Patents

Literature

136results about How to "Strengthen the connection structure" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

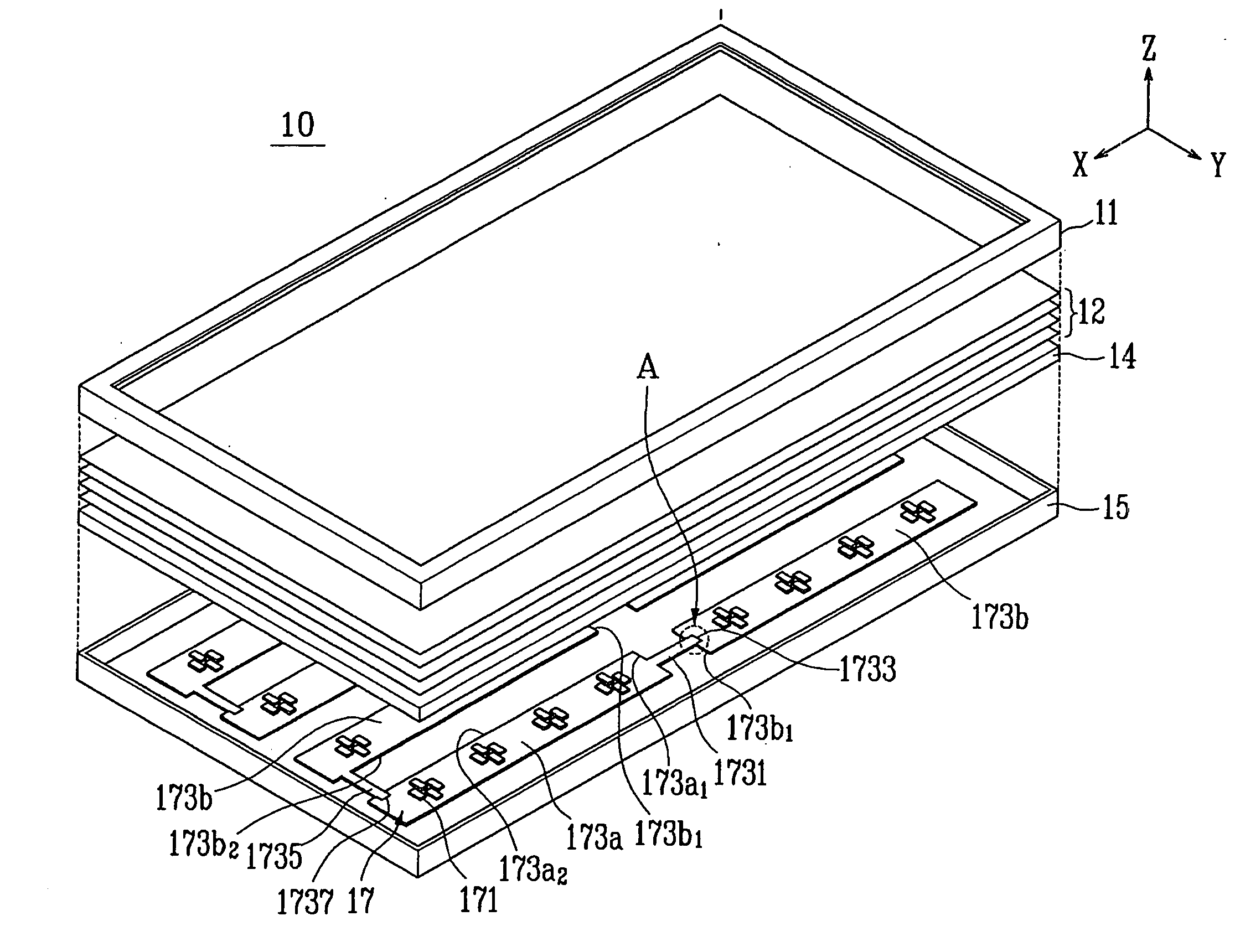

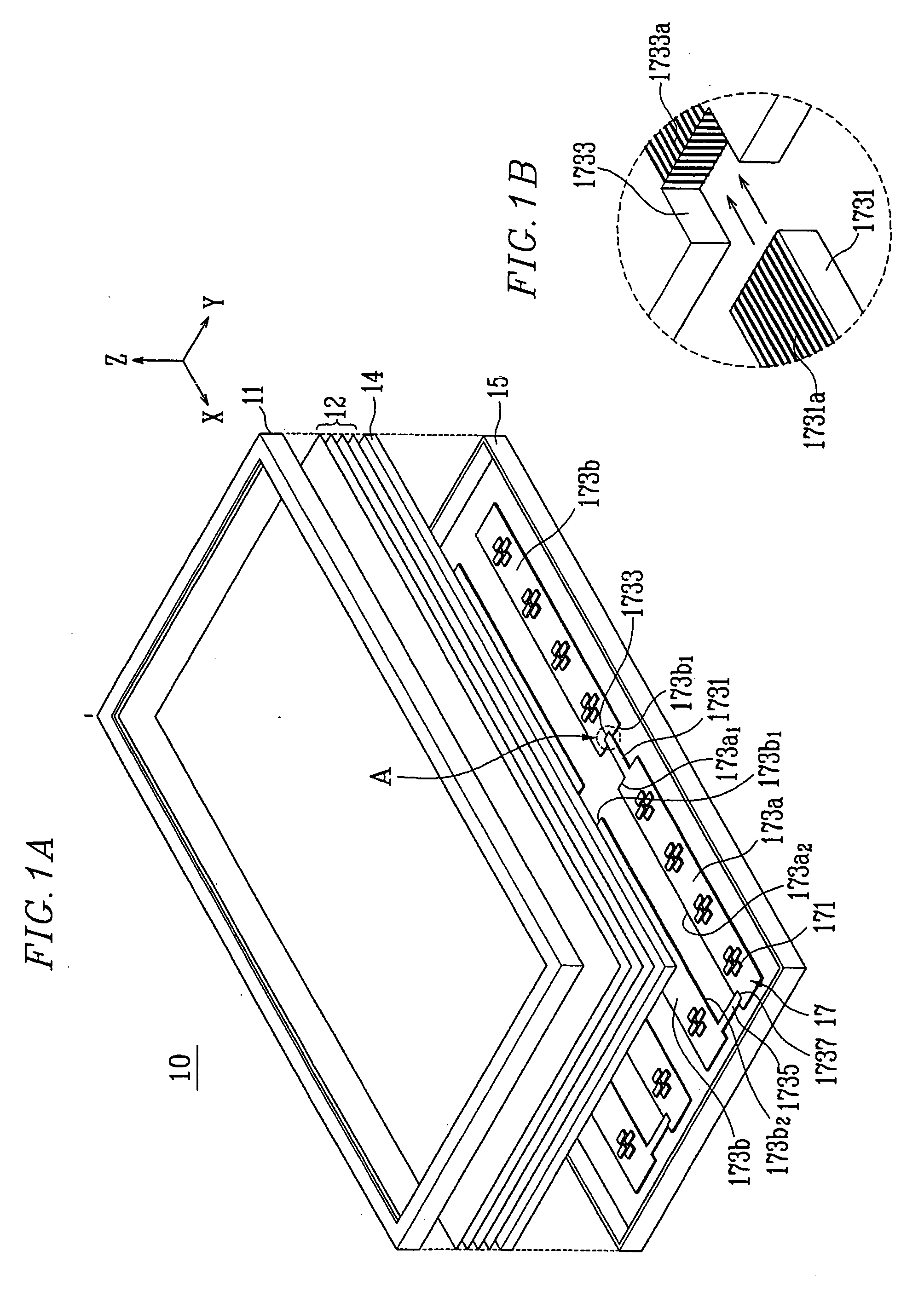

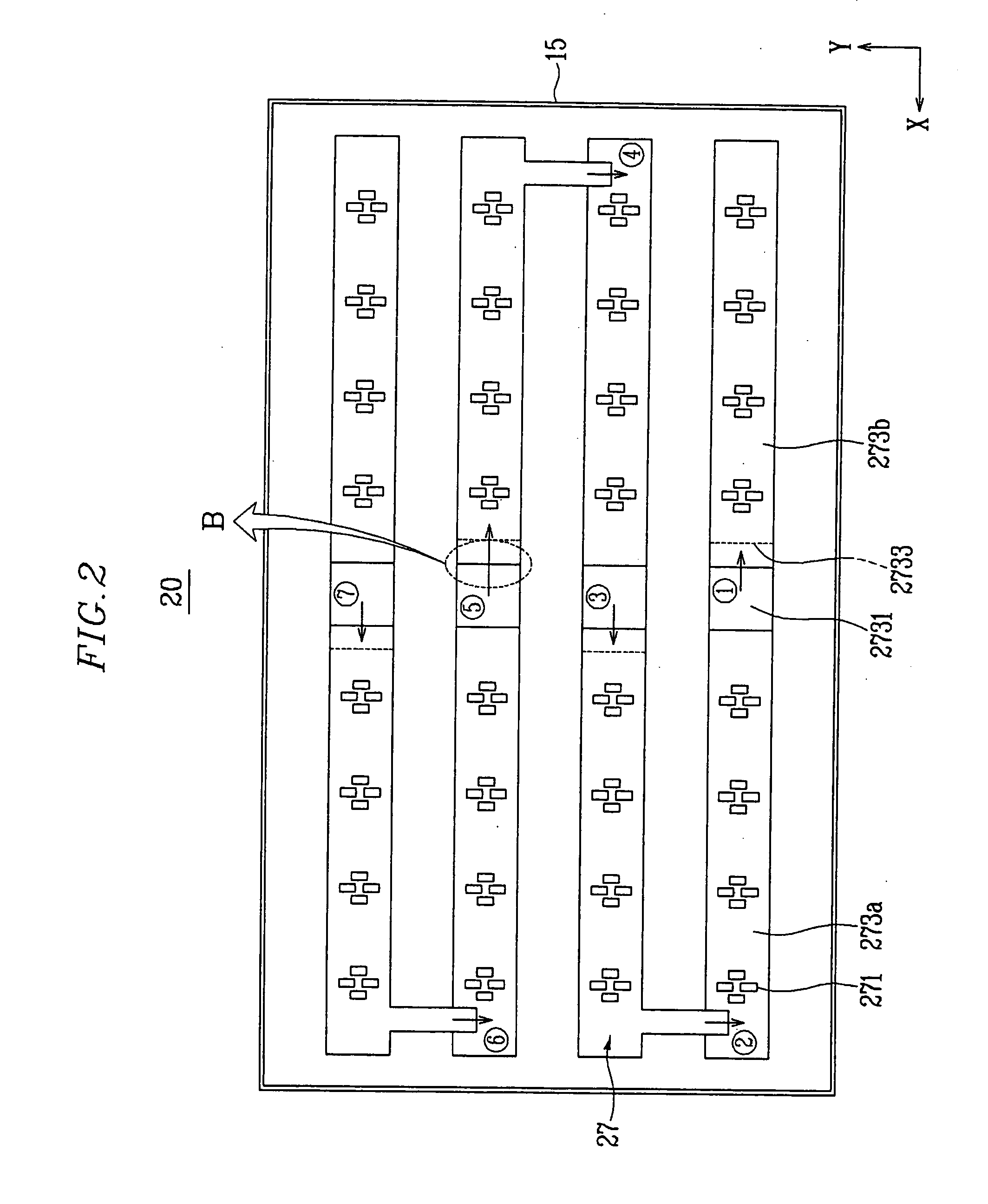

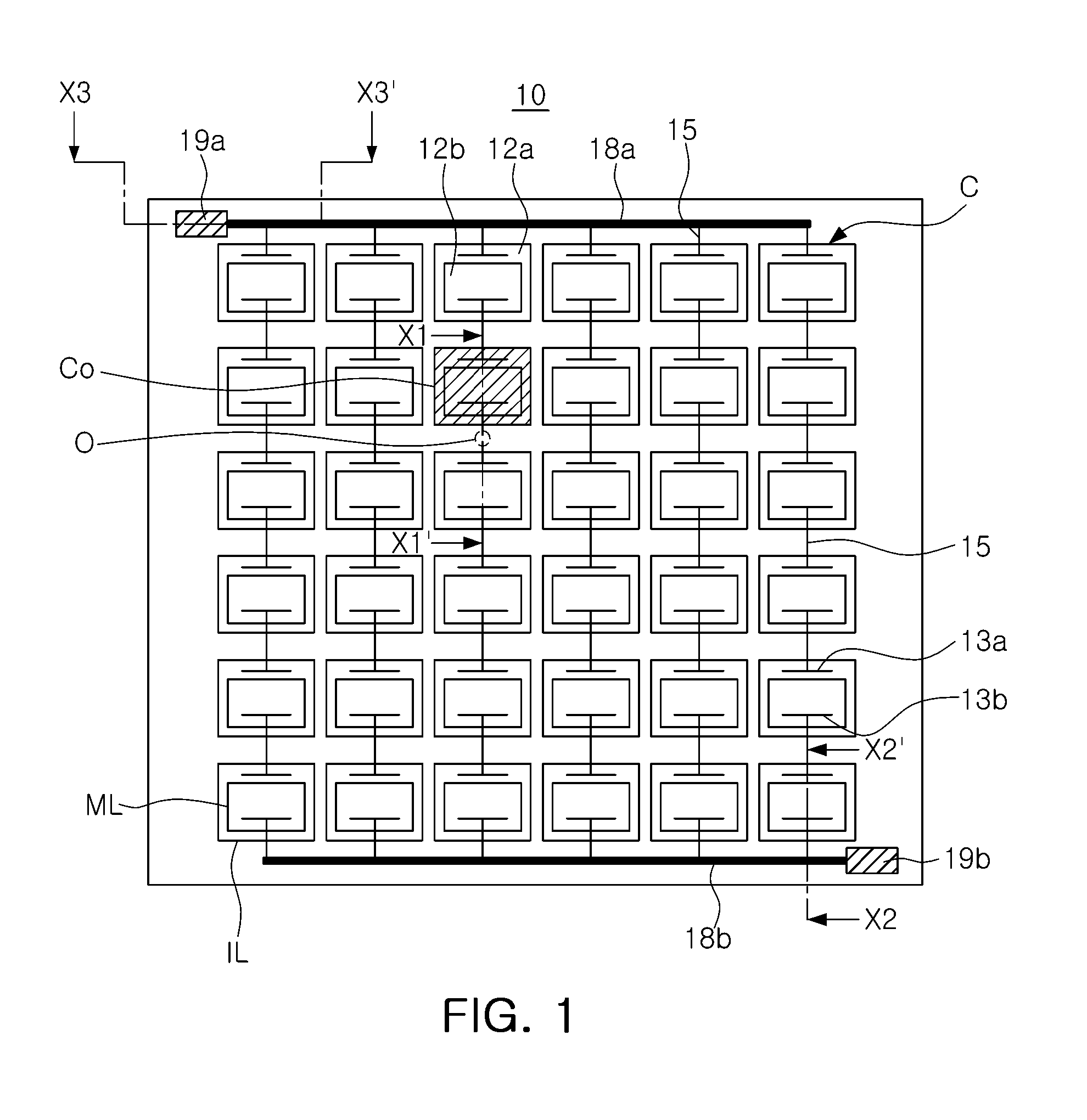

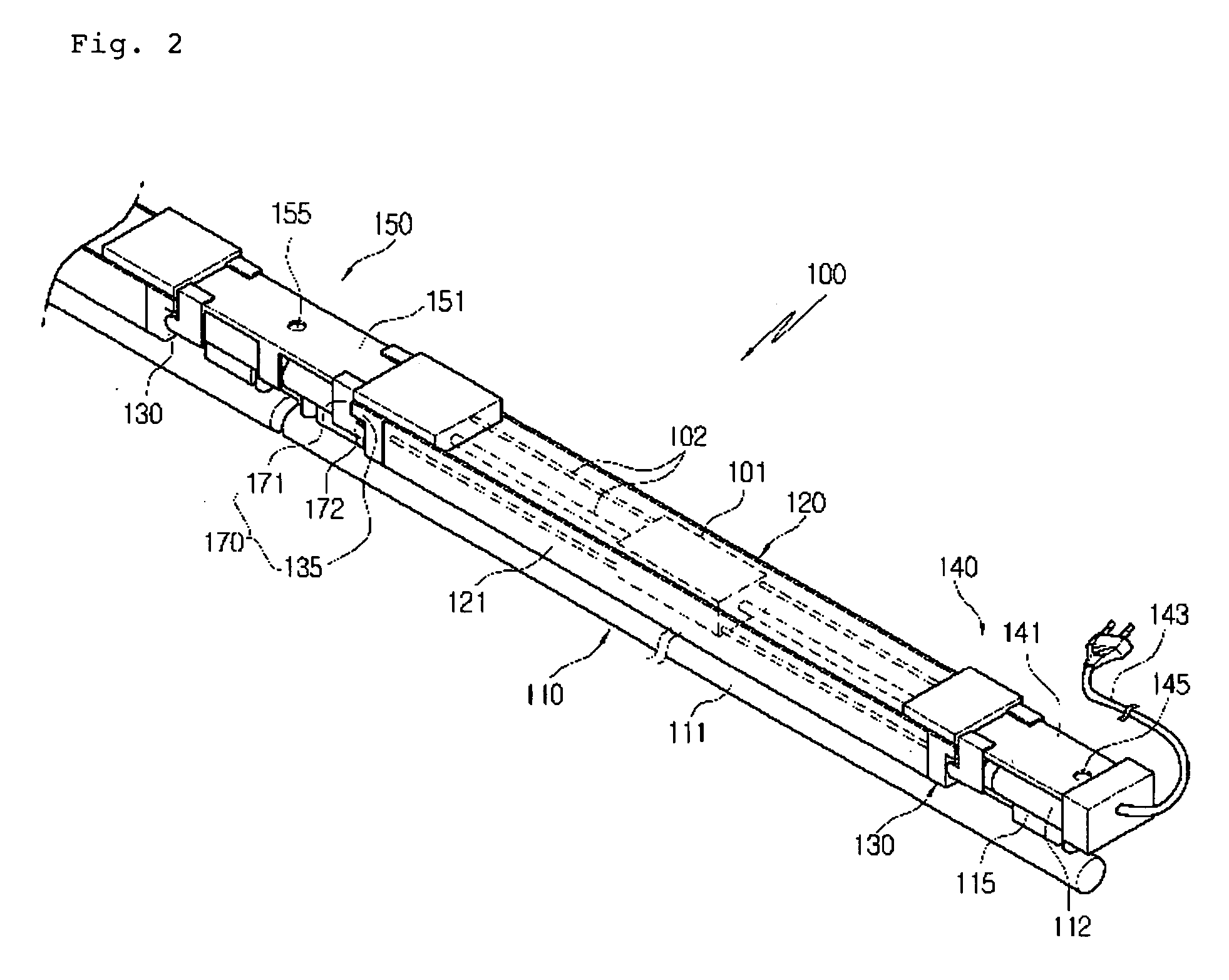

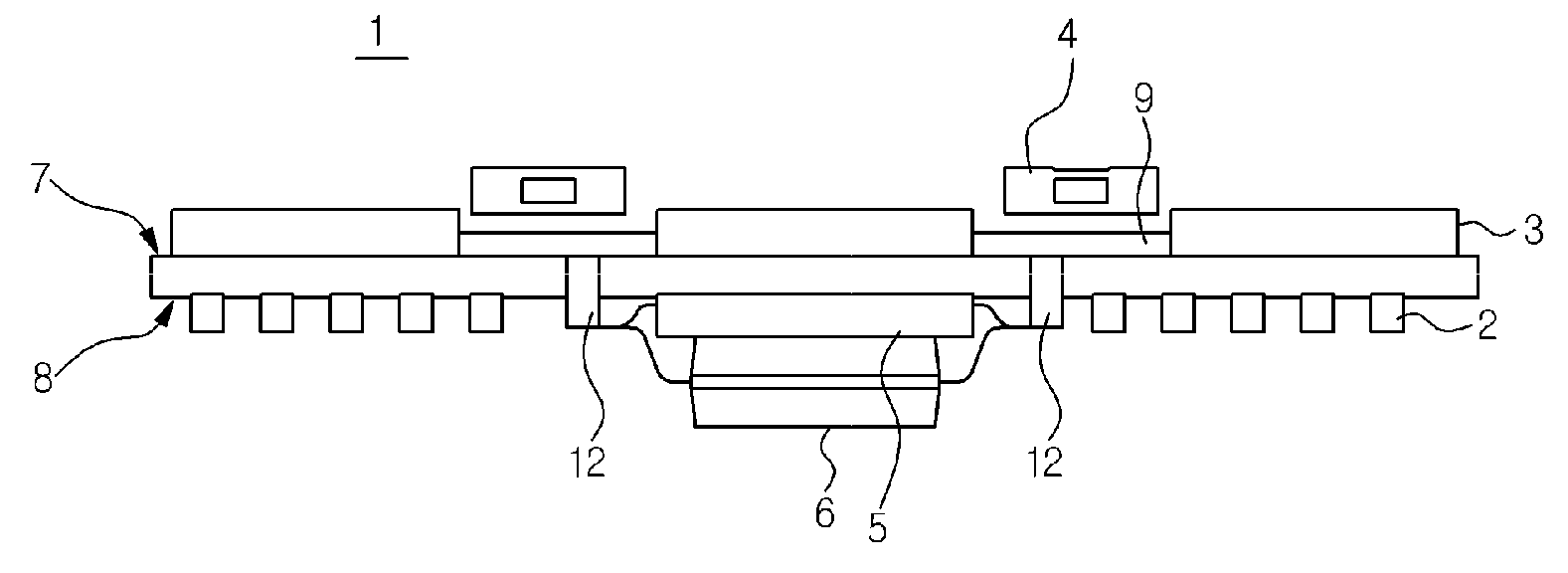

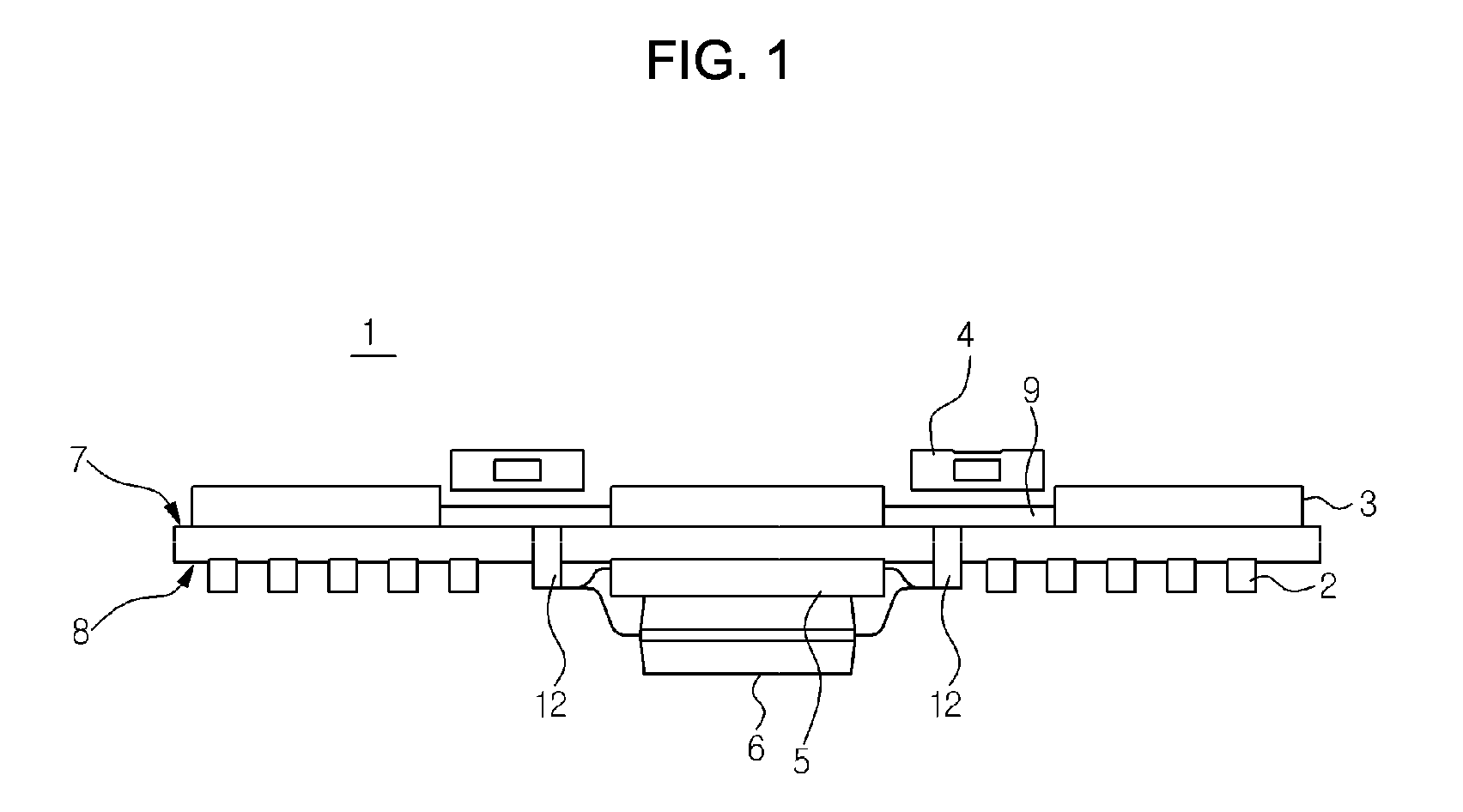

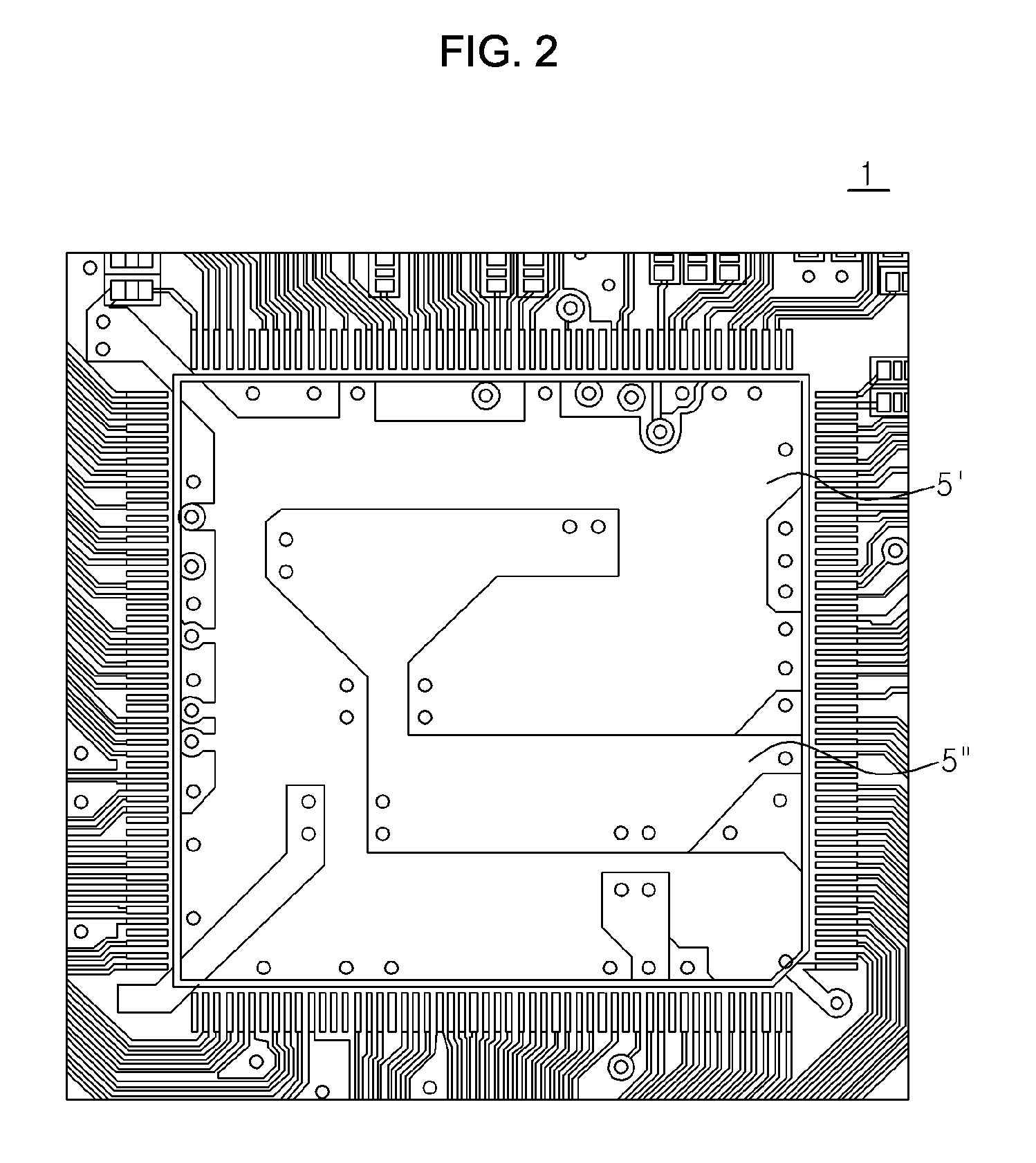

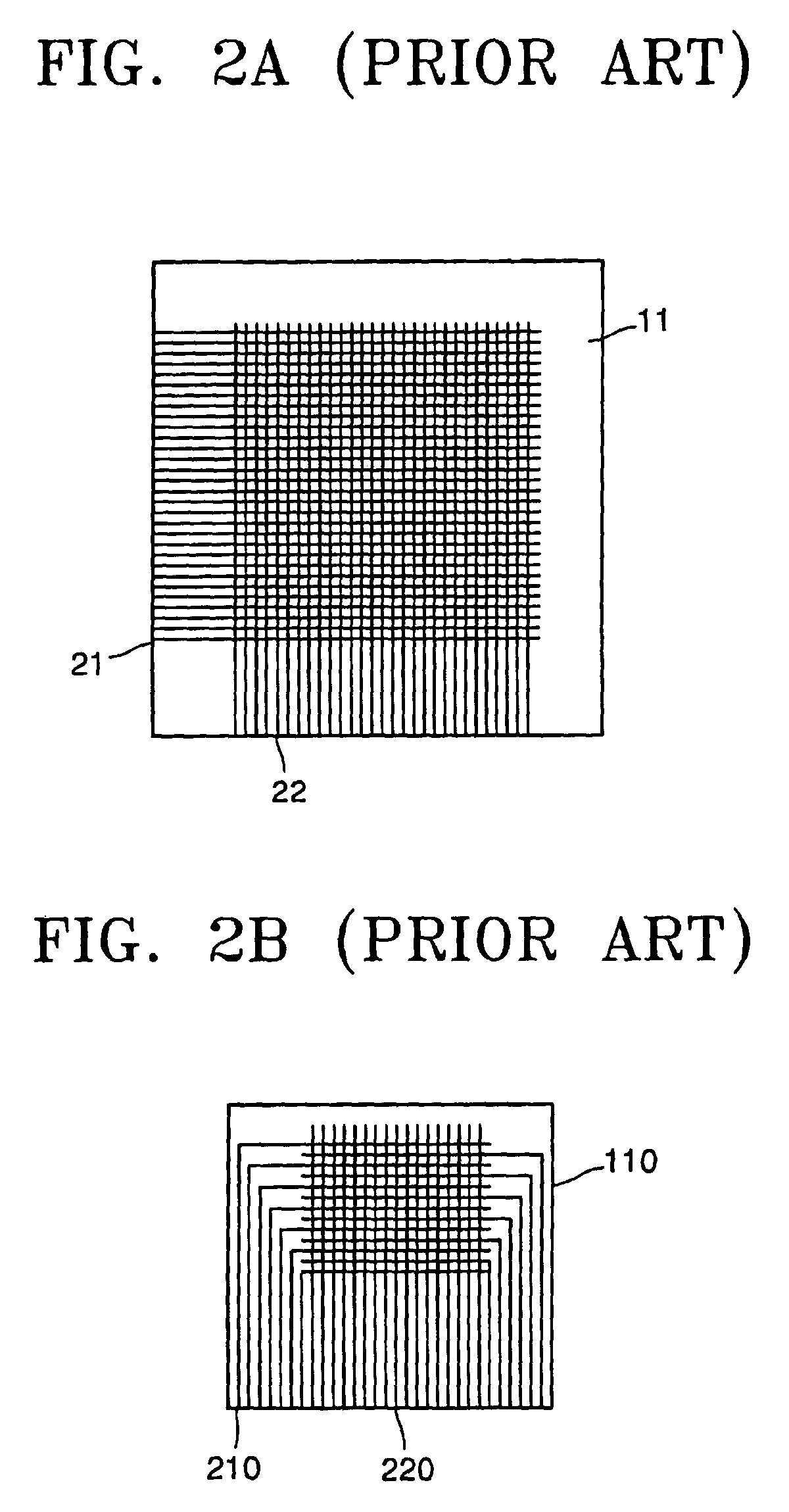

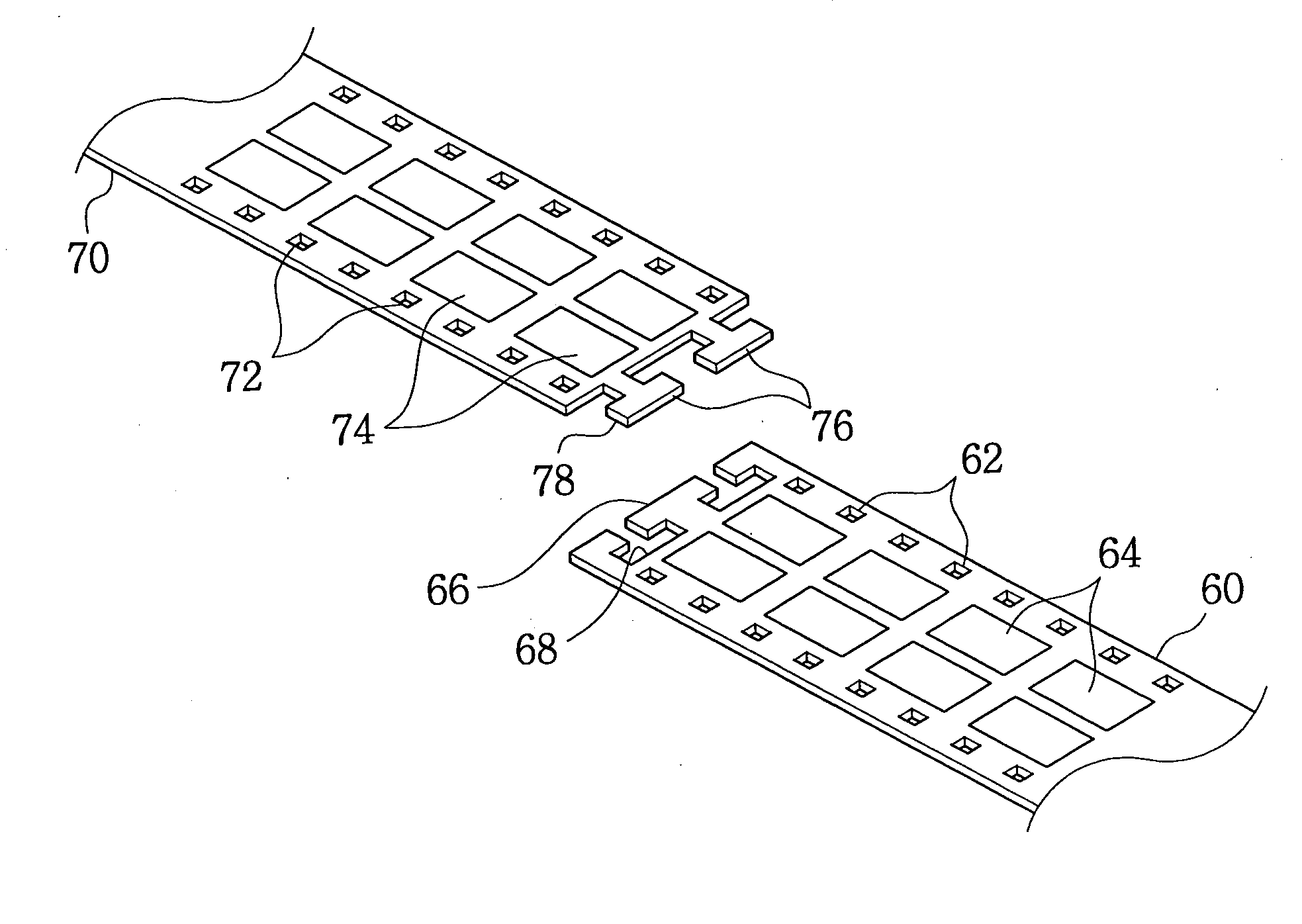

Backlight assembly, display device having the same, and method thereof

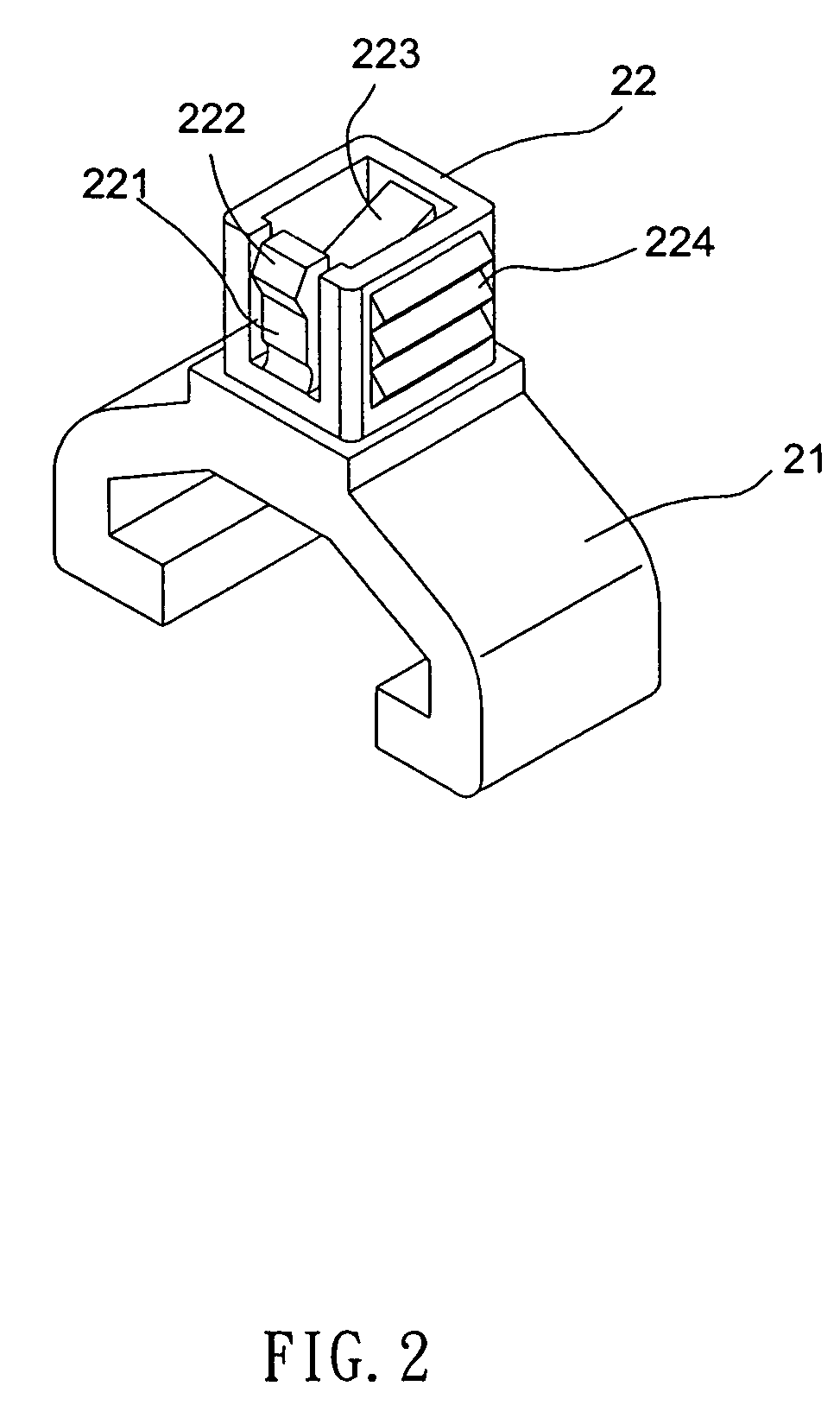

ActiveUS20060289201A1Strengthen the connection structureElectric discharge tubesPrinted circuit aspectsDisplay deviceEngineering

A backlight assembly and a display device having the backlight assembly are provided where the backlight assembly includes a plurality of light sources for emitting light and a plurality of metal core printed circuit boards on which the light sources are mounted. The metal core printed circuit boards are directly connected to each other in predetermined regions to emit light in a surface direction. A method of assembling the backlight assembly is further provided.

Owner:SAMSUNG DISPLAY CO LTD

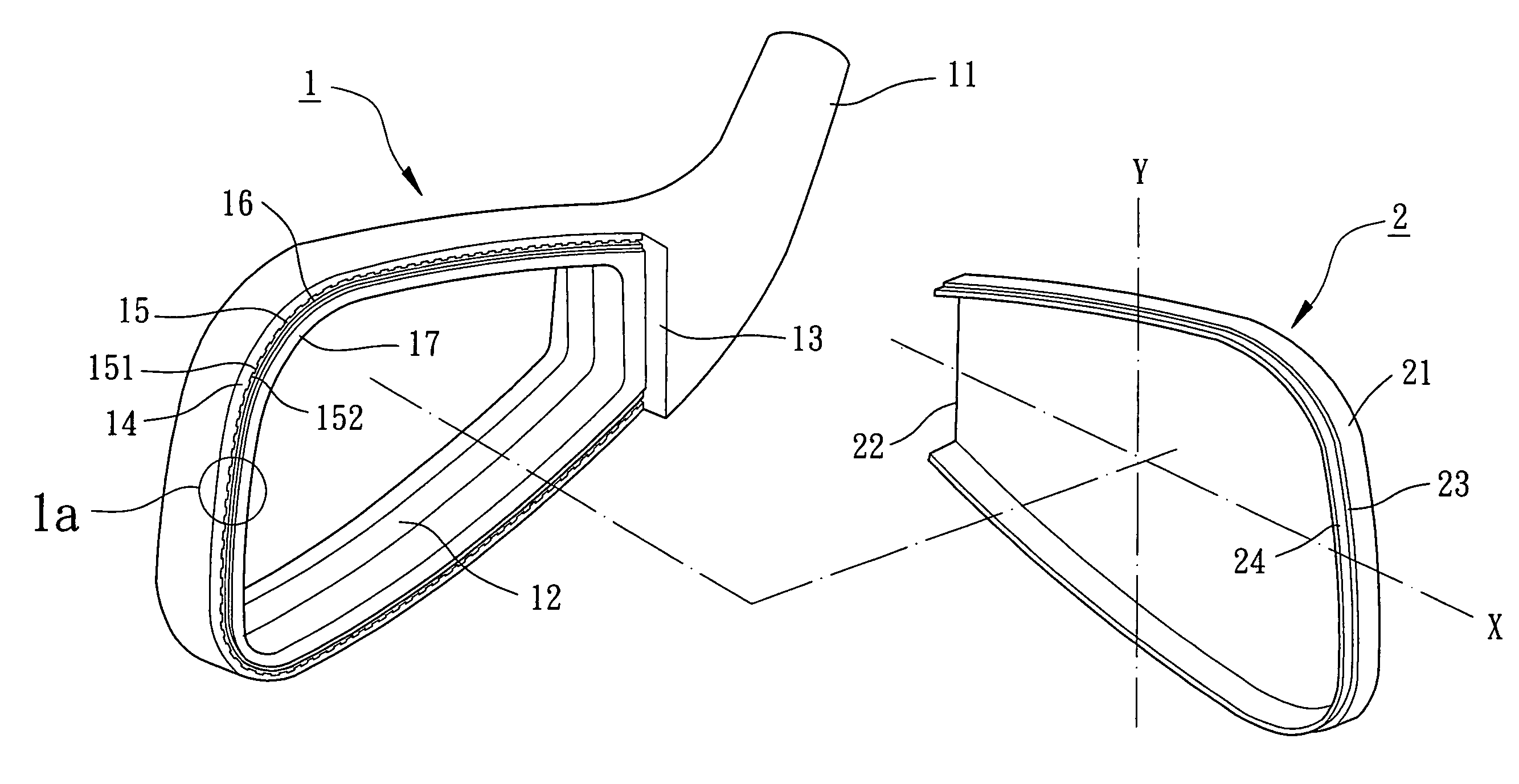

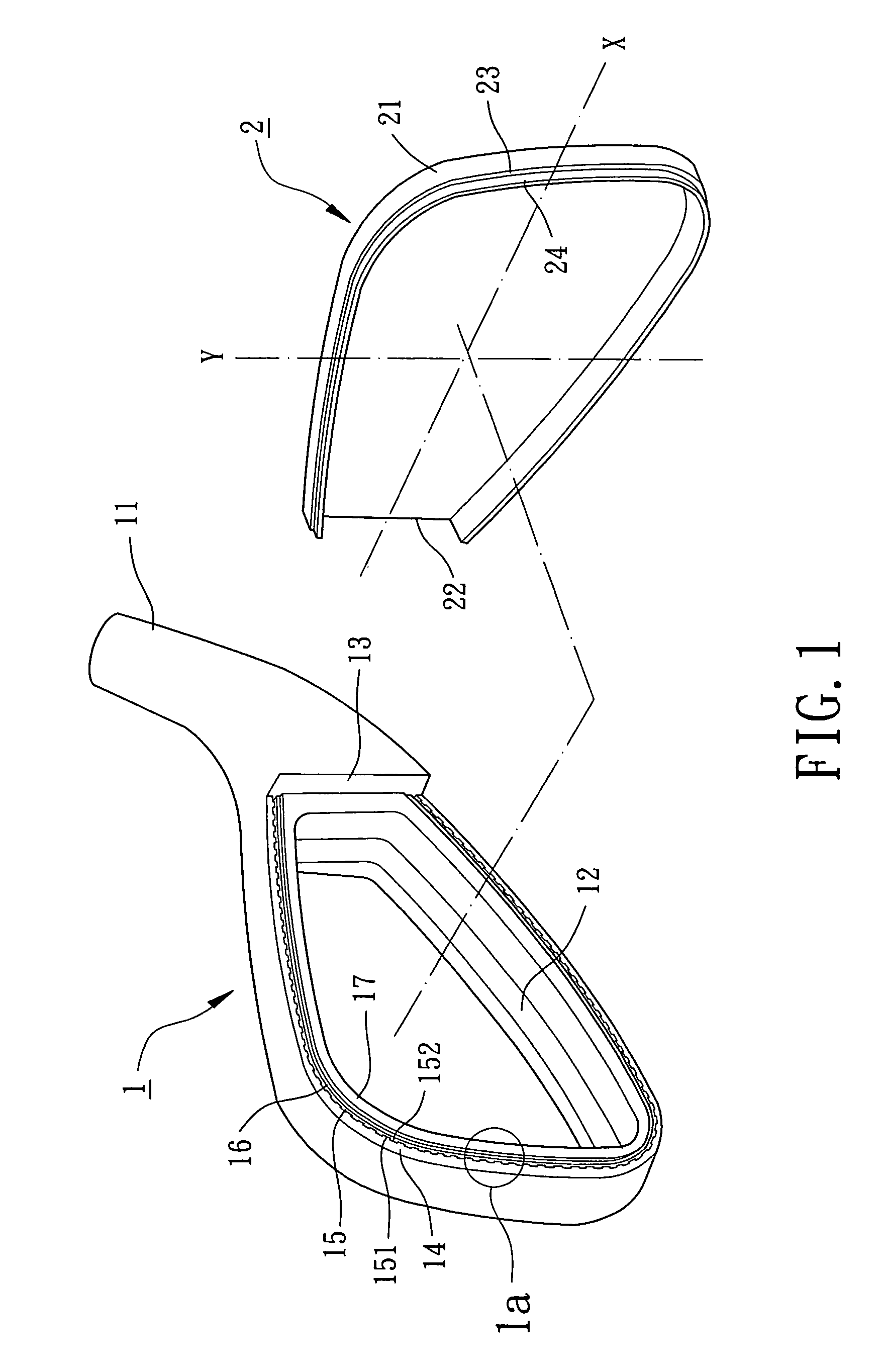

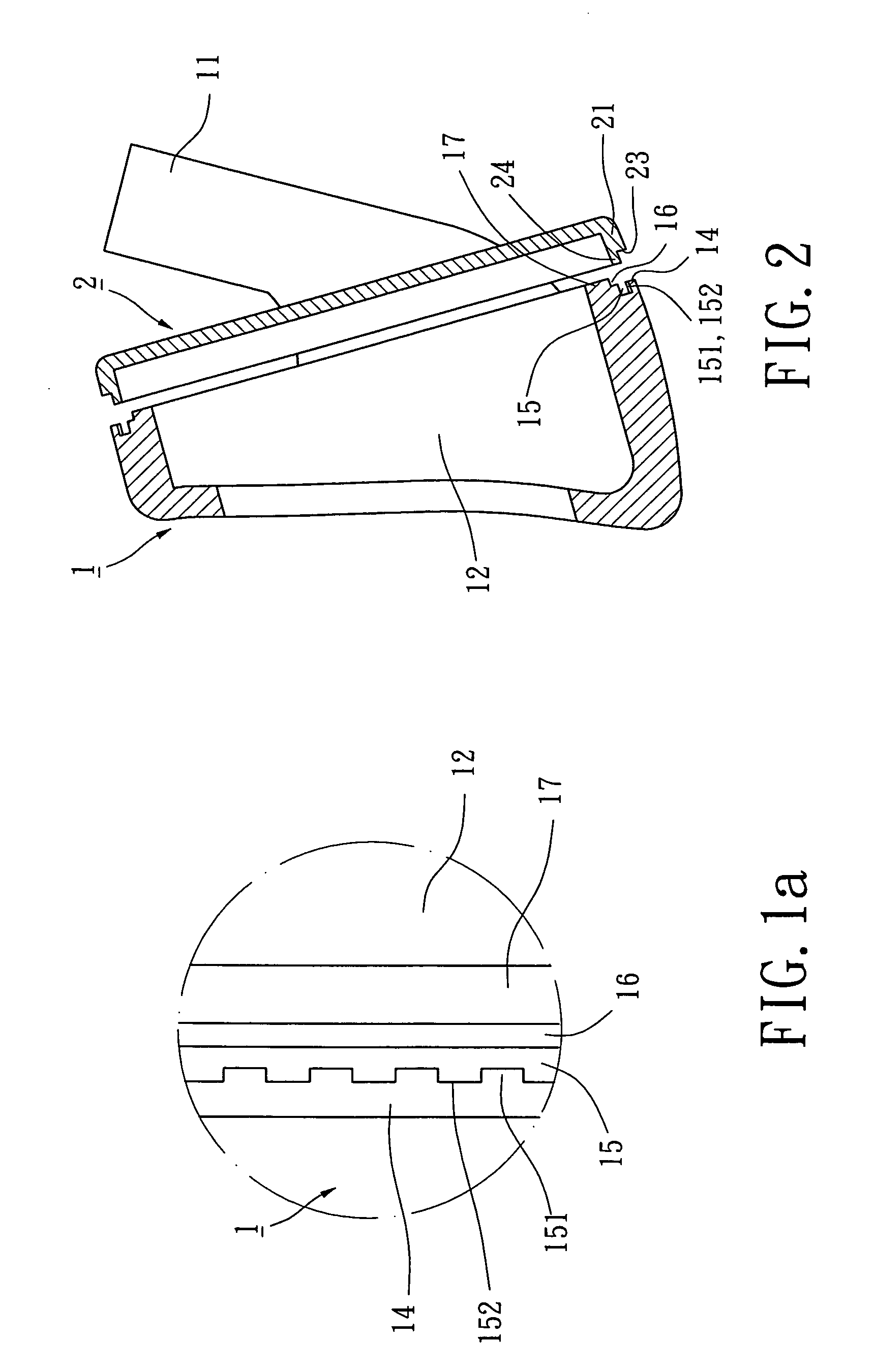

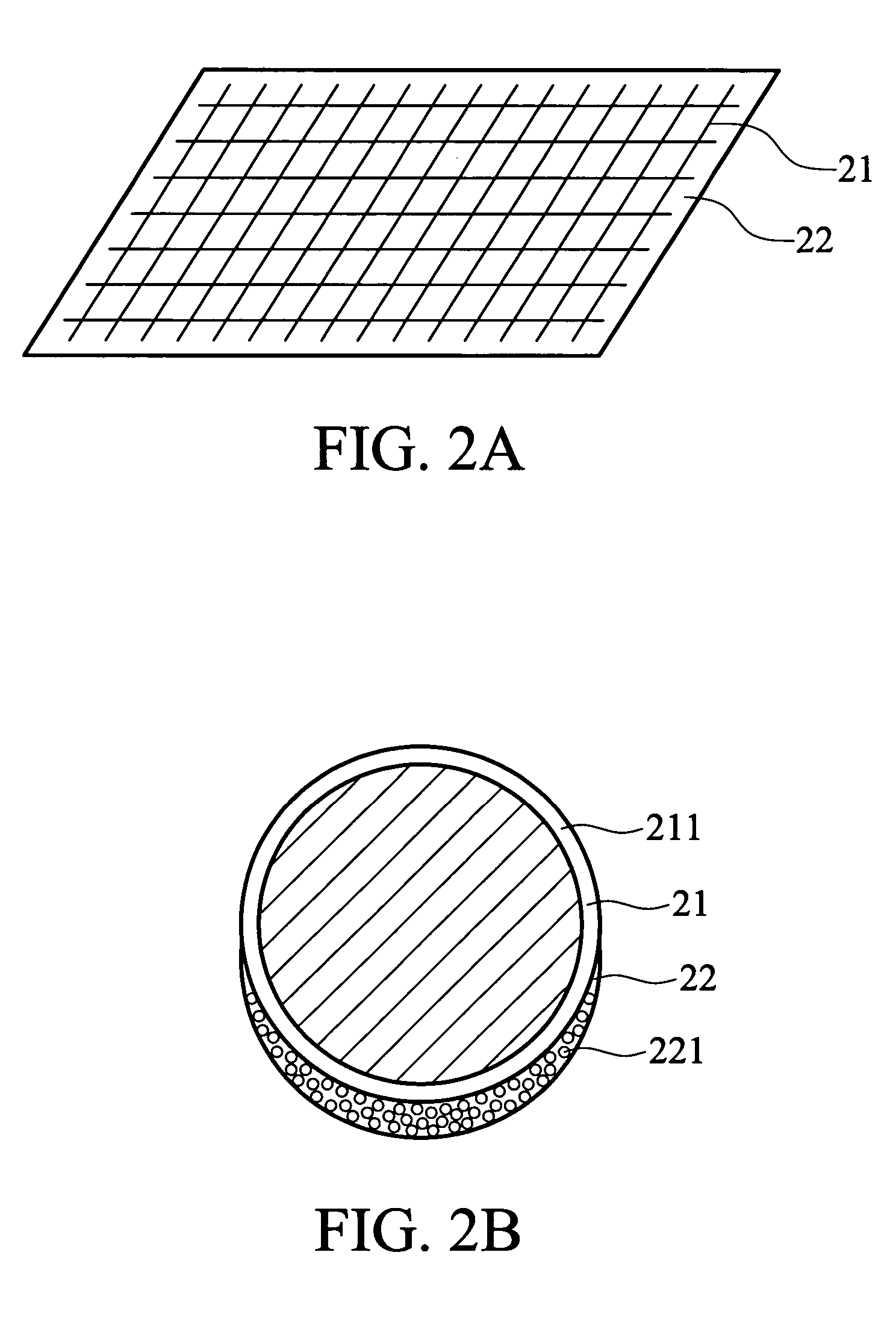

Intensified structure for connecting a golf club head body with a striking plate

A golf club head includes a golf club head body having a connecting groove and a filling space, and a striking plate having an annular upright bent wall and a connecting end. In assembling, the connecting end of the annular upright bent wall of the striking plate is initially inserted into the connecting groove of the golf club head body so that an intensified structure is provided. The filling space of the golf club head body is further filled with a braze material. In brazing, the braze material contained in the filling space of the golf club head body is melted and thus filled within a clearance between the connecting groove of the golf club head body and the connecting end of the striking plate to form a welded layer.

Owner:FUSHENG IND CO LTD

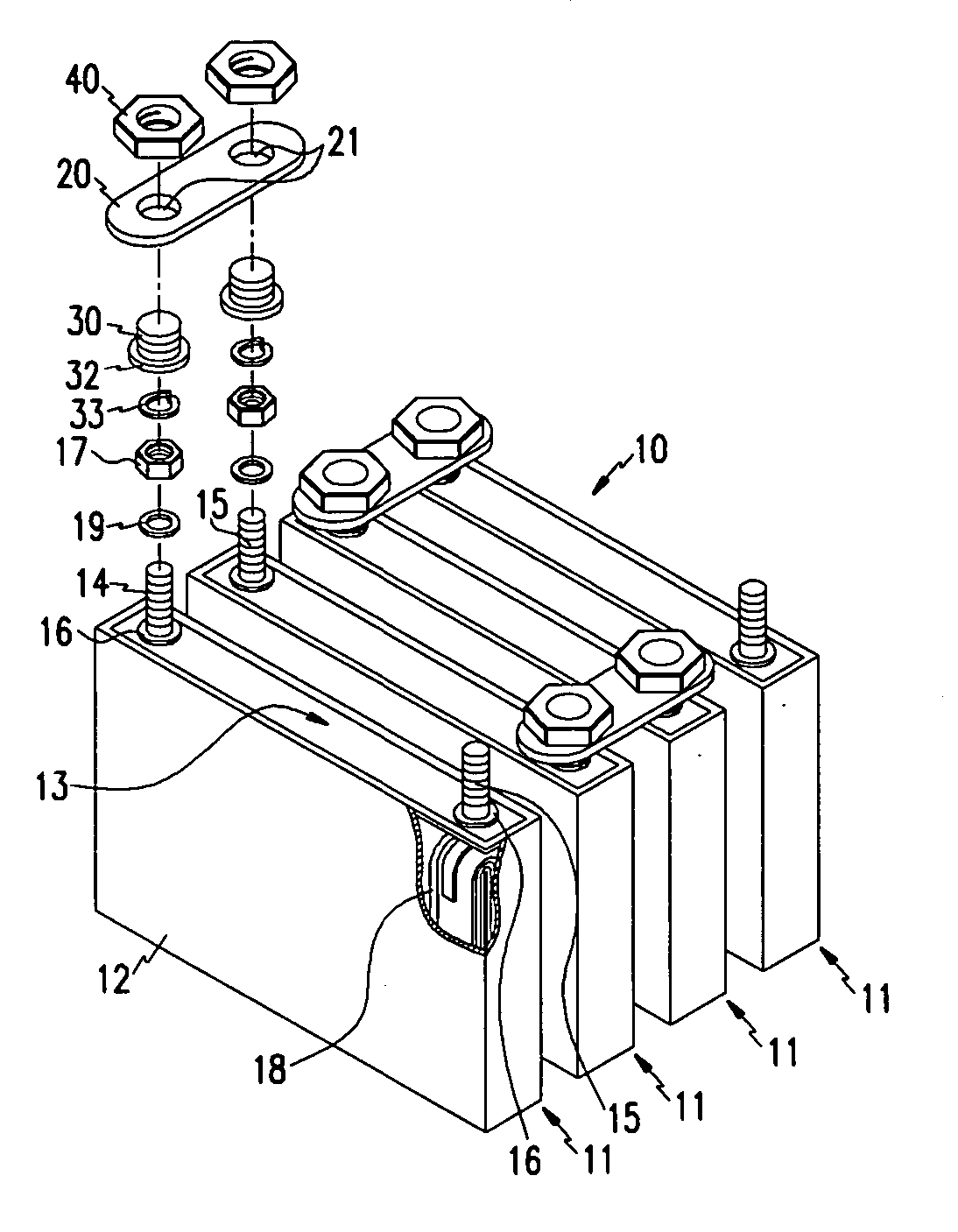

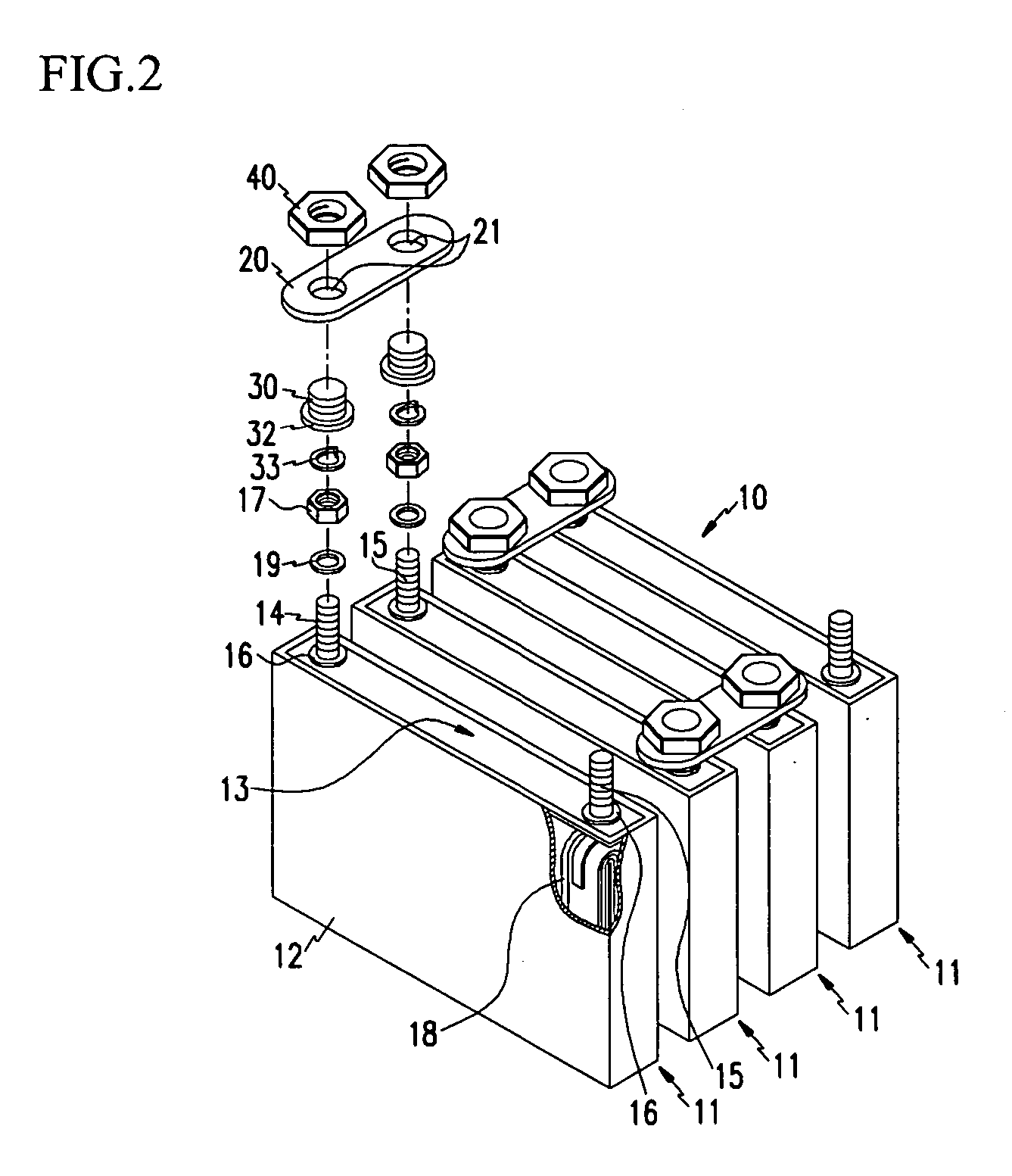

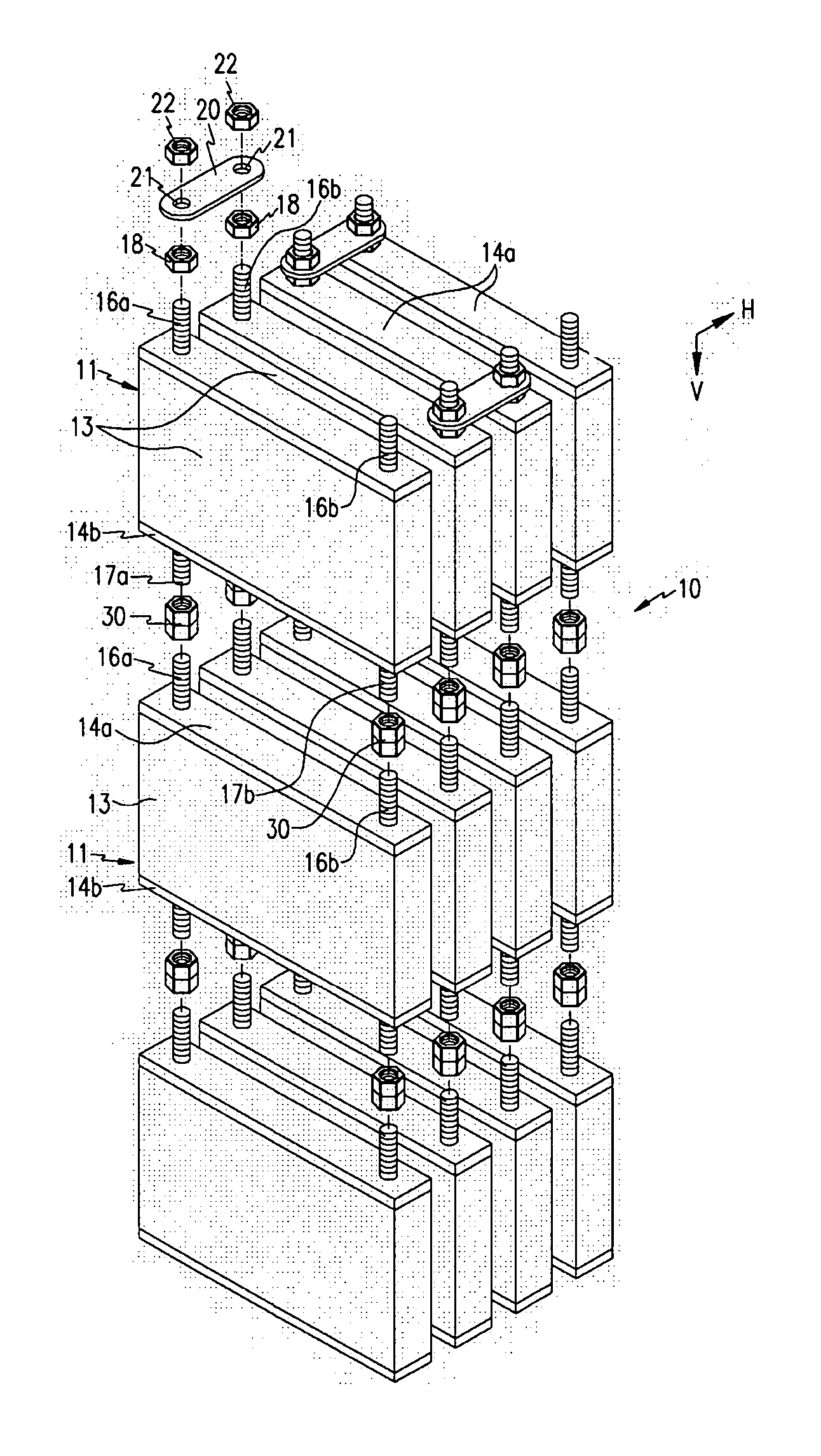

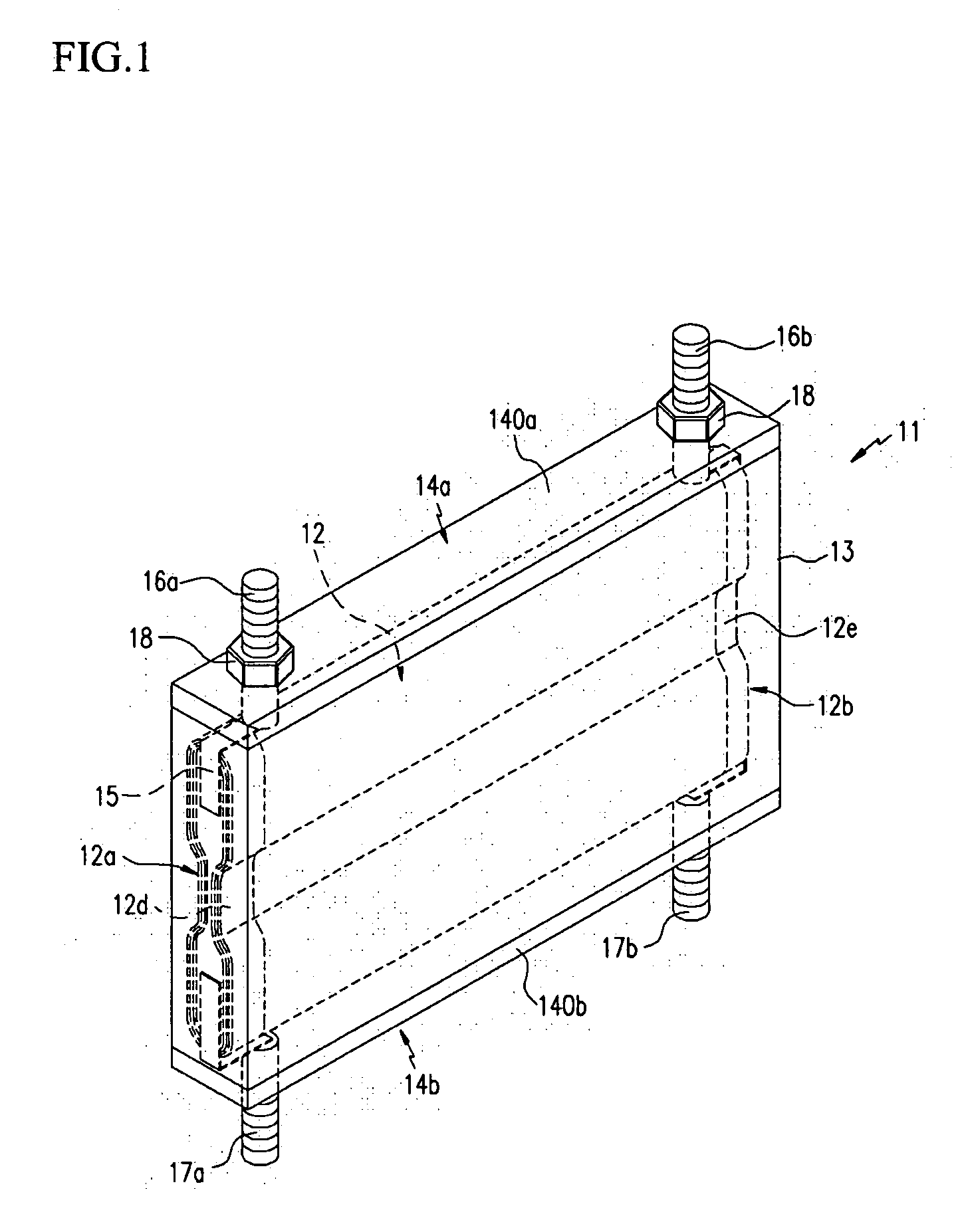

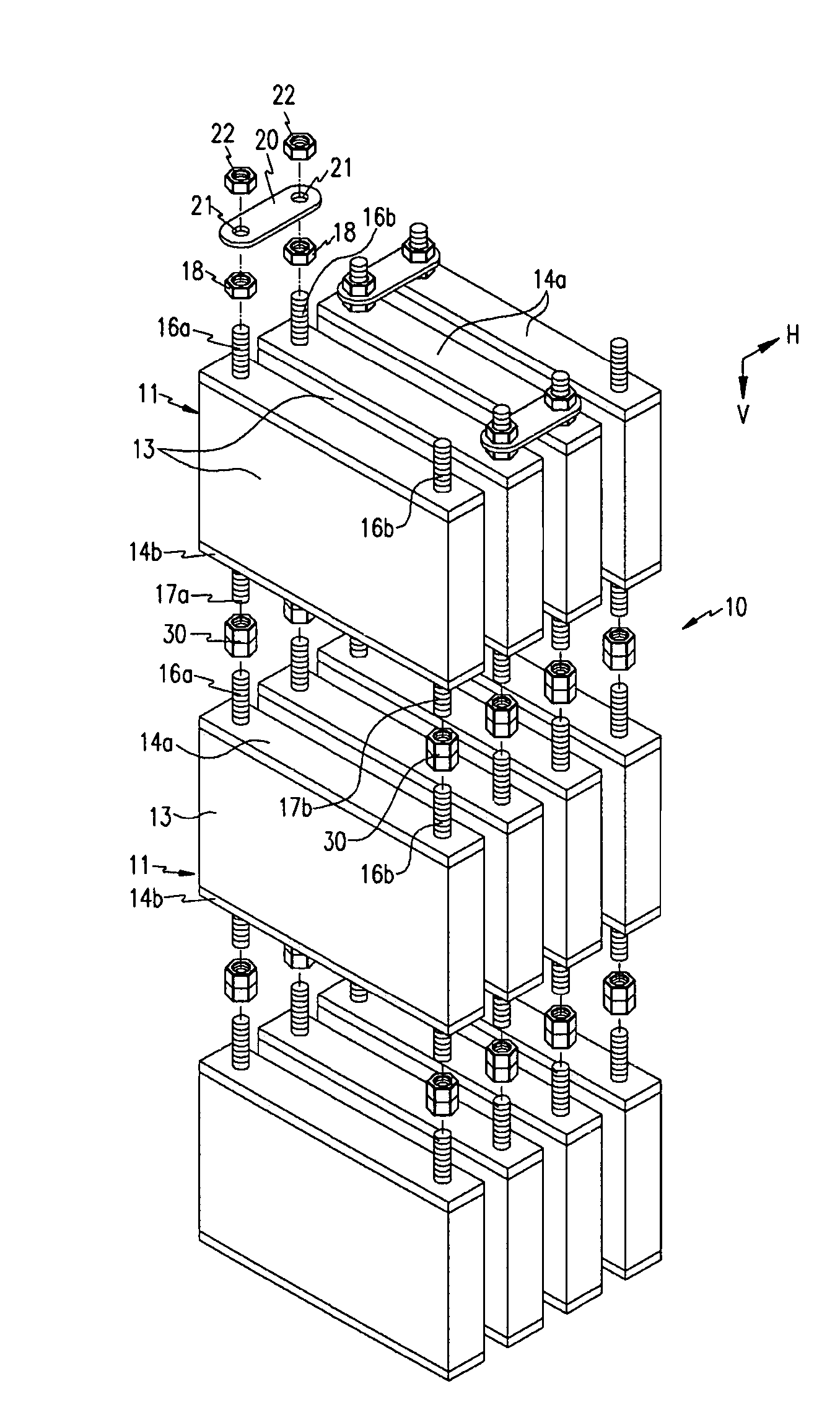

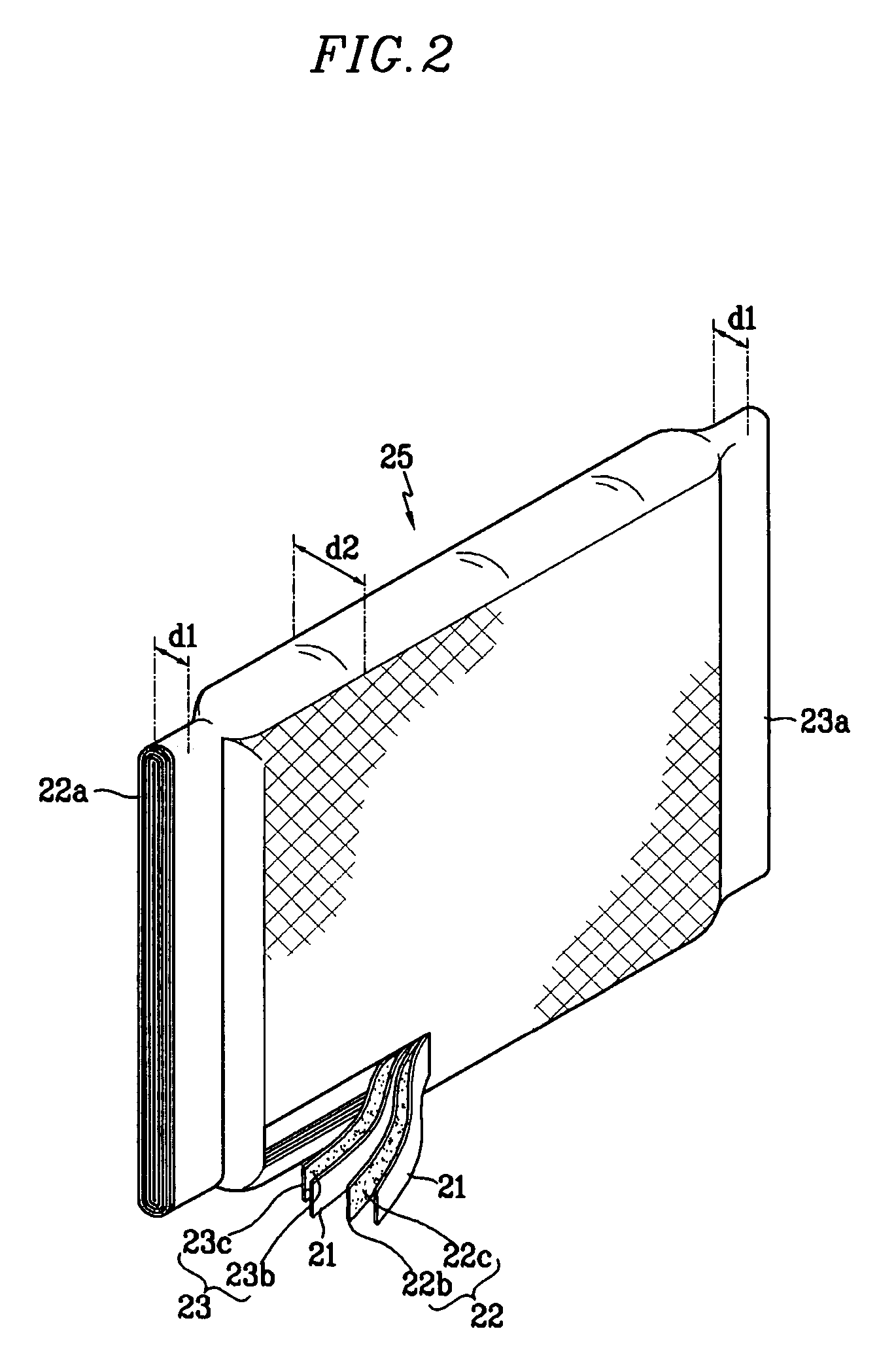

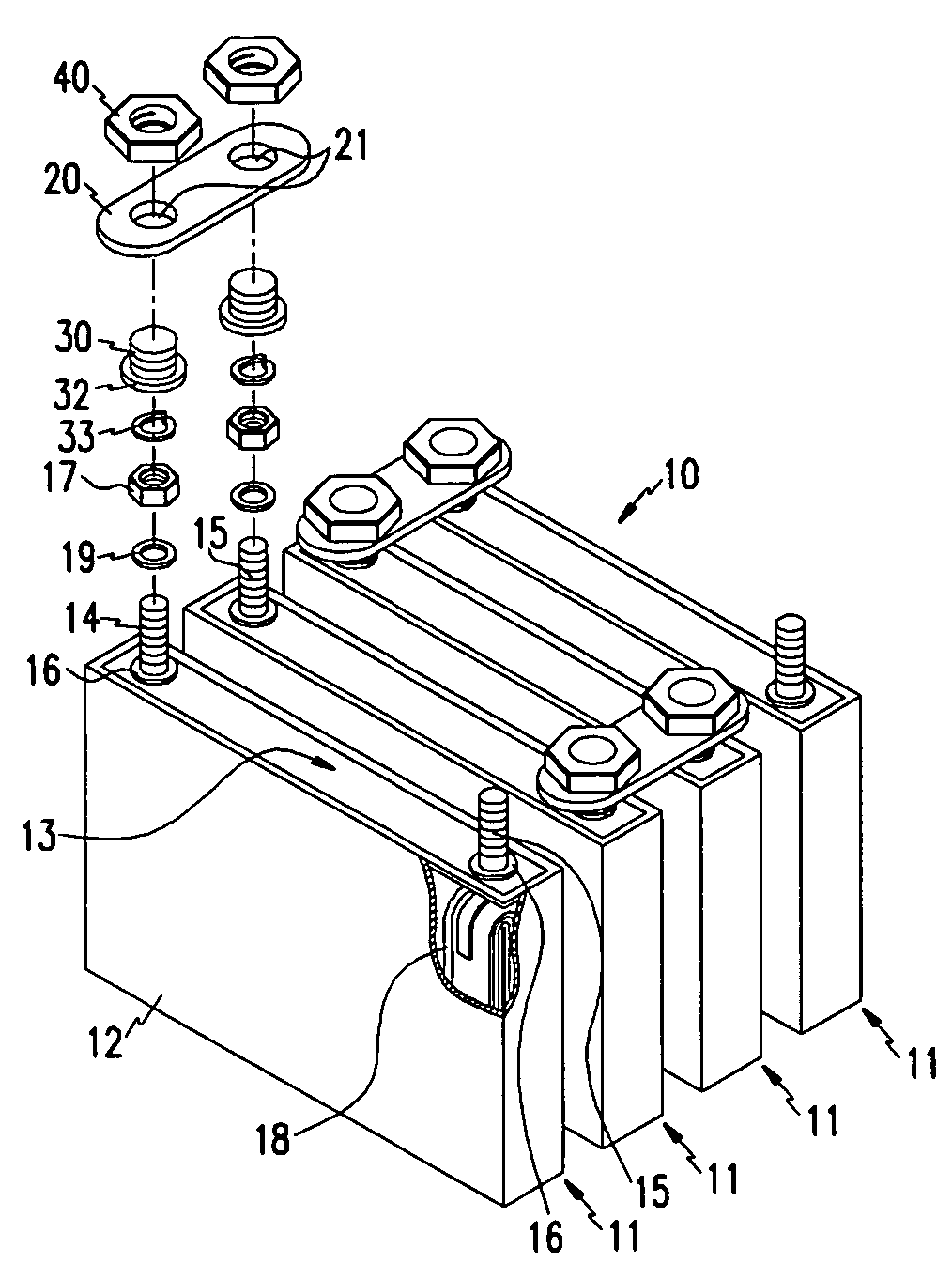

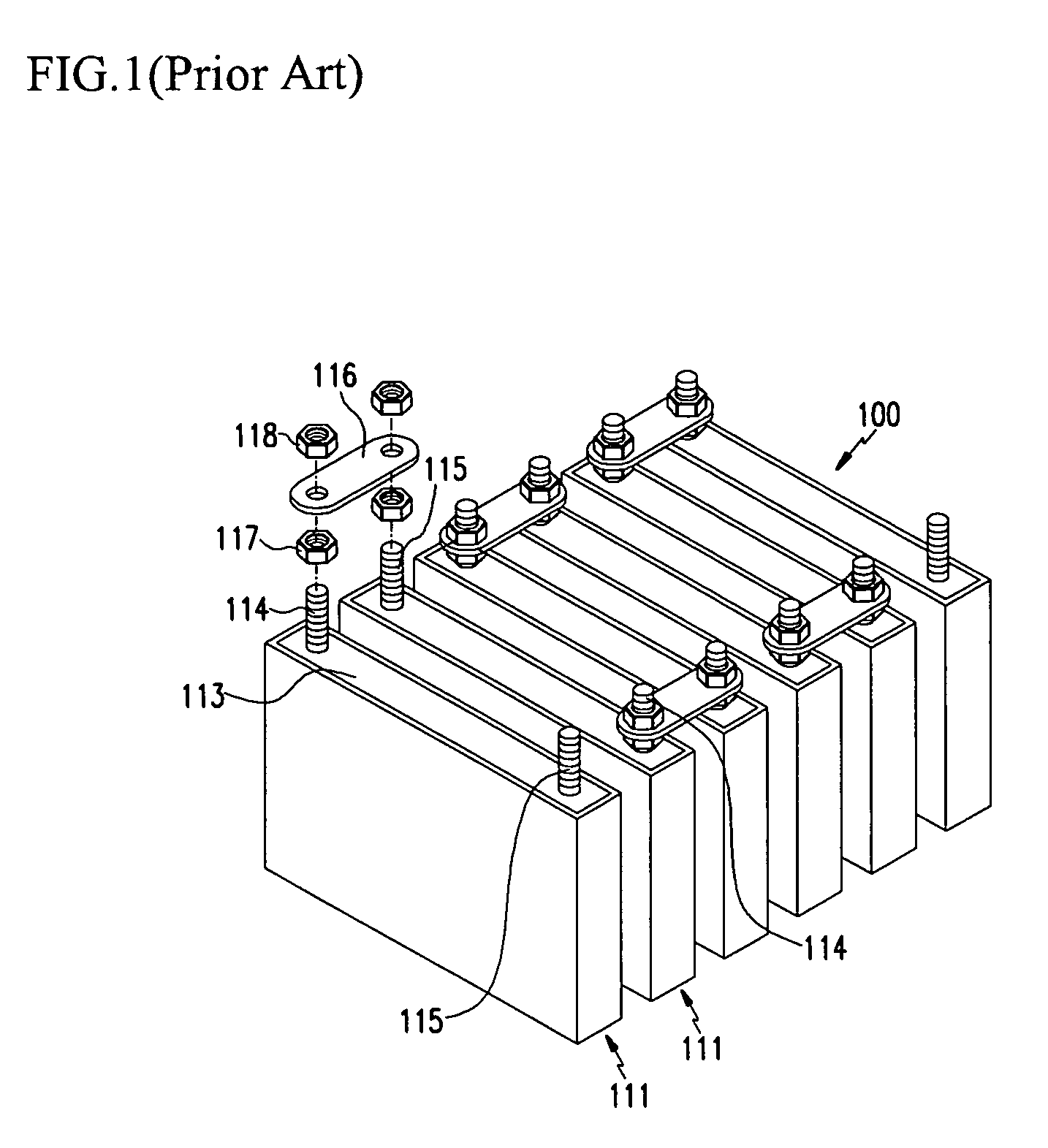

Secondary battery and a secondary battery module using the same

InactiveUS20060094289A1Electric conductivity and current collecting efficiencyMaximize contact areaLarge-sized flat cells/batteriesCurrent conducting connectionsEngineeringFlange

A secondary battery module includes a connector, which electrically connects a first unit battery to an adjacent unit battery. The connector is connected to the first battery through a connecting member, which is connected to a terminal of the first battery. The connecting member has external threads and a flange on which the connector is positioned. The connector is also fitted to the connecting member and fixed thereto through a nut, which is joined with the external threads of the connecting member.

Owner:SAMSUNG SDI CO LTD

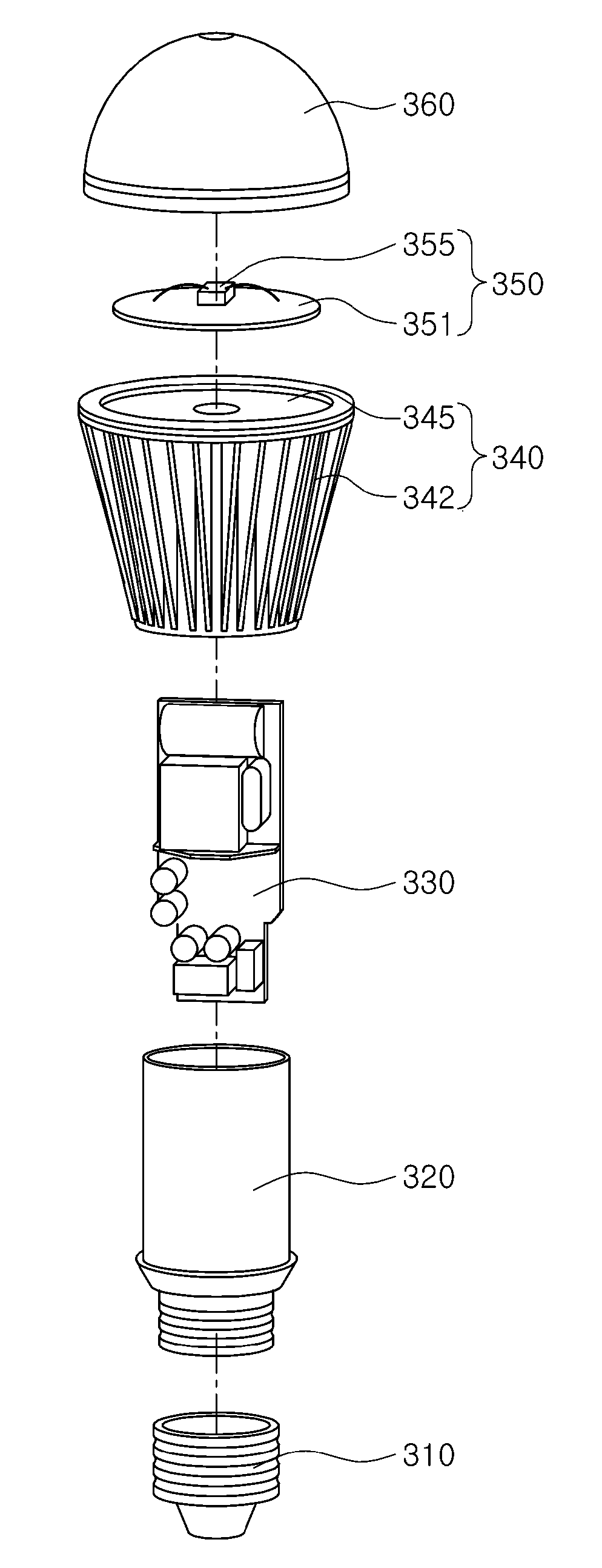

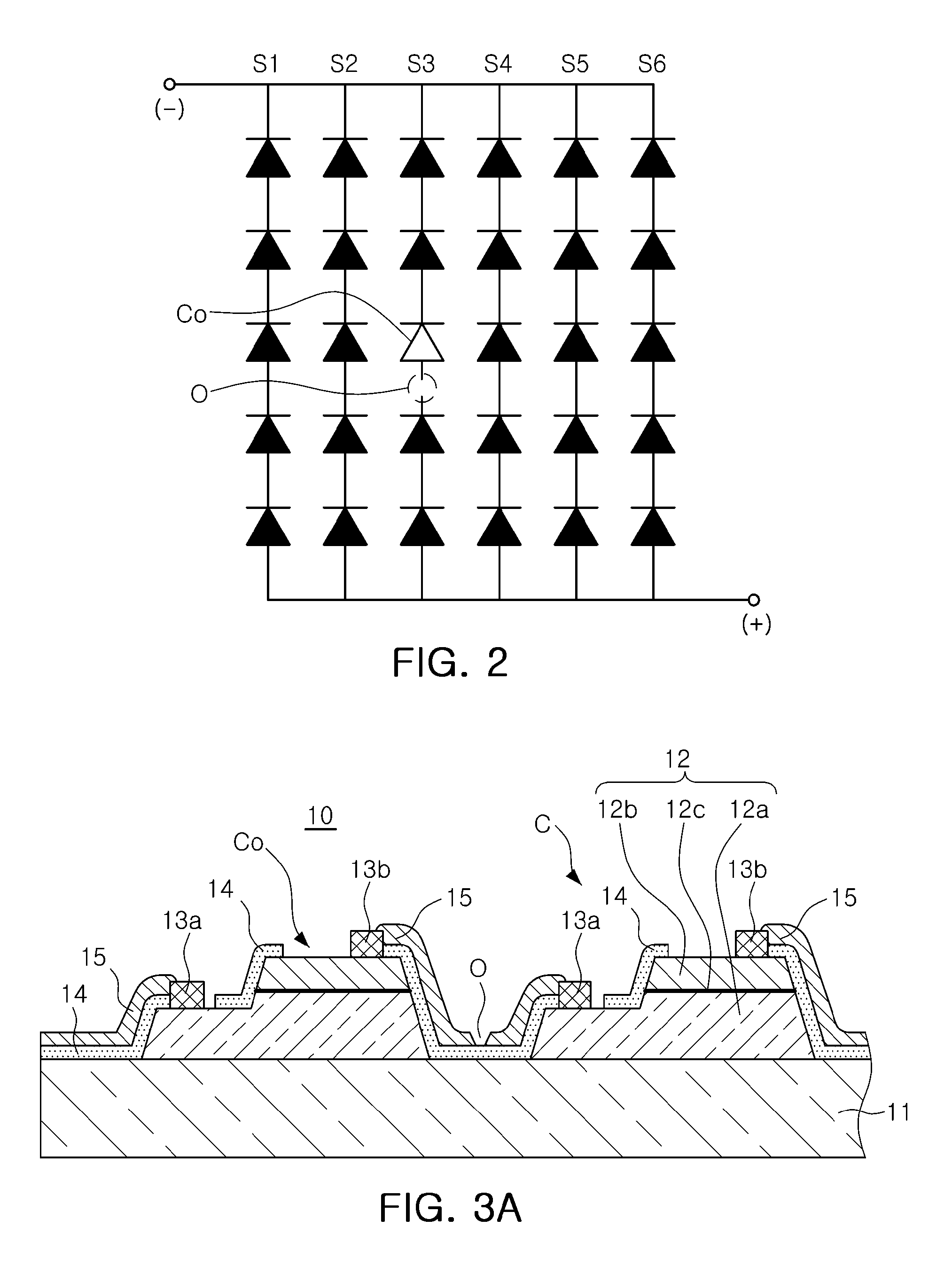

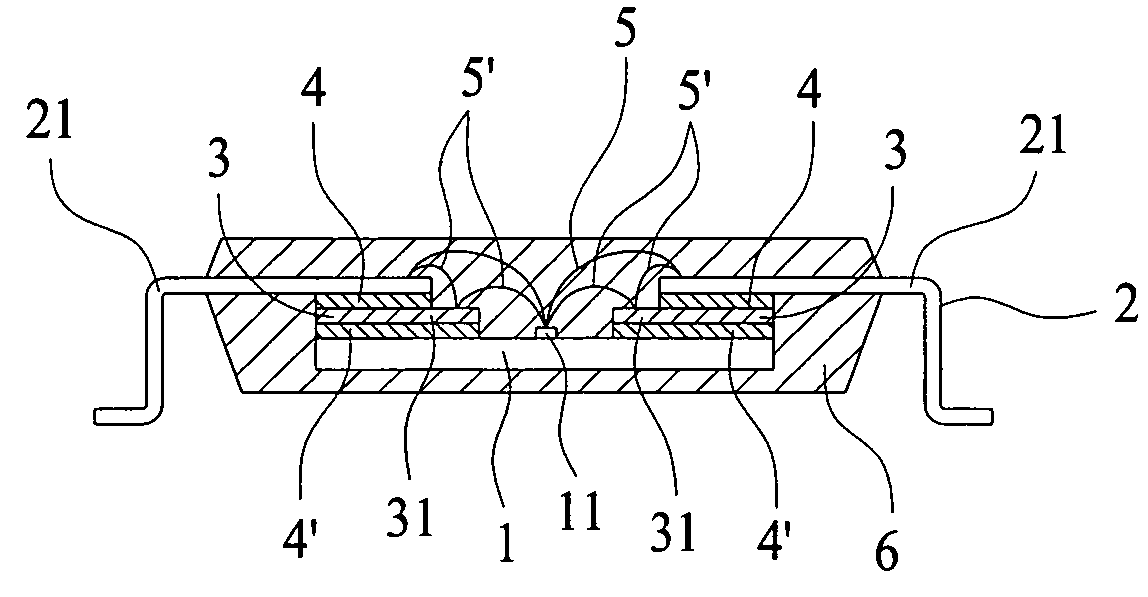

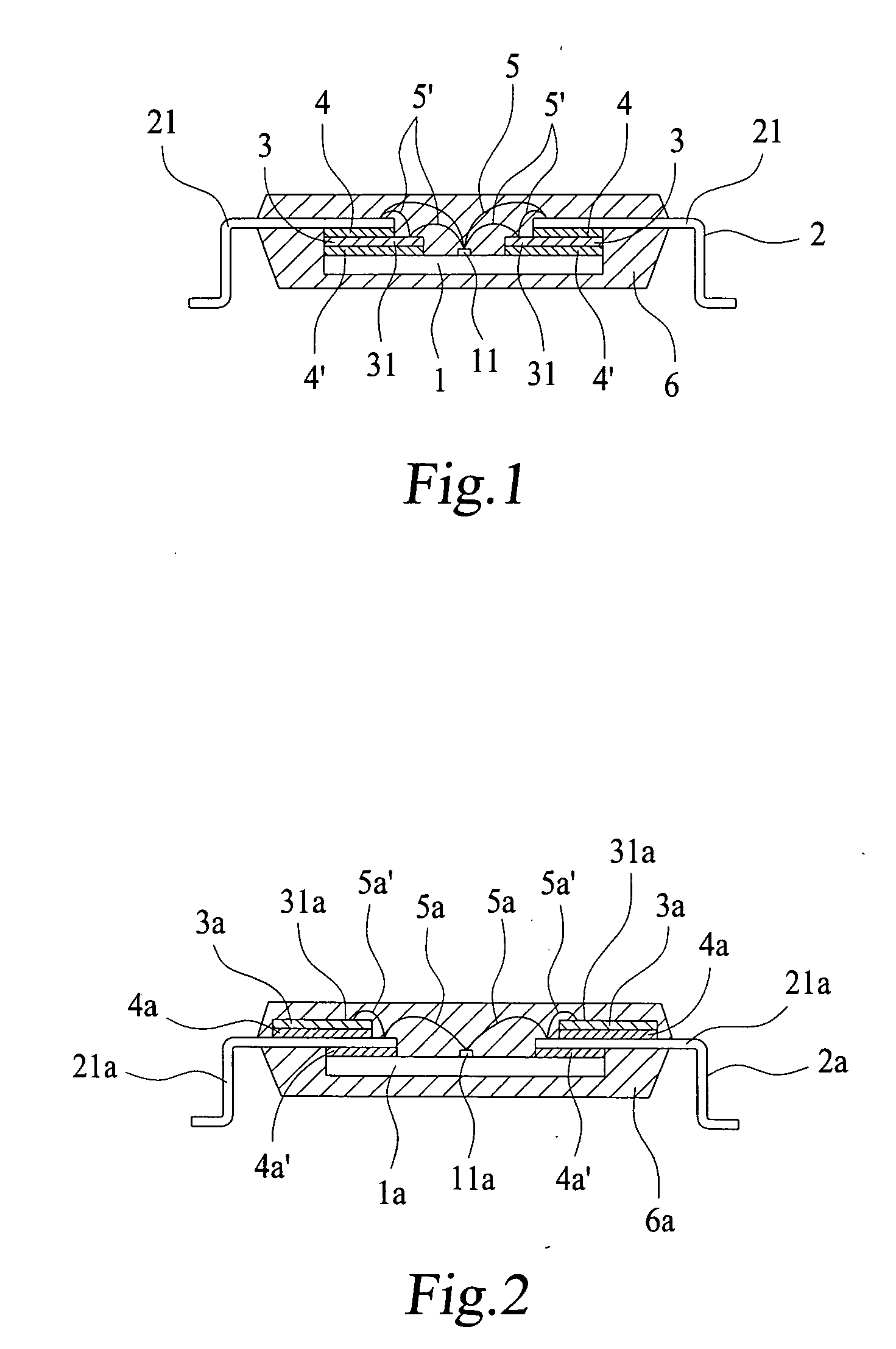

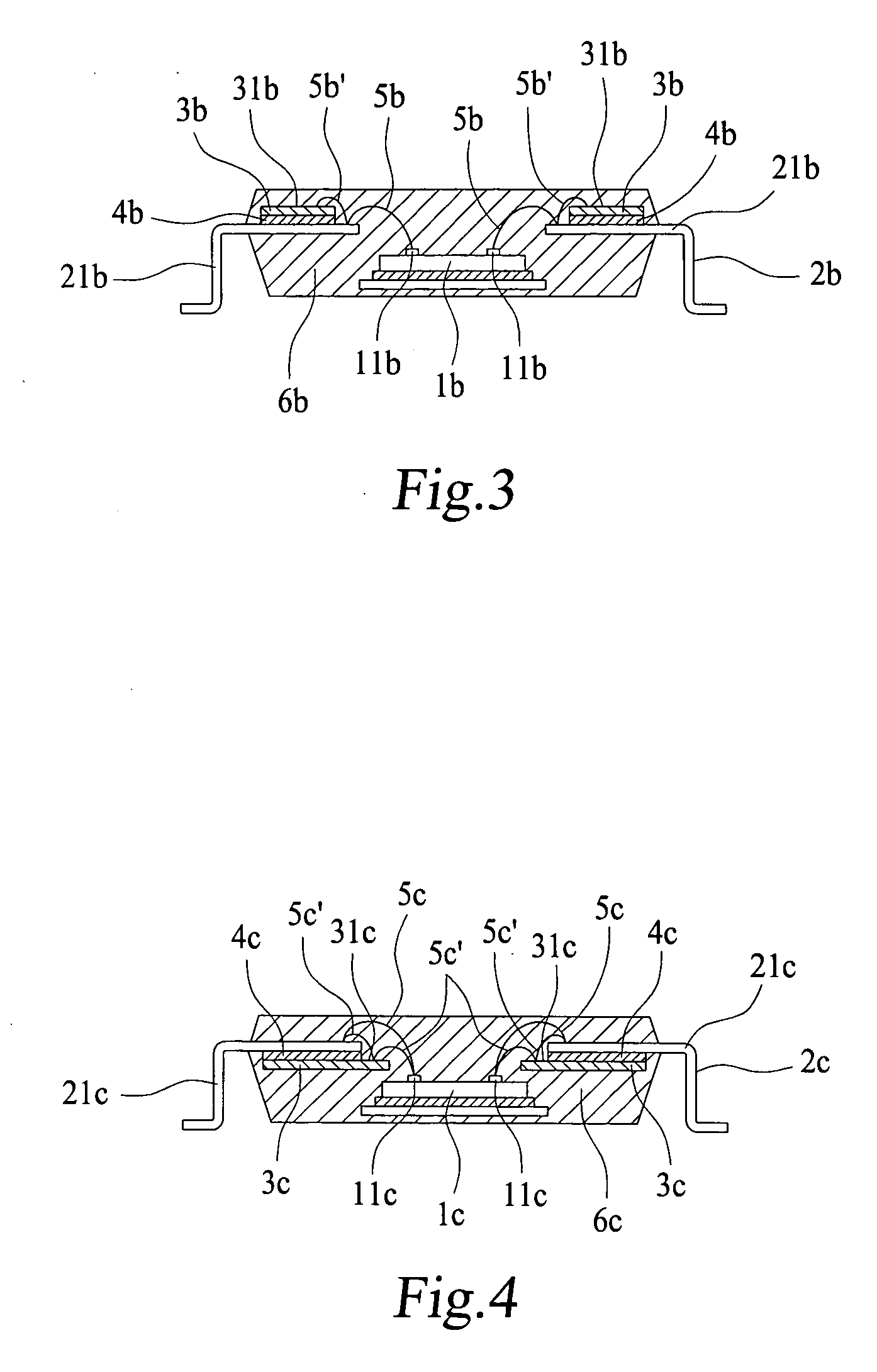

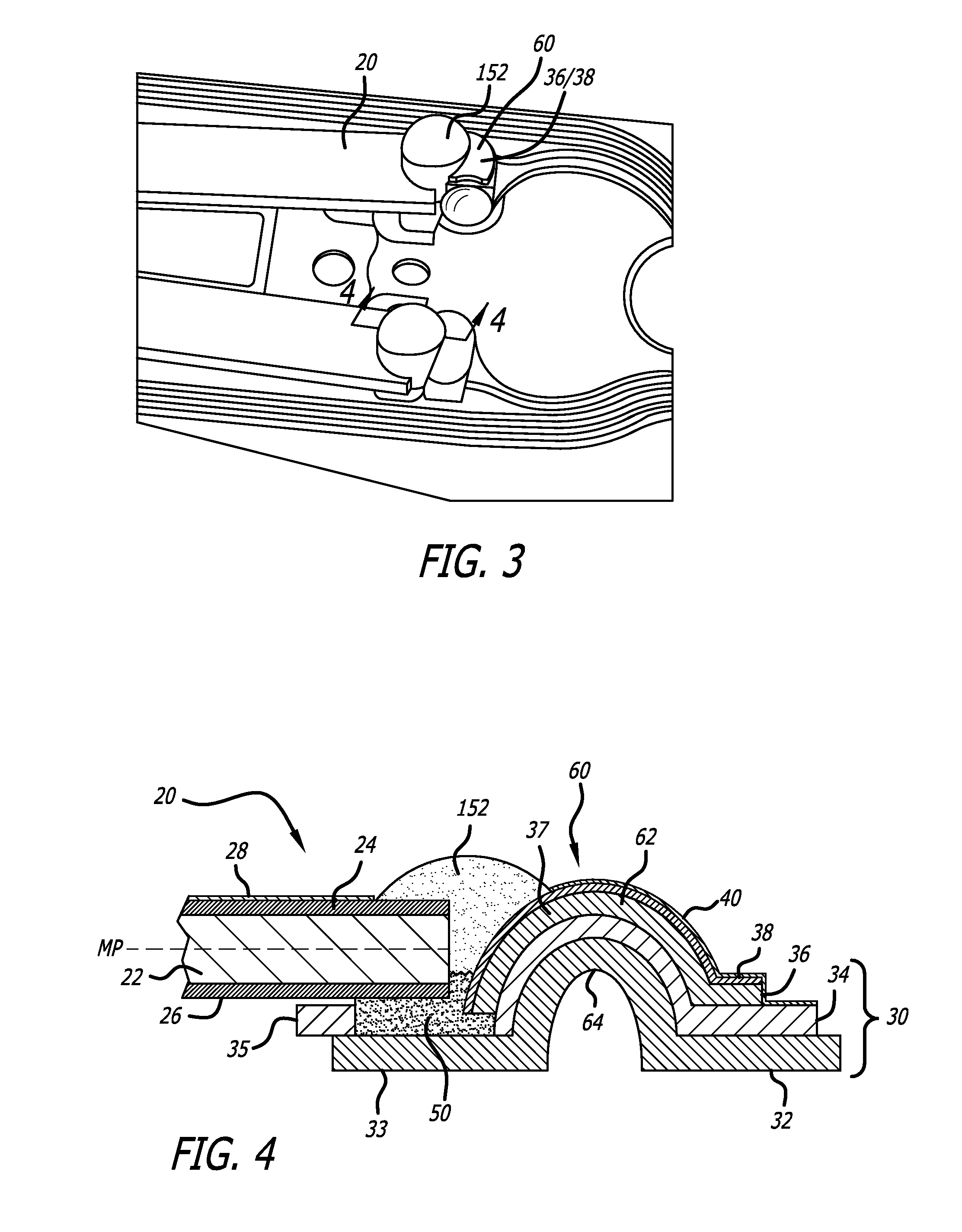

Semiconductor light emitting device having multi-cell array, light emitting module, and illumination apparatus

ActiveUS20110210352A1Increase the areaImprove lighting efficiencySolid-state devicesSemiconductor devicesInsulation layerActive layer

A semiconductor light emitting device includes a substrate; a plurality of light emitting cells disposed on the top surface of the substrate, the light emitting cells each having an active layer; a plurality of connection parts formed on the substrate with the light emitting cells formed thereon to connect the light emitting cells in a parallel or series-parallel configuration; and an insulation layer formed on the surface of the light emitting cell to prevent an undesired connection between the connection parts and the light emitting cell. The light emitting cells comprise at least one defective light emitting cell, and at least one of the connection parts related to the defective light emitting cell is disconnected.

Owner:SAMSUNG ELECTRONICS CO LTD

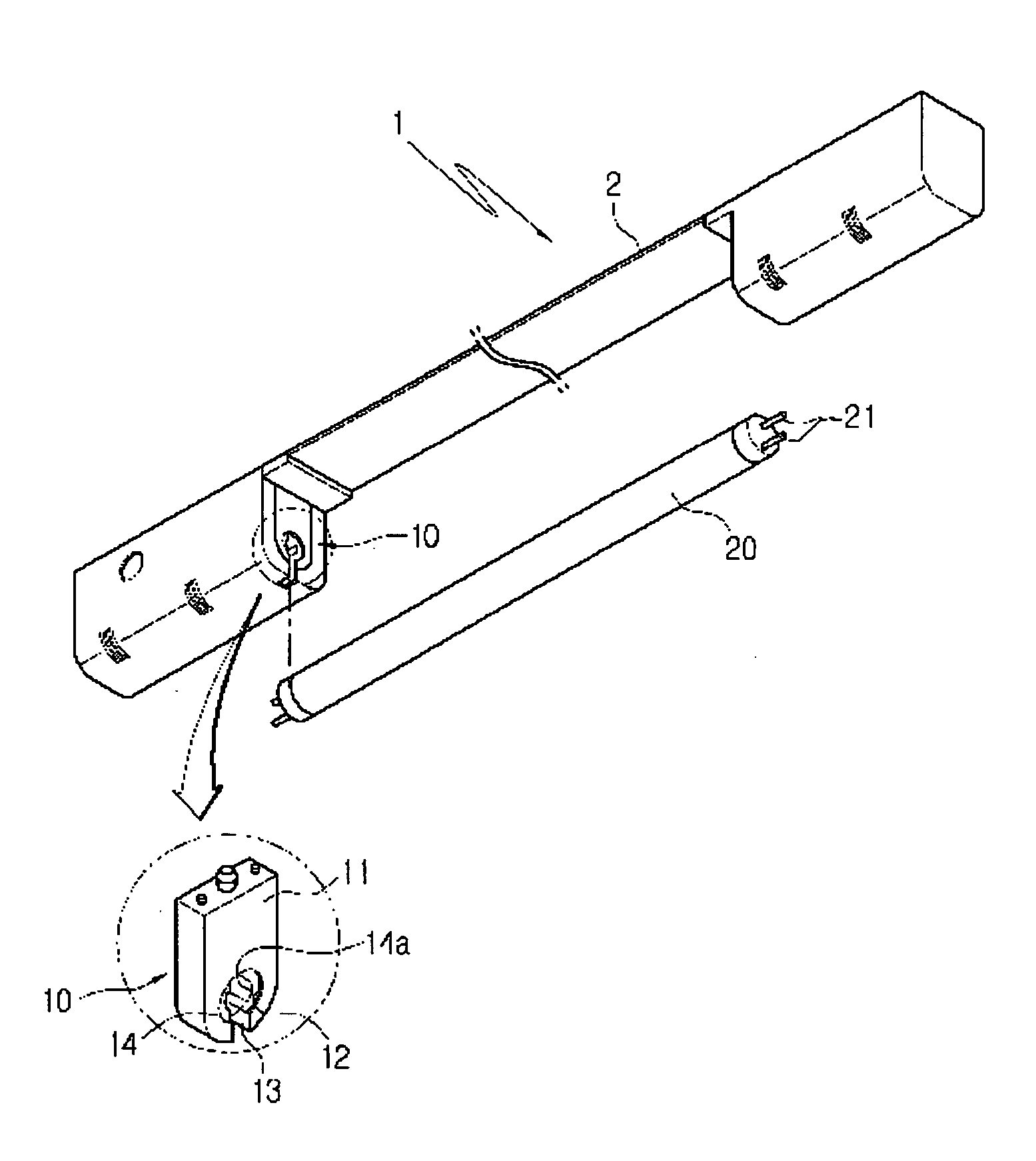

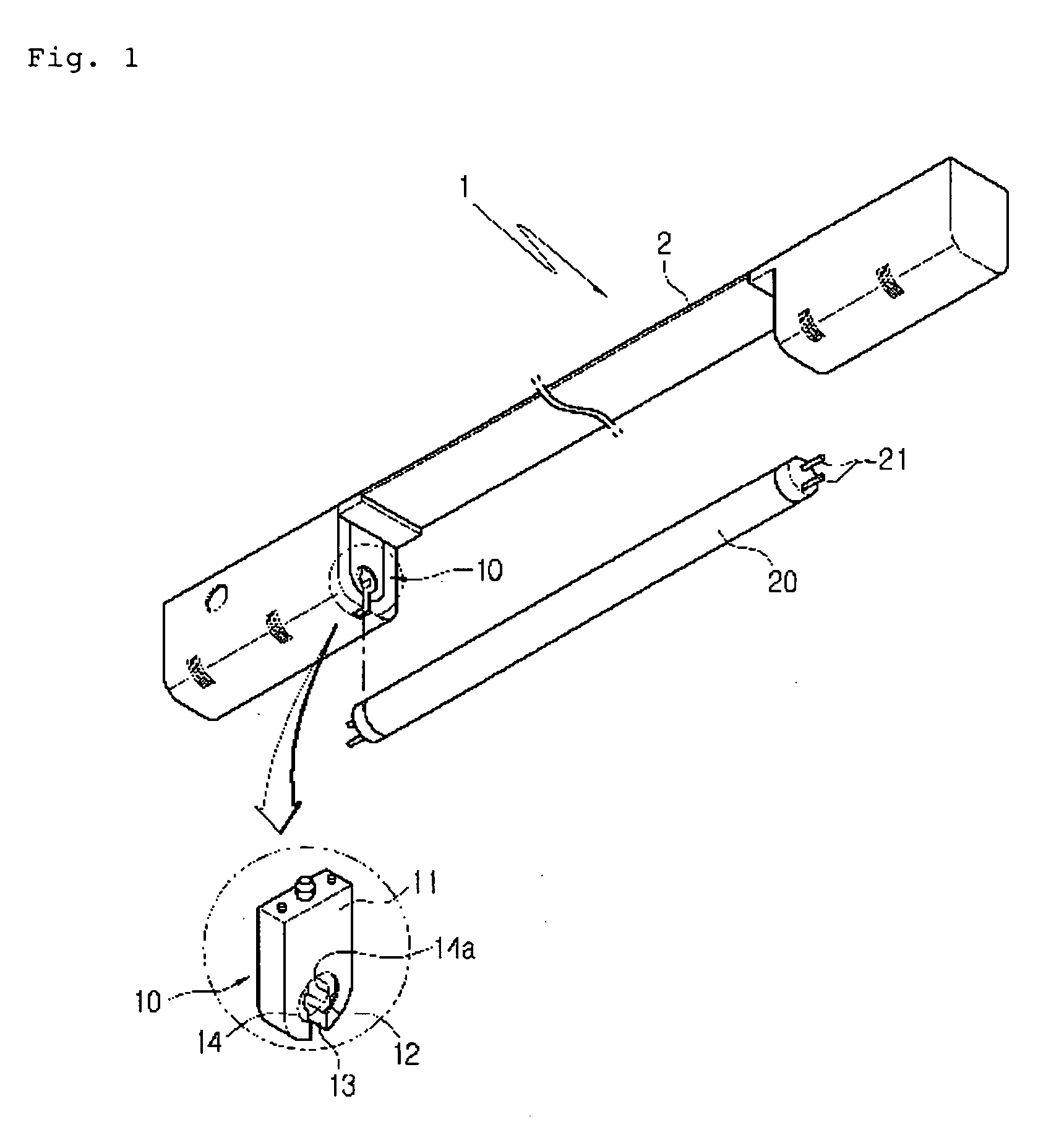

Fluorescent lighting fixtures

InactiveUS20060012981A1Beautiful appearanceImprove lighting effectsCoupling device connectionsNon-electric lightingElectricityFluorescence

The present invention relates to fluorescent lighting fixtures, which are aligned in series at regular intervals, which are easily connected one another, and which prevent discontinuation of illumination occurring between fluorescent lamps. The fluorescent lighting fixture includes: a fluorescent lamp having a tube type lamp body, auxiliary tubes mounted at the tops of both ends of the lamp body, and terminal pins inwardly formed at an end of each auxiliary tube; a body having a stabilizer mounted therein for lighting the fluorescent lamp, connection terminals located at both ends thereof at a predetermined interval and electrically connected with the stabilizer; and sockets mounted at both ends of the body, each of the sockets having a support slit formed in the outer surface thereof for fixing and supporting the terminal pins of the fluorescent lamp, and a receiving slit for allowing the terminal pins to be inserted into the support slit.

Owner:FEELUX CO LTD

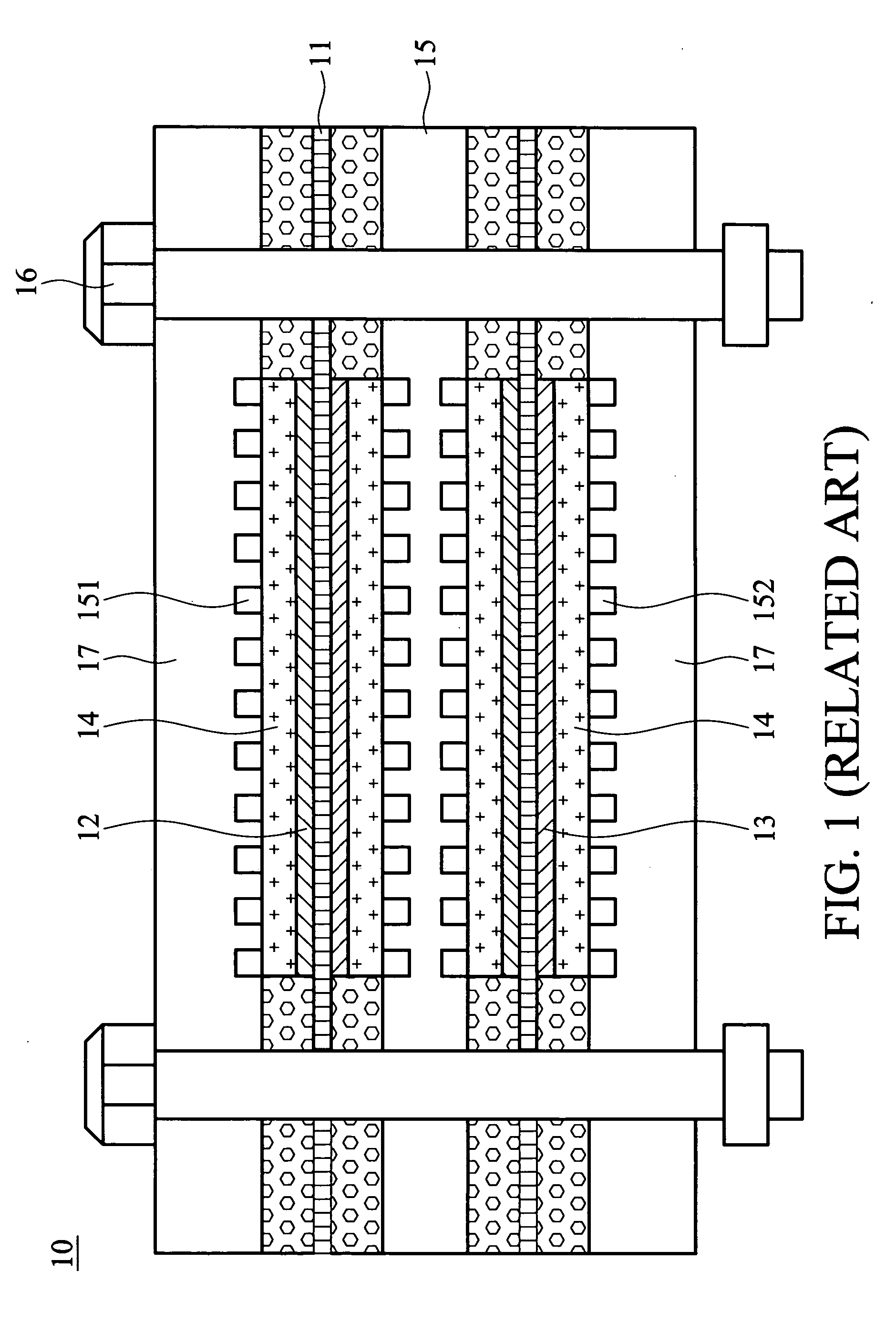

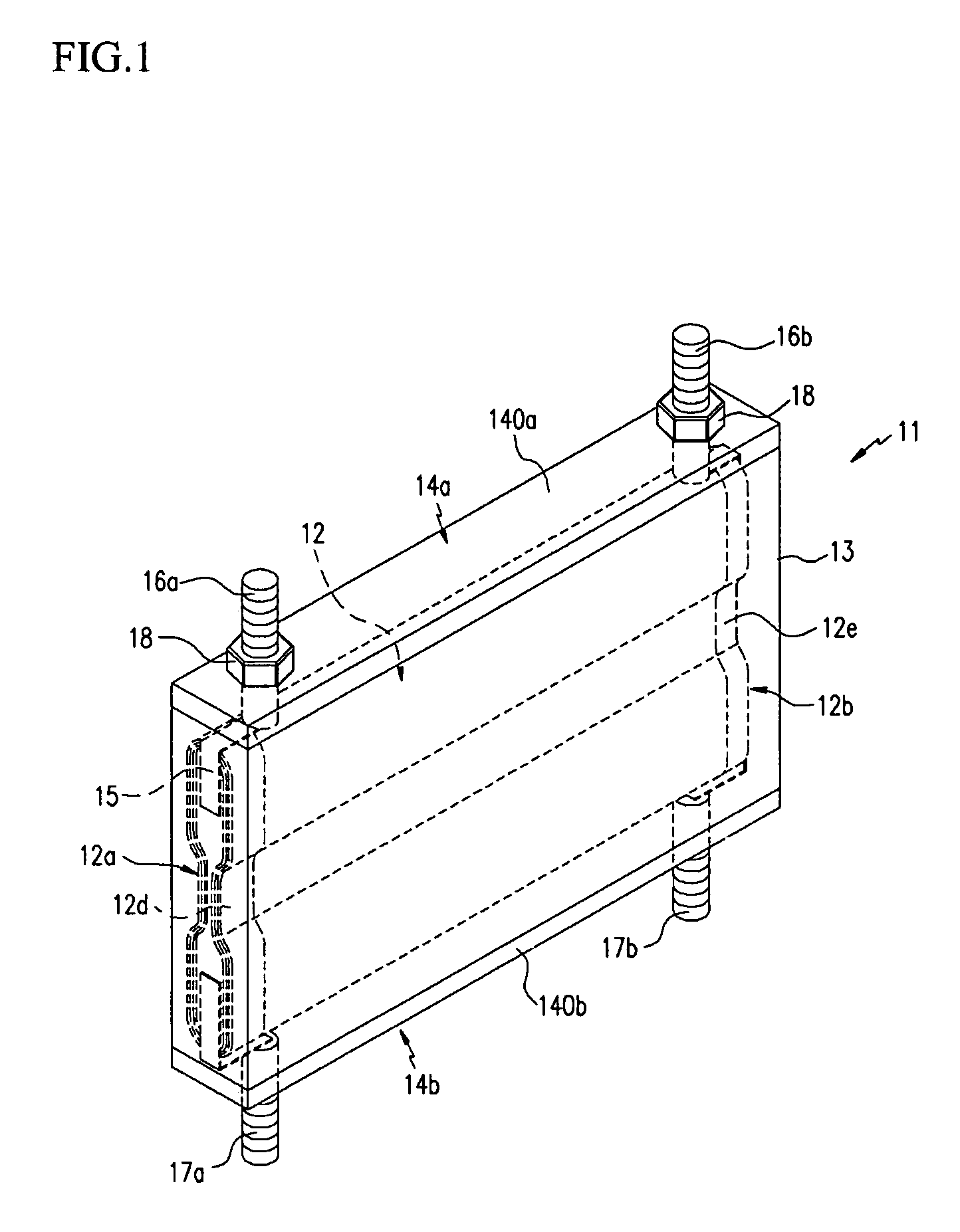

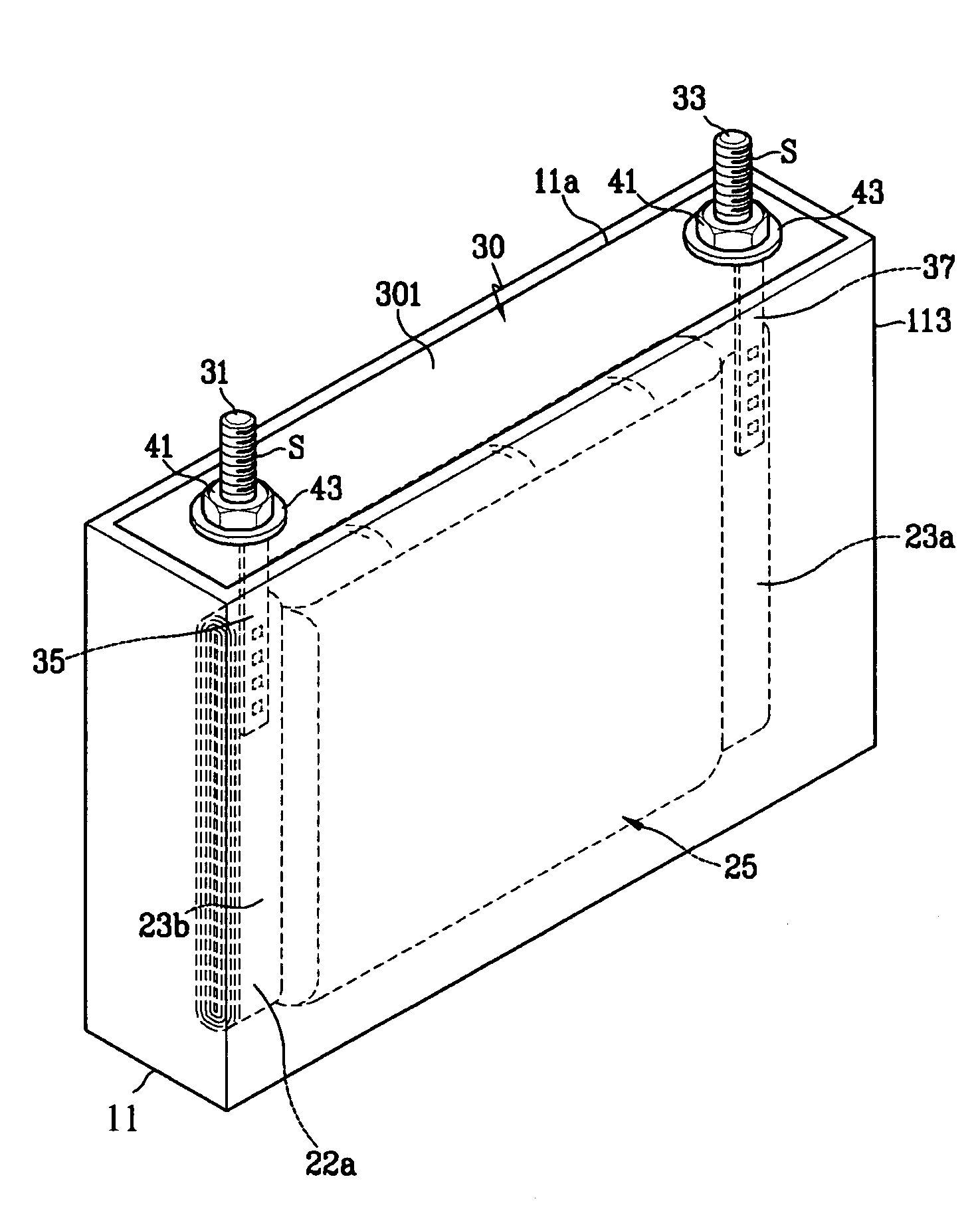

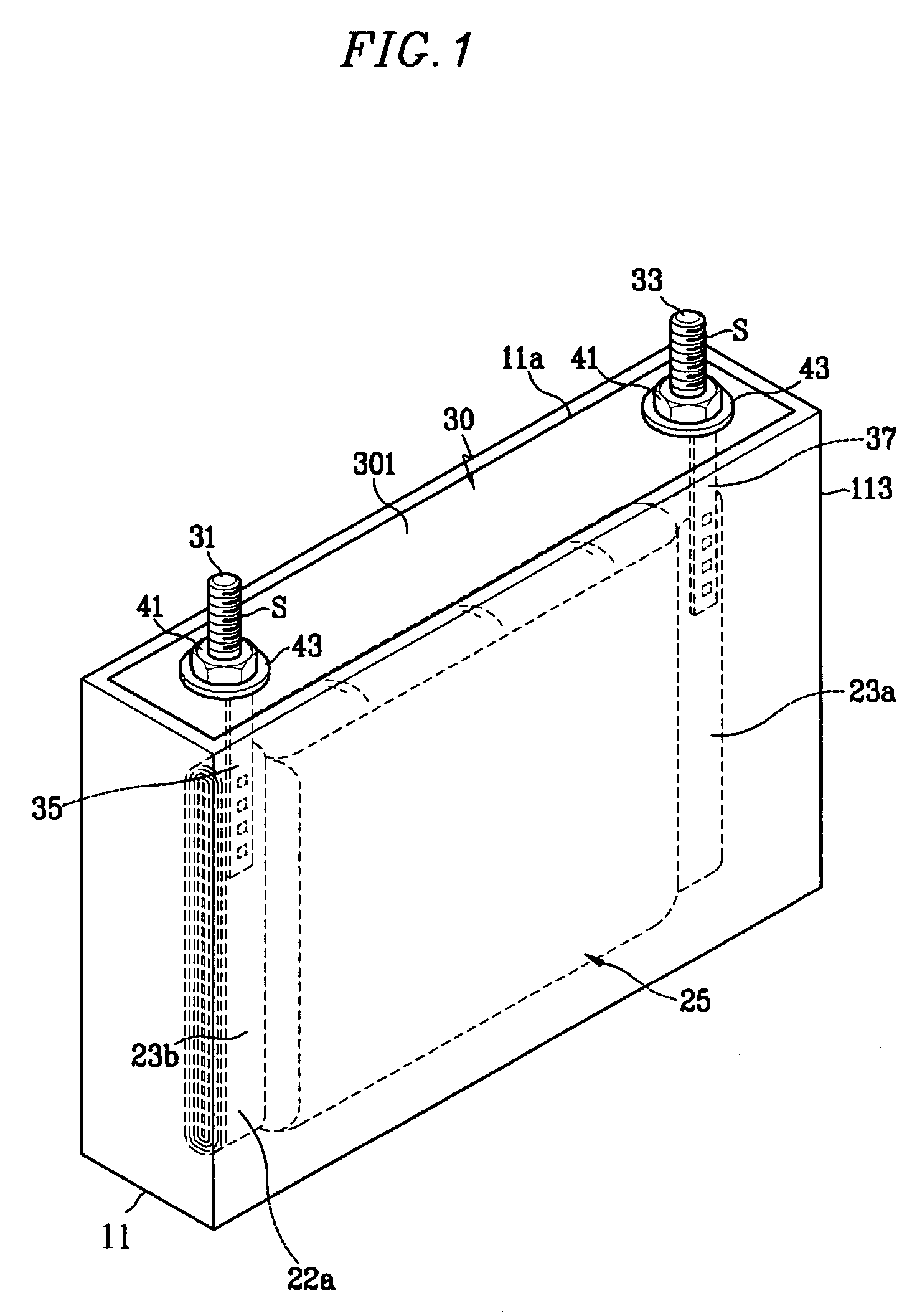

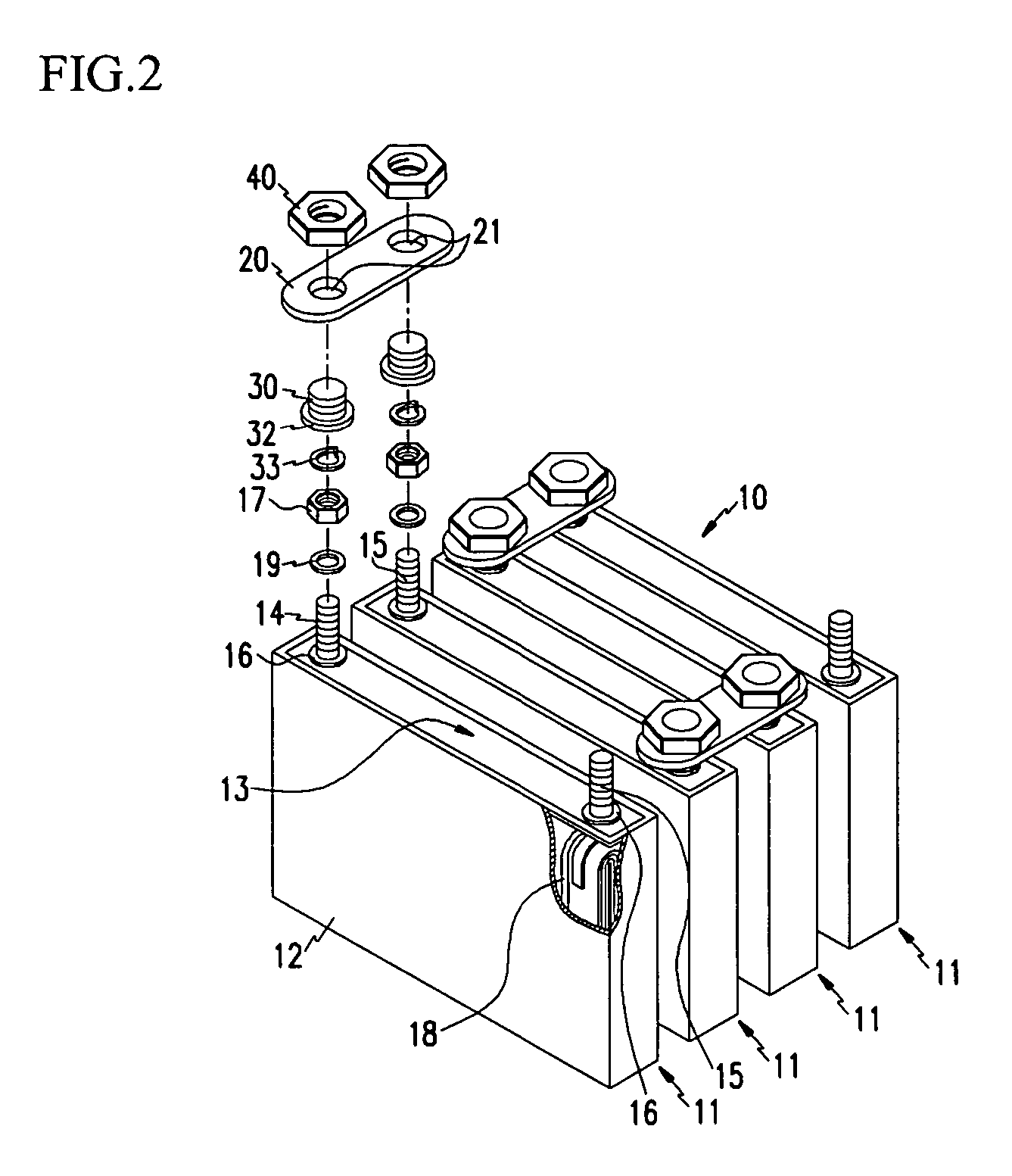

Rechargeable battery and battery module using the same

ActiveUS20050260491A1Improve space utilizationIncrease power and capacity of batteryFinal product manufactureSmall-sized cells cases/jacketsEngineeringElectrical and Electronics engineering

The present invention relates to a rechargeable battery including an electrode assembly comprising a positive electrode, a negative electrode, and a separator interposed therebetween. The battery further comprises a case accommodating the electrode assembly and a plurality of positive electrode terminals and negative electrode terminals that are exposed outside of the case, connected to the case, and coupled to the electrode assembly.

Owner:SAMSUNG SDI CO LTD

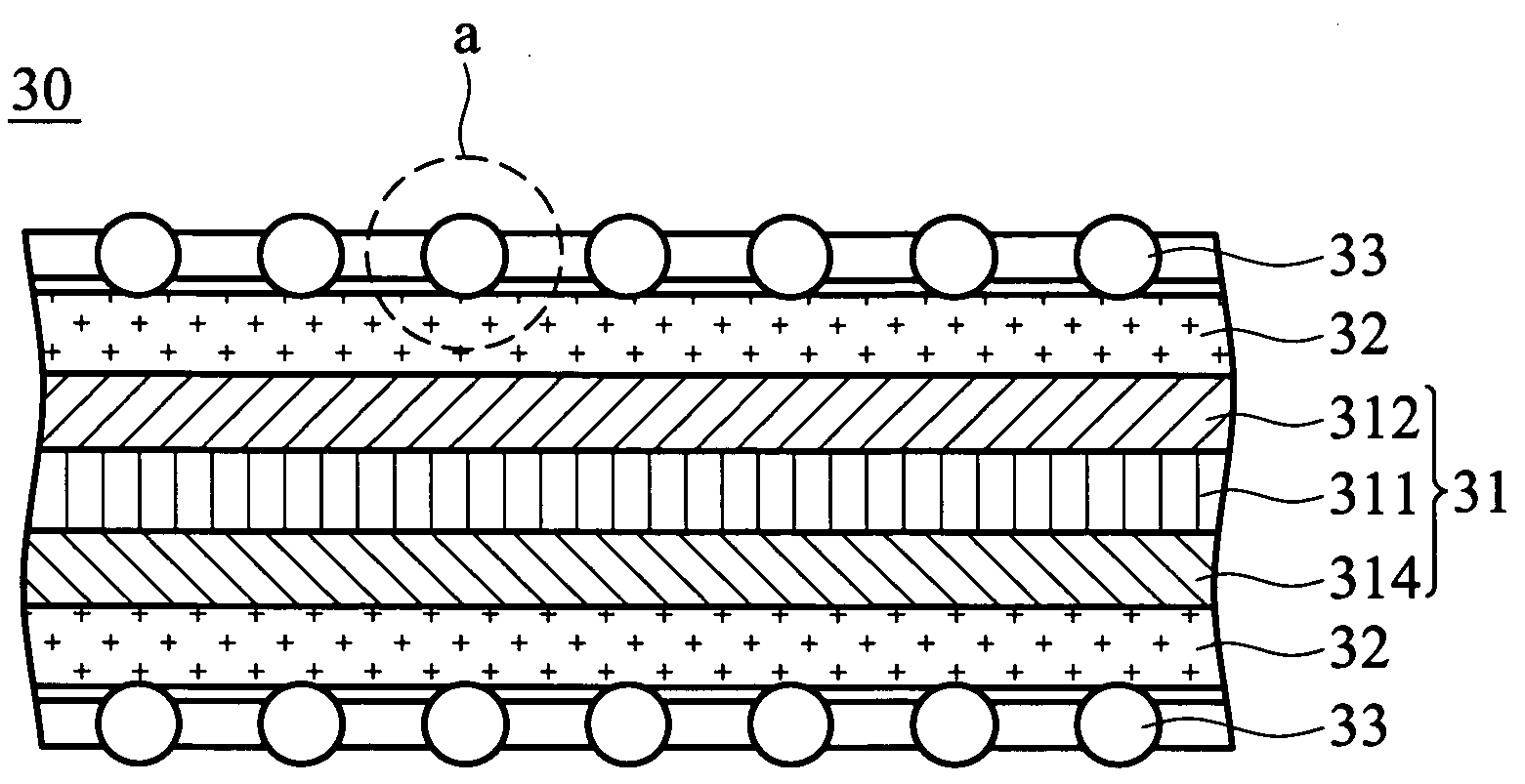

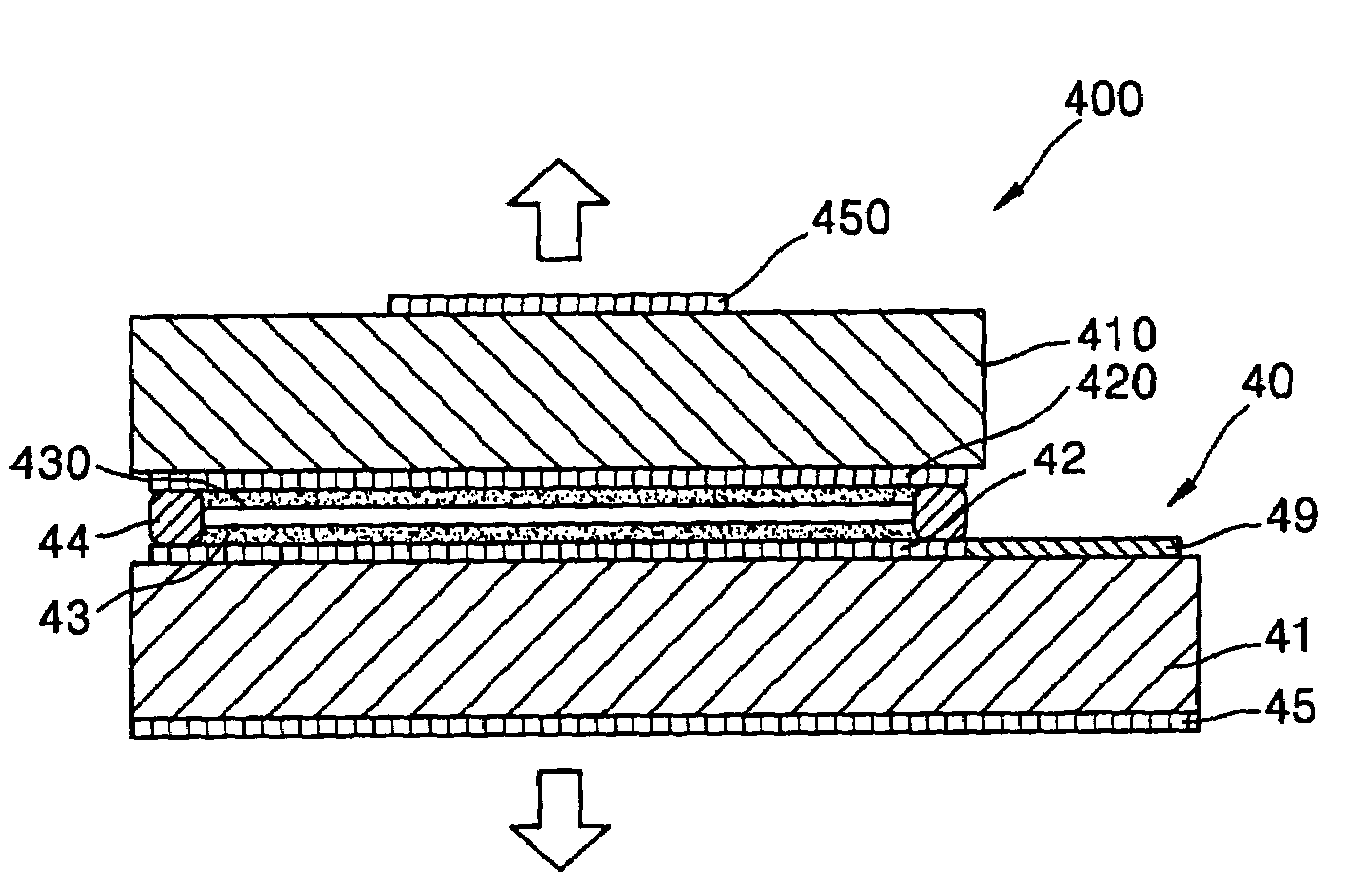

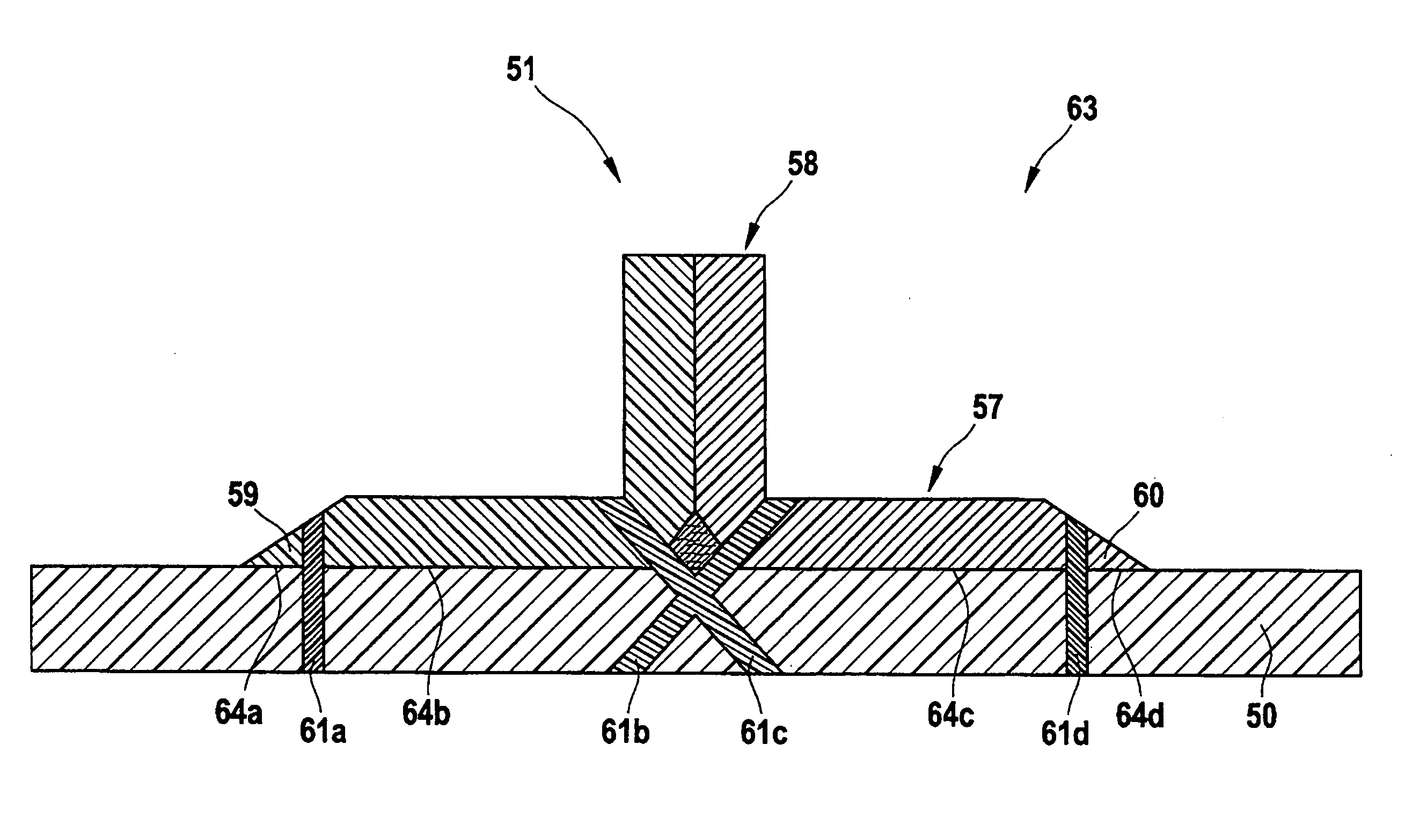

Flat fuel cell assembly and fabrication thereof

ActiveUS20050026026A1Improved connection structureHigh densityLamination ancillary operationsFuel cells groupingMembrane configurationHeat press

A connecting structure of a flat fuel cell assembly. The assembly includes a plurality of fuel cells, each of which has a membrane electrode assembly with an anode, a proton exchange membrane and a cathode combined. Two conductive nets are attached to the surfaces of the anode and the cathode of each membrane electrode assembly by thermosetting adhesive and heat pressing to collect and transmit electrons.

Owner:IND TECH RES INST

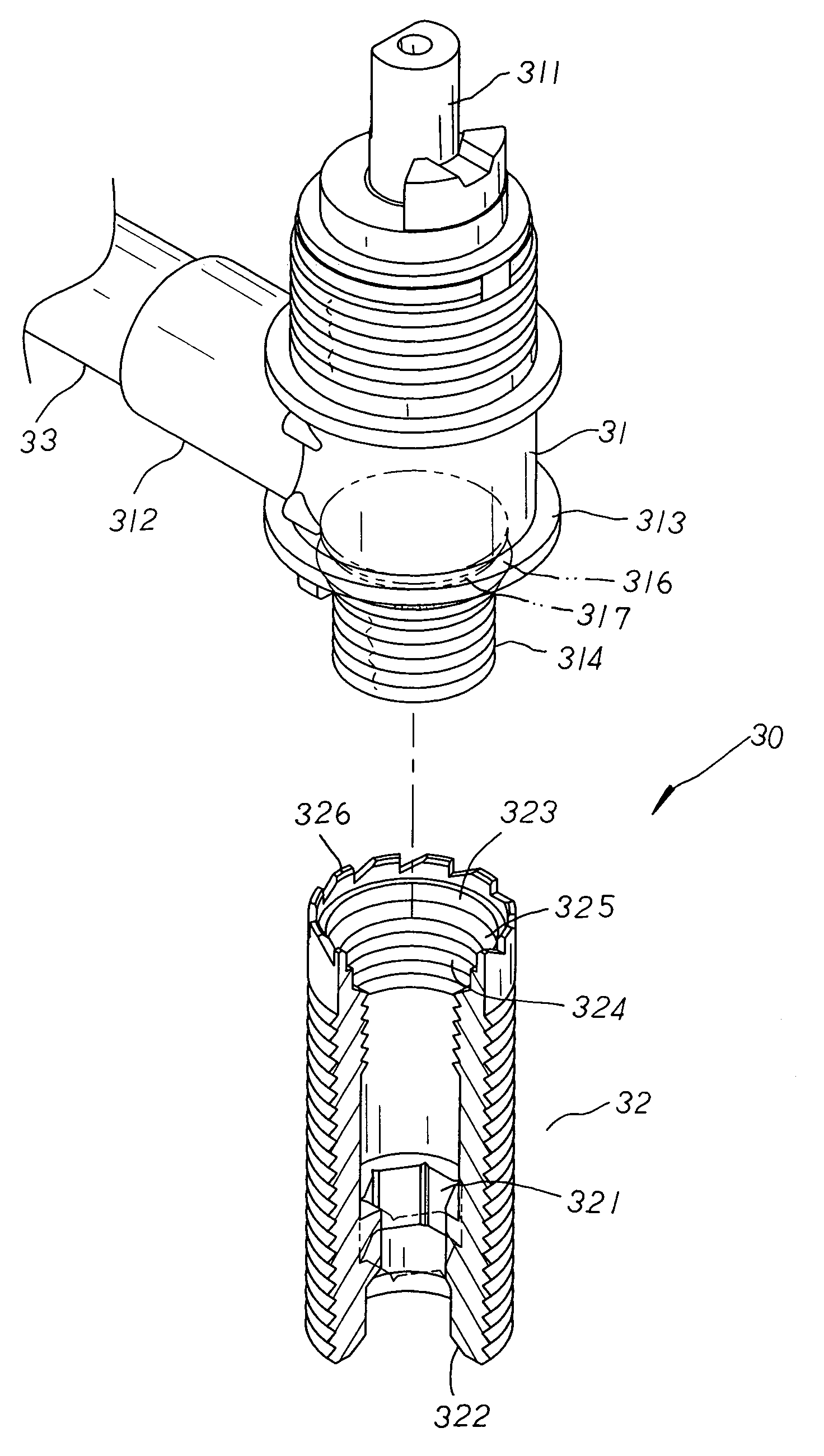

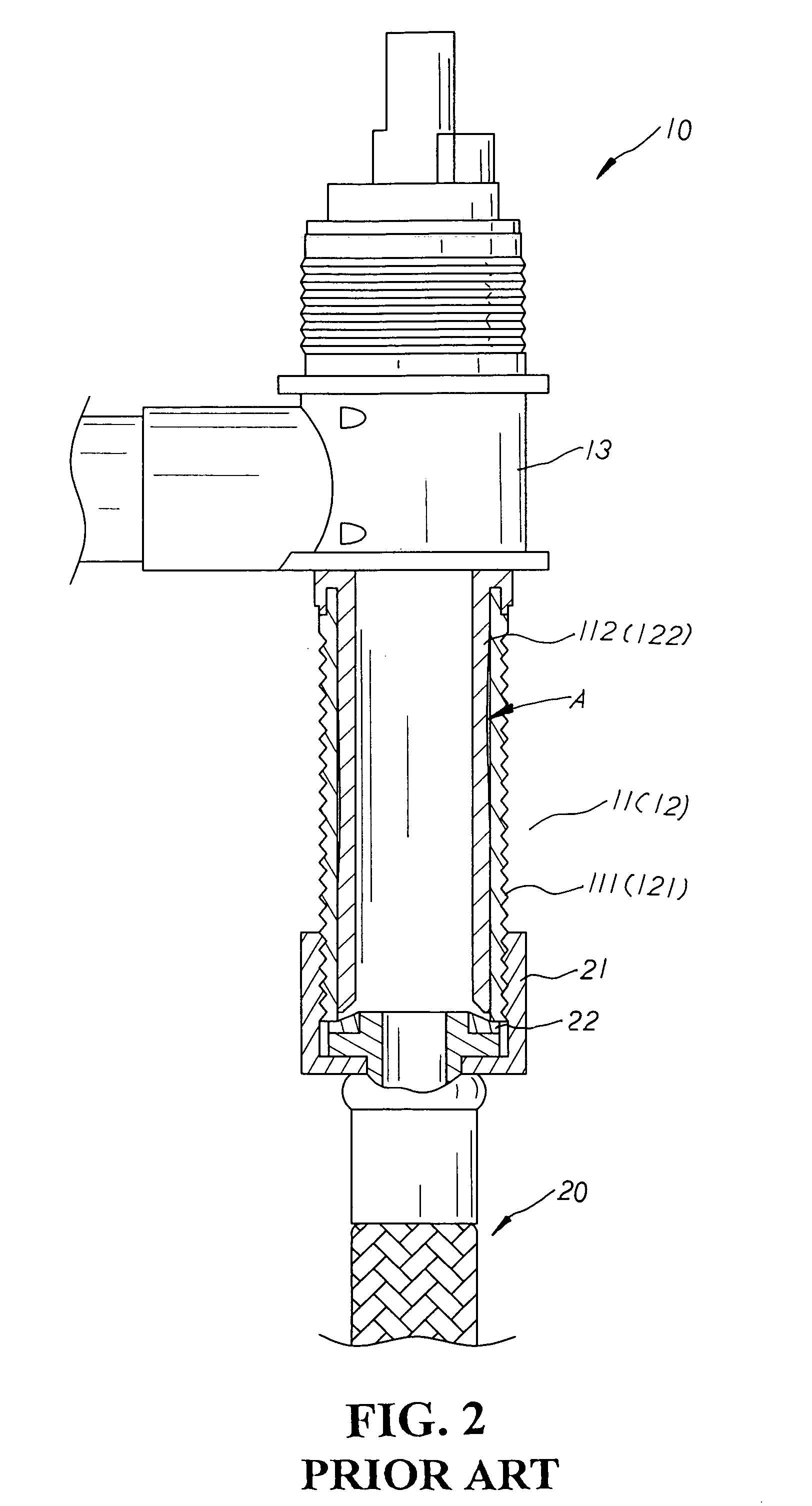

Hot/cold water tube connection structure for plastic faucets

InactiveUS7231936B2Avoid problemsStrengthen the connection structureServomotor componentsJoints with sealing surfacesCouplingEngineering

A hot / cold water tube connection structure for plastic faucets comprises a hot / cold water connector tube made up of a valve seat and a coupling tube wherein the valve seat has a screw tube extending downwards at the bottom of a stop ring, and a sealing ring mounted at an appropriate position of the screw tube thereon to form engaging rings at both sides thereof. The coupling tube has an oblique face indented at one end edge against which a water-sealing hoop mounted at a screw joint of a water inlet tube is securely abutted, and a coupling joint with an internal screw thread section disposed at the inner wall of the other end thereof. Therefore, the connector tube assembled can avoid the problem of gaps found in the conventional tube connection structure, and facilitate an easer replacement thereof due to its separate type of design for economical and eco-protection purposes.

Owner:CHANG KIM

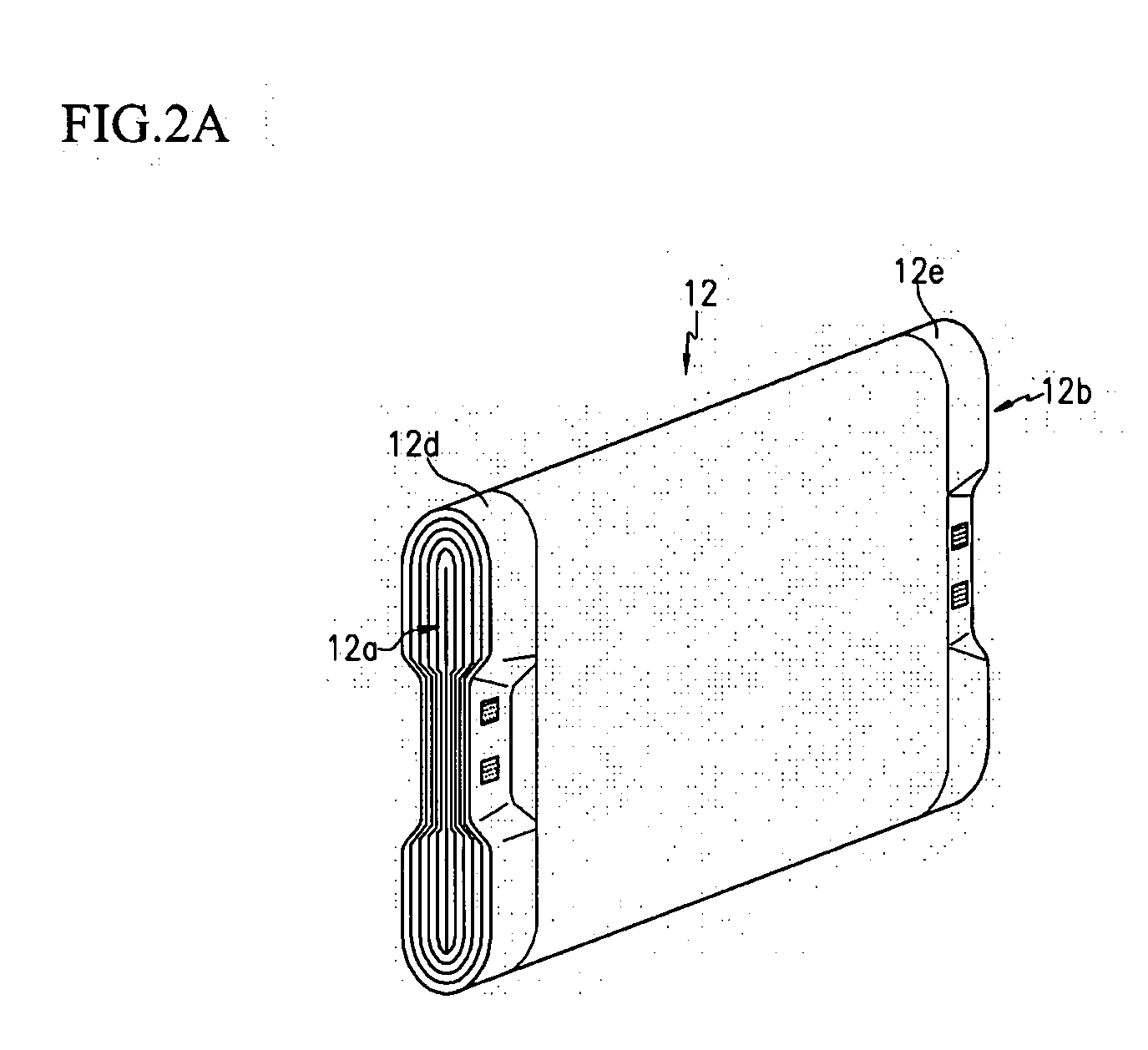

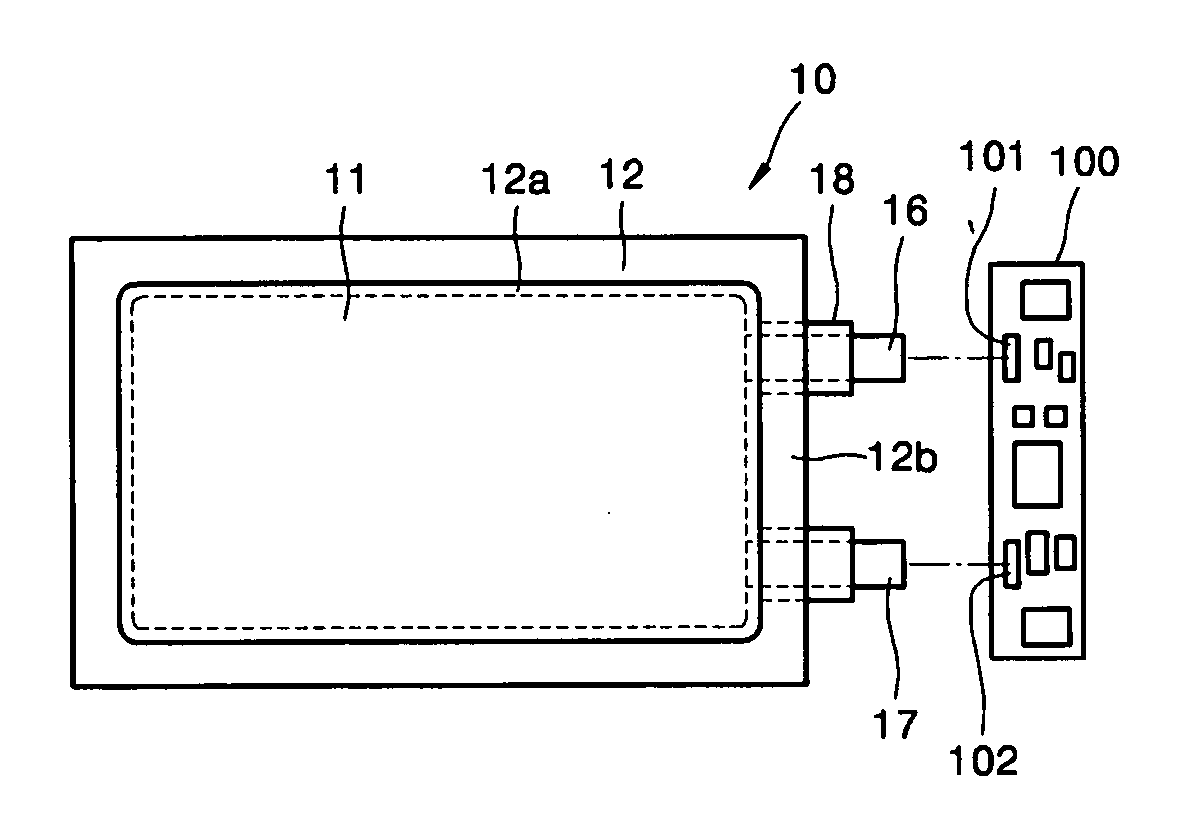

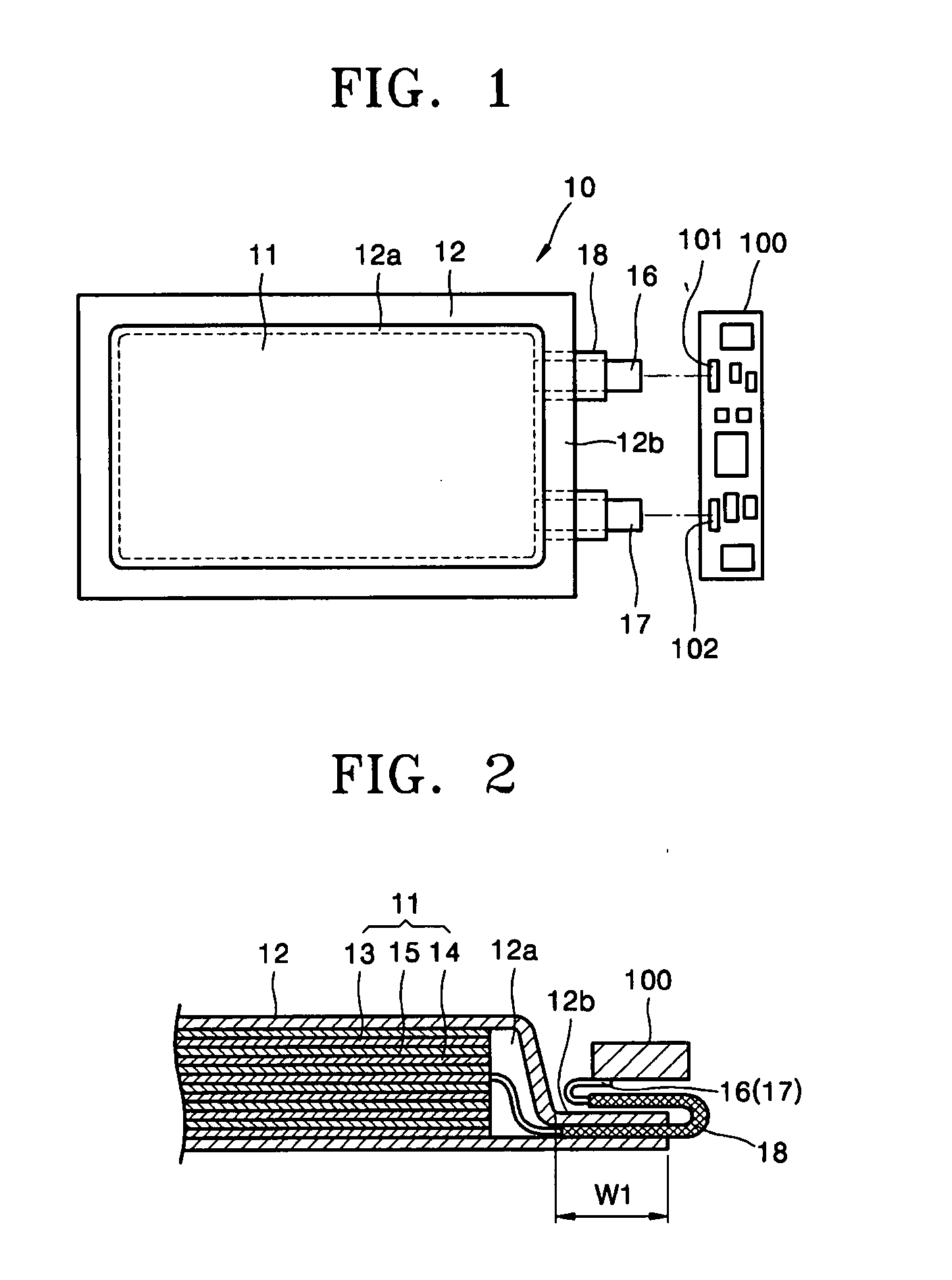

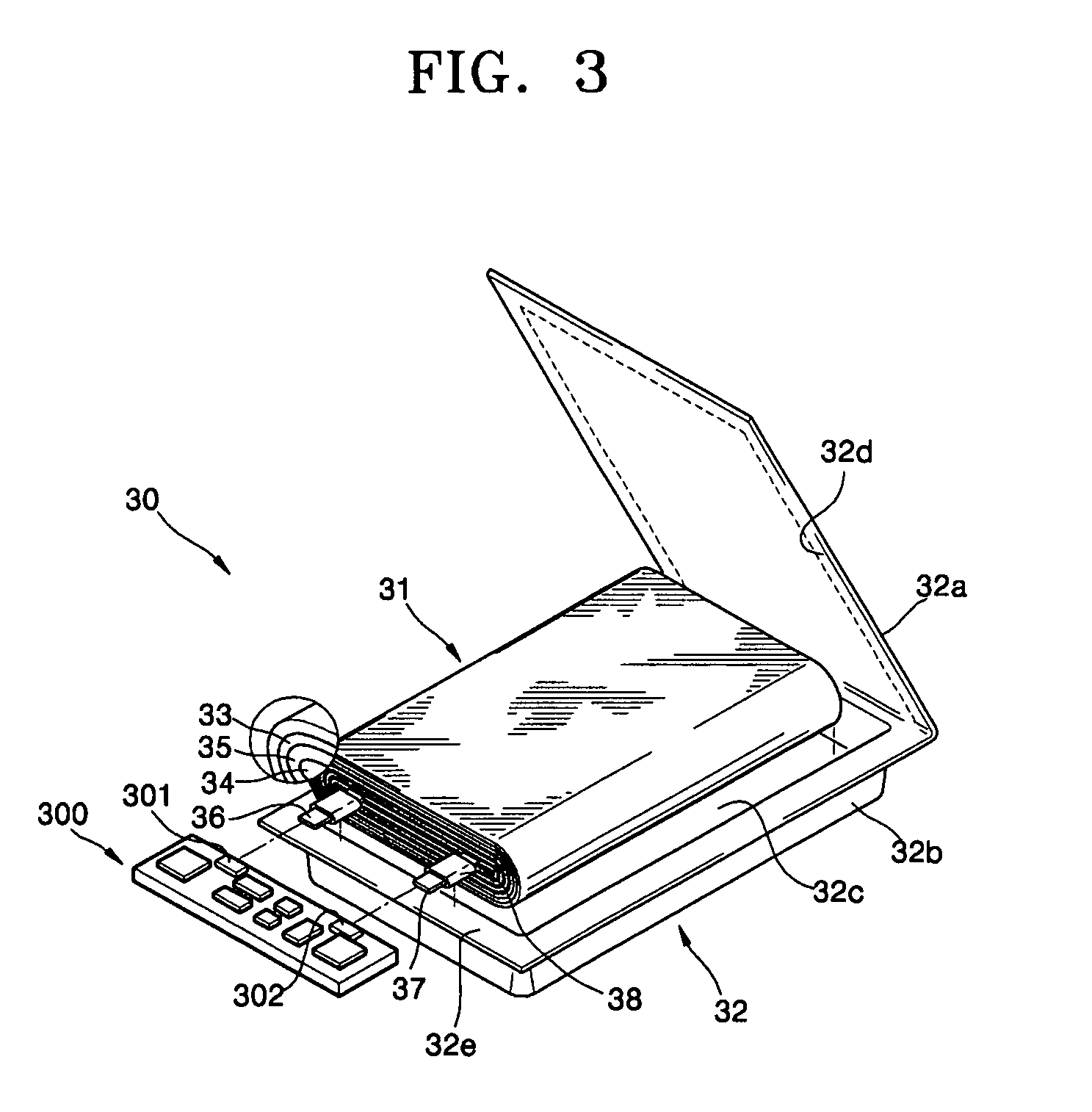

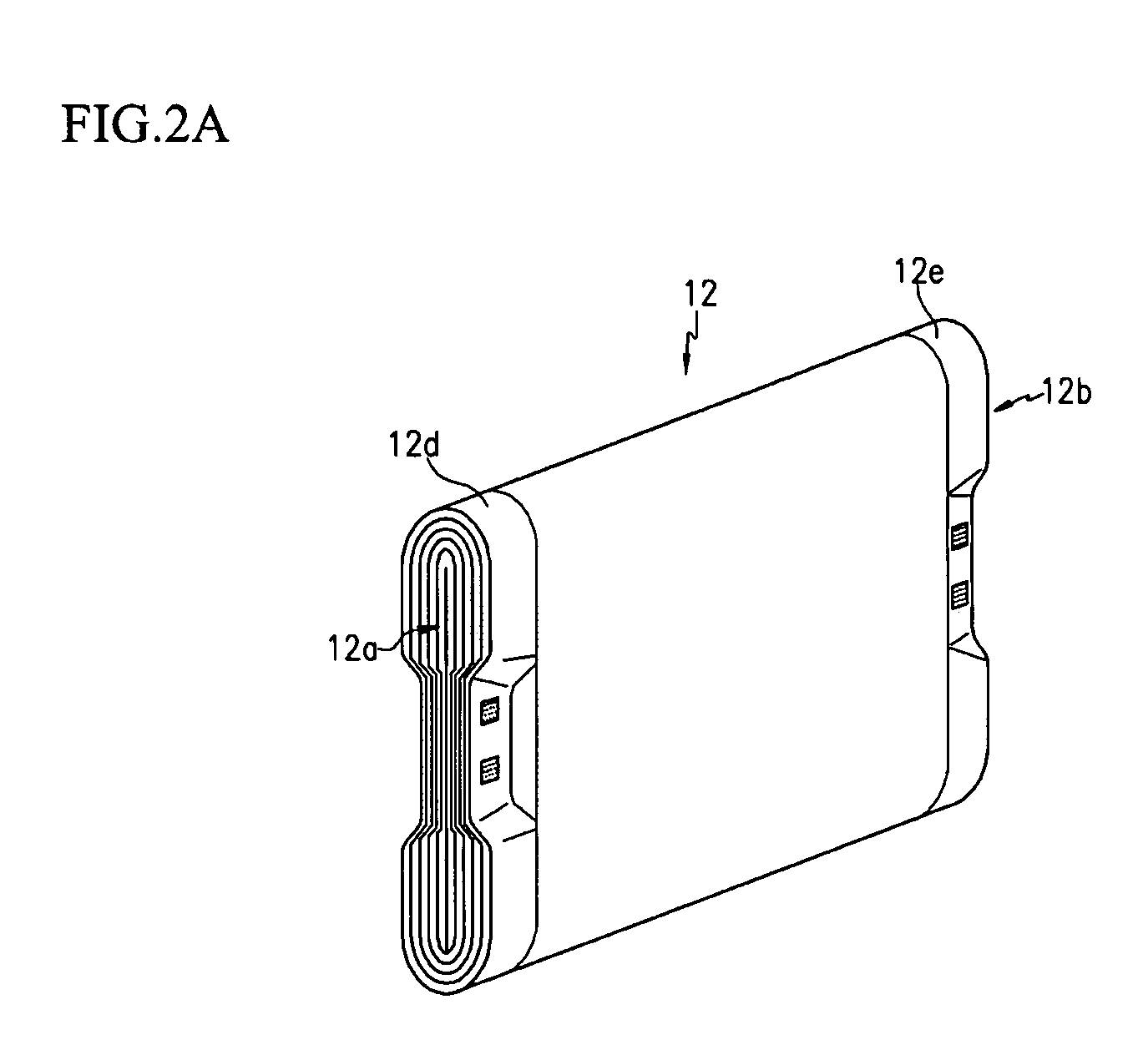

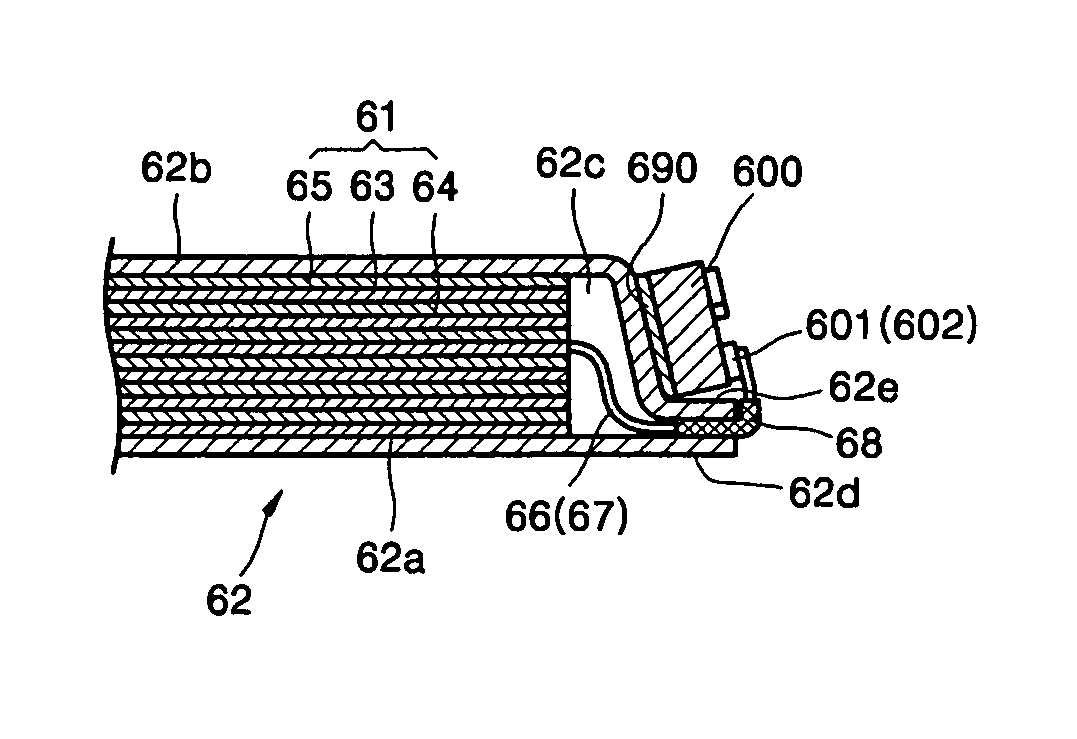

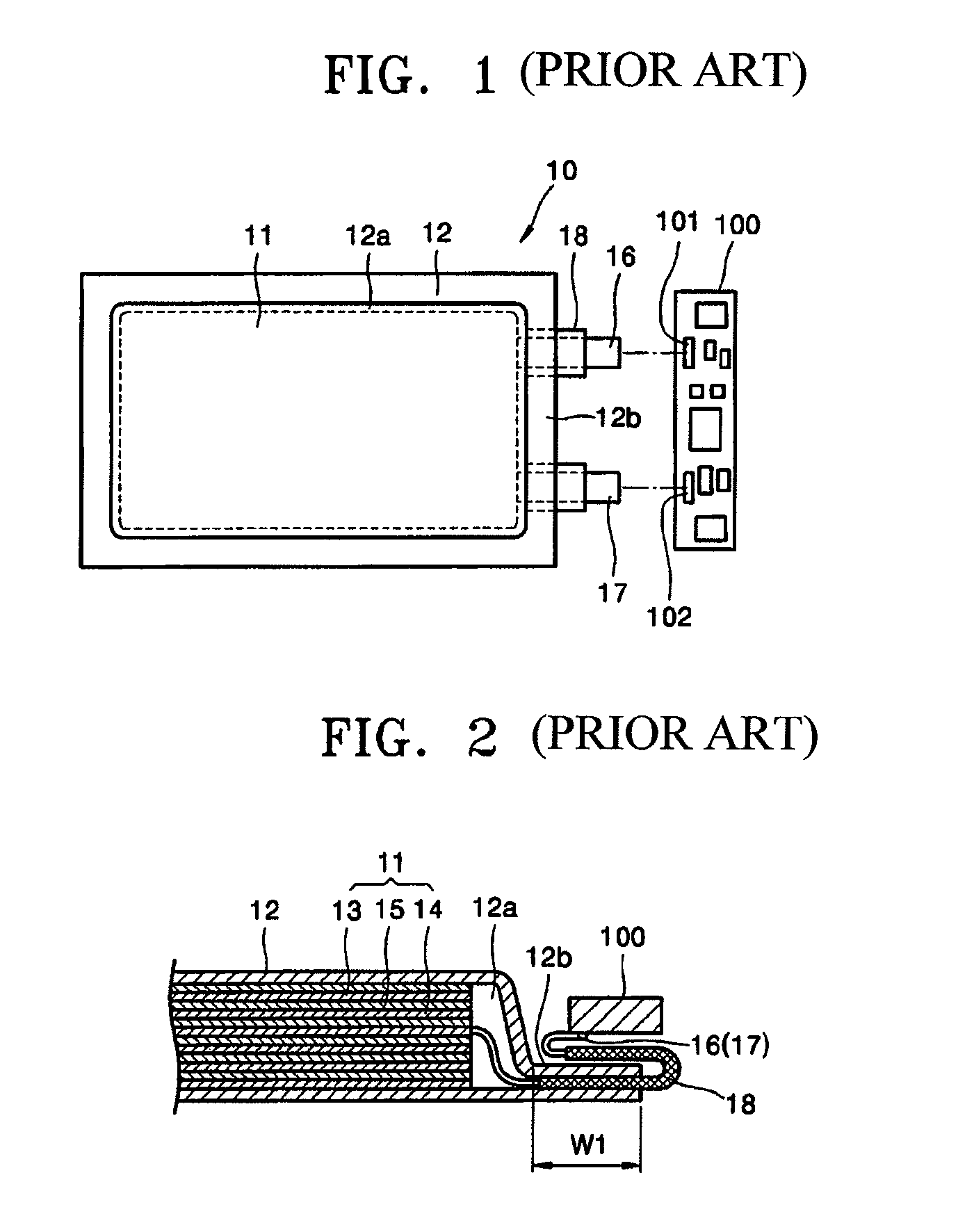

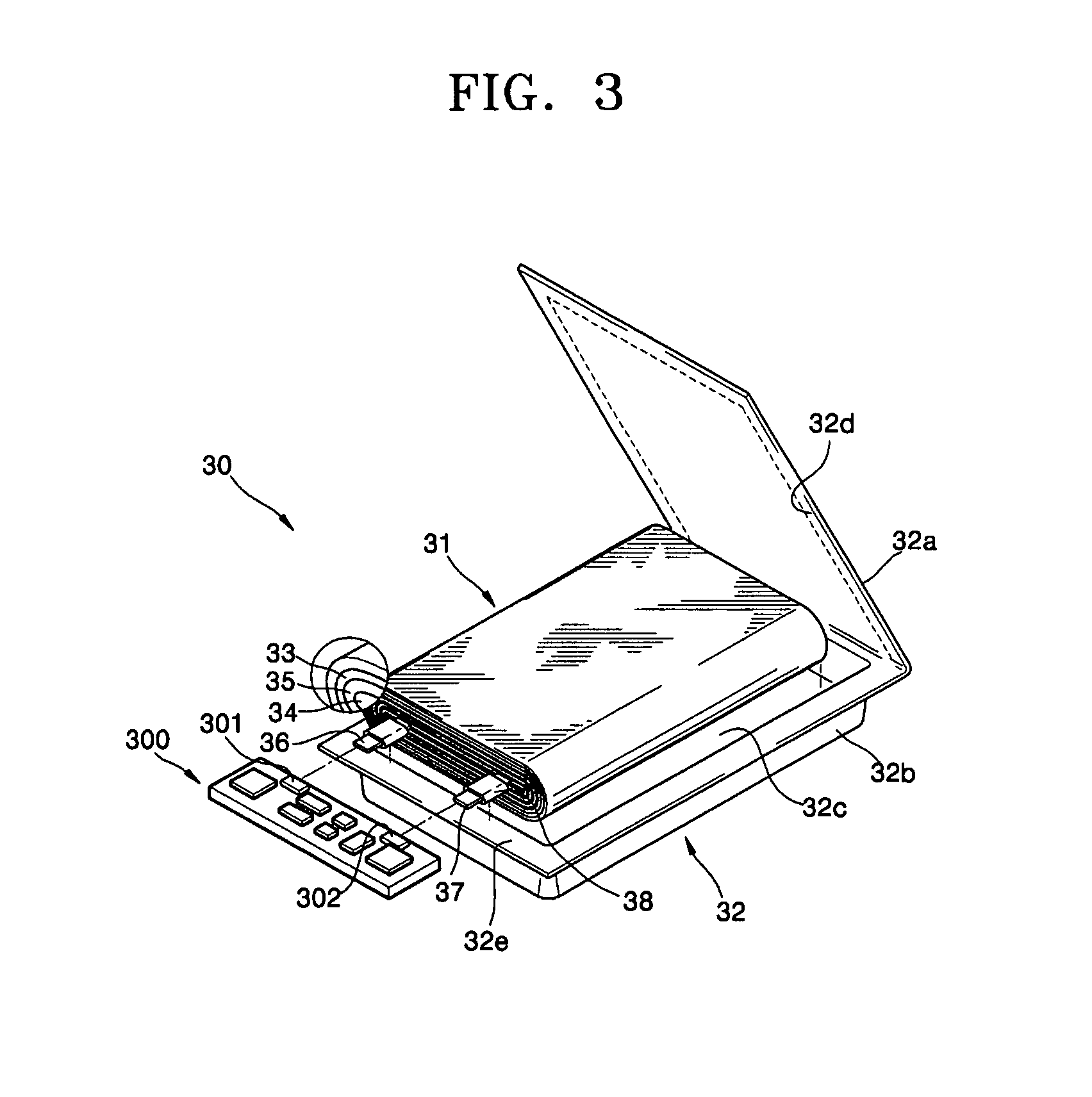

Pouch-type lithium secondary battery and fabrication method thereof

ActiveUS20060068275A1Minimizes seal surfaceStrengthen the connection structureFinal product manufactureCells structural combinationLithiumEngineering

A pouch-type lithium secondary battery including: a battery unit comprising a positive electrode plate, a separator, and a negative electrode plate, wherein the separator is disposed between the positive and negative electrode plates; electrode tabs extending from each of the positive and negative electrode plates of the battery unit, respectively; a case having a space to accommodate the battery unit and sealing surfaces formed along the periphery of the space, wherein the case is sealed at the sealing surfaces by thermal fusion; and a protection circuit board 600 electrically connected to the electrode tabs. The protection circuit board is disposed parallel to an outer wall of the case. Since the electrode tabs are bent in an upright position with respect to the sealing surfaces, and the protection circuit board electrically connected to the bent electrode tabs is disposed between the outer wall of the case and the electrode tabs, the size of the sealing surfaces of the case can be minimized.

Owner:SAMSUNG SDI CO LTD

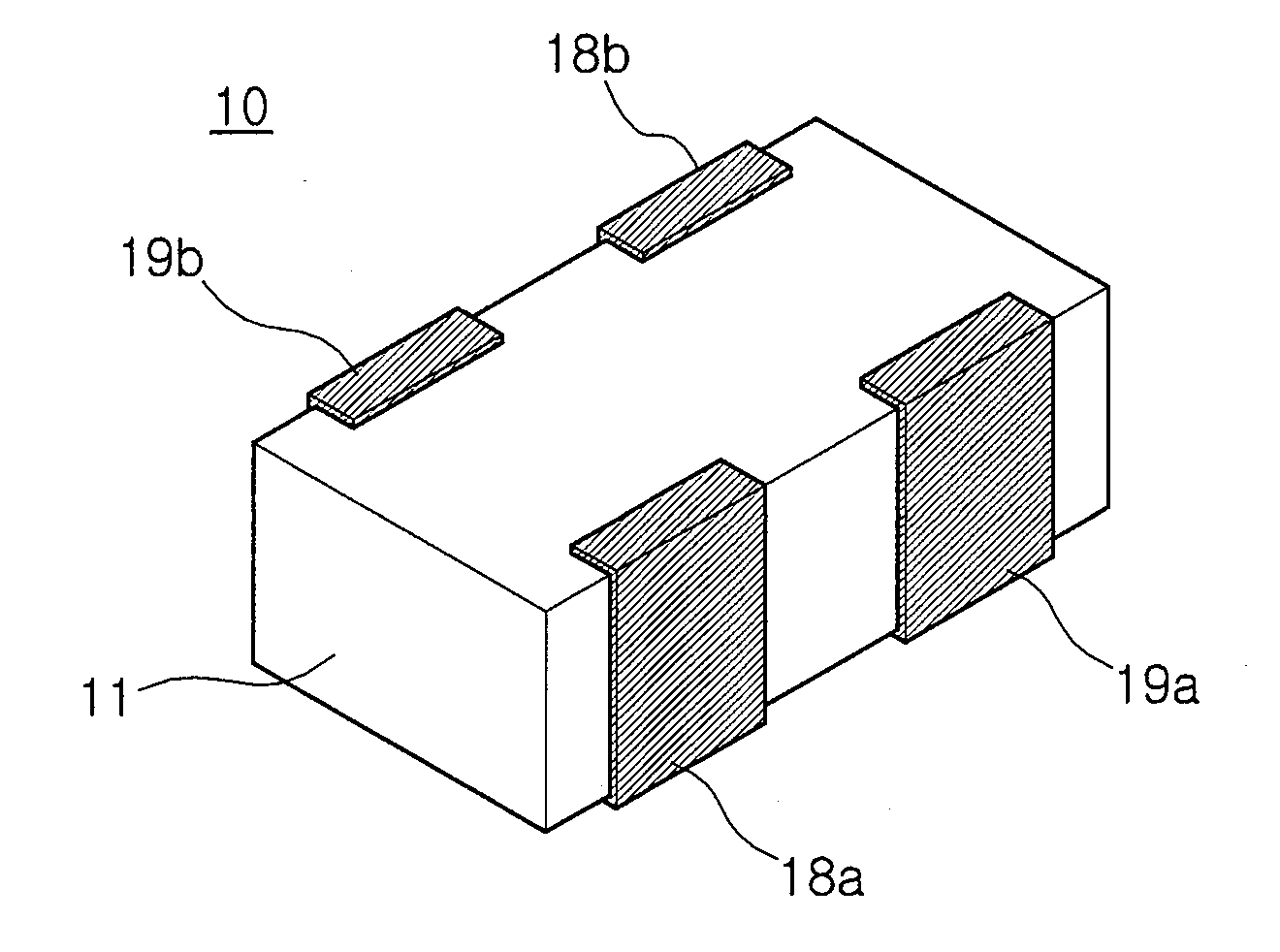

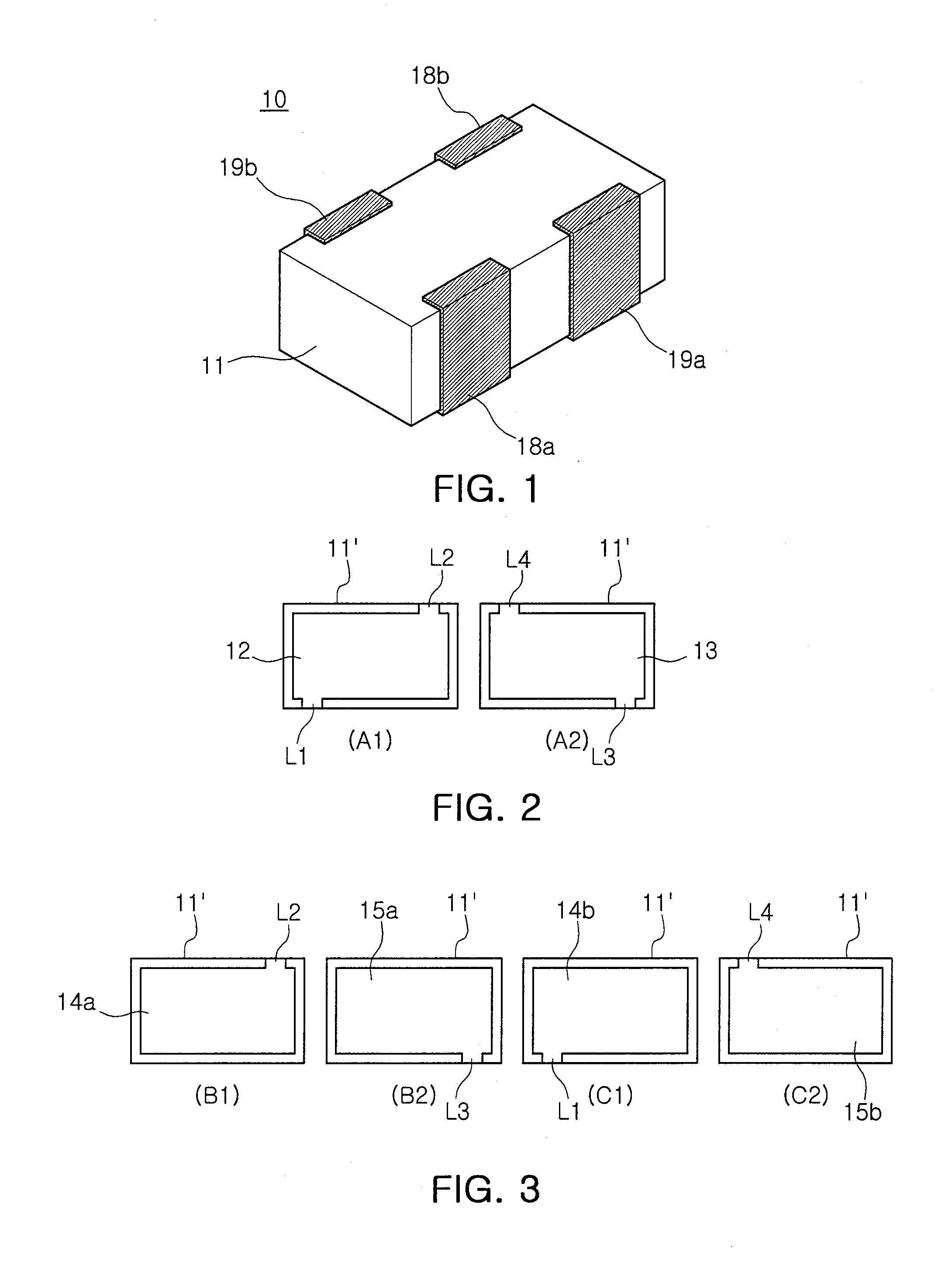

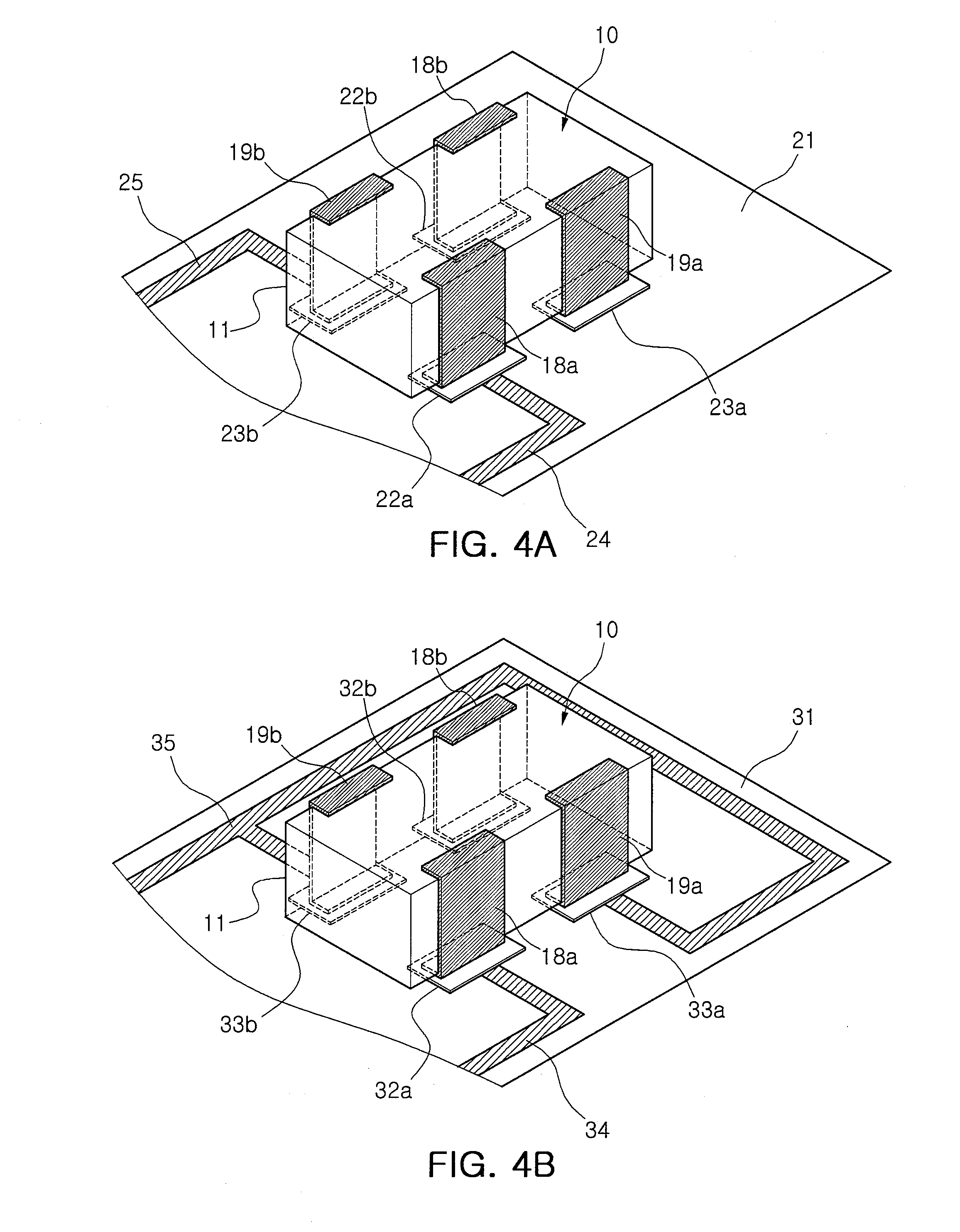

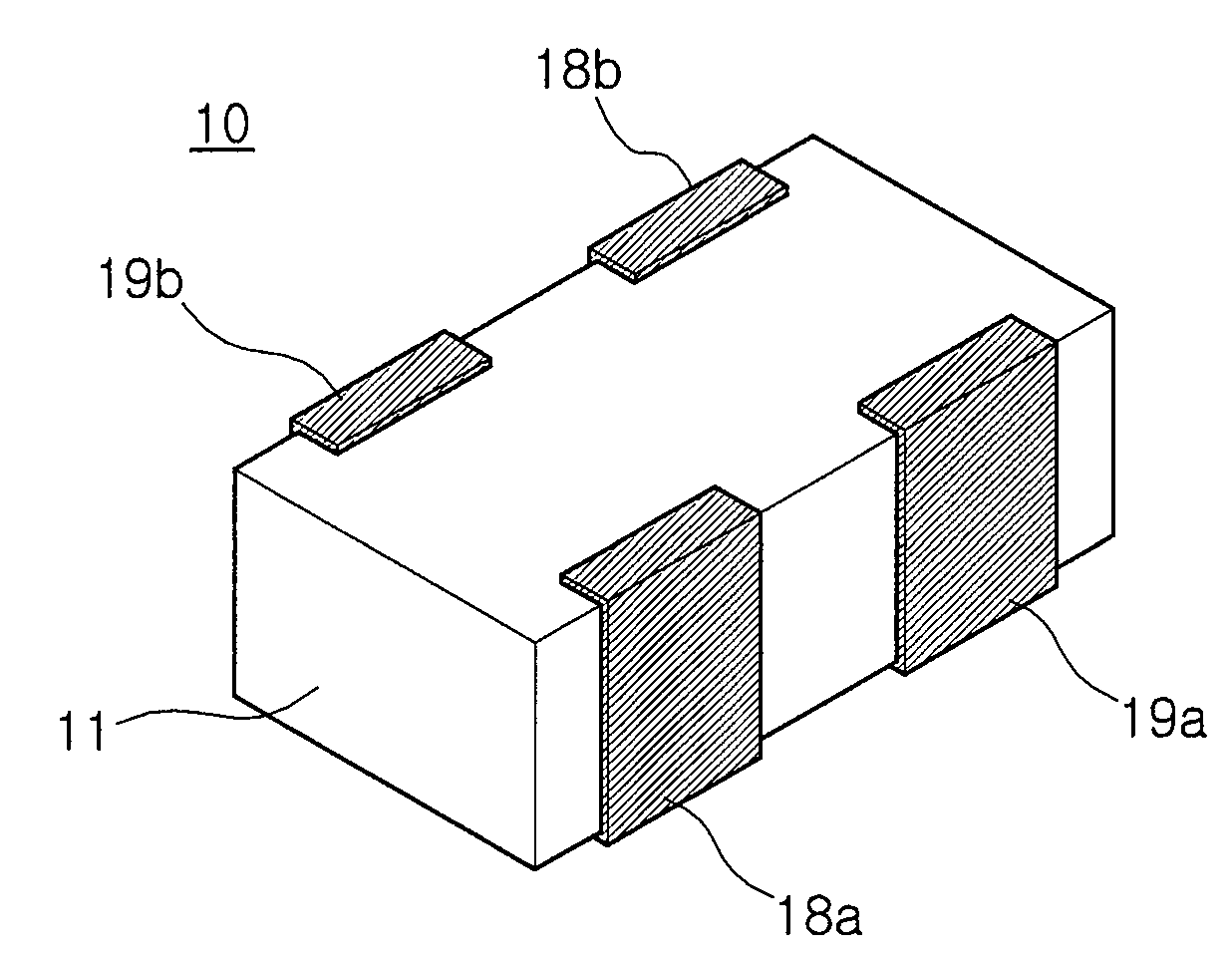

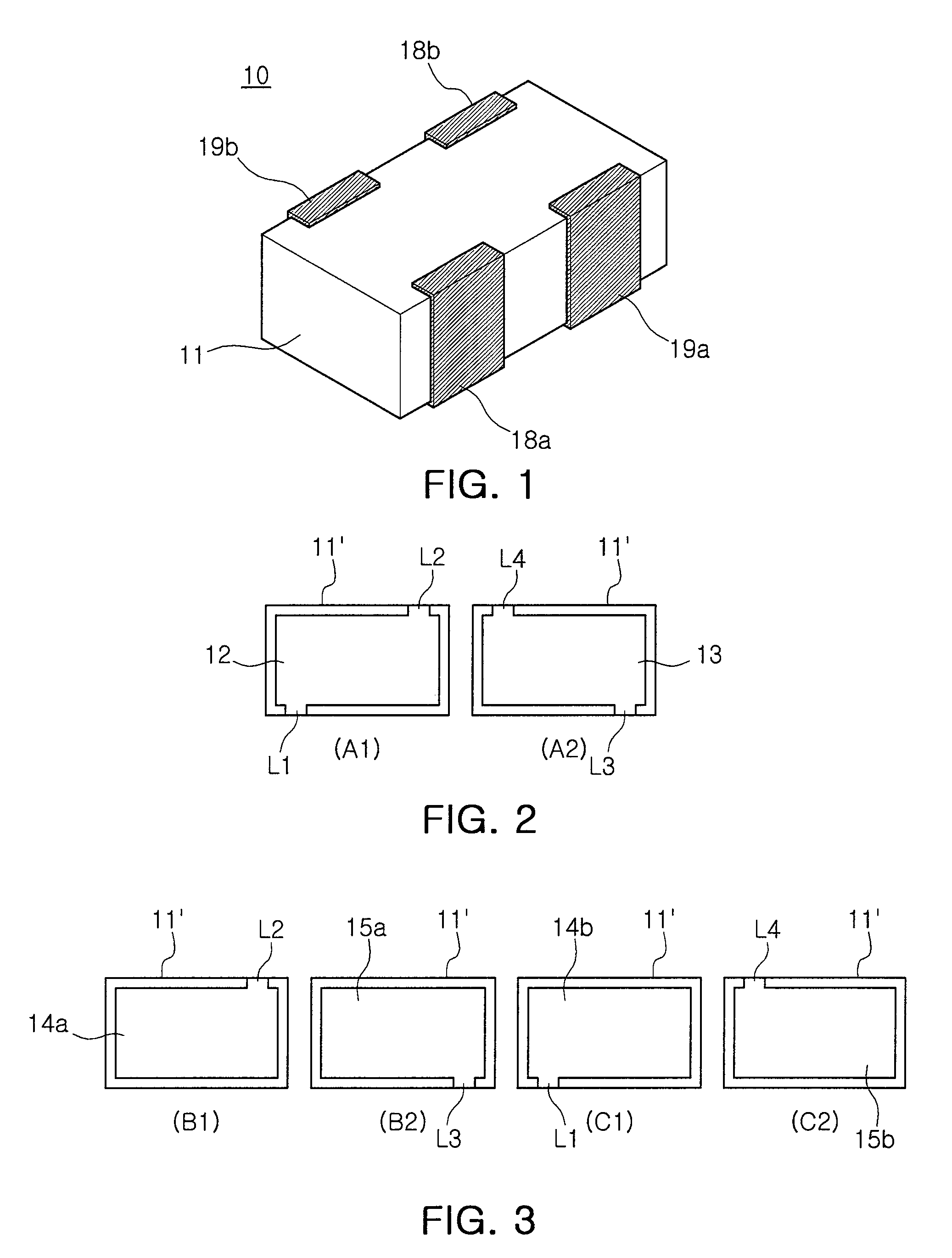

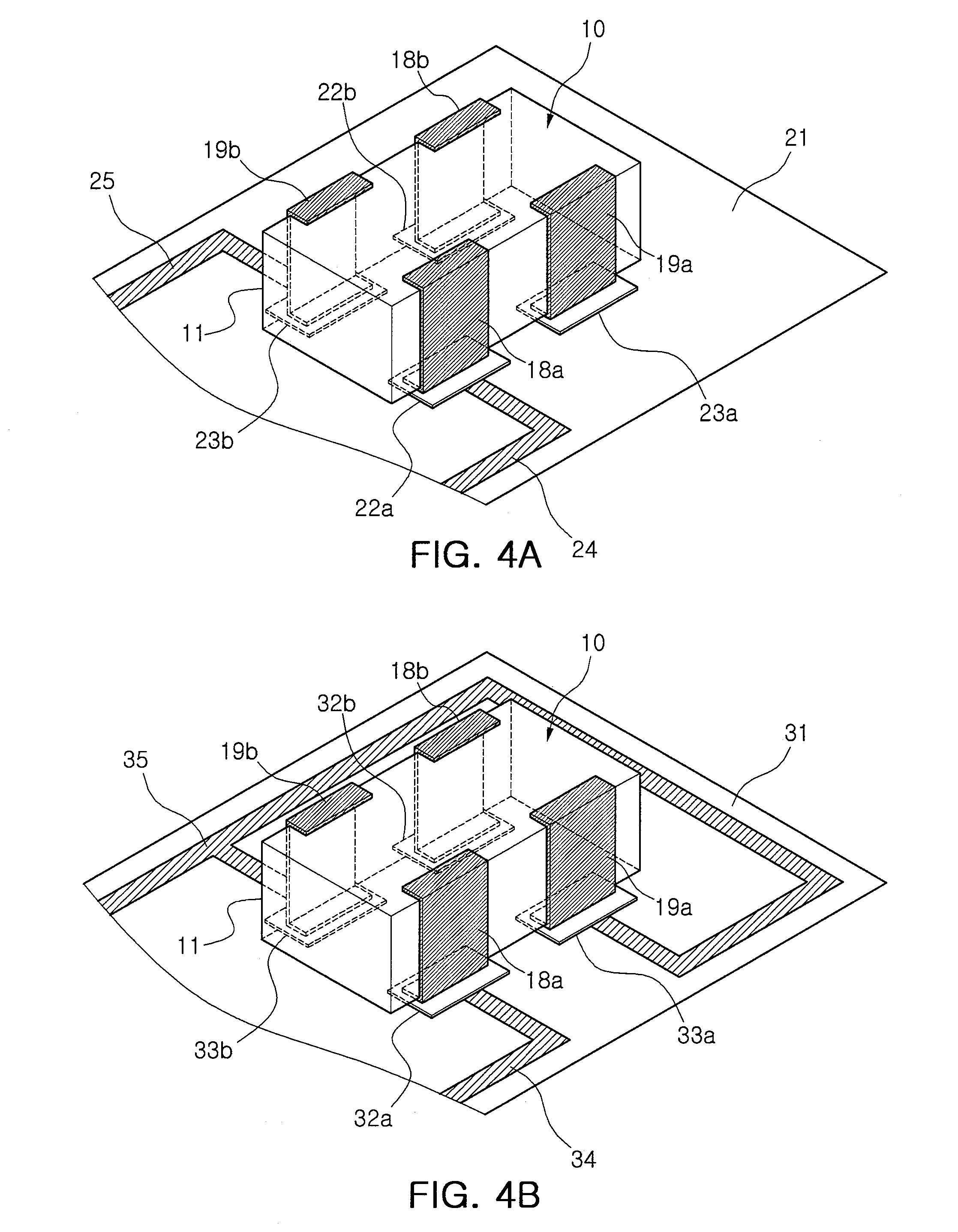

Multilayer capacitor

ActiveUS20090086403A1Strengthen the connection structureFixed capacitor electrodesElectrolytic capacitorsElectrical conductorElectrical polarity

There is provided a multilayer capacitor including an inner connecting conductor of at least one polarity; a plurality of first and second outer electrodes formed on a surface of the body, wherein the inner connecting conductor is connected to a corresponding one of the outer electrodes having identical polarity, a corresponding one of the inner electrodes having identical polarity to the inner connecting conductor includes a plurality of groups each including at least one of the inner electrodes, wherein the inner electrodes of the respective groups are connected to the outer electrodes having identical polarity that are different from one another for each of the groups and electrically connected to the inner connecting conductor through the connected outer electrode.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

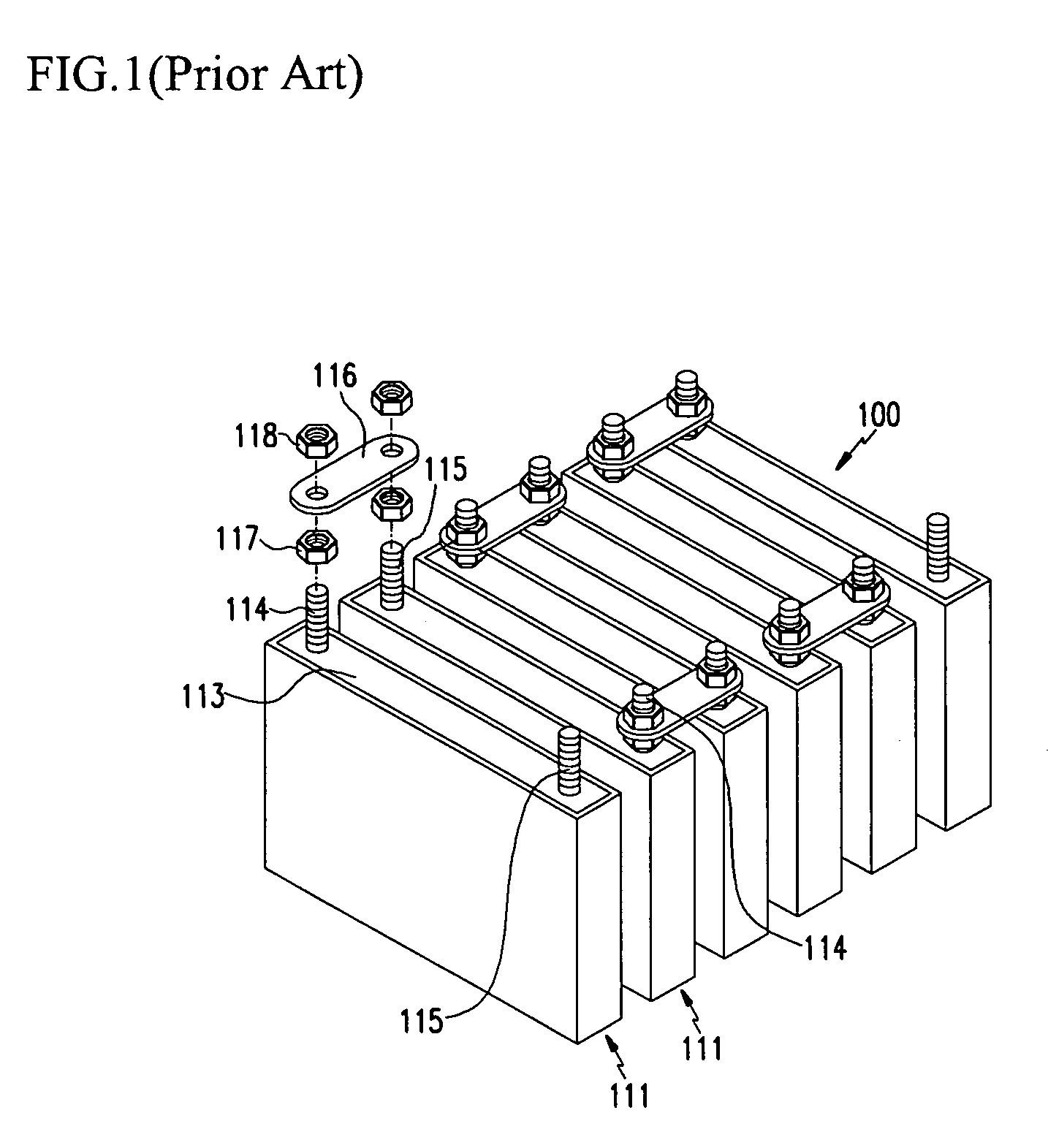

Rechargeable battery and battery module using the same

ActiveUS7393608B2Improve space utilizationIncrease powerFinal product manufactureSmall-sized cells cases/jacketsRechargeable cellElectrical and Electronics engineering

The present invention relates to a rechargeable battery including an electrode assembly comprising a positive electrode, a negative electrode, and a separator interposed therebetween. The battery further comprises a case accommodating the electrode assembly and a plurality of positive electrode terminals and negative electrode terminals that are exposed outside of the case, connected to the case, and coupled to the electrode assembly.

Owner:SAMSUNG SDI CO LTD

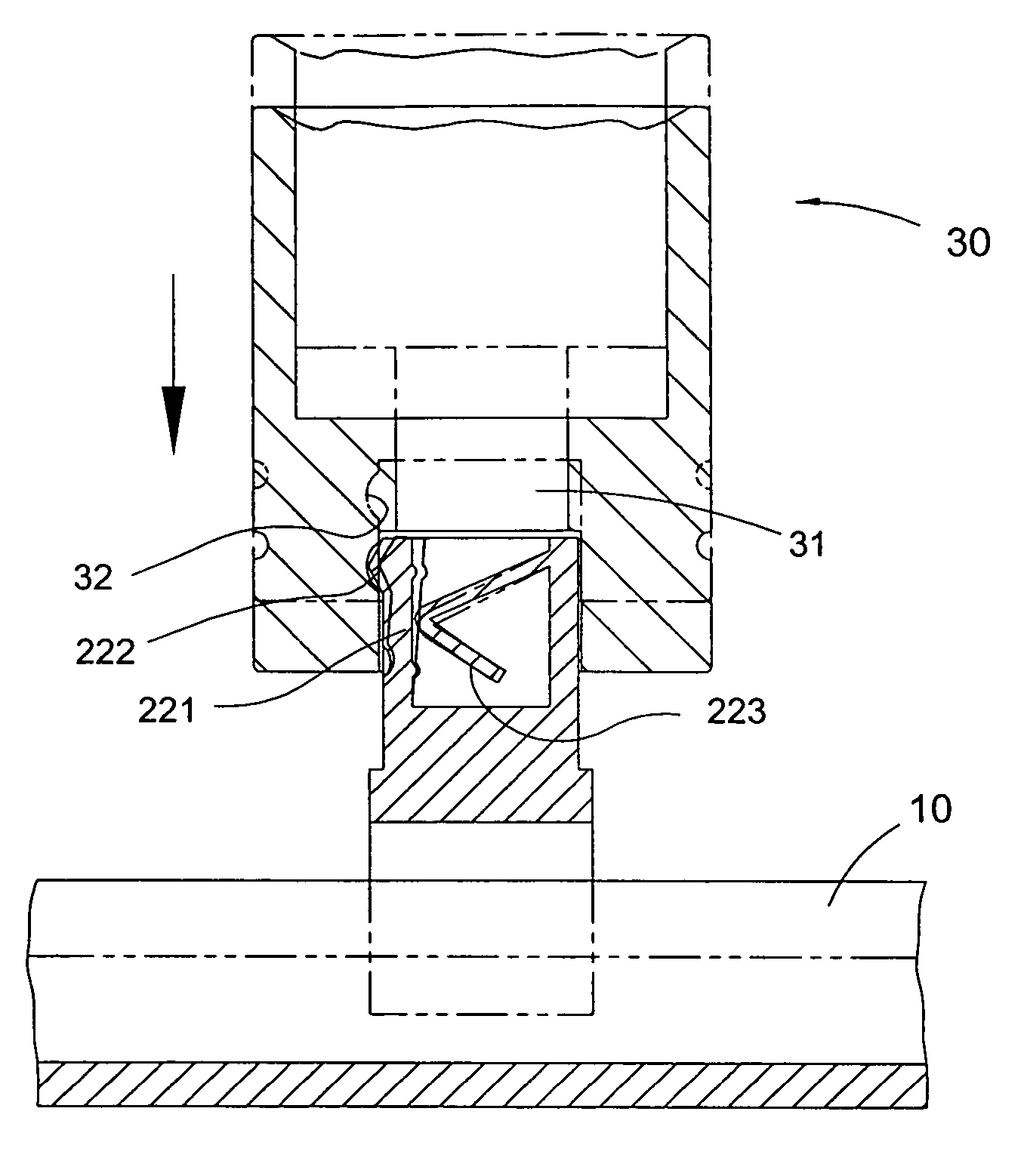

Secondary battery

ActiveUS7745046B2Reduce gapStrengthen the connection structureFinal product manufactureSmall-sized cells cases/jacketsElectrical and Electronics engineeringElectrode

Owner:SAMSUNG SDI CO LTD

Printed circuit board

InactiveUS20100181101A1Reduce simultaneous switching noiseWell formedCross-talk/noise/interference reductionPrinted electric component incorporationTransmitted powerPower noise

A printed circuit board (PCB) reduces a simultaneous switching noise (SSN) causing power noise, thereby reducing radiated electromagnetic interference (EMI). In a double-layered PCB, a first substrate is arranged in parallel with a second substrate while being spaced apart from the second substrate by a predetermined distance. The first substrate includes a ground plane, which is deposited over an entirety of the first substrate. The second substrate includes a power plane deposited at a position of a component mounted to the printed circuit board (PCB) to transmit power to the component. Thus, the power trace of the PCB is simplified in structure, thereby reducing EMI radiation noise.

Owner:SAMSUNG ELECTRONICS CO LTD

Dual-type organic electroluminescence display and manufacturing method thereof

ActiveUS7034452B2Strengthen the connection structureDischarge tube luminescnet screensStatic indicating devicesOrganic electroluminescenceEngineering

Owner:SAMSUNG DISPLAY CO LTD

Packaged chip capable of lowering characteristic impedance

InactiveUS20060131742A1Lower characteristic impedanceReduce electrical noiseSemiconductor/solid-state device detailsSolid-state devicesAdhesiveEngineering

A packaged chip lowering characteristic impedance comprises a chip, a lead wire frame, a plurality of metal layers, adhesive layers, lead wires, and a mold, being formed into TSOP LOC and thin-small-sized packaging types; from a specified site above or under each row of leads of the lead wire frame, metal layers are fixed respectively with adhesives layers to the lead wire frame; lead wires are connected respectively between electrode contacts of the chip and leads of the lead wire frame and a lead wire provided is connected between at least one lead and the metal layer, so the packaged chip using metal layers as a Ground or Power plane is formed; thus, electrical noises and EMI are lowered and a problem of poor transmission of signals is eliminated so that a stable transmission of signals and an efficient transmission speed may be further developed.

Owner:DOMINTECH

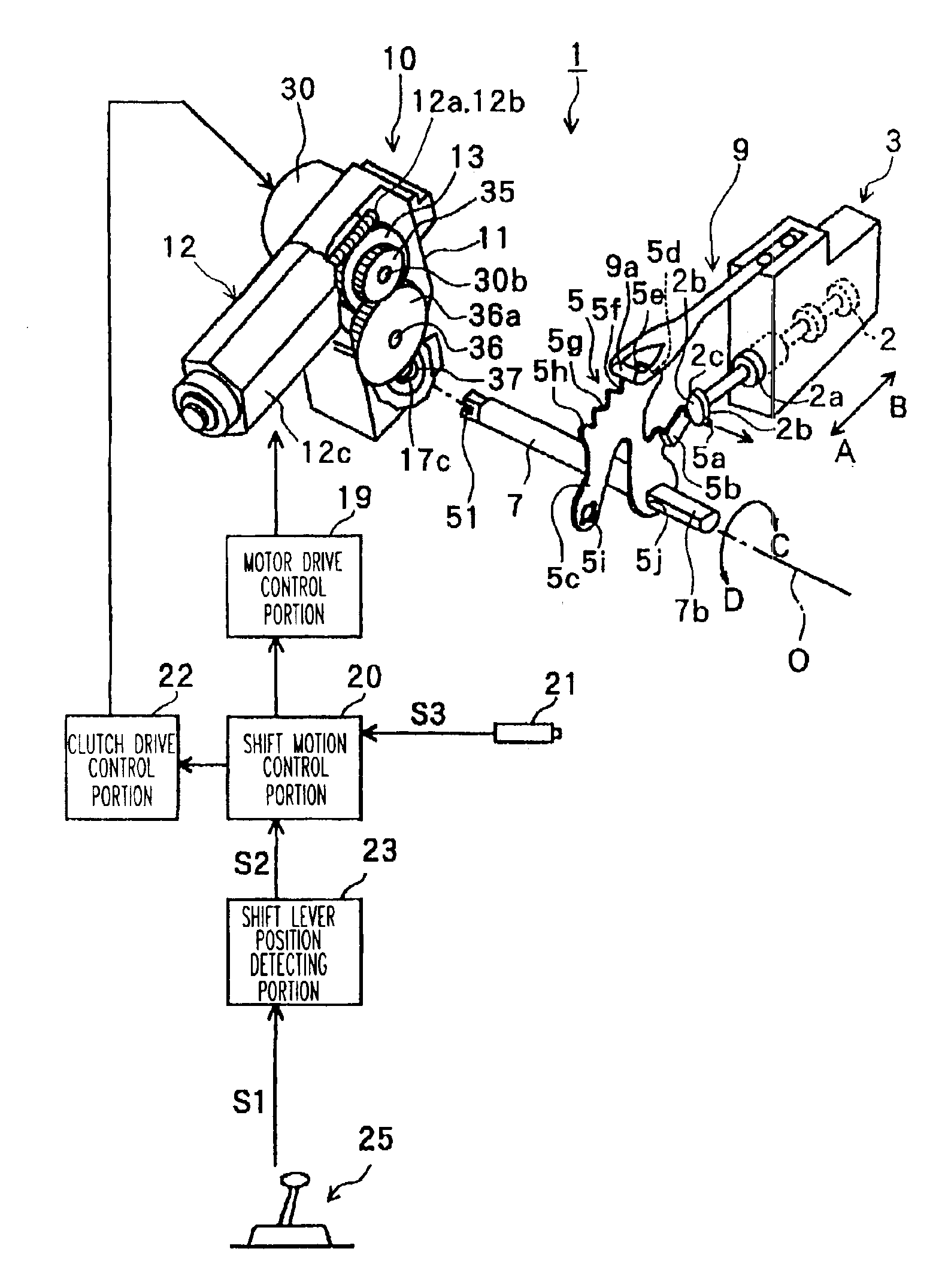

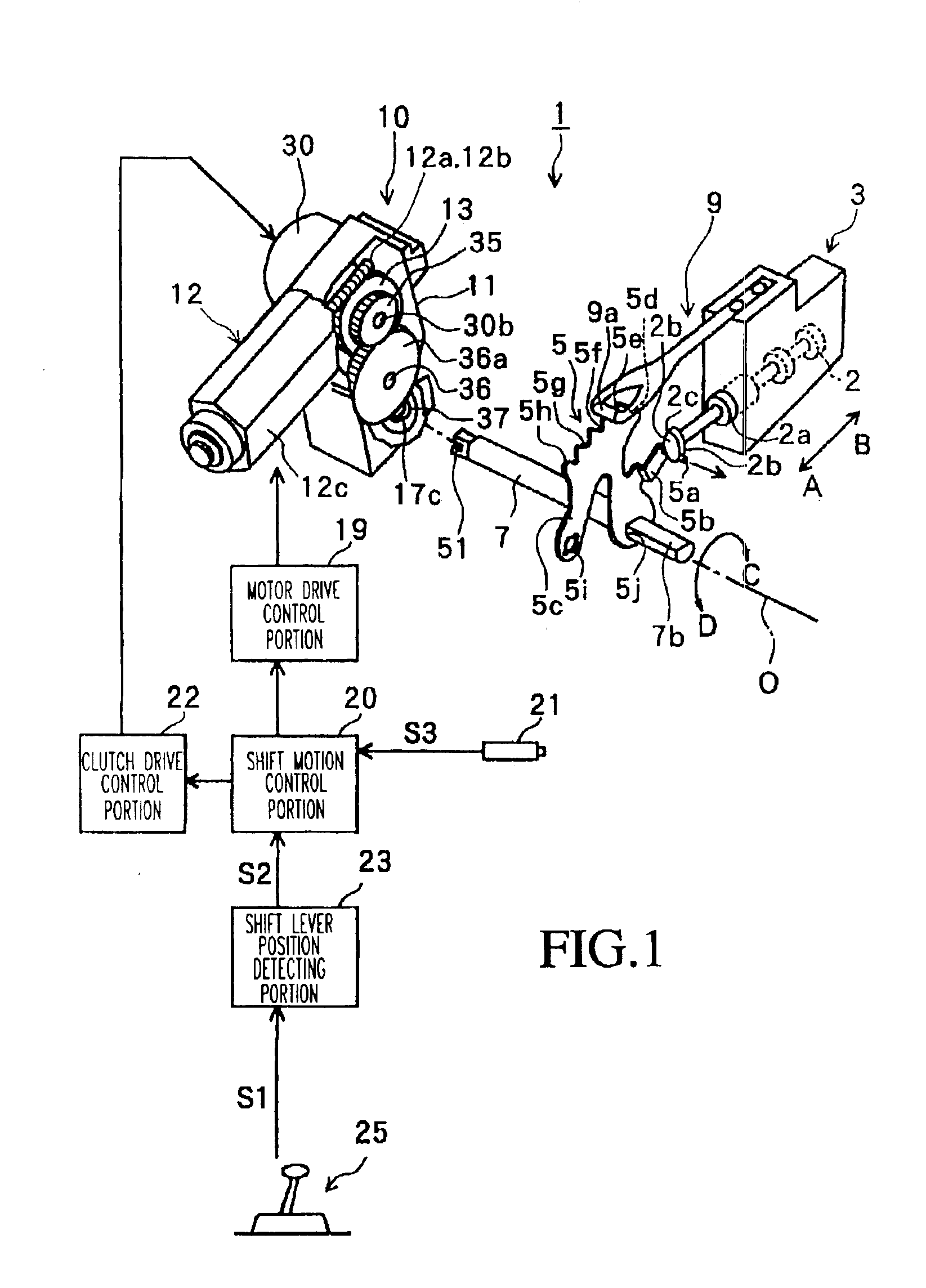

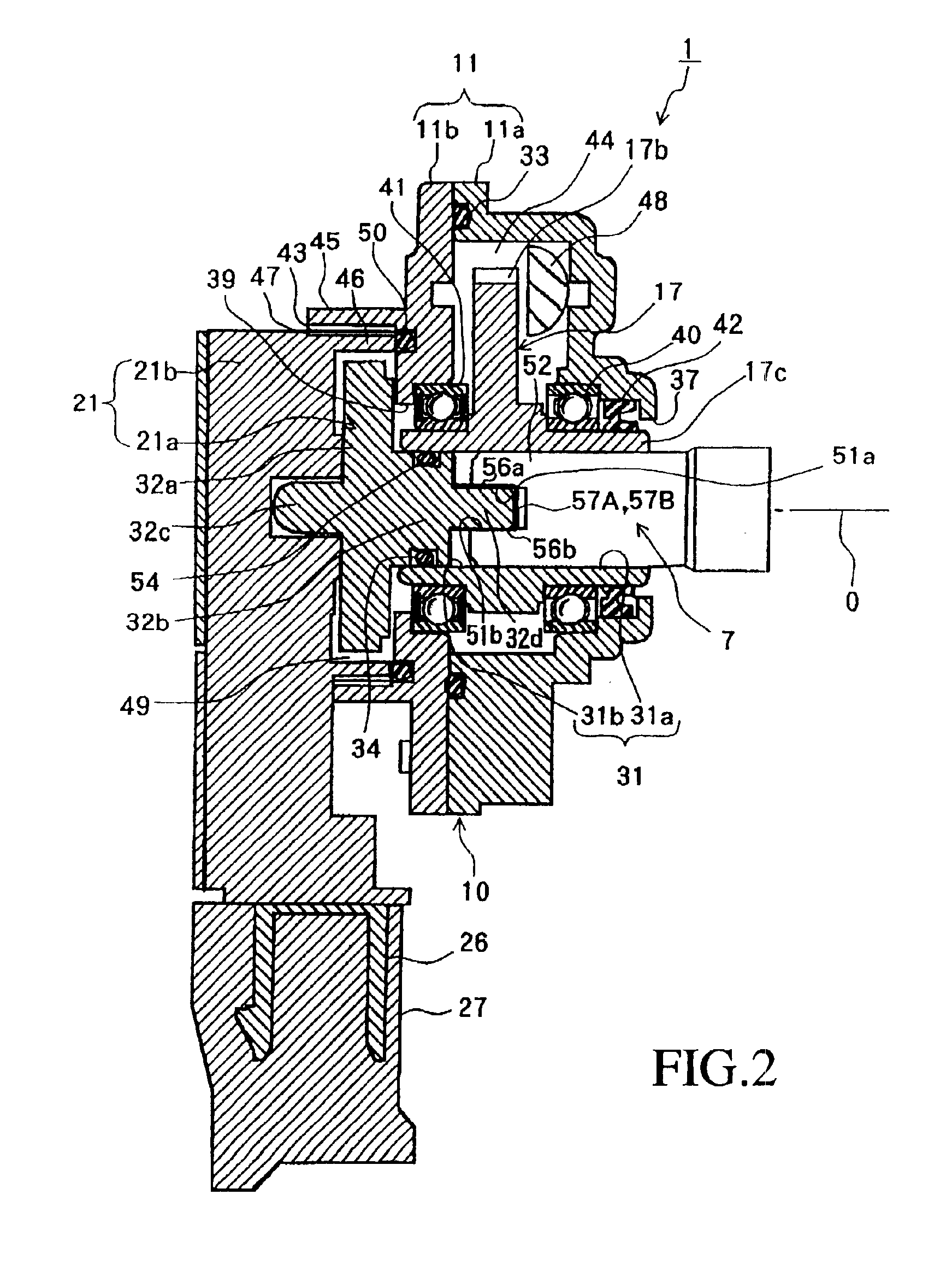

Shift range changeover mechanism

InactiveUS6877390B2Eliminate connectionAccurate rotation positioningGearingGearing controlLocation detectionEngineering

A vehicle range changeover mechanism is driven in response to operation of a shift lever. The range changeover mechanism has an output sector gear that is unrotatably connected to a range control shaft, and a position detecting sensor, a portion of which that is interlocked with and connected to the range control shaft. Looseness between the output sector gear and the position detecting sensor portion is eliminated by provision of a leaf or spring plate, thereby assuring rotation of the position detecting sensor portion corresponding one to one with the rotational motion of the range control shaft.

Owner:AISIN AW CO LTD

Pouch-type lithium secondary battery and fabrication method thereof

ActiveUS8999566B2Minimizes seal surfaceStrengthen the connection structureFinal product manufactureCells structural combinationLithiumEngineering

A pouch-type lithium secondary battery including: a battery unit comprising a positive electrode plate, a separator, and a negative electrode plate, wherein the separator is disposed between the positive and negative electrode plates; electrode tabs extending from each of the positive and negative electrode plates of the battery unit, respectively; a case having a space to accommodate the battery unit and sealing surfaces formed along the periphery of the space, wherein the case is sealed at the sealing surfaces by thermal fusion; and a protection circuit board 600 electrically connected to the electrode tabs. The protection circuit board is disposed parallel to an outer wall of the case. Since the electrode tabs are bent in an upright position with respect to the sealing surfaces, and the protection circuit board electrically connected to the bent electrode tabs is disposed between the outer wall of the case and the electrode tabs, the size of the sealing surfaces of the case can be minimized.

Owner:SAMSUNG SDI CO LTD

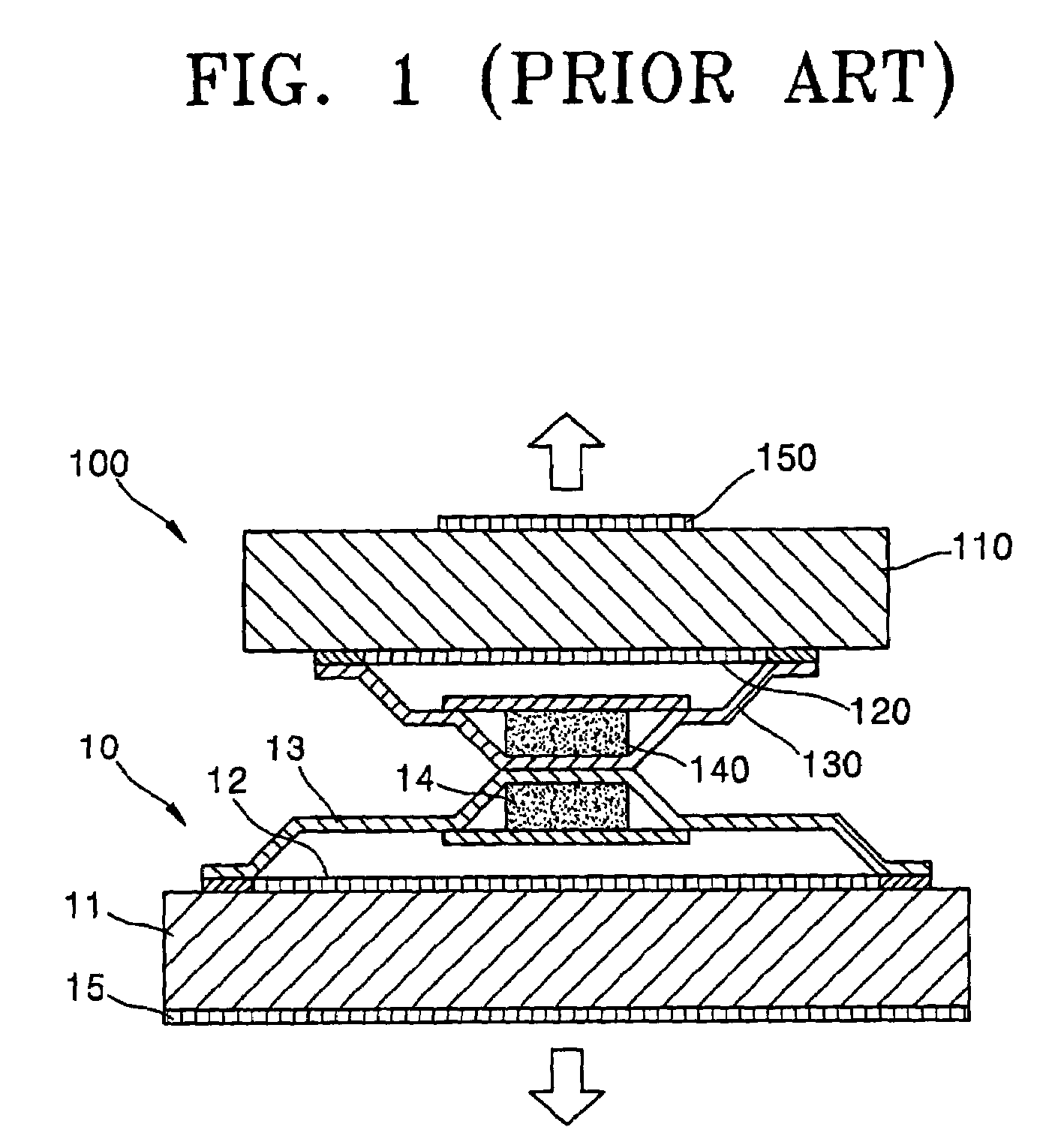

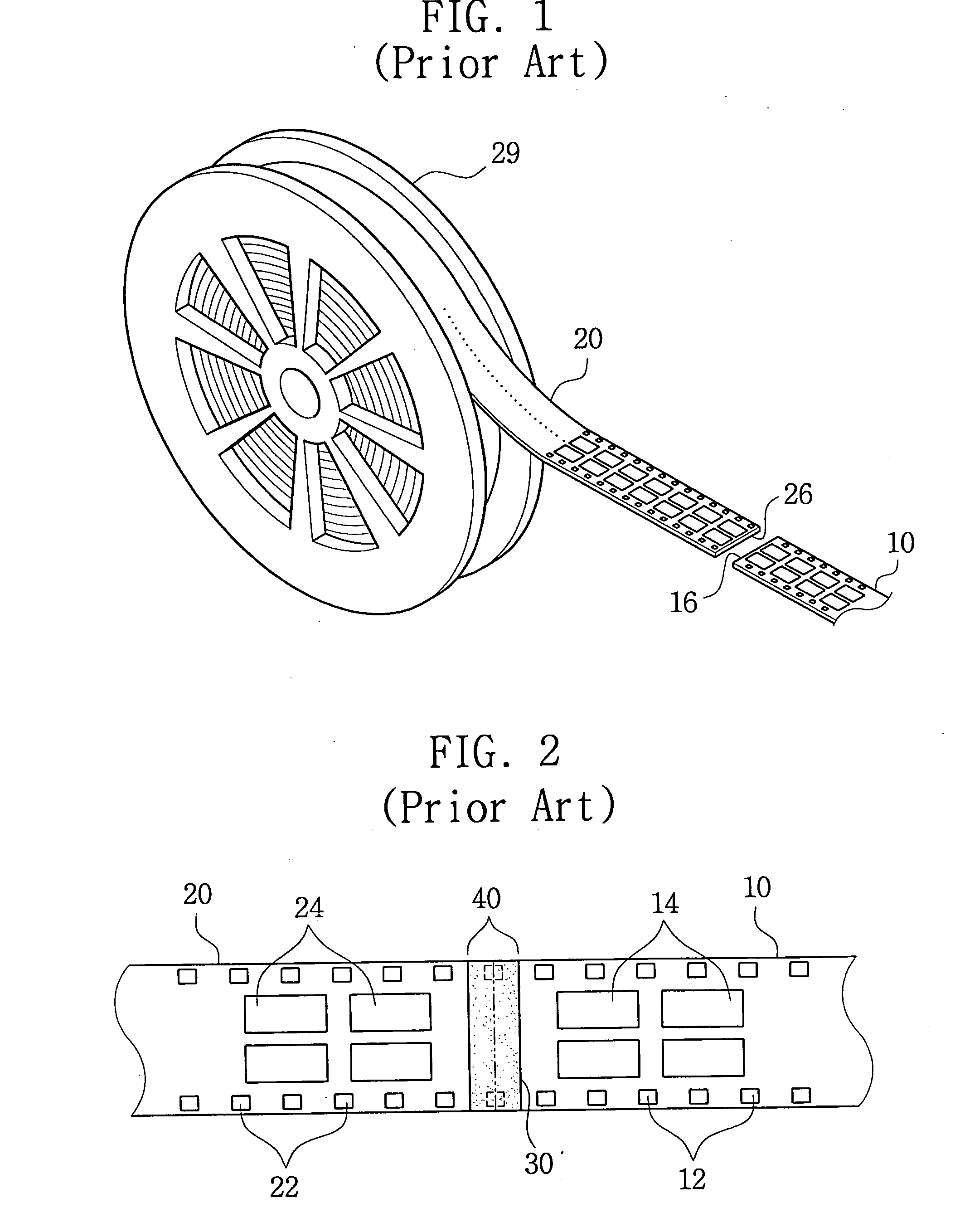

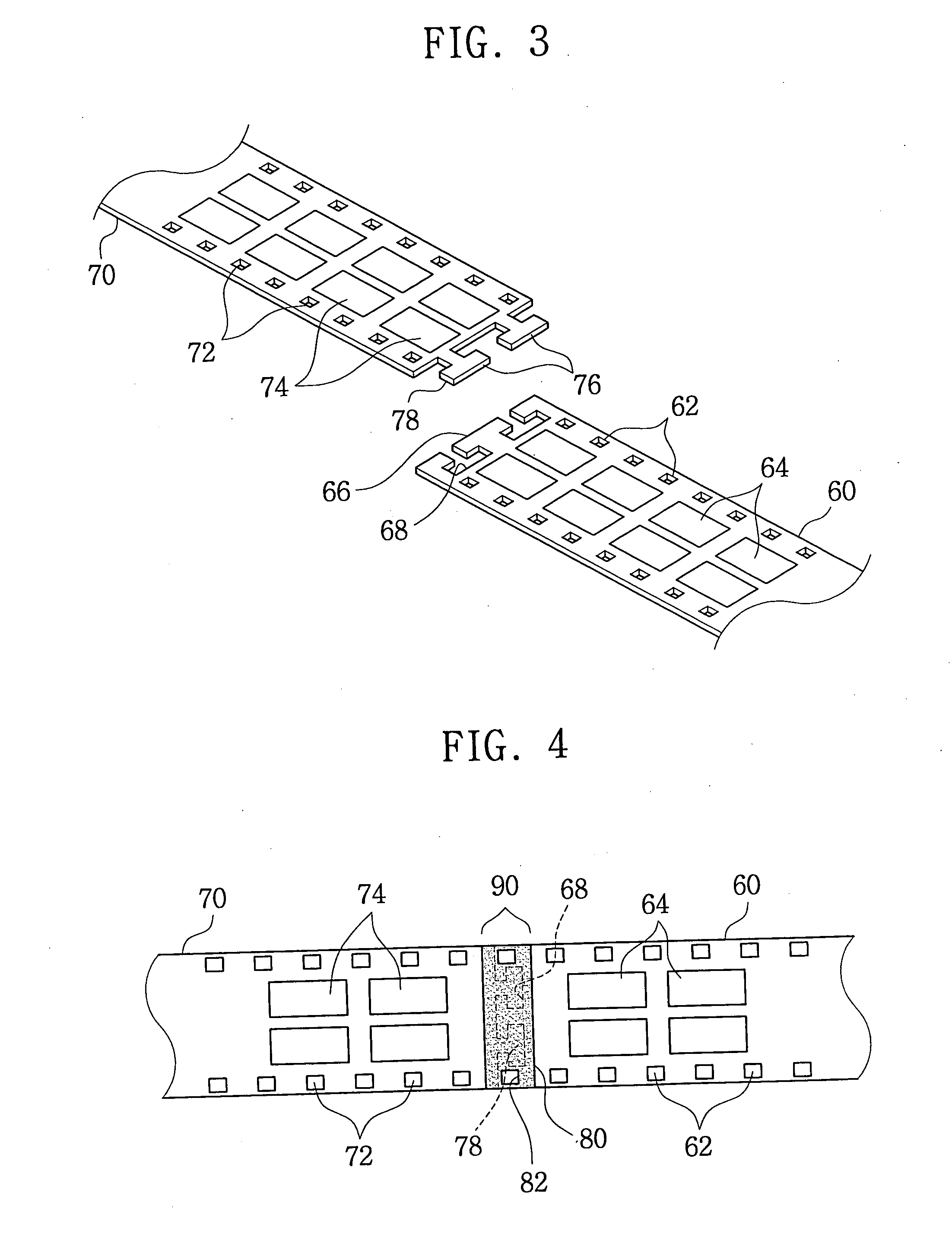

Connection structure of circuit substrate

InactiveUS20050016897A1High tensile strengthAvoid deformationSemiconductor/solid-state device detailsSolid-state devicesEngineeringElectrical and Electronics engineering

The present invention provides an improved connection for circuit substrates. The circuit substrates are connected at concave and convex portions at their ends. The concave portion is formed such that the inside width is larger than the entrance width. The convex portion fits into the concave portion. Thereby, a connected portion of the circuit substrates has increased tensile strength. Furthermore, abnormality of the connected portion of the circuit substrates may be easily perceived.

Owner:SAMSUNG ELECTRONICS CO LTD

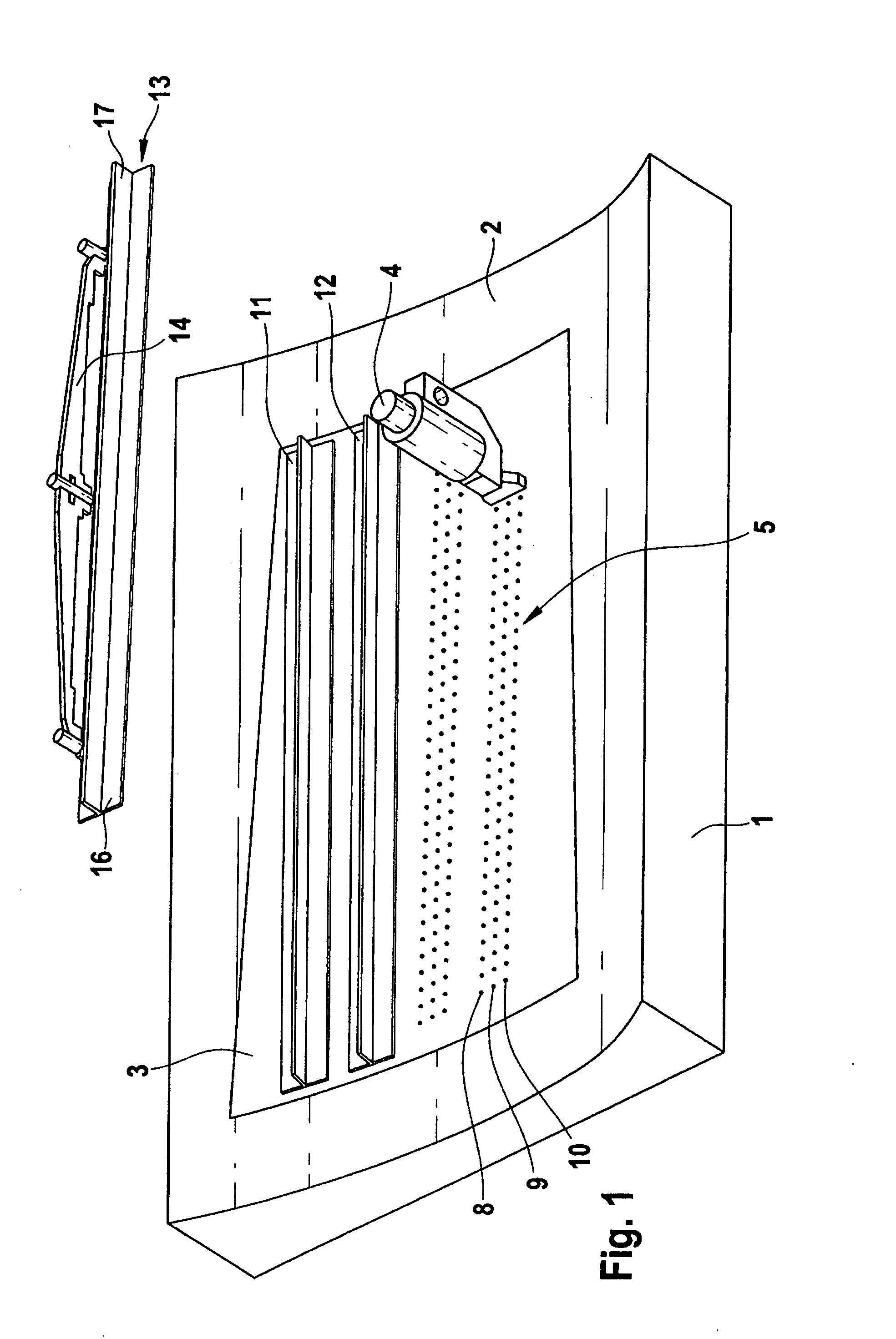

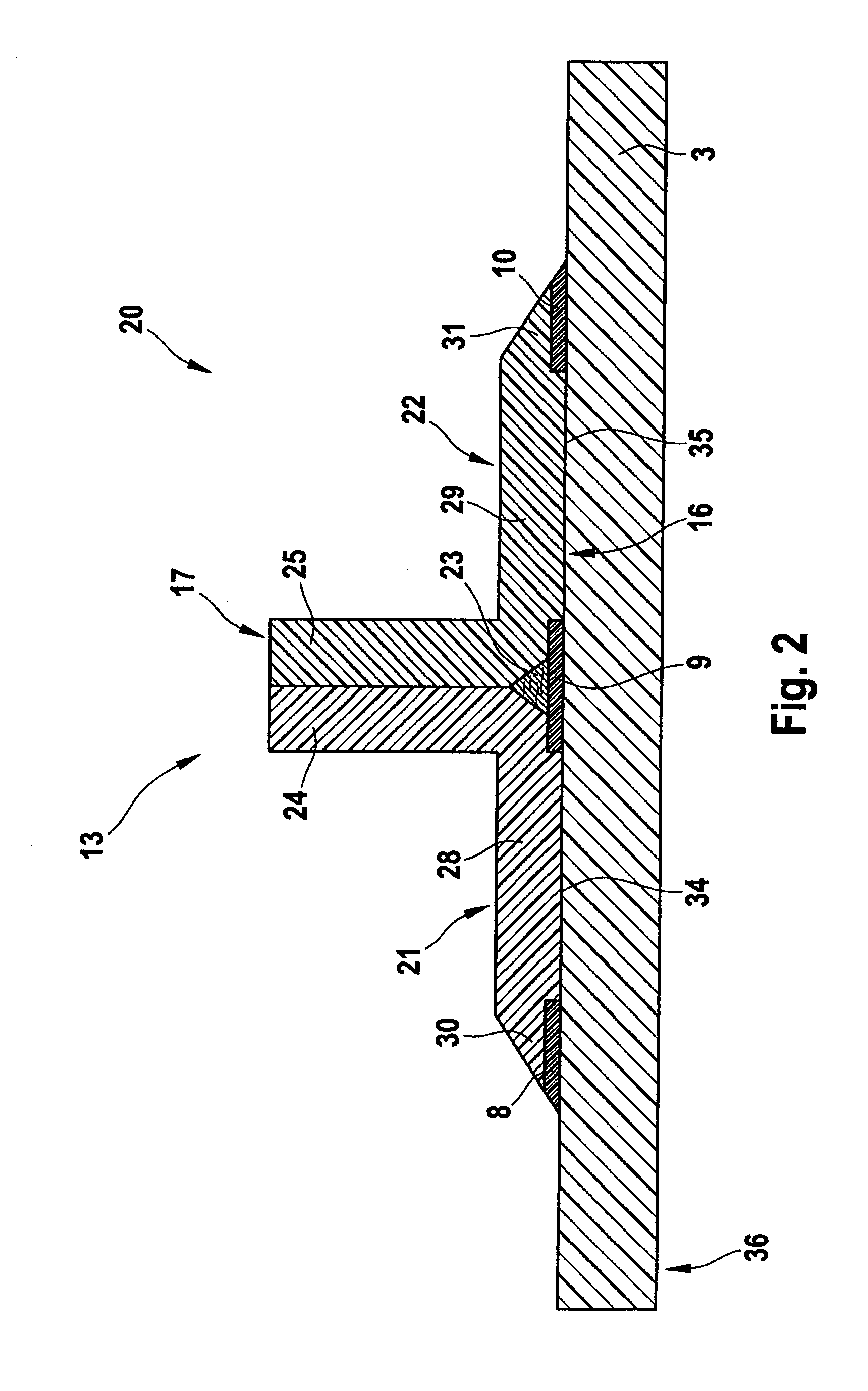

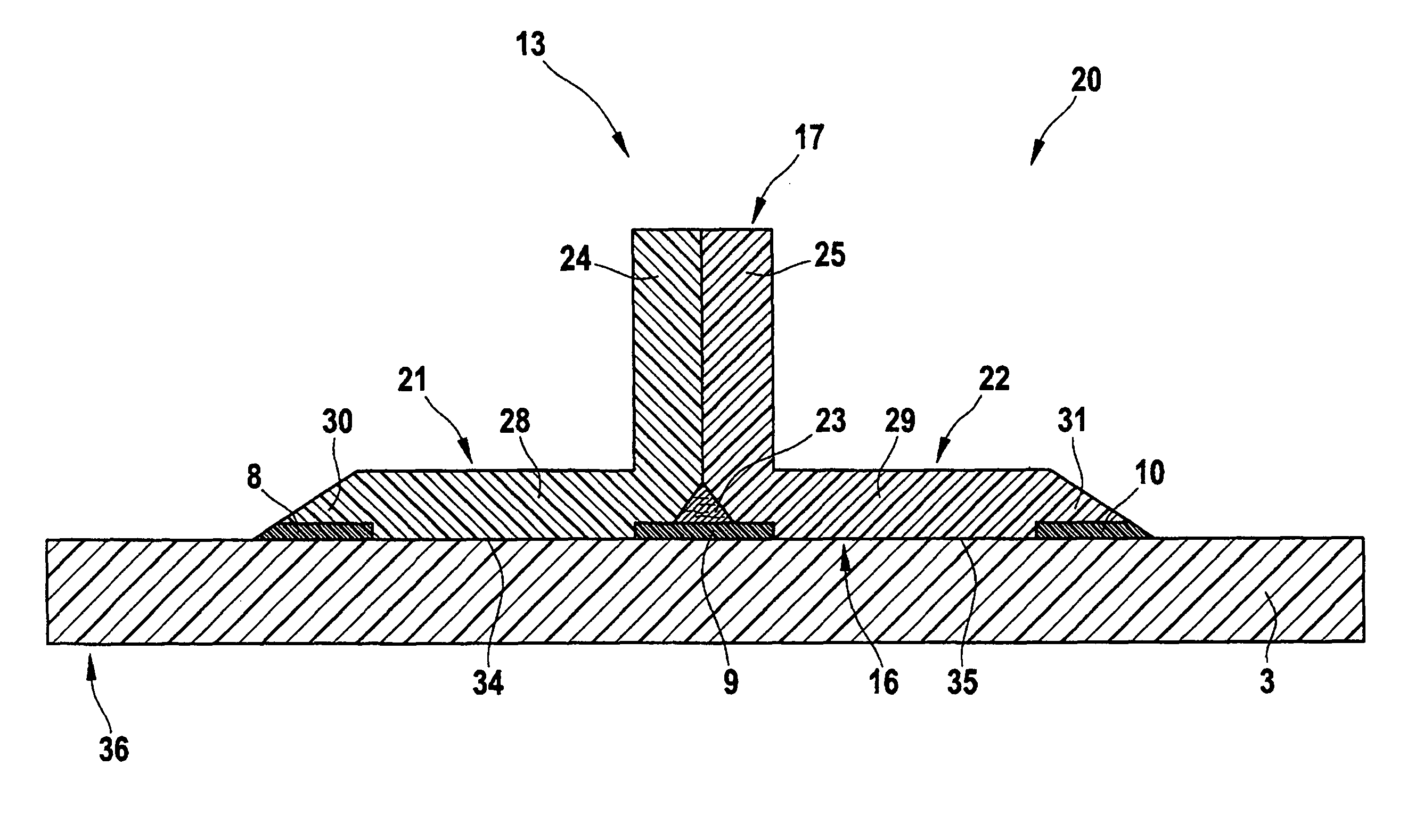

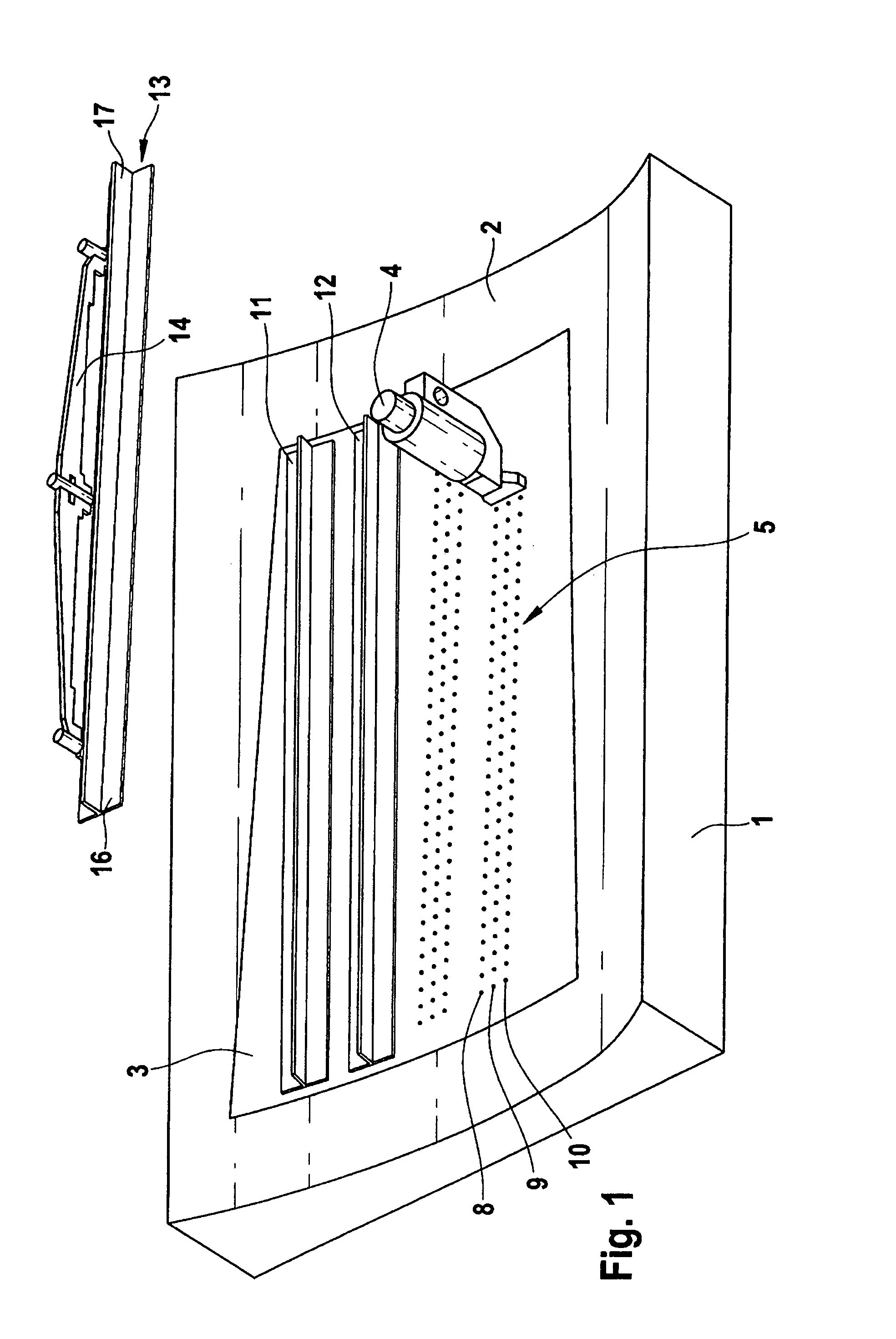

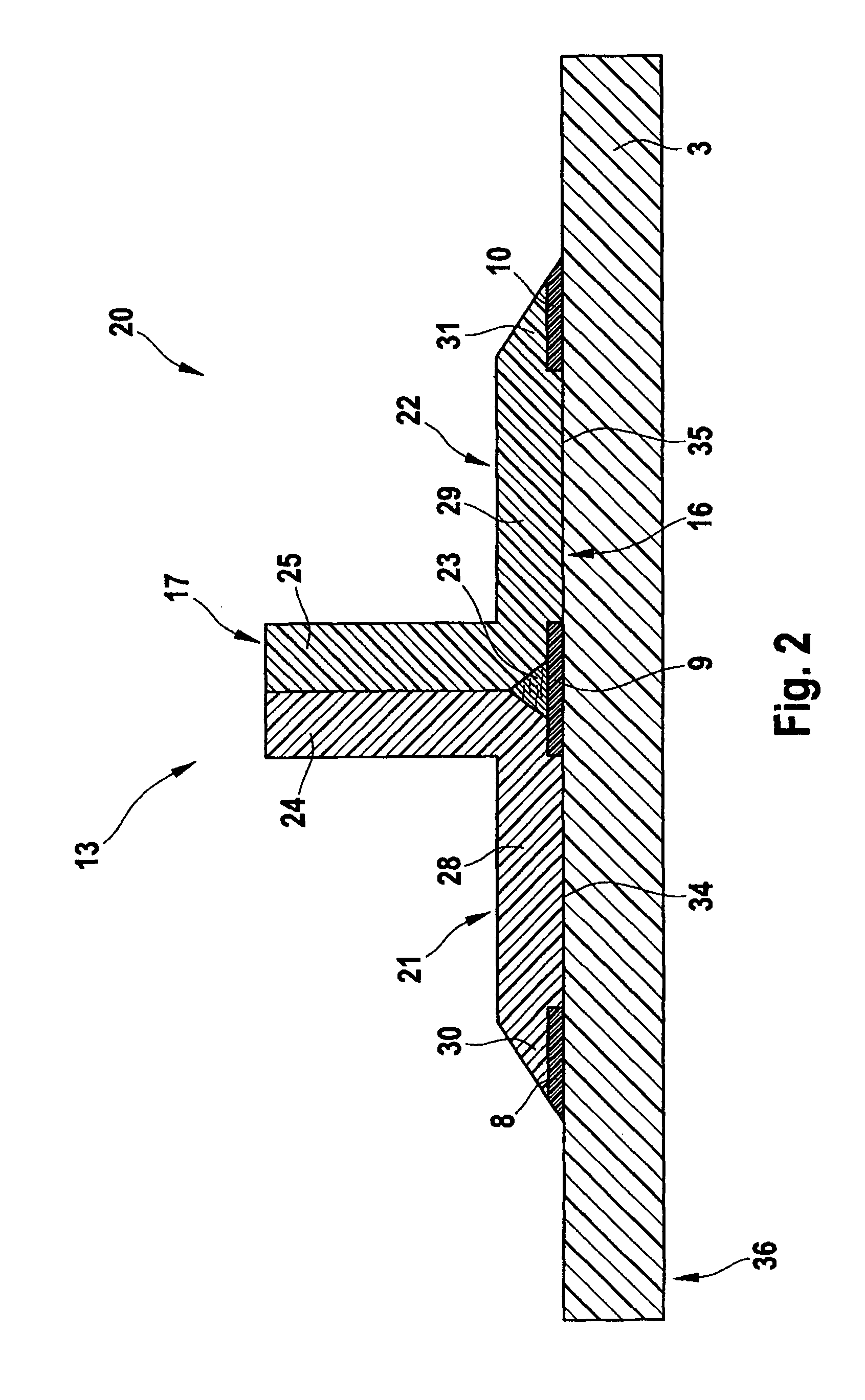

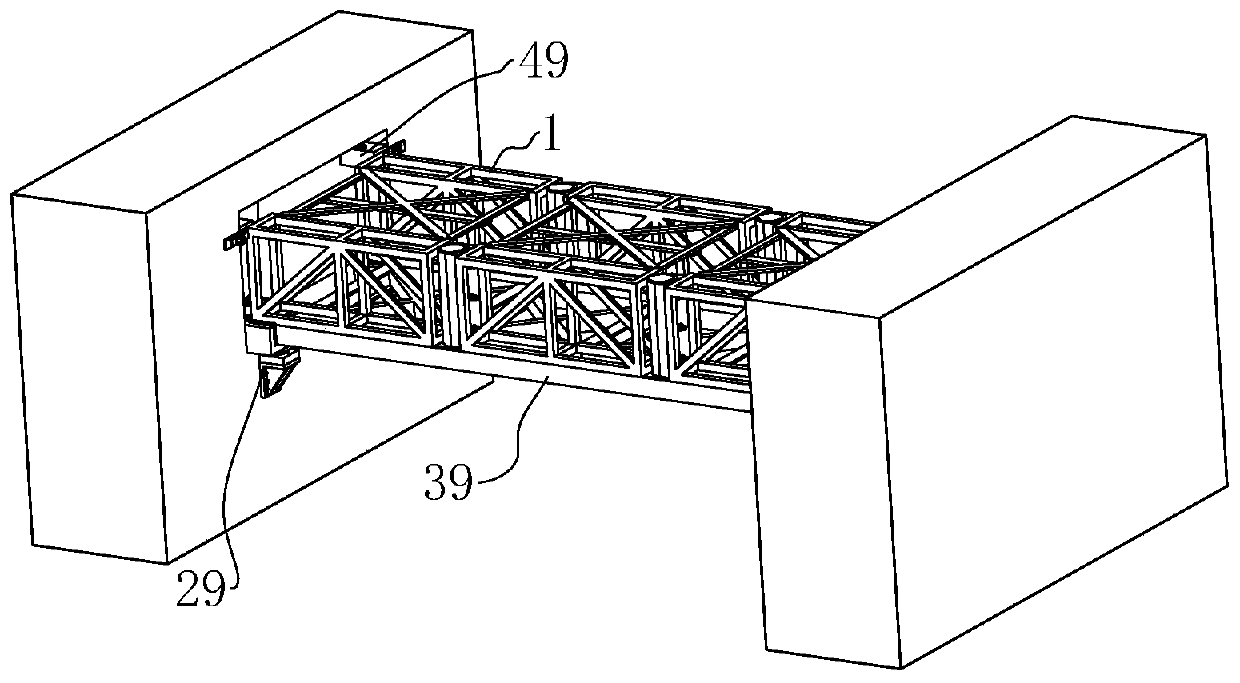

Connecting structure for an aircraft or spacecraft and method for producing the same

ActiveUS20080210824A1Improved connection structureStrengthen the connection structureFuselage framesAircraft stabilisationEnergy absorbingAirplane

The present invention relates to a connecting structure for an aircraft or spacecraft, with a structural component and a stringer. The stringer is connected to the structural component by means of connecting regions. In order to reduce stress peaks that result for example from impact in the structural component, a high impact material is introduced into at least one of the connecting regions to provide a local increase in the energy absorbing capacity of the at least one connecting region.

Owner:AIRBUS OPERATIONS GMBH

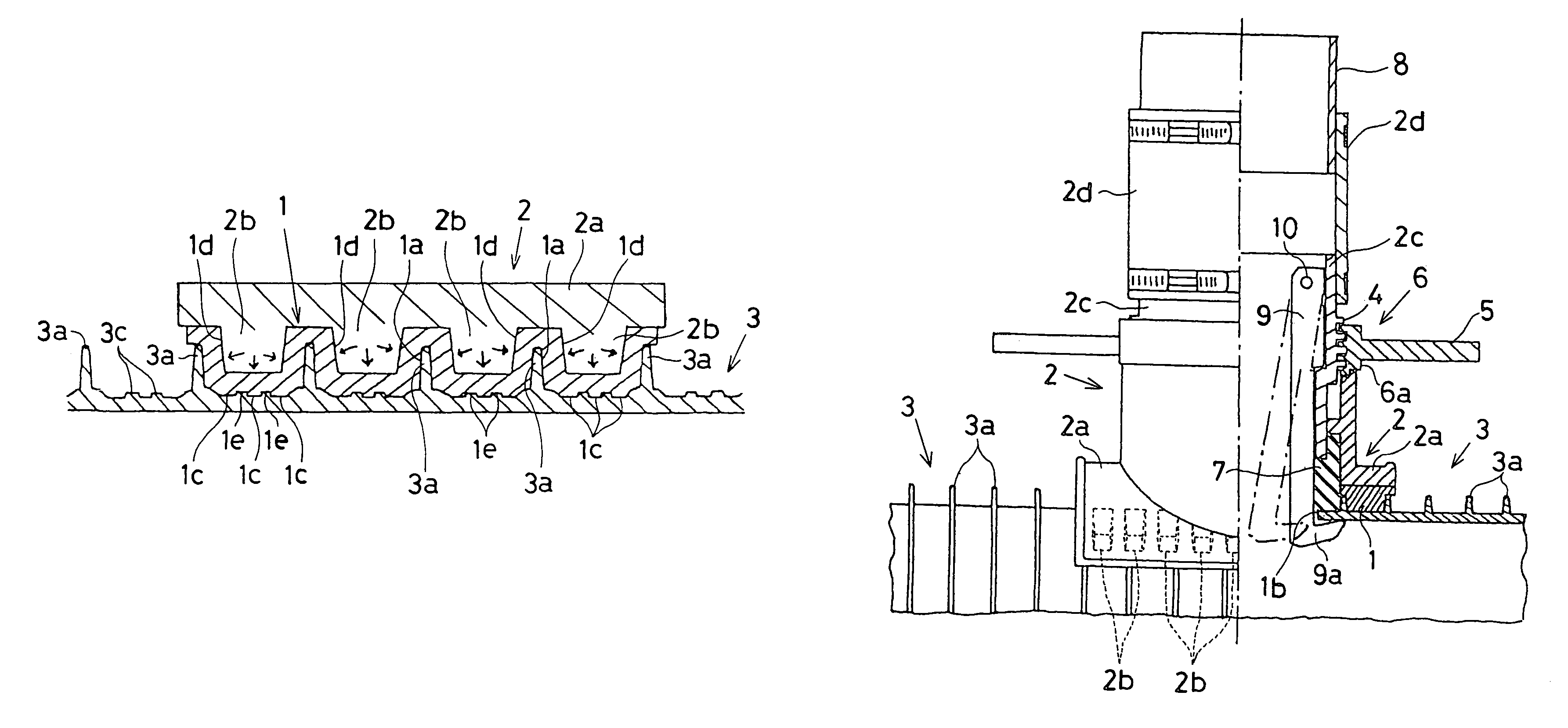

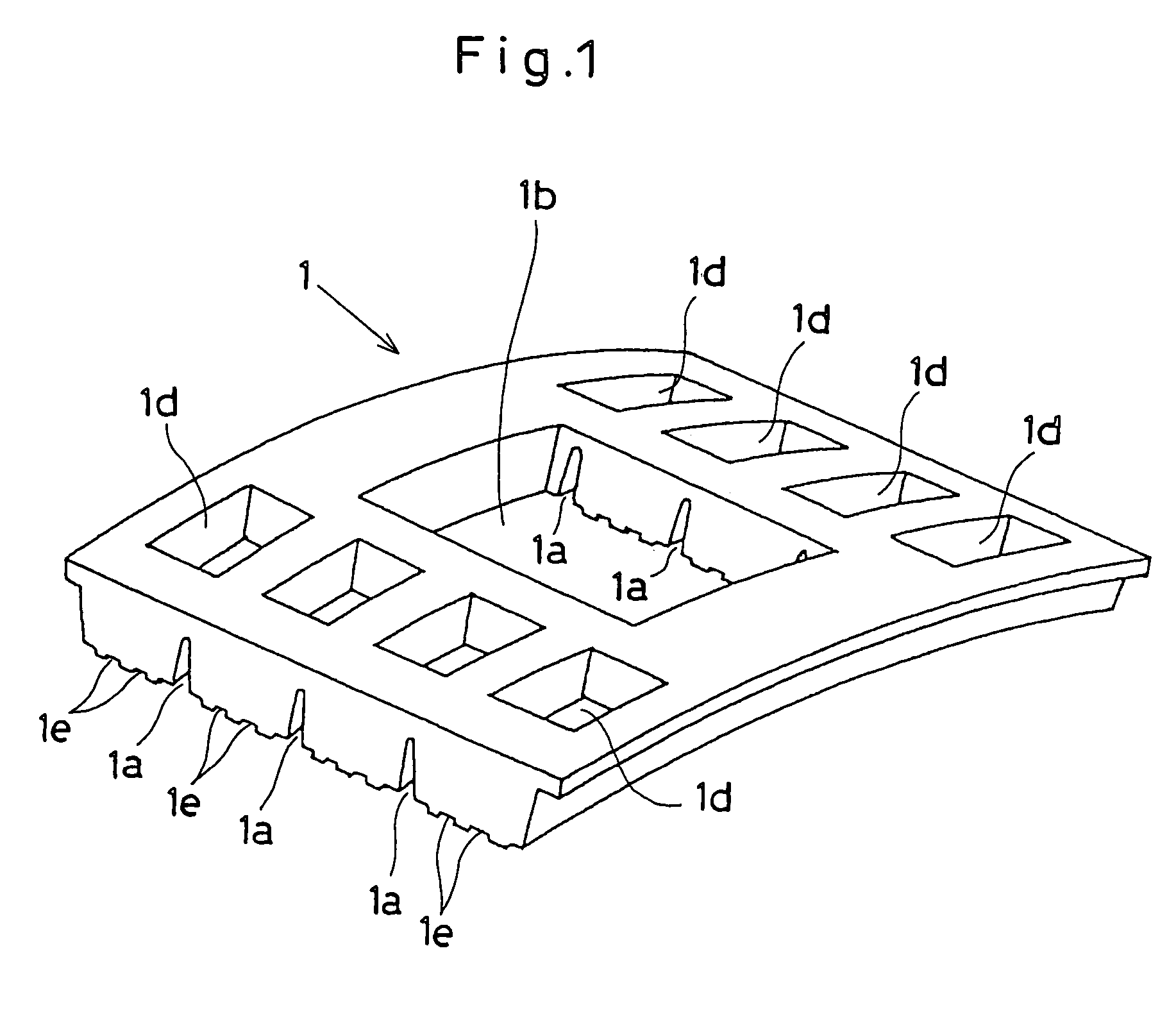

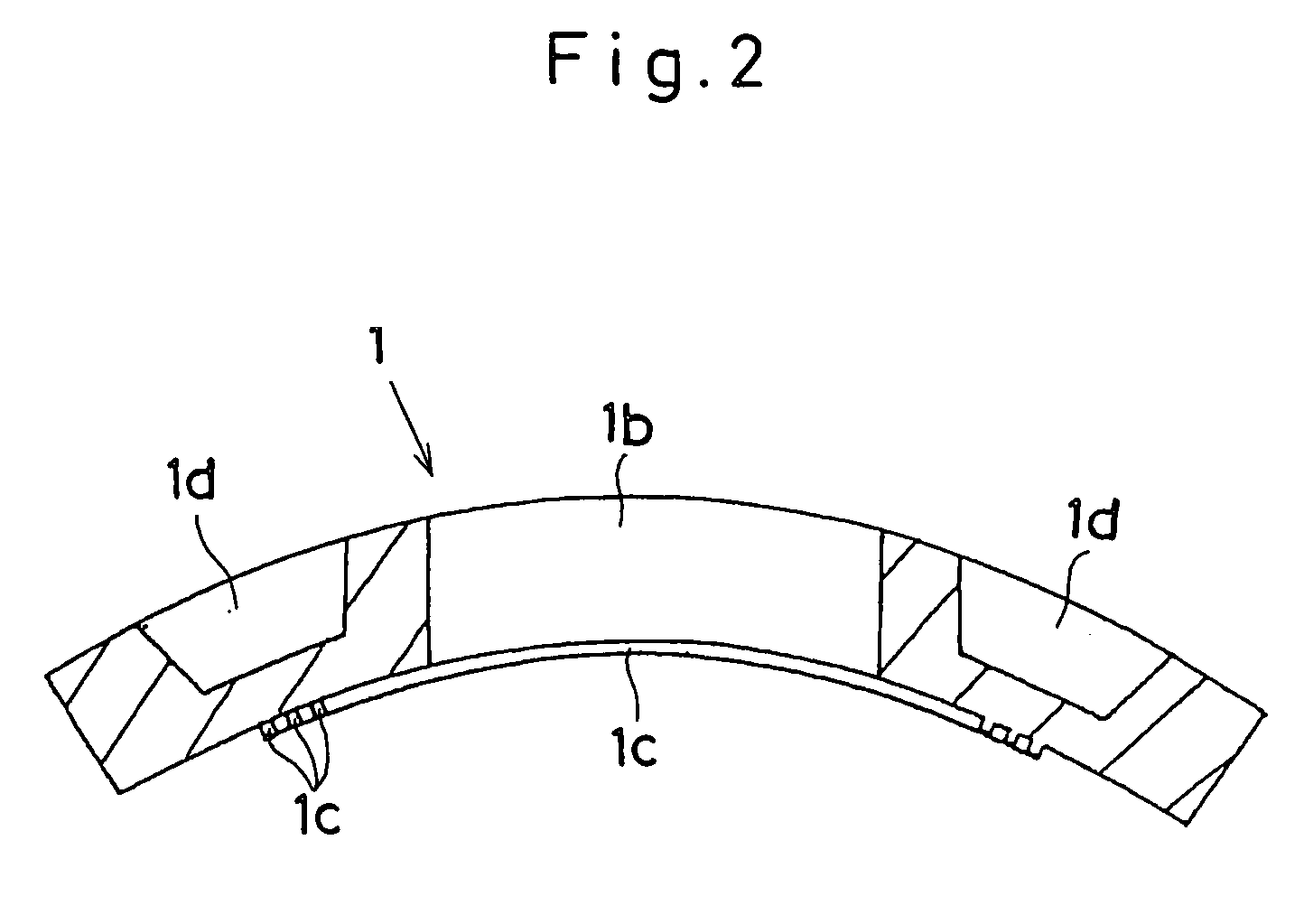

Duct connection assemble between a branch duct and a main duct

InactiveUS7007980B2Strengthen engagement actionEffectively absorb shaking tremor and impactPipeline expansion-compensationBranching pipesEngineeringSealant

A duct connection assemble, whereby upon connecting a saddle flange (2a) of the joint duct (8) to the main ribbed duct (3) through the communication hole (1b), the rubber sealant (1) is interposed between the saddle flange (2a) and a circumferential area of the communication hole (1b) so that protuberances (2b) uniformly press the rubber sealant (1) through the recesses (1d) to tightly engage the saddle flange (2a) against an outer surface of the main ribbed duct (3) through rib-fitting grooves (1a) and the water sealing small projective rings (1c). The joint duct (2) is brought into an elastical engagement with the main ribbed duct (3) to achieve a good water sealing action for an extended period of time.

Owner:SANRITSU CORP

Connecting structure for an aircraft or spacecraft and method for producing the same

InactiveUS7997534B2Strengthen the connection structurePrevent detachment of the stringerFuselage framesAircraft stabilisationFlight vehicleEnergy absorption

The present invention relates to a connecting structure for an aircraft or spacecraft, with a structural component and a stringer. The stringer is connected to the structural component by means of connecting regions. In order to reduce stress peaks that result for example from impact in the structural component, a high impact material is introduced into at least one of the connecting regions to provide a local increase in the energy absorbing capacity of the at least one connecting region.

Owner:AIRBUS OPERATIONS GMBH

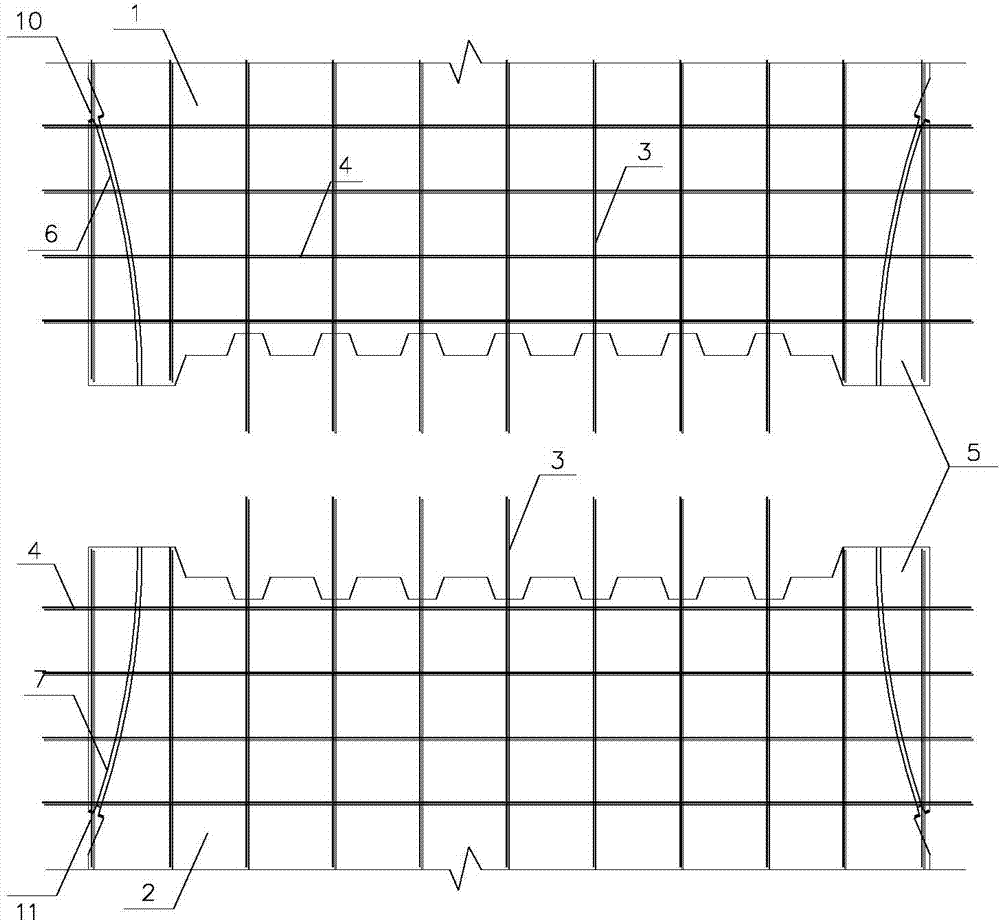

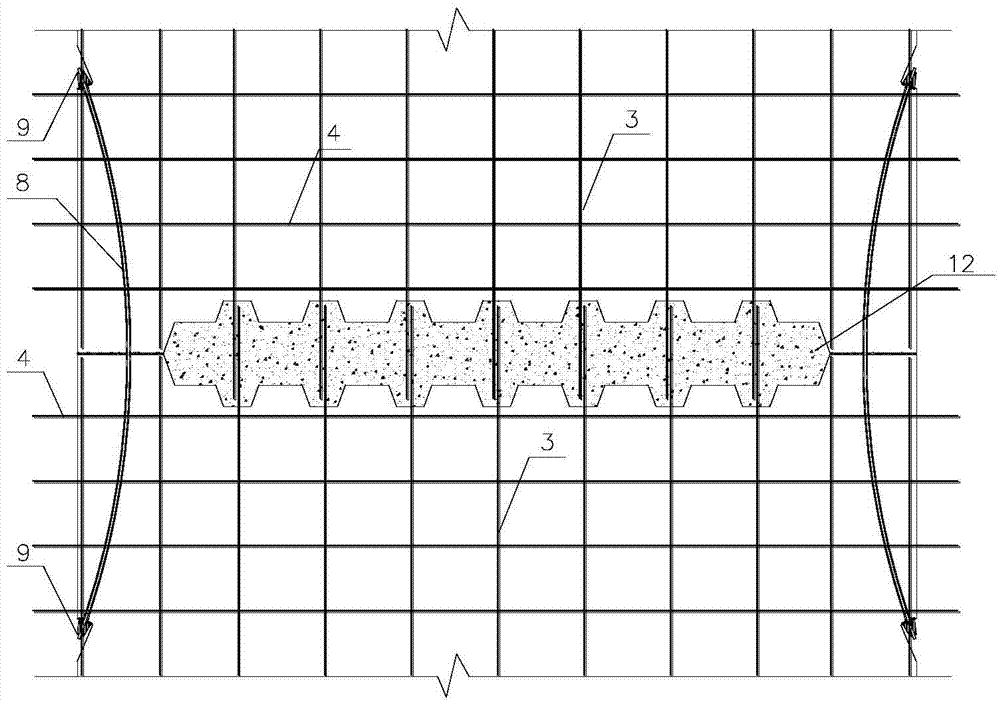

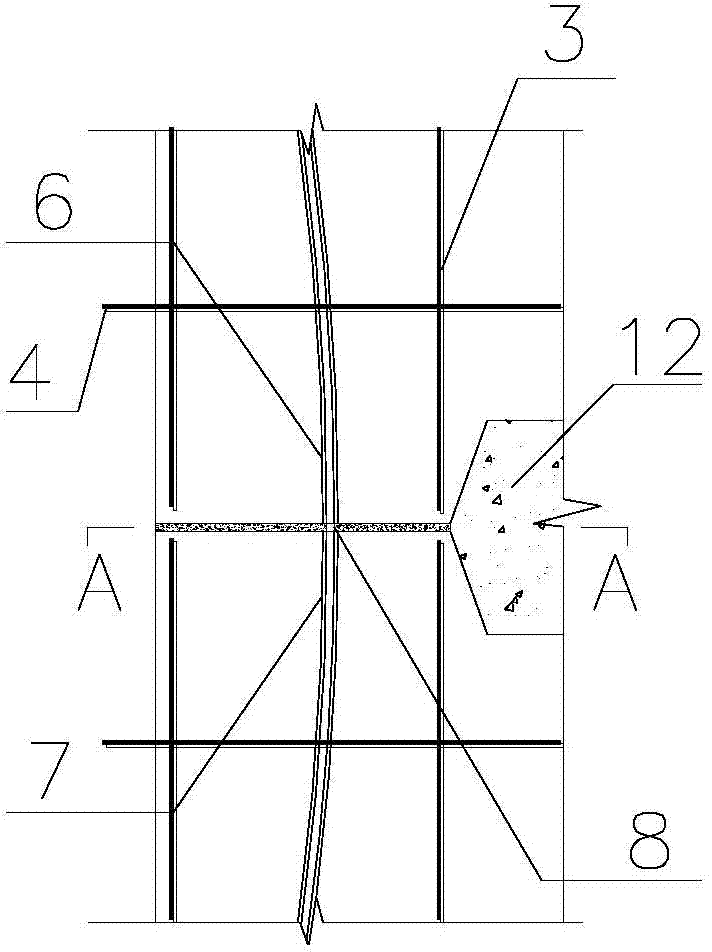

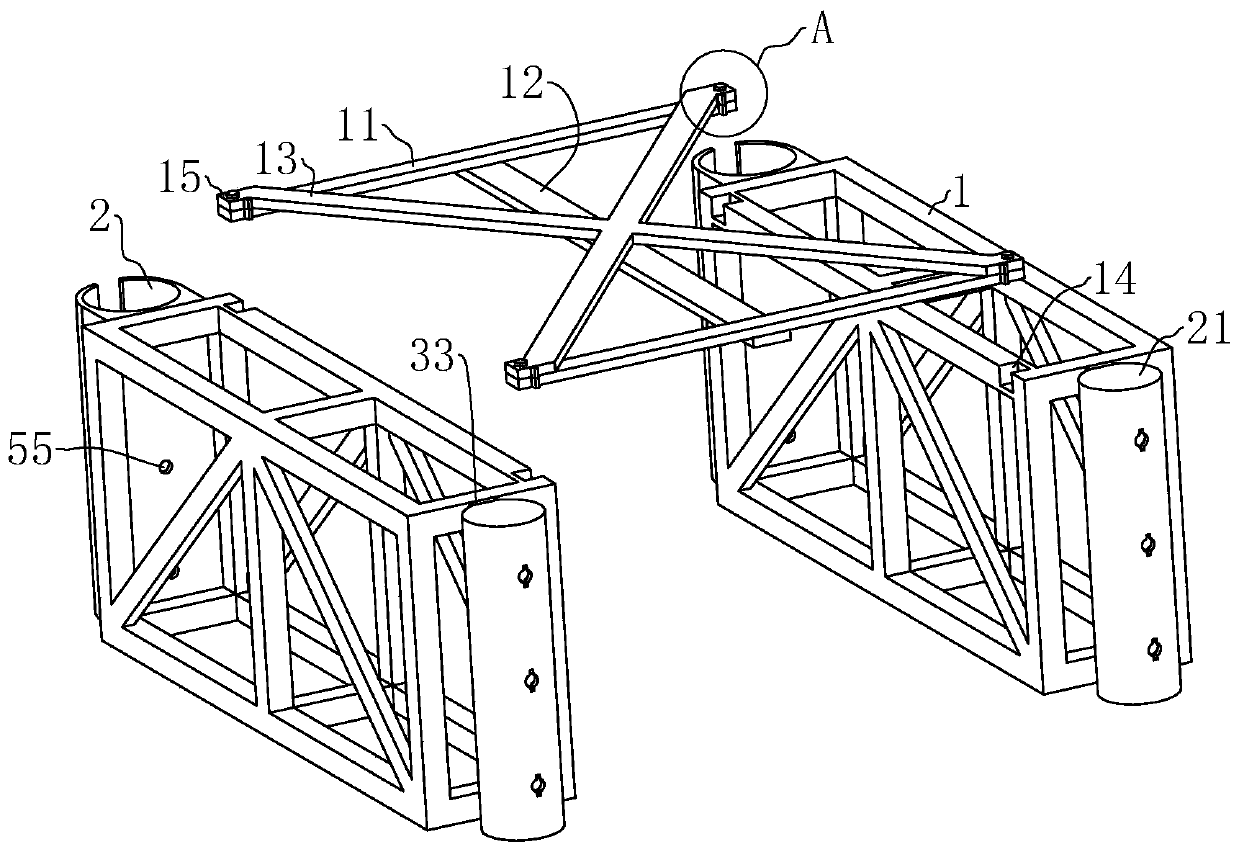

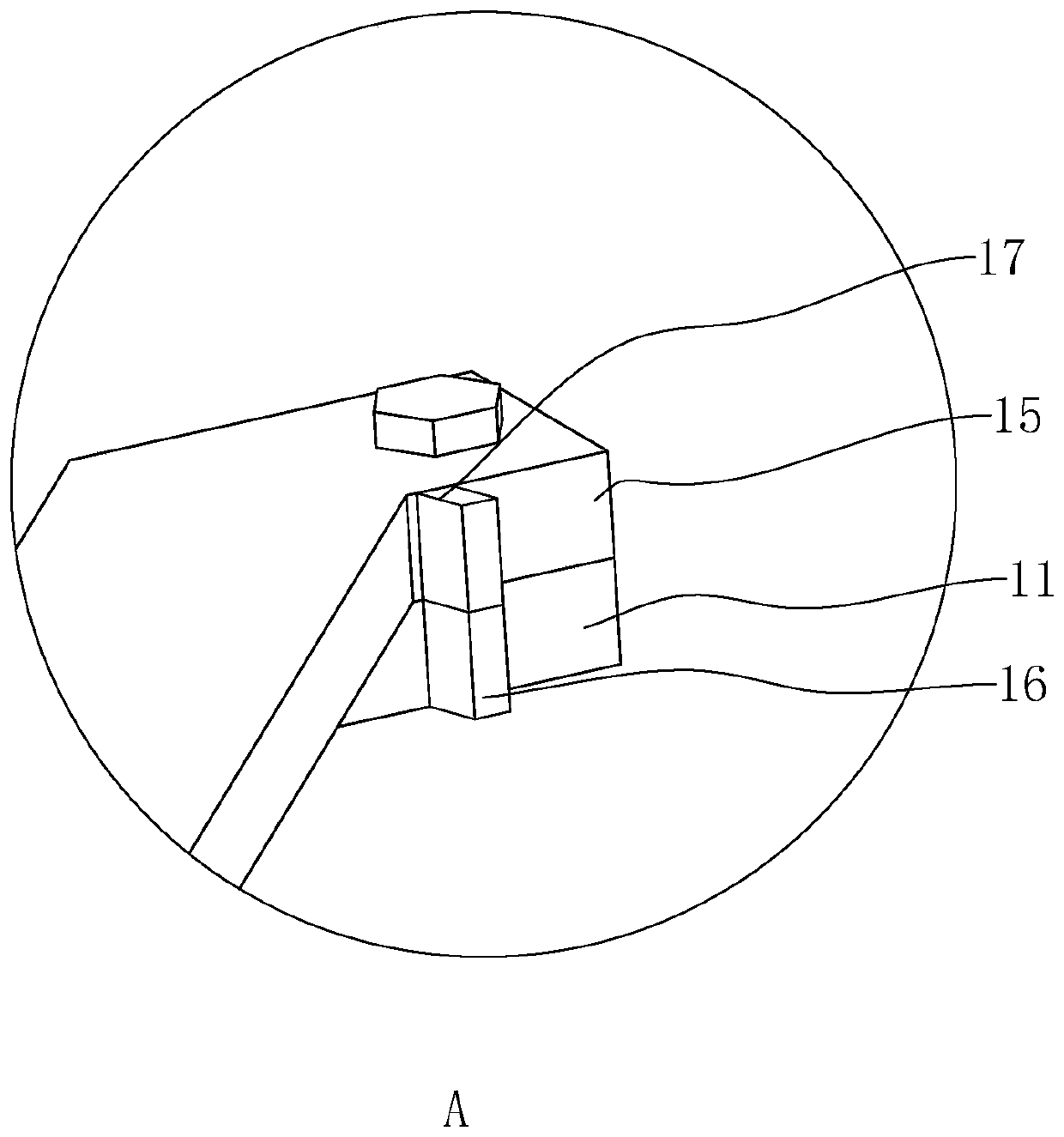

Reinforcement type prefabricated assembly type shear wall structure and construction method thereof

InactiveCN103790267AImprove bending abilityReduce load capacityWallsBuilding material handlingPre stressPre stressing

The invention discloses a reinforcement type prefabricated assembly type shear wall structure. Pre-stressed steel strands penetrate into an upper layer prefabricated wall and a lower layer prefabricated wall connected with the upper layer prefabricated wall adjacently. The invention further discloses a construction method of the reinforcement type prefabricated assembly type shear wall structure. According to the special construction process of a tooth space type connection structure of the assembly type shear wall, in the construction process of the upper layer prefabricated wall, the pre-stressed steel strands are adopted for connecting the adjacent upper layer prefabricated wall and the lower layer prefabricated wall, so that the upper layer prefabricated wall is stabilized on the lower layer prefabricated wall in the period that a concrete structure is cast, temporary supports do not need to be arranged any more, construction is convenient, performance is reliable, and the problems that the assembly type shear wall is difficult in connection construction on site and expensive in manufacturing cost are solved. Meanwhile, an existing connection structure is strengthened.

Owner:TIANJIN UNIV RES INST OF ARCHITECTRUAL DESIGN & URBAN PLANNING +1

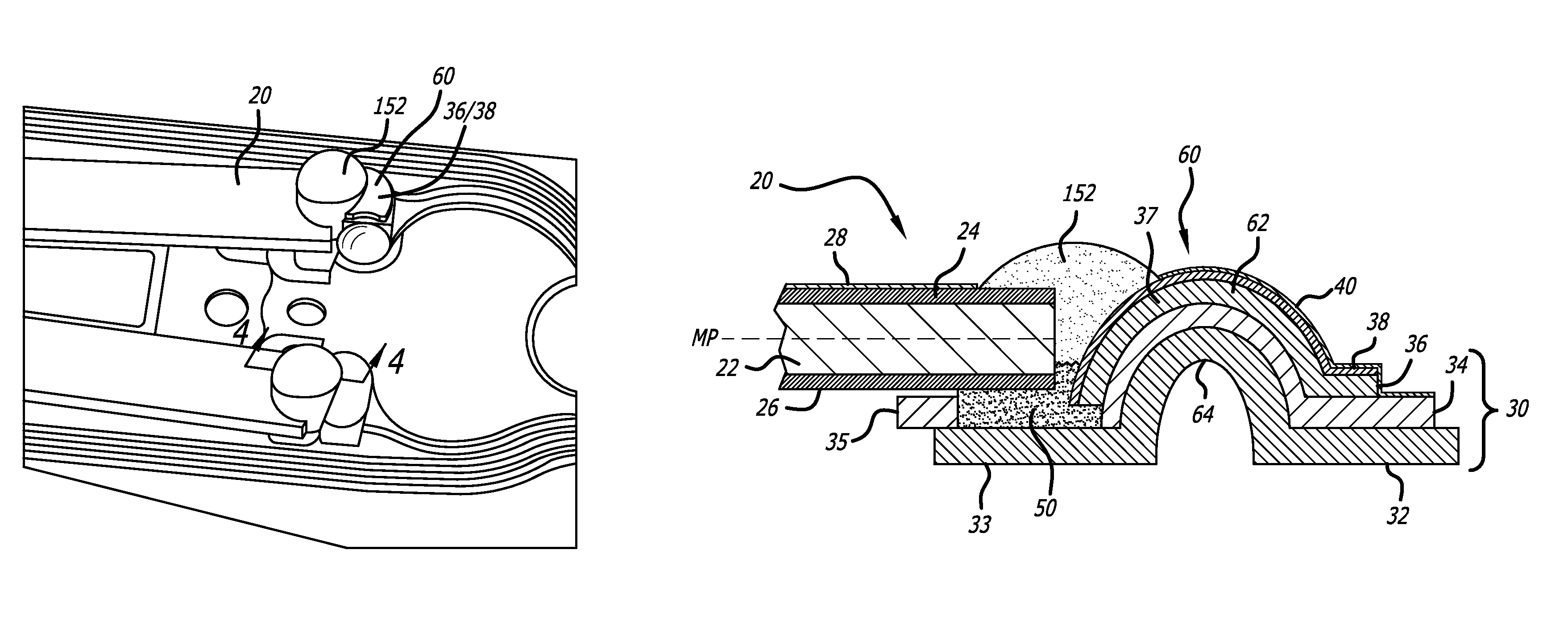

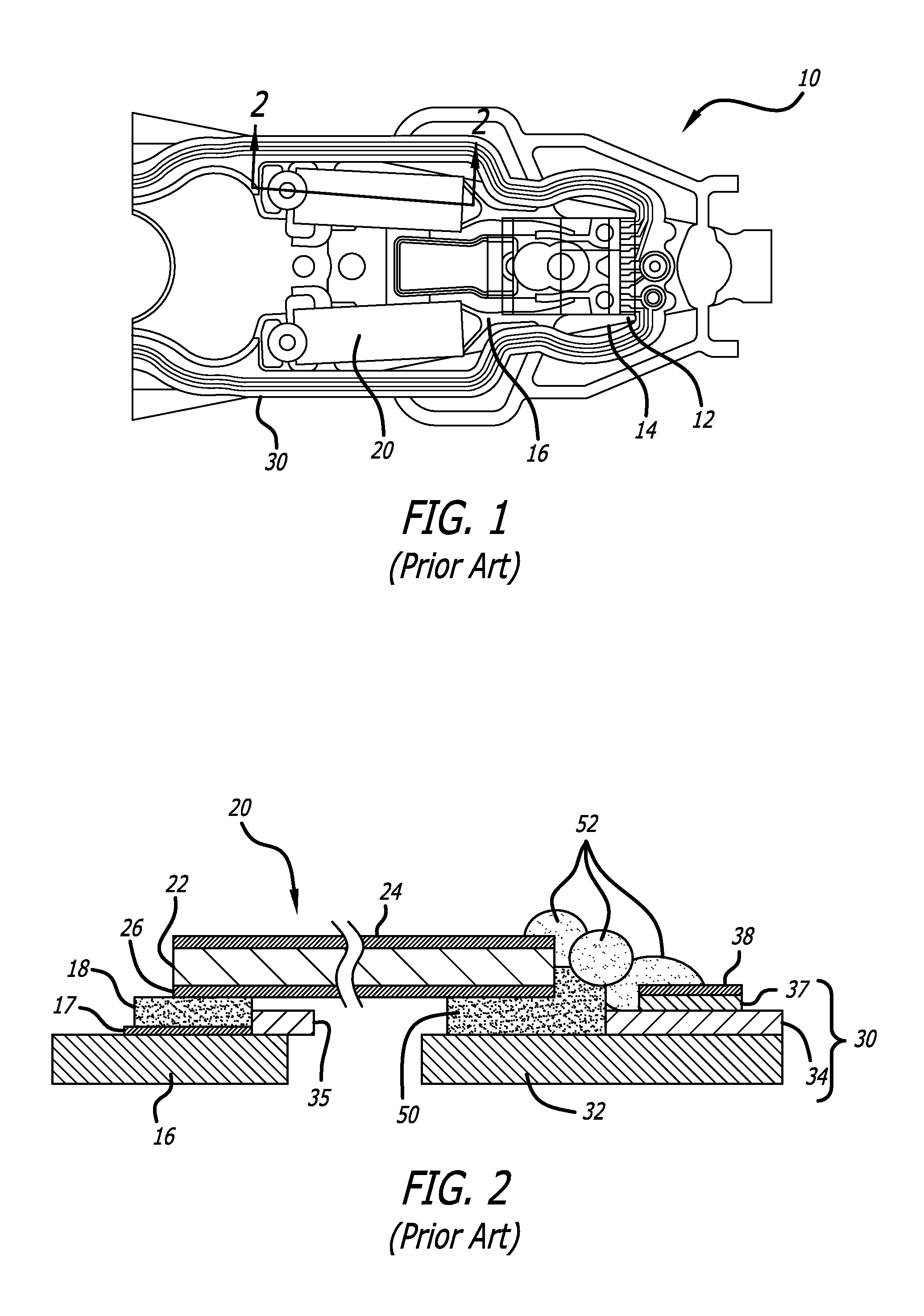

Formed electrical contact pad for use in a dual stage actuated suspension

ActiveUS9105288B1Reduce distanceImproved profileElectrical connection between head and armArm with actuatorsPiezoelectric microactuatorHard disc drive

A flexible electrical circuit such as for use in a hard disk drive dual stage actuated (DSA) suspension has a dimple or other raised feature such as a jog formed in an electrical contact pad. The dimple raises up at least part of the contact pad in height so as to reduce the distance that an electrical bridging component or material such conductive epoxy, solder paste, or jet dispensed solder must traverse in order to complete an electrical connection from the contact pad to an adjacent piezoelectric microactuator or other electrical component for which the electrical circuit carries an electrical signal or electrical power. The reduced distance improves the cleanliness and reliability of the electrical and physical bond, and can allow for electrical connection types that would otherwise be impractical.

Owner:MAGNECOMP

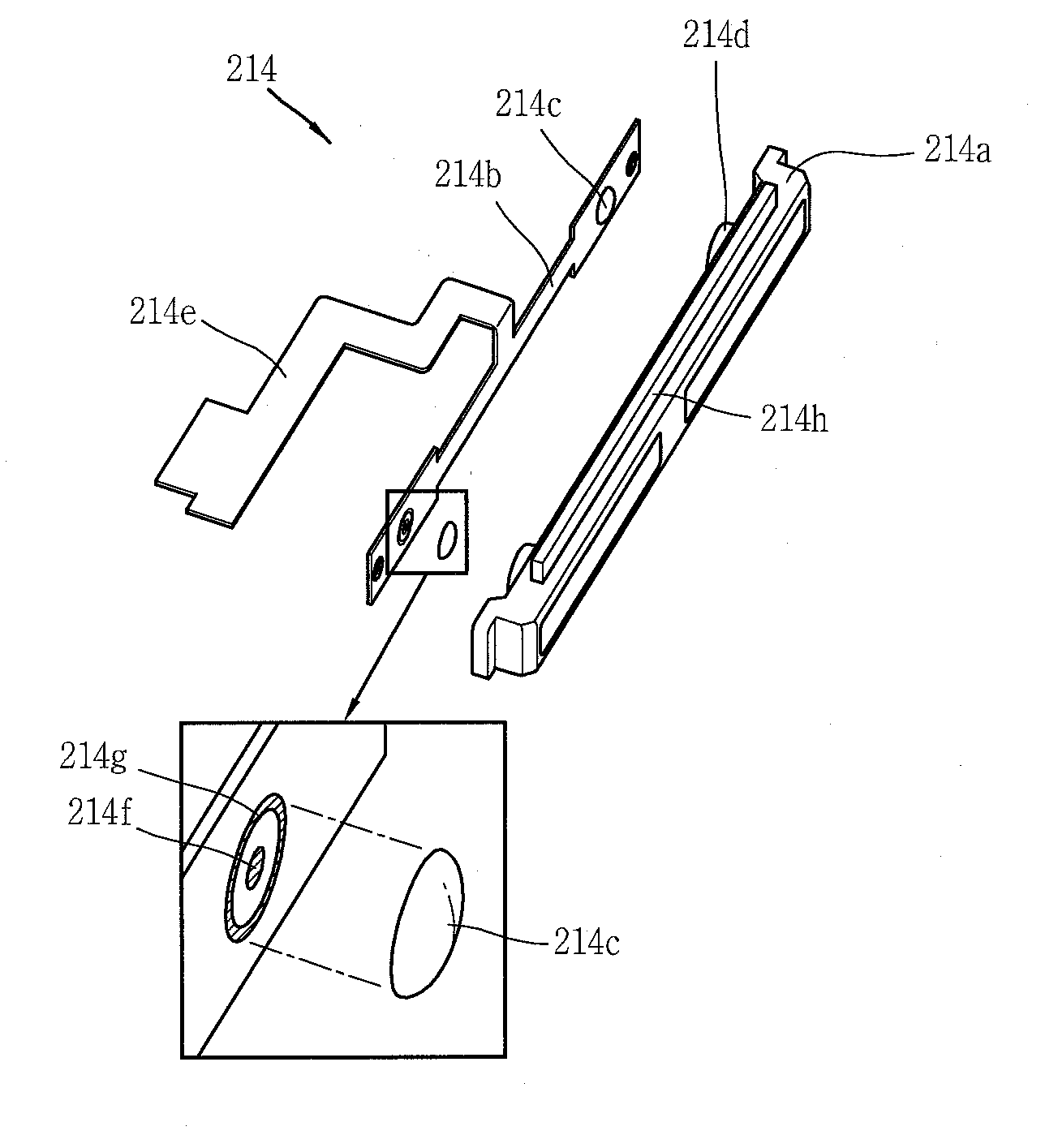

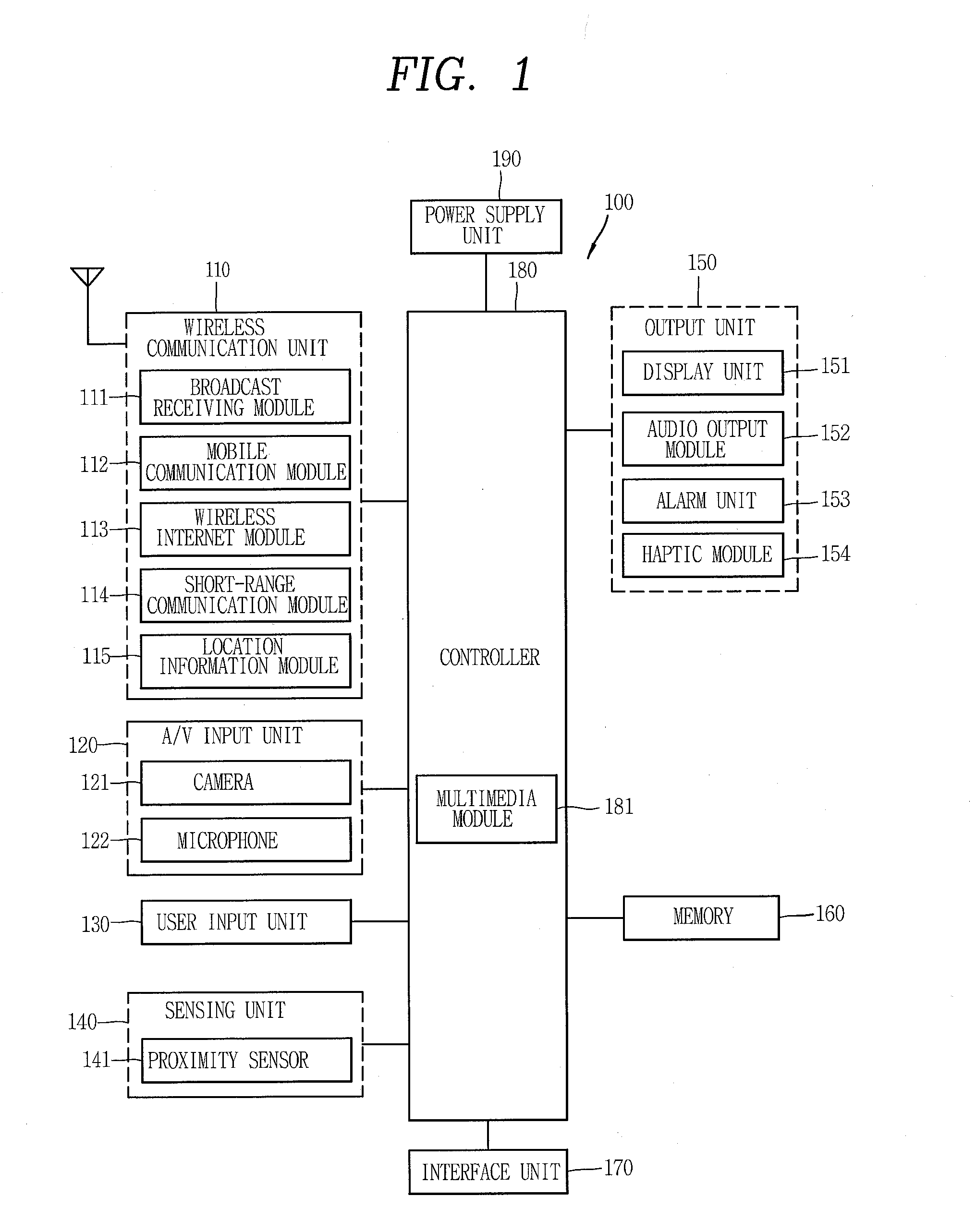

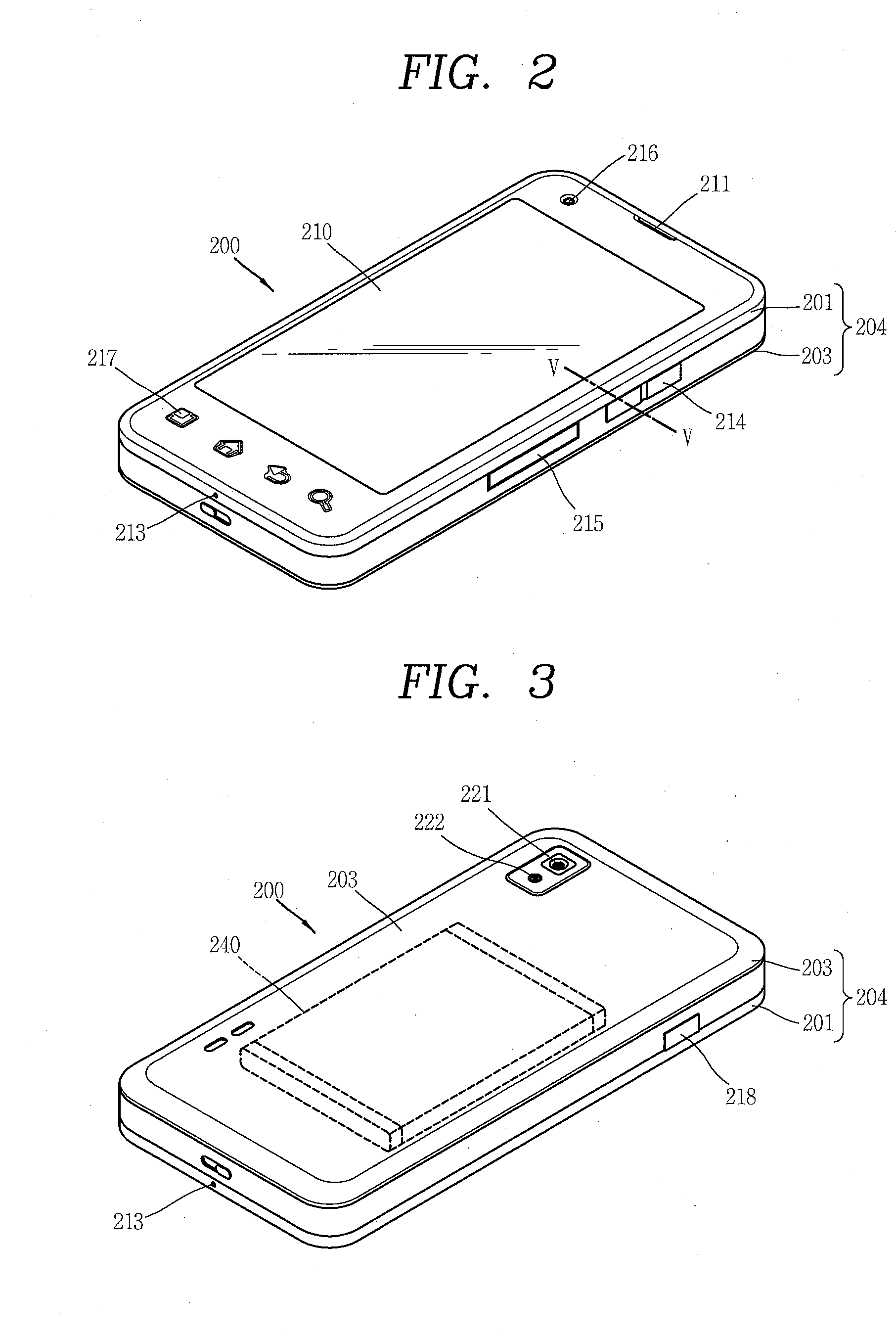

Connection module and mobile terminal having the same

InactiveUS20140302705A1Strengthen the connection structureEmergency casingsElectric discharge tubesEngineeringElectrical and Electronics engineering

Owner:LG ELECTRONICS INC

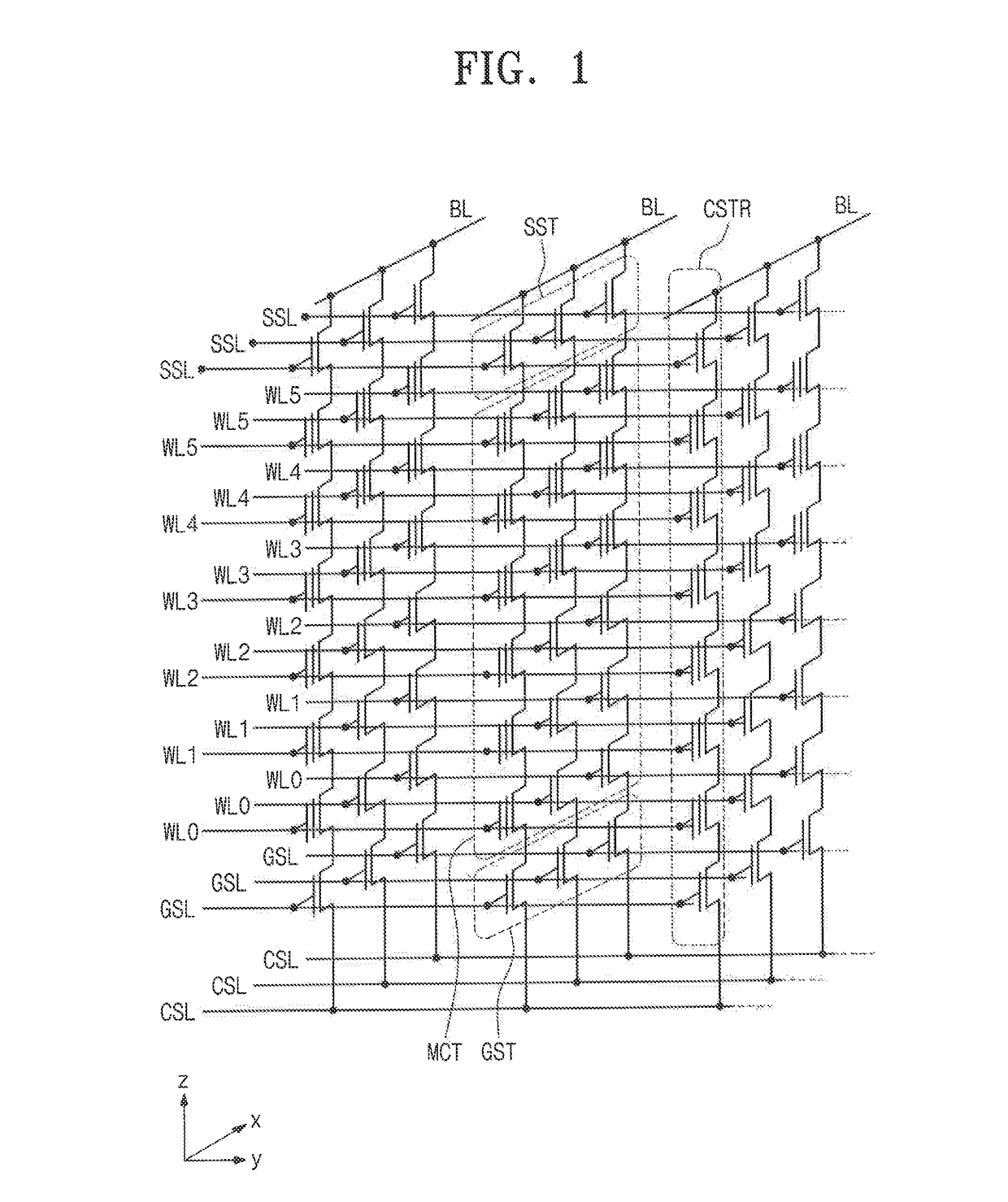

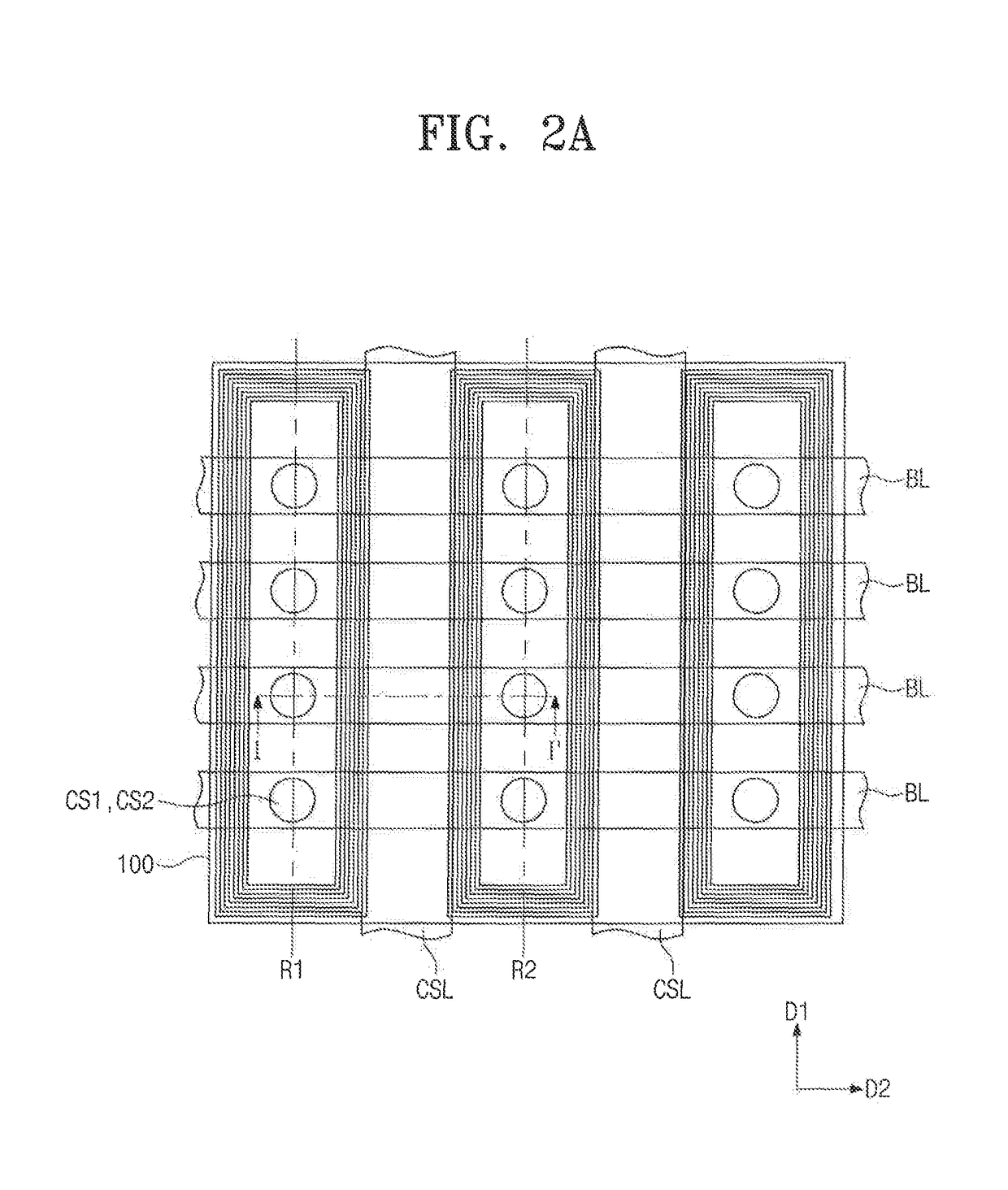

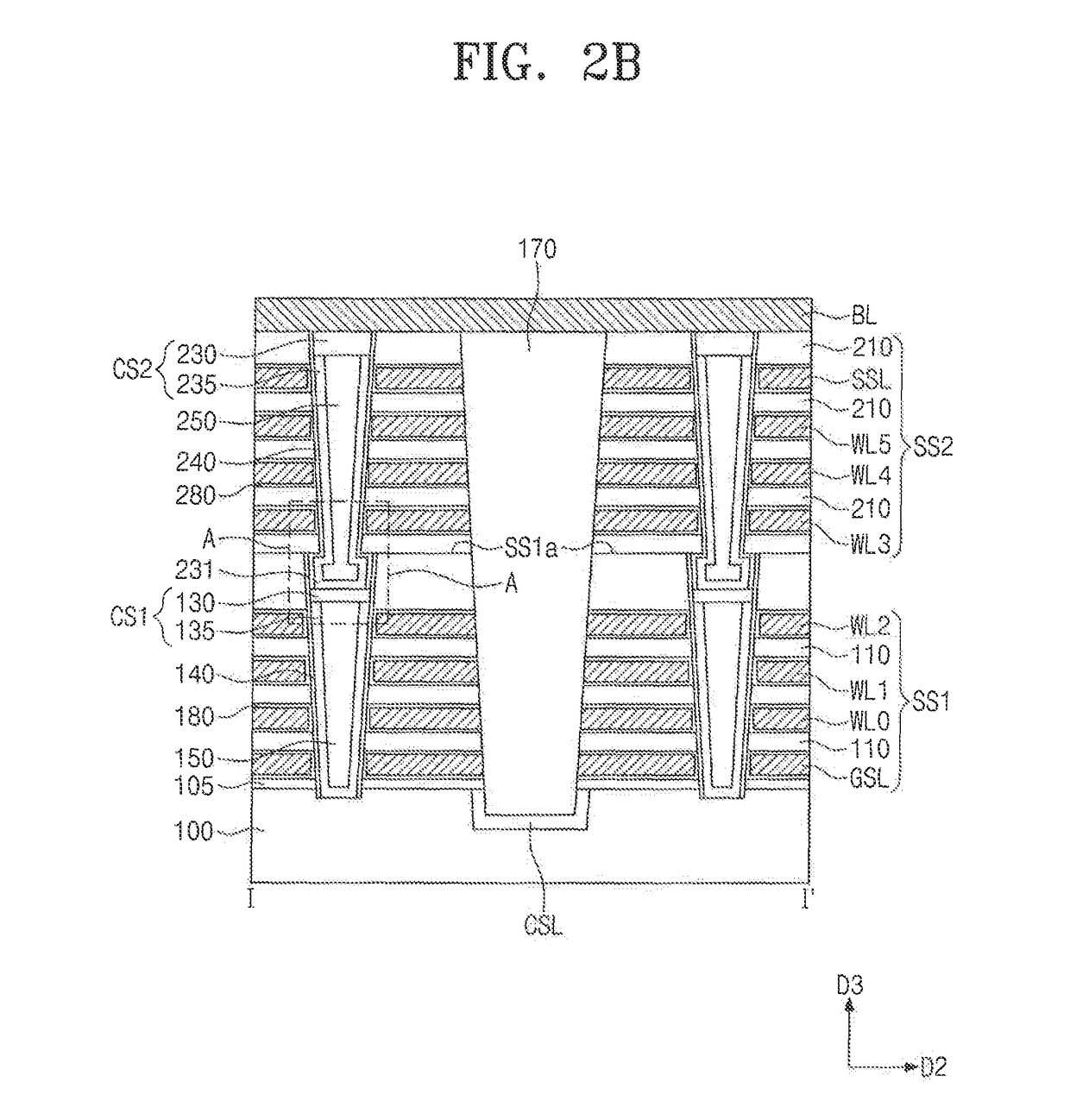

Semiconductor device and method of manufacturing the semiconductor device

ActiveUS10229927B2Strengthen the connection structureSimple manufacturing processSolid-state devicesSemiconductor devicesDevice materialEngineering

A semiconductor device includes a lower stack structure including lower gate electrodes and lower insulating layers that are alternately and repeatedly stacked on a substrate. The semiconductor device includes an upper stack structure including upper gate electrodes and upper insulating layers that are alternately and repeatedly stacked on the lower stack structure. A lower channel structure penetrates the lower stack structure. An upper channel structure penetrates and is connected to the upper stack structure. A lower vertical insulator is disposed between the lower stack structure and the lower channel structure. The lower channel structure includes a first vertical semiconductor pattern connected to the substrate, and a first connecting semiconductor pattern disposed on the first vertical semiconductor pattern. The upper channel structure includes a second vertical semiconductor pattern electrically connected to the first vertical semiconductor pattern with the first connecting semiconductor pattern disposed therebetween.

Owner:SAMSUNG ELECTRONICS CO LTD

Secondary battery and a secondary battery module using the same

InactiveUS7614906B2Electric conductivity and current collecting efficiencyMaximize contact areaLarge-sized flat cells/batteriesCurrent conducting connectionsEngineeringFlange

A secondary battery module includes a connector, which electrically connects a first unit battery to an adjacent unit battery. The connector is connected to the first battery through a connecting member, which is connected to a terminal of the first battery. The connecting member has external threads and a flange on which the connector is positioned. The connector is also fitted to the connecting member and fixed thereto through a nut, which is joined with the external threads of the connecting member.

Owner:SAMSUNG SDI CO LTD

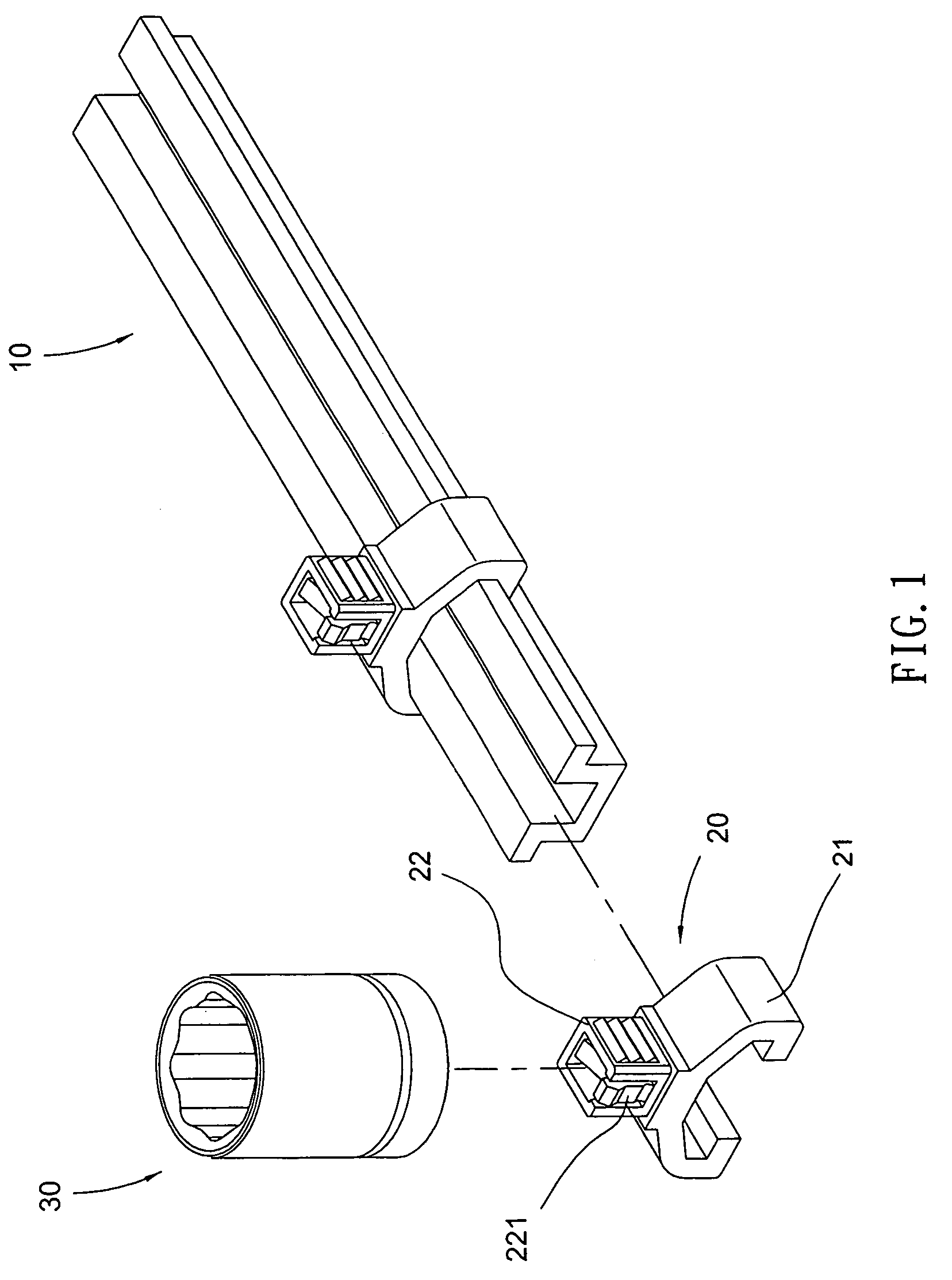

Socket connecting structure

InactiveUS7118406B2Strengthen the connection structureExtended service lifeCoupling device detailsContact members penetrating/cutting insulation/cable strandsMechanical engineeringEngineering

Owner:DANAHER TOOL TAIWAN BRANCH

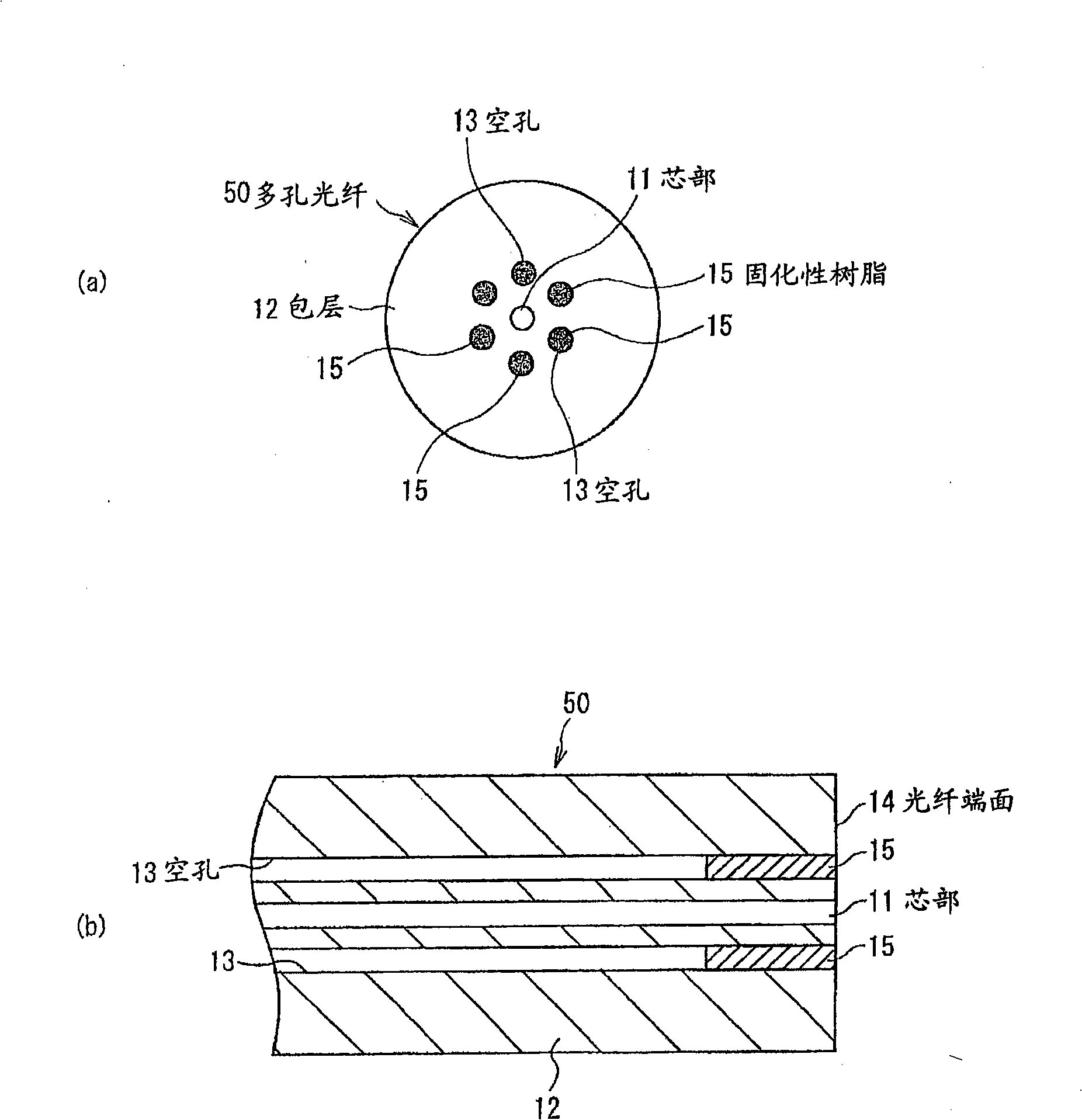

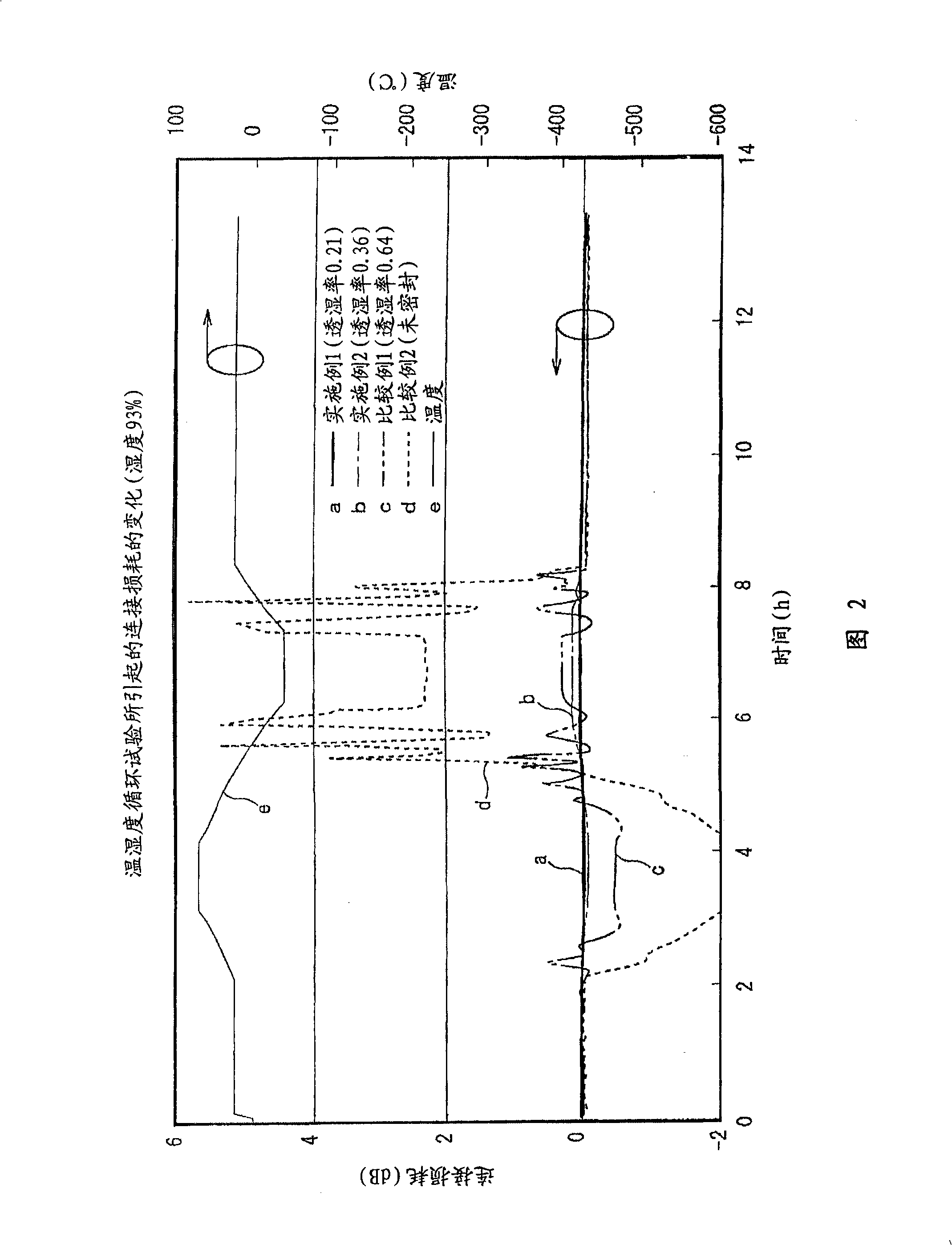

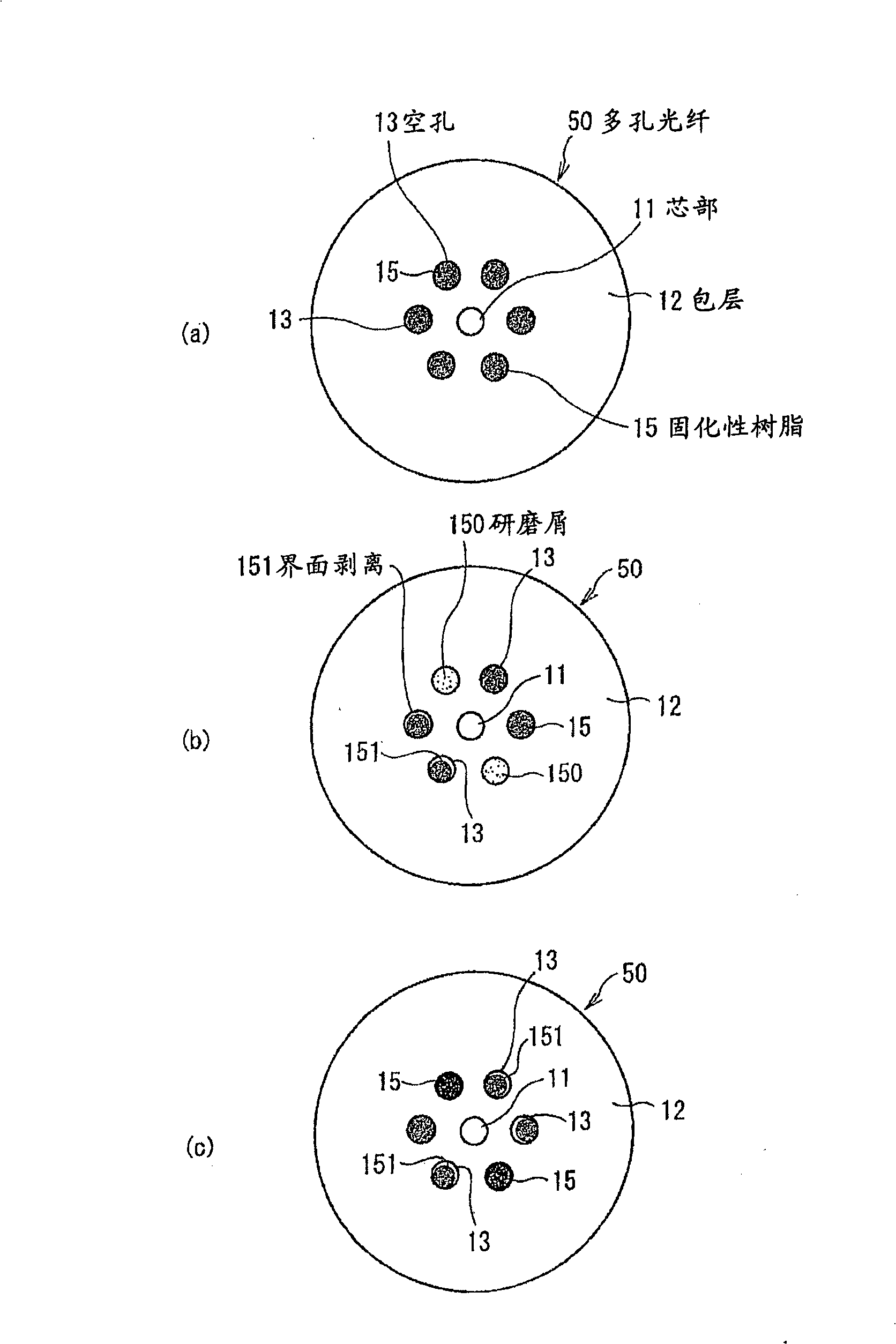

Optical fiber, sealing method for optical fiber end face, connection structure of optical fiber, and optical connector

InactiveCN101311757AImproved face sealing methodStrengthen the connection structureCladded optical fibreCoupling light guidesRefractive indexMoisture permeability

The invention provides an optical fiber with high reliability, sealing method for optical fiber end face, connection structure of optical fiber, and optical connector. The porus optical fiber (50) of the invention is formed by a solid core (11), a clad (12) formed around the core (11), a plurality of holes (13) being formed in the clad with refractive index being 1, and a hardening resin (15) filled in the holes (13) of the optical fiber end face (14). The hardening resin (15) if filled around the optical fiber end face (14) of the plurality of holes (13) and is hardened; the hardening resin (15) having a moisture permeability equal to or less than 0.5 g / cm2.24 hr, or the bonding strength with the glass is 5MPa and the hardness after hardening is the character over 50 expressing by Shore D hardness.

Owner:HITACHI CABLE

Multilayer capacitor

ActiveUS7675733B2Strengthen the connection structureFixed capacitor electrodesFixed capacitor dielectricElectrical conductorElectrical polarity

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com