Patents

Literature

182results about "Generator generated ignition energy" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Multiple operating mode engine and method of operation

InactiveUS6907870B2Easy to operateOvercome deficienciesValve arrangementsElectrical controlControl systemFuel efficiency

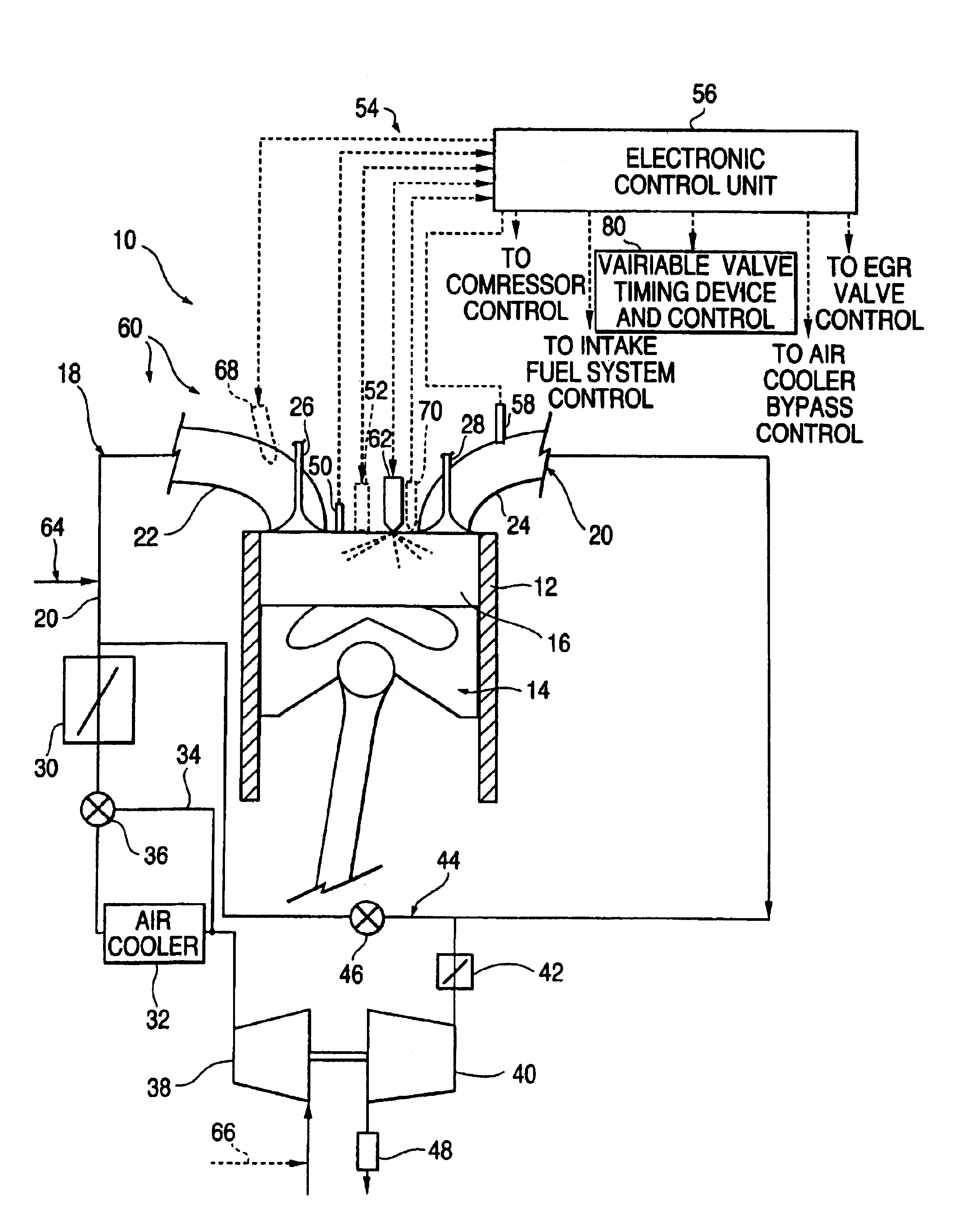

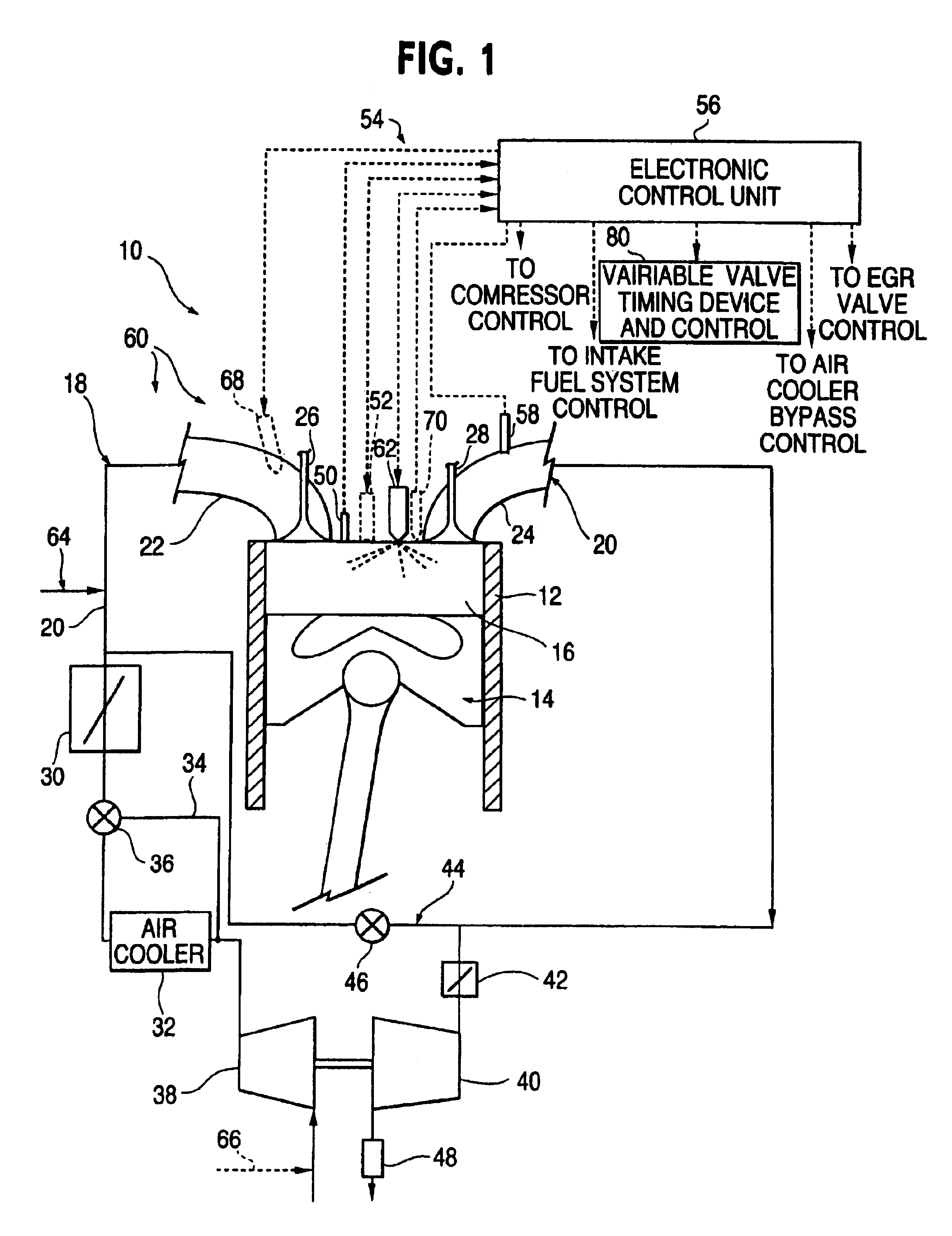

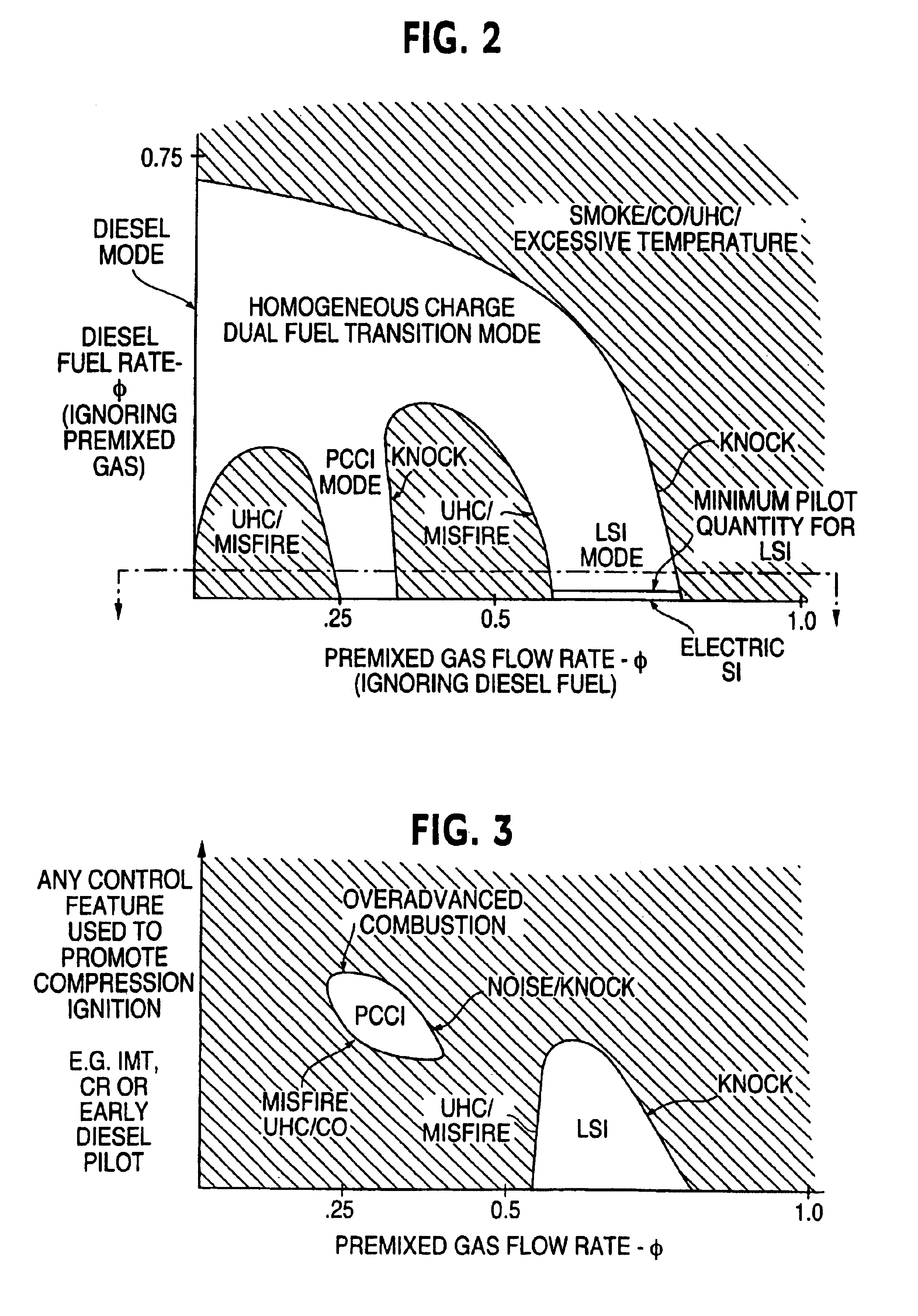

A multi-mode internal combustion engine and method of operating the engine is provided which is capable of operating in a variety of modes based on engine operating conditions to enhance fuel efficiency and reduce emissions. The multi-mode engine include a fuel delivery system and control system for permitting the engine to operate in a diesel mode, a homogeneous charge dual fuel transition mode, a spark ignition or liquid spark ignition mode and / or a premixed charge compression ignition mode. The control system and method permits the engine operation to transfer between the various modes in an effective and efficient manner by controlling one or more fuel delivery devices or other engine components so as to move along a continuous transfer path while maintaining engine torque at a substantially constant level.

Owner:CUMMINS INC

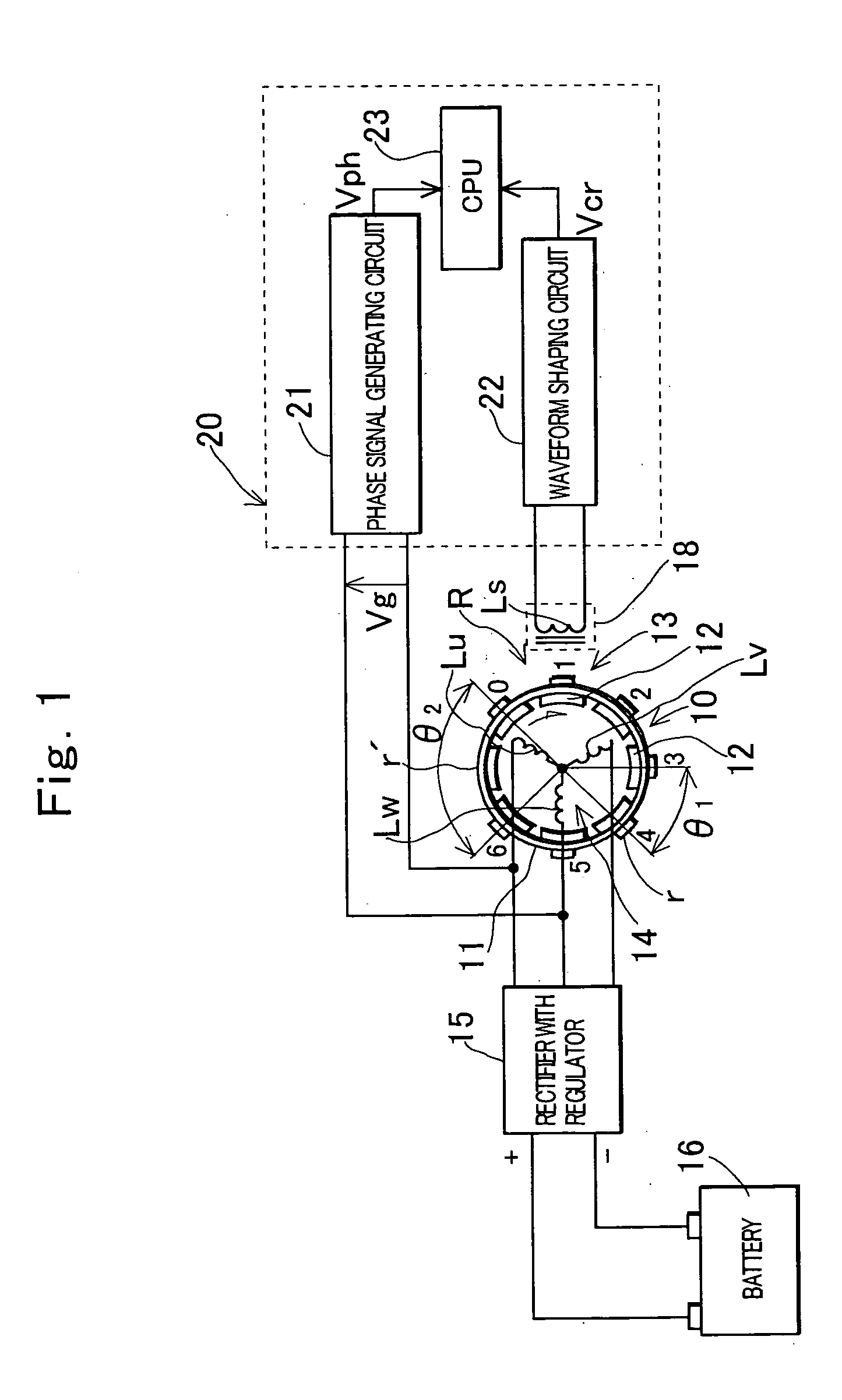

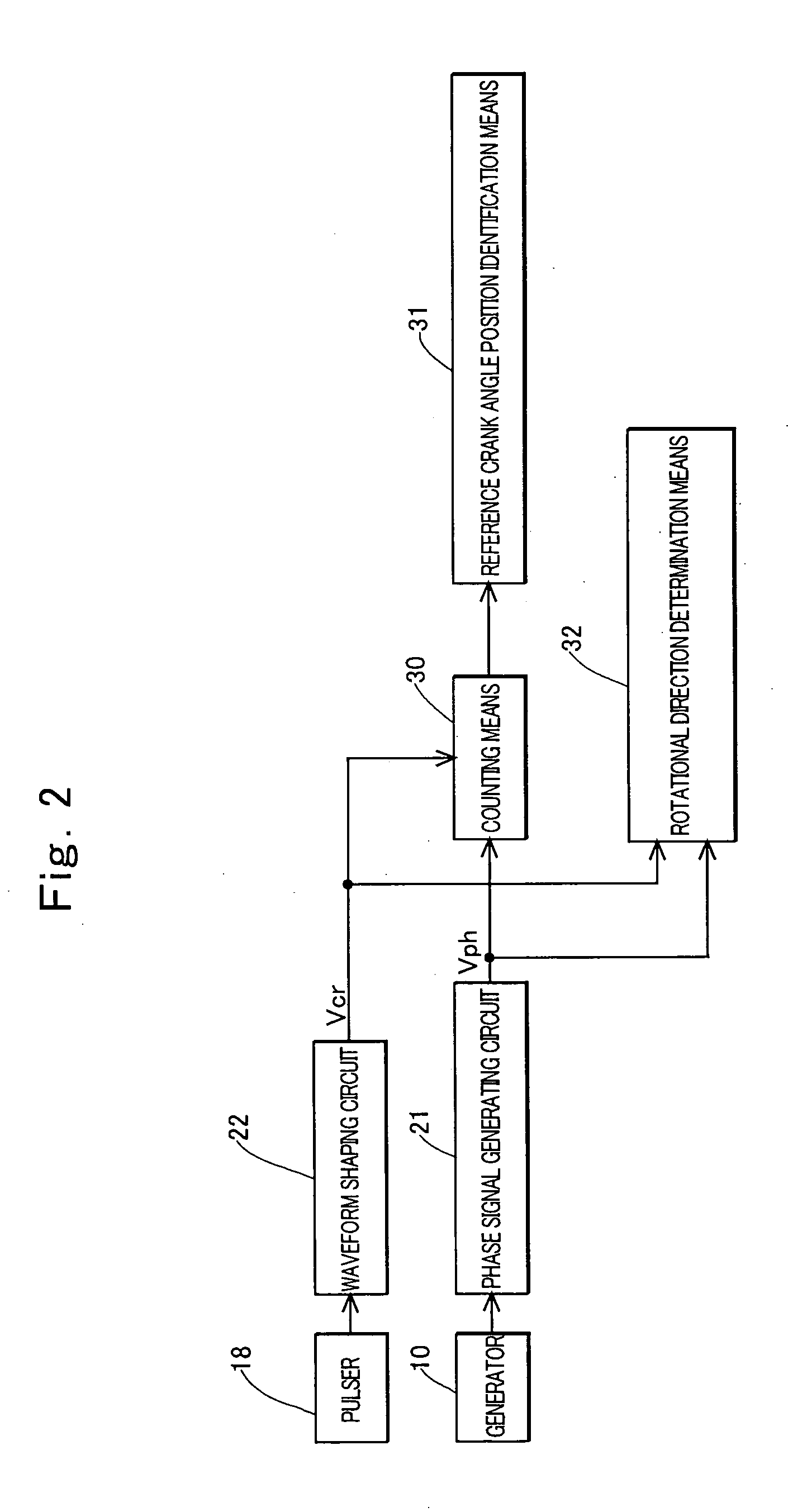

Engine rotation information detection device

ActiveUS20050120782A1Prevent reversalEasy to controlElectrical controlEngine testingEngineeringSignal generator

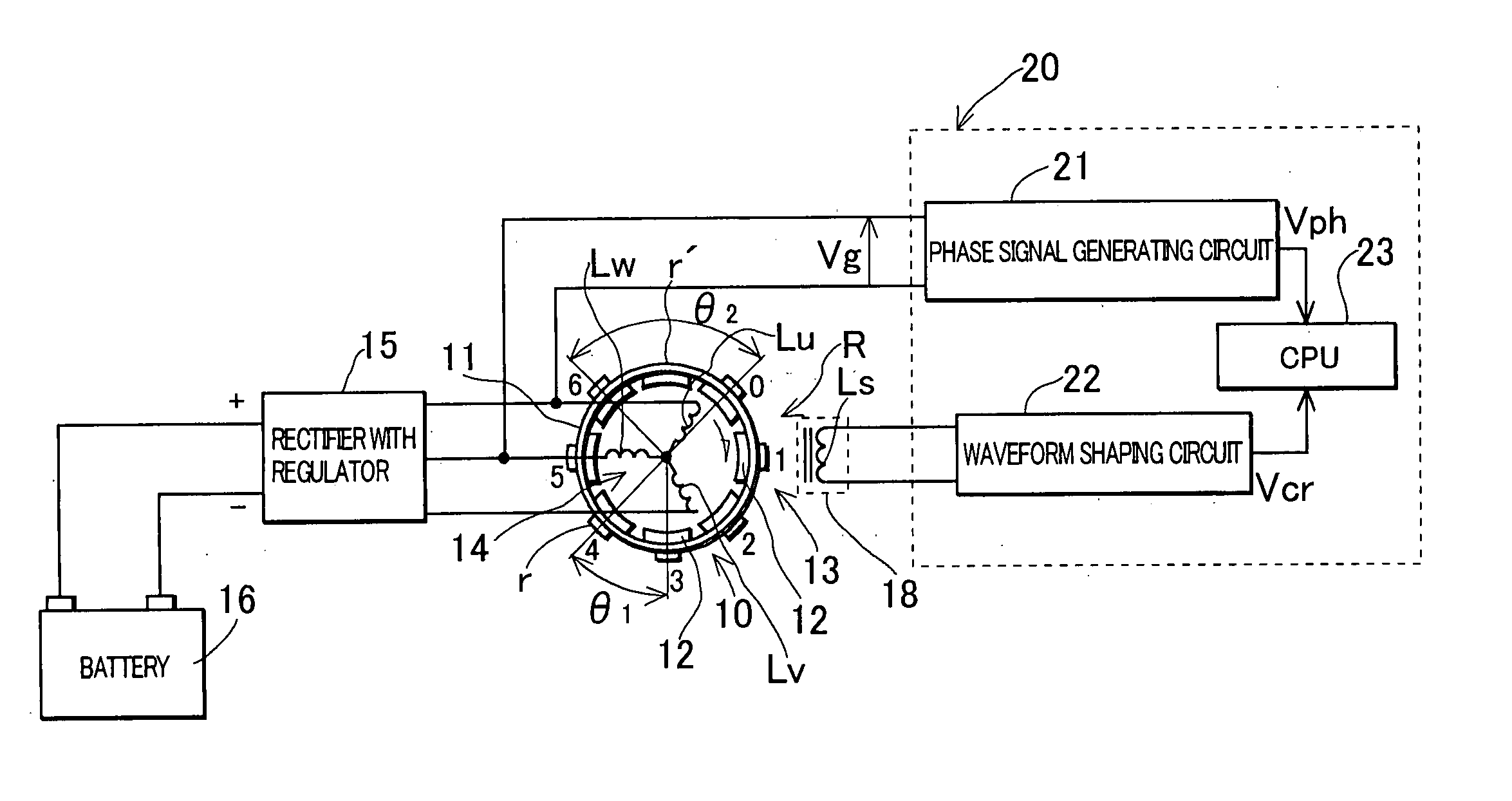

An engine rotation information detection device including: a generator that rotates in synchronization with an engine to output an AC voltage; a pulse signal generator that detects reluctors of a rotor having many reluctors and one reluctor missing portion to generate a pulse; counting means that counts the number of detections of a zero point of a waveform of the AC voltage in each detection section, the detection section being a section between a crank angle position where the pulse signal generator detects an edge of each reluctor and a crank angle position where the pulse signal generator detects a next reluctor; and reference crank angle position identification means that specifies a detection section including the reluctor missing portion from a count value counted by the counting means and identifies a pulse generated at a reference crank angle position based on the specified detection section.

Owner:MAHLE INT GMBH

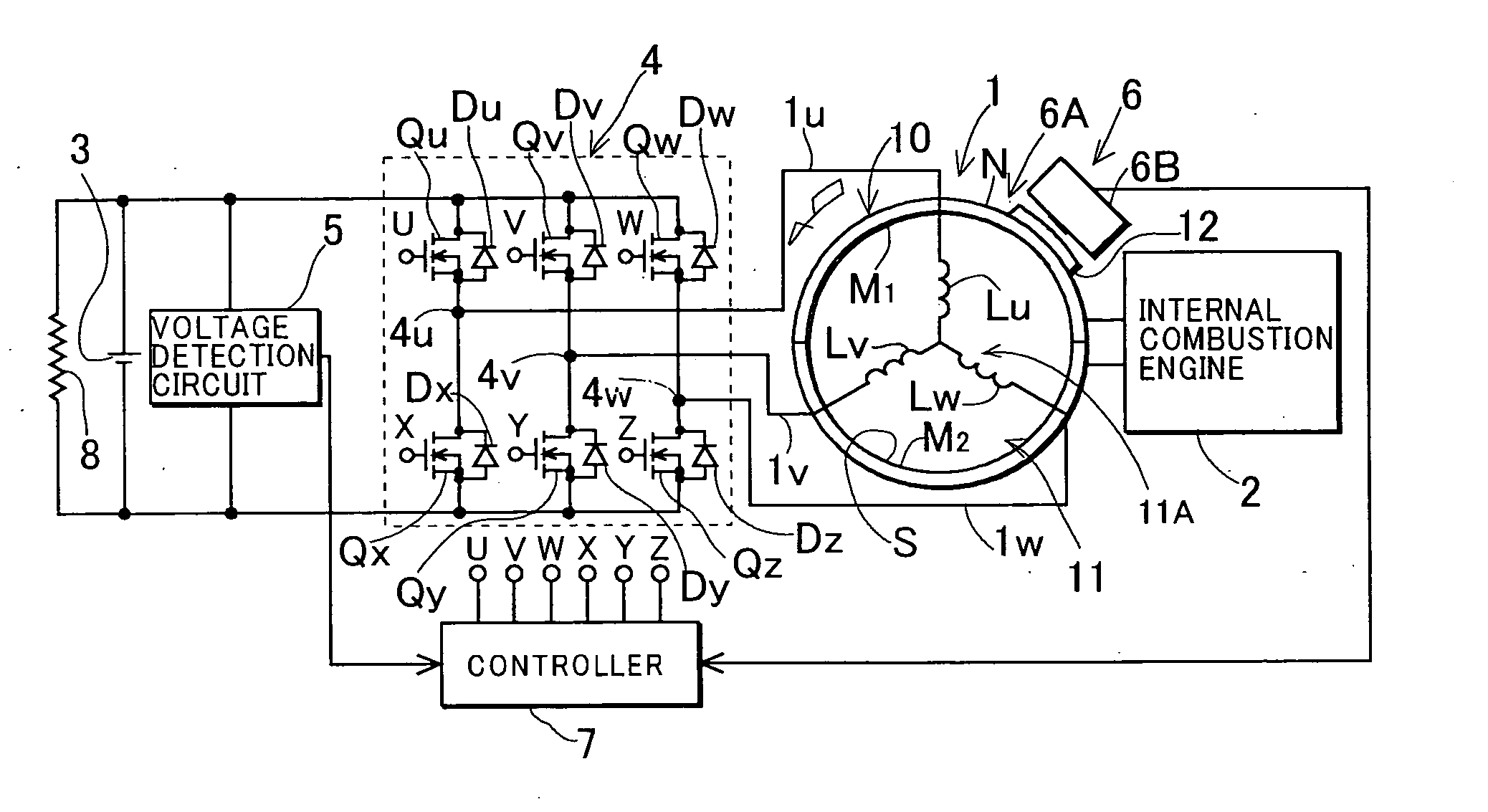

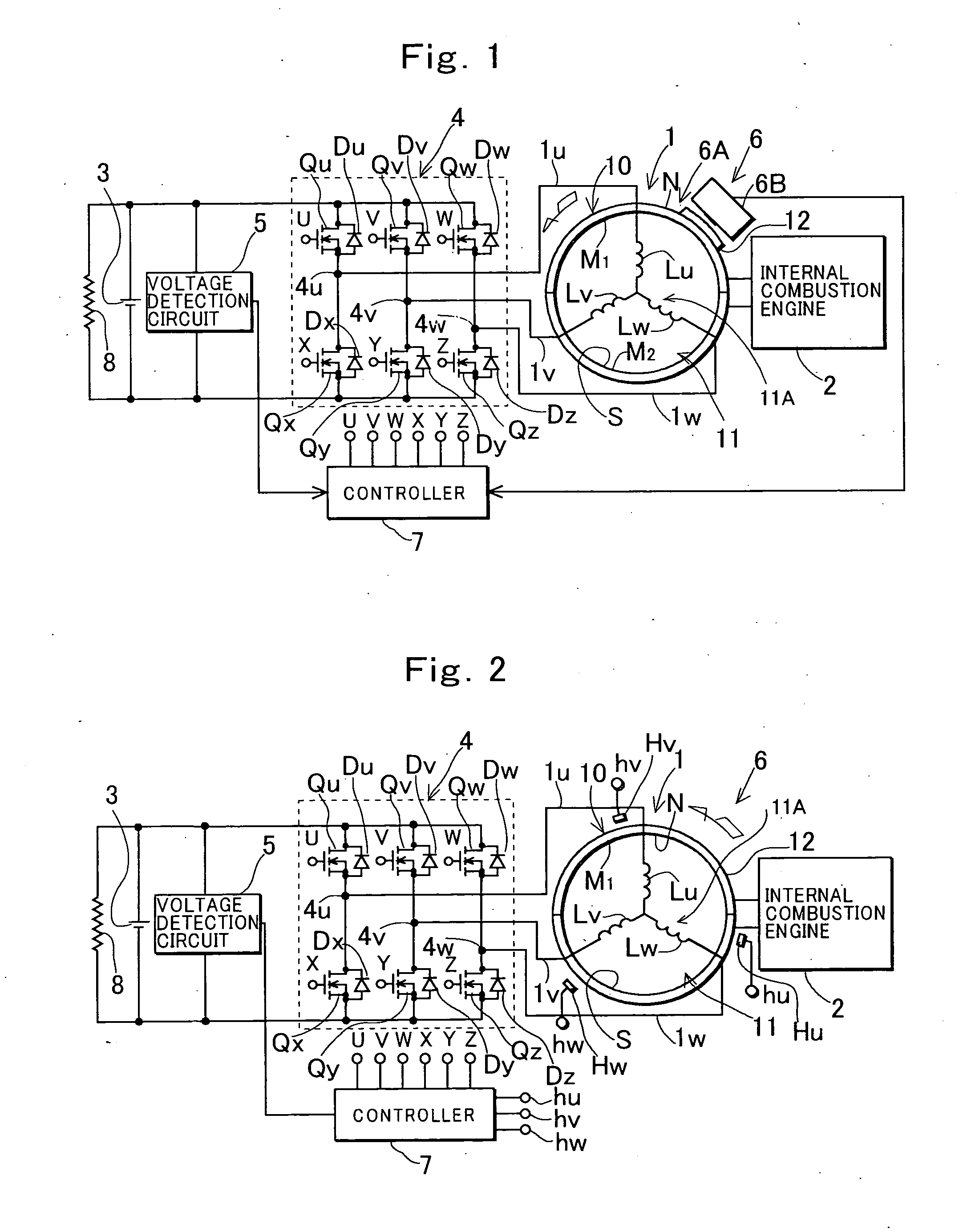

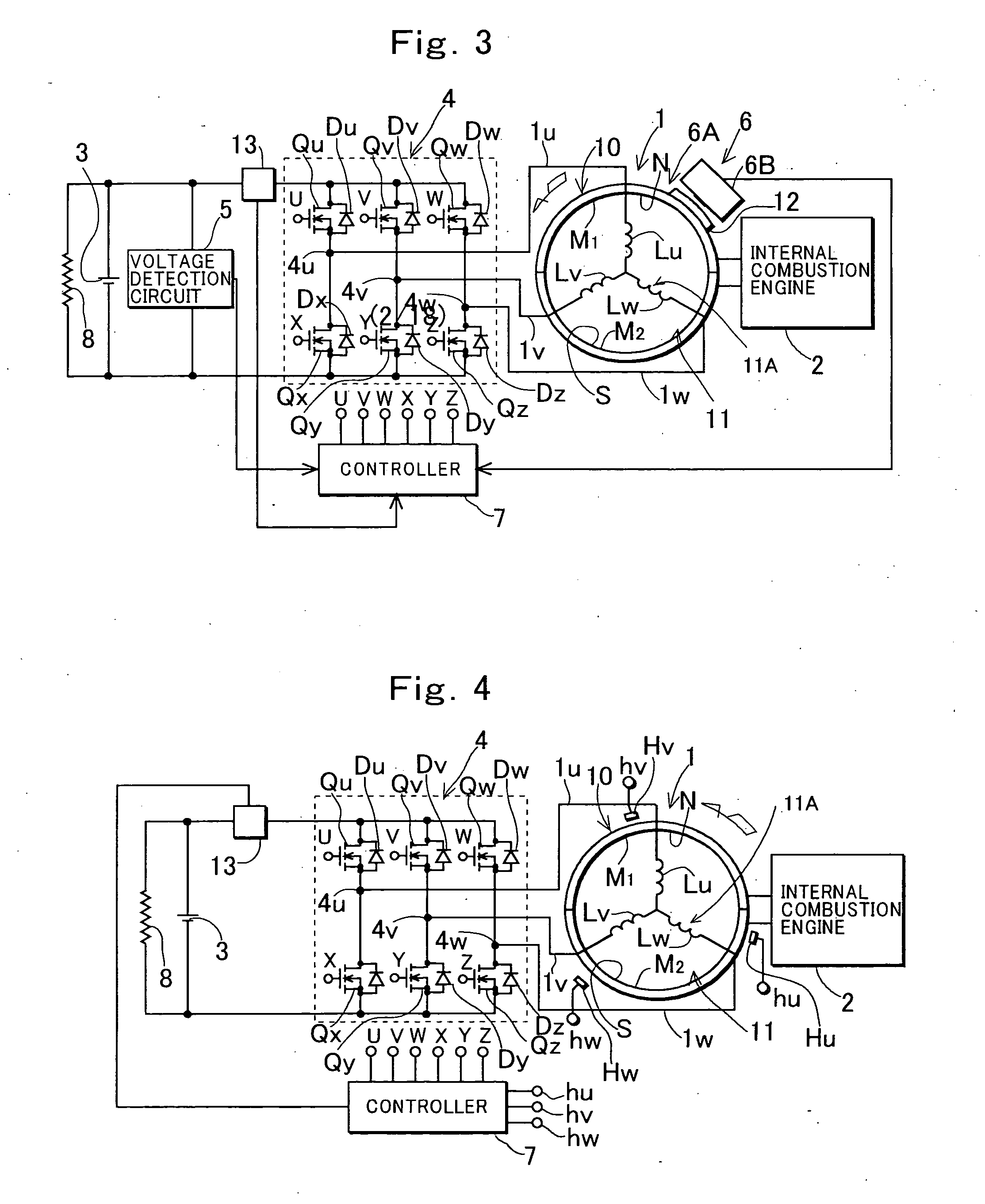

Generating device having magneto generator

ActiveUS20050093520A1Increase in sizeIncrease productionAssociation with control/drive circuitsConversion with intermediate conversion to dcEngineeringControl switch

A generating device that includes an AC / DC conversion unit having a rectifier circuit that rectifies an output of a magneto rotor and applies the output to a battery, and an inverter circuit that converts a voltage of the battery into an AC control voltage and applies the AC control voltage to an armature coil of the magneto generator, performs chopper control that controls switch elements of the inverter circuit so as to interrupt an output current of the magneto generator to control the output of the magneto generator when a rotational speed of the magneto generator is lower than a set speed, and performs drive control that applies the AC control voltage from the battery through the inverter circuit to the armature coil when the rotational speed becomes higher than the set speed, and changes a phase angle of the AC control voltage to control the output of the magneto generator.

Owner:MAHLE INT GMBH

Charged air intake system for an internal combustion engine

InactiveUS6868840B2Increase air densityNon-fuel substance addition to fuelInternal combustion piston enginesDiesel engineExhaust manifold

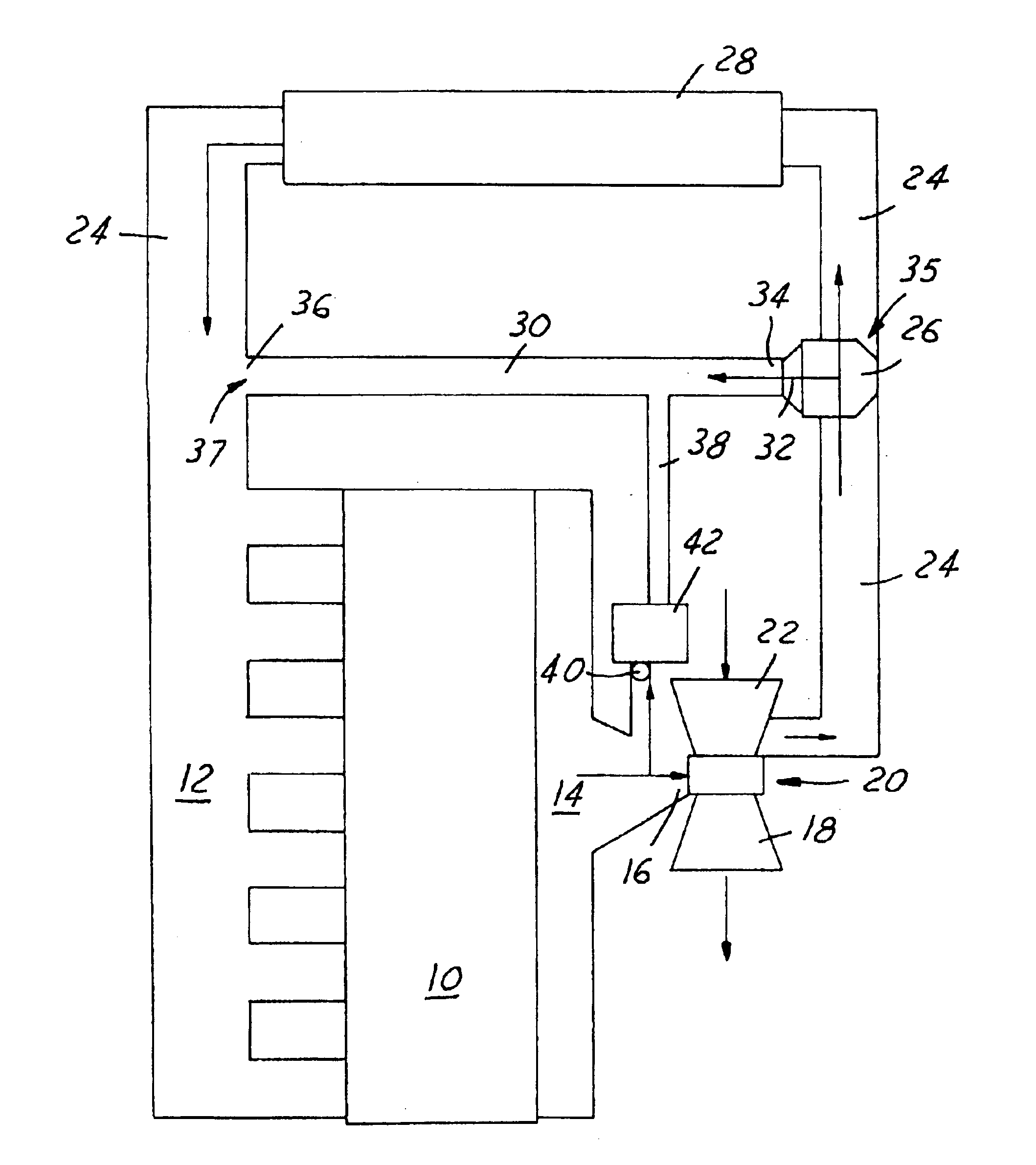

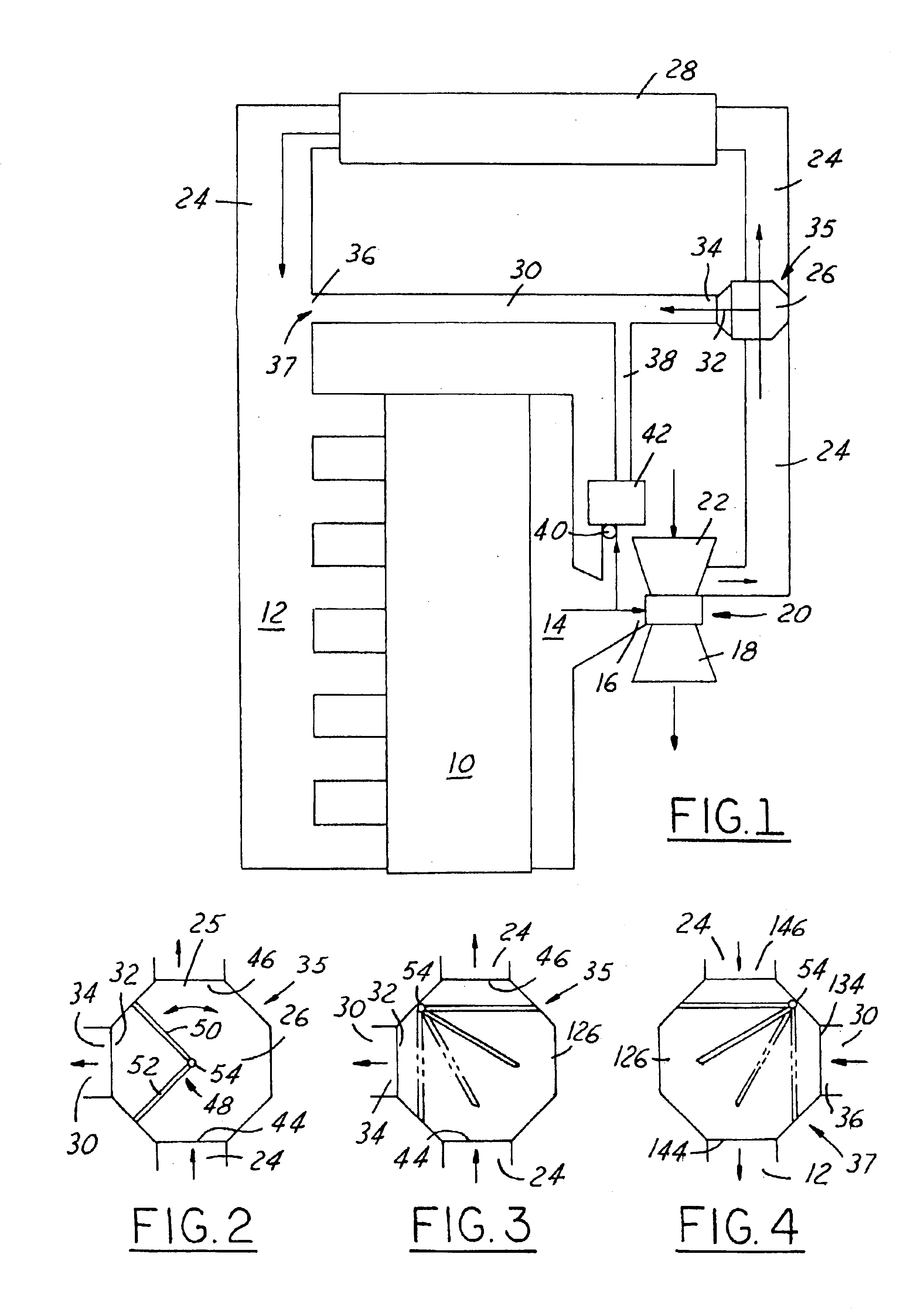

A charge air intake system for a diesel engine (10) includes a first duct (24) and second bypass duct (30) having its upstream and downstream ends connected to the first duct and bypassing a charge air cooler (28) mounted in line with the first duct (24). An EGR conduit (38) leads from the exhaust manifold to the bypass duct (30). A turbo charger furnished charged air to the ducts where a proportioning valve (26) proportions air between the charge air cooler and the bypass duct.

Owner:DETROIT DIESEL CORP

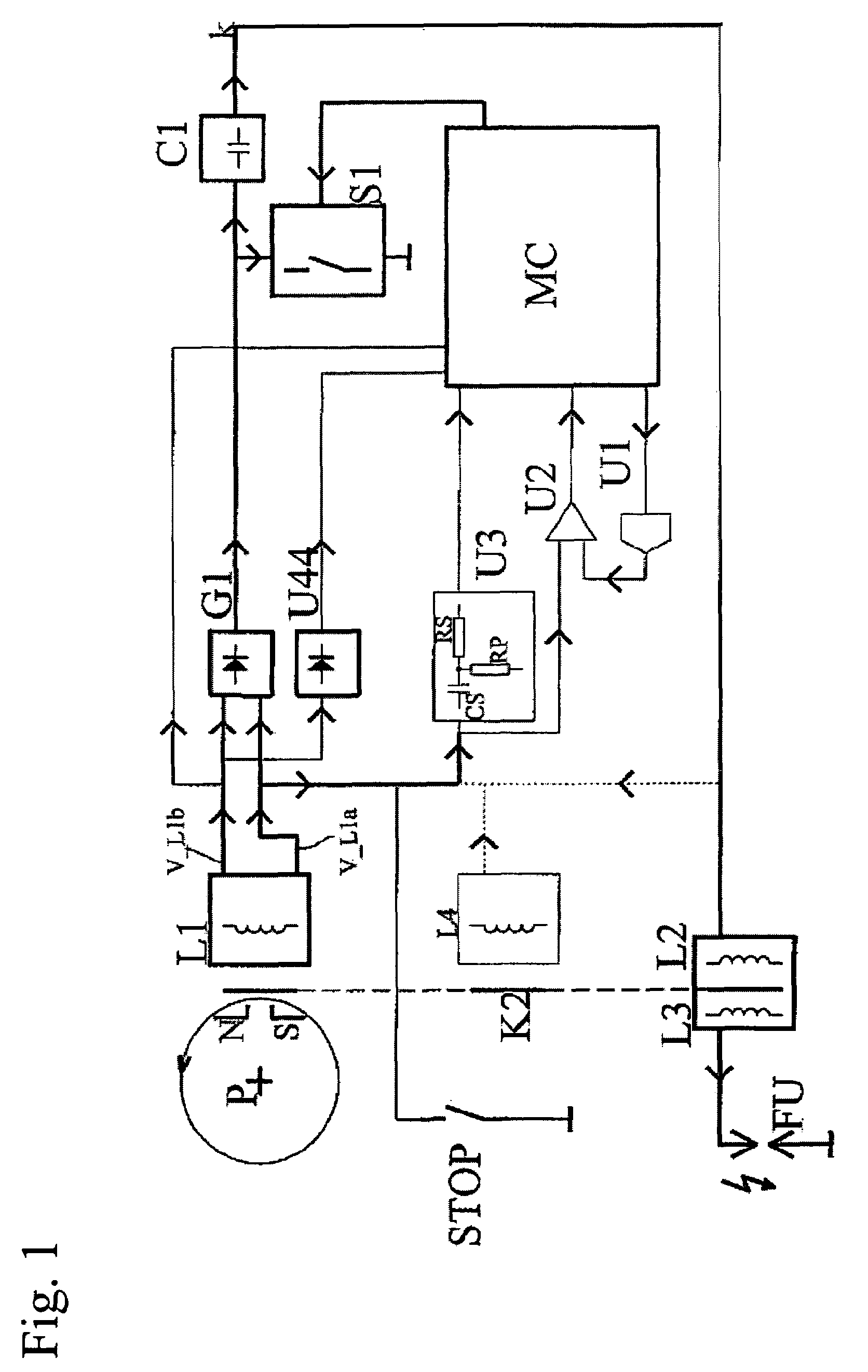

Start safety ignition system

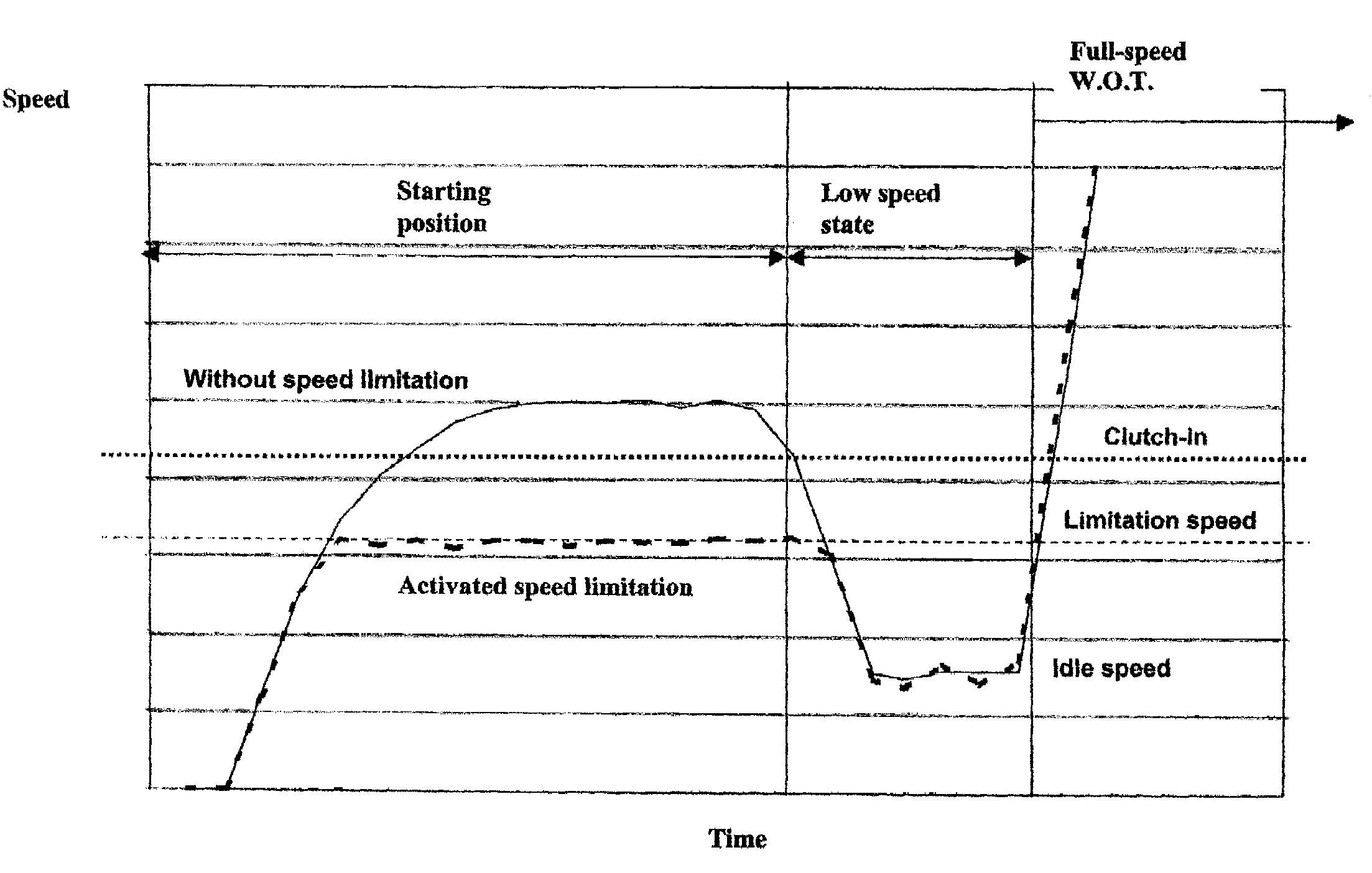

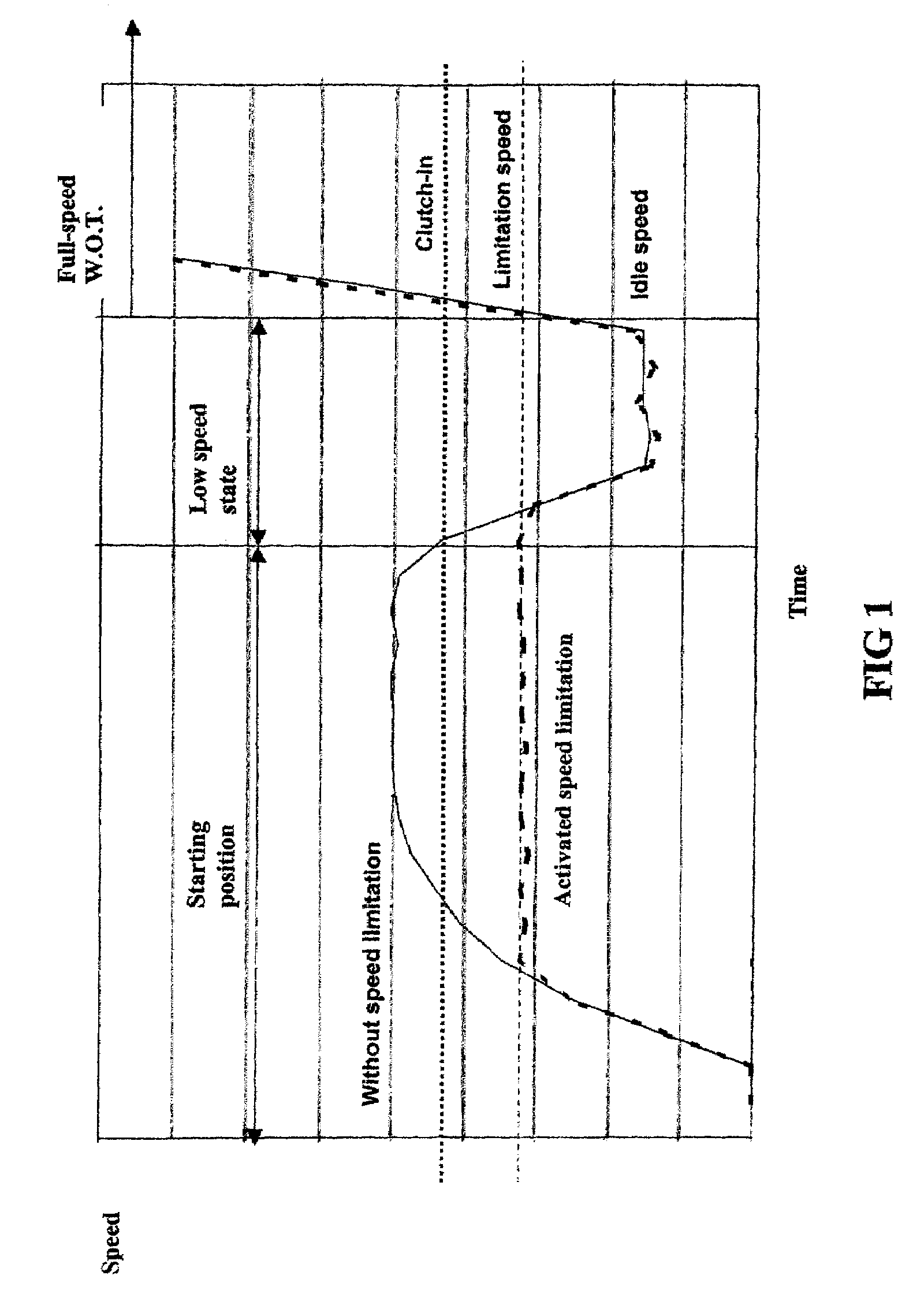

A method for controlling an ignition system of an internal combustion engine having a primary firing pulse generator for charging a capacitor. An electronic switch is included for discharging the capacitor via an ignition coil to generate an ignition voltage. A microcomputer operates the switch to control the ignition timing of the generator. The microcomputer is in communication with a speed sensor that detects the rotational speed of the engine and a speed limitation control that limits the engine speed to a limitation speed below the clutch-in speed of an included centrifugal clutch. The speed limitation control is active or activated when one of either starting the engine or an operating problem of the power tool is detected. The speed limitation control is deactivated when a low speed state of the engine is detected.

Owner:HUSQVARNA AB

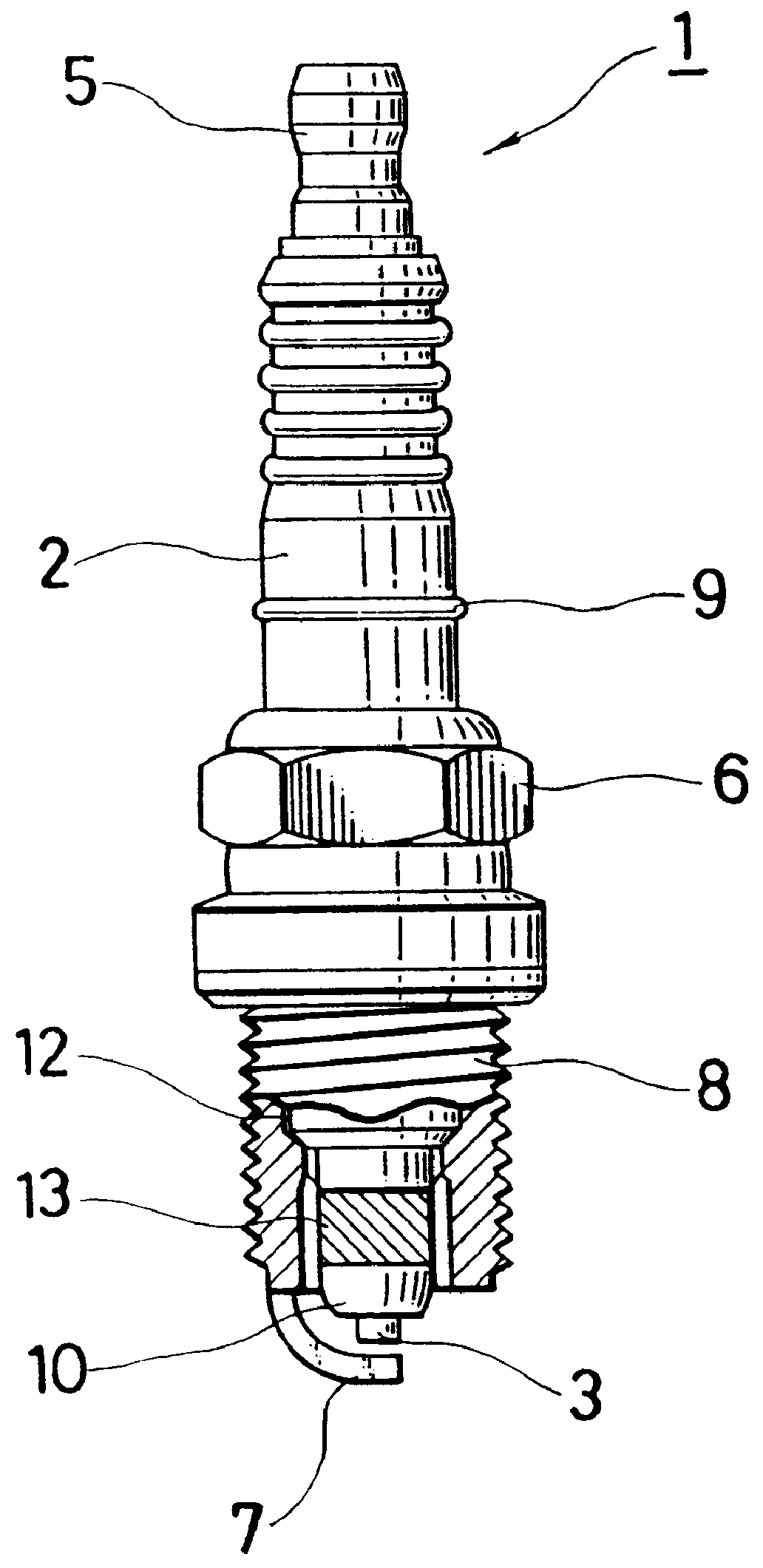

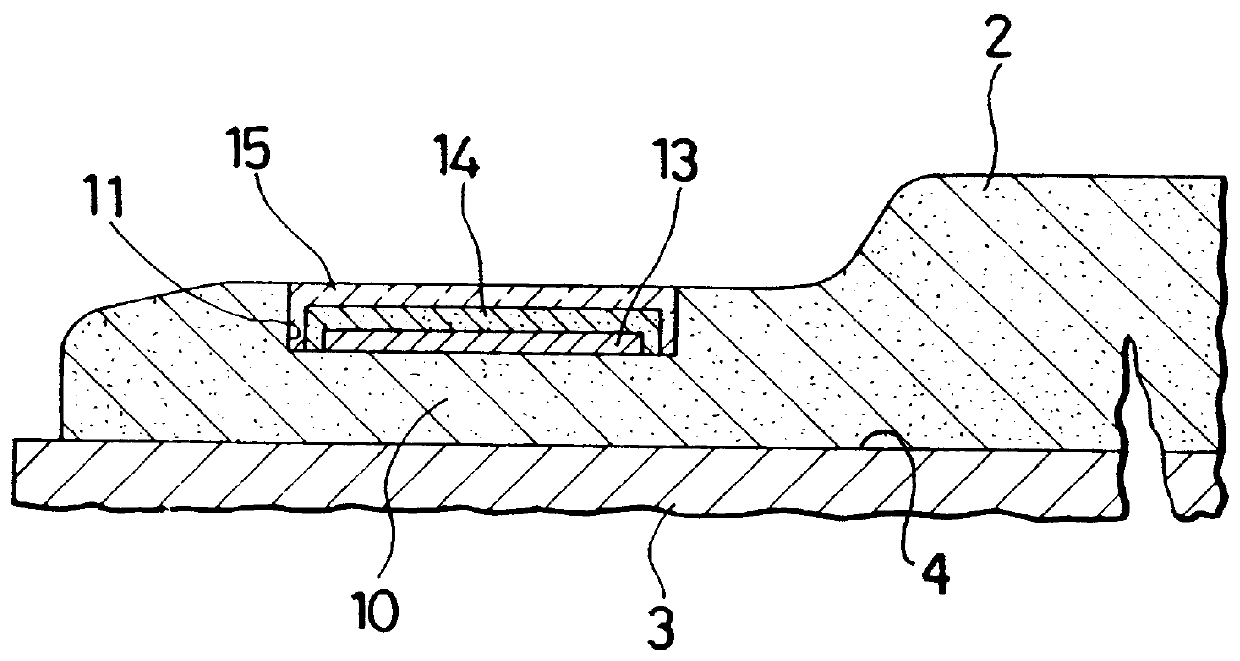

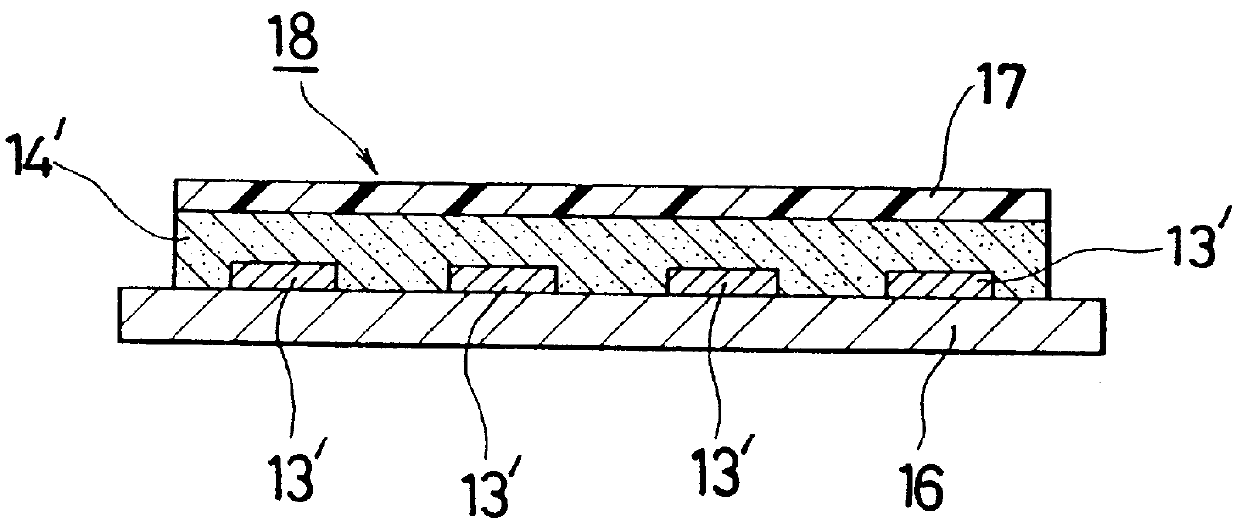

Heater equipped spark plug

InactiveUS6060821ASufficient voltage withstand performanceImprove insulation performanceSpark gapsGenerator generated ignition energyEngineeringMetal

A heater-equipped spark plug comprises an insulator having an insulator nose which holds thereon a center electrode in the vicinity of a free end of an axial bore, a lead wire arranged along a surface of the insulator, a heater formed on the insulator nose by baking a metal paste and connected to the lead wire; and a high softening-point glass layer covering and holding the heater in place with an alumina layer interposed between the high softening-point glass and the heater. Preferably, the alumina layer can have a thickness of 20-200 mu m and the high softening-point glass layer can have a thickness of 30-500 mu m.

Owner:NGK SPARK PLUG CO LTD

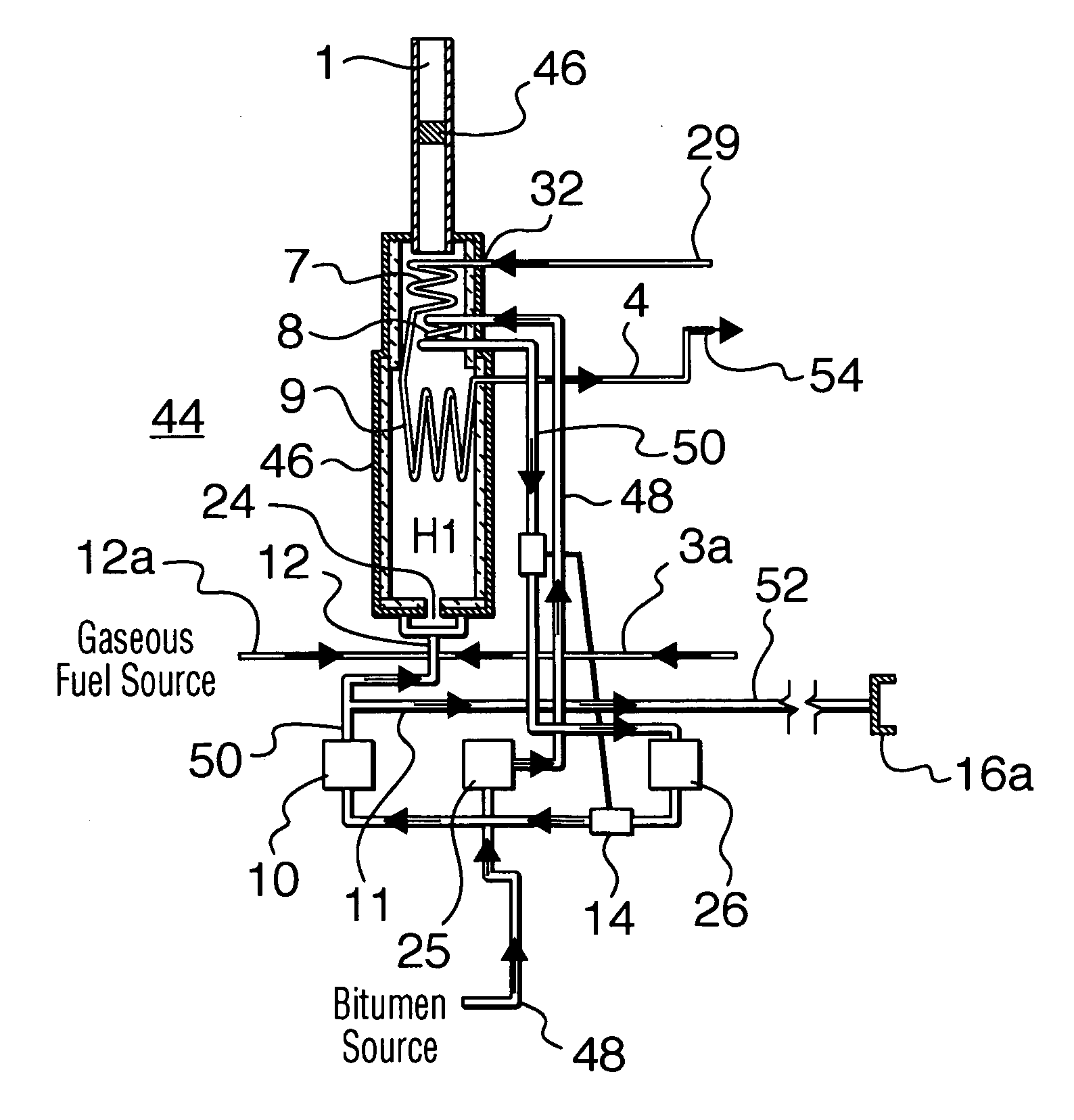

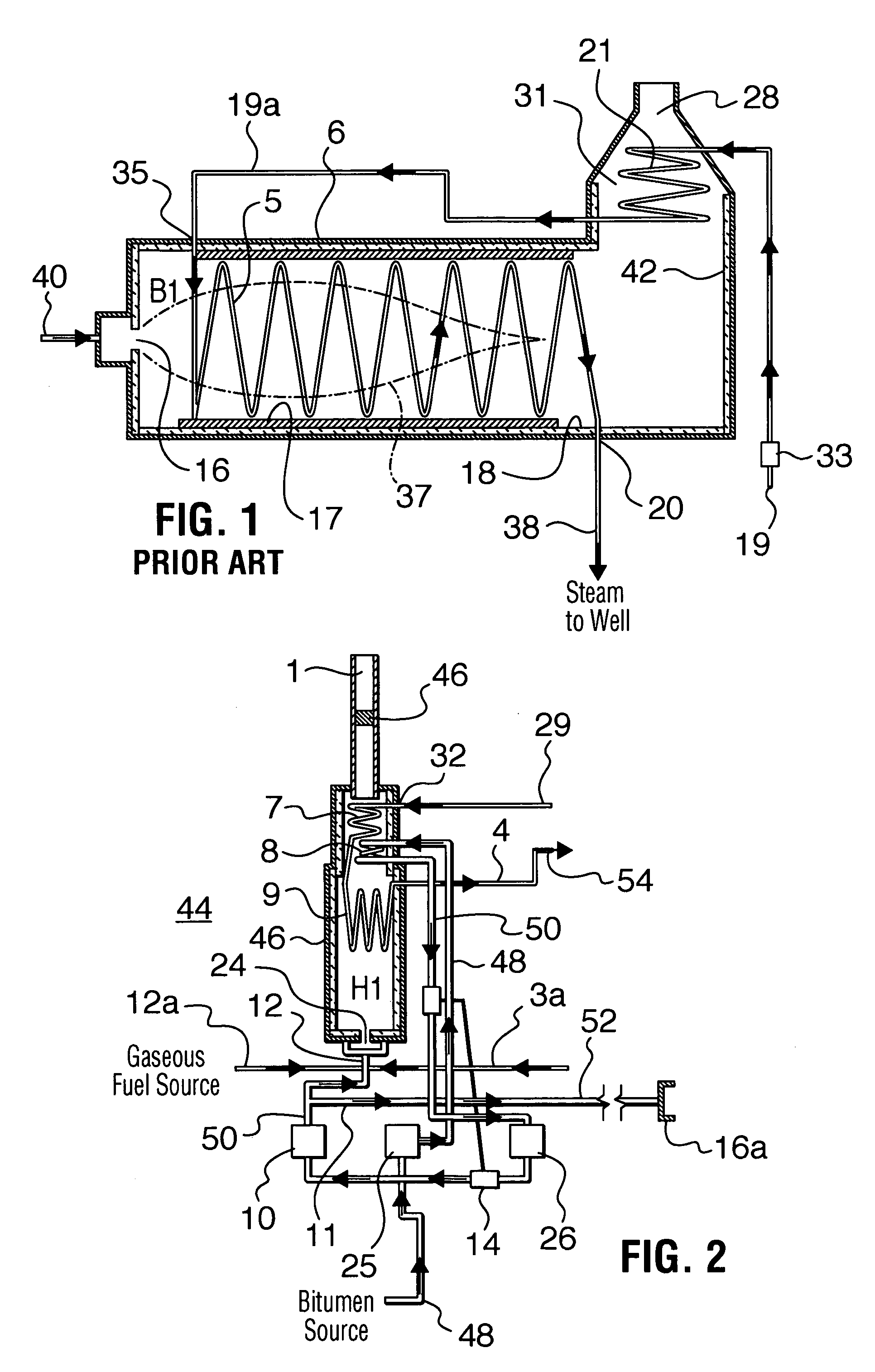

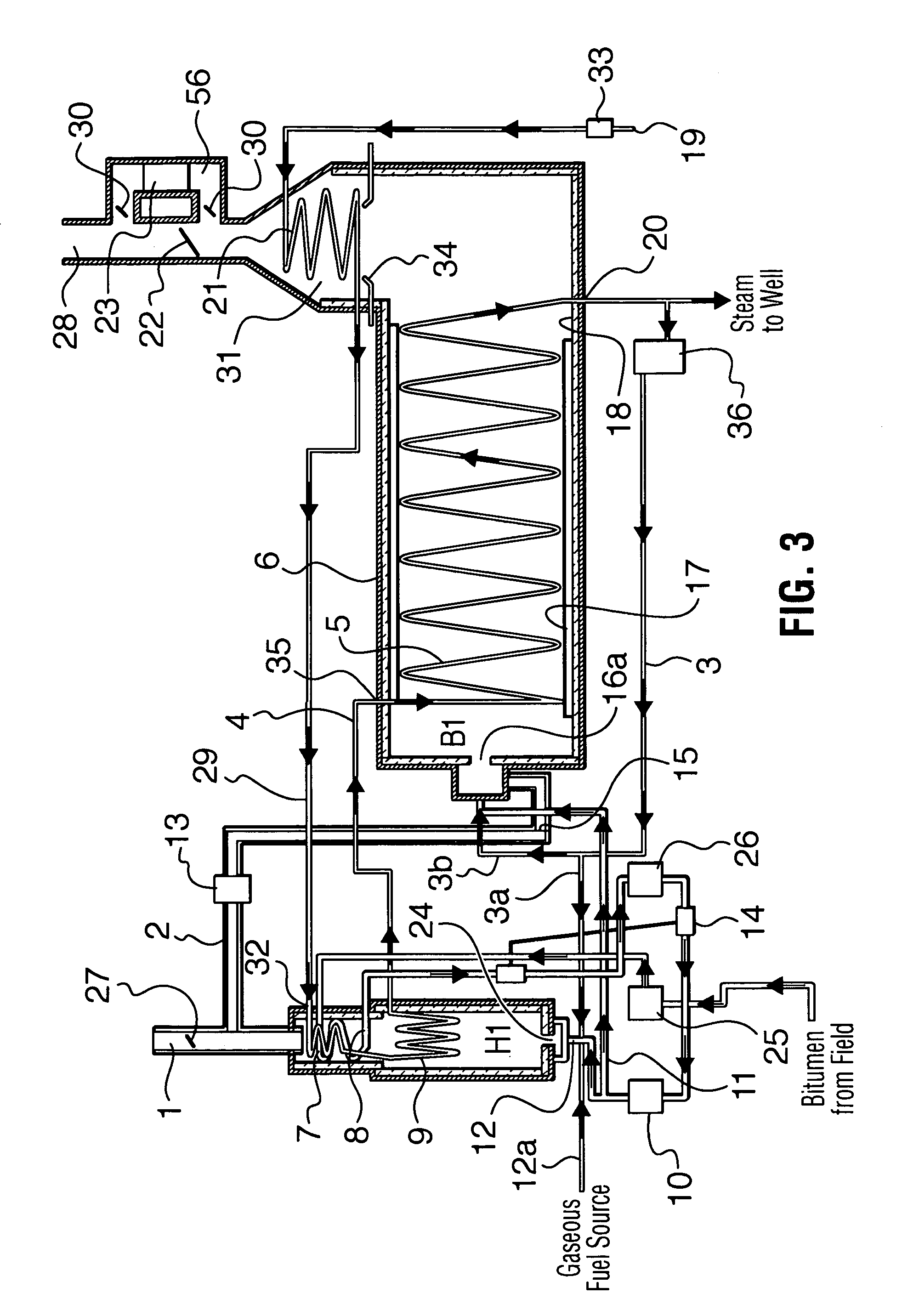

Steam generation apparatus and method

InactiveUS6990930B2Improve steaming qualityEasy to carryFurnace-tube steam boilersSteam/vapor condensersEngineeringLiquid fuel

In one aspect, the invention provides a steam generation apparatus that is liquid fuel fired and addresses conversion of gaseous fuel SIB units to operate with liquid fuel. The invention also relates to a conversion unit for a steam injection boiler, a method for converting a steam injection boiler from gas firing to possible liquid fuel firing and a method for generating steam from a liquid fuel source. The invention employs a fired heater for heating the liquid fuel to a temperature suitable for firing and preheats the water to compensate for the shortfall in heat liberation when a gas boiler is converted to use liquid fuel. In another aspect of the invention, production of steam is achievable consistently by employing step-up heaters with a steam injection boiler. The heaters being connected in parallel to continue heating the water / steam to achieve a higher quality steam over that produced in the boiler while minimizing consideration as to the adverse effects of coil fouling in the boiler.

Owner:ACS ENG TECH

Ignition timing control apparatus and ignition timing control method for internal combustion engine

ActiveUS7712450B2Suppression frequencyInhibitionElectrical controlInternal combustion piston enginesIgnition timingControl theory

In an ignition timing control apparatus for an engine, a KCS learning value learned when the engine is in a given operating state is used in an ignition timing control executed when the engine is in the other operating state. An estimated knocking occurrence ignition timing is set based on a most retarded ignition timing using the KCS learning value. A final ignition timing is set by changing a KCS feedback correction value based on whether knocking occurs when ignition is performed at the estimated knocking occurrence ignition timing. When a point indicating the engine operating state moves into a region where it is difficult to set the estimated knocking occurrence ignition timing, the KCS feedback correction value is changed to retard the final ignition timing, and the final ignition timing is set using the KCS learning value and the changed KCS feedback correction value.

Owner:TOYOTA JIDOSHA KK

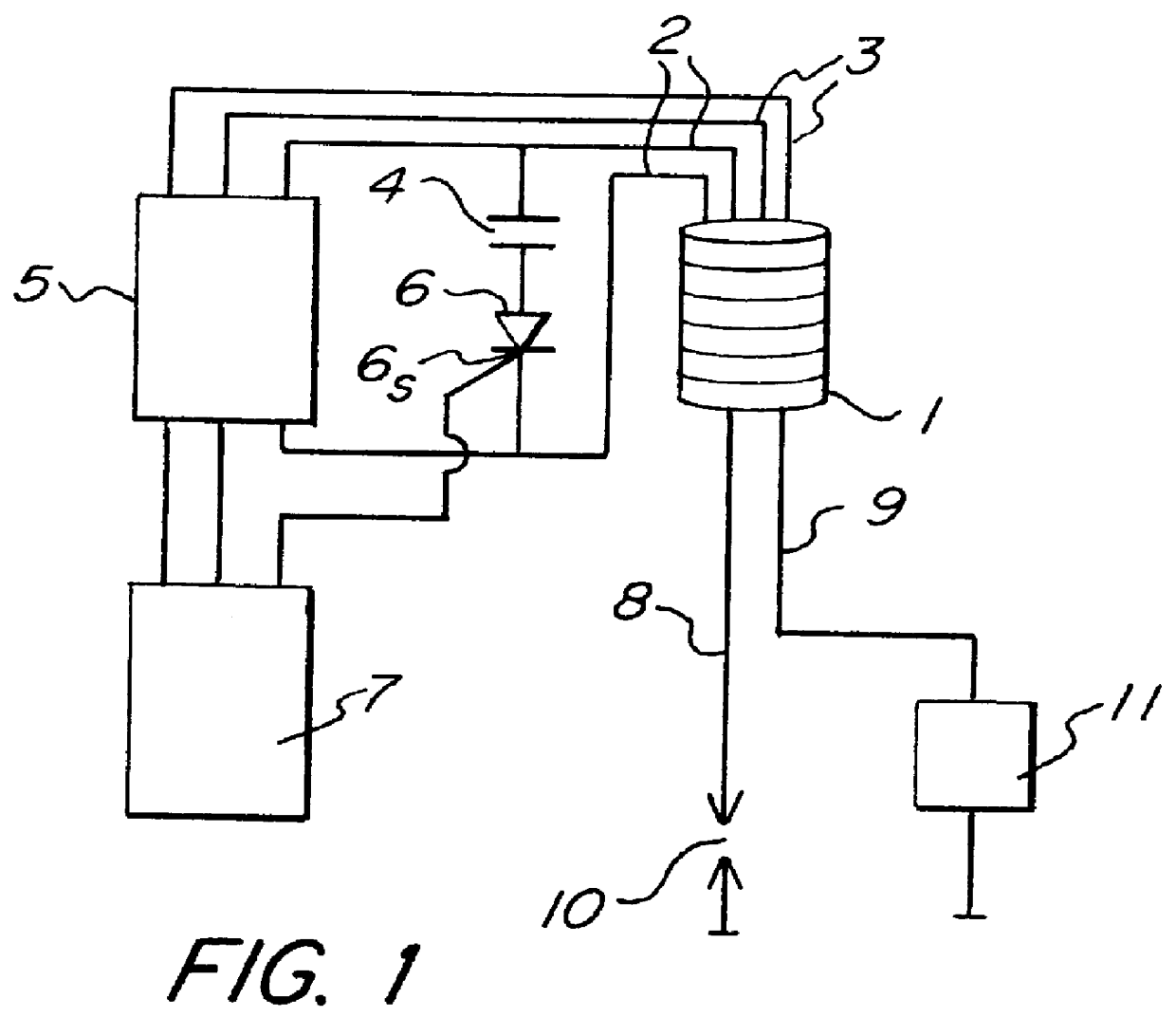

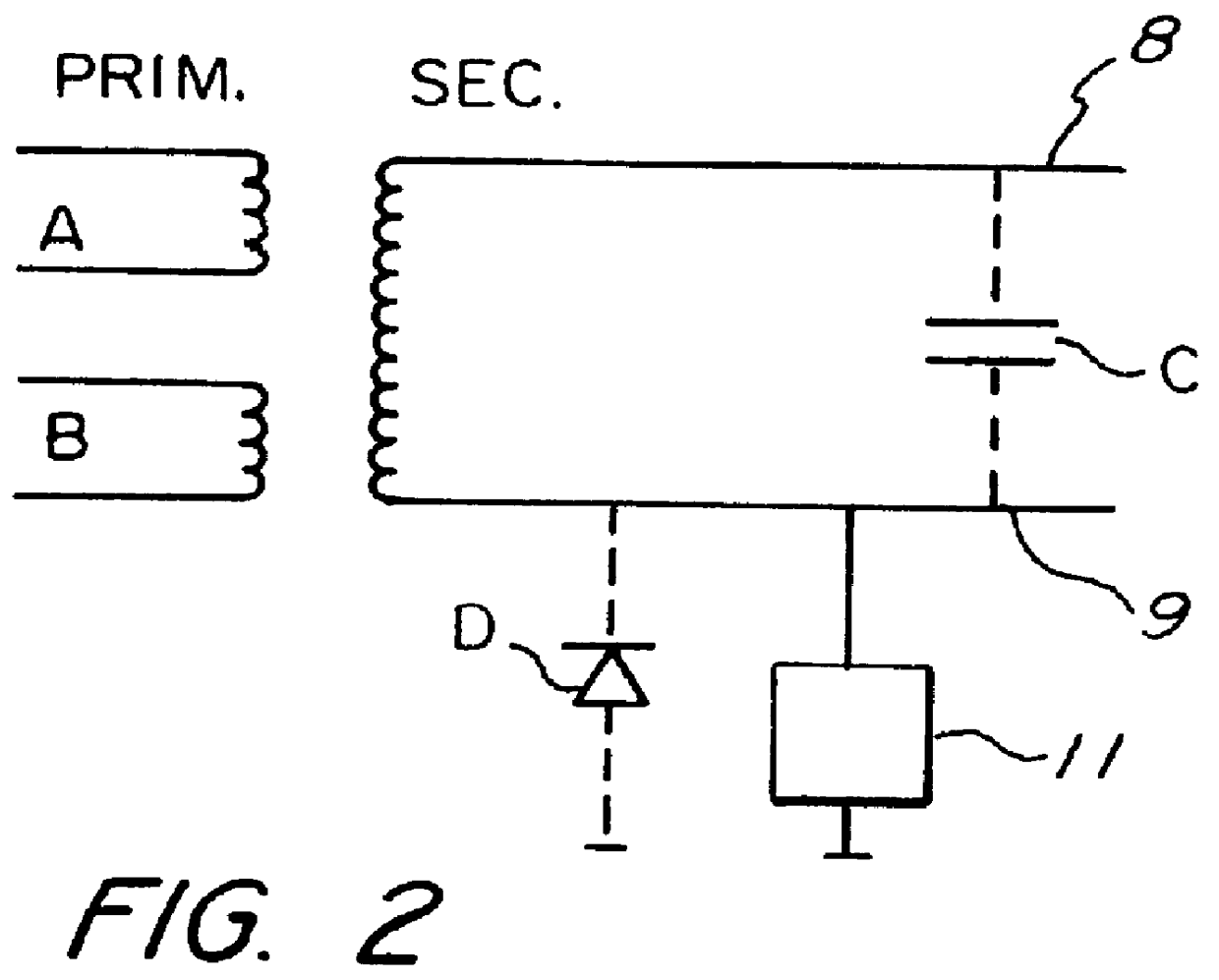

Method of detecting an ionization current

PCT No. PCT / SE97 / 01022 Sec. 371 Date Dec. 10, 1998 Sec. 102(e) Date Dec. 10, 1998 PCT Filed Jun. 11, 1997 PCT Pub. No. WO97 / 47875 PCT Pub. Date Dec. 18, 1997A method for generation of a low test voltage is used for the purpose of detecting an ionization current in the spark gap of an internal combustion engine. The voltage is generated by a controllable ignition magneto (5) arranged in order to charge (2) an ignition capacitor (4). The voltage is applied (3) to the primary side of the ignition device after generation of a spark and after the decay of the spark, after which the ionization current is detected (11) on the secondary side of the ignition device.

Owner:SEM AB

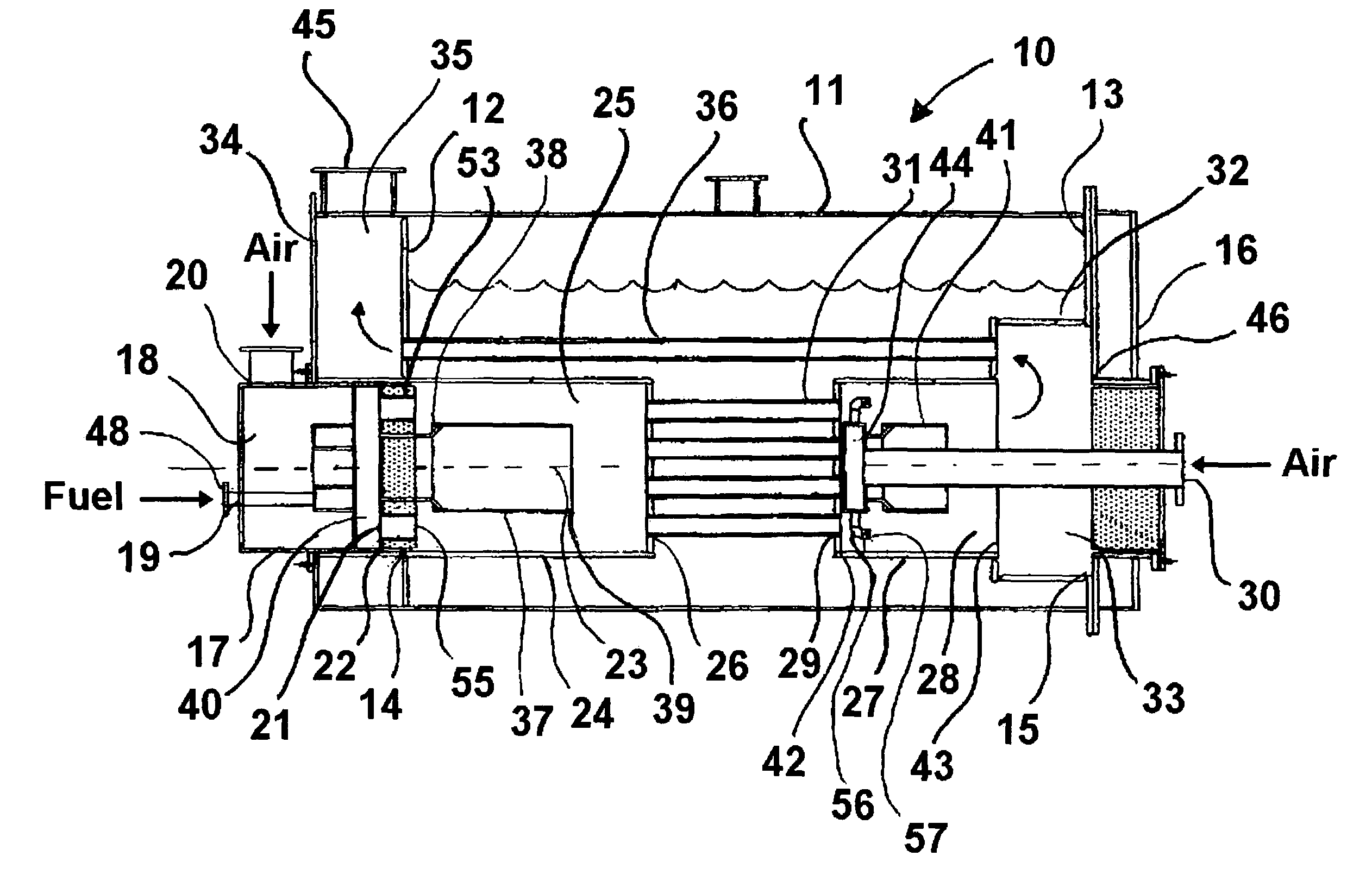

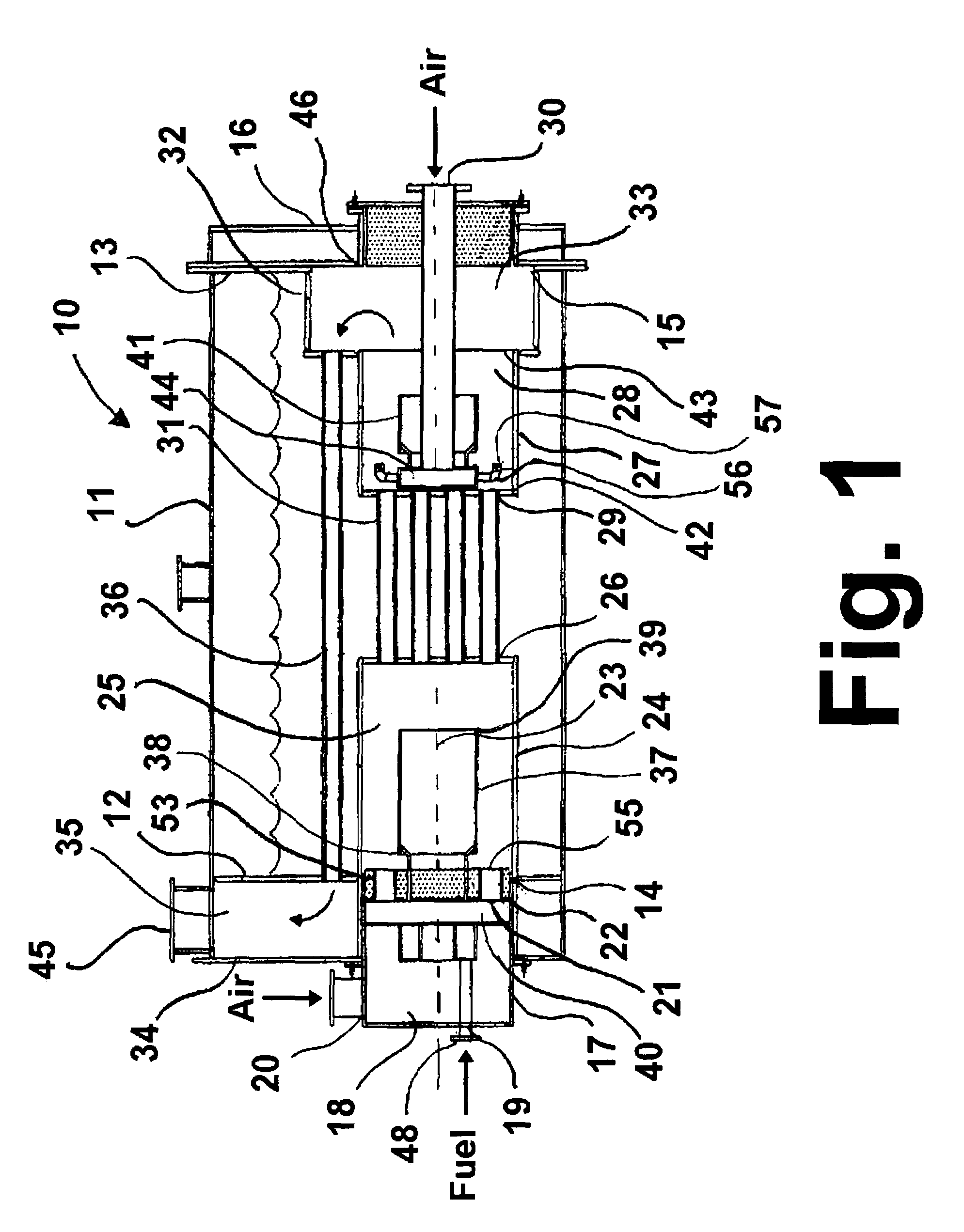

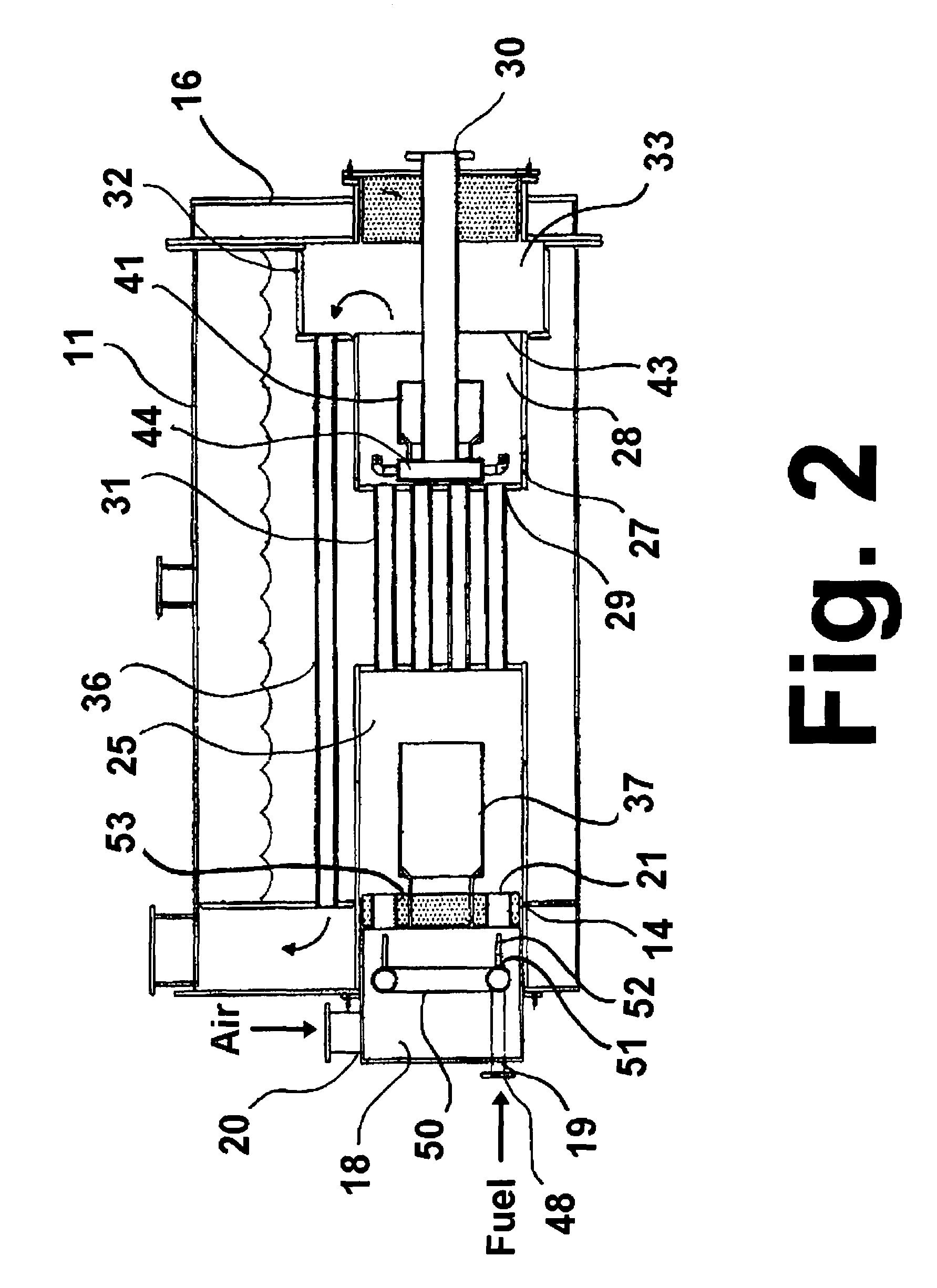

Super low NOx, high efficiency, compact firetube boiler

ActiveUS6971336B1Reduce nitrogen oxide emissionsReducing NO<sub>Furnace-tube steam boilersCombustion enginesCombustion chamberBoiler furnace

A firetube boiler furnace having two combustion sections and an in-line intermediate tubular heat transfer section between the two combustion sections and integral to the pressure vessel. This design provides a staged oxidant combustion apparatus with separate in-line combustion chambers for fuel-rich primary combustion and fuel-lean secondary combustion and sufficient cooling of the combustion products from the primary combustion such that when the secondary combustion oxidant is added in the secondary combustion stage, the NOx formation is less than 5 ppmv at 3% O2.

Owner:GAS TECH INST

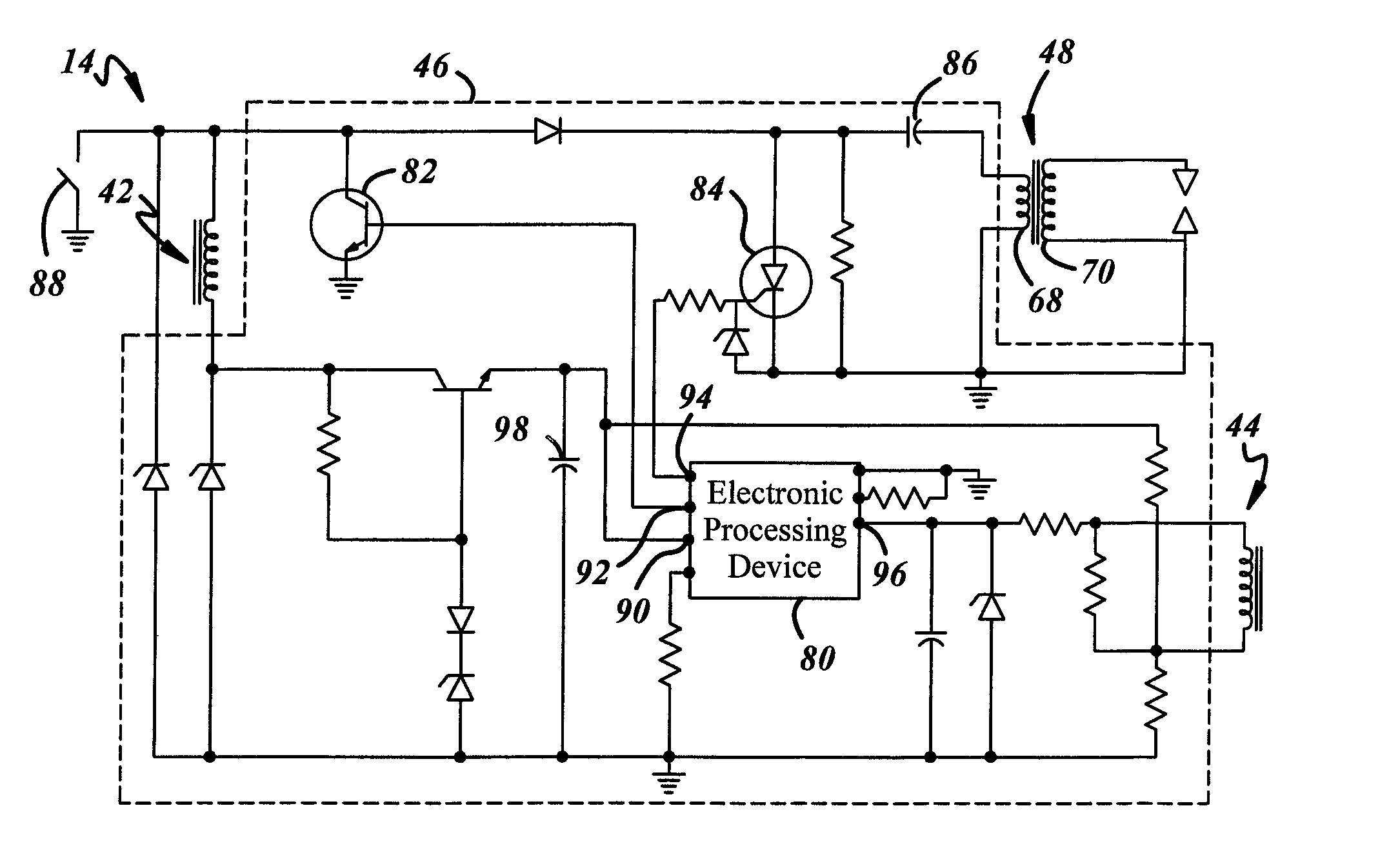

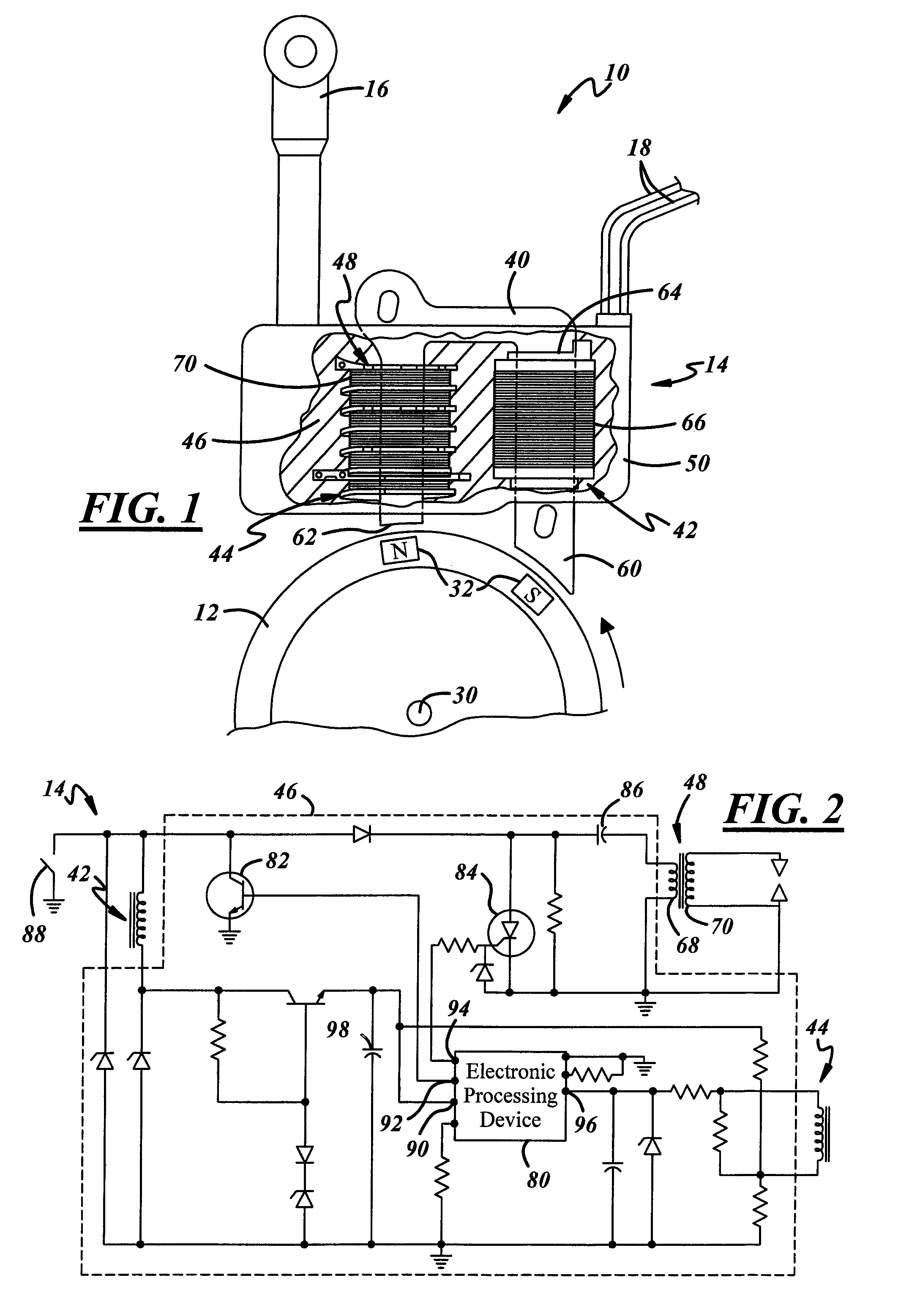

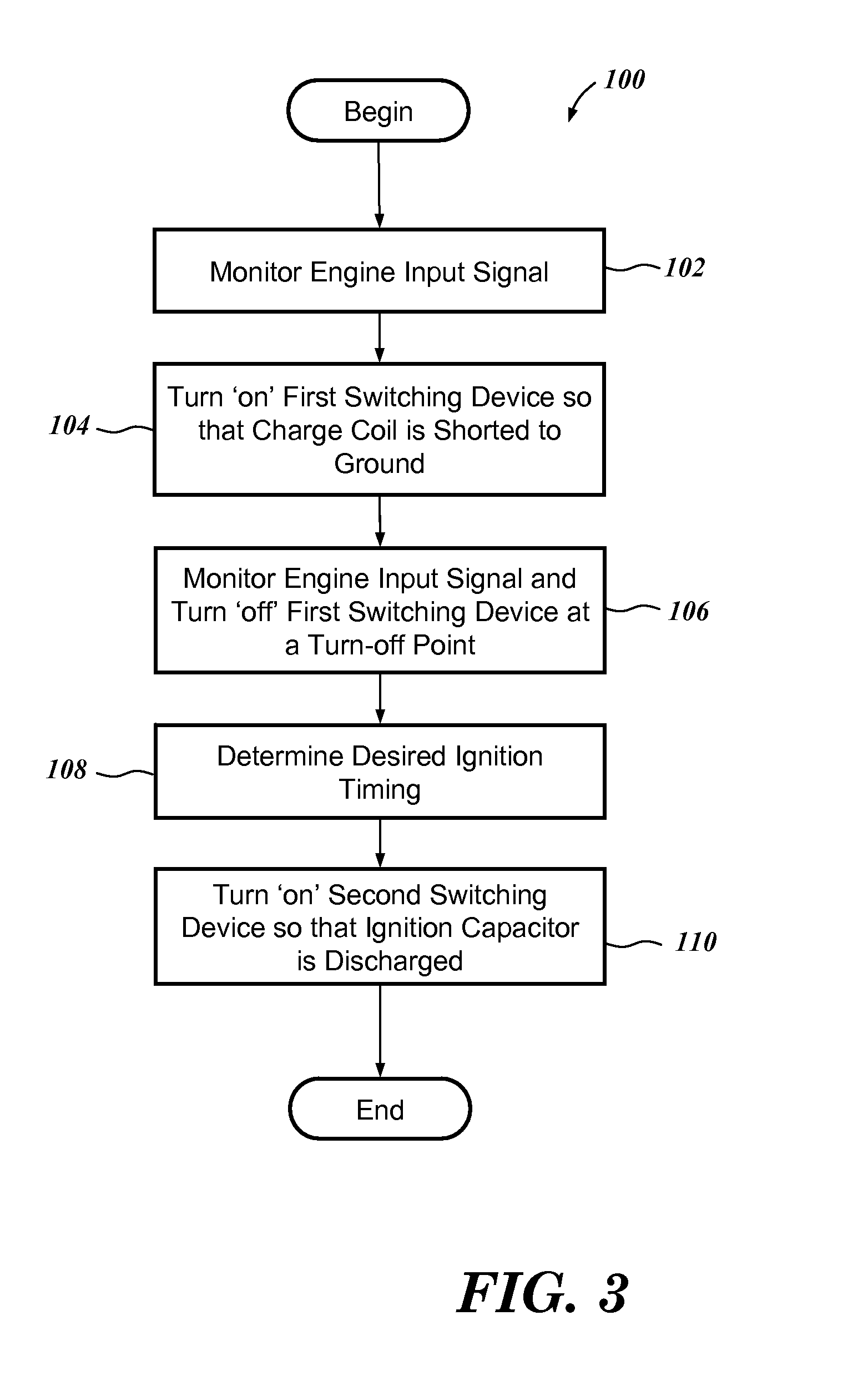

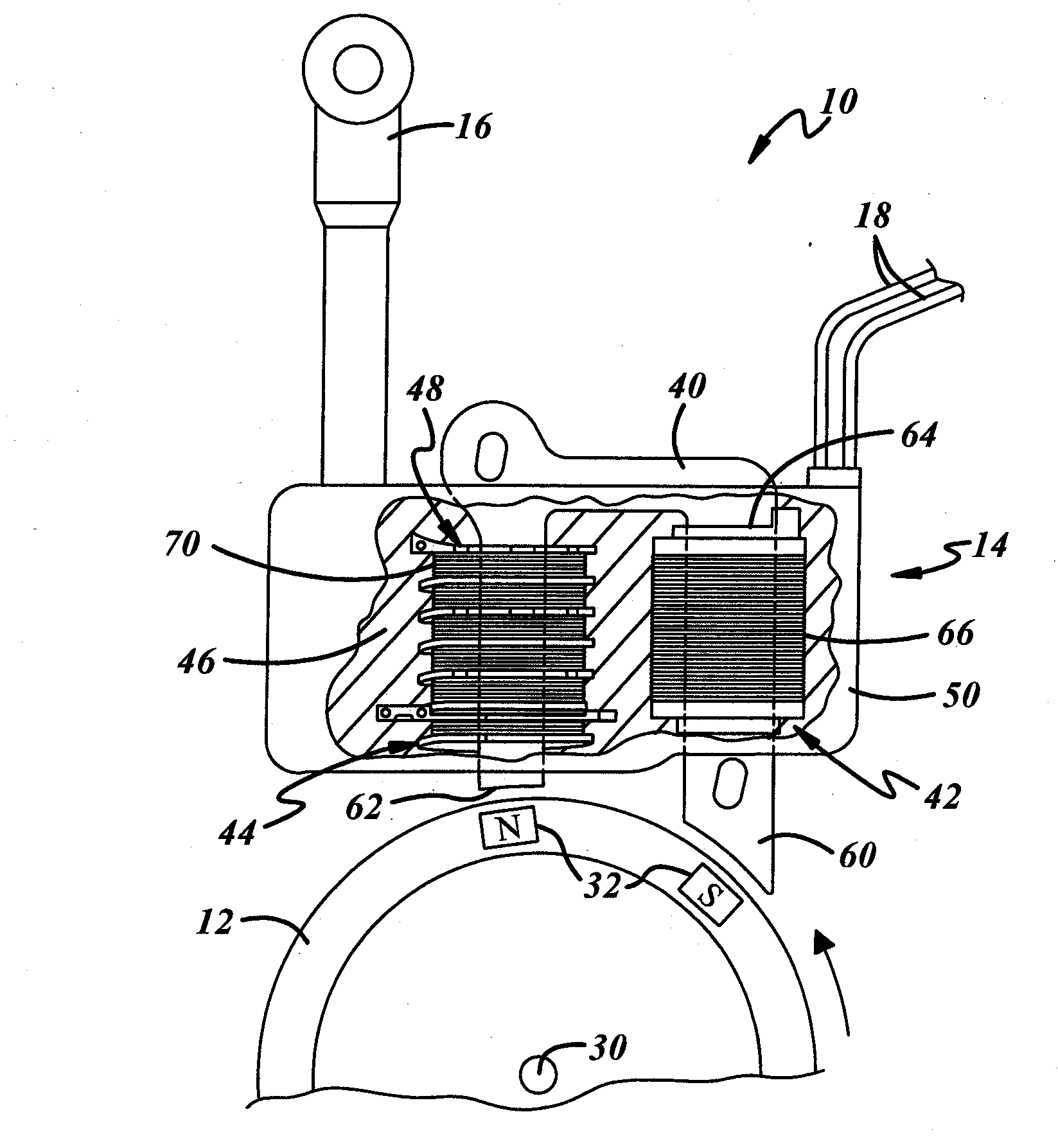

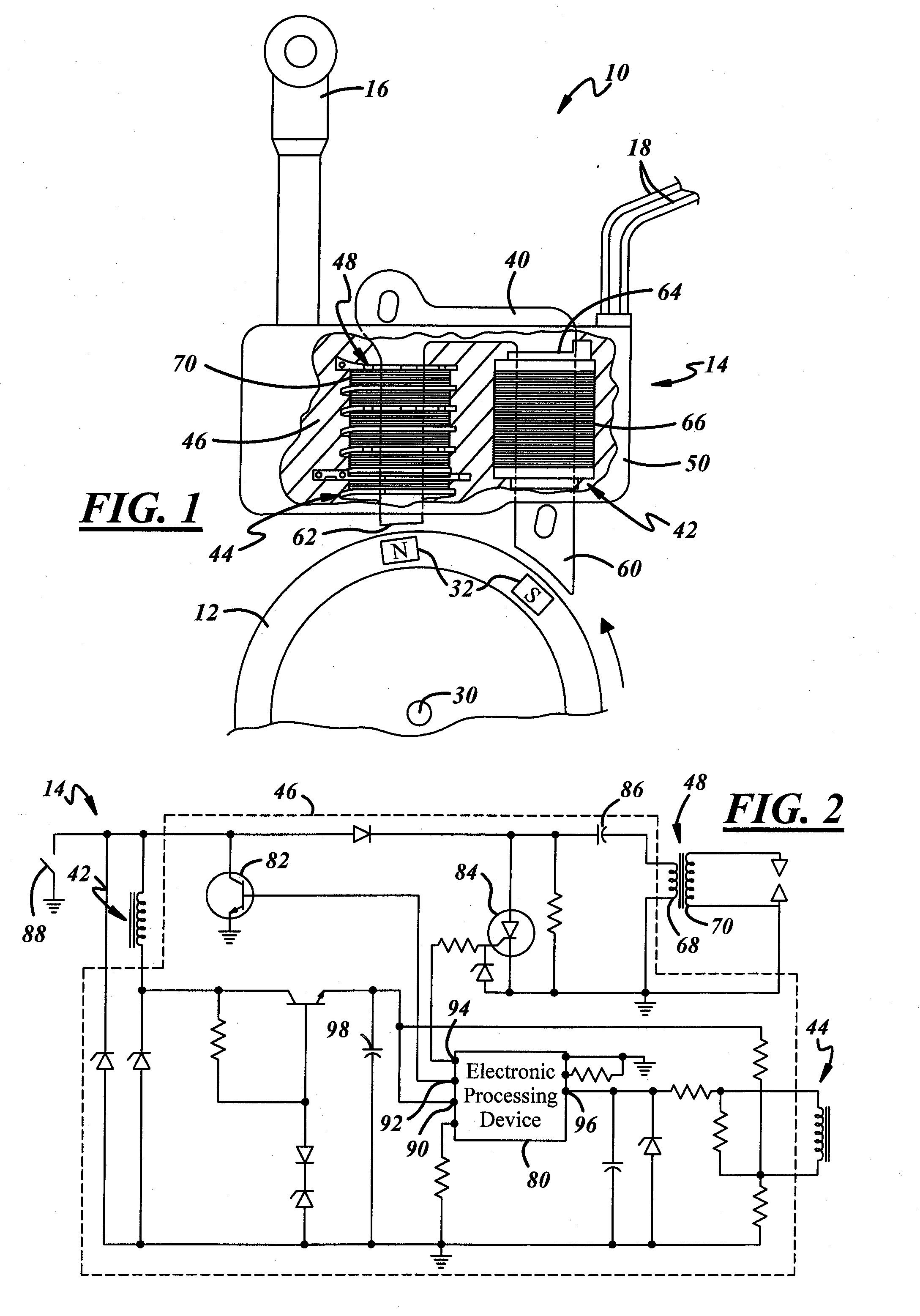

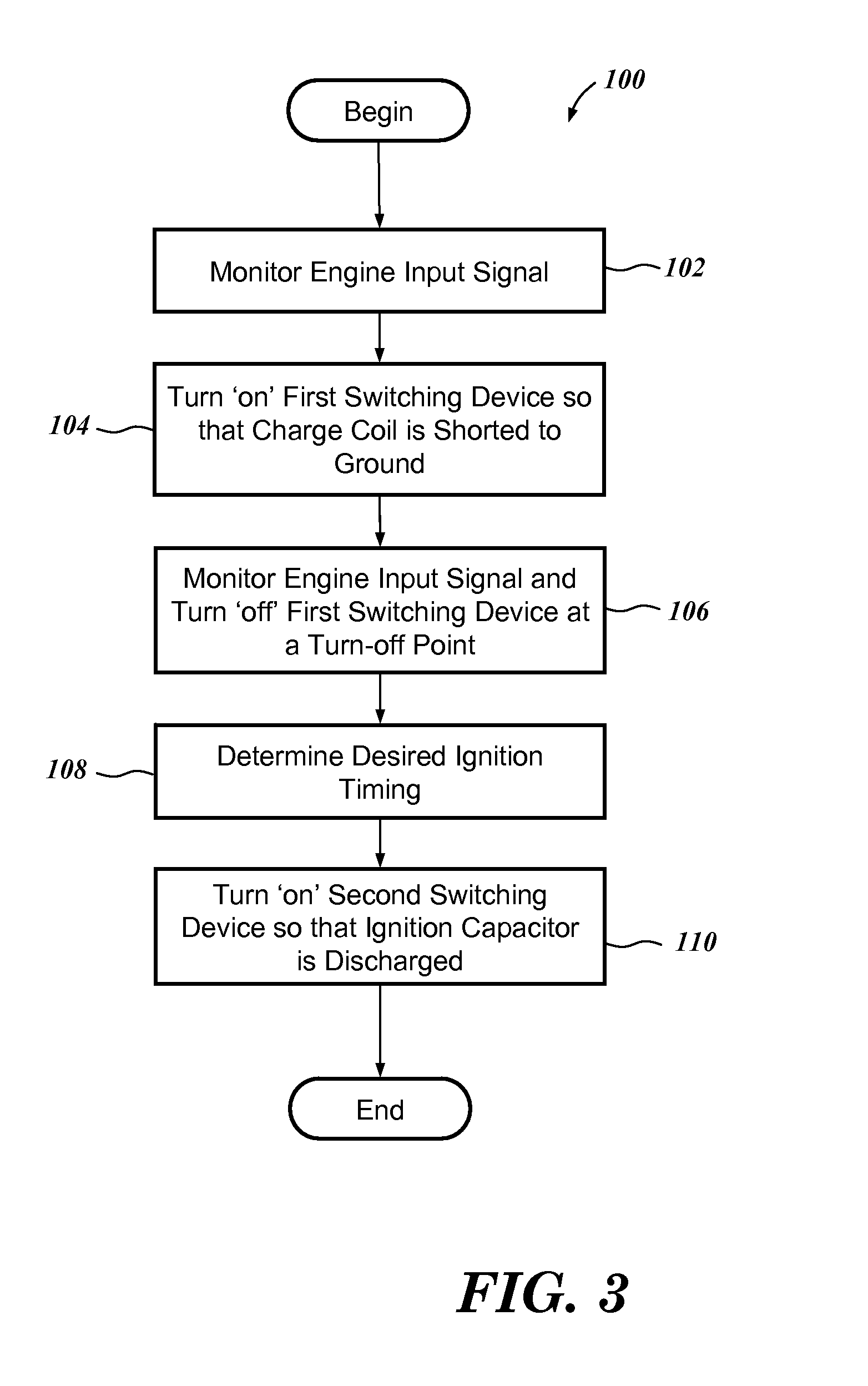

Ignition Module For Use With A Light-Duty Internal Combustion Engine

ActiveUS20080178841A1Low impedance pathAnalogue computers for vehiclesEngine controllersCapacitanceComputer module

A capacitive discharge ignition (CDI) system that can be used with a variety of light-duty internal combustion engines, including those typically employed by lawn, garden, and other outdoor equipment. According to one embodiment, the CDI system includes an ignition module having a first switching device that shorts a charge coil during an initial portion of a charge cycle. Subsequently, the first switching device is turned ‘off’ so that a flyback charging technique charges an ignition capacitor. A second switching device is then used to discharge the ignition capacitor and initiate the combustion process.

Owner:WALBRO LLC

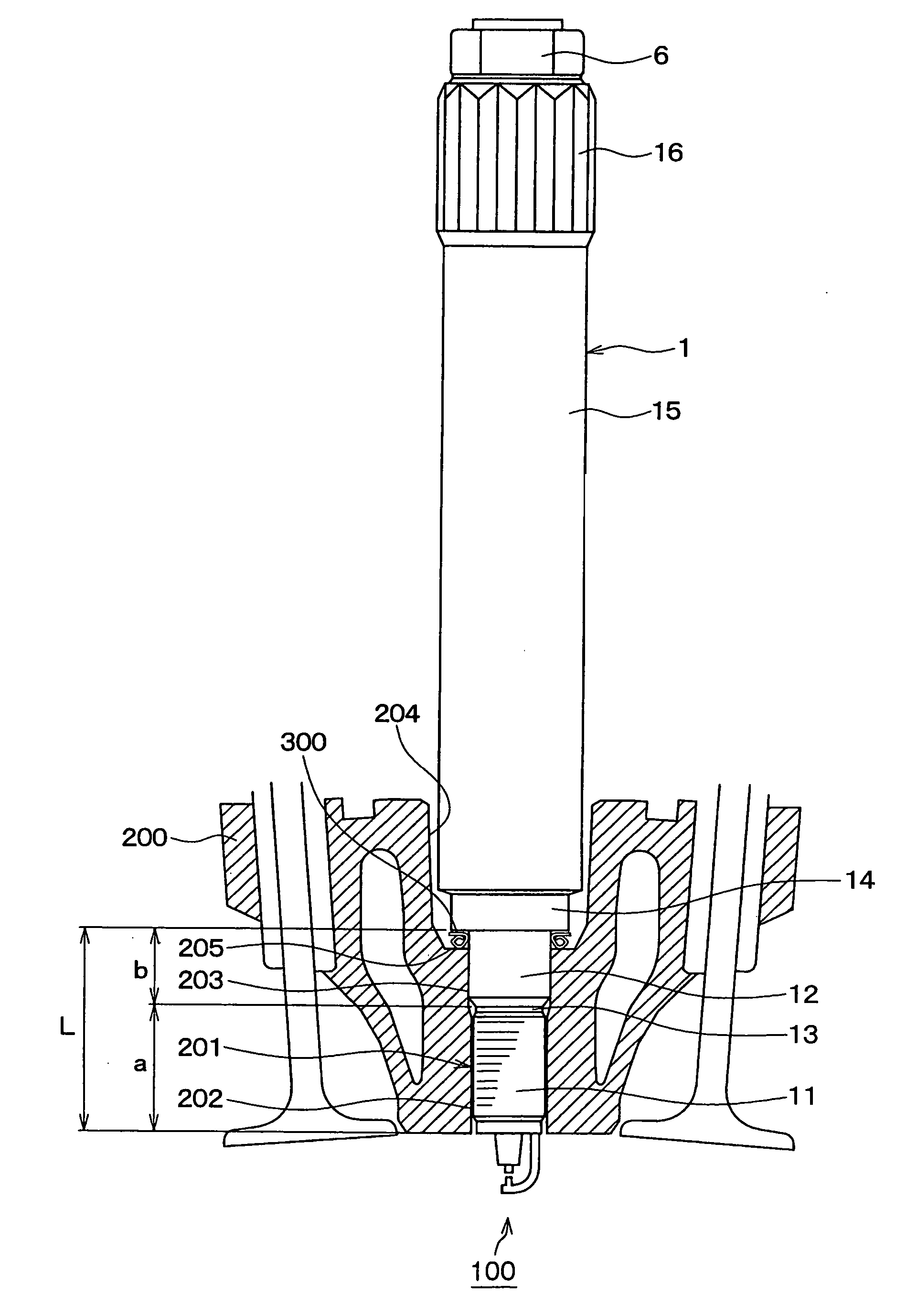

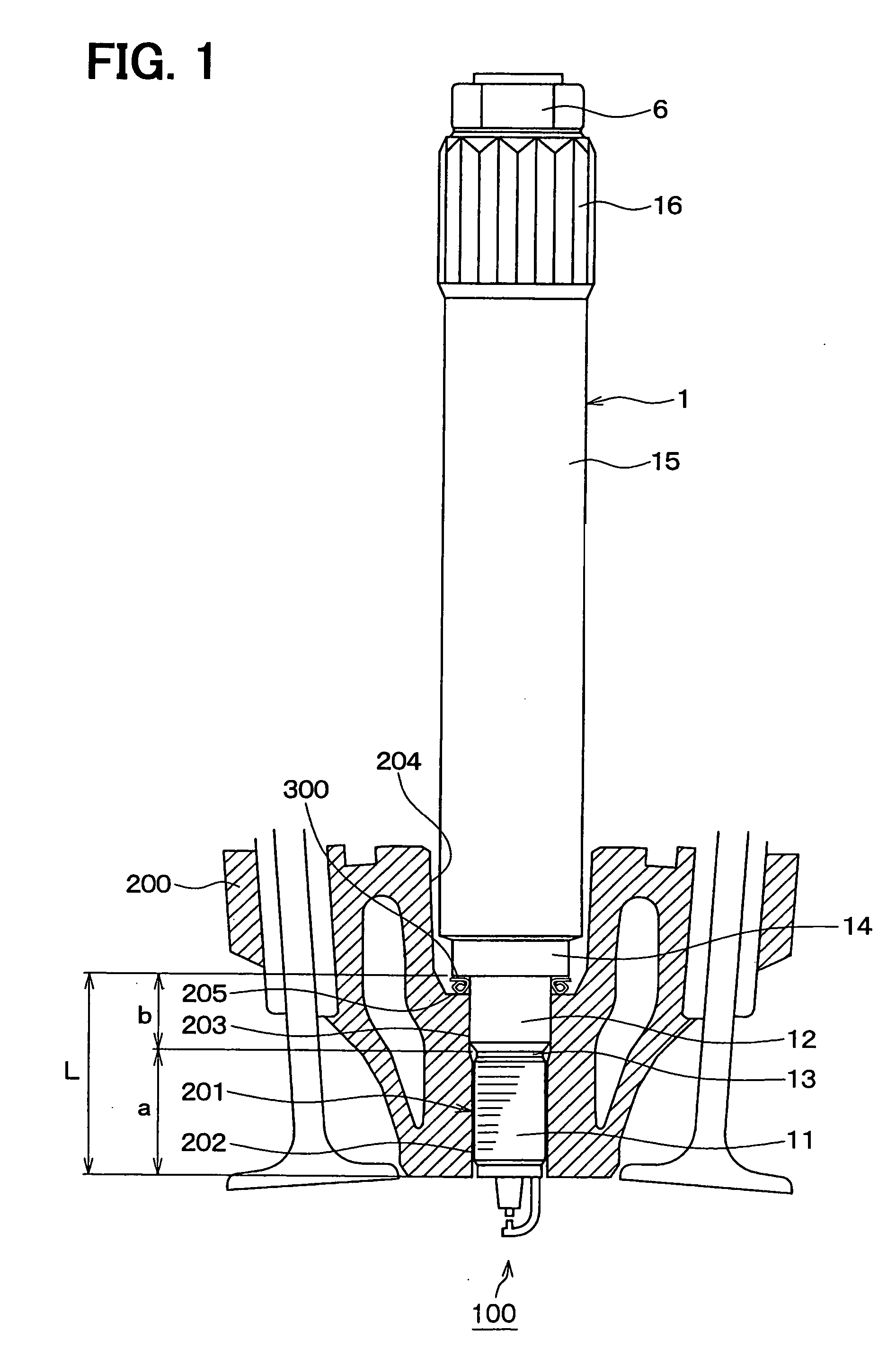

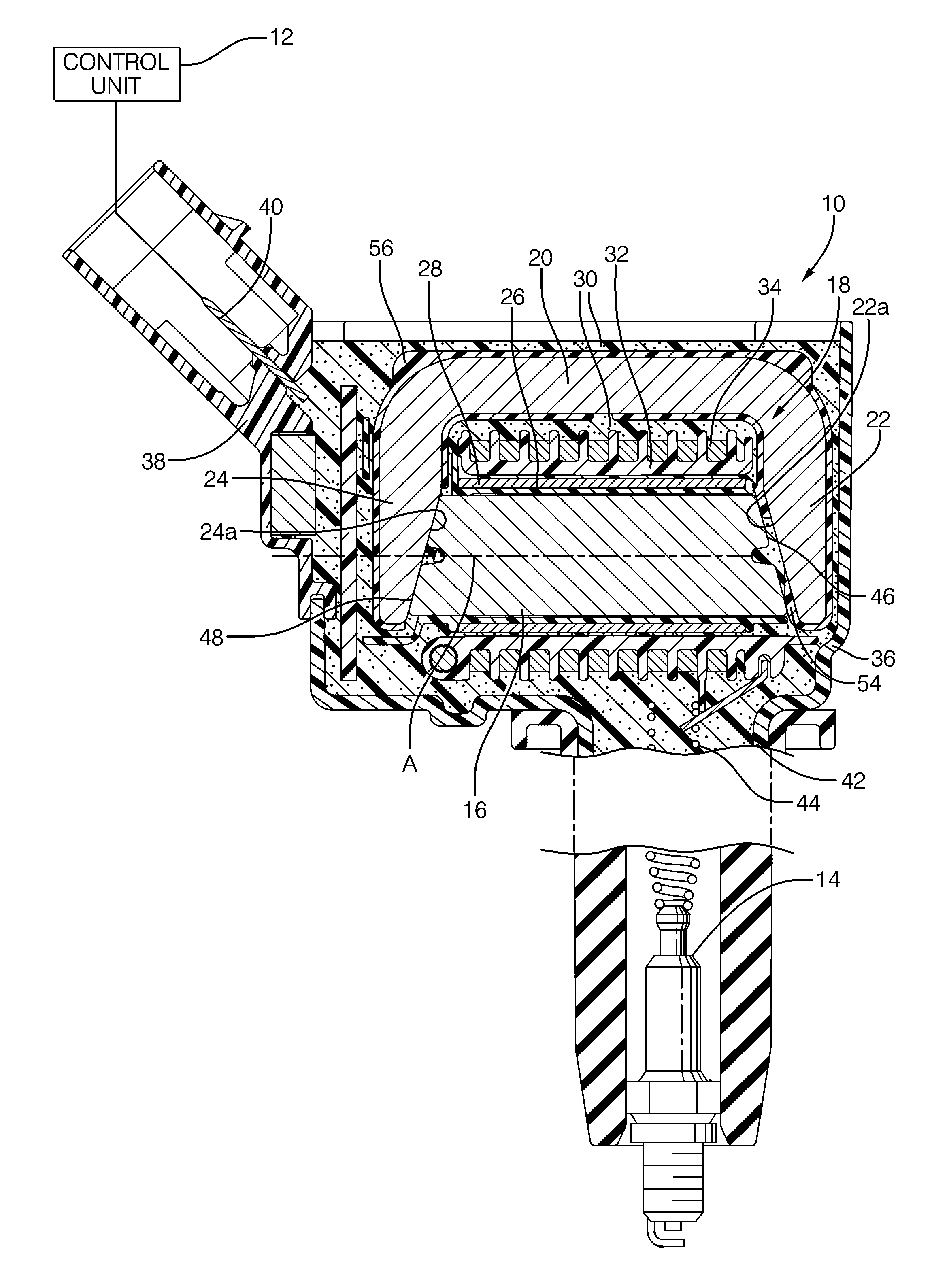

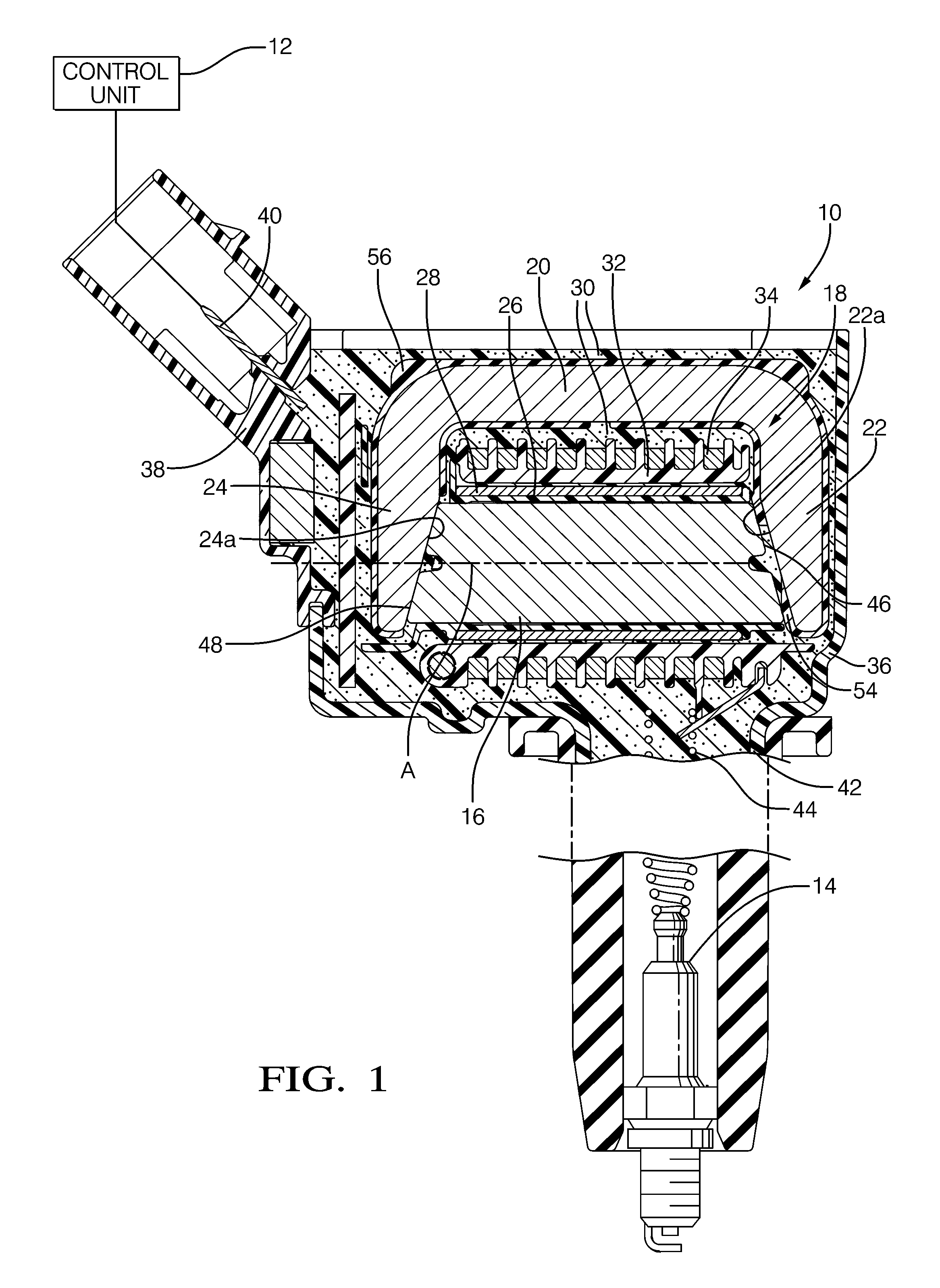

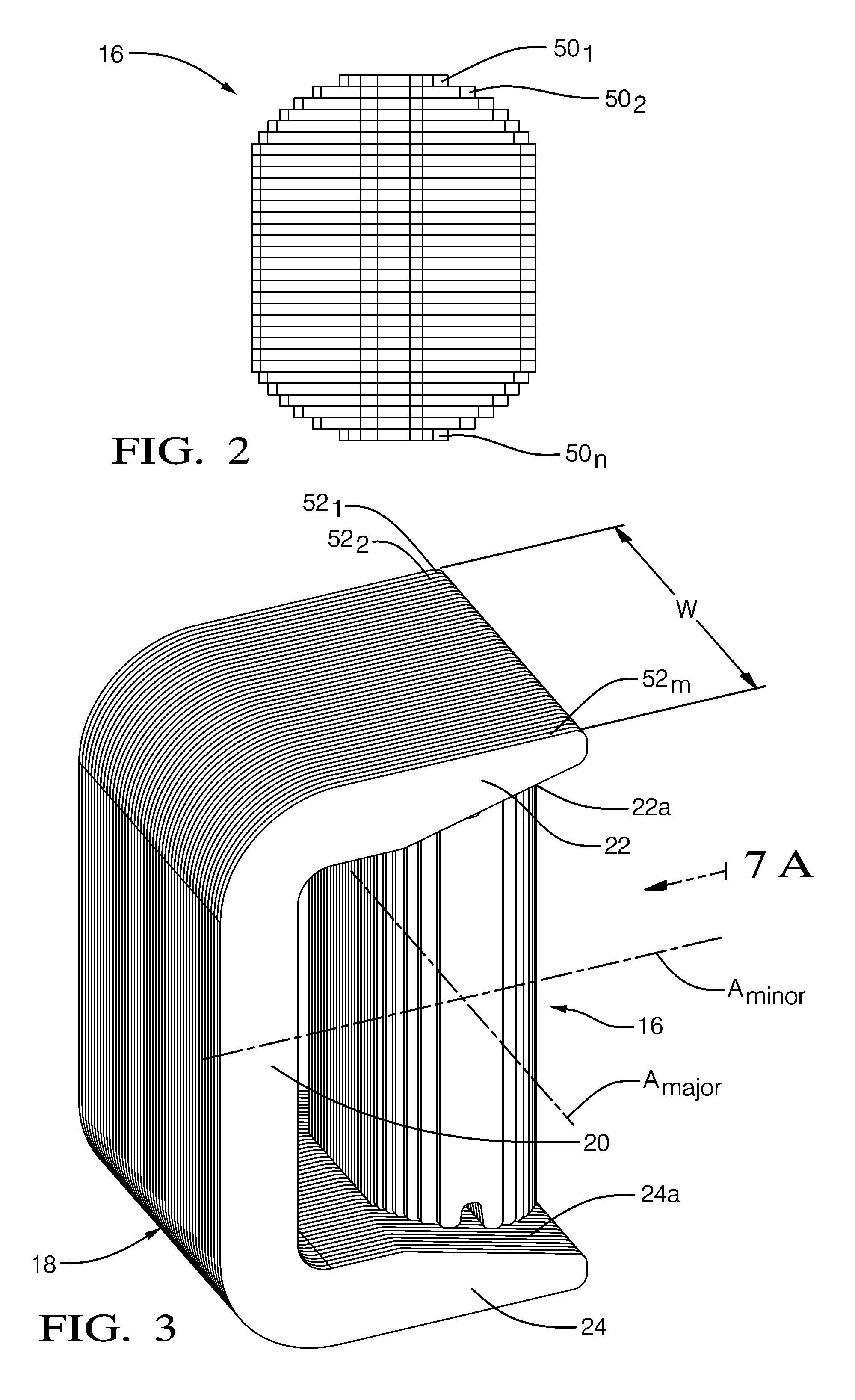

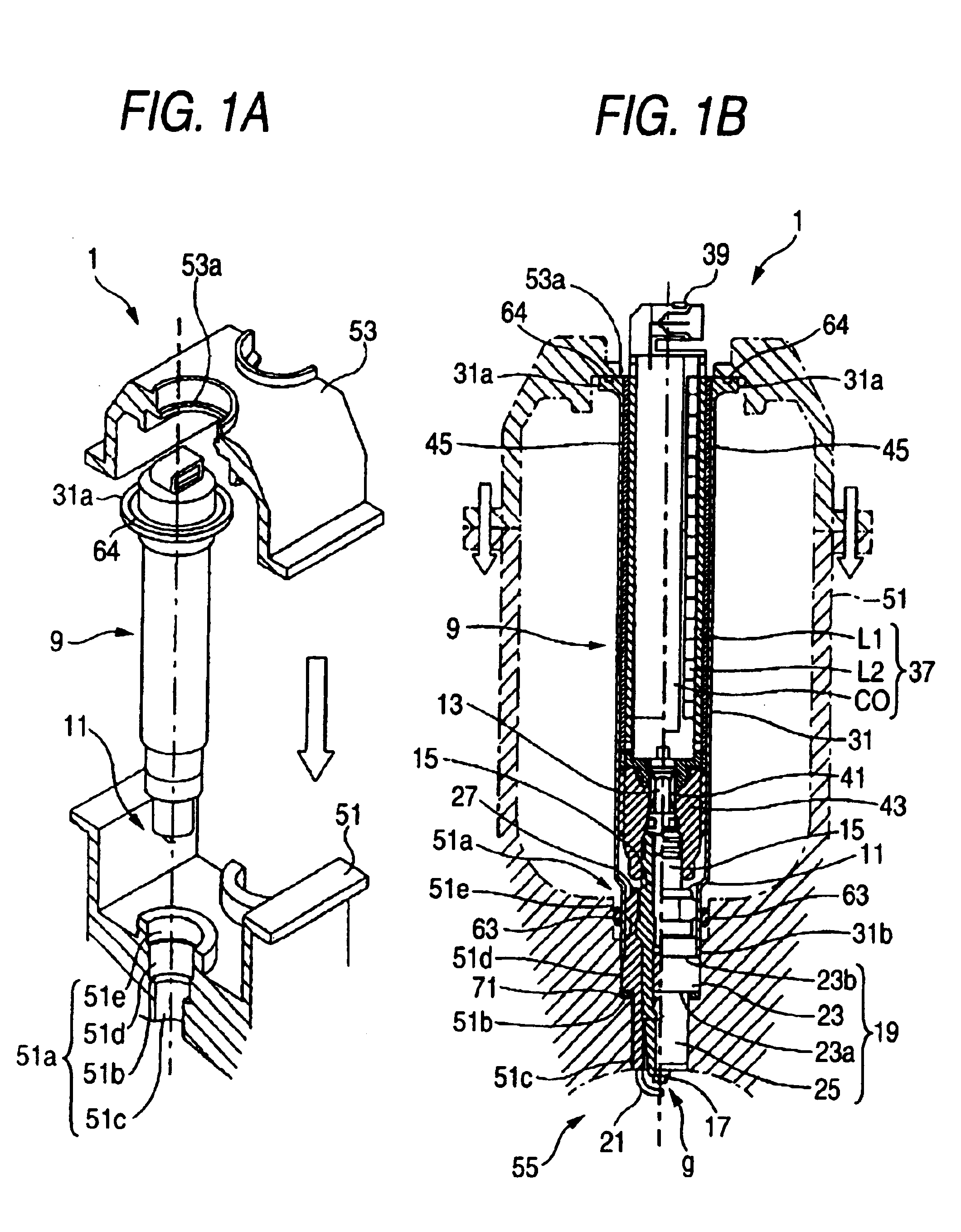

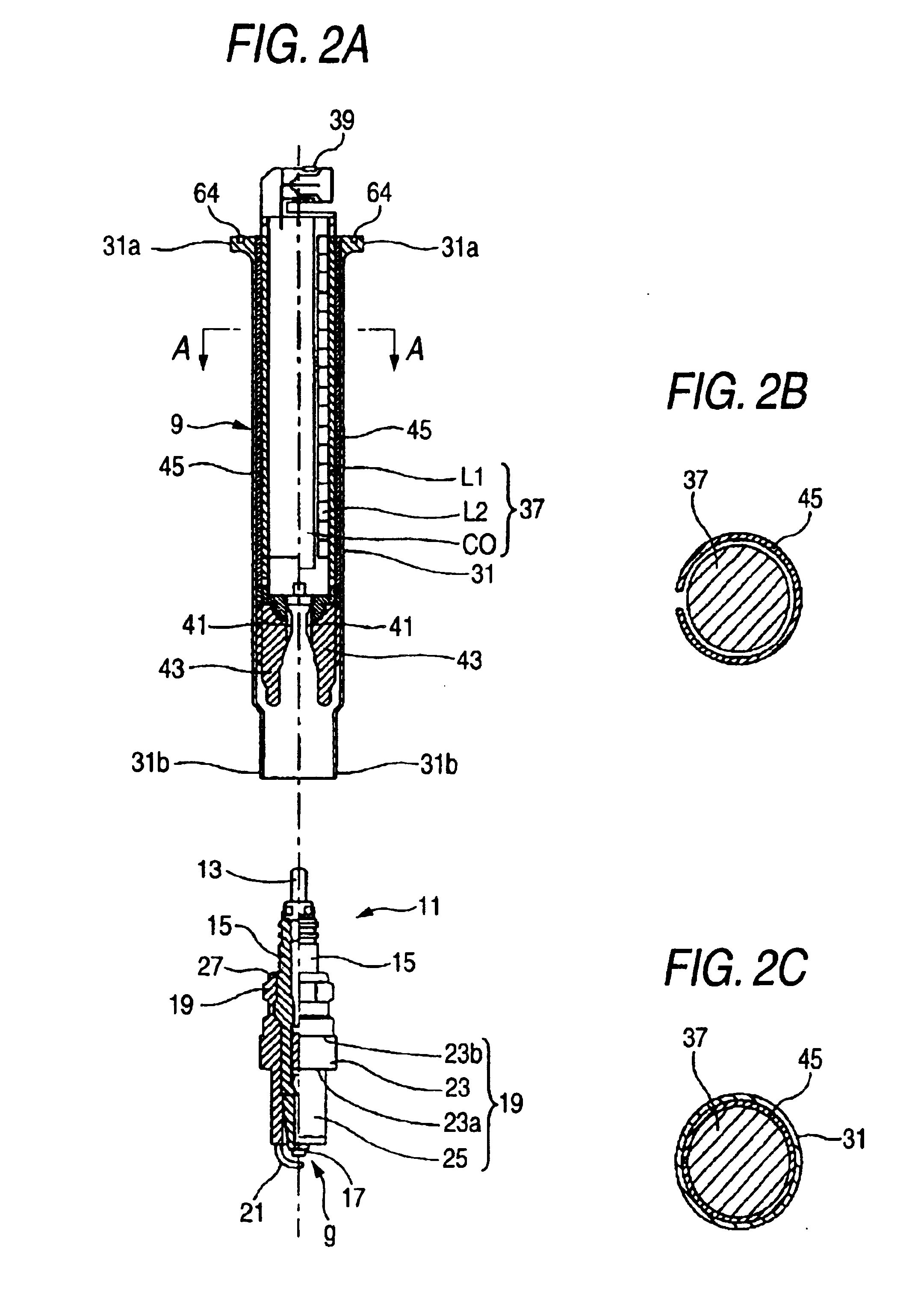

Ignition device for internal combustion engine

InactiveUS20050284454A1Transformers/reacts mounting/support/suspensionSparking plugsCombustion chamberCylinder head

An ignition device for an internal combustion engine has a spark plug, an ignition coil, a housing and a mounting portion. The spark plug is for discharging a current to ignite an air-fuel mixture in a combustion chamber of the internal combustion engine. The ignition coil is for supplying the current to the spark plug. The housing encloses the spark plug and the ignition coil therein. The housing has a mounting portion to be disposed in a mounting hole provided in a cylinder head of the internal combustion engine. The mounting portion includes a screw portion a non-screw portion. The screw portion is to be screw-fastened to the mounting hole. The non-screw portion is not to be screw-fastened to the mounting hole.

Owner:DENSO CORP

Ignition coil

An ignition coil for an internal combustion engine includes a magnetically-permeable core extending along a core longitudinal axis, the core having a pair of end surfaces on axially-opposite ends thereof. The ignition coil also includes a primary winding disposed outward of the core, a secondary winding disposed outward of the primary winding, and a structure comprising magnetically-permeable steel laminations having a base and a pair of legs, the structure defining a magnetic return path. The core is disposed between the pair of legs such that the core longitudinal axis extends through the legs and the end surfaces face toward the legs and at least one of the end surfaces of the core is spaced apart from a respective one of the legs to define an air gap. The structure is over-molded with an over-molding material such that the over-molding material fills at least a portion of the air gap.

Owner:DELPHI TECH IP LTD

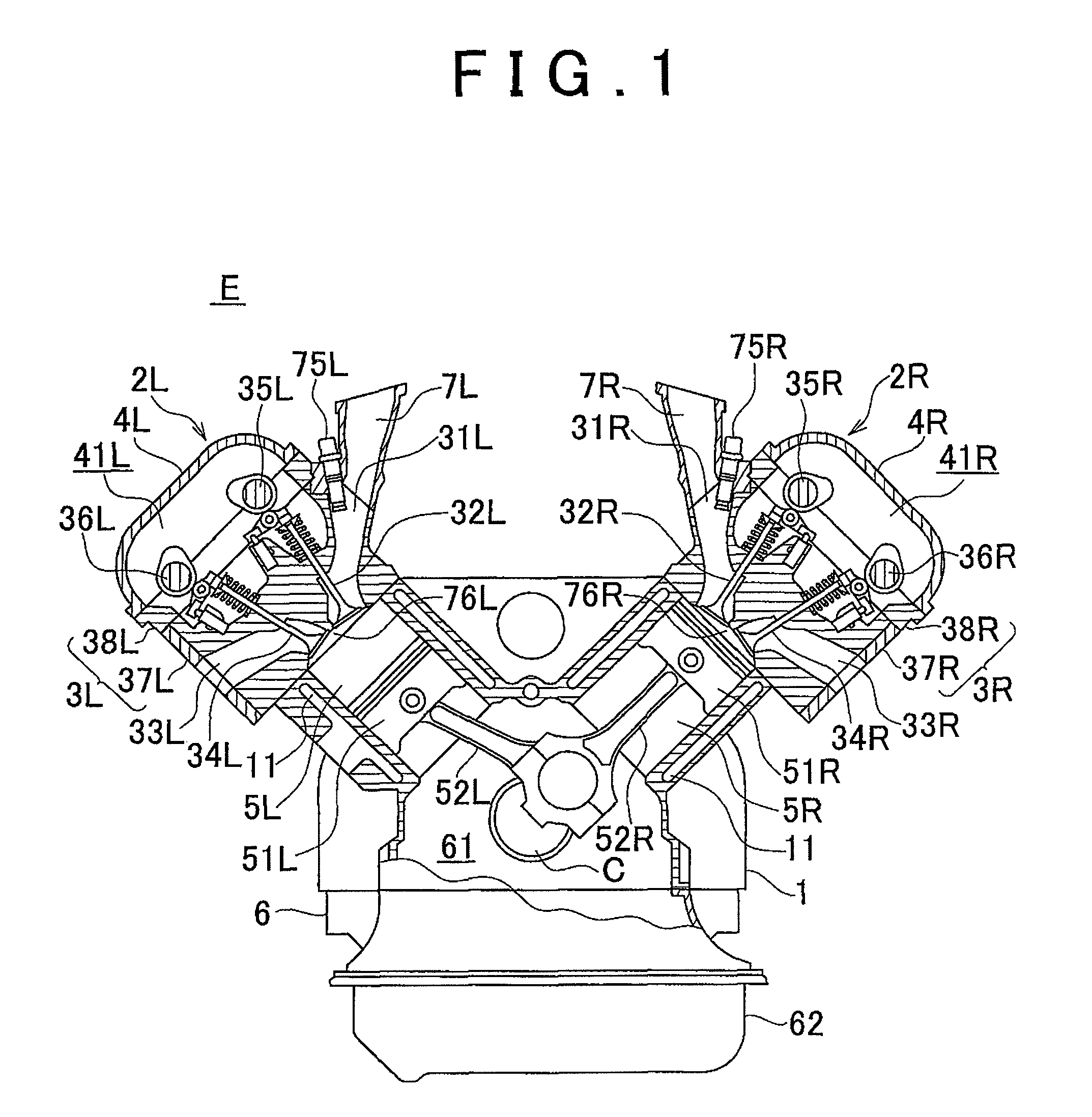

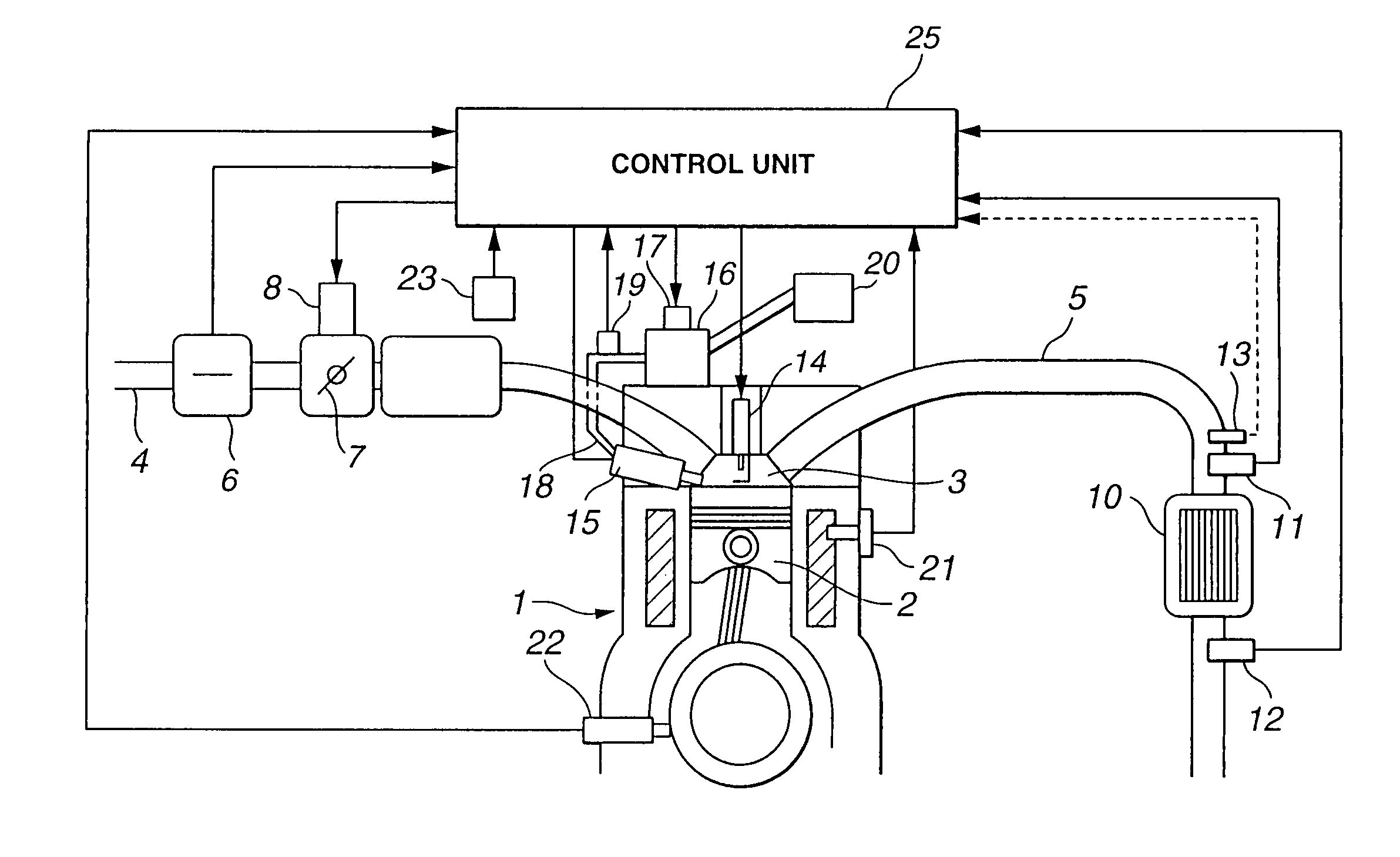

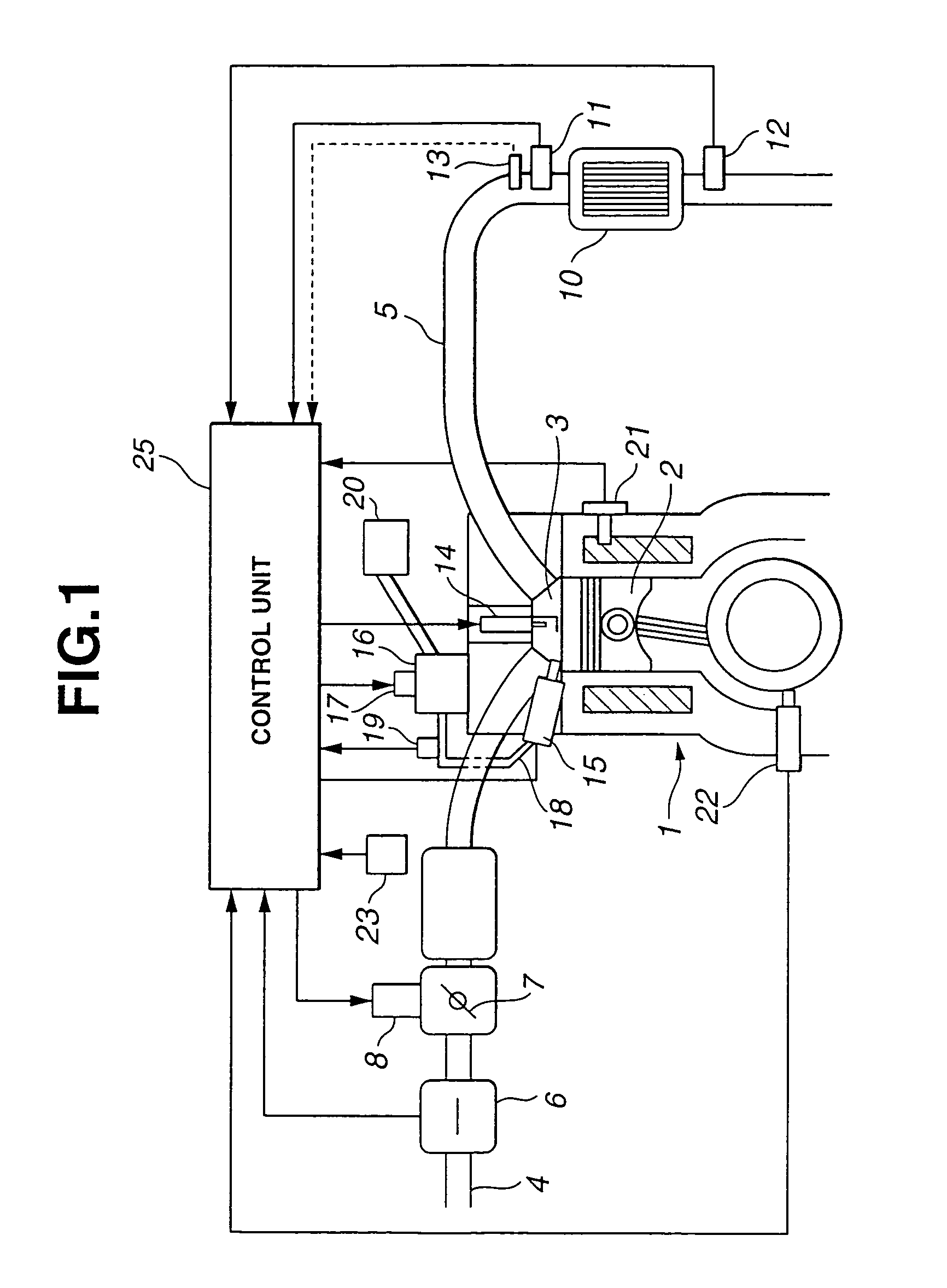

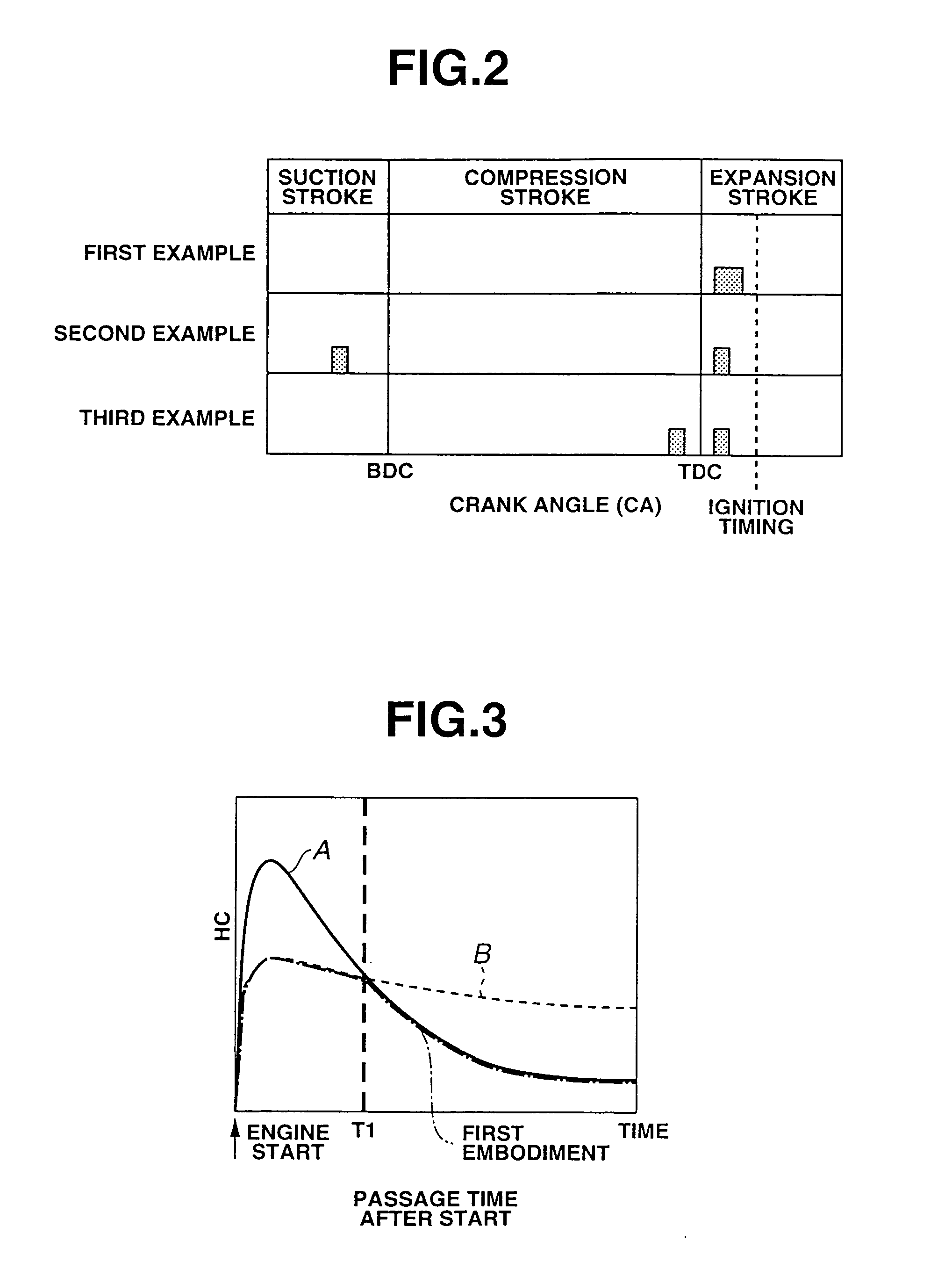

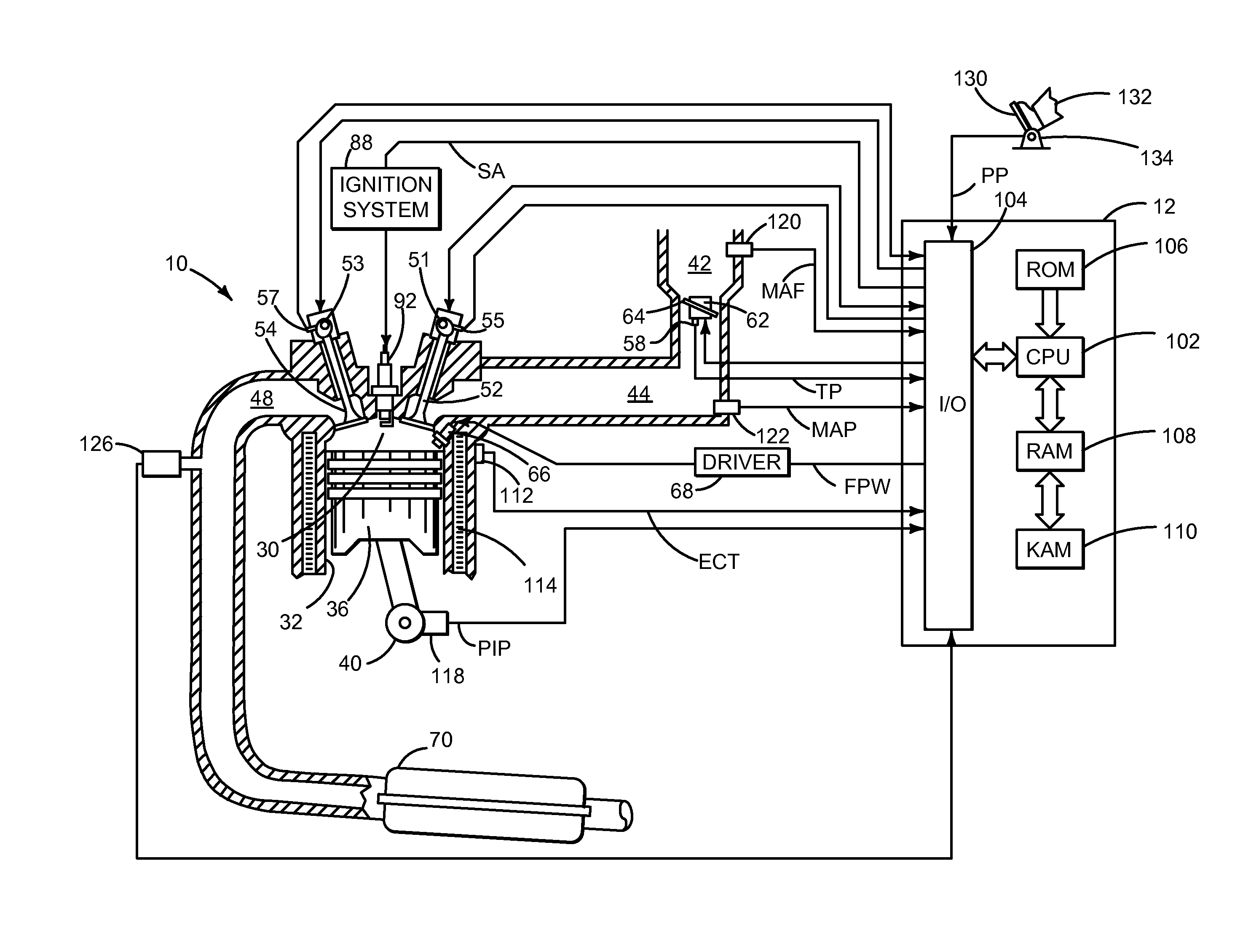

Control method and apparatus for direct injection spark ignited internal combustion engine

ActiveUS7159566B2Good effectShorten the time intervalElectrical controlInternal combustion piston enginesTop dead centerExternal combustion engine

In control method and apparatus for a direct injection spark ignited internal combustion engine, the internal combustion engine comprising a fuel injection valve configured to perform an injection of fuel through an engine cylinder and a spark plug, a super retard combustion comprising: an ignition through the spark plug at a timing after a compression top dead center; and at least once fuel injection in which the injection of fuel is started at a timing after the compression top dead center and before the ignition, during a cold start of the engine, is executed, and an execution of the super retard combustion is inhibited for a predetermined interval of time immediately after the cold start of the engine.

Owner:NISSAN MOTOR CO LTD

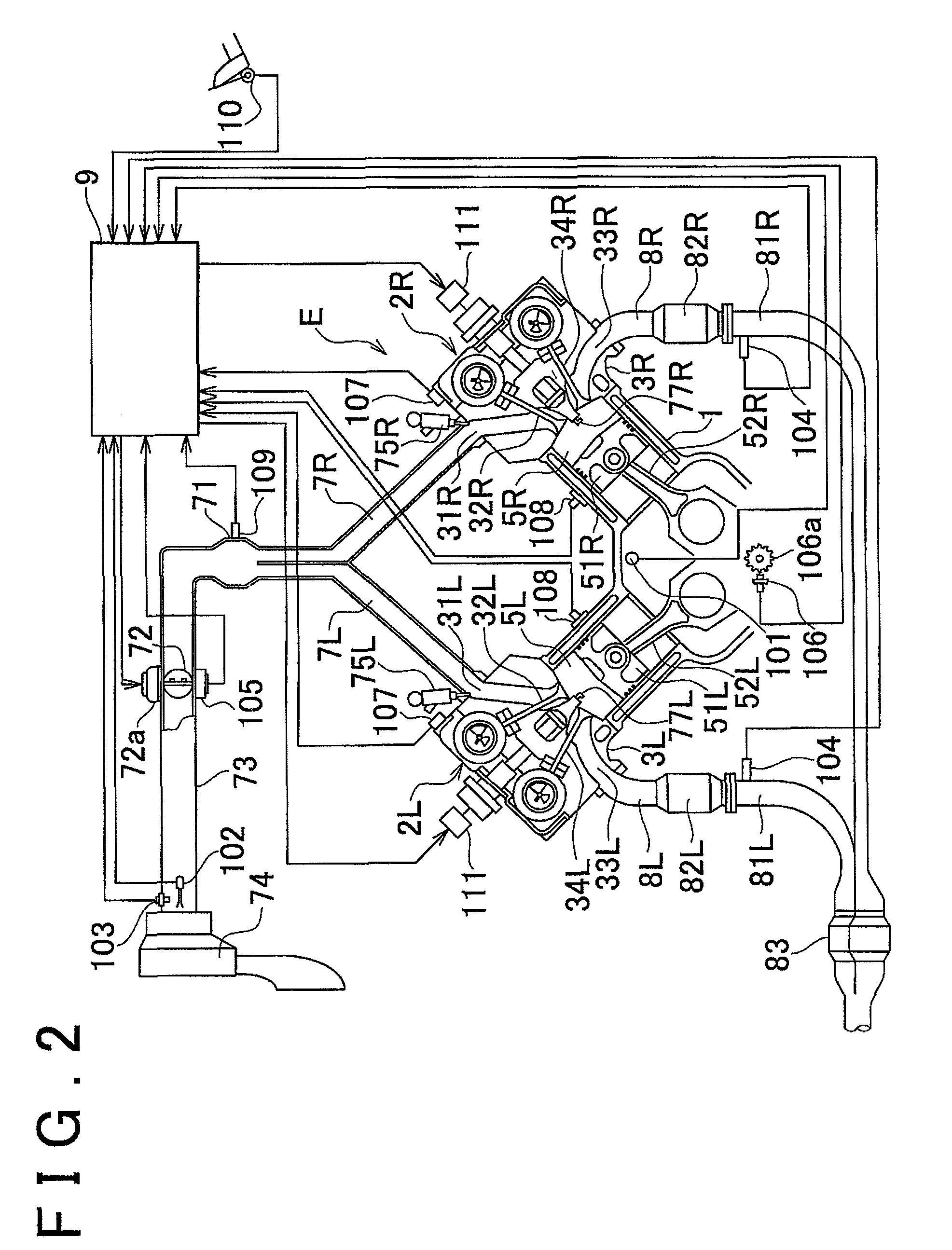

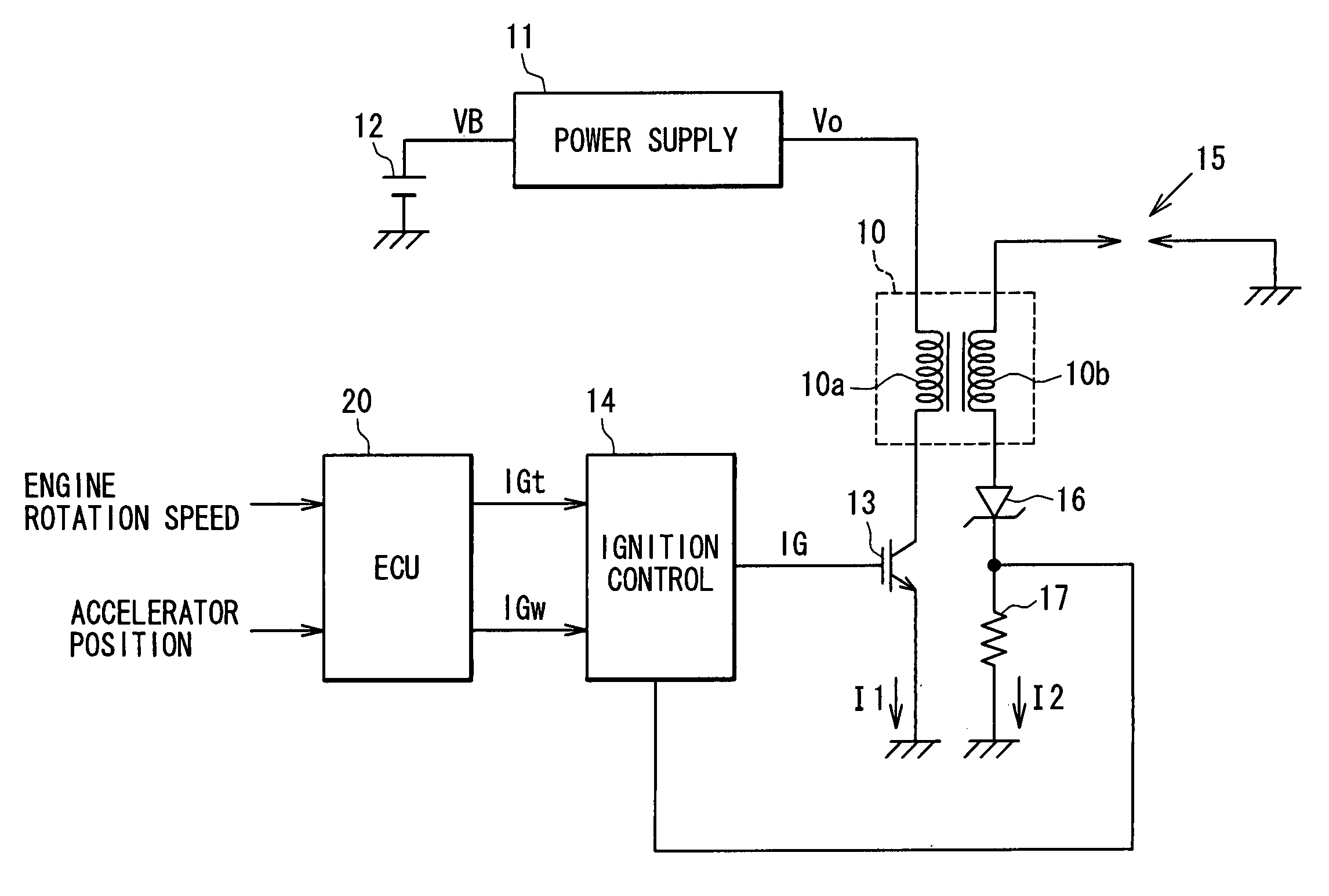

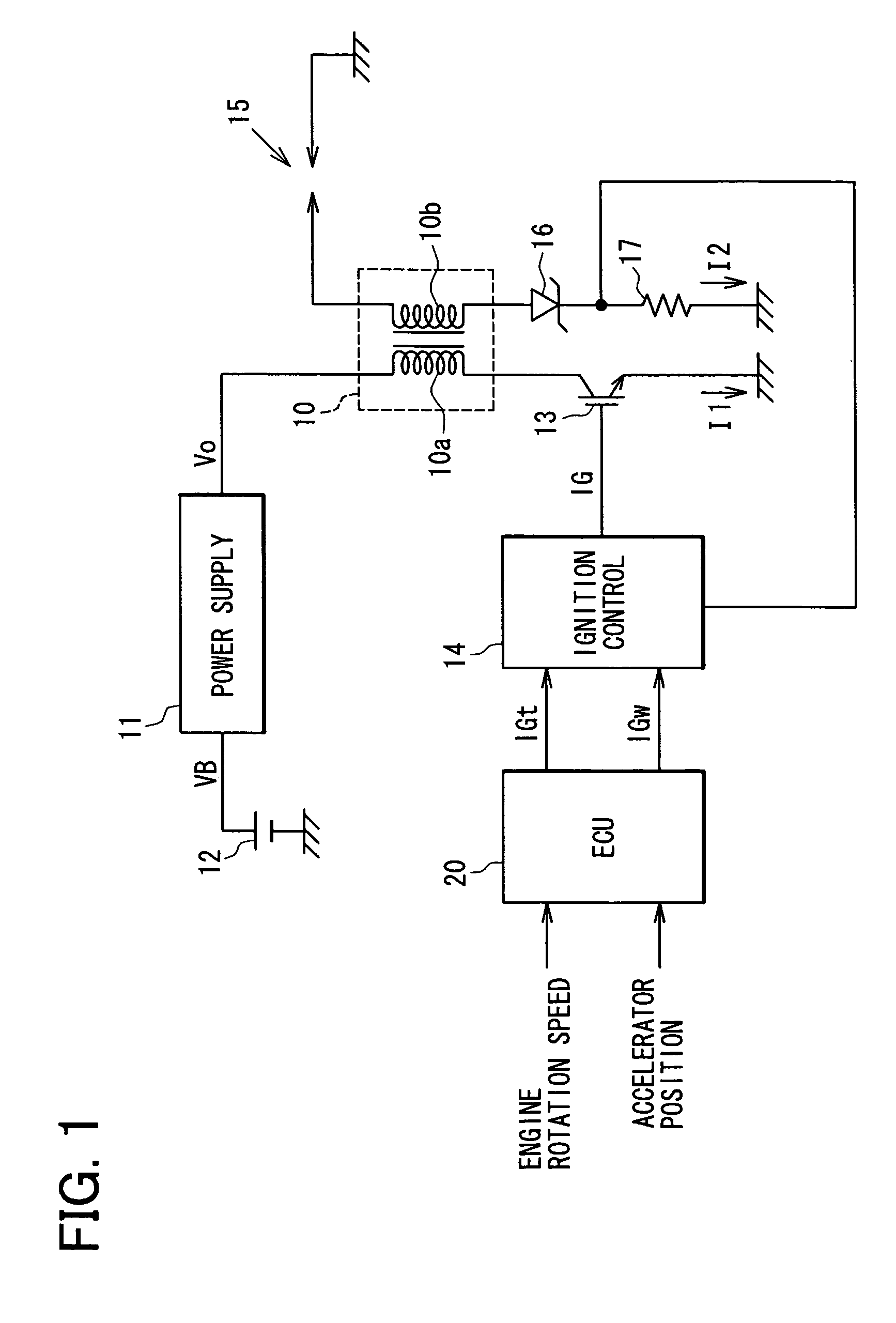

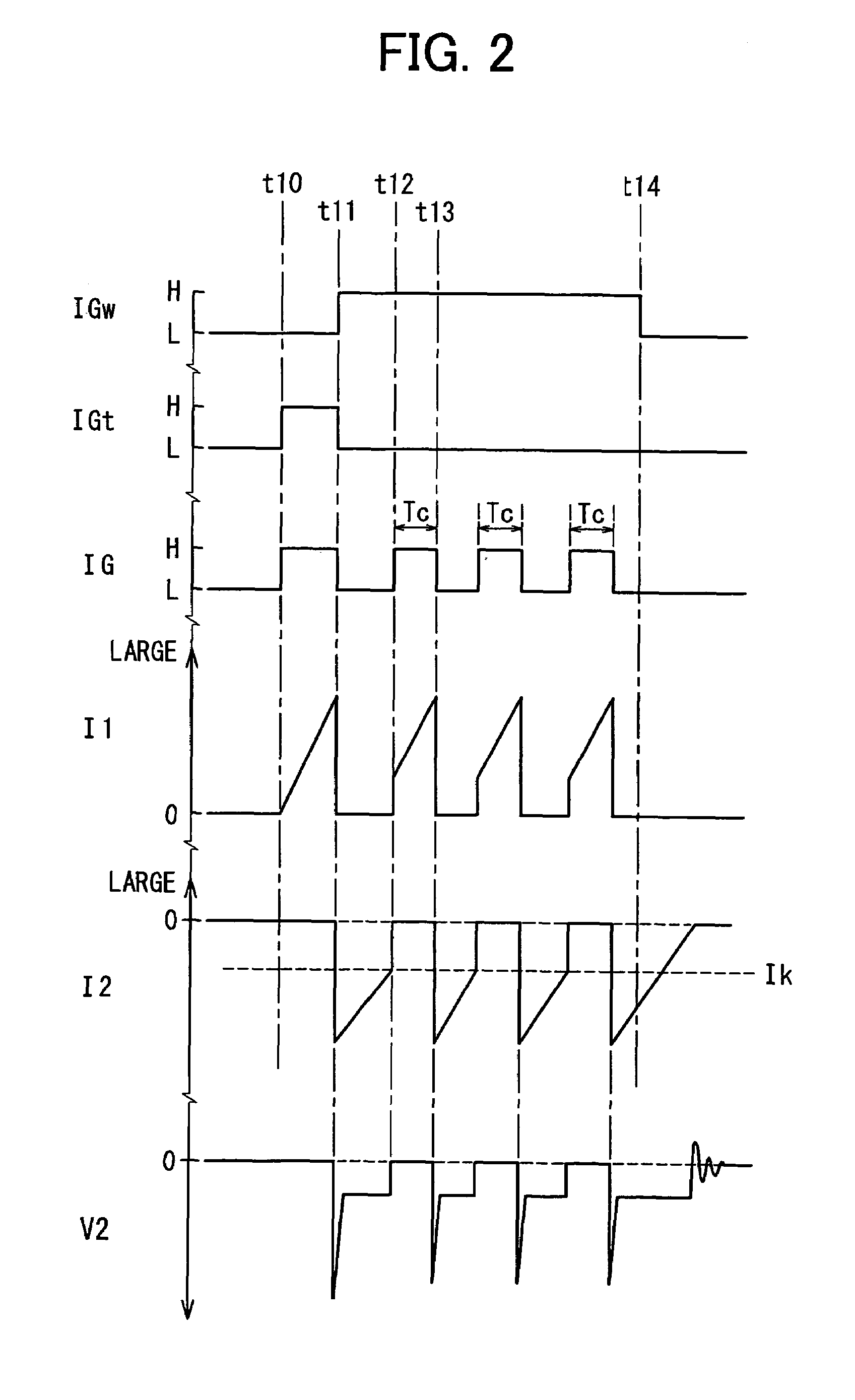

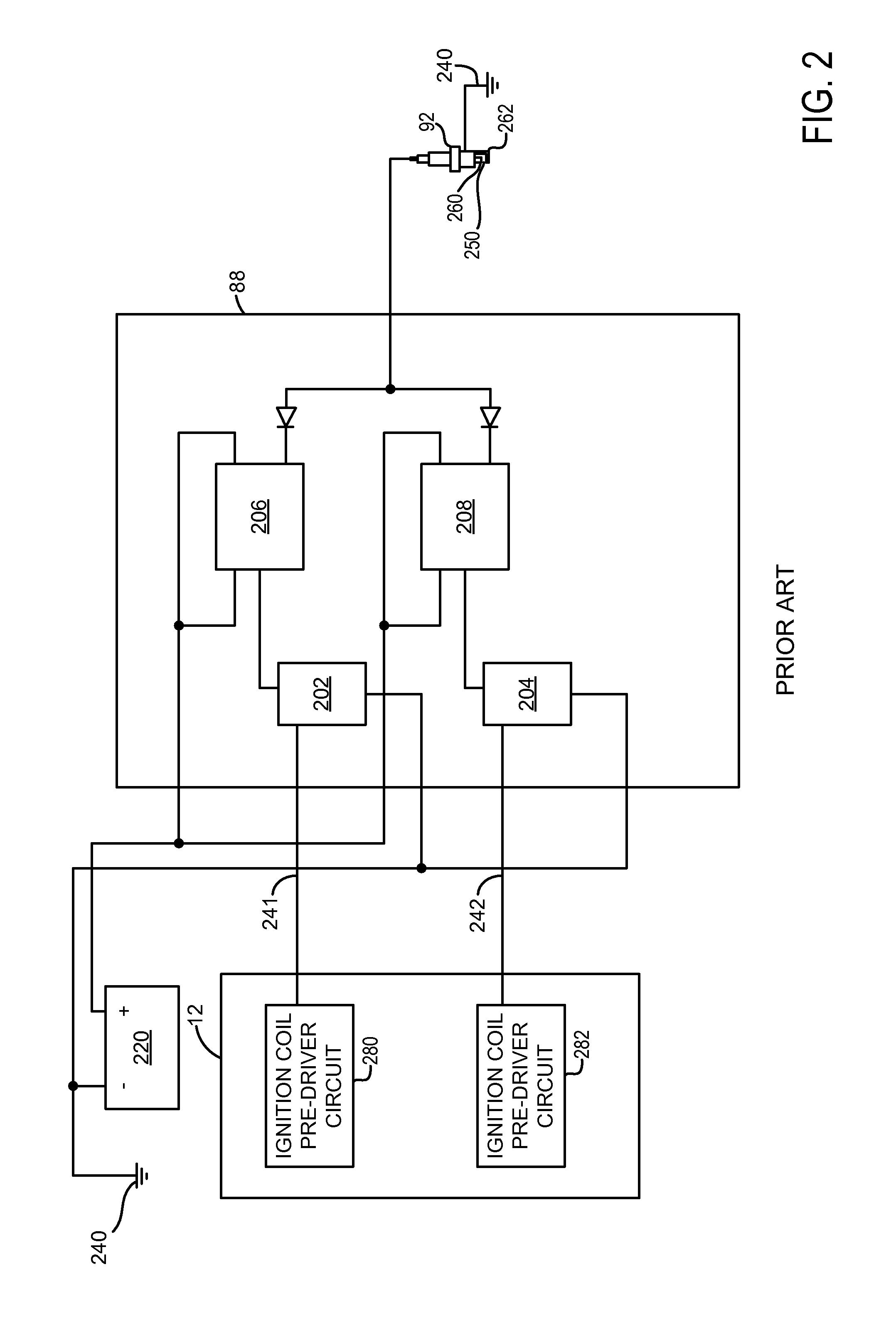

Multiple-spark ignition system for internal combustion engine

ActiveUS7392798B2Improve ignition performanceInternal combustion piston enginesGenerator generated ignition energyIgnition coilMixed gas

Owner:DENSO CORP

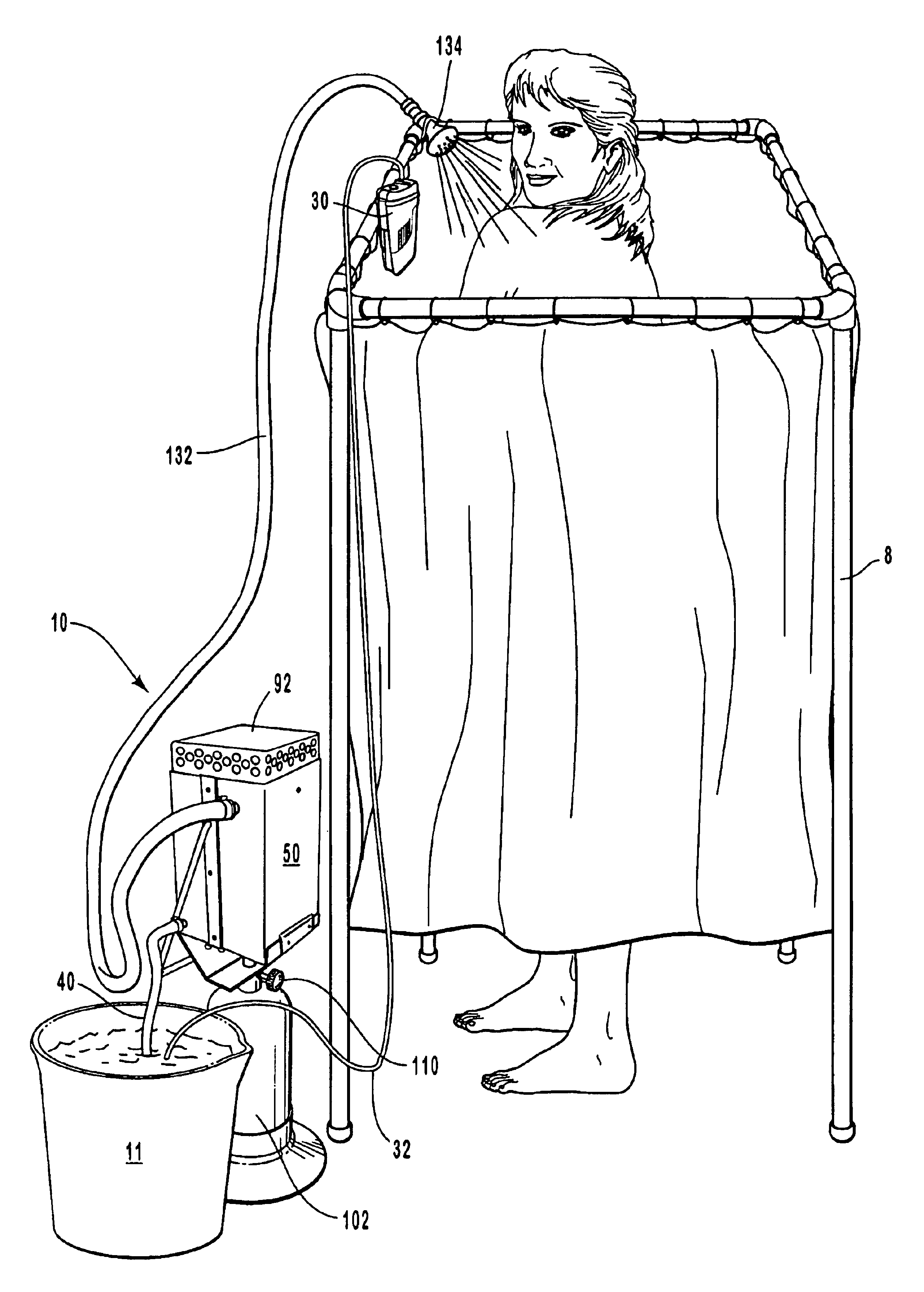

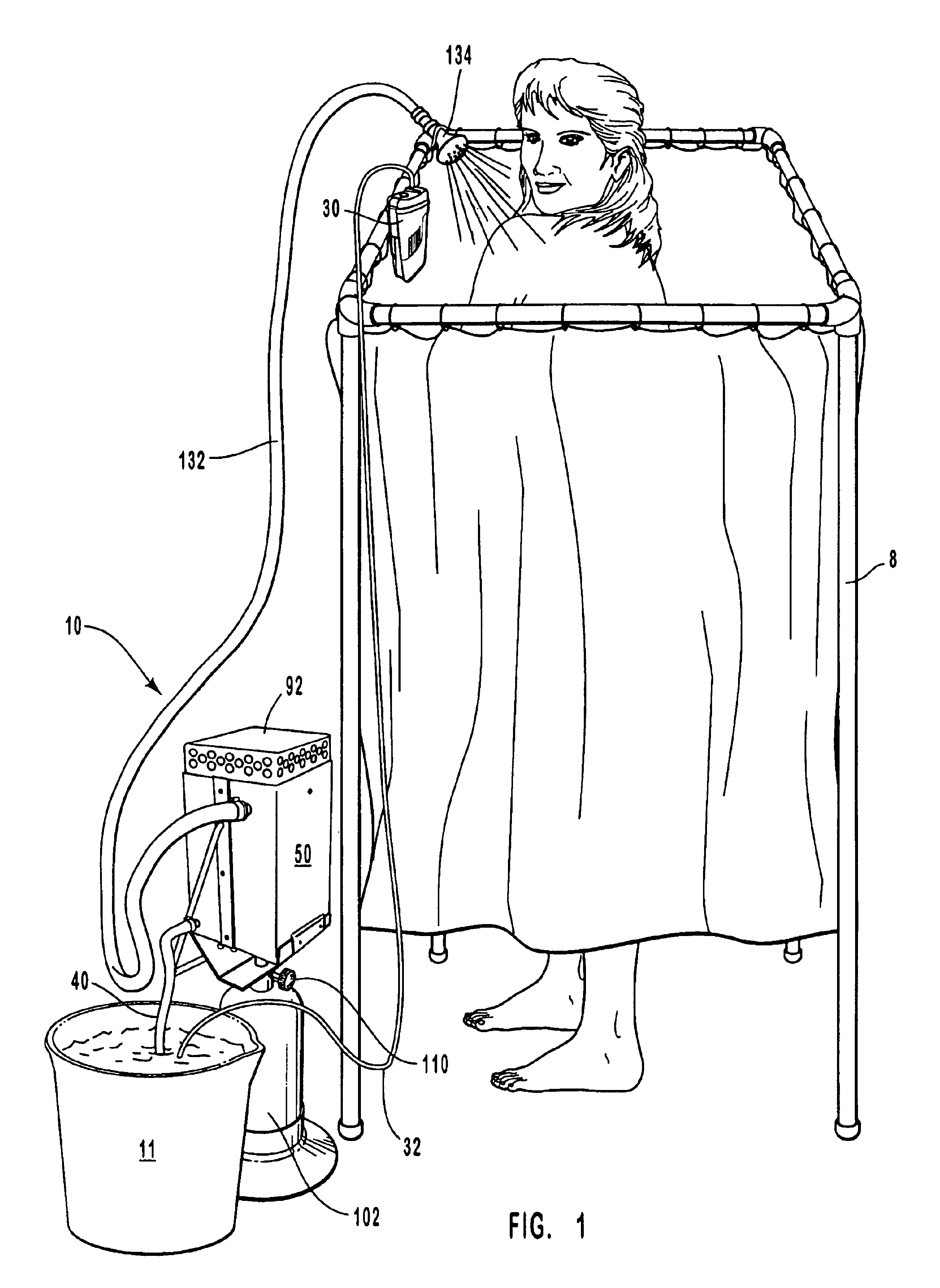

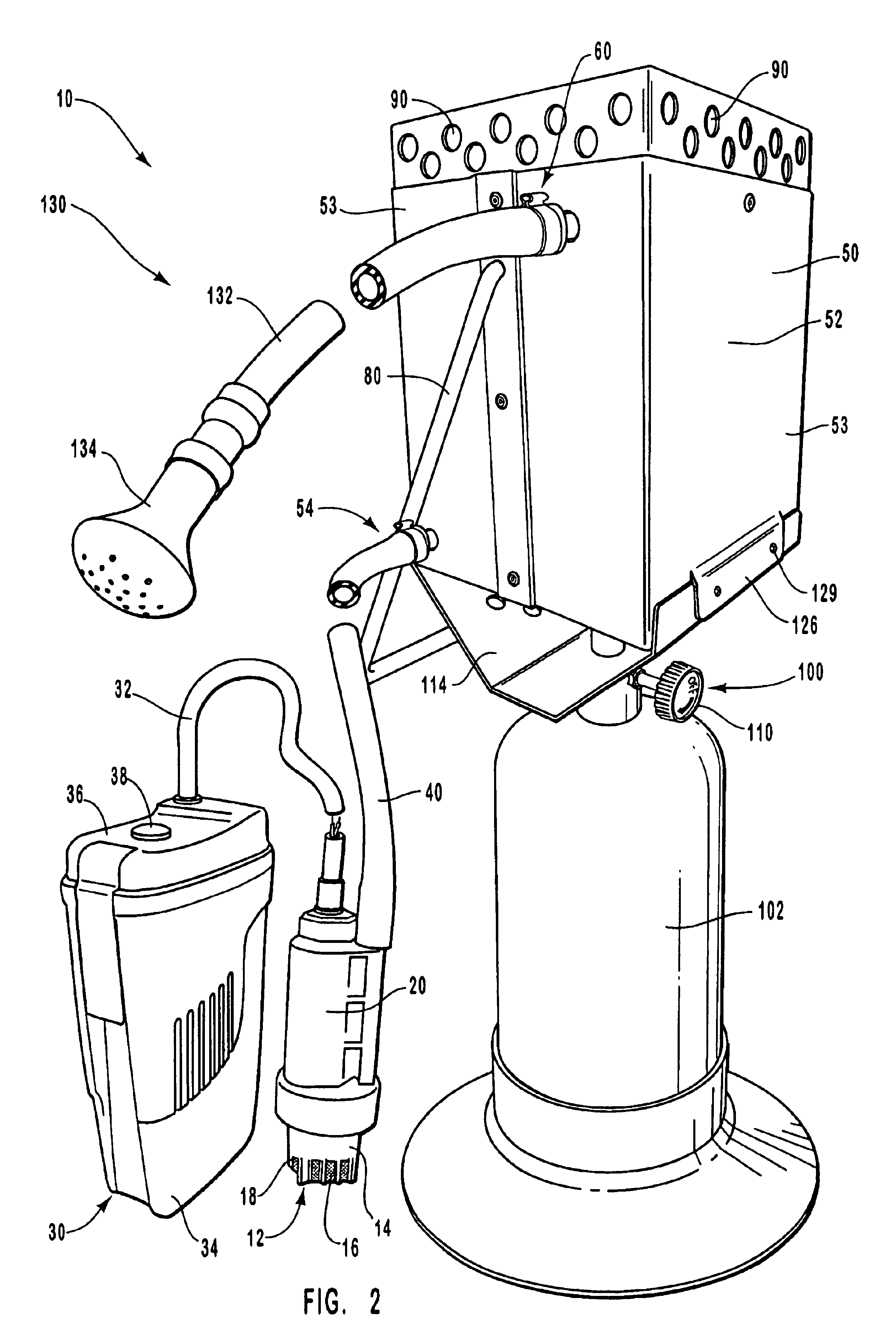

Portable water heater

InactiveUS6978496B2Minimal heat lossProvides heated quickly and efficientlyBathsDouchesWater sourceEngineering

A portable hot water heater for use during camping, boating, hunting, hiking, fishing, backpacking, etc. The hot water heater advantageously efficiently and rapidly heats large quantities of water for hot showers, cooking and cleaning. The hot water heater includes a pump that can draw water from any suitable water source, a power source, a heating assembly that quickly and efficiently heats the water as it flows through the heating assembly. The heating assembly is attached to a shower head or other fixture.

Owner:TAPH

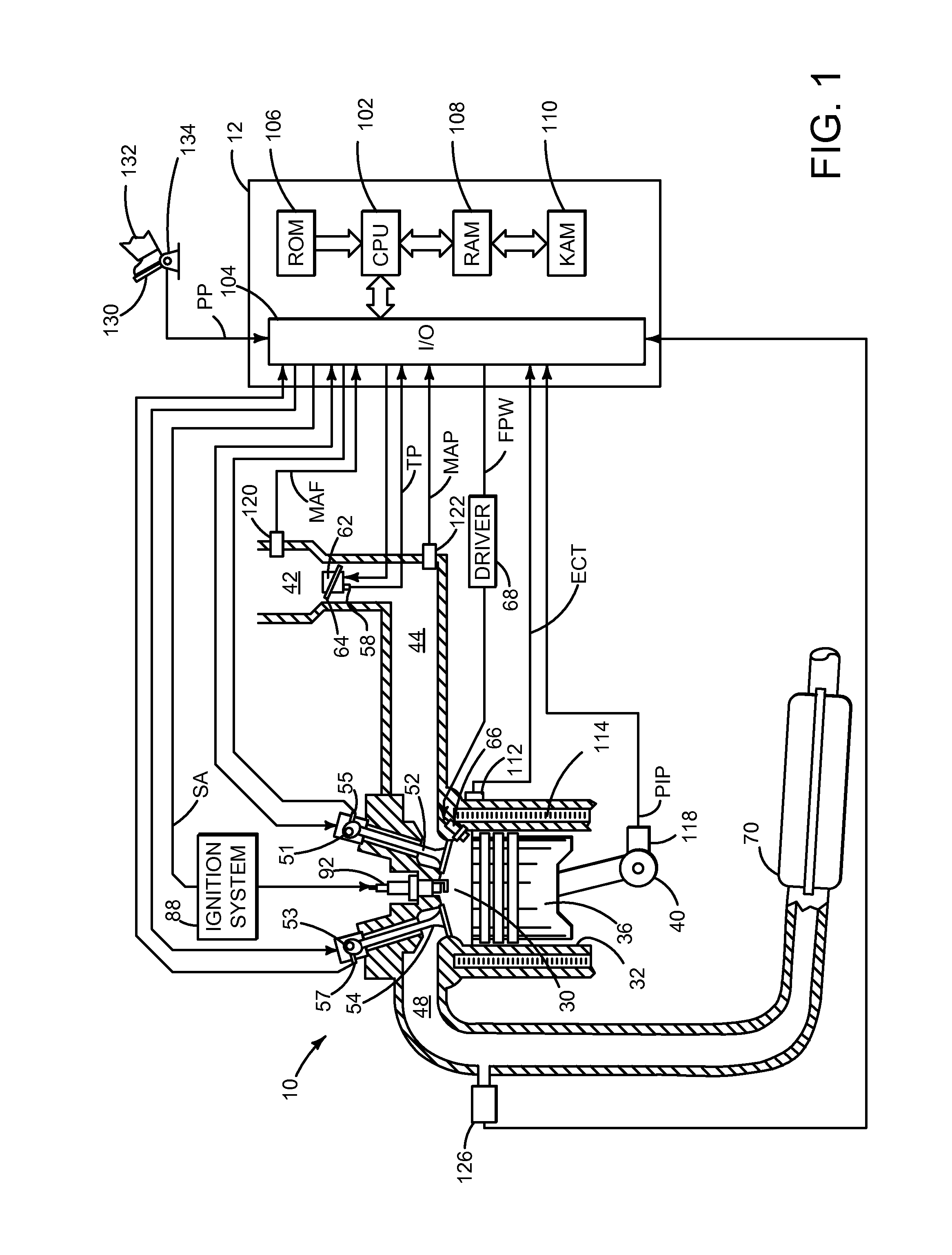

System and method for delivering spark to an engine

ActiveUS20140102412A1Increase the number ofImprove economyGenerator generated ignition energyMachines/enginesElectrical conductorIgnition coil

A system and method for delivering spark to an engine is disclosed. In one example, a single conductor carries a spark signal that is indicative of a desired spark advance for a plurality of ignition coils. The system and method may reduce wiring complexity for spark plugs that are supplied energy via two ignition coils.

Owner:FORD GLOBAL TECH LLC

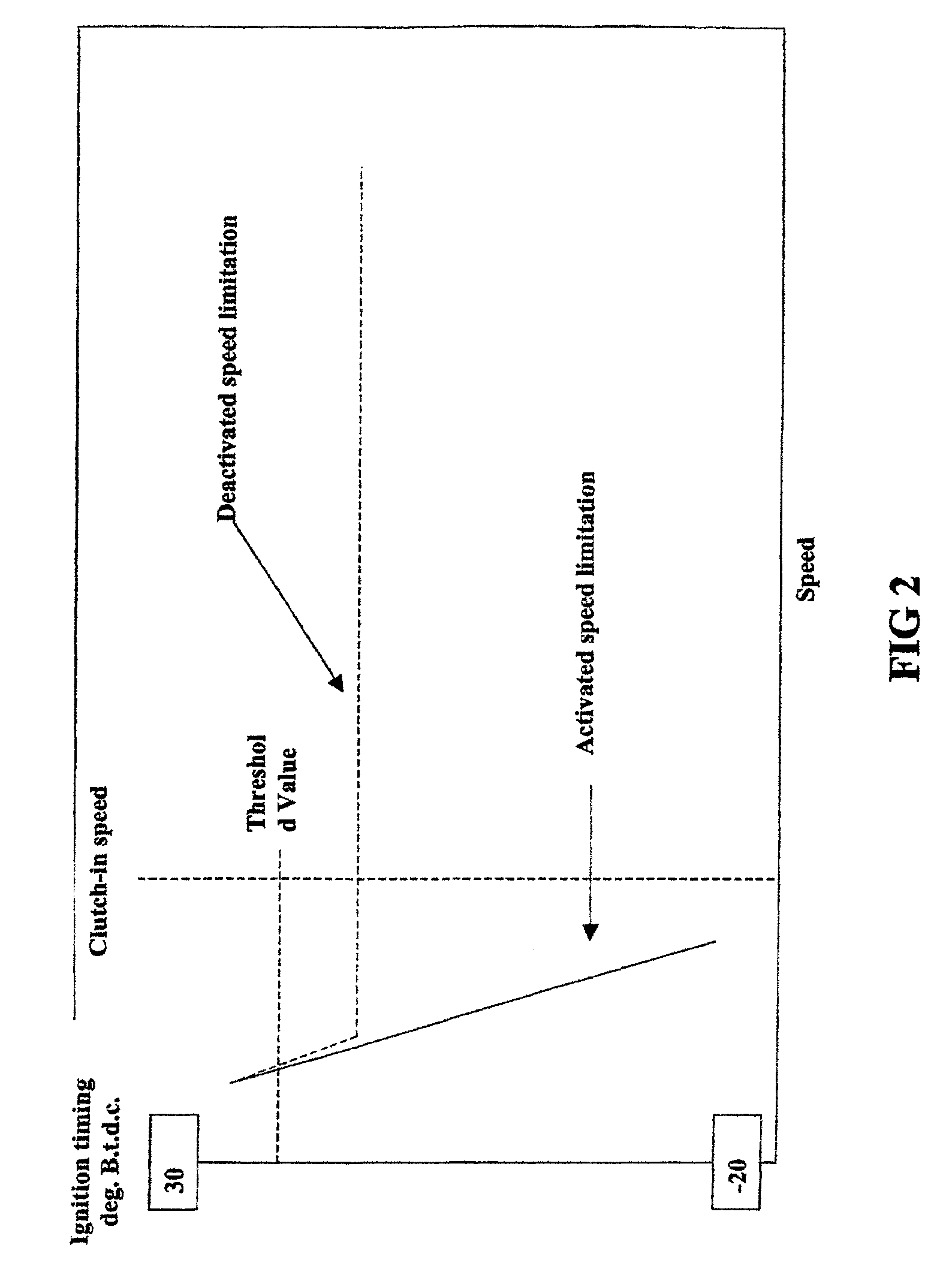

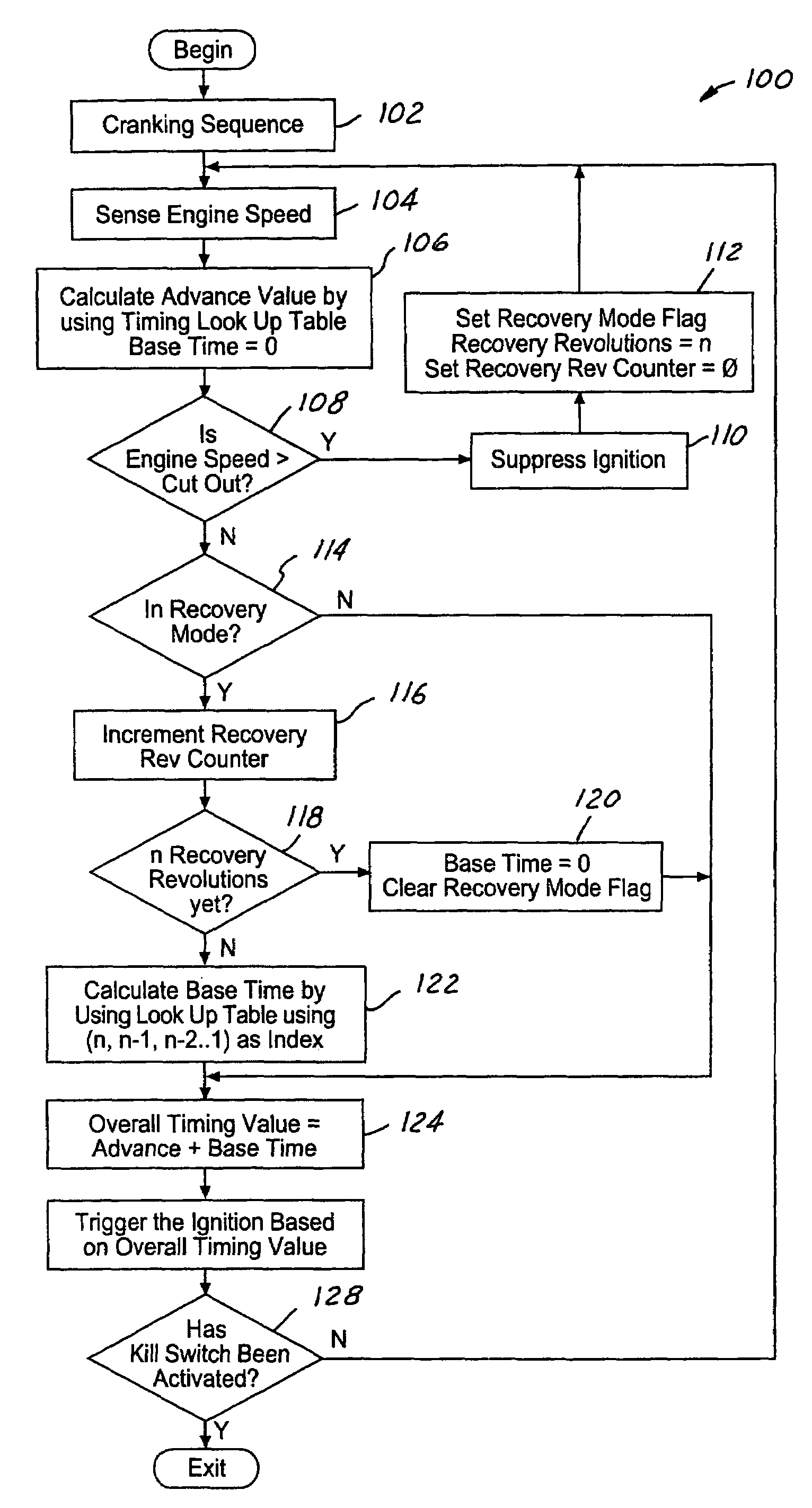

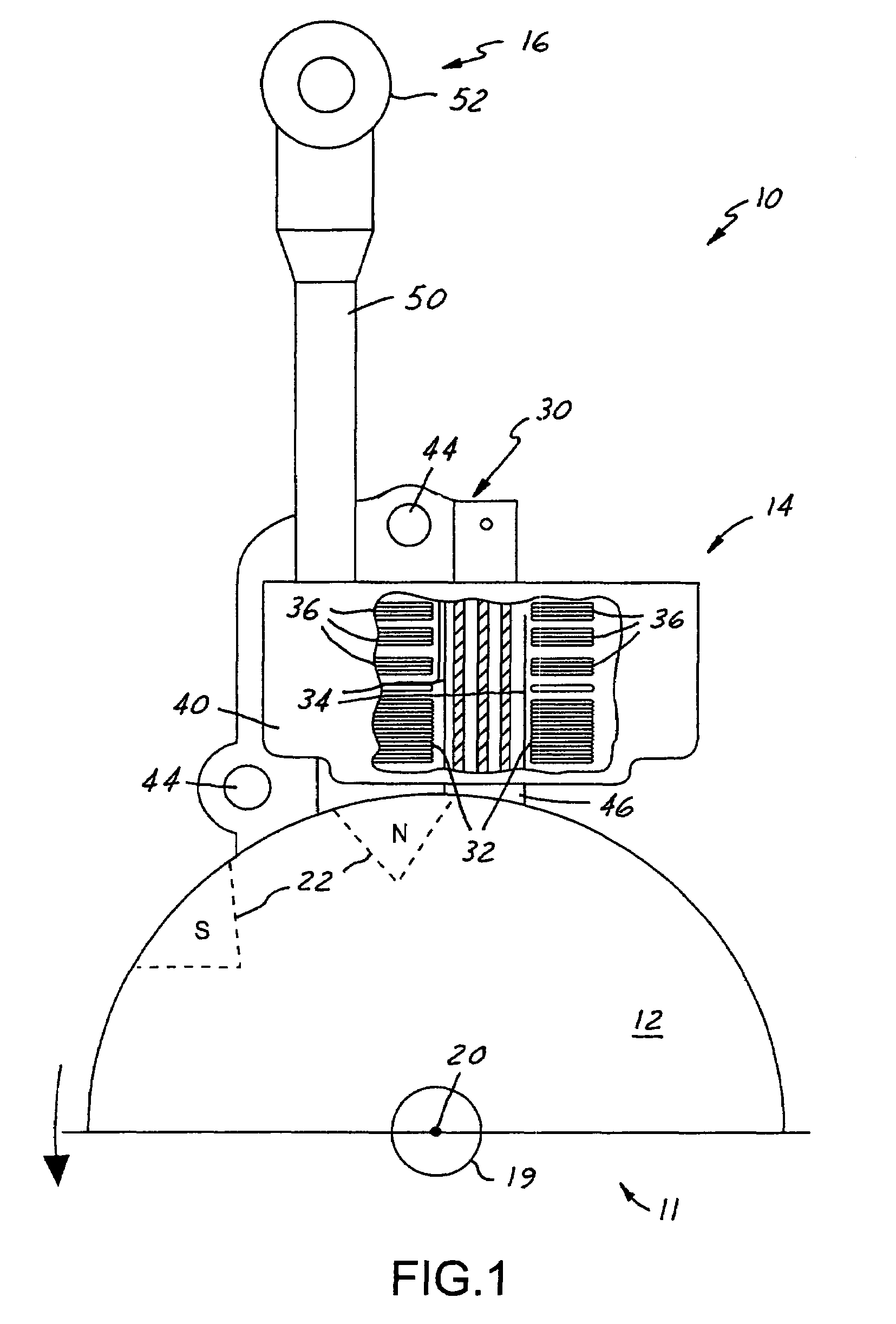

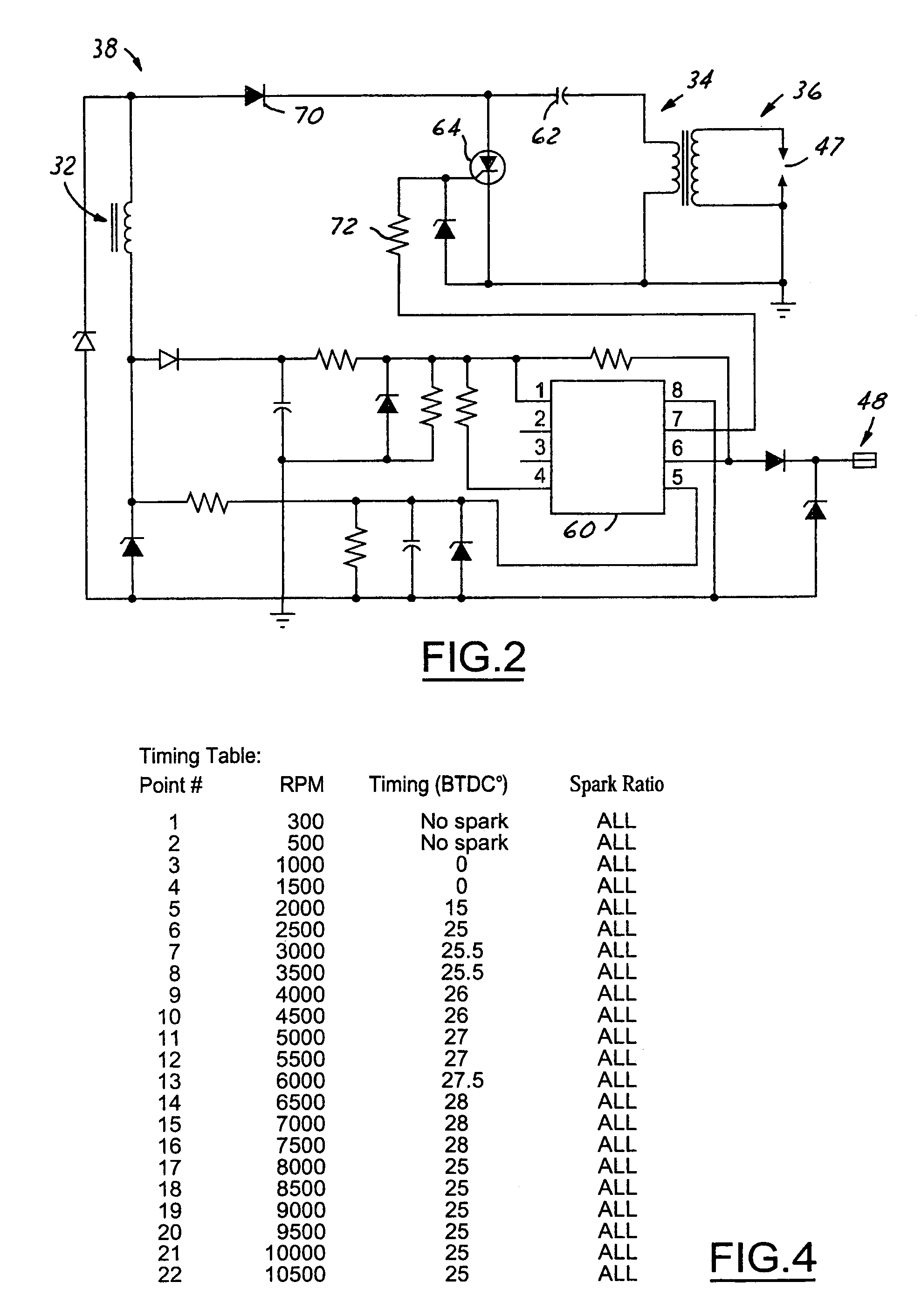

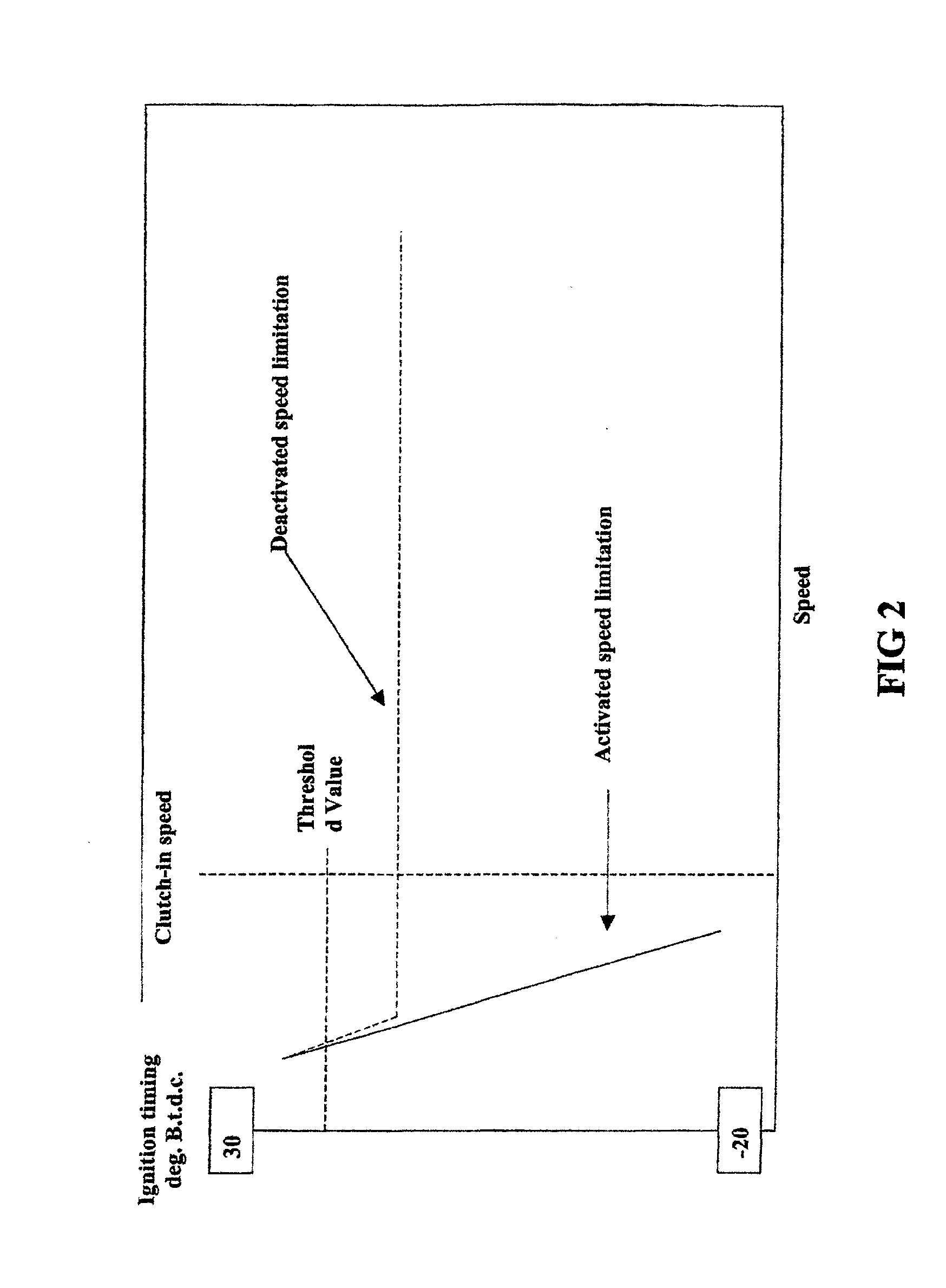

Independent timing retard for engine speed limiting

ActiveUS7040282B2Reduce spikesEasy to adaptGenerator generated ignition energySpeed sensing governorsCombustion chamberMaximum pressure

A method and system for operating an engine wherein ignition of the engine is activated according to a predetermined timing schedule that references engine speed, and the ignition is suppressed above a predetermined engine speed threshold to allow engine speed to fall below the predetermined engine speed threshold. Thereafter, ignition is reactivated according to timing that is retarded relative to the predetermined timing schedule for a predetermined number of engine revolutions substantially when the engine speed has fallen below the predetermined engine speed threshold, thereby mitigating undesirable spikes in combustion chamber maximum pressure.

Owner:WALBRO LLC

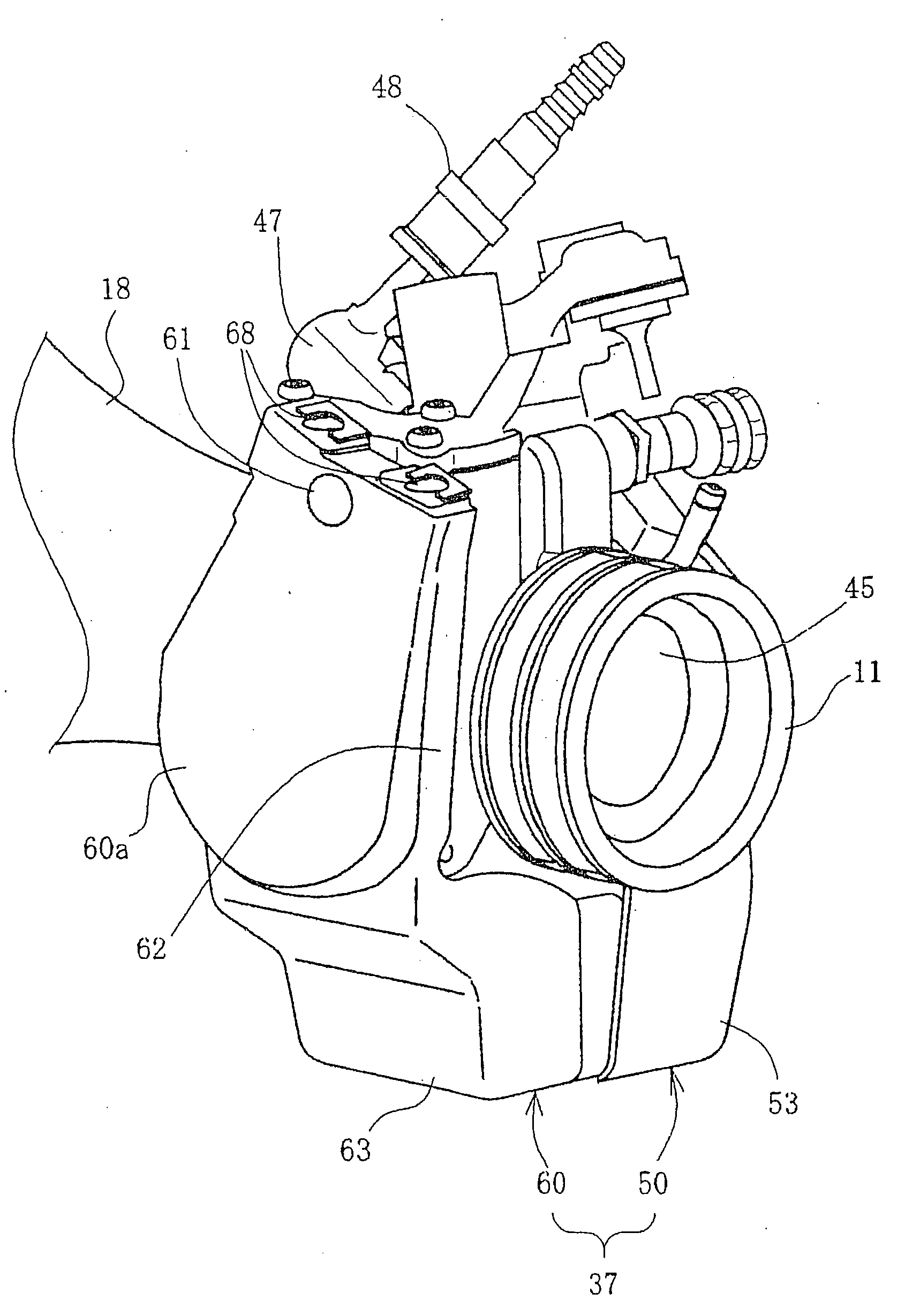

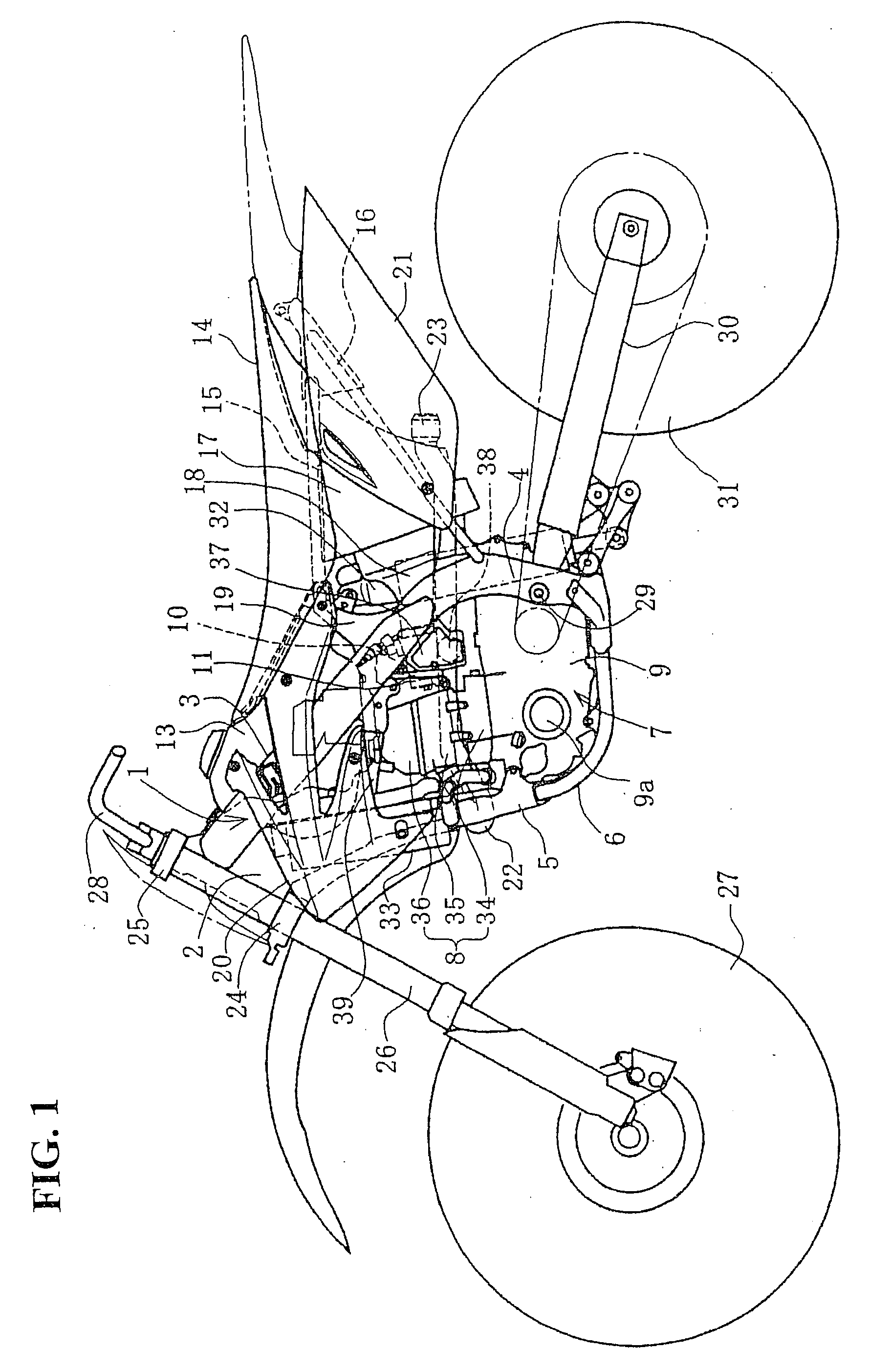

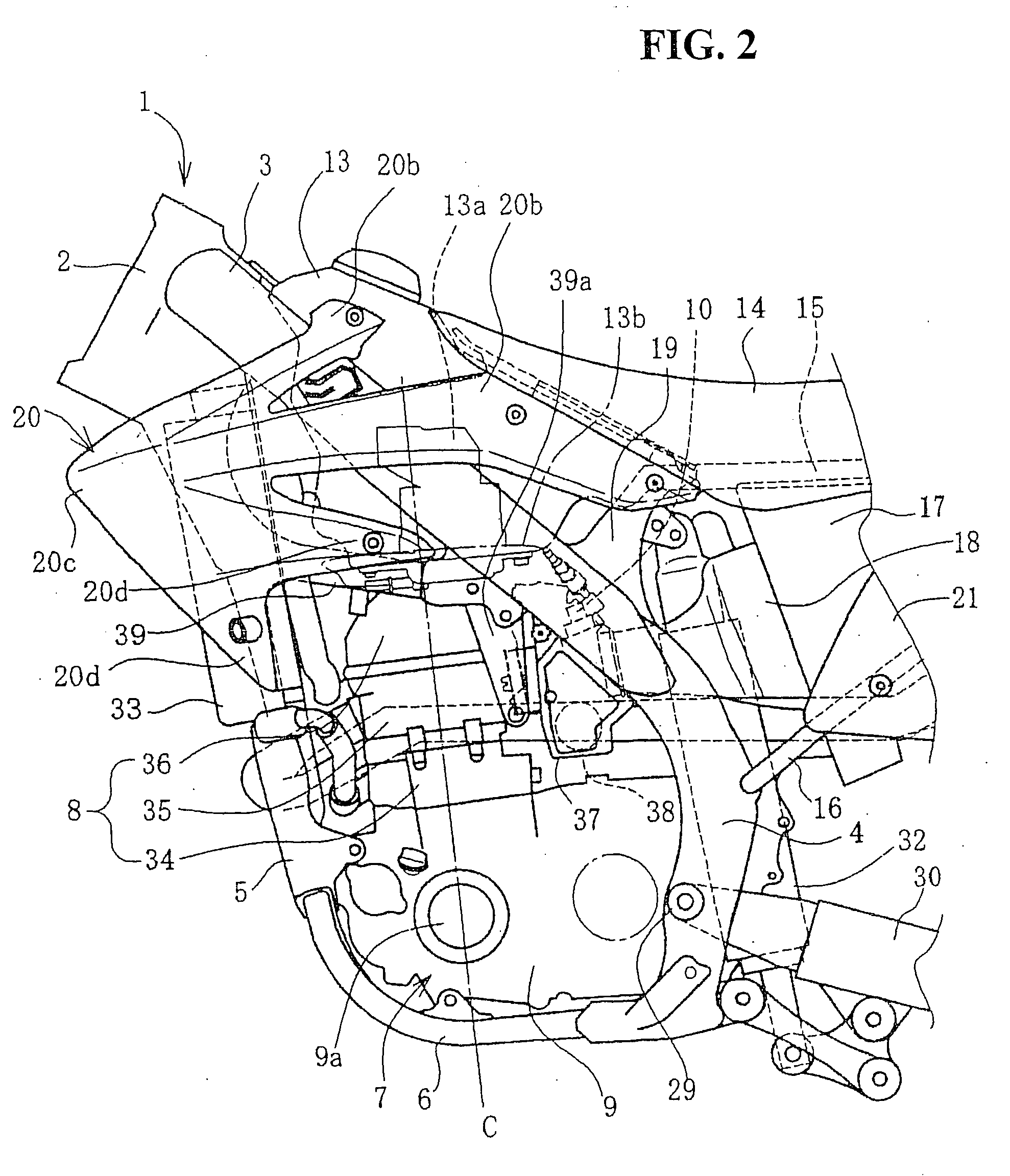

Electric component support structure for motorcycle

ActiveUS20070221169A1Advantageous vibration isolating support structureSolve large capacityCycle equipmentsEngine controllersControl theoryElectrical element

A mounting structure on motorcycle for protecting a capacitor from vibration and heat. In an engine having an upright cylinder a throttle body is connected to an intake path of the cylinder via an insulator, and the throttle body is connected to an air cleaner via a connecting tube. The throttle body is thereby elastically supported relative to the engine and a vehicle body frame via the insulator and the connecting tube. A capacitor is disposed at a position downward of the throttle body. The capacitor is supported integrally with the throttle body using a lower portion of a throttle body cover that covers both left and right sides of the throttle body. A vibration isolating support structure is thus achieved for the capacitor by using the throttle body that is elastically supported.

Owner:HONDA MOTOR CO LTD

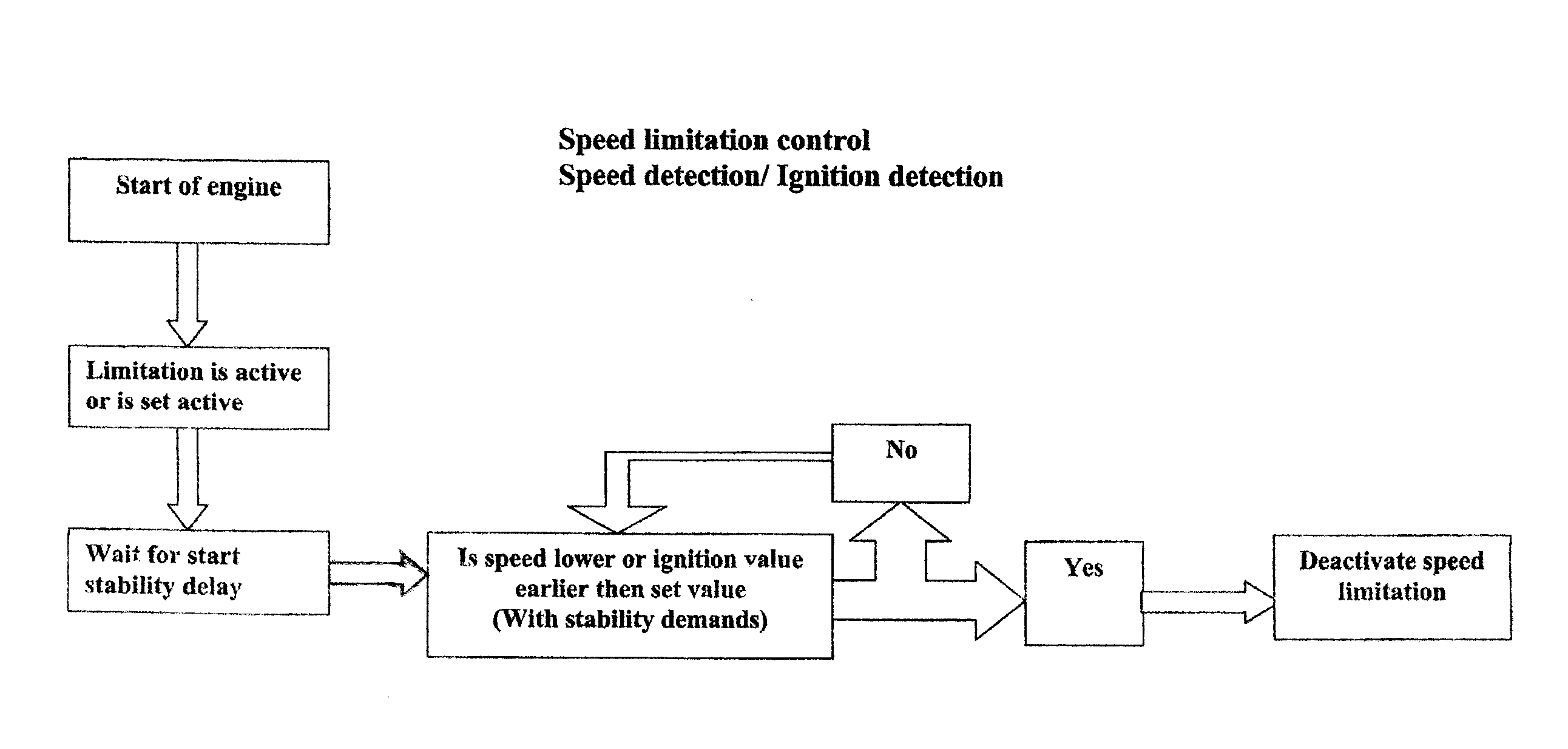

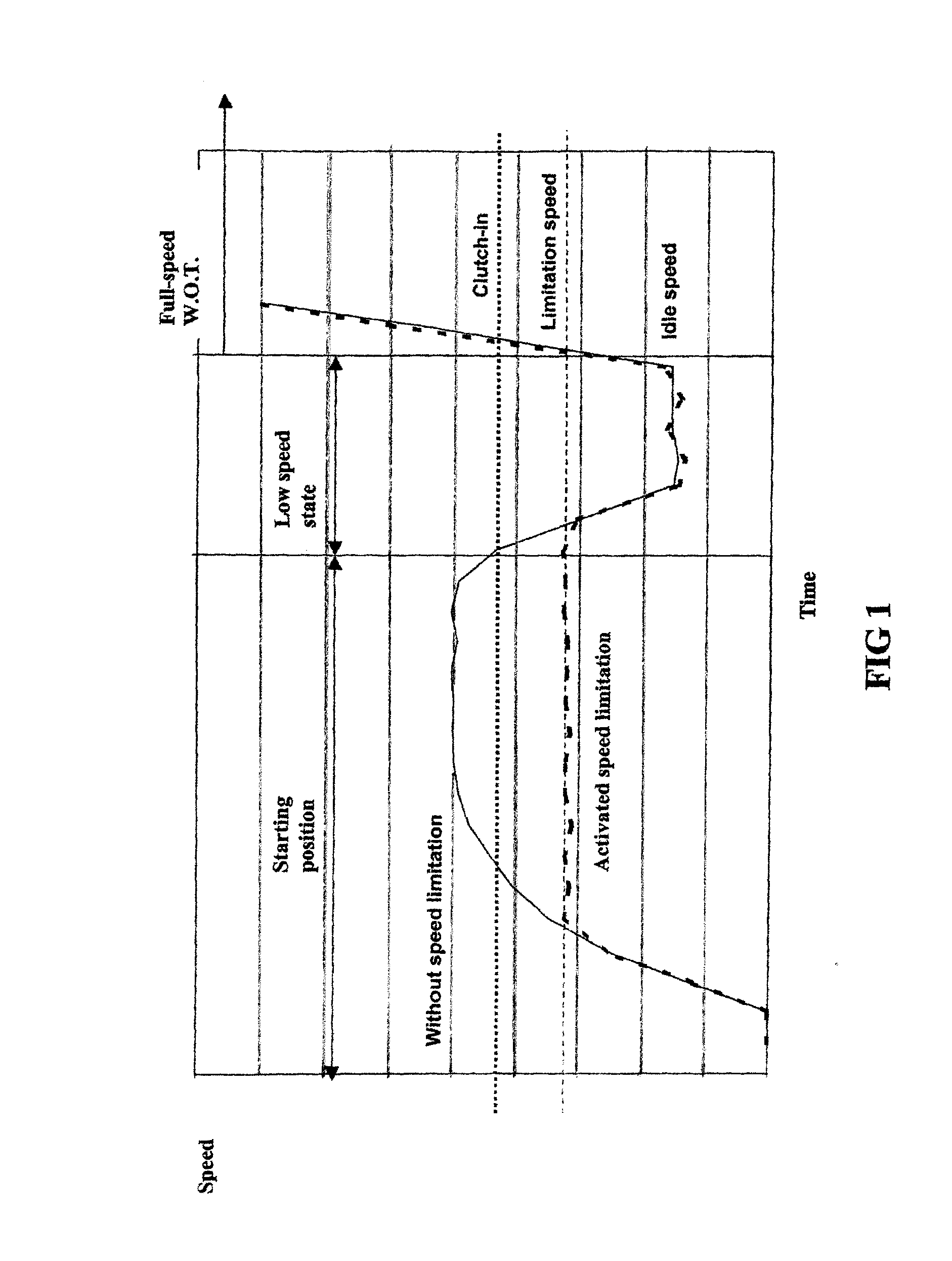

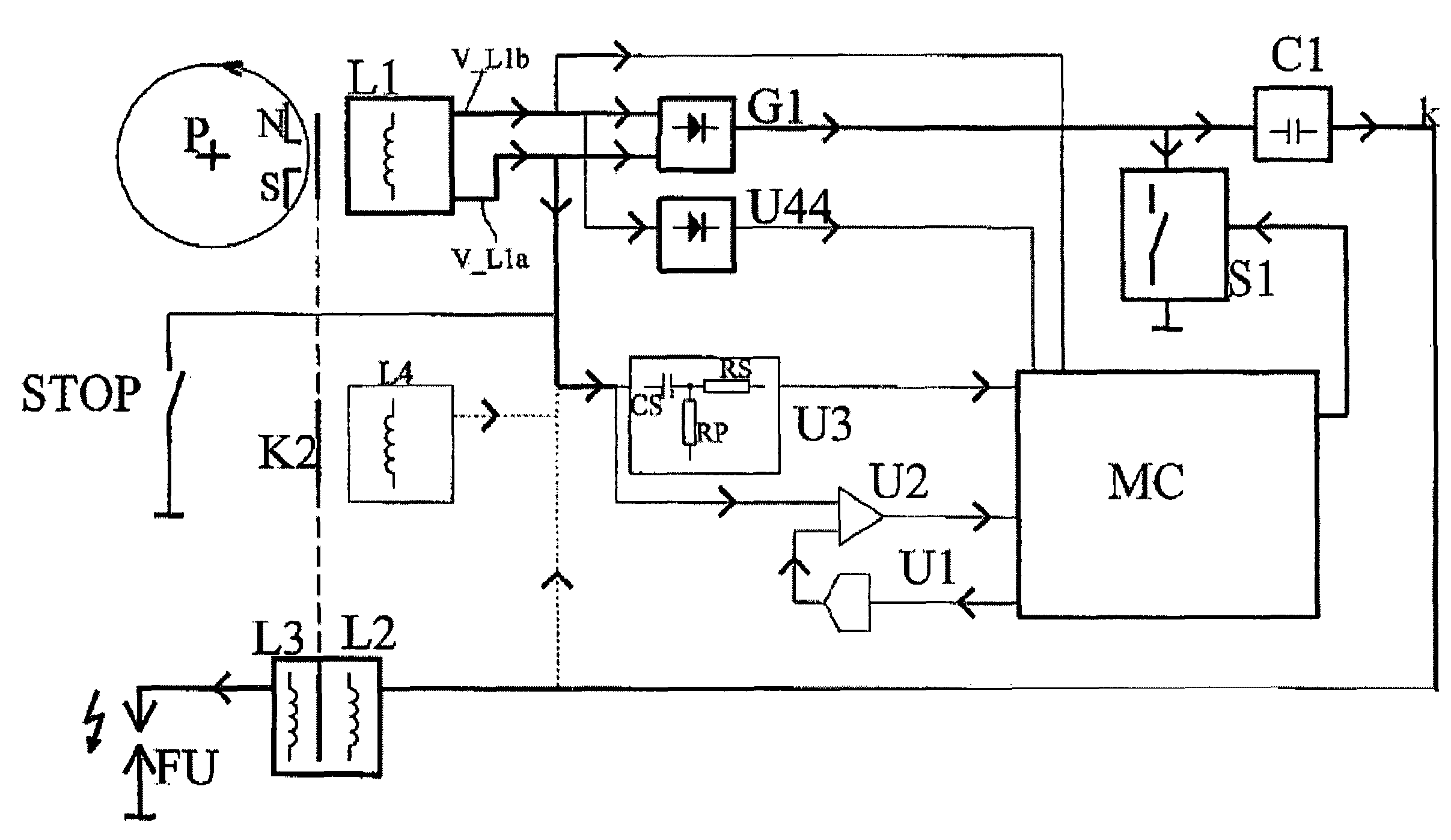

Start safety ignition system

A method for controlling an ignition system of an internal combustion engine having a primary firing pulse generator for charging a capacitor. An electronic switch is included for discharging the capacitor via an ignition coil to generate an ignition voltage. A microcomputer operates the switch to control the ignition timing of the generator. The microcomputer is in communication with a speed sensor that detects the rotational speed of the engine and a speed limitation control that limits the engine speed to a limitation speed below the clutch-in speed of an included centrifugal clutch. The speed limitation control is active or activated when one of either starting the engine or an operating problem of the power tool is detected. The speed limitation control is deactivated when a low speed state of the engine is detected.

Owner:HUSQVARNA AB

Ignition method with stop switch for internal-combustion engines

ActiveUS7156075B2Avoid triggerAvoid ignitionElectric motor startersGenerator generated ignition energyInformation controlSignal on

For stopping an internal combustion engine, a stop switch prevents the triggering of the ignition. A controller in the ignition circuit determines the state of the stop switch by evaluating signals on the state of the internal combustion engine, corresponding information data is generated, and a corresponding stop flag is set and / or enabled. Depending on this information, the activation of the ignition switch, that controls ignition spark, is either blocked or enabled by the controller.

Owner:PRUFREX ELECTRO APPBAU INH HELGA MULLER GEBR DUTSCHKE

Shield and spring interface to a spark plug from a pencil coil

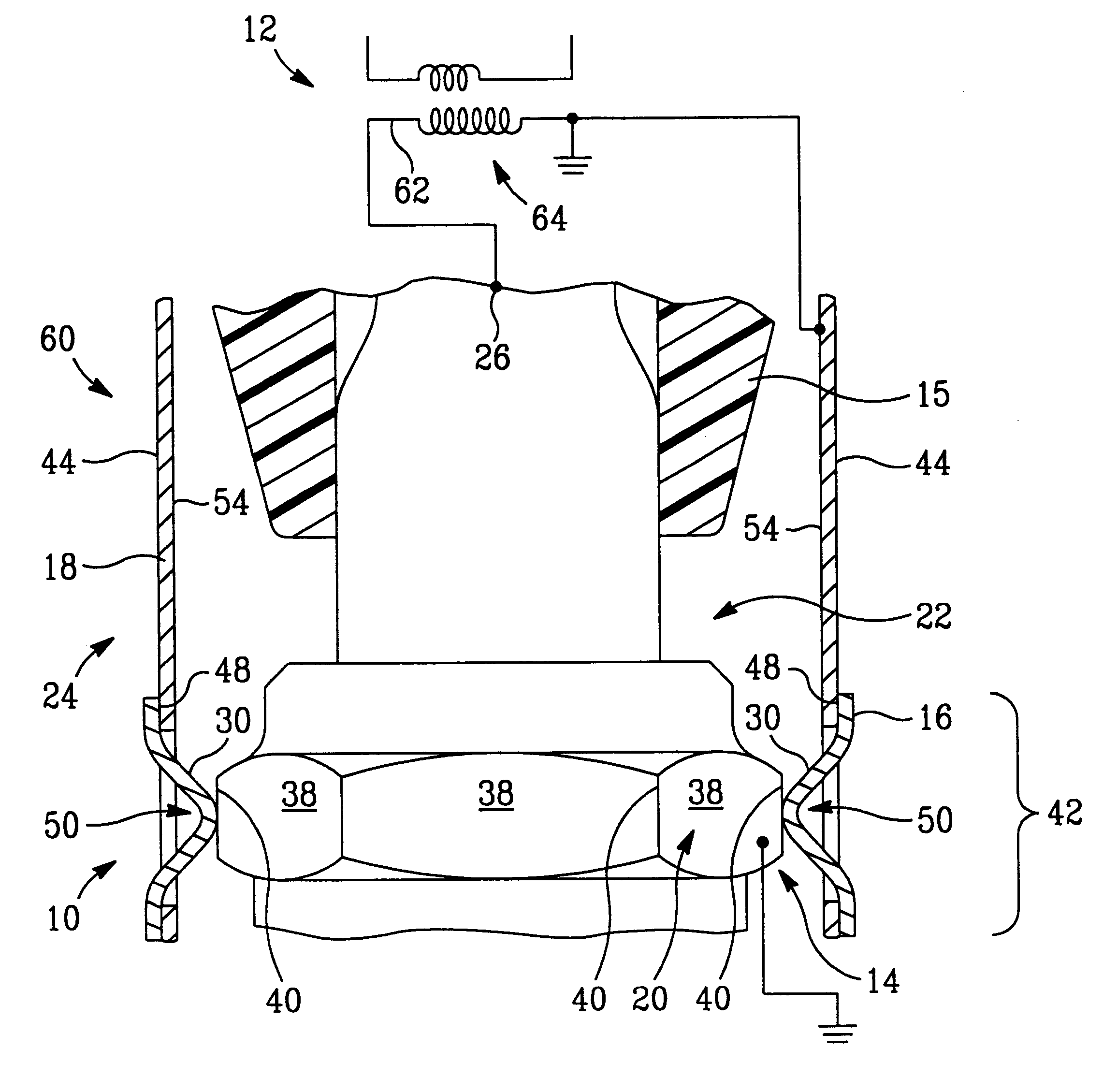

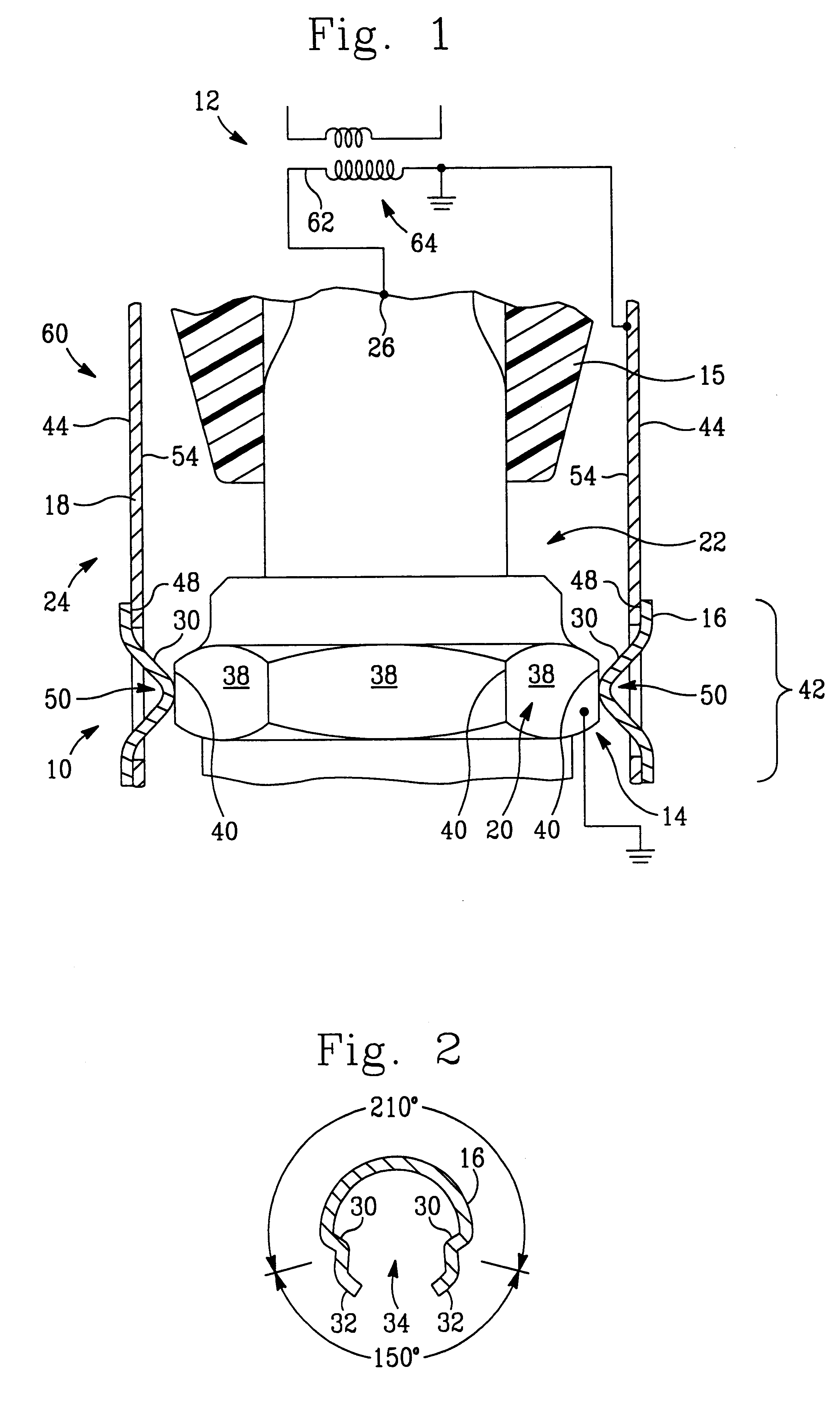

InactiveUS6360706B1Reduce radio frequency interferenceSparking plugsGenerator generated ignition energyLow voltageEngineering

An interface device for interfacing a pencil coil to a spark plug is provided. The interface device comprises a substantially C-shaped spring adapted to mechanically and electrically engage a pencil coil shield and also adapted to make electrical contact with a spark plug ground while the spring remains mechanically and electrically engaged to the pencil coil shield. Also provided is a pencil coil shield assembly for interfacing a pencil coil to a spark plug. The pencil coil shield assembly comprises a substantially cylindrical pencil coil and a spring. The substantially cylindrical pencil coil shield is adapted to surround the pencil coil. The spring is mechanically and electrically engaged with the pencil coil shield and is adapted to make electrical contact with a spark plug ground while the spring remains mechanically and electrically engaged to the pencil coil shield. The interface device and / or pencil coil shield assembly can be configured to reduce RFI from the secondary current winding currents of a pencil coil. In addition, each can be manufactured using inexpensive and uncomplicated manufacturing and installation techniques, and using starting materials and parts that are relatively inexpensive. Also provided is a method of reducing RFI from secondary winding currents of a pencil coil by, among other things, electrically connecting the substantially cylindrical shield to a low voltage terminal of a secondary winding of the pencil coil, and electrically connecting the substantially cylindrical shield to a spark plug ground of a spark plug associated with the pencil coil.

Owner:DELPHI TECH IP LTD

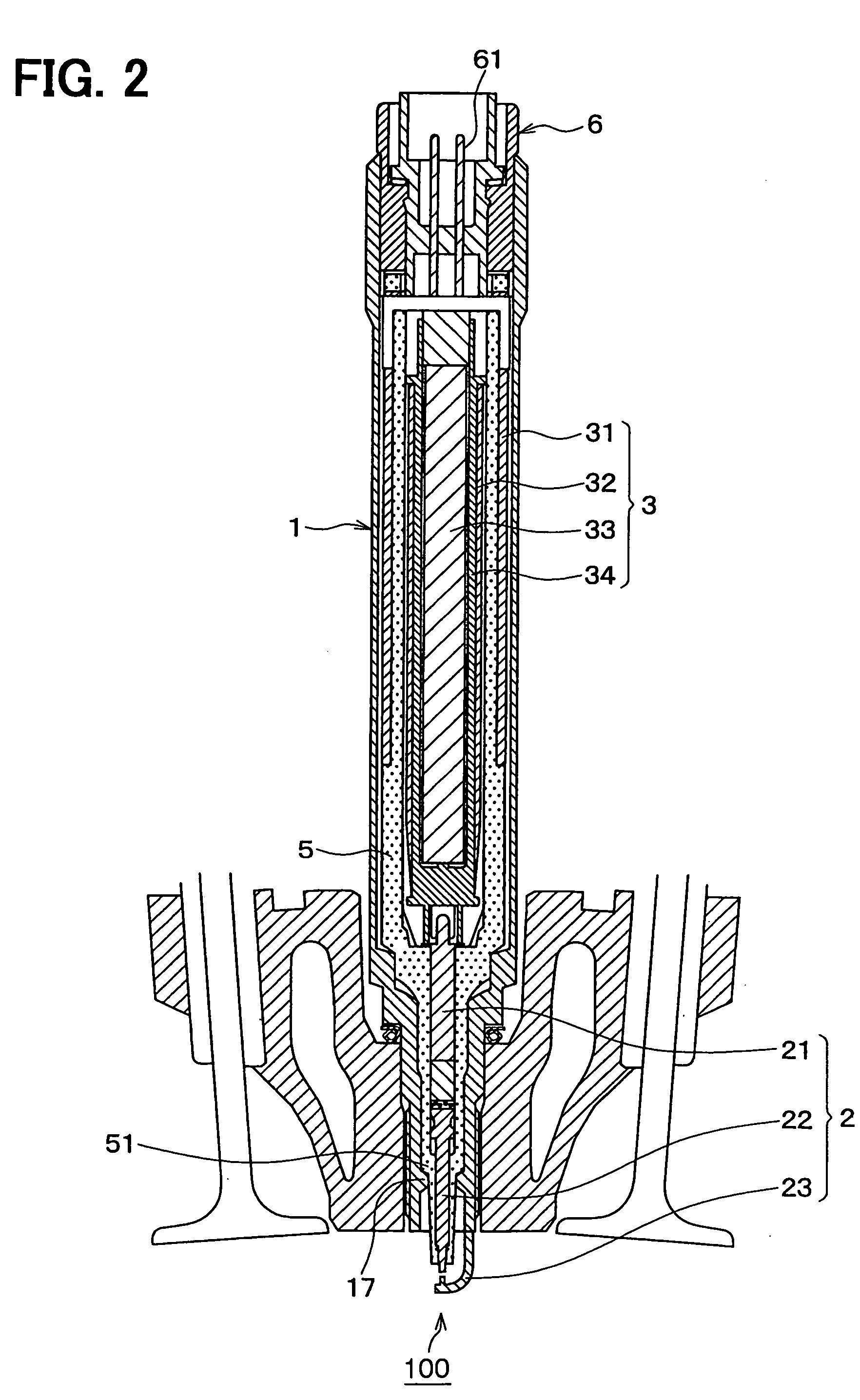

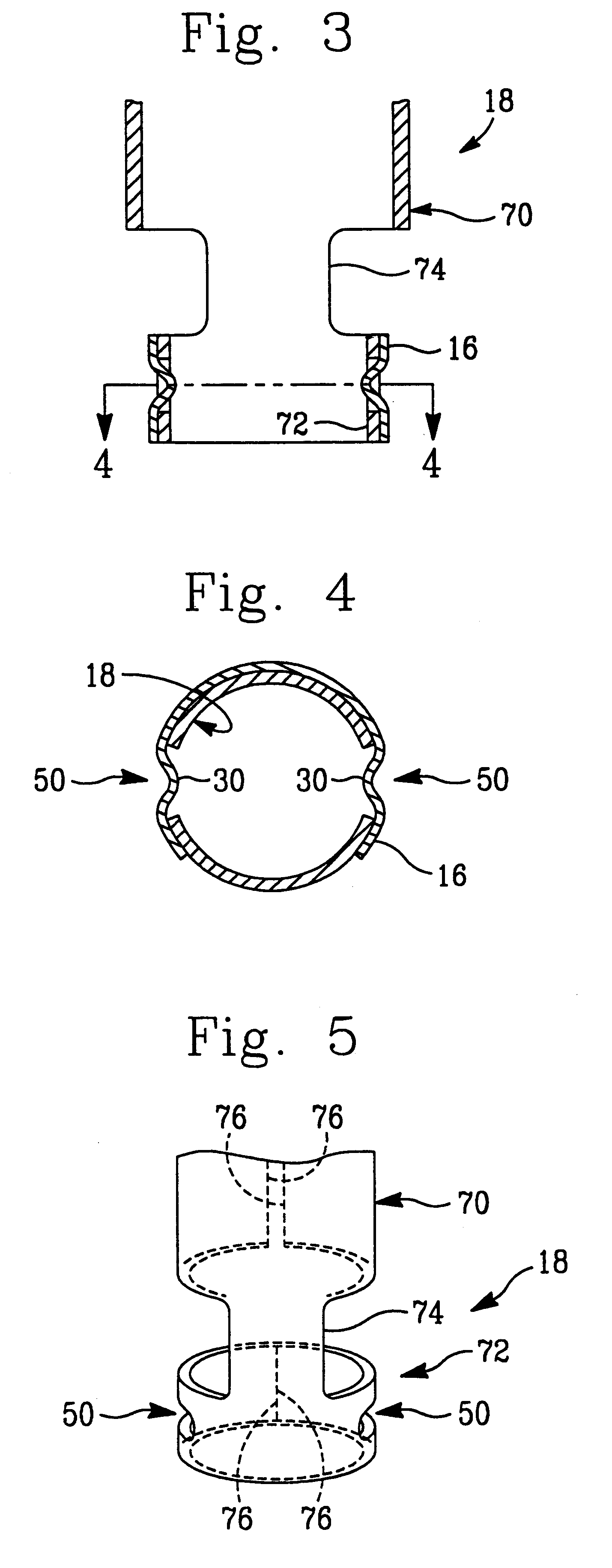

Ignition coil, and internal combustion engine ignition device

InactiveUS6880540B2Accurate detectionImproved contact characteristicsSparking plugsTransformersIgnition coilCylinder head

An object of the present invention is to provide an ignition coil which has a structure to make it possible to connect the ignition coil to a spark plug directly and in which an installation space need not be changed largely when the ignition coil is mounted in a cylinder head, and an internal combustion engine ignition system having the ignition coil.In the present invention, a protection metal pipe (31) of an ignition coil (9) is formed so that a rear end side portion of a spark plug (11) in the rear of a rear end surface (23b) of a collar portion (23) in a metal shell (19) can be received in the inside of the protection metal pipe (31) from a front end (31b). The ignition coil (9) has a structure in which the ignition coil (9) is directly connected to the spark plug (11). The protection metal pipe (31) of the ignition coil (9) is formed to serve also as a plughole pipe, so that the outer diameter of the protection metal pipe (31) can be enlarged up to the outer diameter of a conventional plughole pipe. As a result, a space for installing a coil body portion (37) can be secured largely in the inside of the protection metal pipe (31), so that the installation space need not be changed largely when the ignition coil is mounted in a cylinder head.

Owner:NGK SPARK PLUG CO LTD

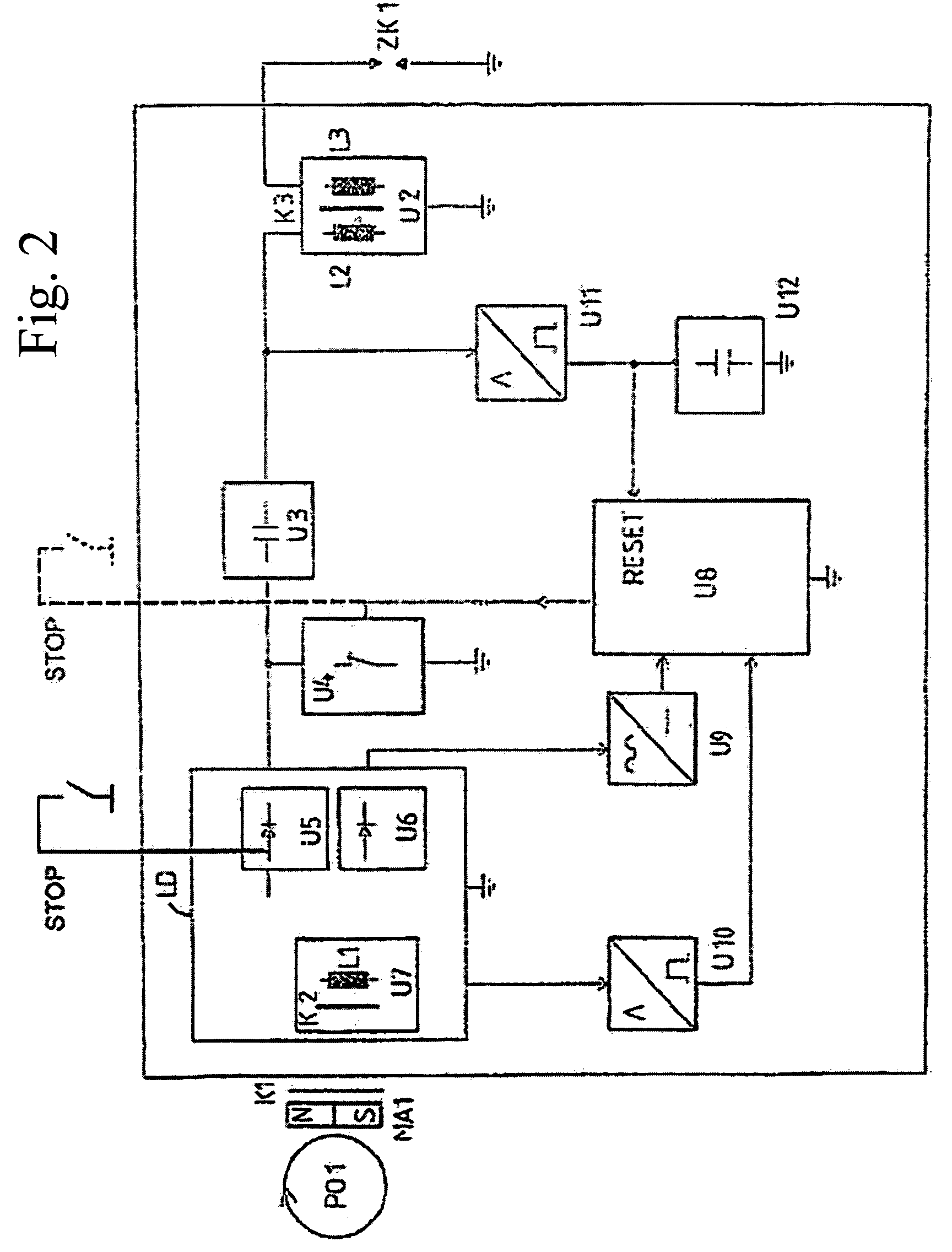

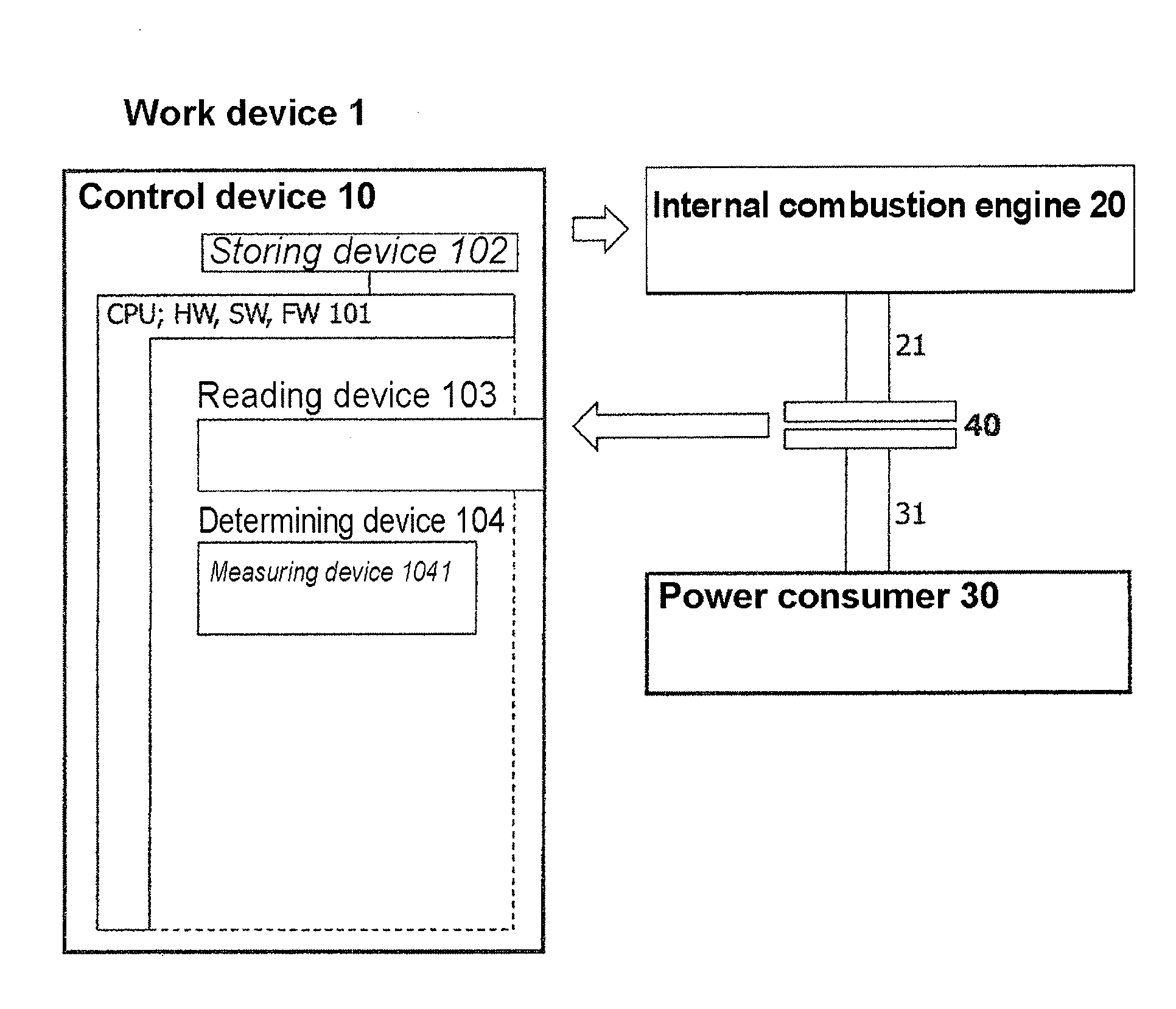

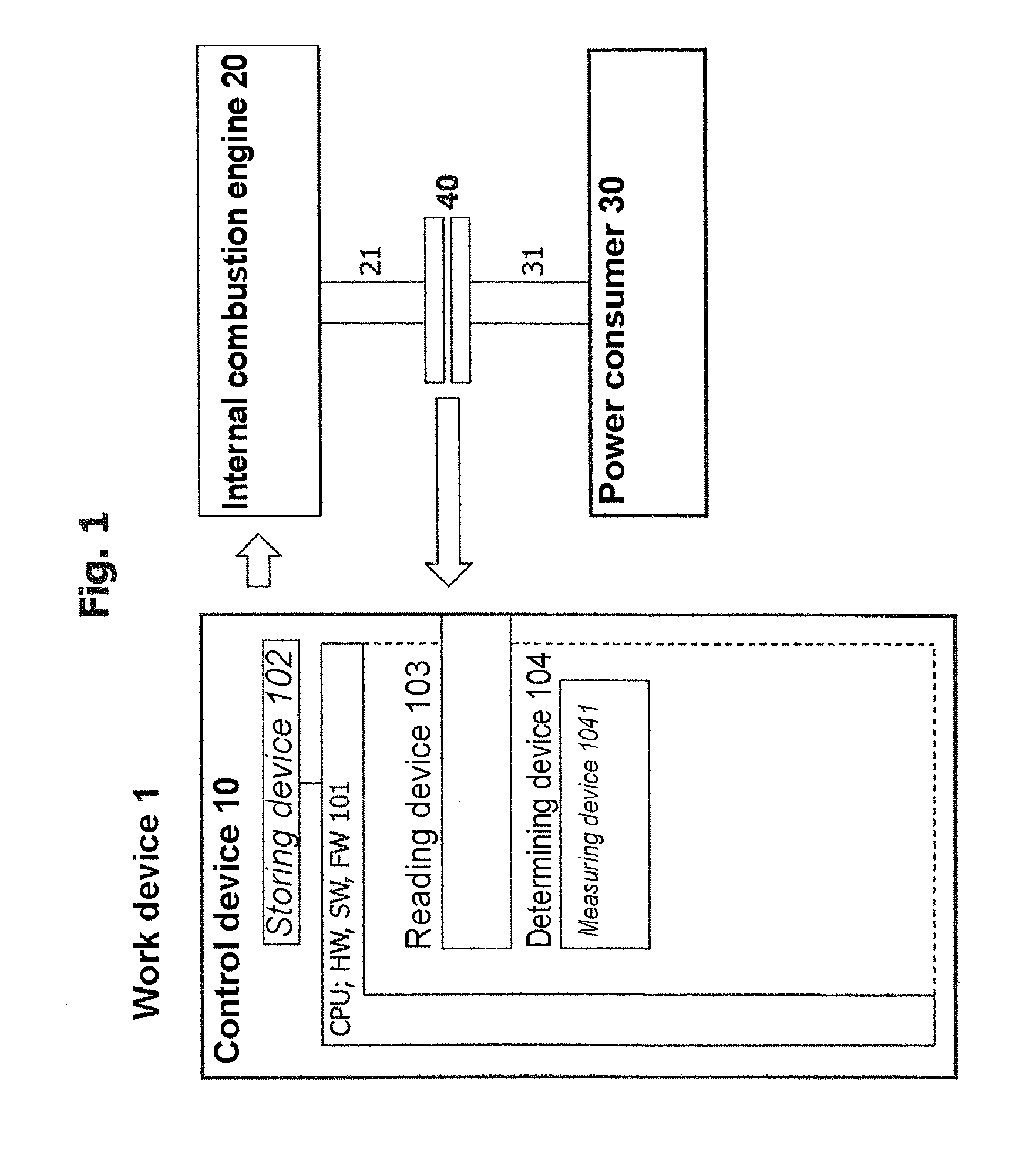

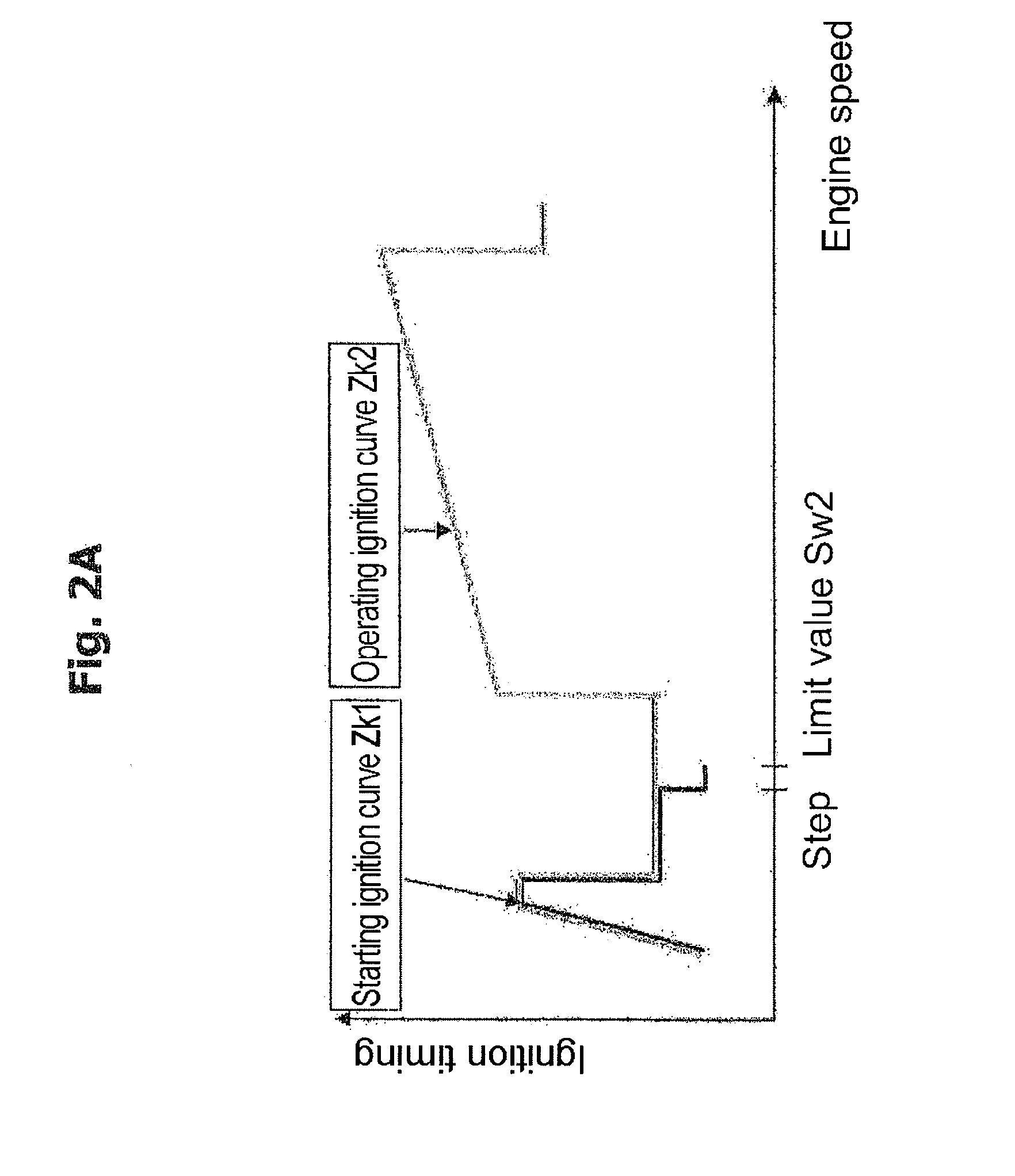

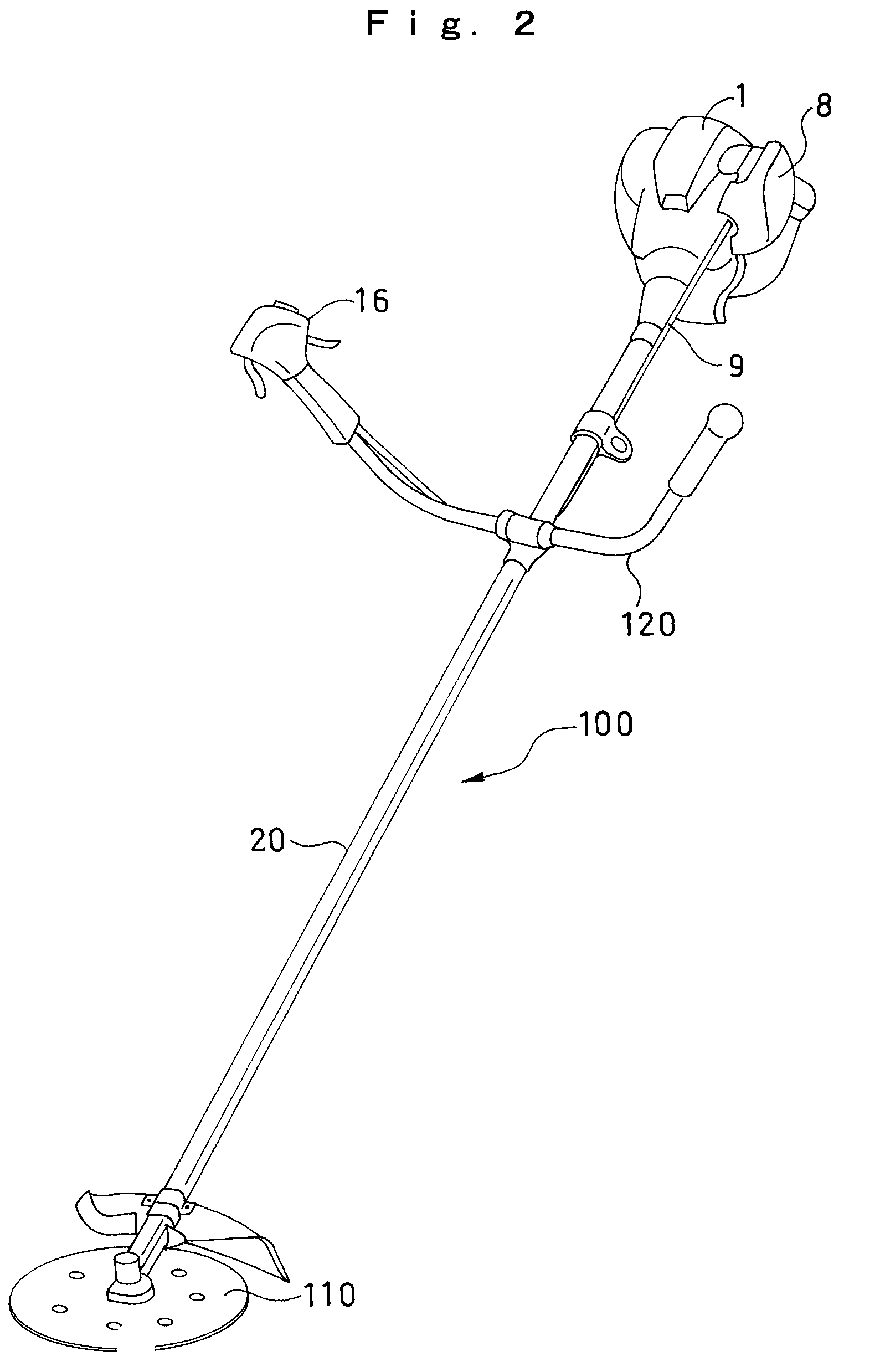

Method and device for controlling the operation of an internal combustion engine of a portable work device

InactiveUS20150345460A1Easy to controlImprove securityAnalogue computers for vehiclesPower operated startersExternal combustion engineInternal combustion engine

The invention relates to a method and a control device for operating an internal combustion engine of a portable work device, said method having the following method steps: a) storing a starting ignition curve for specifying an ignition time after a startup time of the internal combustion engine and an operating ignition curve for specifying the ignition time in a speed range assigned to the nominal operation of the internal combustion engine, b) reading the current engine speed, c) reading at least one time value which indicates the time that has elapsed since a reference time, wherein the reference time can relate to the startup time of the internal combustion engine, and d) determining and / or initiating a switchover process from the starting ignition curve to the operating ignition curve on the basis of the current engine speed and the time value.

Owner:MAKITA CORP +1

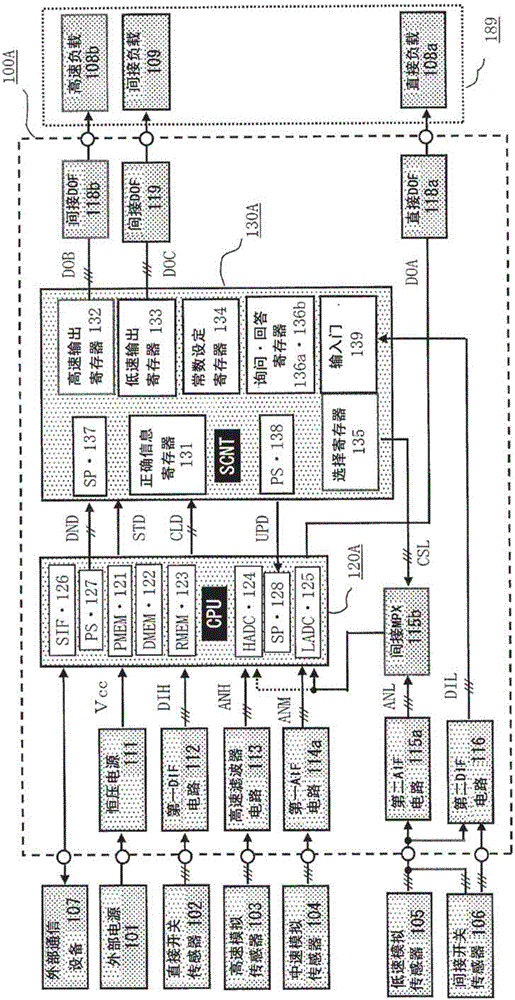

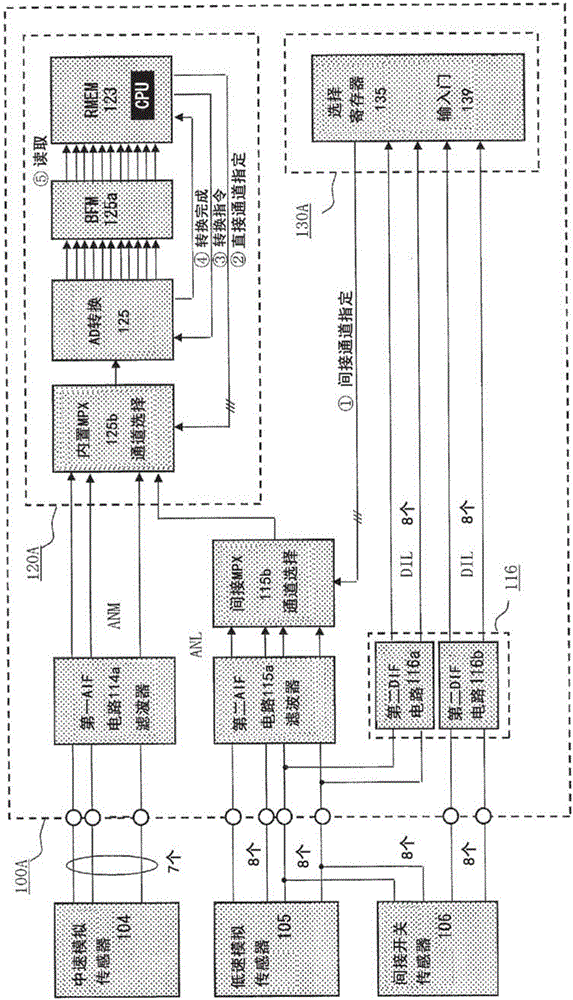

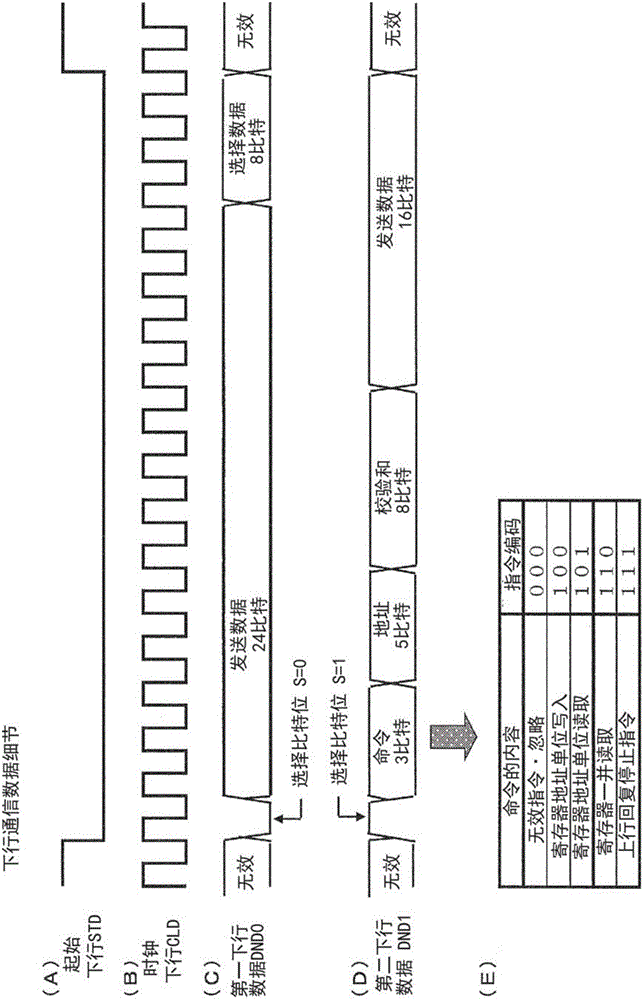

Vehicle-mounted electronic control device

ActiveCN106573583ACut output terminalMiniaturizationProgramme controlElectrical controlLow speedMultiplexer

Down-link communication data DND from a main control circuit unit 120A to a combination control circuit unit 130A are divided into first and second down-link data, and high-speed communication is performed using a down-link clock signal CLD and a transmission start command signal STD. A high-speed load 108b that has been directly driven from the main control circuit unit 120A is indirectly high-speed driven from the combination control circuit unit 130A using the first down-link data. A low-speed analog input signal ANL that has been indirectly input to the combination control circuit unit 130A is input to a specific input channel of a multi-channel AD converter 125 in the main control circuit unit 120A via an indirect multiplexer 115b. By performing channel selection using the down-link communication data DND, the loading of analog signal is performed without depending on the low-speed up-link communication, and the number of points of a medium-speed analog input signal ANM that has conventionally been directly input to the main control circuit unit 120A is decreased, whereby the number of the input and output terminals of the main control circuit unit is decreased and a decrease in size is achieved.

Owner:MITSUBISHI ELECTRIC CORP

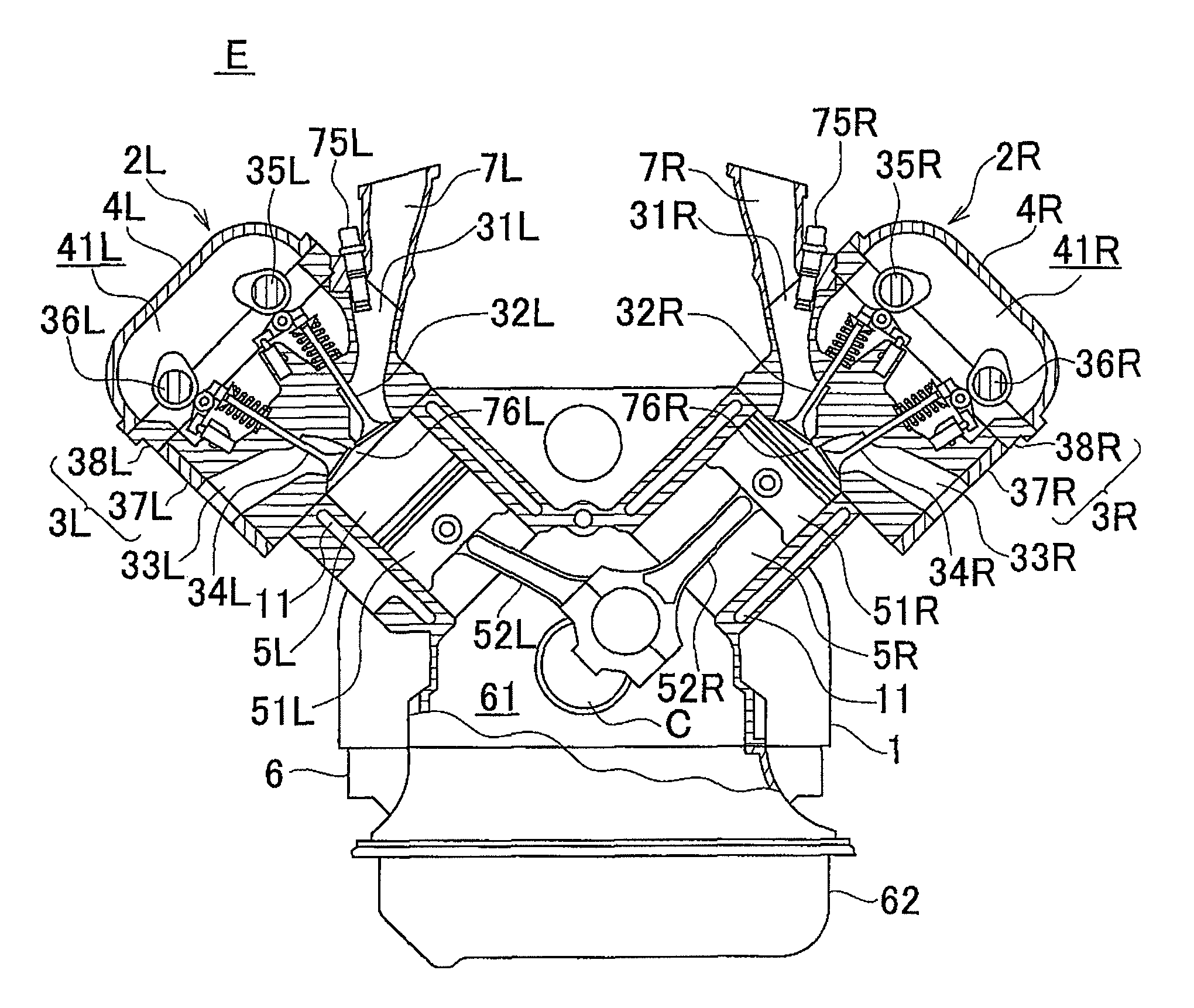

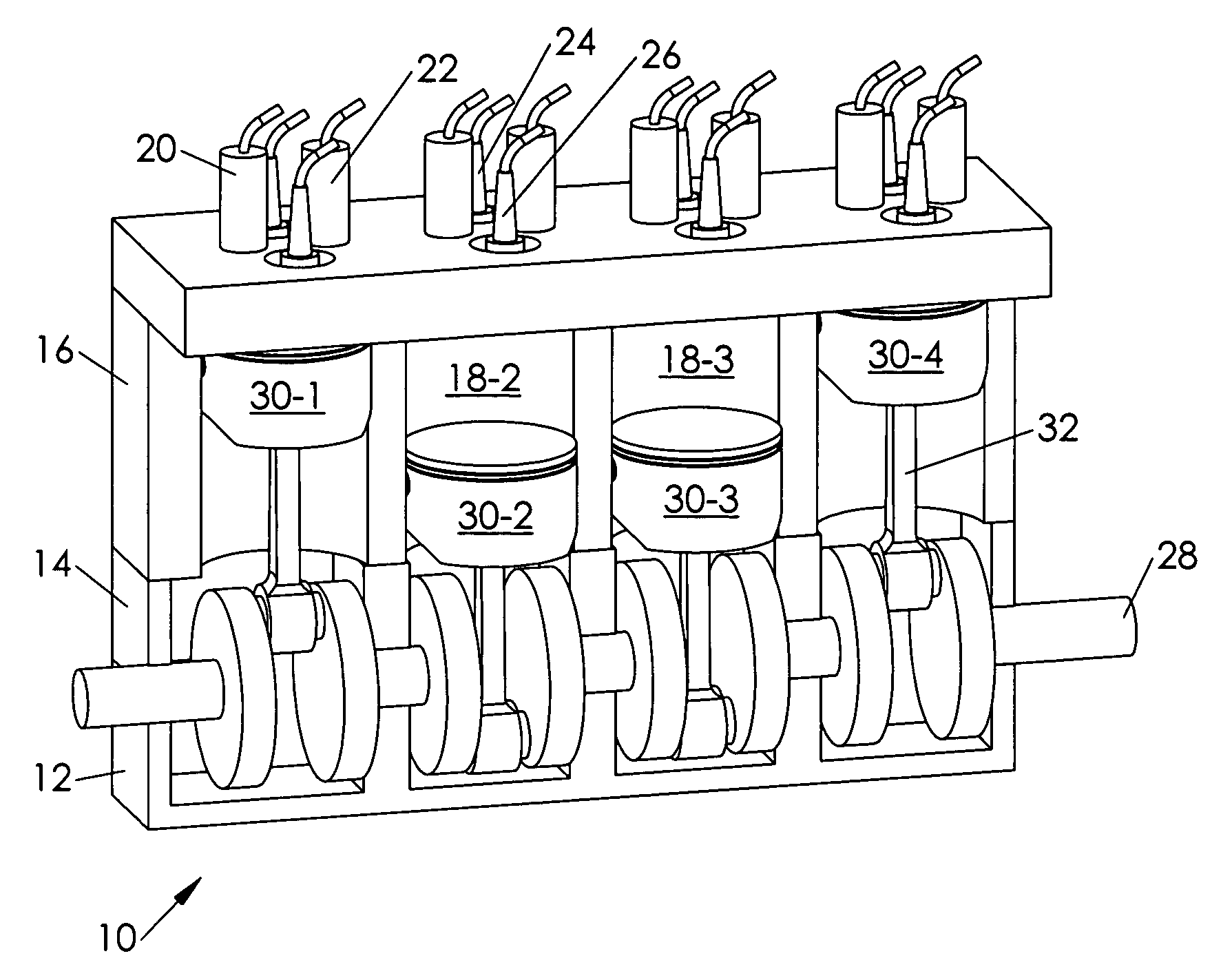

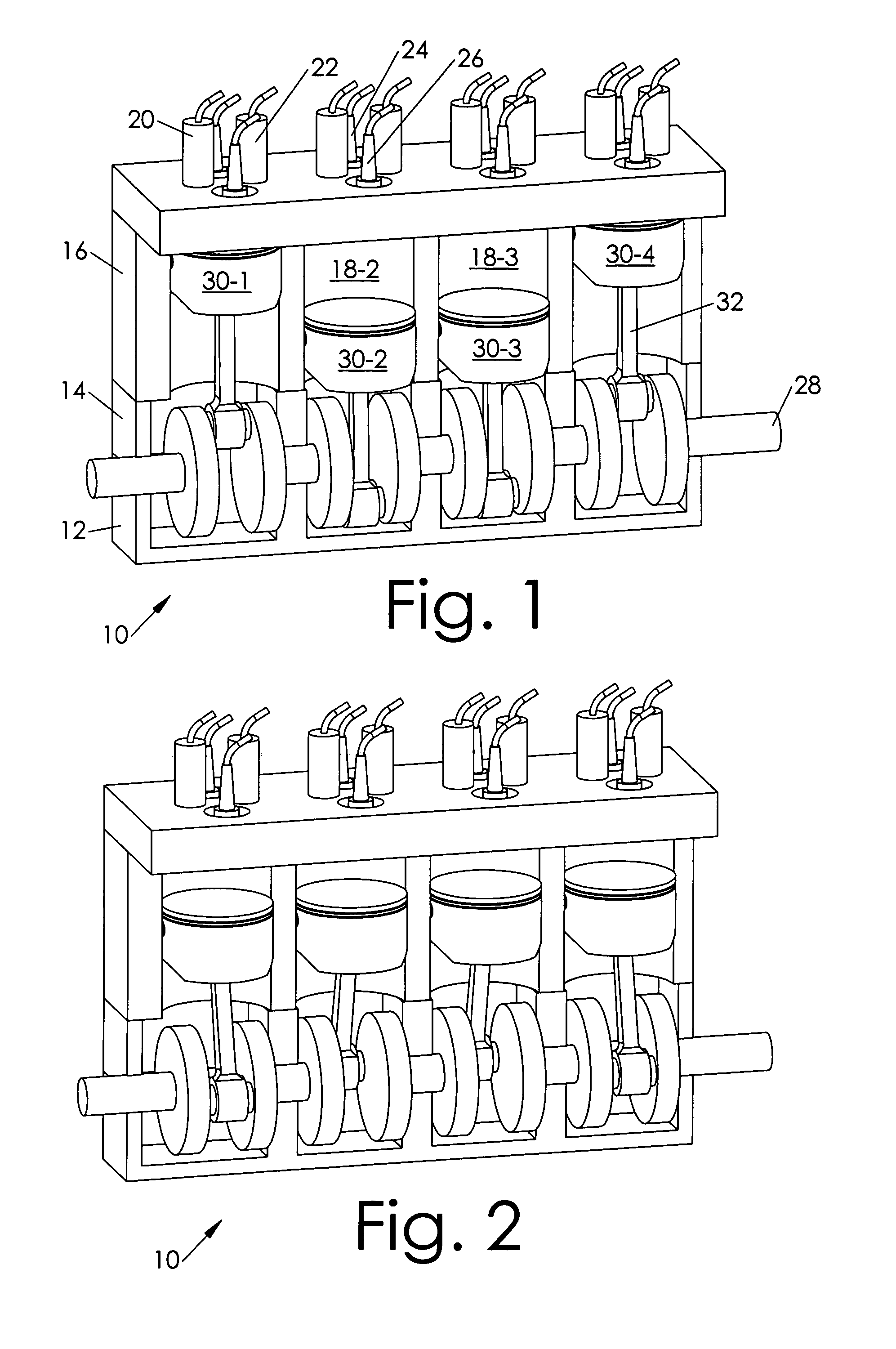

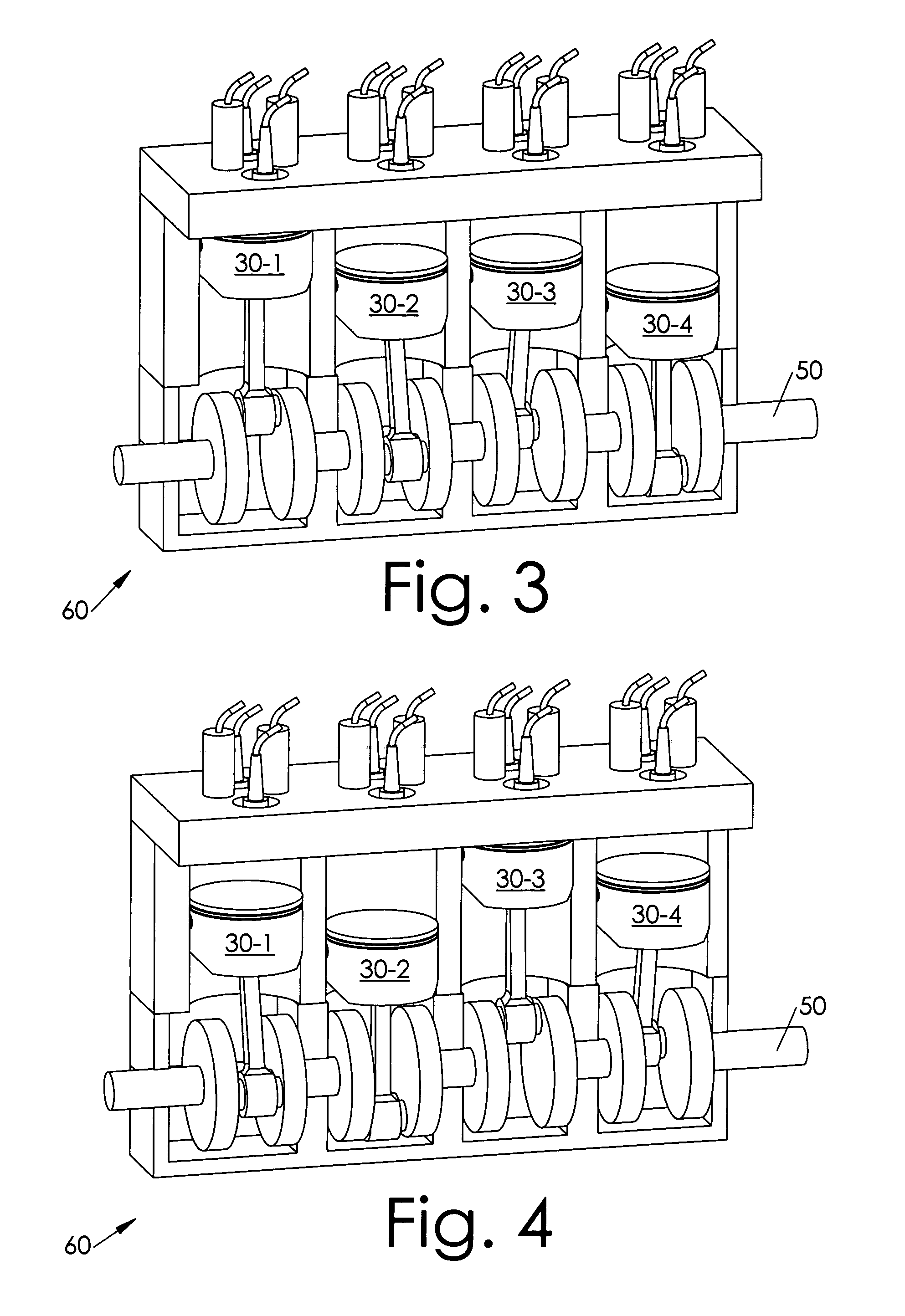

Piston engine with selectable firing order

InactiveUS7063059B2Internal combustion piston enginesOutput powerExternal combustion engineFiring order

A multi-cylinder four-stroke internal combustion engine enabling a method for on-the-fly switching between two or more firing orders. Switching to the new firing order is done without requiring any tear-down of the engine such as to swap camshafts. Switching can be triggered by the rider, or it can be triggered automatically per conditions such as selected gear, RPM range, track location, velocity, and the like.

Owner:MOTOCZYSZ

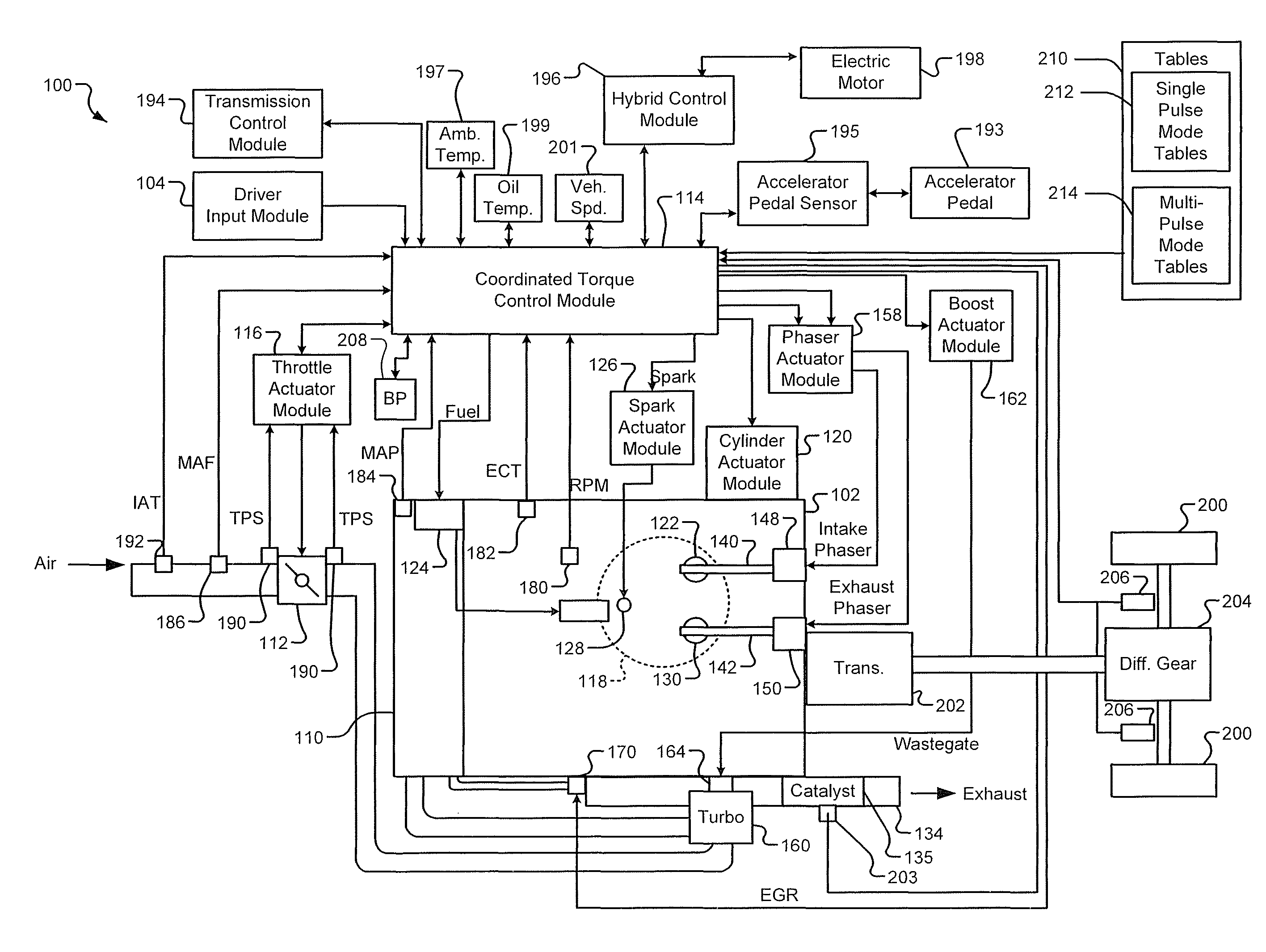

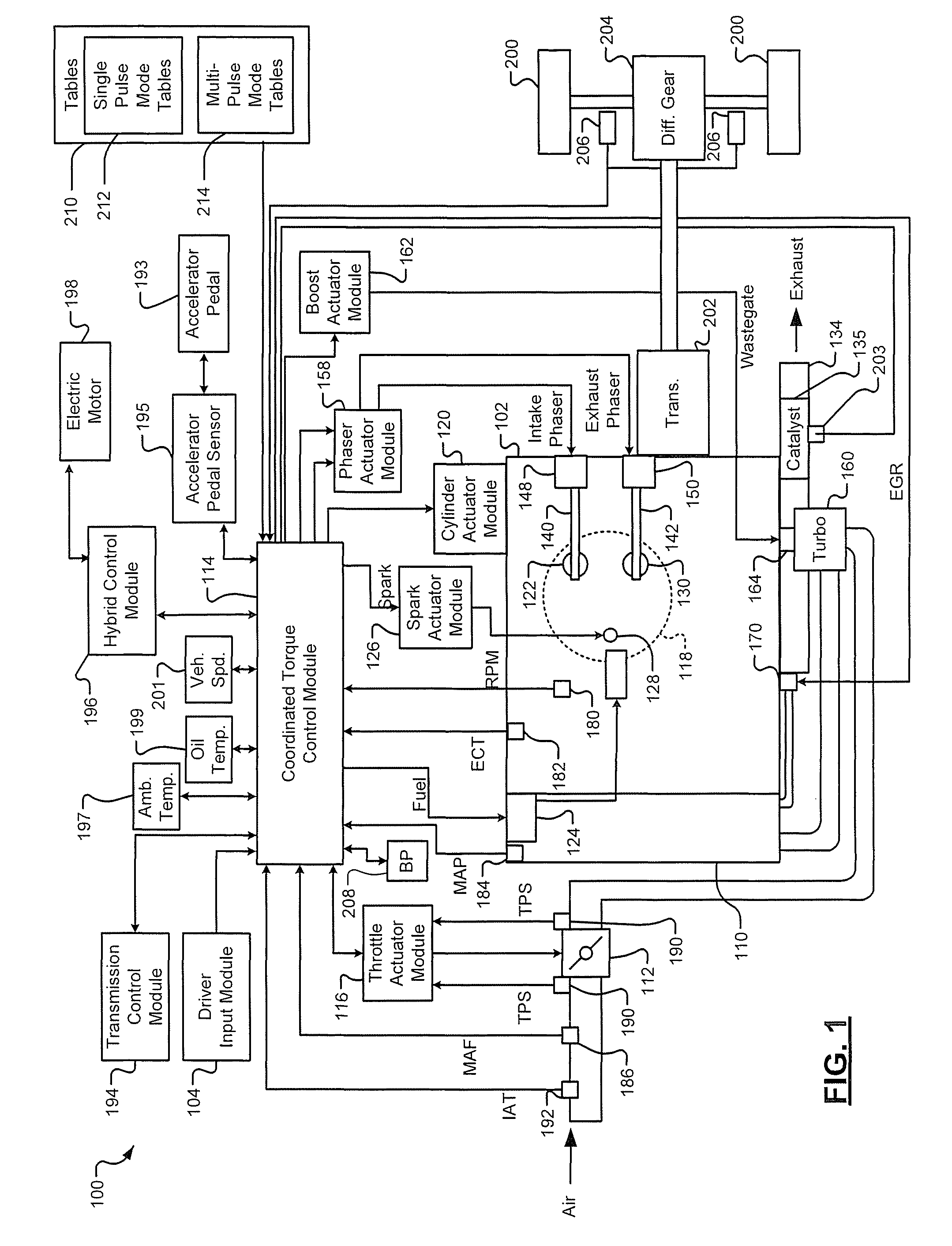

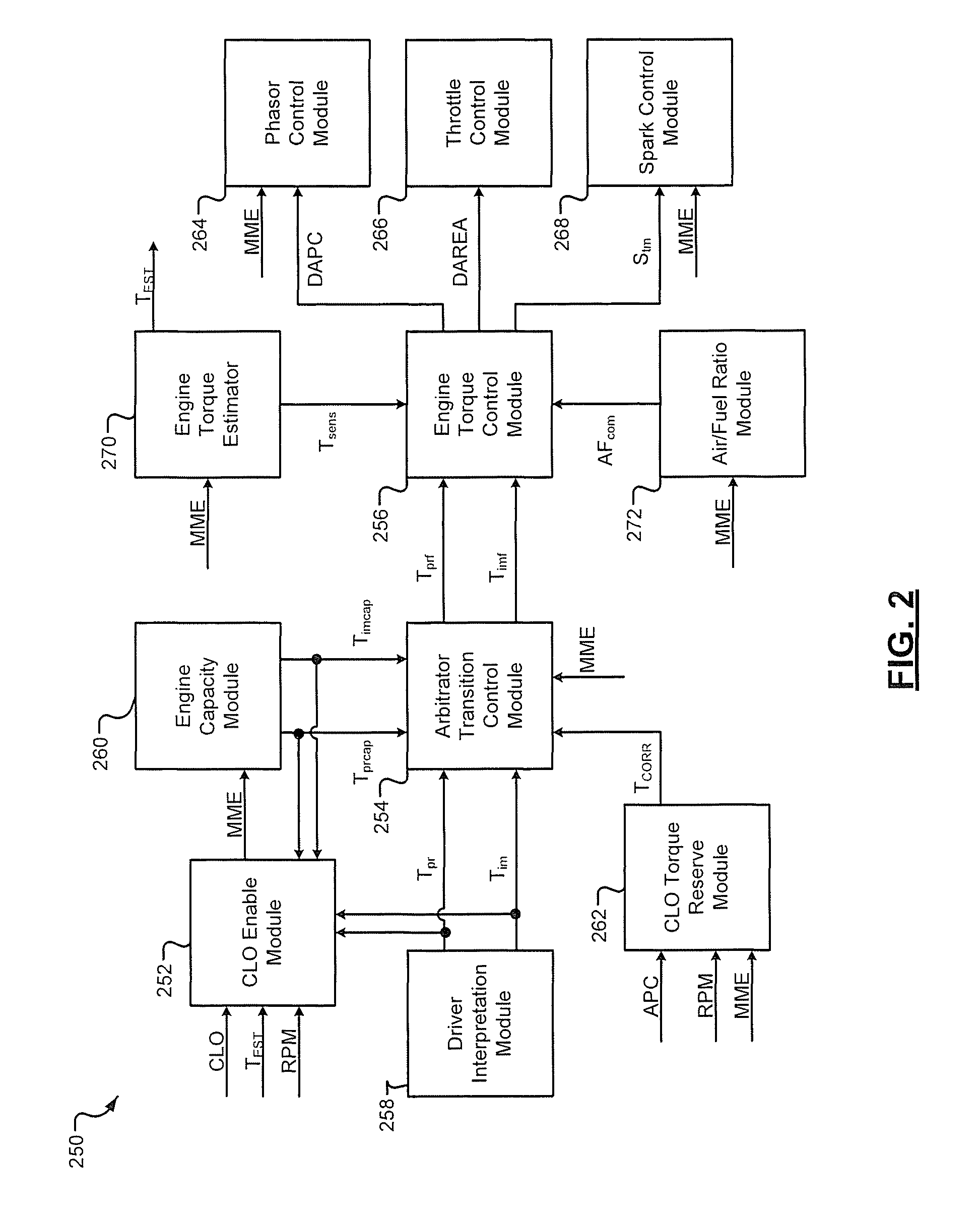

Torque reserve and emission control system for coordinated torque control

InactiveUS7878175B2Analogue computers for vehiclesElectrical controlCombustion chamberControl system

A coordinated torque control system includes a catalyst module that generates a multi-mode enable signal based on a catalyst light off enable signal. A torque reserve module generates a torque reserve signal based on the multi-mode enable signal, an engine speed signal and an air per cylinder signal. The torque reserve module operates in a multi-pulse mode that is associated with injecting N pulses of fuel into a combustion chamber during a combustion cycle of the engine based on the multi-mode enable signal. N is an integer greater than or equal to 2.

Owner:GM GLOBAL TECH OPERATIONS LLC

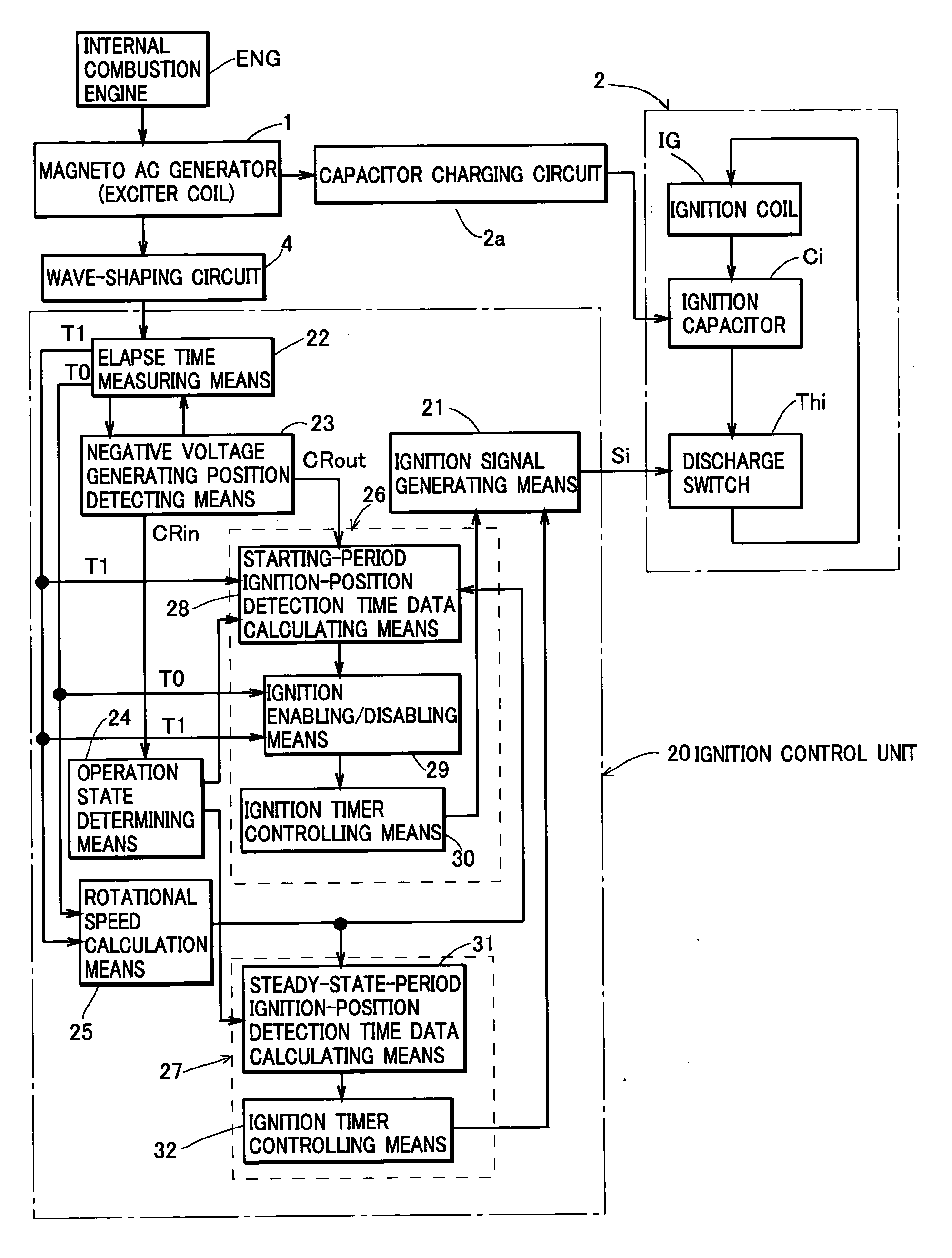

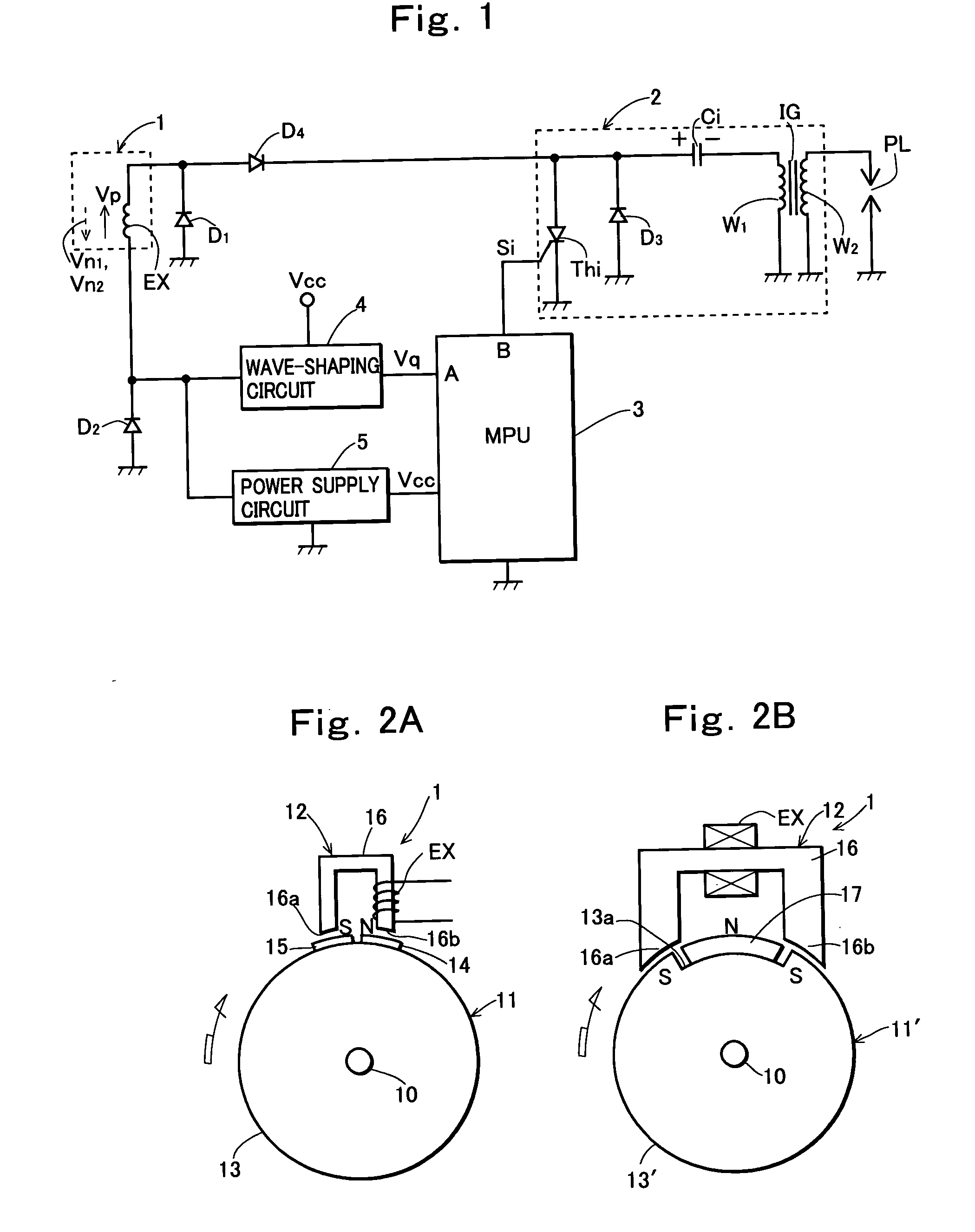

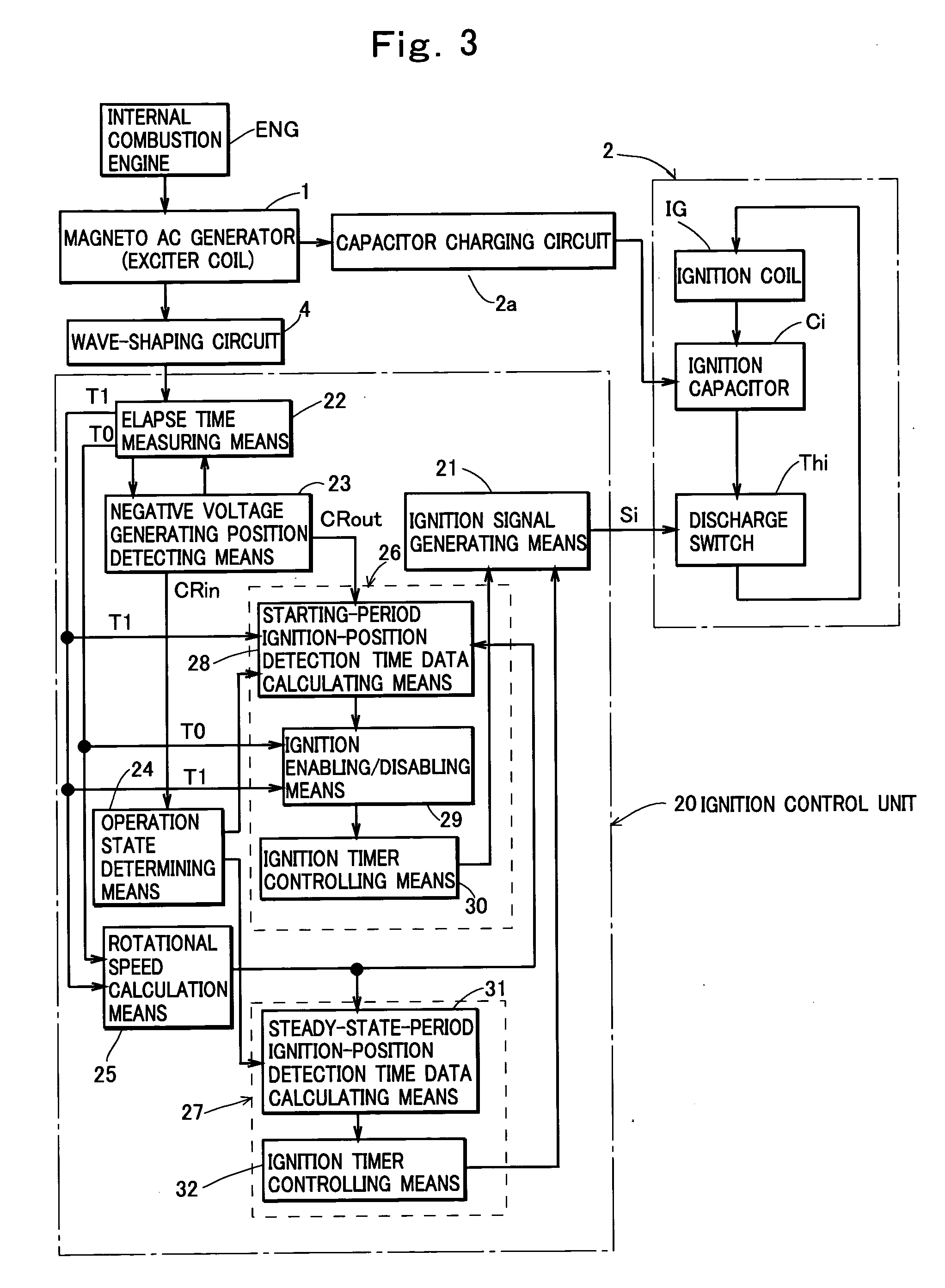

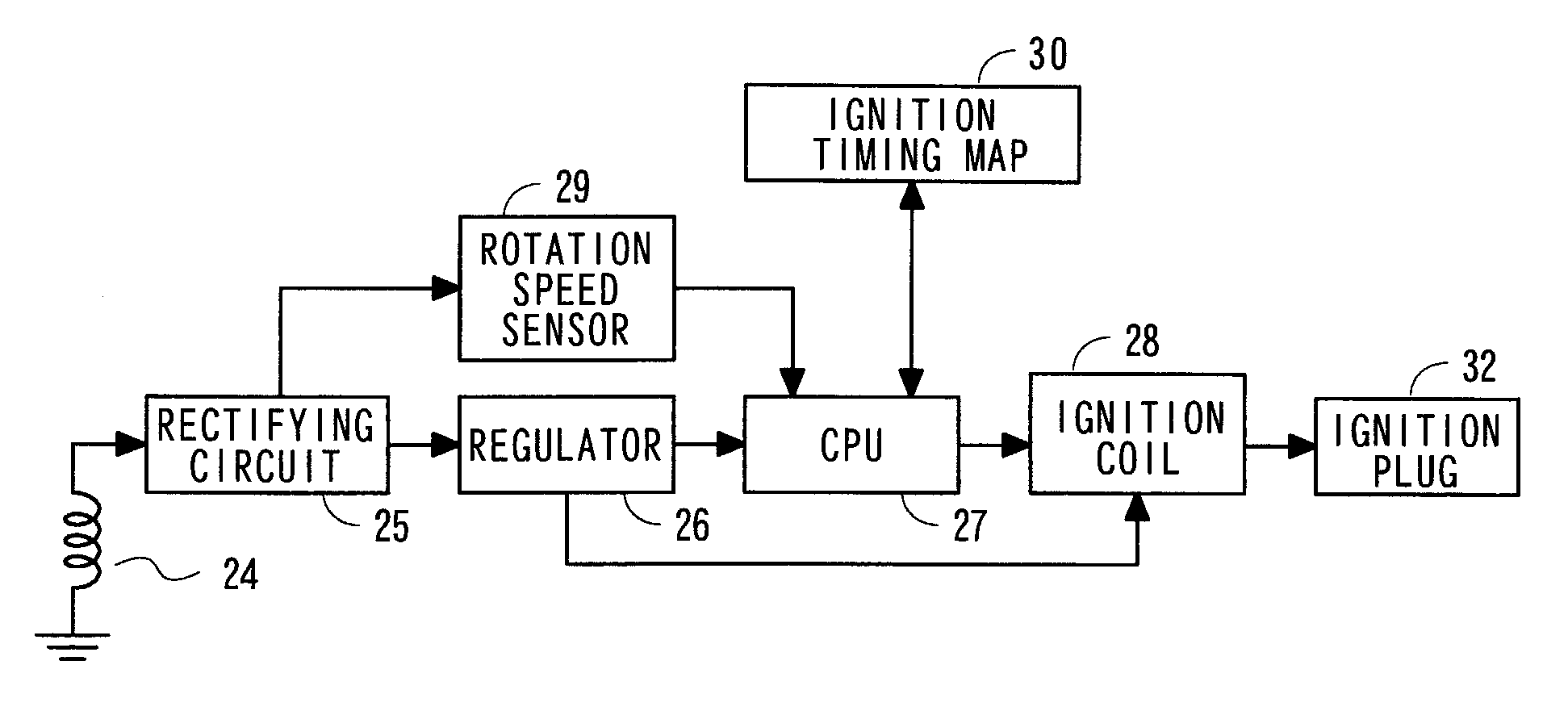

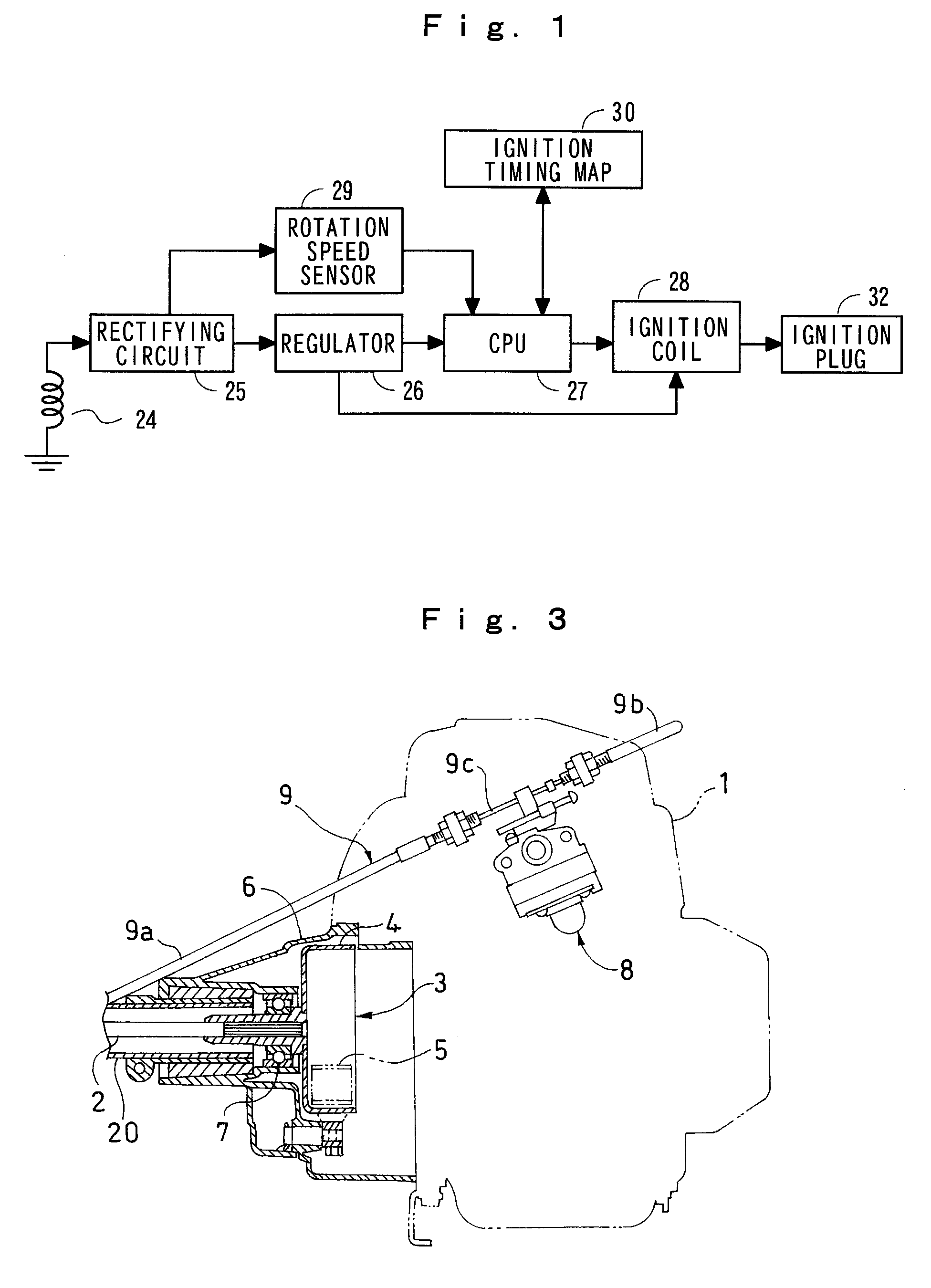

Ignition device for internal combustion engine

ActiveUS20060169249A1Prevent reversalAccurately determineInternal combustion piston enginesGenerator generated ignition energyEngineeringLow speed

A capacitor-discharge-type ignition device for an internal combustion engine, comprising: an exciter coil that generates an AC voltage having a positive half-wave voltage and first and second negative half-wave voltages present before and after the positive half-wave voltage synchronously with rotation of the engine; ignition-position detection time data calculating means that arithmetically operates as ignition position detection time data, the time period that is required for the engine to rotate from the generating position of the second negative half-wave voltage to an ignition position suitable in starting period, at the rotational speed of the engine that is obtained from time period from generation of the first negative half-wave voltage to the generation of the second negative half-wave voltage, and from an angle between the generating position of the first negative half-wave voltage and that of the second negative half-wave voltage, wherein a crank angle position when the measurement of the arithmetically operated ignition position detection time data is completed is determined as an ignition position at a low speed operation of the engine.

Owner:MAHLE INT GMBH

Engine rotation speed controller for working machine

InactiveUS20090101105A1Reduce speedReduce the amount requiredElectrical controlInternal combustion piston enginesLow speedResponse delay

When an engine rotation speed in an engine for working machine without a governor mechanism is increase-and-decrease-controlled by switching ignition timings at a predetermined rotation speed, the response delay of the engine rotation speed with respect to the throttle opening operation is suppressed. The engine rotation speeds for switching the ignition timings are set to 4000 rpm and 5000 rpm. When the throttle opening is increased, a first ignition timing is advanced stepwise to a second ignition timing at the engine rotation speed of 4000 rpm so as to be switched to a rotation control characteristic C30 for high speed rotation. When the throttle opening is decreased, the second ignition timing is retarded stepwise to the first ignition timing at the engine rotation speed of 5000 rpm so as to be switched to a rotation control characteristic C05 for low speed rotation. The switching timing of the rotation control characteristic is different between at increase and decrease of the throttle opening. The difference can be reduced to a small amount ΔTH.

Owner:HONDA MOTOR CO LTD