Patents

Literature

121results about How to "Minimization needs" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

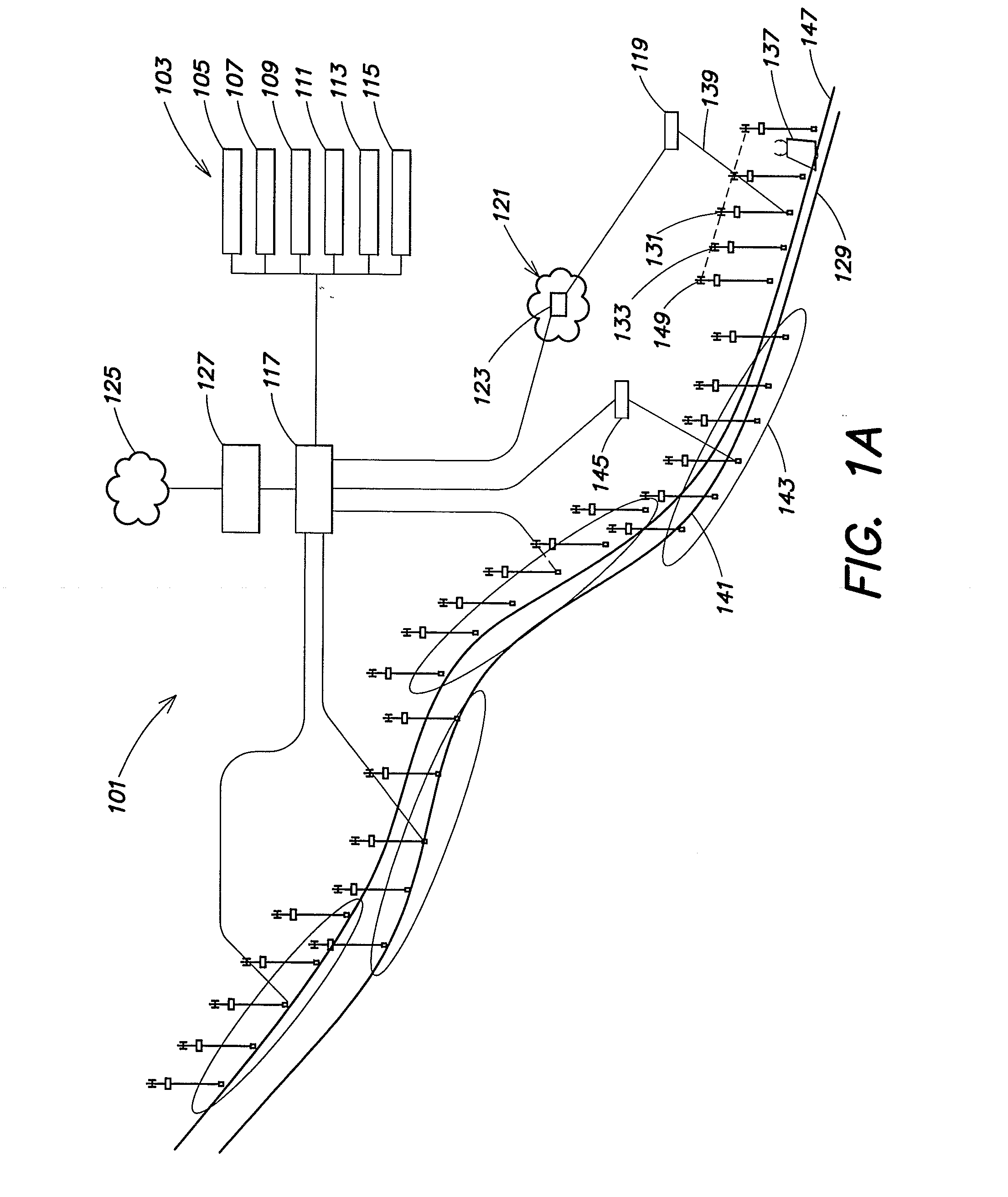

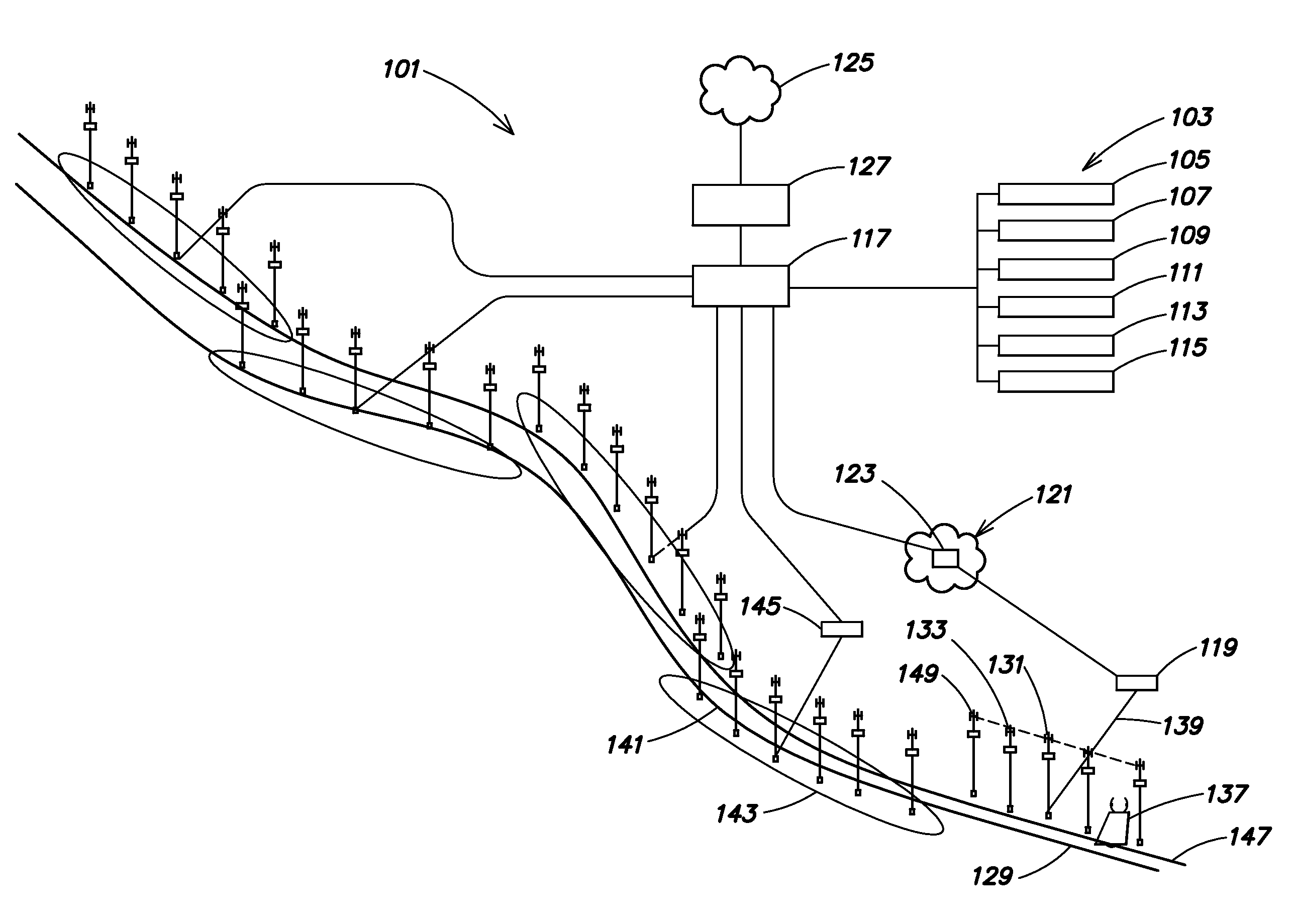

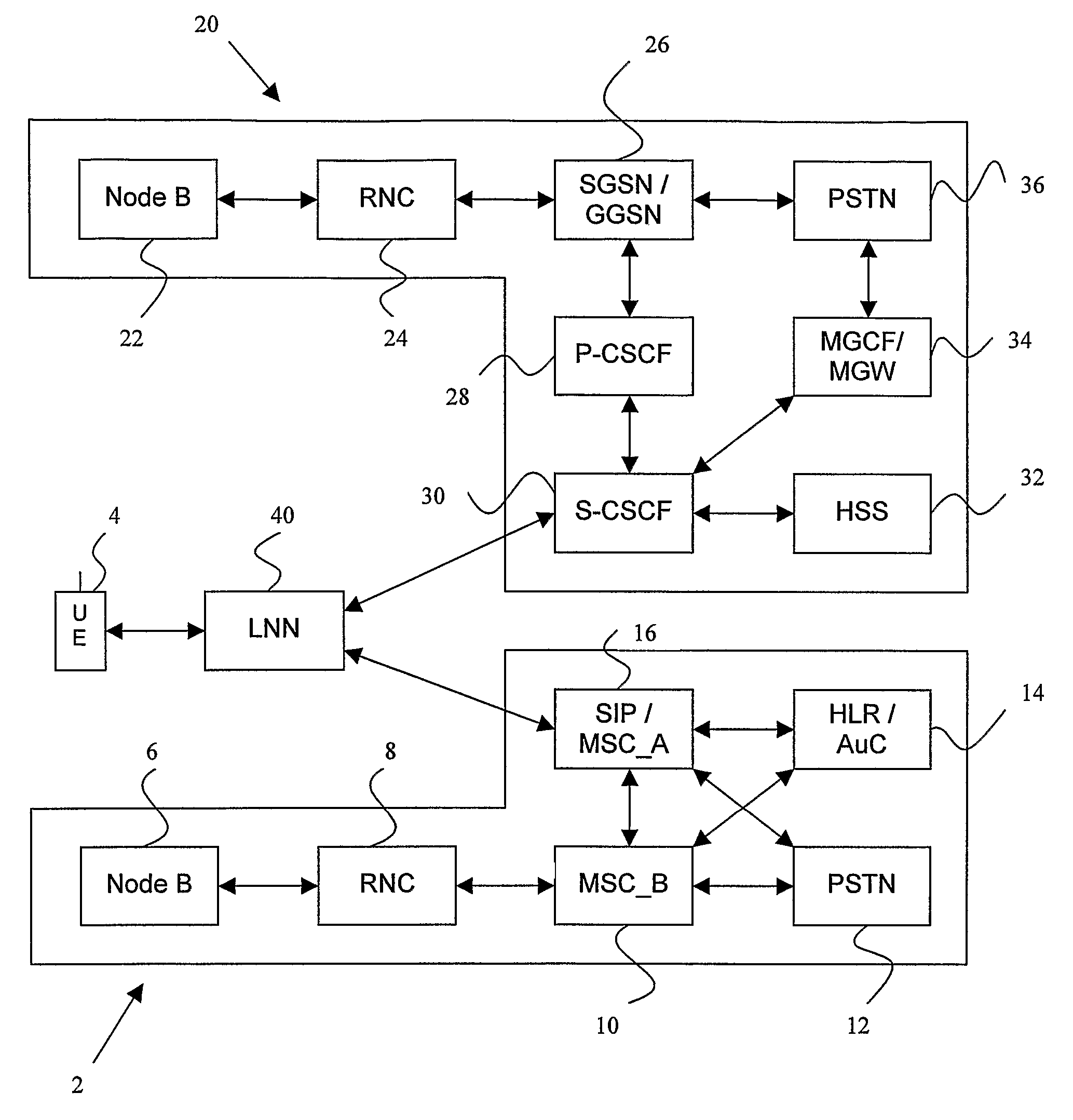

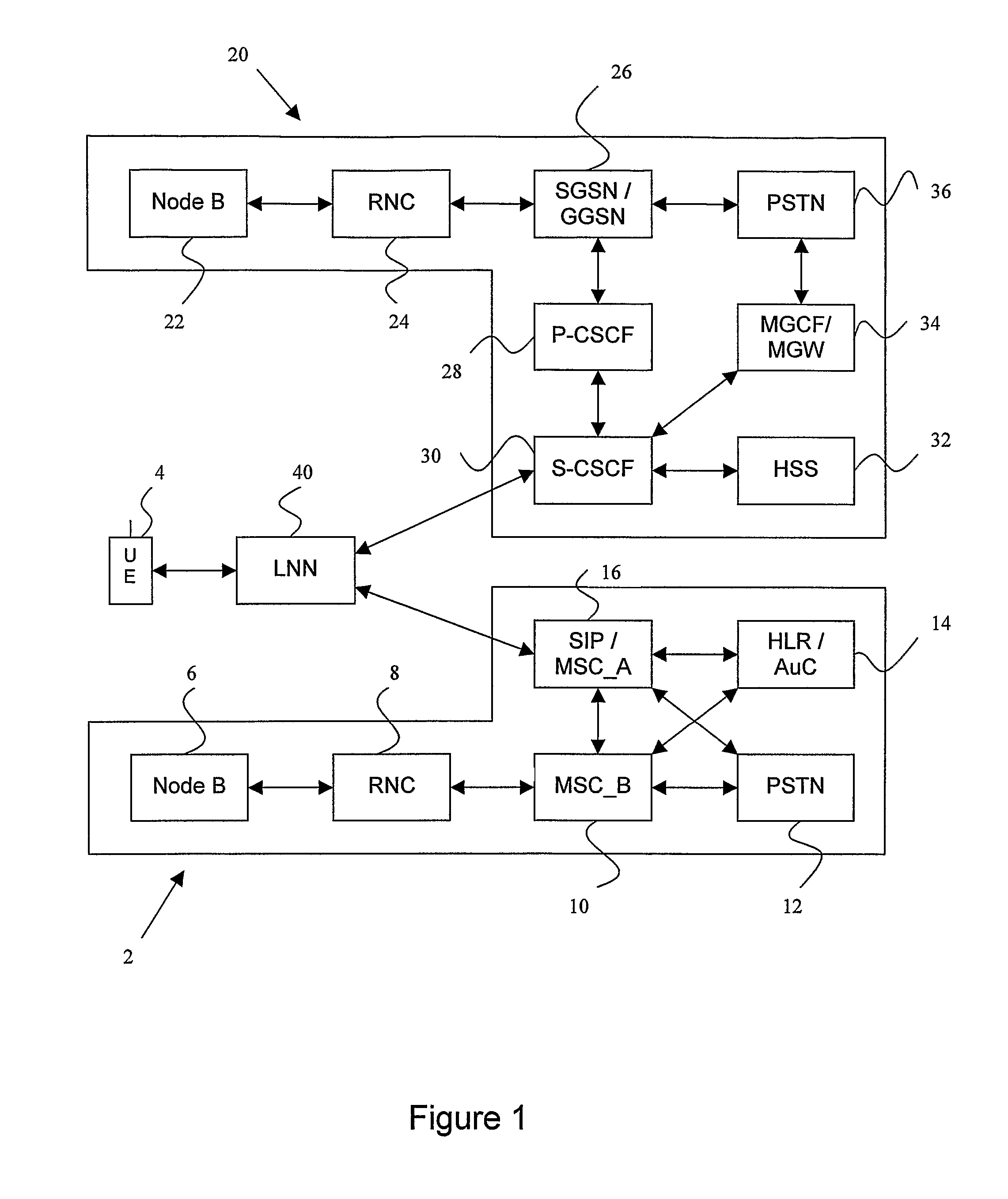

System and method of authenticating mobile devices

ActiveUS20080043655A1Minimize time neededReduce time neededNetwork topologiesTime-division multiplexAsynchronous Transfer ModeGeographic area

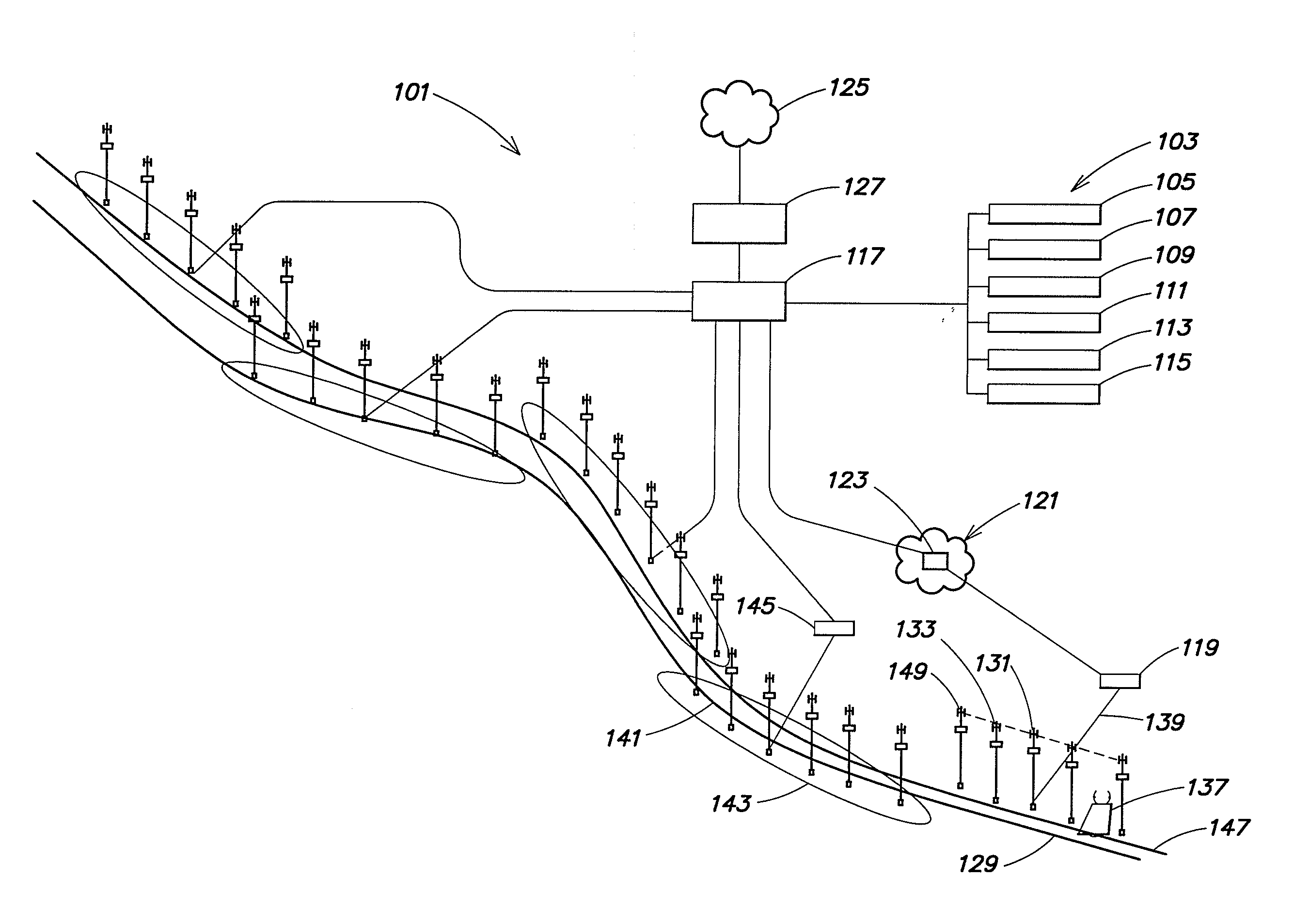

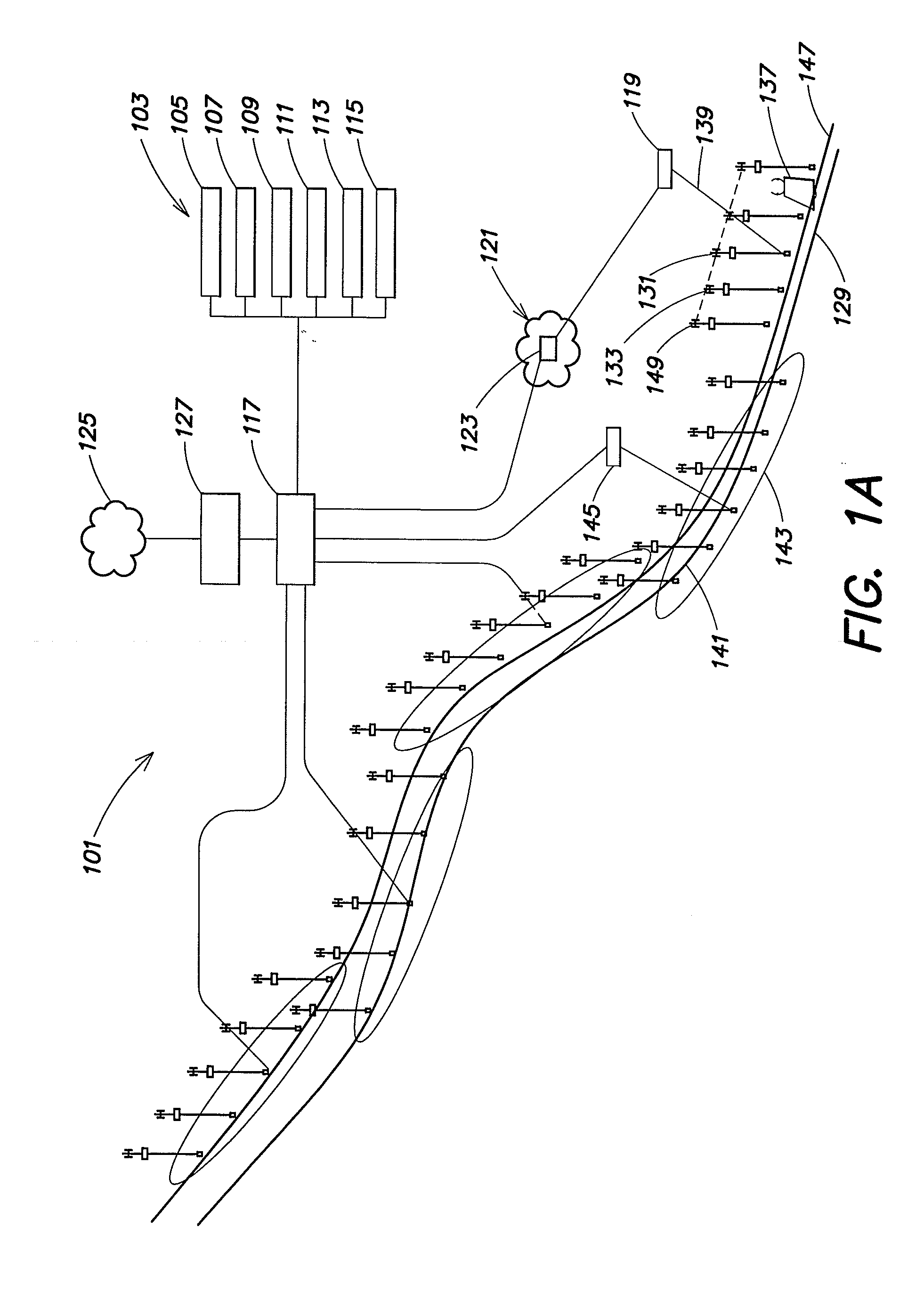

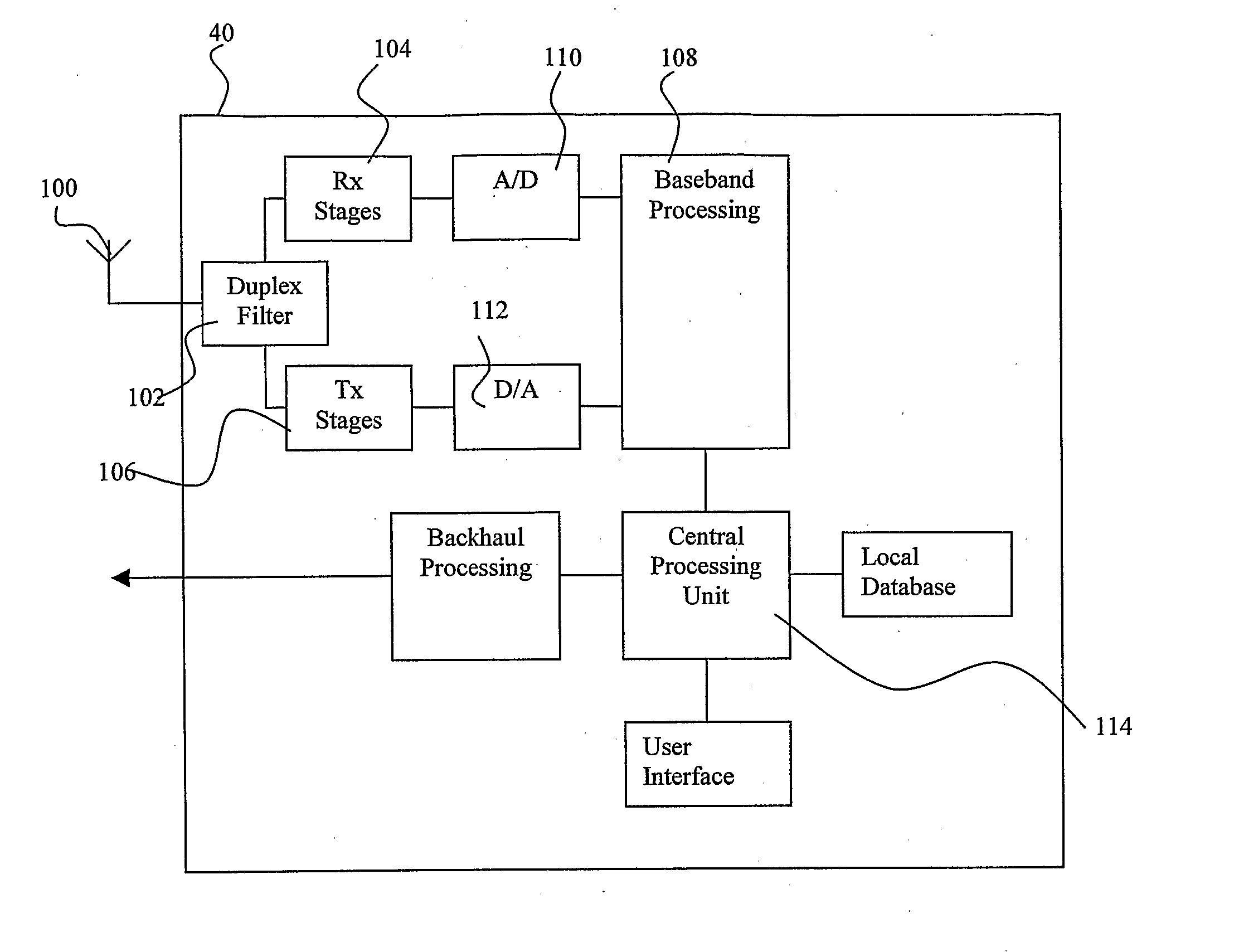

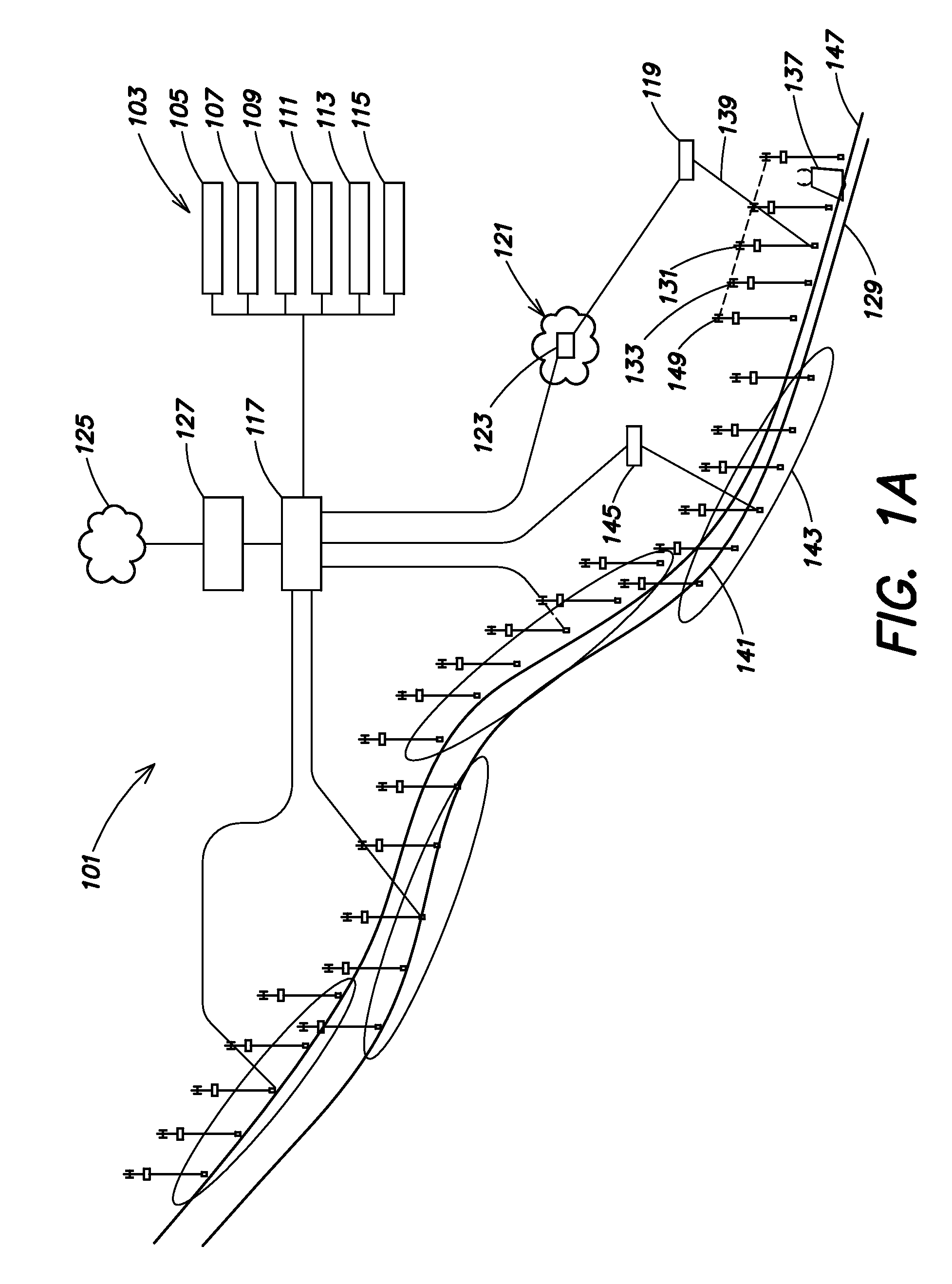

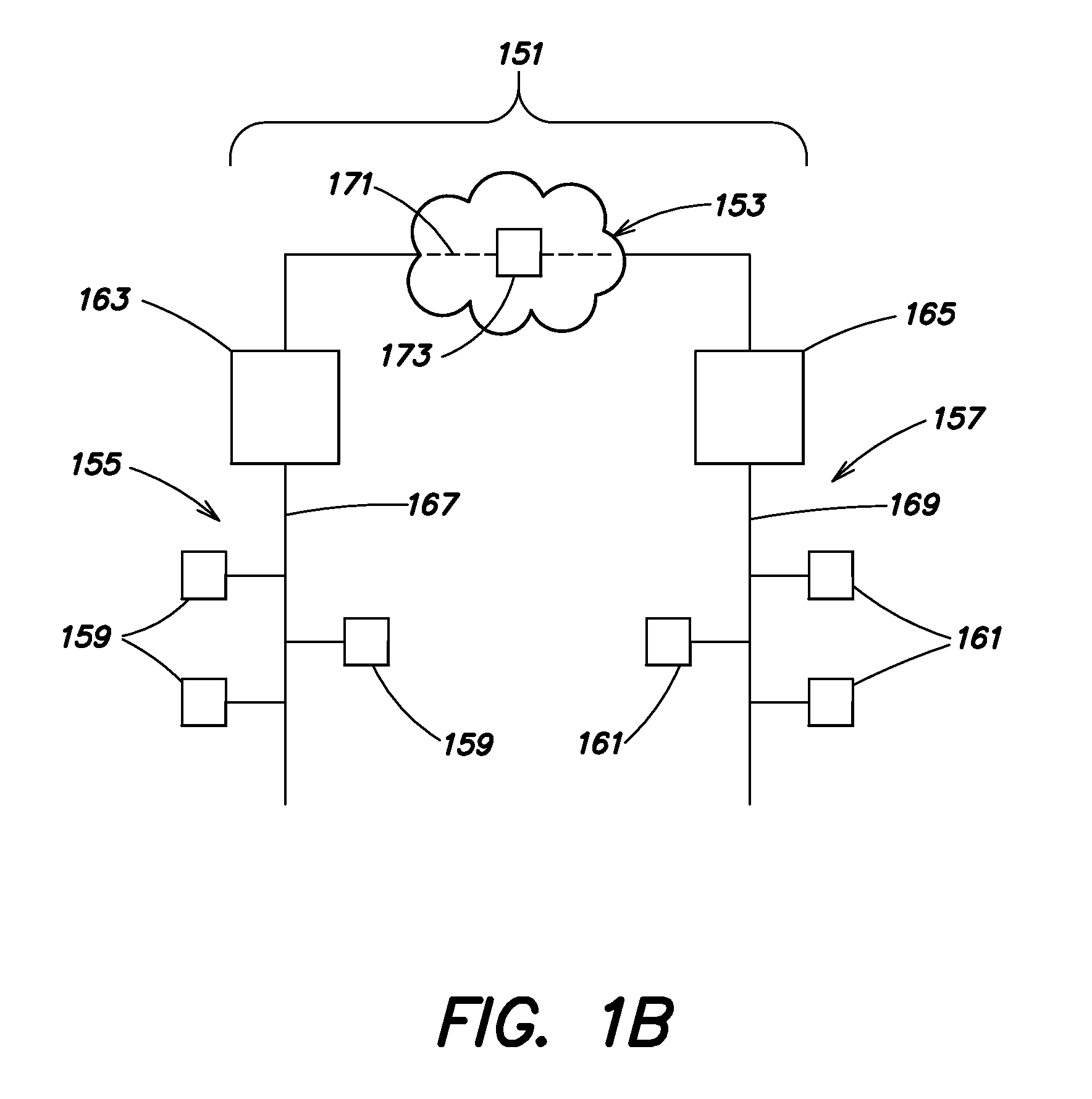

Systems and methods for providing network access to mobile devices that travel with a vehicle, such as a train, a bus, a boat, etc. along or adjacent to a relatively fixed path that may extend over a large geographic area. Mobile devices access the network through stationary access points arranged along or adjacent to the path and communicate with a communication network. The communication network may be arranged as an asynchronous transfer mode (ATM) local area network emulation (LANE) network. One of the mobile devices may be a mobile access point which can couple other mobile devices to the network and record authentication information of other mobile devices so that fast transitions can be made from one stationary access point to another as the vehicle moves along the path.

Owner:WIFI RAIL

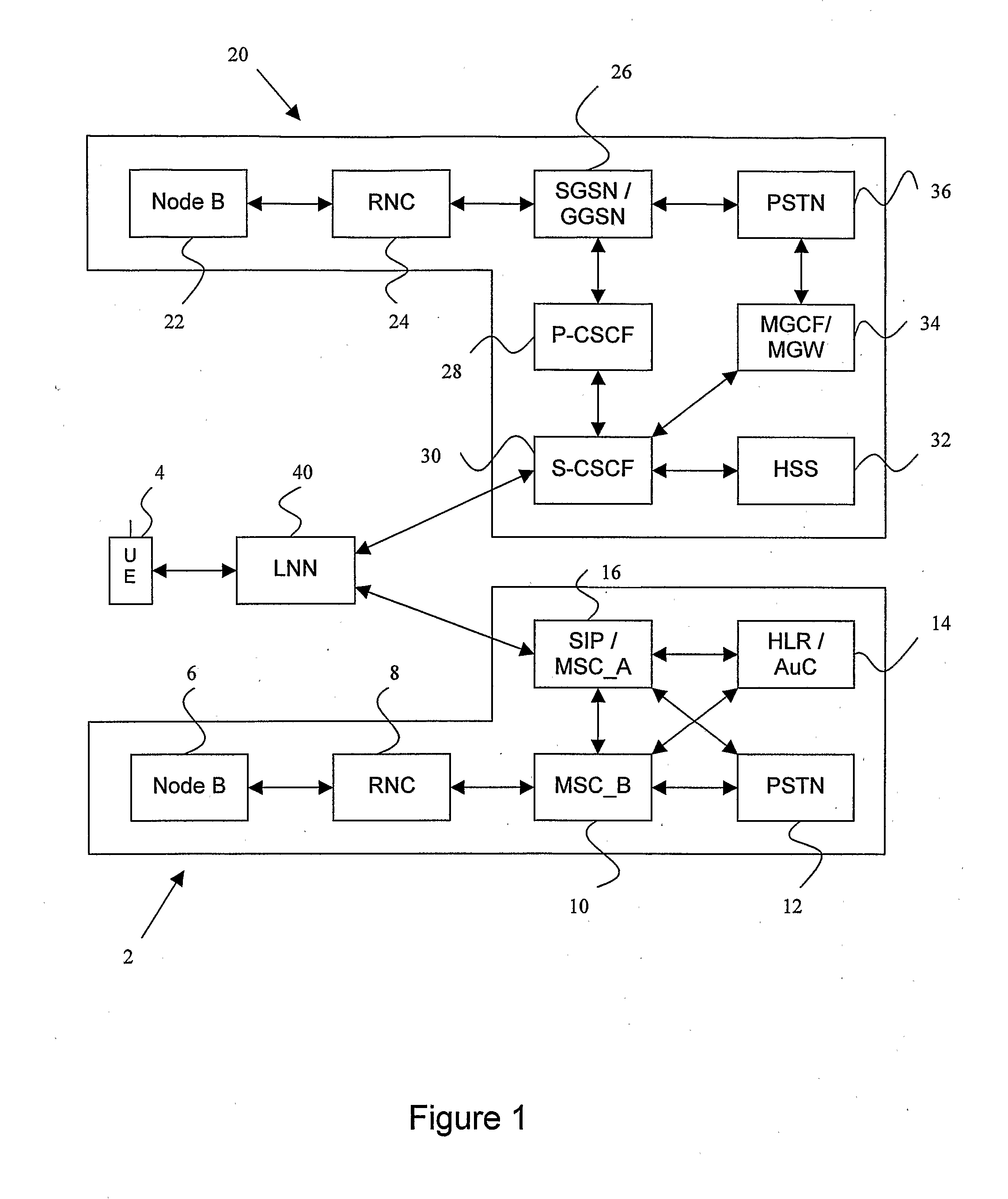

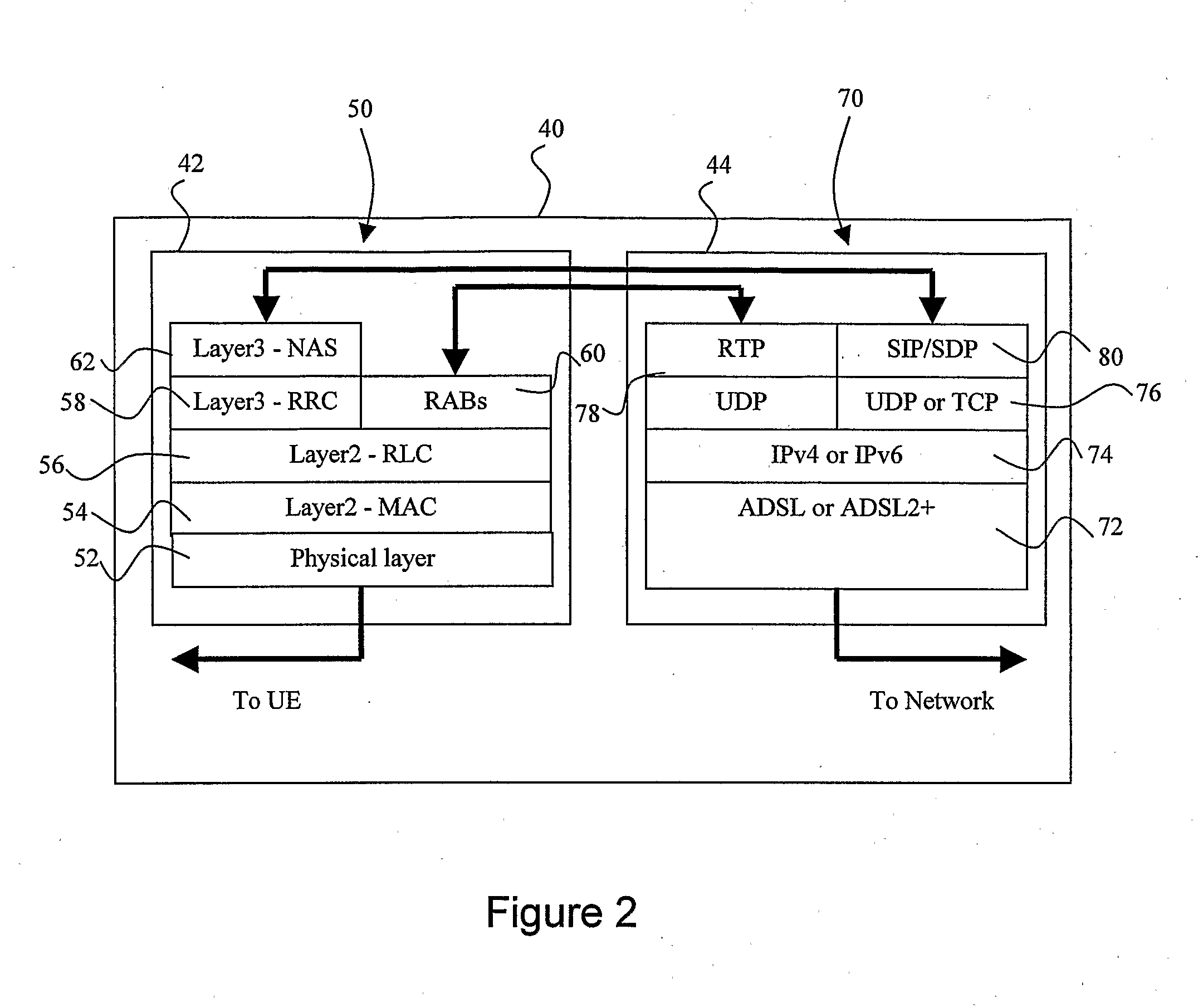

Signal Transmission Method from a Local Network Node

ActiveUS20080069020A1Minimizes power neededImprove interference effectError prevention/detection by using return channelResonant long antennasElectricityData rate

A transmitter is provided having transmission methods that minimize the power needed to ensure reliable reception in a coverage area. In one aspect, data that requires re-transmission as acknowledged mode data is re-transmitted when the power level of the transmission link is higher than a pre-determined level set for reliable reception. The data rate of the re-transmitted data is set according to the difference in the actual power and the pre-determined level. In a second aspect, two transmitting antennae are used to transmit the same signals with a frequency off-set. The frequency off set can be used to determine the phase of the signals being received at the receiver, so that a phase off-set can be introduced to optimise the effect of interference at the receiver.

Owner:BISON PATENT LICENSING LLC

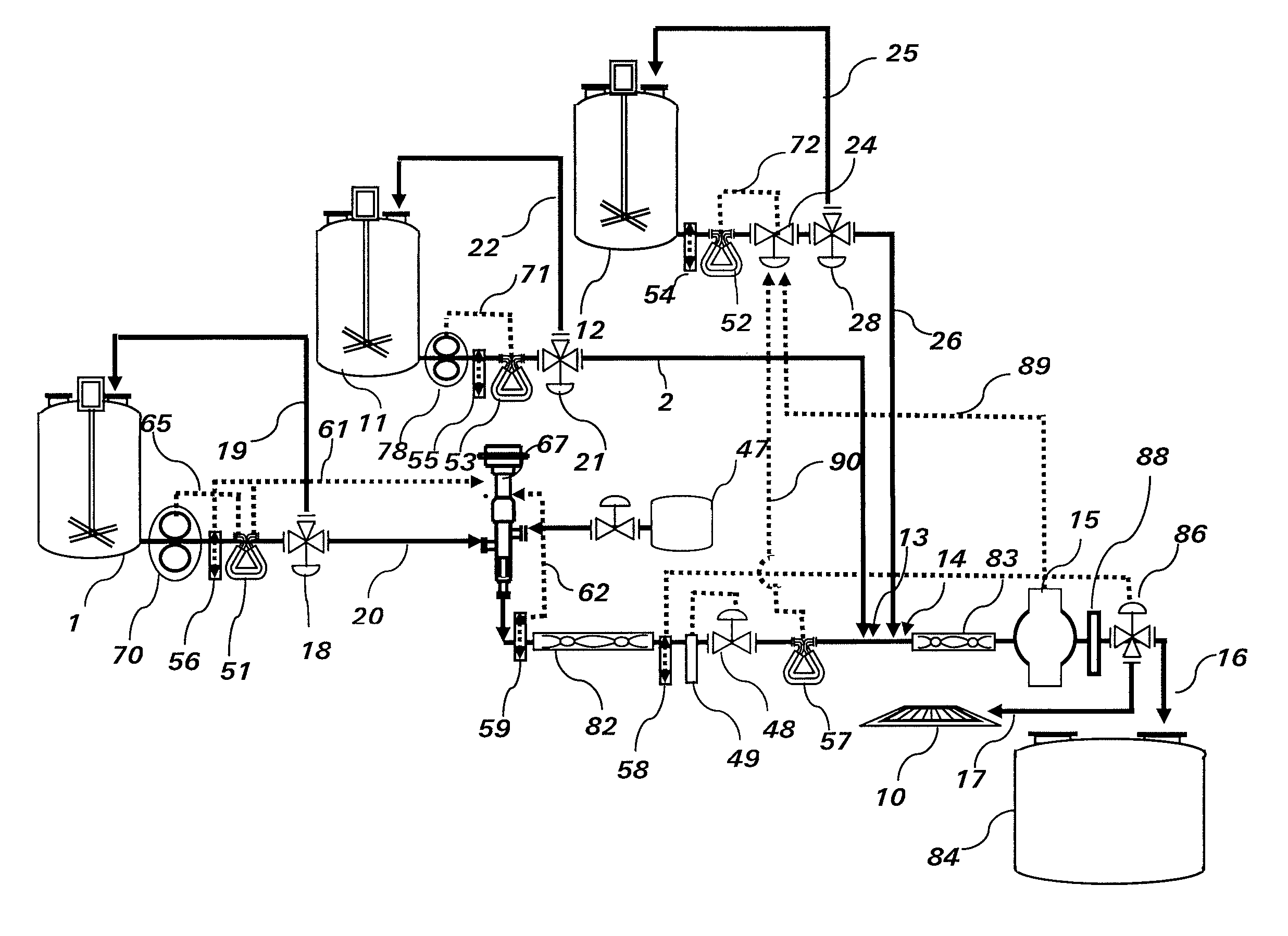

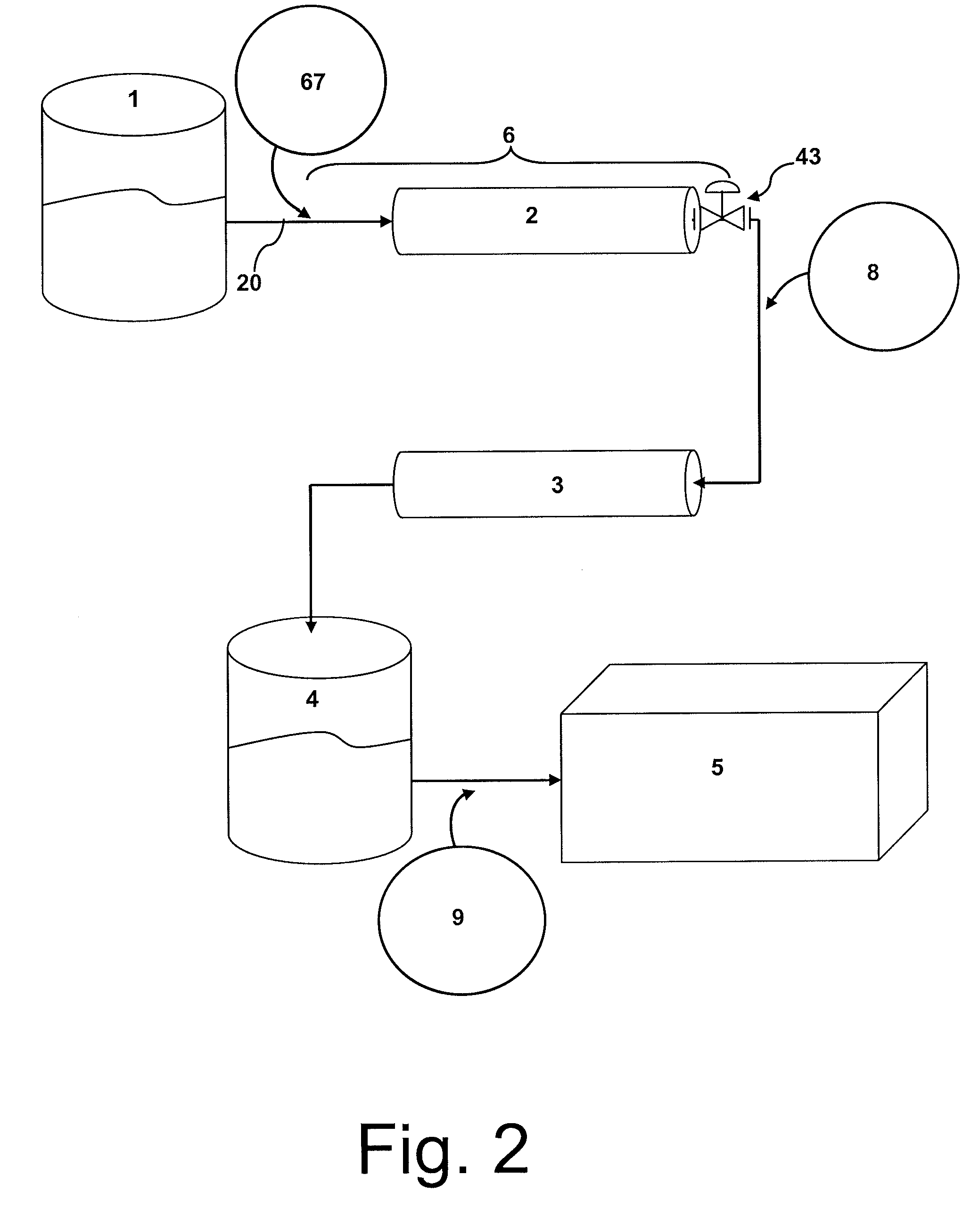

Sterilization of Flowable Food Products

InactiveUS20080160149A1Prevent degradationExtend heating timeCombination devicesAuxillary pretreatmentSporeAlicyclobacillus acidoterrestris

Methods of beverage and flowable food product production using steam injection are provided to efficiently destroy microorganisms able to withstand normal pasteurization temperatures. Microorganisms such as Alicyclobacillus acidoterrestris and its spores may be eliminated from fruit juices and the like while minimizing organoleptic degradation due to heating. The apparatus is capable of pasteurizing, blending and controlling the product specifications of a finished beverage in a continuous matter.

Owner:KRAFT FOODS GLOBAL BRANDS LLC

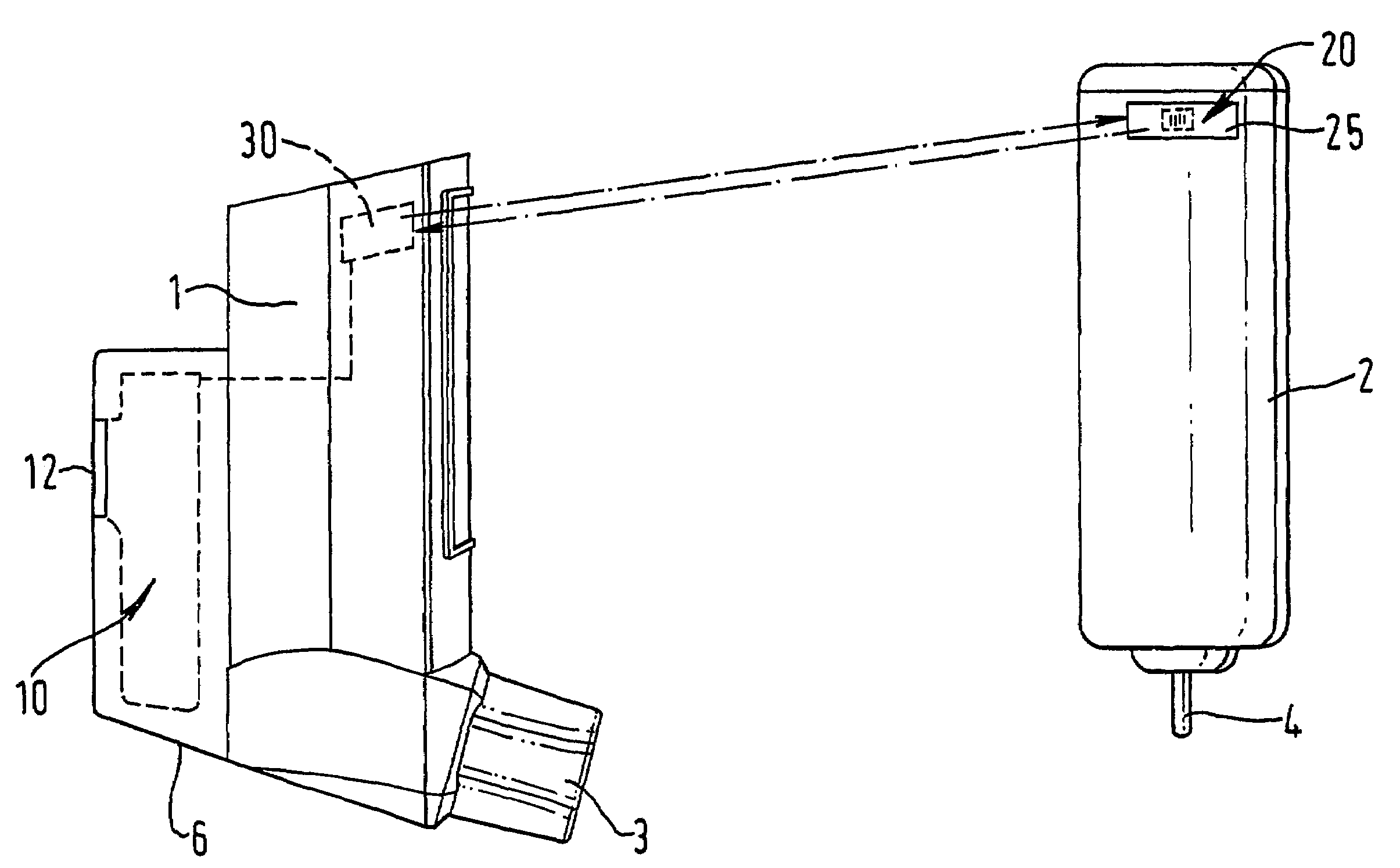

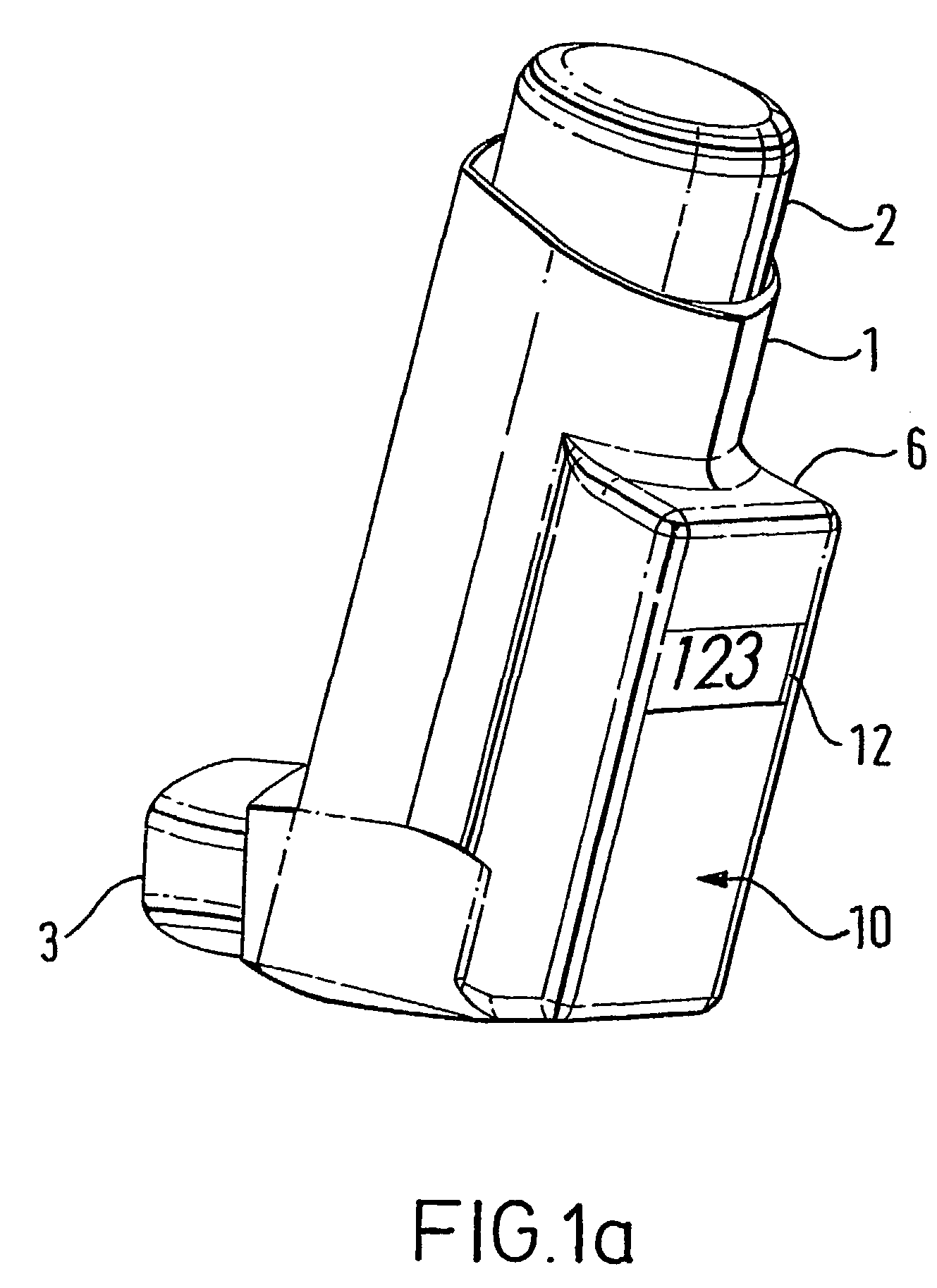

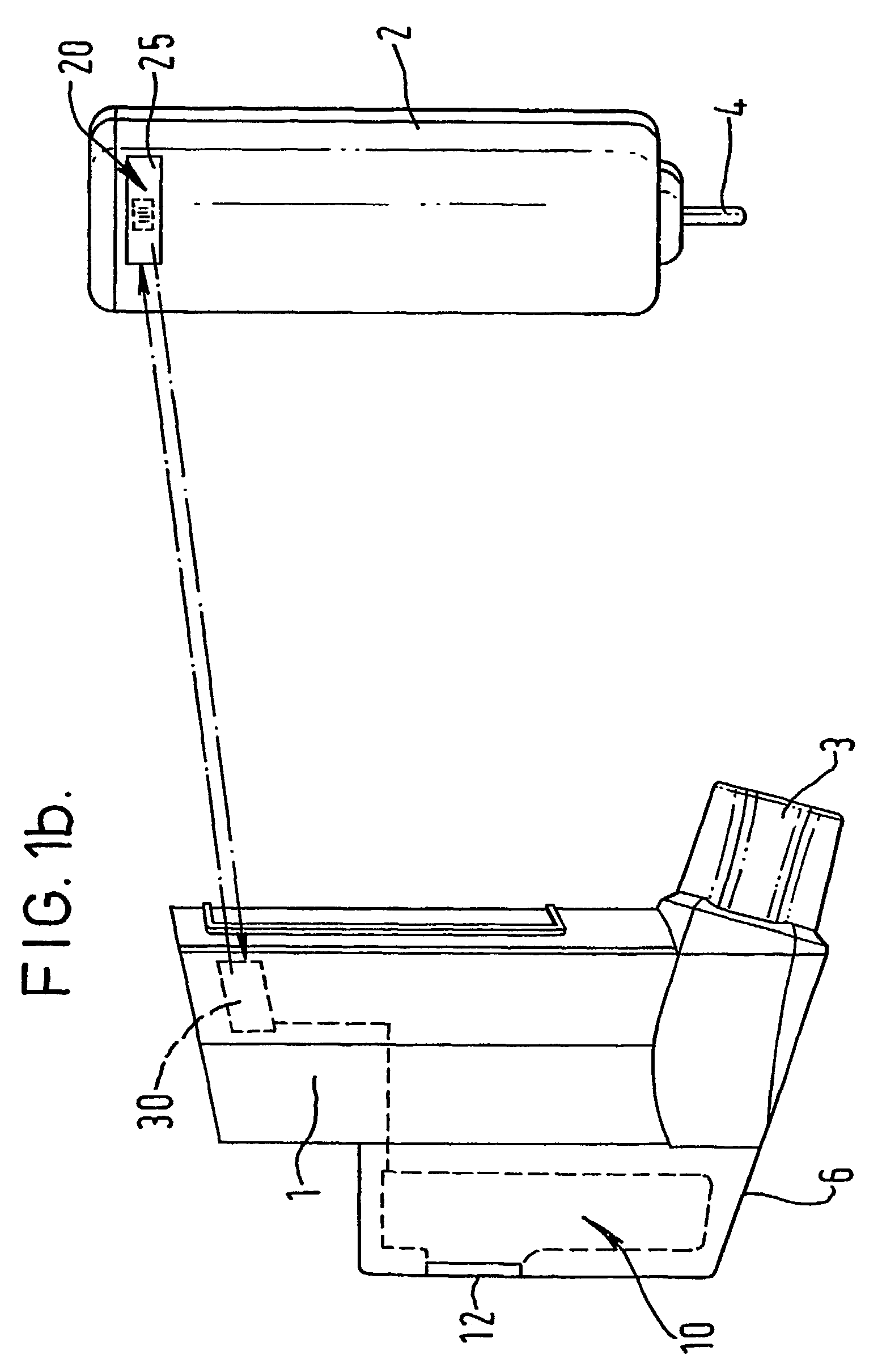

Medicament dispenser

InactiveUS7191777B2Readily and accurately transferableAssist detectionLiquid surface applicatorsPowdered material dispensingMedication DispenserBody shape

A medicament dispenser for use in the storage, presentation and / or dispensing of medicament comprising a body shaped for receipt of a medicament container. In association with the body, there is a first transceiver for transmitting and receiving data. A medicament container is receivable by the body. In association with the medicament container, there is a second transceiver for transmitting and receiving data. Data is transferable in two-way fashion from the first transceiver to the second transceiver. The medicament dispenser may be supplied in kit of parts form.

Owner:GLAXO GROUP LTD

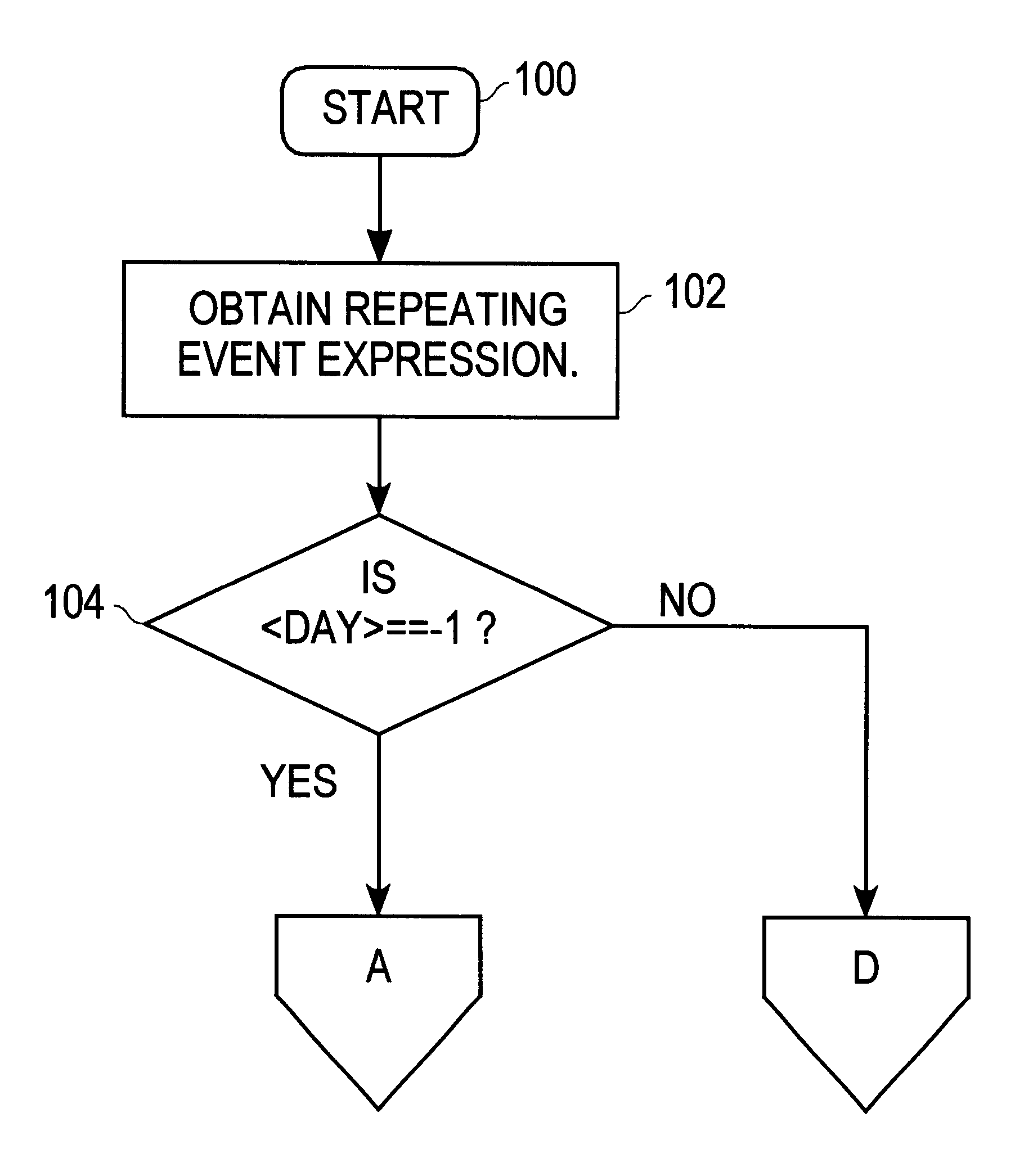

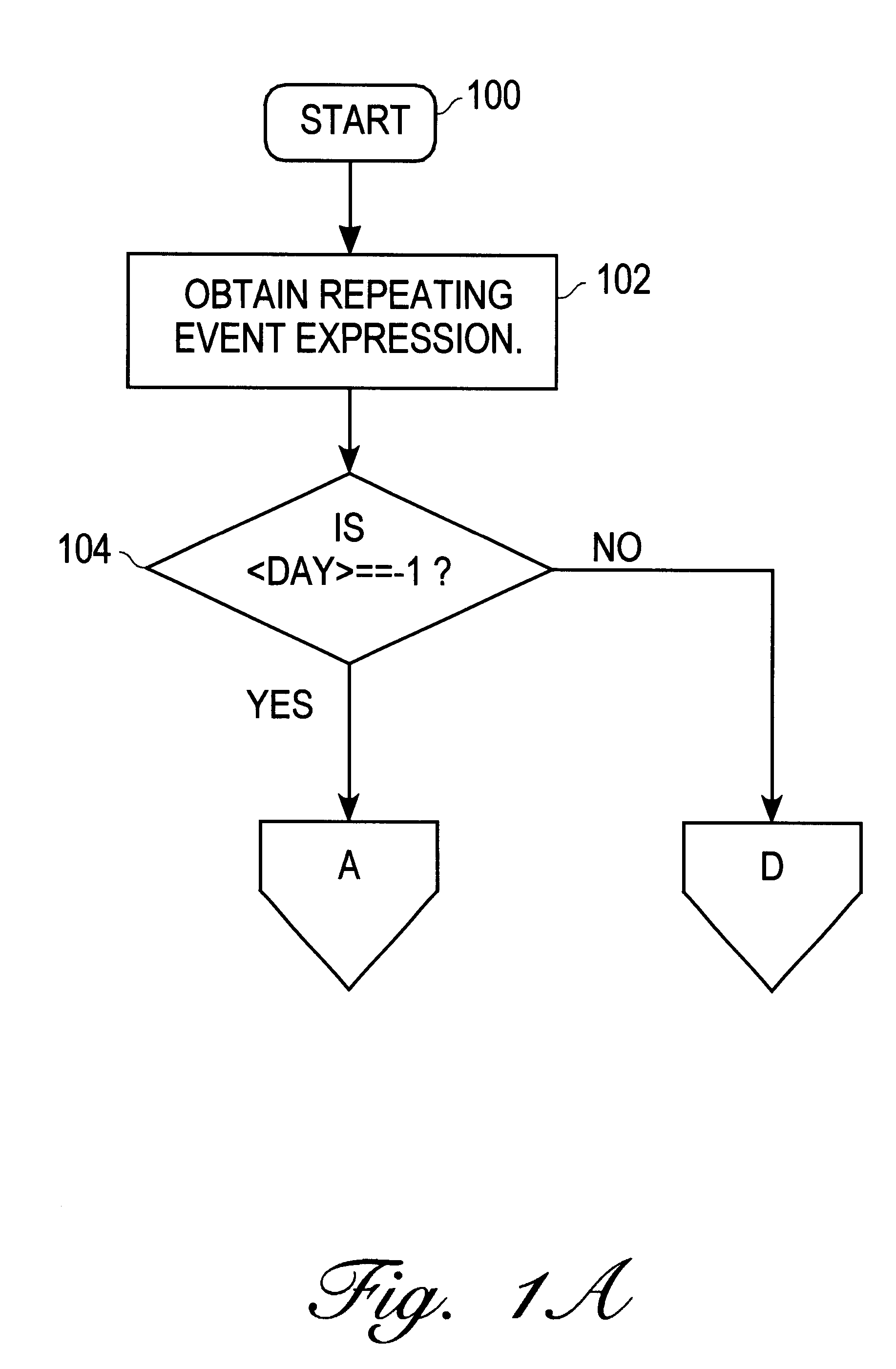

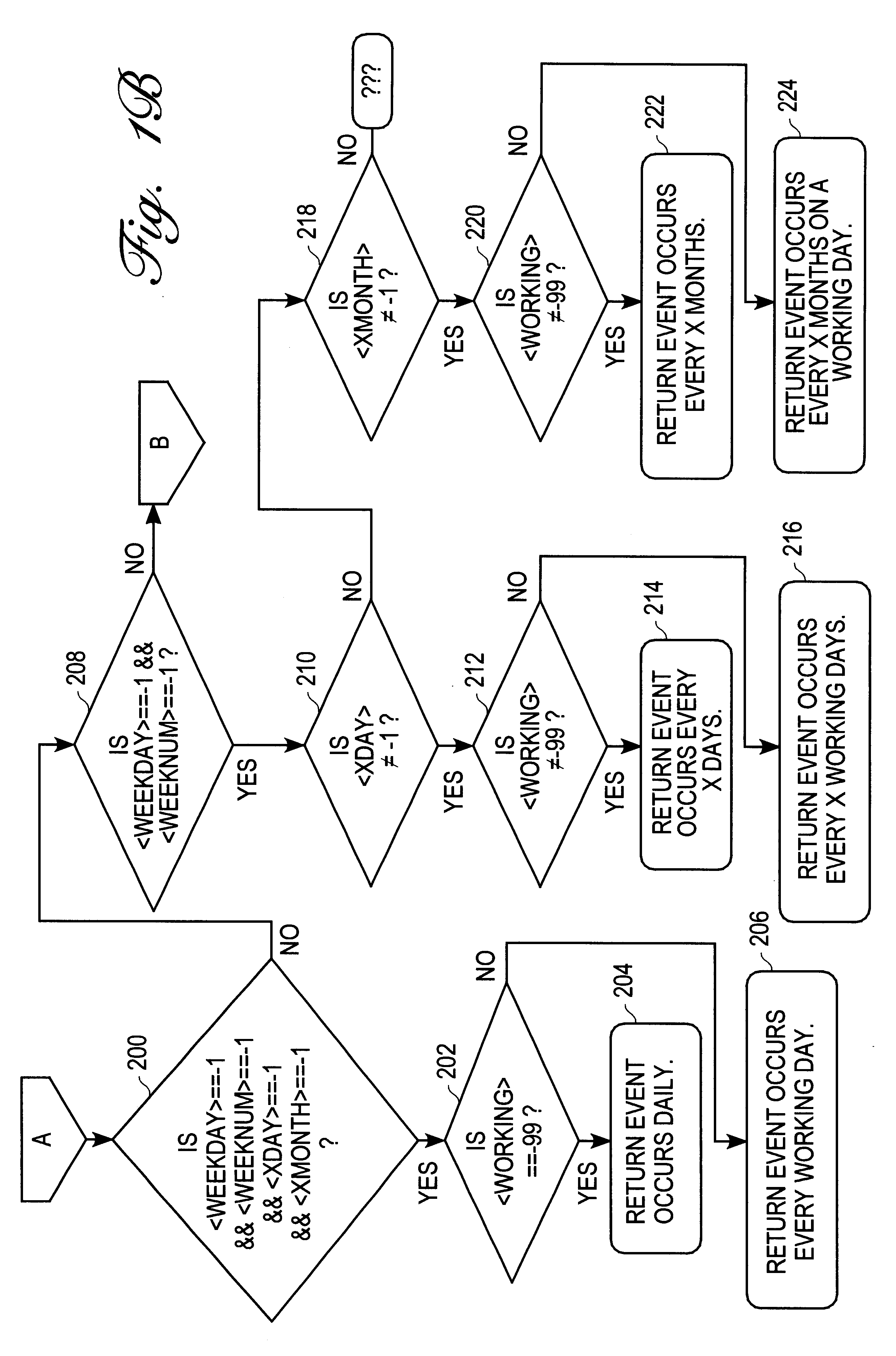

Method and apparatus for generating recurring events in a calendar/schedule system

InactiveUS6272074B1Storage requirement is minimizedMinimization needsVisual indicationOptical signalsInfinite numberData mining

An electronic calendaring and scheduling capability that minimizes storage requirements. Repetitive calendar events are stored as single entries using an expression language. The expression language provides an ability for expressing how often the event recurs. Thus, the days on which the event occurs are computed from an expression stored in a repetitive event. Further, the expression language provides the ability to identify exceptions and to define an infinite number of recurring events from the original recurrent event definition. Events are generated by obtaining a recurrency expression of a first event. The recurrency expression is converted to one or more recurring dates. A beginning date of the first event is also obtained. Using one or more recurring dates and the beginning date, one or more second events are generated in response. The present invention provides the first event and the one or more second events to the users in one or more calendars. The present invention further utilizes a recurrency expression including one or more anti-event expressions. Anti-events have the same format as the recurring event. The anti-event expressions are used to generate one or more exception dates. The exception dates cancel at least one of the recurring dates.

Owner:ORACLE INT CORP

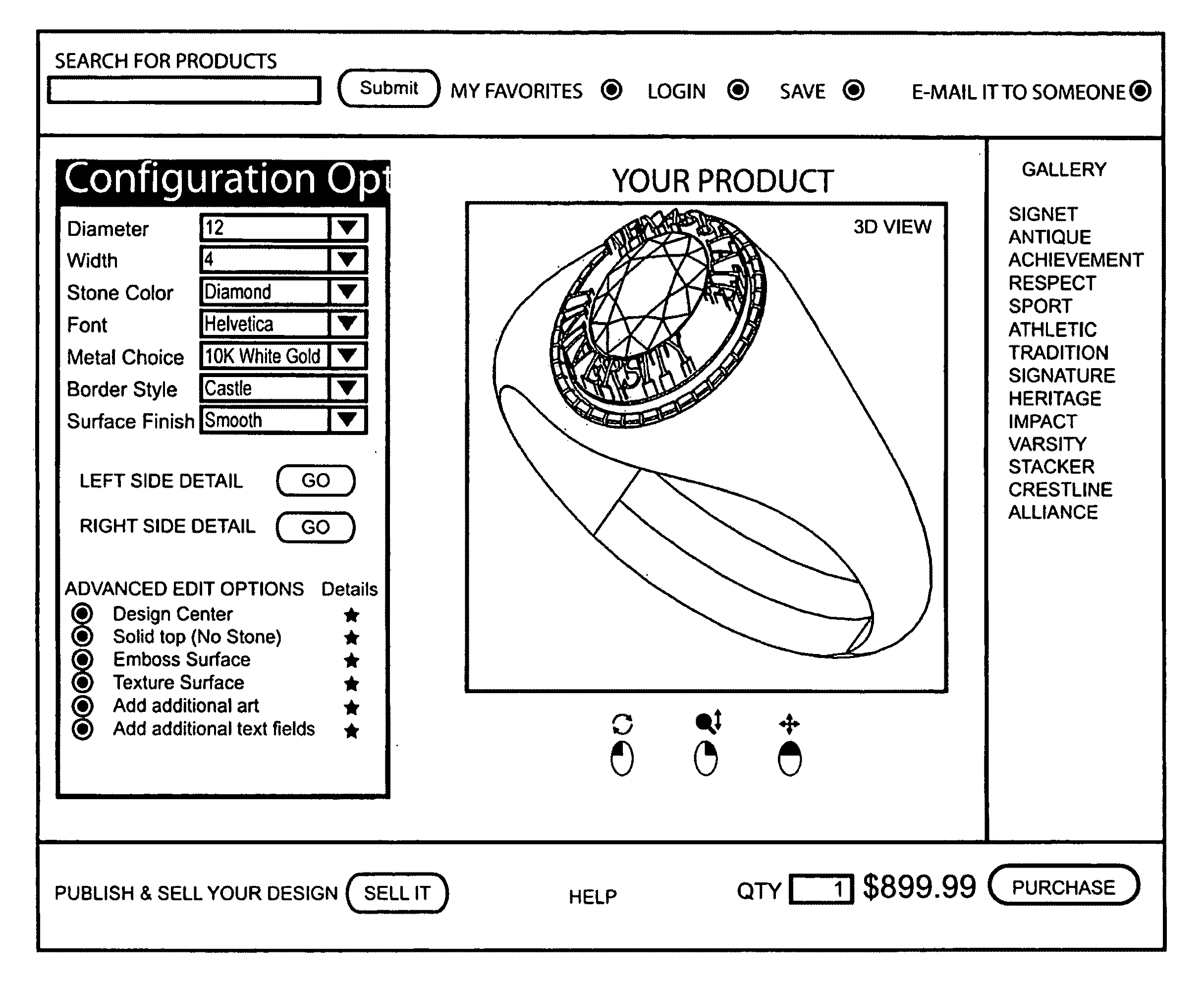

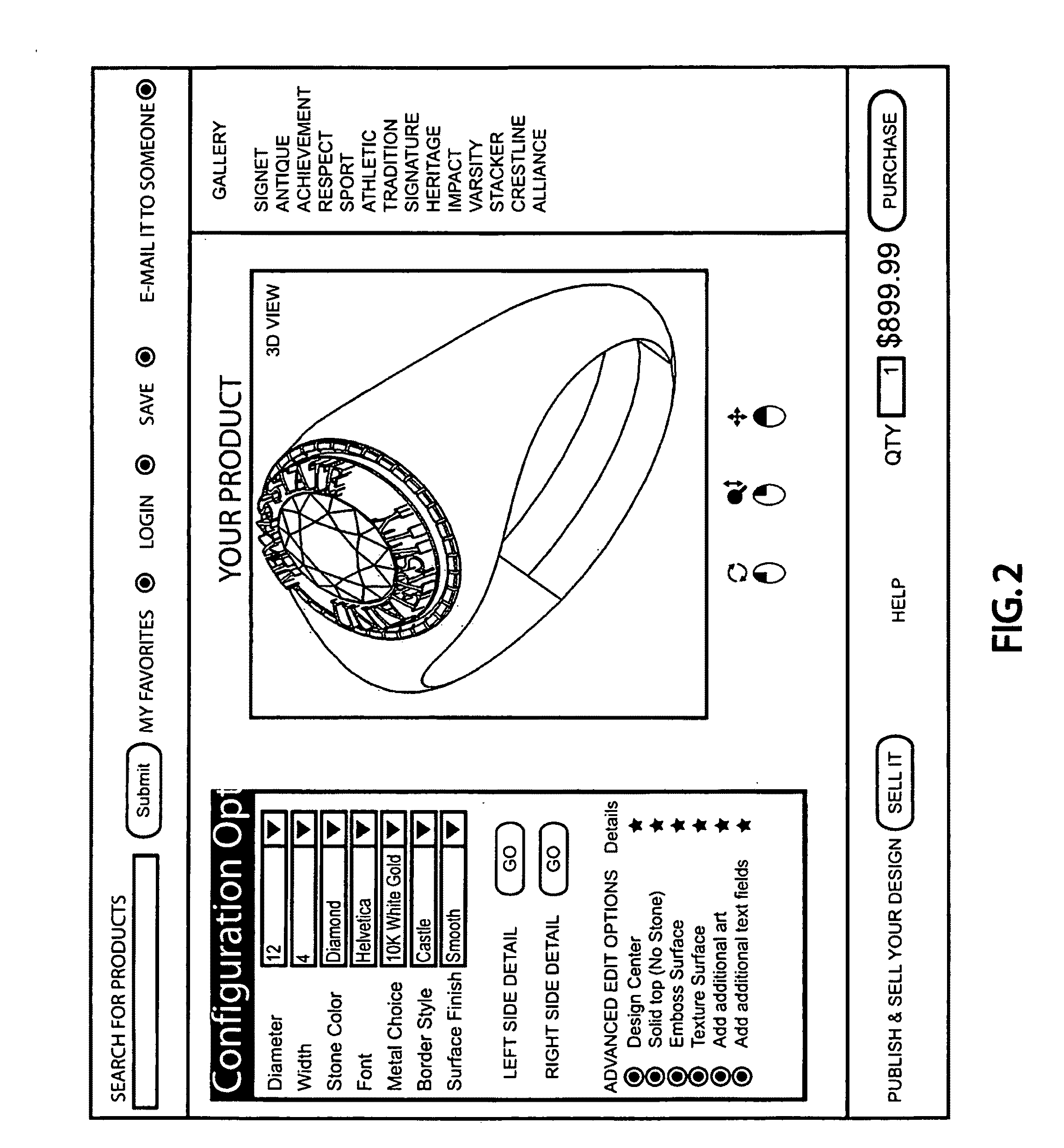

Made-to-order direct digital manufacturing enterprise

ActiveUS20110313878A1Improve business performanceRemoving and minimizing numberGeometric CADAdditive manufacturing apparatusComputer scienceDigitization

Owner:KRAFTWURX INC

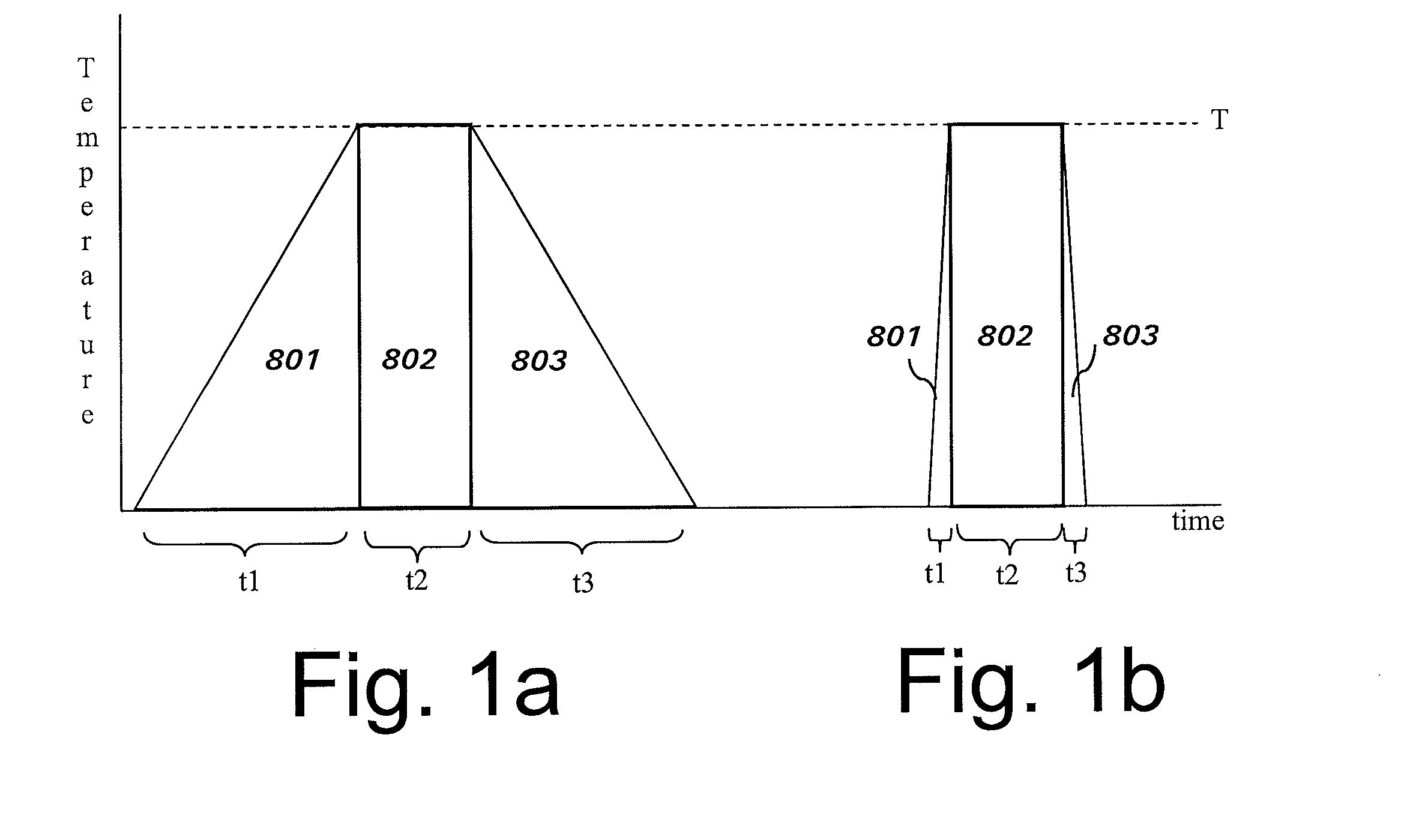

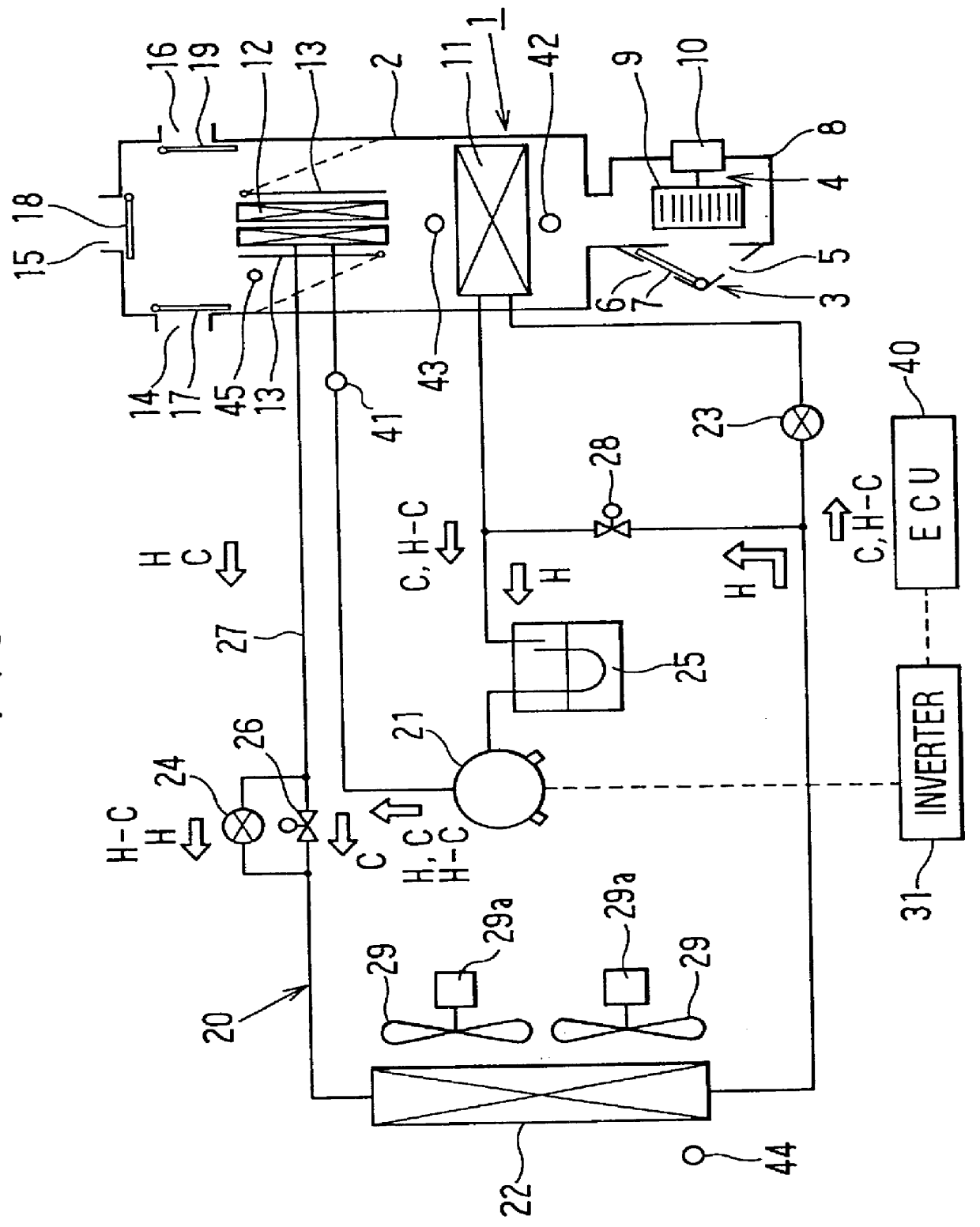

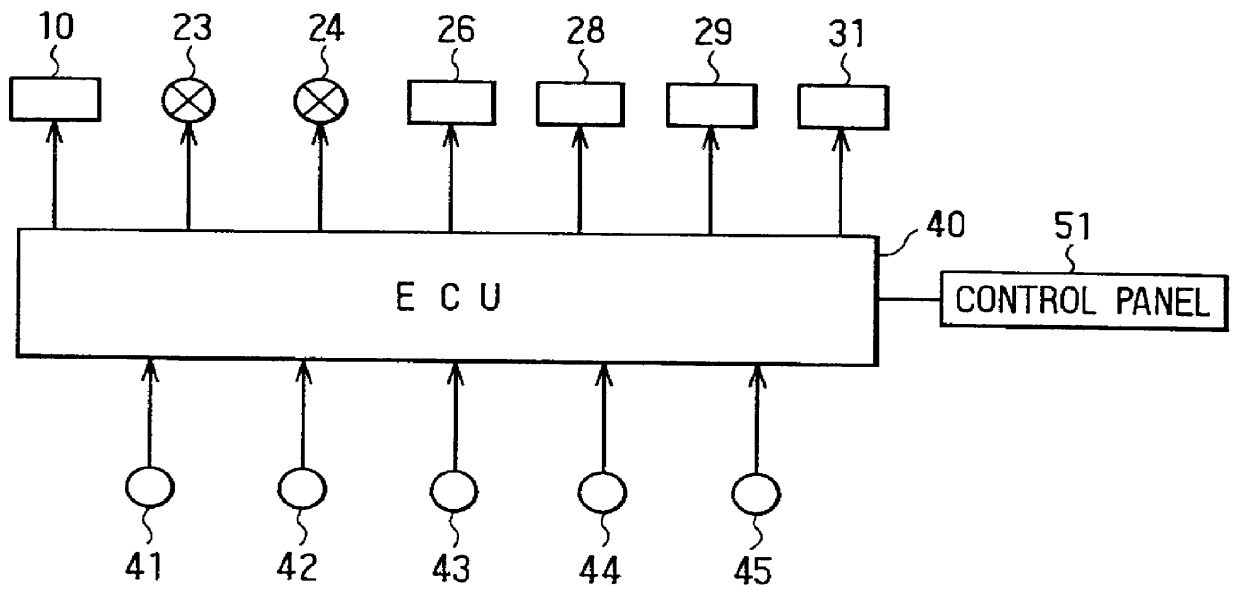

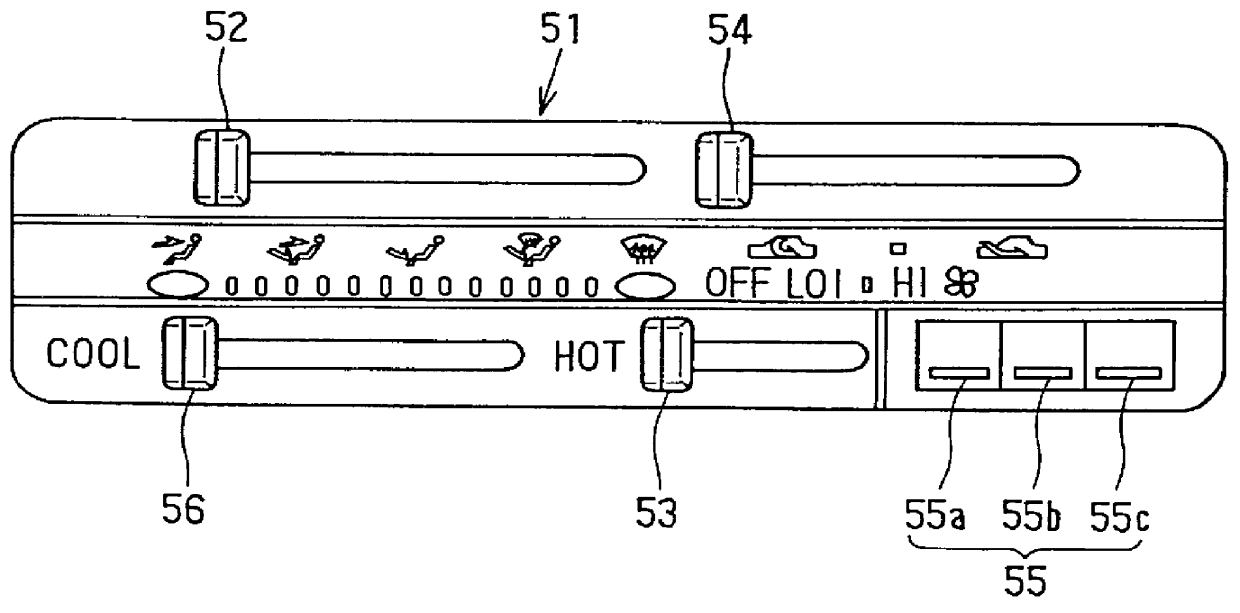

Air conditioner

InactiveUS6035653AMinimizing temperature overshootMinimization needsAir-treating devicesMechanical apparatusResponsivityEngineering

An air conditioner capable of enhancing responsivity of a blowout temperature of conditioned air while preventing occurrence of an overshoot or undershoot condition of the blowout temperature when a user gives an instruction to change the blowout temperature in a dehumidifying operation mode. In a control state, if a set temperature level is adjusted to increase a blowout temperature of conditioned air by increasing the target condenser outlet temperature, the rotating speed of the refrigerant compressor is increased, while the restriction opening of the heating expansion valve is maintained. Thus, the condenser outlet temperature is regulated to the target temperature with minimal undershoot or overshoot of the target temperature.

Owner:DENSO CORP

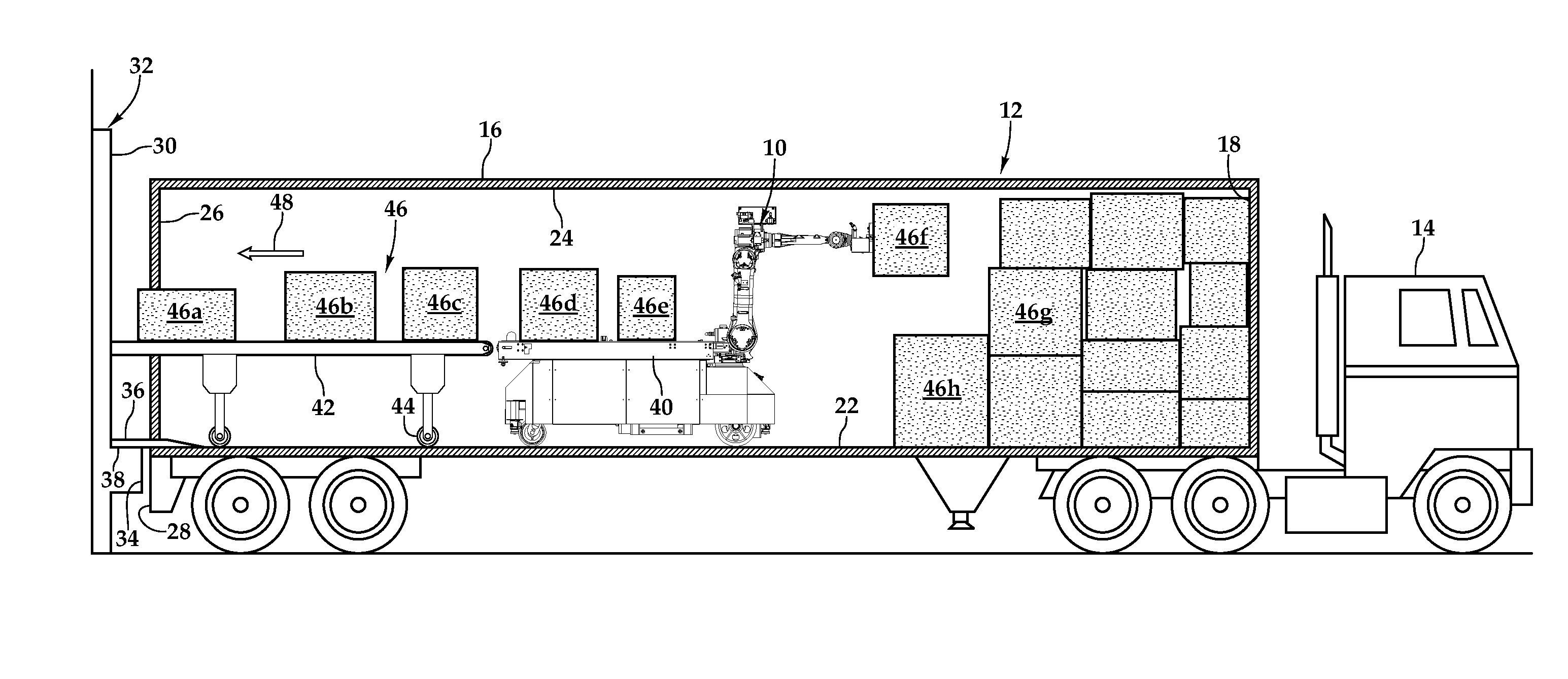

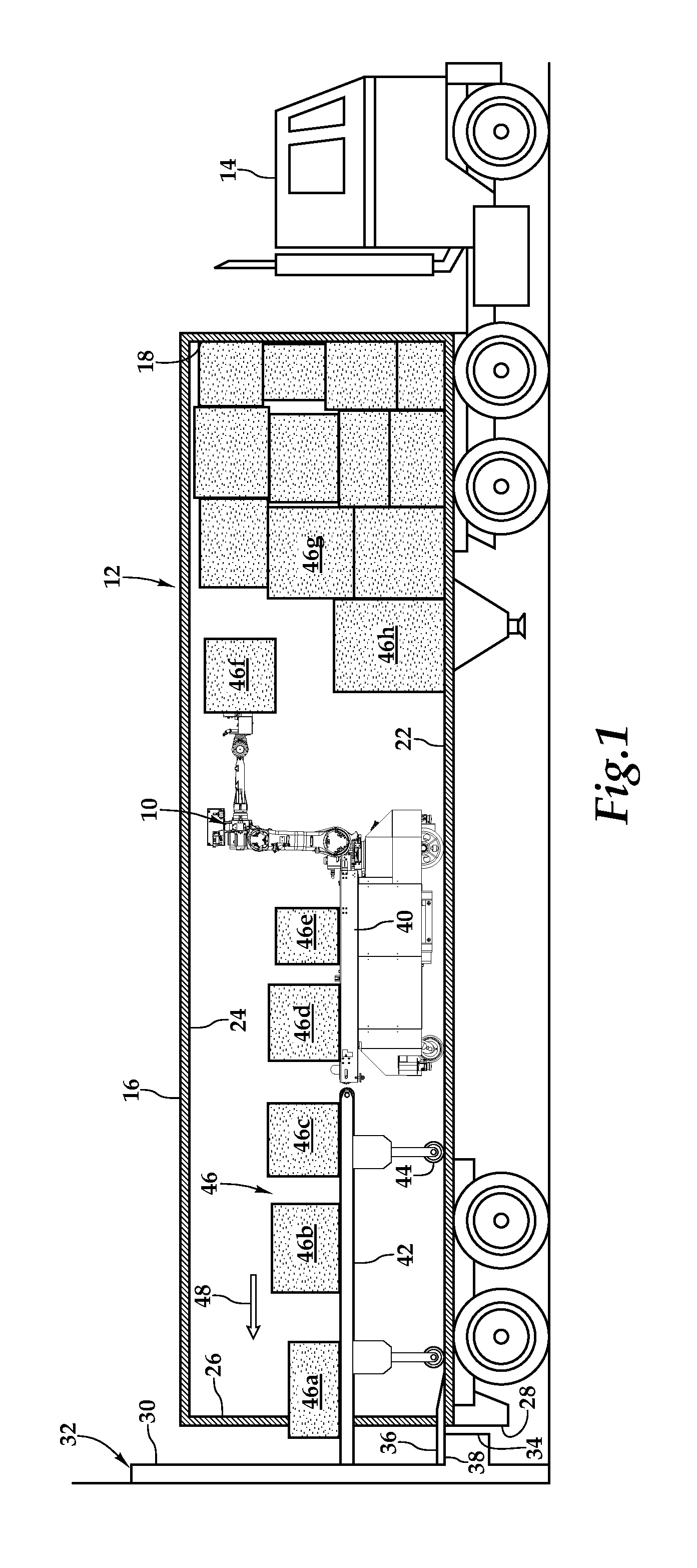

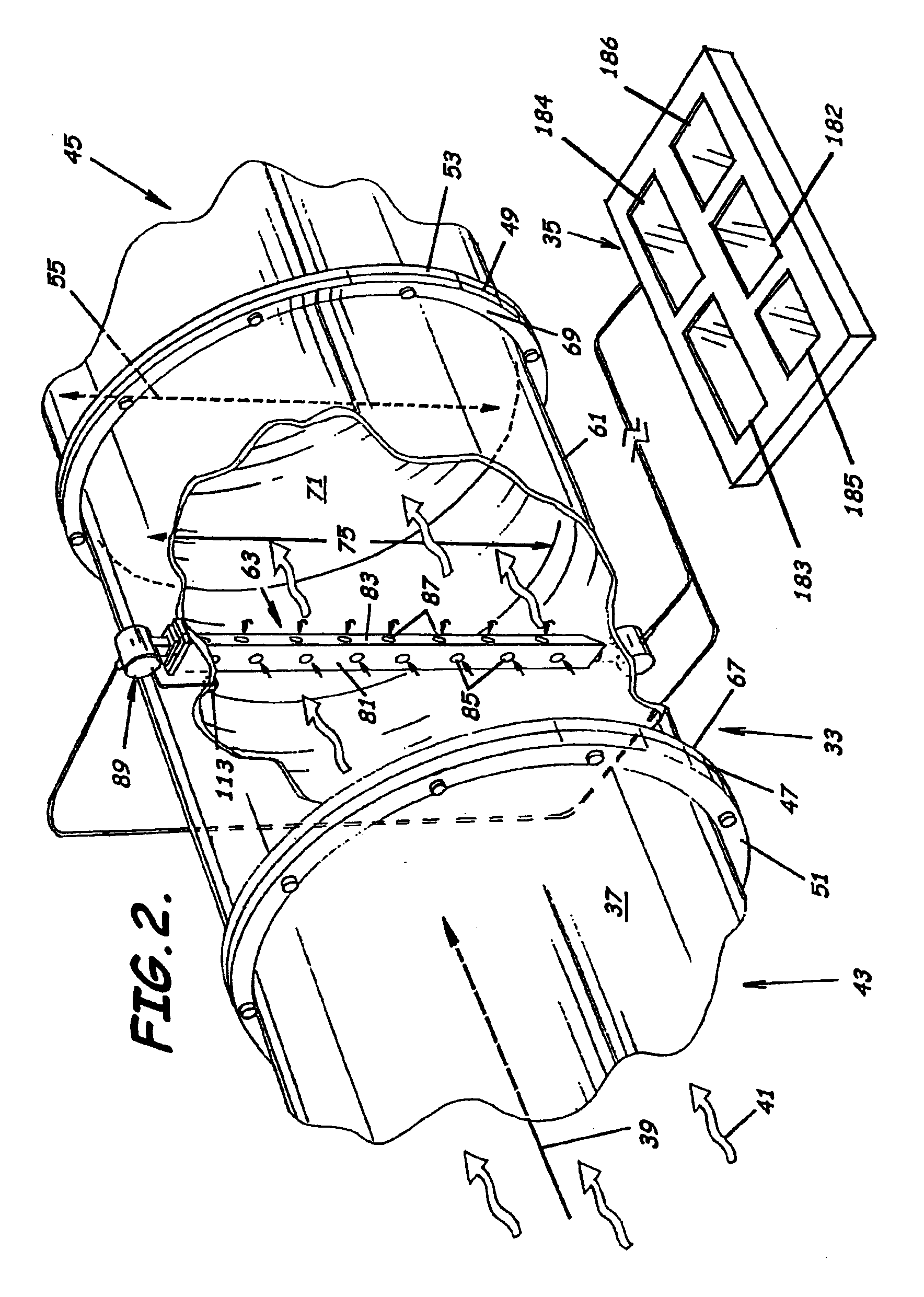

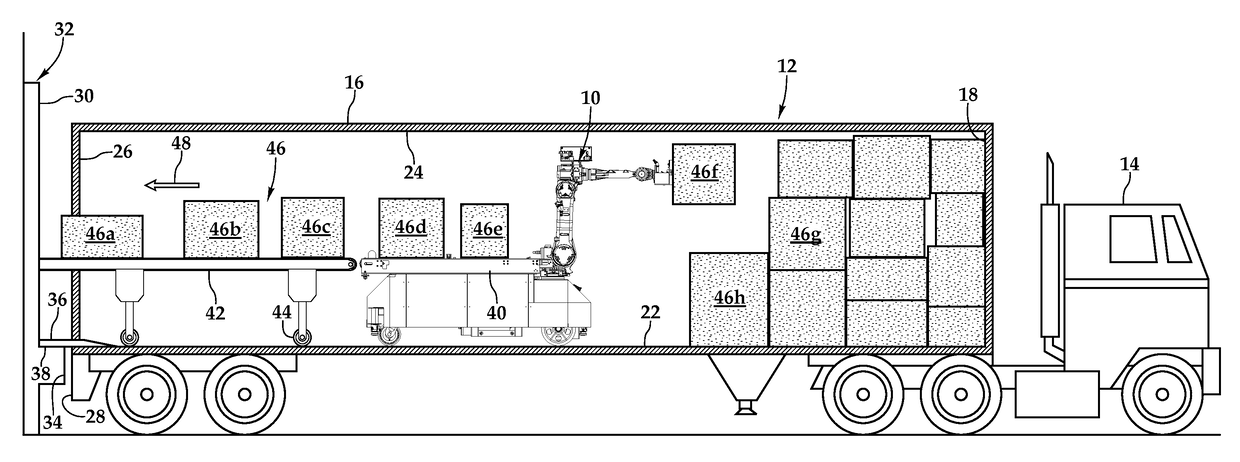

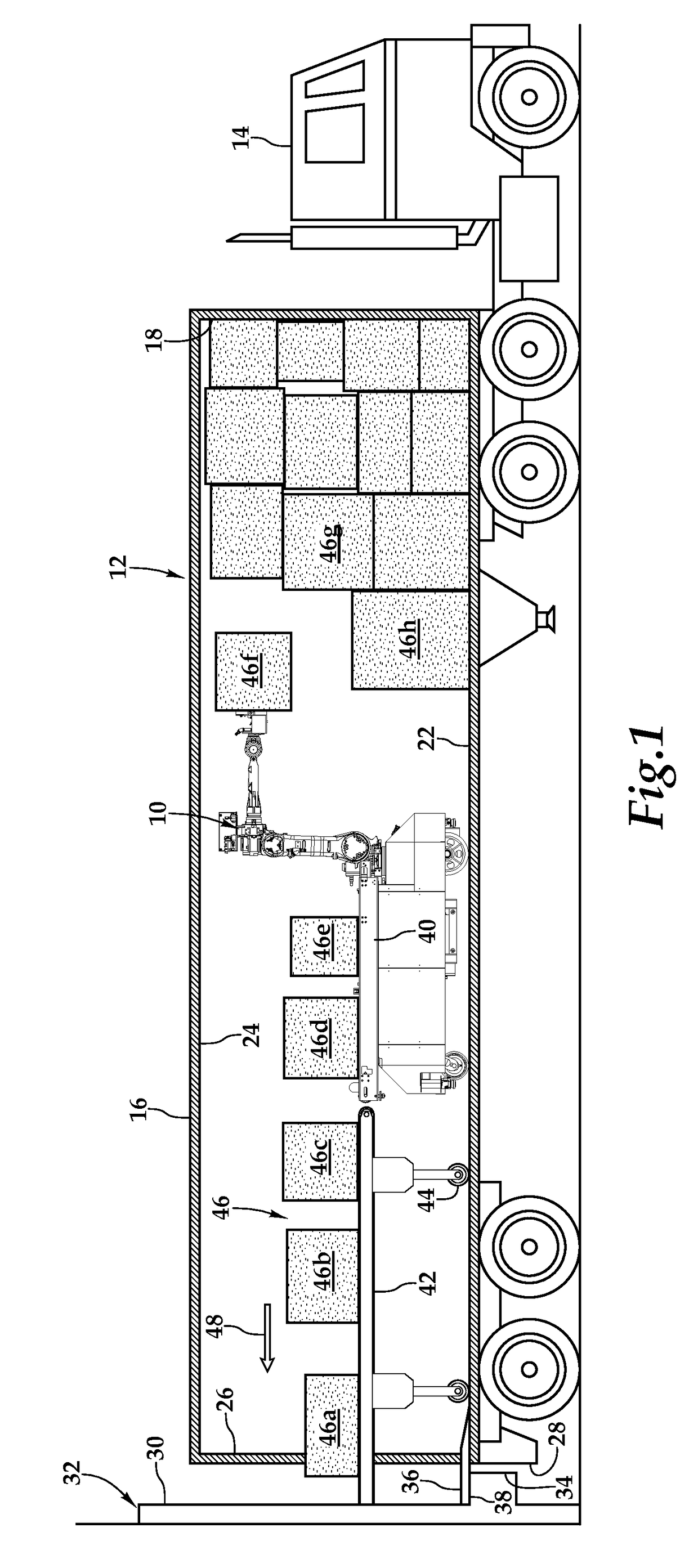

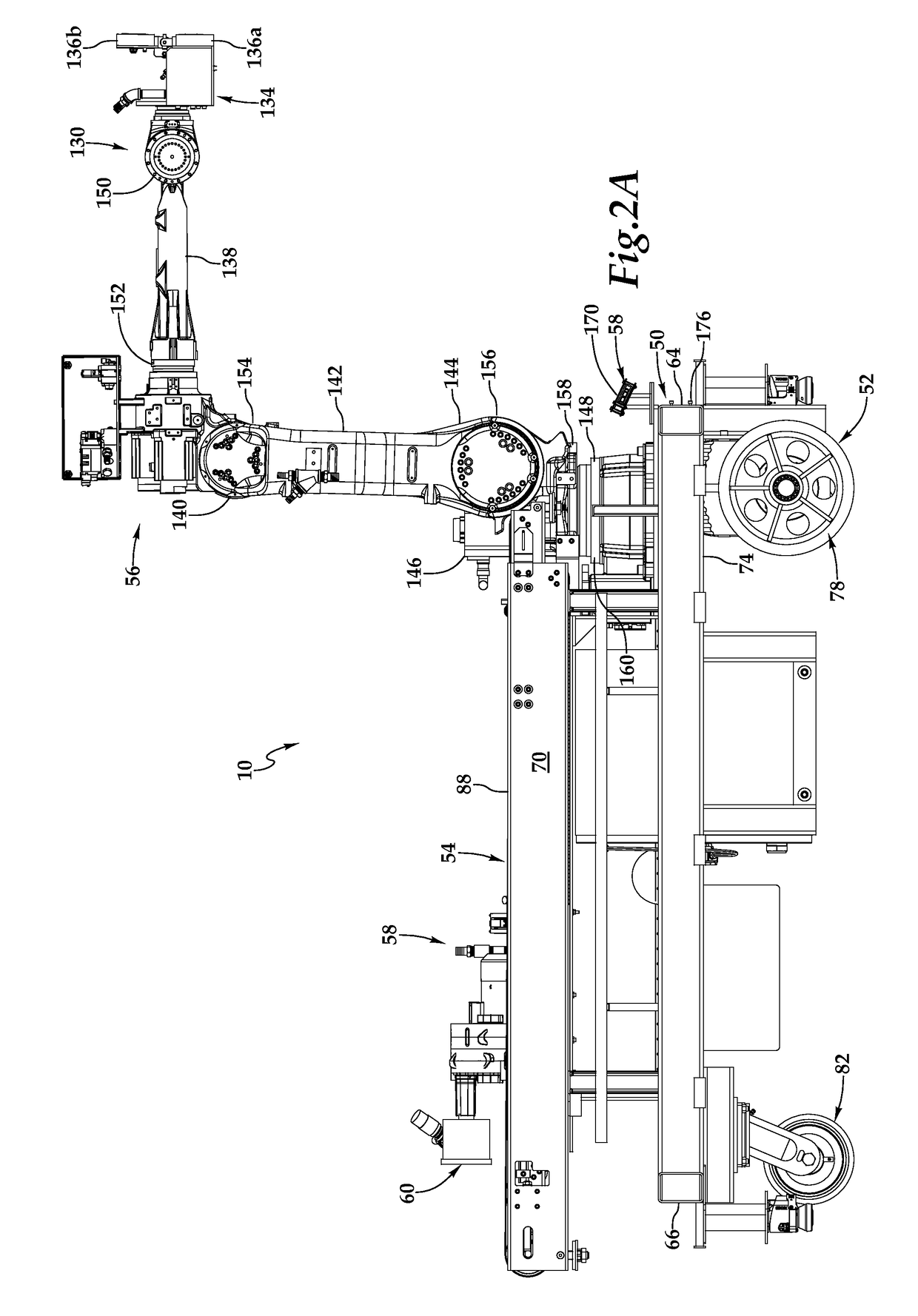

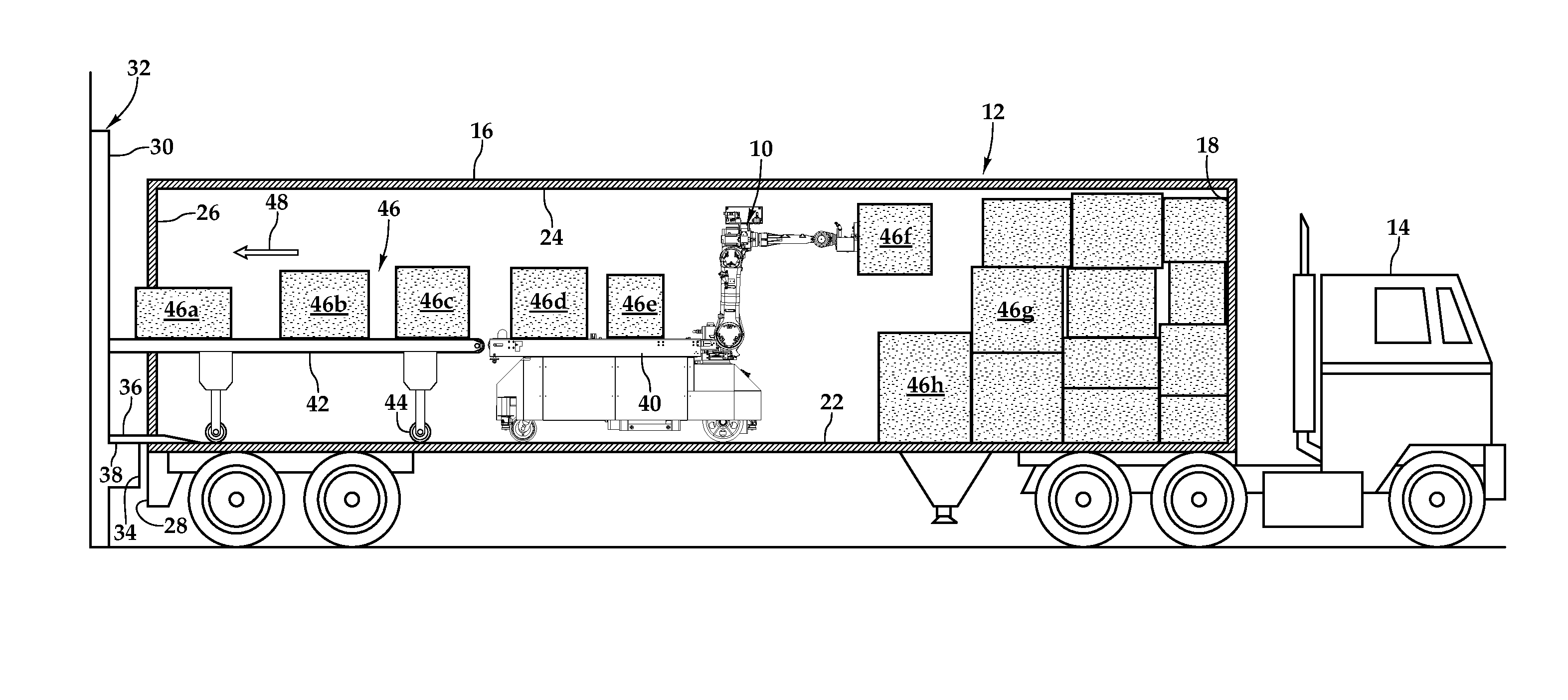

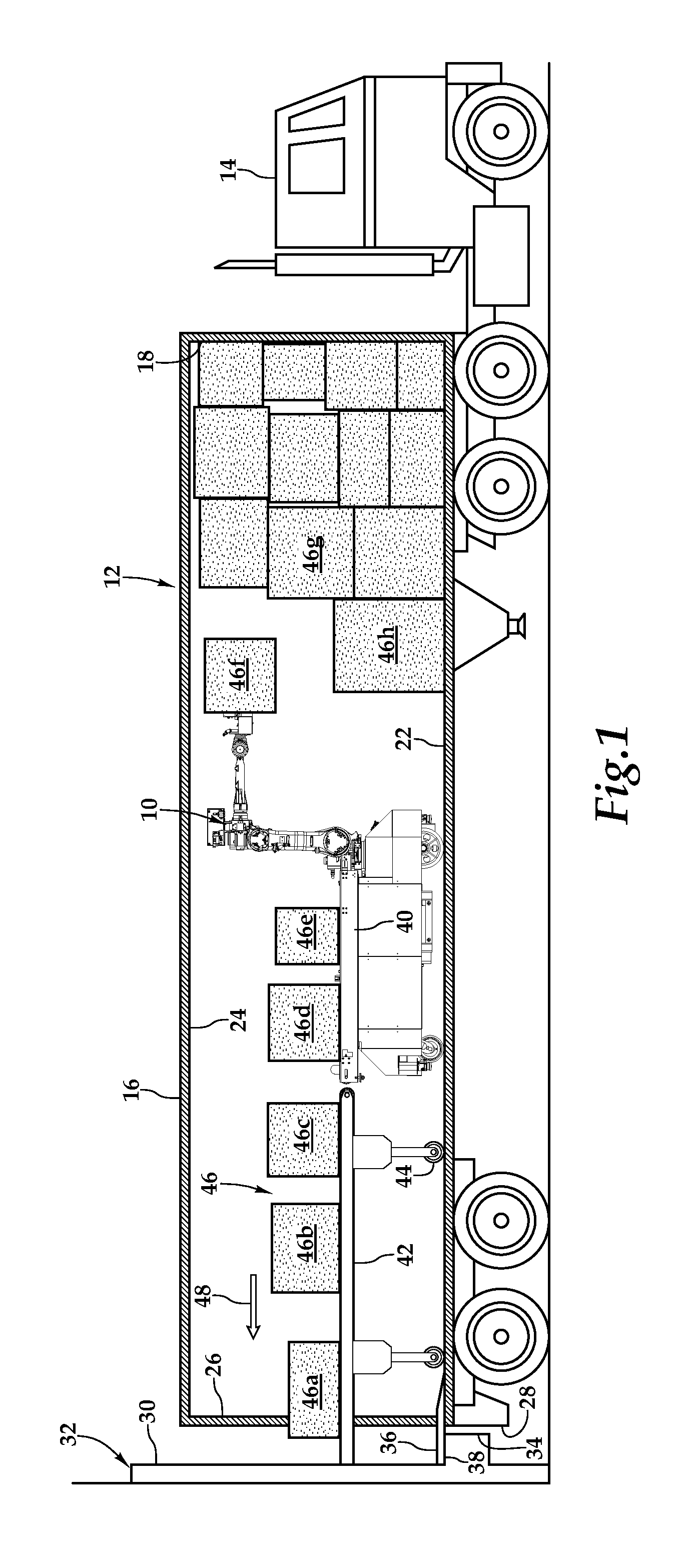

Automated Truck Unloader for Unloading/Unpacking Product from Trailers and Containers

ActiveUS20140205403A1Quantity maximizationProtect and extend lifeProgramme controlProgramme-controlled manipulatorEngineeringBiological activation

An automatic truck unloader for unloading / unpacking product, such as boxes or cases, from trailers and containers is disclosed. In one embodiment, a mobile base structure provides a support framework for a drive subassembly, conveyance subassembly, an industrial robot, a distance measurement subassembly, and a control subassembly. Under the operation of the control subassembly, an industrial robot having a suction cup-based gripper arm selectively removes boxes from the trailer and places the boxes on a powered transportation path. The control subassembly coordinates the selective articulated movement of the industrial robot and the activation of the drive subassembly based upon the distance measurement subassembly detecting objects, including boxes, within a detection space, and dimensions of the trailer provided to the control subassembly.

Owner:WYNRIGHT CORP

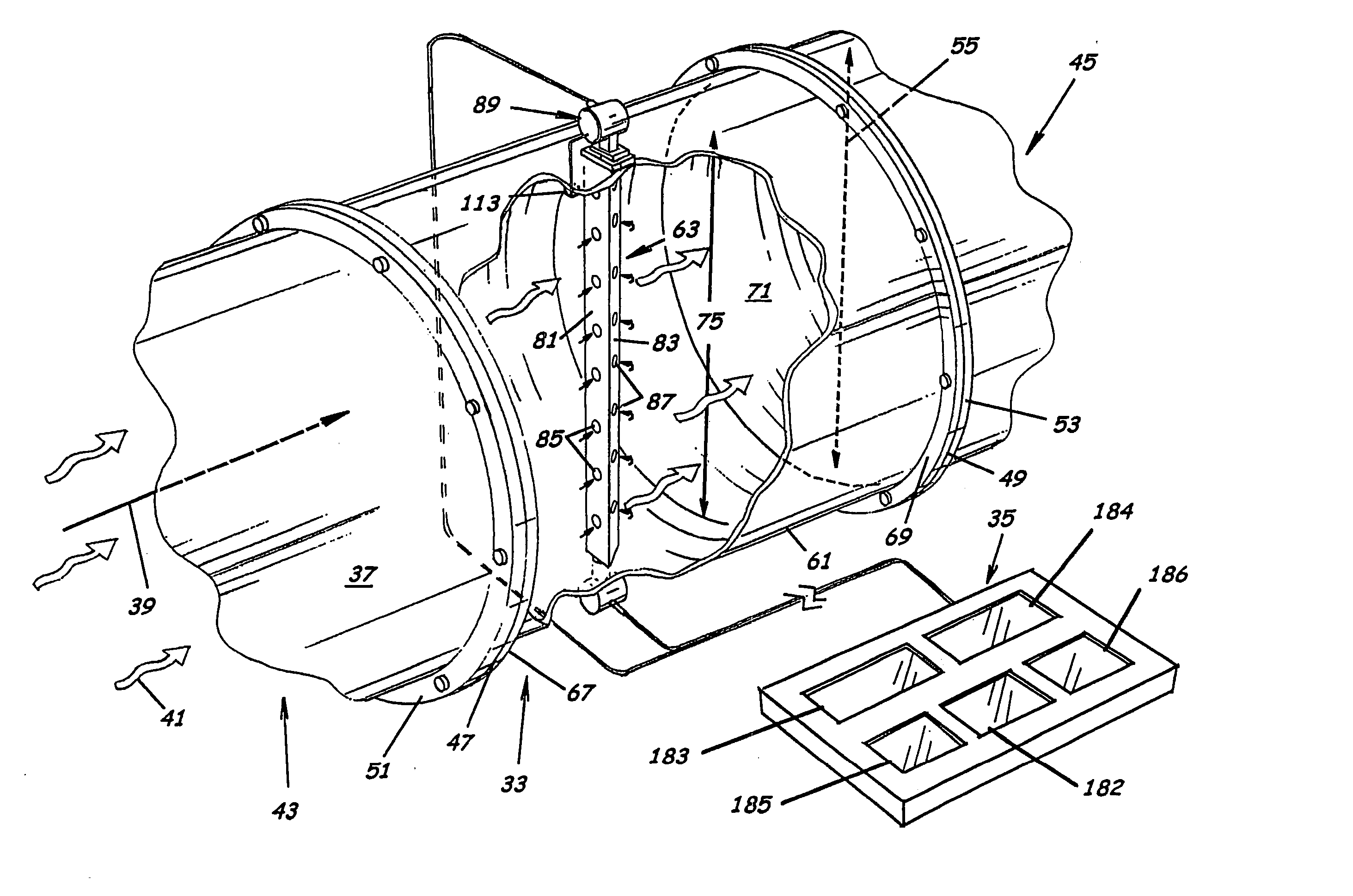

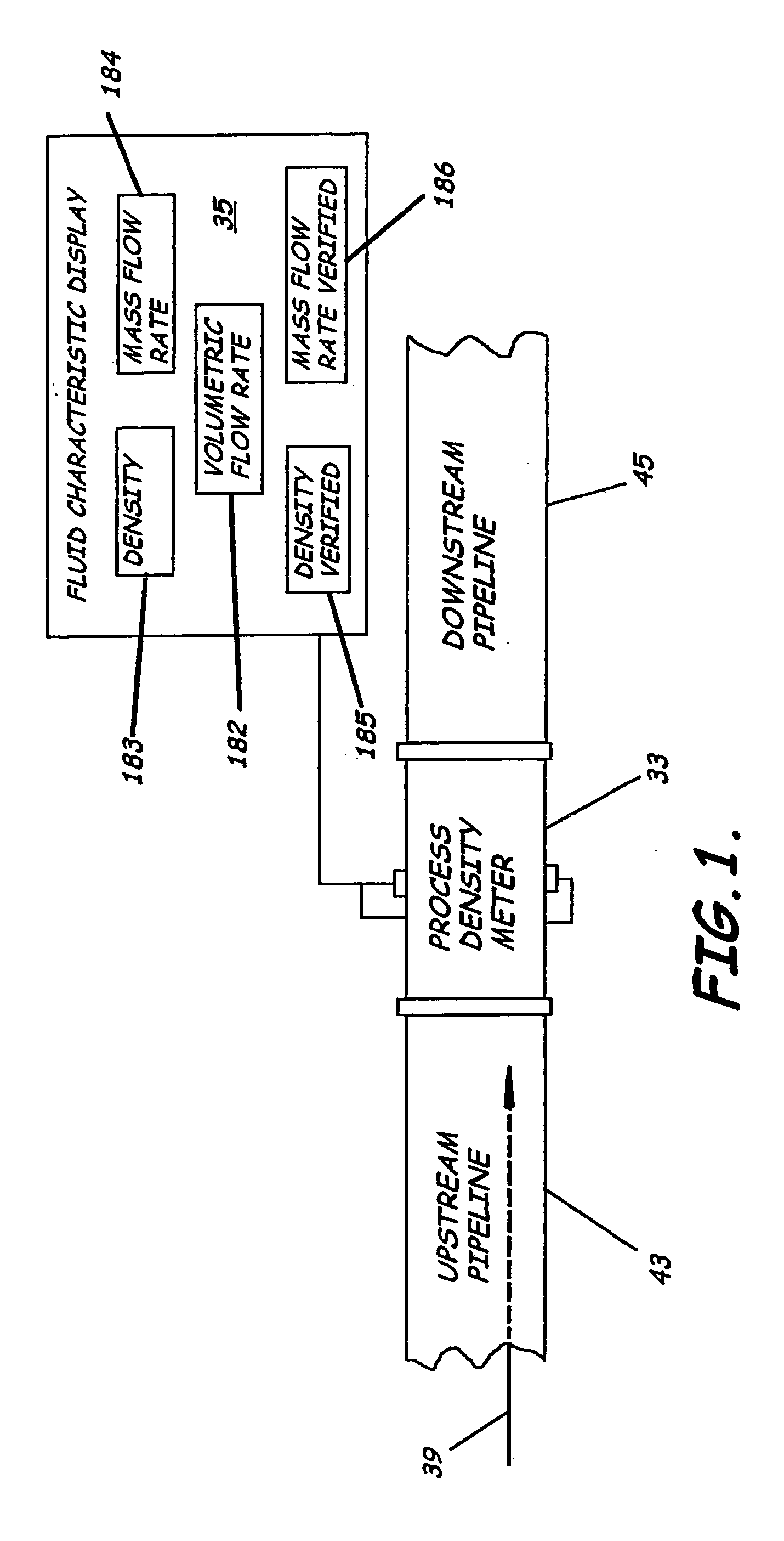

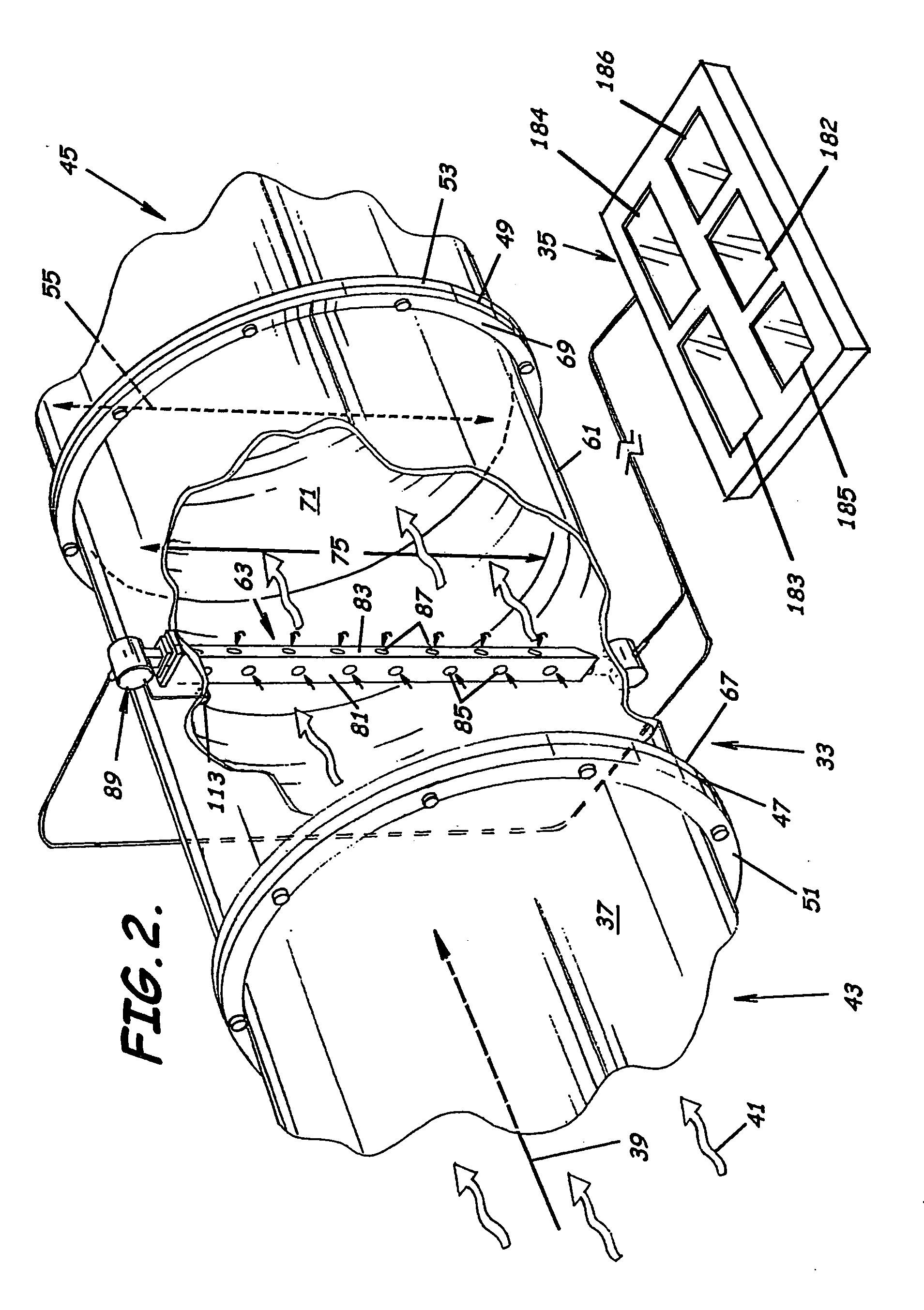

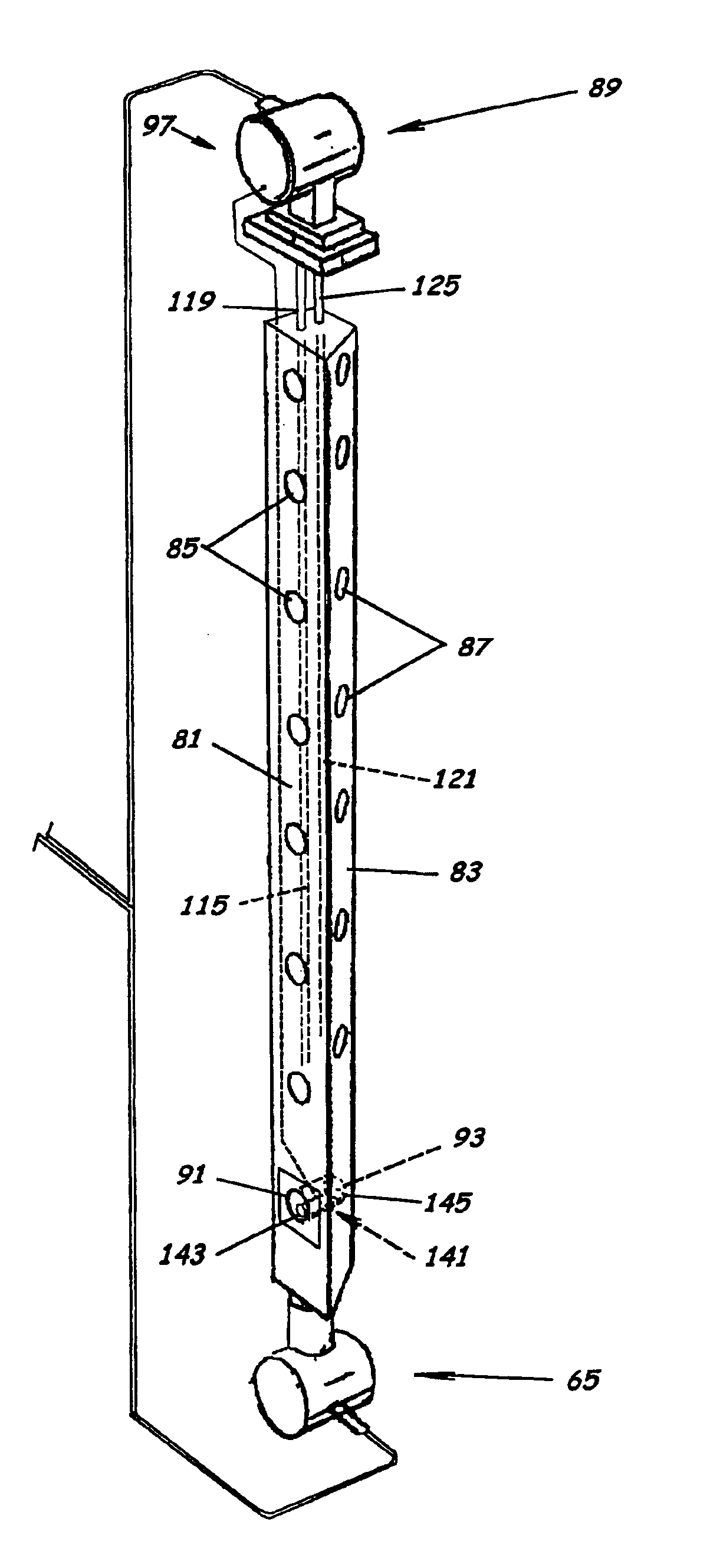

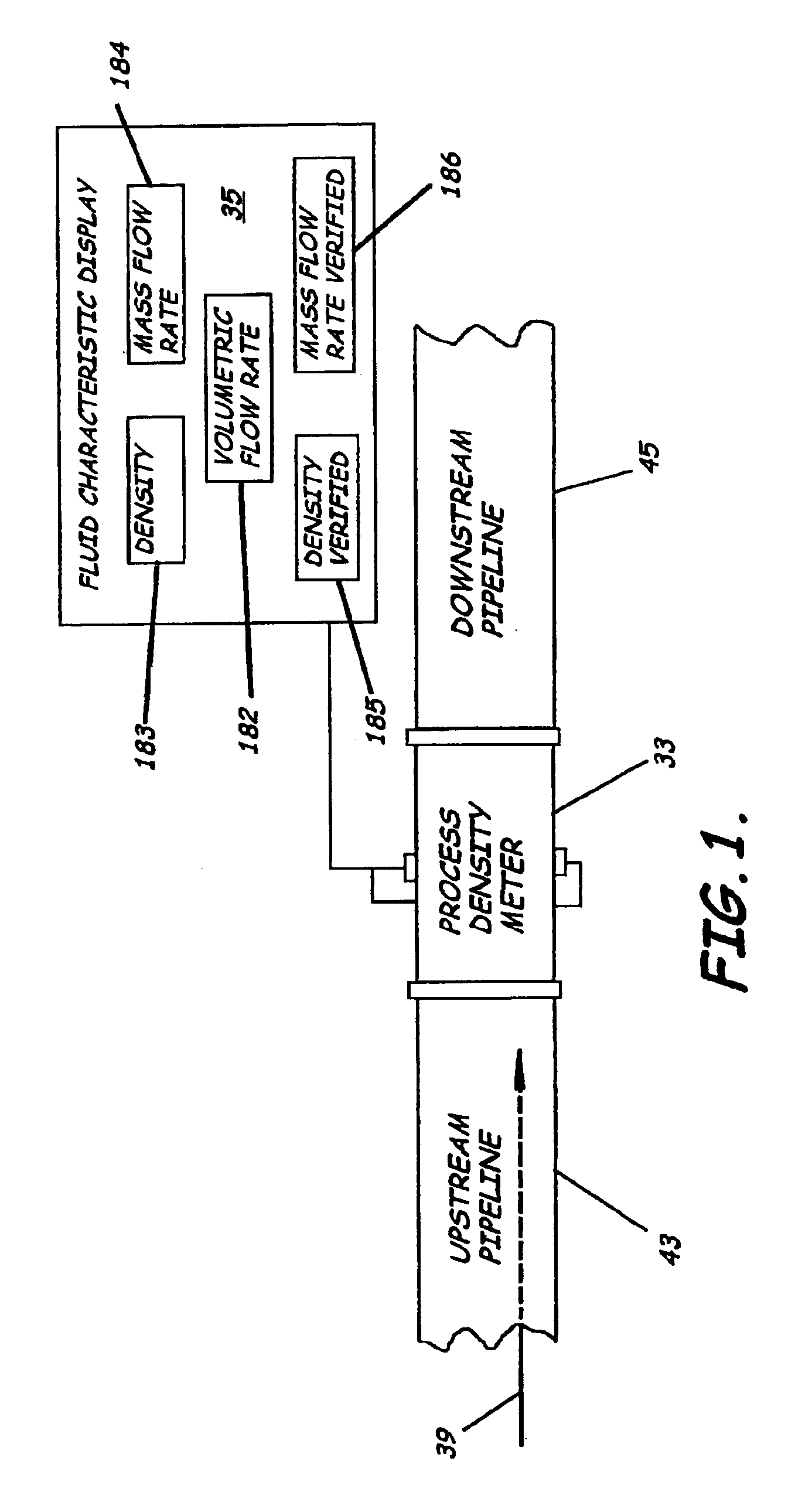

System to measure density, specific gravity, and flow rate of fluids, meter, and related methods

ActiveUS20050034535A1Little maintenanceMinimization needsVolume/mass flow by thermal effectsVolume/mass flow by dynamic fluid flow effectDifferential pressureDisplay device

A system to measure fluid flow characteristics in a pipeline, meter, and methods includes a pipeline having a passageway to transport flowing fluid therethrough, a process density meter including at least portions thereof positioned within the pipeline to provide flowing fluid characteristics including volumetric flow rate, fluid density, and mass flow rate of the flowing fluid, and a fluid characteristic display to display the fluid characteristics. The process density meter includes a vortex-shedding body positioned within the pipeline to form vortices and a vortex meter having a vortex frequency sensor to measure the frequency of the vortices and to determine the volumetric flow rate. The process density meter further includes a differential pressure meter positioned adjacent the vortex-shedding body to produce a differential pressure meter flow rate signal indicative of the density of fluid when flowing through the pipeline. The process density meter also includes a thermal flow meter positioned adjacent the vortex-shedding body to produce a mass flow rate signal indicative of the mass flow rate of fluid when flowing through the pipeline. The process density meter produces an output of a volumetric flow rate, a flowing fluid density, and a mass flow rate to be displayed by the fluid characteristic display.

Owner:SAUDI ARABIAN OIL CO

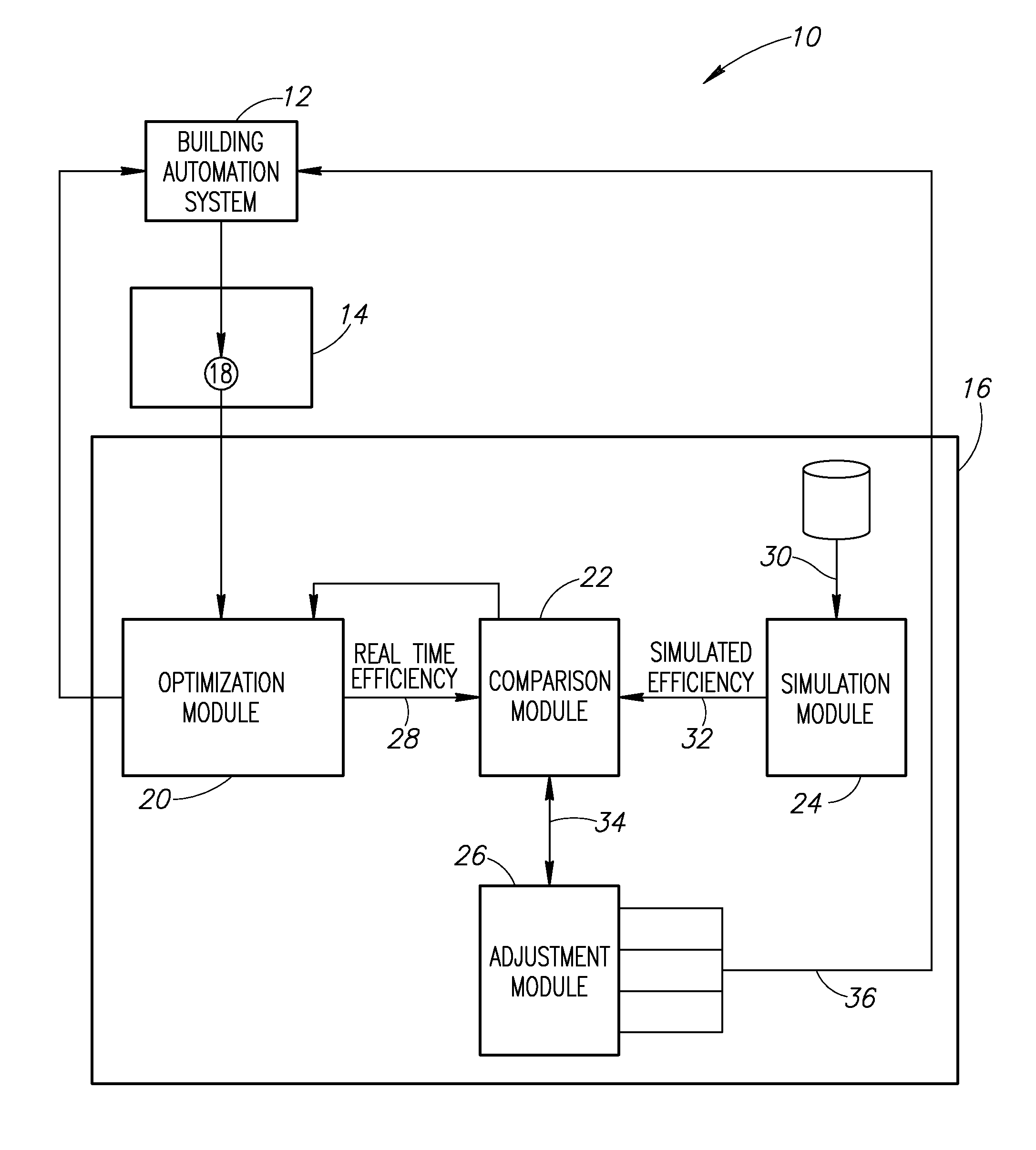

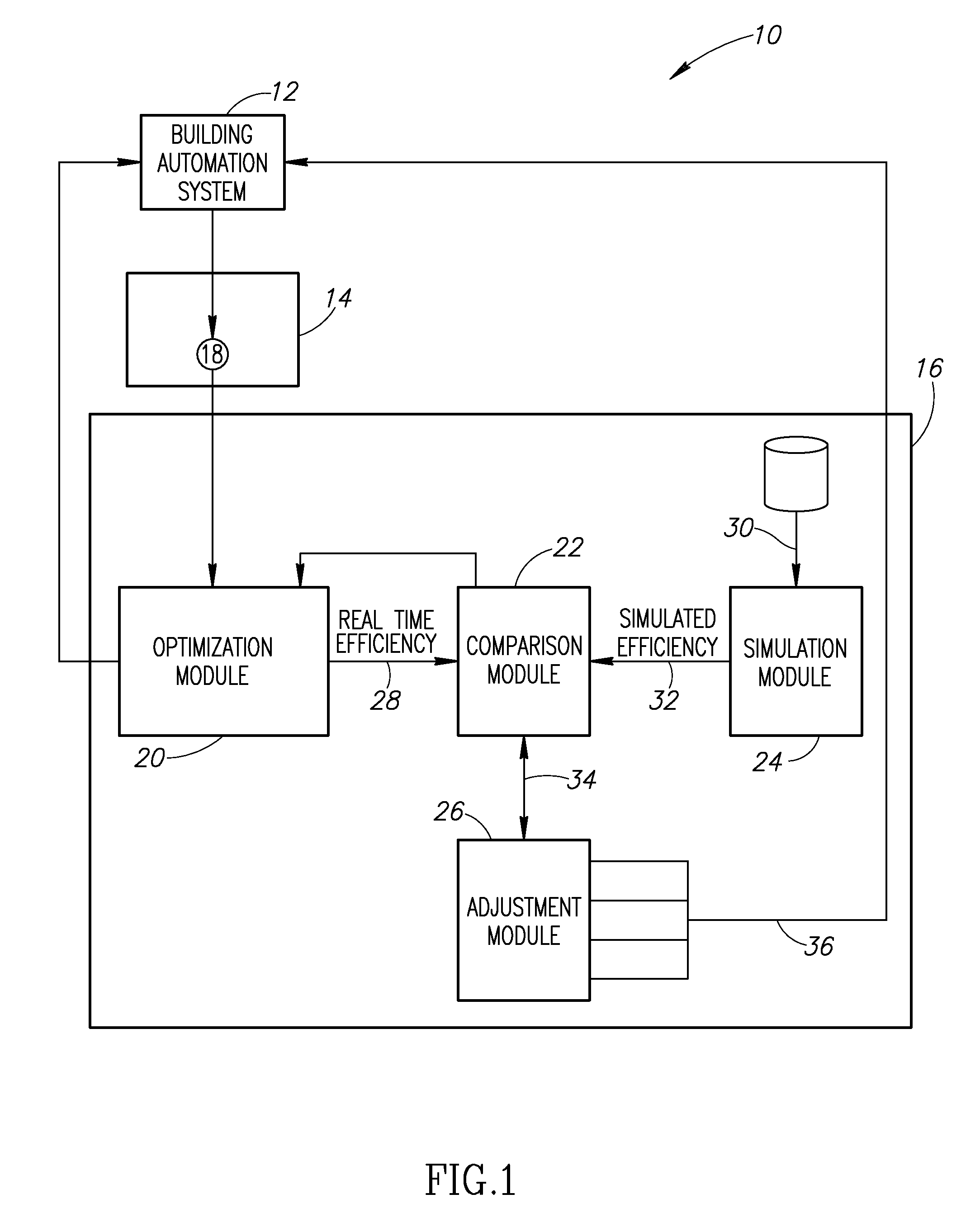

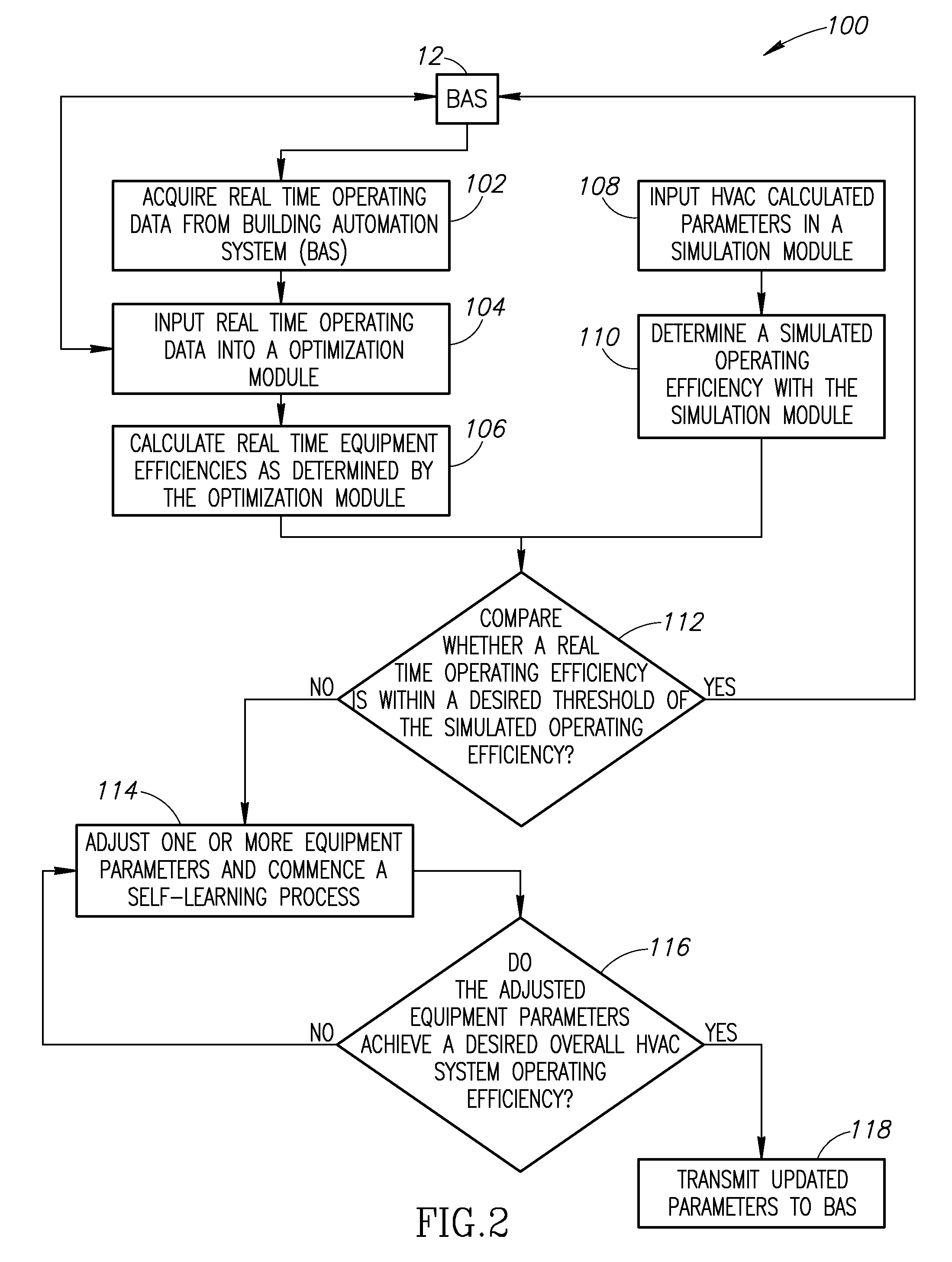

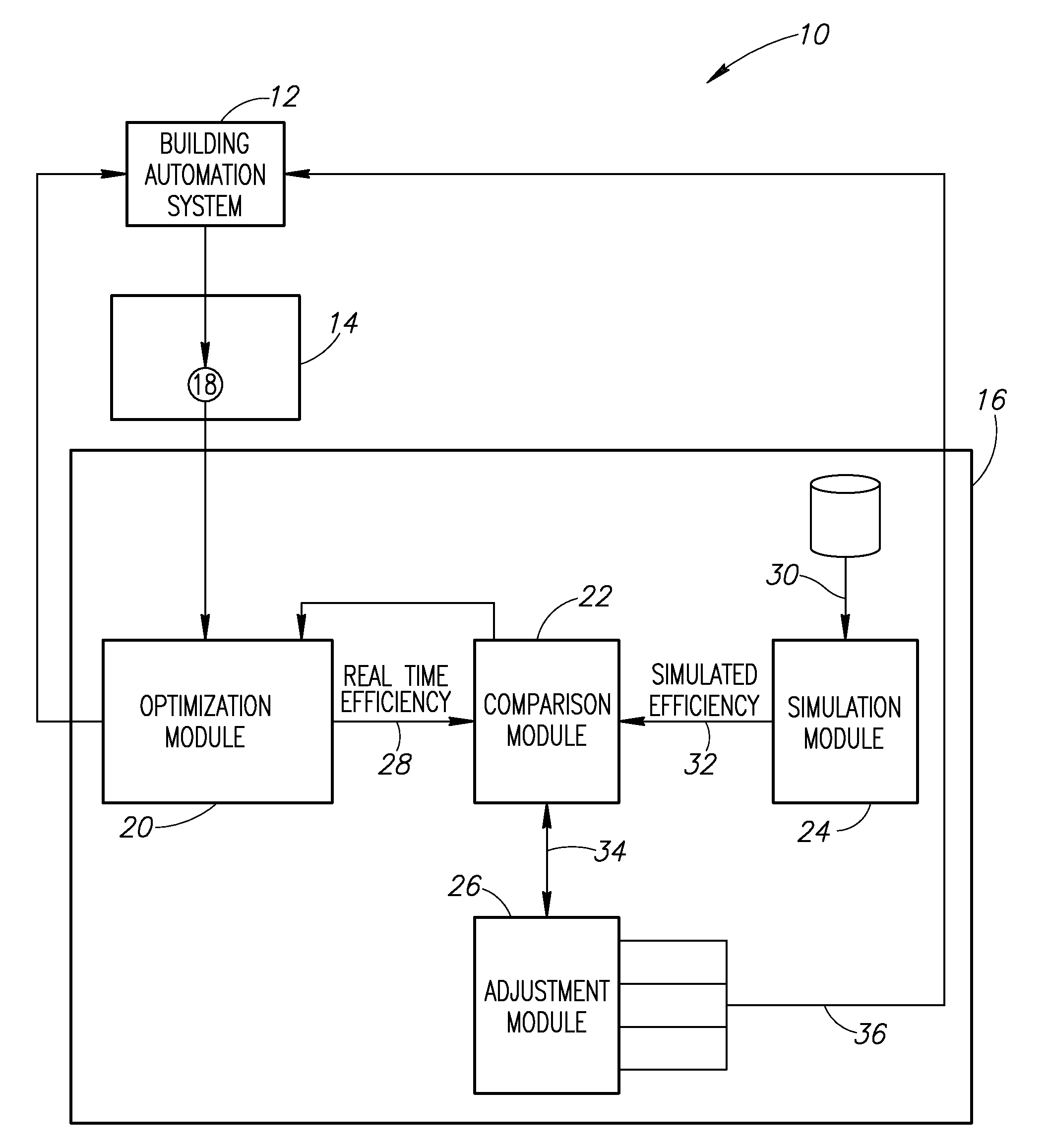

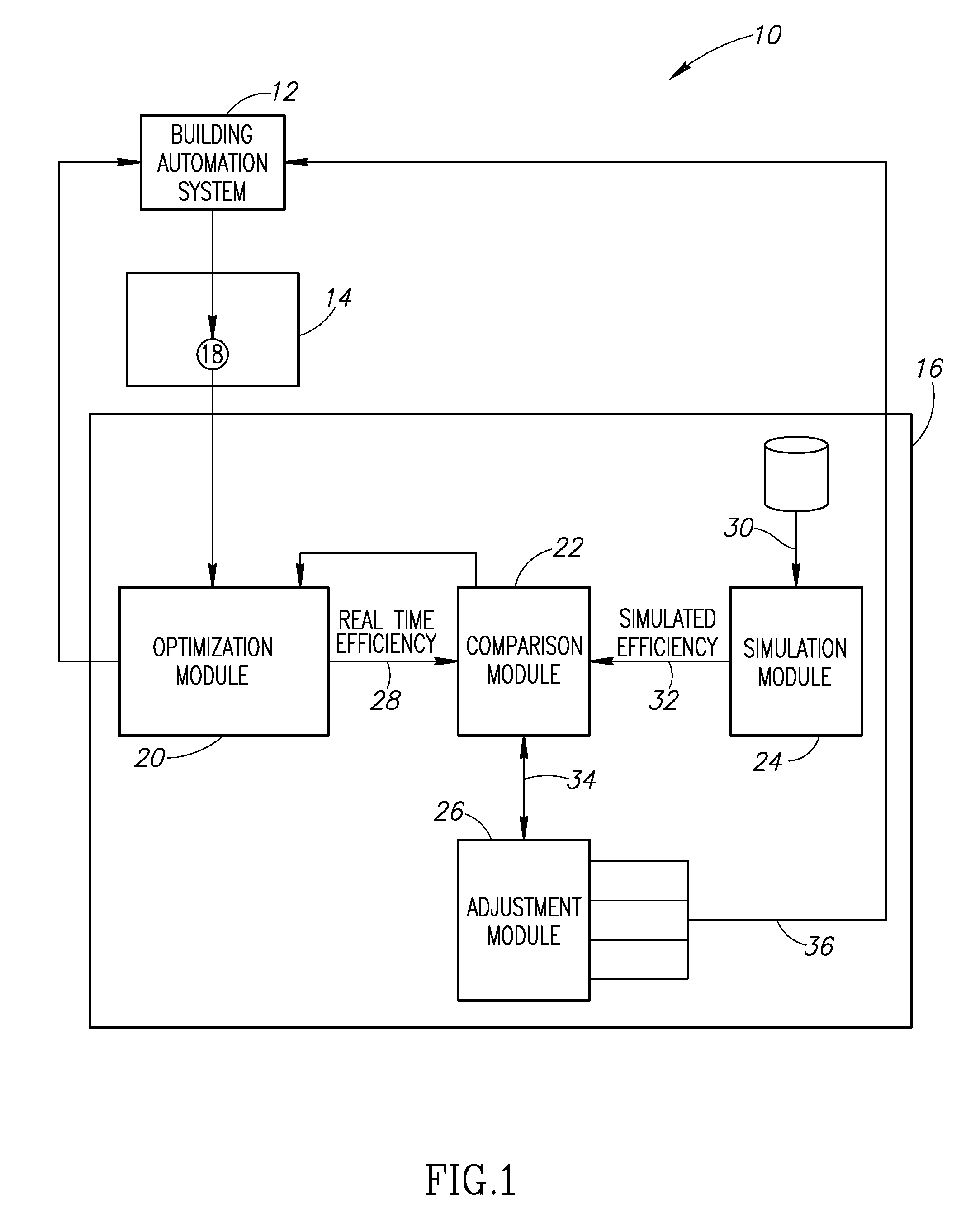

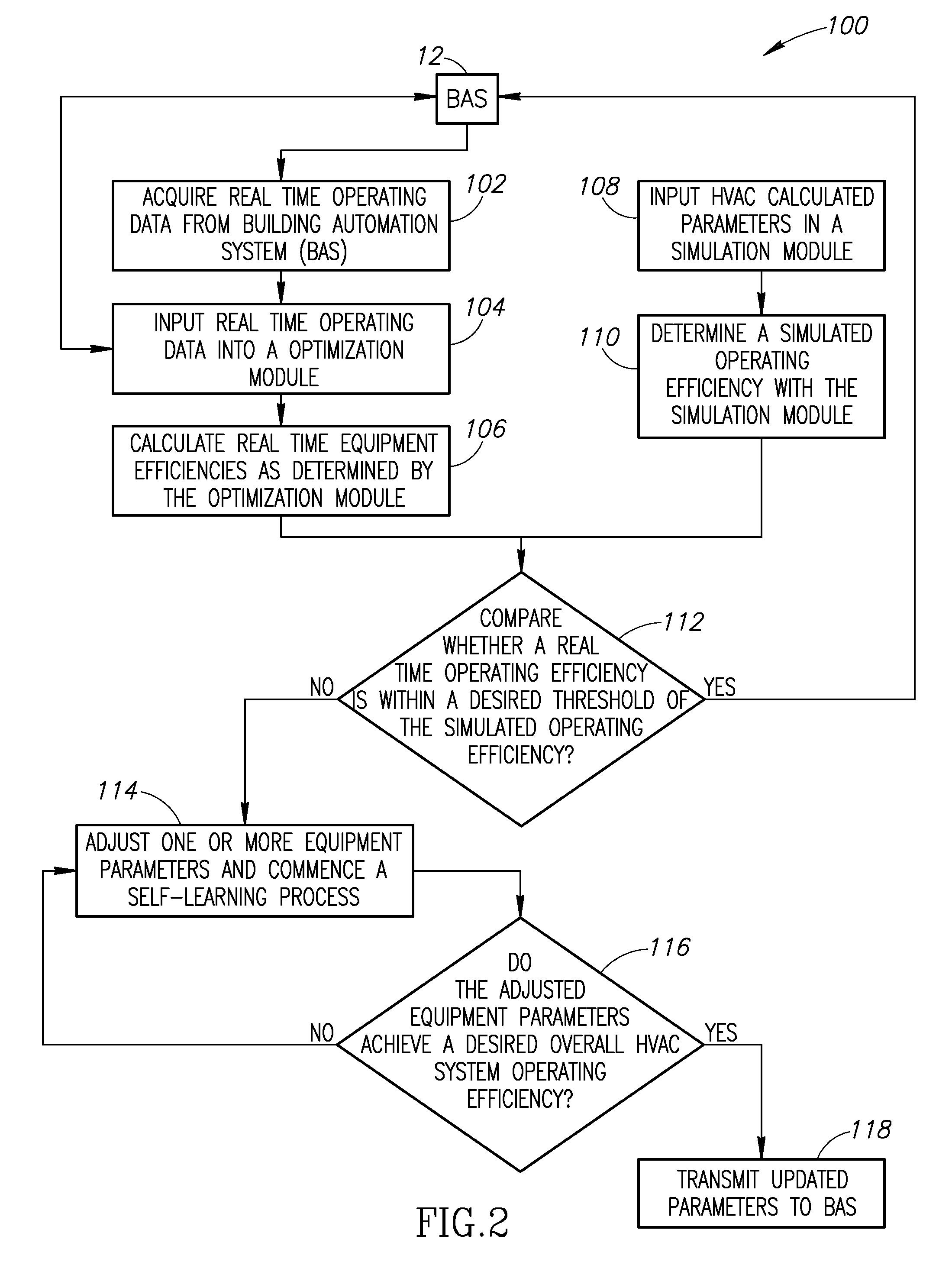

Systems and methods to control energy consumption efficiency

ActiveUS8219250B2Minimization needsMinimum energy wastageProgramme controlSampled-variable control systemsSimulationComputer module

A controller is configured to exchange information with a building automation system and includes various executable programs for determining a real time operating efficiency, simulating a predicted or theoretical operating efficiency, comparing the same, and then adjusting one or more operating parameters on equipment utilized by a building's HVAC system. The controller operates to adjust an operating efficiency of the HVAC system. An adjustment module utilized by the controller may modify the HVAC equipment parameters based on the likelihood that various HVAC equipment operates in parallel and on-line near its natural operating curve. In addition, the adjustment module may include a self-learning aspect that permits the controller to more efficiently make similar, future adjustments as needed.

Owner:OPTIMUM ENERGY

System to measure density, specific gravity, and flow rate of fluids, meter, and related methods

ActiveUS6957586B2Little maintenanceMinimization needsVolume/mass flow by thermal effectsSpecific gravity using flow propertiesDifferential pressureDisplay device

A system to measure fluid flow characteristics in a pipeline, meter, and methods includes a pipeline having a passageway to transport flowing fluid therethrough, a process density meter including at least portions thereof positioned within the pipeline to provide flowing fluid characteristics including volumetric flow rate, fluid density, and mass flow rate of the flowing fluid, and a fluid characteristic display to display the fluid characteristics. The process density meter includes a vortex-shedding body positioned within the pipeline to form vortices and a vortex meter having a vortex frequency sensor to measure the frequency of the vortices and to determine the volumetric flow rate. The process density meter further includes a differential pressure meter positioned adjacent the vortex-shedding body to produce a differential pressure meter flow rate signal indicative of the density of fluid when flowing through the pipeline. The process density meter also includes a thermal flow meter positioned adjacent the vortex-shedding body to produce a mass flow rate signal indicative of the mass flow rate of fluid when flowing through the pipeline. The process density meter produces an output of a volumetric flow rate, a flowing fluid density, and a mass flow rate to be displayed by the fluid characteristic display.

Owner:SAUDI ARABIAN OIL CO

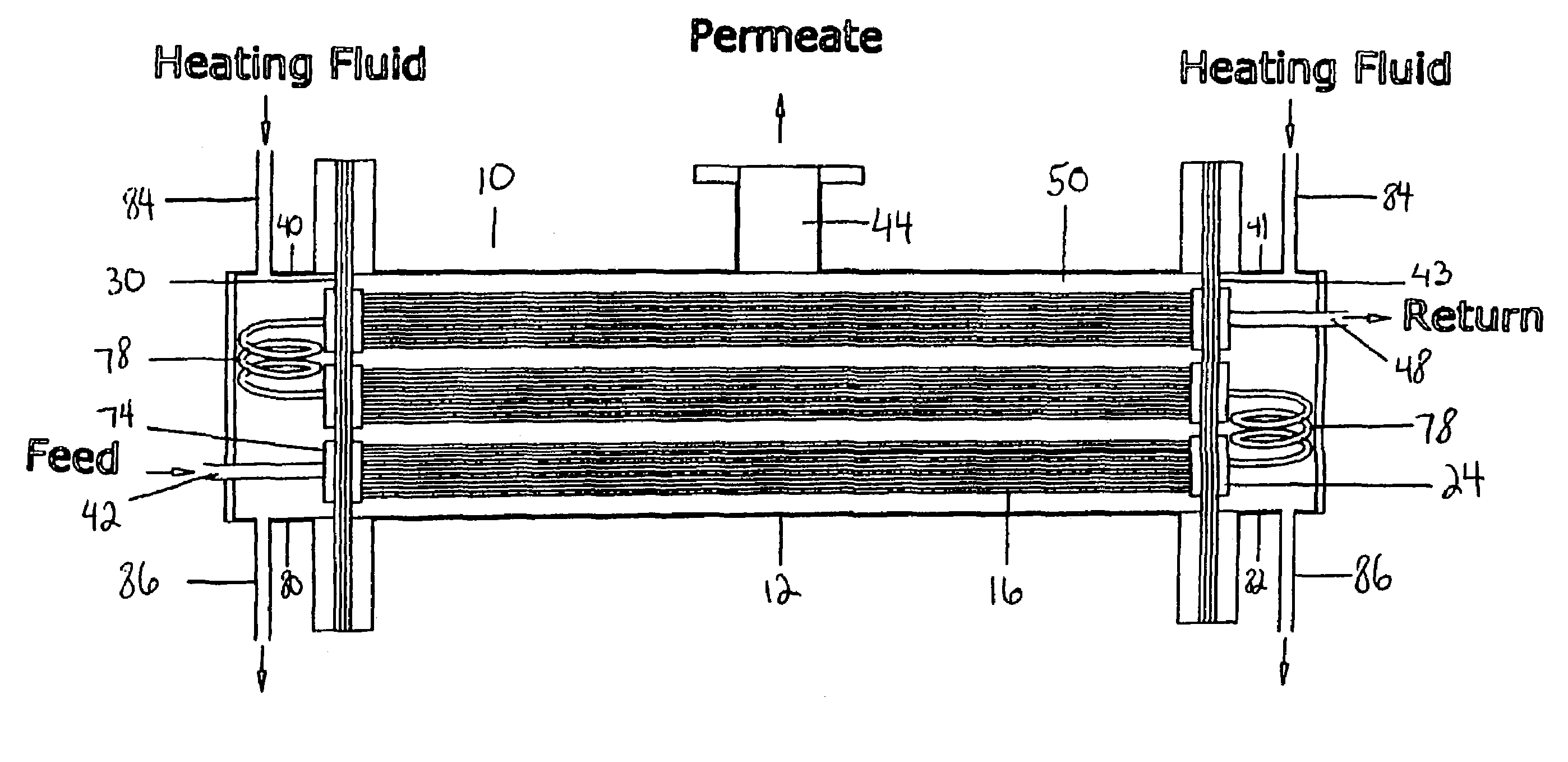

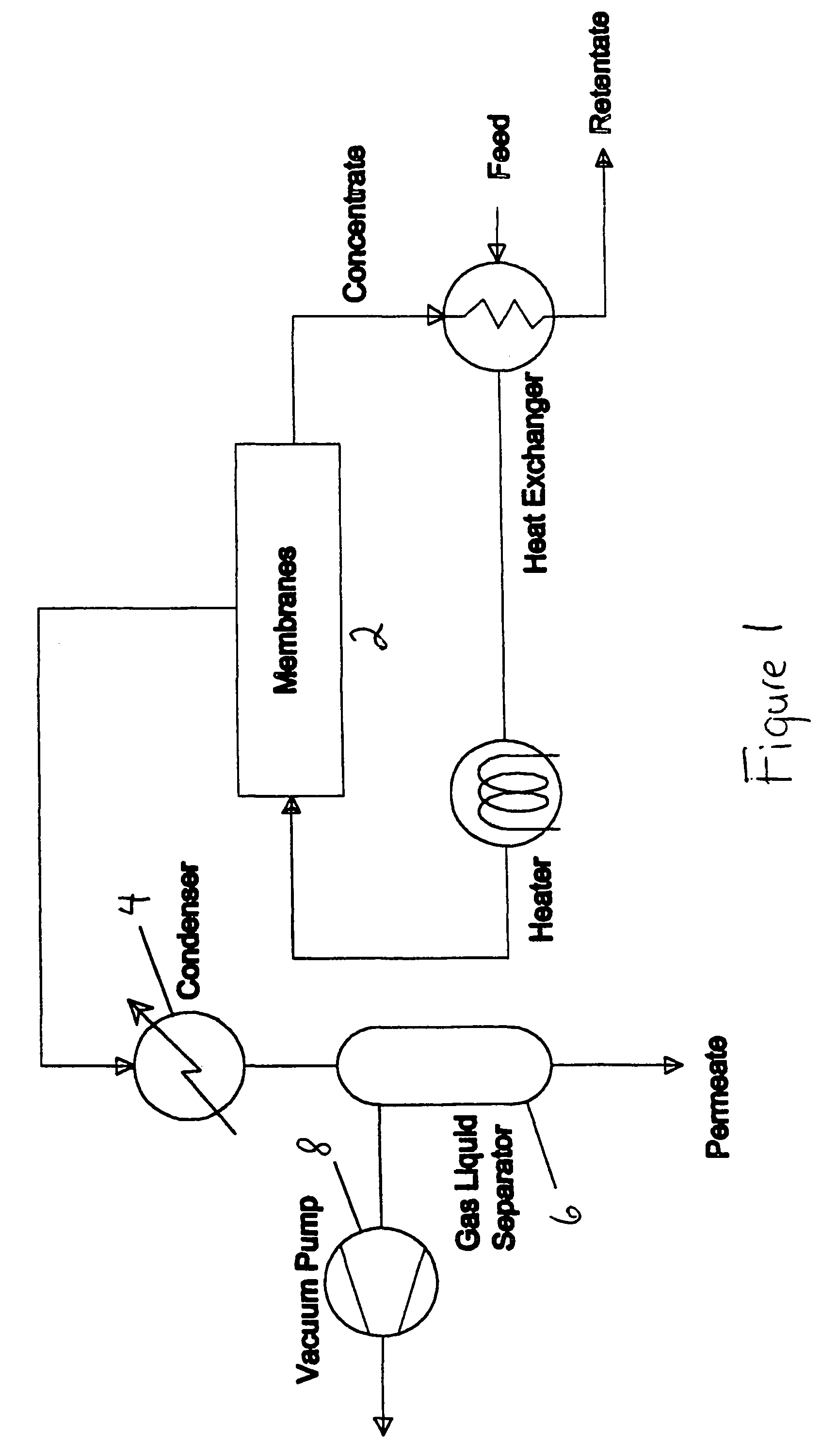

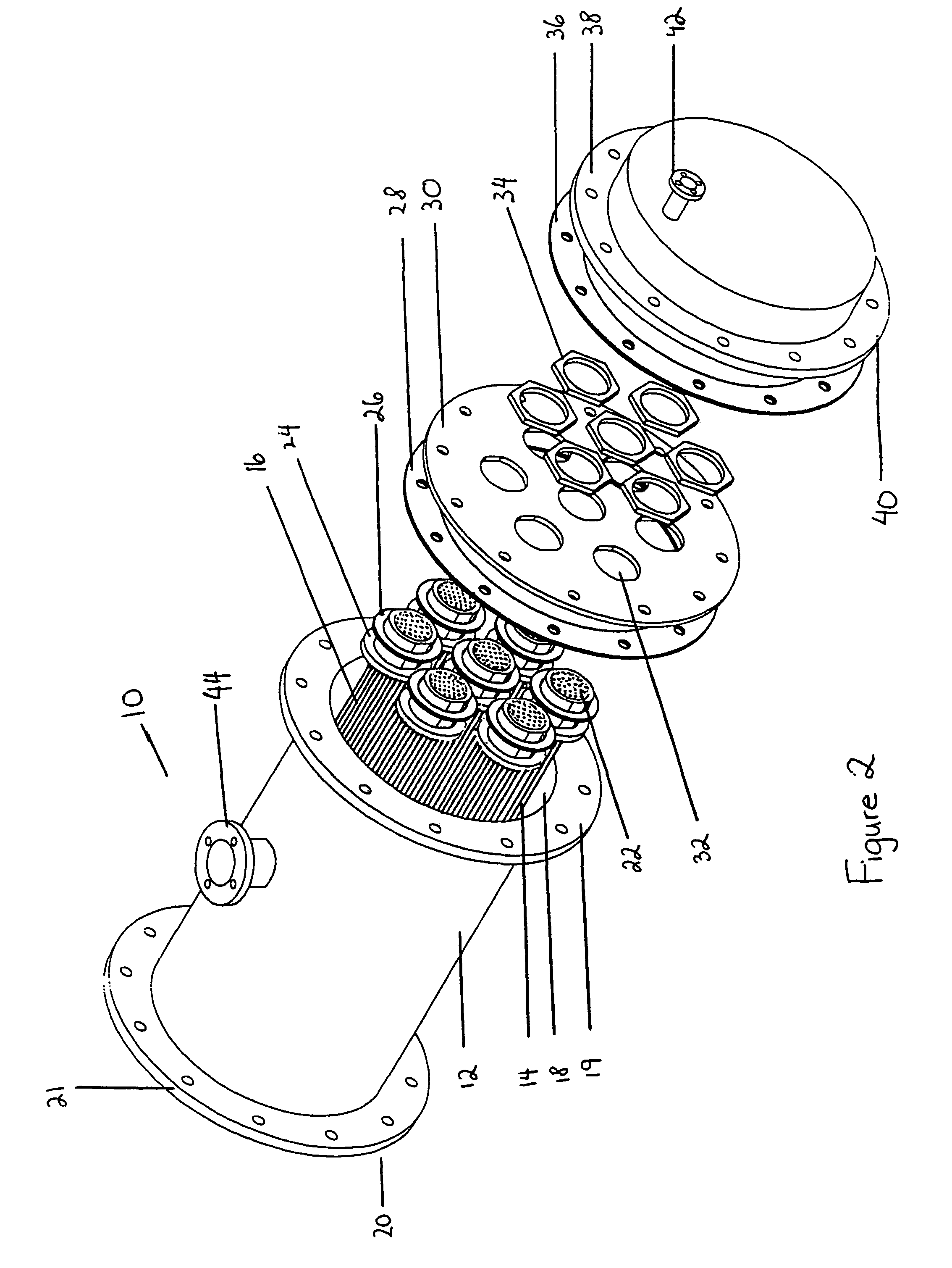

Membrane-assisted fluid separation apparatus and method

InactiveUS7459084B2Easy to disassembleReduce complexityMembranesGeneral water supply conservationFiberHigh concentration

This present invention relates to a fluid separation module adapted to separate a given fluid mixture into permeate and retentate portions using bundles of hollow fiber membranes. The membranes may be composed of different kinds of membranes depending on the application being used to separate the fluid mixture. The fluid separation module may be used to separate fluid mixtures by a number of different processes, including but not limited to, pervaporation, vapour permeation, membrane distillation (both vacuum membrane distillation and direct contact membrane distillation), ultra filtration, microfiltration, nanofiltration, reverse osmosis, membrane stripping and gas separation. The present invention also provides an internal heat recovery process applied in association with those fluid separation applications where separation takes place by evaporation through the membrane of a large portion of the feed into permeate. Desalination and contaminated water purification by means of vacuum membrane distillation are just two examples where the internal heat recovery process may be applied. In these two examples, large portions of the feed are separated by membranes into a high purity water permeate stream by evaporation through the membranes and into a retentate stream containing a higher concentration of dissolved components than present in the feed. In this process the permeate vapour that is extracted from the fluid separation module is compressed by an external compressor to increase the temperature of the vapour higher than the temperature of the feed entering the separation module. Heat from the permeate vapour at the elevated temperature is transferred back to the incoming feed fluid mixture entering the fluid separation module in a condenser / heat exchange.

Owner:LOEB INVESTORS CO 166 LP +1

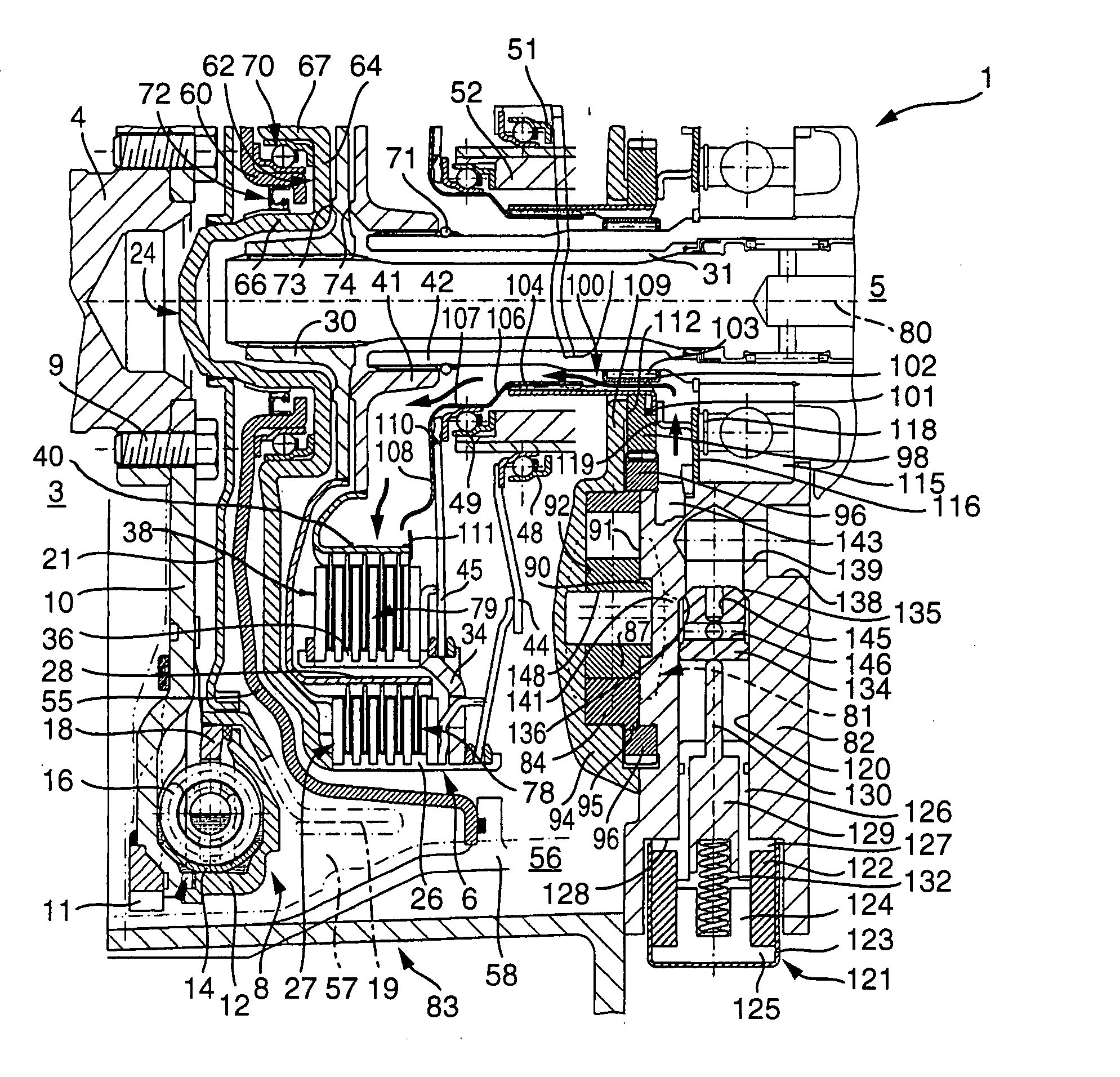

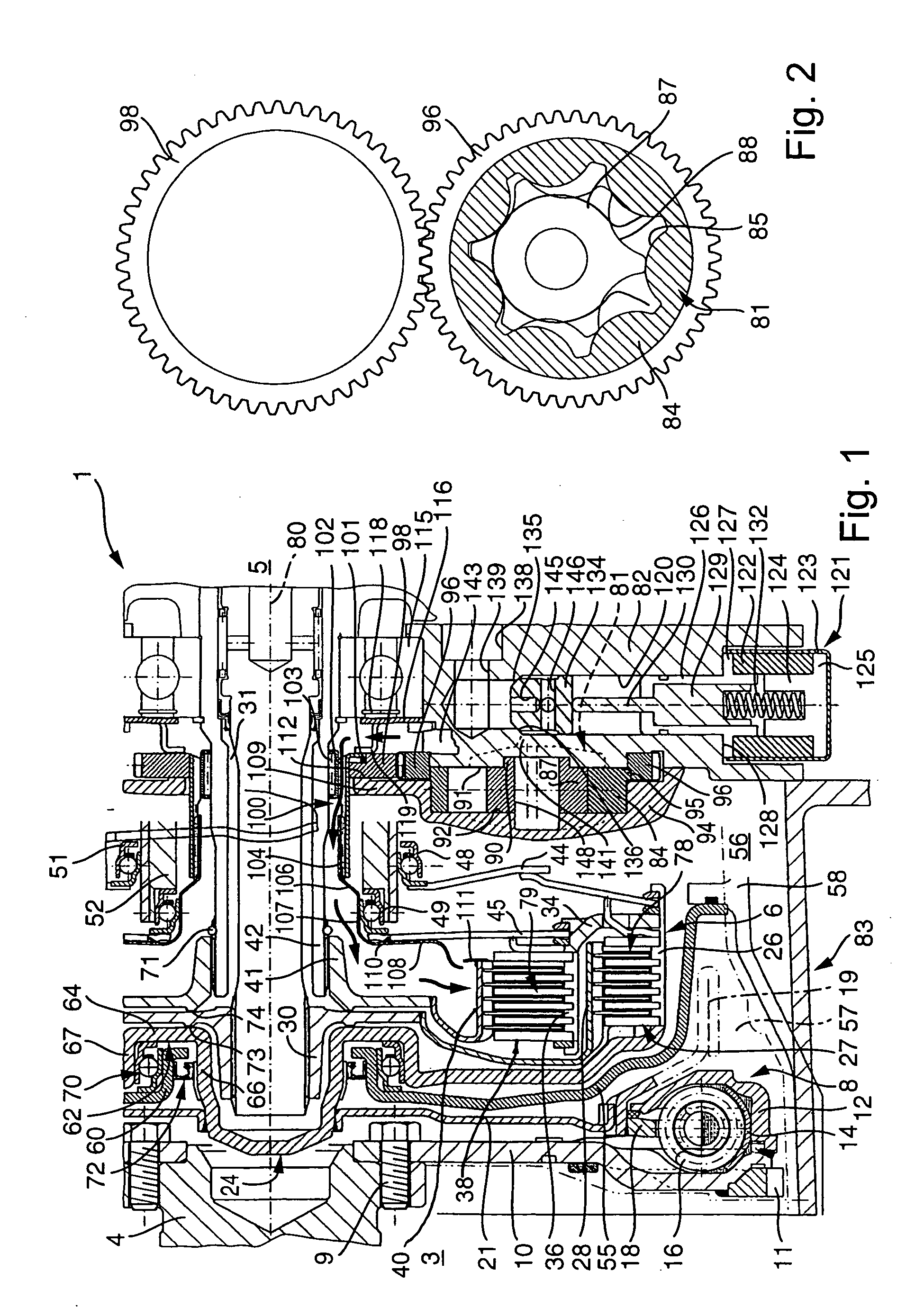

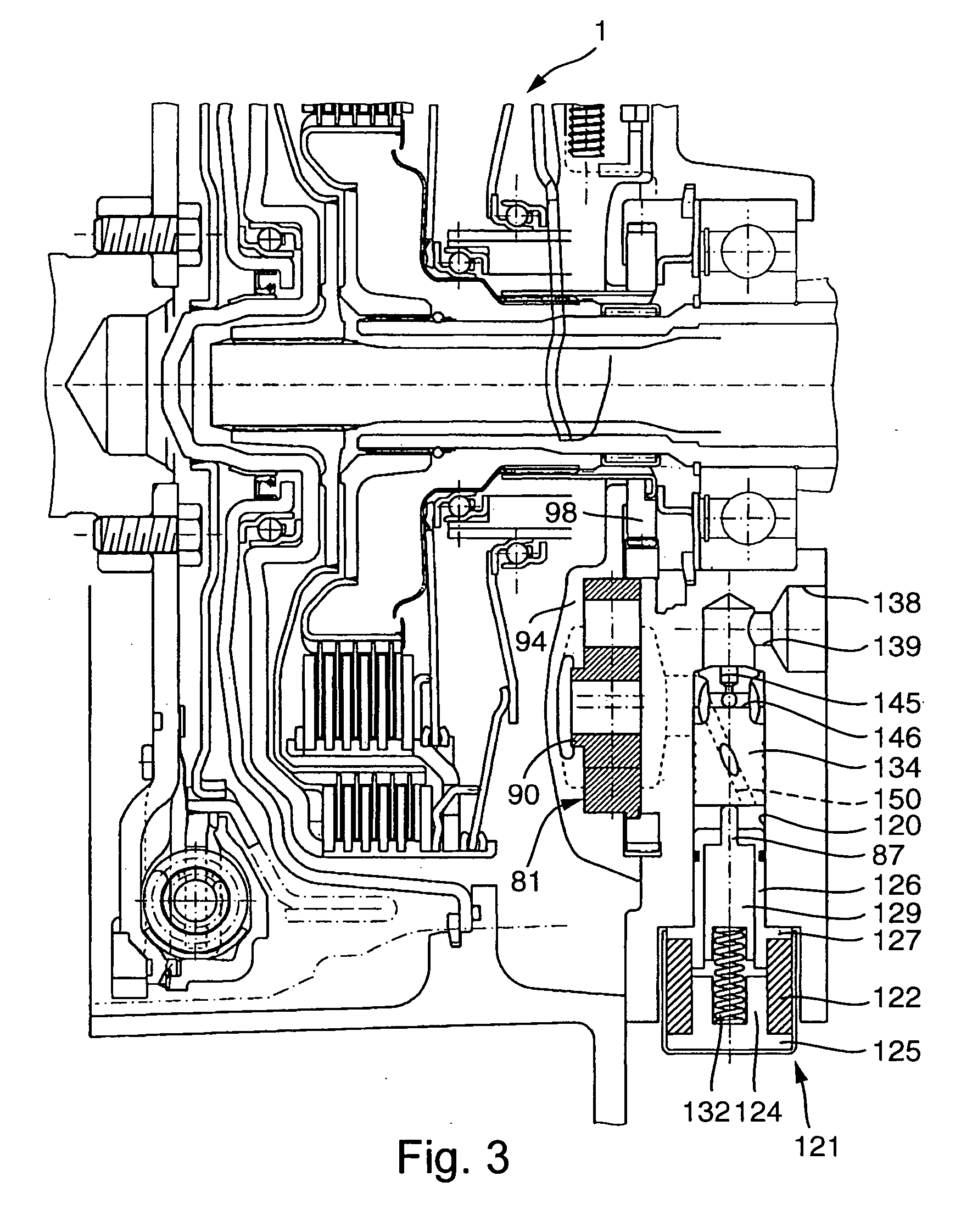

Torque transmitting unit and power train having a torque transmitting unit

InactiveUS20060000684A1Simple to fillCooling becomes necessaryFluid actuated clutchesFriction clutchesCircular discTorque transmission

A torque transmitting unit in the power train of a motor vehicle for transmitting torque between an engine crankshaft, and a transmission having at least one input shaft with at least one friction clutch. The transmission input shaft is coupled with the crankshaft by the friction clutch, which includes friction disks on the power input and / or output sides, and that are pressed together axially along an axis of rotation of the transmission input shaft to form a frictional engagement through a plurality of disks arranged in alternating layers in the axial direction. The disks are pressed against a stop by an actuator and with an actuating bearing interposed, wherein the actuator is connected to a fixed part of the transmission housing in a rotationally fixed connection. The friction clutch is a wet clutch.

Owner:SCHAEFFLER TECH AG & CO KG

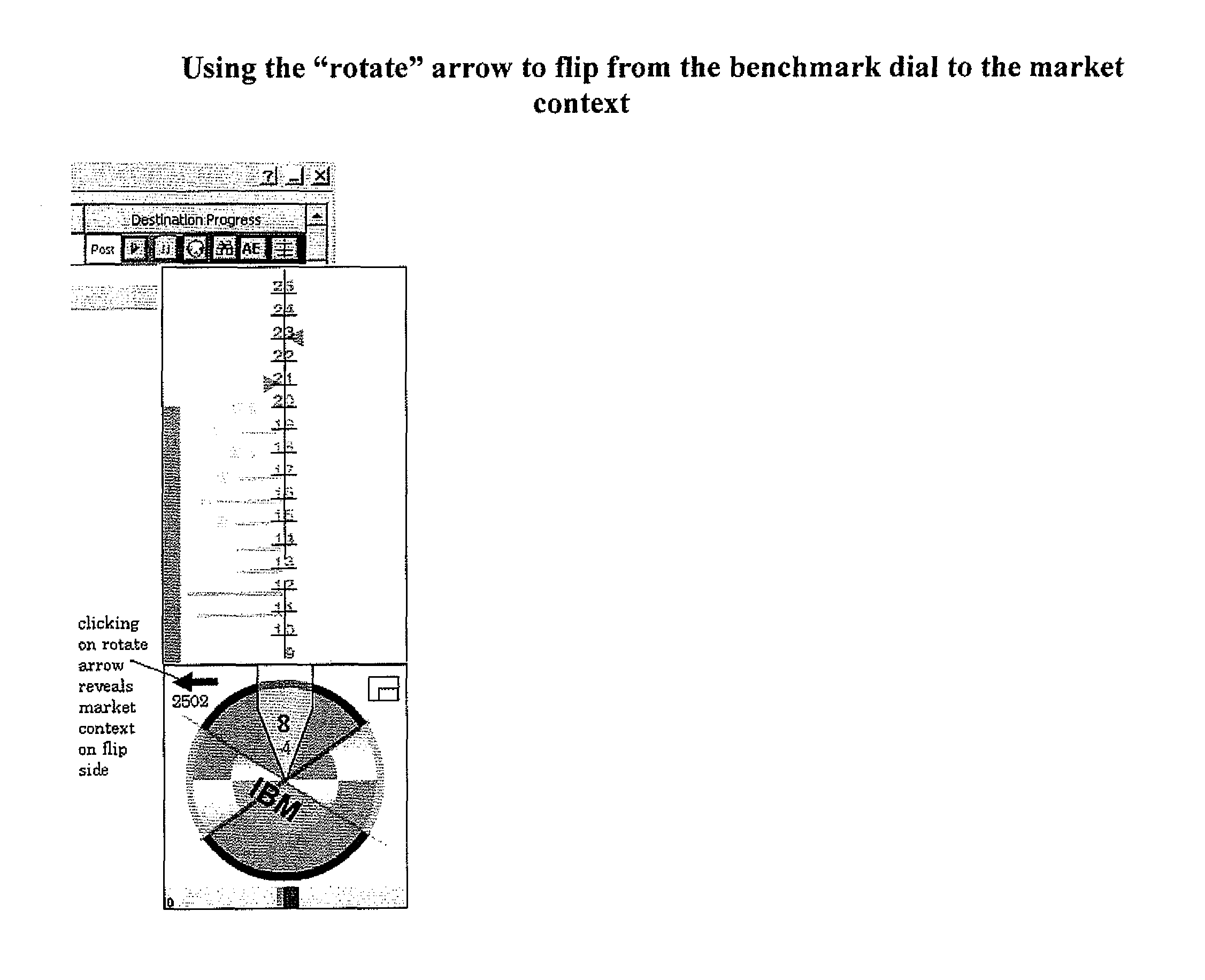

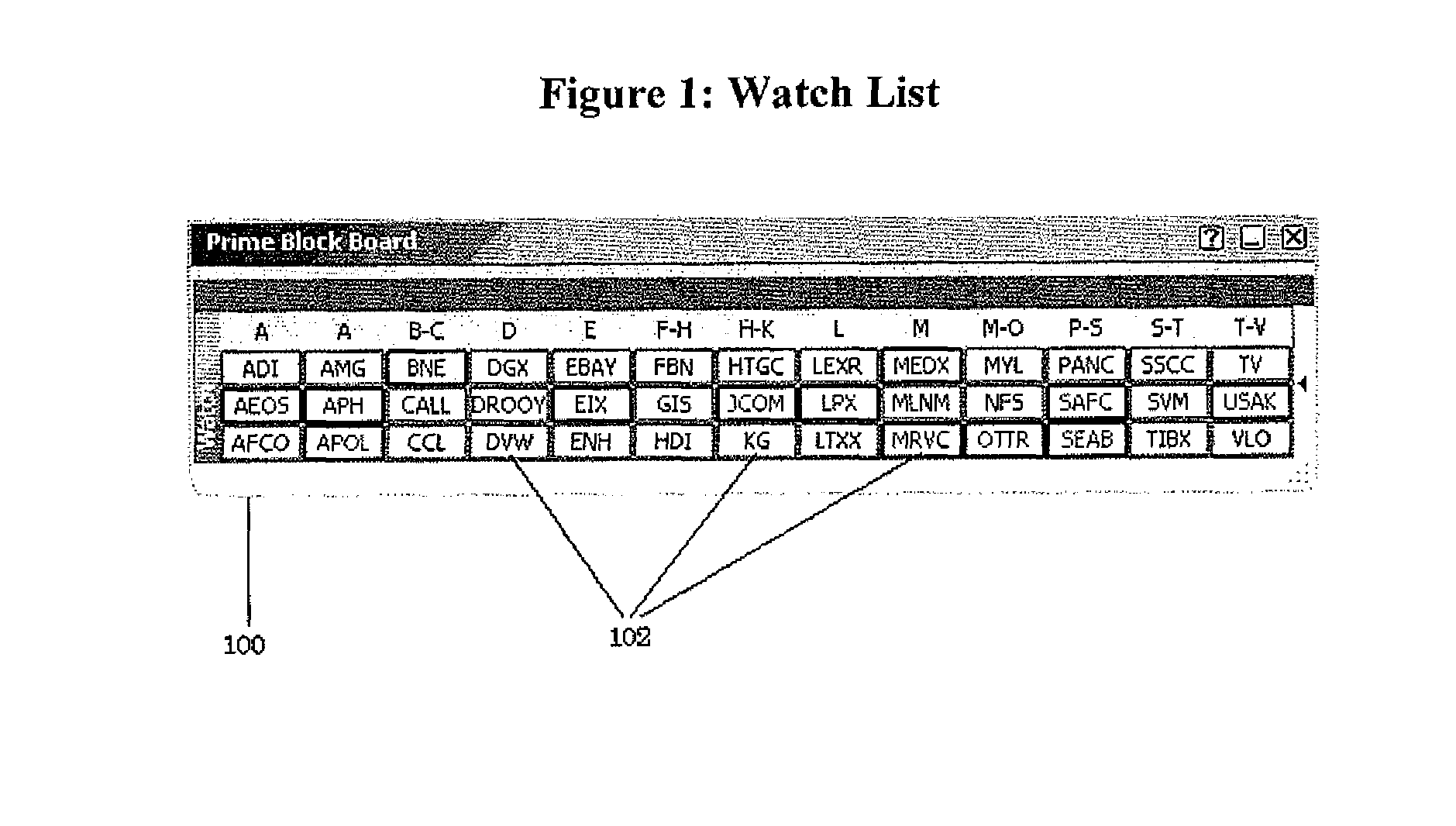

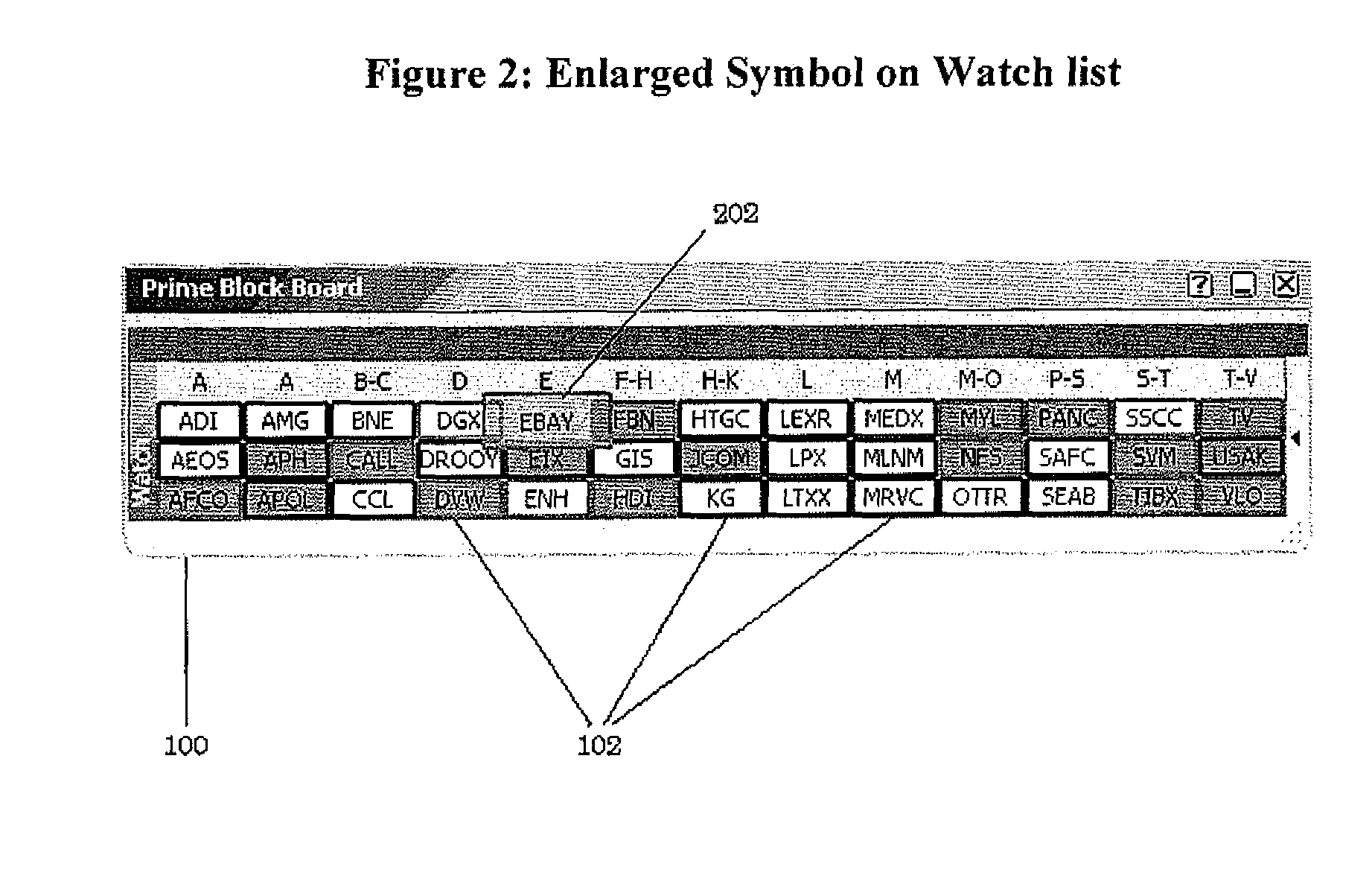

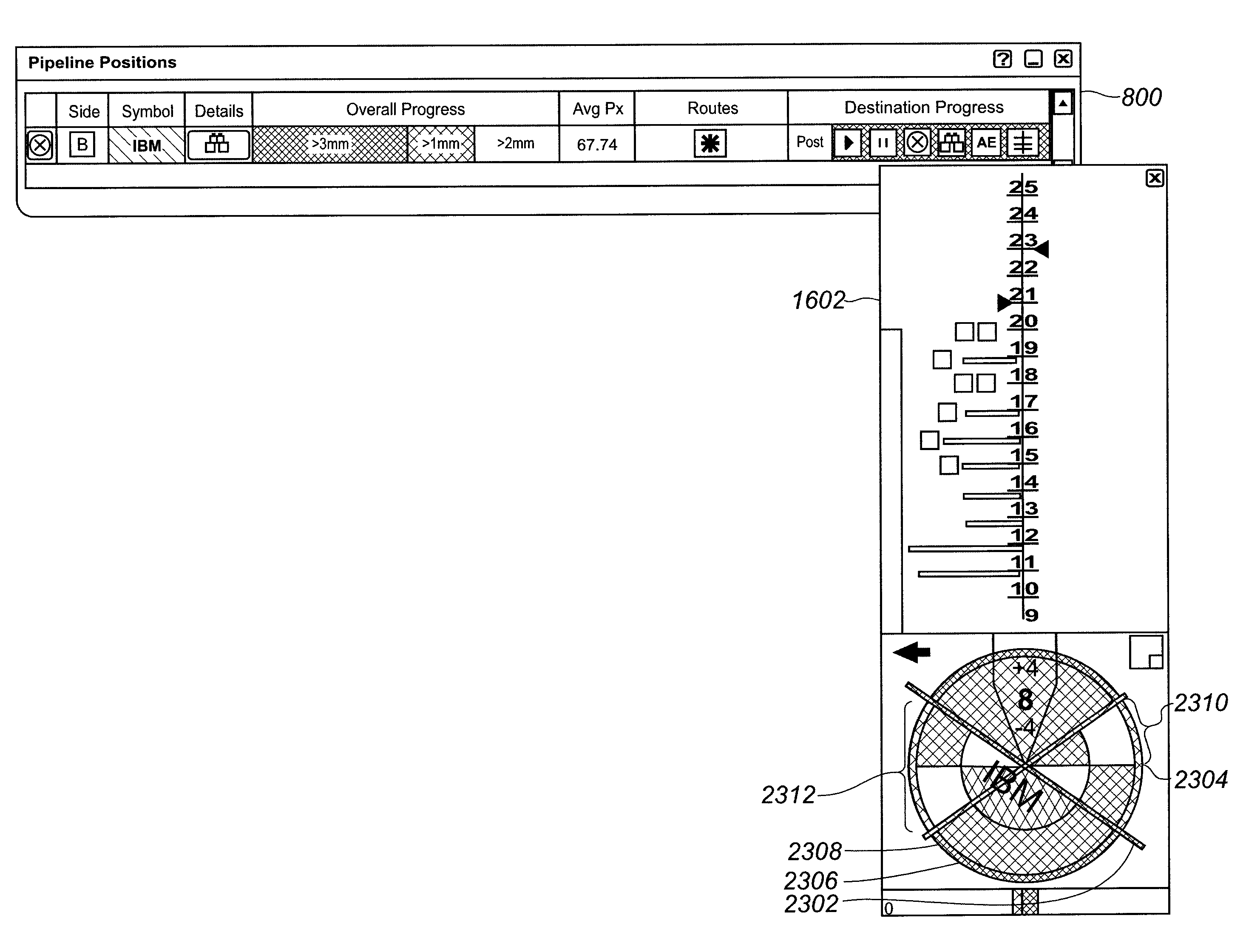

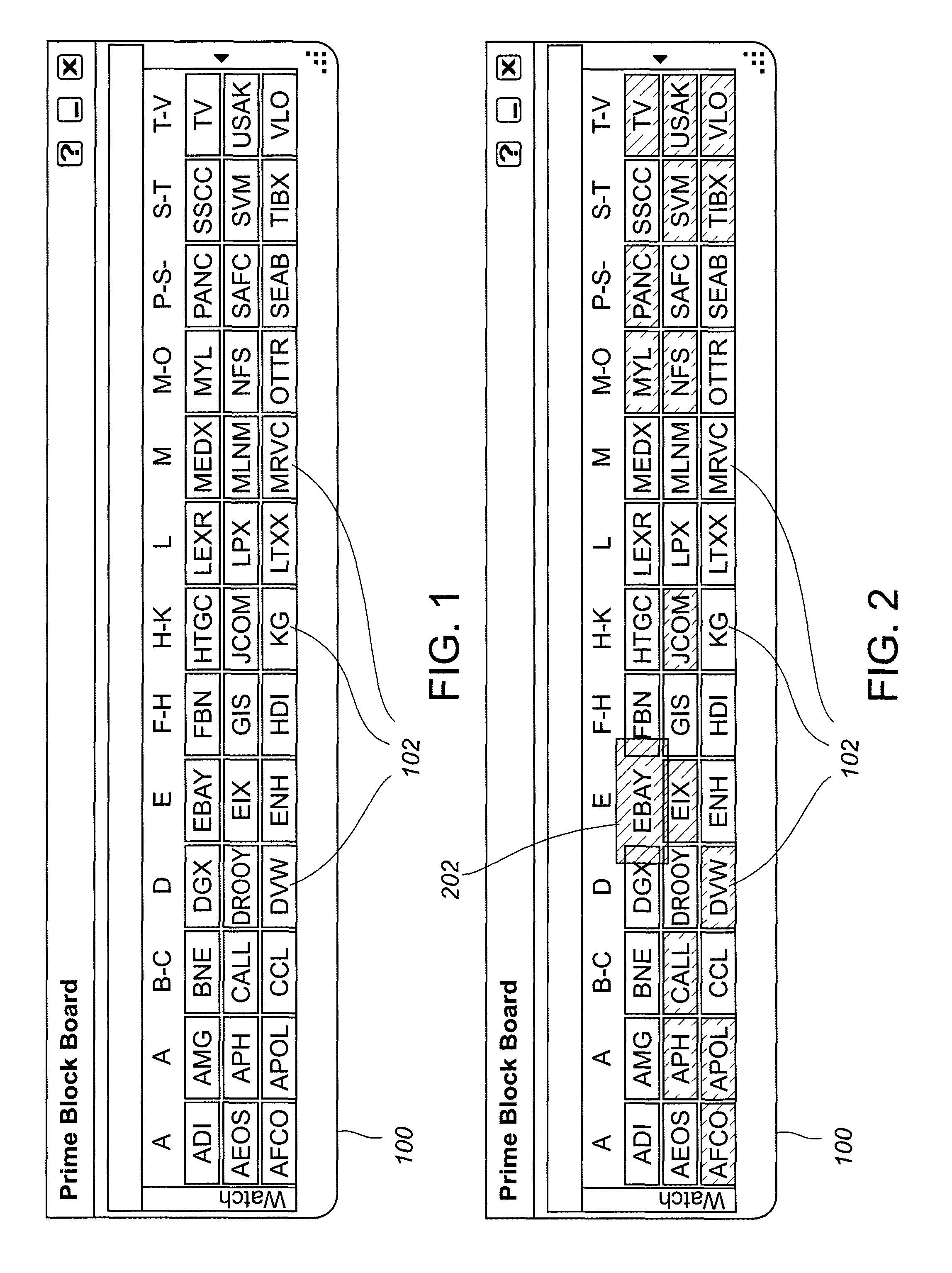

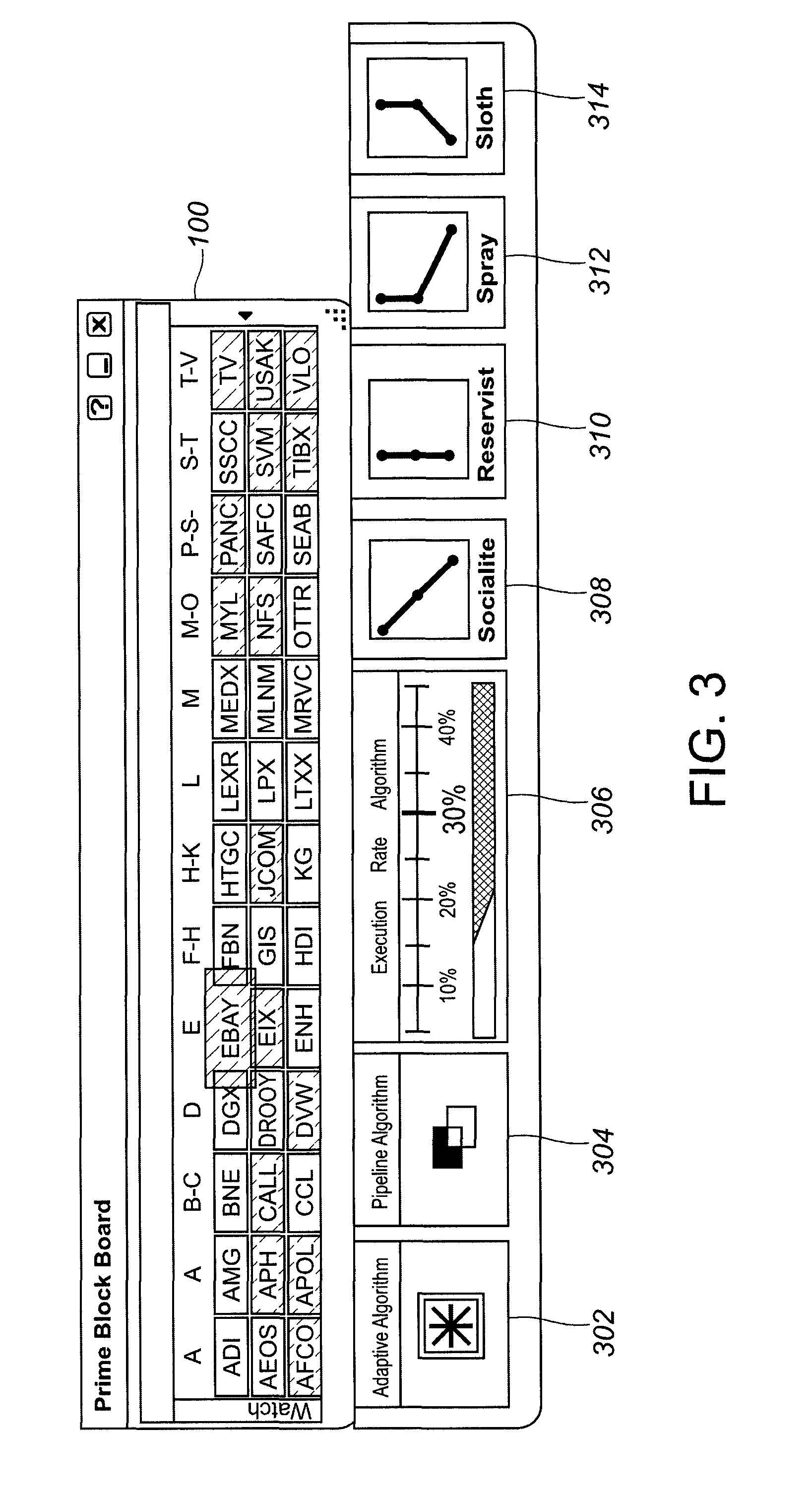

Display of selected items in visual context in algorithmic trading engine

A graphical user interface is used along with an automated algorithm selection function to enable market participants to initiate automated, multi-algorithm trading strategies through a single drag and drop motion. A symbol representing a security can be dragged and dropped onto an icon representing a tactical or strategic algorithm. Other features of the graphical user interface show information such as the progress of the algorithms.

Owner:PORTWARE LLC

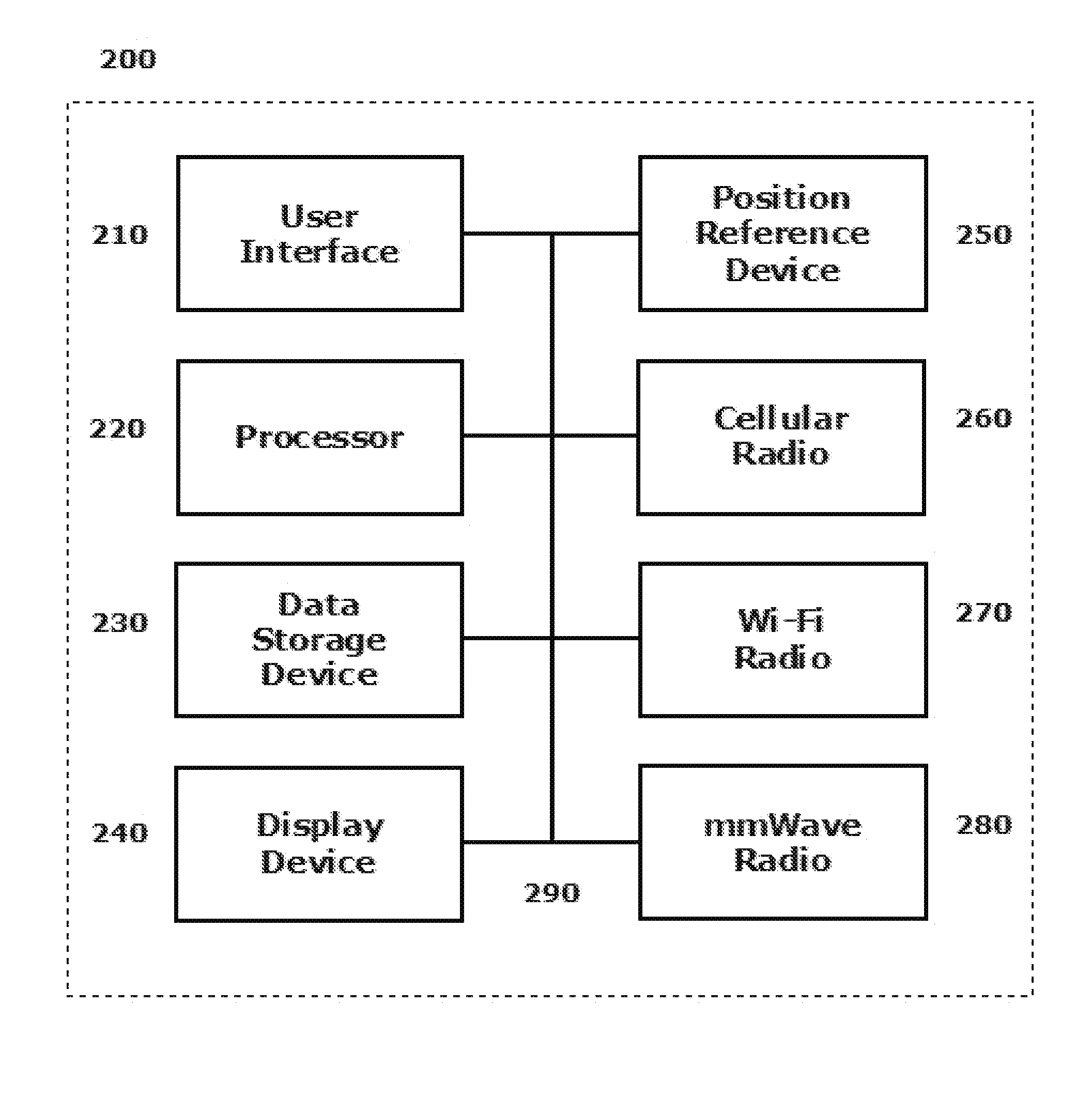

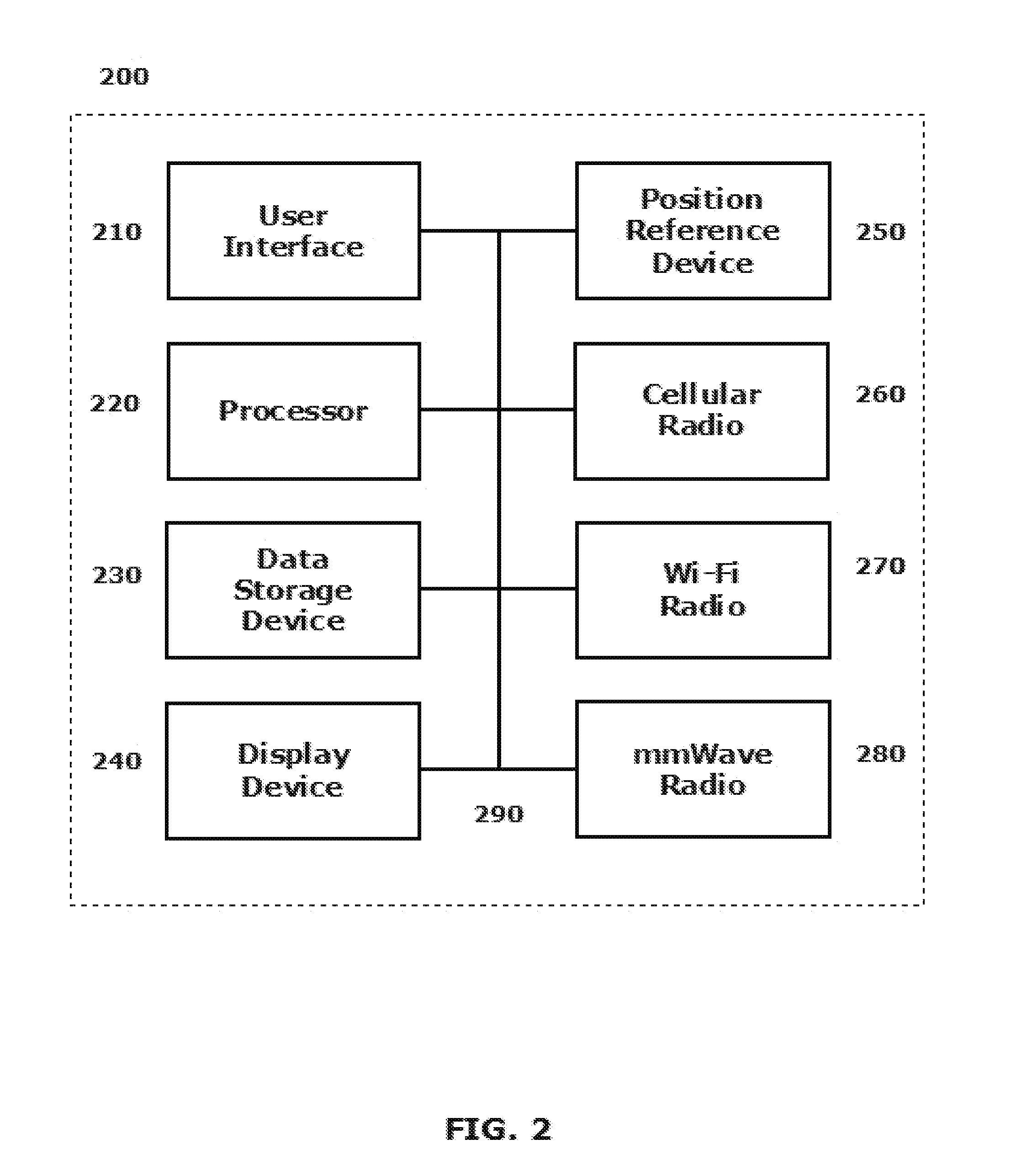

Use of location information in multi-radio devices for mmwave beamforming

ActiveUS20140218236A1Faster and efficient beamformingMinimization needsPosition fixationRadio transmissionWi-FiRadio equipment

A system and method are provided for using location services available from other radios in a multi-radio system to assist a beamforming mechanism, particularly in establishing and maintaining mmWave communication link. A majority of wireless client devices for use in a mmWave communication link are equipped with multiple radios. Many of the “other” radios include technologies that support location based services, including GPS, Wi-Fi and cellular communications. One or more non-mmWave in one device is used to provide relative location information regarding the other device with which the mmWave communication link is to be established. The relative location information is used to derive a direction for communication, and to compute beamforming parameters, in a limited set of transmit / receive sectors where the destination device is likely to be found, in order to streamline the beamforming process.

Owner:INTEL CORP

Systems and methods to control energy consumption efficiency

ActiveUS20100114385A1Minimize time neededImproving building energy management system efficiencyProgramme controlSampled-variable control systemsSimulationComputer module

A controller is configured to exchange information with a building automation system and includes various executable programs for determining a real time operating efficiency, simulating a predicted or theoretical operating efficiency, comparing the same, and then adjusting one or more operating parameters on equipment utilized by a building's HVAC system. The controller operates to adjust an operating efficiency of the HVAC system. An adjustment module utilized by the controller may modify the HVAC equipment parameters based on the likelihood that various HVAC equipment operates in parallel and on-line near its natural operating curve. In addition, the adjustment module may include a self-learning aspect that permits the controller to more efficiently make similar, future adjustments as needed.

Owner:OPTIMUM ENERGY

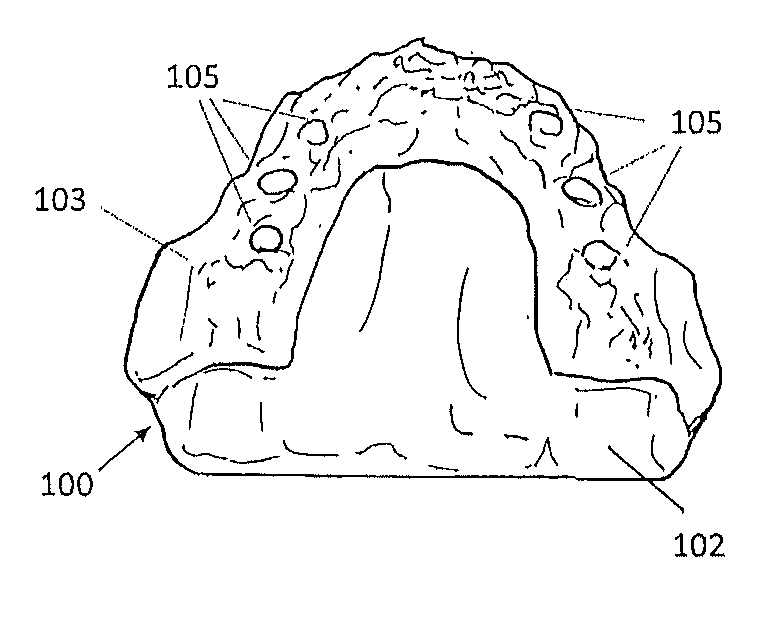

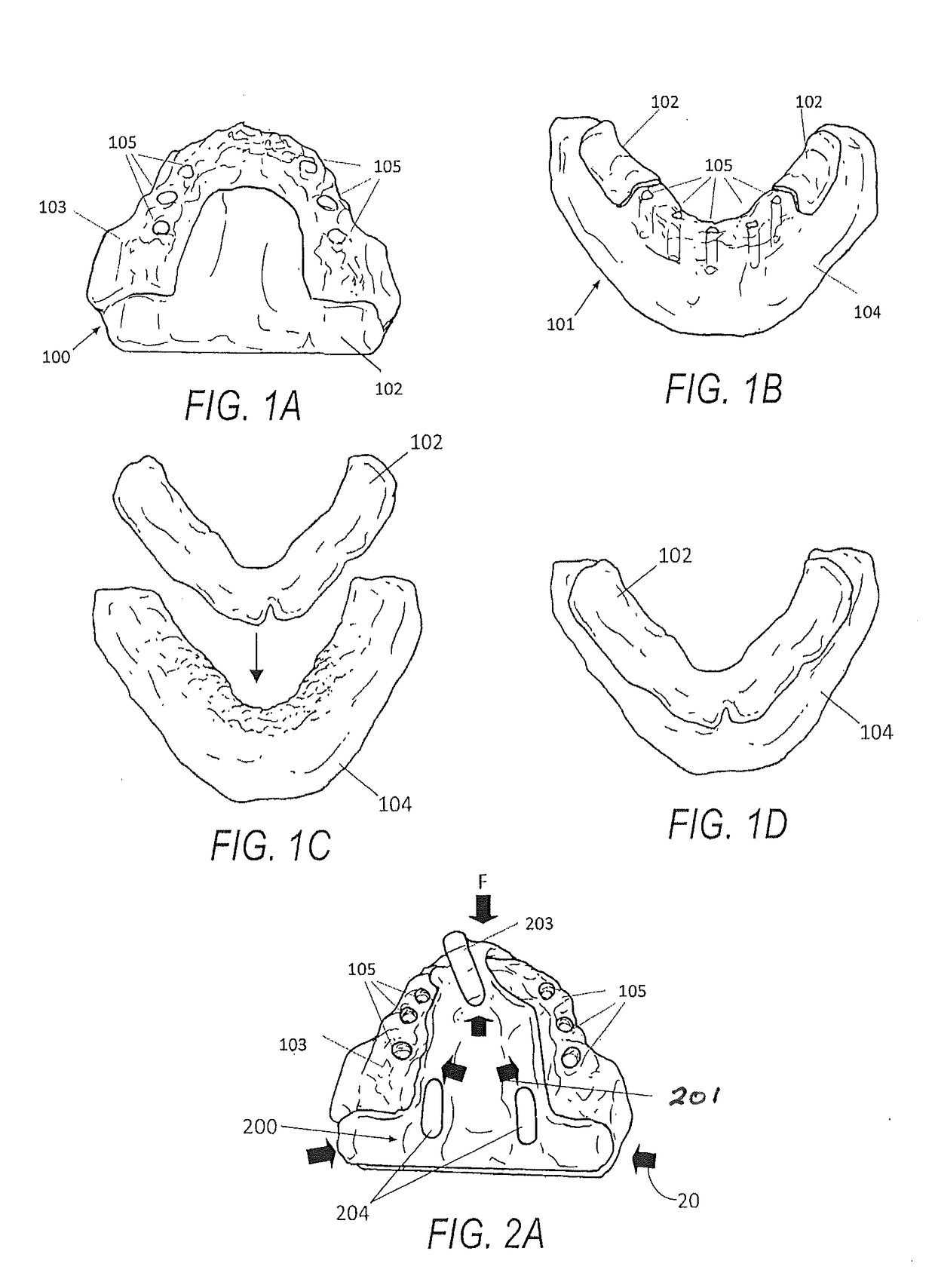

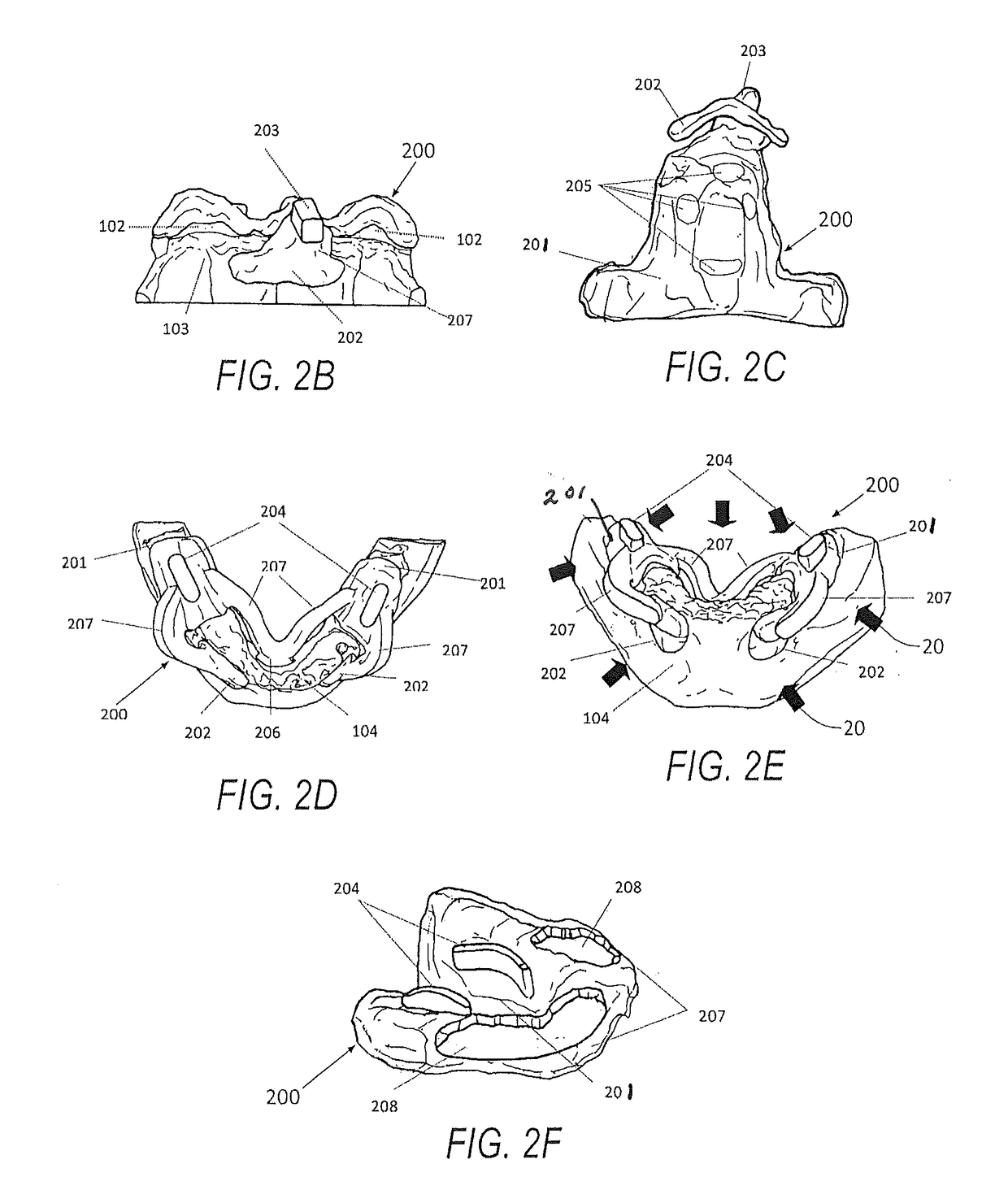

Method of using an endentulous surgical guide

ActiveUS20170112592A1Shorten the timeRelieve pressureDental implantsAdditive manufacturing apparatusBite registrationDental Models

An approach is disclosed that involves creating an updated master dental model of a patient's mouth after an implant surgery by aligning new postoperative oral scan data to pre-existing preoperative oral scan data that is more comprehensive (e.g., it includes bite registration). Before surgery a multi-piece stackable surgical guide set is created using the preoperative oral scan data. The surgical guide set is used to facilitate the surgery. After the surgery at least one piece of the surgical guide set is placed back in a patient's mouth and may act as a reference marker because it was created using the preoperative oral scan data, but is also part of the postoperative mouth configuration since it was used to facilitate the surgery. The affected portion of the mouth may then be digitally scanned directly or indirectly by way of a physical impression with the reference marker in place to determine the new characteristics resulting from the surgery such as new implant installation locations and orientations. The new postoperative oral scan data may be combined with the pre-existing preoperative oral scan data by way of the reference marker (since it is a constant between the two sets of scan data) without having to do such things as take a new bite registration, on which a new implant restoration can be easily created.

Owner:IBUR

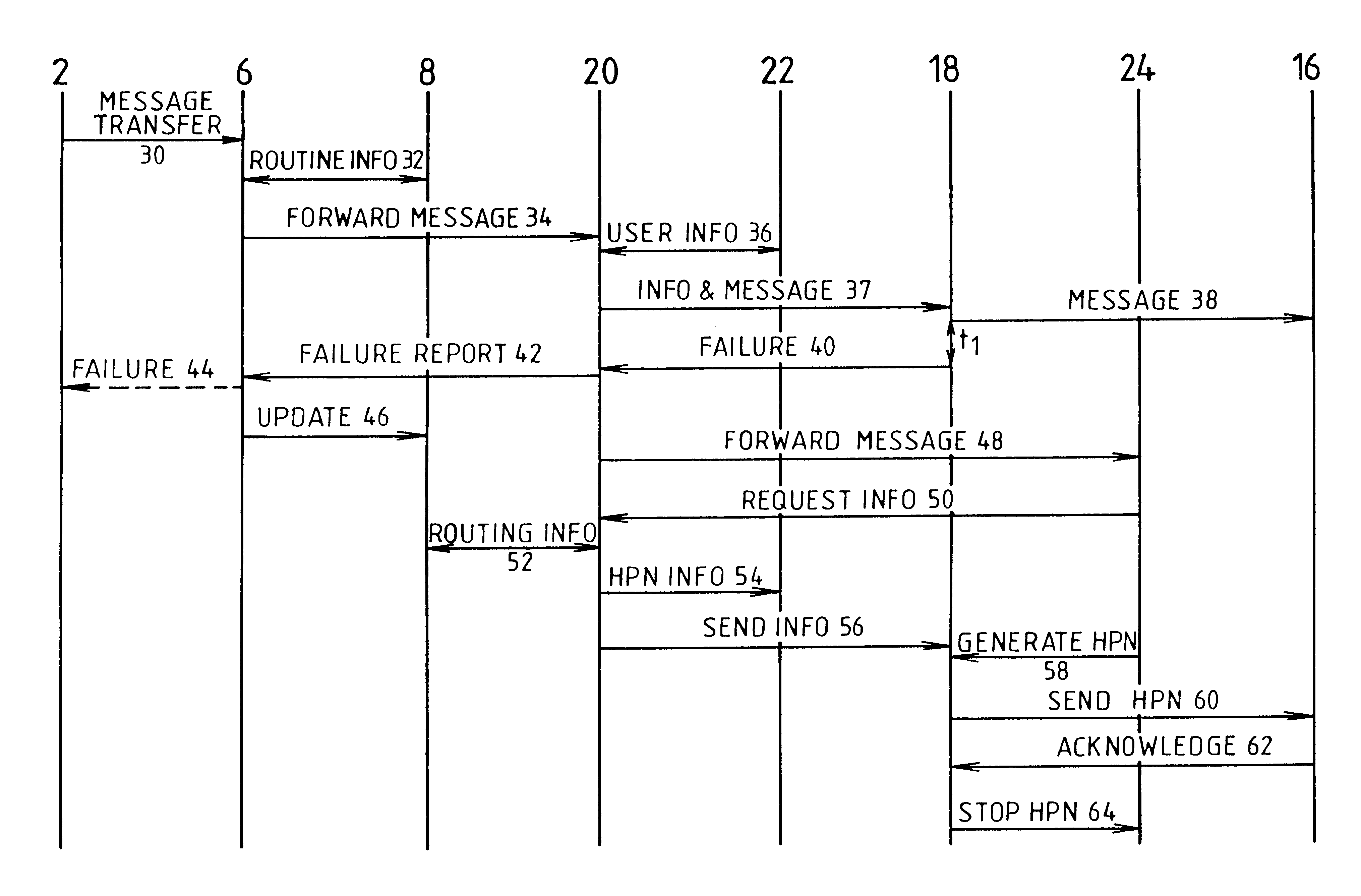

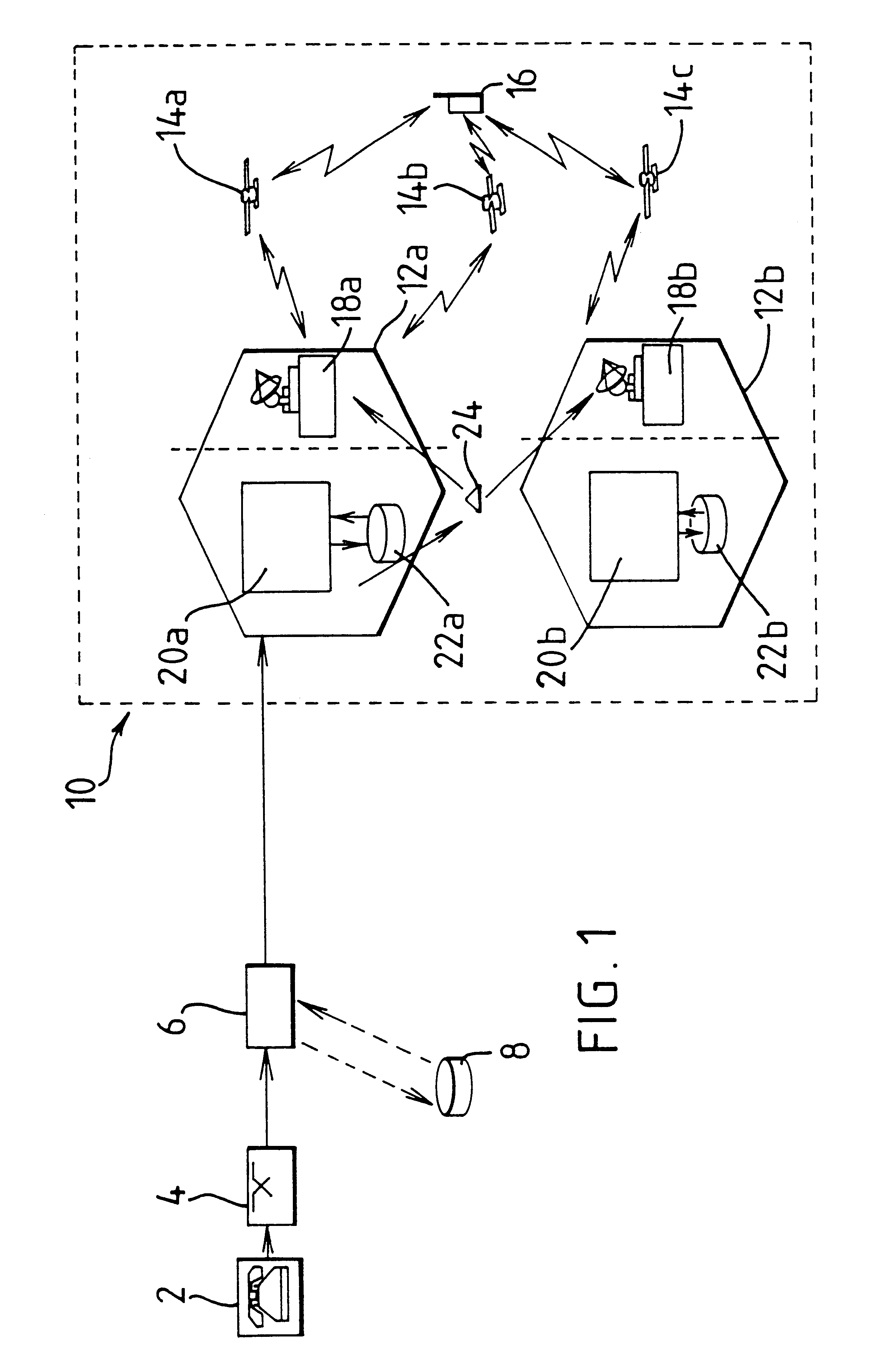

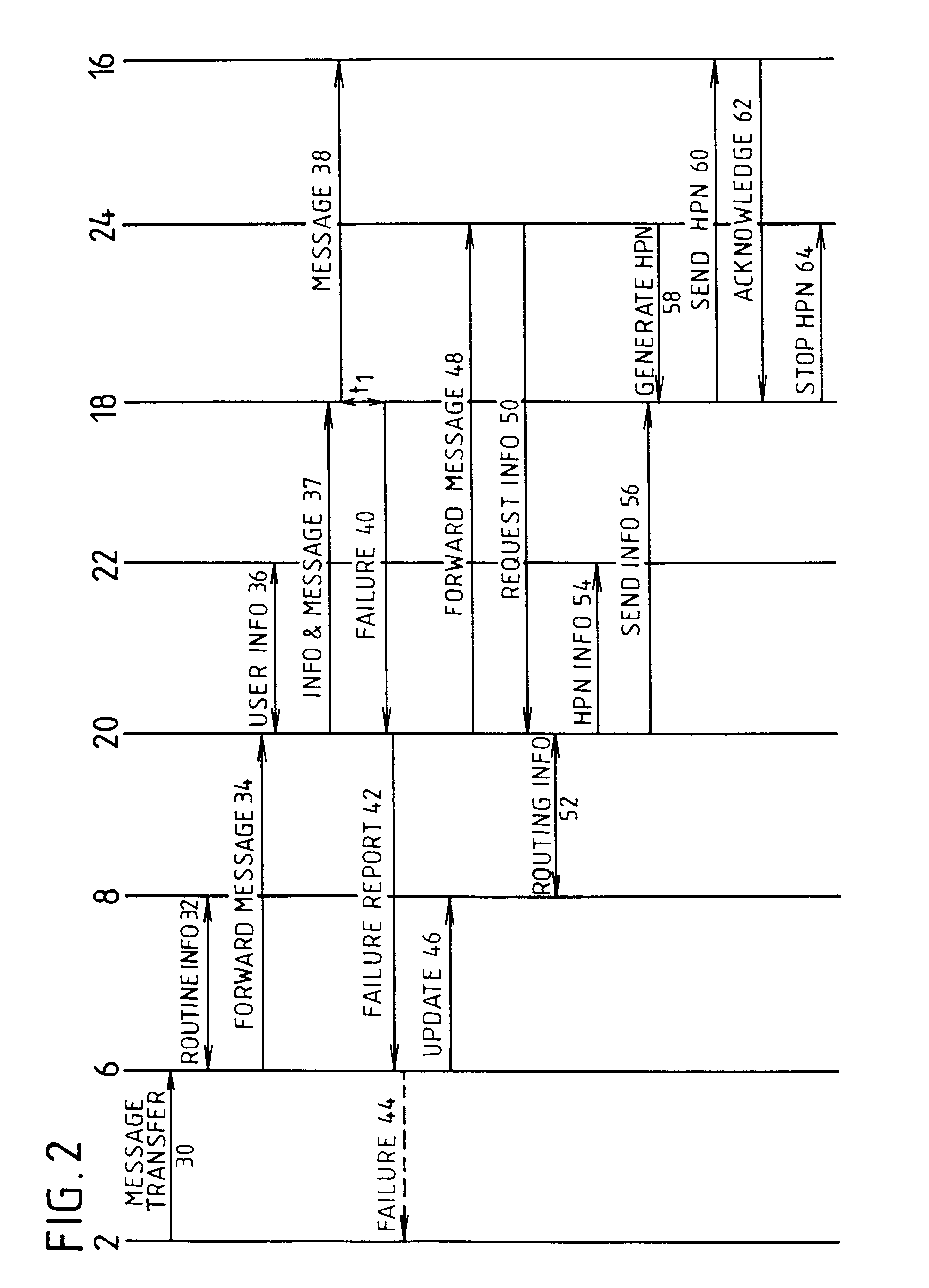

High margin notification method and apparatus

InactiveUS6763240B1Increase profitMinimization needsActive radio relay systemsRadio/inductive link selection arrangementsCommunications systemMobile communication systems

In a mobile communications system 10, a message is sent to a mobile terminal 16 which transmits an acknowledgement signal if the message is received. If the system 10 does not detect an acknowledgement signal, it transmits a high margin notification signal to the mobile terminal 16 to notify the terminal that an attempt was made to send the message. When the mobile terminal 16 has received a notification signal and subsequently comes within range of lower margin signals from the system, it sends a registration signal to the system. The system may then retransmit the message to the mobile terminal 16.

Owner:INMARSAT GLOBAL

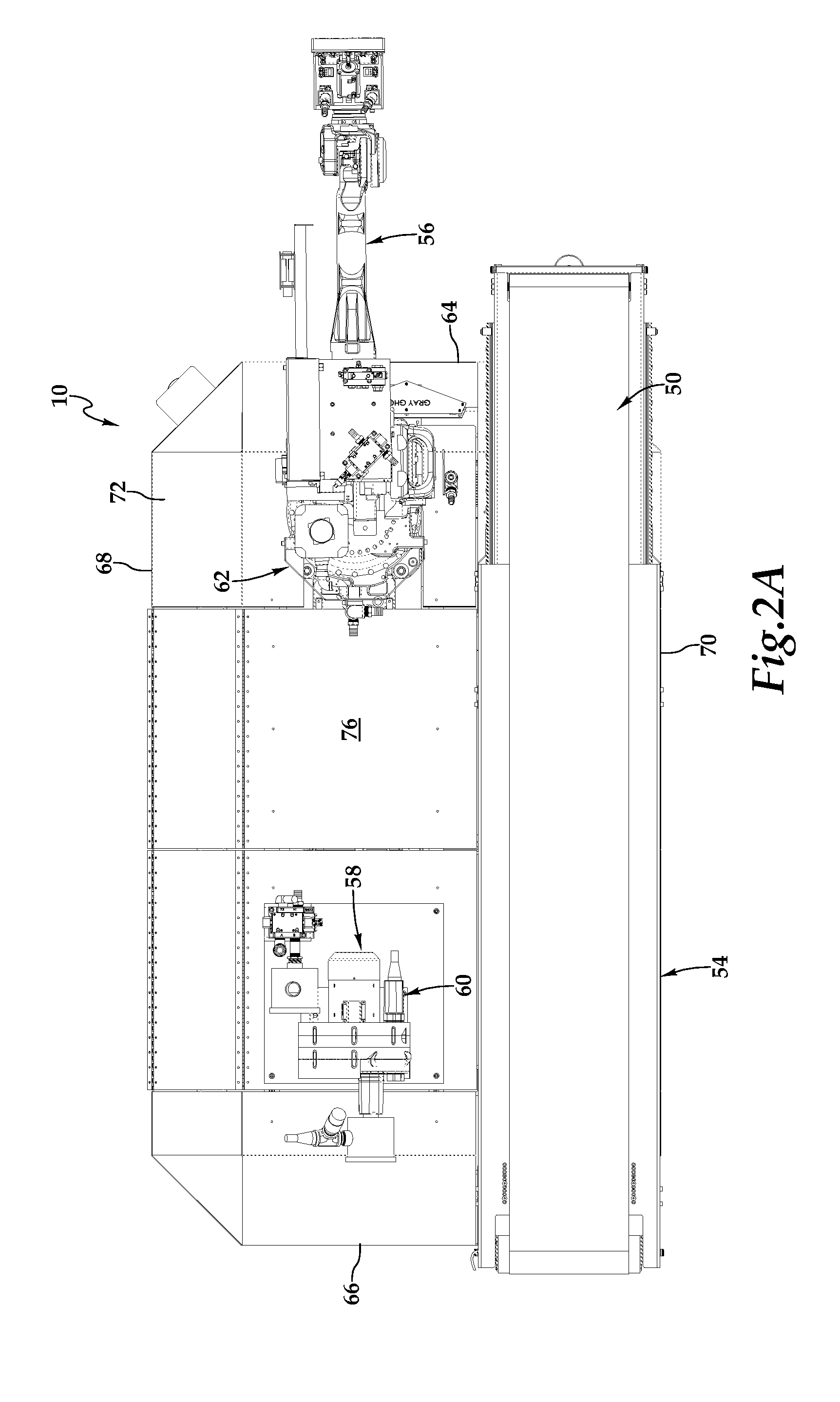

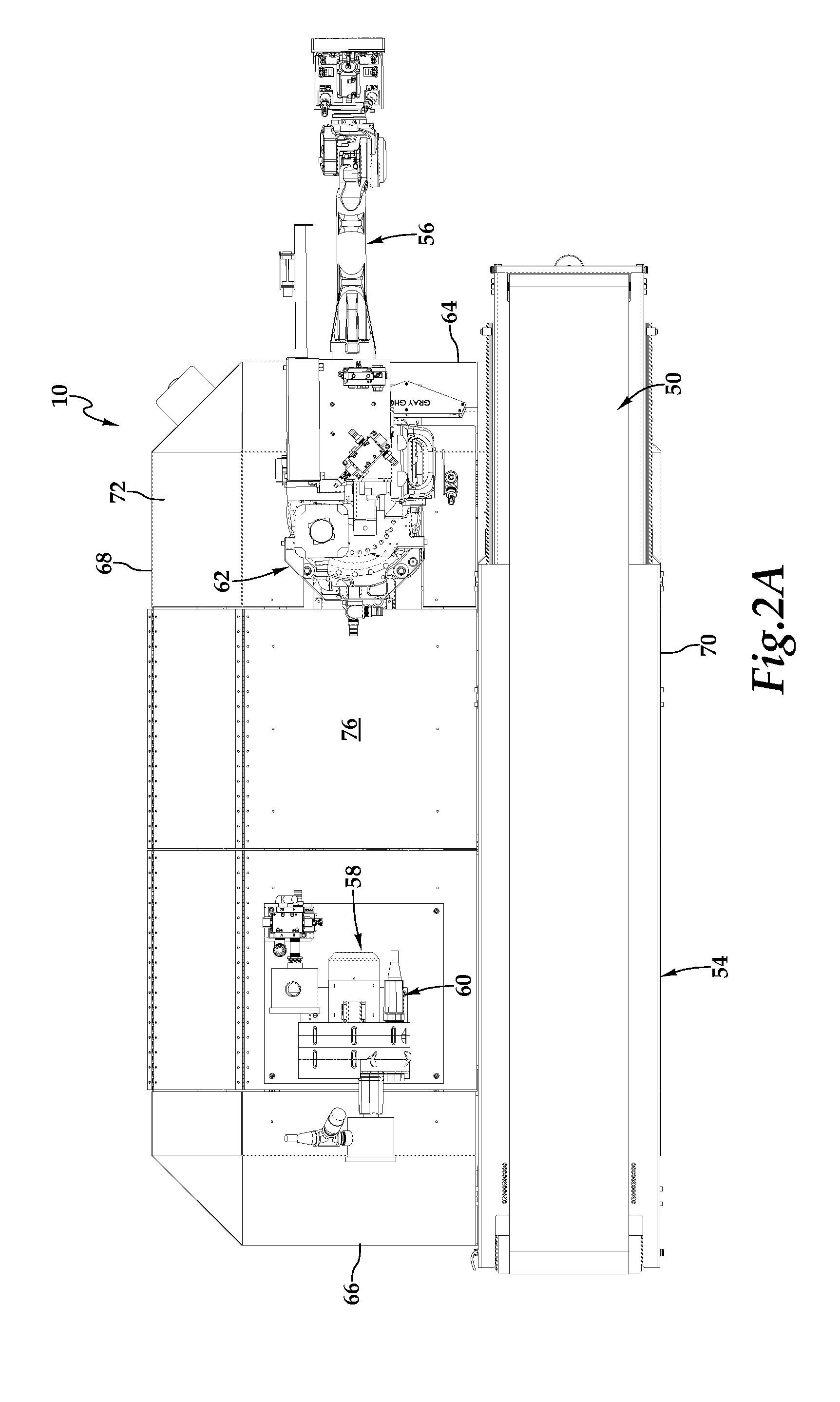

Perception-Based Robotic Manipulation System and Method for Automated Truck Unloader that Unloads/Unpacks Product from Trailers and Containers

ActiveUS20170305694A1Quantity maximizationUse minimizedProgramme-controlled manipulatorConveyorsPattern perceptionEngineering

An automated truck unloader (10) for unloading / unpacking product, such as boxes or cases, from trailers and containers is disclosed. In one embodiment, a mobile base structure provides a support framework for a drive subassembly, conveyance subassembly, an industrial robot (56), a distance measurement subassembly, and a control subassembly (62). Under the operation of the control subassembly, an industrial robot (56) having a suction cup-based gripper arm selectively removes boxes from the trailer and places the boxes on a powered transportation path (88). The control subassembly (62) coordinates the selective articulated movement of the industrial robot (56) and the activation of the drive subassembly based upon a perception-based robotic manipulation system.

Owner:DAIFUKU CO LTD

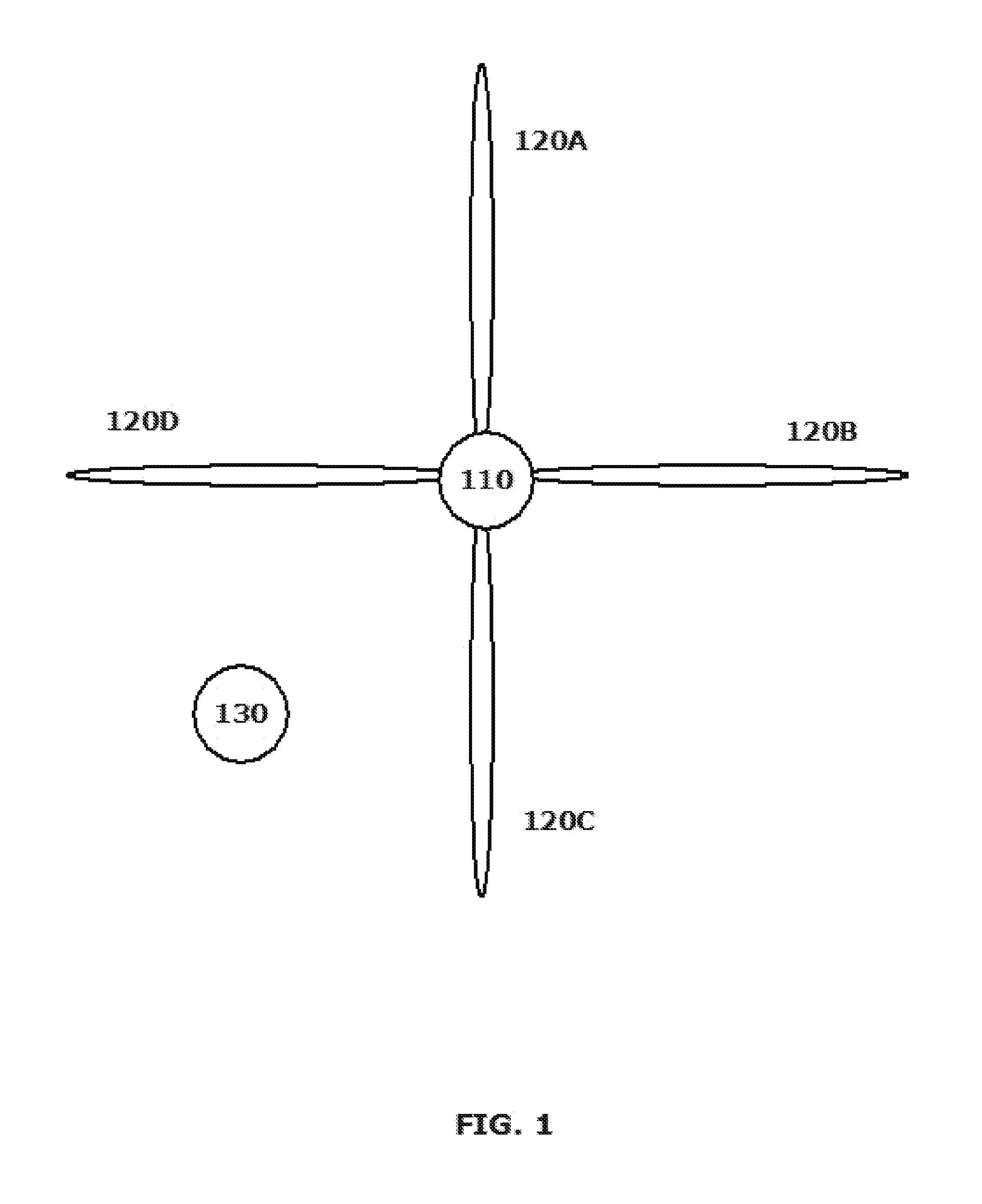

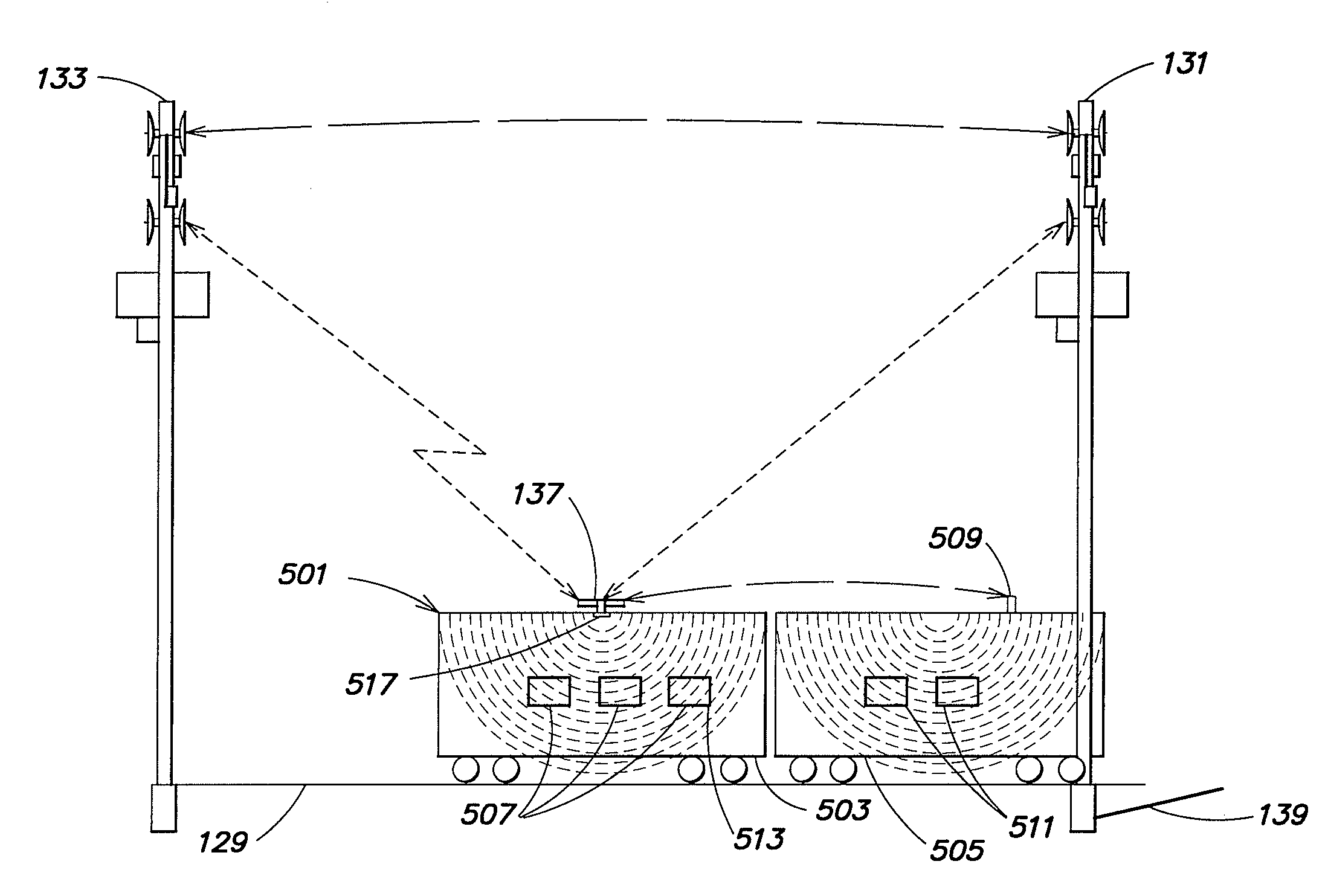

Antenna system for communicating with mobile devices

ActiveUS20080042912A1Minimize time neededShorten the timeAntenna arraysAntenna adaptation in movable bodiesTelecommunicationsMobile device

Systems and methods for providing network access to mobile devices that travel with a vehicle, such as a train, a bus, a boat, etc. along or adjacent to a relatively fixed path that may extend over a large geographic area. Mobile devices access the network through stationary access points arranged along or adjacent to the path and communicate with a communication network. The communication network may be arranged as an asynchronous transfer mode (ATM) local area network emulation (LANE) network. One of the mobile devices may be a mobile access point which can couple other mobile devices to the network and record authentication information of other mobile devices so that fast transitions can be made from one stationary access point to another as the vehicle moves along the path.

Owner:WIFI RAIL

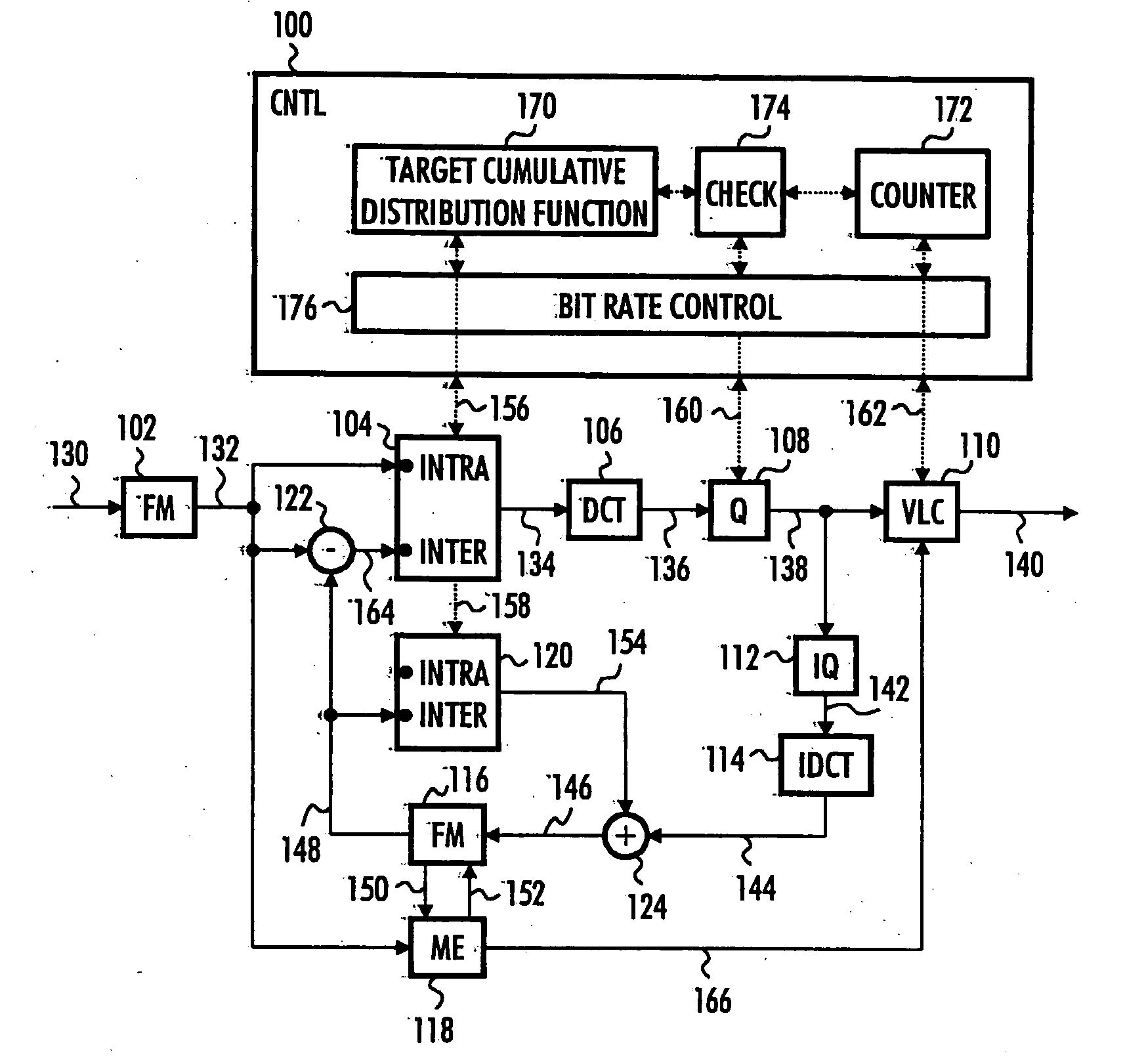

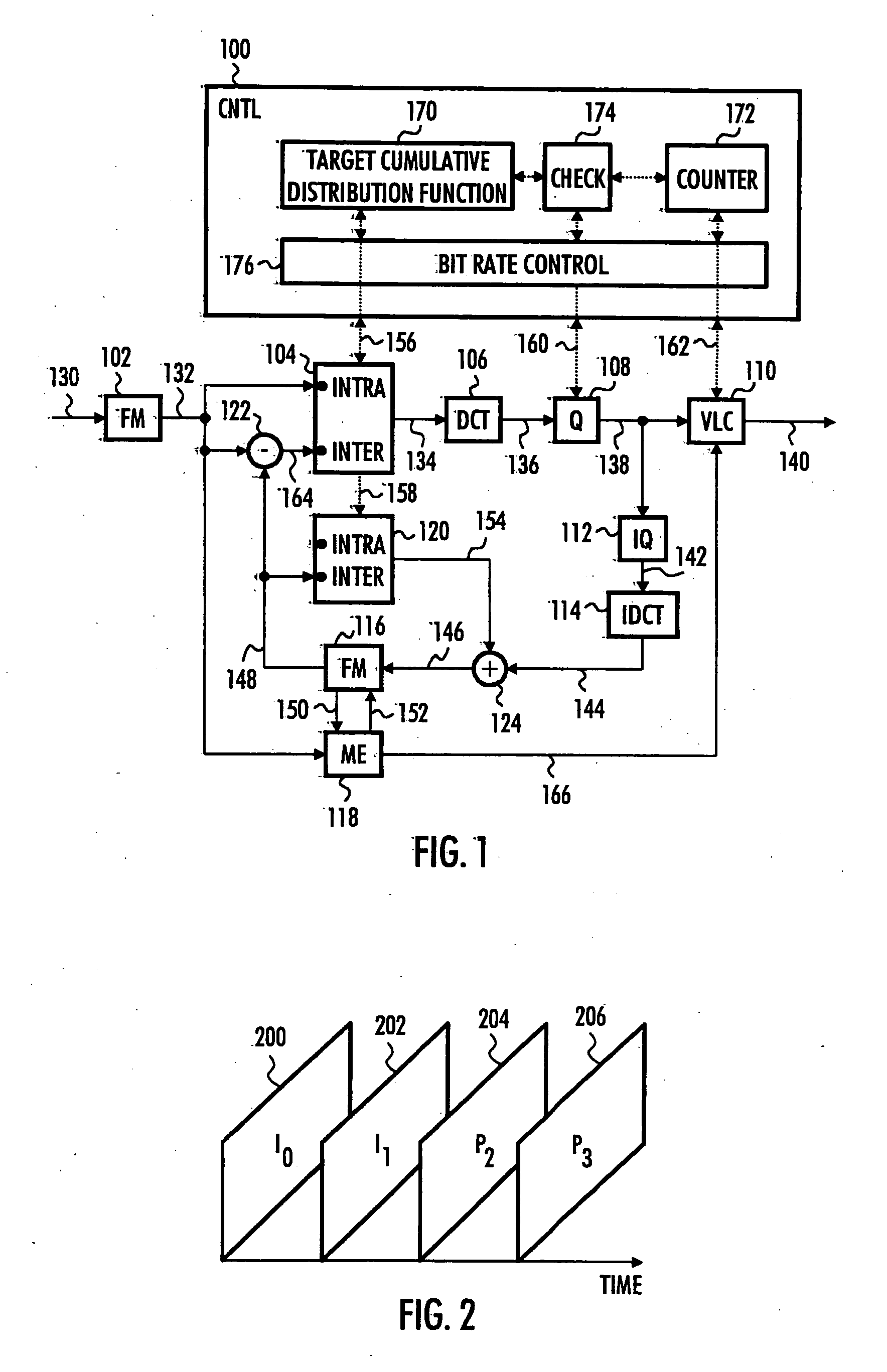

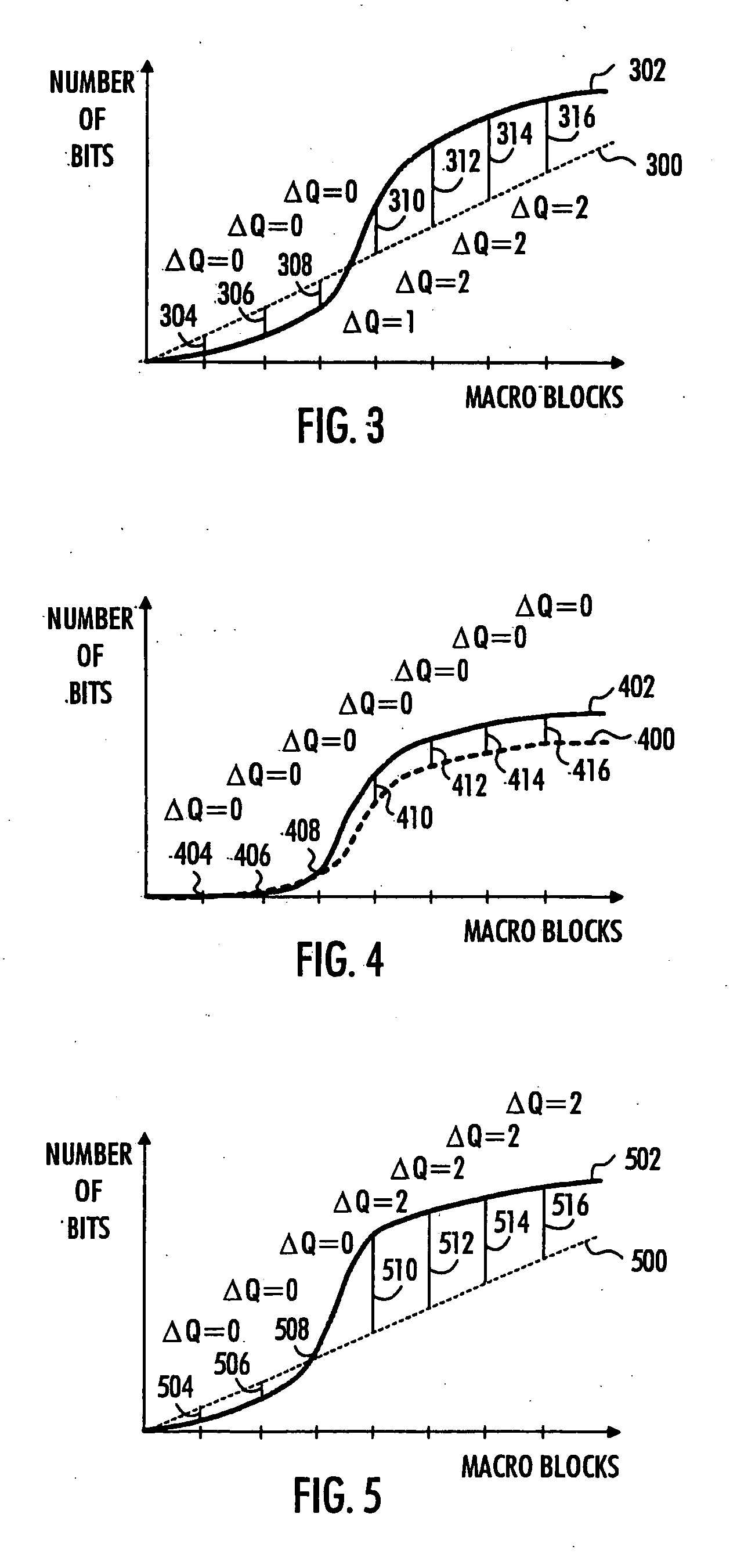

Apparatuses, computer program product and method for bit rate control of digital image encoder

InactiveUS20060062481A1Increase bitrateLimit bit rateCharacter and pattern recognitionDigital video signal modificationEquipment computersDigital image

Apparatuses, a computer program product and a method for controlling a bit rate of a digital image encoder. The bit rate controller includes a target cumulative distribution function computing mechanism predicting the number of encoded bits resulting from an encoding to be performed in the encoder; a counter mechanism counting the number of encoded bits resulting from the encoding; a check mechanism forming an error term from a comparison between a value of the counter and a corresponding value of the target cumulative distribution function; and a bit rate control mechanism adjusting a quantization parameter of the encoding to be continued on the basis of the error term.

Owner:GOOGLE LLC

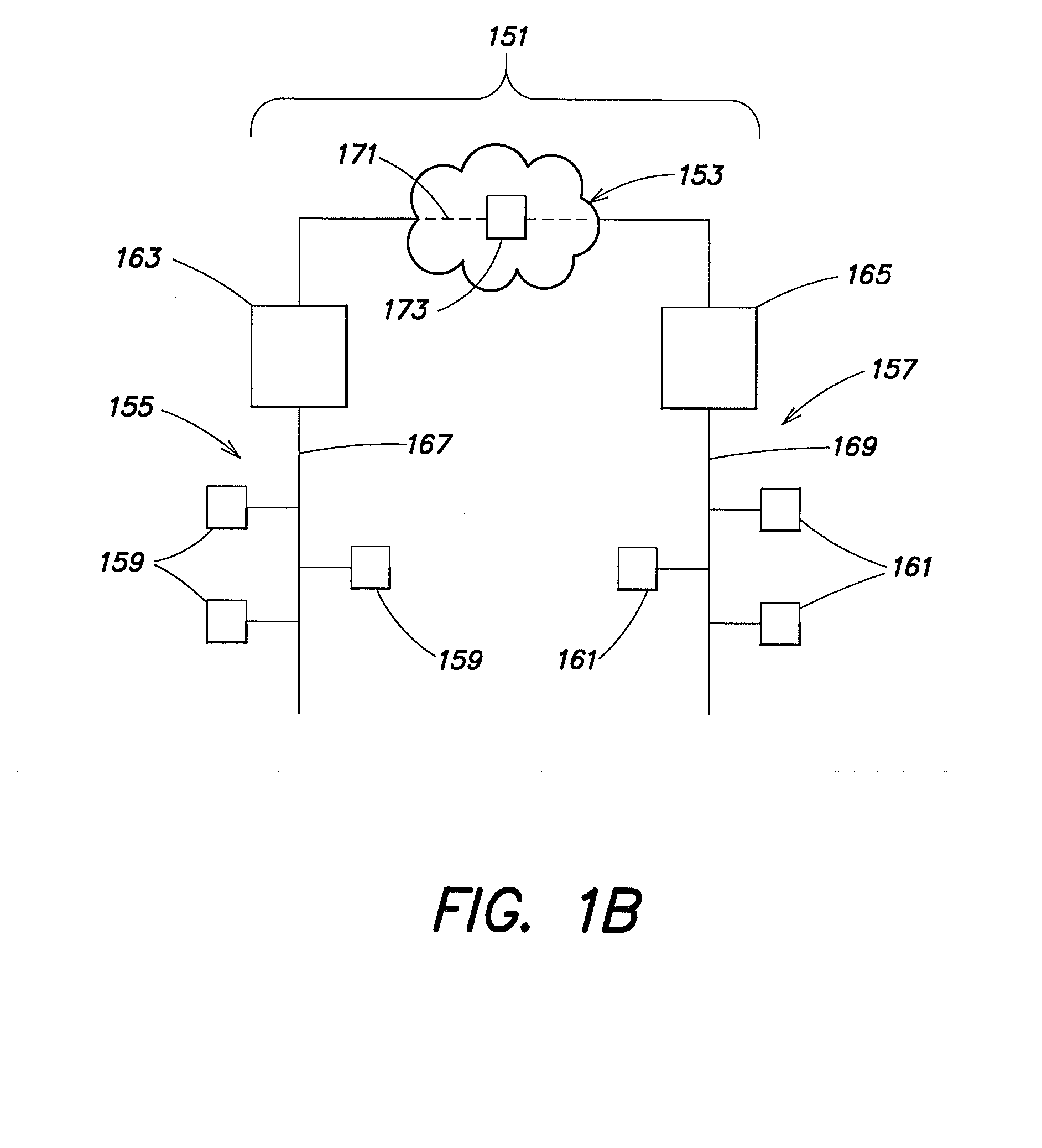

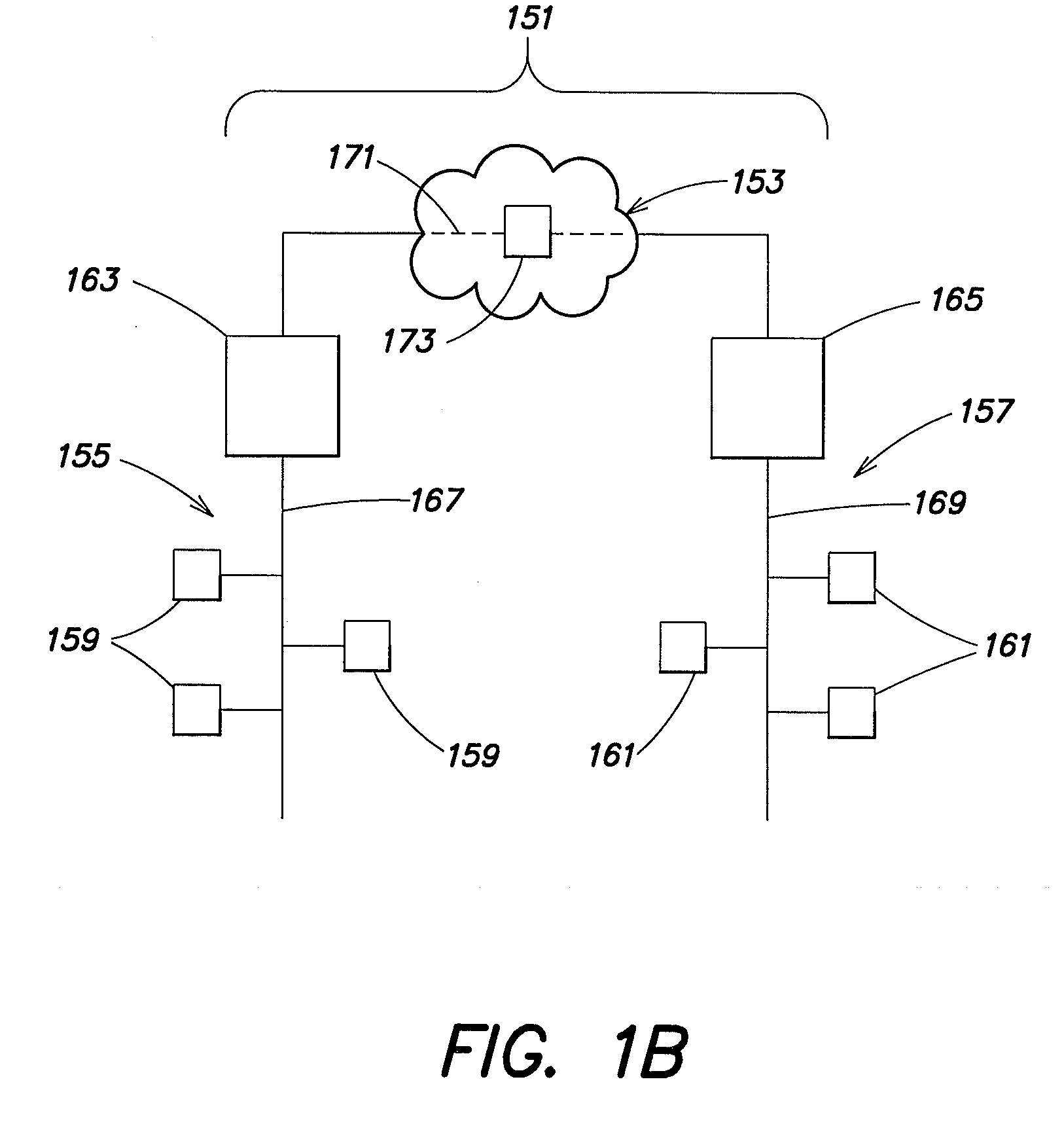

System for providing redundant communication with mobile devices

ActiveUS20080125129A1Minimization needsShorten the timeNetwork topologiesRadio/inductive link selection arrangementsMobile deviceAsynchronous Transfer Mode

Systems and methods for providing network access to mobile devices that travel with a vehicle, such as a train, a bus, a boat, etc. along or adjacent to a relatively fixed path that may extend over a large geographic area. Mobile devices access the network through stationary access points arranged along or adjacent to the path and communicate with a communication network. The communication network may be arranged as an asynchronous transfer mode (ATM) local area network emulation (LANE) network. One of the mobile devices may be a mobile access point which can couple other mobile devices to the network and record authentication information of other mobile devices so that fast transitions can be made from one stationary access point to another as the vehicle moves along the path.

Owner:WIFI RAIL

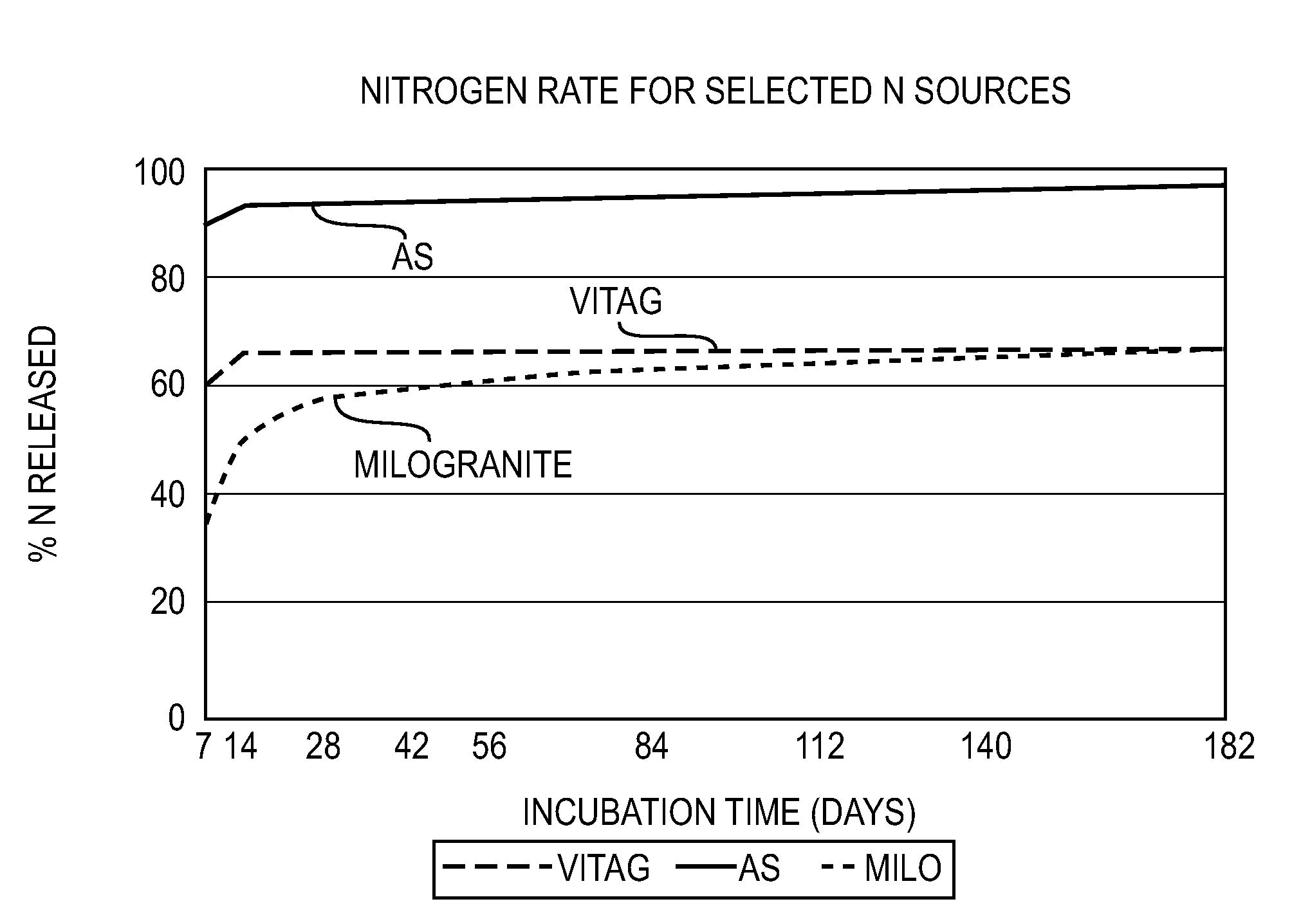

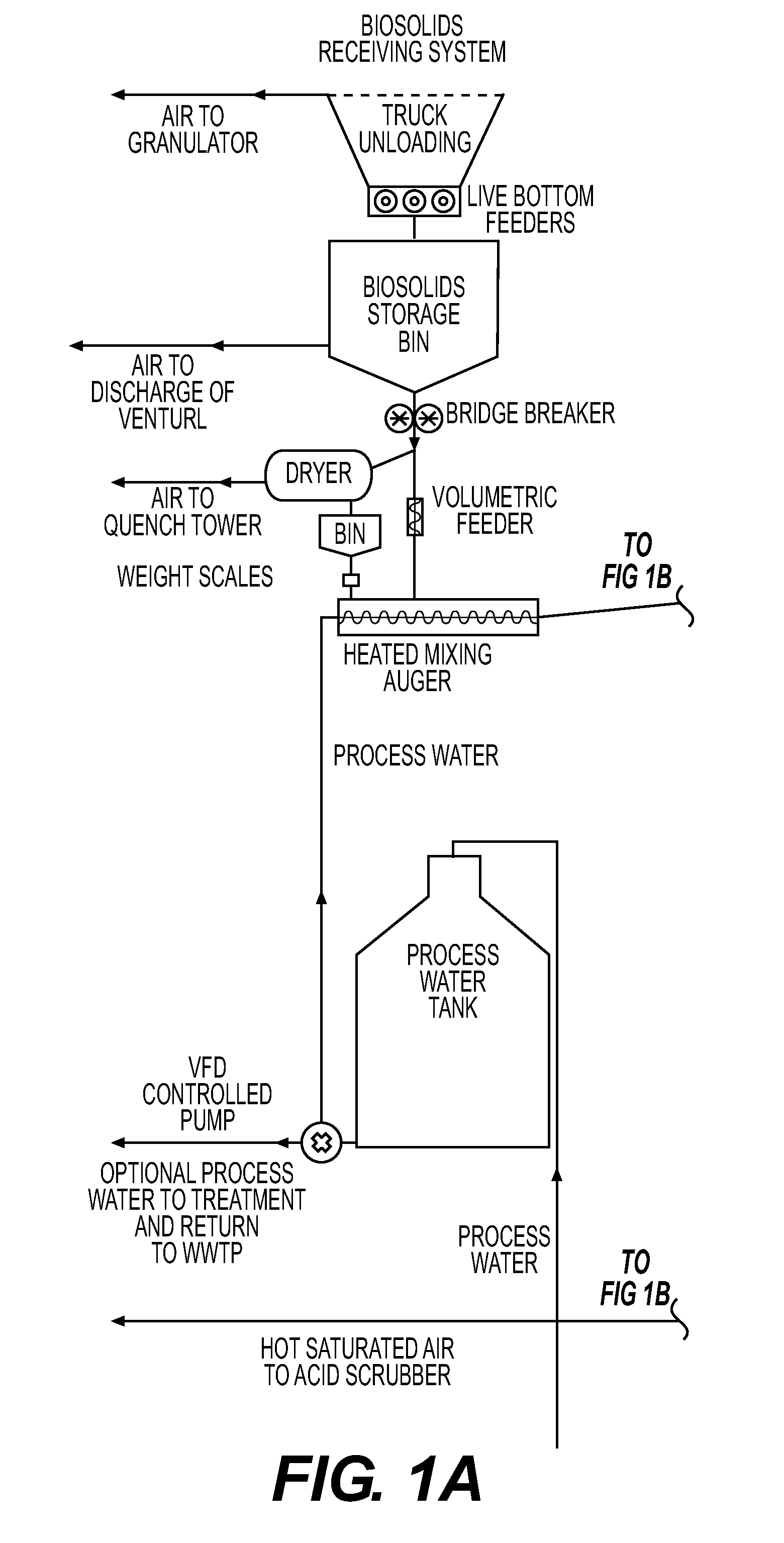

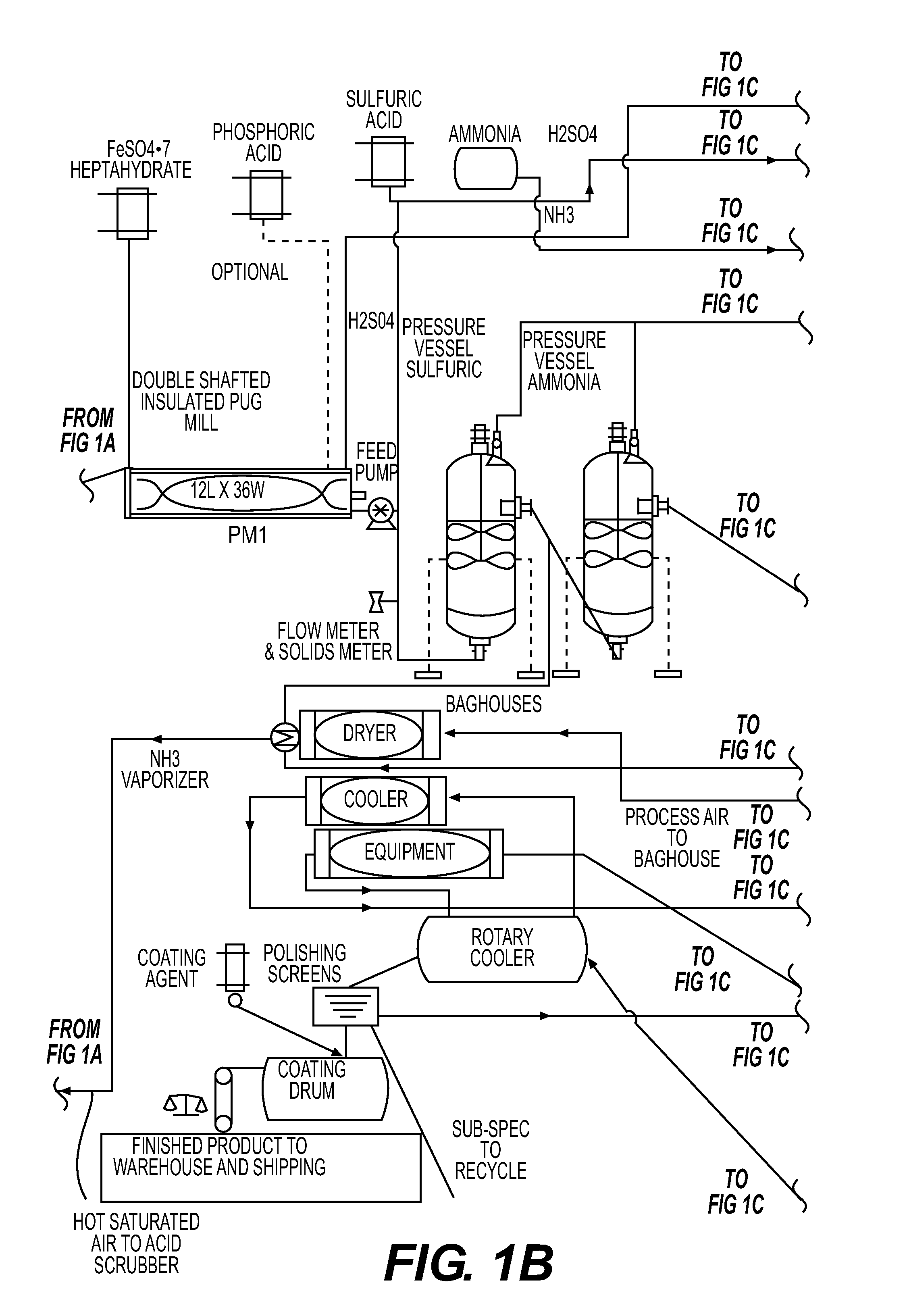

High value organic-enhanced inorganic fertilizers

ActiveUS20120247164A1Increase valueEasy to containCalcareous fertilisersGranule coatingSoil organic matterNitrogen

The invention is directed to manufacture of fertilizer having commercial levels of nitrogen supplemented with organic substances. The process treats organic matter with acid causing hydrolysis of organic polymers after which the mix is injected with nitrogen. The resultant sterilized and liquefied organic matter is disbursed over recycled material for the production of granules. Because the process allows for the controlled addition of acids and ammonia, desired levels of components can be achieved. The process is scalable, odor controlled and safe thereby allowing for the location of biosolid processing facilities in most any location. Further, the fertilizer of the invention provides a dual nitrogen-release profile when applied to crops. After application to soil, fertilizer of the invention releases an immediate bolus of nitrogen, similar to traditional ammonium sulfate, followed by continued slow release of nitrogen typically over a season.

Owner:GENERATE LENDING LLC +1

Methods and systems related to trading engines

At least one aspect comprises a method comprising: (a) receiving electronic data describing a trading order from a market participant; (b) associating the trading order with one or more target brokers, (c) selecting with a processing system one or more first trading algorithms from a plurality of available stored algorithms for execution of the trading order; (d) commencing with the processing system execution of the trading order via the one or more first trading algorithms; (e) evaluating with the processing system quality of execution, during the execution, of the trading order via the one or more first trading algorithms; and (f) if the evaluated quality of execution compares unfavorably to a threshold of acceptability, switching with the processing system the execution of the trading order to one or more second trading algorithms, wherein the processing system comprises one or more processors.

Owner:PORTWARE LLC

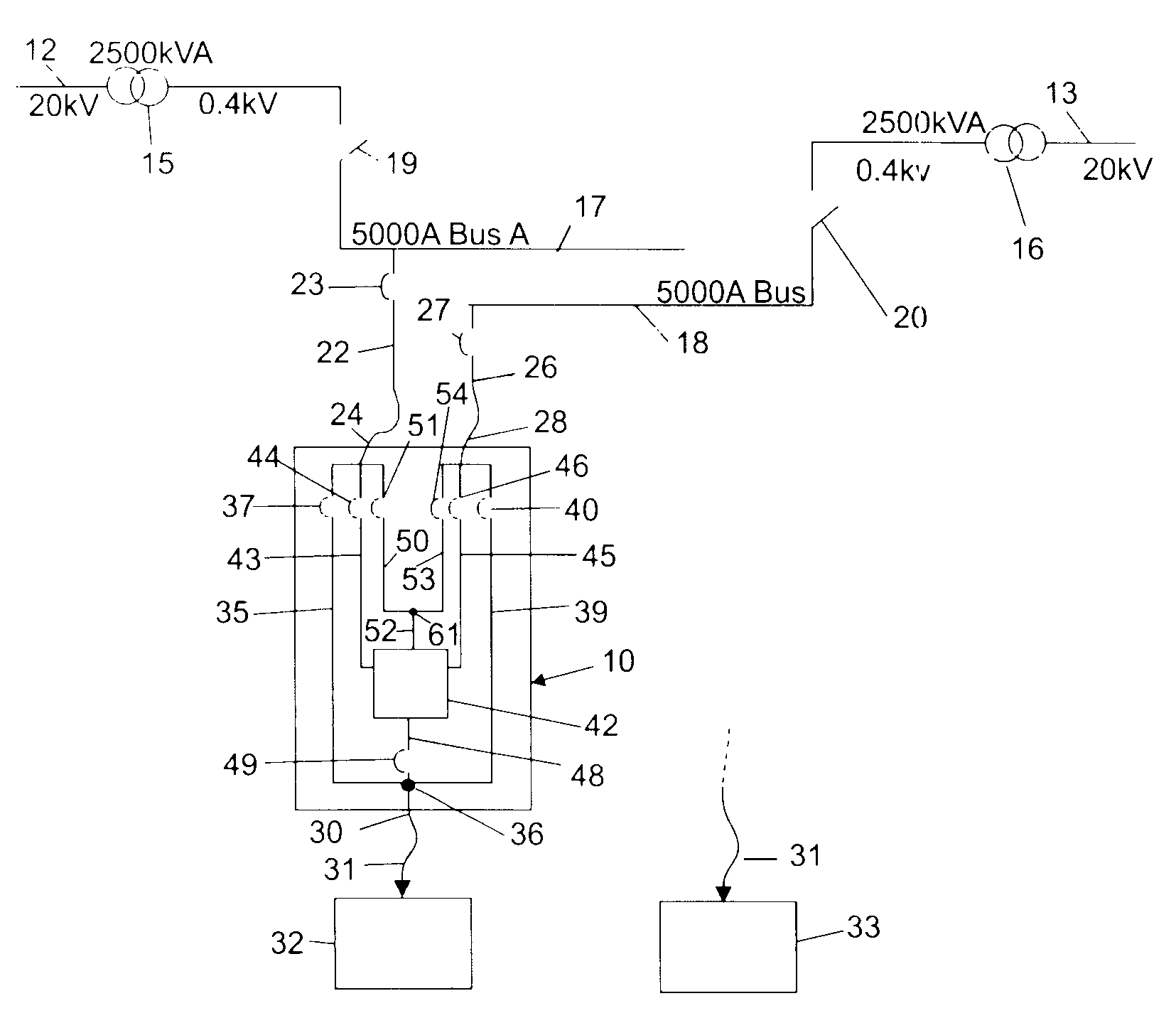

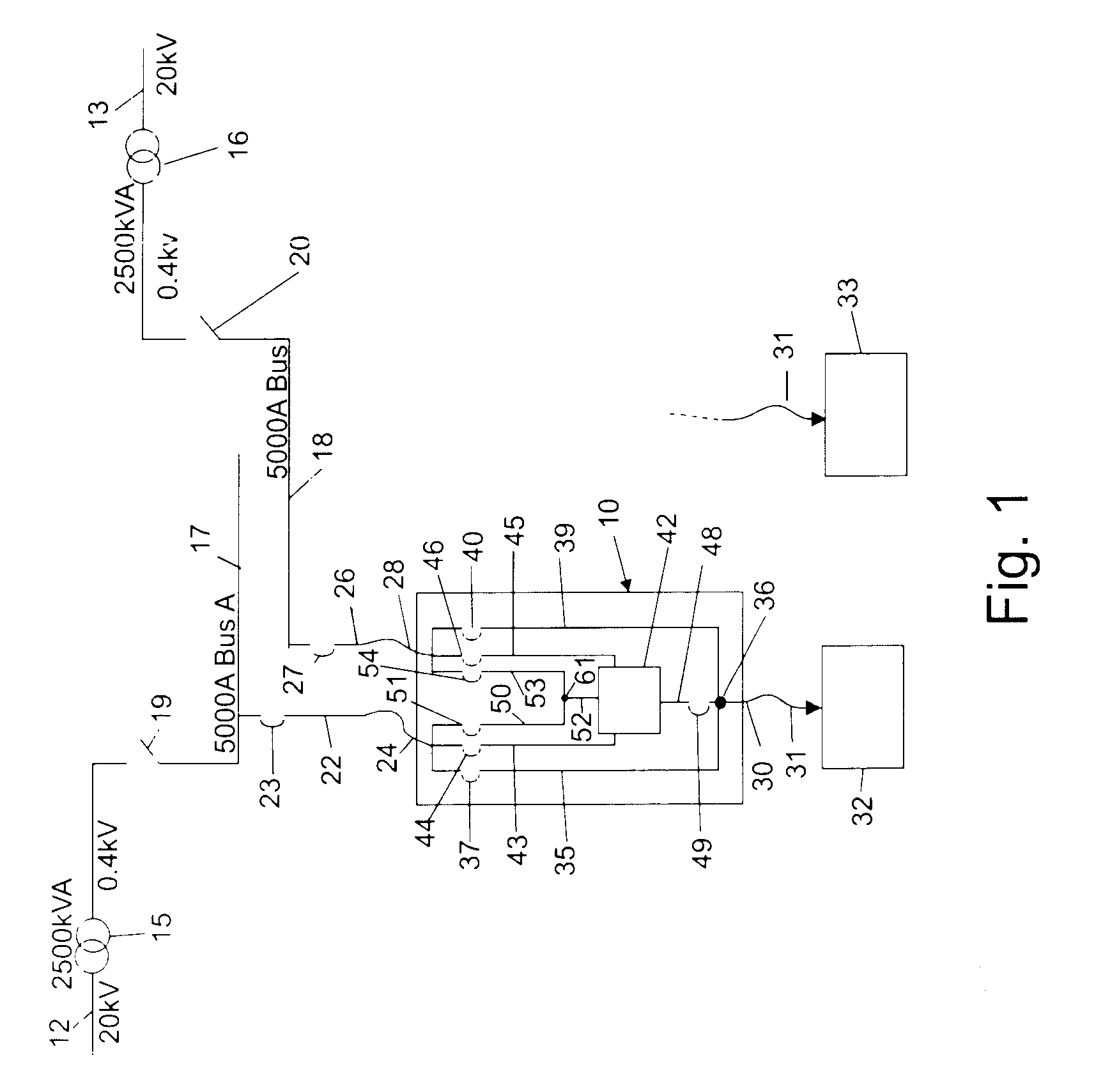

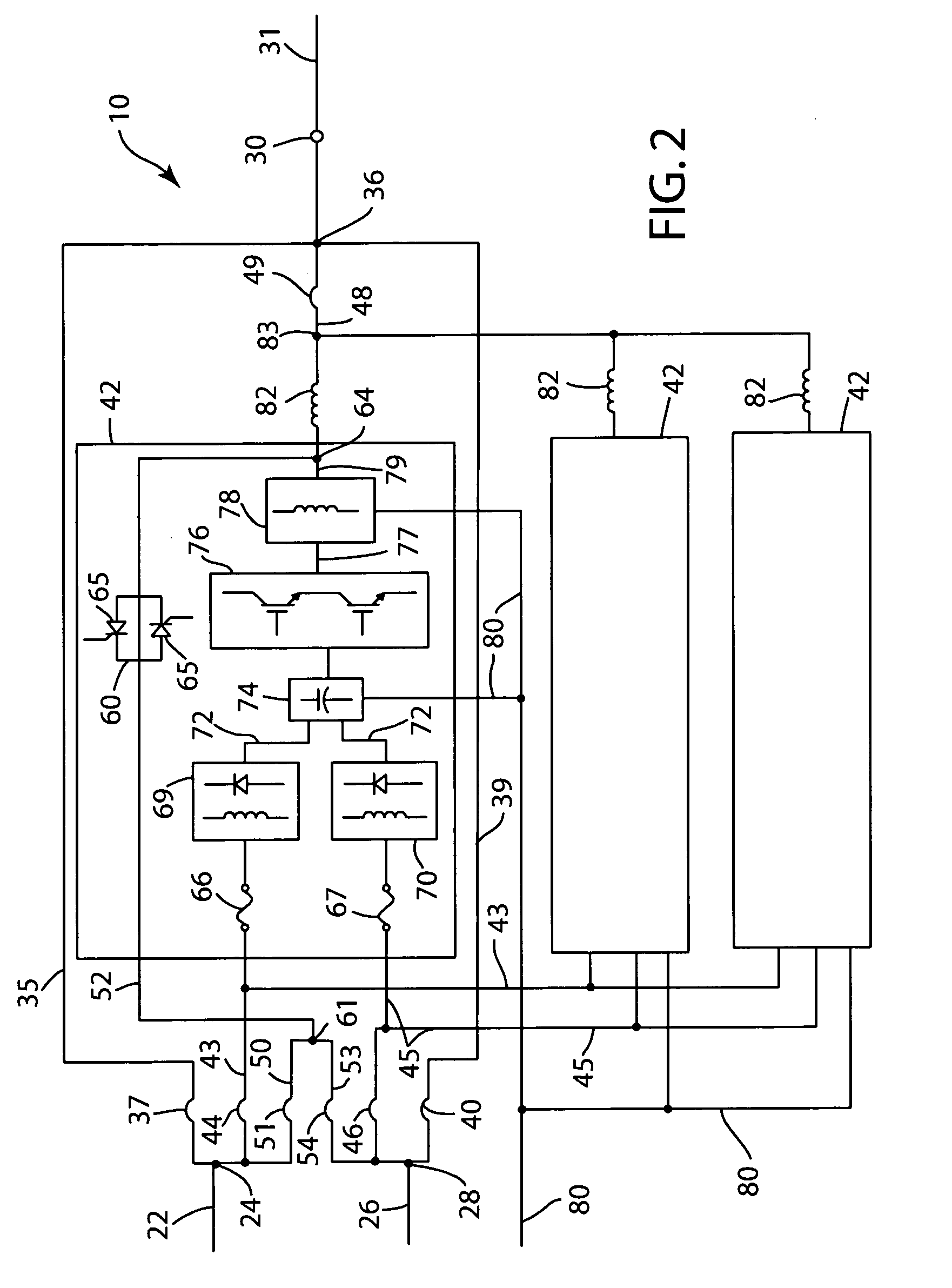

Dual feed power supply systems with enhanced power quality

ActiveUS7129599B2Disrupting functionImprove reliabilityBatteries circuit arrangementsElectric powerCritical loadTransfer switch

Dual feed power supply system provides high reliability of a dual utility feed, with minimal interruptions in power supplied to critical loads during switching, and compensation for voltage sags occurring on the primary power feed. AC input buses are connected through a transfer switching apparatus to phase lines of a distribution bus. The transfer switching apparatus has a first input terminal connected to one of the phase lines of the first input bus and a second input terminal connected to one of the phase lines of the second input bus, and an output terminal connected to one of the phase lines of the distribution bus. Input switches allow switching from one or the other of the AC input buses to the distribution bus, with a fast transfer switch used to interrupt the supply of power from the input buses to the distribution bus during switching of the input switches.

Owner:ROCKWELL AUTOMATION

Automated truck unloader for unloading/unpacking product from trailers and containers

ActiveUS9434558B2Minimization needsMinimize timeProgramme controlProgramme-controlled manipulatorEngineeringTruck

An automatic truck unloader for unloading / unpacking product, such as boxes or cases, from trailers and containers is disclosed. In one embodiment, a mobile base structure provides a support framework for a drive subassembly, conveyance subassembly, an industrial robot, a distance measurement subassembly, and a control subassembly. Under the operation of the control subassembly, an industrial robot having a suction cup-based gripper arm selectively removes boxes from the trailer and places the boxes on a powered transportation path. The control subassembly coordinates the selective articulated movement of the industrial robot and the activation of the drive subassembly based upon the distance measurement subassembly detecting objects, including boxes, within a detection space, and dimensions of the trailer provided to the control subassembly.

Owner:WYNRIGHT CORP

Signal transmission method from a local network node

ActiveUS8503342B2Reliable wayMinimization needsError prevention/detection by using return channelResonant long antennasElectricityData rate

A transmitter is provided having transmission methods that minimize the power needed to ensure reliable reception in a coverage area. In one aspect, data that requires re-transmission as acknowledged mode data is re-transmitted when the power level of the transmission link is higher than a pre-determined level set for reliable reception. The data rate of the re-transmitted data is set according to the difference in the actual power and the pre-determined level. In a second aspect, two transmitting antennae are used to transmit the same signals with a frequency off-set. The frequency off-set can be used to determine the phase of the signals being received at the receiver, so that a phase off-set can be introduced to optimise the effect of interference at the receiver.

Owner:BISON PATENT LICENSING LLC

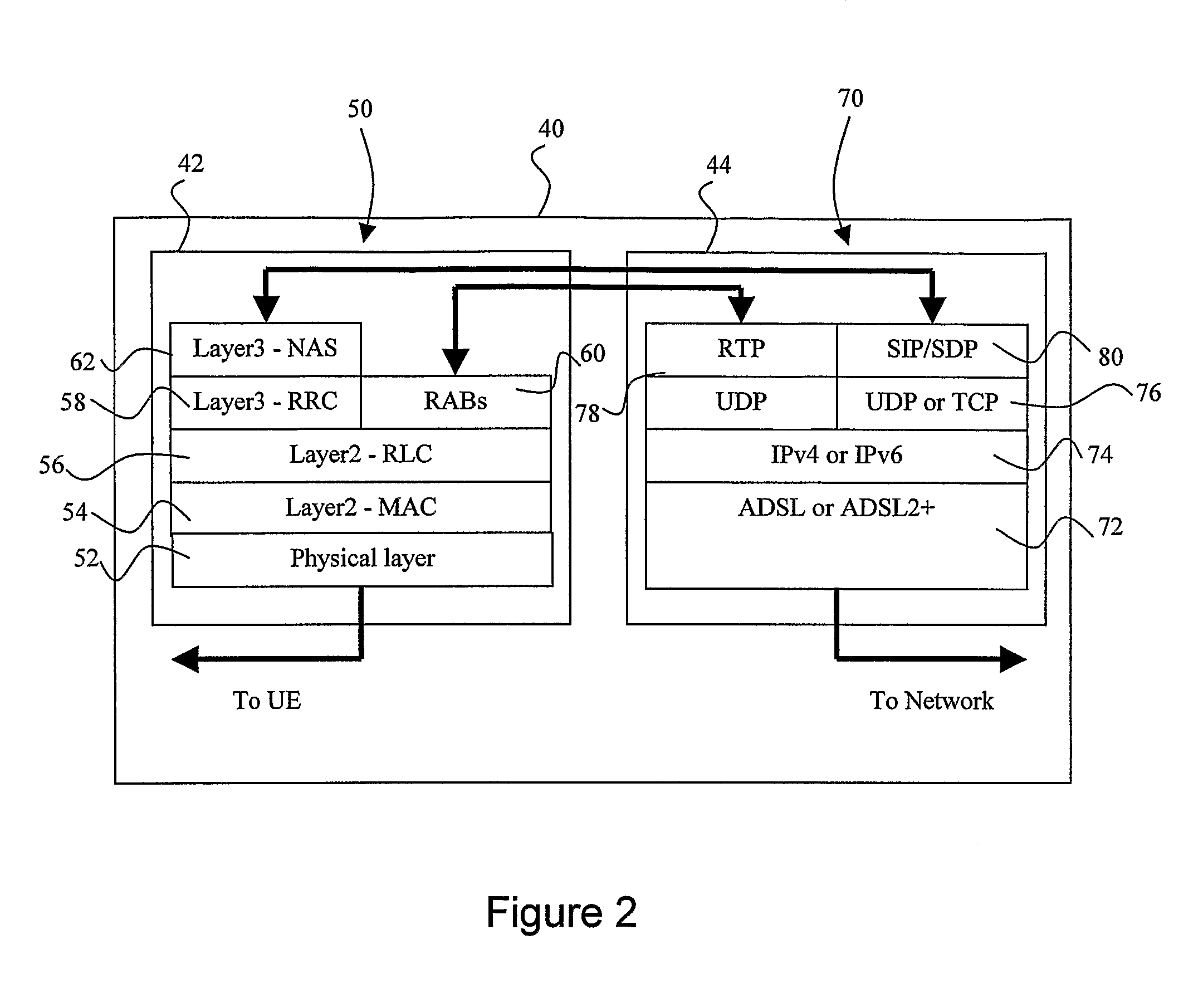

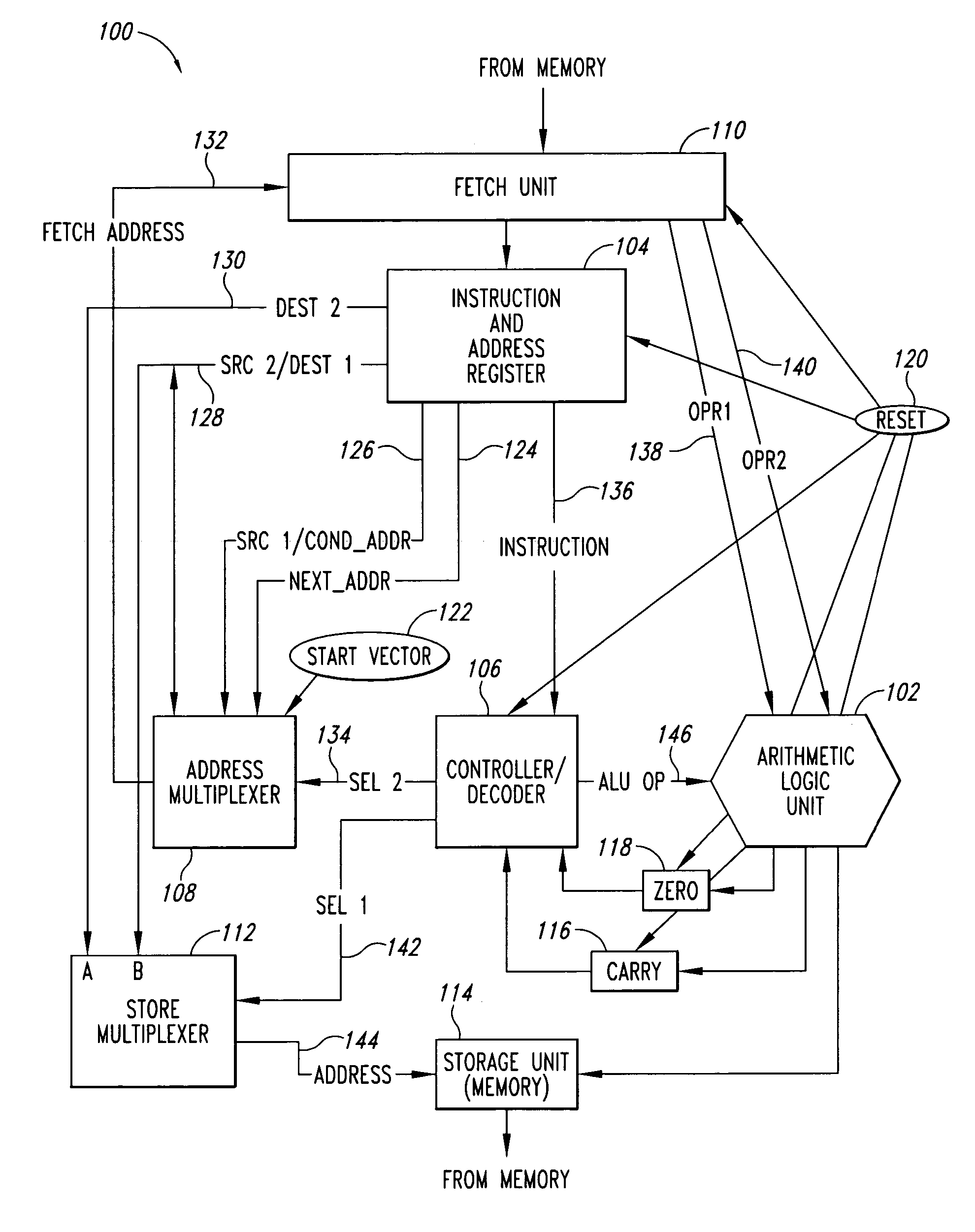

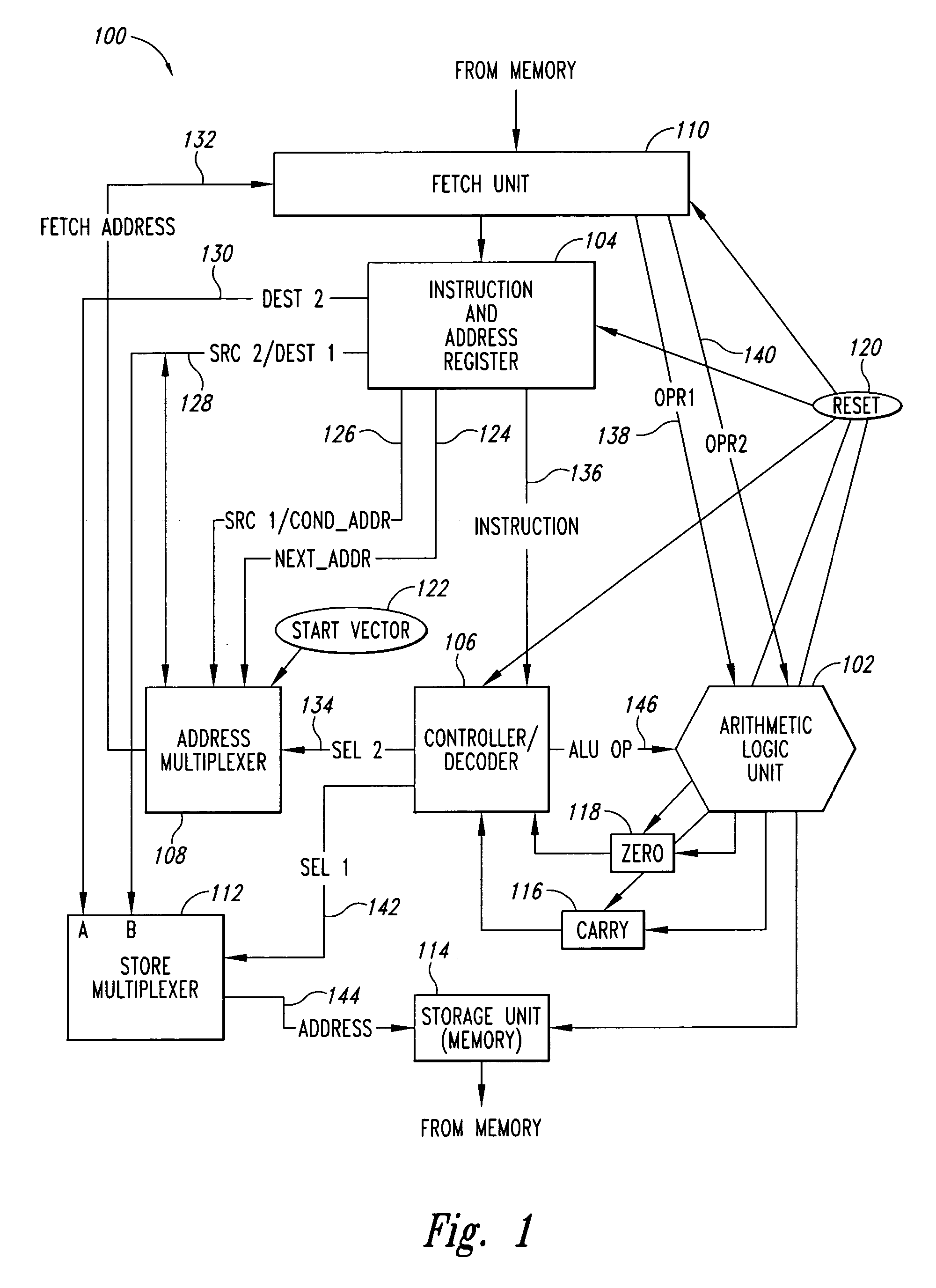

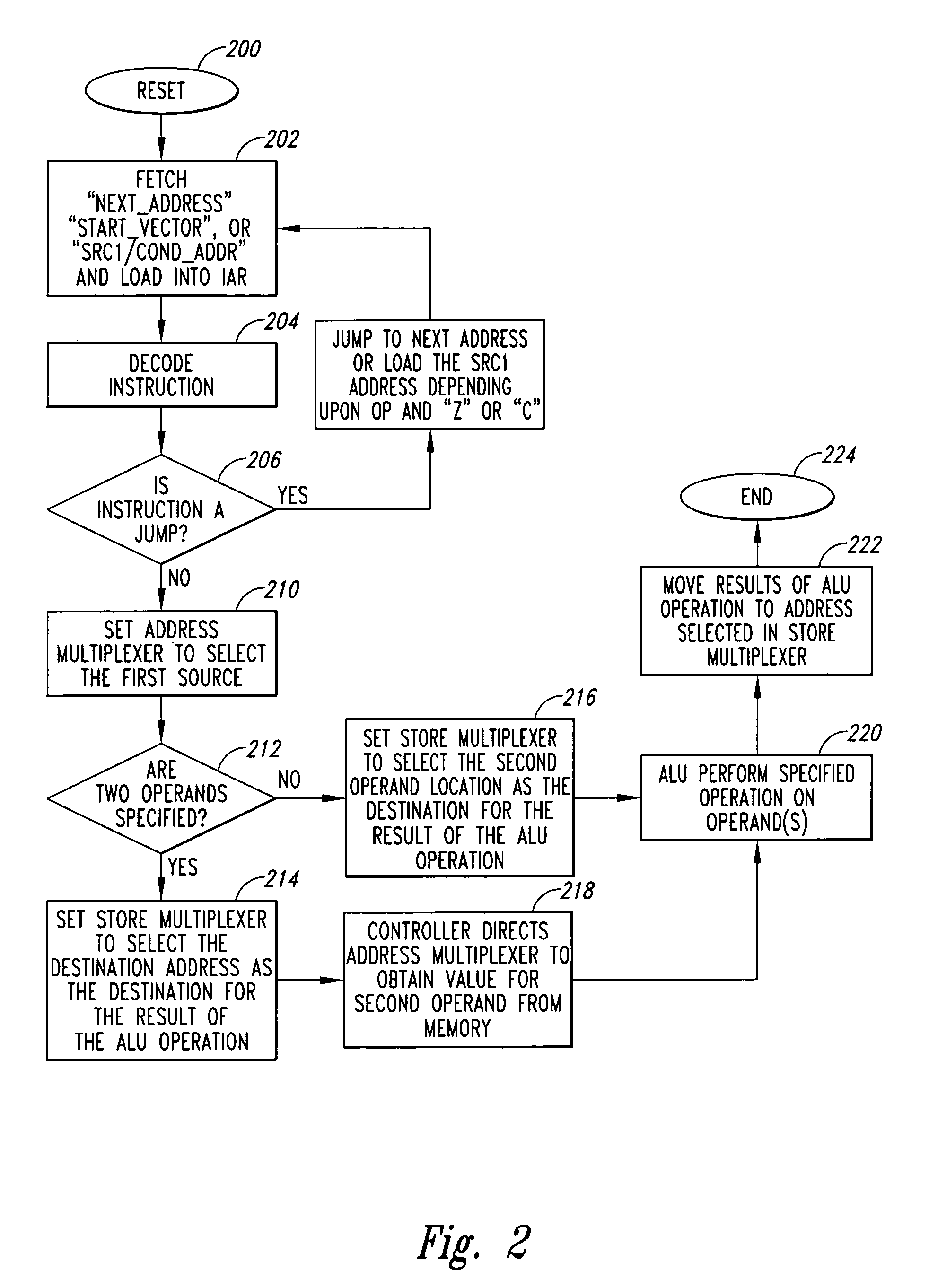

Method and system for substantially registerless processing

InactiveUS7200736B2Direct accessSimple logicInstruction analysisDigital computer detailsArithmetic logic unitData stream

A simple instruction set processor preferably utilizes six primary components: a fetch unit, and instruction and address register, a controller / decoder, an arithmetic logic unit, an address multiplexer, and a storage multiplexer. The processor utilizes a data stream containing within it the address for a subsequent instruction to be executed by the processor, thereby avoiding the need for registers of the type utilized in prior art processors. As a result, the processor utilizes a minimal number of registers to perform its operations. The processor utilizes an instruction set in which every instruction contains a JUMP to the next instruction. By utilizing JUMPs in every instruction and providing the address to which the processor is to JUMP, there is no need for address counters and register pointers. Also, extremely fast state changes are facilitated the contents of only one register identifying a next address must be saved or restored. By eliminating data registers, data streams of any width may be supported by suitably utilizing a plurality of processor connected in parallel. The elimination of multiple registers enables the processor to more easily be embedded within memory arrays themselves. The processor preferably utilizes six primary components: a fetch unit, and instruction and address register, a controller / decoder, an arithmetic logic unit, an address multiplexer, and a storage multiplexer.

Owner:MICRON TECH INC

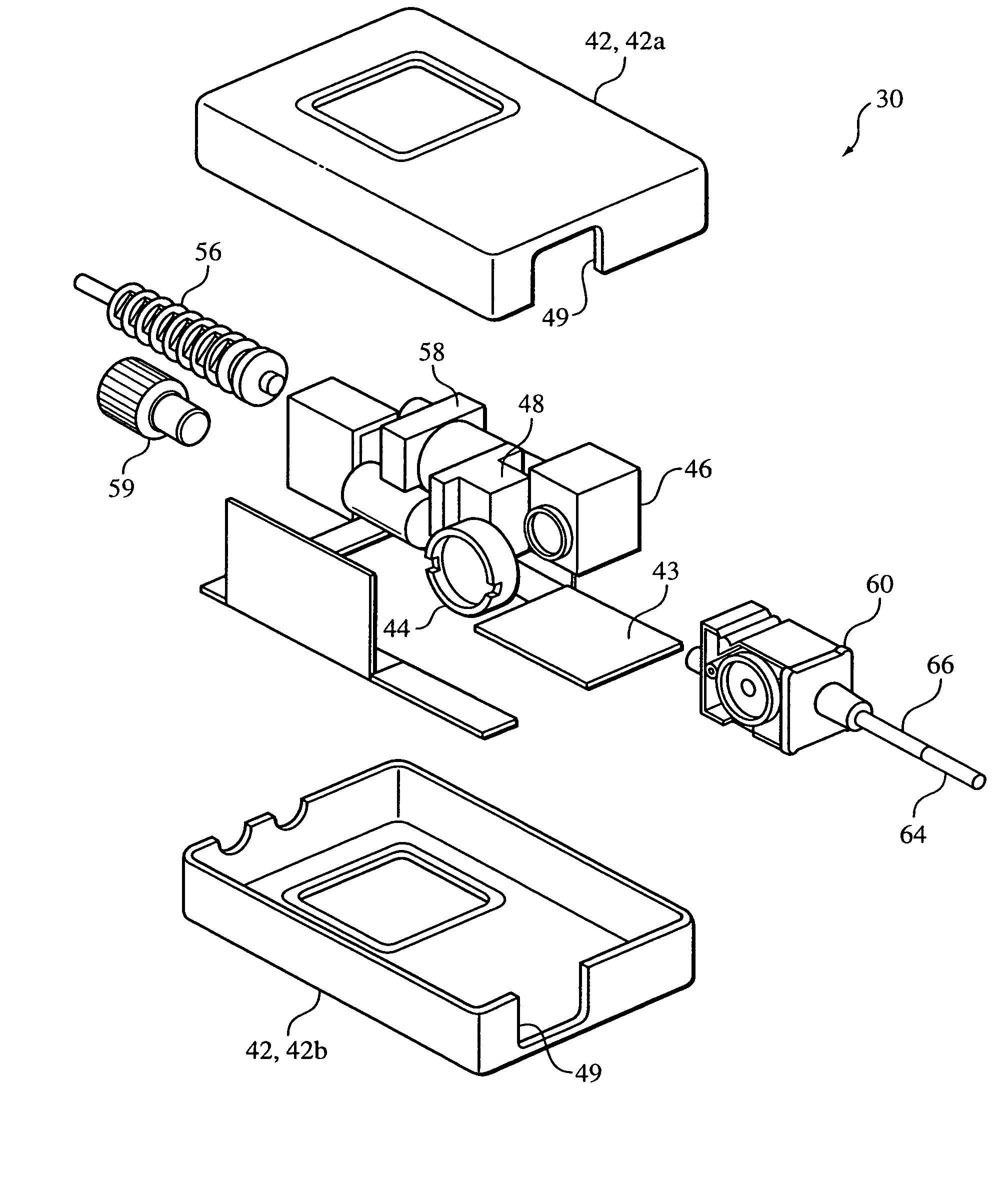

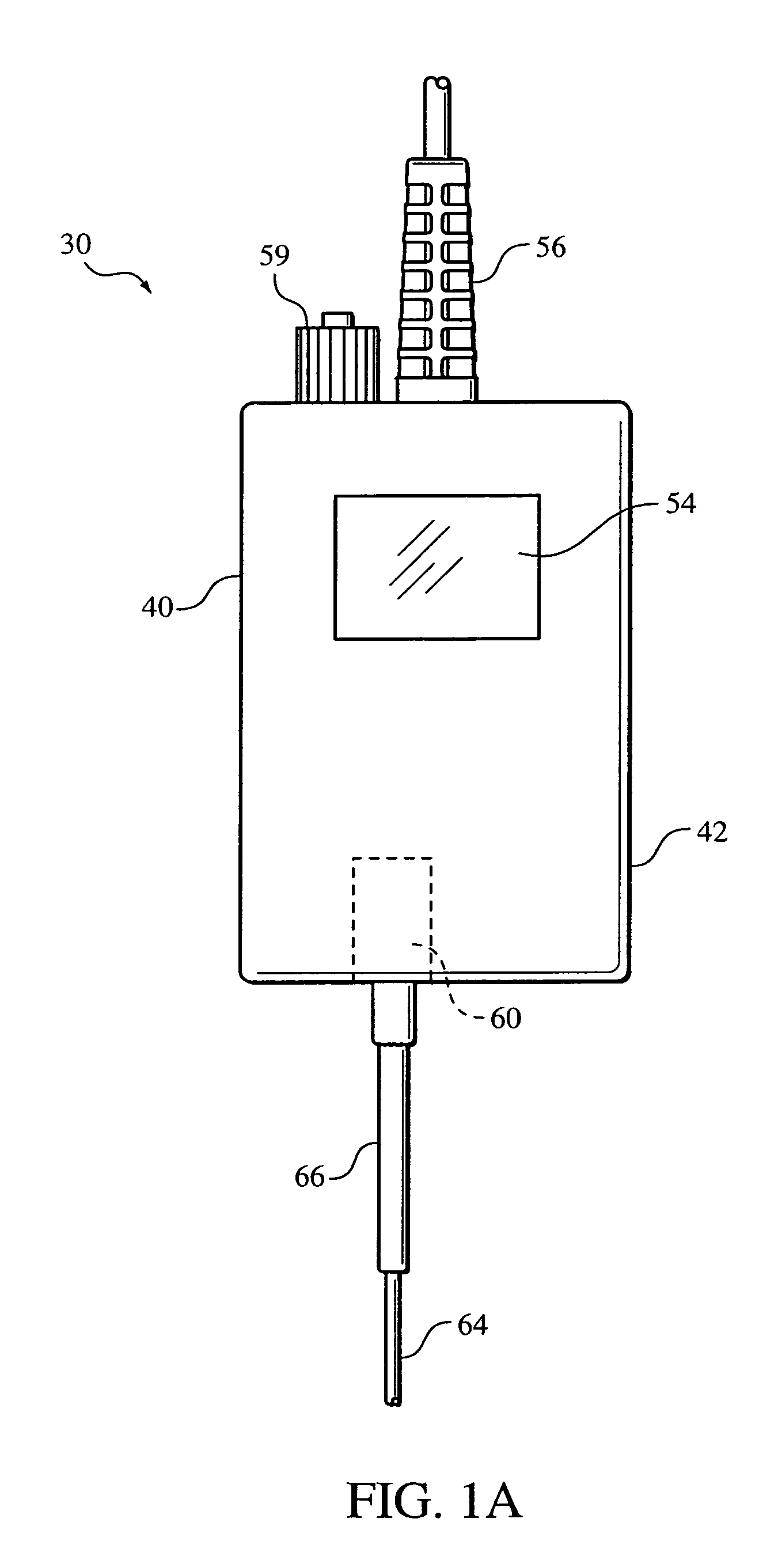

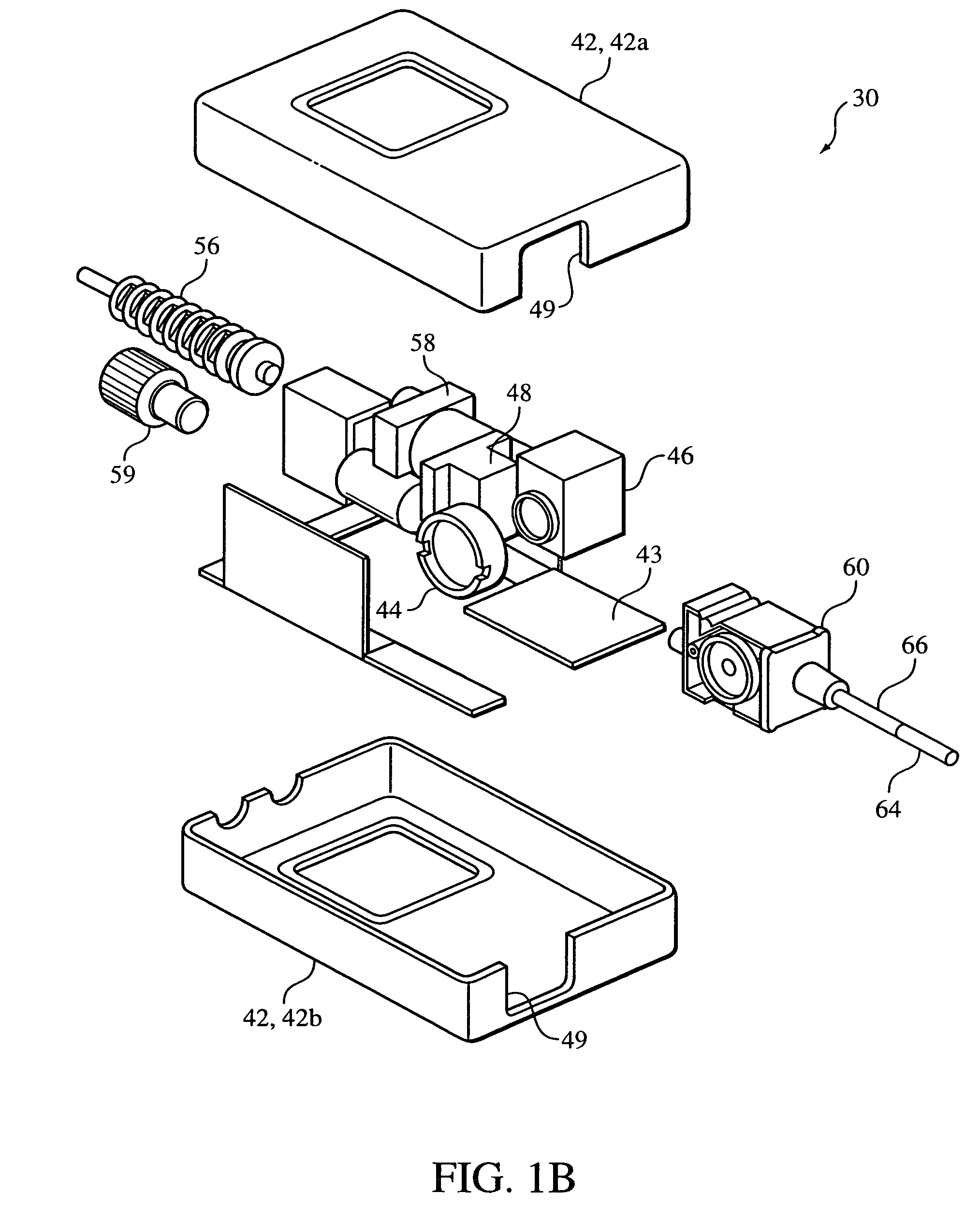

Sidestream gas sampling system with detachable sample cell

InactiveUS7341563B2Minimizes need for preventiveOvercomes shortcomingWithdrawing sample devicesTransmissivity measurementsChemical physicsProduct gas

A sidestream sampling system includes a sidestream gas measurement assembly and a sample cell configured to be assembled therewith. The sidestream gas measurement assembly includes a receptacle for removably receiving at least a portion of the sample cell. The sample cell is coupled to a sampling tube that is configured to communicate with an airway of an individual. When the sample cell is assembled with the sidestream gas measurement assembly, a window of the sample cell is oriented toward a corresponding source and / or detector of the sidestream gas measurement assembly to facilitate monitoring of an amount of at least one gas or vaporized material in an individual's respiration.

Owner:RIC INVESTMENTS LLC

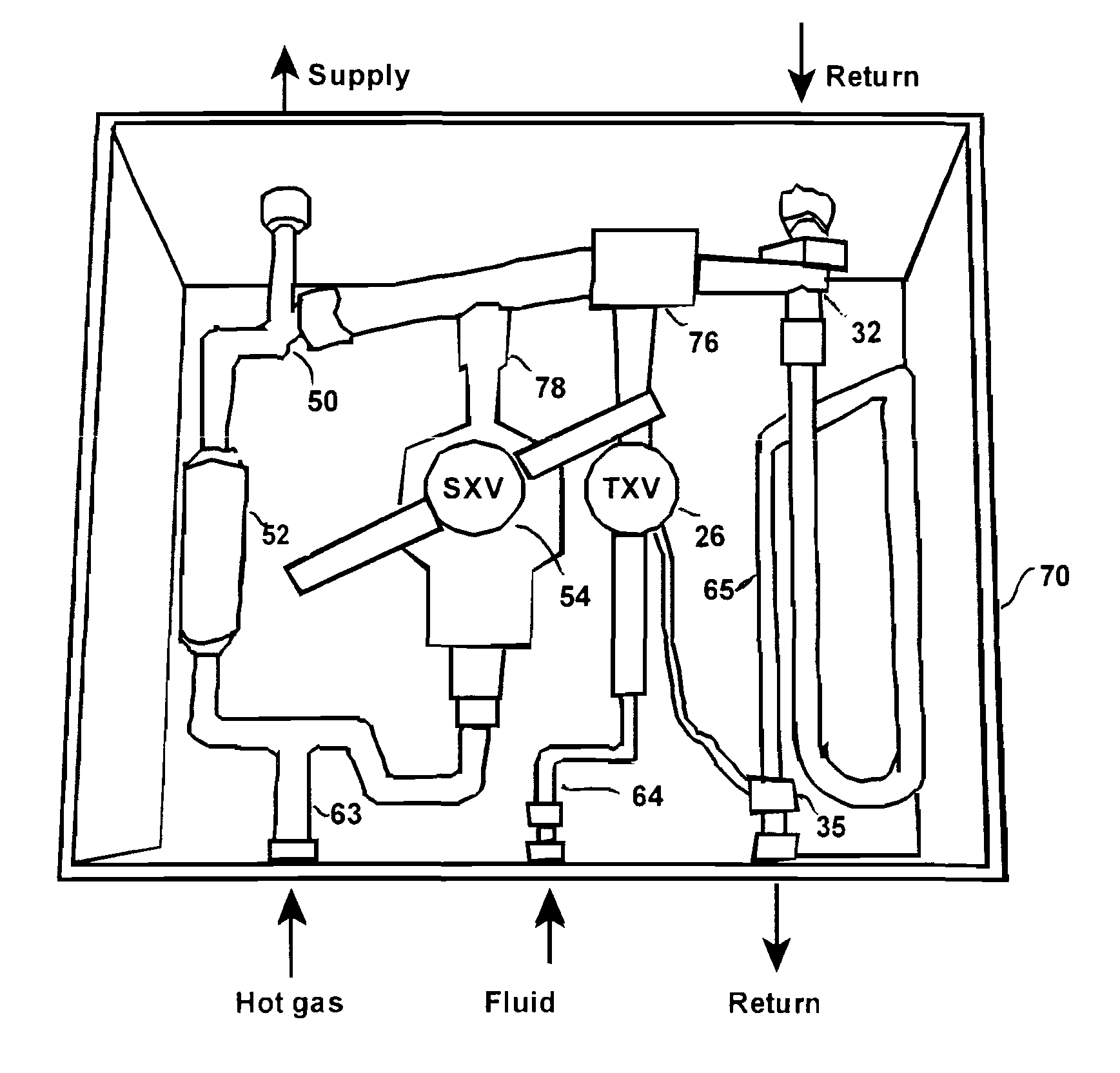

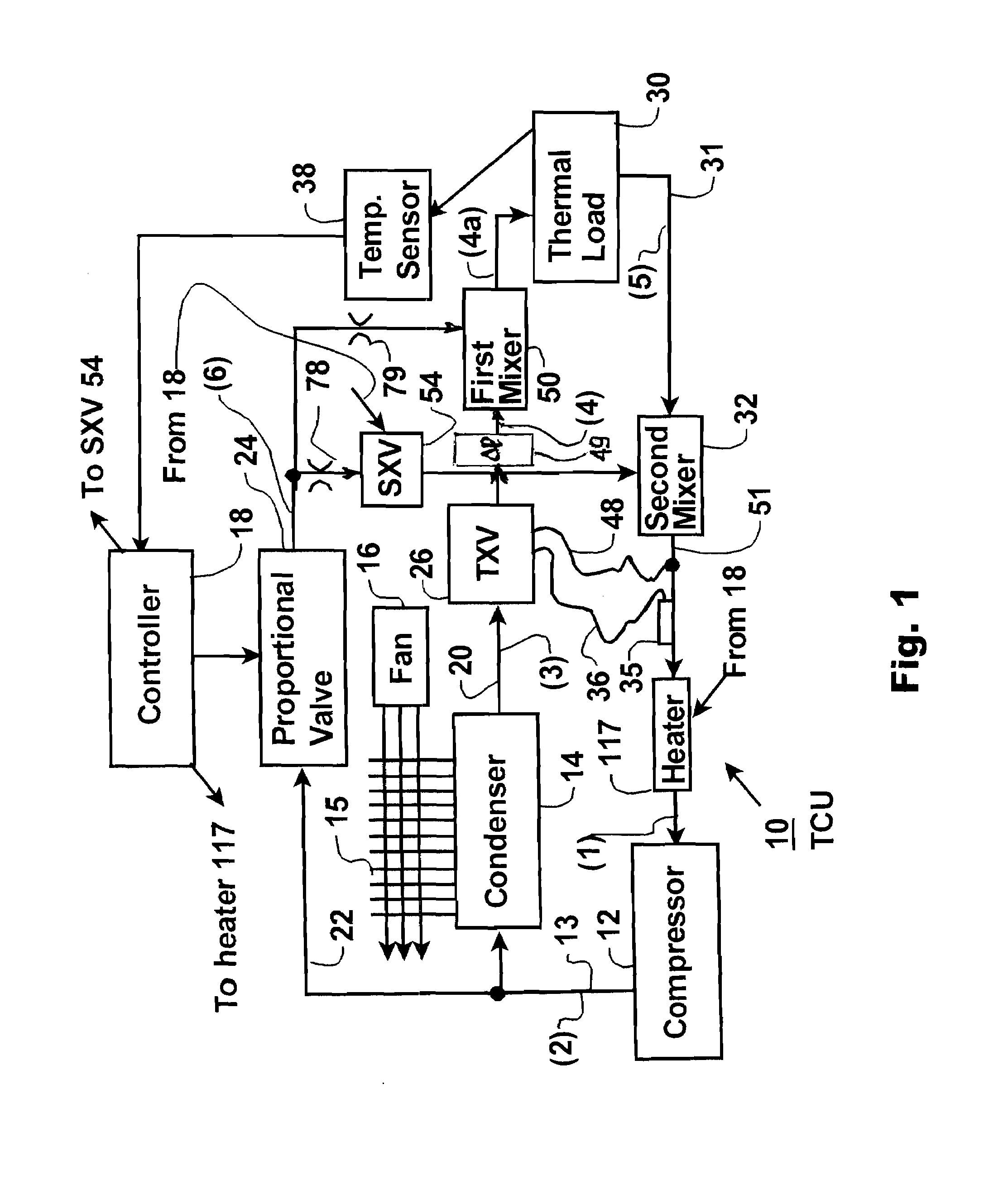

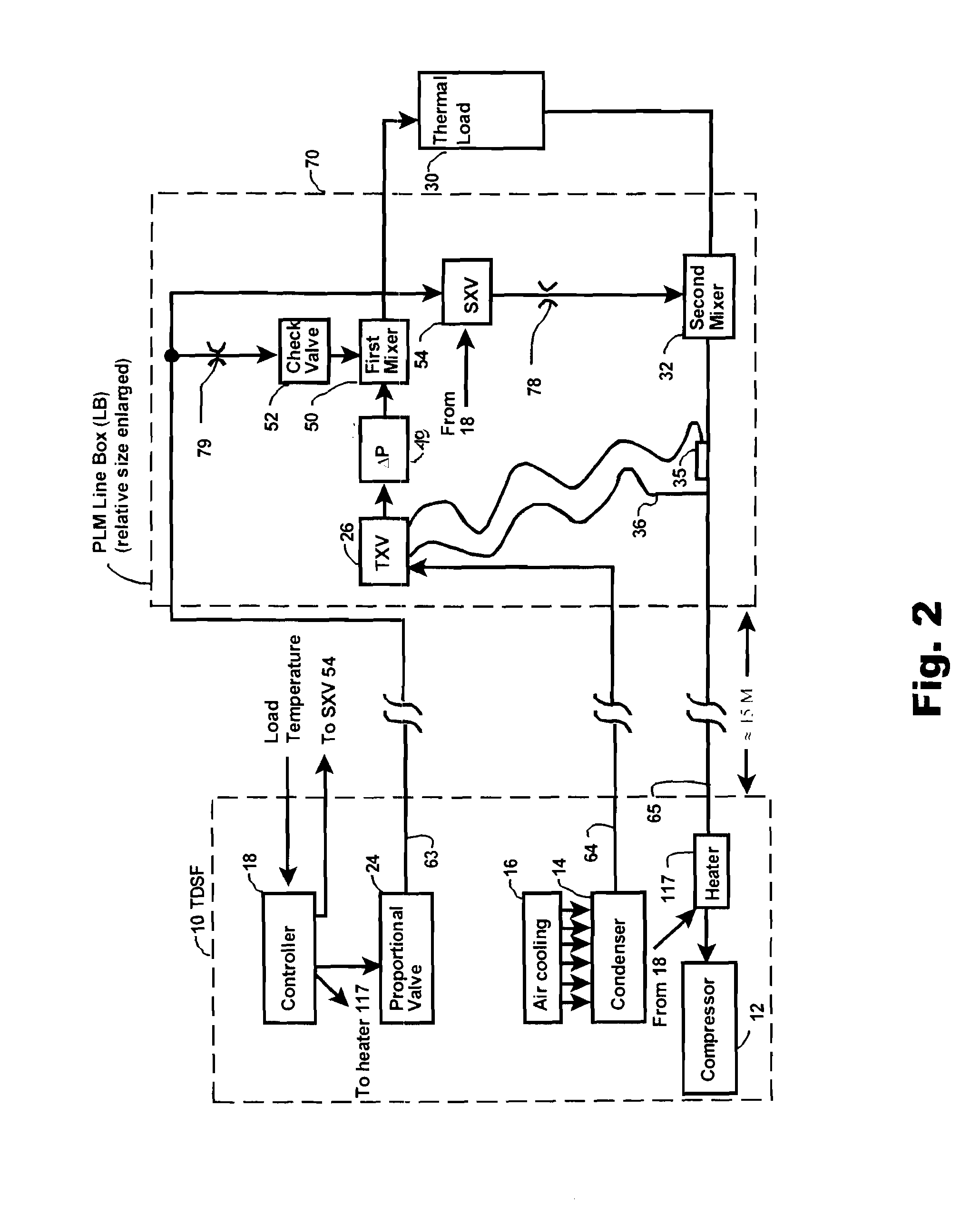

Method and apparatus for thermal exchange with two-phase media

ActiveUS20100076611A1Strict controlHigh heat transfer coefficientControlling ratio of multiple fluid flowsTemperatue controlTemperature controlLine tubing

In a temperature control system using a controlled mix of high temperature pressurized gas and a cooled vapor / liquid flow of the same medium to cool a thermal load to a target temperature in a high energy environment, particular advantages are obtained in precision and efficiency by passing at least a substantial percentage of the cooled vapor / liquid flow through the thermal load directly, and thereafter mixing the output with a portion of the pressurized gas flow. This “post load mixing” approach increases the thermal transfer coefficient, improves control and facilities target temperature change. Ad added mixing between the cooled expanded flow and a lesser flow of pressurized gas also is used prior to the input to the thermal load. A further feature, termed a remote “Line Box”, enables transport of the separate flows of the two phase medium through a substantial spacing from pressurizing and condensing units without undesired liquefaction in the transport lines.

Owner:ADVANCED THERMAL SCI