Patents

Literature

38 results about "Time base generator" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

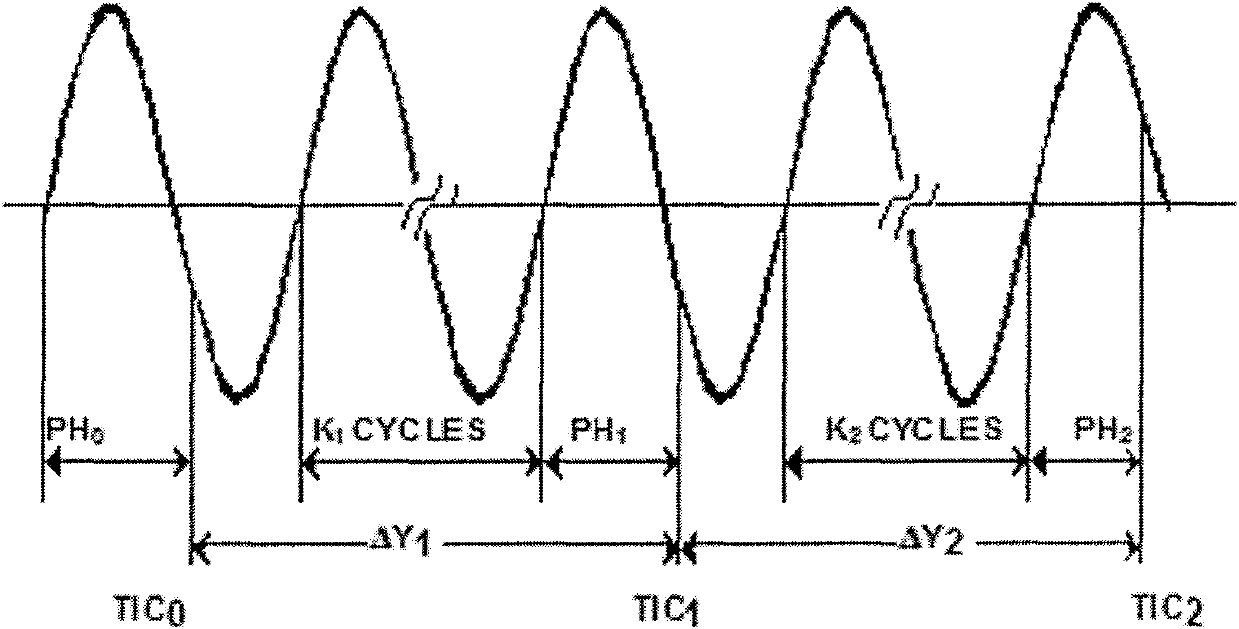

A time base generators, or timebase, is a special type of function generator, an electronic circuit that generates a varying voltage to produce a particular waveform. Time base generators produce very high frequency sawtooth waves specifically designed to deflect the beam in cathode ray tube (CRT) smoothly across the face of the tube and then return it to its starting position.

Integrated gigabit ethernet PCI-X controller

InactiveUS20060143344A1Reduce data latencyEnergy efficient ICTVolume/mass flow measurementTransceiverBus interface

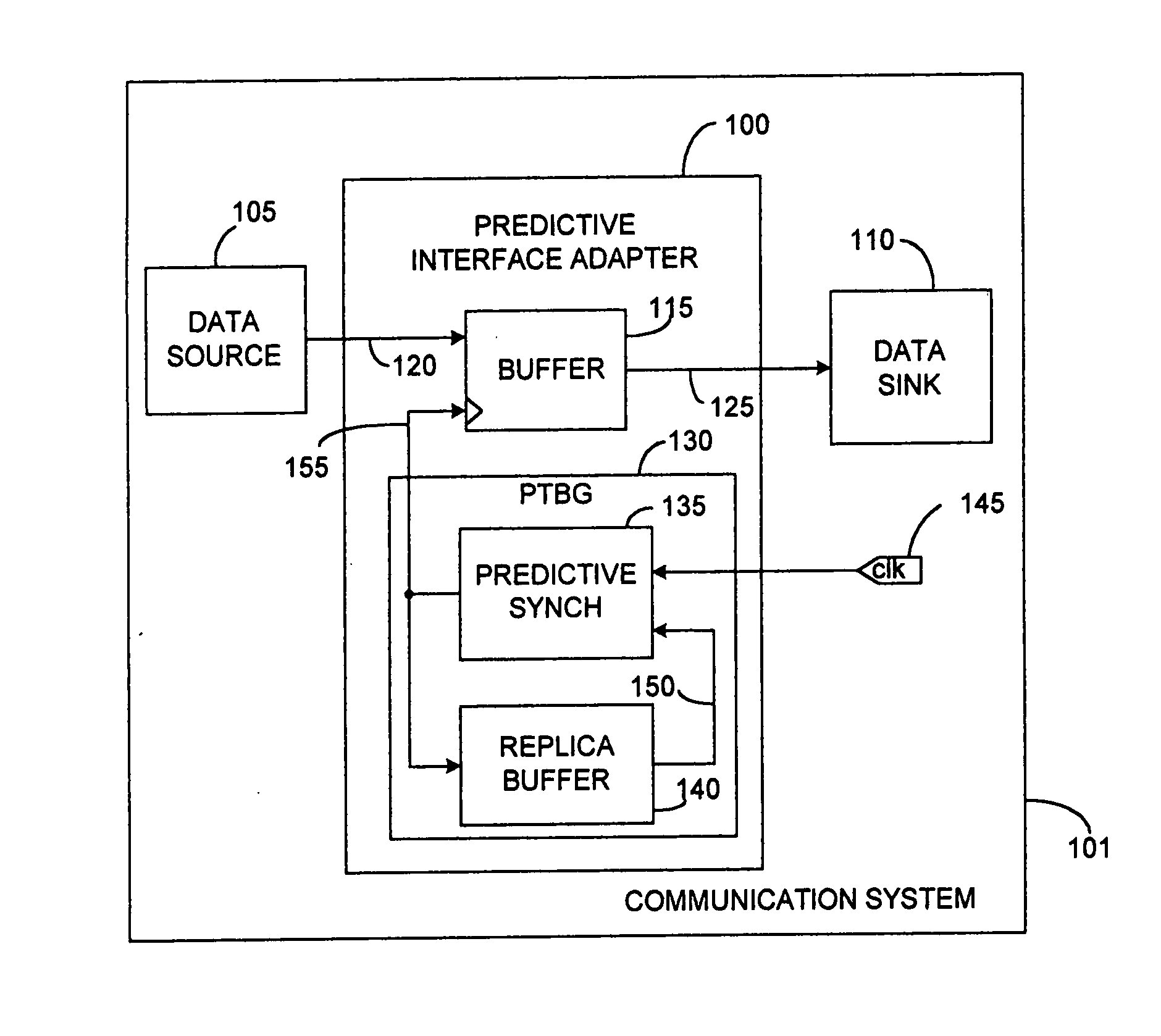

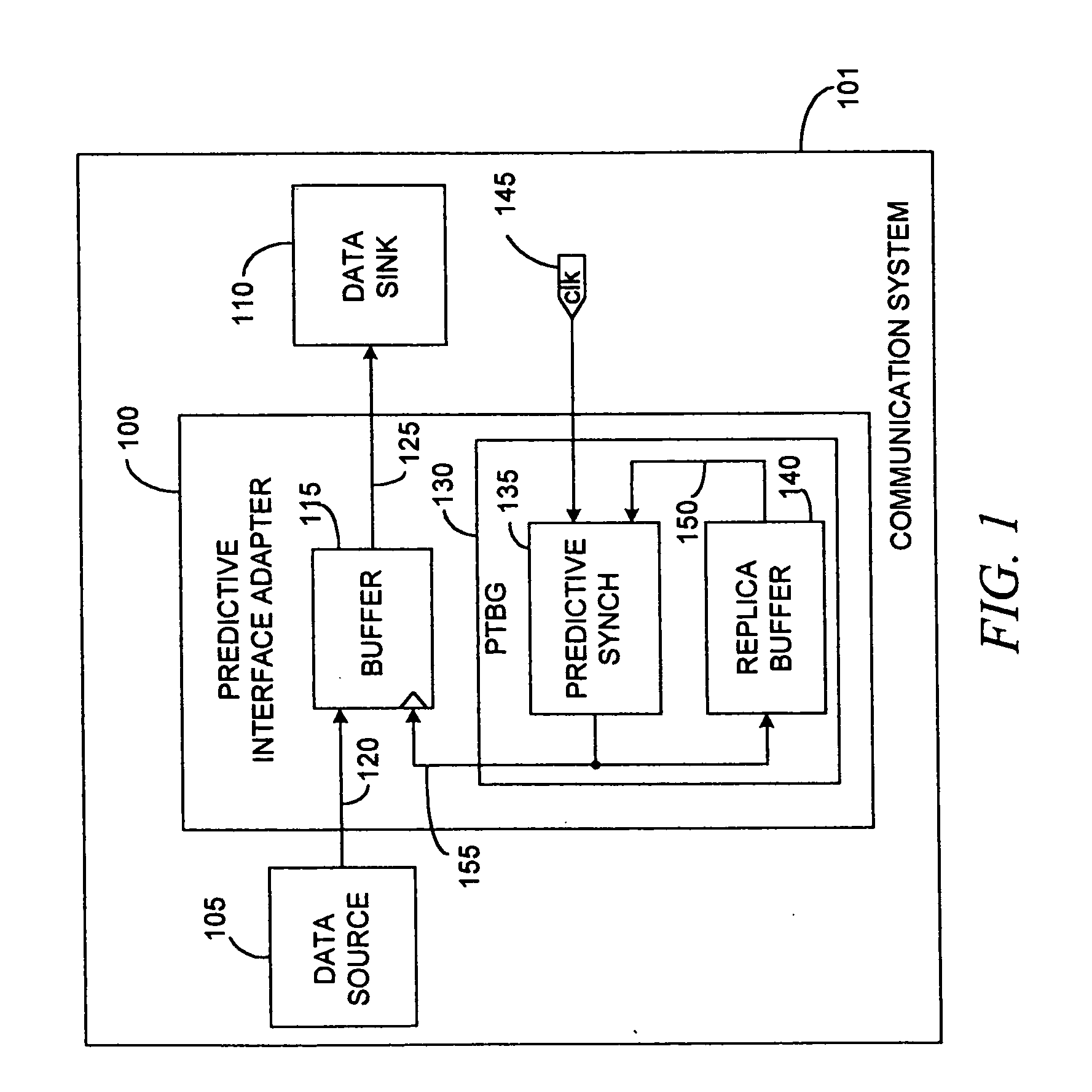

A network controller having a multiprotocol bus interface adapter coupled between a communication network and a computer bus, the adapter including a predictive time base generator; and a management bus controller adapted to monitor and manage preselected components coupled with one of the communication network and the computer bus. The management bus controller is adapted to employ an Alert Standard Format (ASF) specification protocol, a System Management Bus (SMBus) specification protocol, an Intelligent Platform Management Interface (IPMI) specification protocol, a Simple Network Management Protocol (SNMP), or a combination thereof. The network controller also includes a 10 / 100 / 1000BASE-T IEEE Std. 802.3-compliant transceiver and media access controller coupled with the communication network; a buffer memory coupled with the MAC, wherein the buffer memory includes one of a packet buffer memory, a frame buffer memory, a queue memory, and a combination thereof; and a transmit CPU and a receive CPU coupled with the multiprotocol bus interface adapter and the management bus controller. The network controller can be a single-chip VLSI device in an 0.18 micron CMOS VLSI implementation.

Owner:AVAGO TECH INT SALES PTE LTD

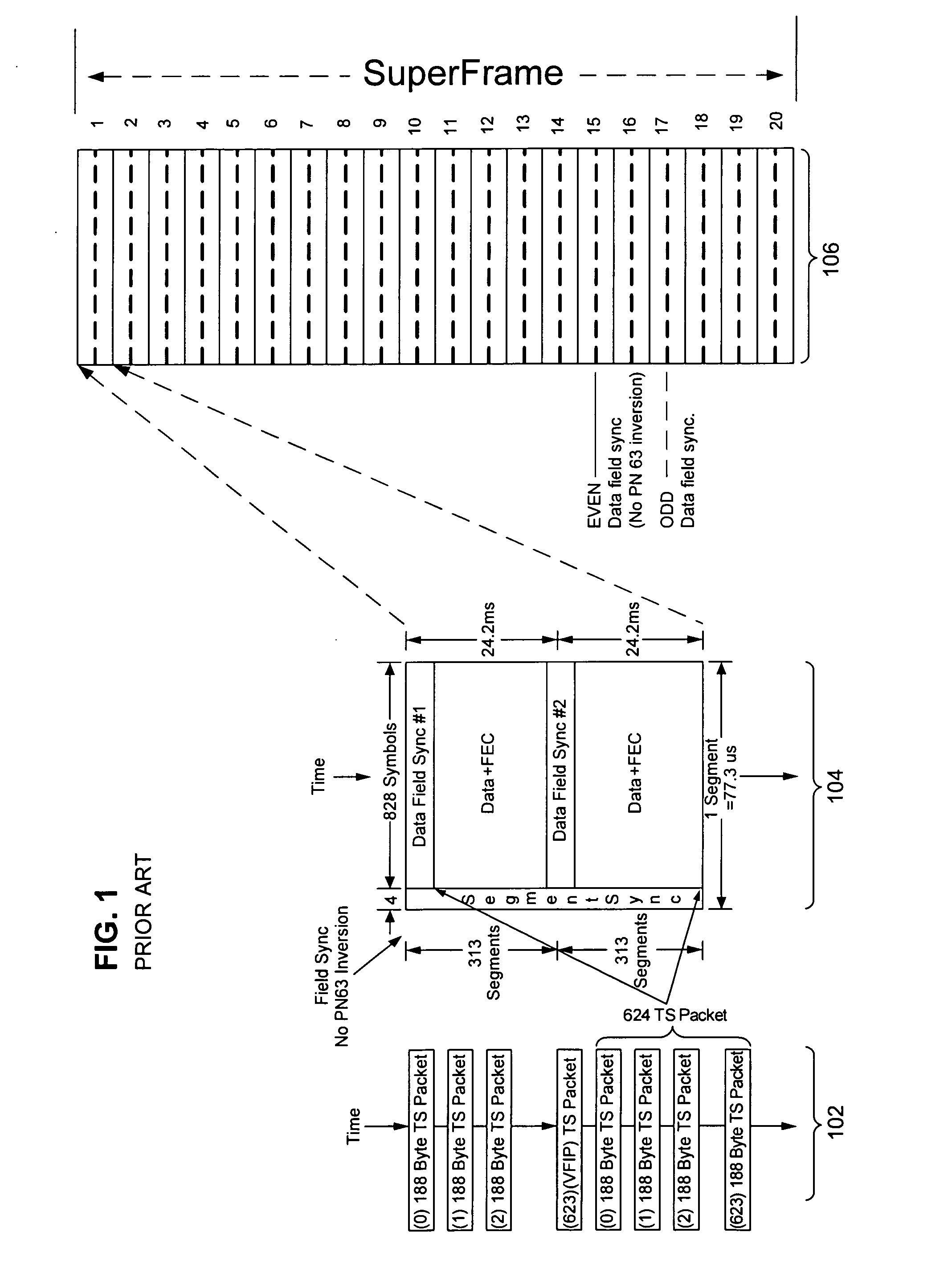

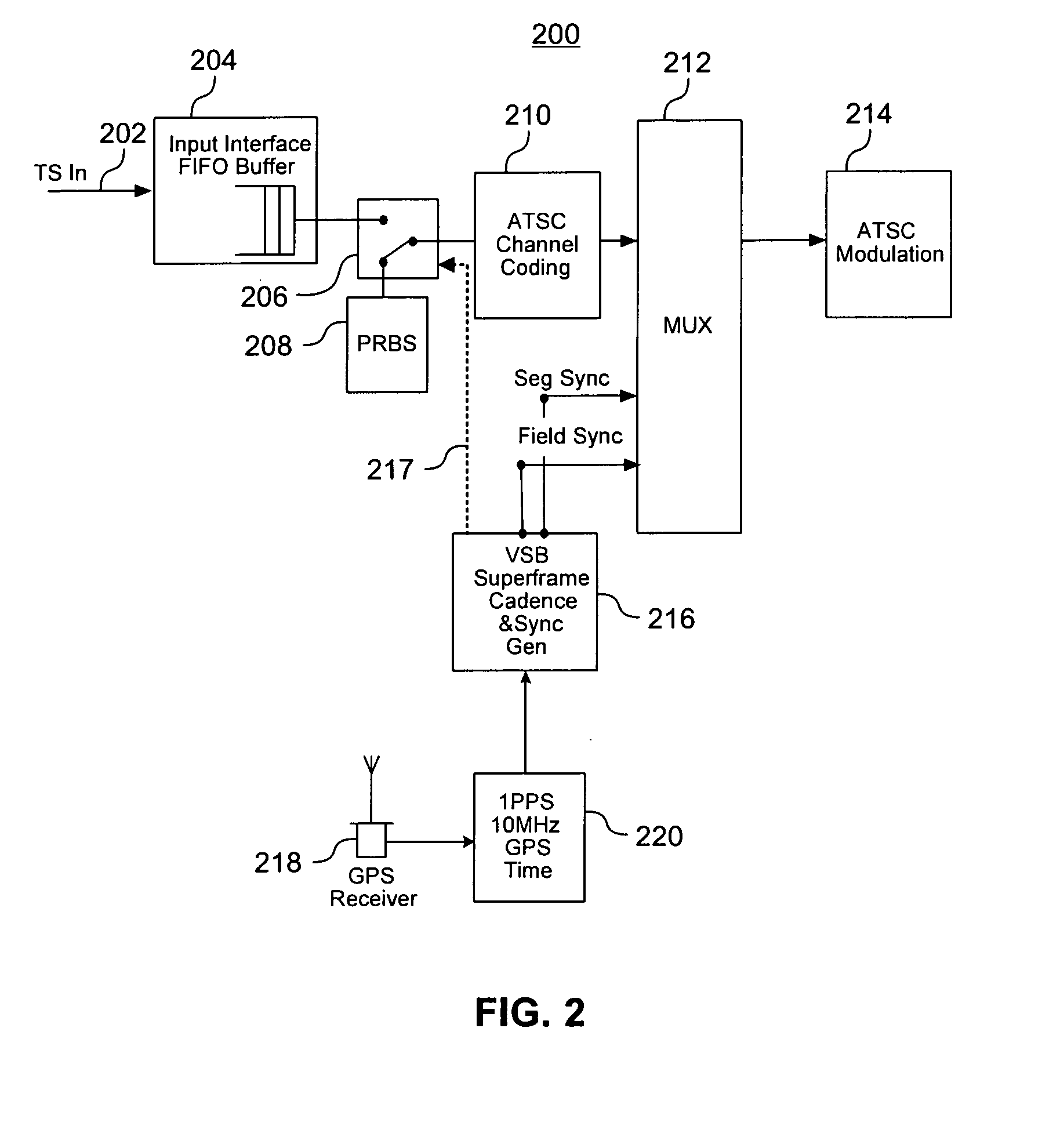

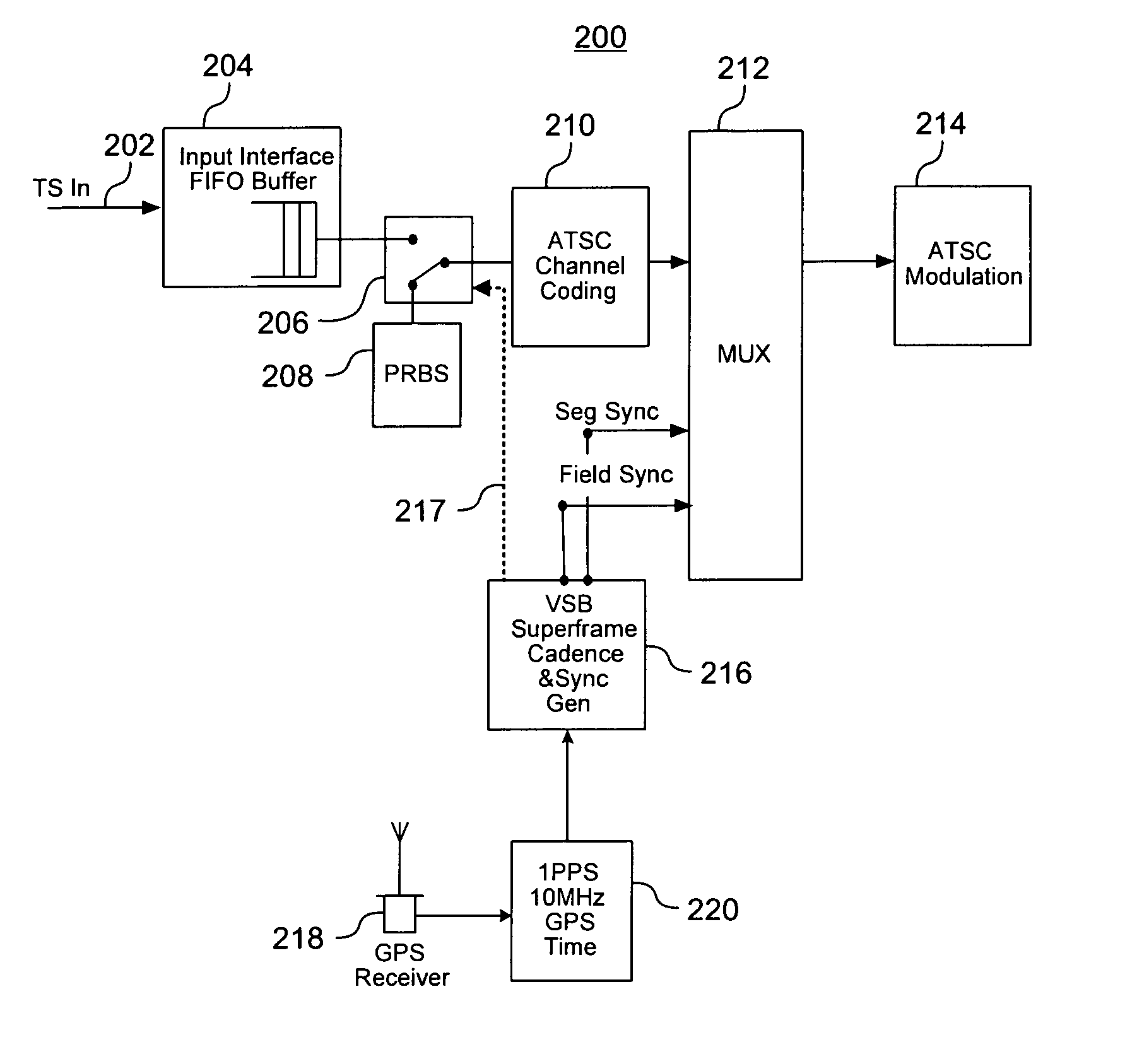

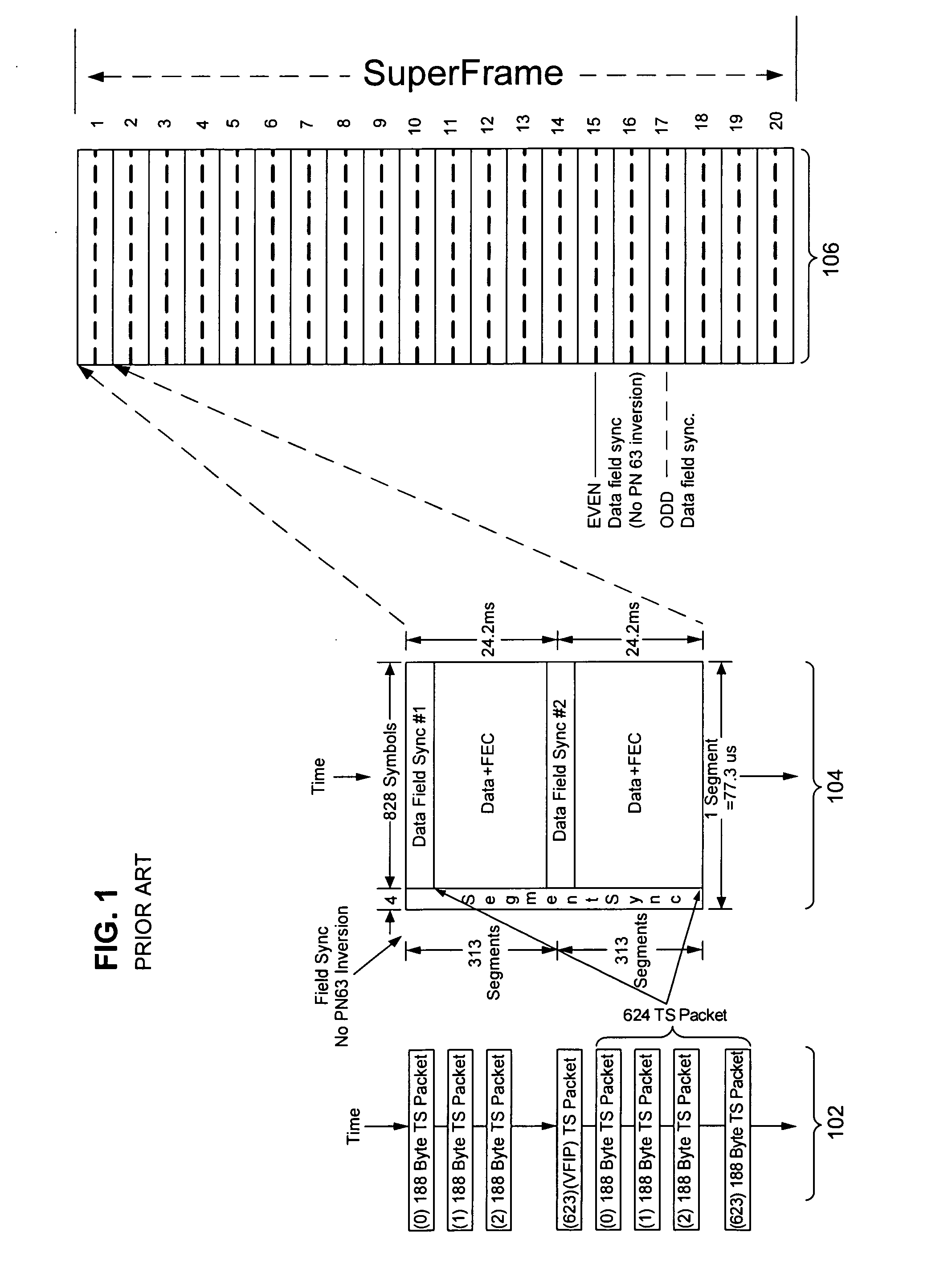

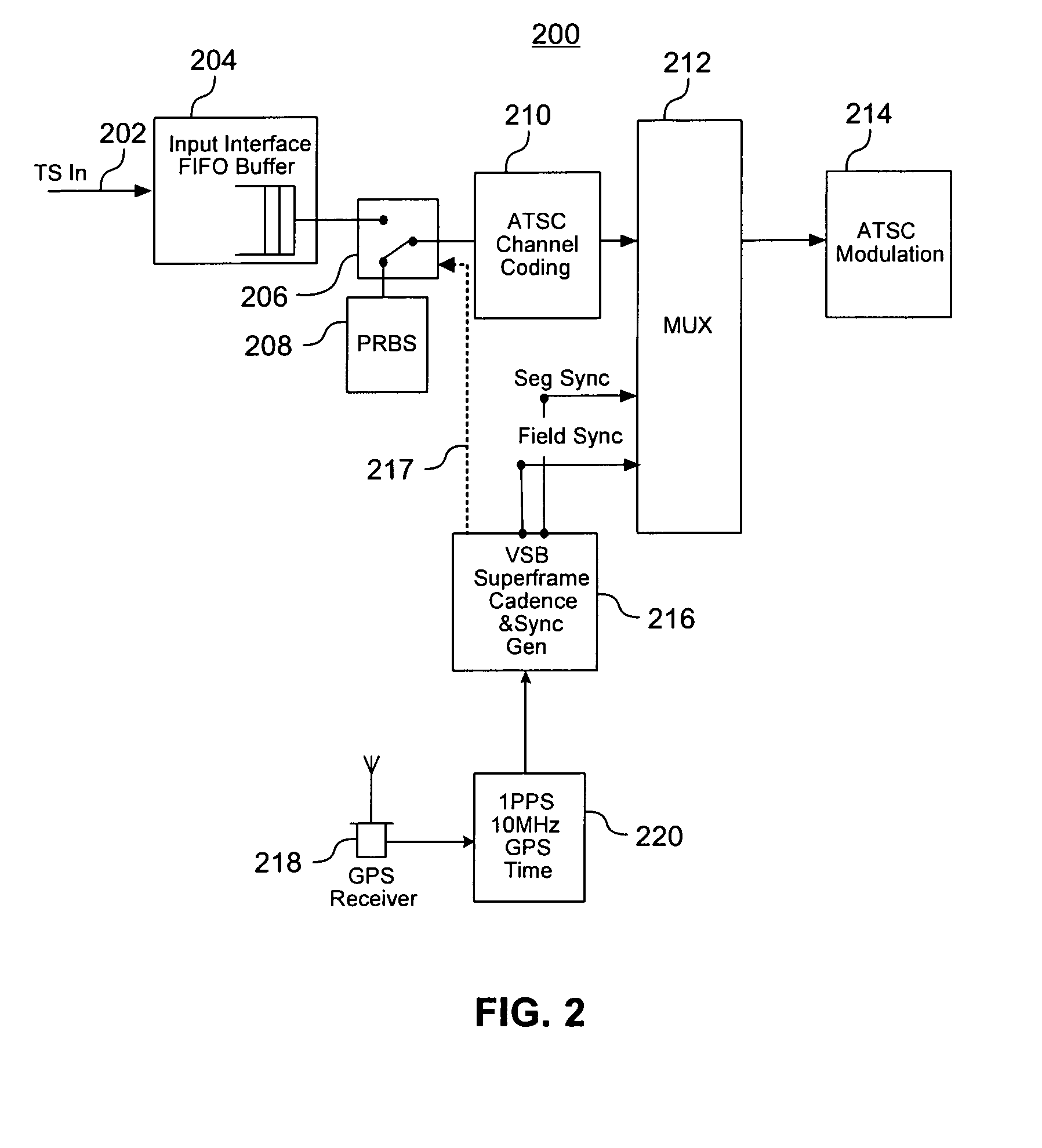

Systems, apparatus, methods and computer program products for providing ATSC interoperability

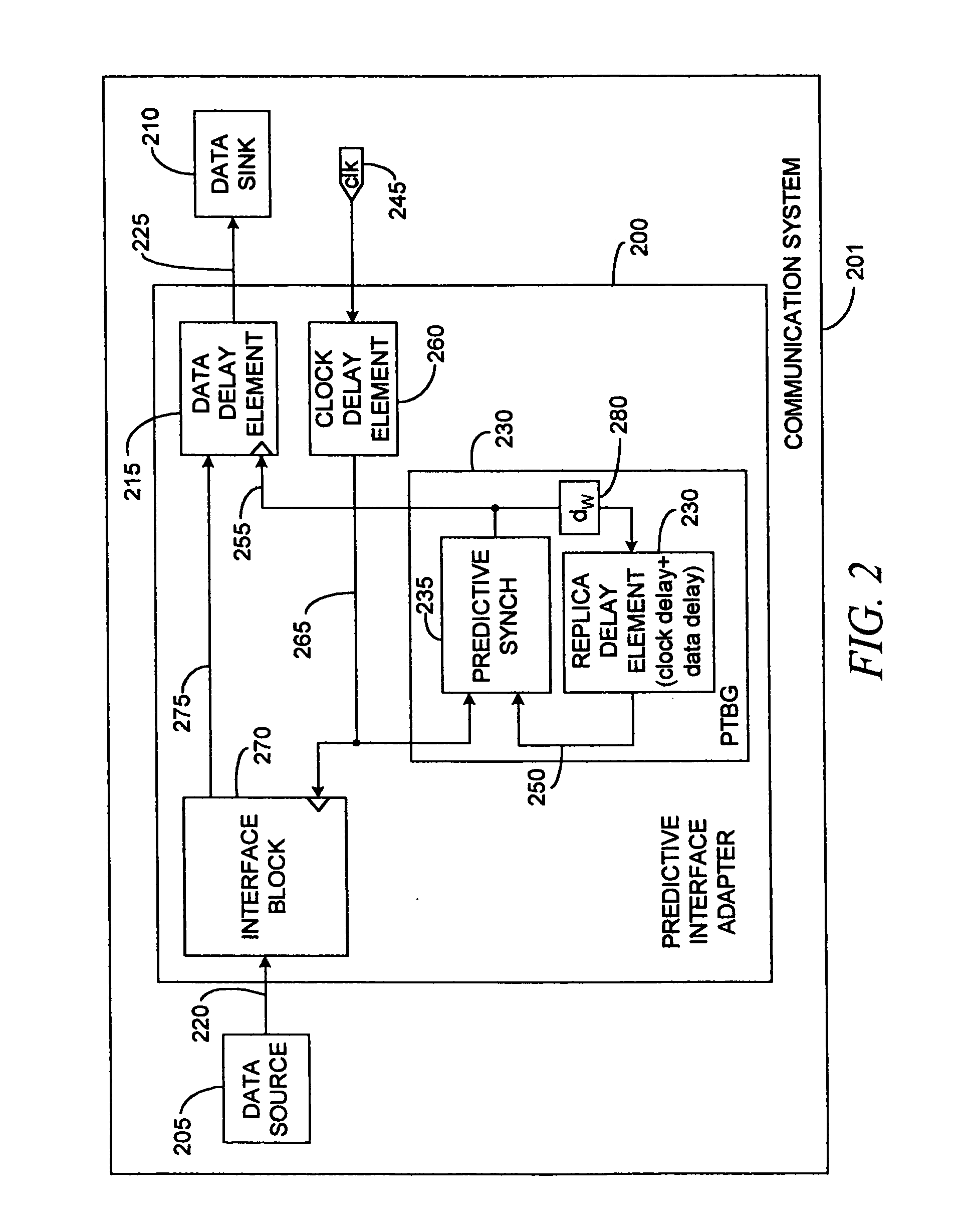

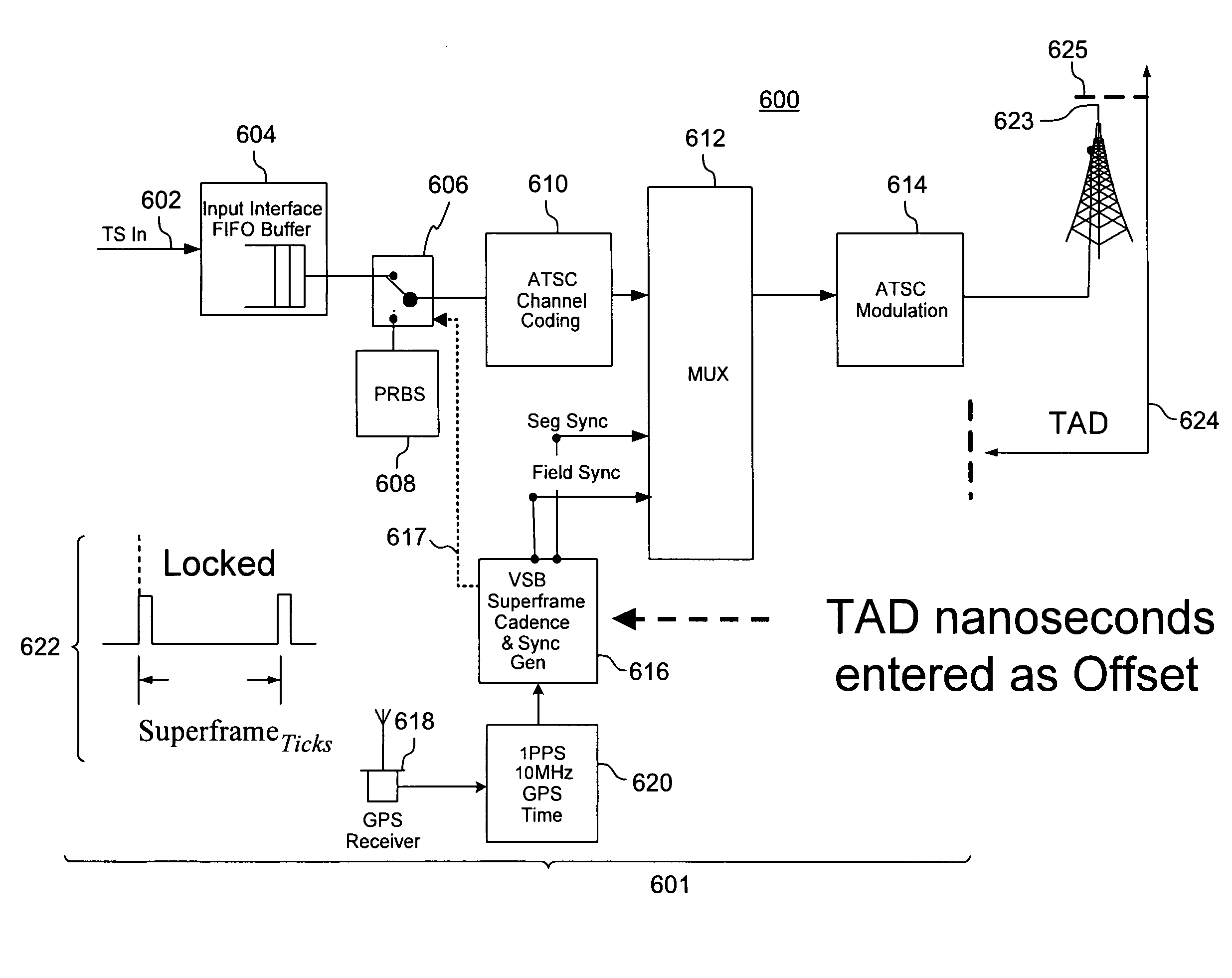

Systems, apparatus, methods and computer program products are provided for causing a dataframe to be emitted at an air interface of an antenna. A memory stores a transmission to antenna delay value (TAD). An offset calculator calculates an offset value based on an epoch of a global timebase generator and the transmission to antenna delay value (TAD). An interface controller in communication with the offset calculator communicates a segment synchronization signal and a field synchronization signal based on the offset value.

Owner:ROHDE & SCHWARZ GMBH & CO KG

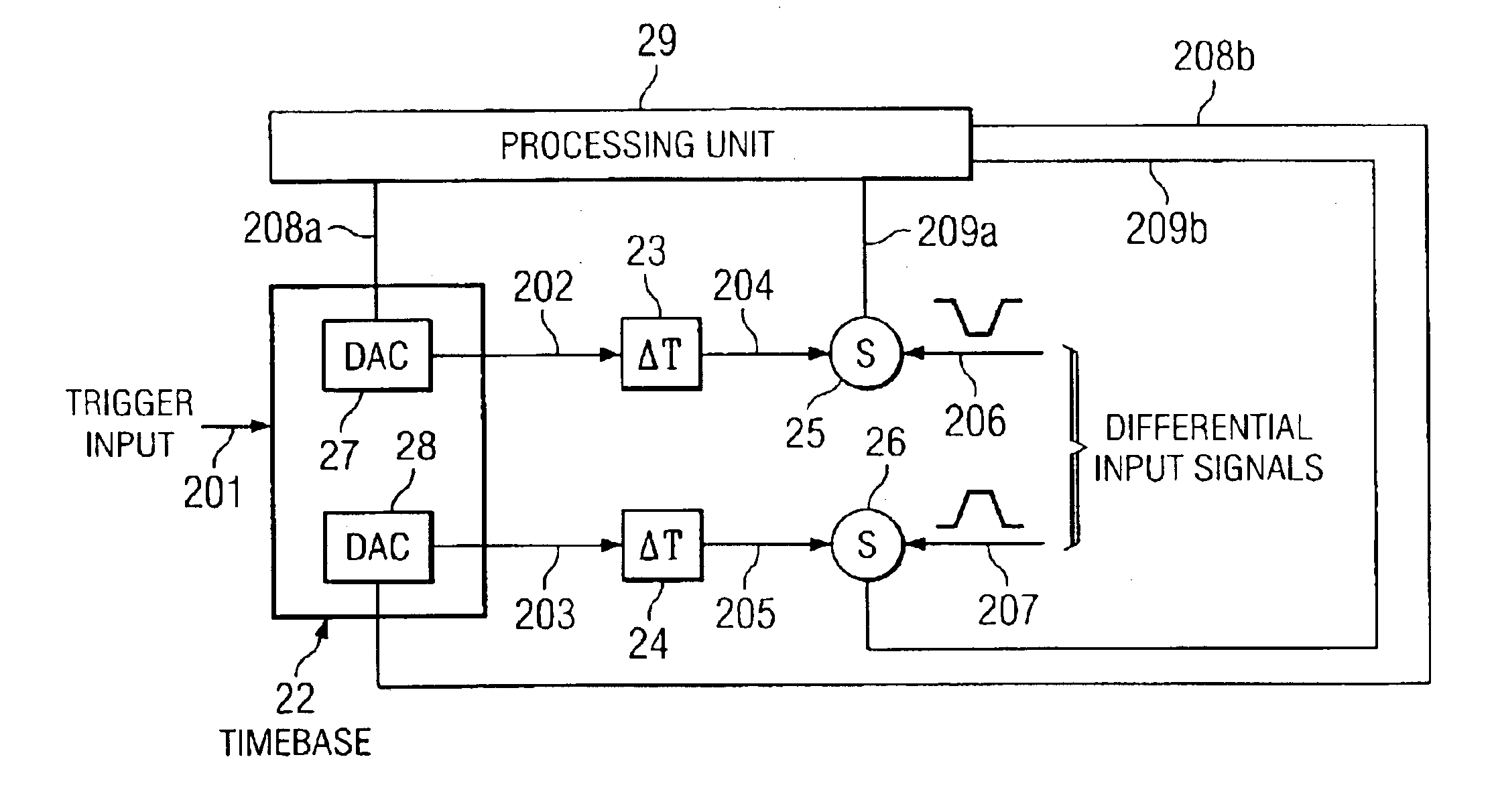

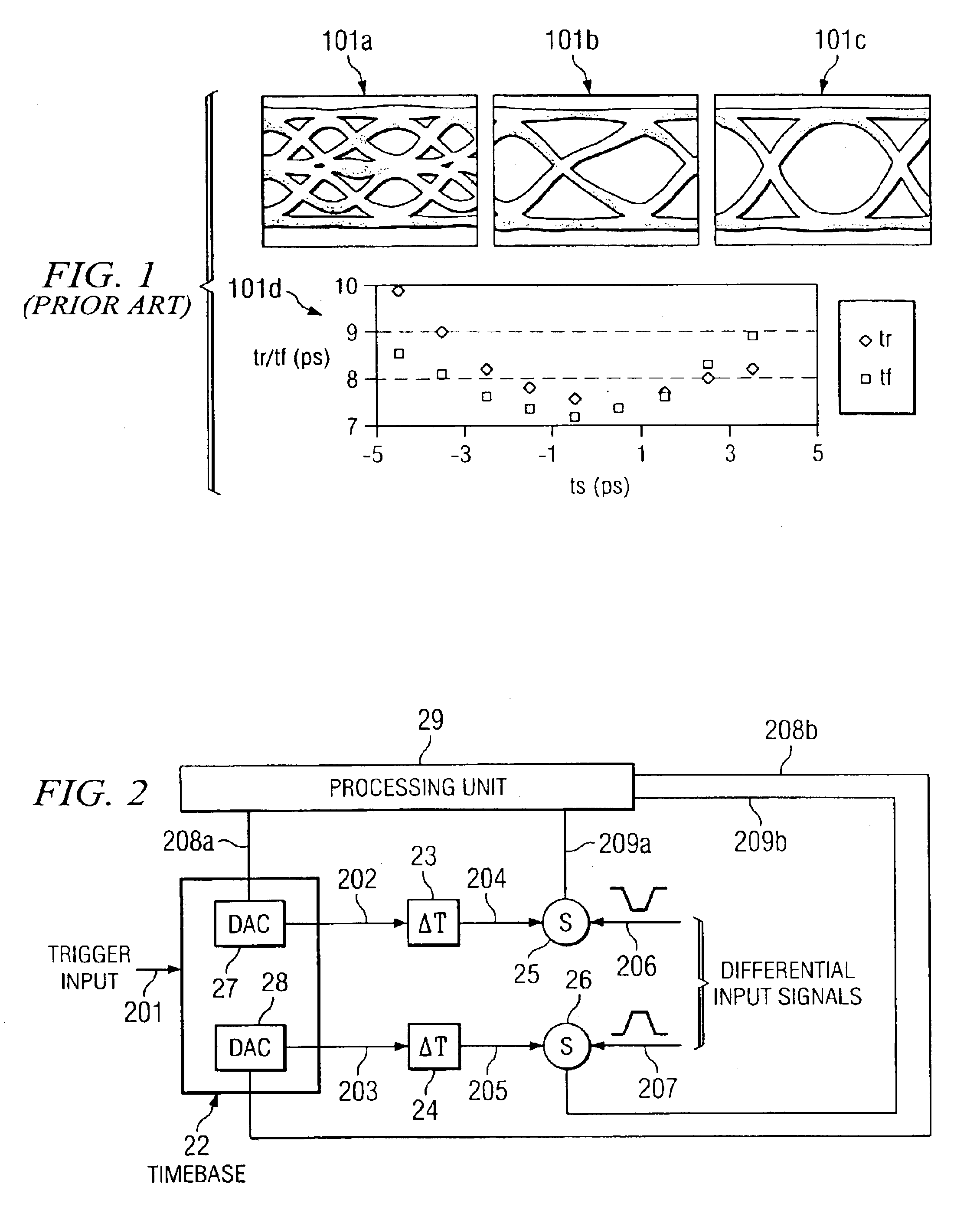

Auto skew alignment of high-speed differential eye diagrams

InactiveUS6909980B2Digital variable displayChannel dividing arrangementsAlgorithmDifferential signaling

Auto-skew alignment of high-speed eye diagrams of a pair of differential signals defines a figure of merit containing time integrals of mathematical functions dependent on magnitudes of the differential signals and related skew, then calculating an optimized skew value that minimizes the figure of merit. Optimally integrals are performed over a random time interval including at least two consecutive bit periods of the differential signals. Calculations include coarse search for optimum skew and fine search using an adaptively decreasing fine skew interval. Data acquisition and control hardware includes paired independent skew circuits and paired sampling circuits coupled to a timebase generator and a processing unit, which performs calculations in accordance with an auto-deskew algorithm. The accuracy of the optimized skew value is limited only by hardware skew resolution which in present implementations is less than or equal to one picosecond.

Owner:AGILENT TECH INC

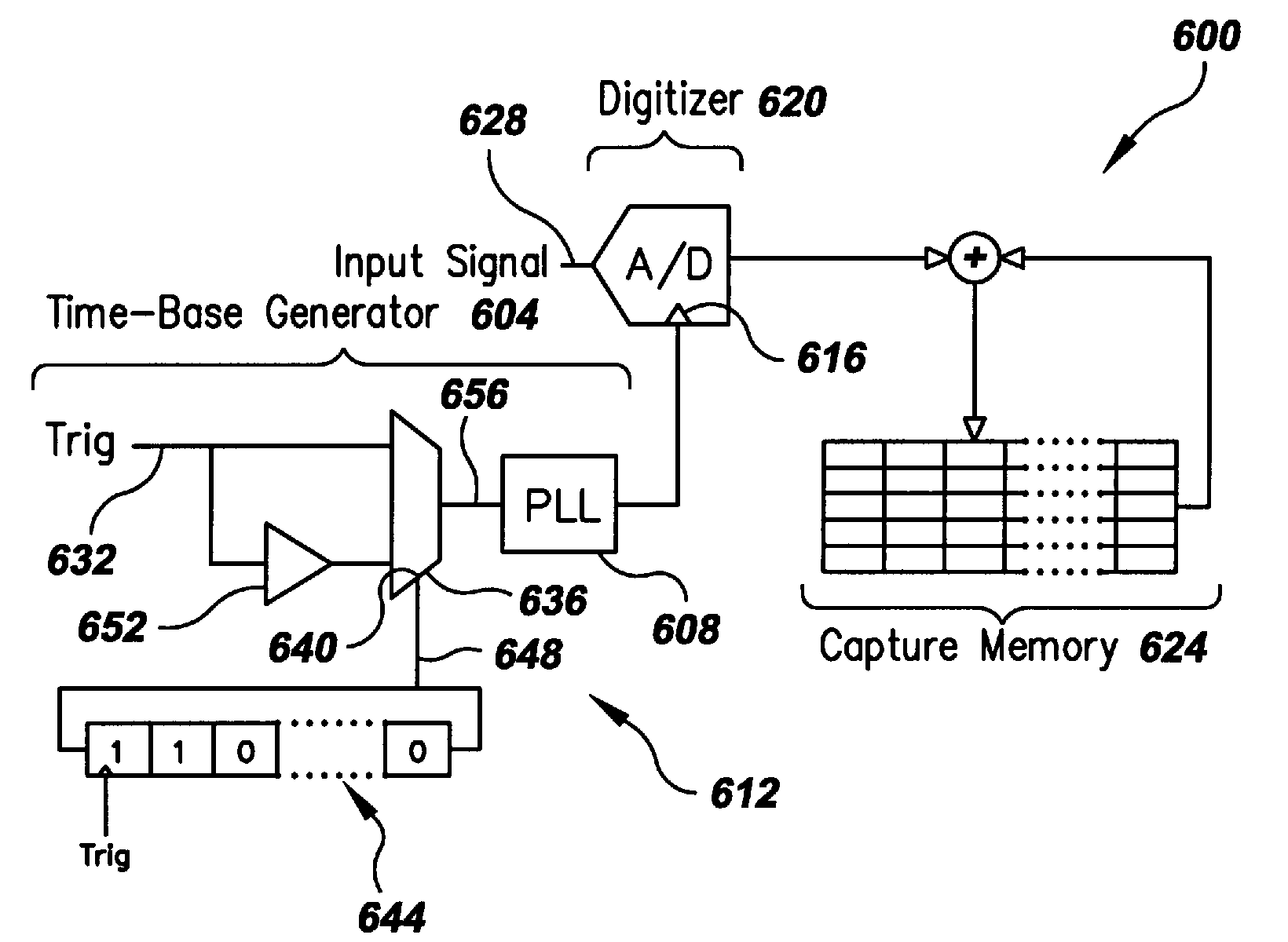

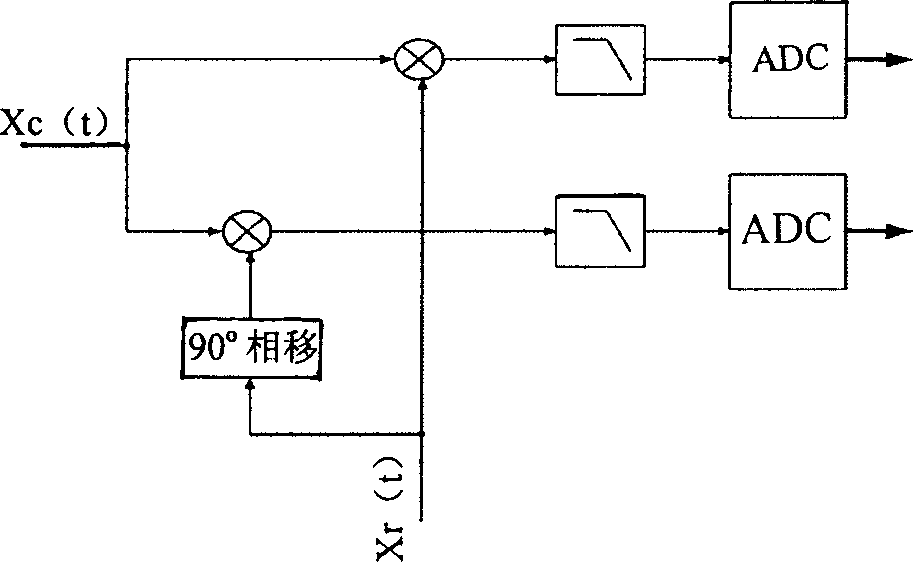

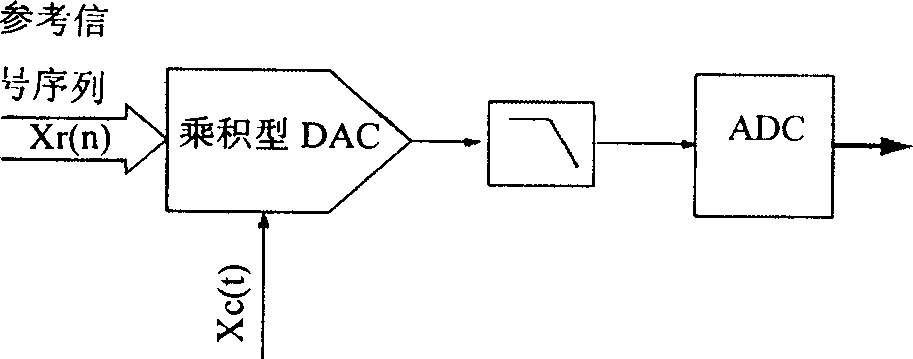

Signal Integrity Measurement Systems and Methods Using a Predominantly Digital Time-Base Generator

InactiveUS20080048726A1Noise figure or signal-to-noise ratio measurementElectrical testingPhase filterEngineering

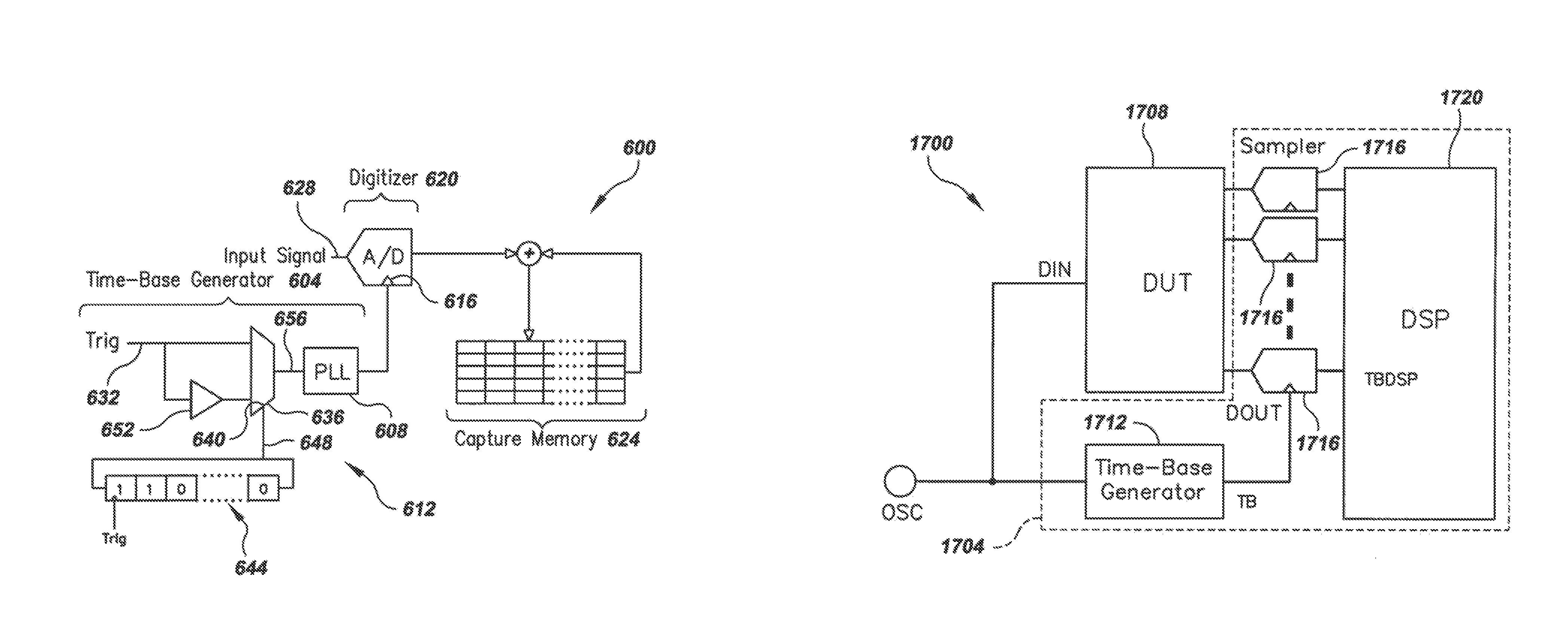

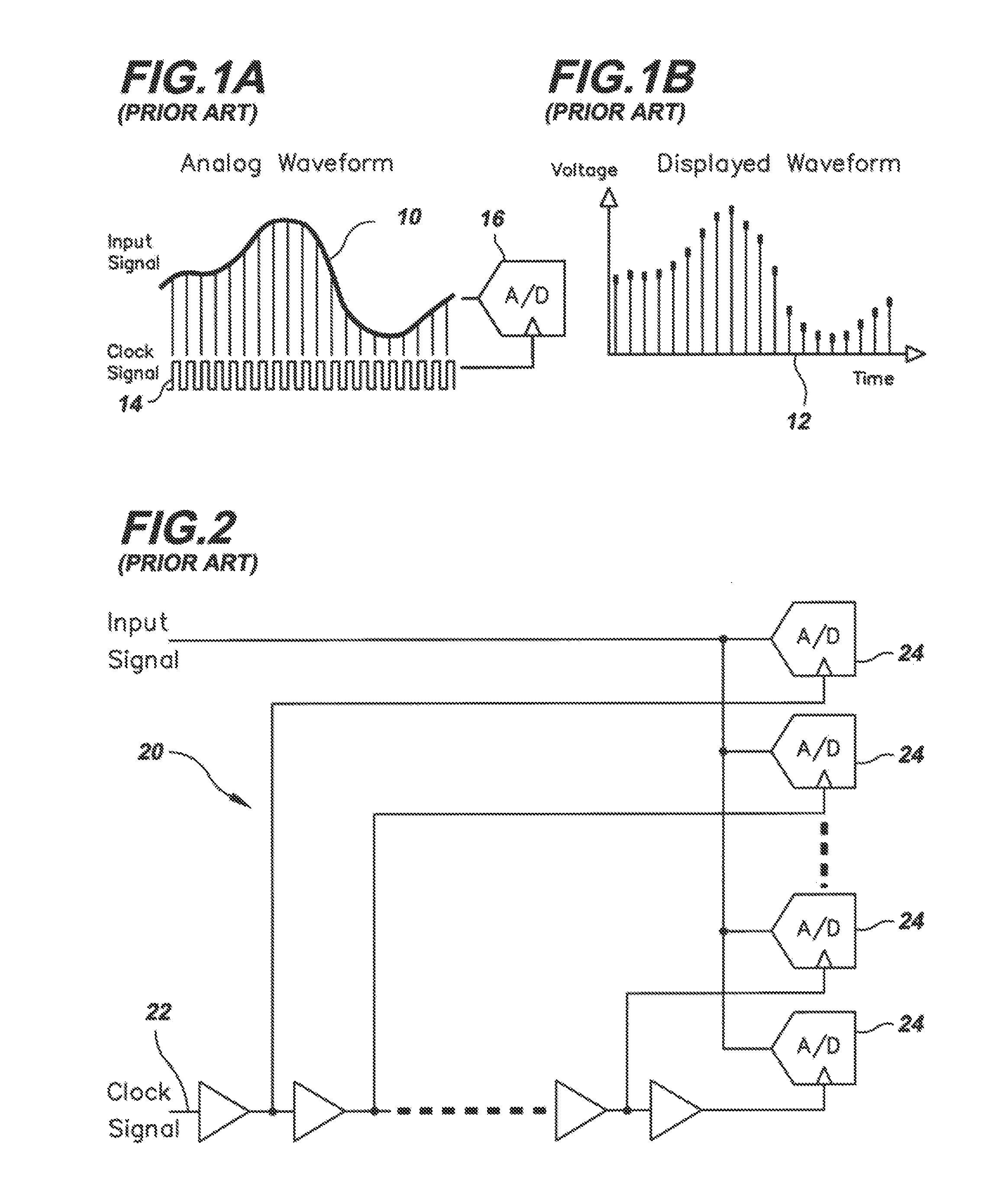

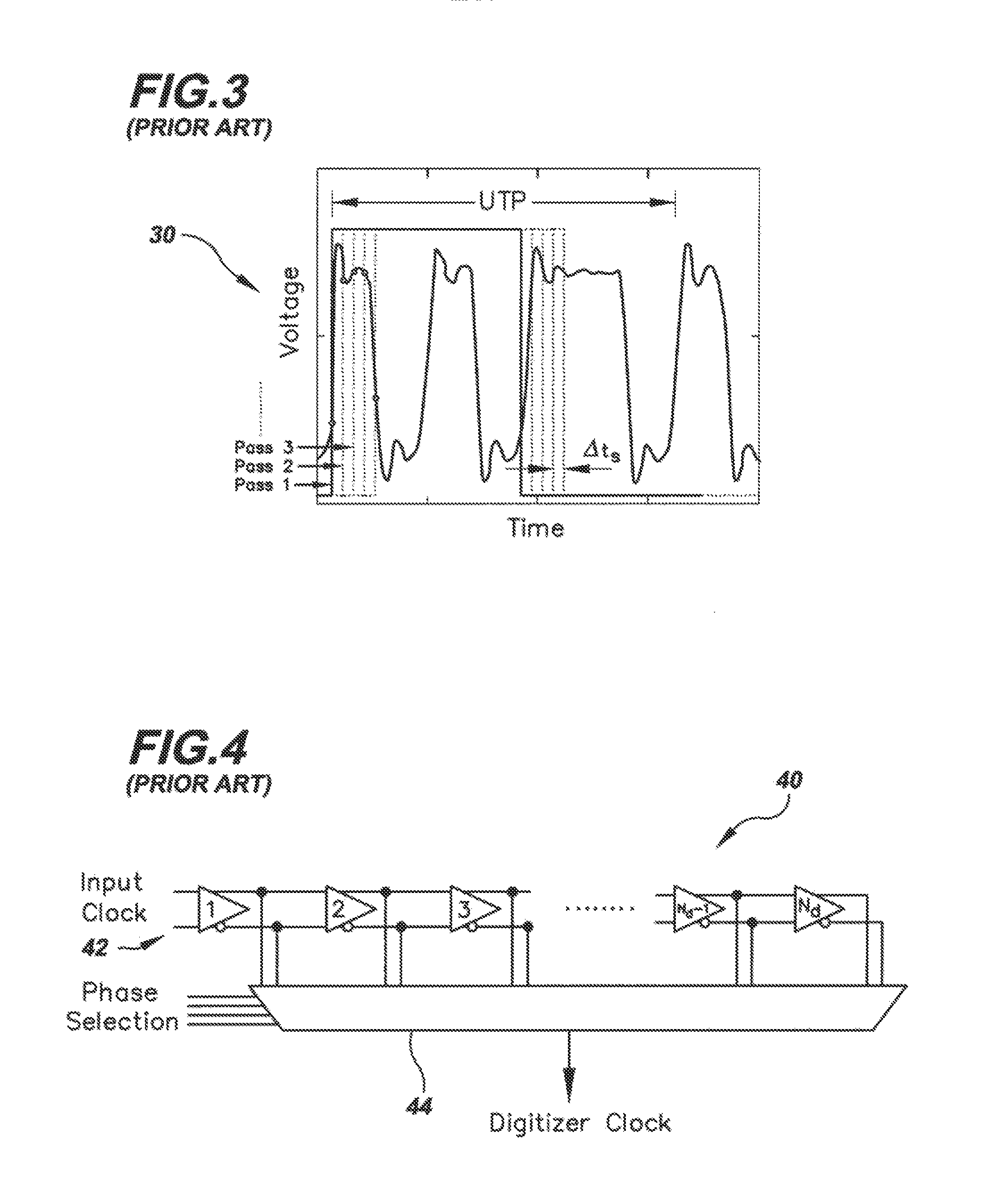

Signal-integrity measurement systems and methods utilizing unique time-base generation techniques for controlling the sampling of one or more signals under test. A time-base generator made in accordance with the present disclosure includes a phase filter and modulation circuitry that generates a rapidly varying phase signal as a function of the output of a sigma-delta modulator. The phase filter filters unwanted high-frequency phase components from the rapidly varying phase signal. The filtered signal is used to clock one or more samplers so as to create sampling instances of the signal(s) under test. The sampling instances are then analyze using any one or more of a variety of techniques suited to the type of signal(s) under test.

Owner:DFT MICROSYST

Multiprotocol computer bus interface adapter and method

Owner:AVAGO TECH INT SALES PTE LTD

Signal integrity measurement systems and methods using a predominantly digital time-base generator

InactiveUS7681091B2Noise figure or signal-to-noise ratio measurementElectrical testingPhase filterEngineering

Signal-integrity measurement systems and methods utilizing unique time-base generation techniques for controlling the sampling of one or more signals under test. A time-base generator made in accordance with the present disclosure includes a phase filter and modulation circuitry that generates a rapidly varying phase signal as a function of the output of a sigma-delta modulator. The phase filter filters unwanted high-frequency phase components from the rapidly varying phase signal. The filtered signal is used to clock one or more samplers so as to create sampling instances of the signal(s) under test. The sampling instances are then analyze using any one or more of a variety of techniques suited to the type of signal(s) under test.

Owner:DFT MICROSYST

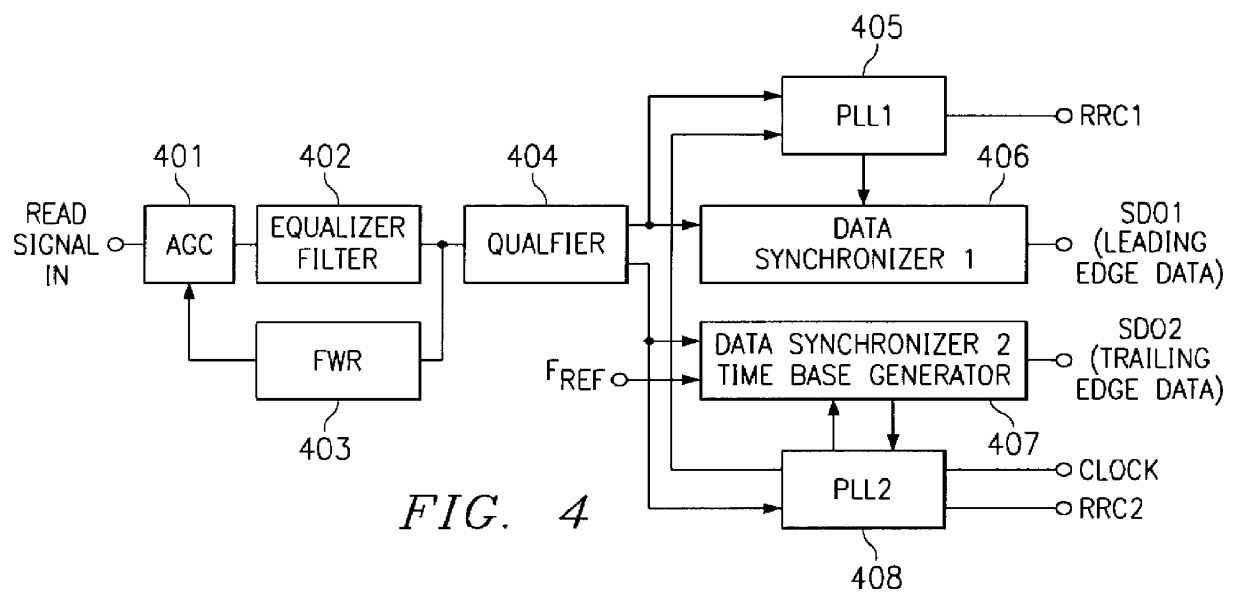

Read channel IC for dual PLL solution

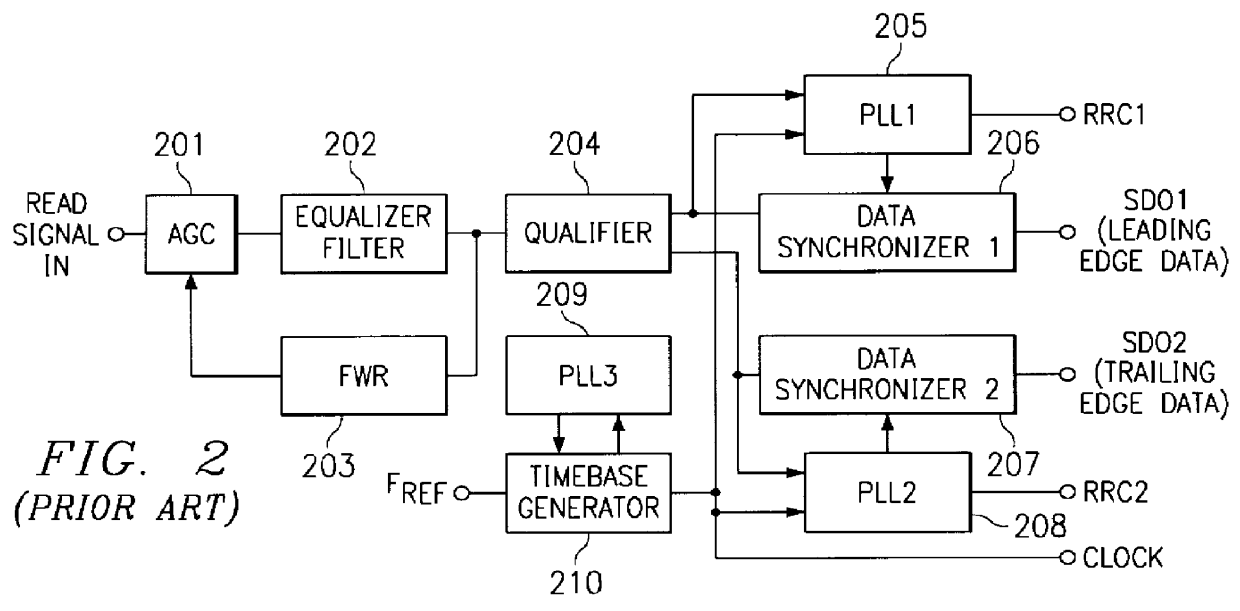

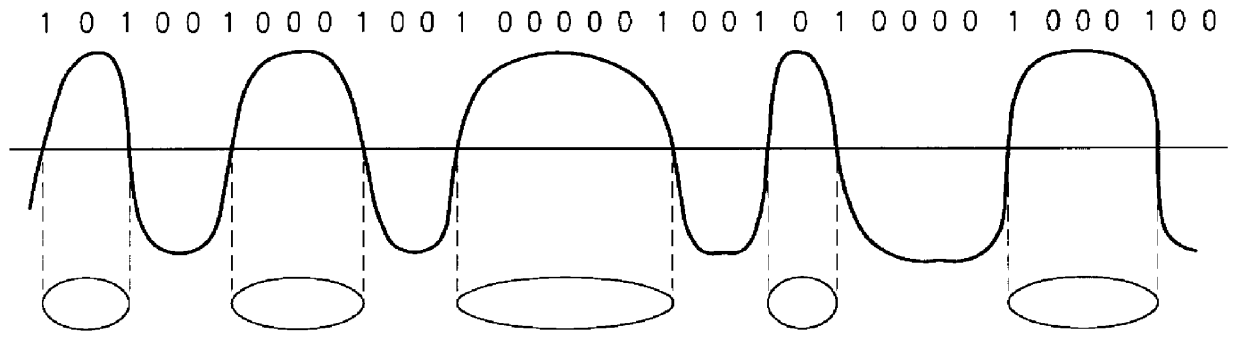

The present invention discloses a fully integrated data synchronization circuit for a disk drive read channel system. The data synchronization system comprises dual data synchronizers to provide read reference clocks. Dual PLL circuits are coupled to the data synchronizers to provide a stable reference frequency to data synchronizers. One of the two data synchronizers is used to obtain leading edge data, while the other is for trailing edge data. Each PLL circuit comprises a phase detector, a charge pump, and a VCO. A loop filter is used in conjunction with a charge pump to control loop characteristics of the PLLs. In an idle mode, one of the PLLs is used as a time base generator to provide a stable reference frequency to data synchronizers. Once data synchronizers achieve lock using the stable reference frequency and switch over to read data, the time base generator PLL is switched over to function as a data synchronizer PLL in a read mode. Thus, one of the PLLs is used as both time base generator and data synchronizer PLL, thereby eliminating the need for extra PLL circuitry and requiring only two PLL circuits to support time base generation and data synchronization.

Owner:SILICON SYST INC

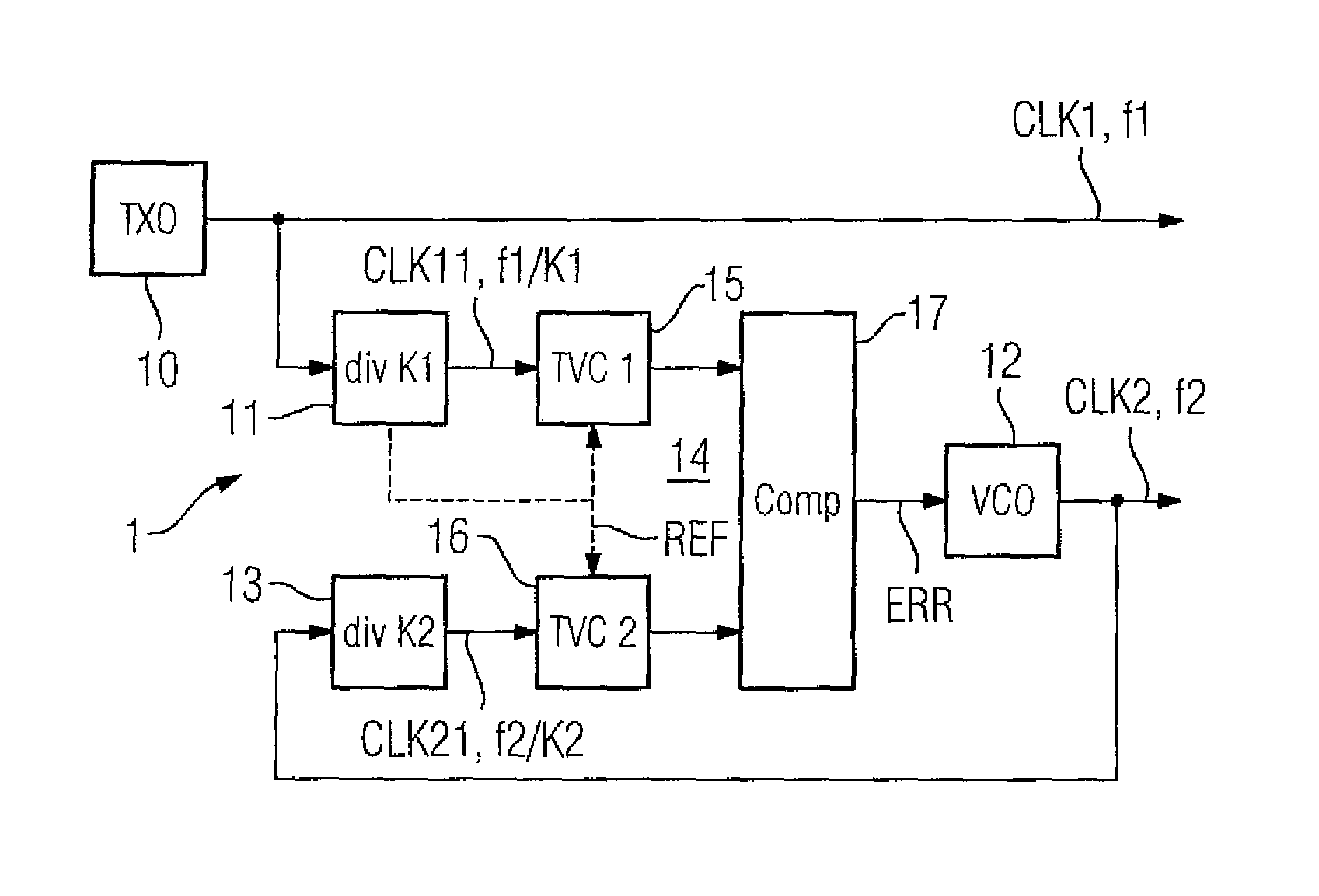

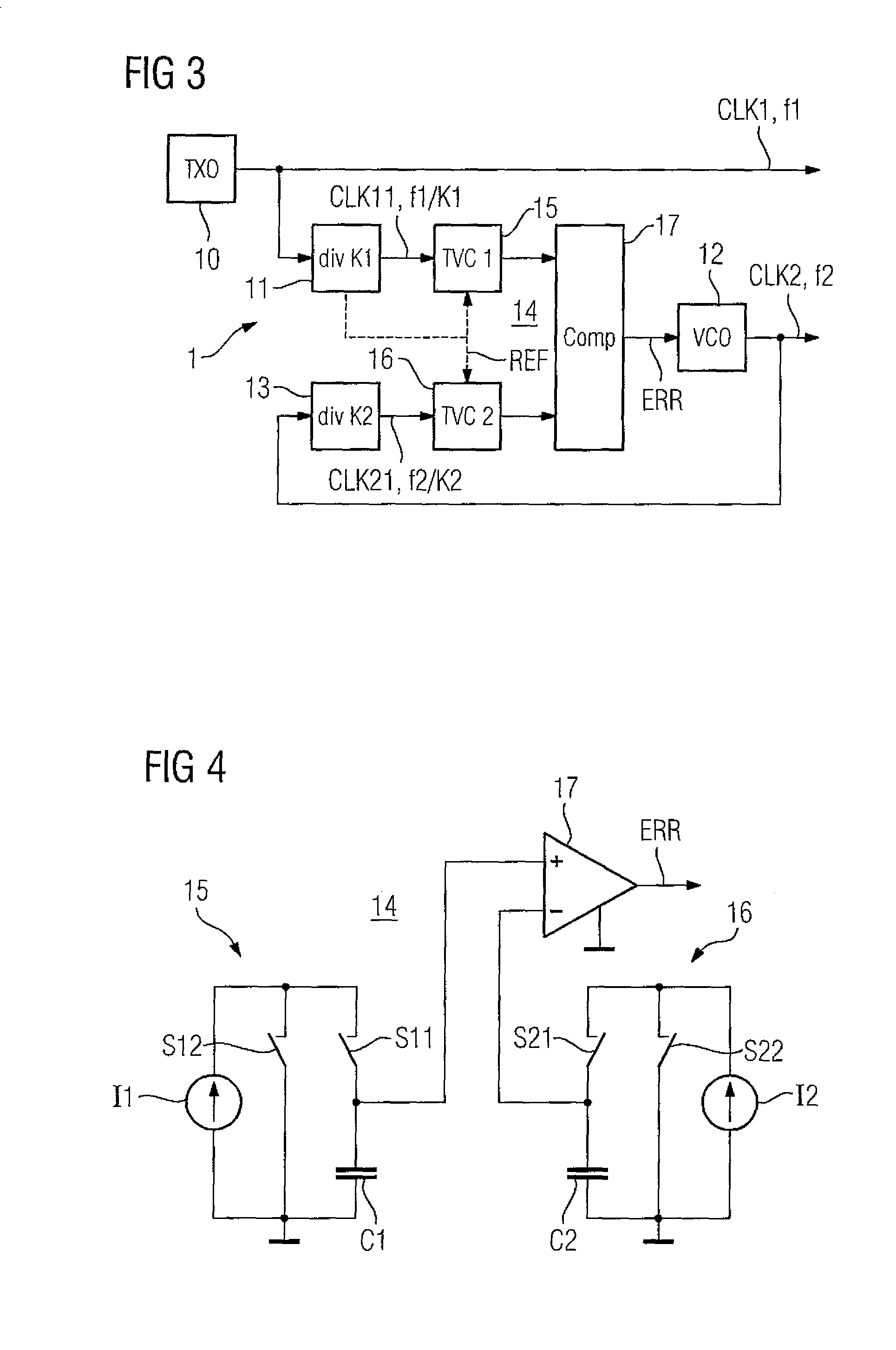

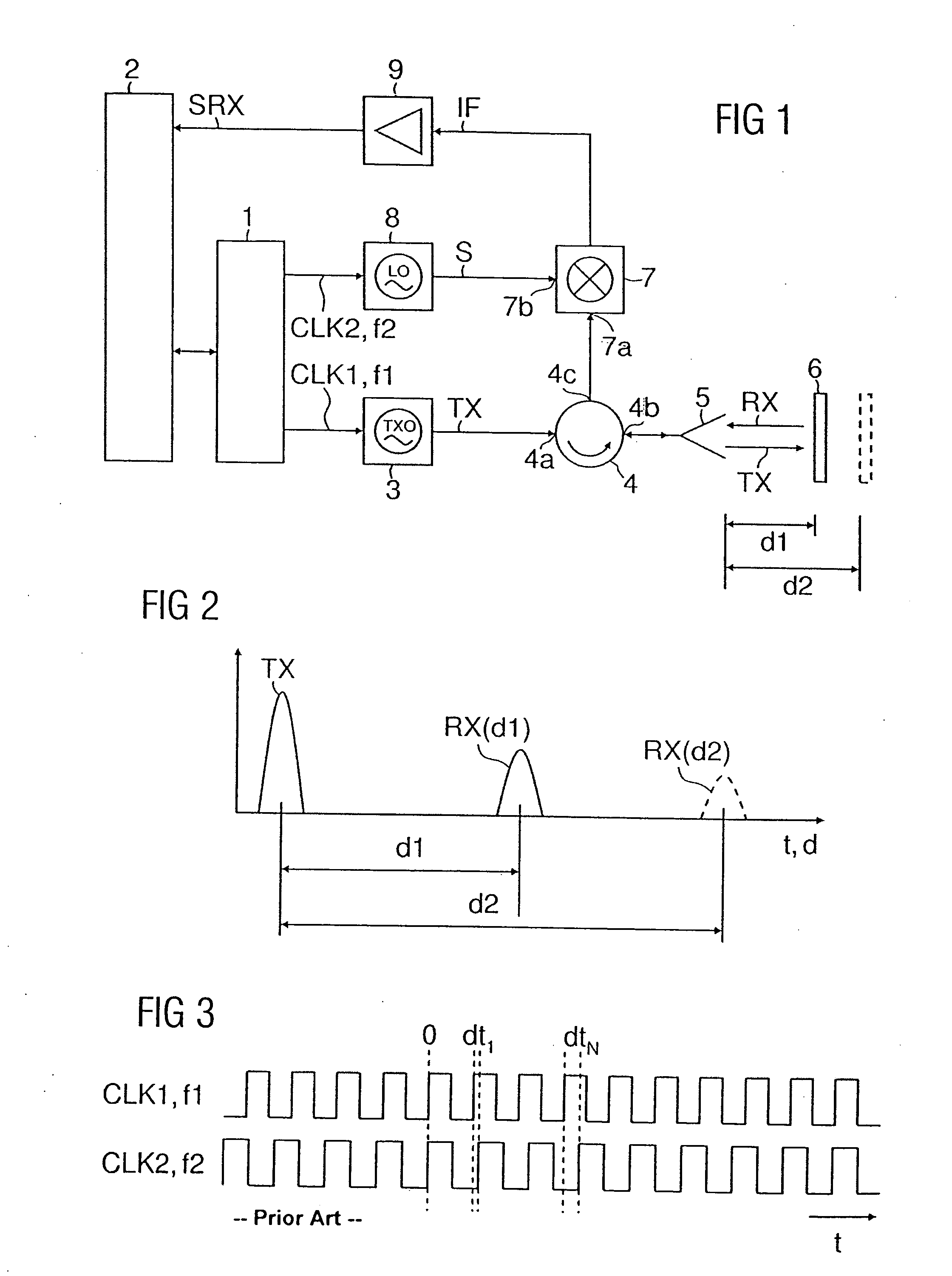

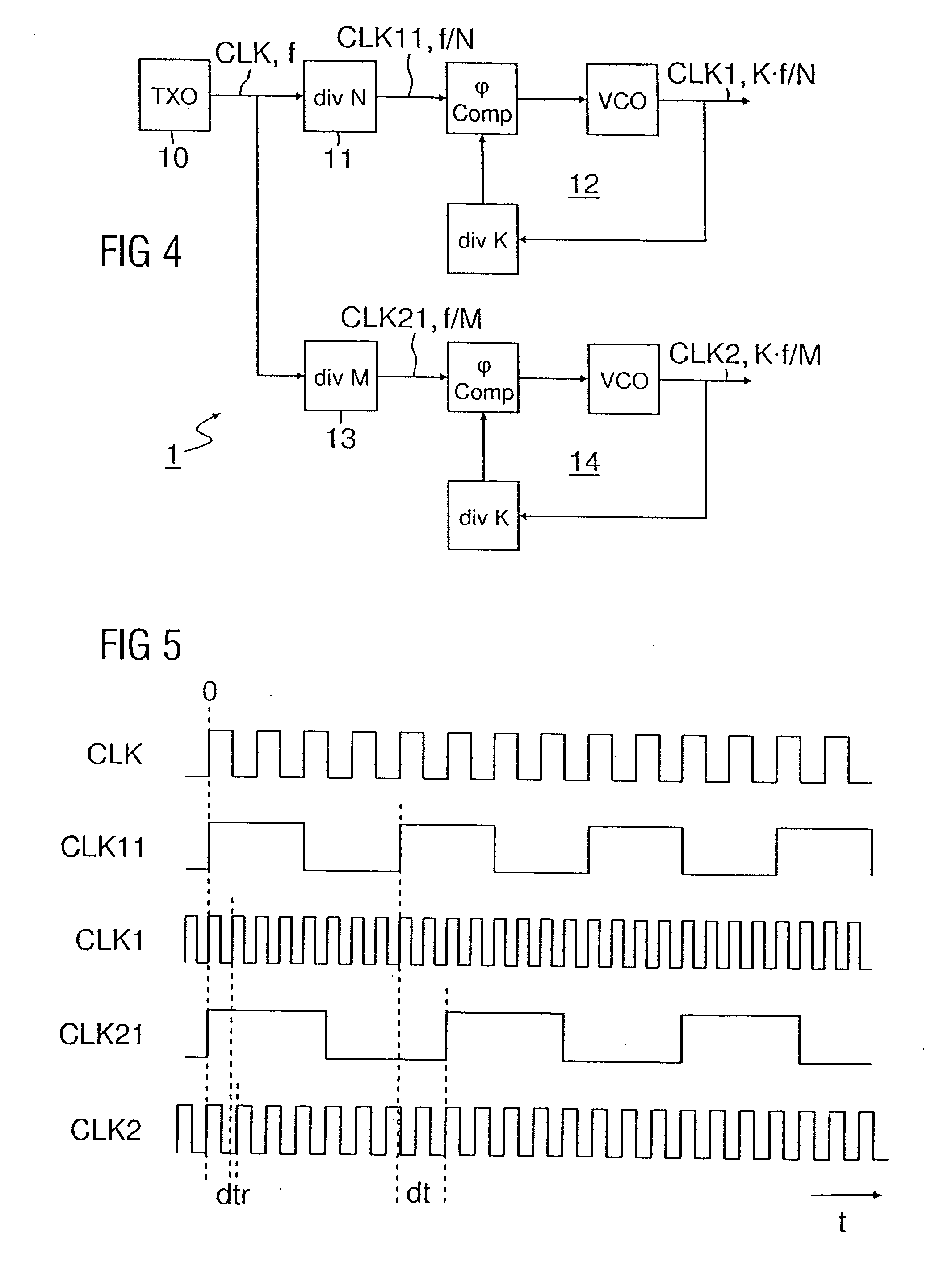

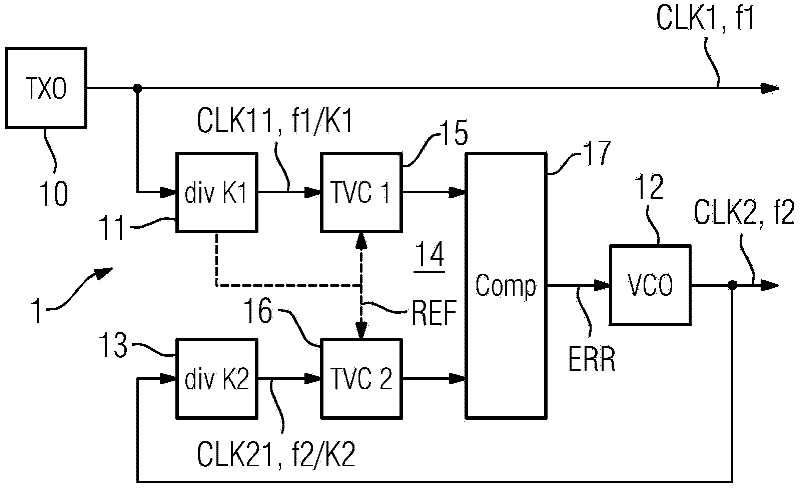

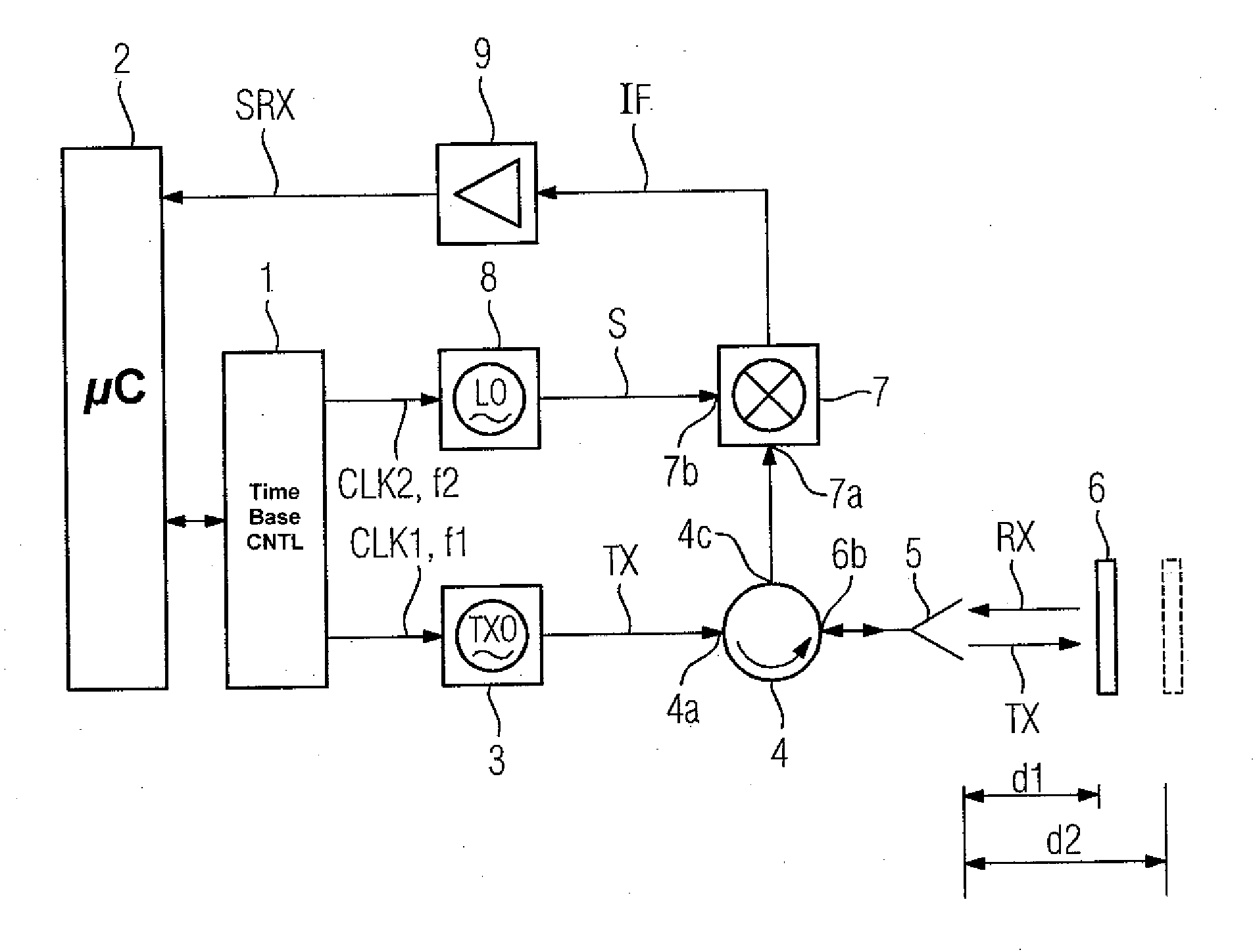

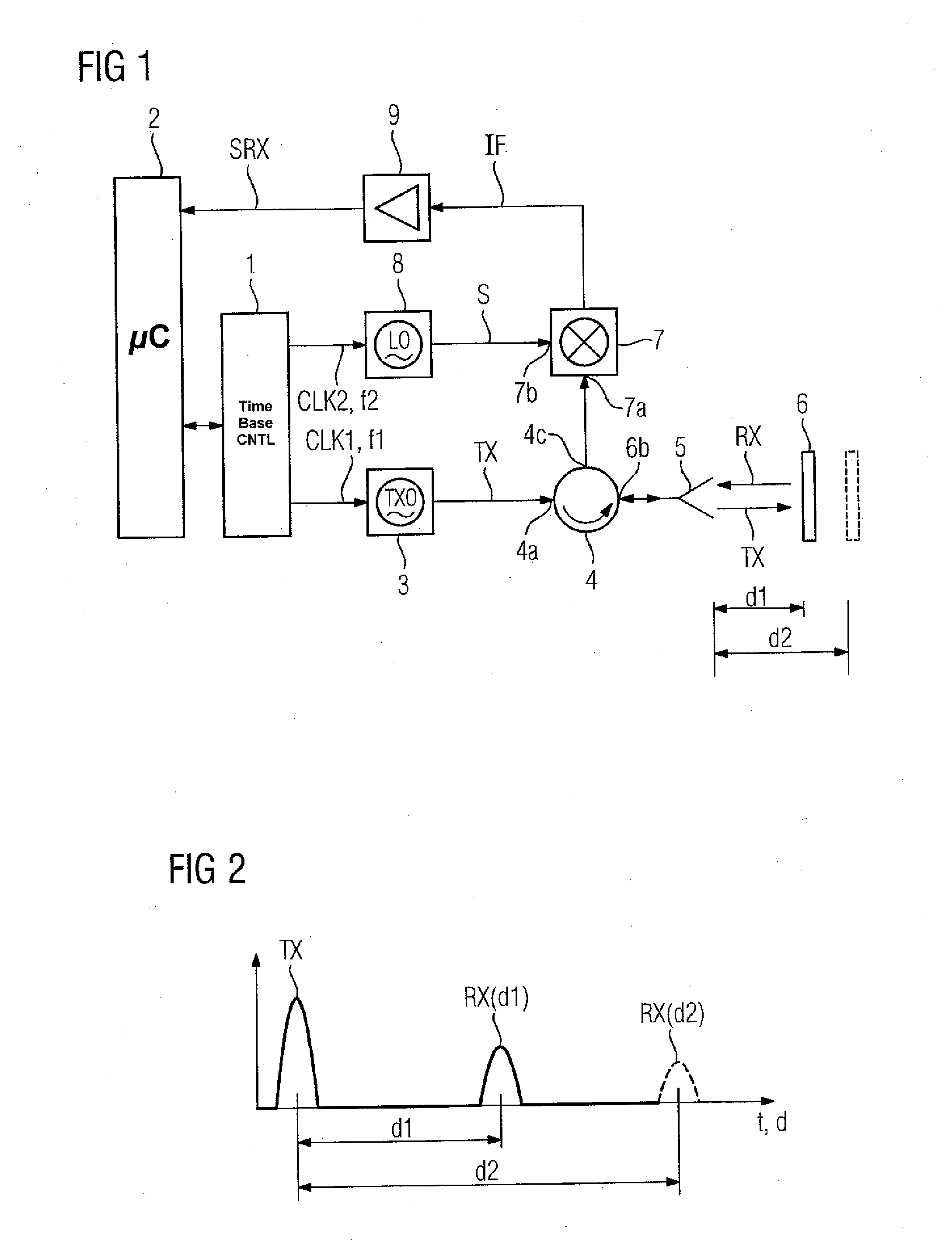

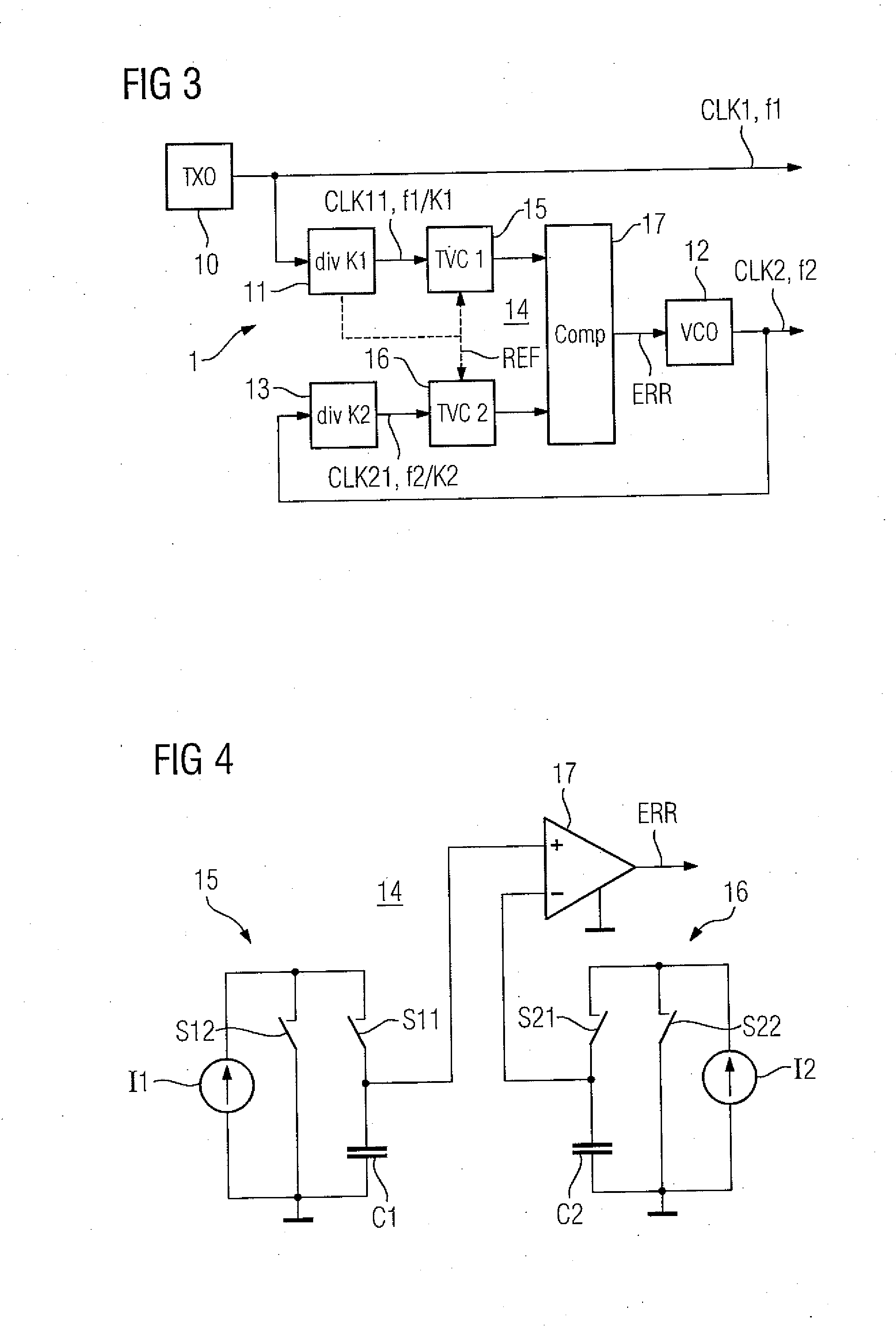

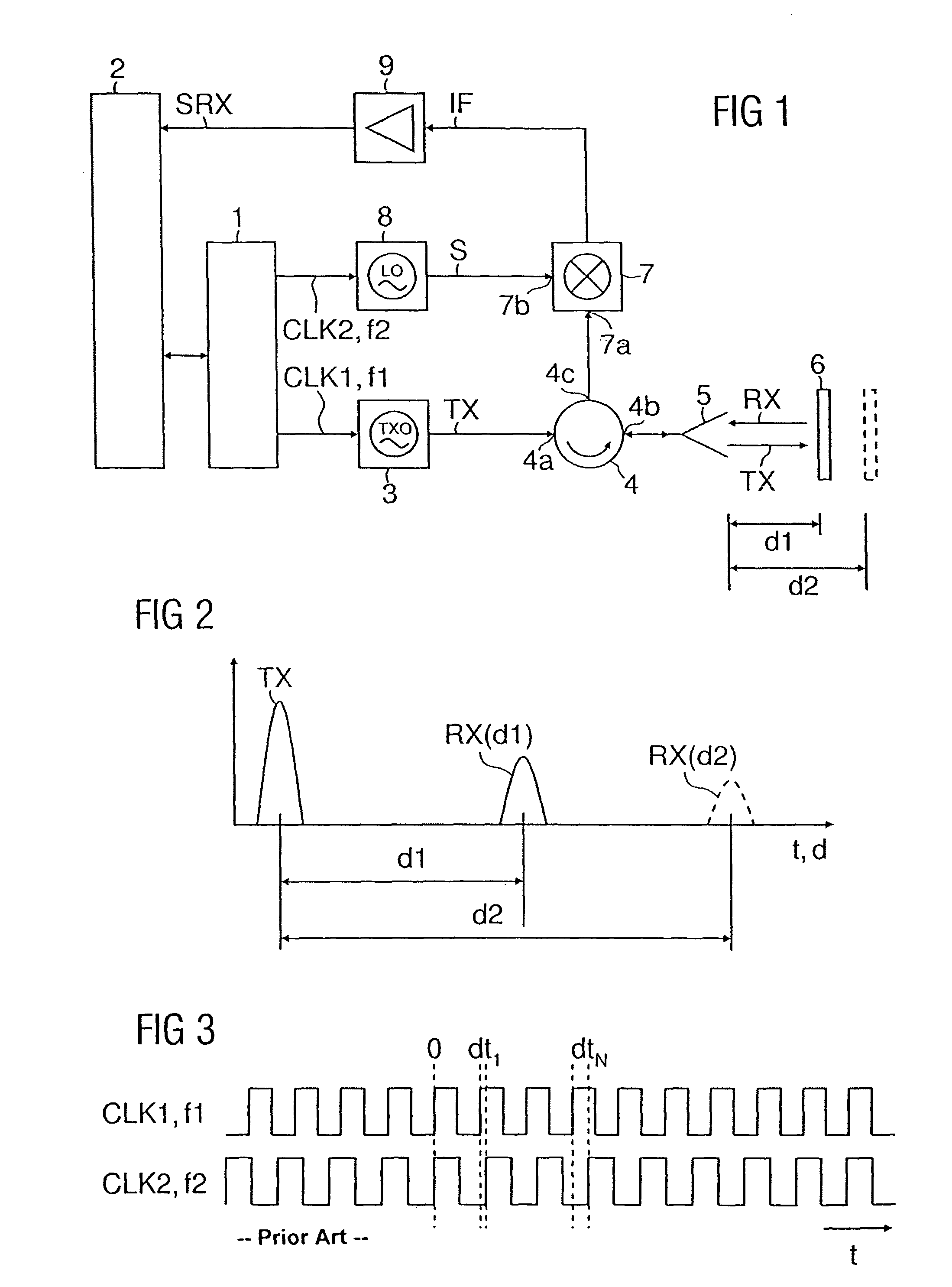

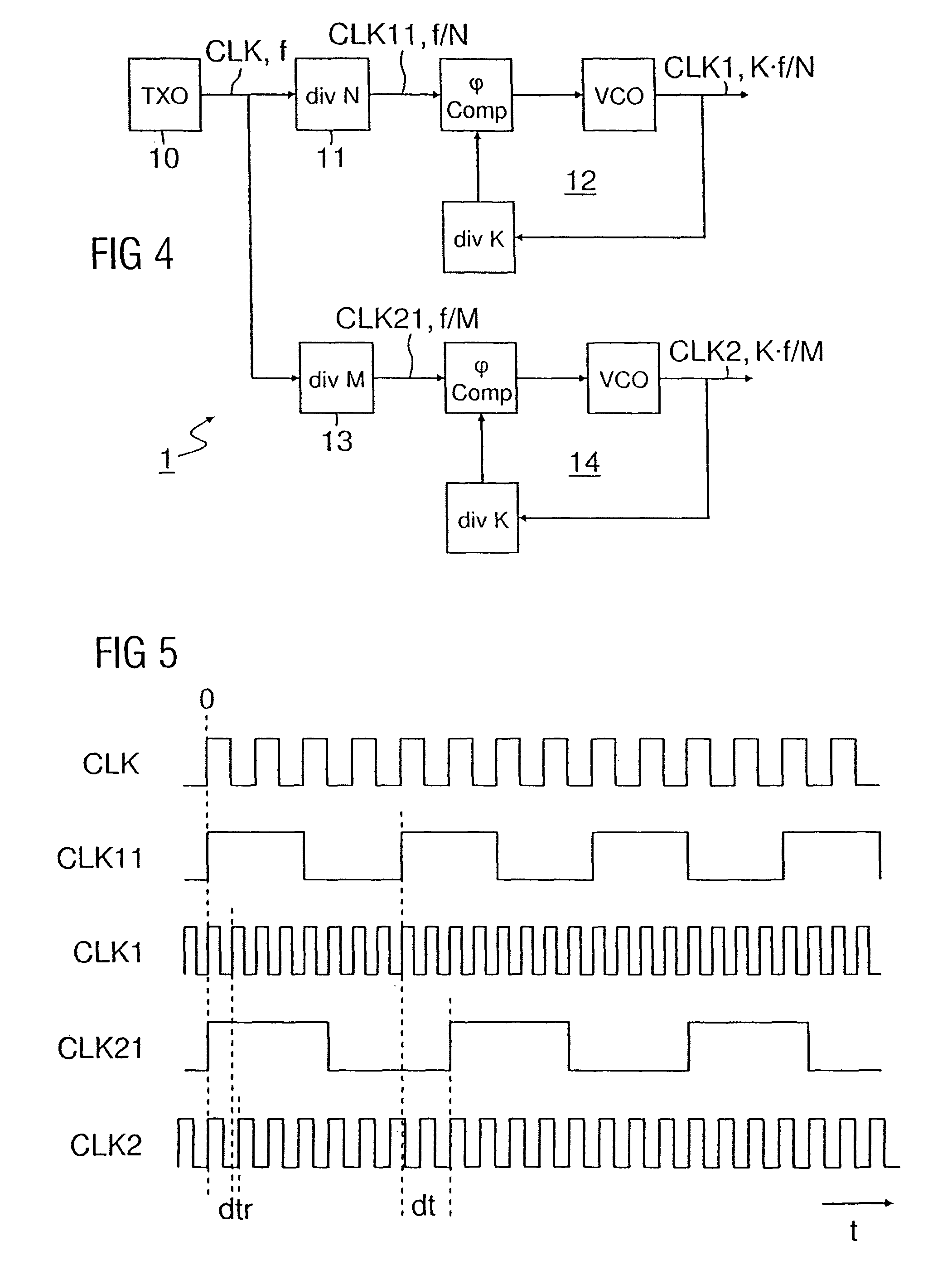

Time base generator and method for providing a first clock signal and a second clock signal

ActiveUS8390348B2Short lock timeMultiple input and output pulse circuitsWave based measurement systemsClock rateEngineering

A time base generator and method for providing a first clock signal and a second clock signal comprising generating the first clock signal at a first clock frequency, dividing the first clock frequency by a first integer to produce a first auxiliary signal, dividing the second clock signal by a second integer to produce a second auxiliary signal, generating an error signal by individually weighting and comparing cycle durations or phasing of the first and second auxiliary signals, and generating the second clock signal by a voltage-controlled oscillator controlled by the error signal such that two clock signals of slightly different frequencies with defined time or phase delay are provided.

Owner:SIEMENS AG

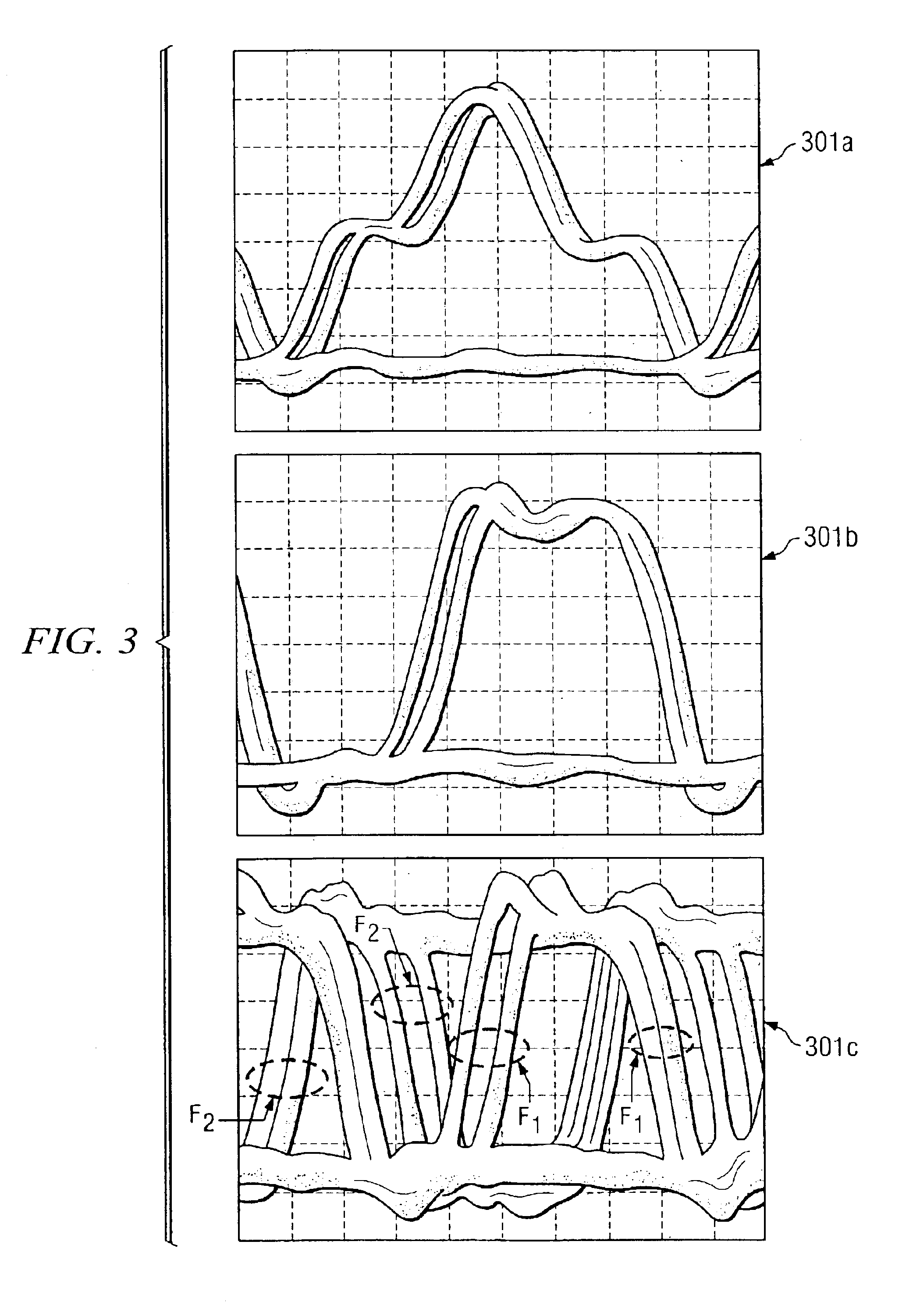

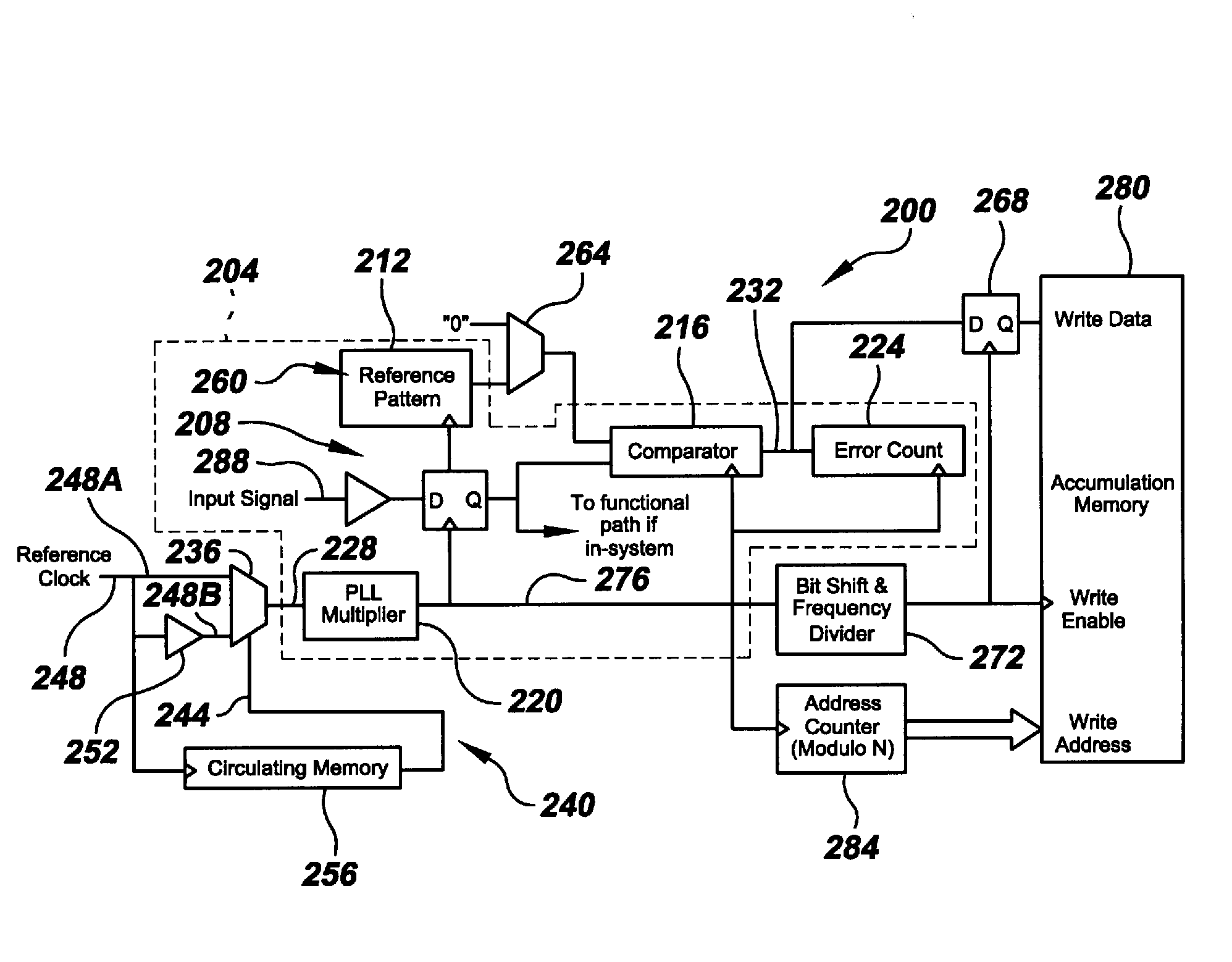

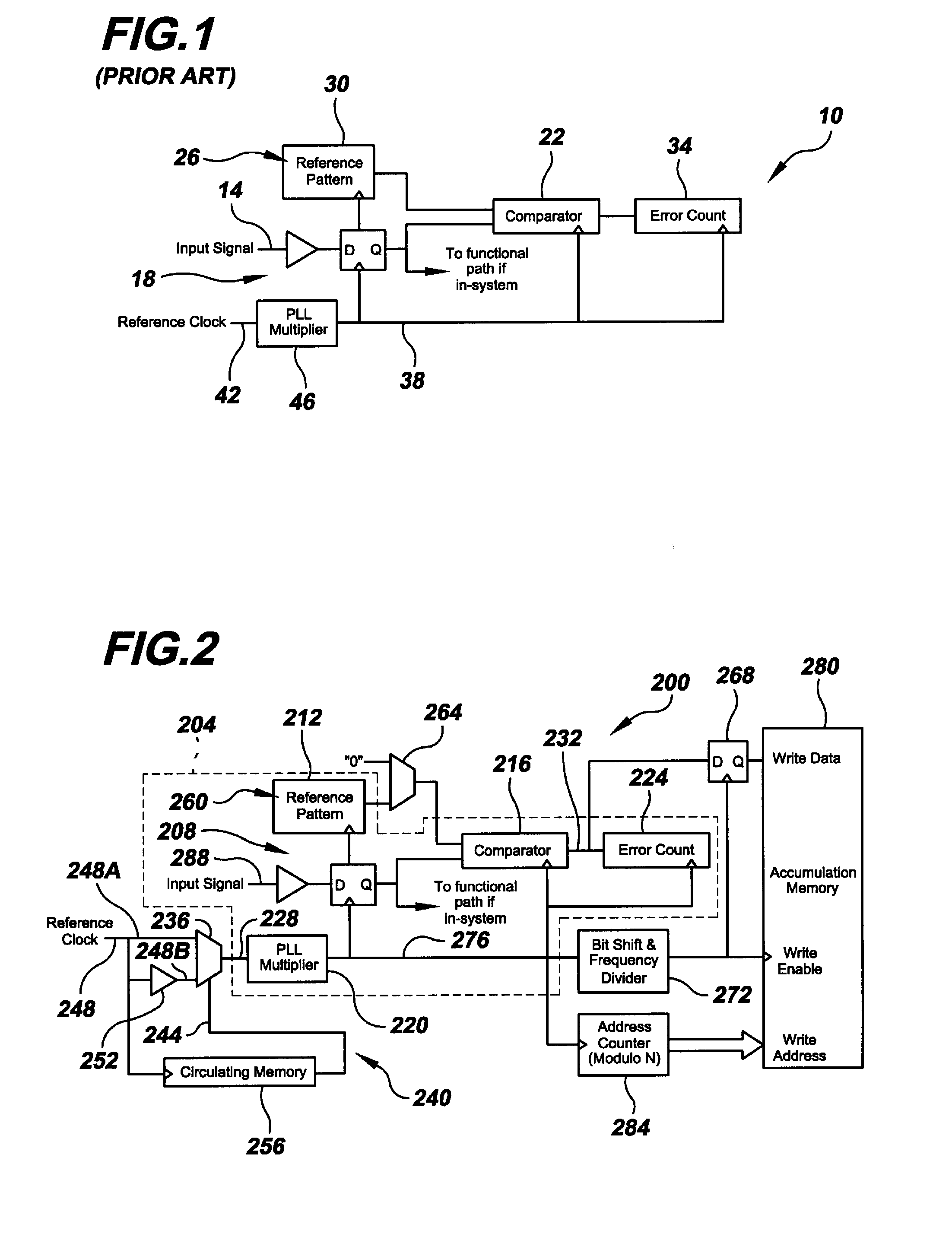

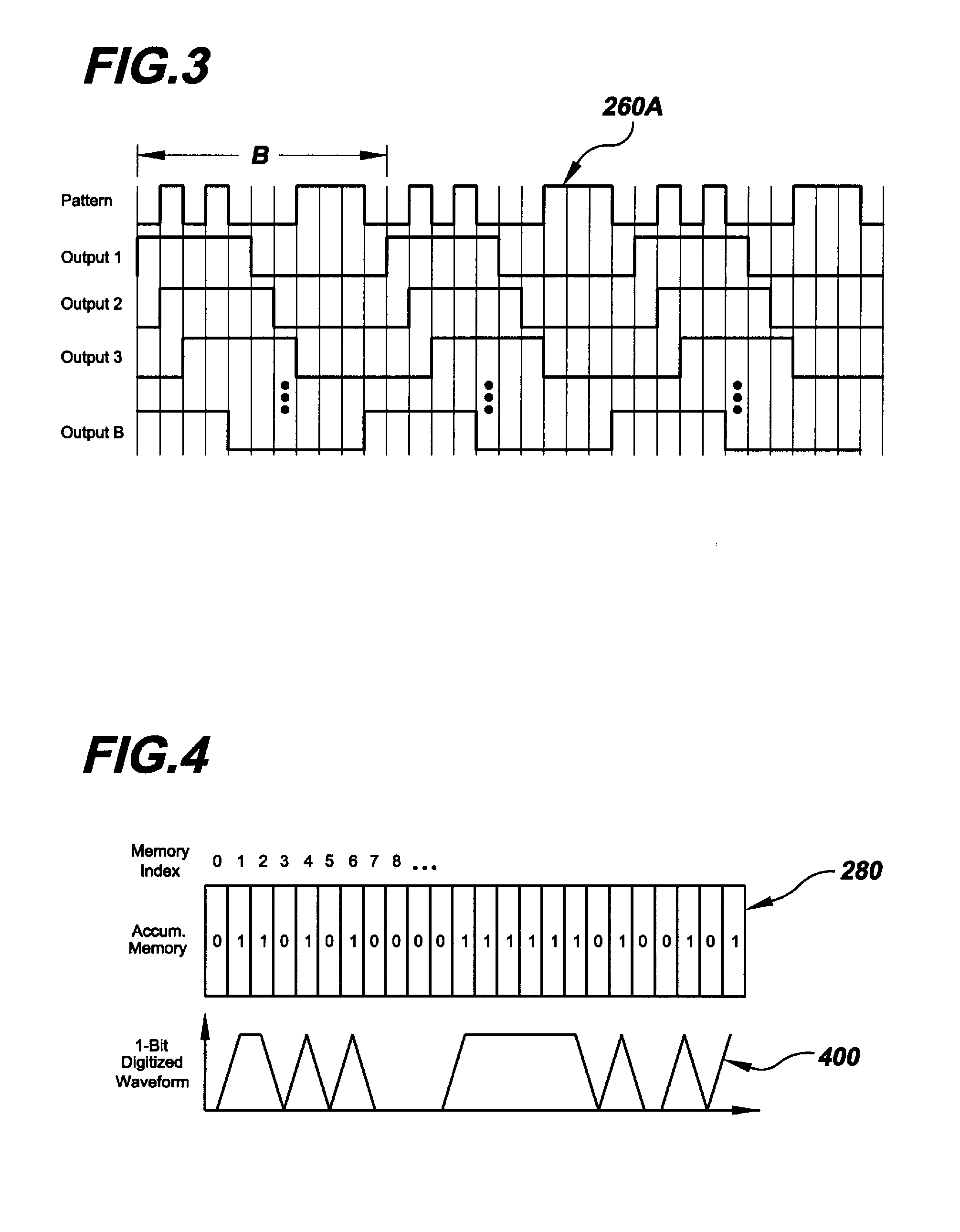

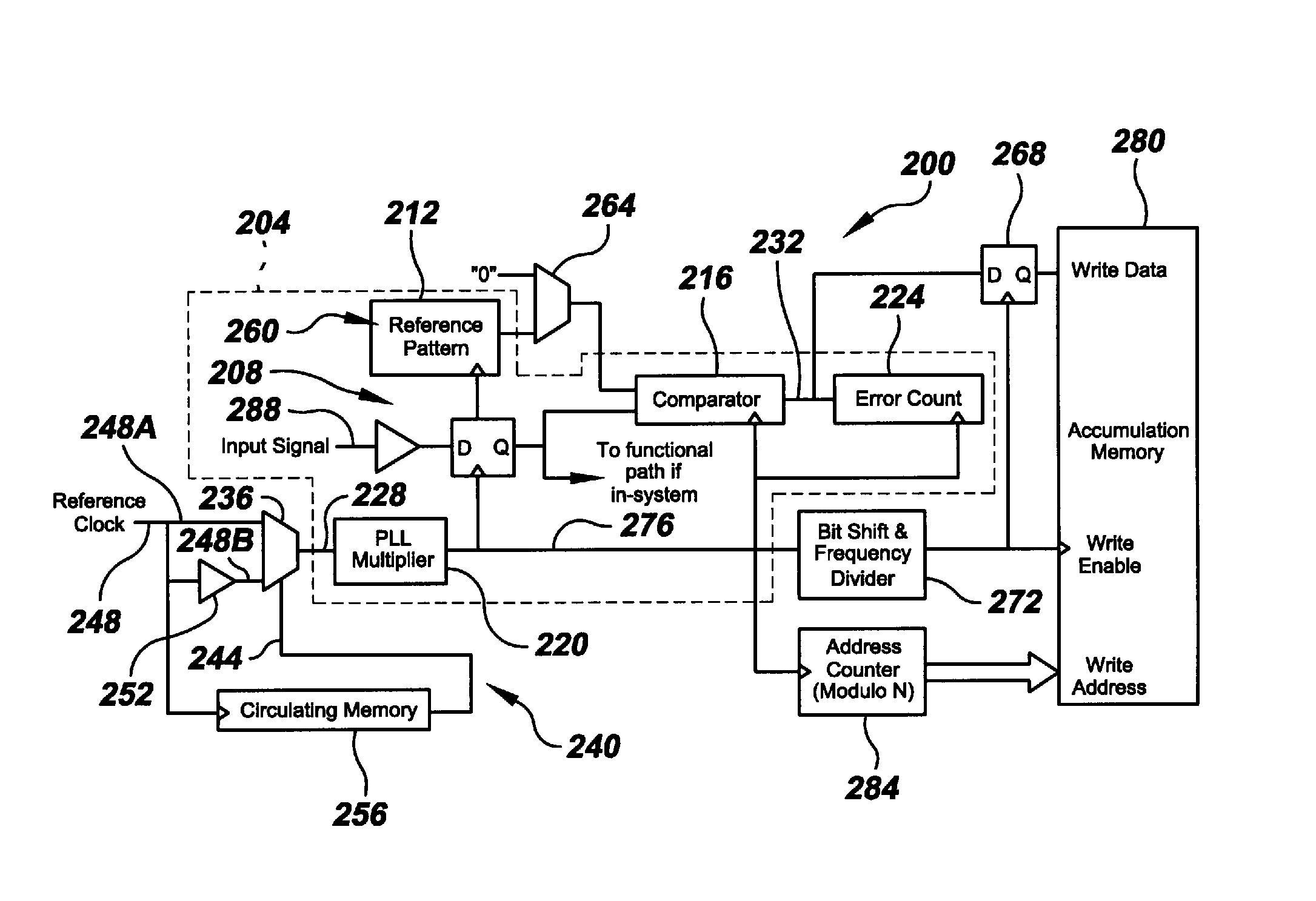

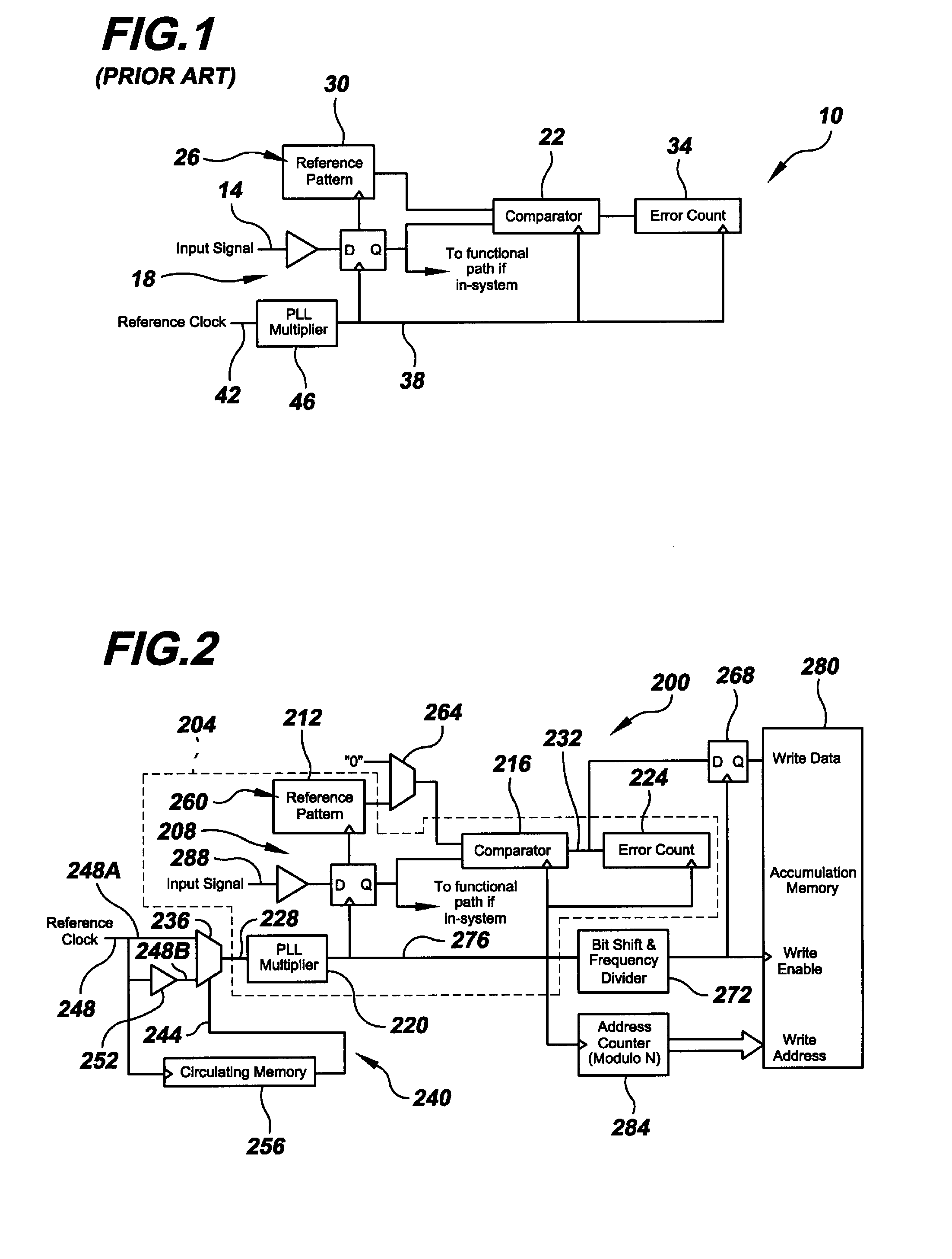

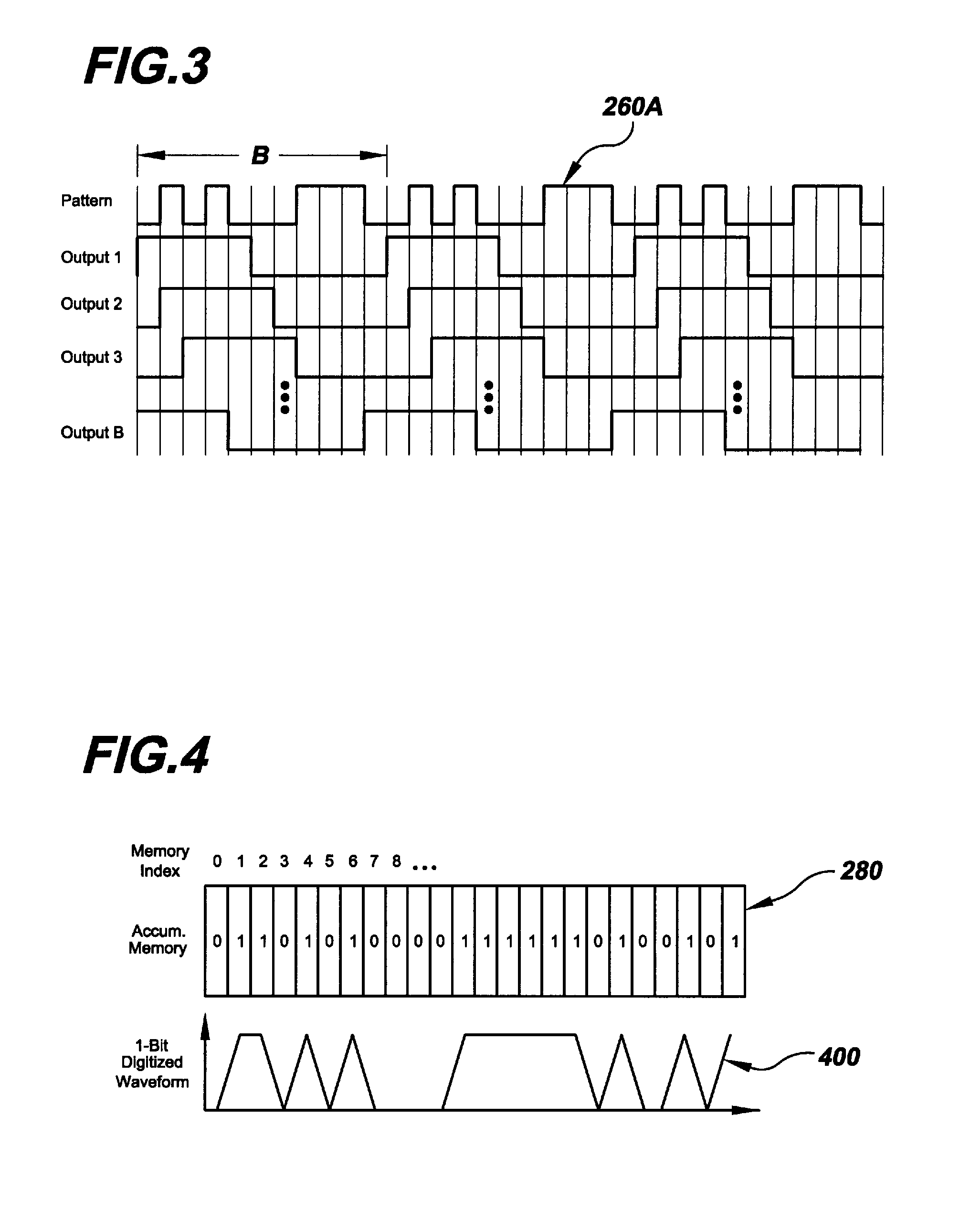

High-Speed Signal Testing System Having Oscilloscope Functionality

A high-speed signal testing system that includes a digital circuitry for providing a pattern tester with oscilloscope functionality at minimal implementation cost. The digital circuitry includes a time-base generator that provides a high-speed repeating time-base signal. The time-base signal, in conjunction with a sub-sampler and an accumulation memory, allows the system to zoom in on, and analyze portions of, one or more bits of interest in a repeating pattern present on the signal under test. Such portions of interest include rising and falling edges and constant high and low bit values.

Owner:DFT MICROSYST

High-speed signal testing system having oscilloscope functionality

A high-speed signal testing system that includes a digital circuitry for providing a pattern tester with oscilloscope functionality at minimal implementation cost. The digital circuitry includes a time-base generator that provides a high-speed repeating time-base signal. The time-base signal, in conjunction with a sub-sampler and an accumulation memory, allows the system to zoom in on, and analyze portions of, one or more bits of interest in a repeating pattern present on the signal under test. Such portions of interest include rising and falling edges and constant high and low bit values.

Owner:DFT MICROSYST

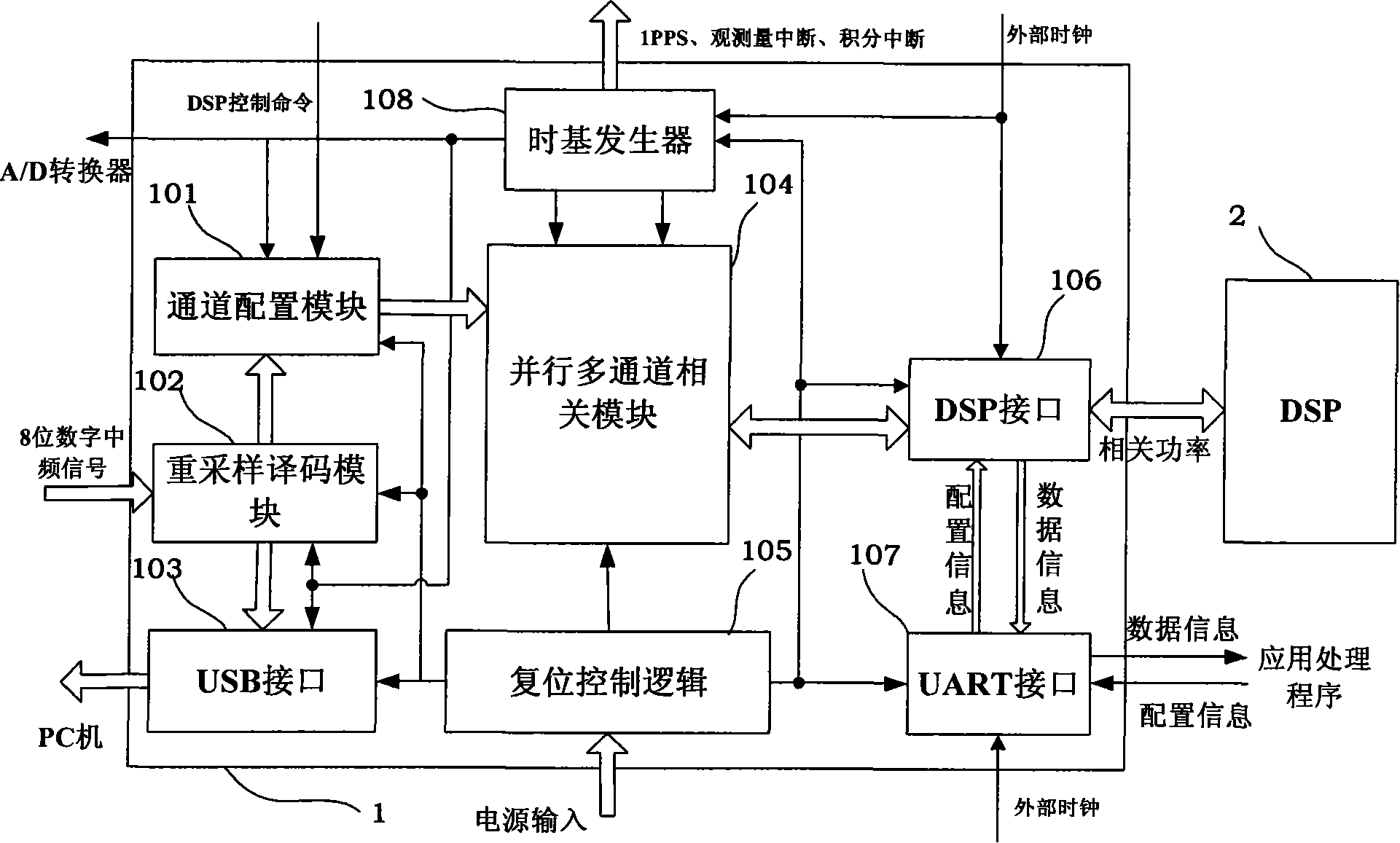

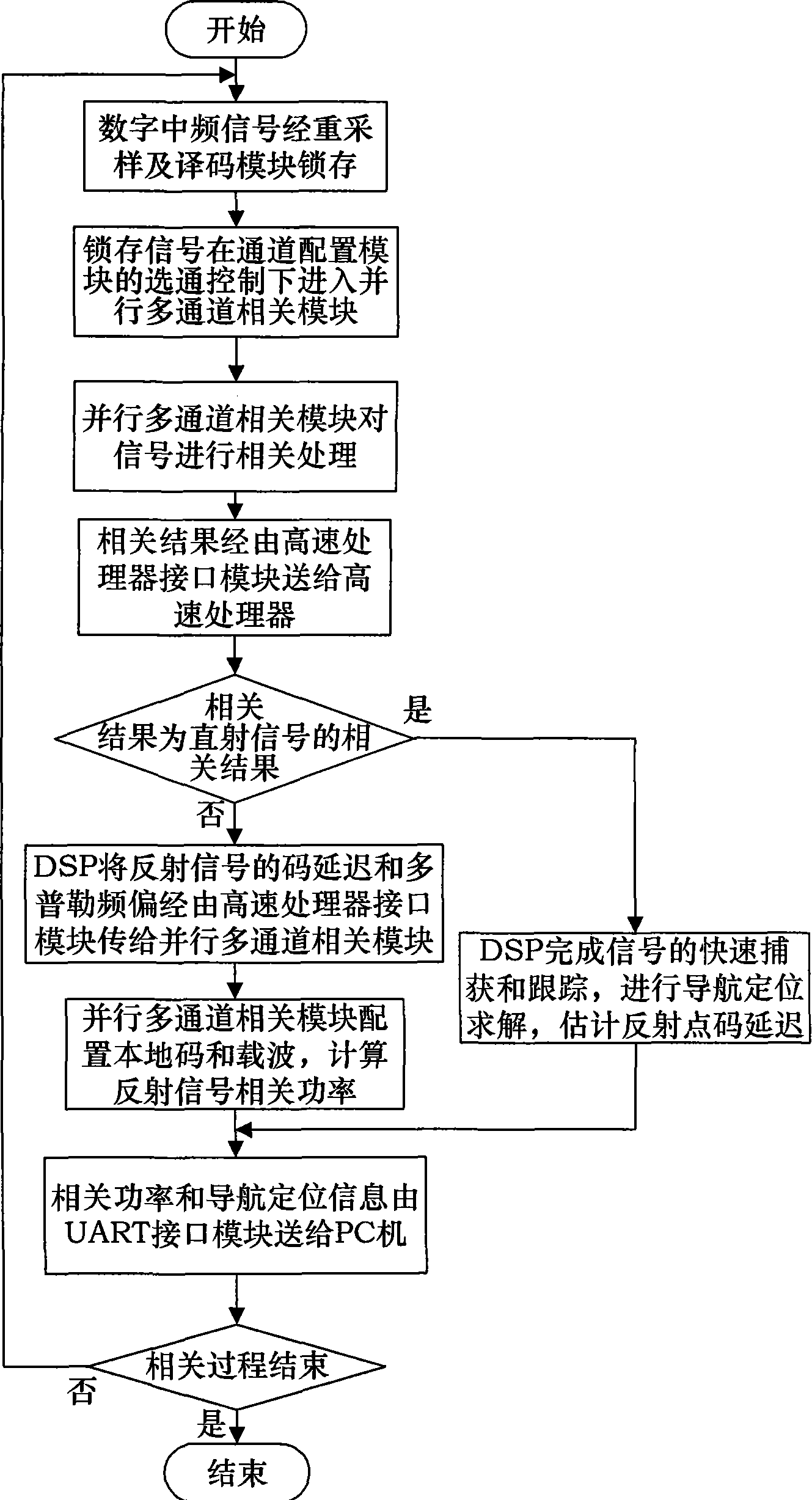

Correlated device capable of receiving and processing reflection signal of navigational satellite

InactiveCN101246212AFlexible and adjustable delayDelayed reflection signalWave based measurement systemsSystem-level simulationData source

The invention discloses a relative device for receiving and processing navigation satellite reflected signal, uses the parallel multi-passage relative module as the core, according to the CPU configuration information, gives relative power outputs at various chip / Doppler time for reflected signal. Parallel multi-passage relative module is controlled by passage configuration module, and is connected with time-base generator, UART interface and DSP interface, every module accepts logistic control of reset control. The device ensures early software development of design, modeling, system-level simulation, IP core integration, and combined verification, and is suitable for various receiver systems and design of configuration function. The invention can process GPS direct signal and reflected signal at the same time, uses direct signal to navigate and position, outputs the power relating to reflected signal under the control of DSP at various delay times.

Owner:BEIHANG UNIV

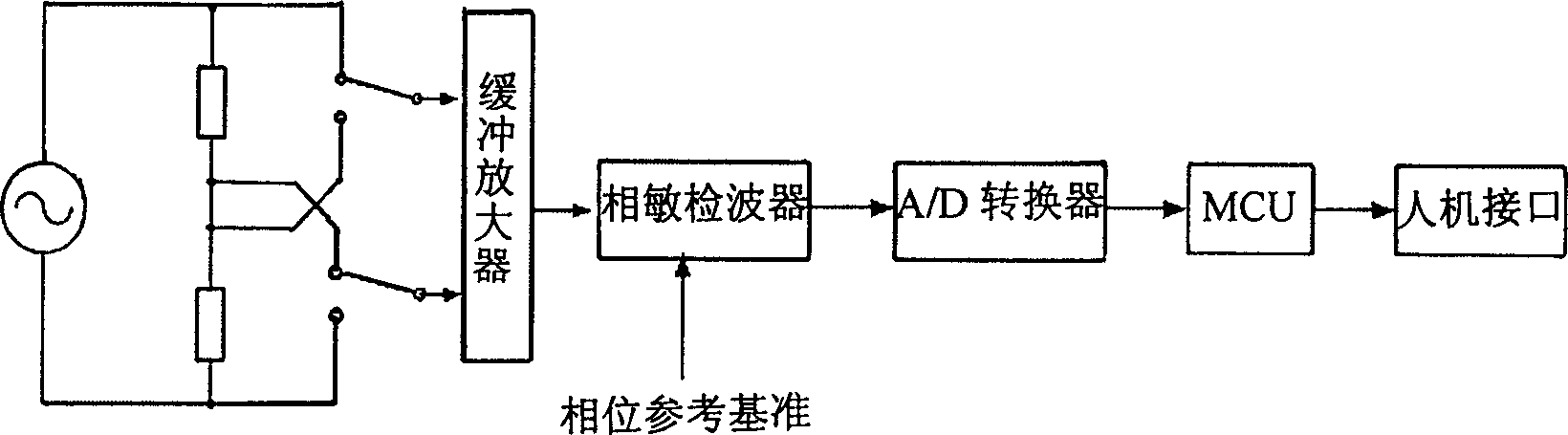

Digital phase-sensitive detector for intelligent element parameter tester

InactiveCN1837834AHigh precisionHigh bandwidthDigital variable displaySemiconductor/solid-state device testing/measurementPhase sensitiveConfusion

This invention relates to a digital phase-sensitive detector for intelligent element parameter tester. Wherein, connecting inputs and outputs of anti-confusion filter to the target element voltage and current signals and signal inputs of two-way sample / holder respectively; connecting the trigger input ports and outputs of sample / holder to the outputs of the time-base generator and signal input ports of high-speed ADC respectively; connecting the output signal of the ADC to the opposite signal data ports of digital phase-sensitive detection algorithm module in series or by parallel; connecting the control port and data wire of FPGA to the opposite orts of ADC; and connecting the output of algorithm module with the main controller in the tester.

Owner:南京长盛仪器有限公司

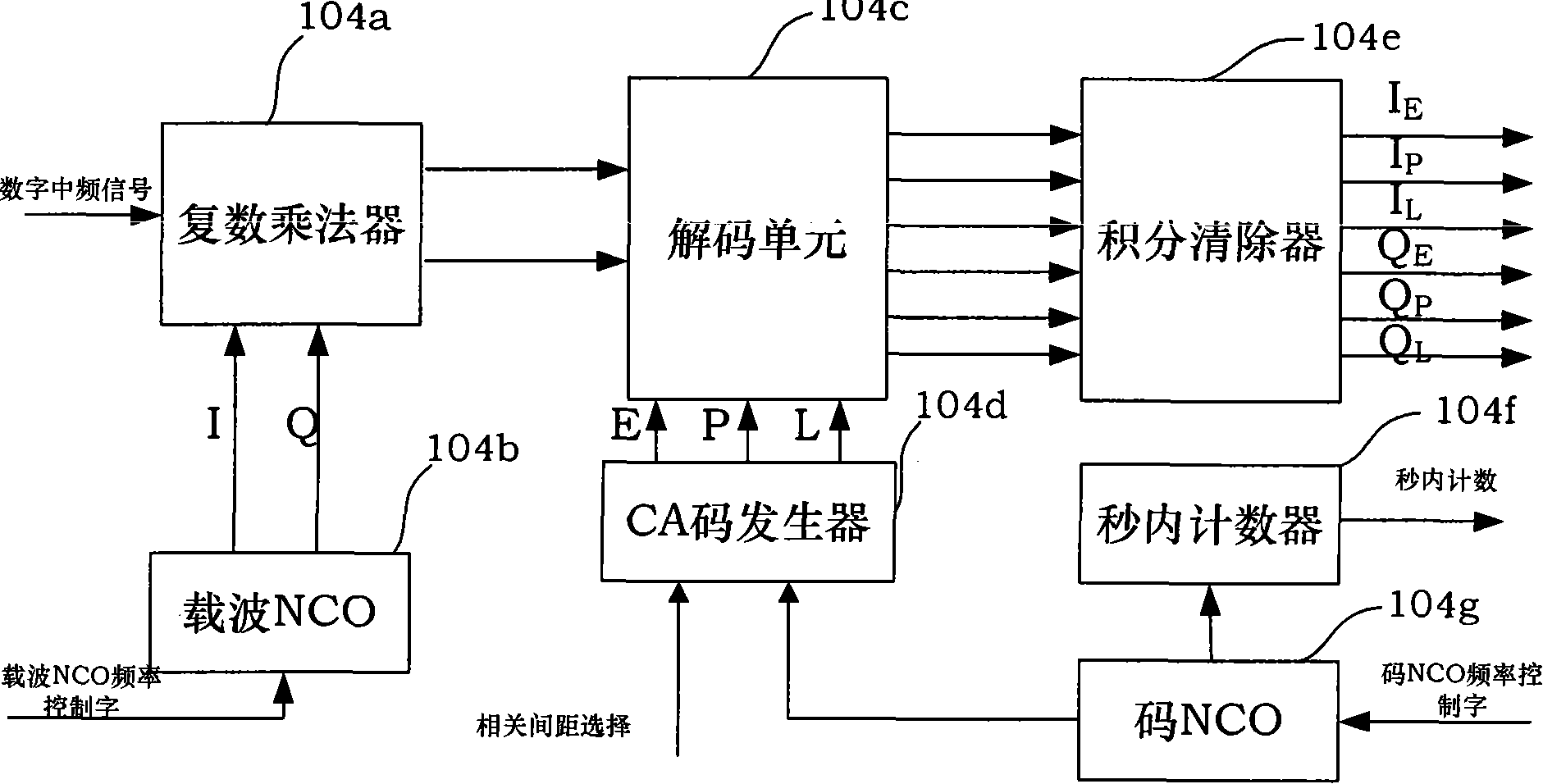

GPS and Glonass multichannel parallel signal tracing method and correlator

The invention discloses a GPS and Glonass multichannel parallel signal tracing method and a correlator, comprising a multichannel correlator. The multichannel correlator comprises a clock generator, a time base generator, registers, an address decoder, a bus interface, a plurality of tracing modules, wherein, the plurality of tracing modules are connected in parallel through bus. The parallelly connected plurality of tracing modules is connected with the clock generator, the time base generator, and the registers, and is connected with the address decoder through the bus interface.

Owner:BEIJING UNISTAR MICROELECTRONICS

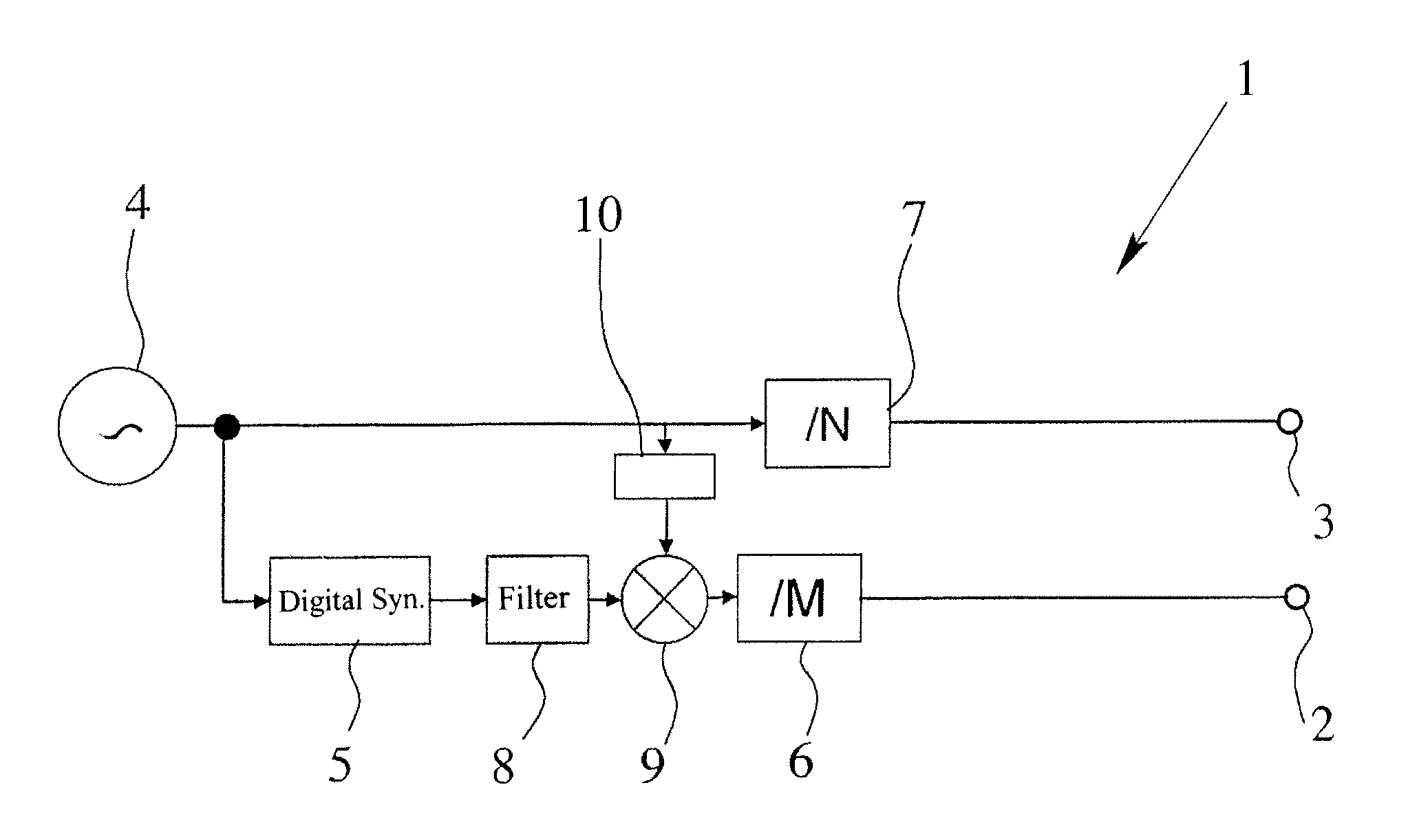

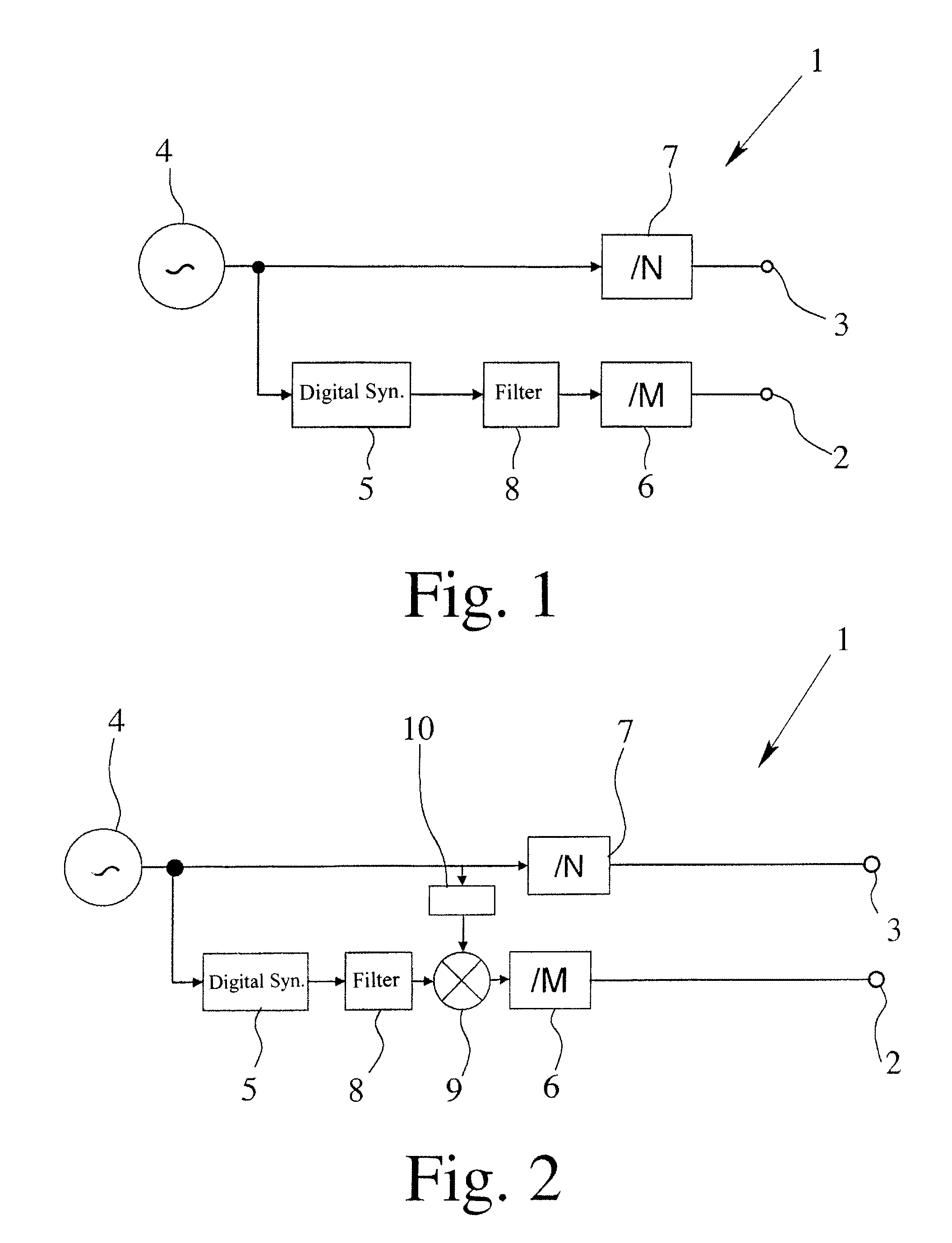

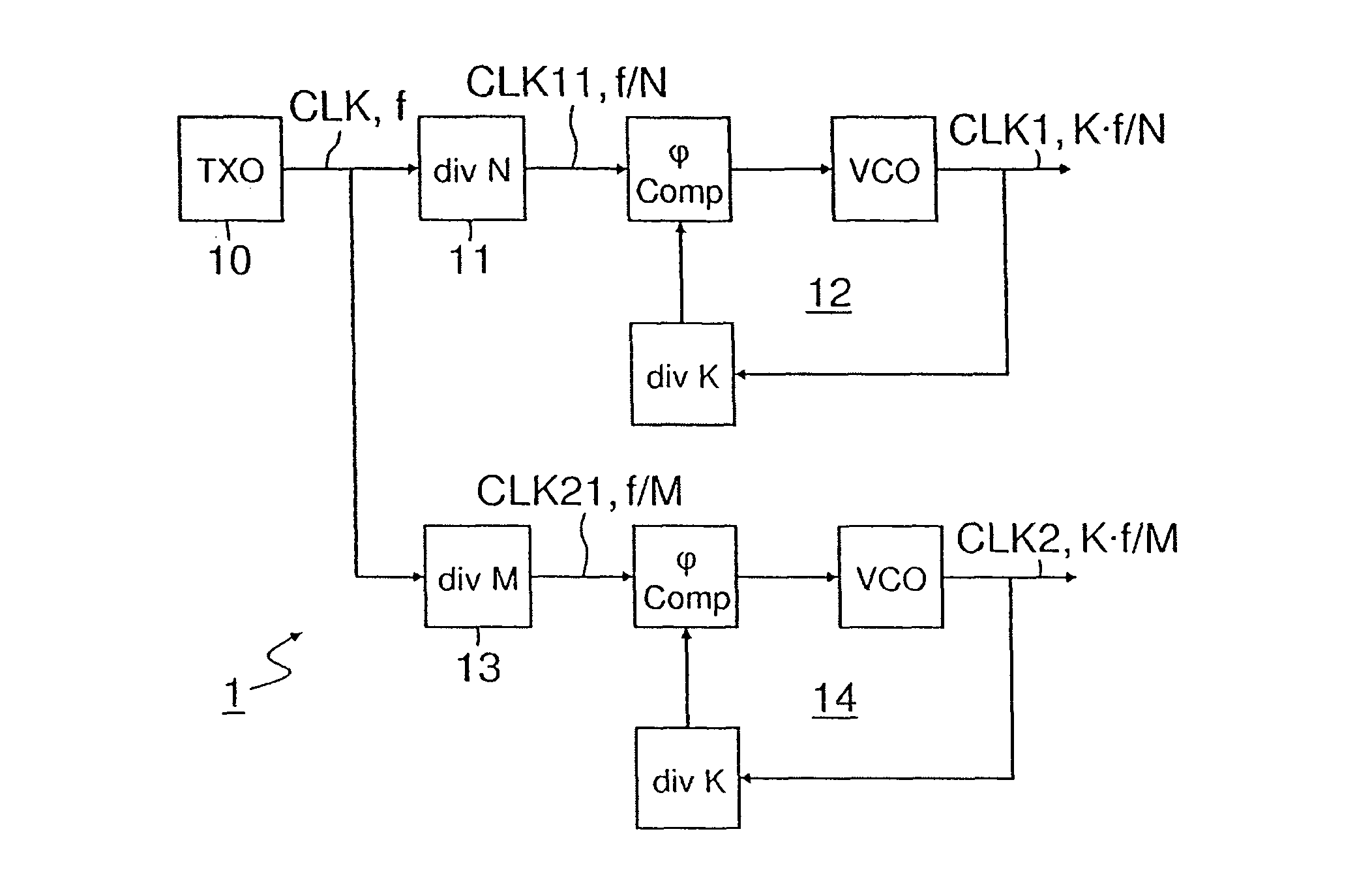

Digital Time Base Generator and Method for Providing a First Clock Signal and a Second Clock Signal

ActiveUS20100201408A1Easy to controlAccurate calculationWave based measurement systemsPulse automatic controlBase frequencySecond ancillary

A digital time base generator and method for providing a first clock signal and a second clock signal in which a base clock signal having a base frequency is generated to provide two clock signals of slightly different frequencies with defined time or phase delay. Here, the base frequency is divided by a first integer to produce a first auxiliary signal, the frequency of the first auxiliary signal is multiplied by a factor to obtain the first clock signal, the base frequency is further divided by a second integer to produce a second auxiliary signal, and the frequency of the second auxiliary signal is multiplied by the factor to obtain the second clock signal.

Owner:SIEMENS AG

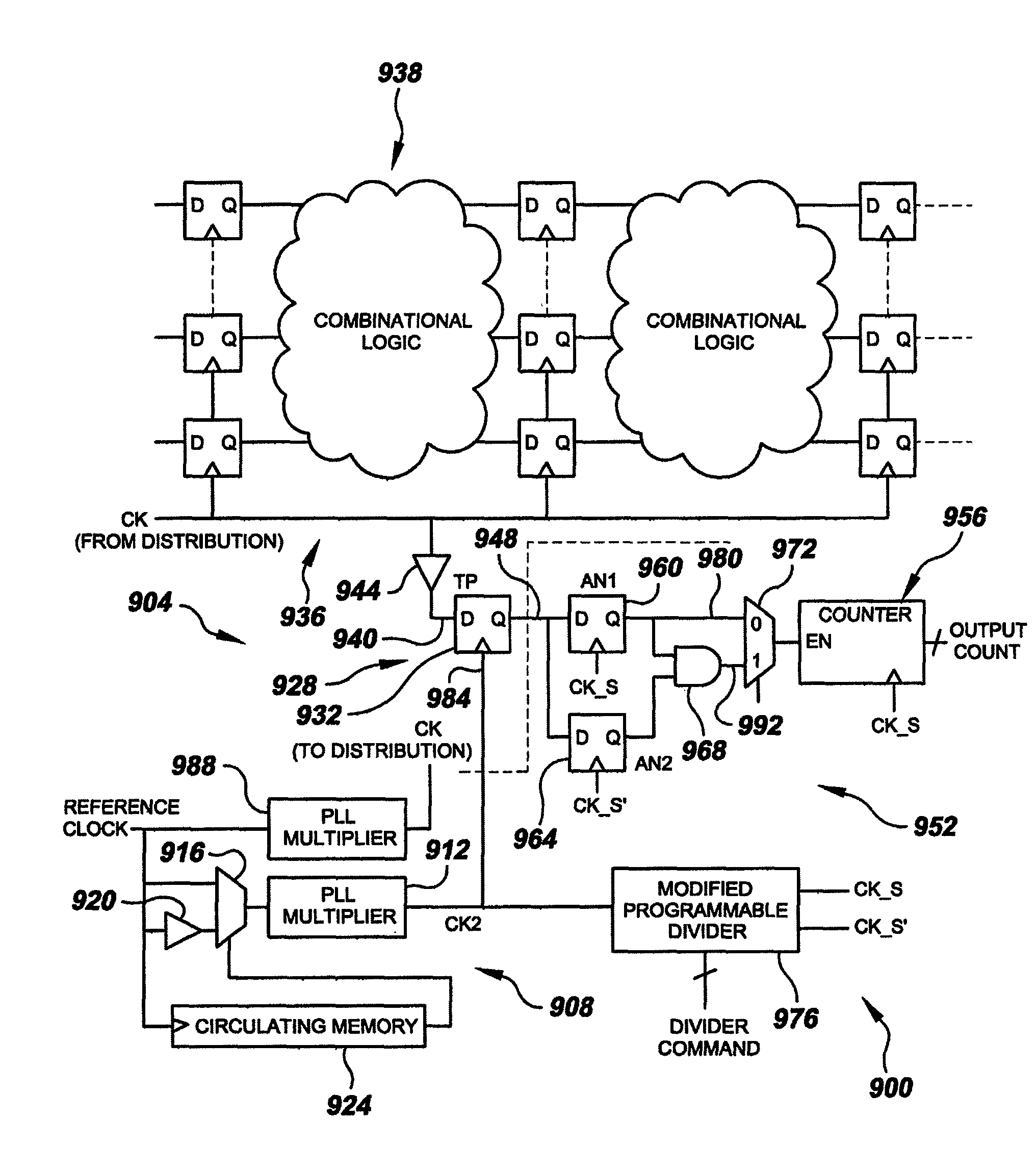

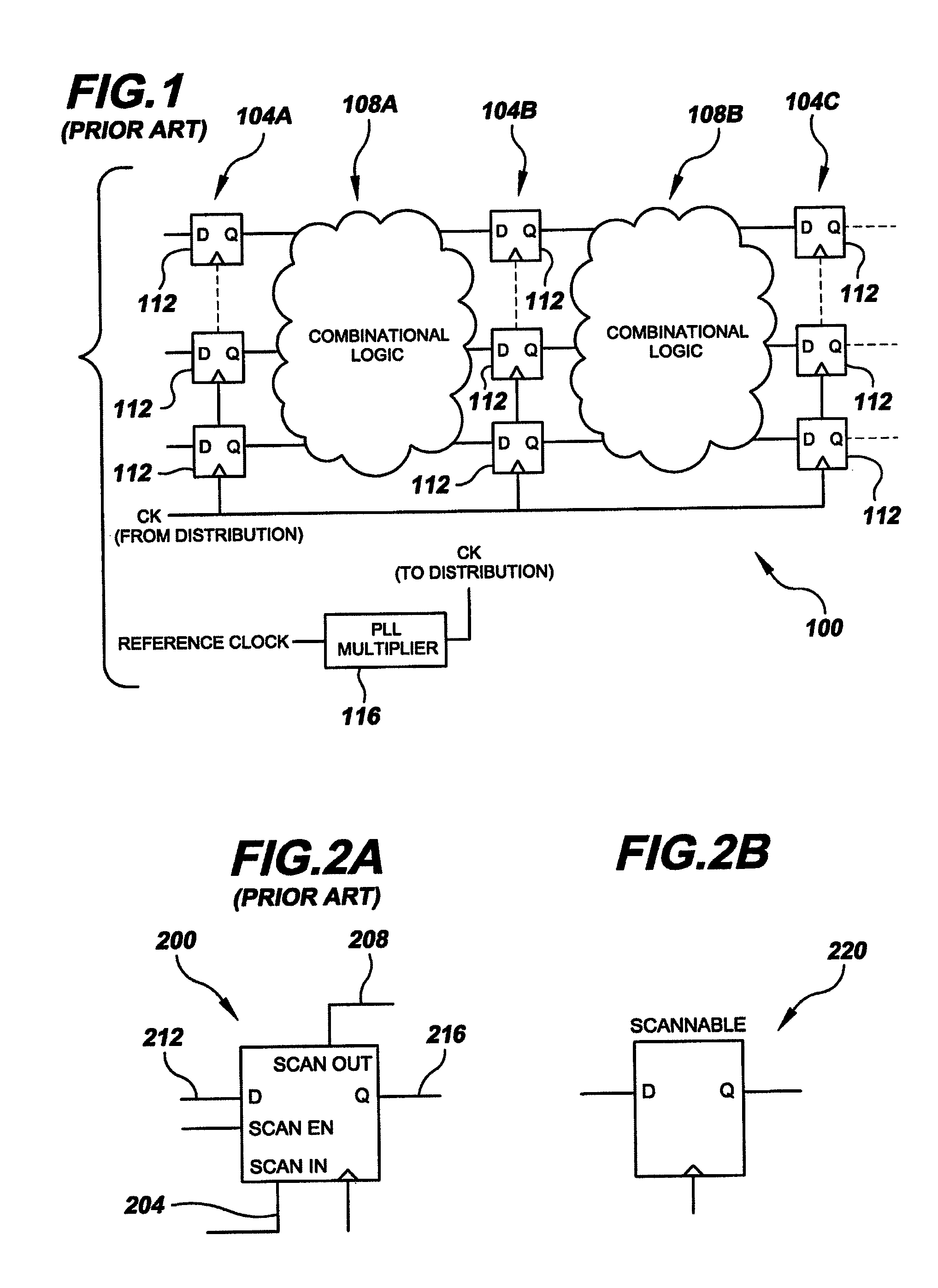

Systems and methods for testing and diagnosing delay faults and for parametric testing in digital circuits

InactiveUS7917319B2Noise figure or signal-to-noise ratio measurementElectronic circuit testingCircuit delayDigital electronics

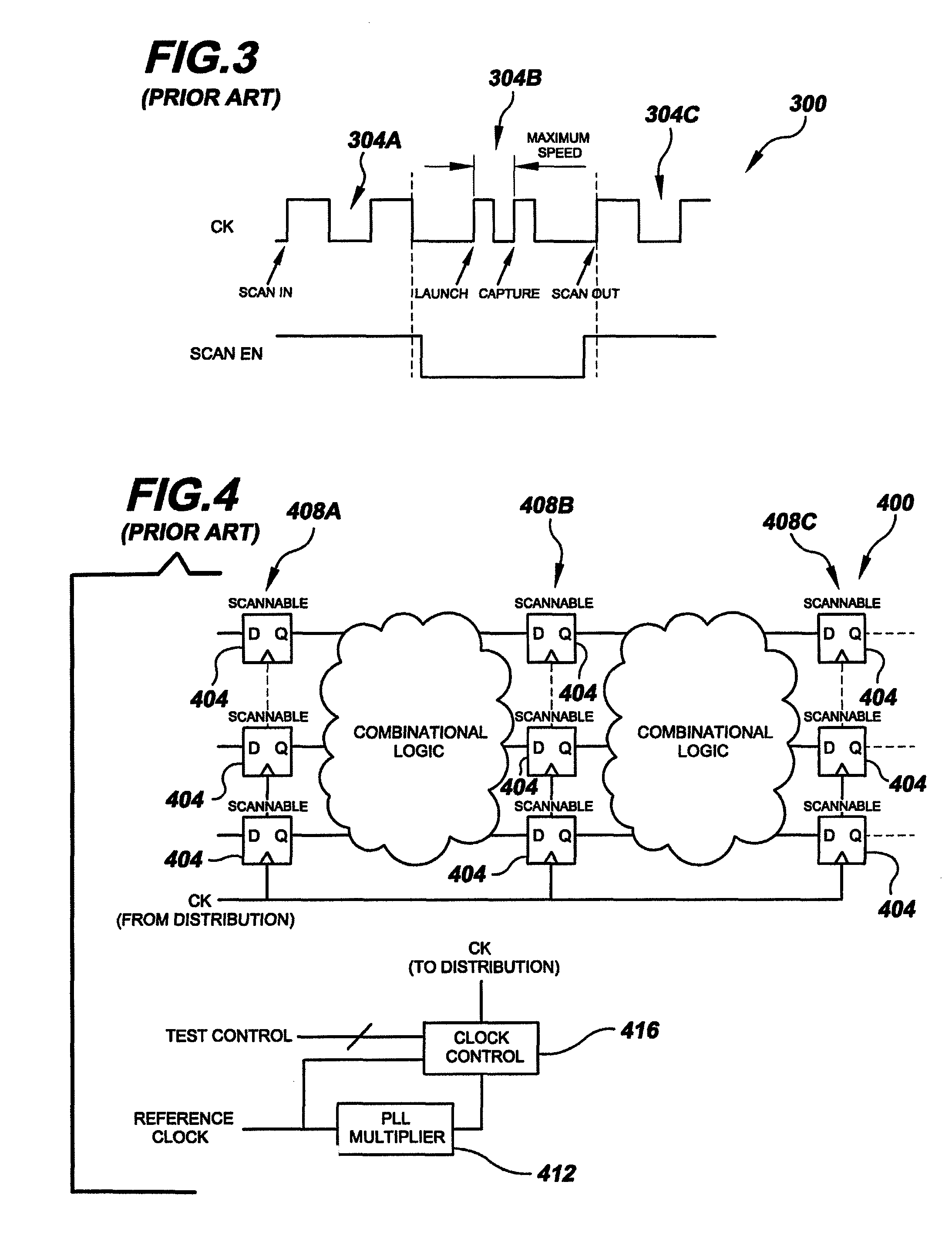

Delay-fault testing and parametric analysis systems and methods utilizing one or more variable delay time-base generators. In embodiments of the delay-fault testing systems, short-delay logic paths are provided with additional scan-chain memory elements and logic that, in conjunction with the one or more variable-delay time-base generators, provides the effect of over-clocking without the need to over-clock. Related methods provide such effective over-clocking. In embodiments of parametric analysis systems, test point sampling elements and analysis circuitry are clocked as a function of the output of the one or more variable-delay time-base generators to provide various parametric analysis functionality. Related methods address this functionality.

Owner:DFT MICROSYST

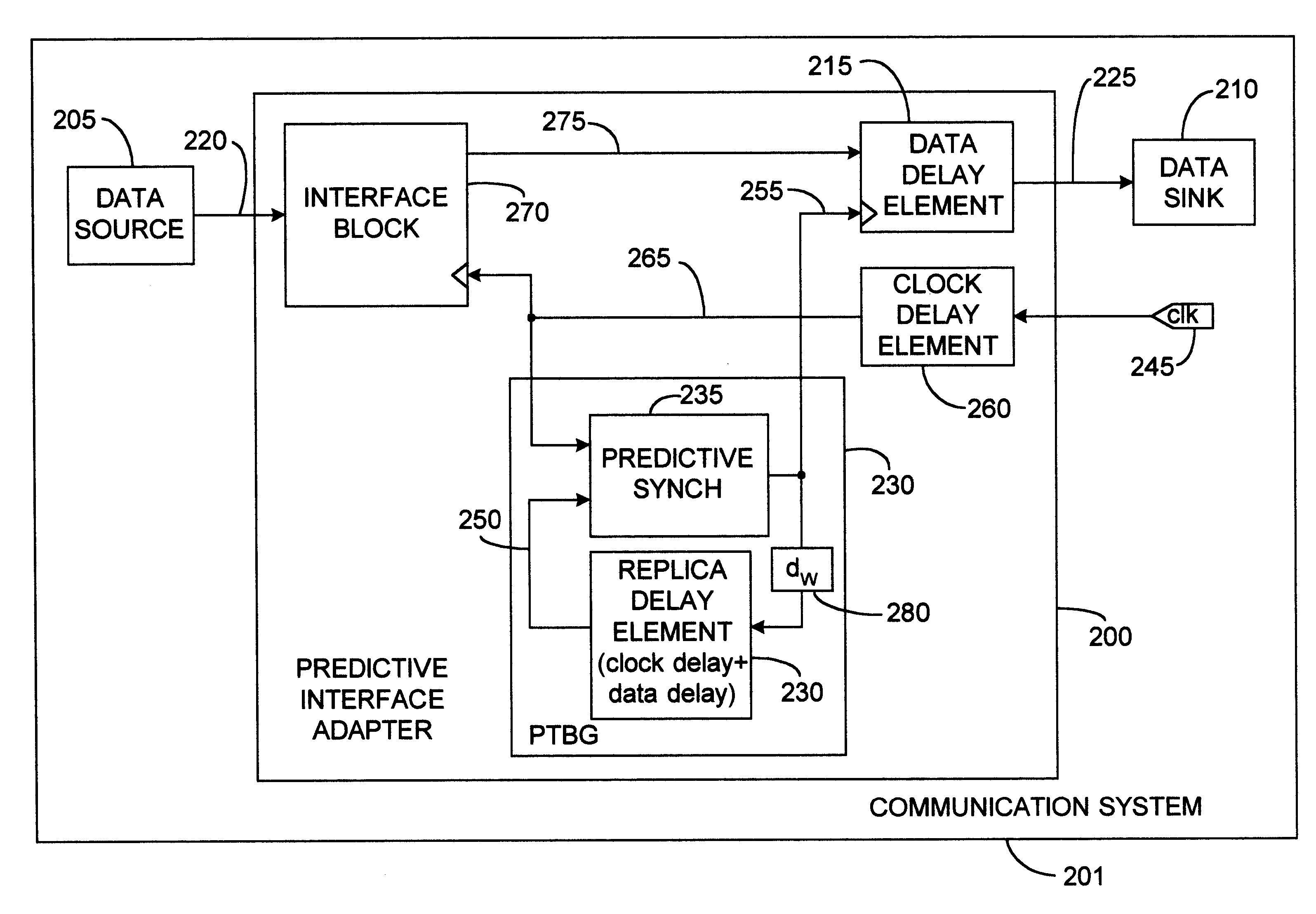

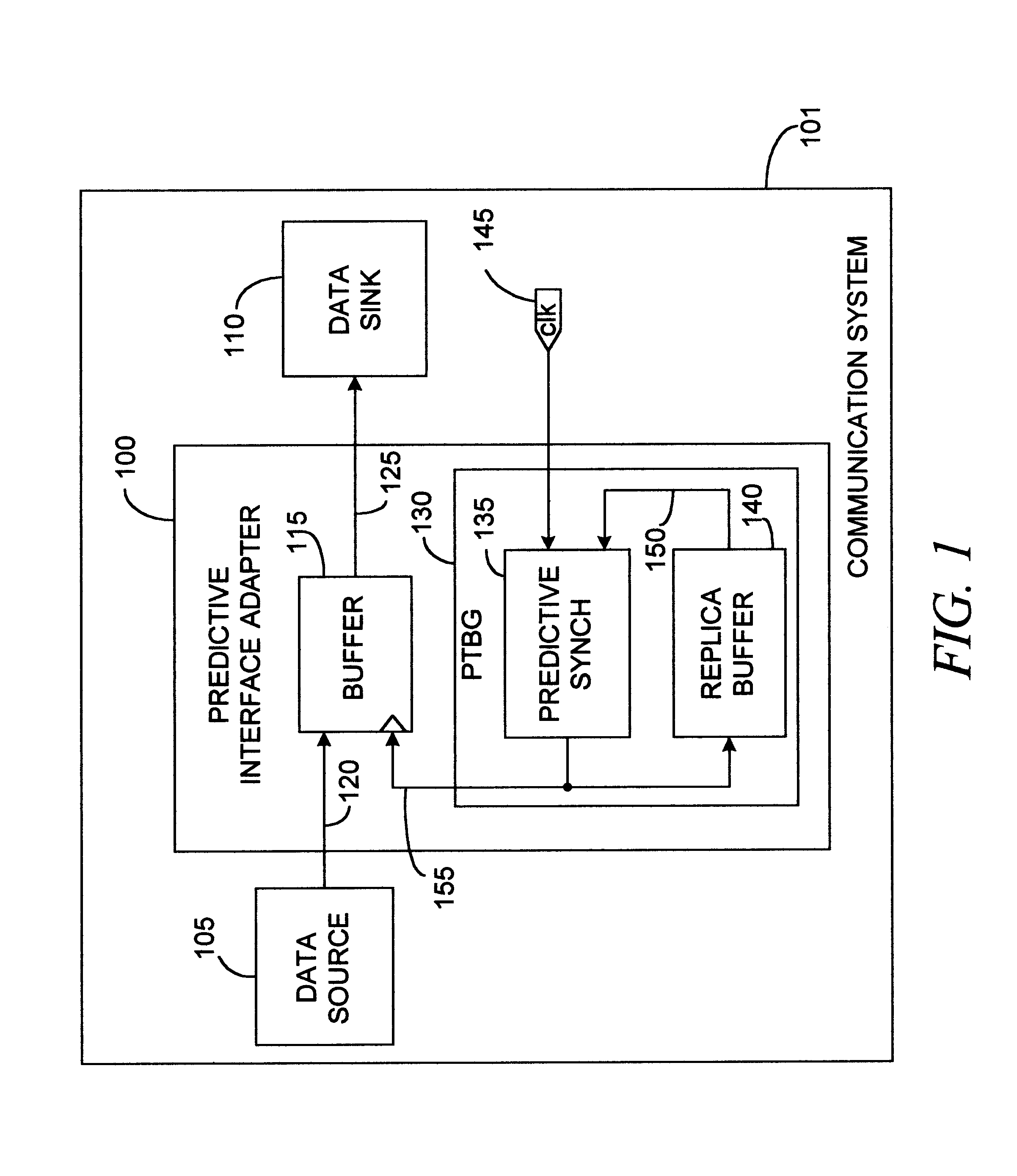

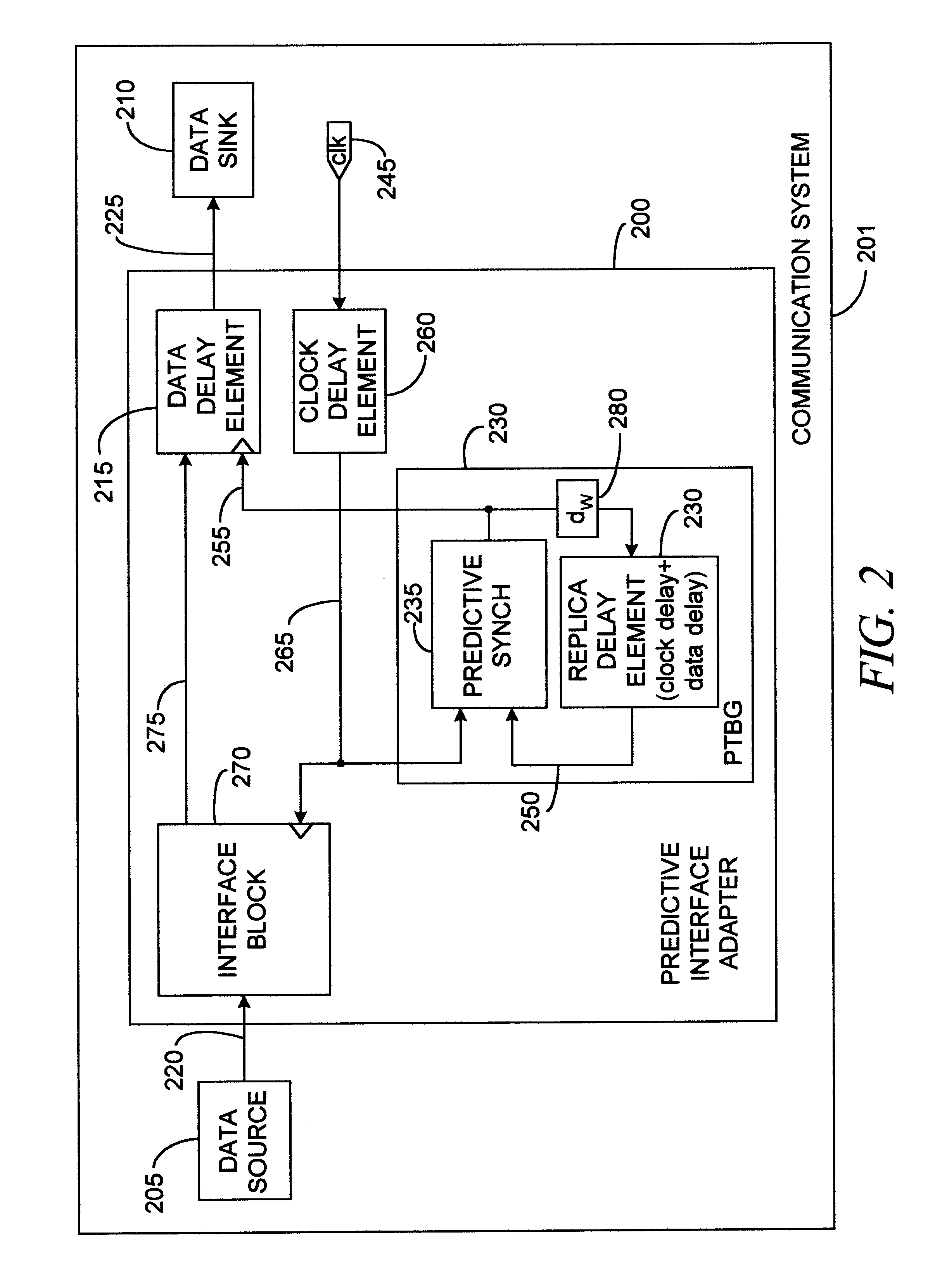

Multiprotocol computer bus interface adapter and method

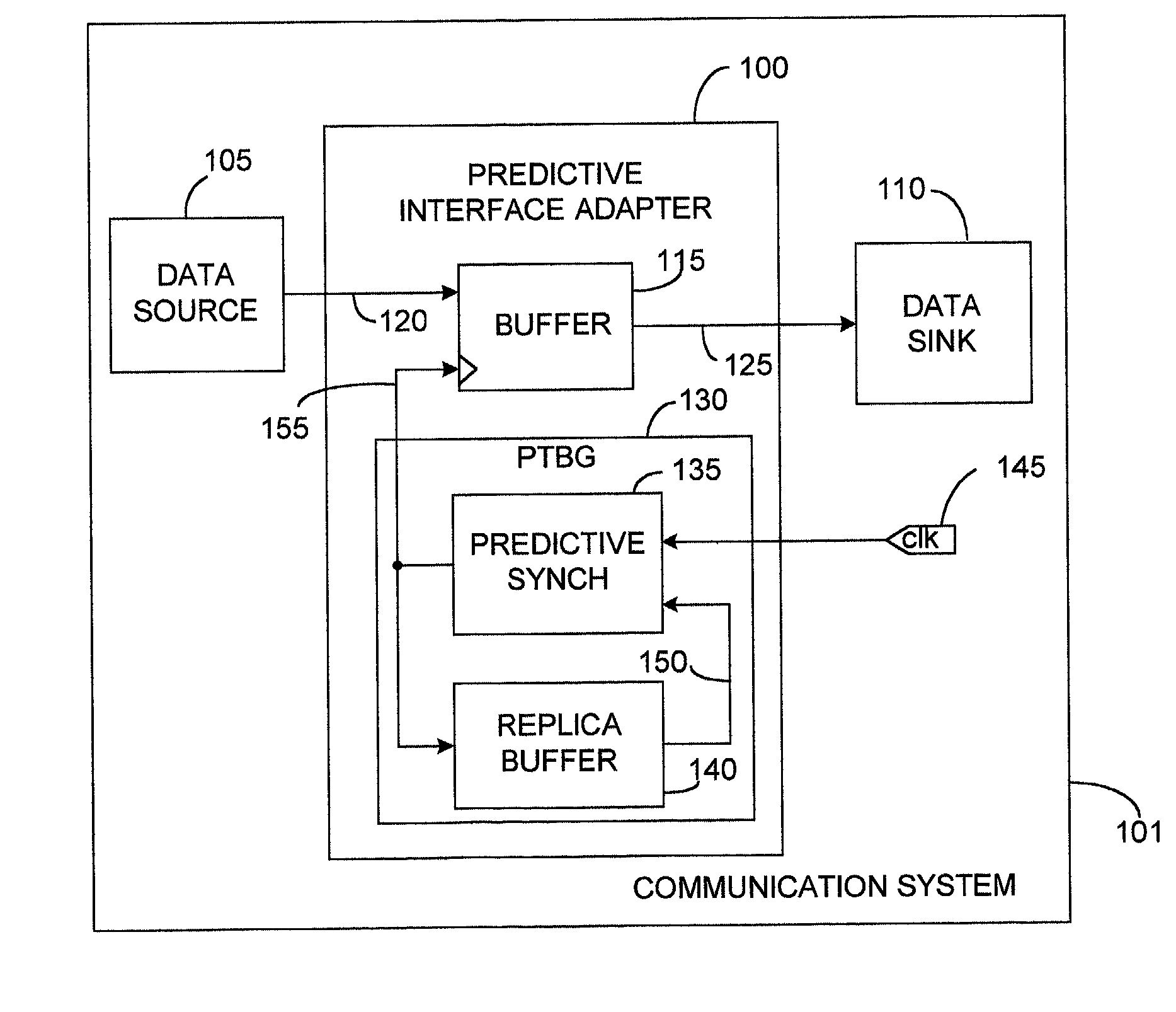

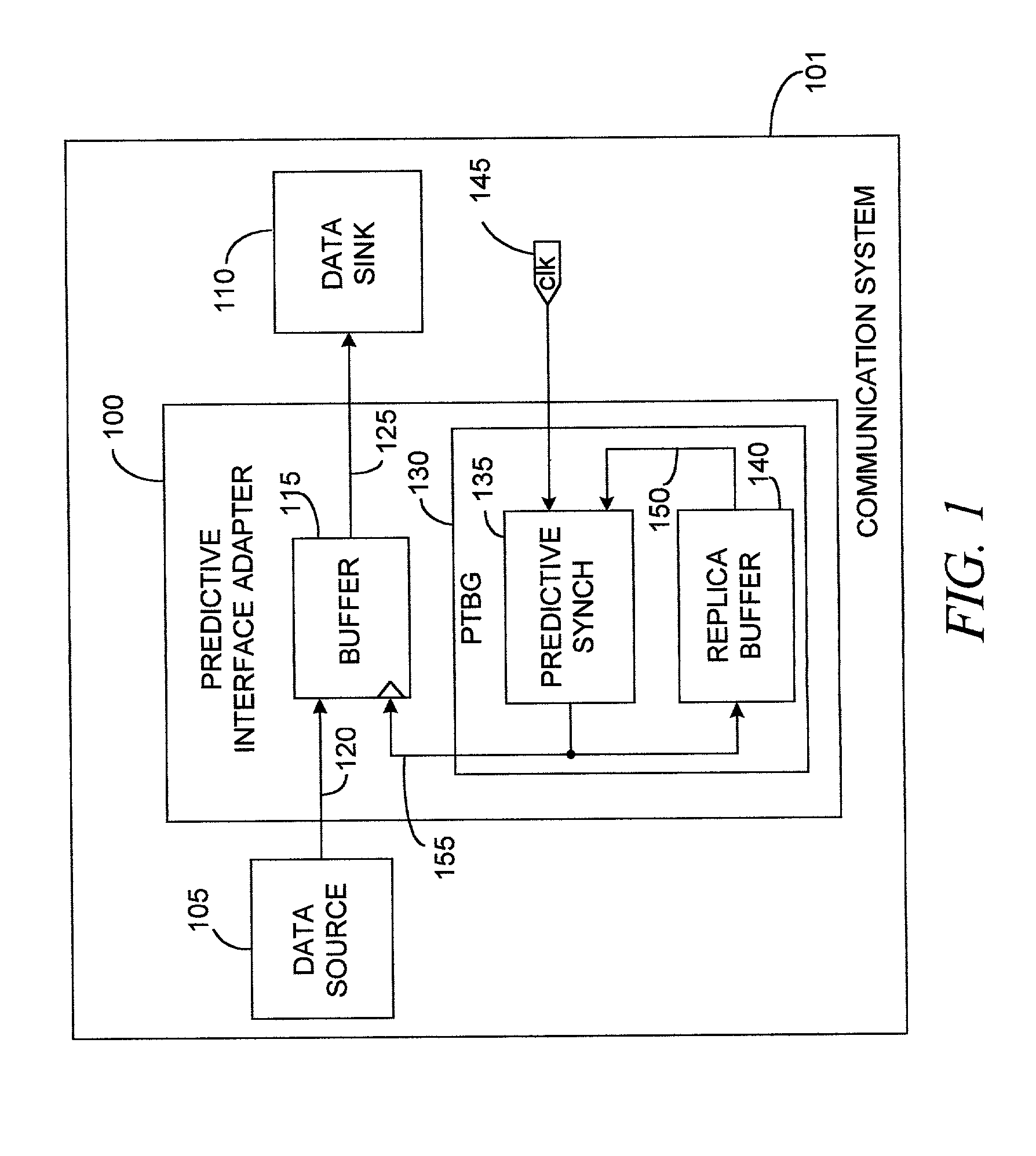

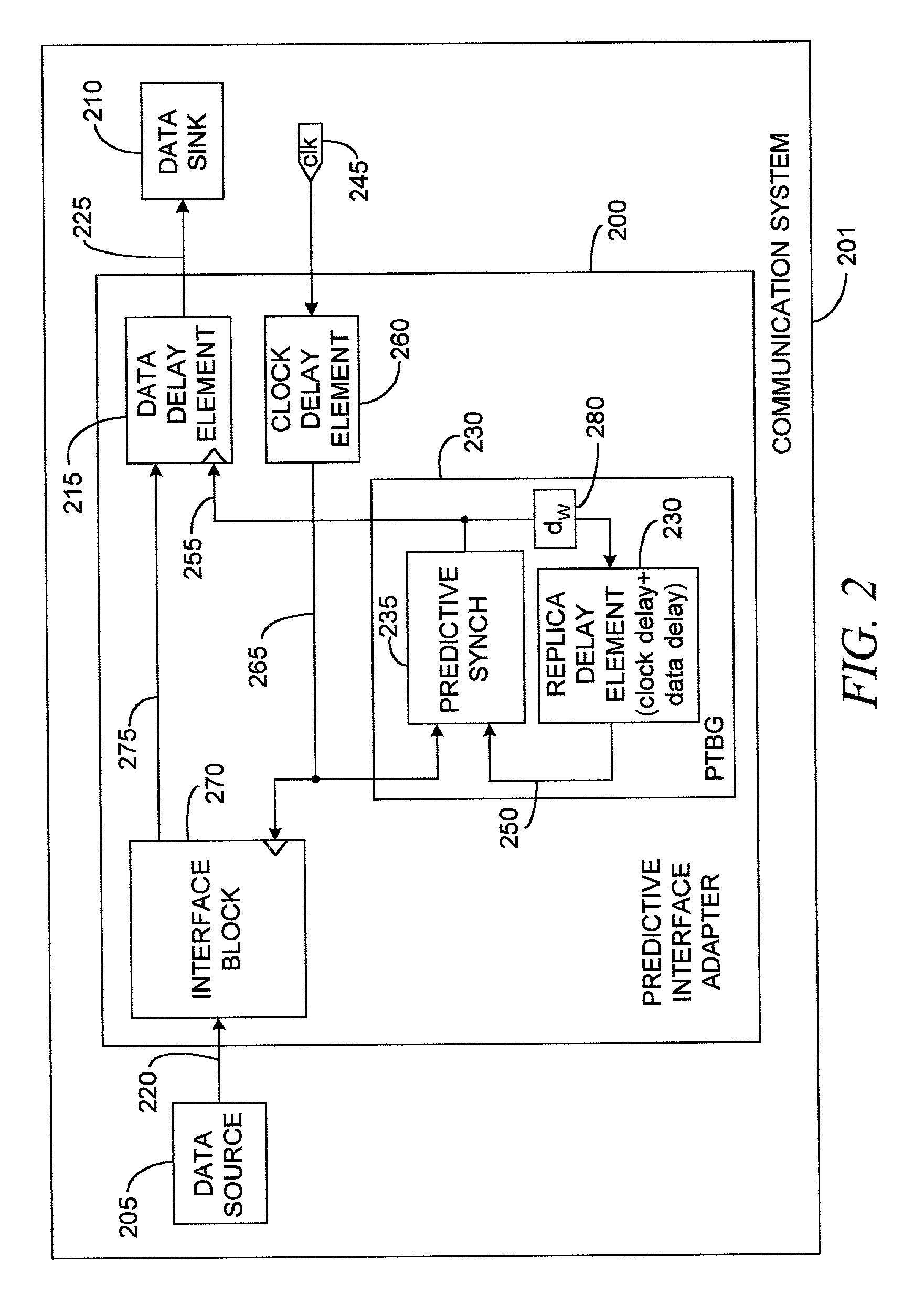

A predictive time base generator having predictive synchronizer and replica delay element coupled with the synchronizer feedback delay loop. The predictive time base generator receives a clock signal delayed by a predetermined clock delay and produces a predictive time signal advanced in time by an amount represented by the replica delay element. The replica delay element can replicate one or both of a predetermined clock delay and a predetermined data delay, substantially nullifying the respective delays in critical signal paths of a device. The replica delay element can include replicas of structure(s) found in an incoming clock path and an outgoing data path, such elements including, for example, voltage level shifters, buffers or data latches, multiplexers, wire element models, and the like. A predictive computer bus interface adapter which incorporates the aforementioned predictive time base generator also is provided. Such a predictive interface adapter can be adapted to be observant of stringent bus protocol timing budgets imposed under the PCI and PCI-X local bus protocol, and to be robust relative to variations in design and fabrication processes, and environmental operating conditions.

Owner:AVAGO TECH INT SALES PTE LTD

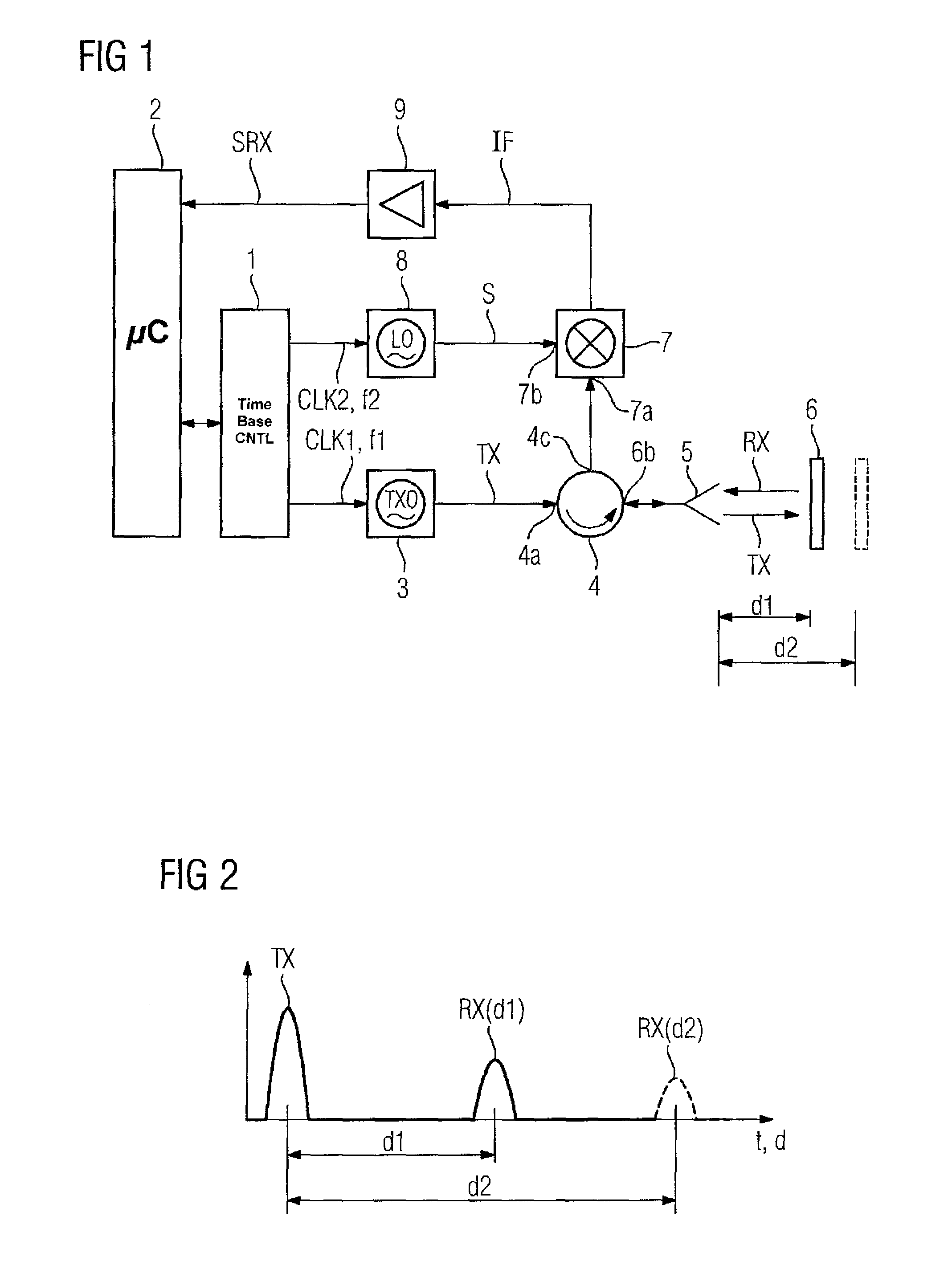

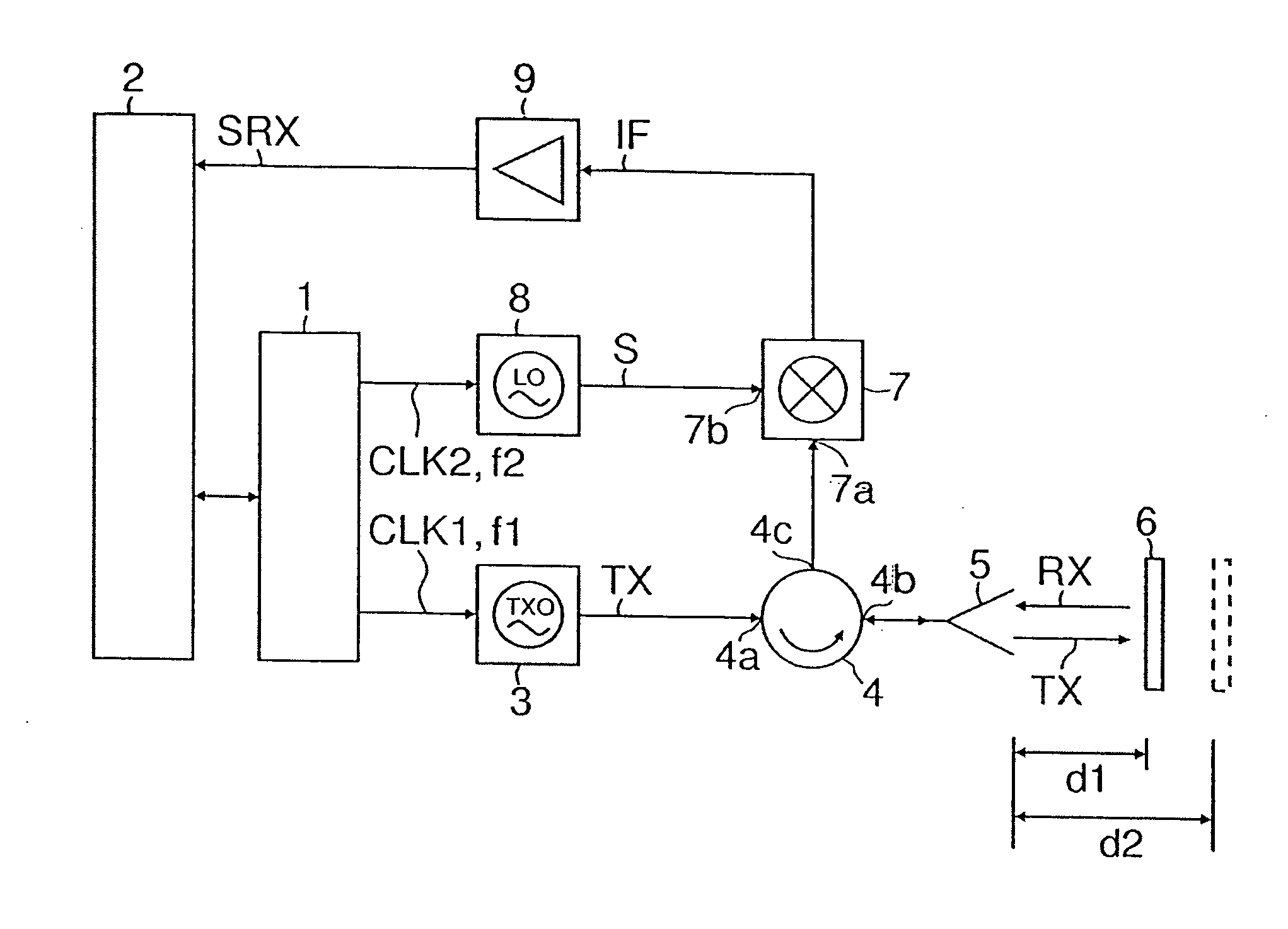

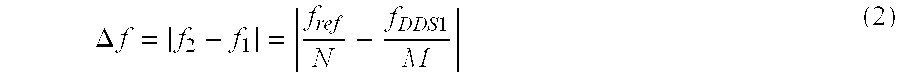

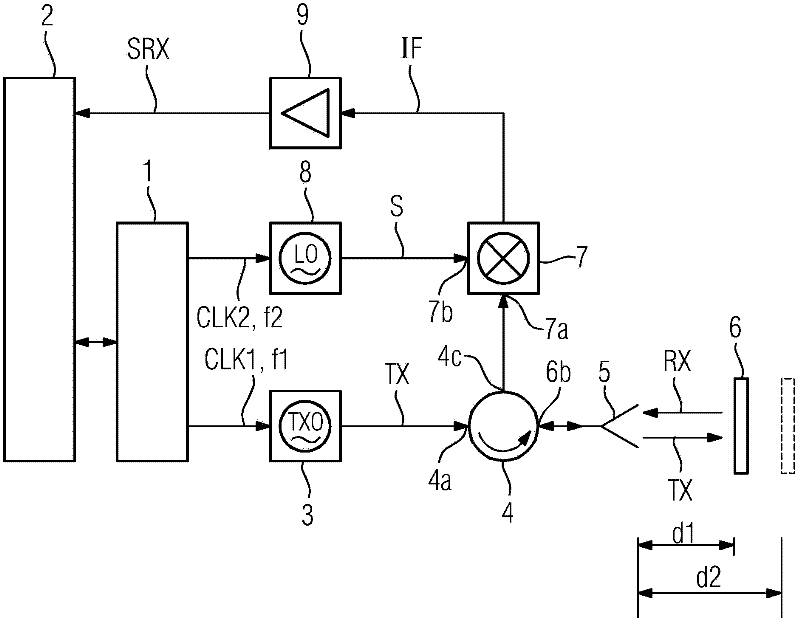

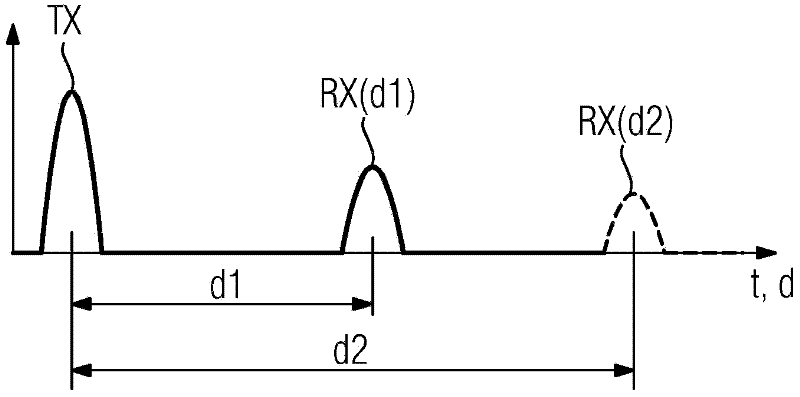

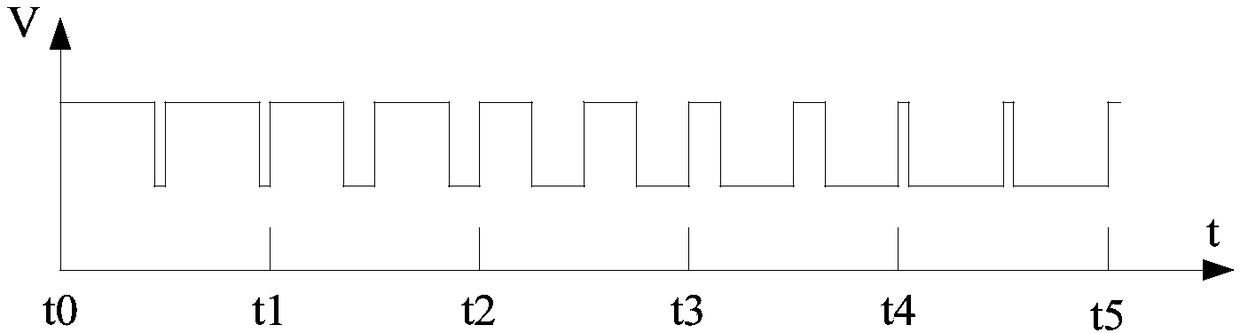

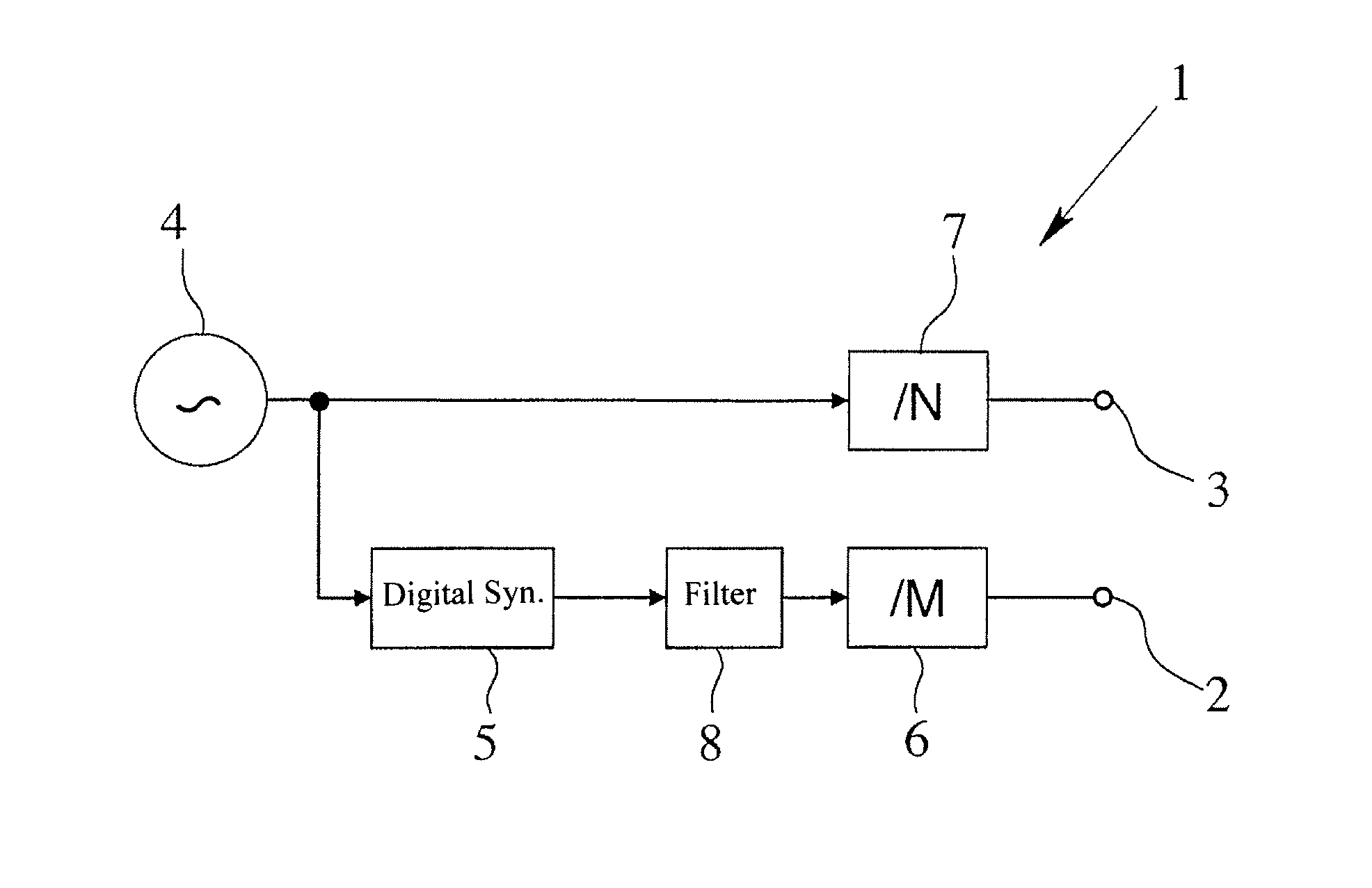

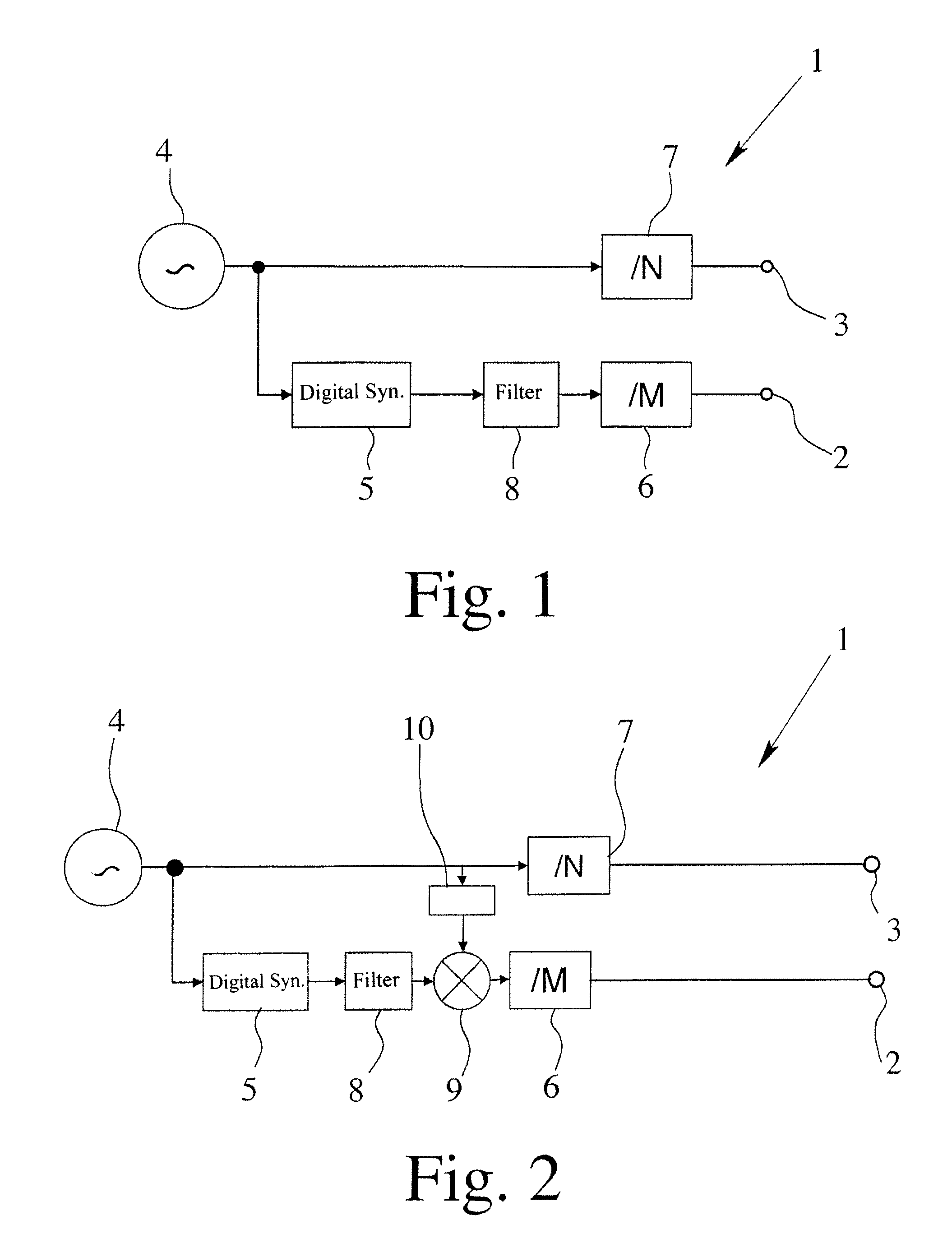

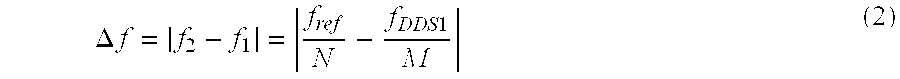

Frequency synthesizer for a level measuring device and a level measuring device

ActiveUS20110006811A1Phase resolutionAvoid noiseDigital data processing detailsOscillations generatorsLow noiseMeasurement device

A frequency synthesizer for a time base generator of a level measuring device which works according to the radar principle, with at least one first output for output of a first frequency signal, with at least one second output for output of a second frequency signal, and with a reference oscillator for producing a reference frequency signal, the first frequency signal and the second frequency signal having a small difference frequency relative to one another, the first frequency signal being producible by interaction of the reference oscillator with a direct digital synthesizer. The first frequency signal and second frequency signal can be generated with especially low noise by the second frequency signal being derived from the reference oscillator without interconnection of a direct digital synthesizer and the direct digital synthesizer being operated such that only a noise spectrum is produced which is at least partially minimized.

Owner:KROHNE MESSTECHNICK GMBH & CO KG

A time base generator and method for providing a first clock signal and a second clock signal

InactiveCN102655403AShorten the timeWave based measurement systemsPulse automatic controlClock rateEngineering

Owner:SIEMENS AG

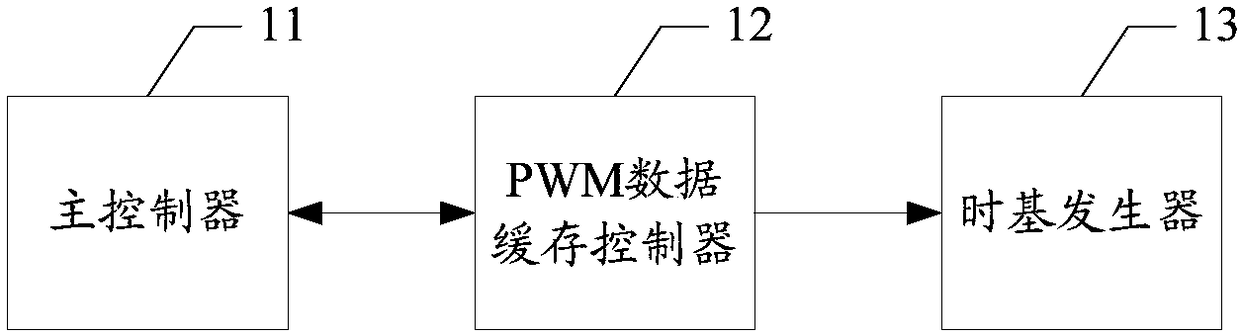

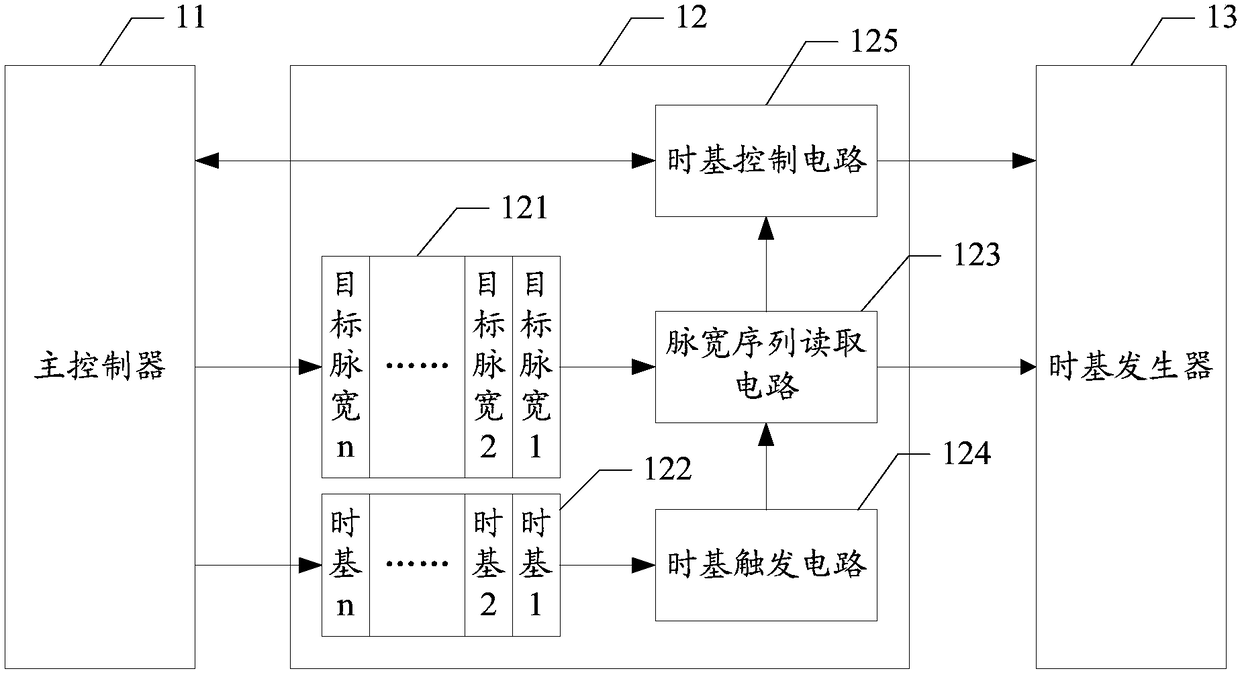

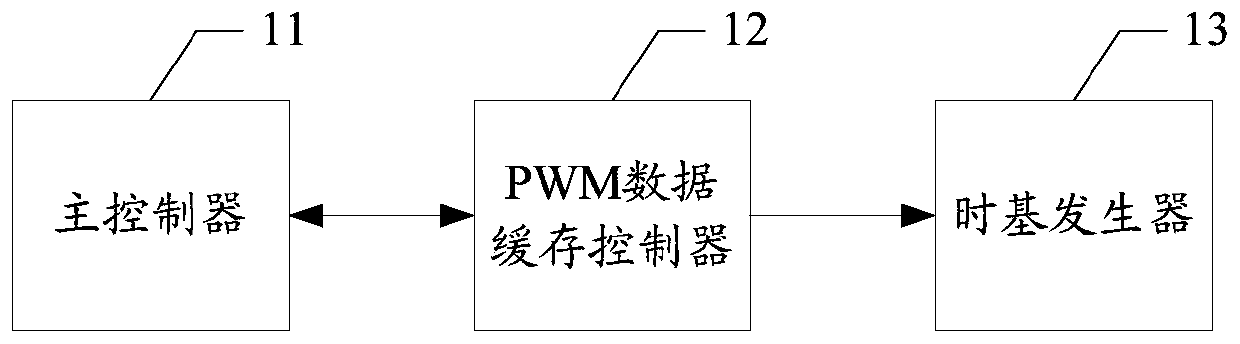

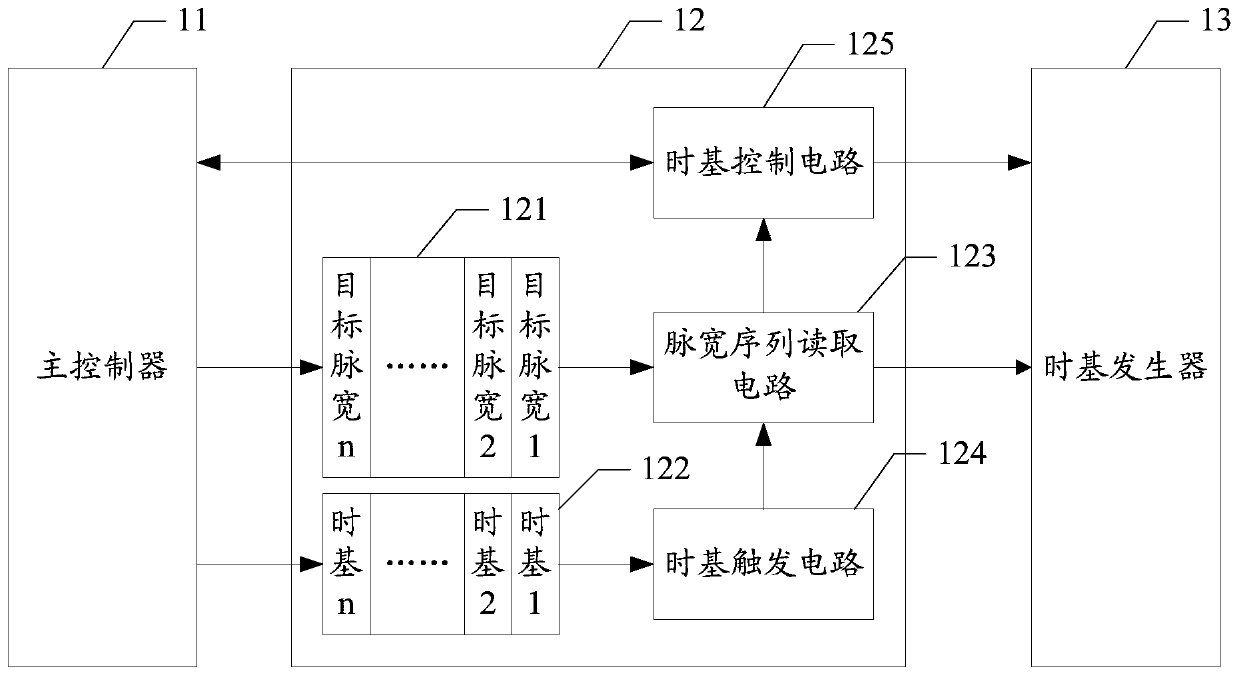

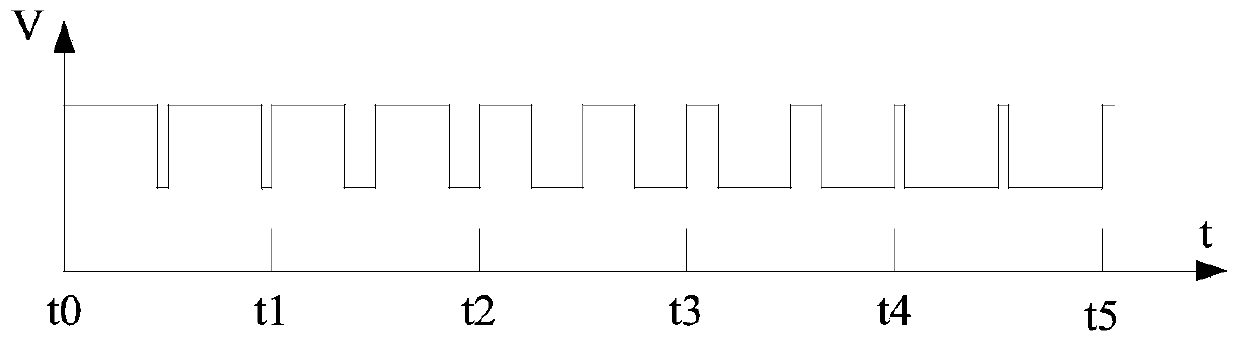

Intelligent lighting control system, intelligent lighting control method and intelligent lighting system

ActiveCN108064099AReduce capacity requirementsReduce computing power requirementsElectrical apparatusElectroluminescent light sourcesSmart lightingControl system

The invention relates to an intelligent lighting control system, an intelligent lighting control method and an intelligent lighting system. The intelligent lighting control system includes a main controller, a PWM data buffer controller and a time base generator; the main controller is suitable for receiving a dimming instruction inputted by a user, generating corresponding target pulse width adjustment parameters according to the dimming instruction, sending the target pulse width adjustment parameters to the PWM data buffer controller, and sending a PWM wave generation instruction to the PWMdata buffer controller; the PWM data buffer controller is suitable for storing the target pulse width adjustment parameters, and controlling the time base generator to generate PWM waves corresponding to the target pulse width adjustment parameters when receiving the PWM wave generation instruction; and the time base generator is suitable for generating the PWM waves corresponding to the target pulse width adjustment parameters, and inputting the generated PWM waves to an LED driving circuit. With the intelligent lighting control system, the intelligent lighting control method and the intelligent lighting system provided by the technical schemes of the invention adopted, the requirements of an LED lighting device for MCU computing performance during dimming can be lowered.

Owner:SHANGHAI EASTSOFT MICROELECTRONICS

Frequency synthesizer for a level measuring device and a level measuring device

A frequency synthesizer for a time base generator of a level measuring device which works according to the radar principle, with at least one first output for output of a first frequency signal, with at least one second output for output of a second frequency signal, and with a reference oscillator for producing a reference frequency signal, the first frequency signal and the second frequency signal having a small difference frequency relative to one another, the first frequency signal being producible by interaction of the reference oscillator with a direct digital synthesizer. The first frequency signal and second frequency signal can be generated with especially low noise by the second frequency signal being derived from the reference oscillator without interconnection of a direct digital synthesizer and the direct digital synthesizer being operated such that only a noise spectrum is produced which is at least partially minimized.

Owner:KROHNE MESSTECHNICK GMBH & CO KG

Time Base Generator and Method for Providing a First Clock Signal and a Second Clock Signal

ActiveUS20120223743A1Short lock timeMultiple input and output pulse circuitsWave based measurement systemsClock rateTime base generator

A time base generator and method for providing a first clock signal and a second clock signal comprising generating the first clock signal at a first clock frequency, dividing the first clock frequency by a first integer to produce a first auxiliary signal, dividing the second clock signal by a second integer to produce a second auxiliary signal, generating an error signal by individually weighting and comparing cycle durations or phasing of the first and second auxiliary signals, and generating the second clock signal by a voltage-controlled oscillator controlled by the error signal such that two clock signals of slightly different frequencies with defined time or phase delay are provided.

Owner:SIEMENS AG

Digital time base generator and method for providing a first clock signal and a second clock signal

ActiveUS8207762B2Easy to controlAccurate calculationWave based measurement systemsPulse automatic controlBase frequencyVIT signals

A digital time base generator and method for providing a first clock signal and a second clock signal in which a base clock signal having a base frequency is generated to provide two clock signals of slightly different frequencies with defined time or phase delay. Here, the base frequency is divided by a first integer to produce a first auxiliary signal, the frequency of the first auxiliary signal is multiplied by a factor to obtain the first clock signal, the base frequency is further divided by a second integer to produce a second auxiliary signal, and the frequency of the second auxiliary signal is multiplied by the factor to obtain the second clock signal.

Owner:SIEMENS AG

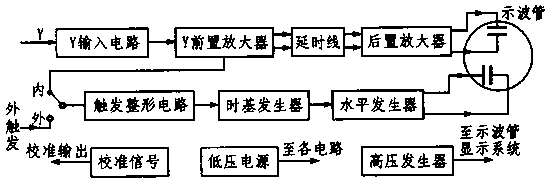

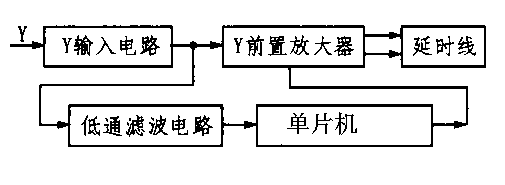

Universal oscilloscope with storage function

InactiveCN103954818AObserve the waveformObserved amplitudeDigital variable displayMicrocomputerMicrocontroller

The invention discloses a universal oscilloscope with a storage function, and belongs to the field of electronic measuring instruments. The universal oscilloscope comprises a Y input circuit, a Y front amplifying circuit, a delay line, a rear amplifying circuit, an oscilloscope tube, a levelness generator, a time-base generator, a trigger waveshaping circuit, a low-pass filter circuit and a single-chip microcomputer. The universal oscilloscope can store measured information in real time and replay an aperiodic single-pulse signal as required or in a one step mode or continuously, and an engineer can completely observe the waveform, amplitude and pulse width of the signal.

Owner:周美玲

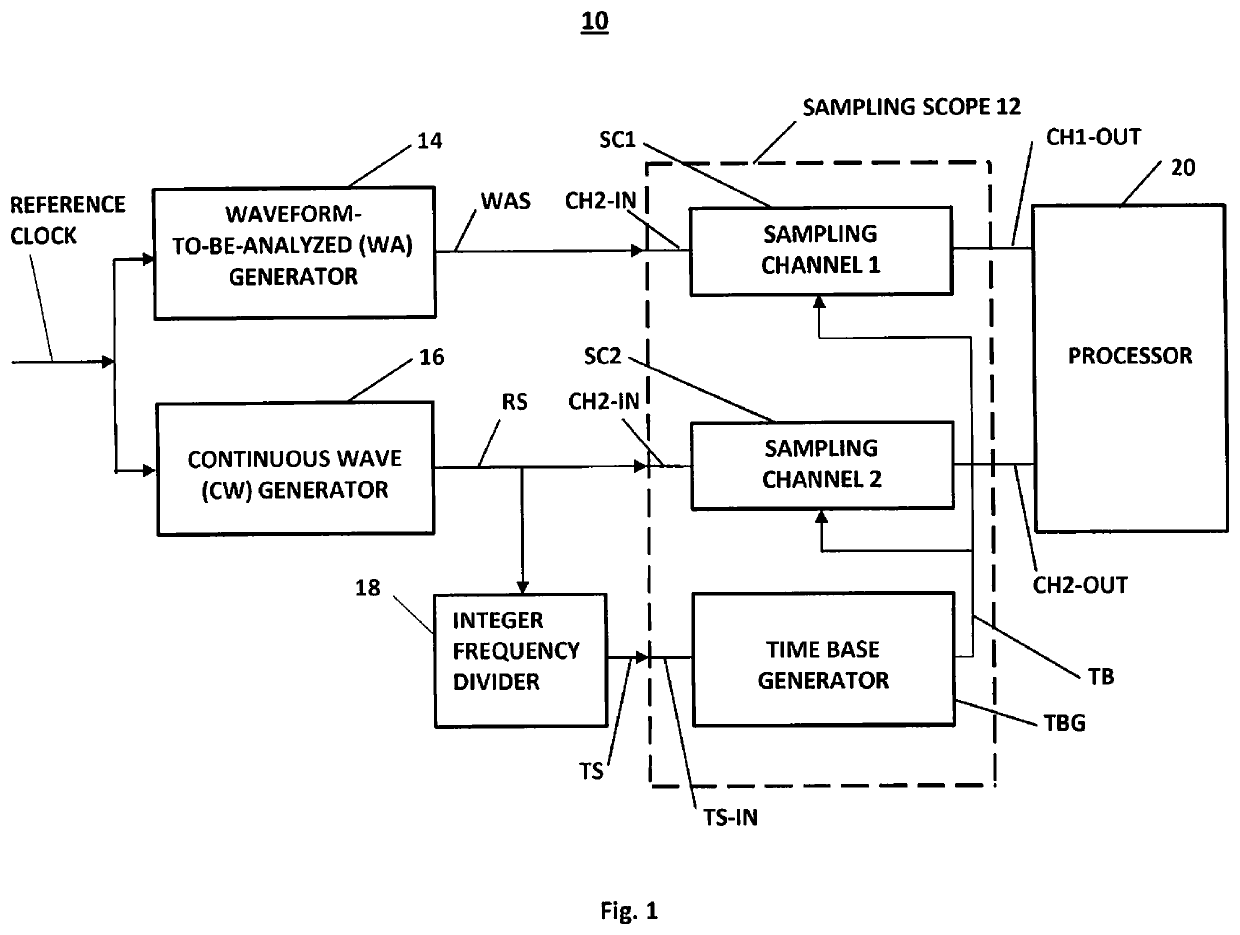

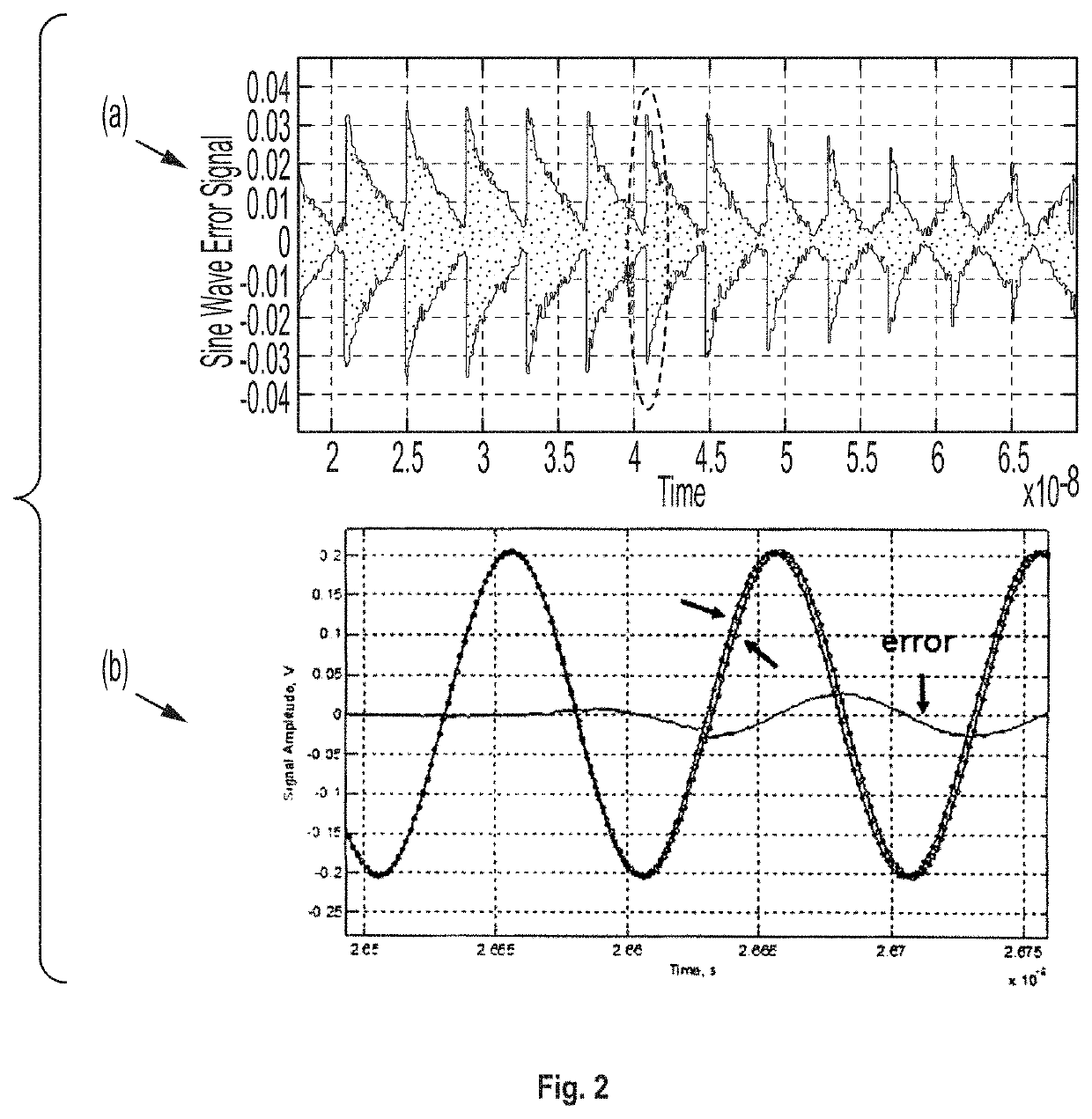

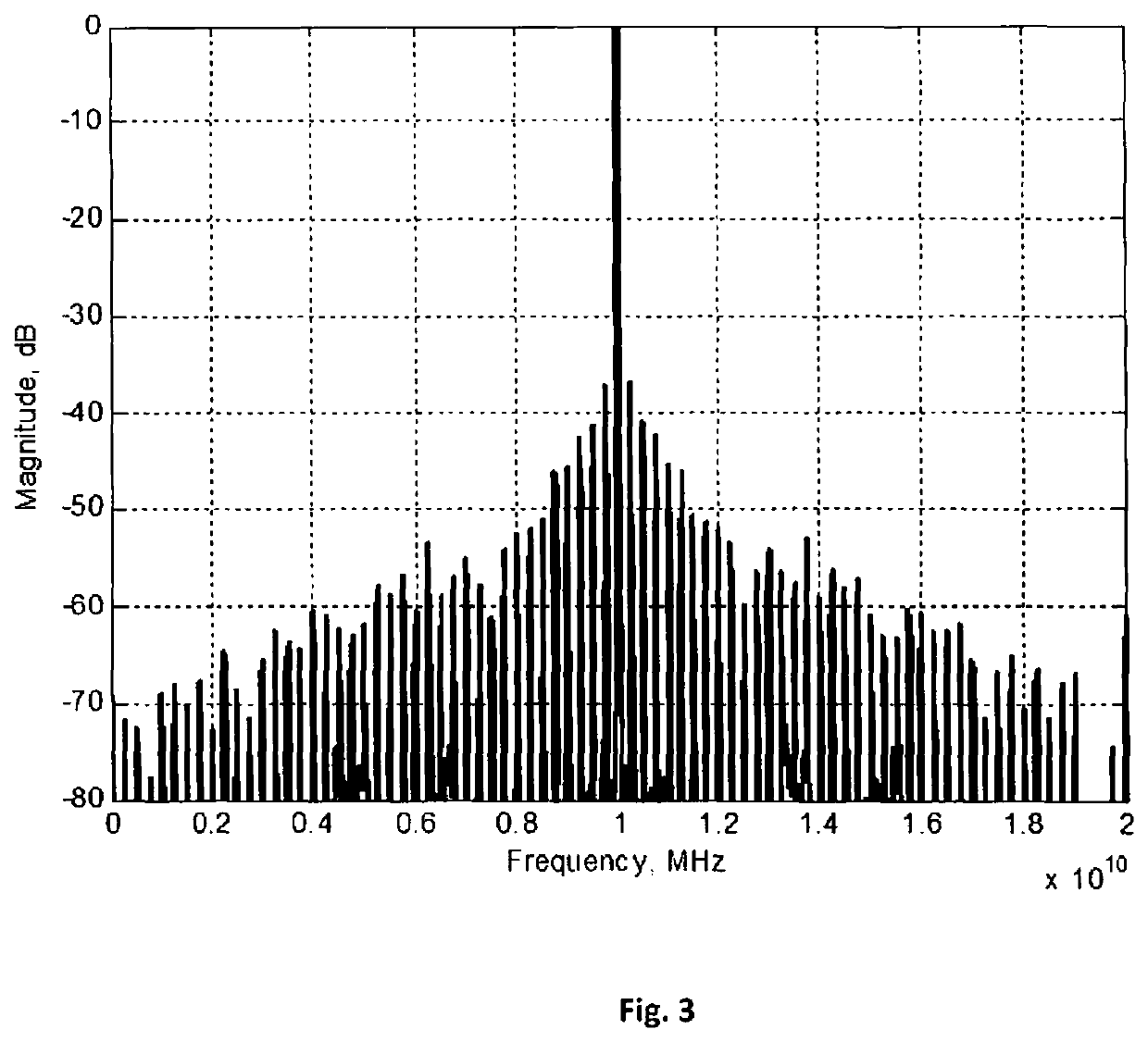

Time base correction method for high accuracy sampling scope-based measurements

ActiveUS10534018B1Reducing time base-caused errorDigital variable displayTesting/calibration of speed/acceleration/shock measurement devicesEngineeringComputational physics

A method and apparatus for resolving time base-generated errors from sampling scope-based measurements. Mutually synchronized repetitive waveform-to-be-analyzed signals (WAS) and repetitive sinusoidal reference signals (RS) are respectively applied to a first channel and a second channel of a sampling scope. A time base generator applies a sampling signal to the first and second channels. An average sine wave period Tav for k samples of RS is determined, followed by determination of phase error φk for each of the k samples, corresponding to phase differences between an ideal sine wave signal and the applied reference sinusoidal signal. Time base error values dk for k samples are calculated from dk=φk*Tav / 2π. Error values dk correct time base errors in the sampling signal, and the WAS is re-sampled at sampling times adjusted by dk.

Owner:GUZIK TECHN ENTERPRISES

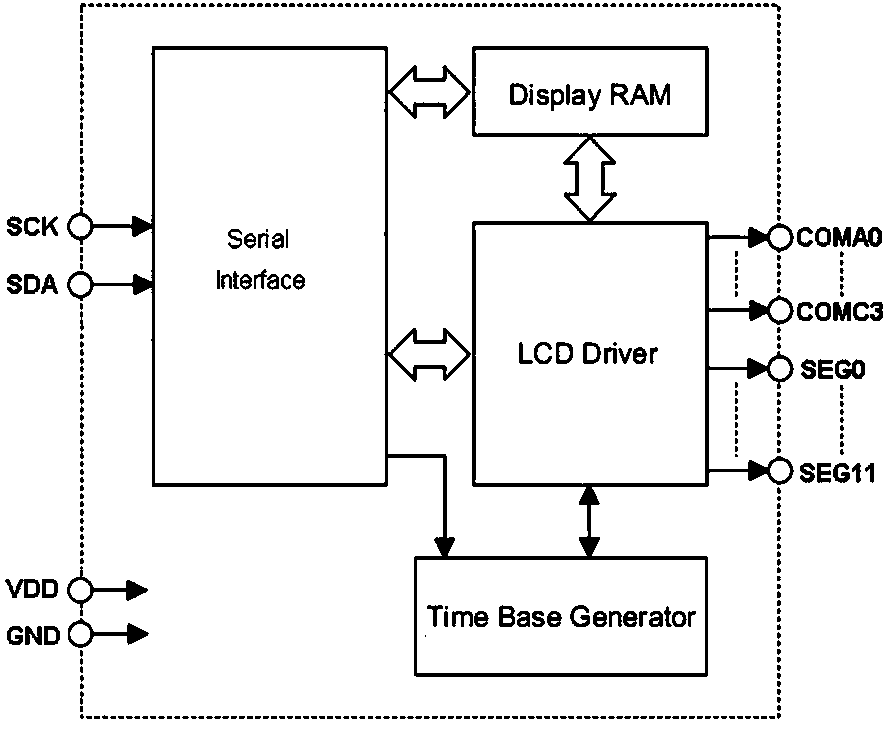

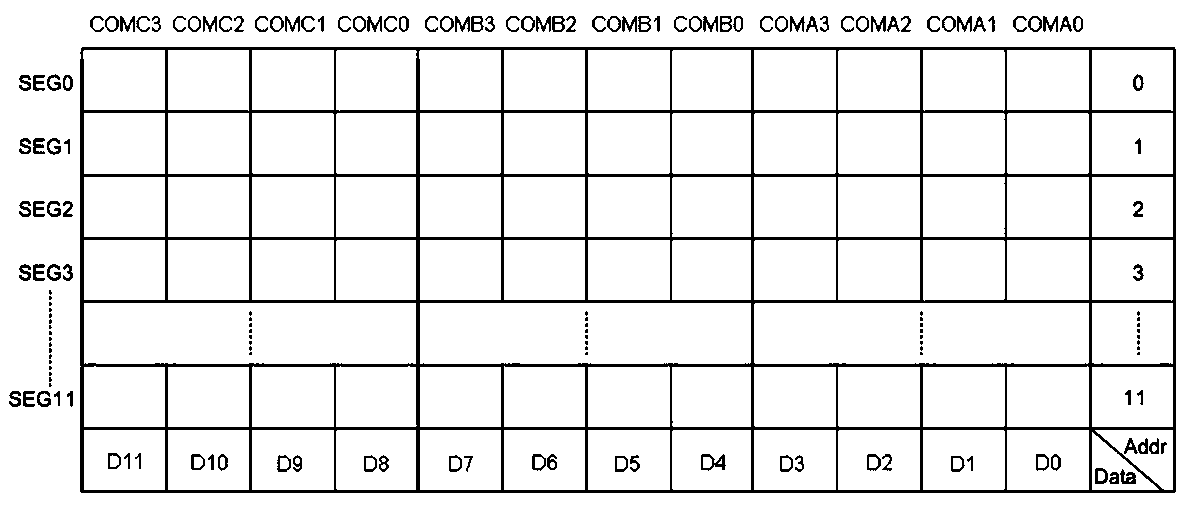

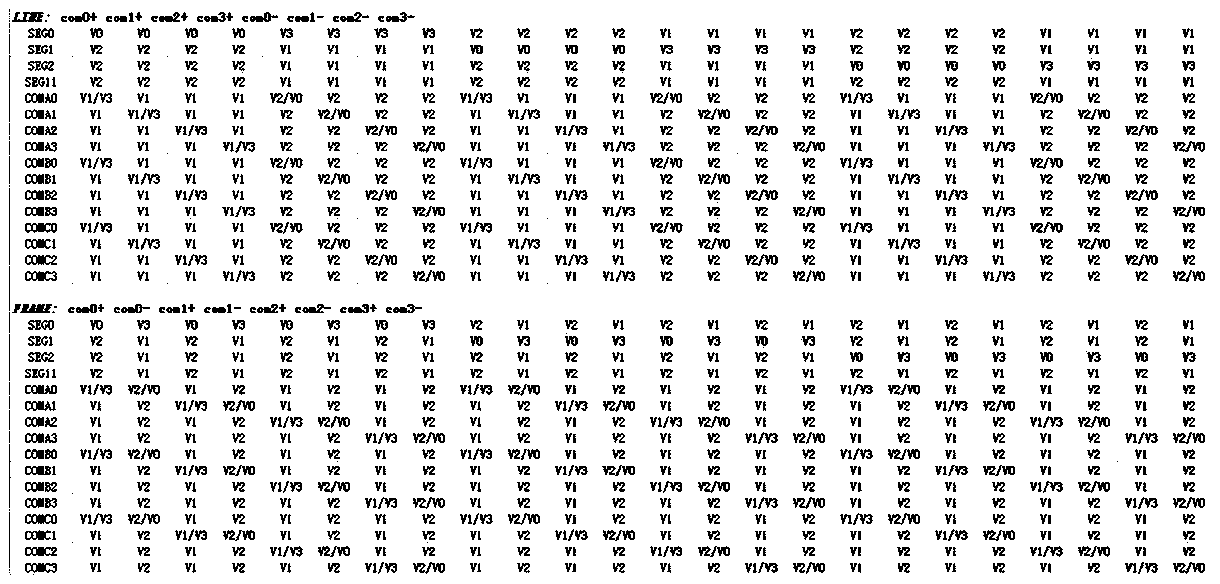

Liquid crystal driving chip capable of reducing number of pins

ActiveCN110718201AReduce the numberReduced pin countStatic indicating devicesHemt circuitsMechanical engineering

The invention discloses a liquid crystal driving chip capable of reducing the number of pins, and belongs to the technical field of liquid crystal driving chips. The liquid crystal driving chip capable of reducing the number of pins comprises an LCD drive and bias circuit, a display RAM, a time base generator, a serial interface module, a serial port module and a serial port module. The LCD driving and biasing circuit, the display RAM and the time base generator are all connected with the serial interface module; the display RAM is connected with the LCD driving and biasing circuit; the time base generator is connected with the LCD driving and biasing circuit, four male electrodes COM and twelve segment electrodes SEG are arranged on the LCD driving and biasing circuit, each male electrodeCOM corresponds to three paths of COM output ends, and each segment electrode SEG corresponds to one path of SEG output end. According to the liquid crystal driving chip capable of reducing the number of the pins, the number of the pins is reduced, and cost is reduced.

Owner:厦门骏陆科技有限公司

Systems, apparatus, methods and computer program products for providing ATSC interoperability

Owner:ROHDE & SCHWARZ GMBH & CO KG

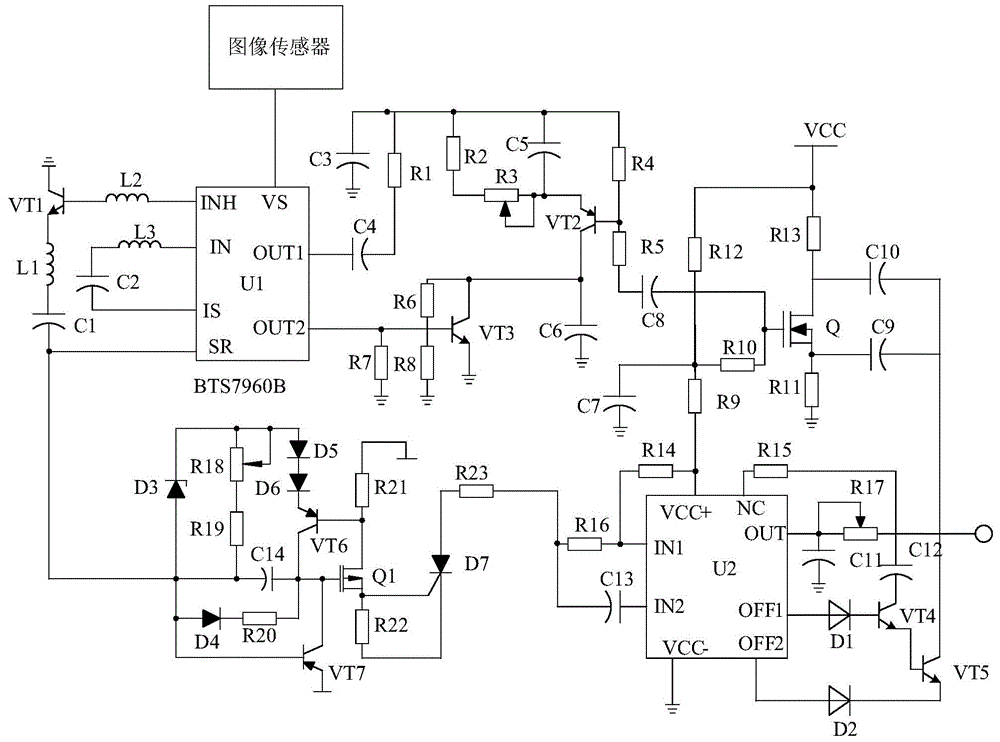

Image processing system based on broad pulse trigger circuit

InactiveCN104917932AGuaranteed treatment effectAvoid distortionTelevision system detailsColor television detailsResistorTime base generator

The invention discloses a stable image processing system comprising a image sensor, an image processing circuit connected with the image sensor, a time base generation circuit connected with the image processing circuit, a signal filtering circuit simultaneously connected with the image processing circuit and the time base generation circuit and a bias amplifying circuit connected with the time base generation circuit. The stable image processing system is characterized by further comprising a phase-shift circuit connected with the bias amplifying circuit; the phase-shift circuit comprises a phase-shift chip U2, a triodeVT4, a triodeVT5, a resistor R14, a capacitor C3 and the like; one end of the resistor R14 is connected with a VCC+ pin of the phase-shift chip U2, and the other end of the resistor R14 is connected with an IN1 pin of the phase-shift chip U2; a cathode of the capacitor C3 is connected with the IN1 pin of the phase-shift chip U2 through a resistor R16, and an anode of the capacitor C3 is connected with an IN2 pin of the phase-shift chip U2. Compared with the prior art, the stable image processing system is provided with the phase-shift circuit to ensure processing effect of the processing system as the voltage is unstable, thus image signal distortion after processing never occurs.

Owner:CHENGDU CHUANGTU TECH

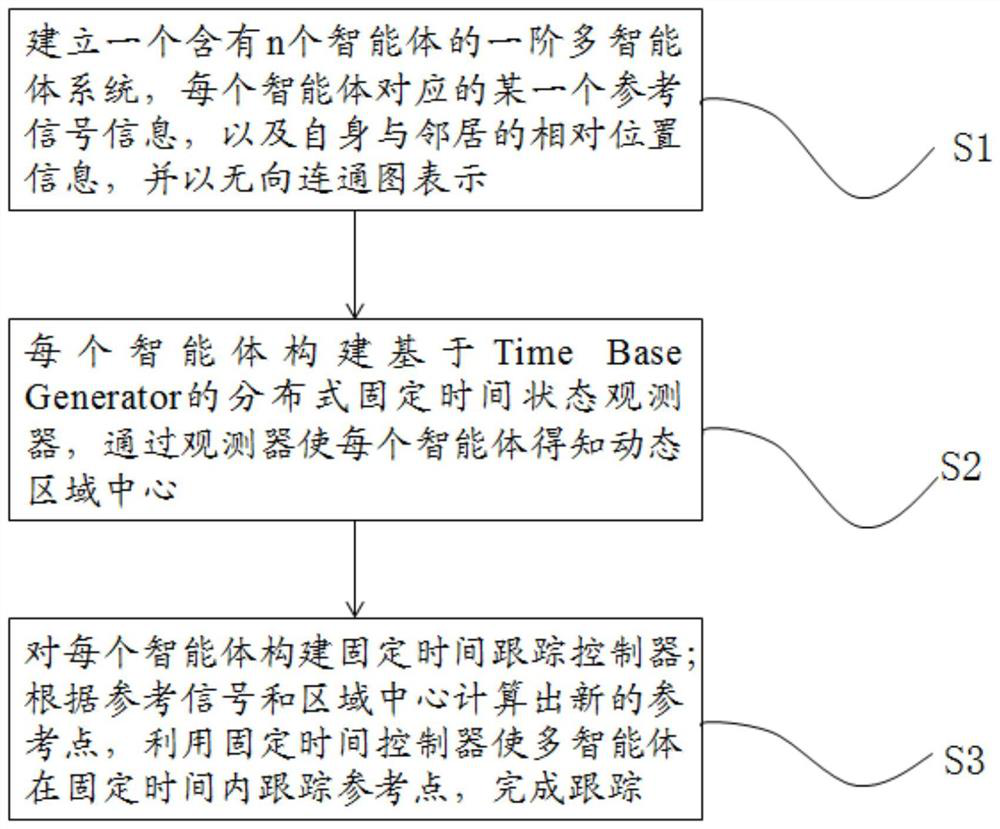

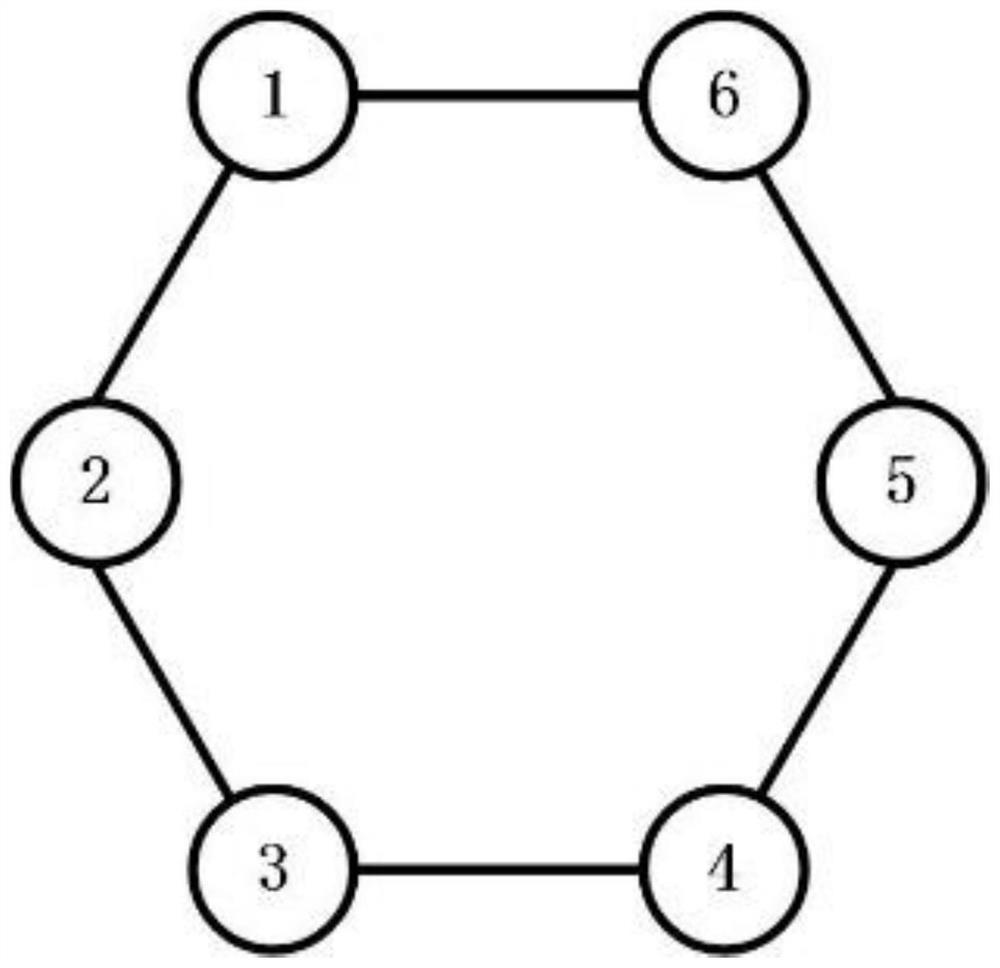

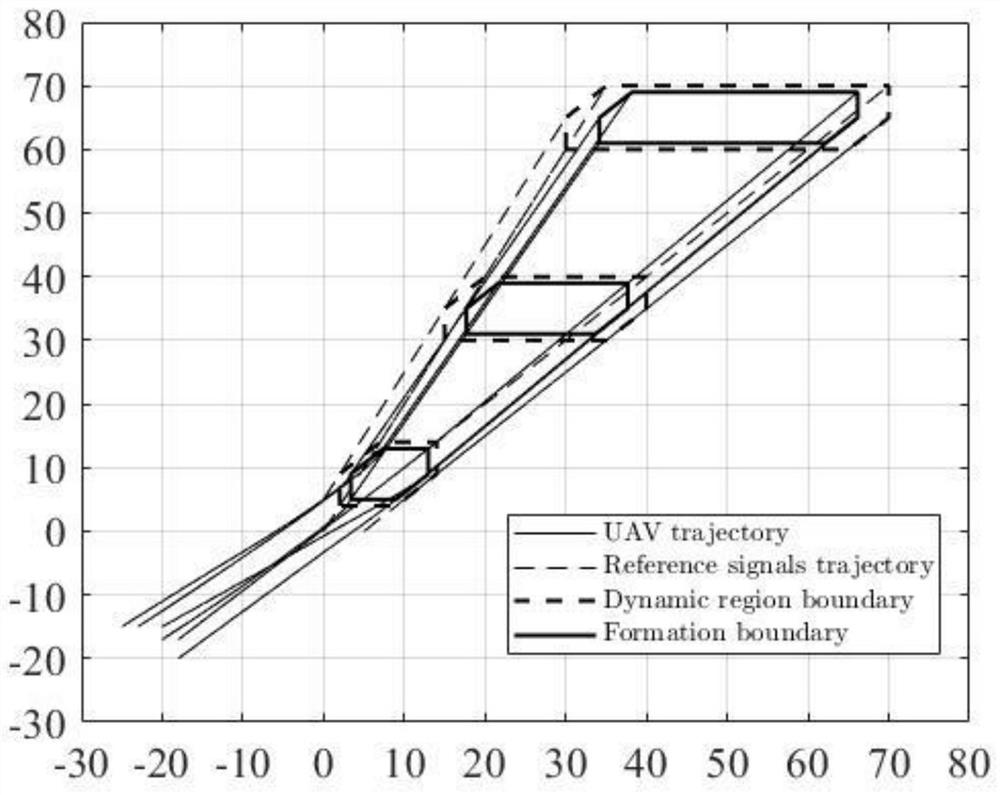

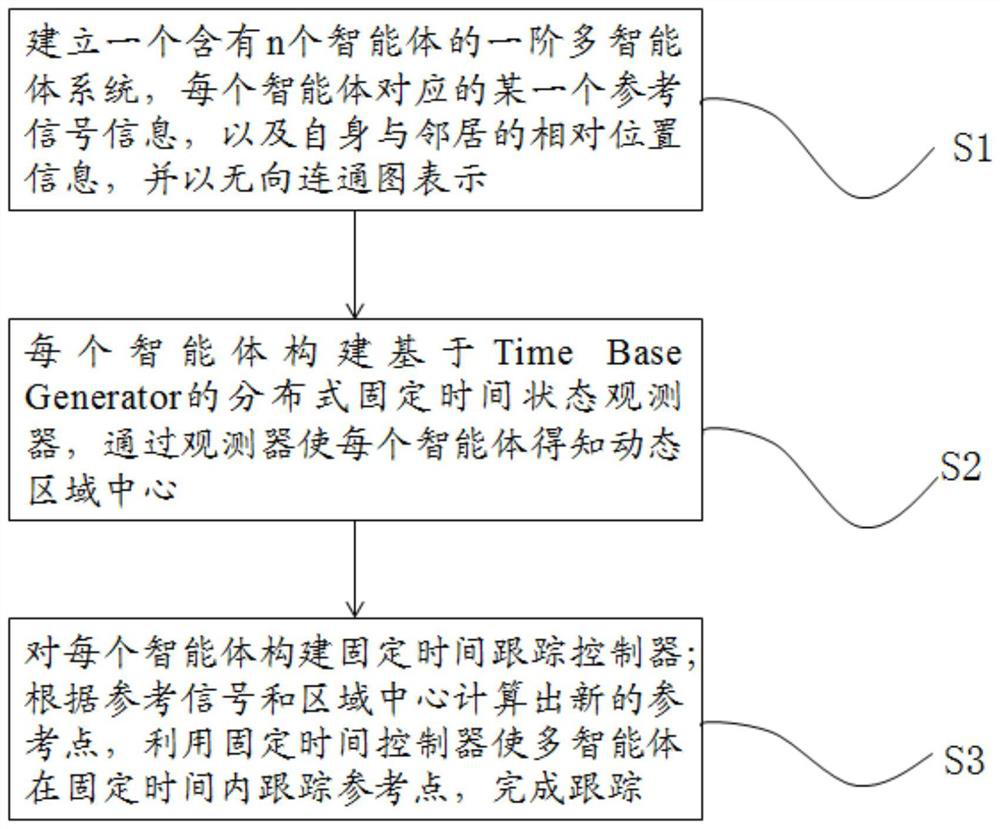

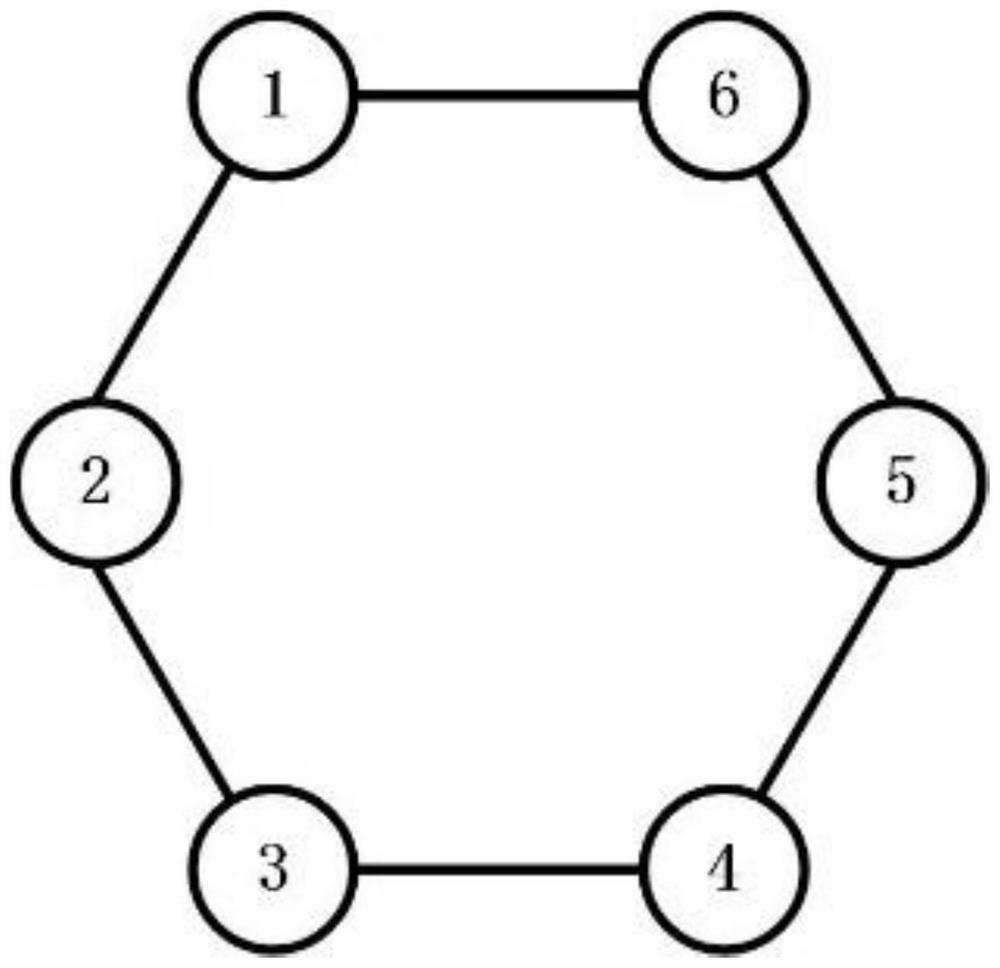

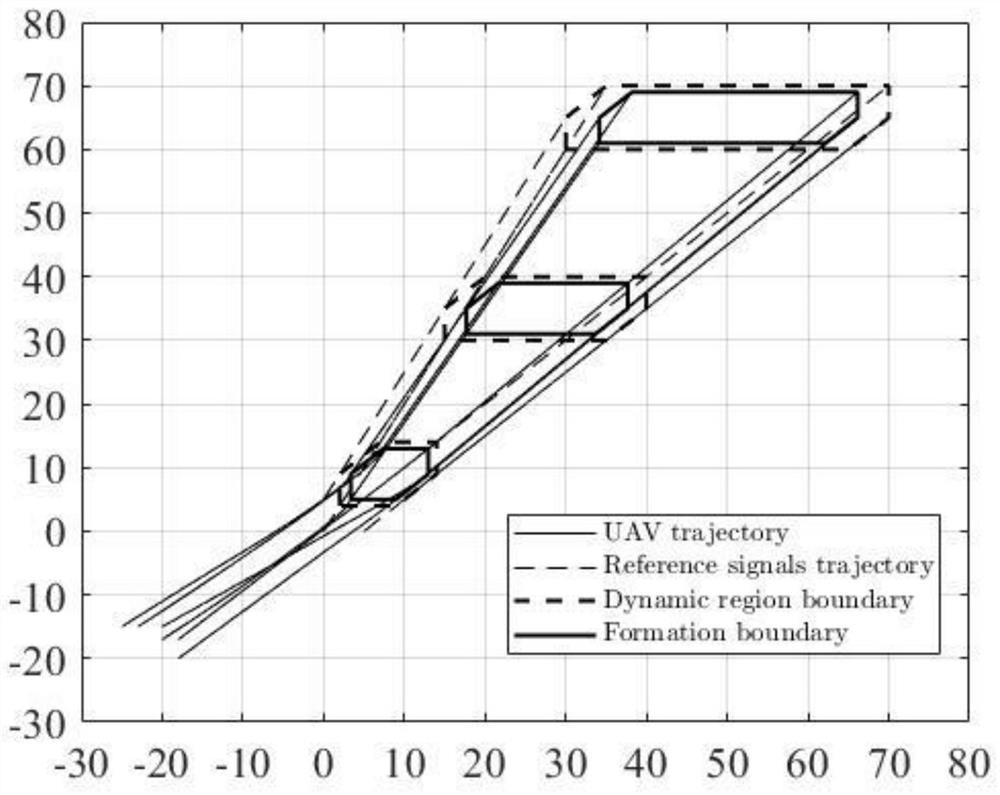

Fixed time dynamic region tracking control method based on Time Base Generator

ActiveCN113093554AFixed-time dynamic region tracking issue fixedThe initial control input is smallTotal factory controlAdaptive controlState observerMulti-agent system

The invention provides a fixed time dynamic region tracking control method based on Time Base Generator, which comprises the following steps of: establishing a fixed time distributed state observer to estimate the central position of a tracked area, and then setting a reference point according to the central position, and finally, designing a fixed time controller to enable the multiple agents to track the reference point within any given time and keep the reference point all the time, so that fixed time dynamic region tracking is realized. According to the method, the stable time is not affected by the initial state of the system, the multi-agent system can track the designated area within any given time, the fixed time method based on Time-Base Generator has smaller energy input and more concise system parameters, and the applicable range of the system is widened.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

Intelligent lighting control system, control method and intelligent lighting system

ActiveCN108064099BReduce computing power requirementsReduce capacity requirementsElectrical apparatusElectroluminescent light sourcesIntelligent lightingLight equipment

Owner:SHANGHAI EASTSOFT MICROELECTRONICS

A Fixed Time Dynamic Area Tracking Control Method Based on Time Base Generator

ActiveCN113093554BFixed-time dynamic region tracking issue fixedThe initial control input is smallTotal factory controlAdaptive controlState observerControl engineering

The invention provides a fixed-time dynamic area tracking control method based on Time Base Generator, which includes the following steps: establishing a fixed-time distributed state observer to estimate the center position of the tracked area, then setting a reference point according to the center position, and finally designing a fixed time The time controller enables the multi-agent to track the upper reference point at any given time and keep it all the time, thus realizing fixed-time dynamic region tracking. The stability time of this method is not affected by the initial state of the system, which enables the multi-agent system to track the specified area at any given time, and the fixed time method based on the Time-Base Generator has a smaller energy input and a more concise system. parameters to improve the applicable scope of the system.

Owner:NORTHWESTERN POLYTECHNICAL UNIV