Patents

Literature

1096results about "Angle demodulation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Individual channel phase delay scheme

ActiveUS20080157867A1Cathode-ray tube indicatorsPhase-modulated carrier systemsEngineeringNoise suppression

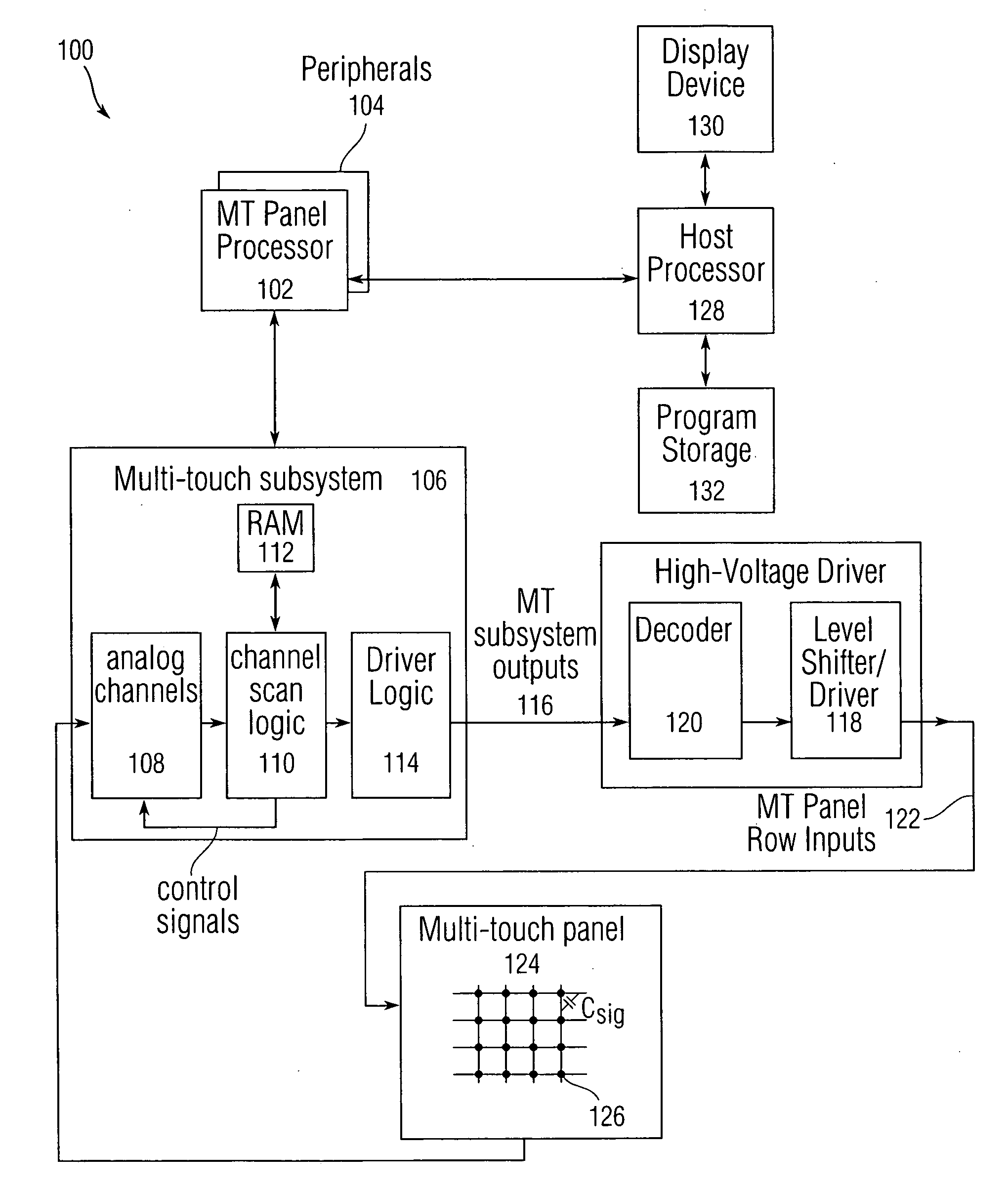

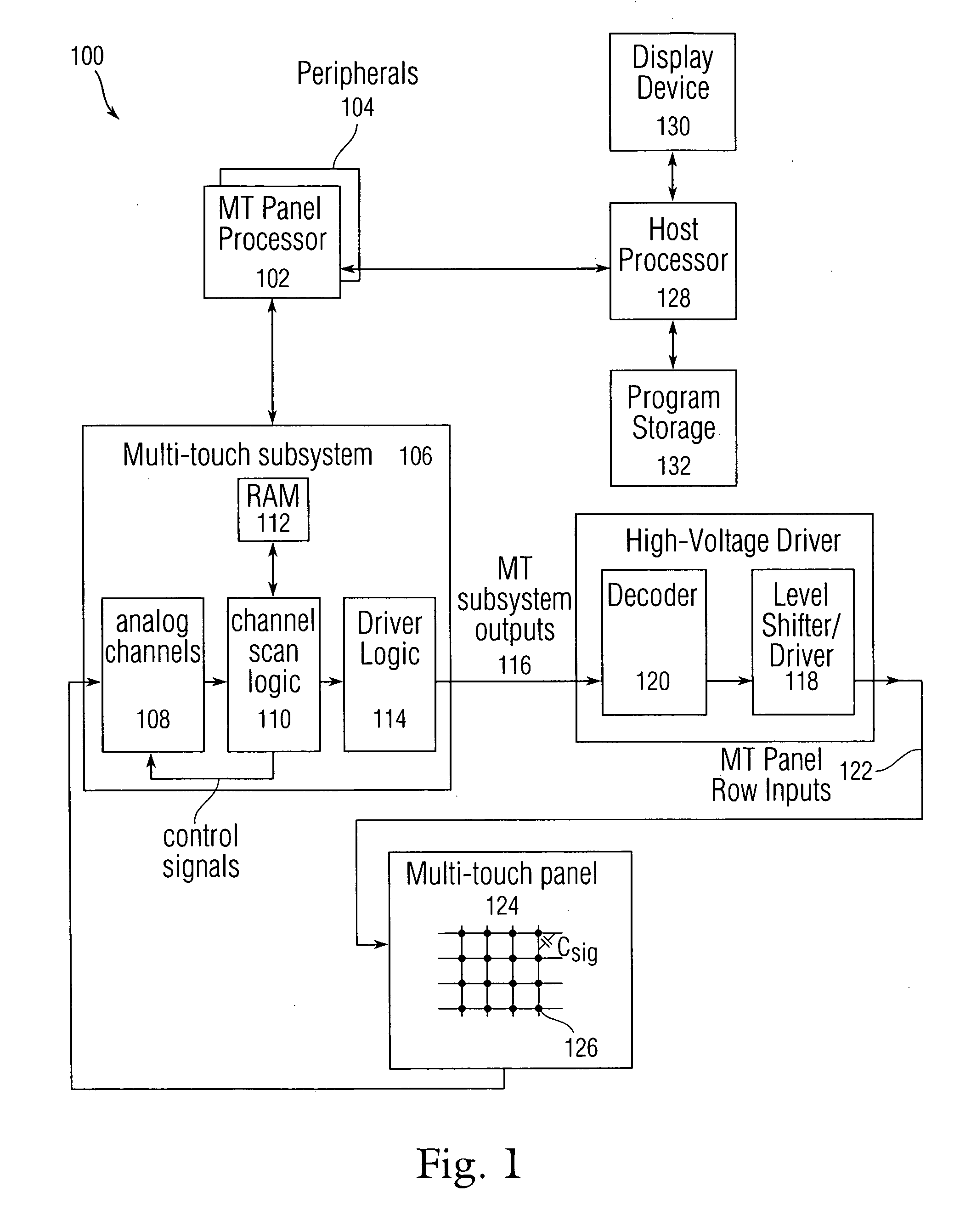

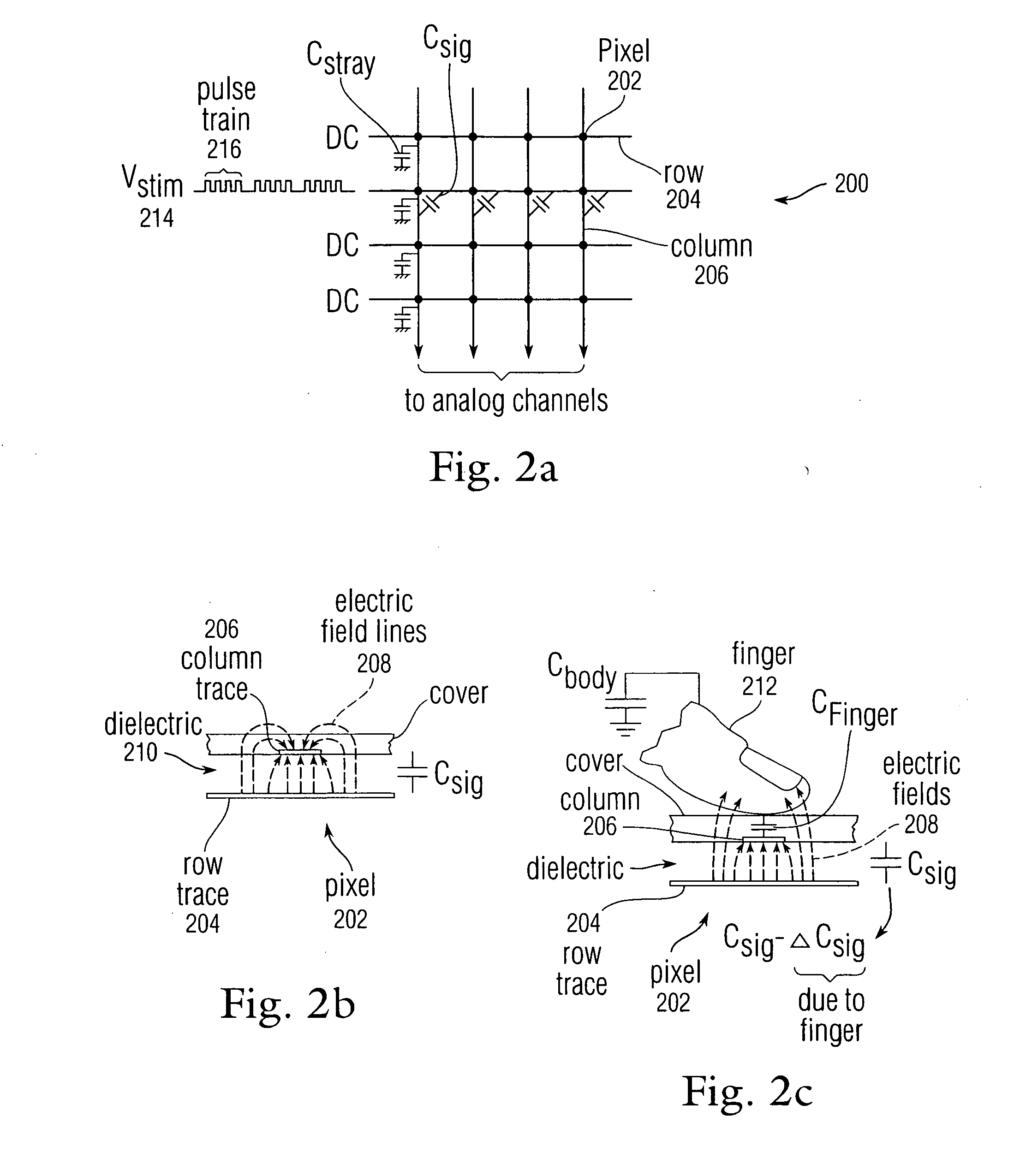

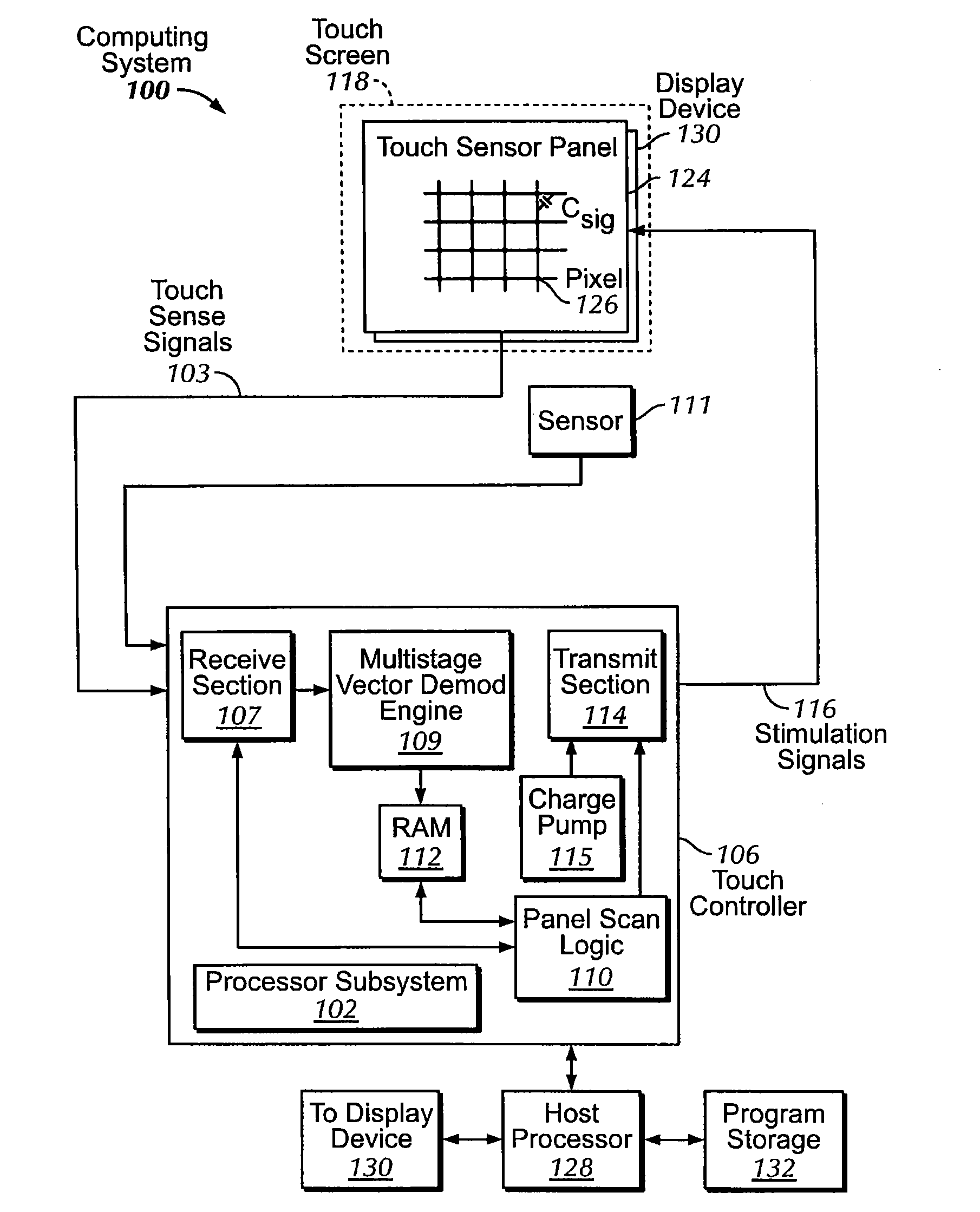

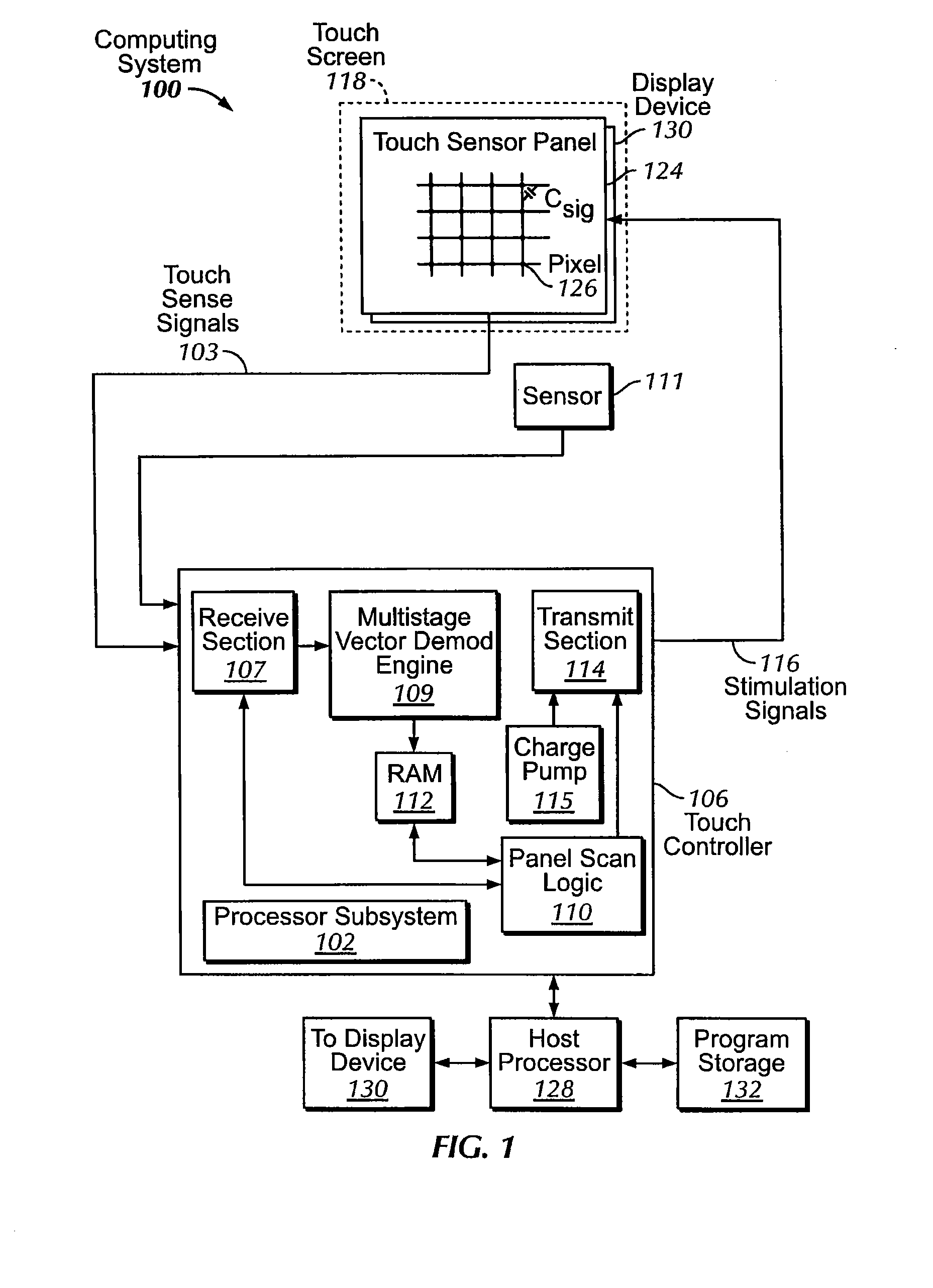

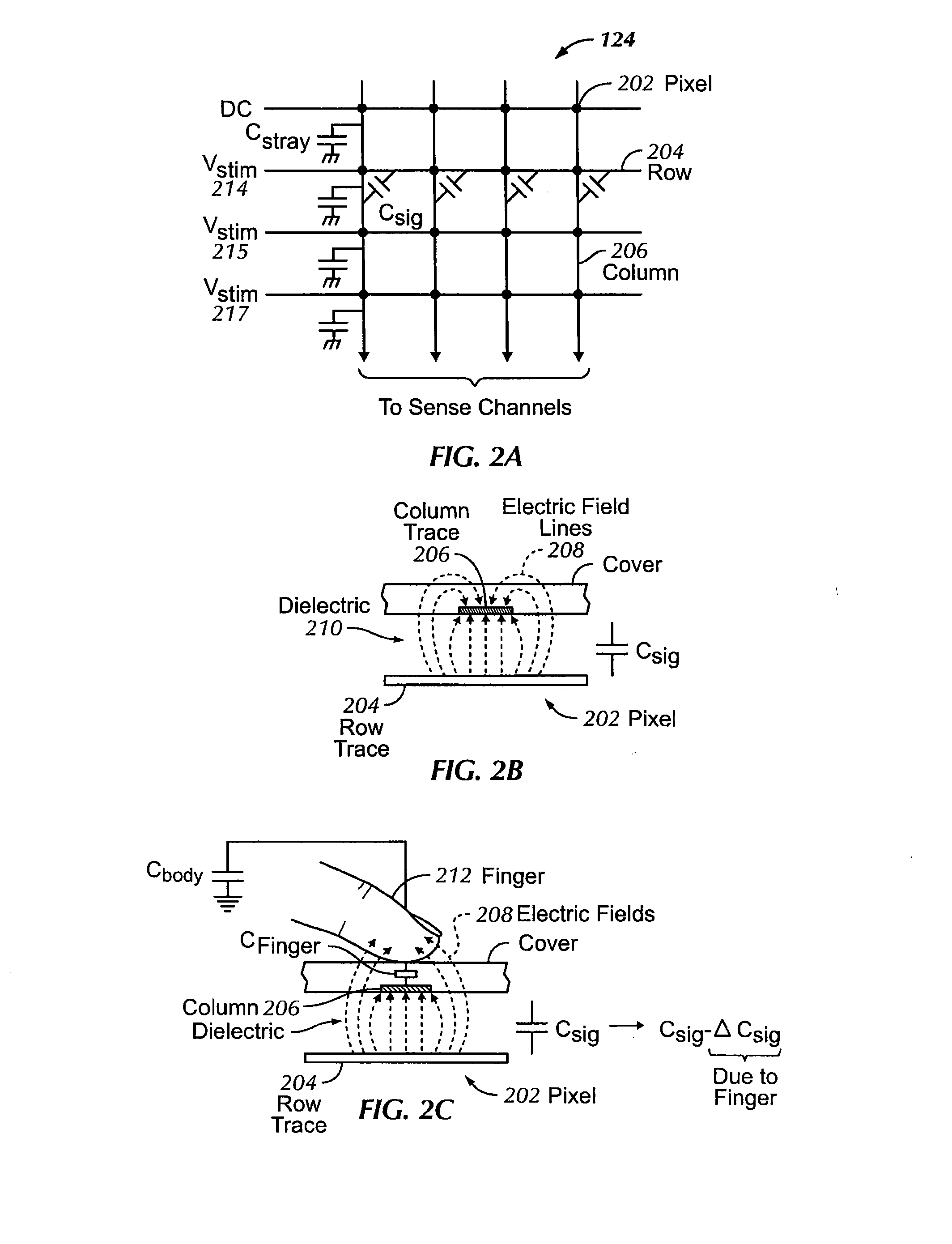

Embodiments of the present invention are directed to processing an incoming signal by using a demodulation signal, while controlling the phase of the demodulation signal in relation to the incoming signal. The incoming signal can be processed by being mixed with the modulation signal at a mixer. The mixing may thus cause various beneficial modifications of the incoming signal, such as noise suppression of the incoming signal, rectification of the incoming signal, demodulation of the incoming signal, etc.

Owner:APPLE INC

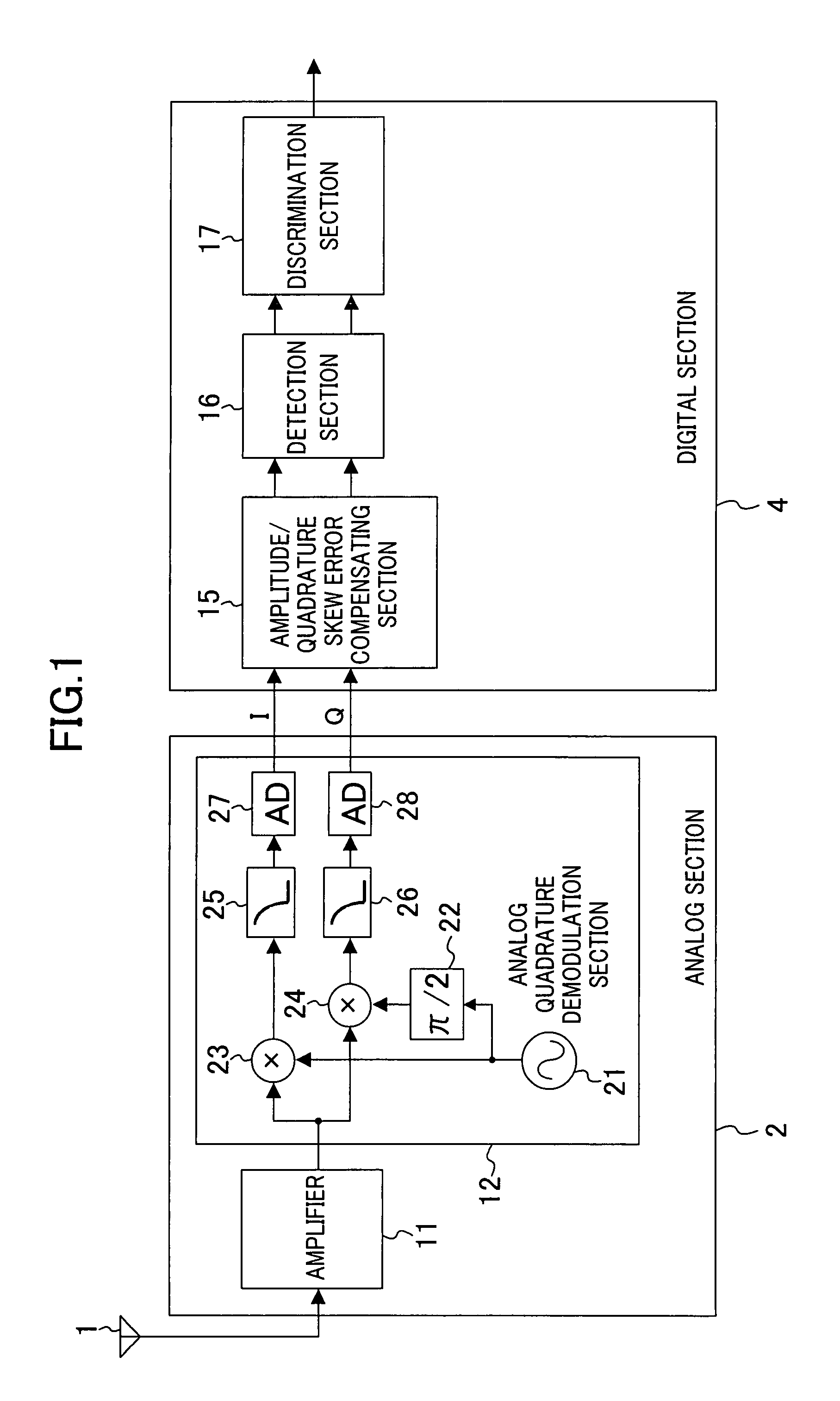

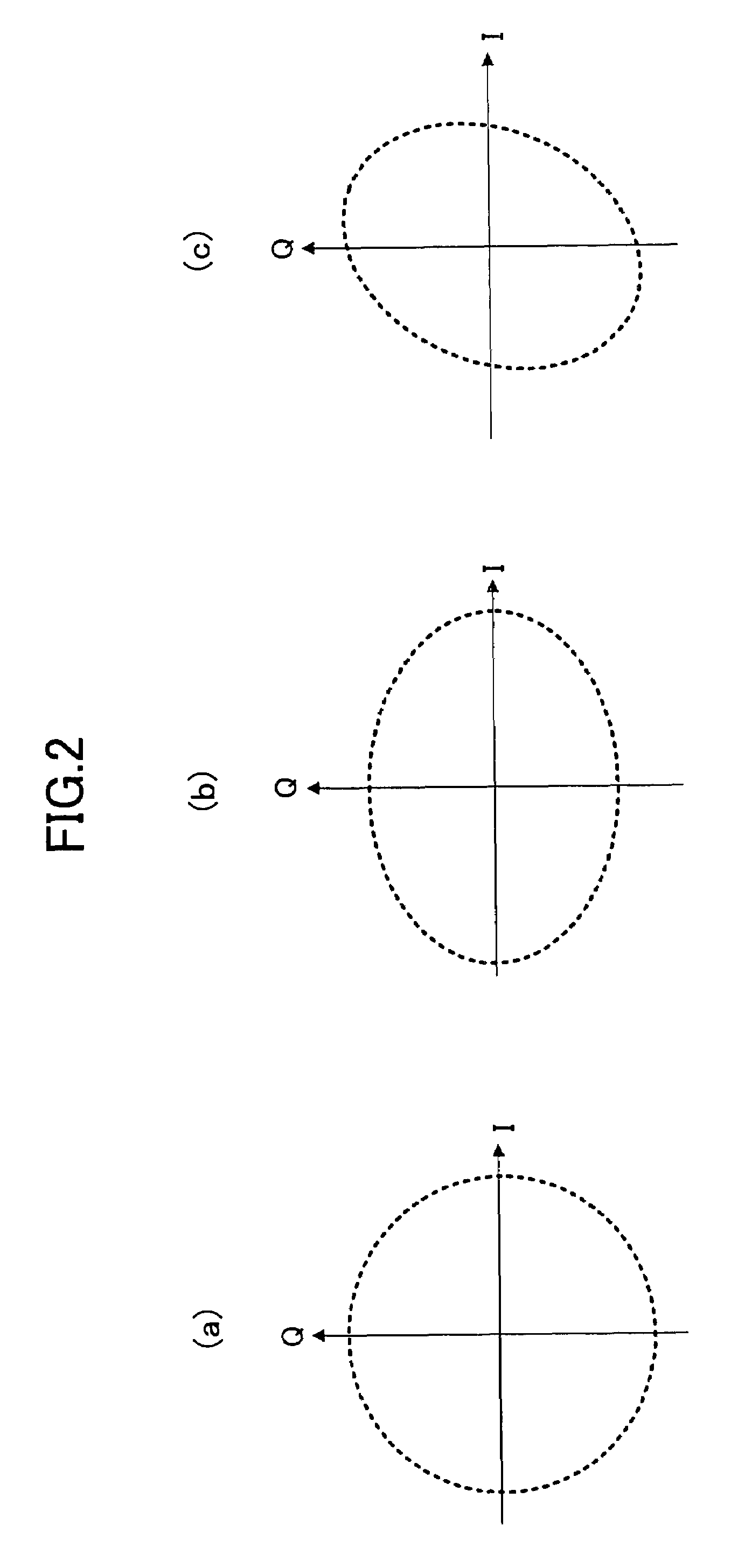

Amplitude error compensating device and quadrature skew error compensating device

InactiveUS7456683B2Error preventionLine-faulsts/interference reductionInformation controlQuadrature demodulation

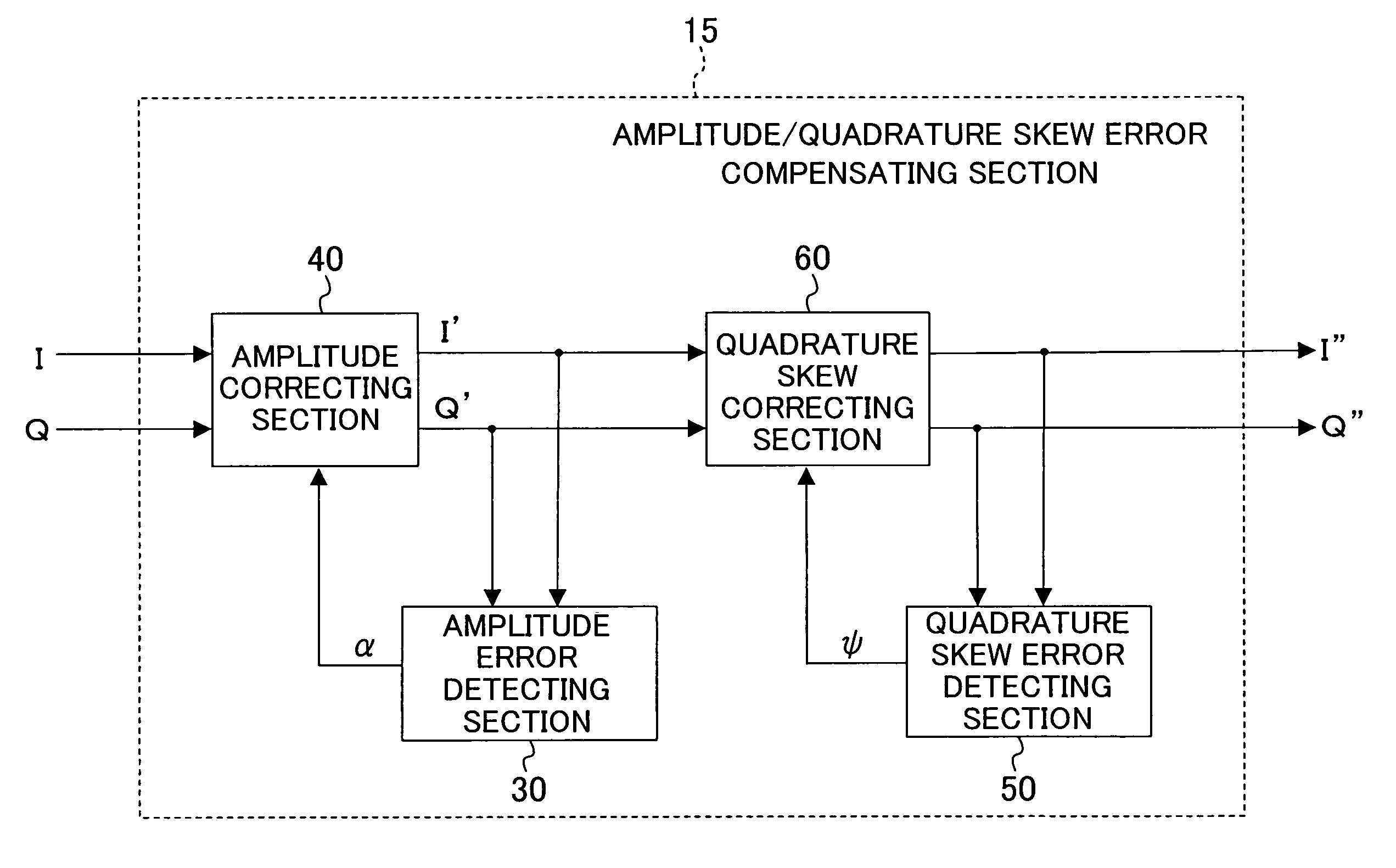

An amplitude error compensating device comprises an amplitude correcting section for performing amplitude correction with respect to an in-phase component and a quadrature component of a complex signal obtained by quadrature demodulation, based on amplitude error information, and outputting a resultant amplitude-corrected complex signal, and an amplitude error detecting section for obtaining the amplitude error information, depending on amplitudes of an in-phase component and a quadrature component of the amplitude-corrected complex signal. The amplitude error detecting section comprises a power difference calculating section for obtaining as a power error a difference in power between the in-phase component and the quadrature component of the amplitude-corrected complex signal, a rotation detecting section for detecting a rotation of a signal point of the amplitude-corrected complex signal, an error information control section for outputting the power error when a rotation of the signal point has been detected, and 0 when a rotation of the signal point has not been detected, and a smoothing section for smoothing an output of the error information control section, and outputting the result as the amplitude error information.

Owner:SOCIONEXT INC

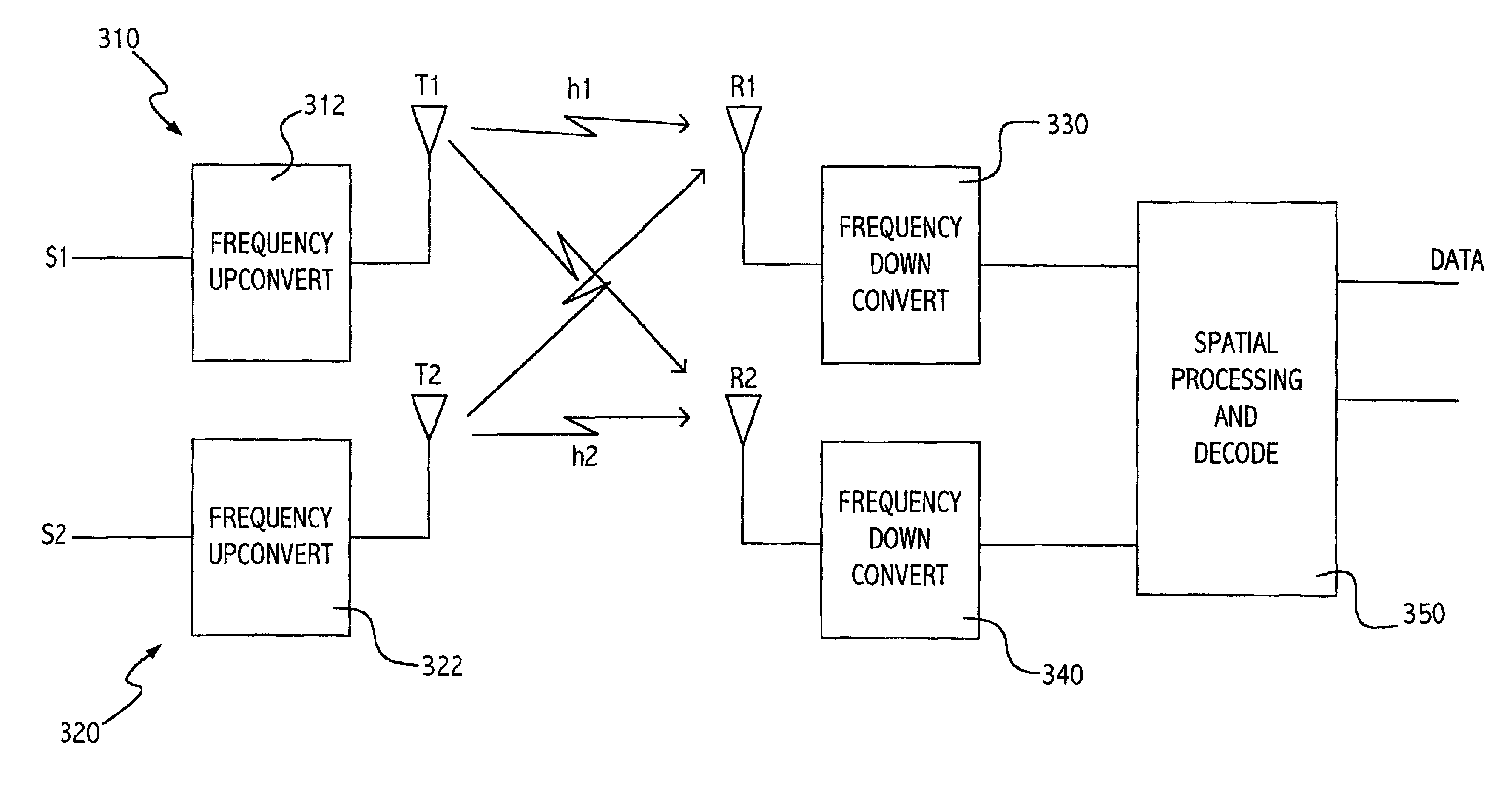

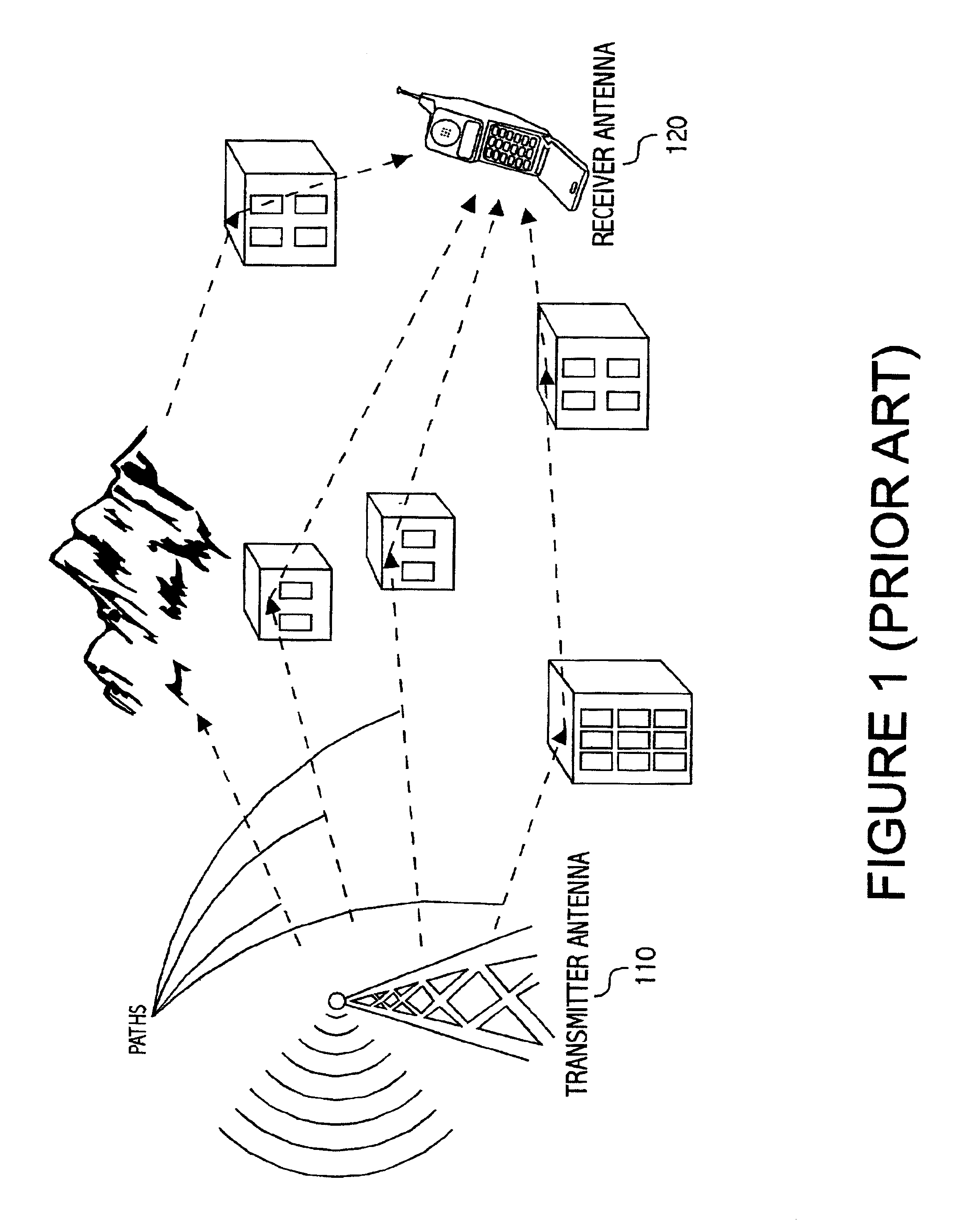

Method and system for multiple channel wireless transmitter and receiver phase and amplitude calibration

InactiveUS6862440B2Low costTransmitters monitoringReceivers monitoringTransmission channelEngineering

The present invention provides a method and system for estimating common amplitude and phase errors of a multiple channel wireless system. The multiple channel wireless system includes a plurality of transmission channels formed between a plurality of transmission antennas and a plurality of receiver antennas. The method includes estimating transmission channel elements between each transmission antenna and receiver antenna pair of the multiple channel wireless system. Calibration symbols are transmitted from each transmit antenna. Signals are received that correspond to the calibration symbols having traveled through the transmission channels. Received calibration symbols are estimated based upon spatial processing of the received signals and the estimated transmission channel elements. Common amplitude and phase errors are estimated for each transmit and receive antenna pair by comparing the transmitted calibration symbols with the received calibration symbols.

Owner:TAHOE RES LTD

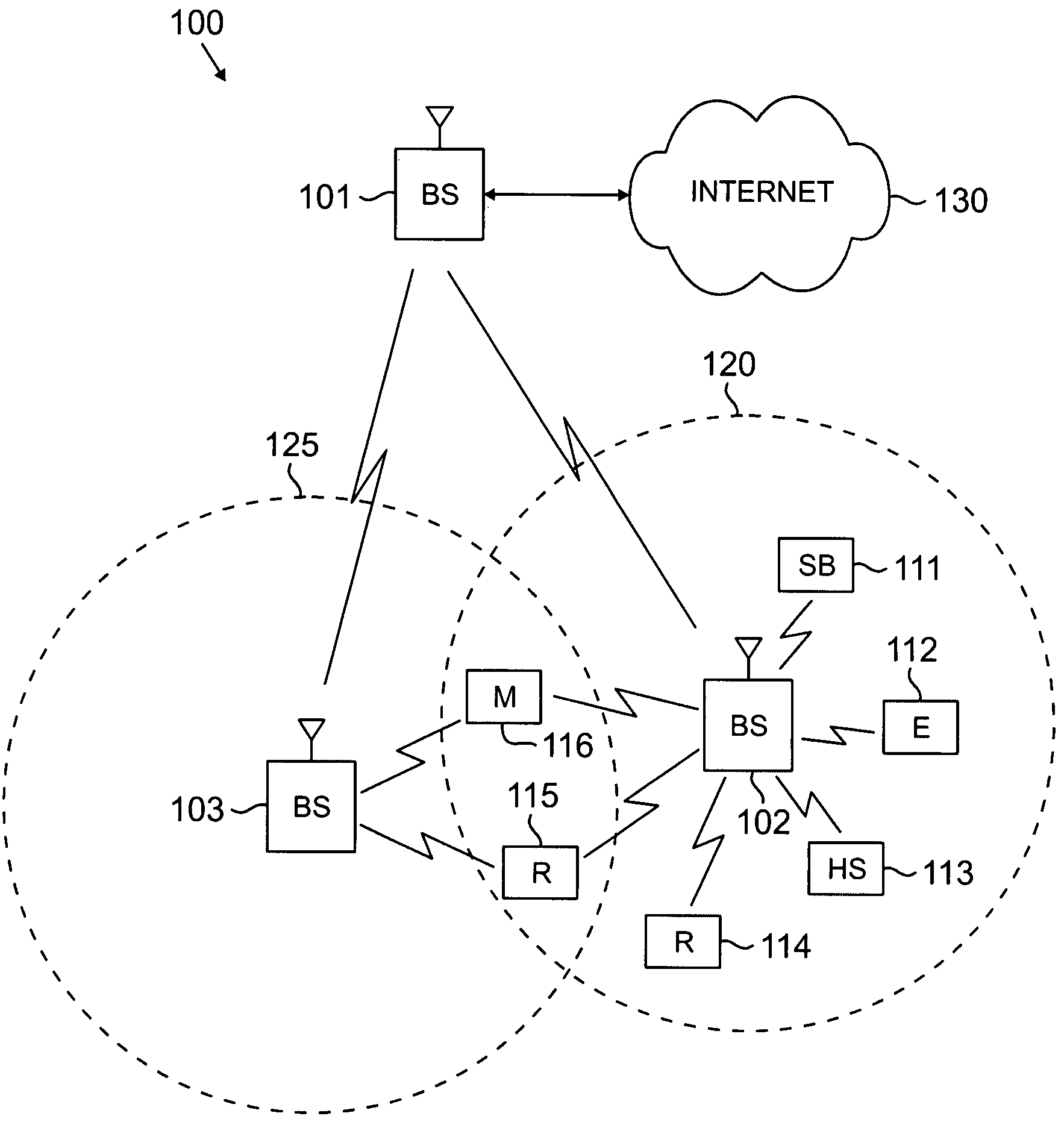

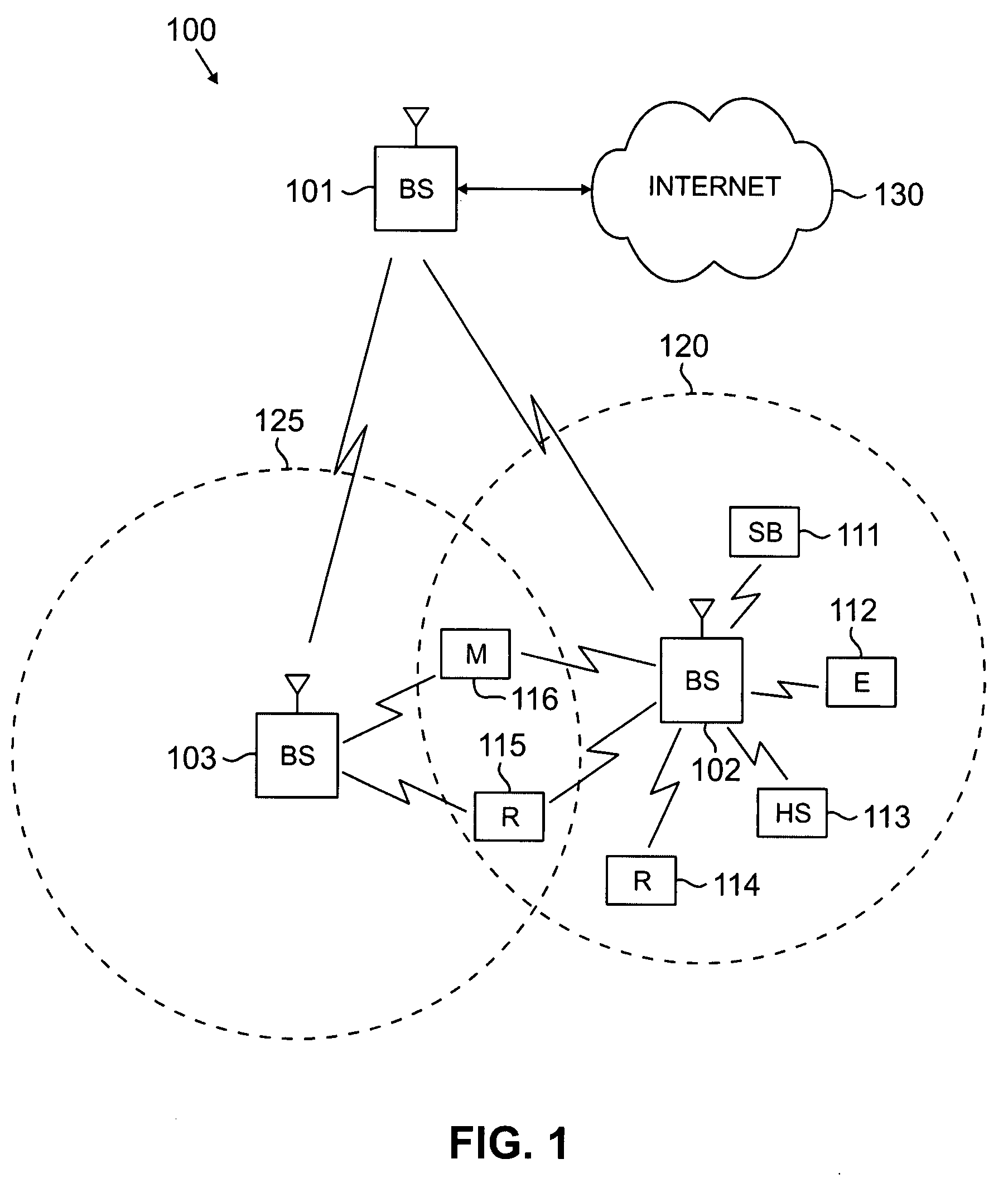

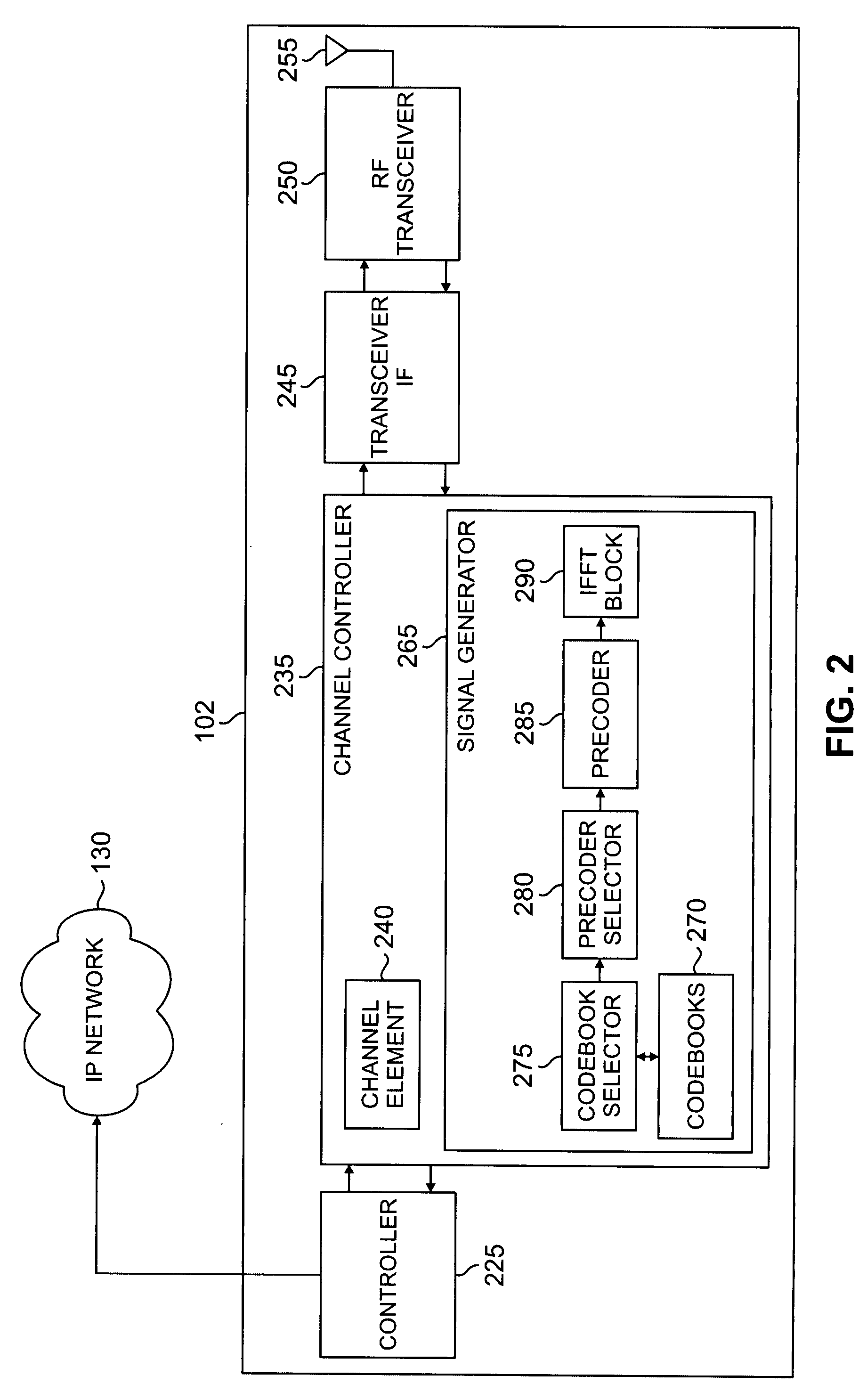

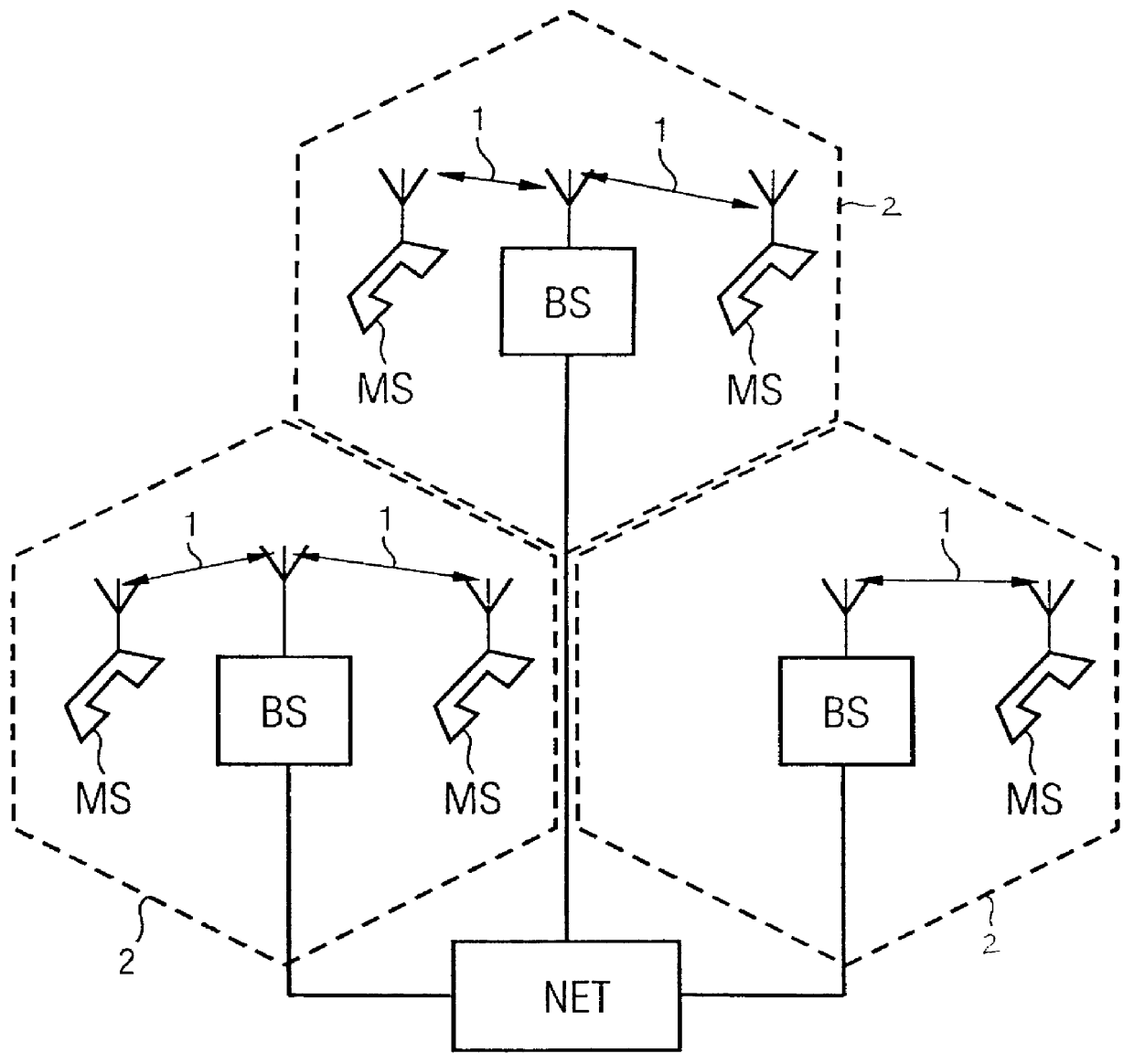

System and method for performing precoding in a wireless communication system

ActiveUS20080080637A1Polarisation/directional diversityFrequency/rate-modulated pulse demodulationCommunications systemDiversity scheme

A base station capable of performing precoding in a wireless communication system is provided. The base station includes a plurality of codebooks and a codebook selector. Each codebook comprises a plurality of composite precoding matrices that are generated based on a corresponding diversity precoding matrix. The codebook selector is operable to select one of the codebooks for use in a communication session with a subscriber station.

Owner:SAMSUNG ELECTRONICS CO LTD

Phase compensation for multi-stimulus controller

Determining a compensated phase matrix for a multi-stimulus demodulation process is provided. A first drive line of a multi-stimulus sensing system is selected, and a stimulation signal is transmitted on the selected drive line. A channel gain resulting from the stimulation signal is measured from a received sense signal resulting from the stimulation signal. The measured channel gain is compared with a known channel gain to obtain an individual phase compensation for the selected drive line. A compensated phase matrix is formed of the individual phase compensation values for multiple drive lines.

Owner:APPLE INC

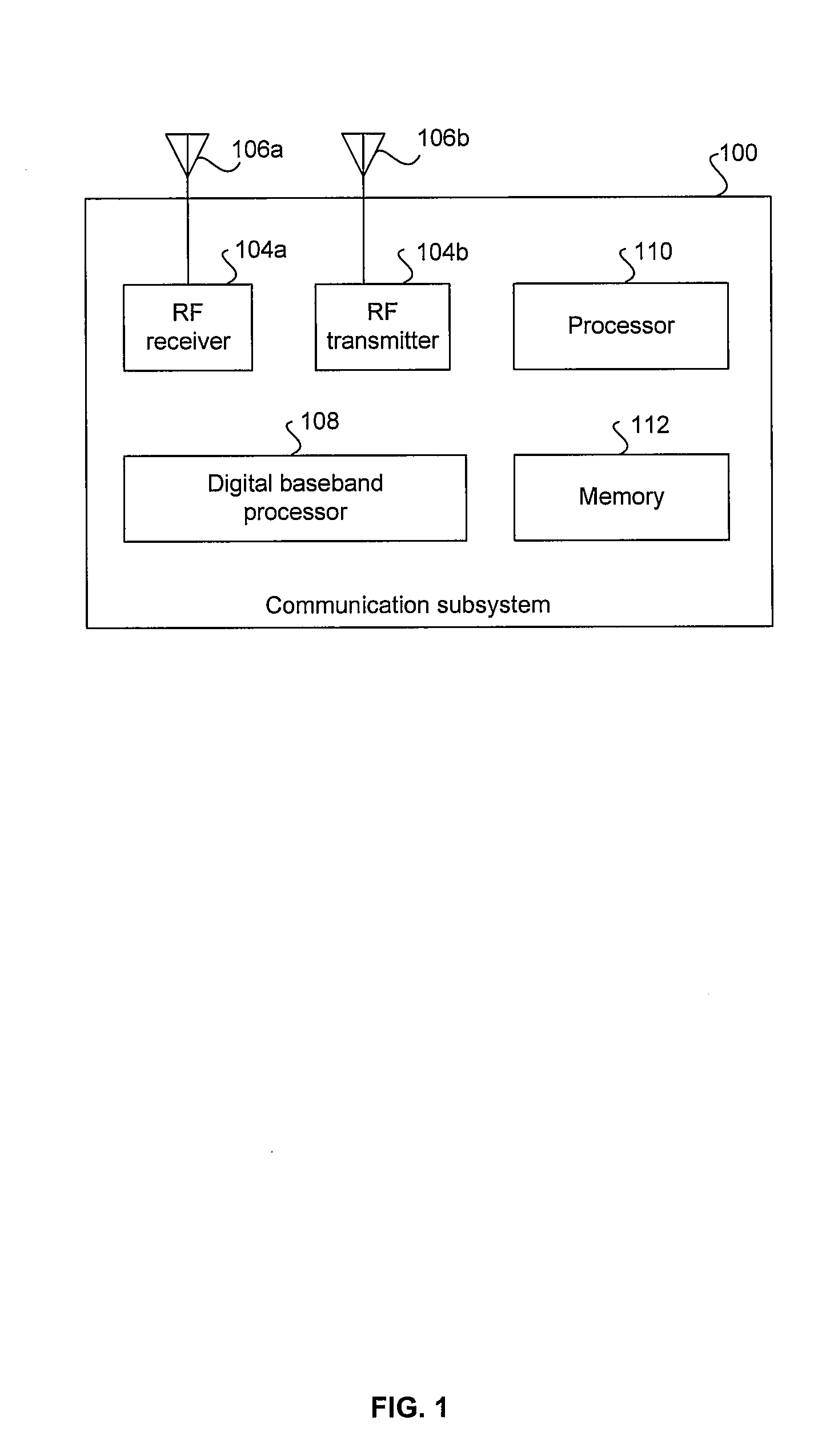

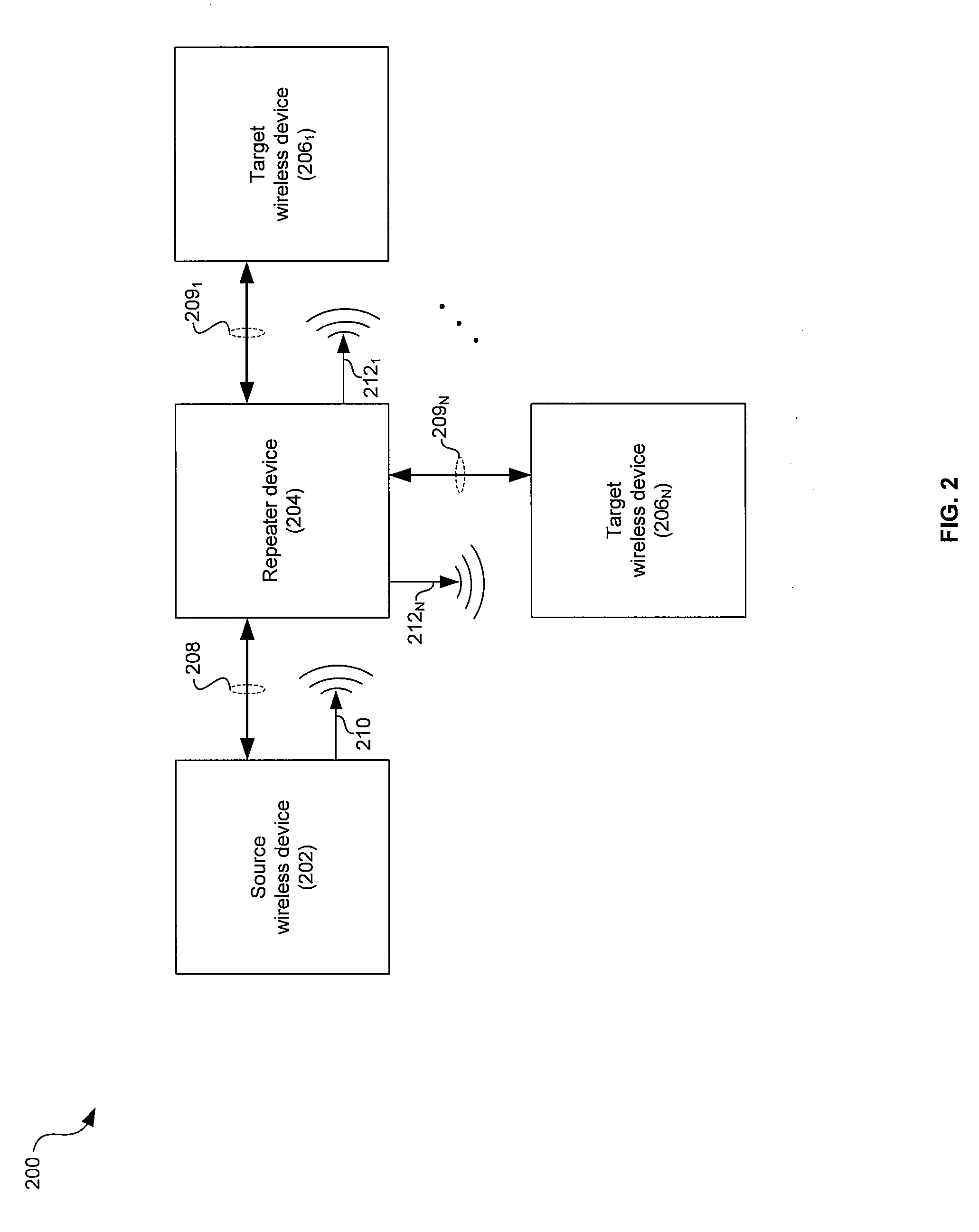

Method And System For Communicating Via A Spatial Multilink Repeater

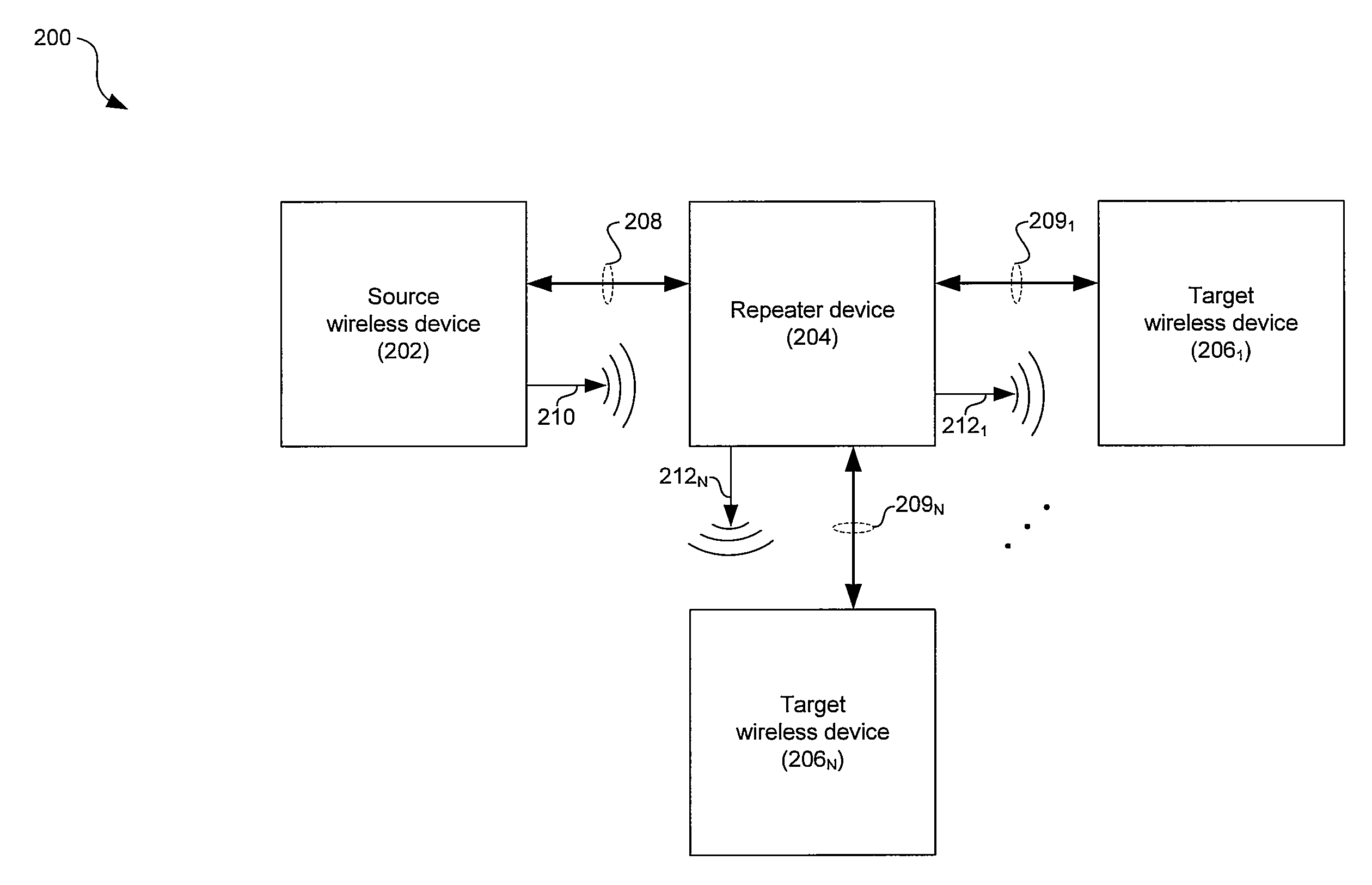

Aspects of a method and system for communicating via a spatial multilink repeater are provided. In this regard, a received signal may be frequency shifted to generate a plurality of repeated signals, wherein each repeated signal may be shifted by a different frequency with respect to the received signal. Each repeated signal may comprise one or more signal components and a phase and / or amplitude of each of the components may be controlled to control a directivity of the repeated signals. Each of the repeated signals may be generated by quadrature down-converting said received signal by mixing the received signal with a first LO signal pair, up-converting the down-converted signal by mixing it with a second LO signal pair, and adding or subtracting an in-phase portion and a quadrature-phase portion of the up-converted signal.

Owner:AVAGO TECH INT SALES PTE LTD

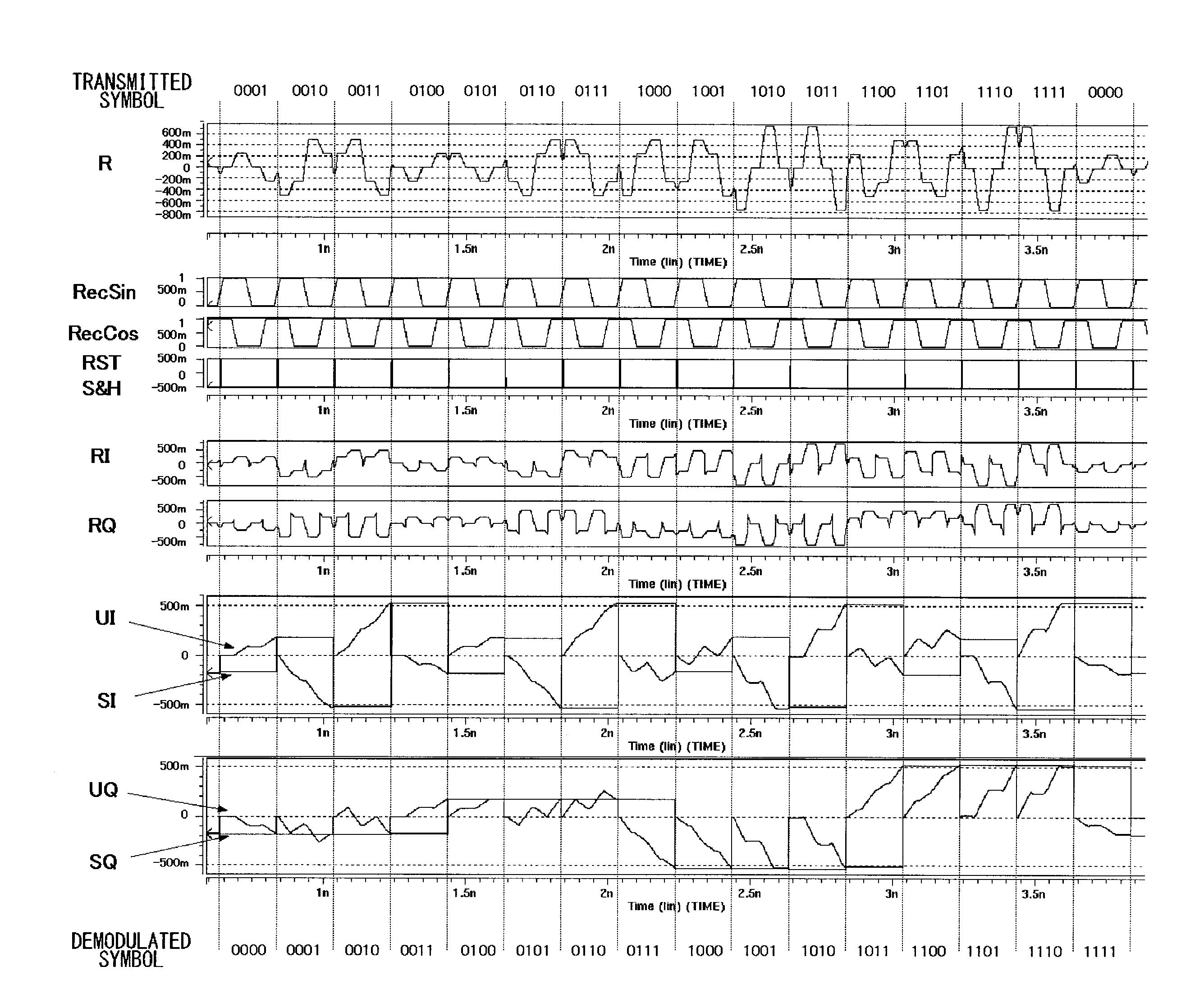

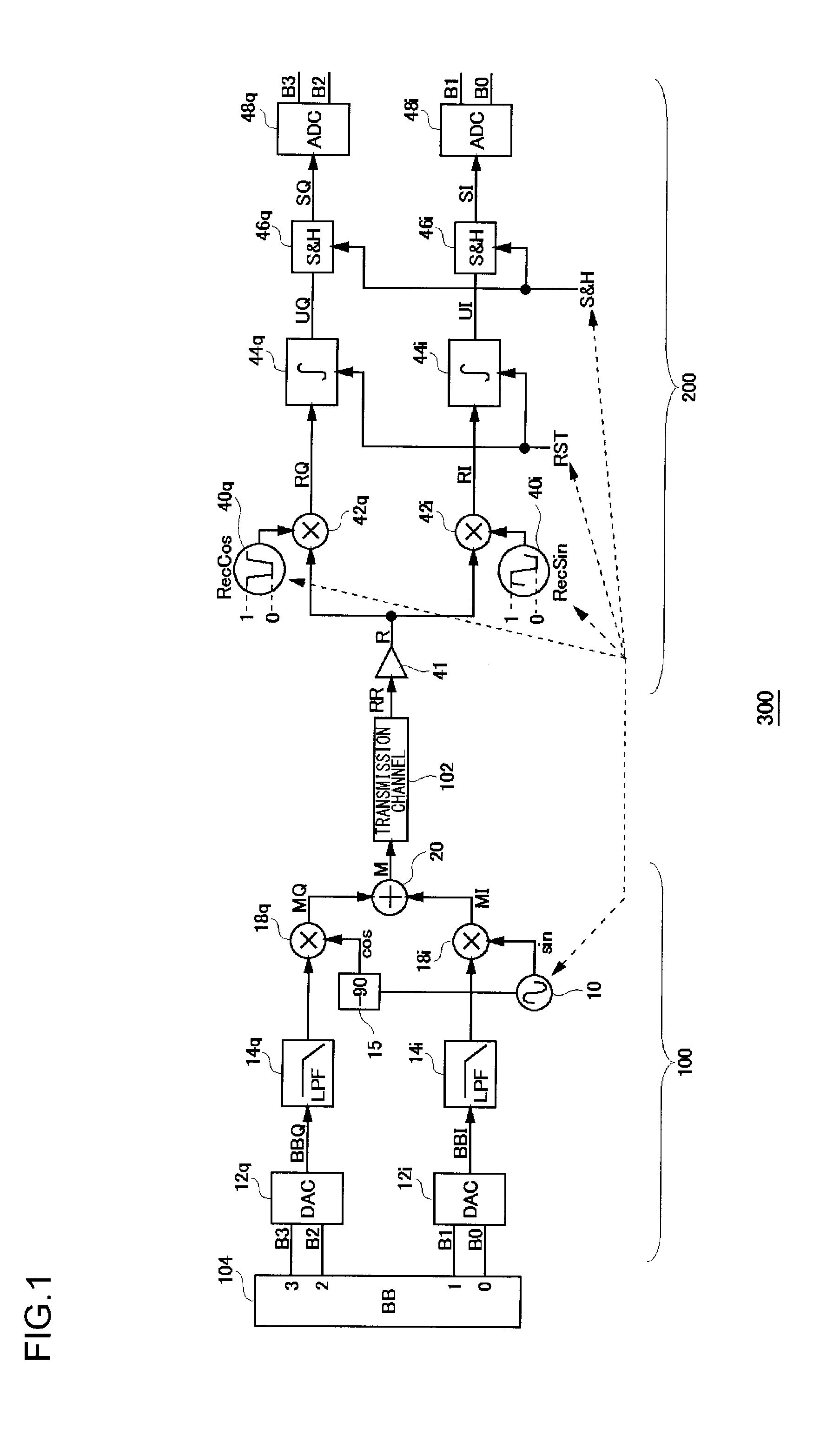

Quadrature amplitude demodulator and demodulation method

InactiveUS20110018626A1Readily implement dataModulation transferencePhase-modulated carrier systemsIntegratorFrequency mixer

A quadrature amplitude demodulator demodulates a modulated signal on which quadrature amplitude modulation is performed. Oscillators generate an in-phase carrier signal having a rectangular wave, a trapezoidal wave or a waveform similar to these, and a quadrature carrier signal, the phase of which is shifted by ¼ cycle relative to the in-phase signal. First and second mixers respectively perform mixing of the modulated signal with the in-phase signal and the quadrature carrier signal. First and second integrators respectively integrate output signals of the first and the second mixers, for a predetermined period in accordance with the cycle of the in-phase carrier signal and the quadrature carrier signal. First and second A / D converters respectively convert outputs of the first and the second integrators into digital values.

Owner:ADVANTEST CORP

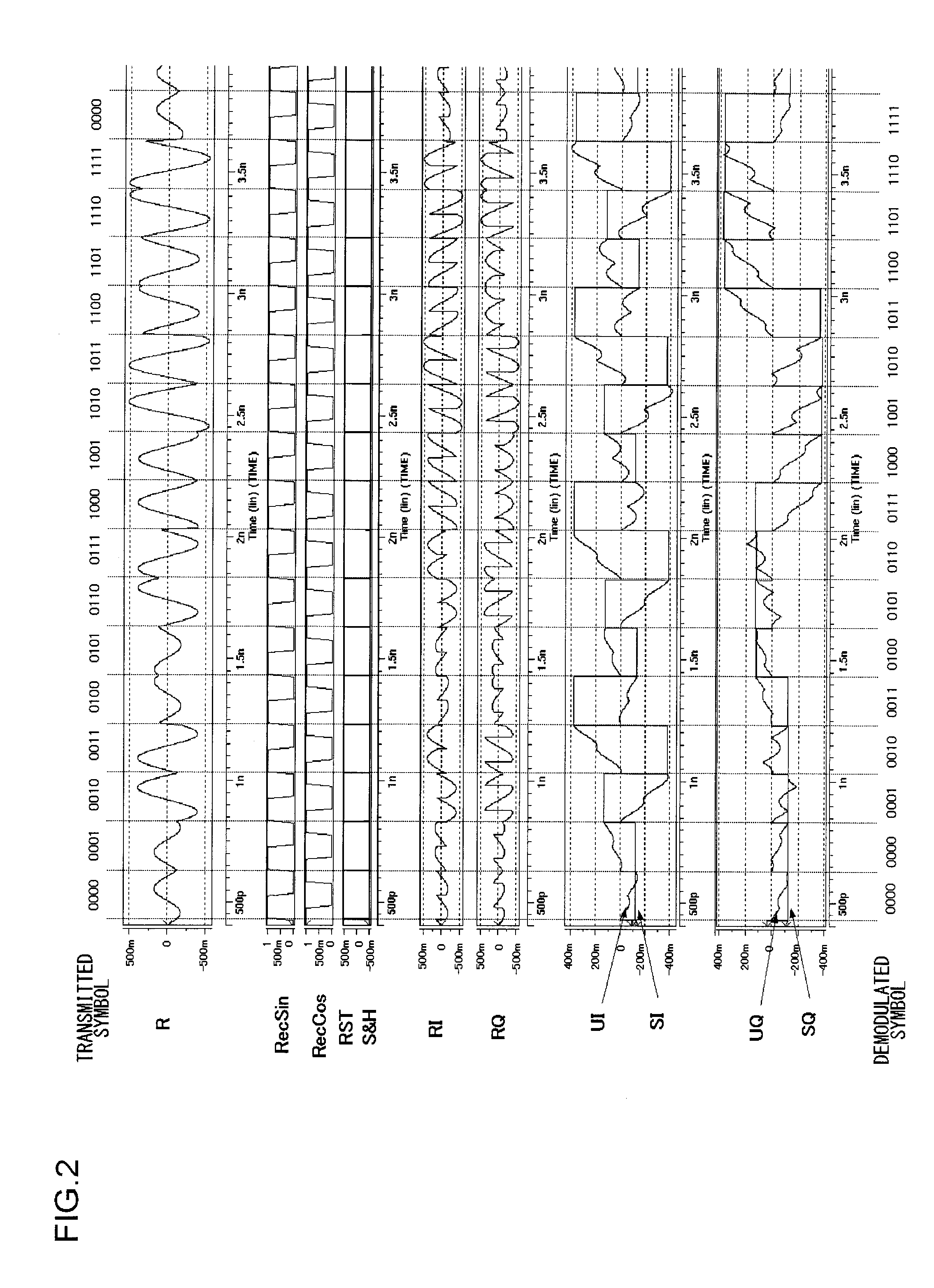

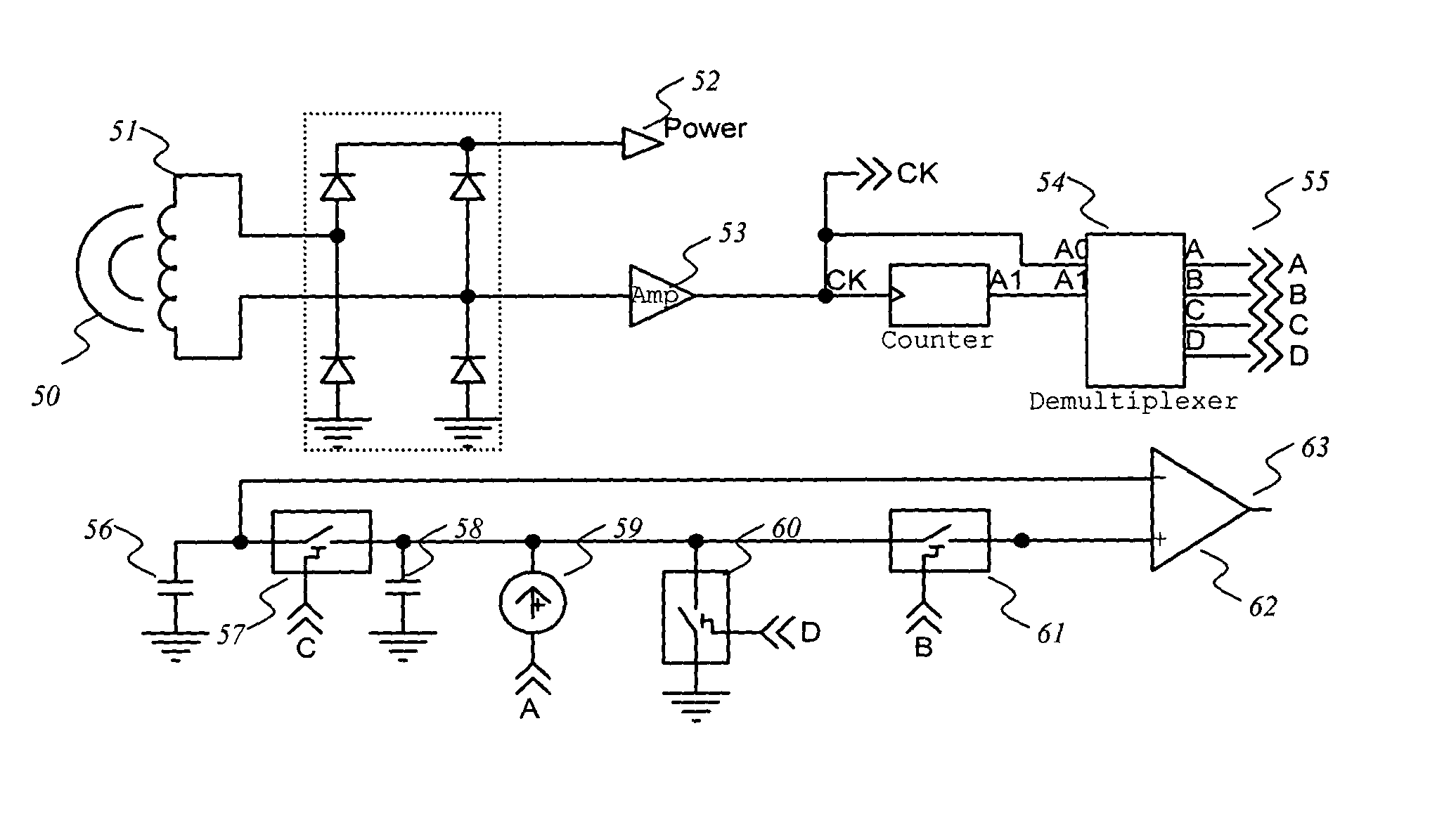

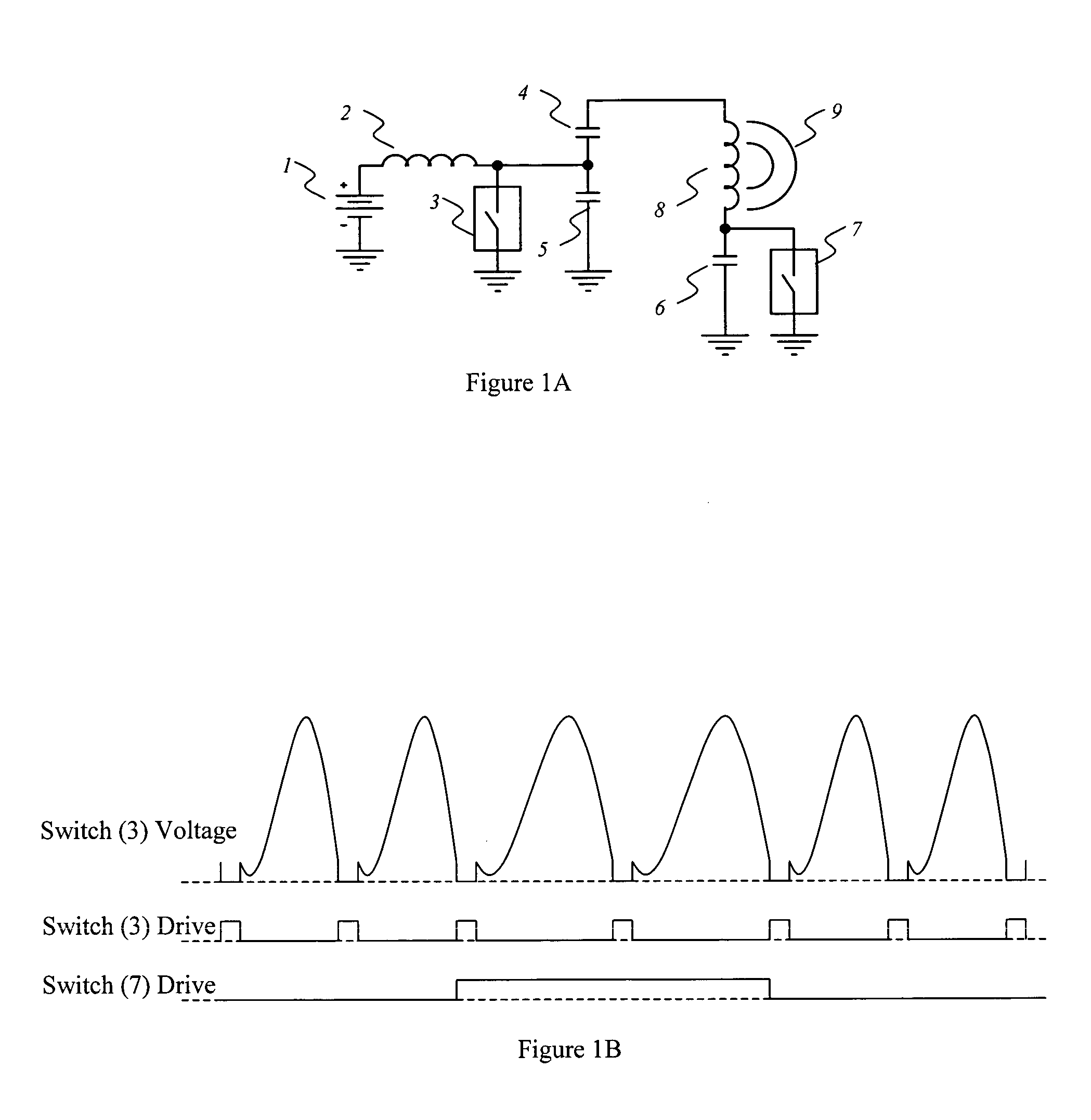

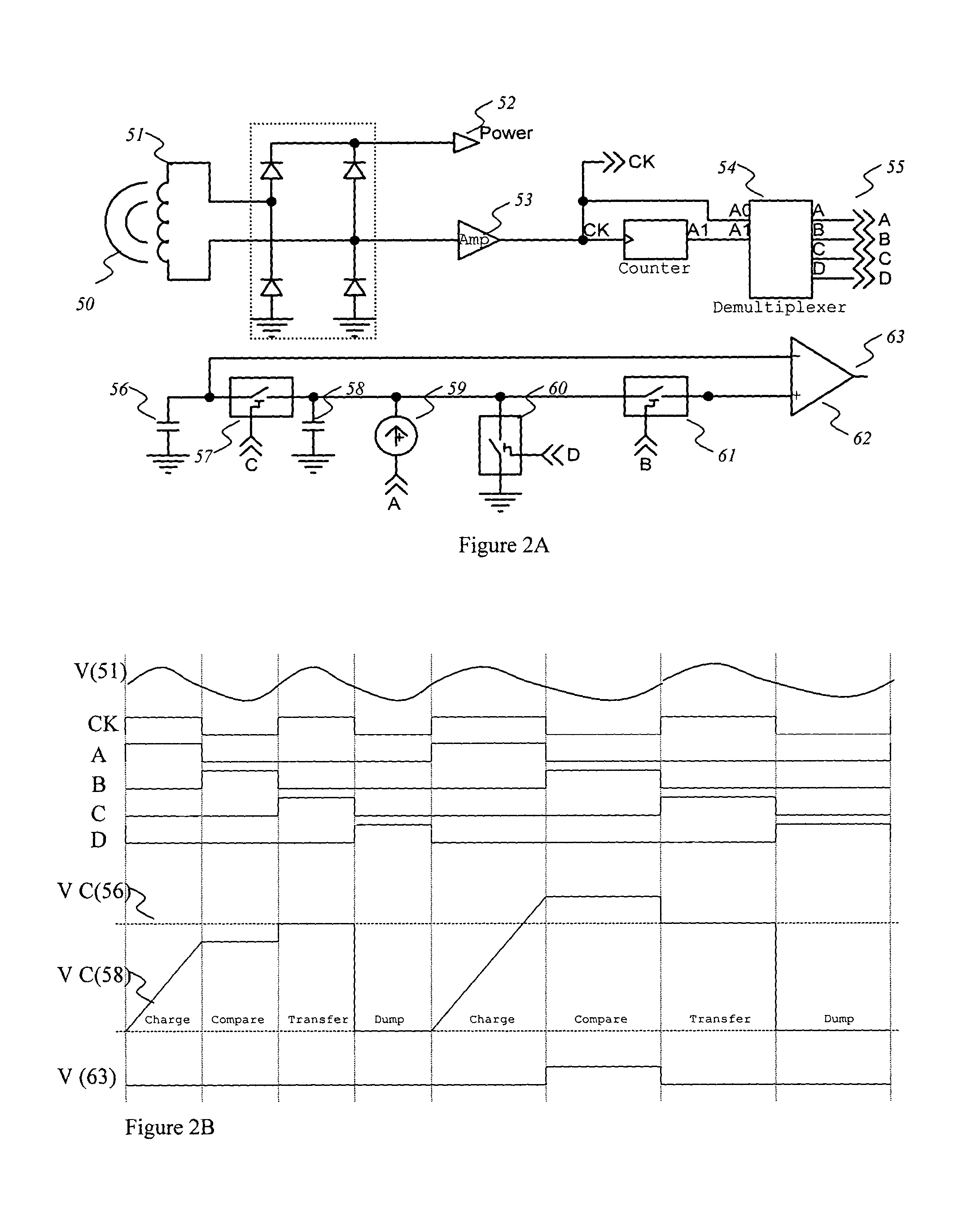

Inductive data and power link suitable for integration

ActiveUS20050063488A1Increase powerImproved telemetry systemElectric signal transmission systemsDiagnosticsData synchronizationTime distortion

A system providing an inductive power and data link between an external transmitter and miniature internal receiver is presented. The system is suited to applications where the receiver must be of a small size and the system must consume very little power, such as an implanted biomedical device. The system is also compatible with systems where bi-directional communications are required. The novel transmitter and receiver form an improved forward data telemetry system. The transmitter consists of a Class-E converter with its optimum operating frequency being synchronously, instantaneously and efficiently altered in accordance with the data to be transmitted, thereby producing an FSK modulated magnetic field of substantially constant amplitude. The constant amplitude output allows for the continuous, data-independent transfer of power to the miniature receiver and its associated electronics. The present invention also represents an improvement over the high efficiency Class-E converters previously patented by the inventors. The receiver consists of a coil and an integrated rectifying system to recover operating power from the incident magnetic field, as well as an FSK demodulator whose operation is based on the multiphase comparison of charging times of integrated capacitors. The described FSK demodulator approach removes deleterious effects resulting from low-frequency changes in the transmitter frequency, and eliminates time distortion artifacts generated by circuit imbalances and asymmetries in the power recovery process. The combination of the transmitter and receiver improvements yields a reliable data transfer system unaffected by circuit imbalances and incidental variations in the amplitude and frequency of the magnetic field.

Owner:LUNA NEURO LLC

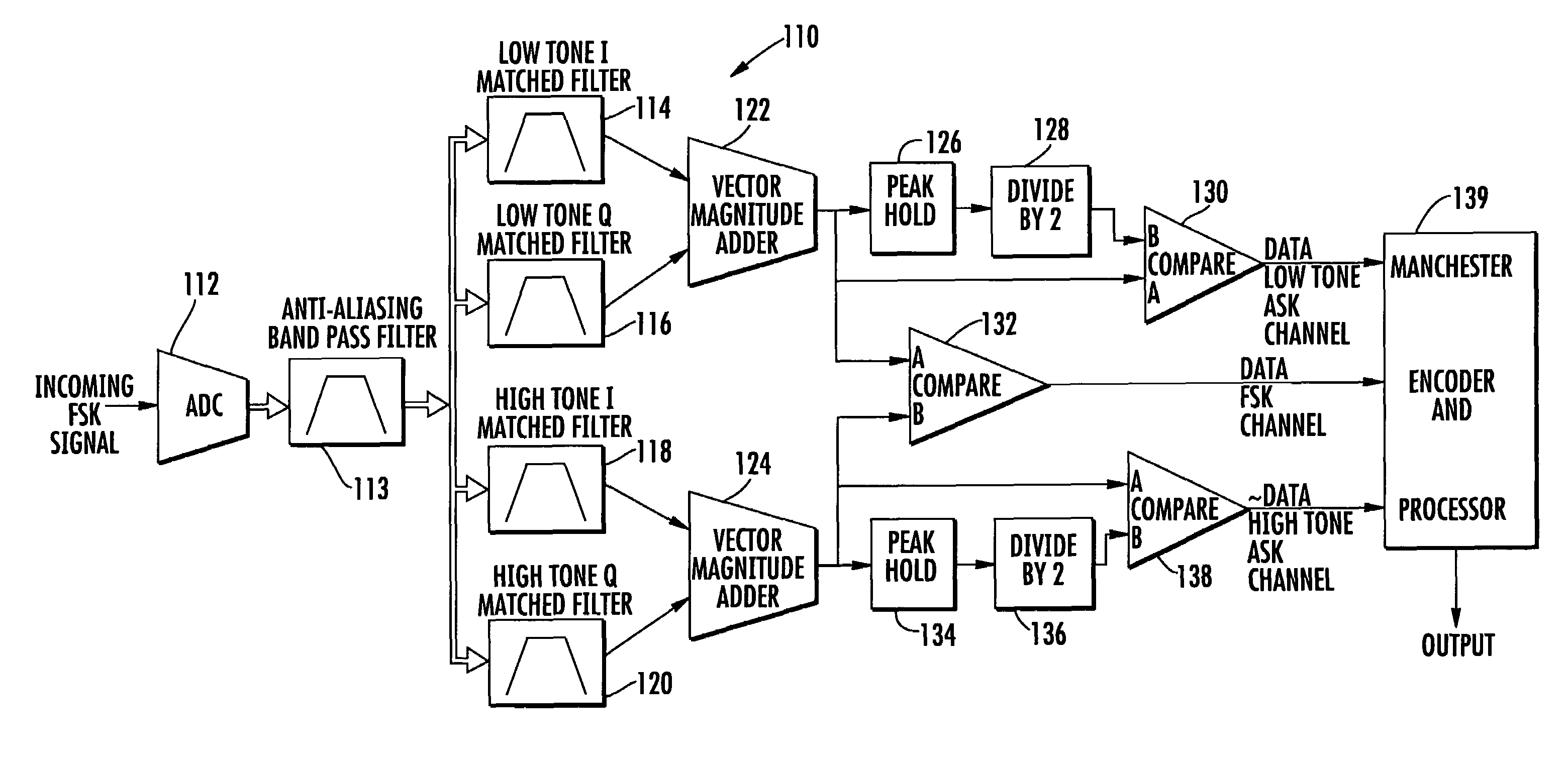

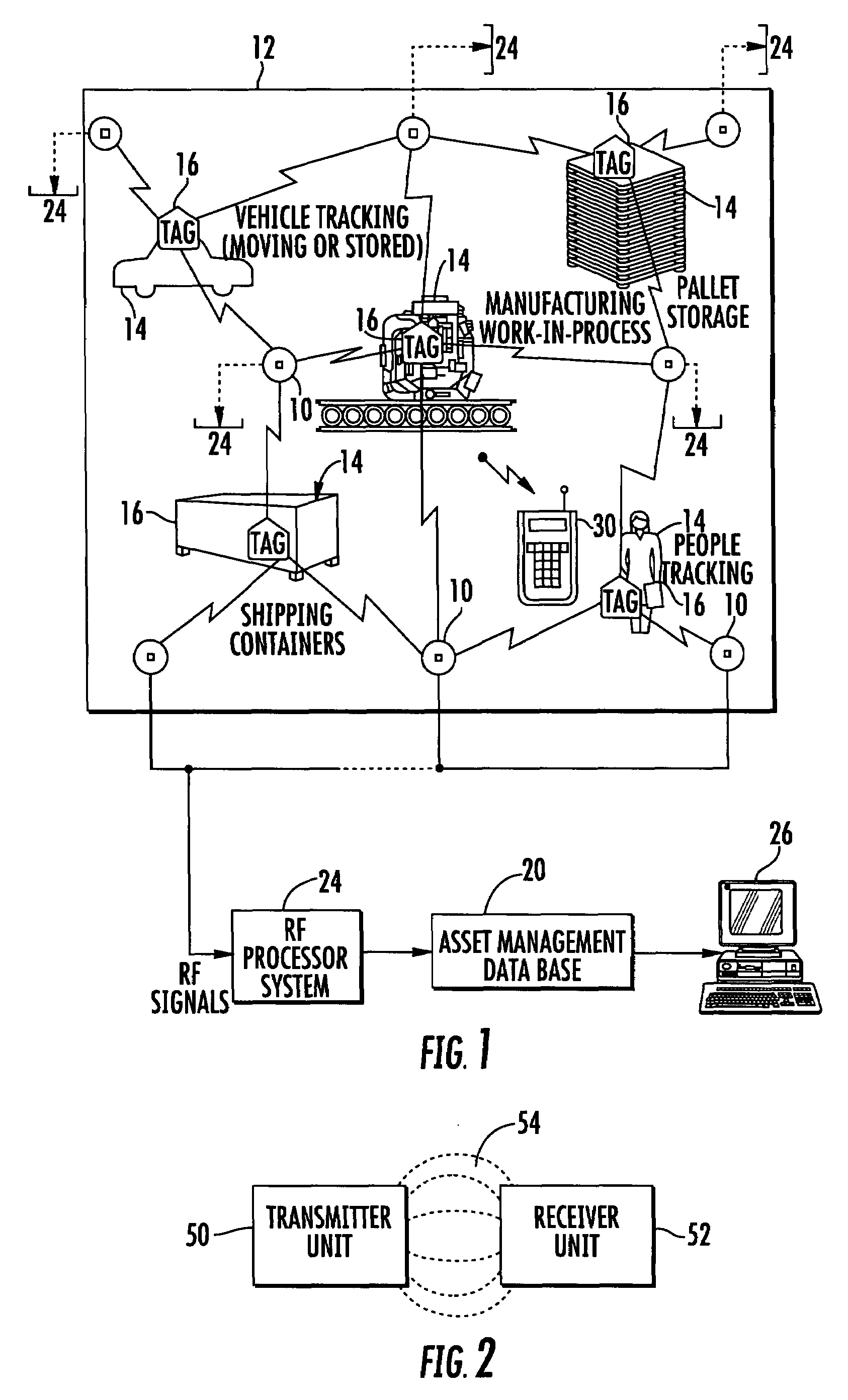

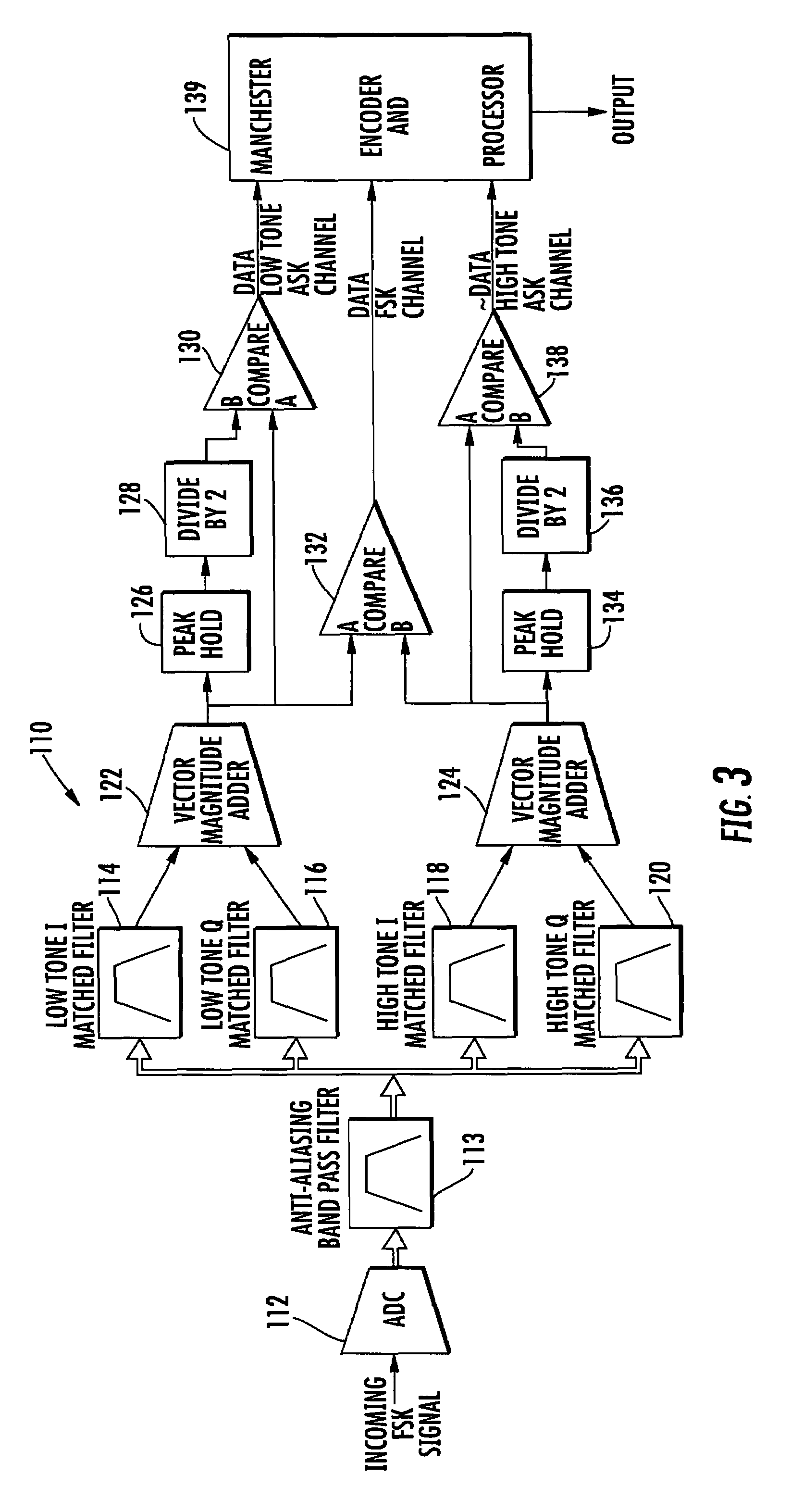

Receiver for object locating and tracking systems and related methods

Owner:ZEBRA TECH CORP

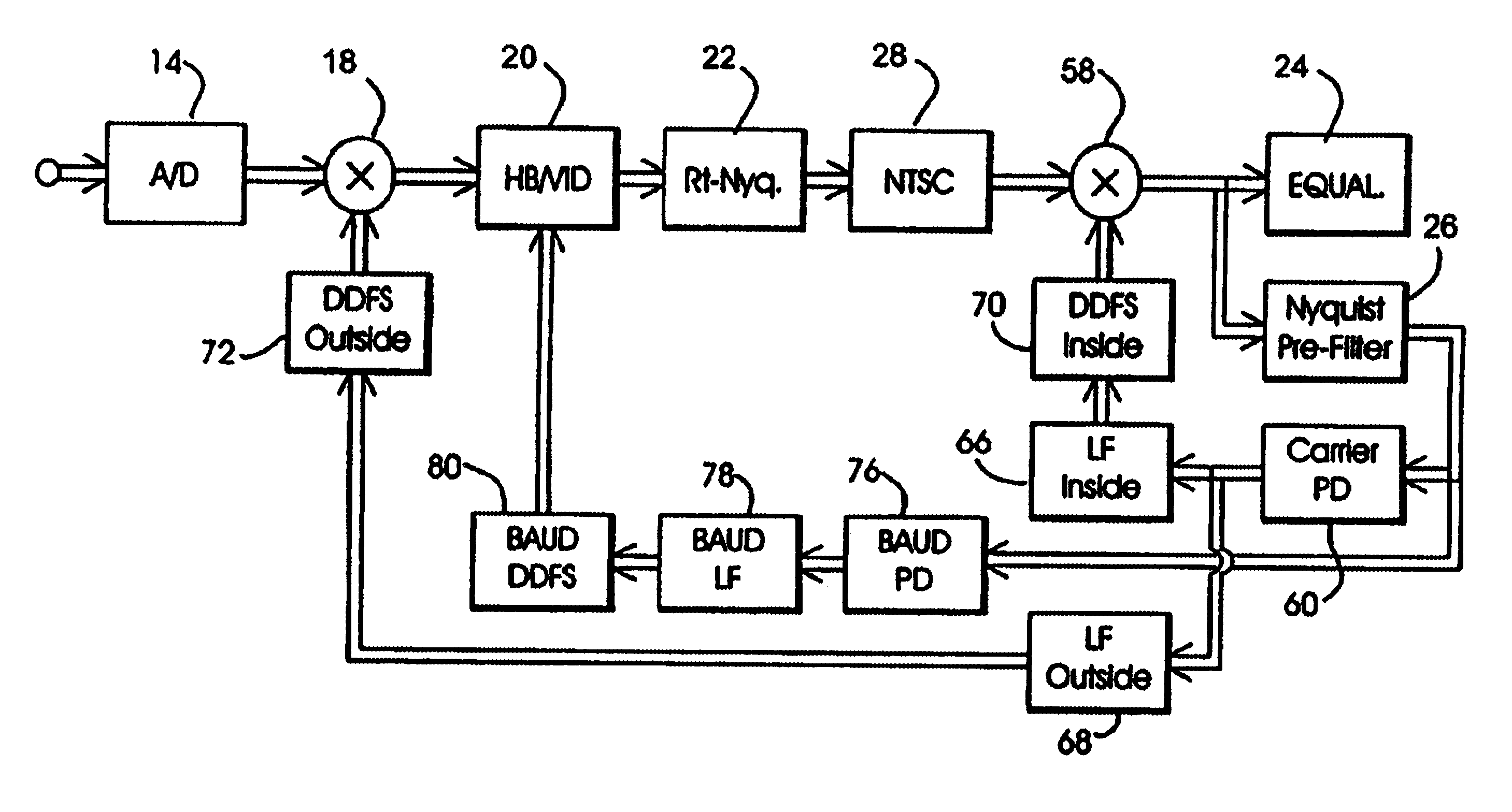

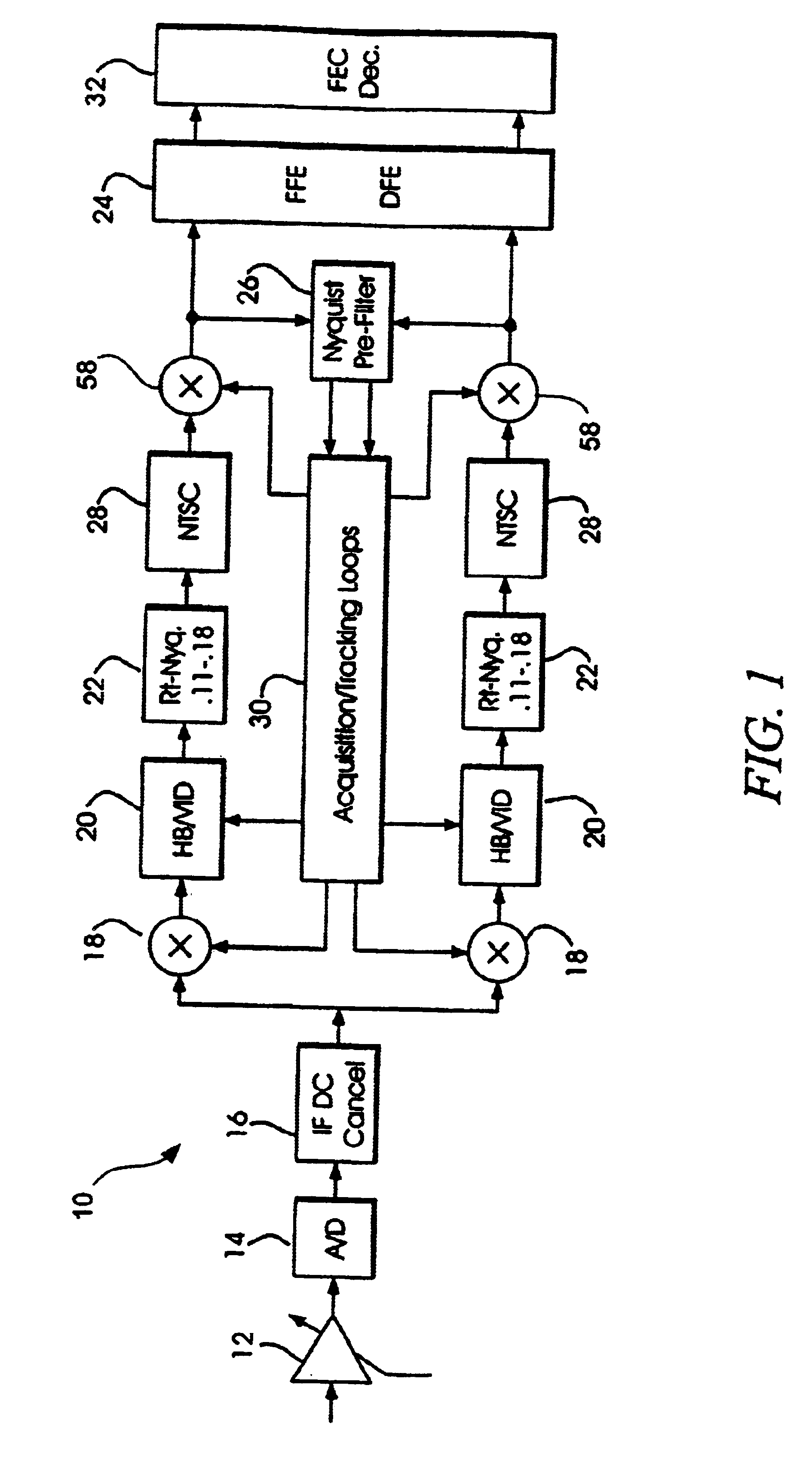

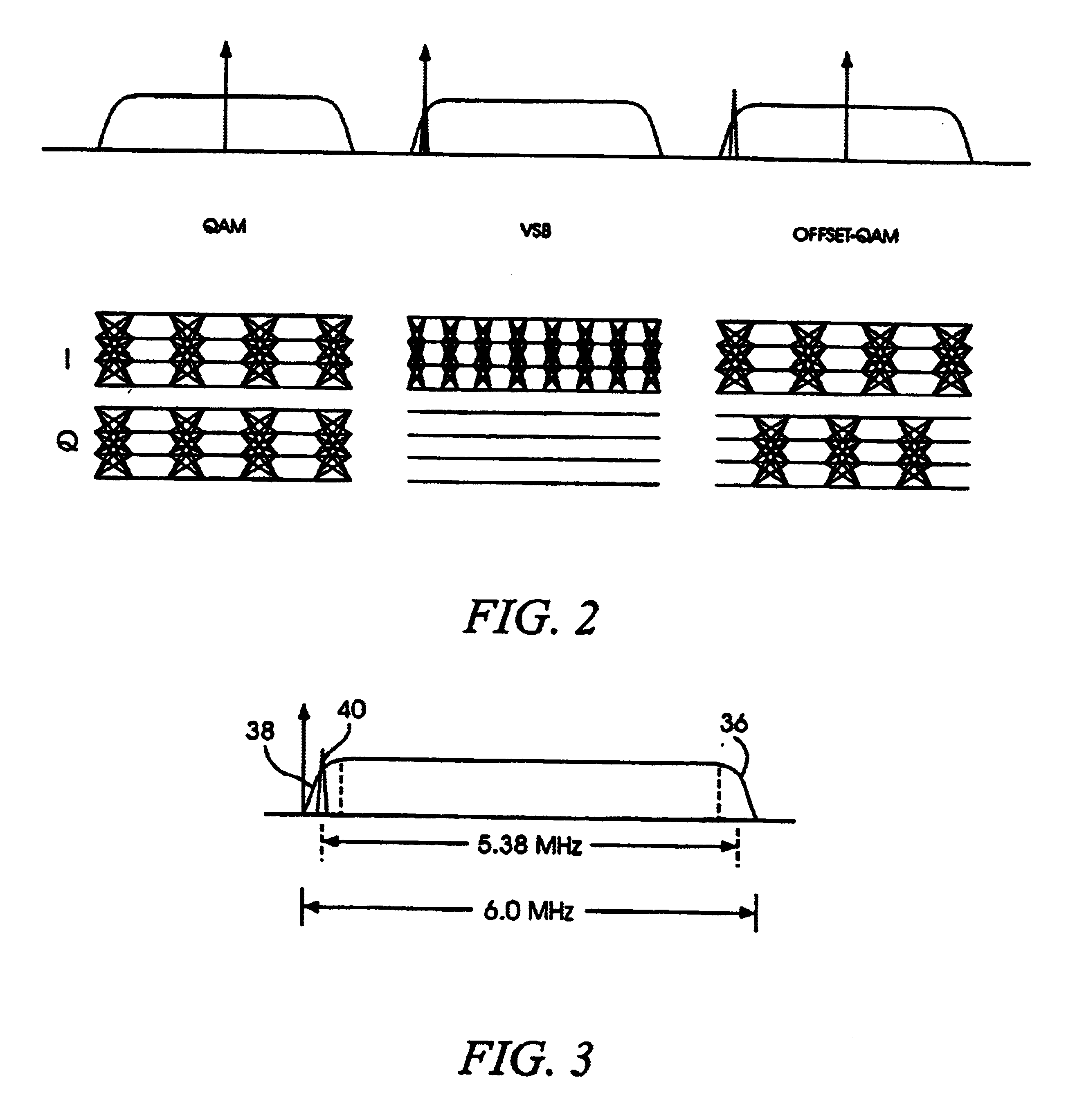

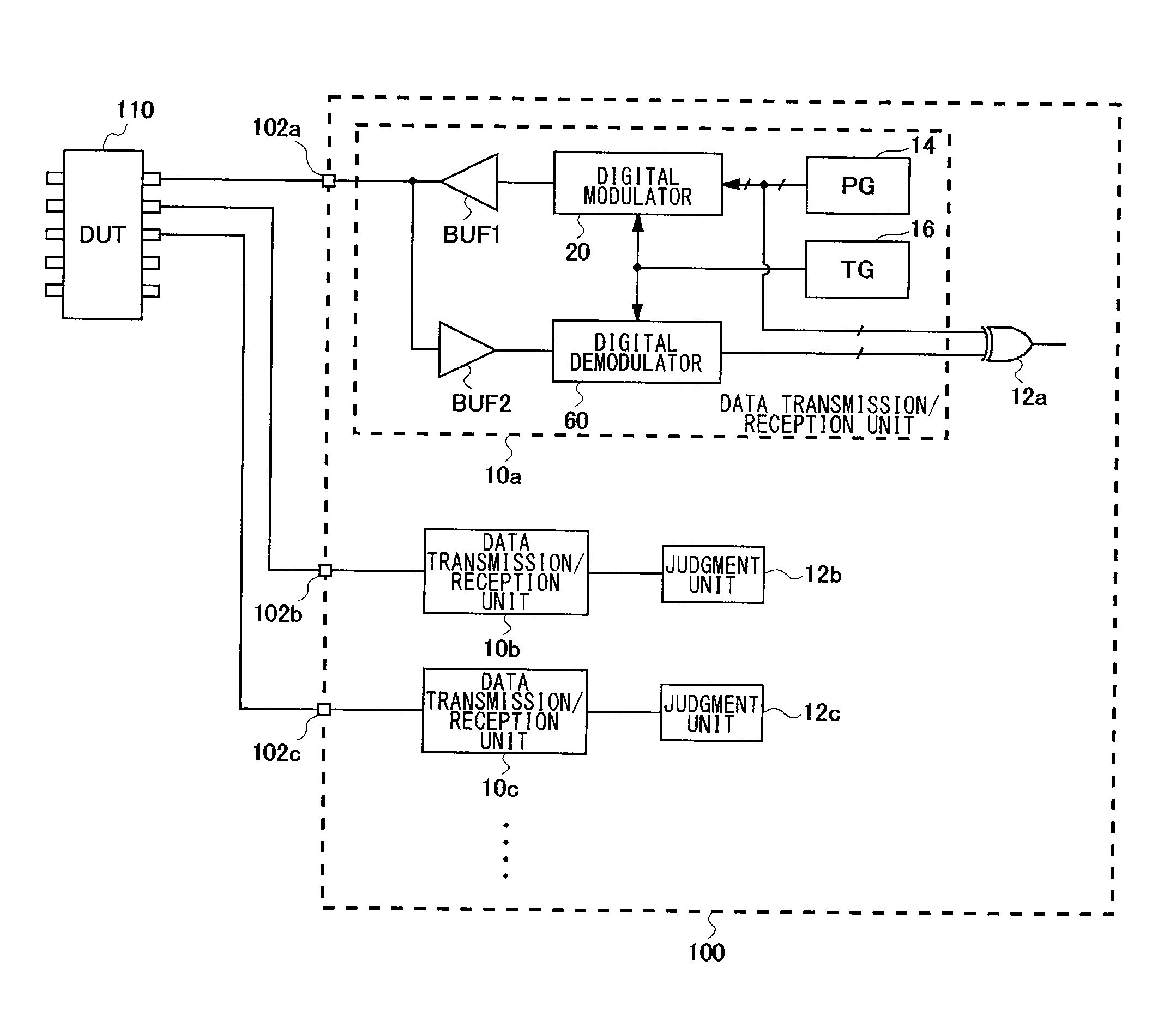

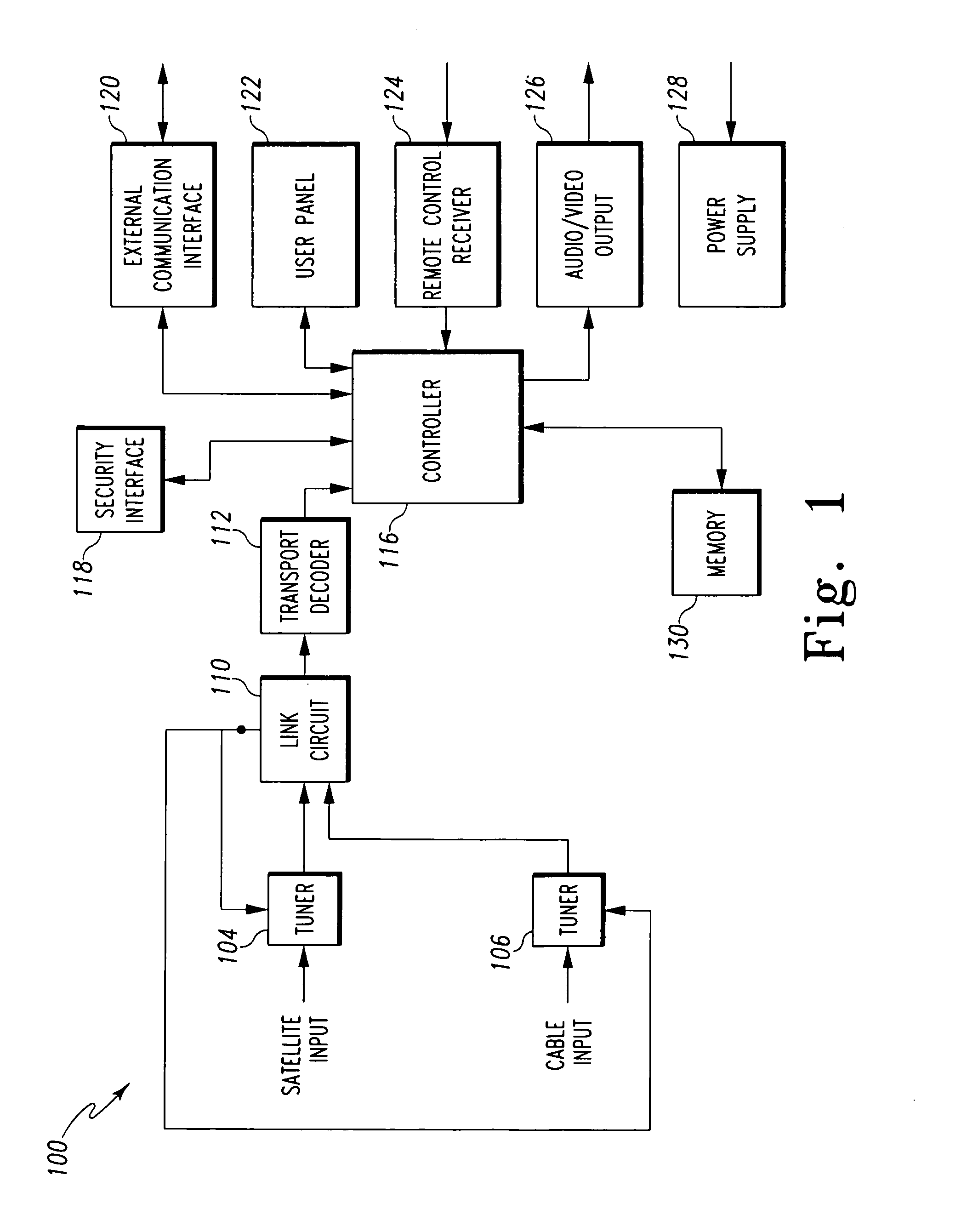

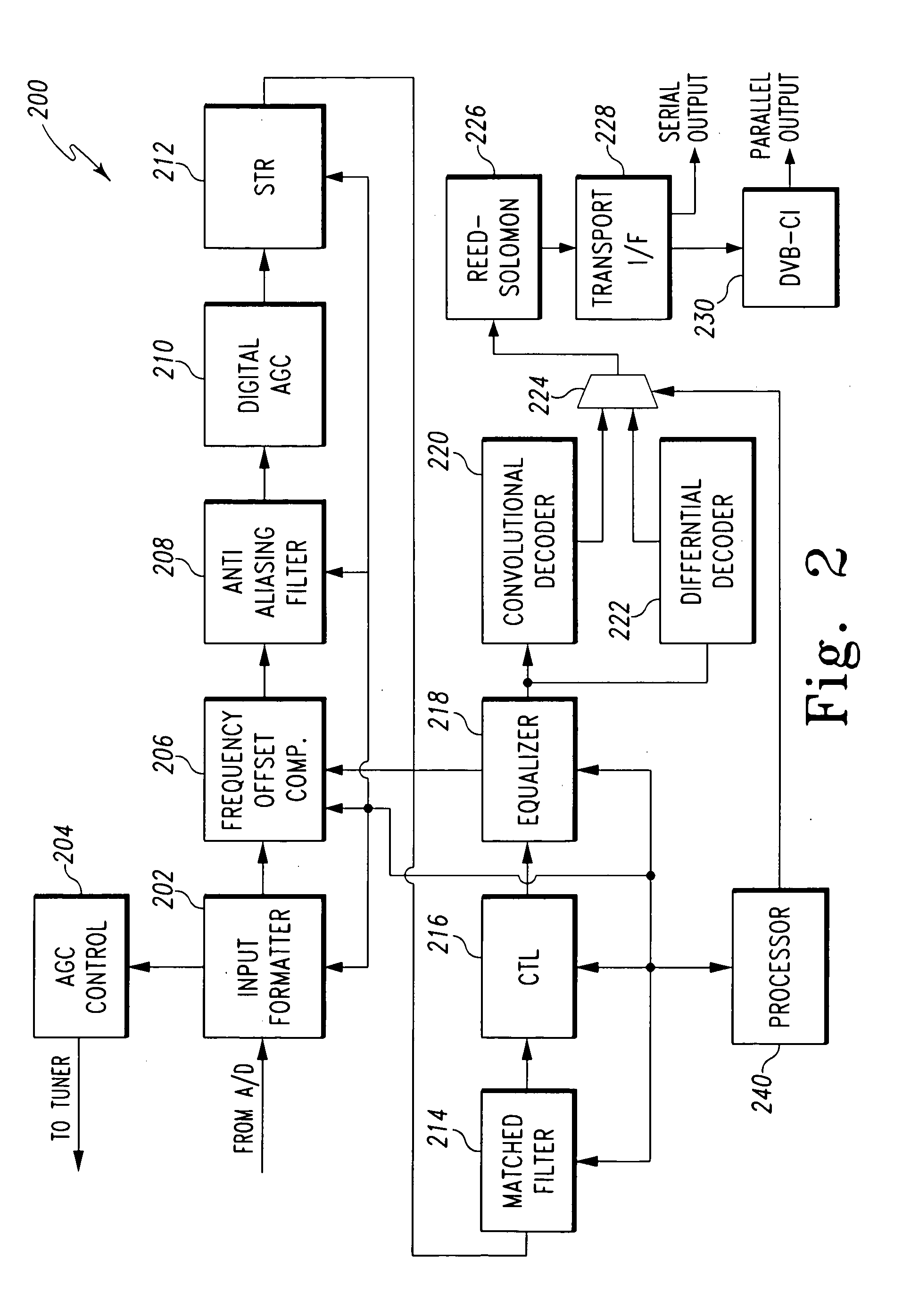

Dual mode QAM/VSB receiver

InactiveUS6842495B1Enhanced reliability symbolic decisionFacilitate decision-makingTelevision system detailsTelevision system scanning detailsPhase detectorTelevision receivers

A television receiver system capable of receiving and demodulating television signal information content that has been modulated and transmitted in accordance with a variety of modulation formats is disclosed. In particular, the system is able to accommodate receipt and demodulation of at least 8 and 16-VSB modulated signals in order to support US HDTV applications, as well as 64 and 256-QAM modulated signals, for European and potential US CATV implementations. The system includes carrier and timing recovery loops adapted to operate on an enhanced pilot signal as well as decision directed carrier phase recovery loops. Phase detectors operate on I and Q rail signals, or generate a Q rail from a Hilbert transform of the I rail. Decision directed loops incorporate a trellis decoder in order to operate on sequence estimated decisions for improved reliability in poor SNR environments.

Owner:AVAGO TECH INT SALES PTE LTD

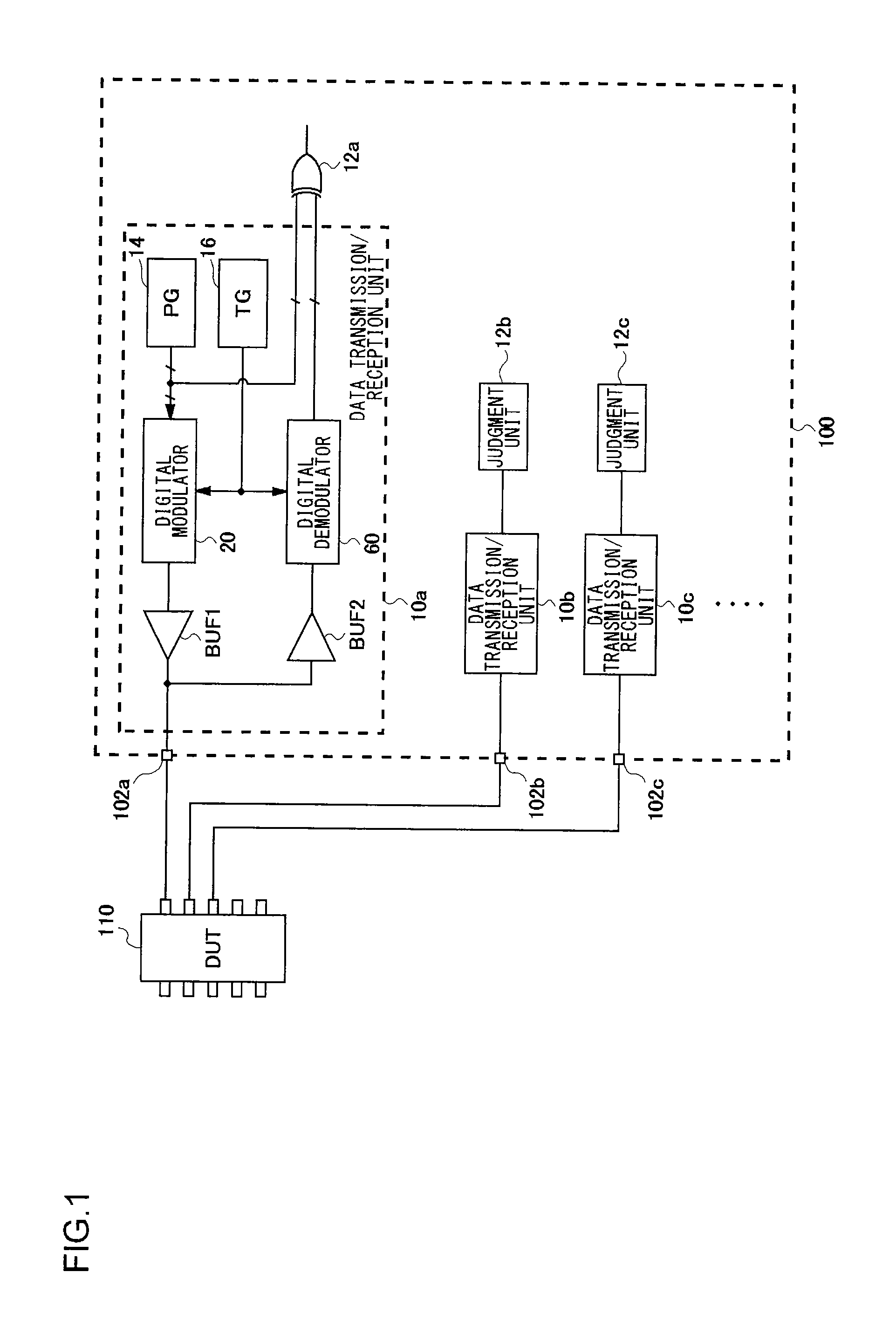

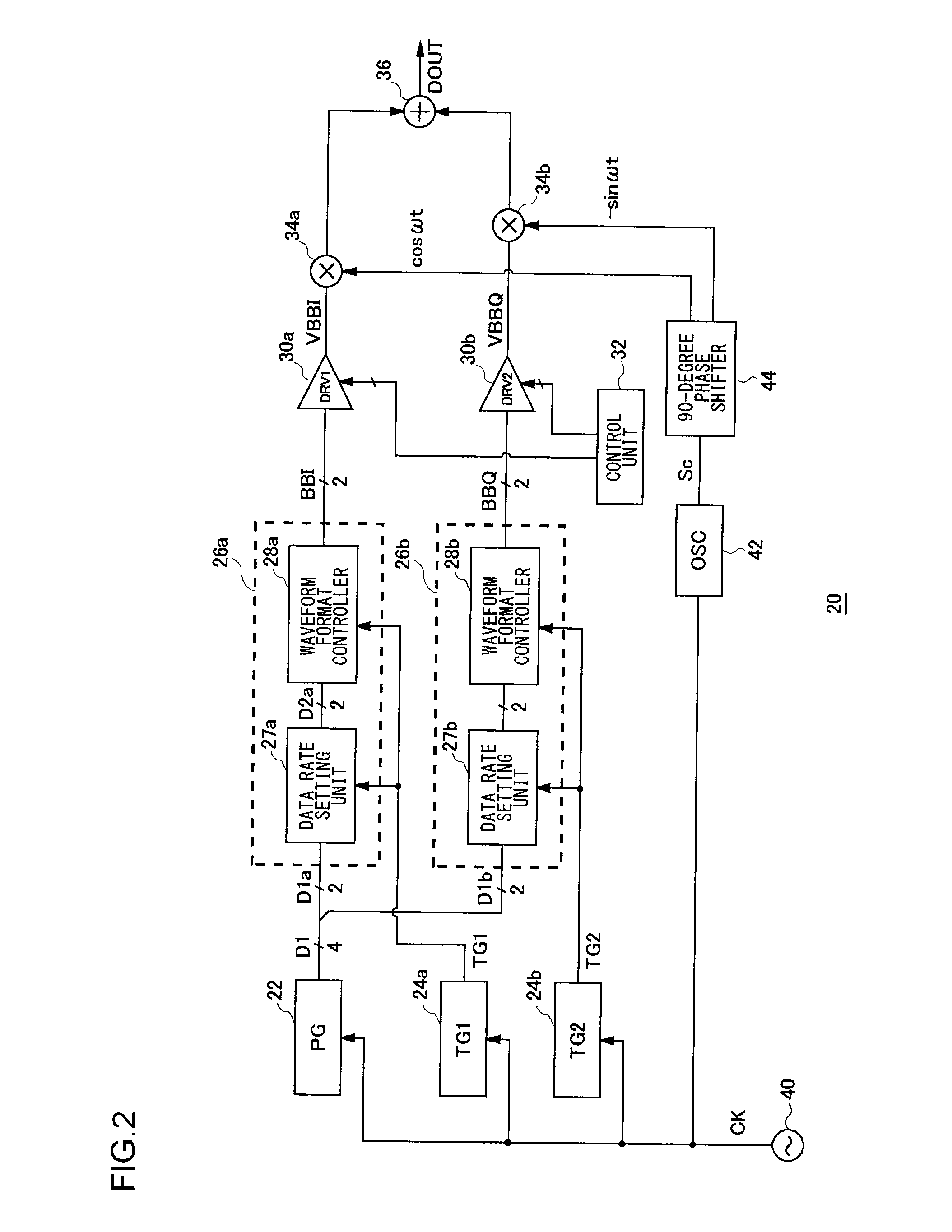

Test apparatus for digital modulated signal

ActiveUS20100321127A1Reduce circuit sizeCalibrating non-linear distortionElectrical testingAngle modulationBinary multiplierCarrier signal

A test apparatus includes digital modulators provided in increments of multiple channels. A baseband signal generator performs retiming of data input as a modulation signal for the in-phase (quadrature) component, using a timing signal the timing of which can be adjusted, thereby generating a baseband signal. A driver generates a multi-value digital signal having a level that corresponds to the baseband signal output from the baseband signal generator. A multiplier amplitude-modulates a carrier signal with the multi-value digital signal. An adder sums the output signals of the multipliers.

Owner:ADVANTEST CORP

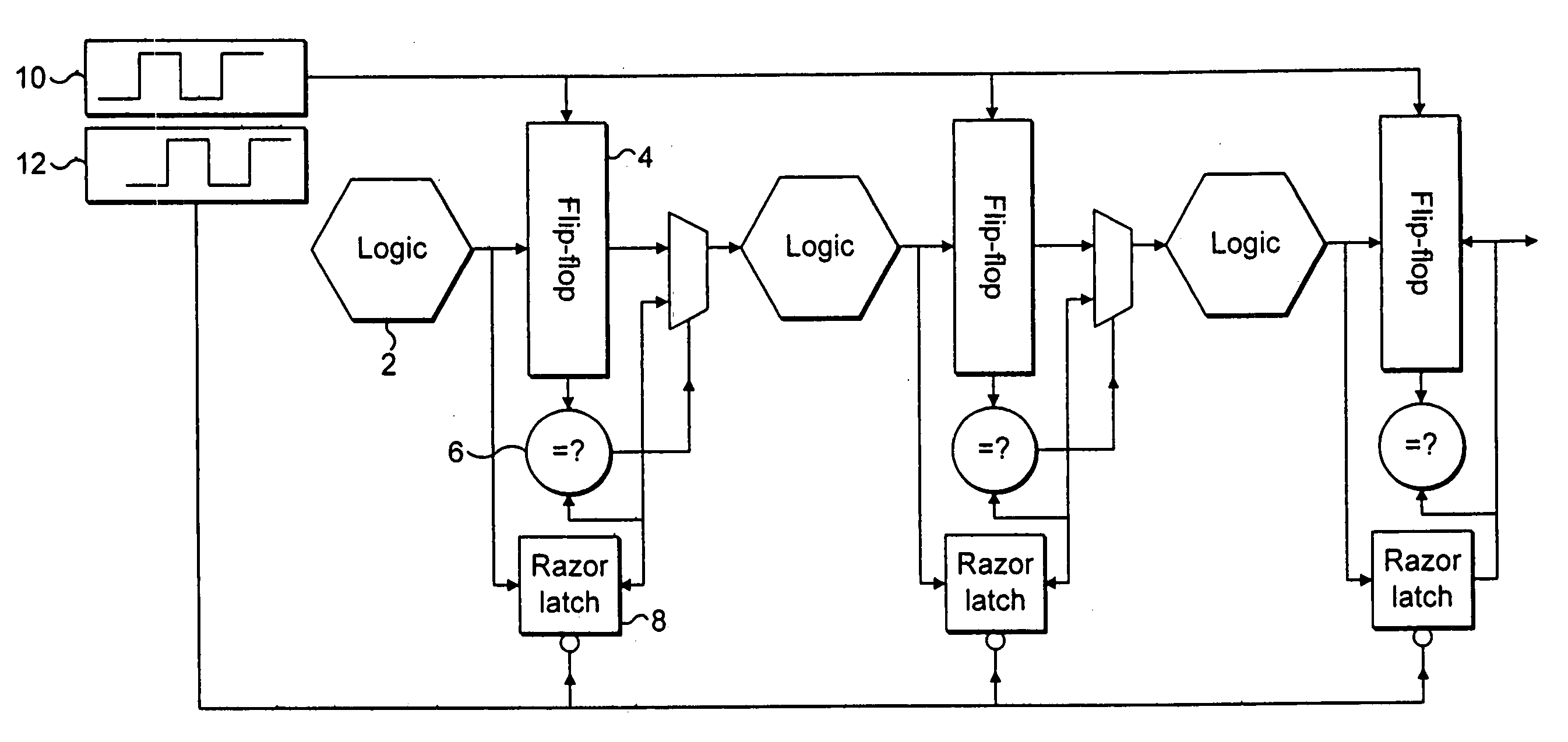

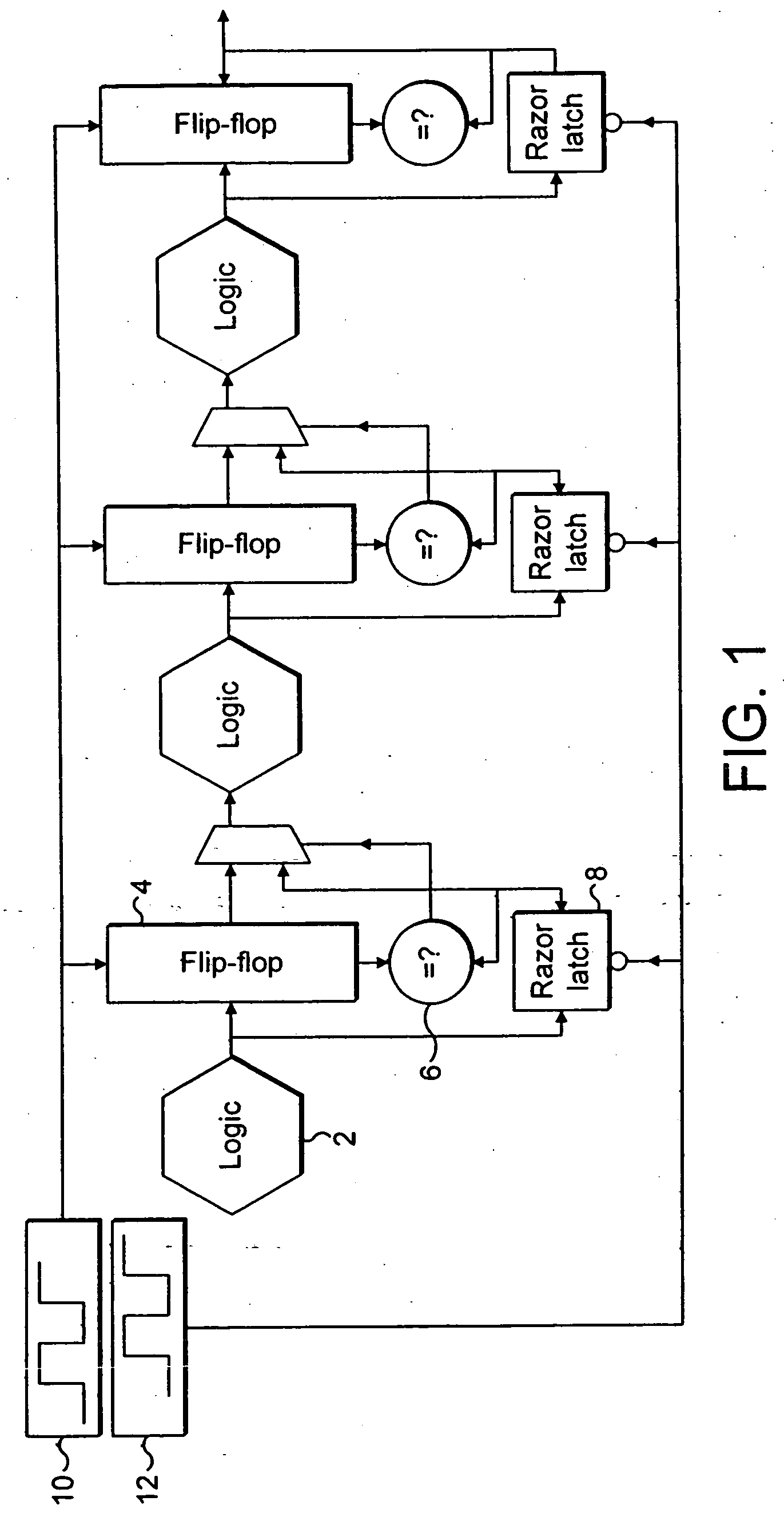

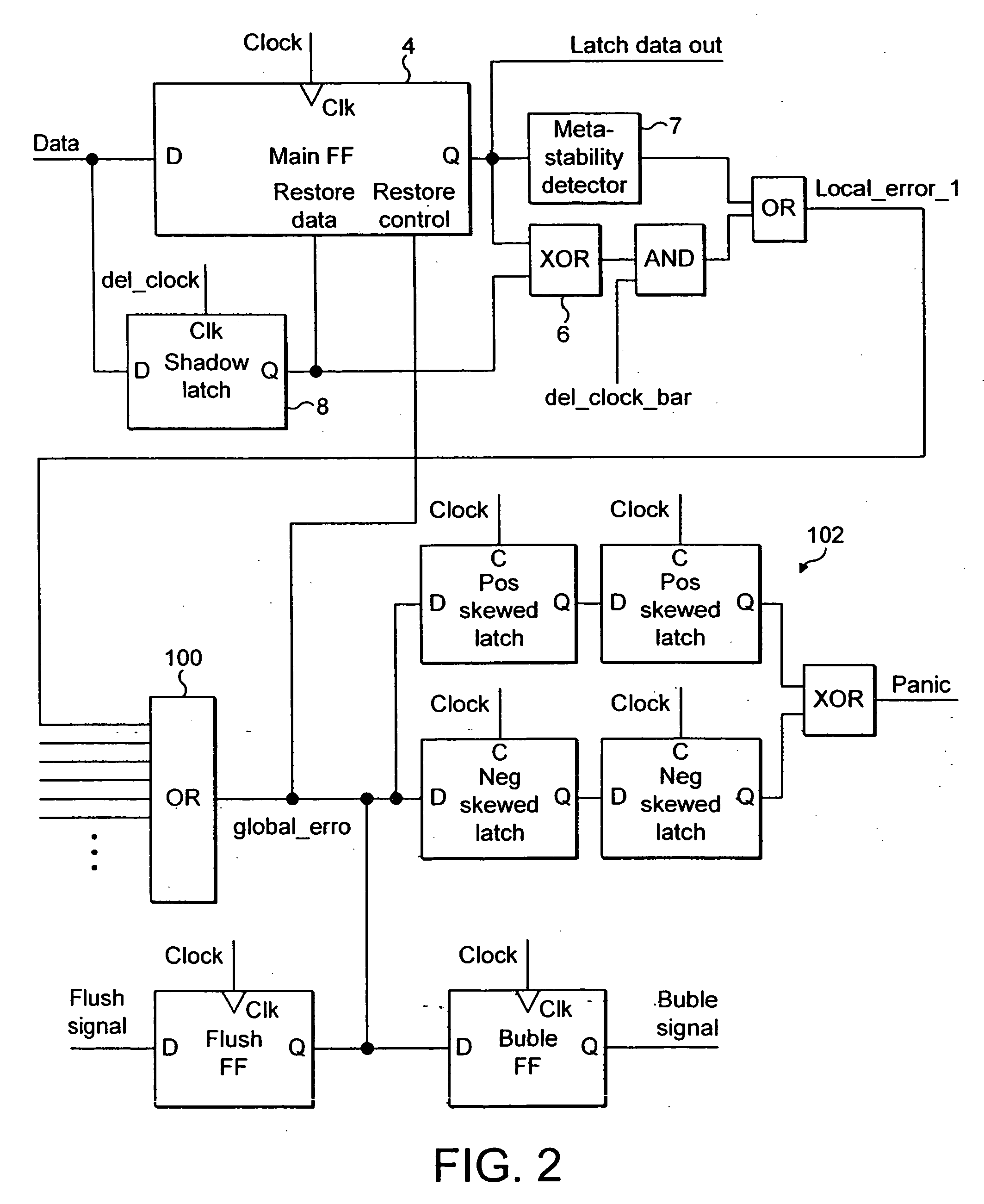

Error recovery within processing stages of an integrated circuit

ActiveUS20050246613A1Easy to modifyReduce the possibilityCode conversionFrequency/rate-modulated pulse demodulationError checkClock rate

An integrated circuit includes a plurality of processing stages each including processing logic 1014, a non-delayed signal-capture element 1016, a delayed signal-capture element 1018 and a comparator 1024. The non-delayed signal-capture element 1016 captures an output from the processing logic 1014 at a non-delayed capture time. At a later delayed capture time, the delayed signal-capture element 1018 also captures a value from the processing logic 1014. An error detection circuit 1026 and error correction circuit 1028 detect and correct random errors in the delayed value and supplies an error-checked delayed value to the comparator 1024. The comparator 1024 compares the error-checked delayed value and the non-delayed value and if they are not equal this indicates that the non-delayed value was captured too soon and should be replaced by the error-checked delayed value. The non-delayed value is passed to the subsequent processing stage immediately following its capture and accordingly error recovery mechanisms are used to suppress the erroneous processing which has occurred by the subsequent processing stages, such as gating the clock and allowing the correct signal values to propagate through the subsequent processing logic before restarting the clock. The operating parameters of the integrated circuit, such as the clock frequency, the operating voltage, the body biased voltage, temperature and the like are adjusted so as to maintain a finite non-zero error rate in a manner that increases overall performance.

Owner:ARM LTD +1

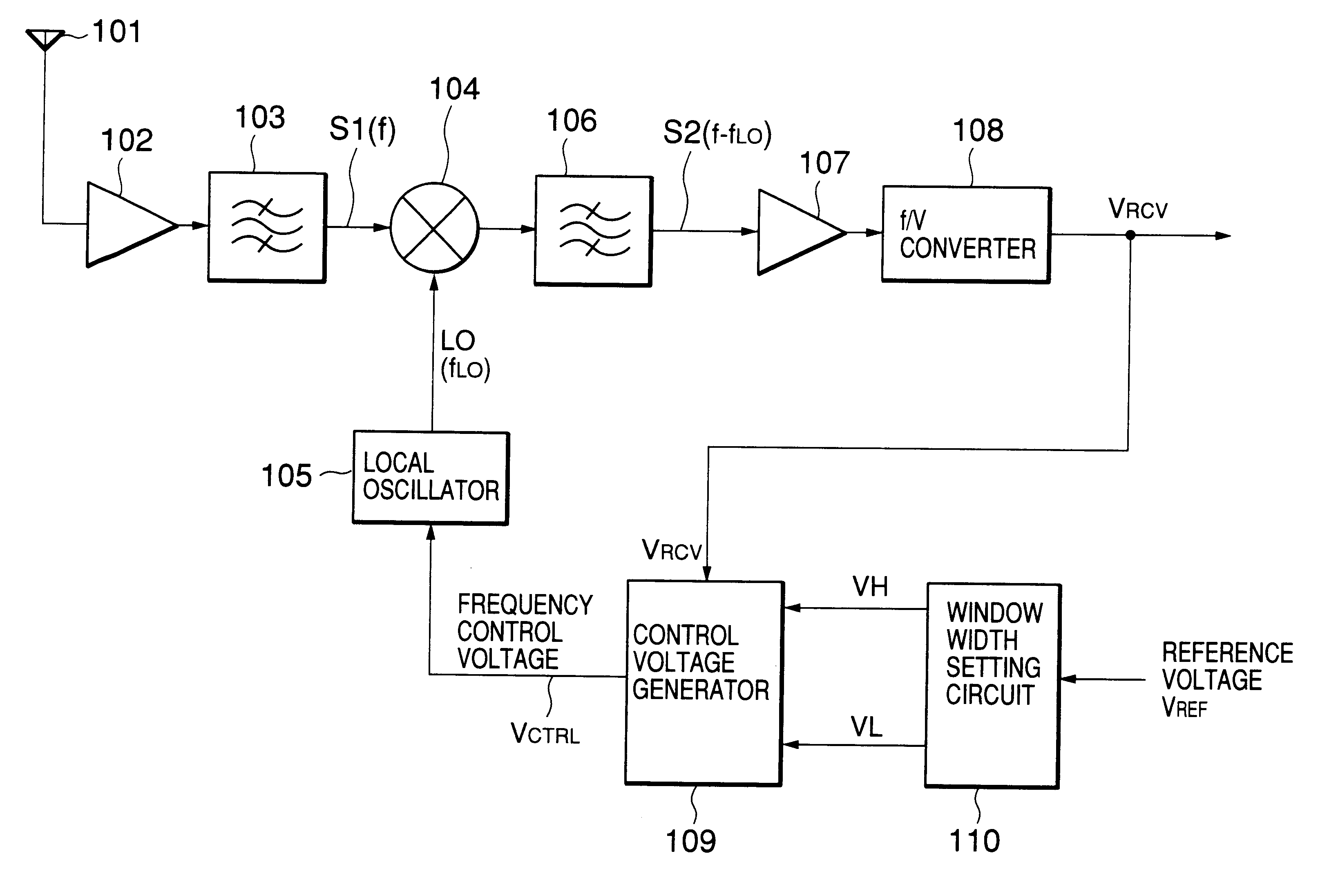

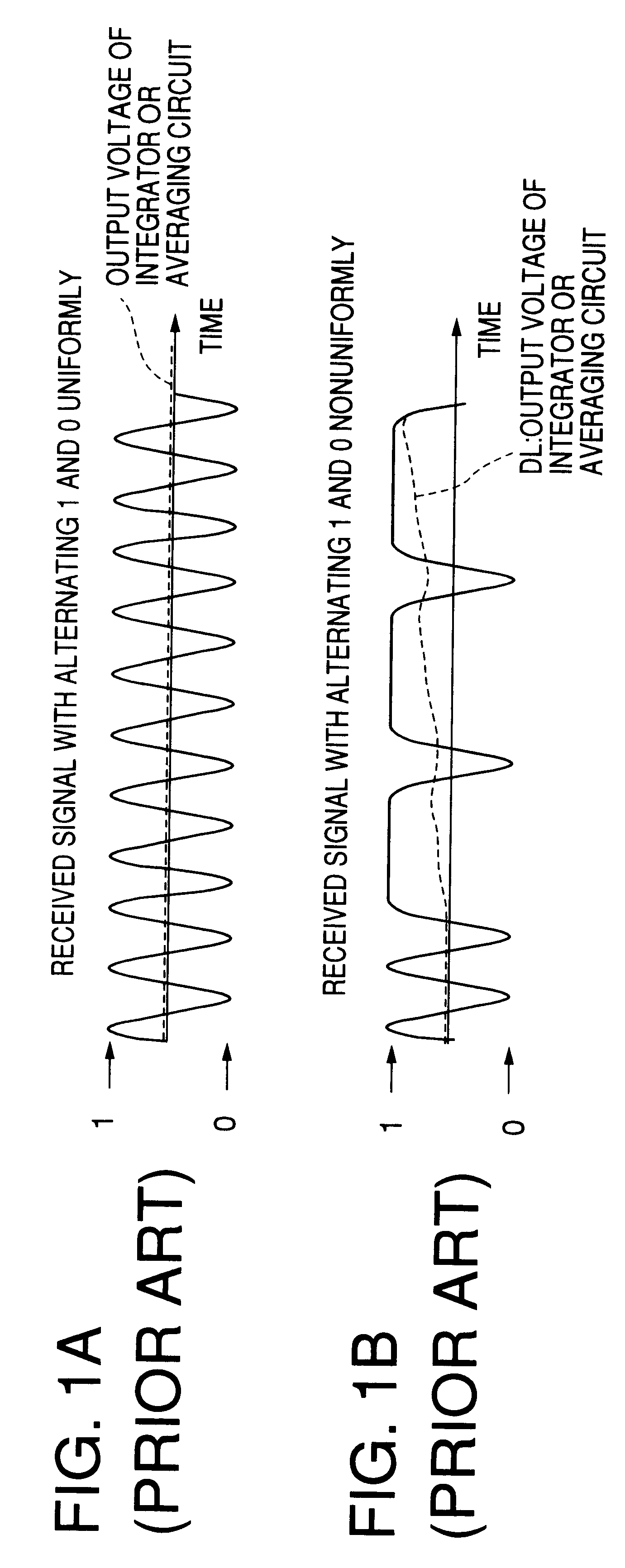

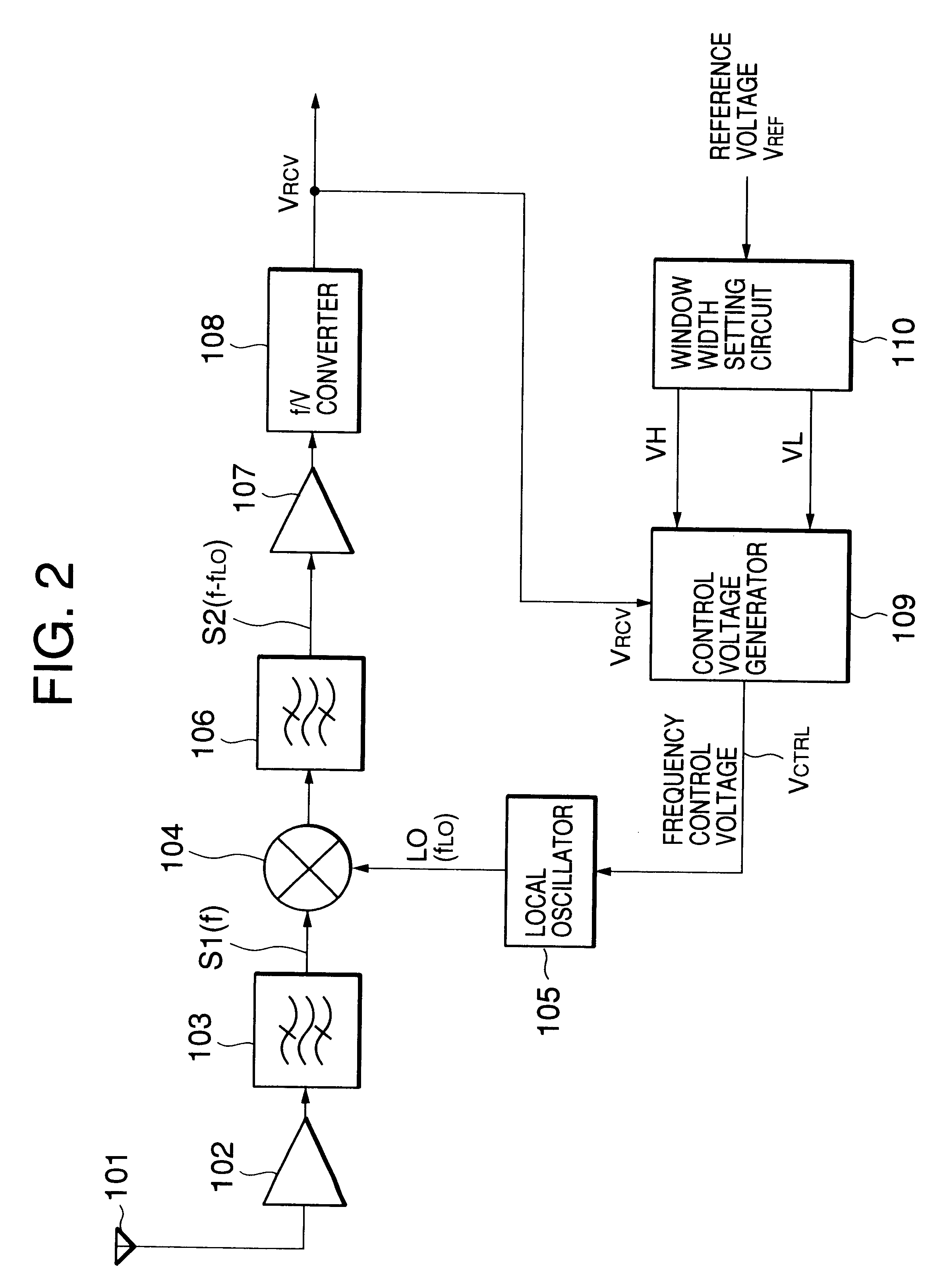

Automatic frequency control in FSK receiver using voltage window deviation

InactiveUS6332007B1Pulse automatic controlAutomatic frequency control detailsLocal oscillatorEngineering

An AFC circuit for controlling an oscillation frequency of a local oscillator is disclosed. An f / V converter converts a frequency of an FSK signal to a received signal voltage varying depending on the frequency of the FSK signal. A window generator generates a voltage window including a reference voltage corresponding to a center frequency of the FSK signal. The oscillation frequency of the local oscillator is controlled depending on a deviation of the received signal voltage from the voltage window so that the received signal voltage falls into the voltage window.

Owner:NEC CORP

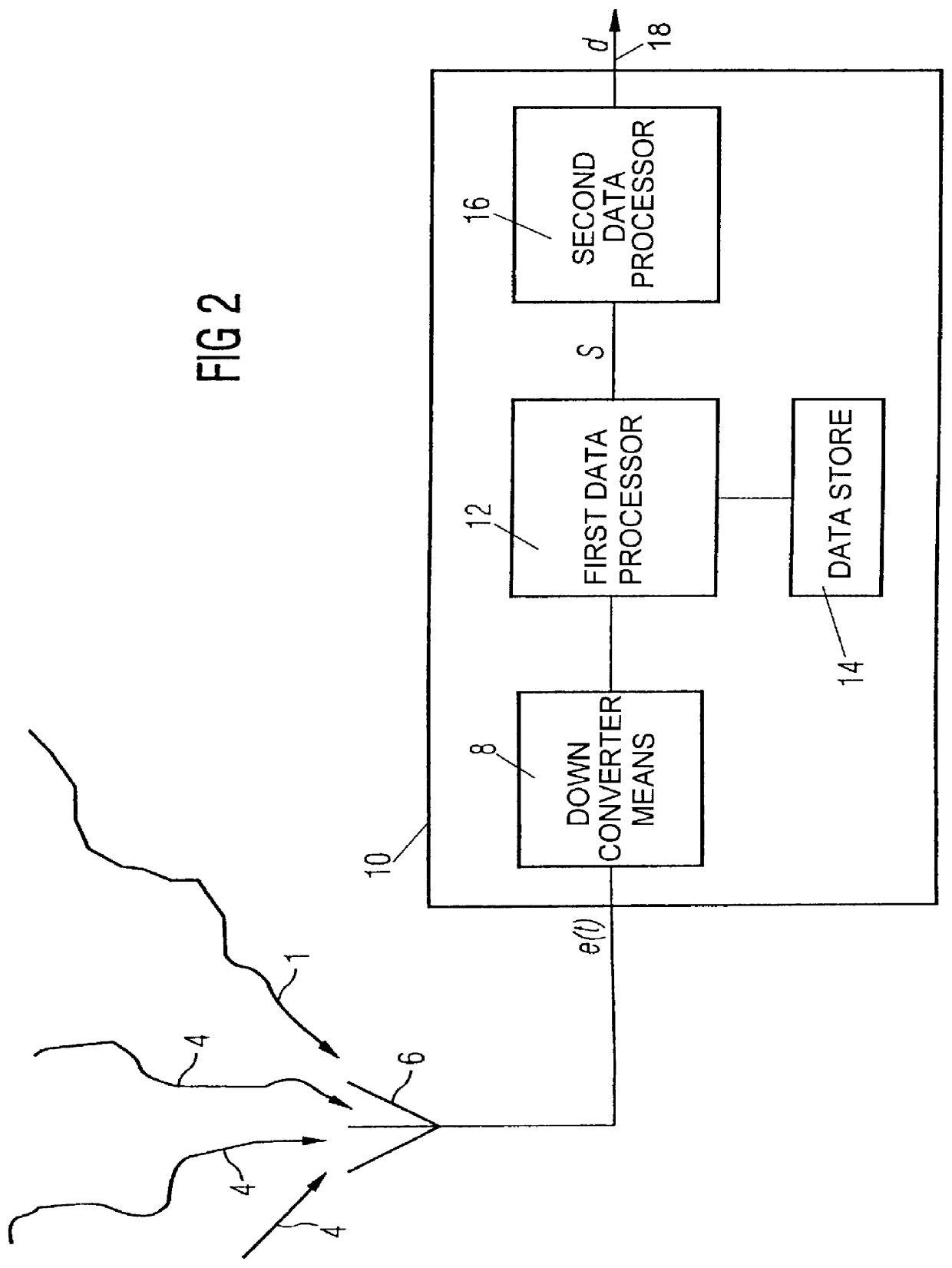

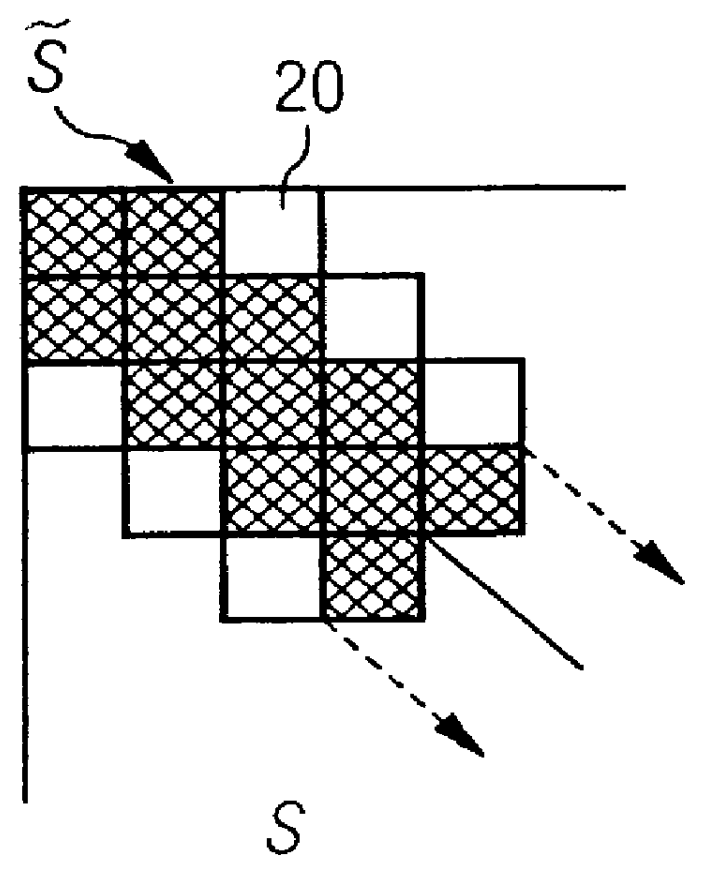

Radio communications receiver and method of receiving radio signals

InactiveUS6064689AImprove abilitiesAvoid detectionError preventionLine-faulsts/interference reductionRadio communicationsRadio signal

A radio communications receiver which detects radio signals and recovers data representative of the radio signals in a presence of contemporaneously detected interfering signals, the radio communications receiver having a detector that detects said radio signals and generates digital base band signals representative of the radio signals, a matrix former that forms a correlation matrix having rows and columns from the base band signals, and a data processor that generates a factor matrix of the correlation matrix, the factor matrix having rows and columns, and recovers data from the factor matrix. The data processor generates the factor matrix by calculating first elements of the factor matrix from the correlation matrix using a factorization algorithm in accordance with a pre-determined structure of the factor matrix, and forming second elements of the factor matrix by selectively copying first elements in accordance with the pre-determined structure.

Owner:NOKIA SIEMENS NETWORKS GMBH & CO KG

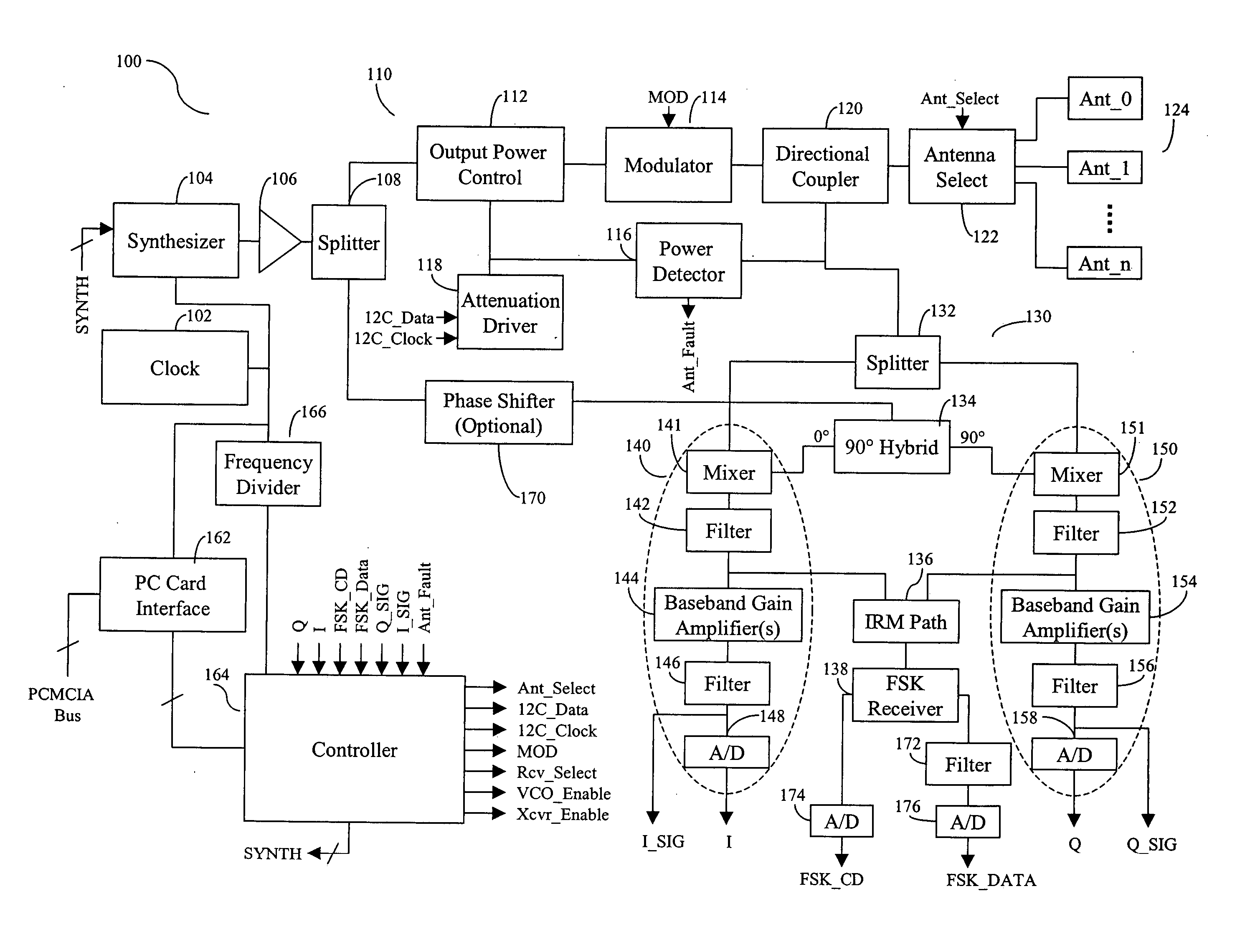

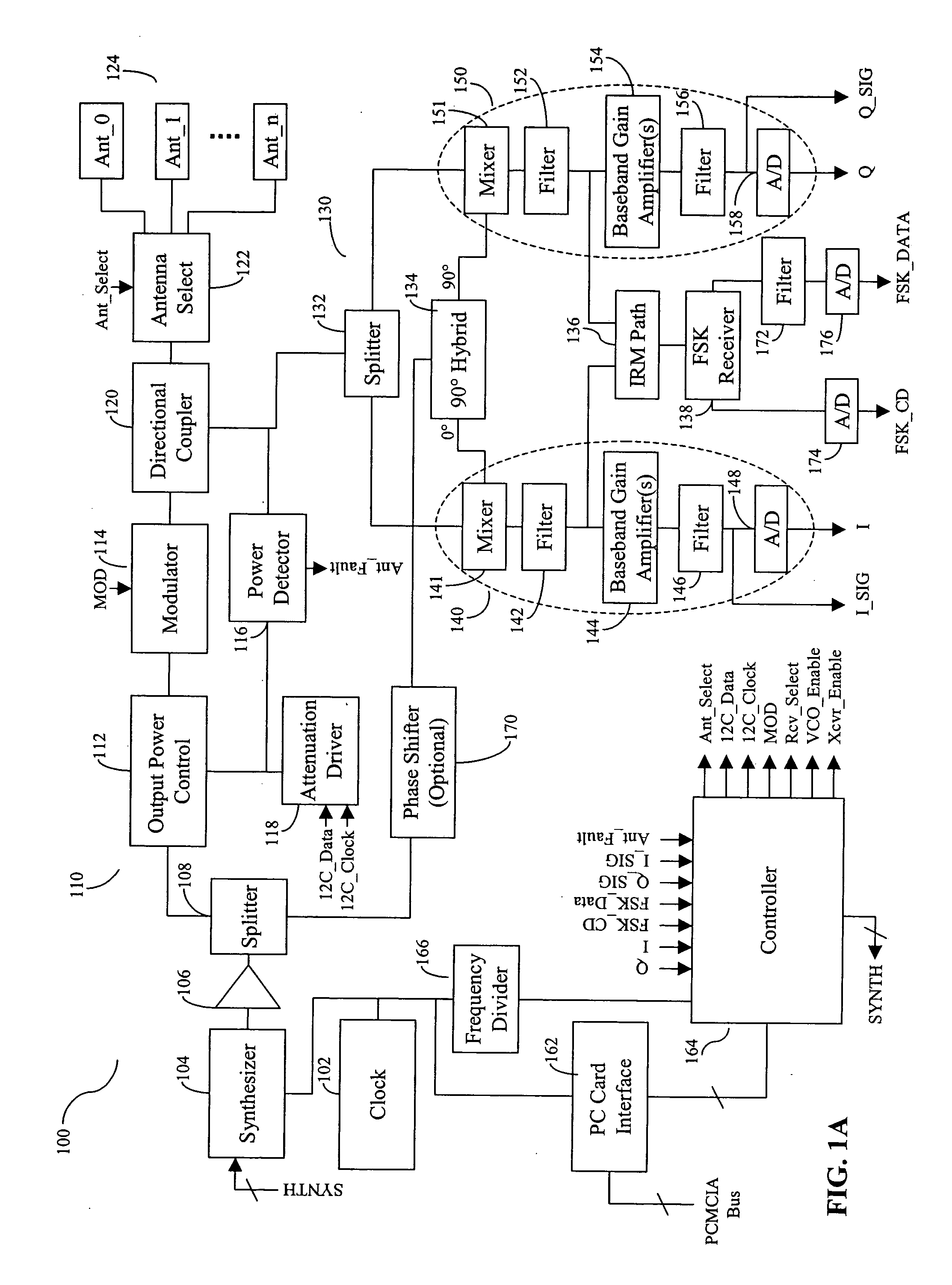

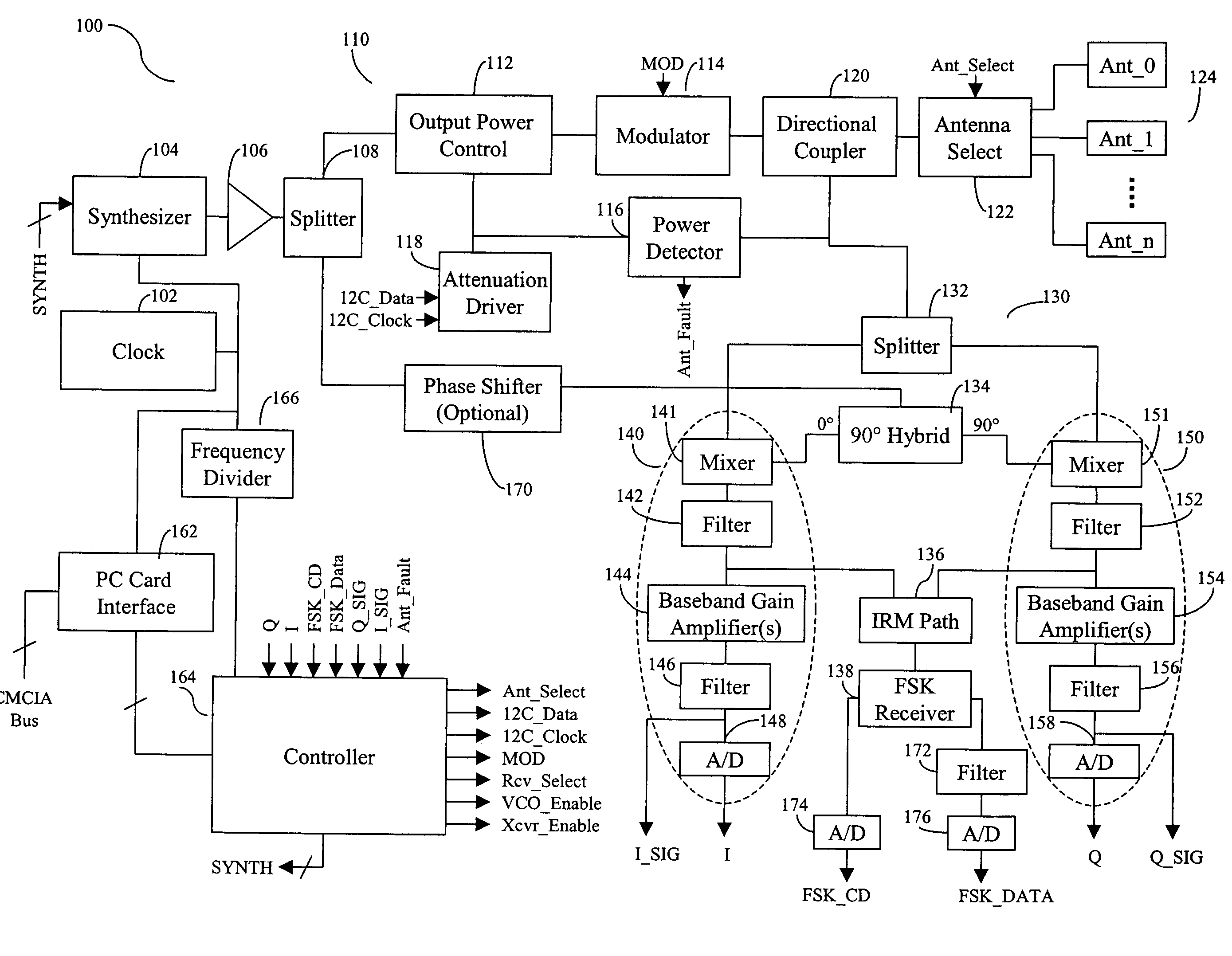

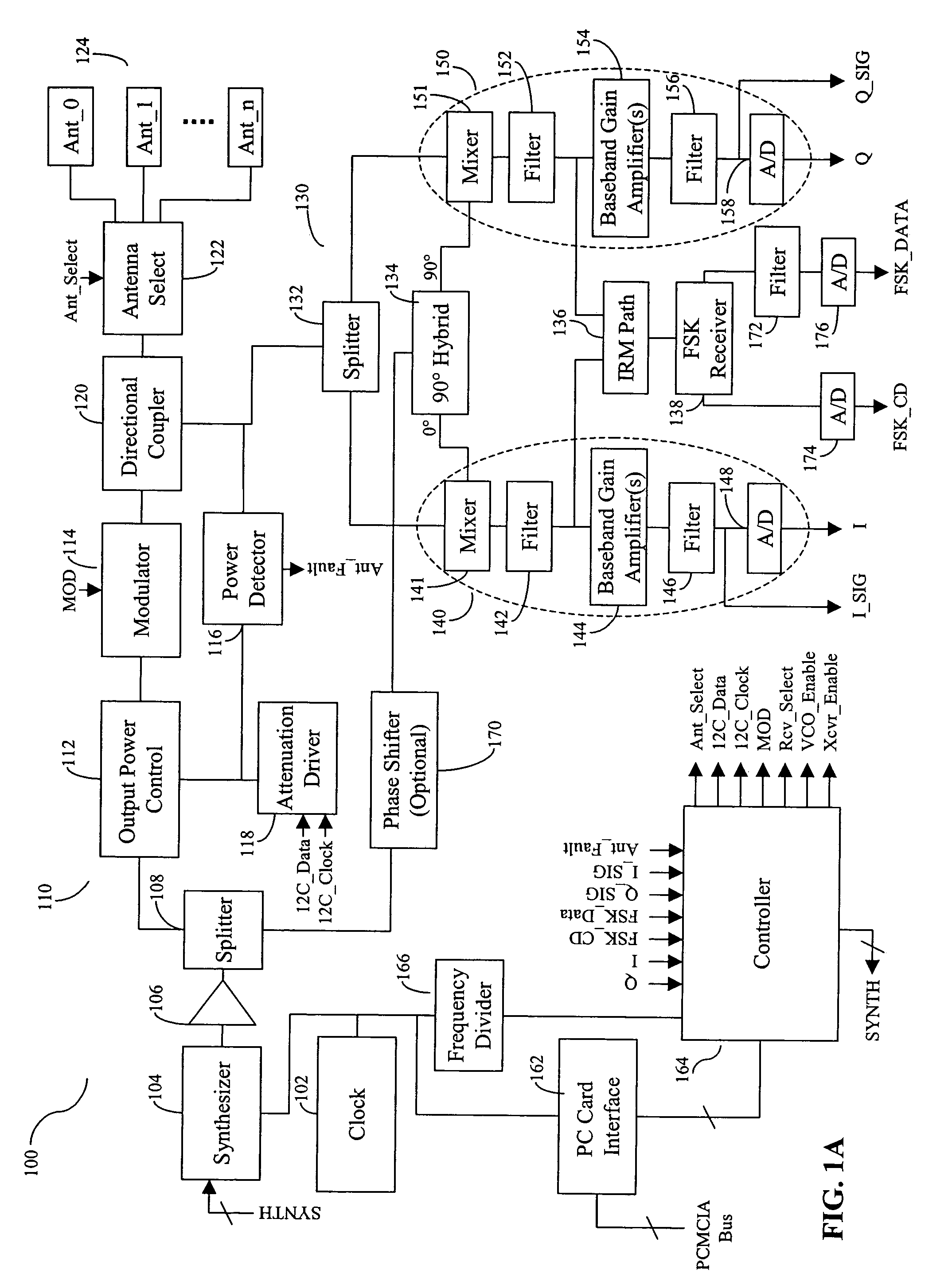

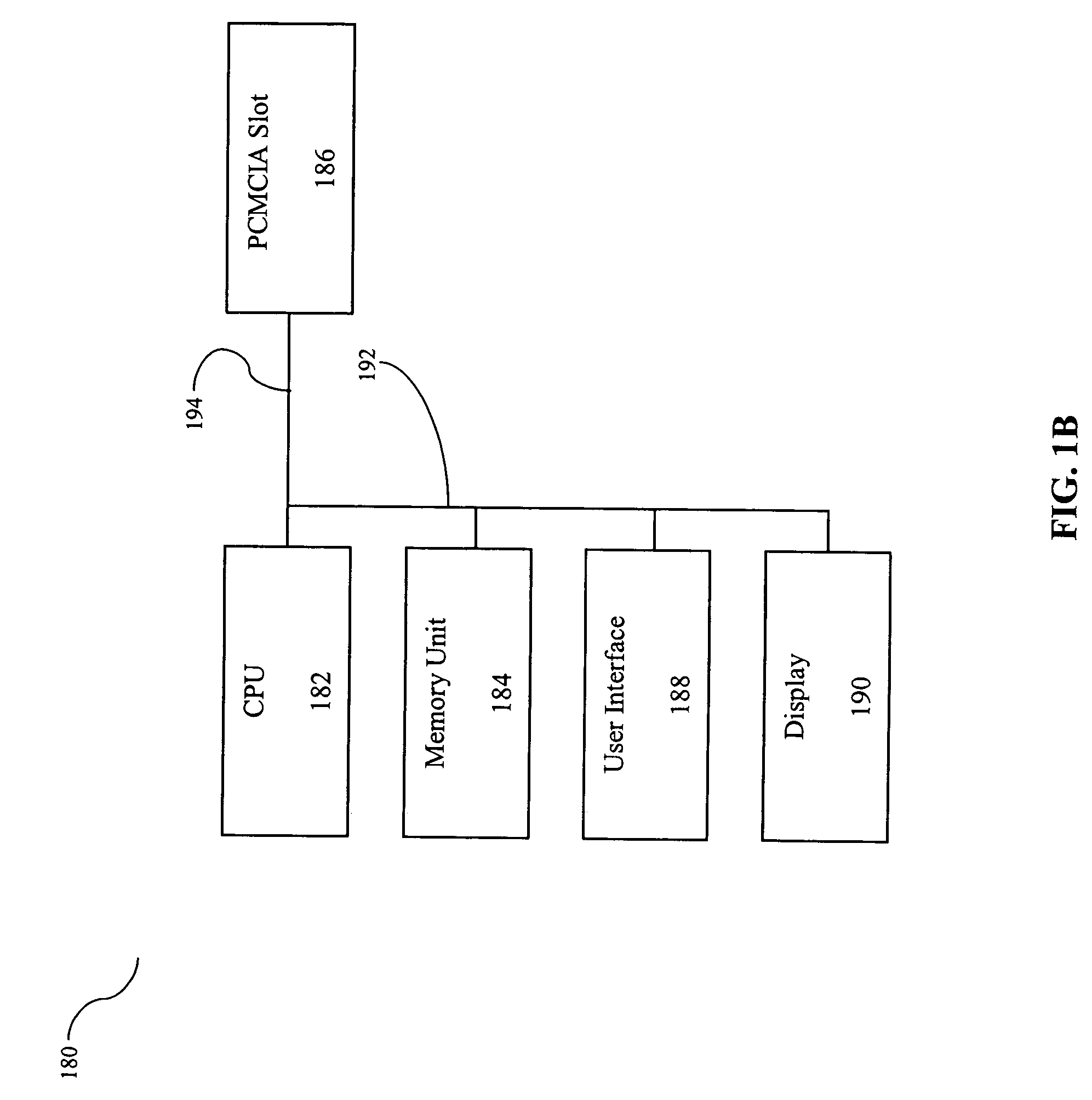

Multiprotocol RFID reader

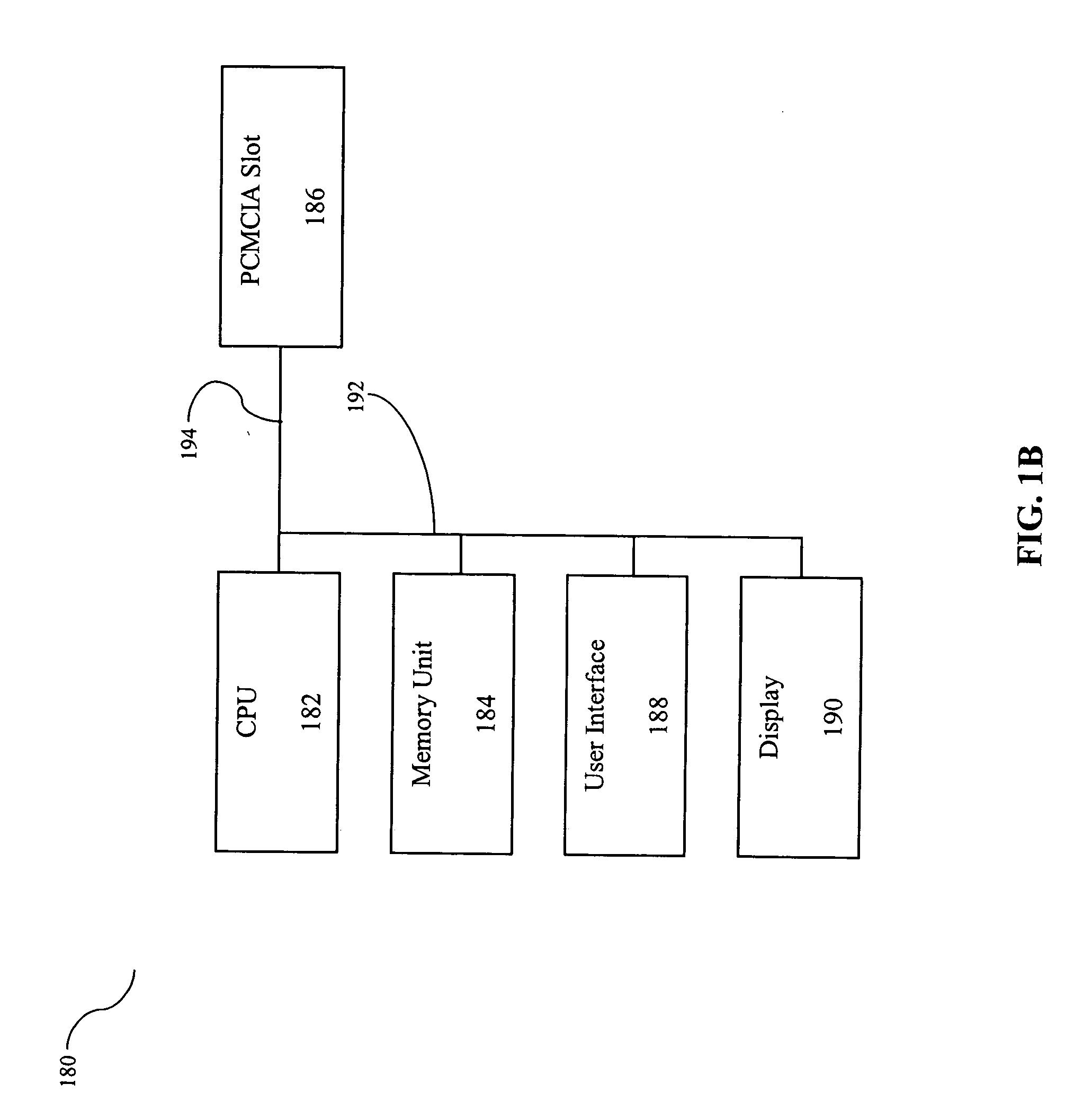

InactiveUS20050231367A1Small sizeHigh sensitivityMemory record carrier reading problemsVisual presentationEngineeringPersonal computer

An RFID reader accessible thorough a personal computer and includes a PC card interface and a controller both operating according to clock signals from a crystal oscillator. The RFID reader further includes a linearized power amplifier modulator in a transmit path, a receive chain capable of demodulating EPCglobal Class_1 and Class_0 signals from RFID tags, and an integrated switching device for selecting one of a plurality of antenna for transmitting or receiving RF signals.

Owner:WJ COMM

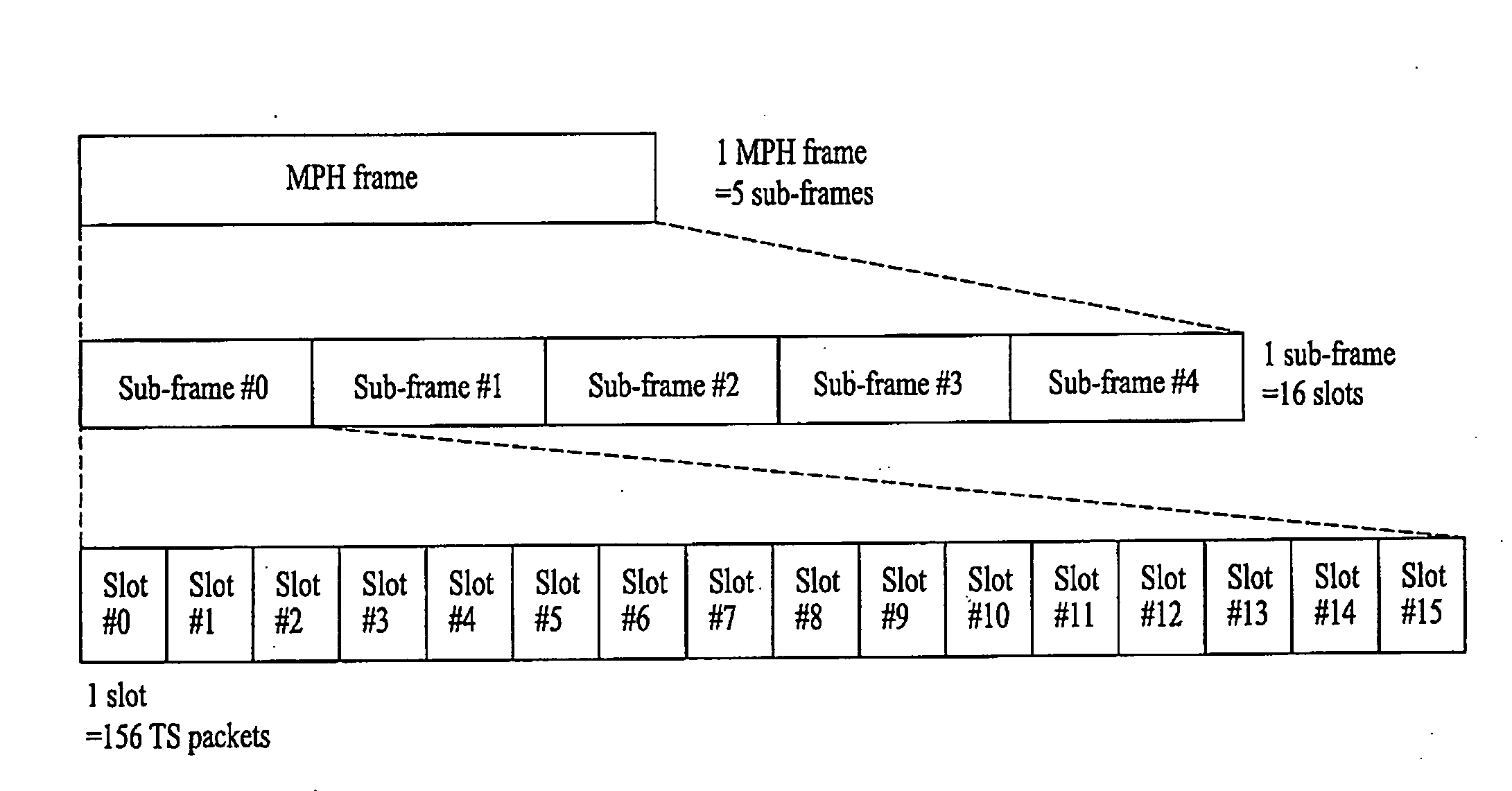

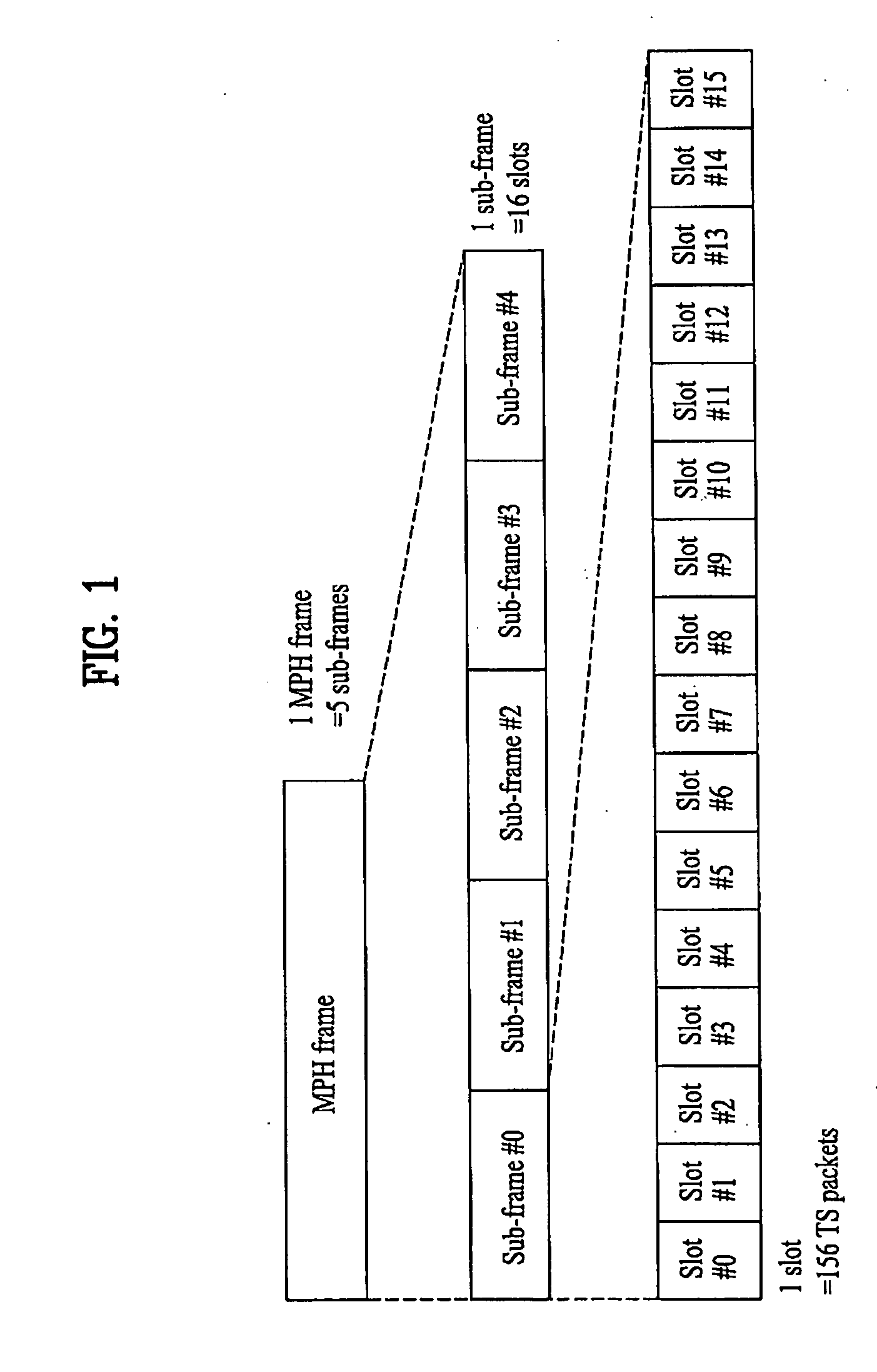

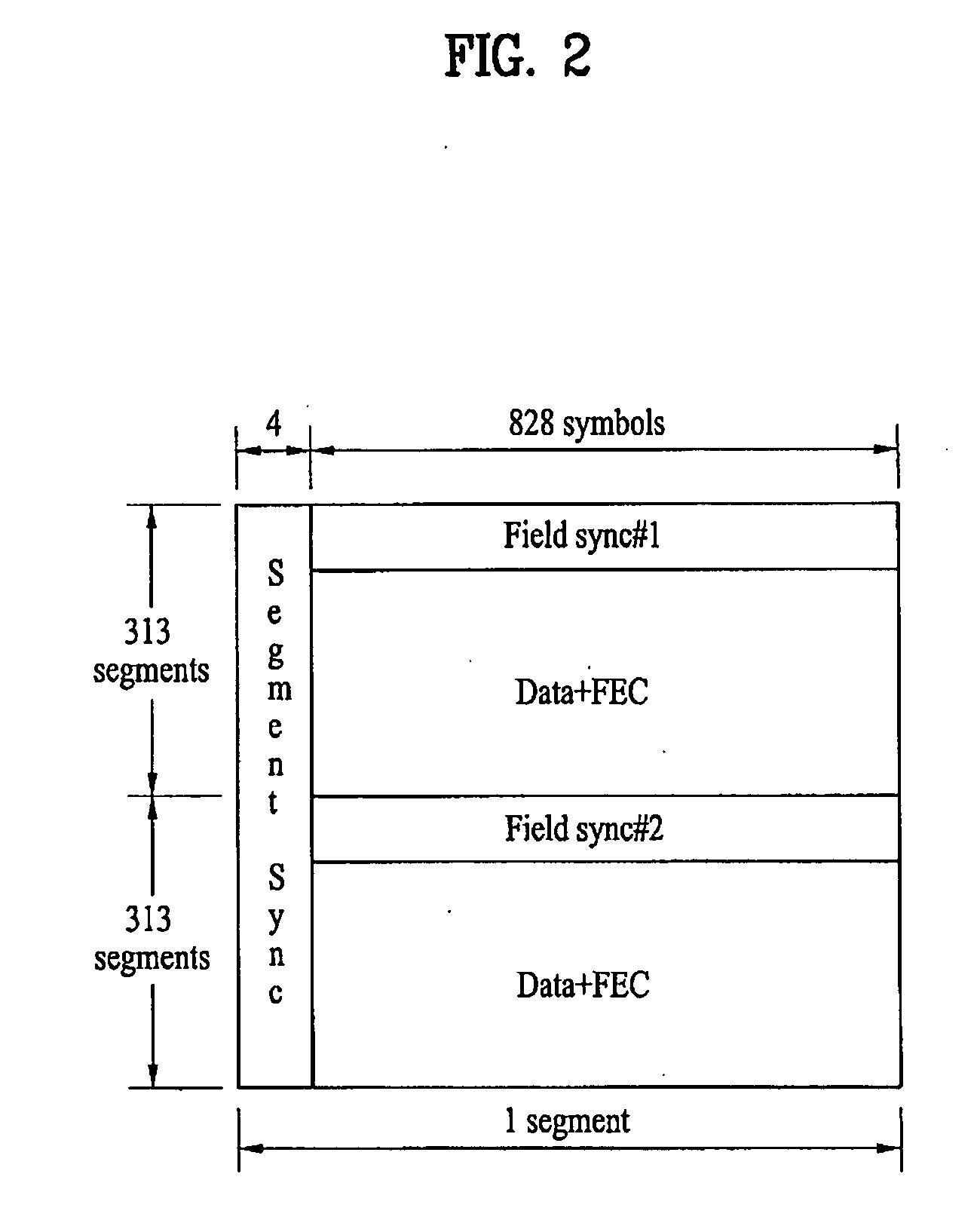

Digital broadcasting system and method of processing data thereof

InactiveUS20090028272A1Improve reception performanceBroadcast specific applicationsSpecific information broadcast systemsMultiplexingMobile business

A digital broadcasting system and data processing method are disclosed, which are highly resistant to channel changes and noise. The present invention includes receiving a broadcast signal having mobile service data and main service data multiplexed with each other from at least one parade, demodulating the broadcast signal, acquiring program table information describing at least one service included in at least one ensemble from the demodulated broadcast signal and decoding the mobile service data associated with a first service using a program table information transport unit in the acquired program table information.

Owner:LG ELECTRONICS INC

Multiprotocol RFID reader

InactiveUS7197279B2Small sizeHigh sensitivityMemory record carrier reading problemsFrequency-modulated carrier systemsEngineeringPersonal computer

An RFID reader accessible thorough a personal computer and includes a PC card interface and a controller both operating according to clock signals from a crystal oscillator. The RFID reader further includes a linearized power amplifier modulator in a transmit path, a receive chain capable of demodulating EPCglobal Class_1 and Class_0 signals from RFID tags, and an integrated switching device for selecting one of a plurality of antenna for transmitting or receiving RF signals.

Owner:WJ COMM

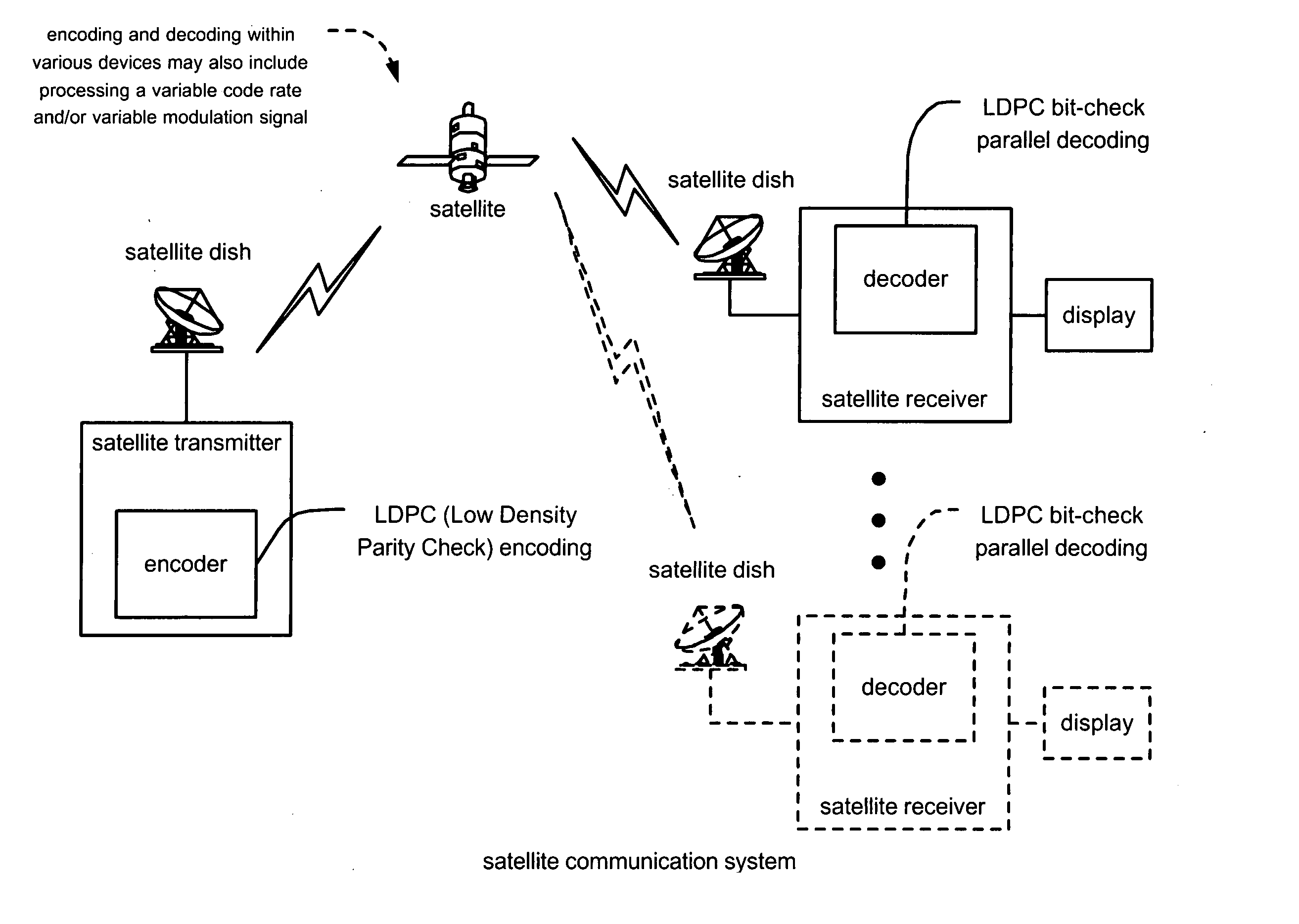

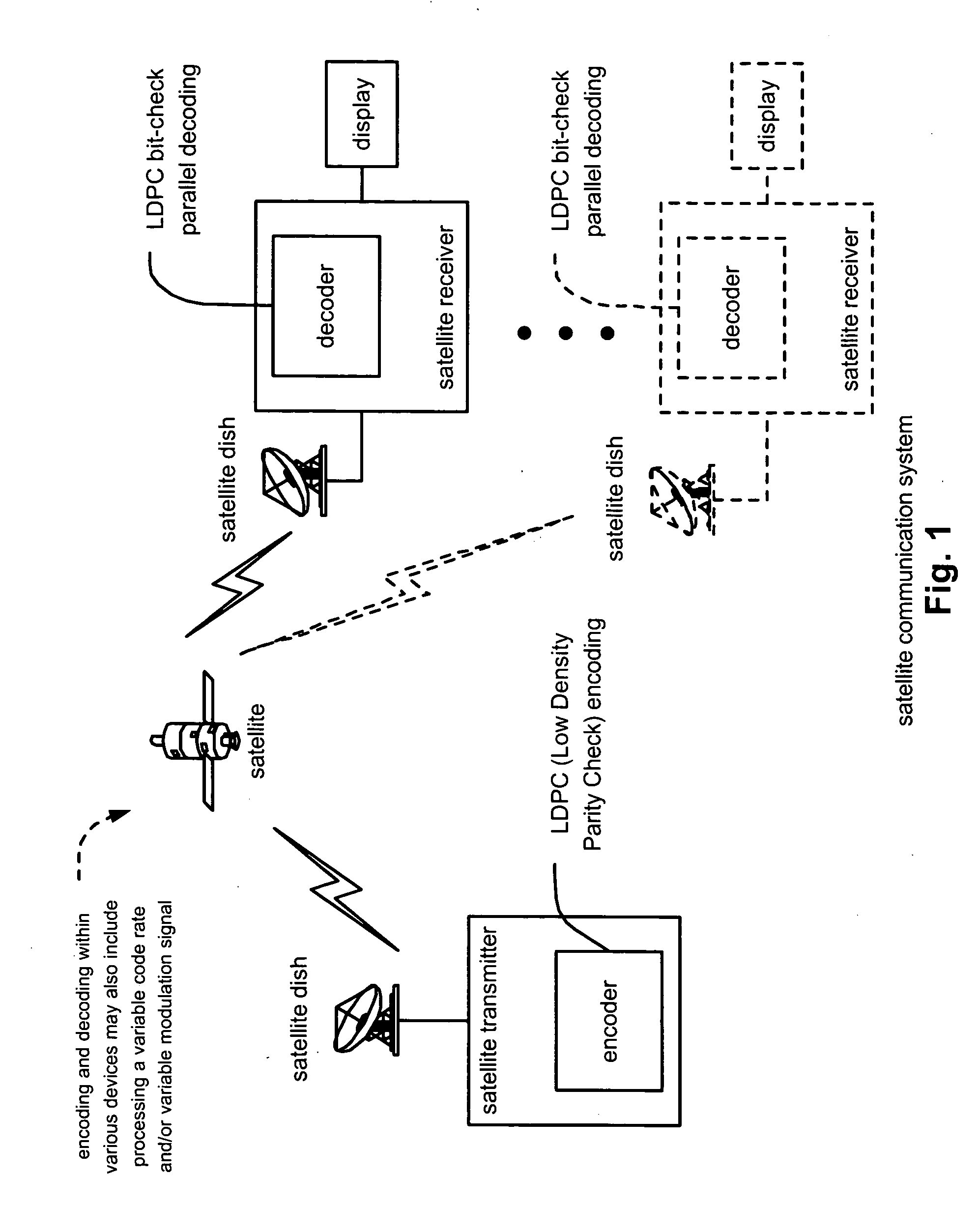

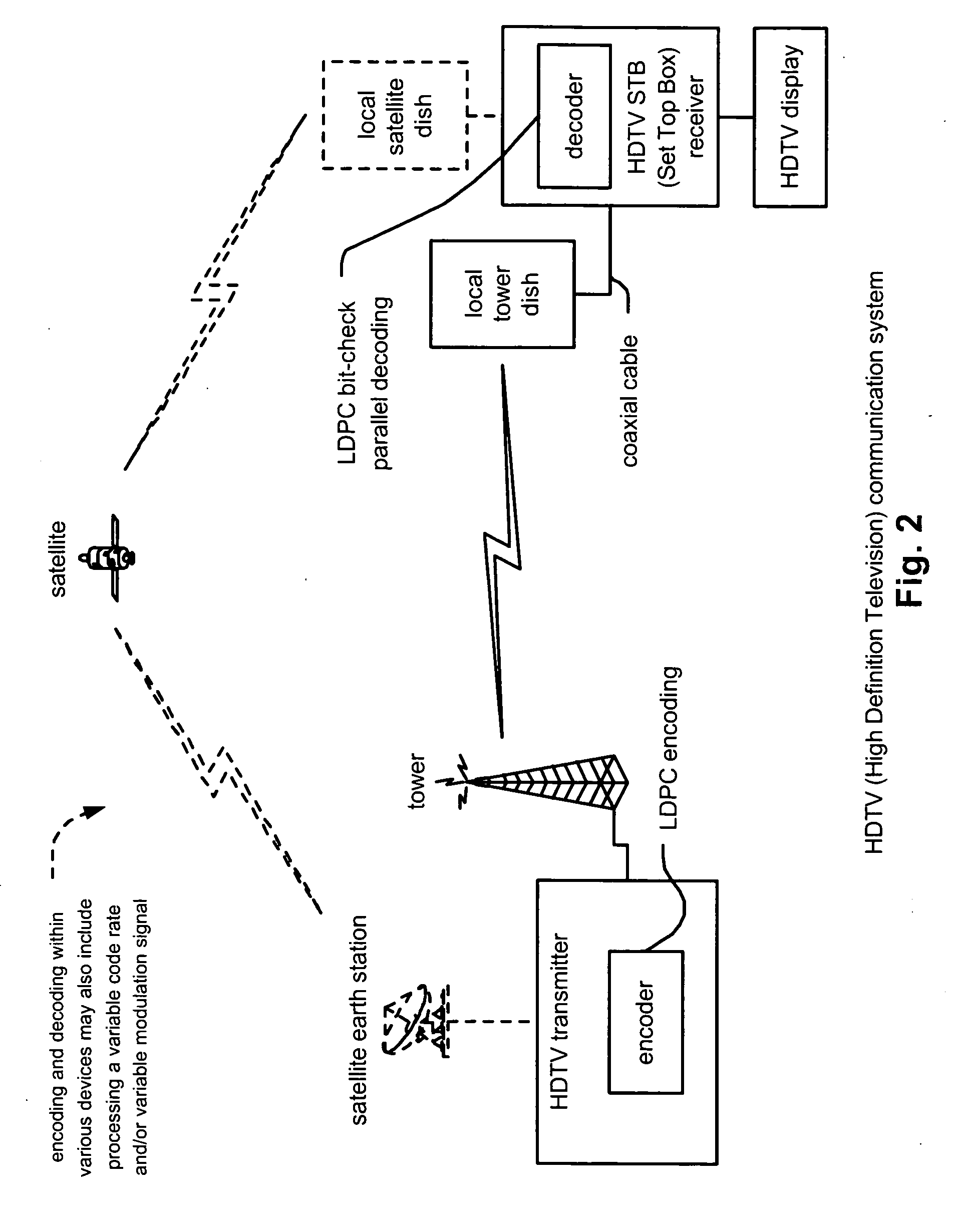

LDPC (Low Density Parity Check) coded signal decoding using parallel and simultaneous bit node and check node processing

InactiveUS20050229090A1Error detection/correctionError correction/detection using multiple parity bitsLow densityComputer science

LDPC (Low Density Parity Check) coded signal decoding using parallel and simultaneous bit node and check node processing. This novel approach to decoding of LDPC coded signals may be described as being LDPC bit-check parallel decoding. In some alternative embodiment, the approach to decoding LDPC coded signals may be modified to LDPC symbol-check parallel decoding or LDPC hybrid-check parallel decoding. A novel approach is presented by which the edge messages with respect to the bit nodes and the edge messages with respect to the check nodes may be updated simultaneously and in parallel to one another. Appropriately constructed executing orders direct the sequence of simultaneous operation of updating the edge messages at both nodes types (e.g., edge and check). For various types of LDPC coded signals, including parallel-block LDPC coded signals, this approach can perform decoding processing in almost half of the time as provided by previous decoding approaches.

Owner:AVAGO TECH INT SALES PTE LTD

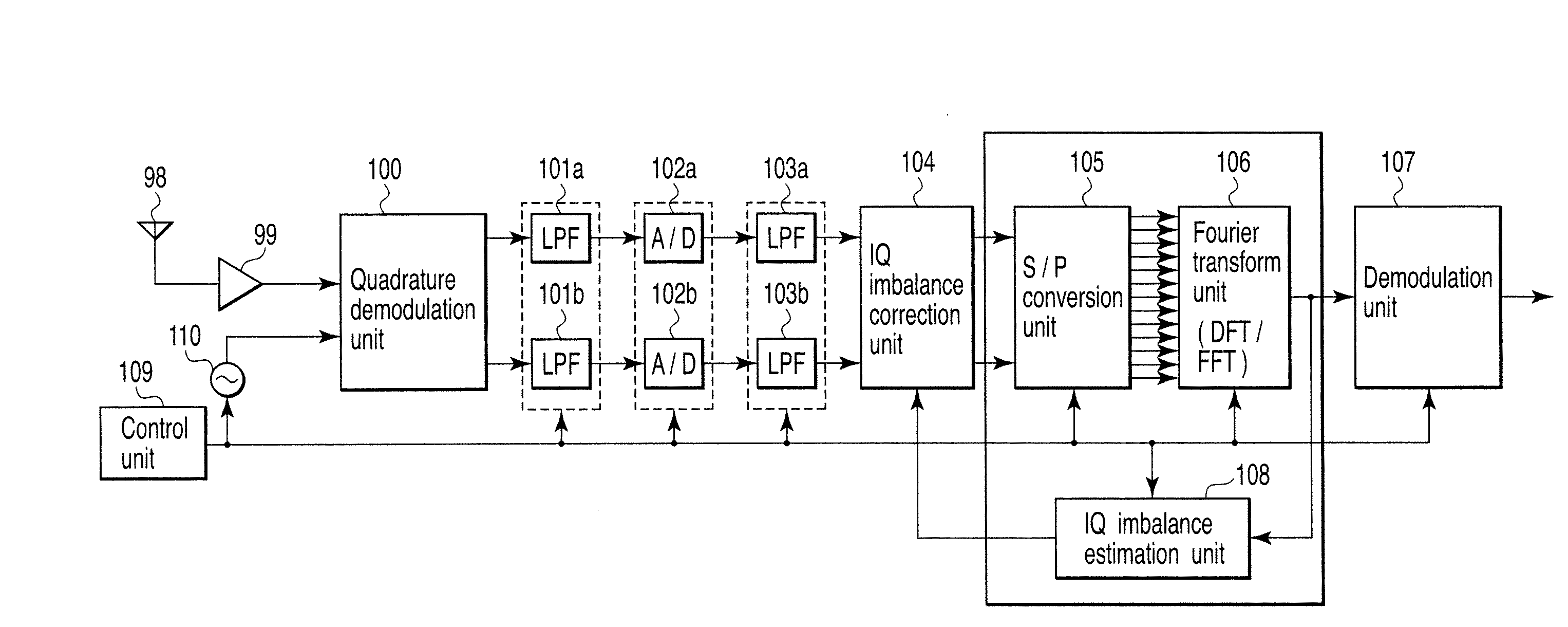

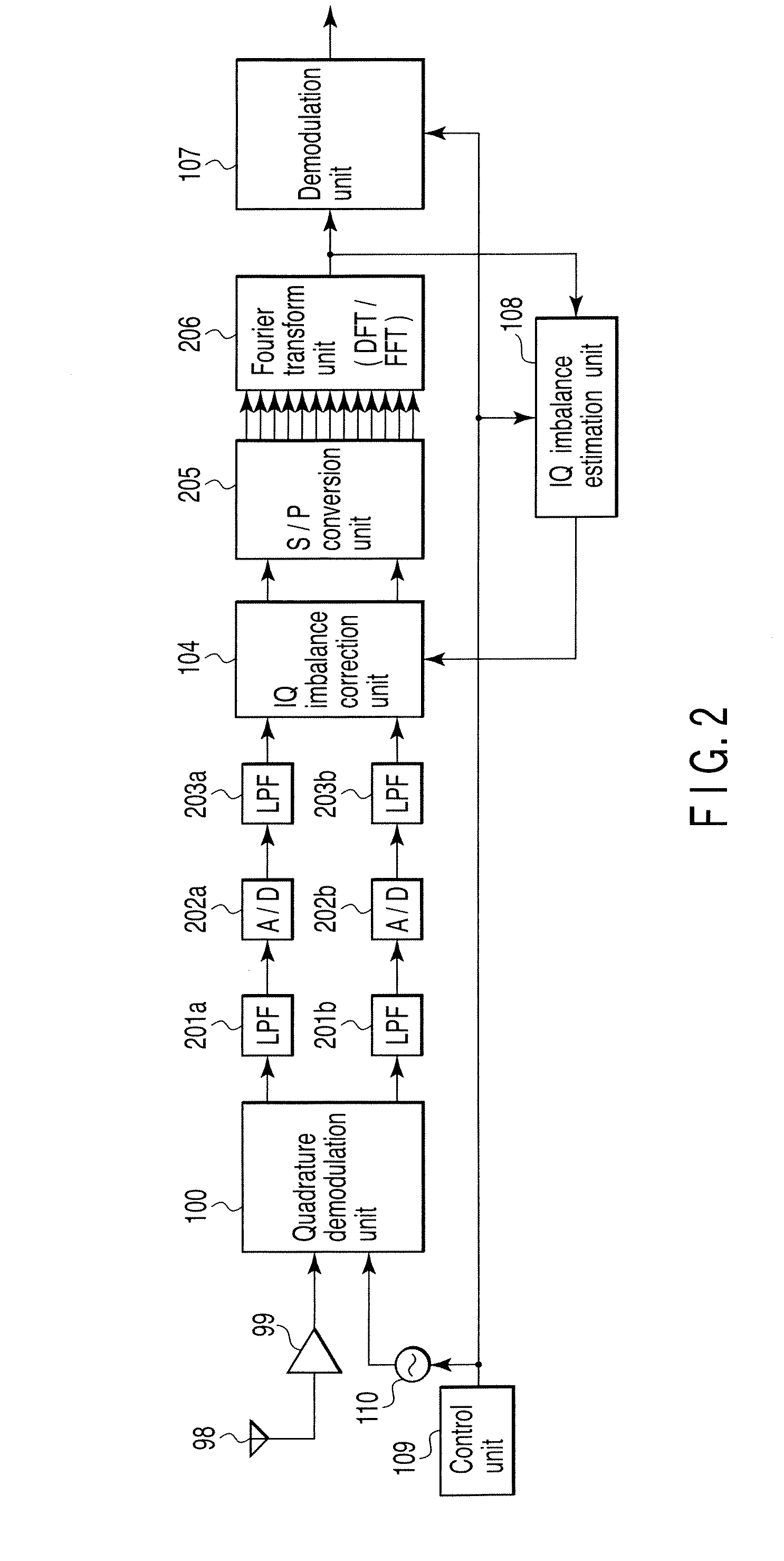

Wireless communication apparatus and receiving method

InactiveUS20080159442A1Single output arrangementsElectric pulse generatorAmplitude distortionTelecommunications

A wireless communication apparatus receives an quadrature modulated signal, generate a local signal having a frequency different from a center frequency of the quadrature modulated signal, performs quadrature demodulation on the quadrature modulated signal by using the local signal, to obtain an I channel signal and a Q channel signal, performs Fourier transform on the I channel signal and the Q channel signal, to obtain signals in a frequency domain, and calculates a first correction coefficient for correcting phase distortion and amplitude distortion caused by the quadrature demodulation by using pairs of signals among the signals, each of the pairs are located at symmetrical frequency positions with respect to the frequency of the local signal.

Owner:KK TOSHIBA

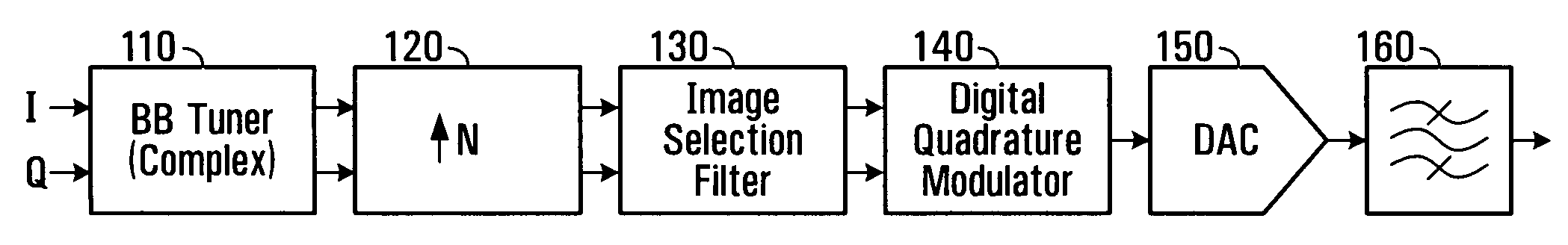

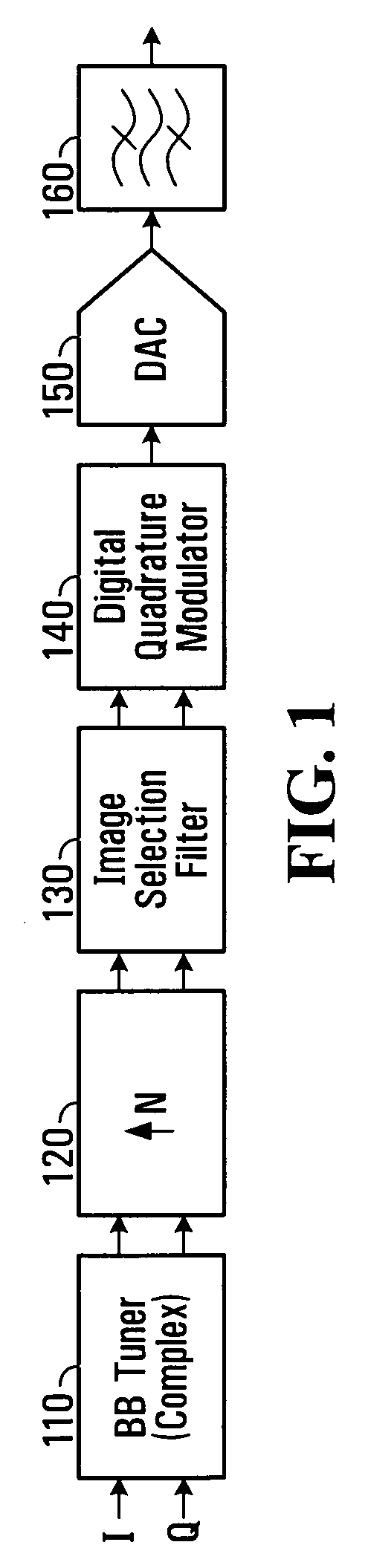

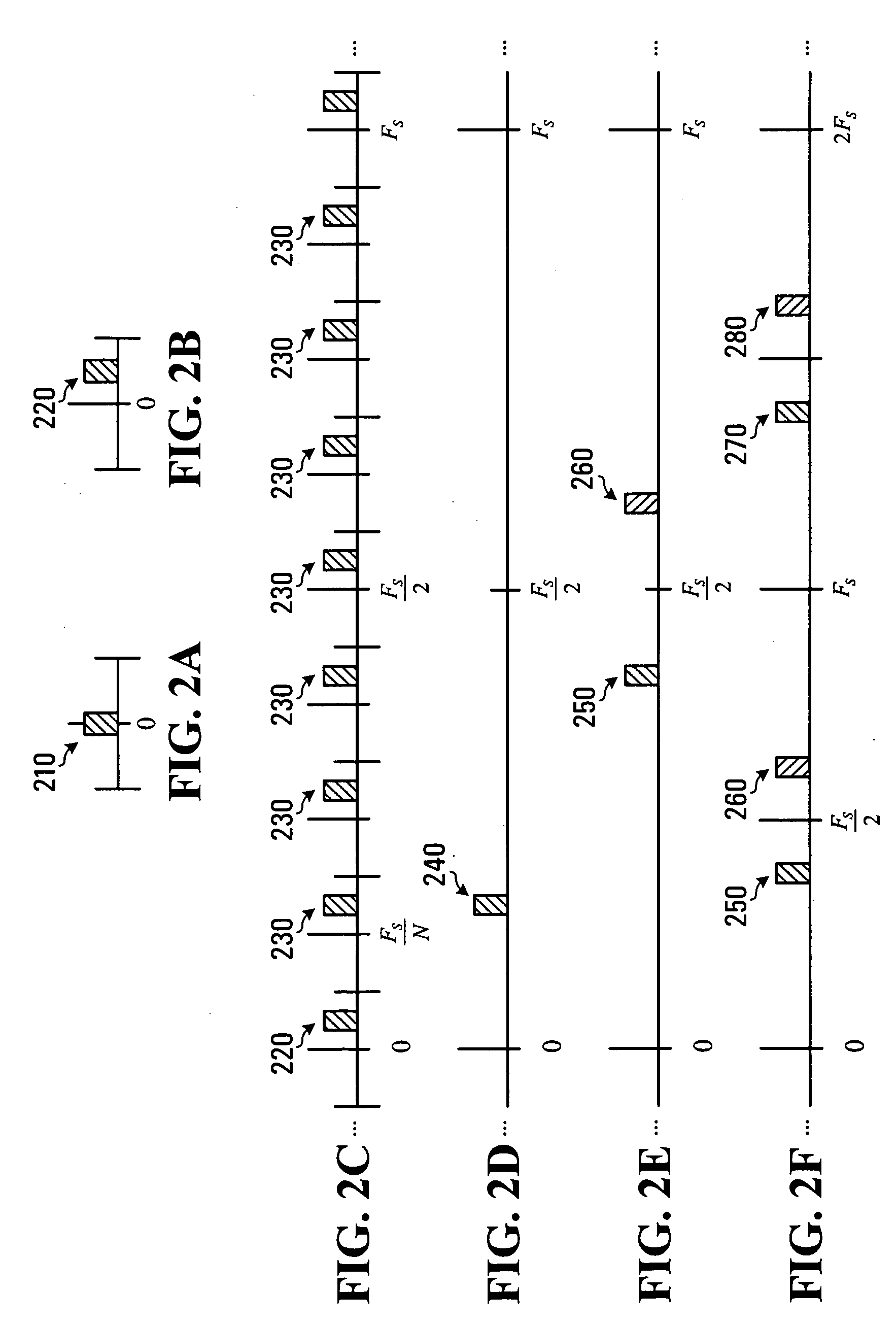

Methods and systems for programmable digital up-conversion

InactiveUS20100098191A1Reduce complexityModulation transferenceDigital technique networkDigital analog converterEngineering

Methods and apparatus are described herein that make use of complex tuning, the inherently repetitive nature of sampled signals, and programmable digital filtering to create a flexible digital up-conversion system that utilizes a digital-to-analog converter (DAC) with a fixed effective sample rate while still being adapted for tunability over a wide frequency range. With a knowledge of the fixed effective sample rate of the DAC and a desired frequency of up-conversion and combining complex tuning at baseband and up-sampling by a factor of N with a programmable passband filter configured to select one of a plurality of signal images resulting from the up-sampling, it is possible to translate a baseband input signal to a wide range of frequencies above or below Fs, without changing the sampling rate of the fixed rate DAC used in the up-conversion process.

Owner:APPLE INC

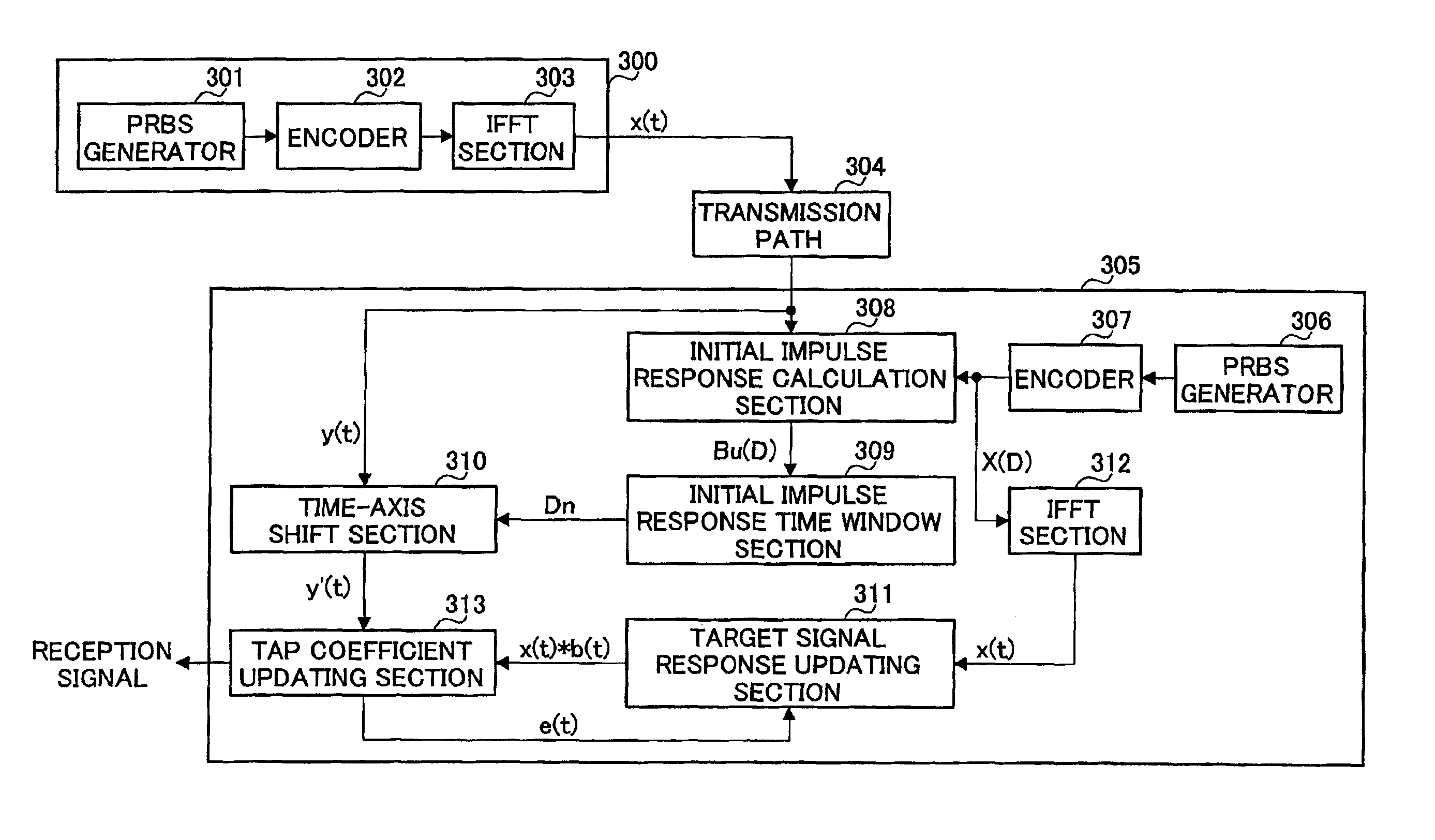

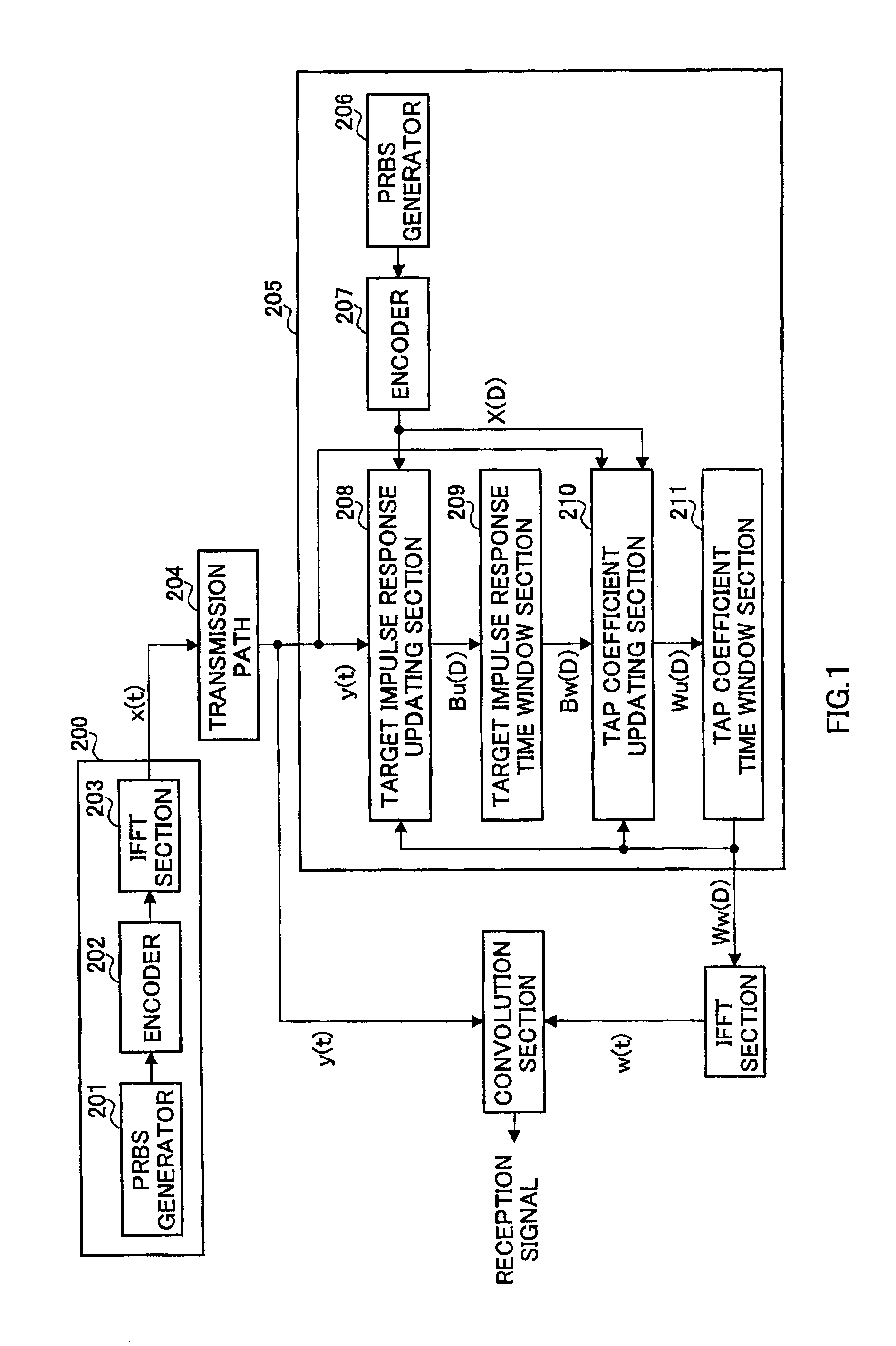

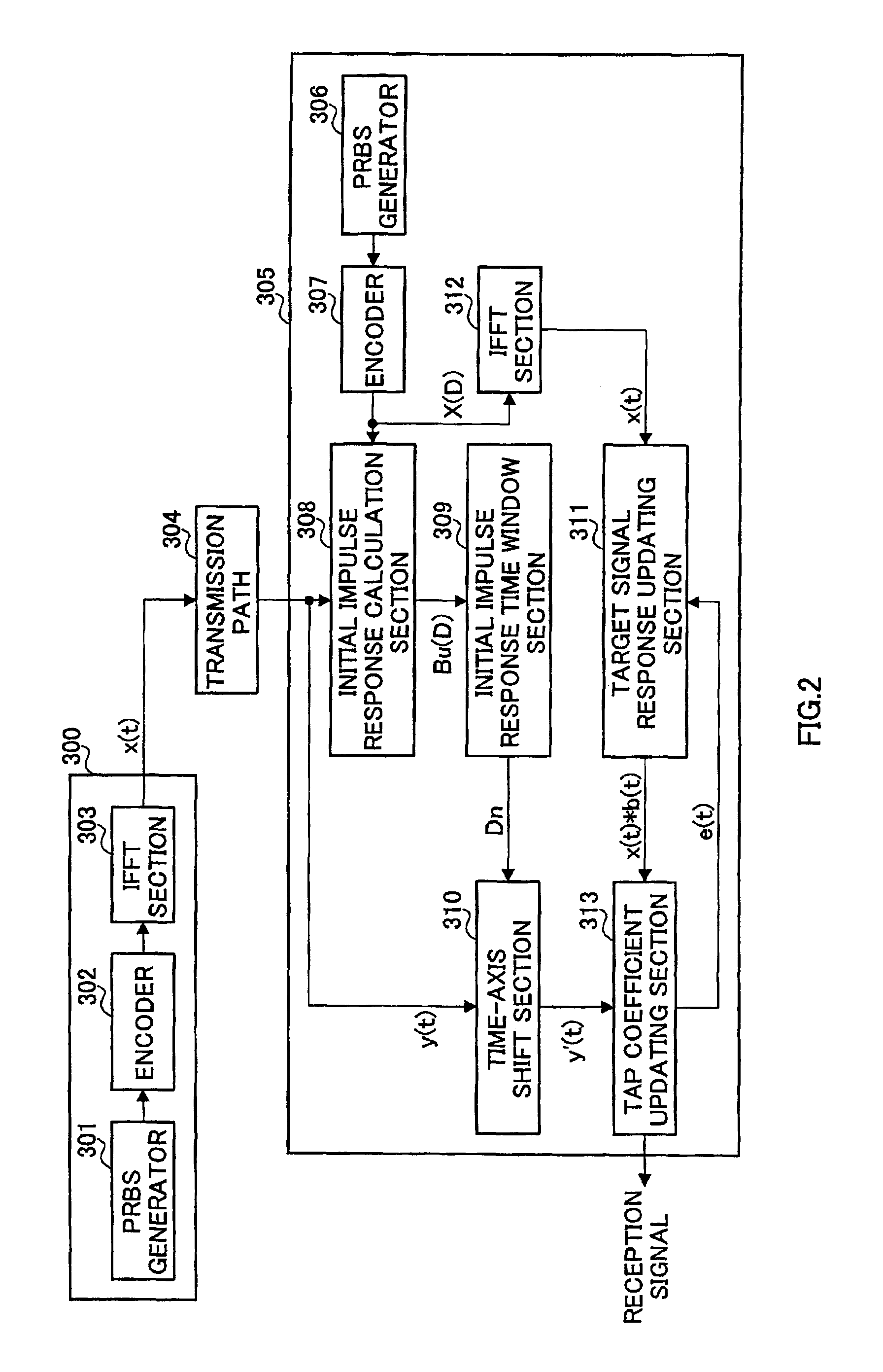

Adaptive equalizer training circuit, modem apparatus and communication apparatus

InactiveUS6928110B2Reduce the amount of errorReduce the amount of calculationMultiple-port networksTransmission control/equlisationModem deviceRenewal time

A training circuit for training a tap coefficient of an adaptive equalizer that performs error calculations in a training process and updating of the tap coefficient in a time area and thereby makes the tap coefficient converge stably in a short time.

Owner:MATSUSHITA GRAPHIC COMM SYST INC

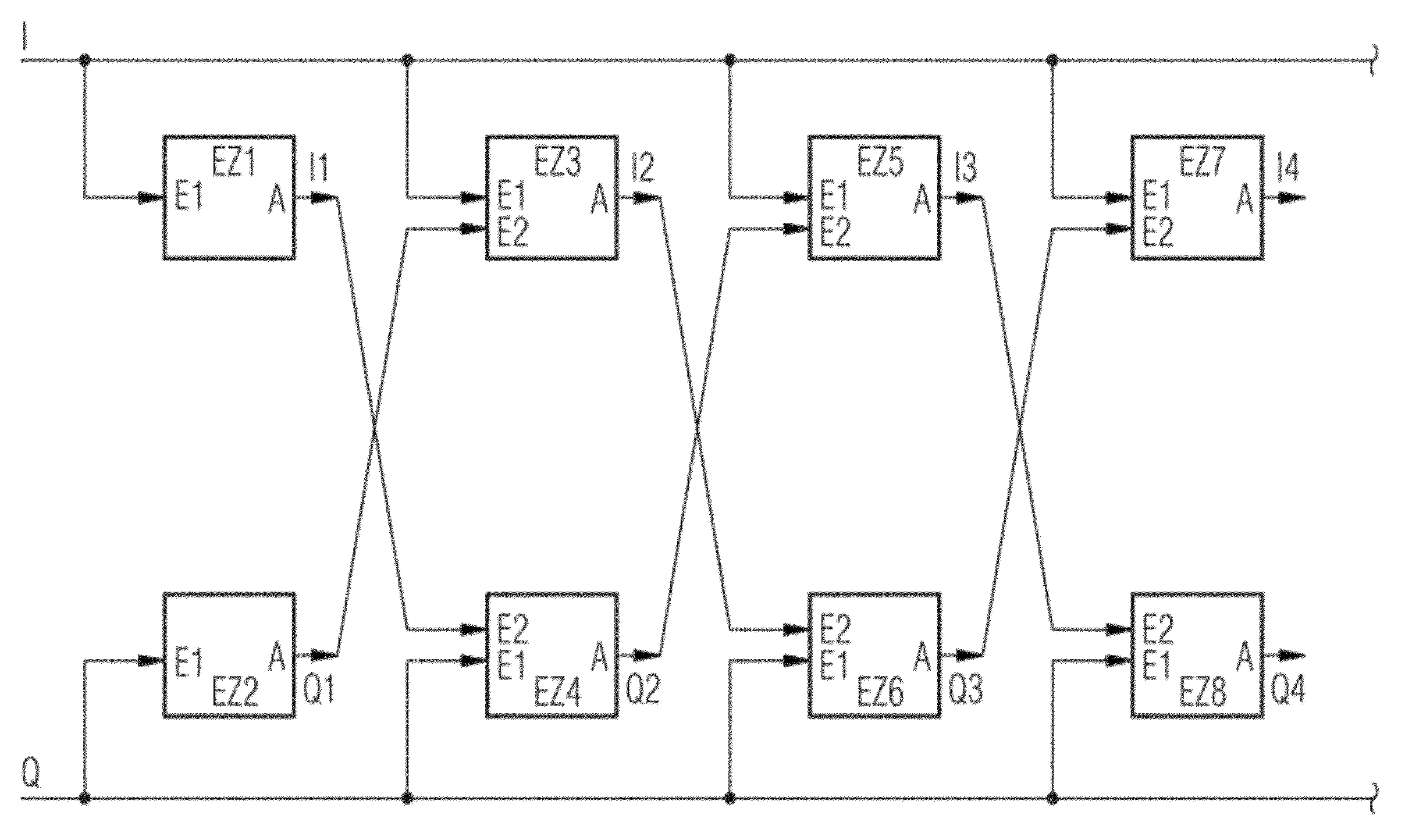

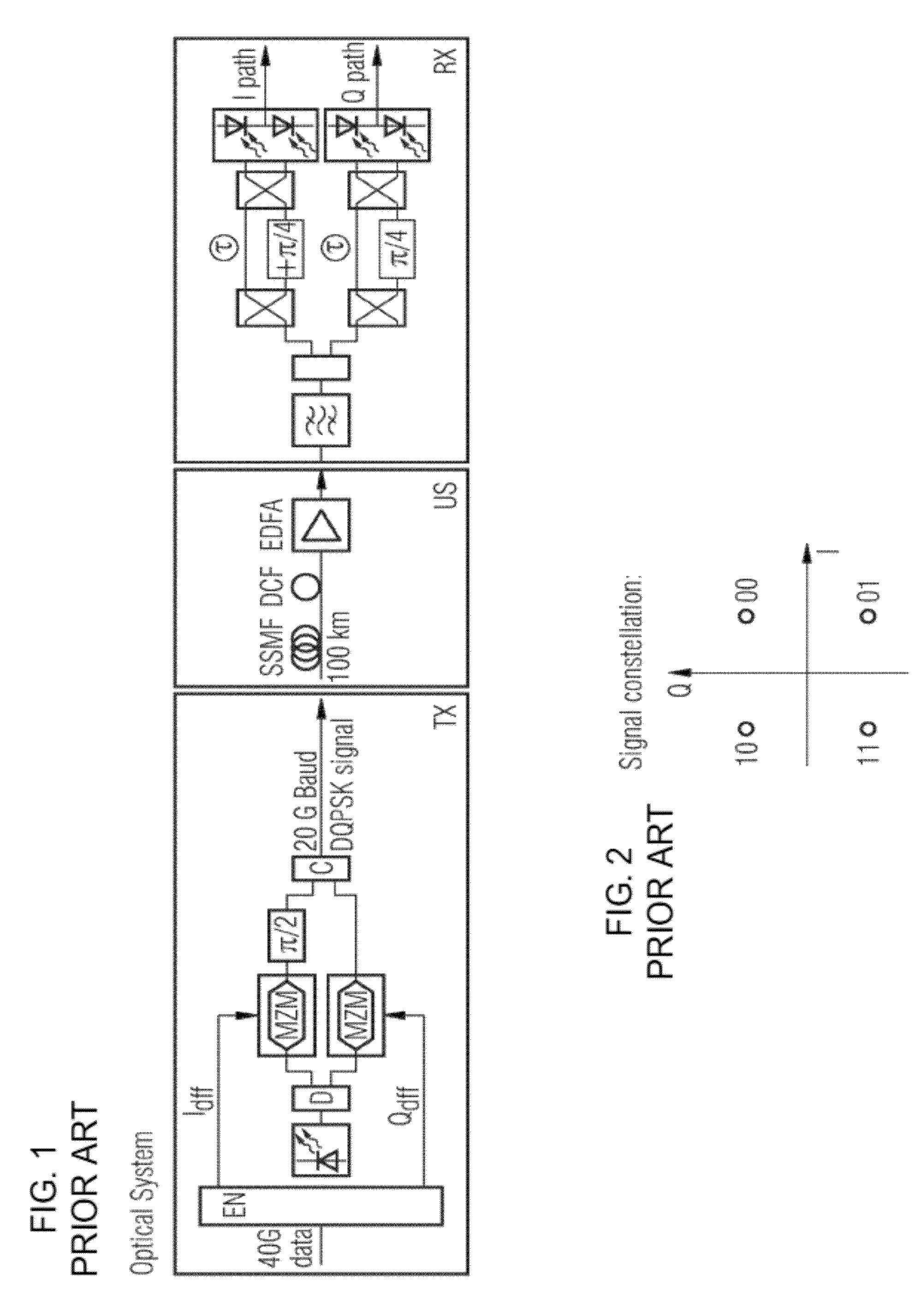

Receiver structure and method for the demodulation of a quadrature-modulated signal

ActiveUS8199803B2Accurate measurementMultiple-port networksDelay line applicationsQuadrature modulationEngineering

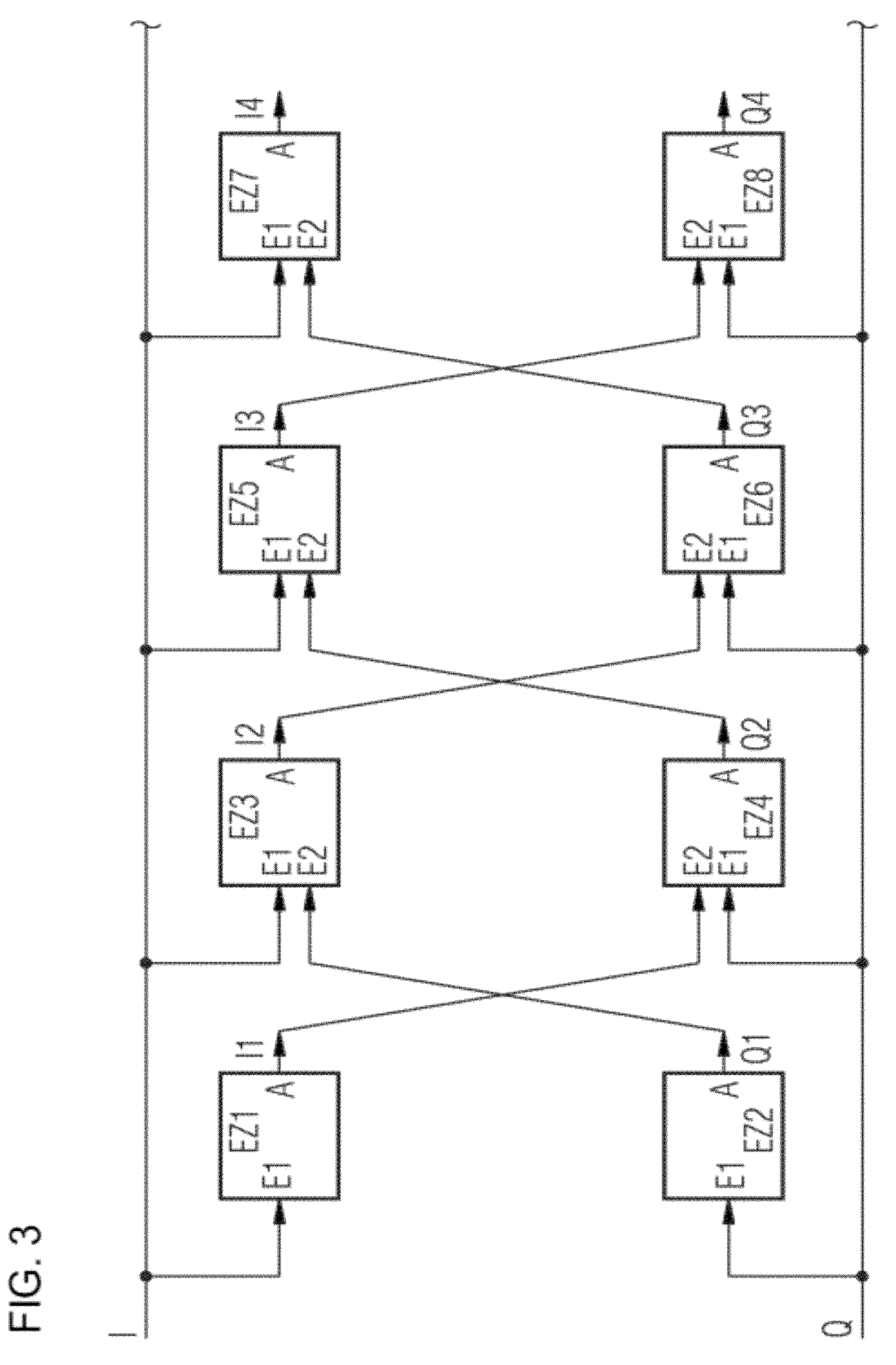

A receiver is provided for a quadrature-modulated signal, which can be divided into an inphase signal and a quadrature signal. The inphase signal is fed to first and third equalizers, and the quadrature signal is fed to second and fourth equalizers, wherein the first and second equalizers each perform a first equalization of the respective signal. An output of the first equalizer is connected to a second input of the fourth equalizer, which, by means of a second equalization of the quadrature signal, transmits an equalized quadrature signal as a function of the previously fed equalized inphase signal of the first equalizer. An output of the second equalizer is connected to the second input of the third equalizer, which, through a second equalization of the inphase signal, transmits an equalized inphase signal as a function of the previously fed equalized quadrature signal of the second equalizer.

Owner:XIEON NETWORKS SARL

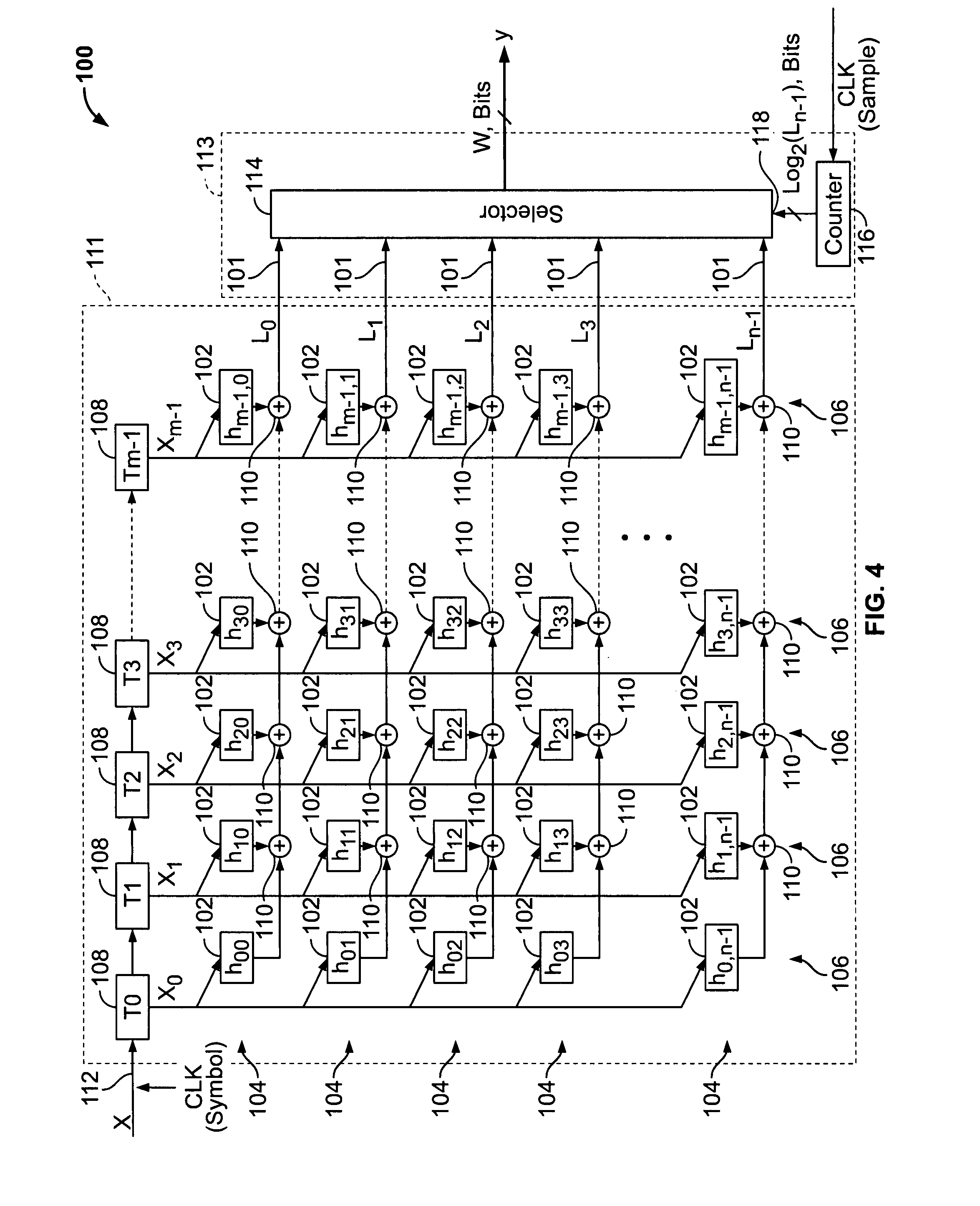

Method and architecture for digital pulse shaping and rate conversion

A method and architecture for pulse shaping are provided. The architecture includes a pulse shaping filter having a plurality of memory elements and a plurality of taps connected to the plurality of memory elements wherein a total number of the plurality of taps is independent of a sampling rate. The pulse shaping filter further includes a selector configured to select outputs from the plurality of taps to define a pulse shaped output.

Owner:EAGLE TECH LLC

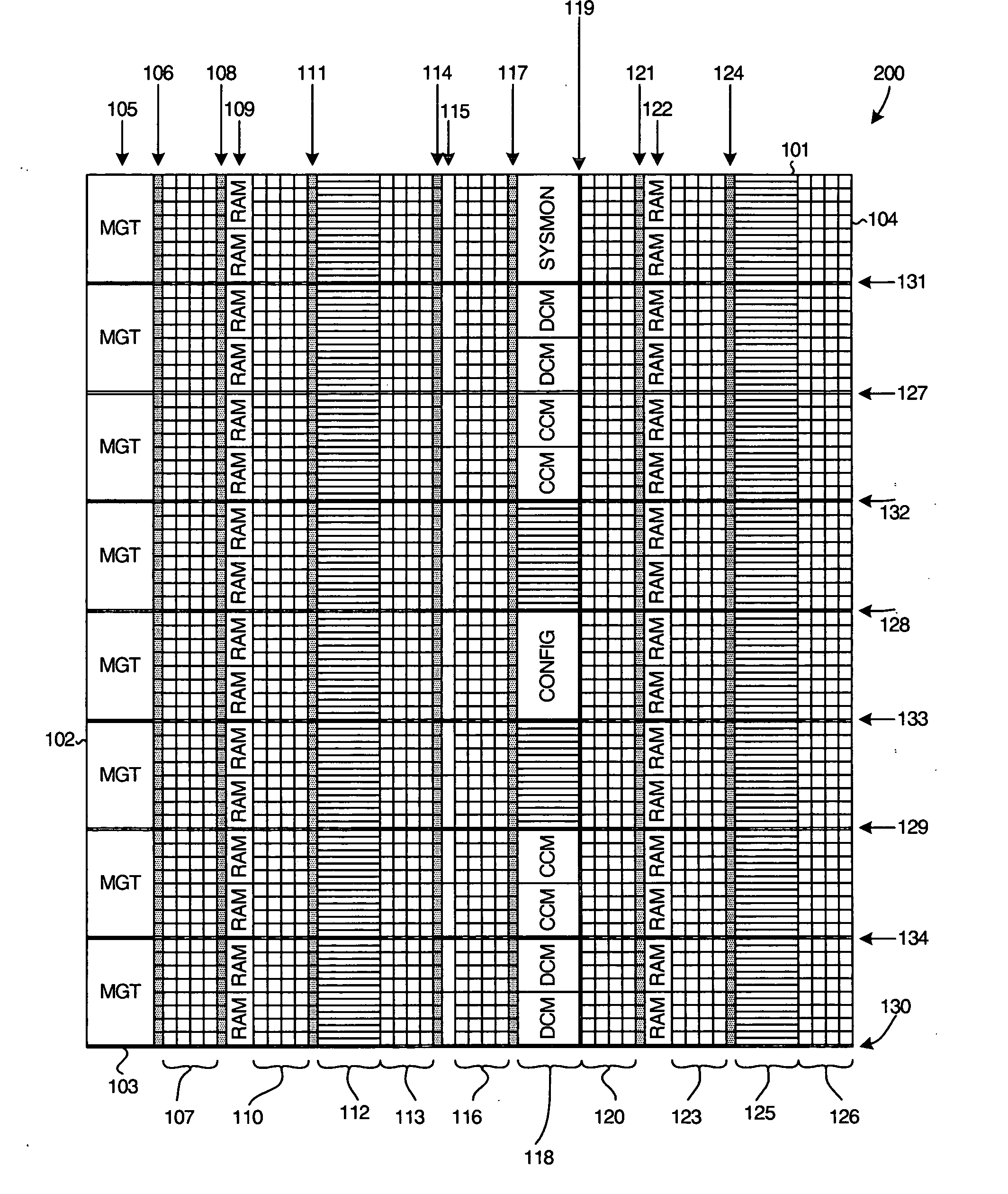

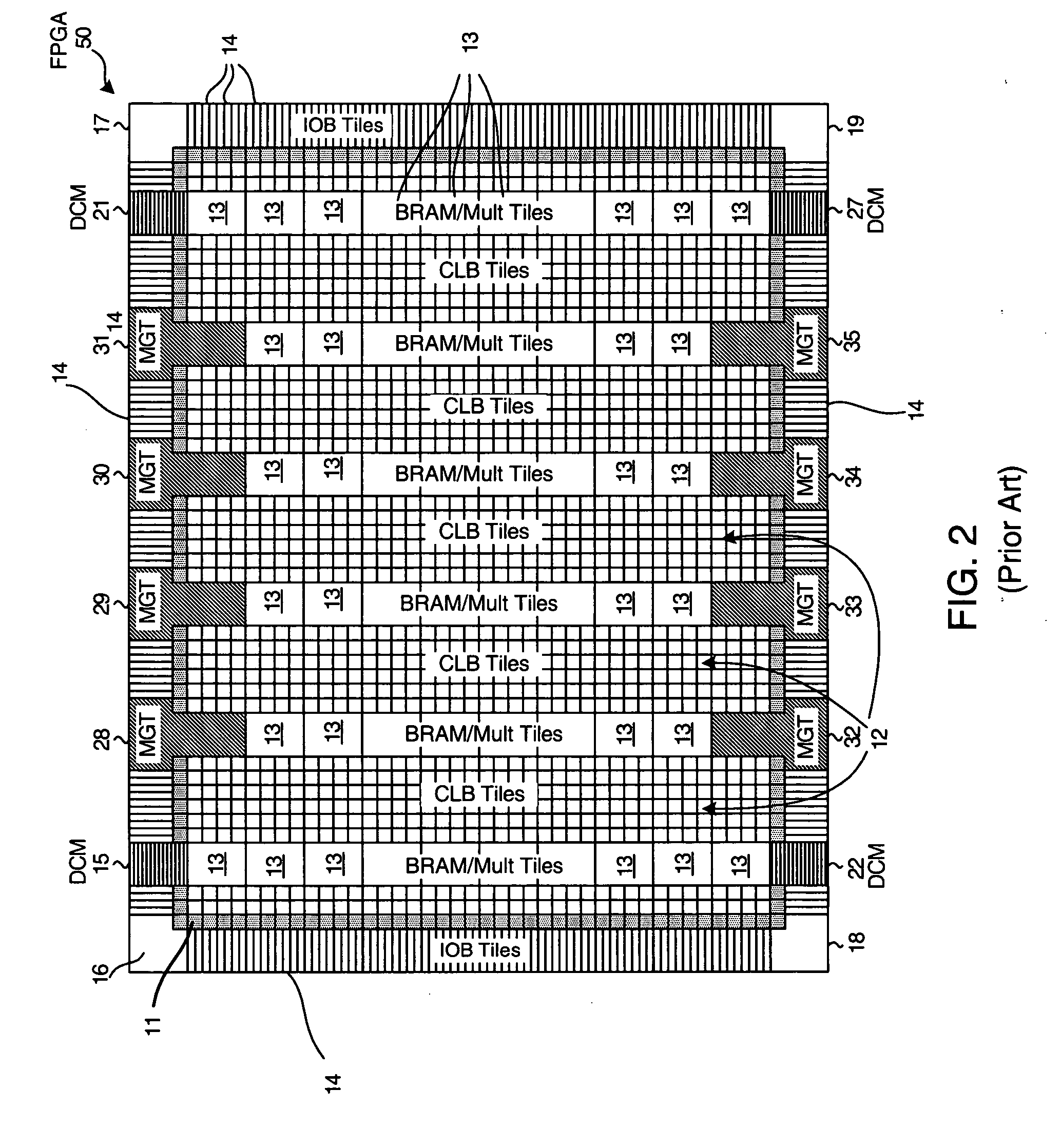

Columnar architecture

ActiveUS20050007155A1Solid-state devicesFrequency/rate-modulated pulse demodulationIntegrated circuitEngineering

An integrated circuit (IC) is disclosed having circuitry arranged in a plurality of columns. A column in the IC is essentially a series of aligned circuit elements of the same type that extends from a first edge of the IC to a second edge. In addition there may be a center column having circuit elements of different types.

Owner:XILINX INC

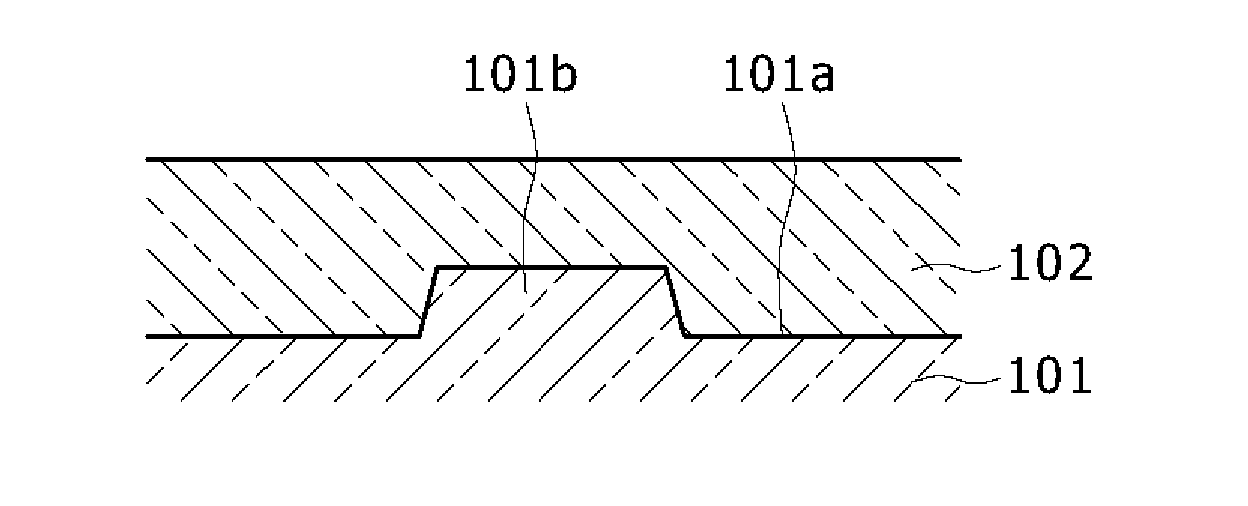

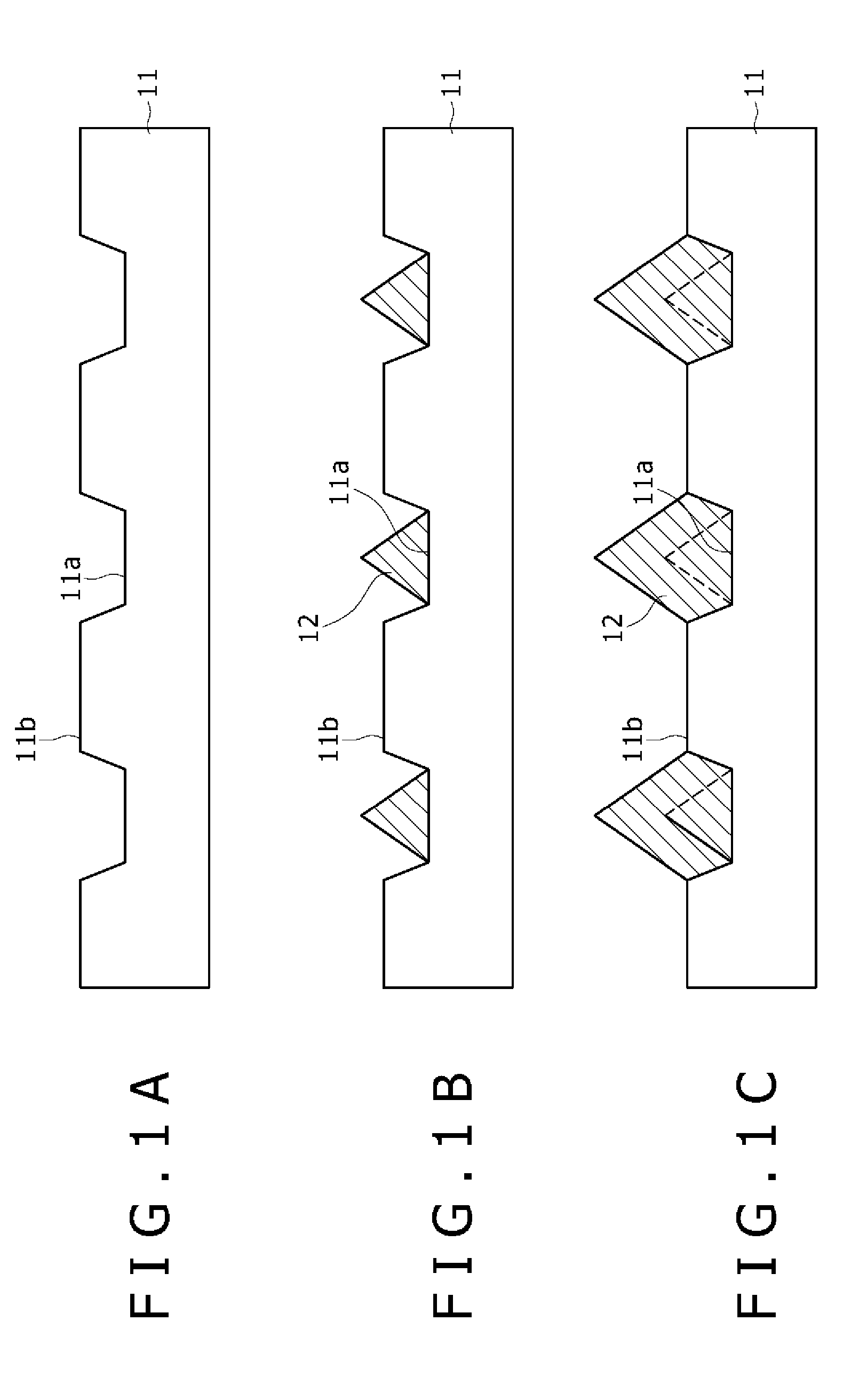

Light-emitting diode, method for making light-emitting diode, integrated light-emitting diode and method for making integrated light-emitting diode, method for growing a nitride-based iii-v group compound semiconductor, light source cell unit, light-emitting diode backlight, and light-emitting diode display and electronic device

InactiveUS20060258027A1Light emission efficiency is reducedImprove light emission efficiencySolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceEngineering

A method for making a light-emitting diode, which including the steps of: providing a substrate having at least one recessed portion on one main surface and growing a first nitride-based III-V group compound semiconductor layer through a state of making a triangle in section having a bottom surface of the recessed portion as a base thereby burying the recessed portion; laterally growing a second nitride-based III-V group compound semiconductor layer from the first nitride-based III-V group compound semiconductor layer over the substrate; and successively growing a third nitride-based III-V group compound semiconductor layer of a first conduction type, an active layer and a fourth nitride-based III-V group compound semiconductor layer of a second conduction type on the second nitride-based III-V group compound semiconductor layer.

Owner:SONY CORP

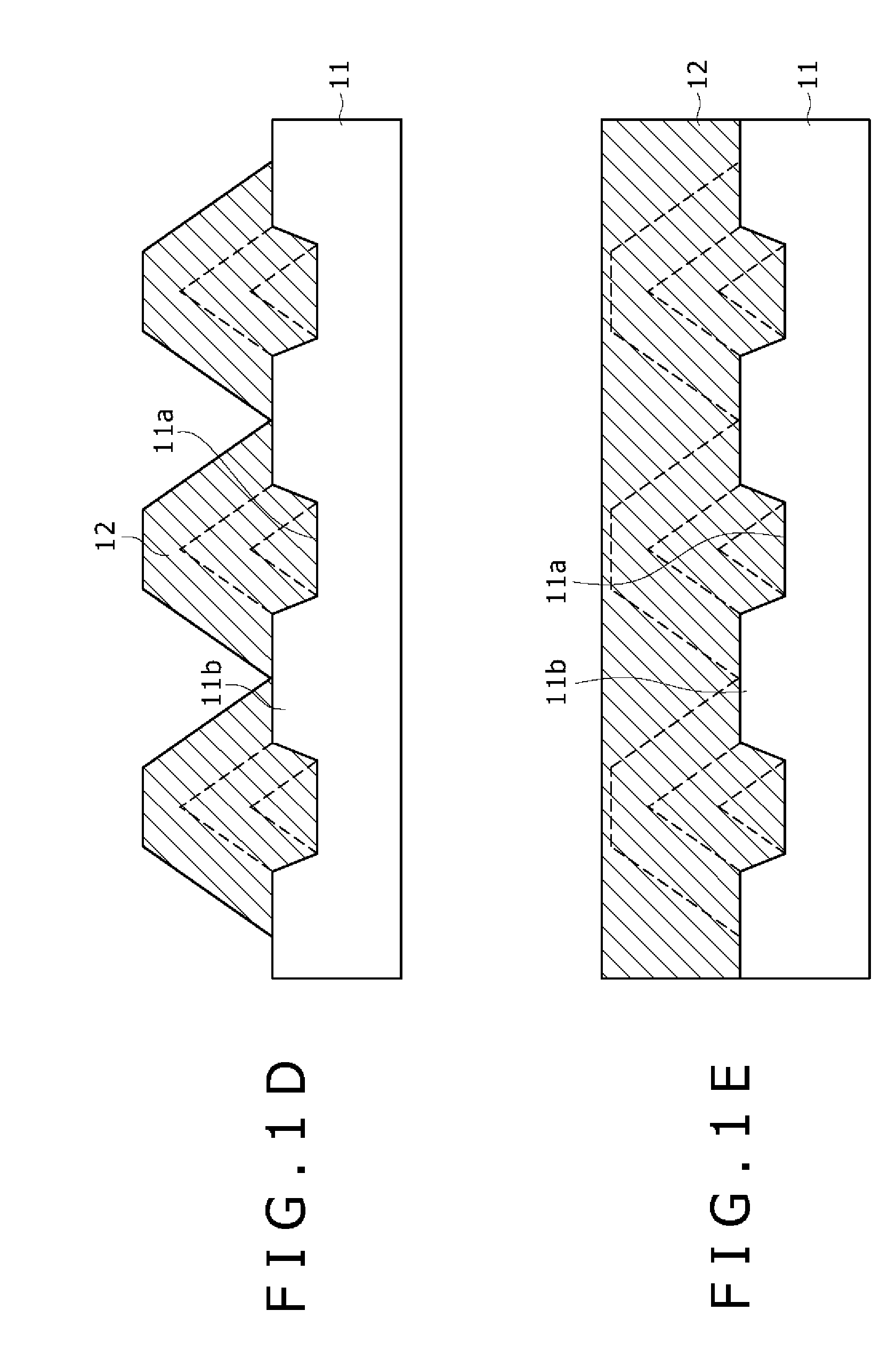

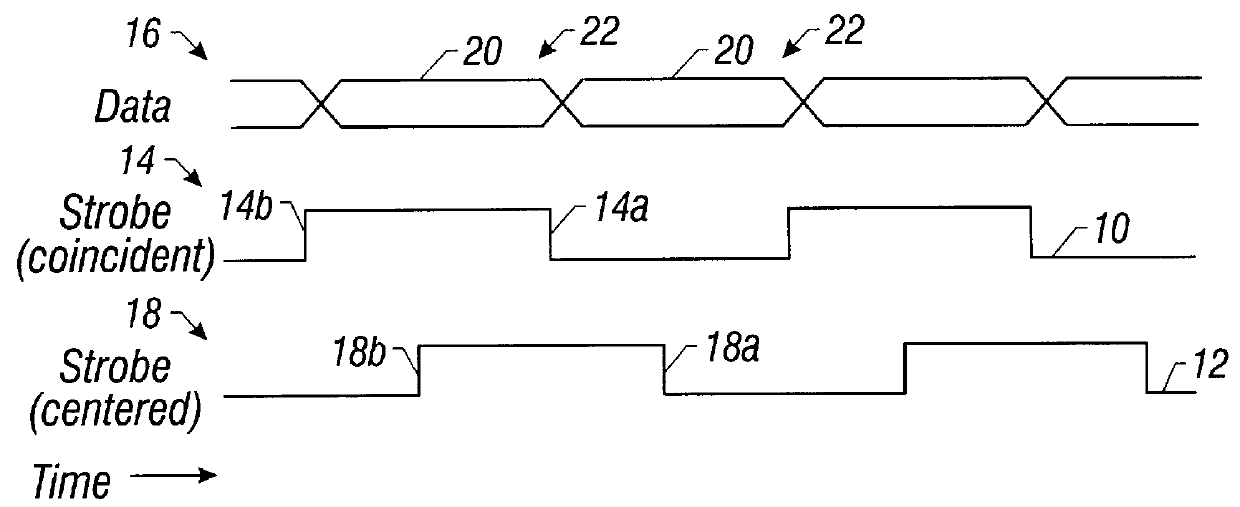

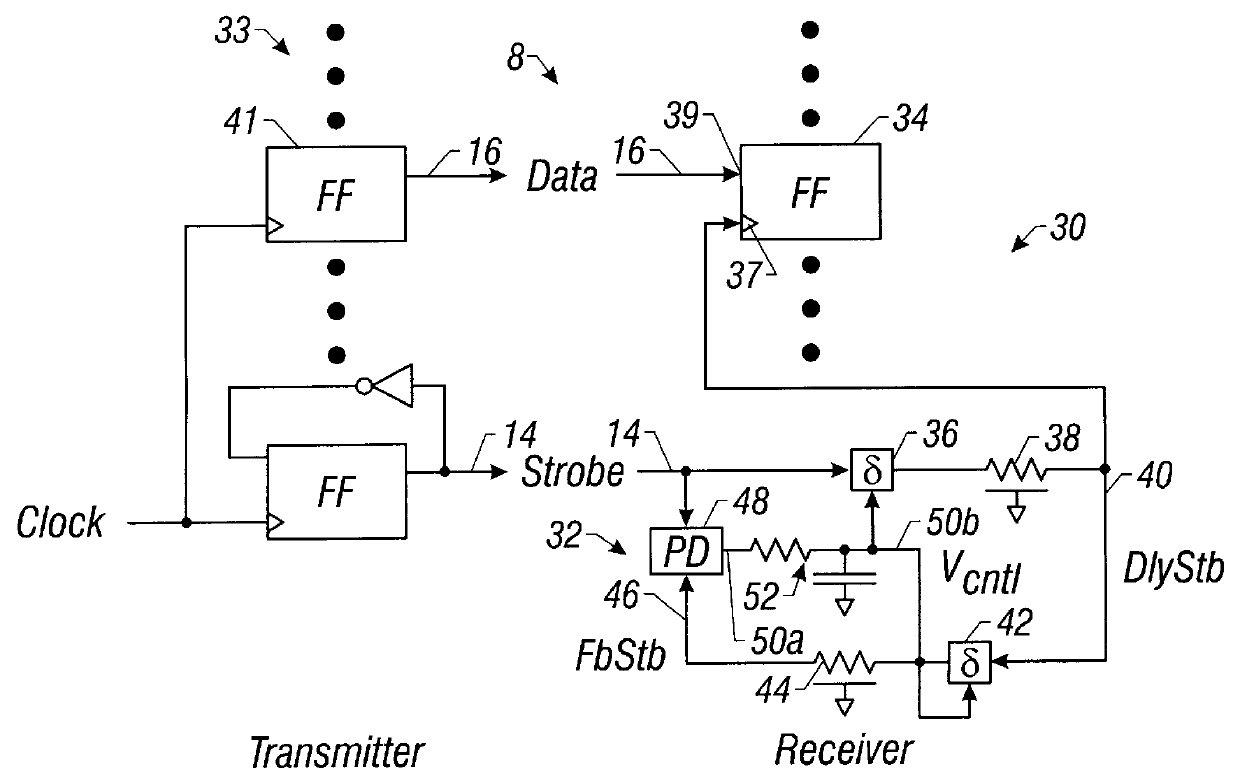

Timing control for input/output testability

InactiveUS6085345AMultiple input and output pulse circuitsPulse automatic controlPhase differenceDelay-locked loop

Circuitry added to chips that use source synchronous techniques reduces difficulties associated with testing the chips. The circuitry increases the ability to use source synchronous techniques for data transmission. The circuitry is implemented in a delayed-lock loop (DLL) in either a transmitter (driver) or a receiver. The DLL measures the phase difference between a strobe signal and a delayed strobe signal. The DLL can be externally controlled by a source selectable input which allows the delay of the delayed strobe signal to be varied to test Tsetup and Thold in the receiver without varying the timings of the strobe signal and the data signals supplied to the chips. A timing measurement circuit having the strobe signal, the delayed strobe signal, and reference signals as inputs may be used to calibrate the phase difference between the strobe signal and delayed strobe signal.

Owner:INTEL CORP

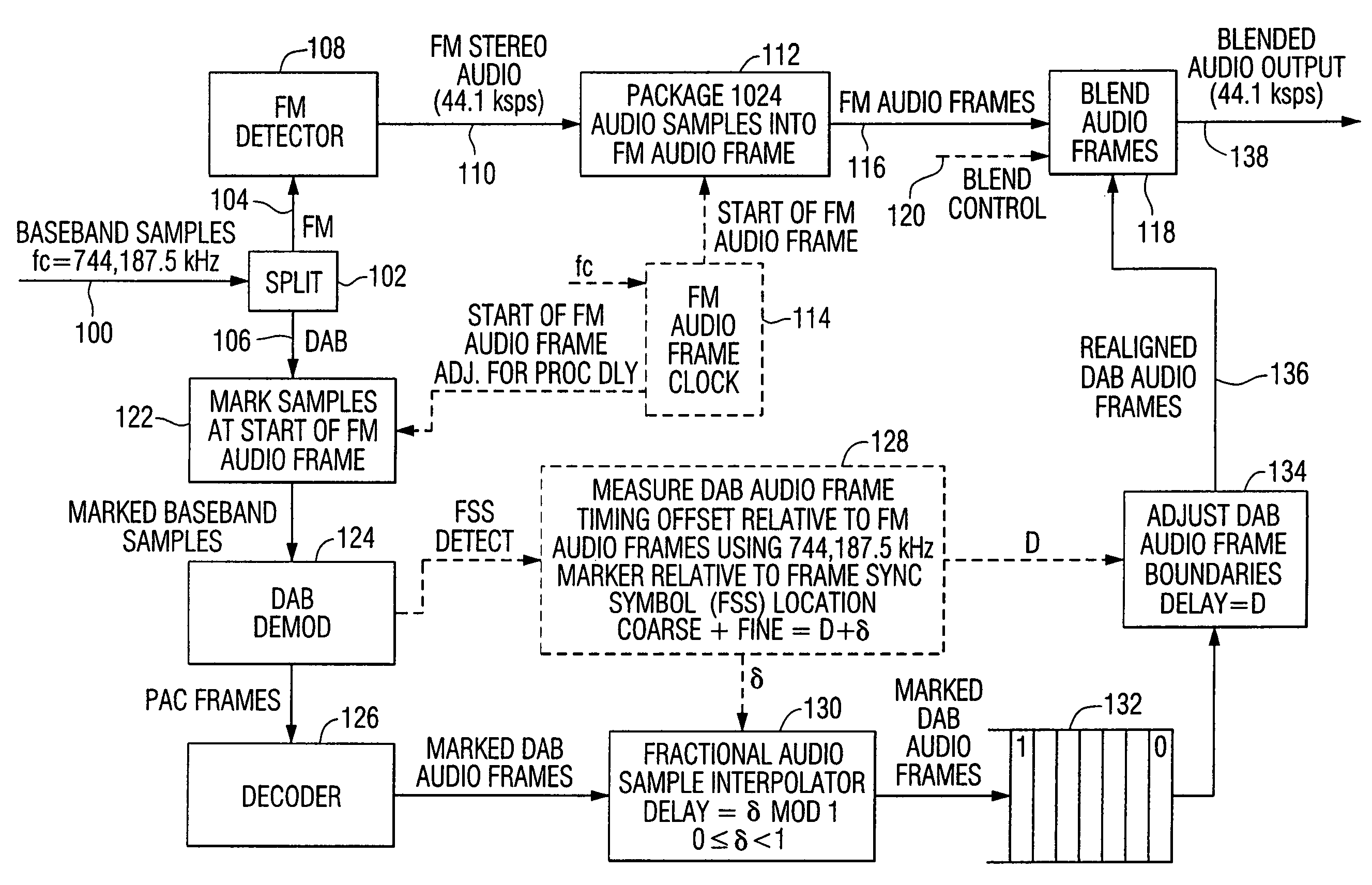

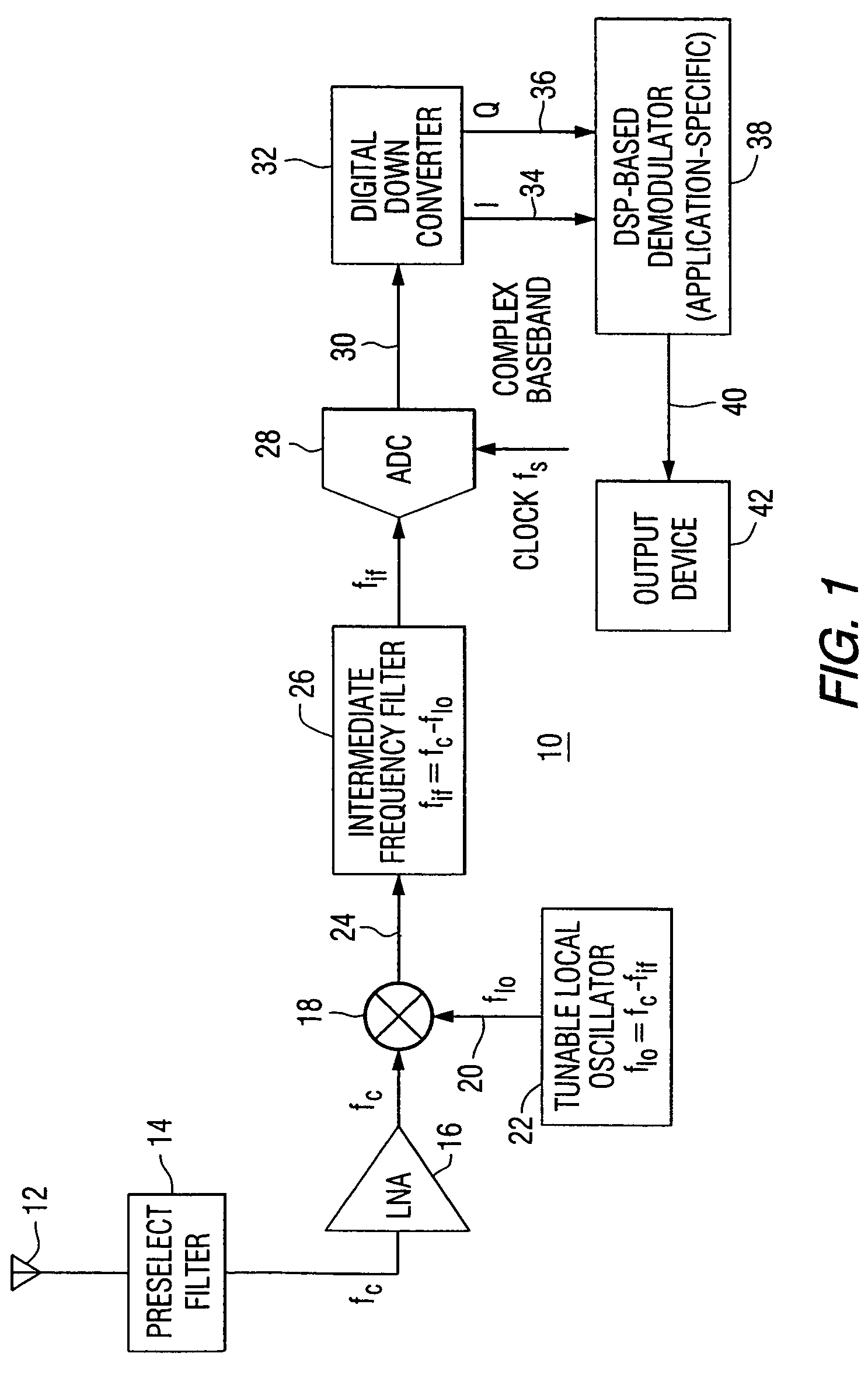

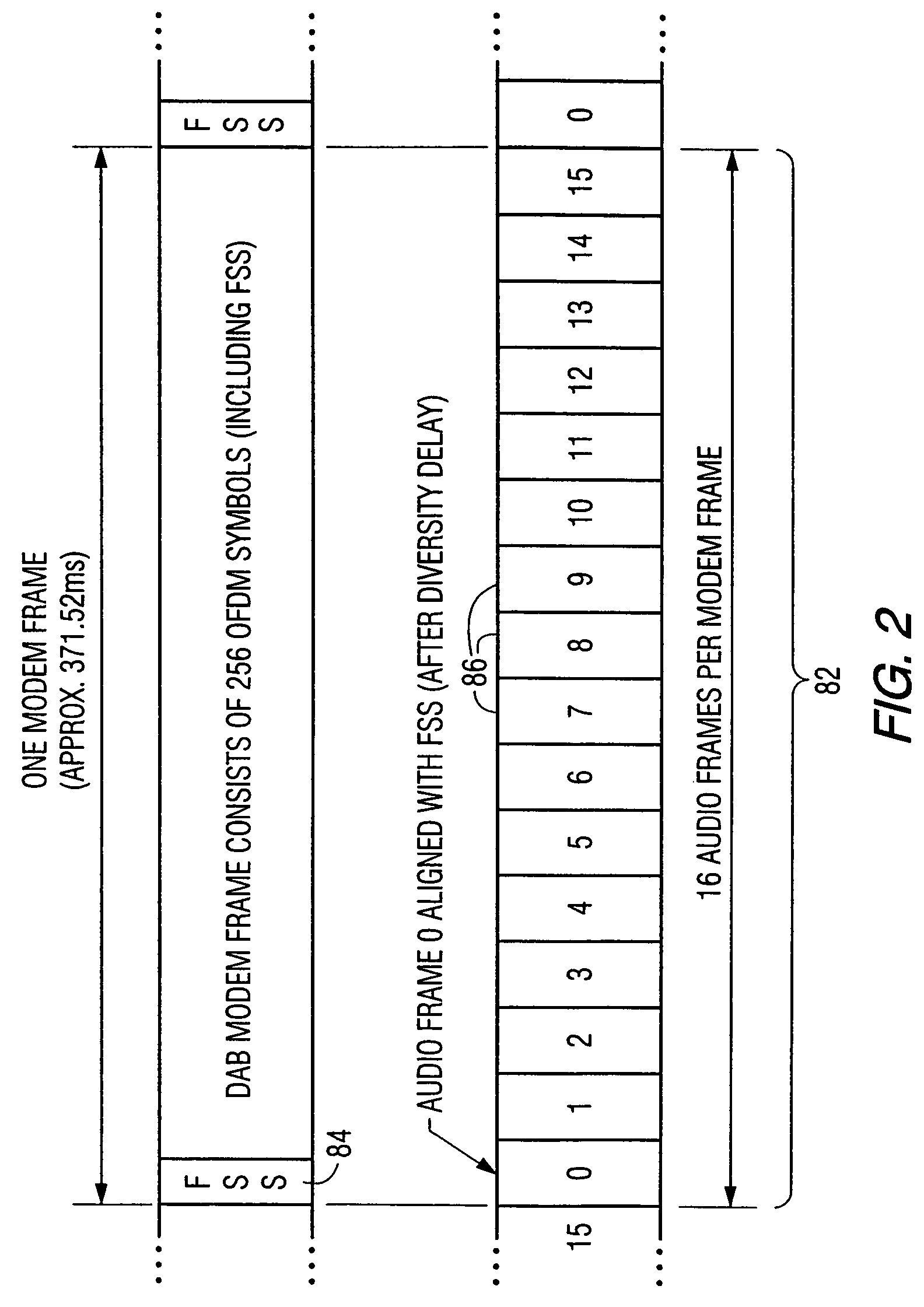

Method and apparatus for blending an audio signal in an in-band on-channel radio system

ActiveUS7546088B2Mitigate intermittent interruptionError preventionFrequency/rate-modulated pulse demodulationIn-band on-channelAudio signal flow

A method for processing a composite digital audio broadcast signal to mitigate intermittent interruptions in the reception of the digital audio broadcast signal, the method comprising the steps of separating an analog audio portion of the digital audio broadcast signal from a digital audio portion of the digital audio broadcast signal, detecting errors in the digital audio portion of the digital audio broadcast signal, adjusting the digital audio portion of the digital audio broadcast signal in response to errors in the digital audio portion of the digital audio broadcast signal to produce an adjusted digital audio portion, and blending the analog audio portion with the adjusted digital audio portion to produce an audio output. A receiver that performs the method is also included.

Owner:IBIQUITY DIGITAL CORP

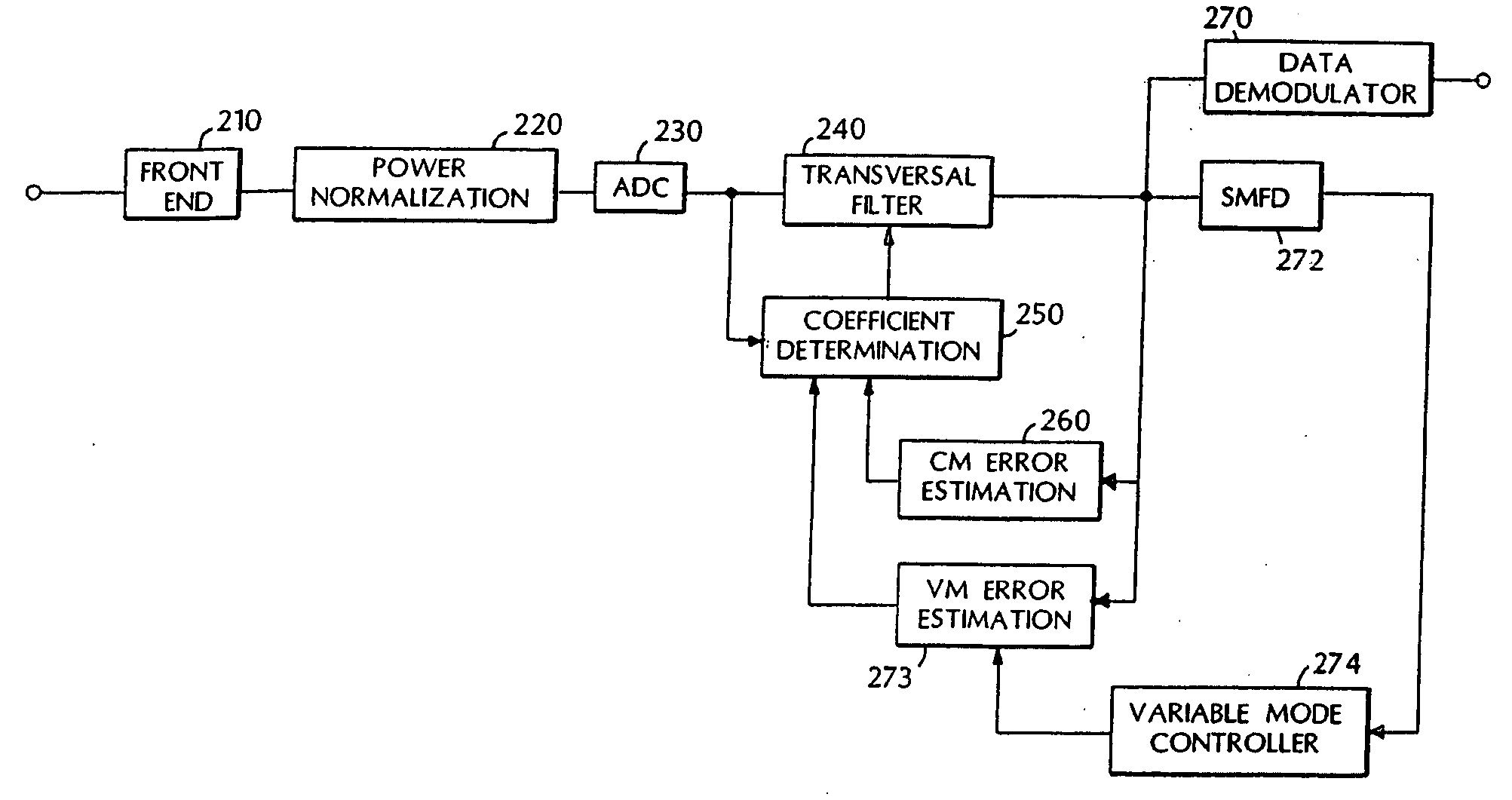

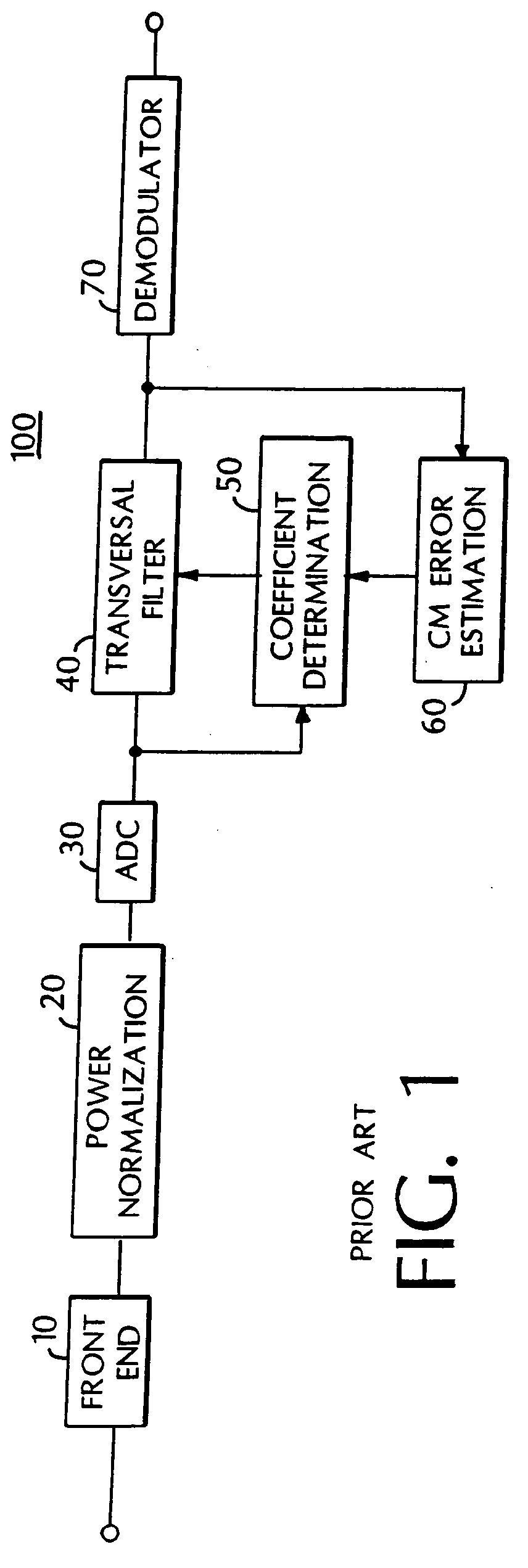

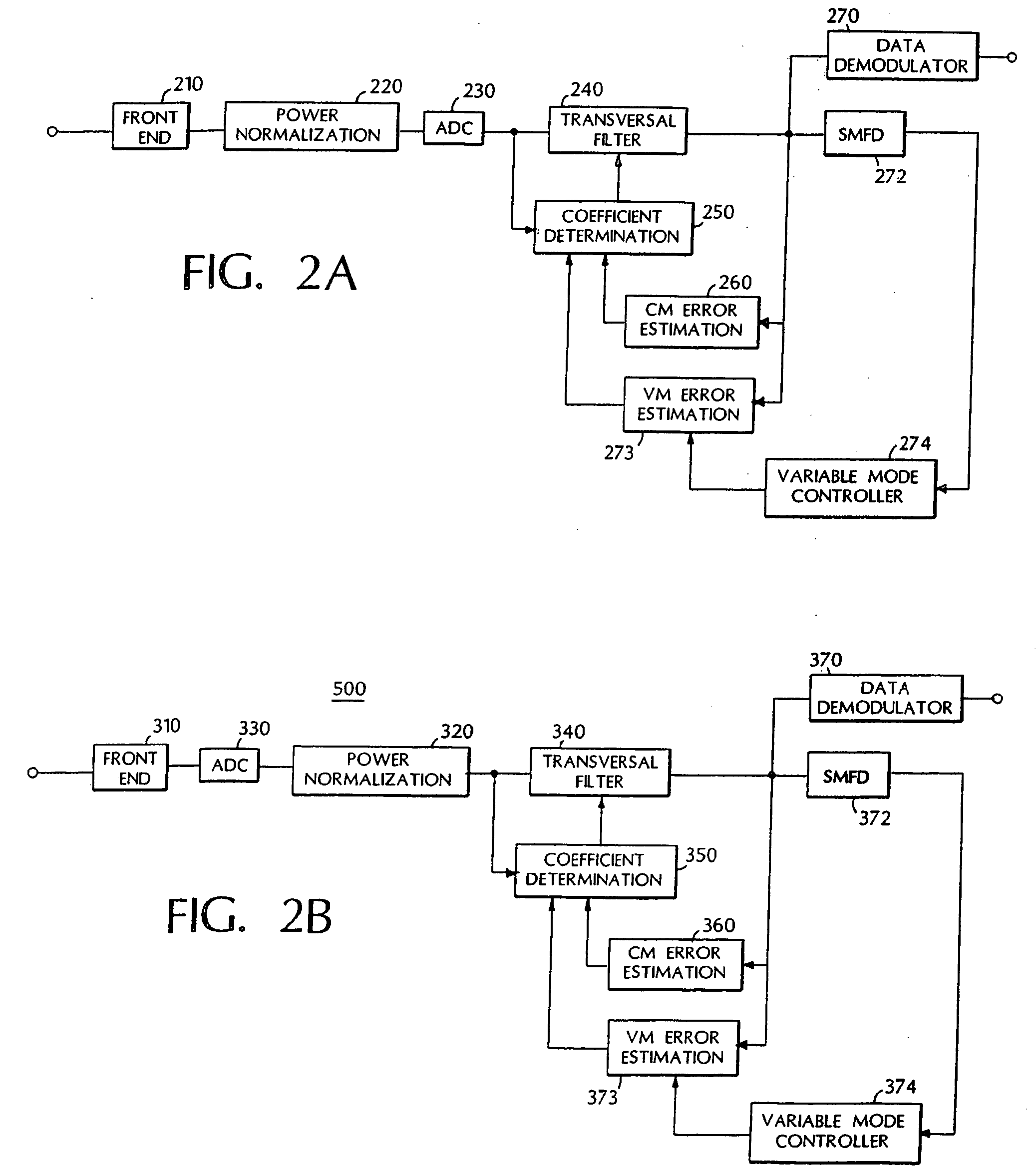

Demodulation

InactiveUS20060152276A1Improve filtering effectImprove adaptabilityMultiple-port networksTransmission control/equlisationFrequency spectrumFrequency detection

Demodulation apparatus includes a transversal filter characterized by coefficients adjusted by a coefficient determiner responsive to a constant modulus error signal and variable mode error signal related to the output of a spectral mean frequency detector having its input coupled to the output of the transversal filter.

Owner:BOSE CORP

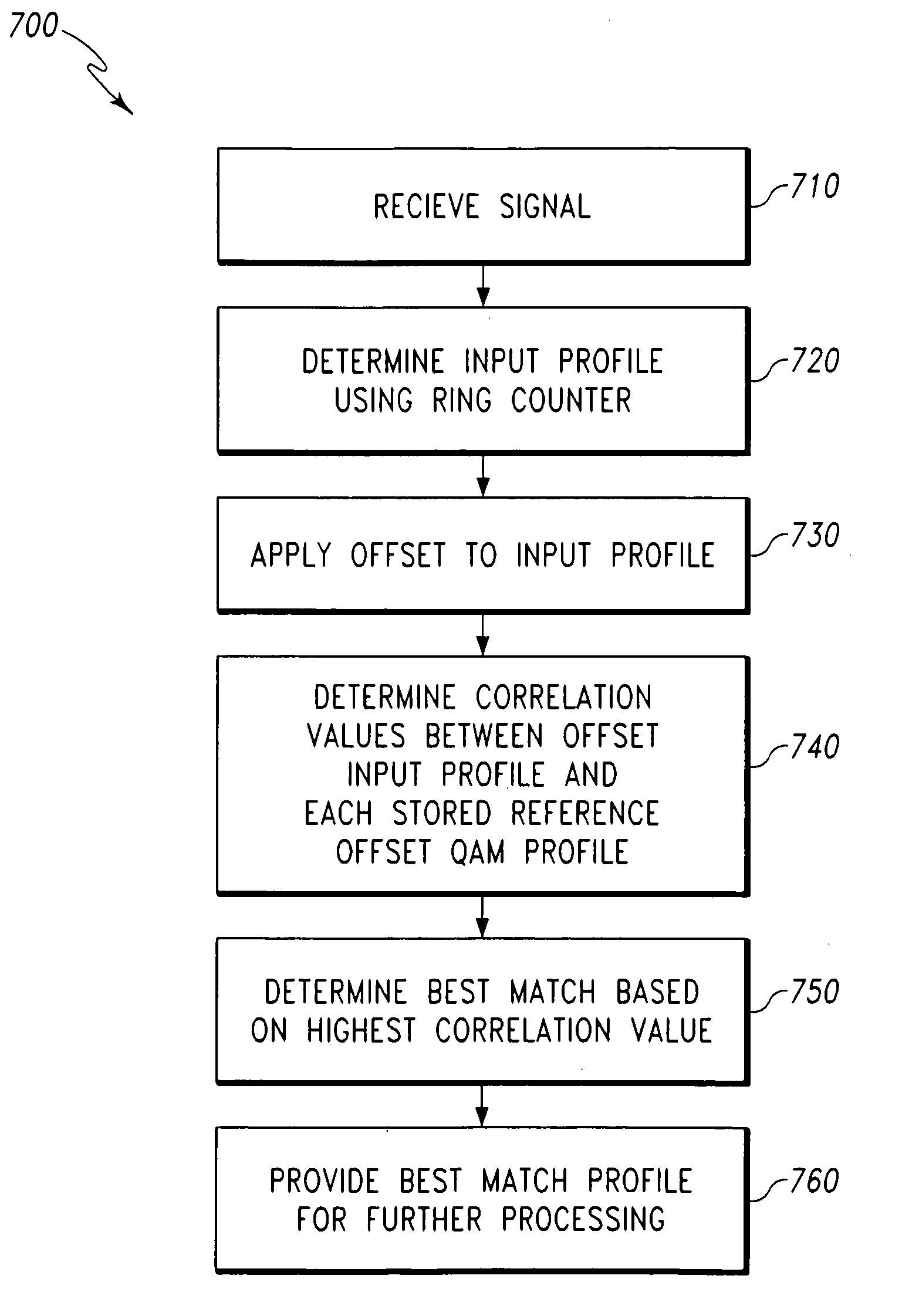

Apparatus and method for determination of signal format

InactiveUS20110074500A1Multiple input and output pulse circuitsMultiple modulation transmitter/receiver arrangementsRing counterSignal analyzer

The determination of the signal modulation format for a channel is an important aspect of the operation of a signal receiver. A method (700) is described including the steps of receiving (710) a signal, comparing (720) a sample of the received signal to a first threshold value and a second threshold value, creating (720) a signal profile based on the comparison, and selecting (750) a modulation format for the received signal based on the signal profile. An apparatus (500) is also described including a ring counter (510) that receives a sample of an input signal, compares the sample to a first threshold value and a second threshold value, and creates a signal profile for the input signal, a signal profiler (550) that compares the signal profile for the input signal to at least two reference profiles, and a detector (560) that determines a modulation format for the input signal based on the comparison in the signal profiler (550).

Owner:MAGNOLIA LICENSING LLC

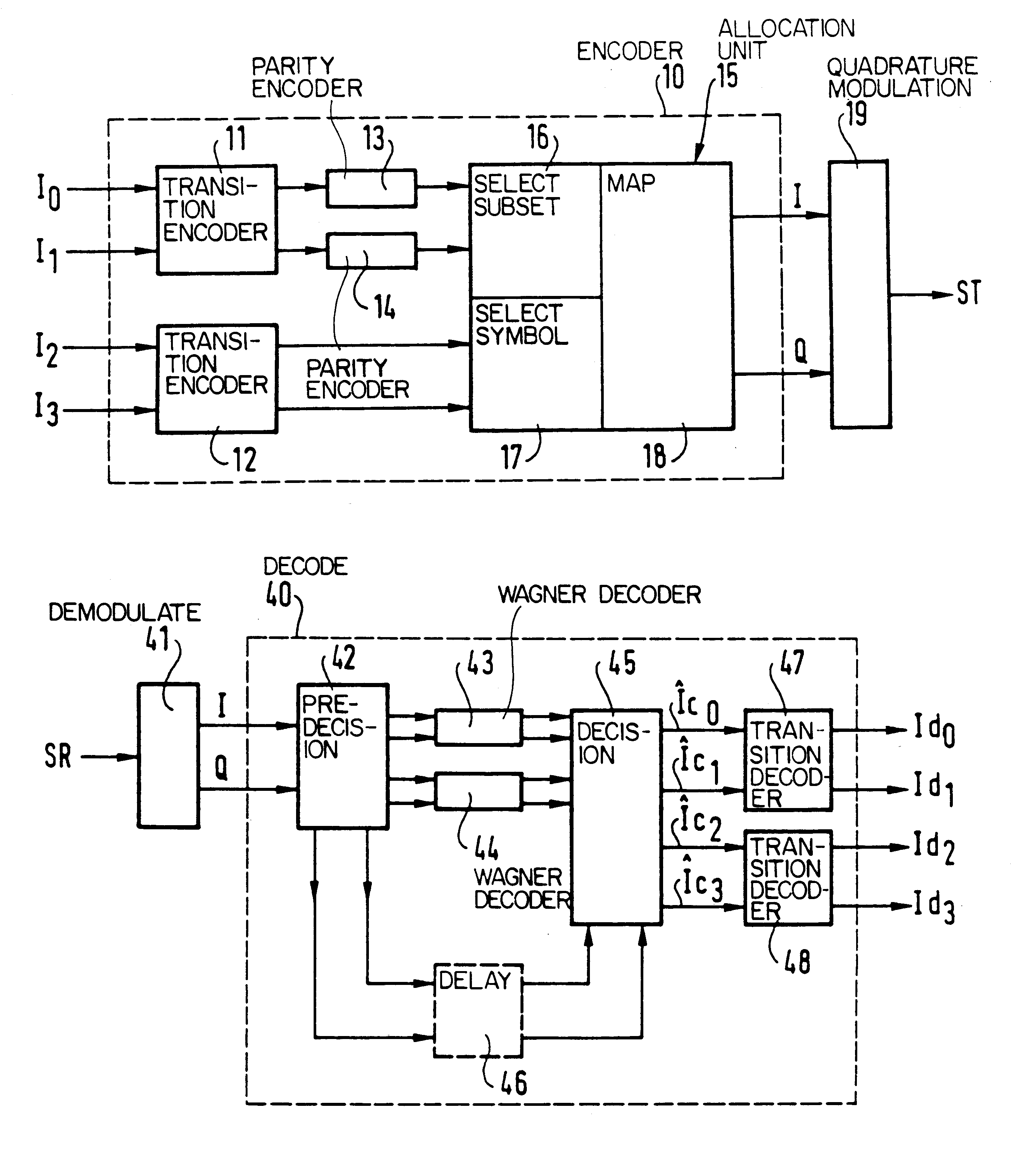

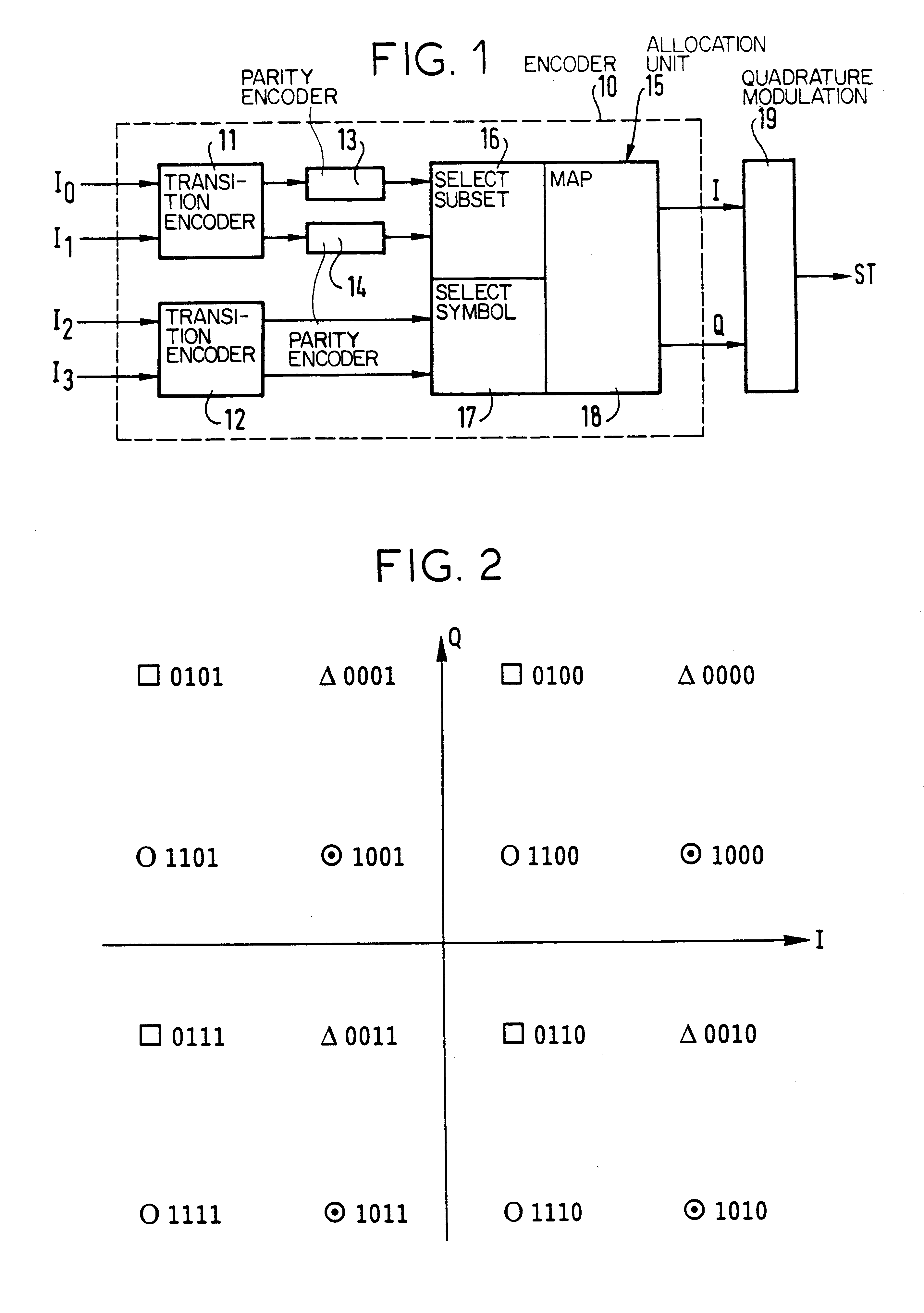

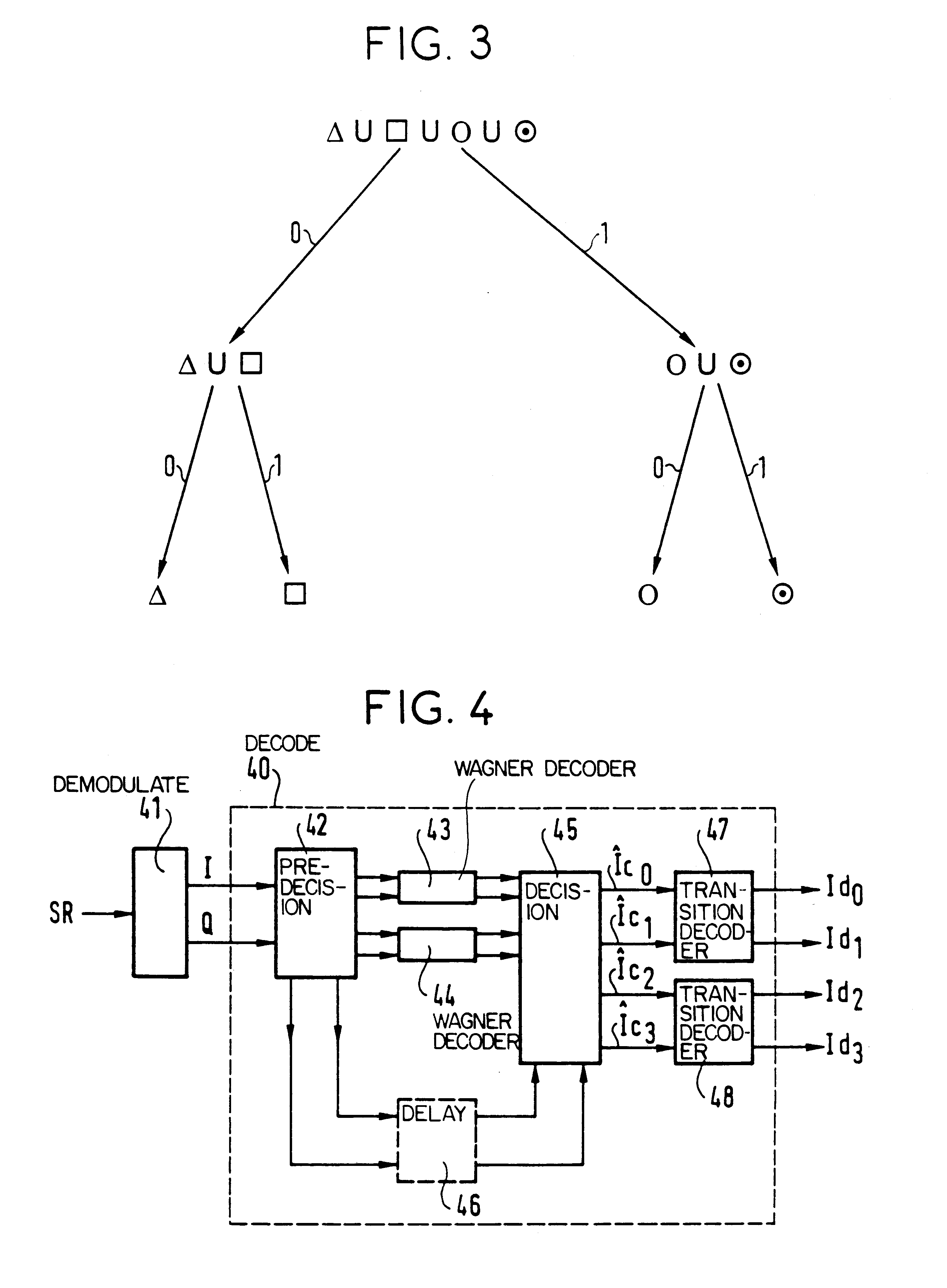

Encoding/decoding system using 16-QAM modulation encoded in multi-level blocks

InactiveUS6195396B1Error correction/detection using block single space codingCode conversionQam modulationAlgorithm

The invention provides a block-encoded modulation scheme using multi-level partitioning techniques. This scheme is made transparent to phase ambiguities of ±pi / 2 and of pi, by means of differential encoding and appropriate mapping, it is applicable to 16-QAM modulation, and it has theoretical encoding gain that is optimal for the rate of the code. The decoder associated with this scheme uses the Wagner algorithm which is much less complicated to implement than the Viterbi algorithm or than the Reed-Solomon algorithm.

Owner:ALCATEL TELSPACE