Patents

Literature

69results about "Dual purpose resist" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

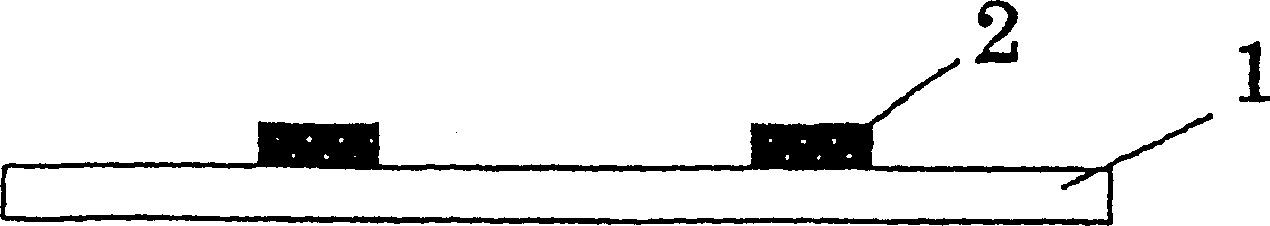

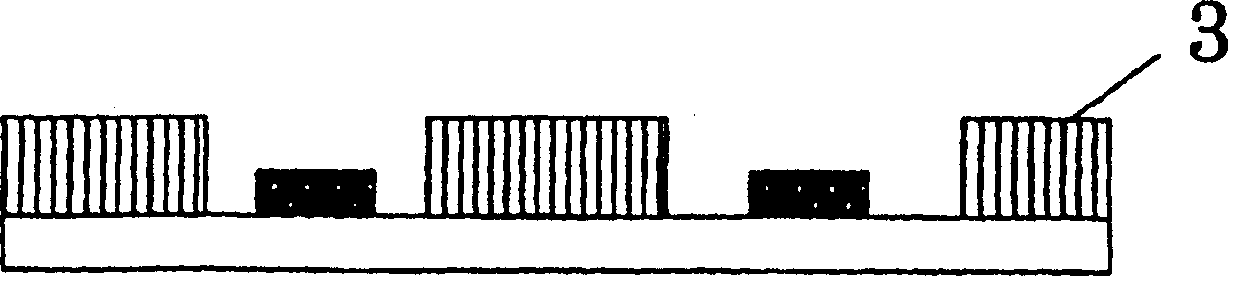

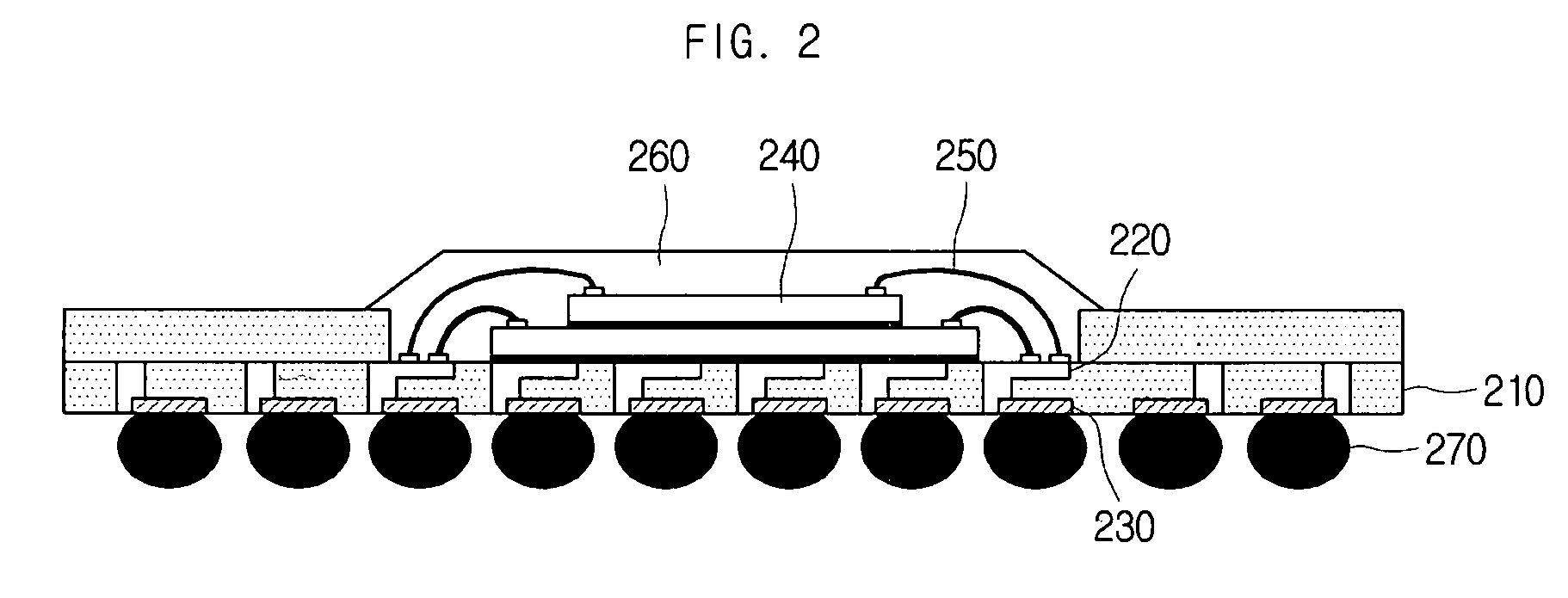

Multi-layer wiring board

InactiveUS20100065313A1Promote lowerHigh density housingCircuit bendability/stretchabilityDual purpose resistHigh densityFlexible electronics

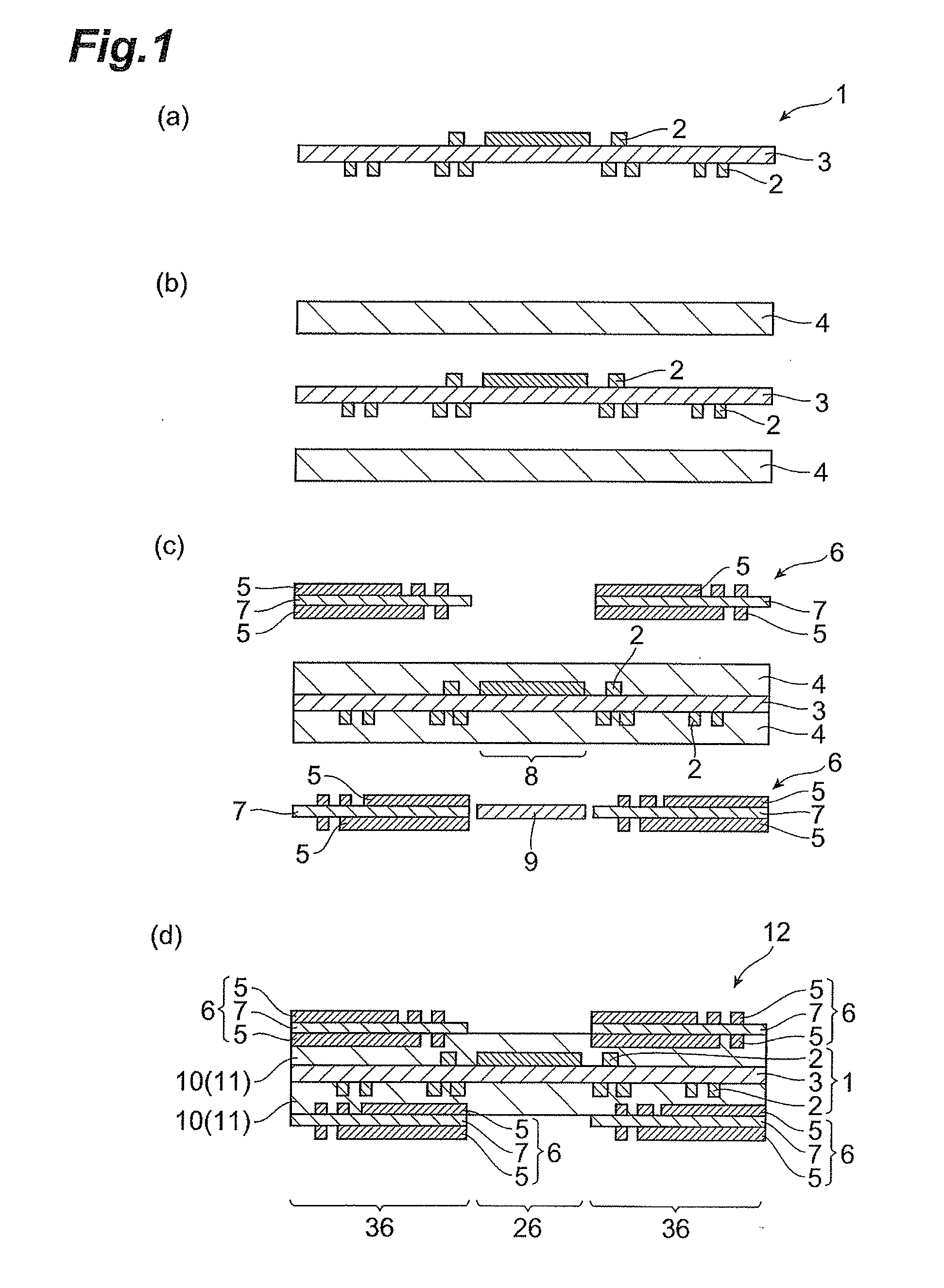

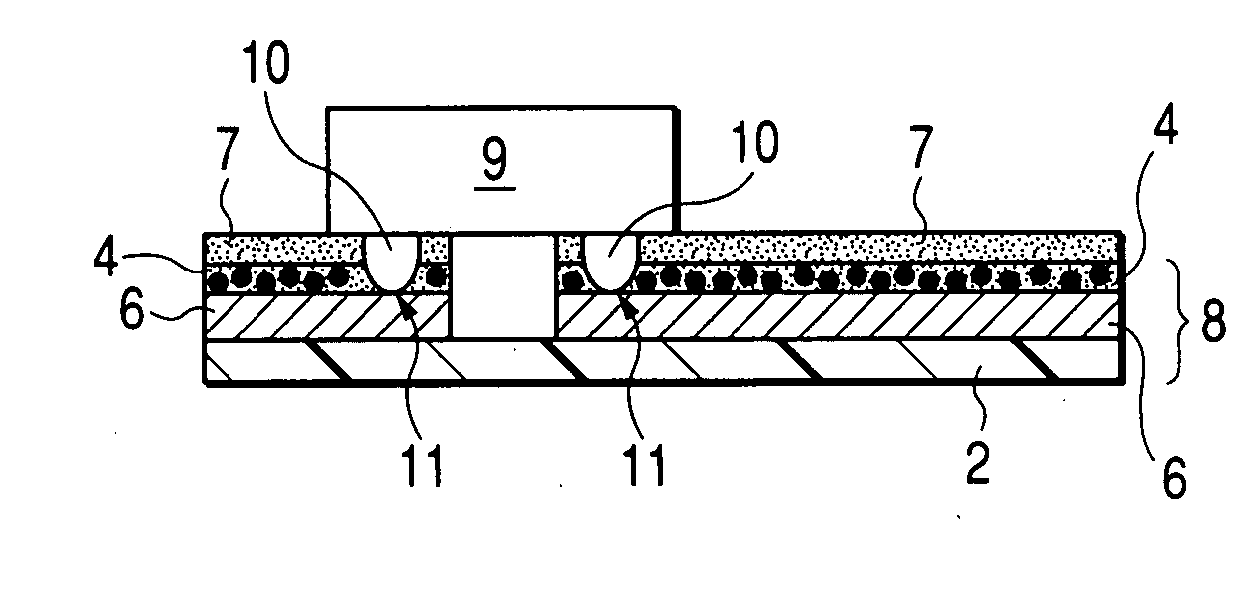

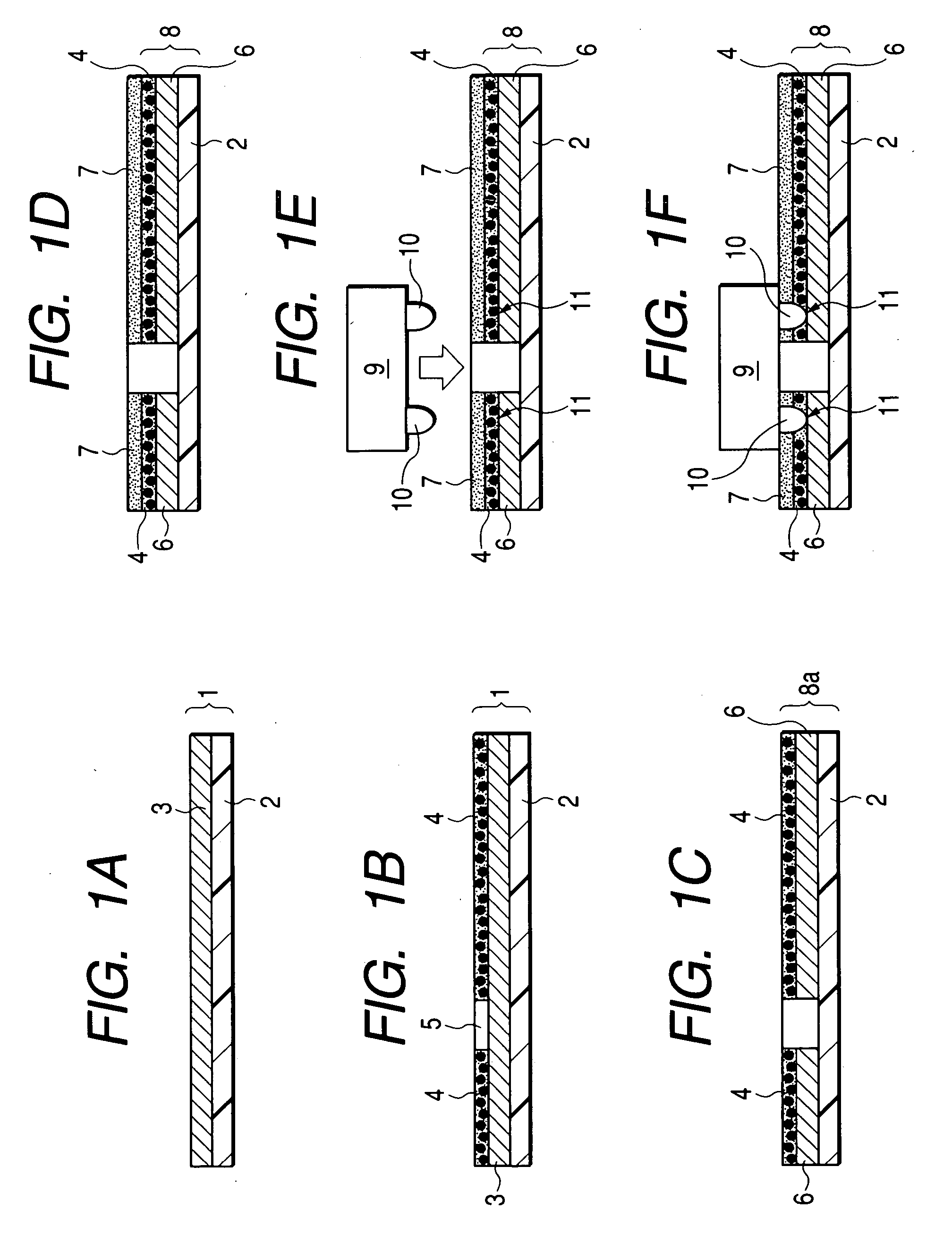

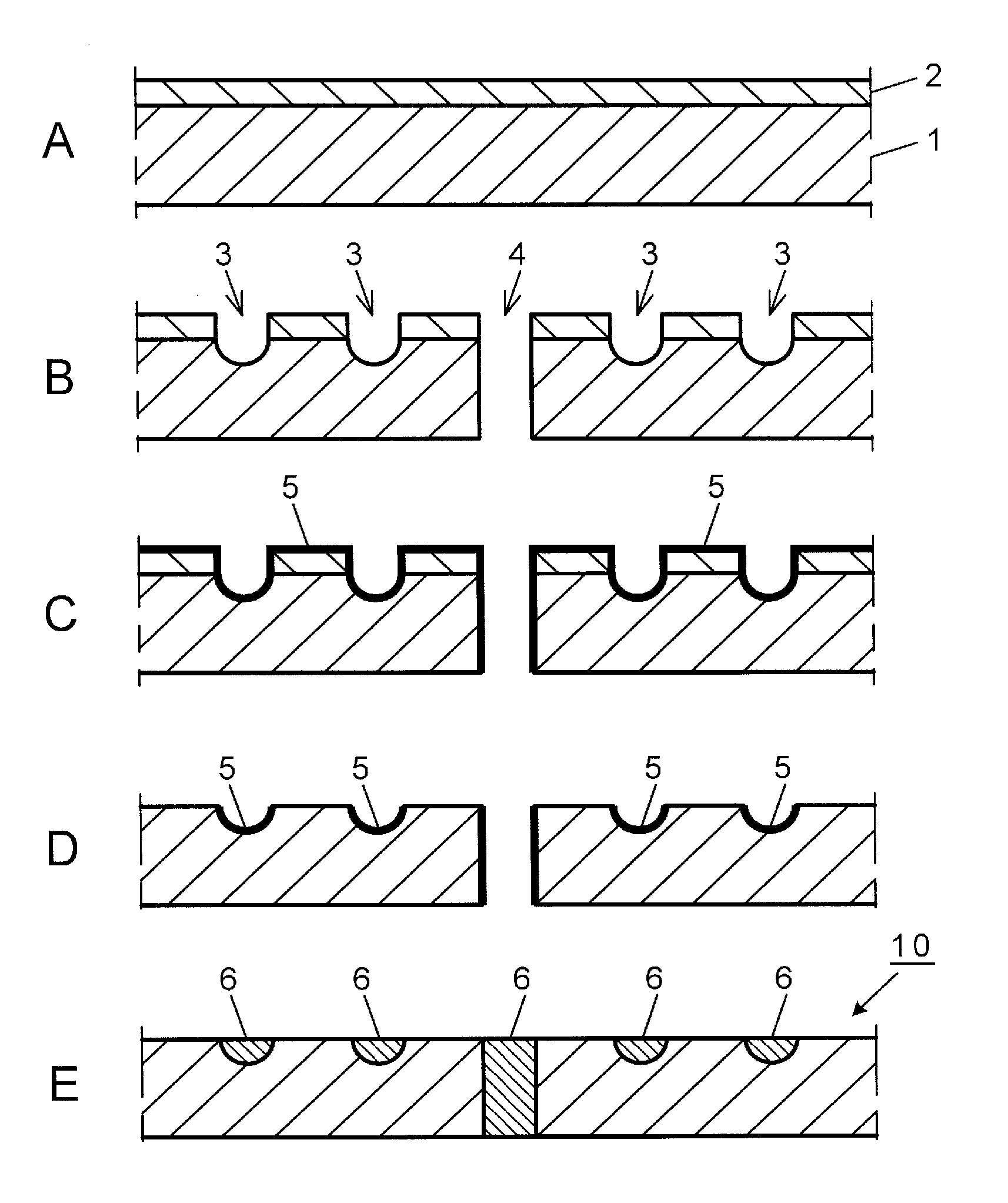

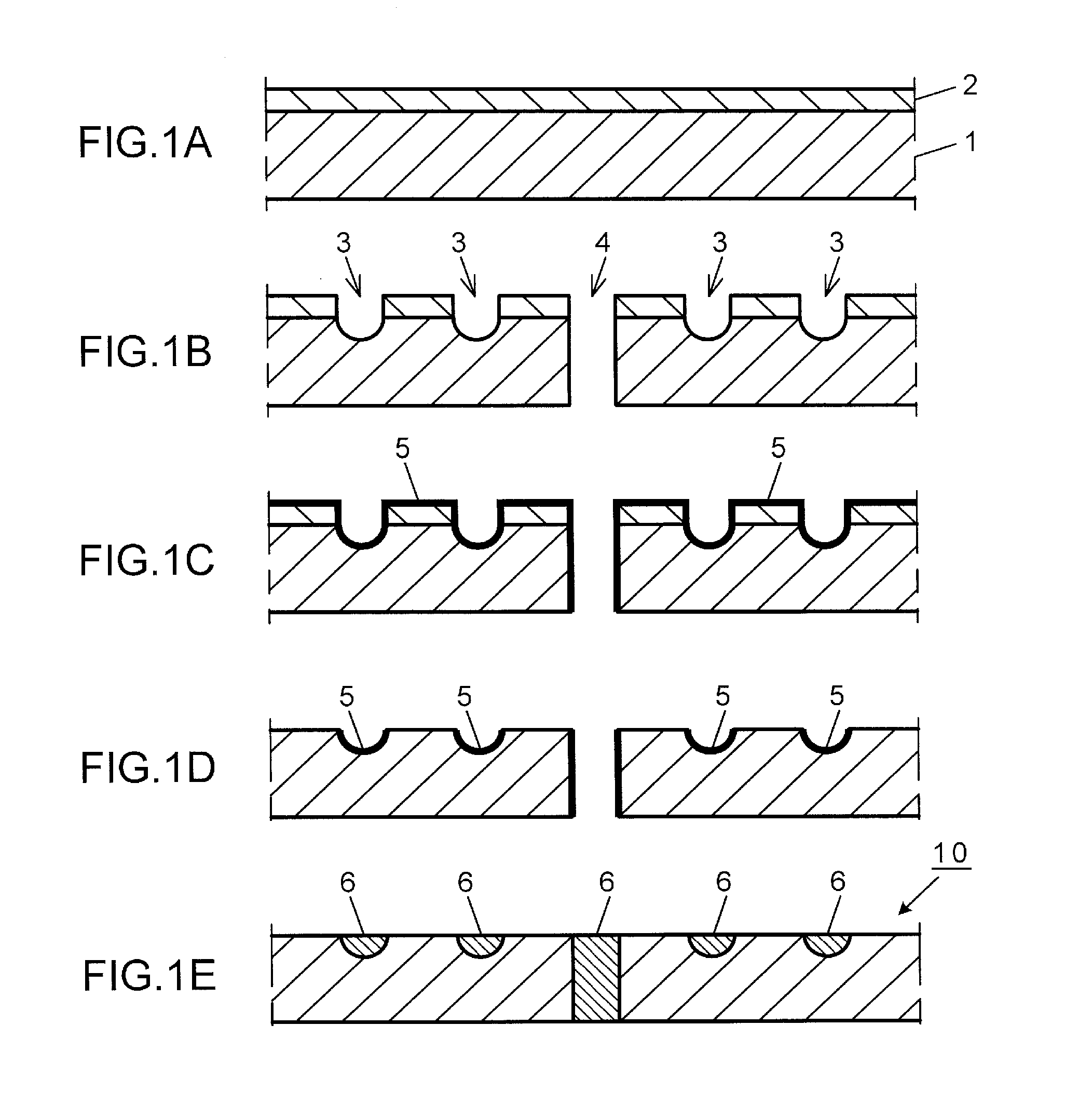

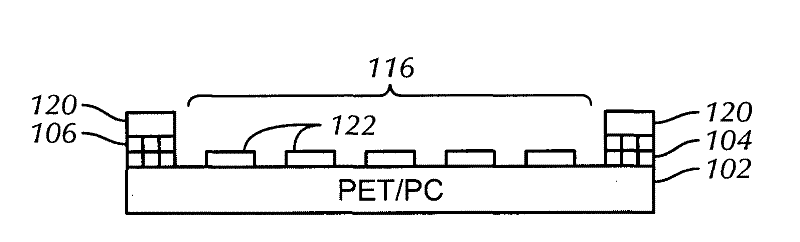

It is an object of the present invention to provide a multilayer circuit board that can be housed at high density in the enclosures of electronic devices. According to a preferred embodiment of the invention, a multilayer circuit board (12) has a structure wherein non-flexible printed circuit boards (6) are laminated via cover lays (10) onto both sides of a flexible printed circuit board (1). In the multilayer circuit board (12), the cover lays (10) protect the regions of the printed circuit board (1) where the printed circuit boards (6) are not situated, while also functioning as adhesive layers (11) for bonding with the printed circuit boards (6). In other words, the same layers are used as the cover lays (10) and adhesive layers (11) in the multilayer circuit board (12).

Owner:HITACHI CHEM CO LTD

Method for manufacturing conductive member, conductive member, and touch panel using same

ActiveUS20150009432A1InhibitionReduce the differenceConductive layers on insulating-supportsDiffusing elementsMetal nanowiresTouch panel

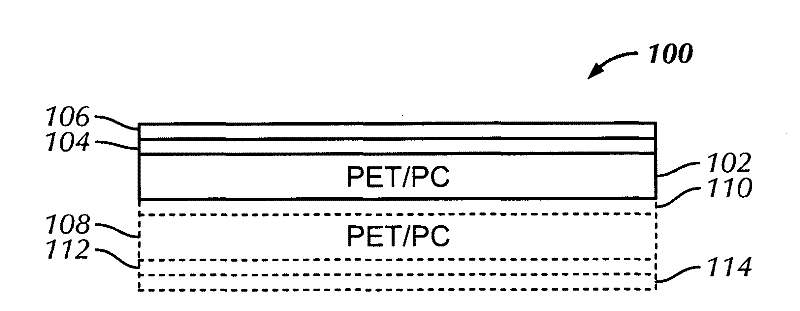

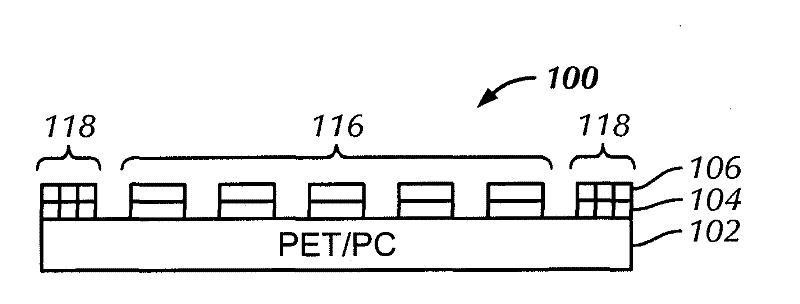

A method for manufacturing of a conductive member includeforming one of a conductive layer including metal nanowires or a light-scattering layer including insulating light-scattering fine particles on a substrate in a pattern shape; andforming the other of the conductive layer including metal nanowires or the light-scattering layer including insulating light-scattering fine particles on a space of the substrate wherein the one of the conductive layer or the light-scattering layer is not formed.

Owner:FUJIFILM CORP

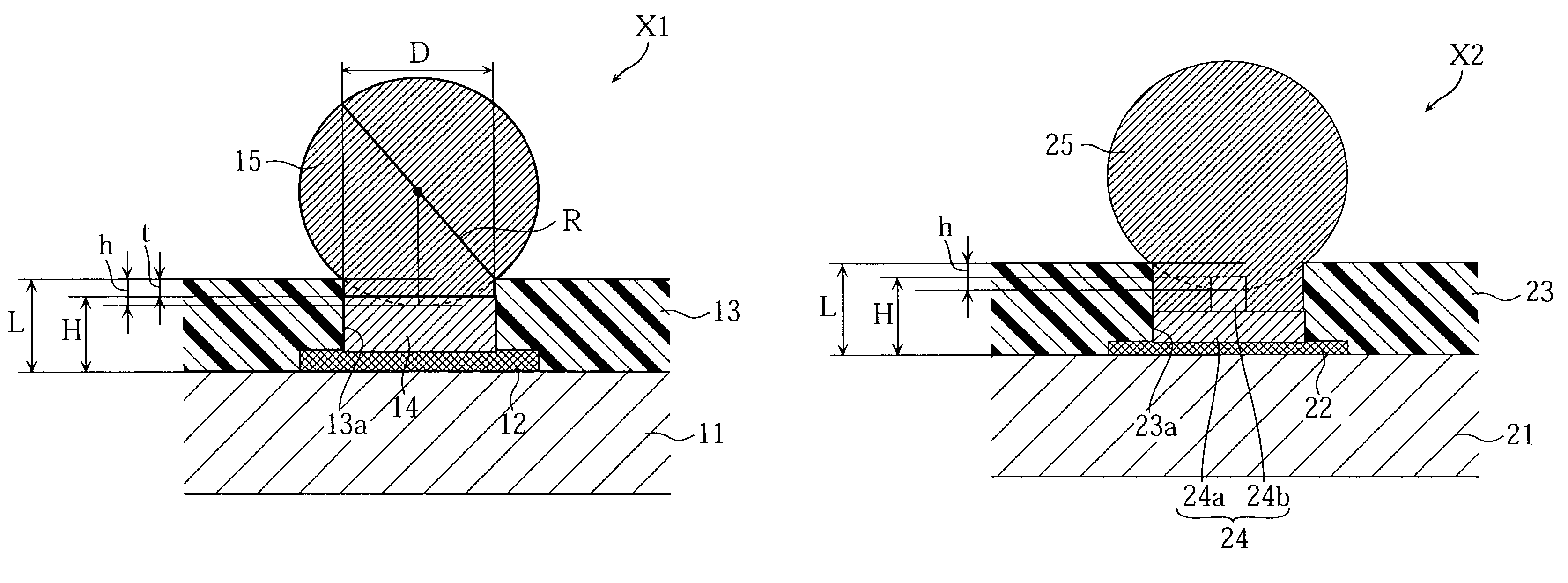

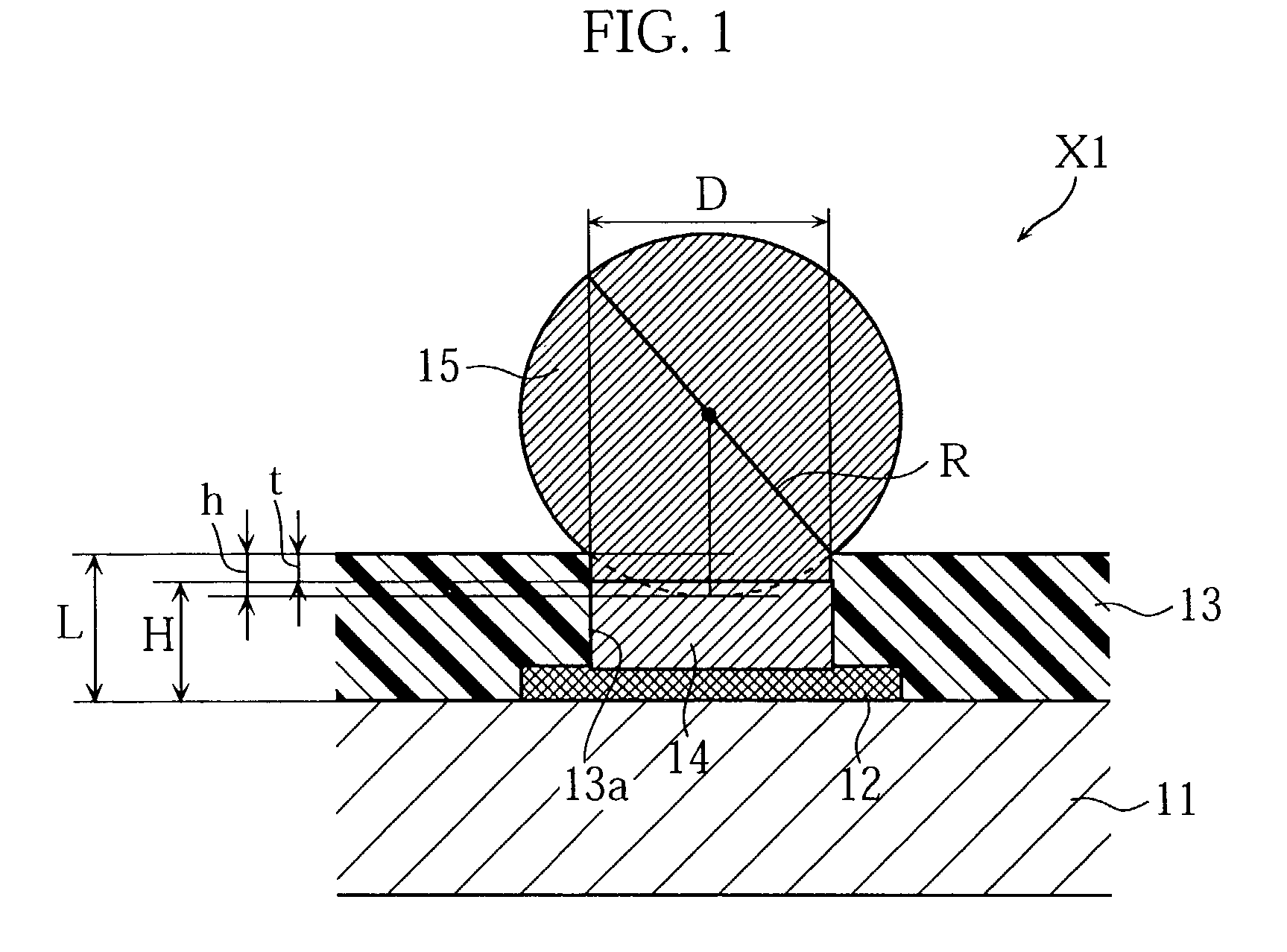

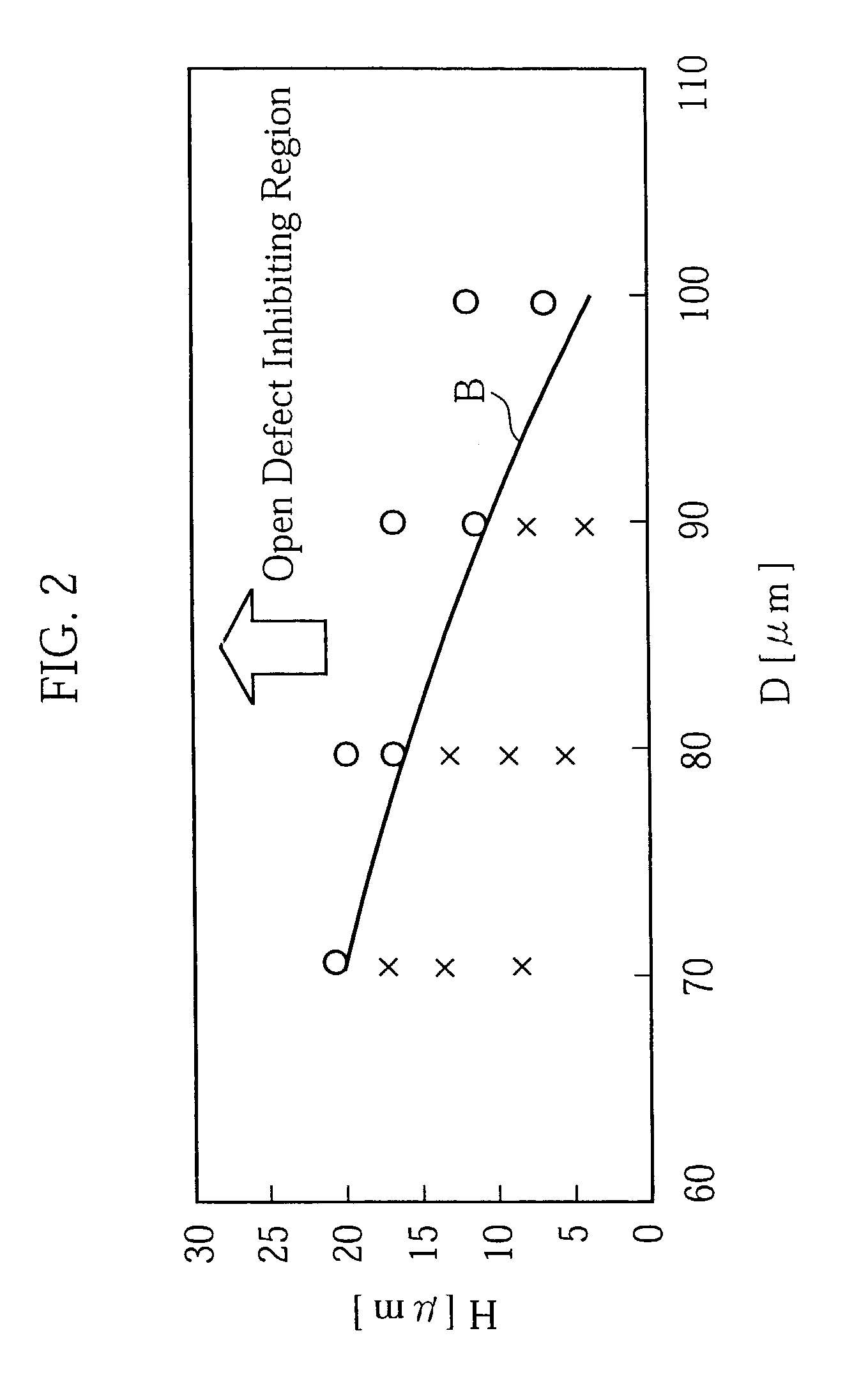

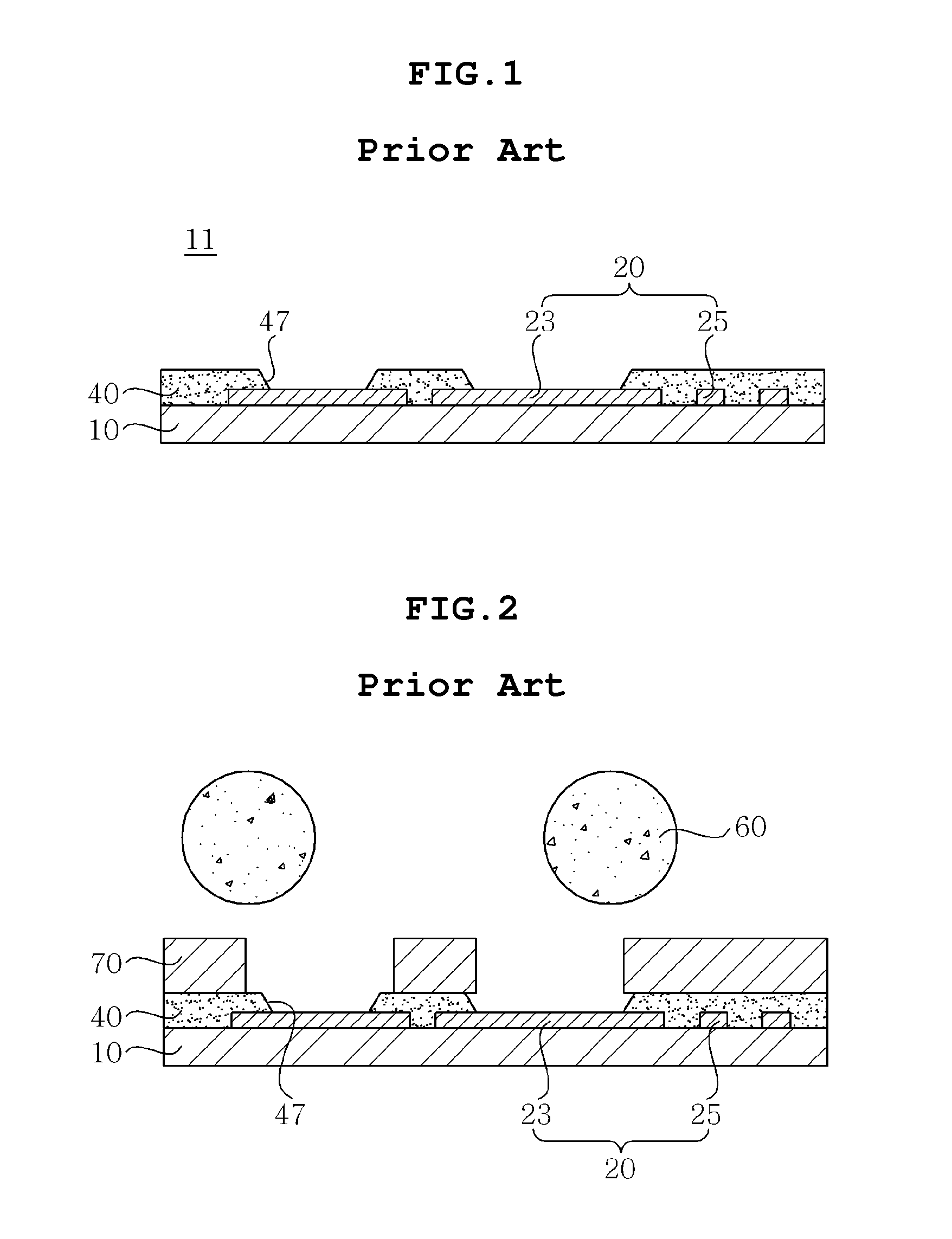

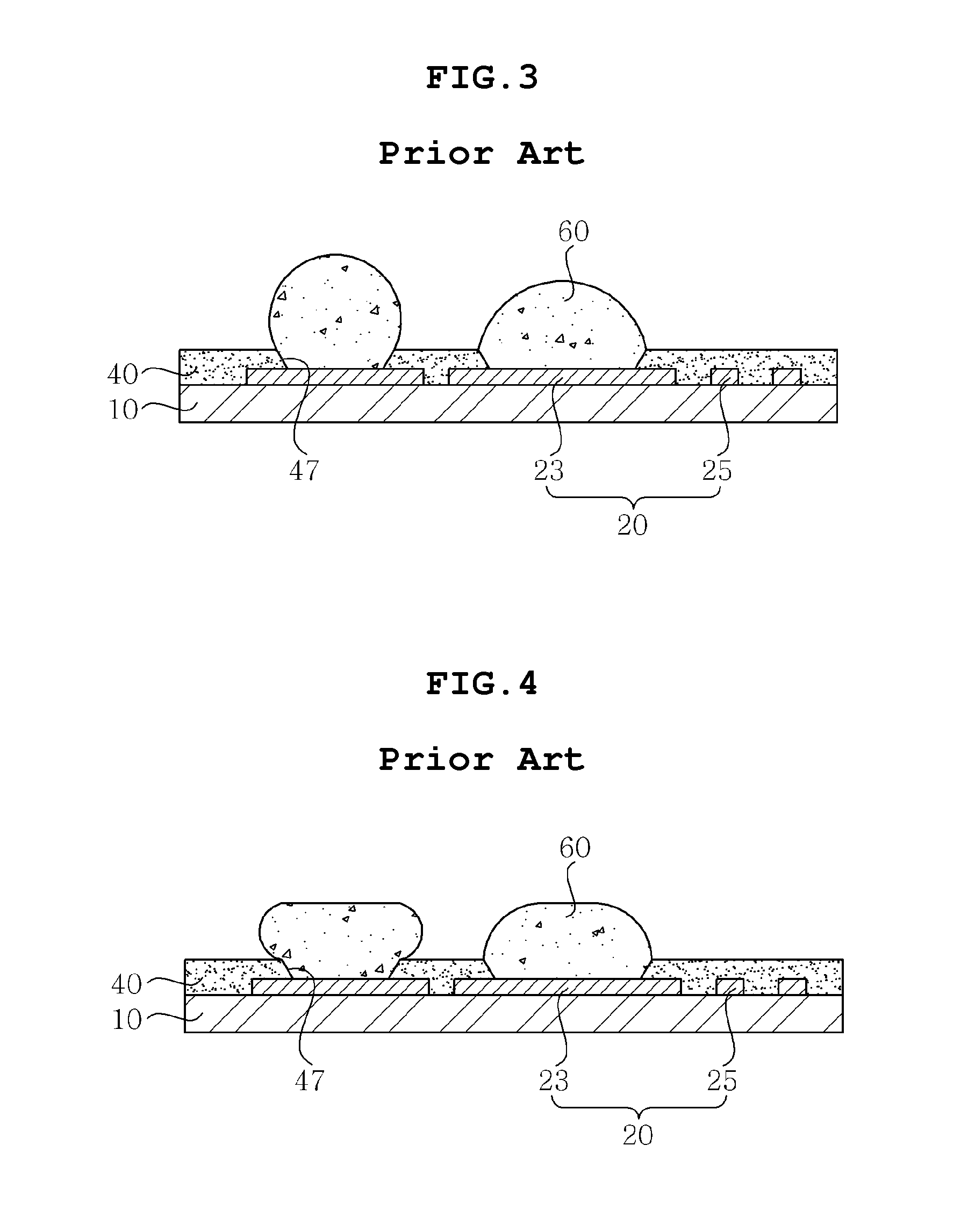

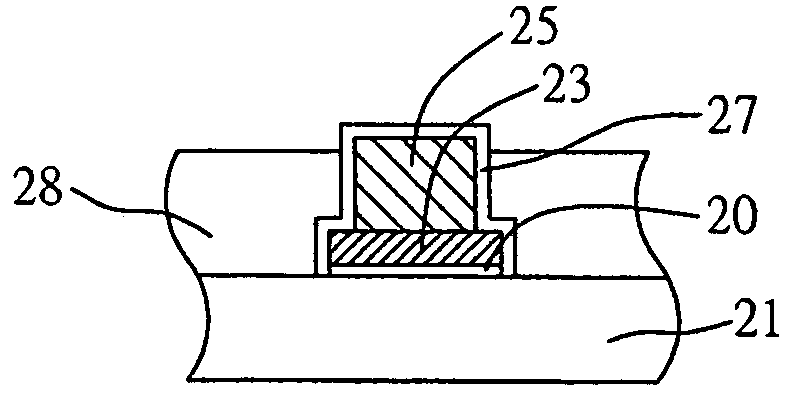

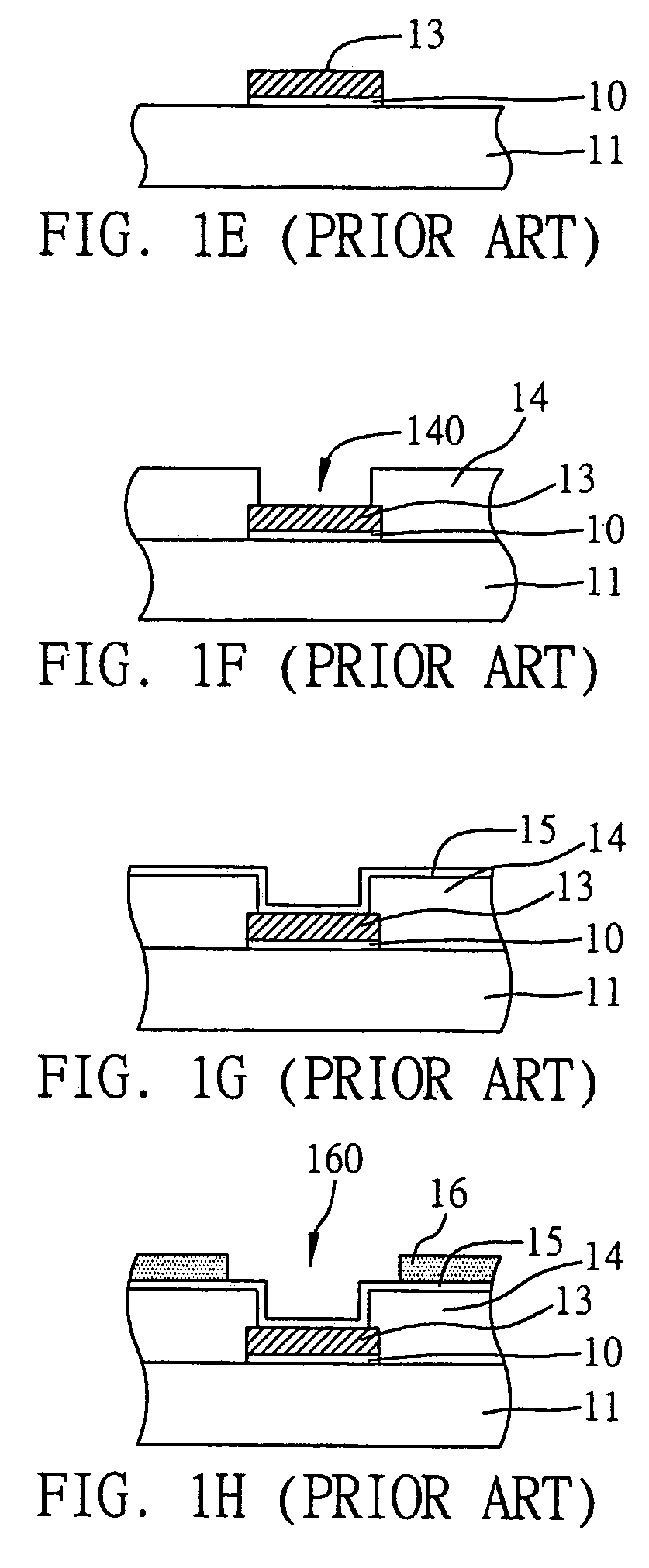

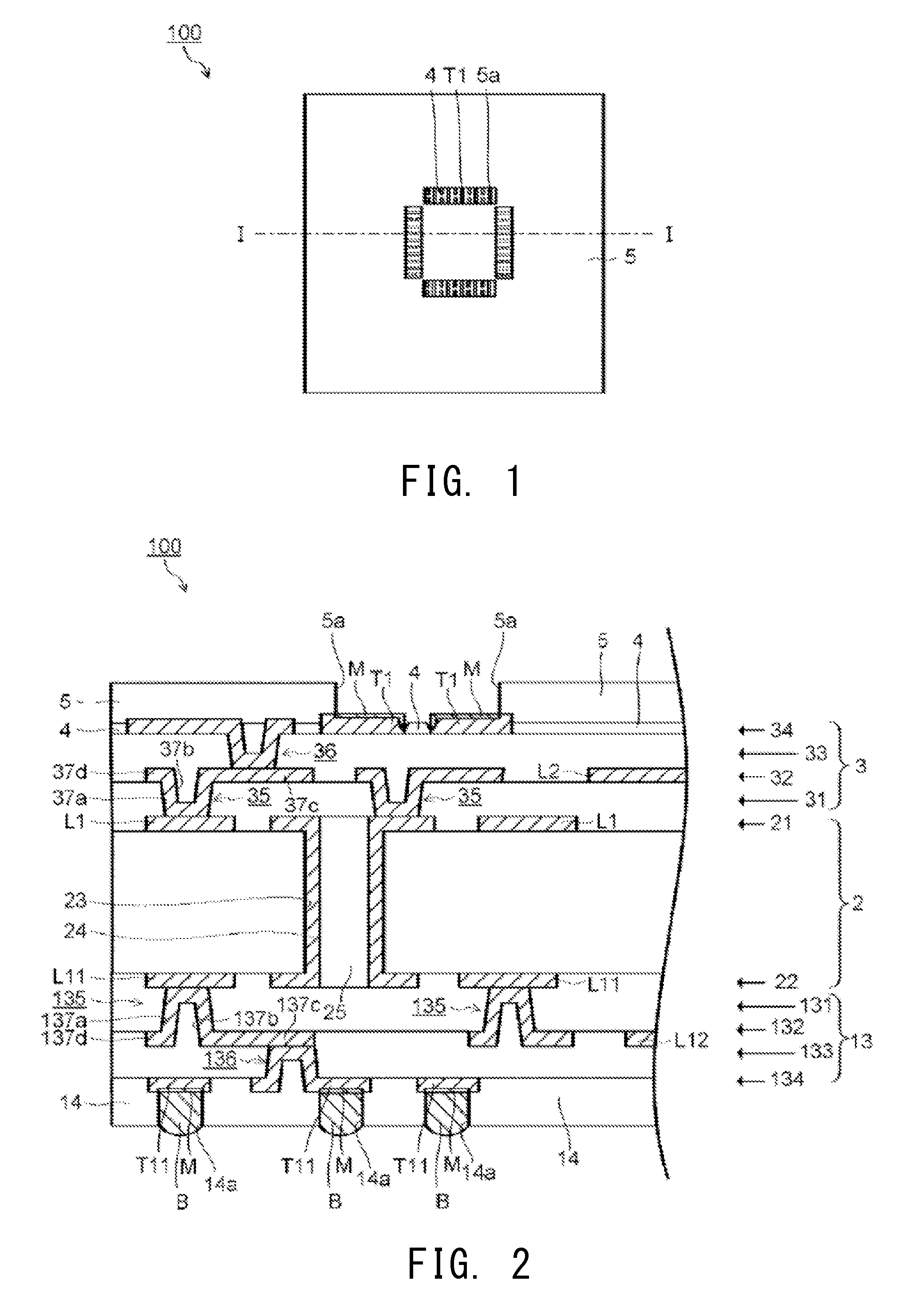

Electronic component with bump electrodes, and manufacturing method thereof

InactiveUS7189927B2Reduce generationAvoid insufficient thicknessFinal product manufactureSemiconductor/solid-state device detailsEngineeringElectronic component

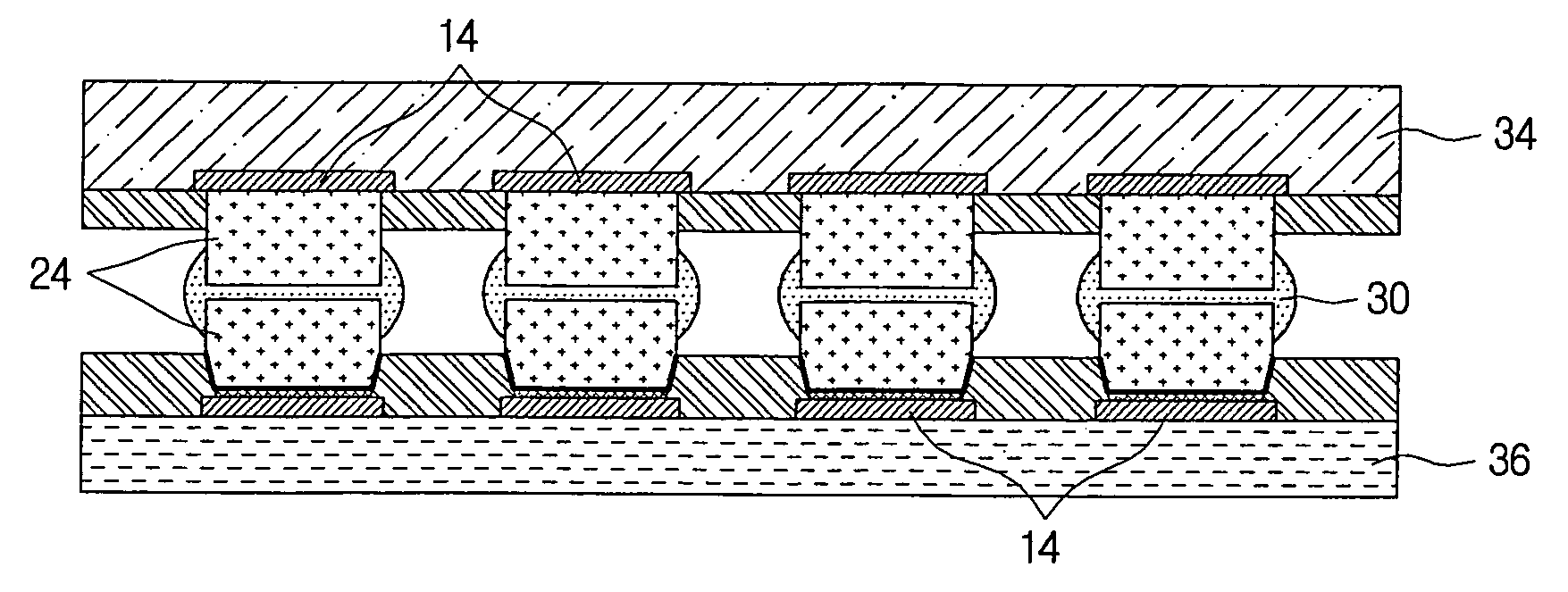

An electronic component with bump electrodes includes a surface-protecting insulating film of adequate thickness and bump elements of adequate height, and allows the occurrence of open defects in the manufacturing process to be appropriately reduced. An electronic component with bump electrodes (X1) includes a substrate (11), electrode pads (12) provided on the substrate (11), an insulating film (13) that has openings (13a) in correspondence with the electrode pads (12) and is laminated and formed on the substrate (11), electroconductive connecting elements (14) provided on the electrode pads (12) in the openings (13a), and bump elements (15) that are in direct contact with the electroconductive connecting elements (14) and project from the openings (13a).

Owner:FUJITSU LTD

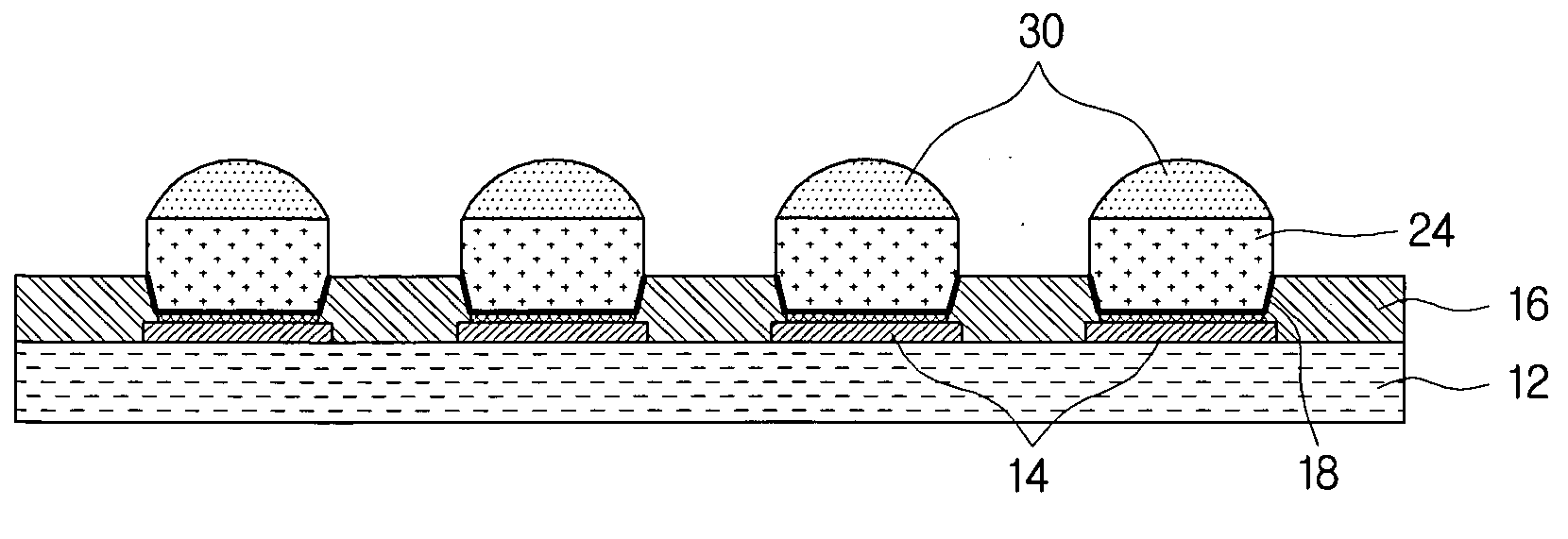

Post bump and method of forming the same

InactiveUS20110012261A1Prevent deviationAvoid flowSemiconductor/solid-state device detailsPrinted circuit aspectsEngineeringSolder form

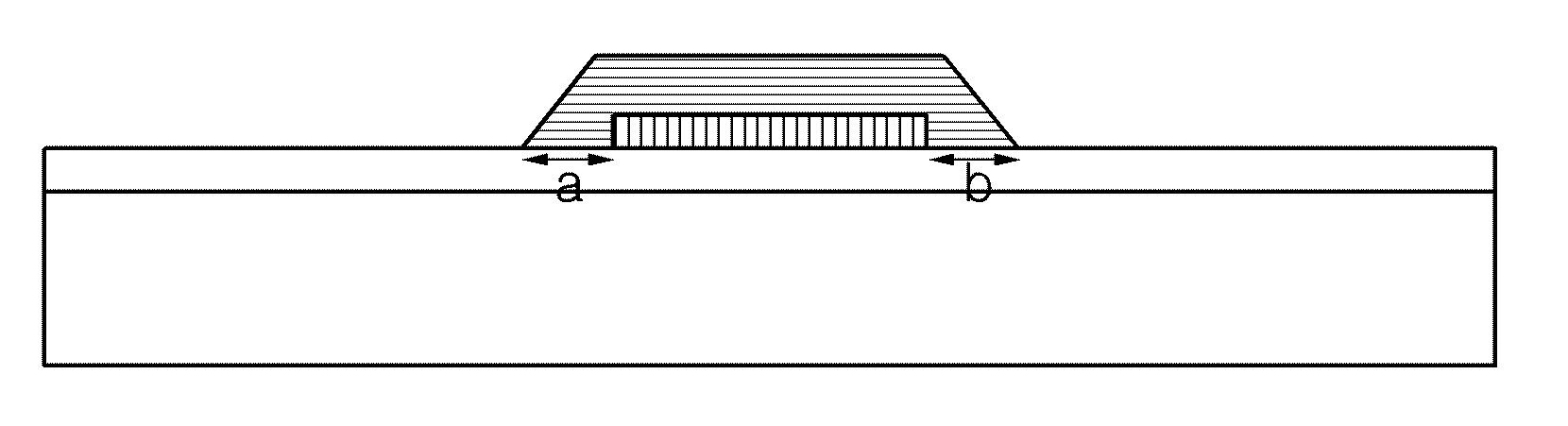

A post bump formed over an electrode pad of a substrate for electrically connecting to an external device, the post bump including a metal post formed over the electrode pad; and a solder formed over the metal post and shaped as a dome, the dome occupying a space defined by imaginary lines extending from a perimeter of the metal post along an axial direction of the metal post.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

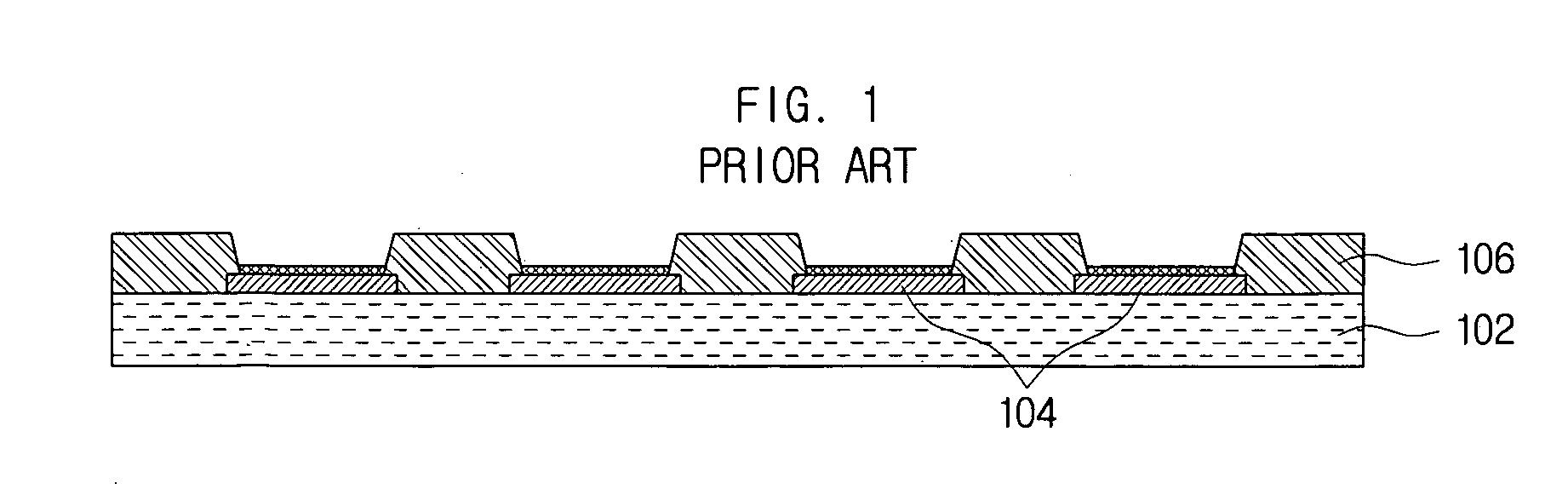

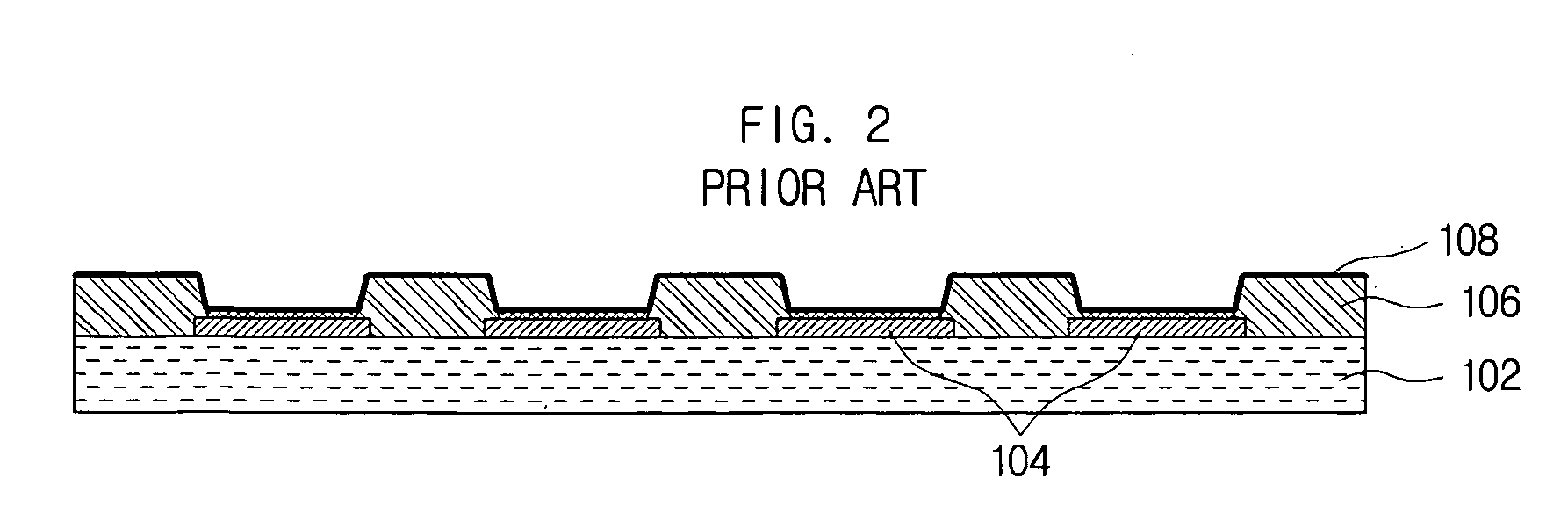

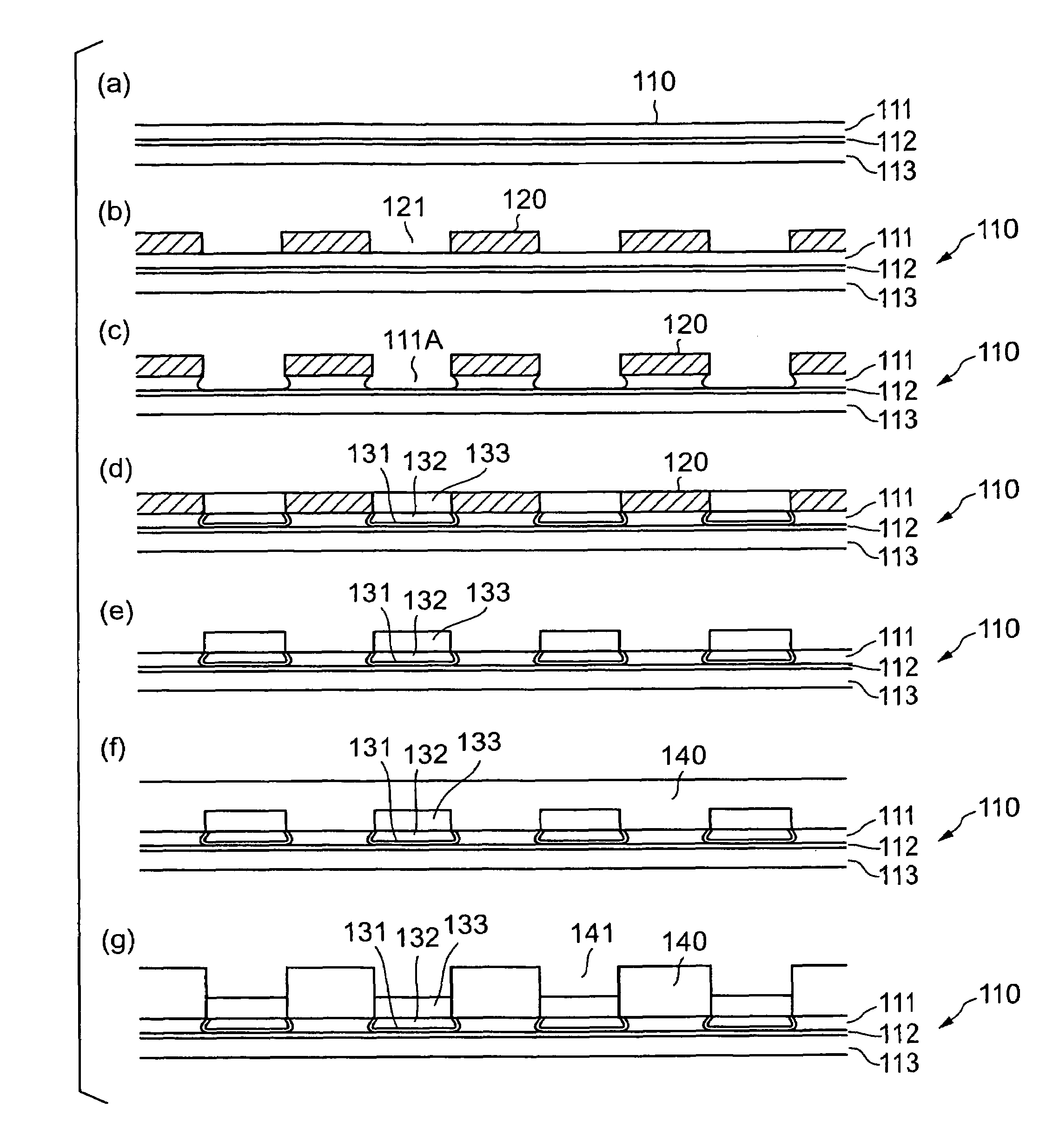

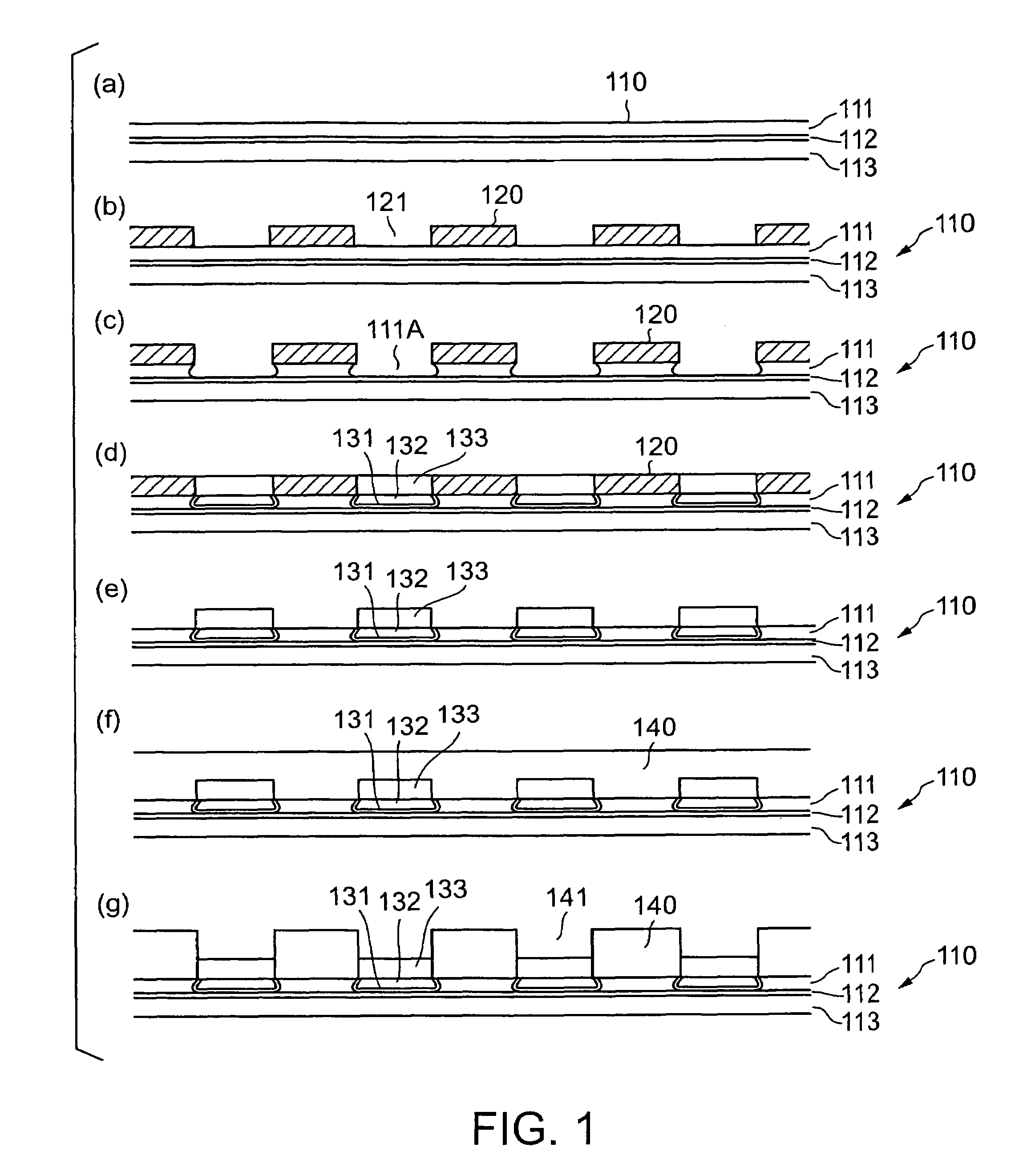

Printed circuit board and method of manufacturing the same

InactiveUS20120138337A1Simple formatReliable formingDual purpose resistConductive pattern formationEngineeringSolder paste

Disclosed herein is a printed circuit board and a method of manufacturing the same, in which a bump is formed using solder paste printing, and a heat radiation layer is formed using a metal layer used in the course of forming the bump, thus simplifying the formation of the bump, reliably mounting the bump, and improving heat-radiating properties.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

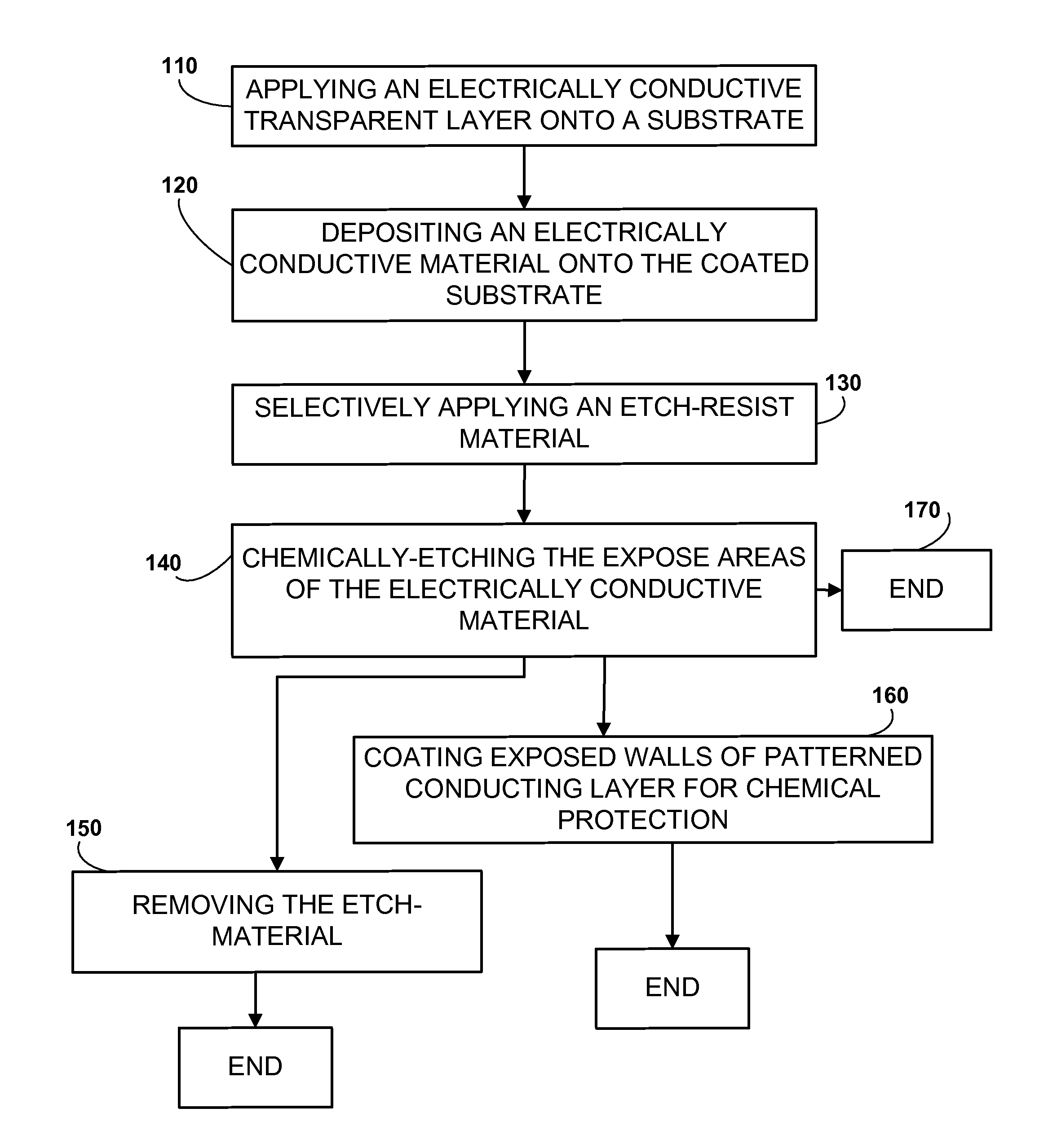

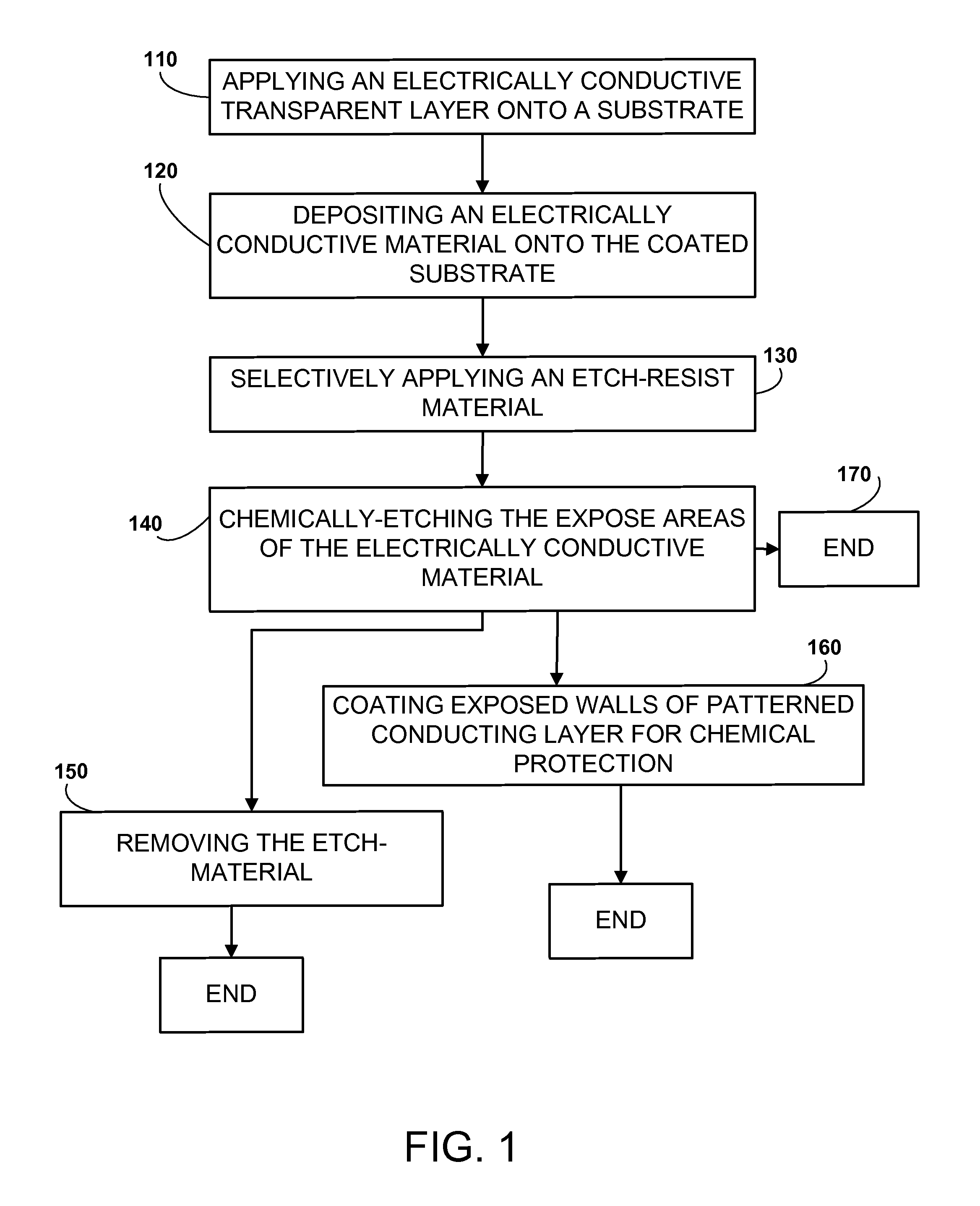

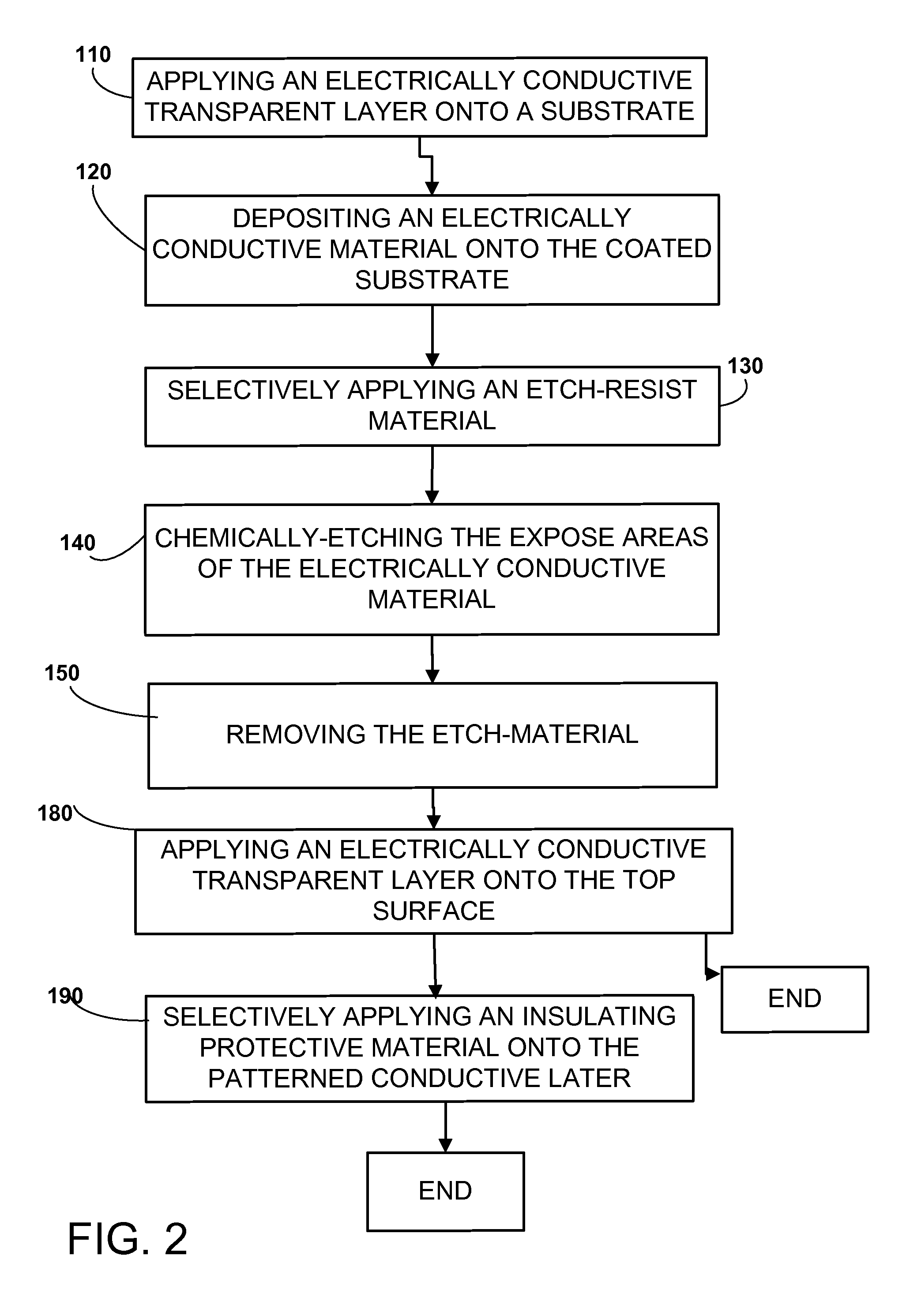

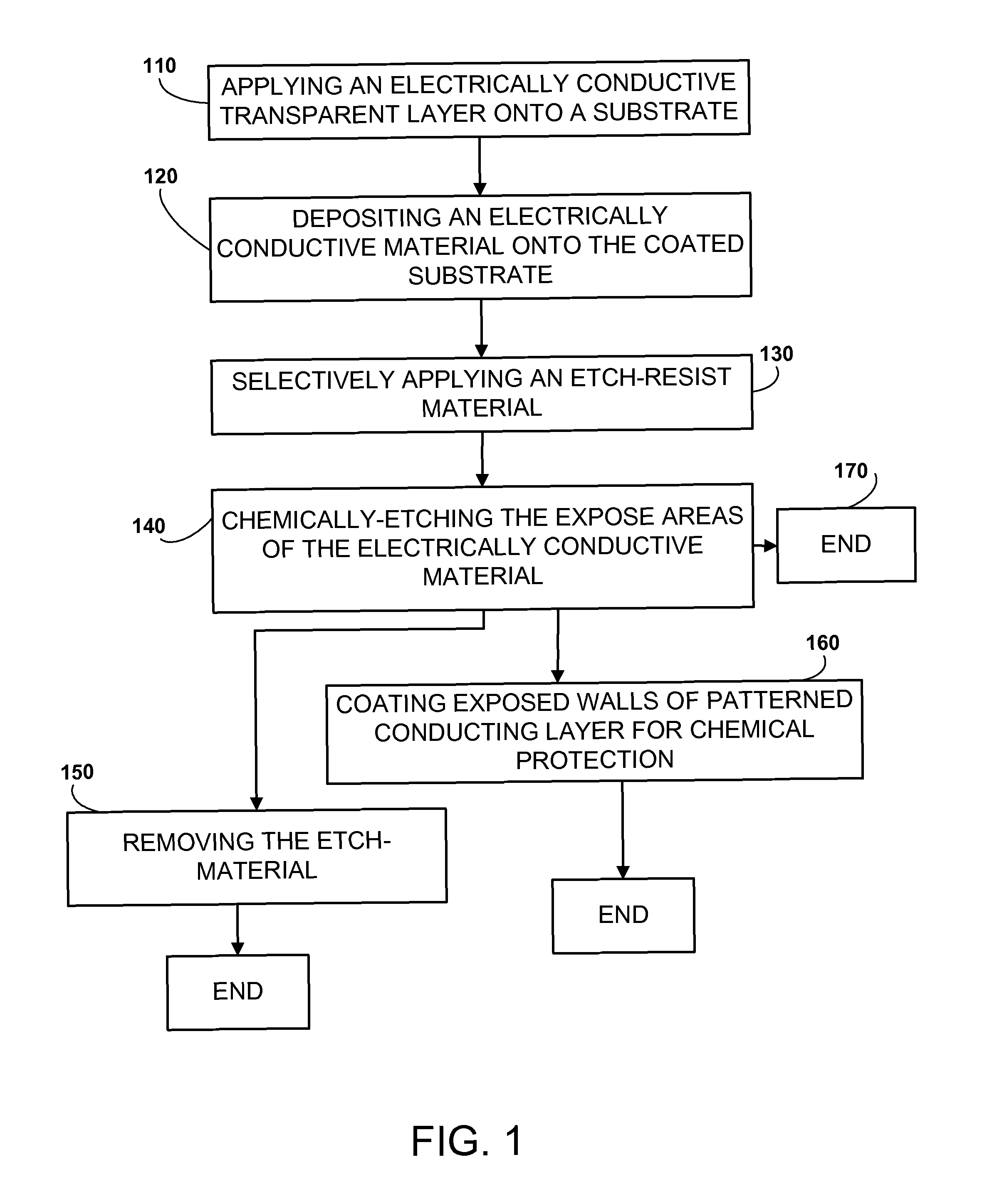

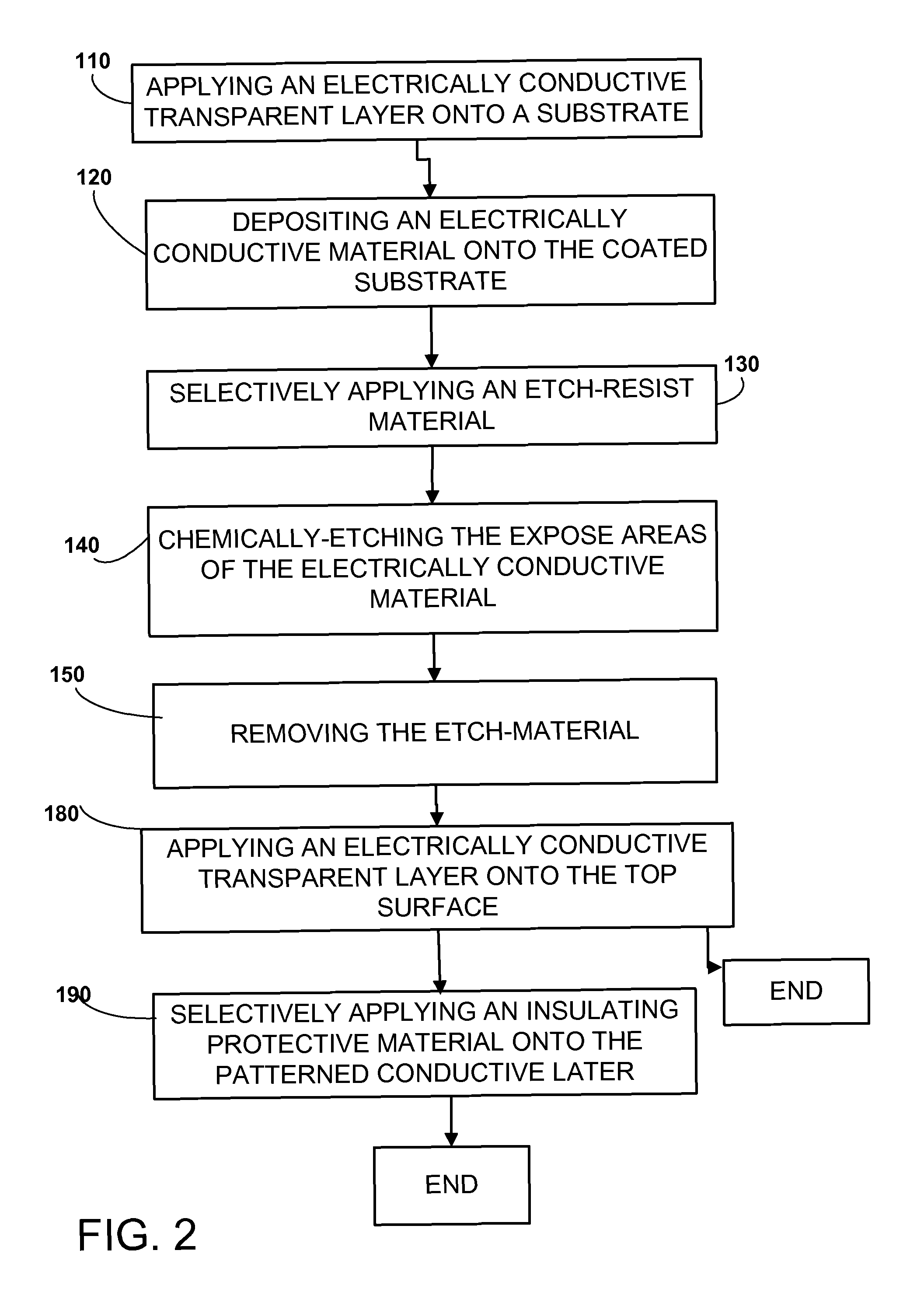

Patterns of conductive objects on a substrate and method of producing thereof

InactiveUS20090293268A1Wave amplification devicesMagnetic/electric field screeningResistConductive materials

According to embodiments of the present invention, a method for manufacturing a pattern of conductive elements on a substrate is provided. The method includes applying a coating layer of electrically conductive transparent compounds onto a substrate; depositing in a vacuum deposition chamber an electrically conductive material onto the coating layer to form an electrically conductive layer; applying an etch-resist material on selective areas of the electrically conductive layer, wherein the selective areas are substantially areas pre-designed to carry the conductive objects; and chemically etching the electrically conductive material from exposed areas of the electrically conductive layer that are not covered by the etch-resist material.

Owner:HANITA COATINGS R C A

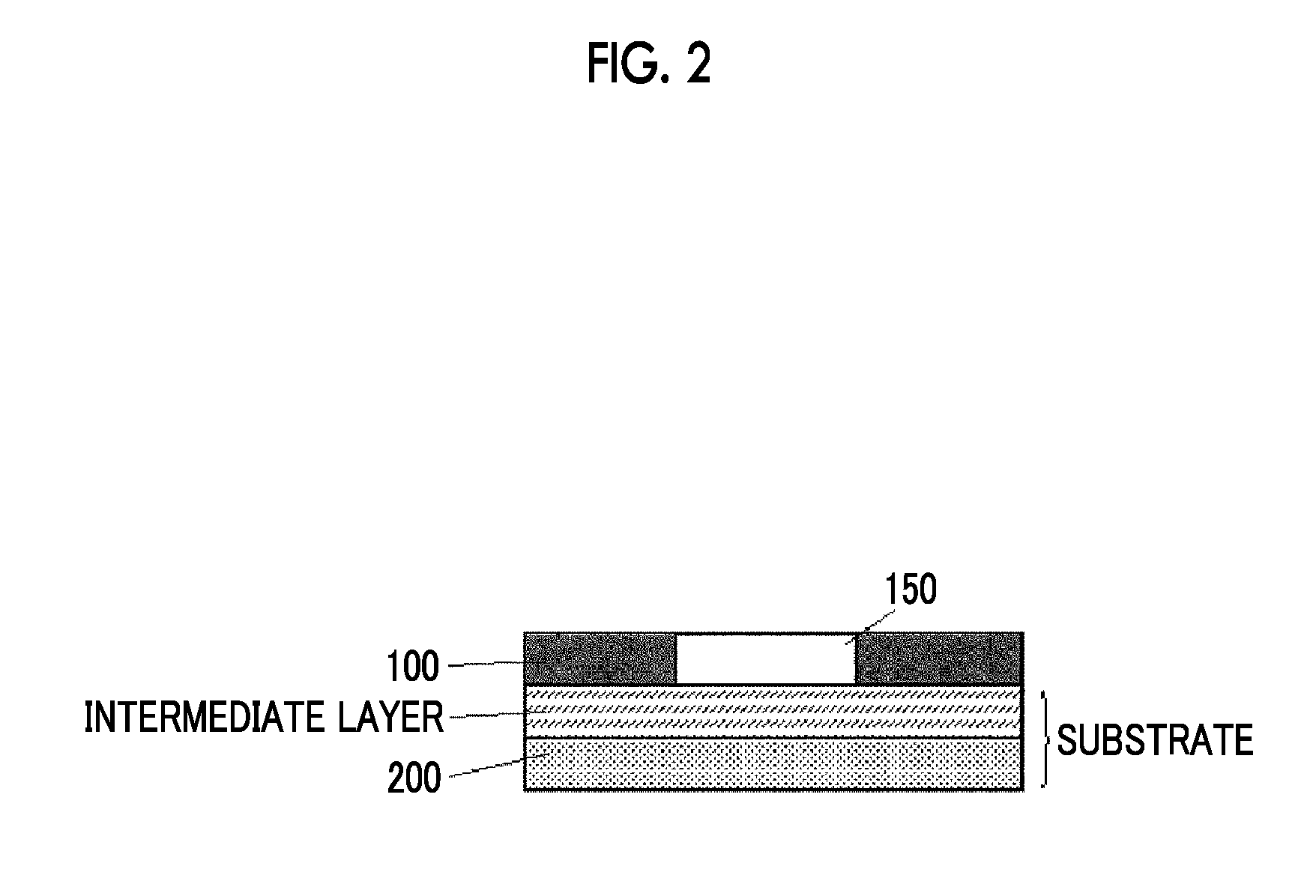

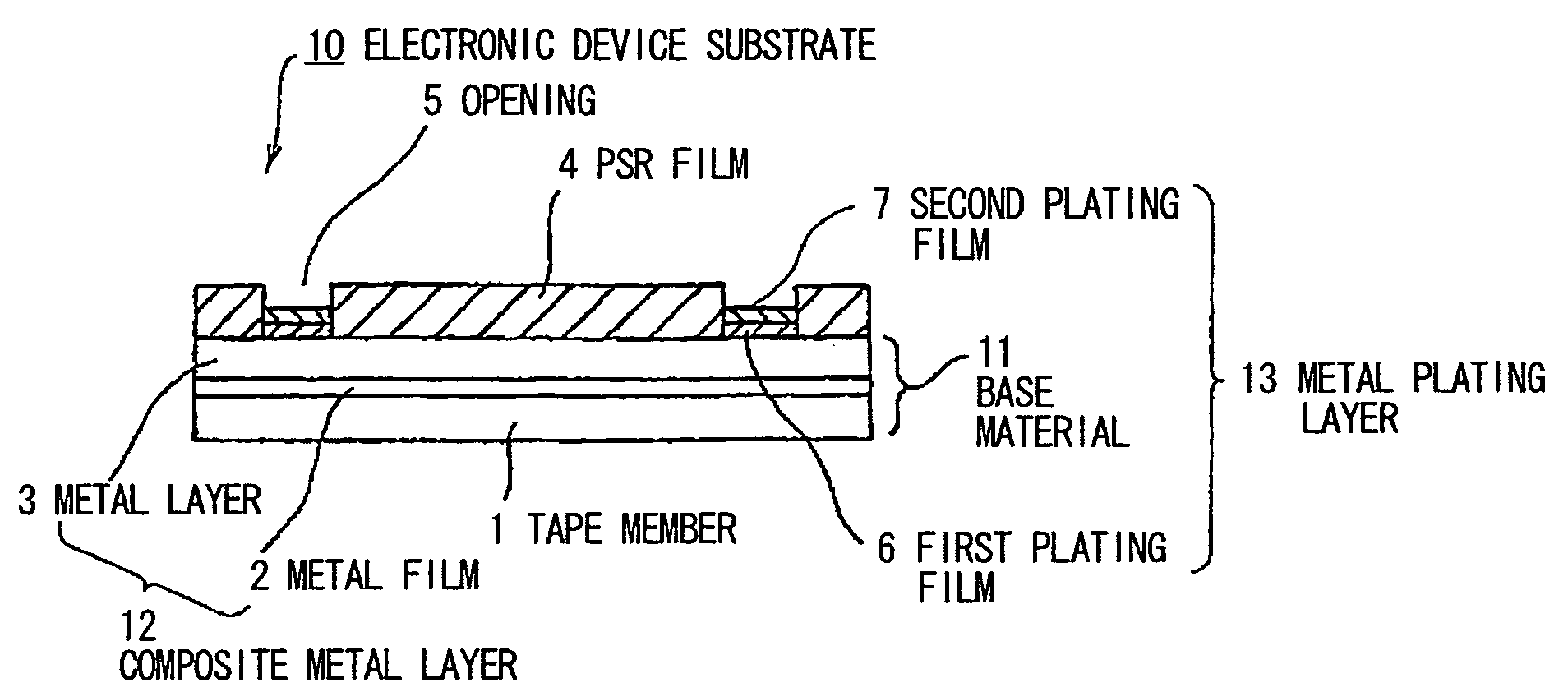

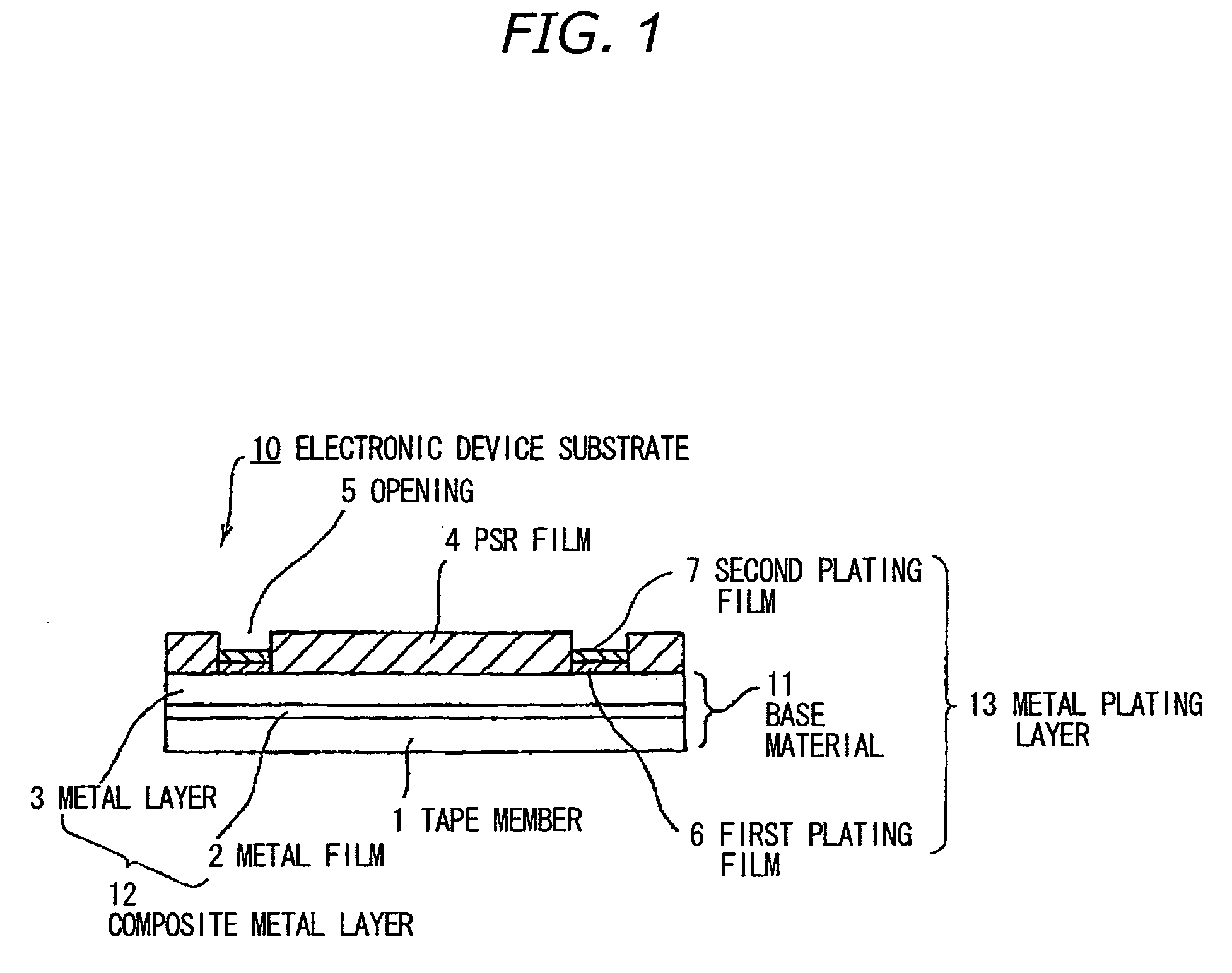

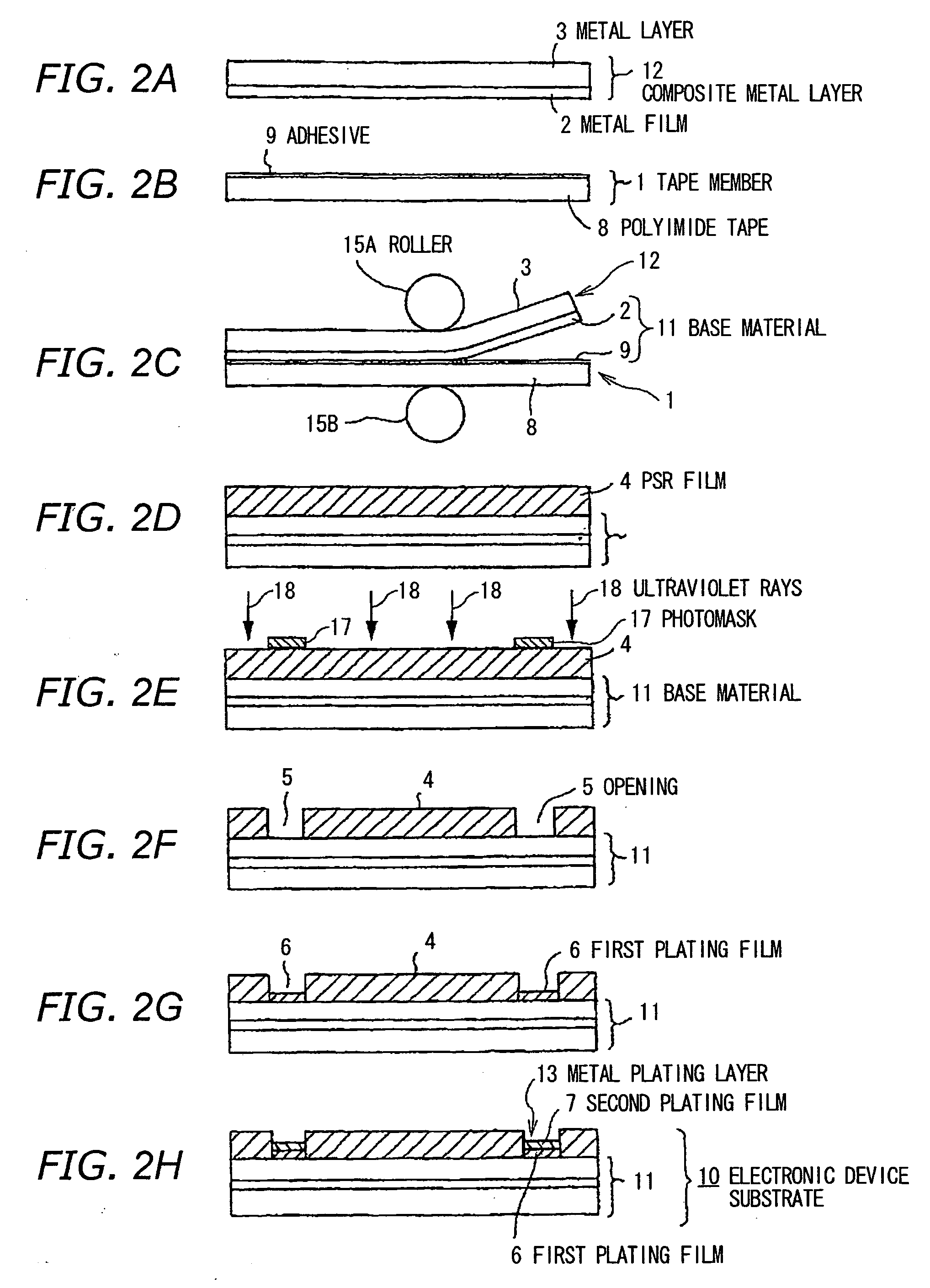

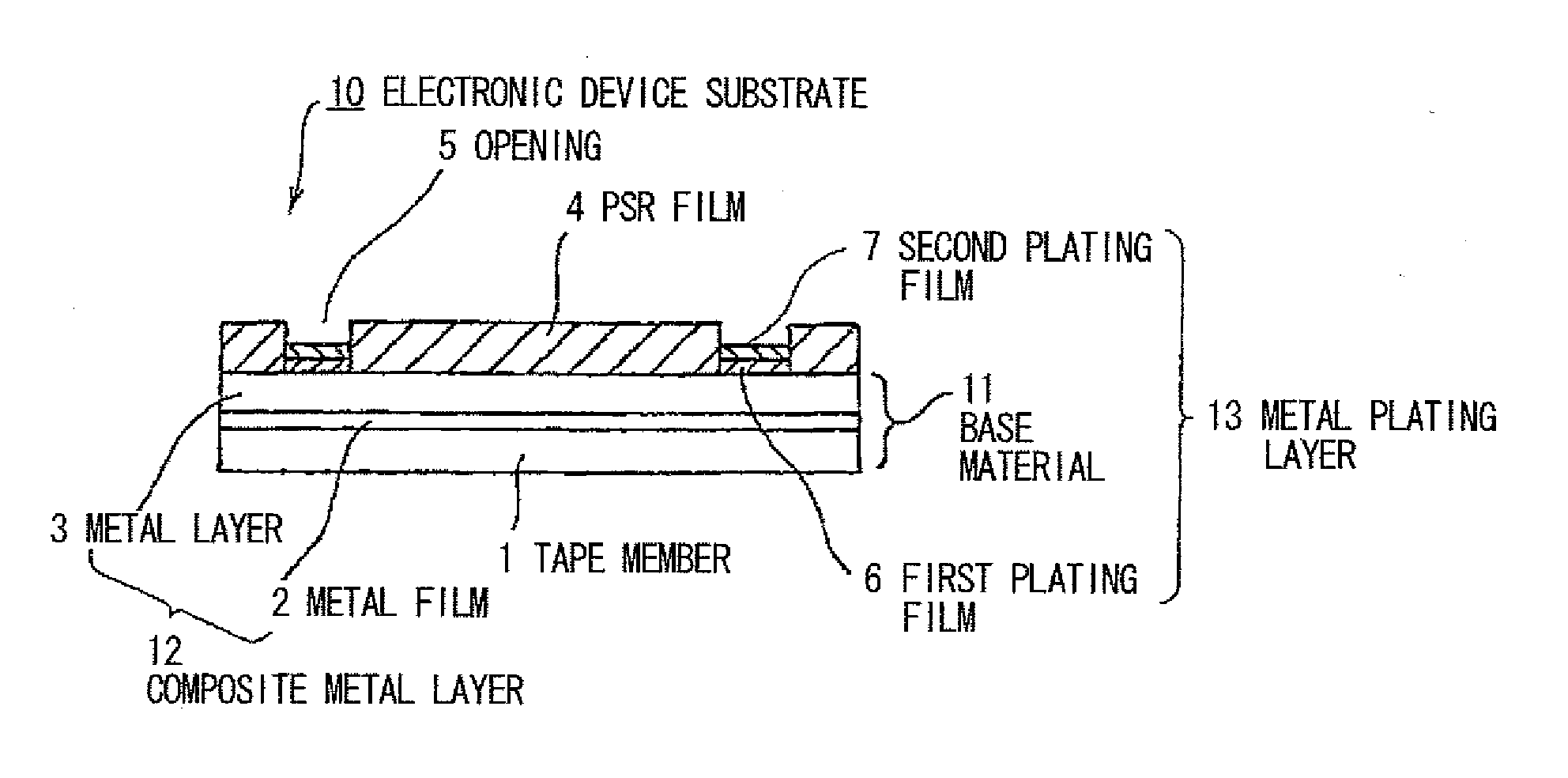

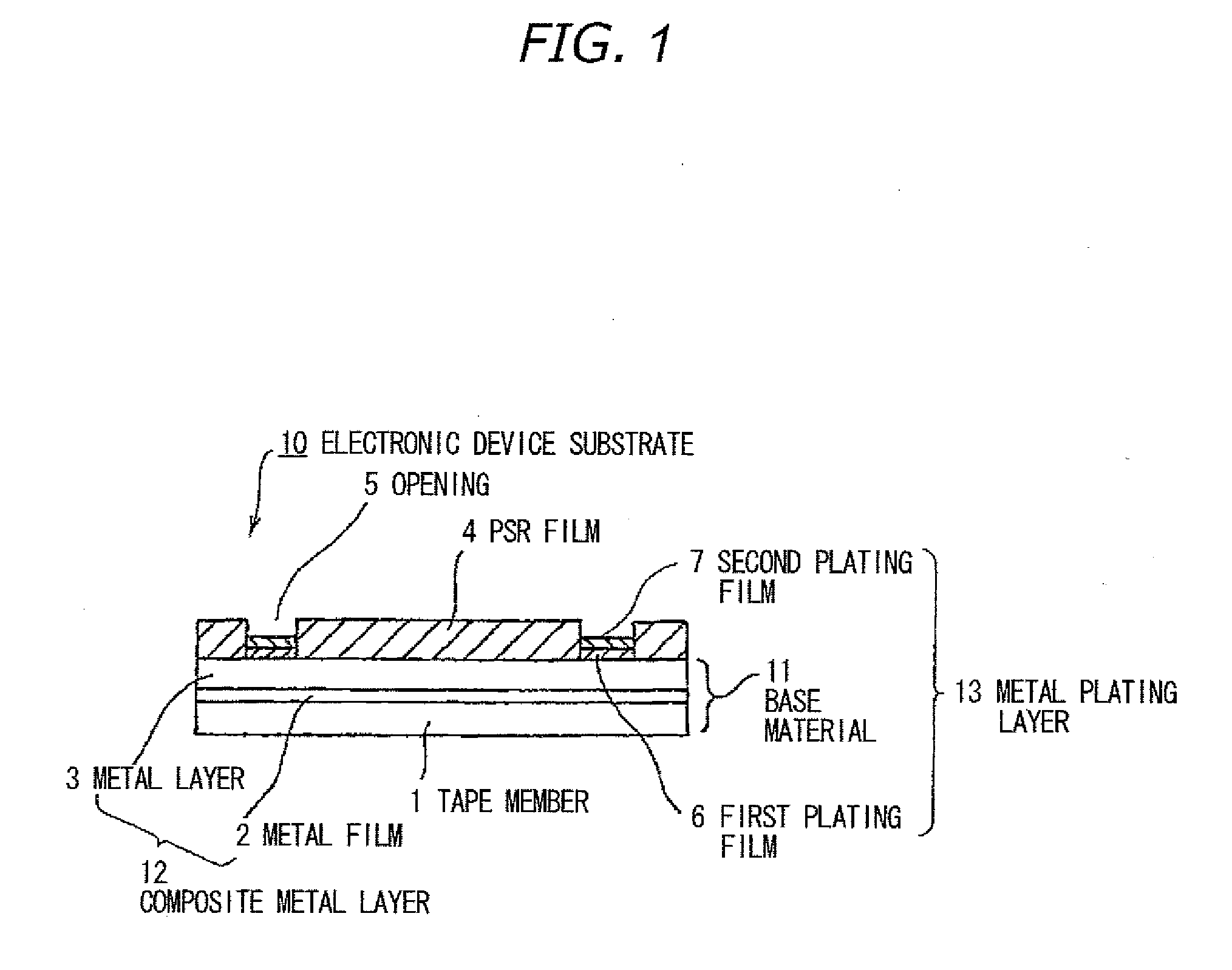

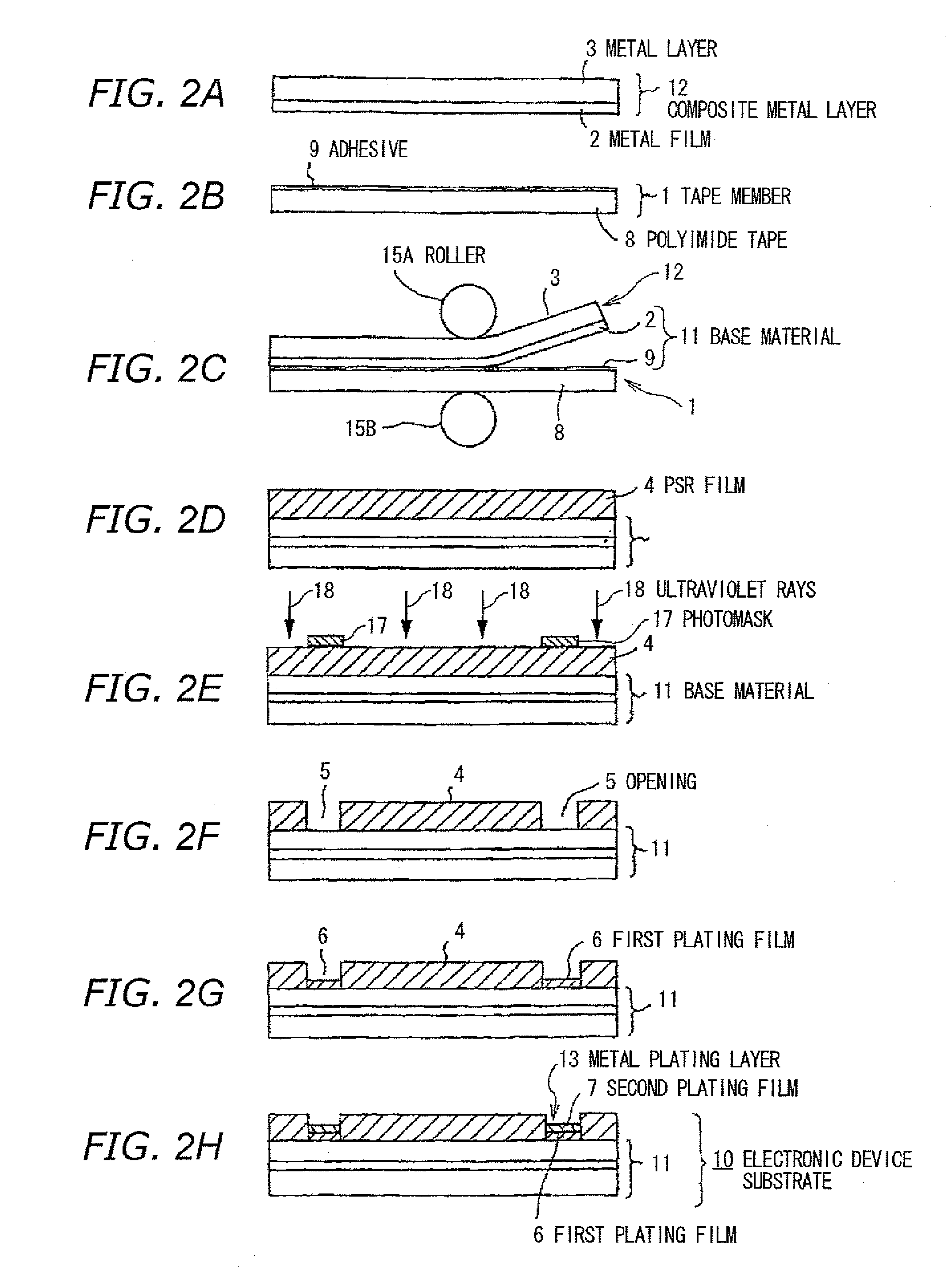

Electronic device substrate, electronic device and methods for making same

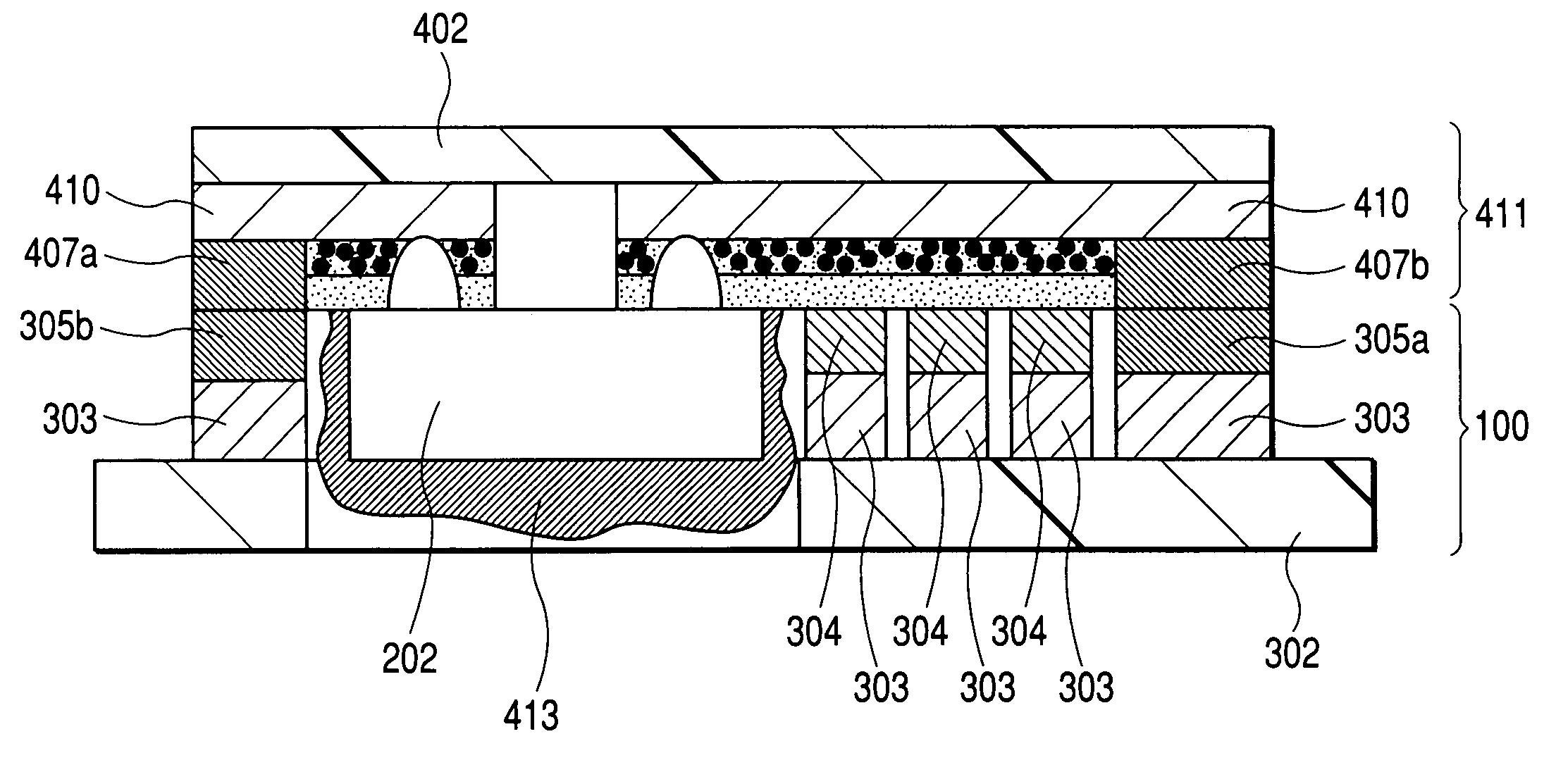

InactiveUS20070269590A1Suppression of increase in mounting areaAvoid crackingSolesPrinted electric component incorporationContact formationInsulation layer

An electronic device substrate having: a base material formed of a thin board; an electrical insulation layer formed on the base material and having plural openings in a thickness direction thereof; and a metal plating layer filled in the plural openings. The base material has a metal layer, a release layer formed contacting the metal layer, and a metal film formed contacting the release layer.

Owner:HITACHI CABLE +1

Post bump and method of forming the same

InactiveUS20090184420A1Avoid flowPrevent deviationSemiconductor/solid-state device detailsPrinted circuit aspectsResistMetallic materials

A post bump and a method of forming the post bump are disclosed. The method of forming the post bump can include: forming a resist layer, in which an aperture is formed in correspondence to a position of an electrode pad, over a substrate, on which the electrode pad is formed; forming a metal post by filling a part of the aperture with a metallic material; filling a remaining part of the aperture with solder; reflowing the solder by applying heat; and removing the resist layer. This method can be utilized to prevent deviations in the plated solder and prevent the unnecessary flowing of the solder over the sides of the metal post during reflowing, so that the amount of solder used can be minimized.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

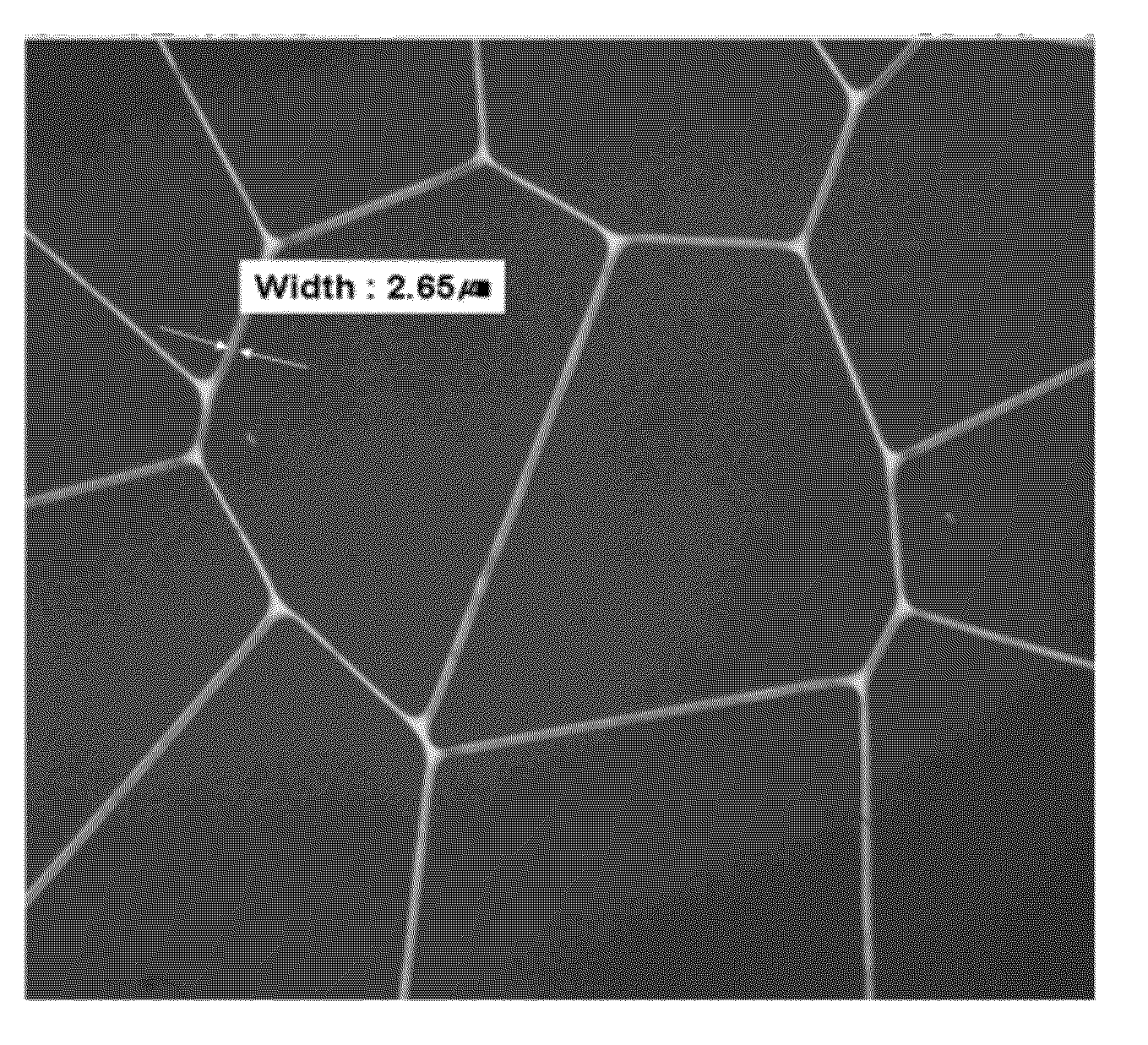

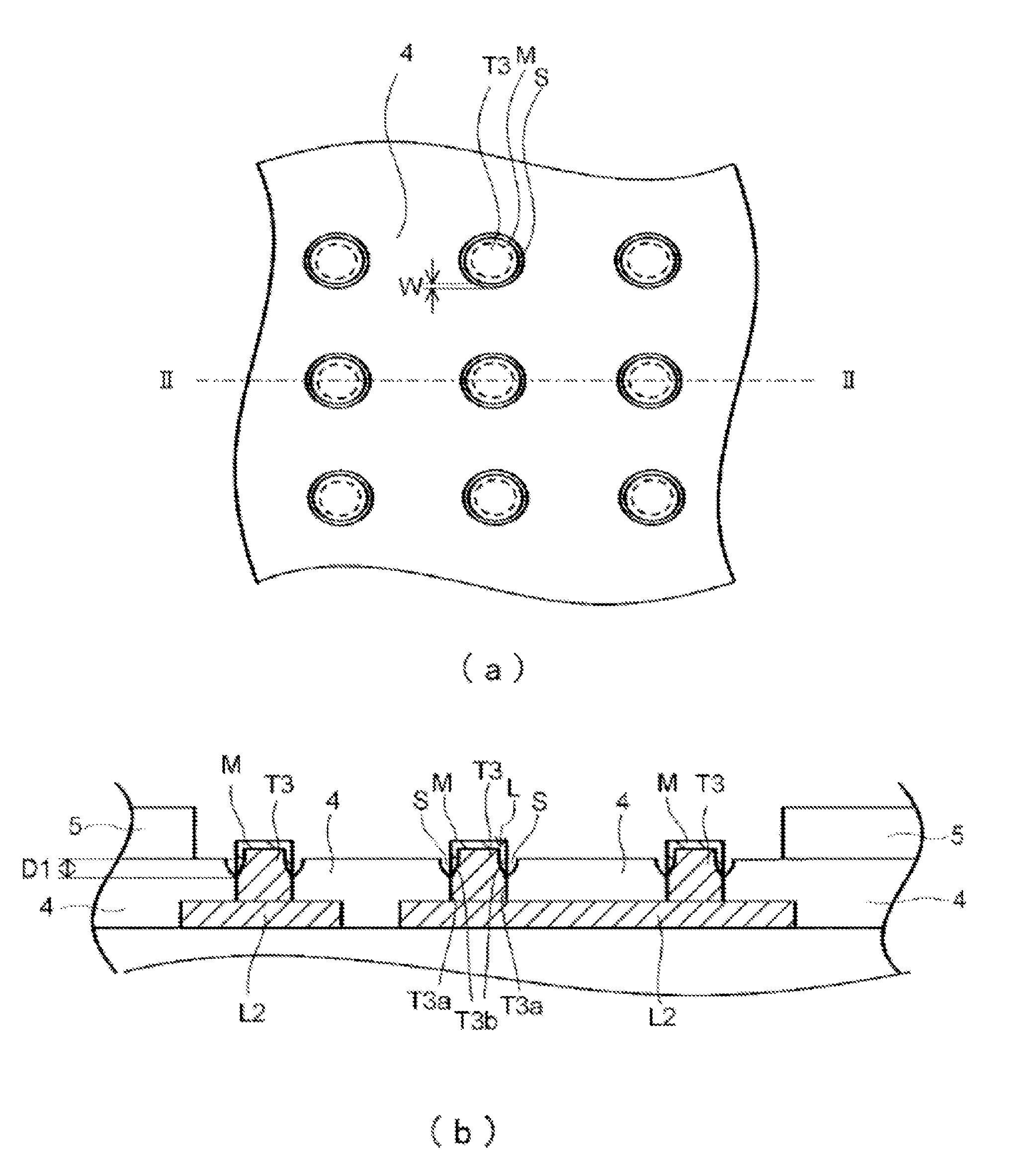

Conductive pattern and manufacturing method thereof

ActiveUS20120031647A1Thin line widthEasy to implementDual purpose resistPhotosensitive material processingResistElectrically conductive

The present invention provides a method for manufacturing a conductive pattern, comprising the steps of: a) forming a conductive film on a substrate; b) forming an etching resist pattern on the conductive film; and c) forming a conductive pattern having a smaller line width than a width of the etching resist pattern by over-etching the conductive film by using the etching resist pattern, and a conductive pattern manufactured by using the same. According to the exemplary embodiment of the present invention, it is possible to effectively and economically provide a conductive pattern having a ultrafine line width.

Owner:LG CHEM LTD

Method of forming buried wiring lines, and substrate and display device using the same

InactiveUS20080239680A1Improve the immunityReduce level differencePrinted circuit aspectsDual purpose resistNanometreCorrosion

An method of forming buried wiring lines makes it possible not to limit usable materials for an insulative plate to those having excellent heat resistance and to improve the corrosion resistance of the terminals provided for the buried wiring lines. The surface of an insulative plate is selectively etched using a mask formed on the surface, thereby forming grooves in the surface. A metallic nanoparticle ink is placed over the whole surface of the plate to fill the grooves with the ink, where the mask is being left. The ink is heated for preliminary curing to form a metallic nanoparticle ink film. The part of the film placed on the mask is selectively removed by detaching the mask, thereby leaving the remainder of the film in the grooves. The remaining film in the grooves is heated for main curing, thereby forming desired buried wiring lines.

Owner:NEC LCD TECH CORP

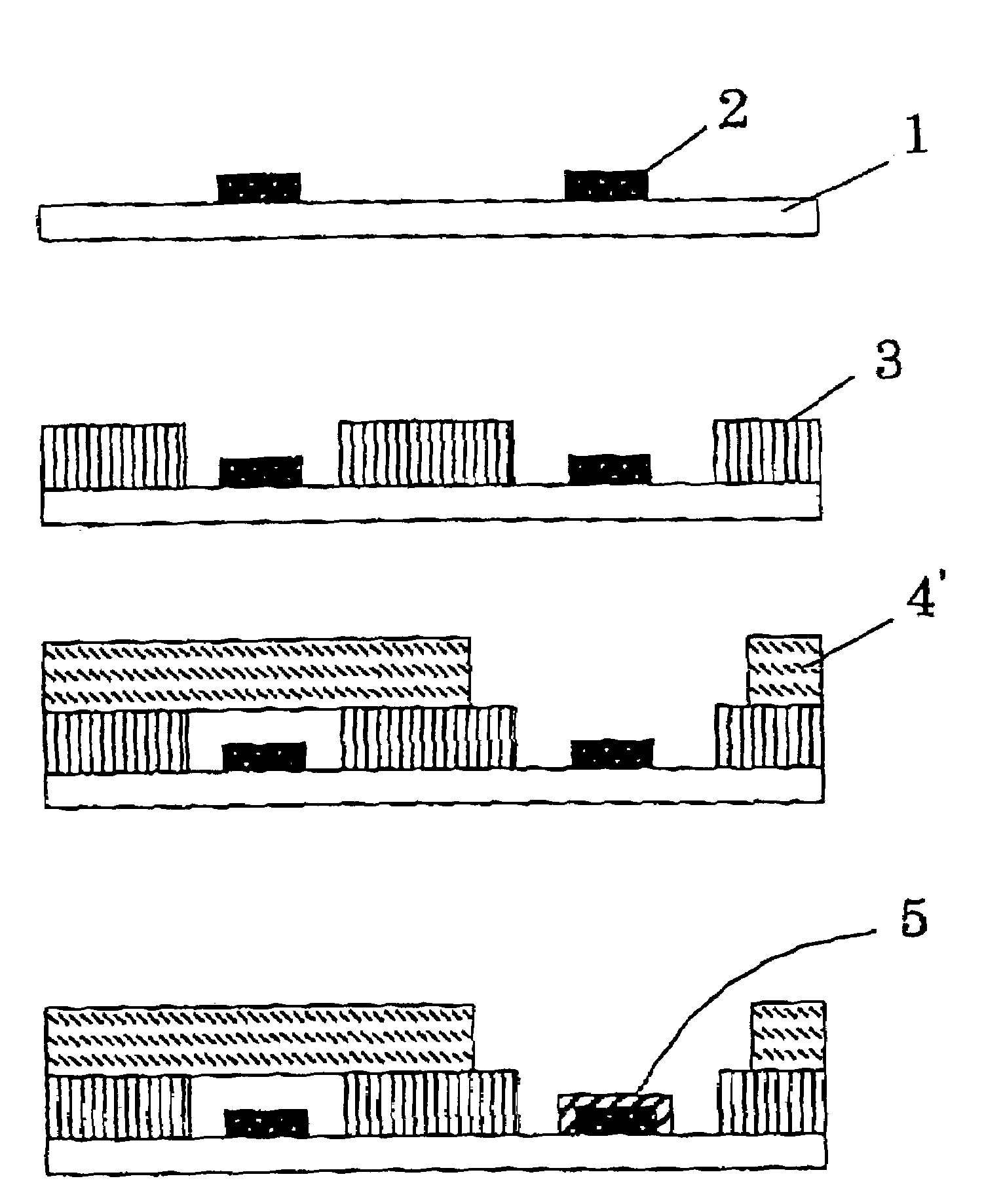

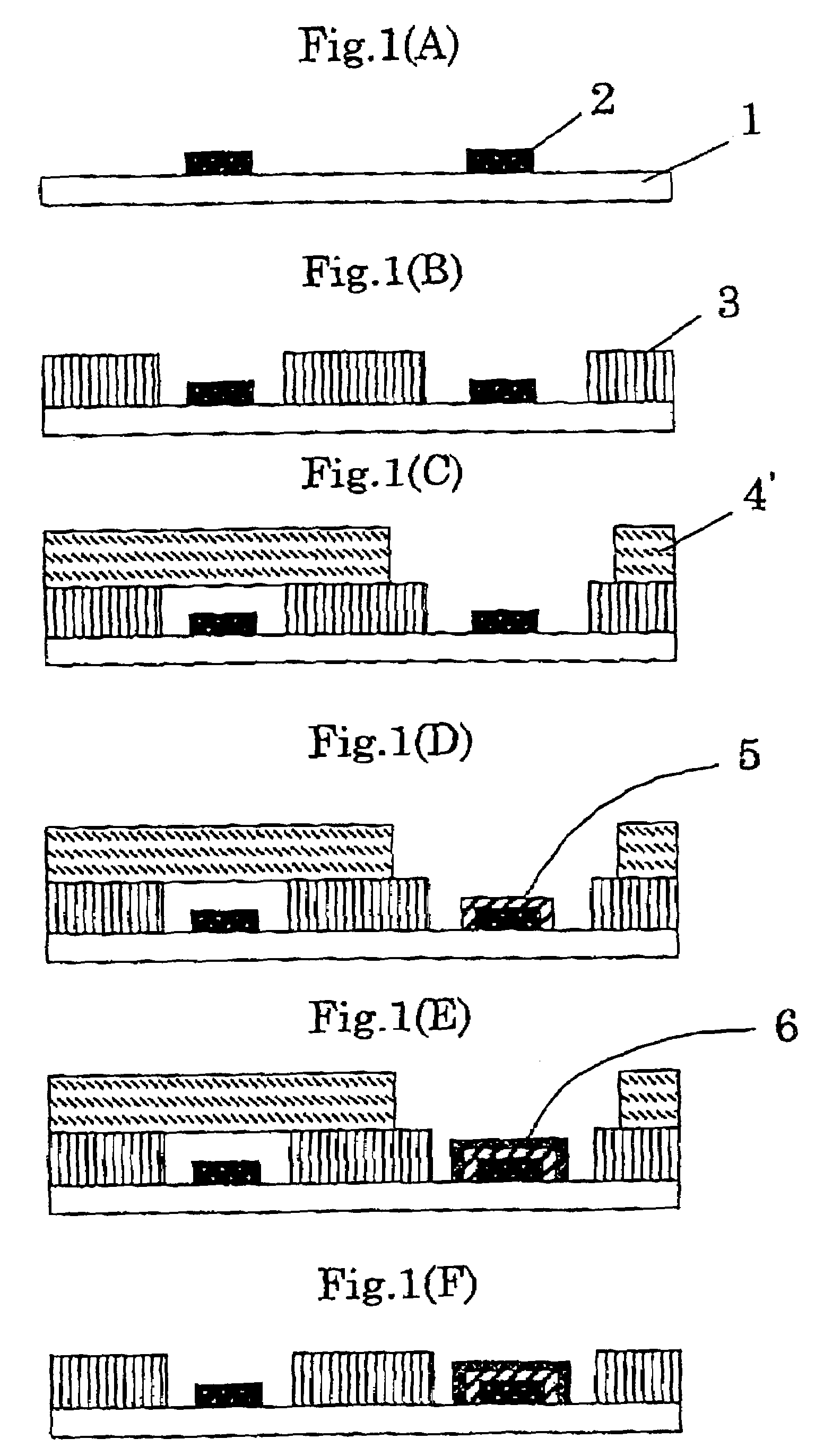

Manufacturing method for electronic component module and electromagnetically readable data carrier

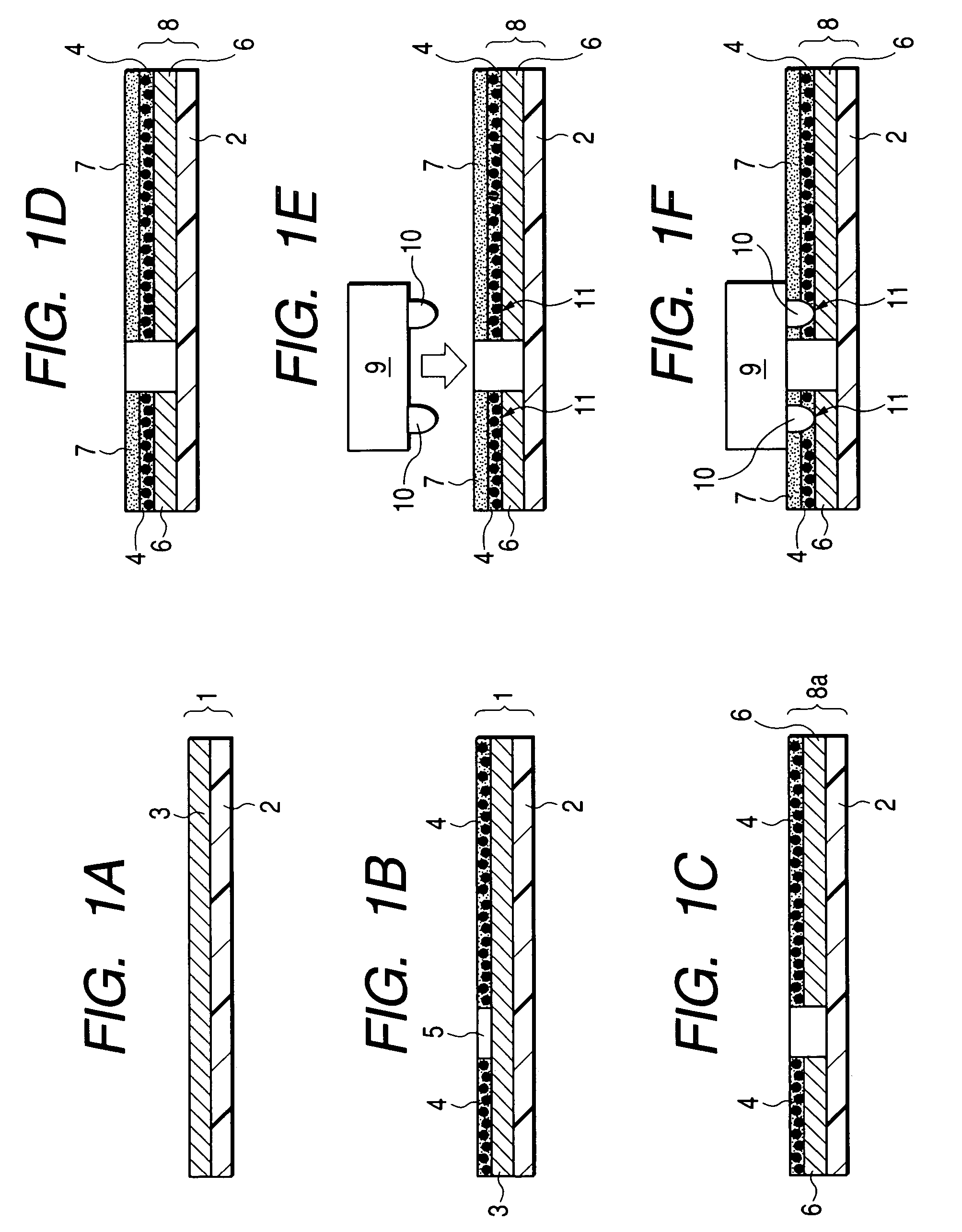

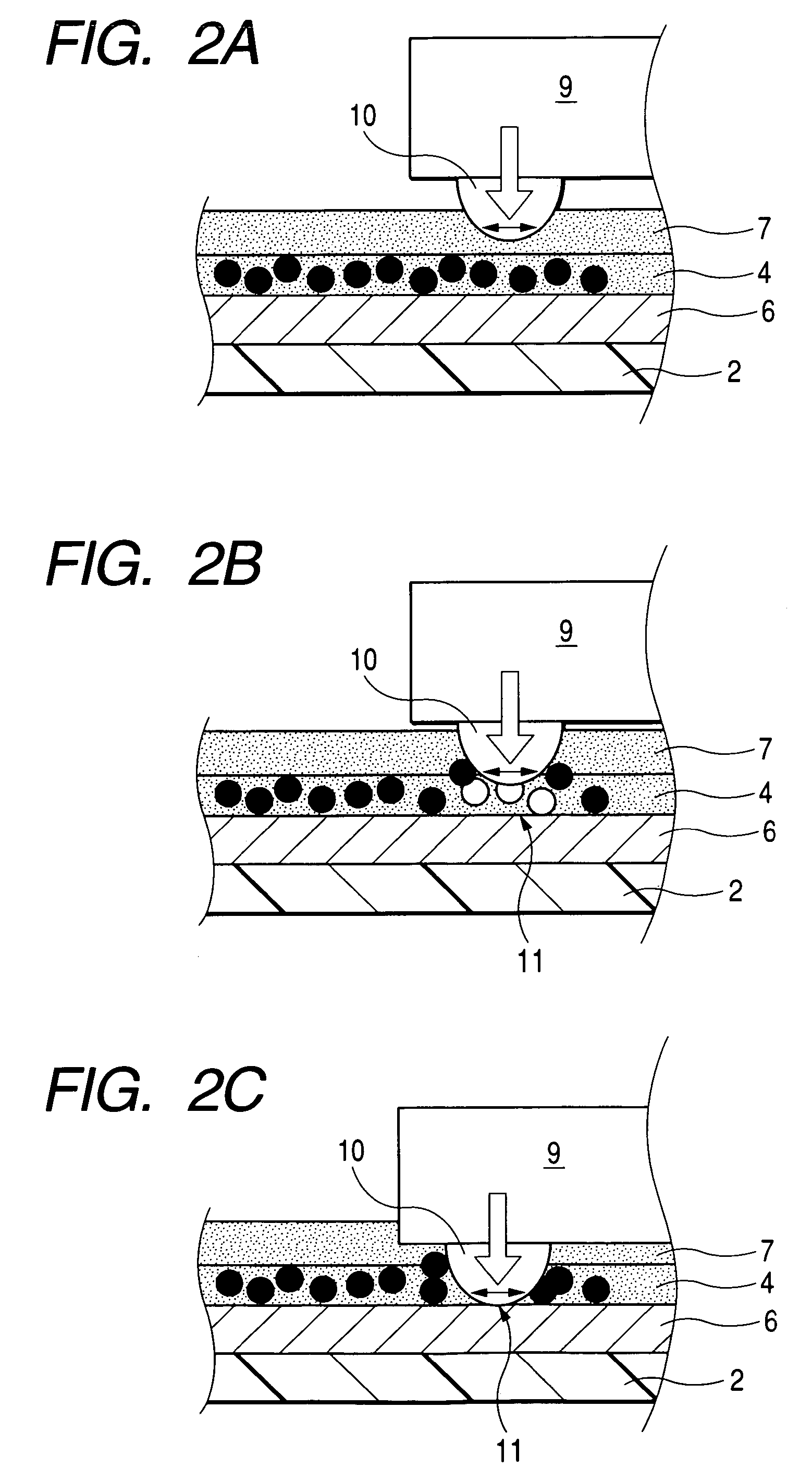

InactiveUS20040112636A1Low costPrevent a short-circuit from occurringPrinted circuit assemblingSemiconductor/solid-state device detailsThermoplasticComputer module

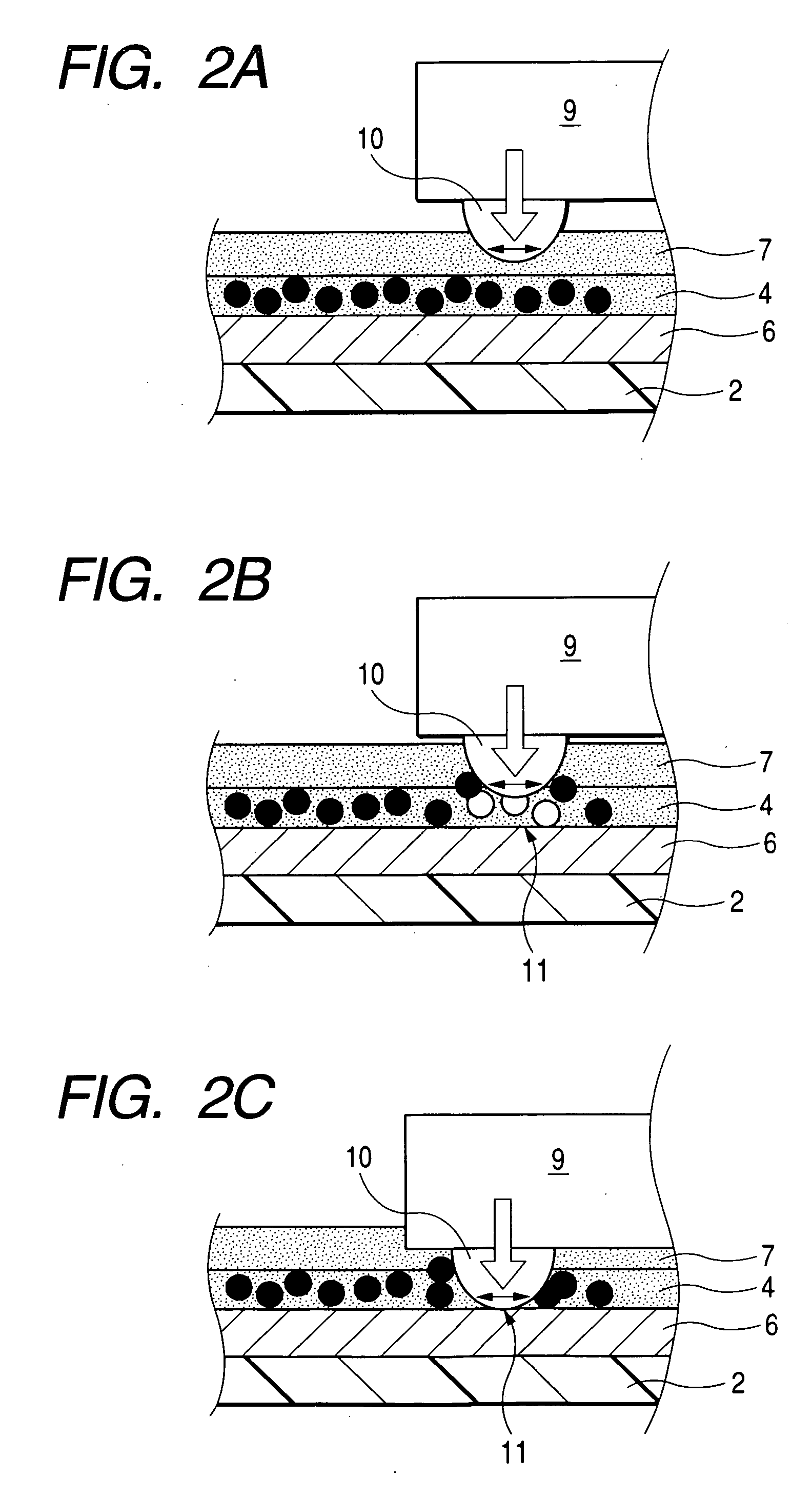

A semiconductor bear chip having a bump subjected to high temperatures is pressed, from the upper side, onto a wiring board including a wiring pattern, a thermosetting resin film covering an electrode area on the wiring pattern and having insulating particles dispersed and included and a thermoplastic resin film covering the thermosetting resin film, while applying a ultrasonic wave, thereby inserting the bumps of the semiconductor bear chip through the thermoplastic resin film and the thermosetting resin film to bond the top end portion of the bump with the electrode area.

Owner:ORMON CORP

Manufacturing method for electronic component module and electromagnetically readable data carrier

InactiveUS7276436B2Printed circuit assemblingSemiconductor/solid-state device detailsThermoplasticComputer module

A semiconductor bear chip having a bump subjected to high temperatures is pressed, from the upper side, onto a wiring board including a wiring pattern, a thermosetting resin film covering an electrode area on the wiring pattern and having insulating particles dispersed and included and a thermoplastic resin film covering the thermosetting resin film, while applying a ultrasonic wave, thereby inserting the bumps of the semiconductor bear chip through the thermoplastic resin film and the thermosetting resin film to bond the top end portion of the bump with the electrode area.

Owner:ORMON CORP

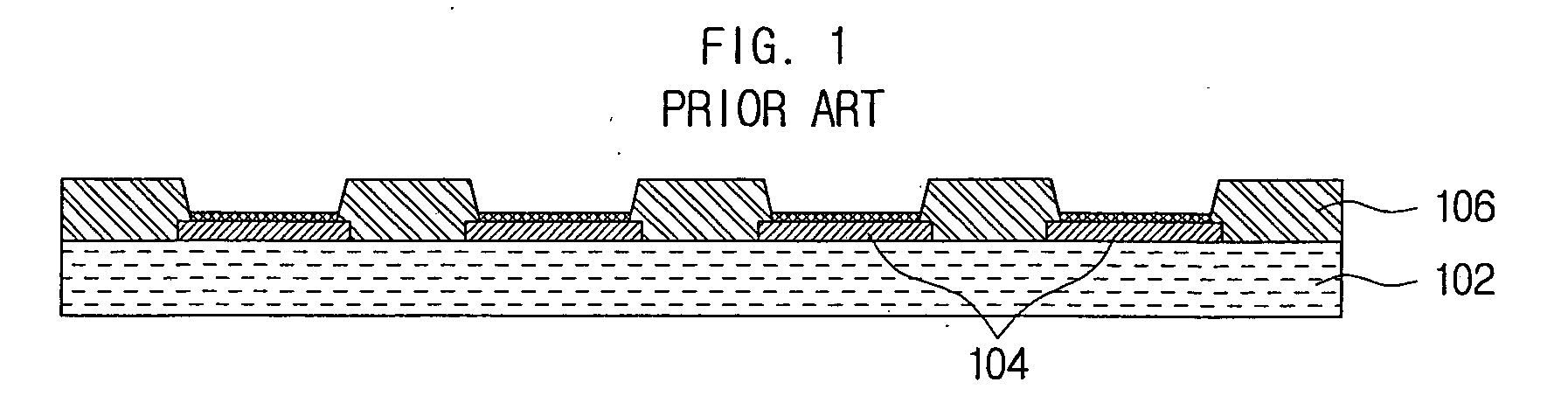

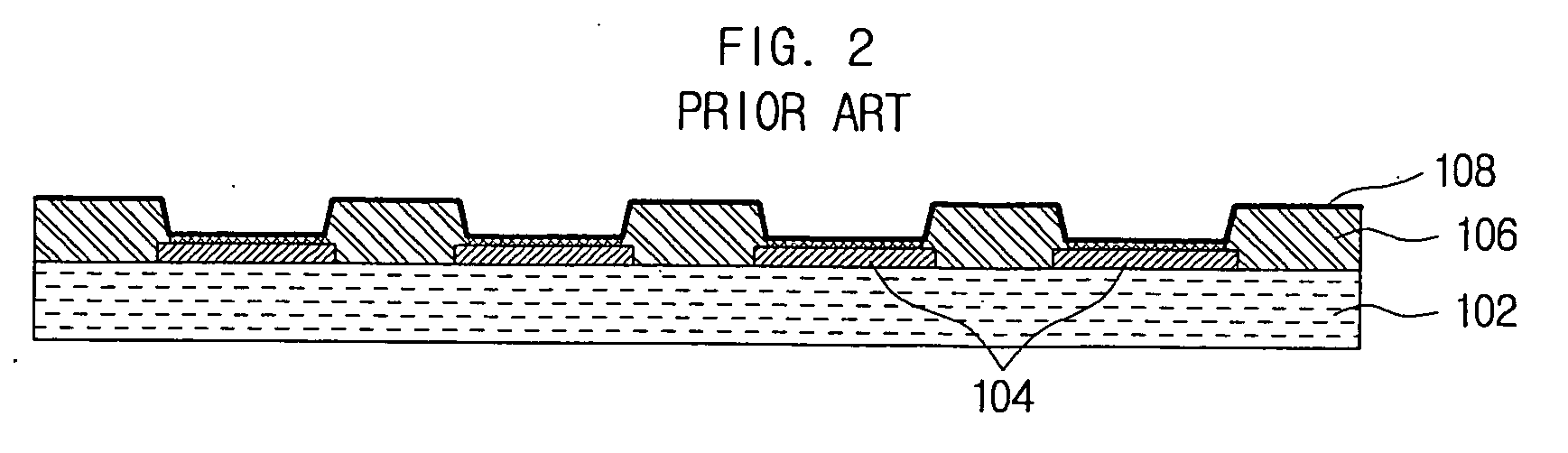

Method for mfg. printed wiring board and photosenstive resin compsn. to be used for it

InactiveCN1500232AExcellent plating resistanceExcellent peelabilitySecond resist patternStacked resist layersResistSolder mask

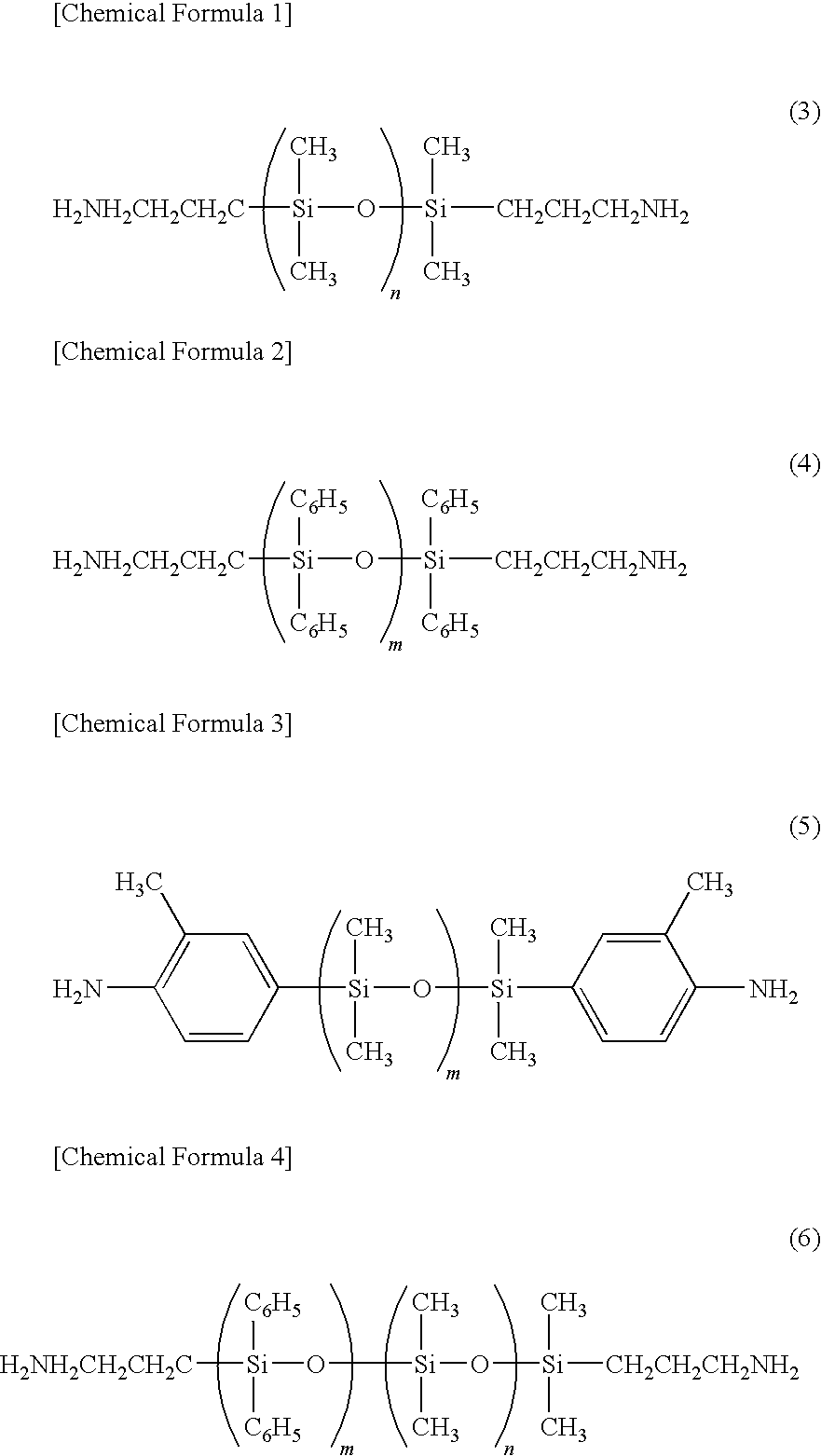

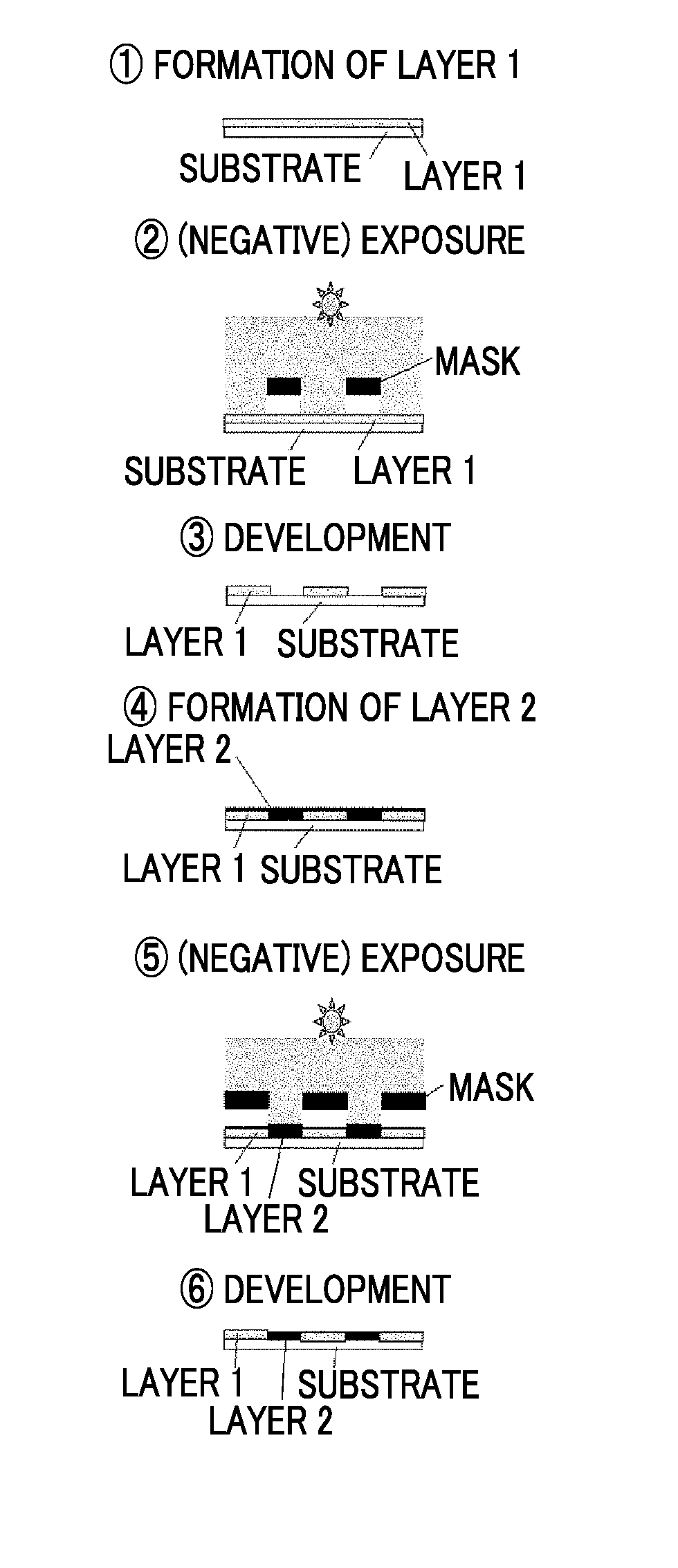

An object of the present invention is to provide a process for producing a printed wiring board, which is advantageous not only in that the reduction in size and increase in density of the wiring board are achieved and further the steps are simplified, but also in that the connection reliability of mount parts and the yield are improved, and a photosensitive resin composition used in the process. The present invention is directed to a process for producing a printed wiring board, comprising the steps of: (i) forming a solder resist on a wiring board having a circuit; (ii) laminating a preliminarily molded layer of a photosensitive resin composition on the solder resist; (iii) subjecting the layer of the photosensitive resin composition to exposure and development to form a resist pattern of the photosensitive resin composition; (iv) subjecting the entire surface of the resultant board to electroless plating, and (v) stripping the layer of the photosensitive resin composition, wherein the steps are conducted in this order, as well as a photosensitive resin composition and the layer thereof used in the process.

Owner:RESONAC CORPORATION

Method for fabricating a packaging substrate

ActiveUS6930044B1Low costAvoid damageSemiconductor/solid-state device manufacturingDual purpose resistResistCopper plating

A method for making a packaging substrate is provided. A thin copper seed layer is formed on a carrier plate. A first resist layer is coated on the thin copper seed layer. The first resist layer defines a wire layout of copper plating area. A layer of copper is then electroplated on the copper plating area to form the wire layout. After this, the first resist layer is stripped to expose the wire layout and the thin copper seed layer. A patterned second resist layer is formed on the wire layout. The patterned second resist layer defines the Ni / Au plating area of the wire layout. The copper seed layer that is not covered by the second resist layer is etched away. A third resist layer is stacked on the second resist layer and defines an Au-plating area of the I / O fingers. Using the third resist layer as a plating hard mask, a layer of Ni / Au layer is plated on the exposed area of the wires. After this step, the second and third resist layers are removed.

Owner:NAN YA PRINTED CIRCUIT BOARD CORPORATION

Printed wiring board and method of manufacturing the same

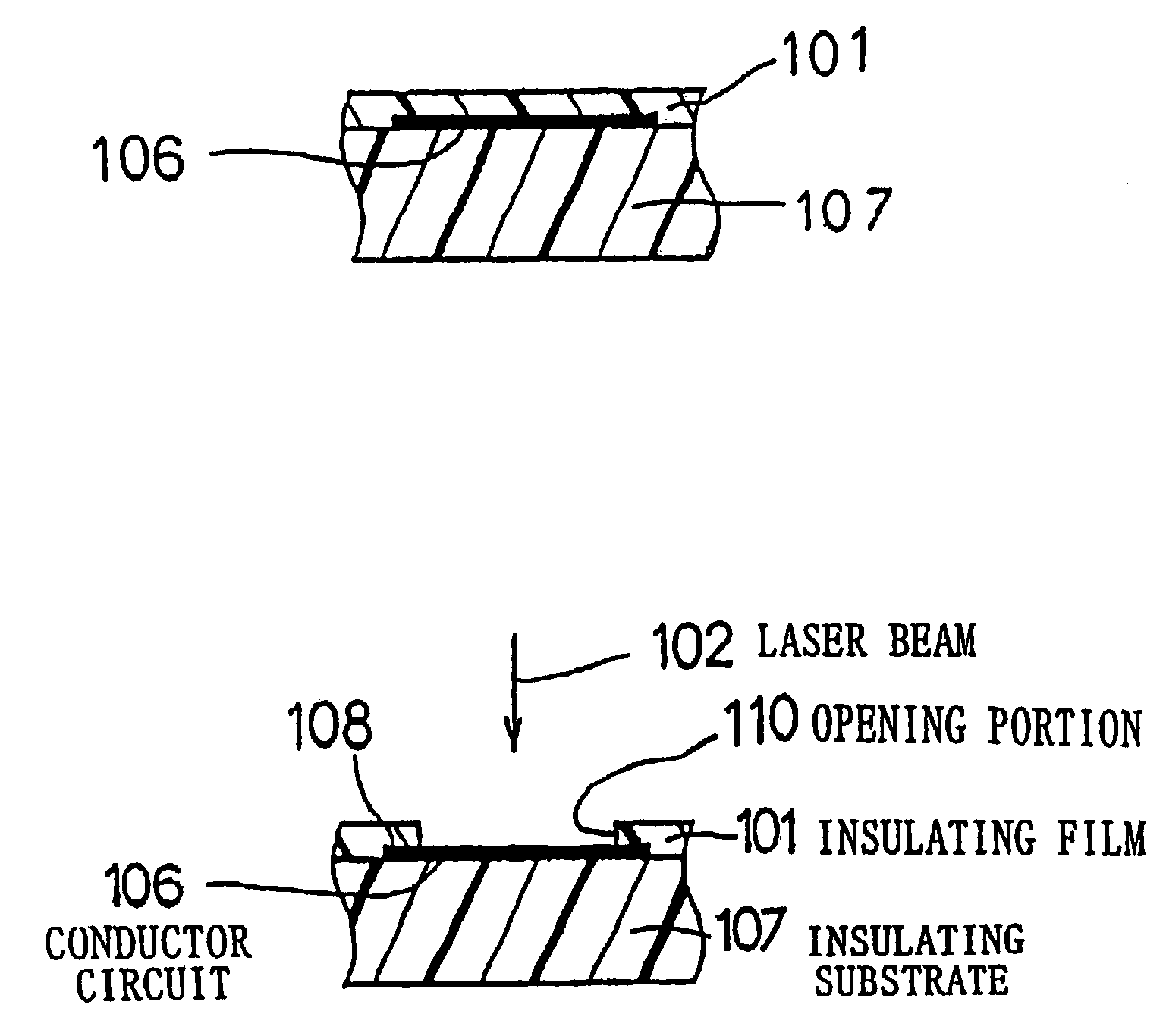

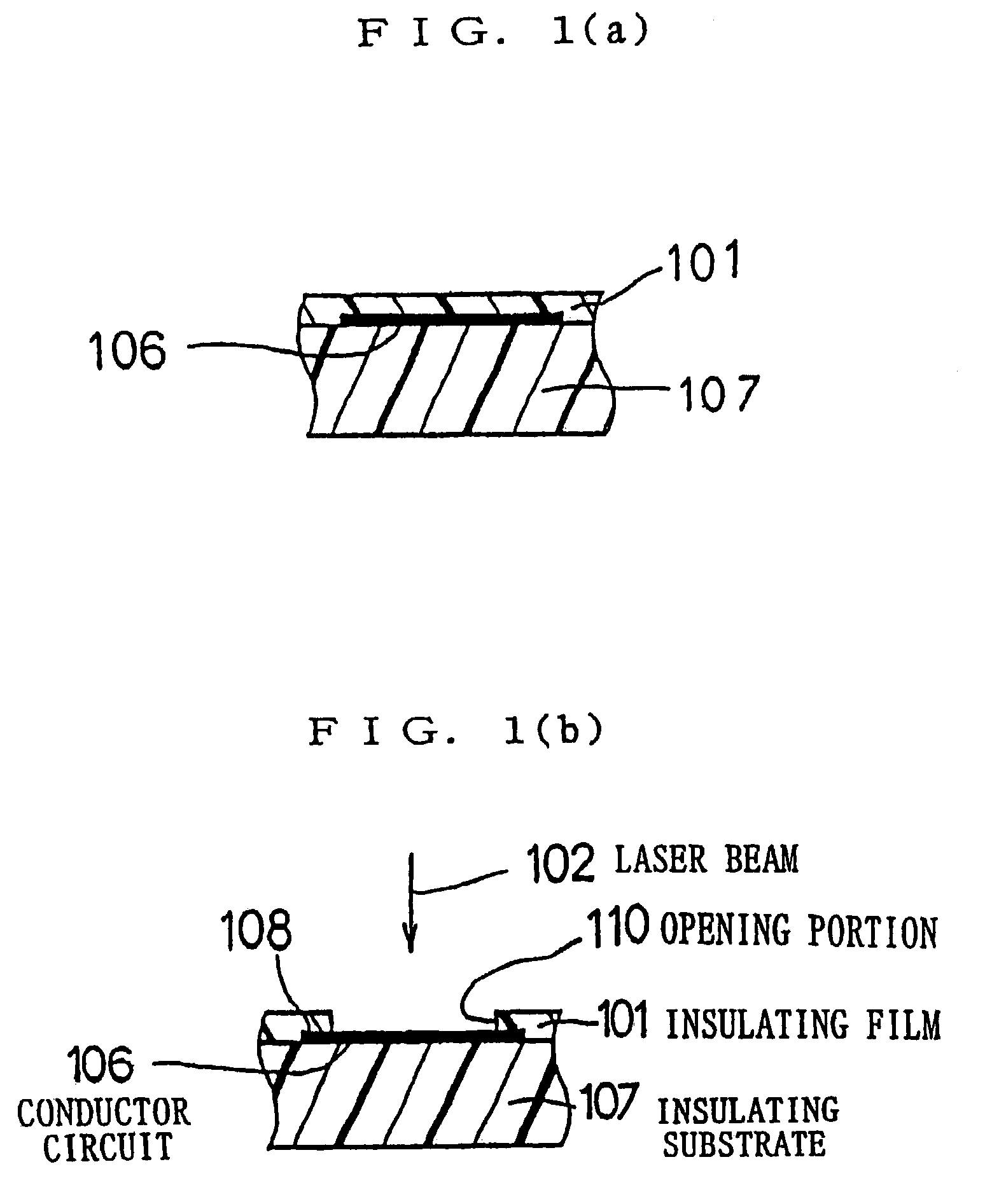

InactiveUS6986917B2Generation of stress of the solder resist is reducedConductor circuit is improvedDecorative surface effectsSemiconductor/solid-state device detailsResistElectrical conductor

A solder resist comprising a thermosetting resin is printed on a surface of an insulating board (7) having a conductor circuit (6). The solder resist is then heat-cured to form an insulating film (1) having a low thermal expansion coefficient. A laser beam (2) is then applied to the portion of the insulating film in which an opening is to be formed, to burn off the same portion for forming an opening (10), whereby the conductor circuit (6) is exposed. This opening may be formed as a hole for conduction by forming a metal plating film on an inner surface thereof. It is preferable that an external connecting pad be formed so as to cover the opening. The film of coating of a metal is formed by using an electric plating lead, which is preferably cut off by a laser beam after the electric plating has finished.

Owner:IBIDEN CO LTD

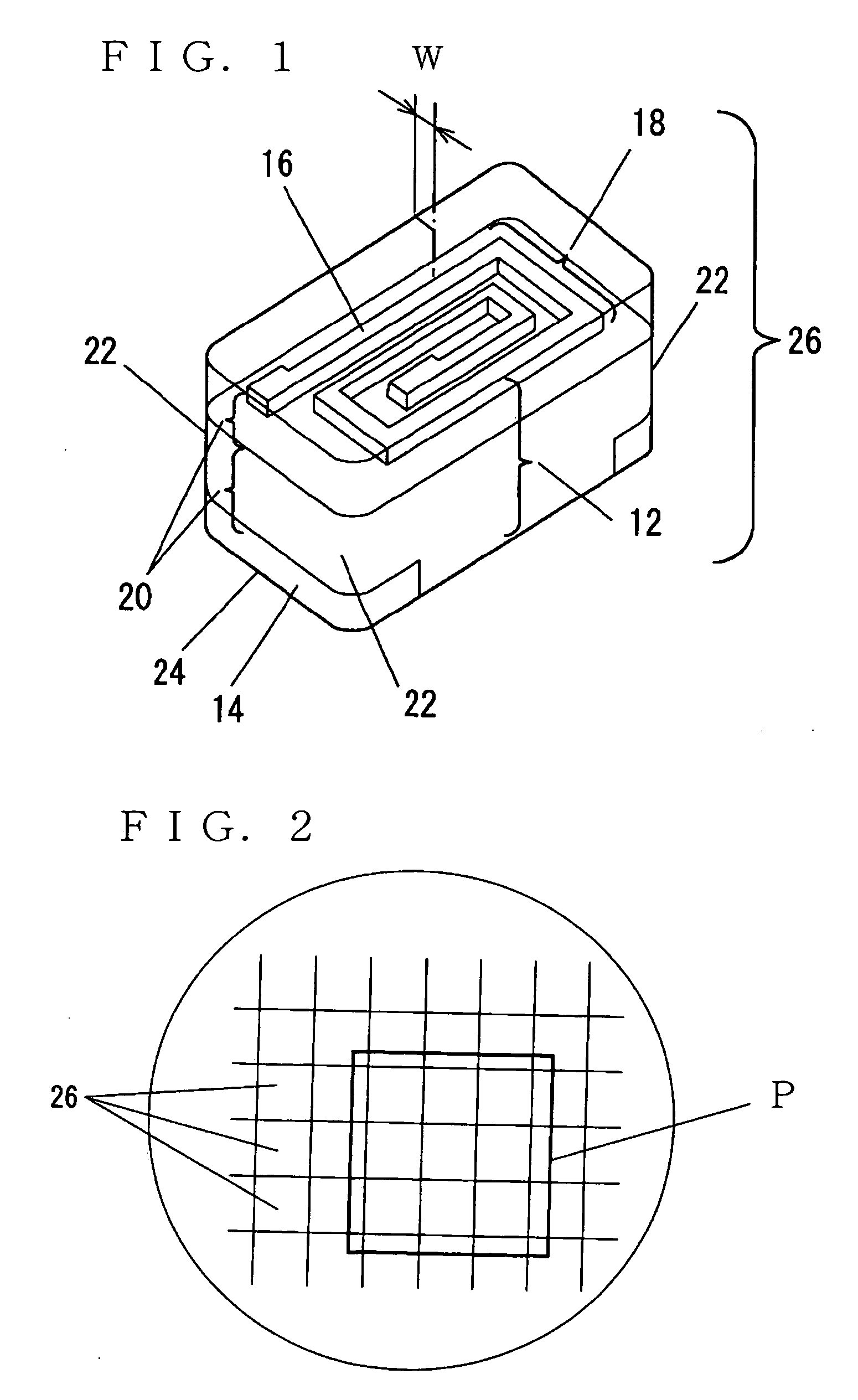

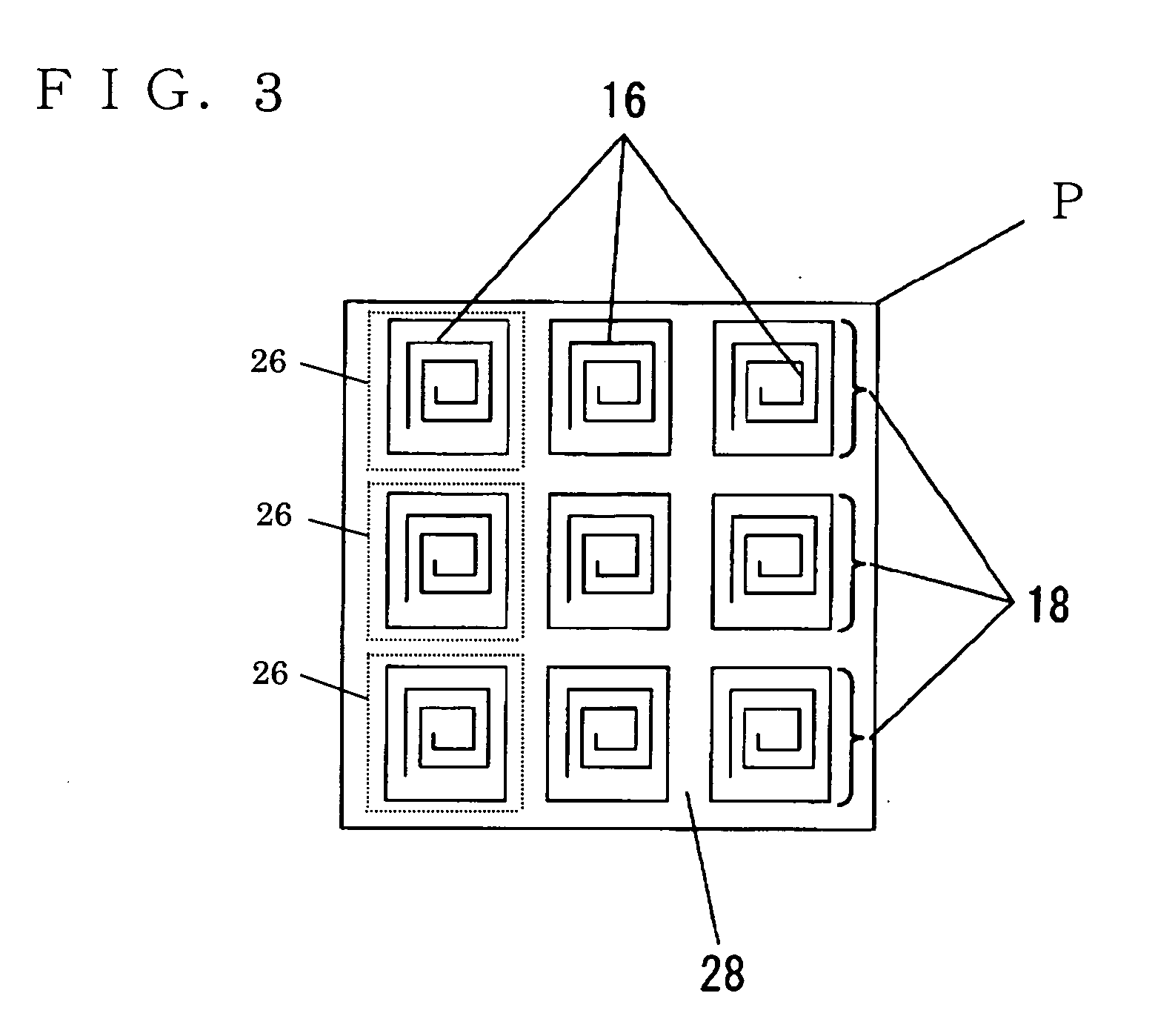

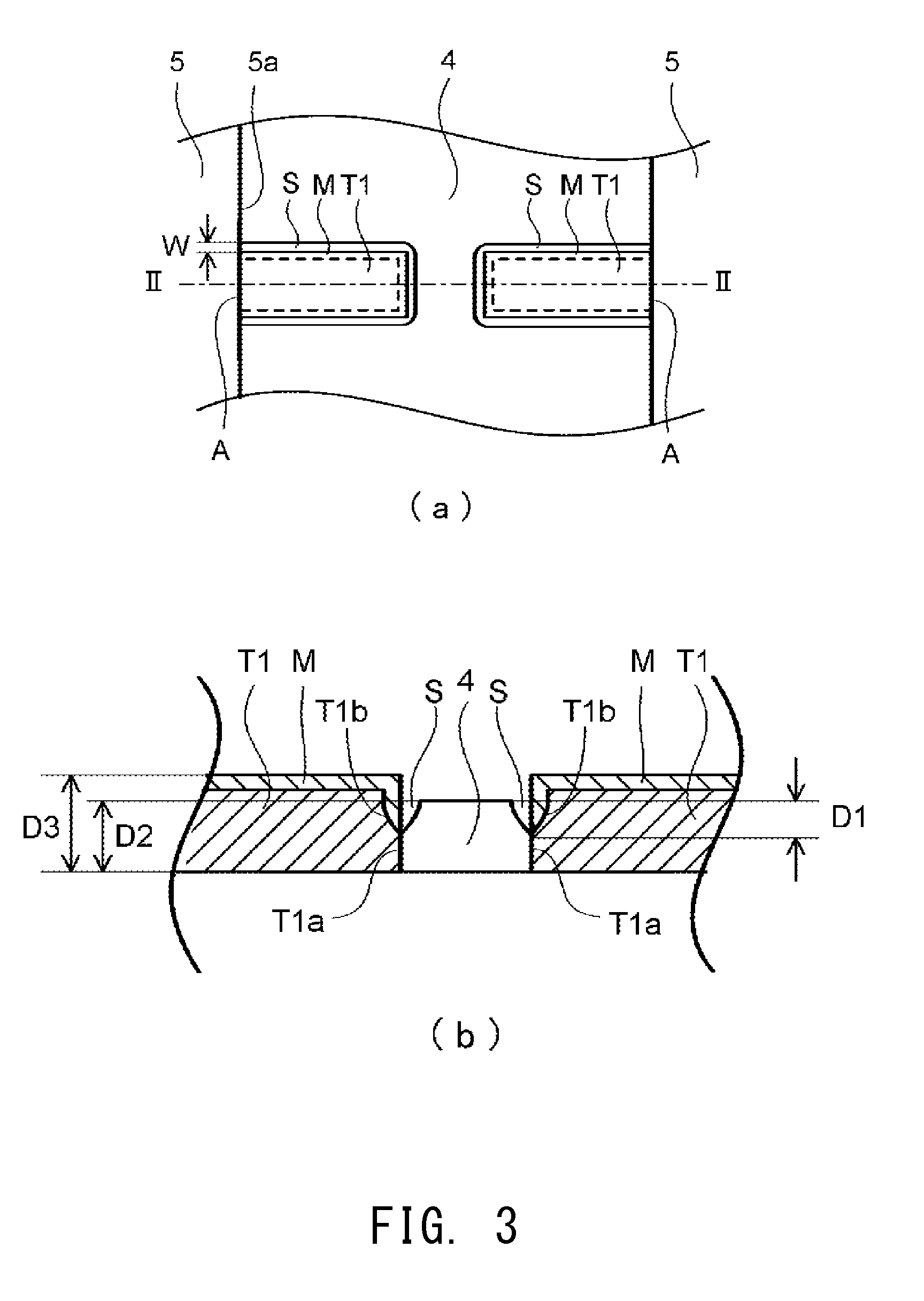

Chip part manufacturing method and chip parts

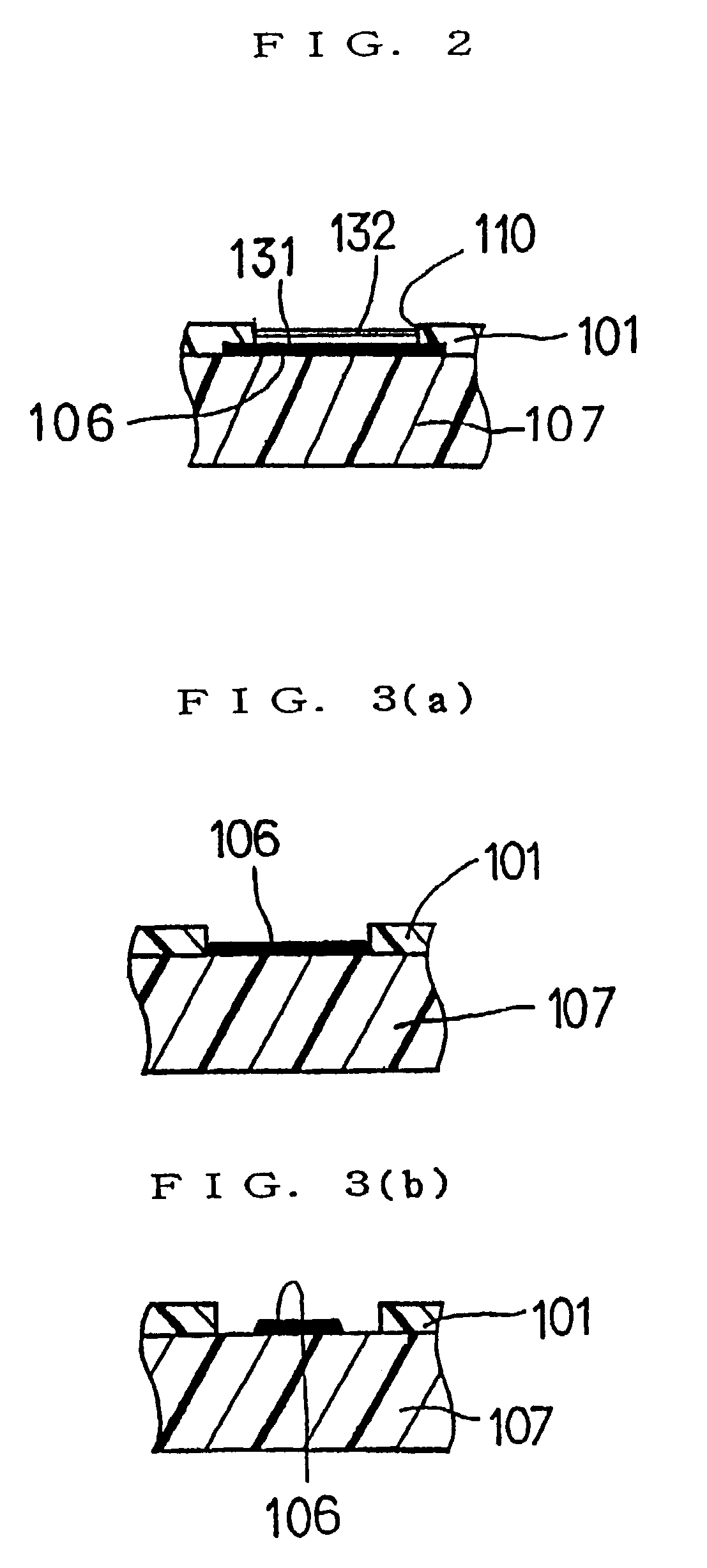

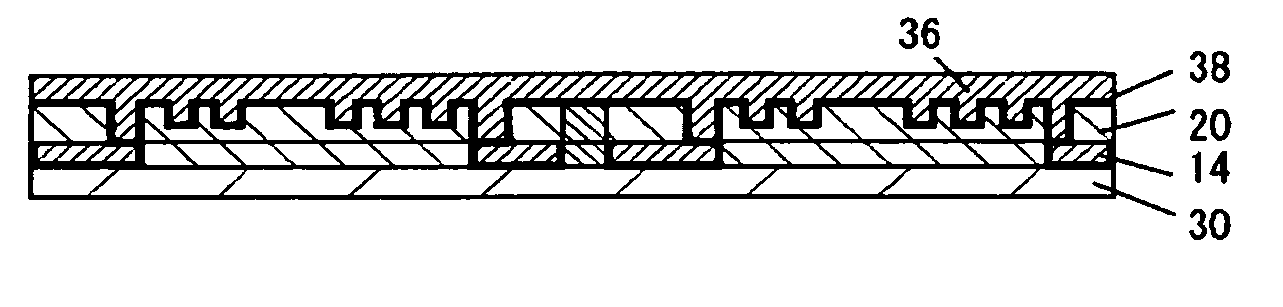

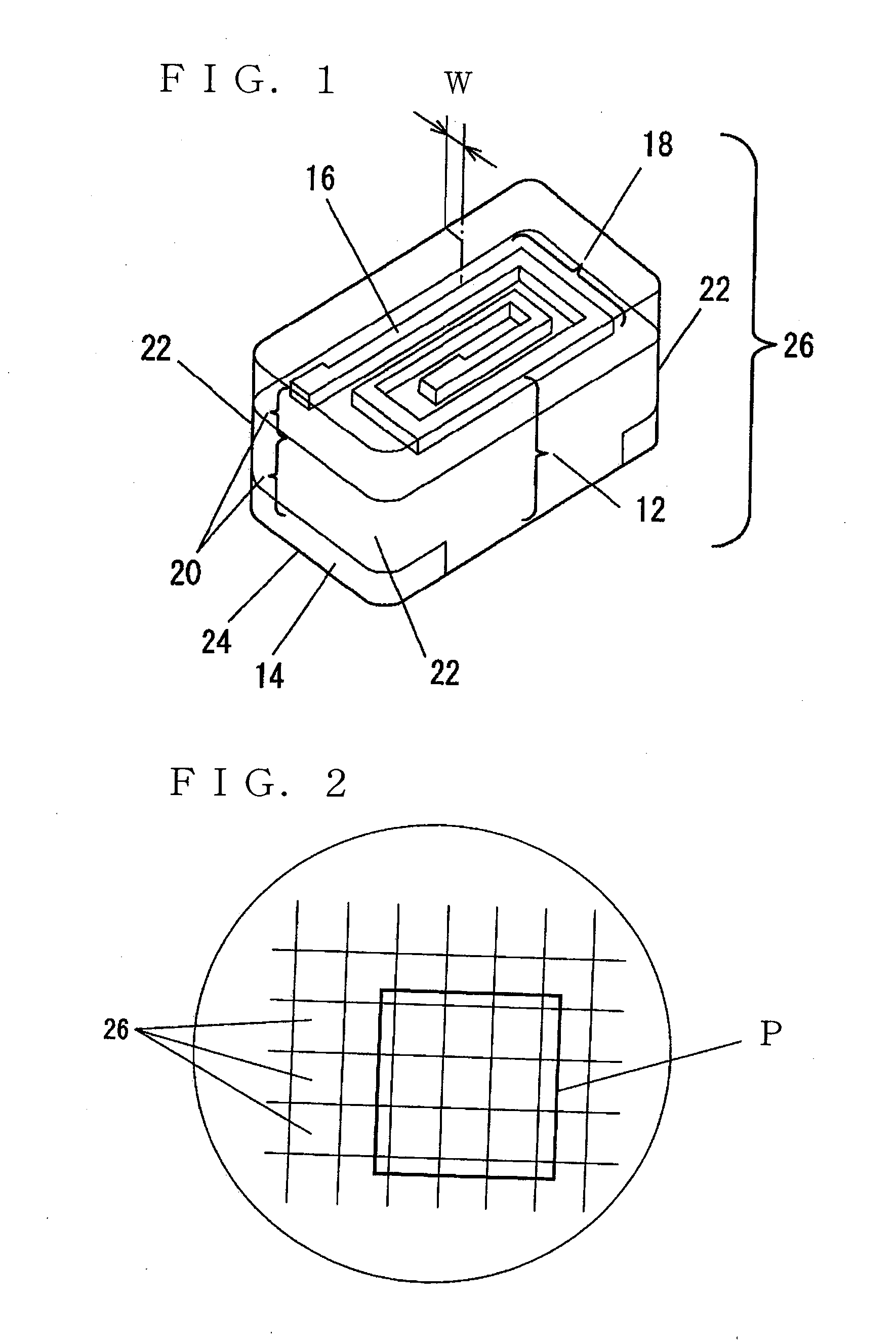

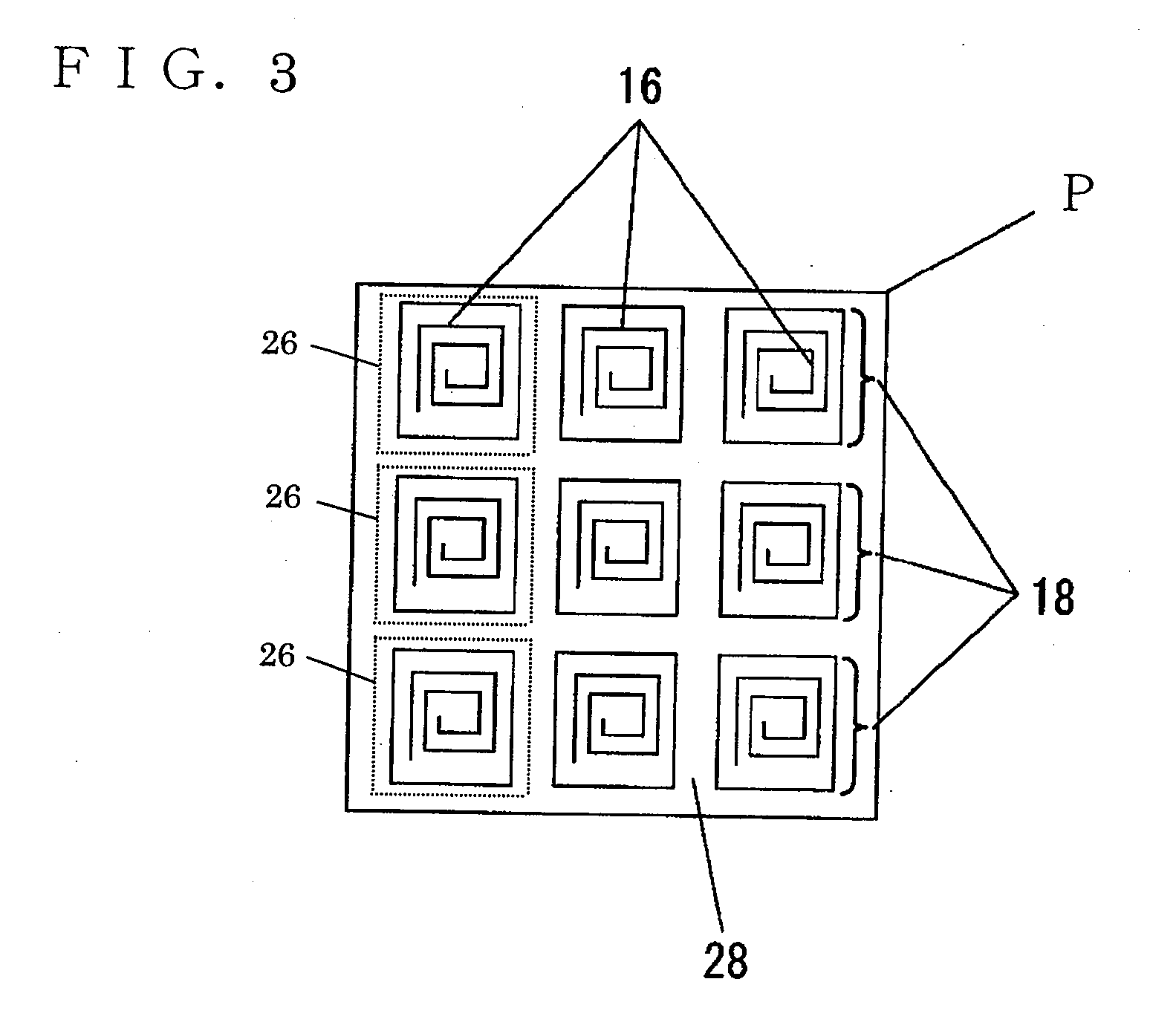

InactiveUS20060091534A1Avoid deformationAvoid problemsSemiconductor/solid-state device detailsPrinted circuit aspectsEngineeringMetal

The present invention provides a chip part manufacturing method comprising a separating process capable of suppressing deformation of chip parts, and also provides chip parts. It comprises a step of forming a plurality of frame-like void portions (32) in one main surface of substrate (30) and insulating resin layer (20) having a spiral void portion (40) disposed in the region thereof, a step of forming metal layer (36) in frame-like void portion (32) and spiral void portion (40) and on insulating resin layer (20), a step of polishing metal layer (36) at least up to the upper surface of insulating resin layer and forming coil section (18) in spiral void portion (40), and a step of forming a metal layer for connecting chip parts to frame-like void portion (32), wherein the metal layer is melted and removed by using an etching agent to separate a plurality of chip parts connected to each other by a frame-like connection.

Owner:PANASONIC CORP

Process for producing printed wiring board and photosensitive resin composition used in the same

InactiveUS7338751B2Improve routing densitySimple stepsPhotosensitive materialsSecond resist patternResistEngineering

An object of the present invention is to provide a process for producing a printed wiring board, which is advantageous not only in that the reduction in size and increase in density of the wiring board are achieved and further the steps are simplified, but also in that the connection reliability of mount parts and the yield are improved, and a photosensitive resin composition used in the process. The present invention is directed to a process for producing a printed wiring board, comprising the steps of: (i) forming a solder resist on a wiring board having a circuit; (ii) laminating a preliminarily molded layer of a photosensitive resin composition on the solder resist; (iii) subjecting the layer of the photosensitive resin composition to exposure and development to form a resist pattern of the photosensitive resin composition; (iv) subjecting the entire surface of the resultant board to electroless plating, and (v) stripping the layer of the photosensitive resin composition, wherein the steps are conducted in this order, as well as a photosensitive resin composition and the layer thereof used in the process.

Owner:HITACHI CHEM CO LTD

Electronic device substrate, electronic device and methods for making same

An electronic device substrate having: a base material formed of a thin board; an electrical insulation layer formed on the base material and having plural openings in a thickness direction thereof; and a metal plating layer filled in the plural openings. The base material has a metal layer, a release layer formed contacting the metal layer, and a metal film formed contacting the release layer.

Owner:RENESAS ELECTRONICS CORP

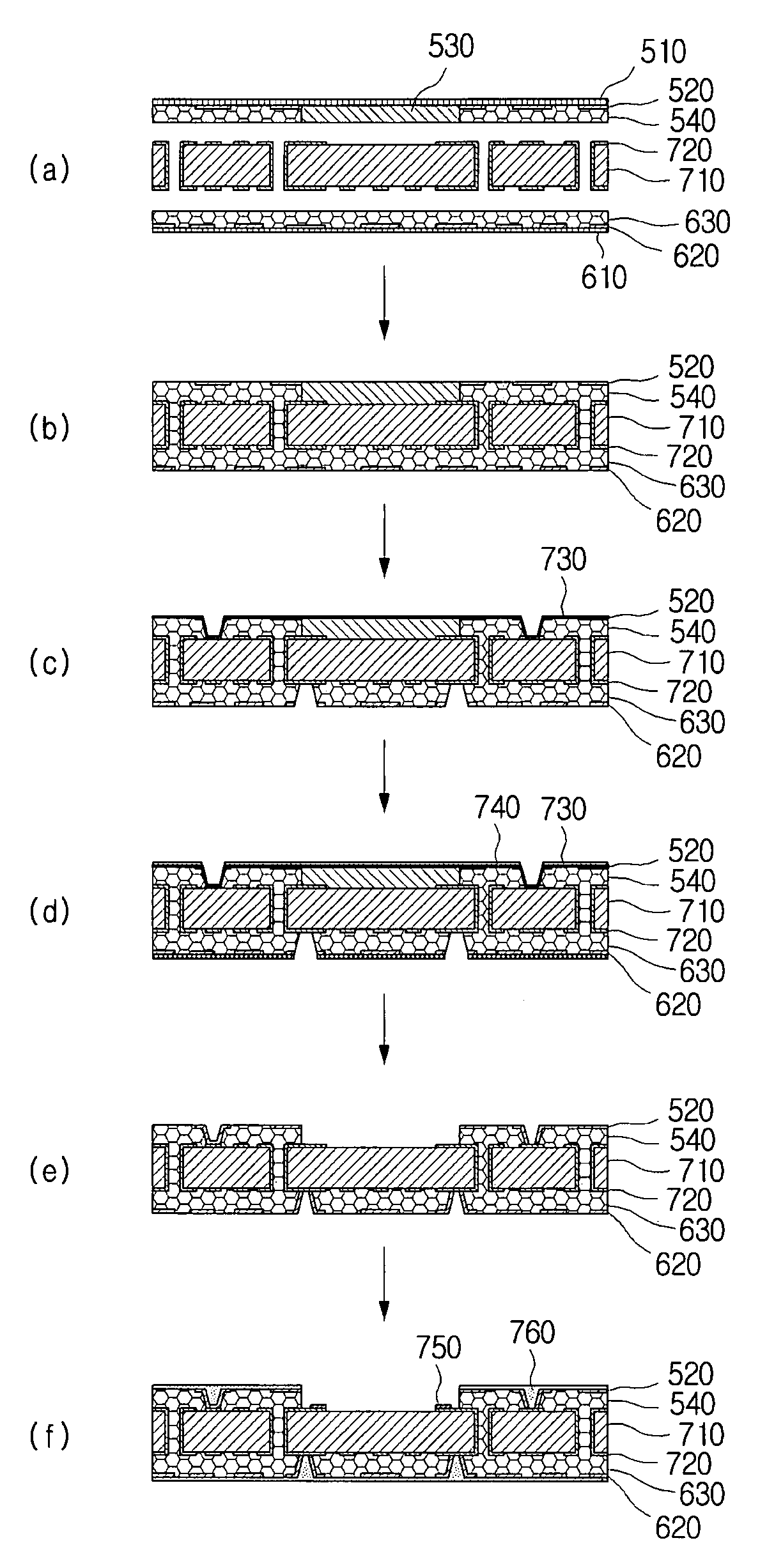

Method for manufacturing a substrate with cavity

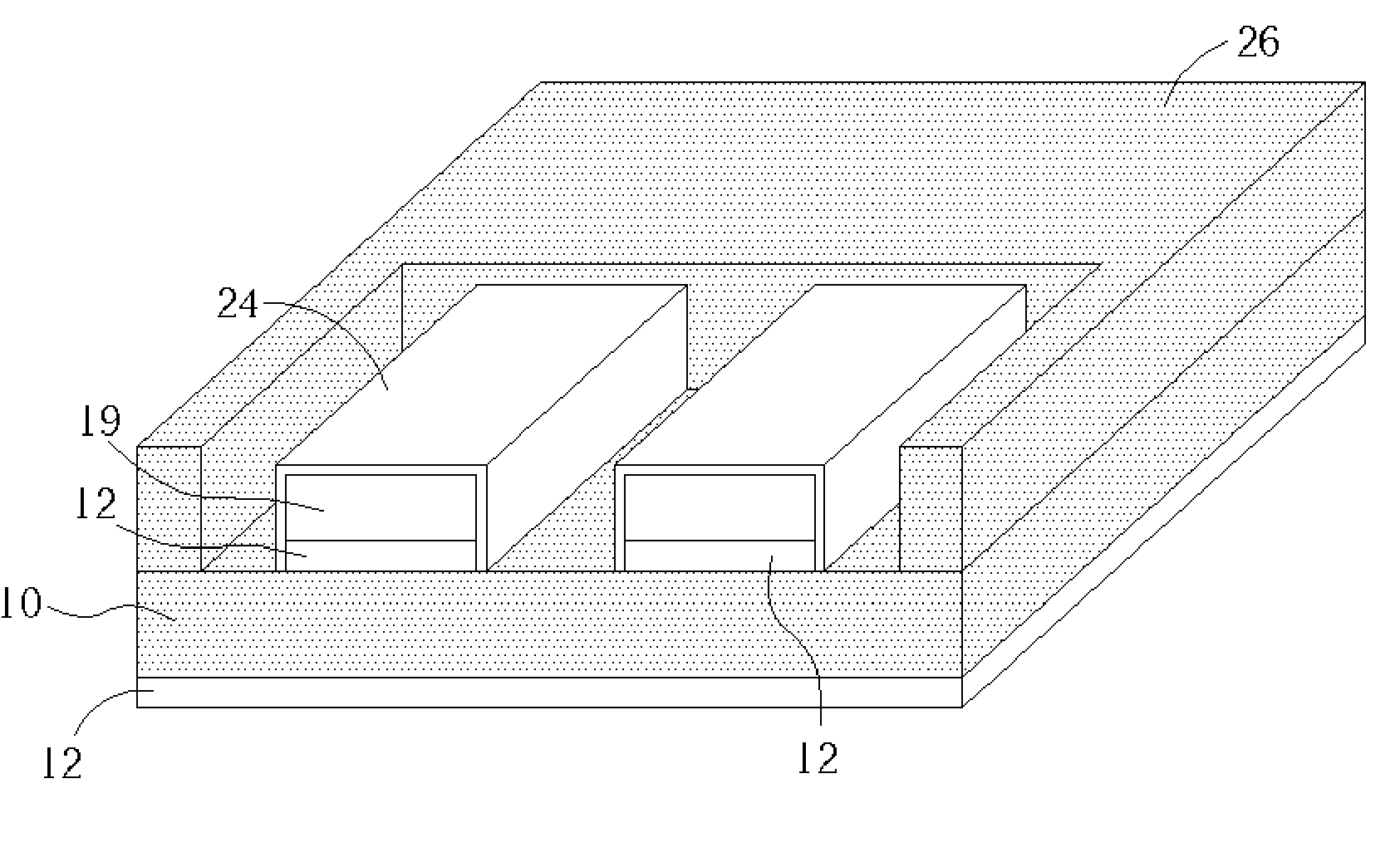

InactiveUS7858437B2Reduce thicknessSemiconductor/solid-state device detailsSolid-state devicesInsulation layerEngineering

An aspect of the present invention features a method for manufacturing a substrate having a cavity. The method can comprises: (a) forming an upper layer circuit on an upper seed layer; (b) laminating a dry film on a portion of the upper seed layer where a cavity is to be formed; (c) fabricating an upper outer layer by forming an insulation layer on top of the upper seed layer and on top and sides of the upper layer circuit; (d) stacking the upper outer layer on one side of a core layer where an internal circuit is formed; (e) removing the upper seed layer; and (f) forming the cavity by removing the dry film. The method for manufacturing a substrate with a cavity according to the present invention can reduce the total thickness of the substrate while the thickness of an insulation layer remains the same, by forming the insulation layer on sides of an external circuit.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

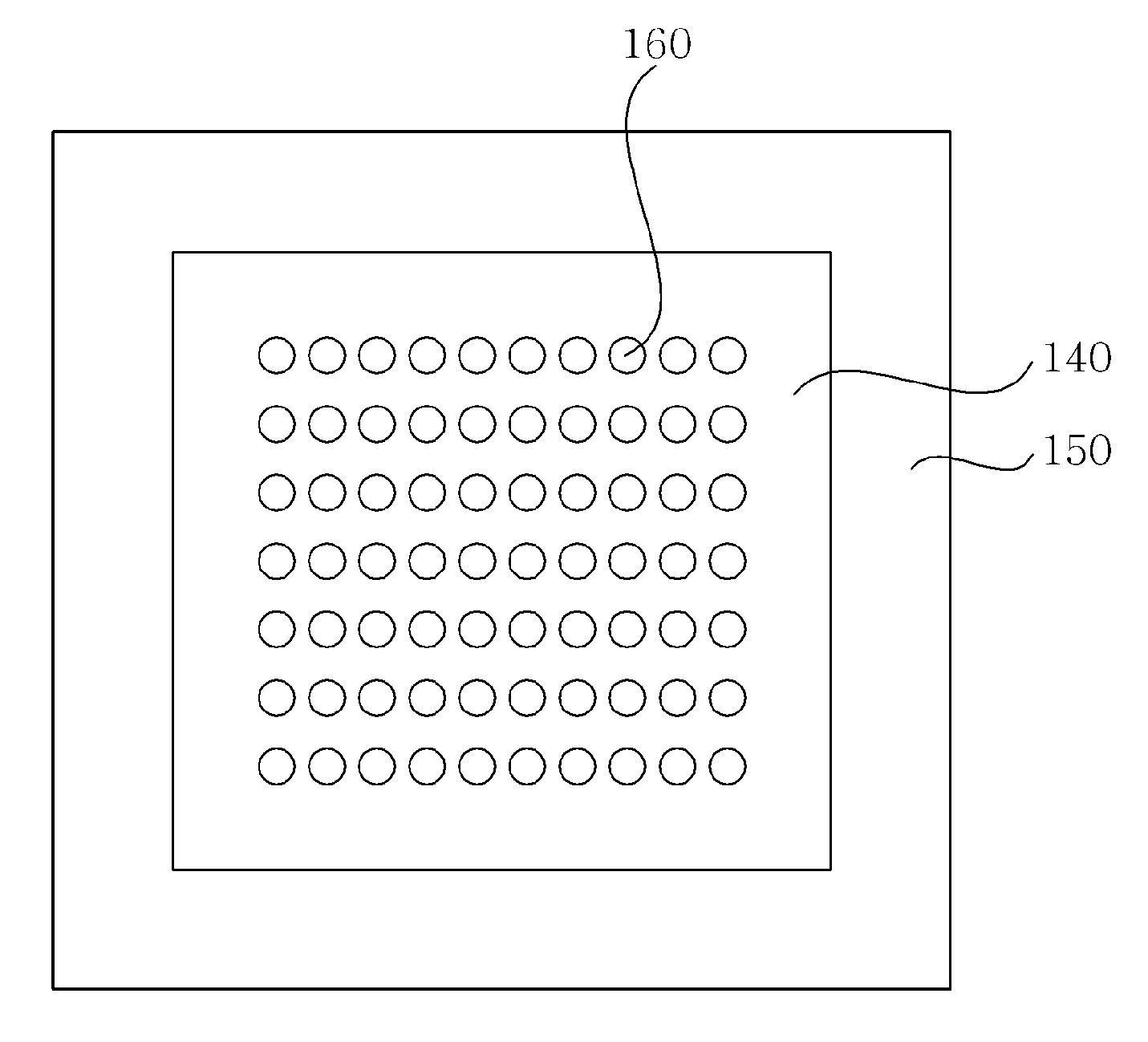

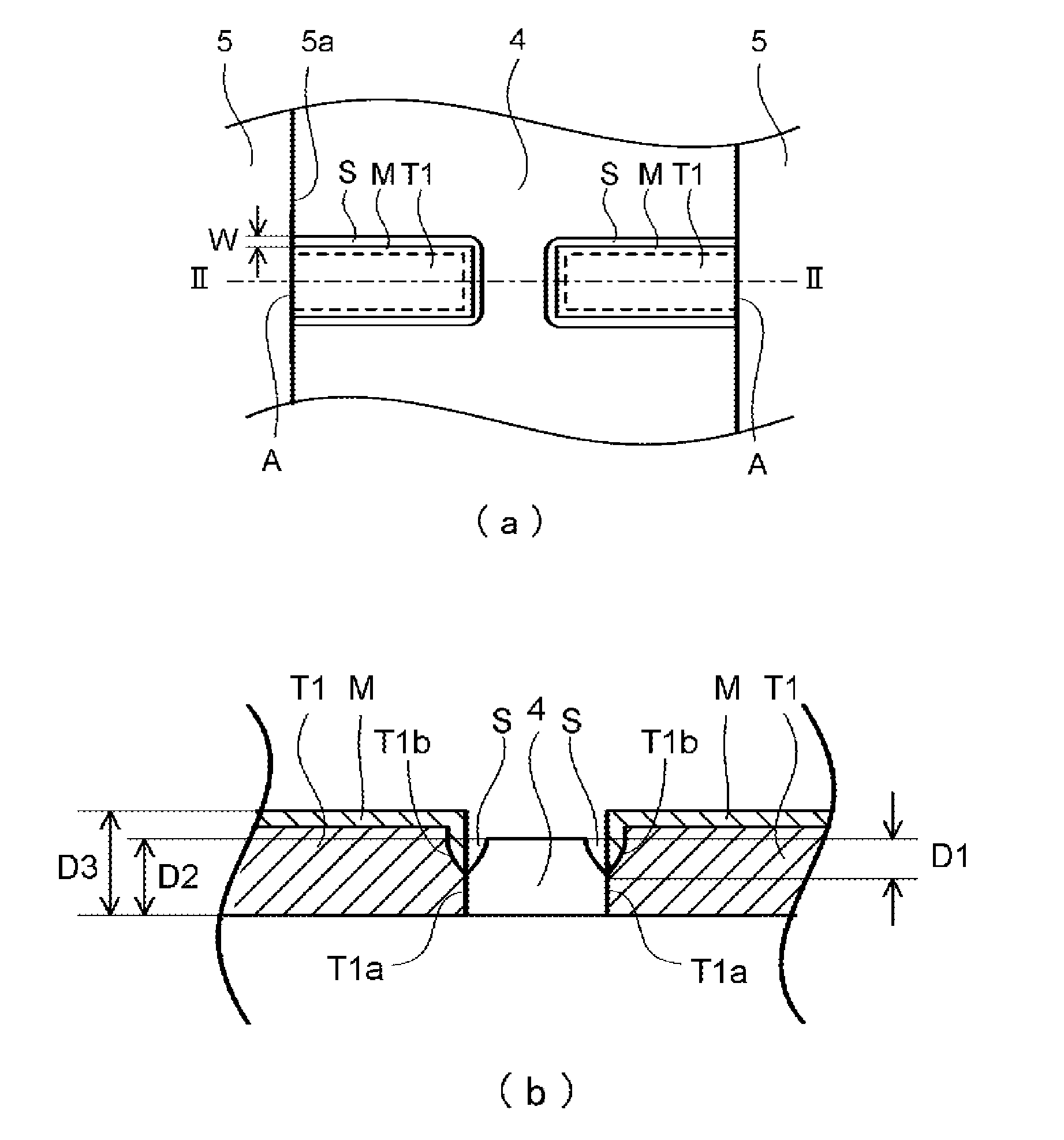

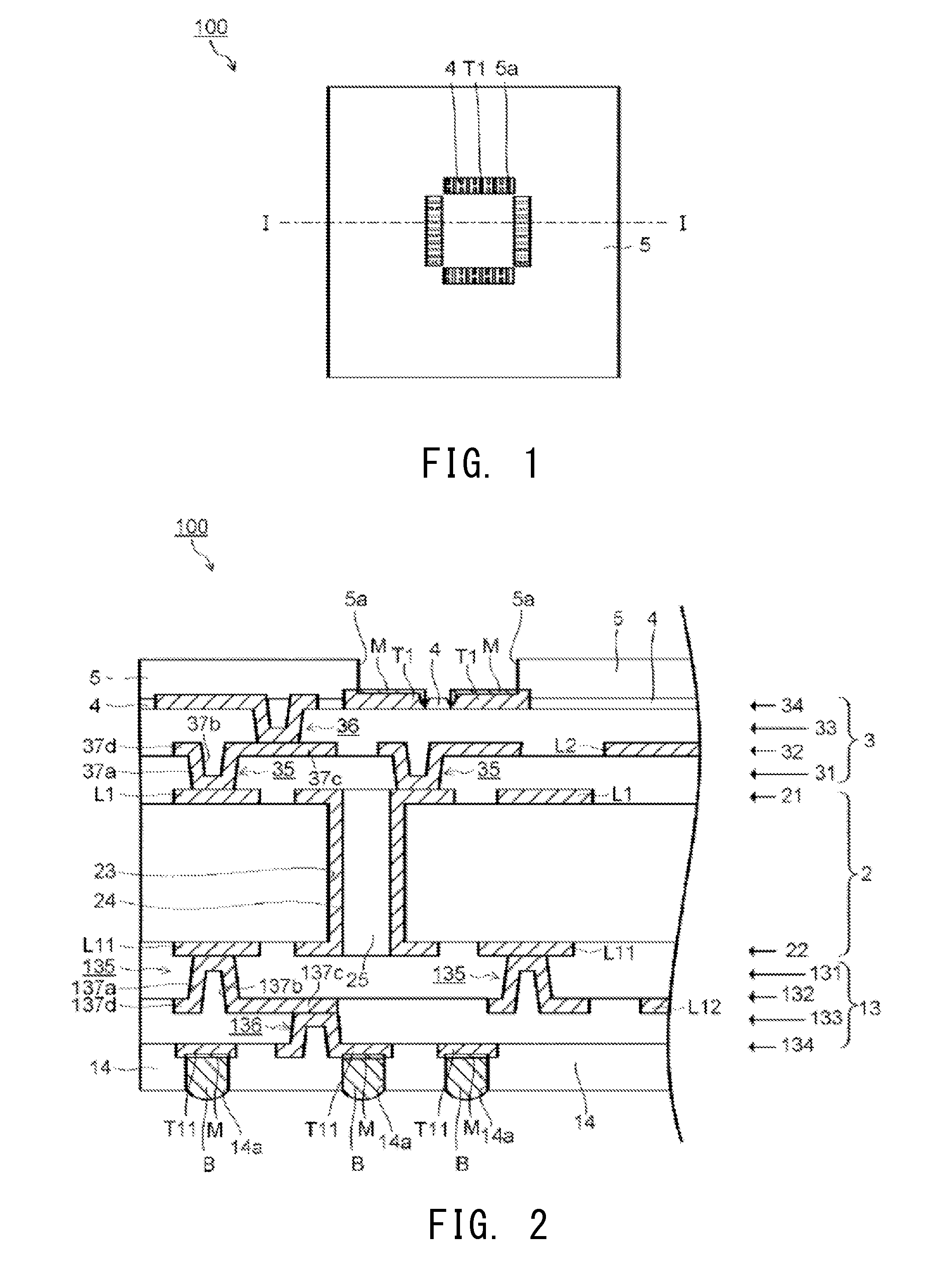

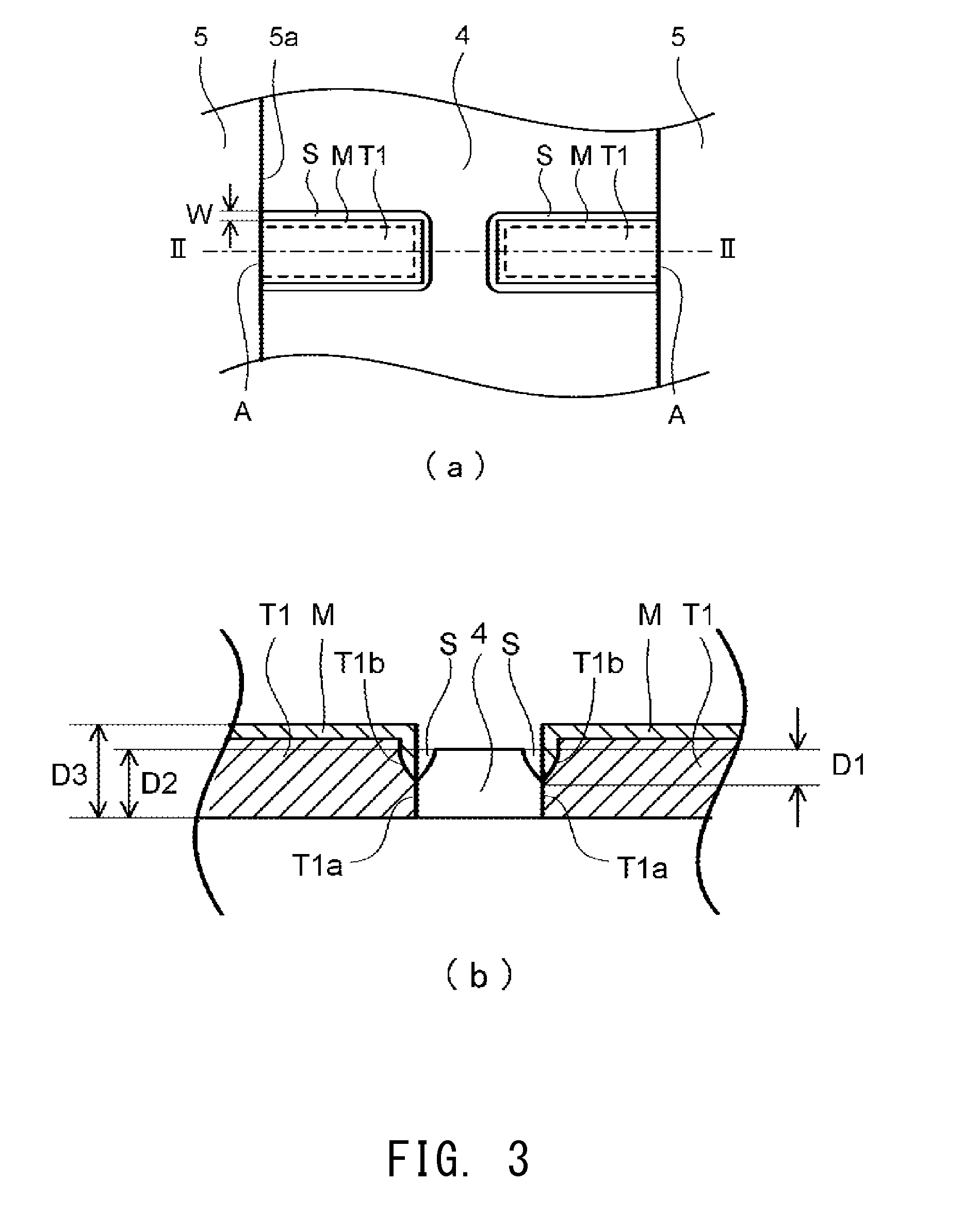

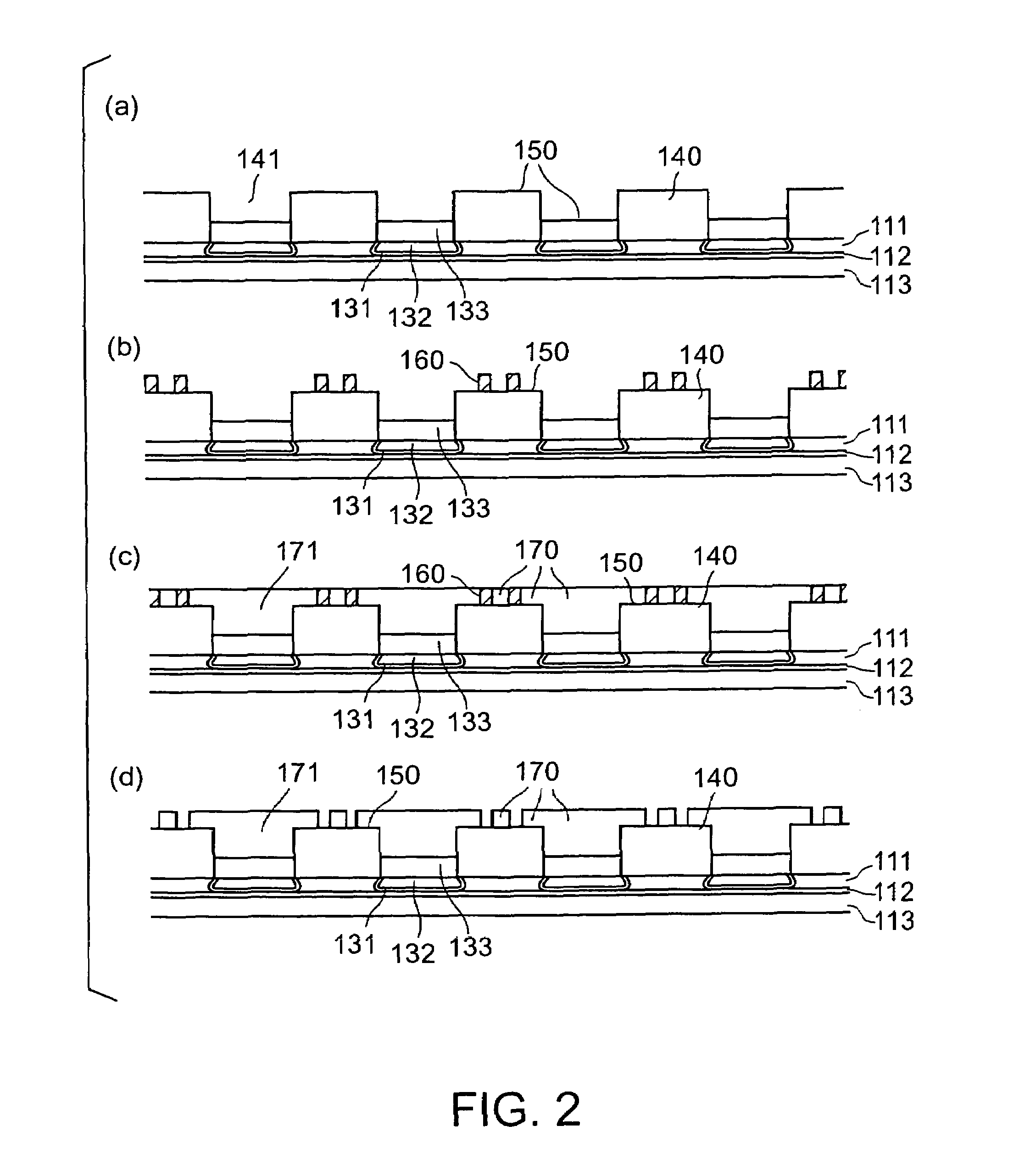

Wiring board

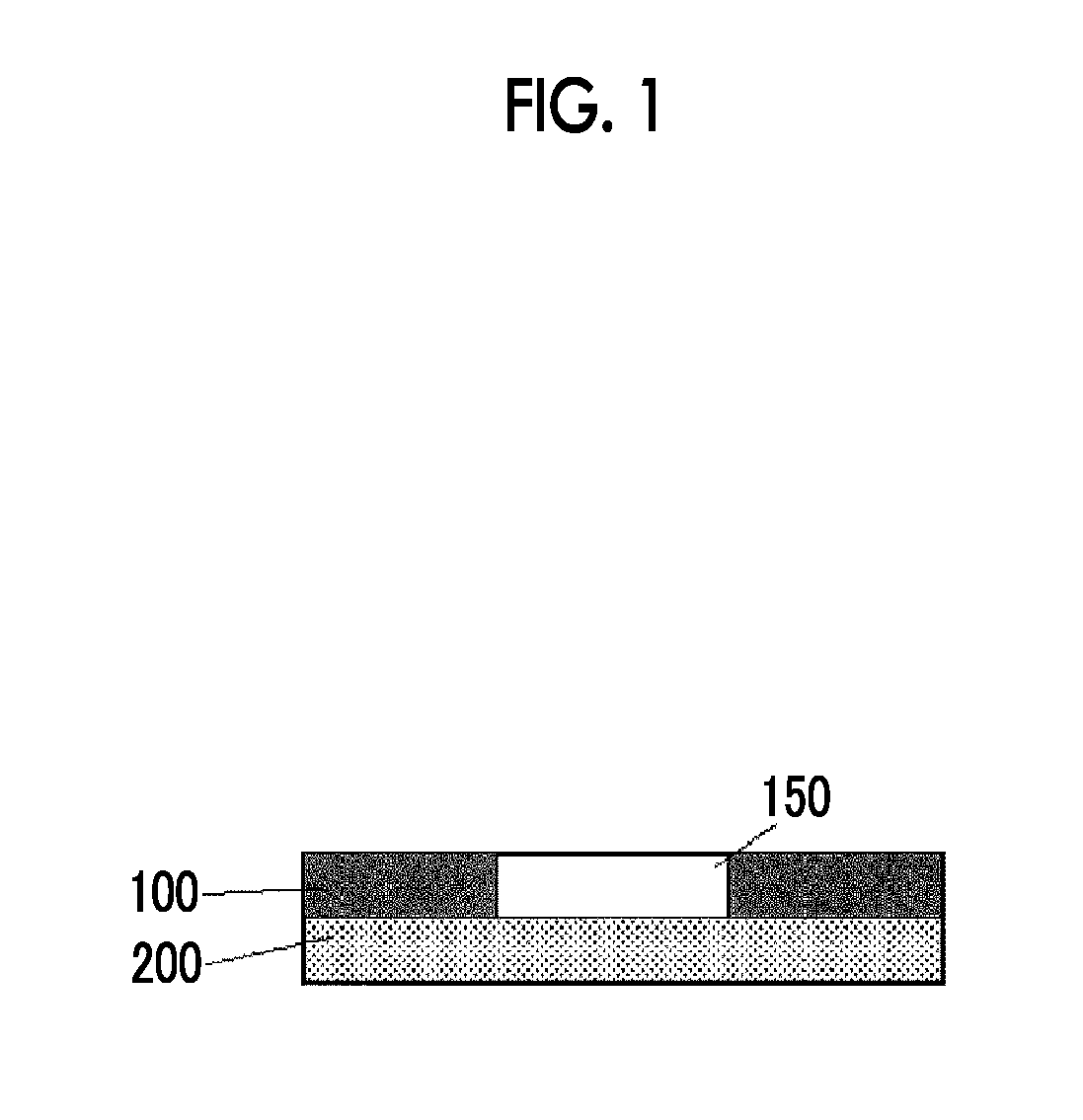

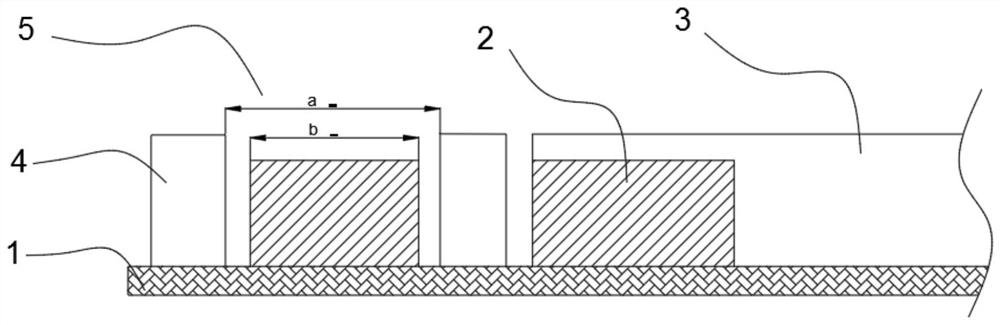

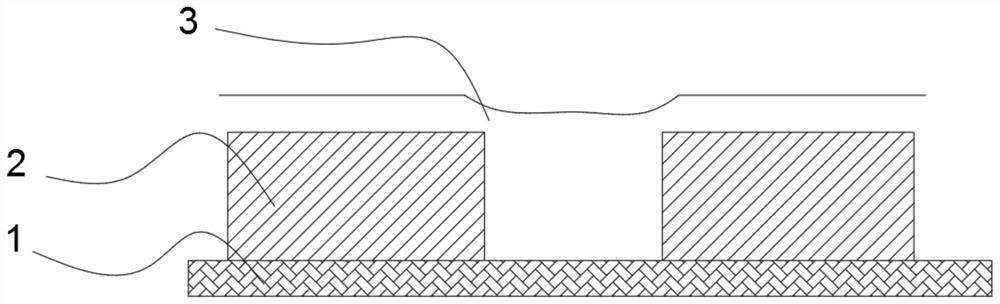

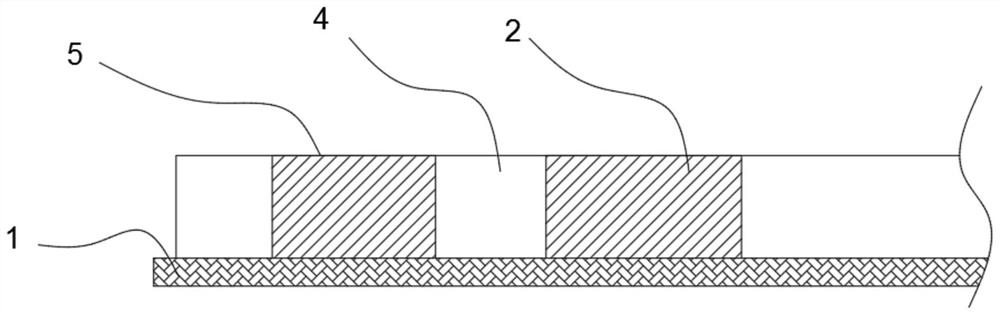

ActiveUS20150027750A1Reduce spacingPrevent short-circuitingPrinted circuit assemblingSecond resist patternInsulation layerElectrical conductor

To provide a wiring substrate which can prevent short circuit between connection terminals, and which realizes reduction of the pitch between the connection terminals. The wiring substrate of the present invention includes a layered structure including one or more insulation layers and one or more conductor layers, and the wiring substrate is characterized in that a plurality of connection terminals are formed on the layered structure so as to be separated from one another; a filling member is filled between the connection terminals; and each of the connection terminals has a side surface composed of a contact surface which is in contact with the filling member, and a spaced surface which is not in contact with the filling member and which is located above the contact surface and below the top surface of the filling member.

Owner:NGK SPARK PLUG CO LTD

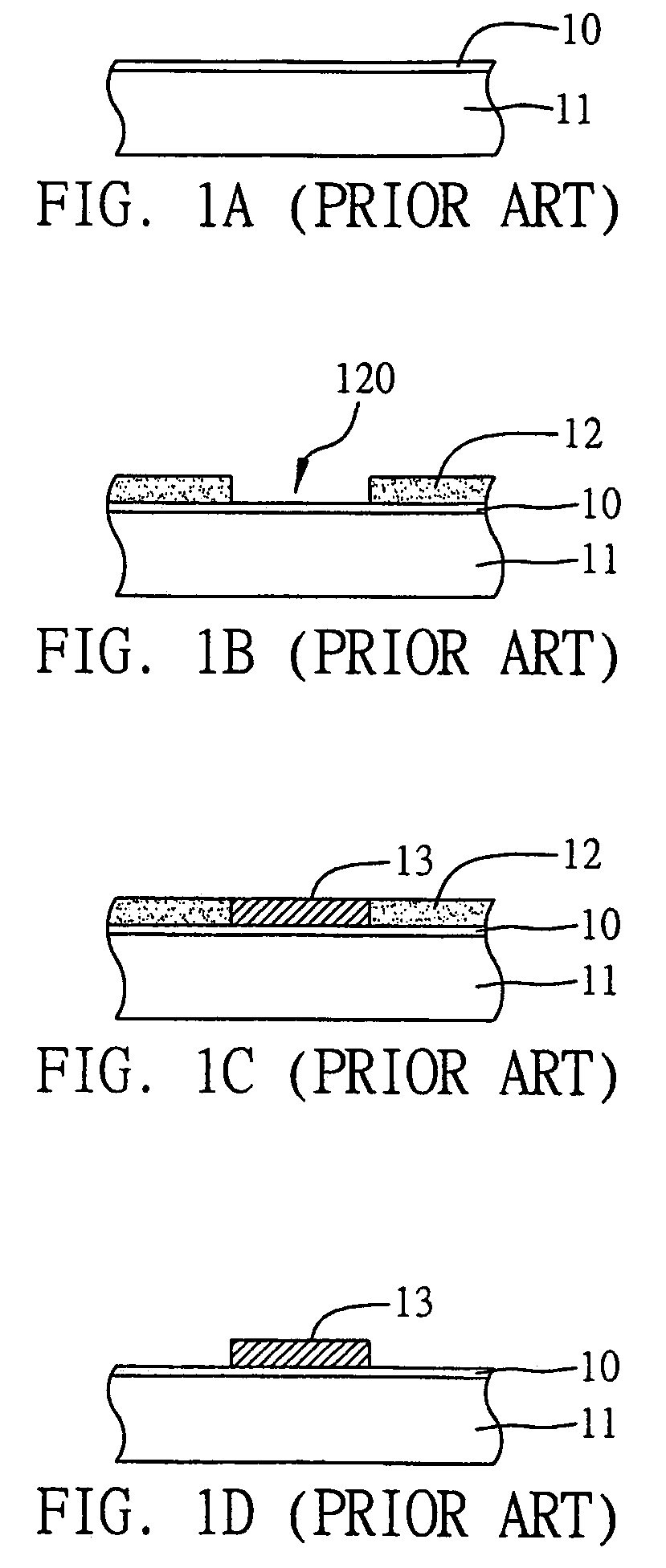

Electrical connector structure of circuit board and method for fabricating the same

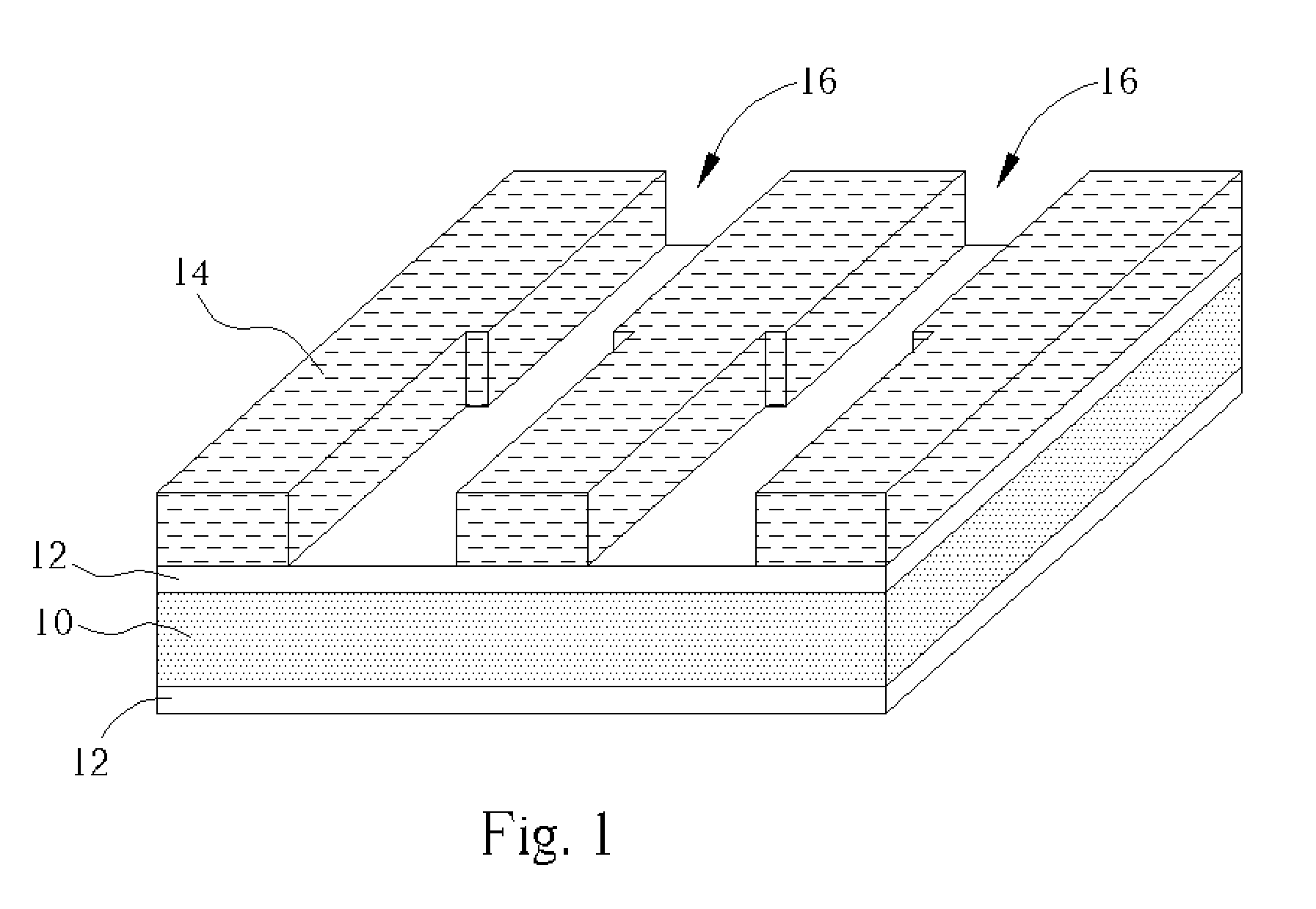

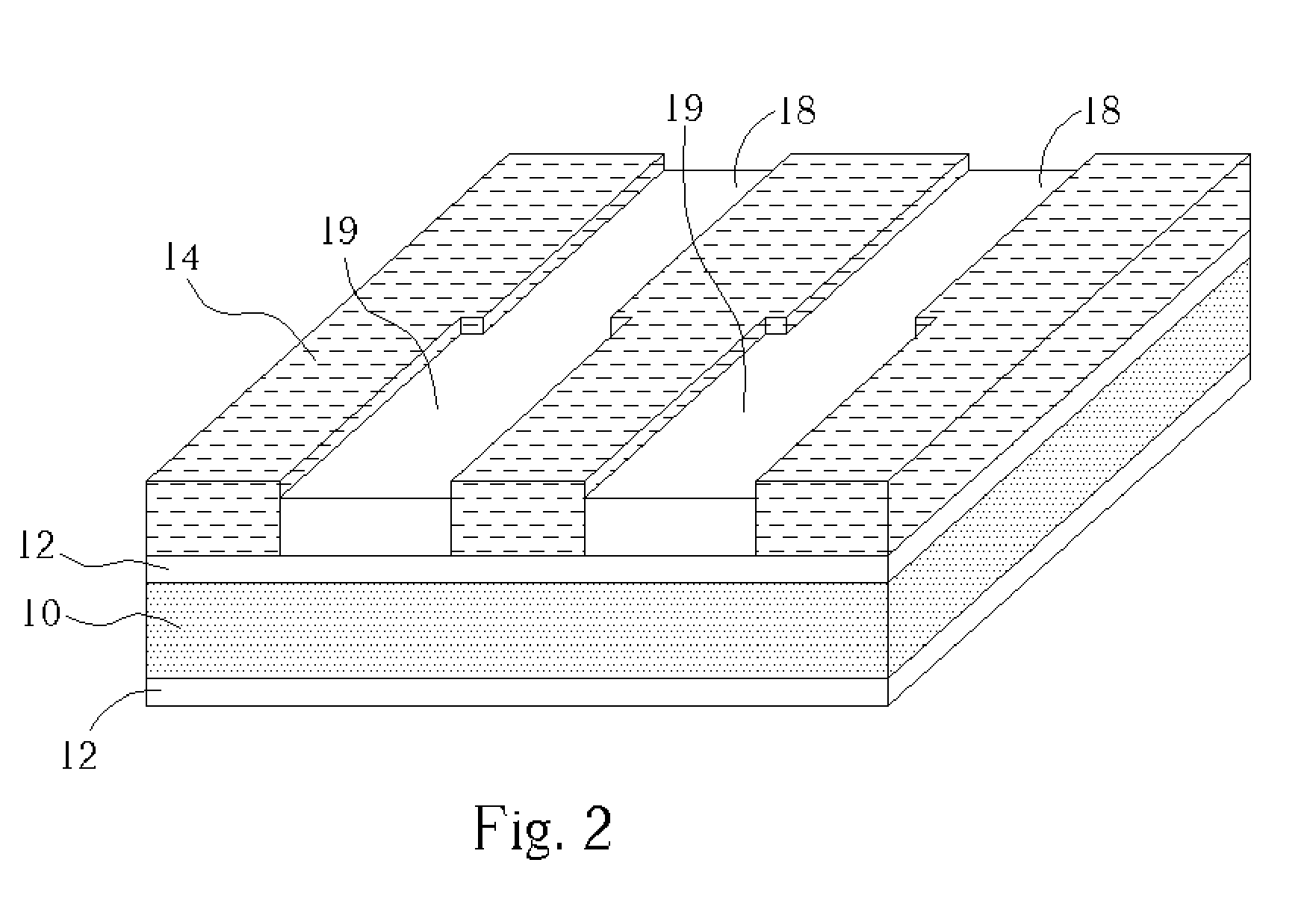

ActiveUS7608929B2Lower requirementDifficult to alignSemiconductor/solid-state device detailsSolid-state devicesResistElectrical connection

An electrical connector structure of circuit board and a method for fabricating the same are proposed. A circuit board having a conductive layer is formed with a first resist layer and a second resist layer thereon, so as to form electrical connection pads and metal bumps on the electrical connection pads. The first and second resist layers are formed with openings therein at positions corresponding to the electrical connection pads and metal bumps, and the exposed conductive layer is removed. An adhesive layer is formed to cover the exposed surfaces of the electrical connection pads and the metal bumps. Then, the second resist layer, the first resist layer and the conductive layer covered by the first resist layer are removed. Later, an insulating protective layer is formed on a surface of the circuit board, and thinned to expose a portion of the adhesive layer, such that electrical connectors of the circuit board are fabricated.

Owner:PHOENIX PRECISION TECH CORP

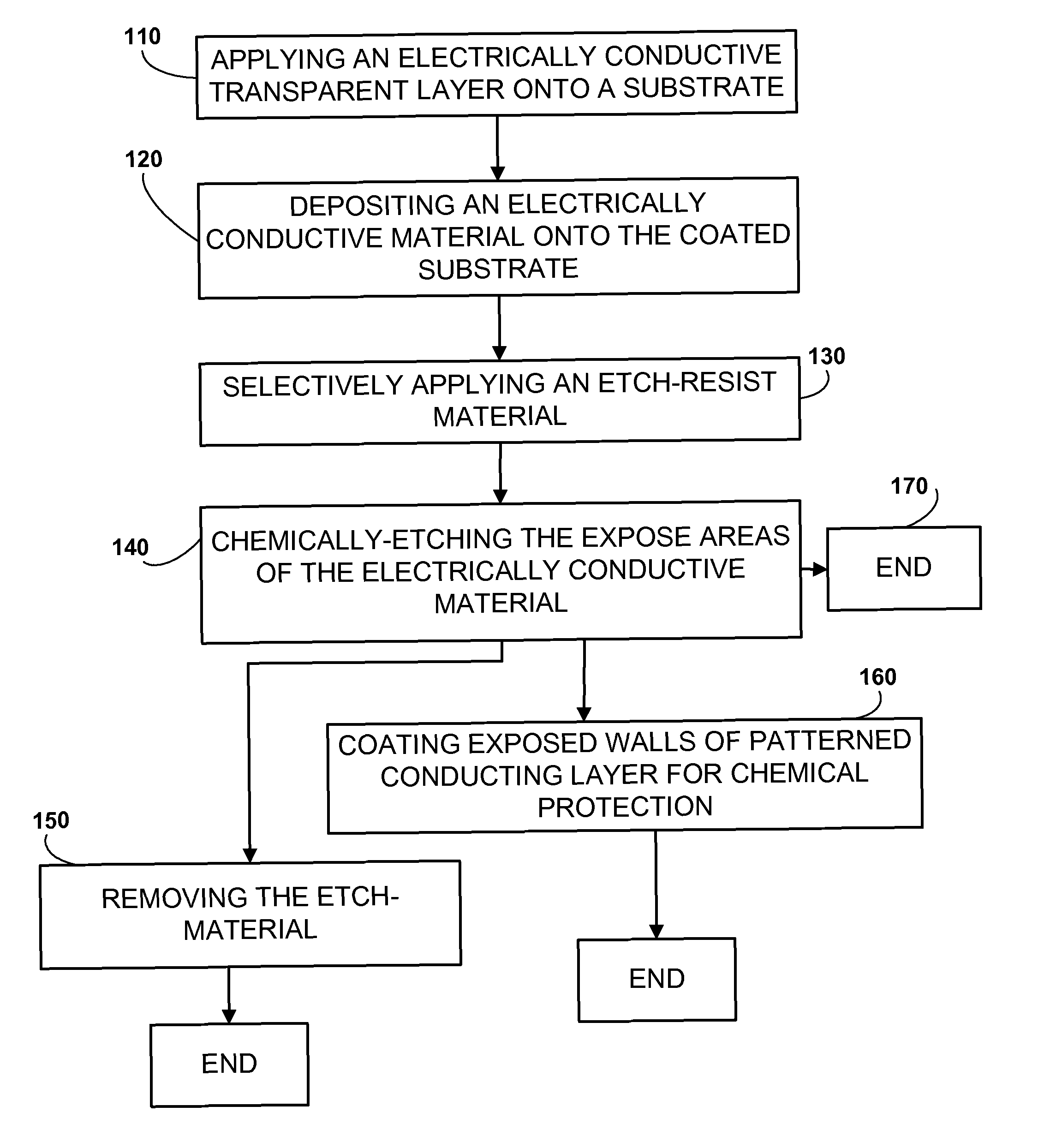

Method of manufacturing a patterned conductive layer

InactiveUS7992293B2Wave amplification devicesMagnetic/electric field screeningResistVacuum deposition

According to embodiments of the present invention, a method for manufacturing a pattern of conductive elements on a substrate is provided. The method includes applying a coating layer of electrically conductive transparent compounds onto a substrate; depositing in a vacuum deposition chamber an electrically conductive material onto the coating layer to form an electrically conductive layer; applying an etch-resist material on selective areas of the electrically conductive layer, wherein the selective areas are substantially areas pre-designed to carry the conductive objects; and chemically etching the electrically conductive material from exposed areas of the electrically conductive layer that are not covered by the etch-resist material.

Owner:HANITA COATINGS R C A

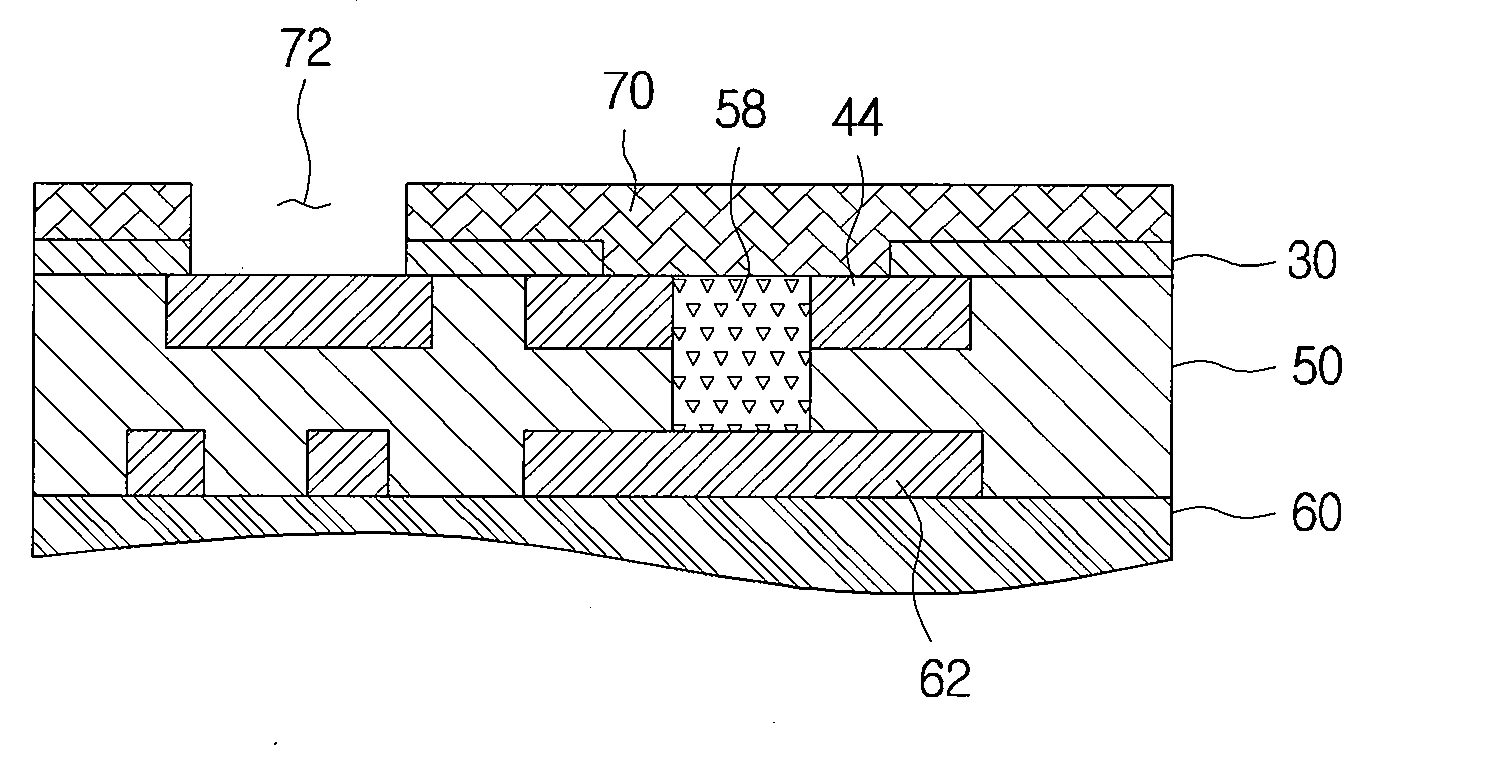

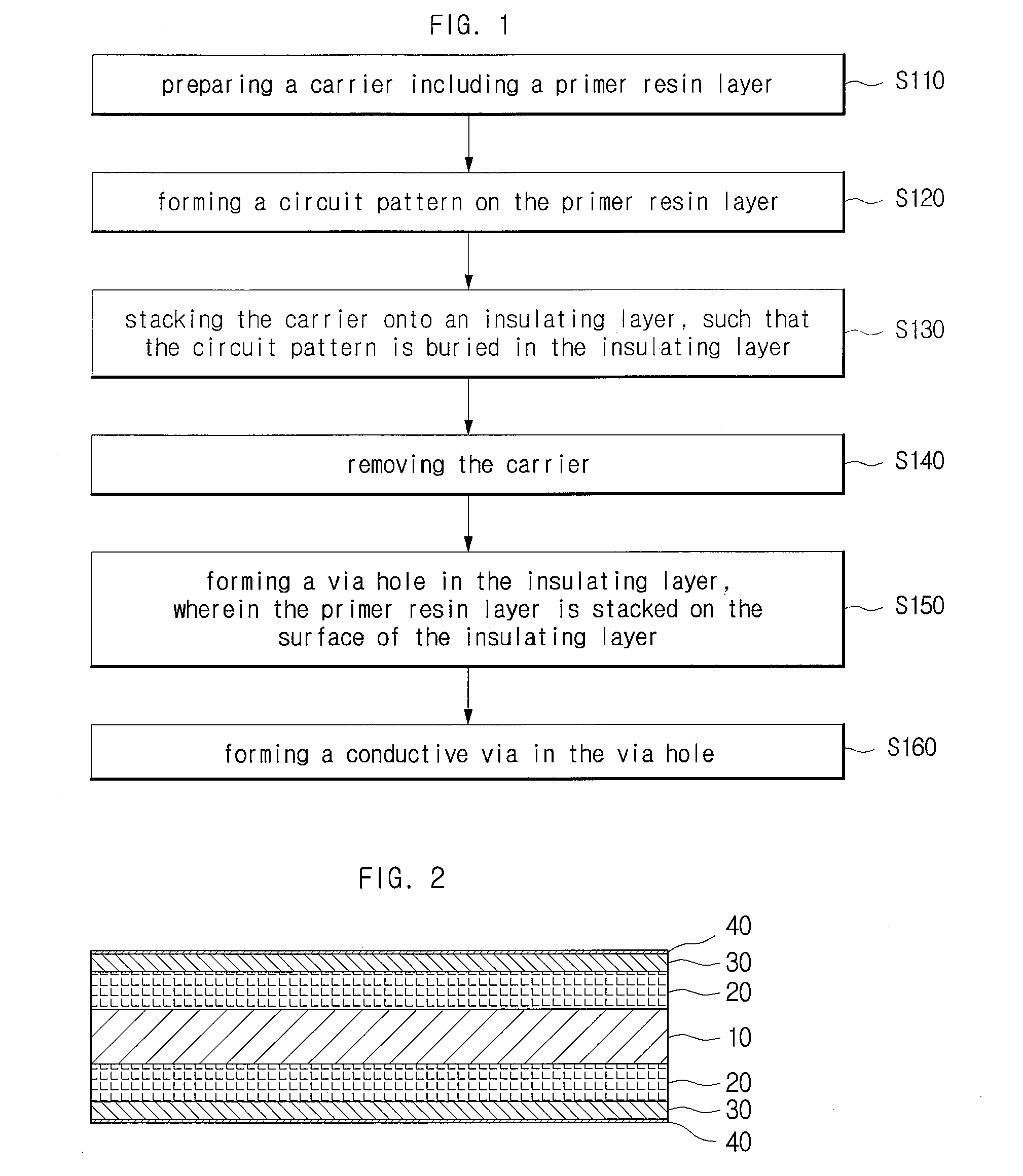

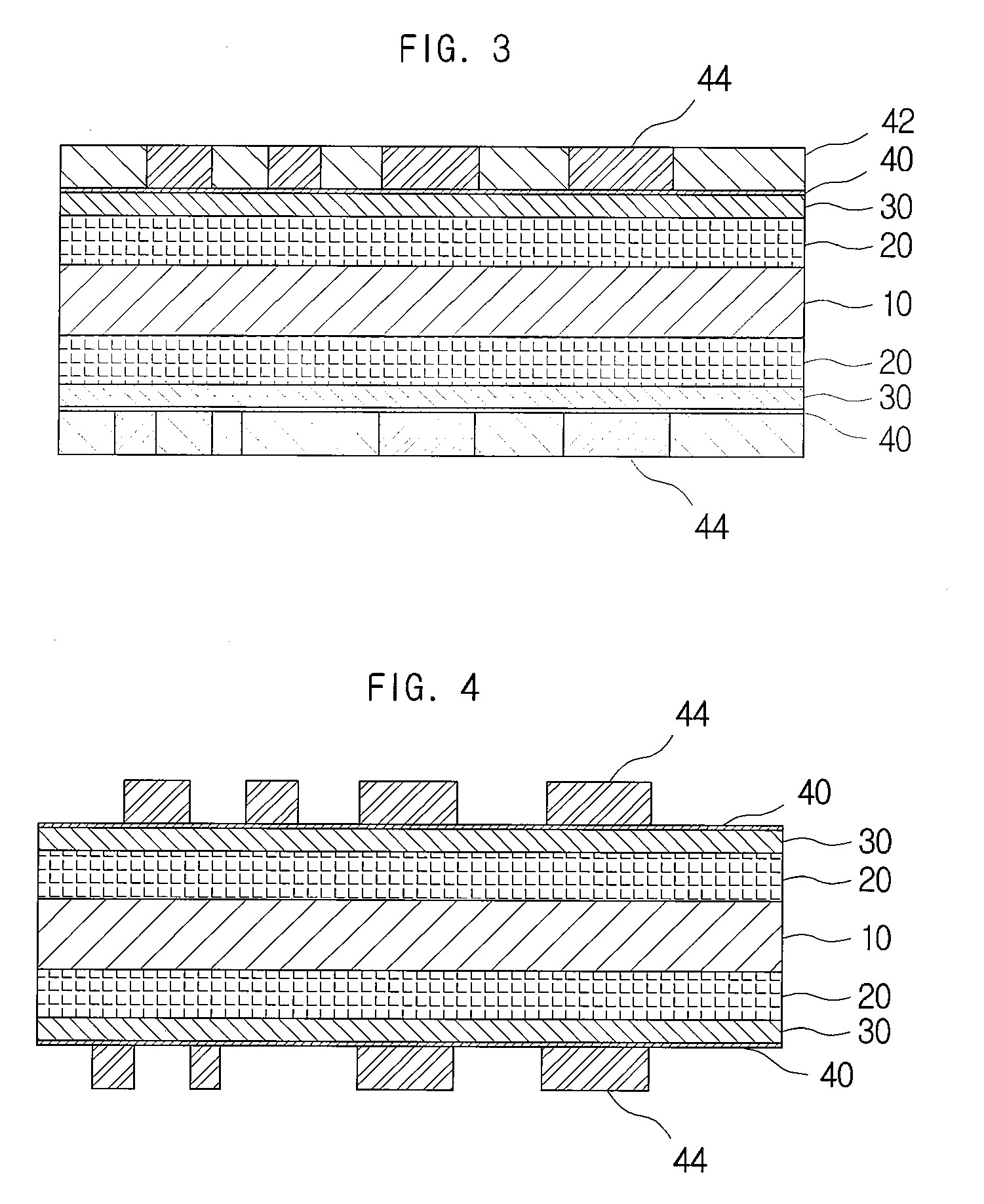

Printed circuit board and manufacturing method thereof

InactiveUS20110088930A1Decorative surface effectsElectrical connection printed elementsEngineeringPrinted circuit board

A printed circuit board and a manufacturing method of the same are disclosed. The method includes: preparing a carrier including a primer resin layer formed thereon; forming a circuit pattern on the primer resin layer; stacking the carrier onto an insulating layer such that the circuit pattern is buried in the insulating layer; removing the carrier; forming a via hole in the insulating layer on which the primer resin layer is stacked; and forming a conductive via in the via hole. The conductive via is formed by forming a plating layer in the via hole and on the primer resin layer and removing a portion of the plating layer formed over the primer resin layer.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

Method for manufacturing insulated conductive pattern and laminate

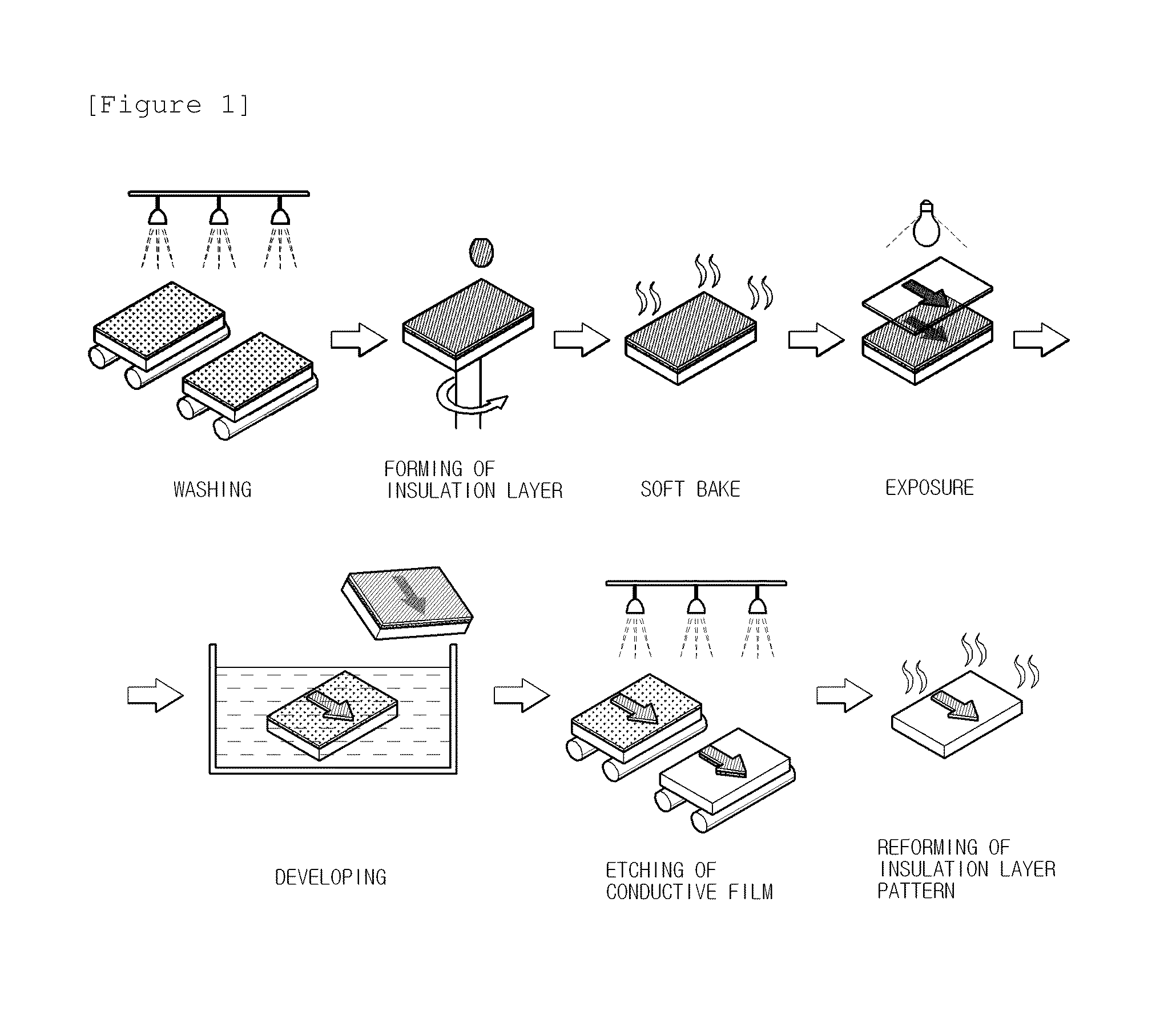

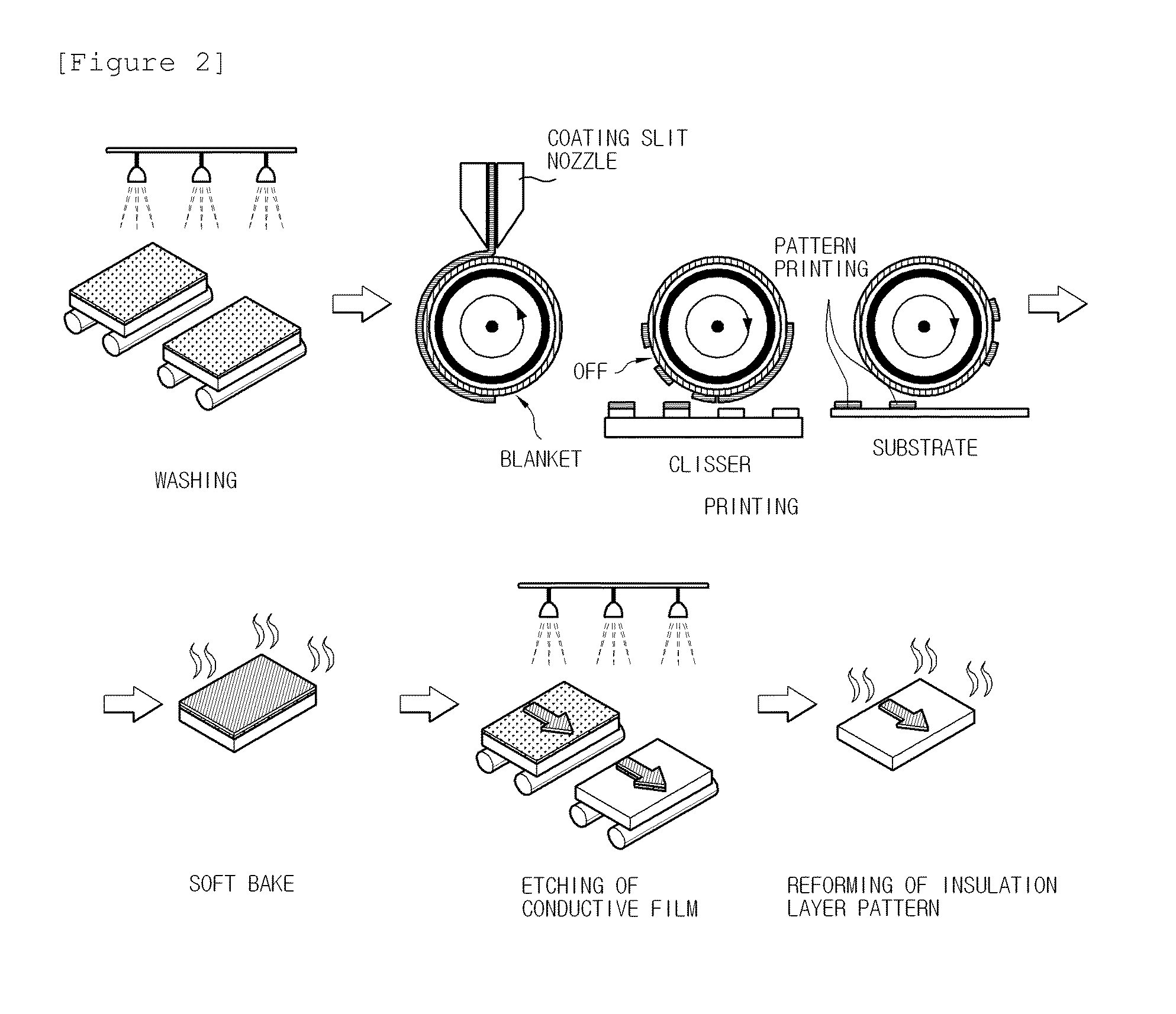

ActiveUS20110290548A1Increase costAvoid it happening againPrinted circuit aspectsDual purpose resistElectrically conductiveEngineering

The present invention provides: a method for manufacturing an insulated conductive pattern, wherein a conductive film and an insulation layer pattern are formed on a substrate, and the insulation layer pattern is reformed to cover a conductive pattern after formation of the conductive pattern by etching the conductive film using the insulation layer pattern as a mask; and a laminate manufactured thereby. According to the present invention, the number of processes is sharply reduced in comparison with the existing processes, and economic efficiency can be greatly improved.

Owner:LG CHEM LTD

Wiring board

ActiveUS9560739B2Prevent short-circuitingReduce spacingPrinted circuit assemblingSecond resist patternInsulation layerElectrical conductor

To provide a wiring substrate which can prevent short circuit between connection terminals, and which realizes reduction of the pitch between the connection terminals. The wiring substrate of the present invention includes a layered structure including one or more insulation layers and one or more conductor layers, and the wiring substrate is characterized in that a plurality of connection terminals are formed on the layered structure so as to be separated from one another; a filling member is filled between the connection terminals; and each of the connection terminals has a side surface composed of a contact surface which is in contact with the filling member, and a spaced surface which is not in contact with the filling member and which is located above the contact surface and below the top surface of the filling member.

Owner:NGK SPARK PLUG CO LTD

Method of manufacturing a wiring board

InactiveUS7325301B2For direct connectionReliable solutionSolid-state devicesSemiconductor/solid-state device manufacturingResistEngineering

A wiring board according to the present invention includes a wiring part formed of one or more layers, a first terminal area disposed on one side of the wiring part in a projecting manner, and a second terminal area disposed on the other side of the wiring part. A resist having an opening for a first terminal area is formed on a surface of a composite made of a plurality of metal layers. A part of a first metal layer of the composite is etched through the opening for a first terminal area to form a hole. The hole is subjected to an electroless plating through the opening of the resist. Thus, the hole is filled with an electroplated layer to form a first terminal area. Then, the resist is removed from the composite, and a wiring layer is formed thereon. Subsequently, a solder resist having an opening for a second terminal area is disposed on the wiring layer. The opening of a second terminal area of the solder resist is subjected to an electroplating so as to form a second terminal area. Removing remaining parts of the composite, a wiring board is completed.

Owner:DAI NIPPON PRINTING CO LTD

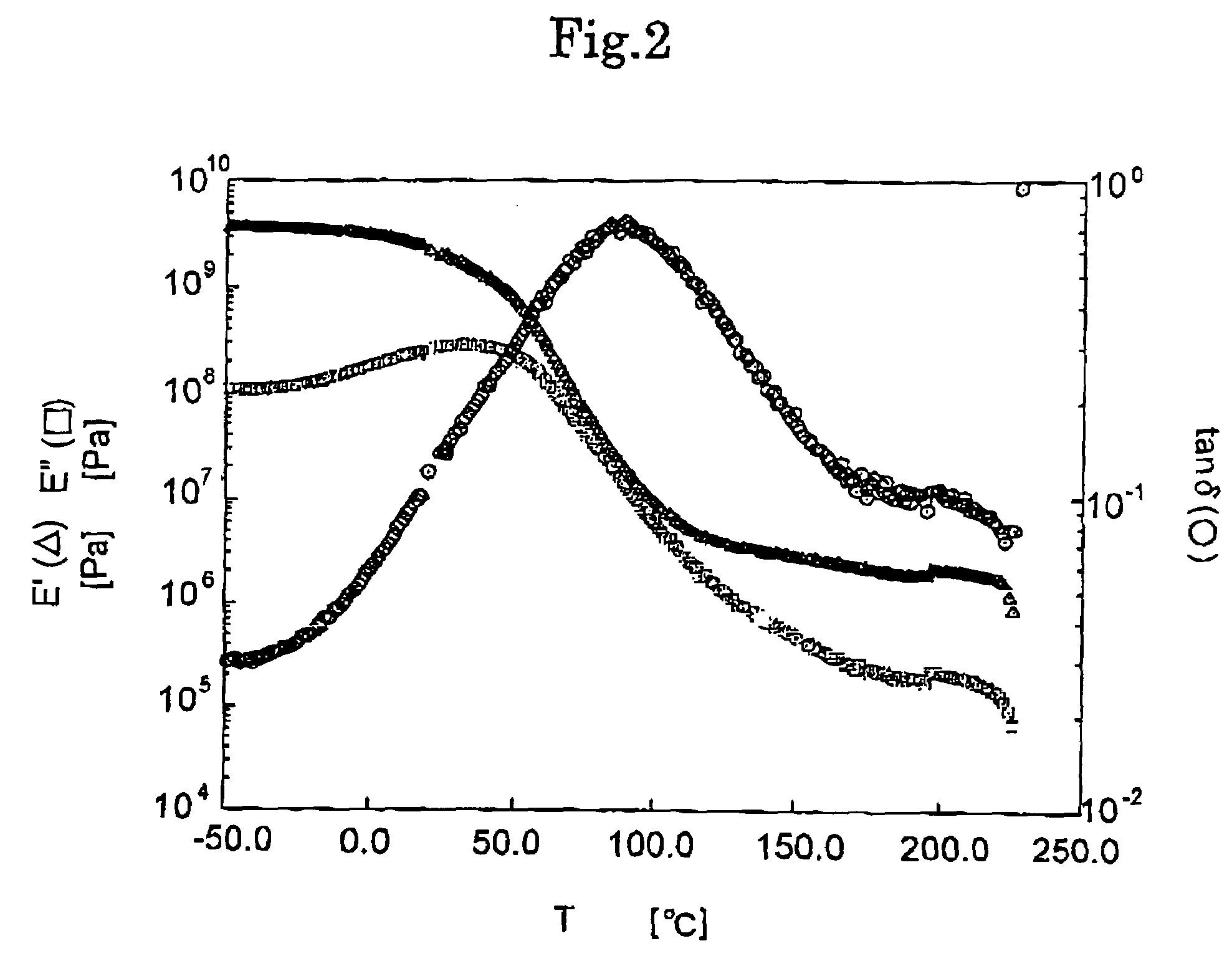

Resin composition and method for producing circuit board

ActiveUS20130337188A1Improve absorption rateImprove circuit board productivityLight absorption dielectricsRadiation applicationsUv absorberWavelength

The present invention relates to a resin composition which includes a copolymer consisting of a first monomer containing a monomer unit having at least one carboxyl group and a second monomer copolymerizable with the first monomer, and also includes an ultraviolet absorber. The resin composition used is a resin composition for which, when ∈1 represents an absorbance coefficient per unit weight of a resin film 2 in a solution prepared by dissolving, in a solvent, the resin film 2 formed by application of the resin composition as a liquid, ∈1 at a light wavelength at which the resin film 2 is to be irradiated is at least 0.01 (L / (g·cm)).

Owner:PANASONIC CORP

Method for fabricating touch sensor panels

InactiveCN102346593ALow costReduce operating costsDual purpose resistAdhesivesResistConductive materials

A method for fabricating a touch sensor panel is disclosed. The method includes providing a substrate for the touch sensor panel, depositing a conductive material layer on a top surface of the substrate, depositing a metal layer on top of the conductive material layer, affixing a resist to a first area of the metal layer, the resist also adapted to serve as a passivation layer during passivation, removing metal from the metal layer outside of the first area; and performing passivation on the substrate while leaving the affixed resist intact.

Owner:APPLE INC

Non-photopolymerization PCB solder resist ink windowing and solder resist oil bridge process

InactiveCN113163615ASolve the problem of solder mask window deviationDual purpose resistNon-metallic protective coating applicationSurface cleaningHigh pressure water

The invention discloses a non-photopolymerization PCB solder resist ink windowing and solder resist oil bridge process, which is used for high-precision PCB micro bonding pad solder resist ink windowing and solder resist oil bridge, and comprises the following steps of S1, manufacturing a blocking point screen, S2, silk-screening ink, S3, carrying out pre-baking treatment, S4, carrying out ink leveling treatment, and leveling the pre-baked solder resist ink by adopting an ink leveling machine, S5, drying and curing treatment: carrying out high-temperature drying and curing on the printed circuit board with the ink leveled, S6, grinding treatment: grinding the ink on the copper surface of the bonding pad to completely expose the copper layer of the bonding pad, and S7, cleaning and drying treatment: cleaning and drying the ground PCB through a horizontal surface cleaning machine, and carrying out micro-etching leveling and cleaning on the exposed copper surface by using a micro-etching leveling liquid and high-pressure water. The process is suitable for any-sizepad windowing and solder resist oil bridge manufacturing, and a powerful quality guarantee is provided for electronic products which are more and more integrated and precise.

Owner:东莞市春瑞电子科技有限公司

Chip part manufacturing method and chip parts

ActiveUS20100255638A1Avoid deformationAvoid problemsPrinted circuit aspectsDual purpose resistMetalElectrical and Electronics engineering

The present invention provides a chip part manufacturing method comprising a separating process capable of suppressing deformation of chip parts, and also provides chip parts. It comprises a step of forming a plurality of frame-like void portions (32) in one main surface of substrate (30) and insulating resin layer (20) having a spiral void portion (40) disposed in the region thereof, a step of forming metal layer (36) in frame-like void portion (32) and spiral void portion (40) and on insulating resin layer (20), a step of polishing metal layer (36) at least up to the upper surface of insulating resin layer and forming coil section (18) in spiral void portion (40), and a step of forming a metal layer for connecting chip parts to frame-like void portion (32), wherein the metal layer is melted and removed by using an etching agent to separate a plurality of chip parts connected to each other by a frame-like connection.

Owner:PANASONIC CORP

Popular searches

Printed circuits structural associations Multilayer circuit manufacture Photomechanical apparatus Transparent dielectrics Cable/conductor manufacture Circuit optical details Liquid/solution decomposition chemical coating Special surfaces Conductive material chemical/electrolytical removal Non-linear optics