Patents

Literature

49results about How to "Complex function" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

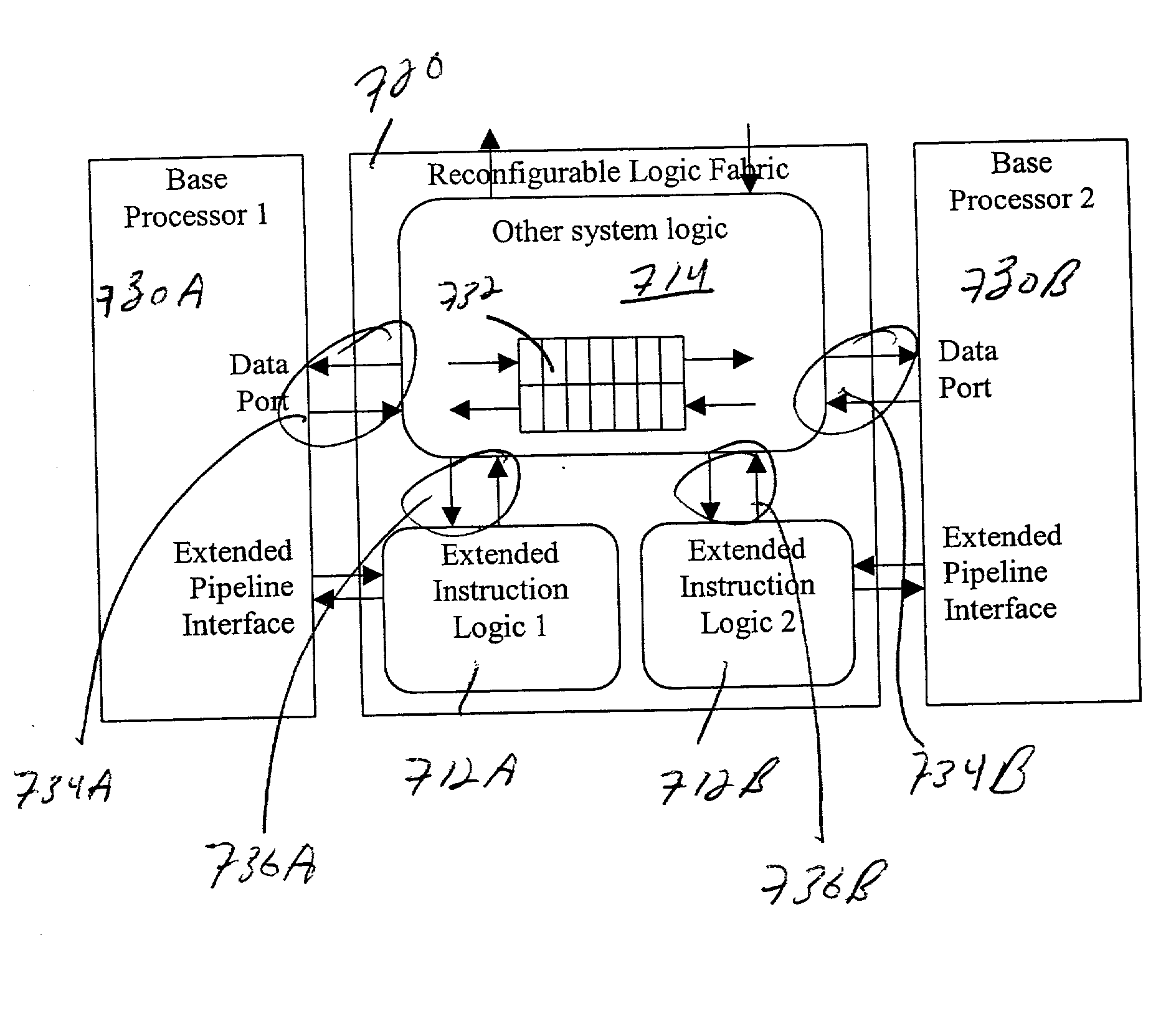

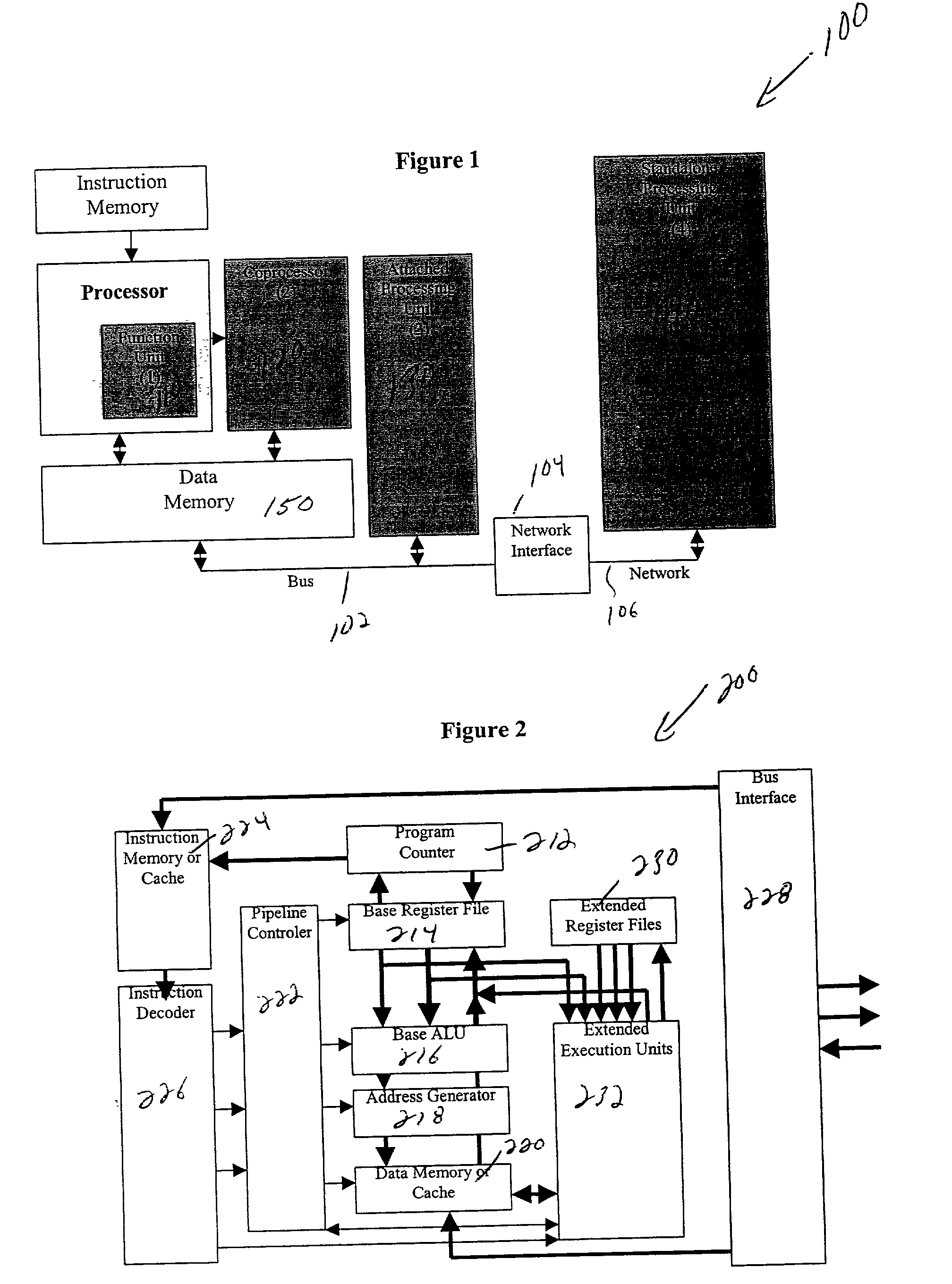

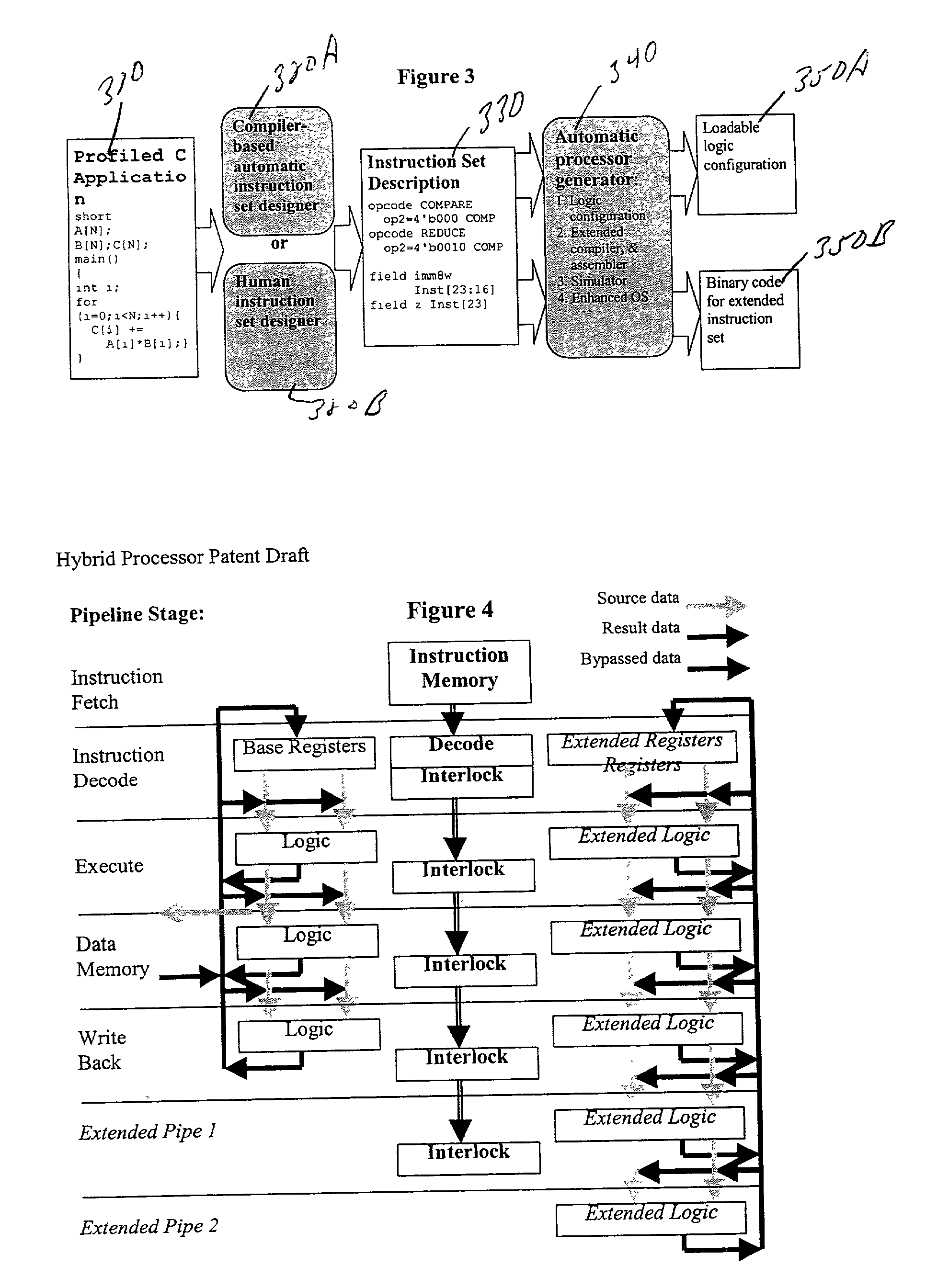

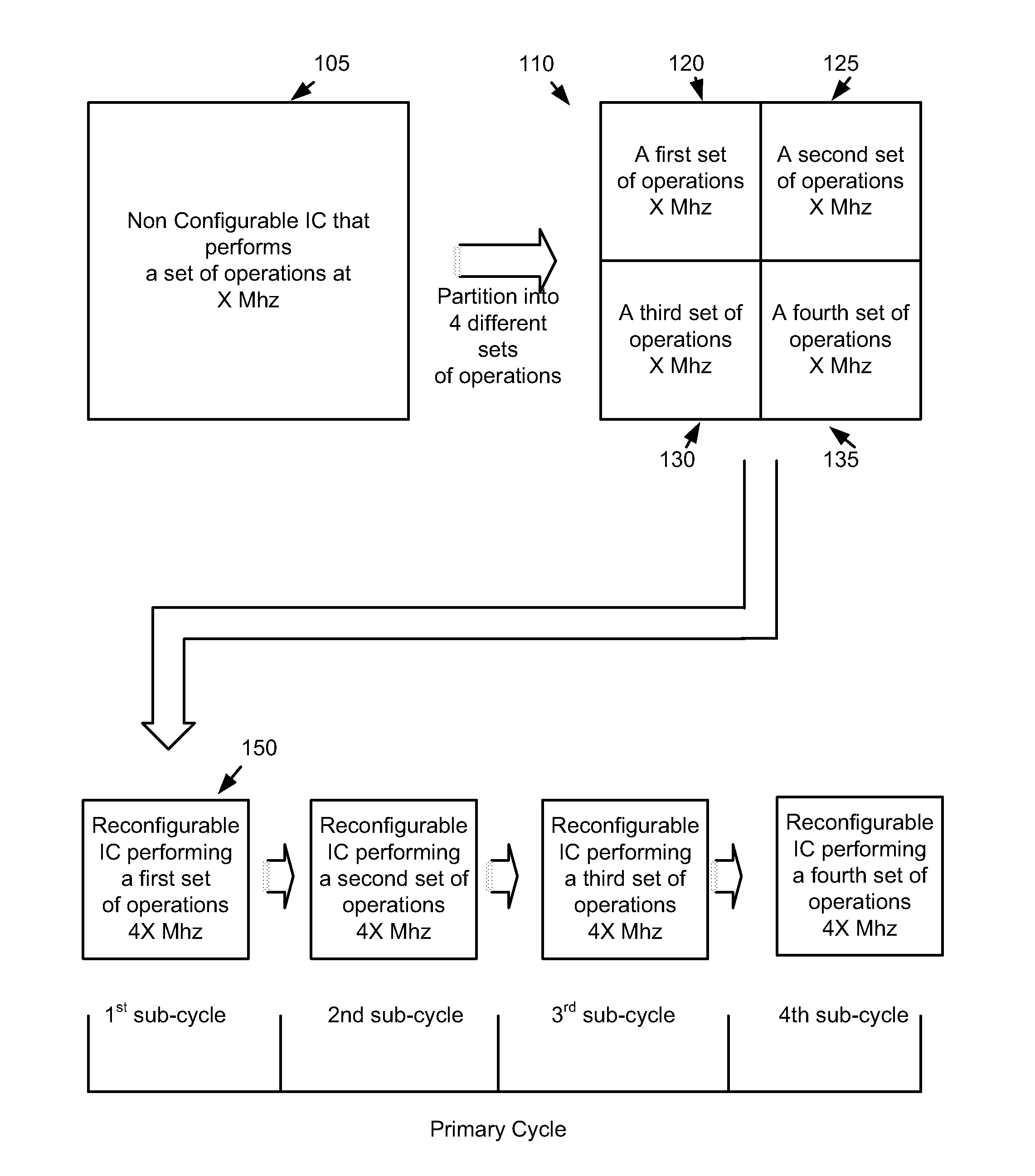

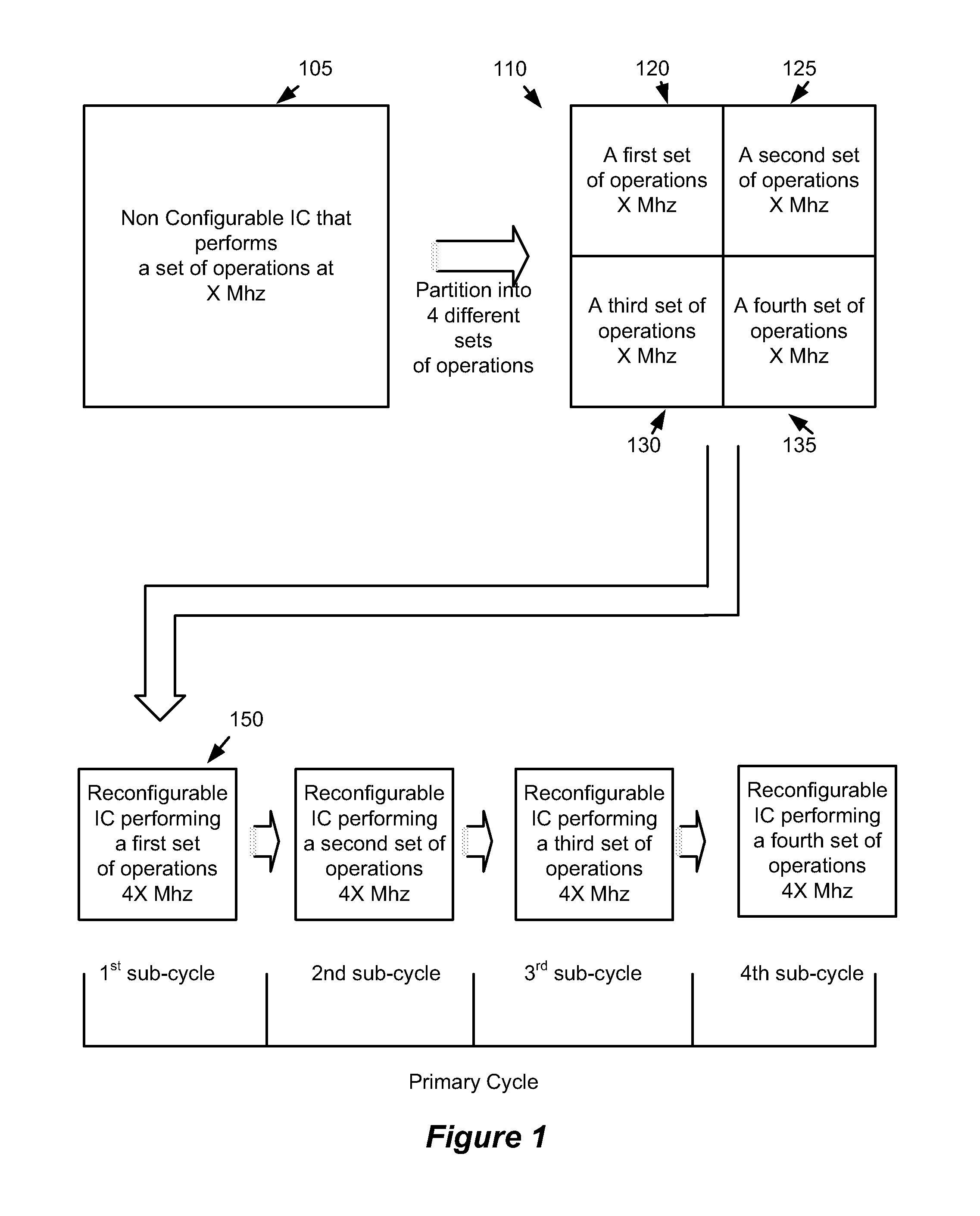

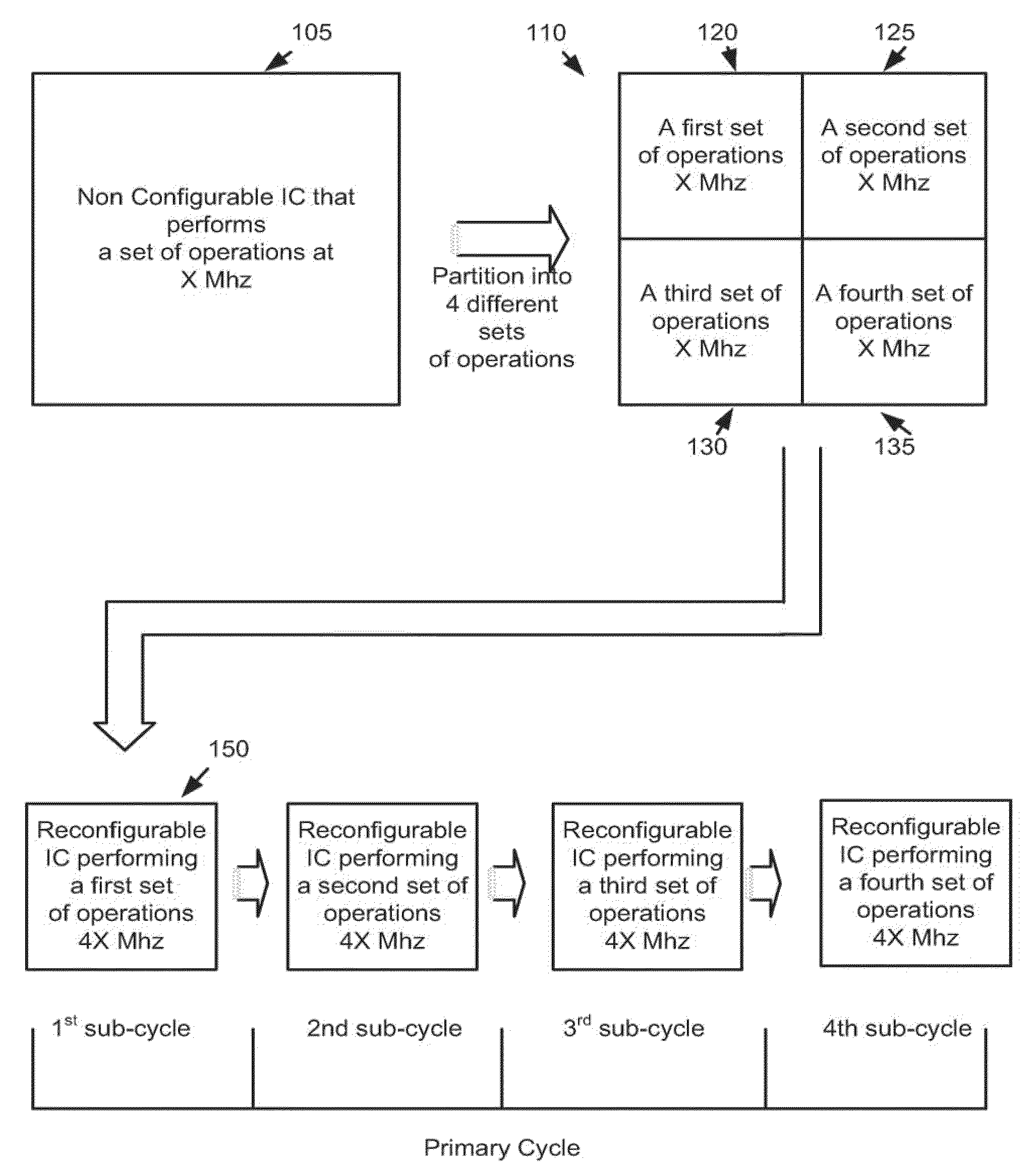

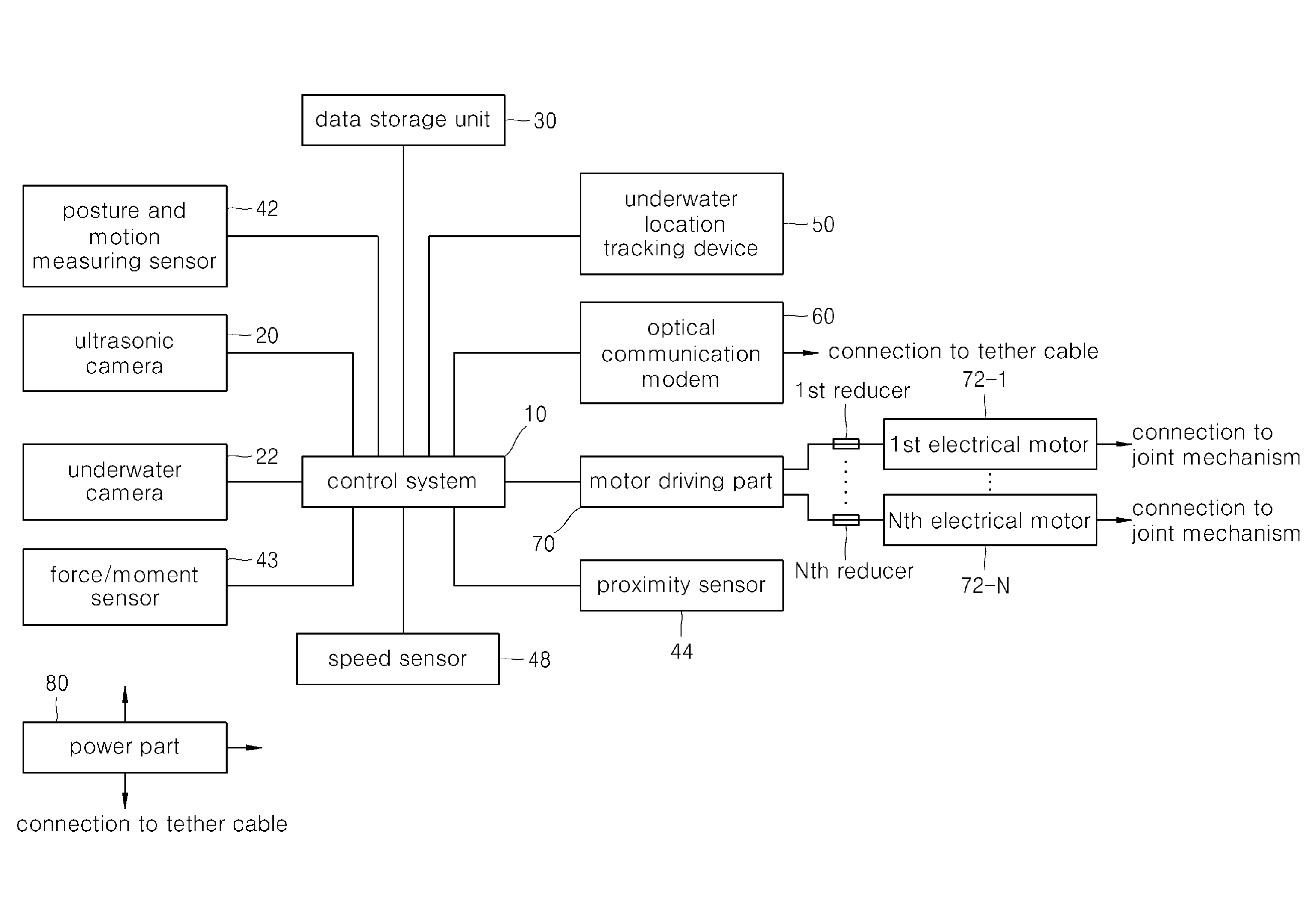

High-performance hybrid processor with configurable execution units

InactiveUS20050166038A1High bandwidthFlexibilityInstruction analysisConcurrent instruction executionHigh bandwidthLatency (engineering)

A new general method for building hybrid processors achieves higher performance in applications by allowing more powerful, tightly-coupled instruction set extensions to be implemented in reconfigurable logic. New instructions set configurations can be discovered and designed by automatic and semi-automatic methods. Improved reconfigurable execution units support deep pipelining, addition of additional registers and register files, compound instructions with many source and destination registers and wide data paths. New interface methods allow lower latency, higher bandwidth connections between hybrid processors and other logic.

Owner:TENSILICA

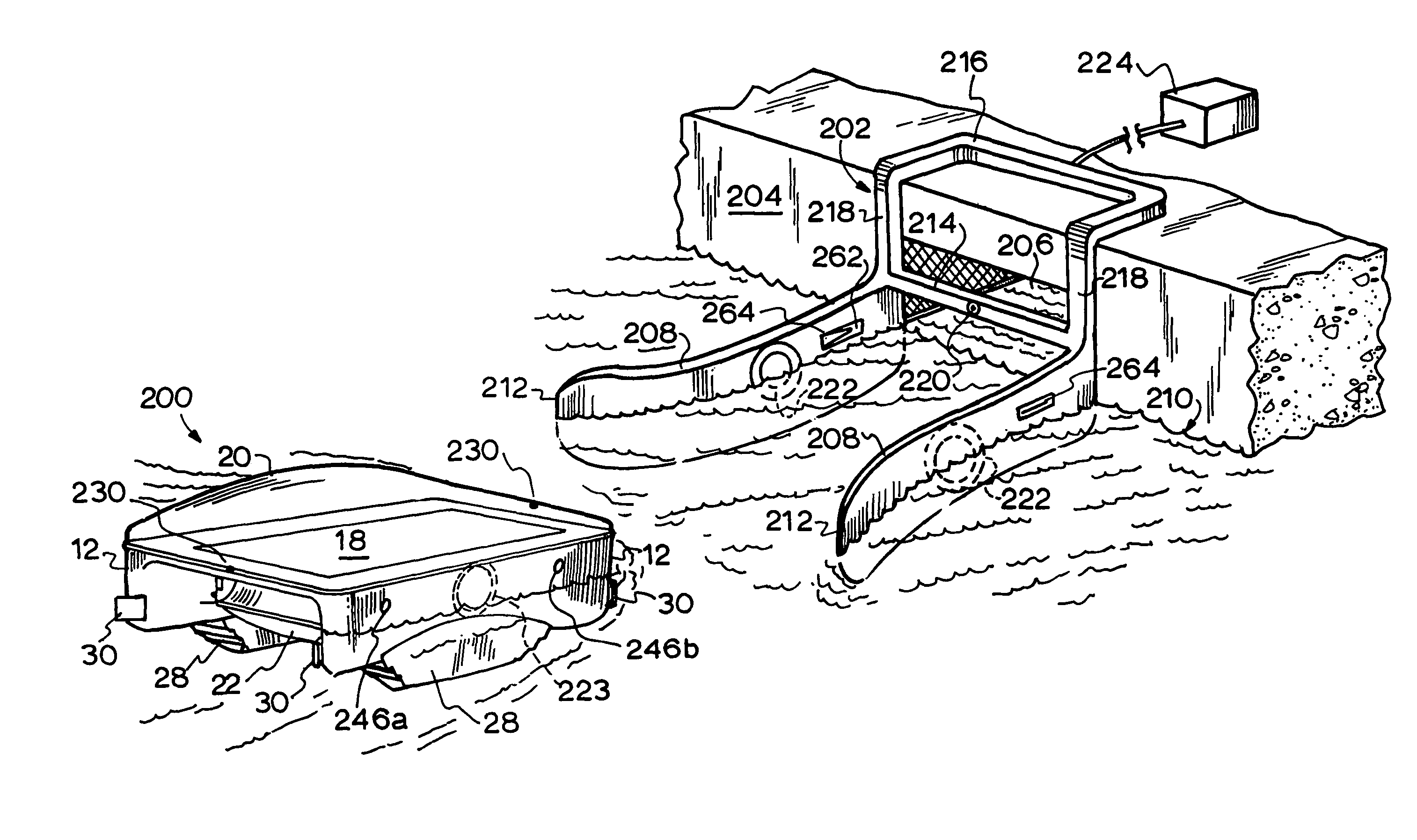

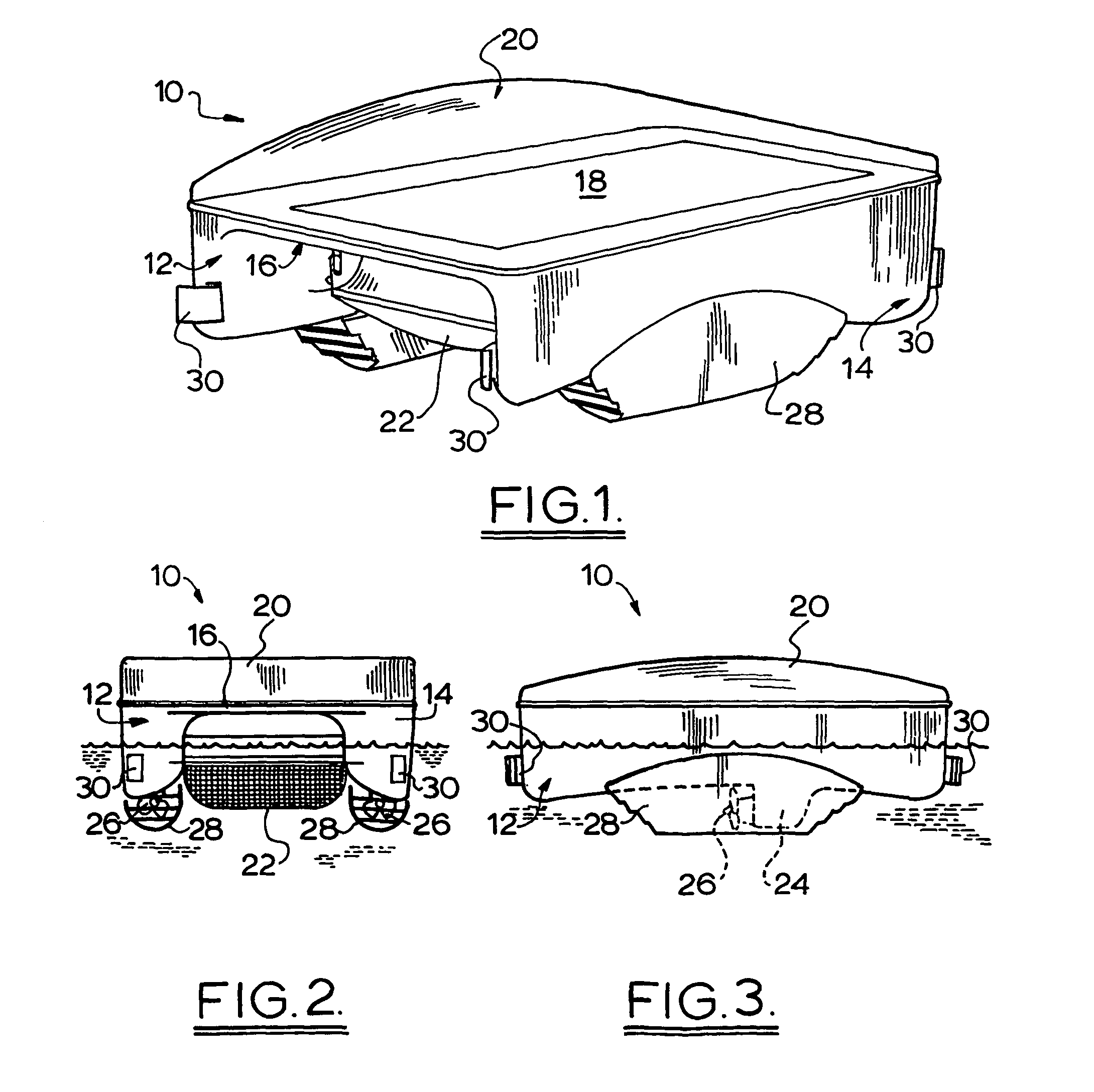

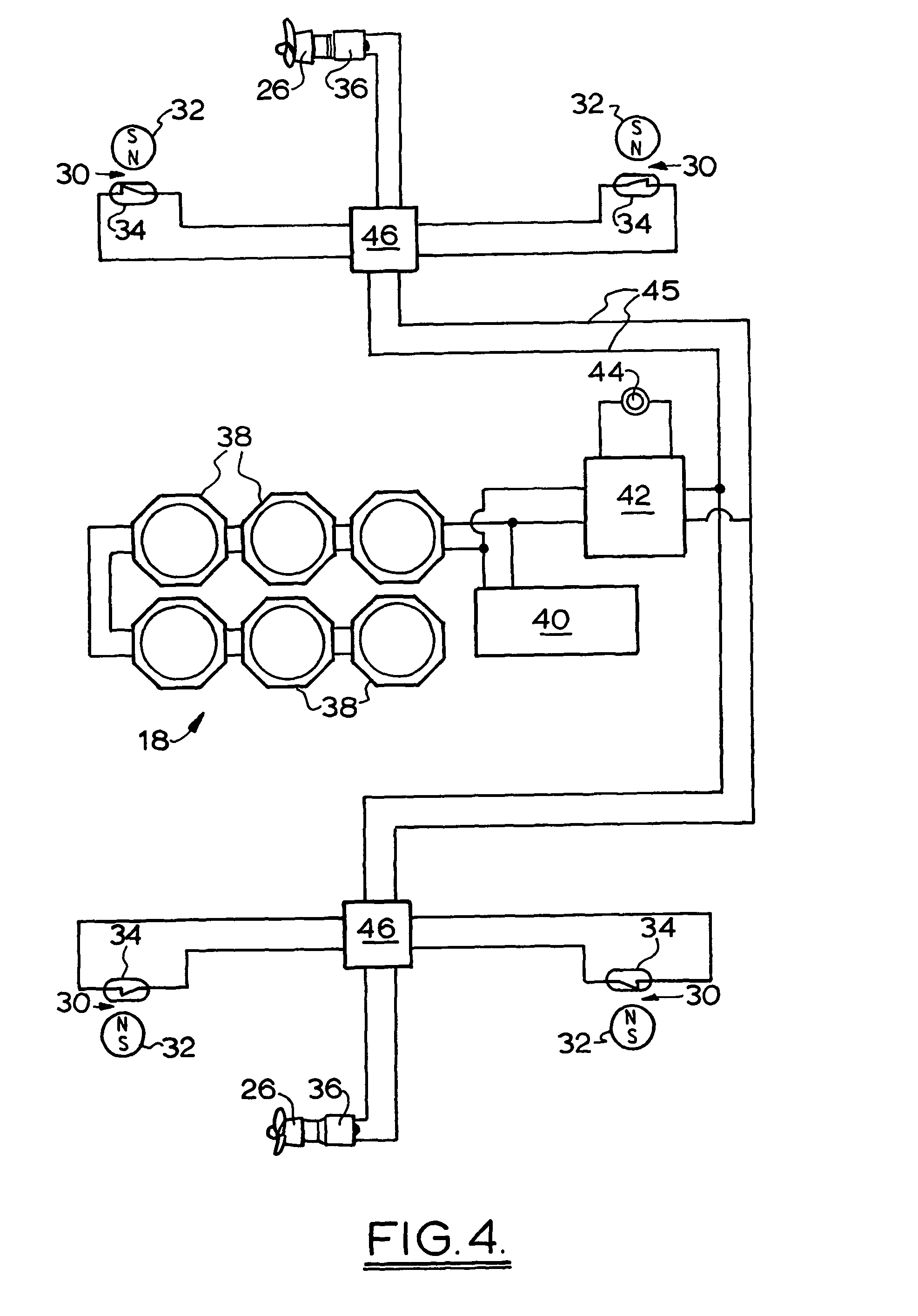

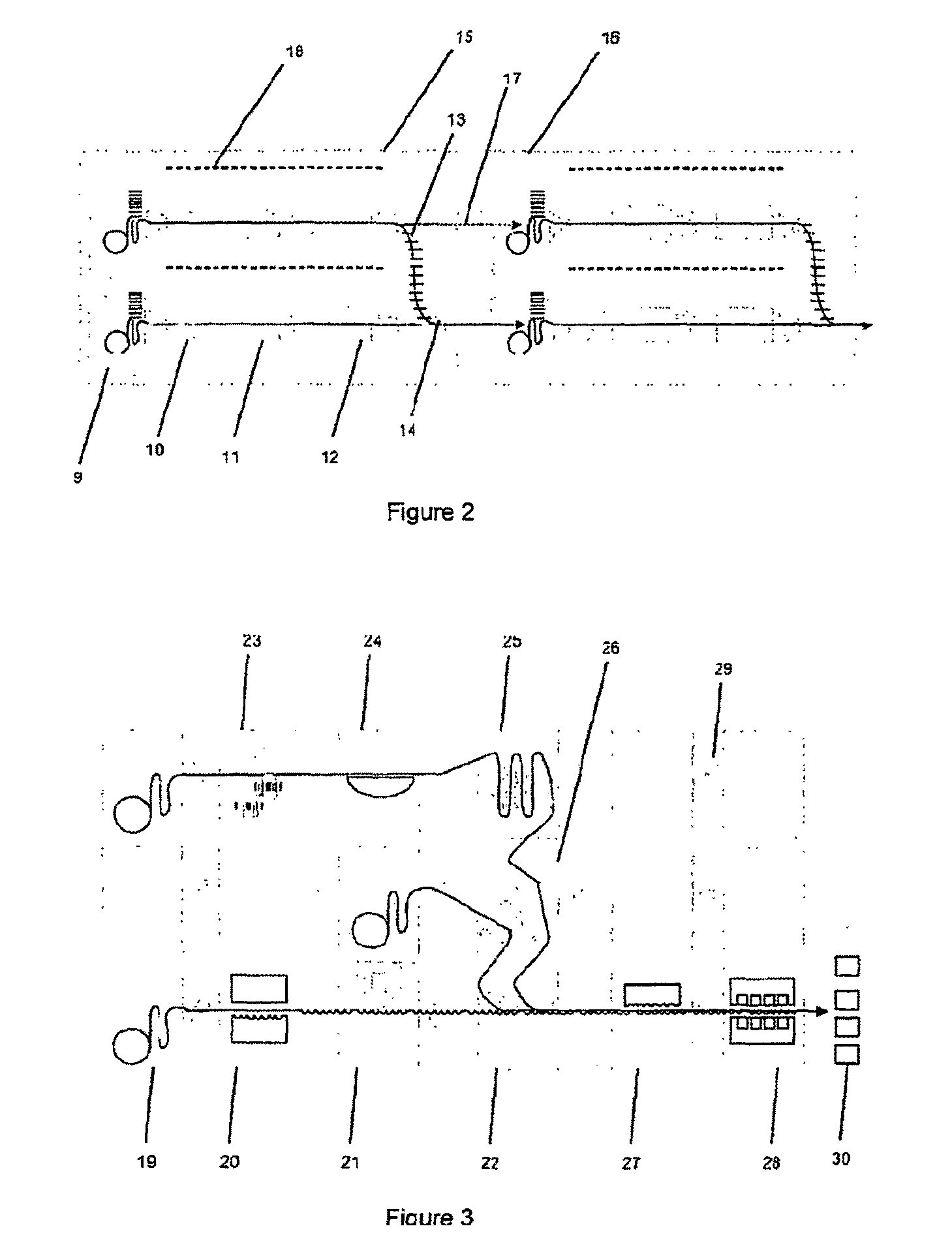

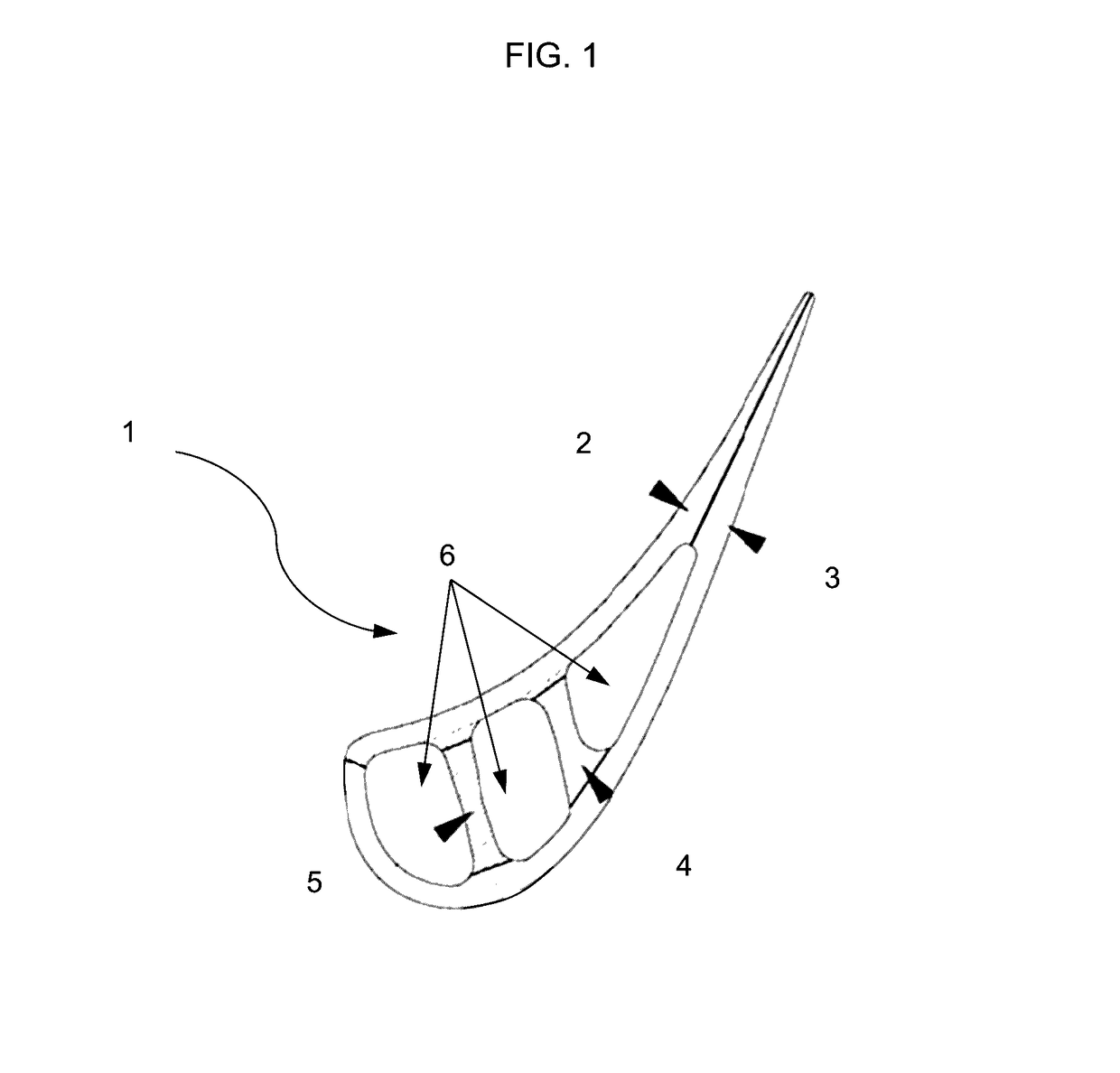

Dual direction water surface skimmer and pool side docking device

InactiveUS7037038B1Convenient lightingComplex functionWater cleaningCharging stationsMarine engineeringWater flow

A water skimmer vessel has two hulls (12, 14) between which a debris collection net or basket-like catcher (22) is arranged. Hinged flaps (68) are provided at each end of the catcher and operate to allow inflow but block outflow of debris from the catcher. Each hull of the vessel is equiped with amoter covered by a guard (28). The vessel may move in either direction and is equipped with sensors (30) on each hulll for effecting the turning and reversing of the vessel upon contact with pool skimmer box inlet (206) and the vessel can be controlled to enter the dock and permit the contents of the catcher to be discharged into the current of pool water flowing into the skimmer box.

Owner:HASKI ROBERT R

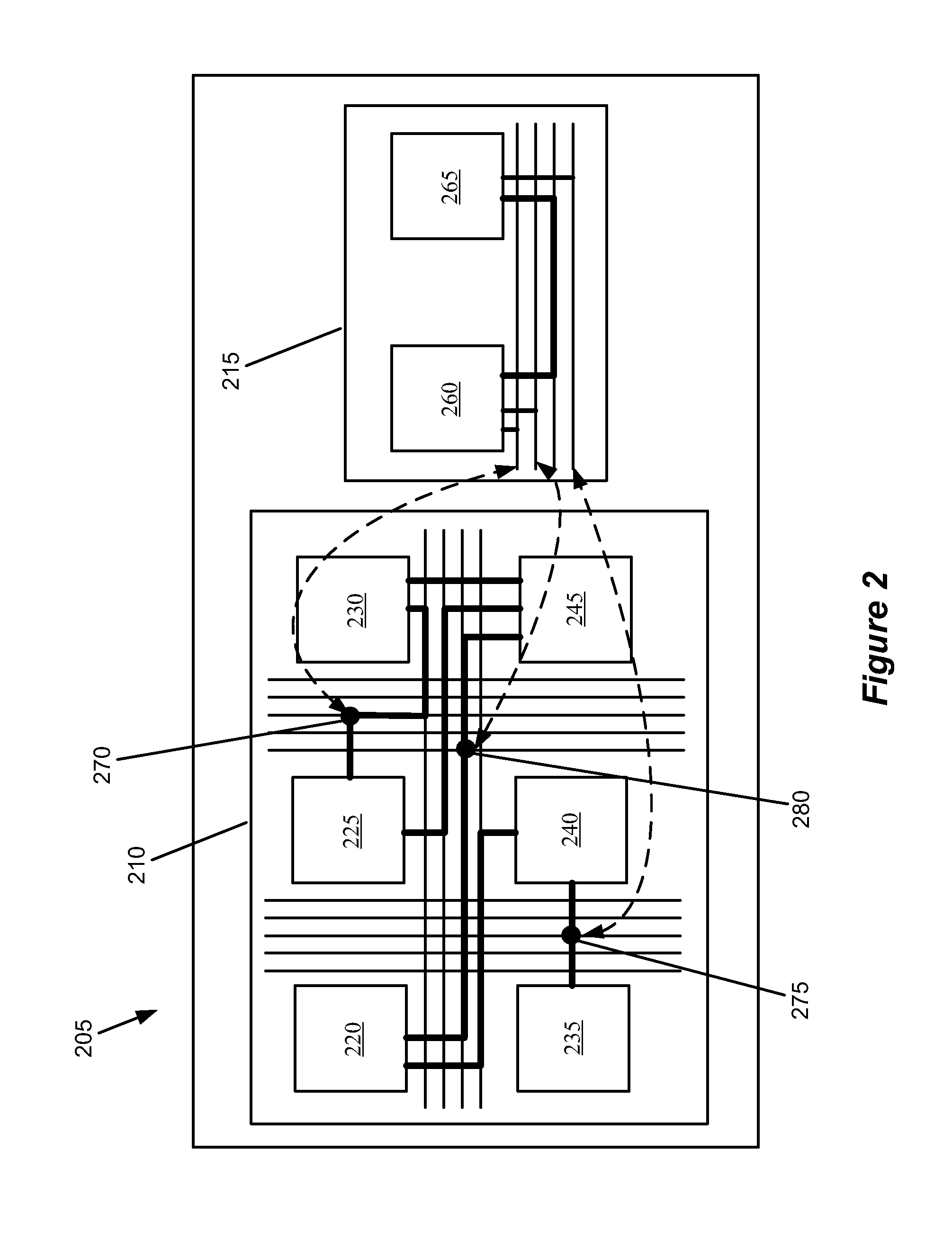

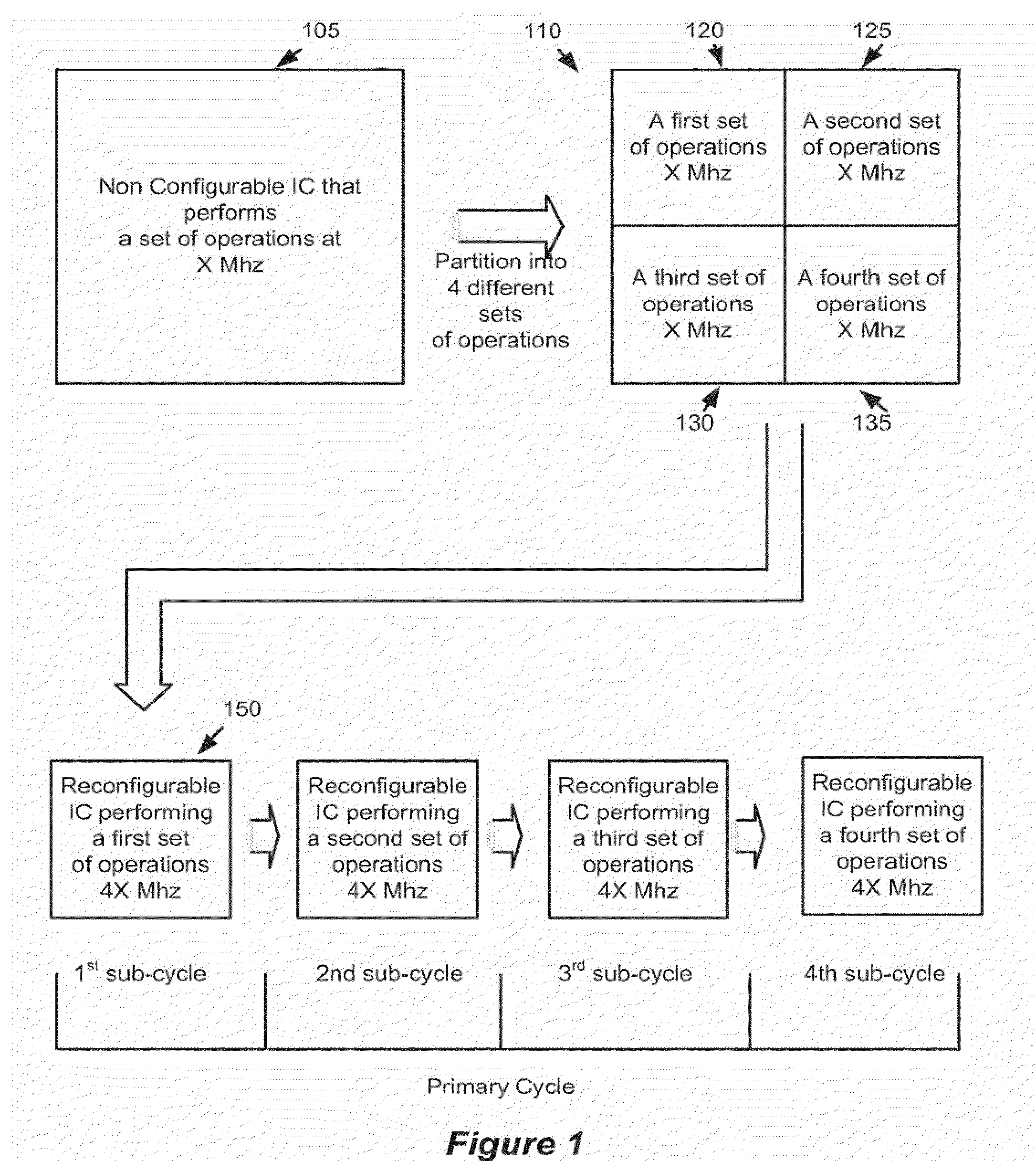

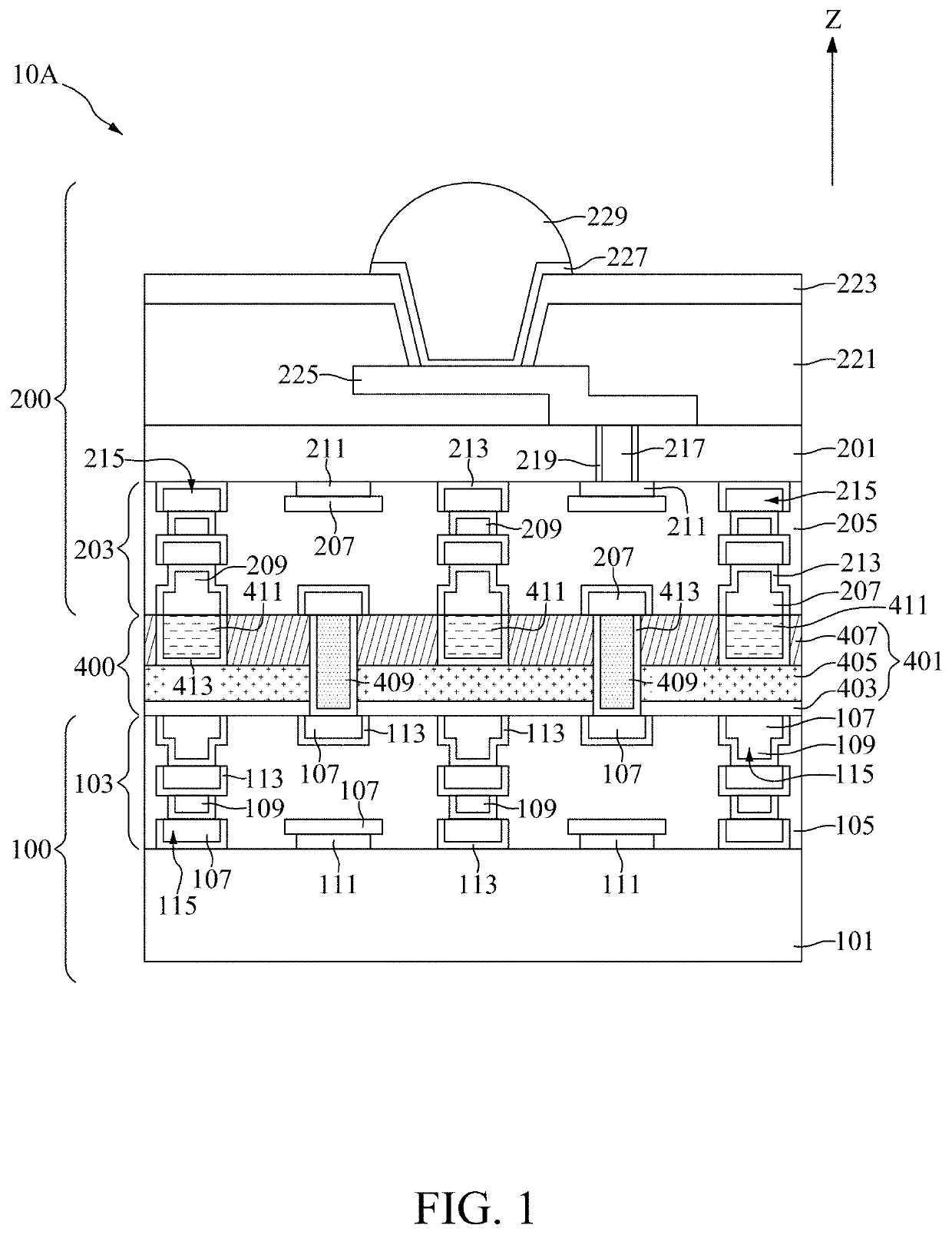

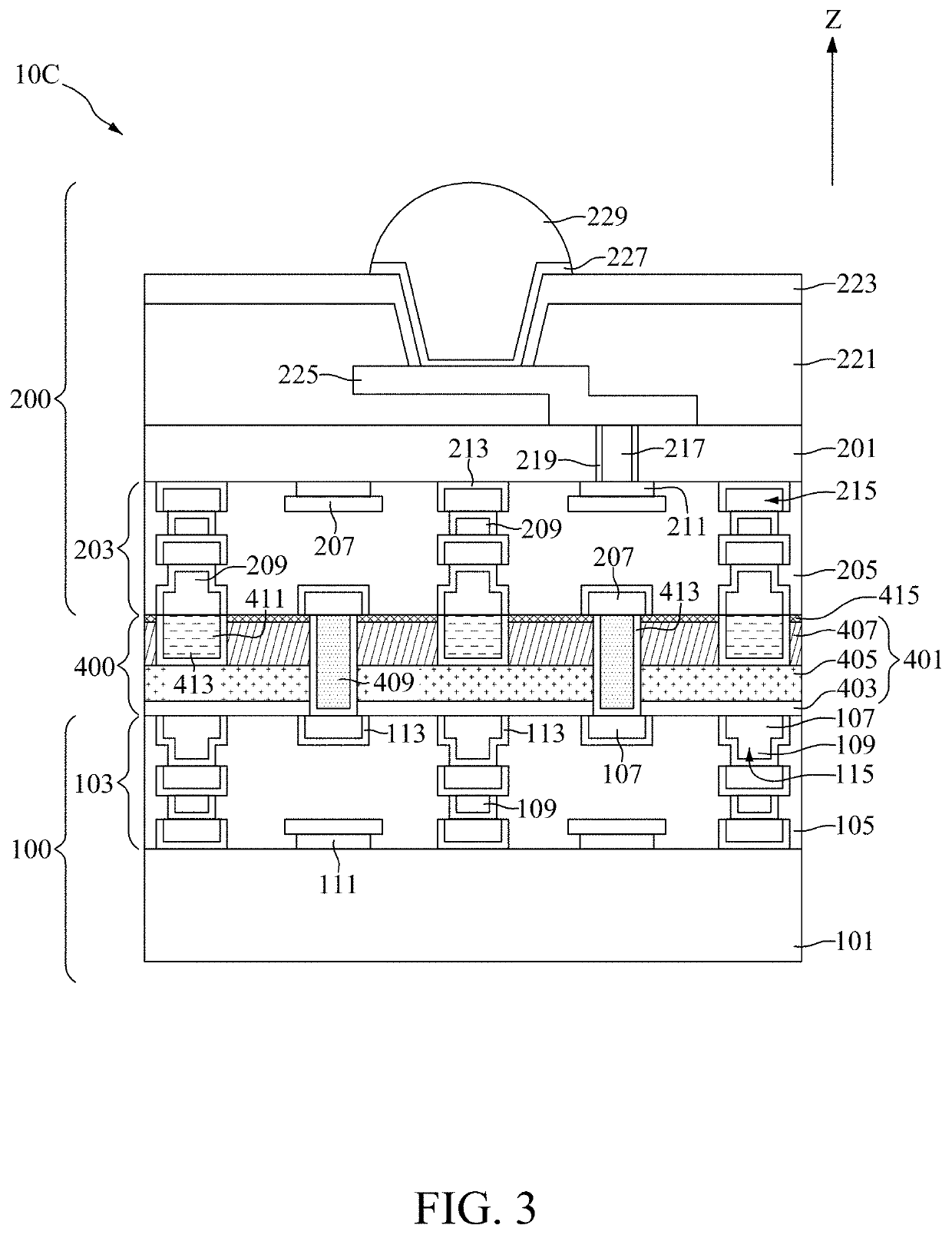

Integrated circuit (IC) with primary and secondary networks and device containing such an IC

ActiveUS20110029830A1Halt operation of systemComplex functionFault responseElectronic circuit testingEngineeringIntegrated circuit

Some embodiments provide an integrated circuit (“IC”) with a primary circuit structure. The primary circuit structure is for performing multiple operations that implement a user design. The primary circuit structure includes multiple circuits. The IC also includes a secondary monitoring structure for monitoring multiple operations. The secondary monitoring structure includes a network communicatively coupled to multiple circuits of the primary circuit structure. The secondary monitoring circuit structure is for analyzing the monitored operations and reporting on the analysis to a circuit outside of the IC.

Owner:ALTERA CORP

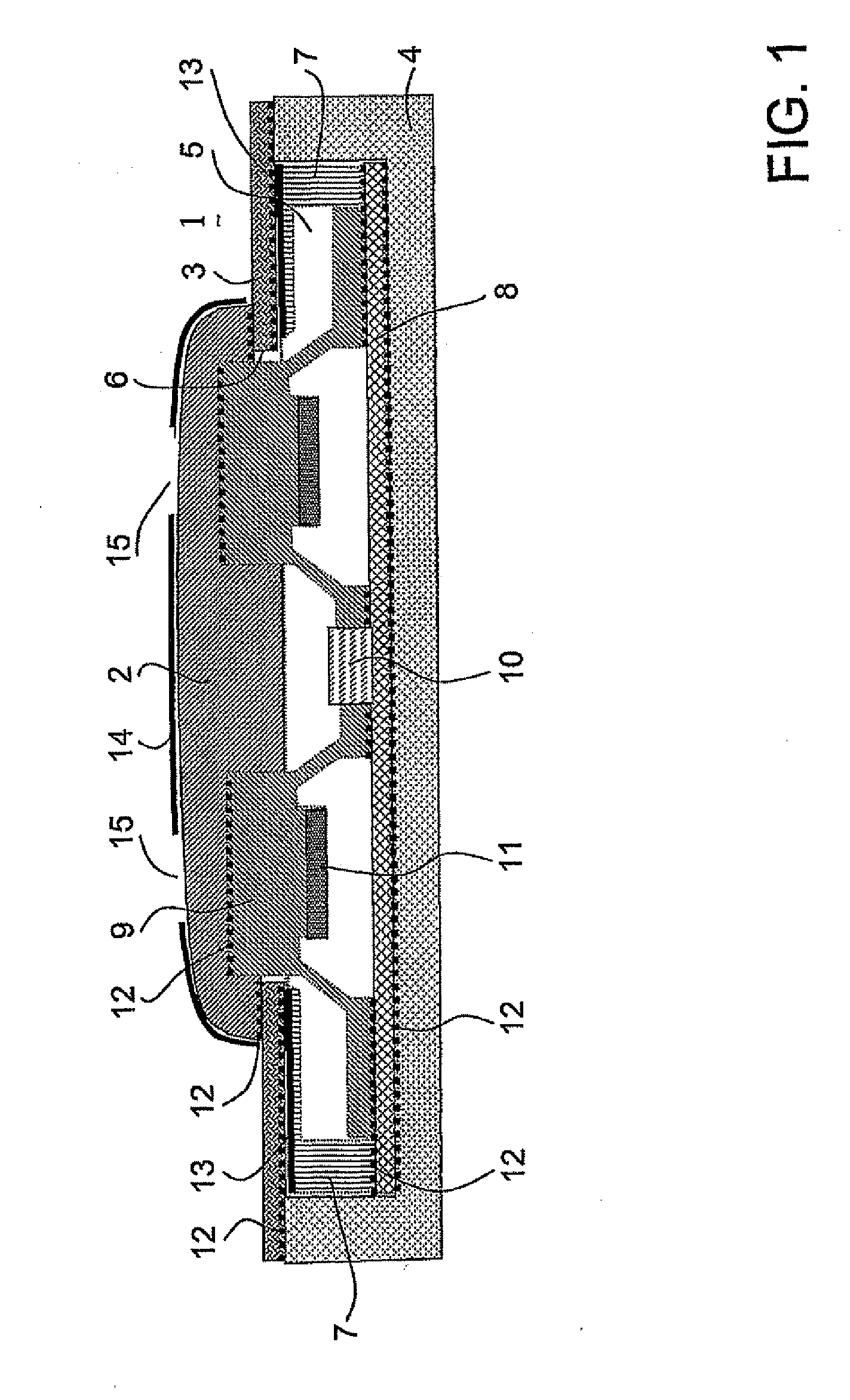

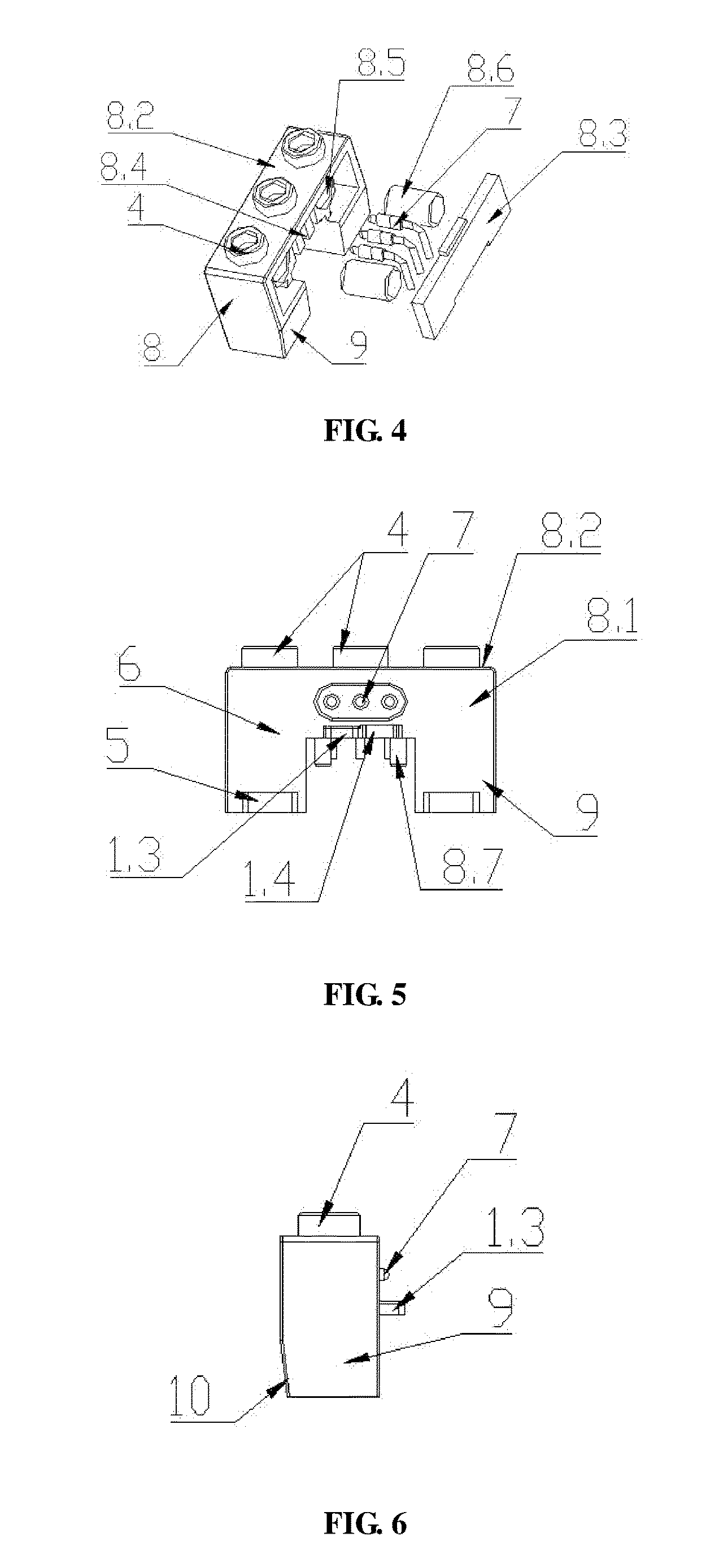

Integrated Switch or Integrated Button

InactiveUS20090301852A1Cost-effectiveComplex functionDashboard fitting arrangementsLegendsEngineeringPush-button

A switch, especially for use in the interior of a vehicle, which is to be embedded at least in part in or on a support that is covered, at least in the area of the switch, with a preferably flexible surface material on the surface thereof. The switch is disposed in an opening of the surface material while including a first zone located substantially in the support and a second push button used for triggering a function. The push button is embodied so as to cover at least some areas of the opening in the surface material and be non-positively and / or positively connected thereto. Also disclosed are a method for assembling such a switch as well as uses thereof as a window control and similar.

Owner:ABATEK INT

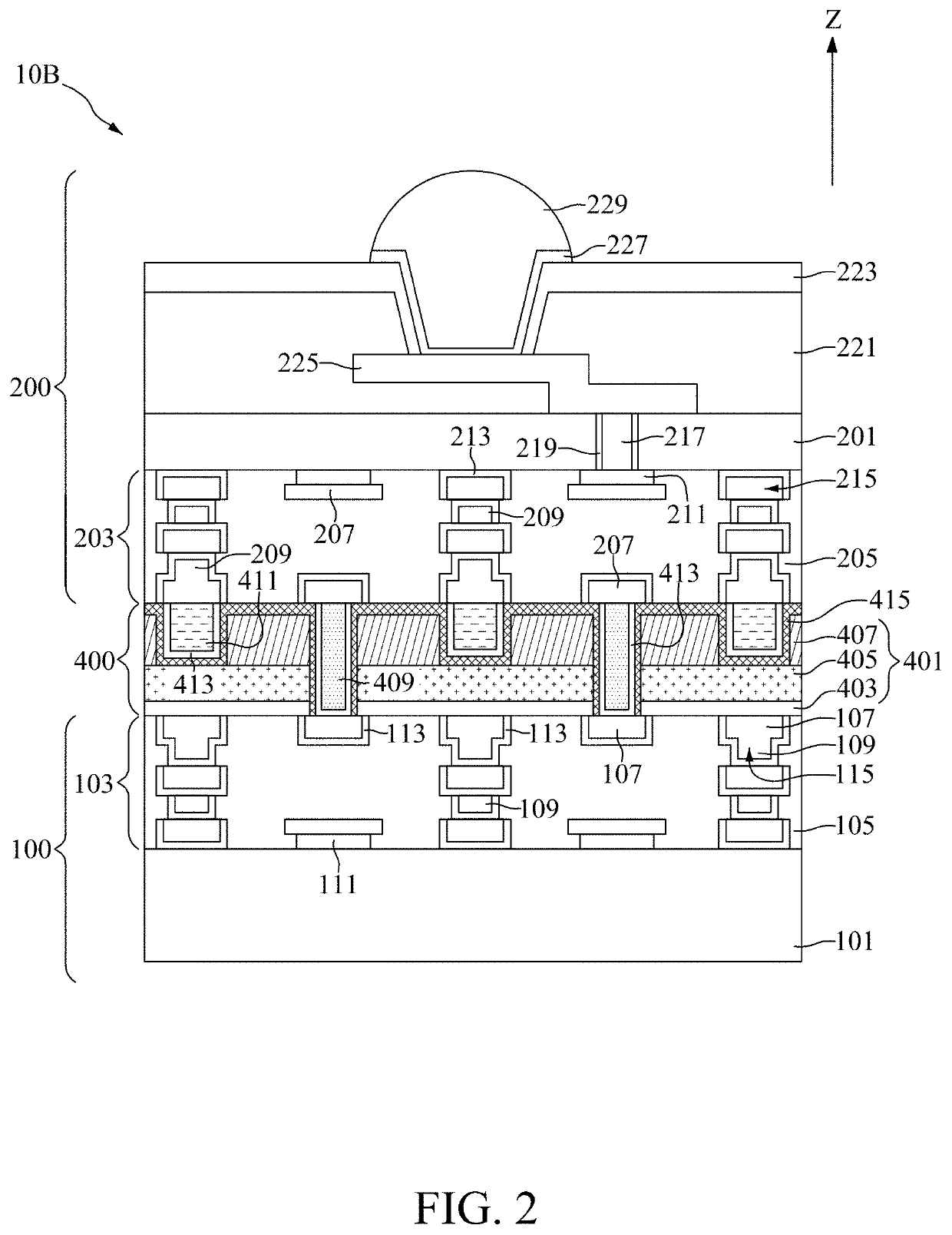

Intergrated circuit (IC) with primary and secondary networks and device containing such IC

ActiveUS20110060546A1Complex functionData detection is convenientResistance/reactance/impedenceElectronic circuit testingTelecommunicationsHemt circuits

Some embodiments provide an integrated circuit (“IC”) with a primary circuit structure. The primary circuit structure is for performing multiple operations that implement a user design. The primary circuit structure includes multiple circuits. The IC also includes a secondary monitoring structure for monitoring multiple operations. The secondary monitoring structure includes a network communicatively coupled to multiple circuits of the primary circuit structure. The secondary monitoring circuit structure is for analyzing the monitored operations and reporting on the analysis to a circuit outside of the IC.

Owner:ALTERA CORP

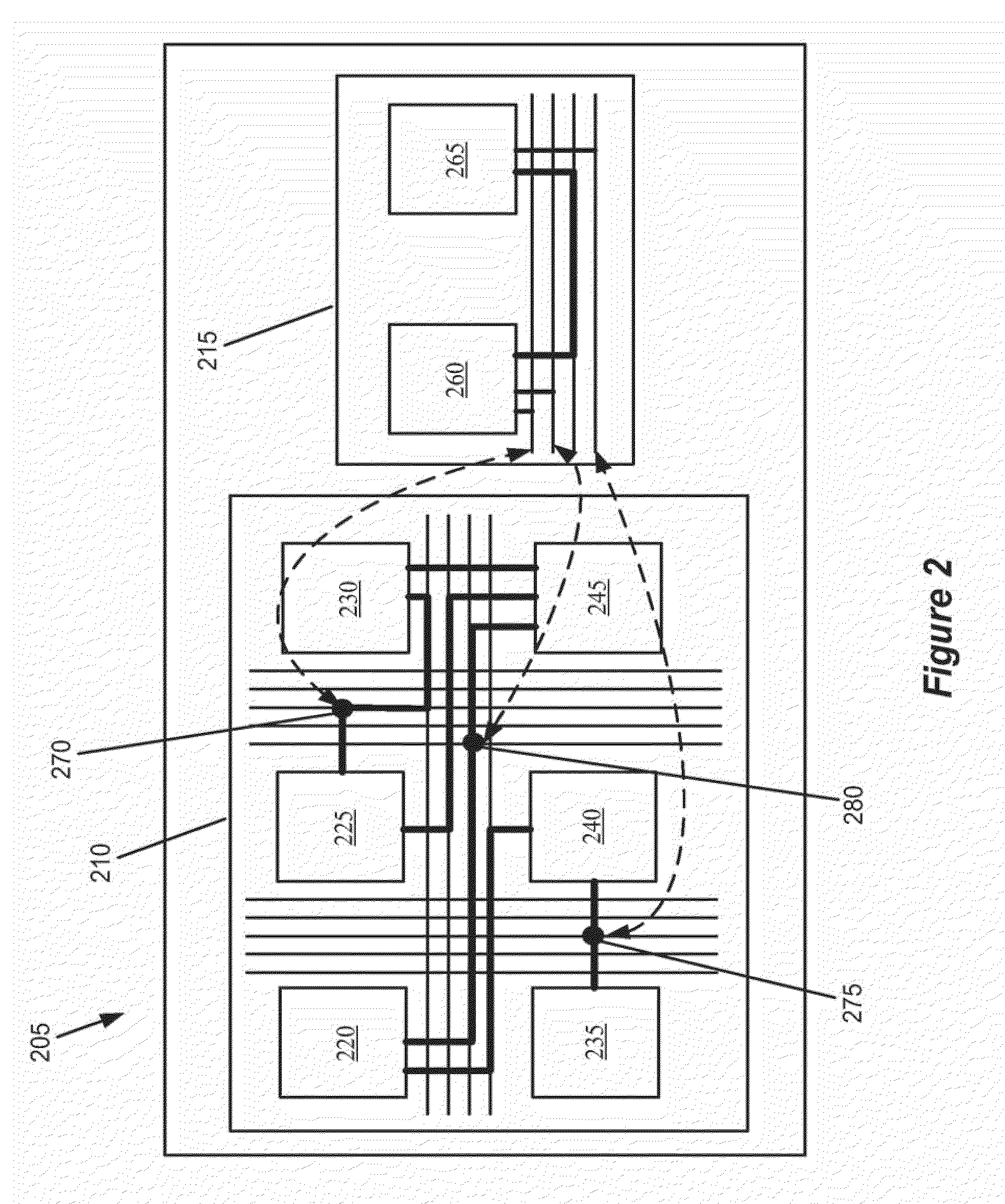

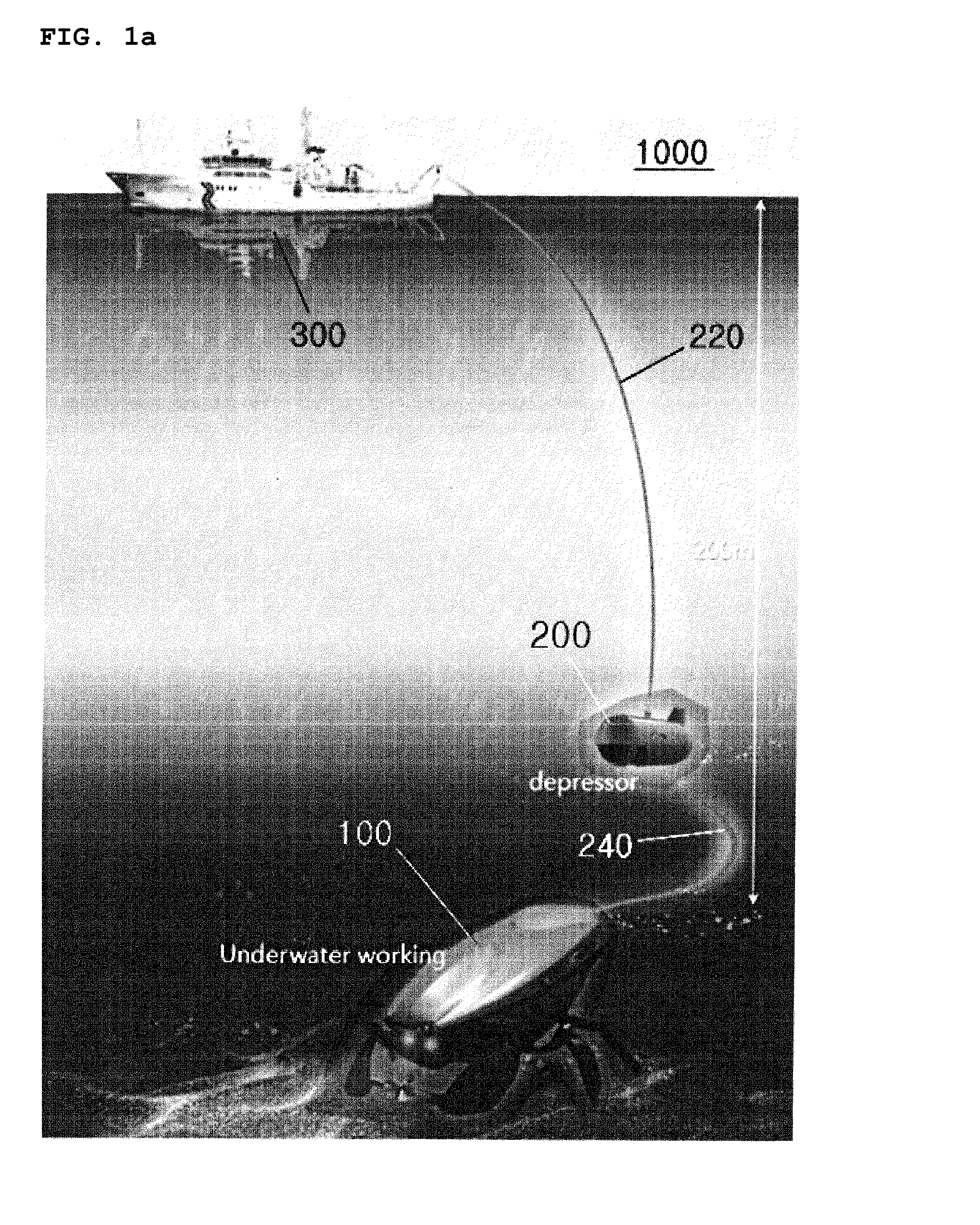

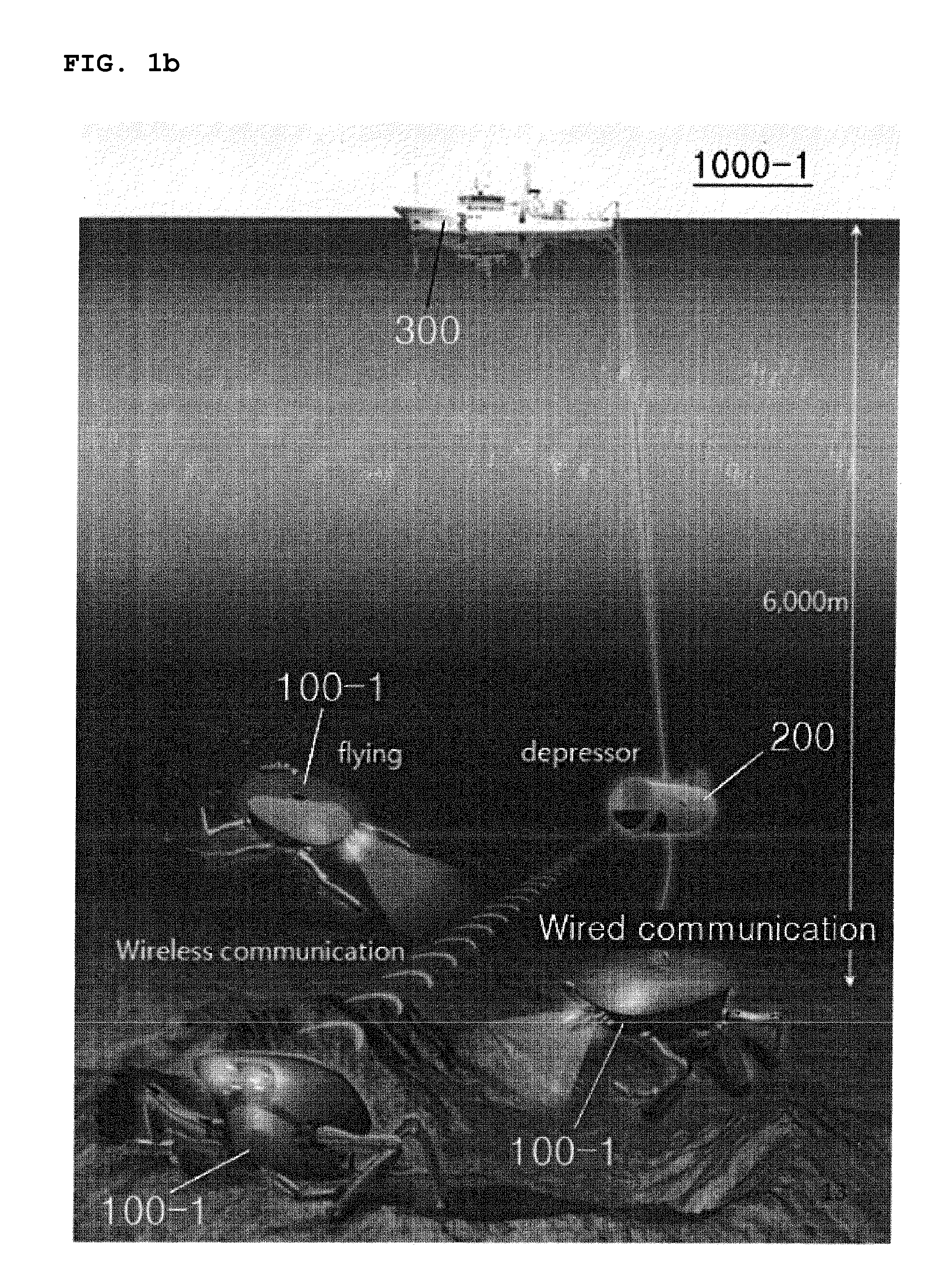

Multi-joint underwater robot having complex movement functions of walking and swimming and underwater exploration system using same

ActiveUS20140343728A1Complex functionEffective performanceProgramme controlProgramme-controlled manipulatorPropellerArthrobotrys

Disclosed is an underwater exploration system using a multi-joint underwater robot having a novel complex movement concept in which the multi-joint underwater robot moves through walking or swimming with multi-joint legs closely to a seafloor, differently from a conventional underwater robot to obtain a thrust through a propeller scheme. The underwater exploration system includes the multi-joint underwater robot having the complex movement function according, a depressor, and a mother ship to store data of an underwater state transmitted from the multi-joint underwater robot and to monitor and control a movement direction of the multi-joint underwater robot. The depressor is connected to the mother ship through a primary cable, the multi-joint underwater robot is connected to the depressor through a second cable, and resistance force of the primary cable is applied to the depressor without being transmitted to the multi-joint underwater robot.

Owner:KOREA INST OF OCEAN SCI & TECH

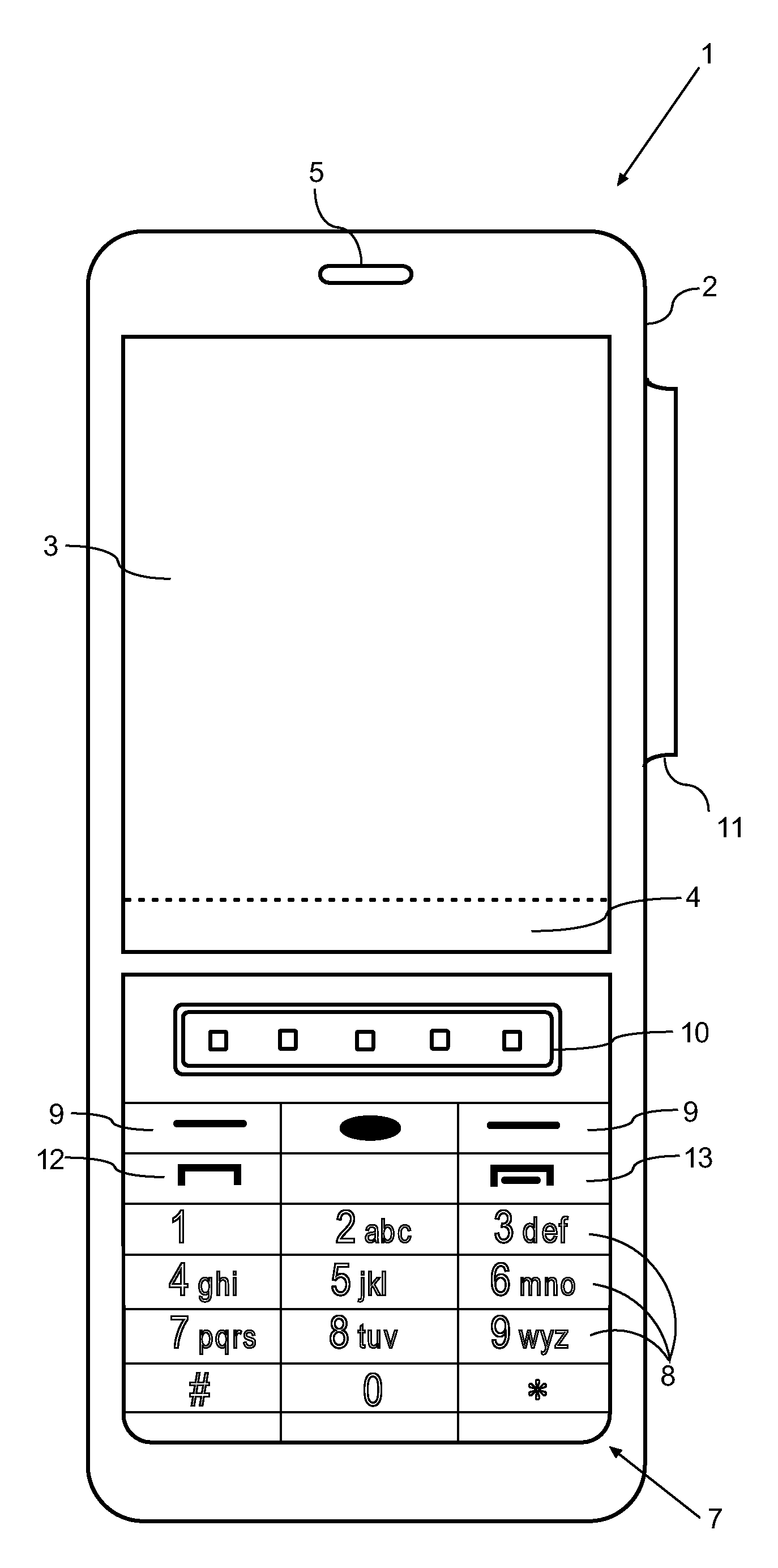

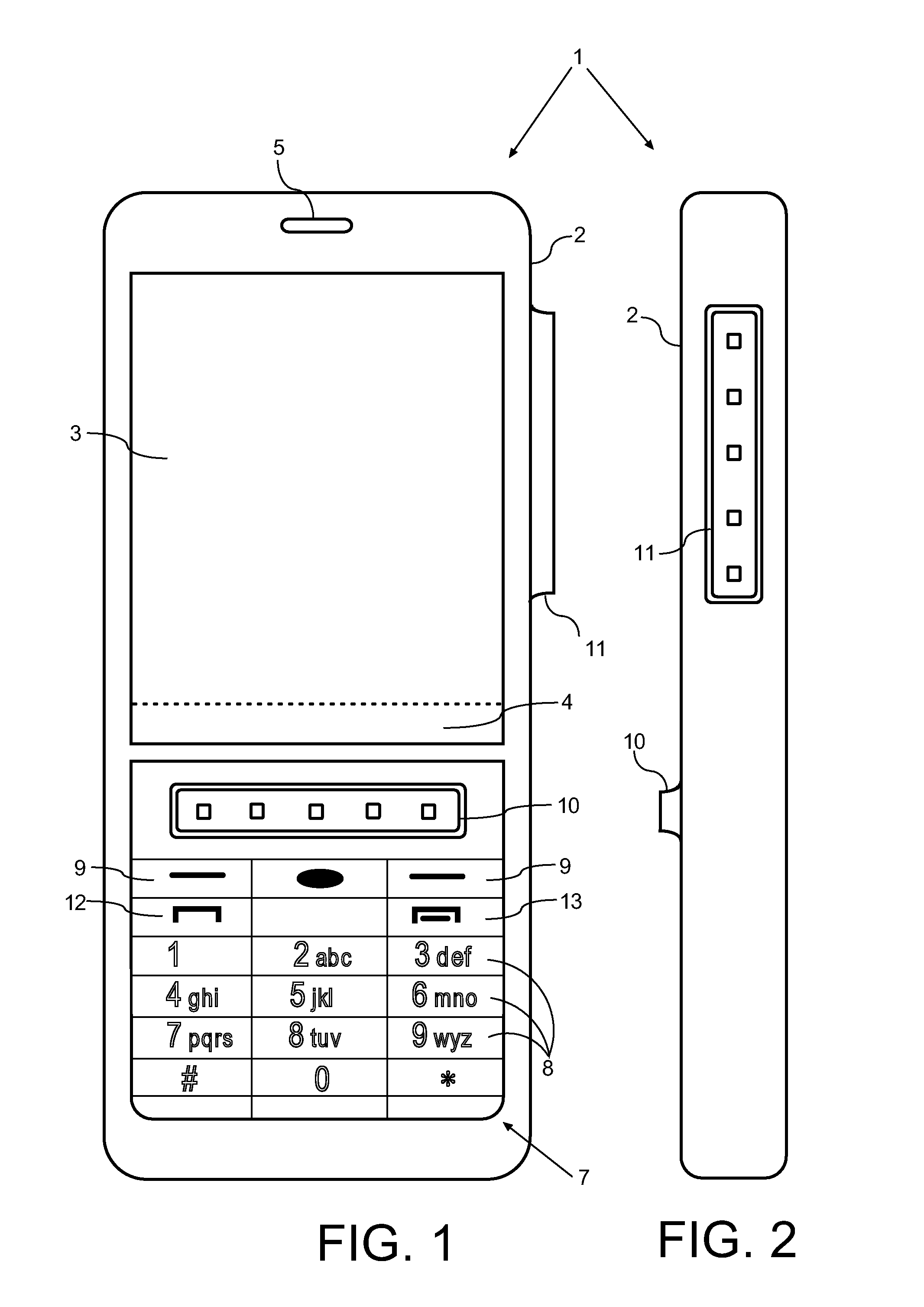

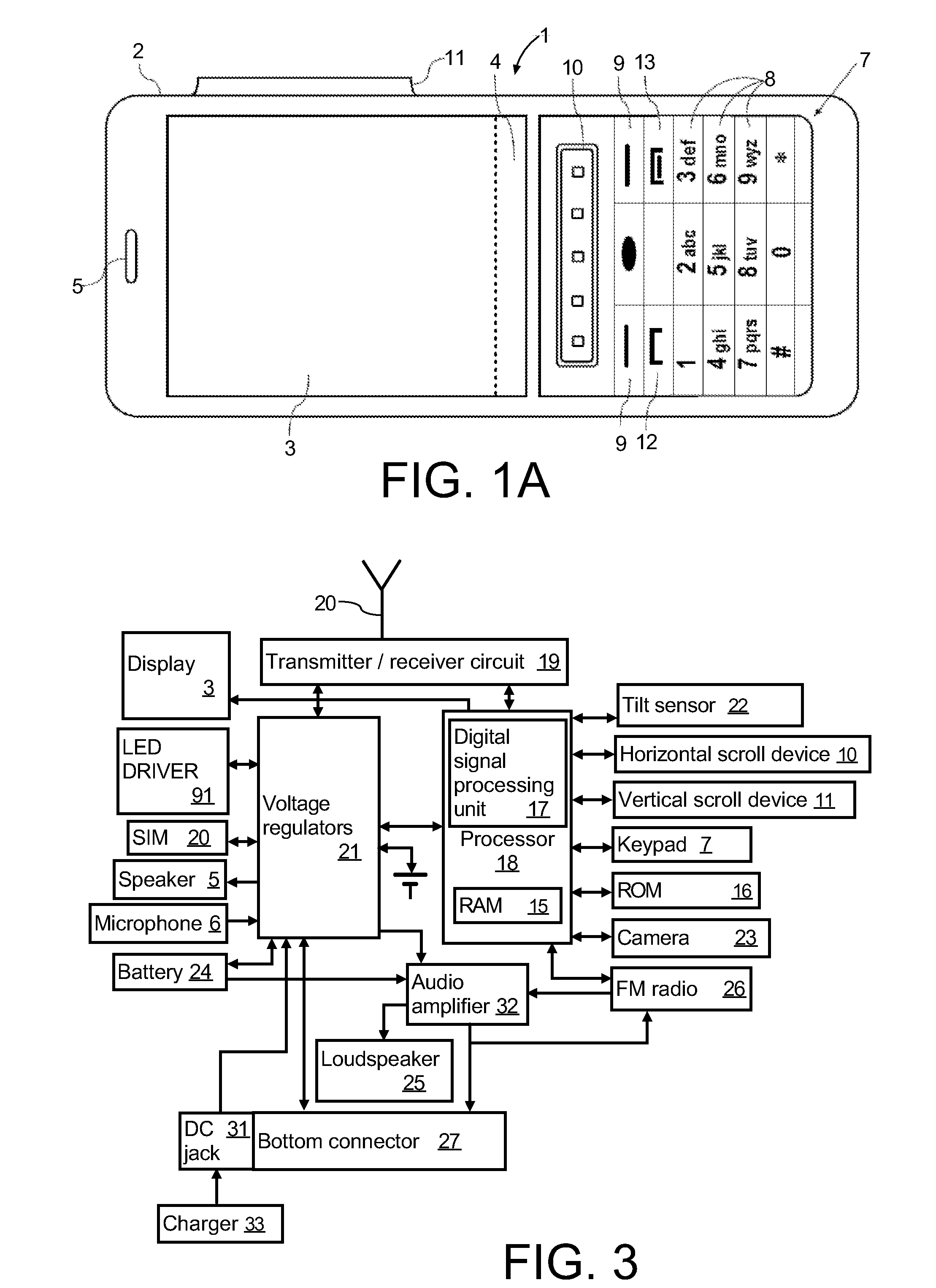

Mobile electronic device with competing input devices

InactiveUS20100201712A1Complex functionIncrease powerInput/output for user-computer interactionCathode-ray tube indicatorsComputer scienceMobile electronics

A mobile electronic device that can be used in at least two different orientations. The mobile electronic device comprises a processor, an orientation sensor, and at least two competing input devices. The processor is configured to enable and disable the competing input devices in accordance with the orientation of the mobile electronic device as detected by the orientation sensor. Alternatively, the processor is configured to assign different control functions to the competing input devices and possibly to interchange these control functions in response to a signal from the orientation sensor. The device may have a scrollbar that is an integral part of a keypad. The device may have a scrollbar that is wrapped around a corner of the device. The device may have two scrollbars that are arranged transversely to one another with the longitudinal extremity of the touch surface one of the scrollbars connecting to the touch surface of the other scrollbar.

Owner:NOKIA CORP

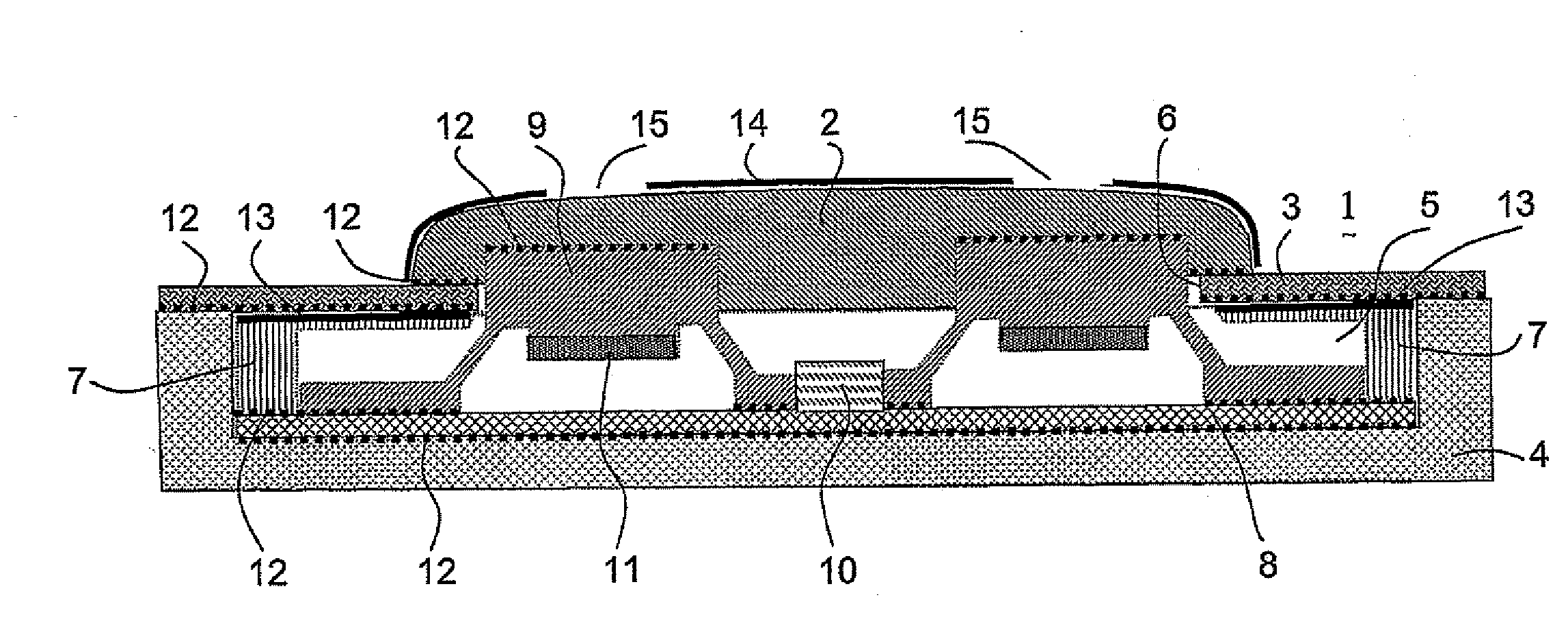

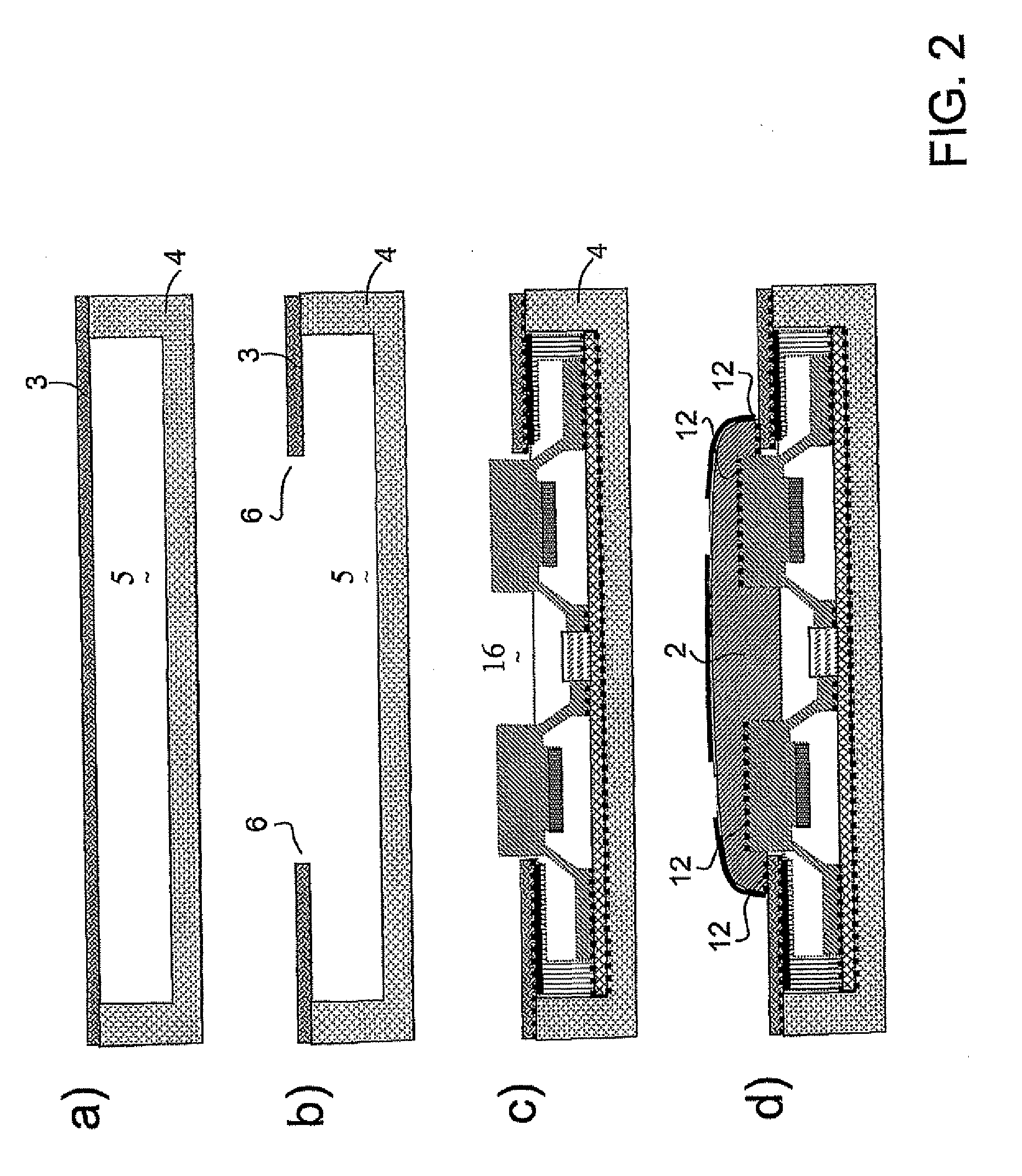

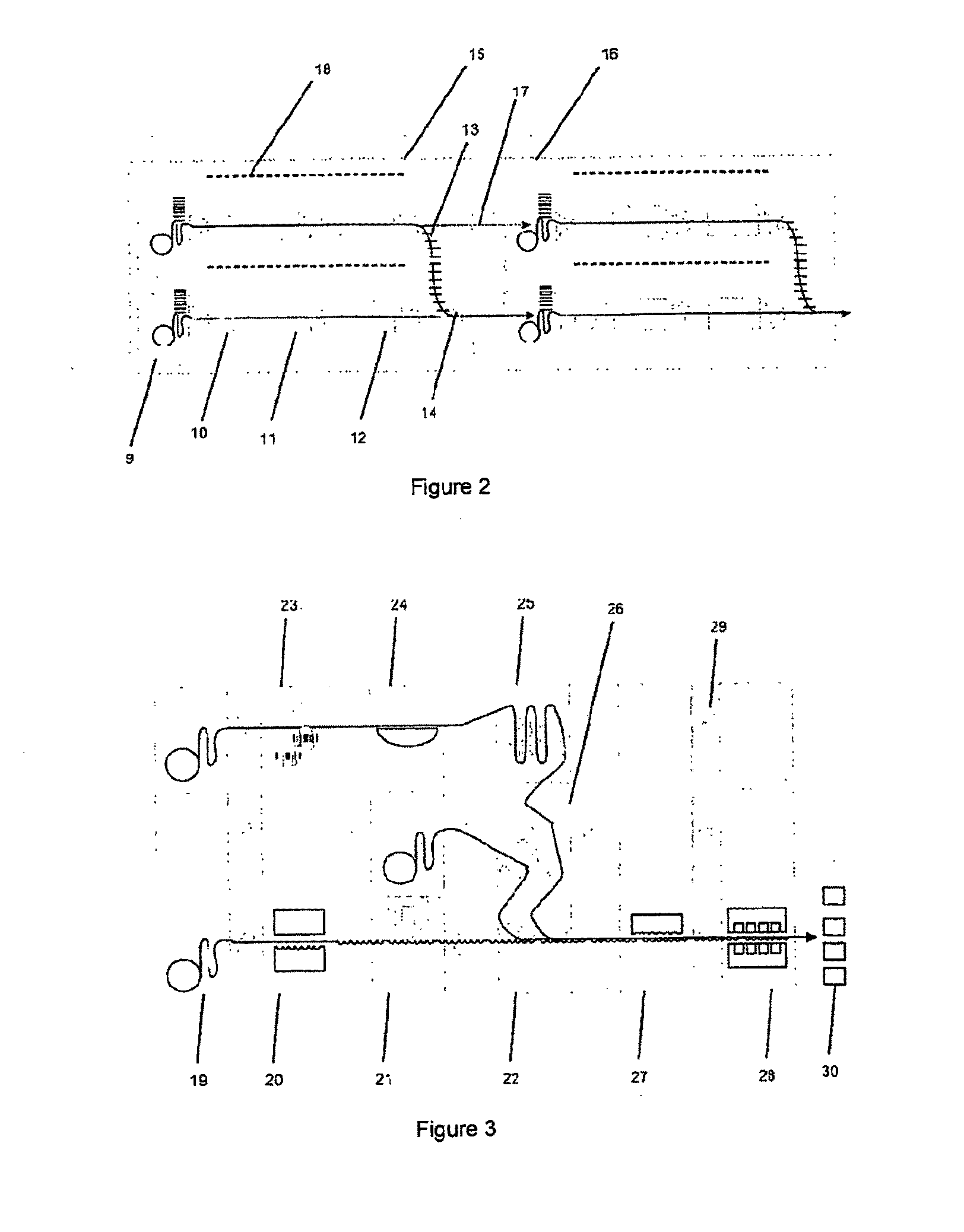

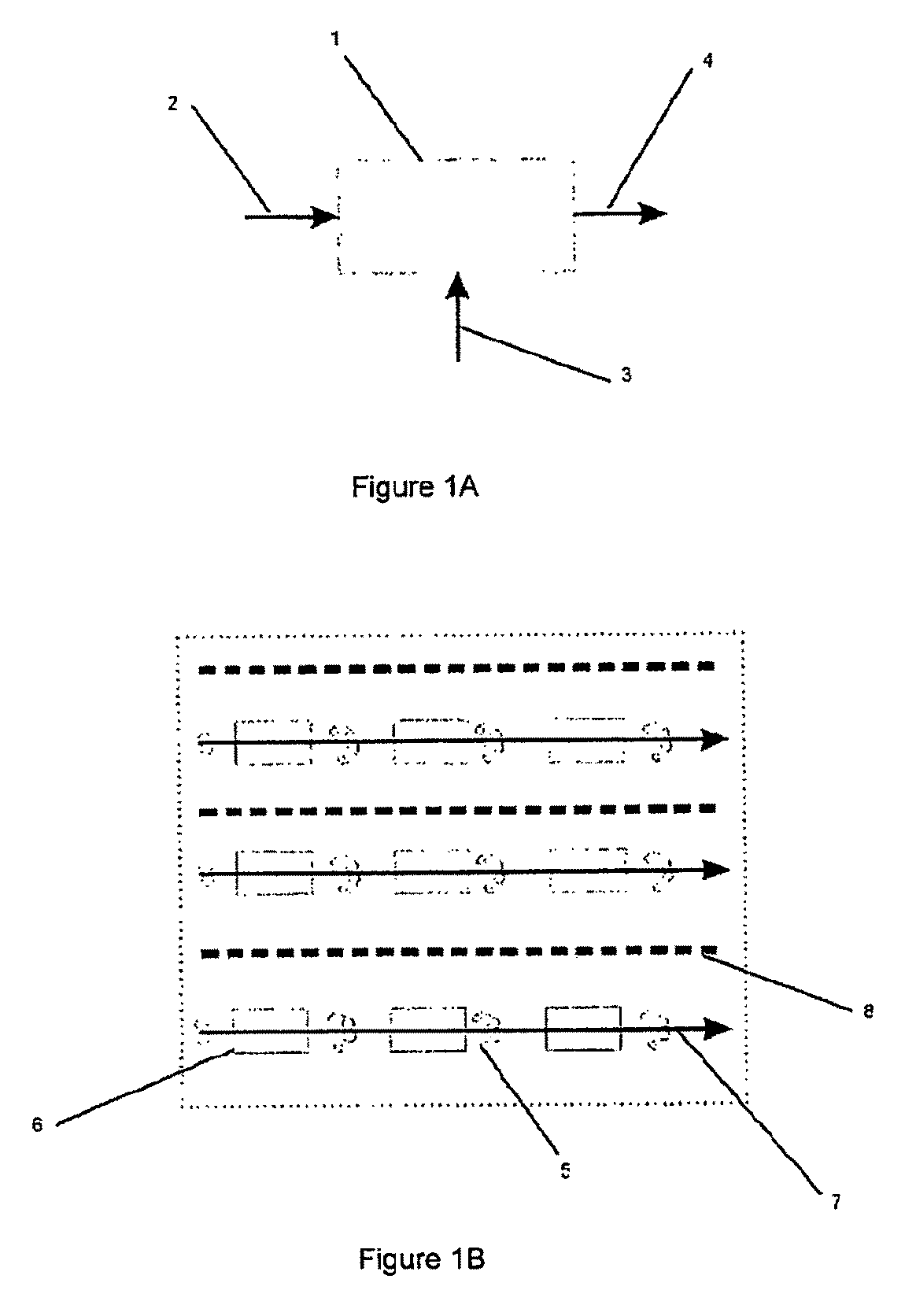

Methods for Low Cost Manufacturing of Complex Layered Materials and Device

InactiveUS20110028293A1Decrease stressRelieve stressBoxes/cartons making machineryPaper/cardboard articlesManufacturing engineeringActuator

A process for manufacturing a device includes performing a plurality of non-bonding processes during at least one web-based manufacturing stage and during at least one sheet-based manufacturing stage. The processes may be performed by a plurality of modules. The modules may be independently controlled and / or monitored. The modules may be interchangeable. One or more modules may receive and / or pass material to another module. The devices that are manufactured may be a layered device, a smart card, a sensor, an actuator, an in vitro diagnostic device, a microfluidic device, or a laminar product. An apparatus for manufacturing device includes at least one web-based manufacturing component and at least one sheet-based manufacturing component. The at least one web-based manufacturing component and the at least one sheet-based manufacturing component are configured to perform a plurality of non-bonding processes.

Owner:MYCROLAB DIAGNOSTICS PTY LTD

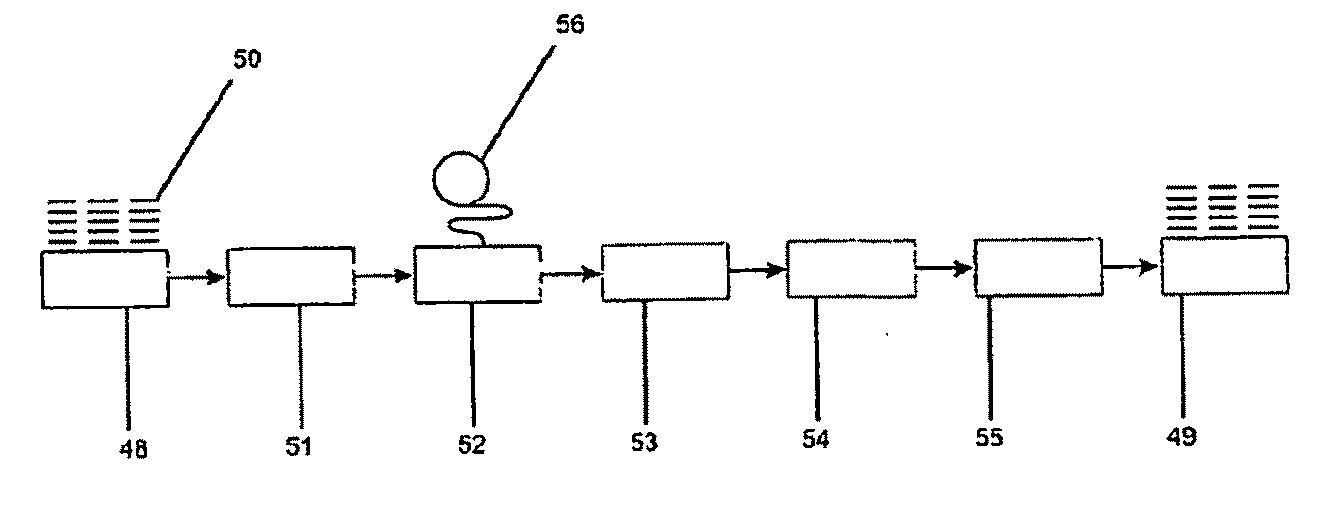

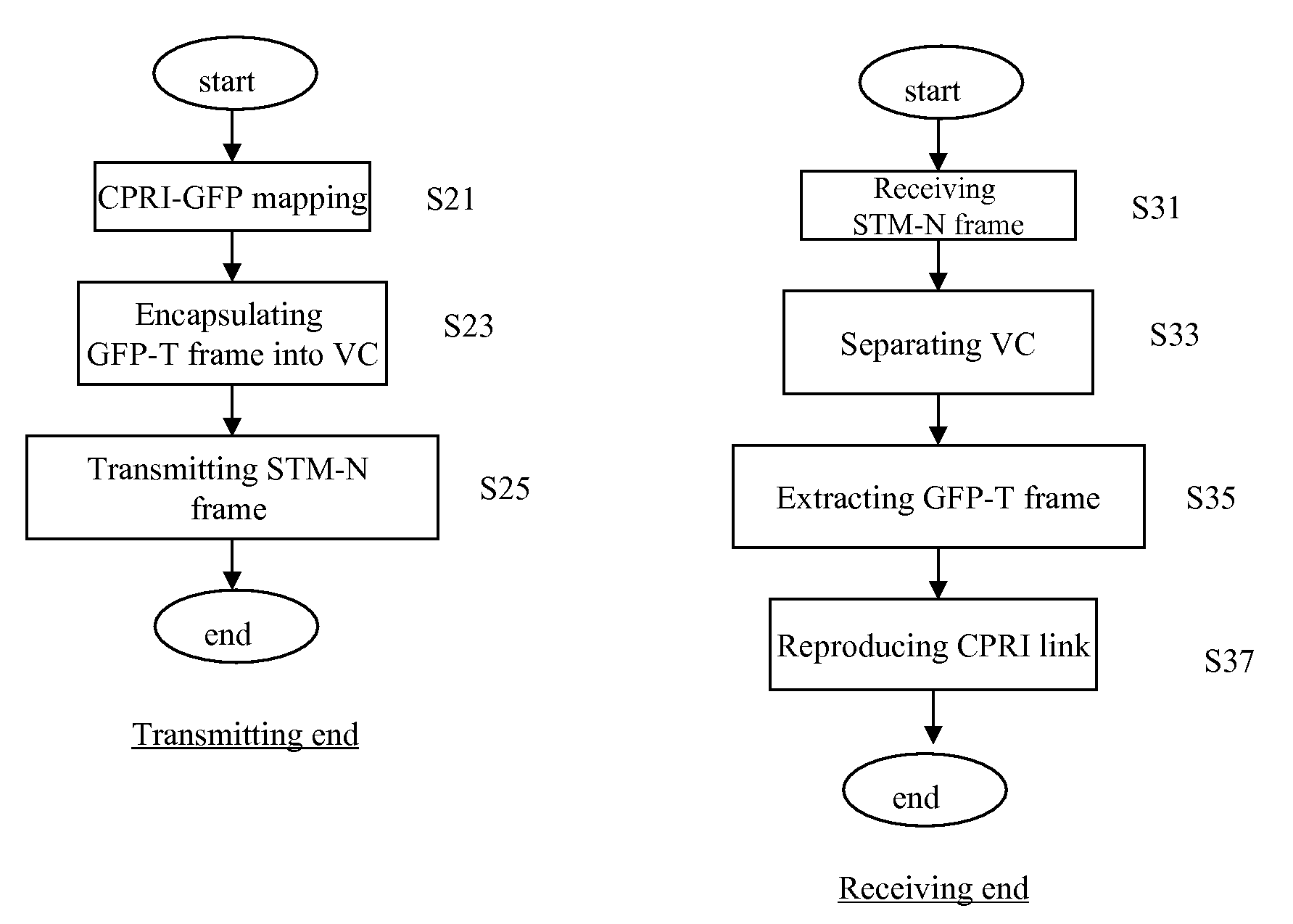

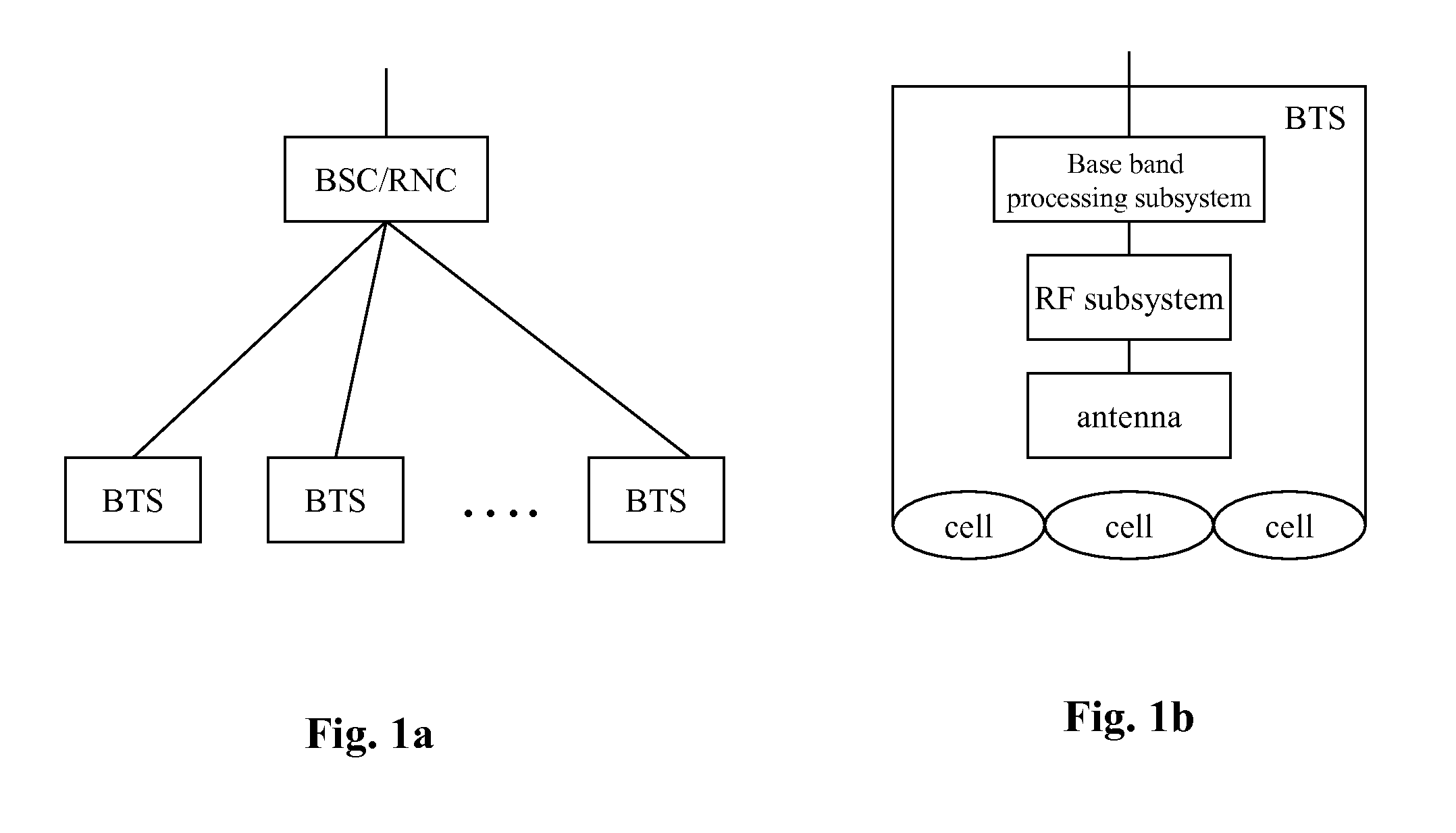

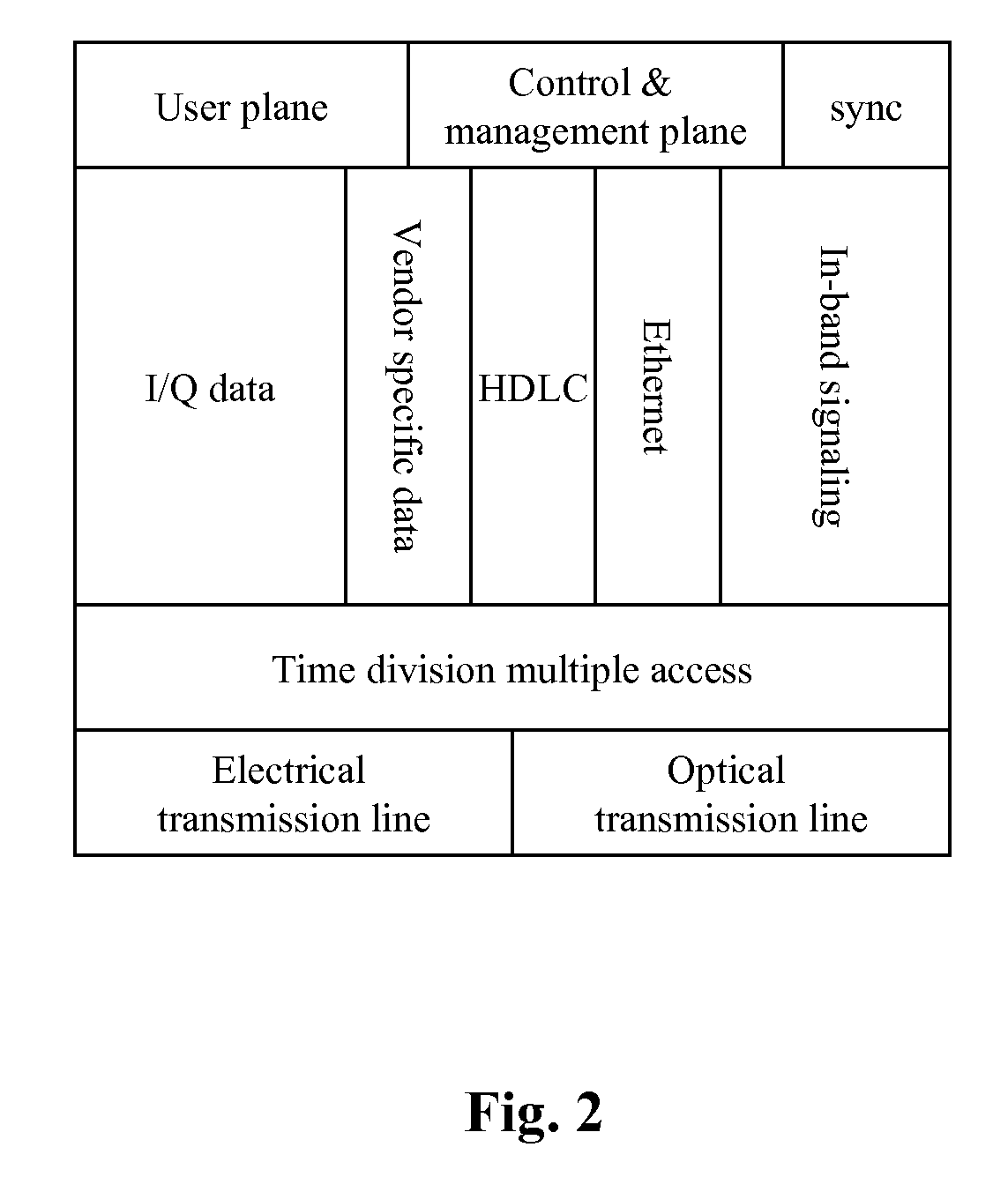

CPRI link multiplex transmission method and system

InactiveUS7680149B2Enhance networking ability and reliabilityFlexible and easy to maintainTime-division multiplexTelecommunicationsComputer science

A communication method between the units of a distributed base station system, characterized by comprising: at the transmitting end, mapping a CPRI link to a GFP-T frame; encapsulating the GFP-T frame into SDH virtual containers to form a STM-N frame; and transmitting the STM-N frame via a SDH line, and at the receiving end, receiving the STM-N frame transmitted via the SDH line; separating the SDH virtual containers from the STM-N frame; extracting the GFP-T frame from the SDH virtual containers; reproducing the CPRI link from the GFP-T frame.

Owner:UTSTARCOM TELECOM CO LTD

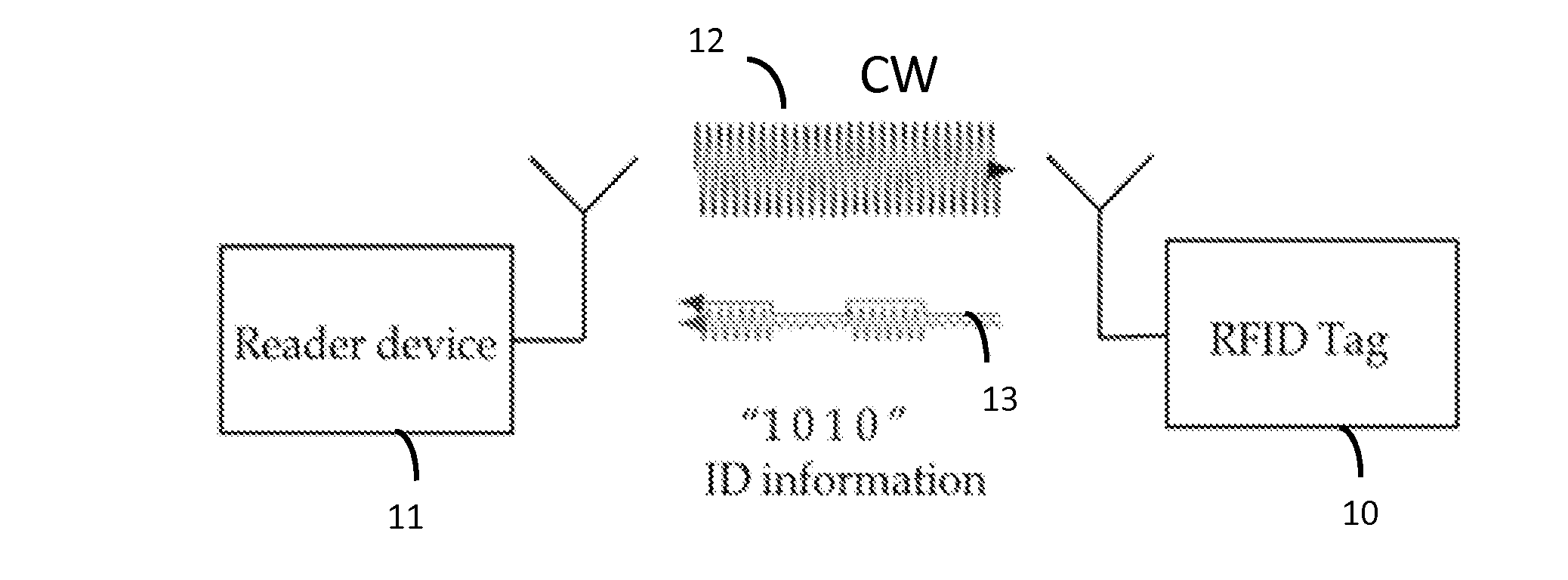

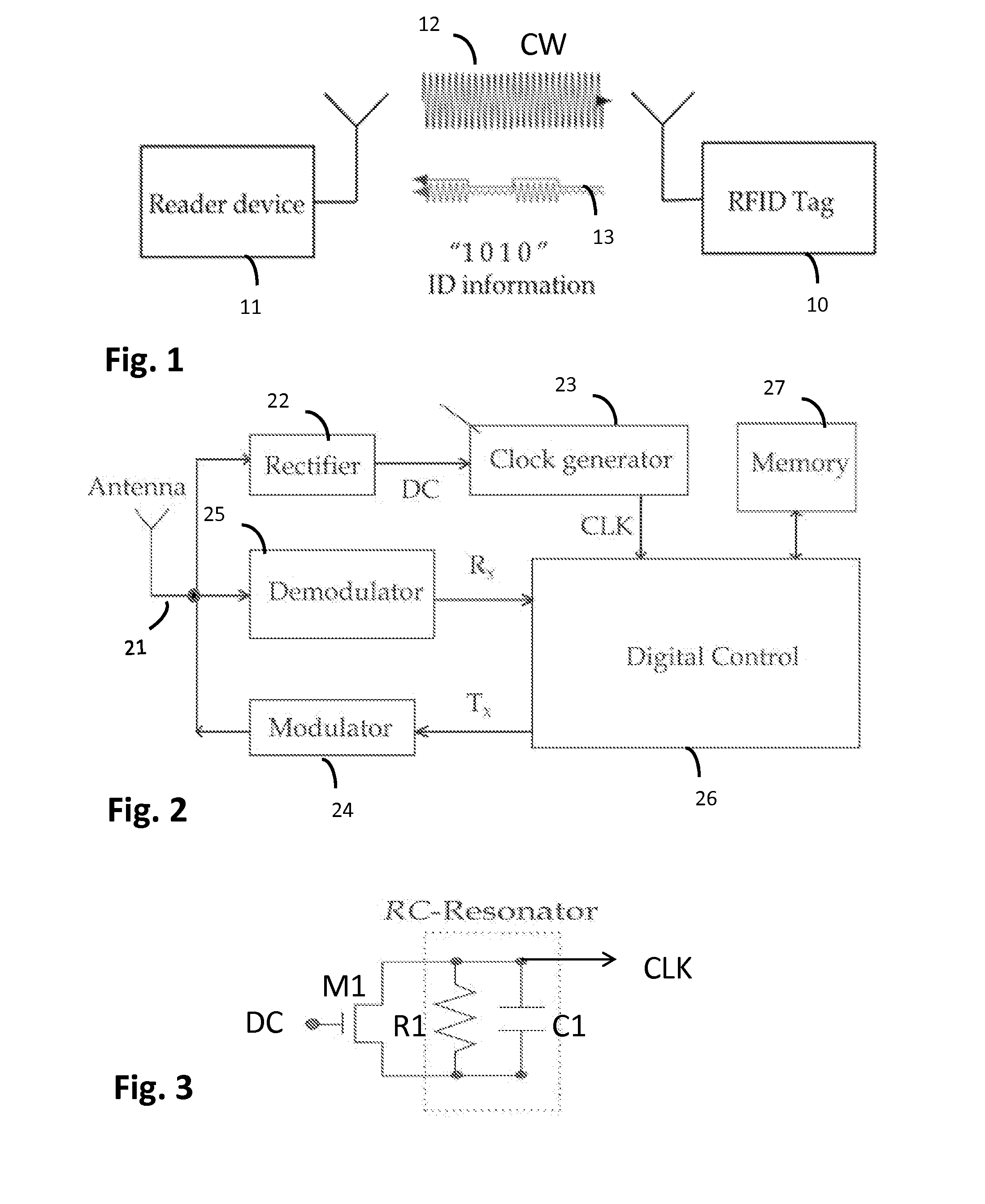

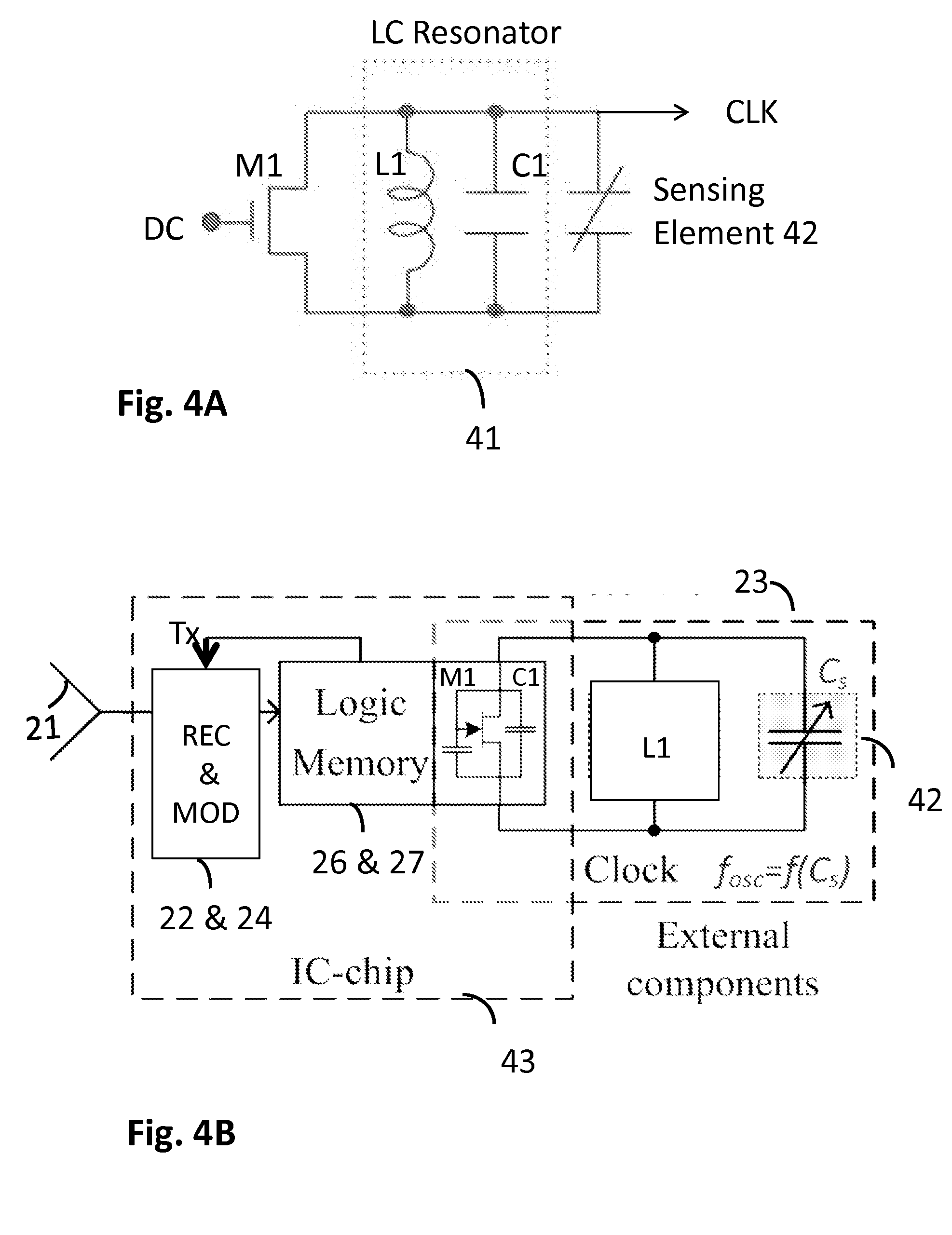

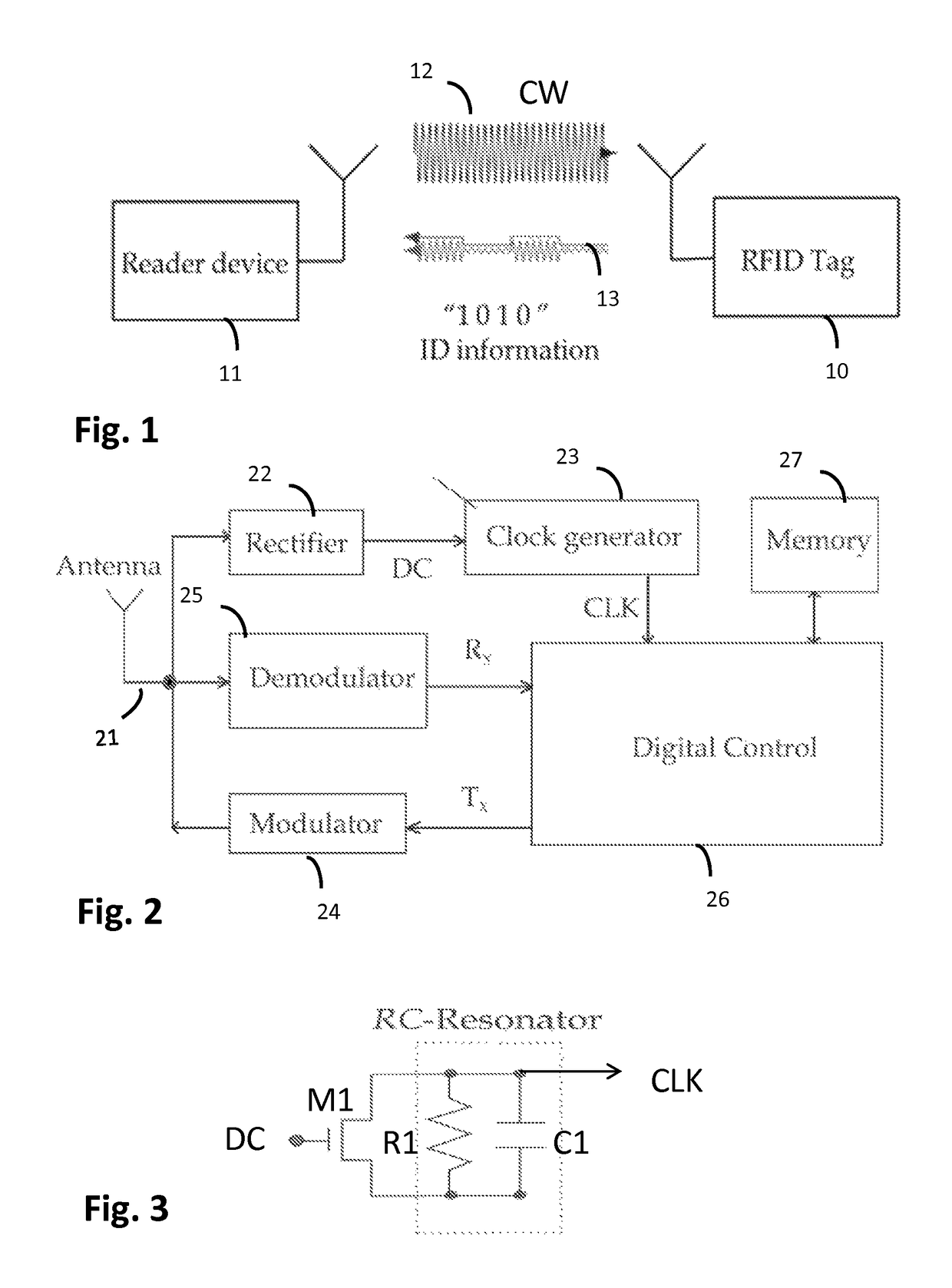

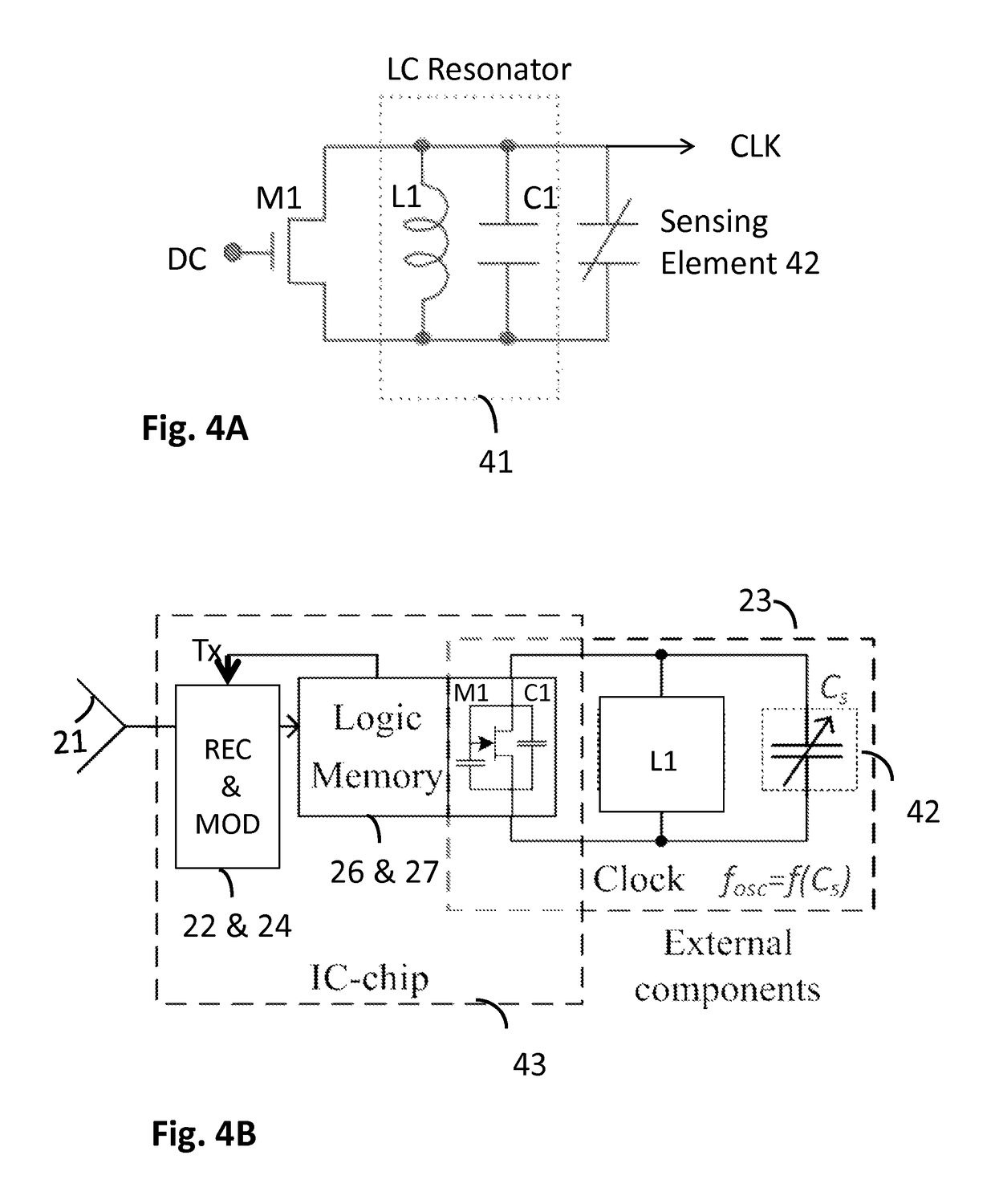

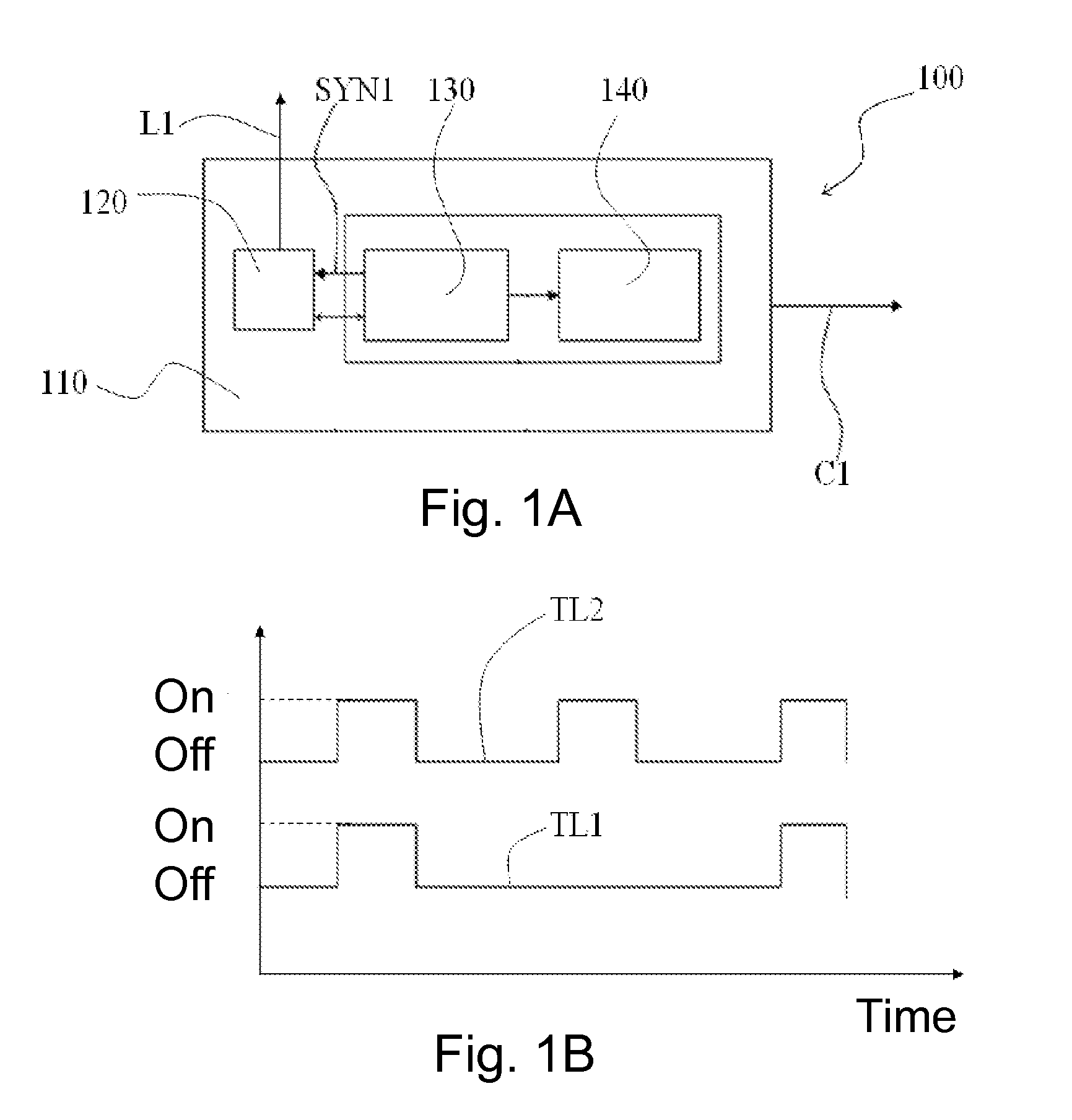

Passive wireless sensor

ActiveUS20160328637A1Long distanceComplex functionWireless architecture usageNear-field in transpondersClock generatorResonator

The RFID sensor tag may include normal RFID circuits and functions (such as rectifier, modulator, logic and memory) as well as a resonator-based clock generator or oscillator. The oscillator is a stable resonator-based oscillator having a high Q value. The resonator-based oscillator is loaded with a sensor element which tunes the oscillation frequency, i.e. the oscillation frequency is sensitive to the measured quantity. Thereby, a passive RFID sensor with a resonator-based oscillator and a sensor element is provided, wherein the oscillation frequency can be made dependent on the sensor element if sensing is required. The concept is compatible for existing RFID tags and can enable the possibility to measure external quantities with-out reducing the read-out distance.

Owner:METSO OUTOTEC (FINLAND) OY

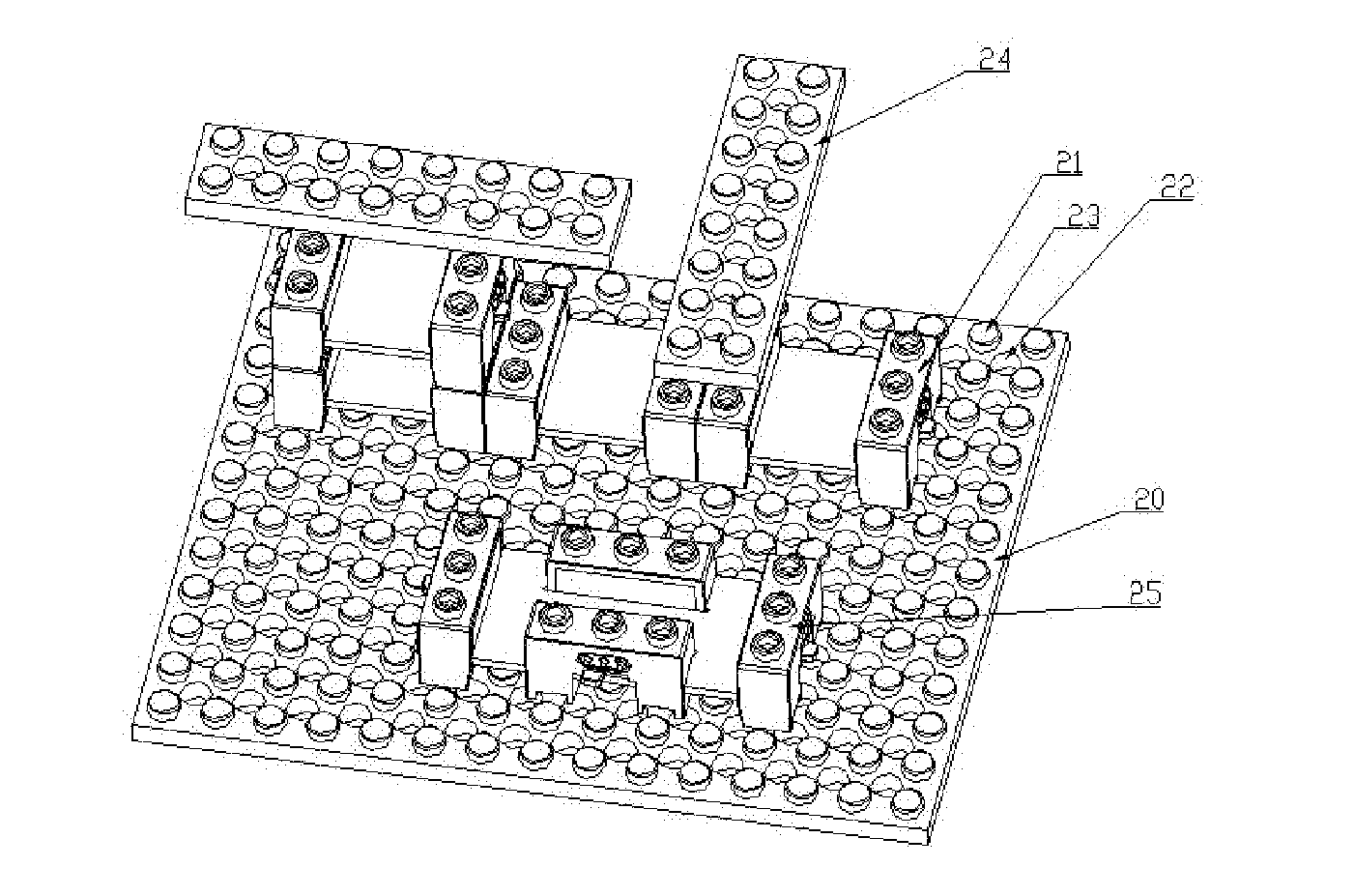

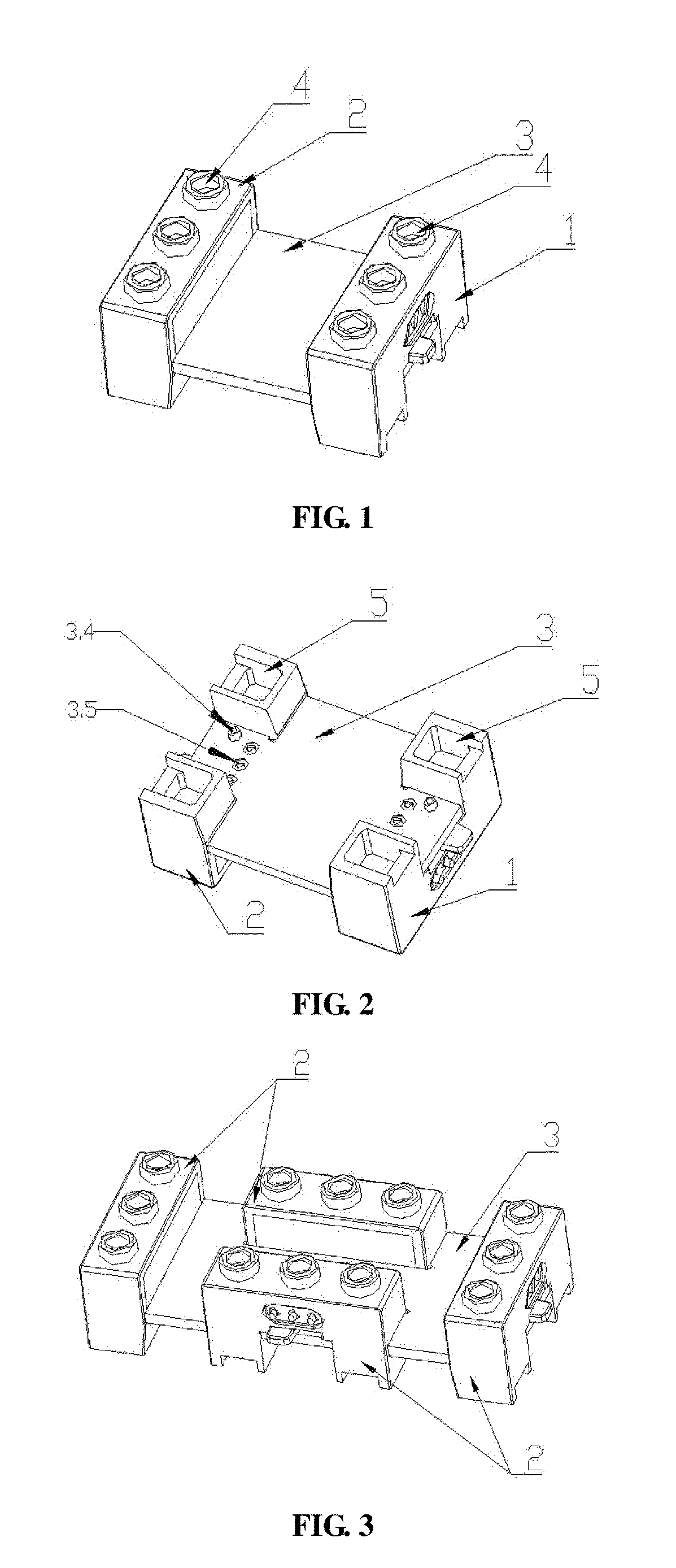

Compatible and Magnetic Absorption-Type Electronic Building Block

Disclosed is a compatible and magnetic absorption-type electronic building block, which comprises a circuit board, a plug connector and a socket connector, wherein the plug connector and the socket connector both comprise an insulation body and a conductive terminal, and the insulation body is arranged with a mounting body and two support feet. A bottom of the mounting body is arranged with an open region, and the mounting body is provided with a butting panel, a top panel and a rear cover. The electronic building block of the invention can not only implement electronic circuit module splicing, but also implement a complex three-dimensional modeling function due to the above specially designed structure. Moreover, the electronic building block can be seamlessly spliced to a common plastic building block in a market.

Owner:HANGZHOU SUZE ELECTRONICS TECH

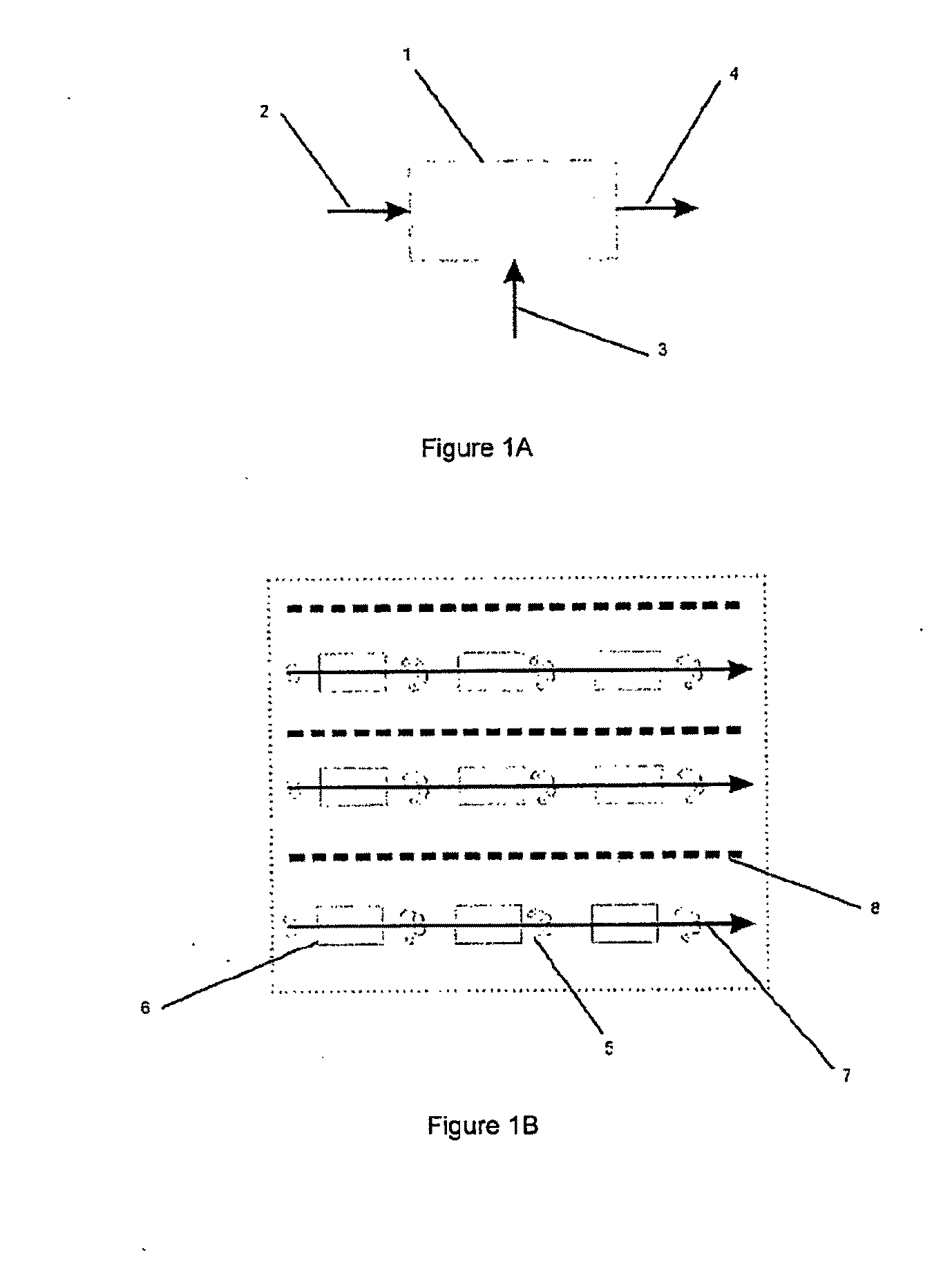

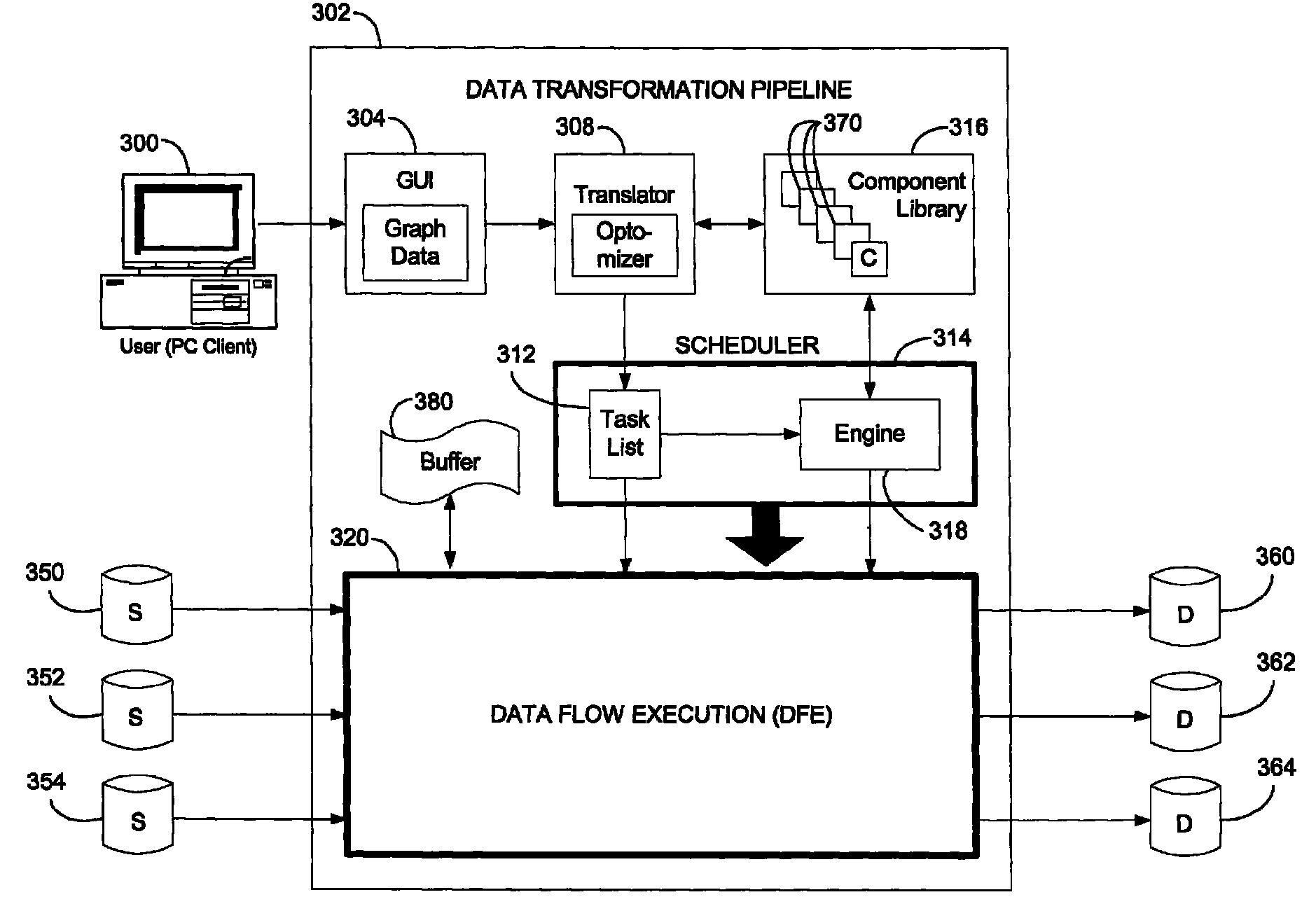

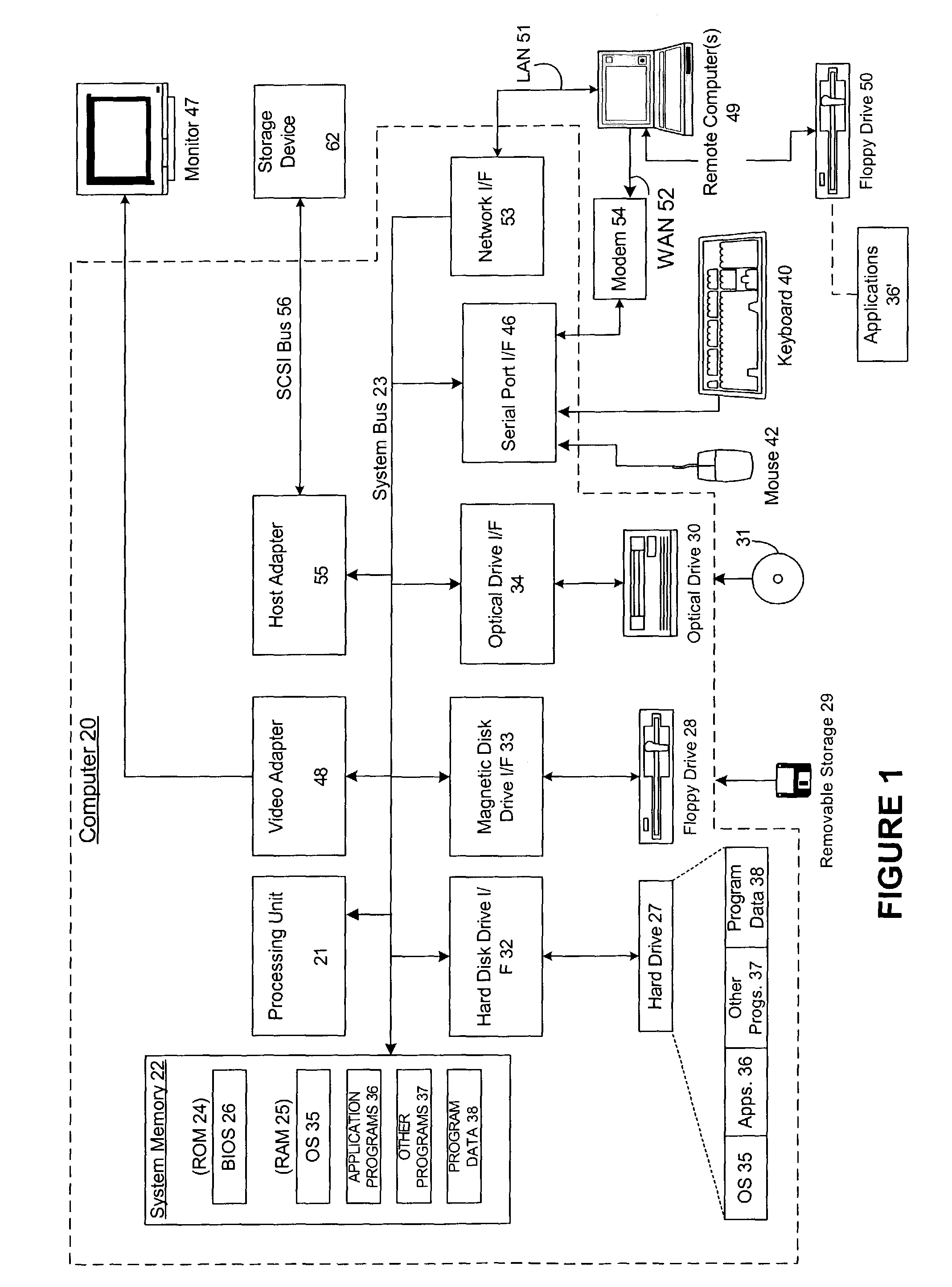

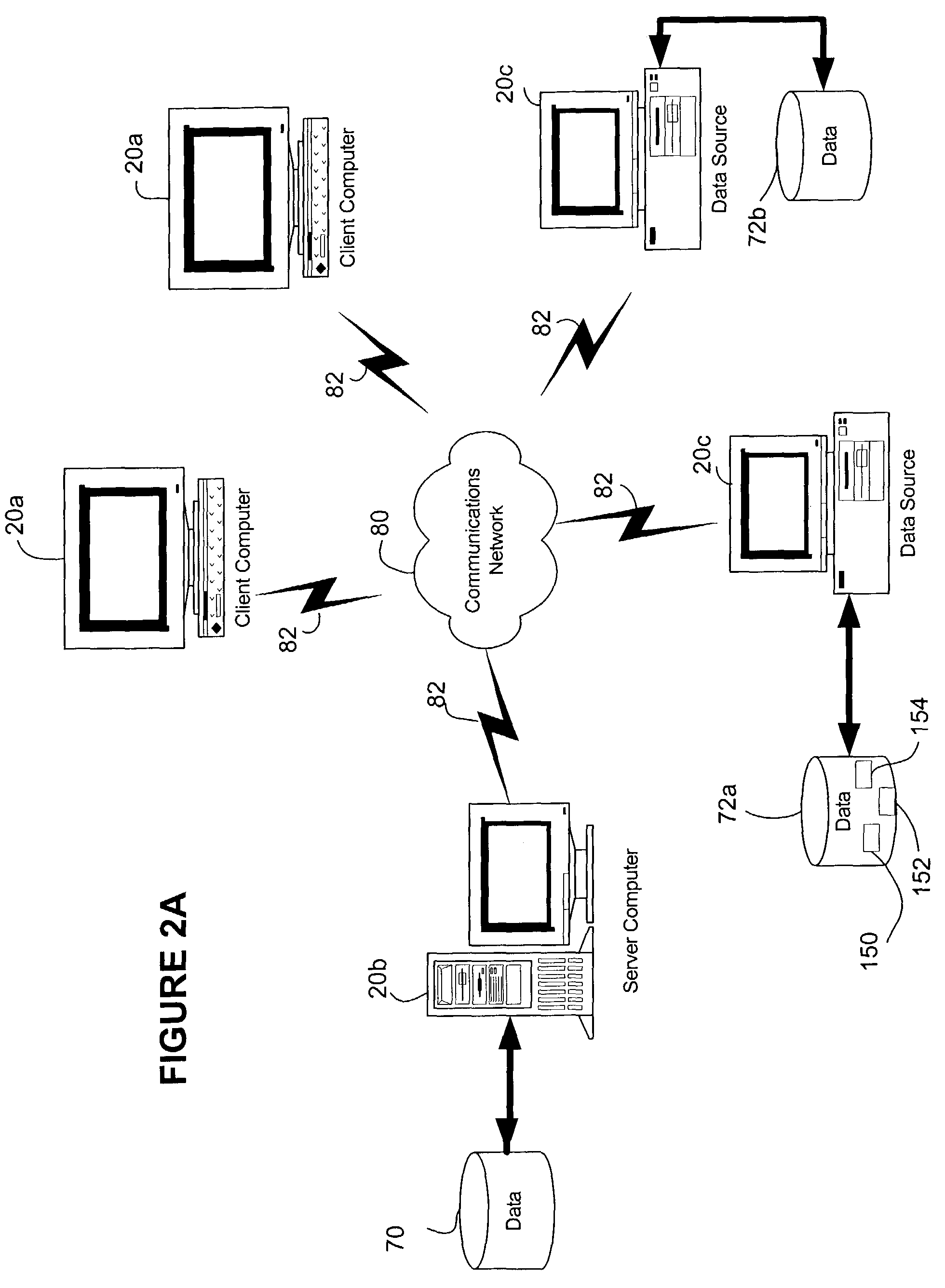

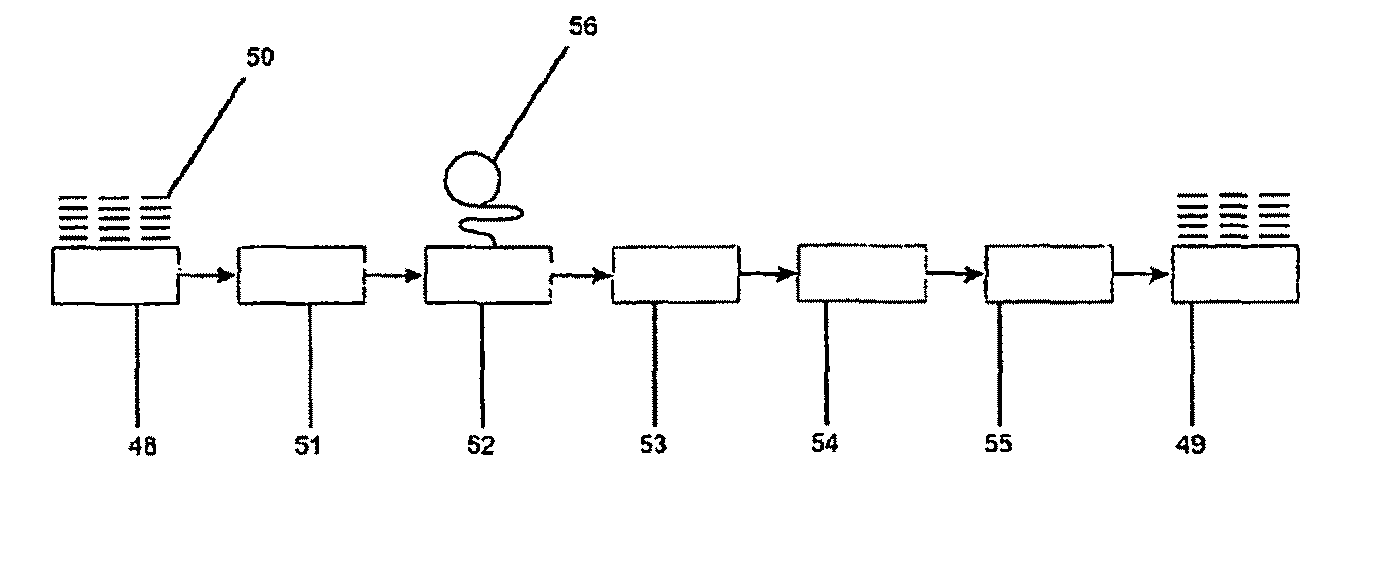

Systems and methods for scheduling data flow execution based on an arbitrary graph describing the desired data flow

ActiveUS7953891B2Complex functionImprove system efficiencyMemory adressing/allocation/relocationMultiprogramming arrangementsData transformationNODAL

The data transformation system in one embodiment, comprises a capability to receive data, a data destination and a capability to store transformed data, and a data transformation pipeline that constructs complex end-to-end data transformation functionality by pipelining data flowing from one or more sources to one or more destinations through various interconnected nodes for transforming the data as it flows. Each component in the pipeline possesses predefined data transformation functionality, and the logical connections between components define the data flow pathway in an operational sense.The data transformation pipeline enables a user to develop complex end-to-end data transformation functionality by graphically describing and representing, via a GUI,a desired data flow from one or more sources to one or more destinations through various interconnected nodes (graph). Each node in the graph selected by the user represents predefined data transformation functionality, and connections between nodes define the data flow pathway.

Owner:MICROSOFT TECH LICENSING LLC

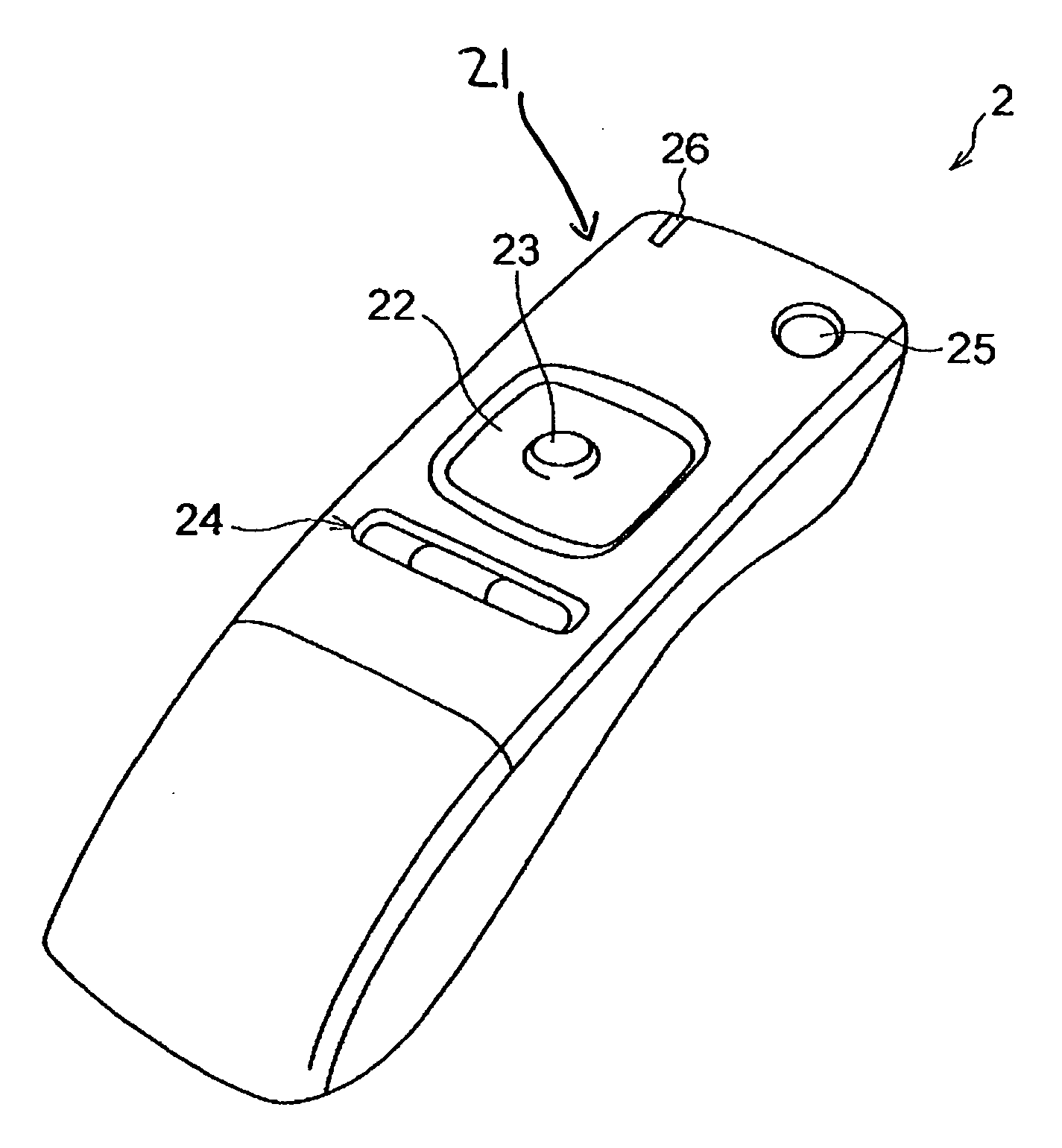

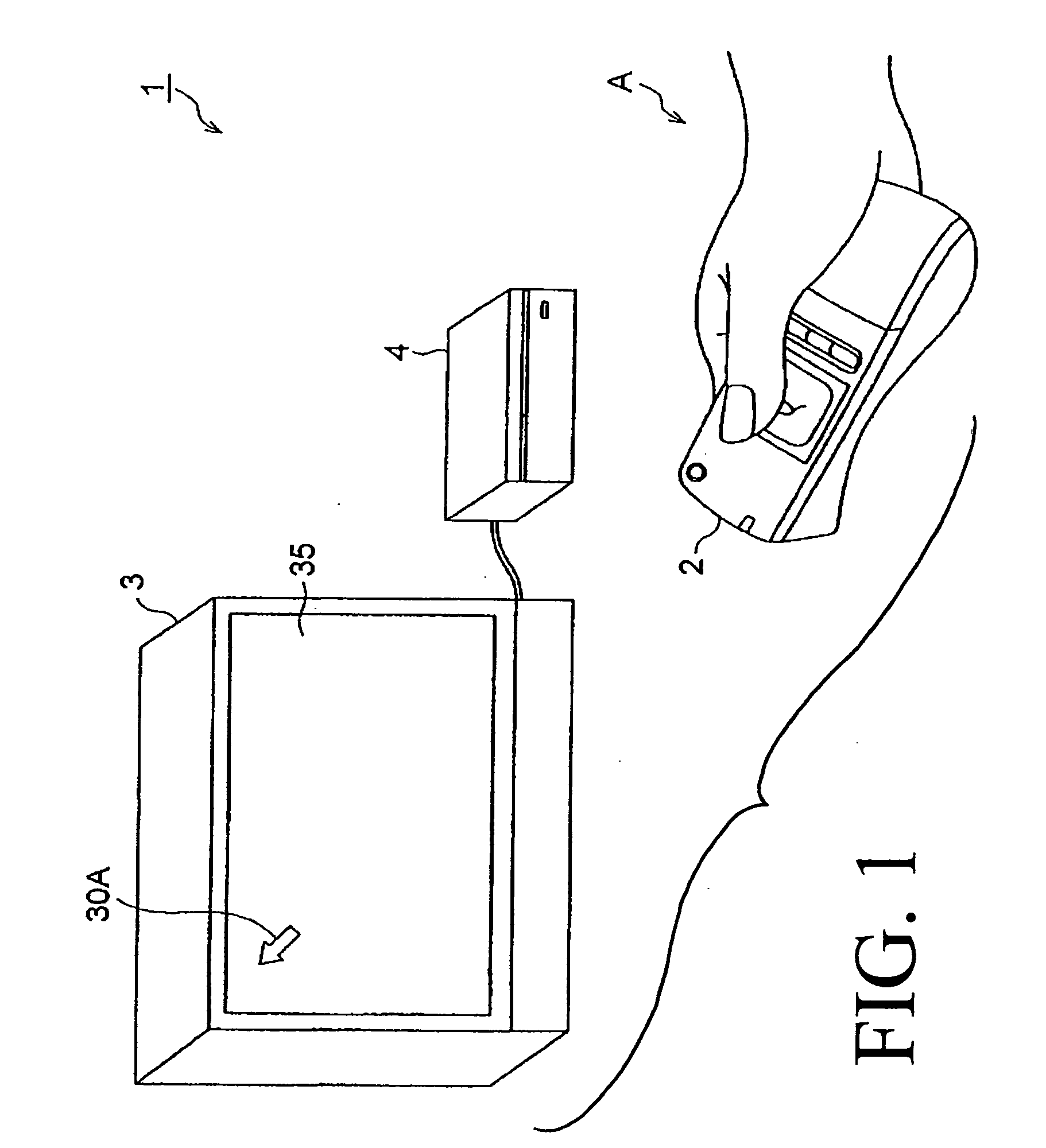

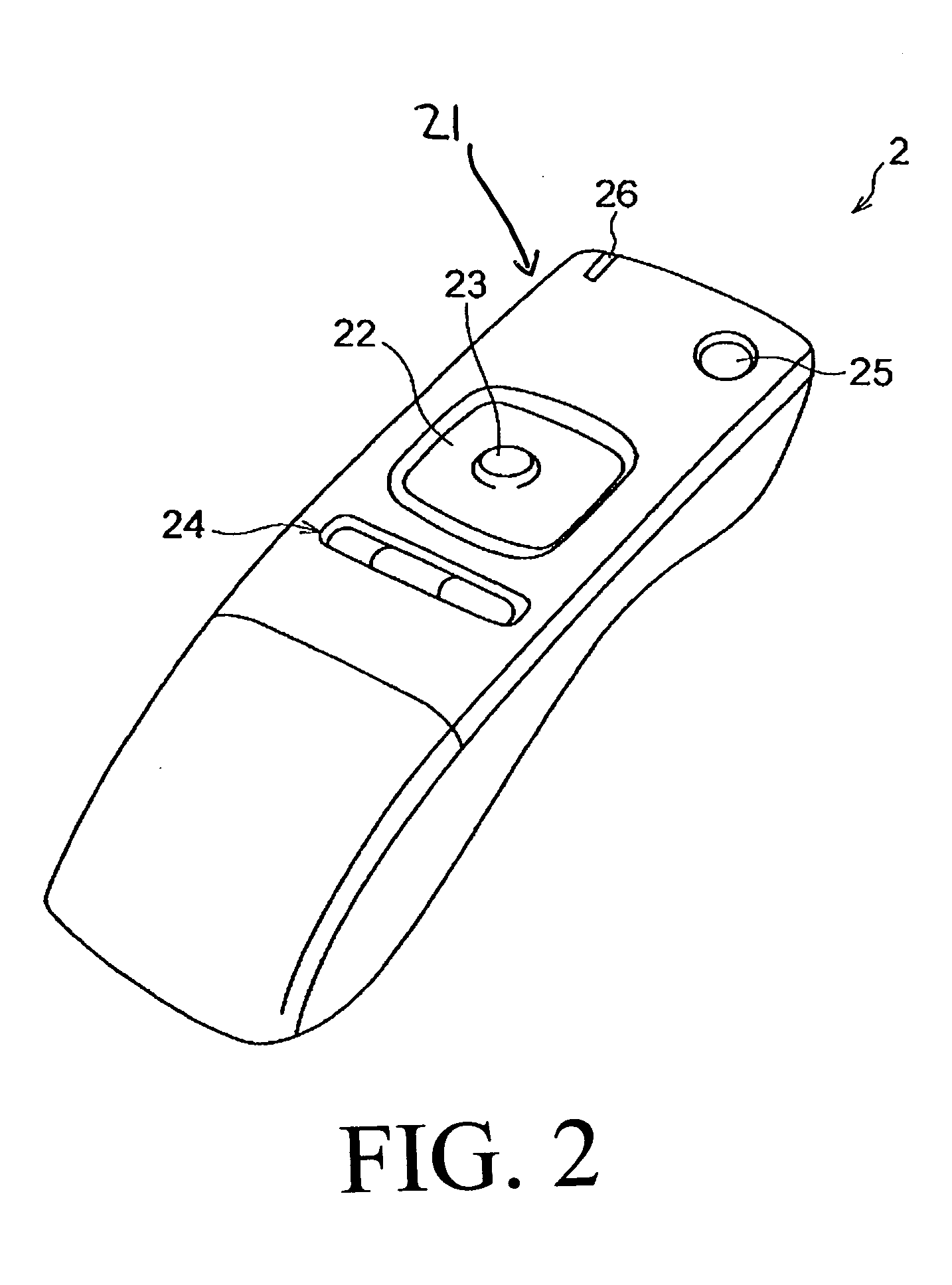

Position input device, remote control device, computer system and electronic equipment

InactiveUS20070176894A1Easy to implementPerformed easily and quicklyTelevision system detailsCathode-ray tube indicatorsWireless transmissionRemote control

A position input device is provided which includes a sensor portion having a detection face, an operation element movable along the detection face of the sensor portion, and a position detection unit which detects the position of the operation element on the detection face. According to additional embodiments, the position input device includes a lid covering the detection face. The lid is movable between opened and closed states, and integrally supports the operation element so as to move integrally with the lid when the lid is opened and closed. A remote control device including the position input device and a wireless transmission unit are also provided. Also provided are computer systems and electronic devices.

Owner:WACOM CO LTD

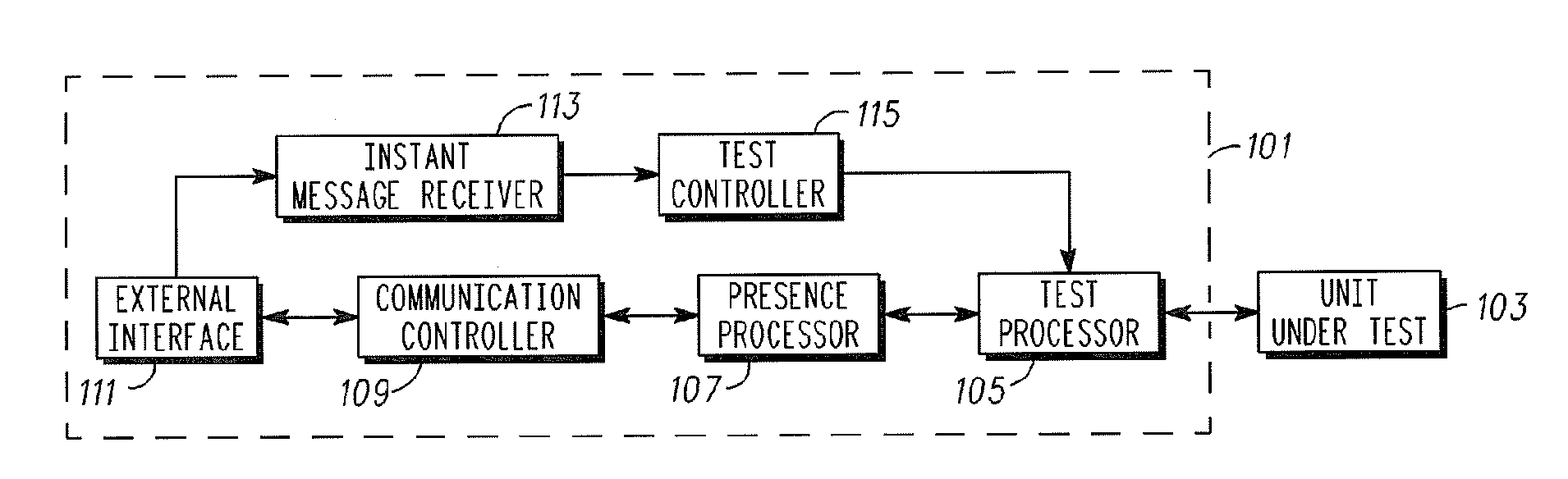

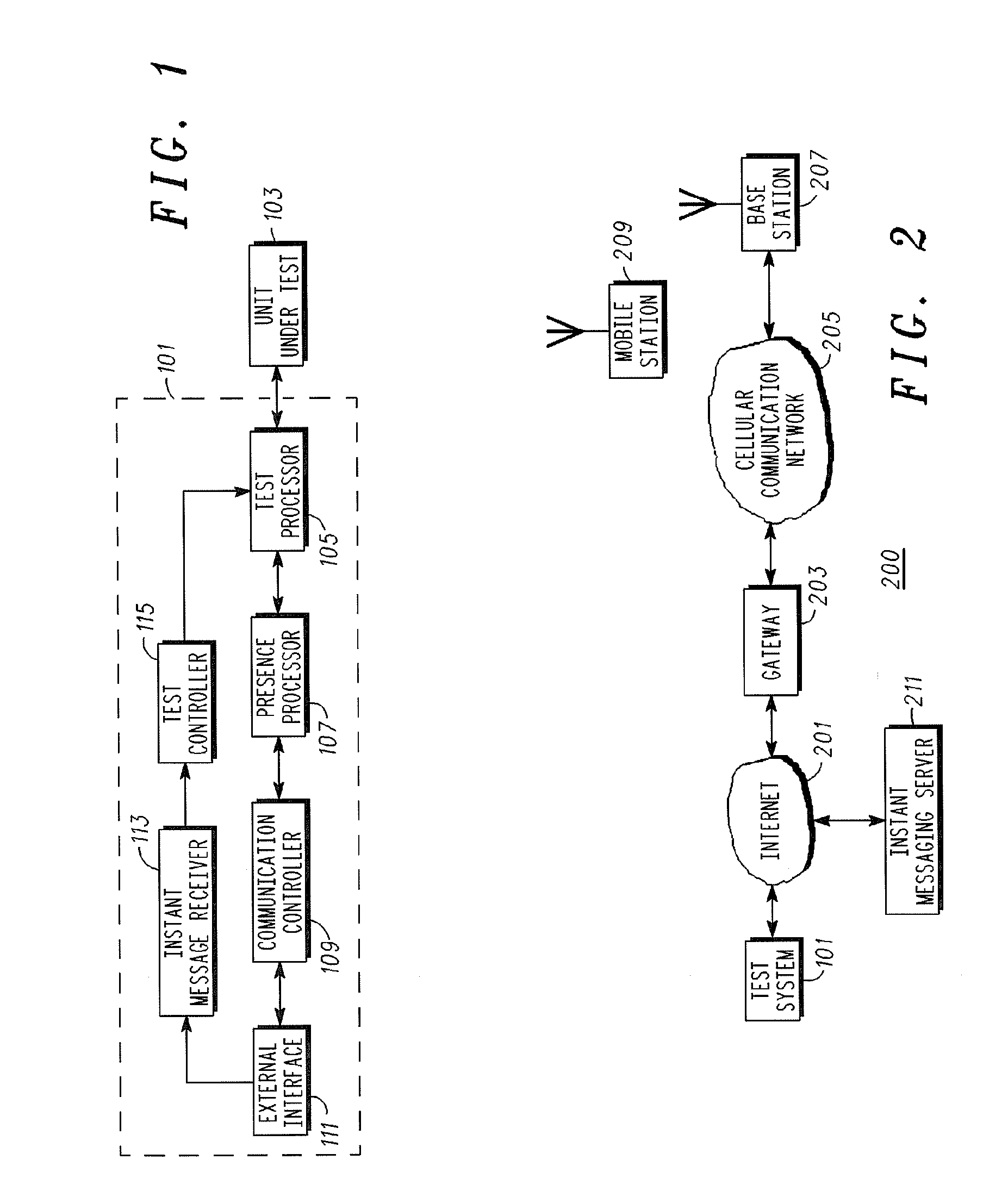

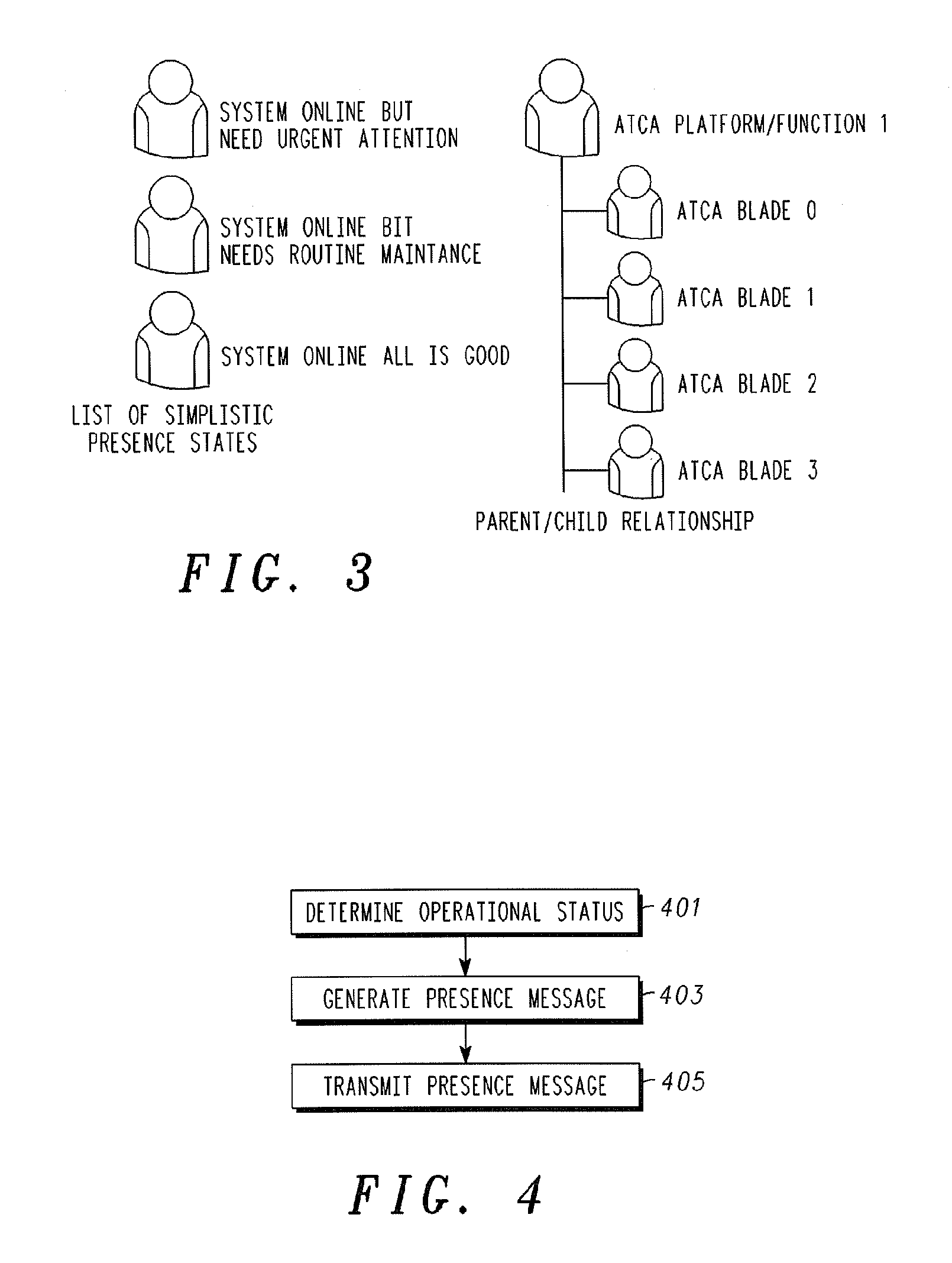

A Test System and Method of Operation

InactiveUS20070291906A1Efficient and low complexity functionalityImprove presentationSupervisory/monitoring/testing arrangementsSubstation equipmentNetwork elementReal-time computing

A test system comprises a test processor which determines an operational status, such as a fault status, for a unit under test. The unit under test may e.g. comprise one or more boards of an electronic assembly. A presence processor generates a presence message in response to the operational status where the presence message is in accordance with a user presence message protocol. A communication controller then transmits the presence message to a remote network element of a communication network. The remote network element may be a presence server which can transmit a presence status update to associated devices. The invention may allow efficient and remote status monitoring for a test system using user presence infrastructure.

Owner:EMERSON NETWORK POWER EMBEDDED COMPUTING

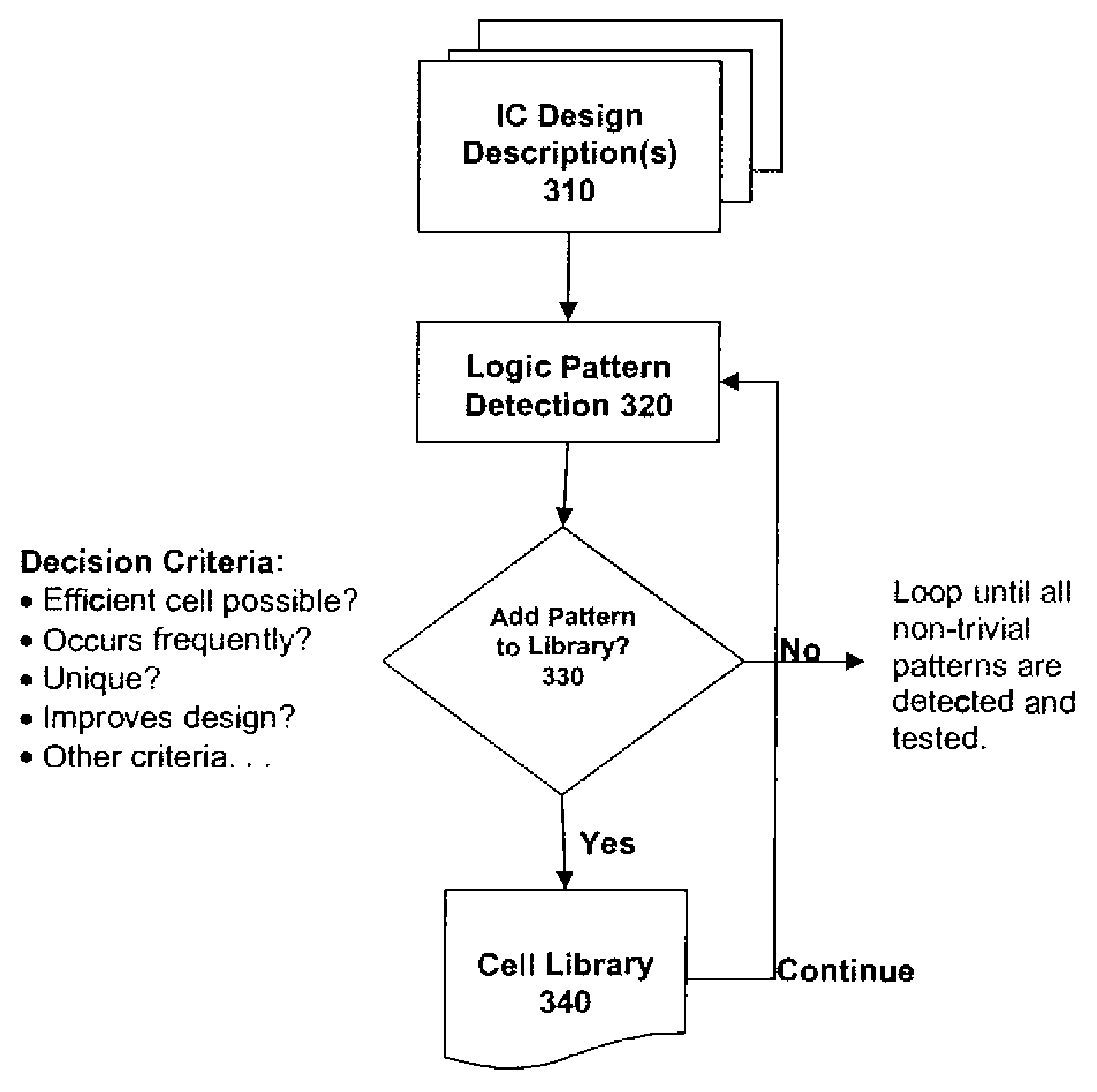

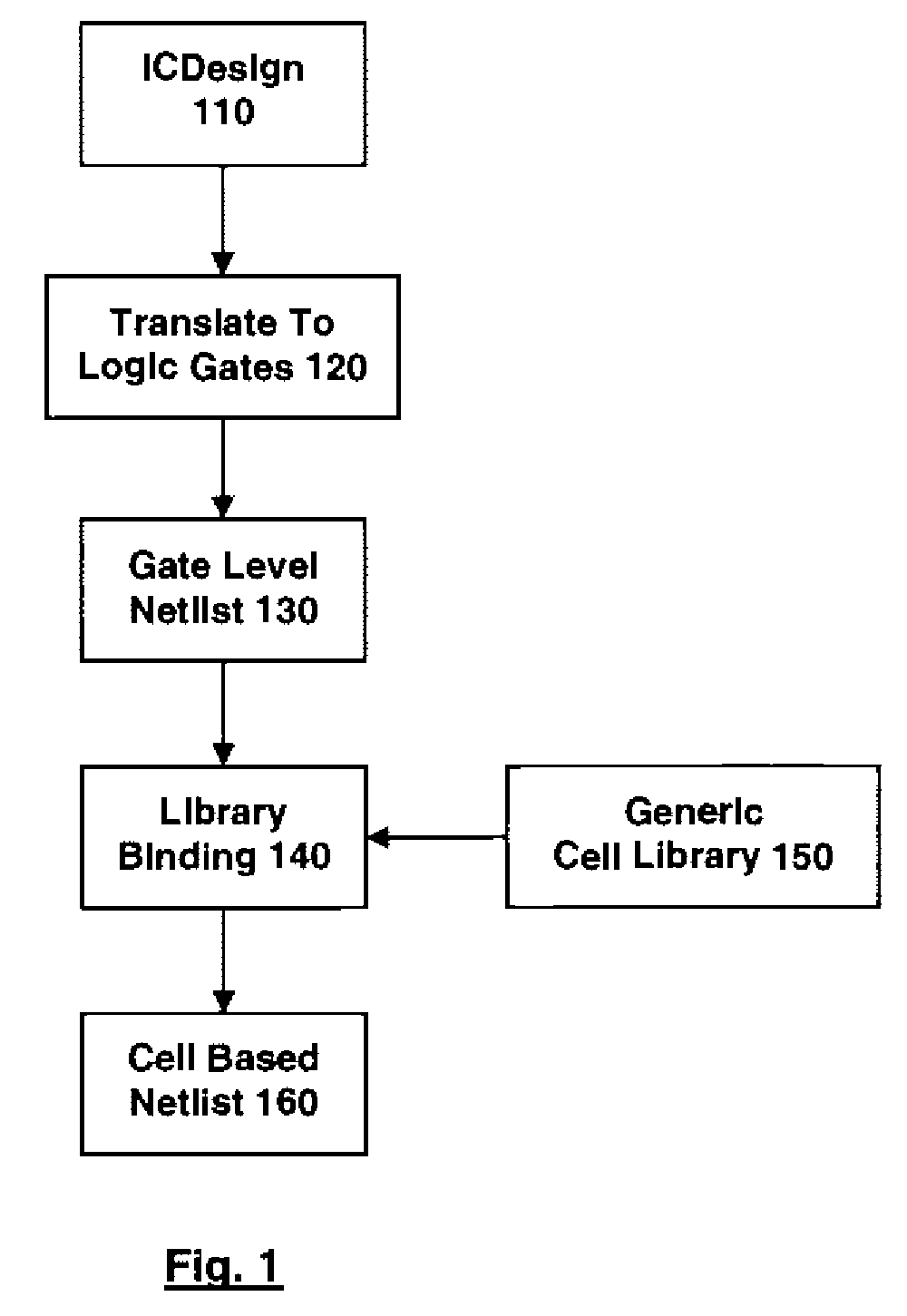

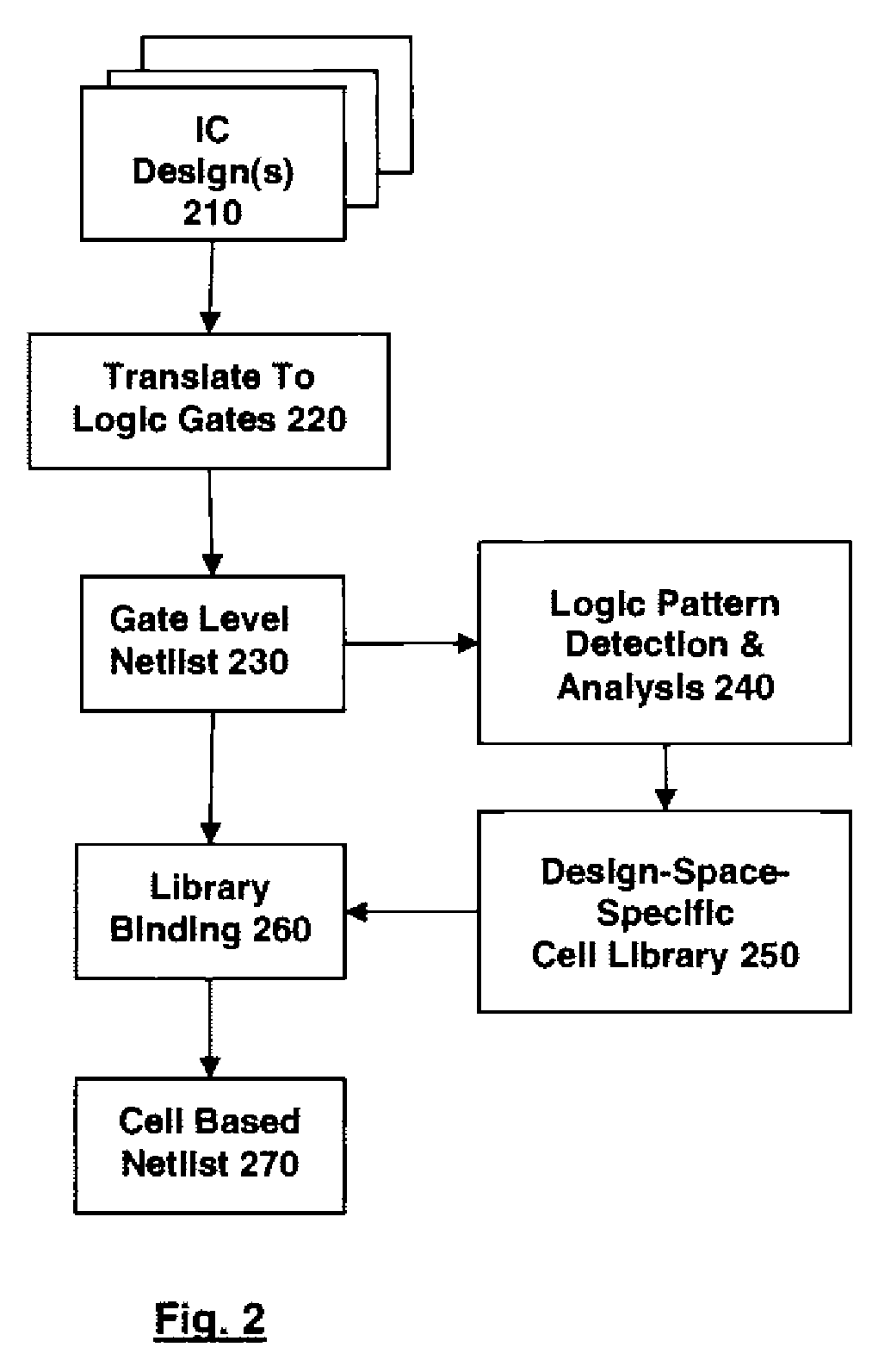

Method For The Definition Of A Library Of Application-Domain-Specific Logic Cells

ActiveUS20080163151A1Complex functionPractical and convenientCAD circuit designSoftware simulation/interpretation/emulationIntegrated circuitTheoretical computer science

The present invention provides in one aspect a method of defining a logic cell library composed of complex functions and simple functions, with some of the complex functions obtained from identifying logic function patterns. In another aspect the present invention provides a method of designing a representation of an integrated circuit that uses complex functions and simple functions, with the complex functions including a plurality of non-standard complex Boolean logic functions that are determined to collectively provide for logic pattern minimization.

Owner:PDF SOLUTIONS INC

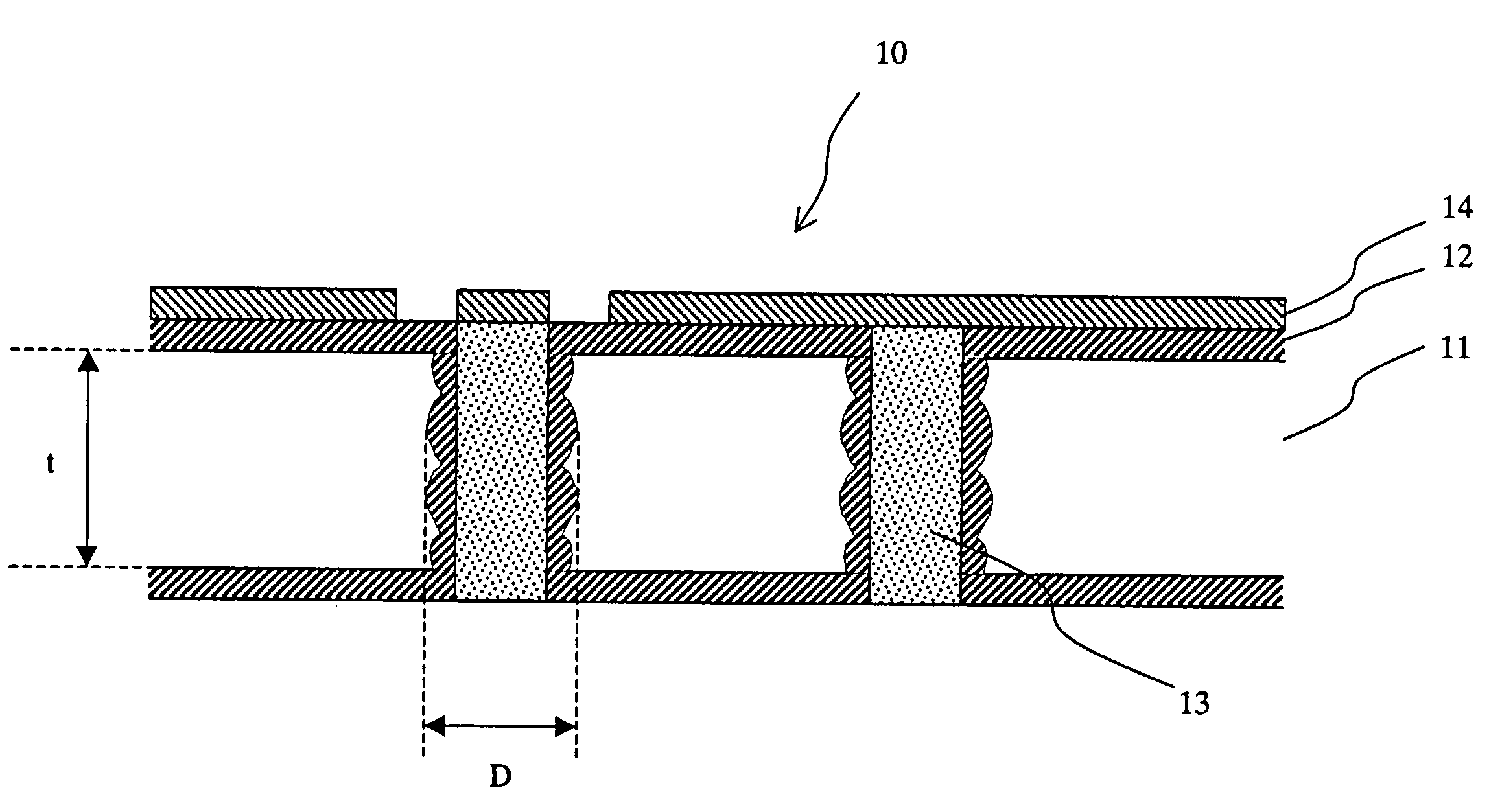

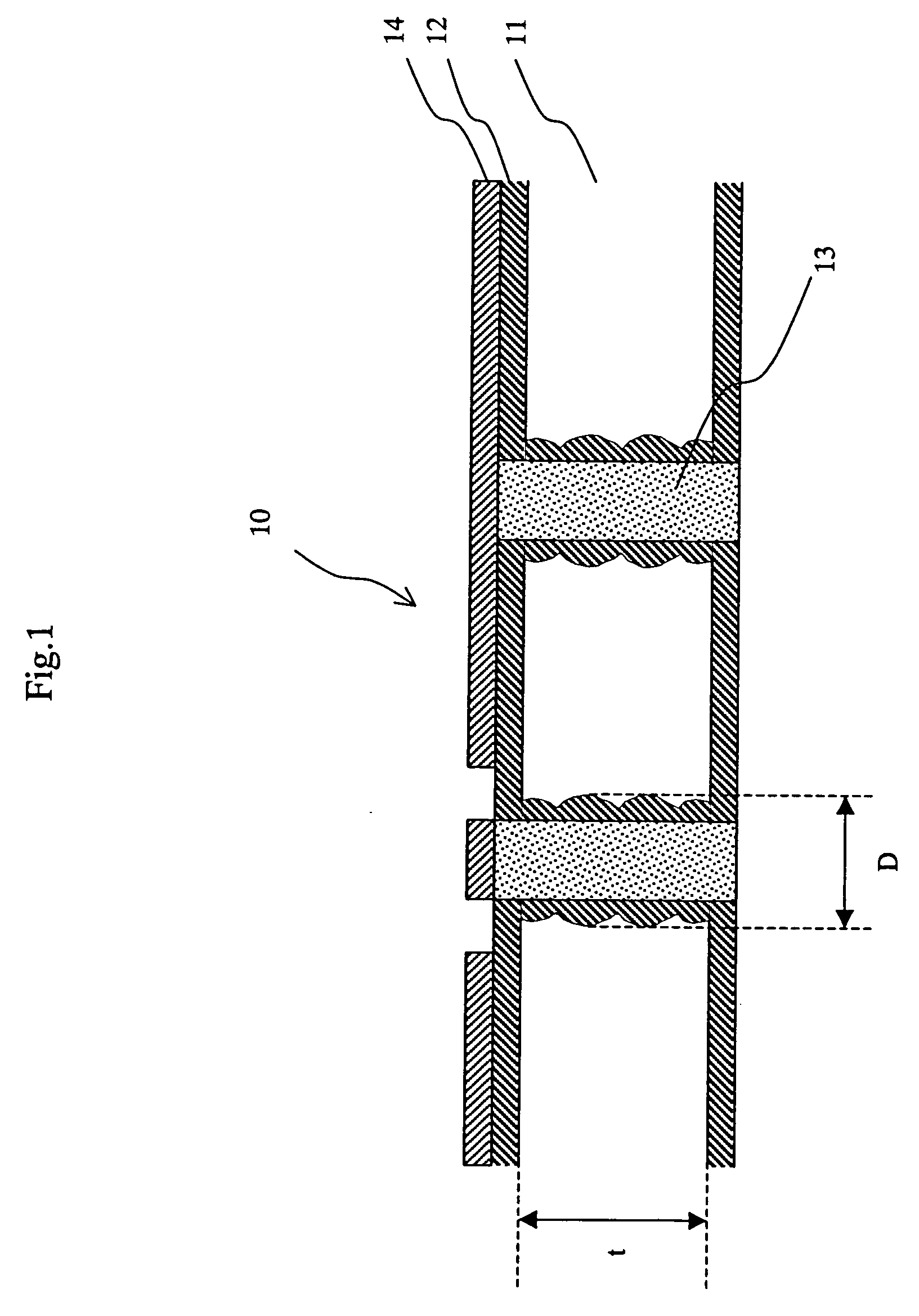

Wiring board and wiring board manufacturing method

InactiveUS20060065439A1Complex functionHigh densityElectrical connection printed elementsCable/conductor manufactureIsotropic etchingMetal

The present invention provides a wiring board including a metal plate that has a through hole formed so as to pass though both surfaces thereof by isotropic etching; an insulating layer that covers both surfaces of the metal plate and the inside surface of the through hole; a wiring layer formed on an upper surface of at least one surface of the insulating layer on; and a conductive via electrode formed in the through hole, wherein a diameter of the through hole is 100 μm or less and a ratio of a thickness of the metal plate to the diameter of the through hole is 1 or more, preferably, 1.2 or more.

Owner:TDK CORPARATION

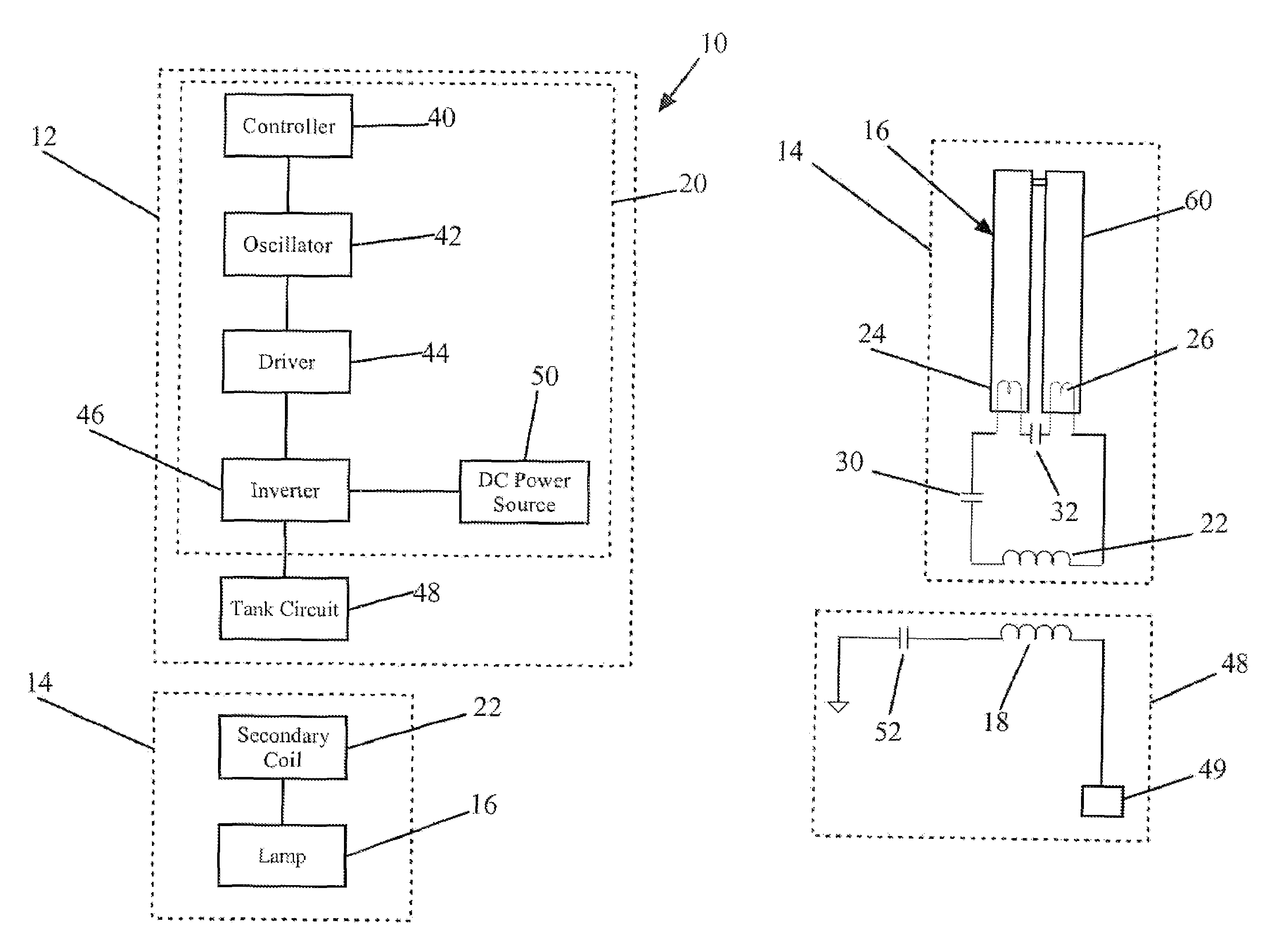

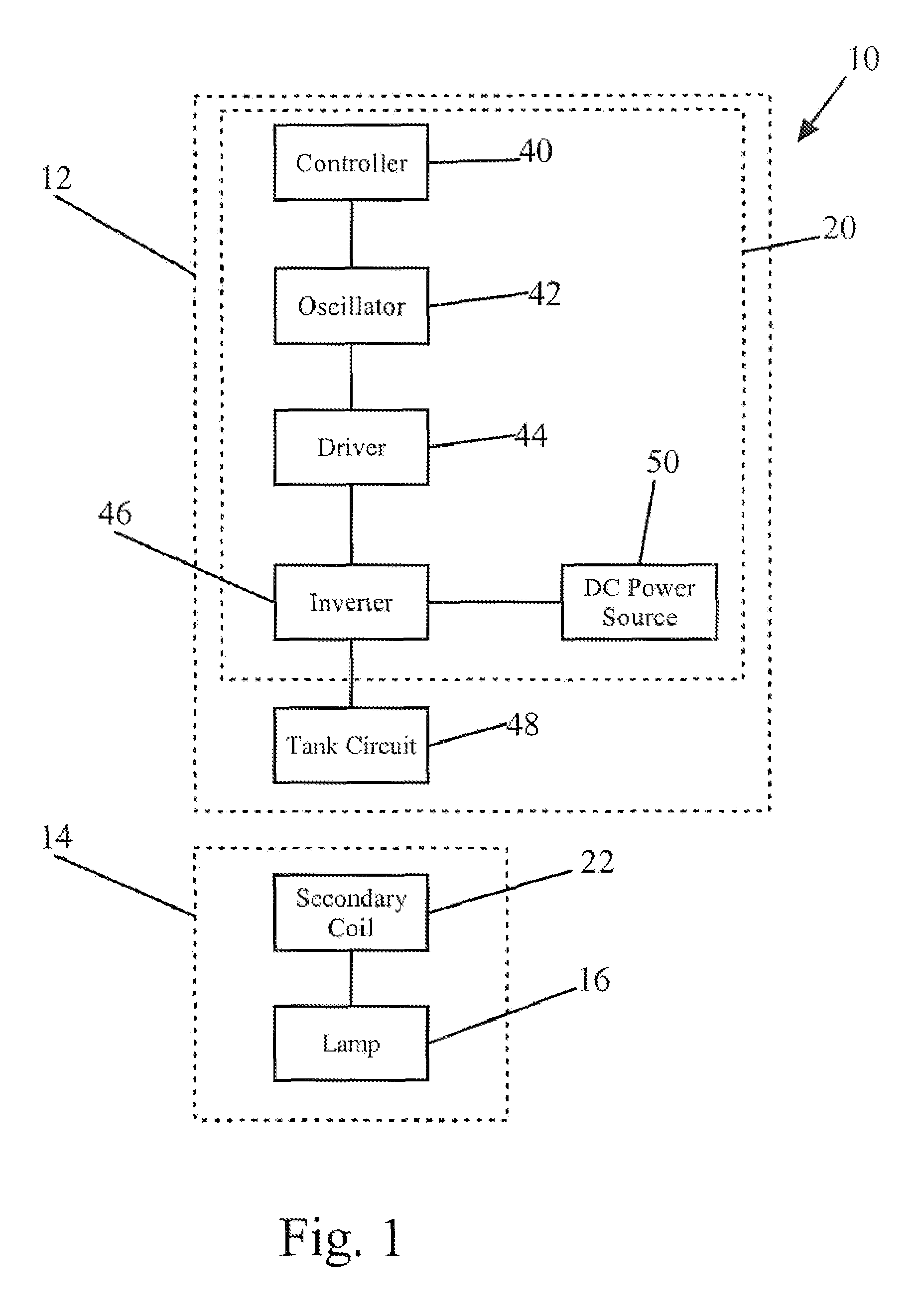

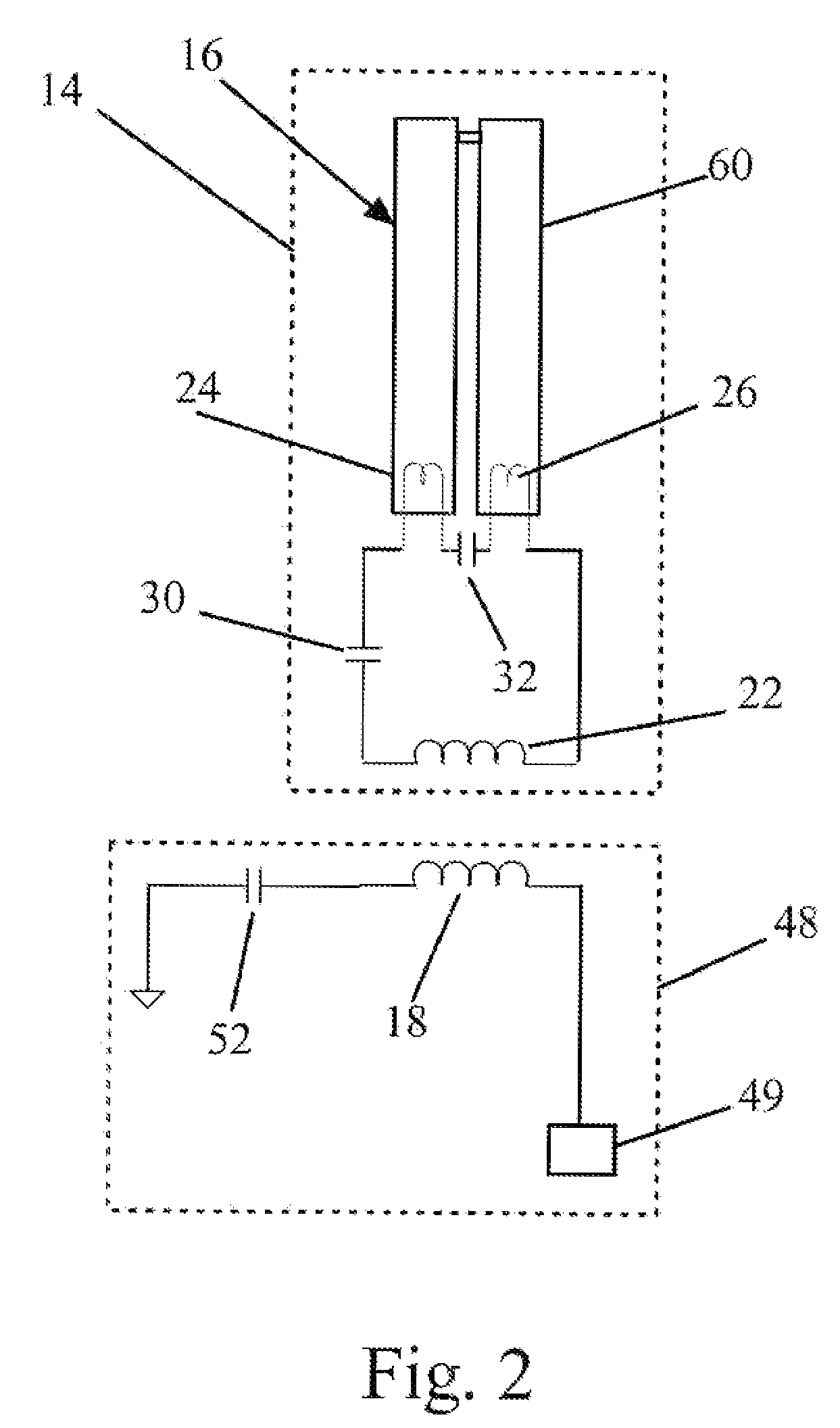

Inductively-powered gas discharge lamp circuit

InactiveUS7592753B2Reduce size and costLess complexElectrical apparatusElectric light circuit arrangementGas-discharge lampElectrical impedance

Owner:ACCESS BUSINESS GRP INT LLC

Passive wireless sensor

ActiveUS10140566B2Long distanceComplex functionWireless architecture usageNear-field in transpondersLine sensorClock generator

The RFID sensor tag may include normal RFID circuits and functions (such as rectifier, modulator, logic and memory) as well as a resonator-based clock generator or oscillator. The oscillator is a stable resonator-based oscillator having a high Q value. The resonator-based oscillator is loaded with a sensor element which tunes the oscillation frequency, i.e. the oscillation frequency is sensitive to the measured quantity. Thereby, a passive RFID sensor with a resonator-based oscillator and a sensor element is provided, wherein the oscillation frequency can be made dependent on the sensor element if sensing is required. The concept is compatible for existing RFID tags and can enable the possibility to measure external quantities with-out reducing the read-out distance.

Owner:METSO OUTOTEC (FINLAND) OY

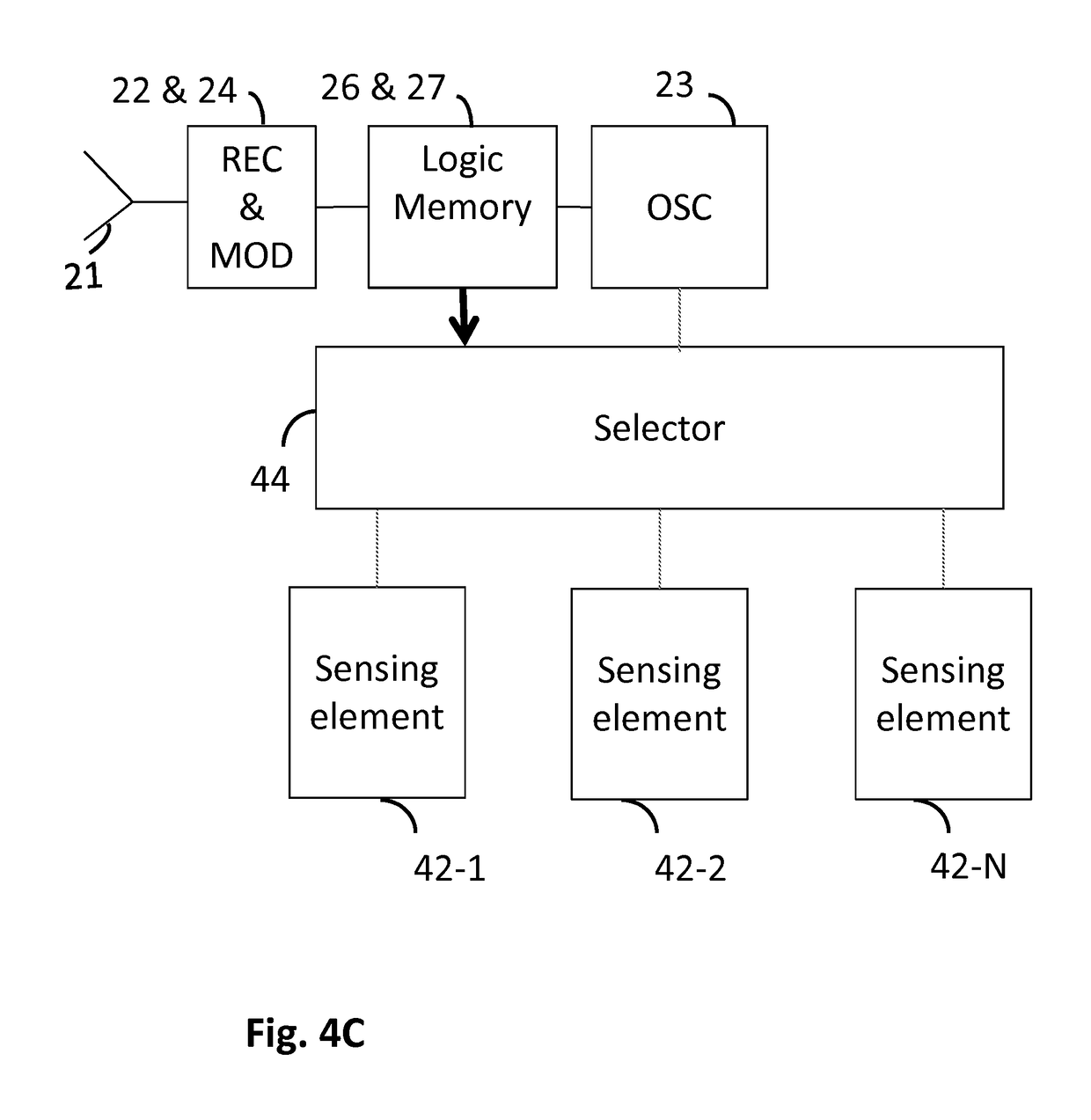

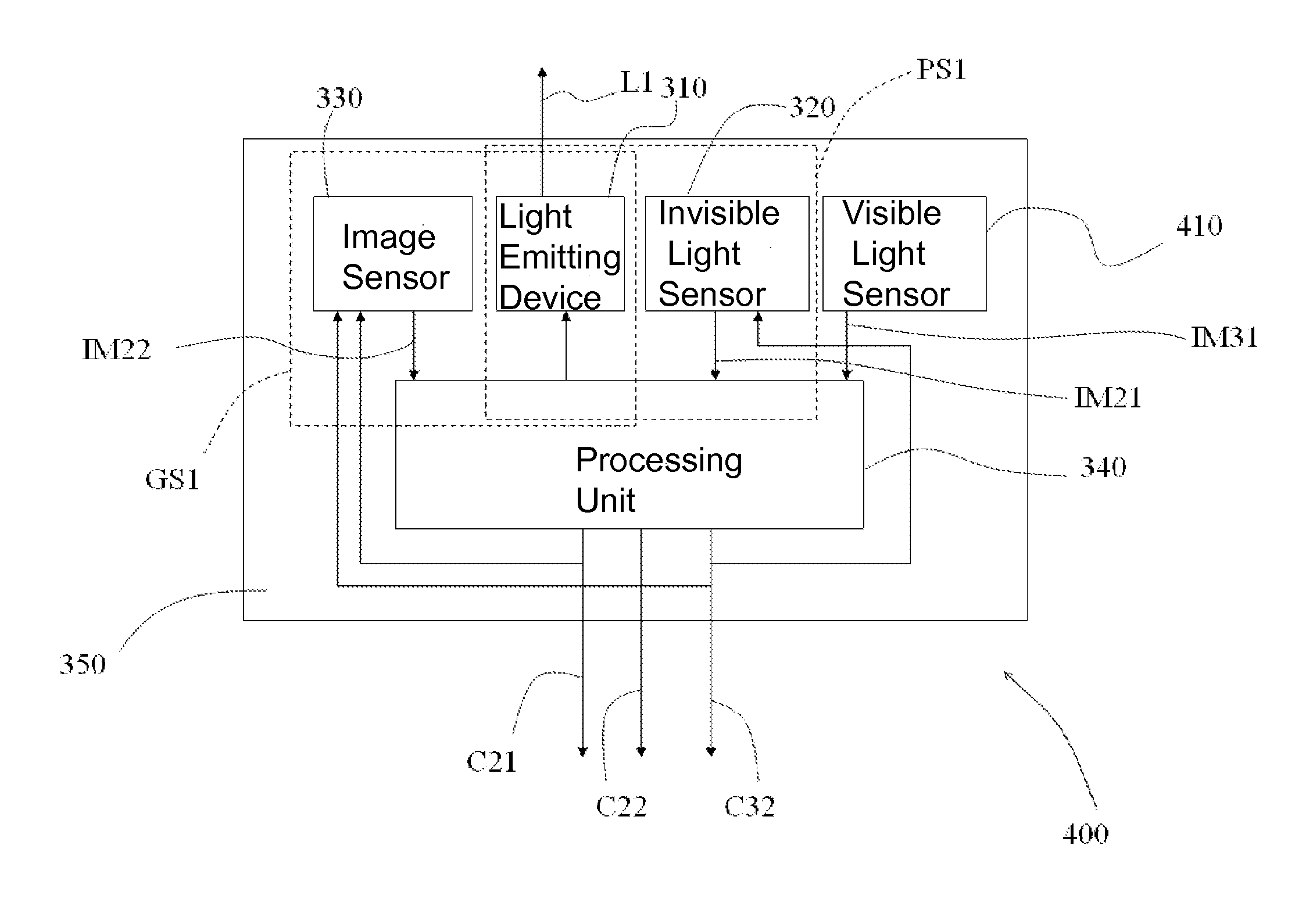

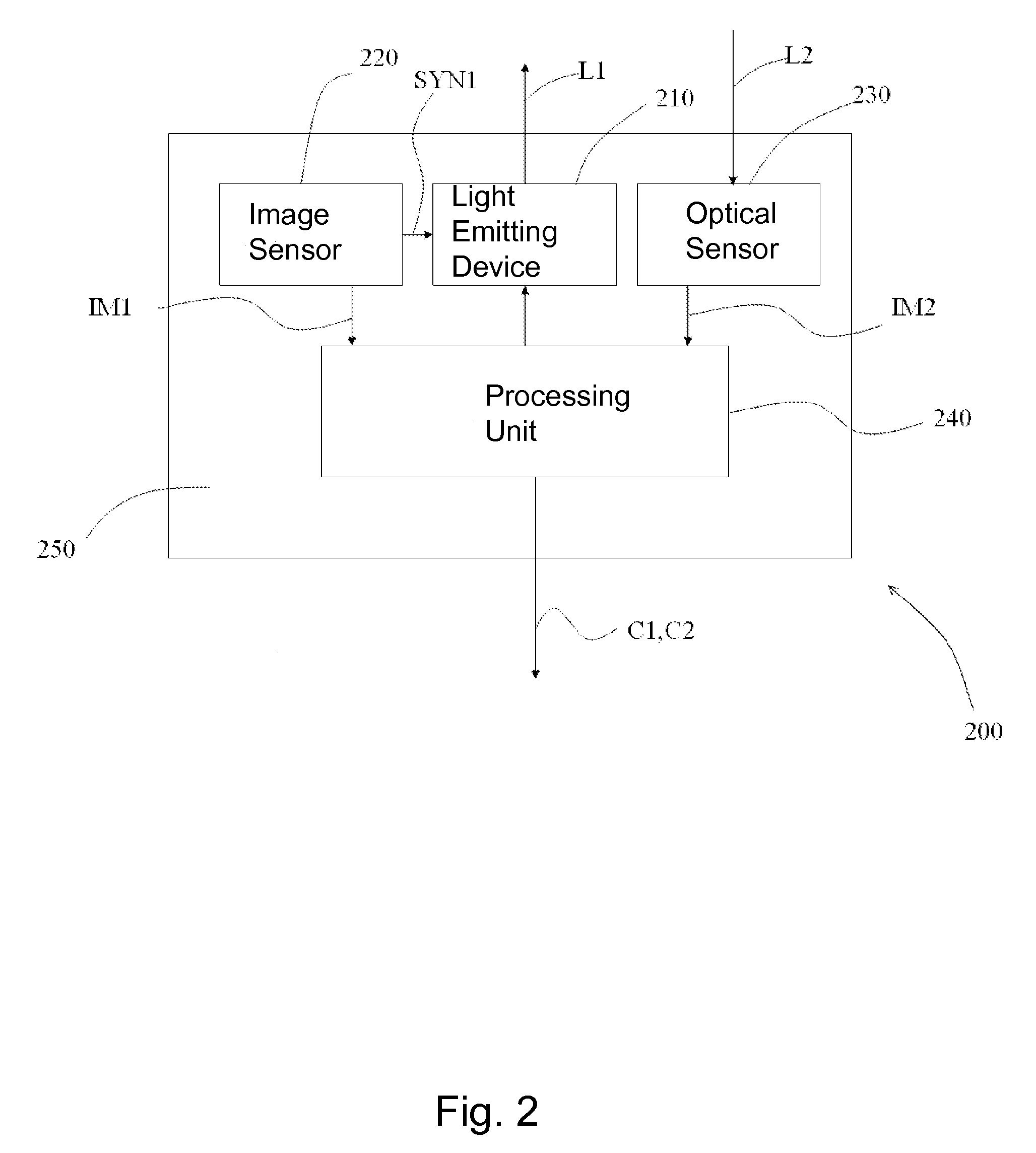

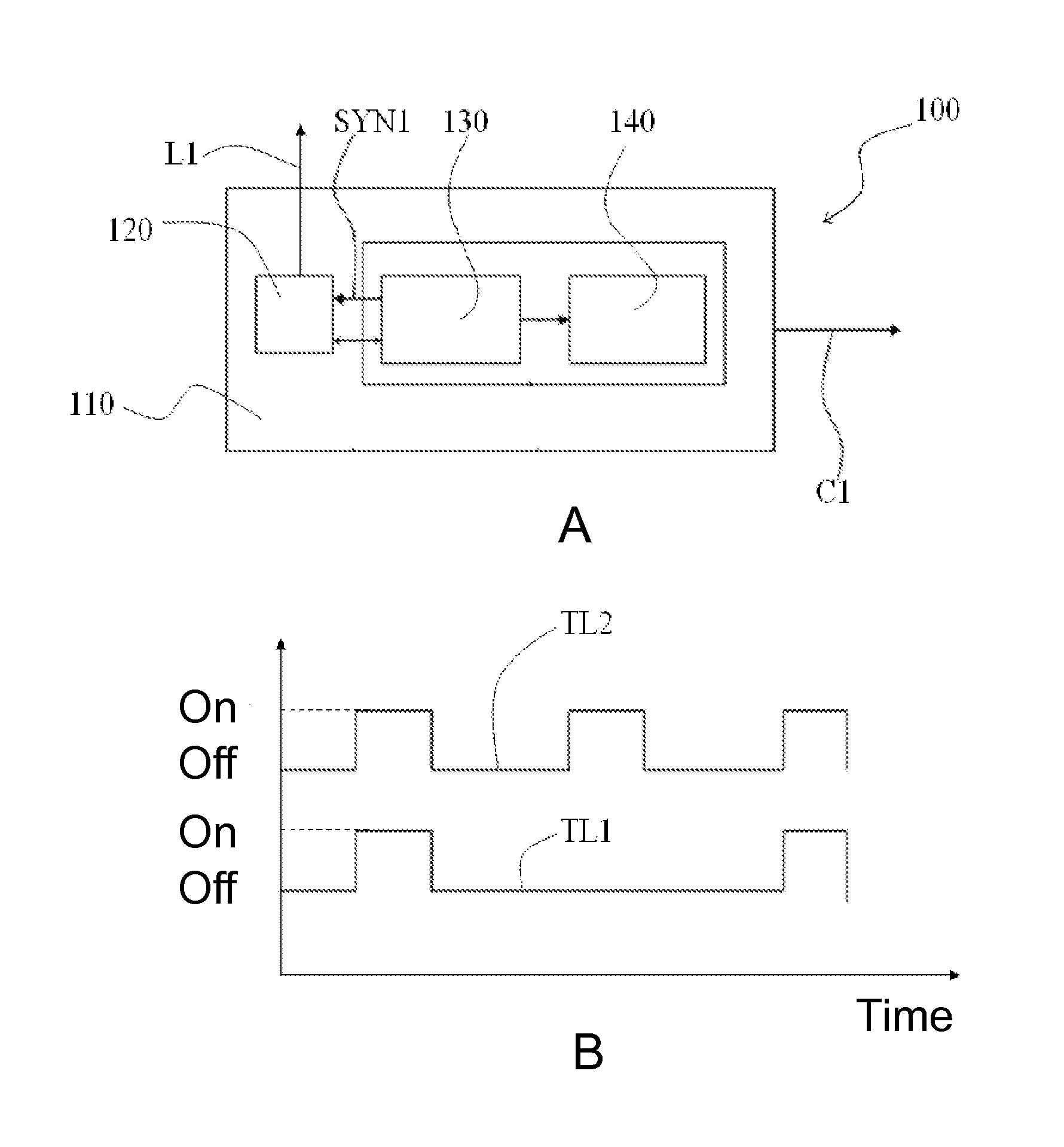

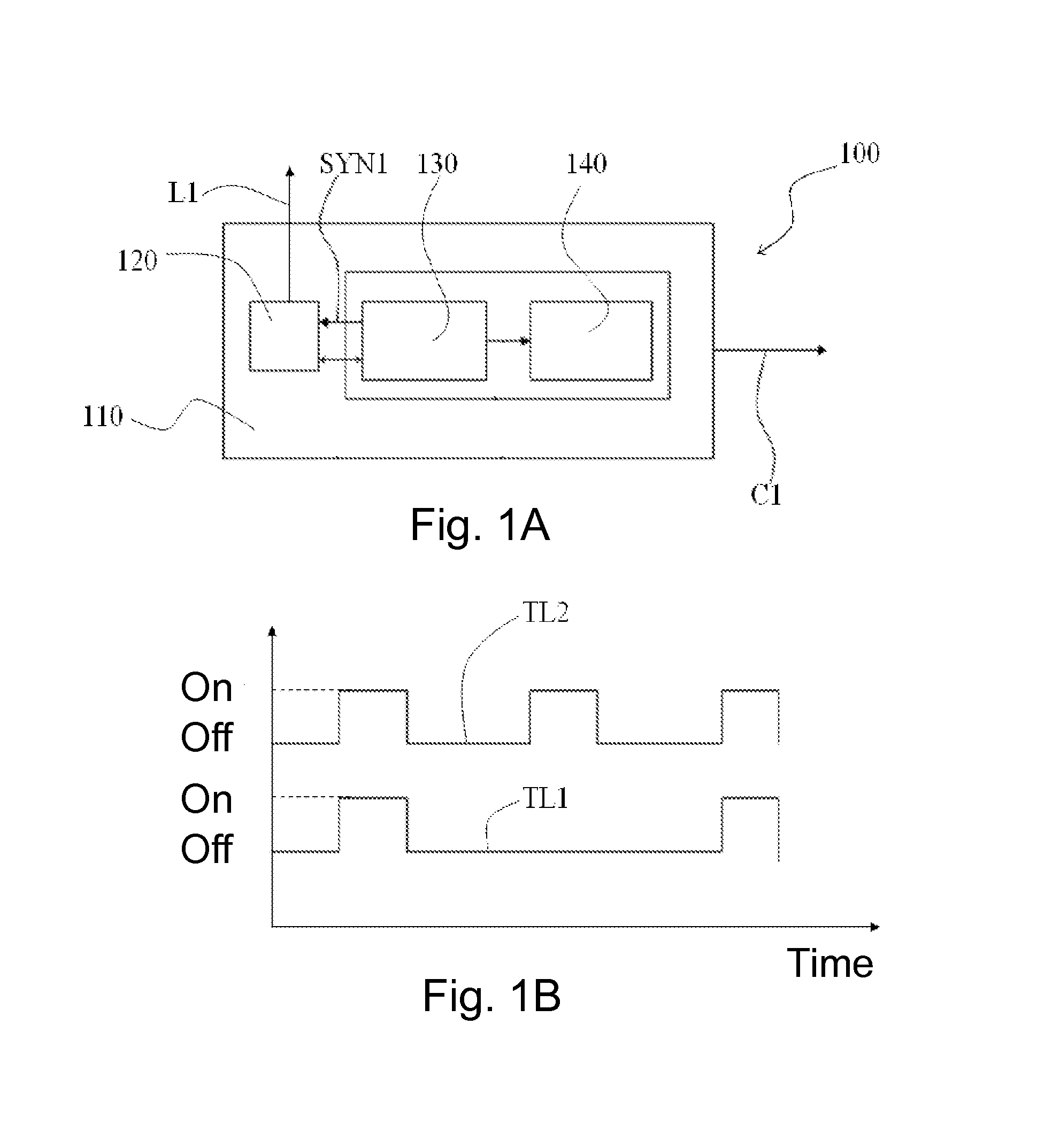

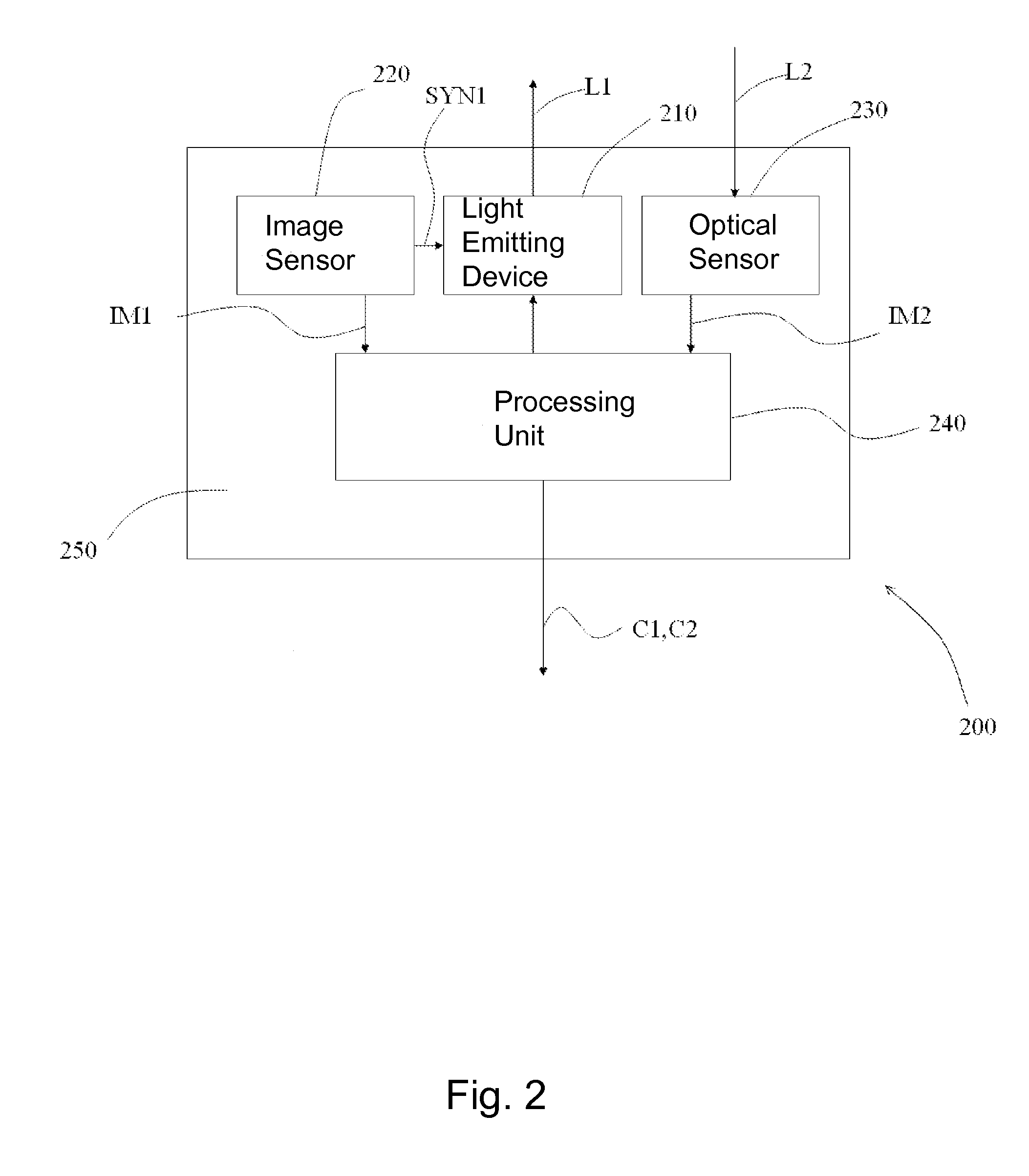

Gesture recognition apparatus and complex optical apparatus

ActiveUS9223407B2Reduce processing timeLower requirementInput/output for user-computer interactionTelevision system detailsLight beamComputer science

The present invention discloses a gesture recognition apparatus including a substrate, a light emitting device, an image sensor and a processing unit. The light emitting device is for emitting a light beam according to a first clock signal. The image sensor is disposed on the substrate and is for receiving the light beam reflected by an object according to a second clock signal to generate an object image. The processing unit is disposed on the substrate and is for recognizing the object image detected by the image sensor to provide a command signal. There is a correlation between a period of the first clock signal and a period of the second clock signal. The present invention also provides a complex optical apparatus.

Owner:PIXART IMAGING INC

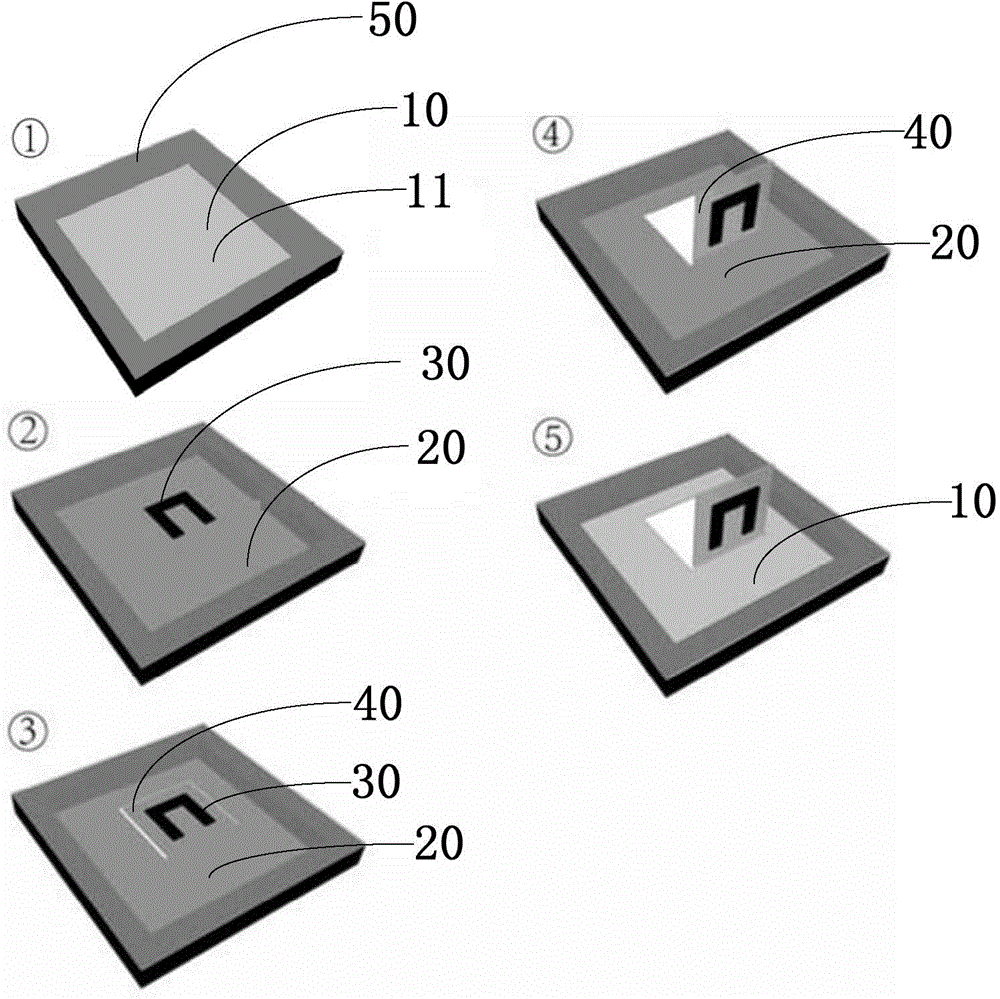

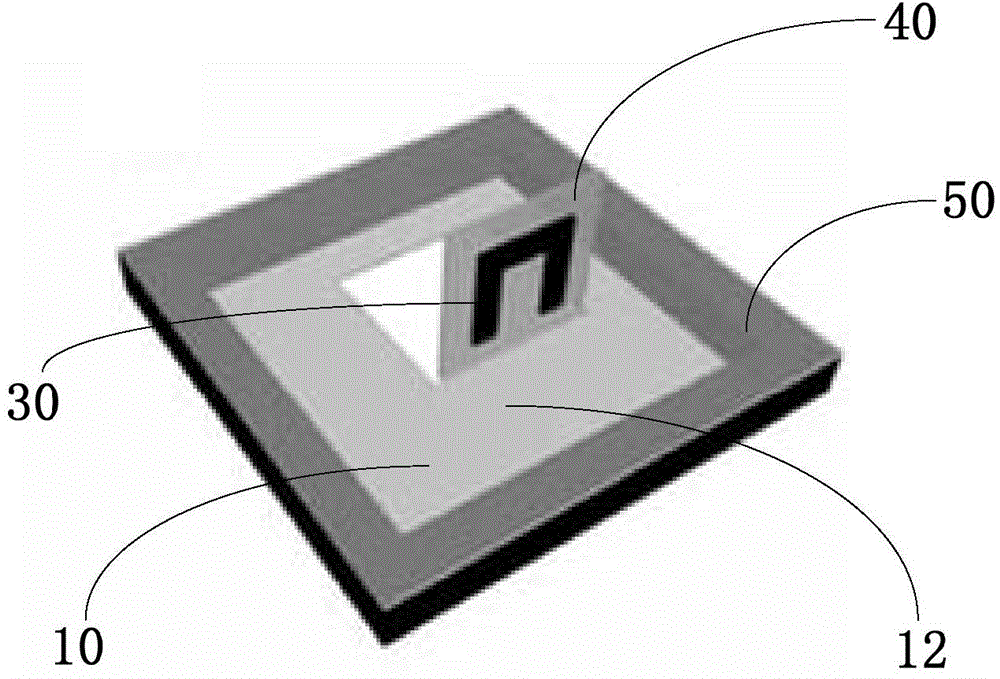

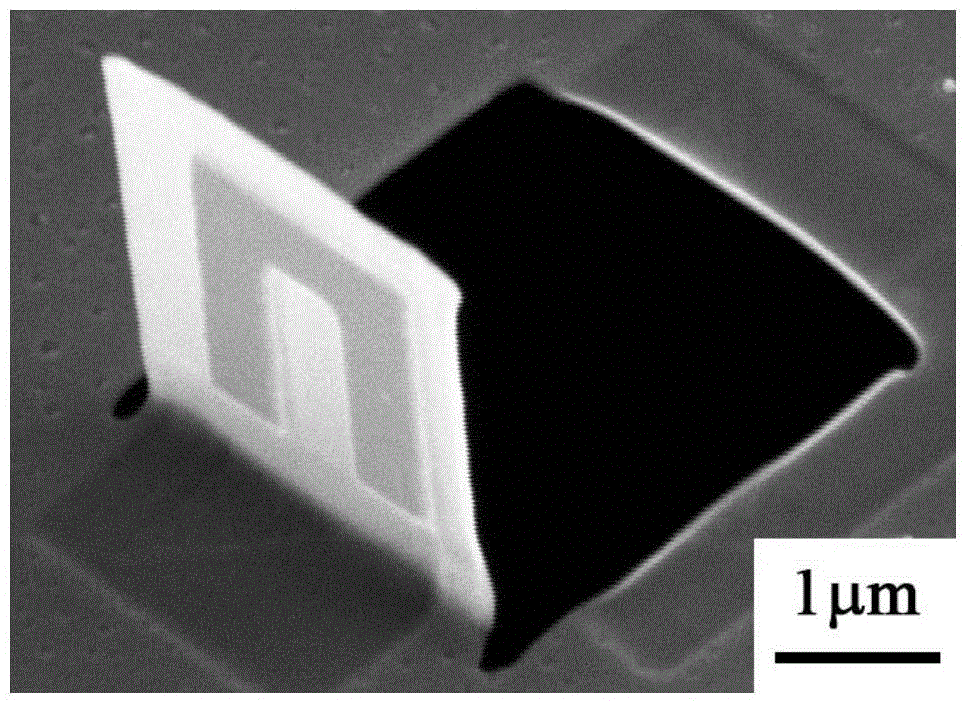

Self supporting three dimension device and preparation method thereof

ActiveCN104599979ADoes not affect insulation propertiesReduce machining accuracySemiconductor/solid-state device manufacturingDielectricIon beam

The invention discloses a self supporting three dimension device and a preparation method thereof. The preparation method of the self supporting three dimension device includes: S1, providing a self supporting insulation dielectric film with a basically flat upper surface; S2, generating a conducting layer and at least one device unit with a preset pattern on the upper surface of the self supporting insulation dielectric film so as to generate a composite layer structure; S3, cutting the composite layer structure so as to obtain at least one suspension portion locally connected with the composite layer structure, wherein each suspension portion is provided with each corresponding device unit; S4, using an ion beam to irradiate the at least one suspension portion so as to deform the conducting layer, and thereby driving each suspension portion to bend around a portion of each suspension portion, connected with the composite layer structure, towards the direction far away from the self supporting insulation dielectric film; S5, removing at least a portion of the conducting layer so as to obtain the self supporting three dimension device. The preparation method of the self supporting three dimension device can prepare a three dimensional structure and micron and nanometer devices which are insulated from one another on the self supporting insulation dielectric film, and has the advantages of being good in controllability, low in cost, and capable of preparing the self supporting three dimension device large in area.

Owner:INST OF PHYSICS - CHINESE ACAD OF SCI

Methods for low cost manufacturing of complex layered materials and device

InactiveUS8220704B2Increase volumeLow costBoxes/cartons making machineryPaper/cardboard articlesBonding processSmart card

Owner:MYCROLAB DIAGNOSTICS PTY LTD

Gesture recognition apparatus and complex optical apparatus

ActiveUS20140139488A1Save power consumptionComplex sensing functionTelevision system detailsInput/output processes for data processingLight beamEngineering

The present invention discloses a gesture recognition apparatus including a substrate, a light emitting device, an image sensor and a processing unit. The light emitting device is for emitting a light beam according to a first clock signal. The image sensor is disposed on the substrate and is for receiving the light beam reflected by an object according to a second clock signal to generate an object image. The processing unit is disposed on the substrate and is for recognizing the object image detected by the image sensor to provide a command signal. There is a correlation between a period of the first clock signal and a period of the second clock signal. The present invention also provides a complex optical apparatus.

Owner:PIXART IMAGING INC

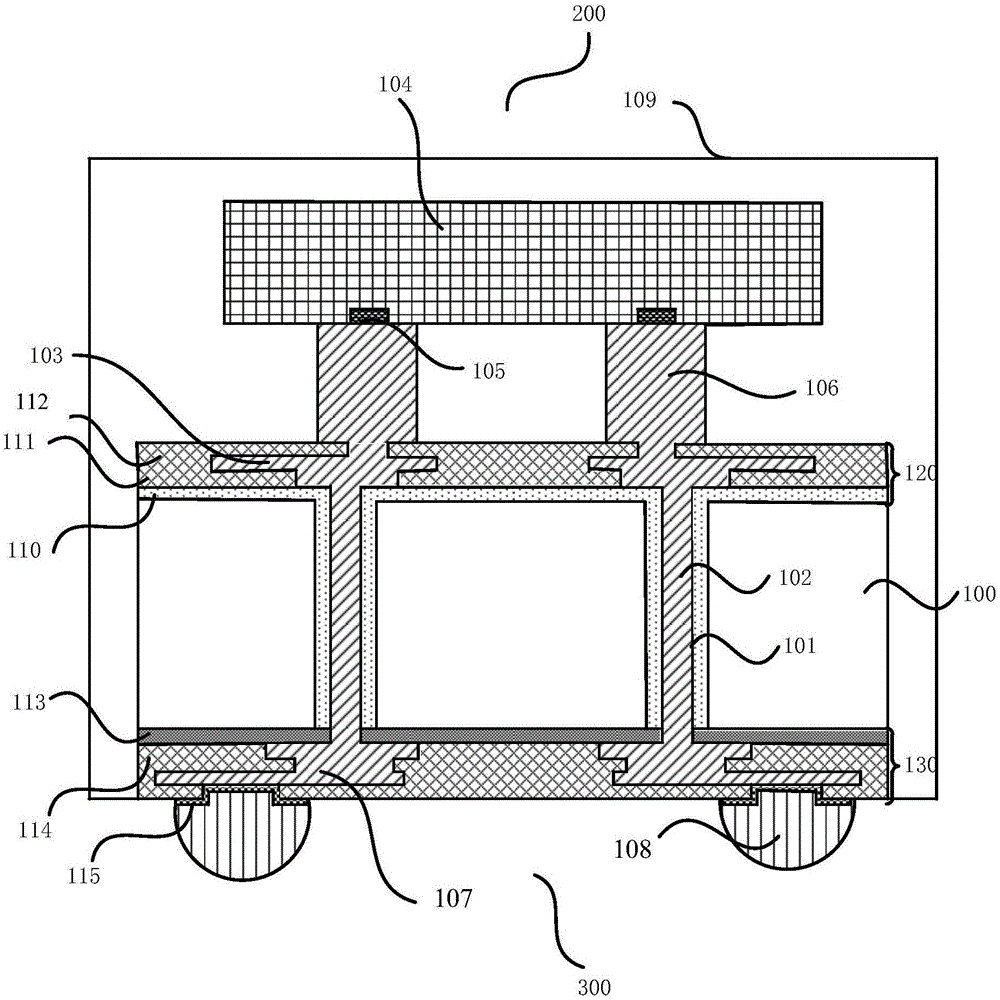

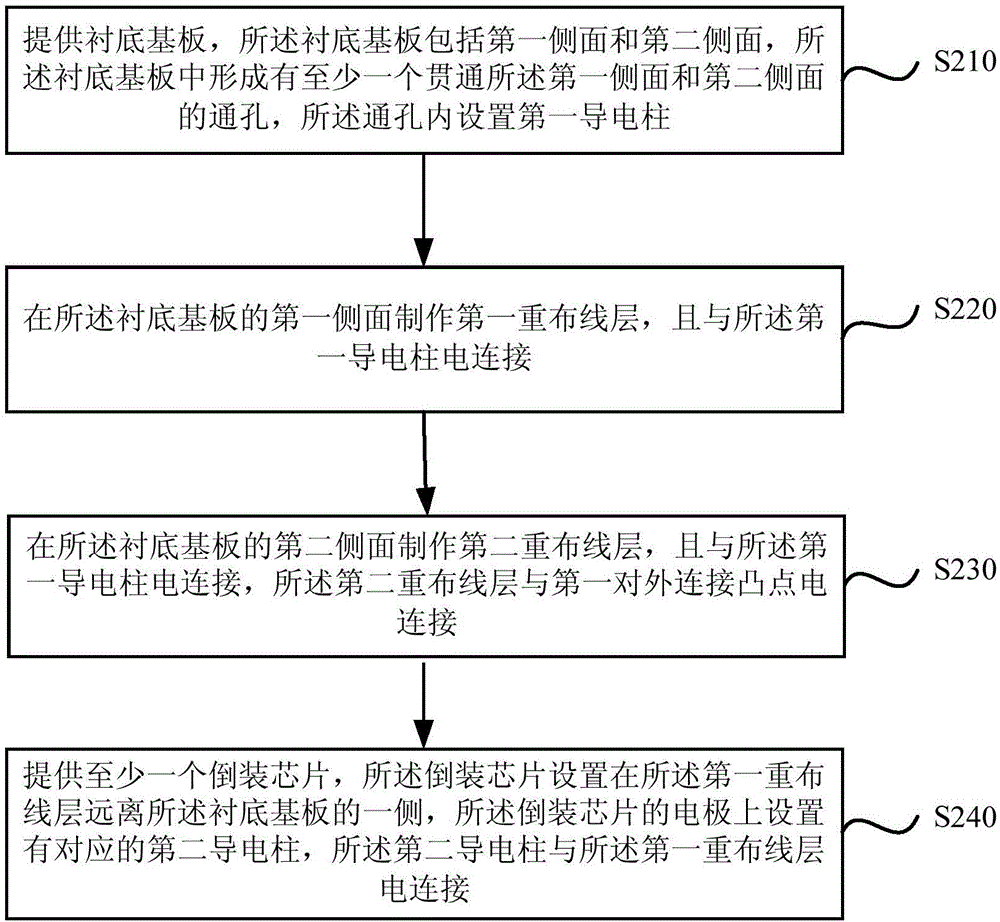

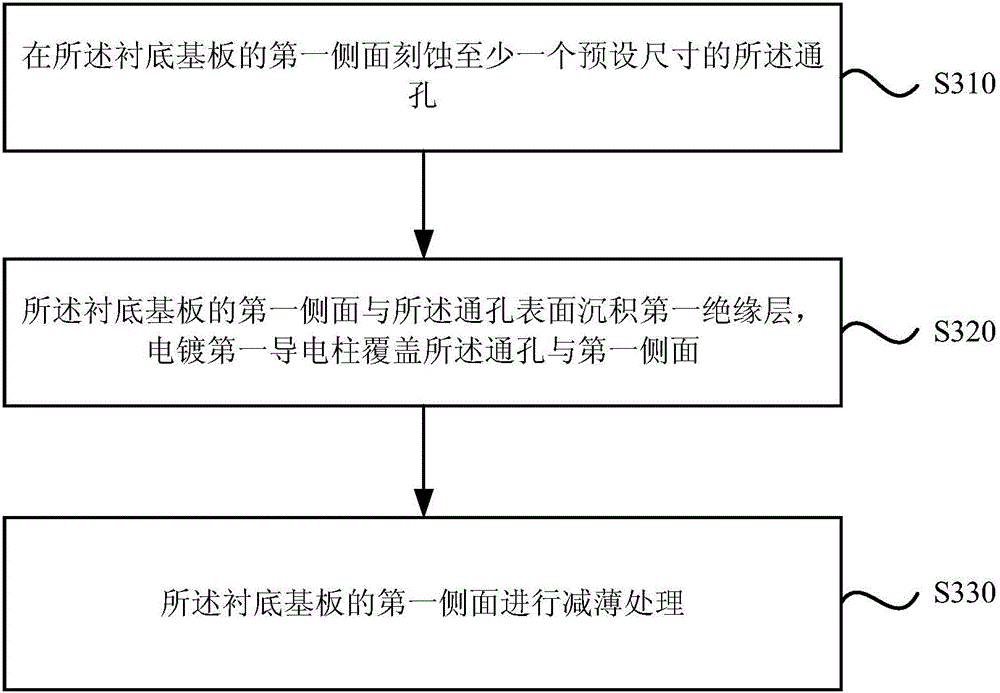

Chip packaging structure and method

InactiveCN106783760AHighly integratedImprove electrical performanceSemiconductor/solid-state device detailsSolid-state devicesEngineeringExternal connection

An embodiment of the invention discloses a chip packaging structure and method. The structure comprises a substrate base board, a first rerouting layer, a second rerouting layer and at least one inverted chip, the substrate base board comprises a first side surface and a second side surface, at least one through hole is formed in the substrate base board and penetrates the first side surface and the second side surface, first conducting posts are arranged in the through holes, the first rerouting layer is arranged on the first side surface of the substrate base board and electrically connected with the first conducting posts, the second rerouting layer is arranged on the second side surface of the substrate base board and electrically connected with the first conducting posts and first external connection projections, the inverted installation chips are arranged on one side of the first rerouting layer far away from the substrate base board, and second corresponding conducting posts are arranged on electrodes of the inverted chips and electrically connected with the first rerouting layer. According to the method, high-integration density of chips is achieved, input / output device interfaces in the unit area of the chips are increased, and electrical properties of the chips are improved.

Owner:NAT CENT FOR ADVANCED PACKAGING

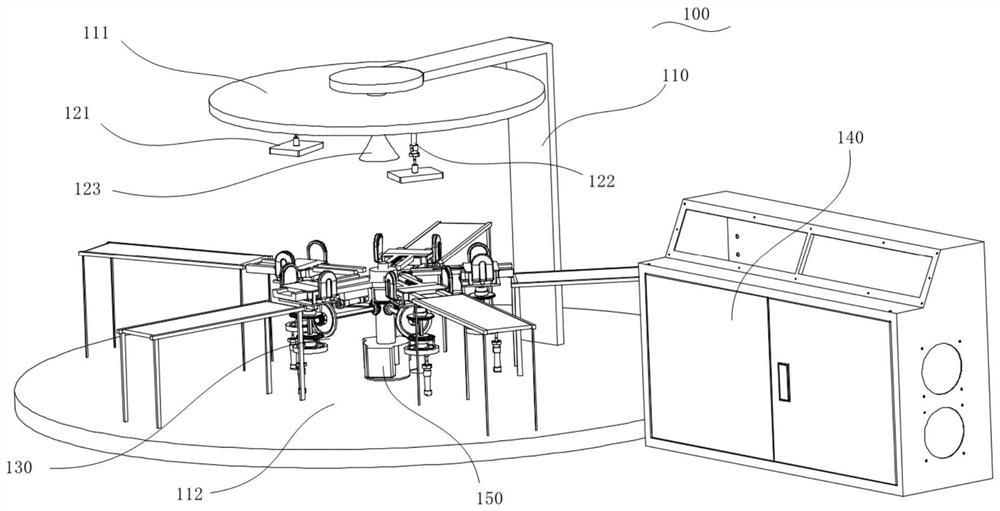

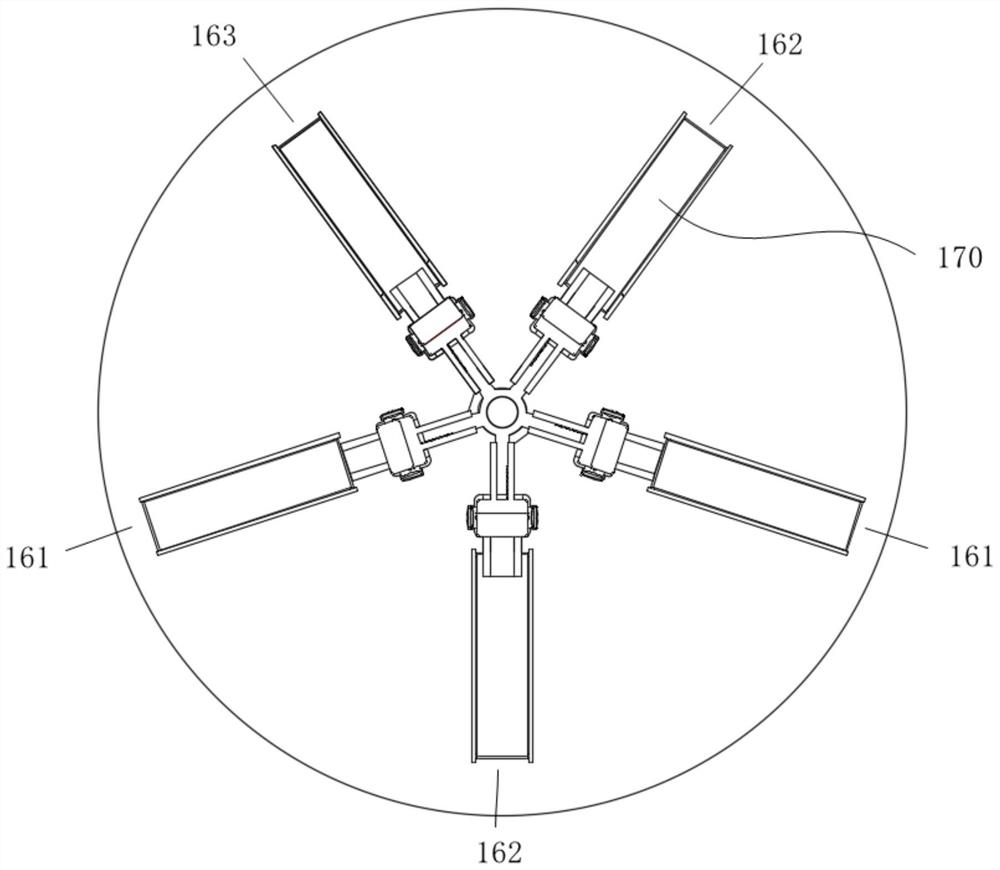

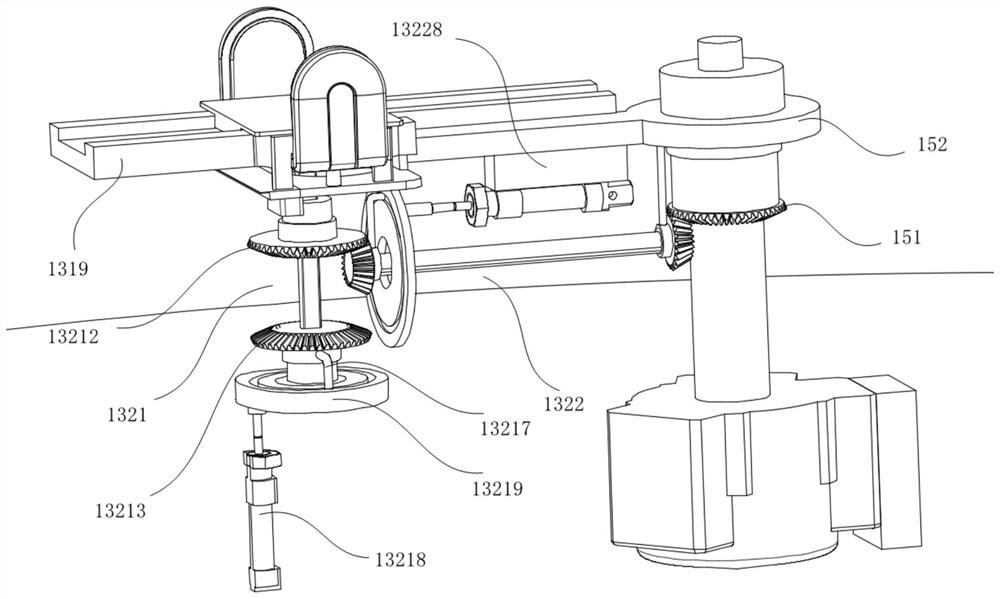

Circuit board automatic detection equipment

InactiveCN112371526AImprove detection efficiencyRealize detectionSortingTransmission beltElectric machinery

The invention discloses automatic circuit board detection equipment. The discloses automatic circuit board detection equipment comprises a rack, a motor, a plurality of conveying belts, a plurality ofmaterial conveying devices, a detection device and a control box, wherein the rack comprises an upper cover and a base plate, the detection device is located on the lower side of the upper cover of the rack, the motor is located in the center position of the base plate of the rack, the multiple material conveying devices are arranged around the motor in the circumferential direction and rotationally connected with the motor, the multiple conveying belts are located on the outer sides of the material conveying devices correspondingly, and each material conveying device comprises a clamping mechanism and a transmission mechanism. By means of the mode, the automatic circuit board detection equipment can rapidly clamp, feed, loosen and discharge a circuit board, detection is conducted at thesame time, and the detection efficiency is greatly improved.

Owner:代国瑞

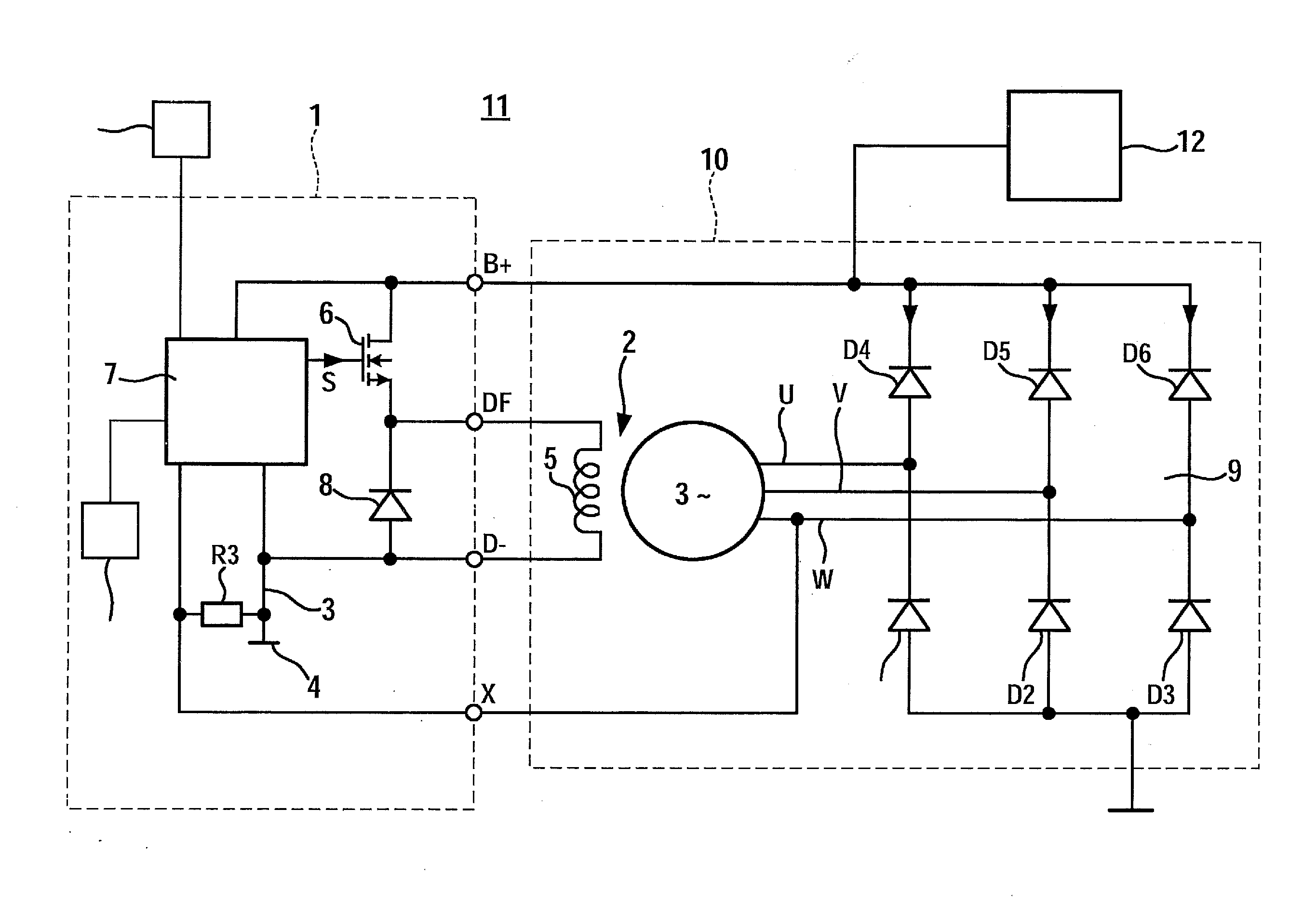

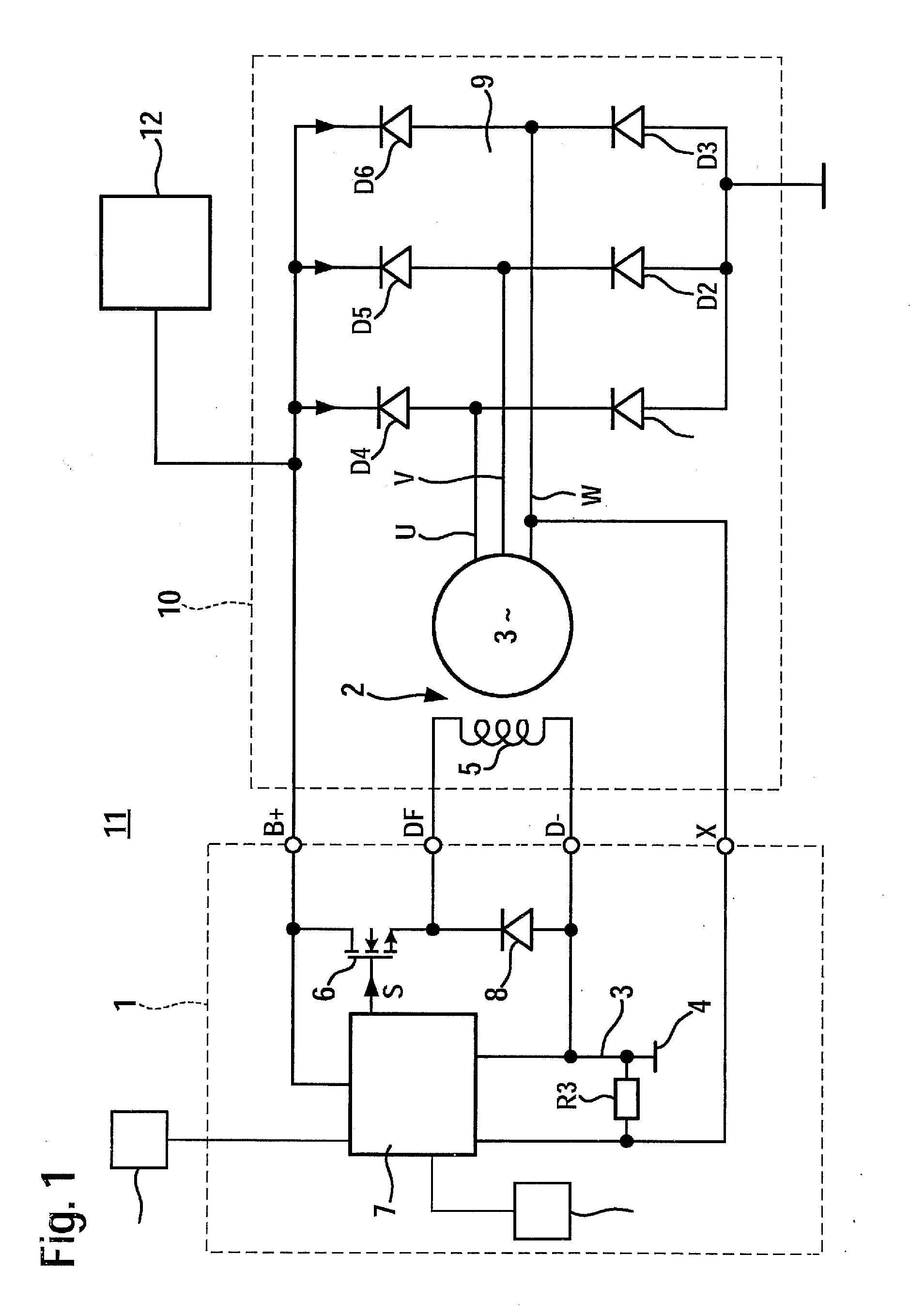

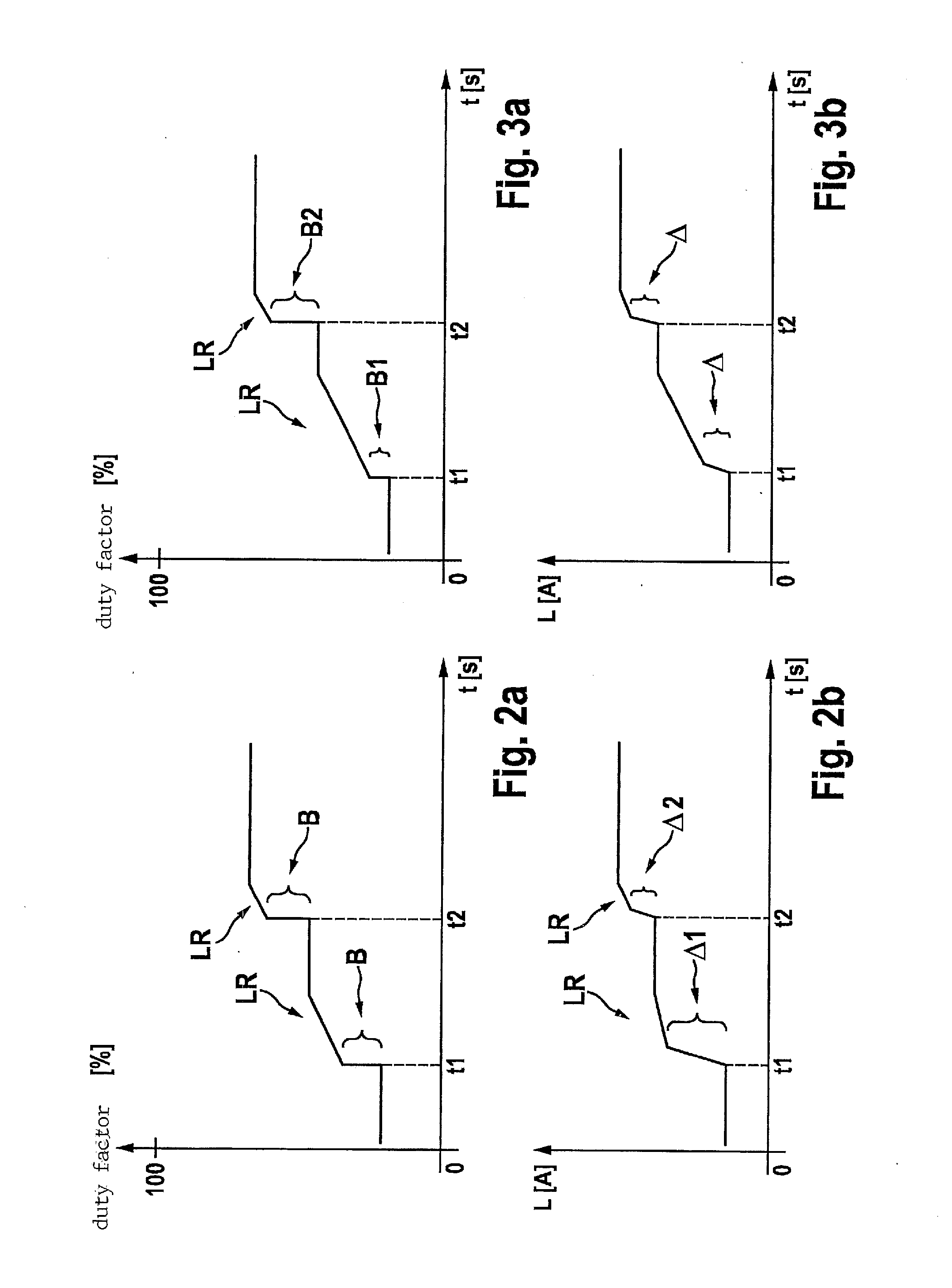

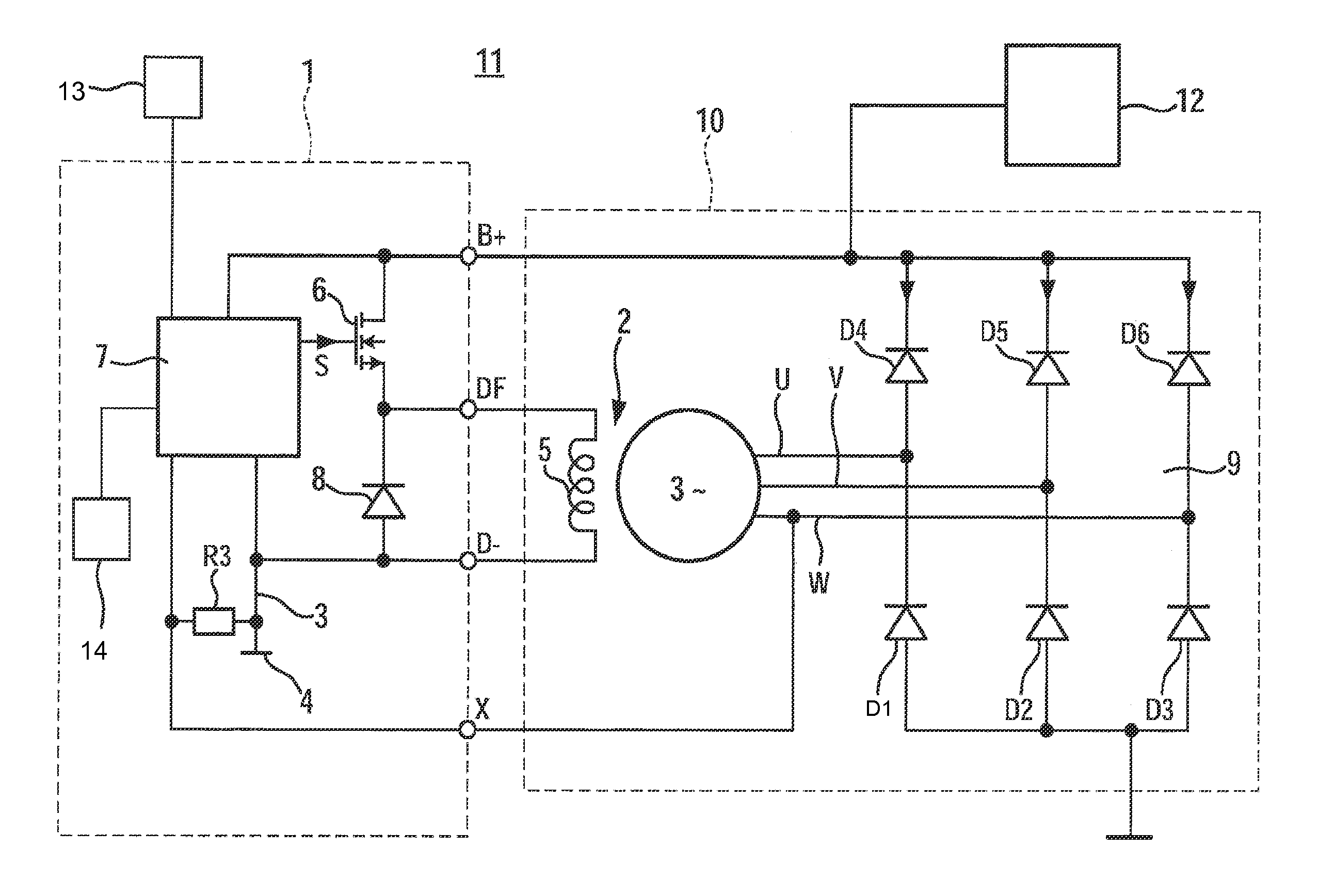

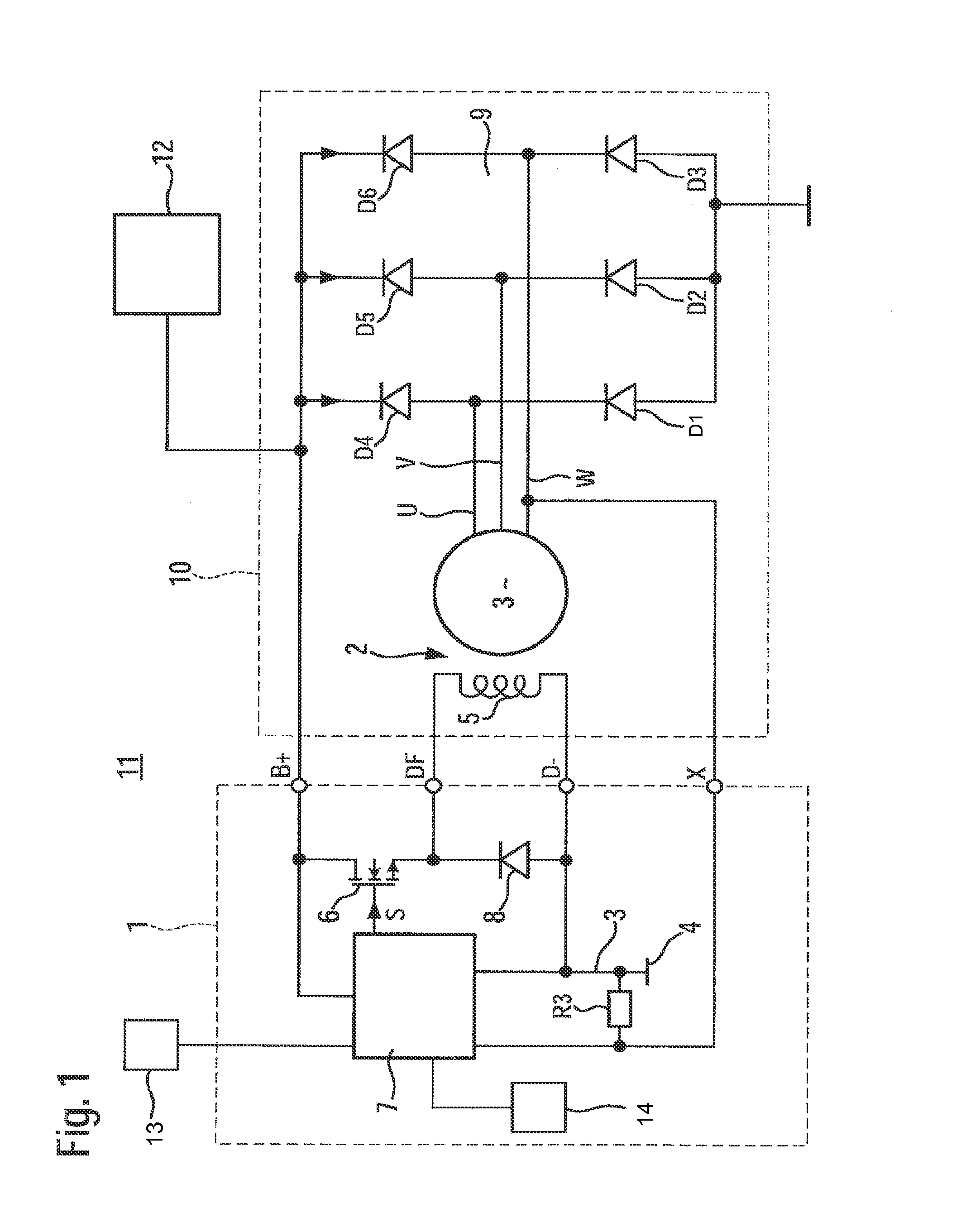

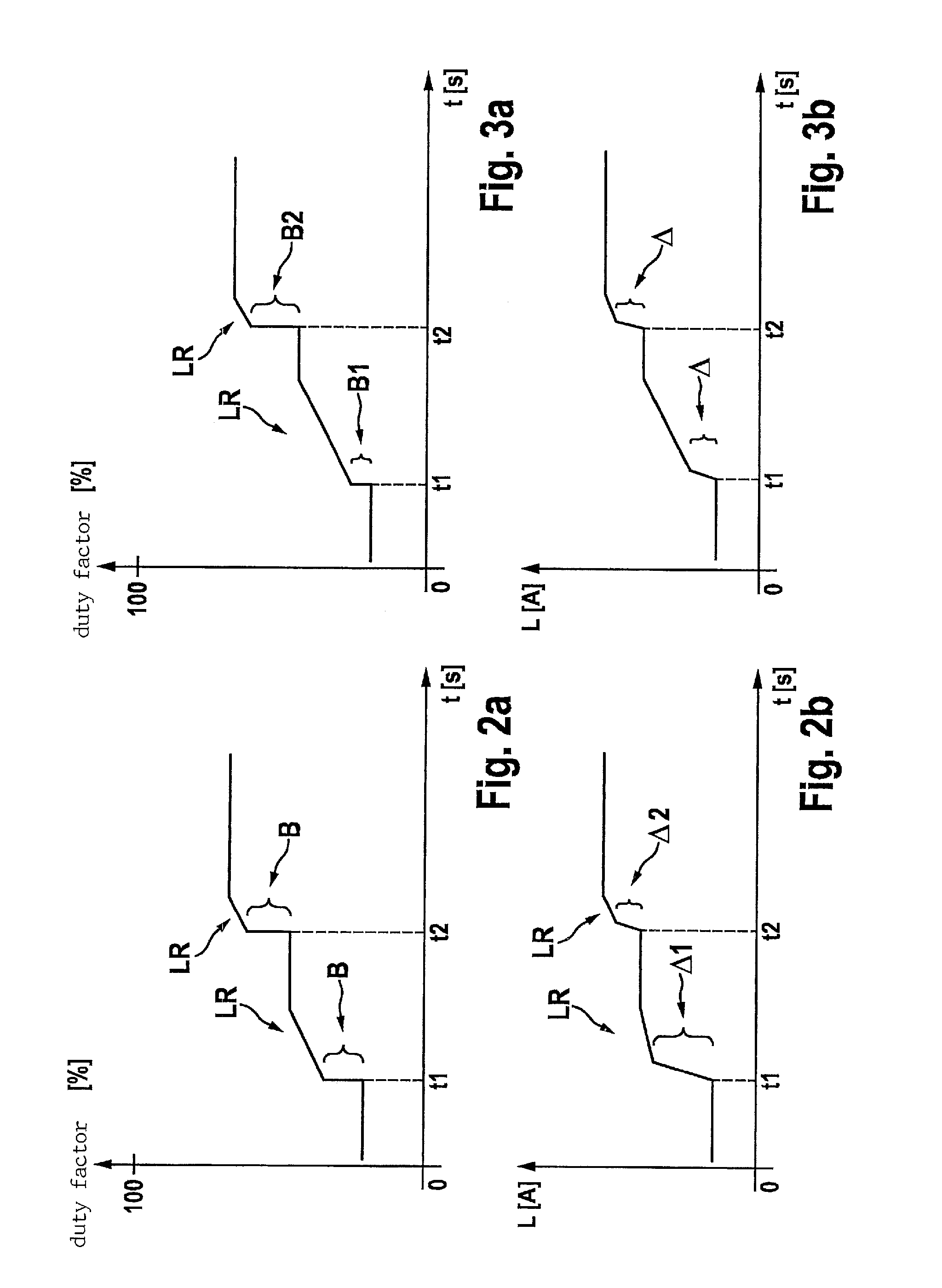

Method and device to compensate for a dip in the output voltage of a motor-vehicle alternator

ActiveUS20130141055A1Point to optimizationComplex functionBatteries circuit arrangementsElectric generator controlAlternatorControl signal

A dip in the output voltage of a motor-vehicle alternator, owing to a connecting of a load or a change in speed, is compensated with the aid of an alternator regulator which provides a control signal that has a duty factor and increases the excitation current of the motor-vehicle alternator. After the occurrence of the voltage dip, in a first step, the duty factor of the control signal is increased by a differential amount, and in a subsequent second step, the rate of correction is limited. After the occurrence of the voltage dip, parameters describing the instantaneous working point of the motor-vehicle alternator are determined, and in the first step, the differential amount is set as a function of the working point.

Owner:SEG AUTOMOTIVE GERMANY GMBH

Pass fail sentencing of hollow components

ActiveUS20170132777A1Complex functionMore passiveImage enhancementImage analysisCost savingsEngineering

Owner:ROLLS ROYCE PLC

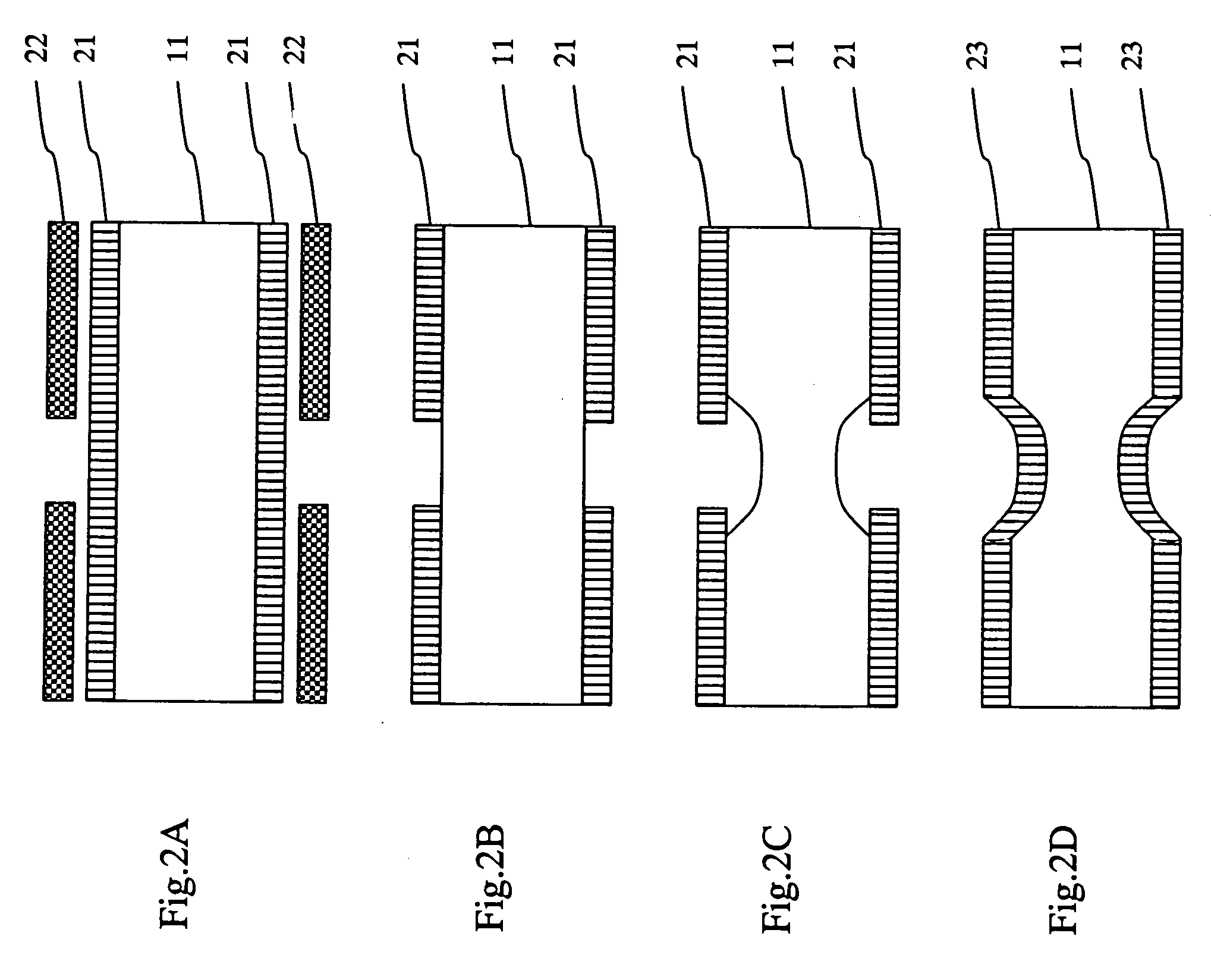

Semiconductor device with conductive protrusions and method for fabricating the same

ActiveUS11127632B1Complex functionSmall volumeSemiconductor/solid-state device detailsSolid-state devicesSemiconductor structureDevice material

The present application discloses a semiconductor device and a method for fabricating the semiconductor device. The semiconductor device includes a first semiconductor structure, a first connecting structure positioned on the first semiconductor structure, and a second semiconductor structure positioned on the first connecting structure. The first connecting structure includes a first connecting insulating layer positioned on the first semiconductor structure, a plurality of first connecting contacts positioned in the first connecting insulating layer, and a plurality of first supporting contacts positioned in the first connecting insulating layer. The top surfaces of the plurality of first connecting contacts contact a bottom surface of the second semiconductor structure. A top surface of the plurality of first connecting contact and a top surface of the plurality of first supporting contact protrude from a top surface of the first connecting insulating layer.

Owner:NAN YA TECH

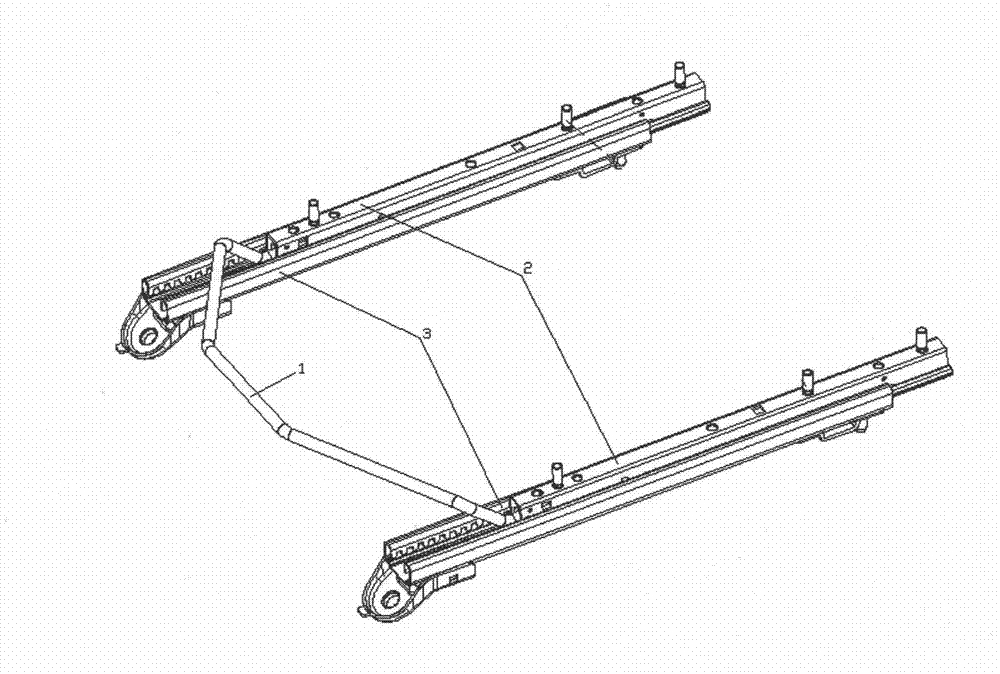

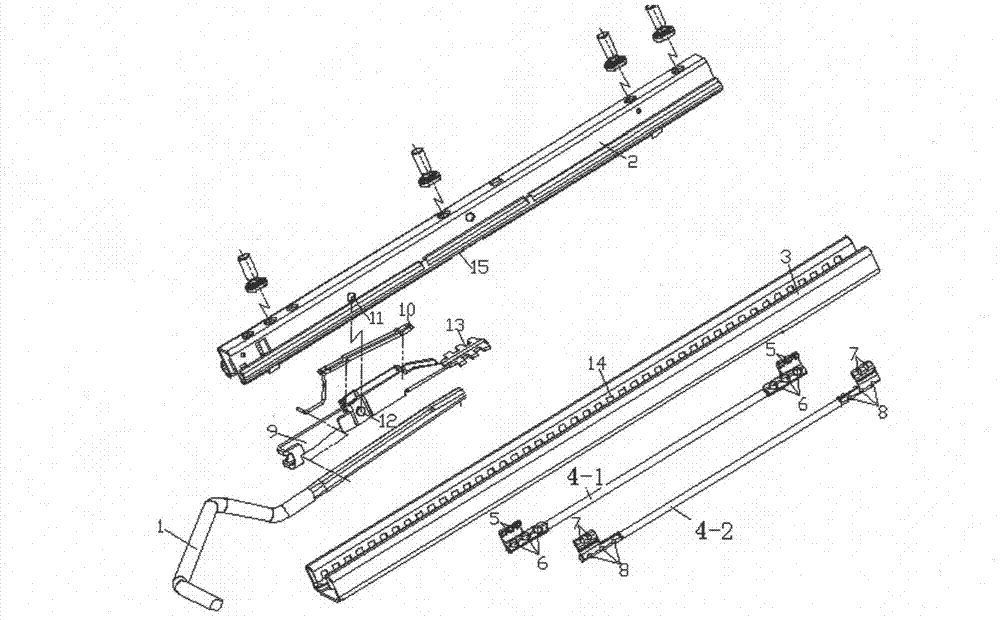

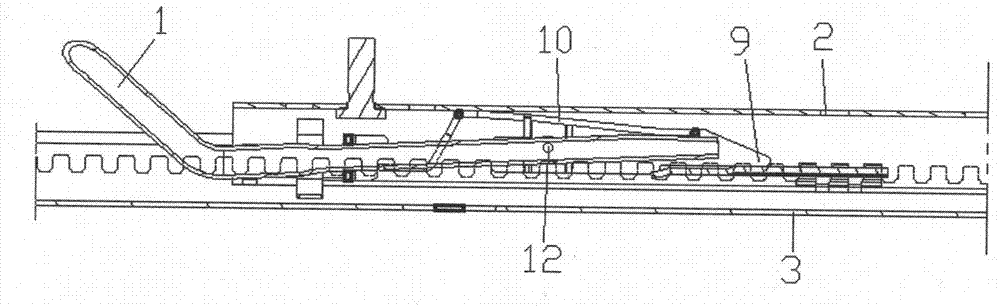

Manual longitudinal sliding rail for car seat

InactiveCN102848936AStress situation improvedAvoid unilateral forceMovable seatsCar seatLocking plate

The invention relates to a manual longitudinal sliding rail for a car seat. The manual longitudinal sliding rail is characterized in that a longitudinal sliding rail mechanism comprises a lower rail, wherein an upper rail is matched on the lower rail in a sliding manner; a cavity is formed between the upper rail and the lower rail; a locking plate penetrated in a connecting part is arranged in the cavity and is hinged with the upper rail; one end of an elastic restoring mechanism is connected with the connecting part while the other end thereof is fixedly connected with the locking plate; at least one side surface in the two side surfaces of the lower rail, facing the upper rail, is provided with a plurality of locking slots; the opening of each locking slot faces the position of the lower rail; and the side of the locking plate, facing the locking slots, is provided with a plurality of locking teeth matched with the locking slots. The manual longitudinal sliding rail disclosed by the invention is simple in structure, and has the locking intensity which meets the compulsive requirements of rules.

Owner:SHANGHAI YANPU METAL PROD

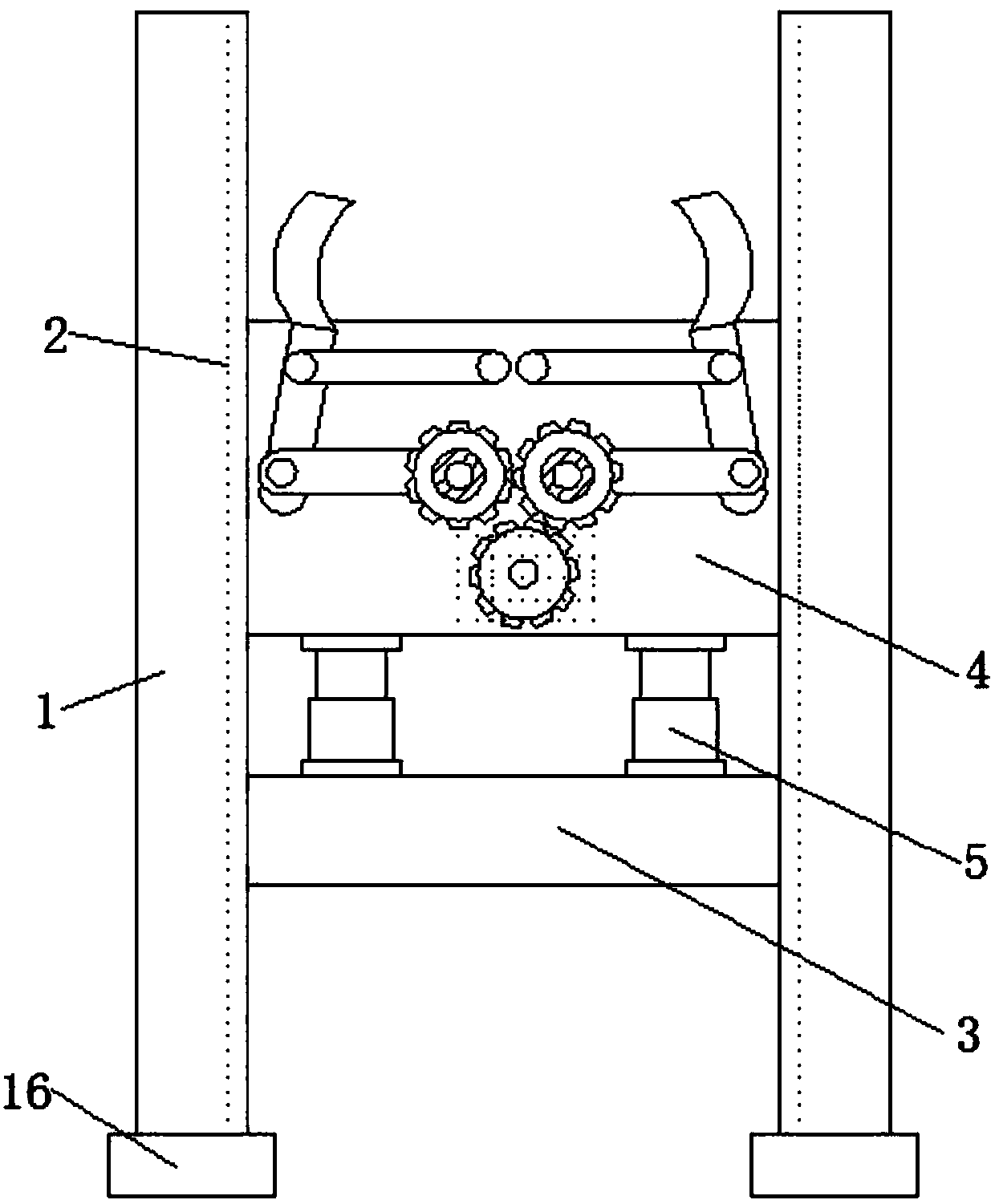

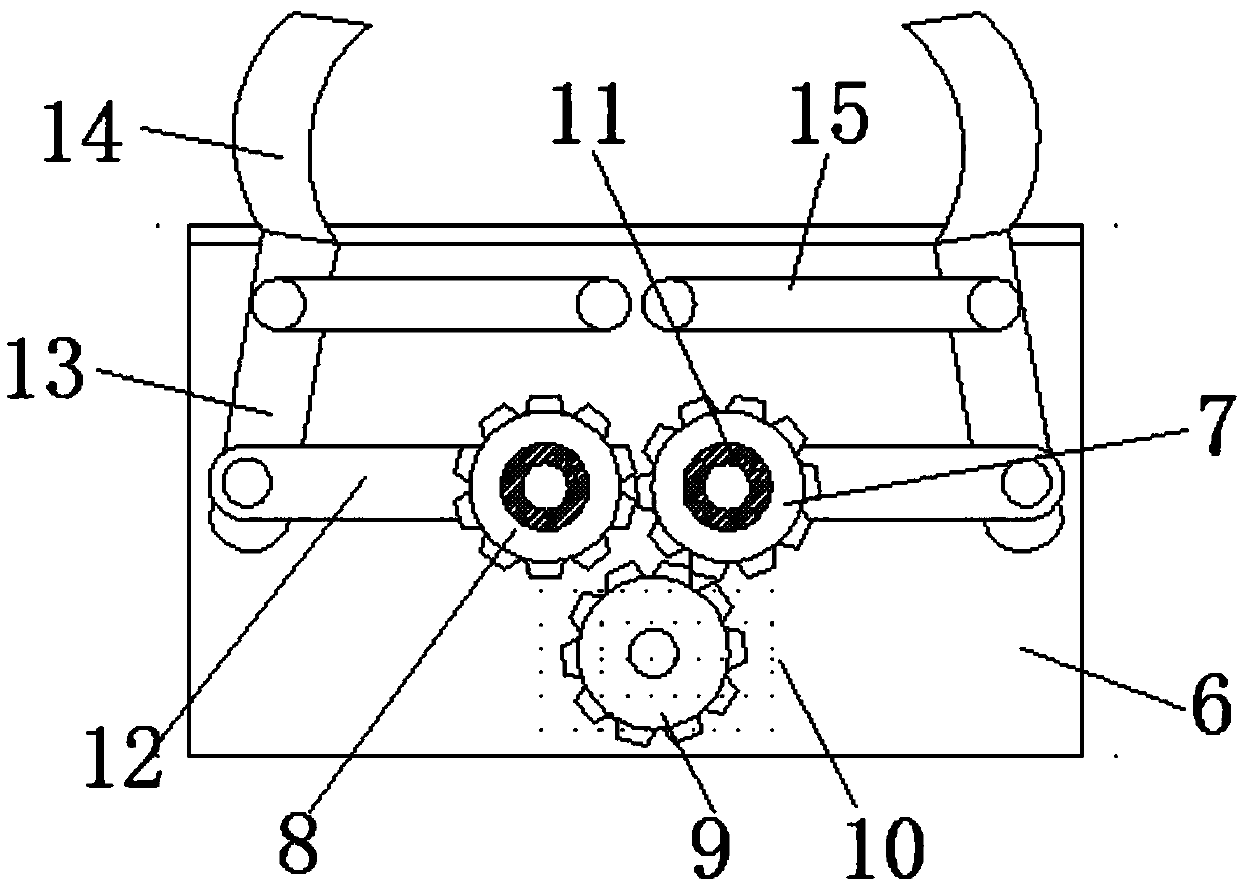

Device for fixing petroleum pipeline

The invention discloses a fixing device for oil pipelines, which comprises two sets of vertically arranged upright columns, a vertically arranged chute is arranged in the adjacent side of the upright columns, and a fixing frame is arranged between the upright columns. A clamping mechanism is provided above the fixed frame, and several telescopic cylinders are arranged between the clamping mechanism and the fixed frame, wherein the clamping mechanism includes a slide plate arranged in the chute. Beneficial effects: through the locking teeth driven by the rotating motor, the first rotating tooth cooperates with the transmission rod under the action of the second rotating tooth, which is convenient for the connecting rod to cooperate with the clamp arm to fix the pipeline, and the fastening pin further strengthens the fixing stability. , the clamping mechanism cooperates with the chute under the action of the telescopic cylinder, which facilitates the adjustment of the height of the pipeline, making it able to adapt to the operation requirements in different environments. It is easy to operate and has complex functions. It is not only low in cost and strong in practicability, but also reusable. Energy saving and environmental protection.

Owner:SHAANXI KERLIMAR ENGINEERS CO LTD

Method and device to compensate for a dip in the output voltage of a motor-vehicle alternator

ActiveUS8963509B2Point to optimizationComplex functionBatteries circuit arrangementsEmergency protective circuit arrangementsAlternatorControl signal

A dip in the output voltage of a motor-vehicle alternator, owing to a connecting of a load or a change in speed, is compensated with the aid of an alternator regulator which provides a control signal that has a duty factor and increases the excitation current of the motor-vehicle alternator. After the occurrence of the voltage dip, in a first step, the duty factor of the control signal is increased by a differential amount, and in a subsequent second step, the rate of correction is limited. After the occurrence of the voltage dip, parameters describing the instantaneous working point of the motor-vehicle alternator are determined, and in the first step, the differential amount is set as a function of the working point.

Owner:SEG AUTOMOTIVE GERMANY GMBH