Patents

Literature

42results about How to "Designed for such use" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

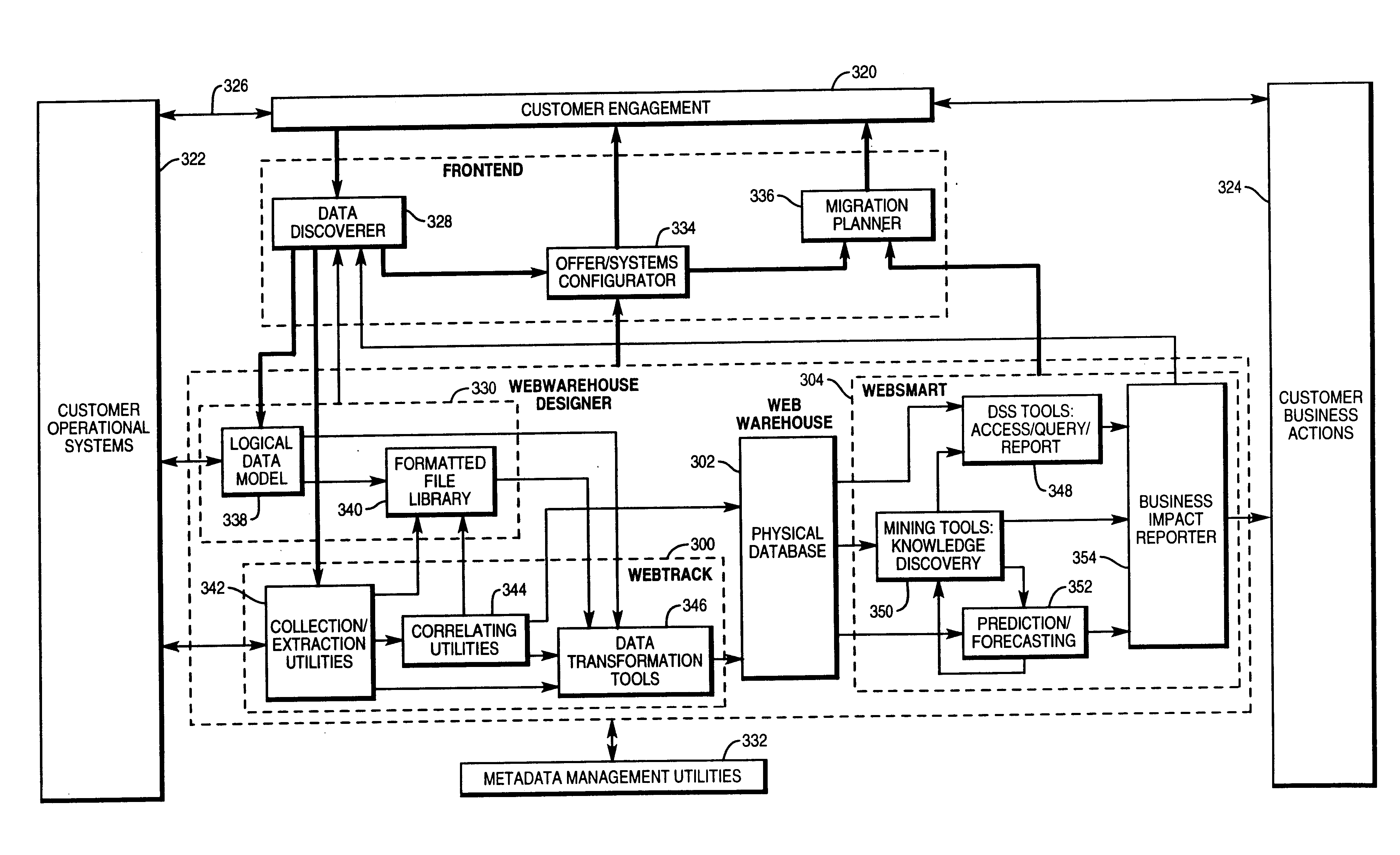

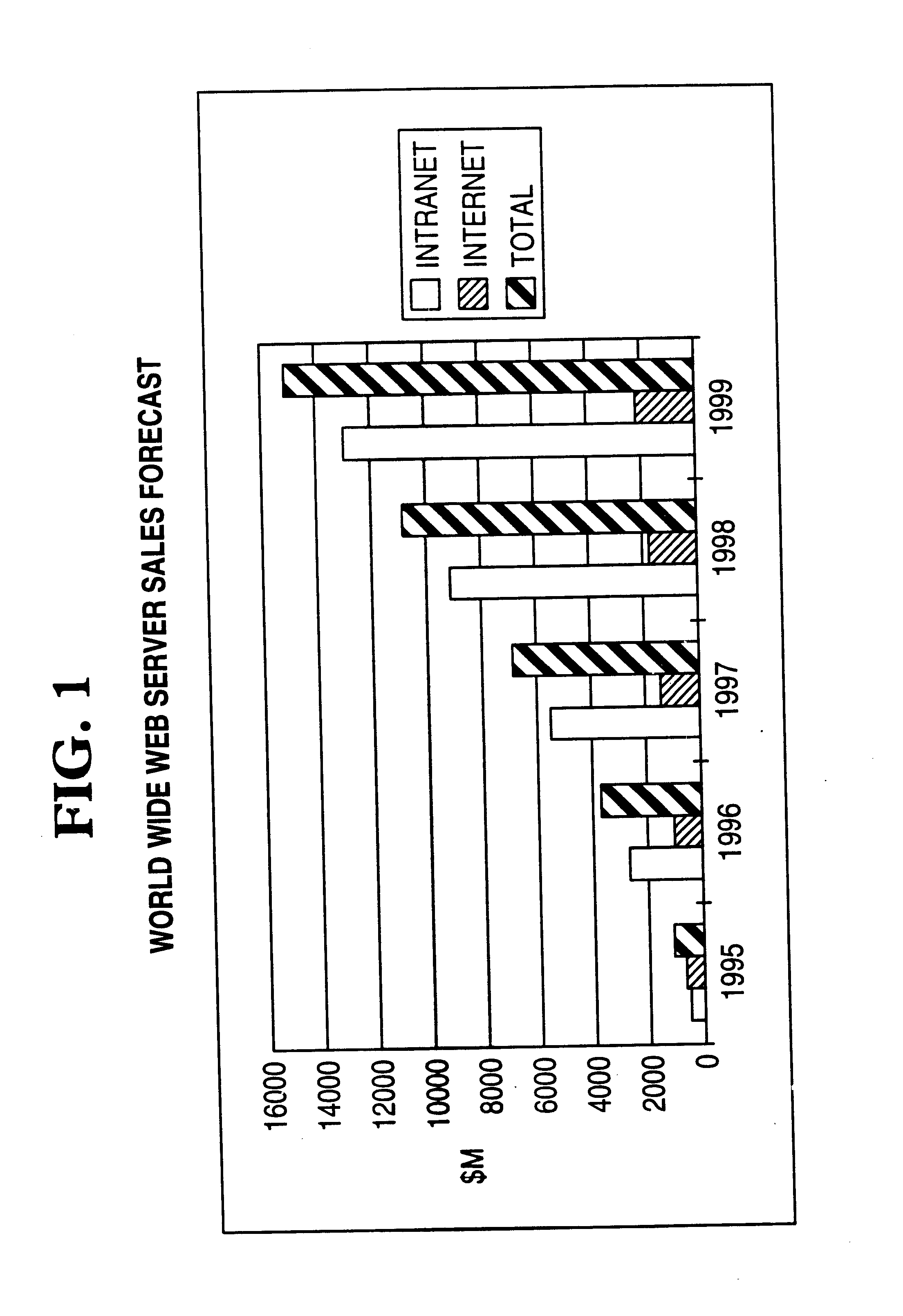

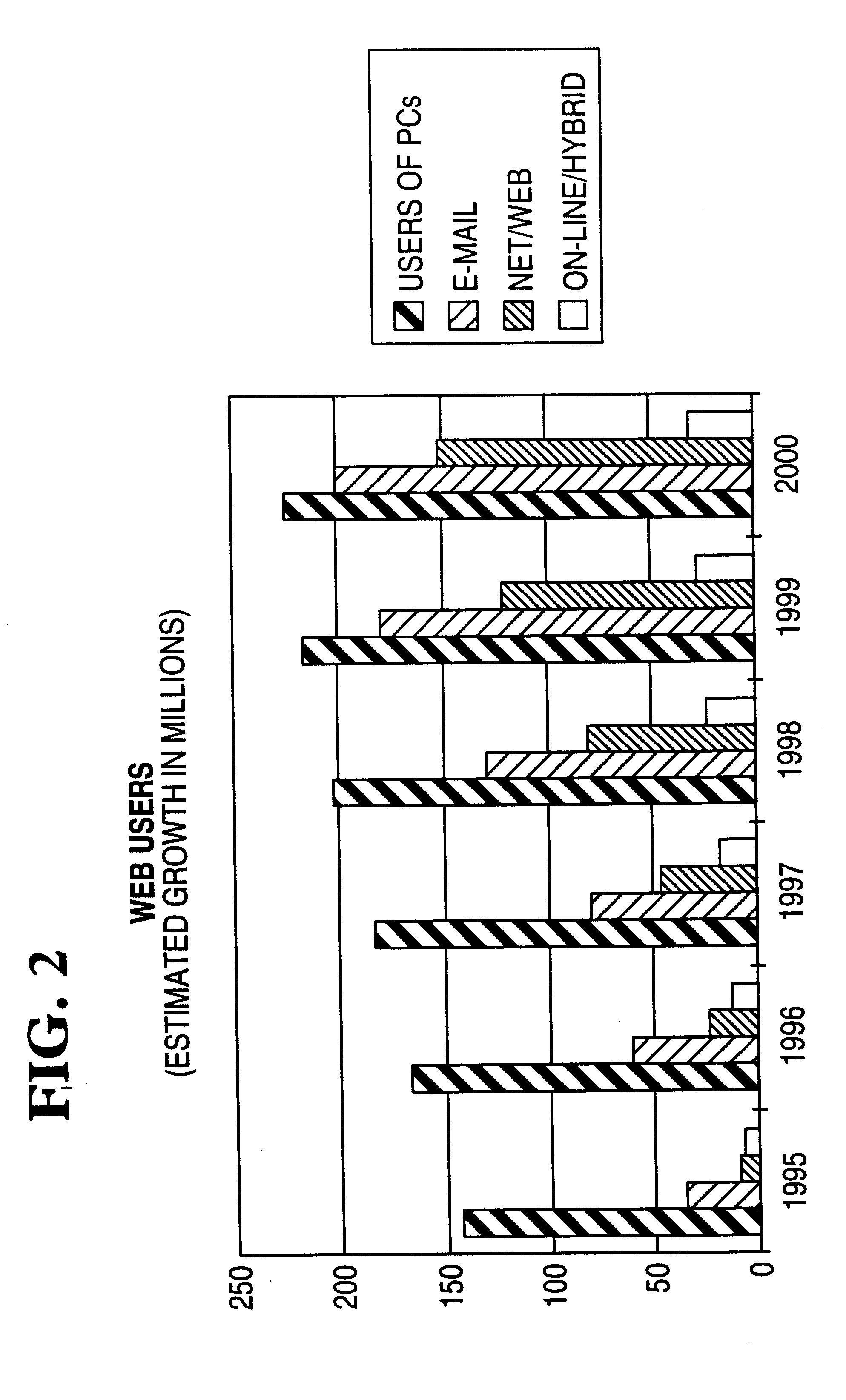

Computer architecture and method for supporting and analyzing electronic commerce over the world wide web for commerce service providers and/or internet service providers

InactiveUS6934687B1Designed for such useFacilitate communicationSpecial data processing applicationsMarket data gatheringData warehousePayment service provider

A computer system that supports and analyzes Internet and / or electronic commerce data includes at least one user station transmitting a user request, and at least one Internet server, connectable to the user station, and providing the user station access to external data sources. The computer system also includes at least one data collection and analysis system. The data collection and analysis system includes at least one analysis module performing statistical and analytical analysis of the Internet and / or electronic commerce data for use by a user in performing one or more business decisions, and at least one Internet and / or electronic commerce data warehouse which is responsively connected to the analysis module and separated from external systems. The data warehouse receives the Internet and / or electronic commerce data, and provides access to the Internet and / or electronic commerce data by the user. The data collection and analysis system also includes at least one data mapping module which searches, collects and transforms the Internet and / or electronic commerce data, and transmits the same to the data warehouse for storage.

Owner:NCR CORP

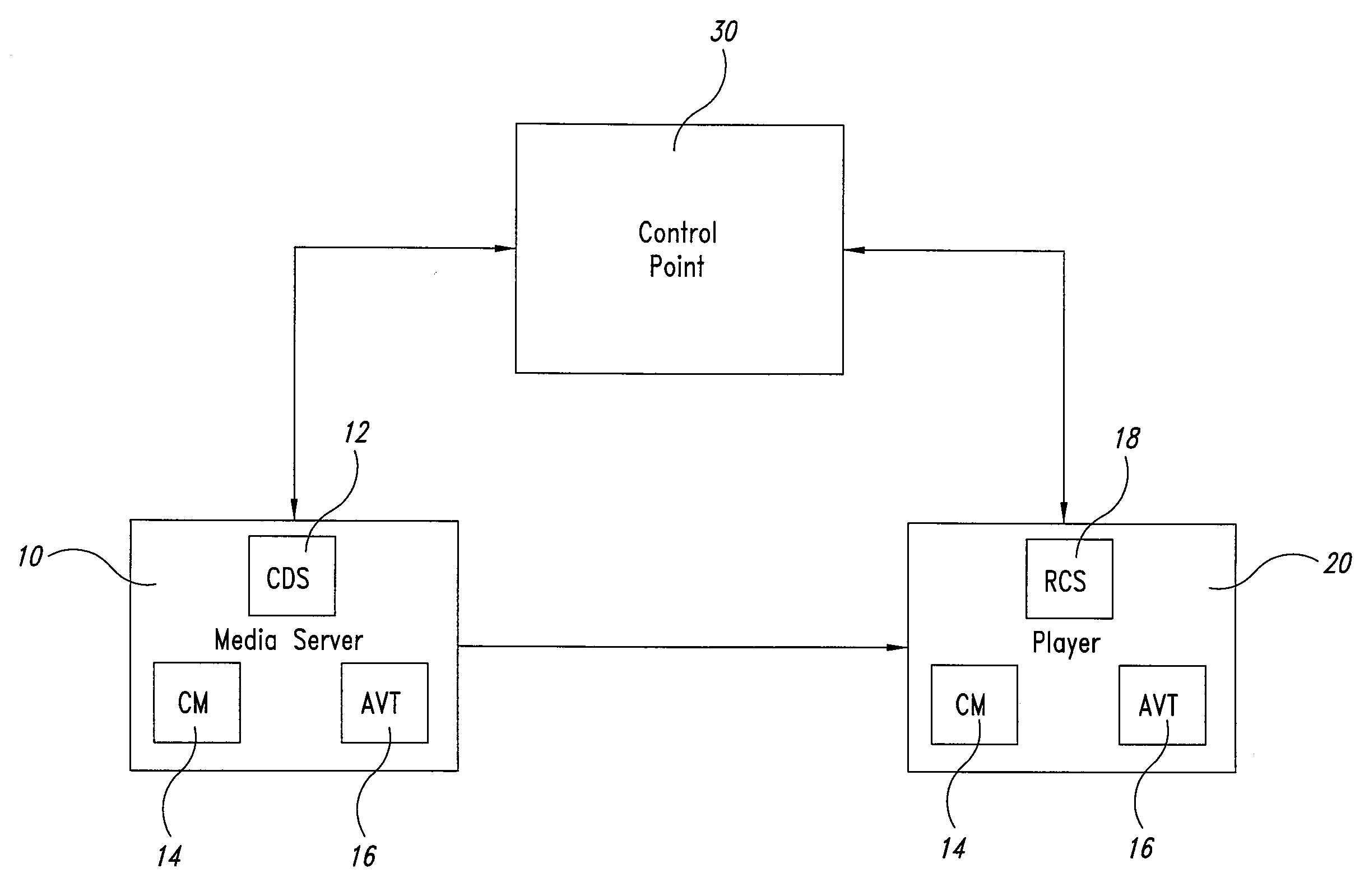

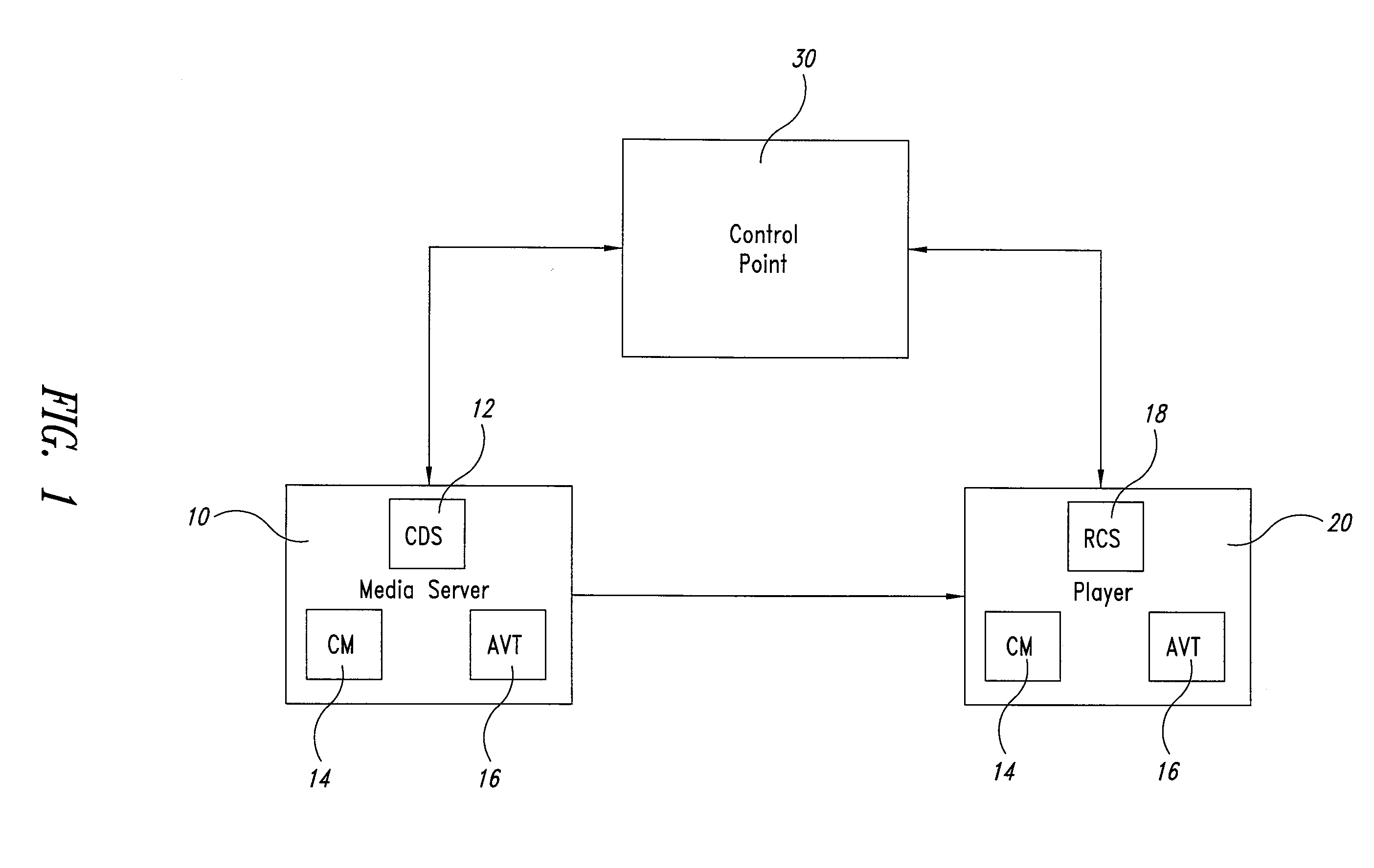

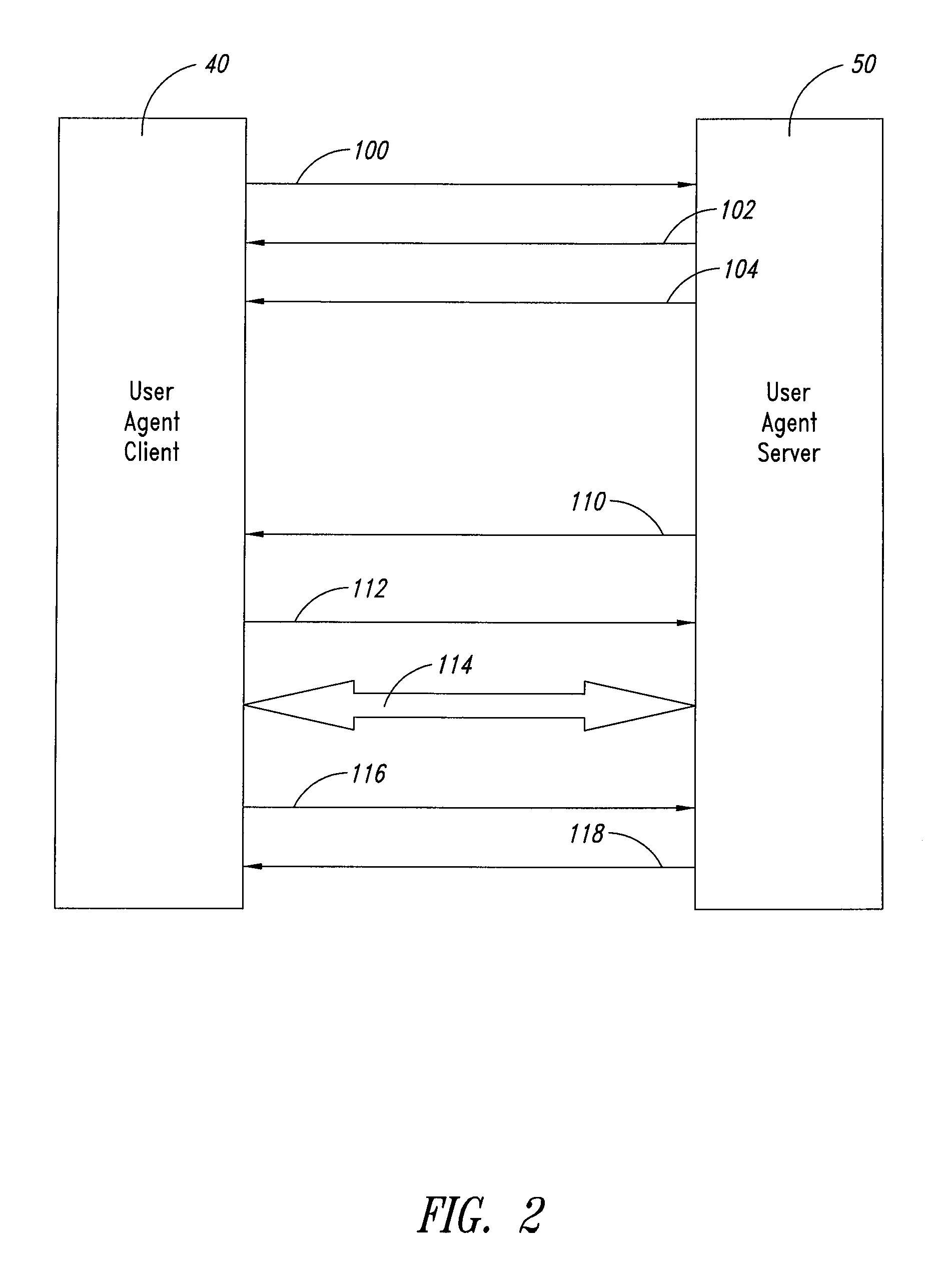

Plug-and-play device for videophony applications on packet-switched networks

InactiveUS20070198669A1Improve performanceReduce complexityDigital computer detailsElectric digital data processingSession Initiation ProtocolThe Internet

A device of a plug-and-play type, which can be integrated in a home network having at least one audio-video Media-Server device or else at least one audio-video Media-Renderer device. The device can be activated for selectively configuring parameters and devices for setting up audio-video calls for connection between the home network and a packet network, such as the Internet. Preferentially, the device is based upon UPnP (Universal Plug-and-Play) technology and uses either a signaling protocol on IP packet network, such as the Session Initiation Protocol (SIP) and ITU-T H.323, or else mobile communications systems, such as the Universal Mobile Telecommunications System (UMTS). The device is able to redirect audio-video streams in the context of a plurality of devices capable of reproducing them and / or to selectively acquire said audio-video streams from a plurality of devices capable of supplying them.

Owner:STMICROELECTRONICS SRL

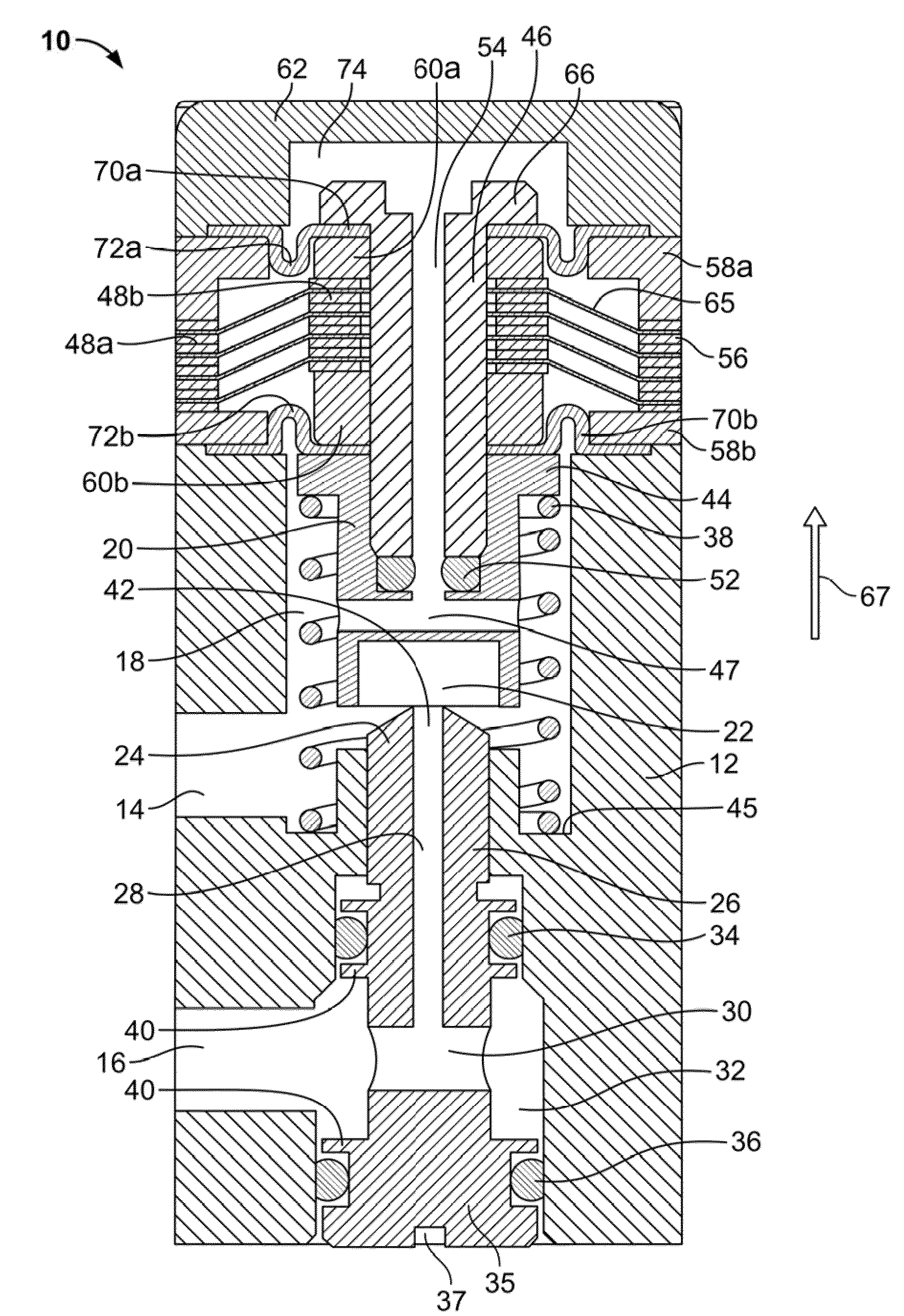

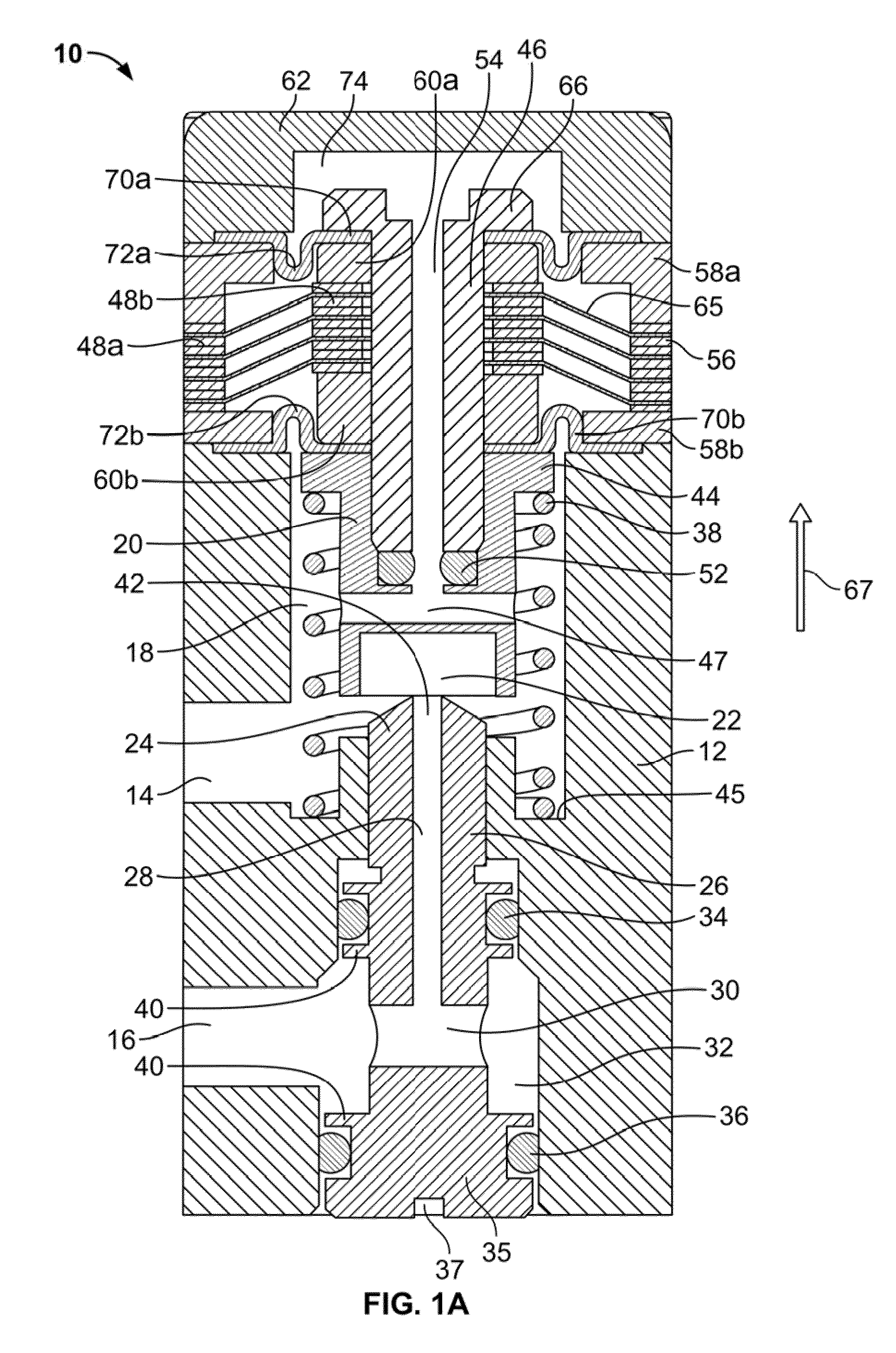

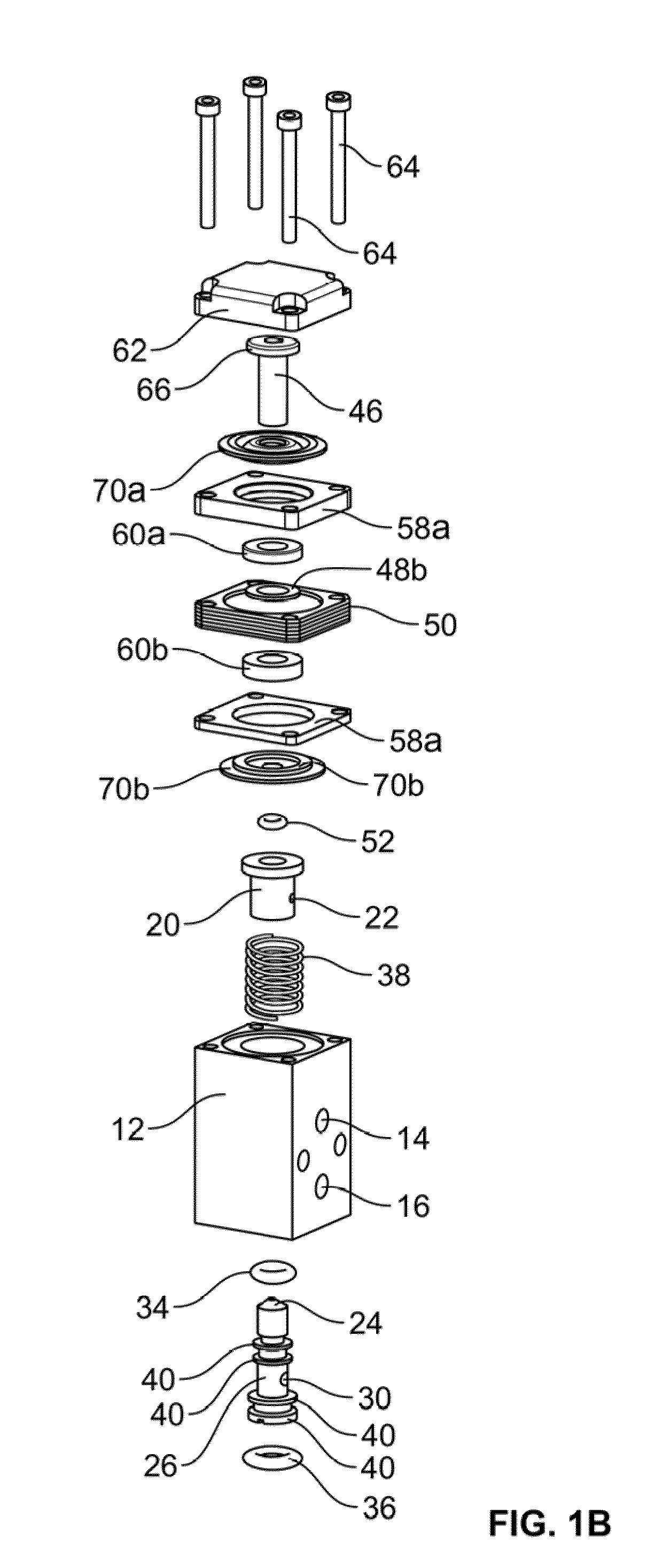

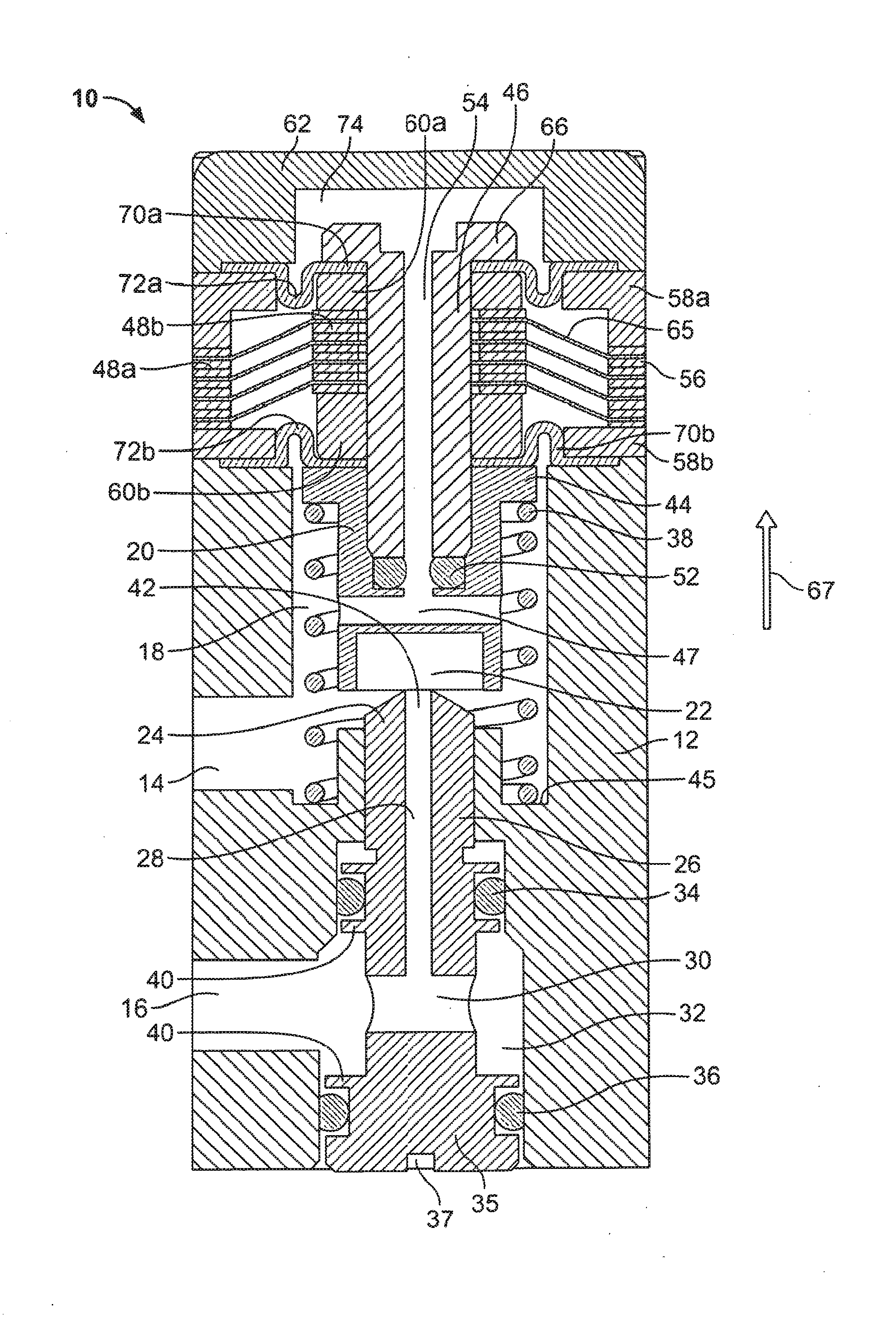

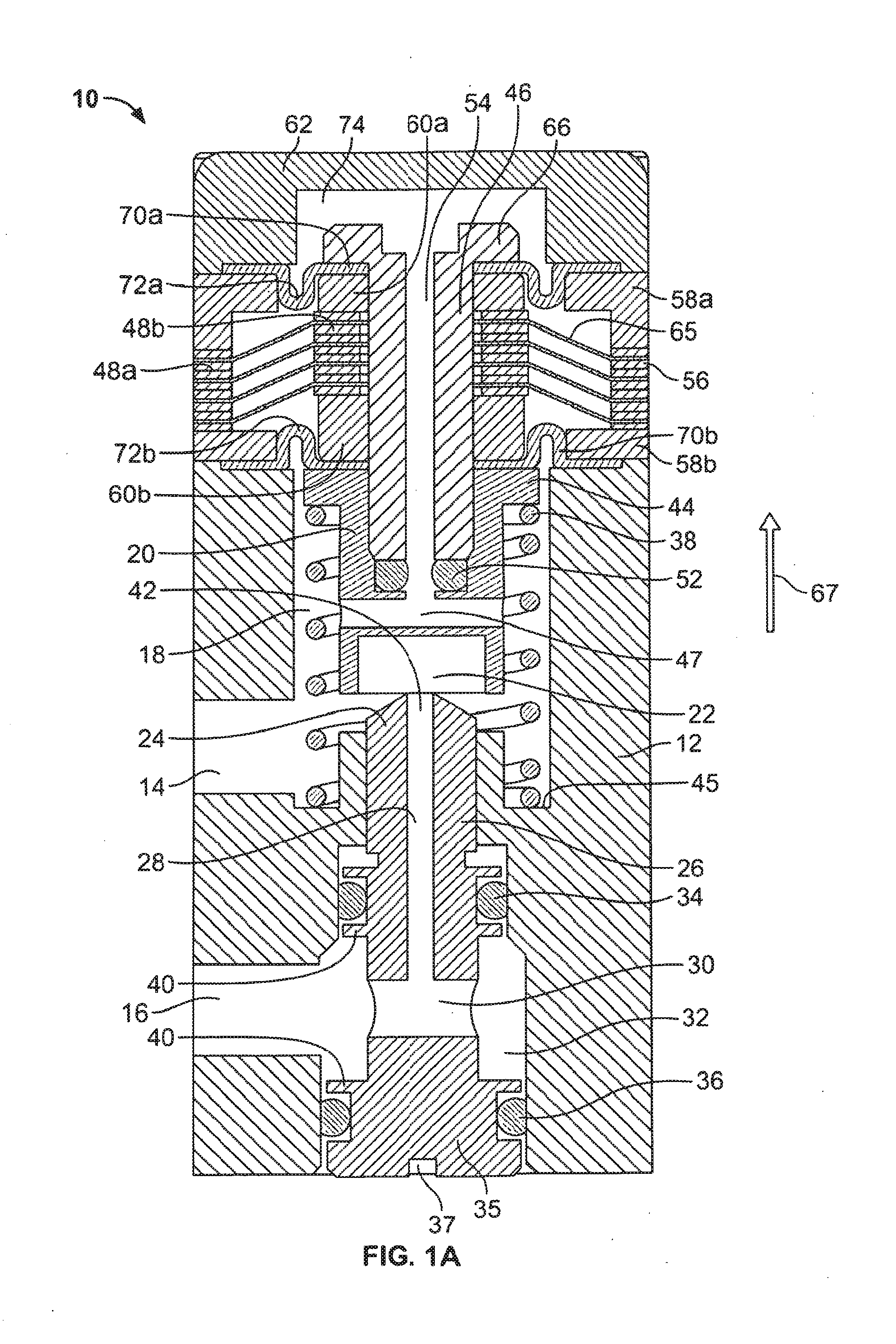

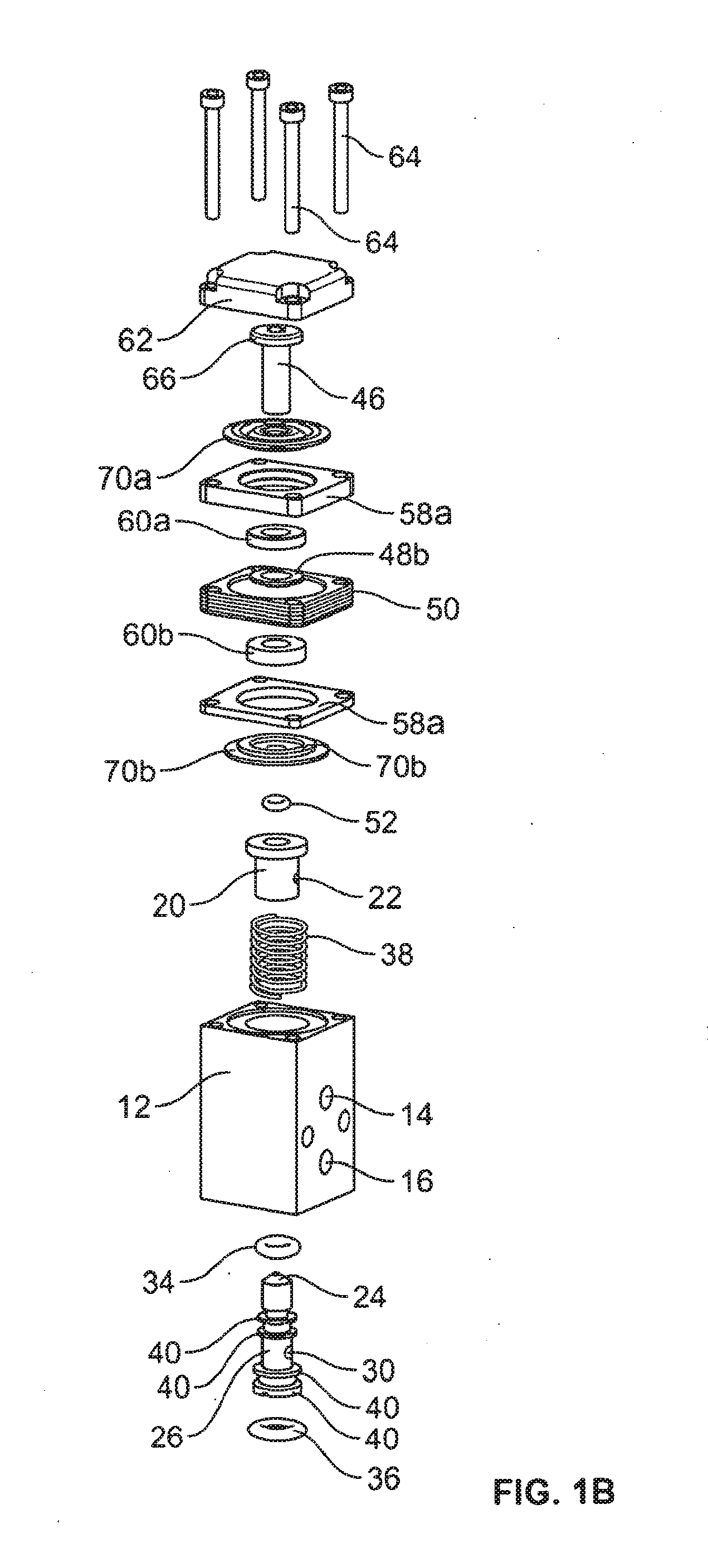

Fluid control systems employing compliant electroactive materials

InactiveUS20090250021A1Easy to adjustLow profileFluid-pressure actuator safetyOperating means/releasing devices for valvesFluid controlControl system

Owner:PARKER HANNIFIN CORP

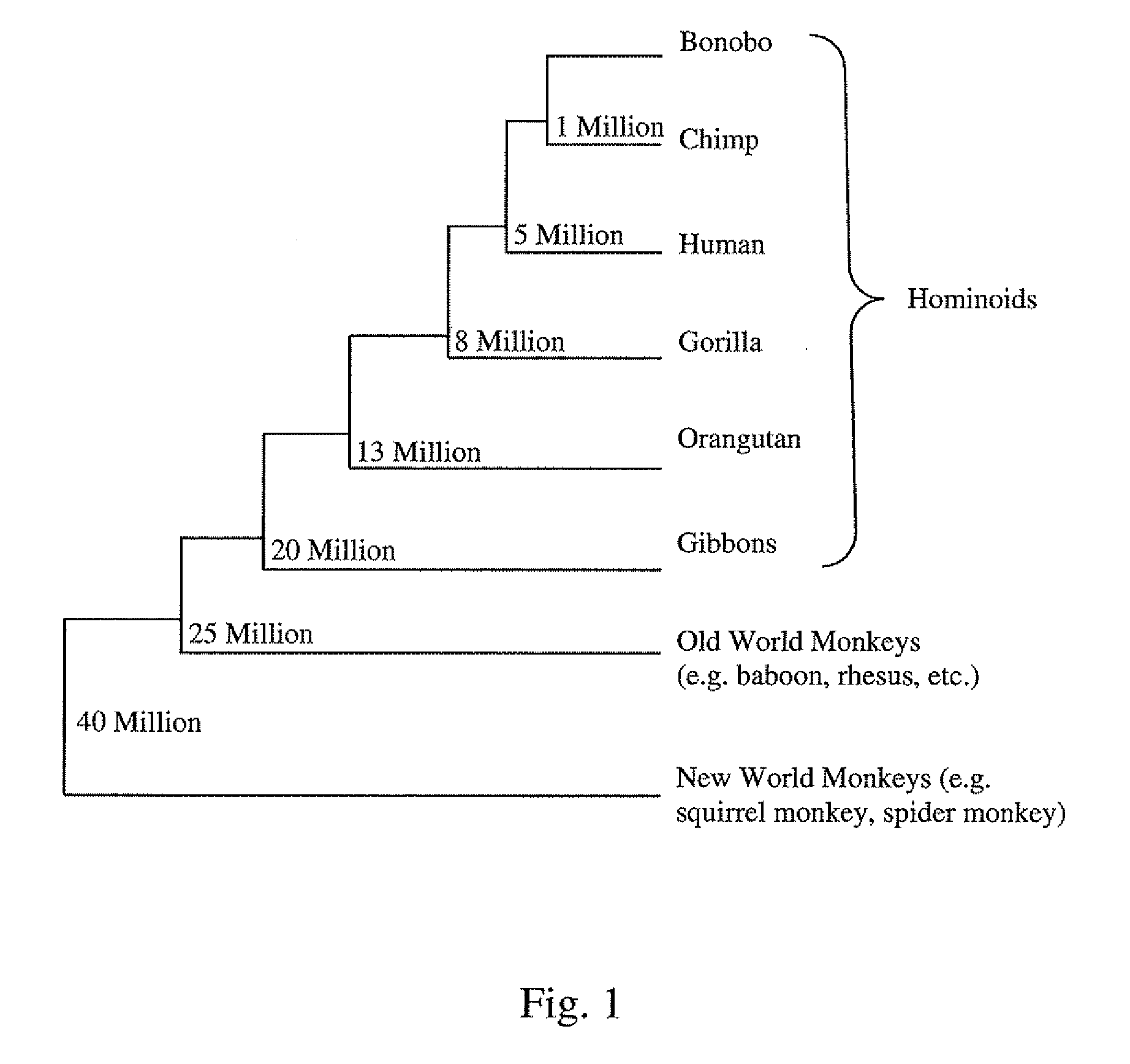

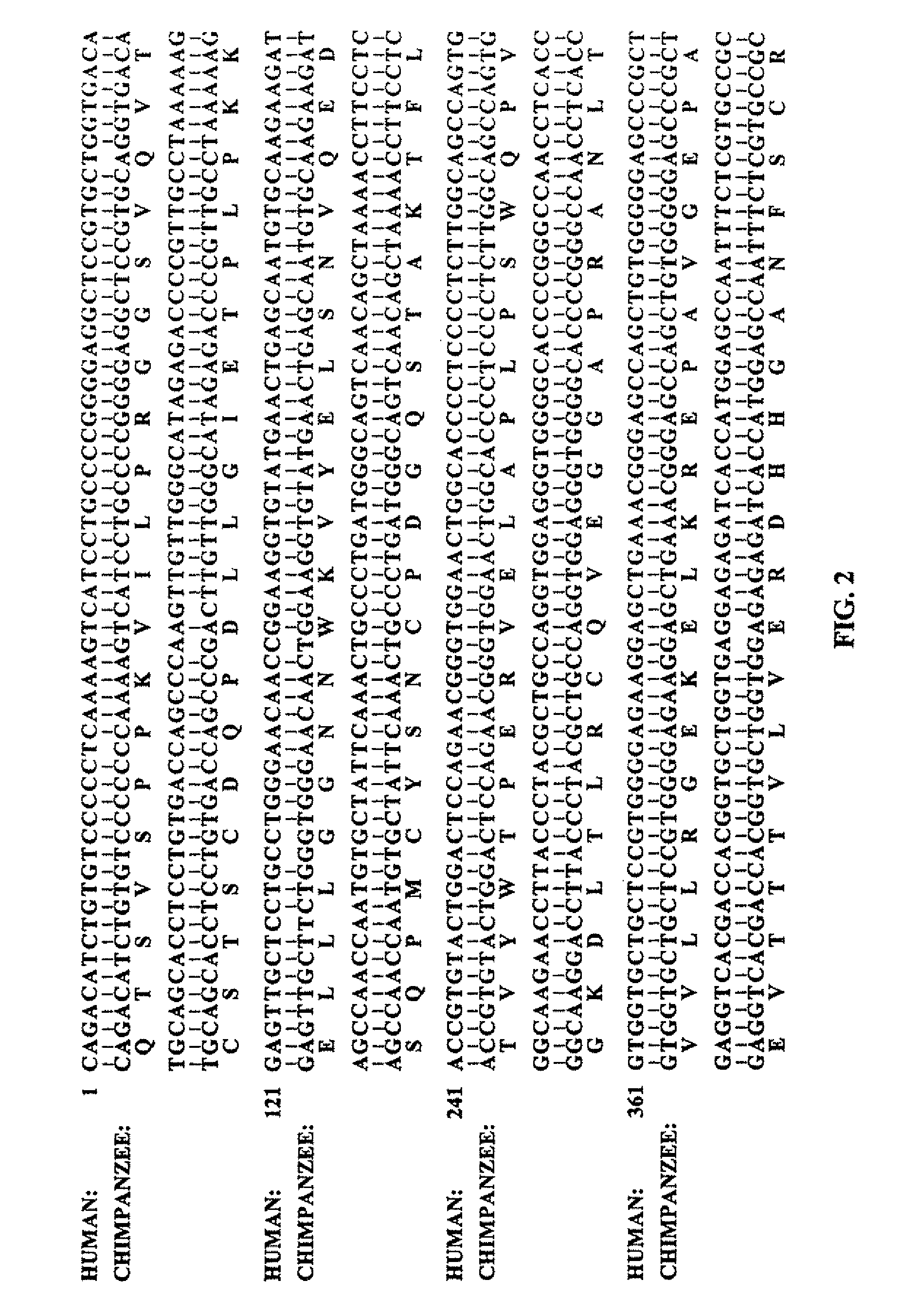

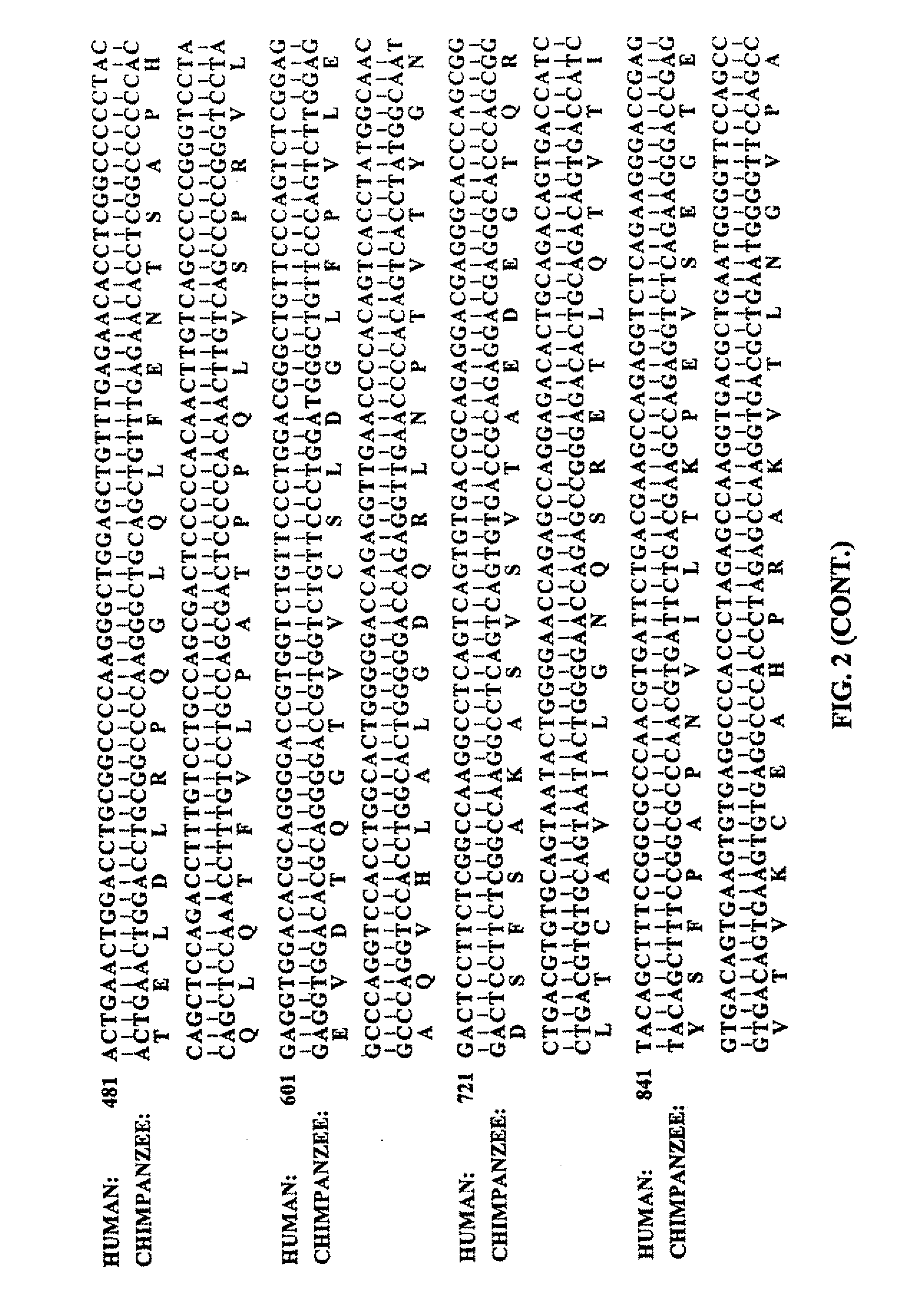

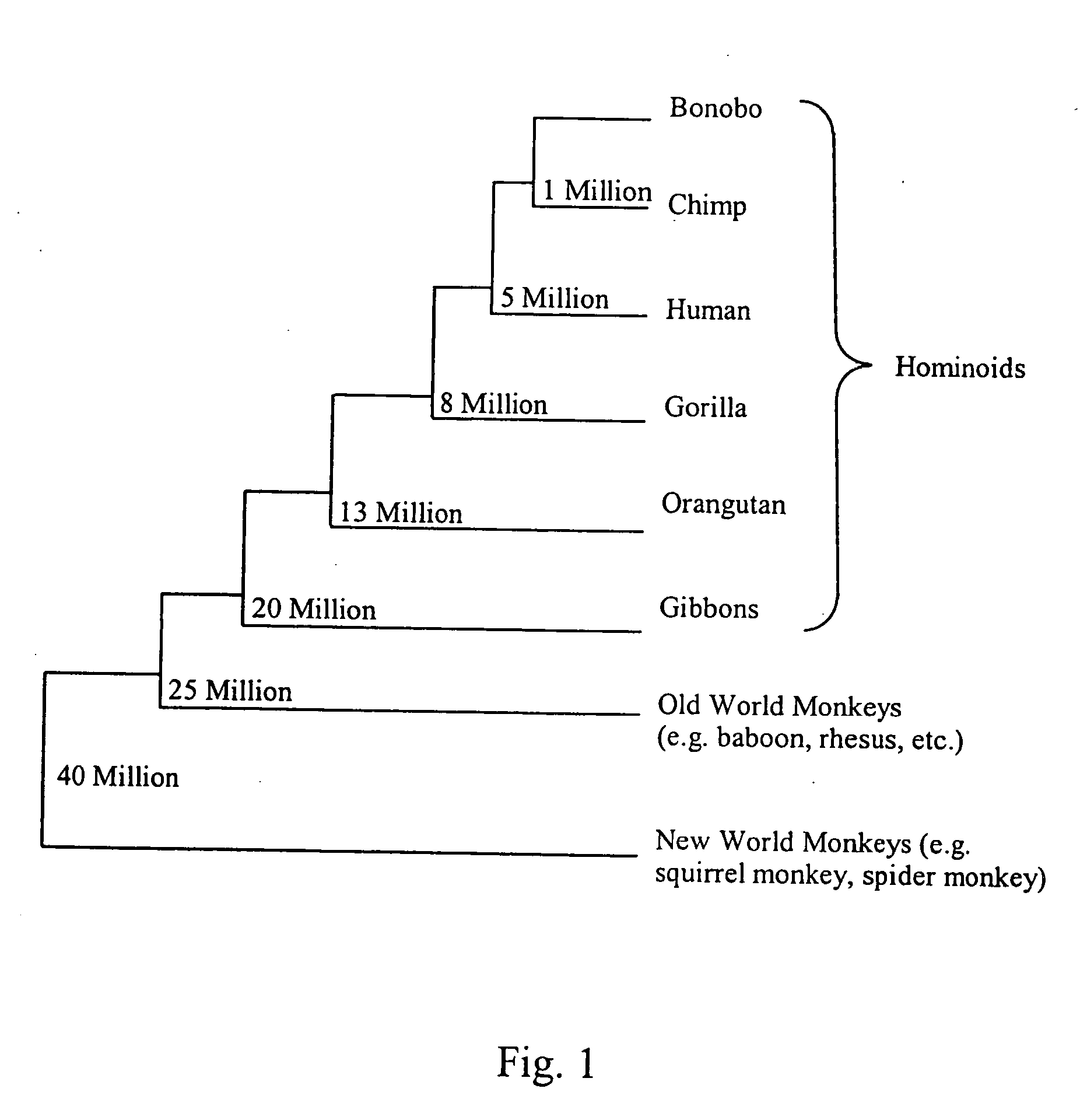

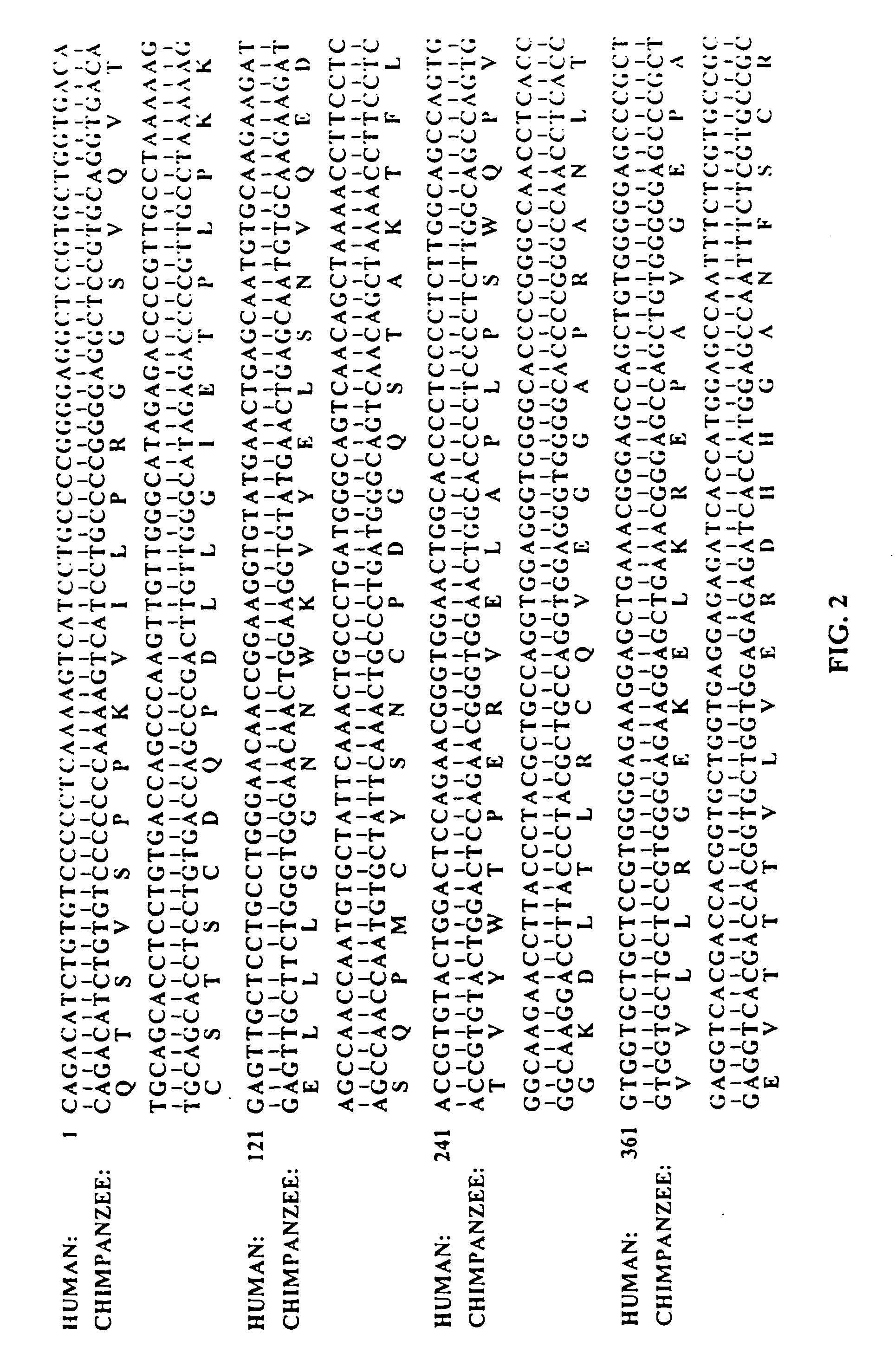

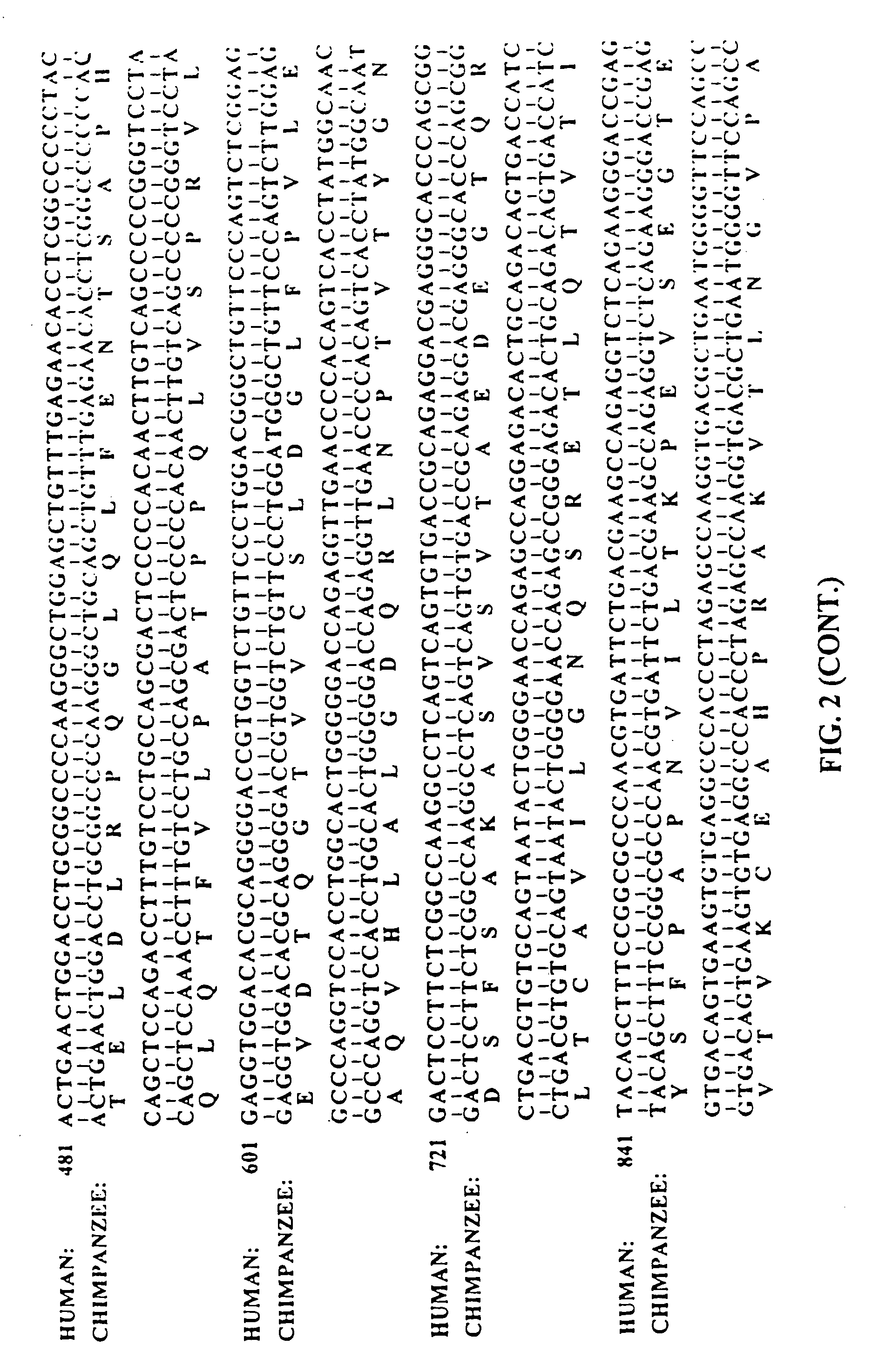

Methods to identify polynucleotide and polypeptide sequences which may be associated with physiological and medical conditions

InactiveUS20090304653A1Extend your lifePositive evolutionarily significant changeBiocideGenetic material ingredientsNucleotideTherapy related

Disclosed are methods to identify an agent which may modulate resistance to HIV-1-mediated disease, comprising contacting at least one agent to be tested with a cell comprising human ICAM-1, and detecting the cell's resistance to HIV-1 viral replication, propagation, or function, wherein an agent is identified by its ability to increase the cell's resistance to HIV-1 viral replication, propagation, or function. Also disclosed are human mutant ICAM-1 polypeptides and methods to treat HIV-1 viral replication, propagation, or function in a human subject by ICAM-1 gene therapy relating to one or more of the following 10 mutations to human ICAM-1: L18Q, K29D, P45G, R49W, E171Q, wherein the mutant ICAM-1 is otherwise identical to human ICAM-1.

Owner:EVOLUTIONARY GENOMICS LLC

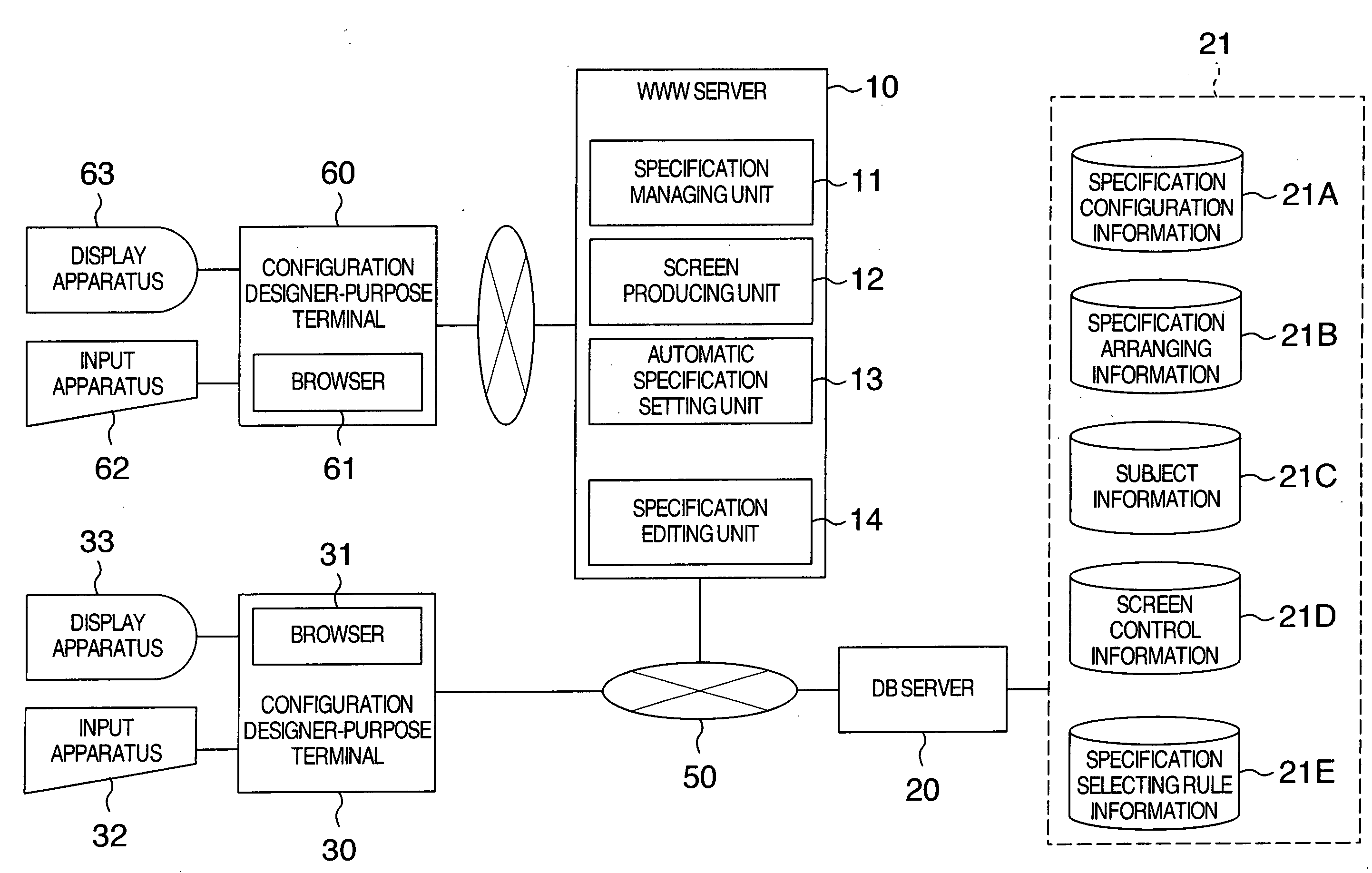

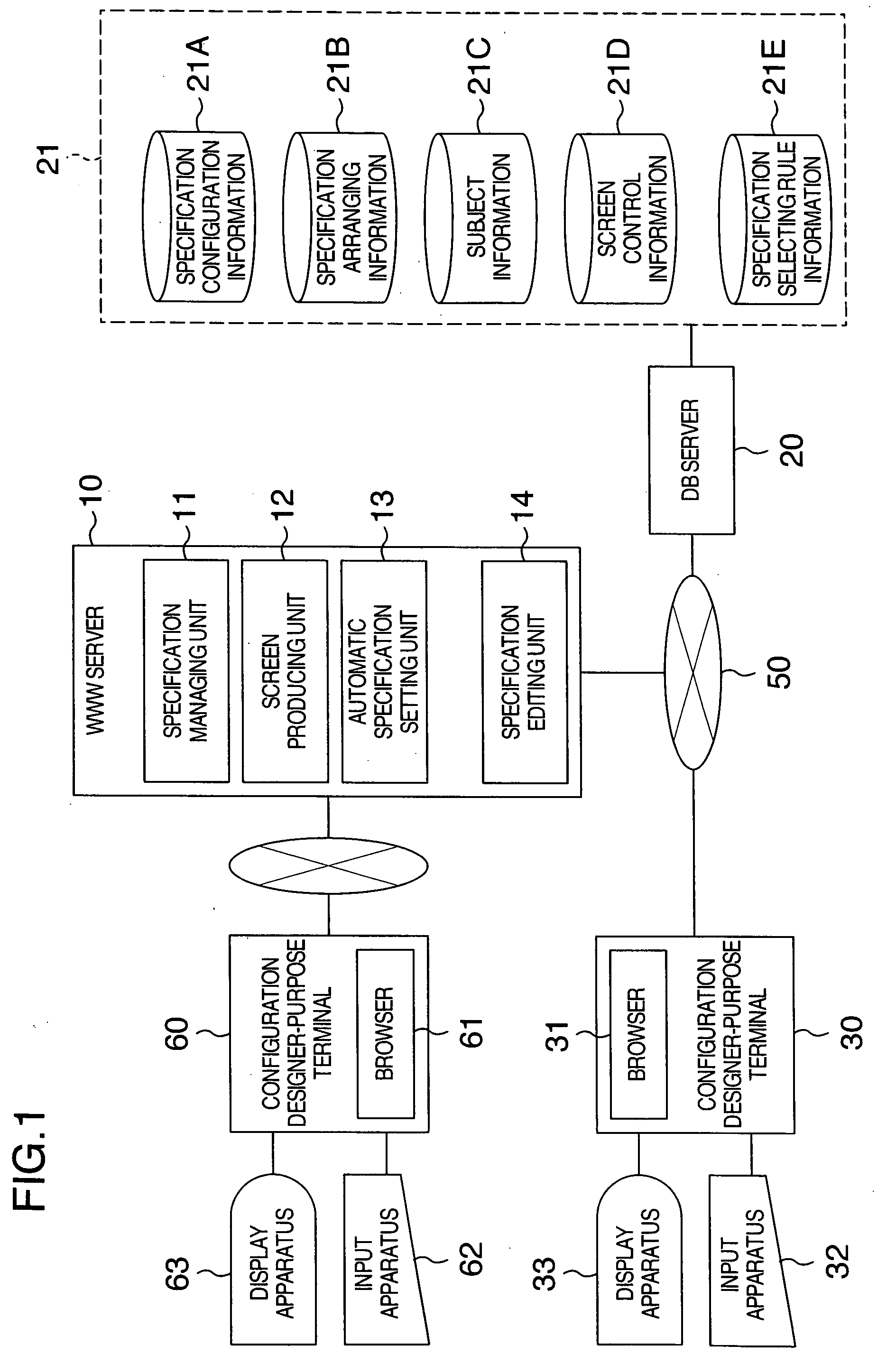

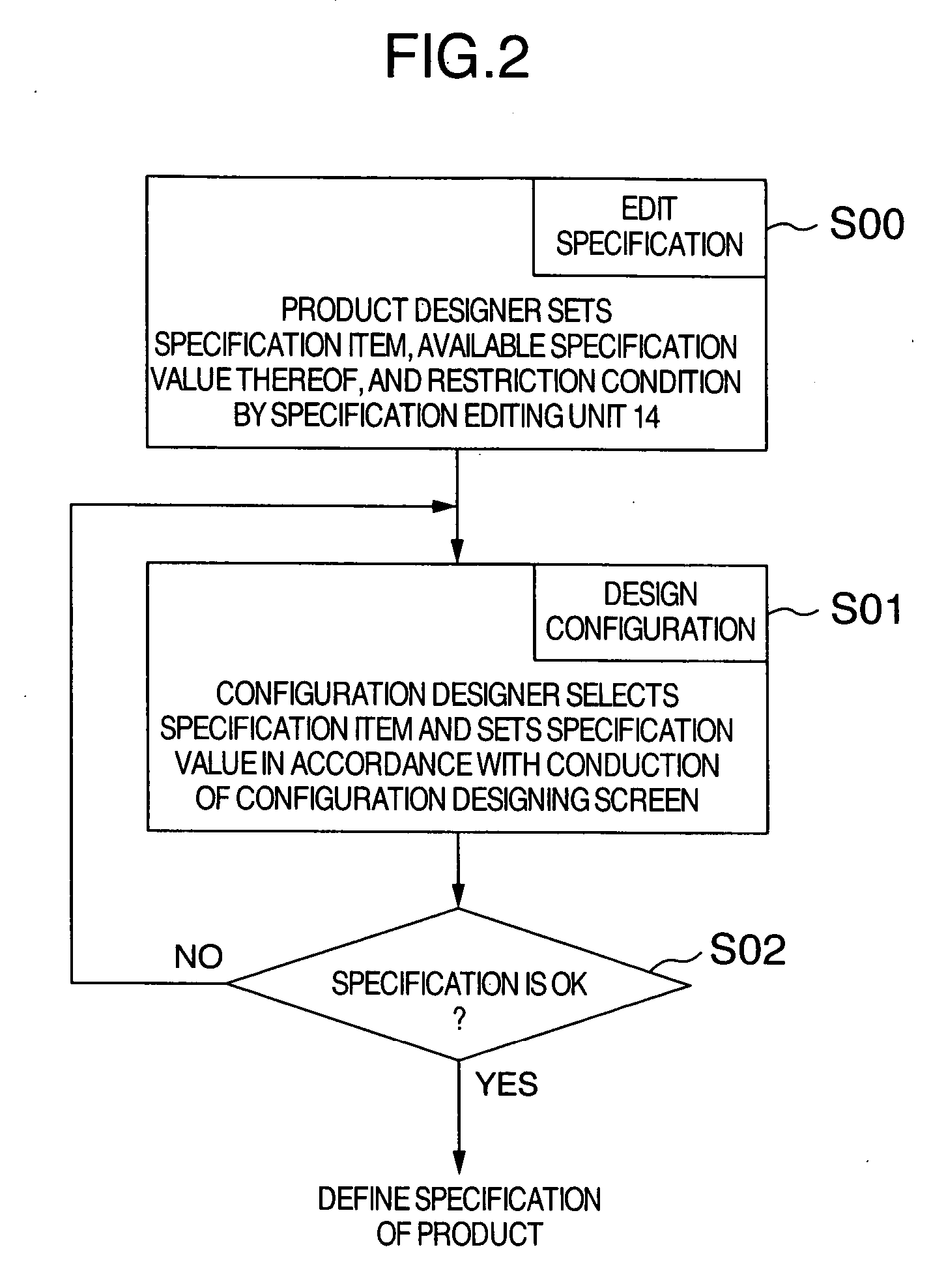

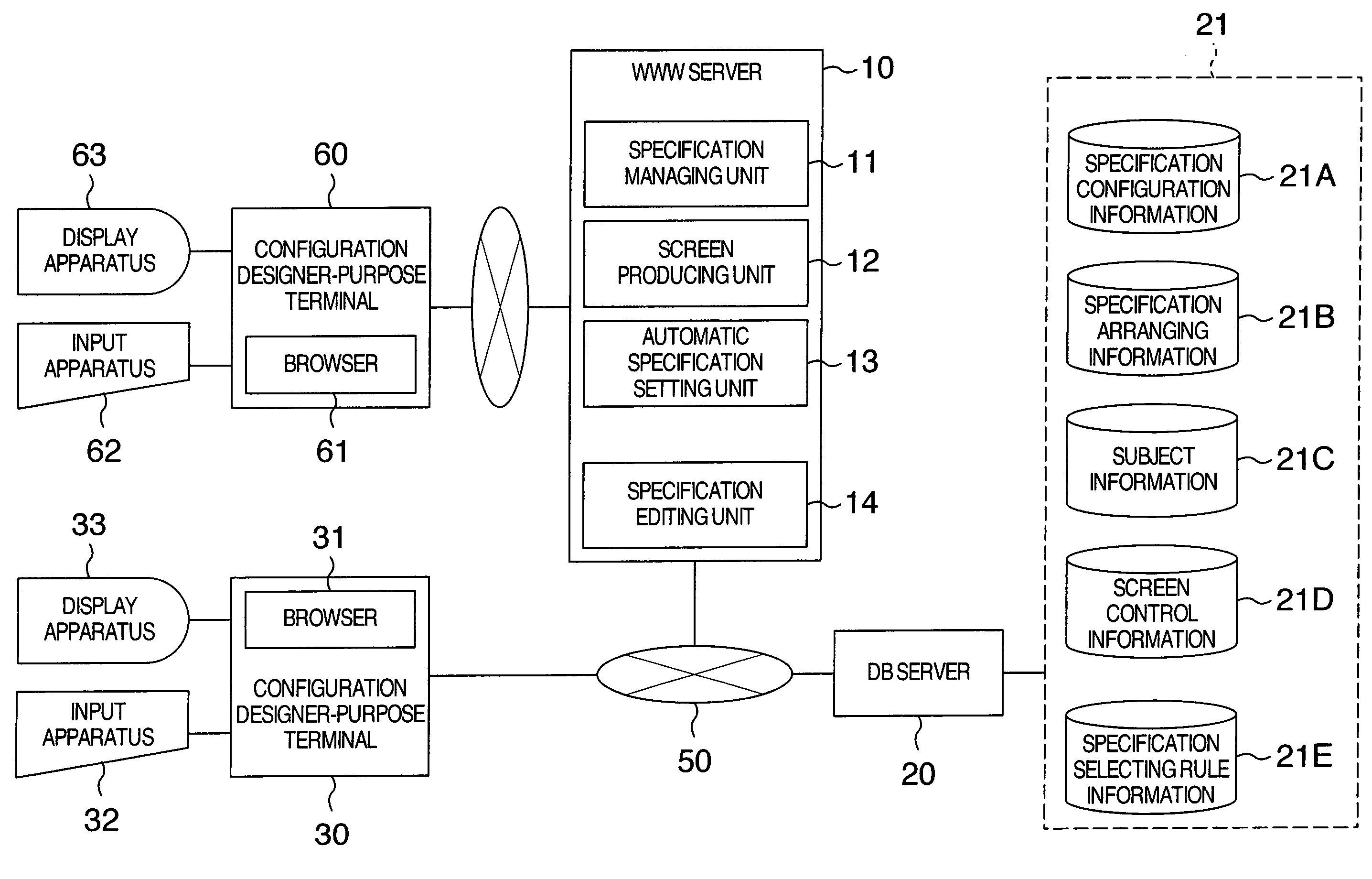

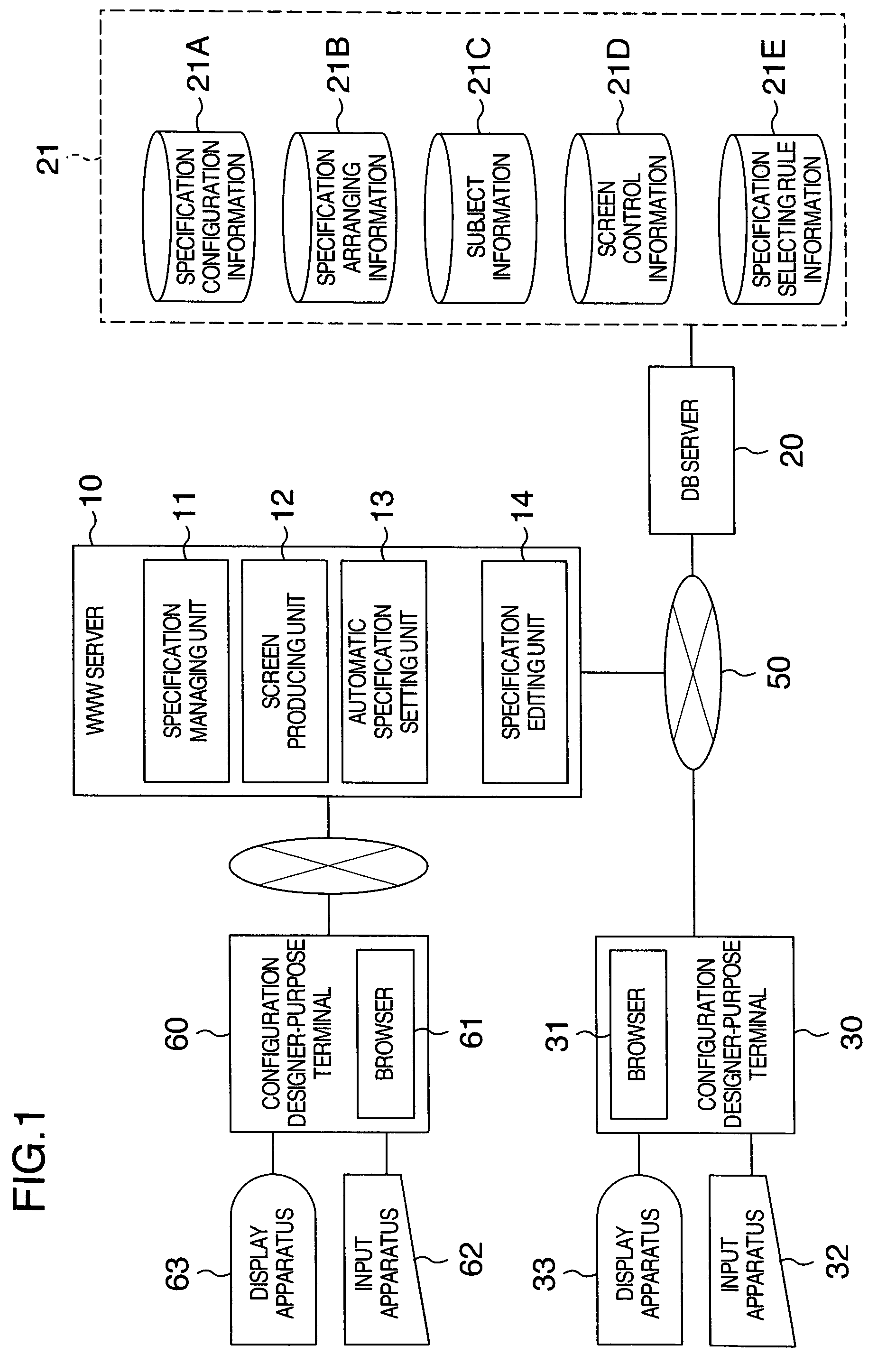

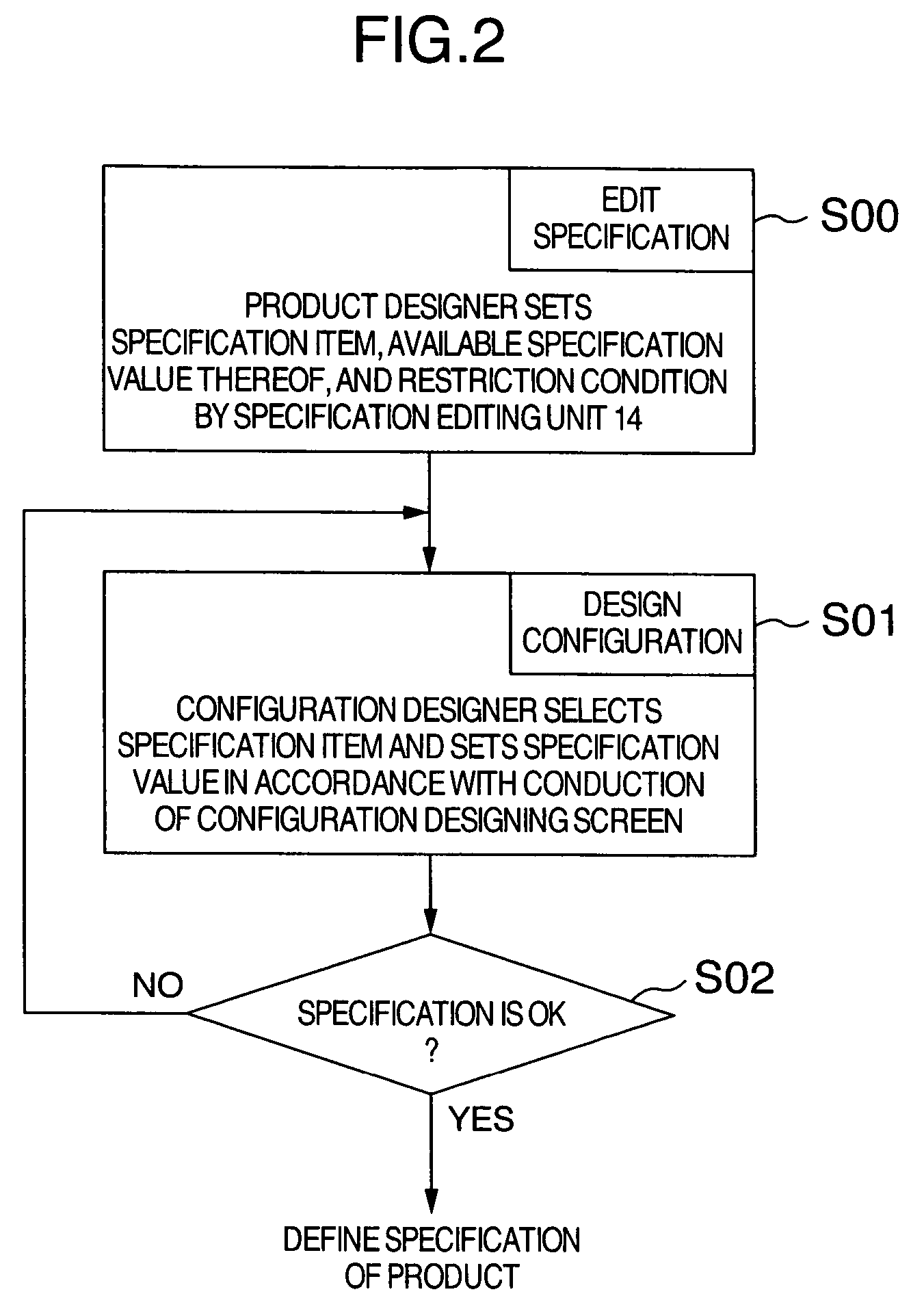

System for aiding the design of product configuration

InactiveUS20060129261A1Production cost be reduceReduces losesCAD network environmentOffice automationEngineeringConfiguration design

While a base model has been determined for a product, in a system for performing a configuration designing operation of the product by setting a specification value to a specification item of the product, a product configuration design aiding system aids that a configuration designer can easily perform the configuration designing operation while following a restriction condition of a specification value of a specification item. A specification configuration information database is constructed which describes restriction conditions available for the specification values with respect to the specification item, and a configuration designing screen for inputting the specification values with respect to the specification item is displayed so as to conduct an input by the configuration designer.

Owner:HITACHI LTD

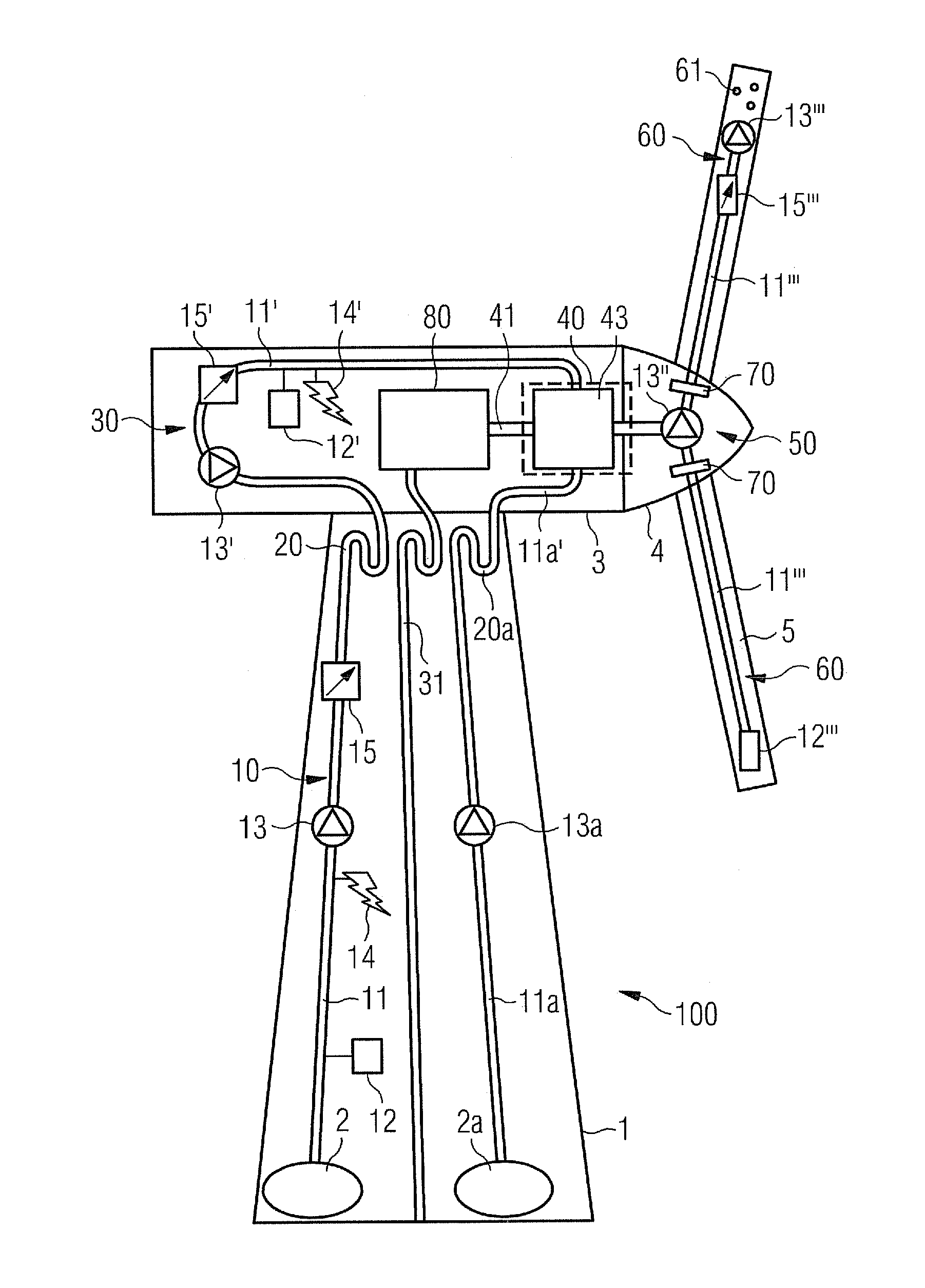

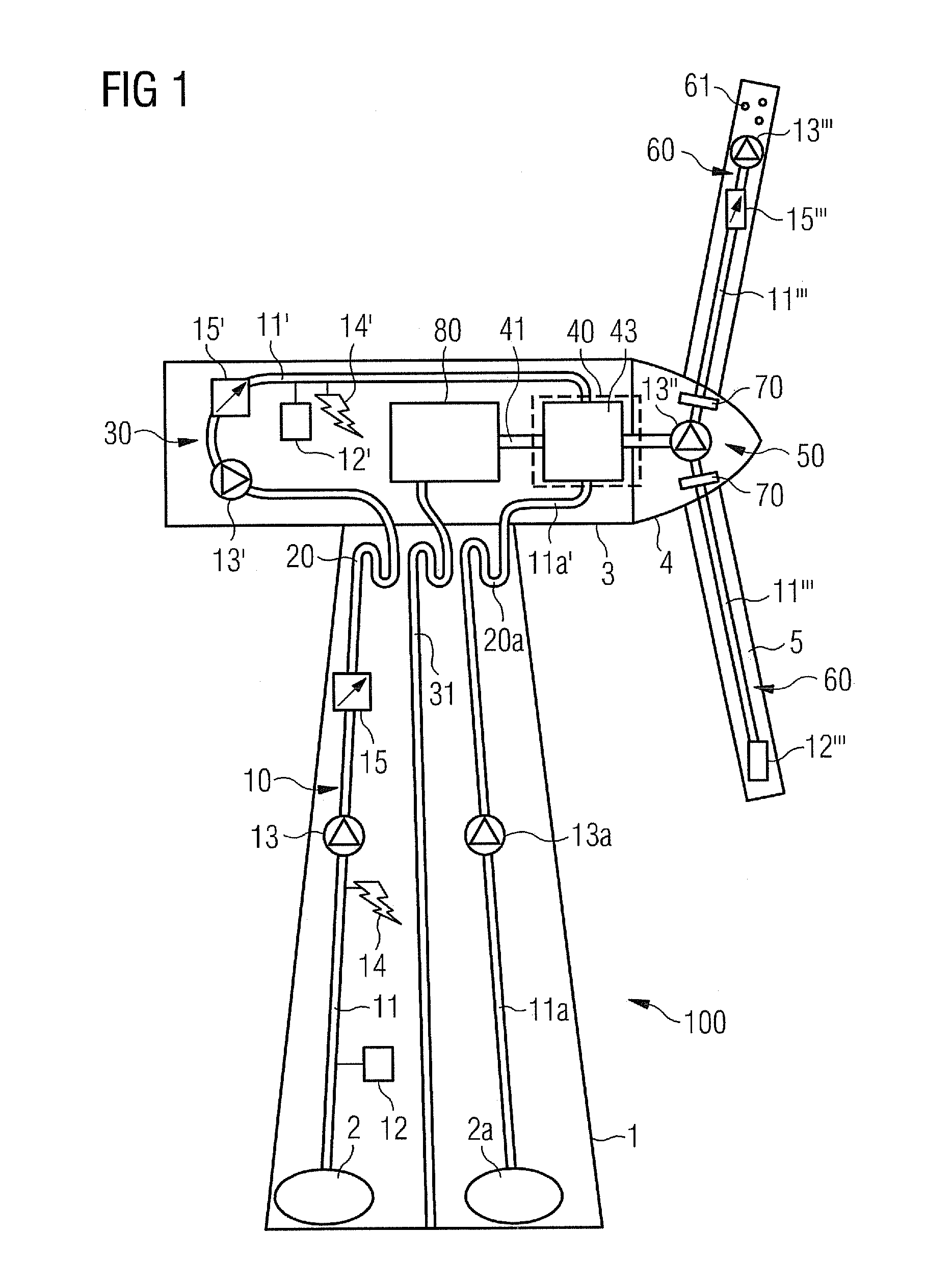

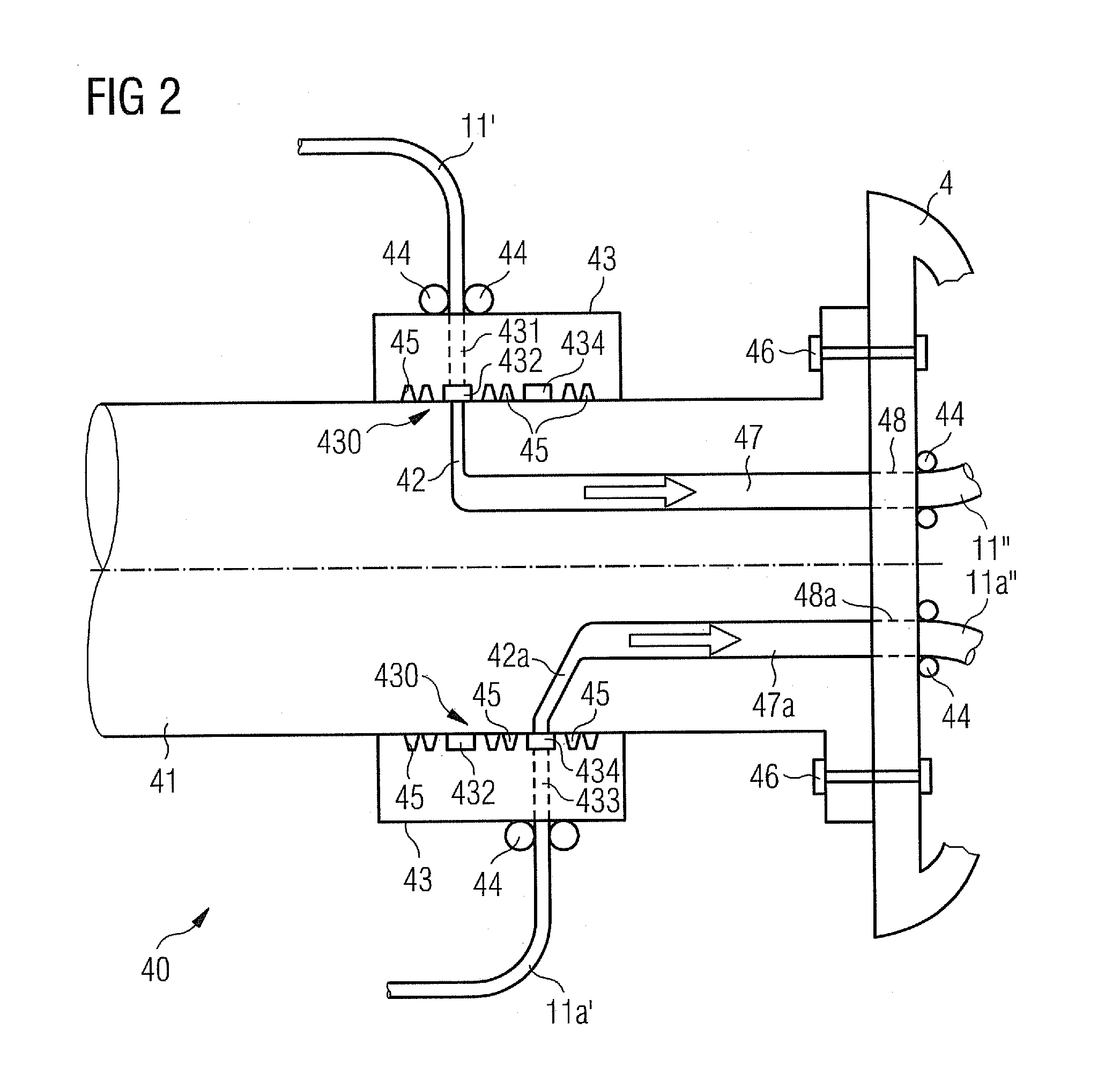

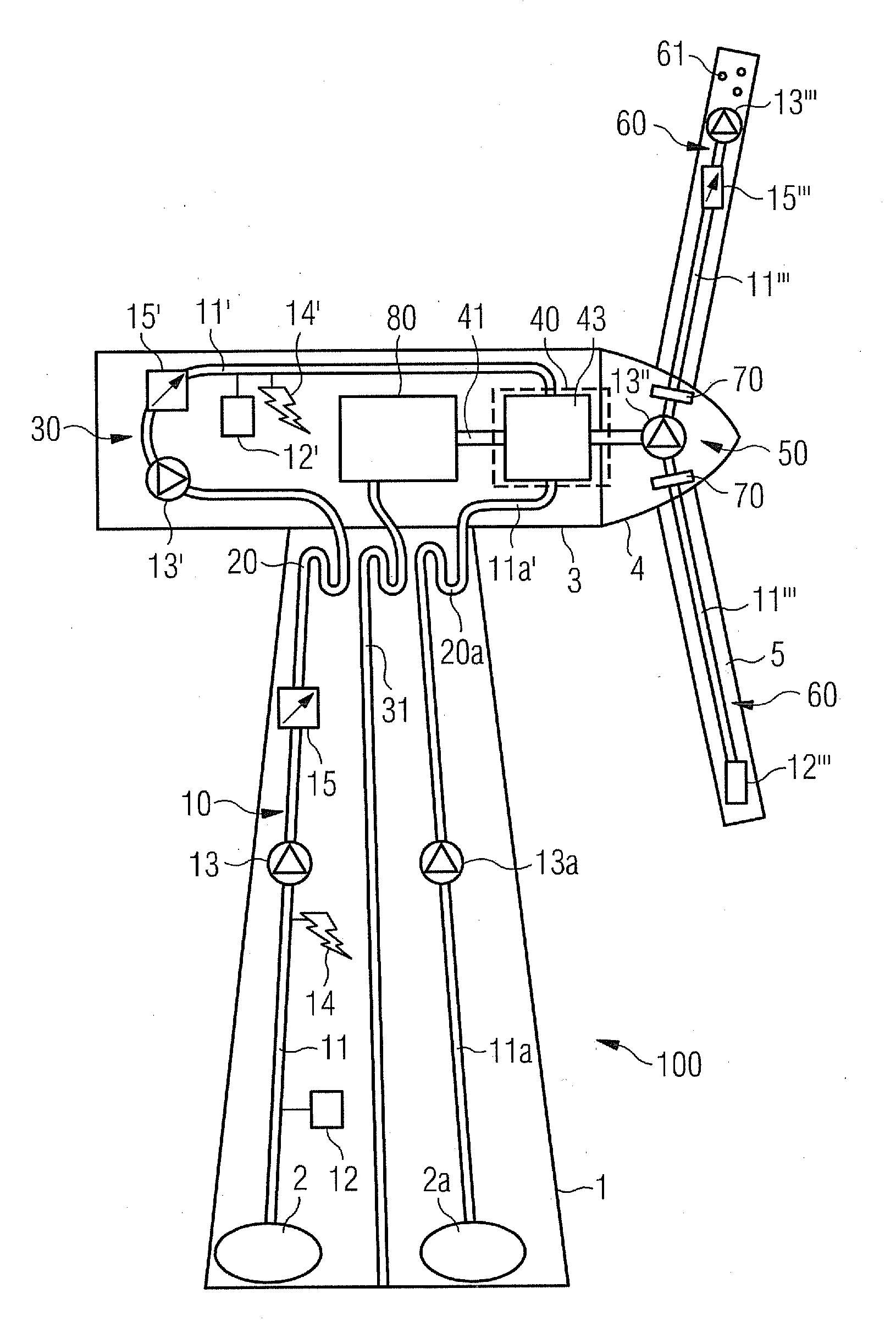

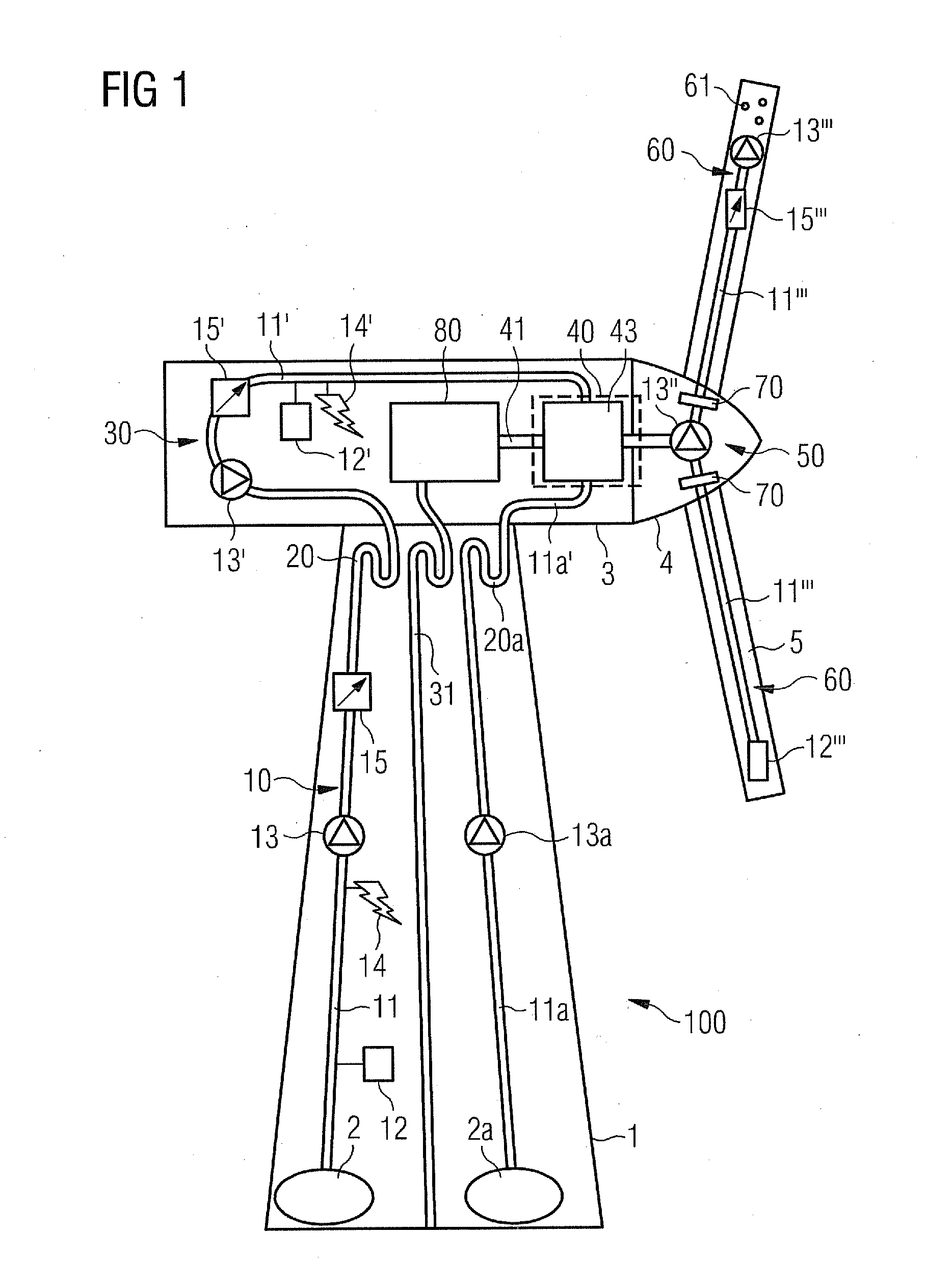

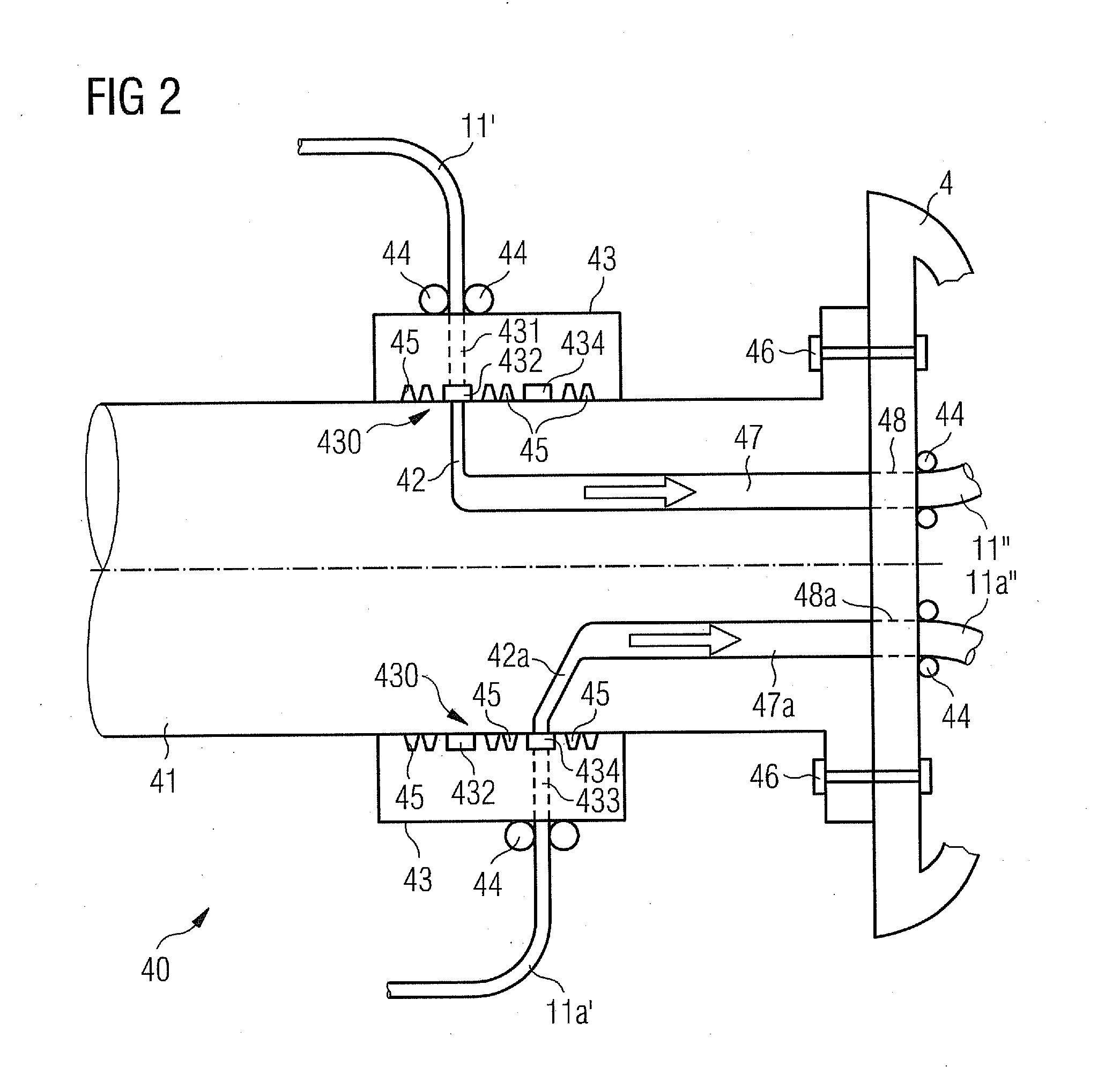

Wind turbine with liquid medium distribution system

A wind turbine with a tower, a nacelle, a main shaft, a hub and blades is provided. The wind turbine also includes a liquid medium distribution system for transport of liquid medium in the wind turbine. The liquid medium distribution system has a first distribution sub-system located in the tower, a second distribution sub-system located in the nacelle, a third distribution sub-system located in the hub, a tower-nacelle-interface connecting the first distribution sub-system to the second distribution sub-system, and a nacelle-hub-interface connecting the second distribution sub-system to the third distribution sub-system. Further, a method of transporting liquid medium in a wind turbine is provided.

Owner:SIEMENS AG

Fluid control systems employing compliant electroactive materials

InactiveUS20160230904A1Easy to adjustLow profileOperating means/releasing devices for valvesMachines/enginesFluid controlControl system

Owner:PARKER HANNIFIN CORP

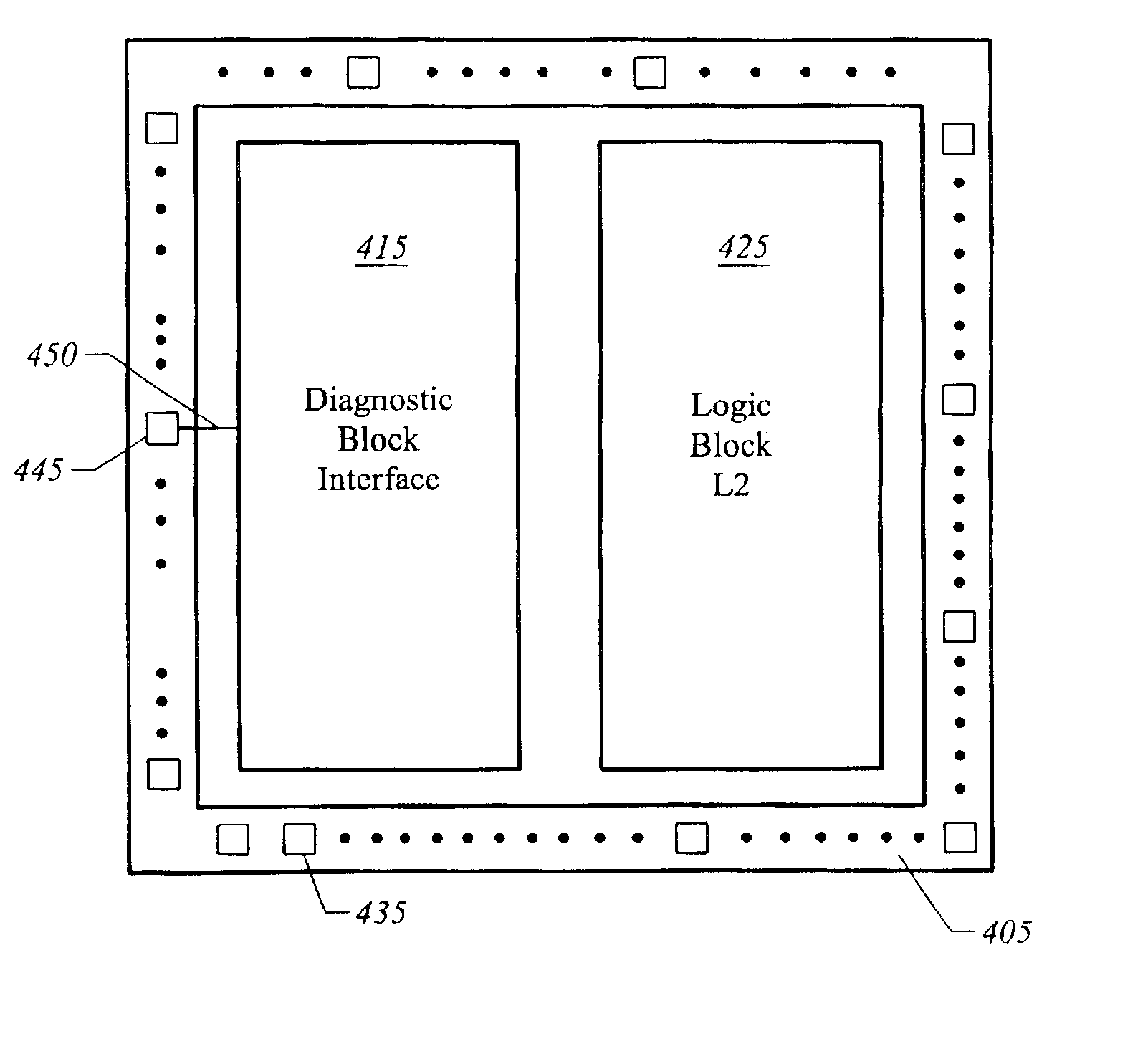

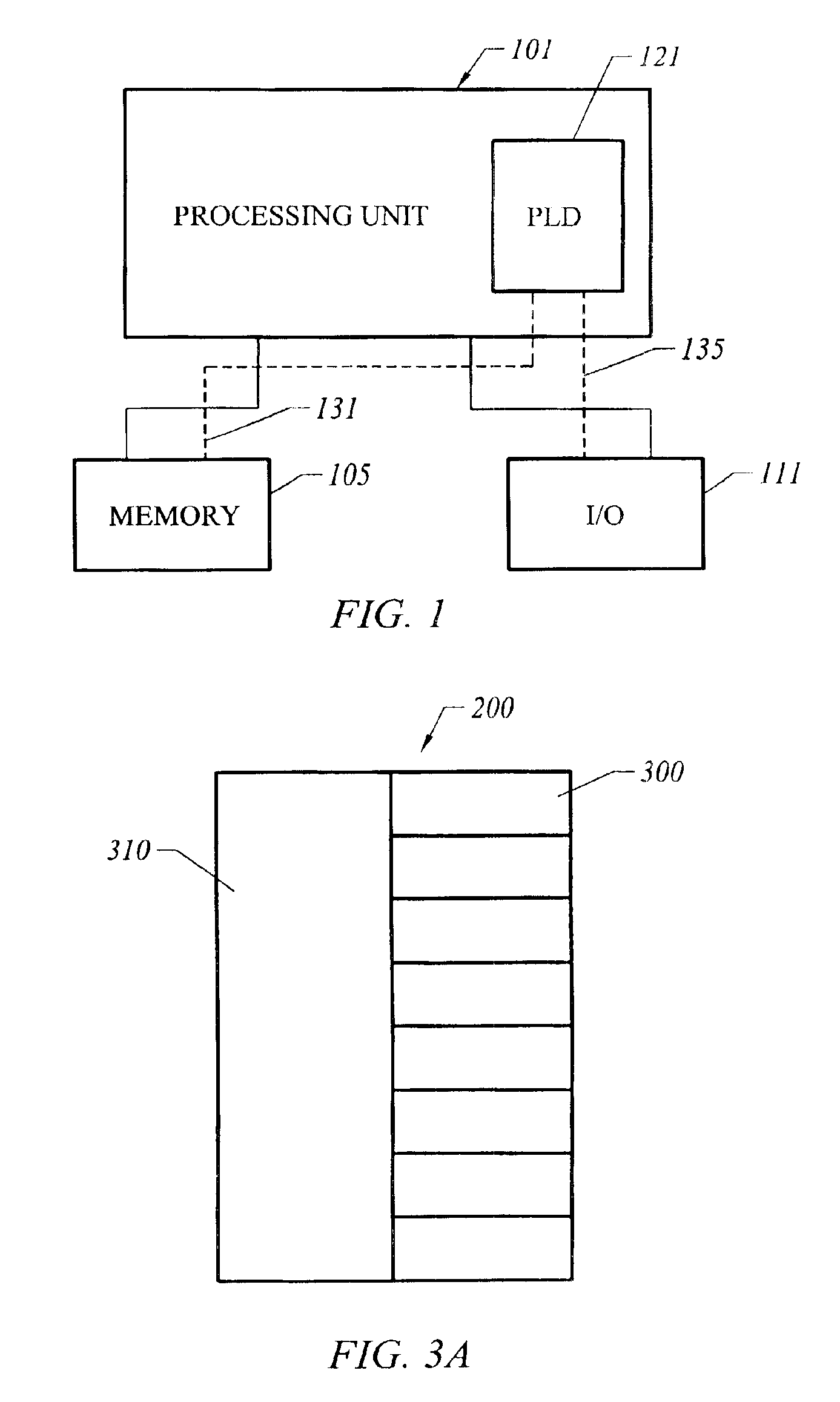

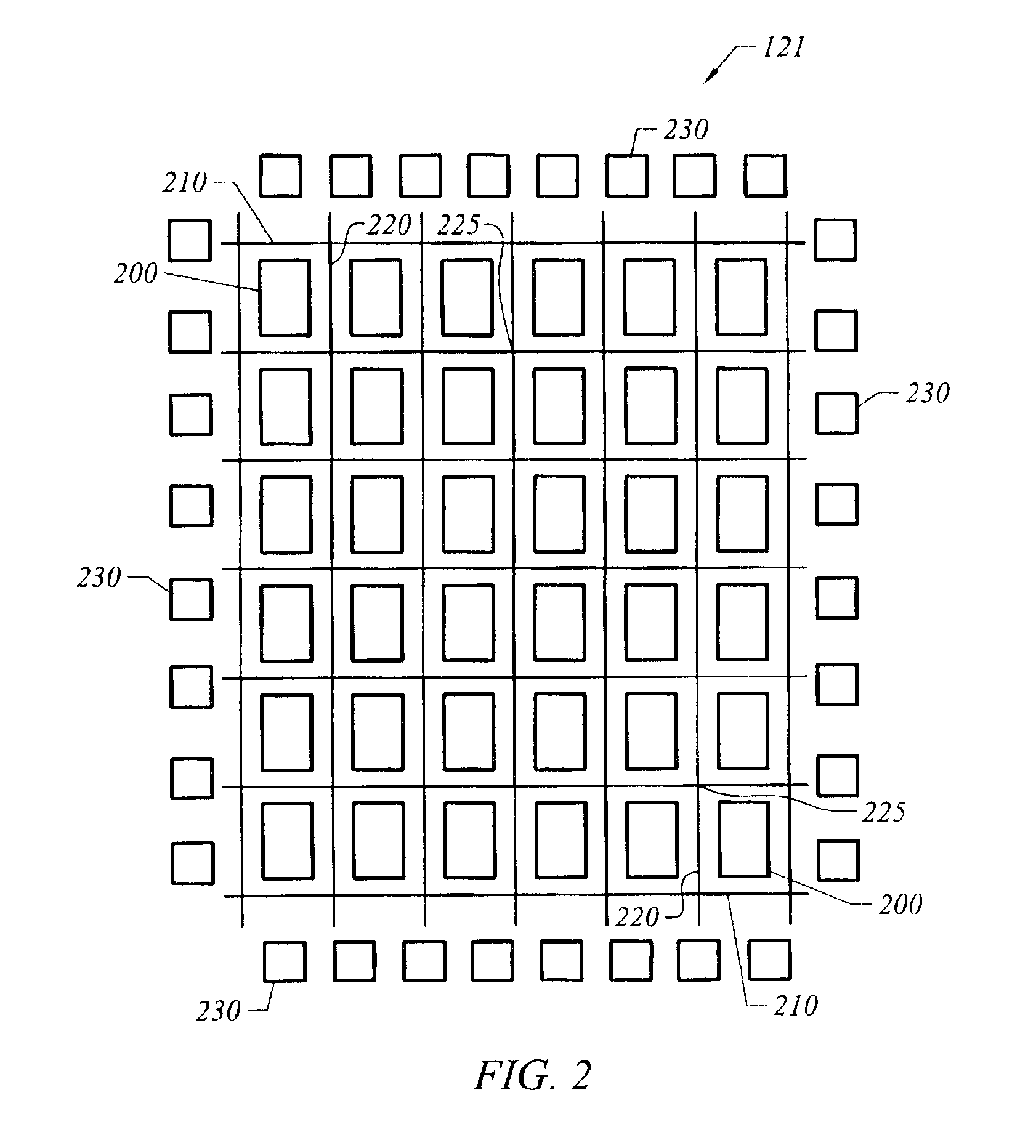

High-performance programmable logic architecture

InactiveUS6882176B1Deal of designDesigned for such useSolid-state devicesLogic circuits using elementary logic circuit componentsProgrammable logic deviceJoint Test Action Group

A programmable logic device architecture. This programmable logic architecture includes a first logic block (425) containing programmable logic elements for performing logic functions. The architecture may also include a diagnostic block interface (415), which interfaces with the first logic block (425), for performing JTAG functions, configuring the first logic block (425), initializing the first logic block (425), interfacing with off-chip diagnostic and test devices and equipment, and performing other similar functions. The first logic block (425) may be programmably coupled to other components on the integrated circuit using a first programmable interconnect network (511). The first logic block (425) includes a plurality of second logic blocks (505) which may be programmably coupled using a second programmable interconnect network (521). The second programmable interconnect network (521) may be programmably coupled to the first programmable interconnect network (511). Furthermore, the plurality of second logic blocks (505) include a plurality of third logic blocks (525) which may be programmably coupled using a third programmable interconnect network (535). A signal from a third logic block (525) may be programmably coupled to the other logic blocks, the diagnostic block interface (415), and other circuitry on the integrated circuit. The internal circuitry of these logic blocks may be monitored through a variety of programmable interconnect paths. This architecture is useful when debugging a design, especially for emulation and prototyping applications.

Owner:ALTERA CORP +1

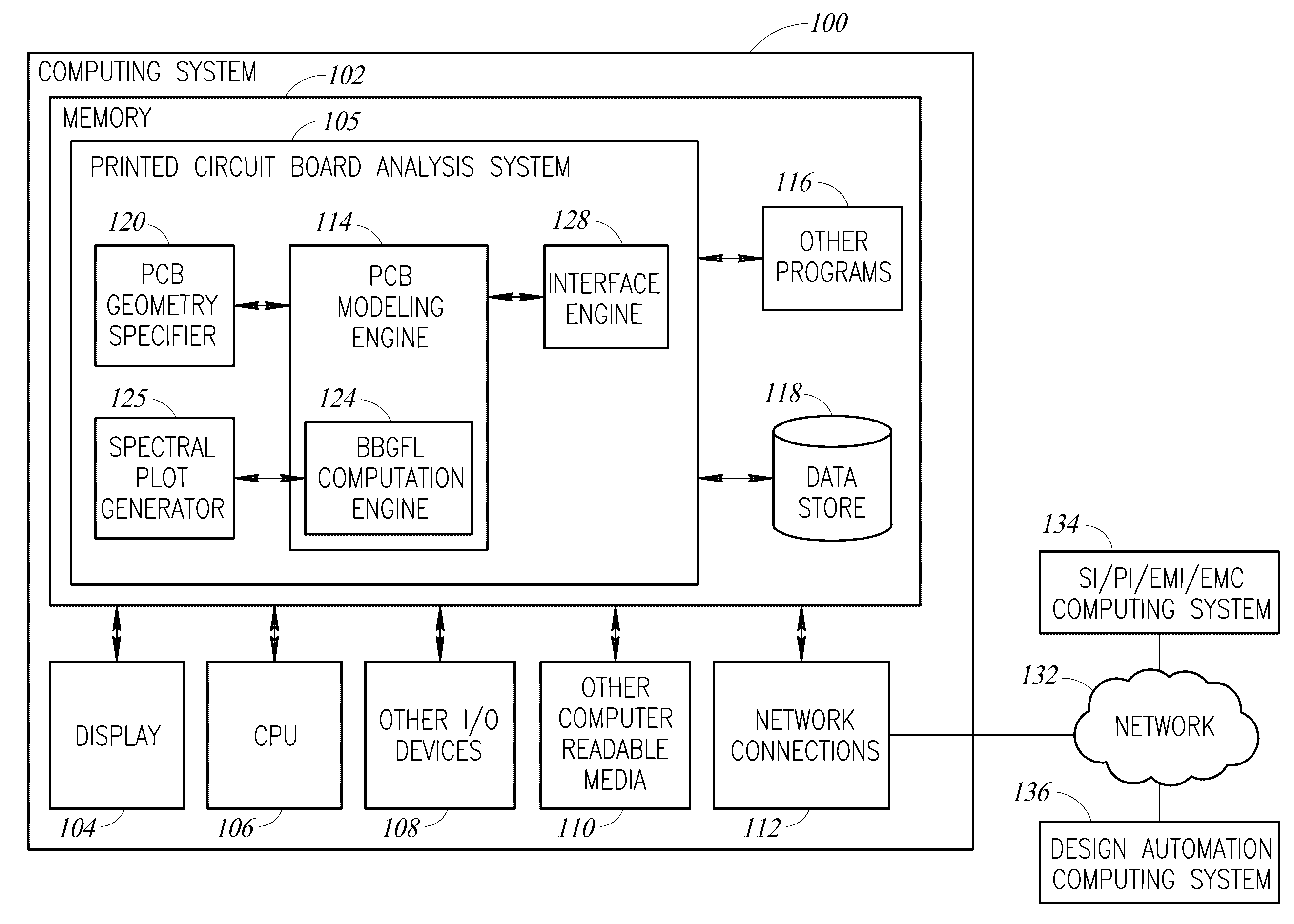

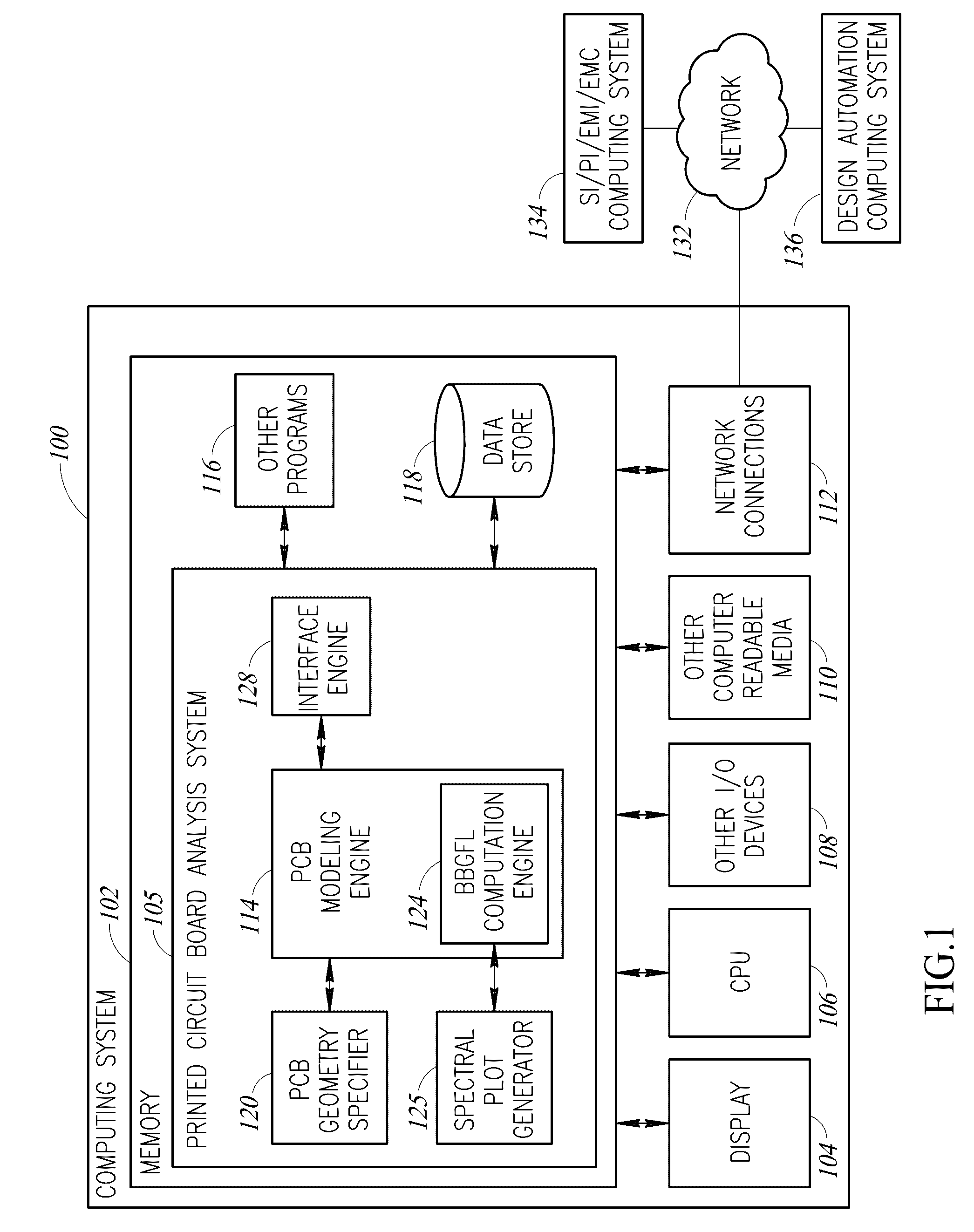

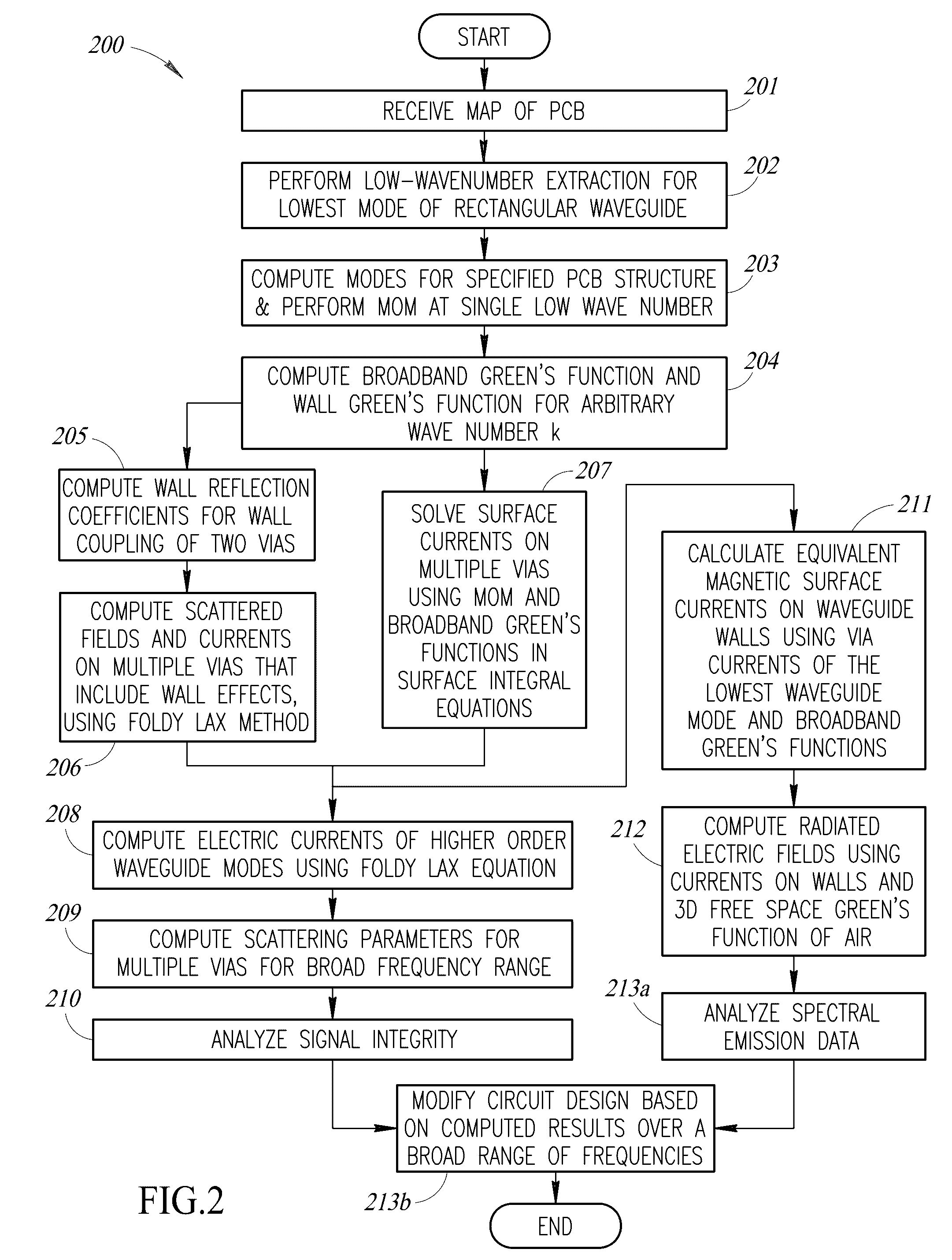

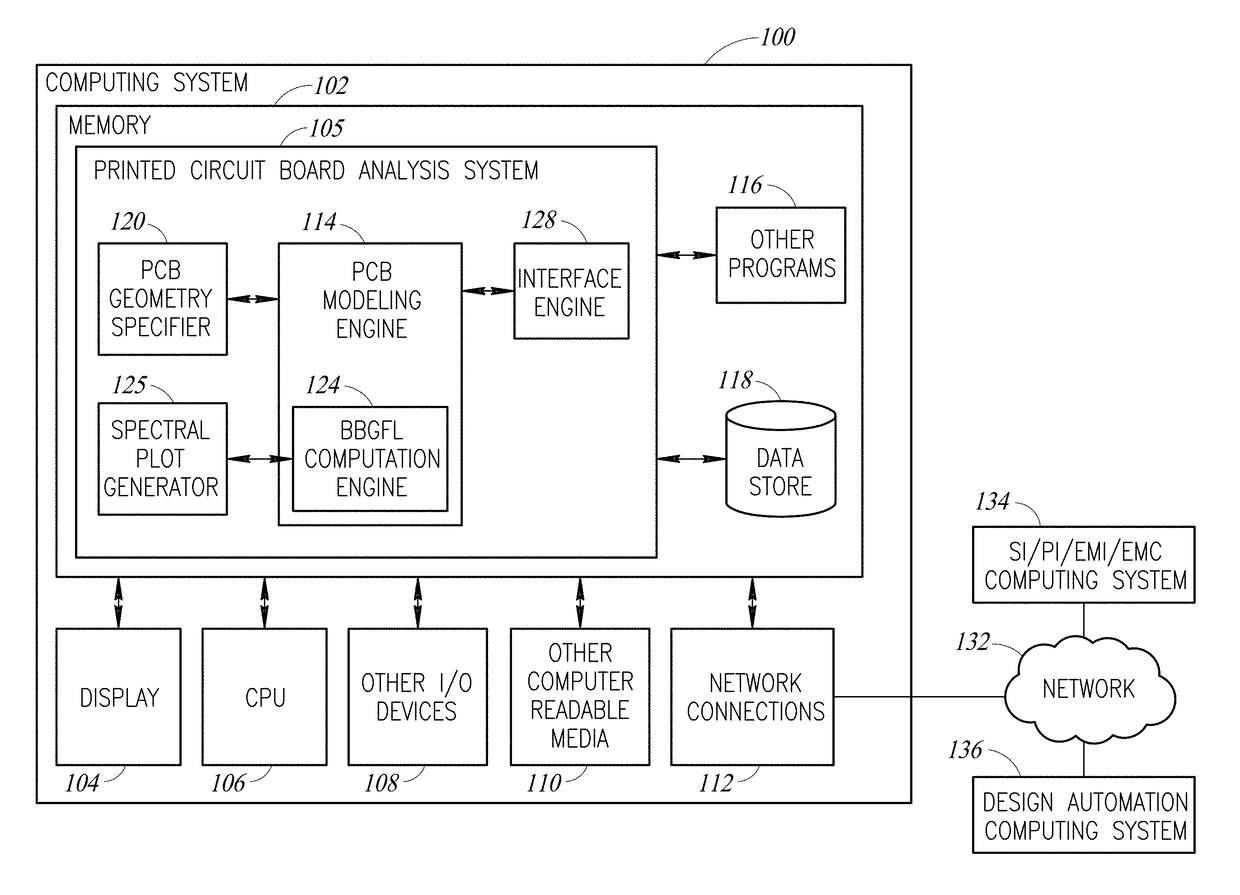

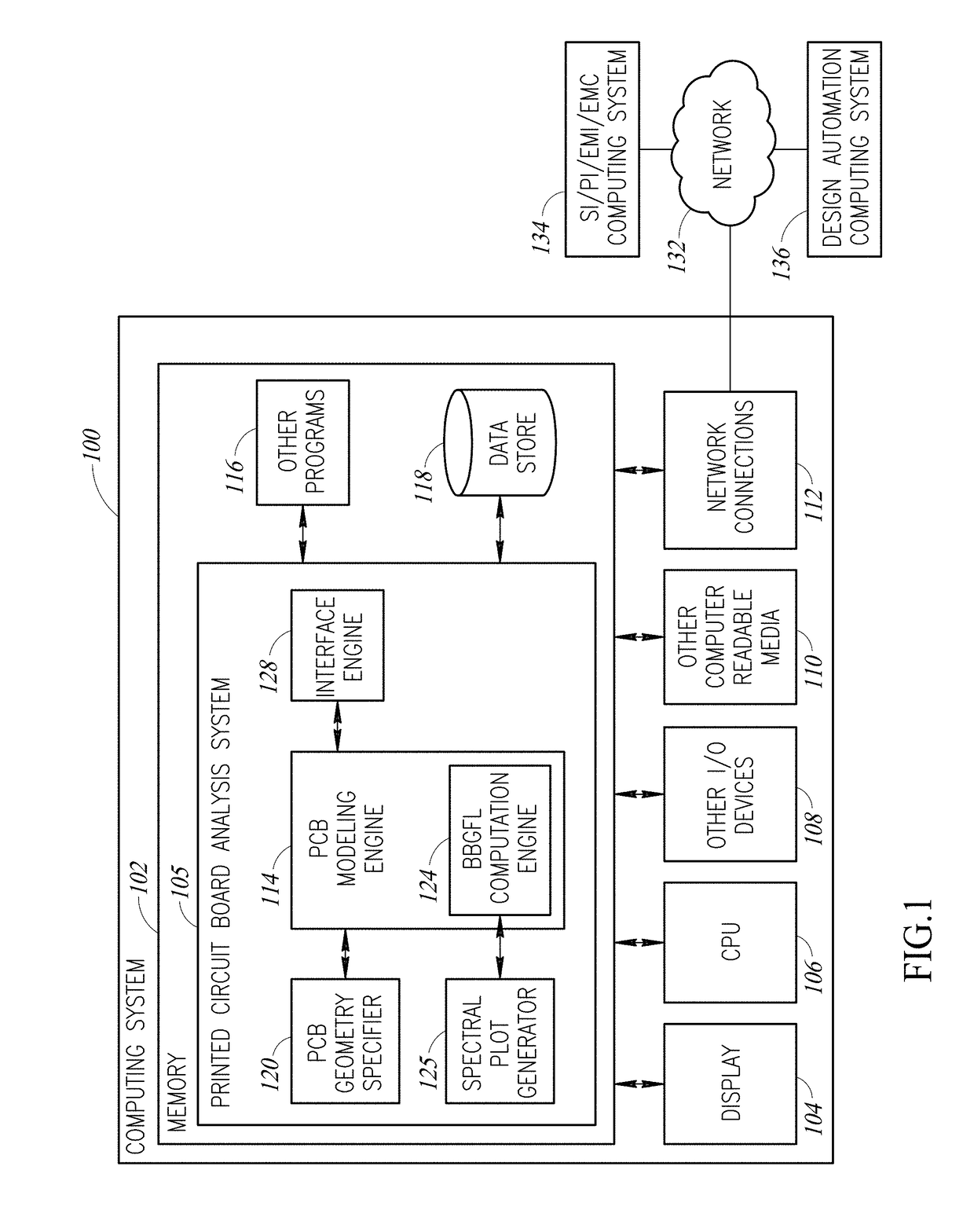

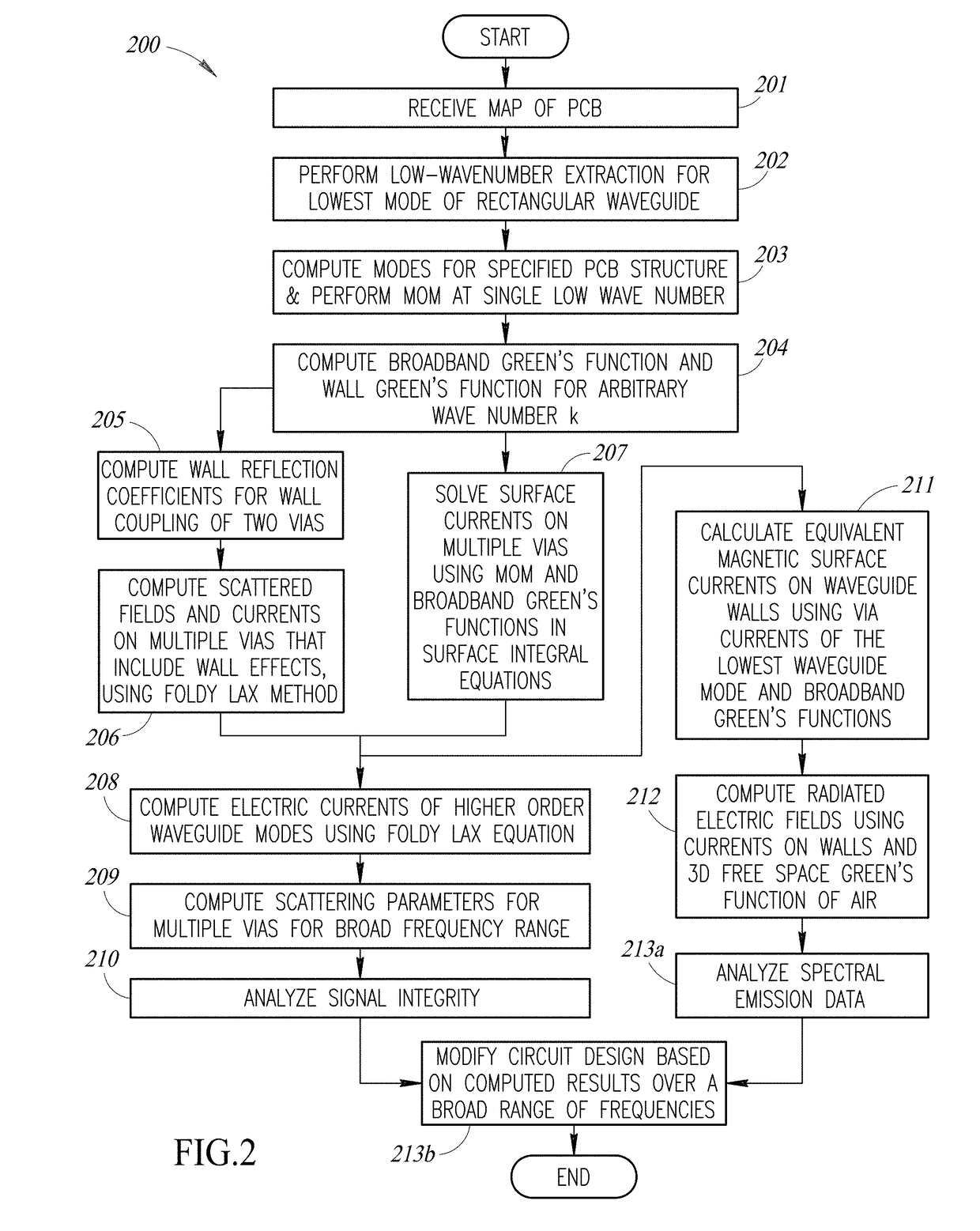

Full wave modeling and simulations of the waveguide behavior of printed circuit boards using a broadband green's function technique

ActiveUS20160314231A1Fast simulationReduce extractionCAD circuit designSpecial data processing applicationsPresent methodFull wave

A broadband Green's function computation technique that employs low wavenumber extraction on a modal summation is used to model the waveguide behavior of electronic components, systems, and interconnects on a printed circuit board. Use of the broadband technique permits discretizing the surface of the printed circuit board across a wide range of frequencies all at once. The broadband Green's function is also extended to via waveguides on circuit boards and power / ground plane waveguides of arbitrary shape. Such a method can analyze a given circuit board geometry over a broad frequency range several hundred times faster than is otherwise possible with existing commercial analysis tools. The present method is useful in electronic design automation for analyzing signal integrity and power integrity, reducing electromagnetic interference and ensuring electromagnetic compatibility.

Owner:TSANG LEUNG W +1

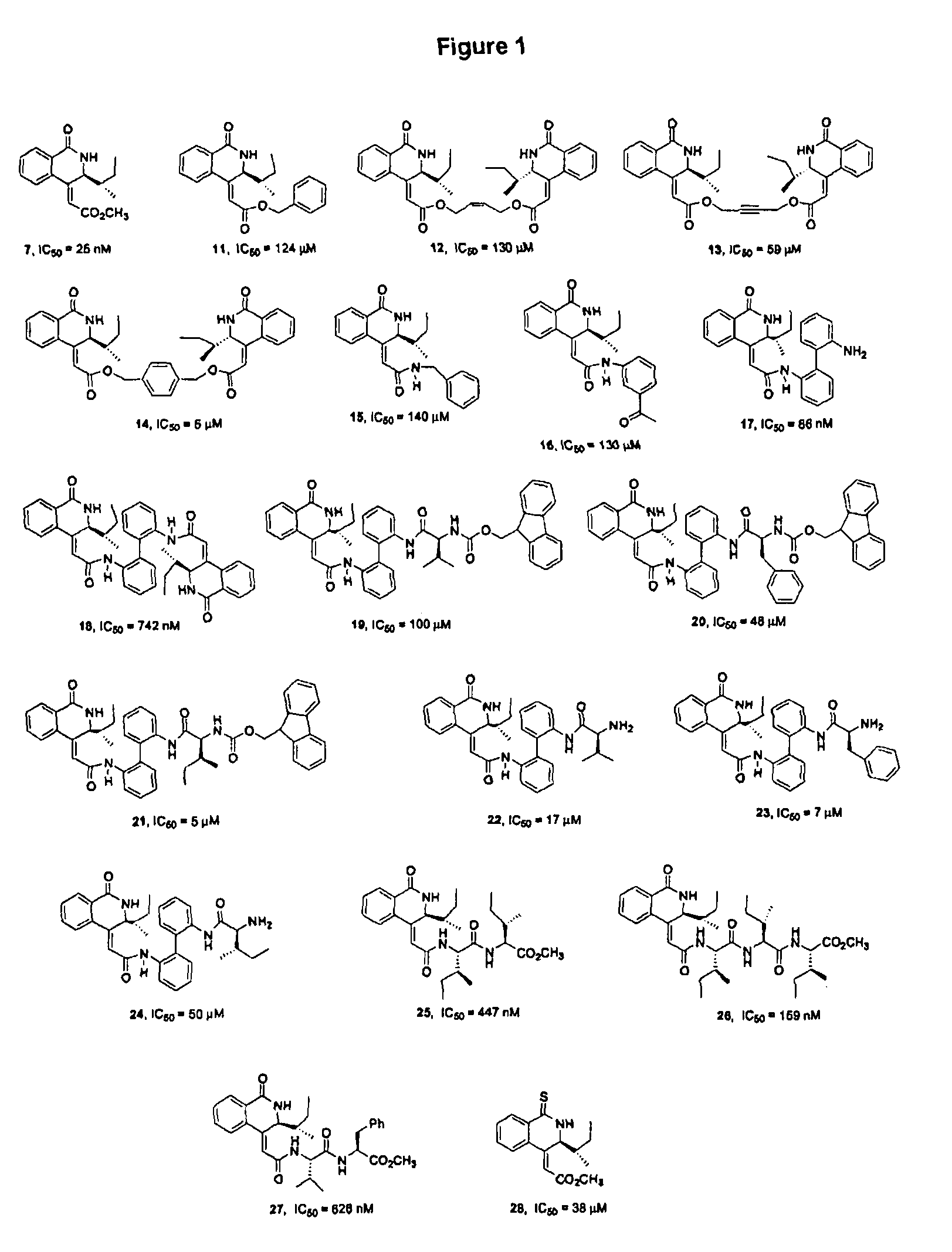

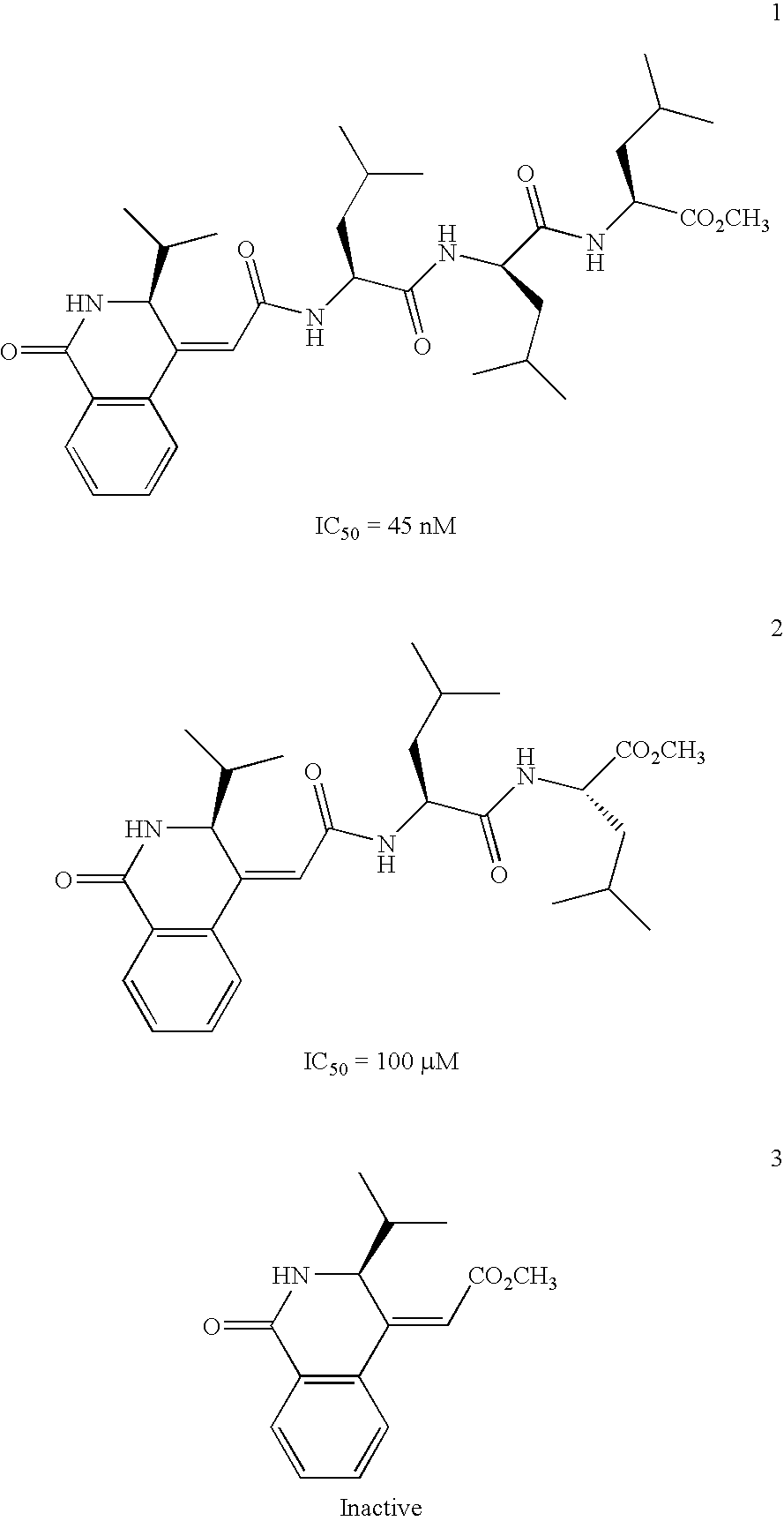

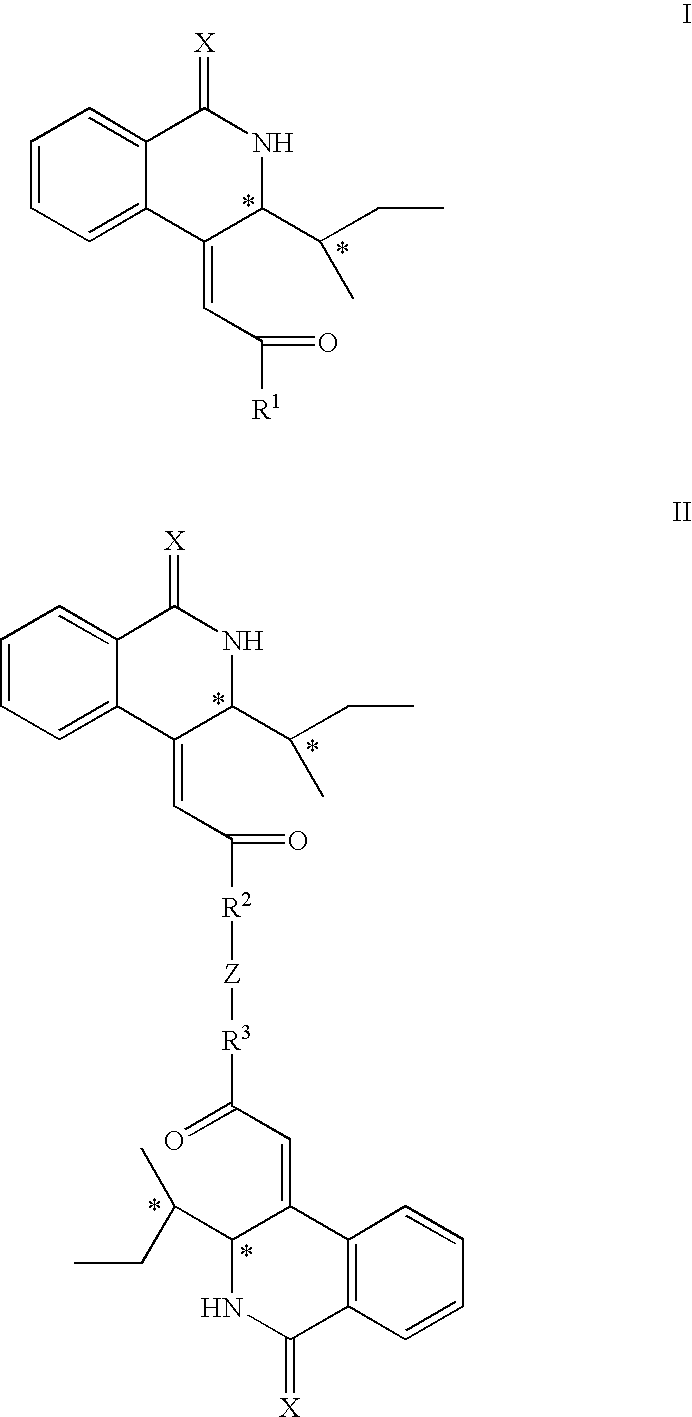

Isoquinoline derivatives as calpain inhibitors

Owner:CONSEJO SUPERIOR DE INVESTIGACIONES CIENTIFICAS (CSIC)

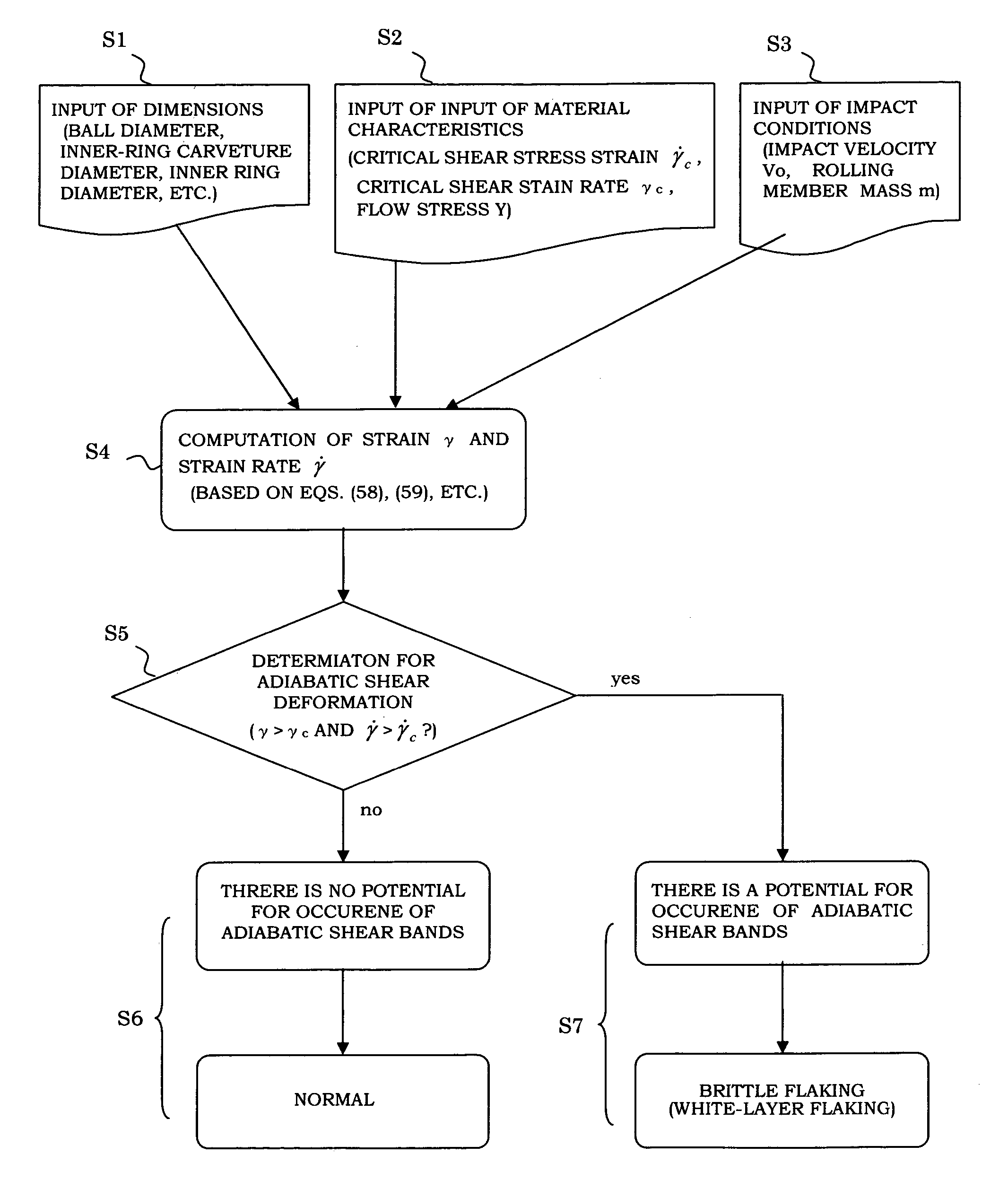

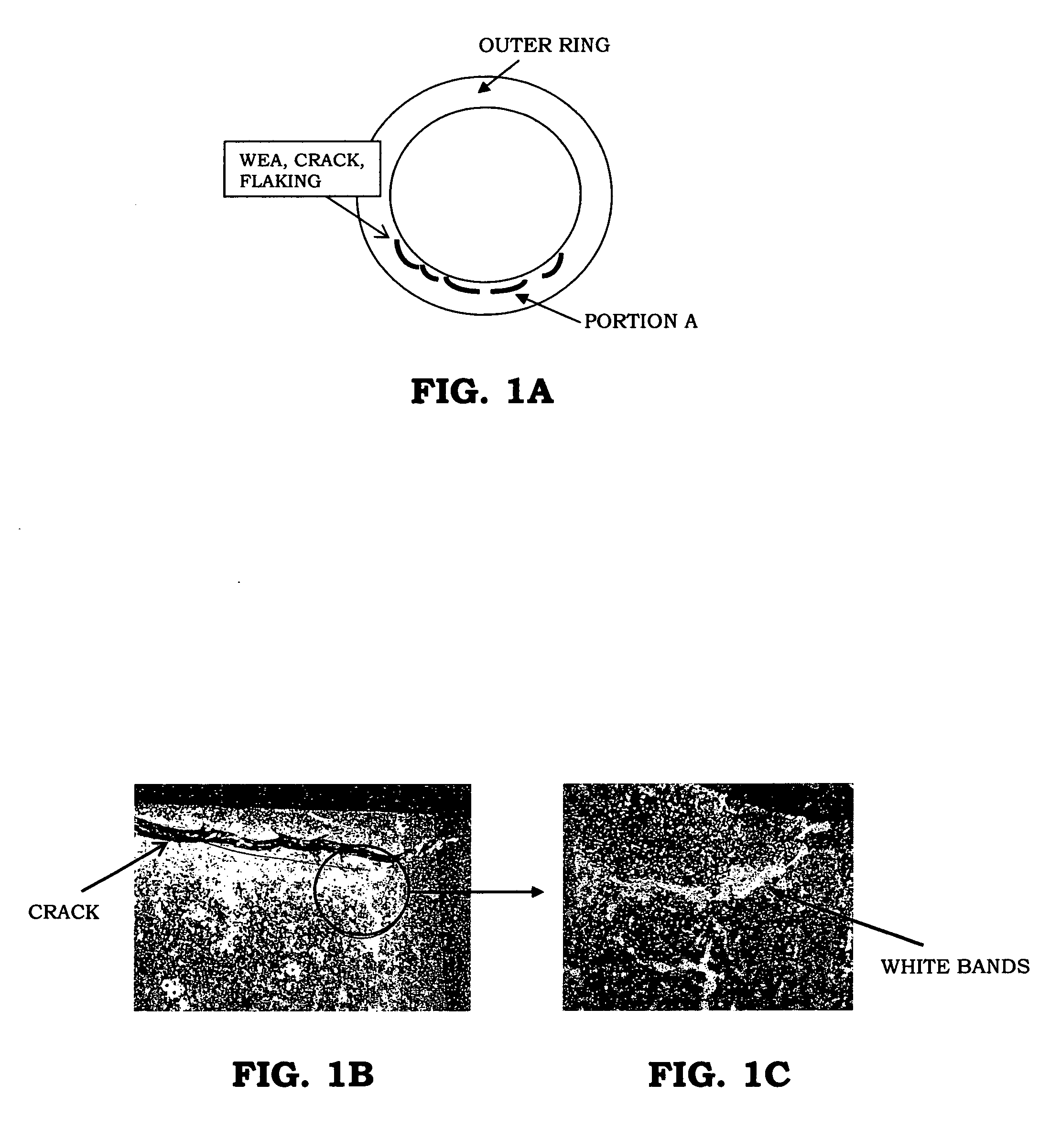

Method and apparatus for designing rolling bearing to address brittle flaking

InactiveUS20060064197A1Clear and correct and simpleBrittle flakingRolling contact bearingsMetal-working apparatusAdiabatic shear bandRolling-element bearing

There is provided a method and apparatus for designing a rolling bearing provided with components including rolling elements, an outer ring, and an inner ring which come into contact with each other. First, it is determined whether or not adiabatic shear bands have a potential for occurrence within at least one of the components, due to the fact that stress is applied to the components, thus causing high deformation rates in the at least one of the components to cause an unstable plastic phenomenon that brings about an adiabatic shear deformation state within the at least one of the components. Then an estimation is made such that brittle flaking resulting from the adiabatic shear bands have a potential for occurrence within the at least one of the components, when it is determined that the adiabatic shear bands have a potential for occurrence.

Owner:DENSO CORP

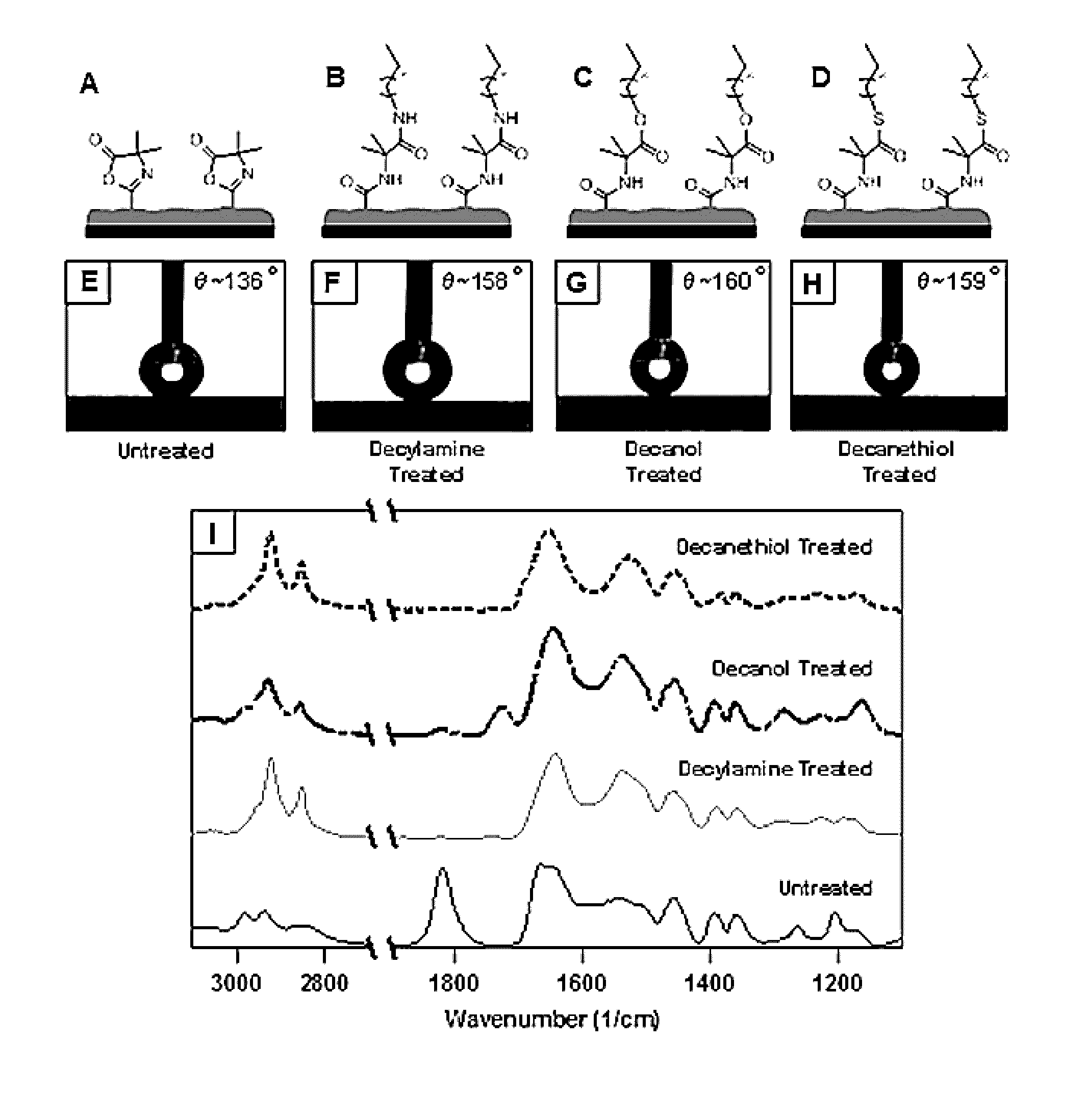

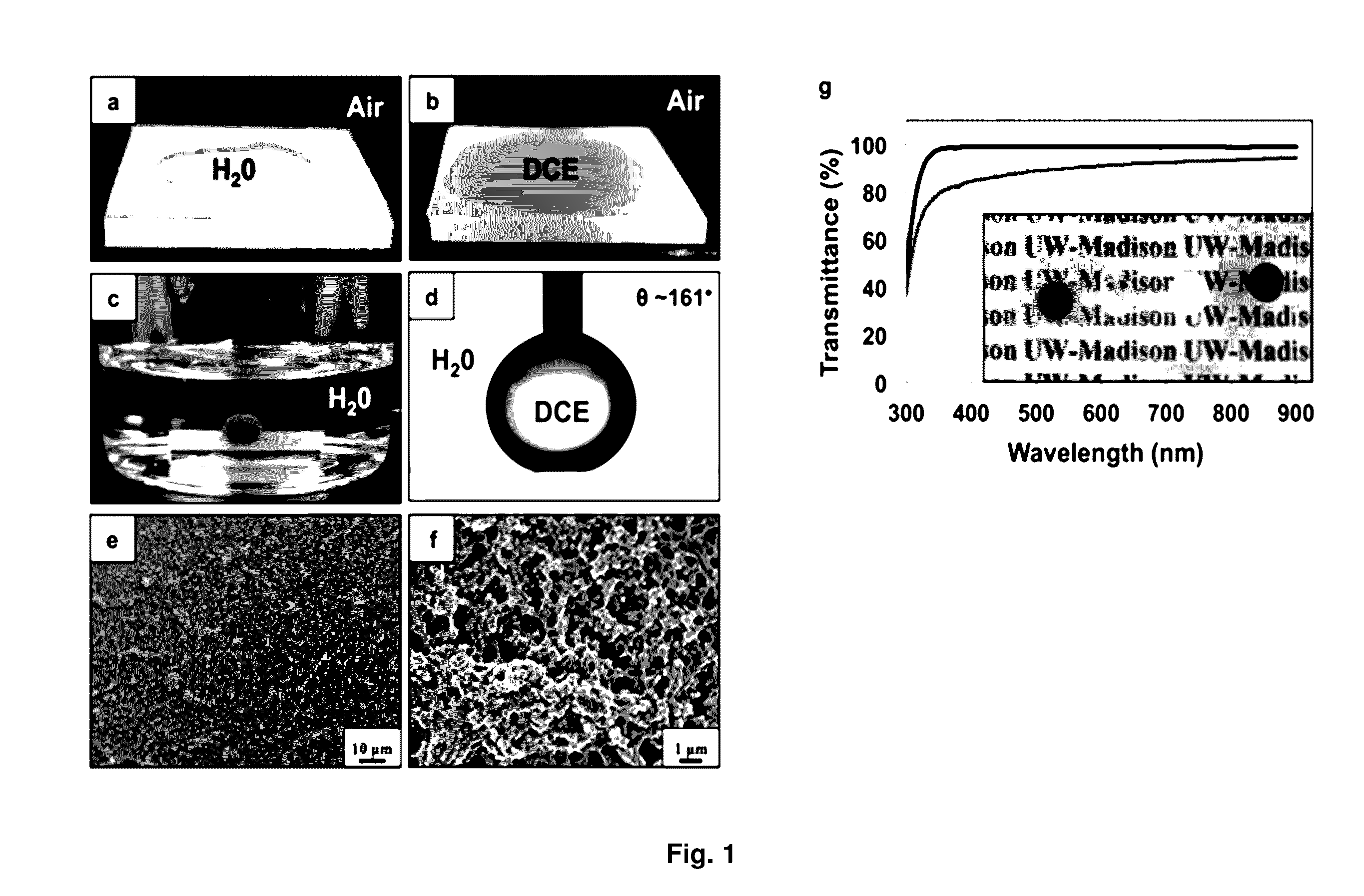

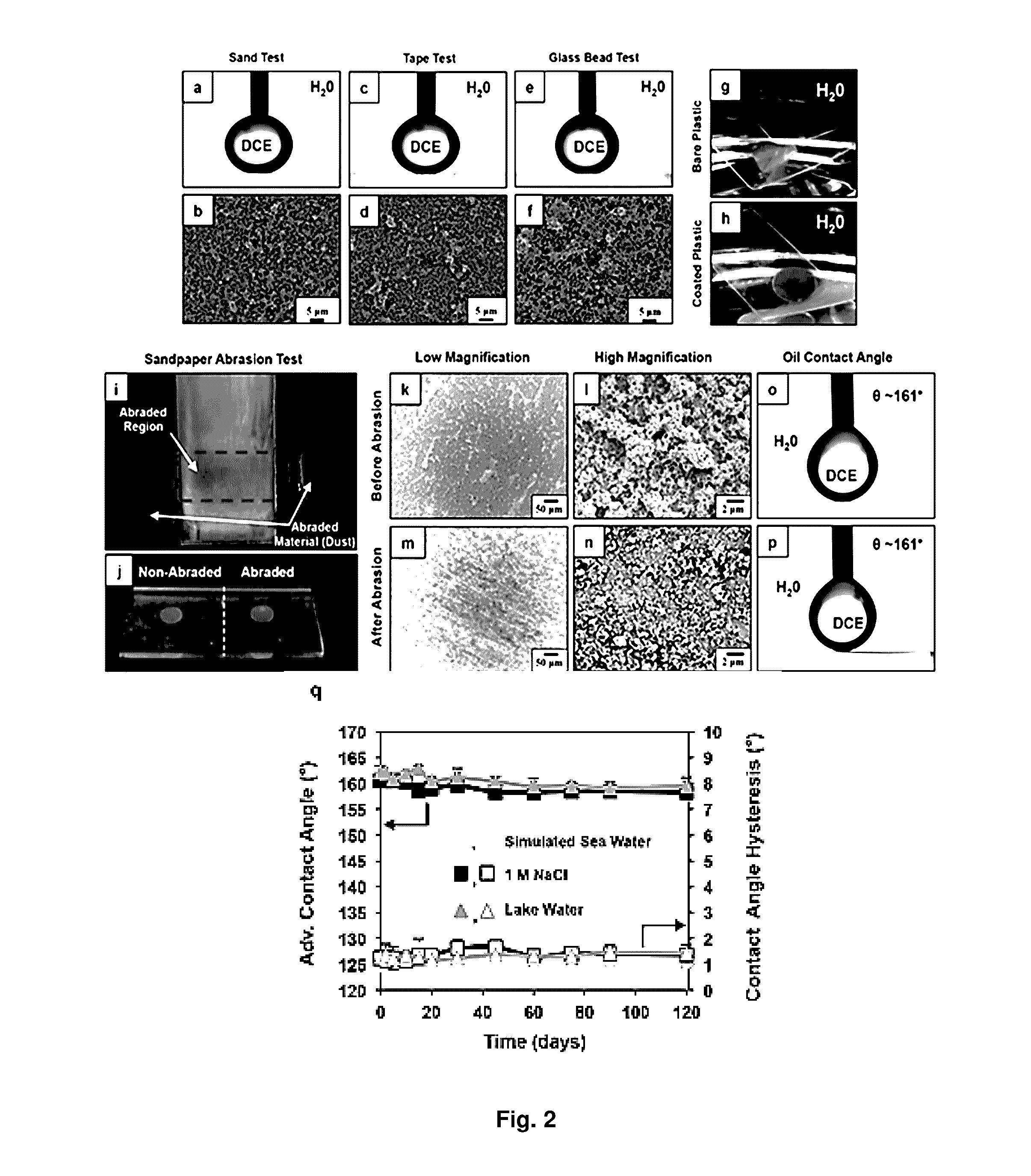

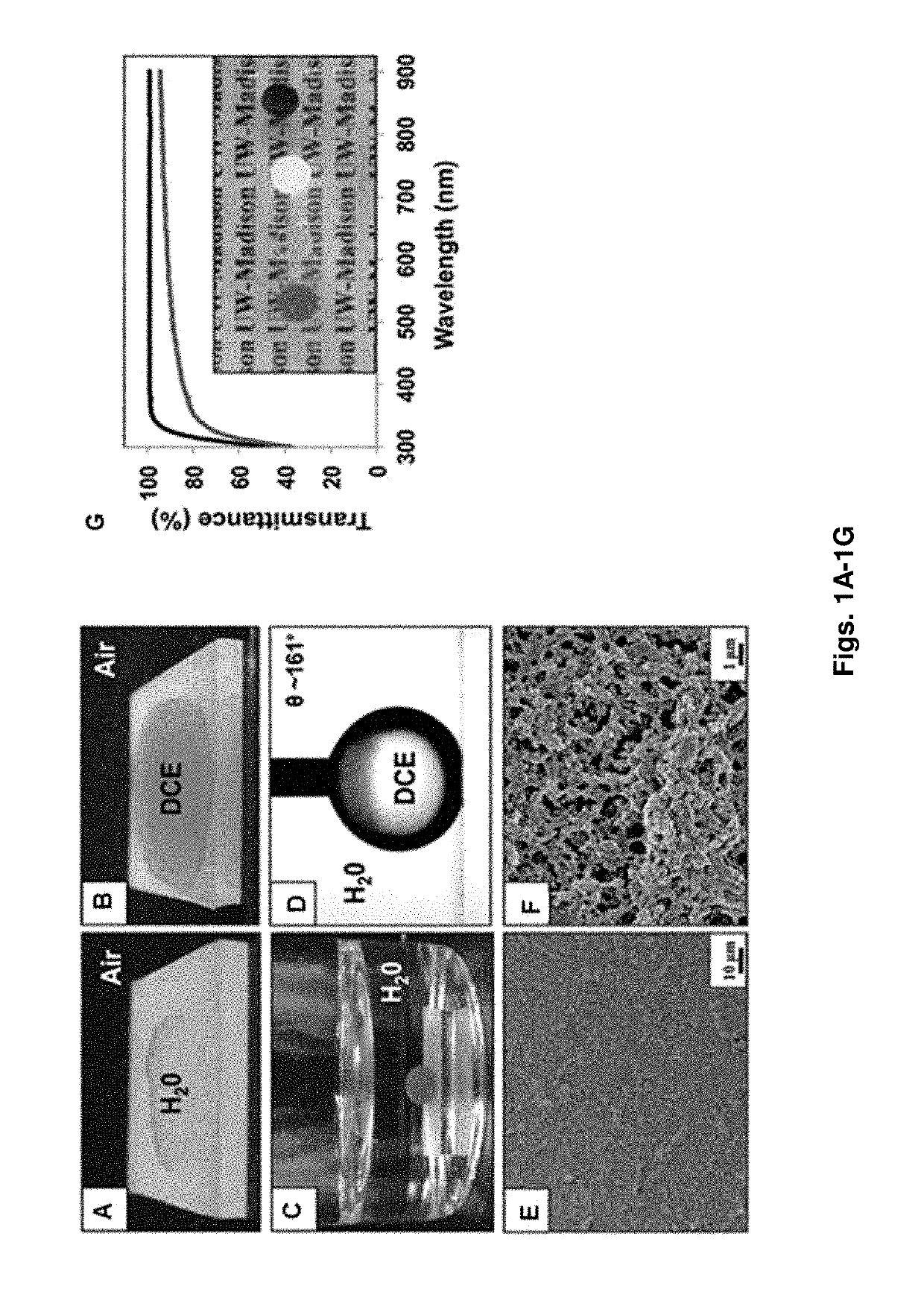

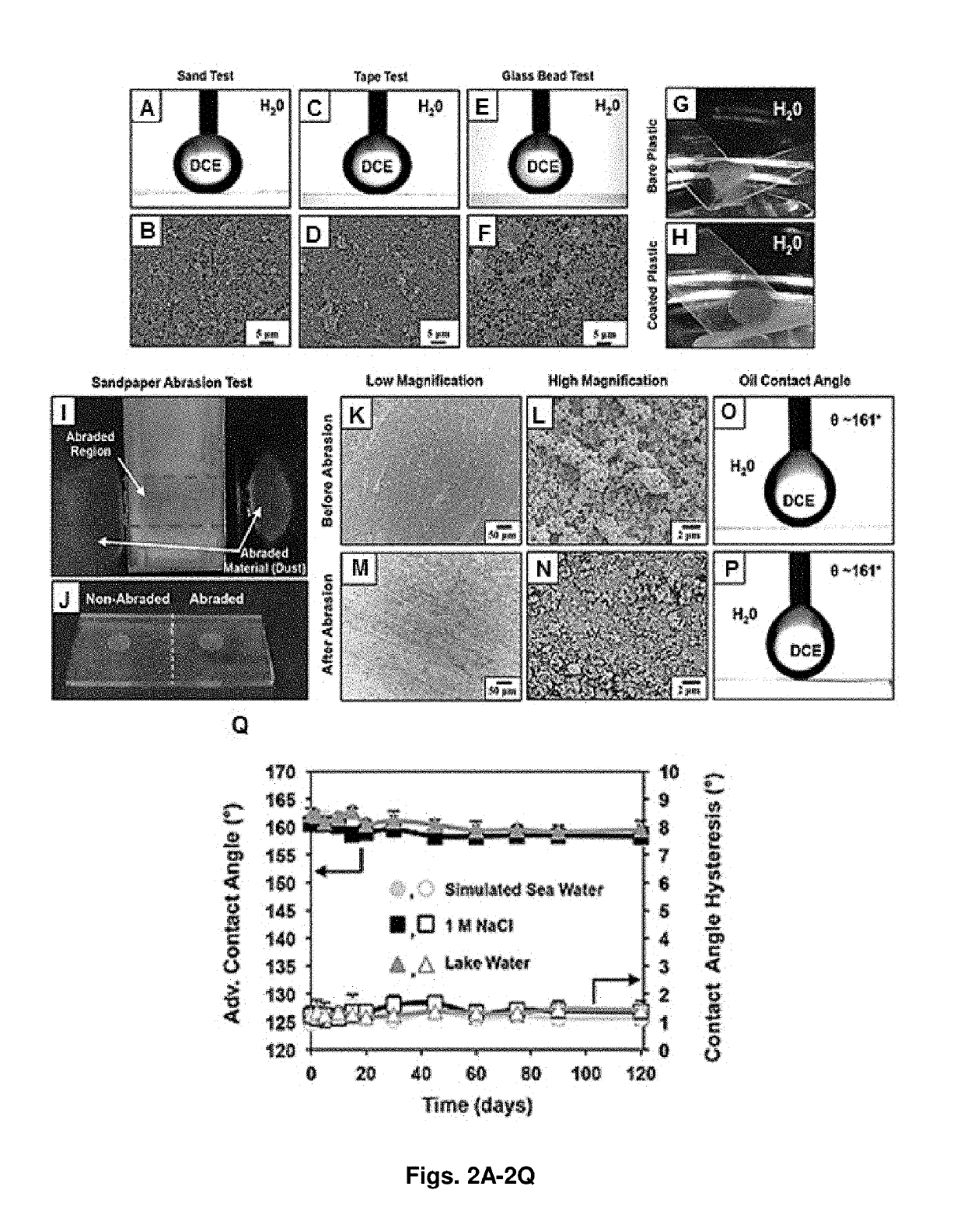

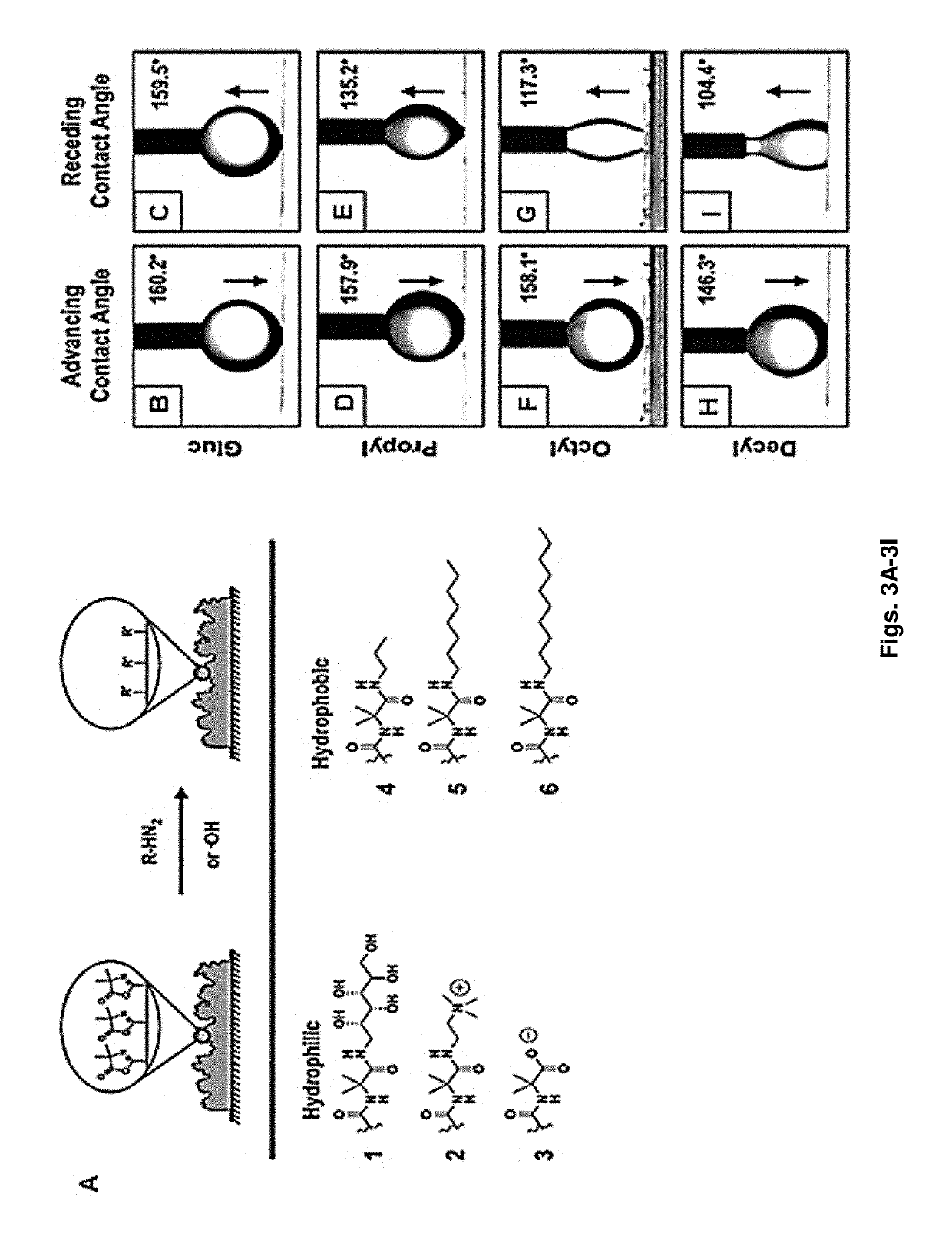

Synthetic Surfaces with Robust and Tunable Underwater Superoleophobicity

ActiveUS20170022372A1Improve structural strengthPromote degradationAntifouling/underwater paintsPaints with biocidesNon wettingAquatic environment

The present invention provides multilayer polymer films, materials and coatings which exhibit robust underwater superoleophobicity and have remarkable structural functional tolerance to a broad range of physical, chemical, and environmental challenges encountered by surfaces deployed in aqueous or aquatic environments. These materials can be fabricated on surfaces of arbitrary shape, size, and composition and provide straightforward means to manipulate surface chemistry and fine-tune other useful features of the interfacial behavior (e.g., underwater oil-adhesiveness). These materials address key obstacles to the application of non-wetting surfaces and anti-fouling ‘super-phobic’ materials in practical, real-world scenarios.

Owner:WISCONSIN ALUMNI RES FOUND

Wind turbine with liquid medium distribution system

A wind turbine with a tower, a nacelle, a main shaft, a hub and blades is provided. The wind turbine also includes a liquid medium distribution system for transport of liquid medium in the wind turbine. The liquid medium distribution system has a first distribution sub-system located in the tower, a second distribution sub-system located in the nacelle, a third distribution sub-system located in the hub, a tower-nacelle-interface connecting the first distribution sub-system to the second distribution sub-system, and a nacelle-hub-interface connecting the second distribution sub-system to the third distribution sub-system. Further, a method of transporting liquid medium in a wind turbine is provided.

Owner:SIEMENS AG

System for aiding the design of product configuration

InactiveUS7467122B2Easy to implementReduce workloadCAD network environmentOffice automationConfiguration designEngineering

While a base model has been determined for a product, in a system for performing a configuration designing operation of the product by setting a specification value to a specification item of the product, a product configuration design aiding system aids that a configuration designer can easily perform the configuration designing operation while following a restriction condition of a specification value of a specification item. A specification configuration information database is constructed which describes restriction conditions available for the specification values with respect to the specification item, and a configuration designing screen for inputting the specification values with respect to the specification item is displayed so as to conduct an input by the configuration designer.

Owner:HITACHI LTD

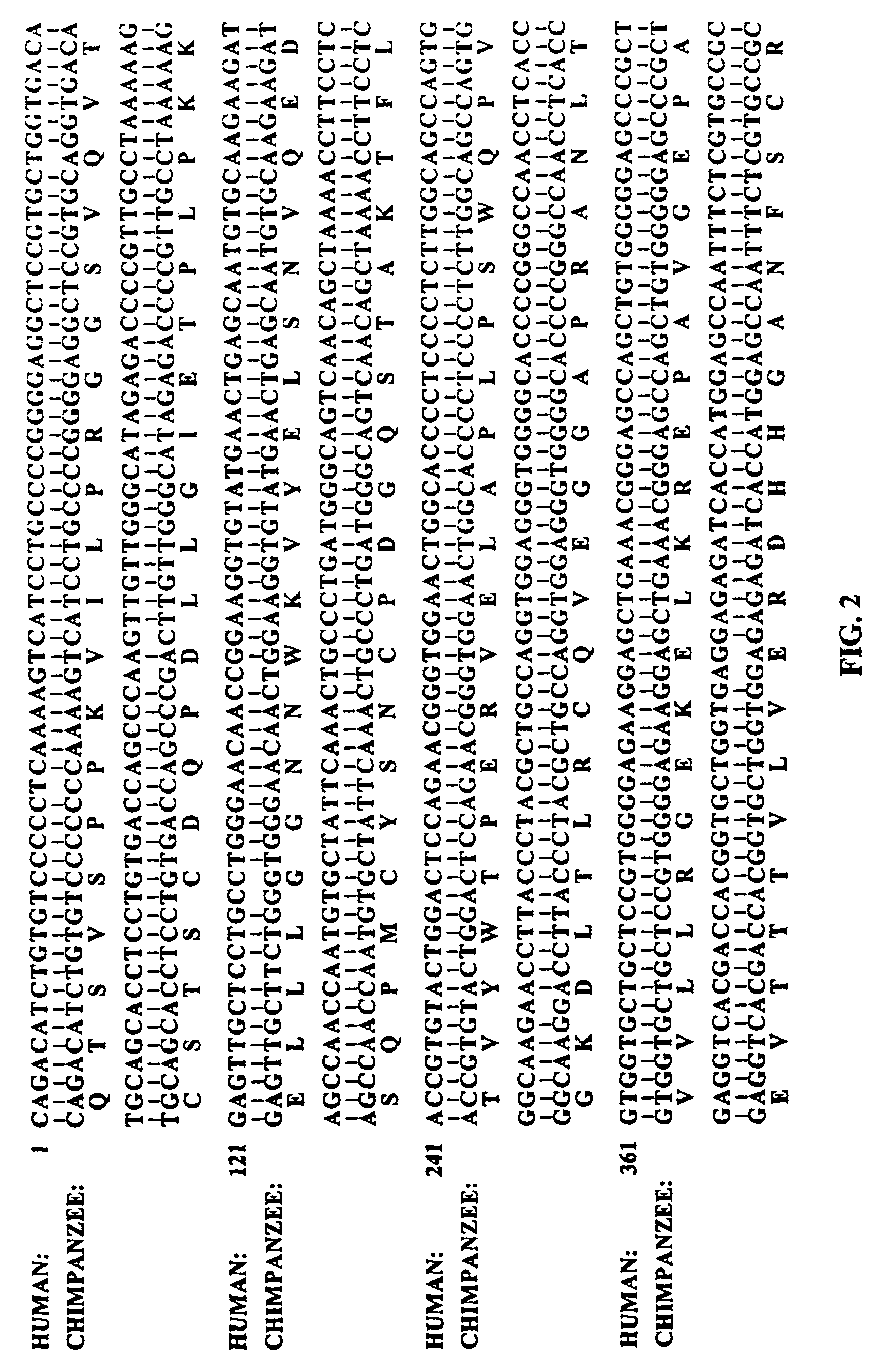

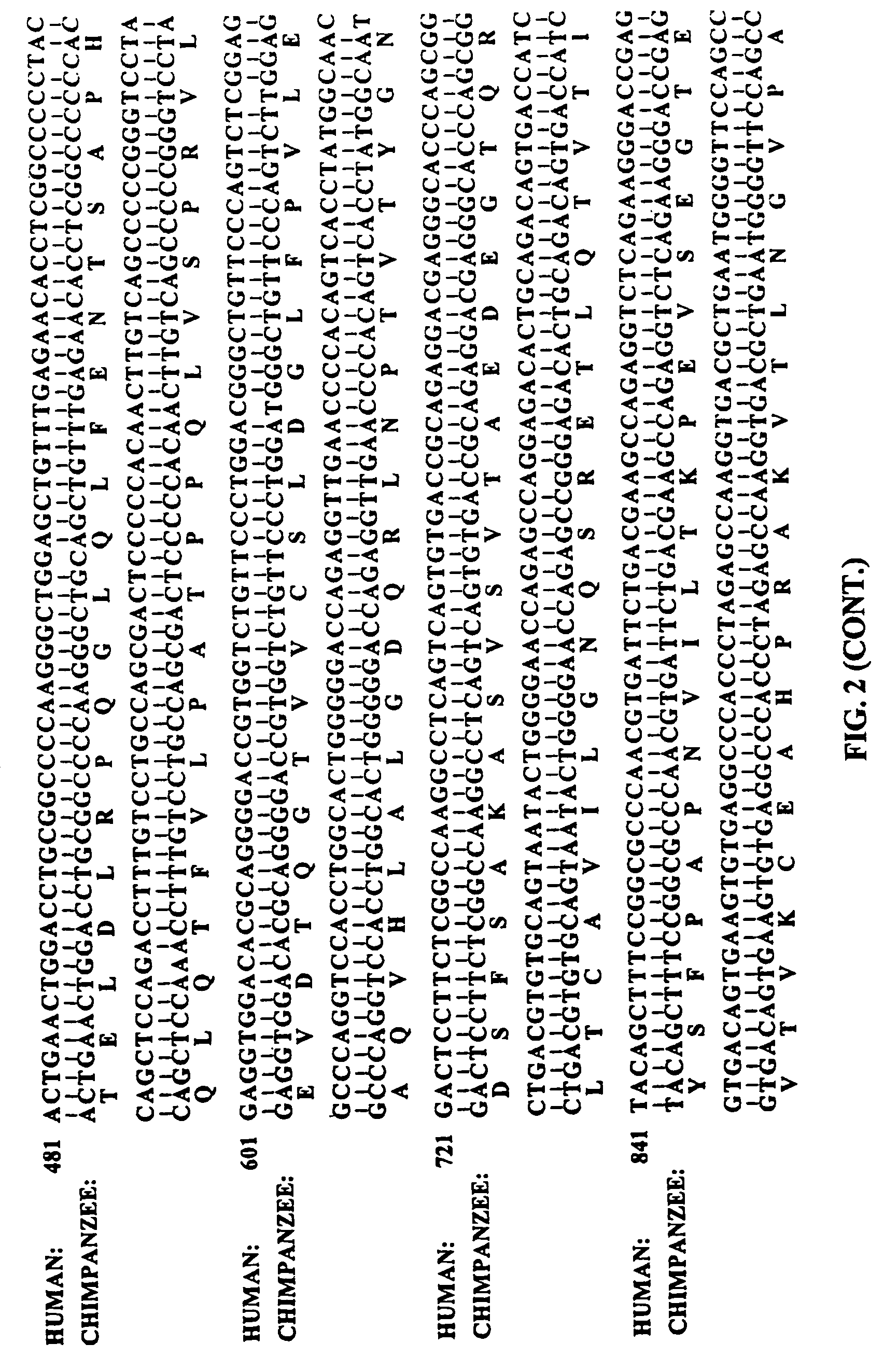

Methods to identify polynucleotide and polypeptide sequences which may be associated with physiological and medical conditions

InactiveUS7247425B2Reduce resistanceImprove developmentCompound screeningApoptosis detectionPolynucleotideICAM-1

The present invention provides methods for identifying evolutionarily significant polynucleotide and polypeptide sequences in human and / or non-human primates which may be associated with a physiological condition, such as enhanced resistance to AIDS infection. The invention also provides methods for identifying evolutionarily significant polynucleotides with mutations that are correlated with susceptibility to diseases, such as ICAM 1. The methods employ comparison of human and non-human primate sequences using statistical methods. Sequences thus identified may be useful as host therapeutic targets and / or in screening assays.

Owner:EVOLUTIONARY GENOMICS LLC

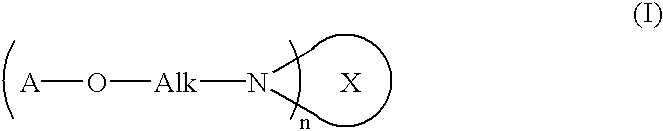

Fullerene derivative and composition comprising the same

InactiveUS20040067892A1Potent photosensitizing actionHighly toxicBiocideNanotechLight irradiationMedicinal chemistry

A fullerene derivative represented by the formula (I): [wherein, A is a residue of monosaccharides or disaccharides, and Alk is a lower alkylene group, the group represented by the formula (X): is a fullerene residual skeleton, and n is an integral number of 1 or 2] or its salt produces a formulation usable for PDT which has more hydrophilicity and lipophilicity, is expected to have selectivity to tumor cells by cell recognition, shows no toxicity to the cells in a dark place and has a cytocidal effect by light irradiation.

Owner:SAN EI GEN F F I +1

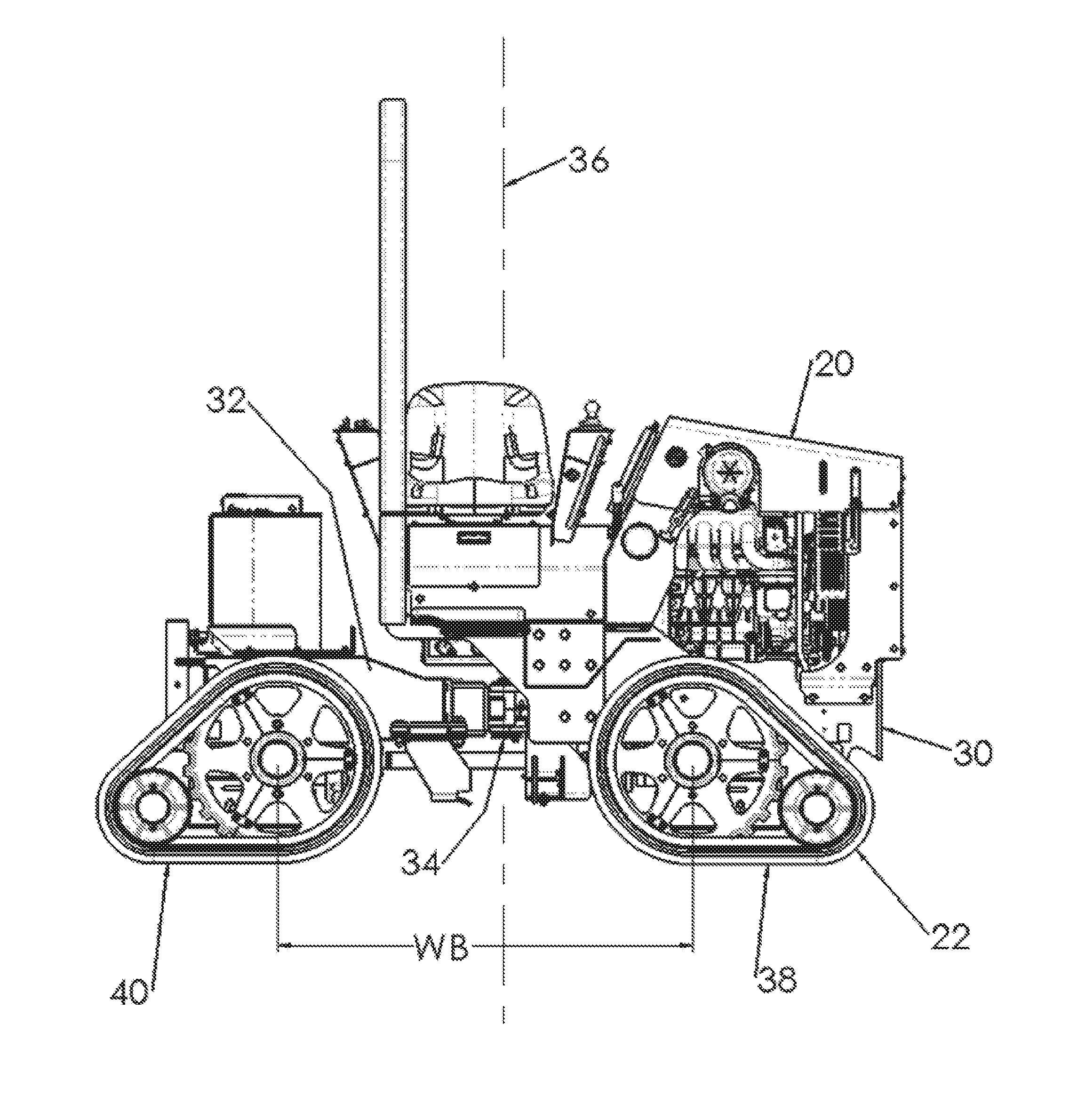

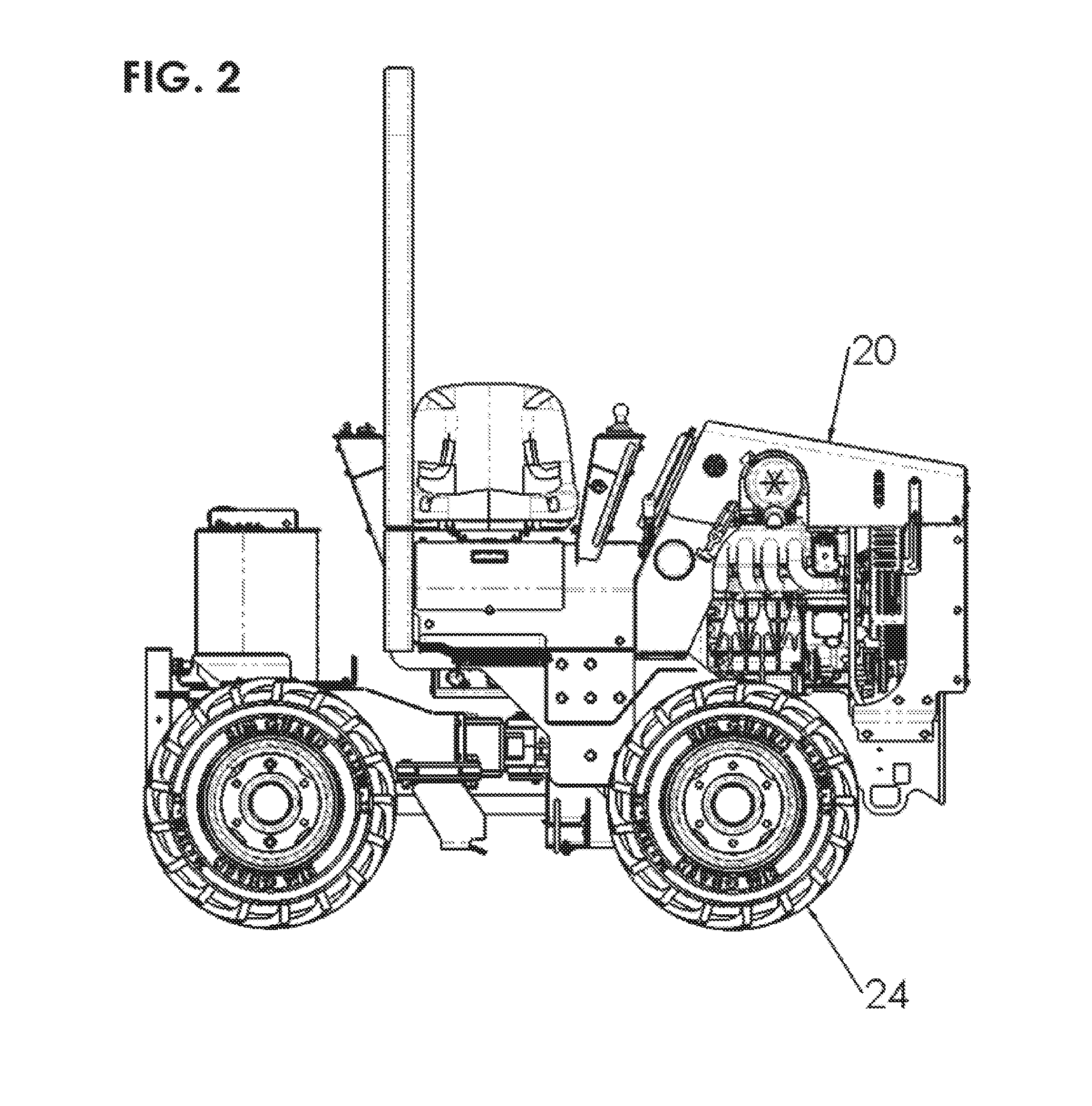

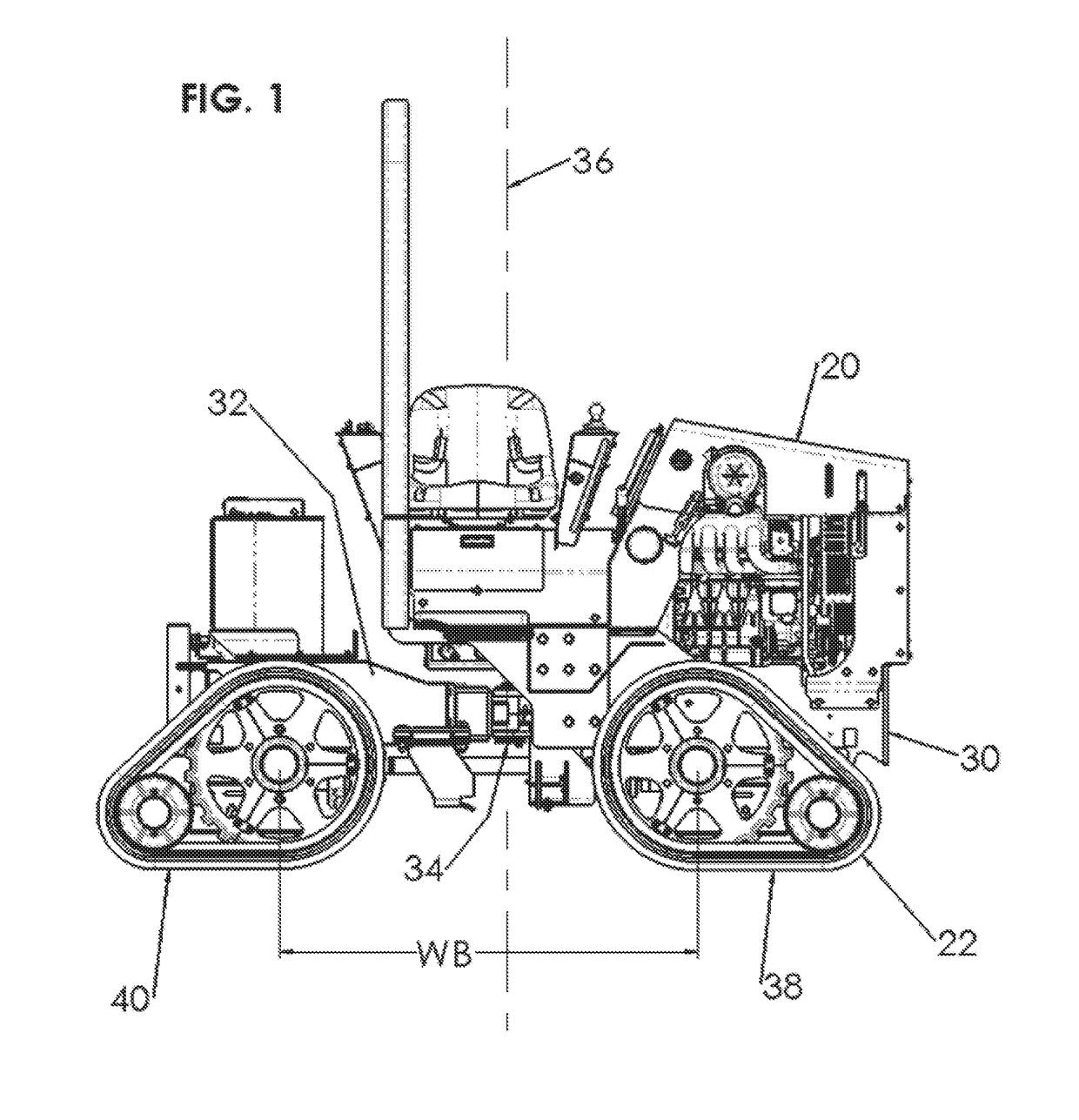

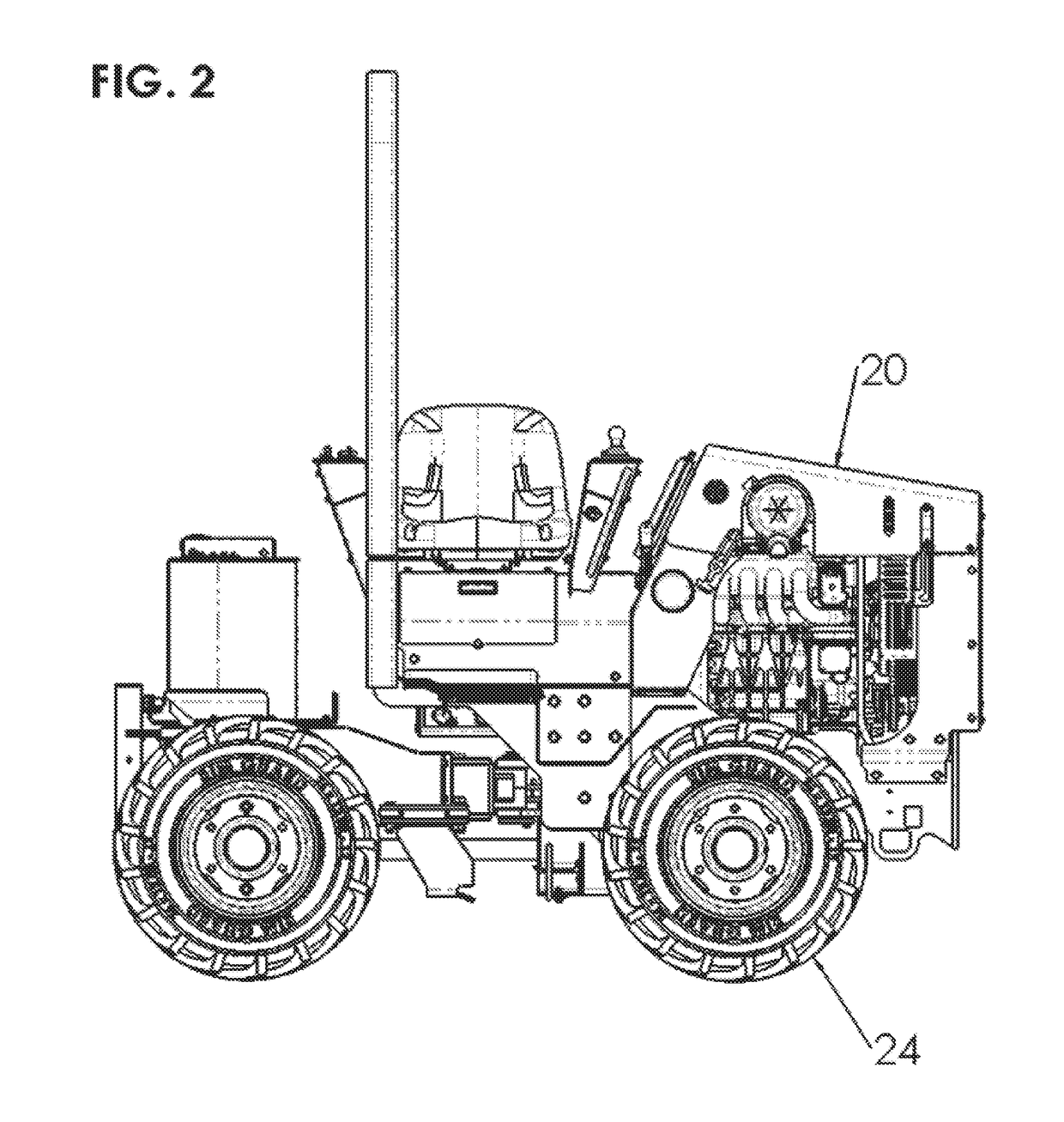

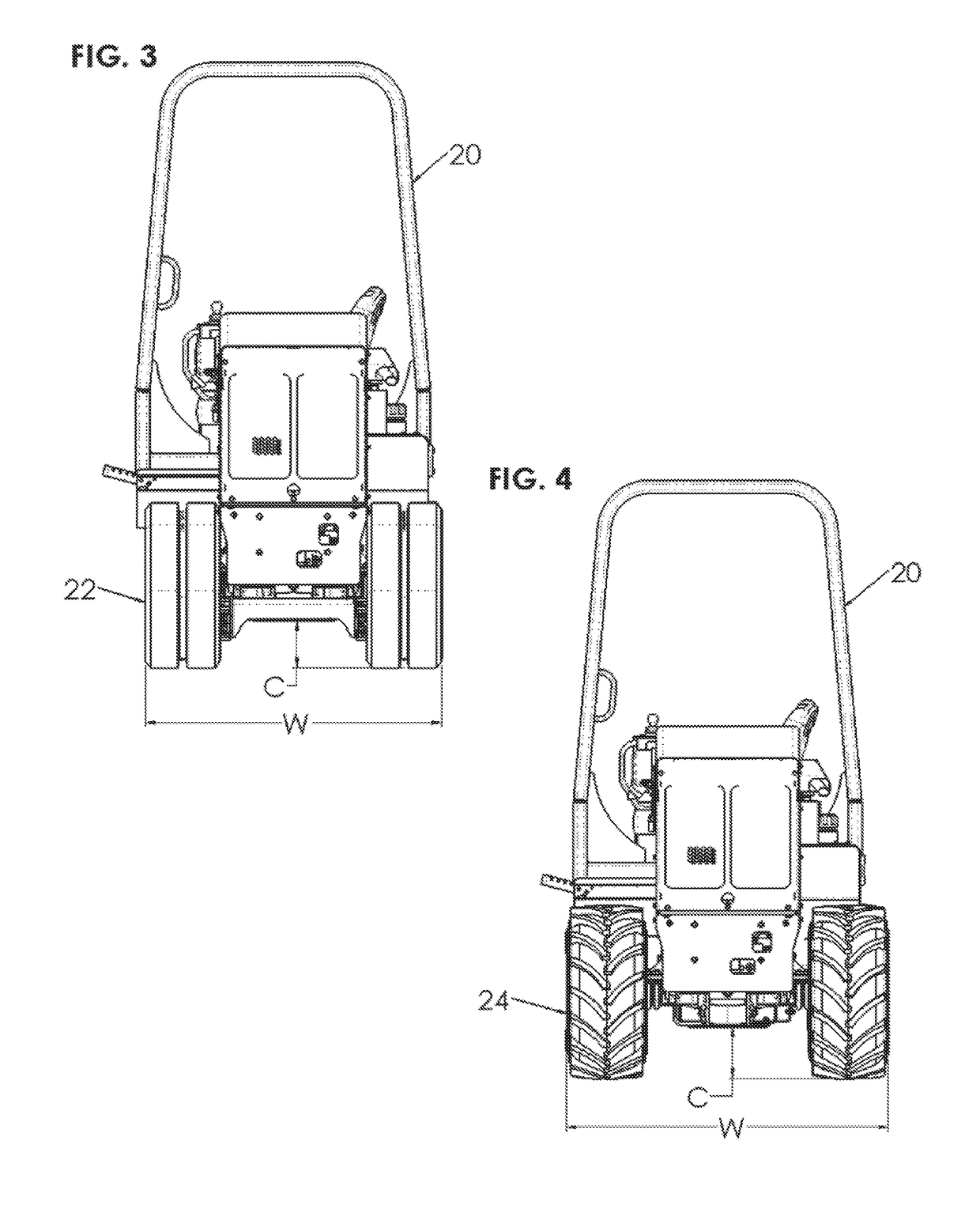

Tractor with track drive

ActiveUS20160221617A1Improve machine performanceEasy to operateSteps arrangementTractor-trailer combinationsDrive wheelIdler-wheel

An off-highway vehicle has a front chassis portion, a rear chassis portion, a front ground drive system and a rear ground drive system. The front chassis portion has a front axle assembly having a front axle housing and a front axle shaft carrying a front wheel hub. The rear chassis portion has a rear axle assembly including a rear axle housing and a rear axle shaft carrying a rear wheel hub. The front ground drive system includes a front drive wheel mounted to the front wheel hub, a front idler wheel mounted to the front axle housing via a front drive frame member in front of the front drive wheel. The rear ground drive system has a rear drive wheel mounted to the rear wheel hub, a rear idler wheel mounted to the rear axle housing via a rear frame member behind the rear drive wheel.

Owner:VERMEER MFG CO

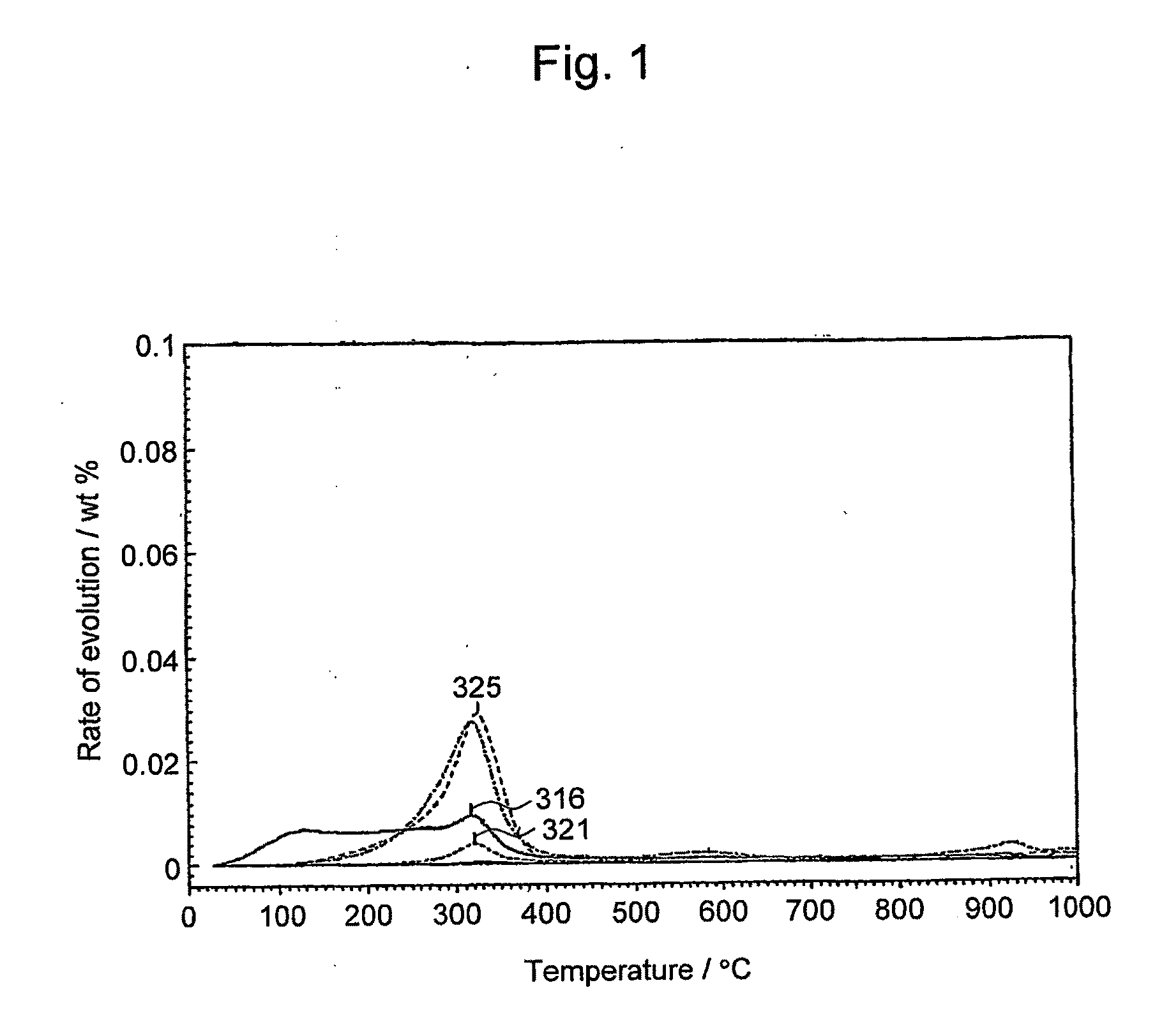

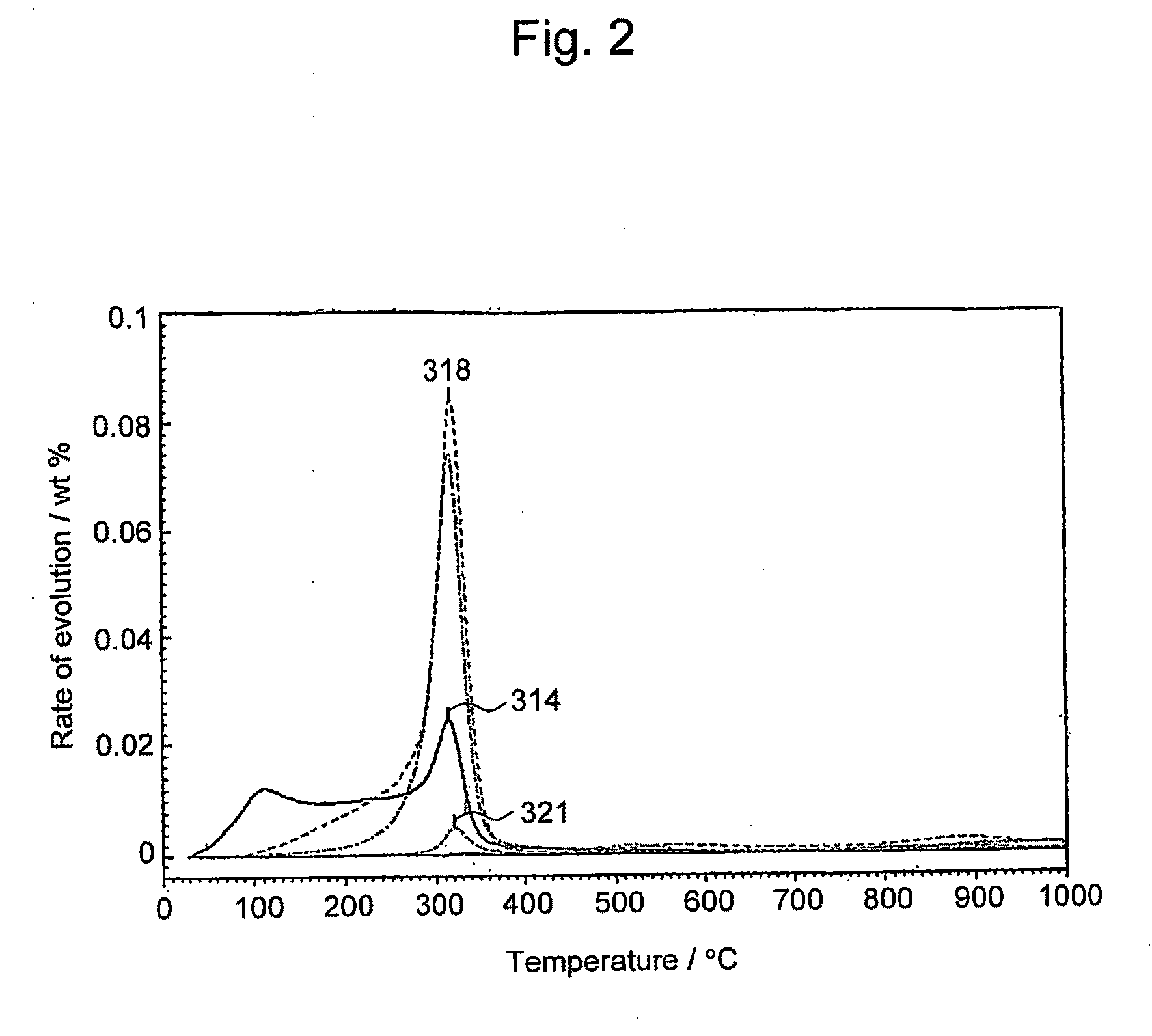

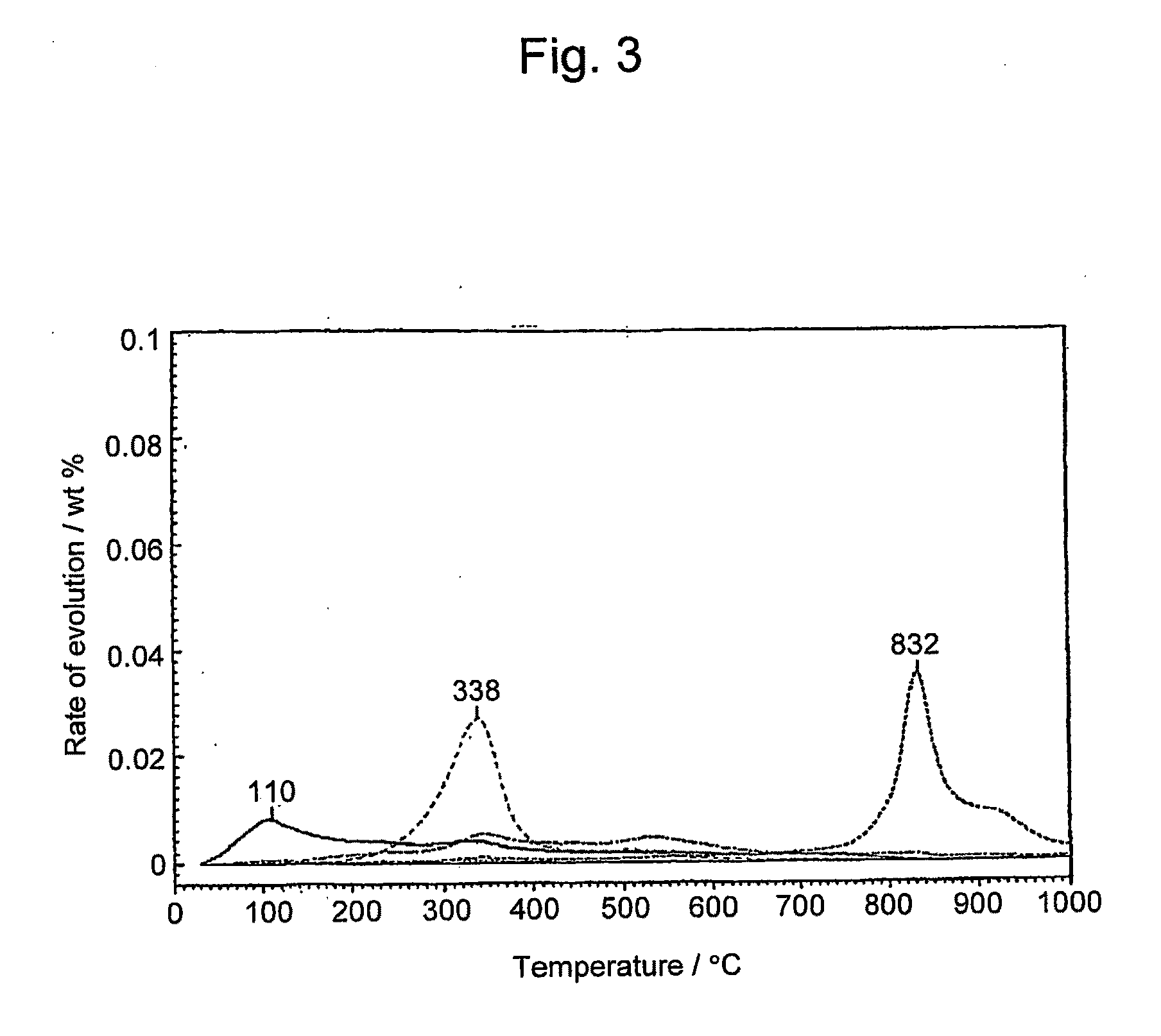

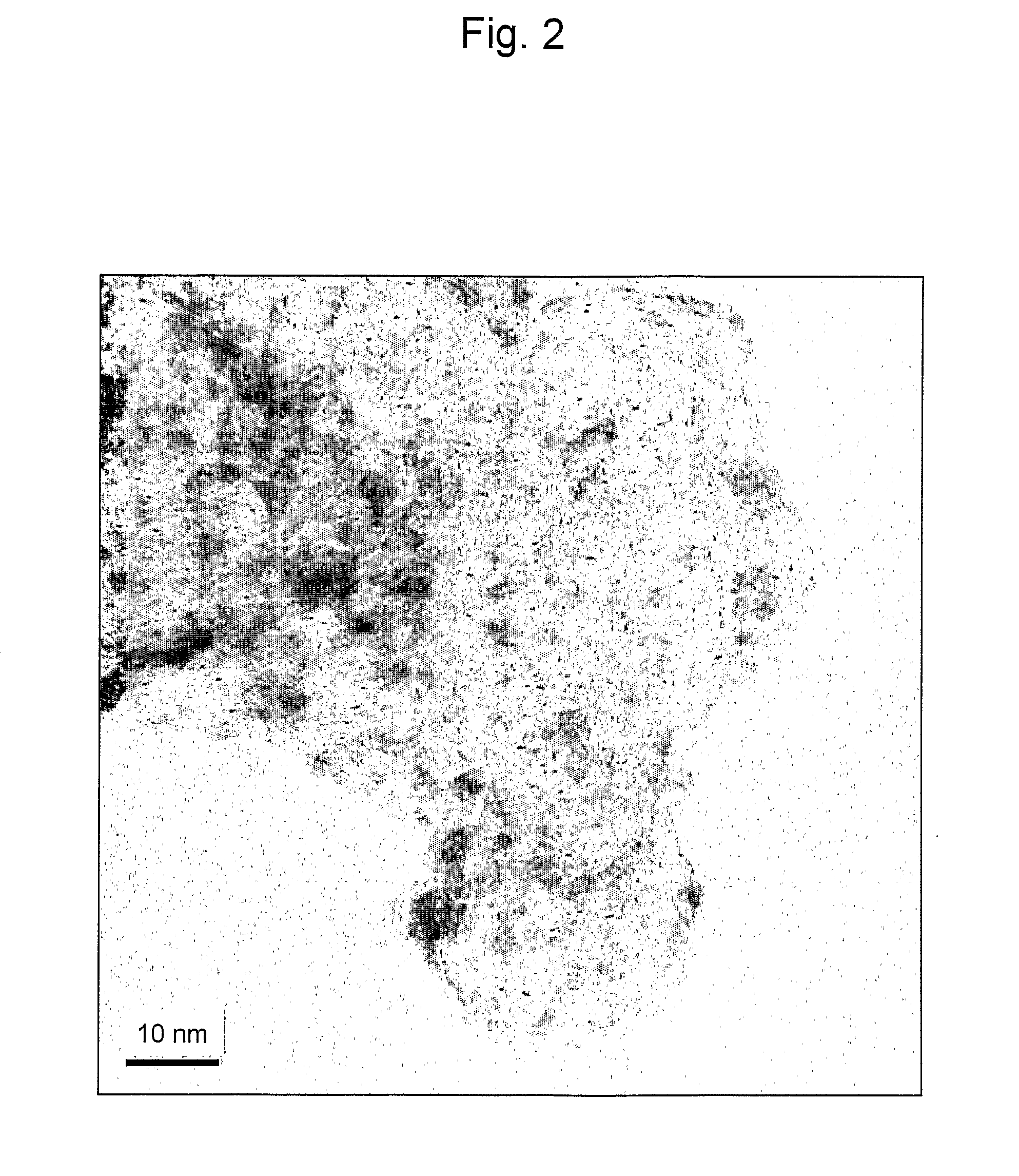

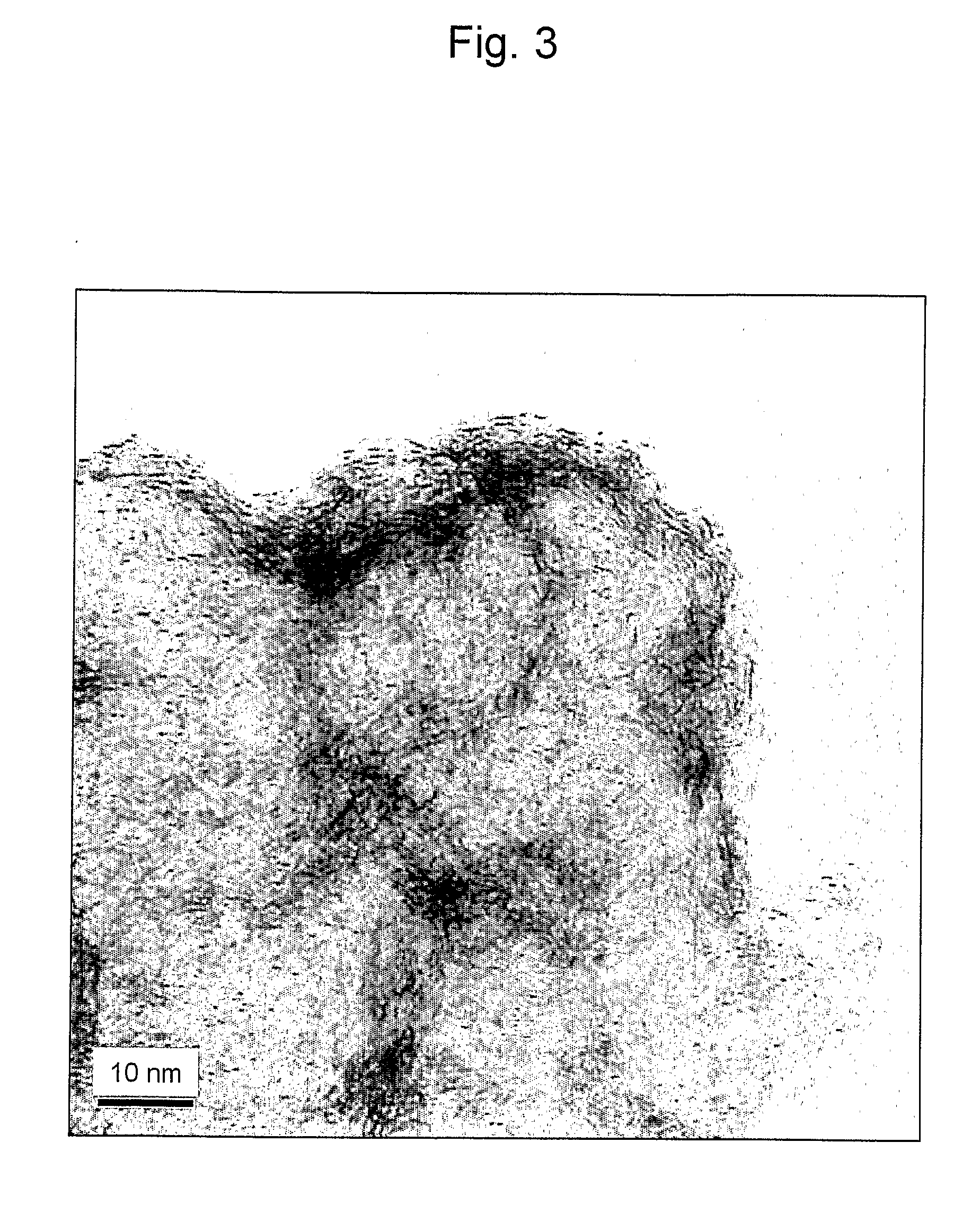

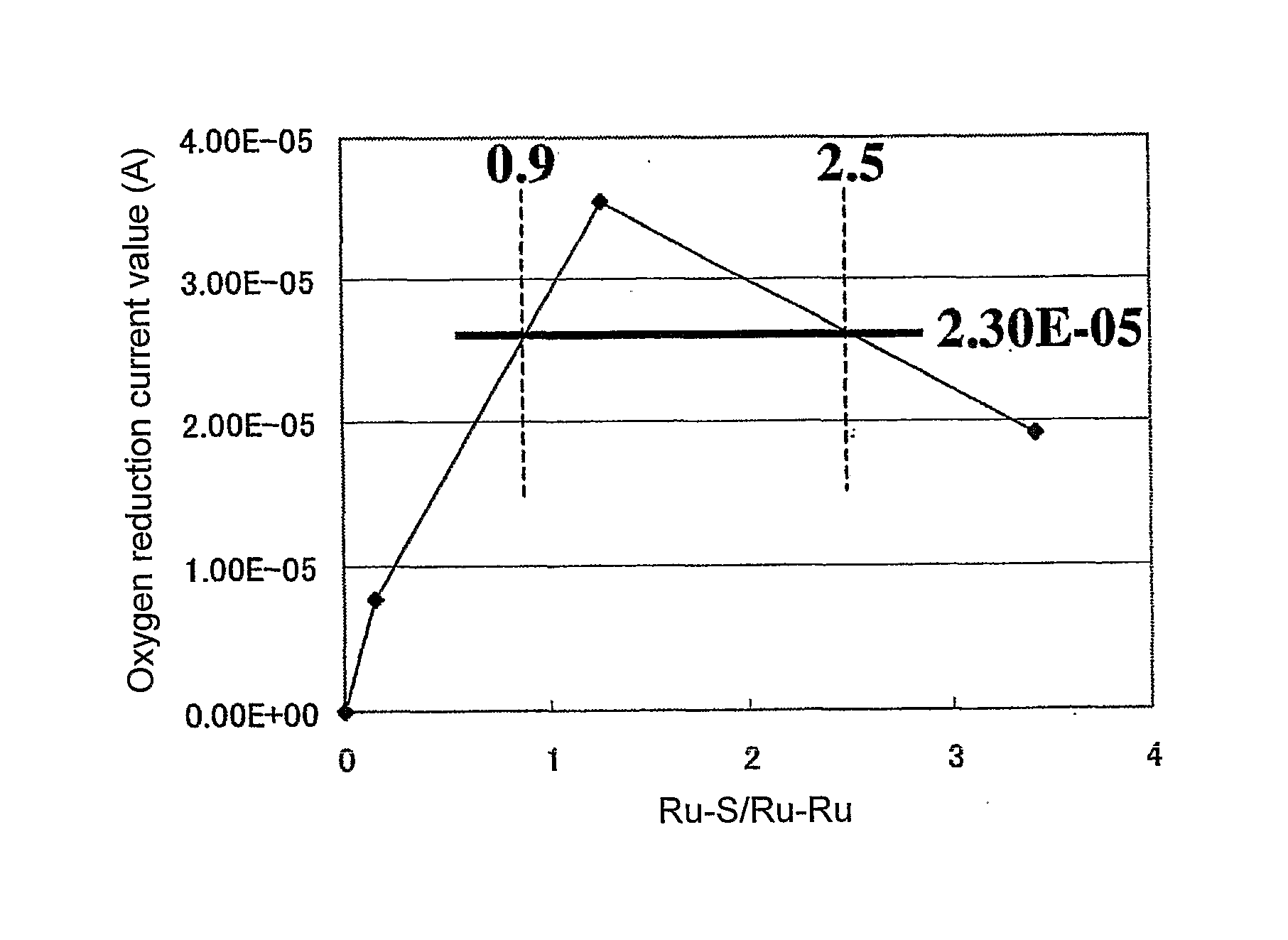

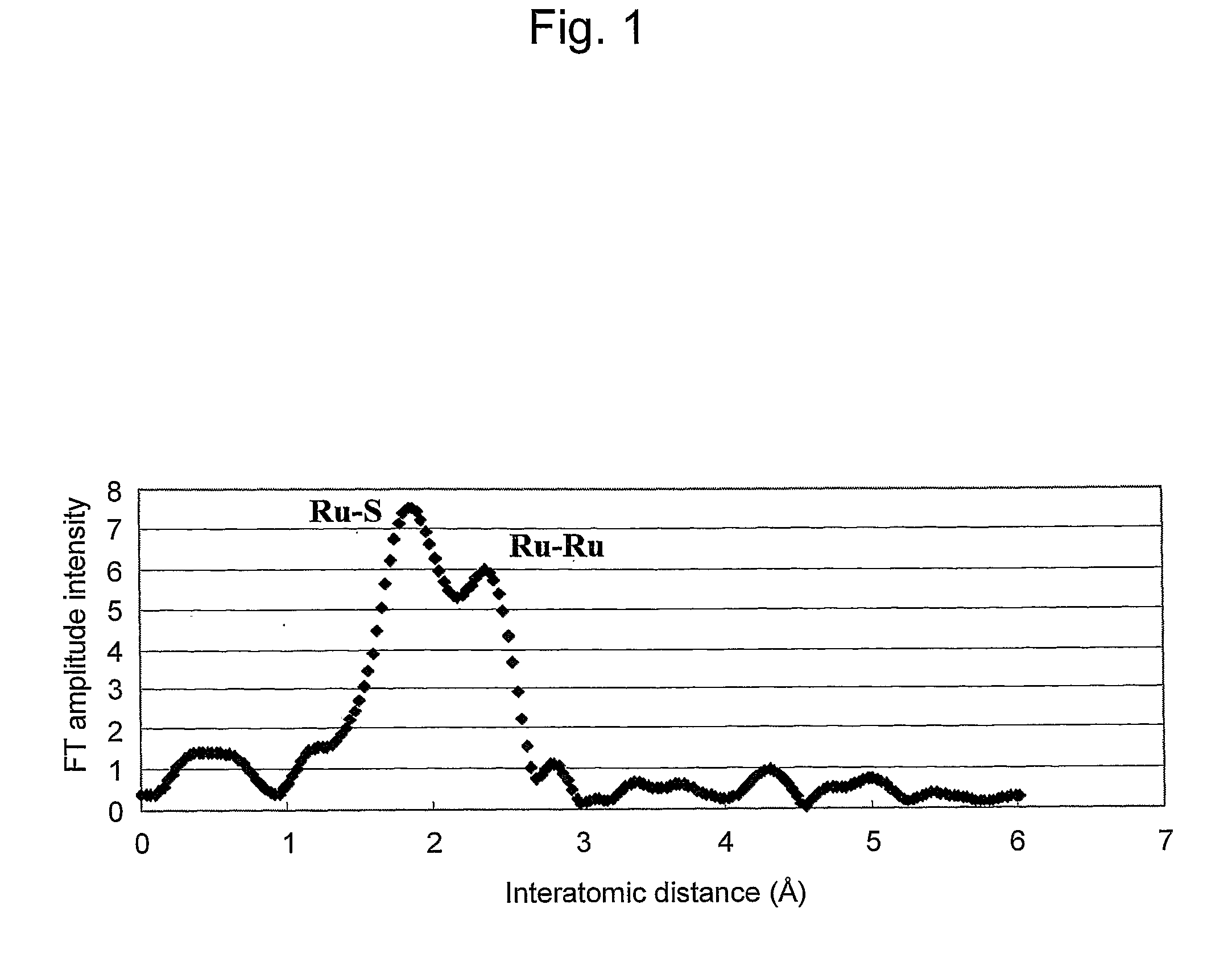

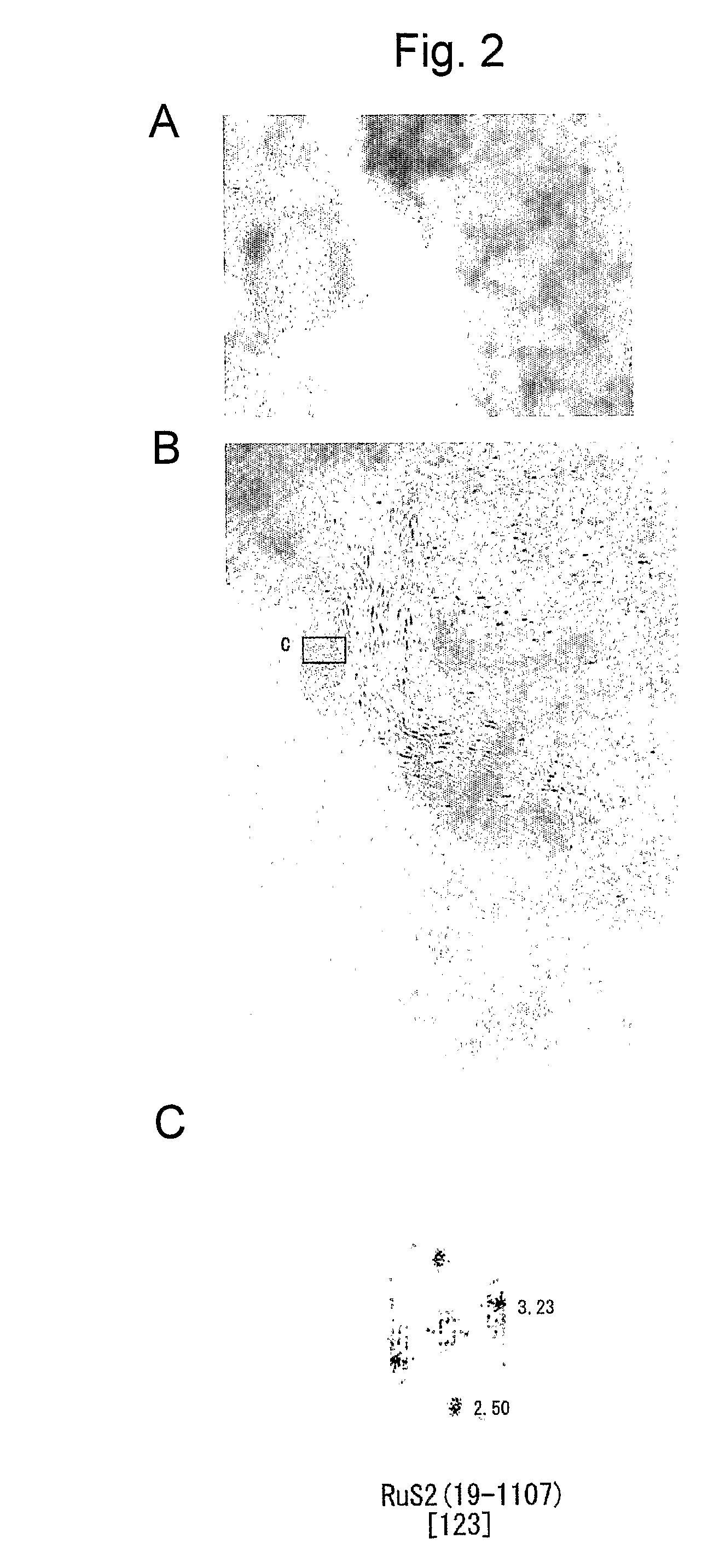

Fuel cell electrode catalyst, method for evaluating performance of oxygen-reducing catalyst, and solid polymer fuel cell comprising the fuel cell electrode catalyst

InactiveUS20110105311A1Improve the level ofHigh activityPhysical/chemical process catalystsCell electrodesFuel cellsSulfur

According to the present invention, a fuel cell electrode catalyst comprising a transition metal element and a chalcogen element and having high activity is provided with an index for performance evaluation that is useful for good catalyst design. Also, a fuel cell electrode catalyst is provided, such catalyst comprising at least one transition metal element and at least one chalcogen element, wherein the value of (transition metal element-chalcogen element coordination number) / (transition metal element-chalcogen element-oxygen coordination number) is 0.27 to 0.71.

Owner:TOYOTA JIDOSHA KK

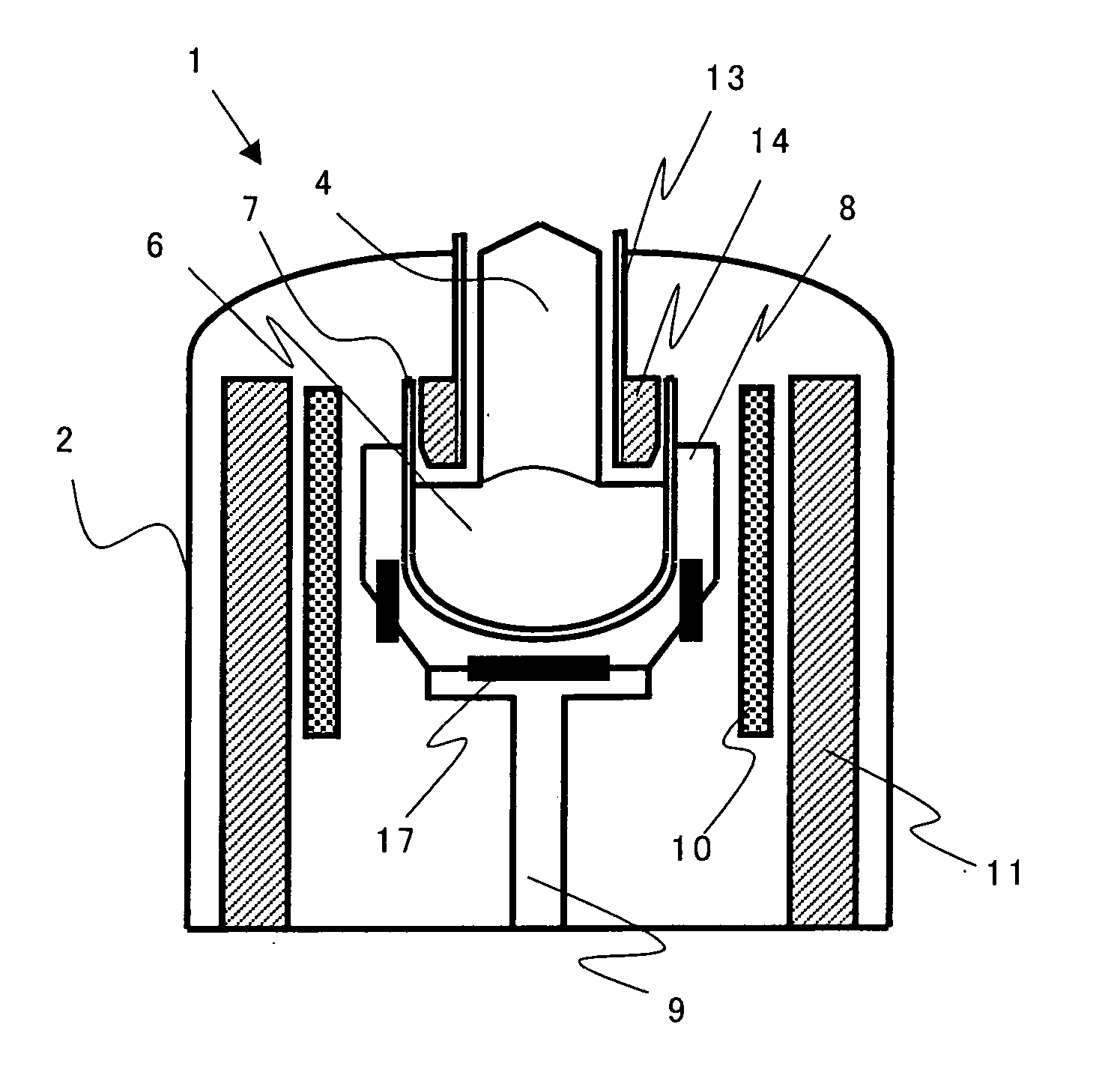

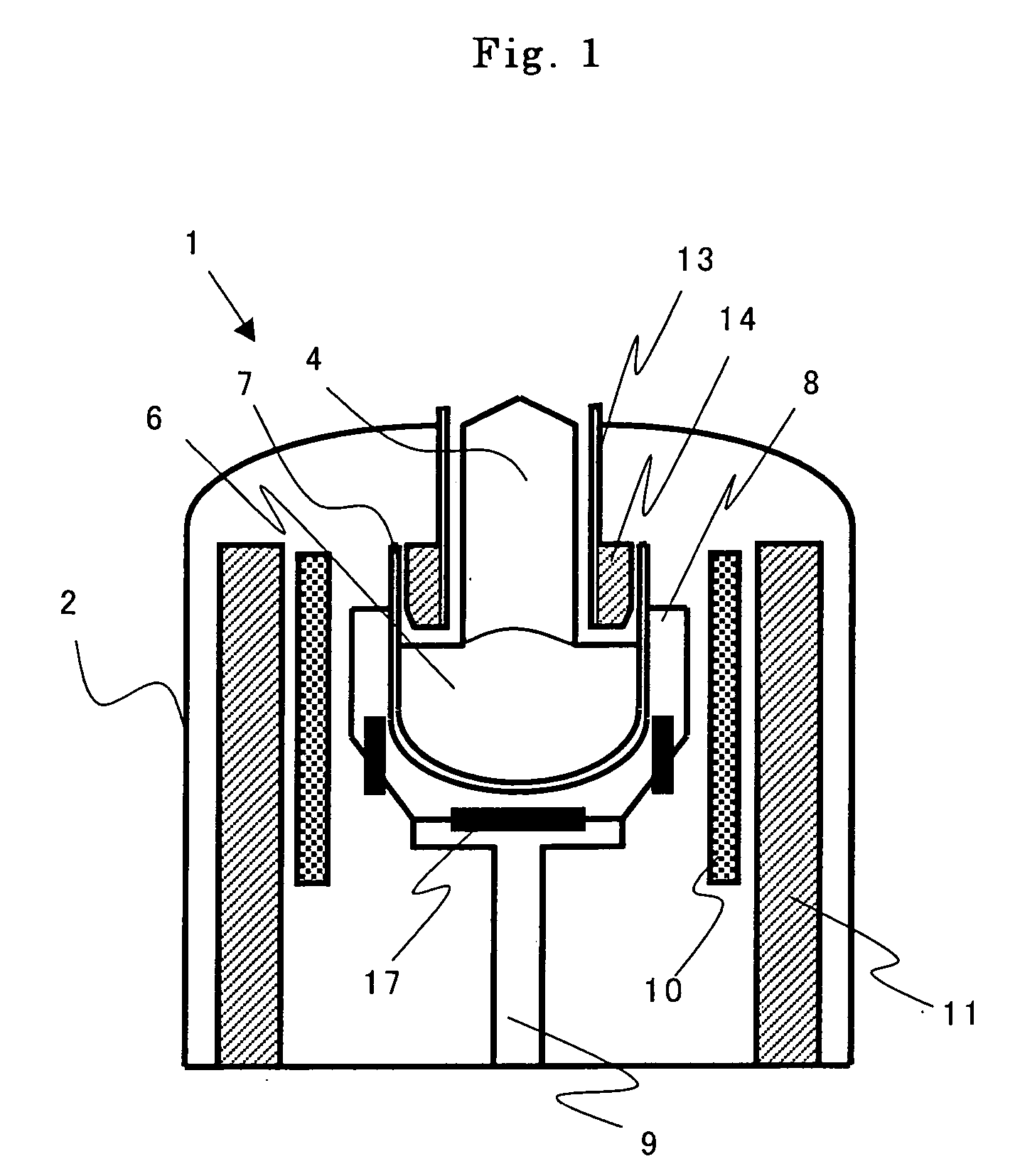

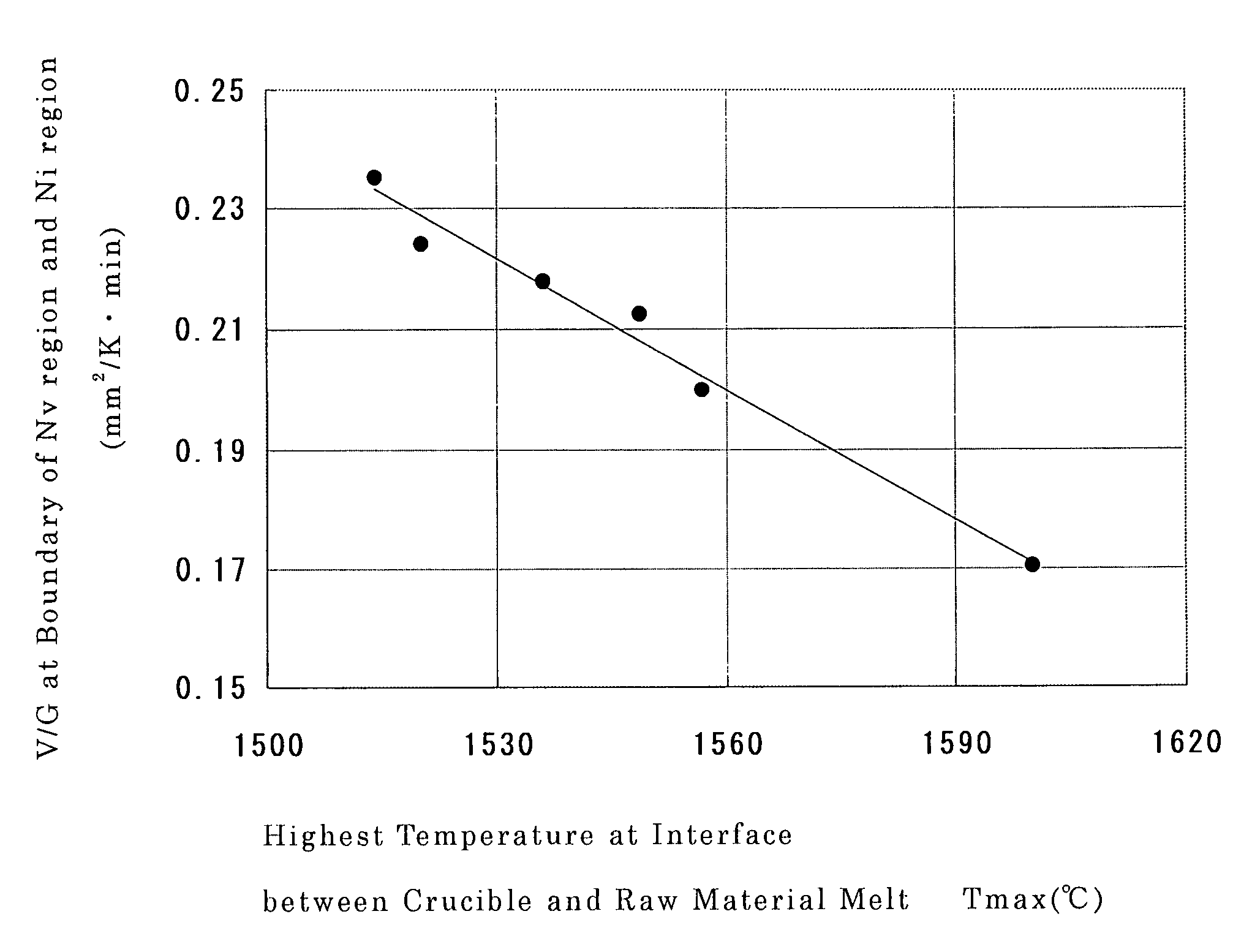

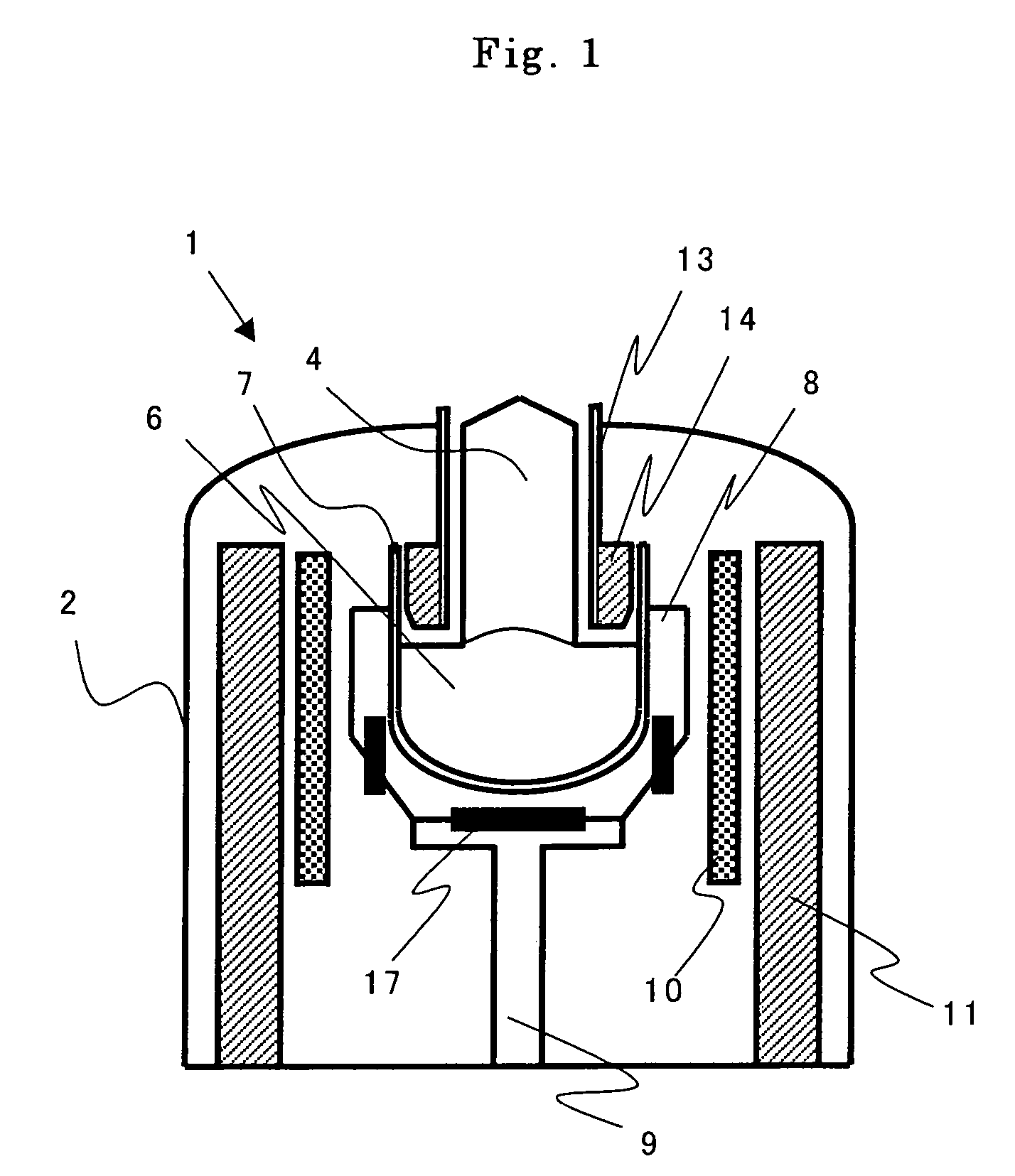

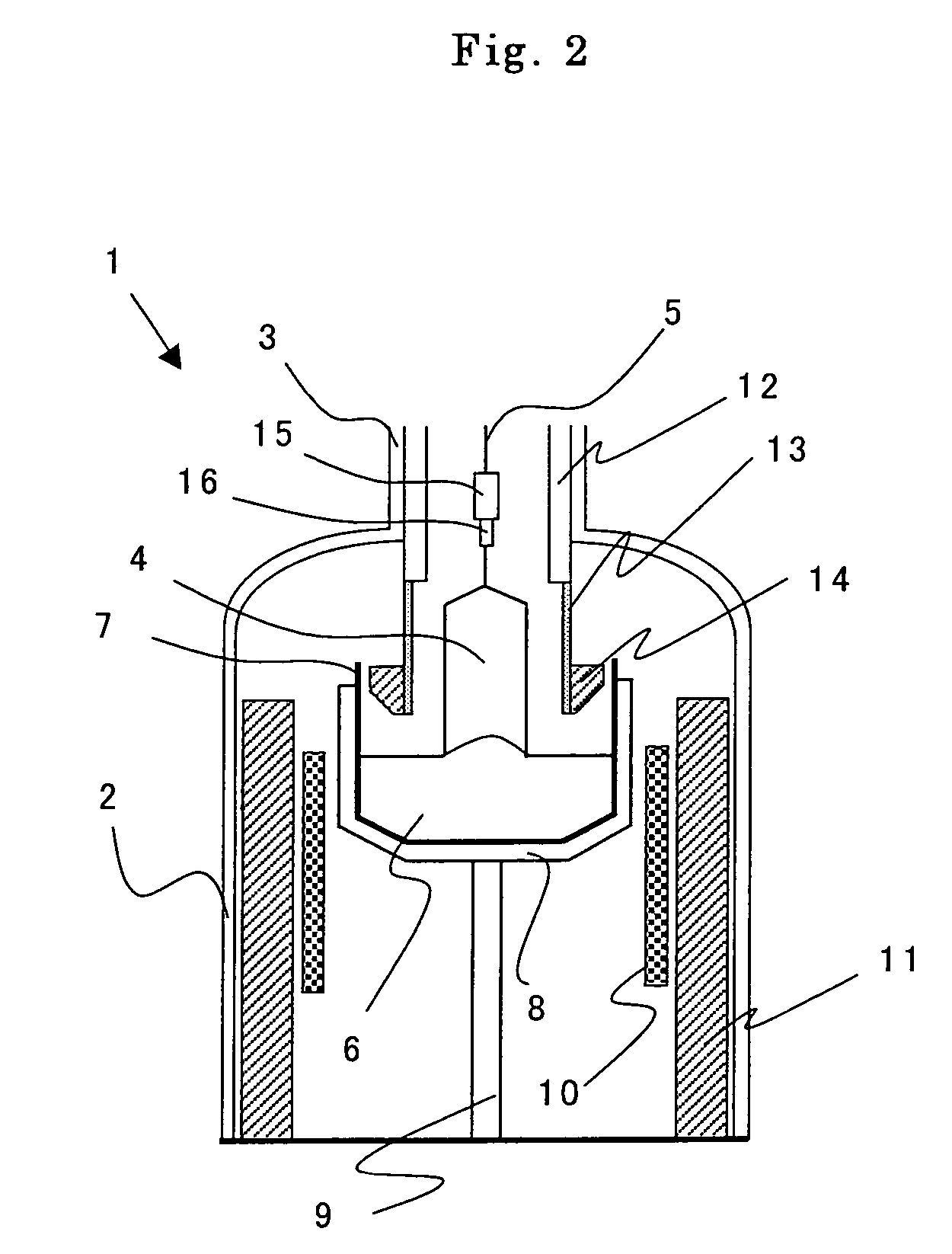

Method for producing single crystal and single crystal

ActiveUS20070000429A1Accurately determineImprove efficiencyPolycrystalline material growthBy zone-melting liquidsCzochralski methodCrucible

The present invention is a method for producing a single crystal by Czochralski method with pulling a seed crystal from a raw material melt, wherein when a pulling rate of pulling a single crystal is defined as V (mm / min), a temperature gradient at a solid-liquid interface is defined as G (K / mm) and a highest temperature at an interface between a crucible and a raw material melt is defined as Tmax (° C.), at least, a range of a value of V / G (mm2 / K·min) including a desired defect region and / or a desired defect-free region is determined according to the Tmax (° C.), and the single crystal is pulled with controlling a value of V / G (mm2 / K·min) within the determined range. There can be provided a method for producing a single crystal in which when a single crystal is pulled with controlling a value of V / G, a value of V / G including a desired defect region and / or a desired defect-free region can be determined more precisely and a single crystal with desired quality can be more surely pulled.

Owner:SHIN-ETSU HANDOTAI CO LTD

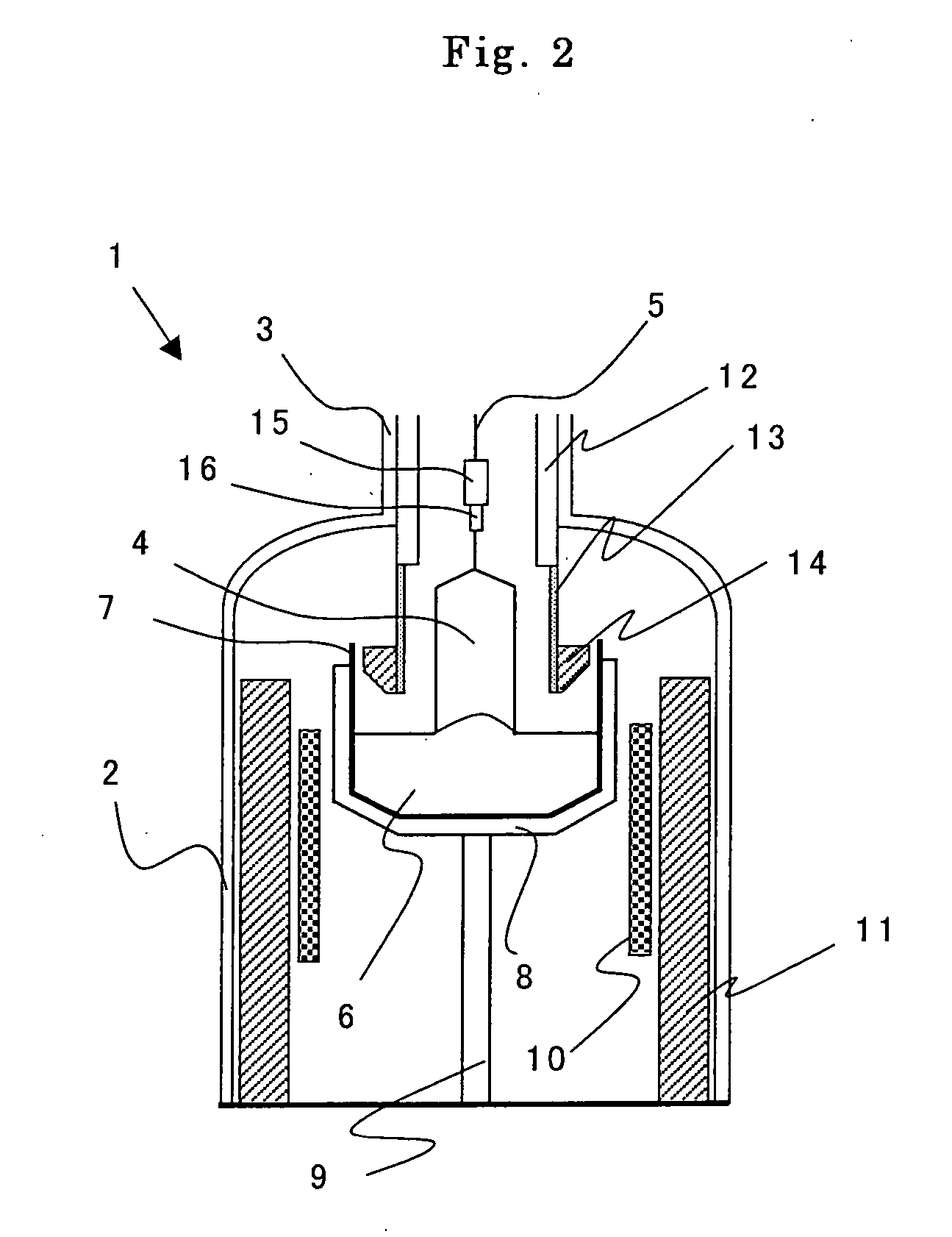

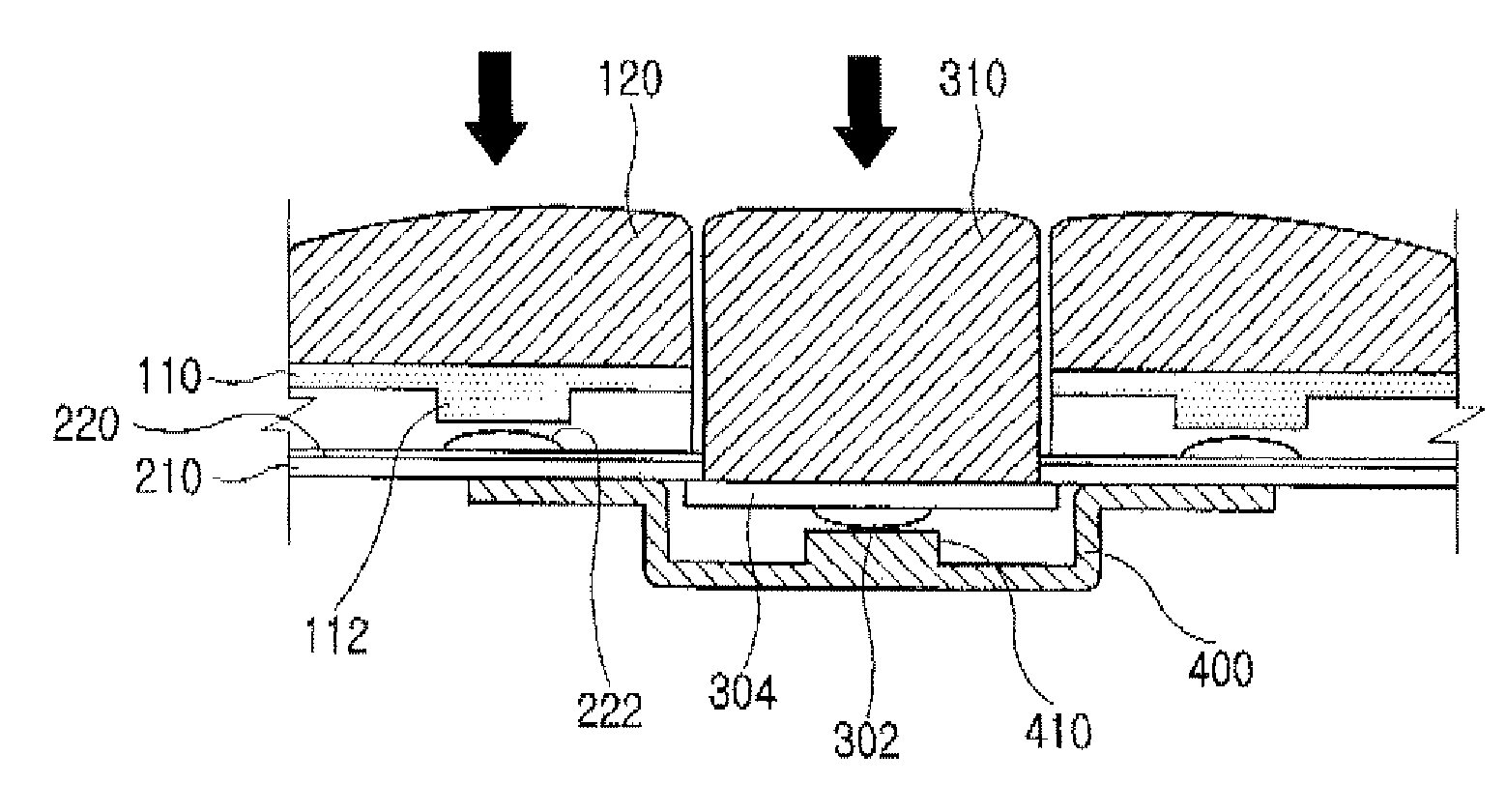

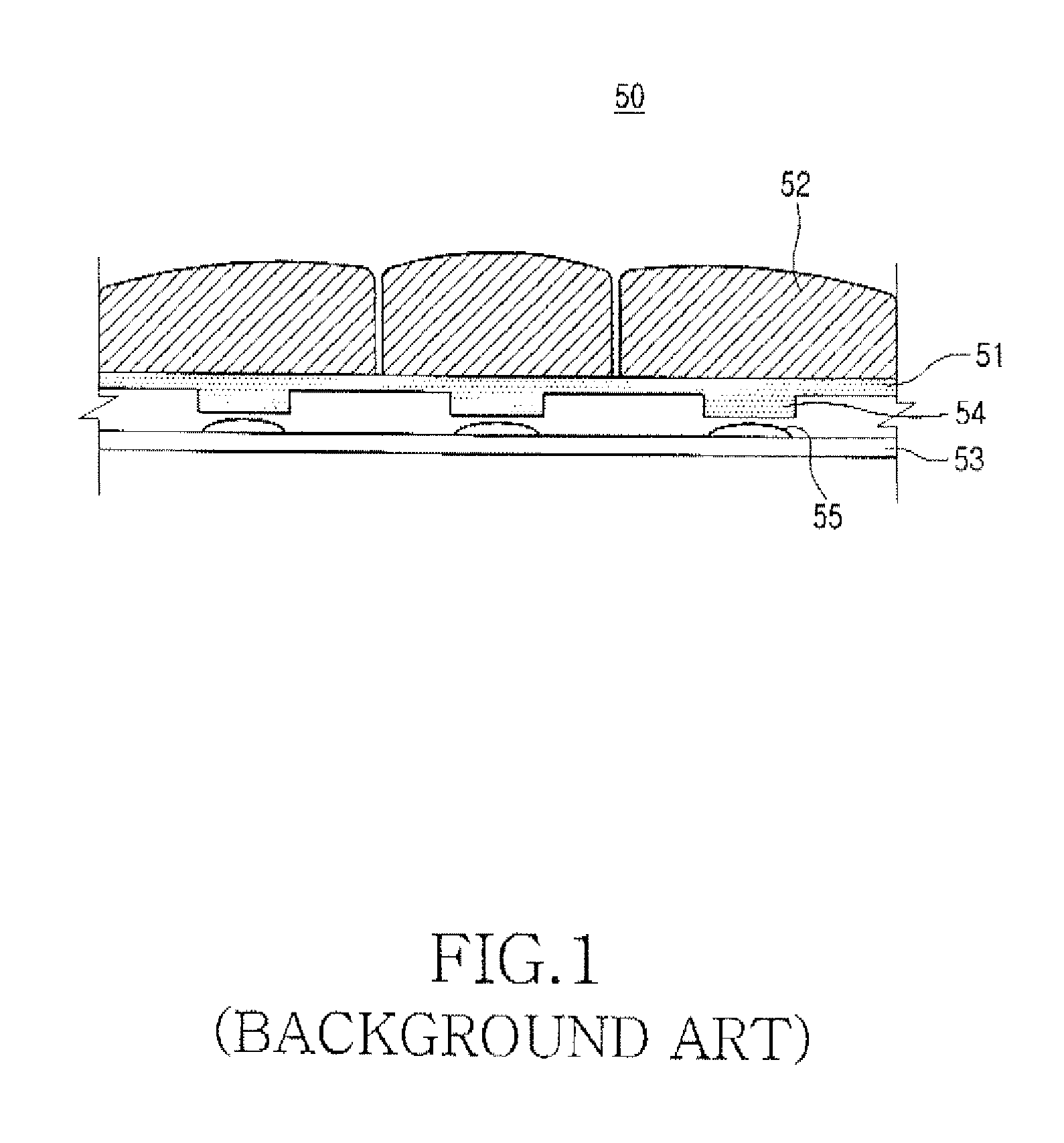

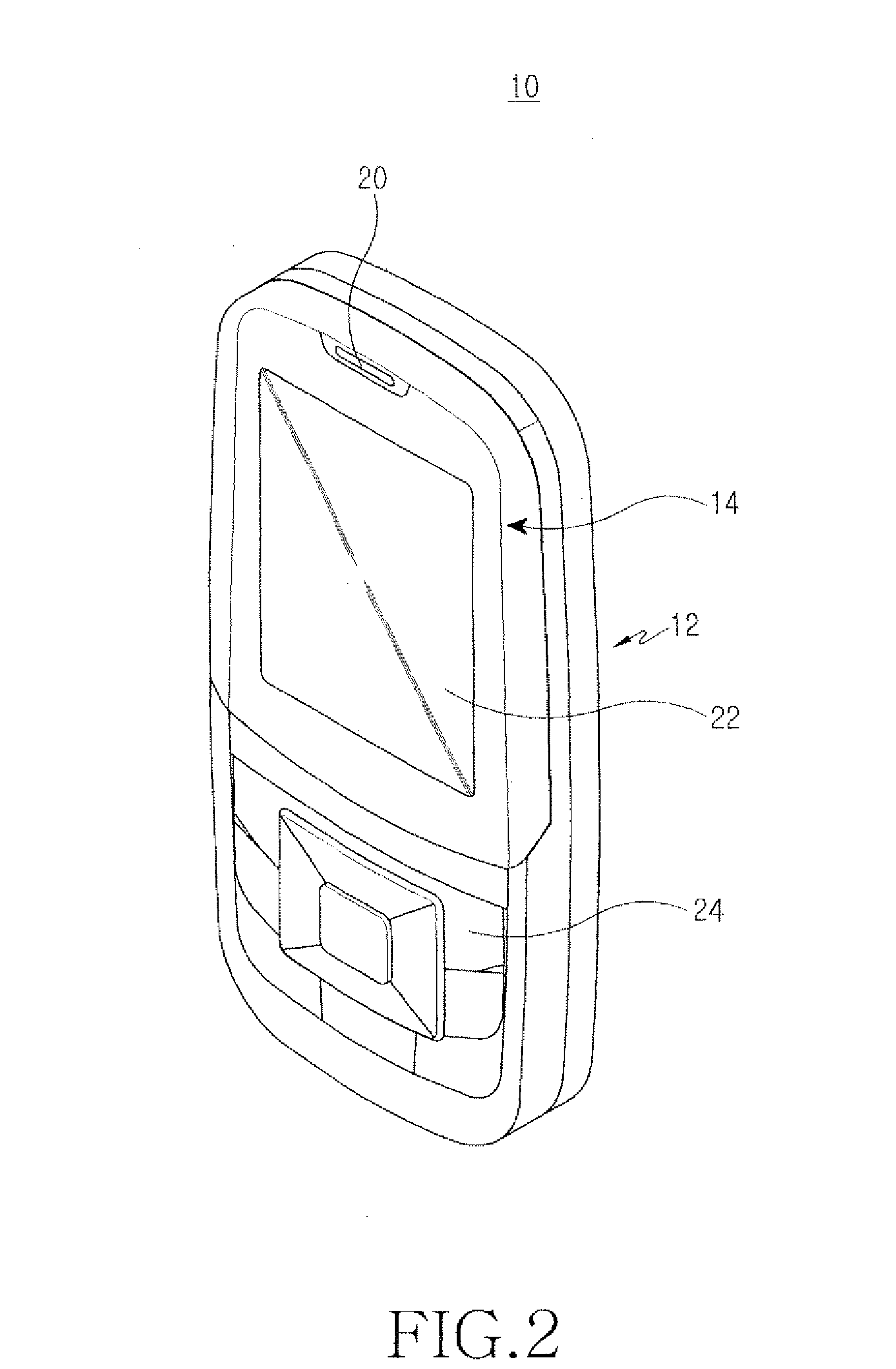

Keypad assembly for portable terminal

InactiveUS7547857B2Shiny appearanceDesigned for such useDigital data processing detailsElectric switchesEngineeringMechanical engineering

Owner:SAMSUNG ELECTRONICS CO LTD

Full wave modeling and simulations of the waveguide behavior of printed circuit boards using a broadband green's function technique

ActiveUS9946825B2Fast convergenceReduce computing costCAD circuit designSpecial data processing applicationsPresent methodFull wave

A broadband Green's function computation technique that employs low wavenumber extraction on a modal summation is used to model the waveguide behavior of electronic components, systems, and interconnects on a printed circuit board. Use of the broadband technique permits discretizing the surface of the printed circuit board across a wide range of frequencies all at once. The broadband Green's function is also extended to via waveguides on circuit boards and power / ground plane waveguides of arbitrary shape. Such a method can analyze a given circuit board geometry over a broad frequency range several hundred times faster than is otherwise possible with existing commercial analysis tools. The present method is useful in electronic design automation for analyzing signal integrity and power integrity, reducing electromagnetic interference and ensuring electromagnetic compatibility.

Owner:TSANG LEUNG W +1

Methods to identify polynucleotide and polypeptide sequences which may be associated with physiological and medical conditions

InactiveUS20050164174A1Reduce resistanceImprove developmentMicrobiological testing/measurementBiological testingNucleotideExon

The present invention provides methods for identifying evolutionarily significant polynucleotide and polypeptide sequences in human and / or non-human primates which may be associated with a physiological condition, such as enhanced resistance to HCV infection. The invention also provides methods for identifying evolutionarily significant polynucleotides with mutations that are correlated with susceptibility to diseases, such as BRCA1 exon 11. The methods employ comparison of human and non-human primate sequences using statistical methods. Sequences thus identified may be useful as host therapeutic targets and / or in screening assays.

Owner:EVOLUTIONARY GENOMICS LLC

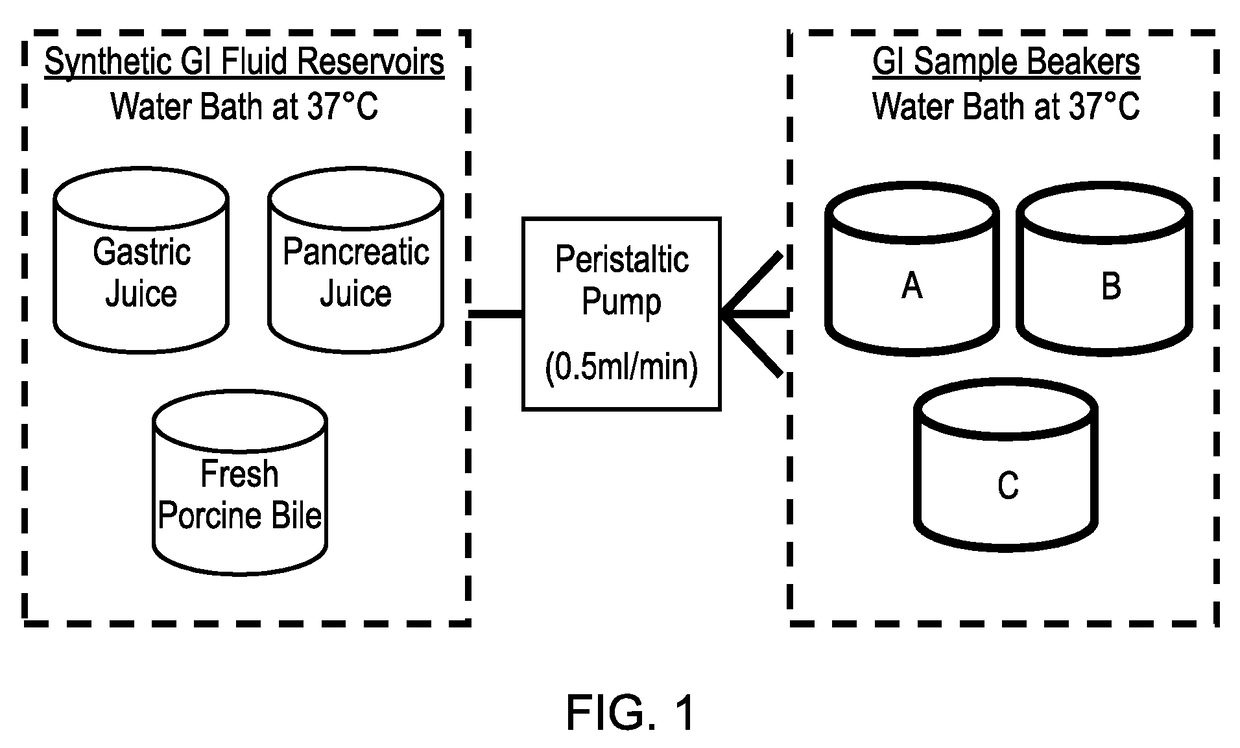

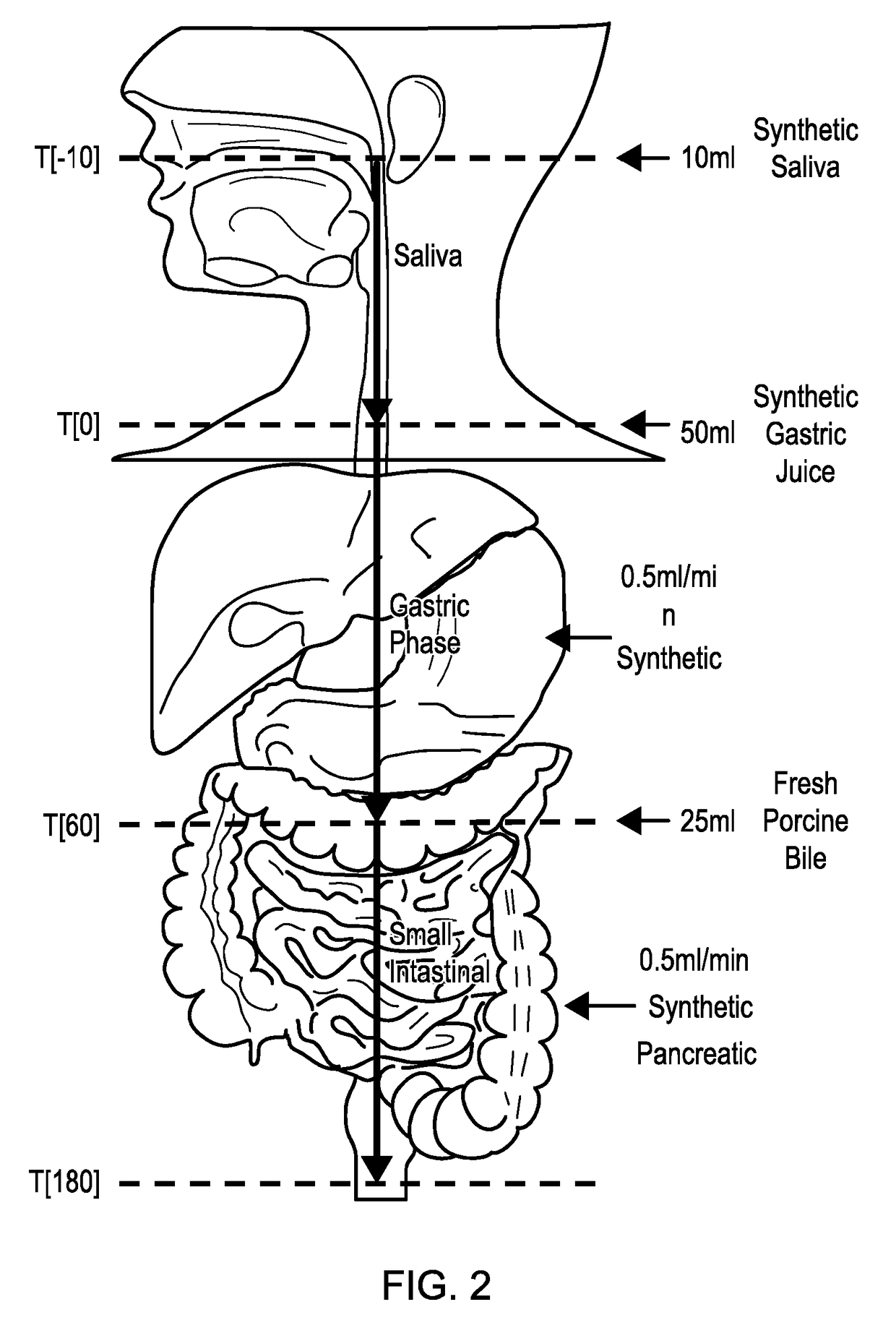

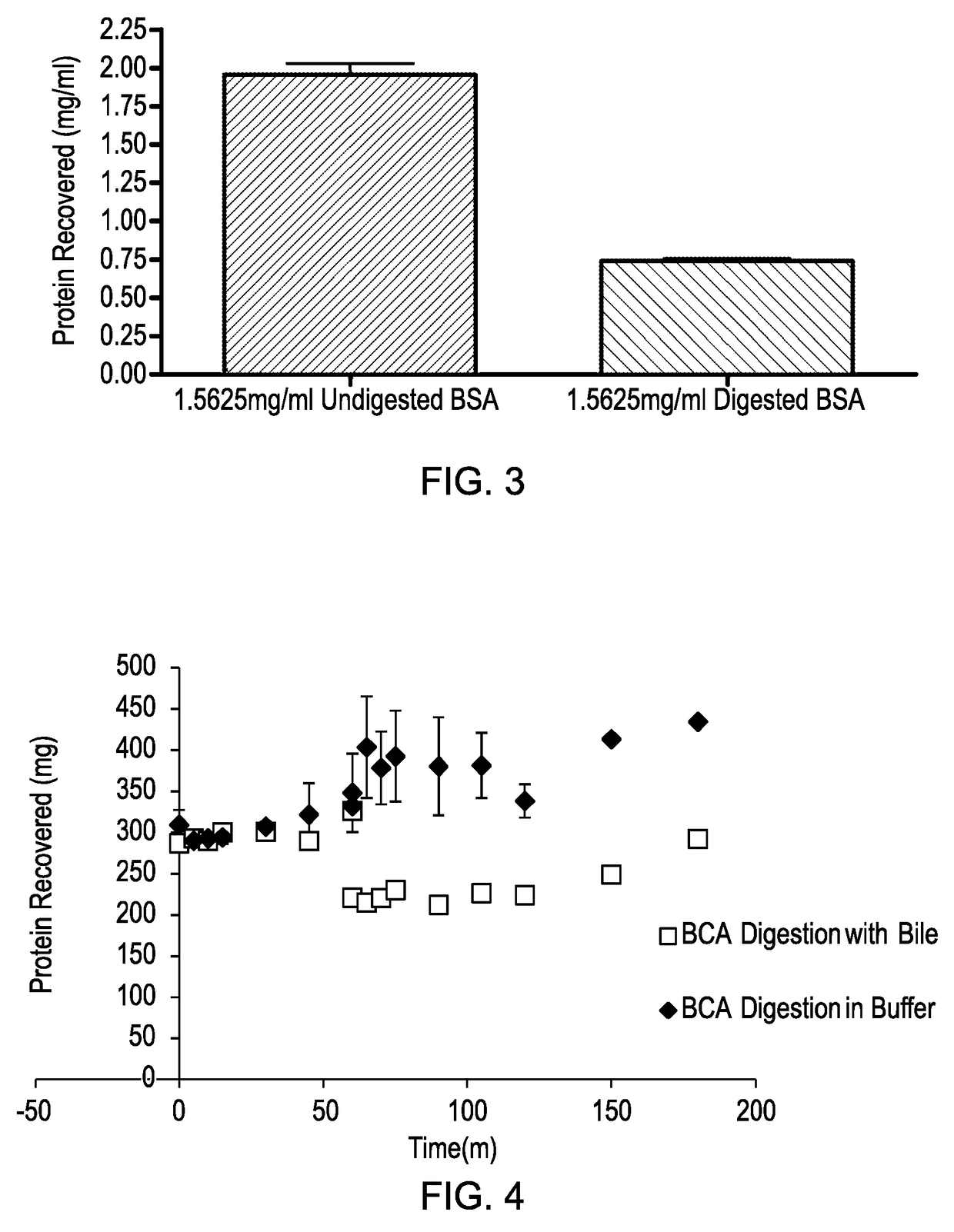

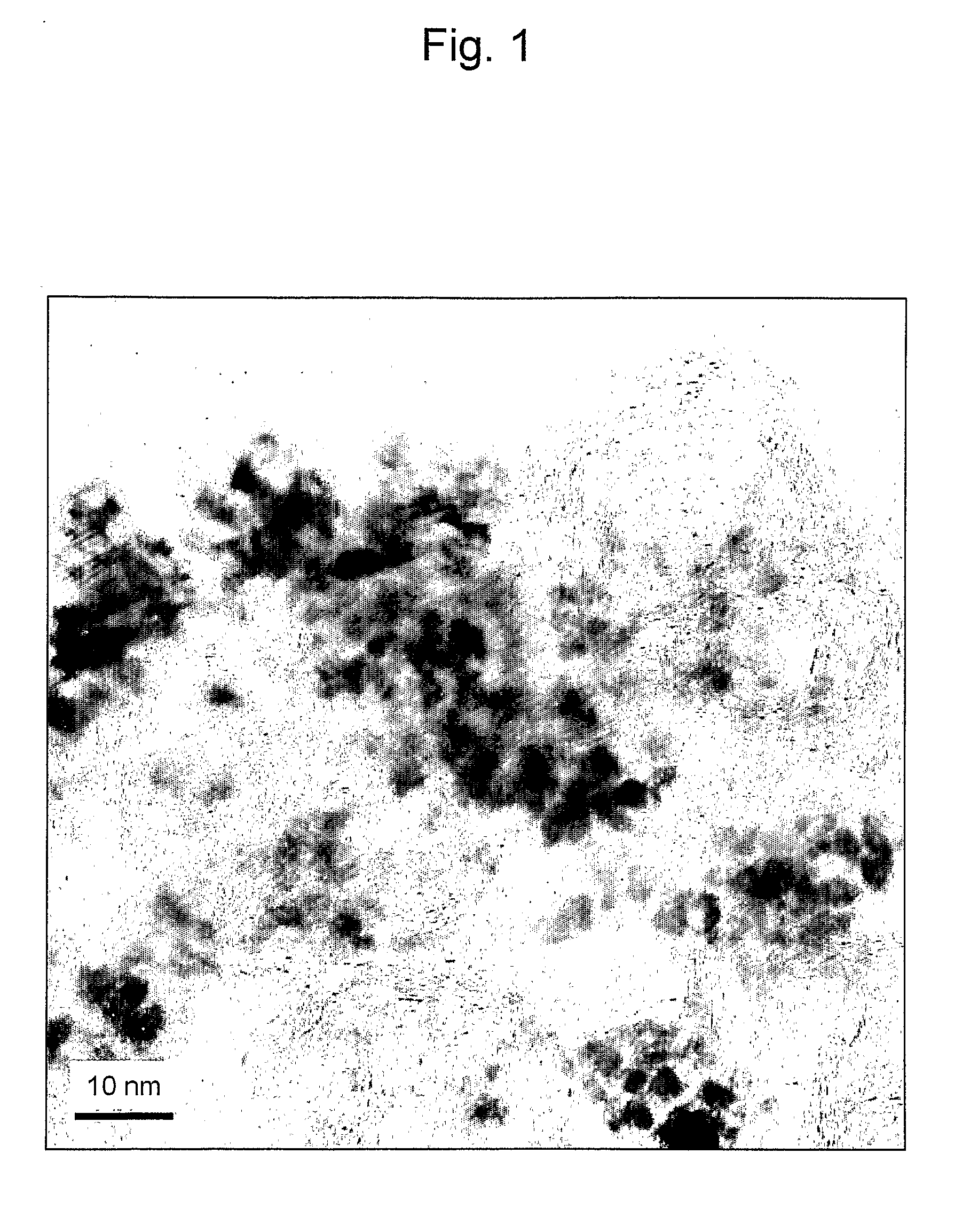

Model gut system

ActiveUS20170160283A1Cost prohibitiveSmall scaleCosmonautic condition simulationsMicrobiological testing/measurementPancreatic juiceDiluent

The invention relates to a Model Gut System (MGS) comprising a pancreatic phase consisting essentially of synthetic pancreatic juice comprising pancreatin and one or more suitable pancreatic diluent(s) at a pH from about 7 to about 9, preferably about 7.9 to about 8.2, and porcine bile.

Owner:NEWCASTLE UNIV

Fuel cell electrode catalyst, method for evaluating performance of oxygen-reducing catalyst, and solid polymer fuel cell comprising the fuel cell electrode catalyst

InactiveUS20110111322A1Improve the level ofHigh activityActive material electrodesSolid electrolyte fuel cellsFuel cellsSulfur

According to the present invention, a fuel cell electrode catalyst comprising a transition metal element and a chalcogen element and having high activity is provided with an index for performance evaluation that is useful for good catalyst design. Also, a fuel cell electrode catalyst is provided, such catalyst comprising at least one transition metal element and at least one chalcogen element which are supported by a conductive carrier, wherein the value of (average electrode catalyst particle size (nm)) / (electrode catalyst particle size distribution (%)) is 0.013 to 0.075.

Owner:TOYOTA JIDOSHA KK

Method for producing a single crystal

ActiveUS7582159B2Accurately determineImprove efficiencyPolycrystalline material growthBy zone-melting liquidsCzochralski methodCrucible

A method for producing a single crystal by Czochralski method with pulling a seed crystal from a raw material melt, wherein in which a range of a pulling rate of pulling a single crystal, a temperature gradient at a solid-liquid interface and a highest temperature at an interface between a crucible and a raw material melt are defined. The single crystal is pulled with controlling the pulling rate and / or the temperature gradient at a solid-liquid interface within the determined range. The method produces a single crystal in which a desired defect region and / or a desired defect-free region can be determined more precisely and a single crystal with desired quality can be more surely pulled.

Owner:SHIN-ETSU HANDOTAI CO LTD

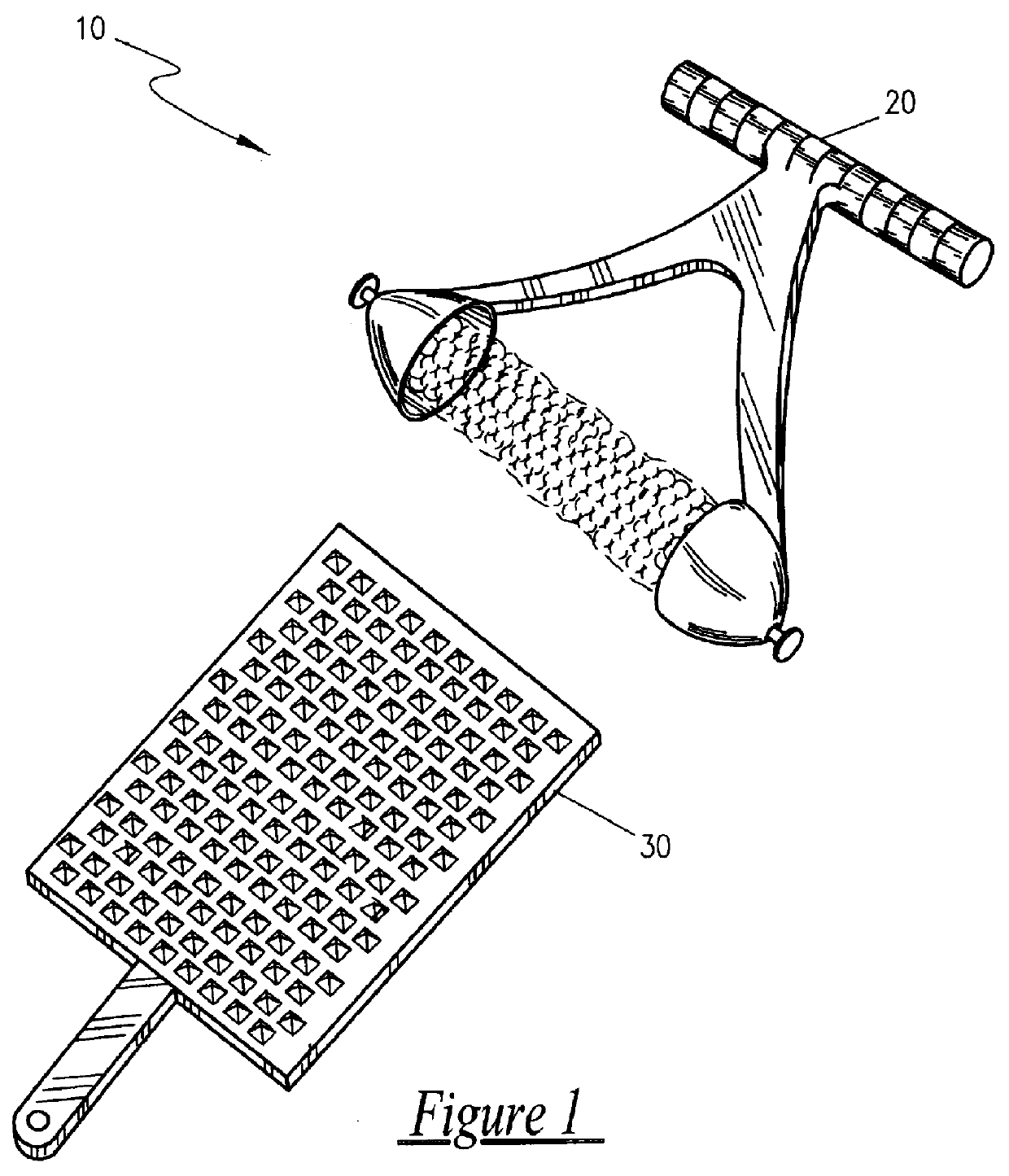

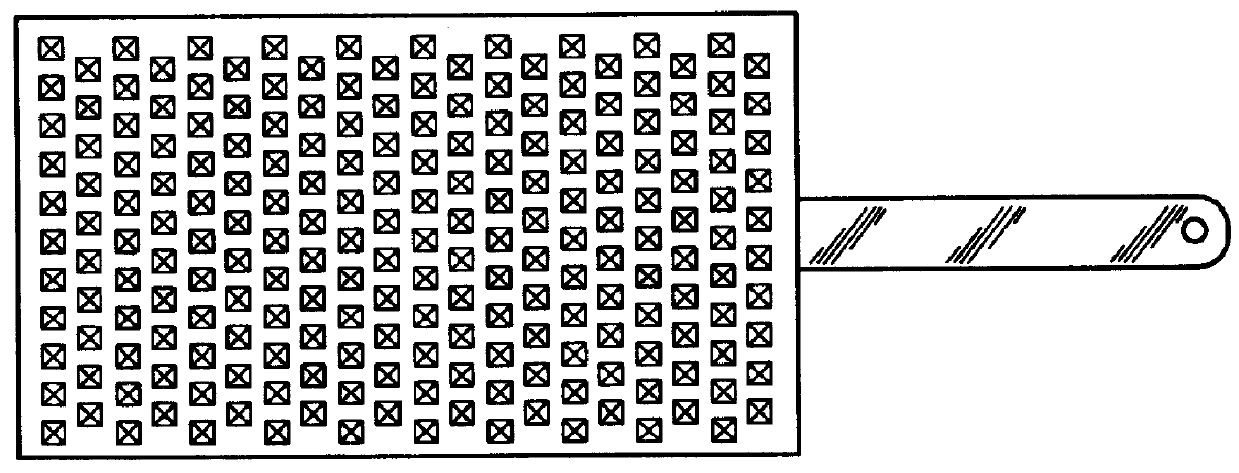

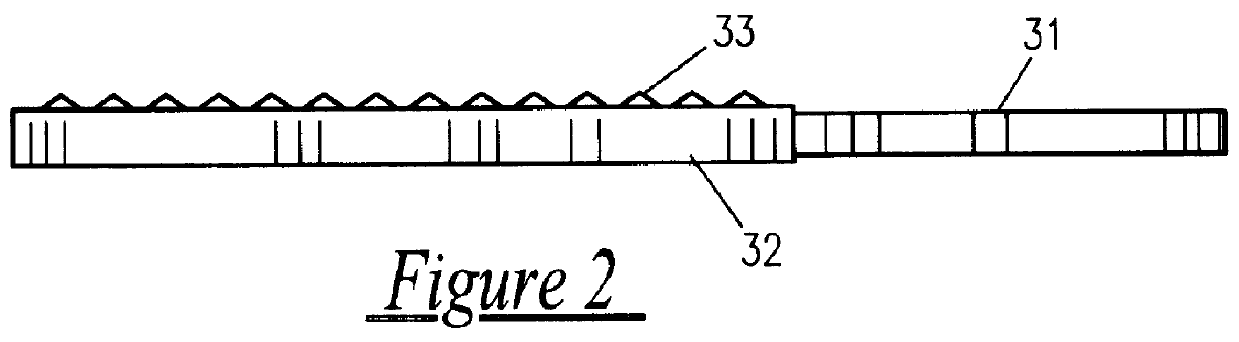

Kernel buster

The present invention is a device to hold an ear of corn while either eating the corn or scraping the kernels off the ear. One inserts the ear of corn between the tensioned corn cob holders-which are a pair of plastic cups. Then, one grasps the handle and rolls the corn cob across the points of the piercing element, the corn cob turns easily in the cups.

Owner:YOUNG MARGERY L

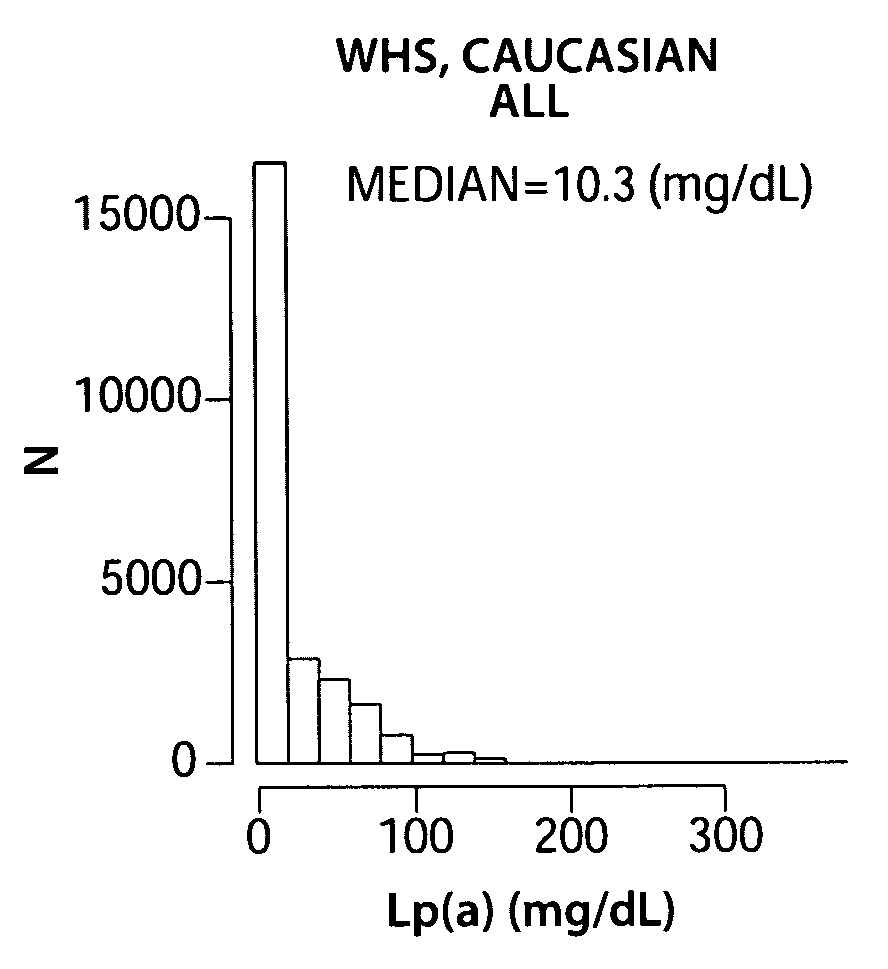

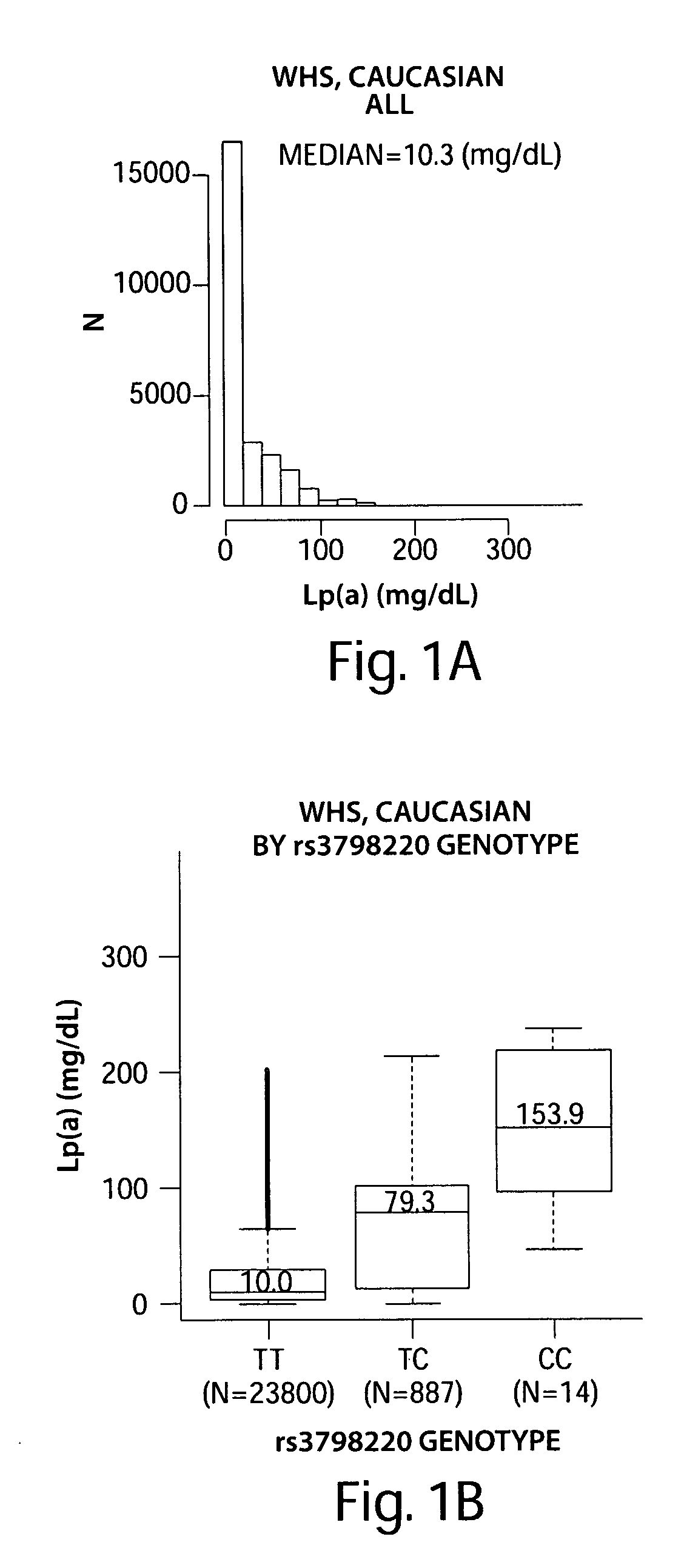

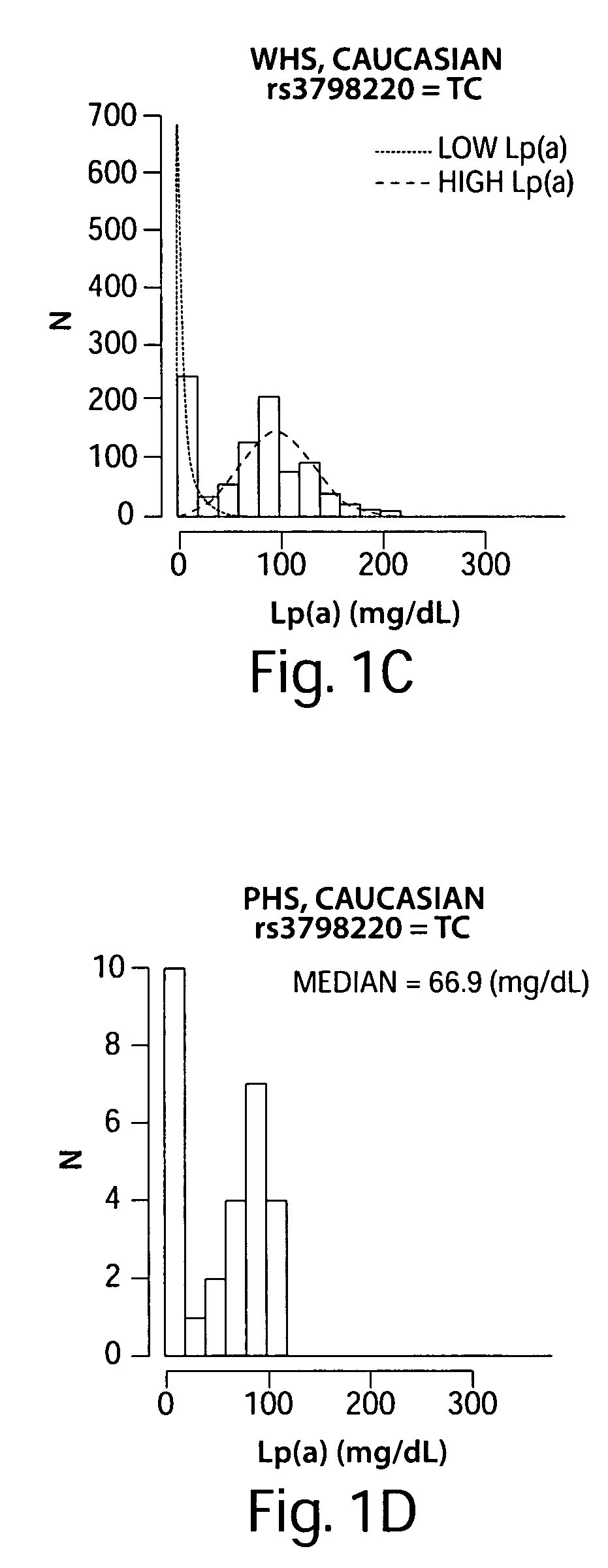

Polymorphism in the apo(a) gene predict responsiveness to acetylsalicylic acid treatment (ridker)

ActiveUS20090004187A1Reduce riskReduce cardiovascular riskBiocideCompound screeningNucleotideBioinformatics

This invention relates to nucleotide polymorphisms in the human Apo(a) gene and to the use of Apo(a) nucleotide polymorphisms in identifying whether a human subject will respond or not to treatment with acetylsalicylic acid.

Owner:APPL BIOSYSTEMS INC +1

Tractor with track drive

ActiveUS10150523B2Easy to convertEfficient preparationSteps arrangementTractor-trailer combinationsDrive wheelEngineering

An off-highway vehicle has a front chassis portion, a rear chassis portion, a front ground drive system and a rear ground drive system. The front chassis portion has a front axle assembly having a front axle housing and a front axle shaft carrying a front wheel hub. The rear chassis portion has a rear axle assembly including a rear axle housing and a rear axle shaft carrying a rear wheel hub. The front ground drive system includes a front drive wheel mounted to the front wheel hub, a front idler wheel mounted to the front axle housing via a front drive frame member in front of the front drive wheel. The rear ground drive system has a rear drive wheel mounted to the rear wheel hub, a rear idler wheel mounted to the rear axle housing via a rear frame member behind the rear drive wheel.

Owner:VERMEER MFG CO

Synthetic surfaces with robust and tunable underwater superoleophobicity

ActiveUS10487217B2Improve structural strengthPromote degradationAntifouling/underwater paintsPaints with biocidesAquatic environmentMaterials science

Owner:WISCONSIN ALUMNI RES FOUND

Fuel cell electrode catalyst, method for evaluating performance of oxygen-reducing catalyst, and solid polymer fuel cell comprising the fuel cell electrode catalyst

InactiveUS20100203420A1Improve the level ofHigh activityPhysical/chemical process catalystsCell electrodesFuel cellsSulfur

According to the present invention, a fuel cell electrode catalyst comprising a transition metal element and a chalcogen element and having high activity is provided with an index for performance evaluation that is useful for good catalyst design. Also, a fuel cell electrode catalyst is provided, such catalyst comprising at least one transition metal element and at least one chalcogen element, wherein the value of (transition metal element−chalcogen element coordination number) / (transition metal element−transition metal element coordination number) is 0.9 to 2.5.

Owner:TOYOTA JIDOSHA KK