Patents

Literature

104 results about "Crt monitor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A cathode ray tube (CRT) monitor is an analog computer display or television set with a large, deep casing. This type of monitor uses streams of electrons that activate dots or pixels on the screen to create a full image. In contrast to this, liquid crystal display (LCD) monitors and plasma television sets,...

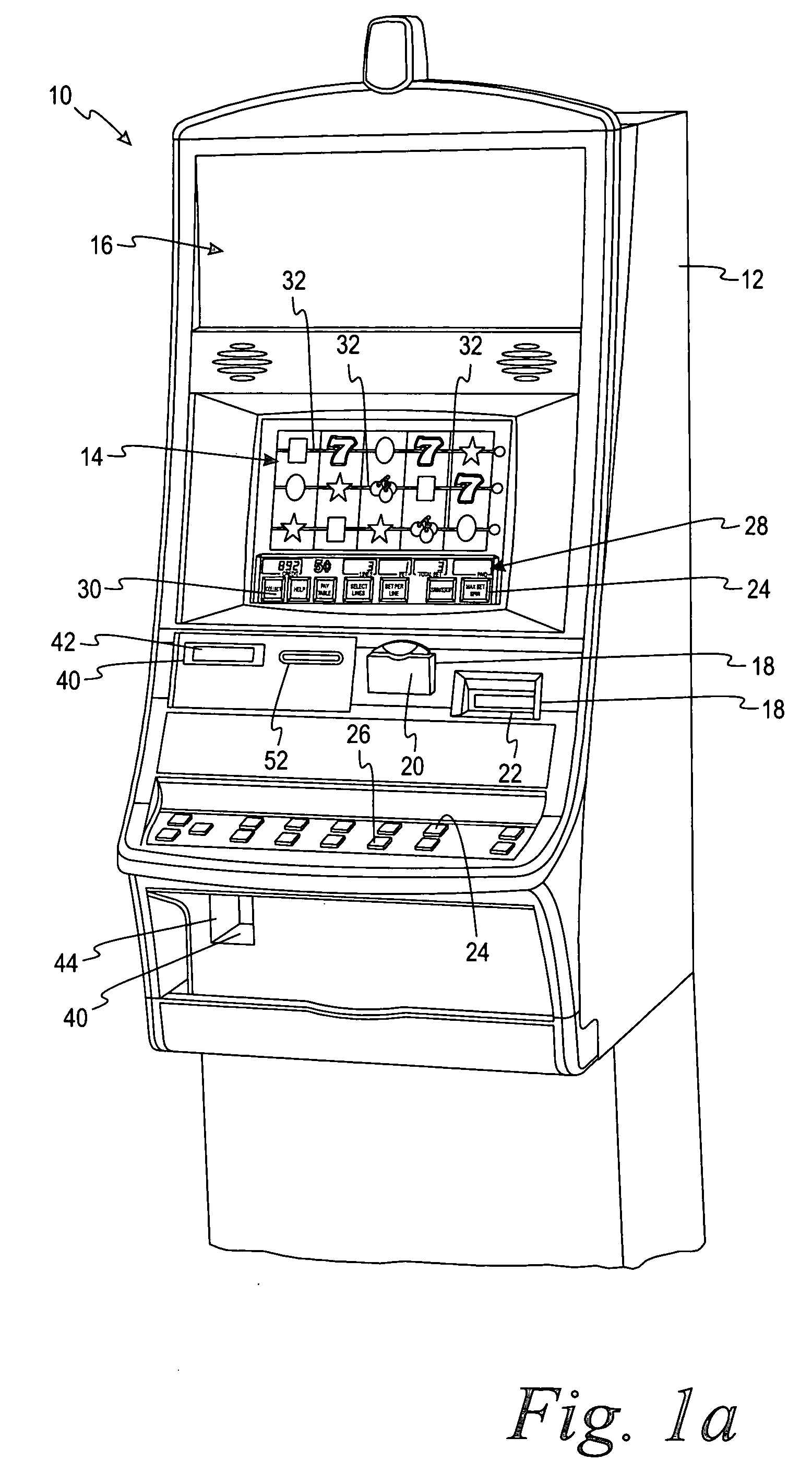

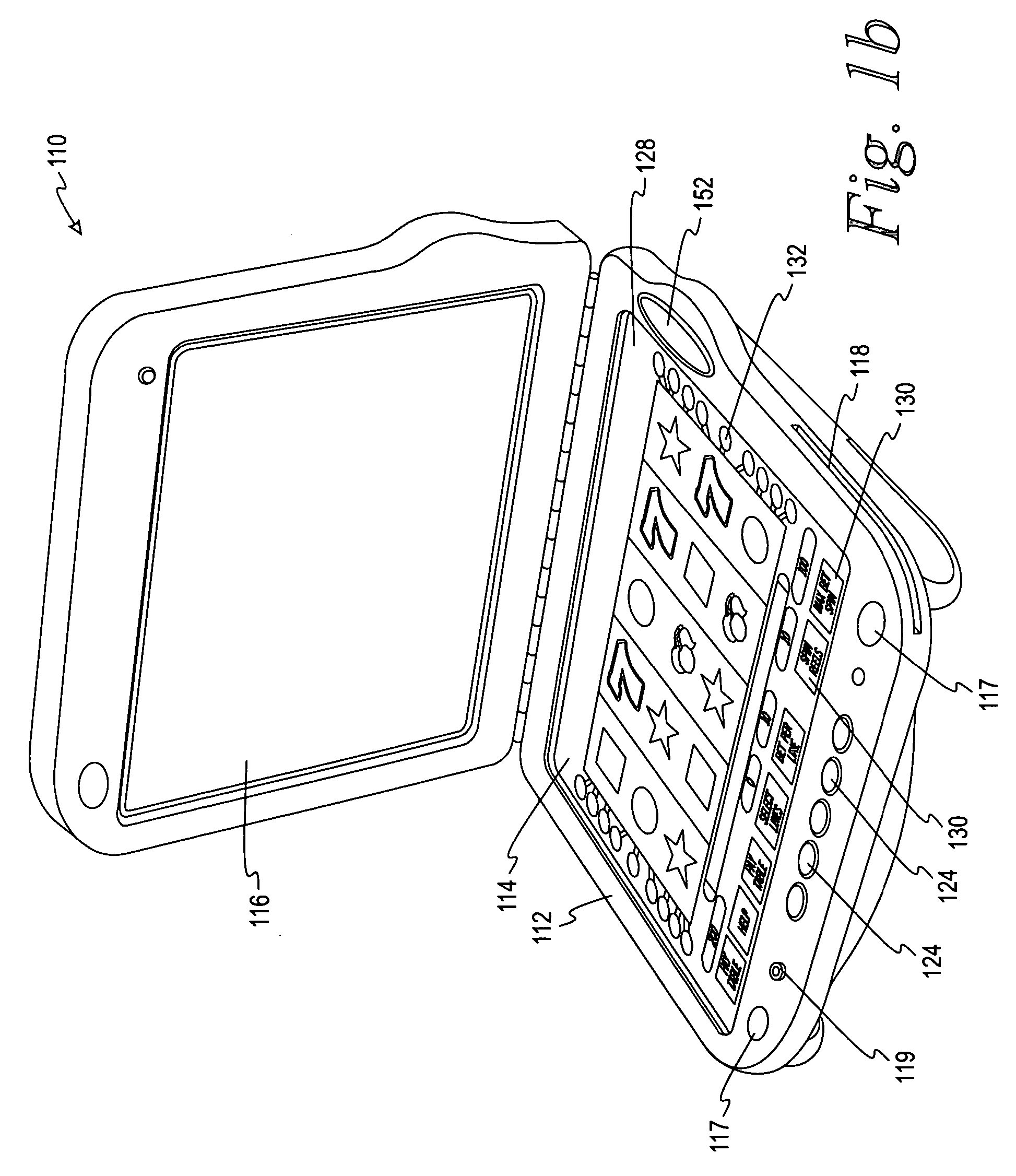

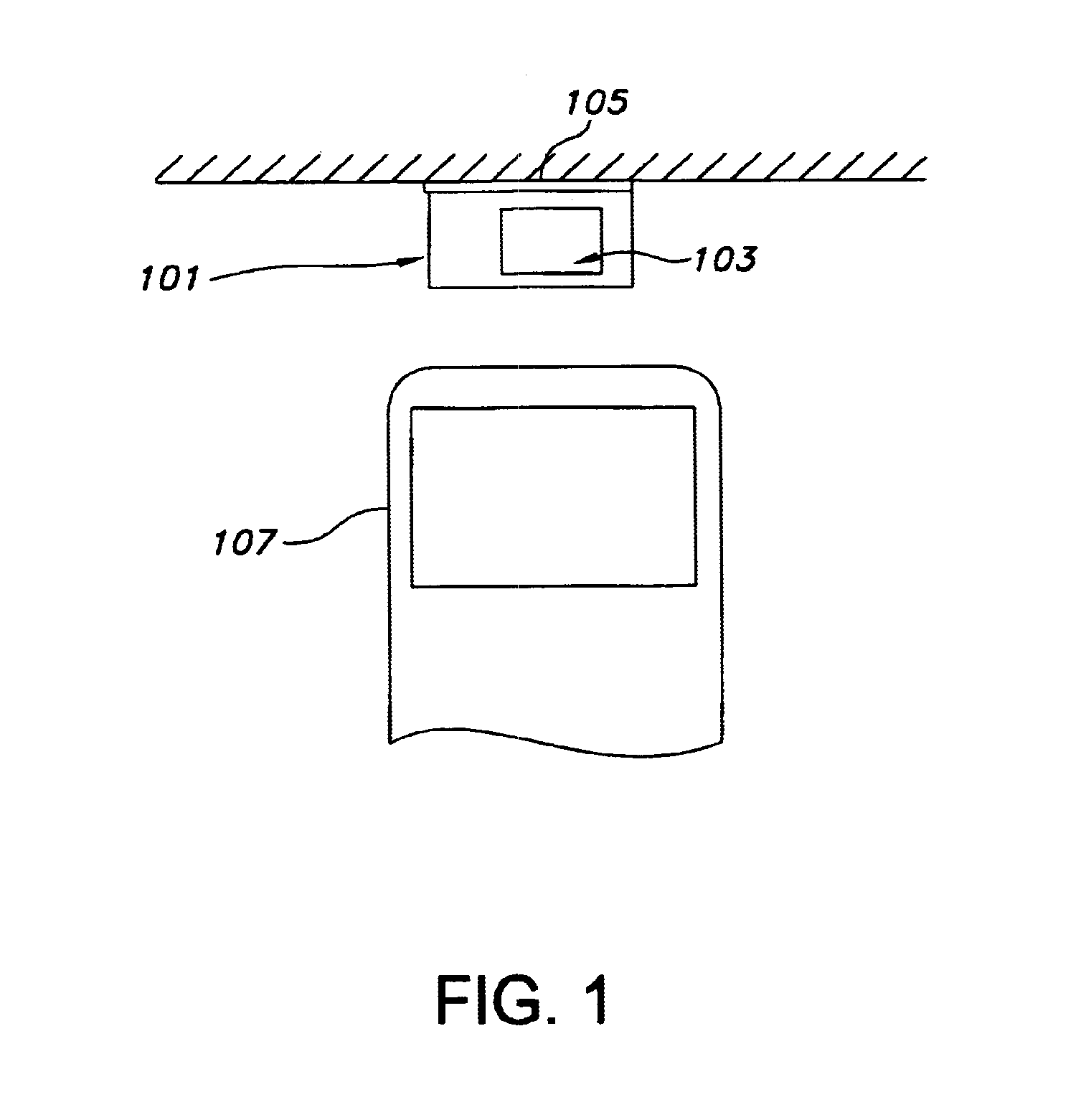

Light sources and displays in a gaming machine

InactiveUS20070010318A1Apparatus for meter-controlled dispensingVideo gamesDisplay deviceCrt monitor

A gaming machine for conducting a wagering game includes a housing that surrounds a light source. The light source emits at least one color of visible light and may include a microdisplay. In one aspect, the light emitters are coupled to optical fibers that guide visible light from the light source to one or more light emitters (such as a tower light, a lighted button, a marquee, or transparent signage). In another, a microdisplay displays an image that is magnified through one or more lenses and projected onto a transparent substrate. The light source may include an LCD display, a CRT display, an incandescent source, or the like. The microdisplay may include a DLP display, a LCoS display, a plasma display, an OLED display, or the like.

Owner:BALLY GAMING INC

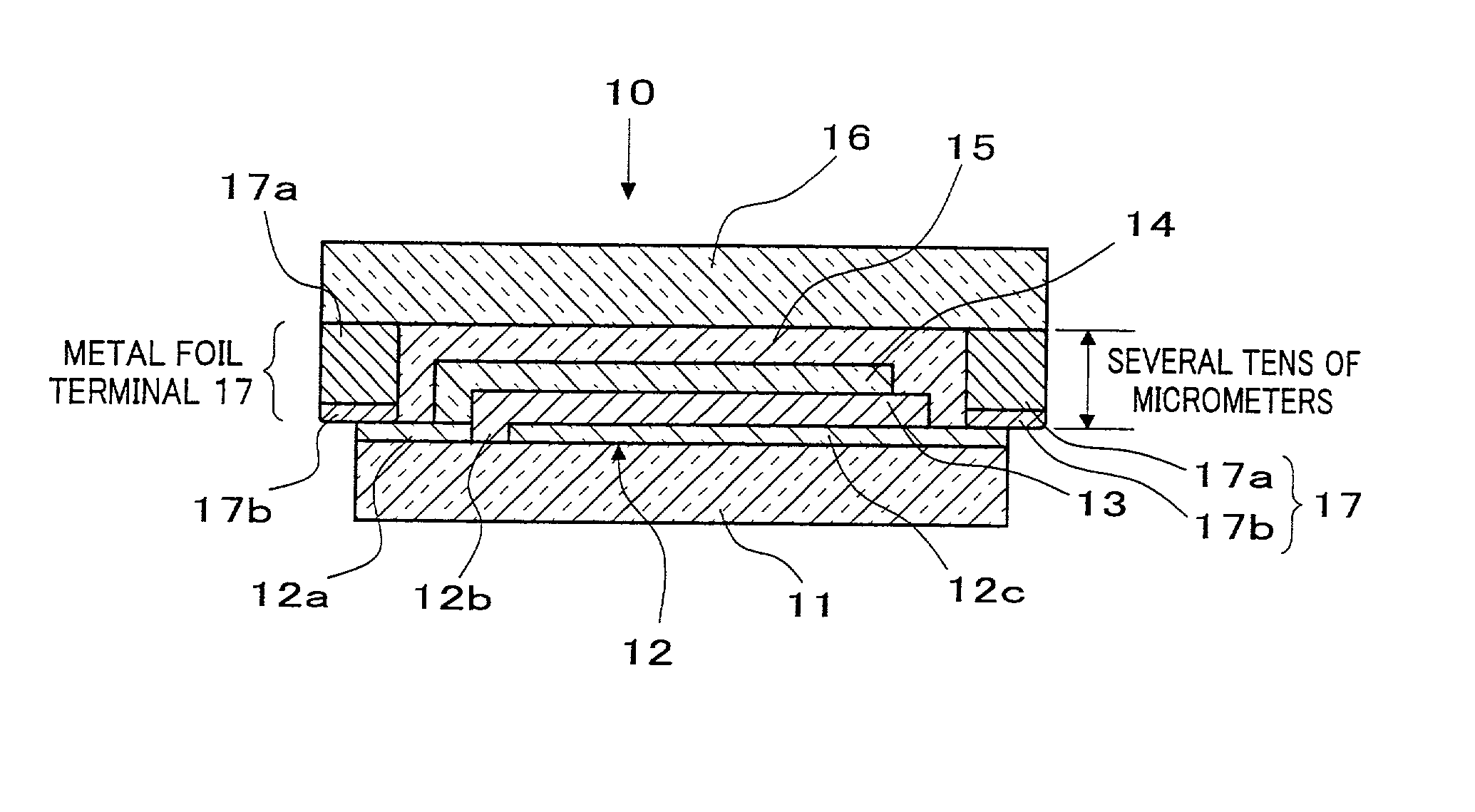

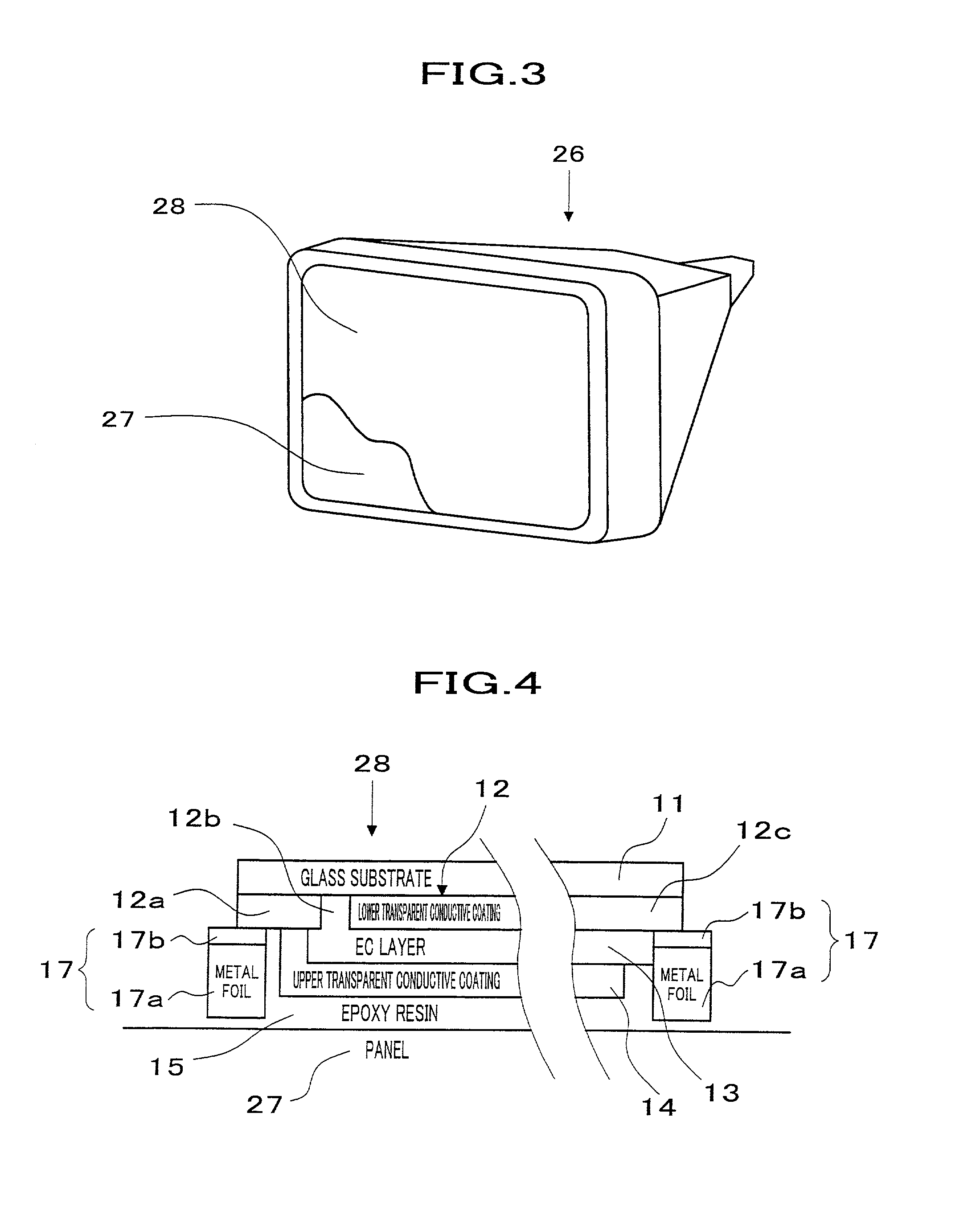

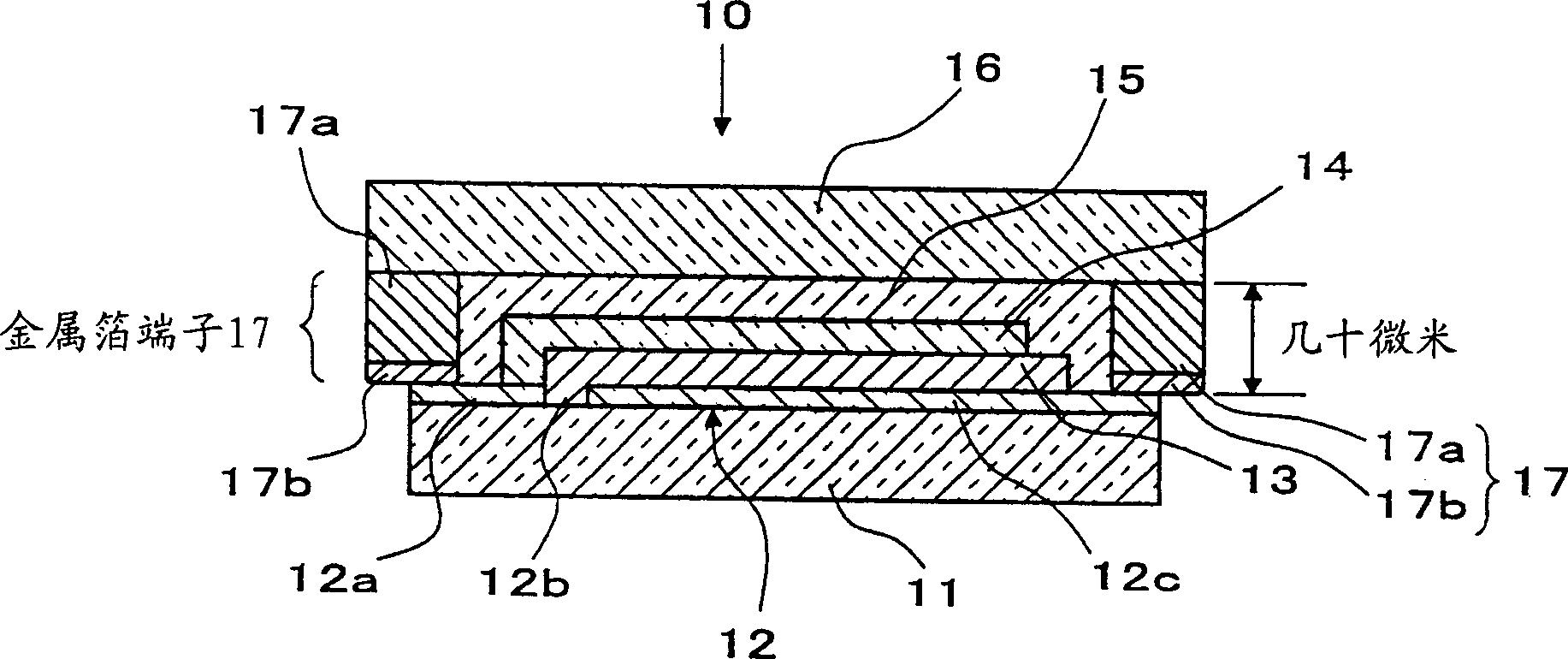

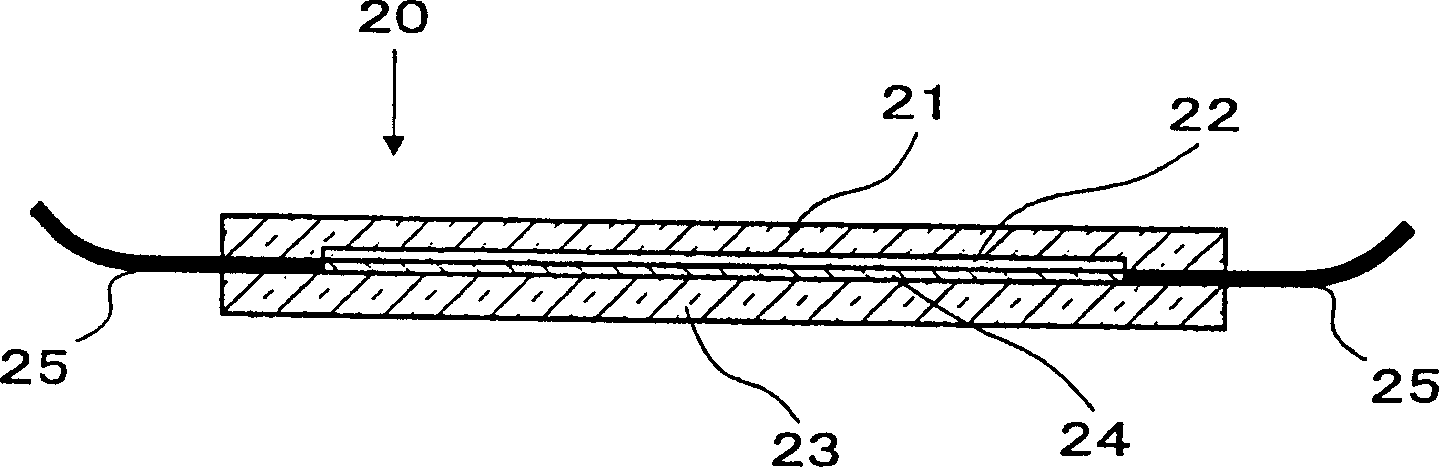

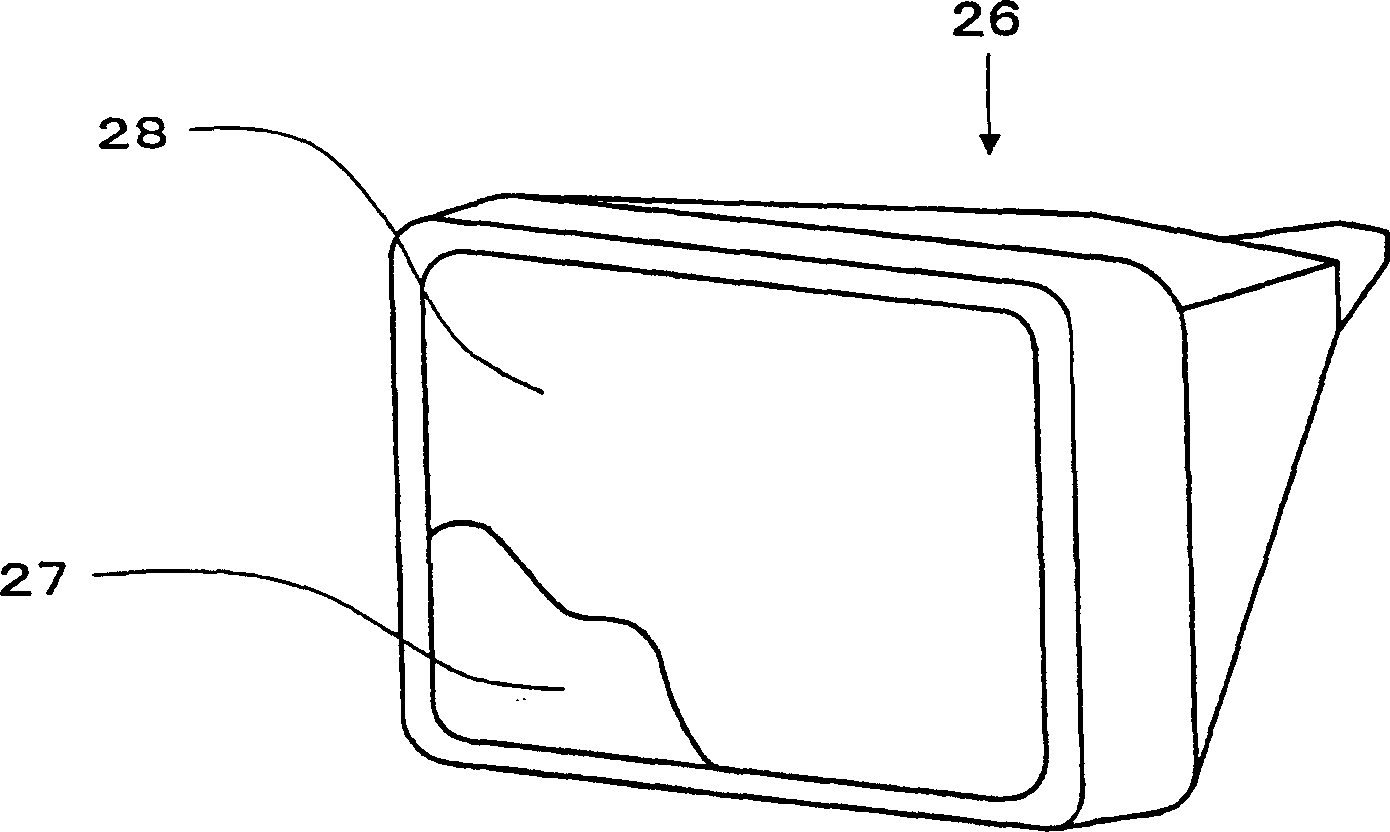

Solid state electrochromic device, and mirror system and crt display using same

InactiveUS20020149829A1Easy to operateAttached with easeTelevision system detailsColor television detailsMetal foilEngineering

There is provided a solid-state electrochromic device including a lower transparent conductive layer (12) formed into filmy shape on a glass substrate, partially provided with a groove (12b), and insulated with the groove (12b), an electrochromic layer (13) layered on the lower transparent conductive layer (12), and an upper transparent conductive layer (14) in direct contact with an insulated portion (12a) of the lower transparent conductive layer. Metal foil terminals (17) made of a metal foil (17a) to which an electrically conductive adhesive material (17b) is applied are bonded to an end of a body portion (12c) of the lower transparent conductive layer and an end of the insulated portion (12a) of the insulated lower transparent conductive layer.

Owner:MURAKAMI CORP

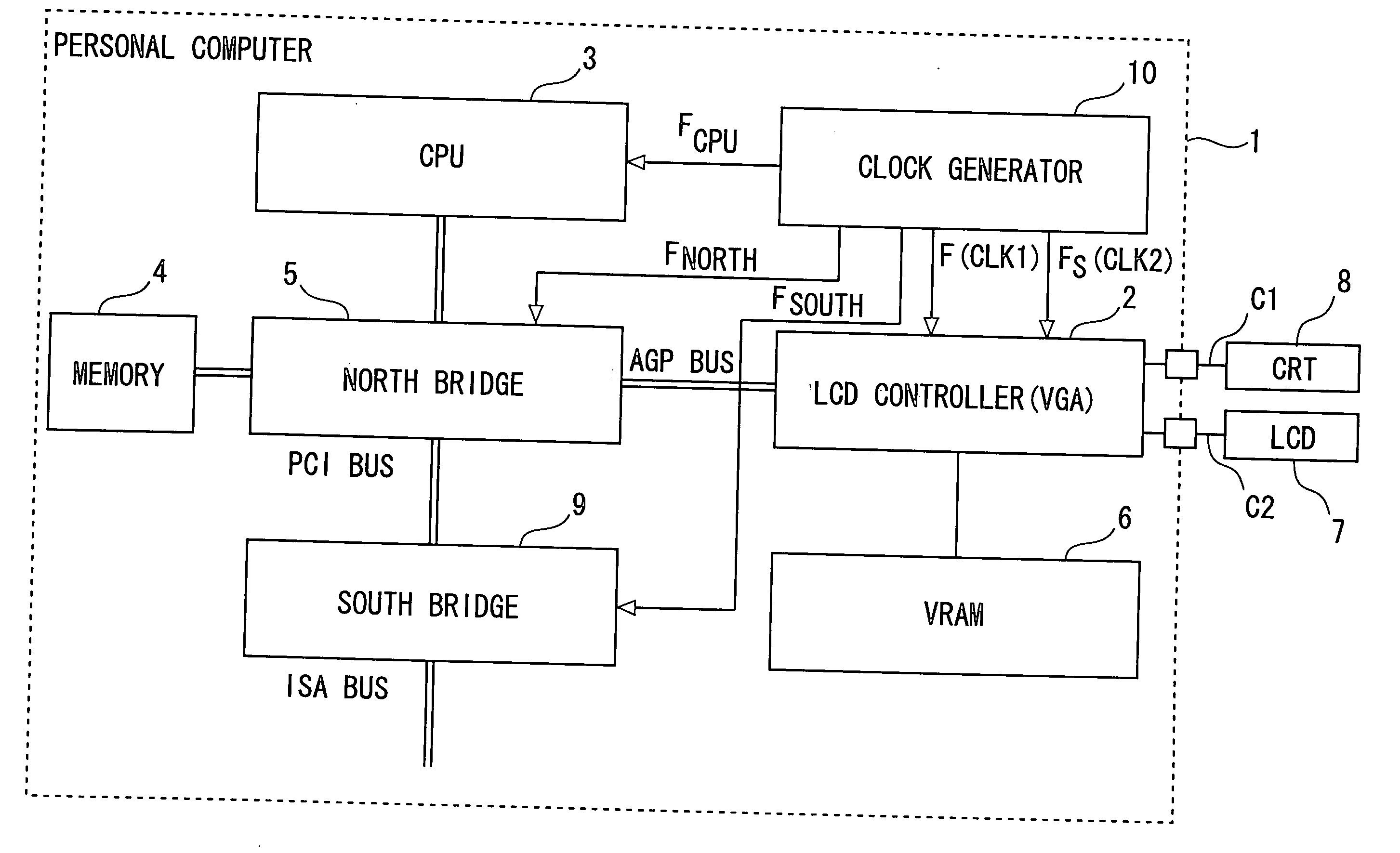

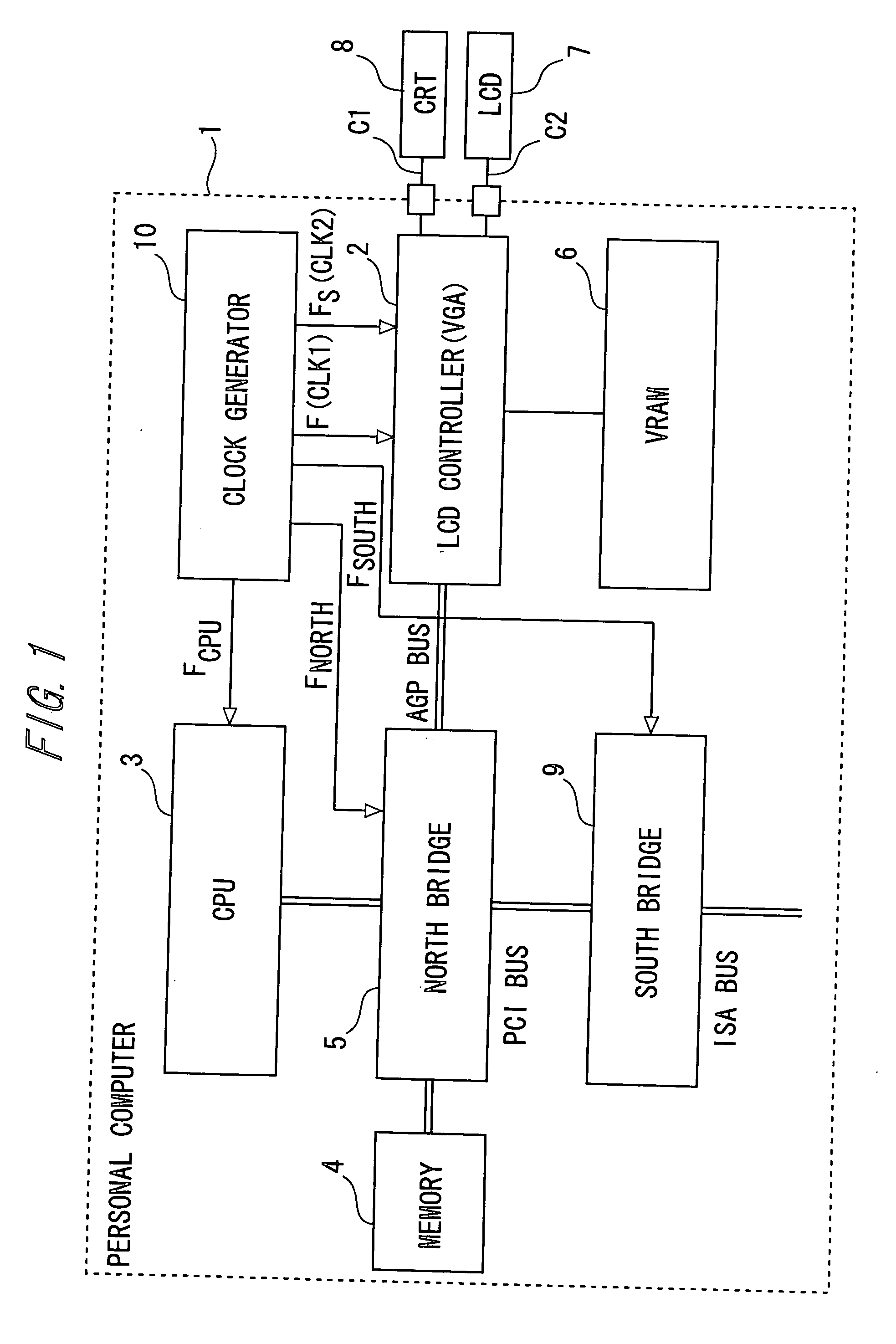

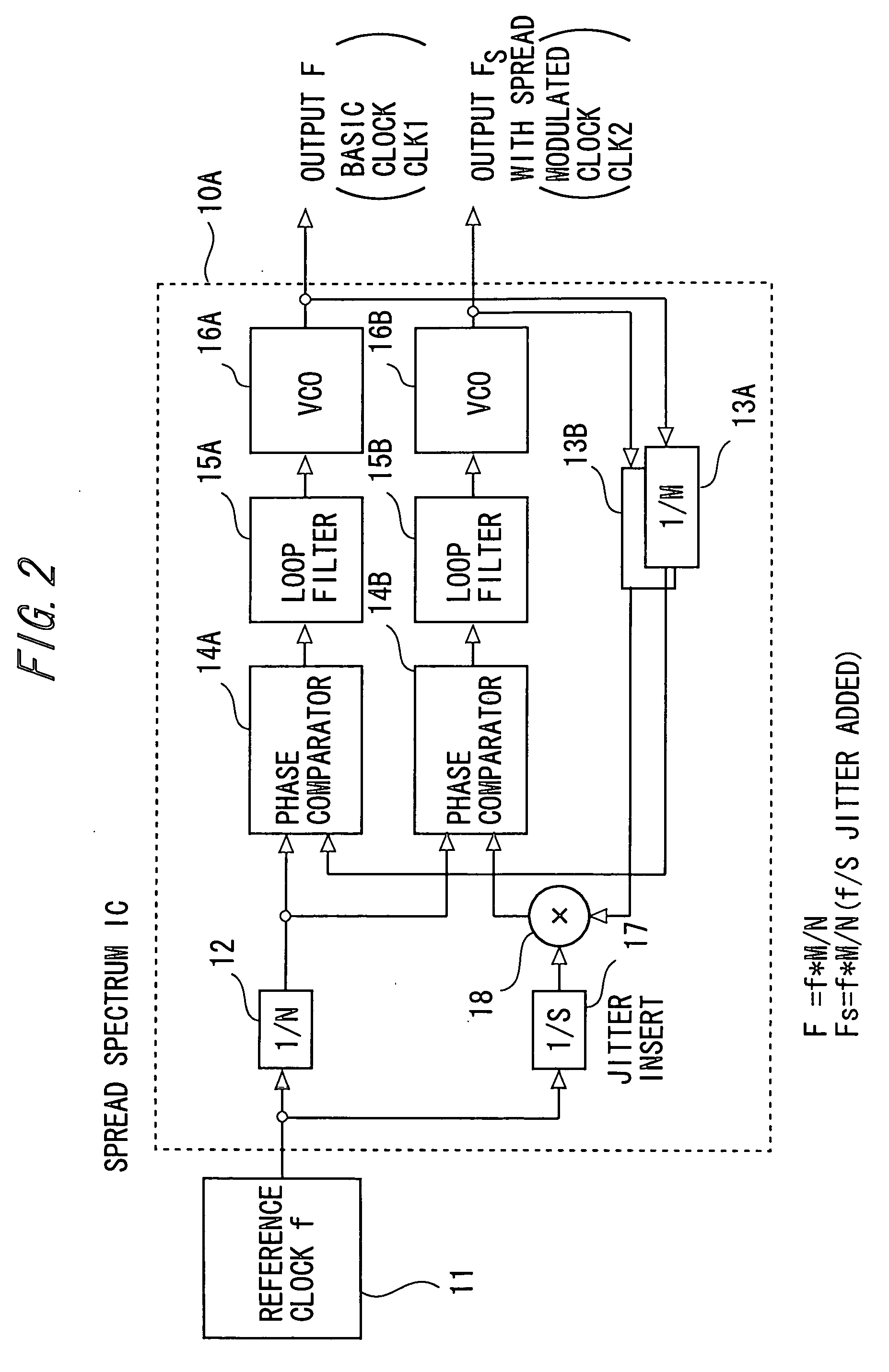

Display control device

InactiveUS20040196212A1Cathode-ray tube indicatorsDigital output to display deviceLiquid-crystal displayData signal

A display control device comprises: a cathode ray tube (CRT) control unit for transferring, to a CRT display, a CRT transfer clock signal, a video data signal and a synchronous signal in accordance with the CRT transfer clock signal generated from a first clock signal having a constant and stable cycle; and a liquid crystal display (LCD) control unit for transferring, to a LCD display, a LCD transfer clock signal, a video data signal and a synchronous signal in accordance with the LCD transfer clock signal generated from a second clock signal as a spread spectrum clocking signal generated based on the first clock signal.

Owner:FUJITSU LTD

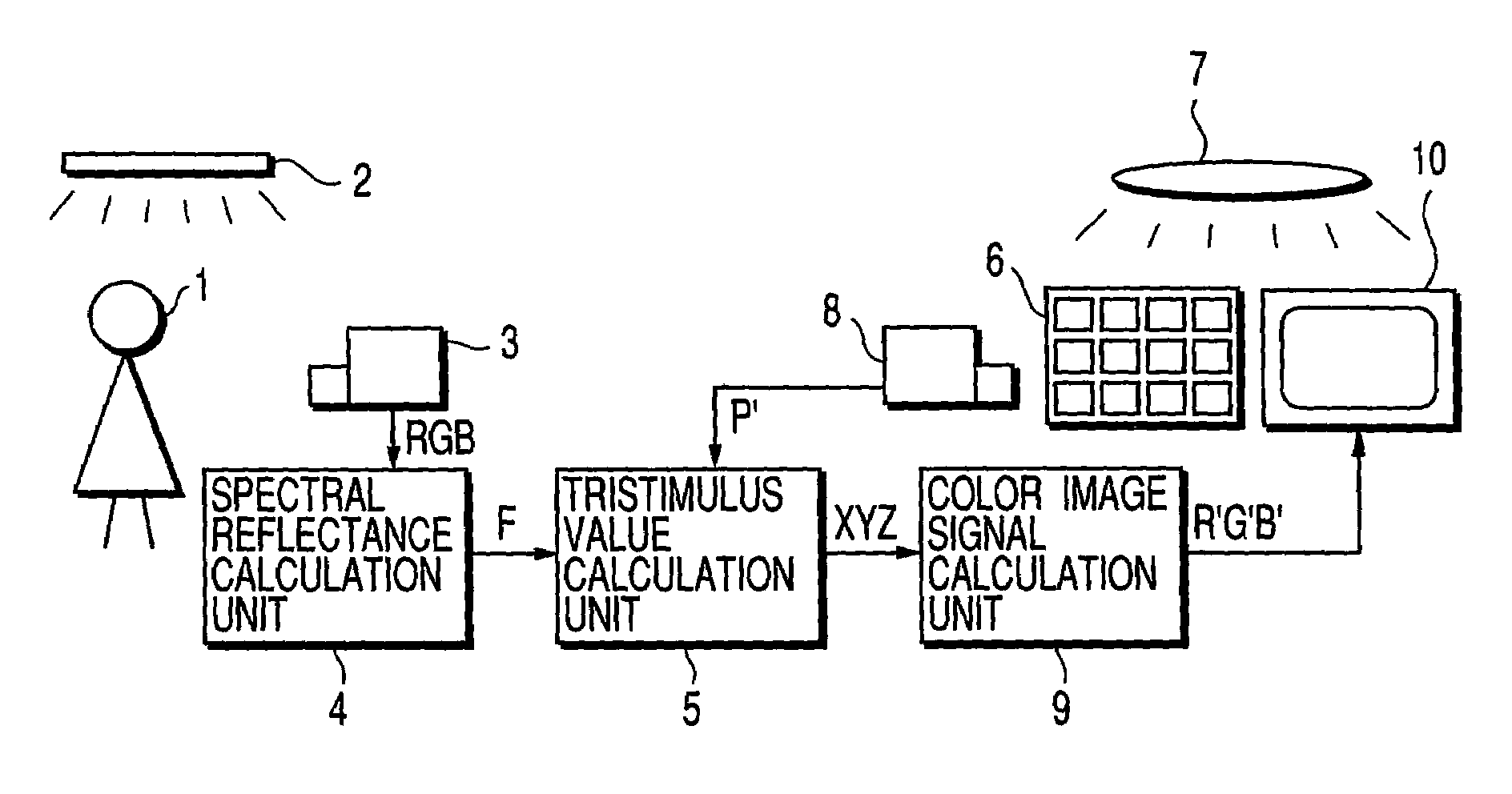

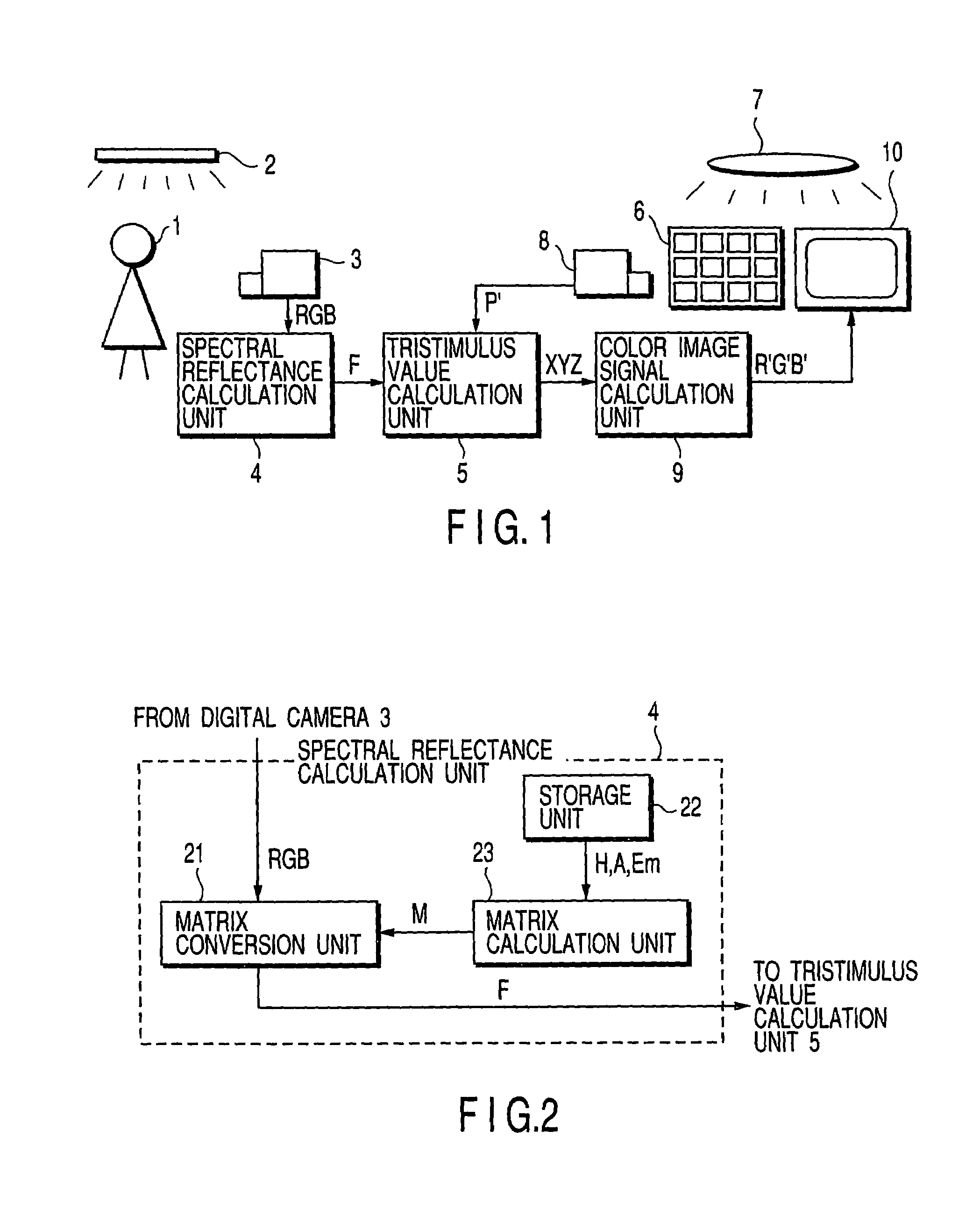

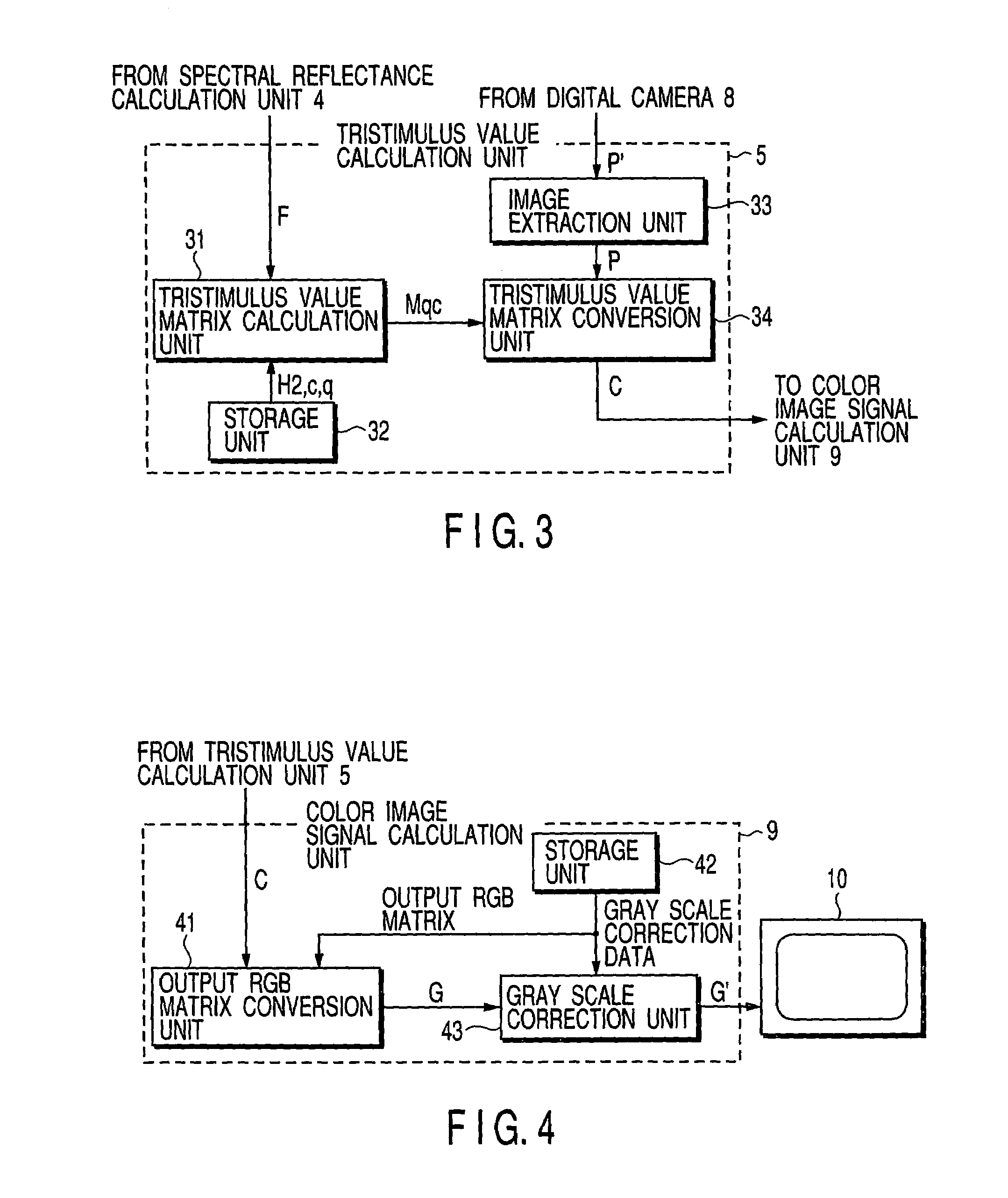

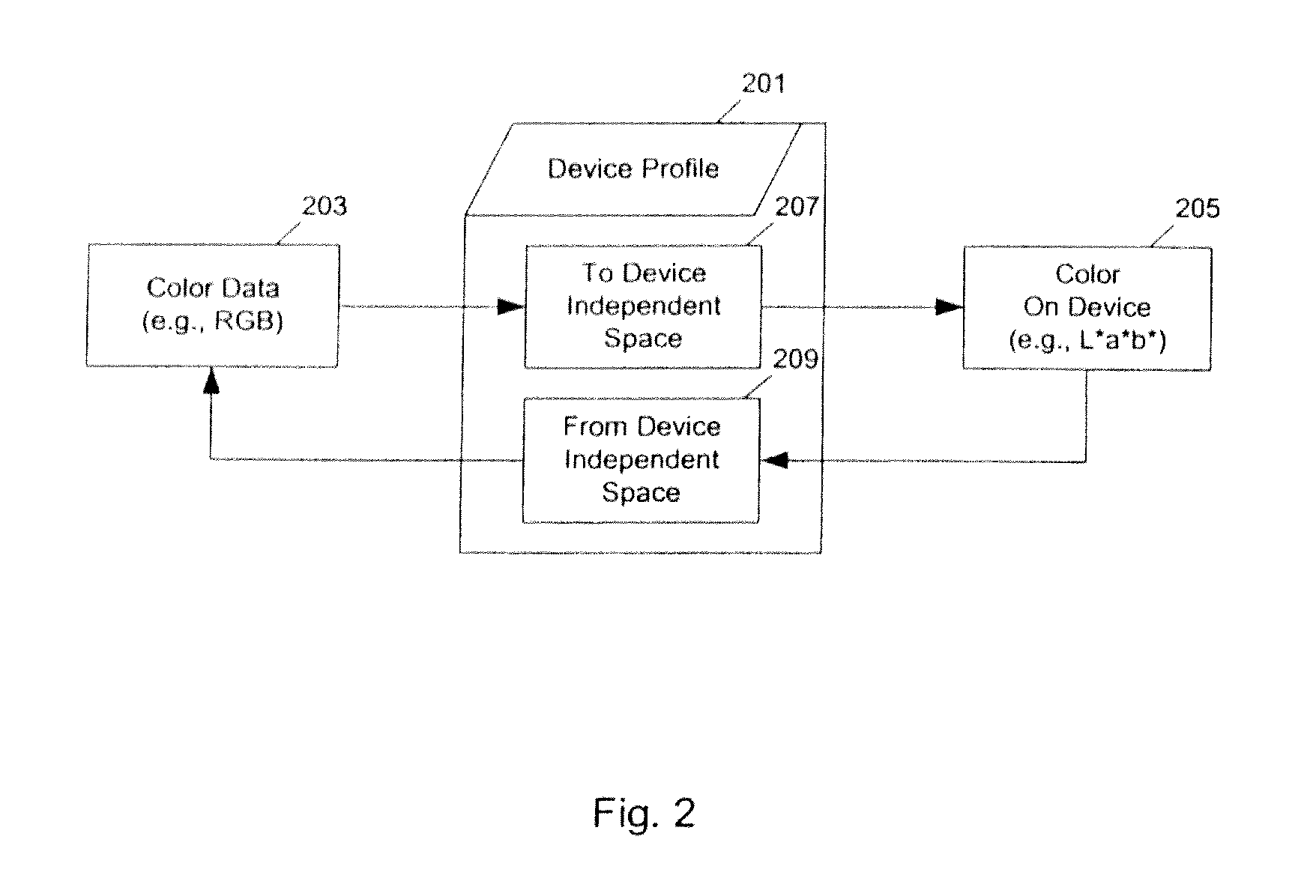

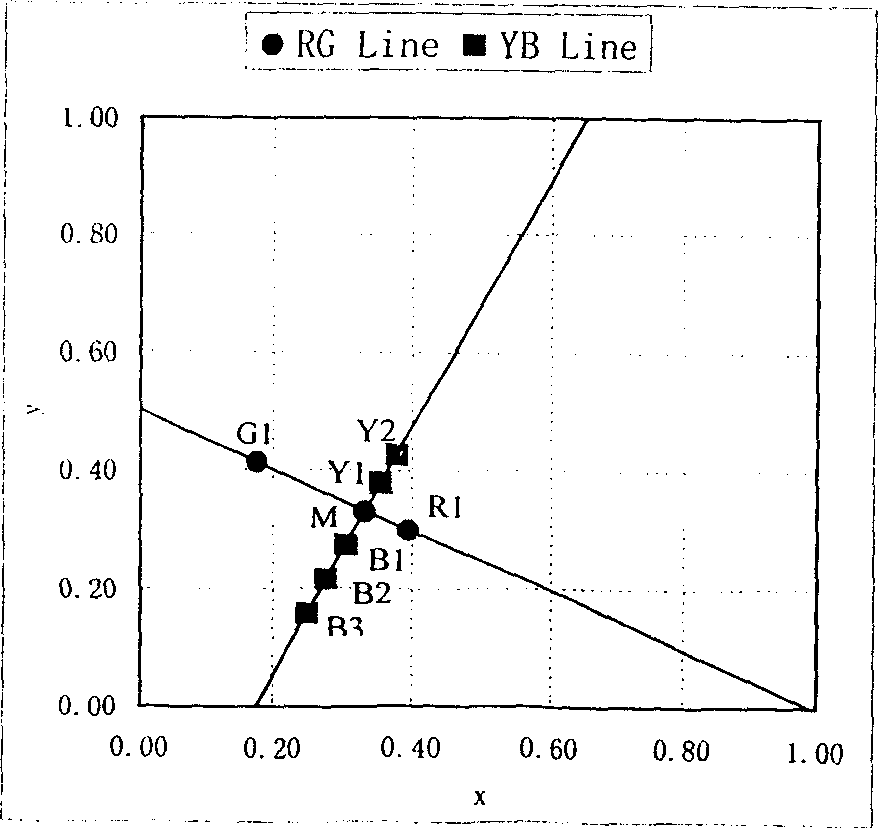

Color reproduction system

InactiveUS6980231B1Highly accurate conversionImprove accuracyTelevision system detailsColor signal processing circuitsColor imageCrt monitor

A color reproduction system includes a tristimulus value calculation unit for calculating tristimulus values (X, Y, Z) under observation illumination light corresponding to the spectral reflectance of an object, which is obtained by a spectral reflectance calculation unit, and a color image signal calculation unit for calculating output color image signals (R′, G′, B′) to a CRT monitor on the basis of the tristimulus values (X, Y, Z). The tristimulus value calculation unit converts spectral reflectance image data (F) of the object into tristimulus value image data (X, Y, Z) under the observation illumination light using the spectral reflectance data of a color chip formed from a plurality of unit color chips, color chip image data (P′) obtained by sensing the color chip with a digital camera under the observation illumination light, spectral sensitivity data of the digital camera, and color matching function data.

Owner:OLYMPUS CORP

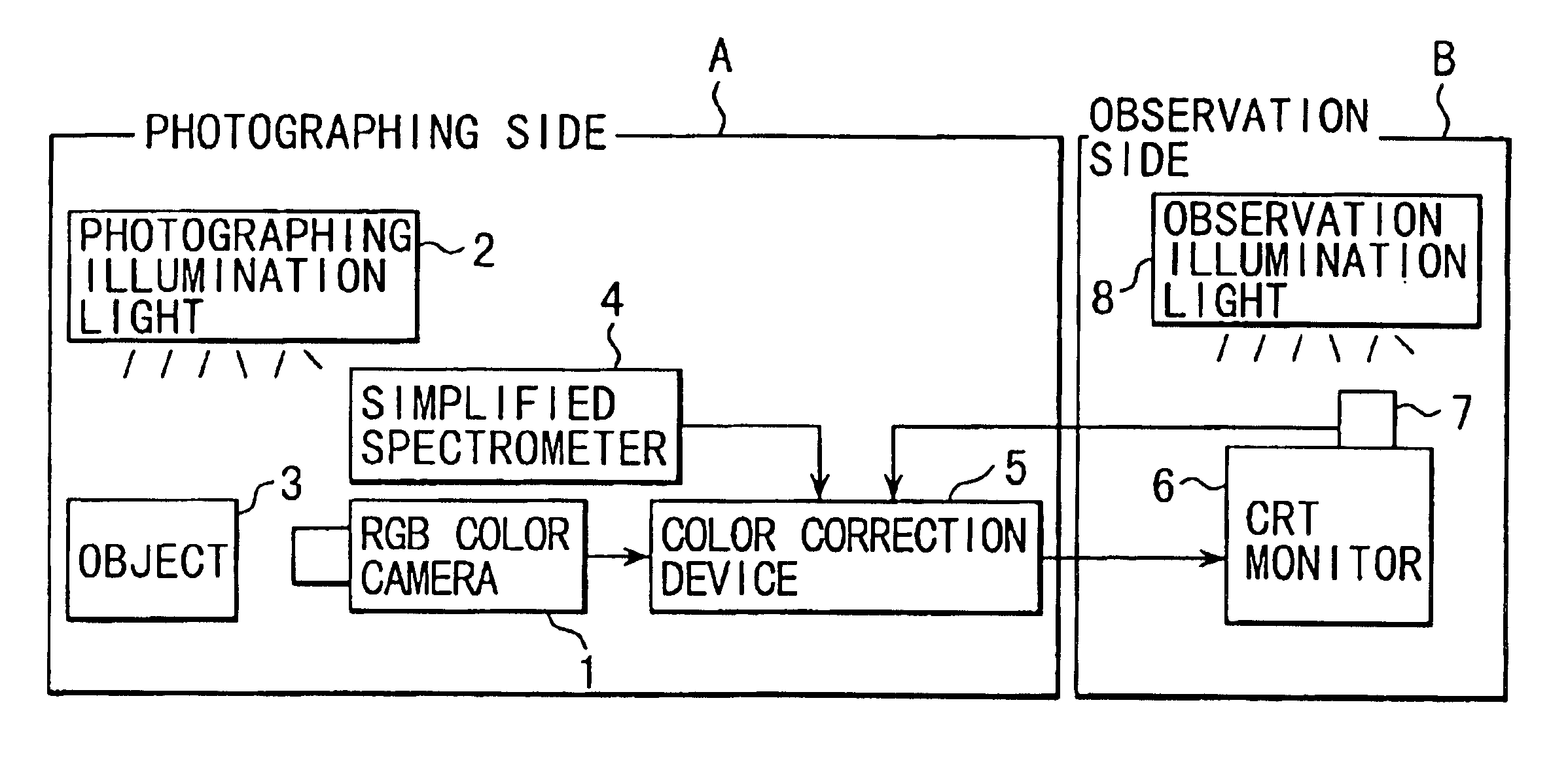

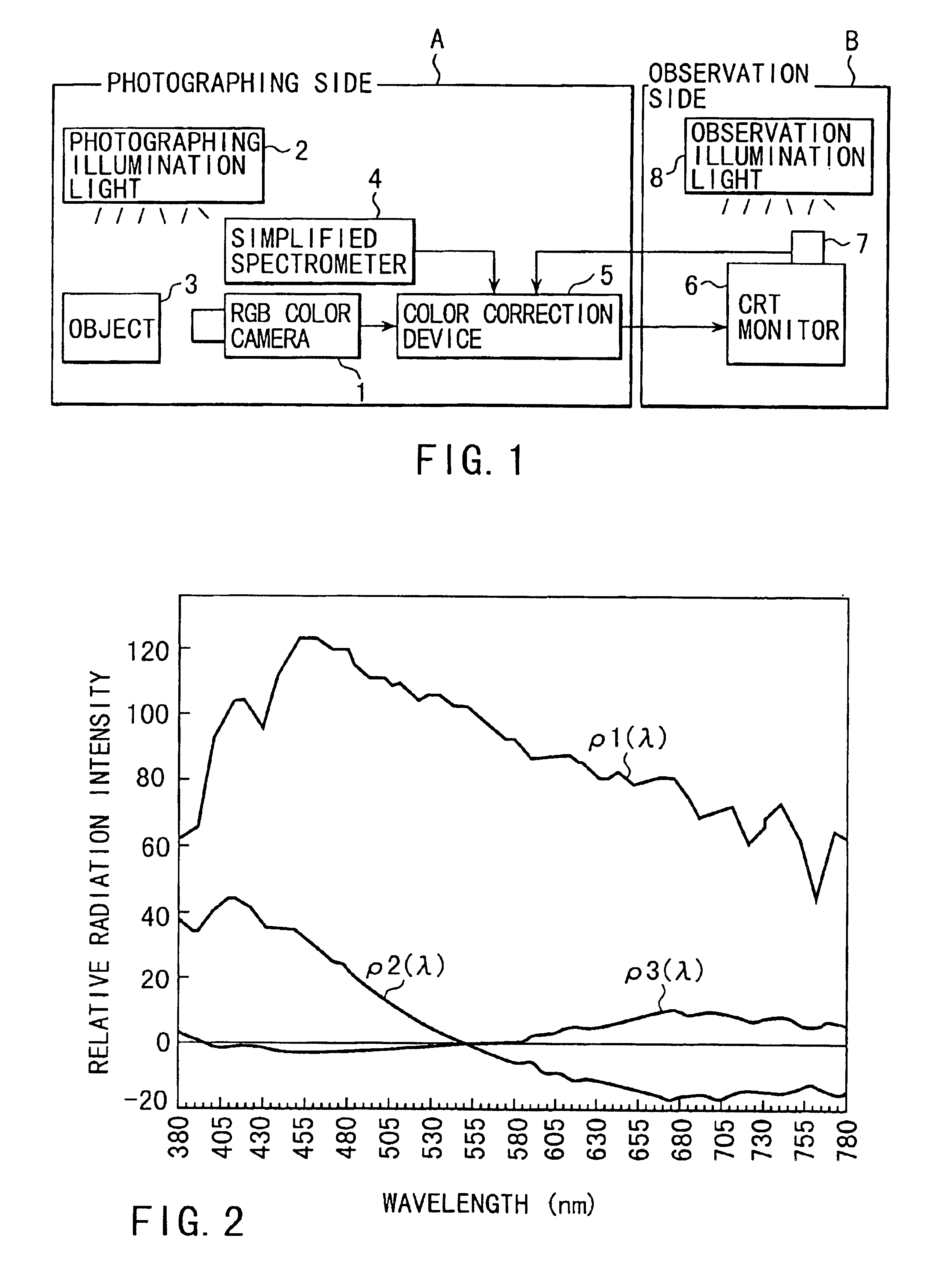

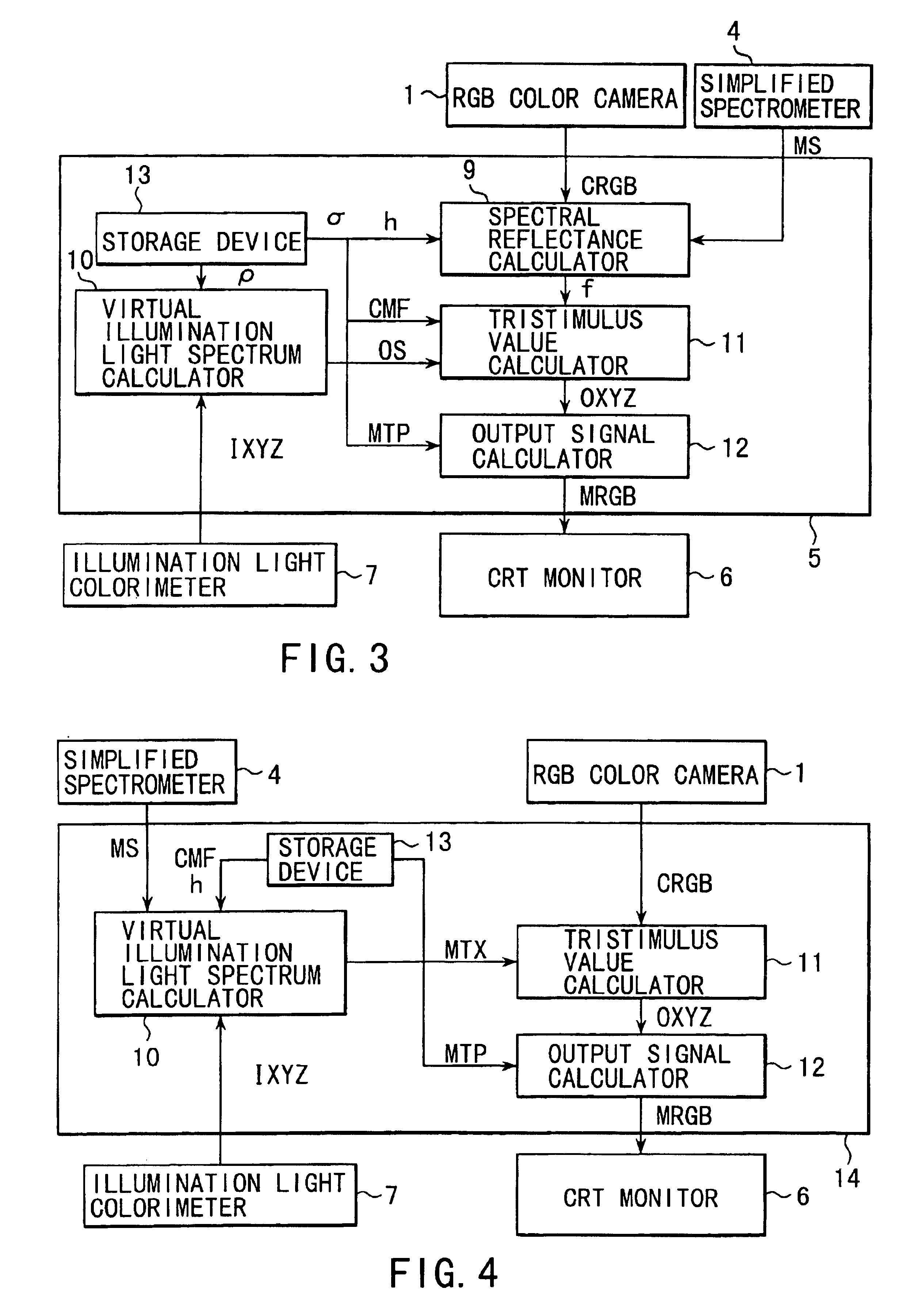

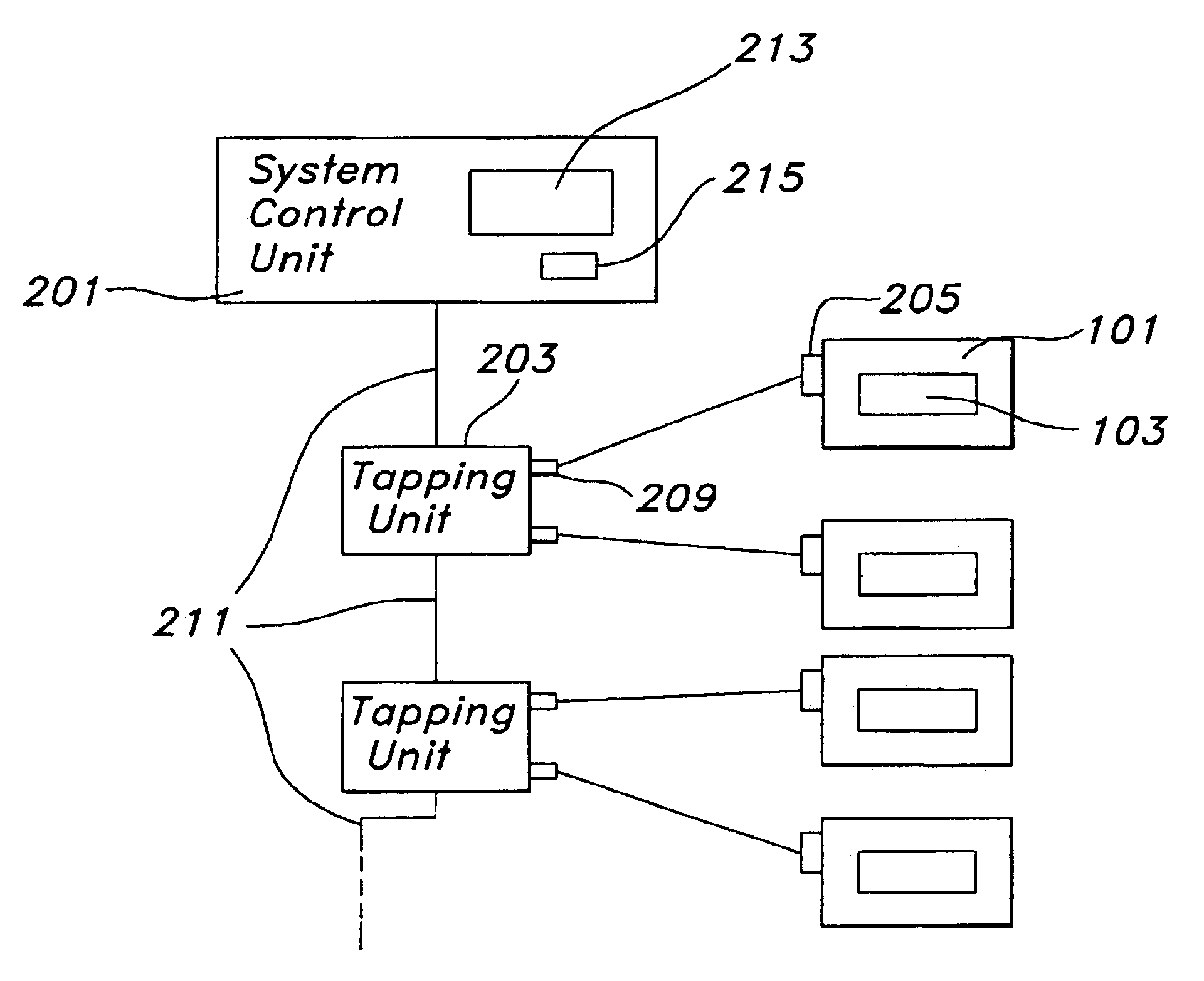

Color reproducing system for reproducing a color of an object under illumination light

InactiveUS6856354B1Easy to measureAccurately reproduces “ appearance ”Television system detailsColor signal processing circuitsColor correctionLighting spectrum

This invention includes an RGB color camera for photographing an object under photographing illumination light, a simplified spectrophotometer for measuring a photographing illumination light spectrum, and a color correction device for calculating tristimulus value data of the object and converting the data into an input signal to a CRT monitor by using monitor profile data. On the observation side, a CRT monitor and illumination light colorimeter for measuring the tristimulus values of observation illumination light are arranged. A color correction device can perform color reproduction without being influenced by changes in the color perception characteristics of a person such as chromatic adaptation by reproducing a virtual illumination light spectrum having tristimulus values equal to those of the observation illumination light without measuring any observation illumination light spectrum.

Owner:OLYMPUS CORP

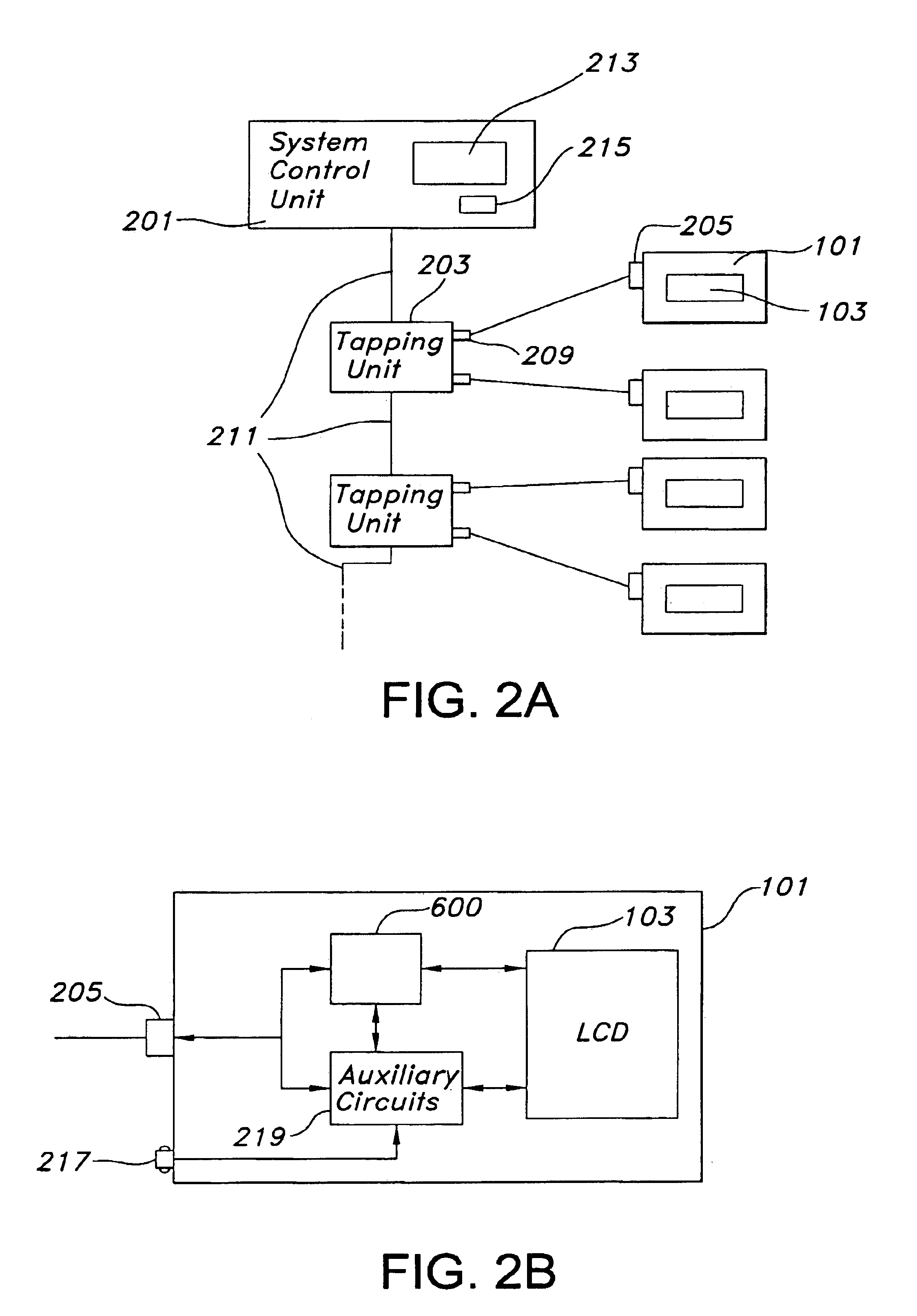

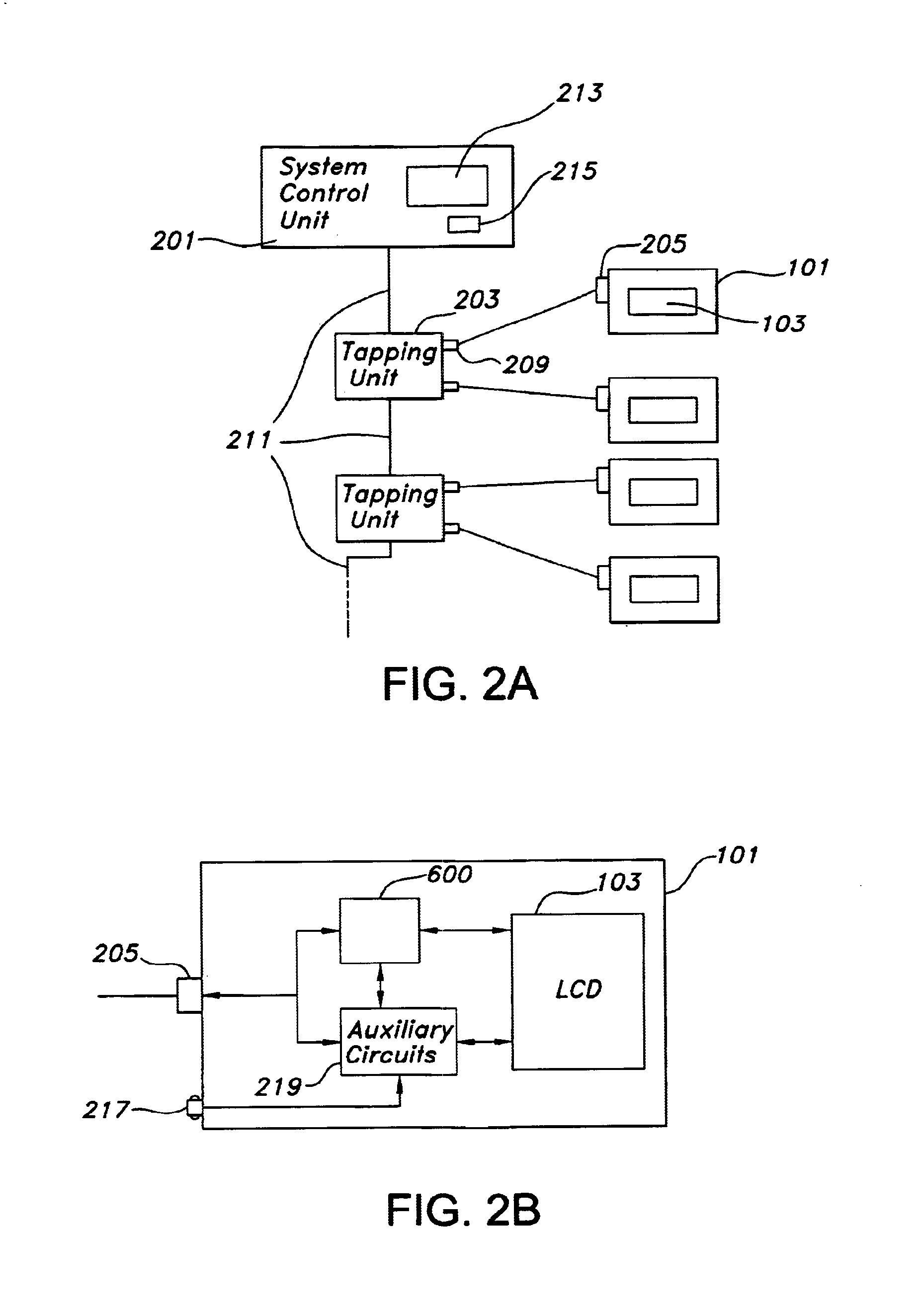

Data request method without using dedicated connections

InactiveUS6918134B1Increase the display interfaceInterfere with performanceTelevision system detailsColor television detailsElectronic systemsLiquid-crystal display

In-flight entertainment systems provide entertainment for passengers on commercial airline flights. Presently, usually on longer flights, video entertainment is commonly available on in-flight passenger entertainment systems. In-flight entertainment systems can display video on a variety of display monitors ranging from a conventional CRT display to a more modern Liquid Crystal Display (LCD). Generally most displays are connected to the aircraft electronic system via a ARINC 722 connector. The ARINC 722 connector commonly provides an electrical interface between the aircraft and the video system, whether the video system is a CRT or LCD type monitor. With the increasing use of LCD monitors there is a greater need for the ability of the display monitor to be able to report its status. The need for status reporting is increased because the LCD monitors are often greater in number than the prior art CRT monitors and because malfunctions are less obvious. Several methods for providing status information from video displays have been proposed. Embodiments of the present invention comprise a system in which data can be requested by repeating commands, such as turn on, a number of times within a predetermined time interval. Because embodiments of the invention use an existing command, which can be the repeated without affecting the functioning of legacy systems, the need for modification of the airline and monitor systems is greatly reduced.

Owner:ROCKWELL COLLINS INC

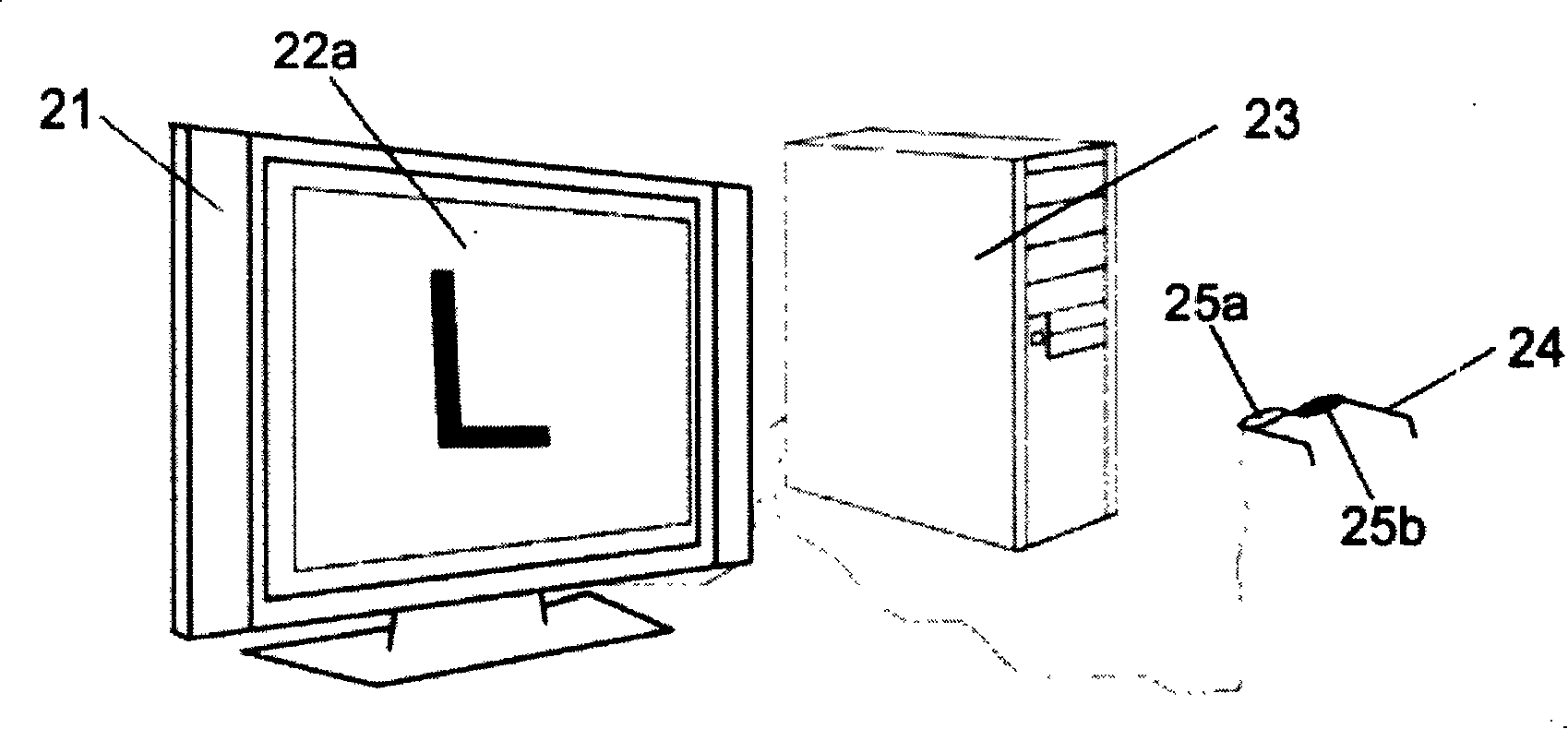

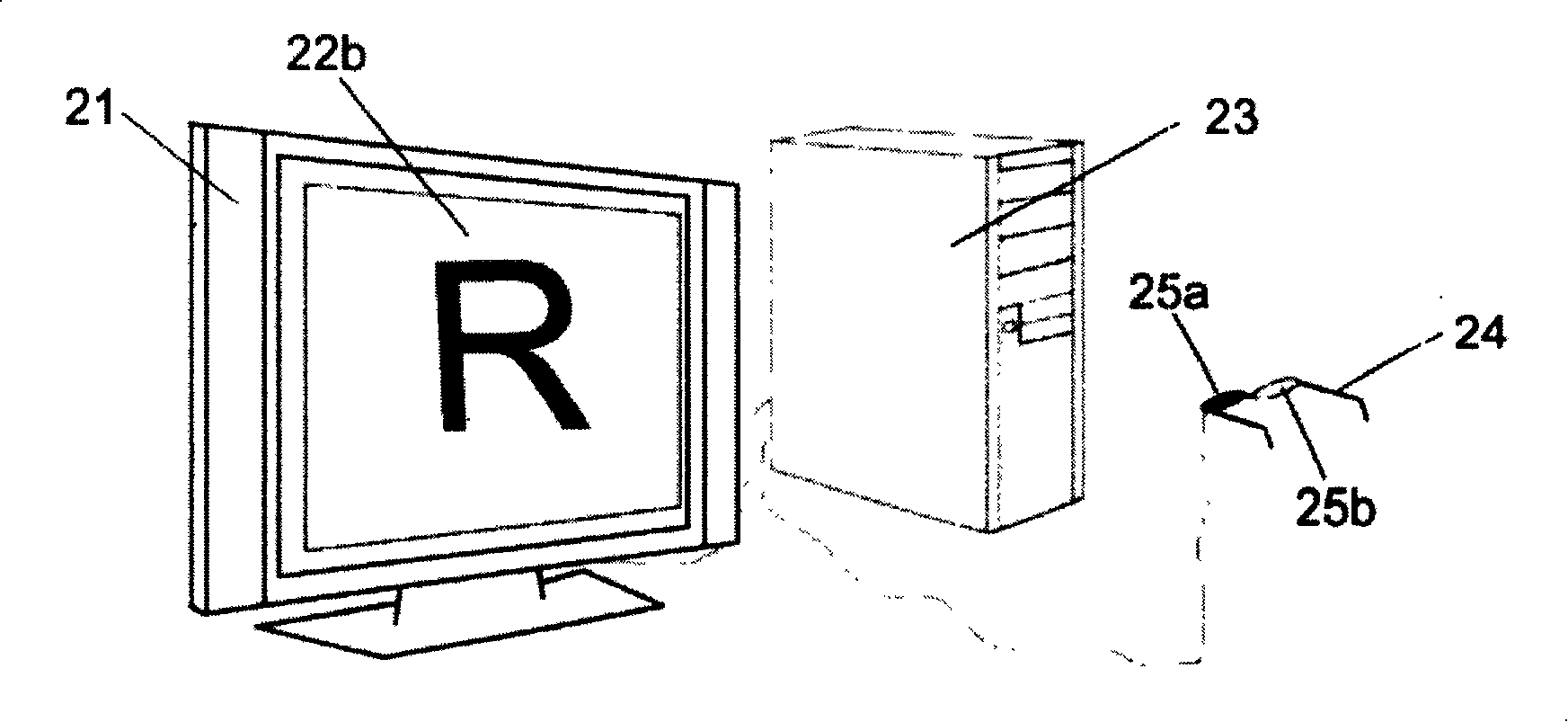

Polarized light grid stereoscopic display device

A three-dimensional display for viewing two-dimensional image and three-dimensional image is provided, which comprises a common two-dimensional image display device (LCD panel, plasma panel and CRT display are all available), a polarized light grid screen and a polariscope, wherein, the polarized light grid screen in the shape of raster comprises two kinds of polarized elements whose polarization orientations are mutually perpendicular lines, which are the first polarized element and the second polarized element. The two polarized elements are overlapped with each other on both horizontal direction and vertical direction. Each polarized element at least corresponds to one subpixel on the display device, which is one of the red subpixel, green subpixel and blue subpixel.

Owner:万双

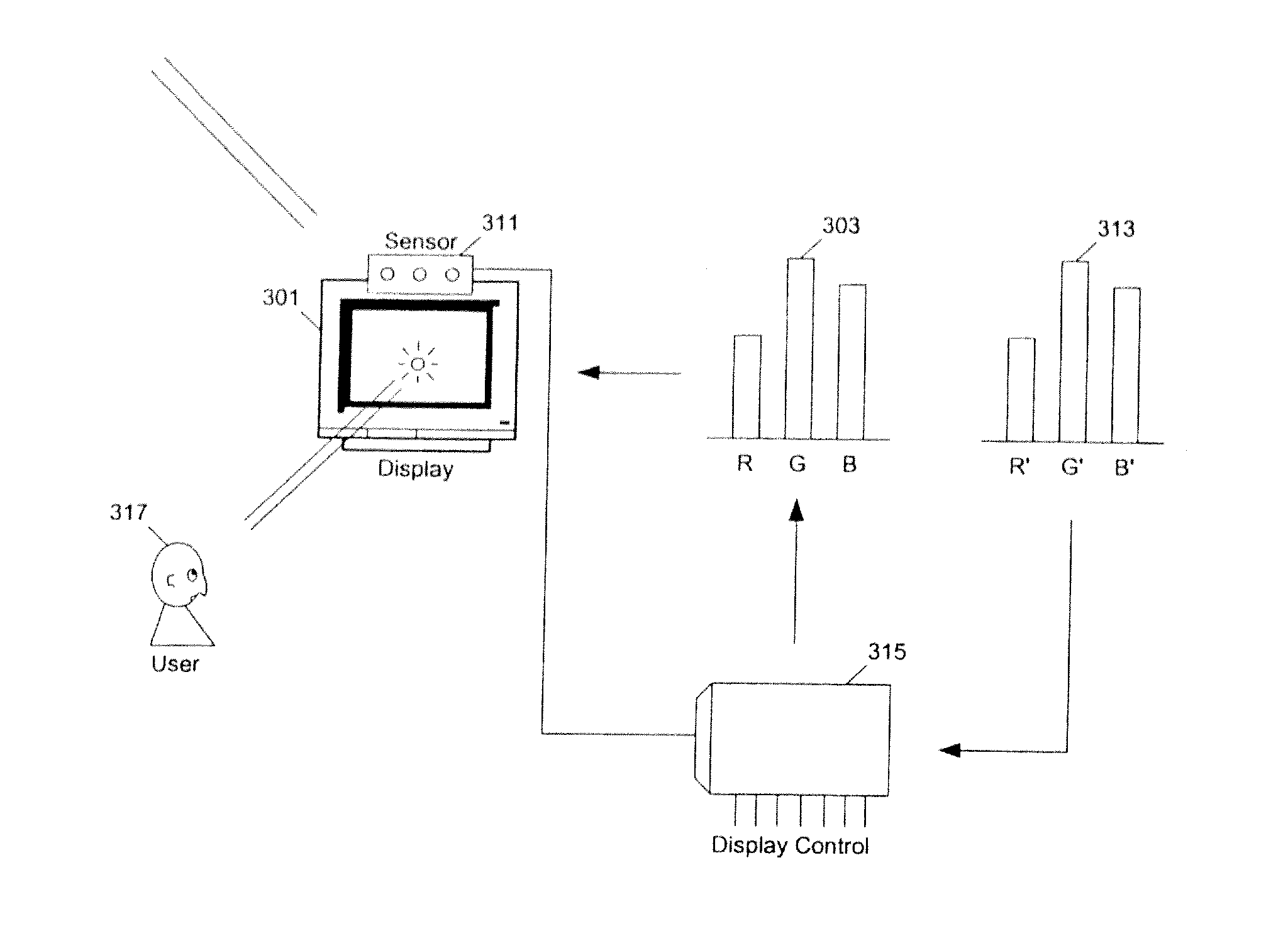

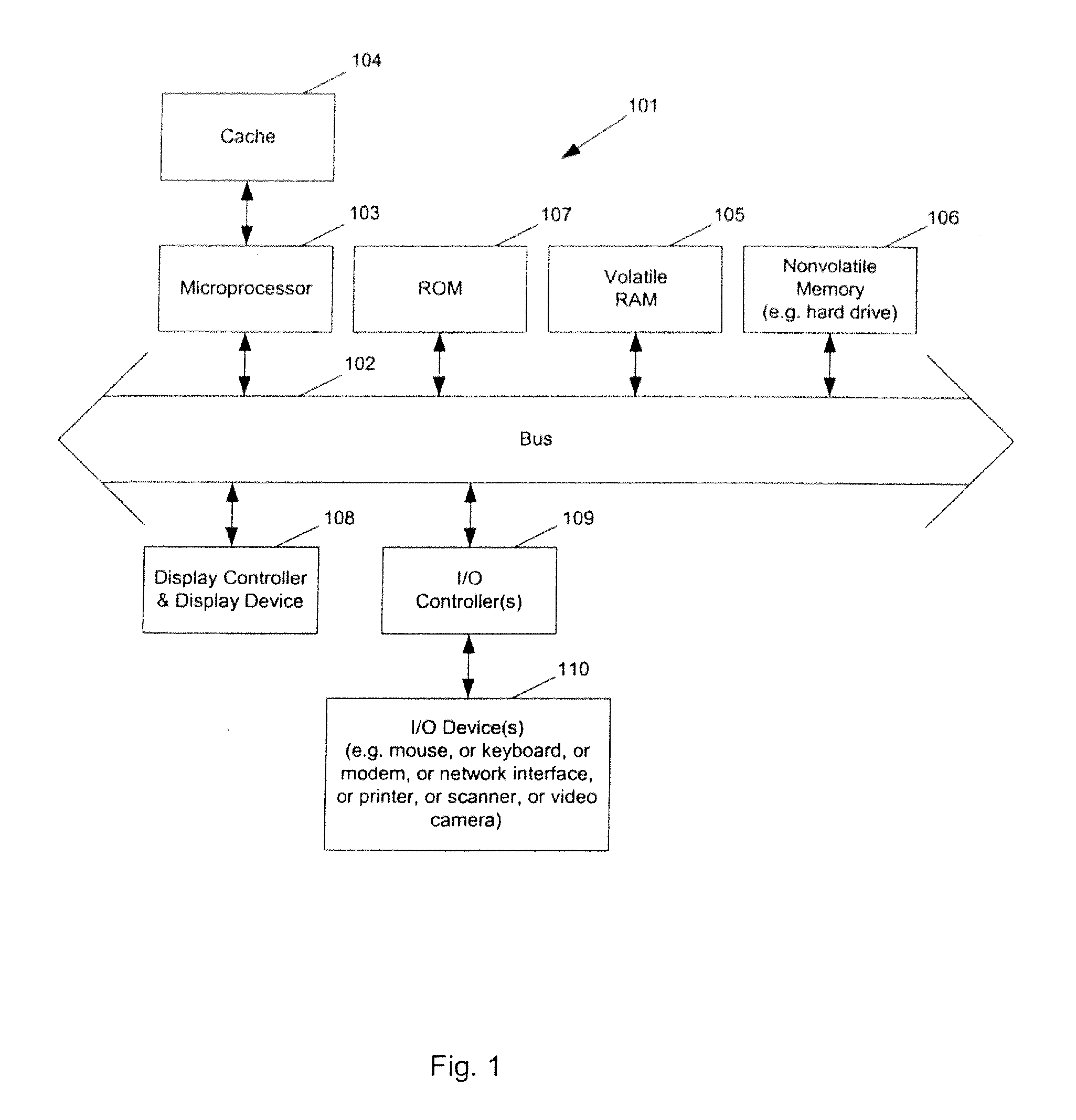

Method and apparatus for color correction of color devices for various operating conditions

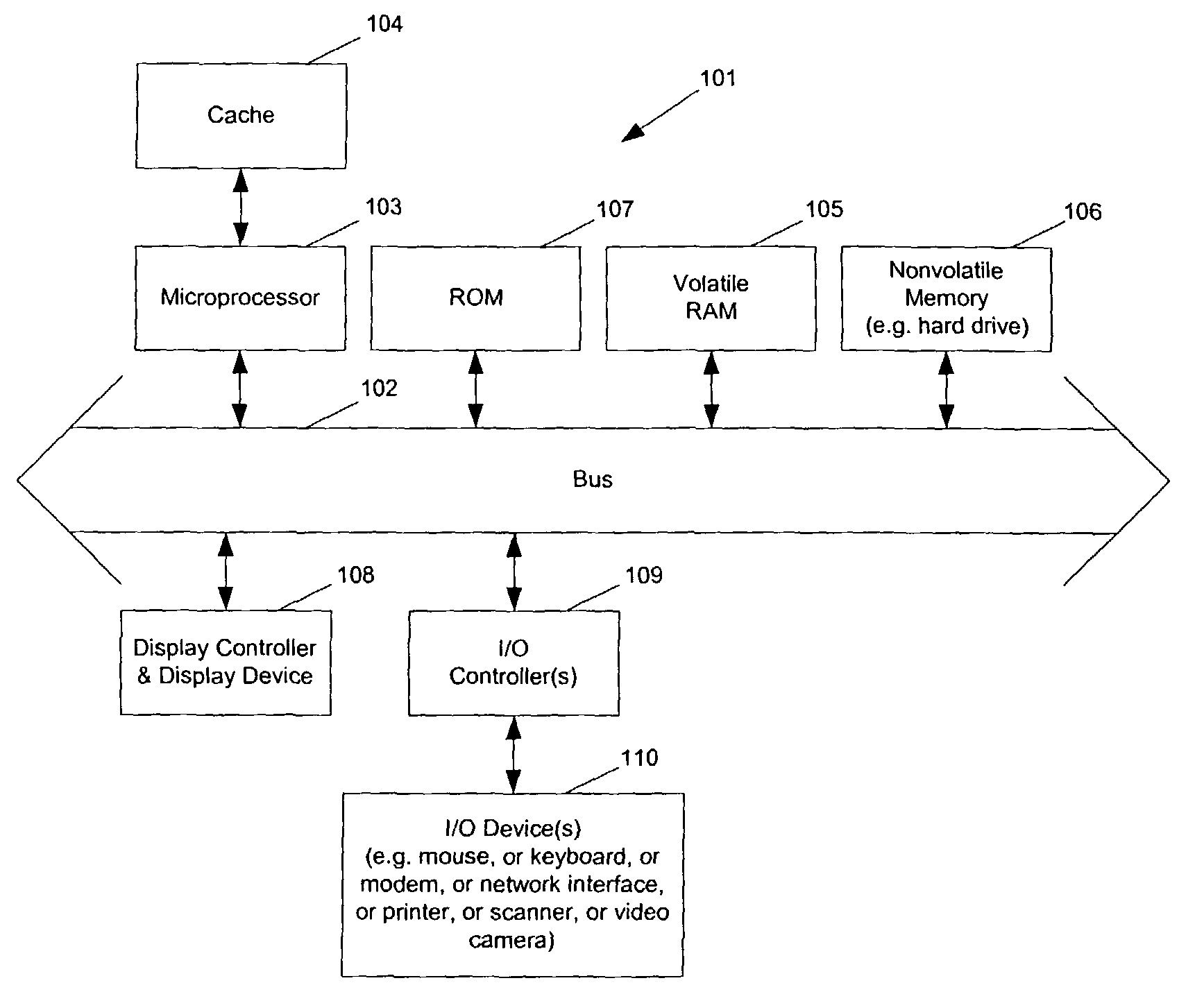

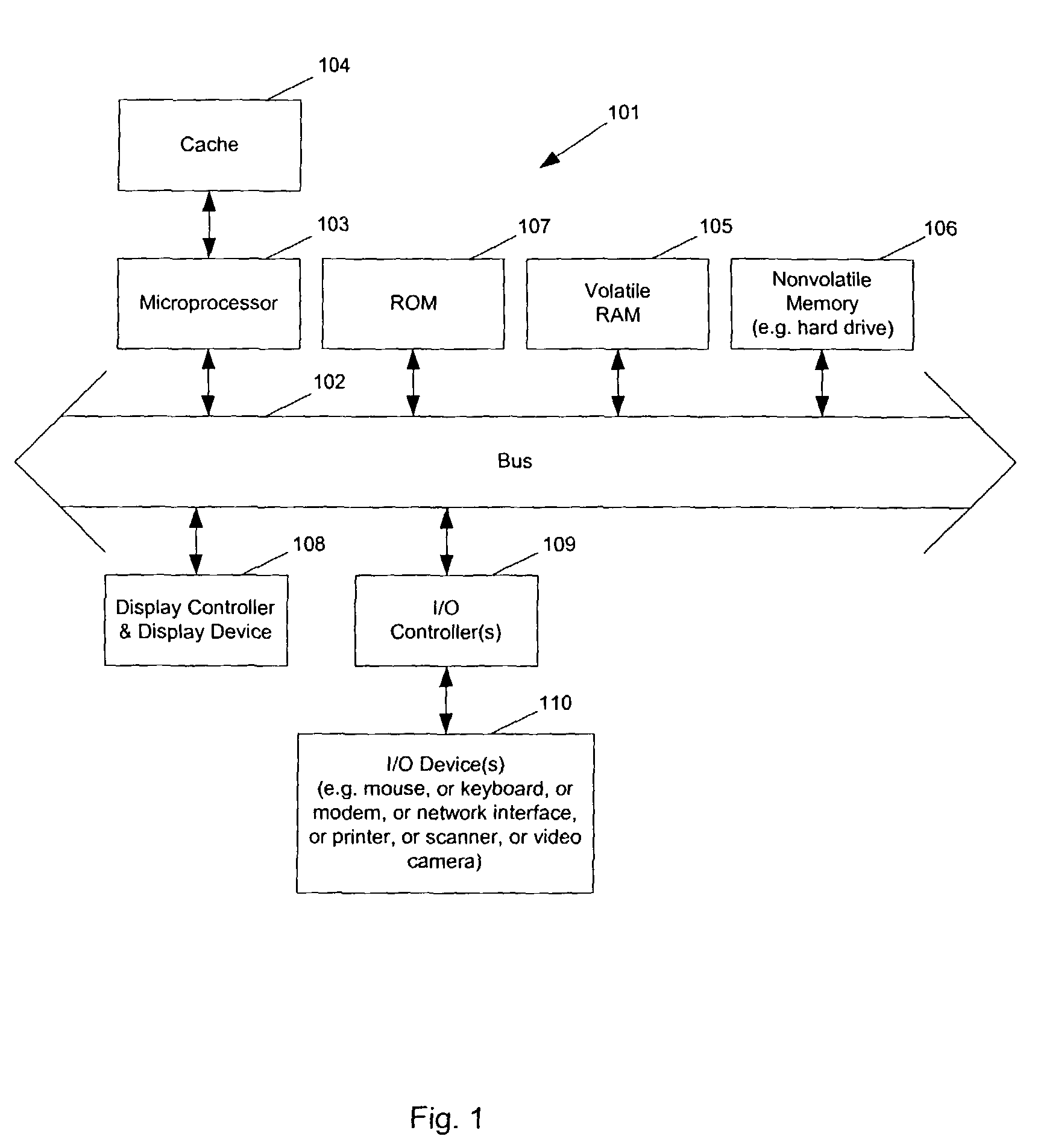

InactiveUS7969478B1Television system detailsColor signal processing circuitsColor correctionDisplay device

Methods and apparatuses for color correction of color device for various operating conditions. In at least one embodiment of the present invention, operating under a current condition, a color correction operation that is derived from color correction operations defined for other conditions is performed on the color data. In another embodiment, a device profile for managing colors for a color device operating under one condition is interpolated from the device profiles for the color device operating under other conditions (e.g., based on the input received from a user interface according to the perception of the user or based on the measurement of a sensor). The interpolation can be based on the input received from a user interface according to the perception of the user or it can be based on the measurement of a sensor or a set of sensors. Various operating conditions for a color device (e.g., a scanner, a camera, a video camera, a printer, a display device such as a CRT monitor or an LCD display panel, a television set, or others) include chromaticity and illumination of ambient light, background color for a display device, characteristics of print media for a printer, humidity, temperature, pressure and ink level for an ink jet printer, the age of a light source for a scanner, and others.

Owner:APPLE INC

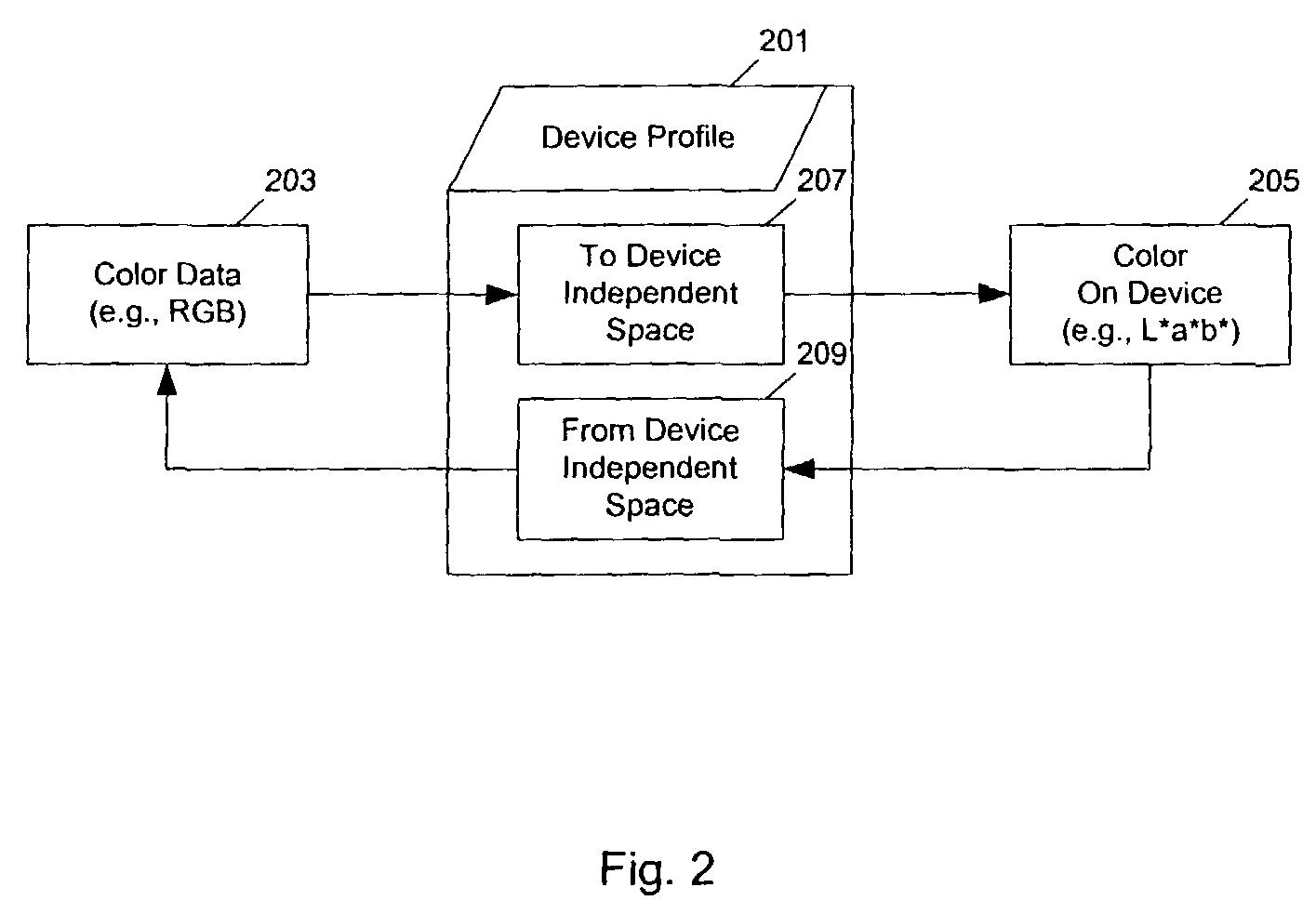

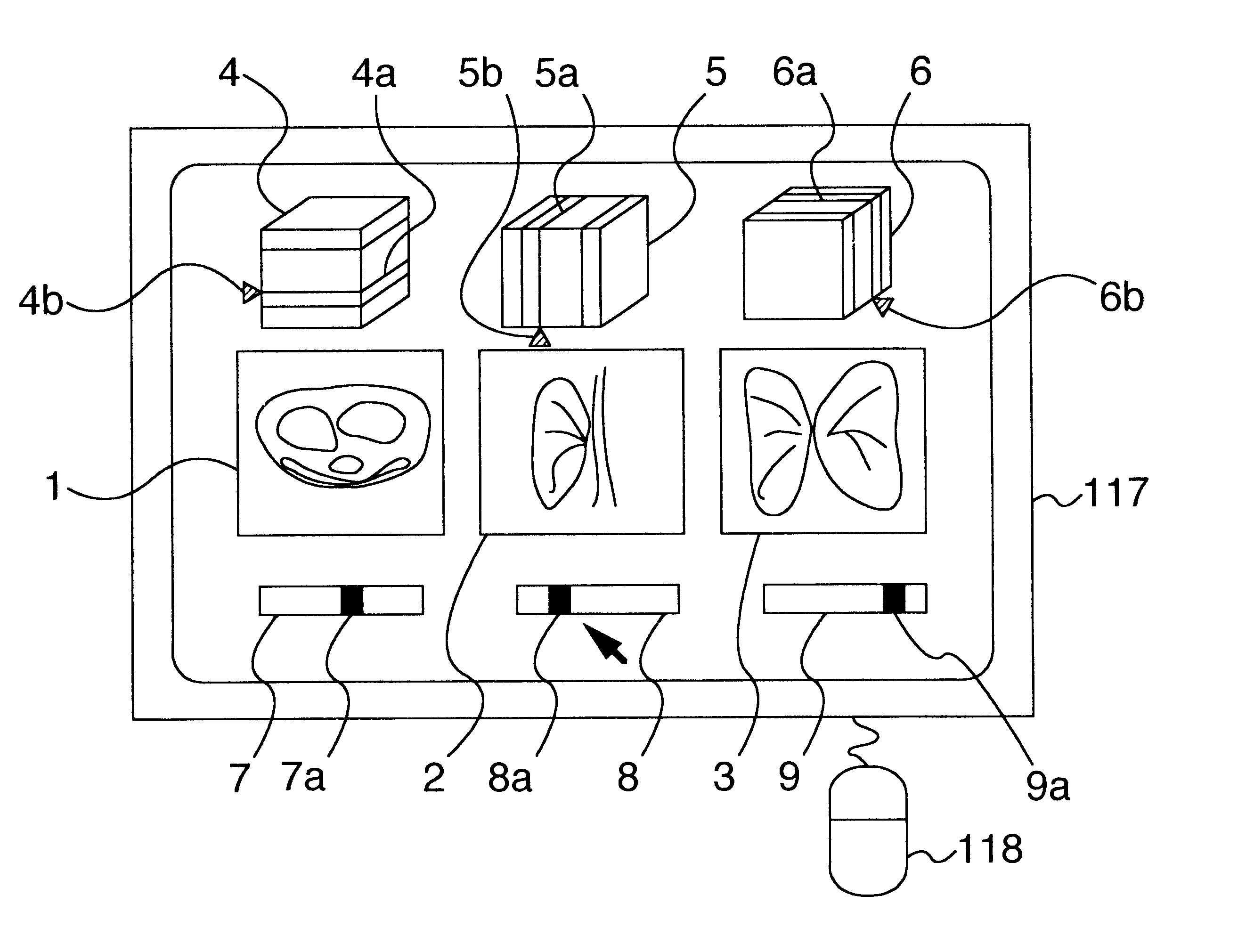

Image display

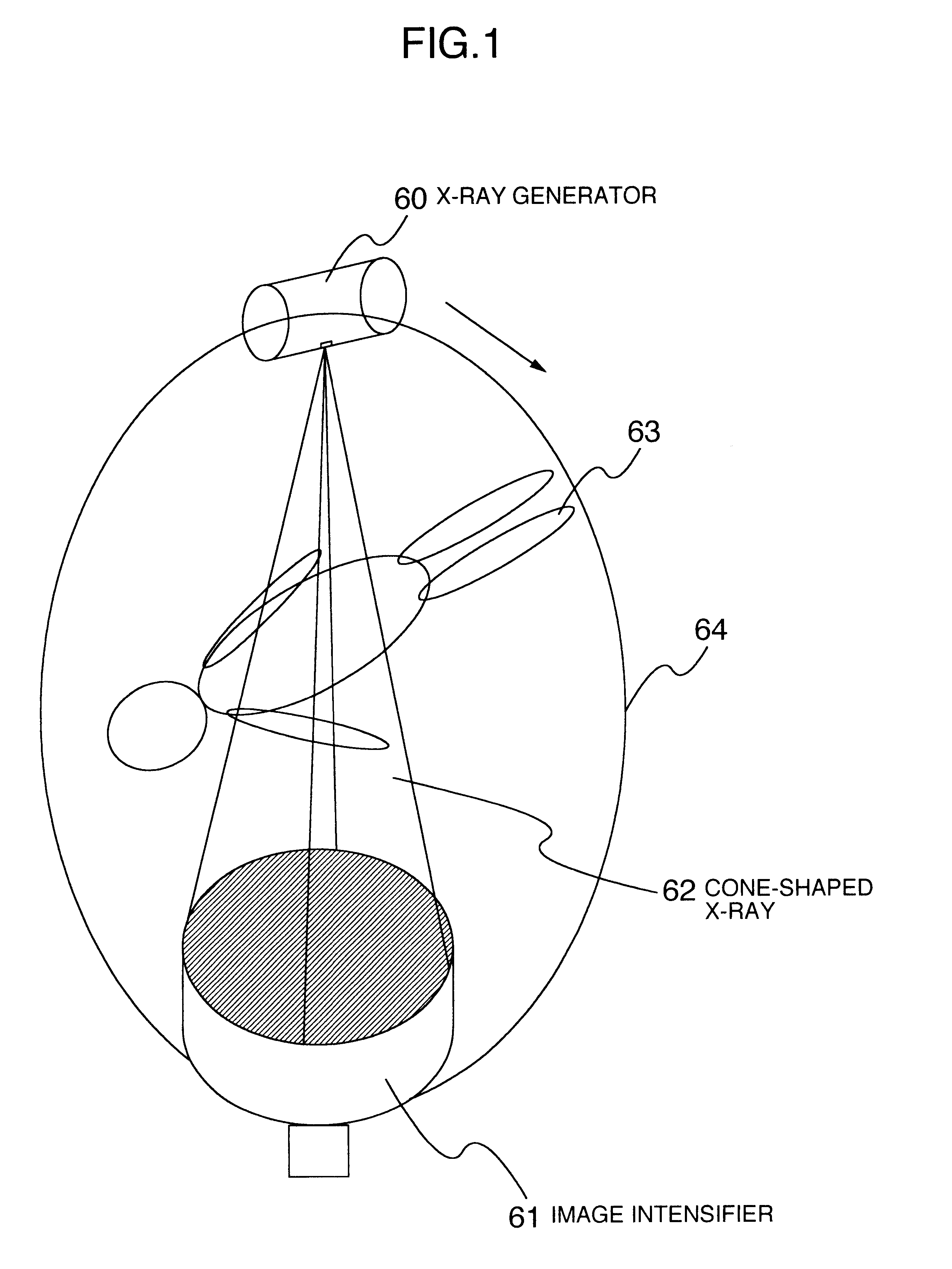

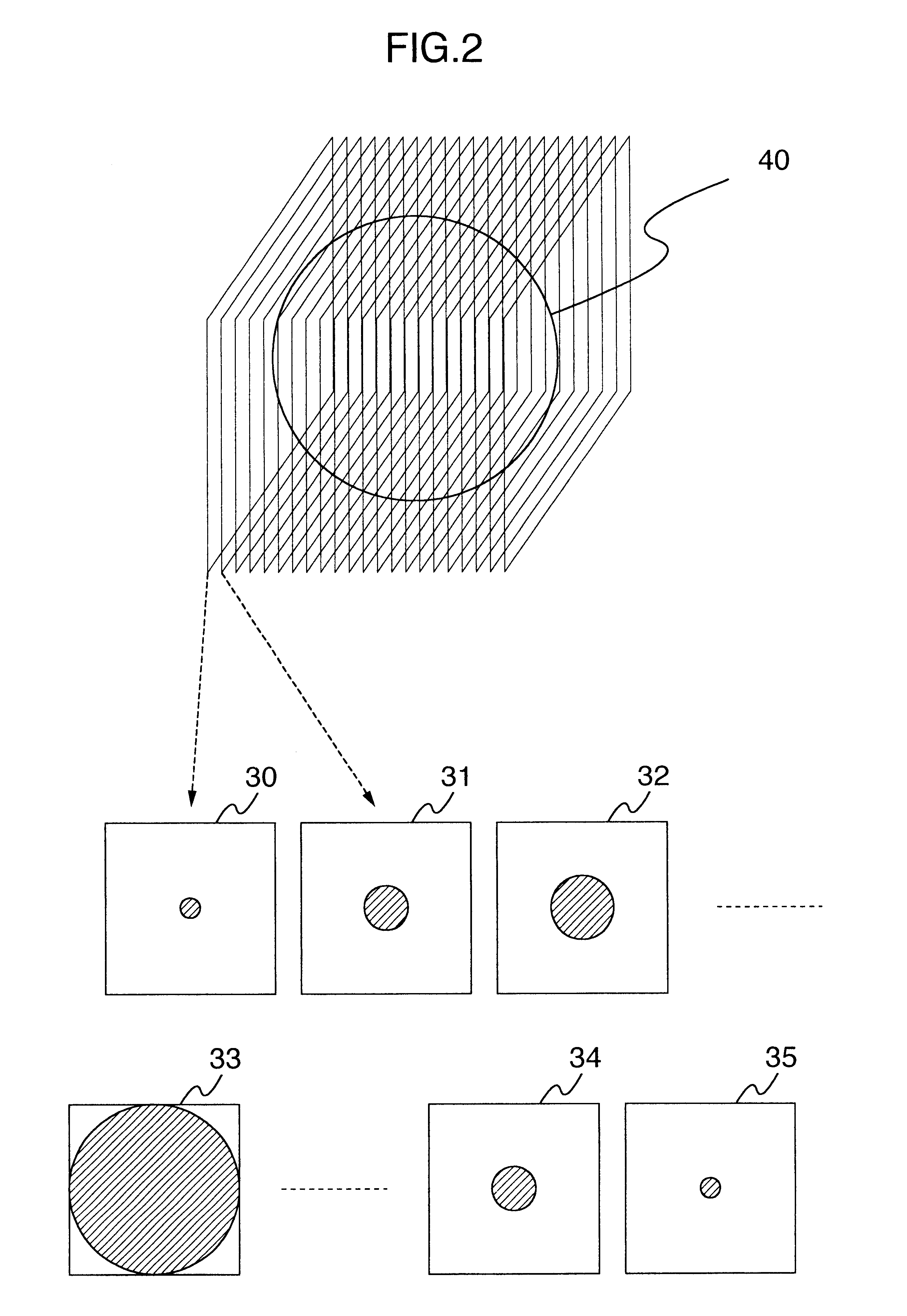

InactiveUS6891963B1Improve efficiencyUsed in small amountUltrasonic/sonic/infrasonic diagnosticsCharacter and pattern recognitionCrt monitorTomographic image

In an image display apparatus capable of storing therein a small amount of images and also capable of displaying two sorts, or more of images within a short time period, an axial image 1, a sagittal image 2, and a coronal image 3, which are loaded from a magnetic disk, are displayed on a CRT monitor 117. Image position indication FIGS. 4, 5, 6 are indicated above the respective tomographic images, and positions of the respective tomographic images are indicated on the respective image position indication FIGS. 4, 5, 6 by employing heavy lines 4a, 5a, 6a, and triangular symbols 4b, 5b, 6b. The positions of the tomographic images can be adjusted by dragging the respective triangular symbols 4b, 5b, 6b by using a mouse 118. Image position input FIGS. 7, 8, 9 are indicated under the respective tomographic images, and the positions of the respective displayed tomographic images are indicated on the image position input FIGS. 7, 8, 9 by way of drag bars 7a, 8a, 9a. Alternatively, the positions of the tomographic images may be adjusted by dragging the drag bars 7a, 8a, 9a by using the mouse 118.

Owner:HITACHI MEDICAL CORP

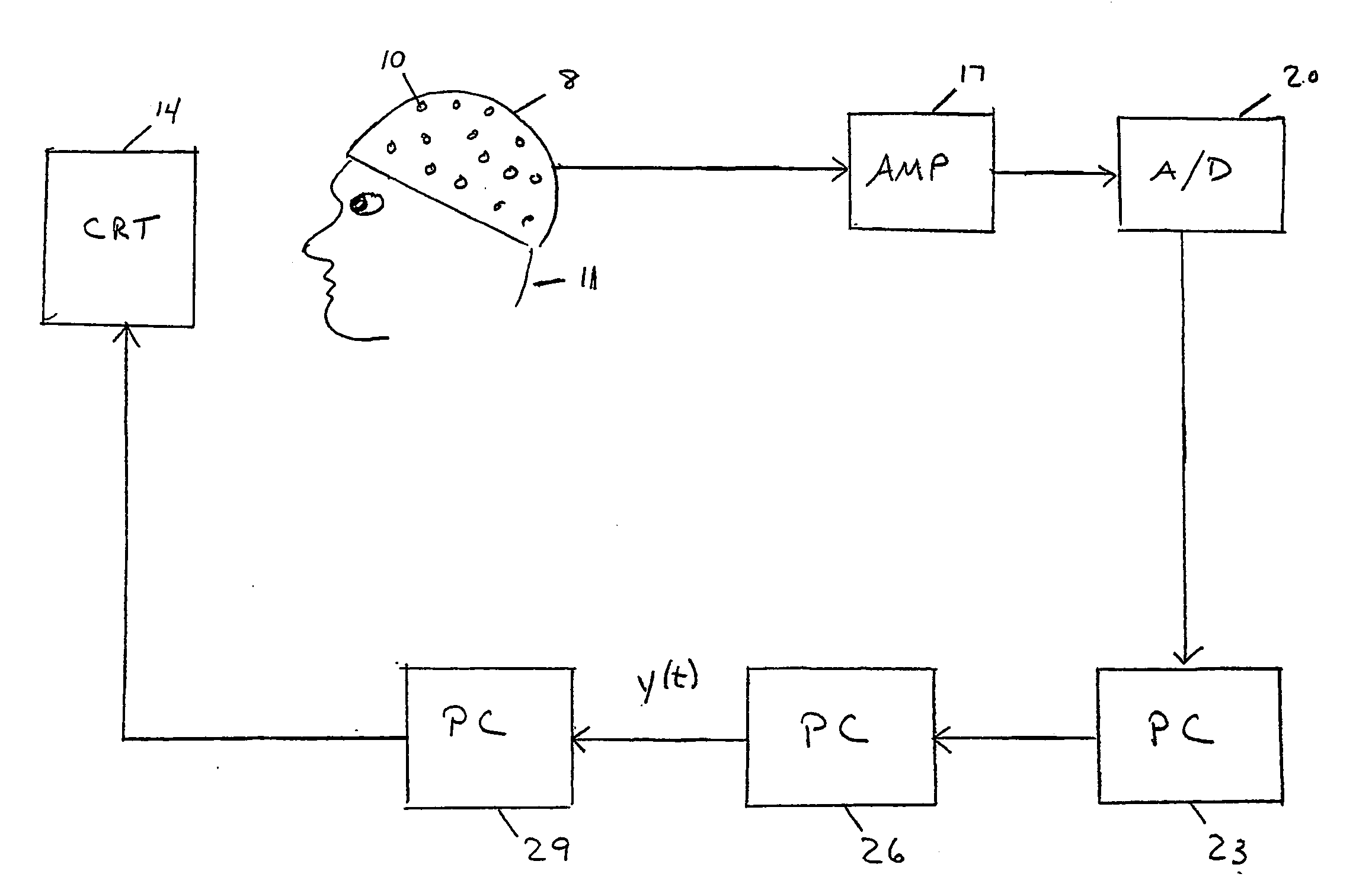

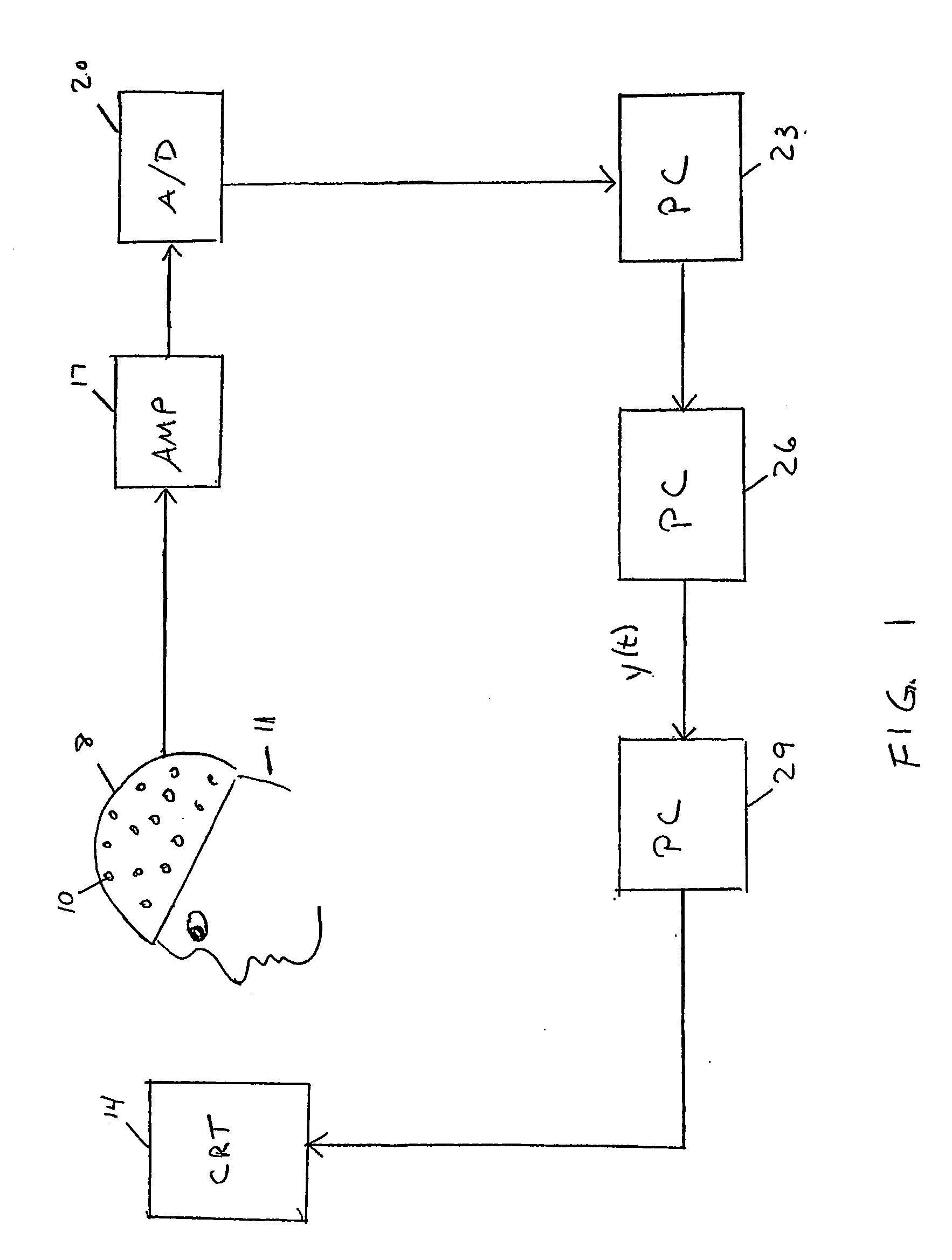

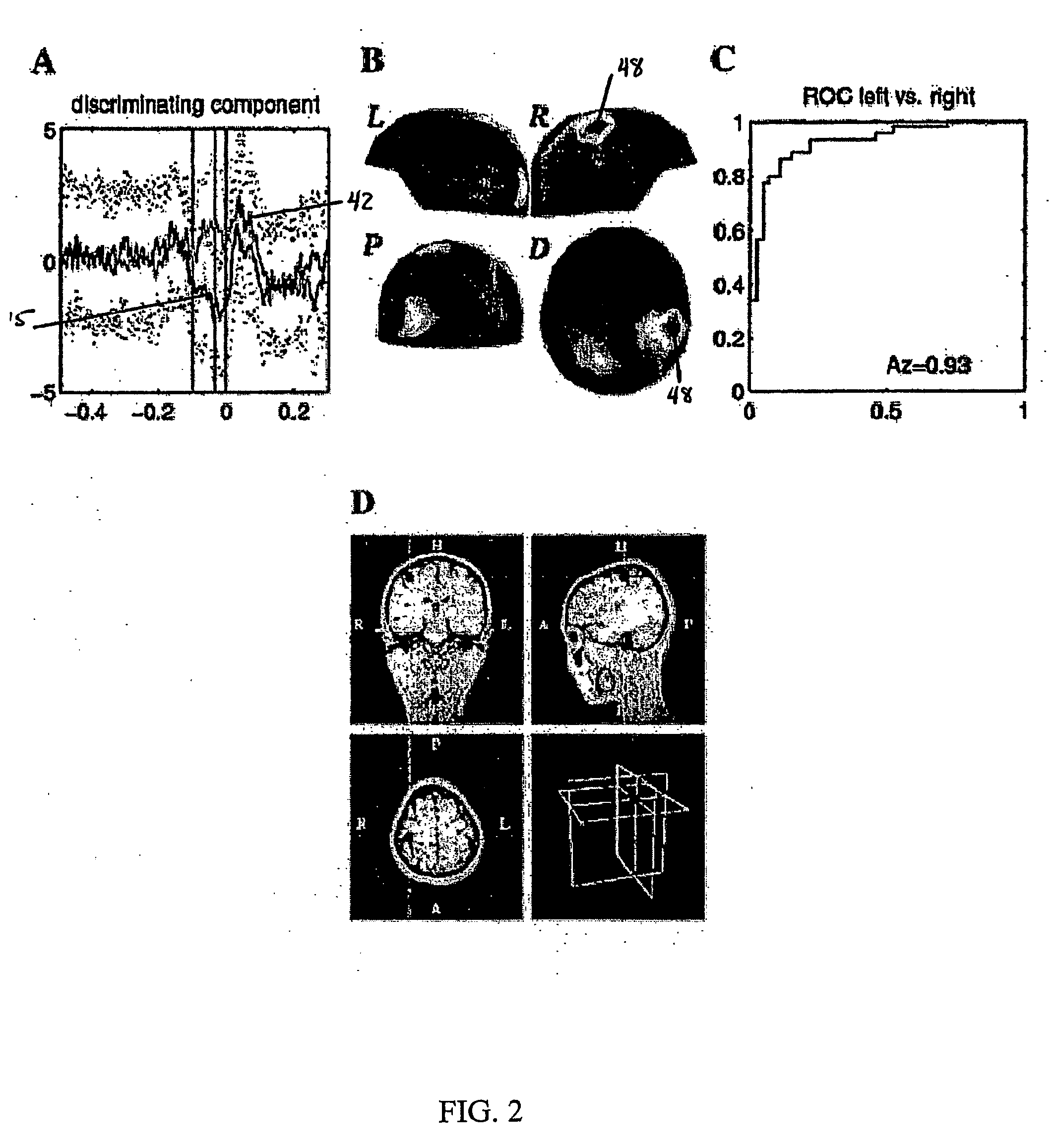

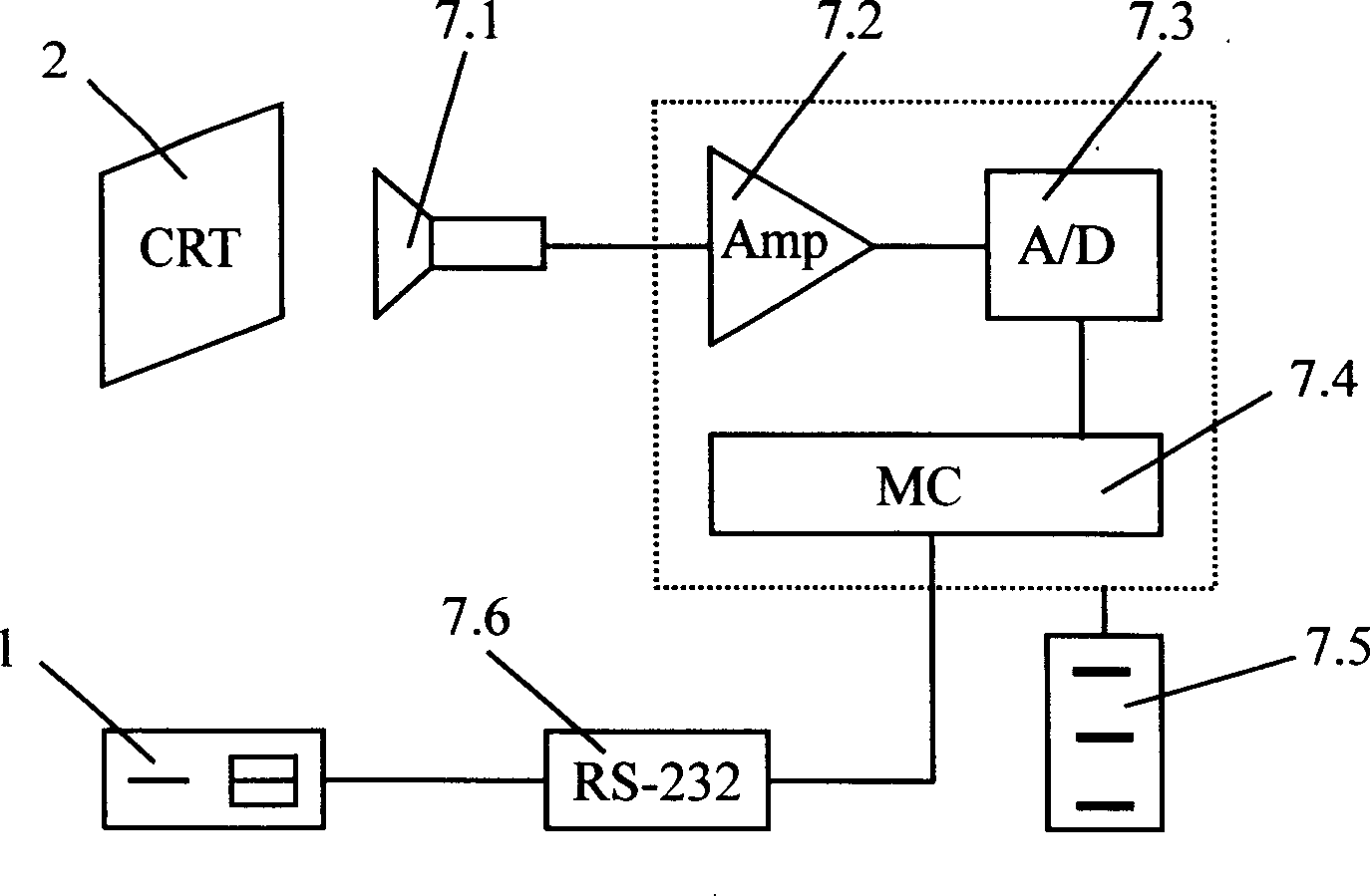

Single trial detection in encephalography

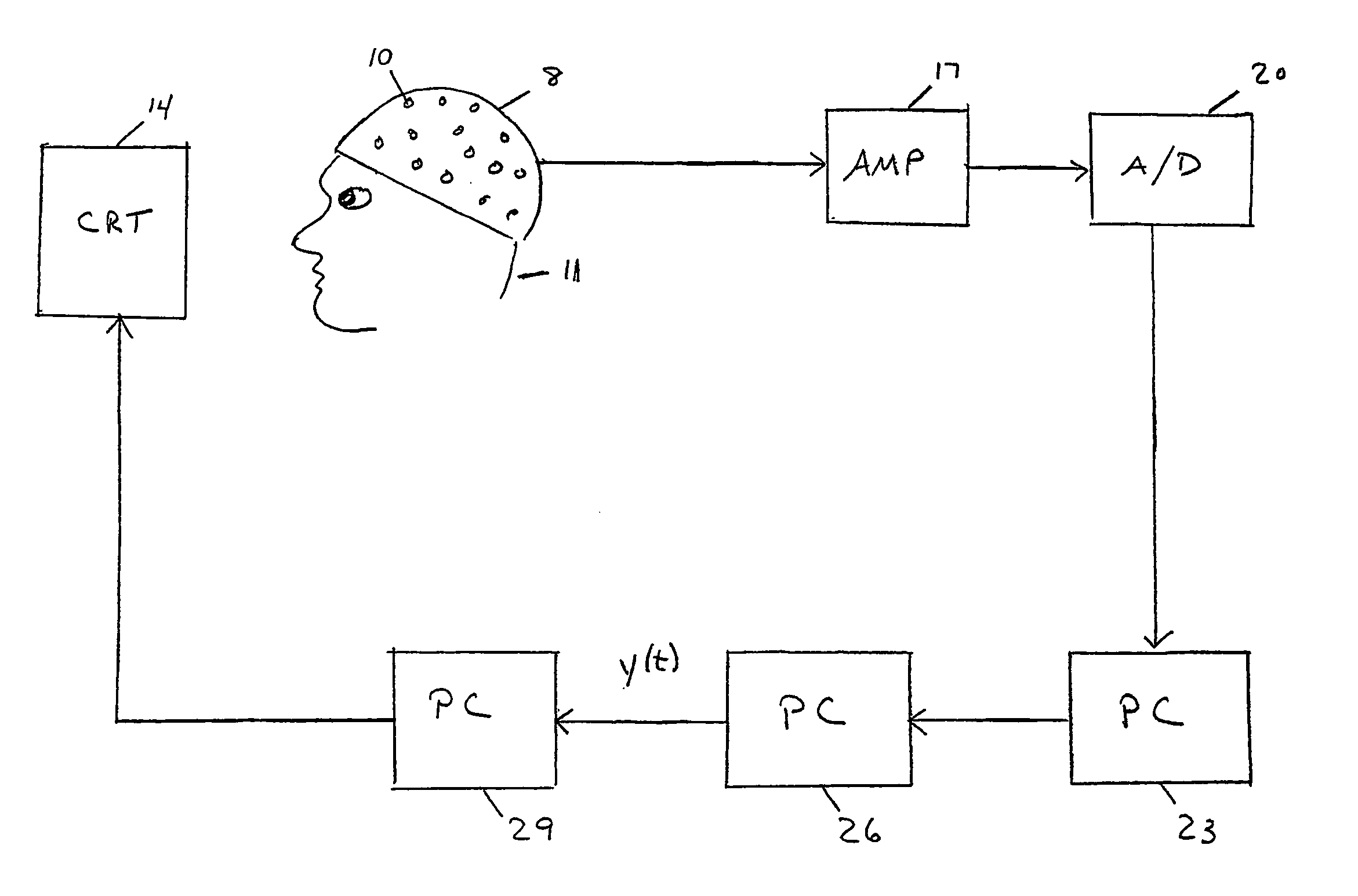

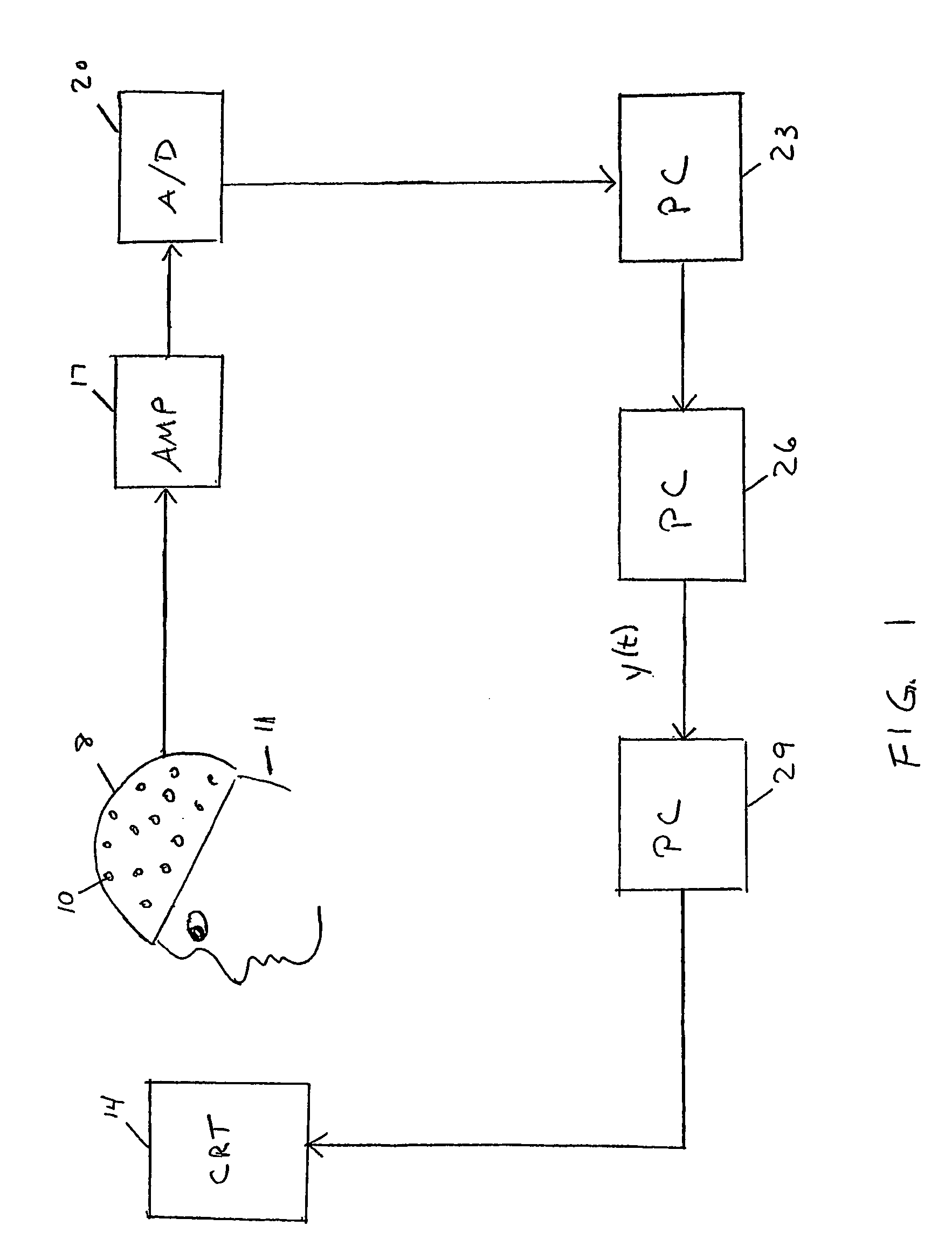

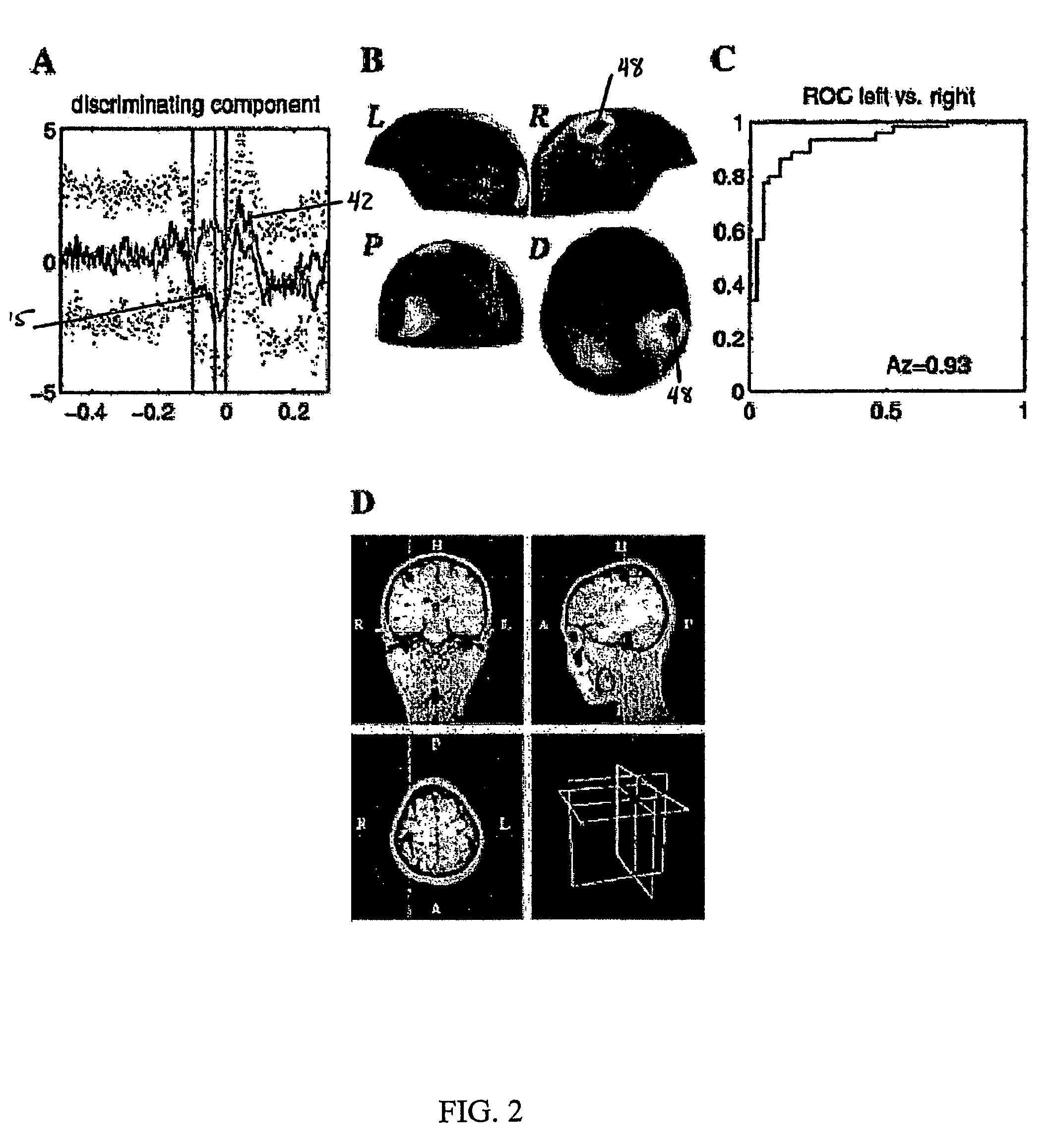

ActiveUS20090326404A1Performance maximizationGood single trial discriminationElectroencephalographySensorsAudio power amplifierSignal on

An EEG cap (8) having 64 or 128 electrodes (10) is placed on the head of the subject (11) who is viewing CRT monitor (14). The signals on each channel are amplified by amplifier (17) and sent to an analog-to-digital converter (20). PC (23) captures and records the amplified signals and the signals are processed by signal processing PC (26) performing linear signal processing. The resulting signal is sent back to a feedback / display PC (29) having monitor (14).

Owner:THE TRUSTEES OF COLUMBIA UNIV IN THE CITY OF NEW YORK

Method and apparatus for color correction of color devices for various operating conditions

InactiveUS20110249141A1Television system detailsColor signal processing circuitsColor correctionDisplay device

Methods and apparatuses for color correction of color device for various operating conditions. In at least one embodiment of the present invention, operating under a current condition, a color correction operation that is derived from color correction operations defined for other conditions is performed on the color data. In another embodiment, a device profile for managing colors for a color device operating under one condition is interpolated from the device profiles for the color device operating under other conditions (e.g., based on the input received from a user interface according to the perception of the user or based on the measurement of a sensor). The interpolation can be based on the input received from a user interface according to the perception of the user or it can be based on the measurement of a sensor or a set of sensors. Various operating conditions for a color device (e.g., a scanner, a camera, a video camera, a printer, a display device such as a CRT monitor or an LCD display panel, a television set, or others) include chromaticity and illumination of ambient light, background color for a display device, characteristics of print media for a printer, humidity, temperature, pressure and ink level for an ink jet printer, the age of a light source for a scanner, and others.

Owner:CHEN KOK +3

Single trial detection in encephalography

An EEG cap (8) having 64 or 128 electrodes (10) is placed on the head of the subject (11) who is viewing CRT monitor (14). The signals on each channel are amplified by amplifier (17) and sent to an analog-to-digital converter (20). PC (23) captures and records the amplified signals and the signals are processed by signal processing PC (26) performing linear signal processing. The resulting signal is sent back to a feedback / display PC (29) having monitor (14).

Owner:THE TRUSTEES OF COLUMBIA UNIV IN THE CITY OF NEW YORK

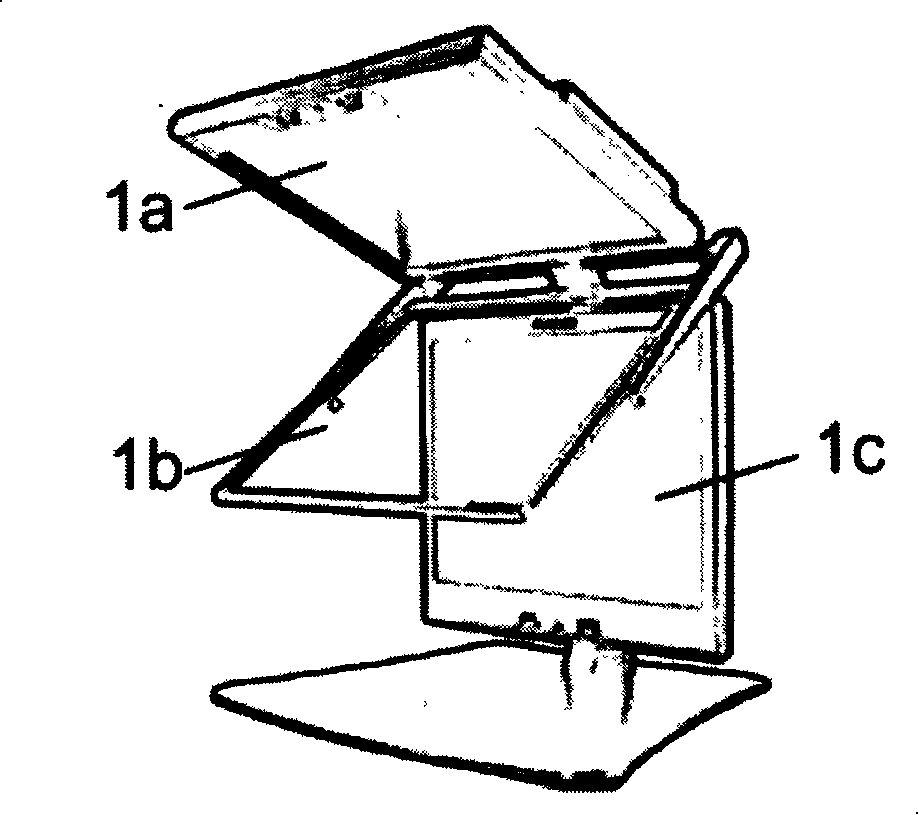

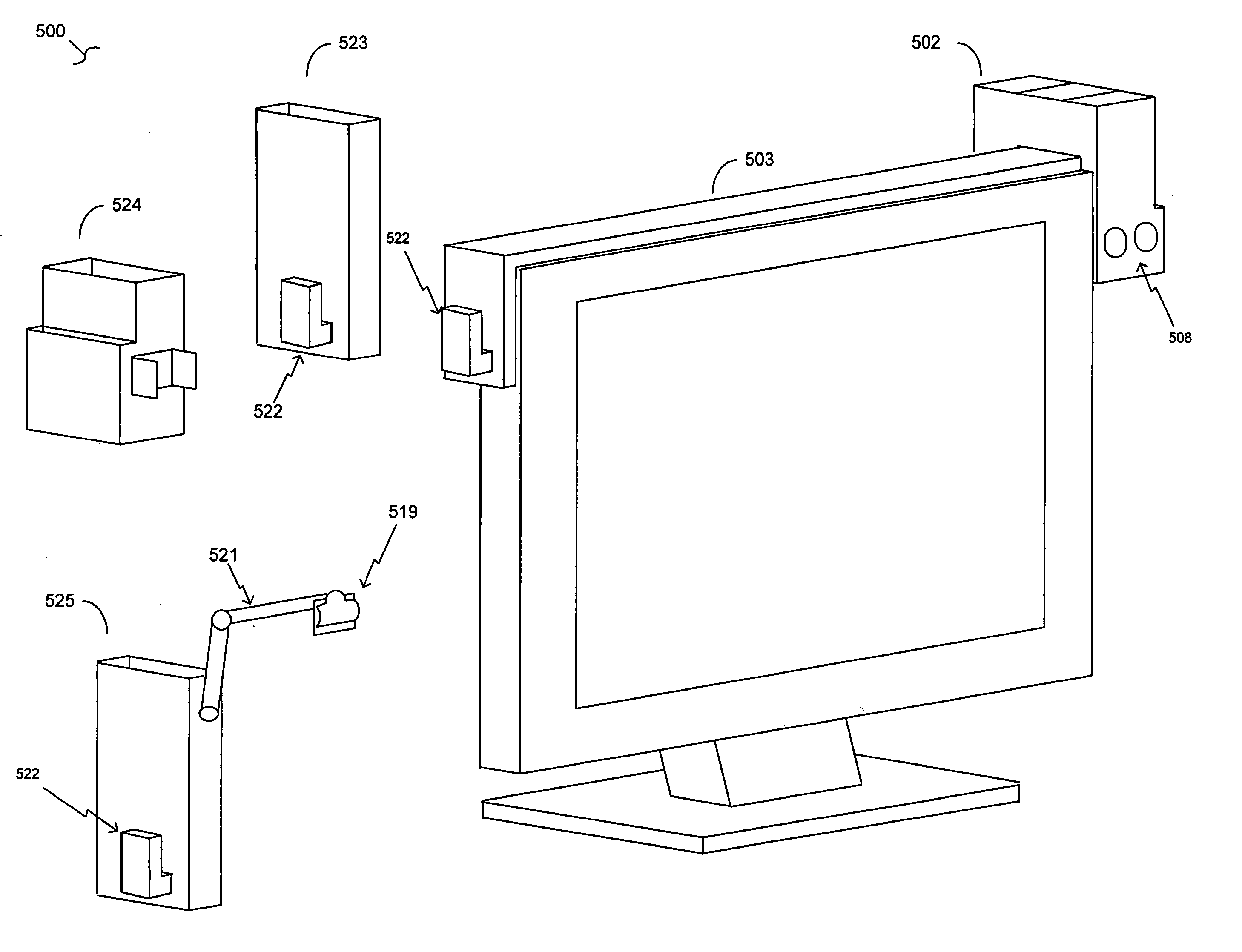

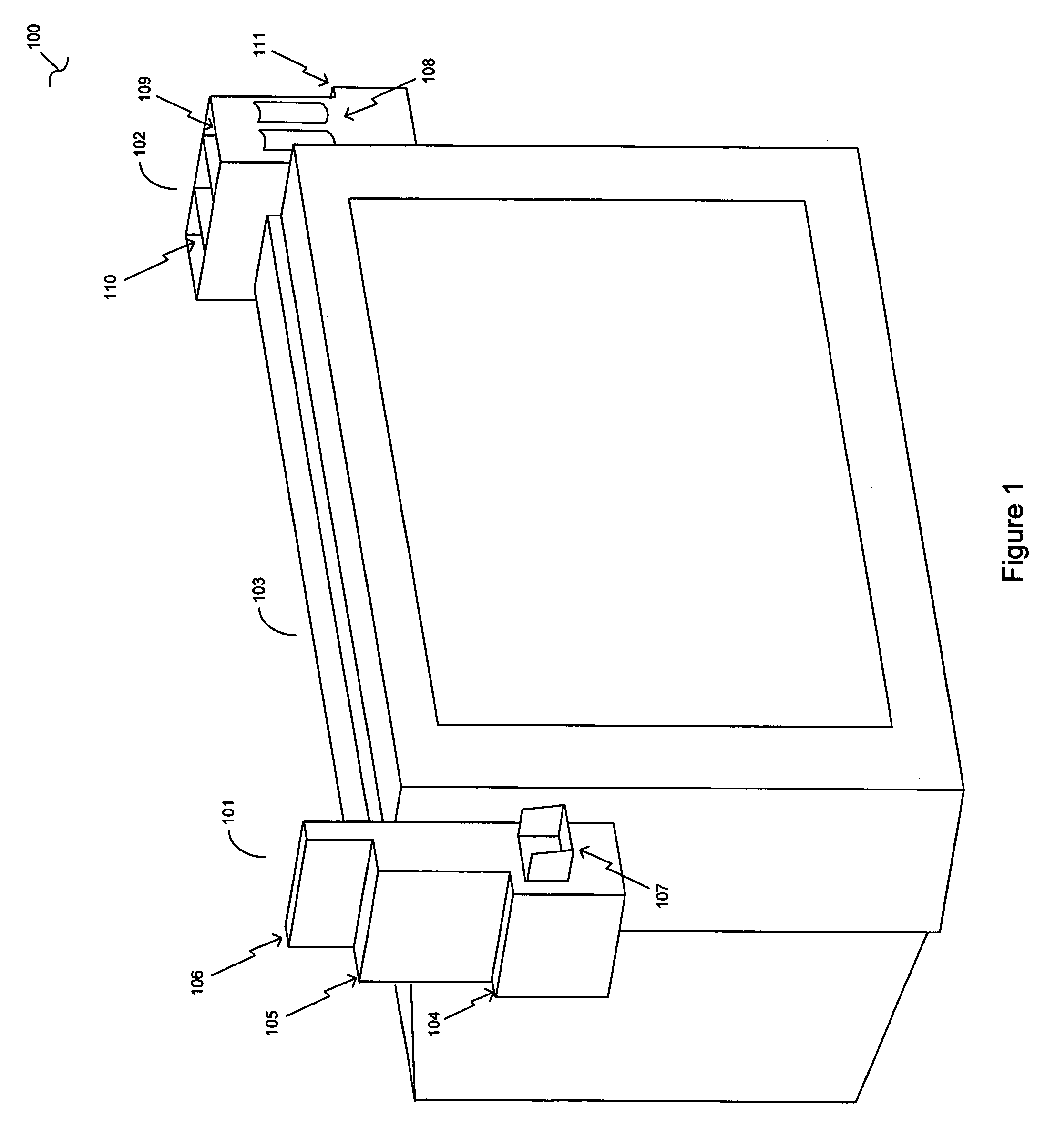

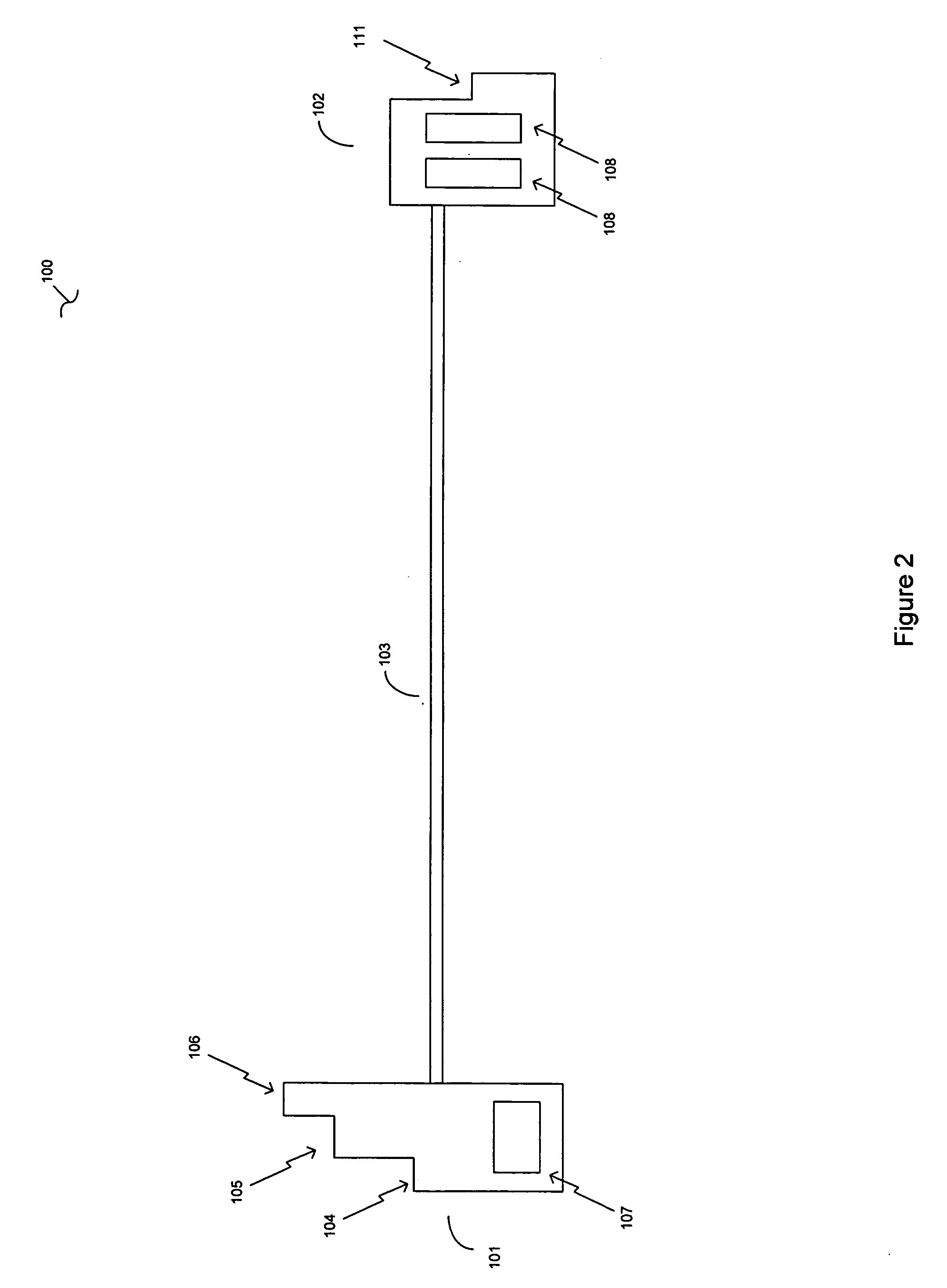

Computer monitor organizer

An organizer is adapted for use with a viewing device such as a computer monitor. The monitor organizer includes a left organizer module, a right organizer module, and a connector 103. The organizer modules may be formed to provide holders or other organizing functionality such as document holders, cell phone holders, writing instrument holders, envelope holders, post-it holders, business card holders, file or paper holders, and the like. The organizer modules may be detachable or permanent, and may allow additional modules to be attached. A rear module or modules may also be included, and the monitor organizer may be adapted to work on a variety of viewing devices including CRT monitors as well as flat panel monitors. The monitor organizer may also expand or contract to accommodate monitors of different external dimension.

Owner:DICKERSON MARK

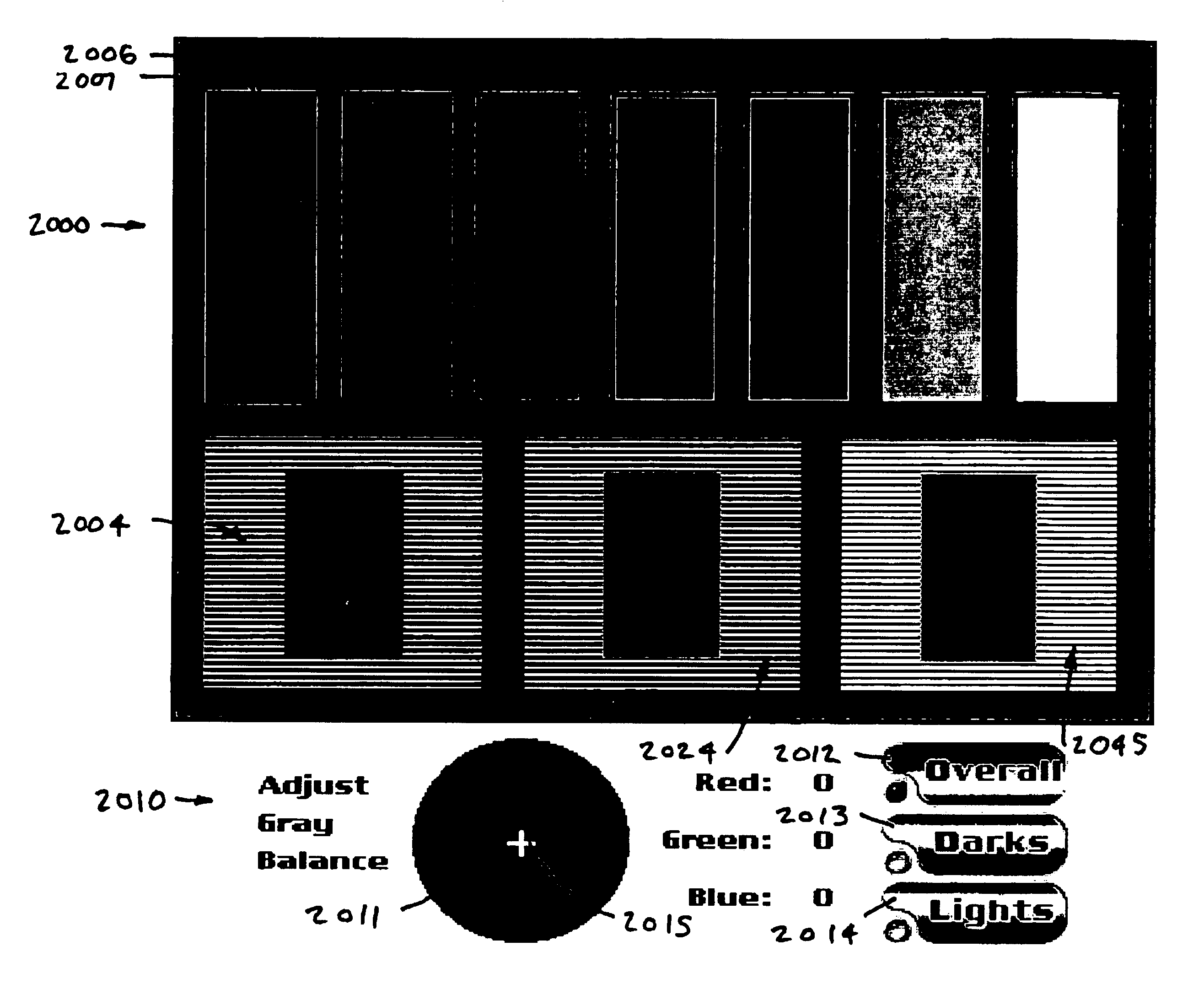

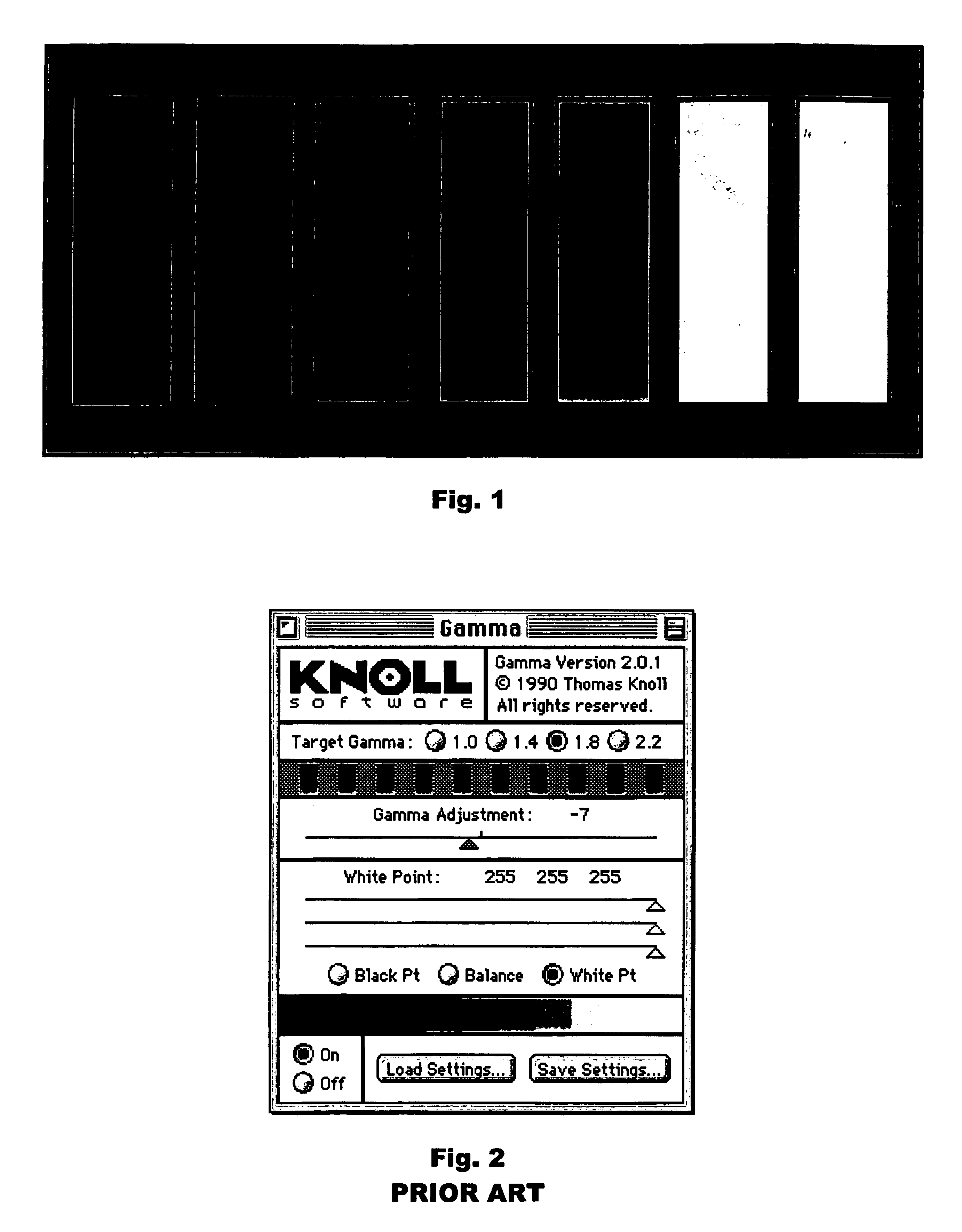

Visual calibration target set method

A novel process of visual calibration of a computer display or the like in volves adjusting the appearance and relative appearance of targets and su targets displayed on the display. An objective method is provided for determining the precisely optimal brightness setting for CRT displays, which method is also applicable to the setting of the “Black Level” control on some FPDs. A precise method is provided to visually determine conformity of a display's tonality to a given standard tone curve, for example a gamma 1.8 curve, which is embodied in one of the preferred calibration target sets. The need to sense and therefore be able to control and to verify the correct gray balance of the entire tone scale of the display is met. The problem of verifying the similarity of the tone curve in the display profile and that of the actual calibration is solved. By converting a preferred RGB gamma target into CIE Lab image data through an ideal display profile of the correct gamma, a new kind of target is taught.

Owner:HOLMES JOSEPH

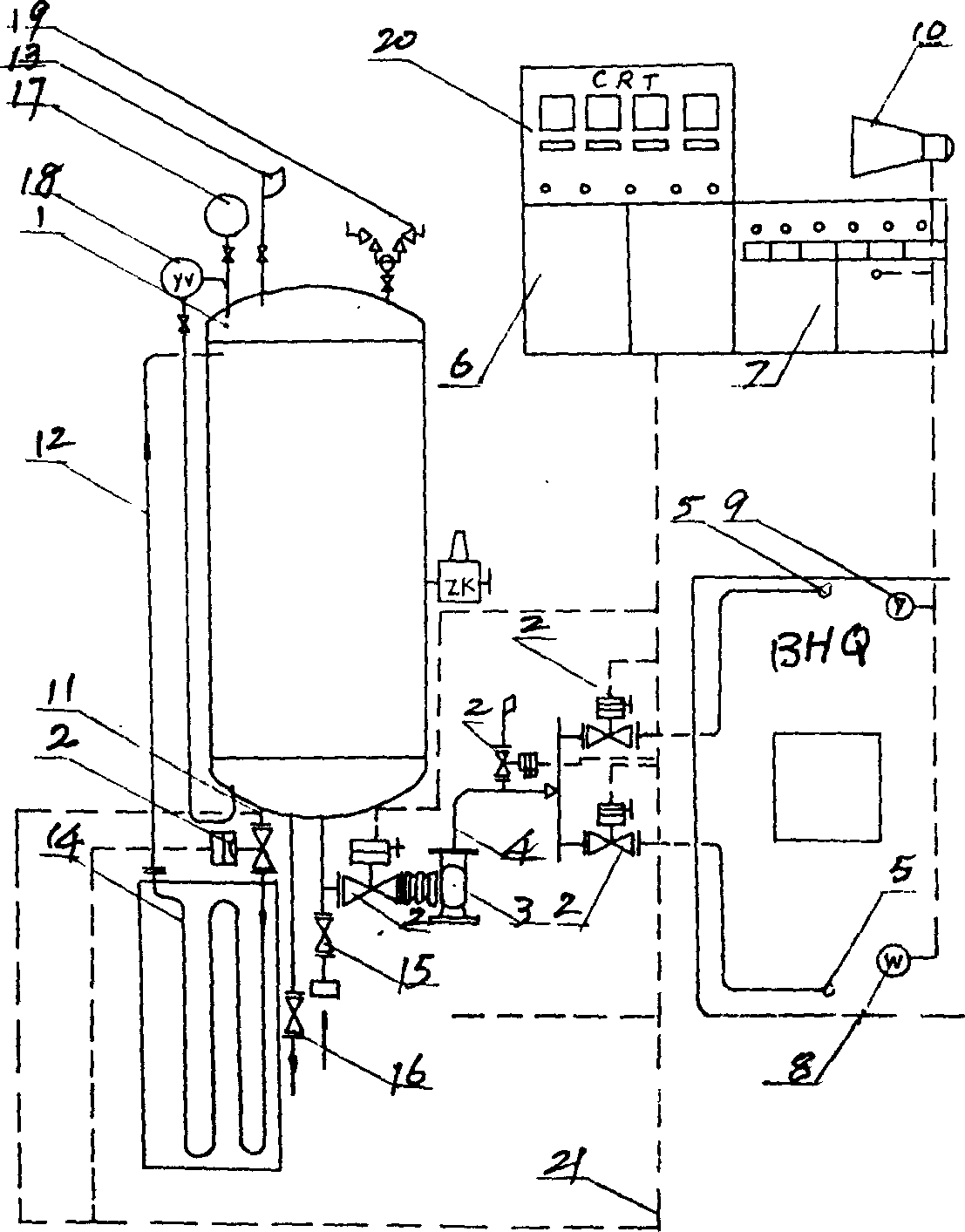

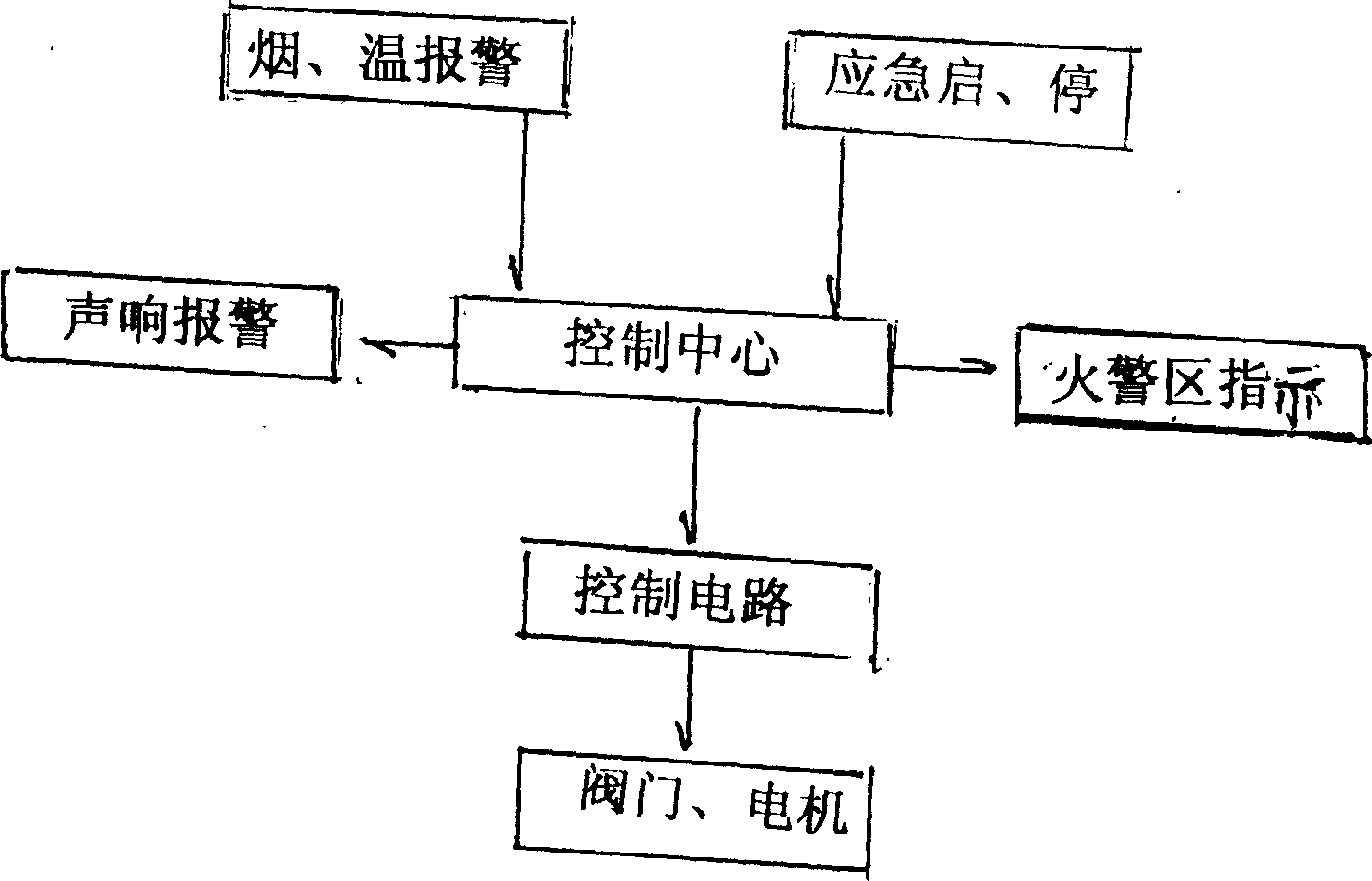

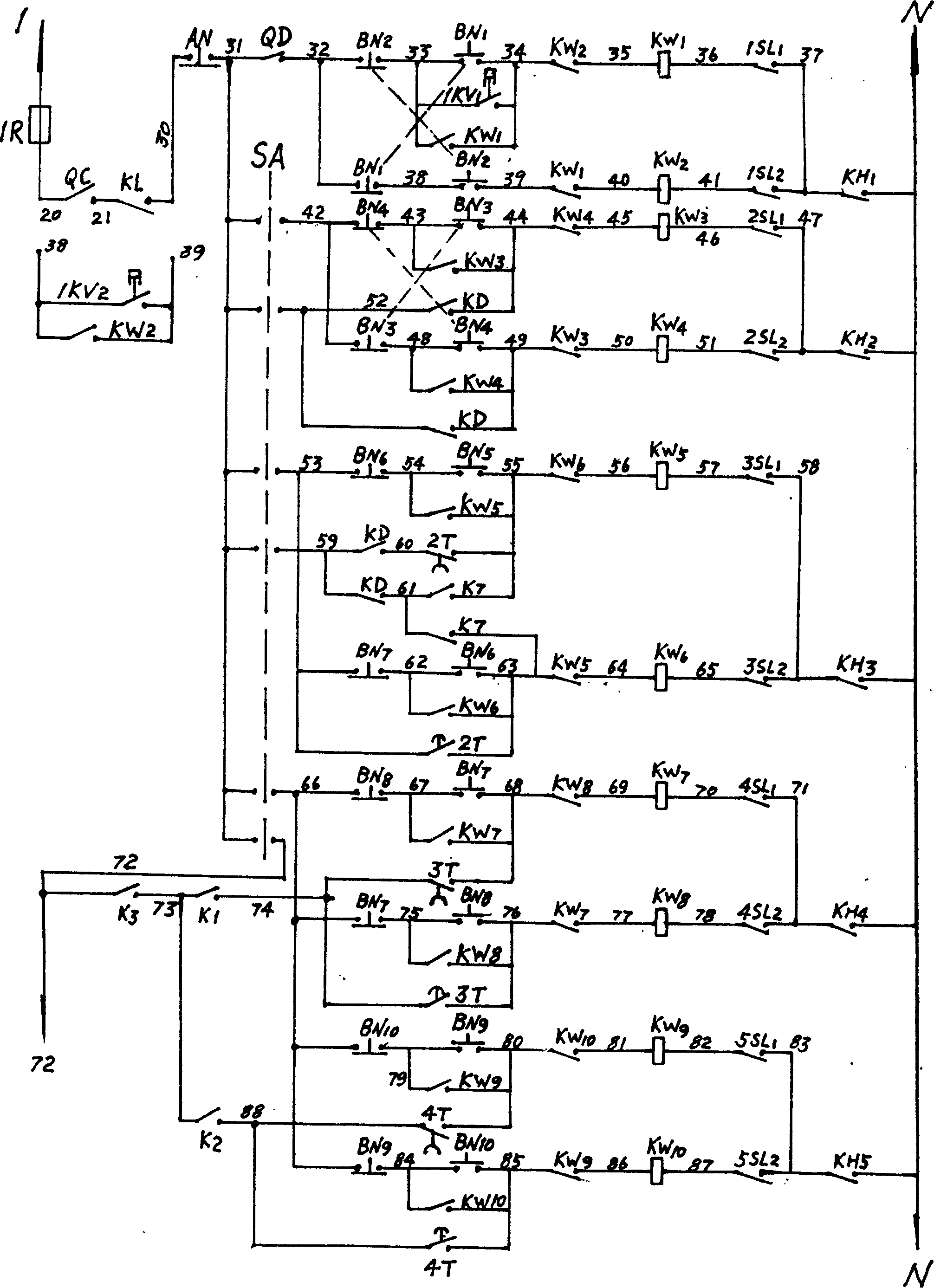

Fire extinguishing apparatus using liquid nitrogen as fire extinguishing agent

The invention is a kind of extinguishing device which uses liquid nitrogen as extinguishing agent. The tin is made upof stainless steel wire vacuum clamp and adiabatic outer laye which is winded by aluminium and platinum. There is pressure gage, liquid leveler, air relief valve, safety valve. The bottom has a liquid charging valve and a purifying valve; one side has a evaporating device and the other side has a liquid nitrogen setting device. The electric control system is made up of linkage controller, extinguishing control plate, temperature sensing detector, annunciator and CRT monitoring device, they are connected by circuit. The control is divided into manual control and automatic control. The liquid nitrogen setting device is made up of electric self-control valve, ultralow temperature liquid pump, adiabatic pipe and nozzle.

Owner:姜华

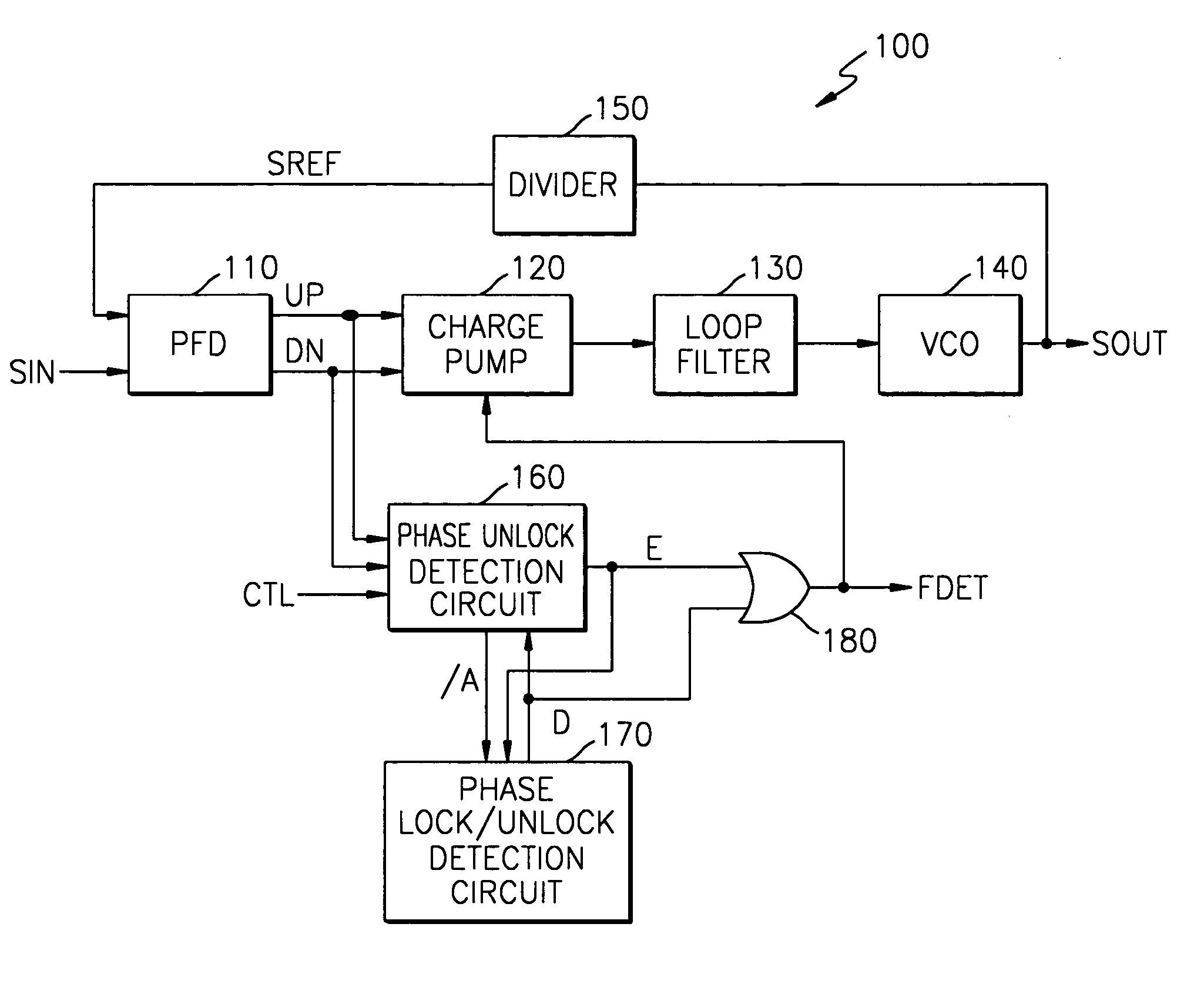

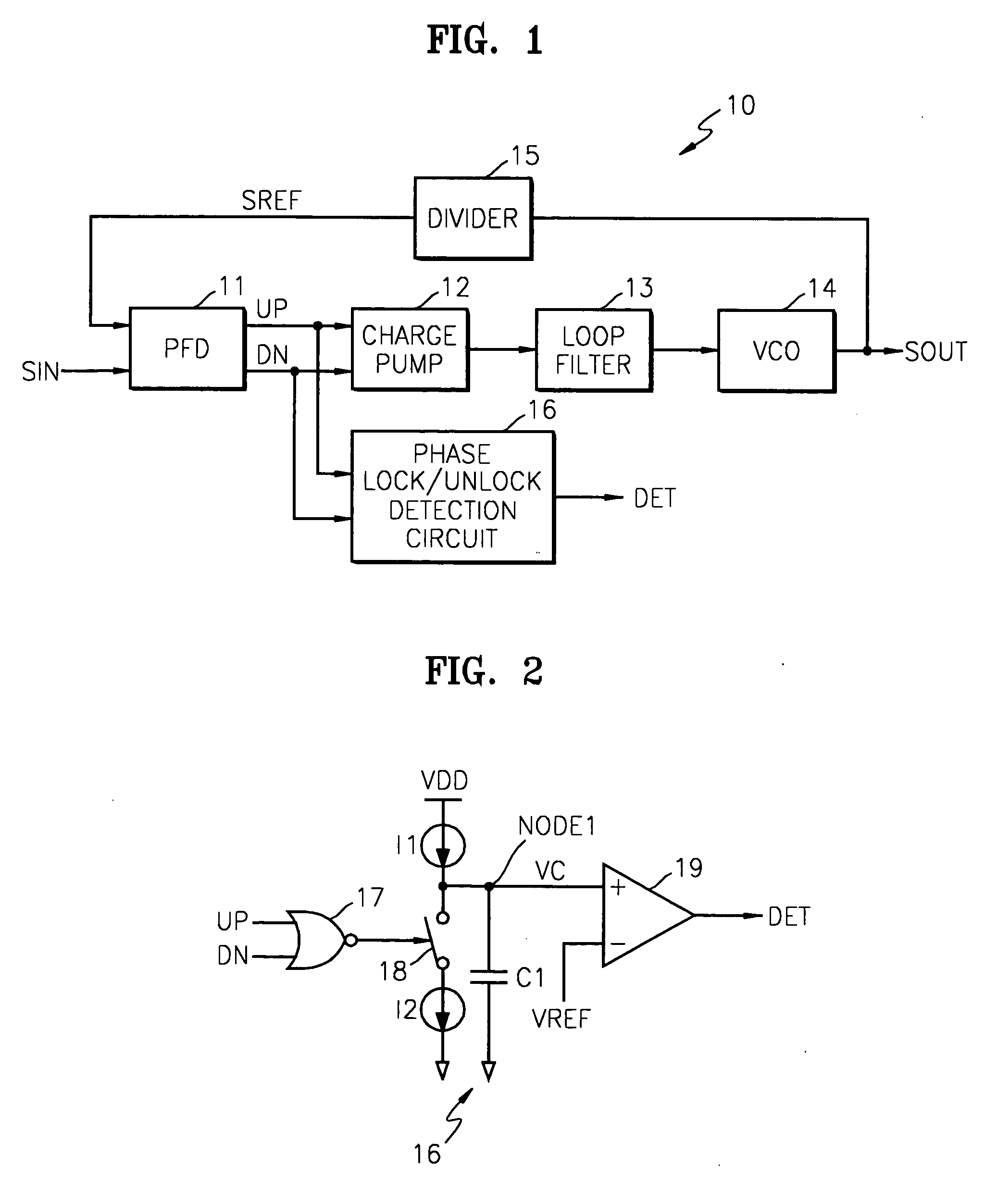

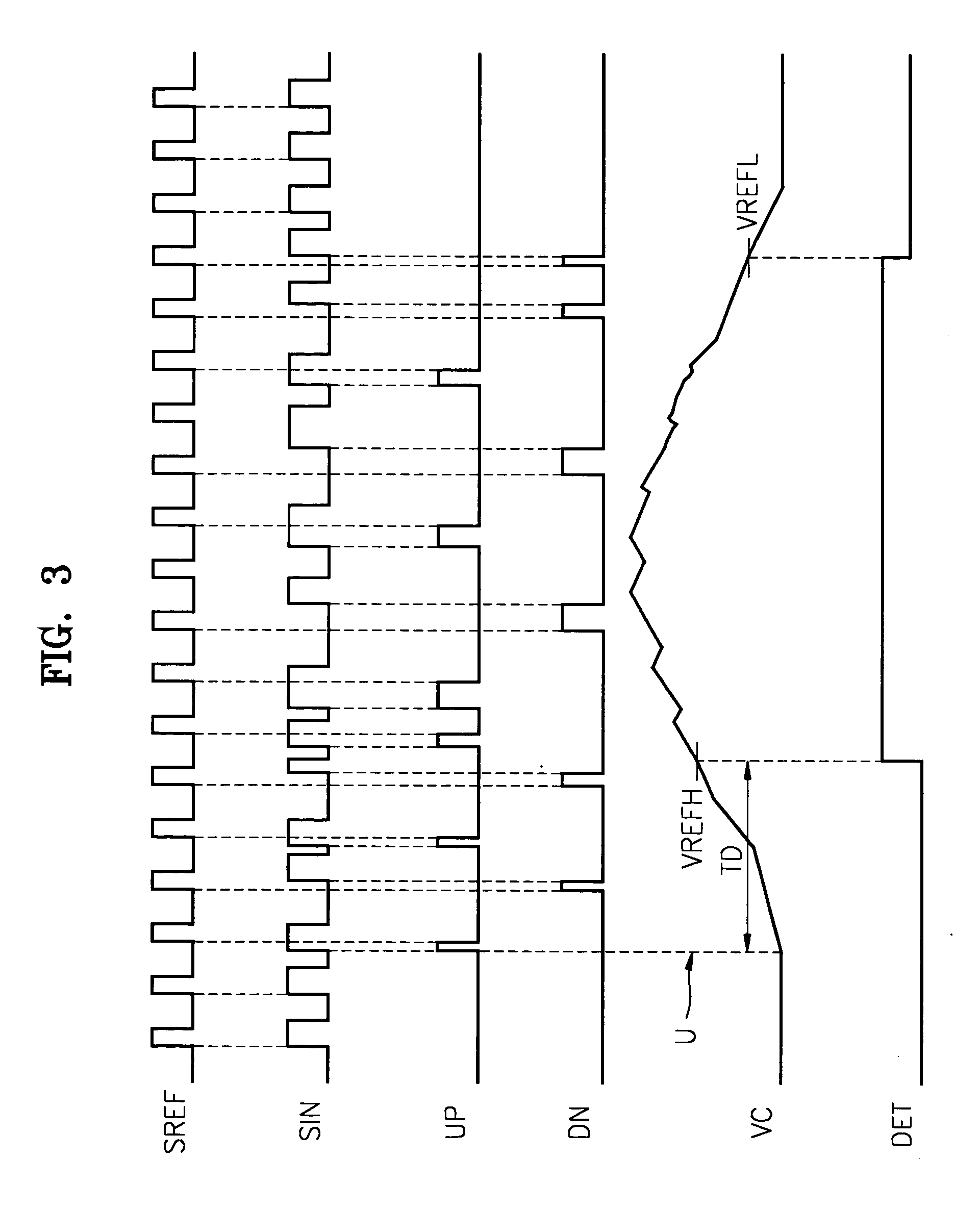

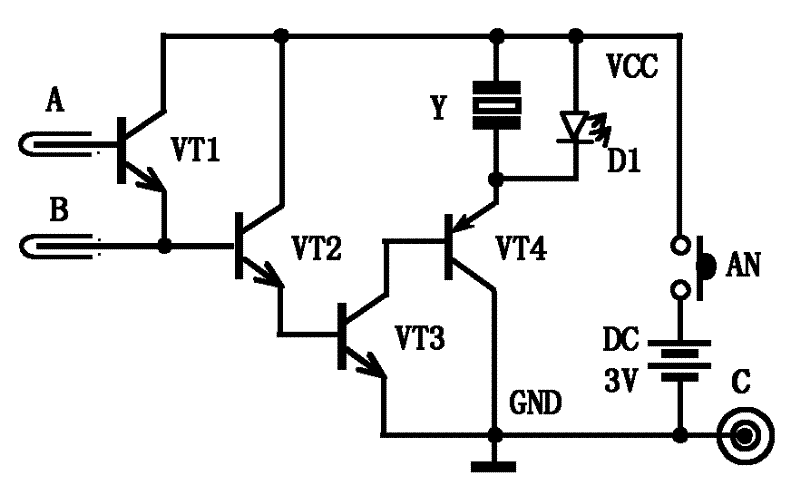

Phase locked loop with improved phase lock/unlock detection function

There is provided a phase locked loop (PLL) having an improved phase unlock detection function. The PLL generates a clock pulse signal at a frequency from a synchronization signal of a cathode ray tube (CRT) monitor. The PLL includes a phase frequency detector (PFD), a charge pump, a loop filter, a Voltage Controlled Oscillator (VCO), a divider, a phase unlock detection circuit, a phase lock / unlock detection circuit, and an output circuit. The PFD compares a phase and frequency of a synchronization signal to that of a reference signal, and outputs an up or down signal. The charge pump outputs a pumping current in response to the up or down signal. The loop filter outputs a control voltage according to the pumping current. The VCO outputs a clock pulse signal having a frequency determined by a control voltage. The divider divides the clock pulse signal by a division ratio and outputs a reference signal. The phase unlock detection circuit detects an initial generation of a phase unlock from the up or down signal, outputs a first detection signal, and outputs an internal control signal according to the up or down signal. The phase lock / unlock detection circuit outputs a second detection signal, in response to the internal control signal and the first detection signal. The output circuit performs a logic operation on the first detection signal and the second detection signal and outputs a third detection signal. Therefore, the PLL having the improved phase lock / unlock detection function can improve system stability in mode switching of a CRT monitor, by quickly detecting an initial generation of phase unlock without a time delay.

Owner:SAMSUNG ELECTRONICS CO LTD

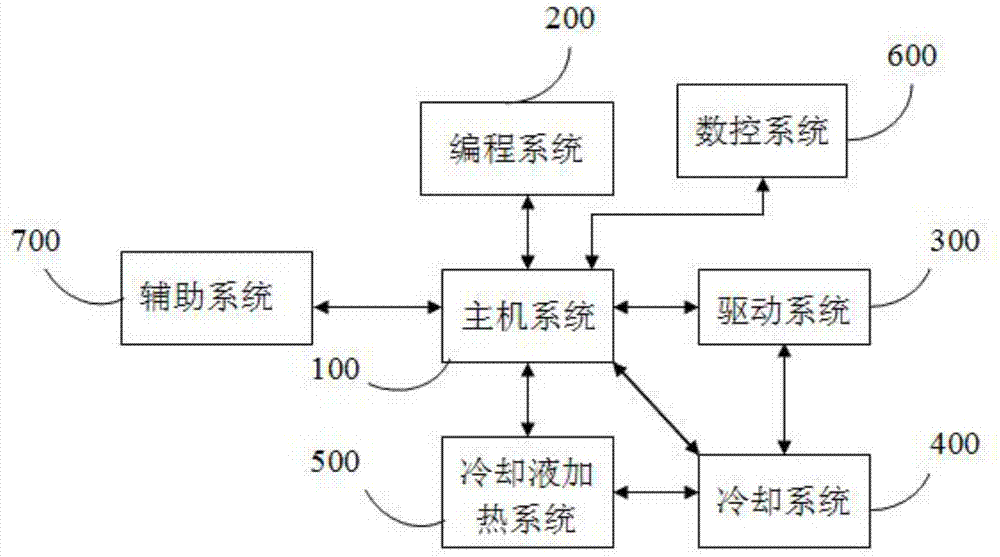

Numerical control machine tool provided with coolant device and coolant heating device

InactiveCN105436986AEfficiently provideProvided in a safe and orderly mannerMaintainance and safety accessoriesCoolant flowEngineering

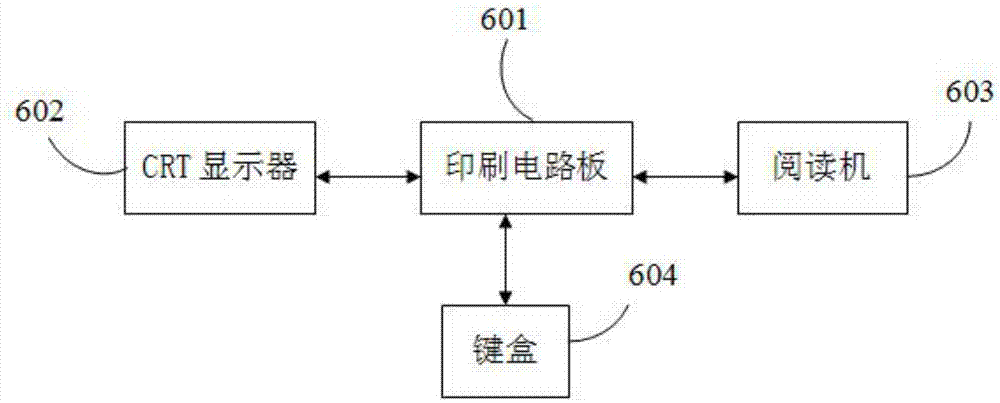

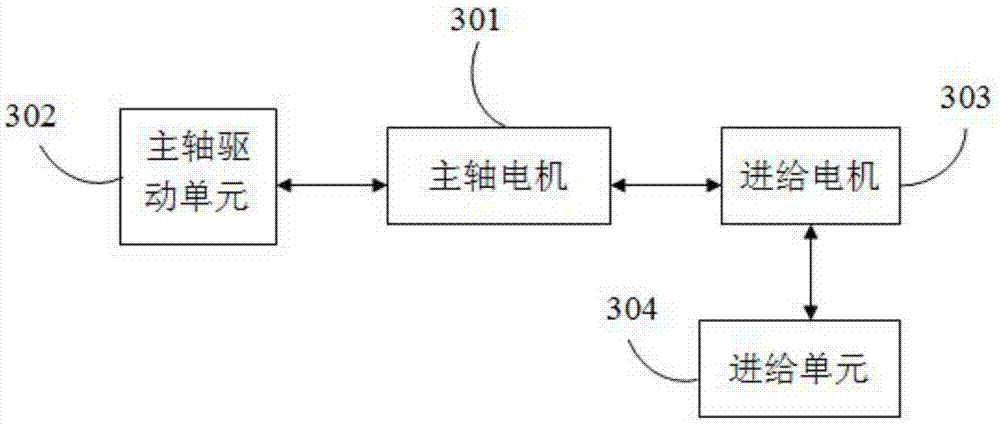

The invention discloses a numerical control machine tool provided with a coolant device and a coolant heating device, and belongs to the technical field of the numerical control machine tools. The numerical control machine tool comprises a main machine system, a programing system, a driving system, a cooling system, a coolant heating system, a numerical control system and an auxiliary system, wherein the numerical control system comprises a printed circuit board, a CRT (Cathode Ray Tube) display, a key box and a paper tape reader; the driving system comprises a spindle driving unit, a feed unit, a spindle motor and a feed motor; the cooling system comprises a coolant pump, a coolant box, coolant, a coolant pump control system, a coolant supply system, a coolant stopping system and a detection system; and the coolant heating system comprises a heating device, a switching system, a power supply, a temperature sensor, a coolant flow velocity sensor and an acousto-optic alarming device. The numerical control machine tool can remove cut chips, can provide the coolant efficiently, safely and orderly, and can heat the coolant.

Owner:QINGHAI MOLD MFG TECH CO LTD

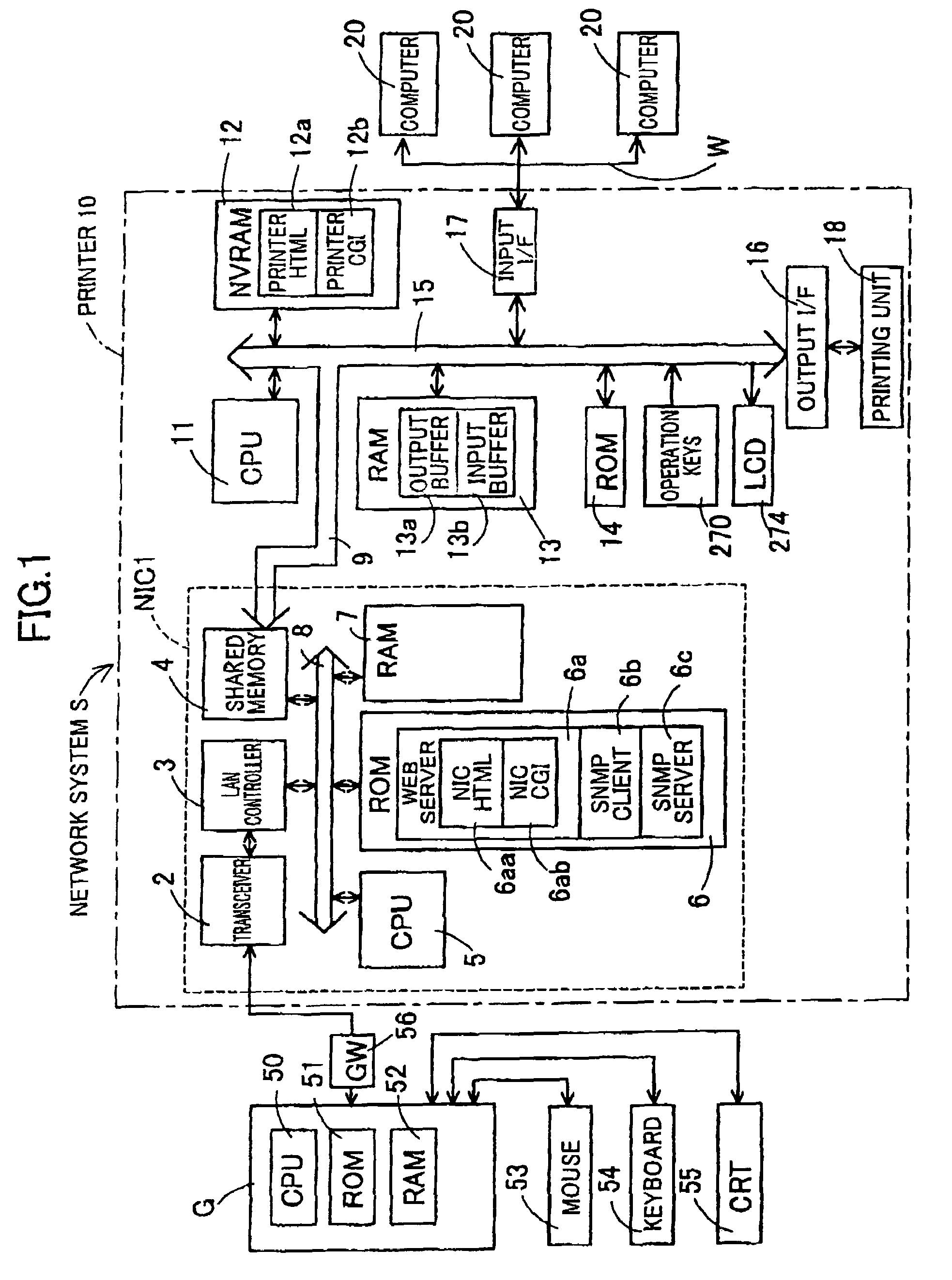

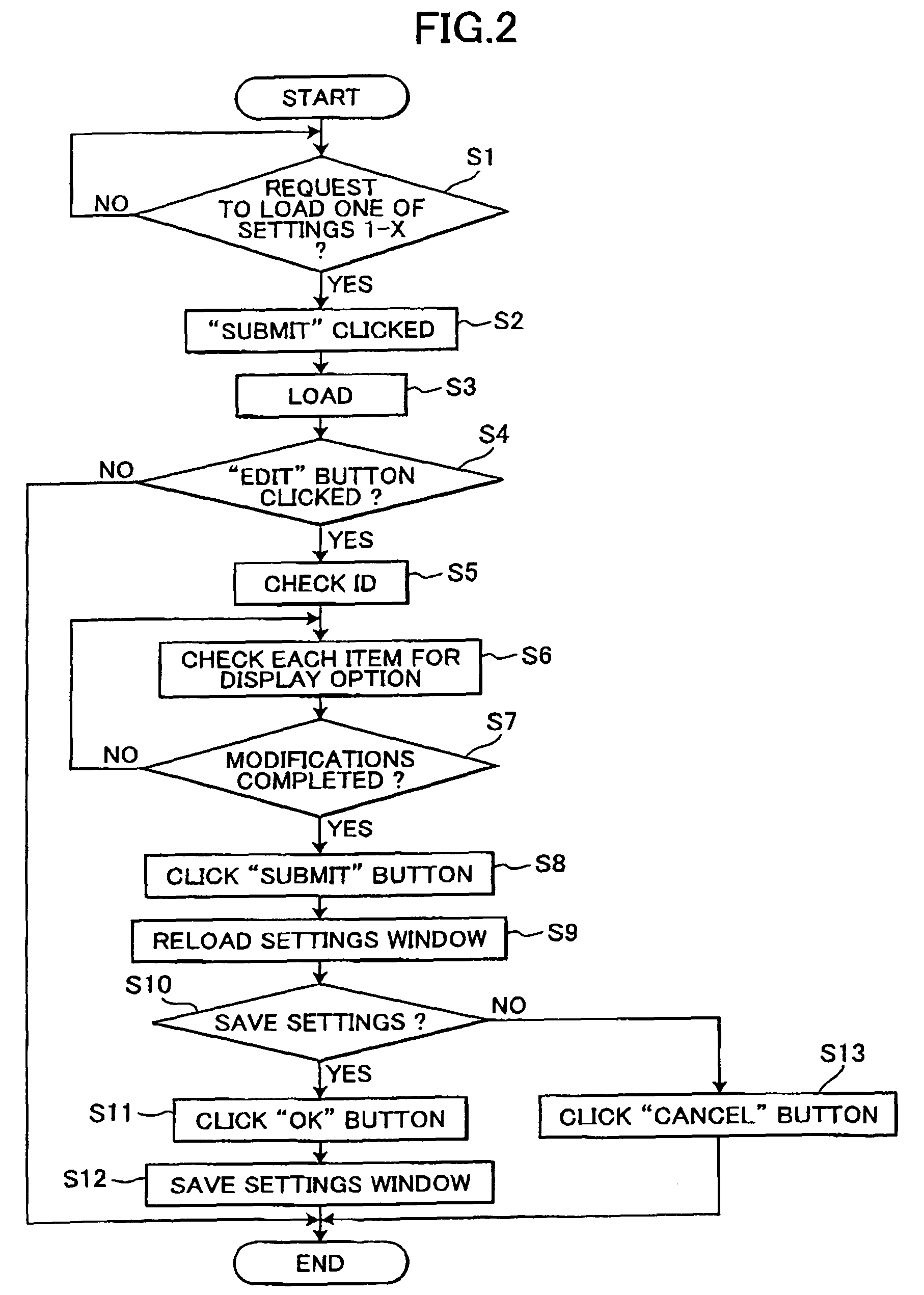

Image forming device and network system

ActiveUS7542159B2Easy to editData processing applicationsDigital data processing detailsData setImage formation

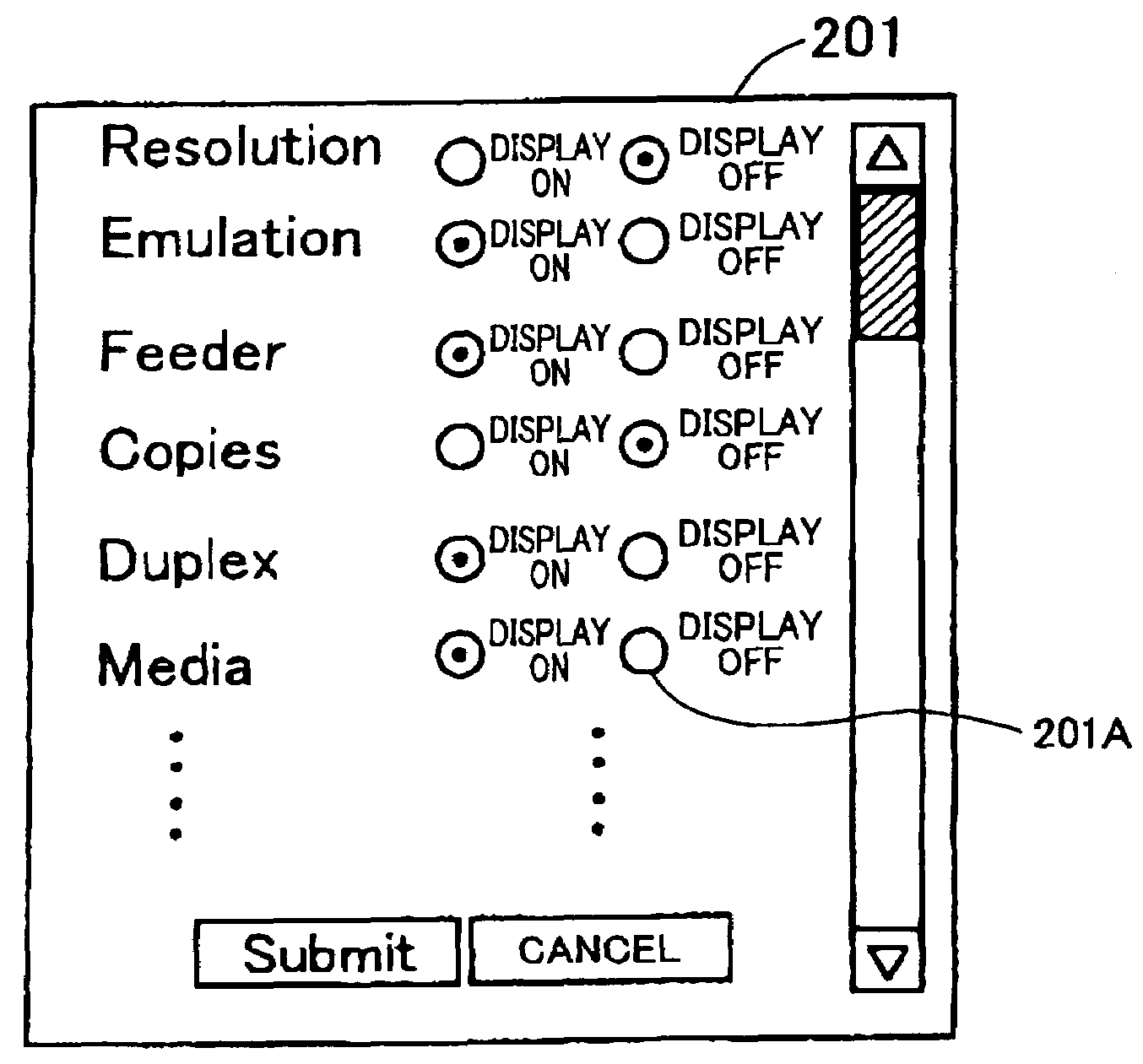

When the printer 10 receives a request signal from one of the administrative computer G and the computers 20 indicating that the user has used the mouse 53 to click the “Edit” button displayed on the CRT monitor 55 (S4), then the printer 10 transmits data for the edit wizard 201 for modifying setting items displayed in the print function settings wizard 202 to the administrative computer G or the computer 20 corresponding to the ID data set attached to the request signal. The user uses the mouse 53 to click on either “Display on” or “Display off” next to each setting item in the edit wizard 201 displayed on the CRT monitor 55 (S6), enabling the user to re-edit setting items displayed in the print function settings wizard 202 (S7-S13).

Owner:BROTHER KOGYO KK

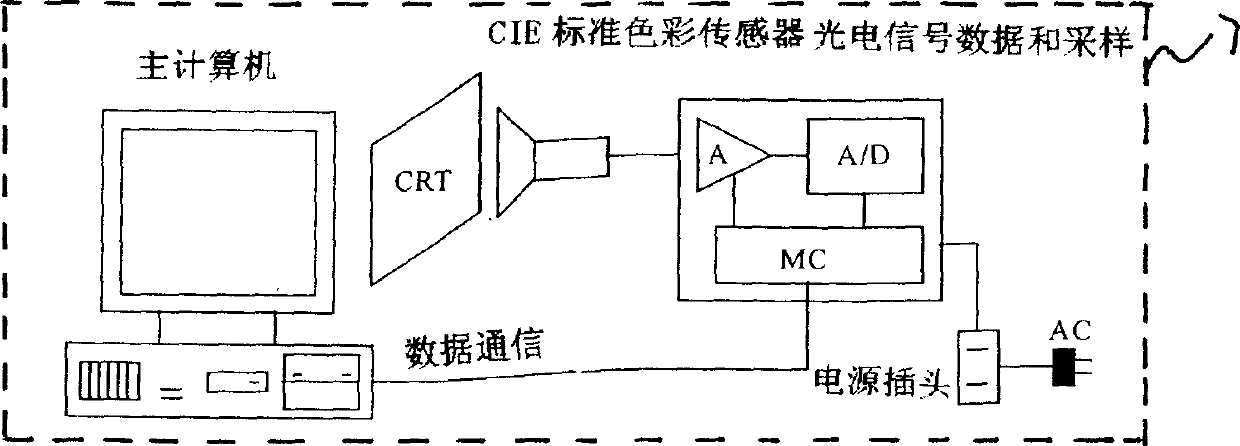

Color anomaly quantitative detection instrument

InactiveCN1559338AAchieving psychophysical quantitative testingImprove detection efficiencyEye diagnosticsSpecial data processing applicationsCrt monitorVisual perception

A quantitative tester of color anomalopia is composed of computer, high-performance color CRT display, standard photoelectric scaling system for human eyes, dedicated responsekeyboard, printer, light shield andmandible supporter. It has high automation level.

Owner:杭州泰来医疗器械有限公司

Backlight Apparatus and Liquid Display Apparatus

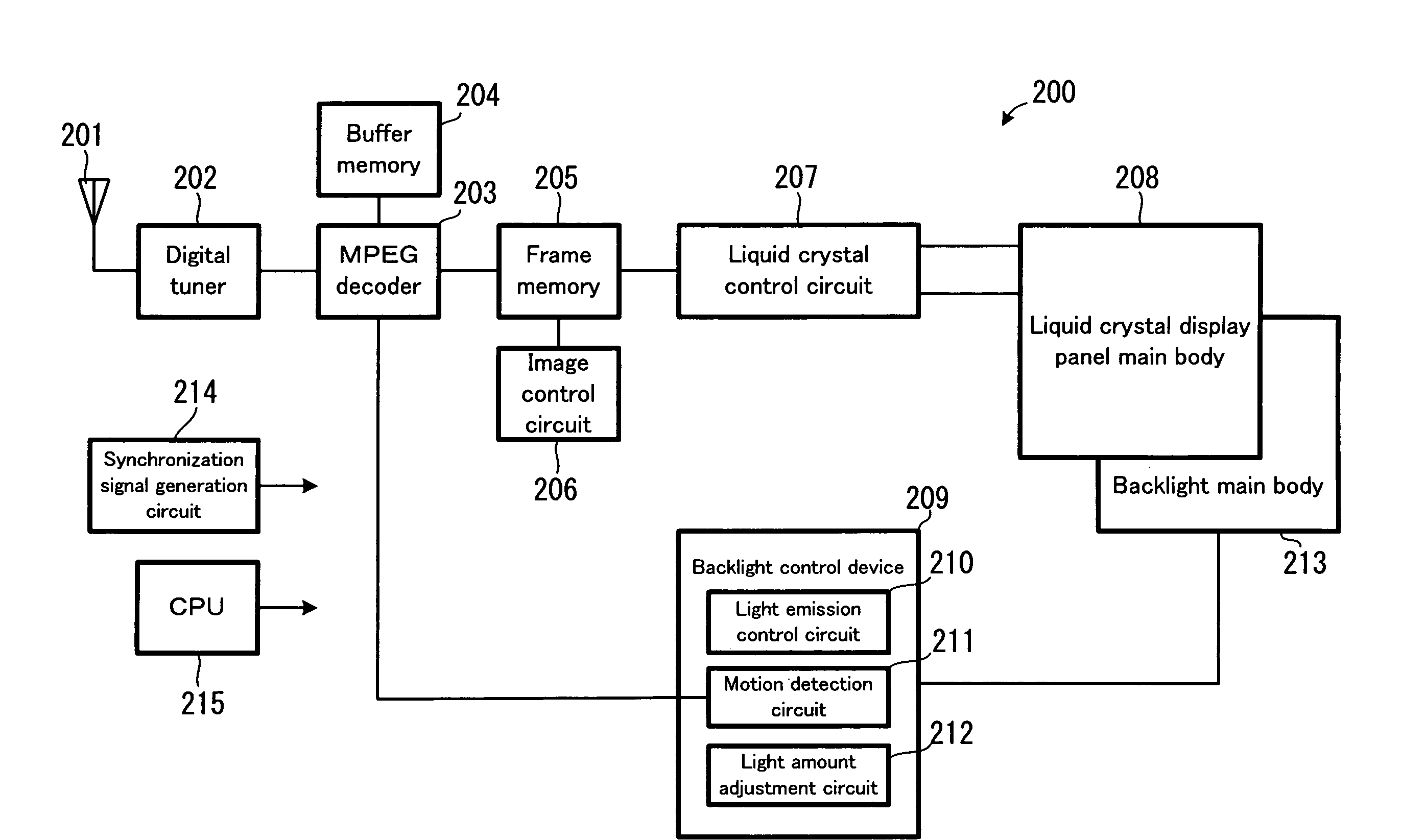

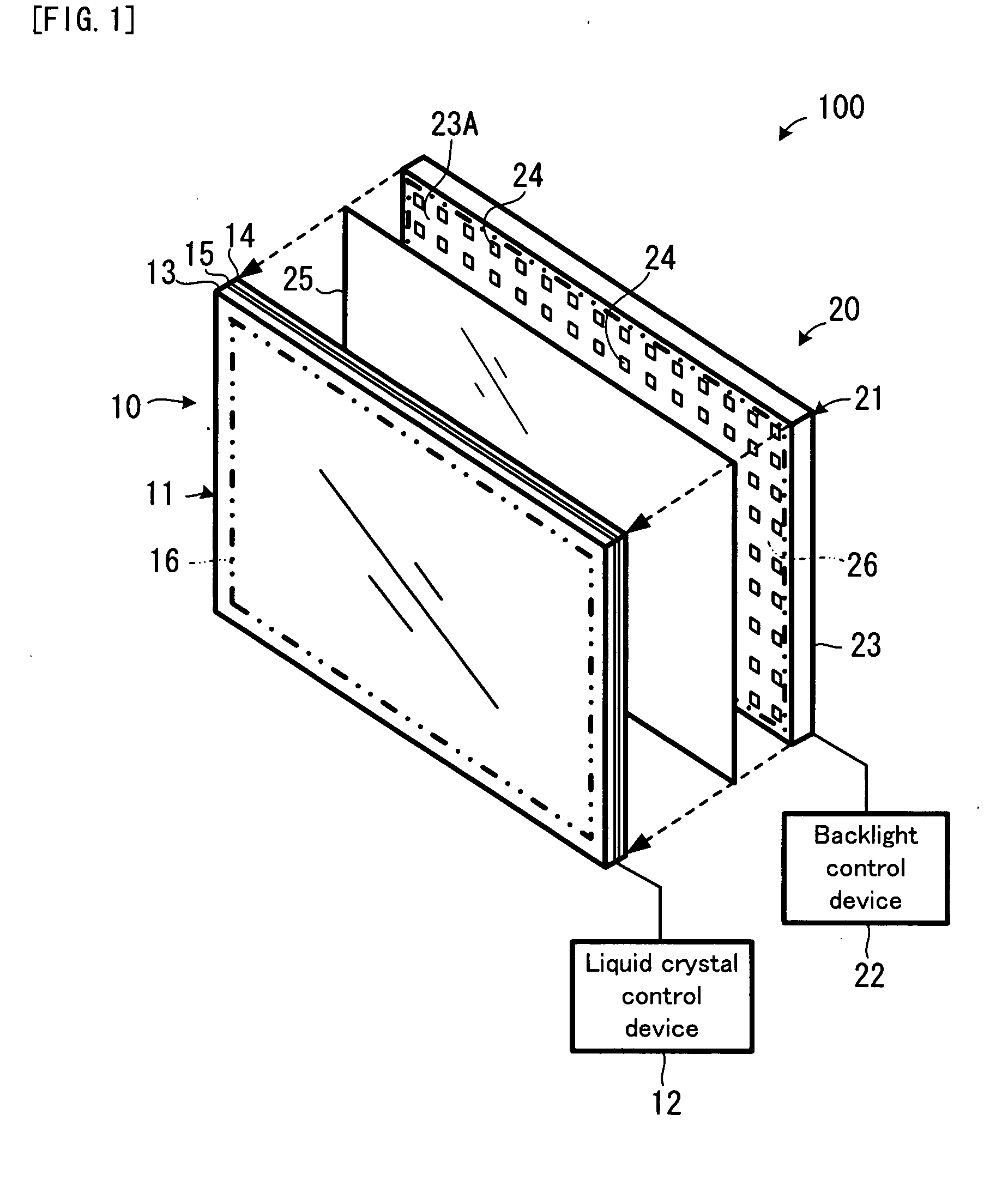

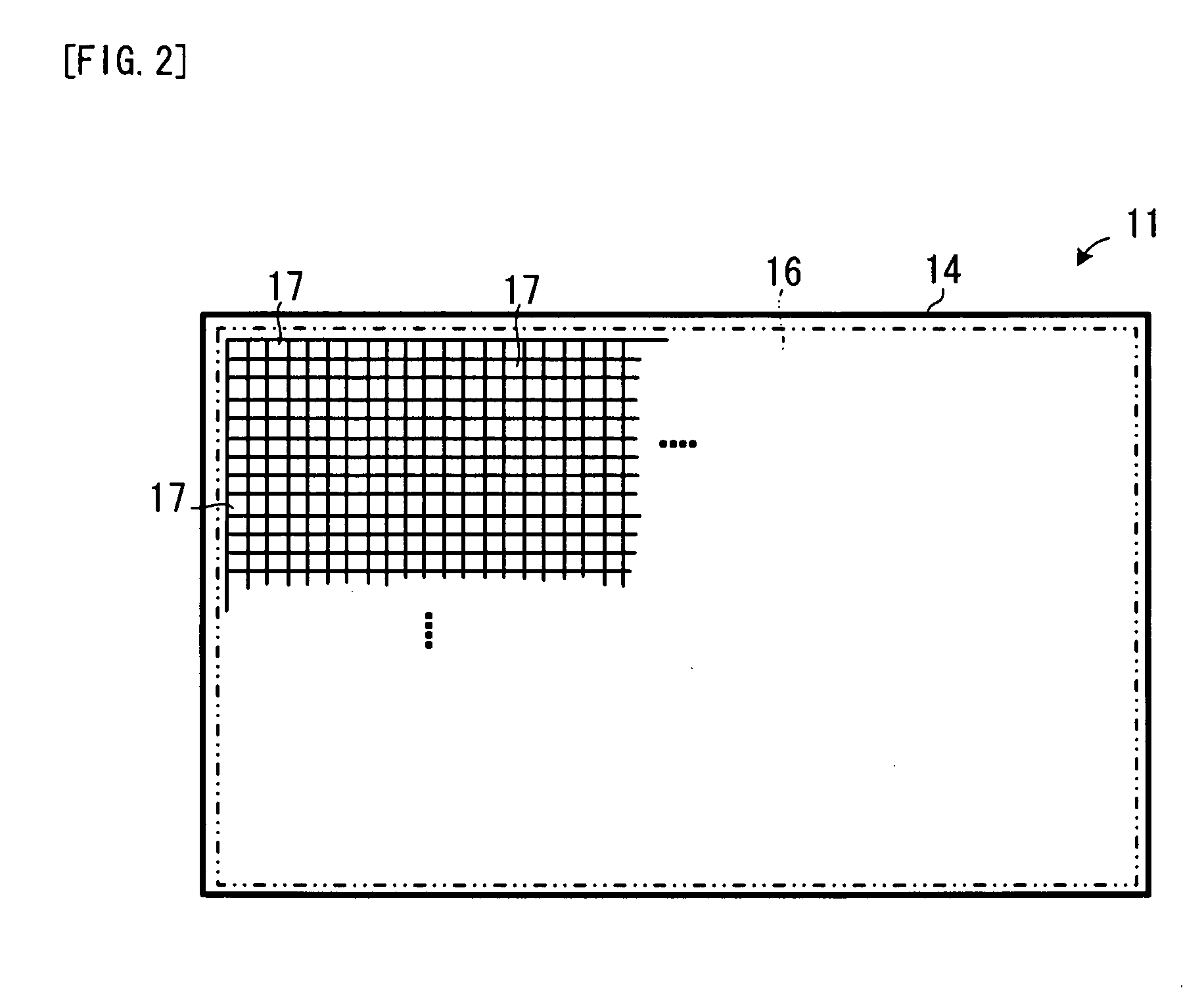

InactiveUS20090153773A1Sufficient effect of eliminating the blur in the motion pictureIncrease the effect of eliminating the blur in the motion pictureStatic indicating devicesIlluminated signsLiquid-crystal displayCrt monitor

By controlling light emission, non-emission, and light intensity of each of the light emitting elements arranged on a backlight unit, a point-shaped light emitting point is created and the light emitting point is moved along the arrangement of pixels formed on a liquid crystal display panel unit. By moving the light emitting point as if an electron beam were scanning in the CRT display, it is possible to enhance the dynamic image blur removal effect.

Owner:PIONEER CORP

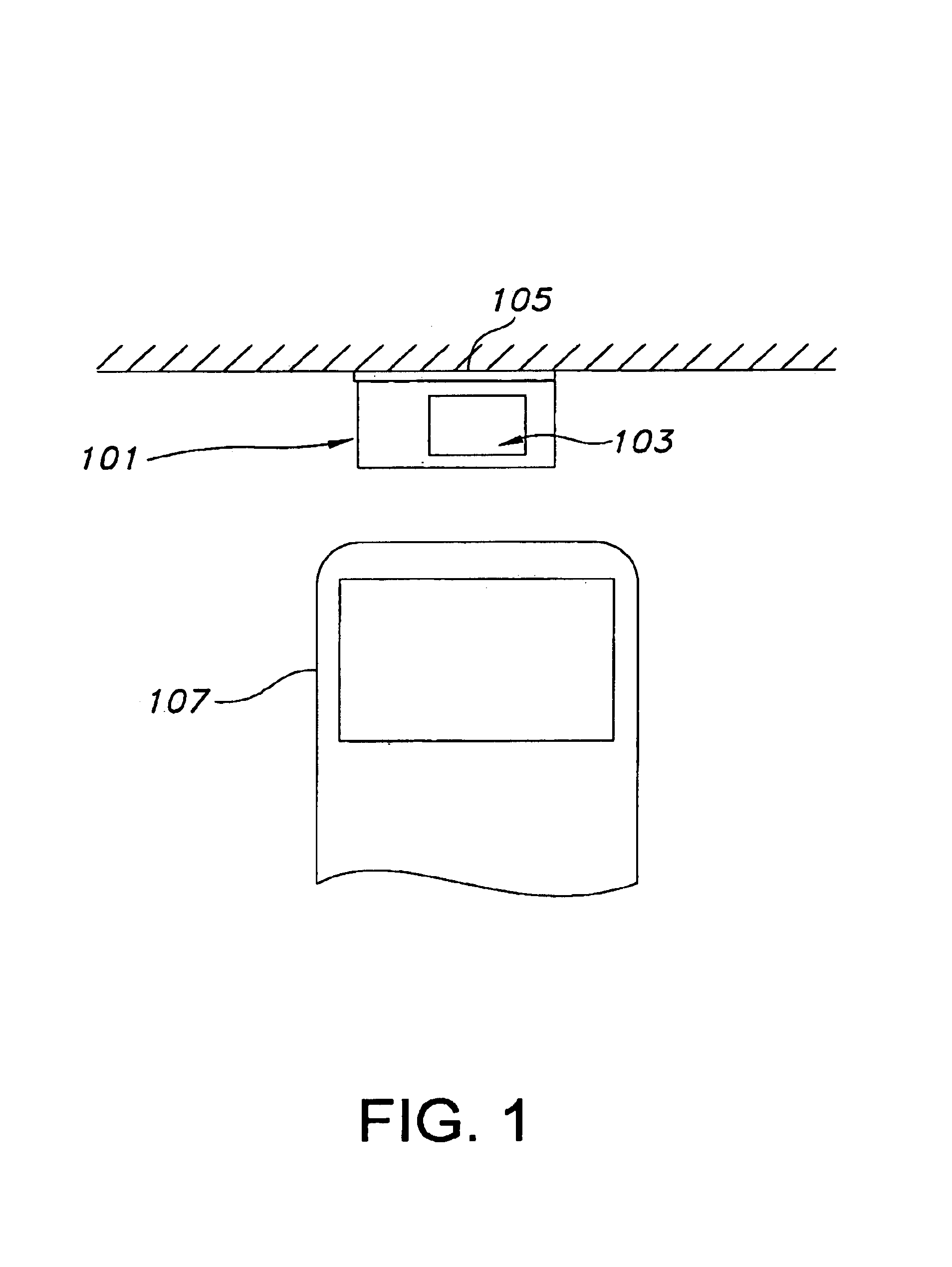

System and method for test data reporting using a status signal

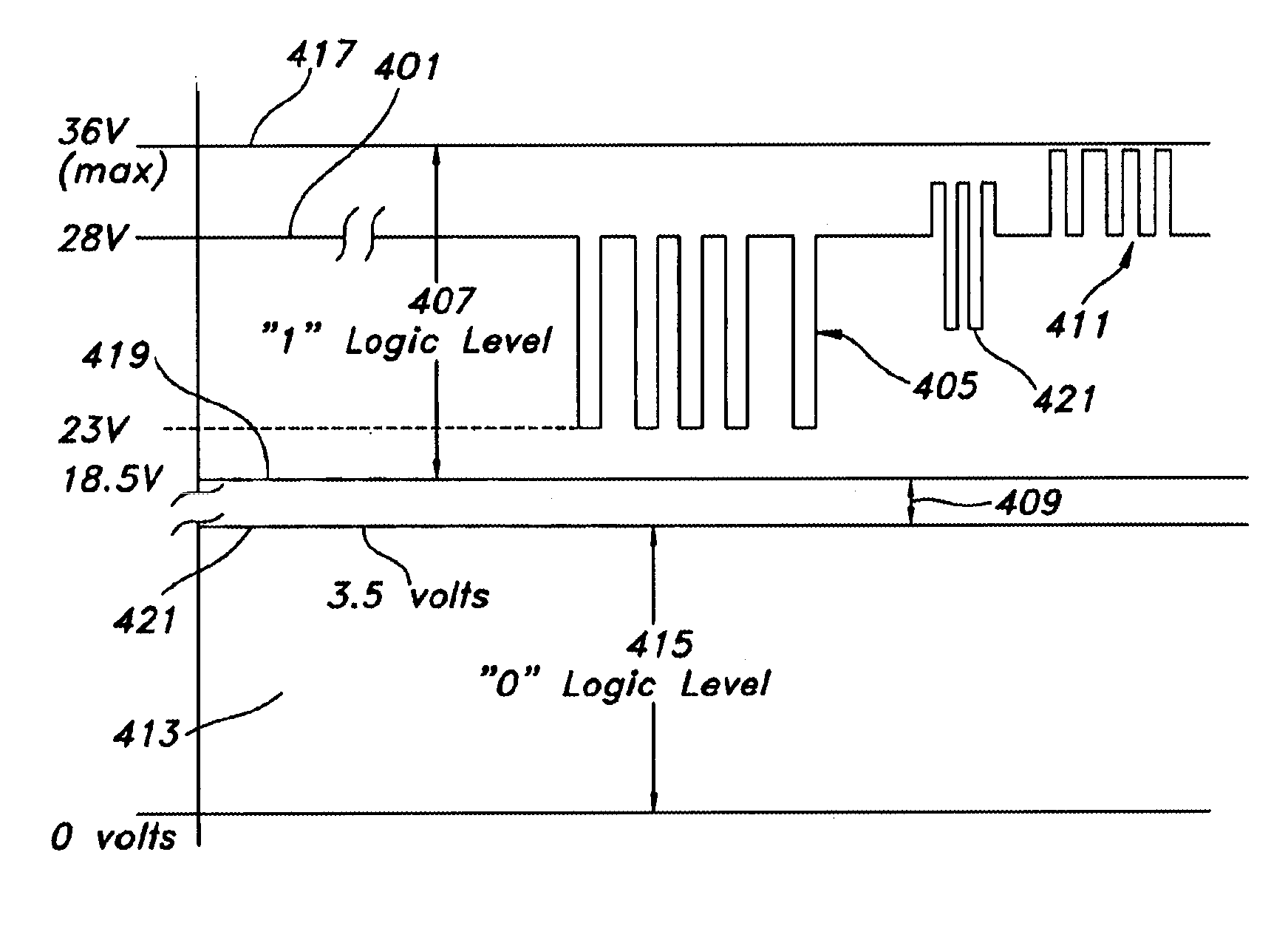

InactiveUS7009601B1Increase the display interfaceInterfere with performancePulse modulationCathode-ray tube indicatorsElectronic systemsLiquid-crystal display

In-flight entertainment systems provide entertainment for passengers on commercial airline flights. Presently, usually on longer flights, video entertainment is commonly available on in-flight passenger entertainment systems. In-flight entertainment systems can display video on a variety of display monitors ranging from a conventional CRT display to a more modern Liquid Crystal Display (LCD). Generally most displays are connected to the aircraft electronic system via a ARINC 722 connector. The ARINC 722 connector commonly provides an electrical interface between the aircraft and the video system, whether the video system is a CRT or LCD type monitor. With the increasing use of LCD monitors there is a greater need for the ability of the display monitor to be able to report its status. The need for status reporting is increased because the LCD monitors are often greater in number than the prior art CRT monitors and because malfunctions are less obvious. Several methods for providing status information from video displays have been proposed. Embodiments of the present invention comprise a system wherein the display status information is superimposed upon a 28-volt monitor on-indicator signal, which currently is contained within the ARINC 722 connector which couples the display to the aircraft wiring. Because embodiments of the invention use an existing signal and superimpose further data upon it, the need for modification of the airline and monitor systems is greatly reduced.

Owner:ROCKWELL COLLINS INC

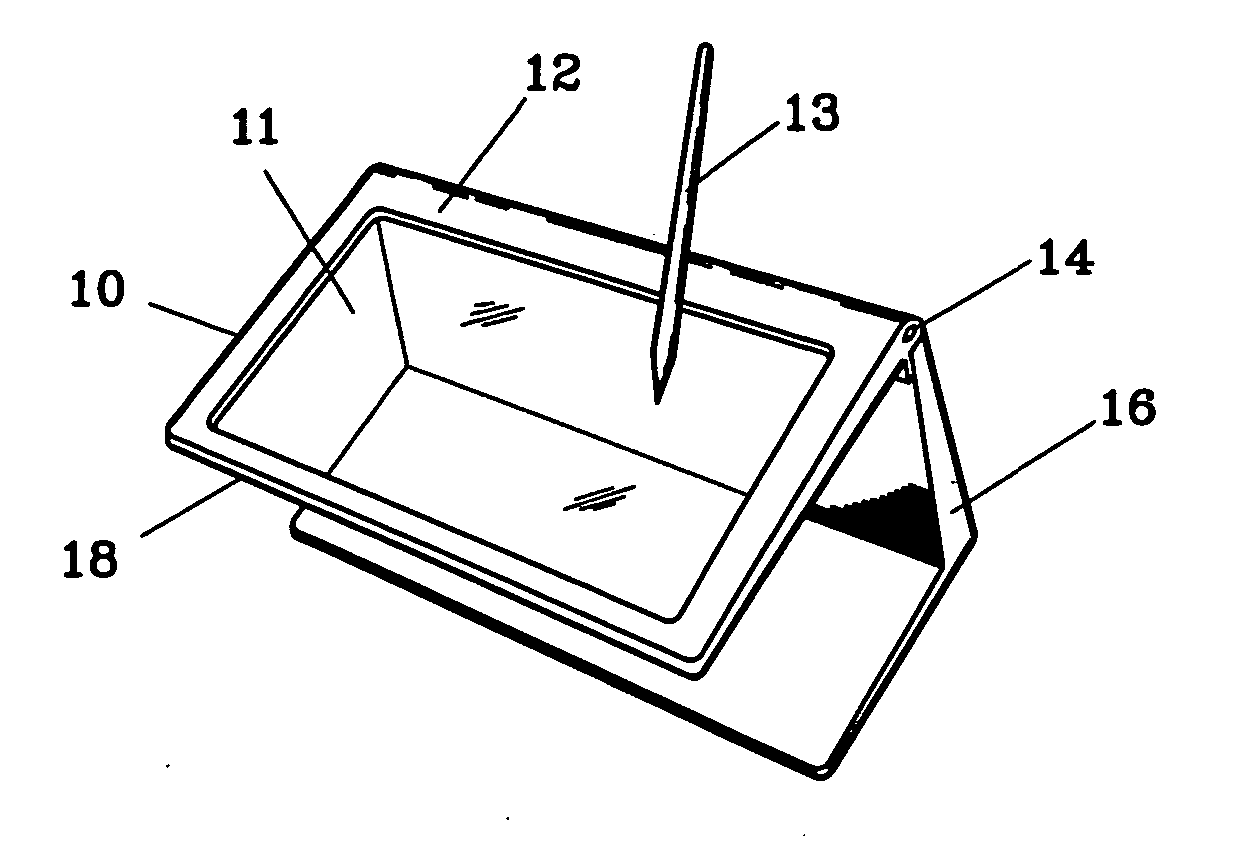

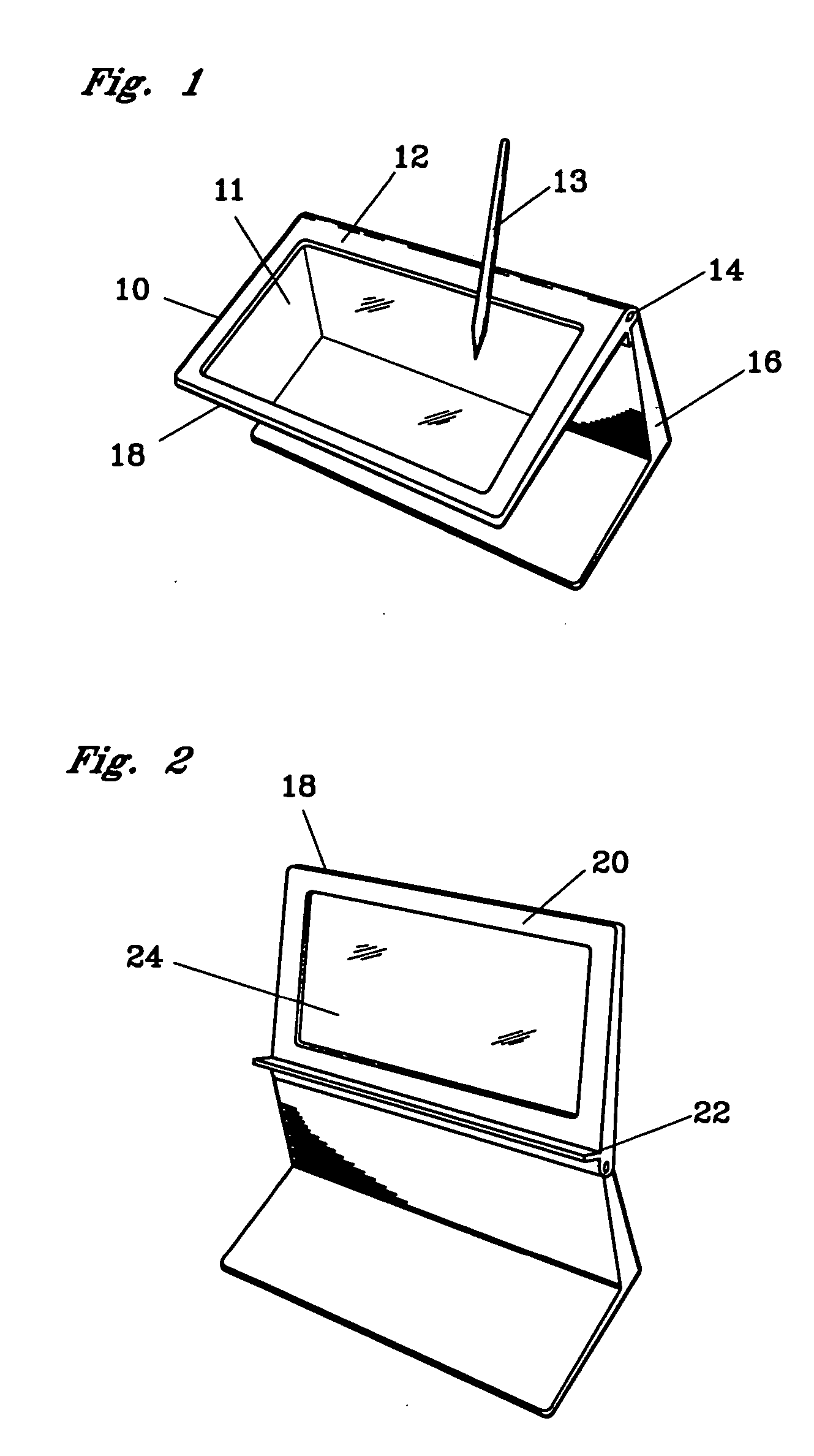

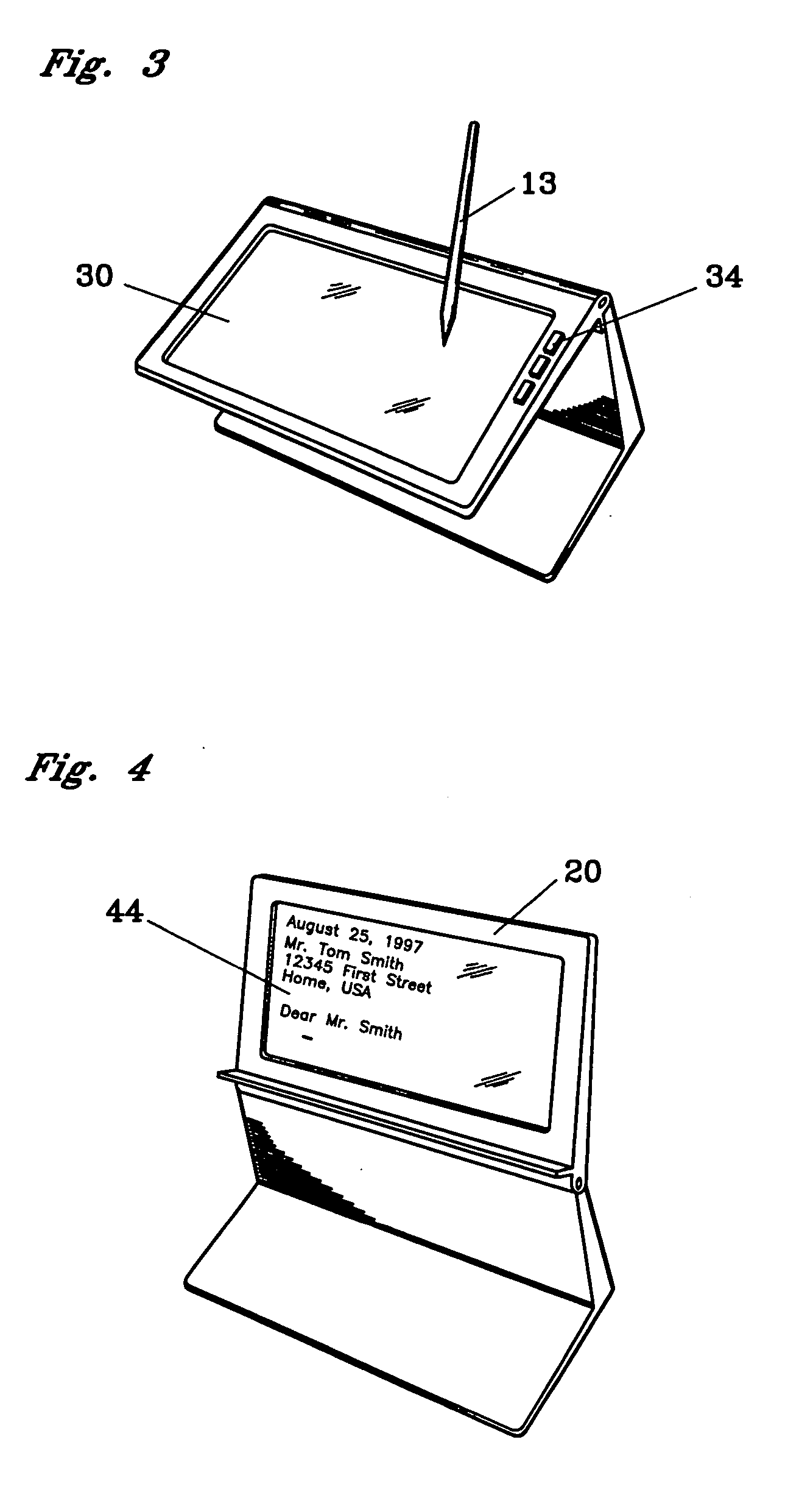

Electronic sketch pad and auxiliary monitor

InactiveUS20040183747A1Not impair vision and operationEasy to operateInput/output for user-computer interactionDigital data processing detailsWord processingPersonal computer

An electronic sketch pad and auxiliary monitor to be used as a peripheral to personal computers. The electronic sketch pad and auxiliary monitor slides under or attaches to the computer keyboard and is used as an auxiliary monitor to the primary CRT monitor. The electronic sketch pad is above and parallel to the key tops, and can be adjusted to give enough room so you can still operate the keyboard. If you are video teleconferencing with a client or colleague you can sketch an idea on the electronic sketch pad and send it without interrupting your primary monitor screen. The operator can move the electronic sketch pad from an optimal sketch position to an optimal auxiliary monitor position below the primary monitor. Now while having a WEB screen on the primary monitor you can be taking notes, doing word processing or working other programs on the auxiliary monitor. With multi-monitor software the sketch pad and auxiliary monitor are in front of the operator relieving the need to twist the operators neck to the side, and saving desk space that would have been needed for a conventional CRT auxiliary monitor and digitizer.

Owner:TRENT CHELSEA

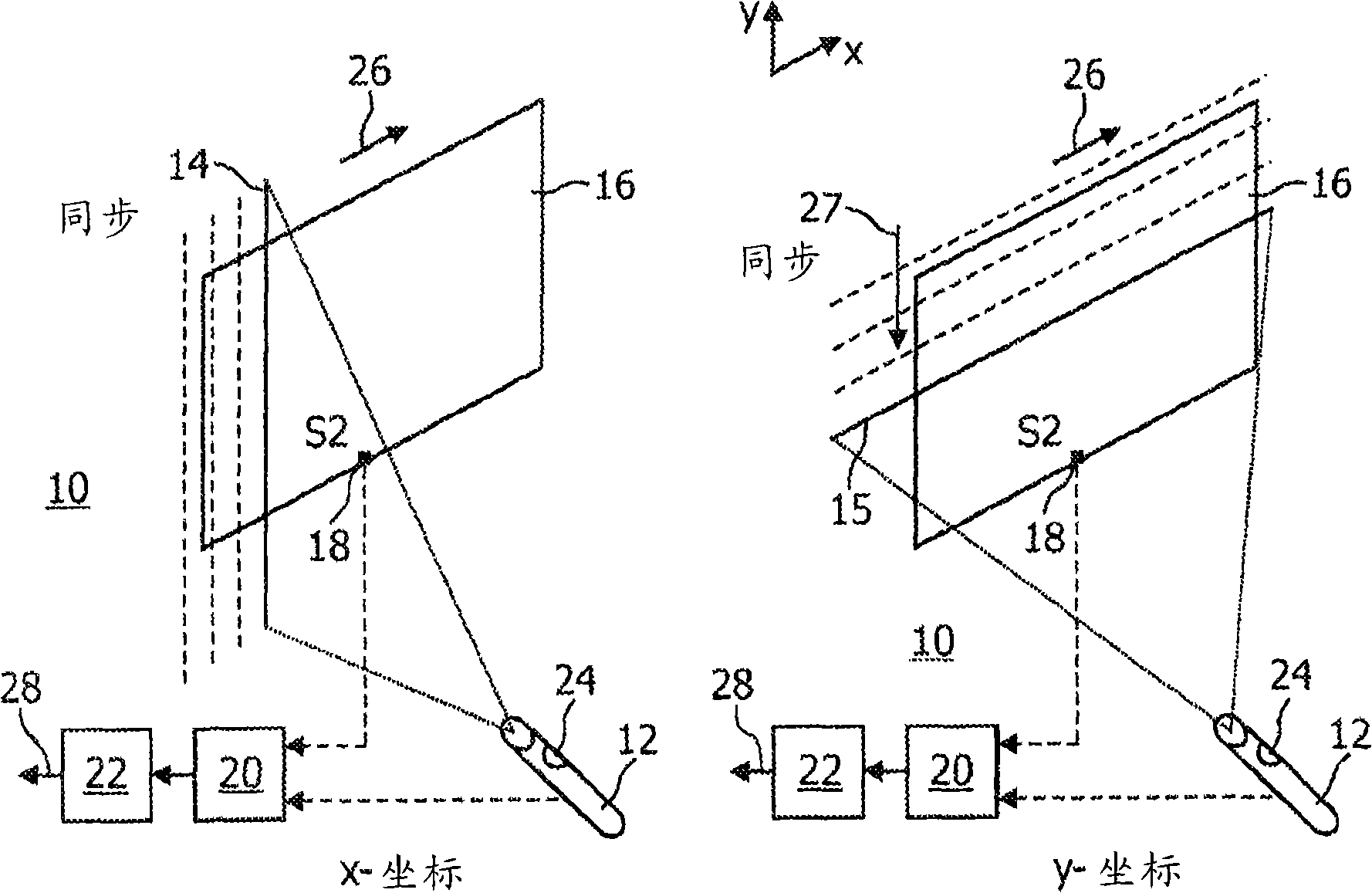

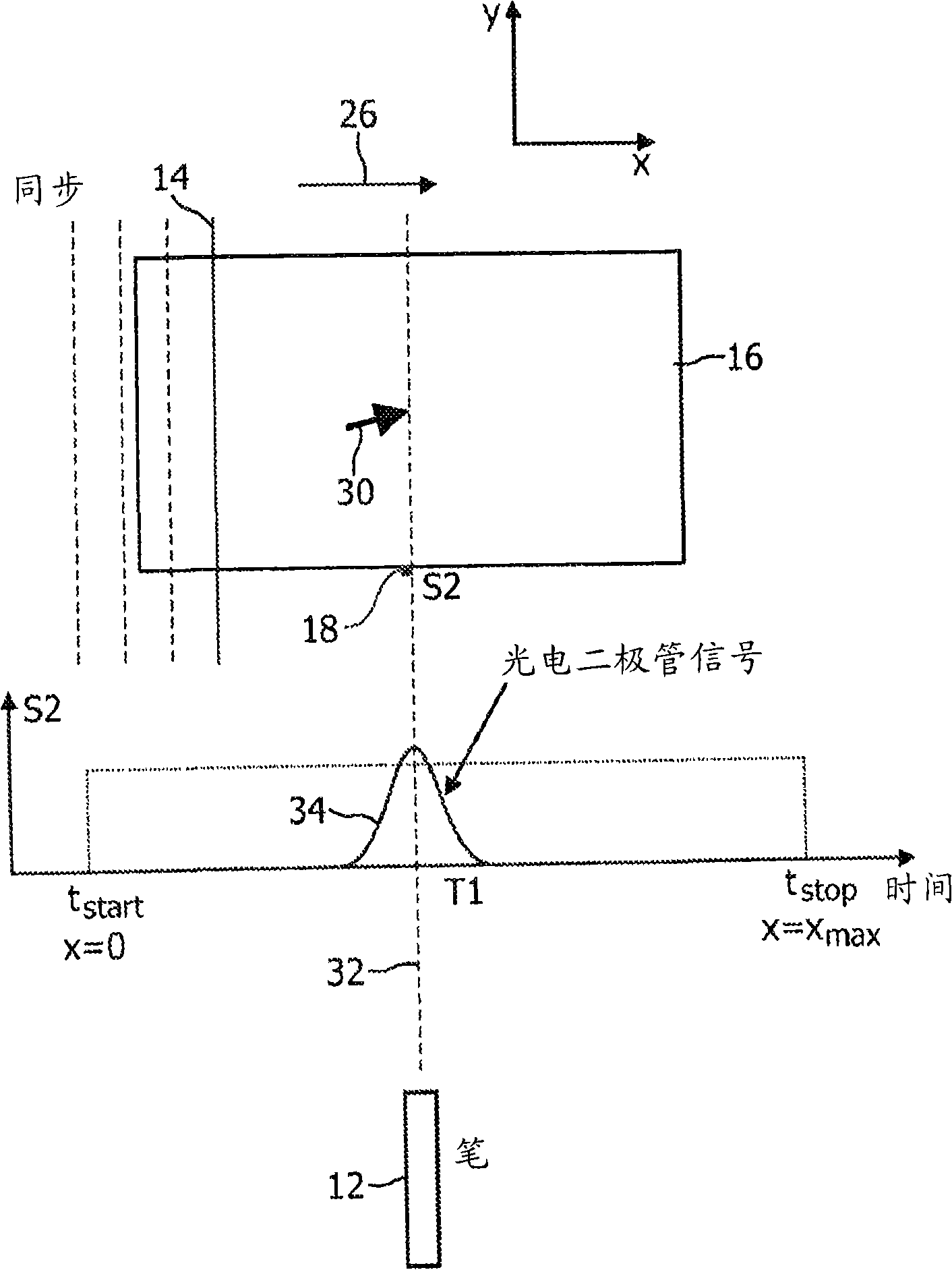

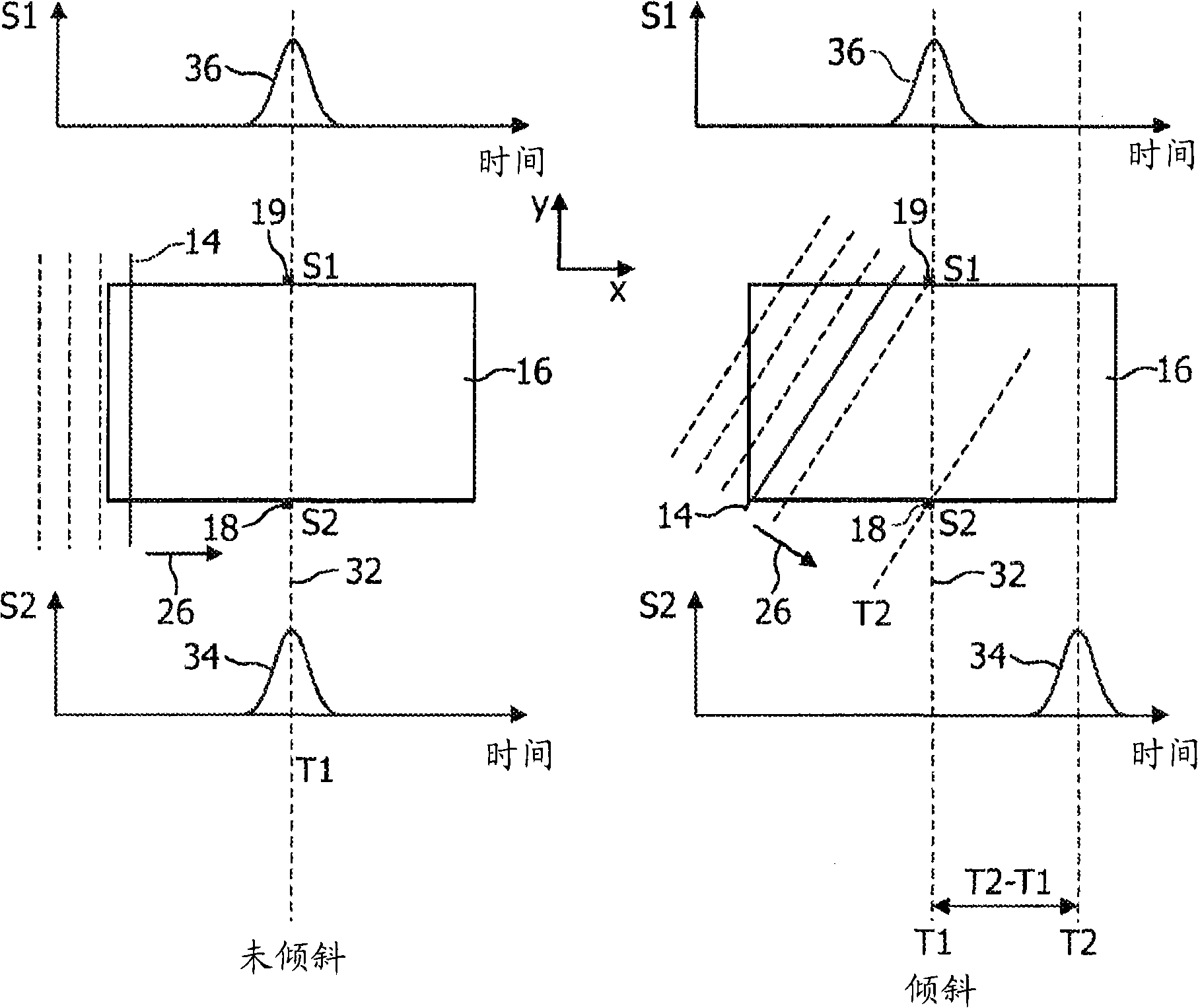

Light pen input system and method, particularly for use with large area non-CRT displays

InactiveCN101322092AImprove convenienceLow costInput/output for user-computer interactionLight sensingCRTS

The invention relates to a light pen input system with a light pen which is adapted to generate at least one scanning light line sweep for scanning a surface such as for example a display screen. The time from starting a scan until a light sensing element placed at a known position detects a scanning light line is measured and processed for determining the coordinates of the pointing position of the light pen. Thus, an ''inverse'' light pen is provided which may be implemented at low costs and which may be used with non-CRT displays. Furthermore, the system is independent of the display screen size.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

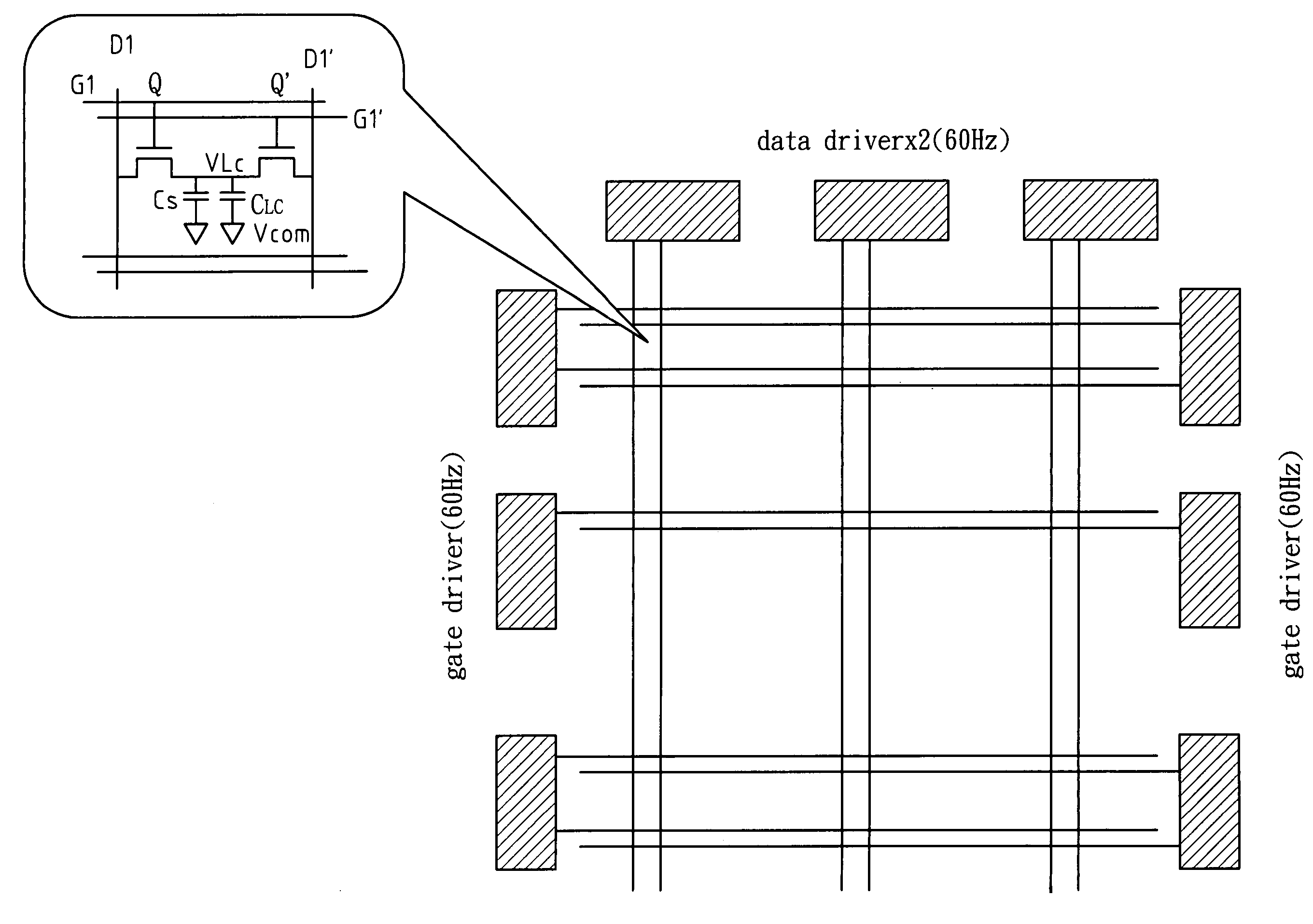

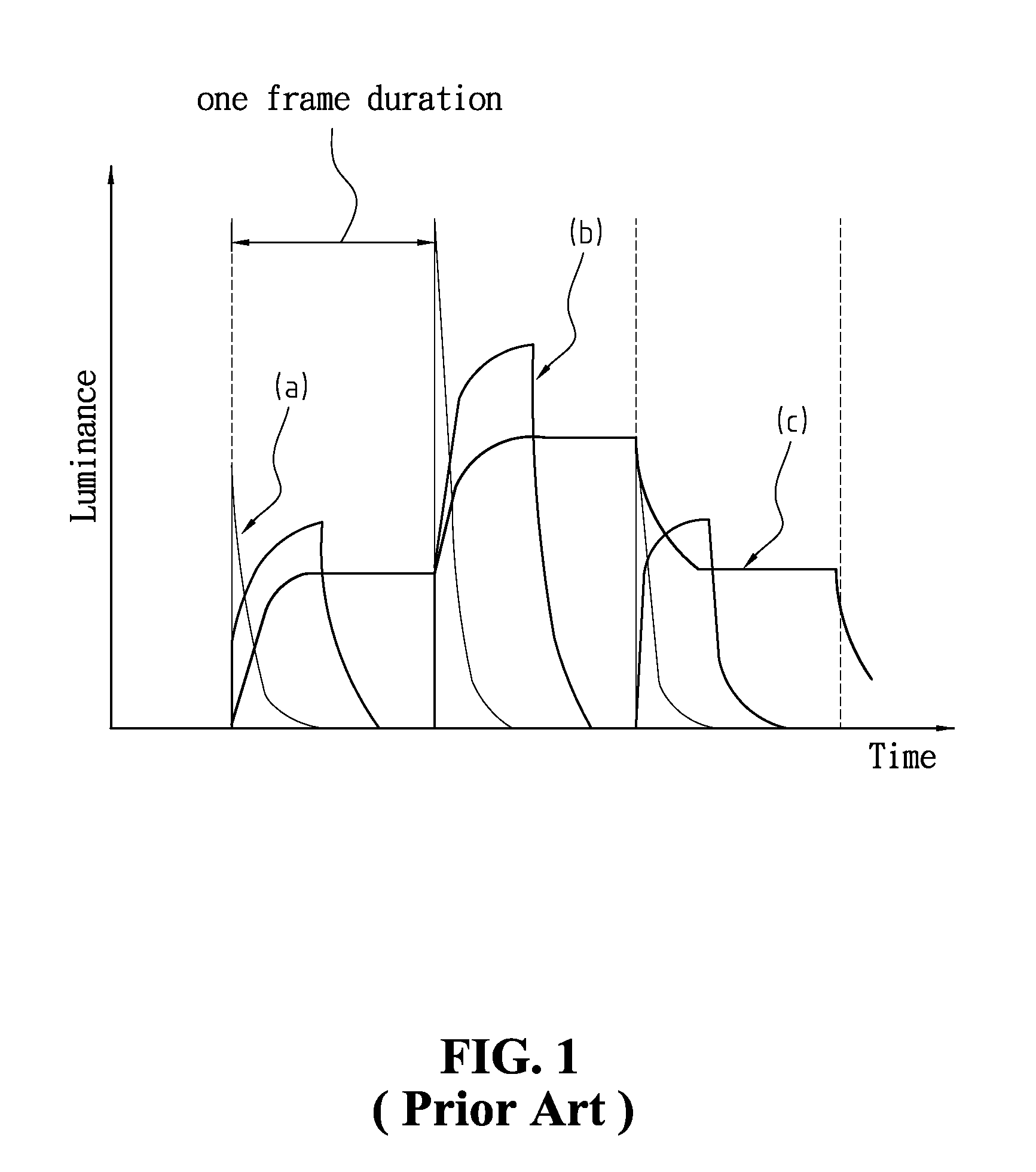

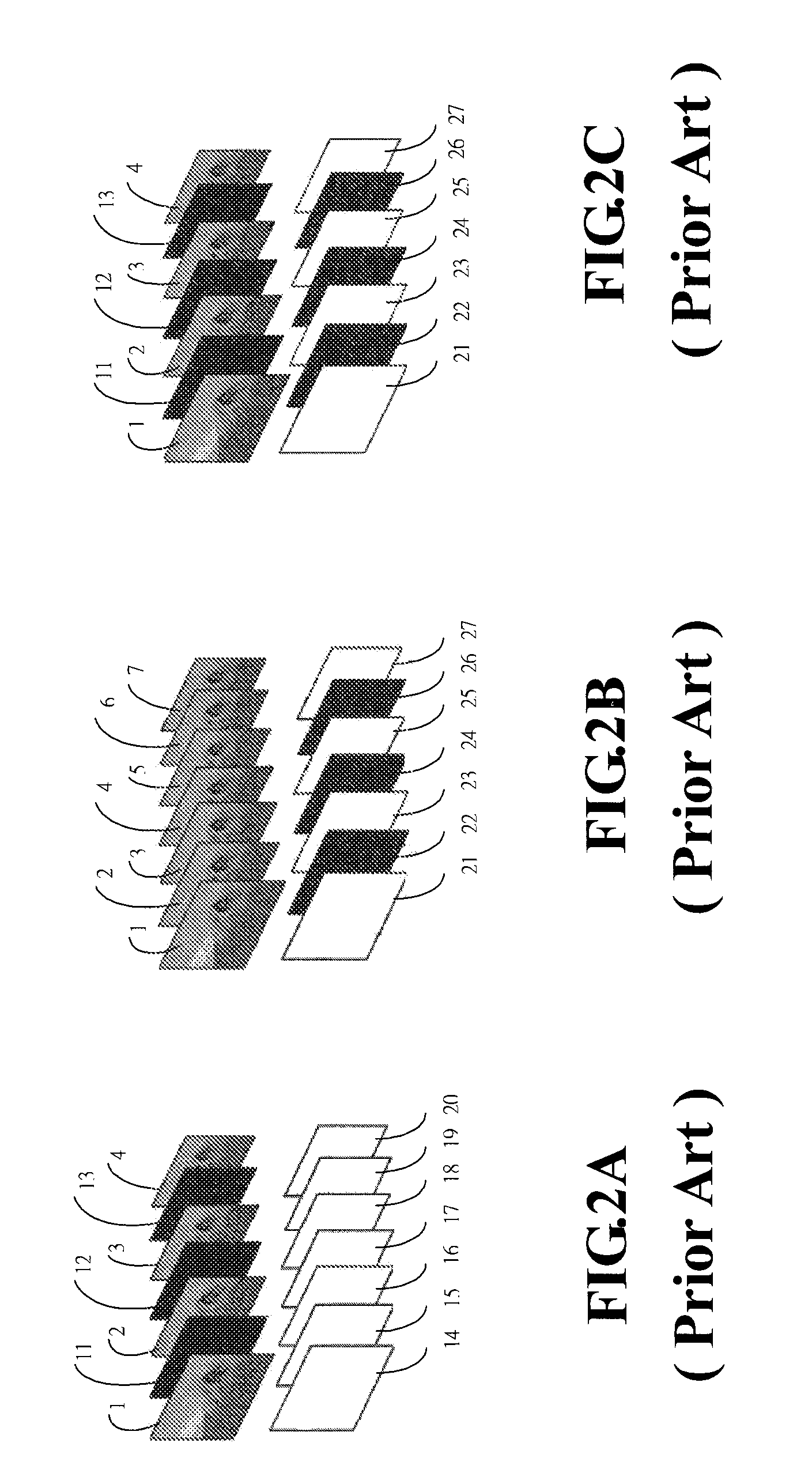

Method and device for simulating an impulse-type CRT display

InactiveUS7324933B2Quality improvementEffectively eliminate the “after-image”Static indicating devicesAnalogue computers for electric apparatusInput controlCrt monitor

Method and device for simulating an impulse-type CRT display is provided, in which the device has first and second input control lines, first and second input data lines, first and second capacitors, a driving voltage output line, and a first transistor having a gate connected to the first input control line, a source connected to the first input data line, and a drain connected to the driving voltage output line, the first capacitor and the drain of a second transistor that is similarly connected to various elements as in the first transistor. The two capacitors are connected to ground respectively, and the driving voltage output line is to output the simulation driving voltage to the pixels of an LCD panel. The first and second input control lines are connected to a first and second gate driver, and the first and second data lines are connected to a data driver respectively.

Owner:VASTVIEW TECH

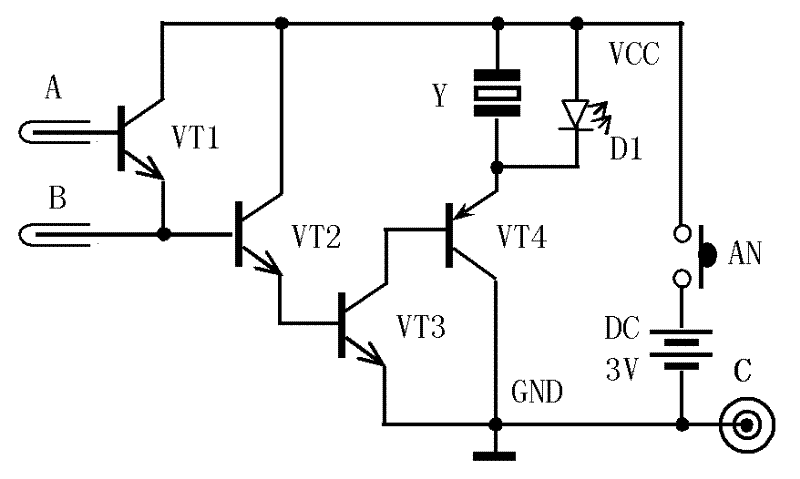

High-performance induction type electroscope

InactiveCN102435823AReduced drive power requirementsCurrent/voltage measurementLow voltageEngineering

The invention relates to a high-performance induction type electroscope, which consists of a direct-current power supply DC, a key switch AN, an induction electrode A, an induction electrode B, a touch electrode C, a homopolar Darlington circuit, a heteropolar Darlington circuit and an acoustooptical reminding circuit. A traditional test pencil can only normally work by leading the test contact of the test pencil to be directly contacted with a charged metal object to form a complete loop. The high-performance induction type electroscope disclosed by the invention can normally work without being directly contacted with the charged object, and the charged object can be metal or an electrostatic object or a nonmetal body, such as a computer cathode ray tube (CRT) display or a color TV kinescope and the like. The high-performance induction type electroscope disclosed by the invention not only is suitable for detecting low voltage but also is suitable for monitoring 220 V alternating current with higher potential or the electrostatic object and is extremely handy in use. The various traditional test pencils can be completely replaced by the actions and the functions of the high-performance induction type electroscope.

Owner:刘喆

Solid state electrochromic element and mirror device and CRT display comprising it

Owner:MURAKAMI CORP

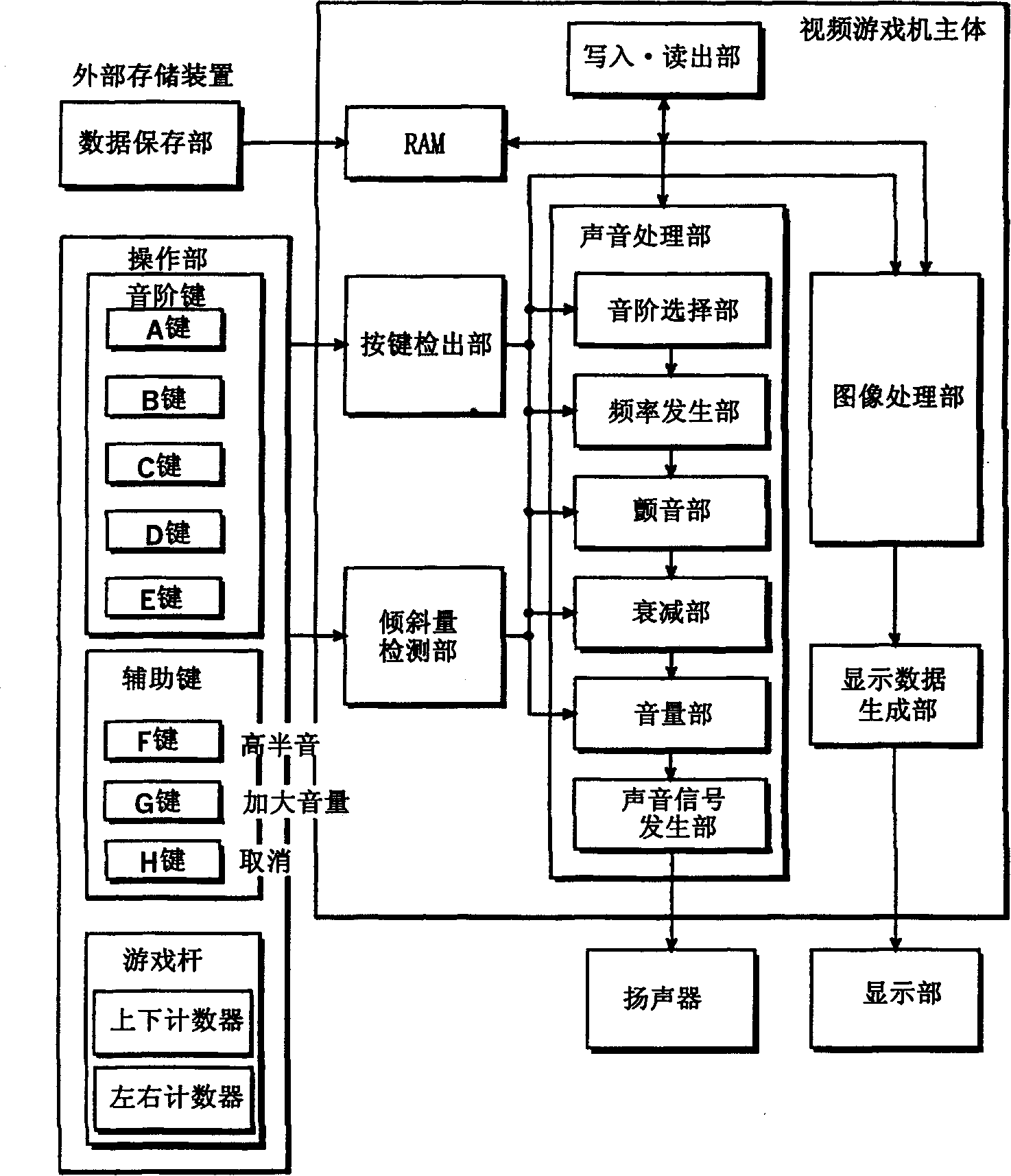

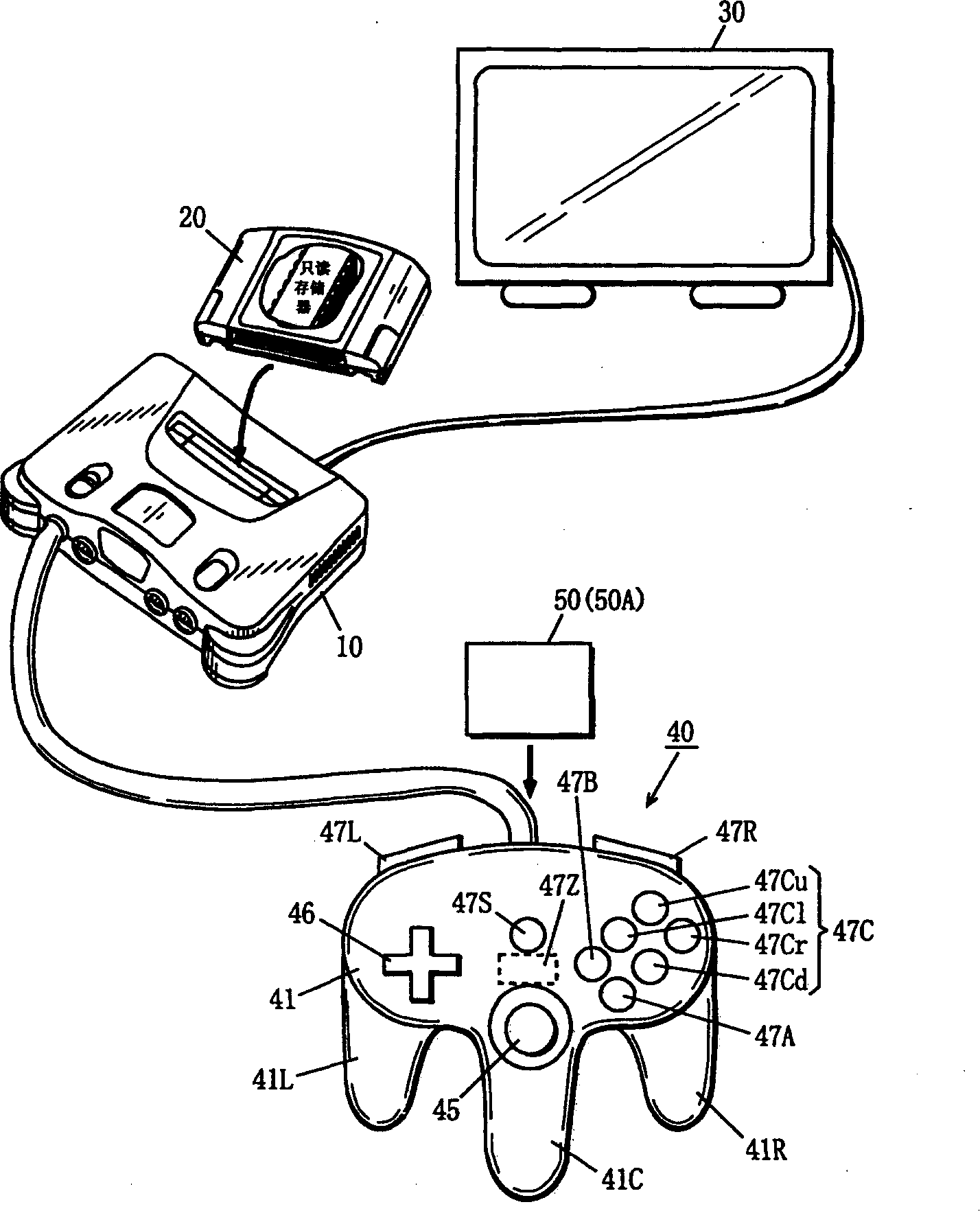

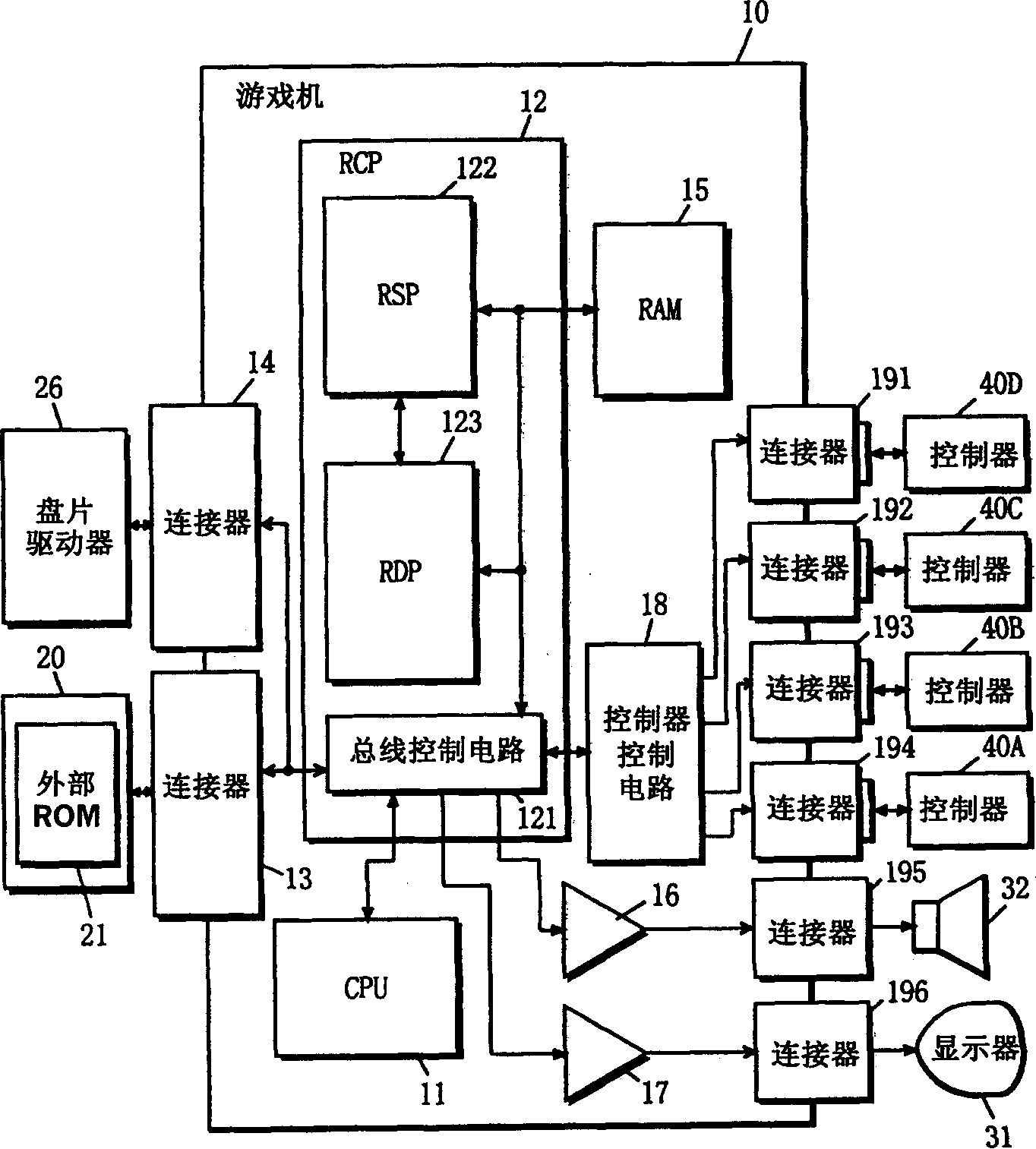

Sound generator and video game machine employing it

InactiveCN1279803ARich soundEasy to adjustElectrophonic musical instrumentsVideo gamesJoystickData storing

When any of push-button switches on a controller 40 is pressed in a sound input mode, a video game machine body 10 generates and temporarily stores frequency data of a tone corresponding to the pressed switch. At this time, when a joystick 45 on the controller 40 is tilted to a predetermined direction, the video game machine body 10 changes the generated frequency data according to the amount of tilt of the joystick 45. It is therefore possible to input various sounds in tone using a limited number of switches. The frequency data stored in the video game machine body 10 is read later to be converted into audio signals, and outputted from a speaker incorporated in a CRT display 30. When a melody based on the inputted sound coincides with a melody set in advance, the video game machine body 10 makes various changes in the progress of the game. For example, a hero character is warped to a position that is different from the present position, or provided with various items.

Owner:NINTENDO CO LTD

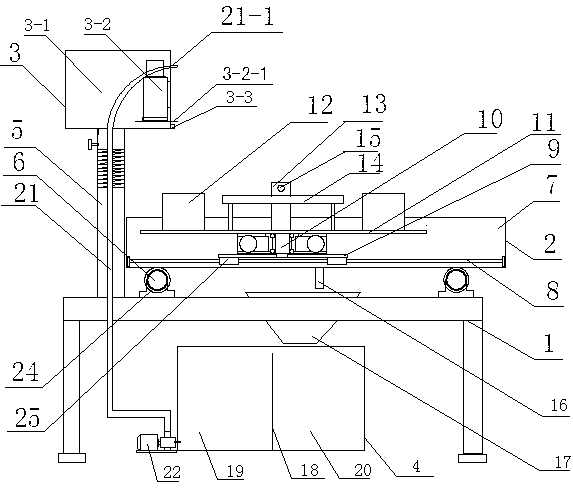

Automatic cutting separator for waste CRT (cathode ray tube) display

ActiveCN103011574AAdaptableReduce labor intensityGlass severing apparatusWater channelDisplay device

The invention discloses an automatic cutting separator for a waste CRT (cathode ray tube) display, and relates to the technical field of metallurgy and mechanical engineering. The waste CRT display automatic cutting separator provided by the invention comprises a support, a cutting table, a cutter and a circulating water channel; two long slideways are connected above the support; the cutting table comprises a water tank which is arranged above the two long slideways and is internally provided with two short slideways; the two short slideways are connected with a cutting table base; a rotary table is arranged above the cutting table base; the upper surface of the rotary table is provided with four rubber blocks; the outer sides of the rubber blocks are provided with CRT spacing blocks; the outer sides of the CRT spacing blocks are provided with handles; the CRT spacing blocks are provided with spacing bolts; water discharging holes are arranged on the bottom of the water channel; the support is provided with a chute; a circulating water tank is internally separated into a left chamber and a right chamber through an overflow baffle plate; the left chamber is communicated with a water pipe; a circulating water pump is arranged between the left chamber and the water pipe; the top end of the water pipe is provided with a water nozzle; and the cutter comprises a cutter box body and an electric cutter. The waste CRT display automatic cutting separator provided by the invention is simple and reasonable in structure, and is simple and flexible to operate.

Owner:YANGZHOU NINGDA NOBLE METAL CO LTD

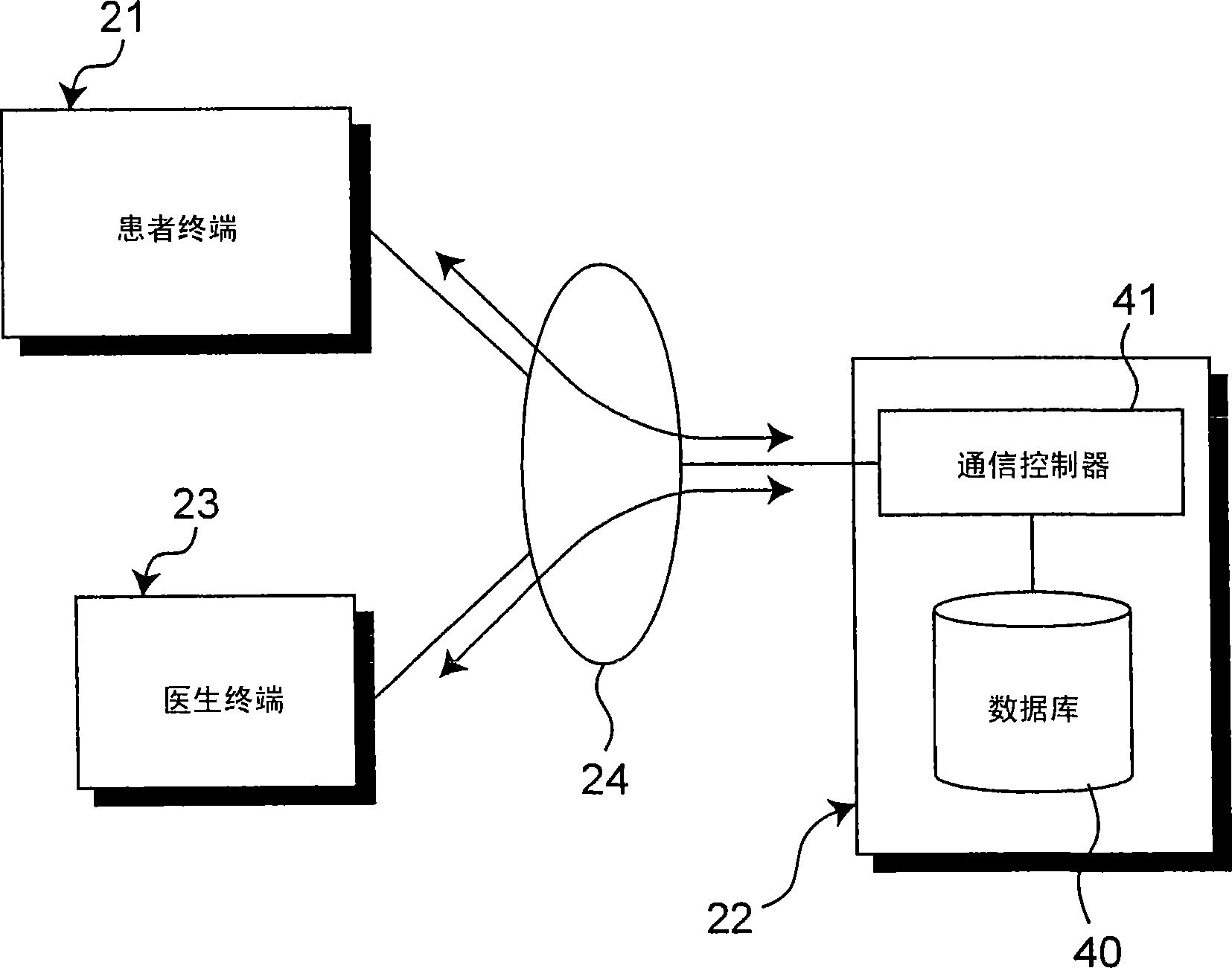

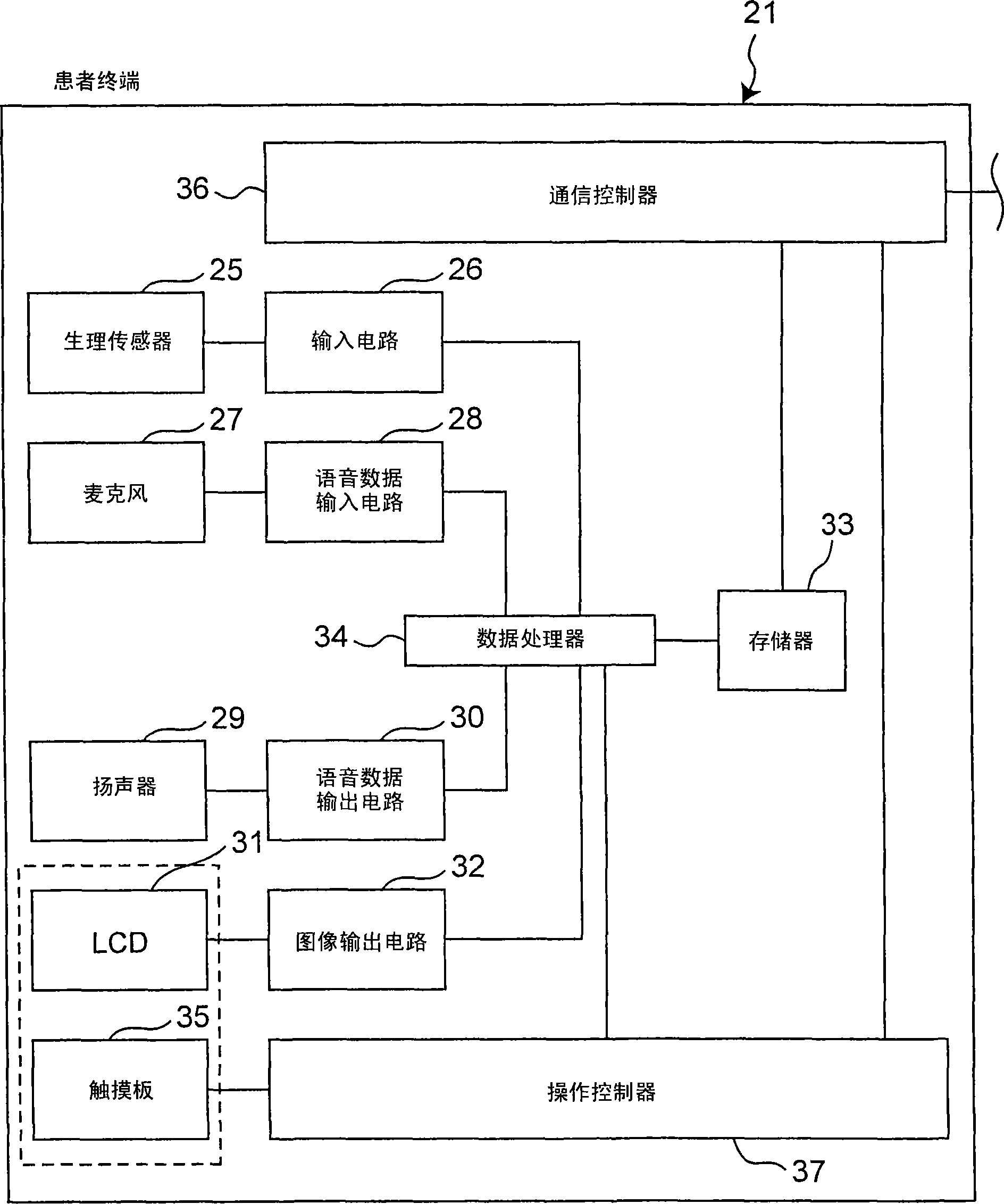

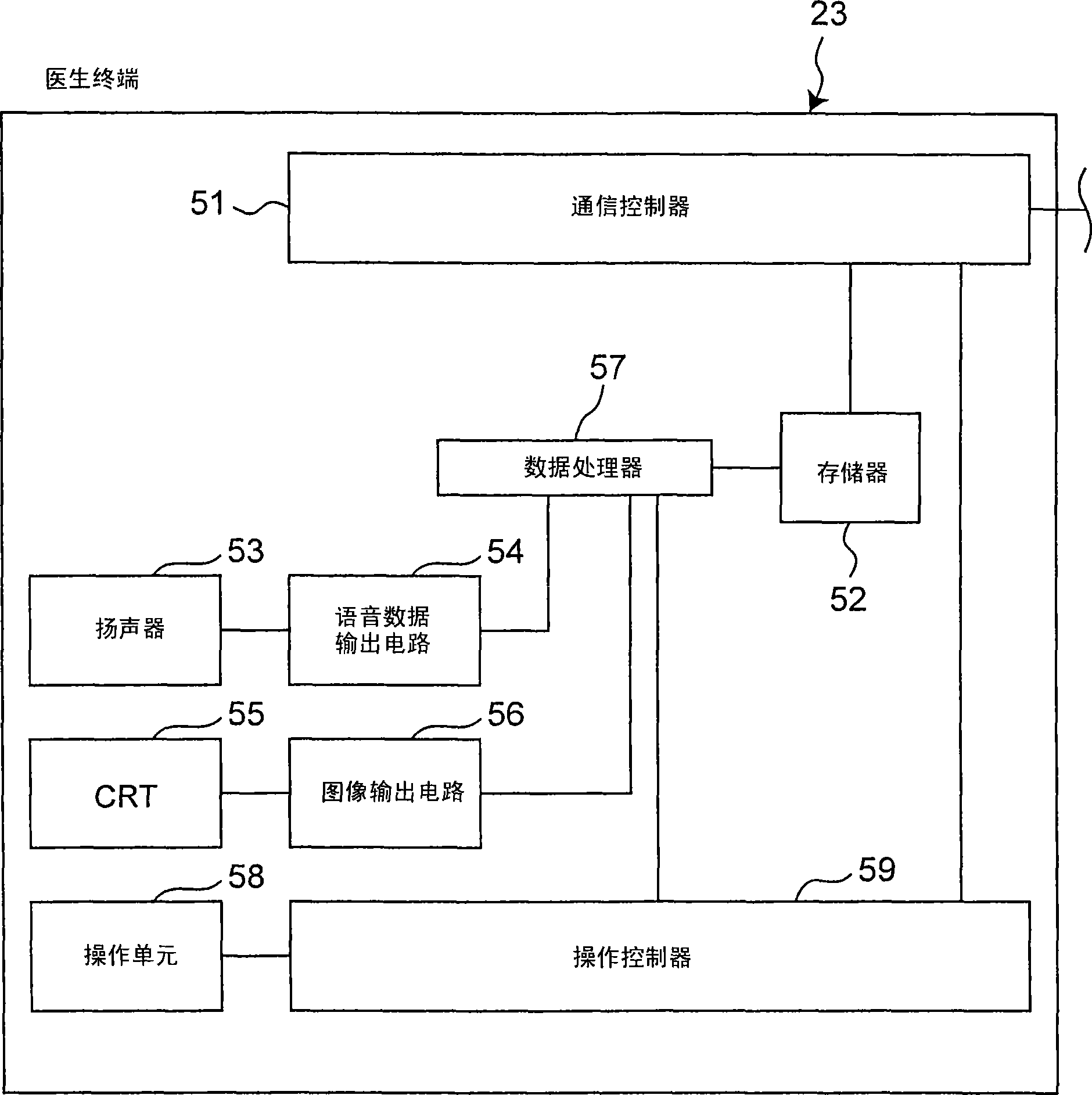

Health data collection apparatus

InactiveCN1867291AAchieve smooth communicationBig amount of dataDiagnostic recording/measuringSensorsDatabase servicesLoudspeaker

A health data collection apparatus for realizing a higher-quality health care. A patient terminal (21) includes a data processing part (34) for associating and storing, in a memory (33), bio-data acquired by a vital sensor (25) with voice data inputted from a microphone (27). The bio-data and voice data stored in the memory (33) are transmitted to a center server (22) via a communication network (24) and stored into a database server (40). A doctor terminal (23) includes a memory (52) for storing therein the bio-data and voice data received from the database server (40), and also includes a data processing part (57) for associating and outputting, to a CRT display (55) and a speaker (53), the bio-data and voice data stored in the memory (52).

Owner:PANASONIC CORP

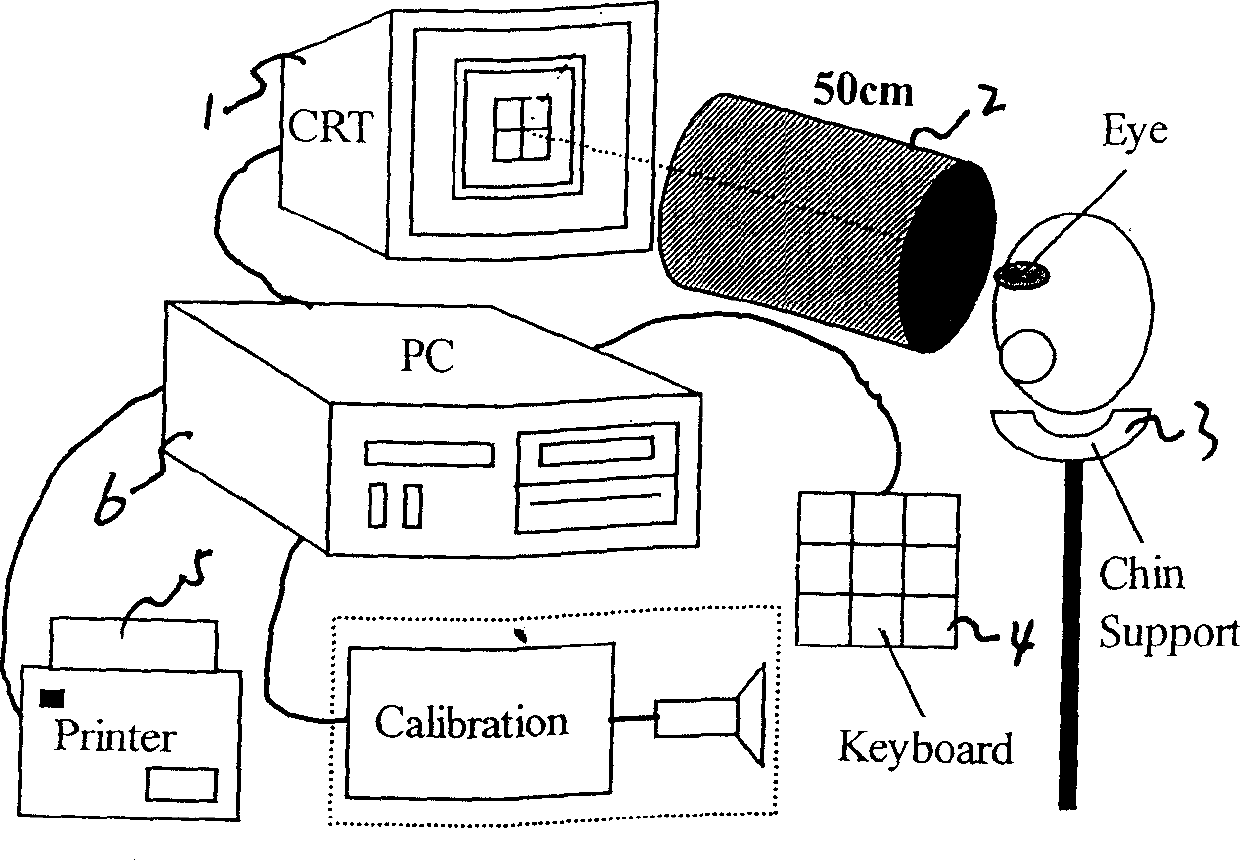

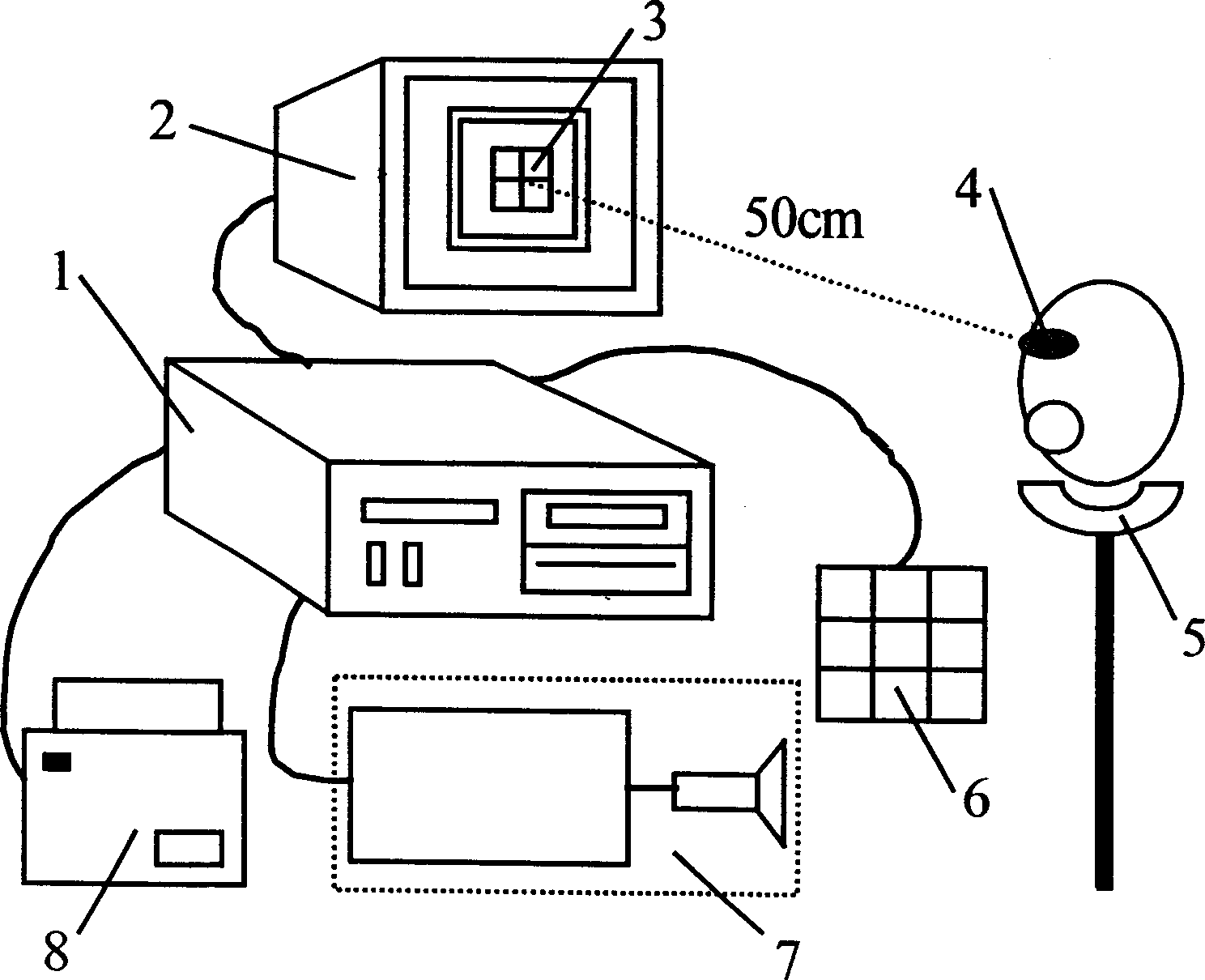

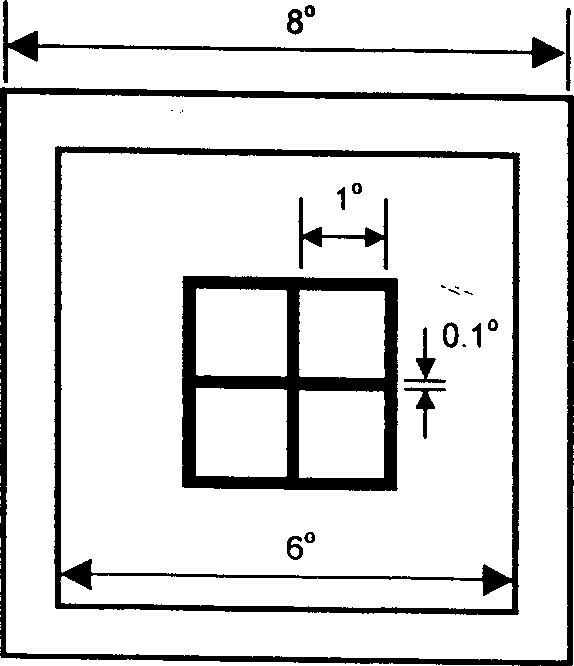

Colour vision-identification characteristic automatic quantitative testing system

InactiveCN1404792ADurable and stable precisionDurable and stable repeatabilityEye diagnosticsCRTSColor discrimination

The present invention discloses an autoamtic quantitative test system of color visual discriminatory acuity. Said system comprises main computer PC machine, color CRT display, lower jaw support, special-purpose respose keyboard, photoelectric scaling system and printer, and the main computer PC machine is respectively connected with color CRT display on central position of whose screen a color irritation test block formed from four 1 degree X 1 degree small squares can be formed, special-purpose response keyboard, printer and photoelectric scaling system by means of RS-232 serial interface, and the lower jaw support is placed in the front of colour CRT display. Said invention utilizes the computer-controlled colour CRT analogous color simulation display technique and other test measures to test color discrimination of visual sense of human eye.

Owner:ZHEJIANG UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com