Patents

Literature

105results about "Threshold modification in field effect transistors" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

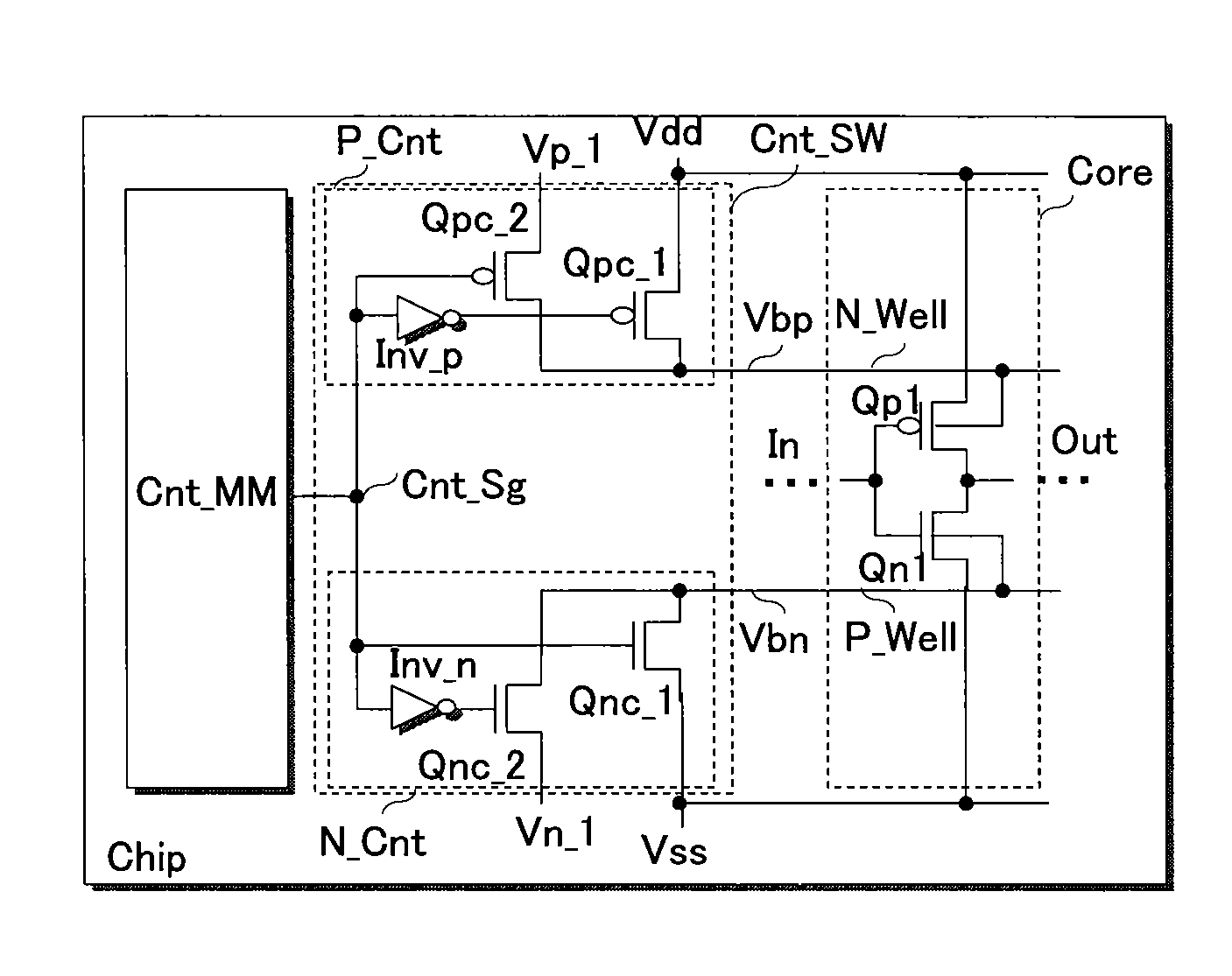

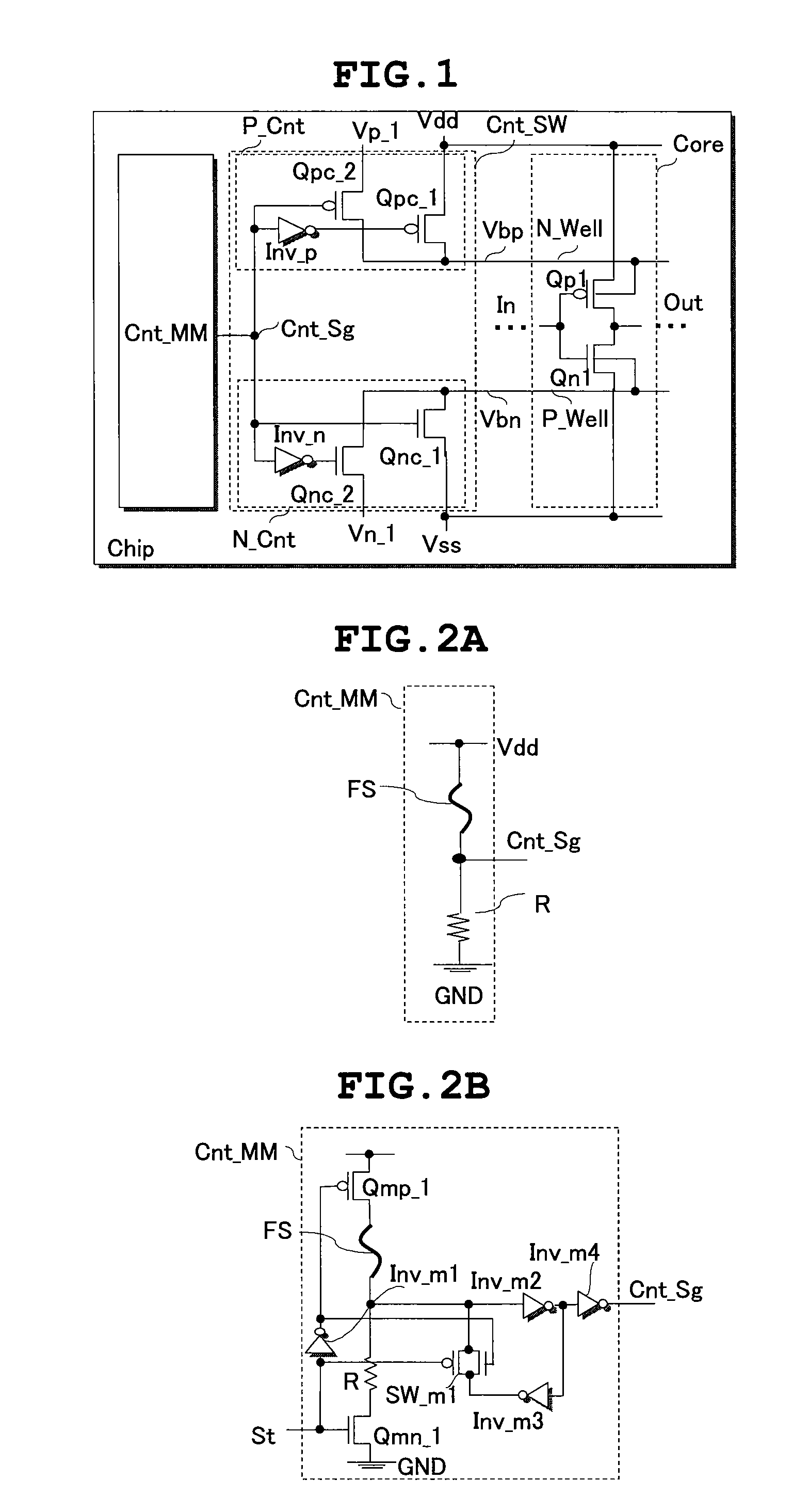

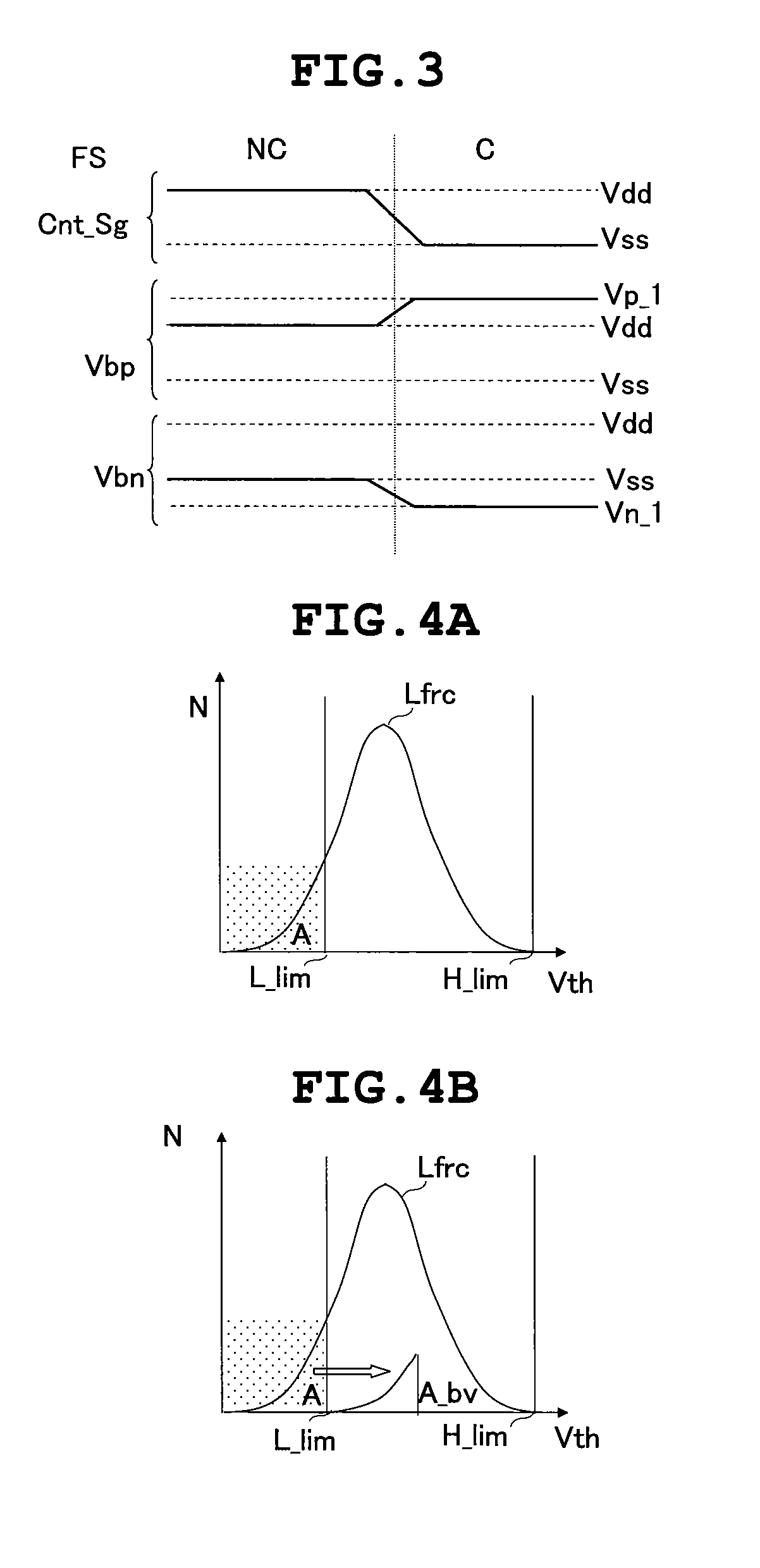

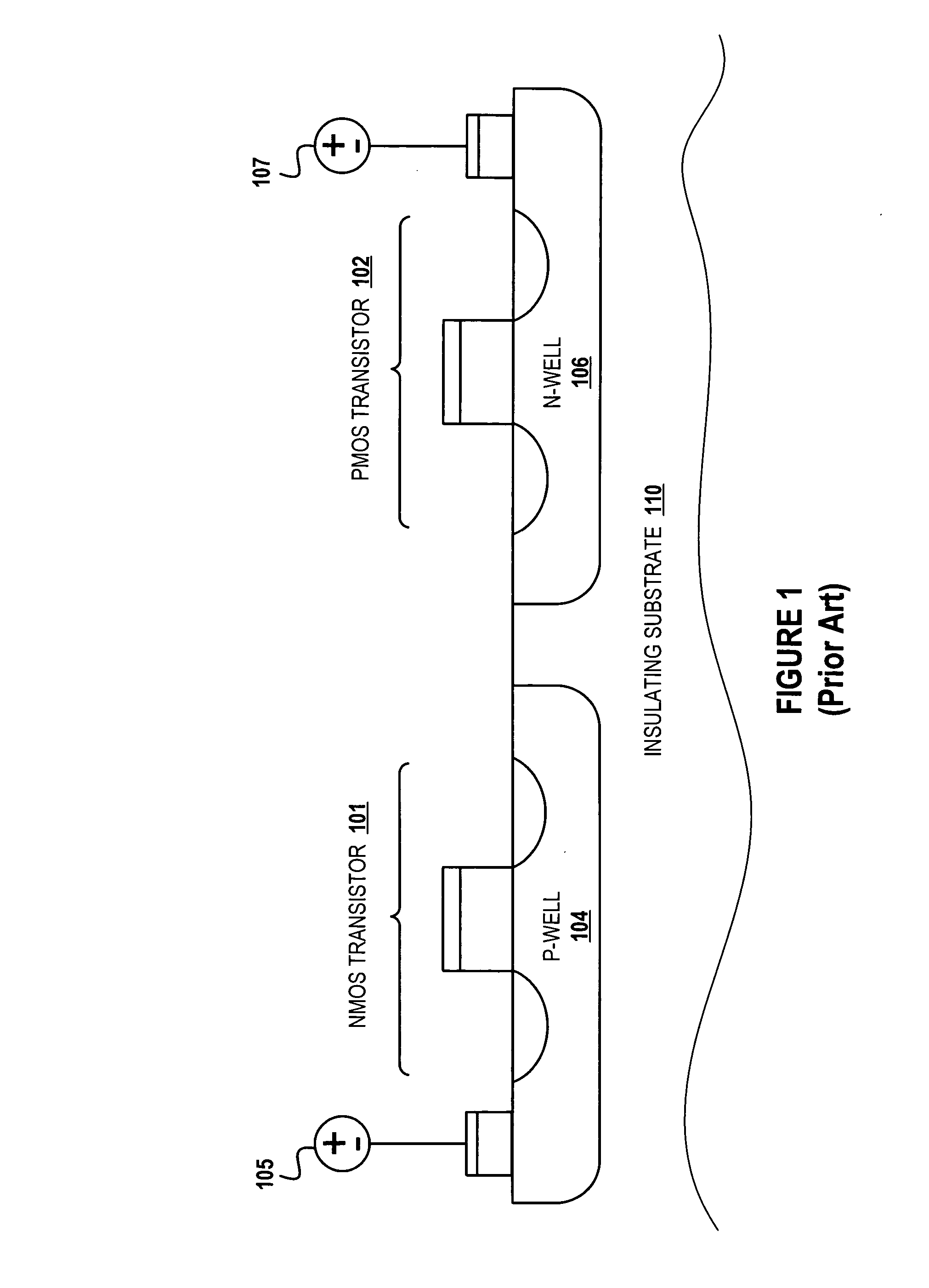

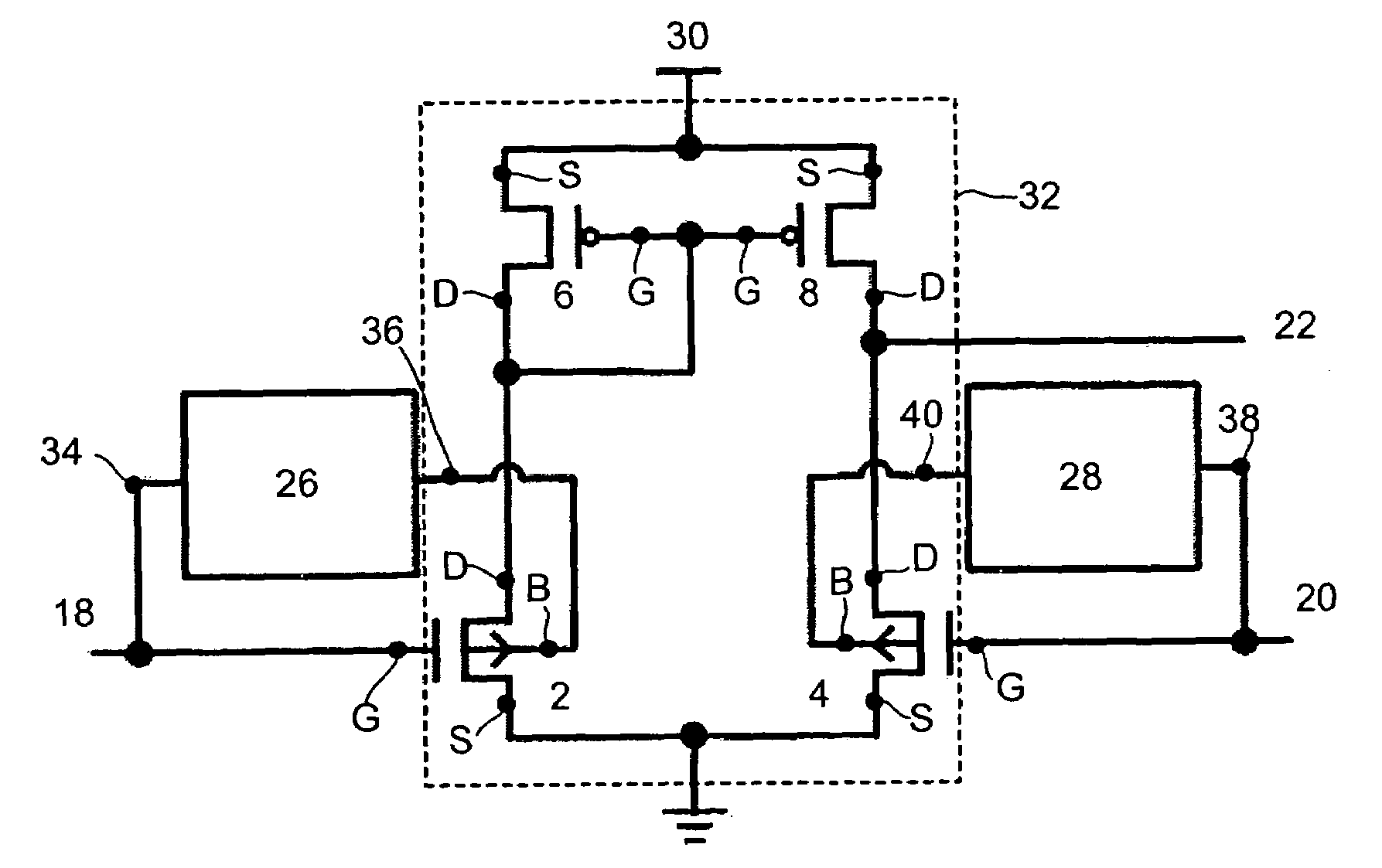

Semiconductor integrated circuit and manufacturing method therefor

InactiveUS20080143423A1Improve production yieldLittle overheadTransistorSolid-state devicesCMOSControl switch

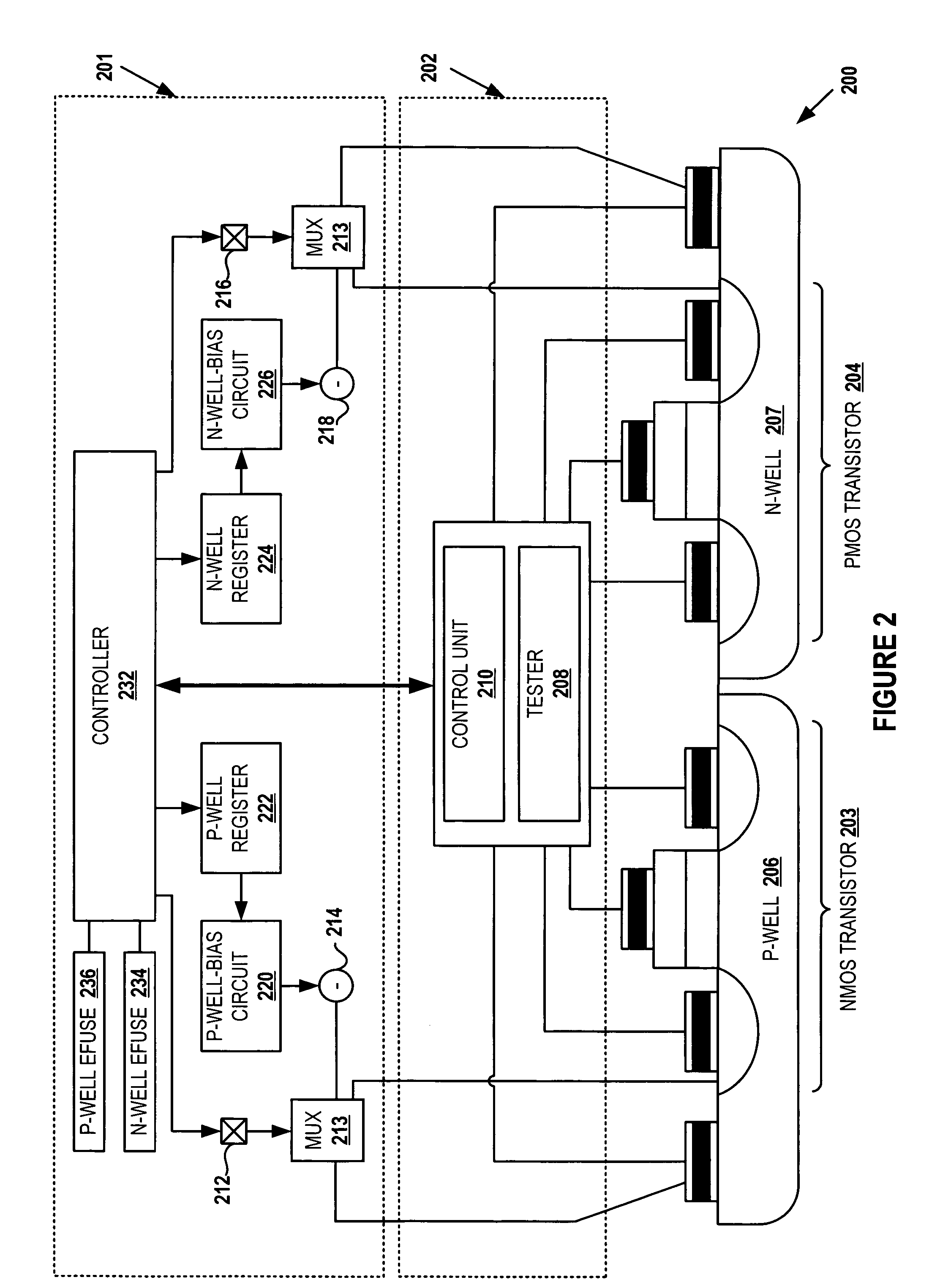

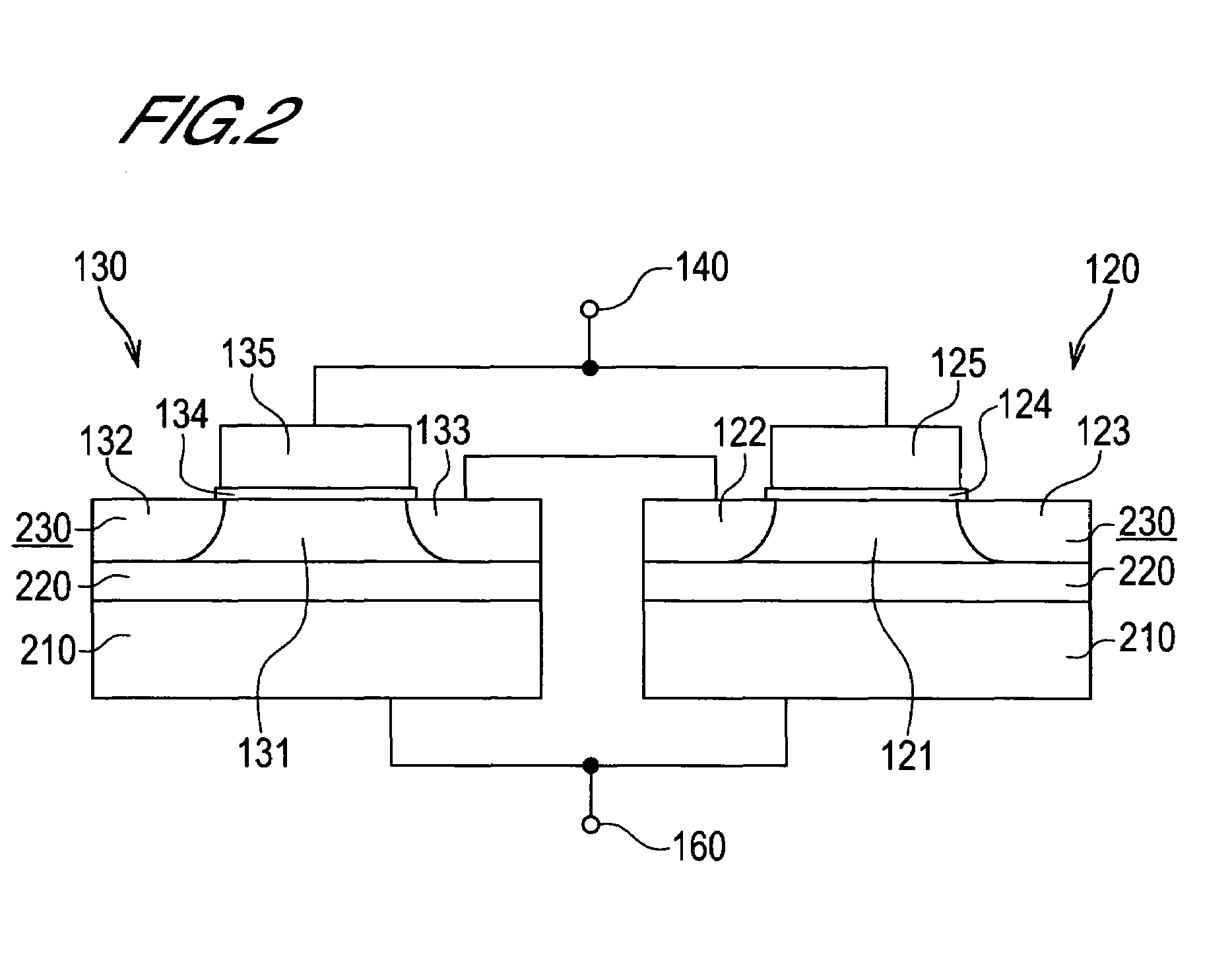

The present invention is directed to realize high manufacture yield and compensate variations in threshold voltage of a MOS transistor with small overhead. A semiconductor integrated circuit includes a CMOS circuit for processing an input signal in an active mode, a control switch, and a control memory. The control switch supplies a pMOS body bias voltage and an nMOS body bias voltage to an N well in a pMOS transistor and a P well in an nMOS transistor, respectively, in the CMOS circuit. The control memory stores control information indicating whether or not the pMOS body bias voltage and the nMOS body bias voltage are supplied from the control switch to the N well in the pMOS transistor and the P well in the nMOS transistor, respectively, in the CMOS circuit in the active mode.

Owner:RENESAS ELECTRONICS CORP

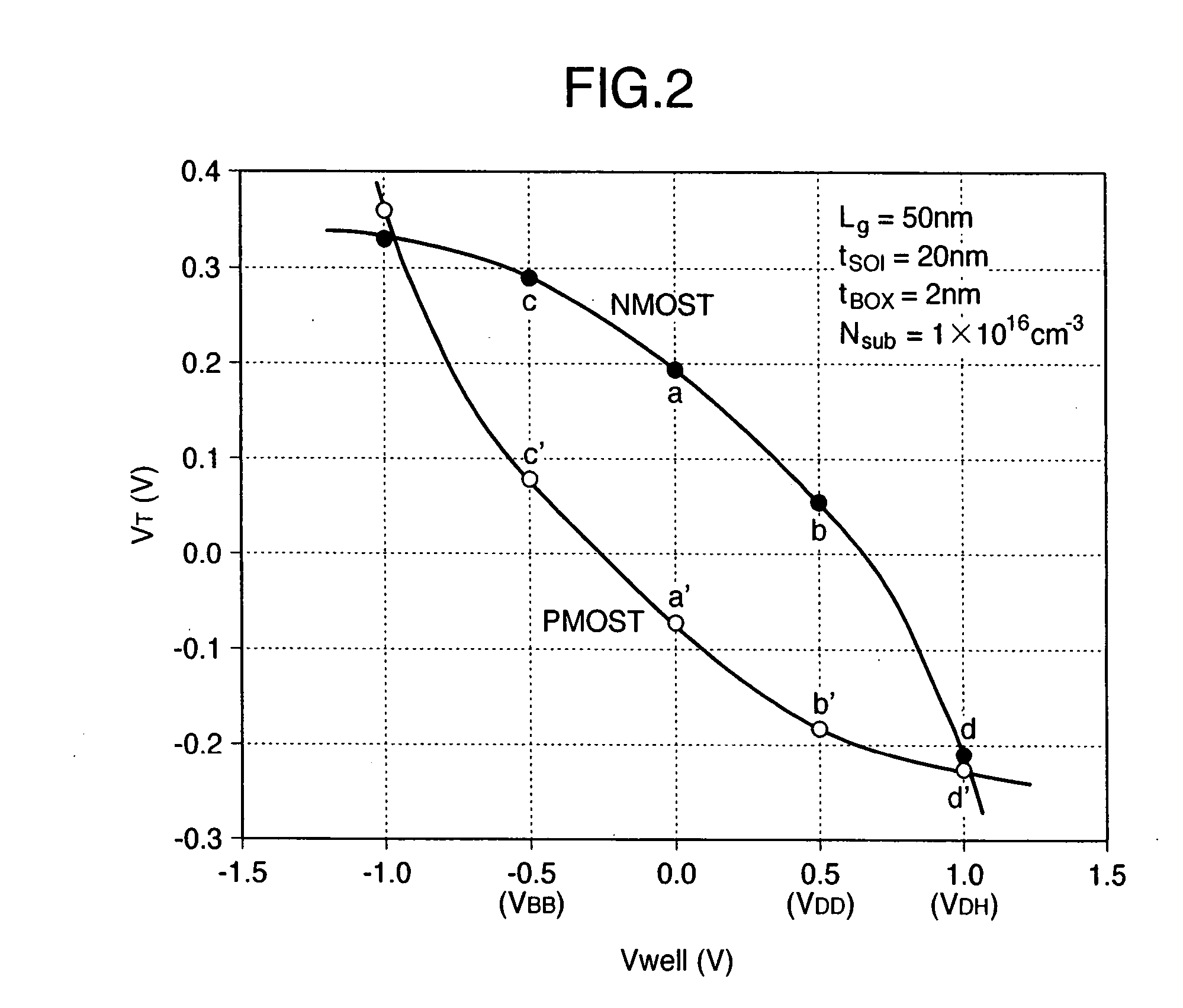

Semiconductor devices

InactiveUS20070152736A1Effective conditionsEffective structureSolid-state devicesSemiconductor/solid-state device manufacturingCMOSVoltage amplitude

Owner:HITACHI LTD

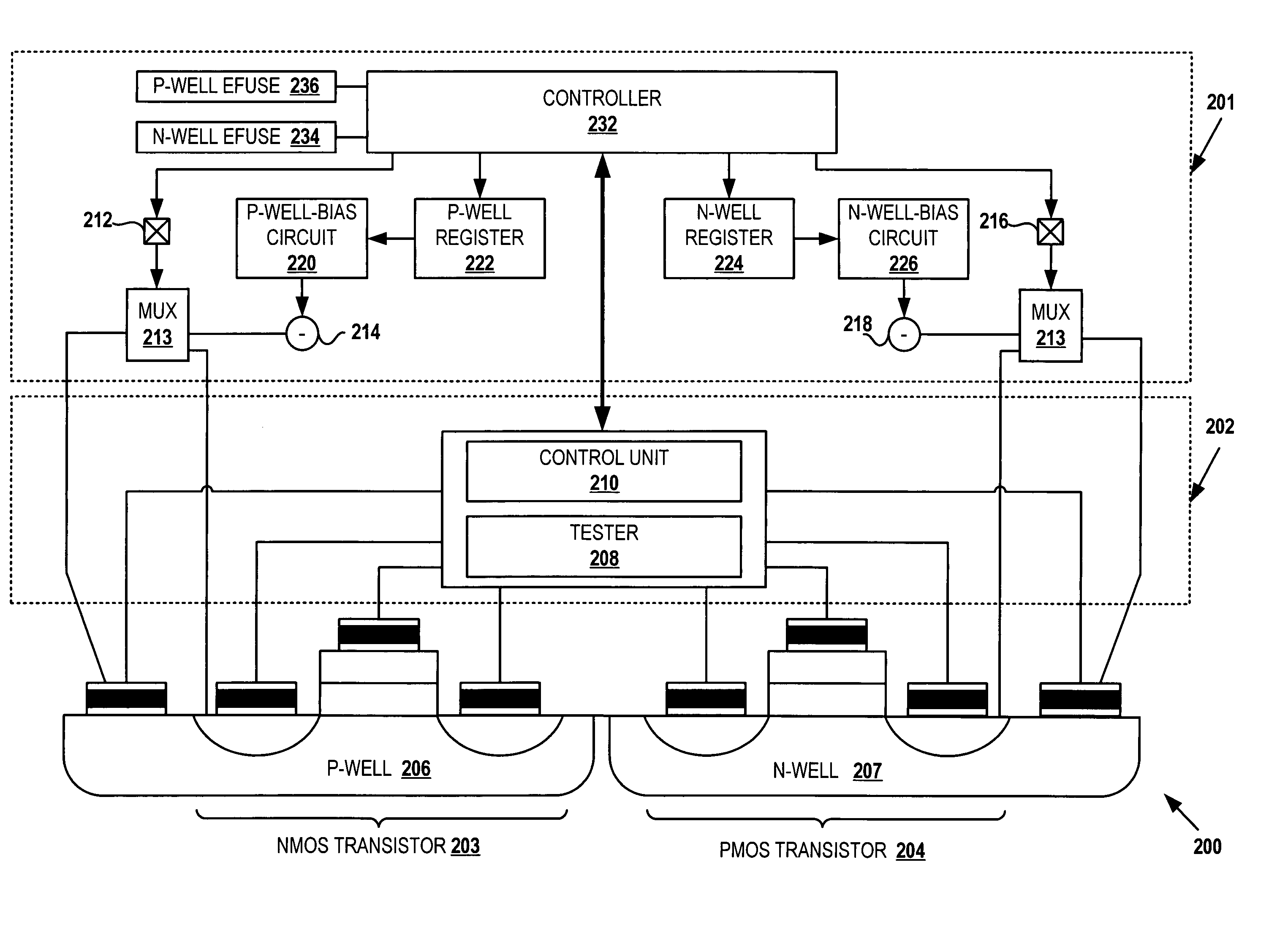

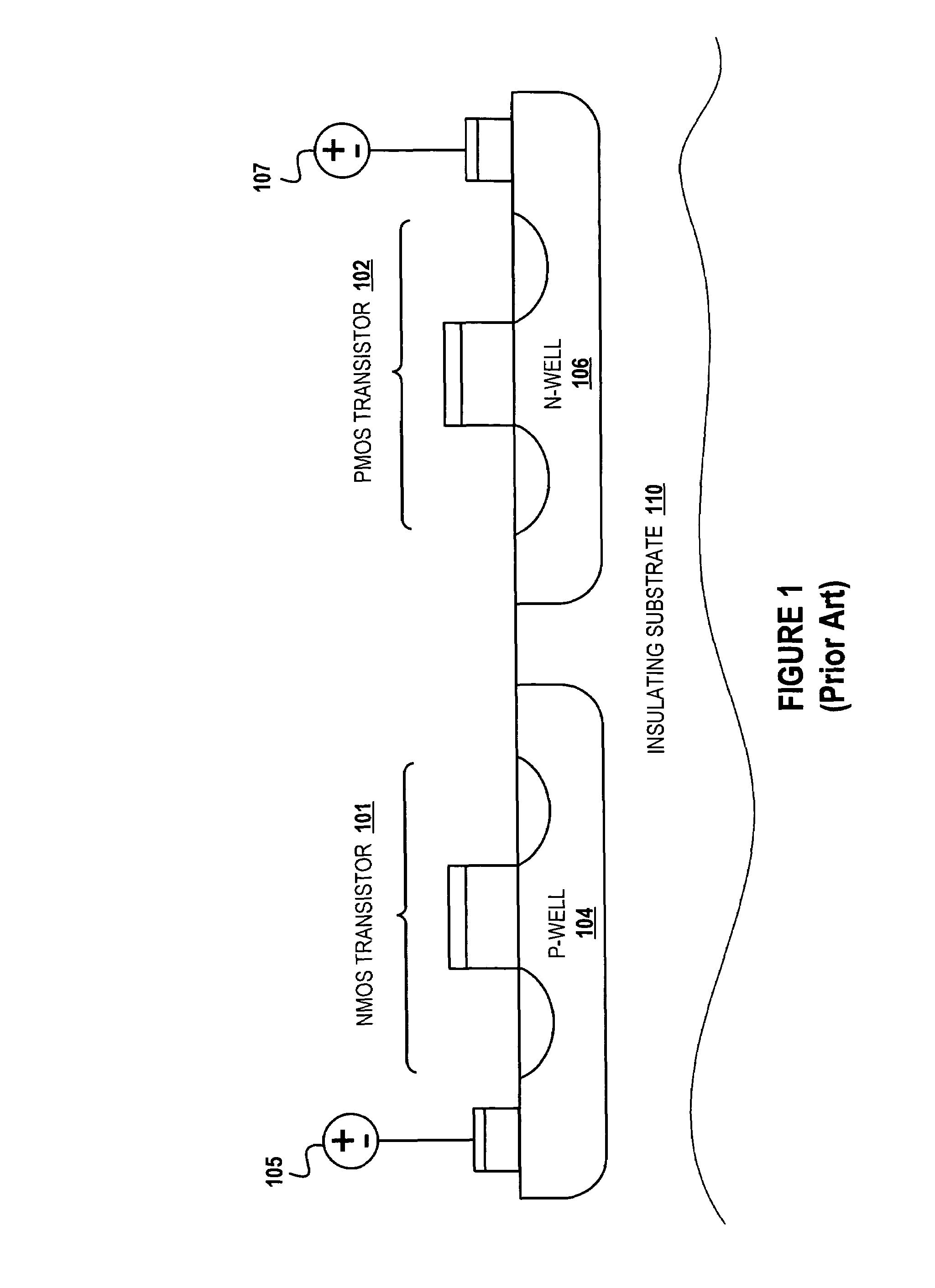

System, method and program product for well-bias set point adjustment

ActiveUS7274247B2Power reduction by control/clock signalThreshold modification in field effect transistorsPower modeProcessor register

A well-bias system dynamically adjusts well-bias set points to optimal levels across an integrated circuit (IC) for enhanced power savings and component reliability during a standby or low-power mode of operation. A controller within the IC determines if the chip power supply voltage will be reduced during an imminent standby or low power mode and sets a register controlling a negative well-bias set point for asserting well-bias to charge wells of the IC accordingly. To minimize leakage current without compromising reliability, the well-bias set point is set to (1) an optimal well-bias set point if a reduced supply voltage is to be applied to the IC, or (2) a minimum well-bias set point when a nominal or high supply voltage is to be applied to the IC.

Owner:NXP USA INC

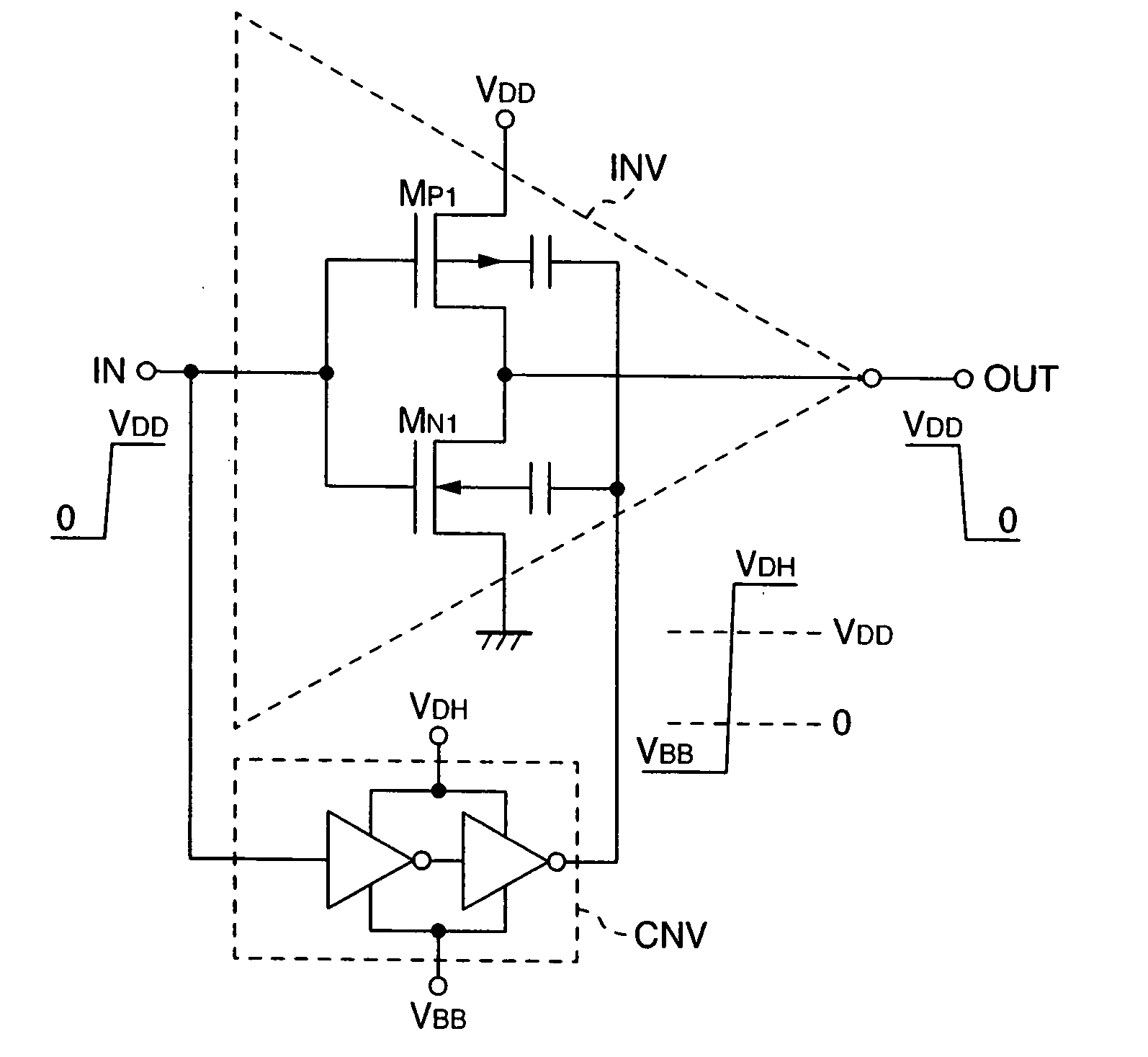

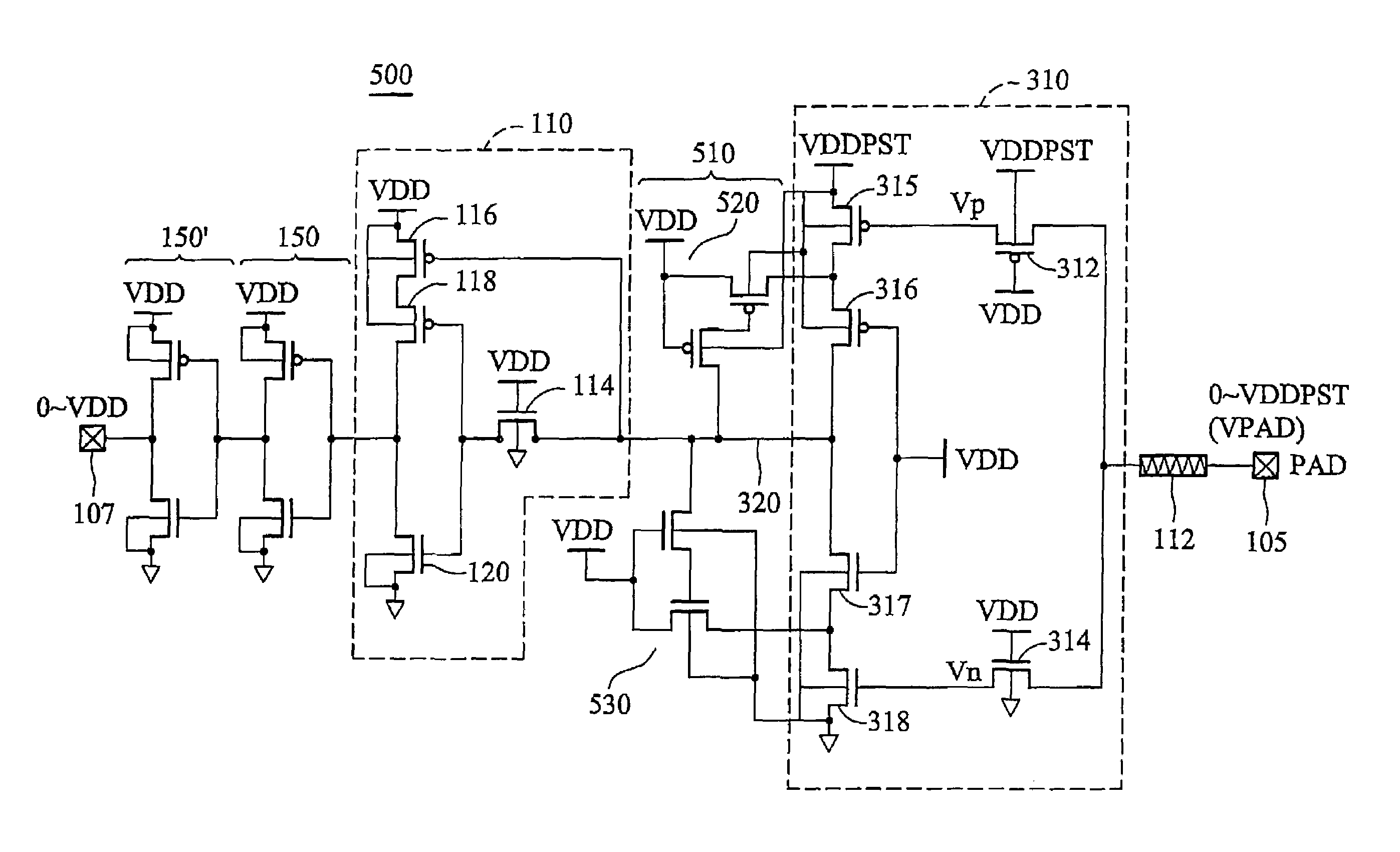

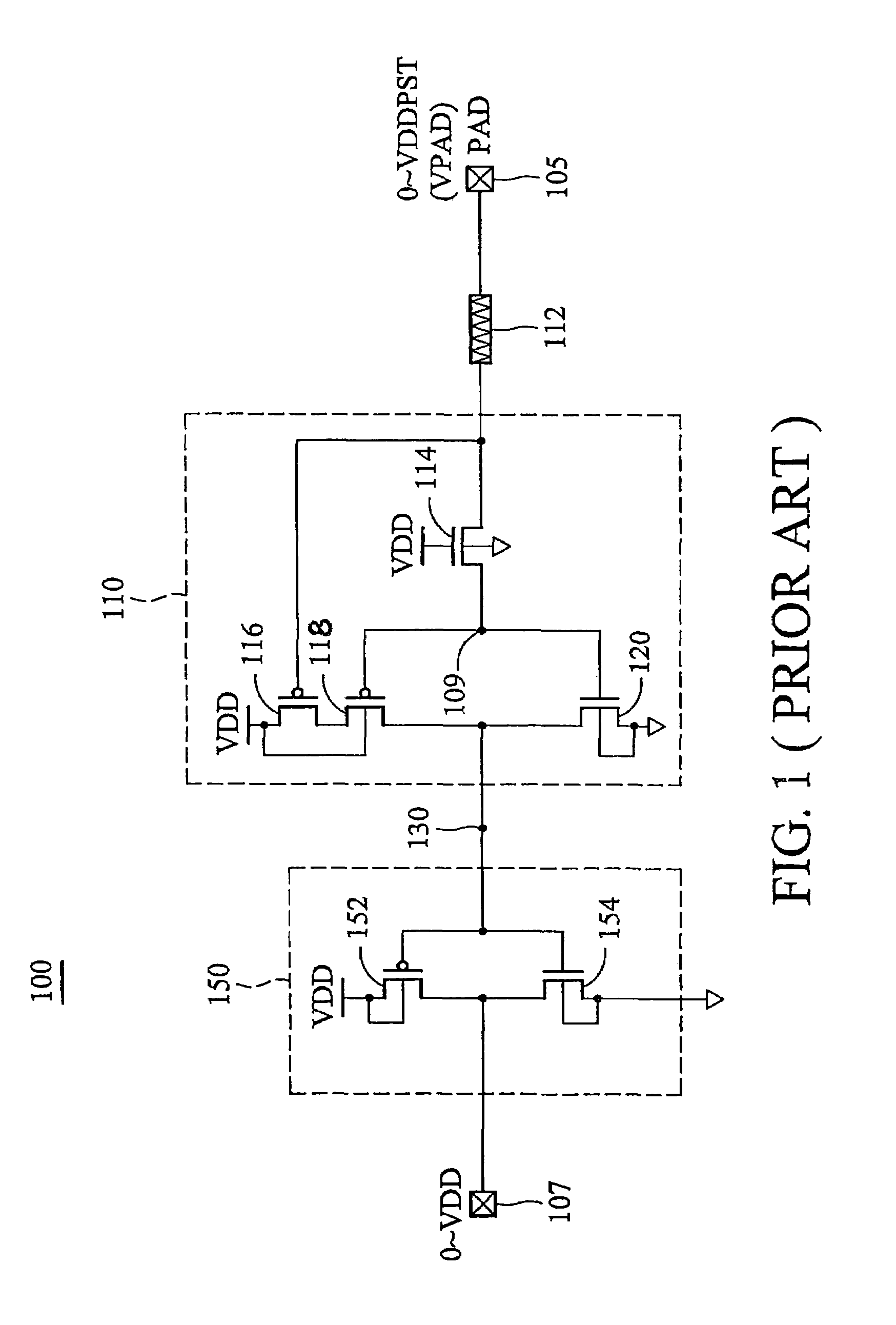

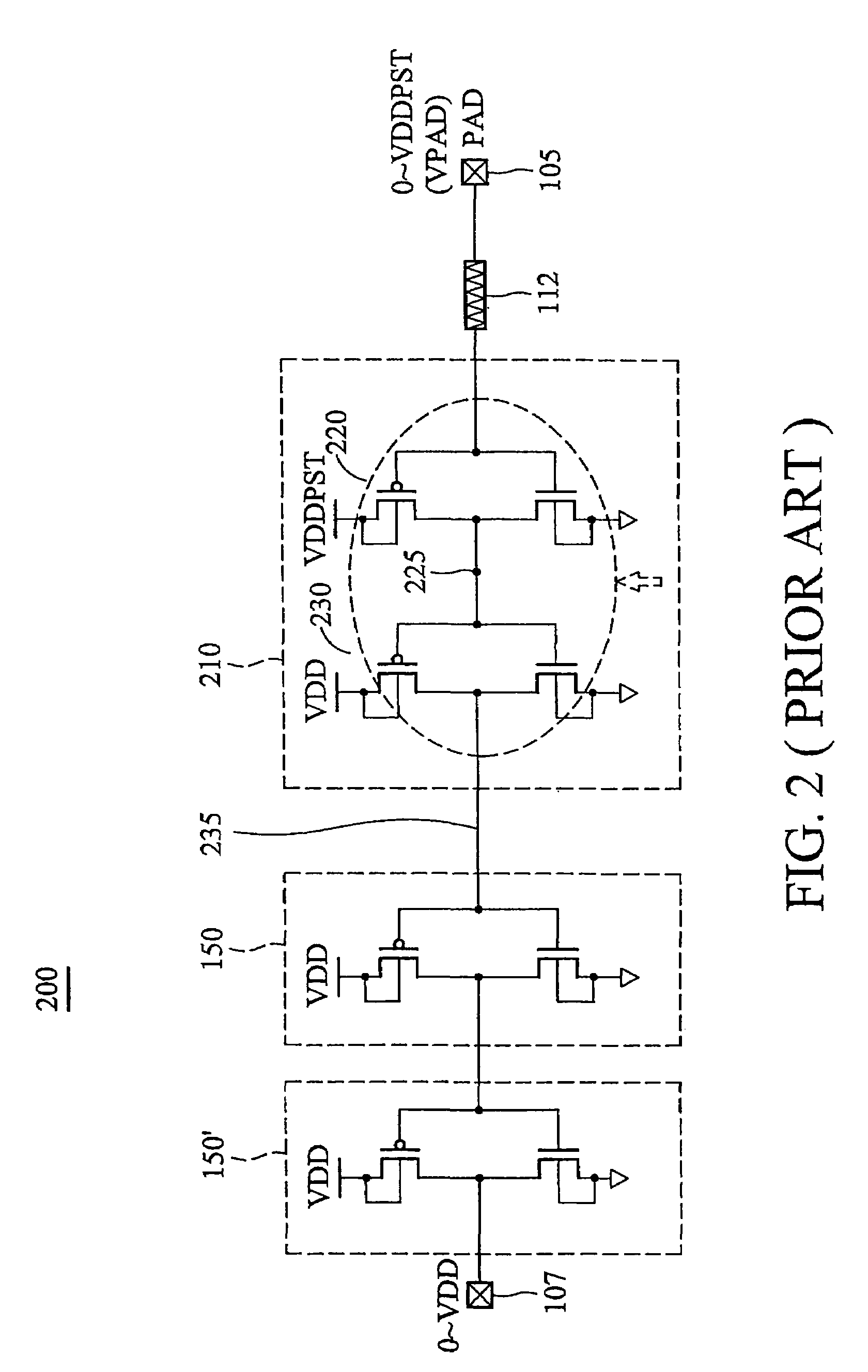

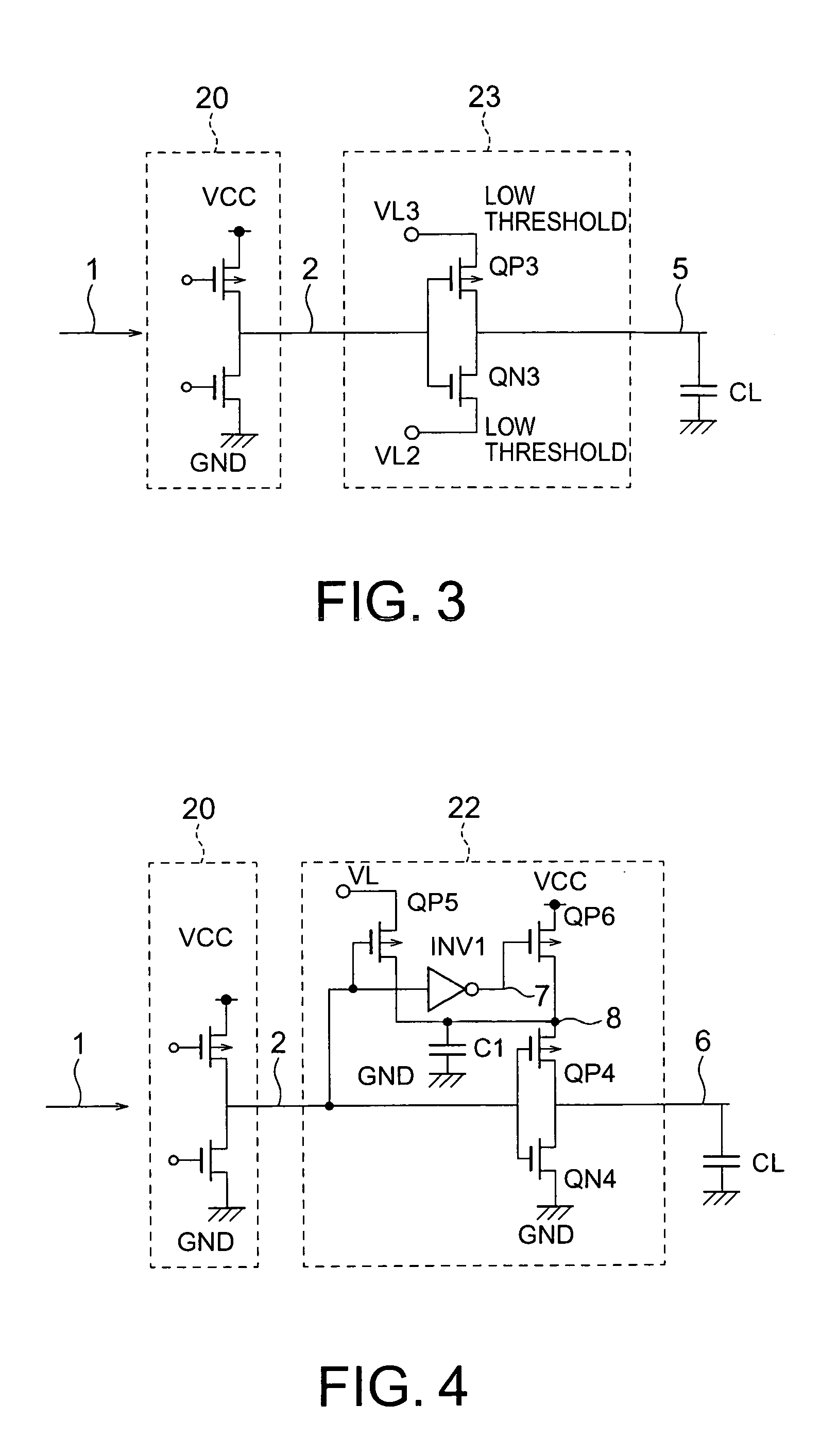

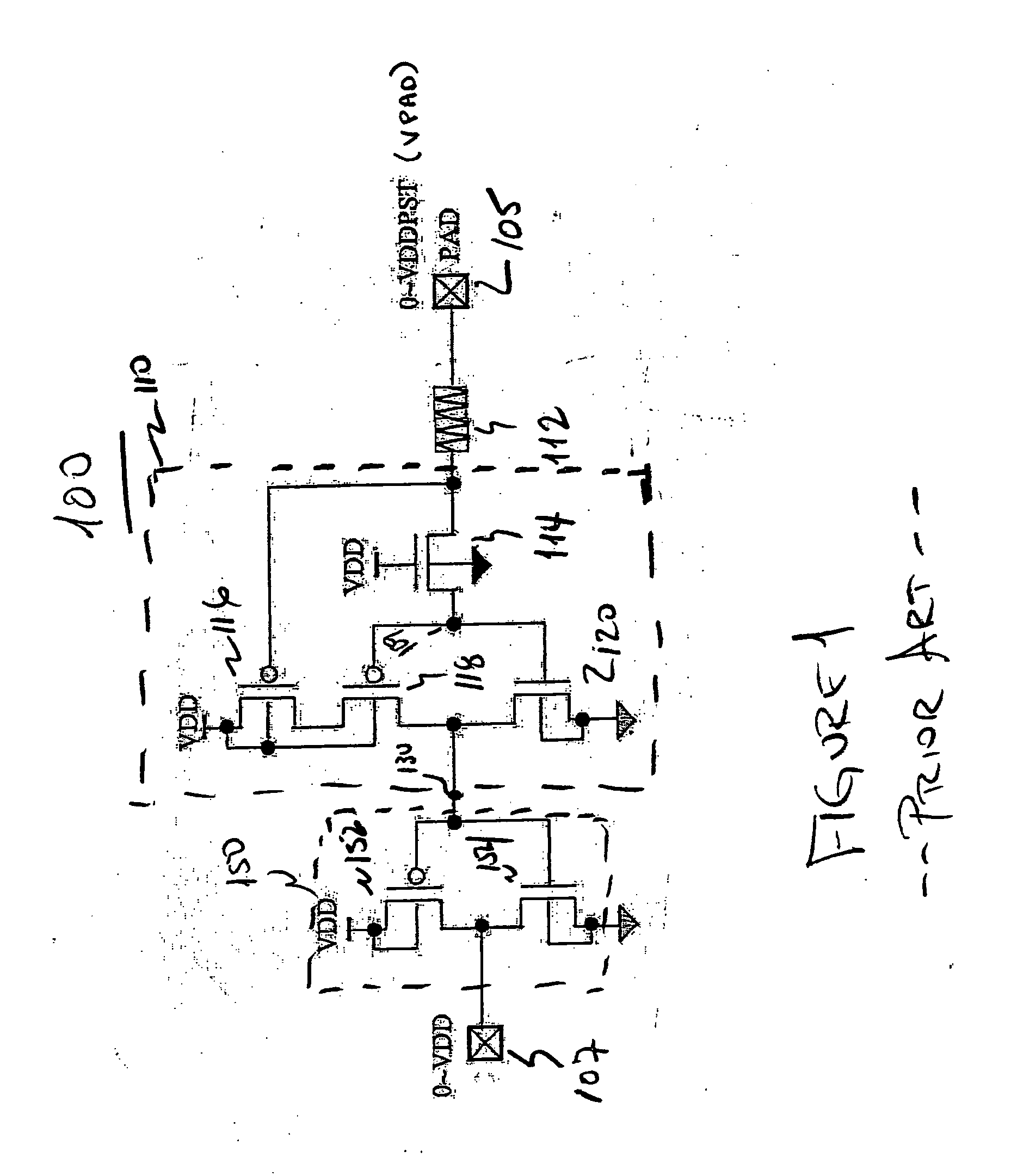

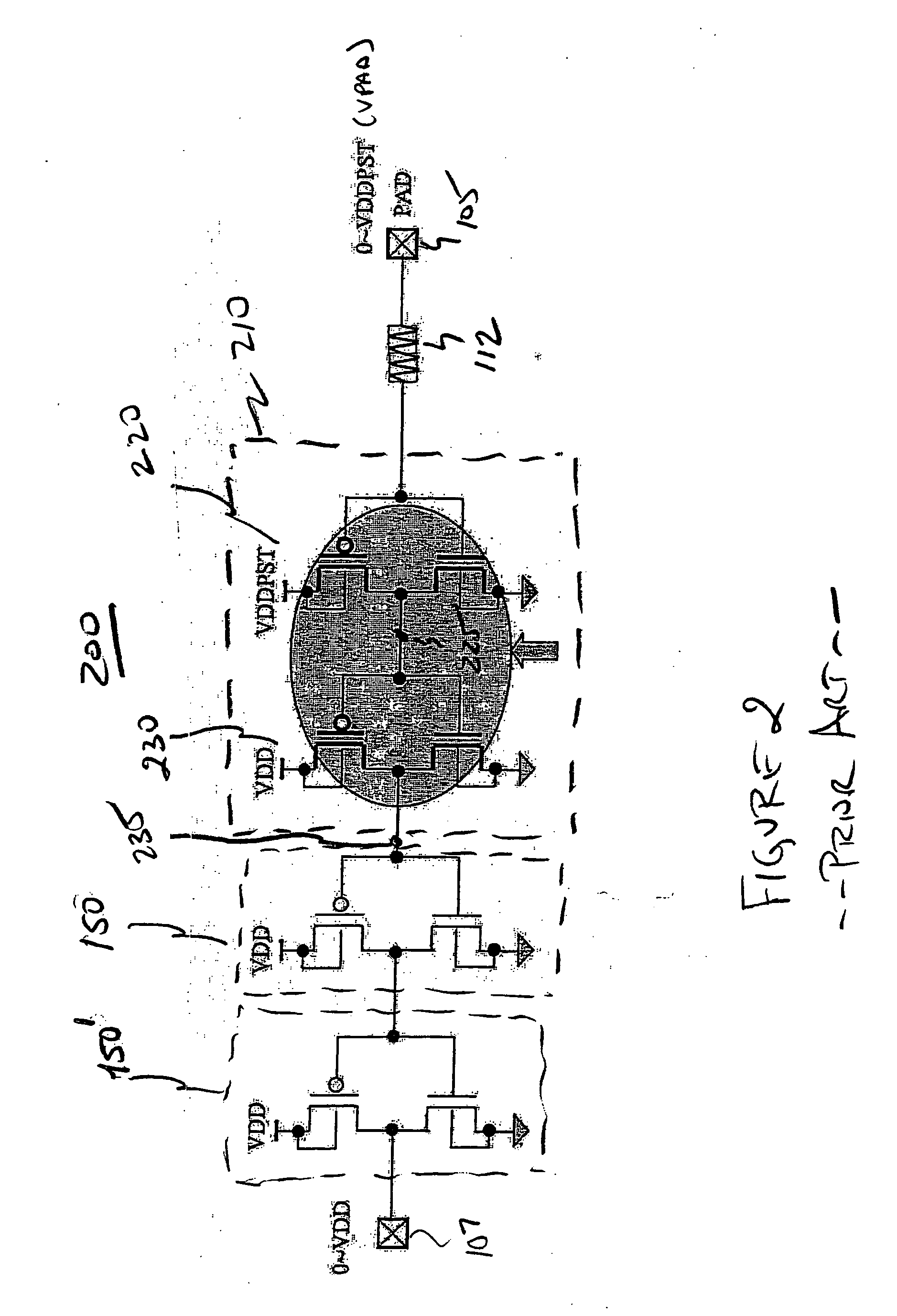

Input buffer structure with single gate oxide

InactiveUS7173472B2Pulse automatic controlInstant pulse delivery arrangementsLow voltage circuitsLevel shifting

An input buffer for interfacing a high voltage signal received at an input node to a low voltage circuit comprising low voltage devices is provided. The buffer includes a threshold adjustment circuit including an inverter coupled to a threshold adjusted output node. The inverter includes low voltage devices and is coupled between a high supply voltage node and a ground node. The inverter includes a first and second transistors having biasing nodes coupled to a low voltage supply node of the low voltage circuit and coupled to the threshold adjusted output node. The adjustment circuit provides at the threshold adjusted output node an inverted signal corresponding to the high voltage input signal. The buffer also includes a level shifting circuit including low voltage devices and provides a low voltage signal corresponding to the high voltage input signal in response to said inverted signal.

Owner:TAIWAN SEMICON MFG CO LTD

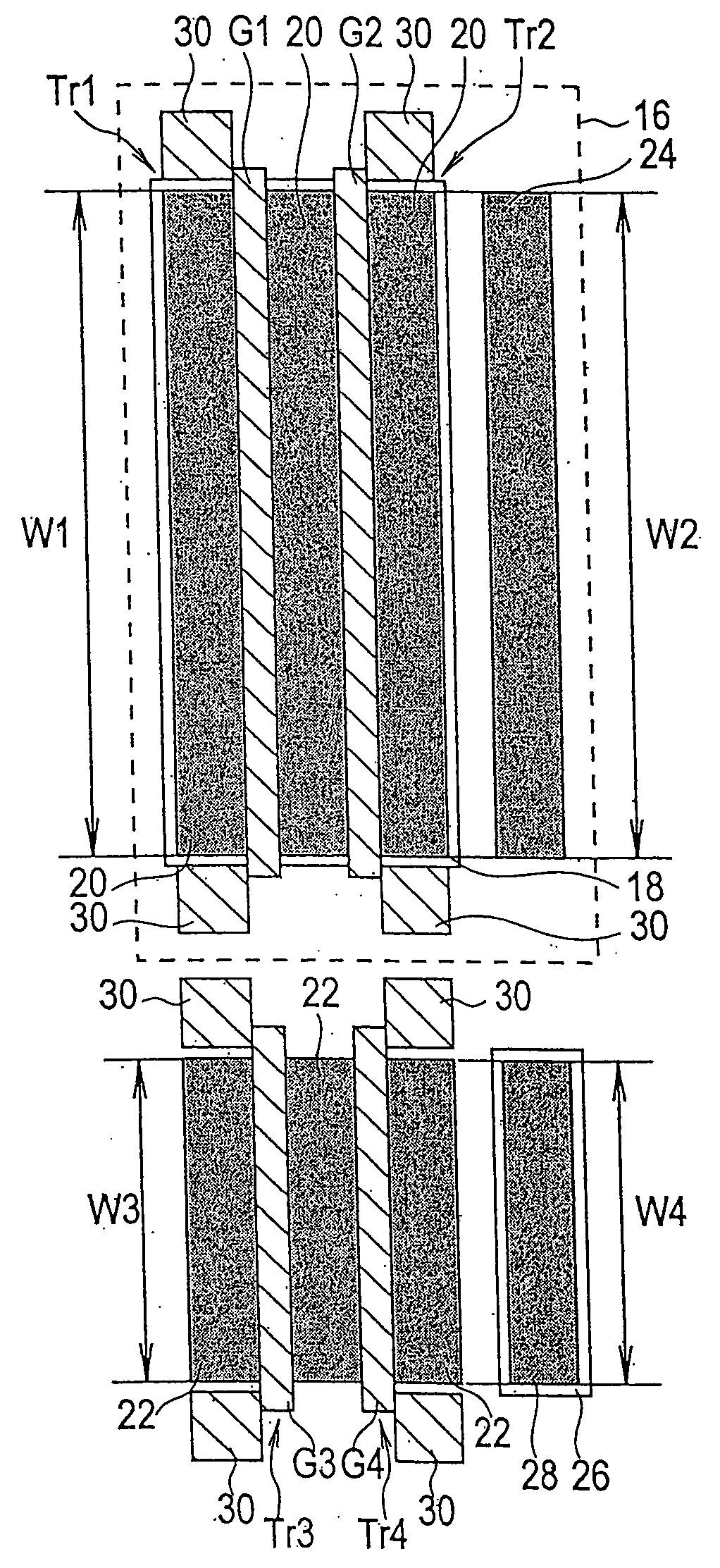

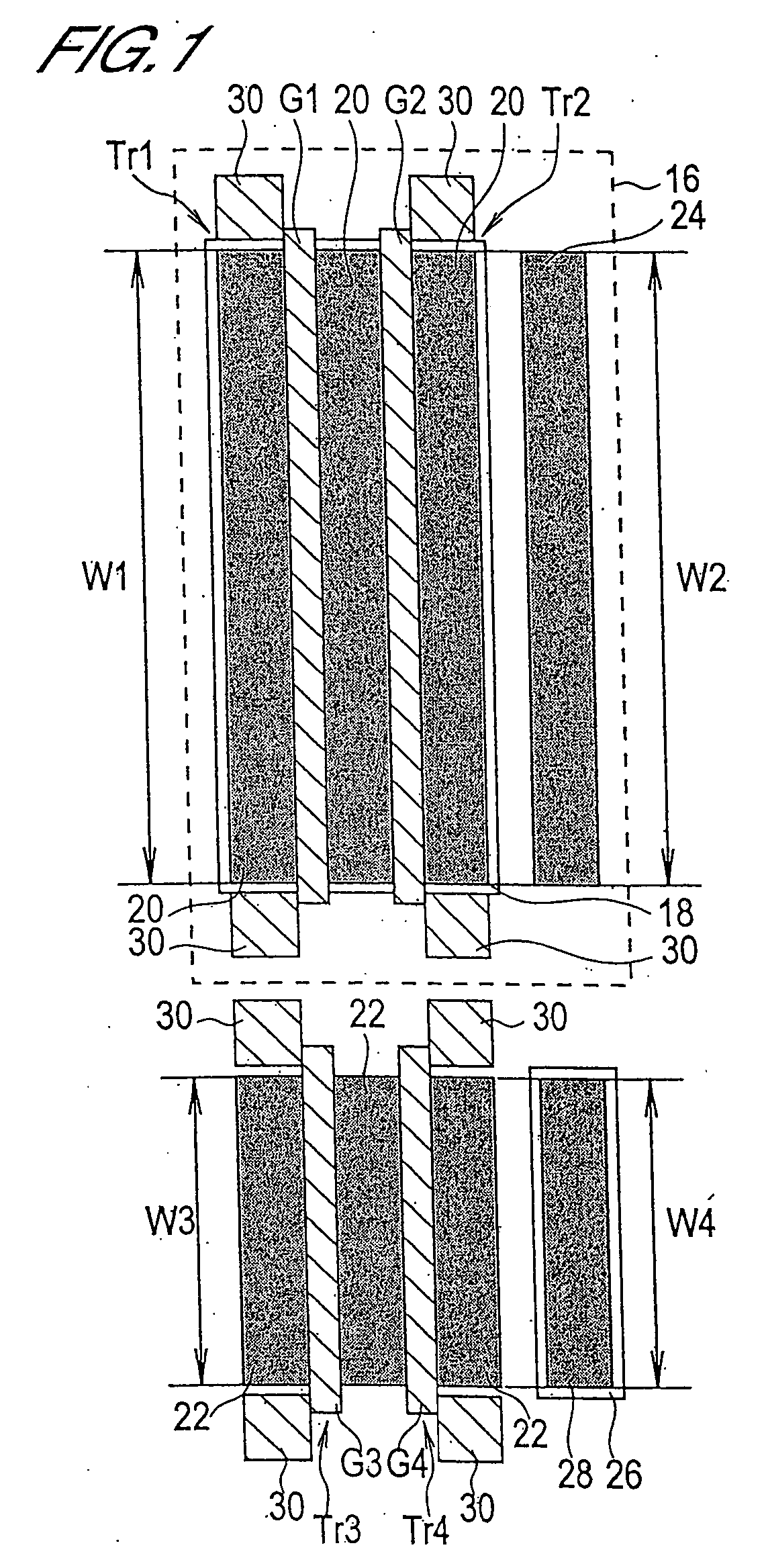

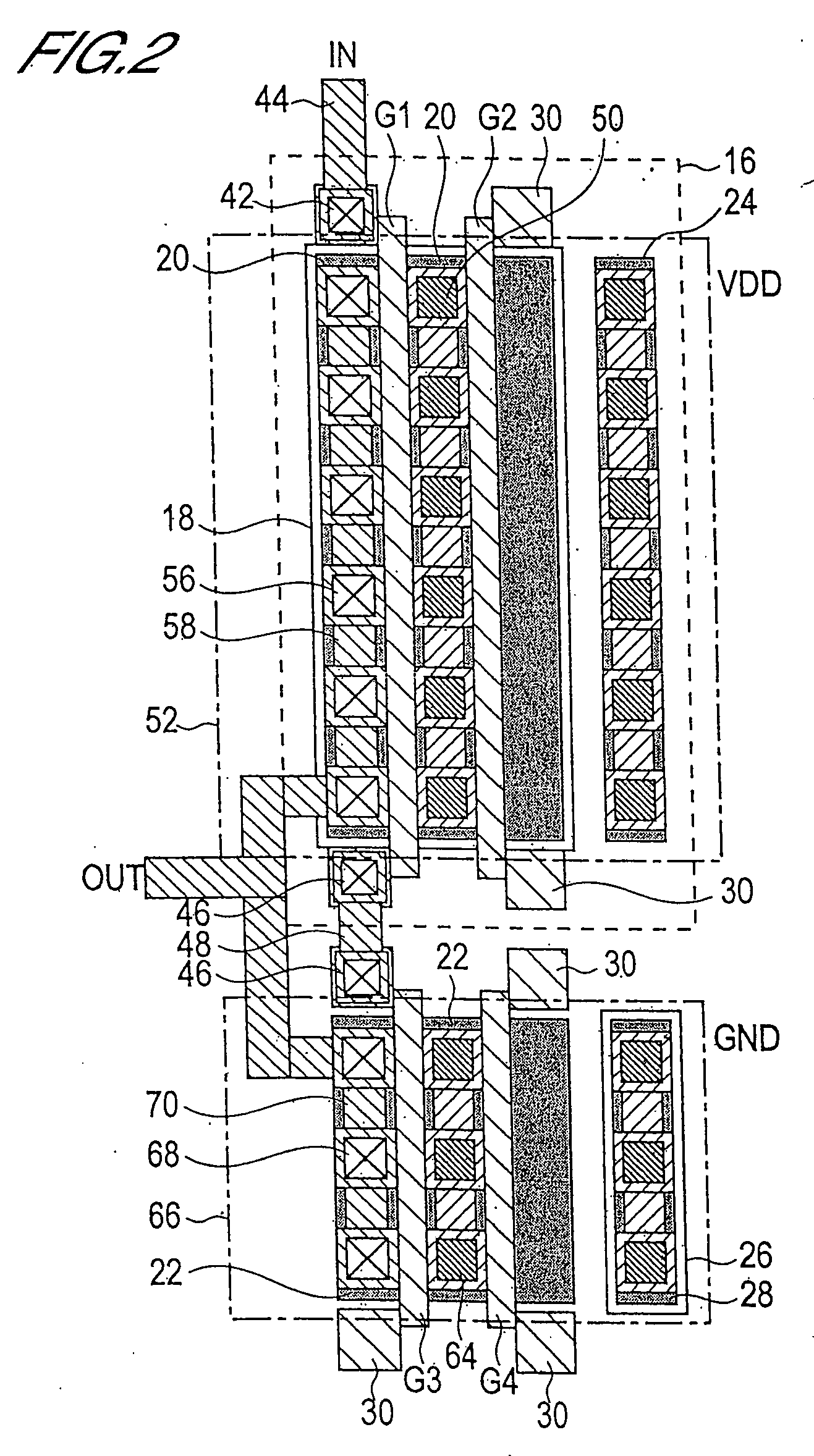

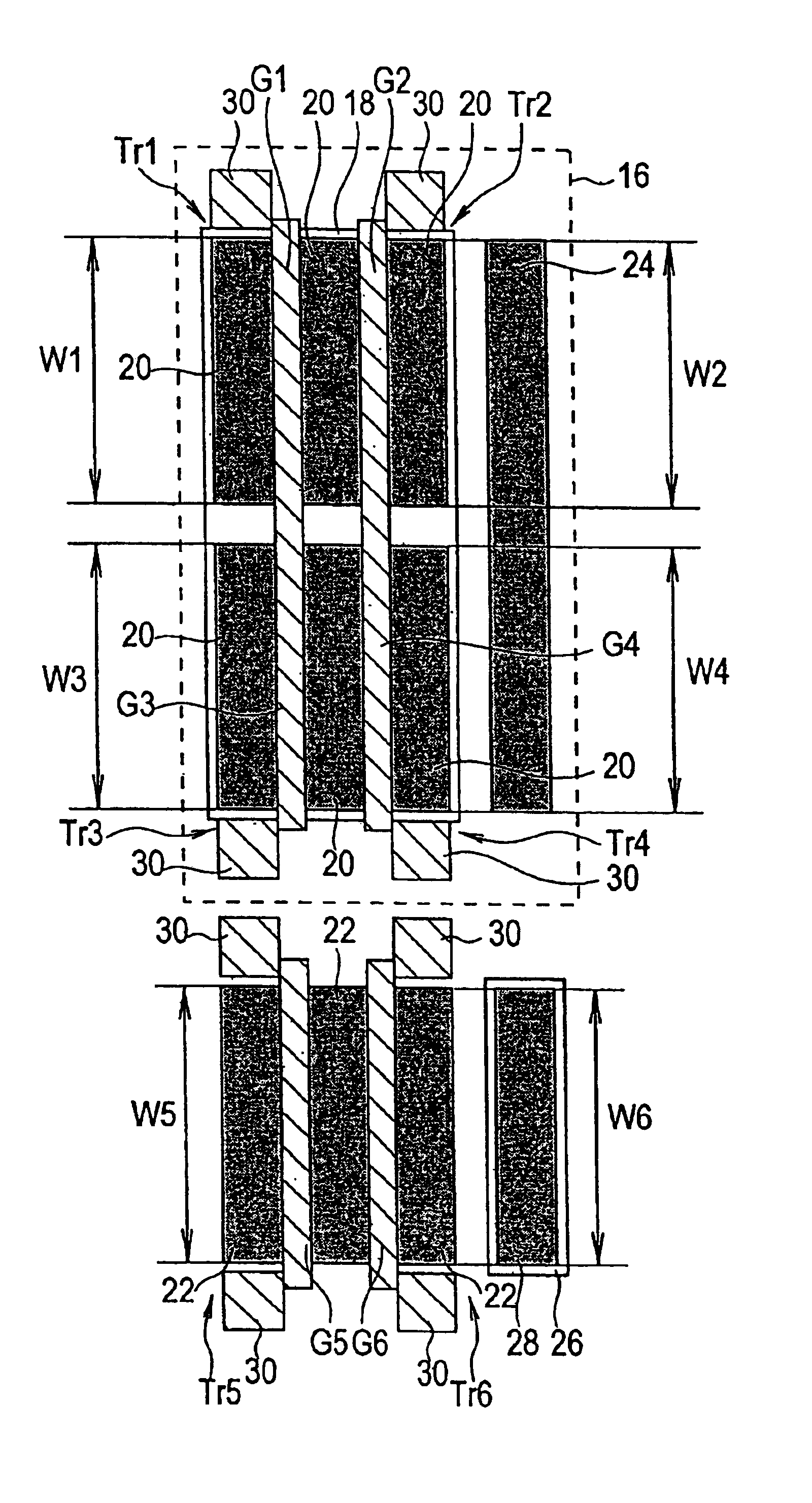

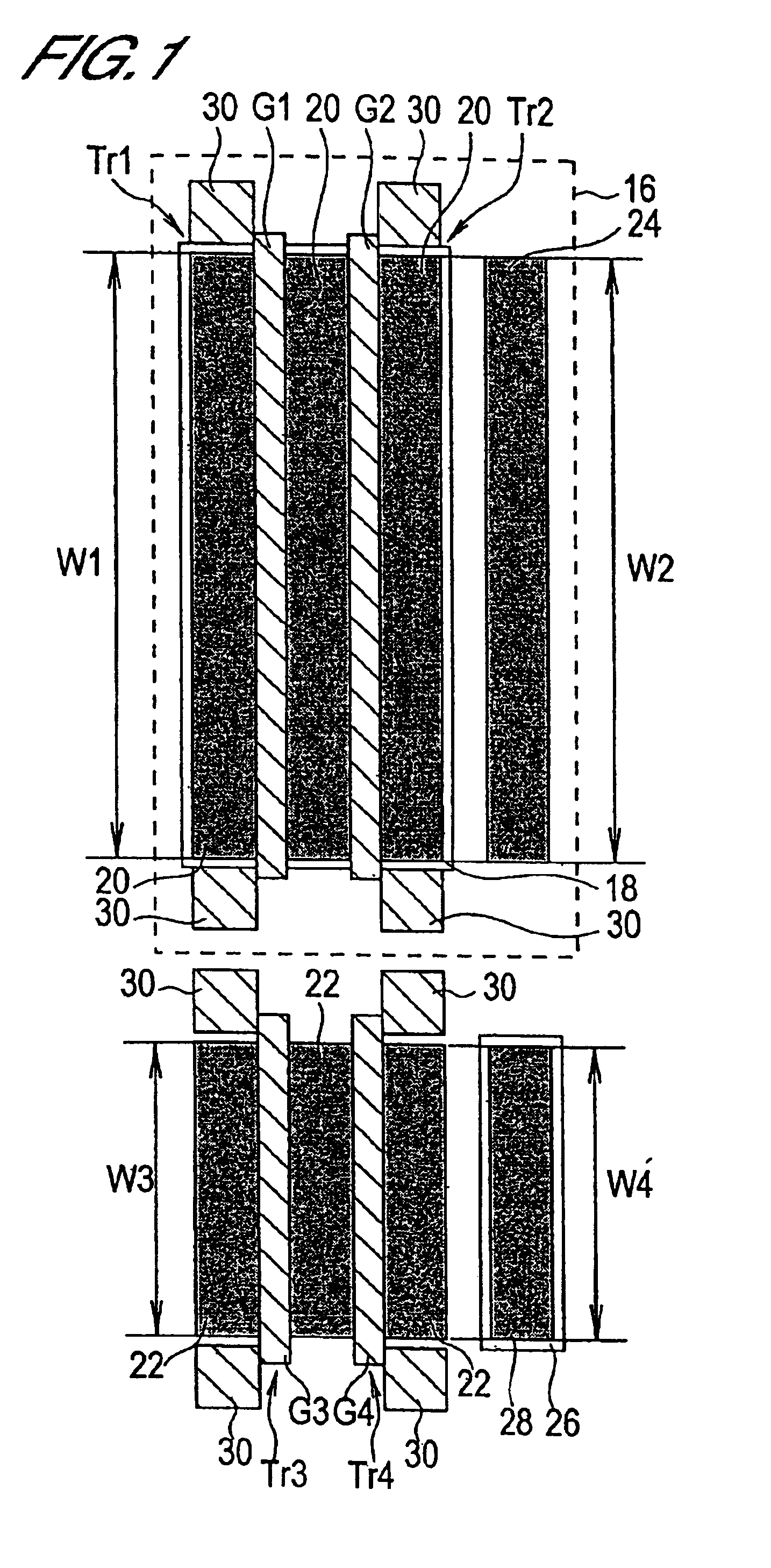

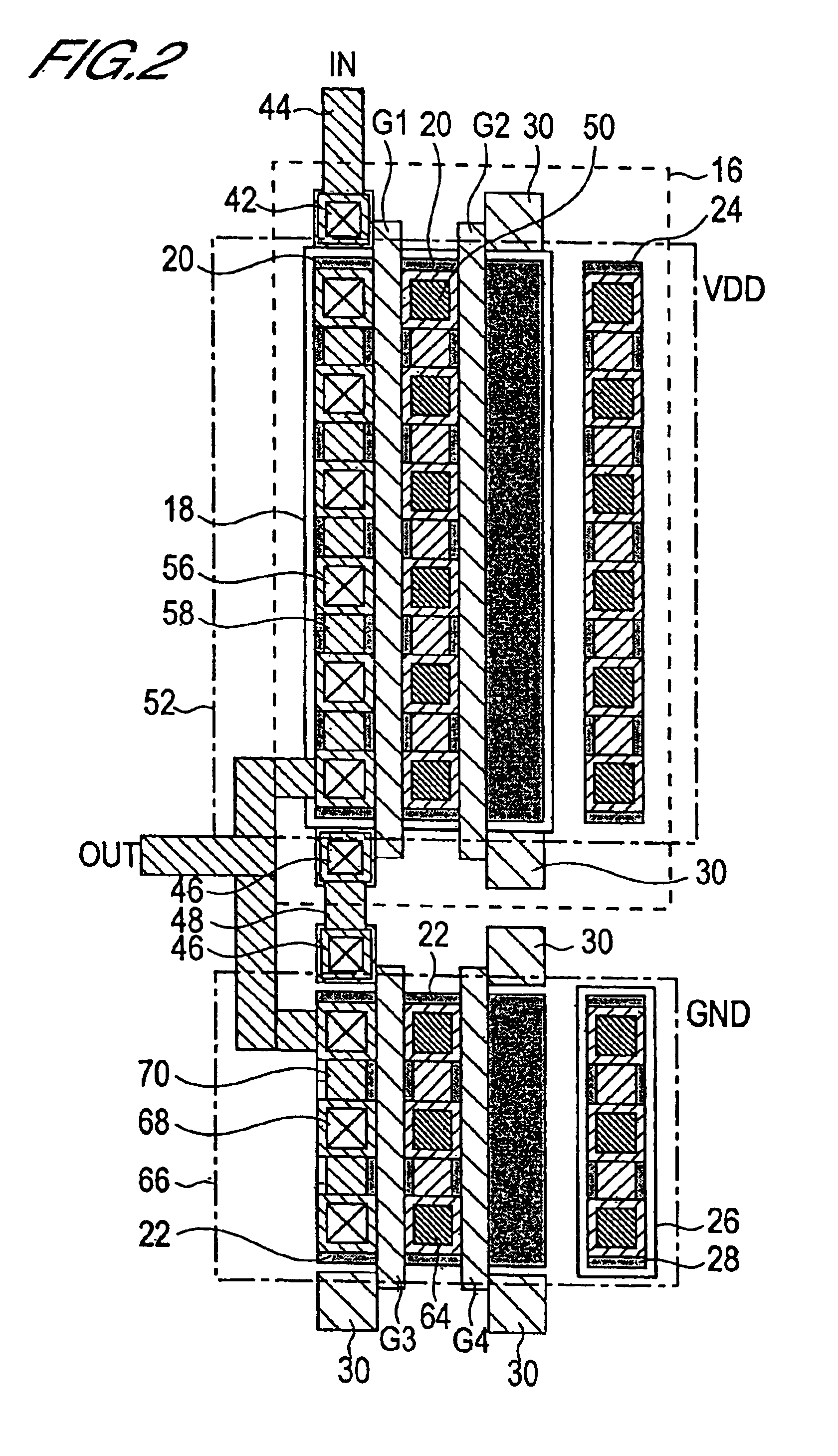

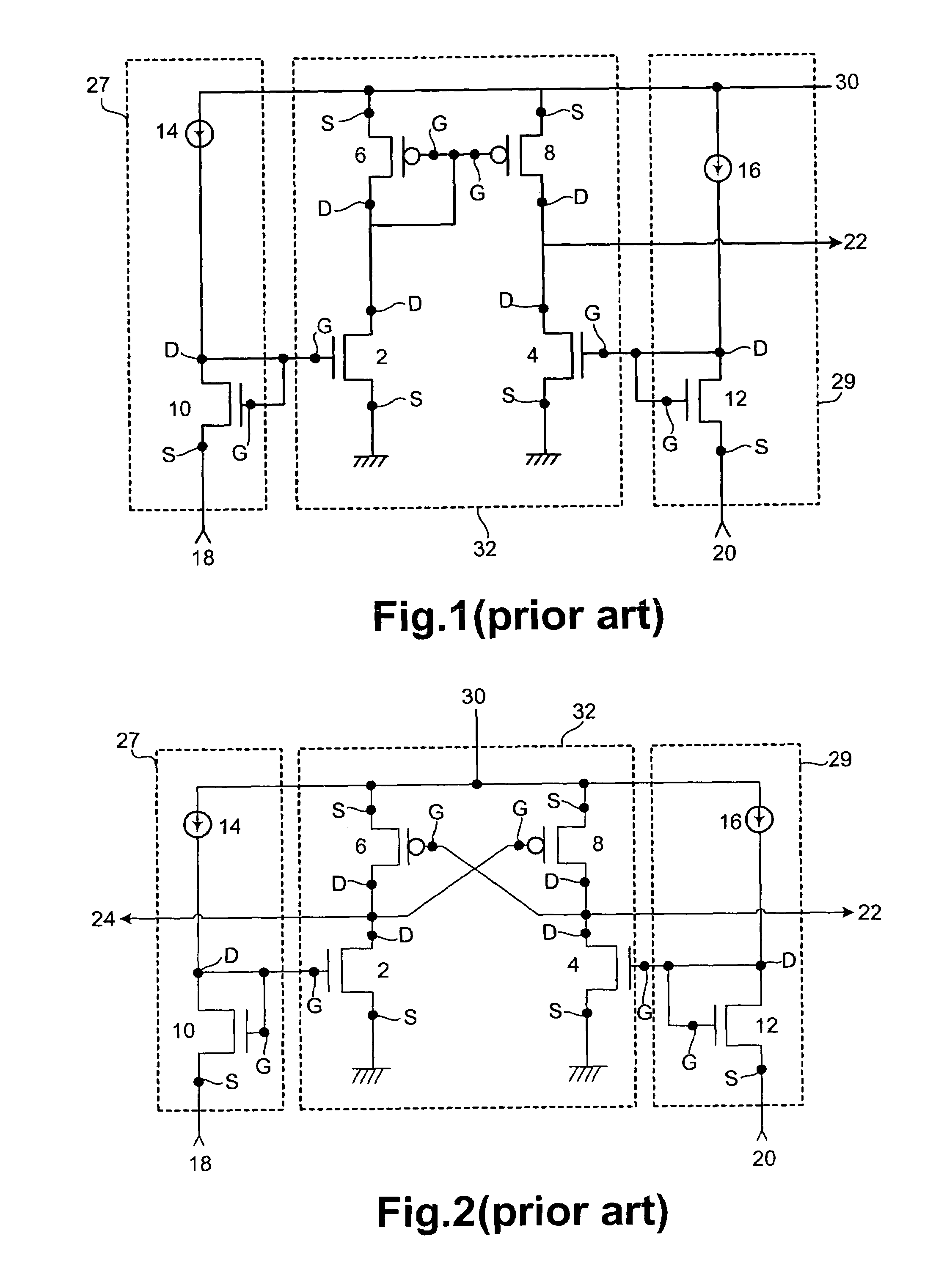

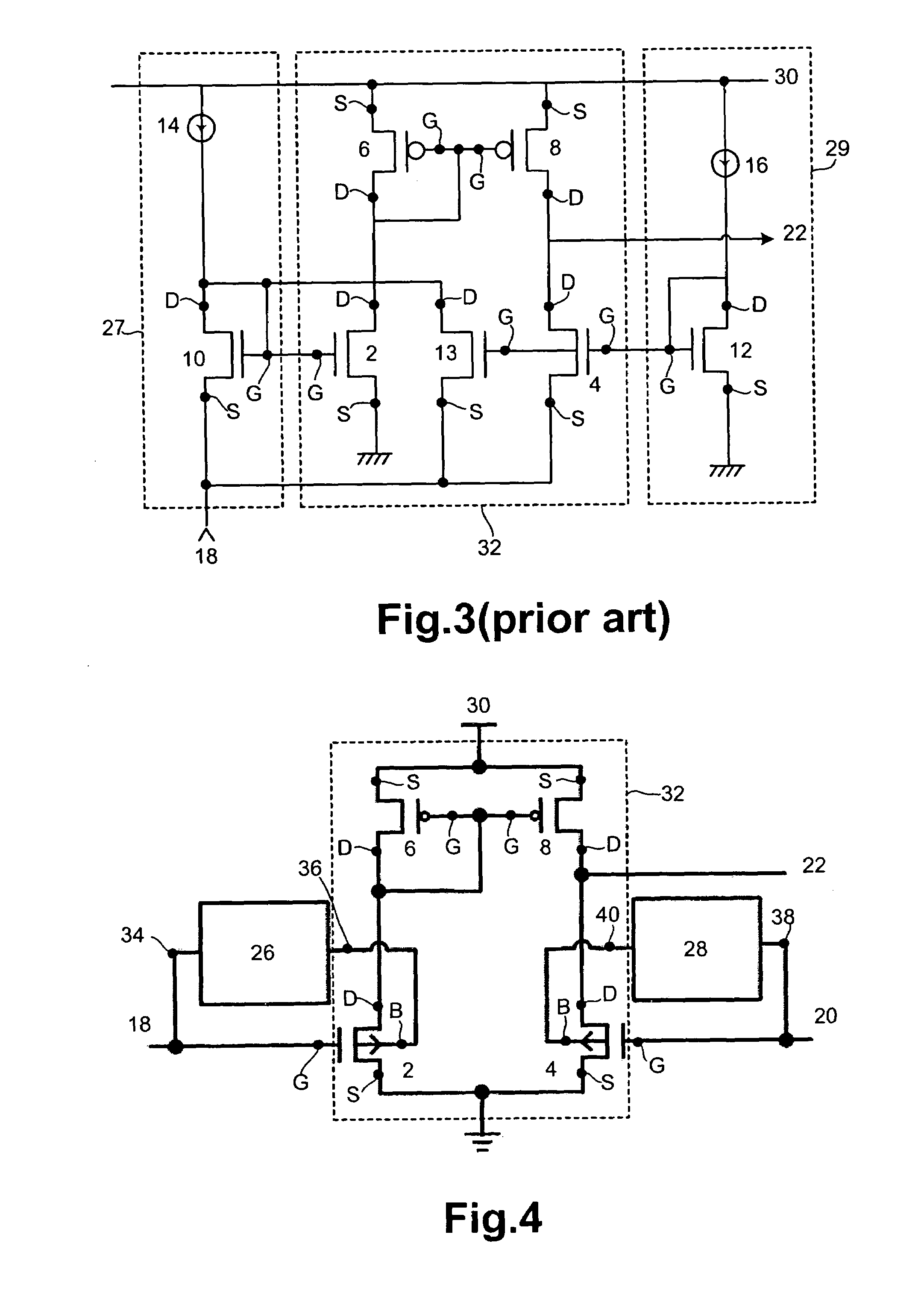

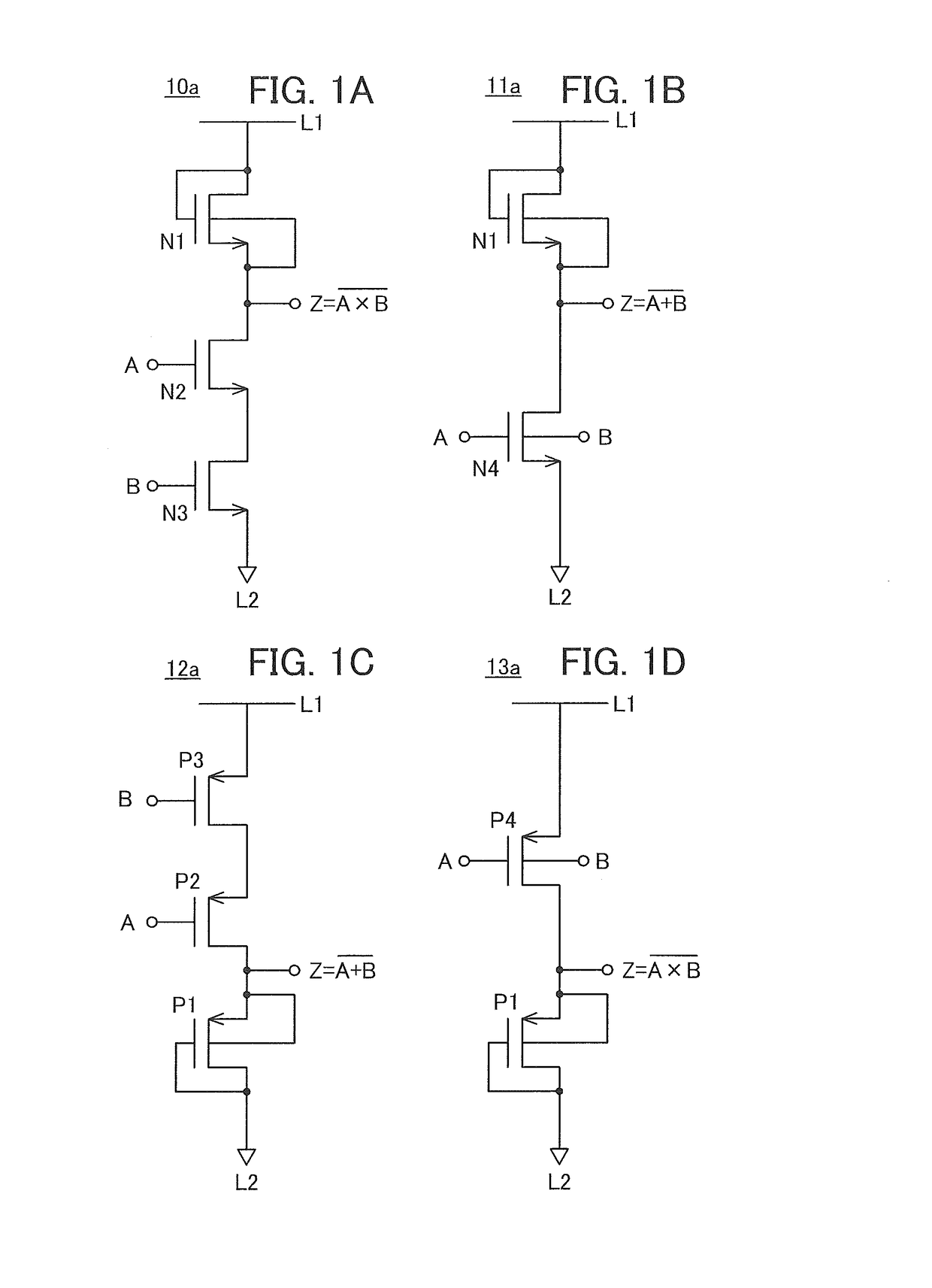

Basic cells configurable into different types of semiconductor integrated circuits

The basic cell constituted by a semiconductor integrated circuit comprises two PMOS transistors and two NMOS transistors. By setting the gate widths of the gates of these transistors to prescribed lengths, the efficiency of use of elements within the basic cell is improved, and fine adjustment of the threshold voltage Vth and delay time Tpd becomes possible.

Owner:LAPIS SEMICON CO LTD

Basic cells configurable into different types of semiconductor integrated circuits

The basic cell constituted by a semiconductor integrated circuit comprises two PMOS transistors and two NMOS transistors. By setting the gate widths of the gates of these transistors to prescribed lengths, the efficiency of use of elements within the basic cell is improved, and fine adjustment of the threshold voltage Vth and delay time Tpd becomes possible.

Owner:LAPIS SEMICON CO LTD

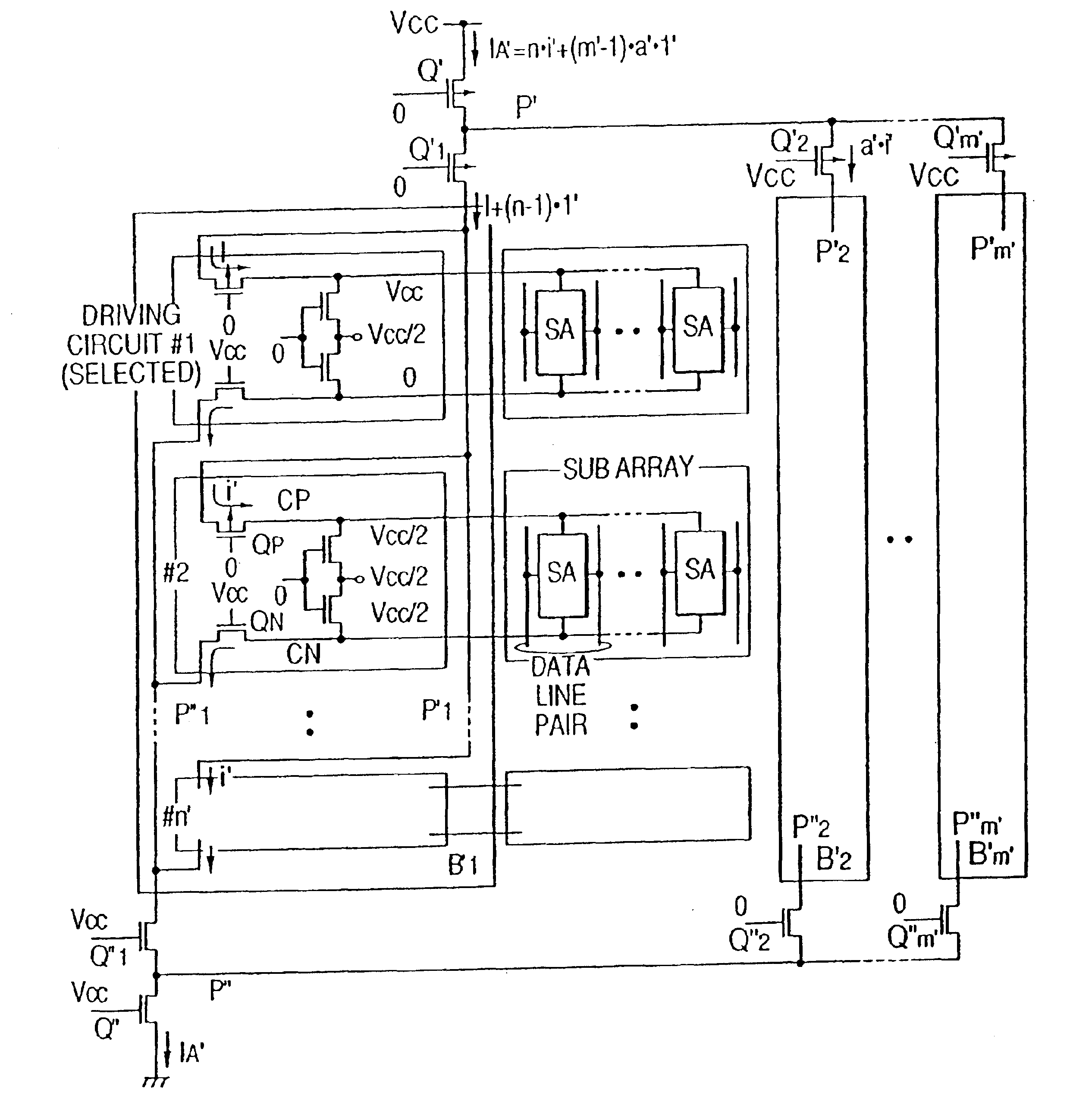

Semiconductor integrated circuits with power reduction mechanism

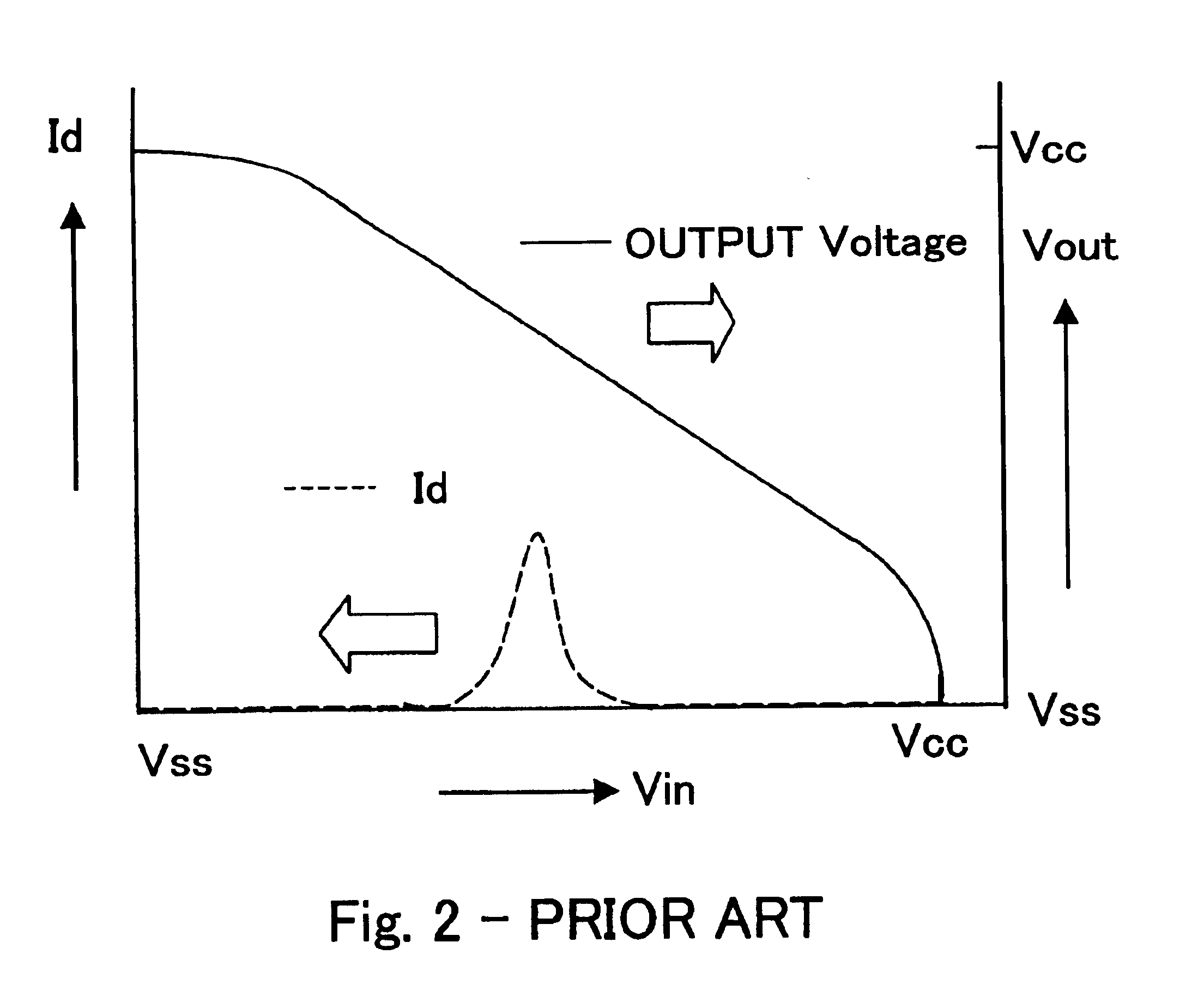

InactiveUS6838901B2Total current dropReduce leakage currentPower reduction by control/clock signalSemiconductor/solid-state device manufacturingEngineeringDrain current

Power dissipation of a semiconductor integrated circuit chip is reduced when it is operated at an operating voltage of 2.5 V or below. A switching element is provided in each circuit block within the chip. Constants of the switching element are set so that leakage current in each switching element in their off-state is smaller than the subthreshold current of MOS transistors within the corresponding circuit block. Active current is supplied to active circuit blocks, while switching elements of non-active circuit blocks are turned off. Thus, dissipation currents of non-active circuit blocks are limited to leakage current value of corresponding switching elements. Thus, the sum of dissipation currents of non-active circuit blocks is made smaller than the active current in the active circuit blocks. As a result, power dissipation in the semiconductor integrated circuit chip can be reduced even in the active state.

Owner:PS4 LUXCO SARL

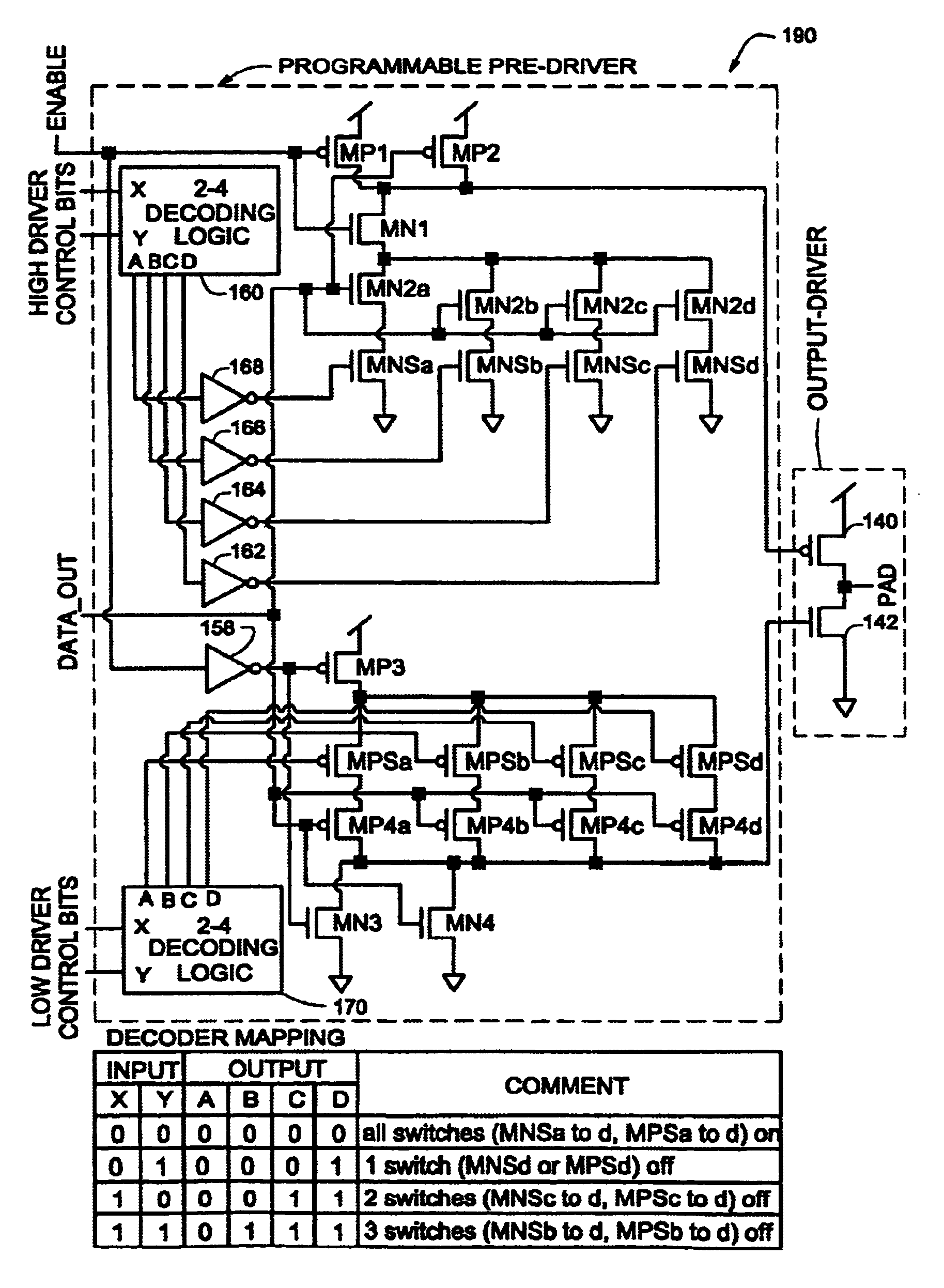

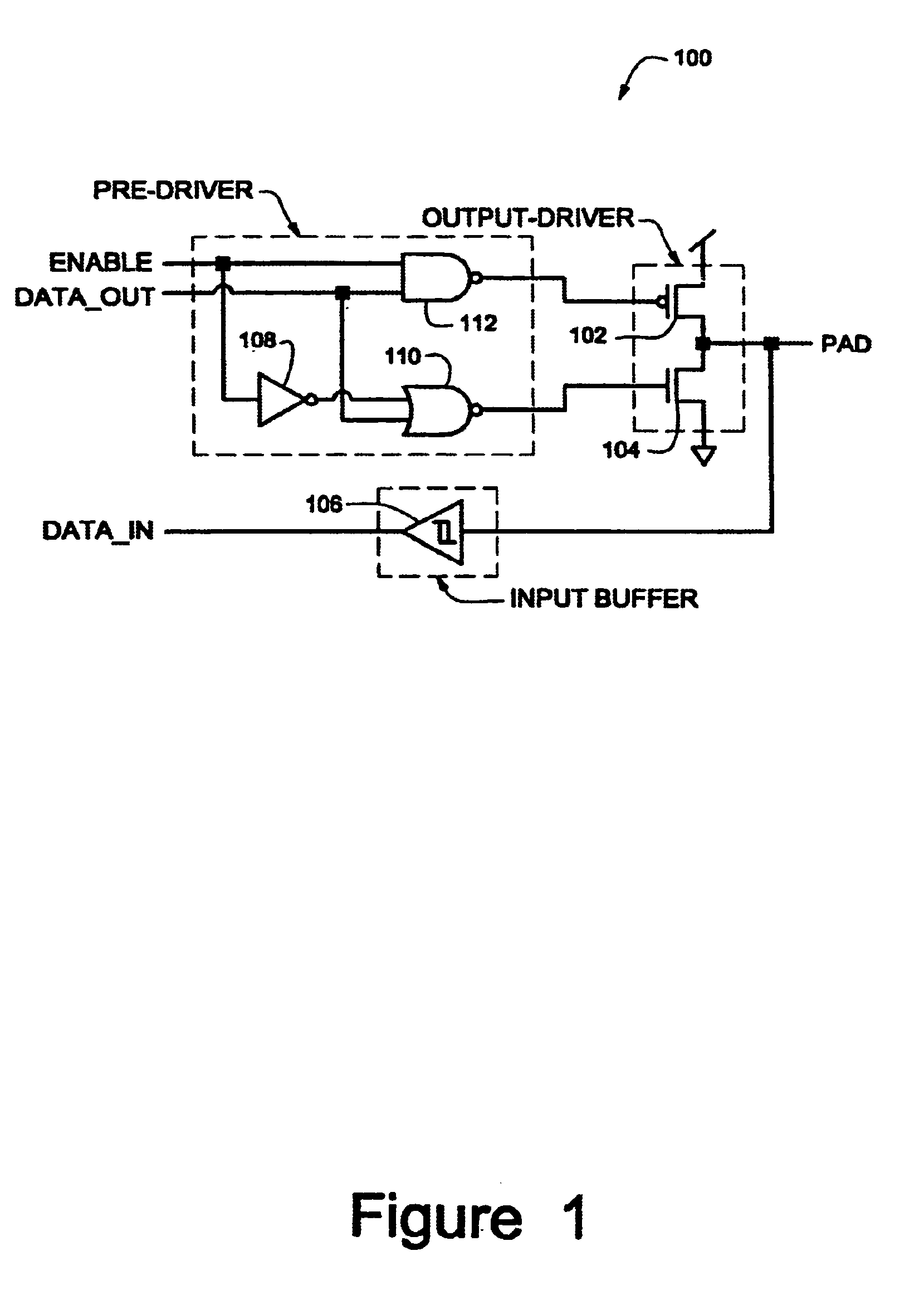

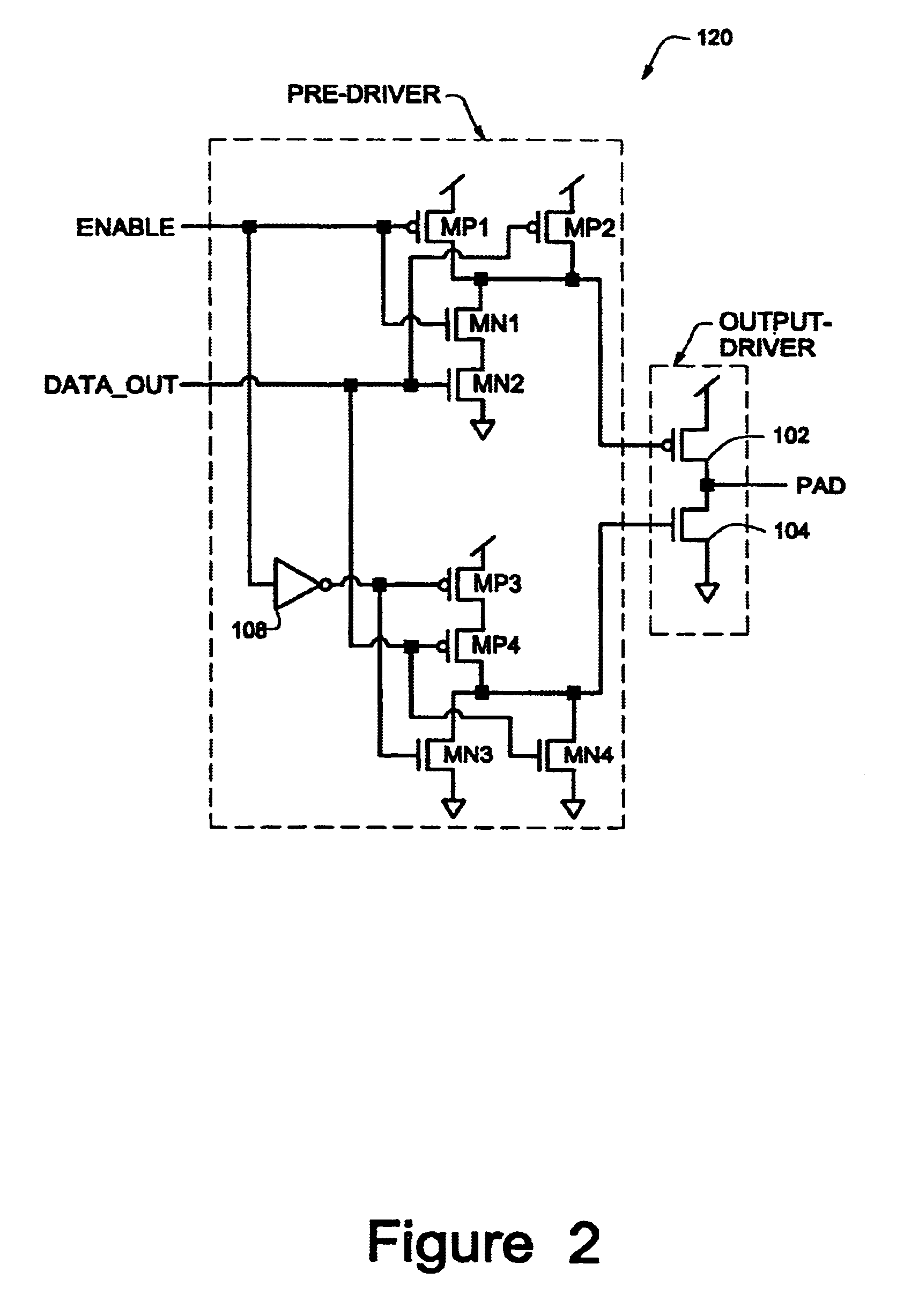

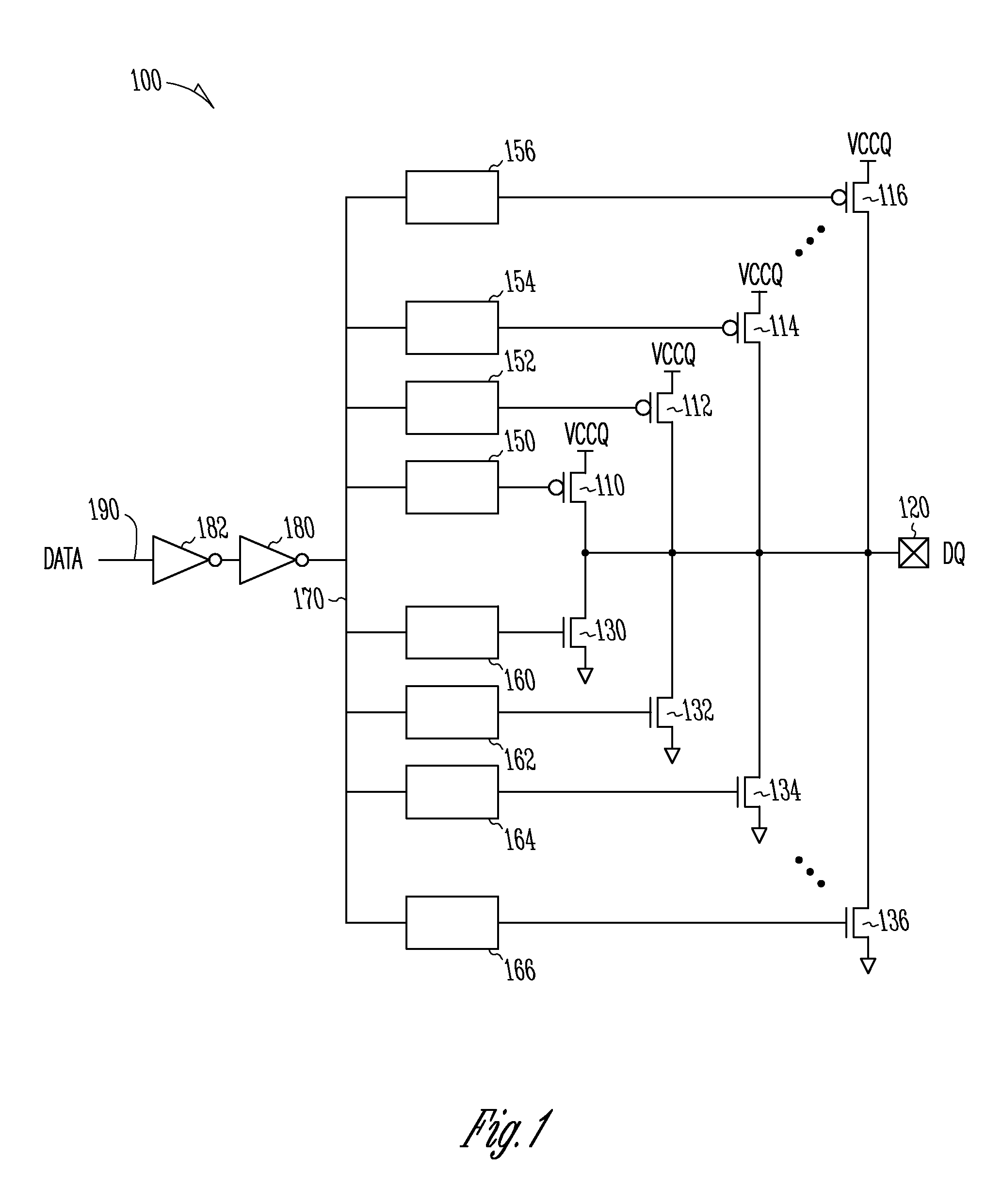

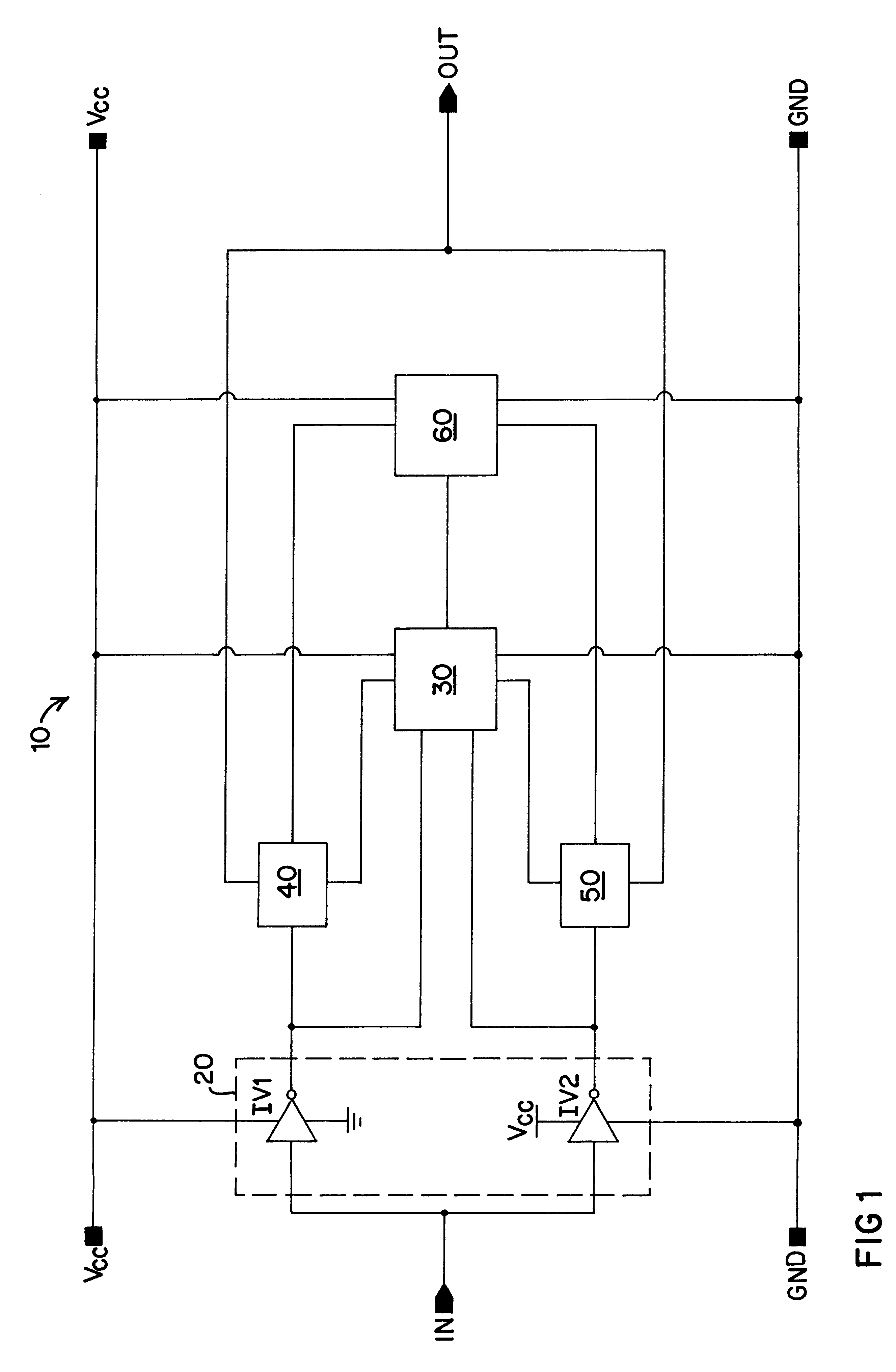

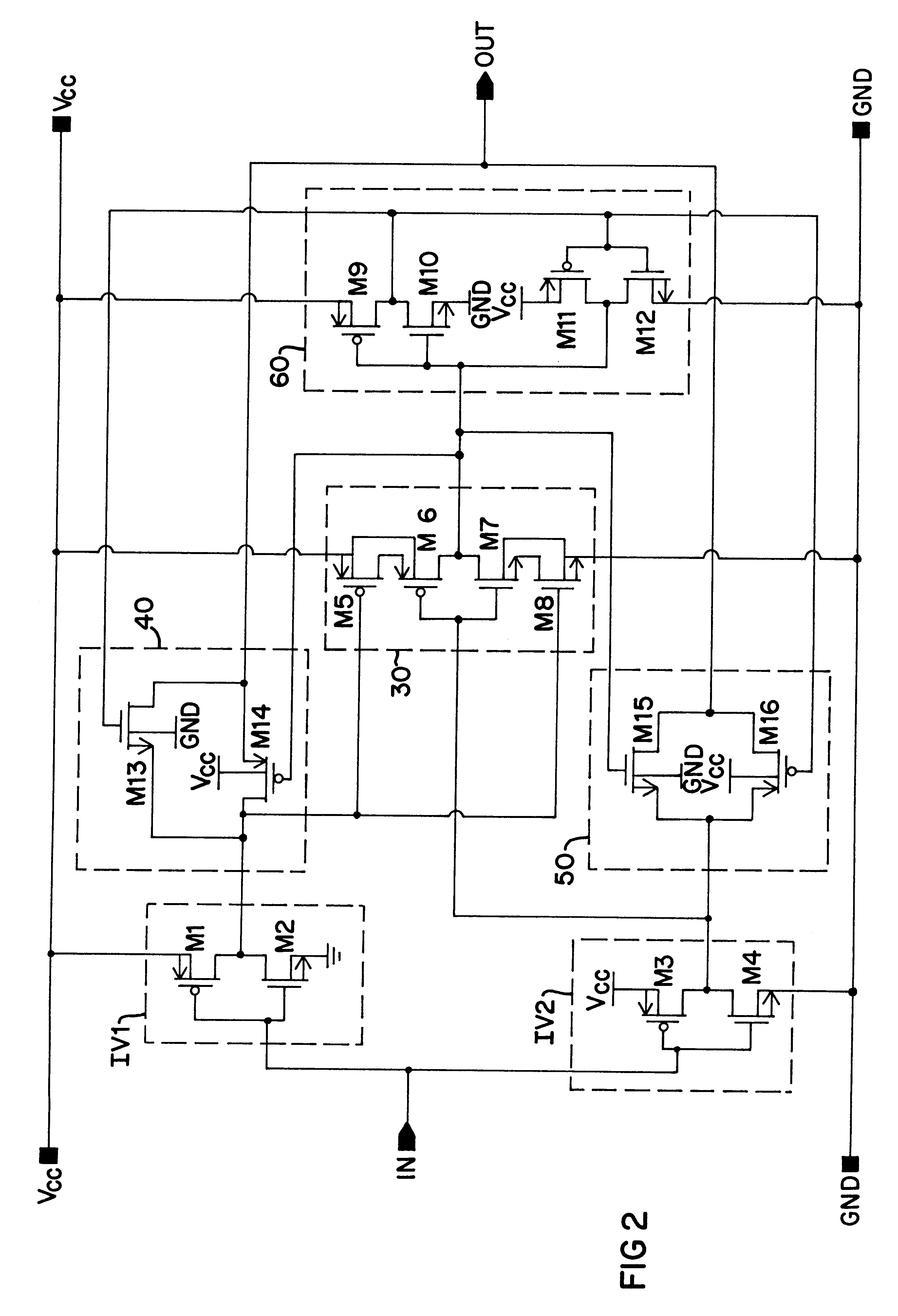

Apparatus and method for a programmable trip point in an I/O circuit using a pre-driver

InactiveUS6970015B1Threshold modification in field effect transistorsElectronic switchingSchmitt triggerEngineering

The invention enables the performance of the input and output stages of an I / O circuit to be modified after an IC is manufactured. In one embodiment, the I / O circuit includes an output driver, programmable pre-driver, programmable Schmitt-trigger input buffer, control circuit and logic circuit. Depending on the number of pull-up and pull-down MOS transistor pairs or “cells” that are enabled in the programmable pre-driver and their different sizes, the overall sizing ratio imbalance between the transistors may be programmed. In particular, the high and low trip points for activation of the output driver is related to an imbalance in the overall sizing ratio of transistors enabled in the programmable pre-driver. This affects the timing characteristics of the output driver.

Owner:NAT SEMICON CORP

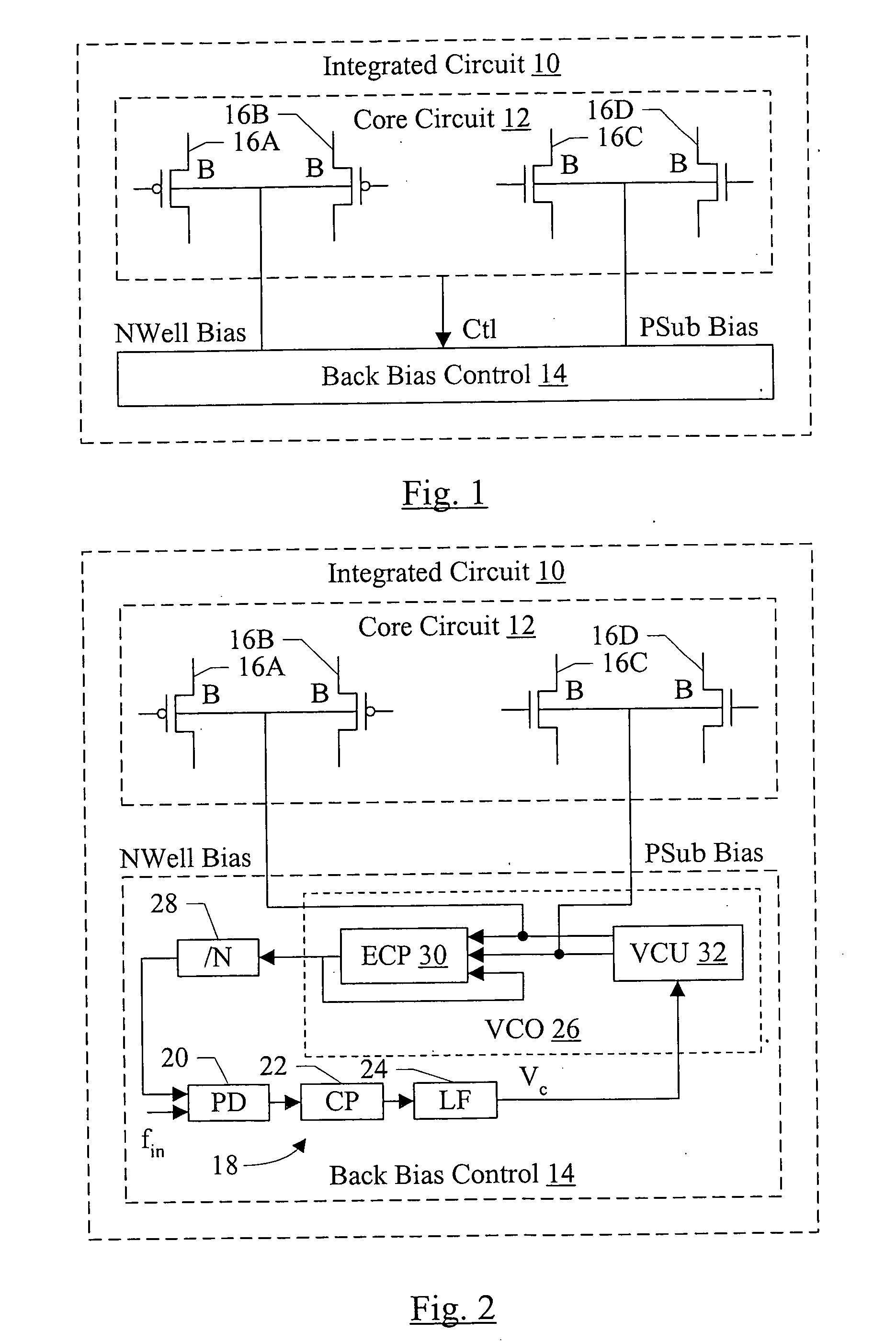

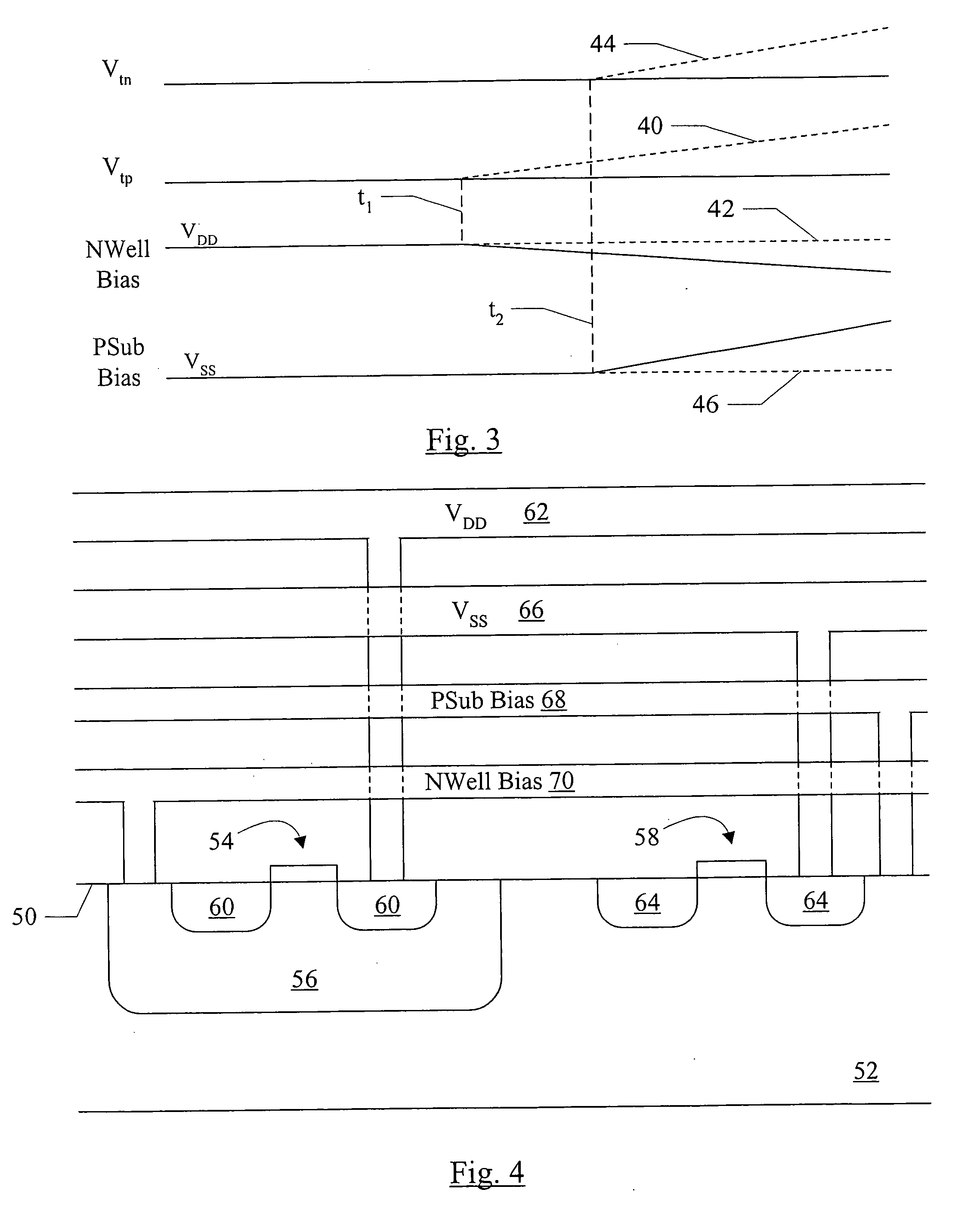

System, method and program product for well-bias set point adjustment

ActiveUS20060220726A1Power reduction by control/clock signalThreshold modification in field effect transistorsPower modeProcessor register

A well-bias system dynamically adjusts well-bias set points to optimal levels across an integrated circuit (IC) for enhanced power savings and component reliability during a standby or low-power mode of operation. A controller within the IC determines if the chip power supply voltage will be reduced during an imminent standby or low power mode and sets a register controlling a negative well-bias set point for asserting well-bias to charge wells of the IC accordingly. To minimize leakage current without compromising reliability, the well-bias set point is set to (1) an optimal well-bias set point if a reduced supply voltage is to be applied to the IC, or (2) a minimum well-bias set point when a nominal or high supply voltage is to be applied to the IC.

Owner:NXP USA INC

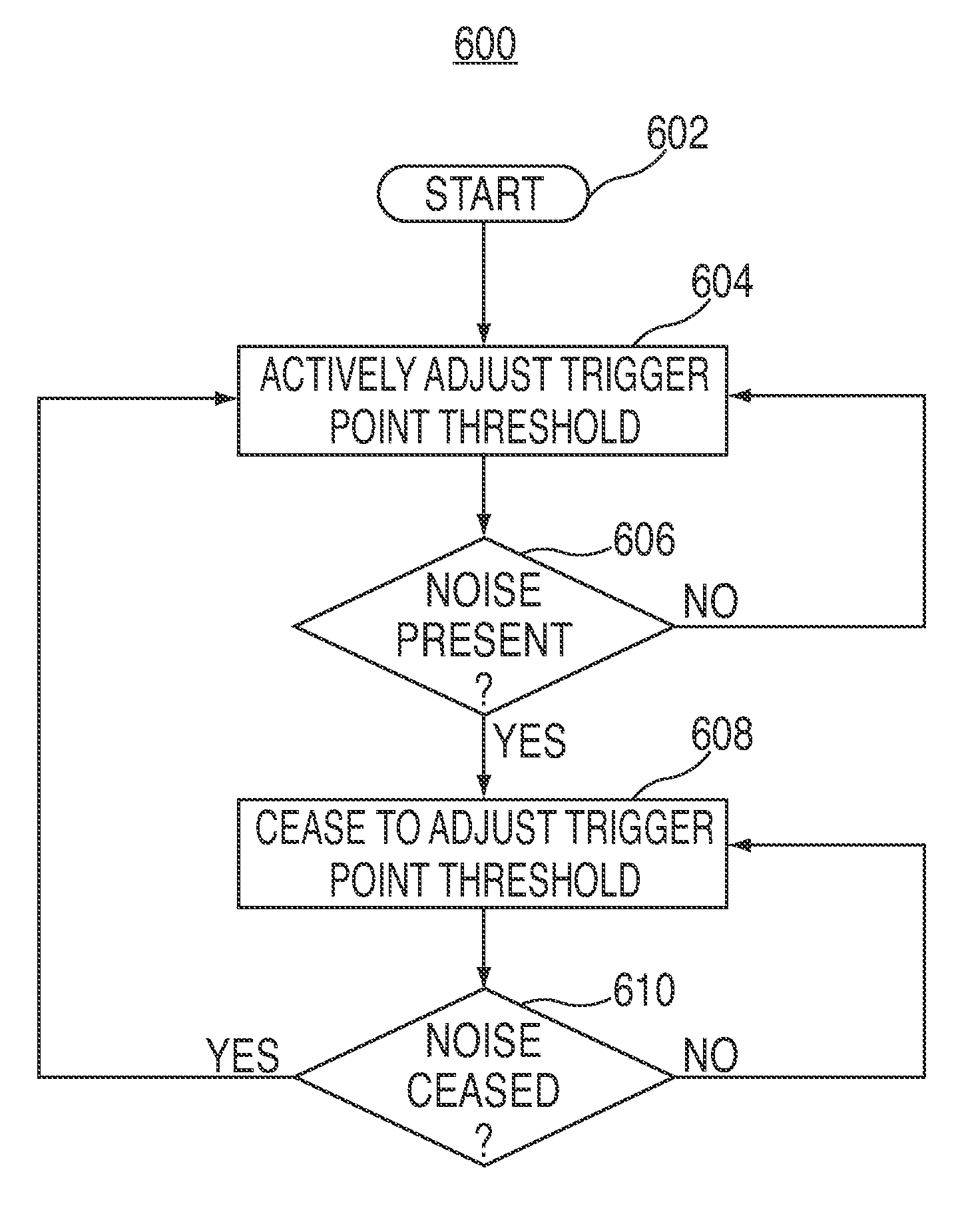

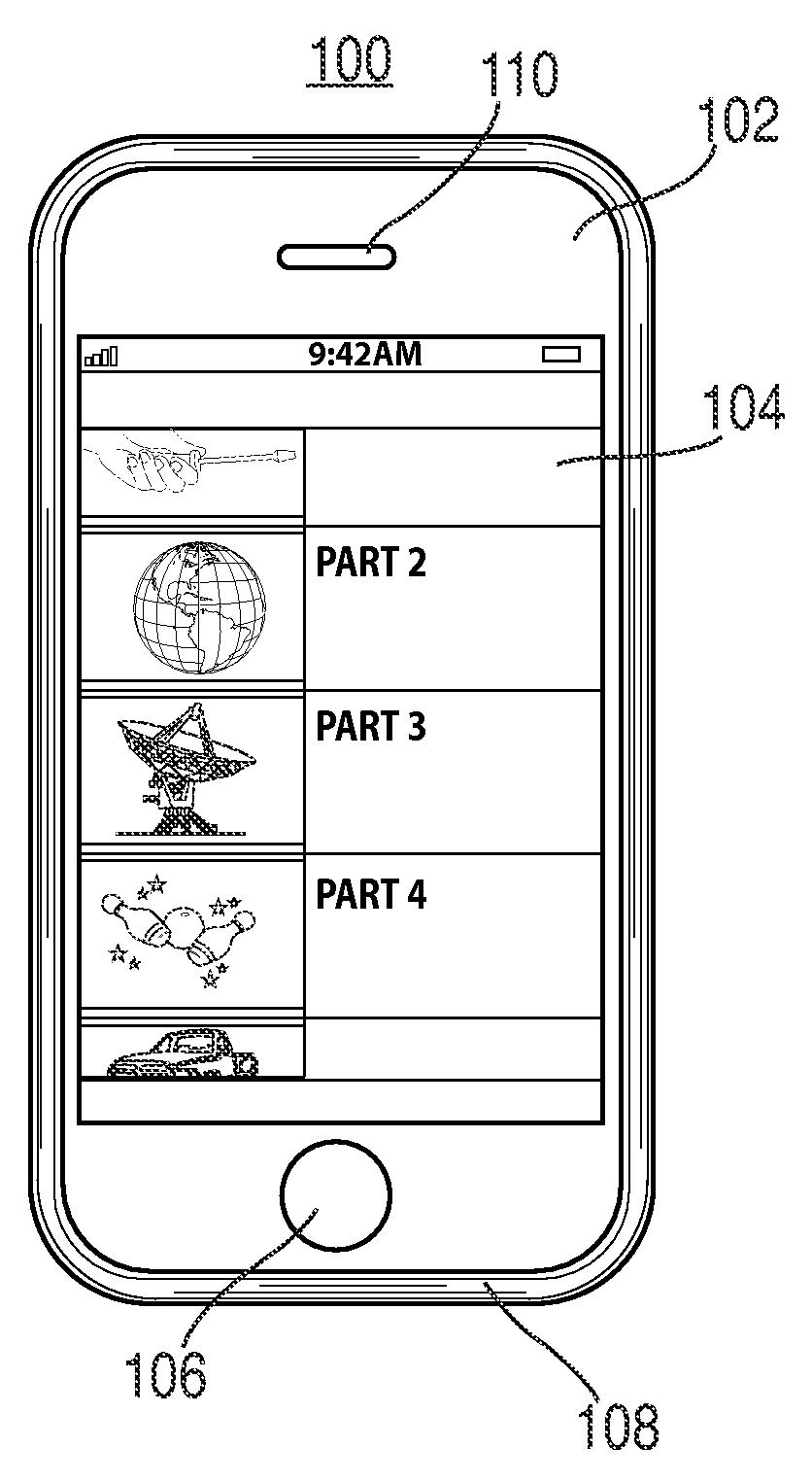

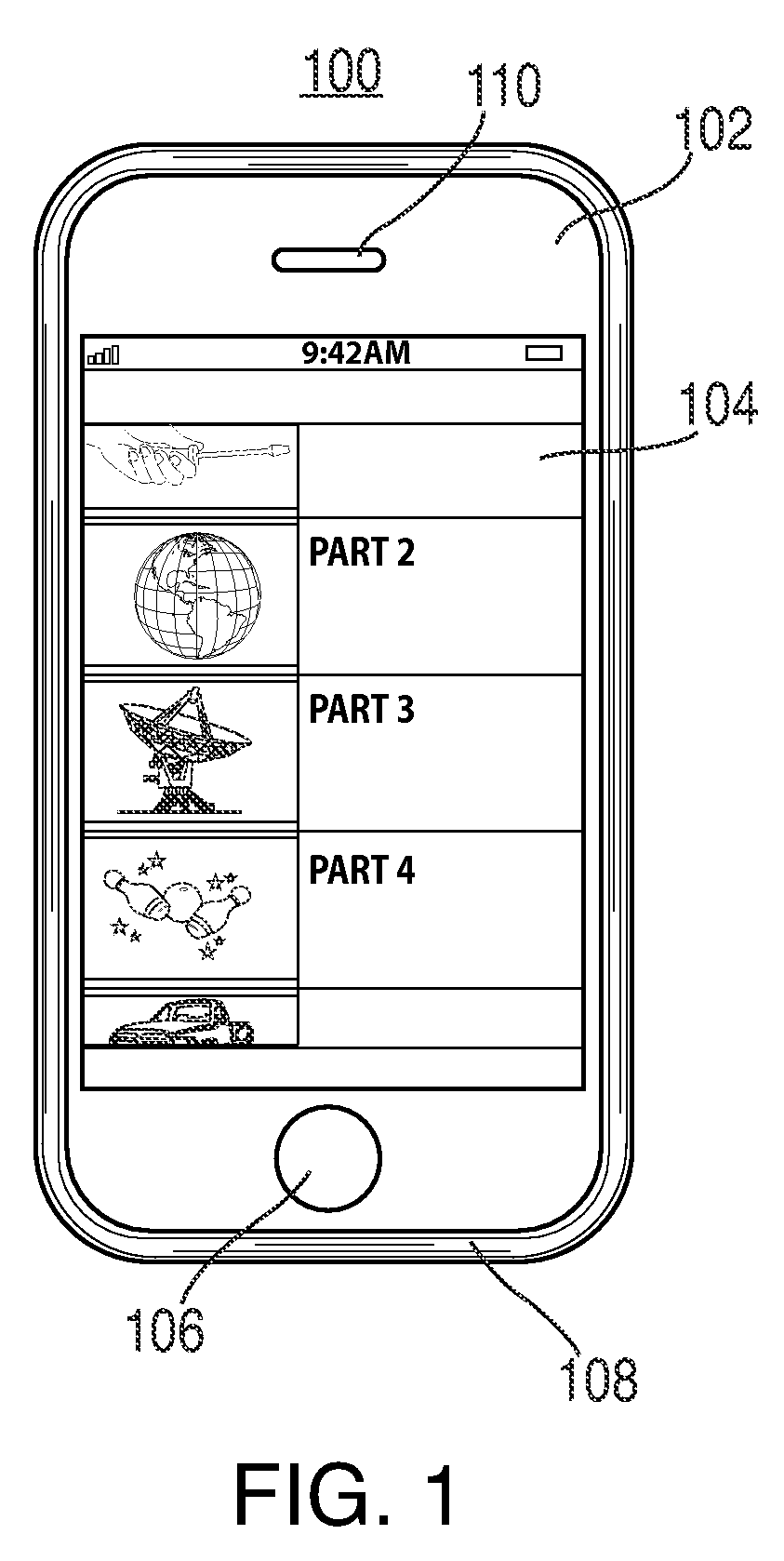

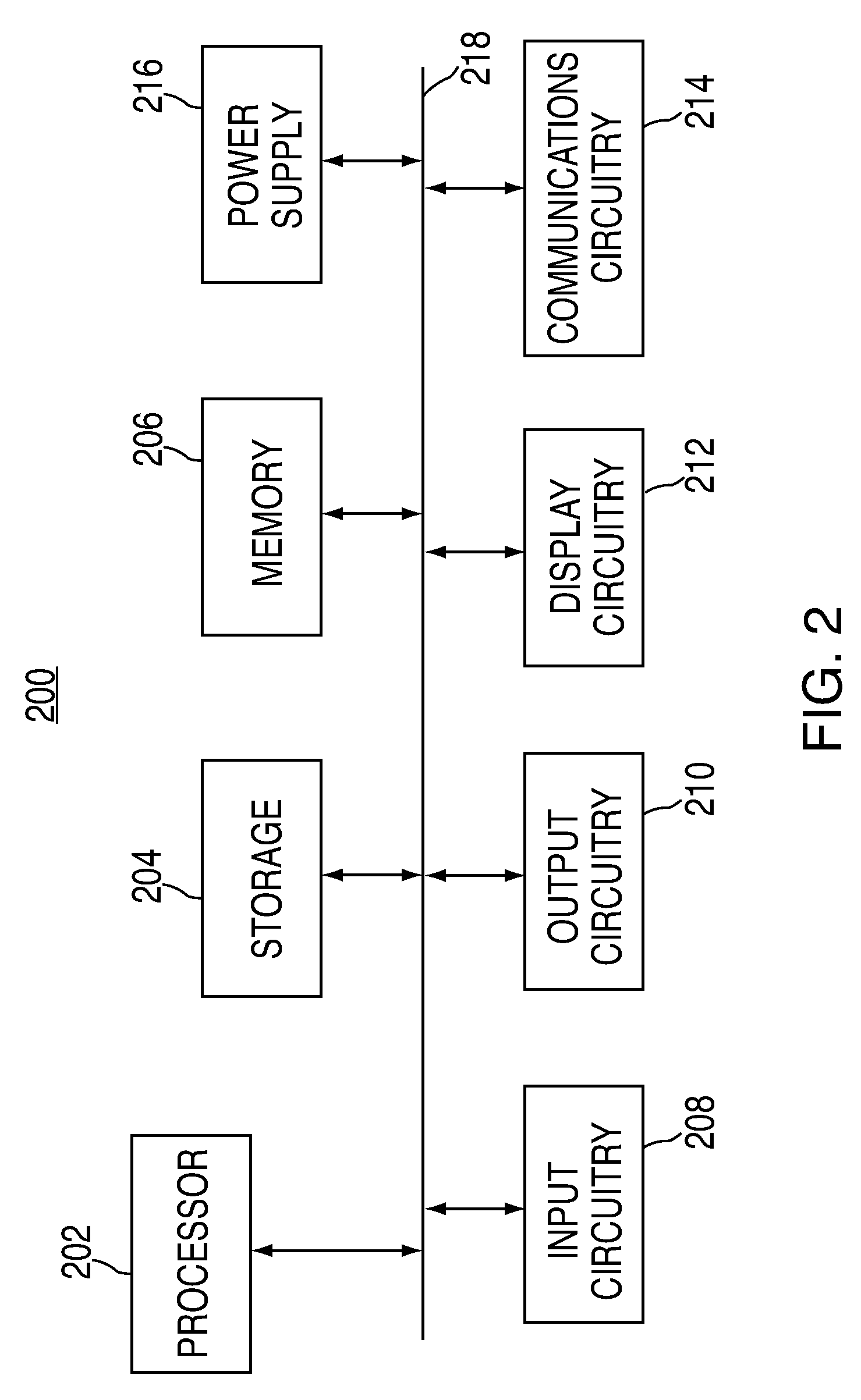

Reducing errors in data by dynamically calibrating trigger point thresholds

InactiveUS7786755B2Reliability increasing modificationsThreshold modification in field effect transistorsComputer scienceTiming data

Methods, systems, computer readable media and means for reducing errors in data caused by noise are provided. In some embodiments of the present invention, circuitry of the device receives timing data from one or more other circuitries and identifies noiseless periods from the timing data. The circuitry then actively adjusts the trigger point threshold of data being transmitted to and / or from the circuitry only during the noiseless periods. The circuitry subsequently monitors the timing data to identify noise periods. In response to identifying a noise period, the device ceases to adjust the trigger point threshold until the noise period is over.

Owner:APPLE INC

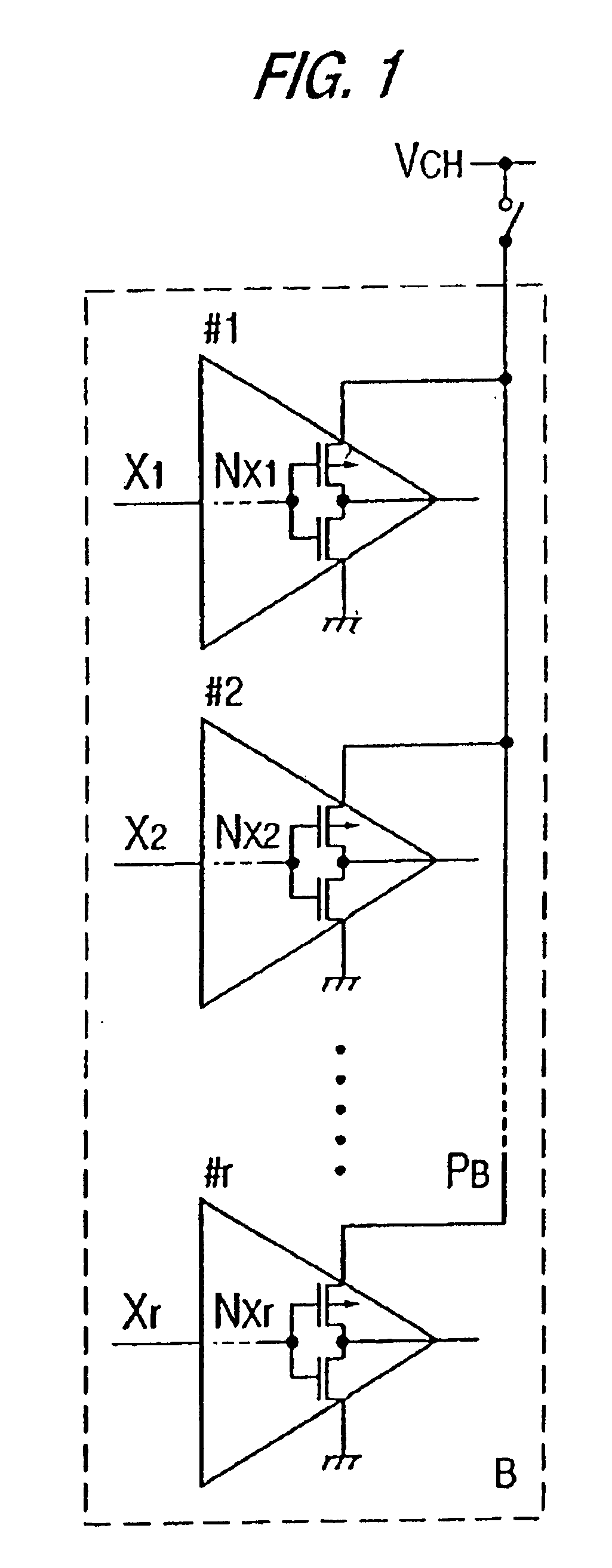

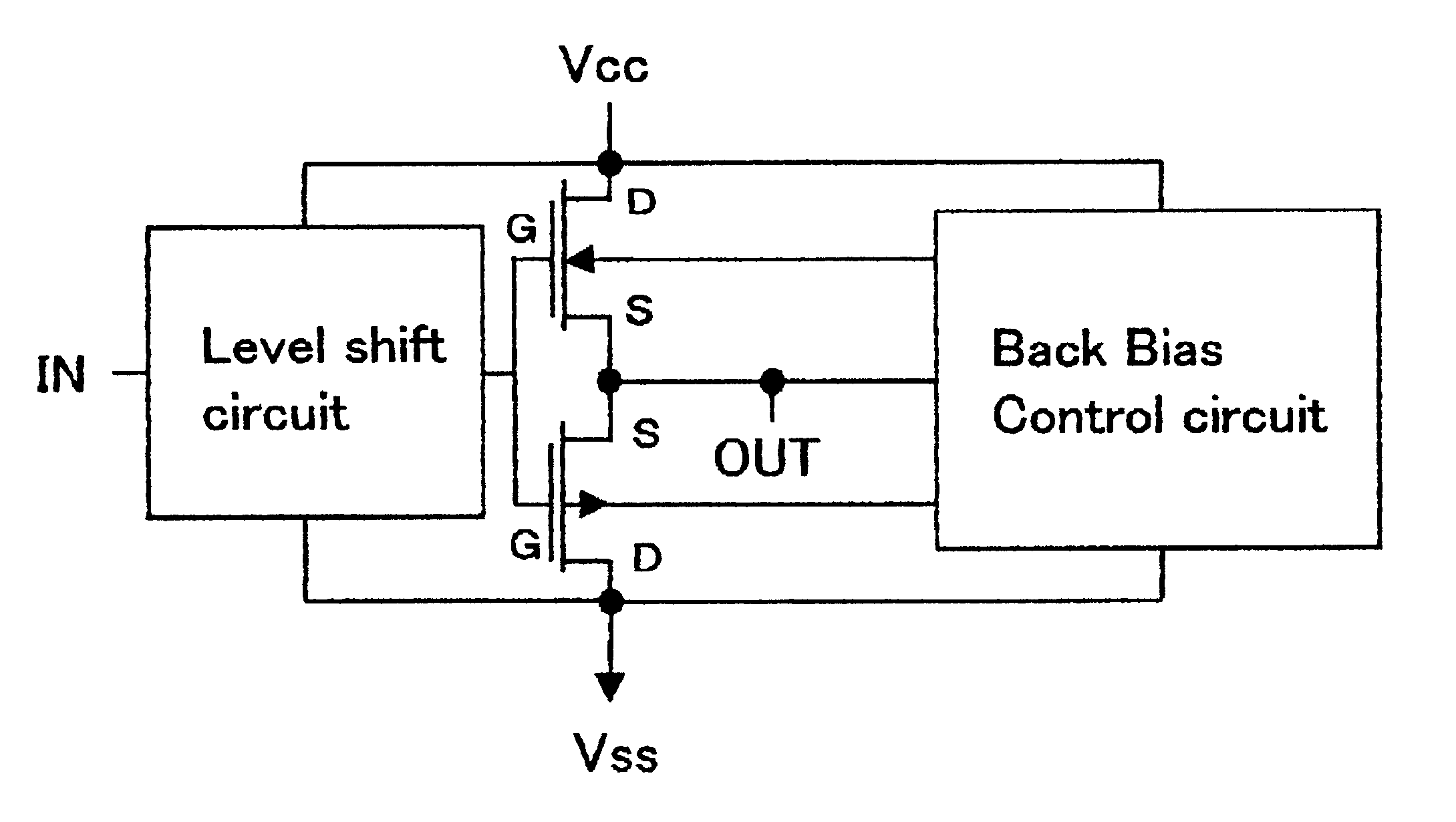

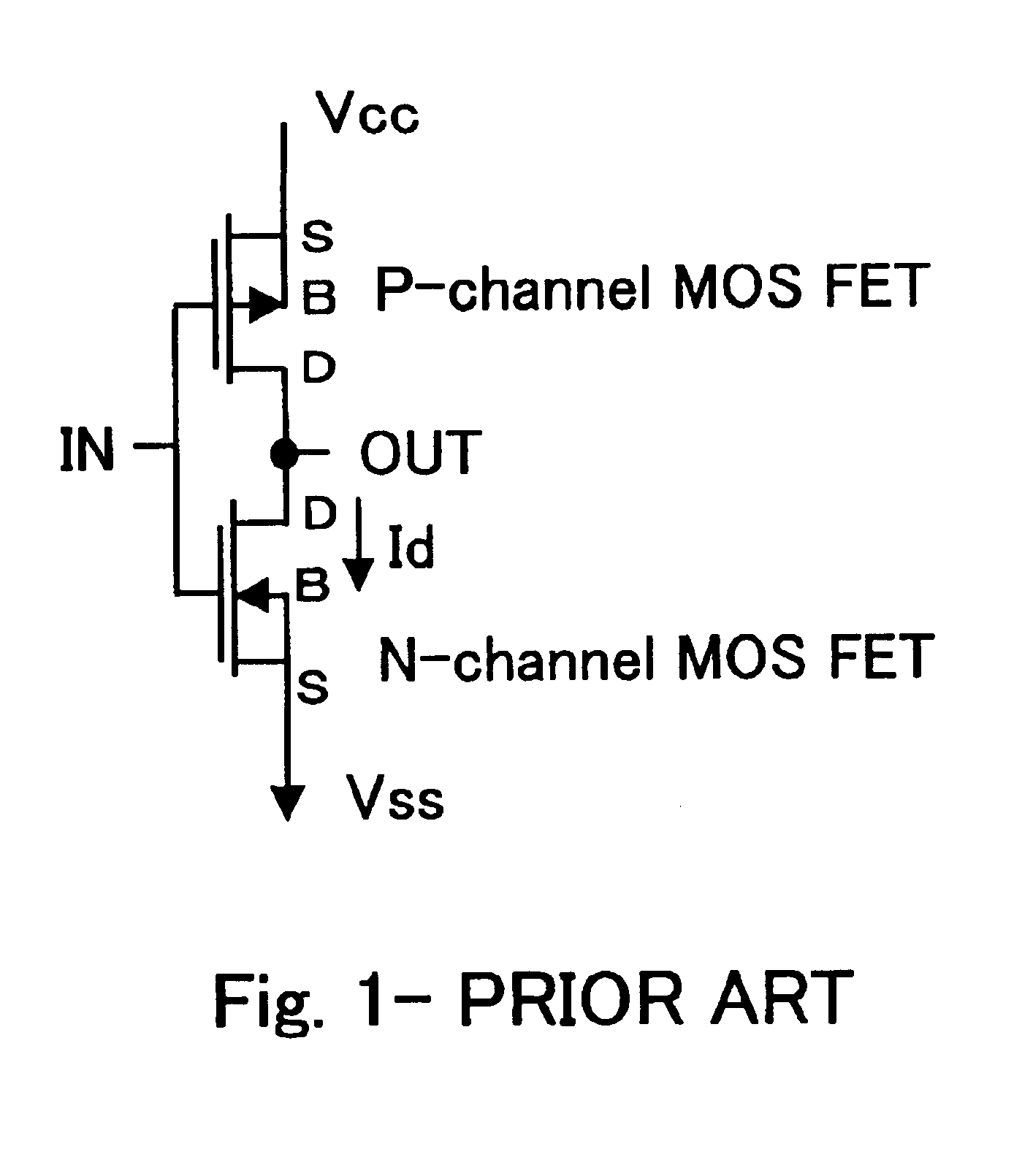

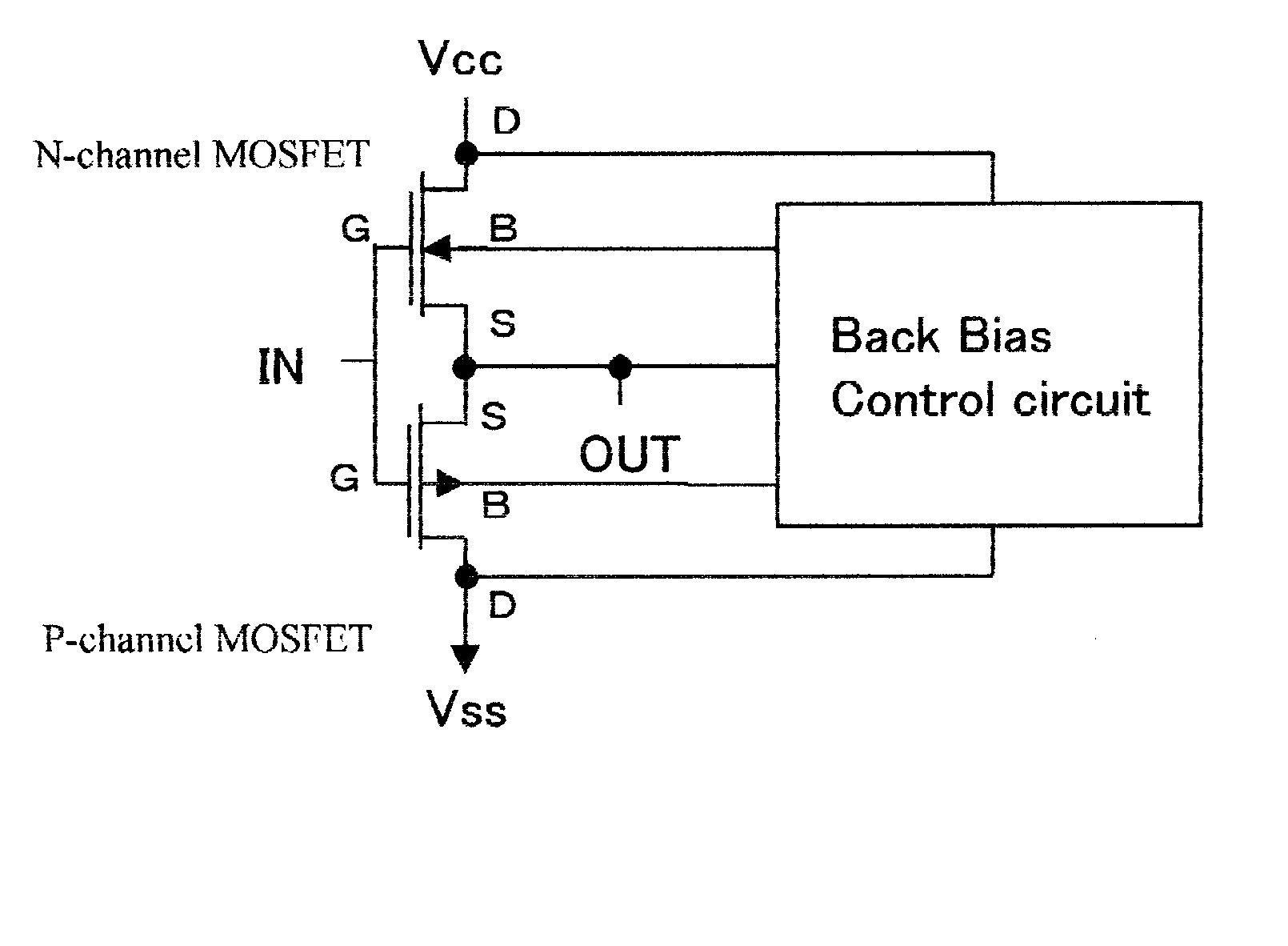

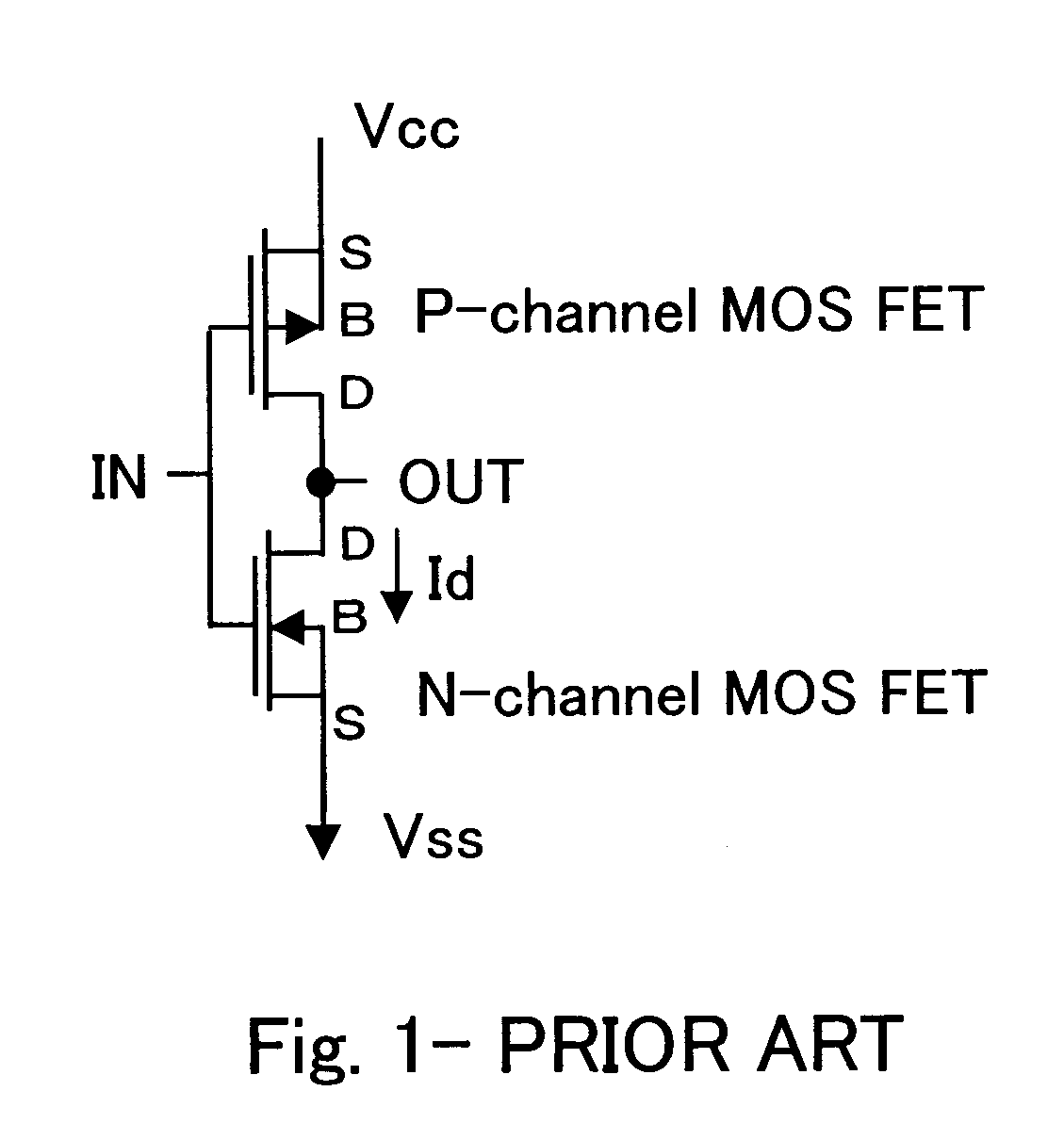

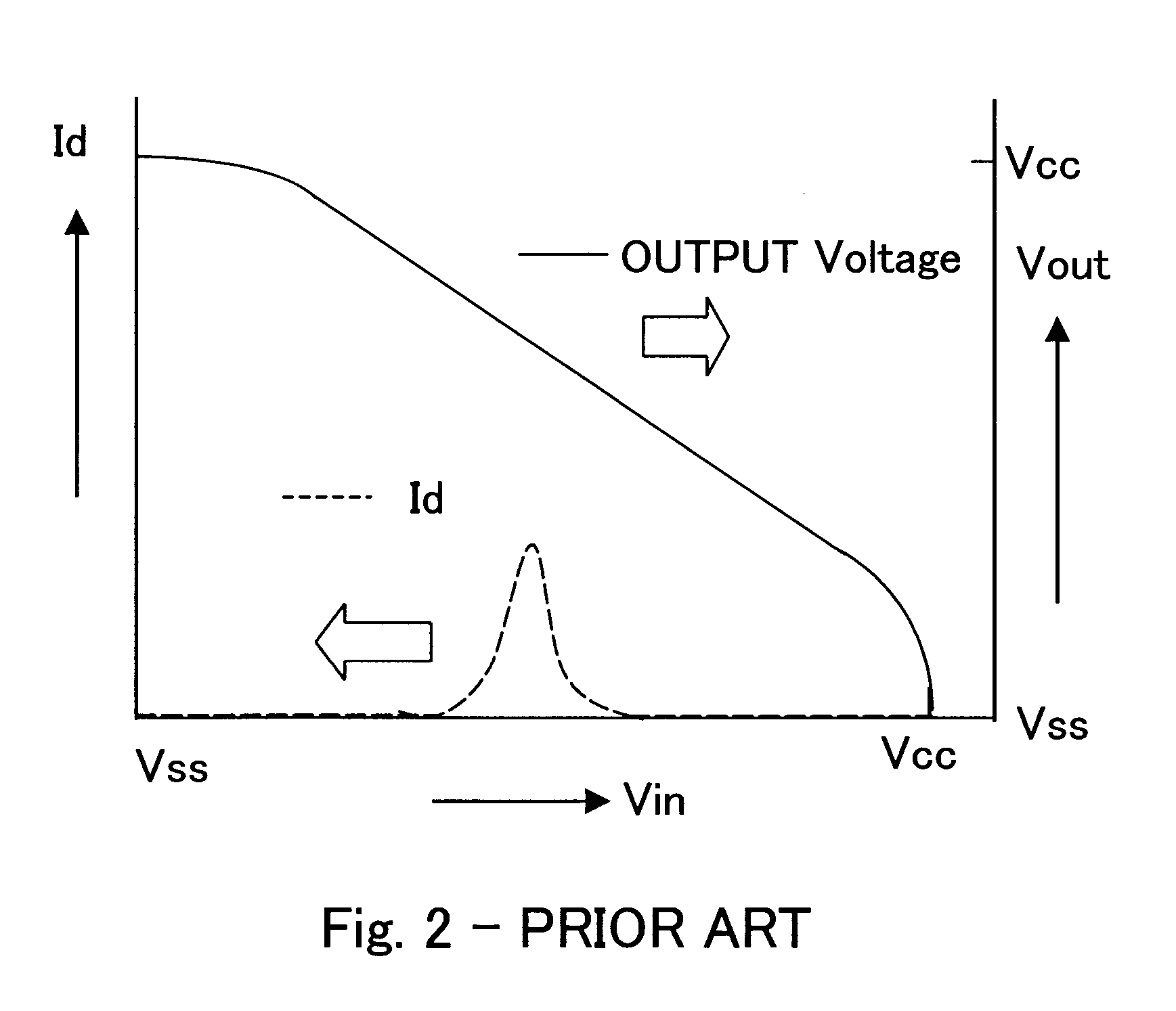

Complementary source follower circuit controlled by back bias voltage

InactiveUS6765430B2Improve performanceReduce usageTransistorThreshold modification in field effect transistorsBack biasPower usage

A complementary source follower circuit has an N-channel type transistor and a P-channel transistor. The threshold voltage of each transistor is independently controlled by a back bias voltage control circuit so that the input voltage and the output voltage relationship can be made linear without the use of an additional circuit such as a level shifting circuit. Also, power consumption can be reduced when the circuit is in standby mode by using the back bias voltage control circuit to achieve non-linearity. A back bias voltage control circuit can also be used to control the threshold voltage of a transistor in series with a resistance load to reduce power usage.

Owner:RPX CORP

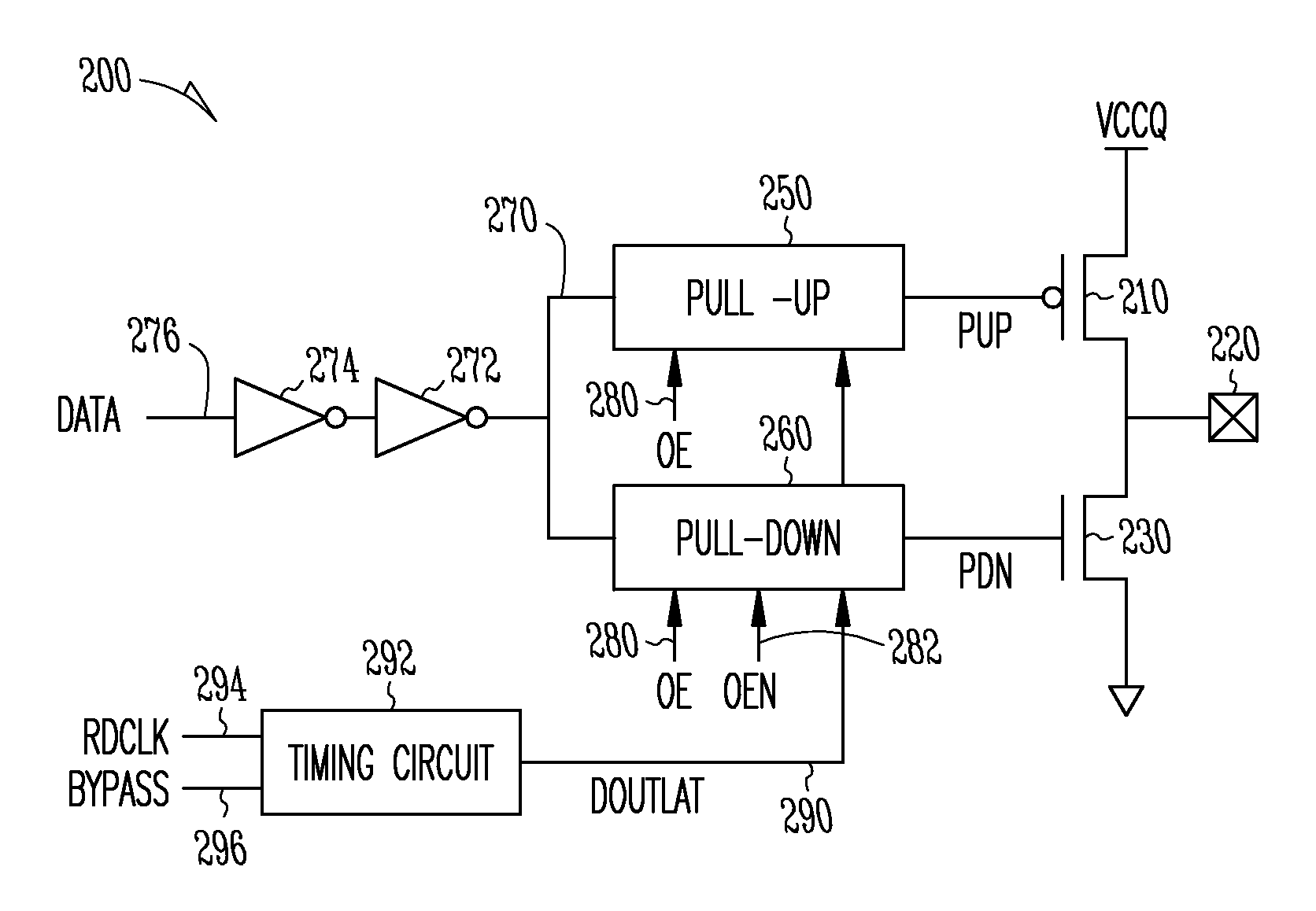

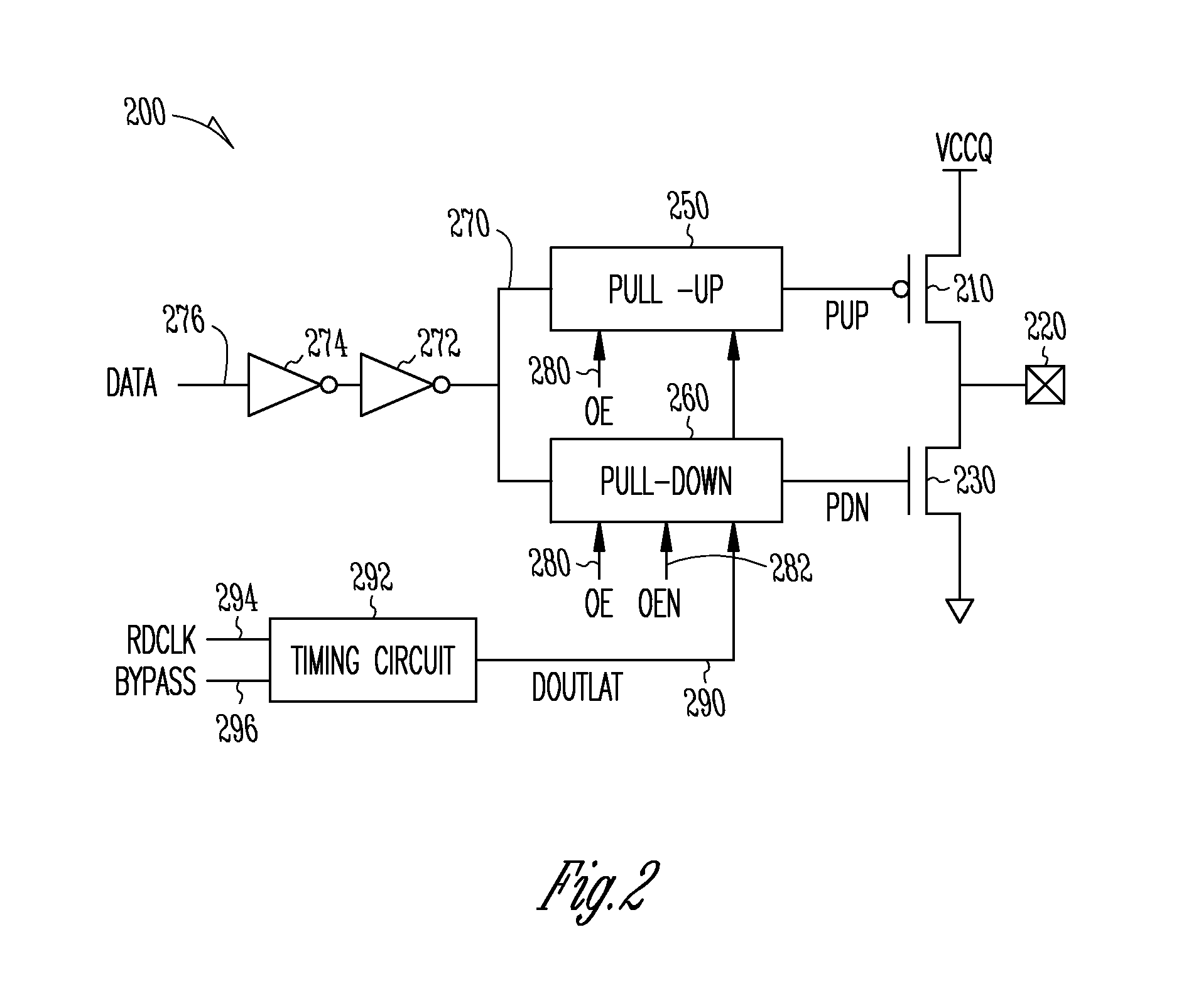

Slew rate modulation

ActiveUS20130147532A1Read-only memoriesThreshold modification in field effect transistorsSignal onTime of arrival

Apparatus and methods may operate so that arrival times of a data signal at gates of transistors are controlled to switch the transistors at different times to modulate the slew rate of a signal on a node. Additional embodiments are also described.

Owner:MICRON TECH INC

Reducing errors in data by synchronizing operations with noiseless periods of data transmission

InactiveUS20090202002A1Function increaseThreshold modification in field effect transistorsCathode-ray tube indicatorsData transmissionComputer science

Methods, systems, computer readable media and means for reducing errors in data caused by noise are provided. In some embodiments of the present invention, timing data is transferred from first circuitry to second circuitry. From the timing data, one or both of the first circuitry and the second circuitry detect whether noise is present as a result of the operations of the first circuitry. If it is detected that noise is present the second circuitry waits for the cessation of the noise before functioning again. If it is detected that no noise is present, the second circuitry functions.

Owner:APPLE INC

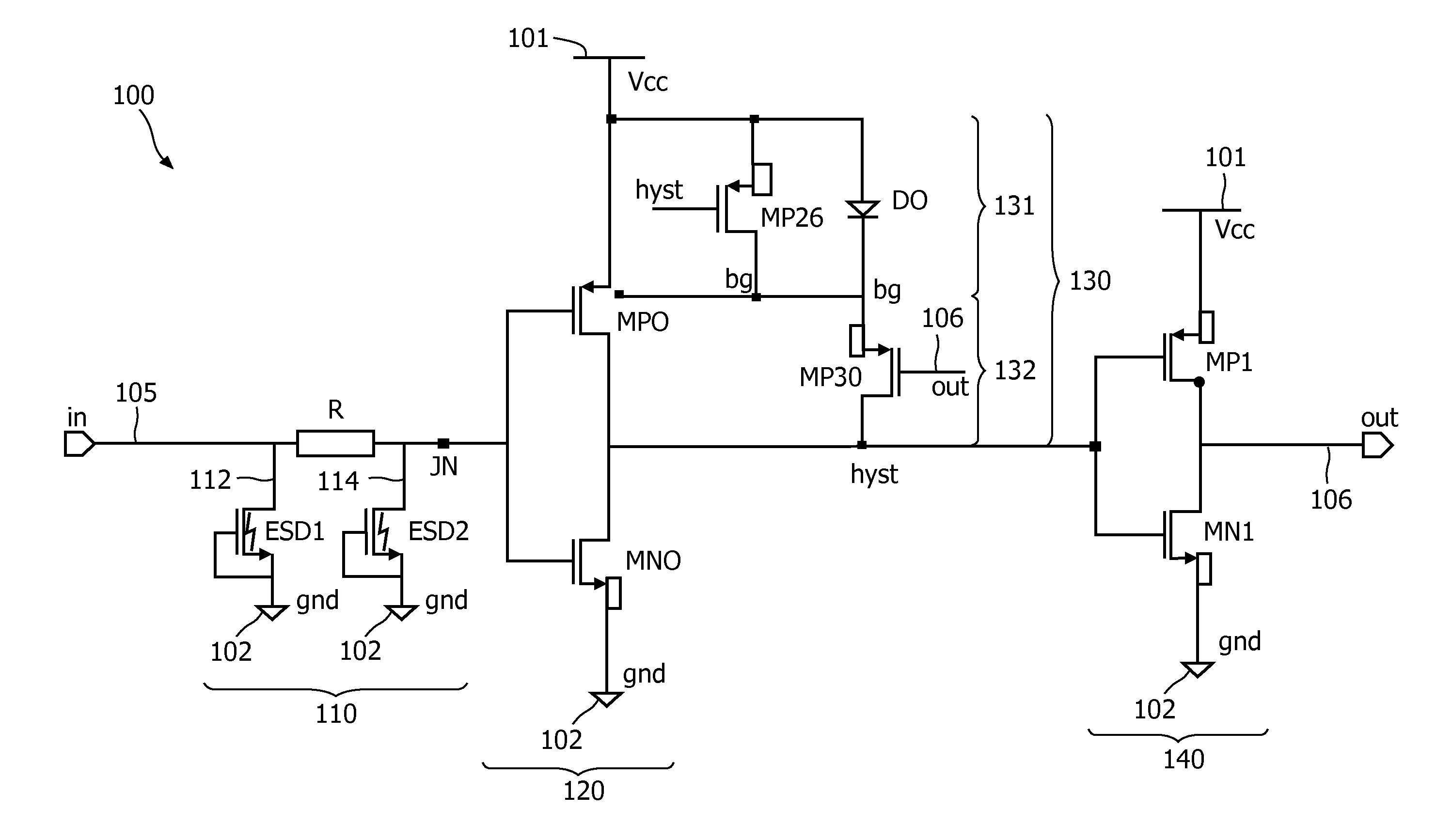

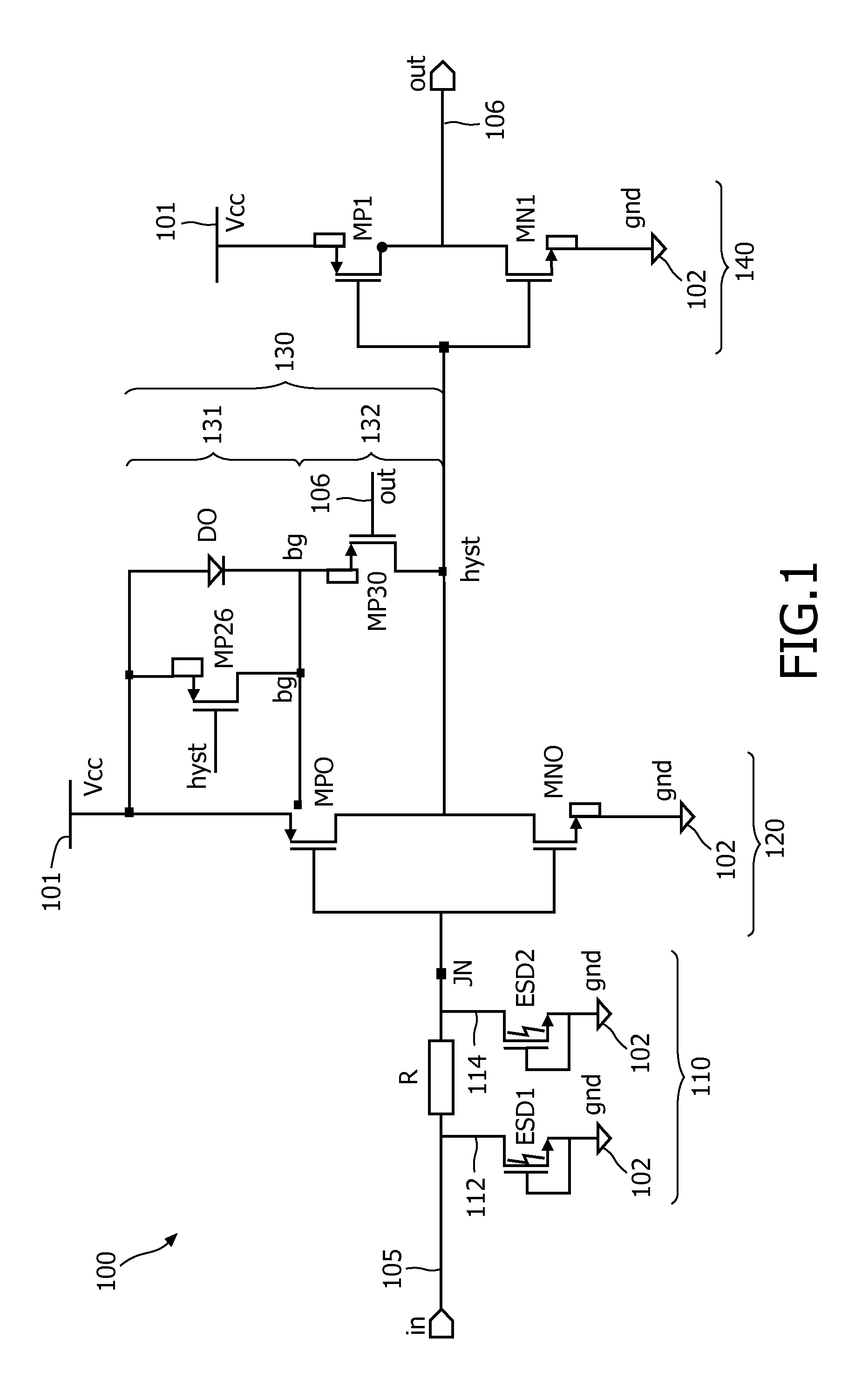

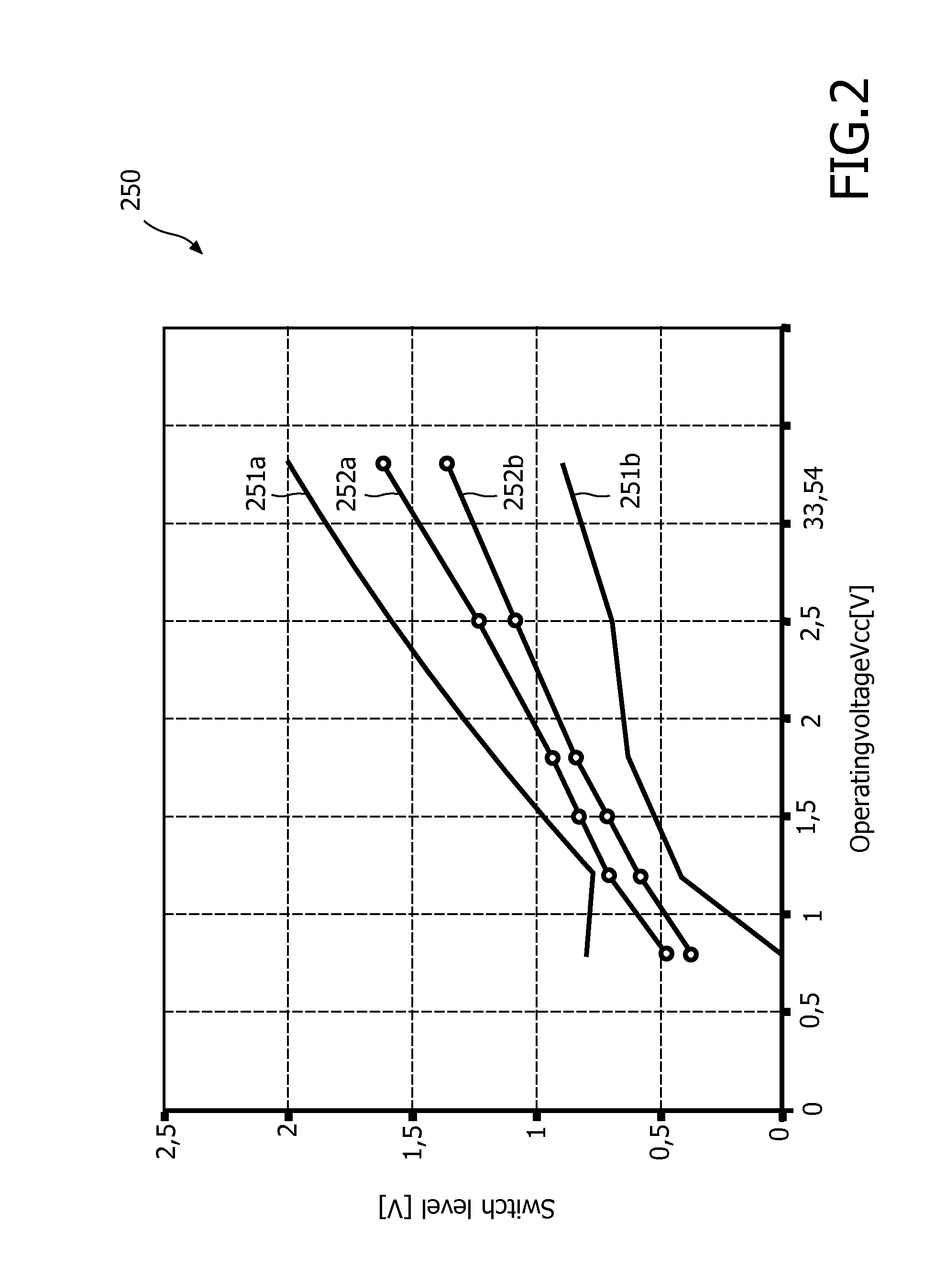

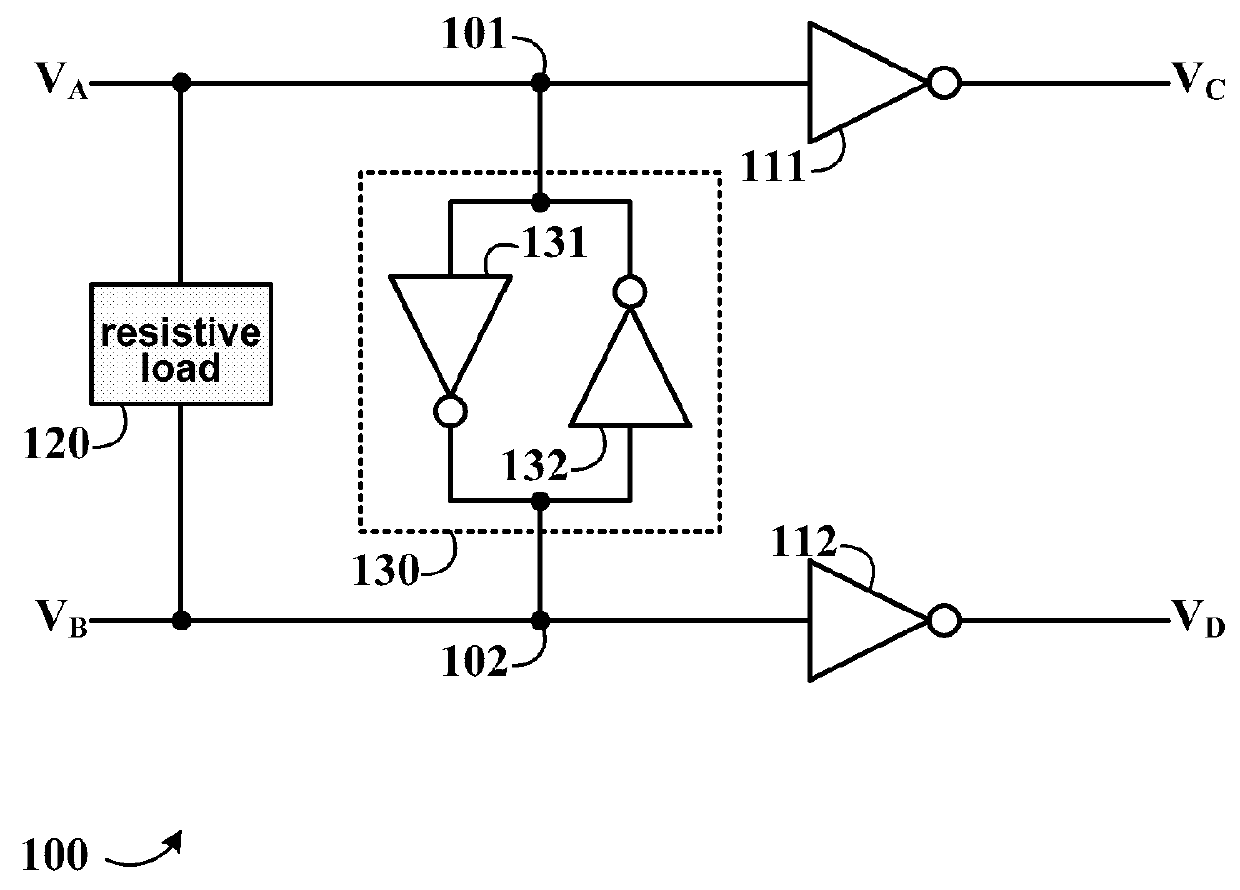

Transformation of an input signal into a logical output voltage level with a hysteresis behavior

InactiveUS20090009217A1Improved hysteresis behaviorLogic circuits characterised by logic functionLogic circuits coupling/interface using field-effect transistorsHysteresisElectrical conductor

It is described a circuit and a method for transforming an input signal into a logical output. The circuit (100) comprises an inverter stage (120), connected in between the first conductor (101) and the second conductor (102). The inverter stage (120) includes a MOS switch (MP0), which comprises a first terminal being connected to the first conductor (101), a second terminal being connected to an output node (hyst), a gate terminal being connected to an input node (JN), and a back gate terminal. The circuit (100) further comprises a voltage divider (130), connected in between the first conductor (101) and the output node (hyst), wherein the voltage divider (130) provides a divider output node (bg) being connected to the back gate terminal. The circuit (100) represents an input cell having an improved hysteresis behavior over the total operating voltage range. This is achieved by adjusting the back gate voltage of the MOS switch (MP0) during a transition from an input level Low to an input level High. This causes a temporarily increased threshold voltage for turning off the MOS switch (MP0) during the transition.

Owner:NXP BV

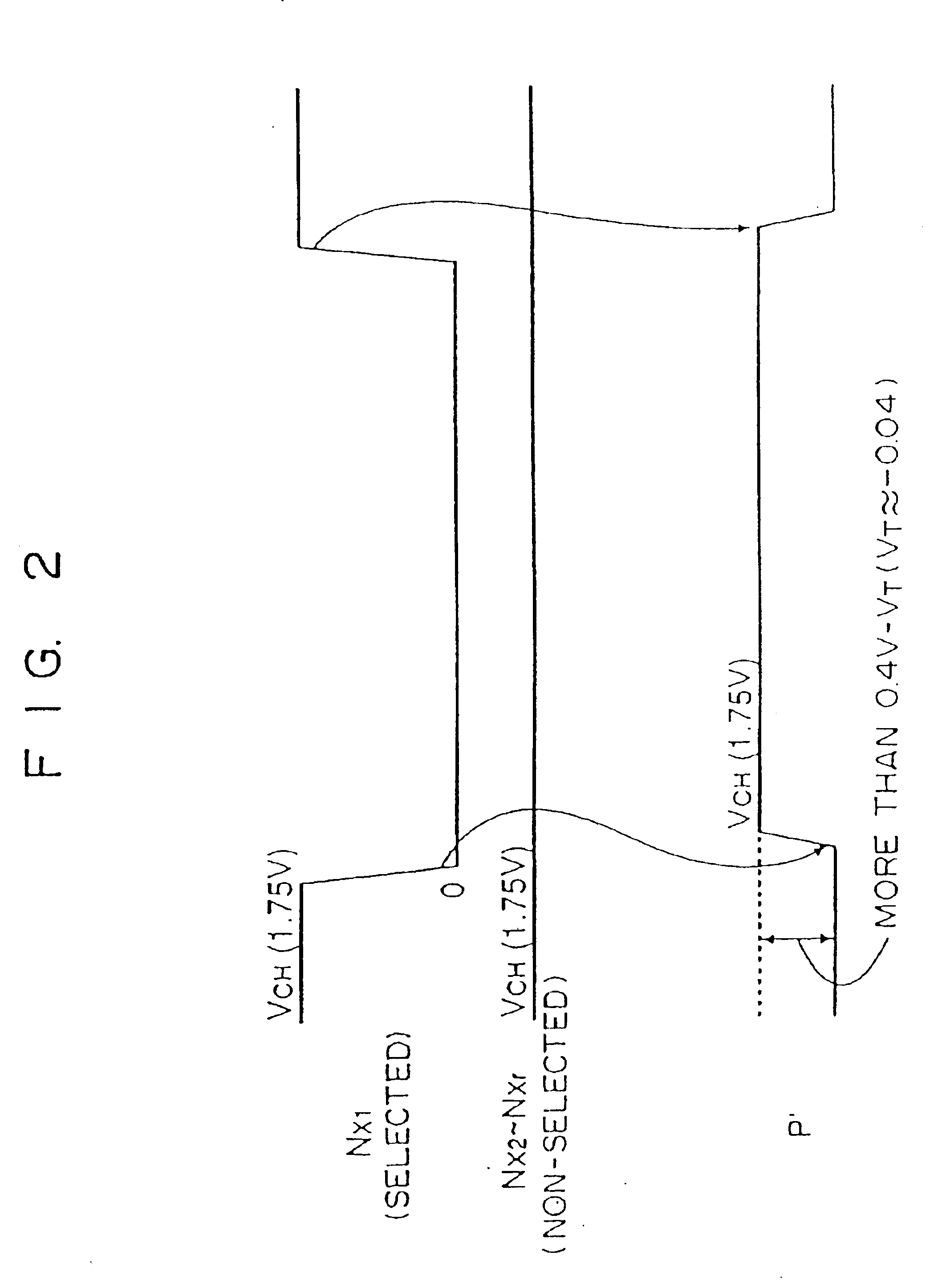

Semiconductor circuit device

ActiveUS7224186B2CurrentReduce leakage currentPower reduction in field effect transistorsSwitching accelaration modificationsVoltage amplitudeLow voltage

Owner:LONGITUDE LICENSING LTD

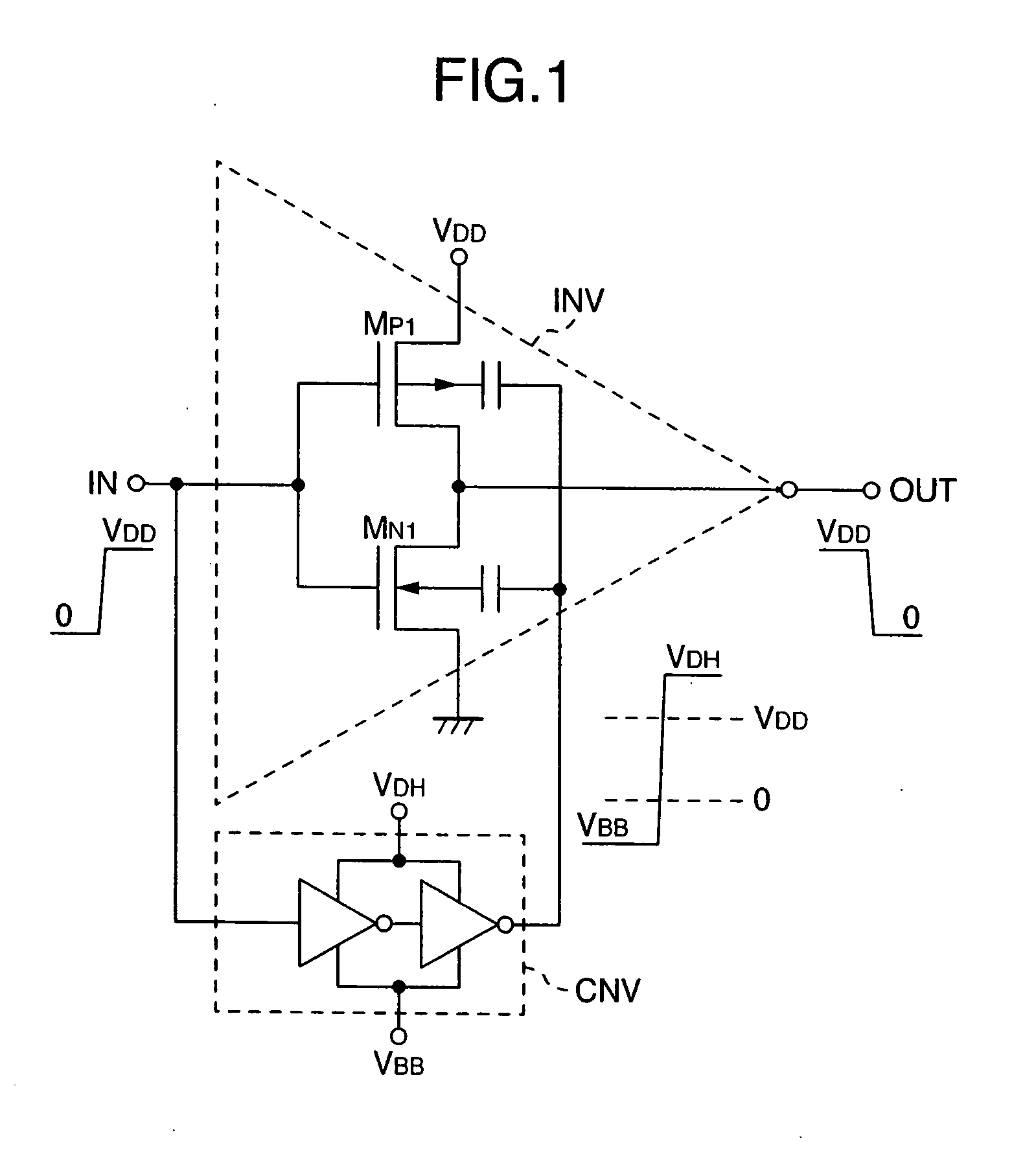

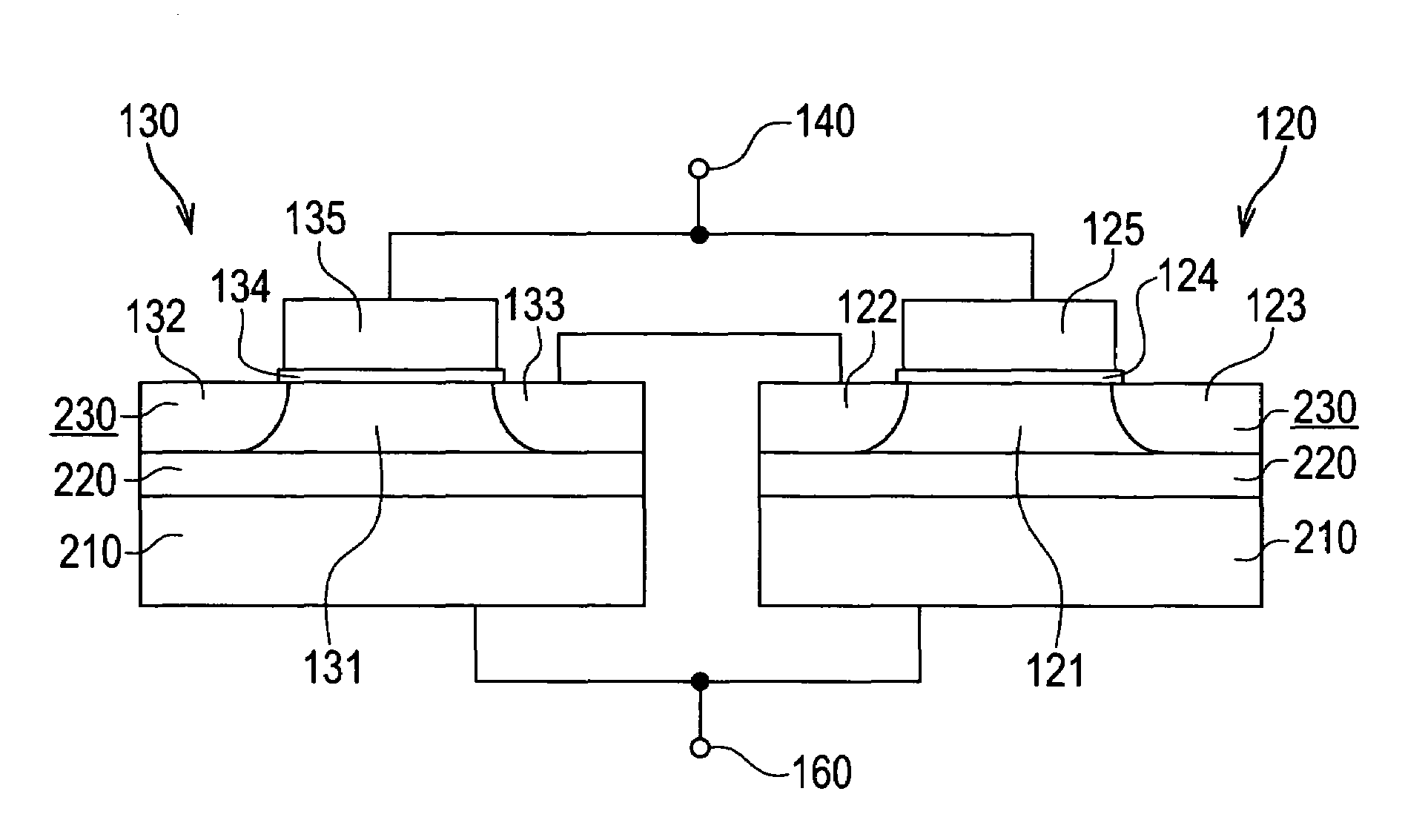

Level shifter with body-biased circuit

InactiveUS7123236B2Increase speedReduce power consumptionPower reduction in field effect transistorsStatic indicating devicesLiquid-crystal displayThin-film-transistor liquid-crystal display

A level shifter, with body-biased circuits, is provided for applying in a thin film transistor liquid crystal display (TFT-LCD). The body-biased circuits are configured to bias the bodies of the input terminal transistors of the level shifter so that the threshold voltages of the input terminal transistors are adjustable. This level shifter is capable of operating at a high frequency with low power consumption while a low-level signal is inputting.

Owner:INNOLUX CORP

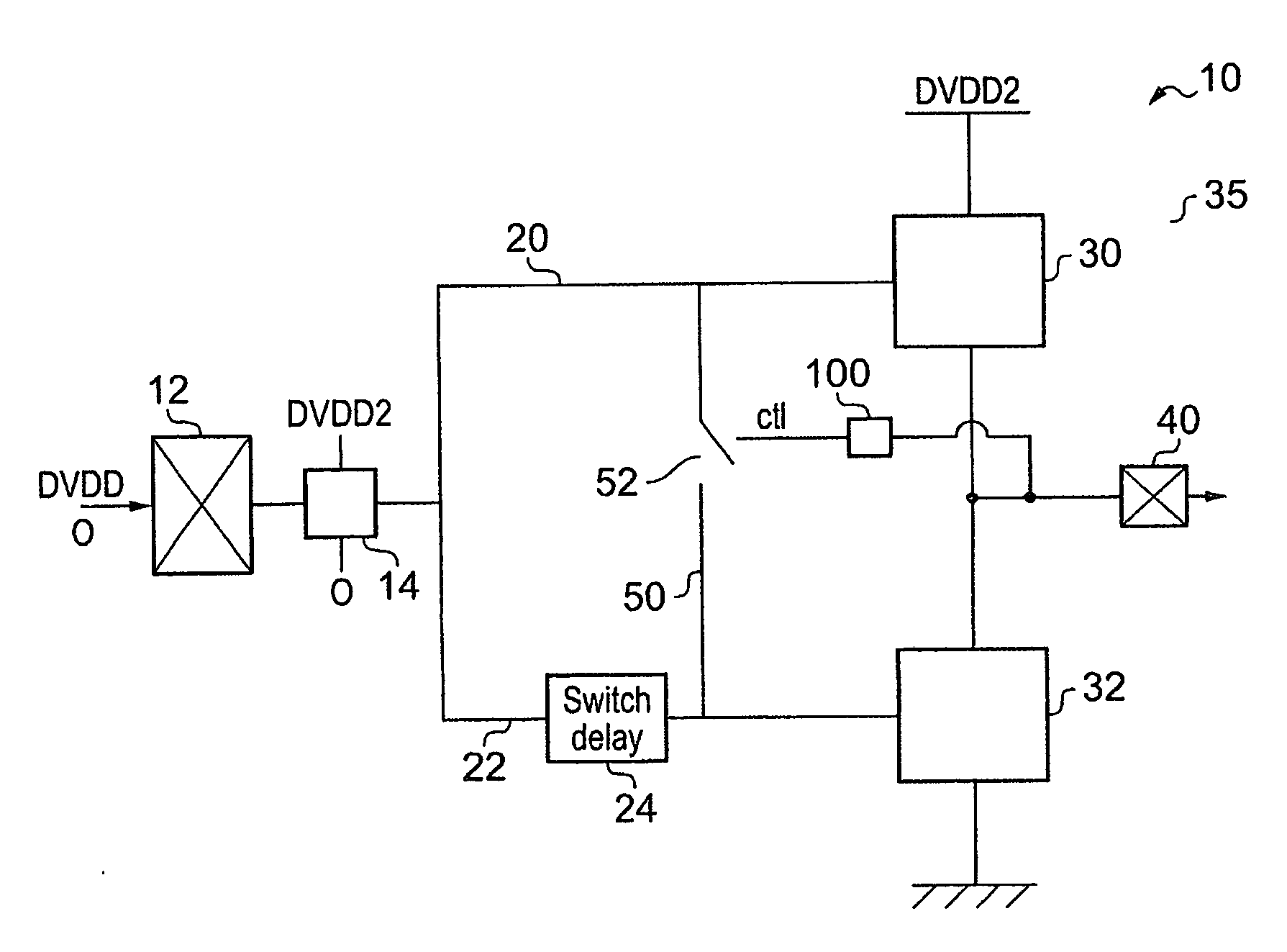

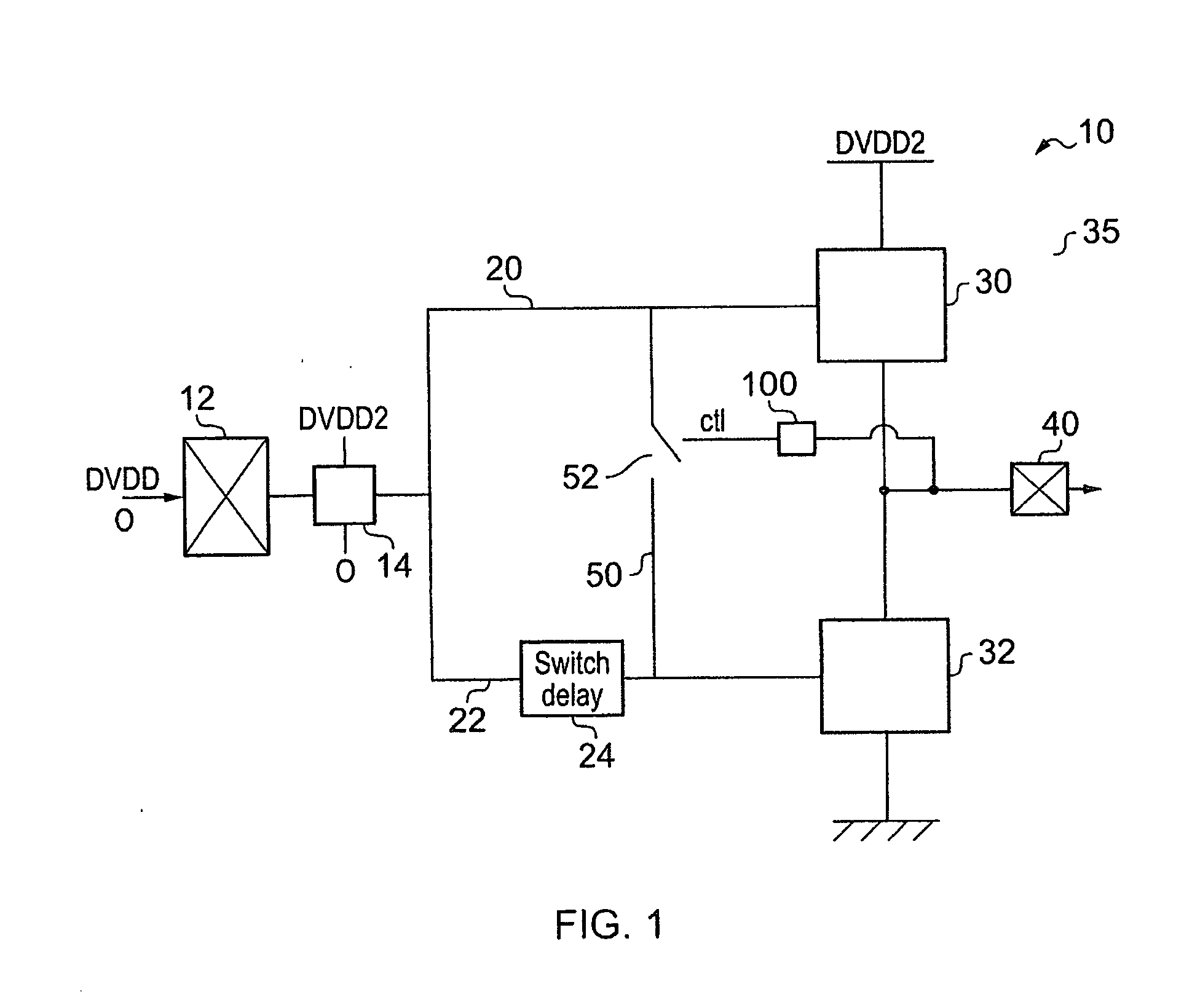

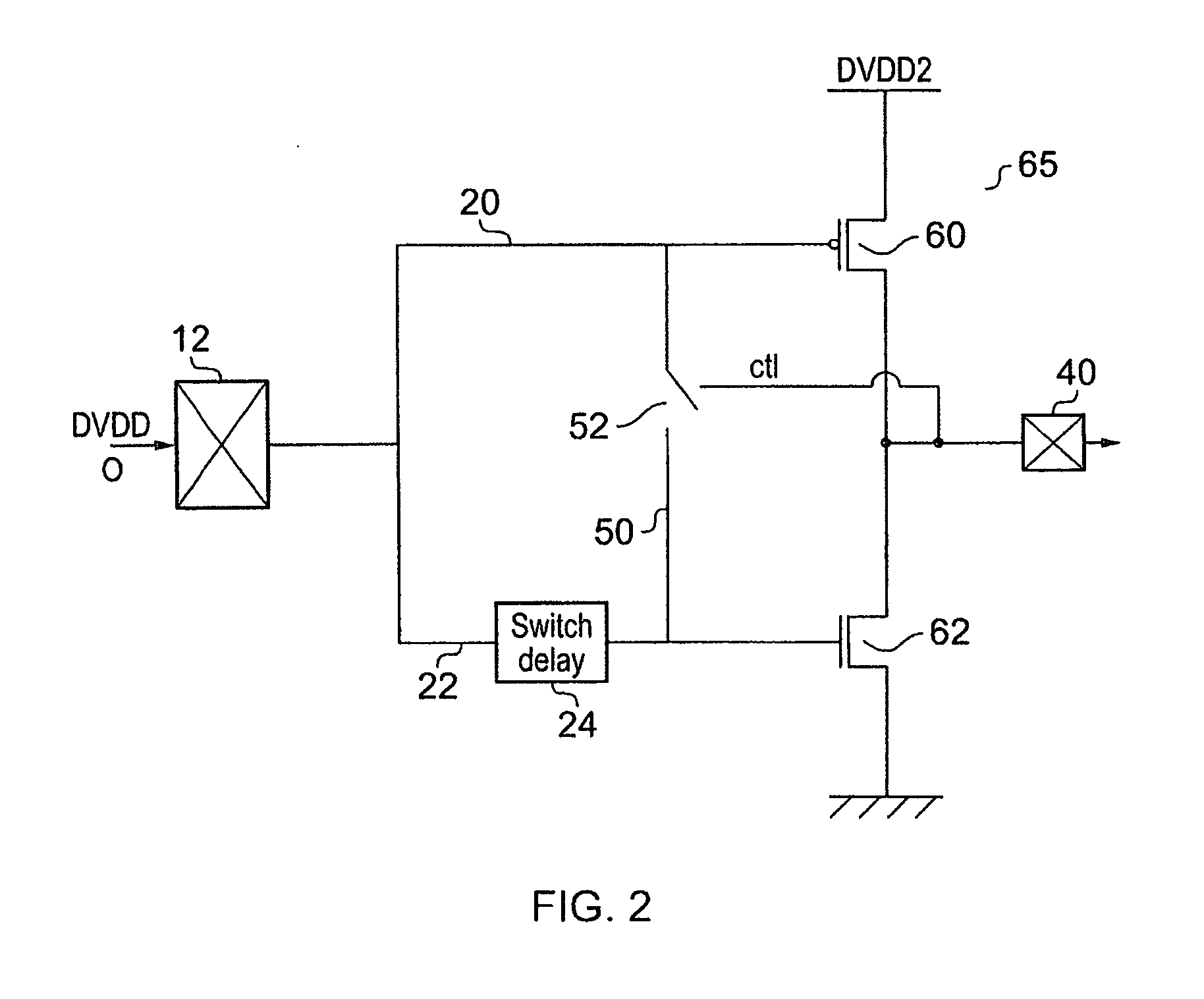

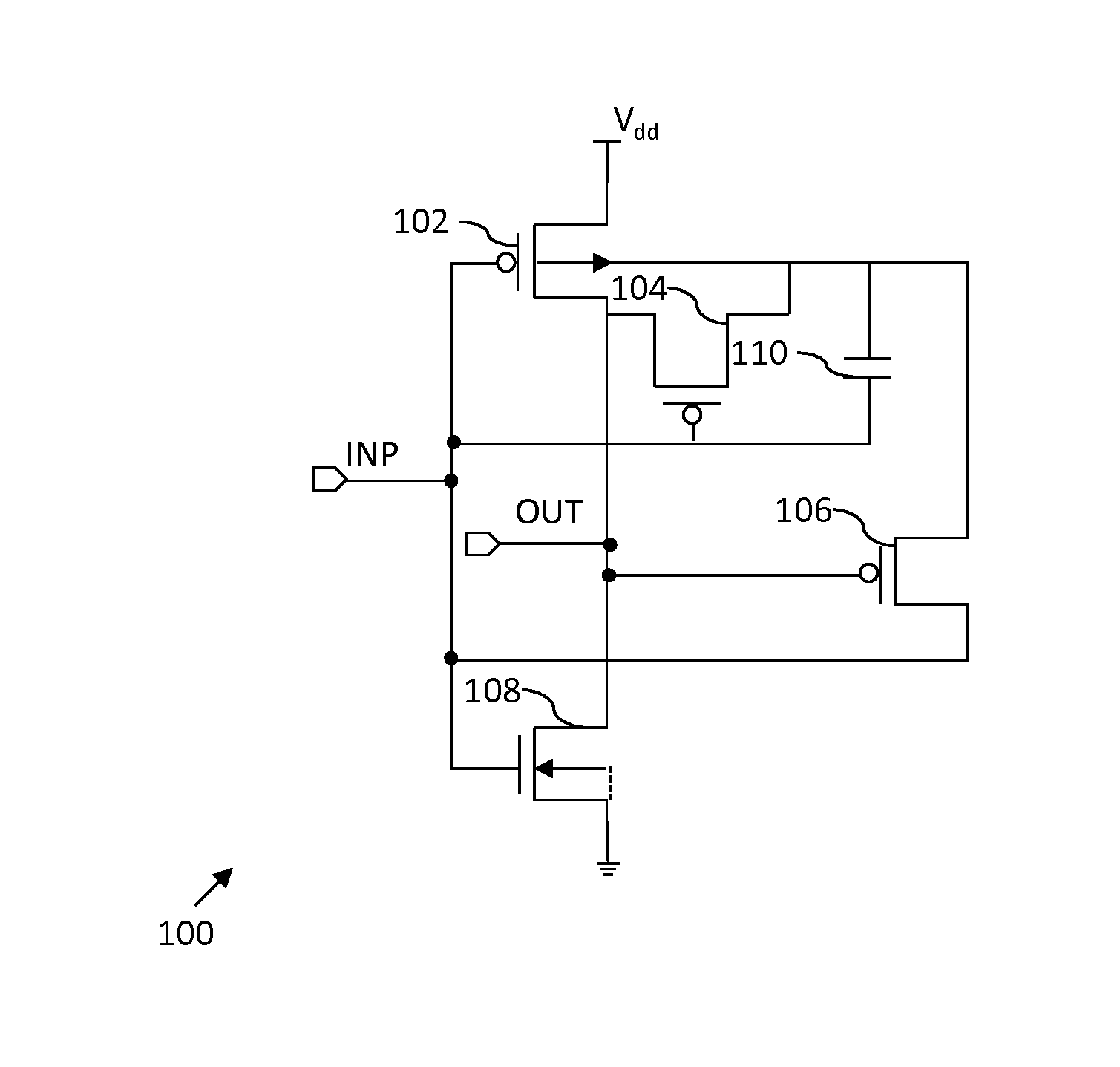

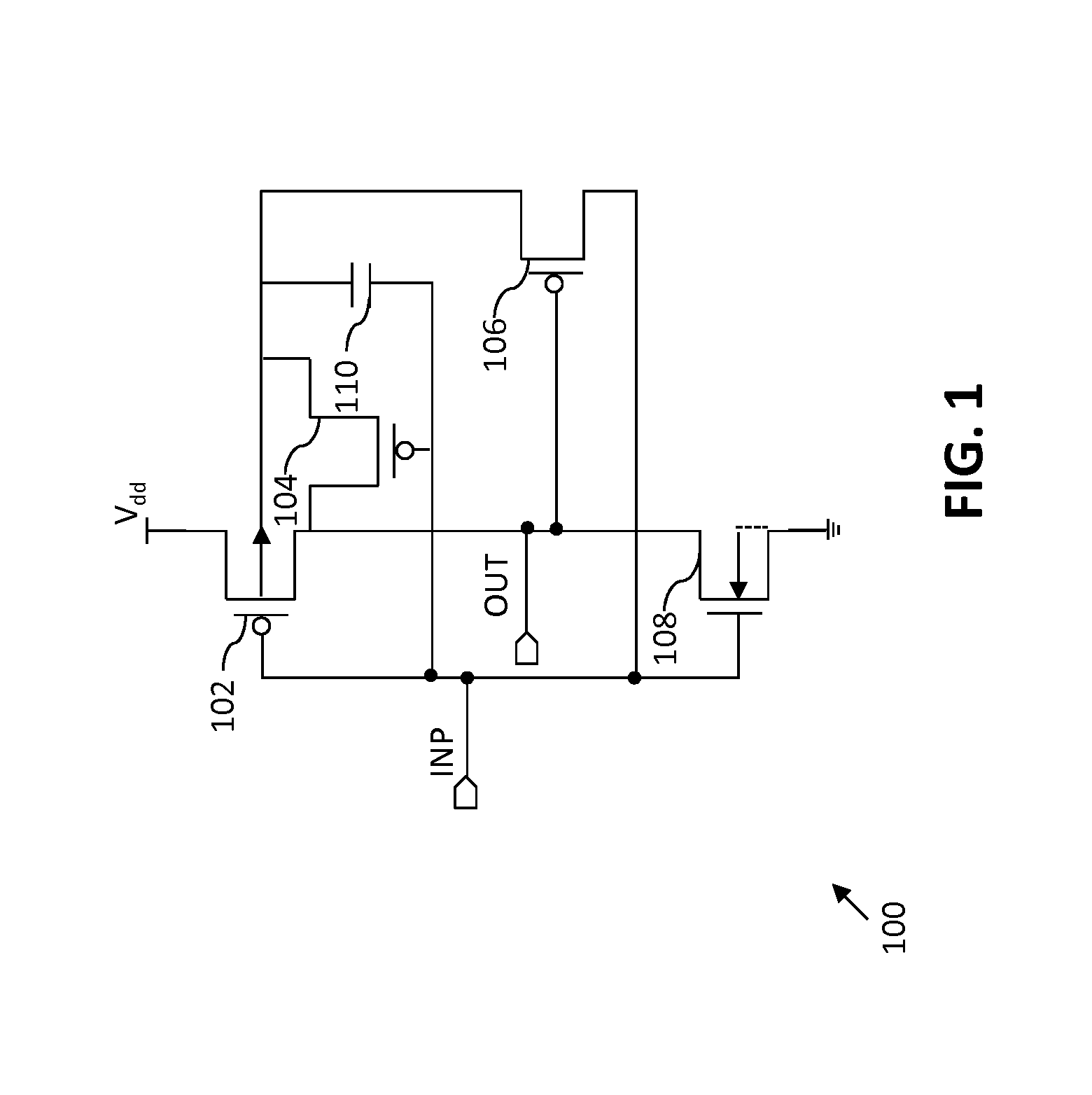

Circuitry for processing signals from a higher voltage domain using devices designed to operate in a lower voltage domain

ActiveUS20100264976A1Reduce voltagePulse automatic controlPulse shapingLow voltageHigh voltage source

An apparatus is disclosed for receiving input signals in a first higher voltage domain and for generating and outputting signals in a second lower voltage domain, said apparatus comprising: an input pad for receiving said input signals in said first higher voltage domain; output circuitry comprising a plurality of devices arranged between a high voltage source of said second lower voltage domain and a low voltage source, said plurality of devices being arranged in a first set and a second set, said first set being arranged between said high voltage source and said output and said second set being arranged between said output and said low voltage source, said output circuitry being configured to switch to output a first predetermined value in response to a rising input signal exceeding an upper threshold value and to switch to output a second predetermined value in response to a falling input signal falling below a lower threshold value; a first input path for sending said received input signals to a first input of said first set; a second input path for sending said received input signals to a second input of said second set; wherein said second input path comprises a switch delay device for reducing a voltage of said received input signal such that on a rising input signal, said input signal has reached a higher value when said output circuitry switches in response to said input signal than it would have reached had said input signal voltage not been reduced; and a controllable connecting path between said first and second inputs for connecting said first and second inputs together in response to detection of said first predetermined value at said output and for not connecting said first and second inputs together in response to detection of said second predetermined value at said output.

Owner:ARM LTD

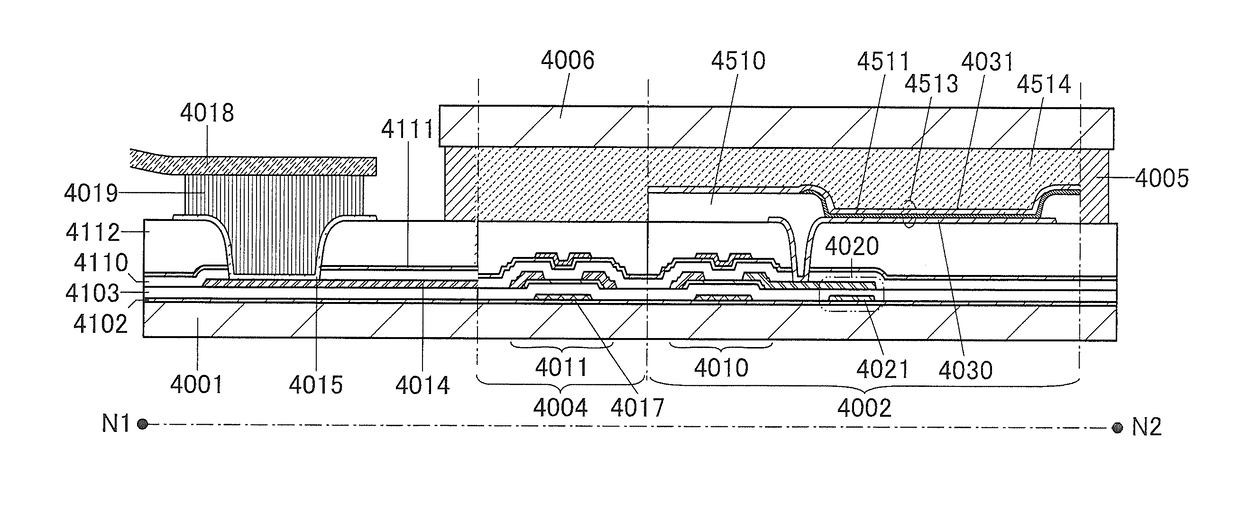

Semiconductor Device

InactiveUS20170110453A1Reduce power consumptionReduce areaTransistorLogic circuits characterised by logic functionEngineeringSemiconductor

A semiconductor device with a small number of transistors is provided. The semiconductor device includes a first transistor, a second transistor, a third transistor, a first wiring, and a second wiring. The first transistor includes a first gate and a second gate. The first gate and the second gate overlap with each other with a semiconductor therebetween. The first wiring and the second wiring are supplied with a high power supply potential and a low power supply potential, respectively. A first terminal of the first transistor is electrically connected to the first gate and the first wiring. A second terminal of the first transistor is electrically connected to the second gate. The second terminal of the first transistor is electrically connected to the second wiring through the second transistor and the third transistor. The first transistor, the second transistor, and the third transistor are preferably n-channel transistors.

Owner:SEMICON ENERGY LAB CO LTD

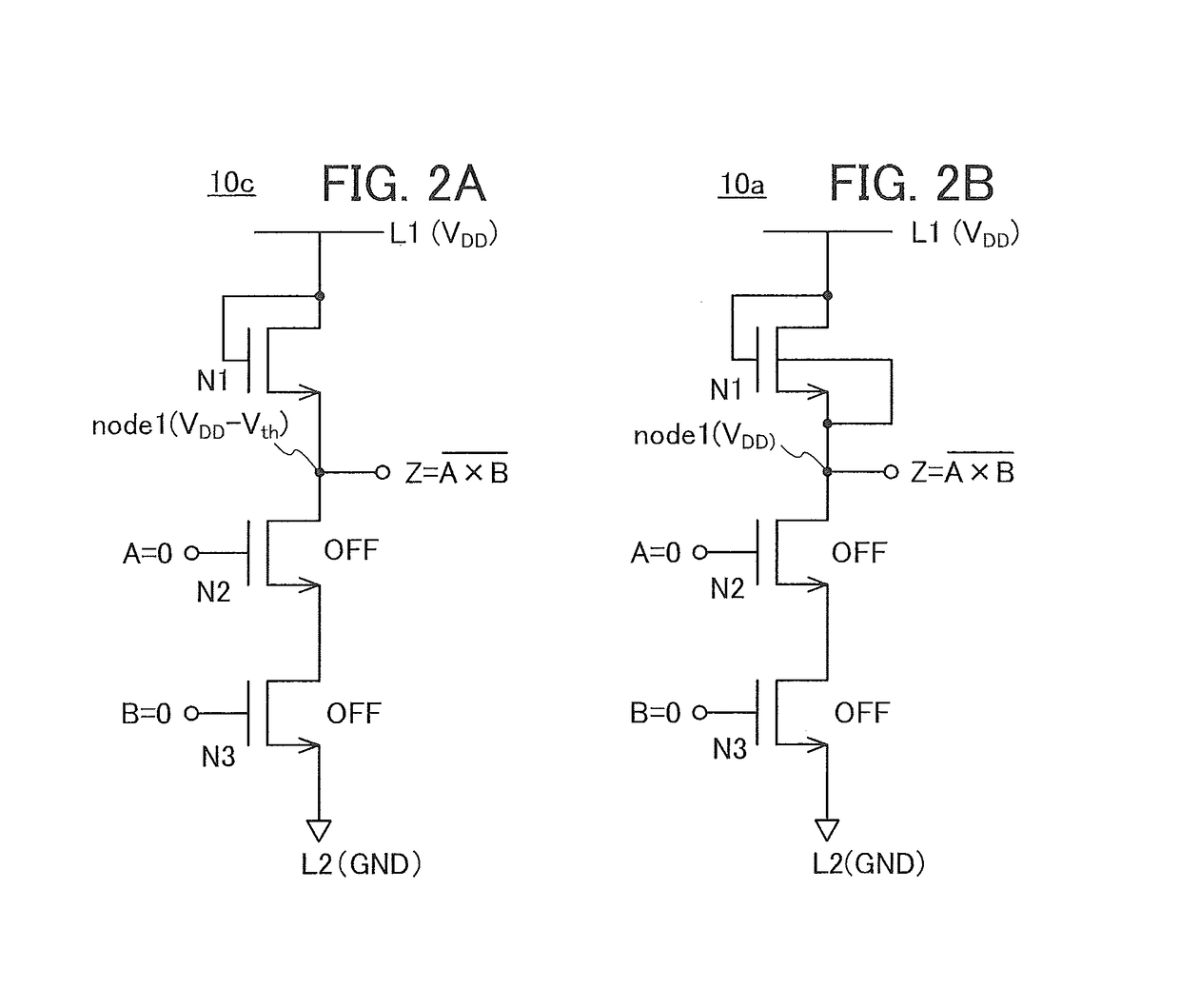

Semiconductor device with an enhancement type field effect transistor in which threshold voltage is dependent upon substrate bias voltage

An enhancement mode field effect transistor whose operation threshold value varies greatly according to the substrate voltage. This field effect transistor is implemented by substituting the gate electrode of a depression mode field effect transistor for a gate electrode of the conductivity type opposite to that of a channel formation region, or a midgap gate electrode. In a preferred embodiment of the present invention, this field effect transistor is provided between a CMOS structure logic gate and a ground line. As a result, the leak current when the field effect transistor is not operating can be diminished without reducing the operational speed of the logic gate.

Owner:LAPIS SEMICON CO LTD

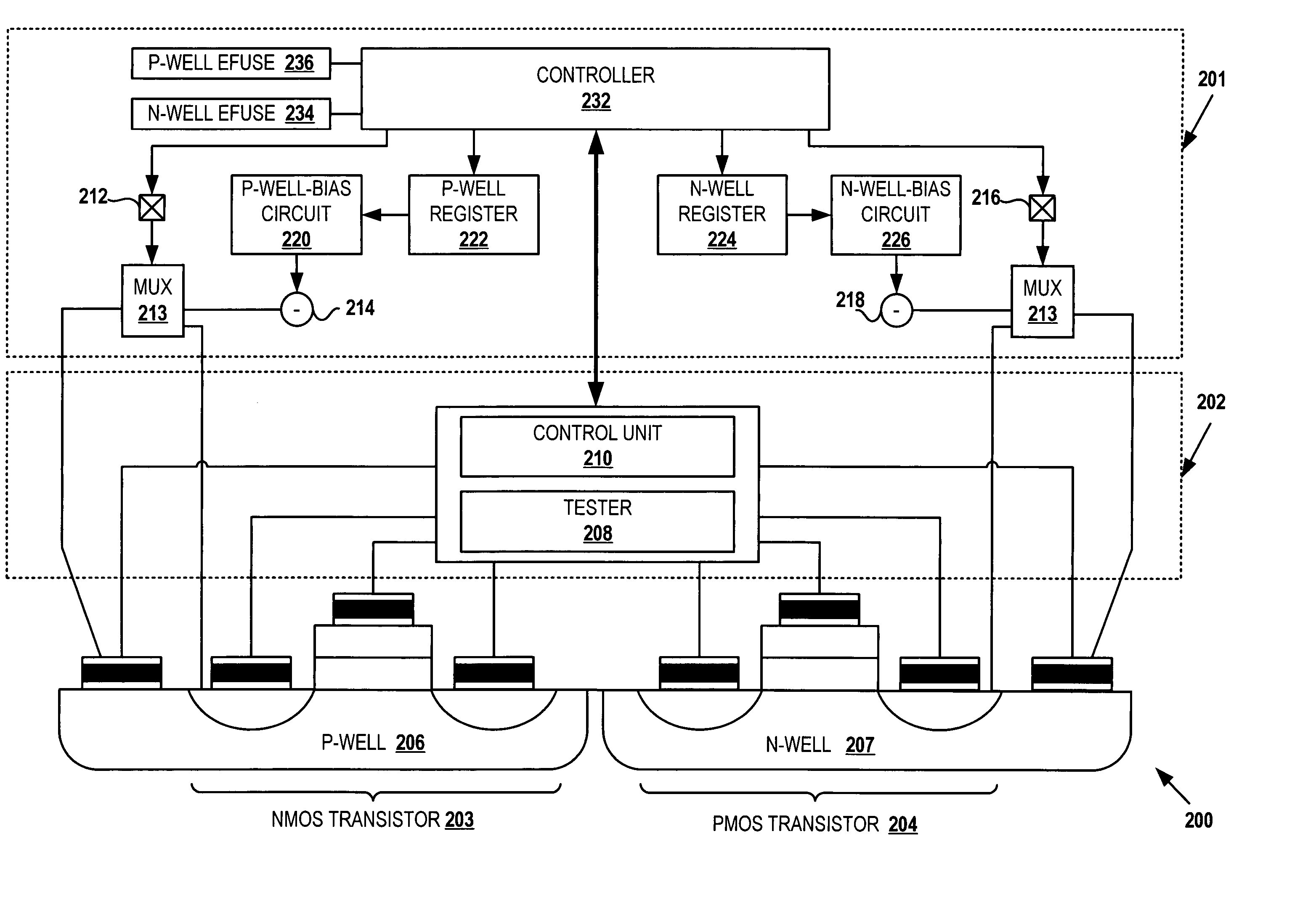

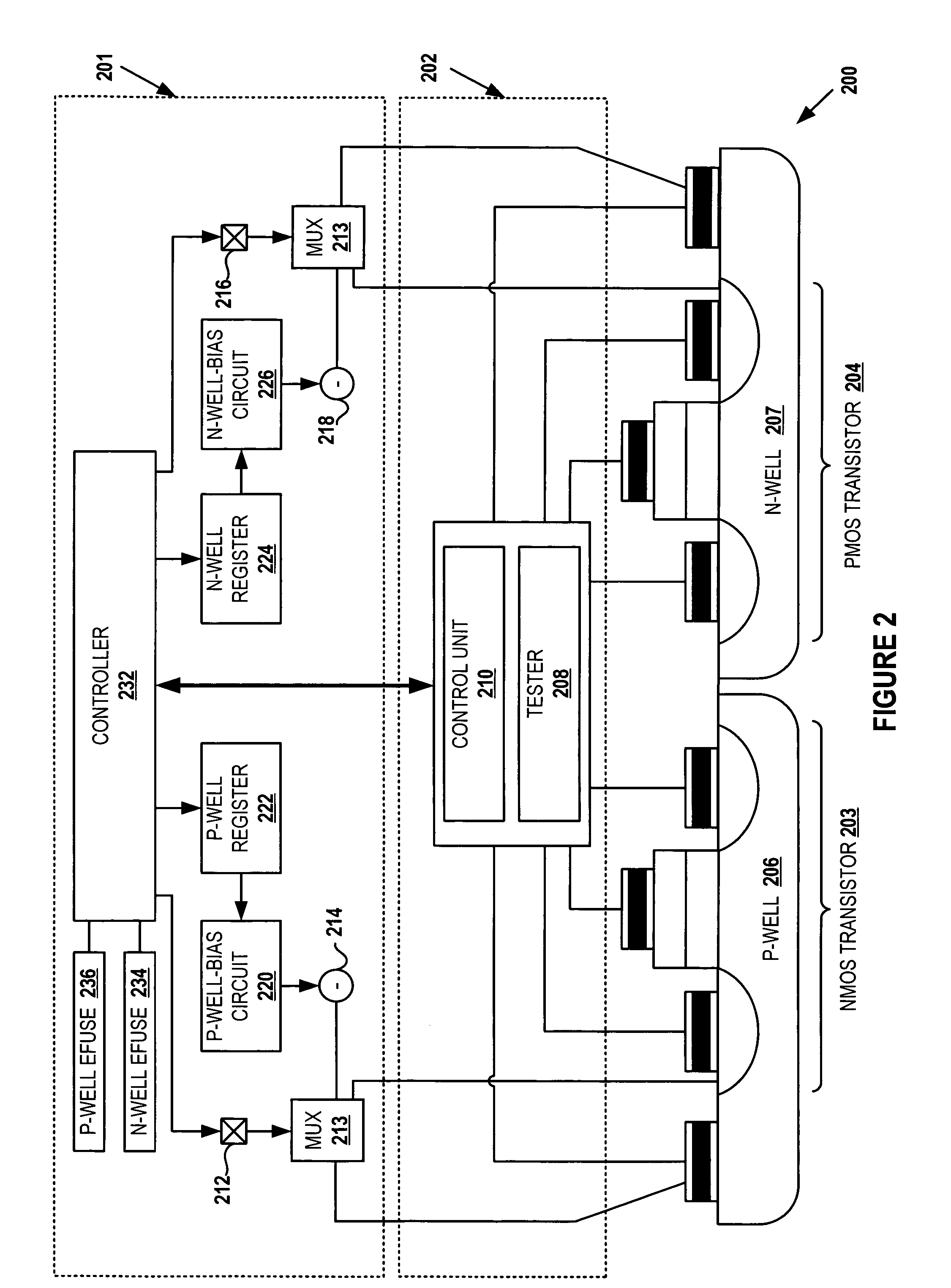

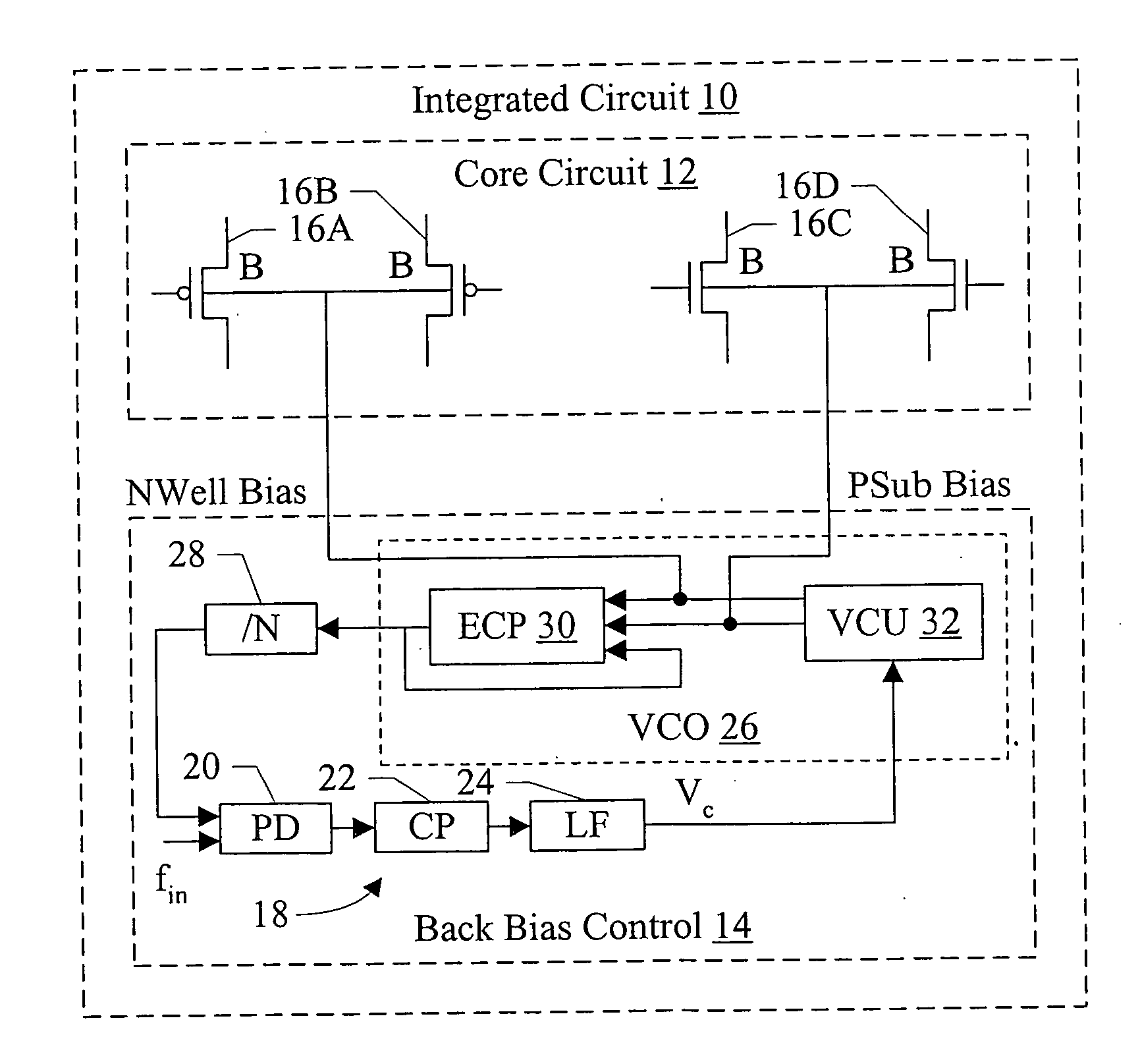

Wearout compensation mechanism using back bias technique

InactiveUS20070139098A1Compensation changesThreshold modification in field effect transistorsElectric pulse generator detailsBack biasSubstrate bias voltage

In one embodiment, an integrated circuit comprises a first circuit and a control unit coupled to the first circuit. The first circuit comprises at least one transistor and implements one or more operations for which the integrated circuit is designed. The control unit is configured to generate at least one substrate bias voltage for the first circuit.

Owner:APPLE INC

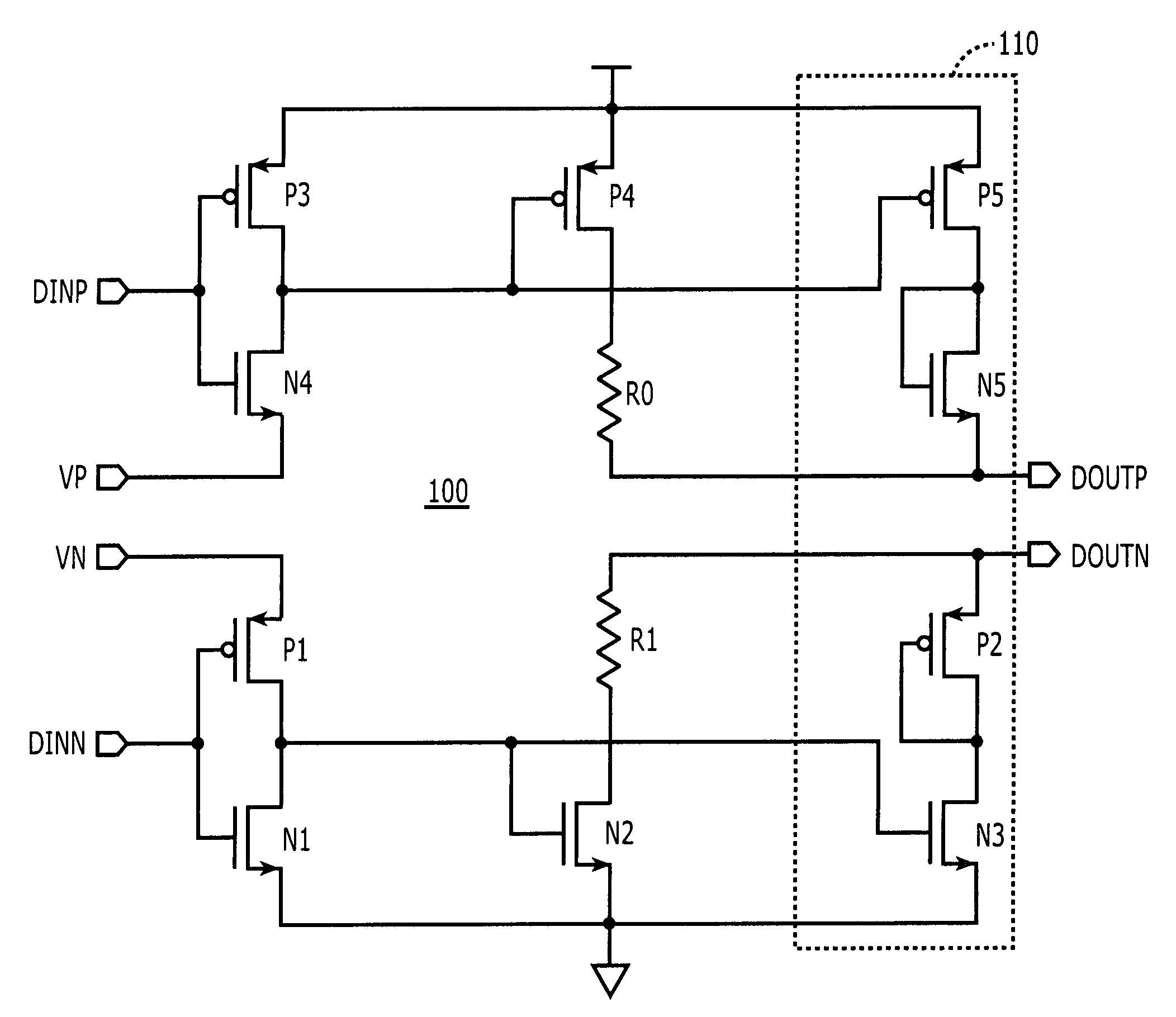

Impedance-matched output driver circuits having enhanced predriver control

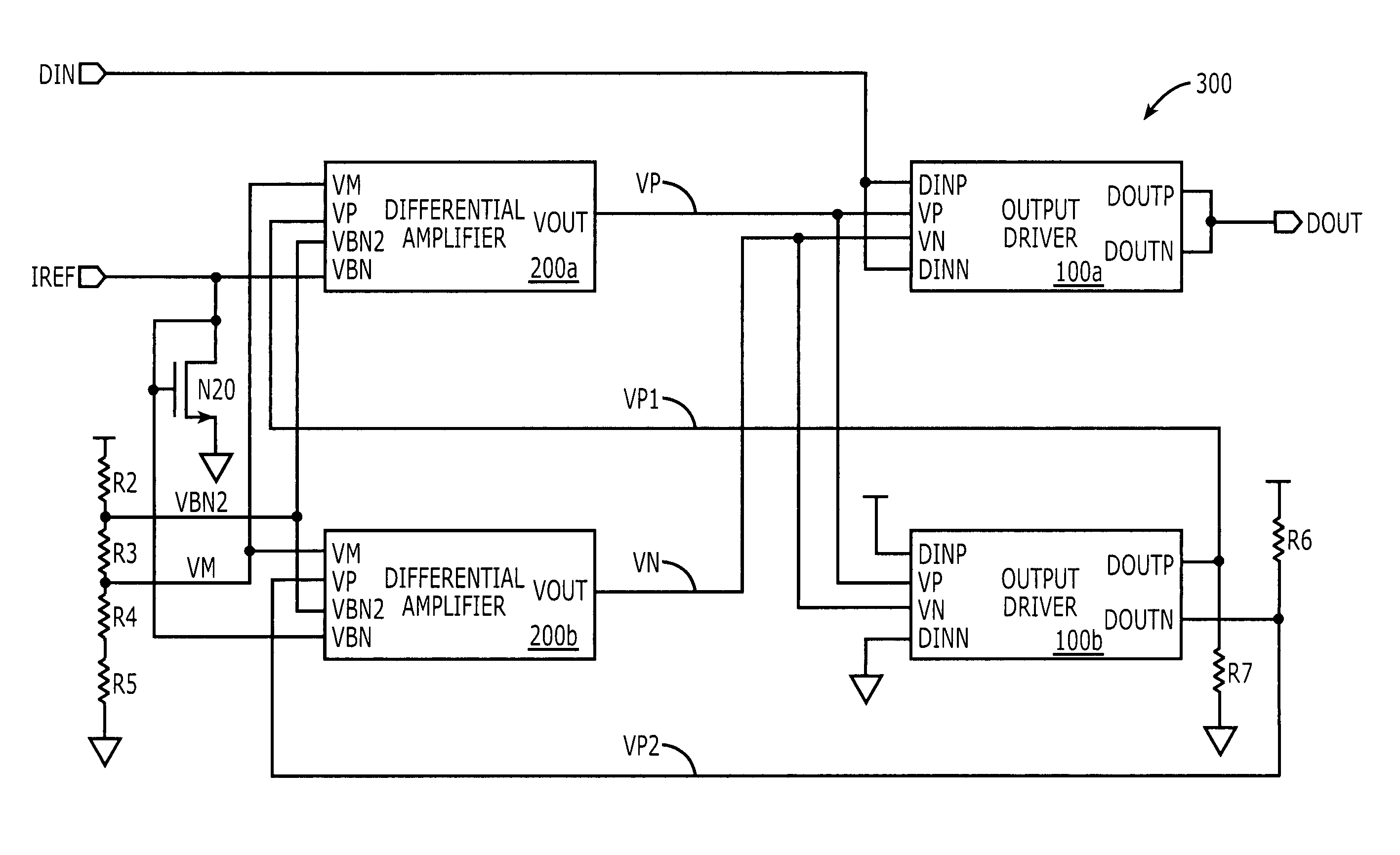

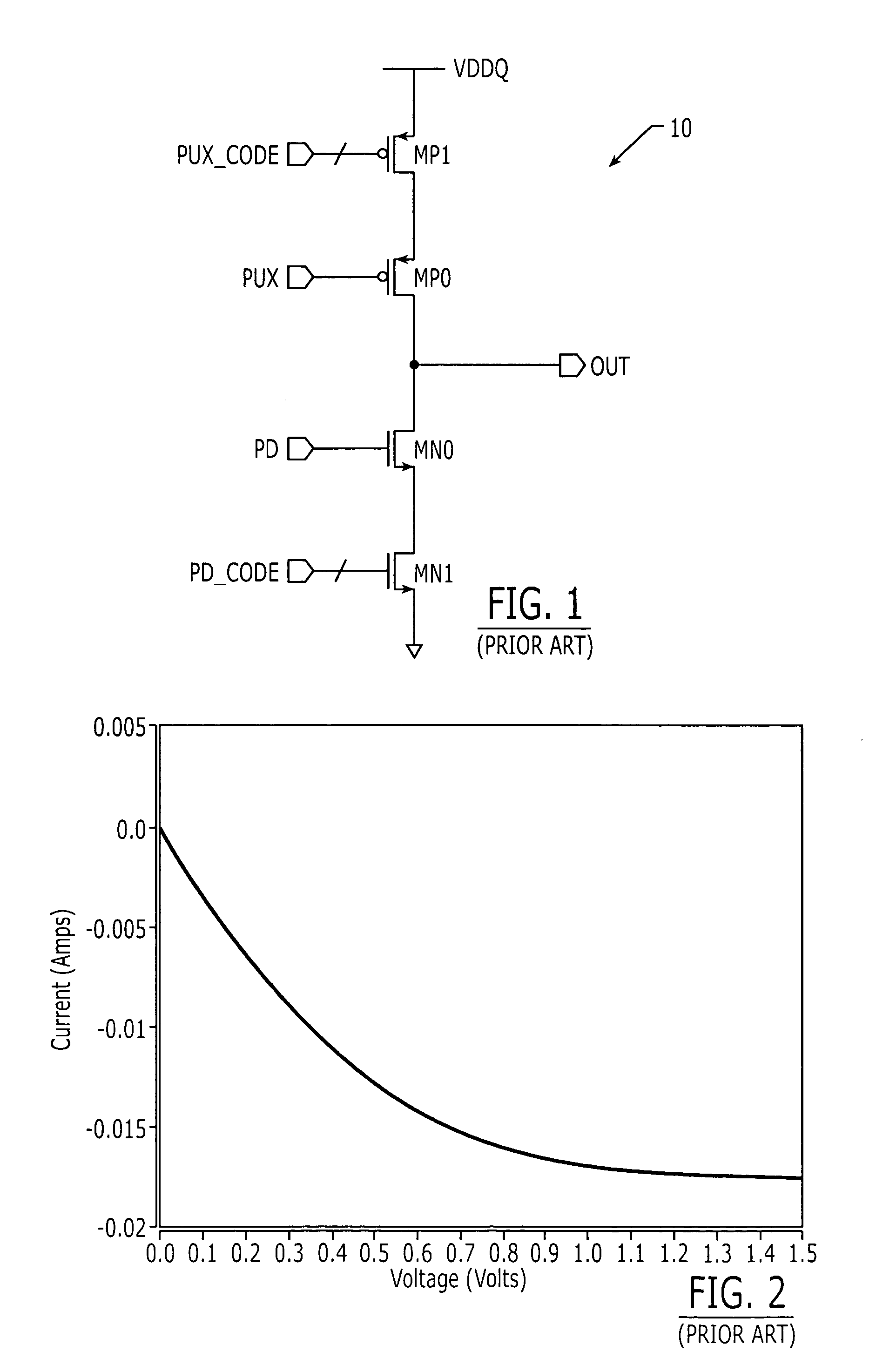

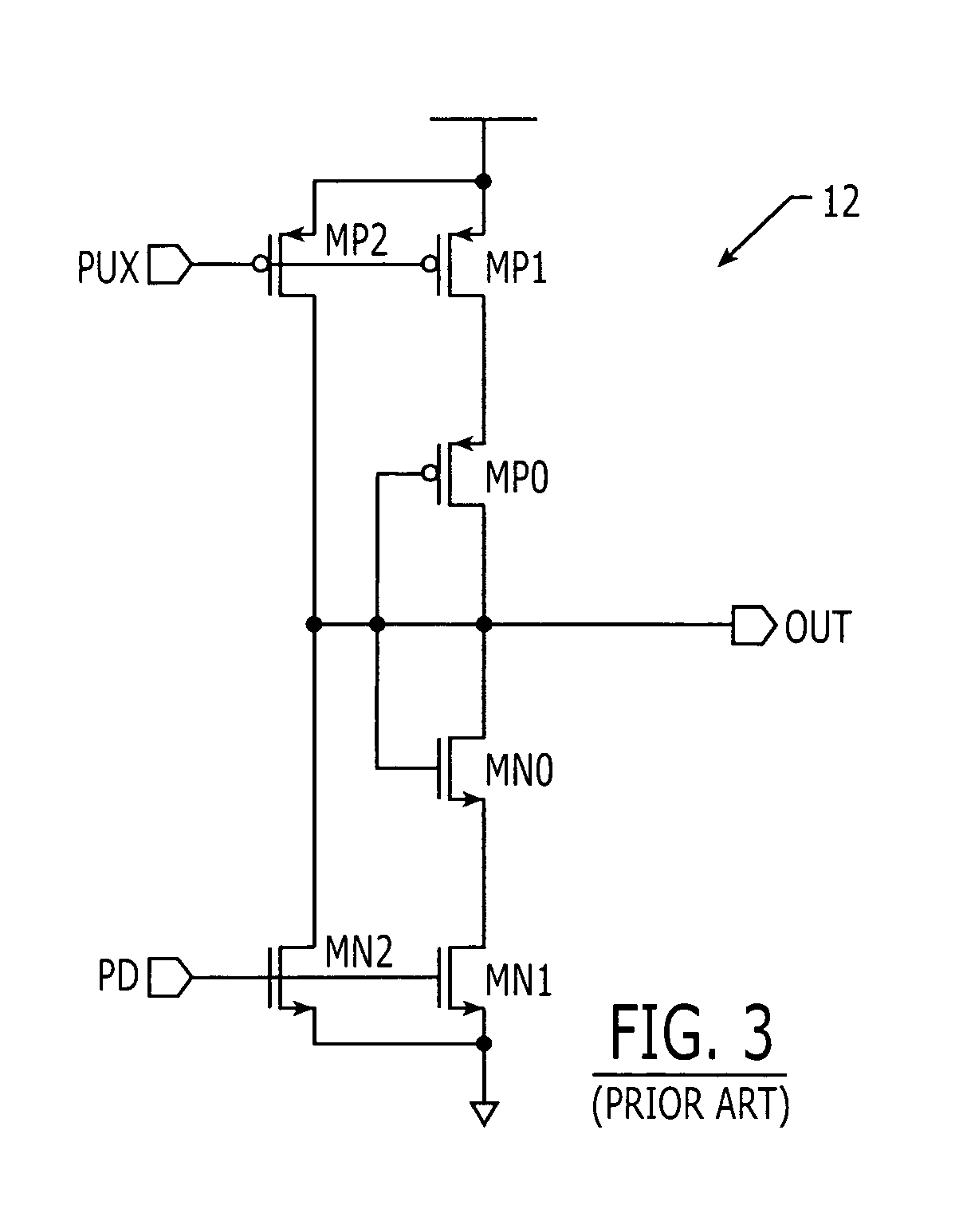

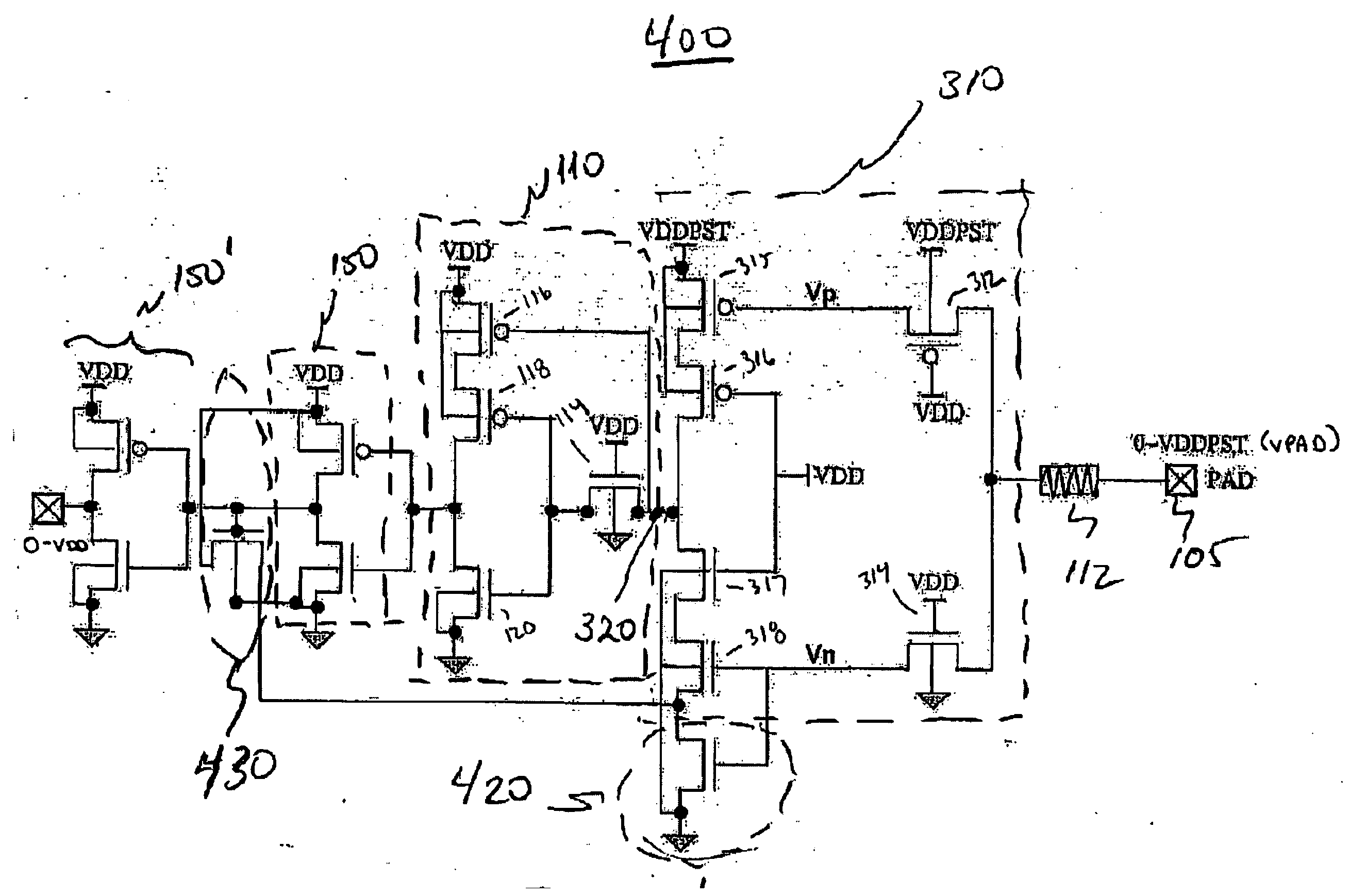

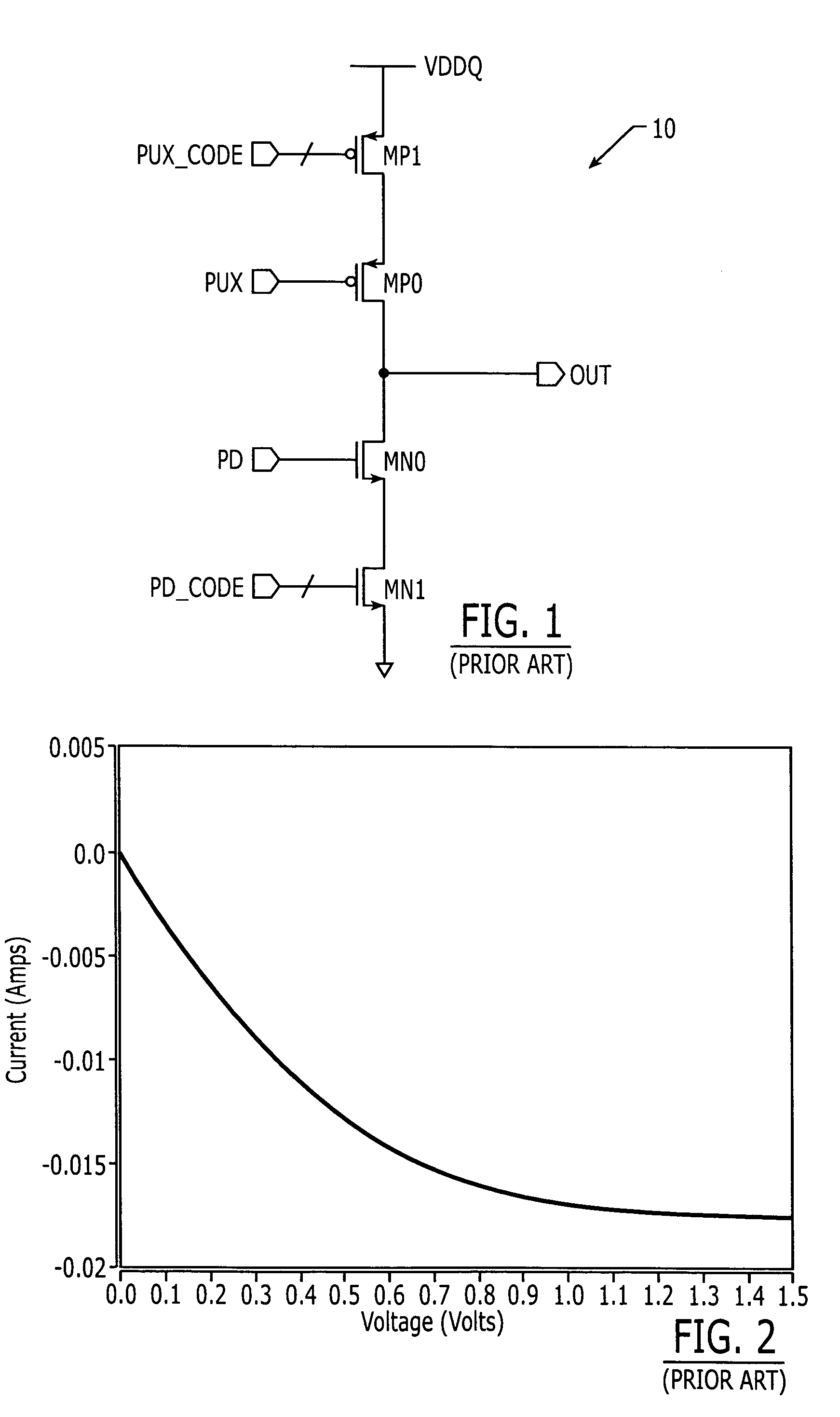

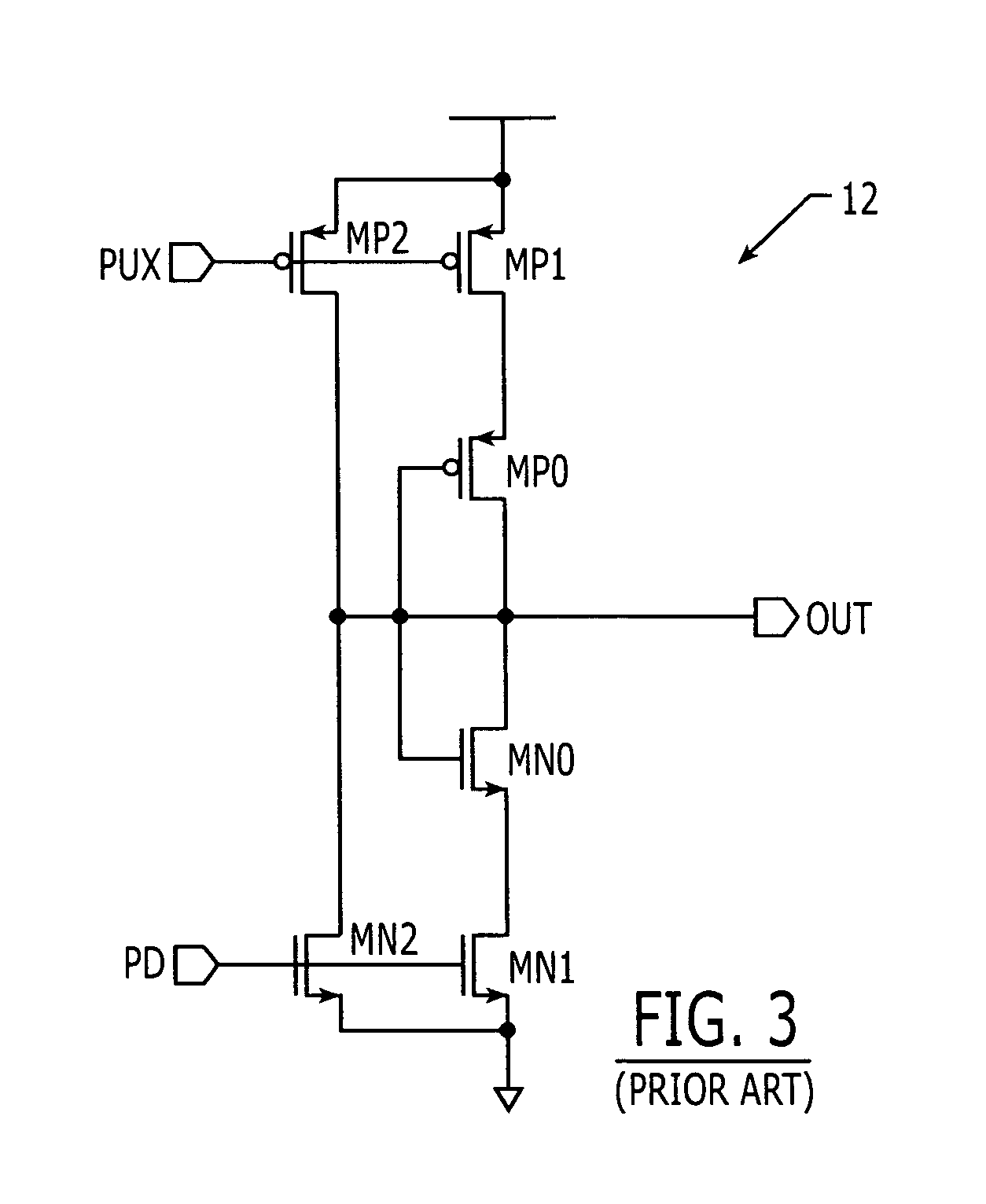

ActiveUS6967501B1Improve operating characteristicsDegree of improvementInput/output impedence modificationReliability increasing modificationsDriver circuitImage resolution

Impedance-matched output driver circuits utilize predriver circuits with analog control to provide enhanced operating characteristics. This analog control may be provided by an analog loop containing differential amplifiers that set the resolution limit of the output driver circuit. These output driver circuits include a first PMOS pull-up transistor having source and drain terminals electrically connected in series in a pull-up path of the output driver circuit. An NMOS pass transistor has a first current carrying terminal electrically connected to a gate terminal of the first PMOS pull-up transistor and a second current carrying terminal configured to receive a P-type analog reference voltage (VP). This P-type reference voltage controls the conductivity of the first PMOS pull-up transistor in the pull-up path. A gate terminal of the NMOS pass transistor is responsive to a pull-up data input signal (DINP). A first NMOS pull-down transistor has source and drain terminals that are electrically connected in series in a pull-down path of the output driver circuit. A PMOS pass transistor is provided having a first current carrying terminal electrically connected to a gate terminal of the first NMOS pull-down transistor and a second current carrying terminal configured to receive an N-type analog reference voltage (VN). This N-type reference voltage controls the conductivity of the first NMOS pull-down transistor in the pull-down path. A gate terminal of the PMOS pass transistor is responsive to a pull-down data input signal (DINN).

Owner:INTEGRATED DEVICE TECH INC

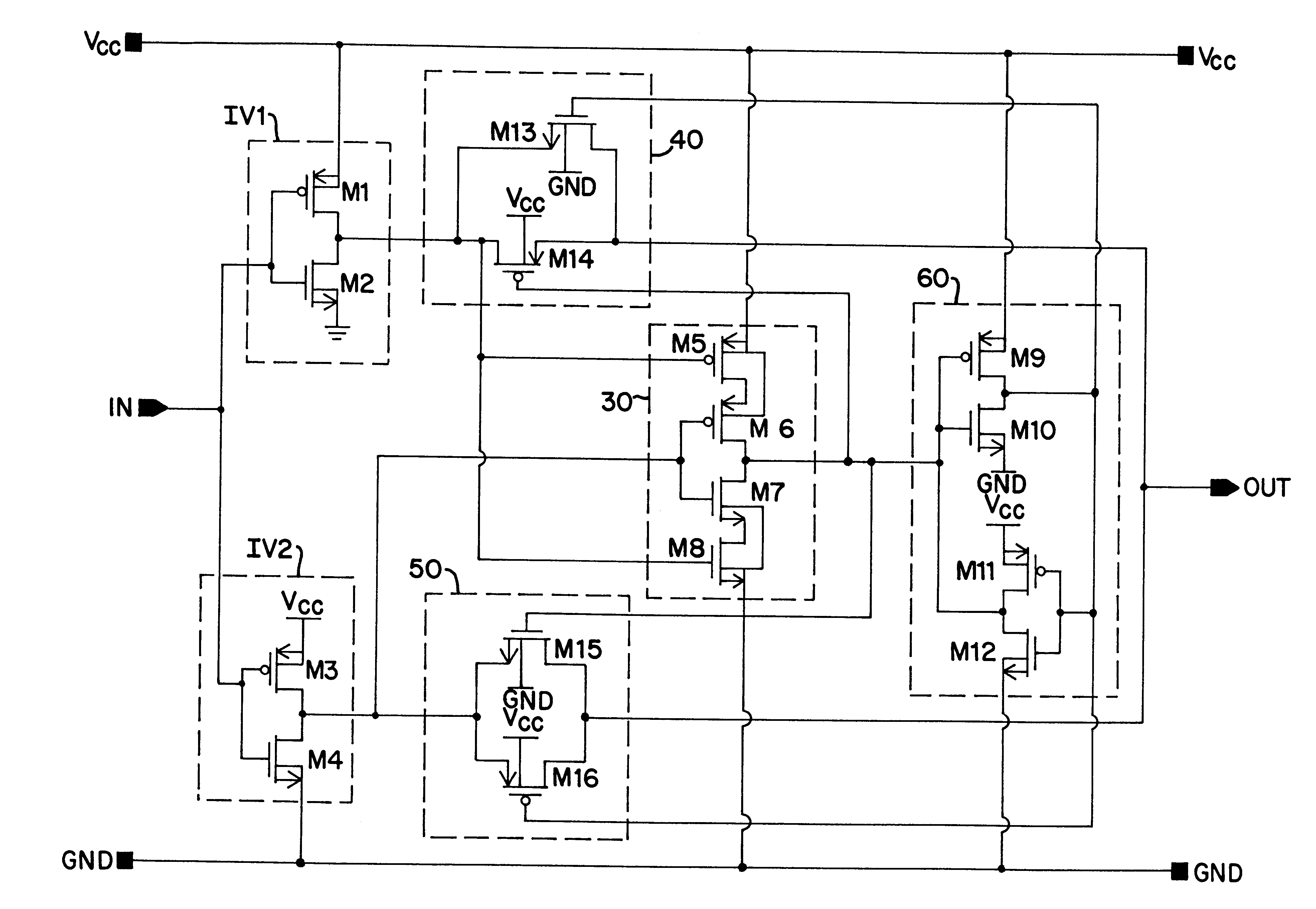

Circuit for dynamic switching of a buffer threshold

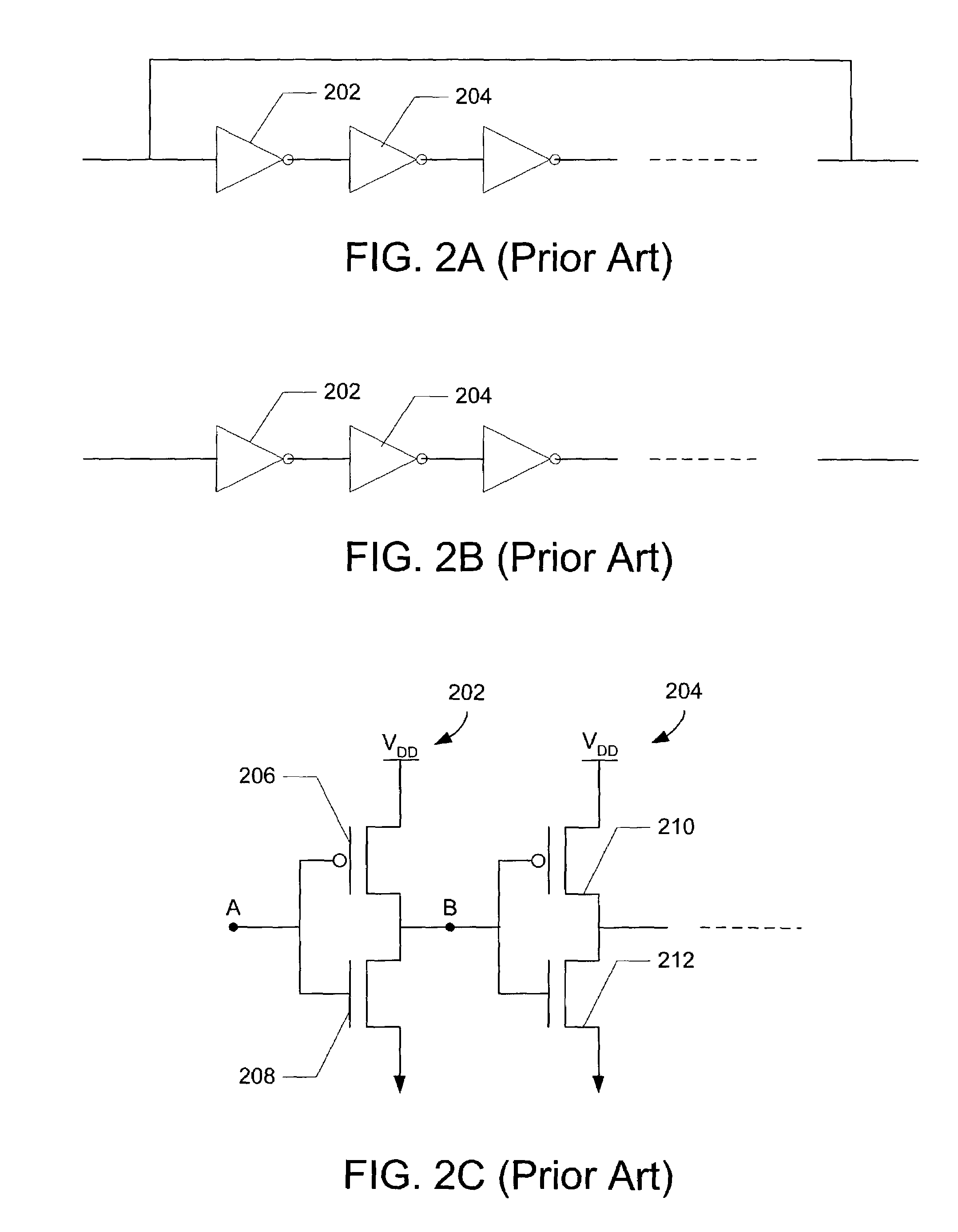

InactiveUS6198308B1Reduce degradationReduce sensitivitySwitching accelaration modificationsThreshold modification in field effect transistorsPropagation delayThreshold potential

A buffer circuit for providing dynamic threshold control. The buffer circuit includes a pair of input inverters designed with different skewed threshold potential characteristics. The outputs of the skewed inverters are directed to a logic circuit designed to select either the faster or the slower signal received from the two inverters for transmission to passgate devices coupled to the respective inverters. Only one of the passgate devices is enabled to ensure that only one of the output signals from the two inverters is propagated through the buffer. A latch is preferably connected between the logic circuit and the two passgate devices to maintain the states of the inverters and the logic circuit. The circuit can be designed to define the threshold potential at which switching will occur so as to reduce propagation delay or increase it as desired. It is therefore possible using the circuit to increase transmission rates with minimal affect on signal noise.

Owner:SEMICON COMPONENTS IND LLC

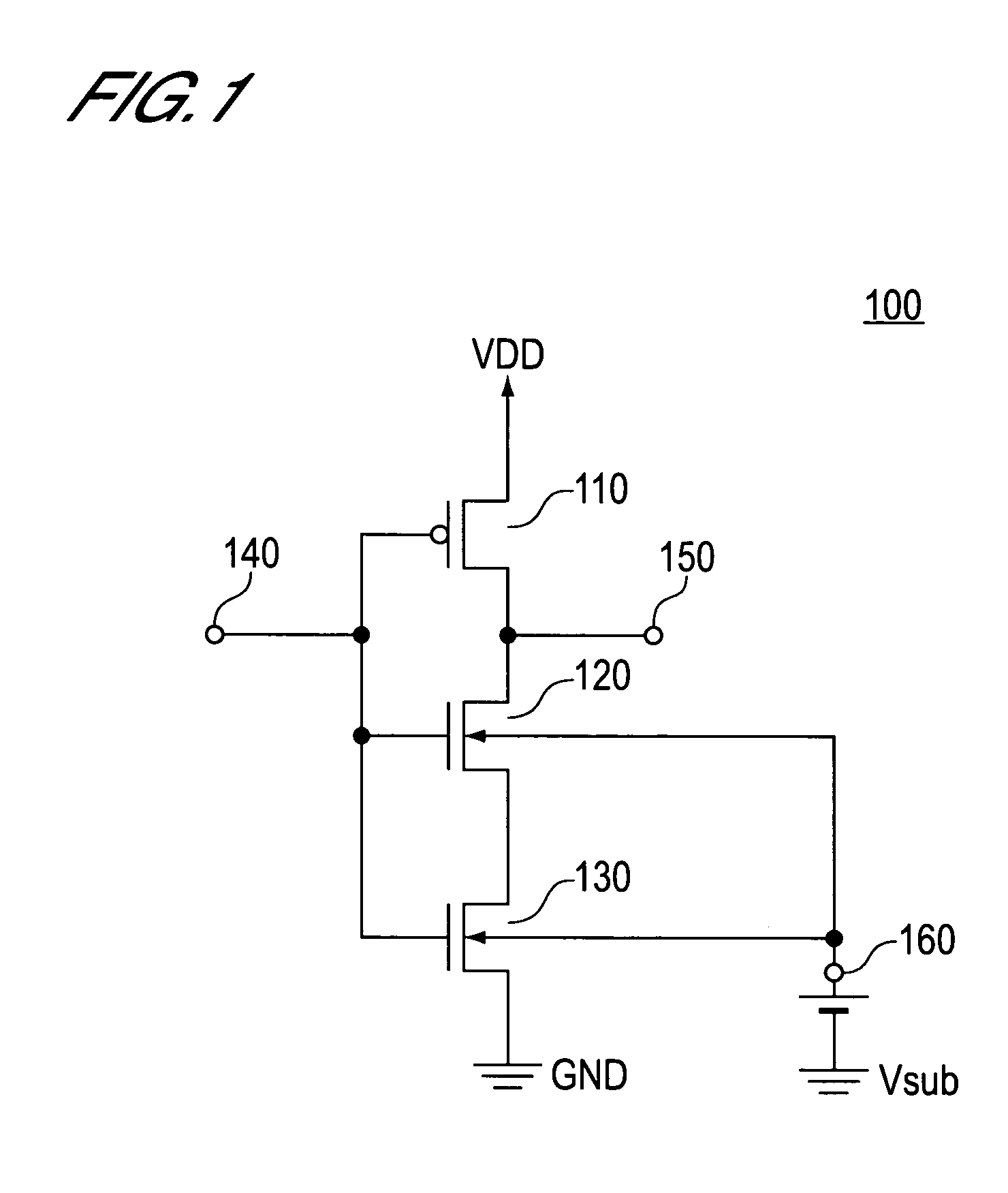

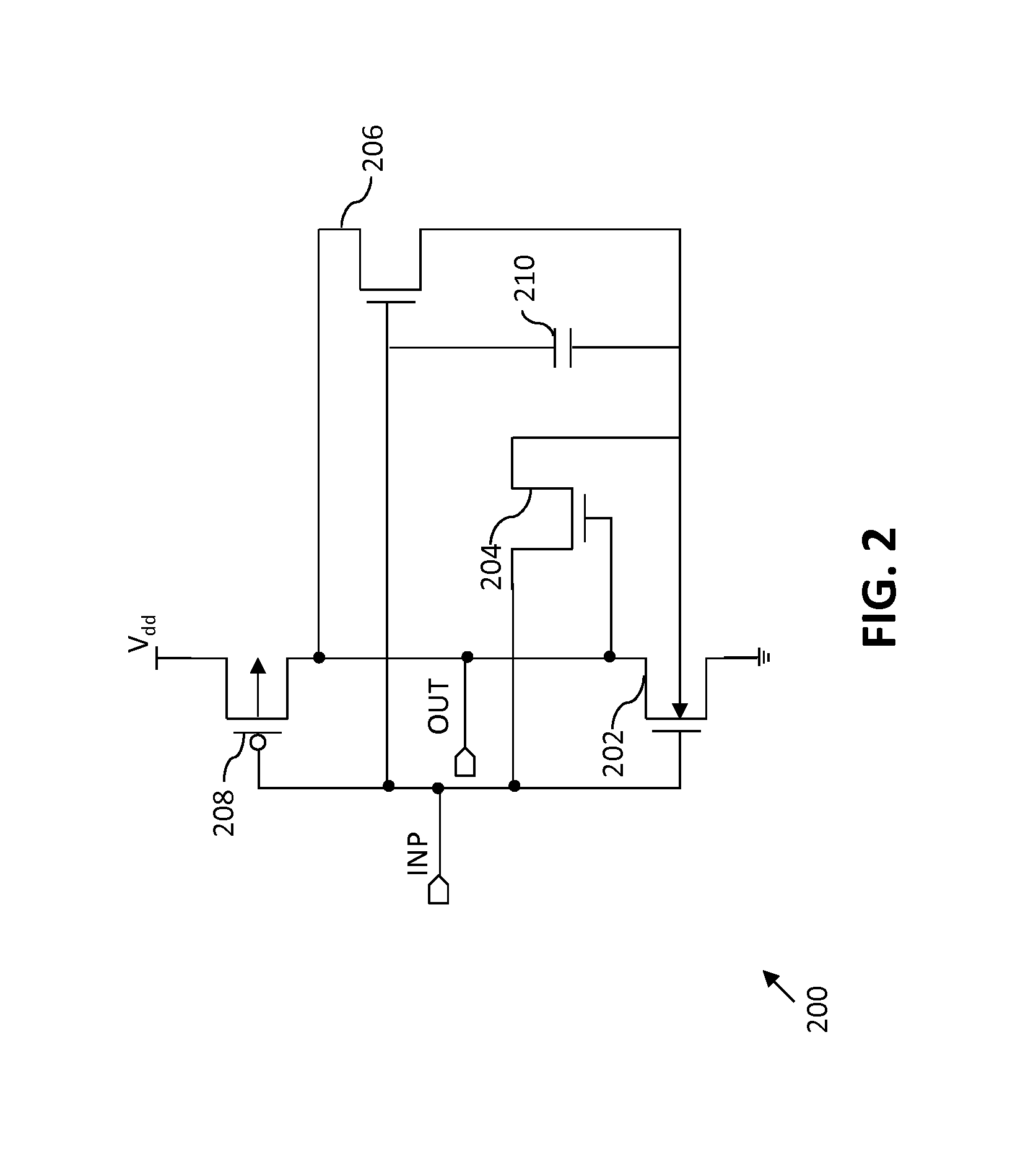

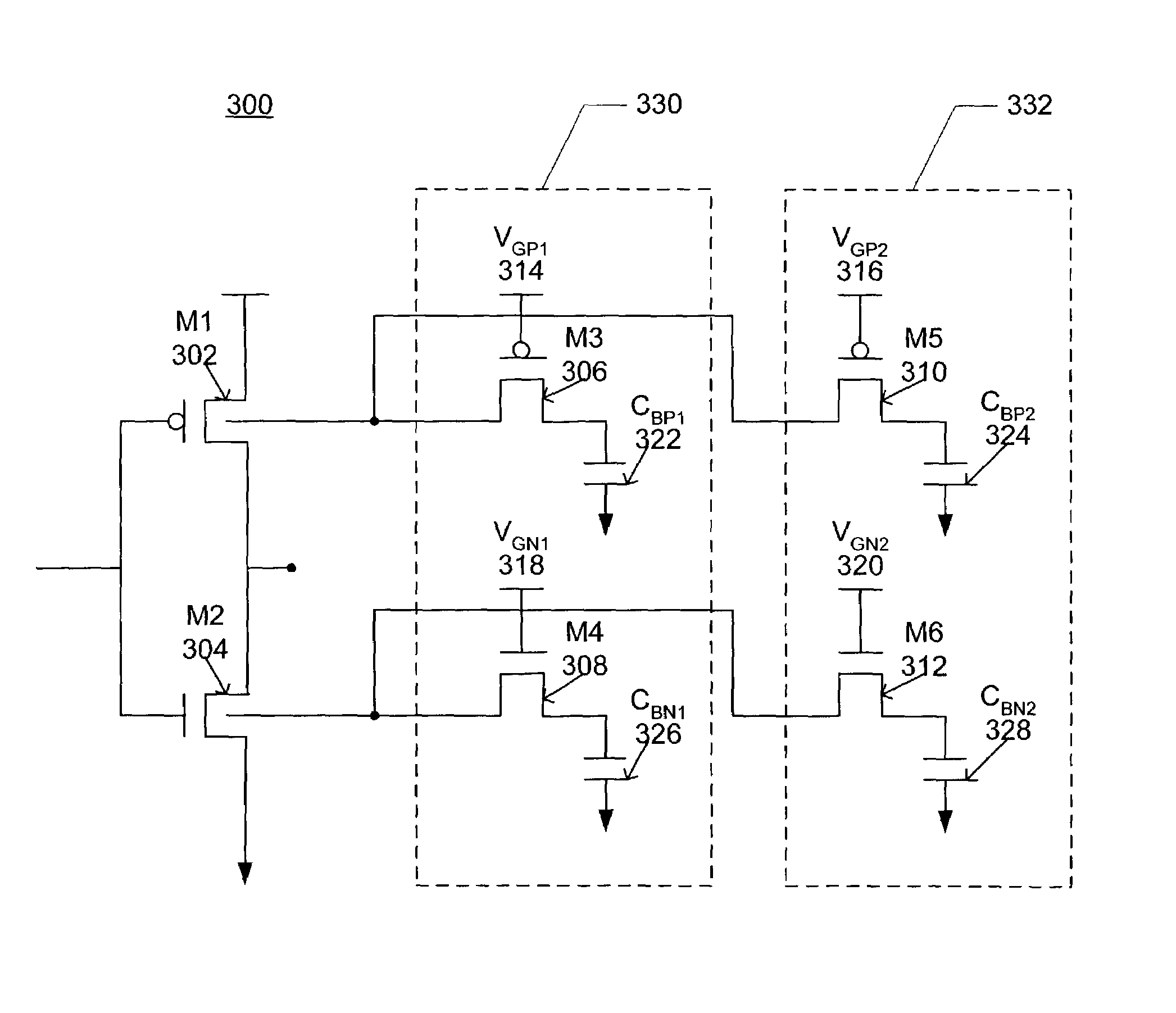

MOS transistor with forward bulk-biasing circuit

ActiveUS8803591B1Threshold modification in field effect transistorsElectric pulse generator detailsLeakage power dissipationState switching

Forward bulk biasing circuitry for PMOS and NMOS transistors is provided. The bulk biasing circuitry includes two N-type MOS transistors, two P-type MOS transistors, and two capacitors. The forward bias to a bulk terminal of a transistor increases a threshold voltage of a transistor, thereby reducing a transition time and improving the performance of the transistor. The forward bias is provided only when the transistor transitions from one state to another, thereby reducing leakage power dissipation during active and standby modes of an integrated circuit that includes the transistor.

Owner:NXP USA INC

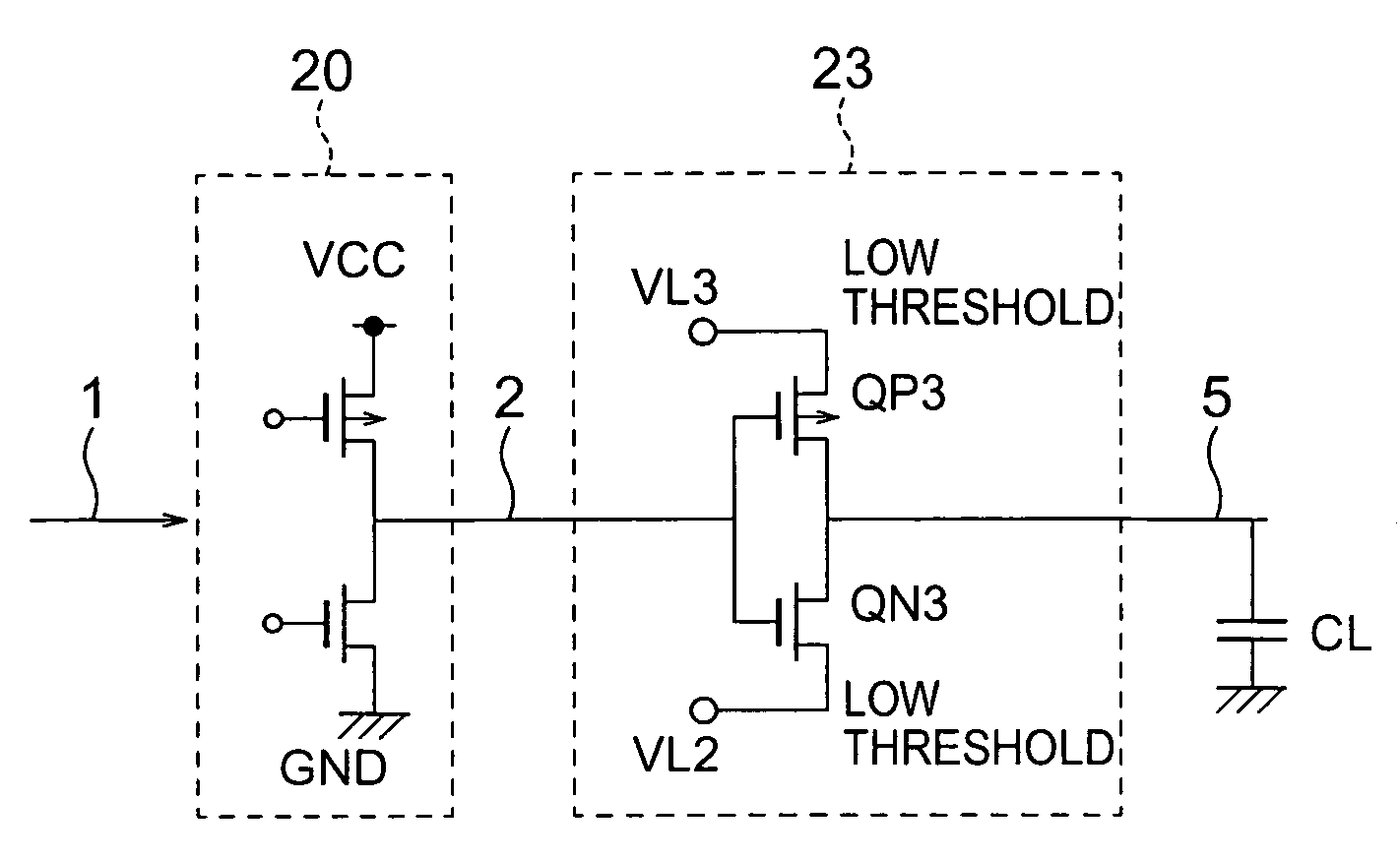

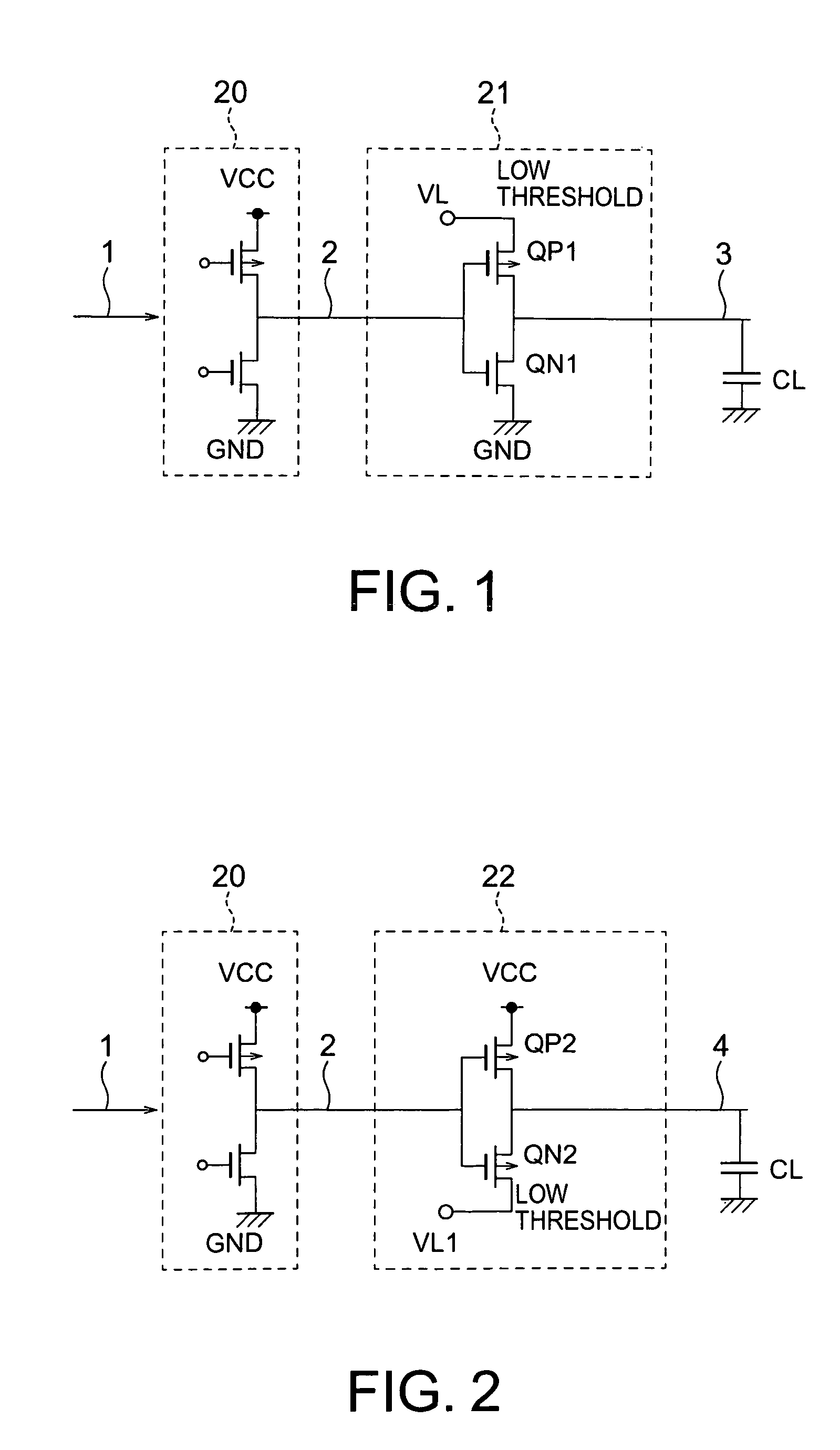

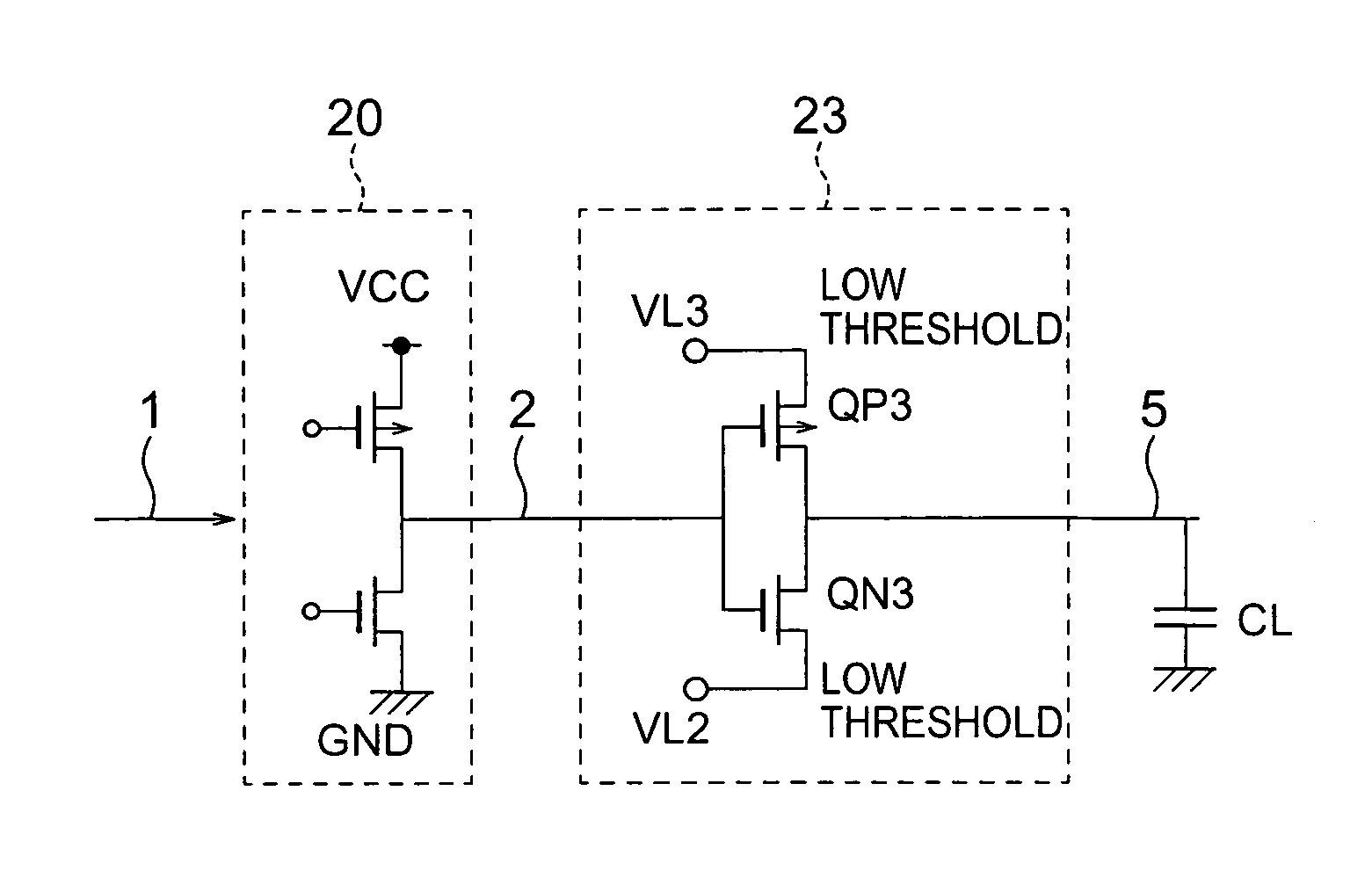

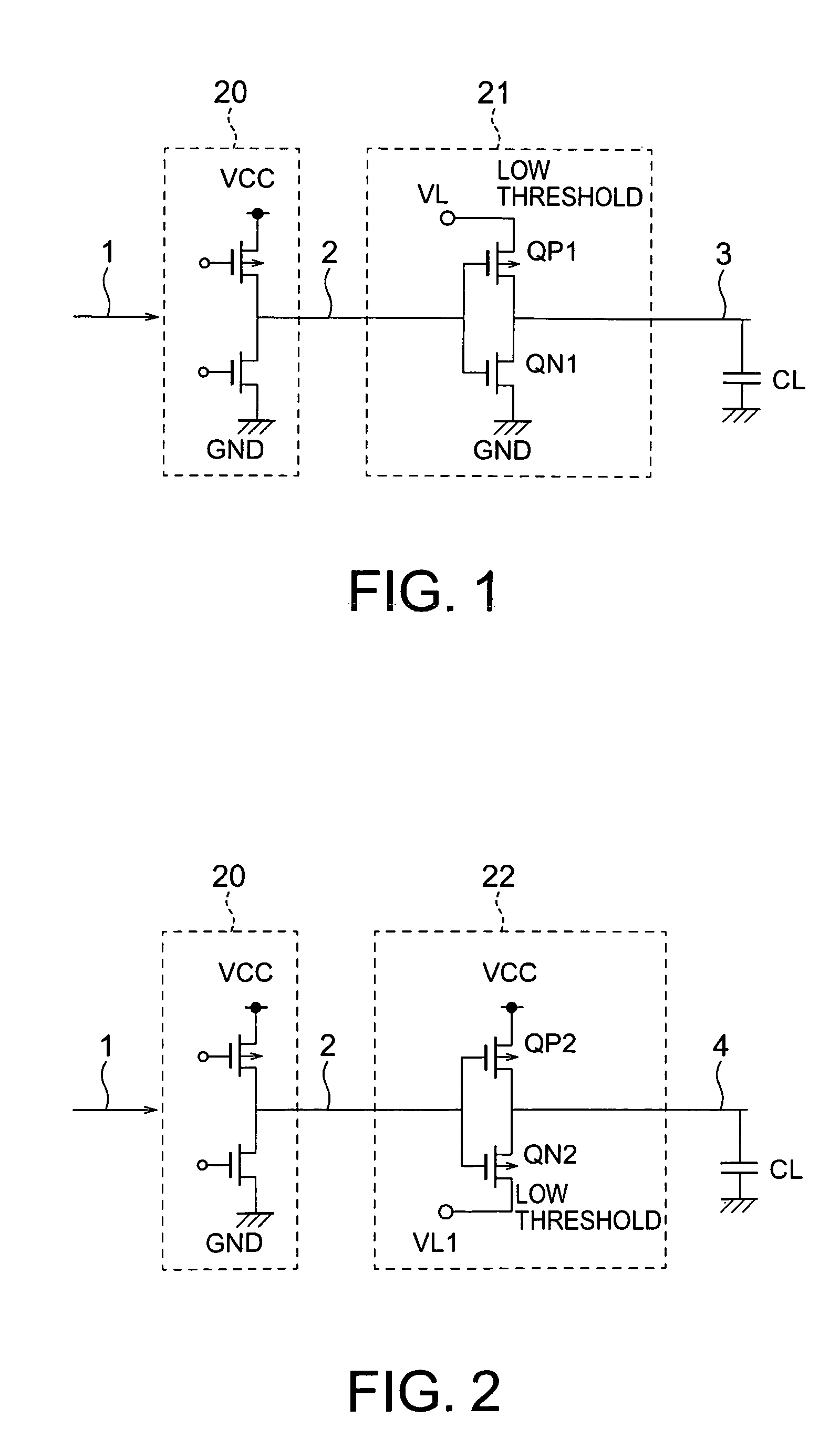

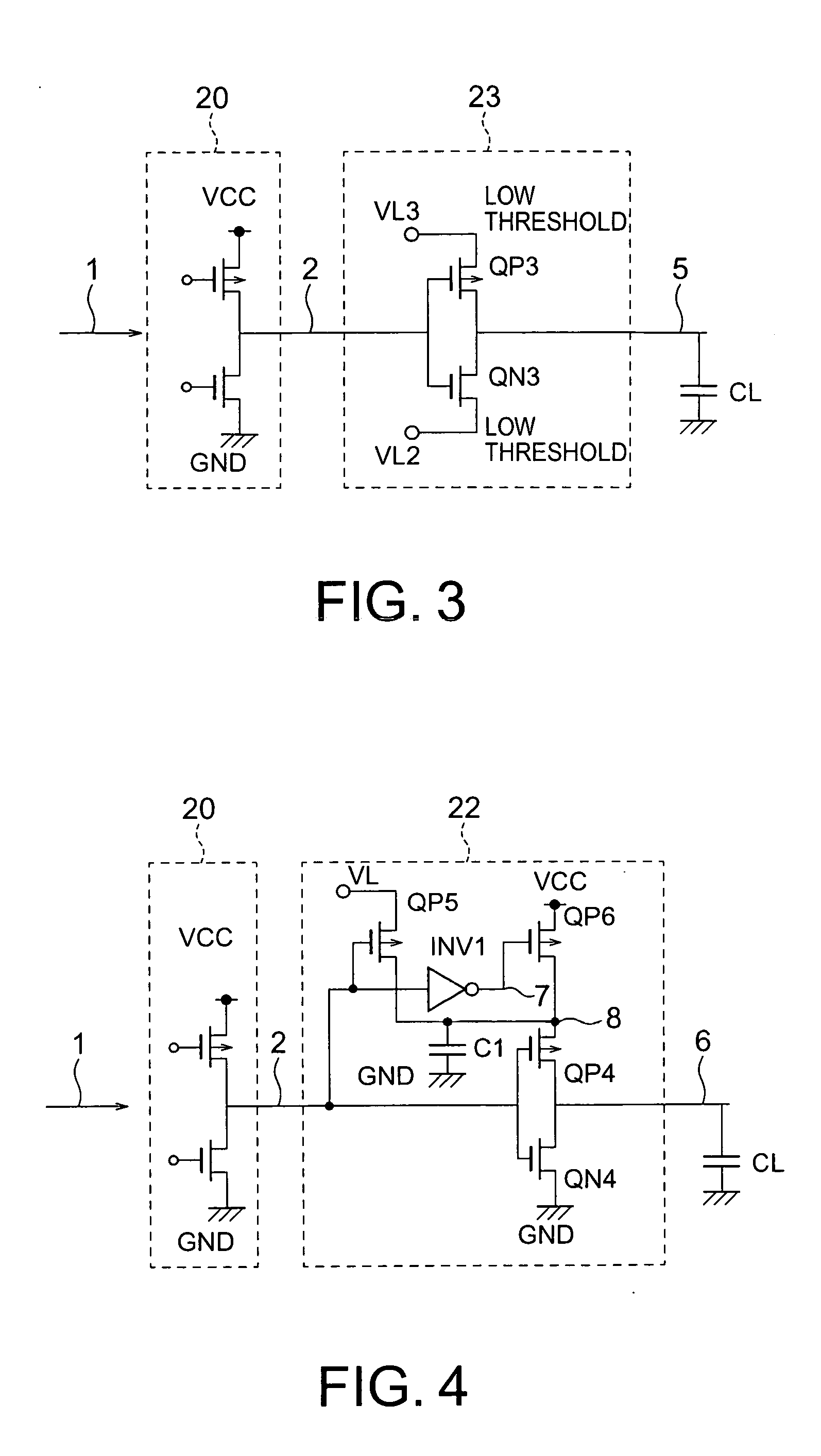

Semiconductor circuit device

ActiveUS20050184759A1CurrentReduce leakage currentPower reduction in field effect transistorsSwitching accelaration modificationsVoltage amplitudeLow voltage

The present invention relates to a semiconductor circuit device including a logic circuit and a signal line driving circuit. The logic circuit is operated at high supply voltage and outputs a signal with a high voltage amplitude. The signal line driving circuit receives a lower supply voltage and has a low-threshold transistor. With the above configuration, a signal can be transmitted at a high speed with a low voltage amplitude and low power consumption. Thus, the semiconductor circuit device including the signal line driving circuit can reduce operating current and can be operated with a low amplitude and low standby current at a high speed.

Owner:LONGITUDE LICENSING LTD

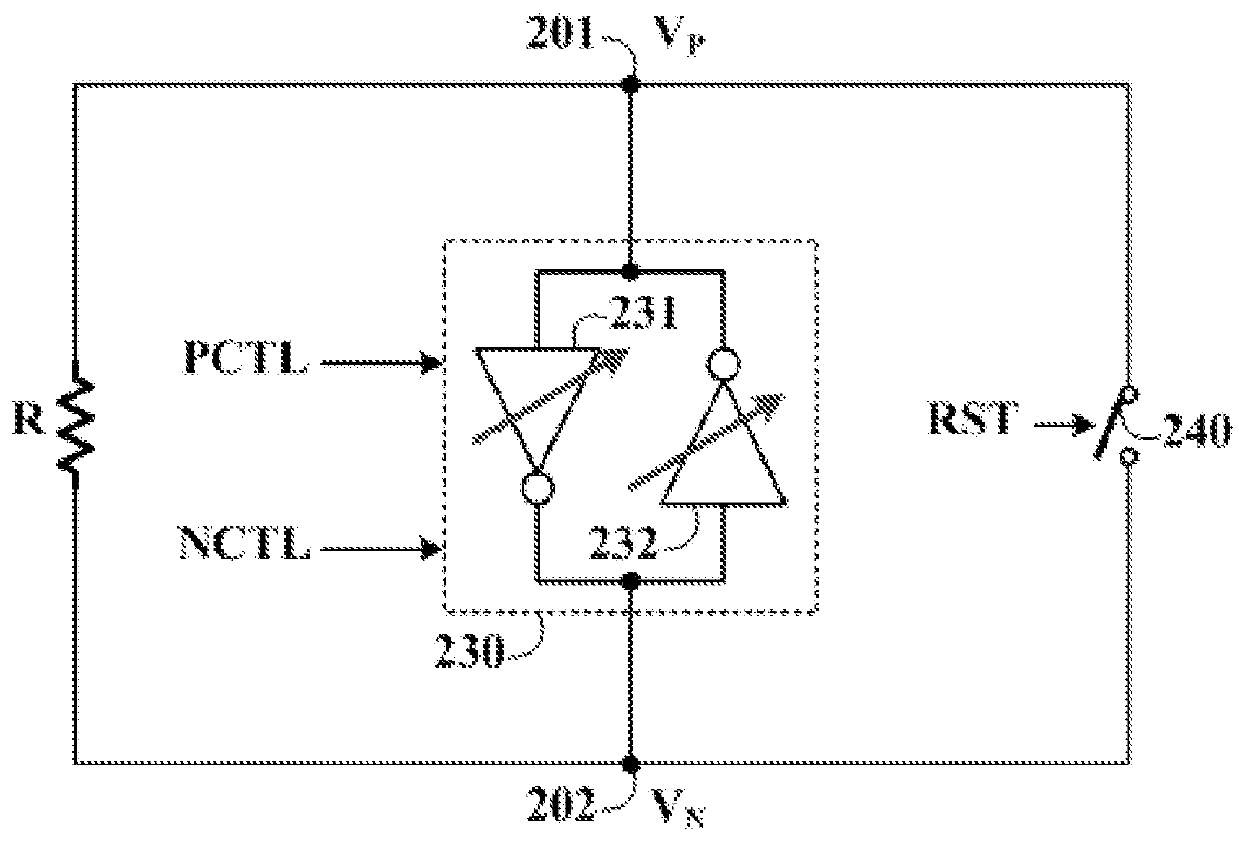

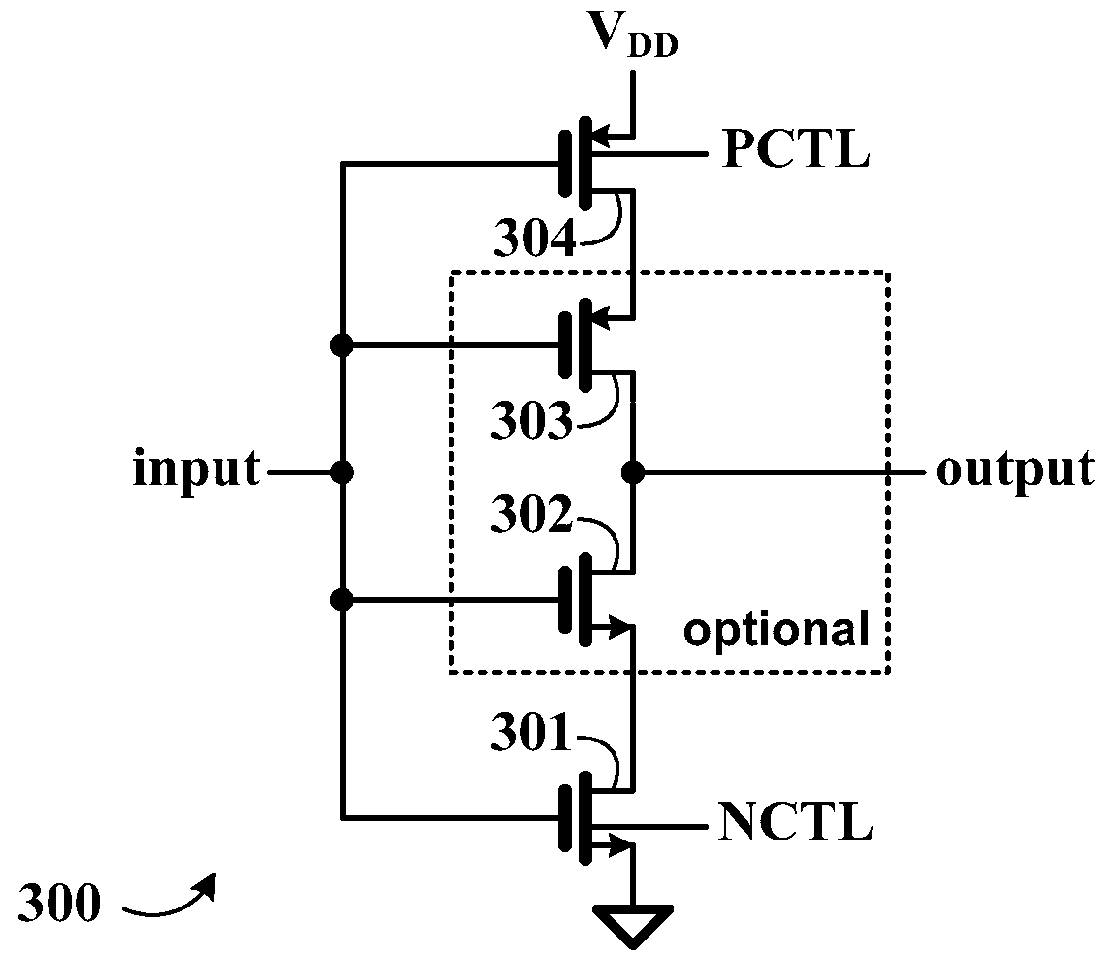

Method and apparatus for calibrating CMOS inverter

ActiveUS20160036419A1Correct offsetThreshold modification in field effect transistorsPulse generation by gas-filled tubesPower inverterCMOS

A circuit and method for calibrating CMOS (complementary metal-oxide semiconductor) inverters are provided. In a circuit, a first tunable CMOS inverter, controlled by a control signal, receives a first voltage from a first circuit node and outputs a second voltage to a second circuit node. A second tunable CMOS inverter, controlled by the control signal, receives the second voltage from the second circuit node and outputs the first voltage to the first circuit node. A resistor couples the first circuit node to the second circuit node. A switch, controlled by a reset signal, conditionally shorts the first circuit node to the second circuit node. A finite state machine receives the first voltage and the second voltage and outputs the reset signal and the control signal, wherein the control signal is adjusted based on a difference between the first voltage and the second voltage.

Owner:REALTEK SEMICON CORP

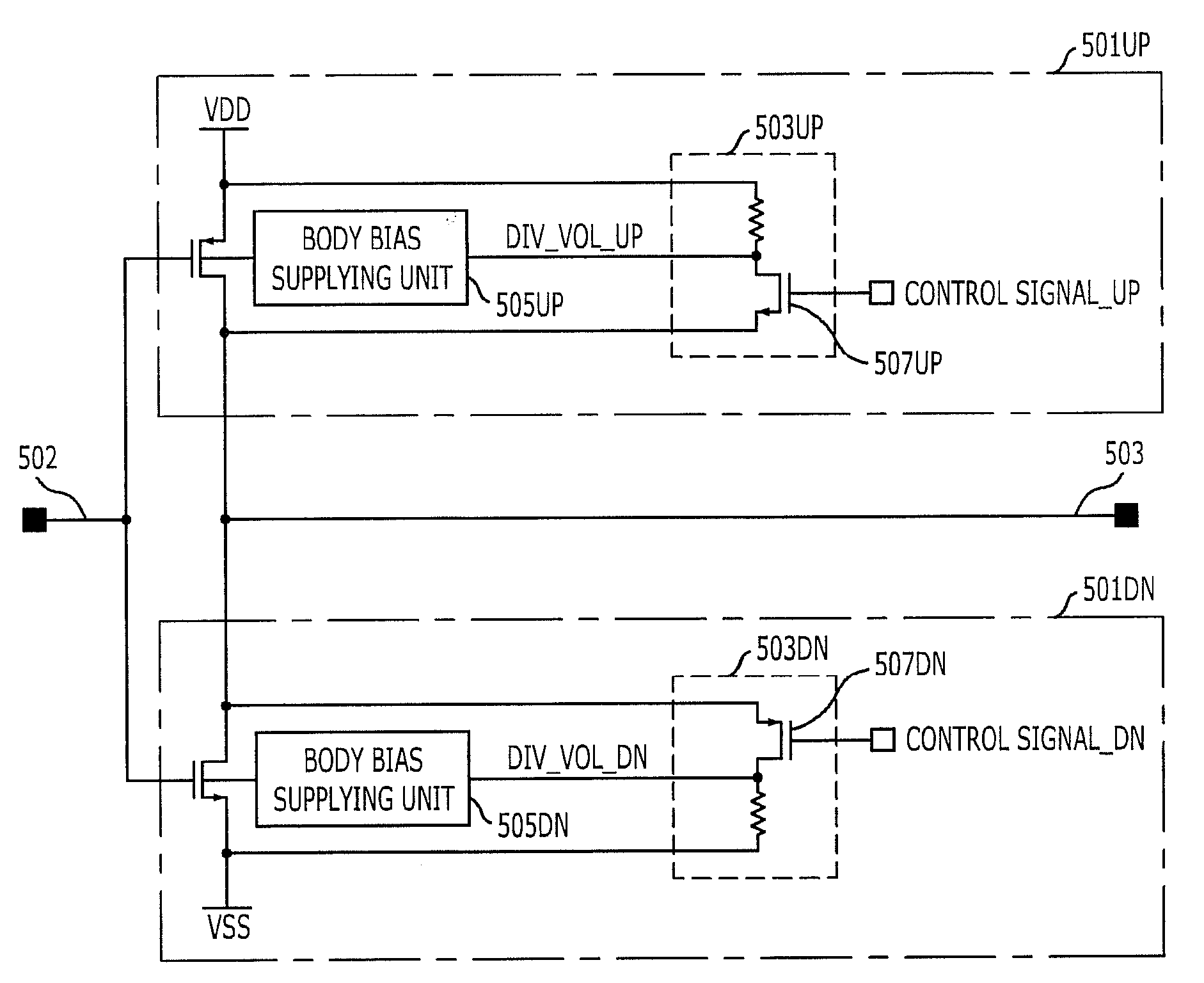

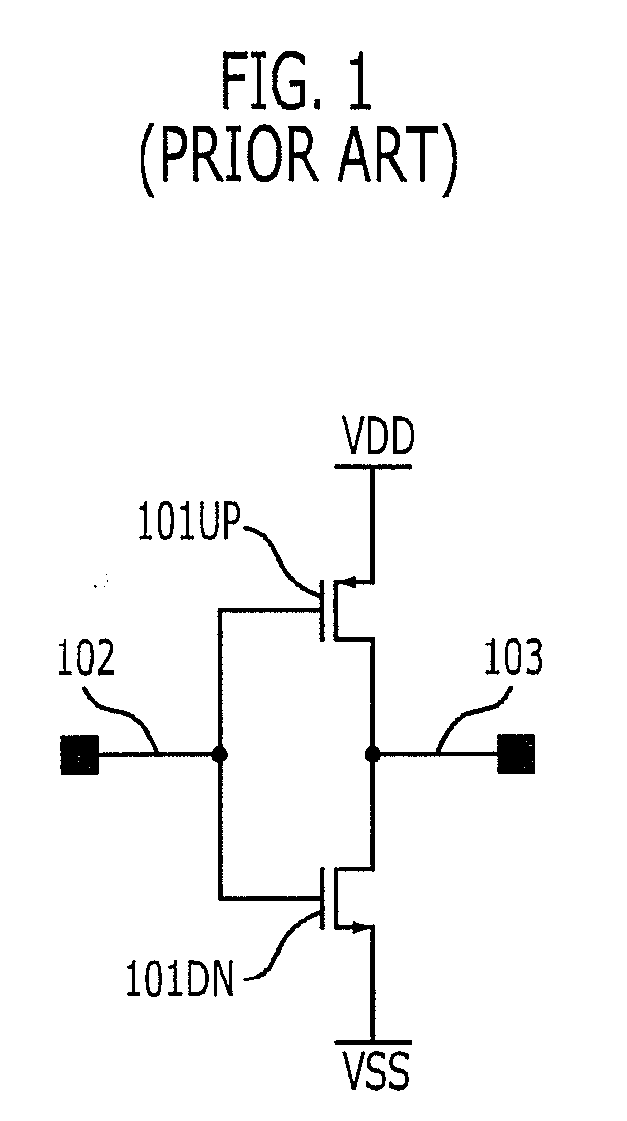

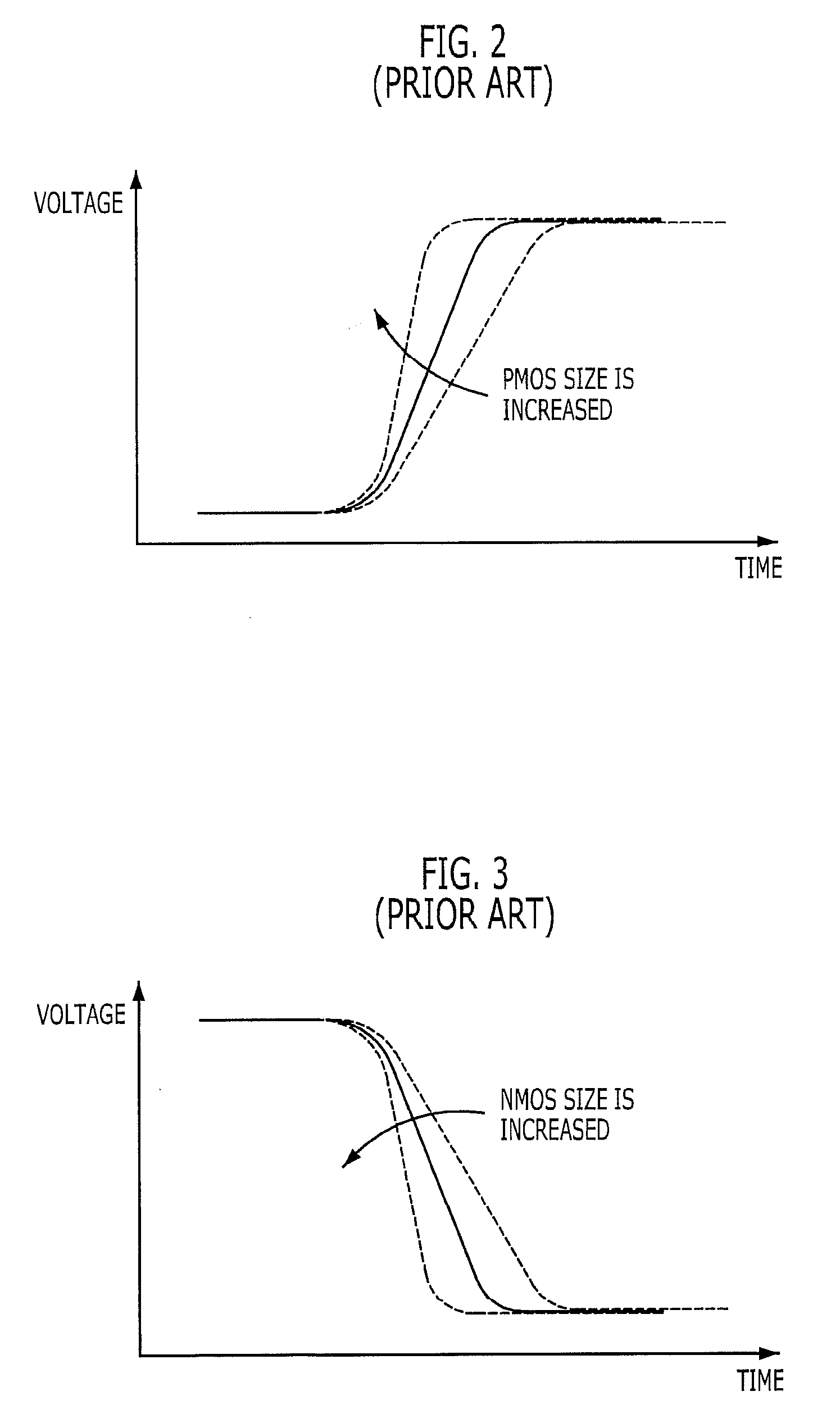

Output driving device

InactiveUS20090243667A1Threshold modification in field effect transistorsElectronic switchingPush pullSlew rate

An output driving device capable of improving a slew rate is provided. The output driving device includes a push-pull type driving unit configured with a pull-up PMOS transistor and a pull-down NMOS transistor, wherein body biases of the pull-up PMOS transistor and the pull-down NMOS transistor are controlled for control of a slew rate of an output signal of the driving unit.

Owner:SK HYNIX INC

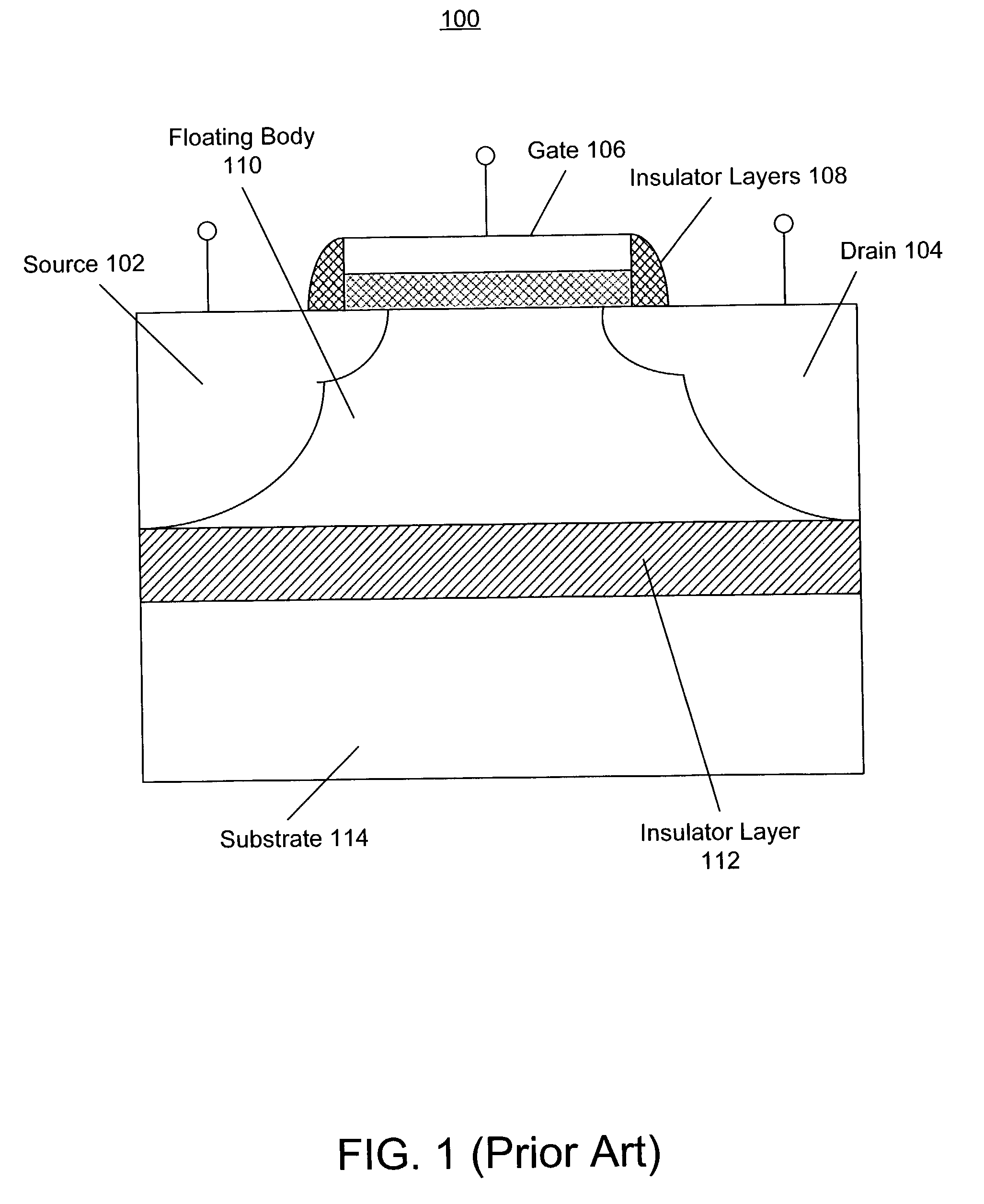

Emulation of long delay chain by ring oscillator with floating body-tied body devices

InactiveUS7205825B2Reduce in quantityAccurate measurementTransistorThreshold modification in field effect transistorsP channelCapacitor

A method and apparatus for reducing the number of stages for measuring first and second switching speeds for PD / SOI transistors uses an inverter circuit which includes: a p-channel body-tied transistor; an n-channel body-tied transistor, coupled at their drains and gates; and a first and a second group of components tied to the bodies of the transistors. The first group restores body potentials for the transistors if the inverter circuit belongs to an even numbered stage of a ring oscillator. The second group provides body potentials for the transistors if the inverter circuit belongs to an odd numbered stage. After each transition of a waveform, the body potentials for the PD / SOI transistors are restored to the original potentials as stored in the capacitors. In this manner, a much smaller ring oscillator with fewer number of stages may be used to accurately measure the first and second switching speeds.

Owner:GLOBALFOUNDRIES INC

Input buffer structure with single gate oxide

InactiveUS20050270079A1Pulse automatic controlInstant pulse delivery arrangementsLow voltage circuitsLevel shifting

Owner:TAIWAN SEMICON MFG CO LTD

Resistance load source follower circuit

InactiveUS20050007182A1Eliminate gapsTransistorInstant pulse delivery arrangementsElectrical resistance and conductanceBack bias

A complementary source follower circuit has an N-channel type transistor and a P-channel transistor. The threshold voltage of each transistor is independently controlled by a back bias voltage control circuit so that the input voltage and the output voltage relationship can be made linear without the use of an additional circuit such as a level shifting circuit. Also, power consumption can be reduced when the circuit is in standby mode by using the back bias voltage control circuit to achieve non-linearity. A back bias voltage control circuit can also be used to control the threshold voltage of a transistor in series with a resistance load to reduce power usage.

Owner:RPX CORP

Impedance-matched output driver circuits having enhanced predriver control

ActiveUS7053661B1Degree of improvementImprove linearityInput/output impedence modificationReliability increasing modificationsDriver circuitImage resolution

Impedance-matched output driver circuits utilize predriver circuits with analog control to provide enhanced operating characteristics. This analog control may be provided by an analog loop containing differential amplifiers that set the resolution limit of the output driver circuit. These output driver circuits include a first PMOS pull-up transistor having source and drain terminals electrically connected in series in a pull-up path of the output driver circuit. An NMOS pass transistor has a first current carrying terminal electrically connected to a gate terminal of the first PMOS pull-up transistor and a second current carrying terminal configured to receive a P-type analog reference voltage (VP). This P-type reference voltage controls the conductivity of the first PMOS pull-up transistor in the pull-up path. A gate terminal of the NMOS pass transistor is responsive to a pull-up data input signal (DINP). A first NMOS pull-down transistor has source and drain terminals that are electrically connected in series in a pull-down path of the output driver circuit. A PMOS pass transistor is provided having a first current carrying terminal electrically connected to a gate terminal of the first NMOS pull-down transistor and a second current carrying terminal configured to receive an N-type analog reference voltage (VN). This N-type reference voltage controls the conductivity of the first NMOS pull-down transistor in the pull-down path. A gate terminal of the PMOS pass transistor is responsive to a pull-down data input signal (DINN).

Owner:INTEGRATED DEVICE TECH INC

Popular searches

Digital storage Reliability increase in field effect transistors Semiconductor lamp usage Semiconductor devices Electric variable regulation Electric pulse generator Logic circuits using elementary logic circuit components Voltage/current interference elimination Logic circuit coupling/interface arrangements Computation using denominational number representation