Patents

Literature

162results about How to "Big screen" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

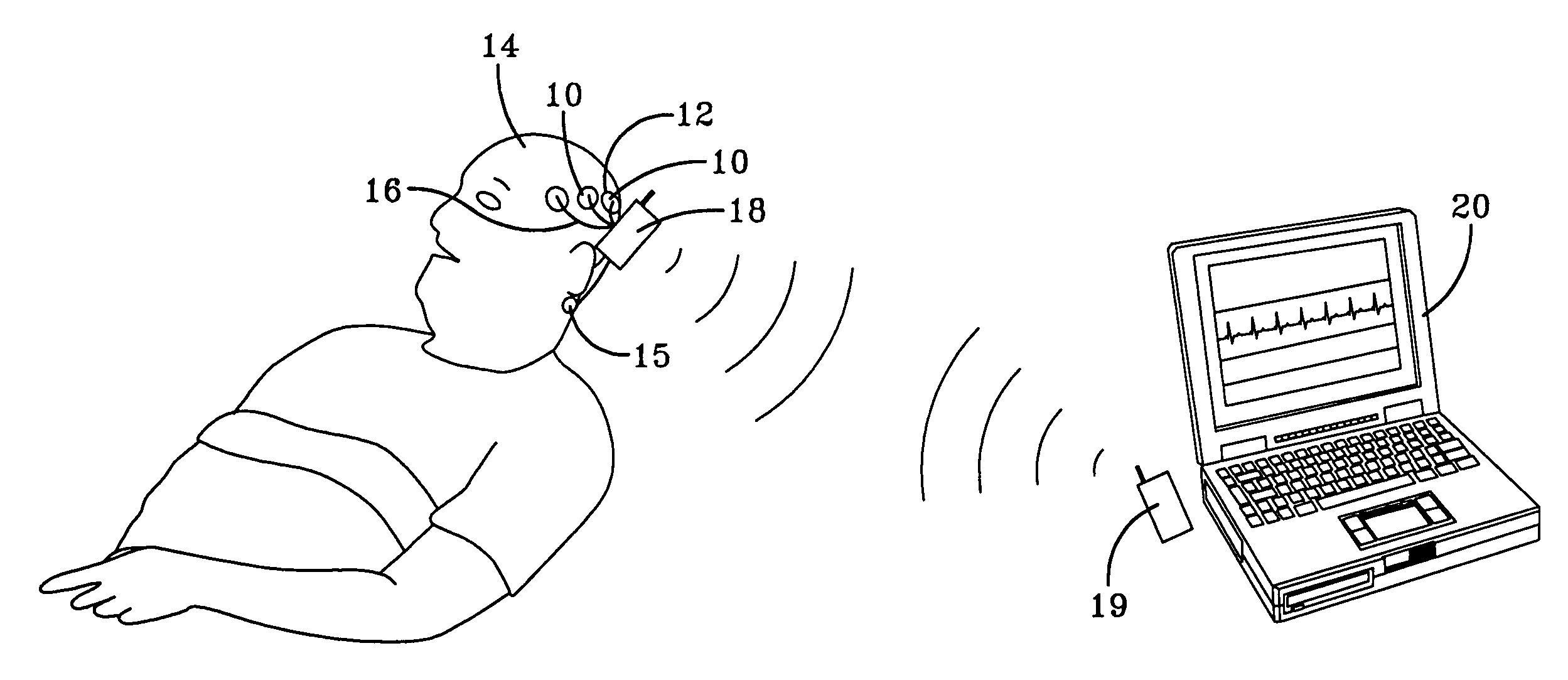

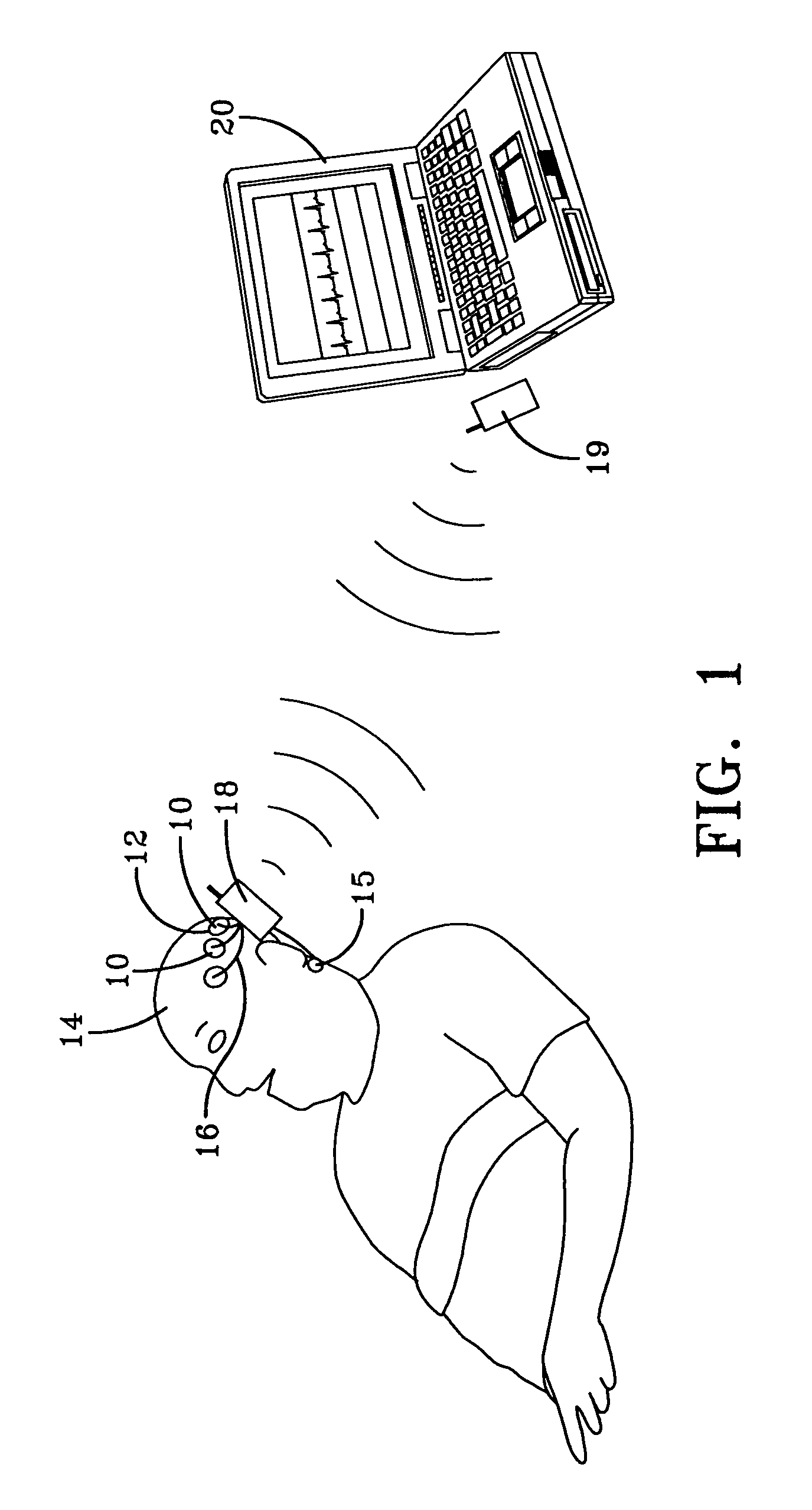

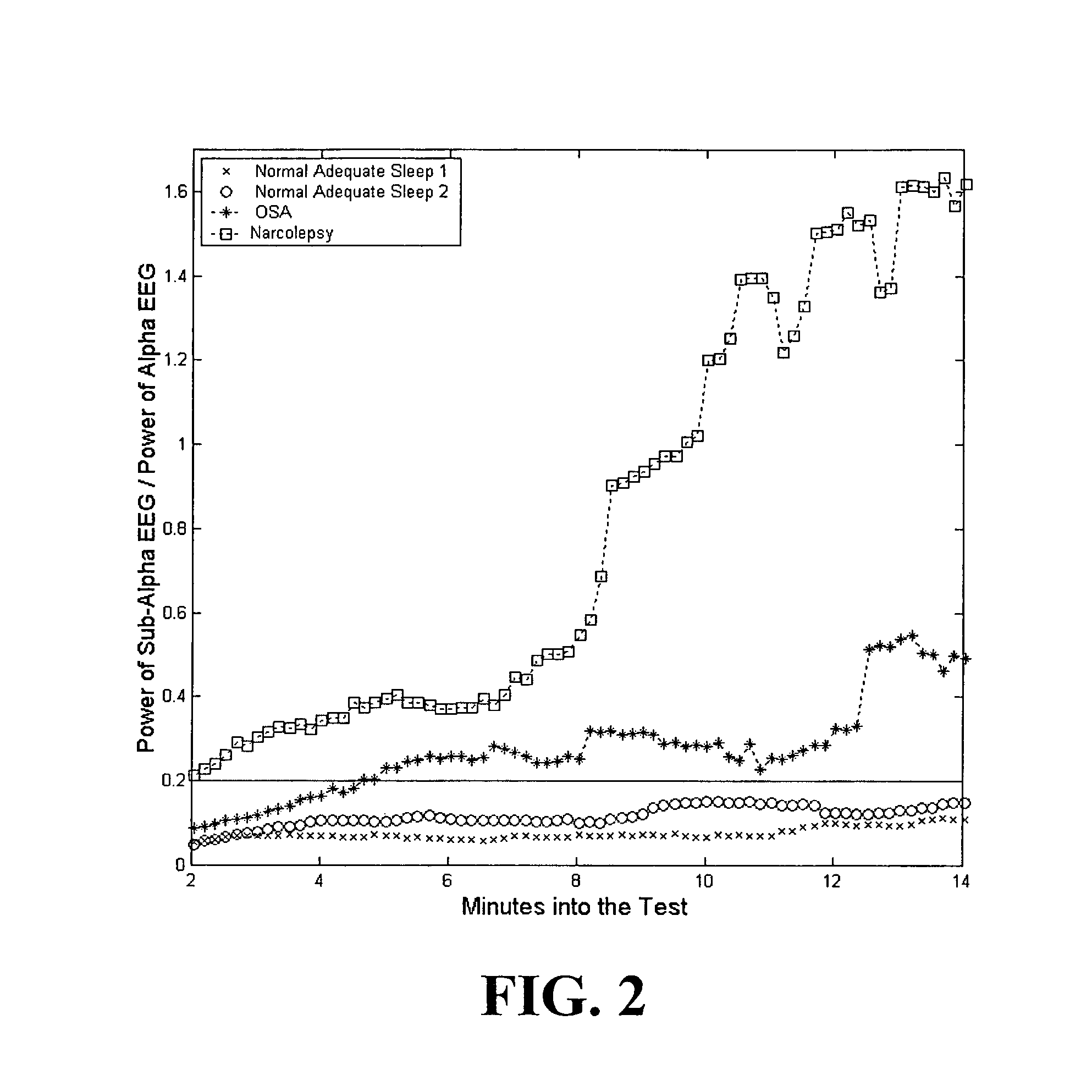

Quantitative sleep analysis method and system

InactiveUS6993380B1Sure easyLow costElectroencephalographySensorsExcessive daytime sleepinessStimulant

The present invention relates to a method of analyzing a subject for excessive daytime sleepiness, and more particularly to a quick (short duration), quantitative method of sleep disorder analysis. The present invention additionally relates to a method, which can be used to quantitatively measure the treatment endpoints for the subject, i.e., appropriate levels of stimulants. Additionally, the present invention relates to a device for sleep disorder analysis.

Owner:CLEVELAND MEDICAL DEVICES

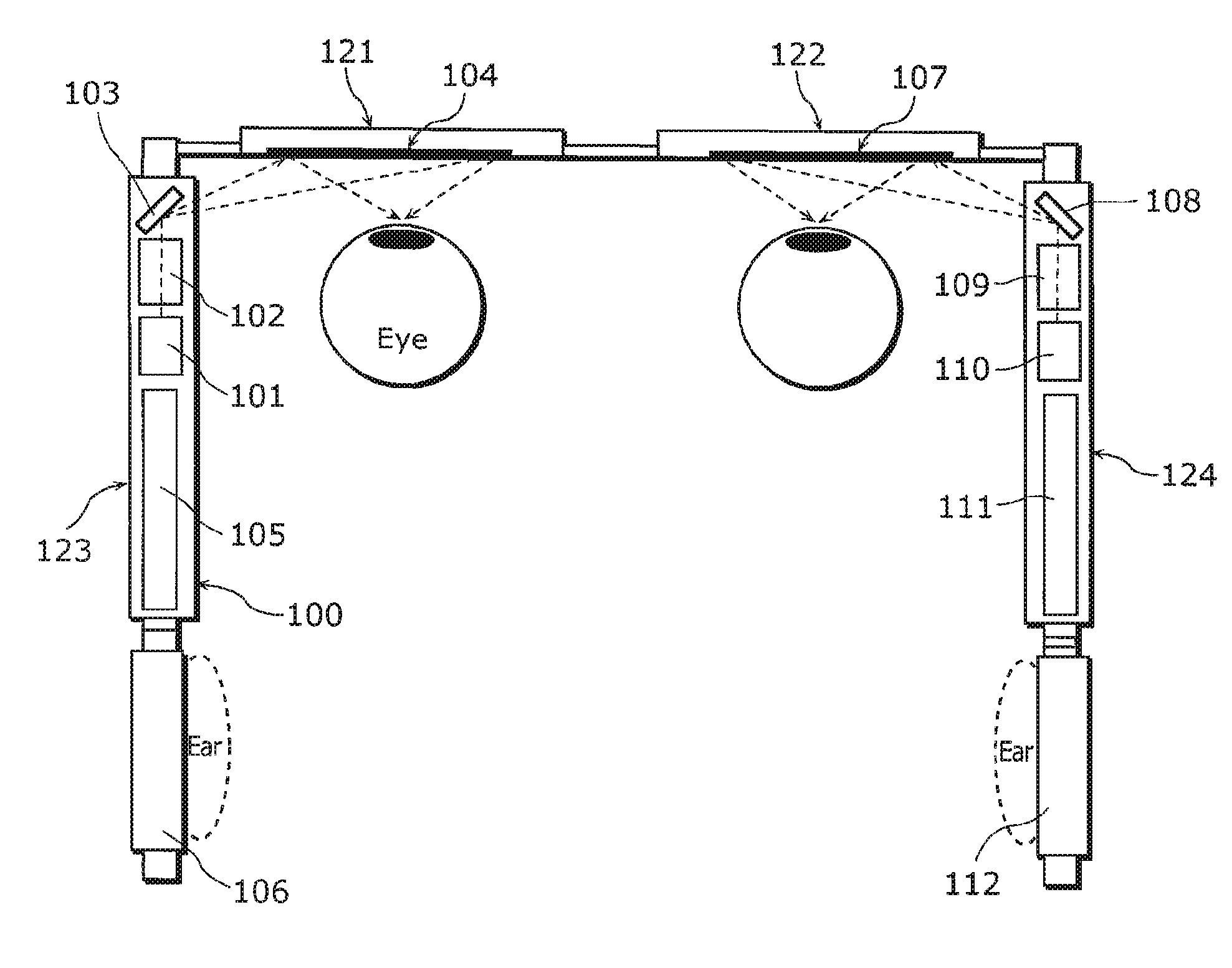

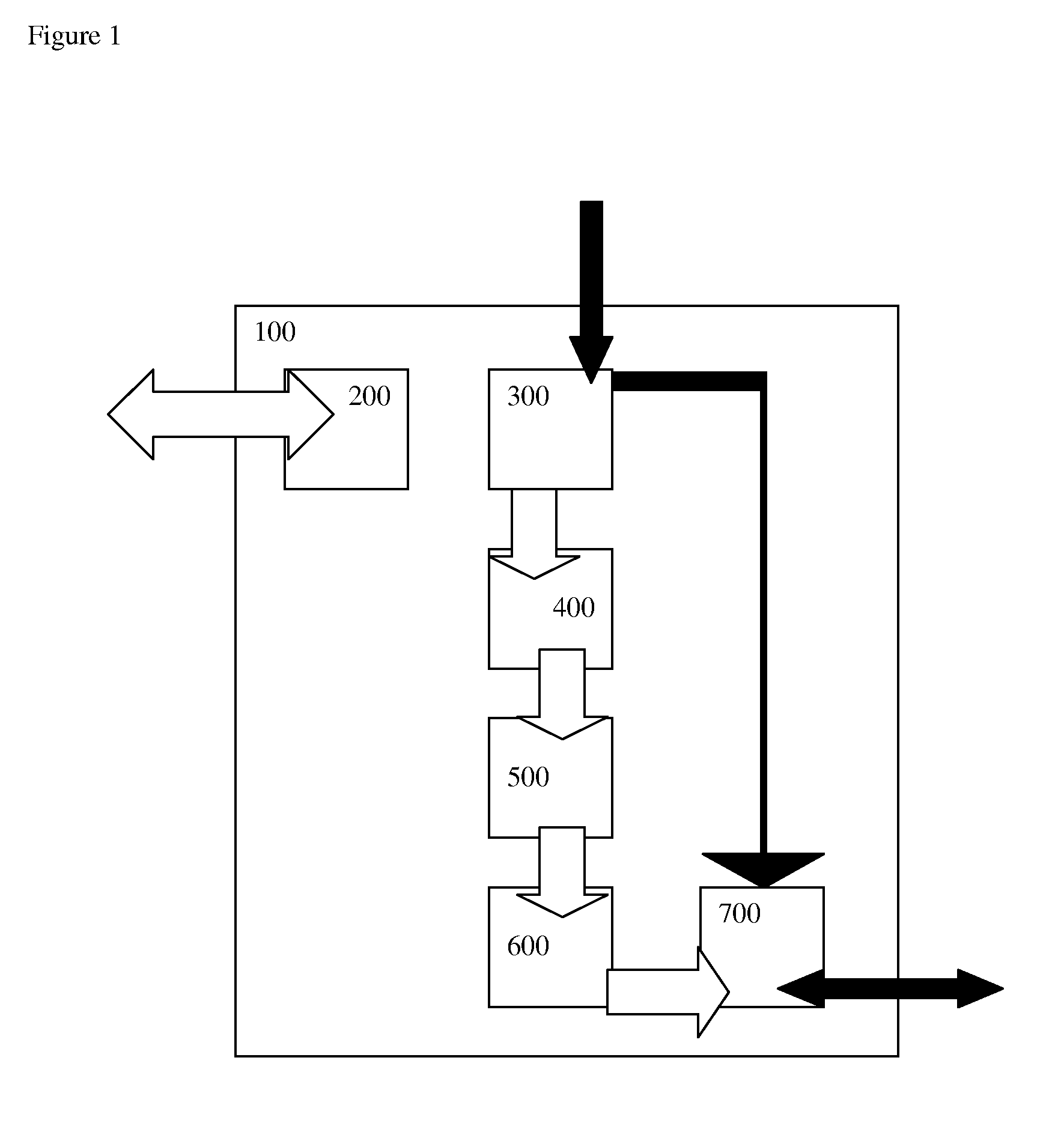

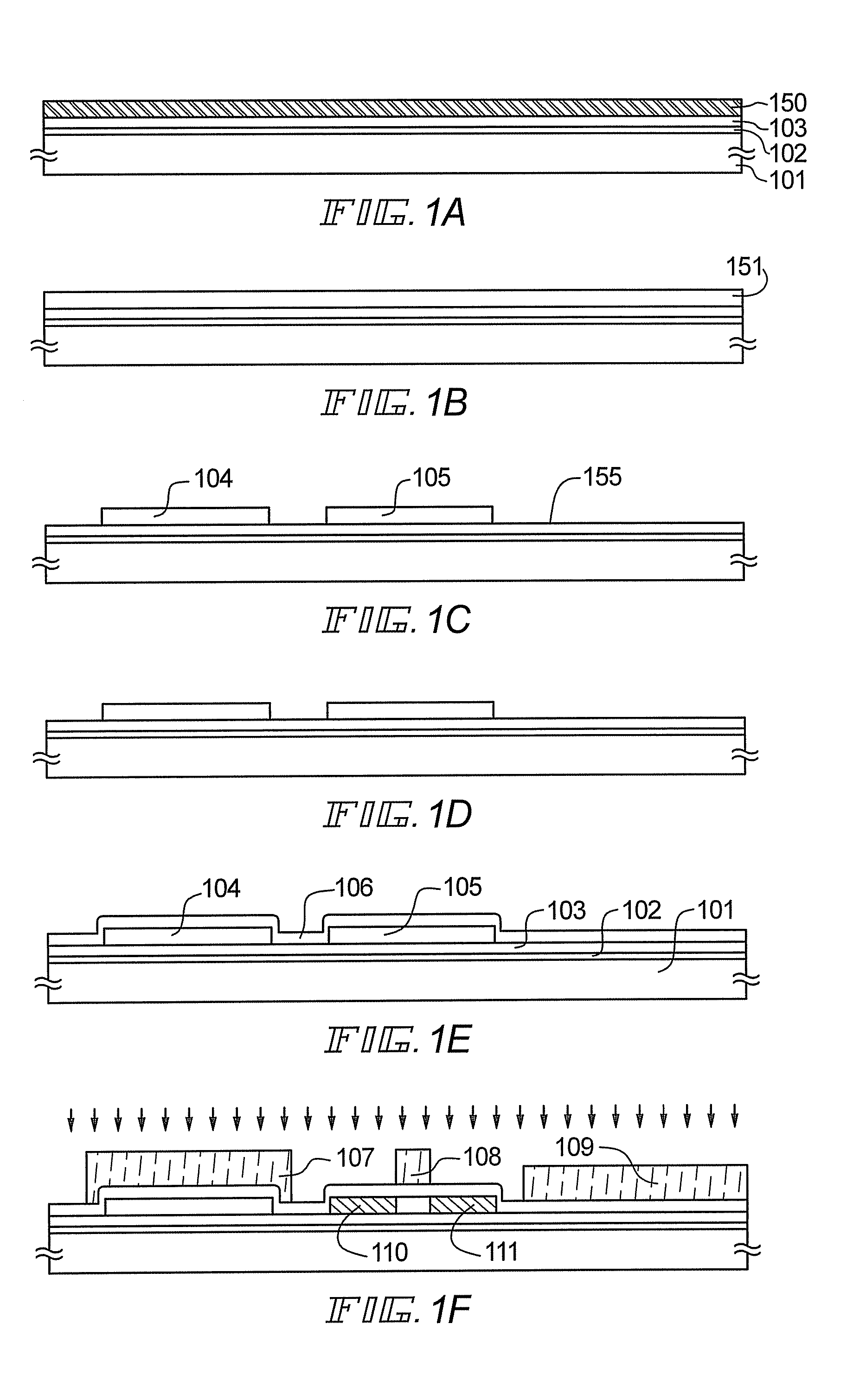

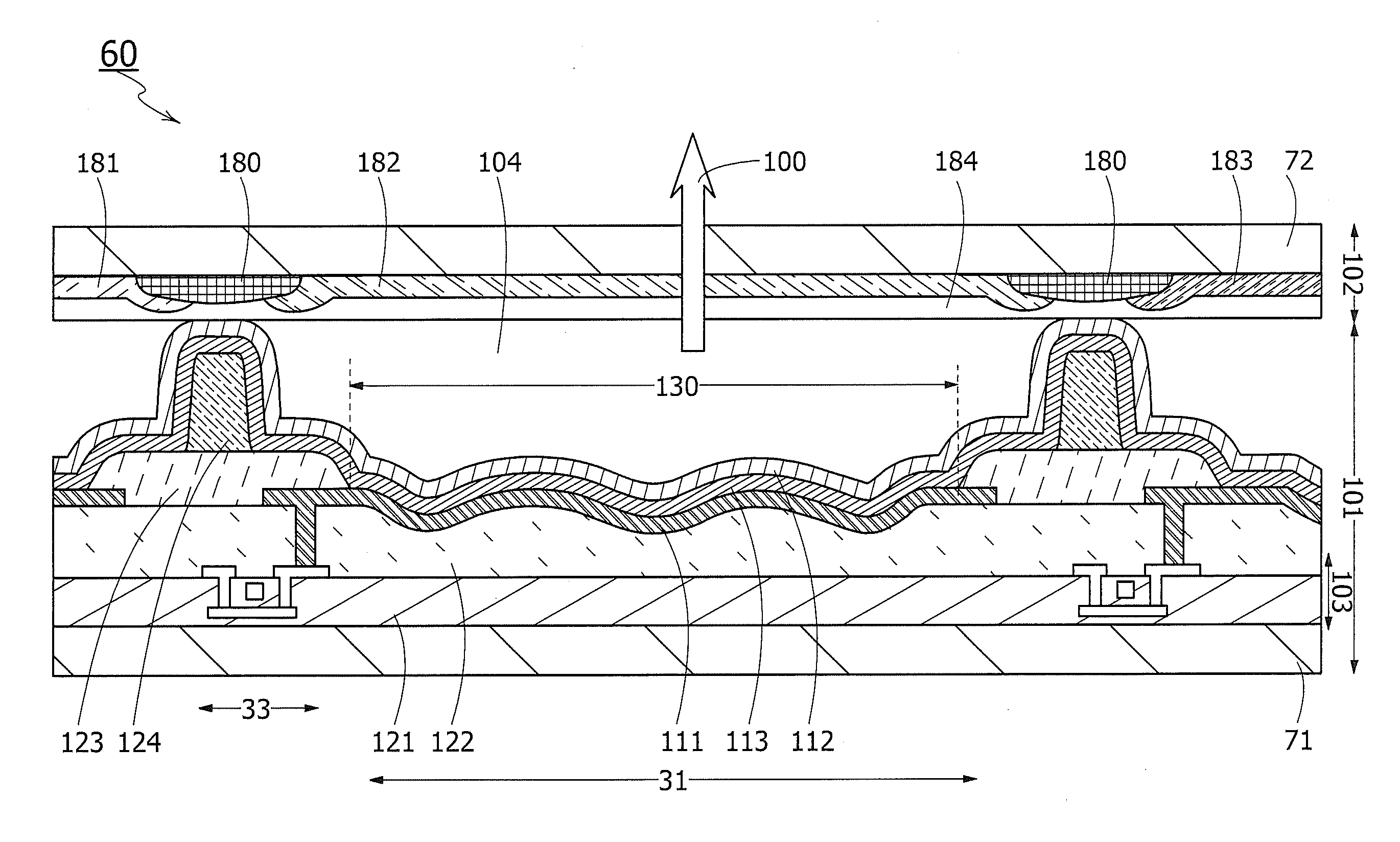

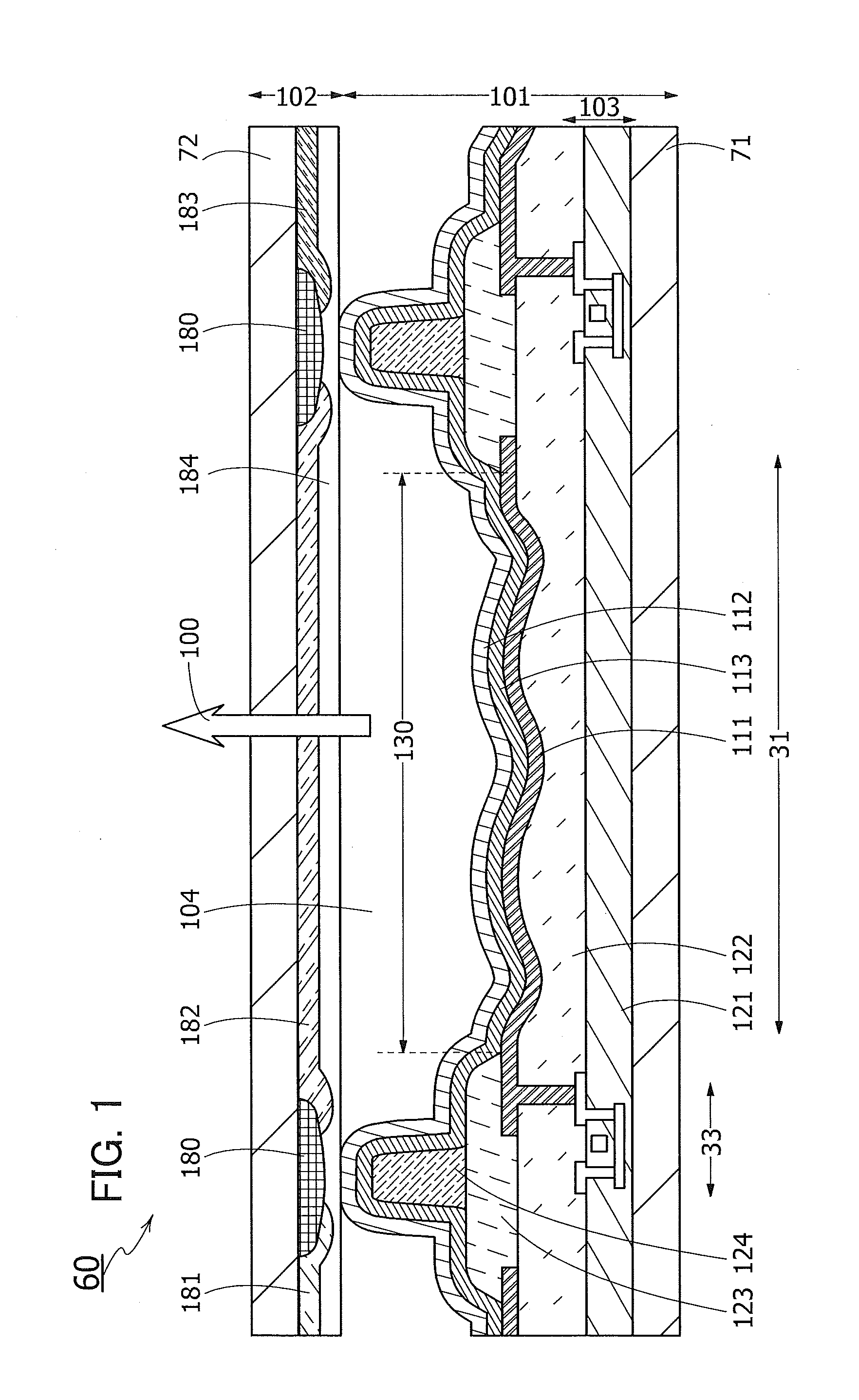

Display apparatus

ActiveUS20100097580A1Reduce problemLower efficiencyProjectorsCathode-ray tube indicatorsDistortionLight source

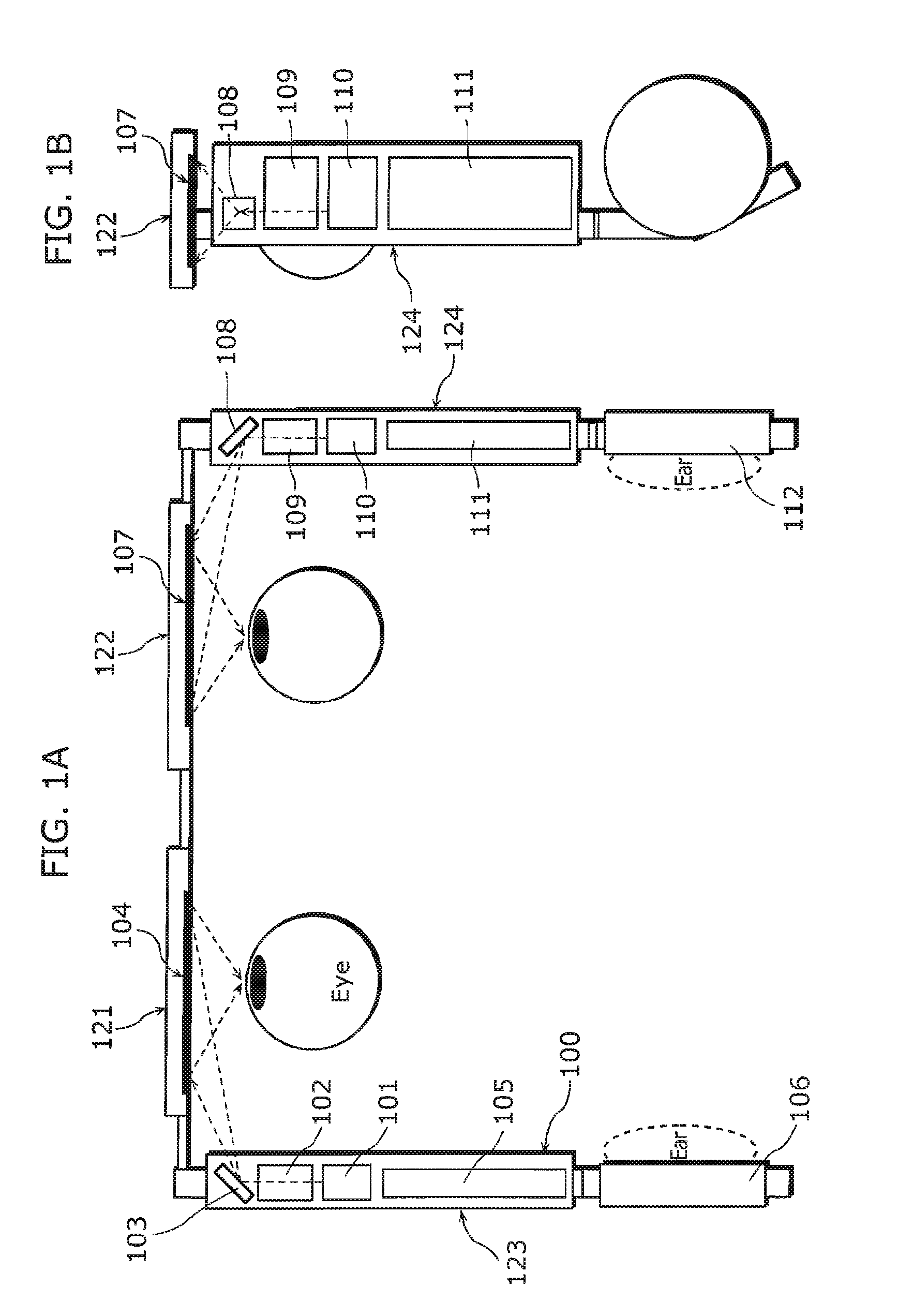

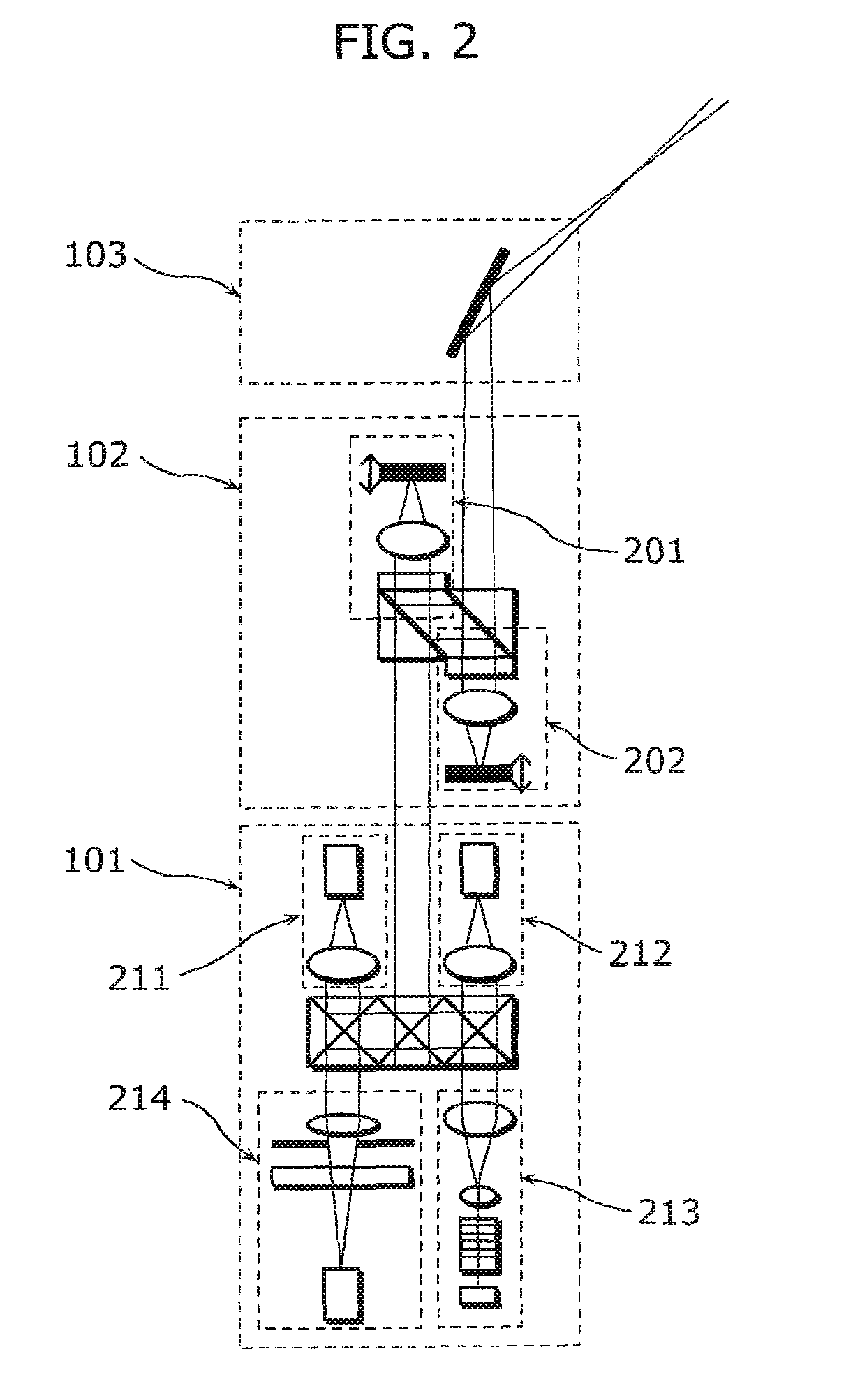

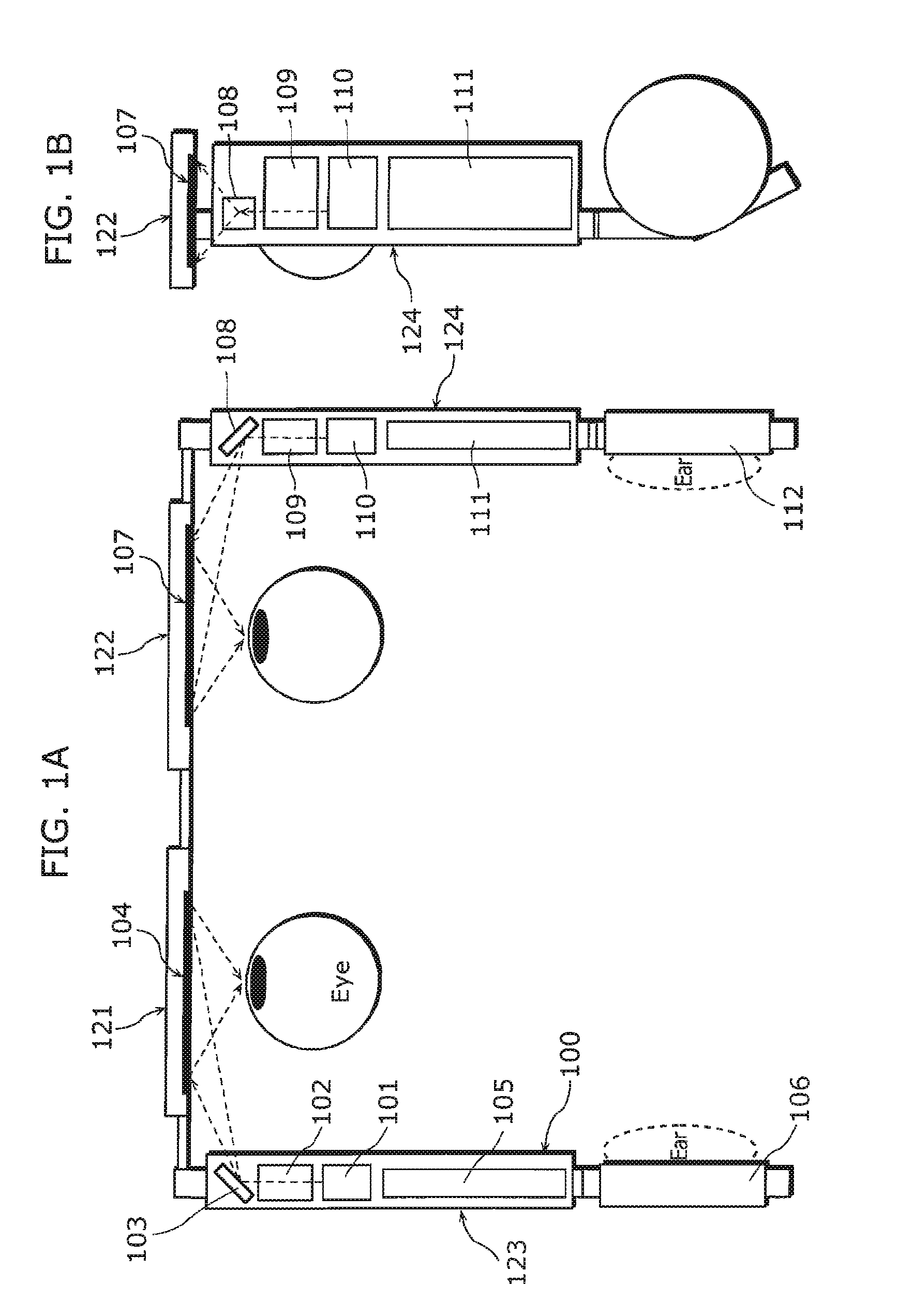

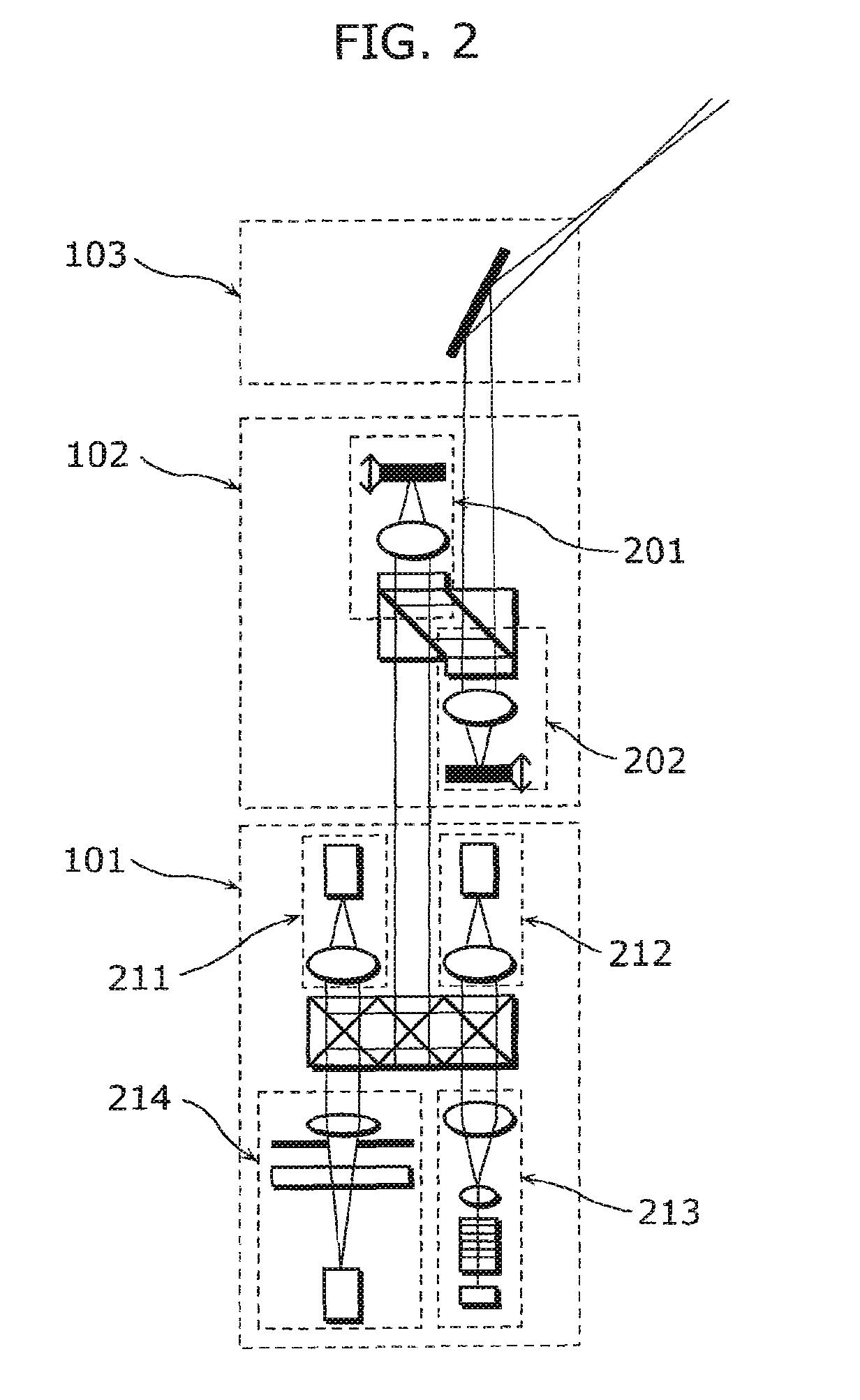

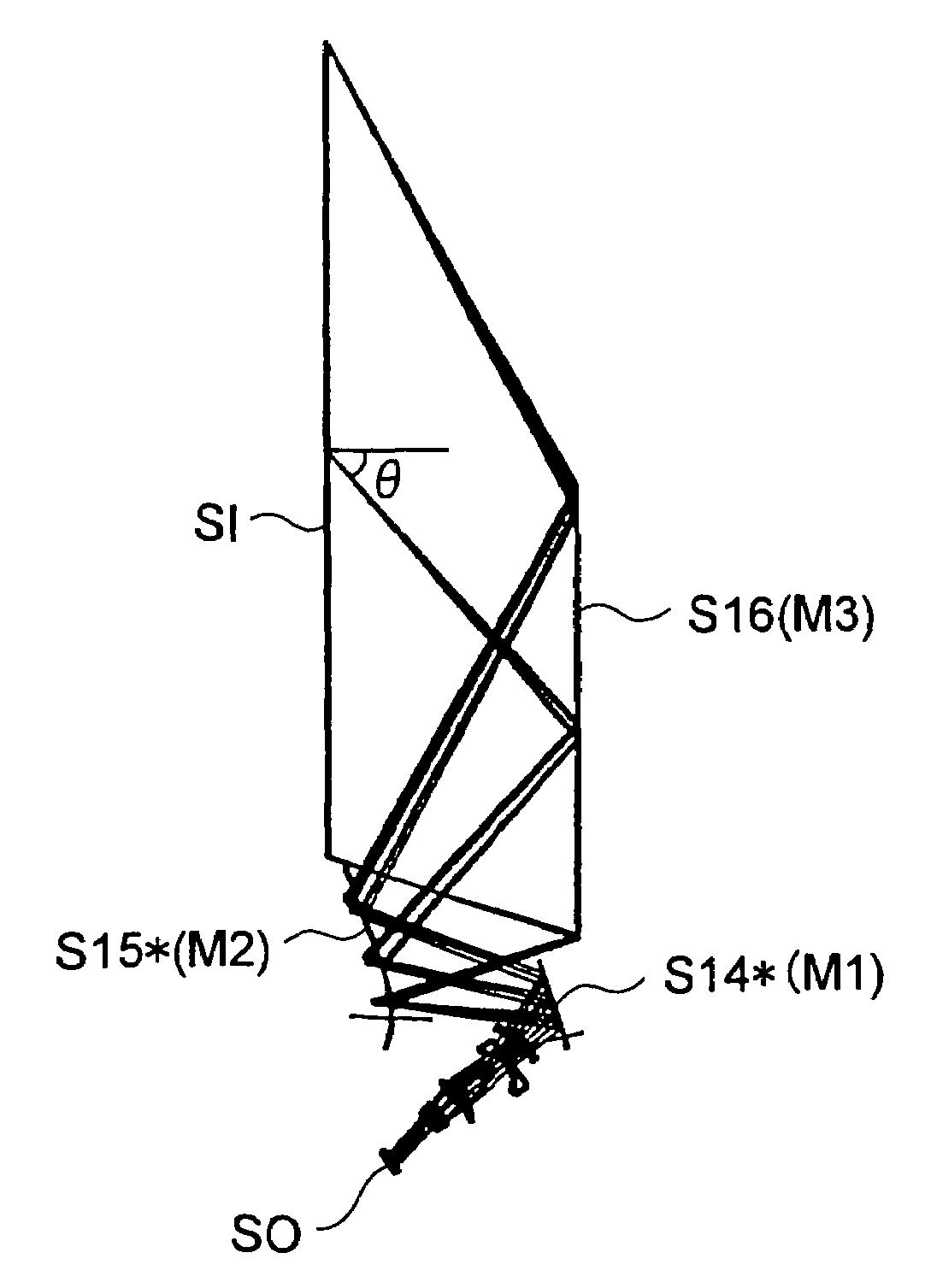

A display apparatus that displays an image on a retina of a user, the display apparatus comprising: an image output unit (100) which includes a light source (101, 110), a wavefront shape change unit (102, 109), and a scan unit (103, 108) and is configured to output display light for displaying the image; and a deflection unit (104, 107) configured to deflect, toward an eye of the user, the display light outputted by the image output unit (100). The deflection unit (104, 107) has a deflection characteristic of suppressing image distortion caused by a change in relative position of the deflection unit (104, 107) with respect to a pupil of the user.

Owner:PANASONIC CORP

Display apparatus

ActiveUS8246170B2Reduce decreaseLow efficiencyProjectorsCathode-ray tube indicatorsShape changePupil

A display apparatus that displays an image on a retina of a user, the display apparatus comprising: an image output unit (100) which includes a light source (101, 110), a wavefront shape change unit (102, 109), and a scan unit (103, 108) and is configured to output display light for displaying the image; and a deflection unit (104, 107) configured to deflect, toward an eye of the user, the display light outputted by the image output unit (100). The deflection unit (104, 107) has a deflection characteristic of suppressing image distortion caused by a change in relative position of the deflection unit (104, 107) with respect to a pupil of the user.

Owner:PANASONIC CORP

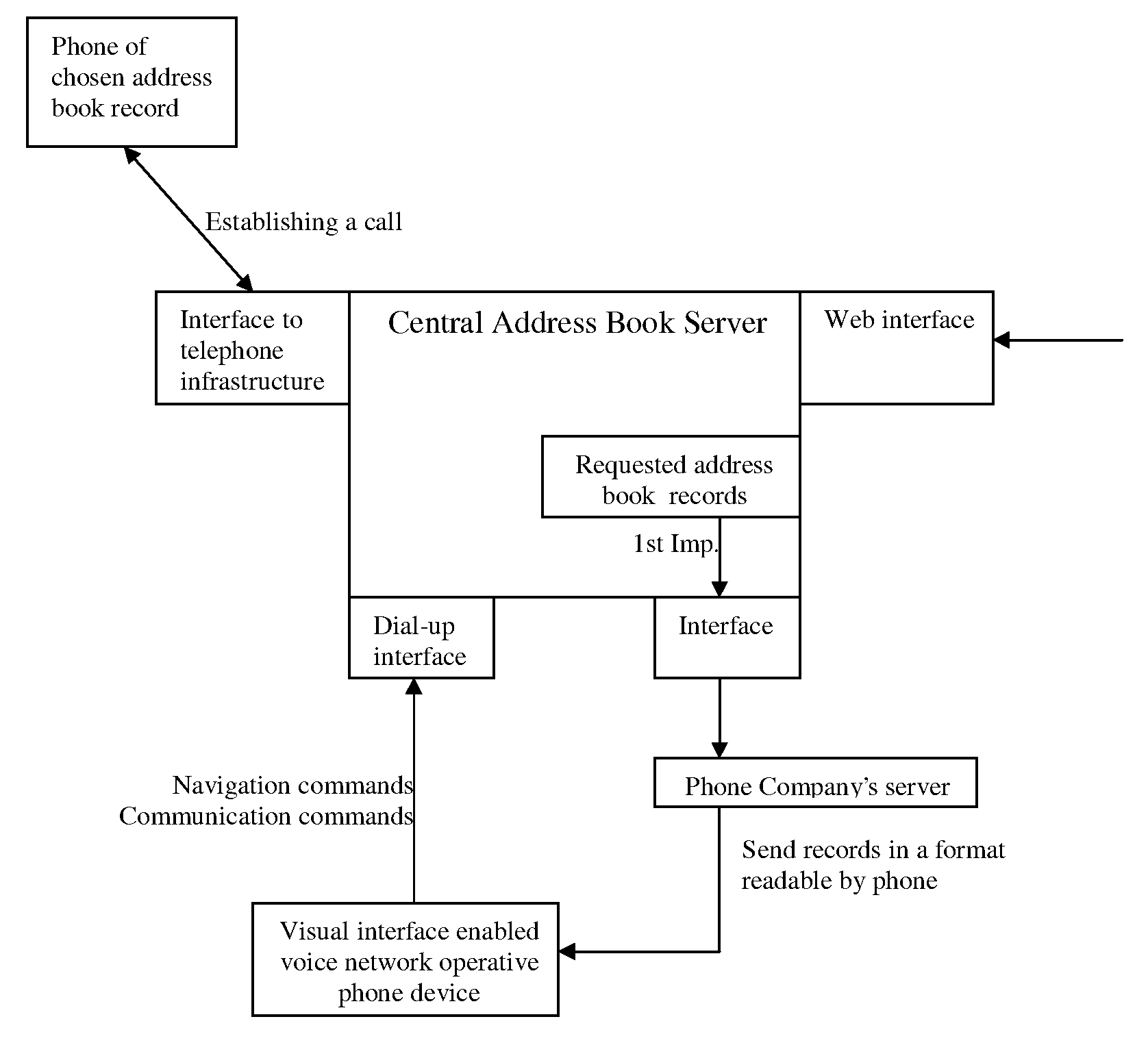

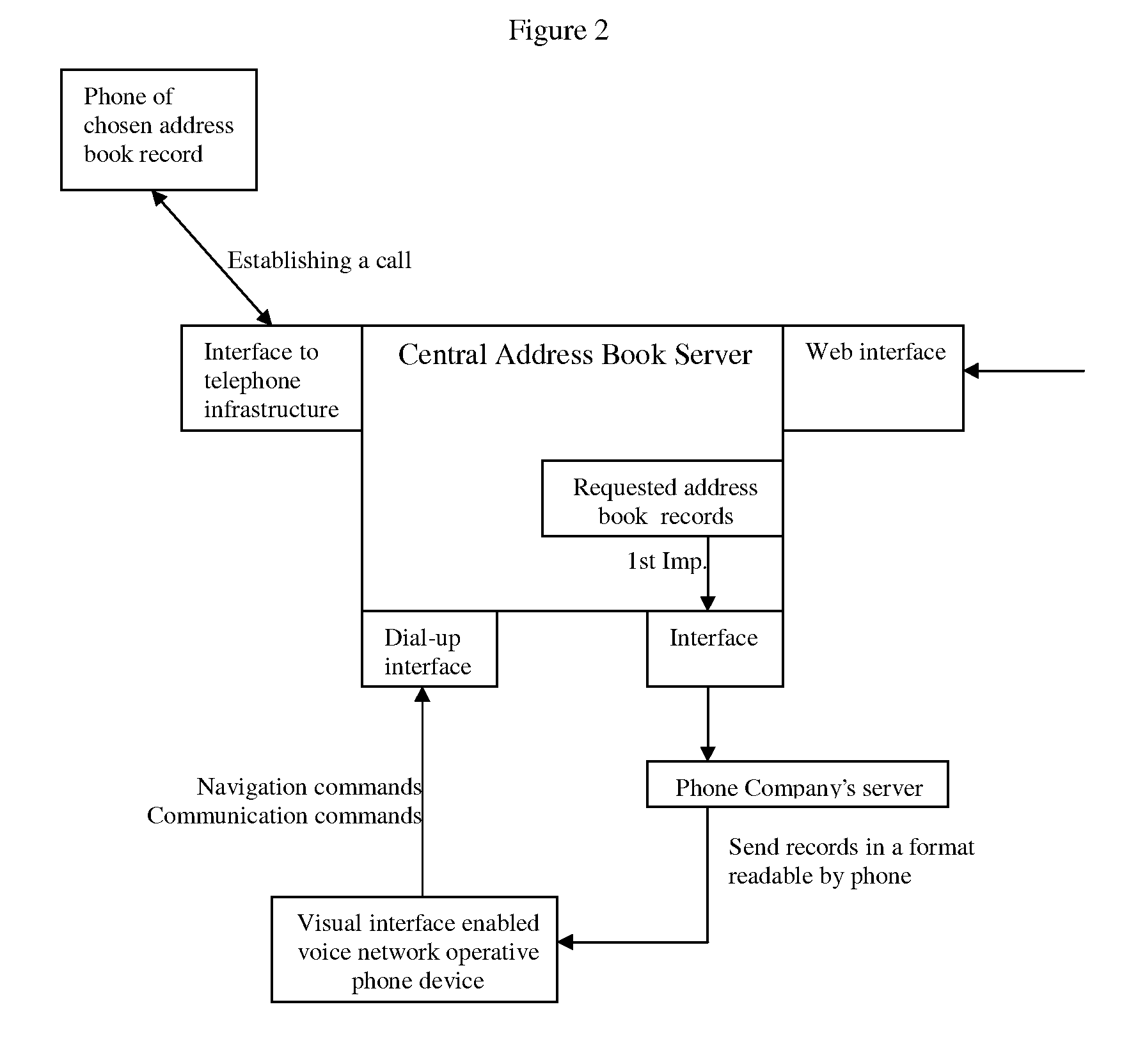

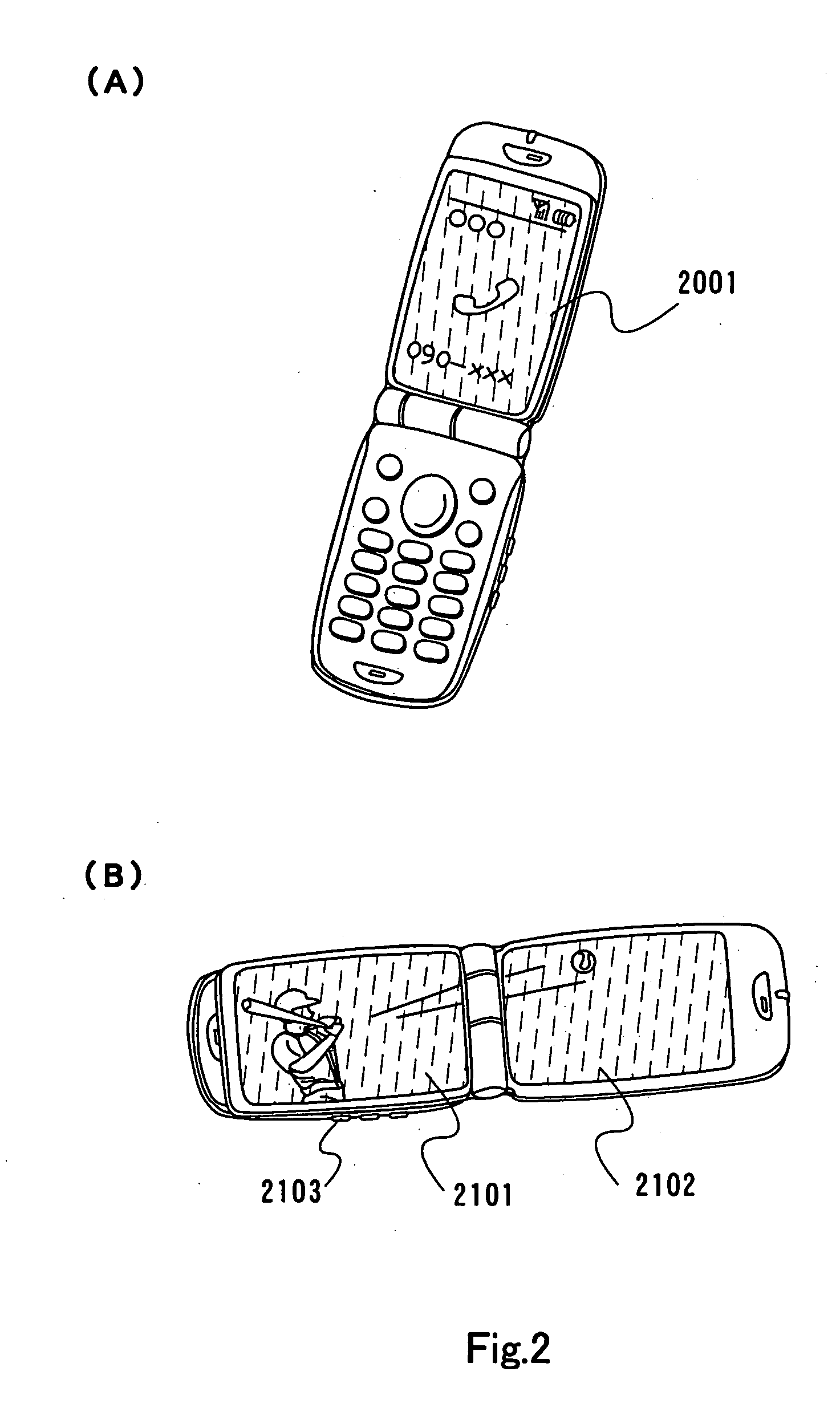

Method for Interacting Via an Internet Accessible Address-Book Using a Visual Interface Phone Device

InactiveUS20070280445A1Simplification for convenience-amongLeast expensiveTelephonic communicationNetwork connectionsEmail addressAddress book

From a visual-interface-enabled voice-network-operative telephone device, a user navigates an Internet based address-book, and upon finding a desired record in the address-book, the user will cause a server associated with the address-book to initiate a call or a message to a device associated with the electronic address stored in the record (e.g. telephone number, VOIP address, email address, etc.). This is done by the server (A) receiving access to an internet accessible address-book; (B) accepting a dial-up connection from a user, wherein the dial-up is from a visual-interface-enabled voice-network-operative telephone device; (C) receiving navigation commands from the device; (D) sending at least one portion of a record in the address-book to the device; and optionally thereafter accepting a communications command from the device relating to an electronic address sent by the server to the device to establish a voice connection with the address or to send a message to the address.

Owner:BROADPHONE

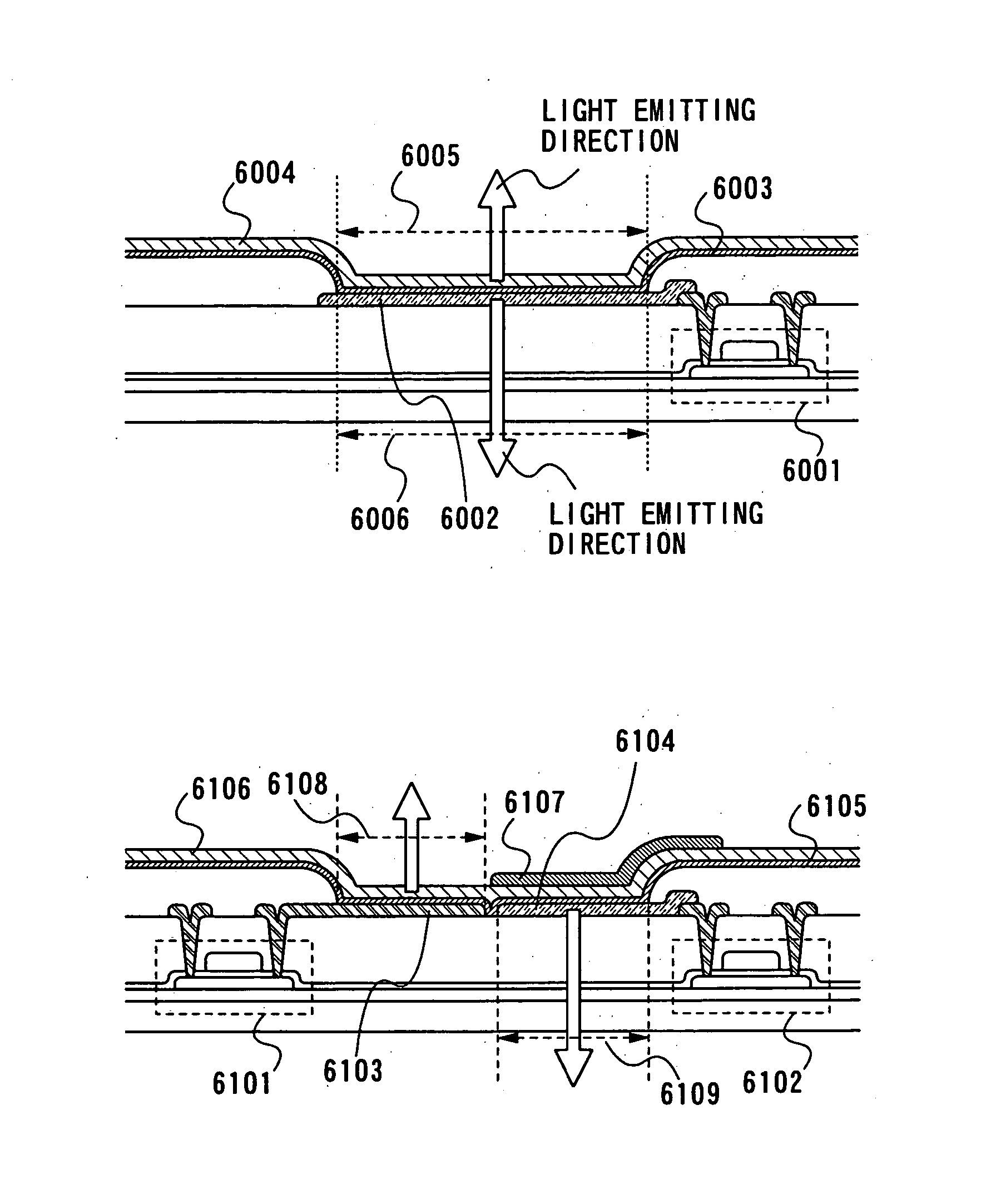

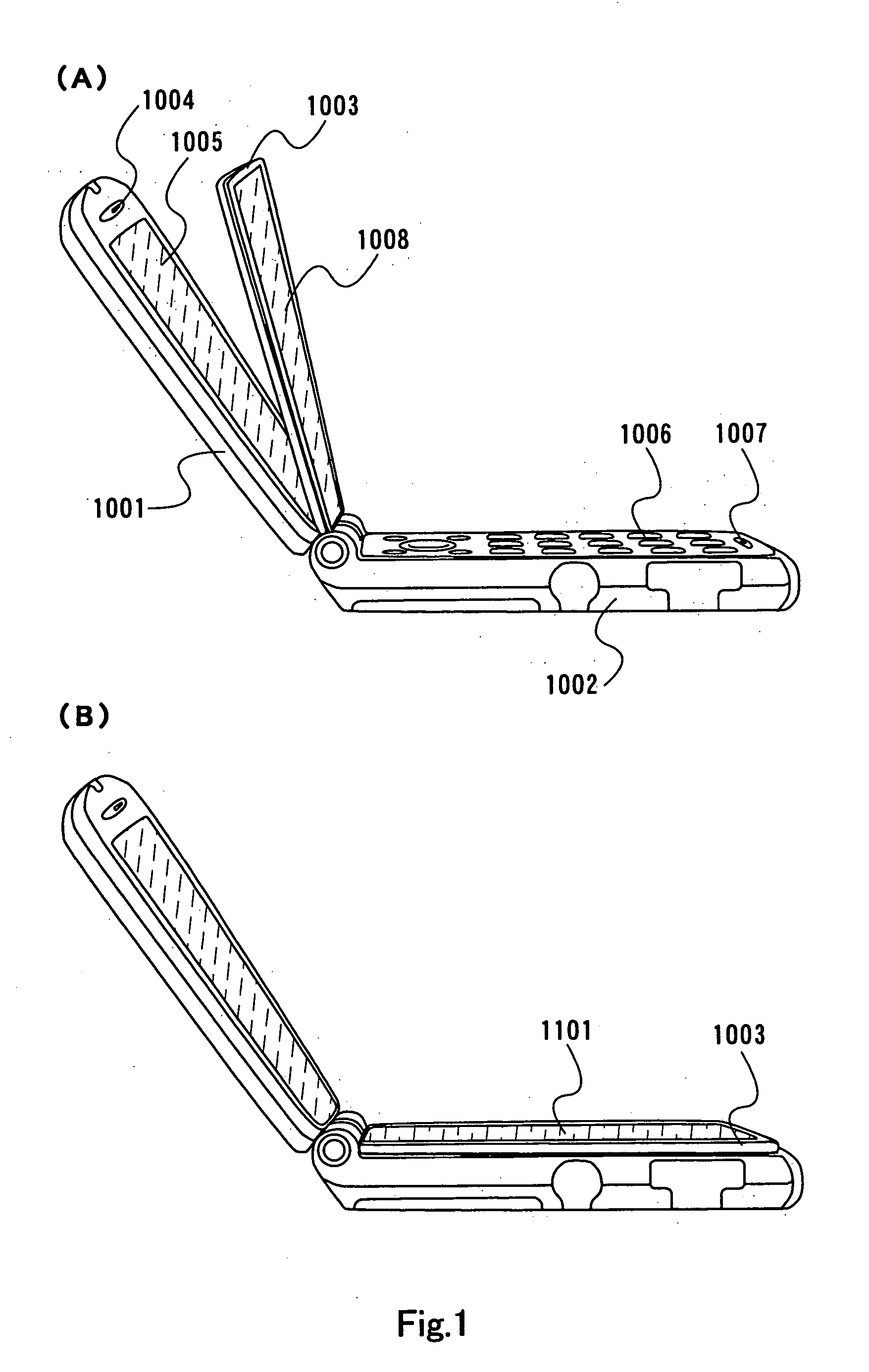

Display device and electronic appliance

ActiveUS20050040753A1Increase added valueReduce weightDischarge tube luminescnet screensDevices with multiple display unitsDisplay deviceEngineering

A dual light emission panel (panel capable of displaying images on both screens) is mounted in a display device or a portable information terminal to achieve a module with a small volume. The display device of the invention comprises a display screen, a first housing and a second housing that are connected to each other, and a dual light emission panel including display screens each on the front side and the back side. The dual light emission panel is connected to the first housing, disposed between the first housing and the second housing when overlapping the first housing, and rotated around a connecting point of the dual light emission panel and the first housing.

Owner:SEMICON ENERGY LAB CO LTD

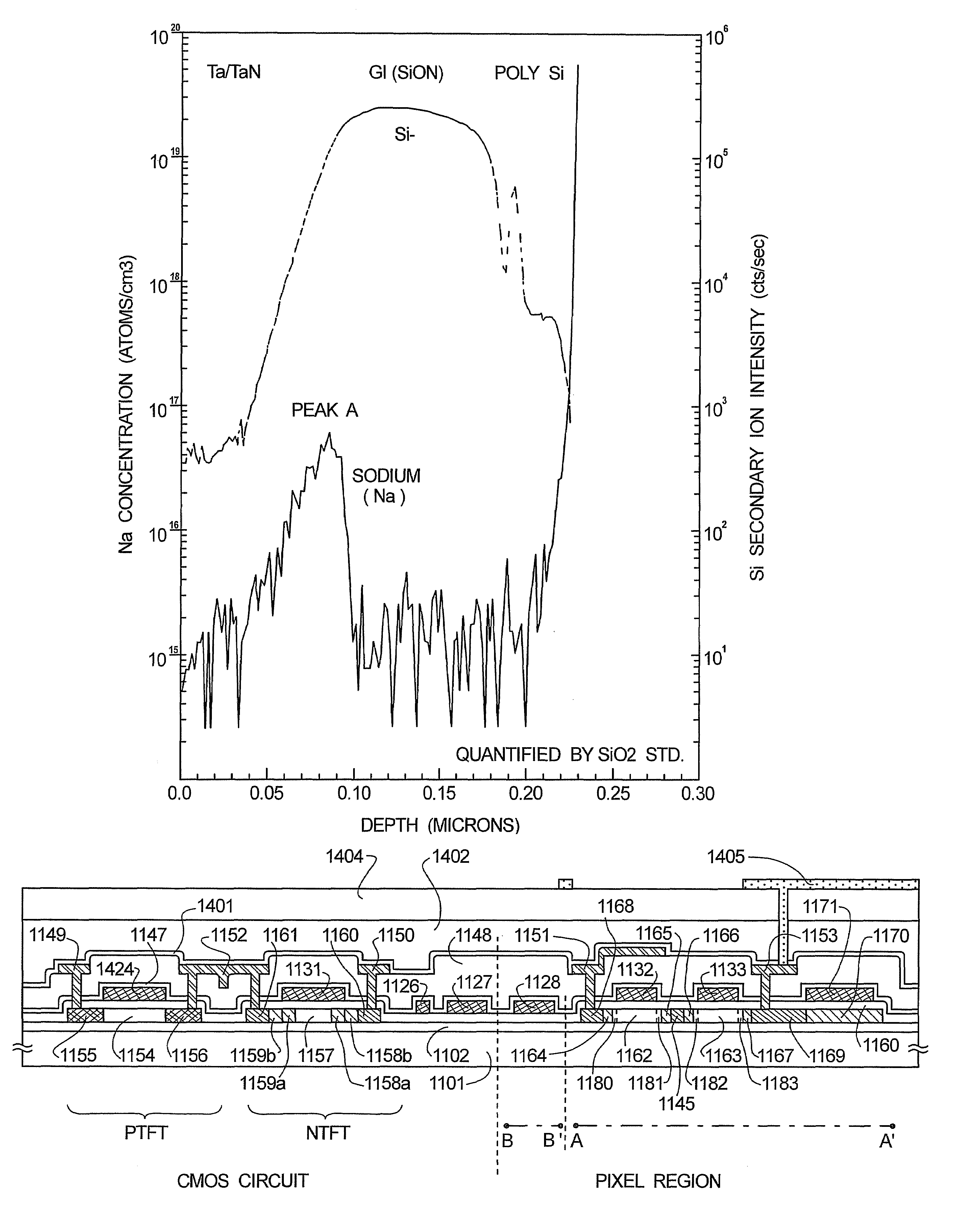

Method of manufacturing a semiconductor device

InactiveUS7402467B1Avoid erosionRemove pollutantsSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

A reduction in contaminating impurities in a TFT, and a TFT which is reliable, is obtained in a semiconductor device which uses the TFT. By removing contaminating impurities residing in a film interface of the TFT using a solution containing fluorine, a reliable TFT can be obtained.

Owner:SEMICON ENERGY LAB CO LTD

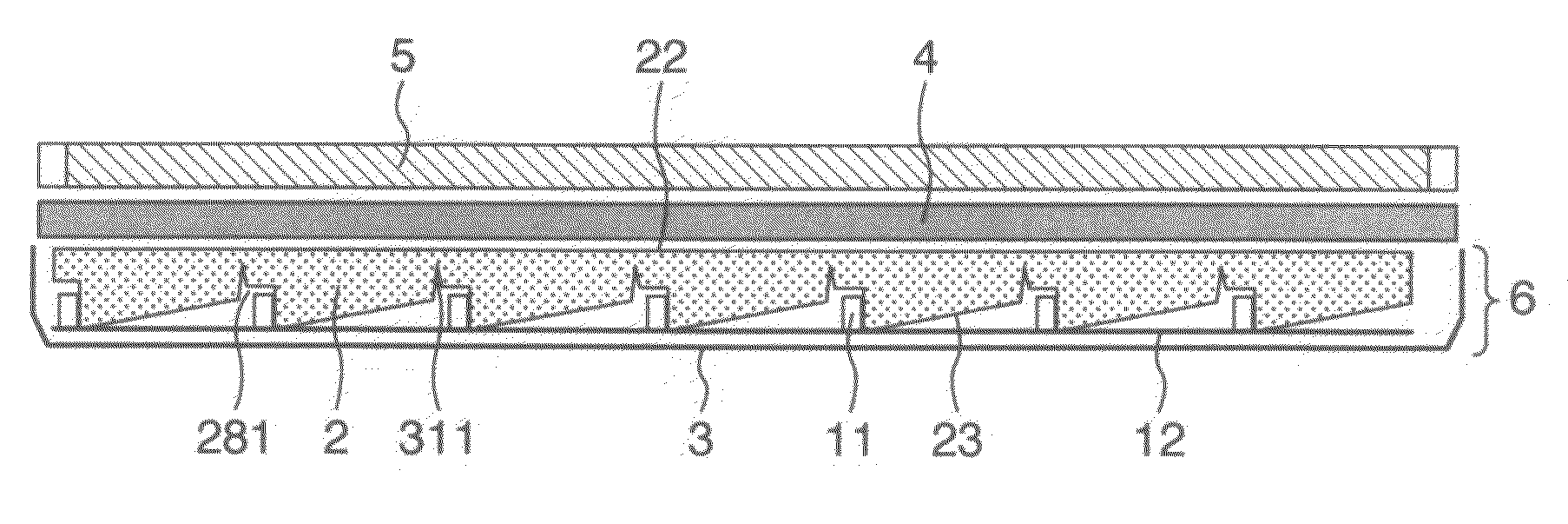

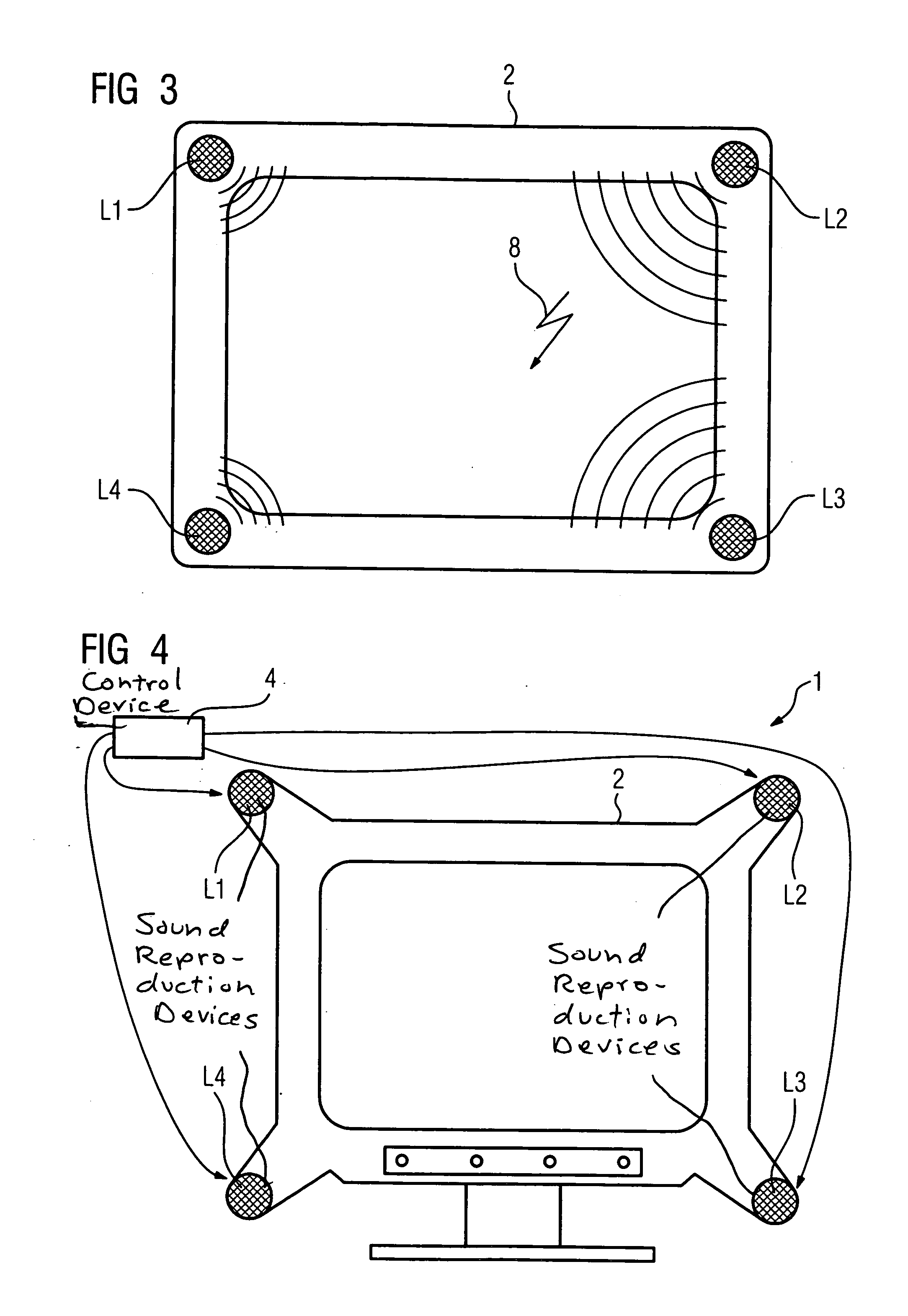

Display apparatus and back light unit to be used therefor

InactiveUS20090303410A1Big screenControl performancePlanar/plate-like light guidesNon-linear opticsLiquid crystalLight wave

A back light unit includes a light source unit combined with an optical waveguide having translucency to guide a light of light source in a direction of liquid crystal panel, and a chassis for holding or supporting the light source unit. The optical waveguide is formed in plate-like shape, a face opposing to the back face of liquid crystal panel is used as a light emitting surface, a face opposing to the chassis is used as a reflecting face for reflecting a light, one of a plurality of side faces adjacent to light emitting surface and reflecting face is used as a light incidence surface where a light from the light source is injected. The light source unit is arranged in multiple in a horizontal direction or a vertical direction of the liquid crystal panel, in the back face side of the liquid crystal panel.

Owner:HITACHI LTD

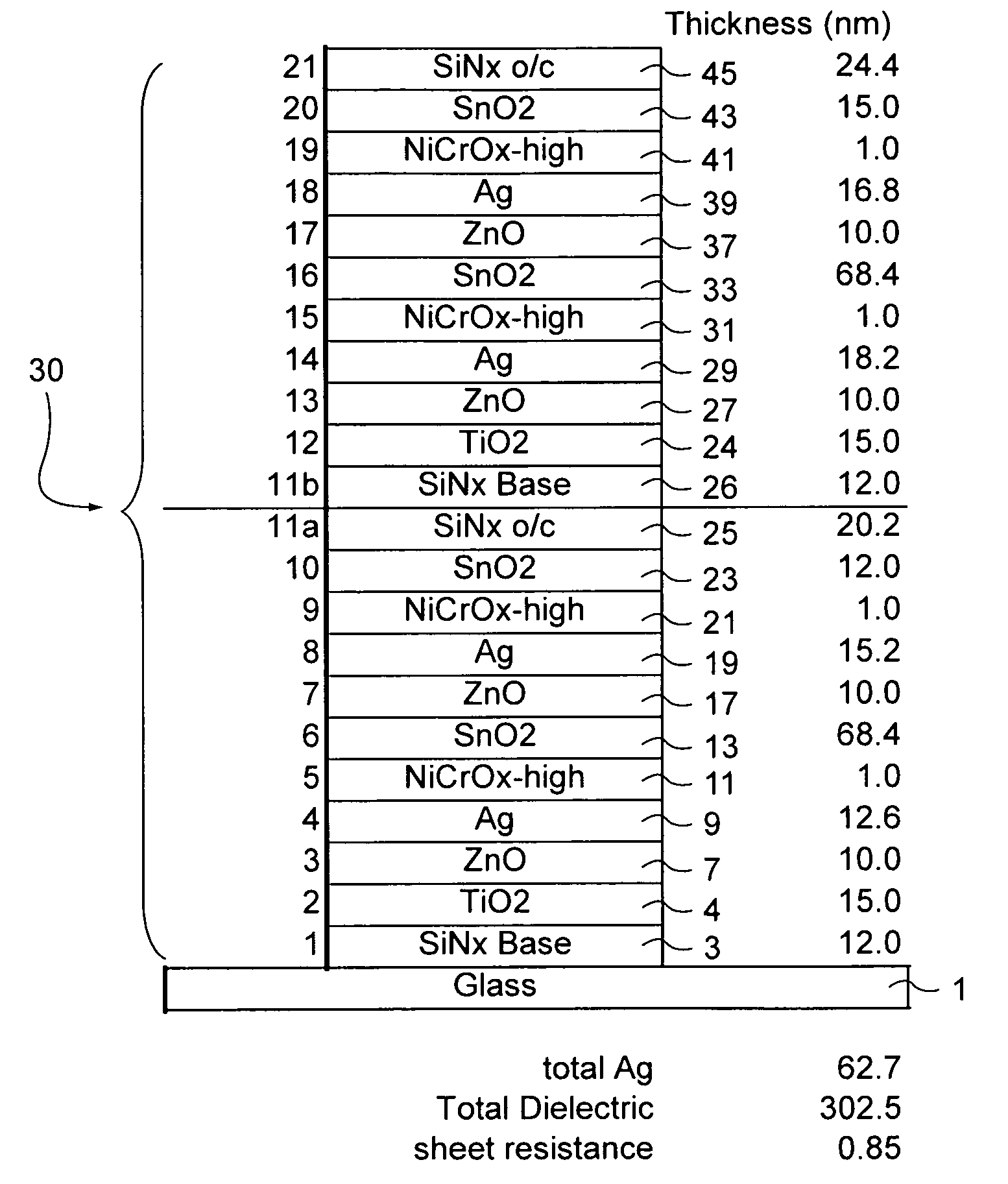

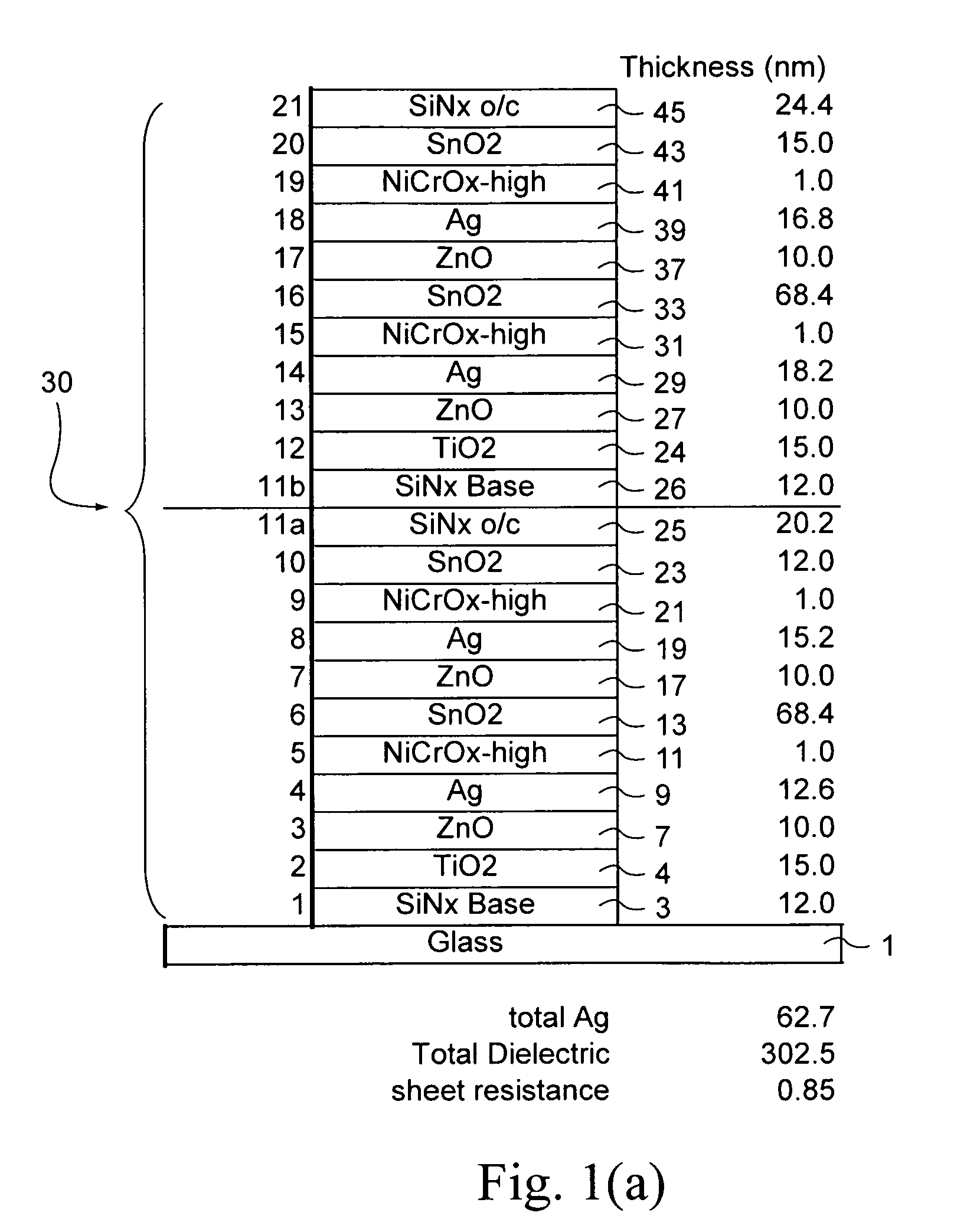

Plasma display panel including frameless EMI filter, and/or method of making the same

ActiveUS20100046191A1Easy to makeImprove display effectMagnetic/electric field screeningAlternating current plasma display panelsInfraredConductive coating

A plasma display panel (PDP) includes a frameless EMI filter supported by a glass substrate for blocking / shielding substantial amounts of electromagnetic waves, with the filter being supported by a side of the substrate opposite a viewer. In certain example embodiments, the PDP filter includes a transparent conductive coating (TCC) for electromagnetic interference (EMI) and near infrared (NIR) blocking without the need for a conductive, peripheral buss bar. Additionally, in certain example embodiments, the need for a conductive frame is reduced or eliminated. The filter has high visible transmission, and is capable of blocking / shielding electromagnetic waves.

Owner:GUARDIAN GLASS LLC

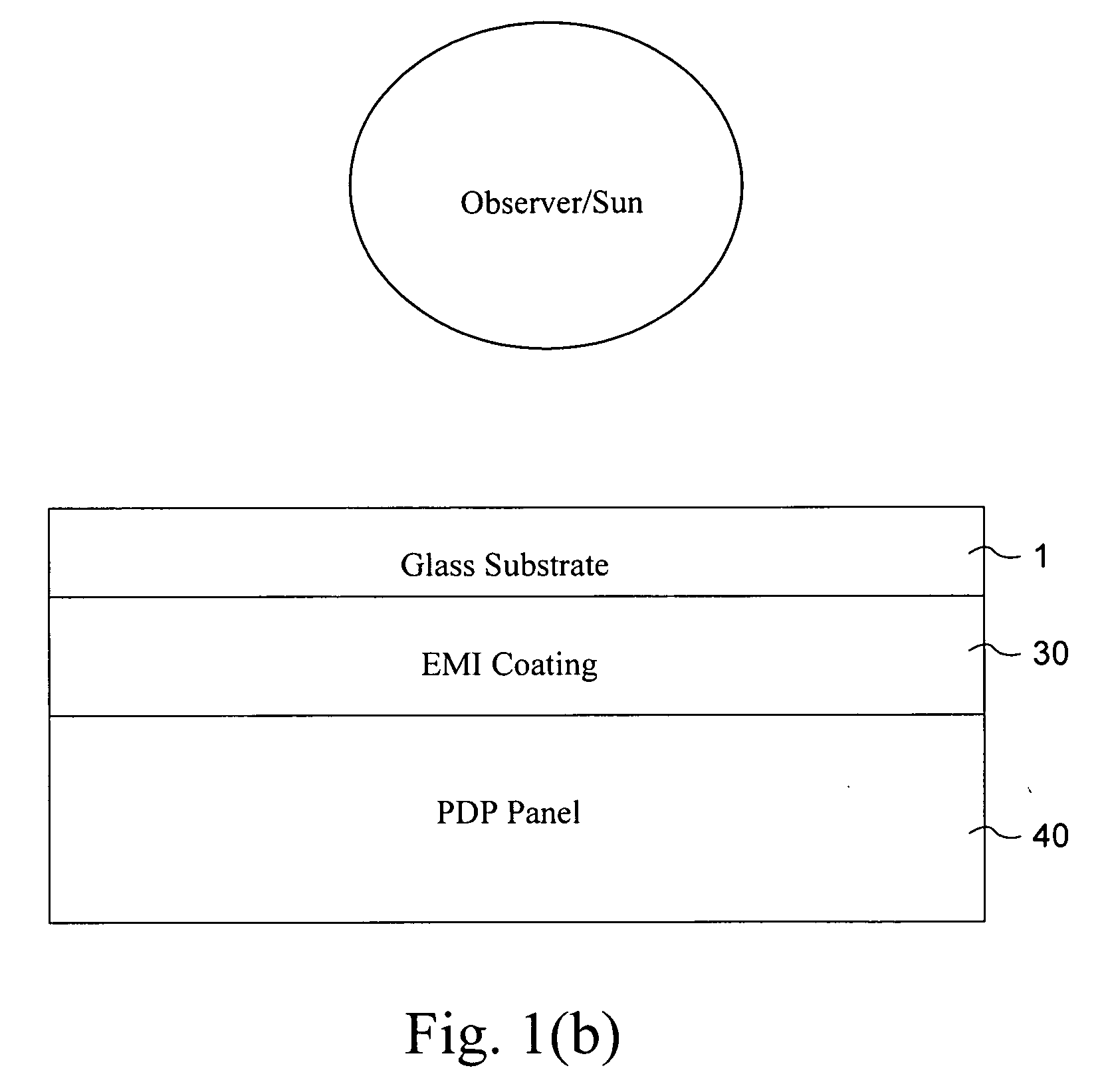

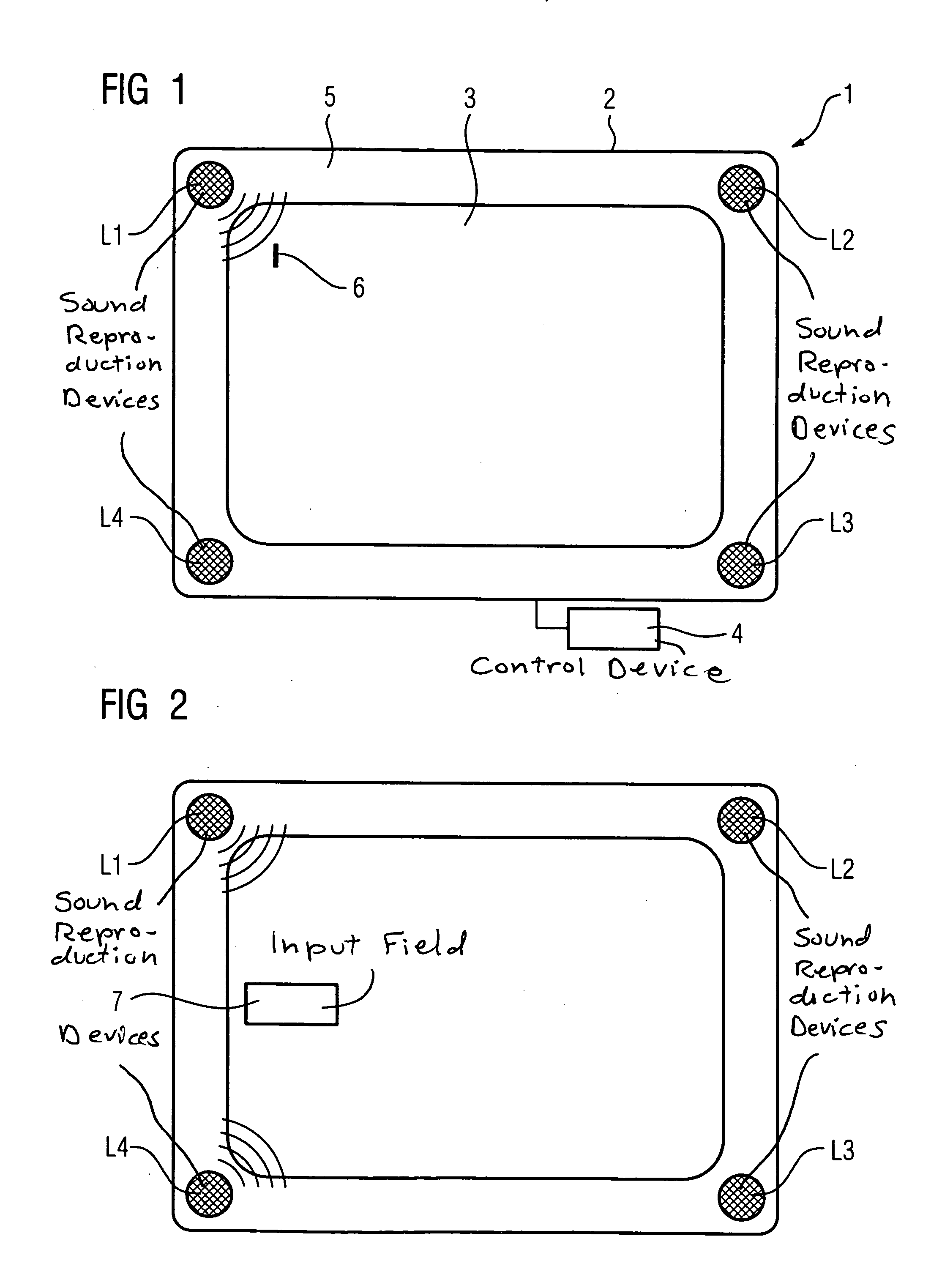

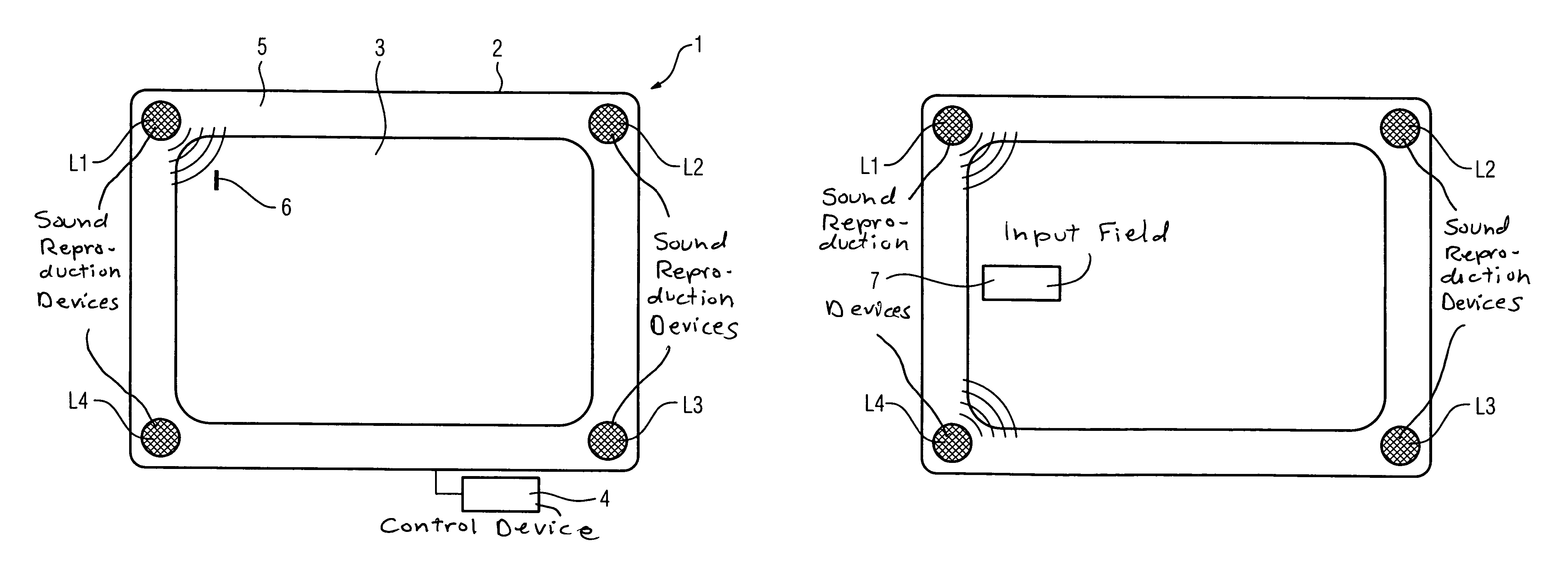

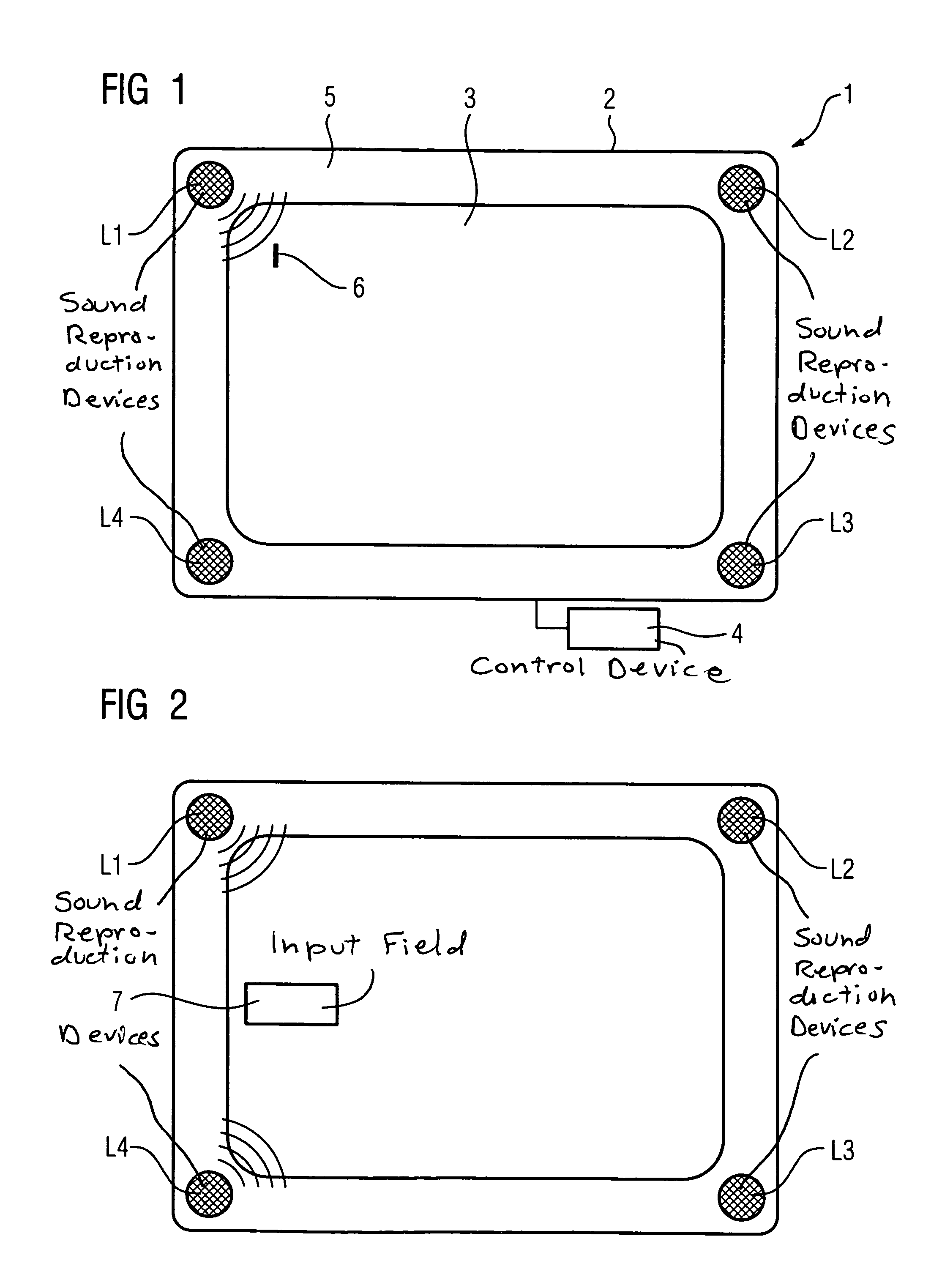

Reproduction apparatus with audio directionality indication of the location of screen information

InactiveUS20050047624A1Simple and fast and secure recognitionBig screenTelevision systemsLoudspeaker spatial/constructional arrangementsDirection informationComputer science

A reproduction device has at least one screen for displaying information, with at least four sound reproduction devices respectively at the corners of the screen, which are separately driven depending on the local screen position of a user-relevant item of information such that direction information relating to the screen information is conveyed to the user by the resulting acoustic signal that is produced by the combined, individual driving, which is perceivable by the user.

Owner:SIEMENS HEALTHCARE GMBH

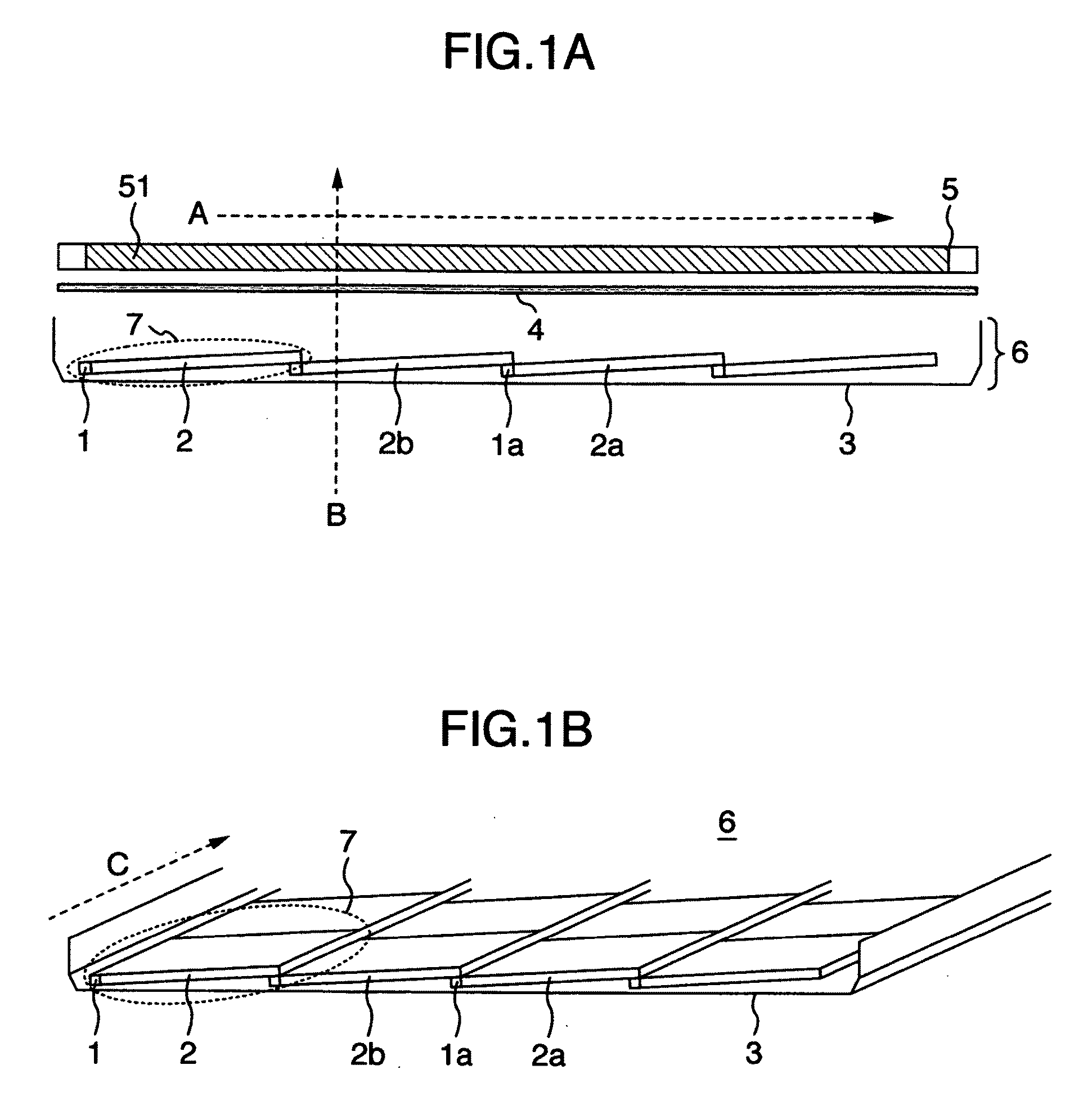

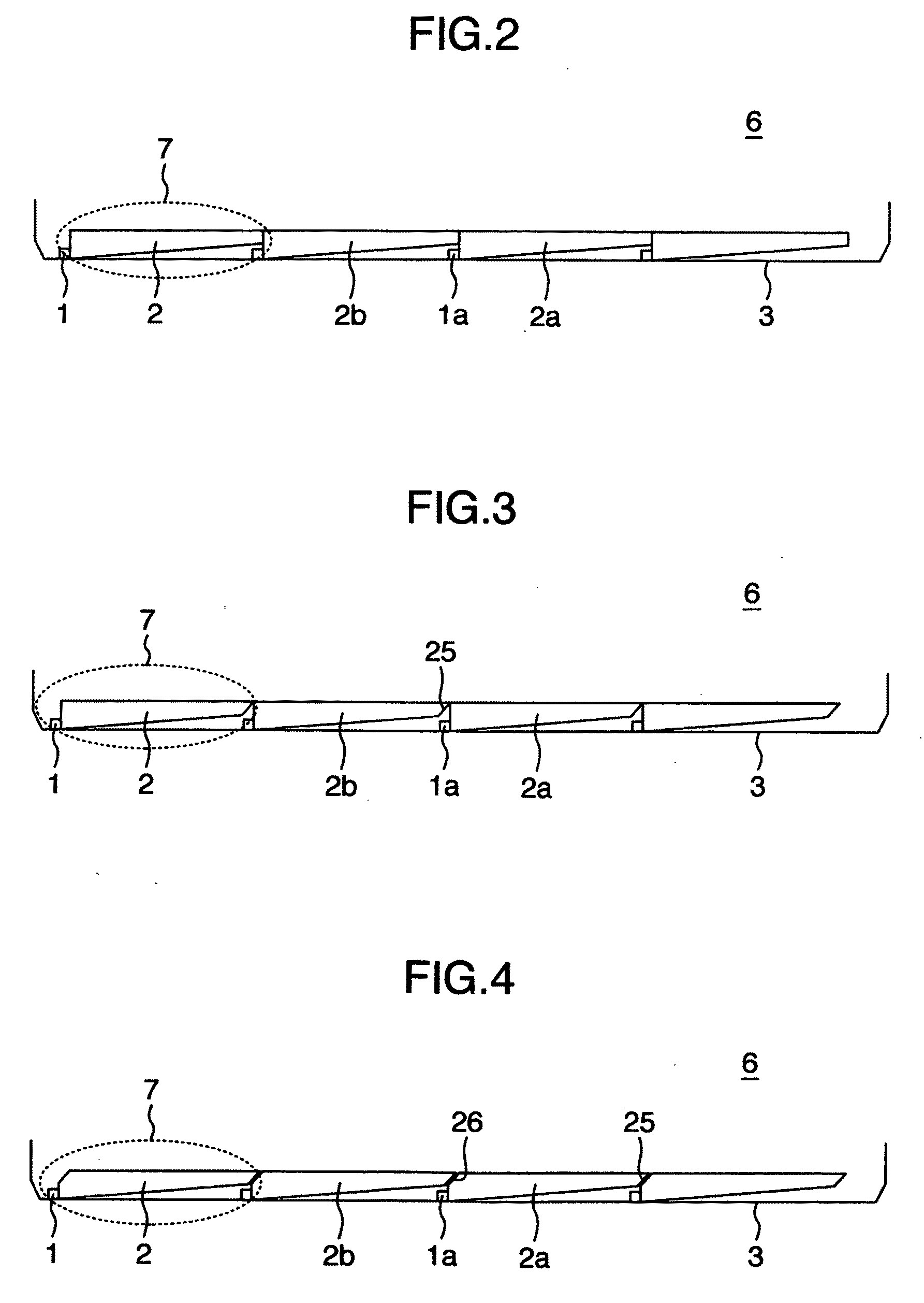

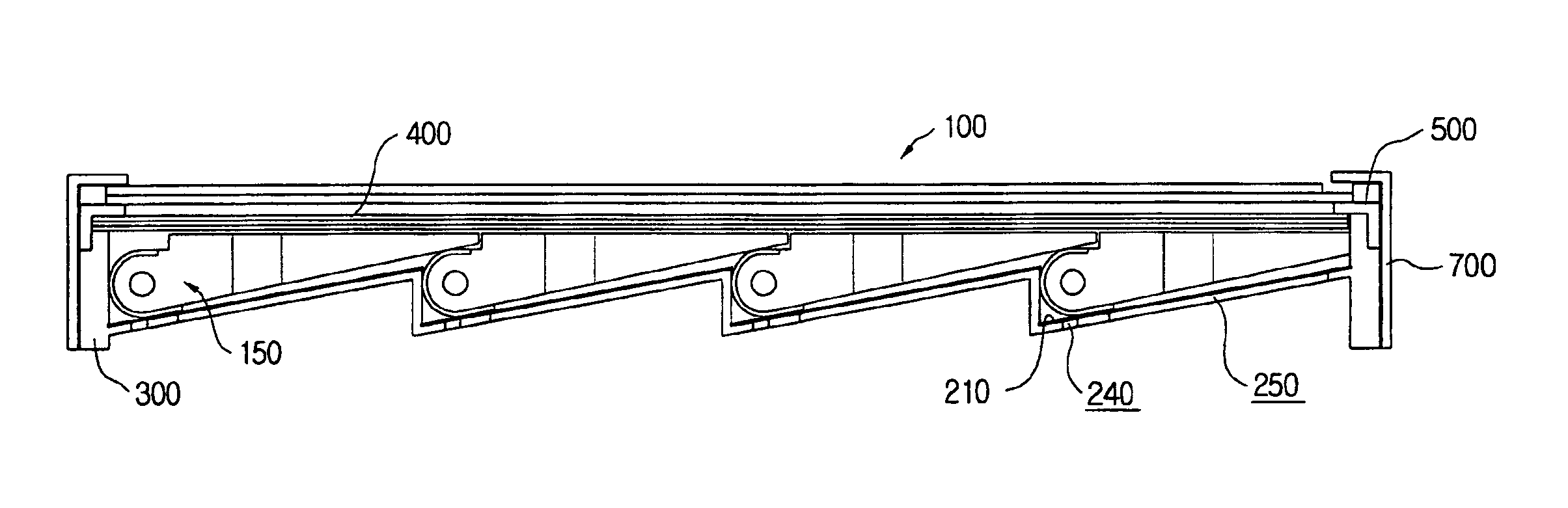

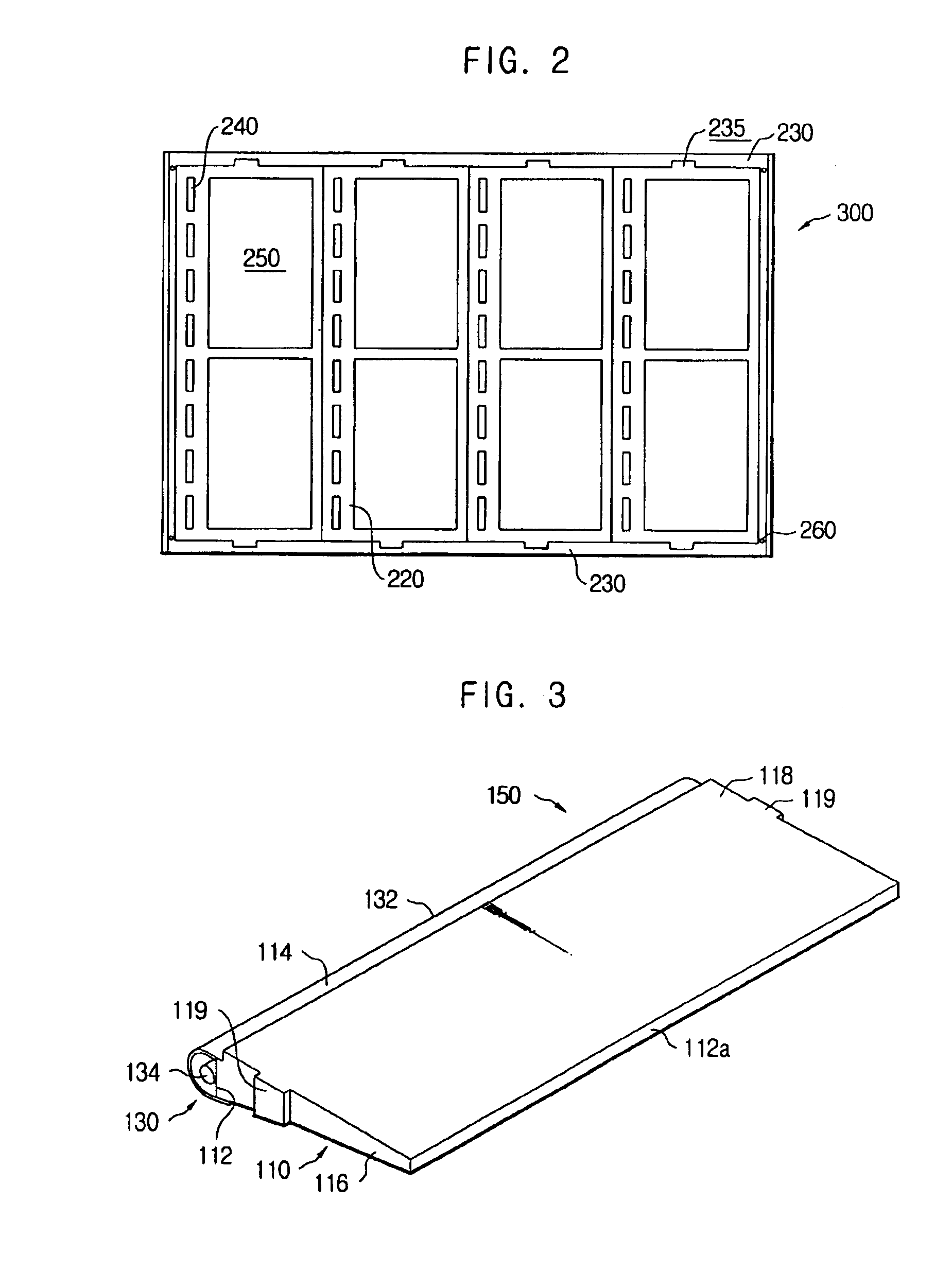

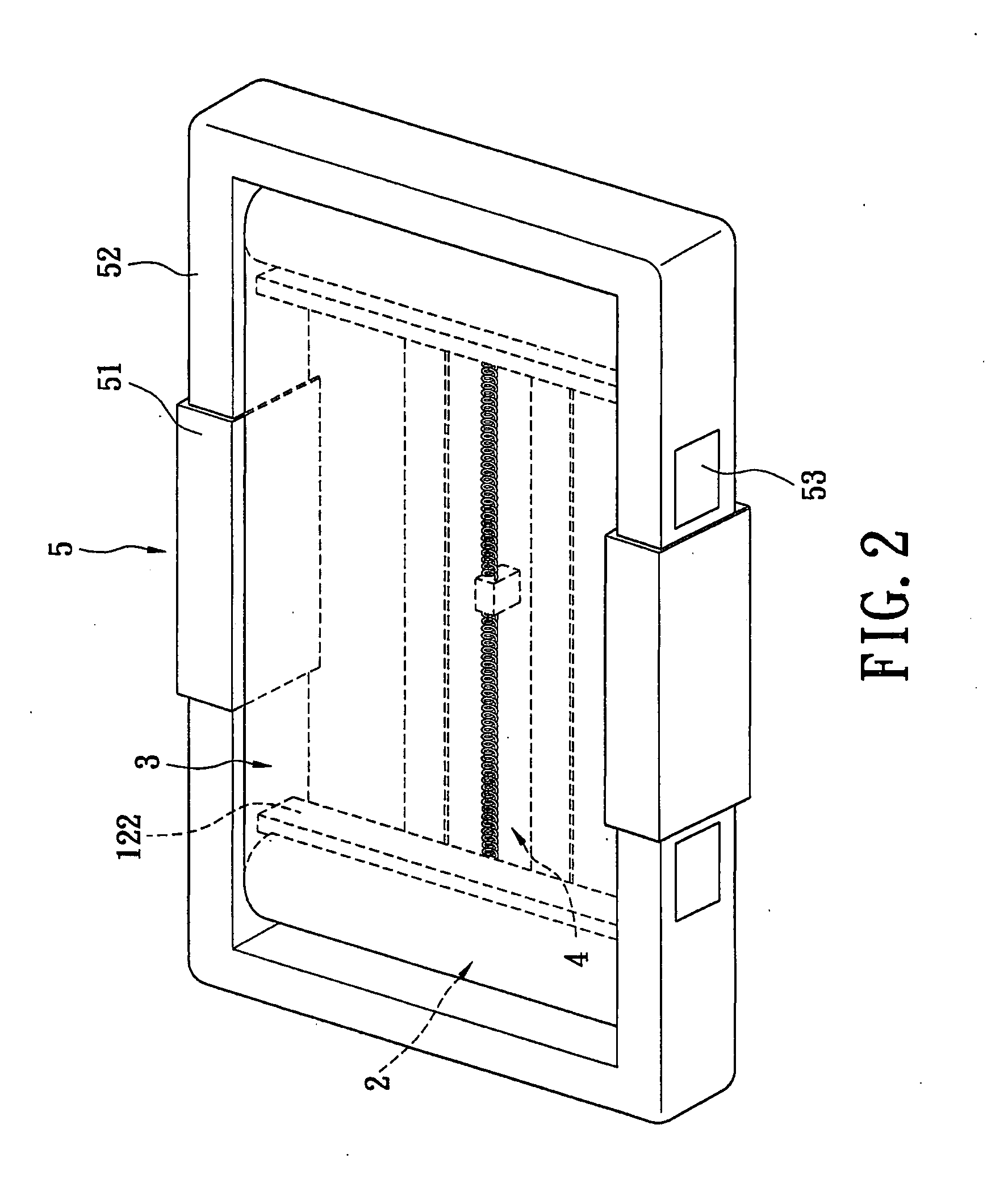

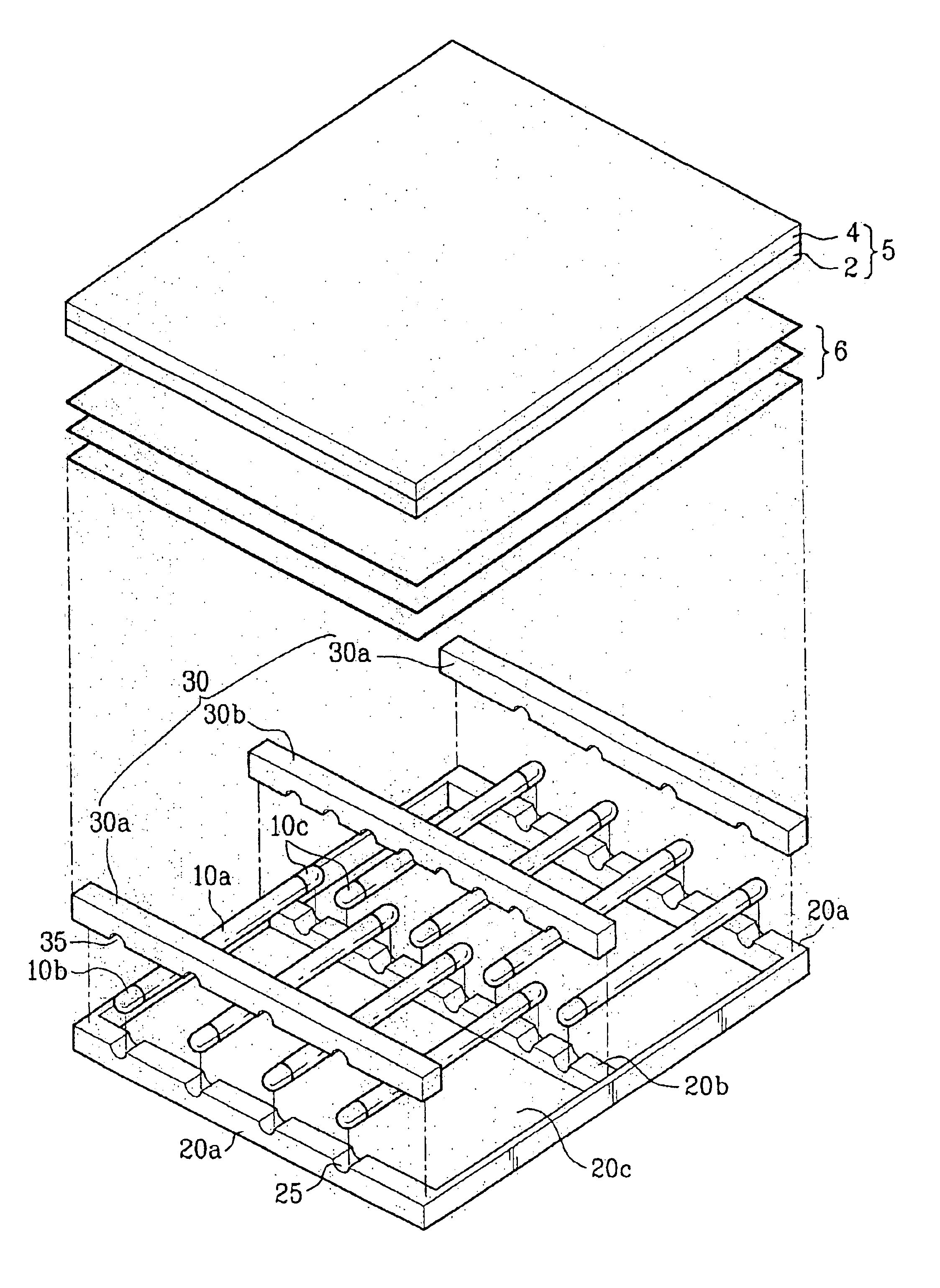

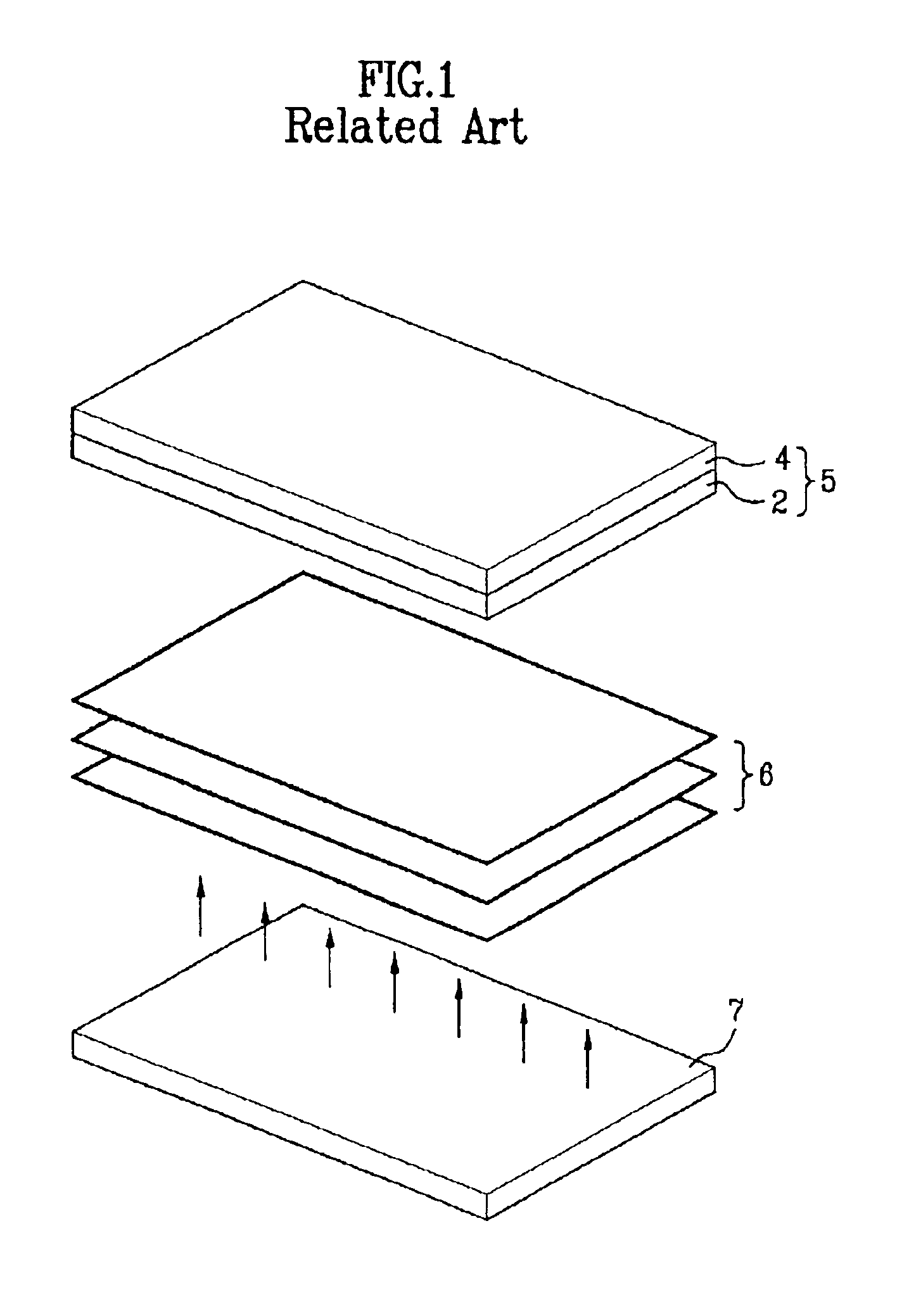

Liquid crystal display including at least two light guiding plates abutting each other

InactiveUS6927812B2Large screen sizeBig screenMechanical apparatusMeasurement apparatus componentsLiquid-crystal displayLight guide

A liquid crystal display of a large screen size, a slim thickness and light weight is disclosed. The liquid crystal display includes a light supply unit group having at least two light guiding plates arranged in parallel and at least one lamp unit coupled to one side of the light guiding plate. A light control element is mounted on an upper surface of the light supply unit group, and uniformly controls luminance between the light guiding plate and the lamp unit. A reflective plate is disposed on a rear surface of the light supply unit group and has a shape corresponding to the rear surface of the light supply unit group. A back light assembly includes a receiving container that receives the light supply unit group, the light control element, and the reflective plate.

Owner:SAMSUNG DISPLAY CO LTD

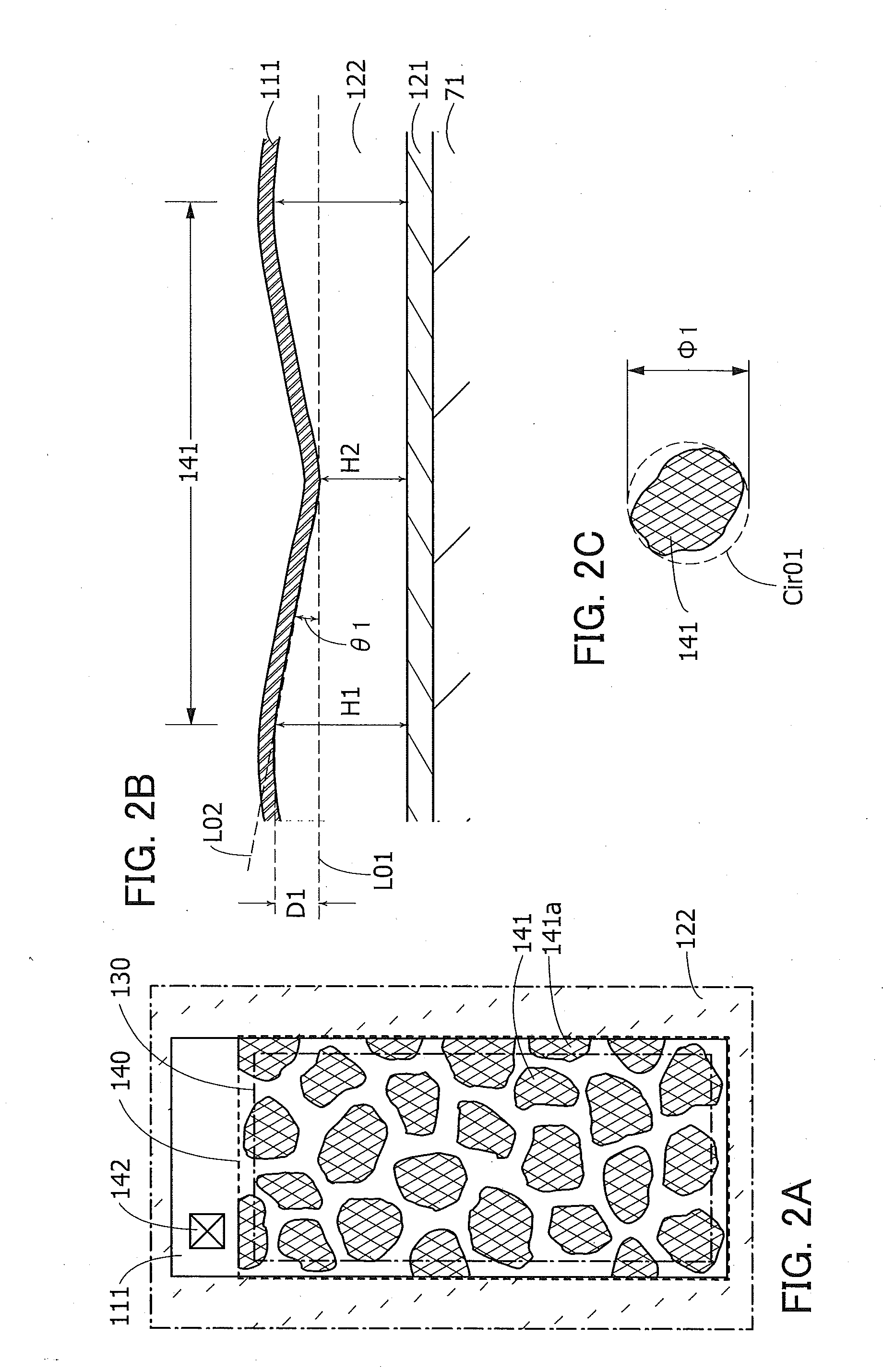

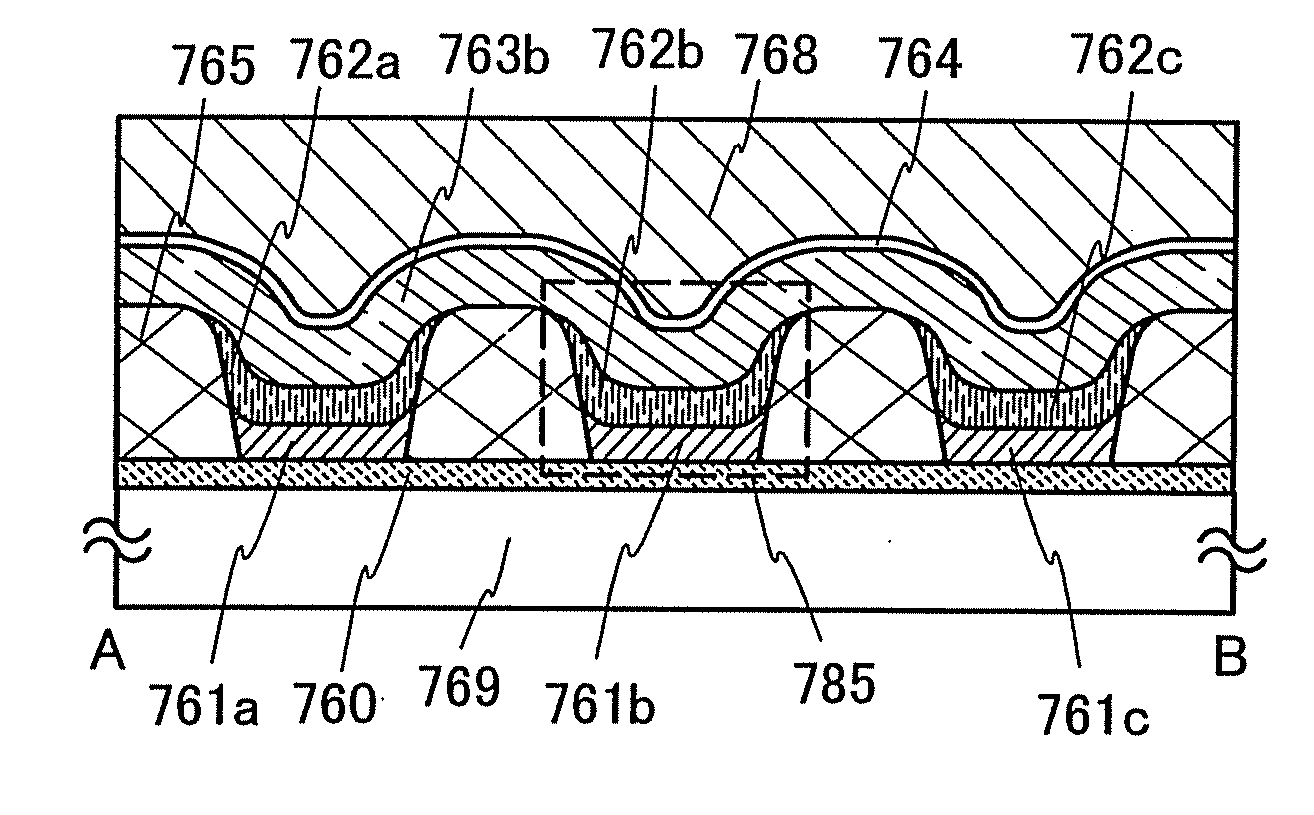

Light-Emitting Device

ActiveUS20140306241A1Increase of surface irregularityHigh definitionSolid-state devicesSemiconductor devicesRotational symmetrySurface shape

In a light-emitting device where reflective electrodes are regularly arranged, occurrence of interference fringes due to reflection of light reflected by the reflective electrode is inhibited. A surface of the reflective electrode of a light-emitting element is provided with a plurality of depressions. The shapes of the plurality of depressions are different from each other and do not have rotational symmetry. Irregularity of the surface shape of the reflective electrode is increased, which inhibits interference of light reflected by the reflective electrode. To form the plurality of depressions in the surface of the reflective electrode, for example, a surface of an insulating layer that is a base of the reflective electrode is made uneven. Reflecting the surface shape of the insulating layer, the reflective electrode has an uneven surface.

Owner:SEMICON ENERGY LAB CO LTD

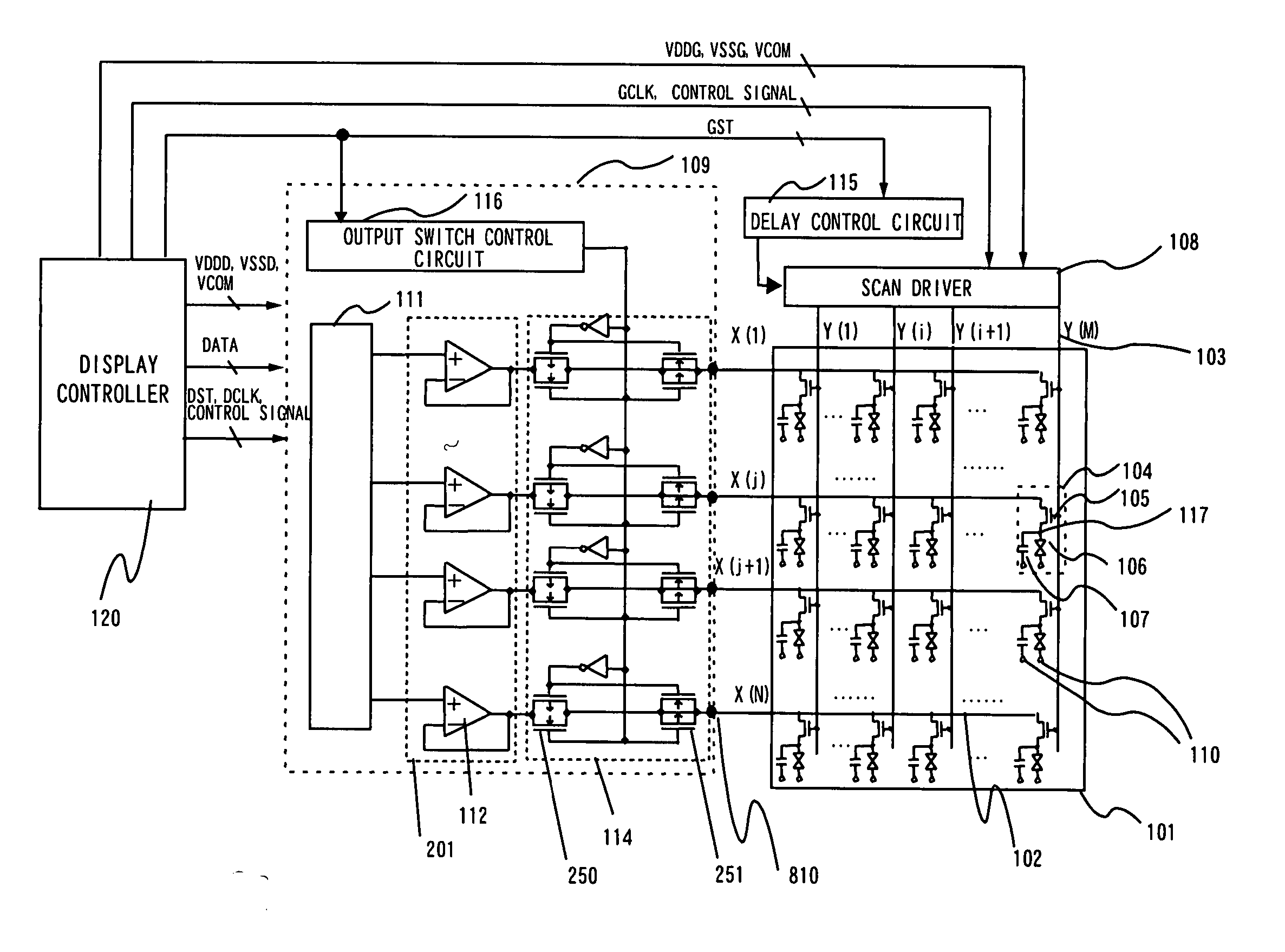

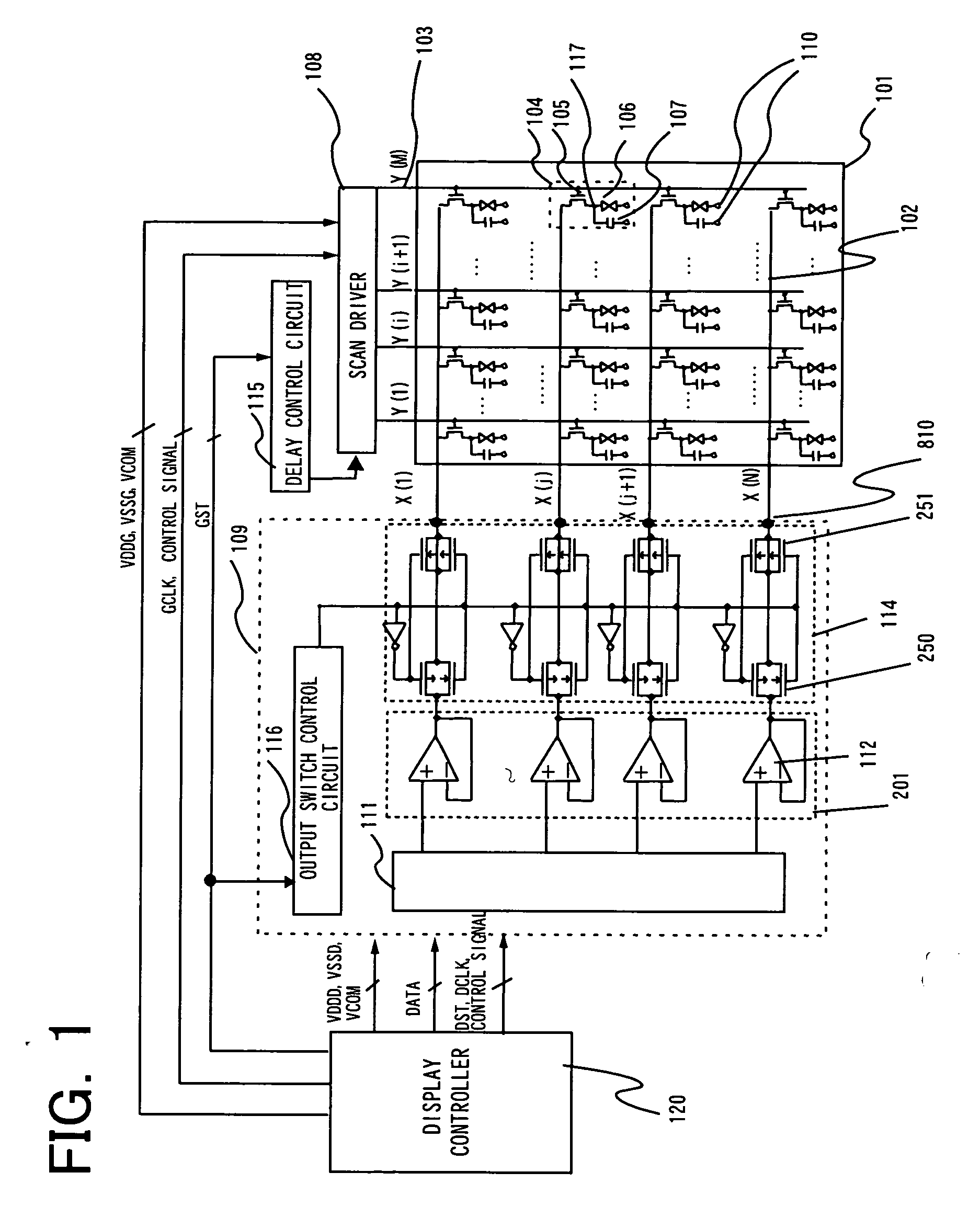

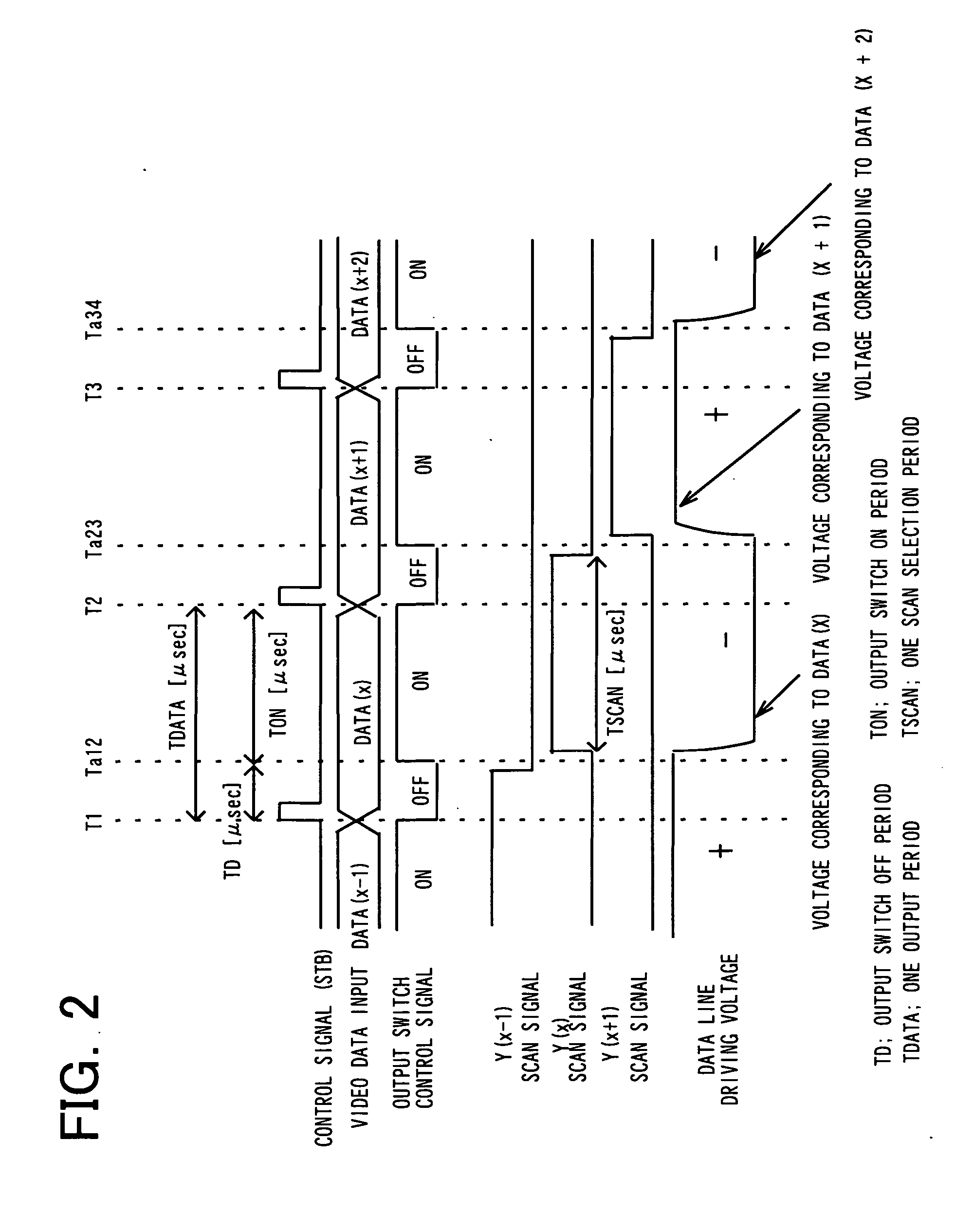

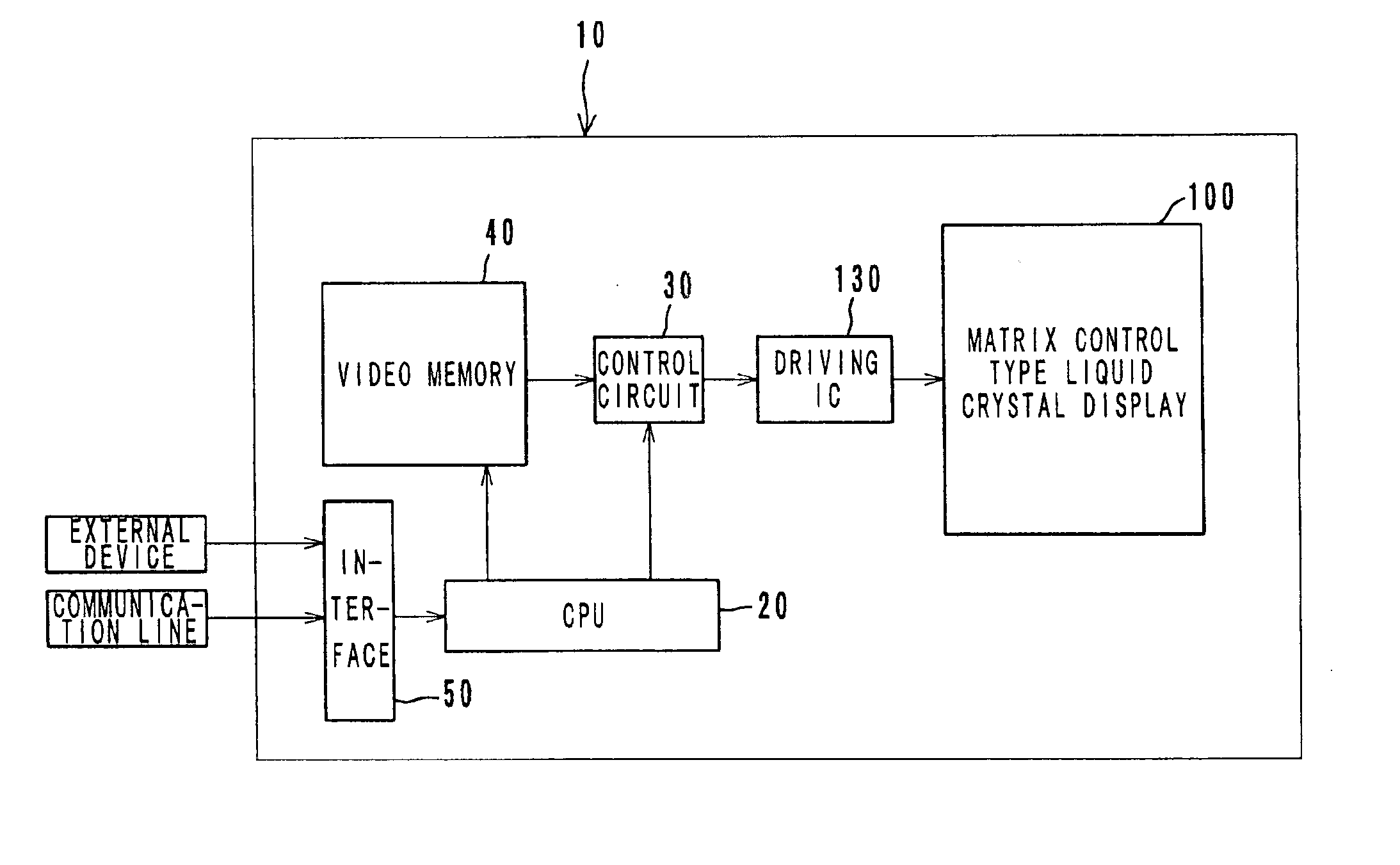

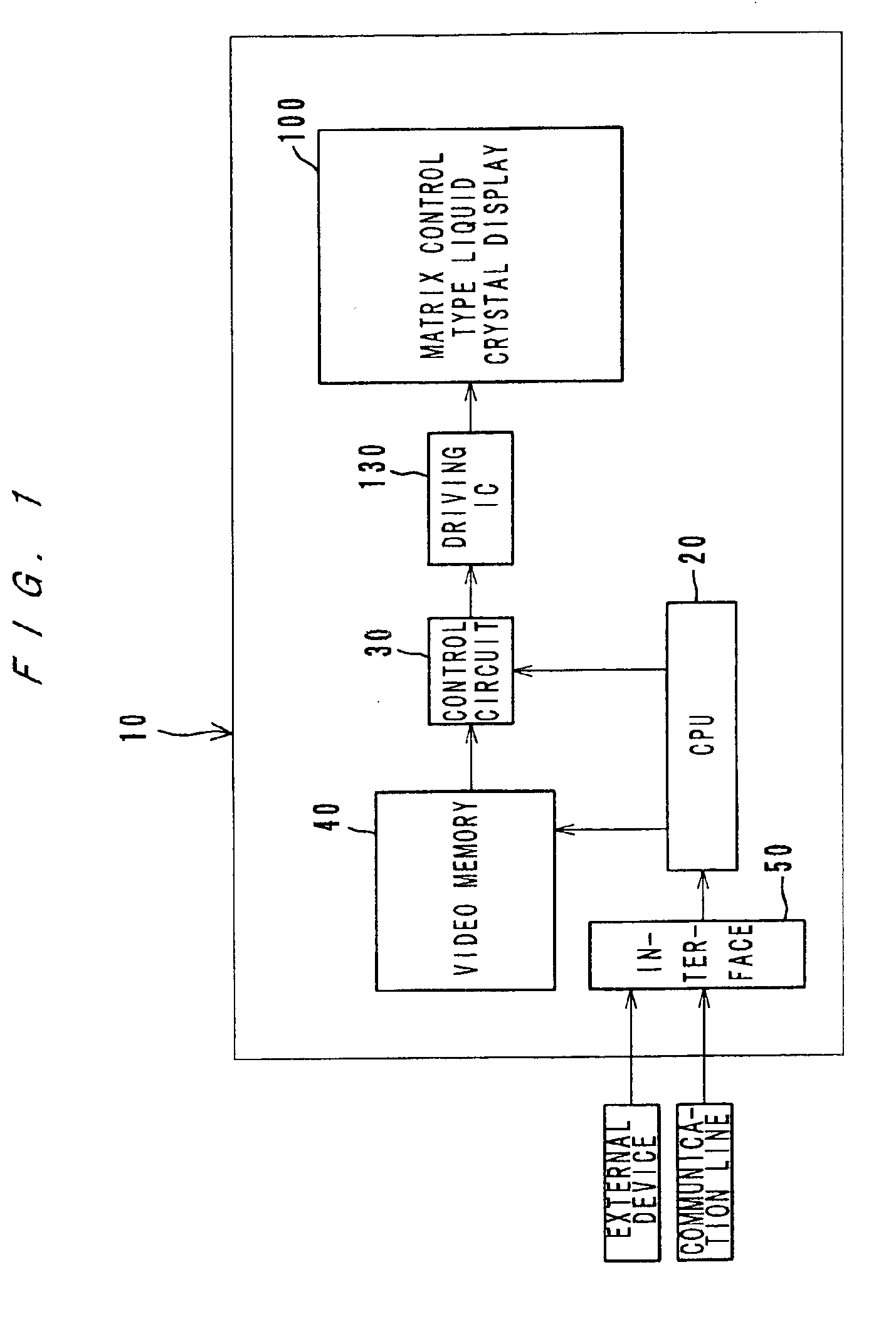

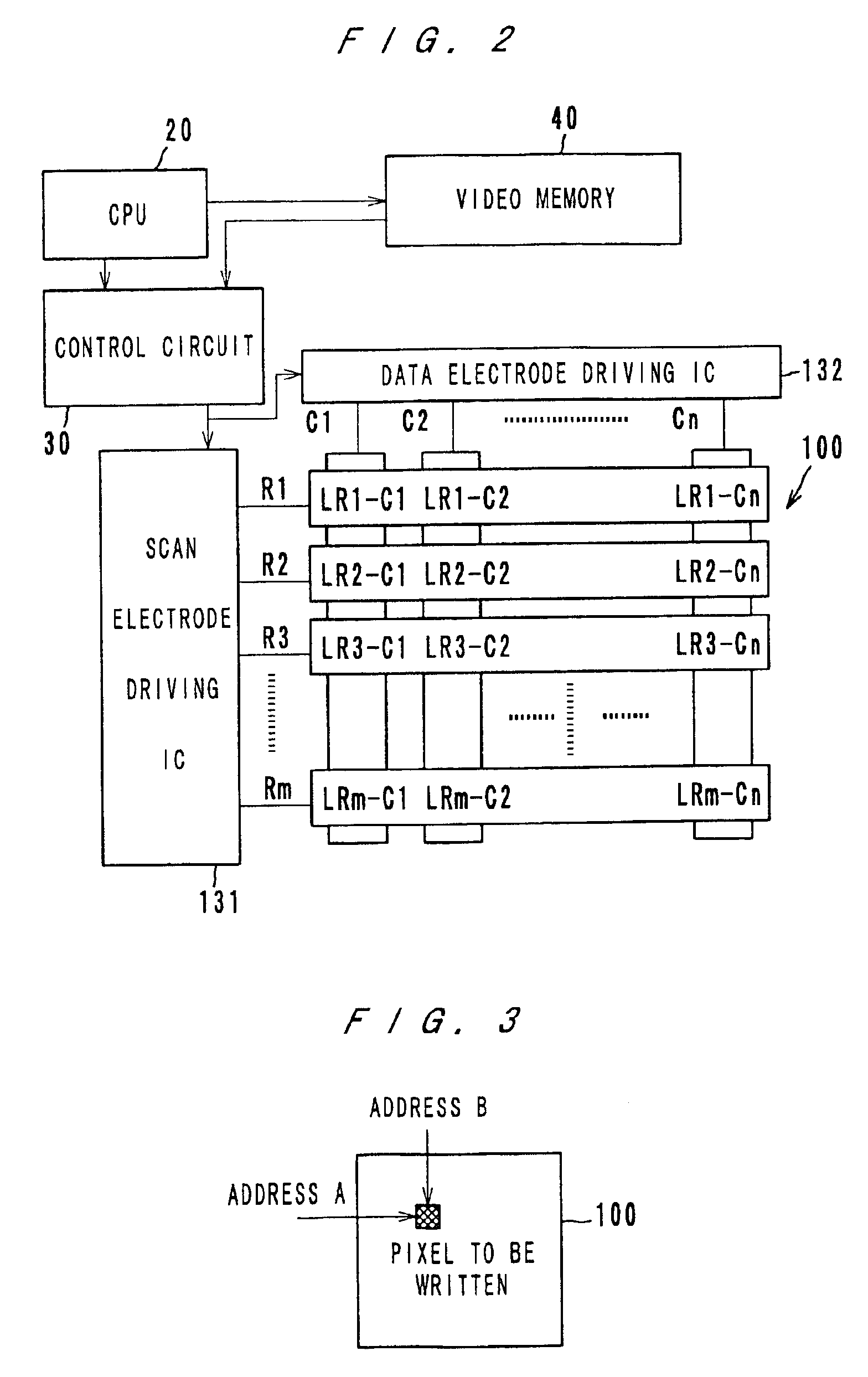

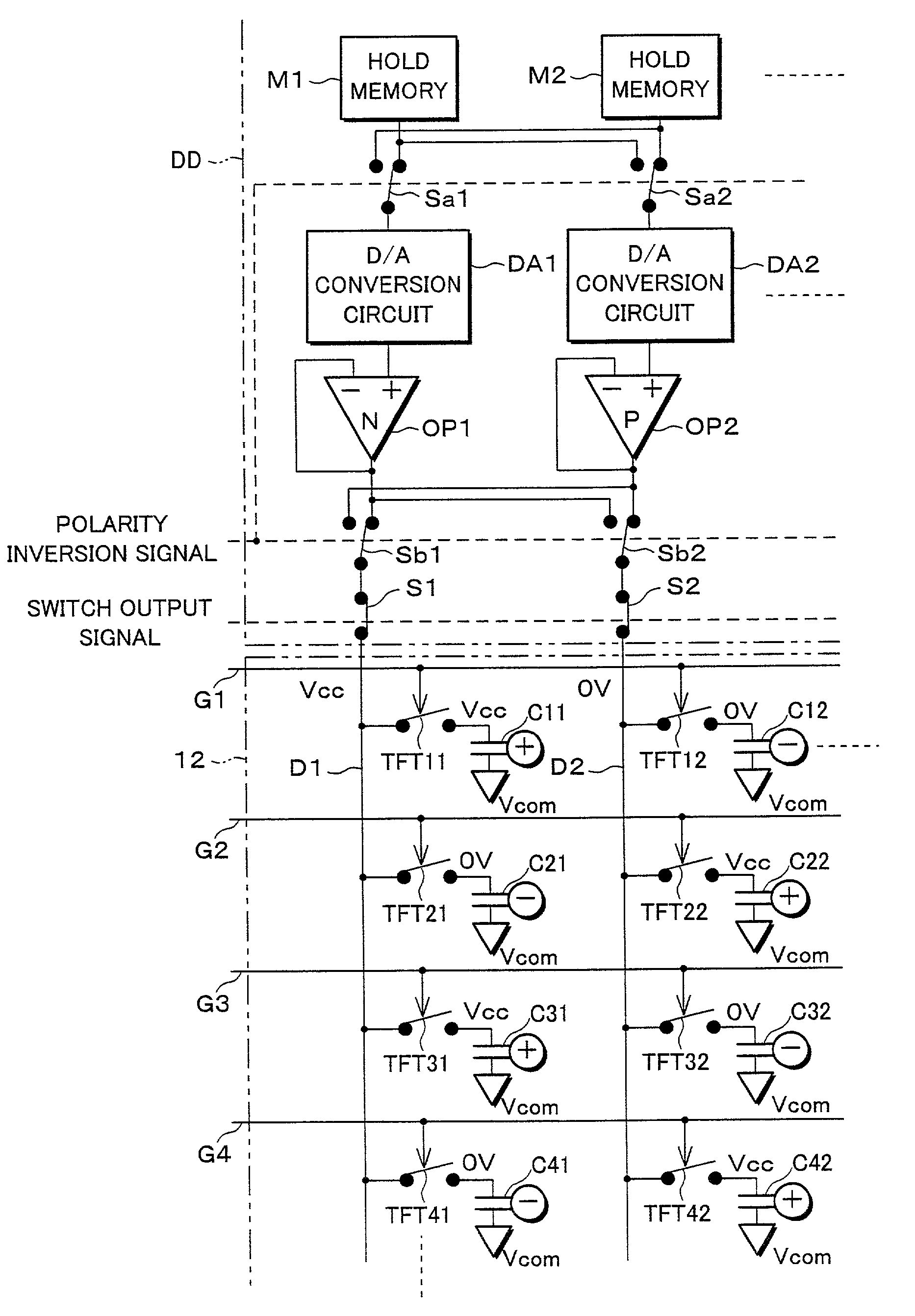

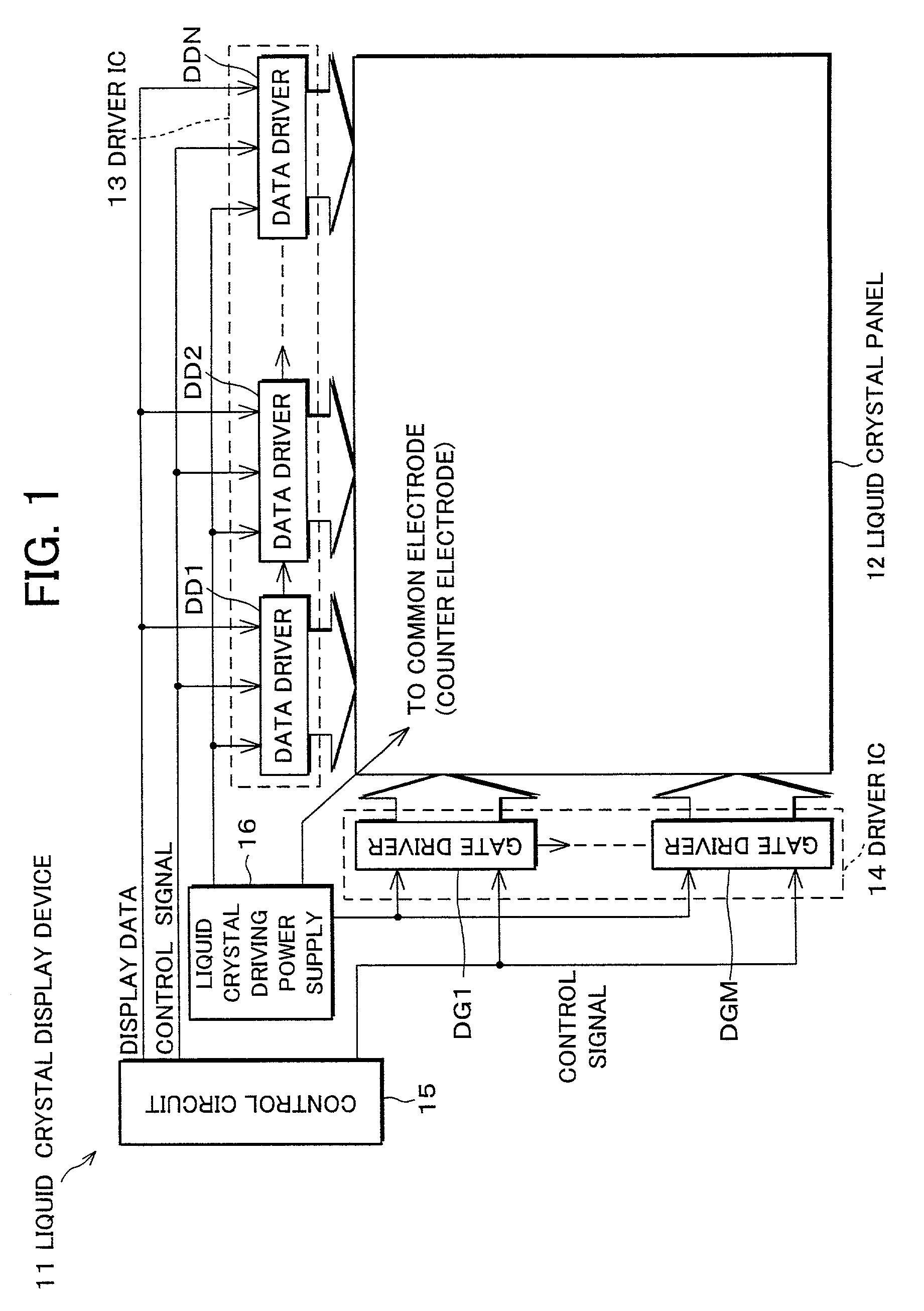

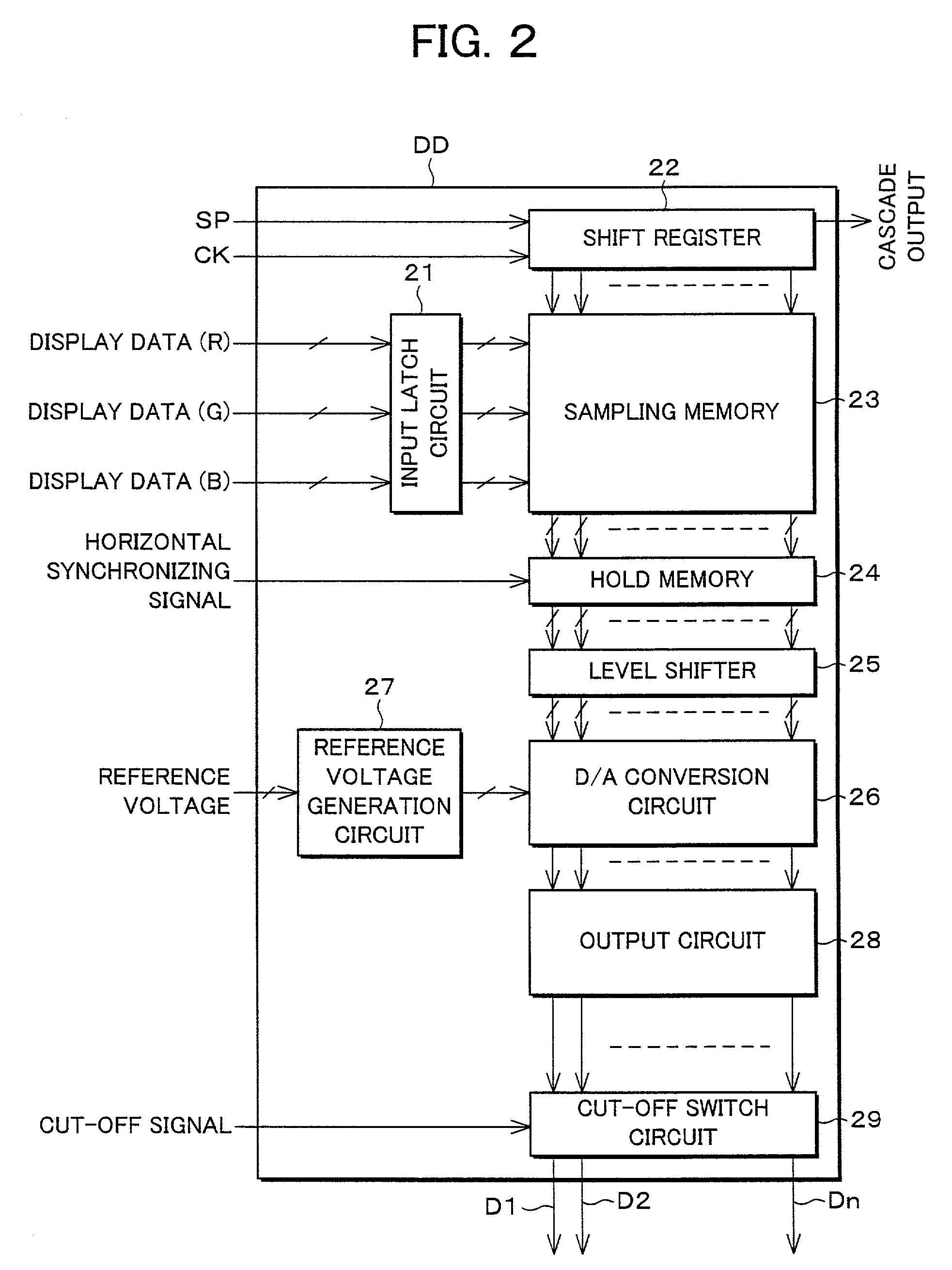

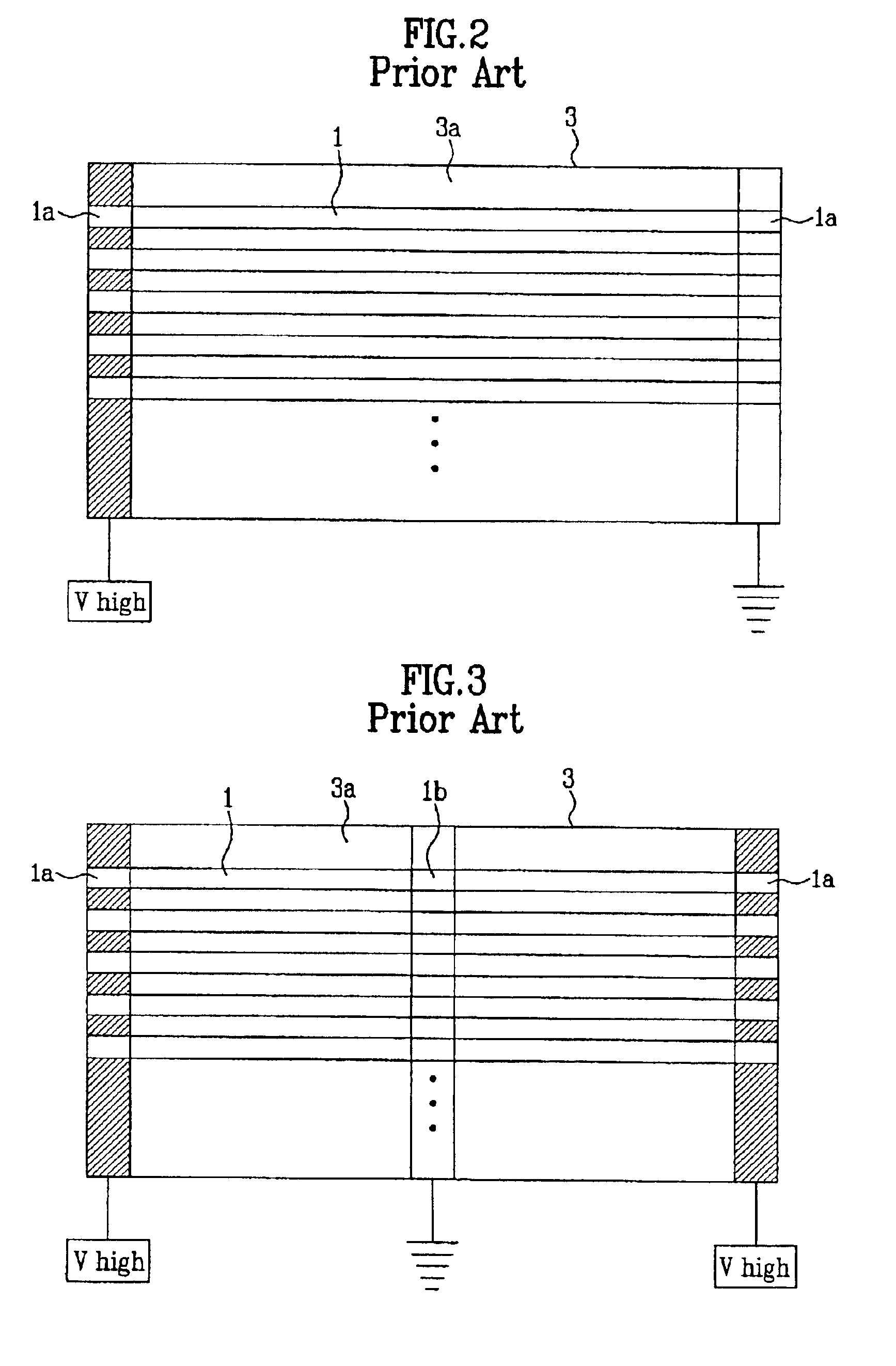

Active matrix type display device and driving method thereof

ActiveUS20060244710A1Improve rendering capabilitiesImprove display qualityCathode-ray tube indicatorsInput/output processes for data processingAudio power amplifierActive matrix

Disclosed is a display device including display unit, a column driver, a delay control circuit, an output switch control circuit, and a display controller. The display unit includes a plurality of pixel electrodes arranged at intersections between a plurality of data lines and a plurality of scan lines in a matrix form and TFTs. One of a drain and a source of each of the TFTs is connected to a corresponding one of the pixel electrodes. The other one of the drain and the source of each of the TFTs is connected to a corresponding one of the data lines, and a gate of each of the TFTs is connected to a corresponding one of the scan lines. The scan driver supplies a scan signal to each of the scan line in a preset scan cycle. The column driver includes D / A converter circuits for converting video data to gray scale signals, a plurality of buffer amplifiers for sequentially amplifying and outputting the gray scale signals in a preset output cycle, and an output switch circuit including a plurality of switches connected to output terminals of the buffer amplifiers and the data lines, respectively. The delay control circuit controls the scan driver so that the preset scan cycle is delayed from the preset output cycle just by a preset delay time. The output switch control circuit controls the output switch circuit to be kept off during the preset delay time. The display controller controls the video data, scan driver, column driver, delay control circuit, and output switch control circuit, respectively.

Owner:RENESAS ELECTRONICS CORP

Reproduction apparatus with audio directionality indication of the location of screen information

InactiveUS7602924B2Simple and fast and secure recognitionBig screenGain controlAdvertisingDirection informationComputer science

A reproduction device has at least one screen for displaying information, with at least four sound reproduction devices respectively at the corners of the screen, which are separately driven depending on the local screen position of a user-relevant item of information such that direction information relating to the screen information is conveyed to the user by the resulting acoustic signal that is produced by the combined, individual driving, which is perceivable by the user.

Owner:SIEMENS HEALTHCARE GMBH

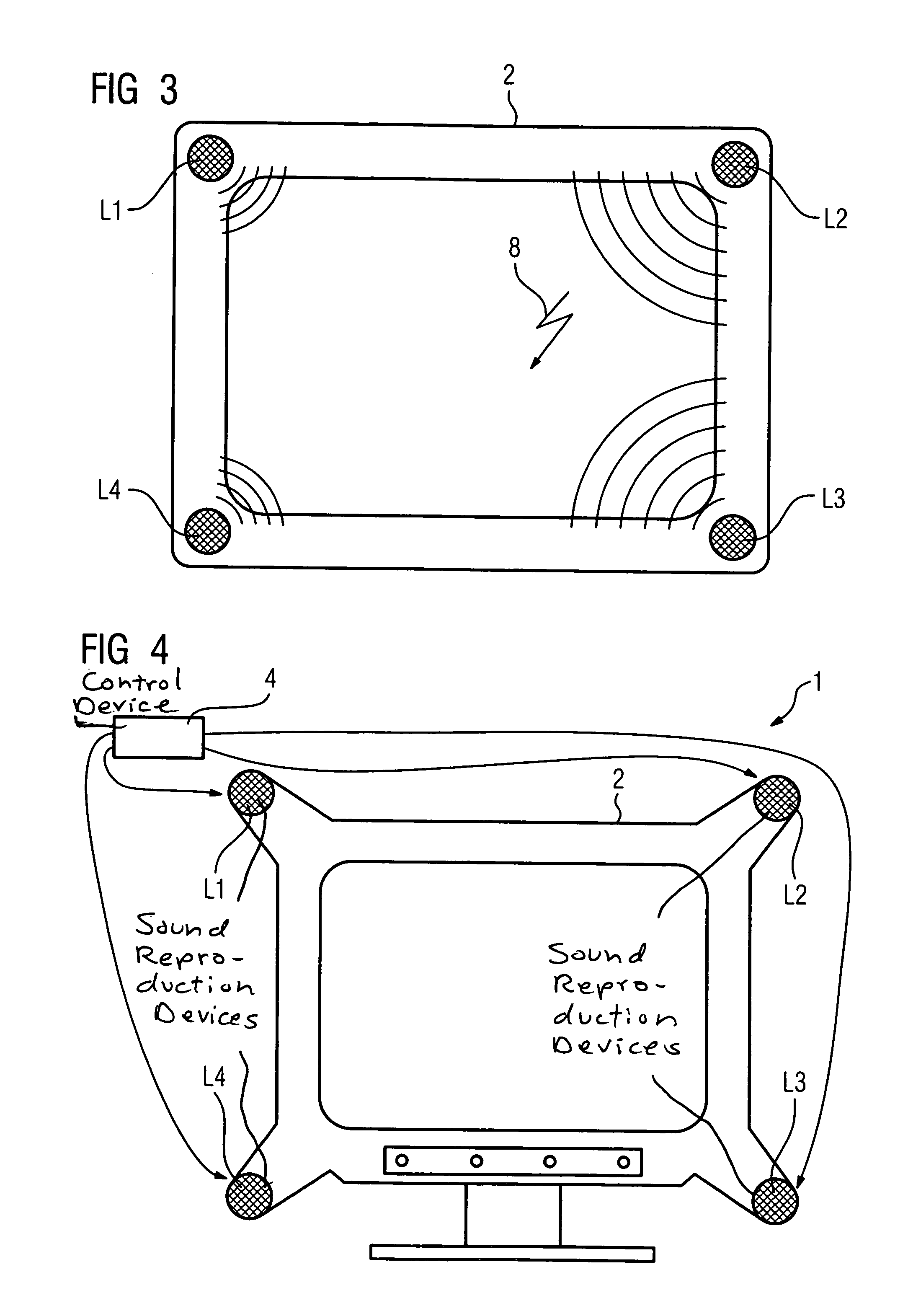

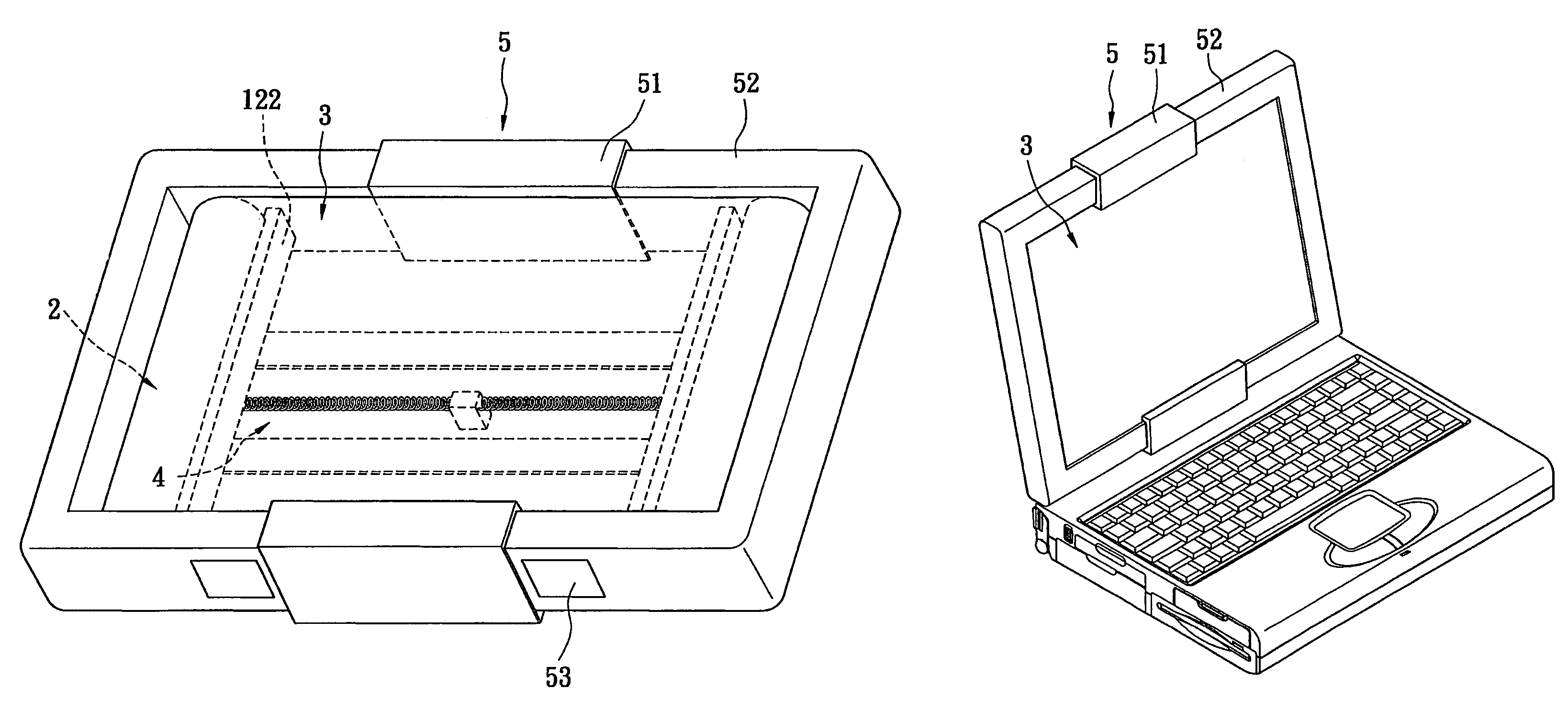

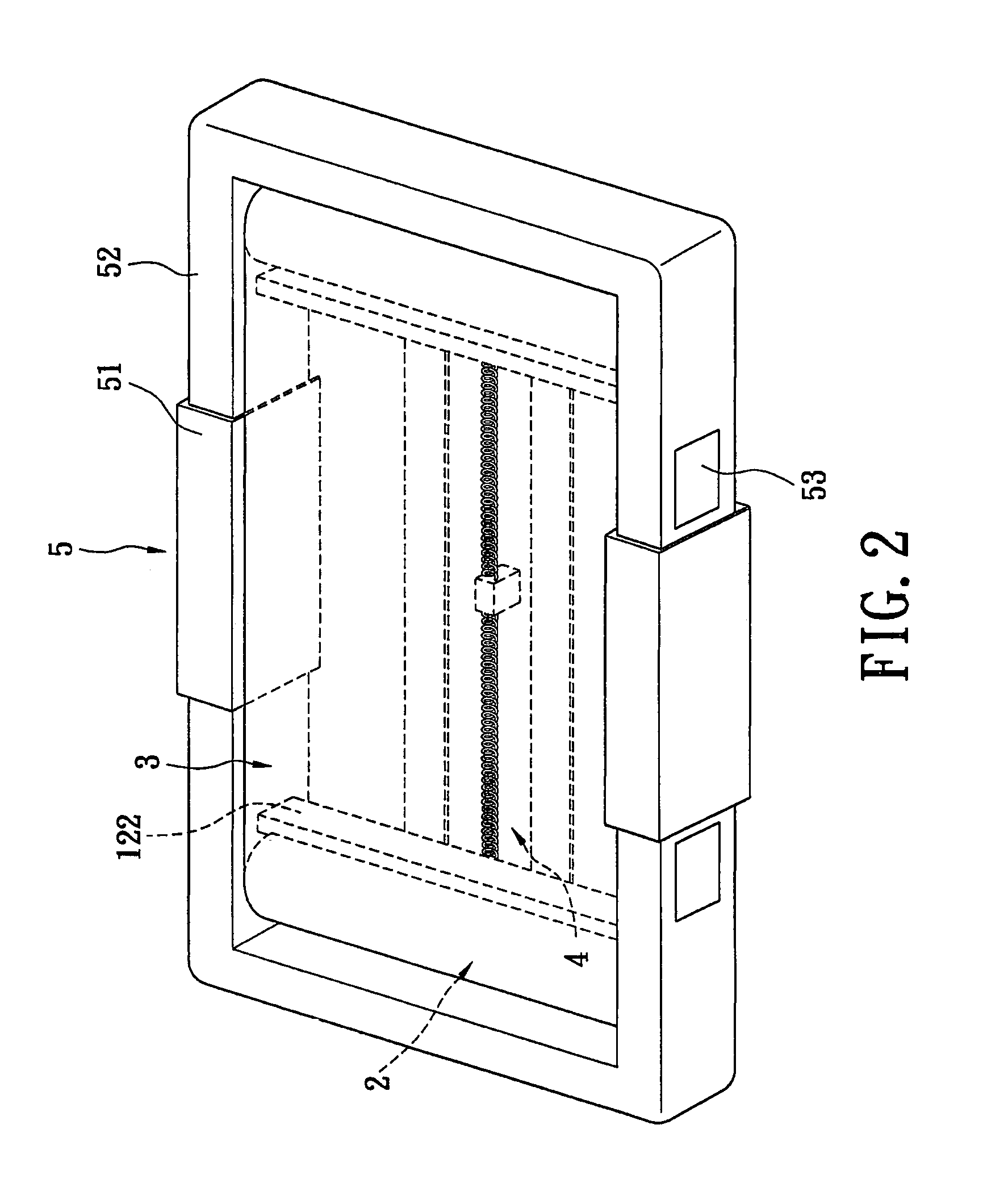

Variable-sized screen

InactiveUS20070146243A1Avoid smallDimension of will varyTelevision system detailsStatic indicating devicesFixed frameDisplay device

A variable-sized screen includes a support, at least one scrolling device and a flexible display. The support has a fixing frame and a movable frame, which are retractably connected. The scrolling device and the flexible display are assembled on the support. The flexible display is wrapped around the support, and the size of the flexible display is variable due to displacement of the support. When the support changes size through a retracted movement of the movable frame and the fixing frame, the flexible display also changes size correspondingly and the size of the screen becomes variable. Therefore, the dimensions of the screen and electronic products are not limited, and the display device has the advantages of a big screen yet is still portable and convenient for a user.

Owner:LITE ON TECH CORP

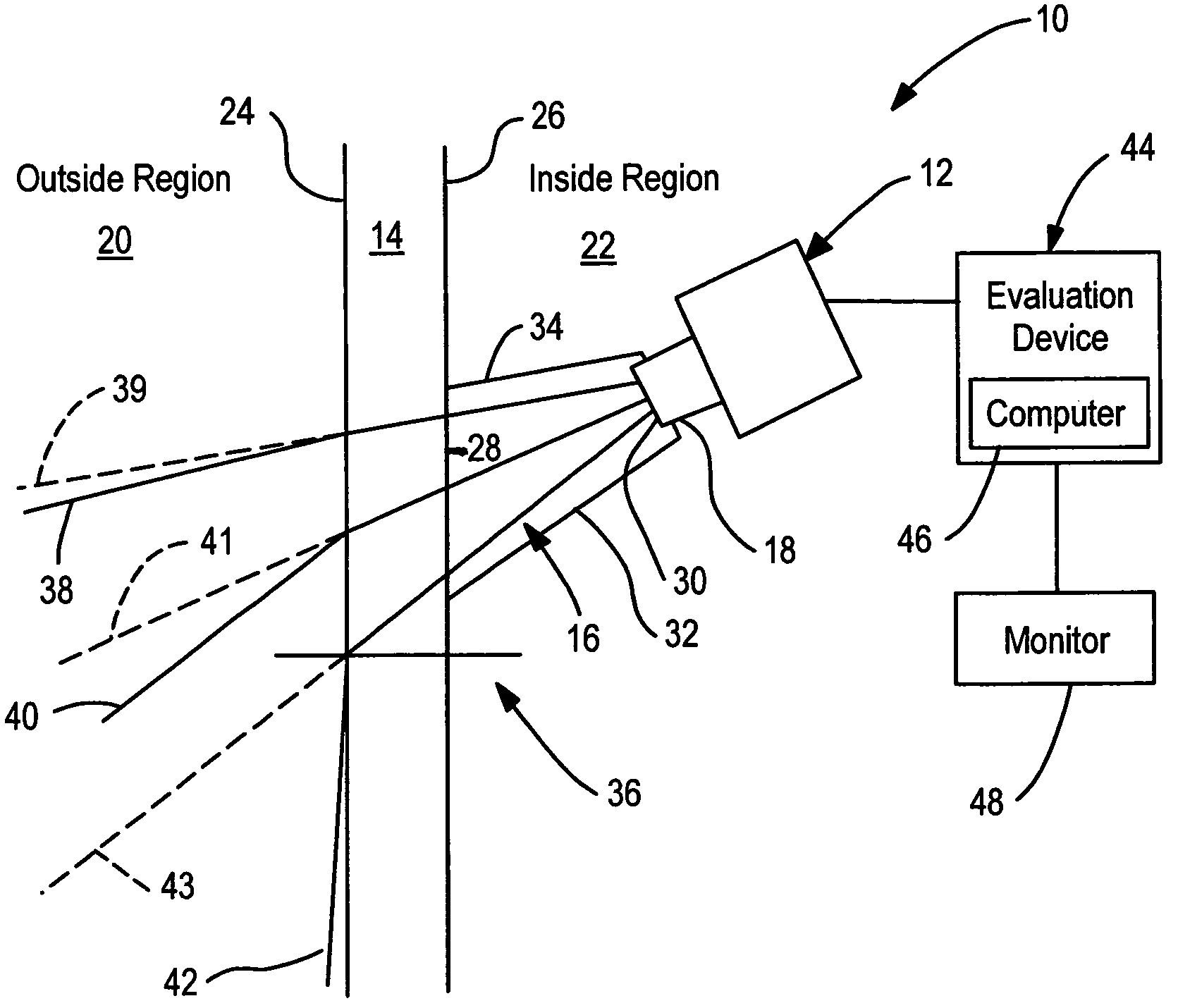

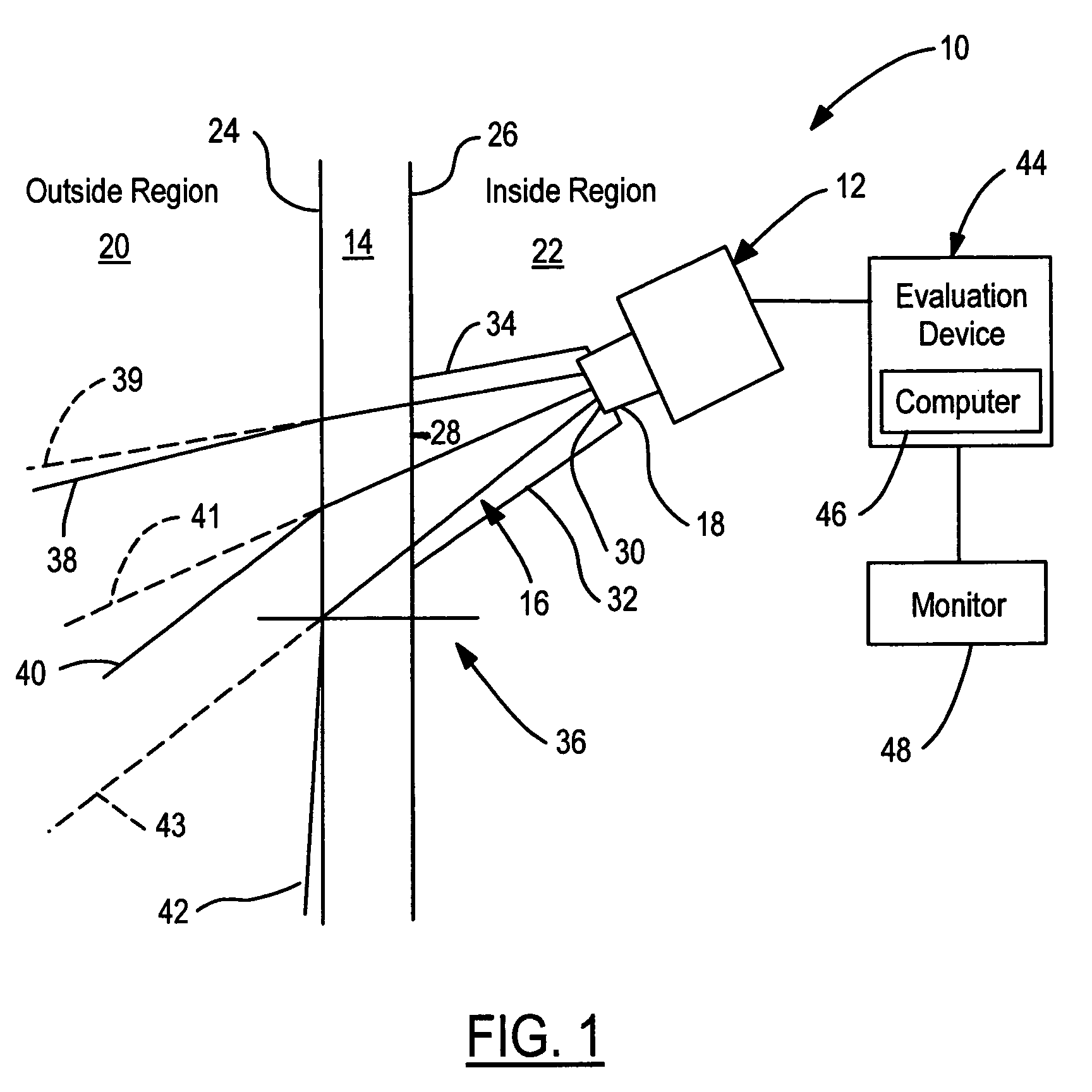

Camera arrangement behind an inclined pane

ActiveUS7811011B2Avoid reflectionsAngular region detected by a camera through the pane isConcealed burglar systemsColor television detailsCamera lensLight guide

A camera arrangement includes a camera having a lens pointed at a pane and being separated from the pane. A light-guiding element is between the camera lens and the pane. The light-guiding element guides at least light which is incident on the pane in a grazing manner from a direction of incidence to the camera.

Owner:LEOPOLD KOSTAL GMBH & CO KG

Information display apparatus

InactiveUS6888522B1Without consume electric powerLow costStatic indicating devicesInput/output processes for data processingLiquid-crystal displayLiquid crystal

An information display apparatus which has a liquid crystal display which uses chiral nematic liquid crystal with a memory effect and can be driven by a matrix driving method. The screen of the display is divided along a scanning line into a still picture display area and a motion picture display area. The information display apparatus may have a first display and a second display on one screen. The first display is a reflective type liquid crystal display with a memory effect, which has an advantage of saving energy, and is used exclusively to display a still picture. The second display is a liquid crystal display which requires only a short time for writing. Information to be written in a short time, such as inputted information, is displayed on the second display.

Owner:MINOLTA CO LTD

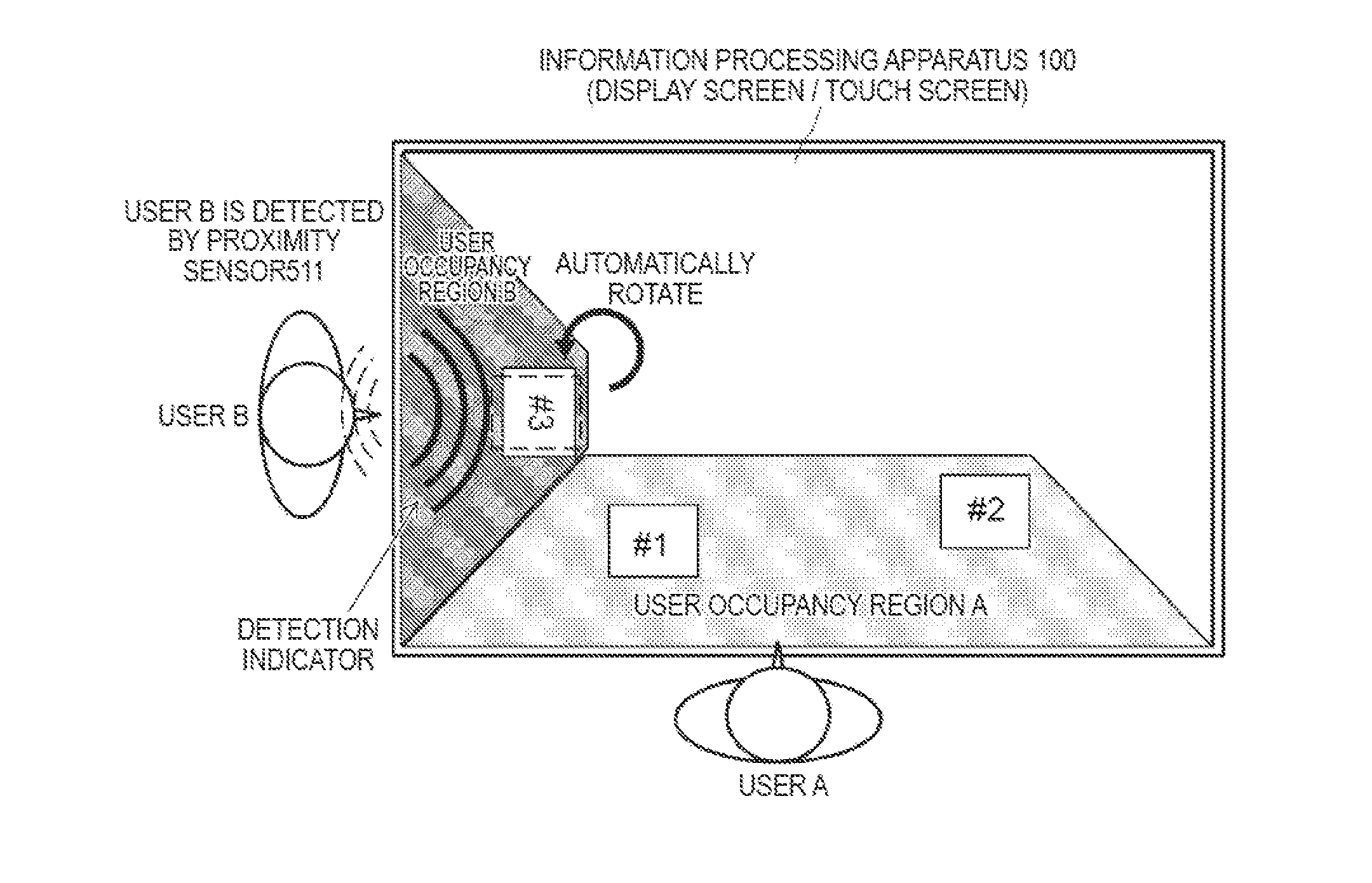

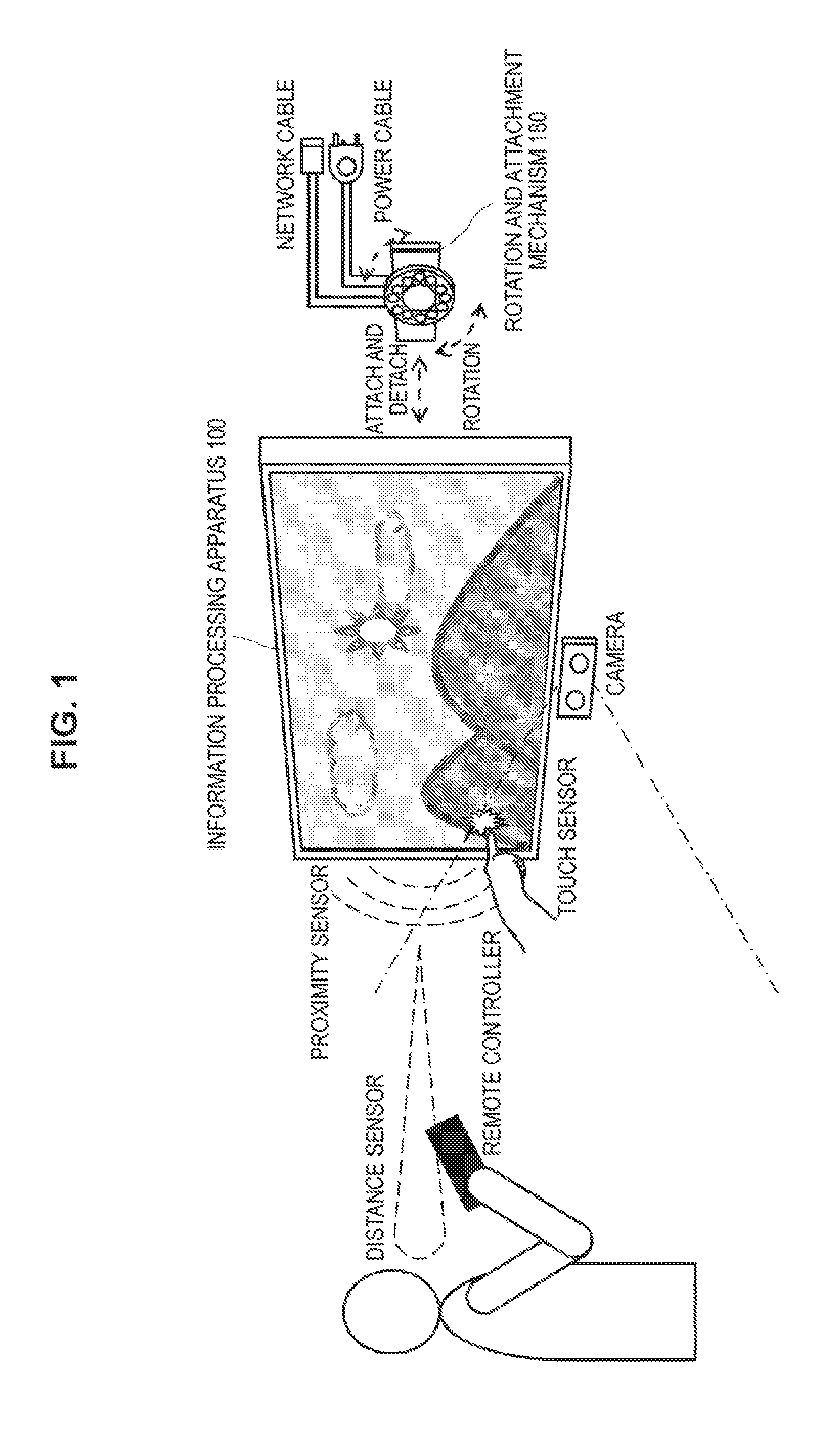

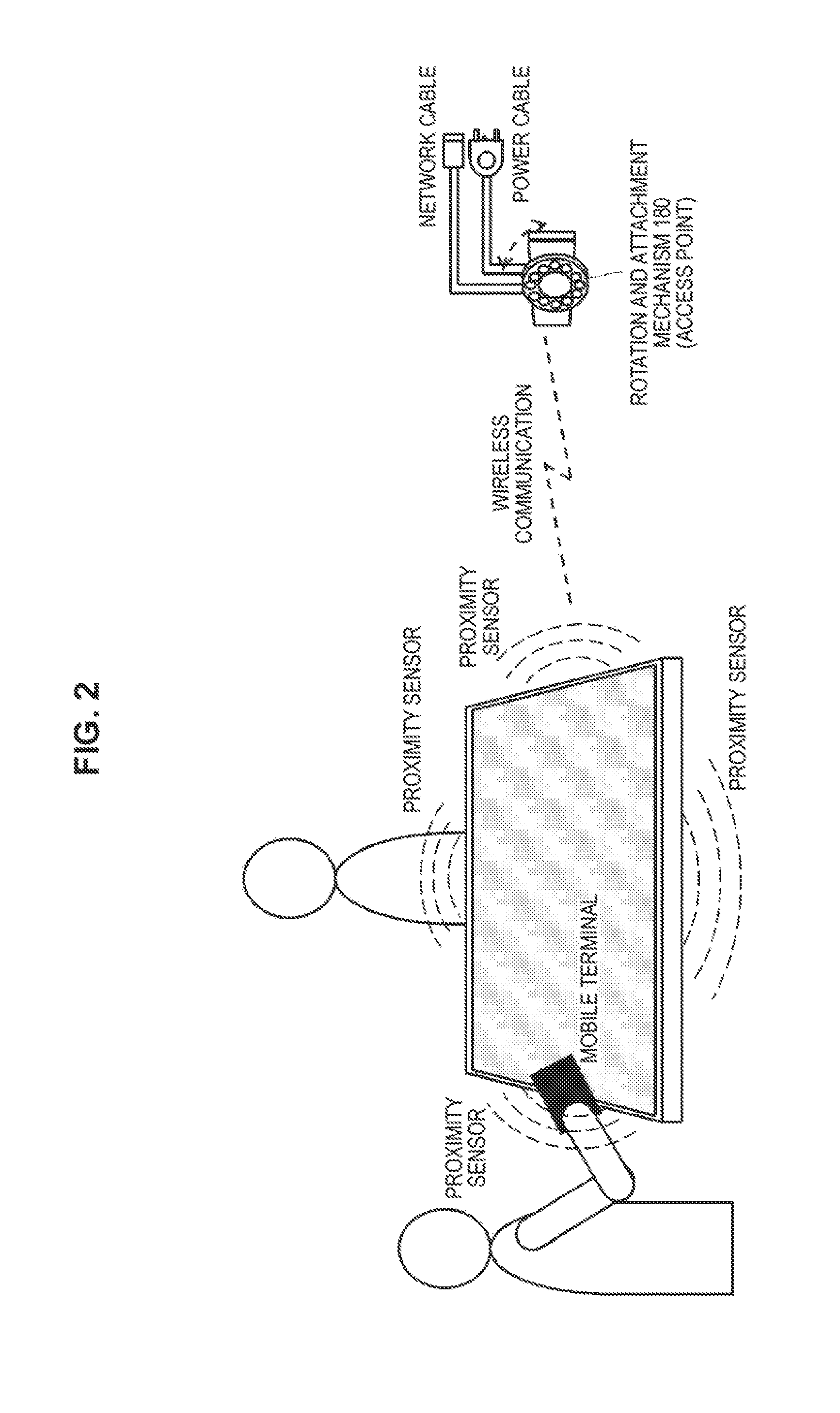

Information processing apparatus and information processing method, and computer program

ActiveUS20140354695A1Improve user convenienceEasy to seeGeometric image transformationCathode-ray tube indicatorsInformation processingImaging processing

There is provided an information processing apparatus including a display part to display video content on a screen, a rotation angle detection part to detect a rotation angle of the screen, a display formation determination part to determine a display formation of video content at any rotation angle of the screen or during transition of the rotation, and an image processing part to perform an image processing in accordance with the display formation determined by the display formation determination part such that the video content is conformed to the screen which is tilted by the rotation angle detected by the rotation angle detection part.

Owner:SATURN LICENSING LLC

Variable-sized screen

InactiveUS7440265B2Big screenDimension of will varyTelevision system detailsStatic indicating devicesFixed frameDisplay device

A variable-sized screen includes a support, at least one scrolling device and a flexible display. The support has a fixing frame and a movable frame, which are retractably connected. The scrolling device and the flexible display are assembled on the support. The flexible display is wrapped around the support, and the size of the flexible display is variable due to displacement of the support. When the support changes size through a retracted movement of the movable frame and the fixing frame, the flexible display also changes size correspondingly and the size of the screen becomes variable. Therefore, the dimensions of the screen and electronic products are not limited, and the display device has the advantages of a big screen yet is still portable and convenient for a user.

Owner:LITE ON TECH CORP

Display Device and Method for Manufacturing Display Device

InactiveUS20090096364A1Low costImprove productivityDischarge tube luminescnet screensLamp detailsImaging qualityDisplay device

To provide a display device with higher image quality and reliability or a large-sized display device with a large screen at low cost with high productivity. A function layer (such as a coloring layer or a pixel electrode layer) used in the display device is formed by discharging a liquid function-layer-forming material to an opening formed with a layer including a first organic compound which has a C—N bond or a C—O bond in the main chain as a base and a layer including a second organic compound as a partition. The fluorine density exhibiting liquid repellency to the liquid function-layer-forming material, which is attached to a surface of the layers including organic compounds, is controlled, whereby a liquid repellent region and a lyophilic region can be selectively formed.

Owner:SEMICON ENERGY LAB CO LTD

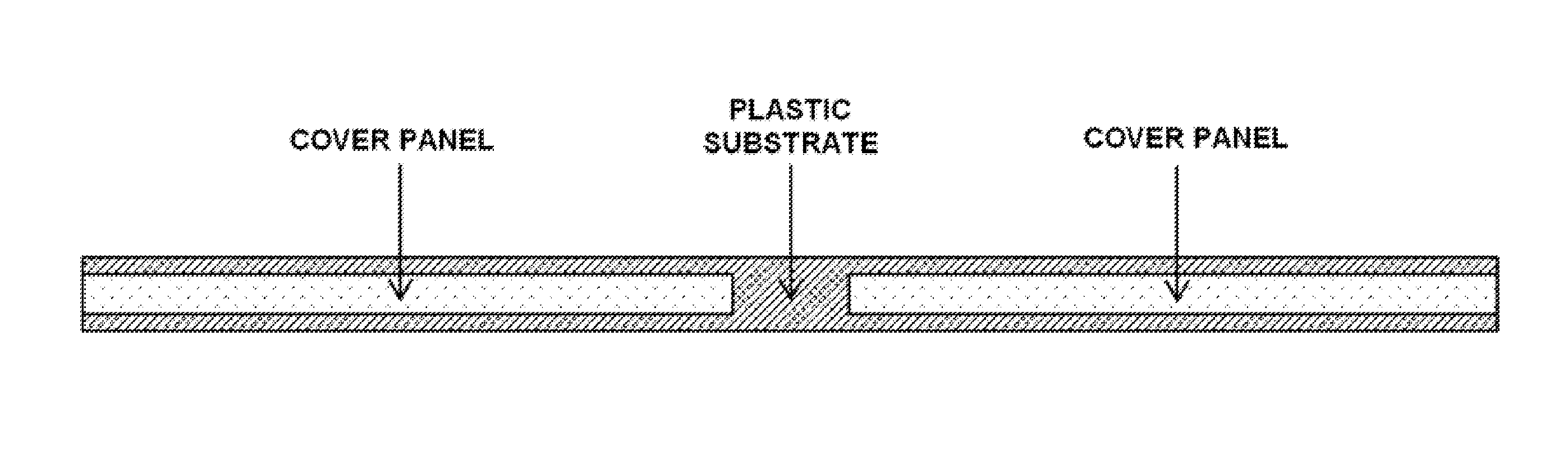

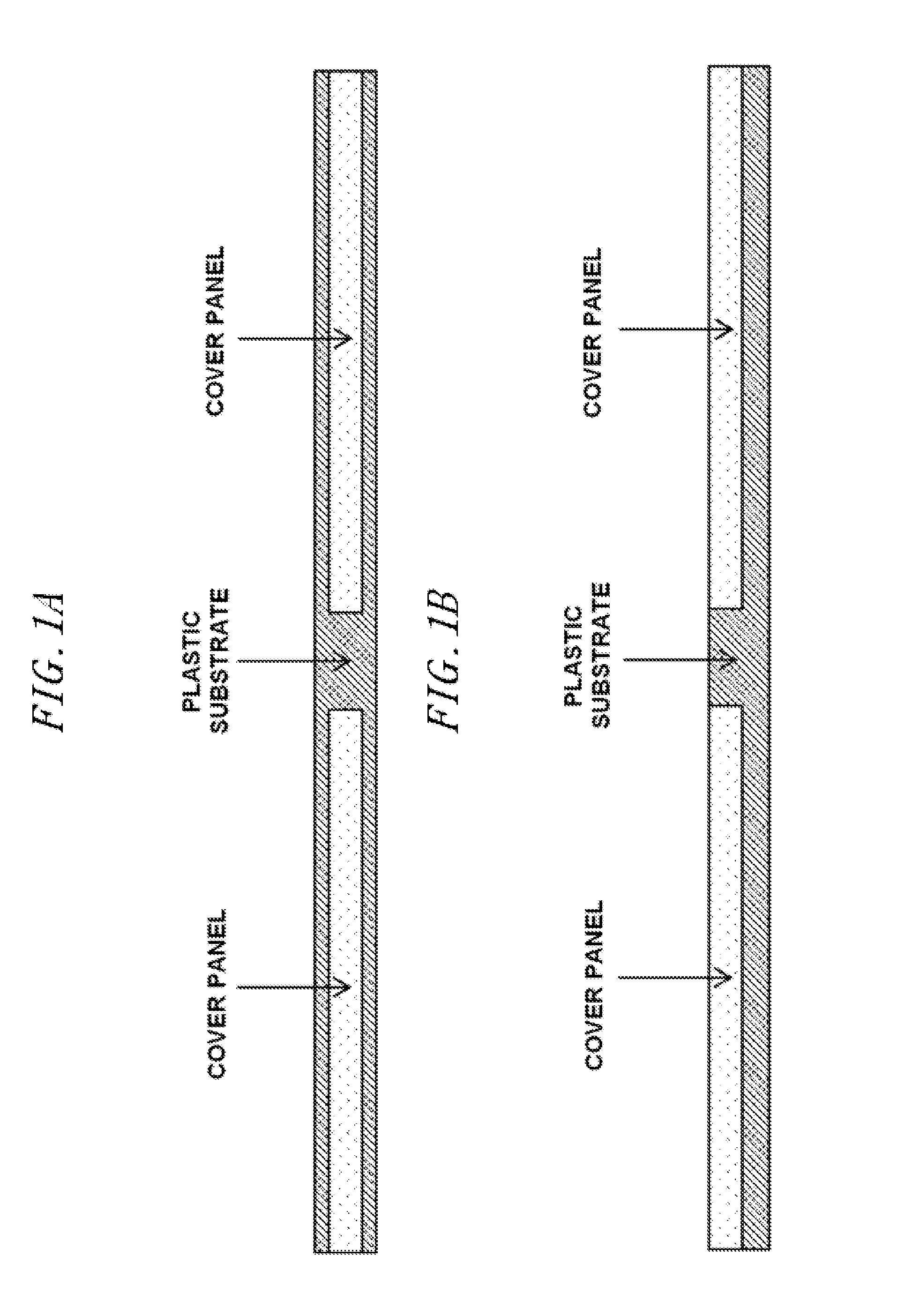

Foldable transparent composite cover window, manufacturing method of the same, and foldable display device containing the same

InactiveUS20150004334A1Minimize any discontinuityHigh portabilityPaper/cardboard articlesGlass/slag layered productsEngineeringDisplay device

A foldable transparent composite cover window, a manufacturing method therefore, and a display device including the foldable transparent composite cover window are provided.

Owner:KOREA ADVANCED INST OF SCI & TECH

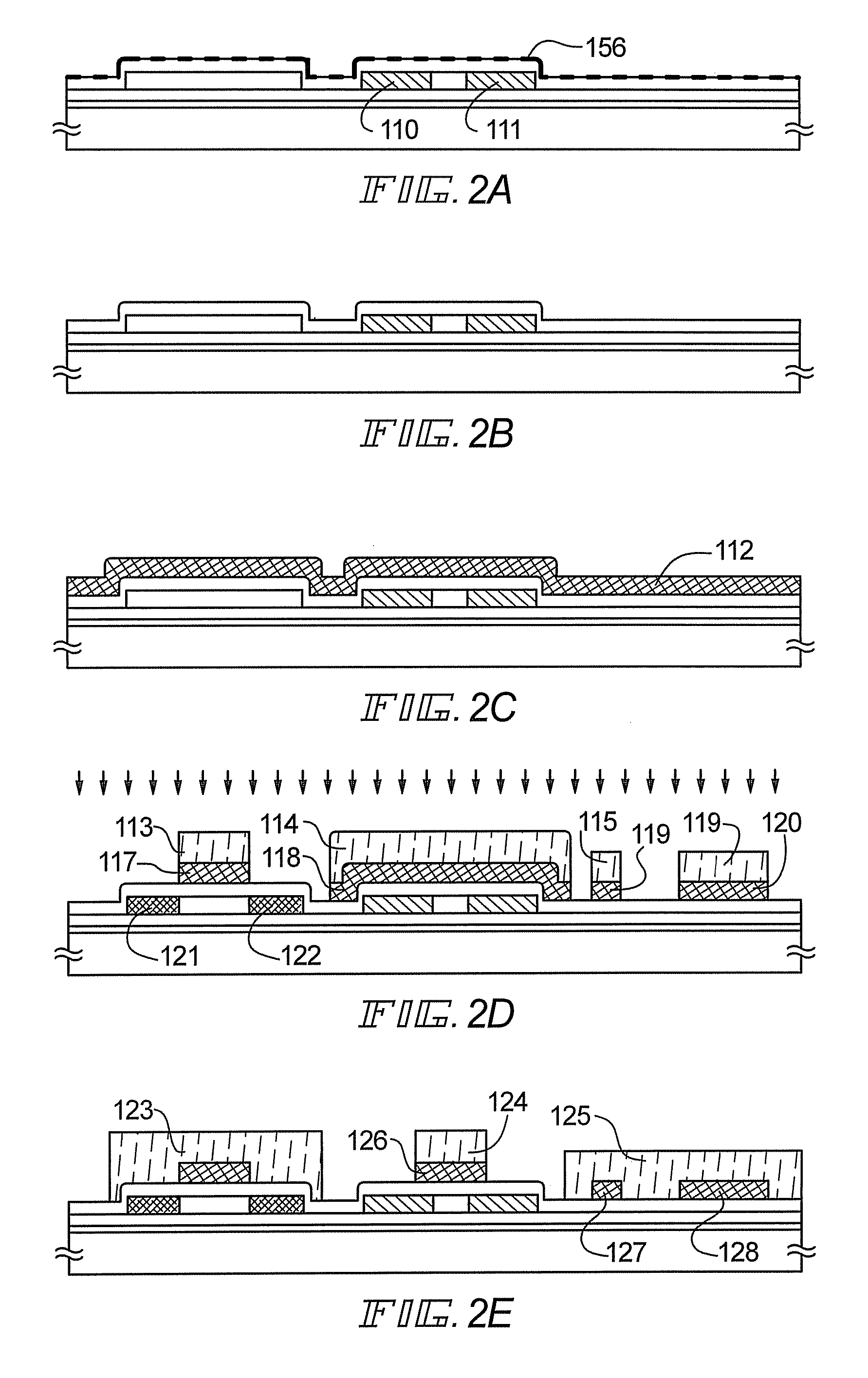

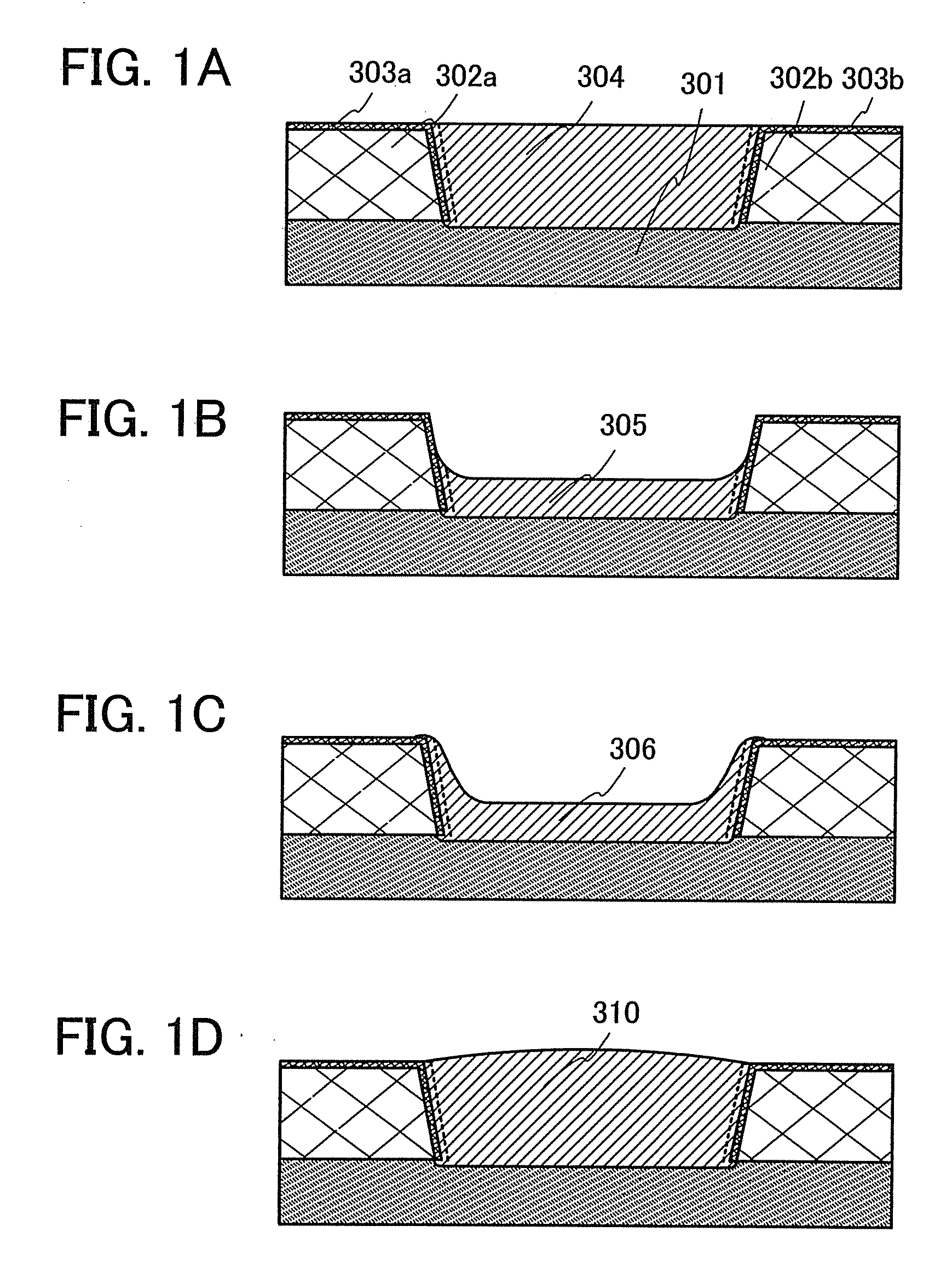

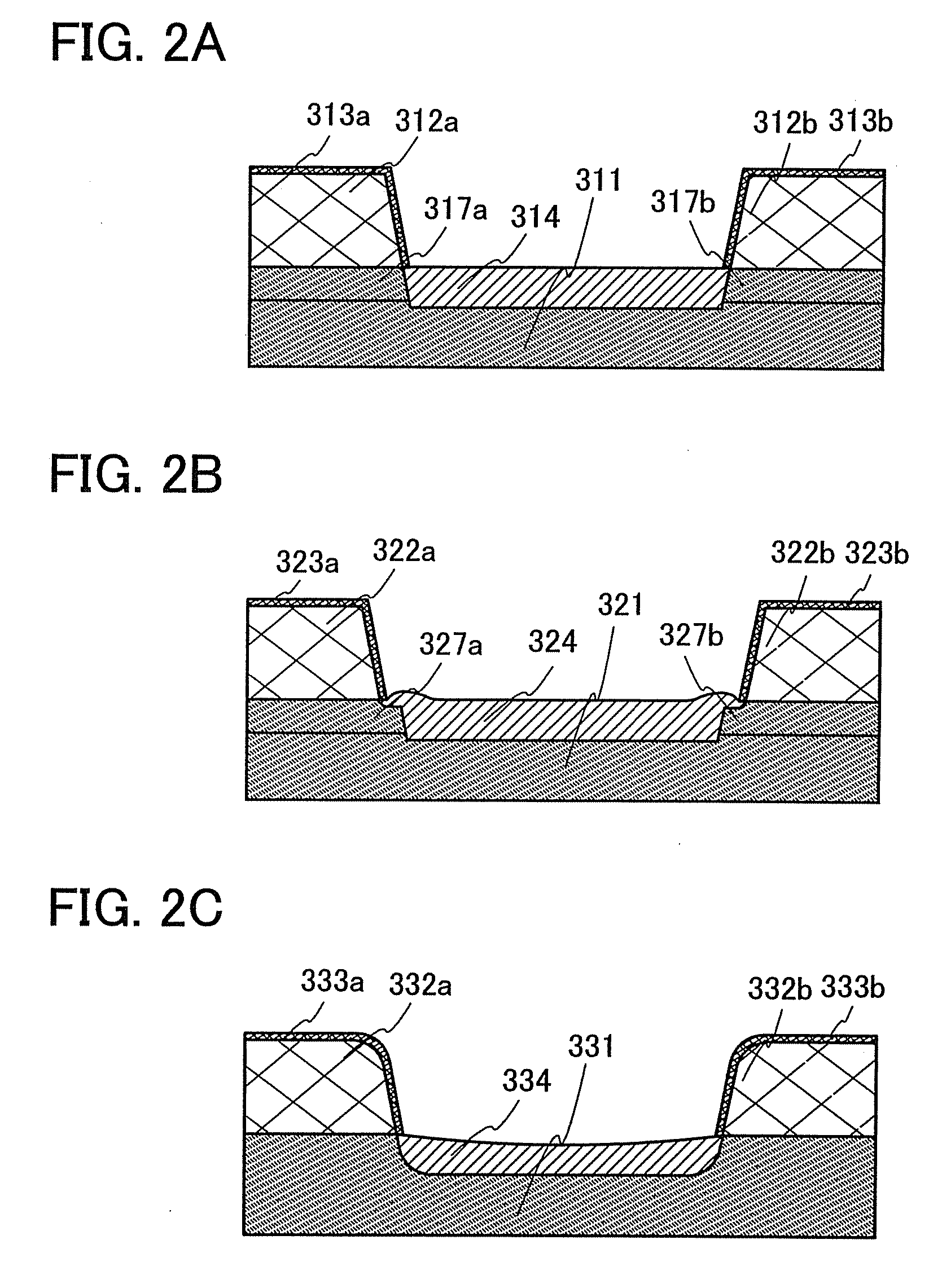

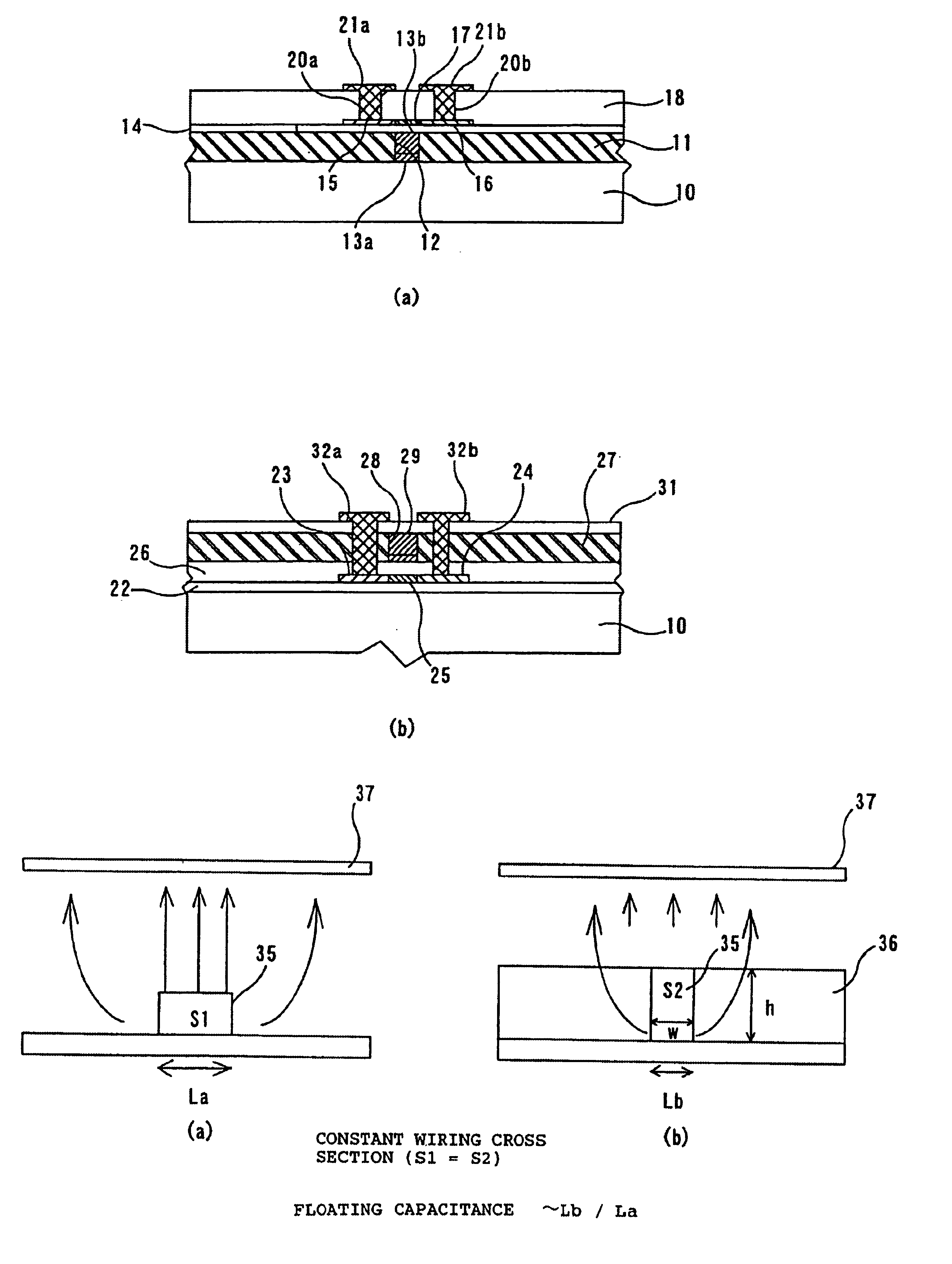

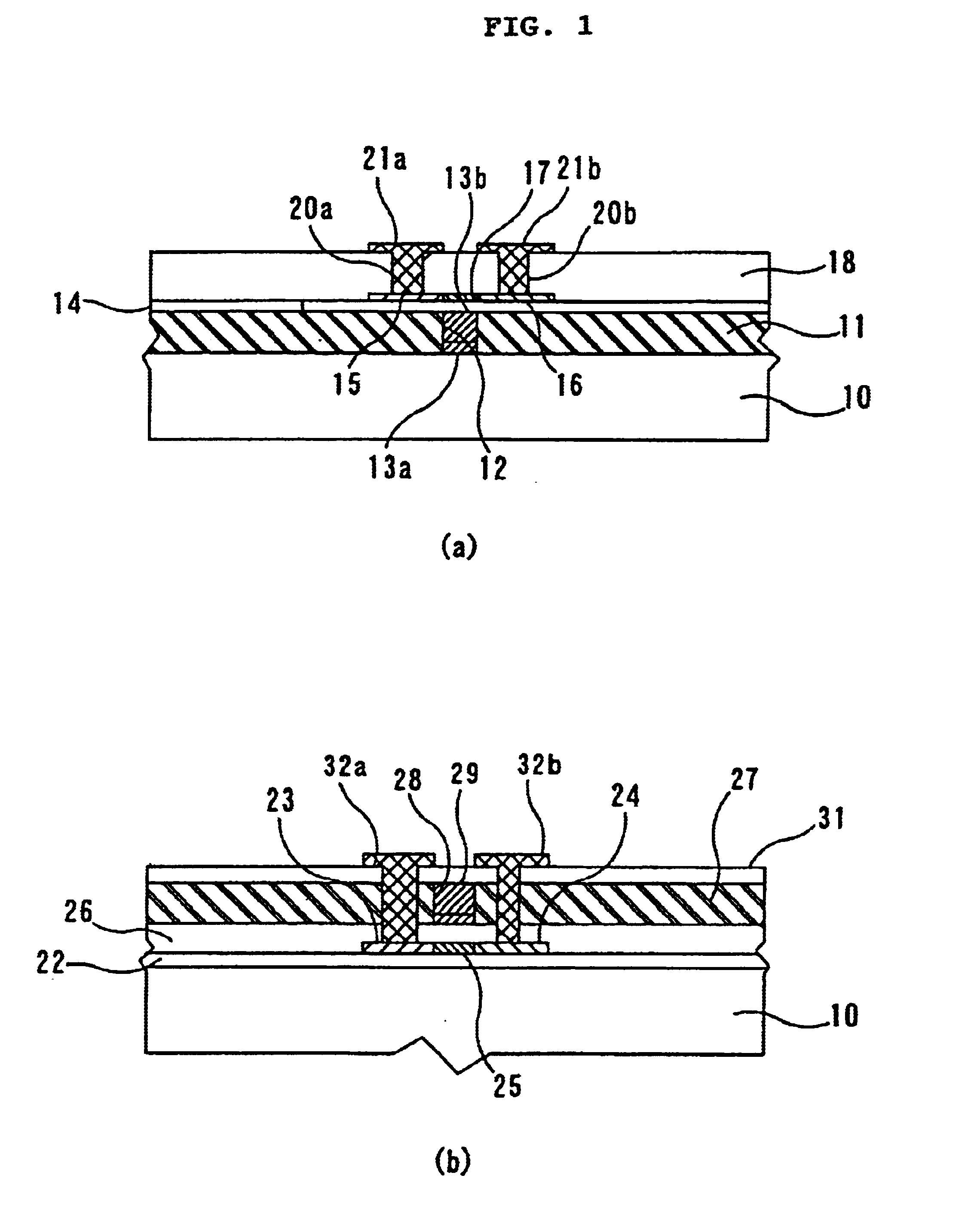

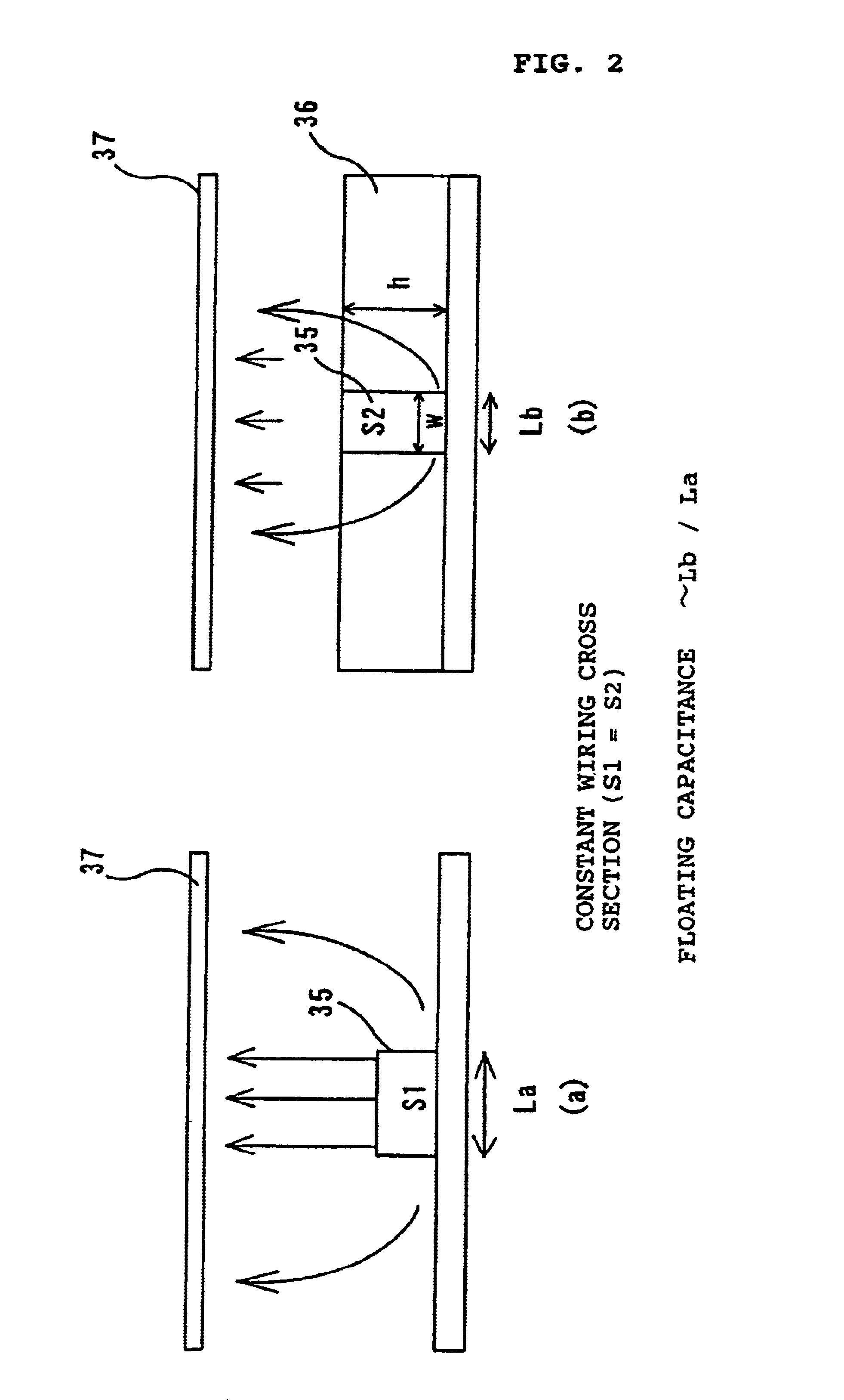

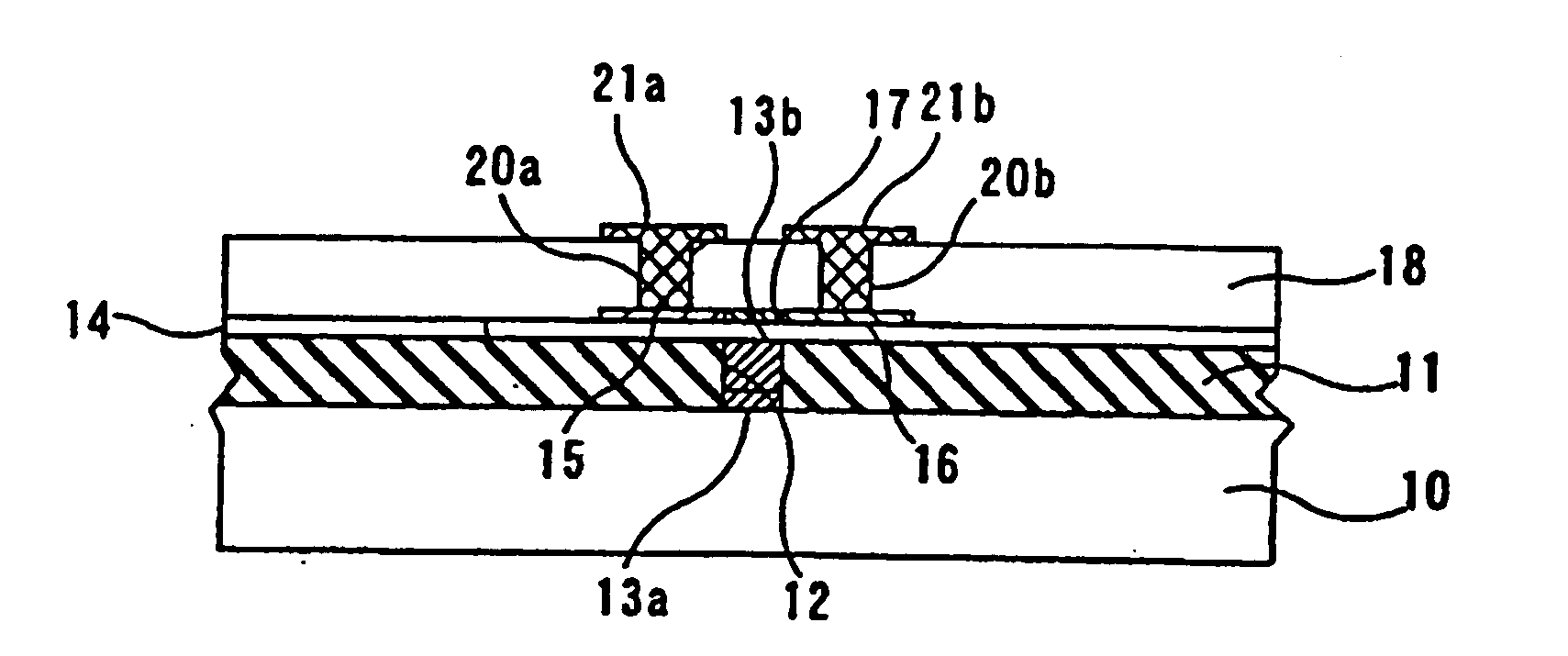

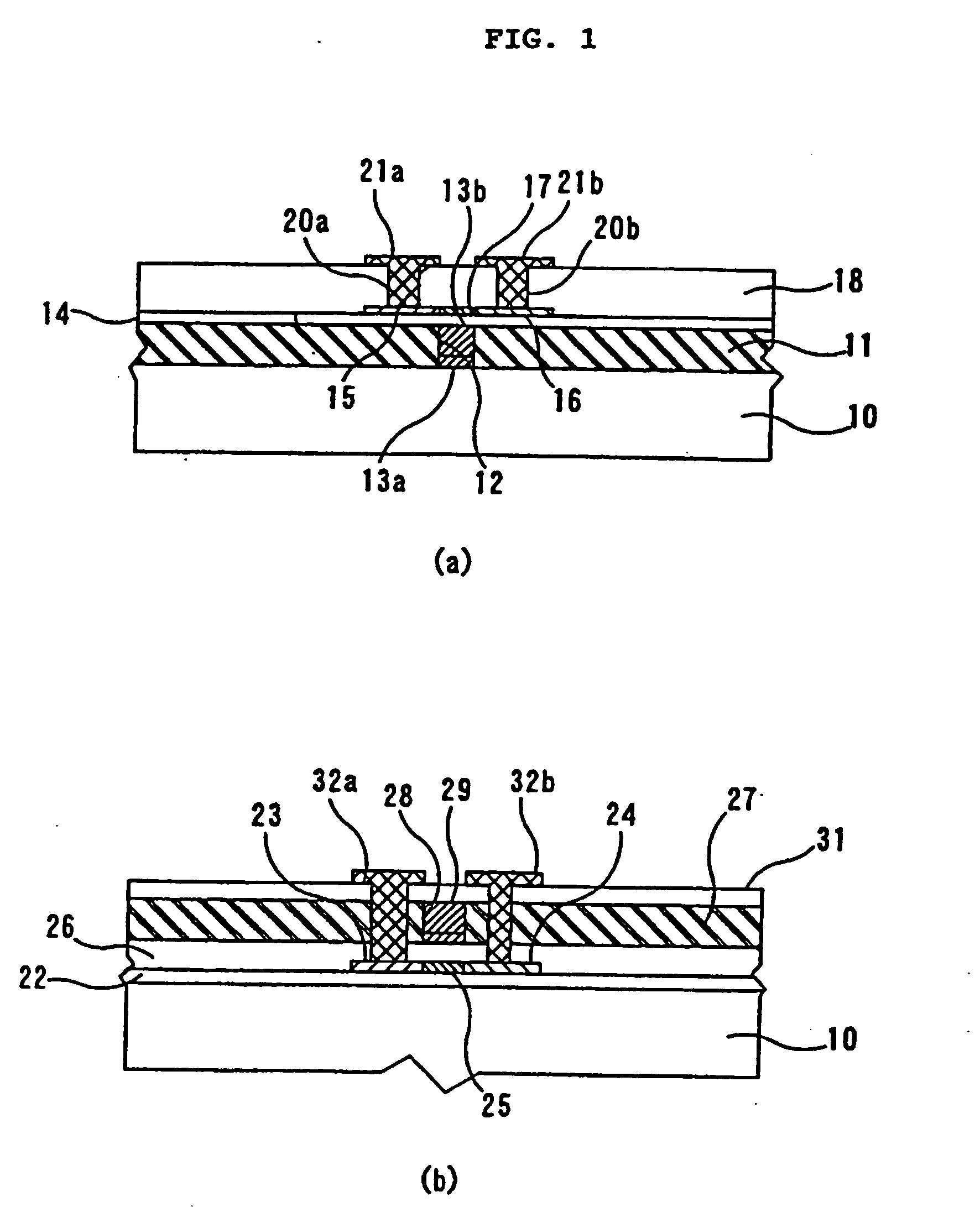

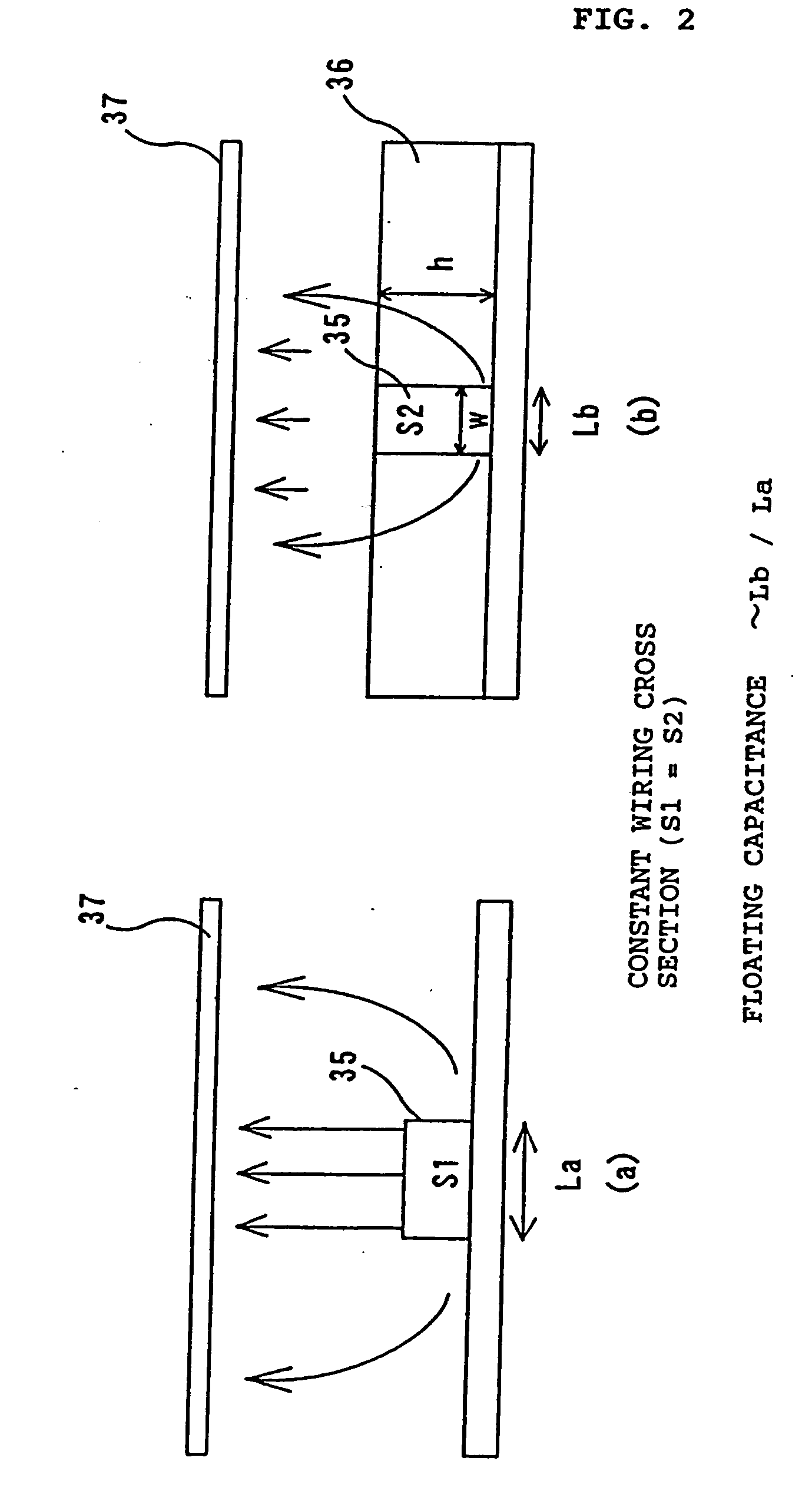

Thin-film transistor structure, method for manufacturing the thin-film transistor structure, and display device using the thin-film transistor structure

InactiveUS6952036B2Big screenHigh definitionTransistorSemiconductor/solid-state device detailsDisplay deviceEngineering

The present invention provides a thin film transistor structure in which at least a trench is formed in an insulating polymer film formed on a substrate. In the thin film transistor structure, a trench formed in the insulating polymer film accommodates a gate wiring constituted of a plurality of conductive layers. Provided also are a method of manufacturing the thin film transistor structure, and a display device including a thin film transistor array composed of the thin film transistors constituted as described above.

Owner:IBM CORP

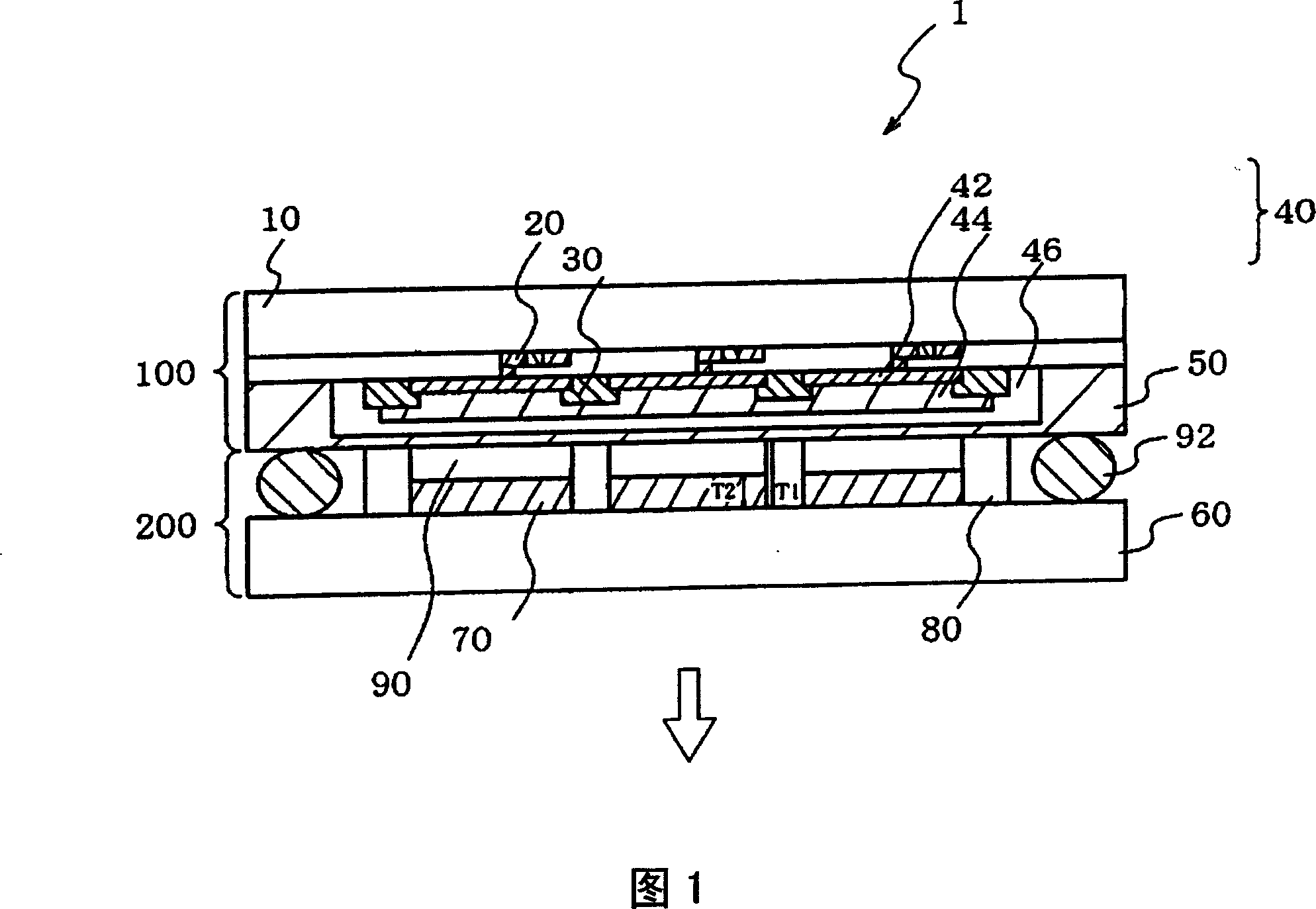

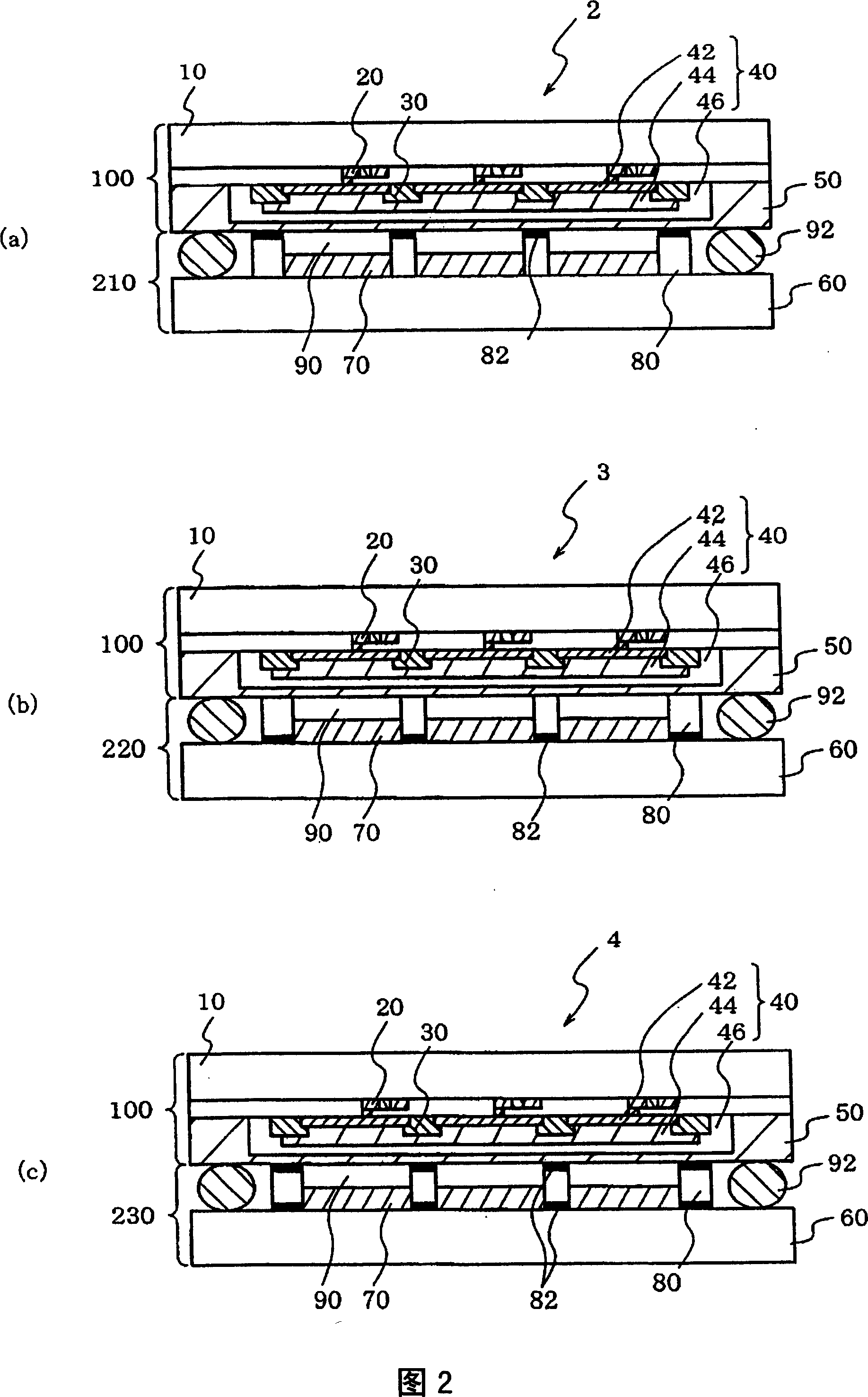

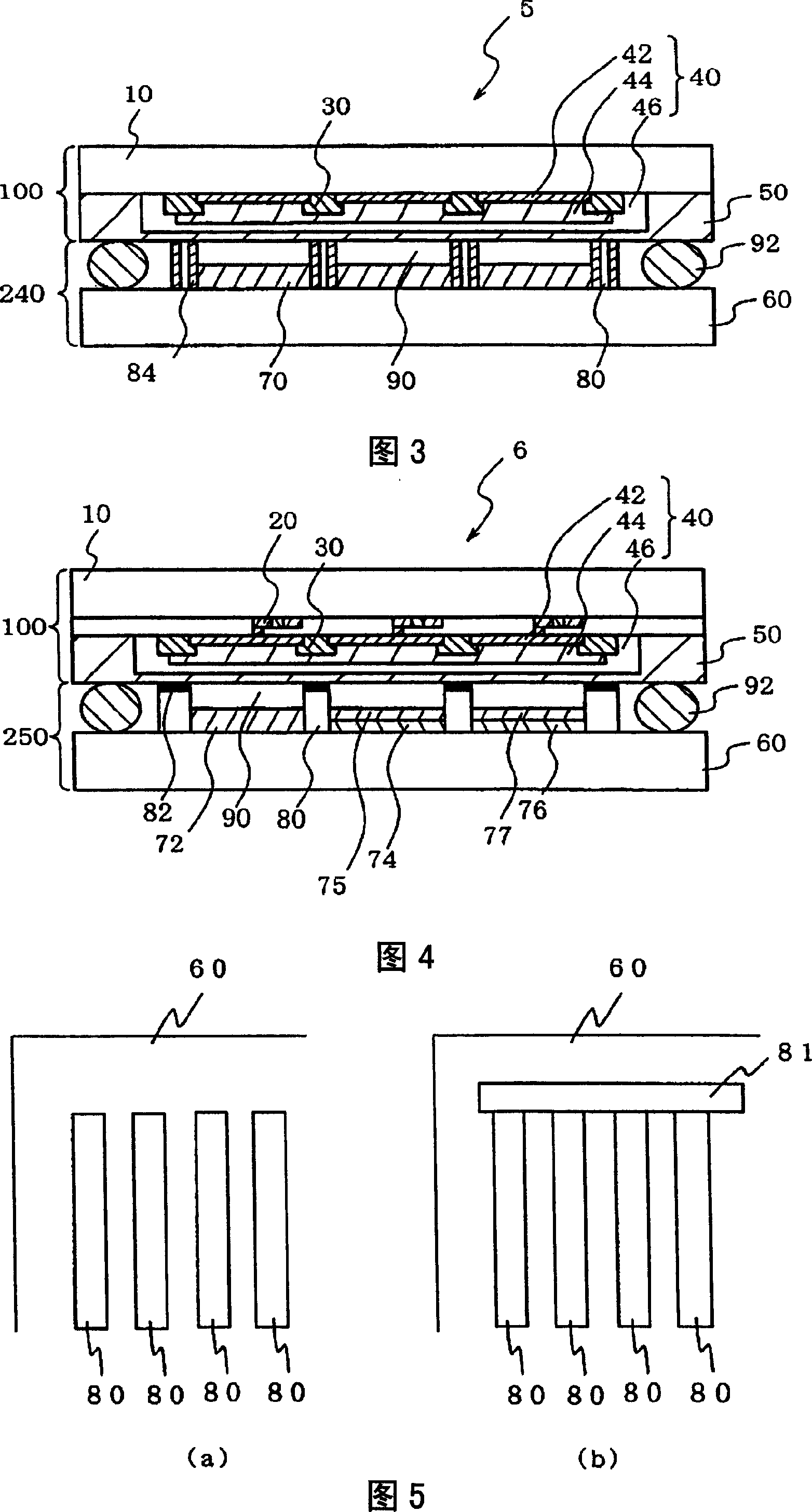

Organic EL display device

InactiveCN1969595AIncreased fluorescence conversion efficiencyImprove luminous efficiencyElectroluminescent light sourcesSolid-state devicesOn boardDisplay device

In an organic EL display device, an organic EL board (100) wherein an organic EL element (40) is formed on a first board (10), and a color conversion board (200) wherein a color conversion layer (70) is formed on a second board (60) are arranged by permitting the organic EL element (40) to face the color conversion layer (70). A transparent wall (80) which is thicker than the color conversion layer (70) is provided between the color conversion layers (70) of the color conversion board (200). The wall (80) is a partition wall for separating the color conversion layer (70), and is also a spacer between the organic EL board (100) and the color conversion board (200). A sealing medium (90) is provided between the walls (80) with the color conversion layer (70).

Owner:IDEMITSU KOSAN CO LTD

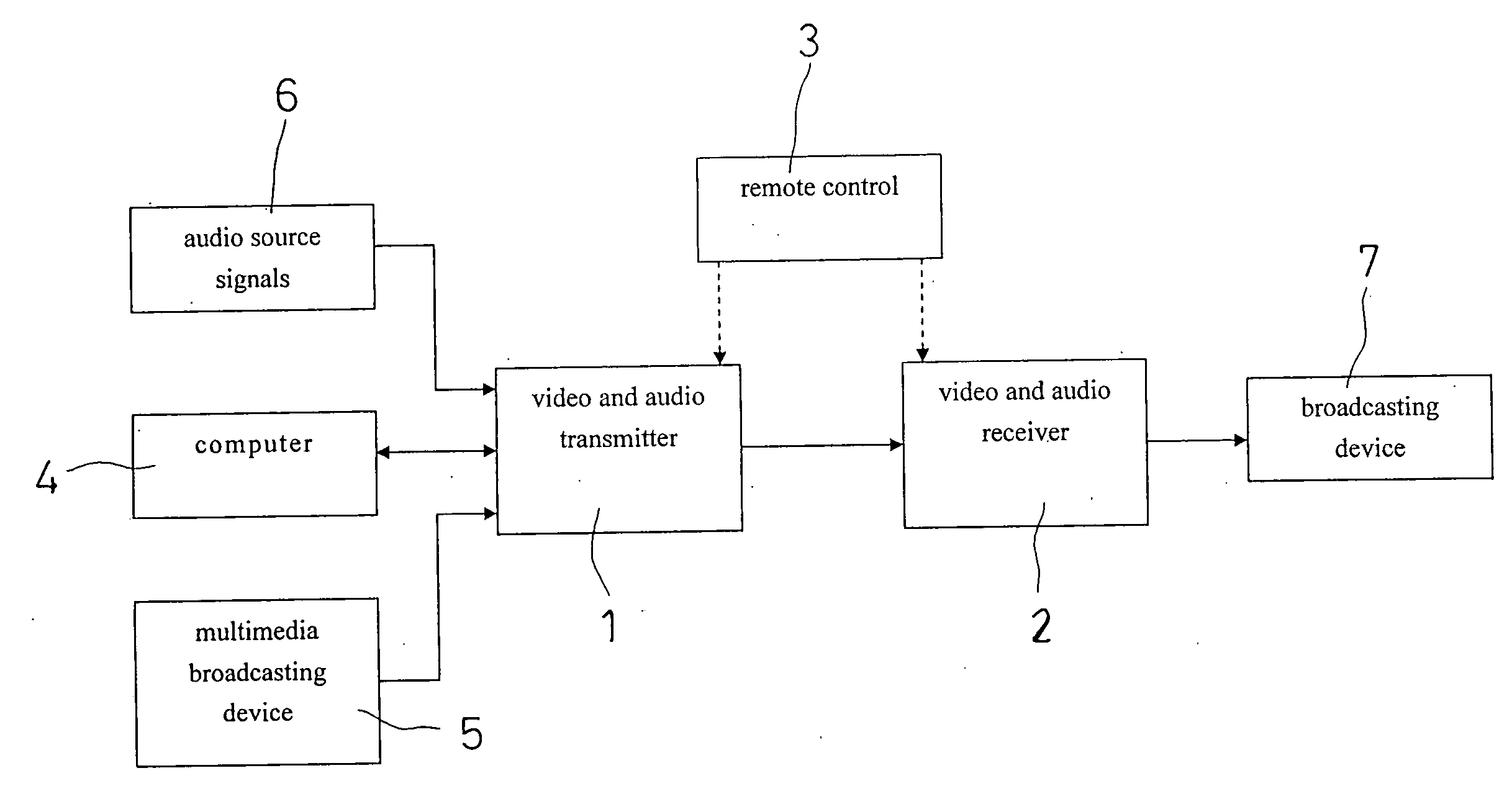

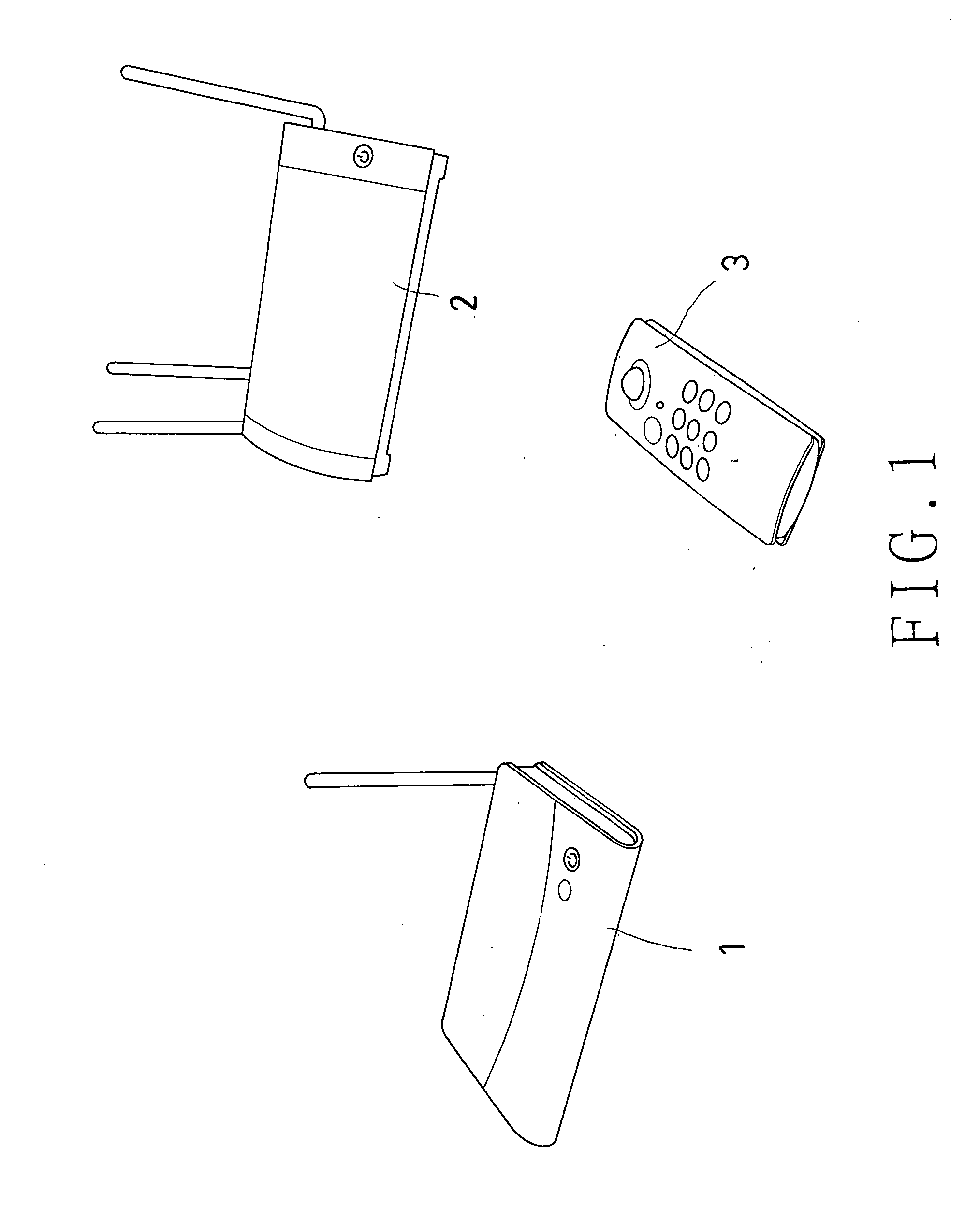

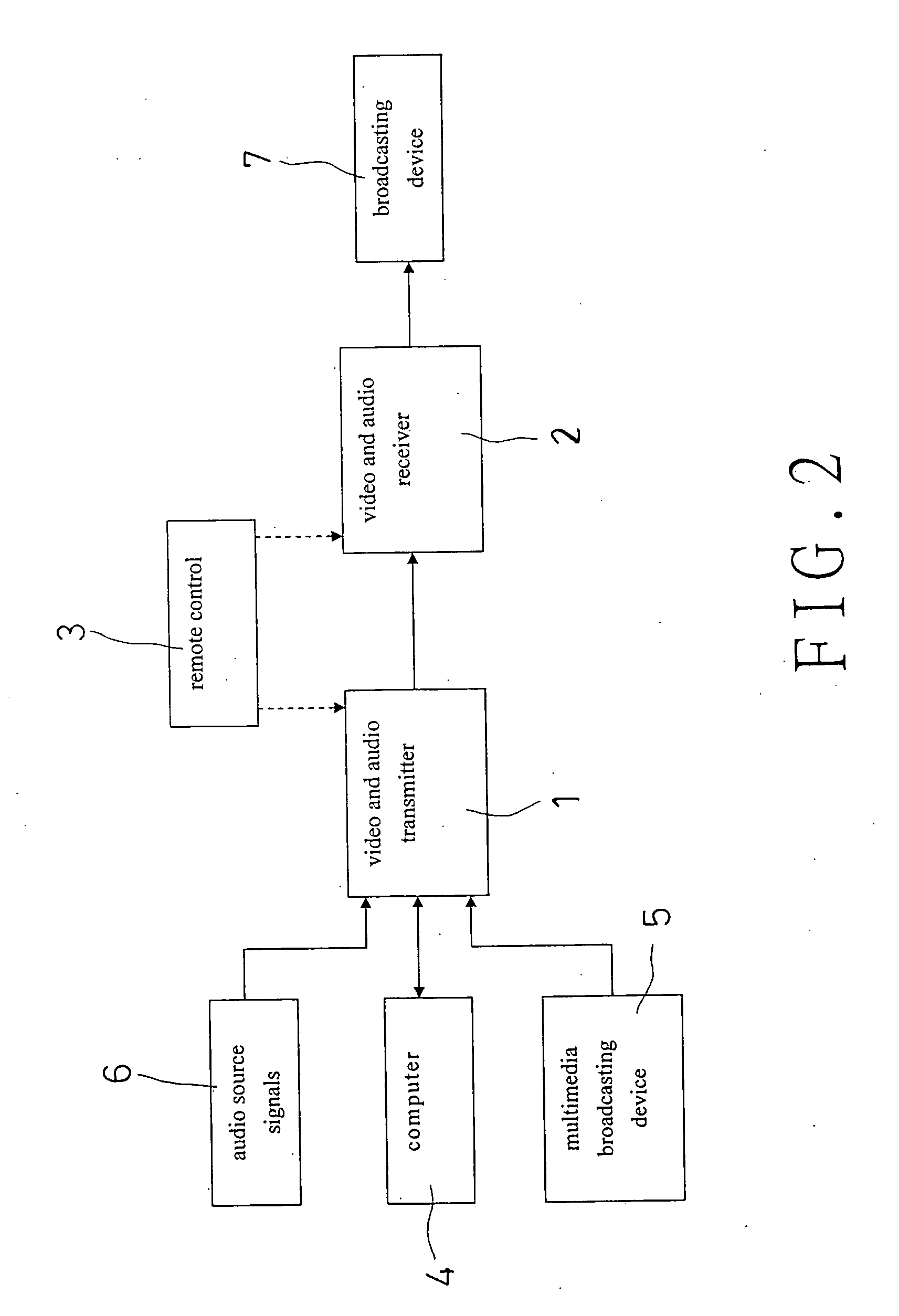

Wireless video and audio broadcasting device

InactiveUS20090254953A1Improve image qualityImprove sound qualityTwo-way working systemsSelective content distributionOverhead projectorRemote control

A broadcasting device includes a video and audio transmitter, several video and audio receivers to wirelessly receive signals from the video and audio transmitter, and a remote control; the video and audio transmitter is connected to a multimedia broadcasting device such as computers, MP3, MP4, CD and DVD players; the video and audio receivers are each connected to a respective second broadcasting device such as televisions, overhead projectors, stereos, and speakers so that video and audio information contained in the multimedia broadcasting device can be transmitted through the transmitter, received with the receivers, and broadcasted through the second broadcasting devices connected to the receivers; the remote control is used to control the video and audio transmitter and the broadcasting devices connected to the receivers.

Owner:JOW TONG TECH CO LTD

Thin-film transistor structure, method for manufacturing the thin-film transistor structure, and display device using the thin-film transistor structure

InactiveUS20050250262A1Big screenHigh definitionTransistorSemiconductor/solid-state device manufacturingDisplay deviceEngineering

The present invention provides a thin film transistor structure in which at least a trench is formed in an insulating polymer film formed on a substrate. In the thin film transistor structure, a trench formed in the insulating polymer film accommodates a gate wiring constituted of a plurality of conductive layers. Provided also are a method of manufacturing the thin film transistor structure, and a display device including a thin film transistor array composed of the thin film transistors constituted as described above.

Owner:INT BUSINESS MASCH CORP

Image display device

InactiveUS6977635B2Simple structureBig screenCathode-ray tube indicatorsInput/output processes for data processingShortest distanceDisplay device

A line inverse driving method is performed by outputting voltages for gradation display in mutually reverse polarities with respect to pixels adjacent in a data signal line direction. A separation switch is provided between an output stage of a data driver and a data signal line to separate them. In a blanking period, the data signal line is cut off, and in the selection-scanning period of a scanning signal line to be scanned first, the scanning signal line to be scanned next is also subjected to the selection-scanning. With this structure, respective charges in adjacent pixel capacitors are neutralized, and it is therefore possible to reduce a power consumption. Further, since a short-circuit can be performed at short distance, the problem of dull waveform can be suppressed, thereby realizing an image display device suited for a large screen.

Owner:SHARP KK

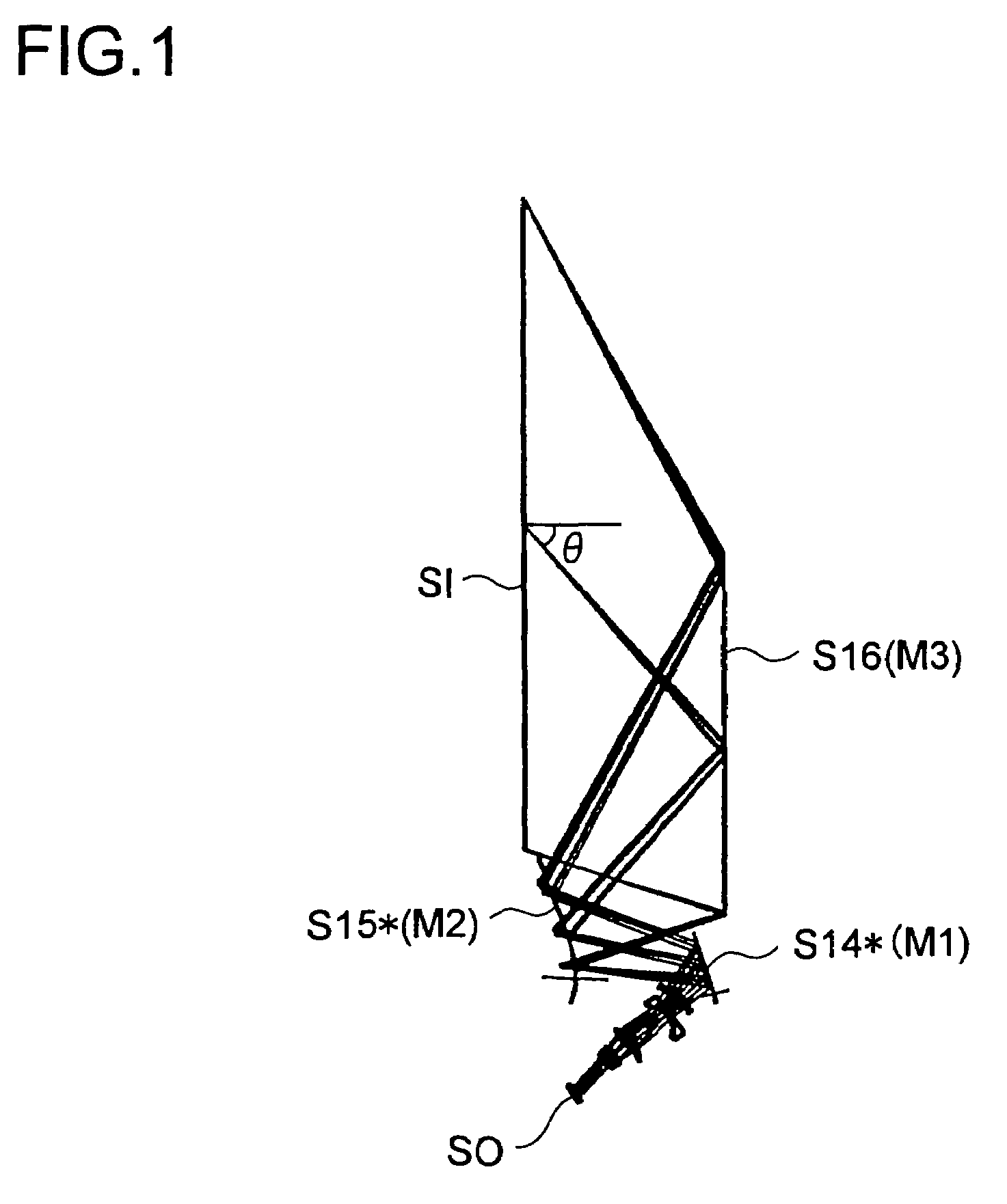

Projection optical system

A projection optical system for performing enlargement projection from a primary image surface on the reduction side to a secondary image surface on the enlargement side has, from the primary image surface side, a lens optical system including two or more lens elements sharing a common rotation-symmetry axis and each having an optical power, a first reflective optical element having an optical power, and a second reflective optical element having a negative optical power. The projection optical system is non-telecentric toward the reduction side, and a prescribed condition is.

Owner:KONICA MINOLTA OPTO

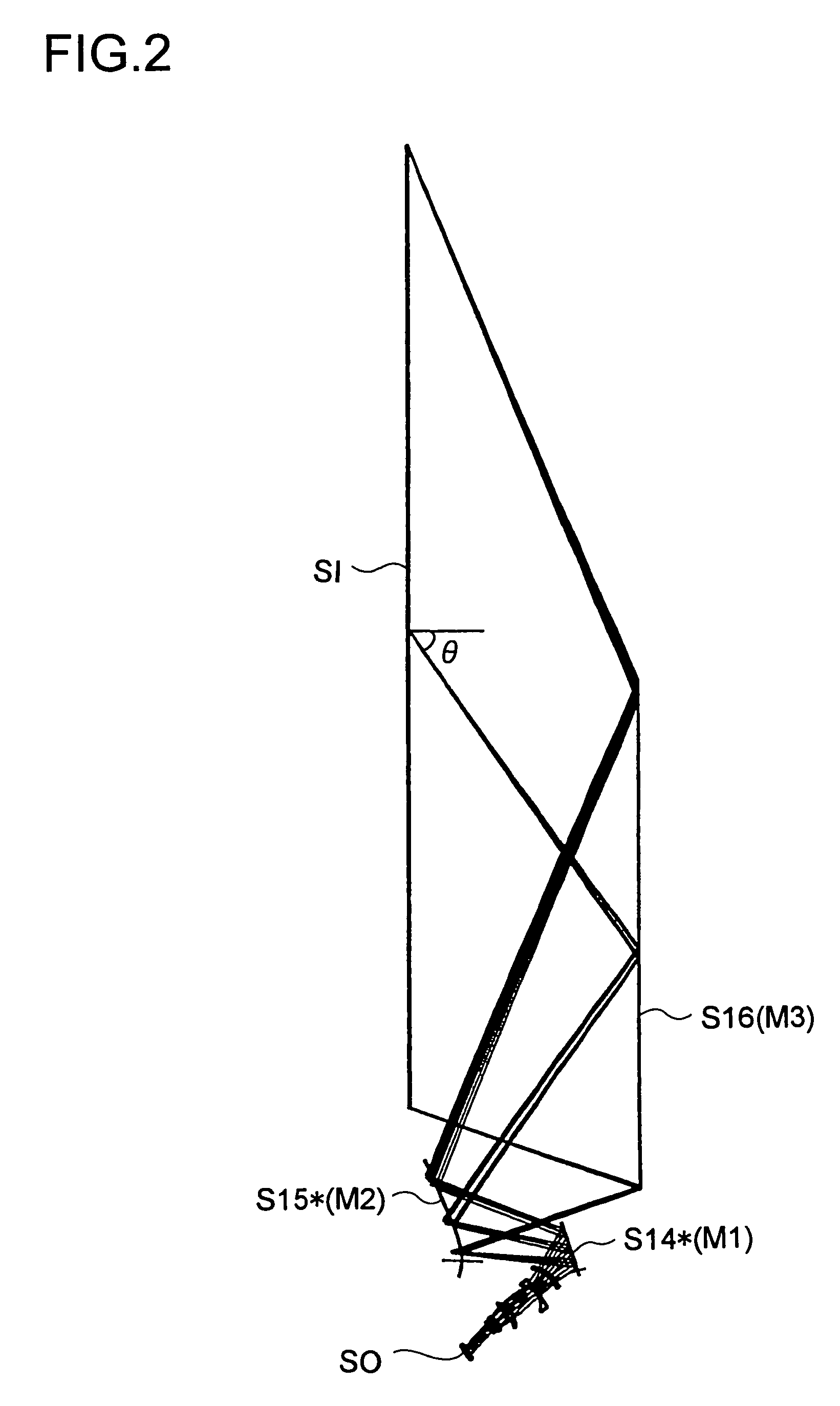

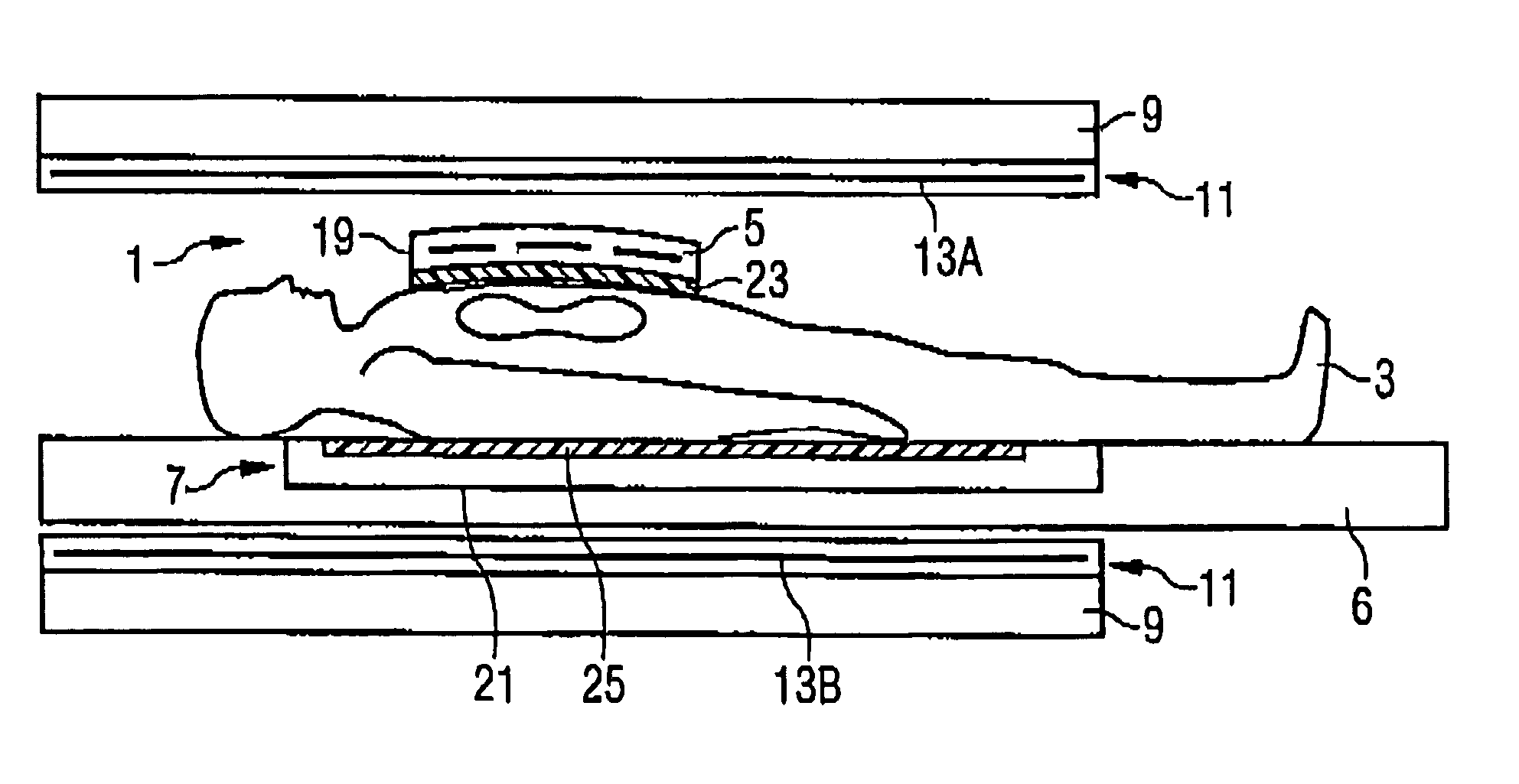

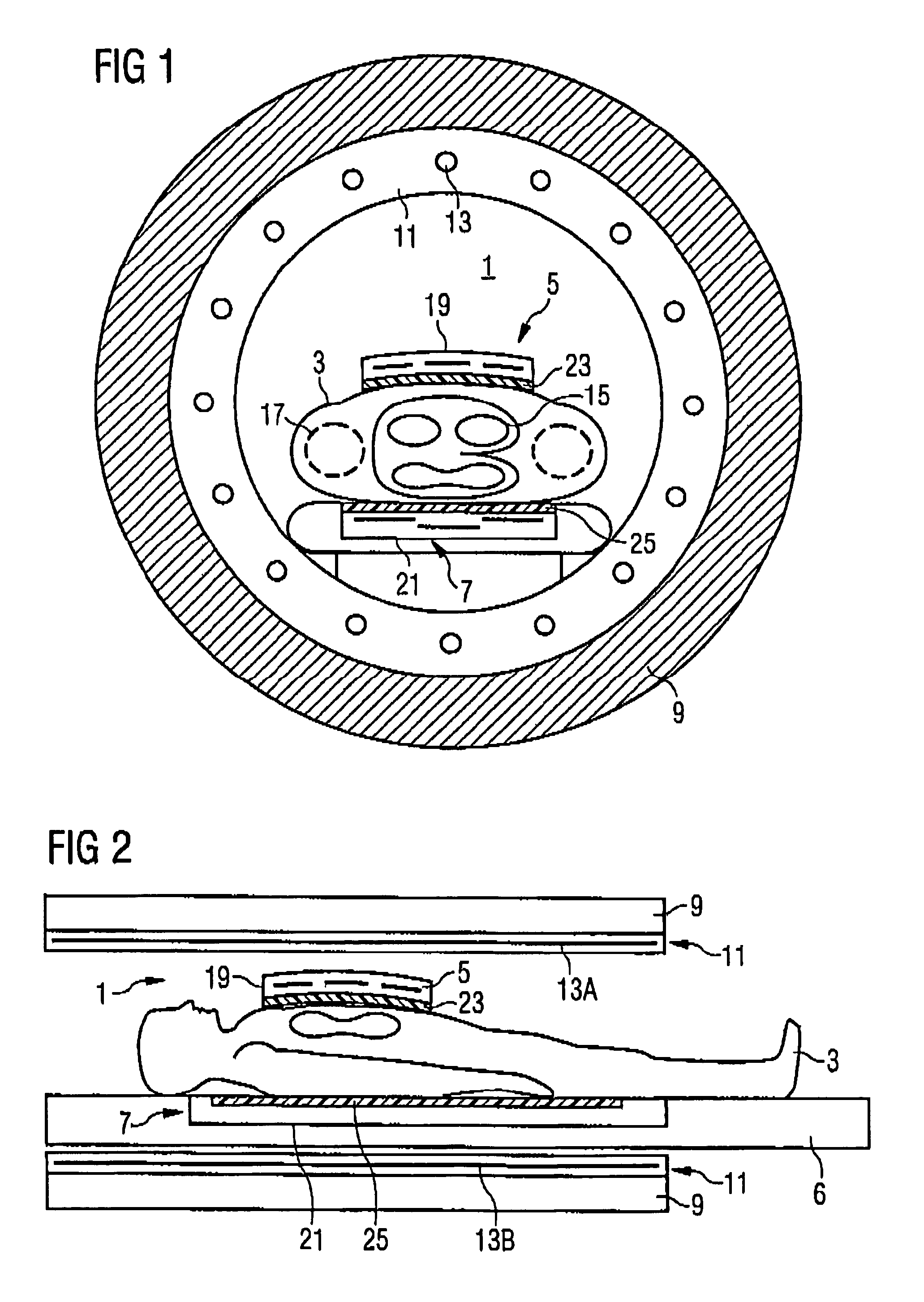

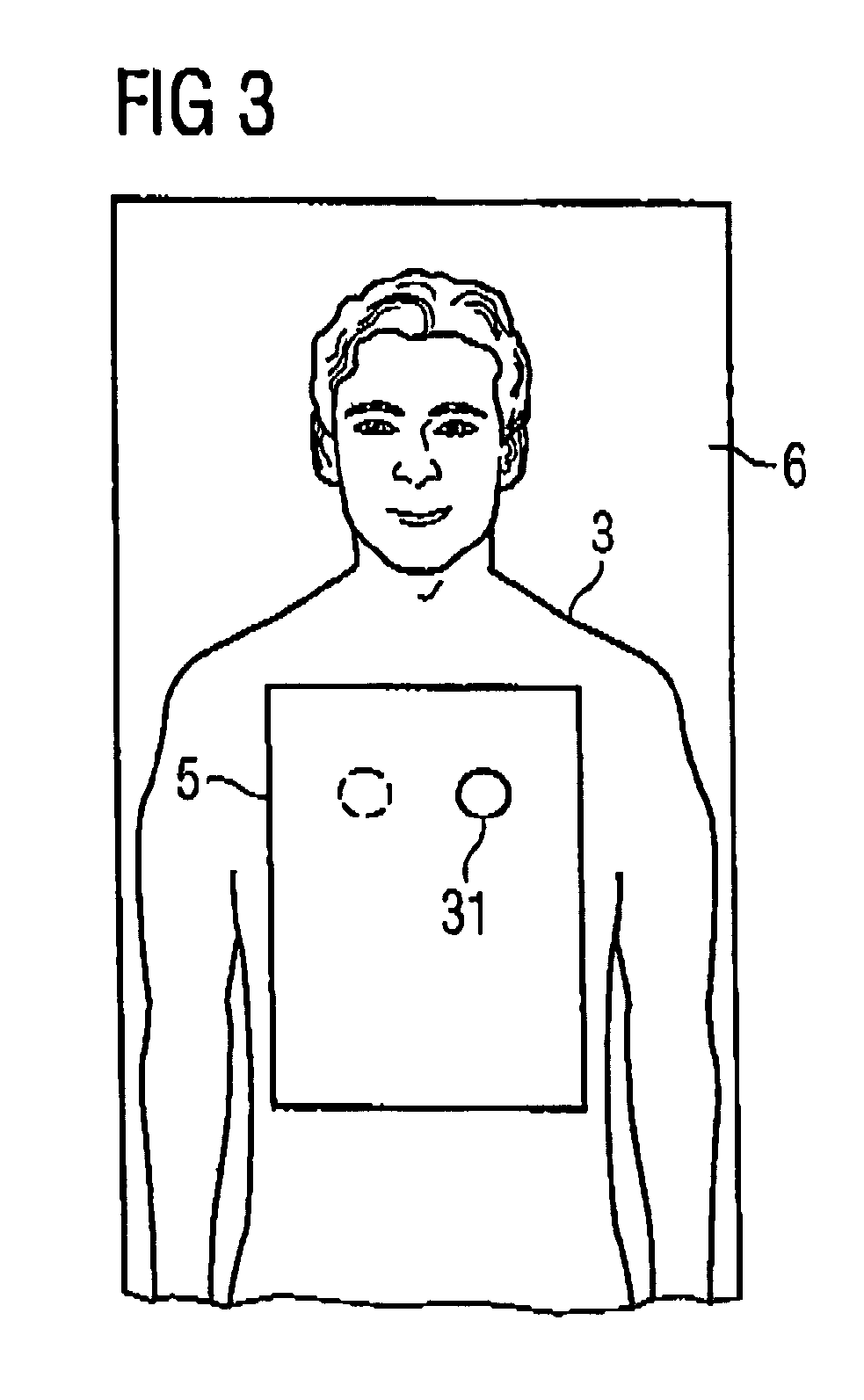

Local coil unit for a magnetic resonance apparatus

InactiveUS7002347B2Precise positioningReduce couplingMagnetic measurementsDiagnostic recording/measuringB1 fieldMR - Magnetic resonance

A local coil unit for a magnetic resonance apparatus, which radiates a radio-frequency field into an examination subject, has a housing and at least a part of the housing is formed of an insulating dielectric material that passively compensates for an inhomogeneity in the high-frequency field in the subject. The material has a relative dielectric value εr of greater than 50, preferably greater than 100, and a dielectric loss factor tan δ of less than 2.5×10−2, preferably less than 1×10−3. In the dielectric material displacement currents are generated which create an additional magnetic field that compensates for the minima in the B1 field as a result of the eddy currents arising in the patient due to the radio-frequency radiation.

Owner:SIEMENS HEALTHCARE GMBH

Back light for liquid crystal display

InactiveUS6939020B2Reduce voltageBig screenNon-electric lightingMeasurement apparatus componentsLiquid-crystal displayEngineering

Owner:LG DISPLAY CO LTD

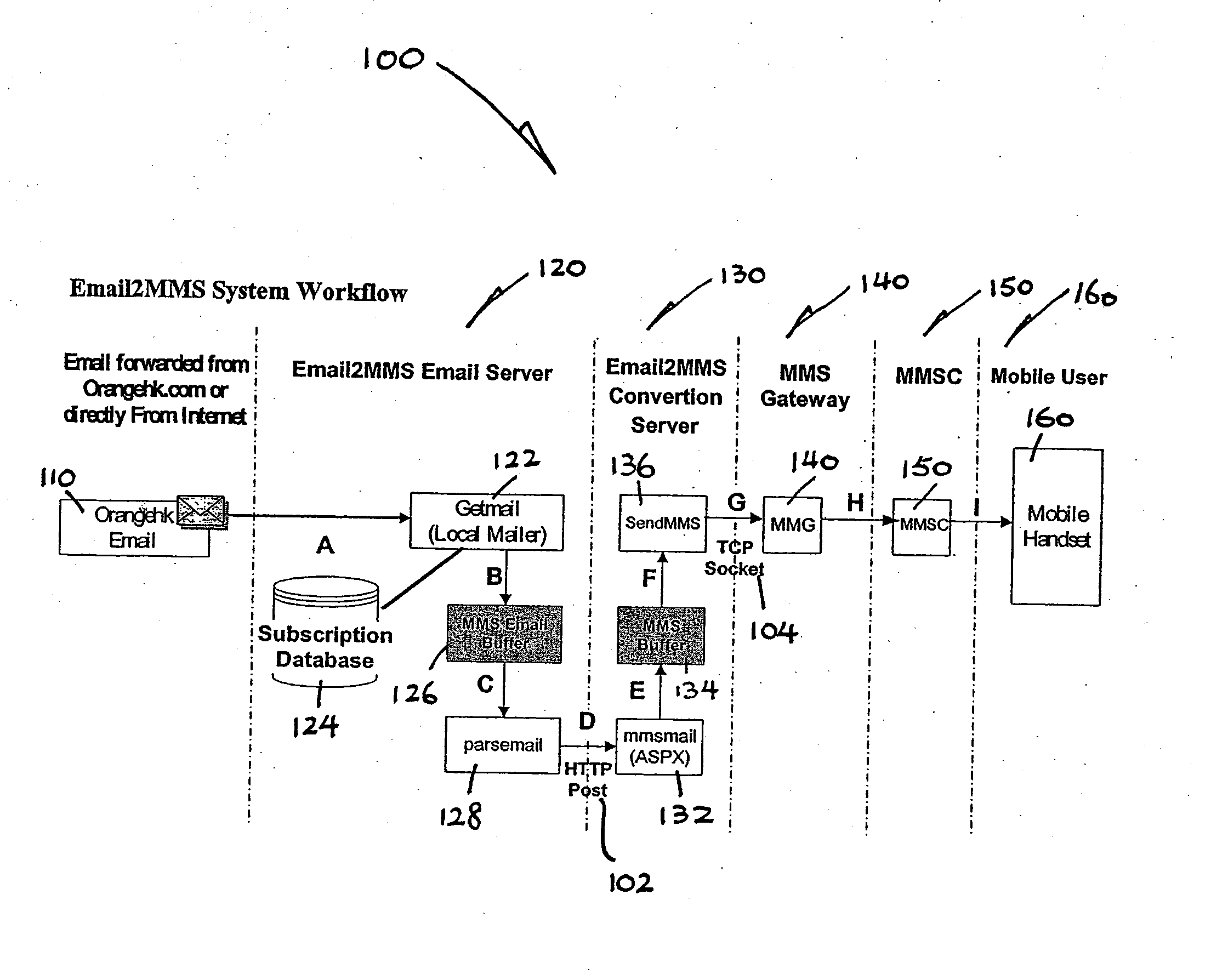

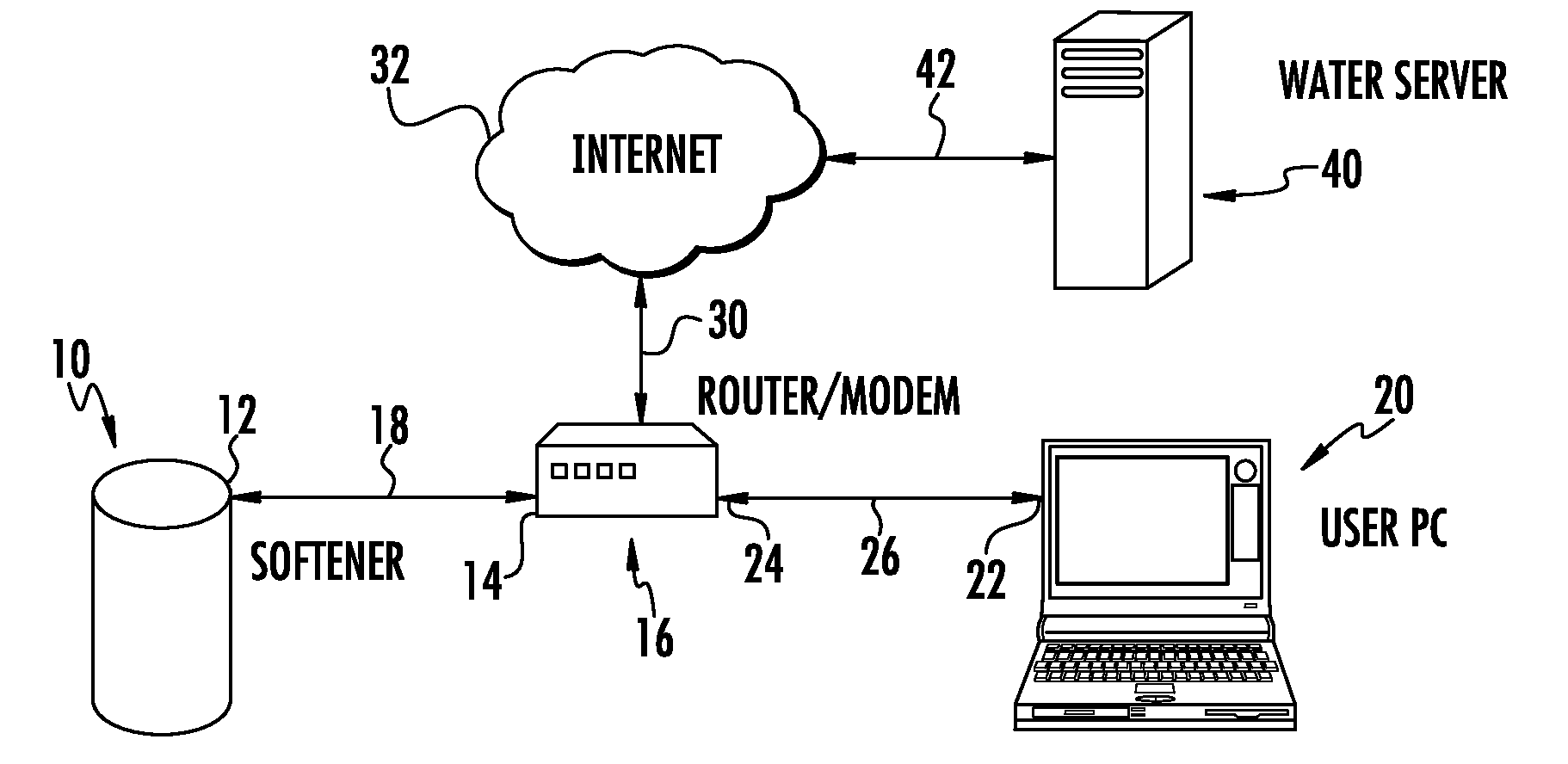

Multi-language wireless email transmission method for mobile communication

InactiveUS20050144243A1Readily availableBig screenNatural language translationMultiple digital computer combinationsWireless transmissionMulti language

A method of wireless transmission of an email having a content in a language unsupported in a mobile communication system by Multimedia Messaging Service (MMS) to a recipient using a mobile phone. An email server receives the email and extracts from the email text information indicative of the recipient and relating to content. A conversion server, connected to the email server, converts the content information from text into an image and composes a MMS message including the image. A MMS message transmitter, connected to the conversion server, transmits the MMS message to the mobile phone. Multi-language (supported and unsupported languages) wireless email transmission is thus made possible.

Owner:HUTCHISON WHAMPOA ENTERPRISES

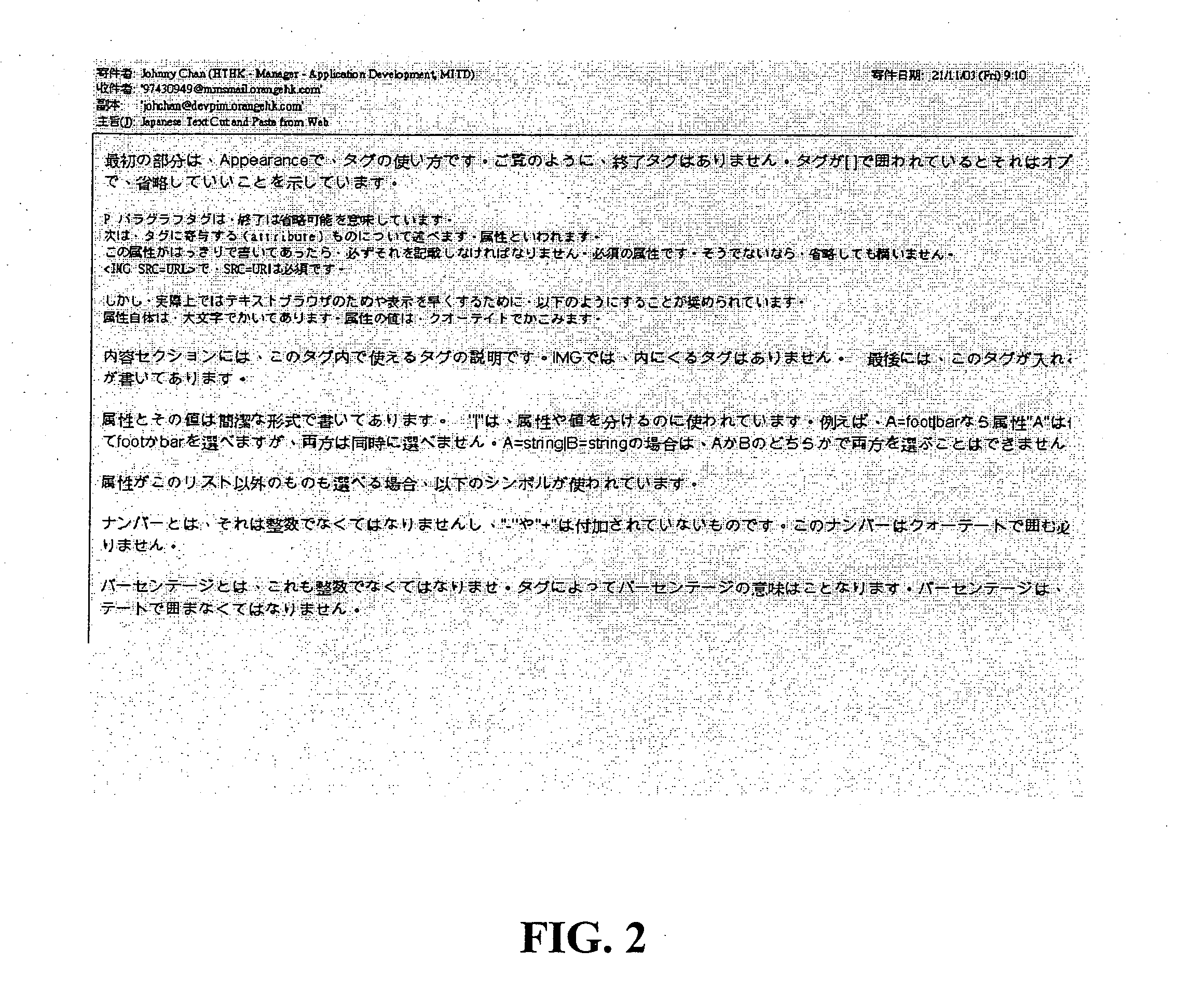

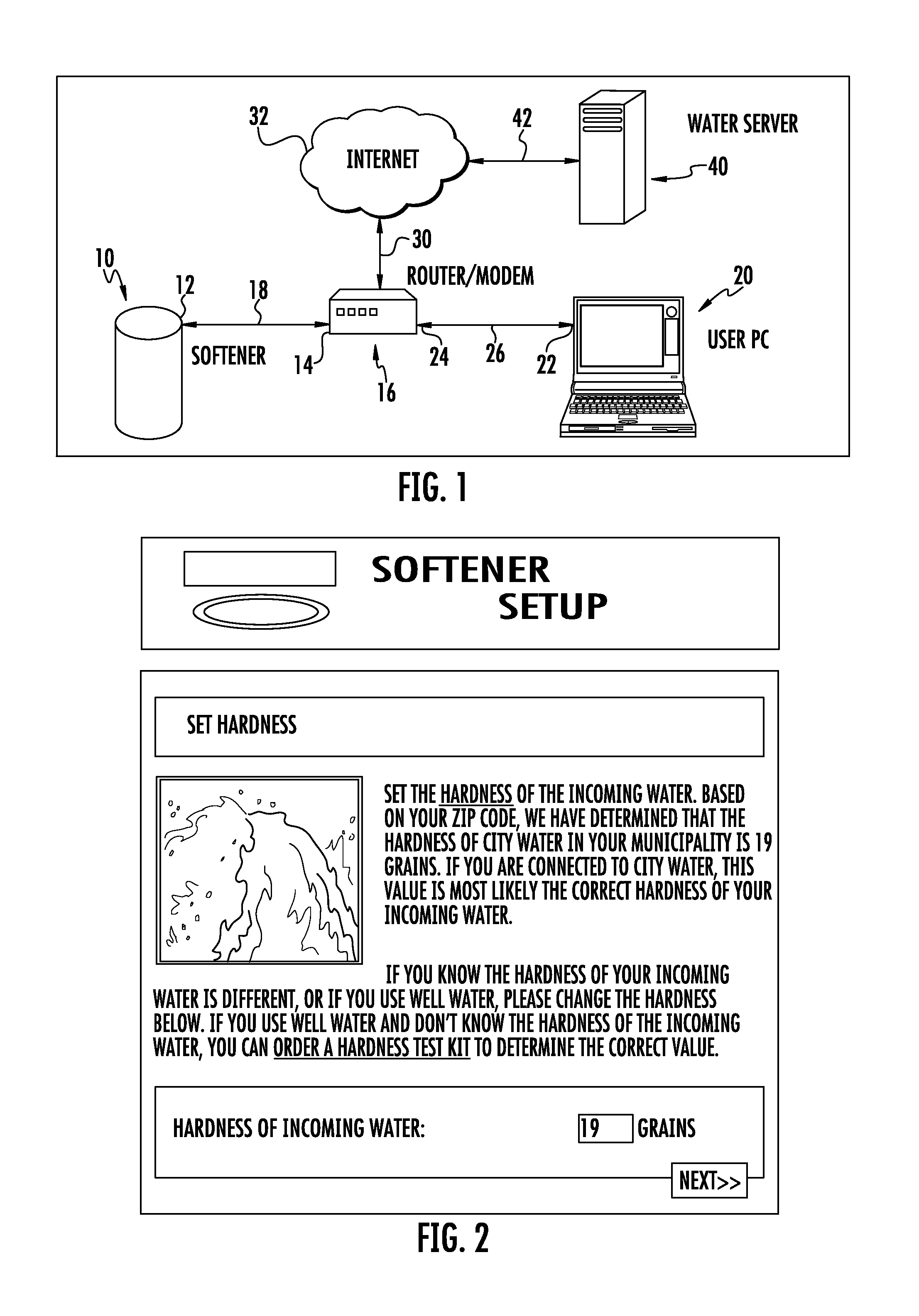

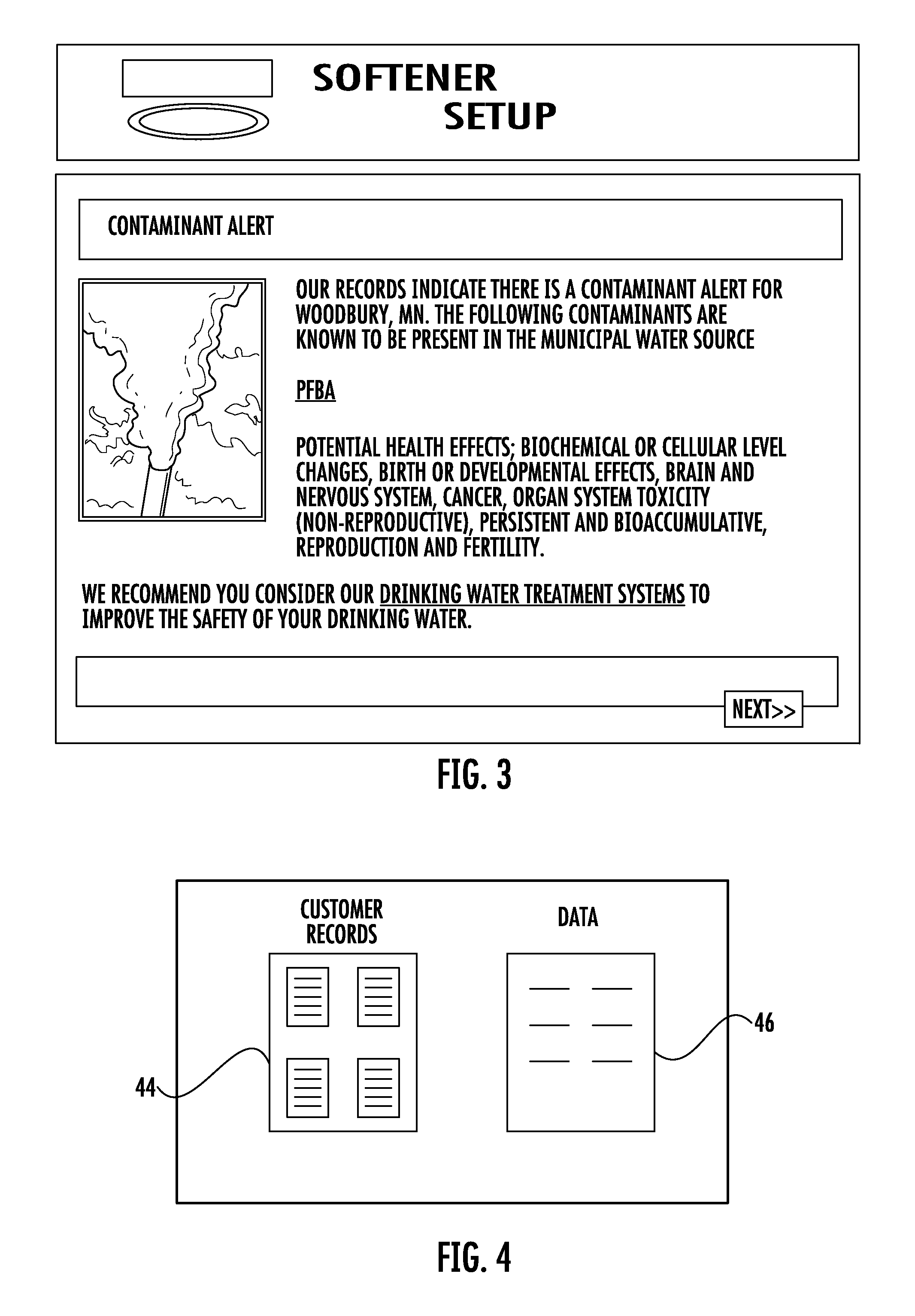

Remotely controlled water treatment system and a method of remotely controlling a water treatment system

InactiveUS20120078722A1Simplifying setup and ongoing operation and maintenanceSimple interfaceMultiple digital computer combinationsBuying/selling/leasing transactionsWeb serverWater treatment system

A water treatment system, such as a water softener, is remotely operated and a method of remotely controlling a water treatment system. In a first embodiment, the water treatment system having a web server is delivered and installed on the users LAN. The user PC is redirected by a remote server to the water treatment system by use of the water treatment system MAC address, IP protocol address and user information. In this manner, the user is able to control the water treatment system and communicate with the remote server. In a second and third embodiment, the water treatment system and user PC communicate indirectly via the remote server. In the second embodiment, the water treatment system is provided with a wireless network interface to couple to the remote server. In the third embodiment, the water treatment system is provided with an internet interface.

Owner:ECOWATER SYST