Patents

Literature

79results about How to "Minimize misalignment" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Image adjustment derived from optical imaging measurement data

Owner:CARL ZEISS MEDITEC INC

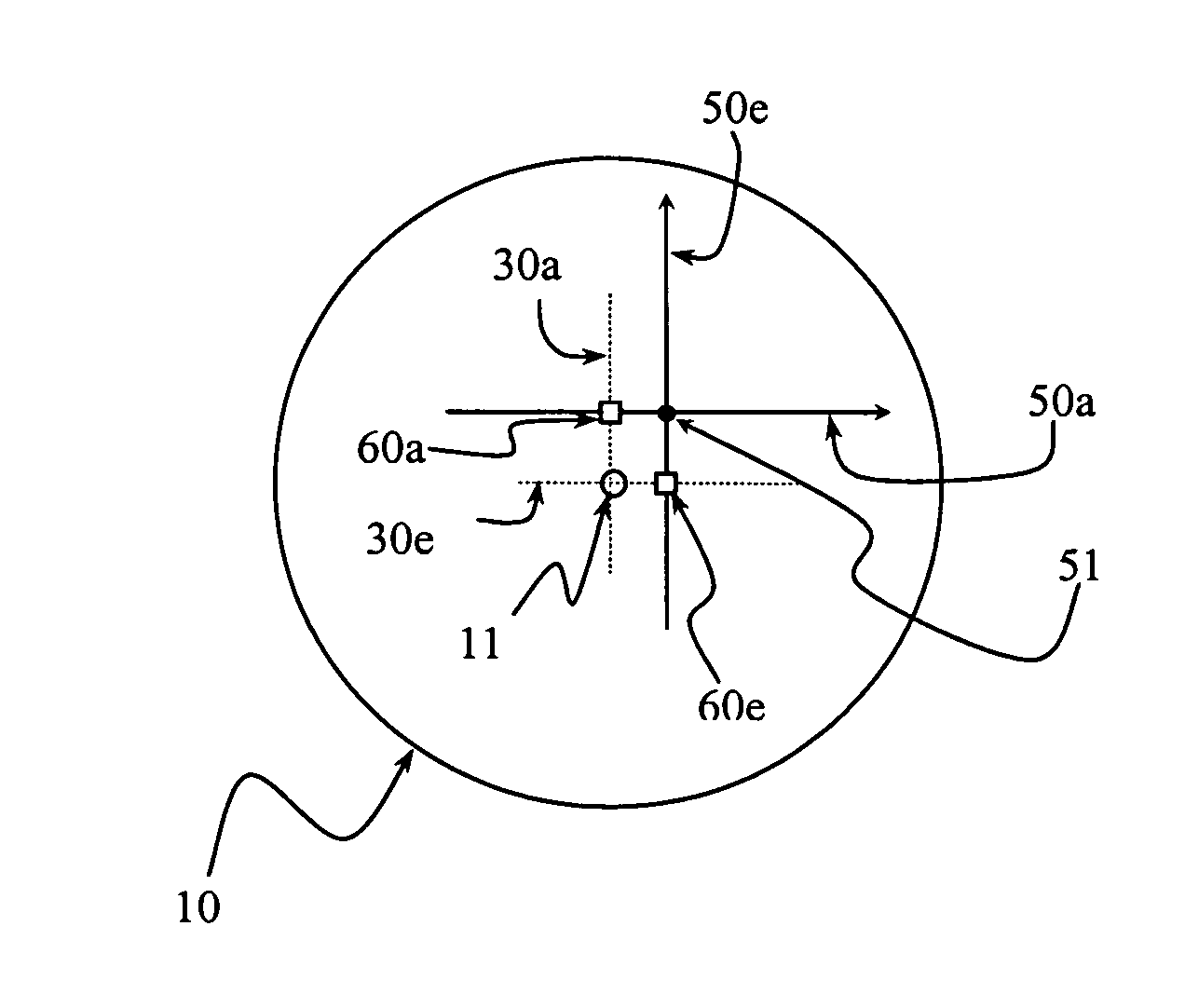

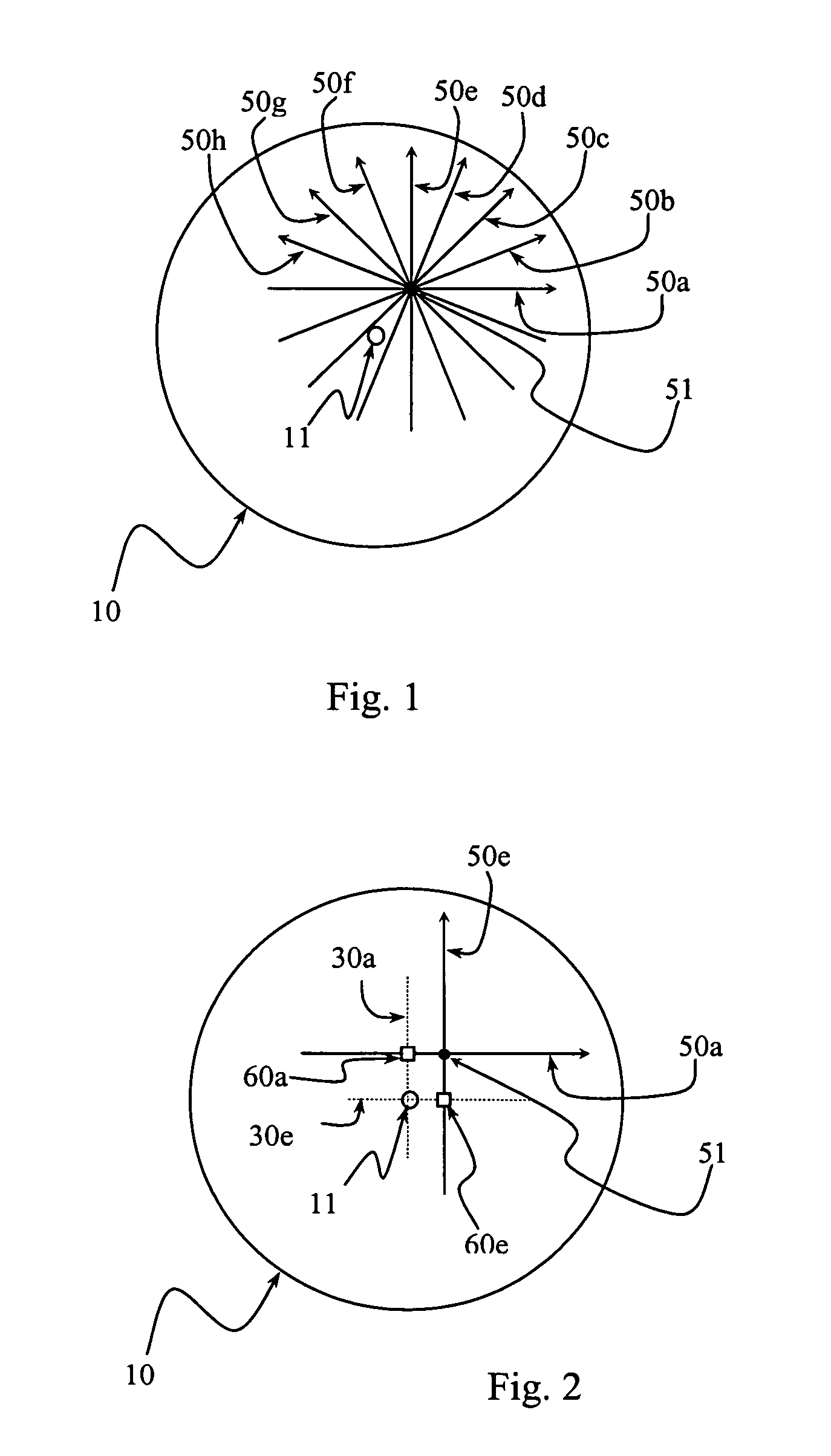

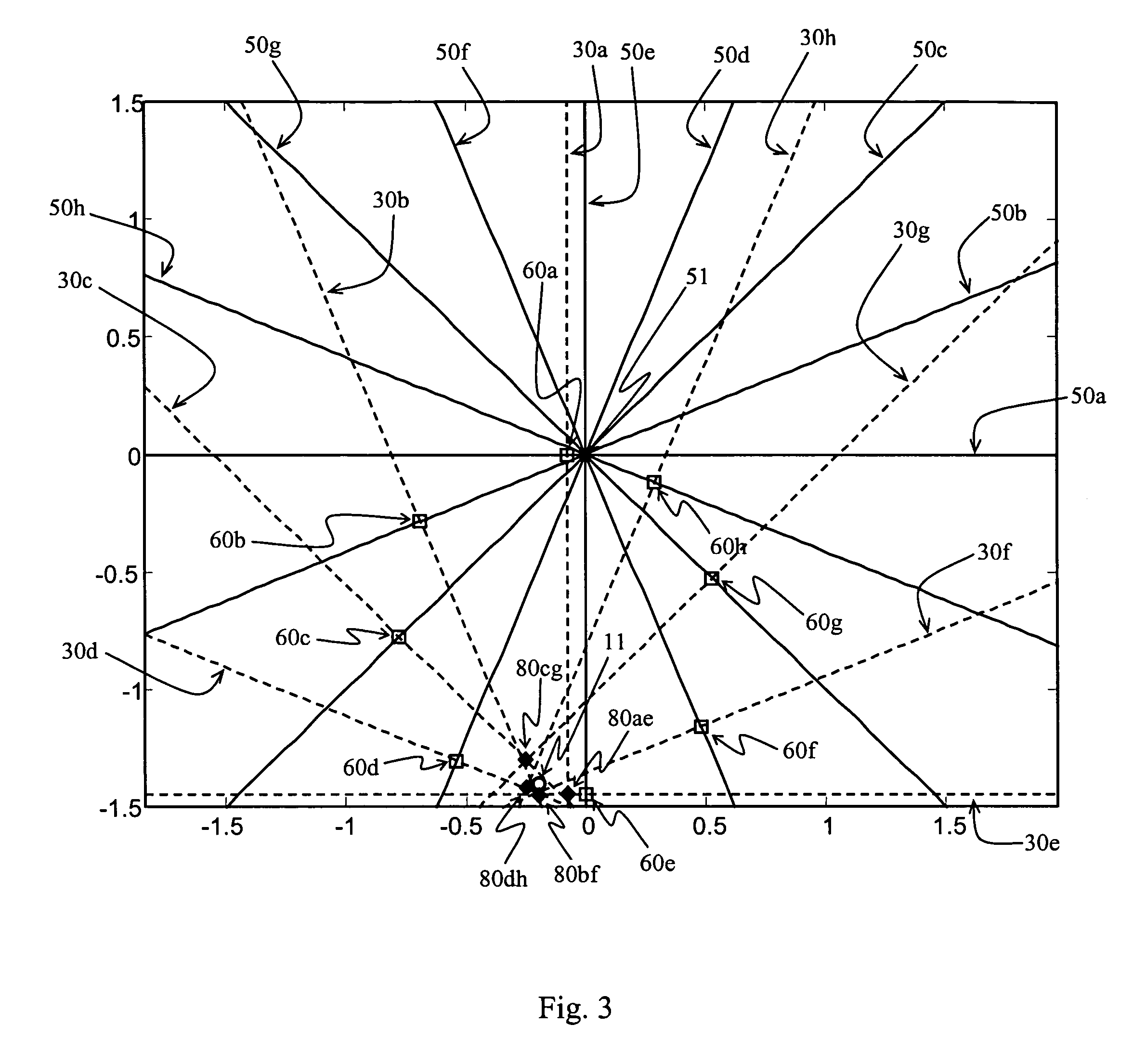

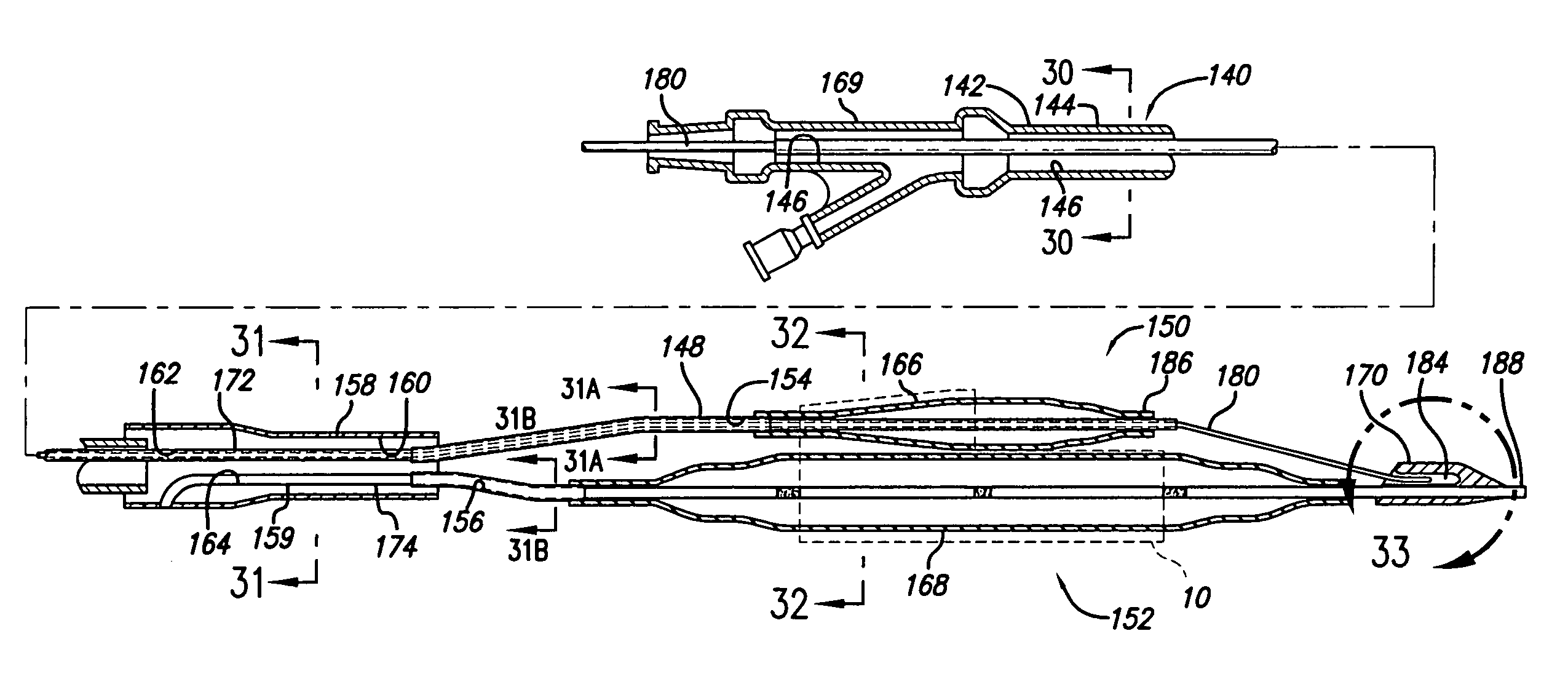

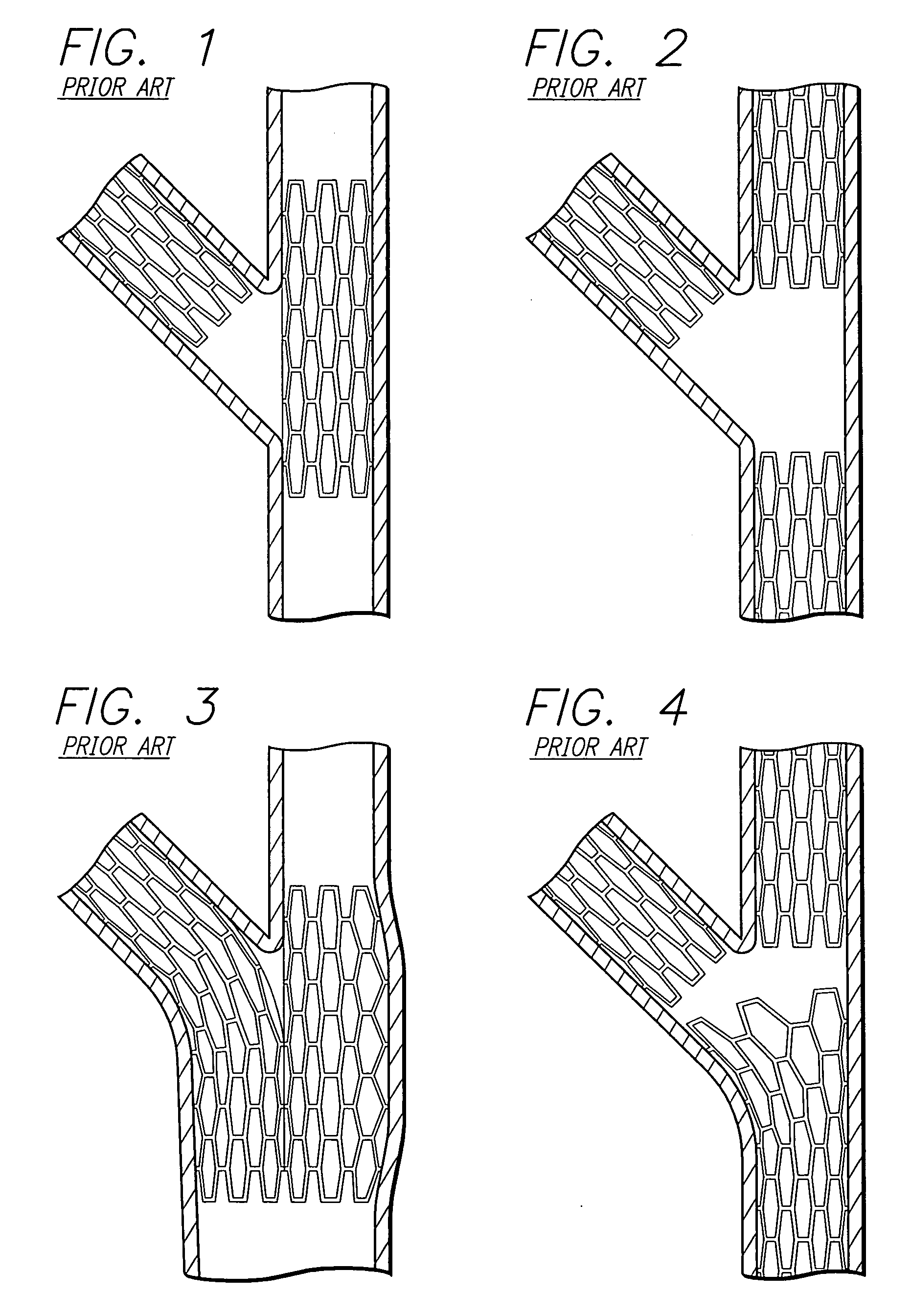

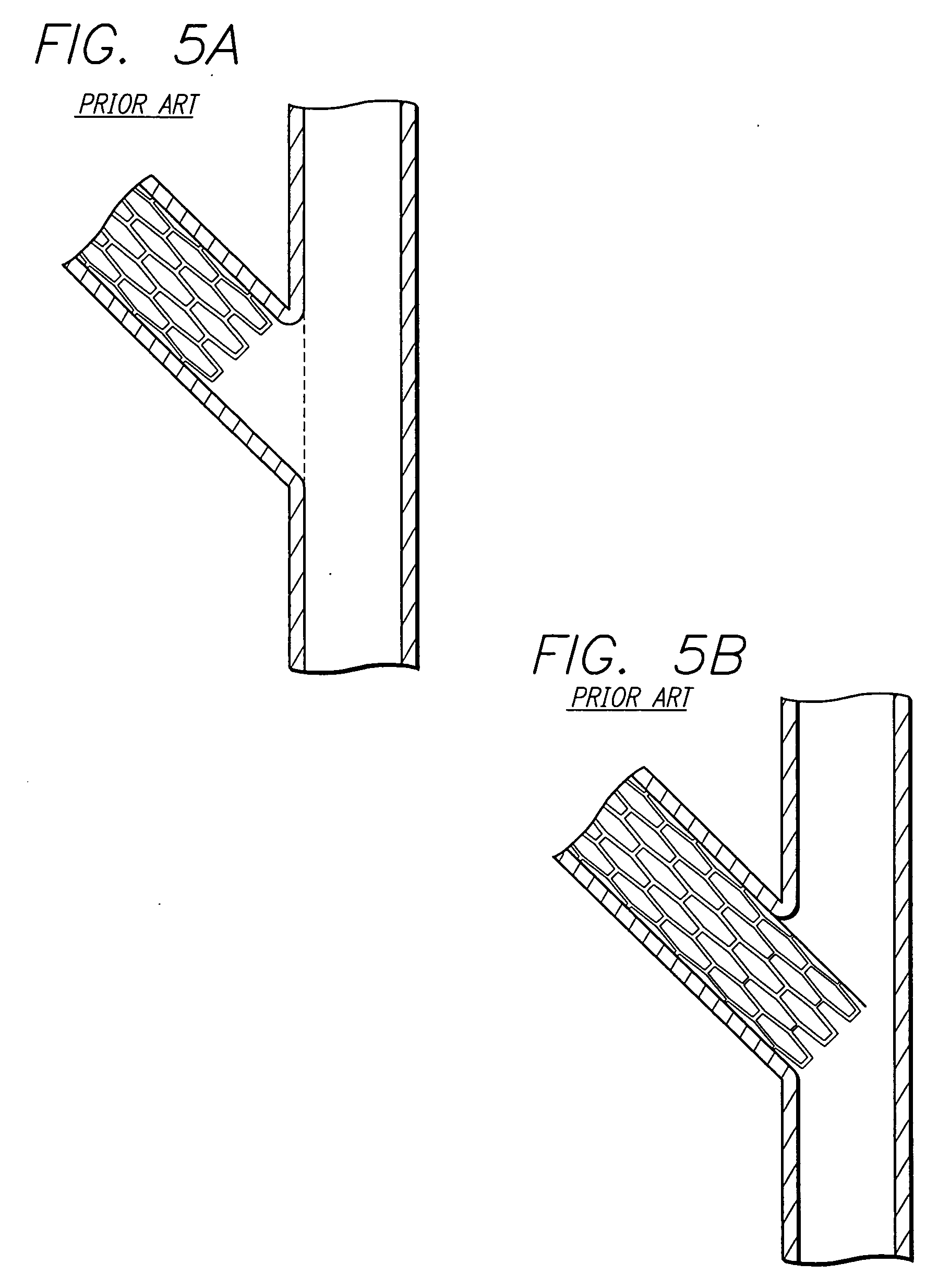

Catheter assembly and method for treating bifurcations

InactiveUS20080009933A1Improve delivery capabilitiesSave effortStentsBlood vesselsInsertion stentBlood vessel

An improved stent design and stent delivery catheter assembly for repairing a main vessel and a side branch vessel forming a bifurcation. The stent includes rings aligned along a common longitudinal axis and connected by links, where the stent has one or more portals for aligning with and partially expanding into the opening to the side branch vessel. The stent is implanted at a bifurcation so that the main stent section is in the main vessel, and the portal section covers at least a portion of the opening to the side branch vessel. A second stent can be implanted in the side branch vessel and abut the expanded central section to provide full coverage of the bifurcated area in the main vessel and the side branch vessel. Radiopaque markers on the stent and on the tip of the delivery catheter assist in aligning the portal section with the opening to the side branch vessel.

Owner:ABBOTT CARDIOVASCULAR

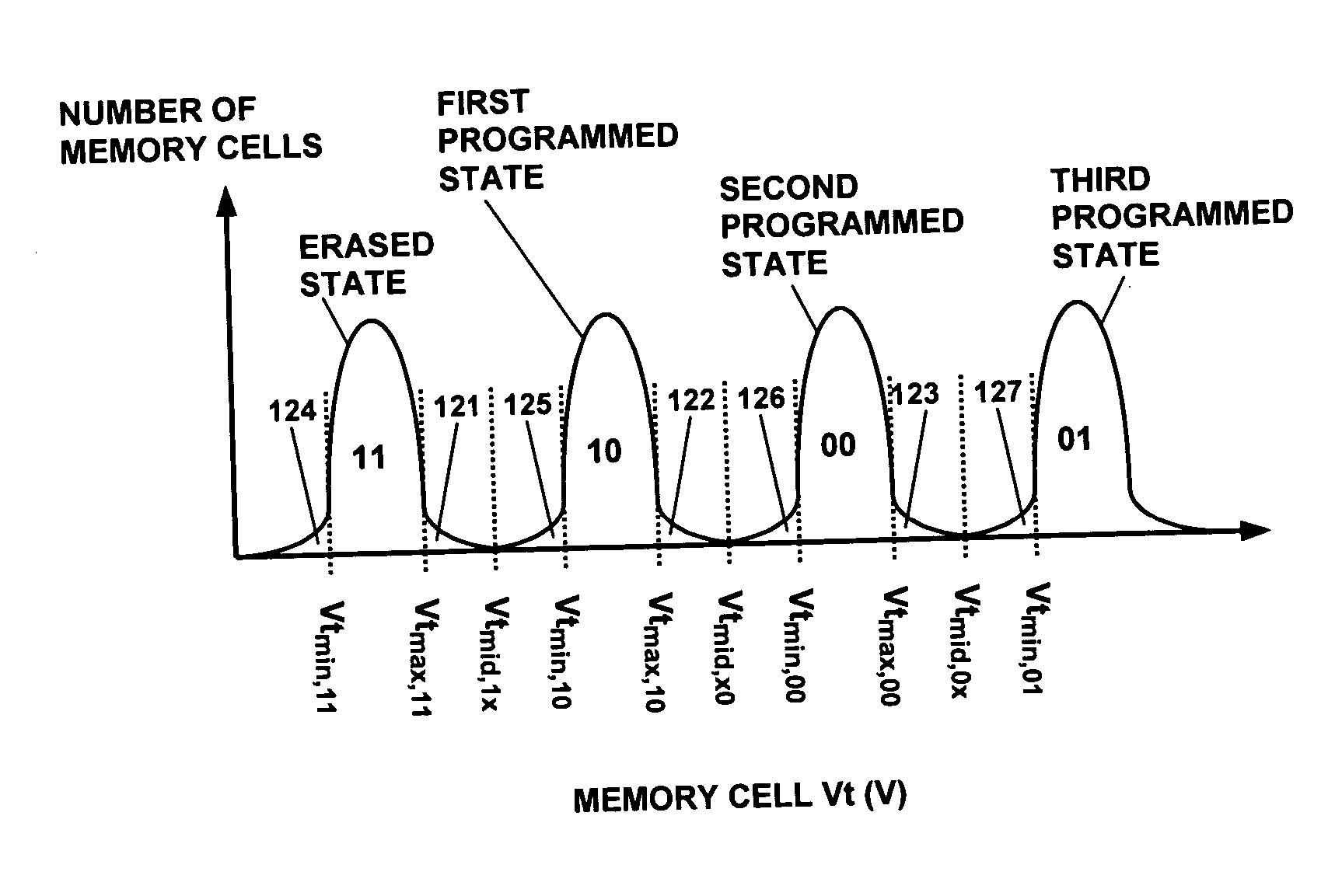

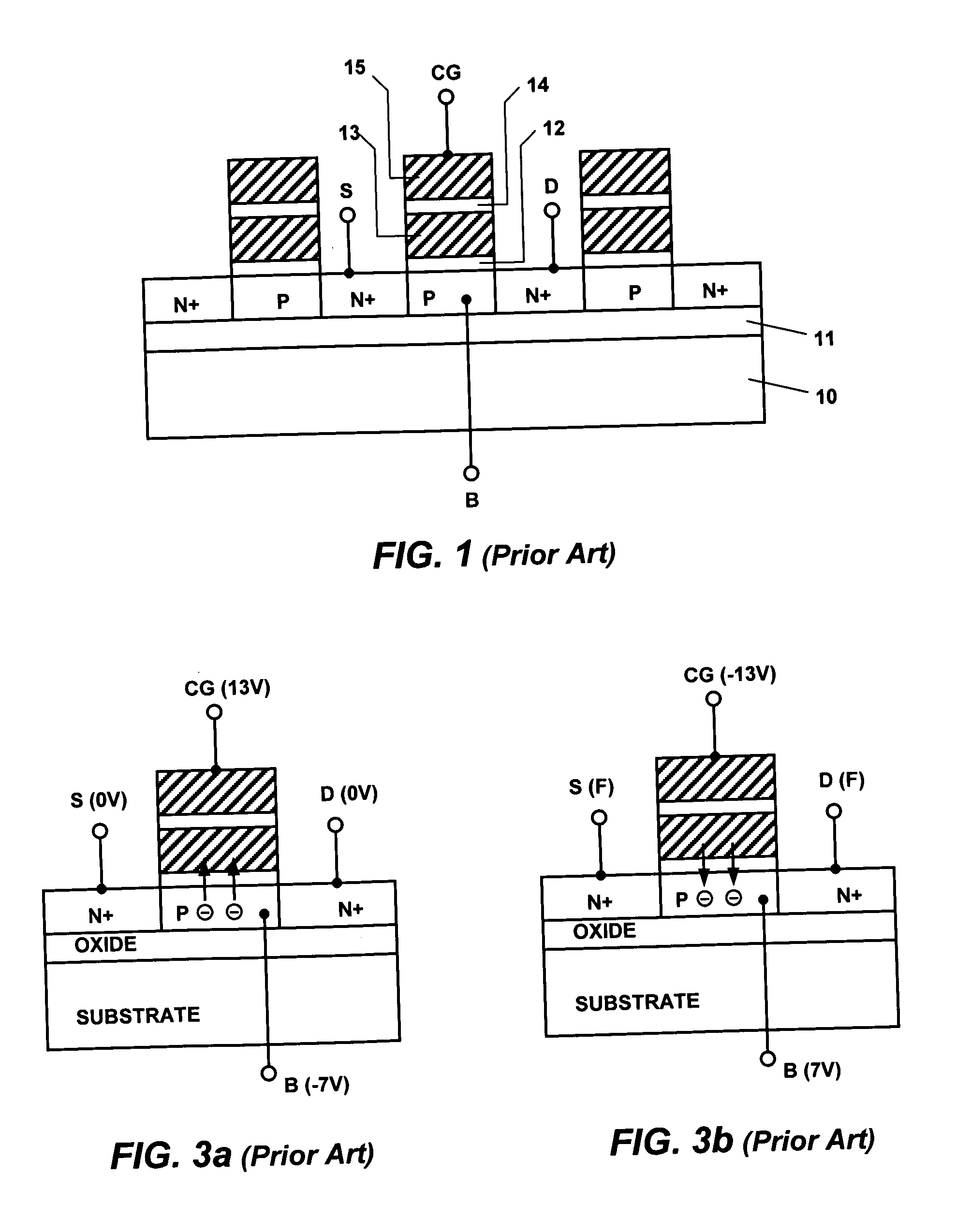

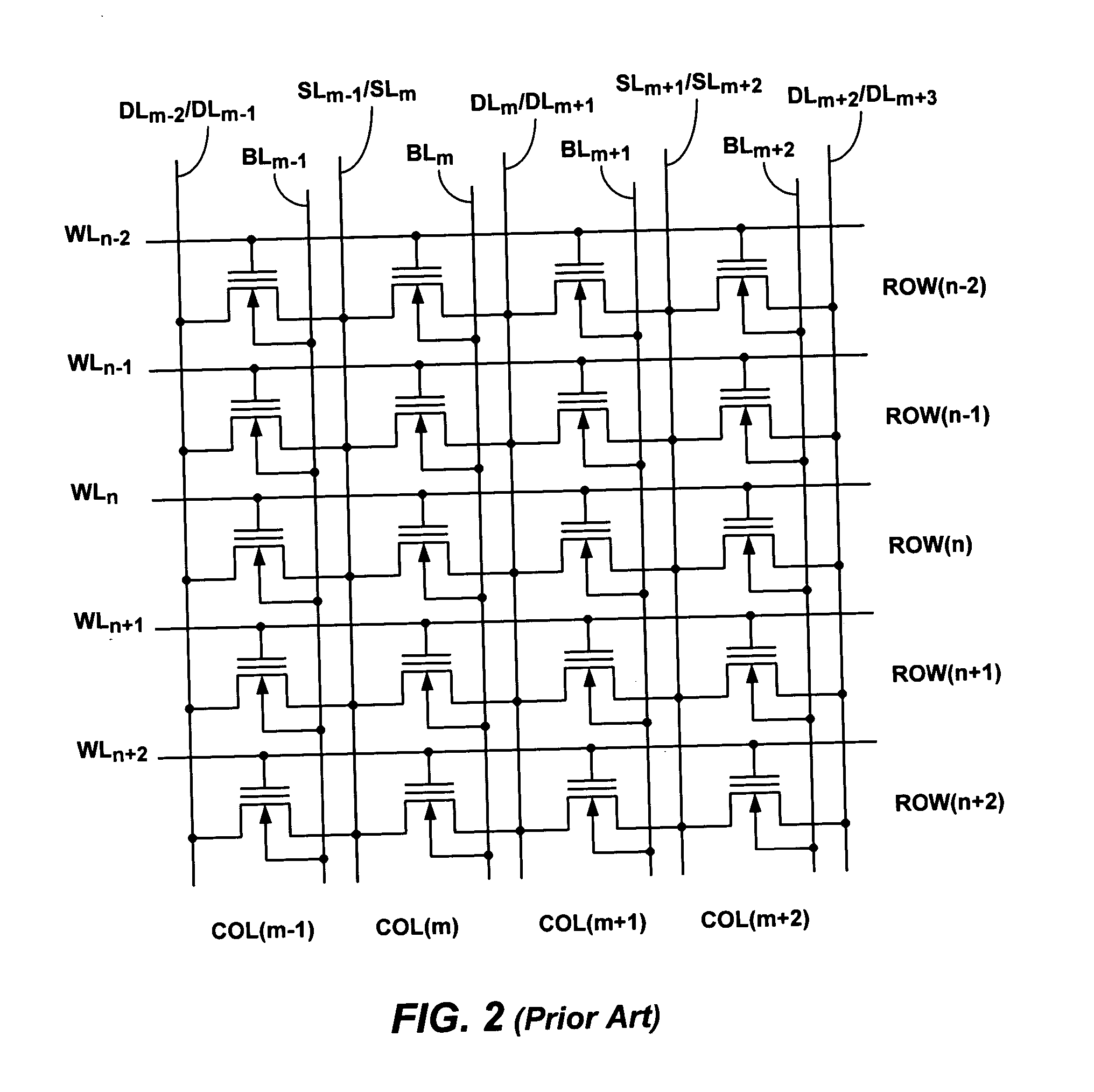

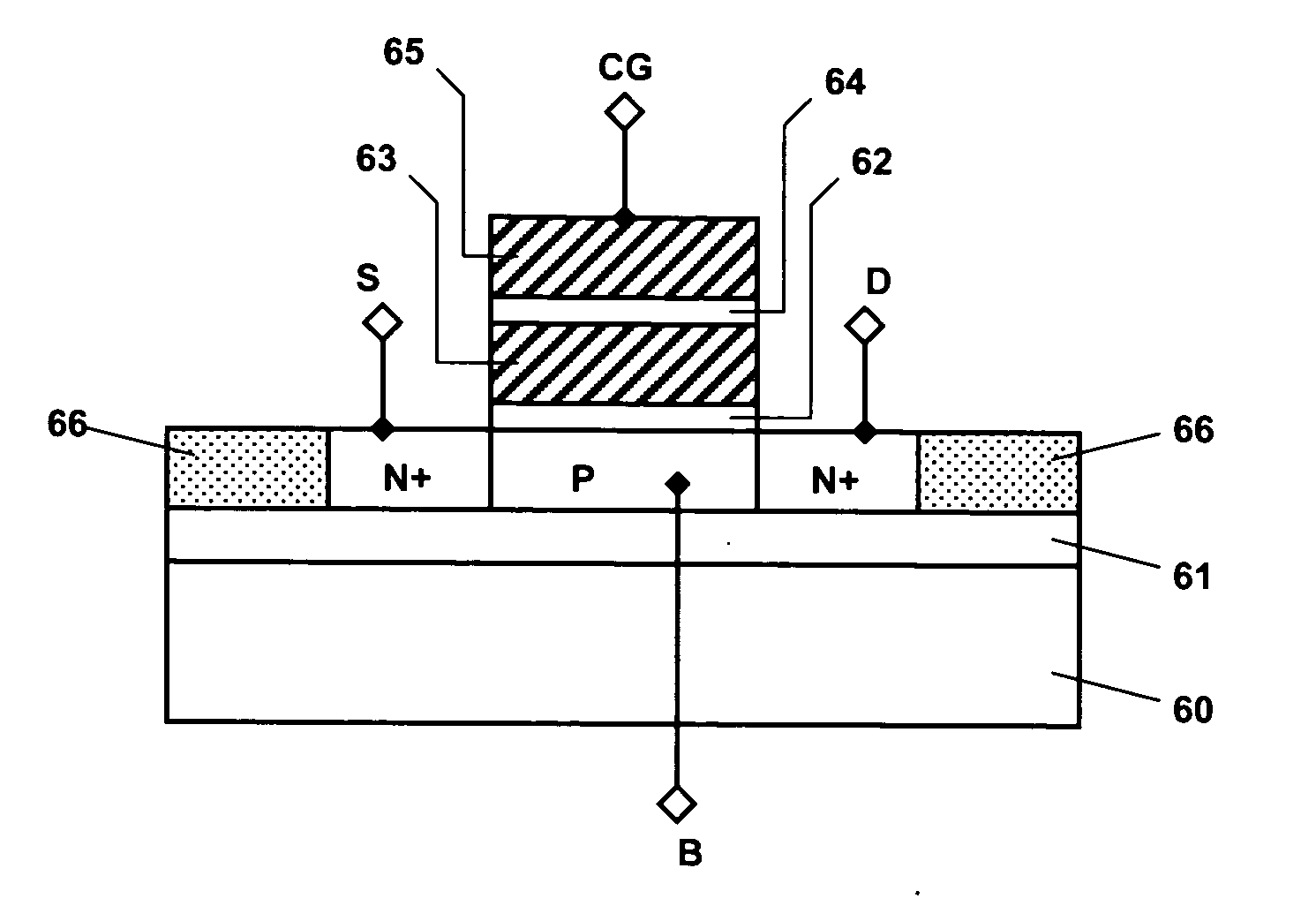

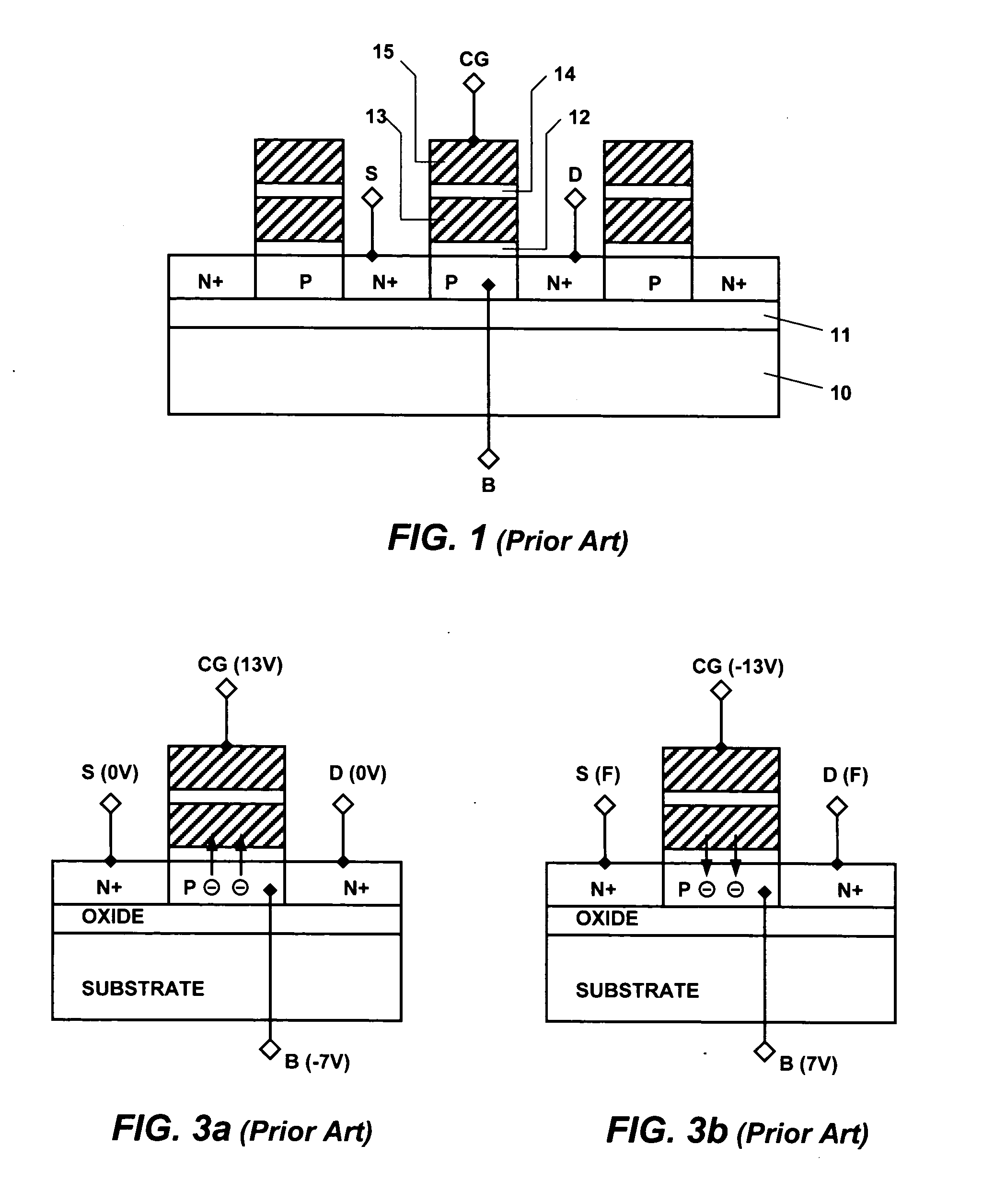

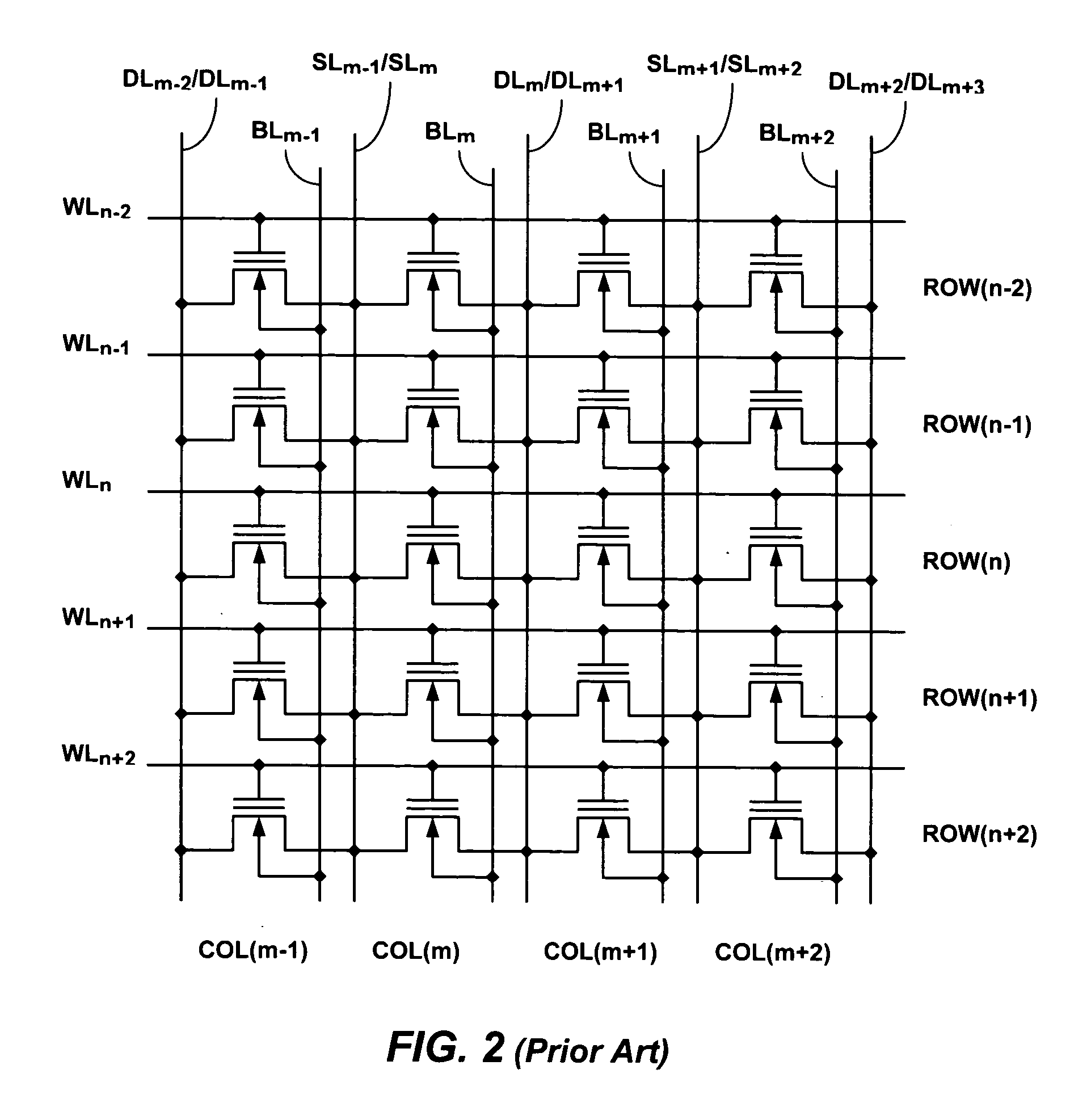

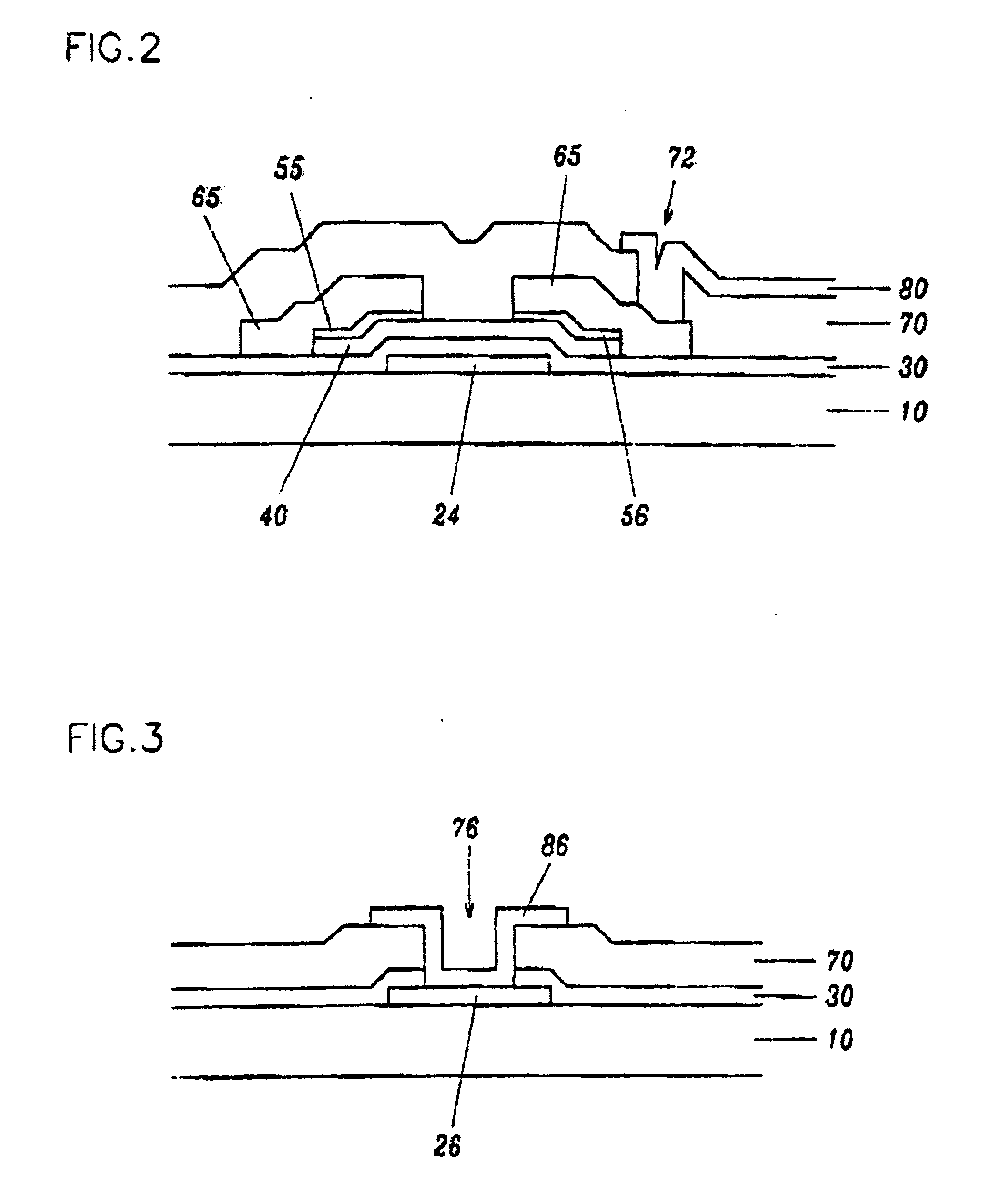

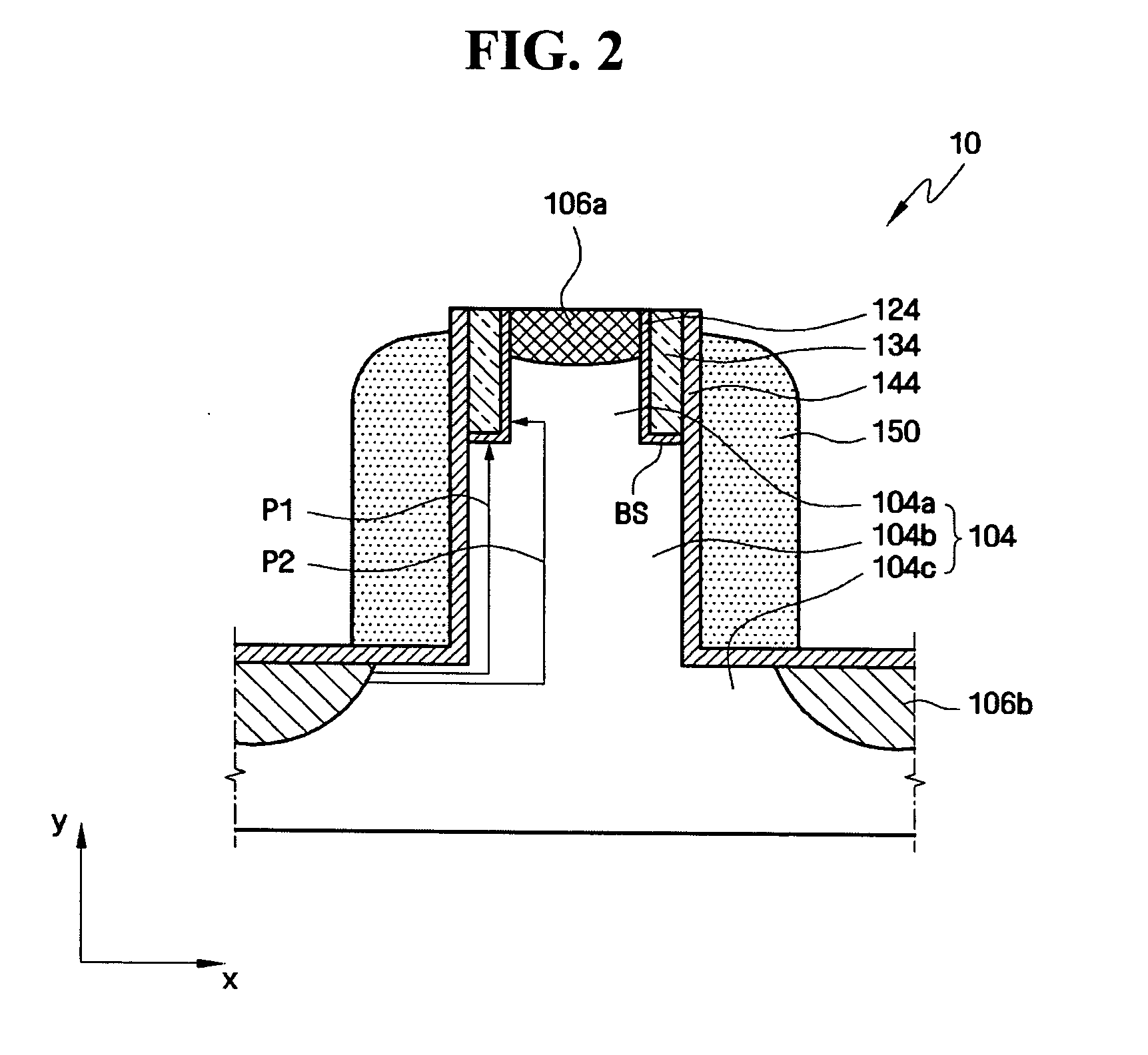

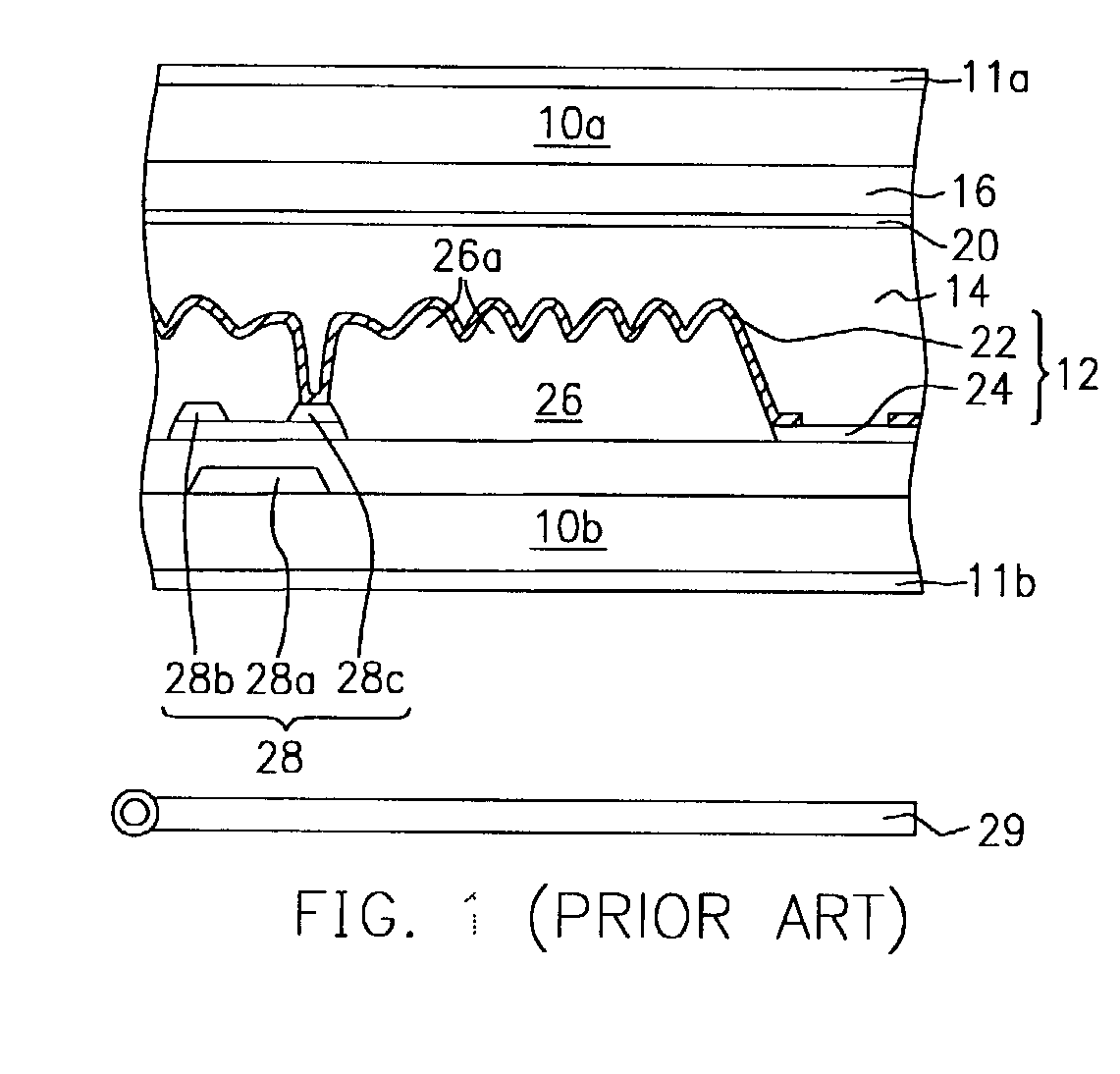

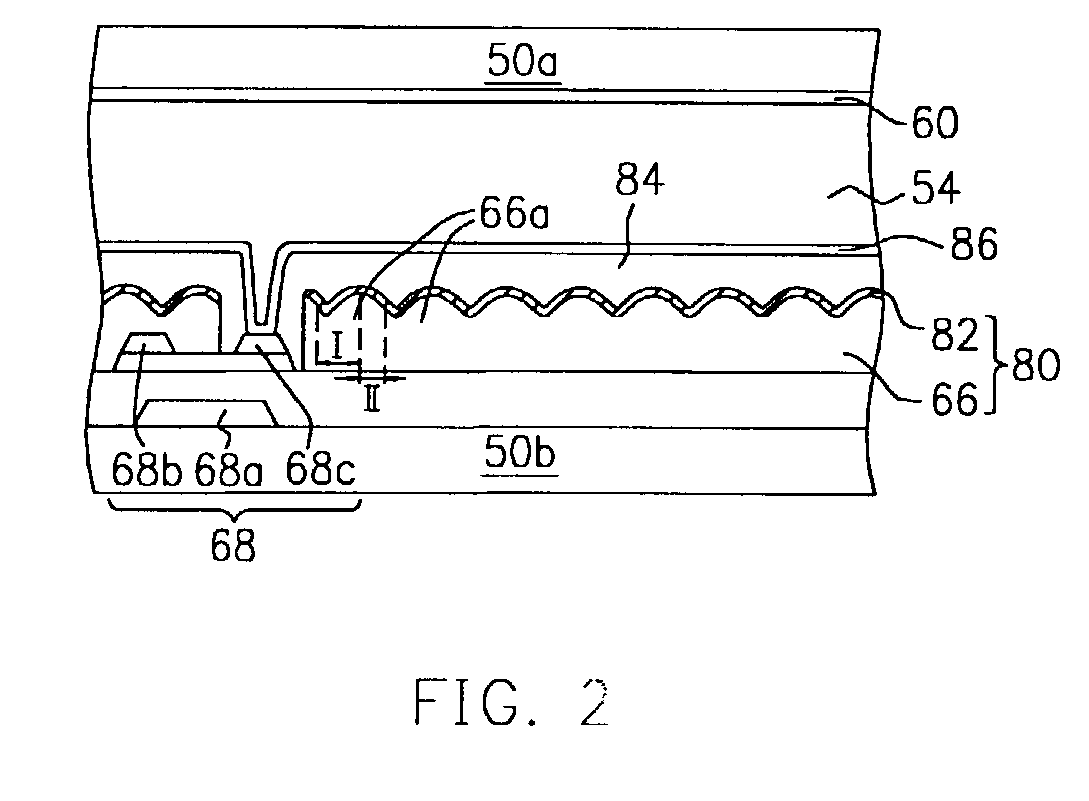

Nor-type channel-program channel-erase contactless flash memory on SOI

InactiveUS20060018164A1Improve good performanceImprove circuit performanceTransistorSolid-state devicesProgrammable read-only memoryDevice material

A semiconductor device having an electrically erasable programmable read only memory (EEPROM) comprises a contactless array of EEPROM memory cells disposed in rows and columns and constructed over a silicon-on-insulator wafer. Each EEPROM memory cell comprises a drain region, a source region, a gate region, and a body region. The semiconductor device further comprises a plurality of gate lines each connecting the gate regions of a row of EEPROM memory cells, a plurality of body lines each connecting the body regions of a column of EEPROM memory cells, a plurality of source lines each connecting the source regions of a column of EEPROM memory cells, and a plurality of drain lines each connecting the drain regions of a column of EEPROM memory cells. The source lines and the drain lines are buried lines, and the source regions and the drain regions of a column of EEPROM memory cells are insulated from the source regions and the drain regions of the adjacent columns of EEPROM memory cells.

Owner:WU KOUCHENG

Nor-type channel-program channel-erase contactless flash memory on SOI

InactiveUS20050179079A1Improve good performanceImprove circuit performanceTransistorSolid-state devicesProgrammable read-only memoryDevice material

A semiconductor device having an electrically erasable programmable read only memory (EEPROM) comprises a contactless array of EEPROM memory cells disposed in rows and columns and constructed over a silicon-on-insulator wafer. Each EEPROM memory cell comprises a drain region, a source region, a gate region, and a body region. The semiconductor device further comprises a plurality of gate lines each connecting the gate regions of a row of EEPROM memory cells, a plurality of body lines each connecting the body regions of a column of EEPROM memory cells, a plurality of source lines each connecting the source regions of a column of EEPROM memory cells, and a plurality of drain lines each connecting the drain regions of a column of EEPROM memory cells. The source lines and the drain lines are buried lines, and the source regions and the drain regions of a column of EEPROM memory cells are insulated from the source regions and the drain regions of the adjacent columns of EEPROM memory cells.

Owner:WU KOUCHENG

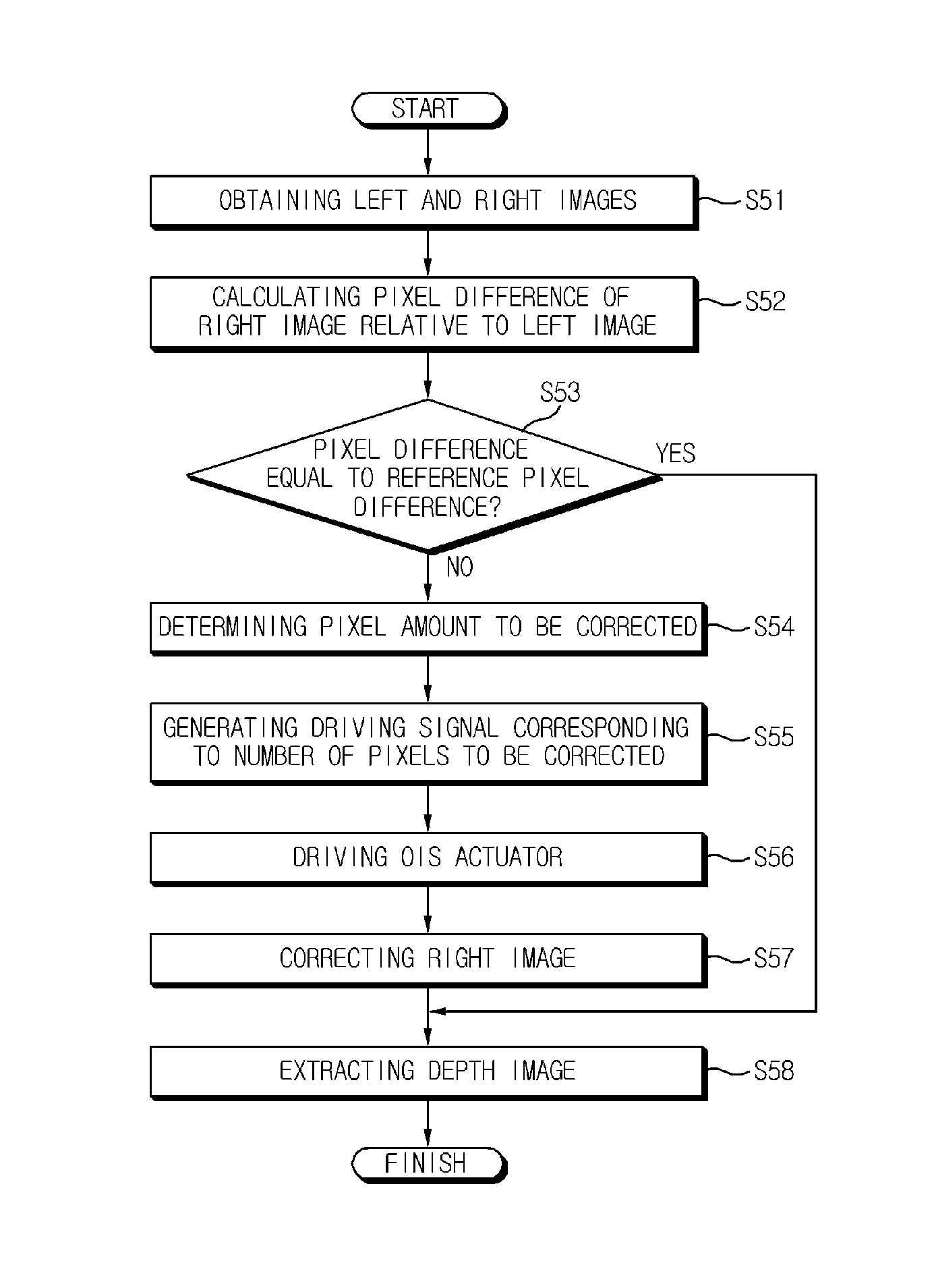

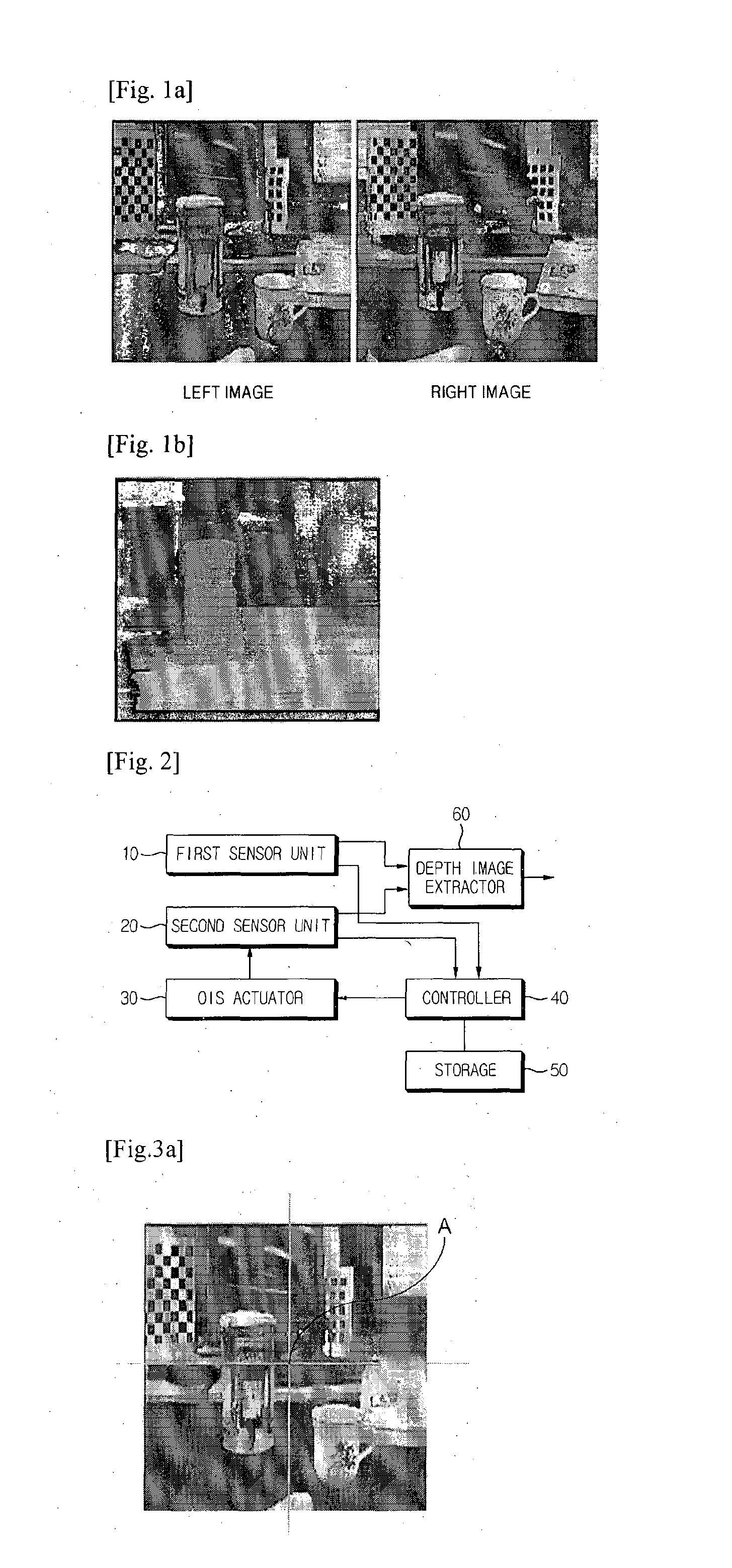

Apparatus and Method for Eliminating Noise in Stereo Image

Apparatus and method for eliminating noise in stereo image are disclosed, the method according to an exemplary embodiment of the present invention comprising, obtaining a first image captured by a first sensor unit and a second imaged captured by a second sensor unit; calculating a pixel difference of the second image relative to a first image based on a predetermined reference point; determining a pixel amount of the second image to be calibrated using a reference pixel difference and the pixel difference; and generating a driving signal for driving an Optical Image Stabilizer (OIS) actuator using the pixel amount to be calibrated.

Owner:LG INNOTEK CO LTD

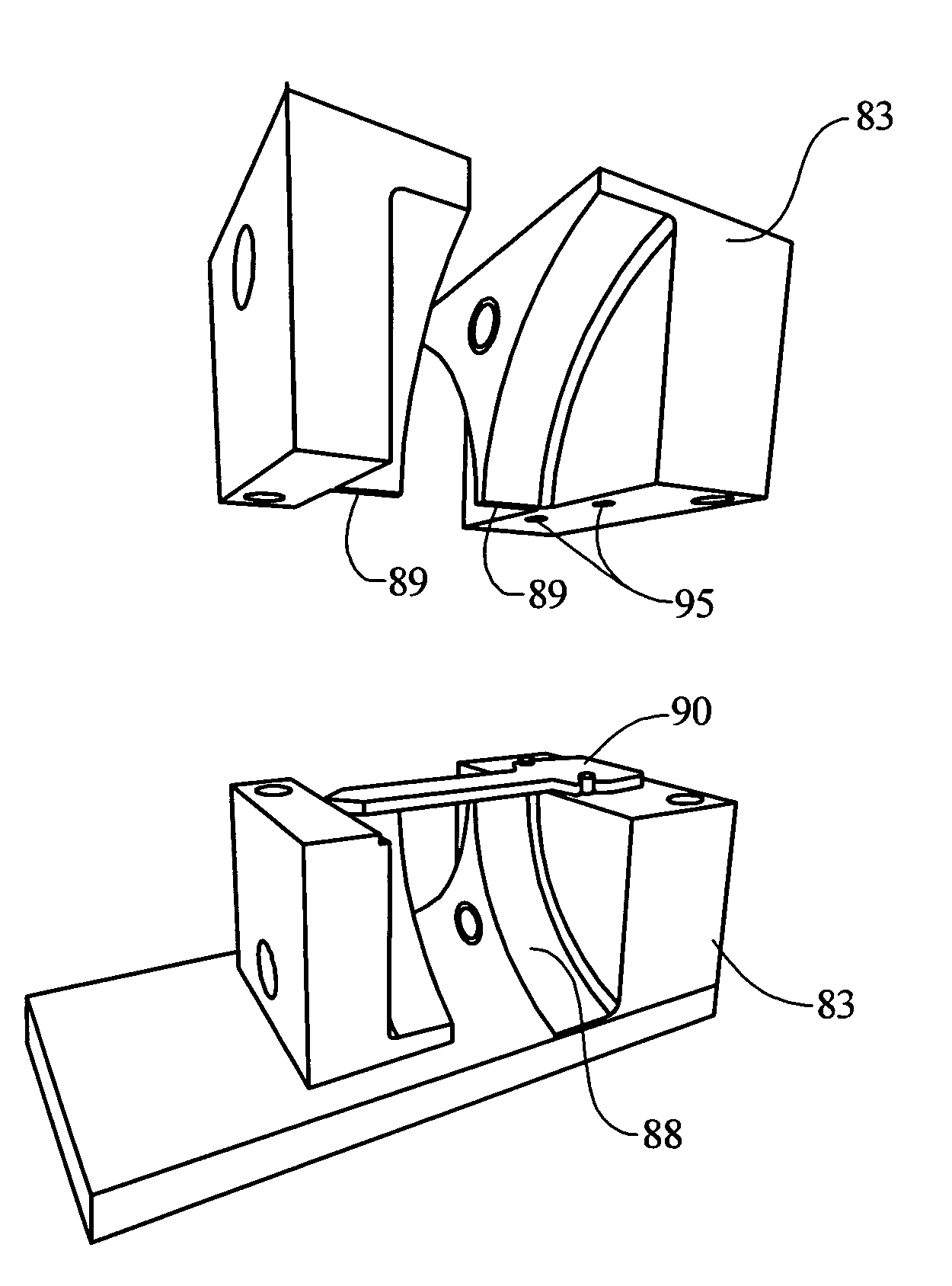

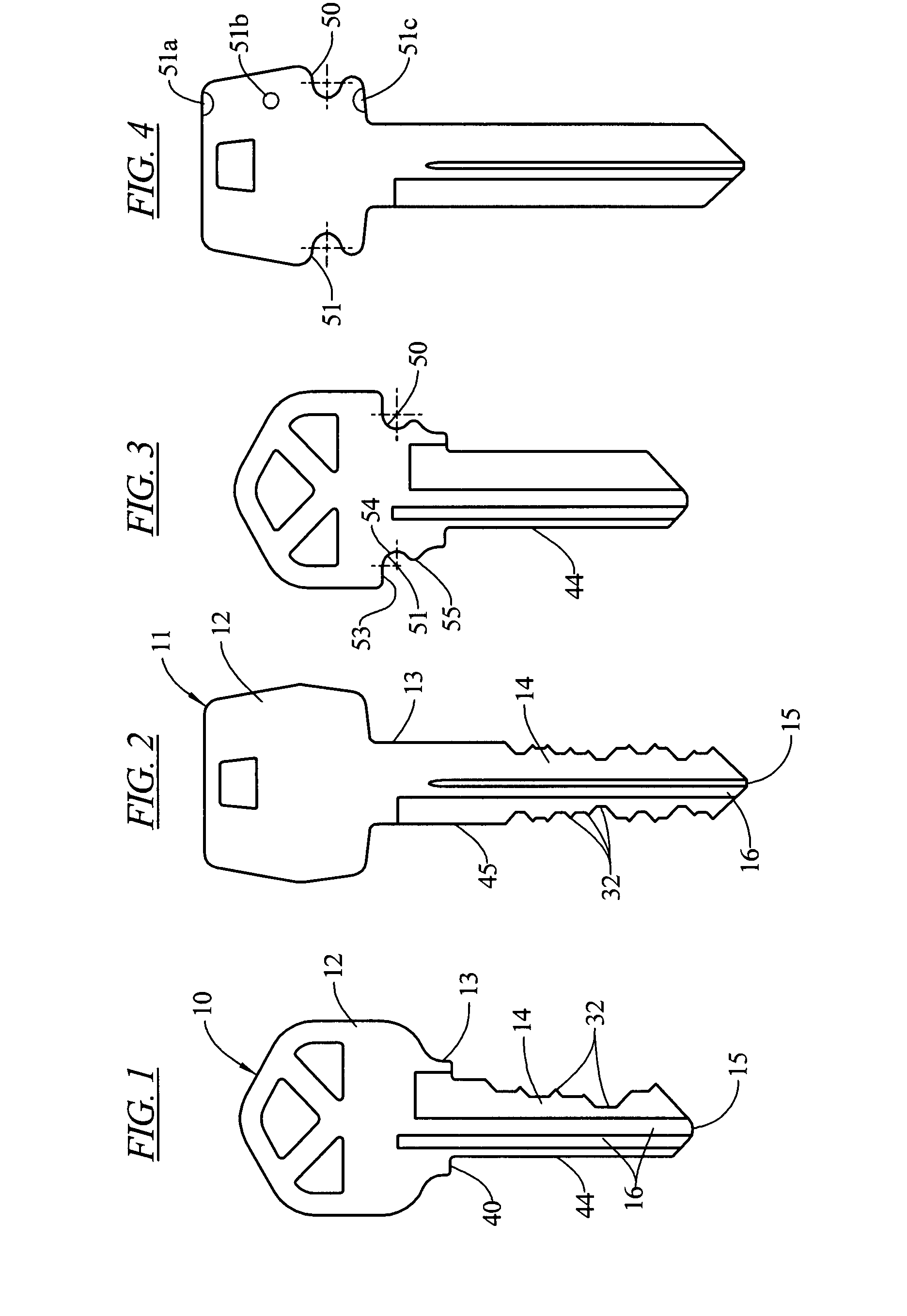

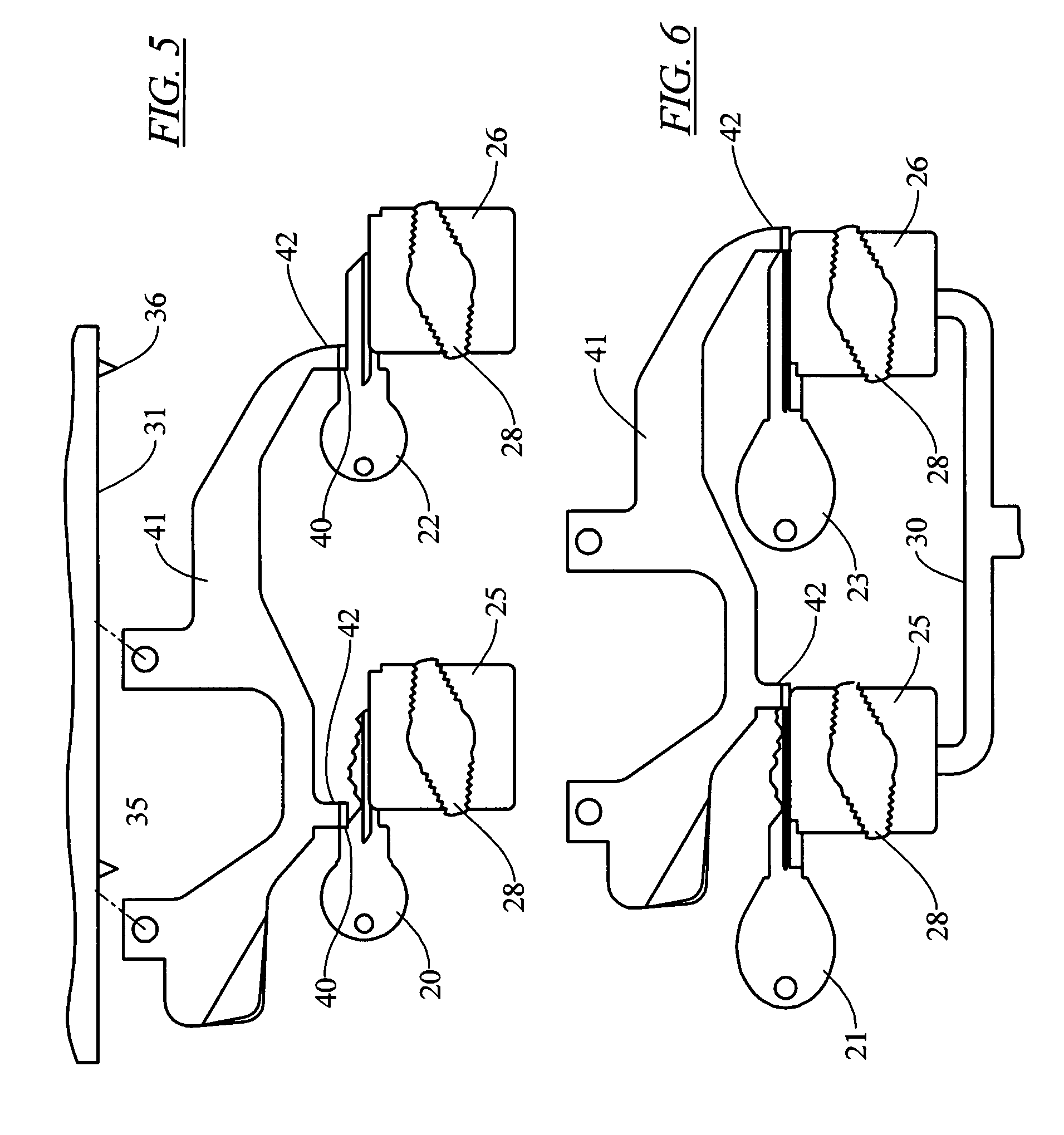

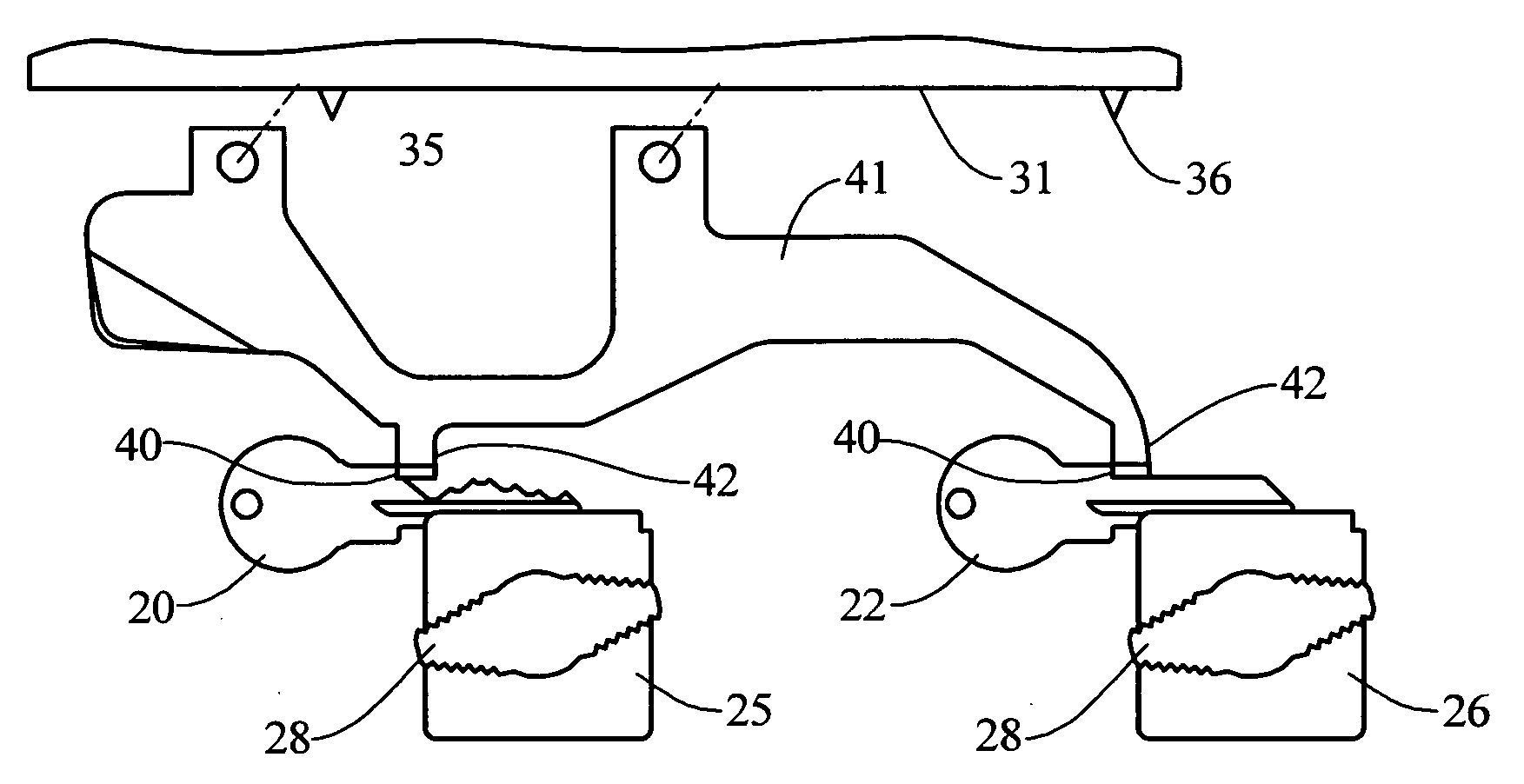

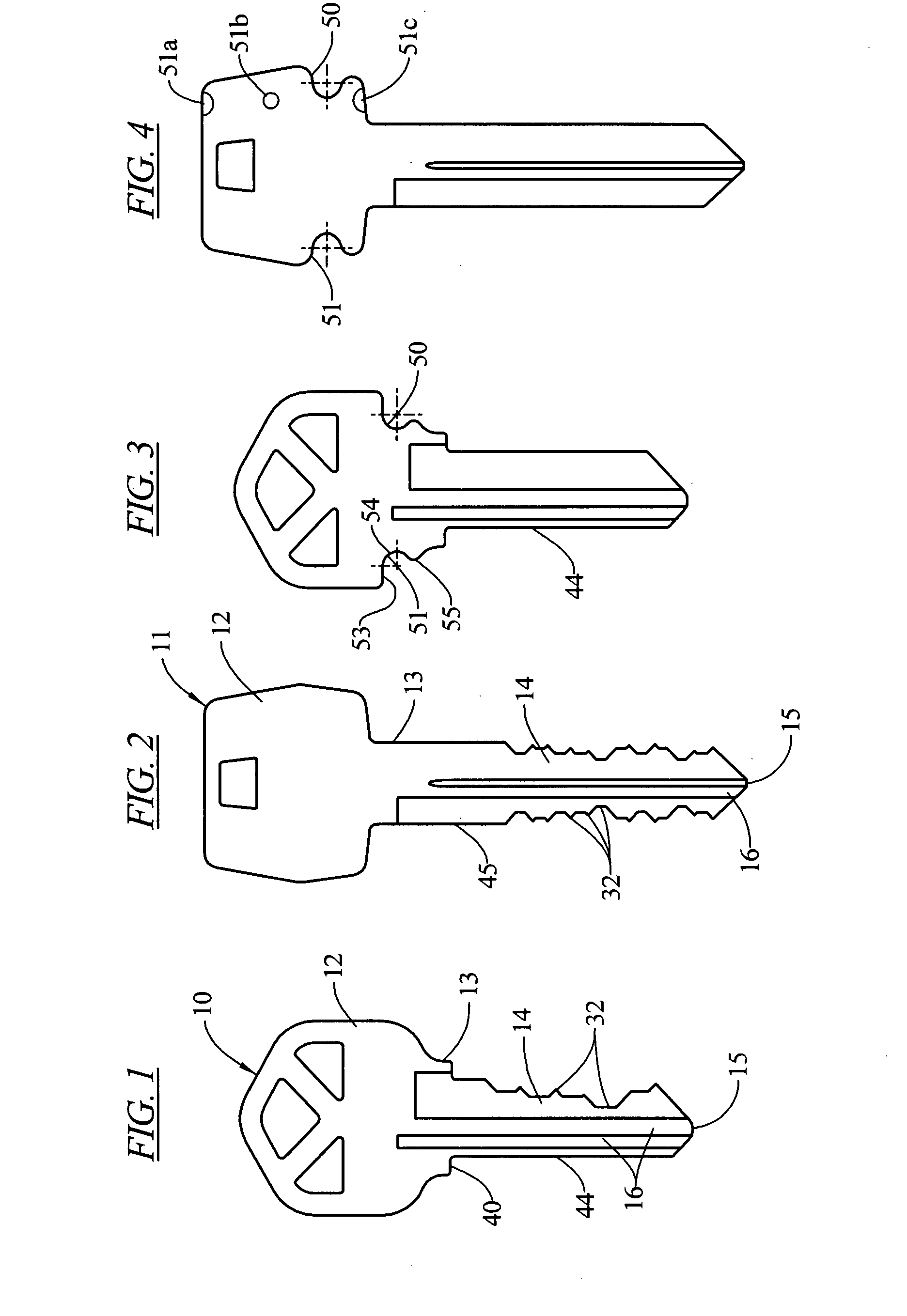

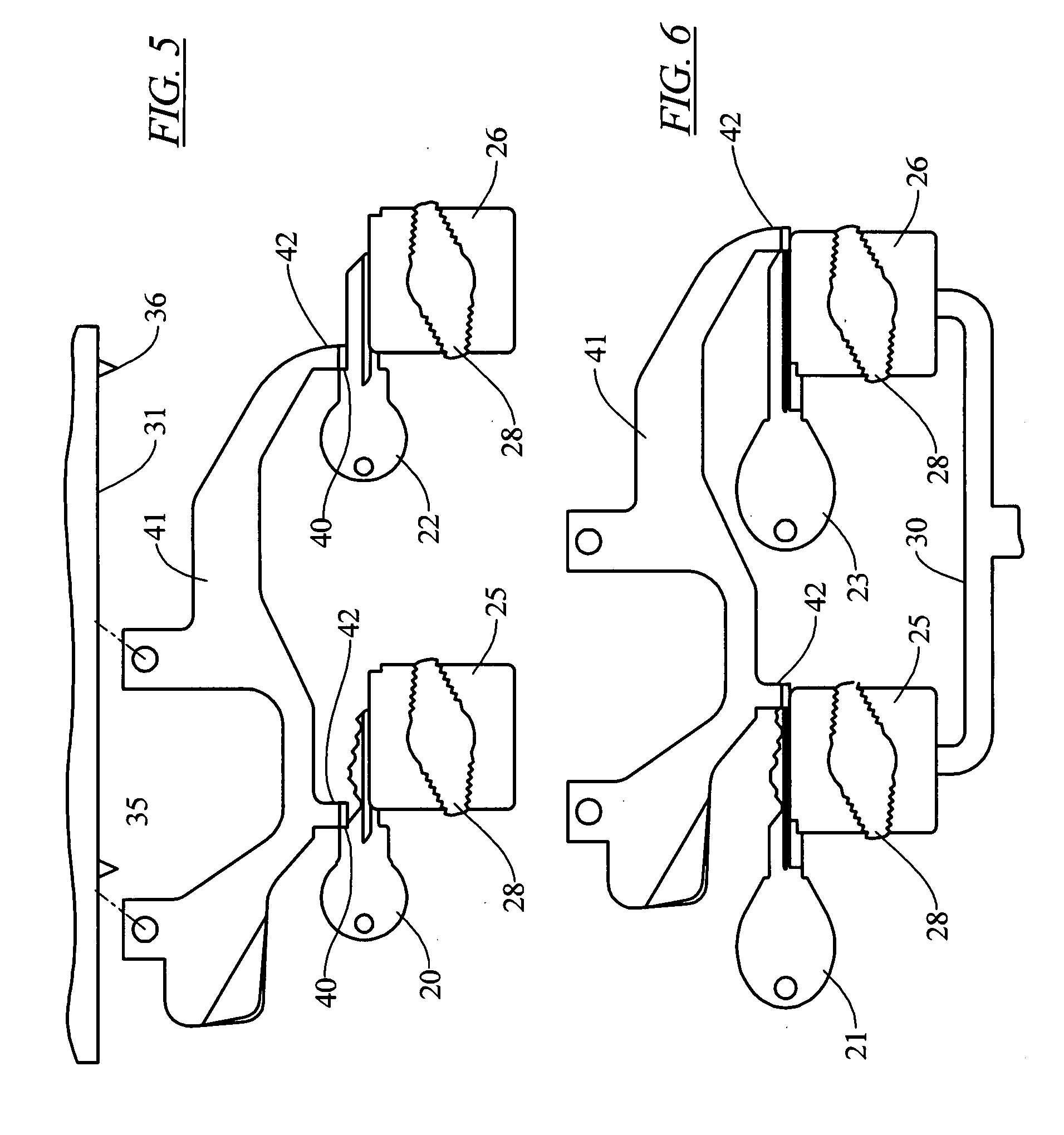

Ez key registration assembly

InactiveUS7918629B2Precise positioningReduce cutting vibrationWorkpiece holdersMilling machinesEngineeringMechanical engineering

A locating system and method for accurately positioning key blanks with respect to a key cutter where the key head is clamped between opposing jaws with the key blade working edges projecting therefrom, the key head is provided with shaped recesses having at least a partially specifically shaped edge wall and wherein at least one jaw member is provided with a projection having a correspondingly shaped sidewall, the pin being positioned with respect to the clamp such that when the key blank head is abutted against the pin with the key blank edge configuration mating to the pin sidewall configuration, the key blade will project from the jaw in a proper position for engagement by either the bitting follower or bitting cutter respectively.

Owner:KABA ILCO CORP

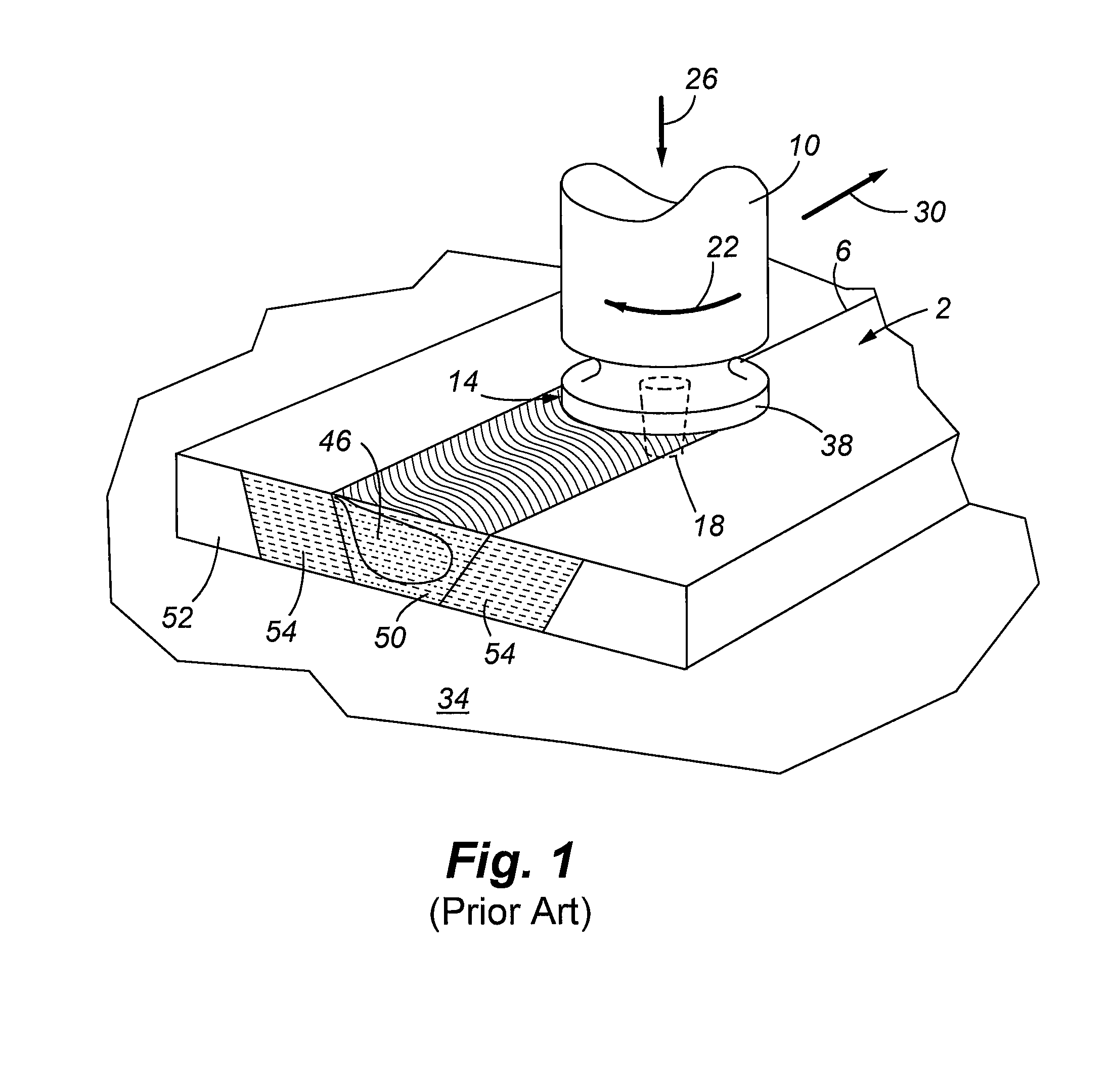

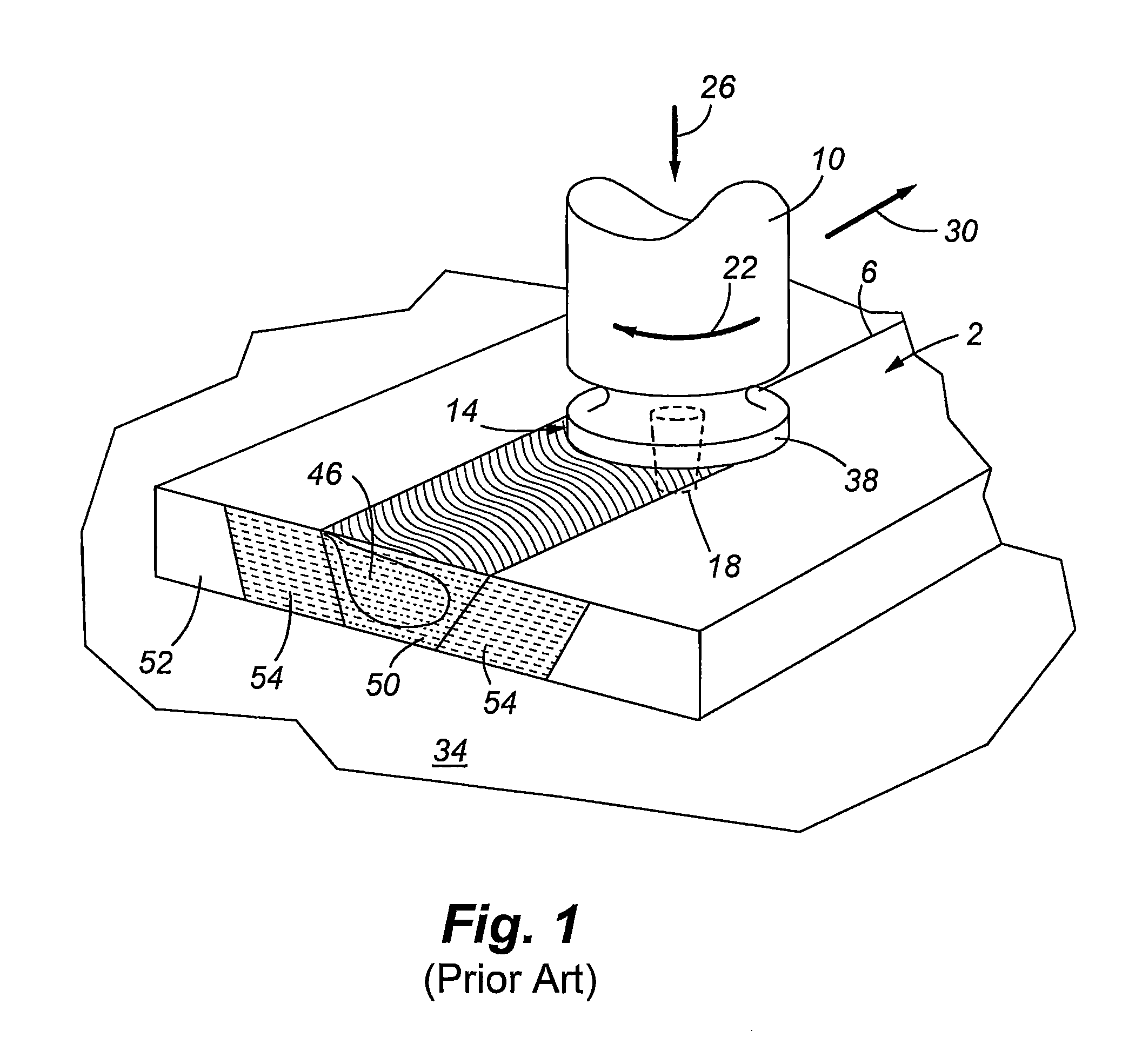

Friction stir welding apparatus, system and method

ActiveUS7866532B1Easy to useManpowerWelding/cutting auxillary devicesAuxillary welding devicesEngineeringMechanical engineering

A method of performing friction stir welding is provided herein. More specifically, traditional friction stir welding requires a rotatable head that is forced against a plurality of work pieces to bond the same. The rotational and normal forces generated by the friction stir welding tool are generally reacted by a backing plate, anvil, mandrel or other mechanisms, such hardware are subject to the applied forces and are often supported with additional internal supports. Conversely, a method of performing a friction stir weld is described that omits the need for such a backing member and internal supports as it is performed using a self reacting pin tool.

Owner:UNITED LAUNCH ALLIANCE

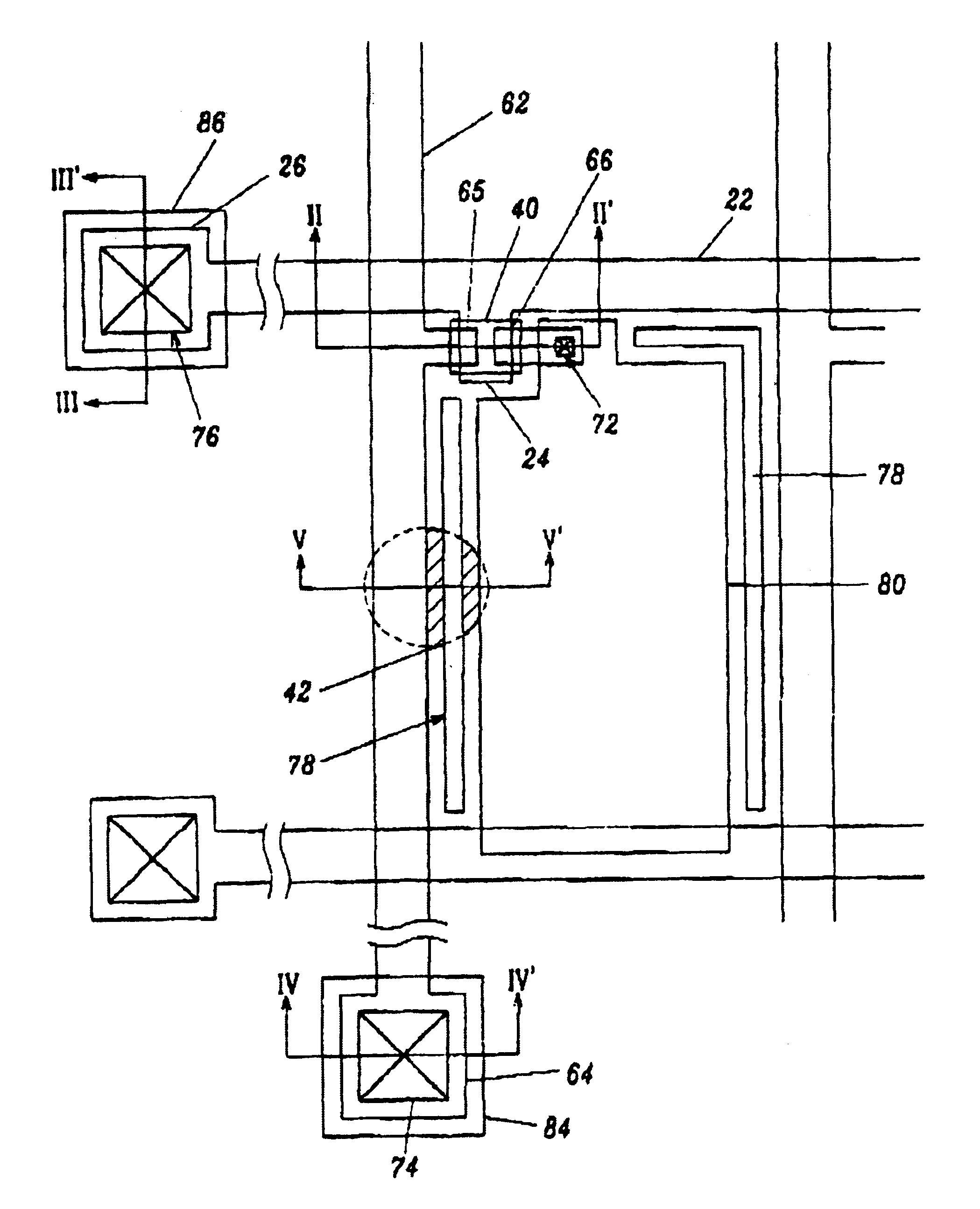

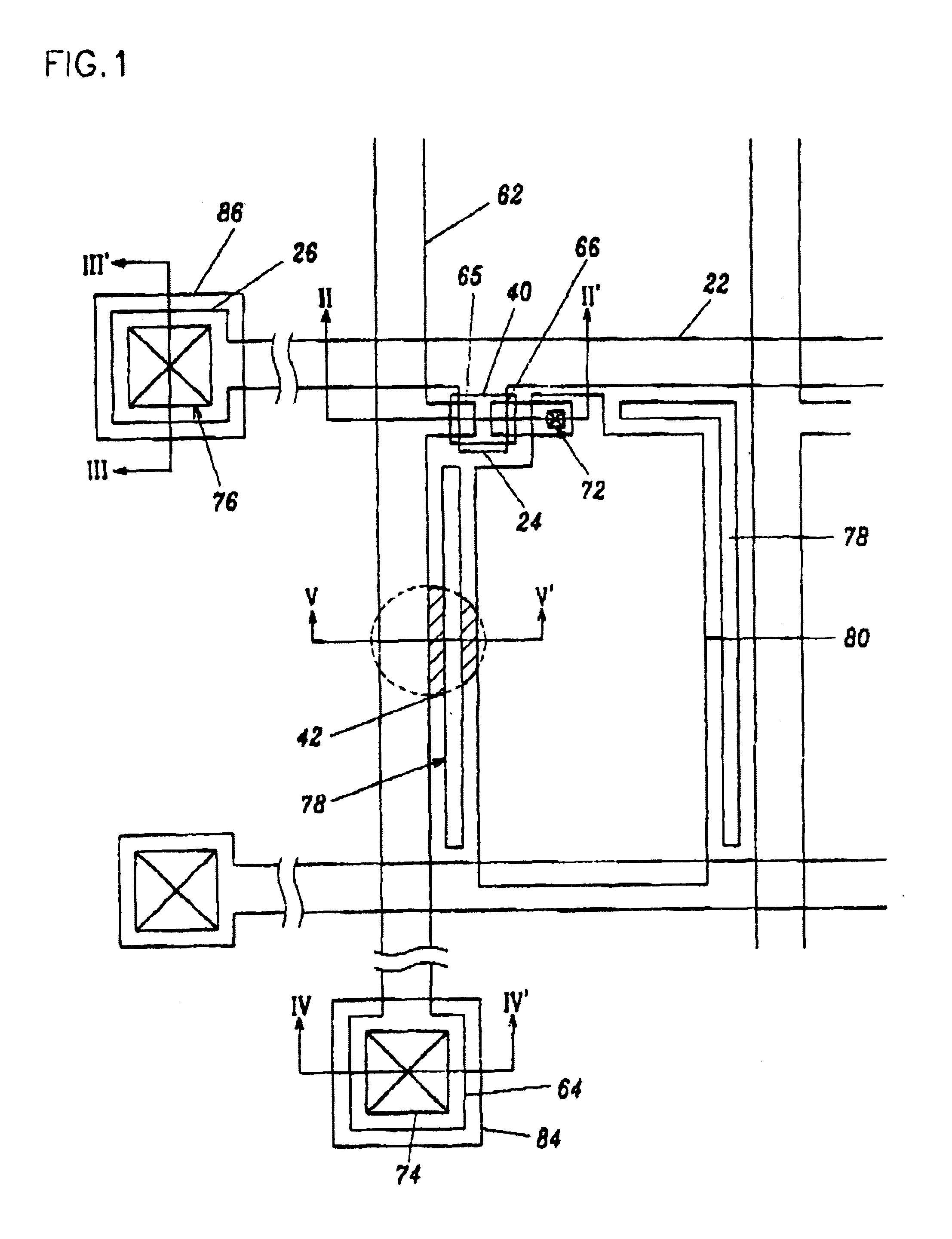

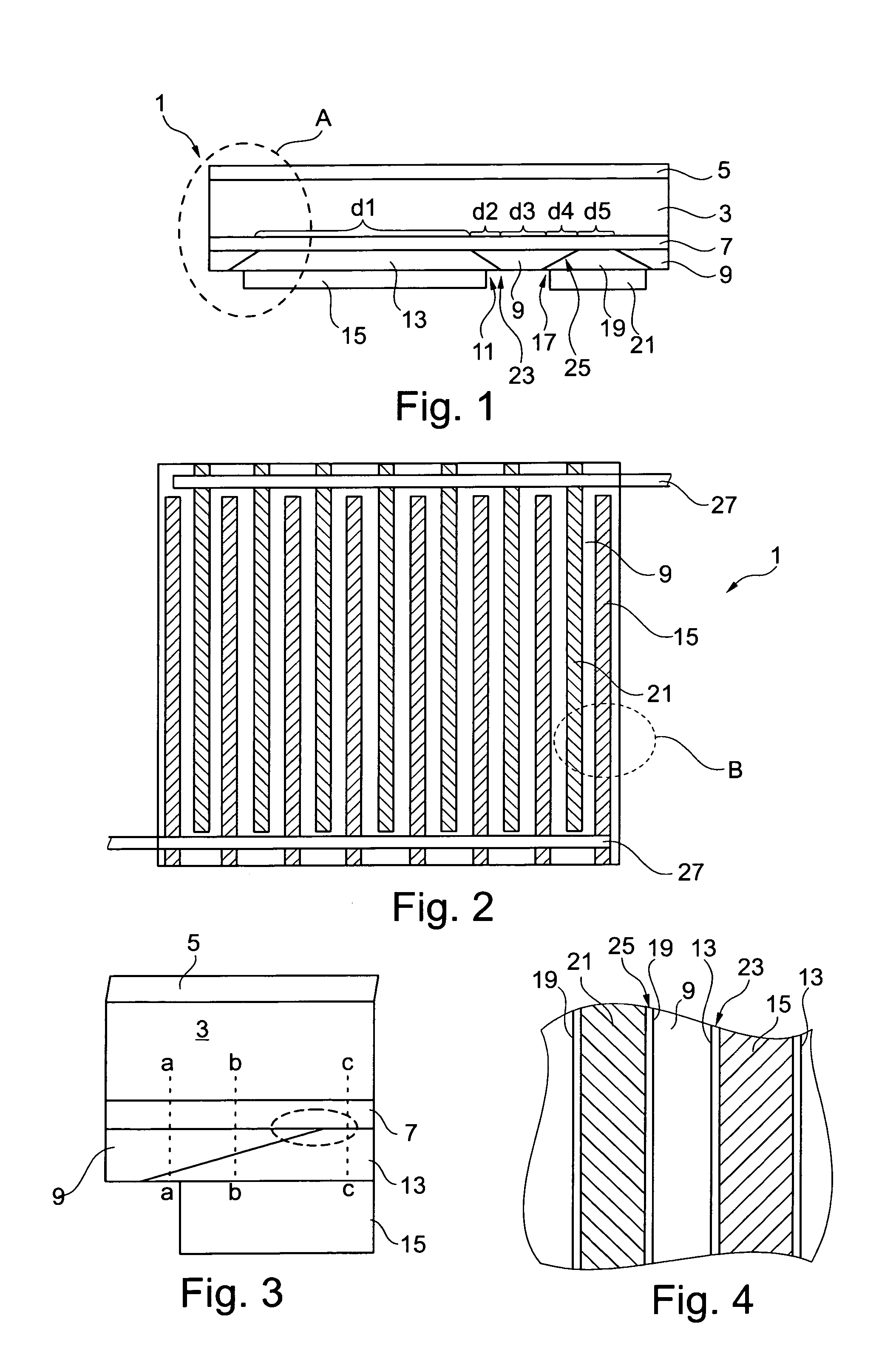

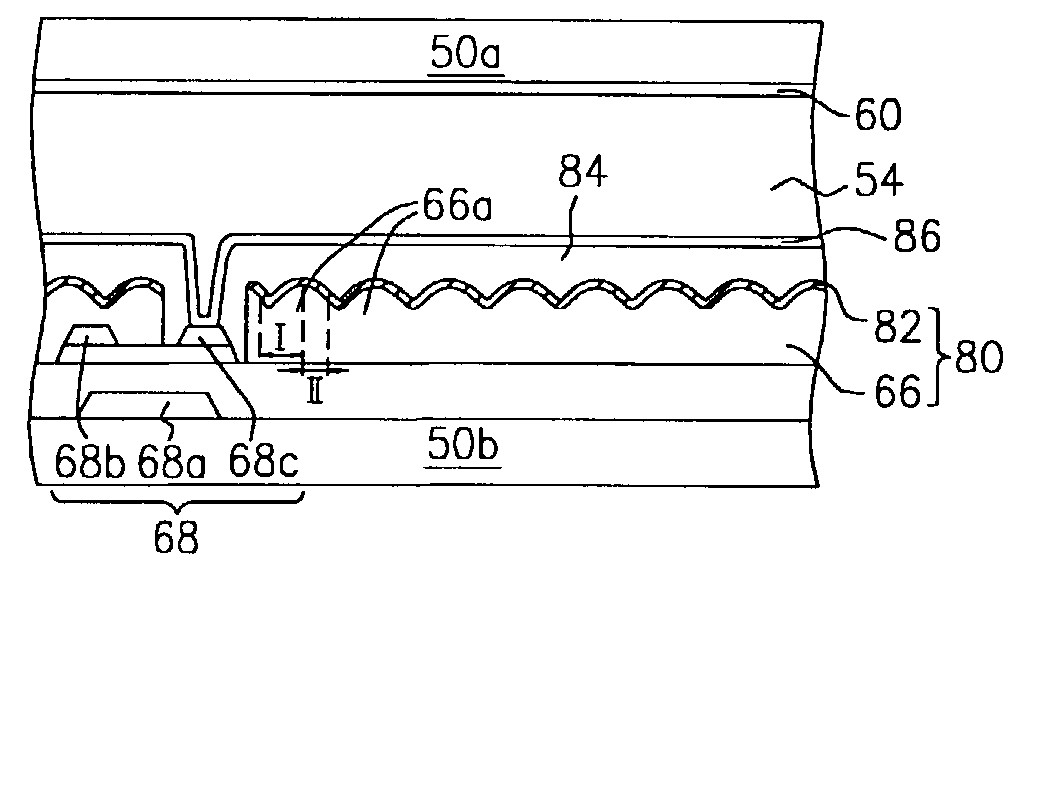

Thin film transistor array panel for a liquid crystal display

InactiveUS6900854B1Reduce defectReduce pixel defectsSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceLiquid-crystal display

A gate wire including a gate line extending in the horizontal direction, and a gate electrode is formed on an insulating substrate. A gate insulating layer is formed on the gate wire and covers the same. A semiconductor pattern is formed on the gate insulating layer 30, and formed on the semiconductor pattern are a data wire having a date line in the vertical direction, a source electrode, a drain electrode separated from the source electrode opposite the source electrode with respect to the gate electrode, and an align pattern located on both sides of the data line. A passivation layer is formed on the data wire and the align pattern, and has contact holes exposing the drain electrode and an opening exposing the substrate between the data line and the align pattern. Here, the align pattern adjacent to the data line is exposed through the opening, and the semiconductor pattern and the gate insulating layer are under-cut. A pixel electrode connected to the drain electrode through the contact hole is formed on the passivation layer. Here, the opening is located between the data line and the pixel electrode. In this structure, misalignment occurring in the manufacturing process of a thin film transistor panel for a liquid crystal display is minimized, and stitch defects are prevented by uniformity forming a coupling capacitance between the data line and the pixel electrode. Shorts between the data line and the pixel electrode are prevented by forming the opening between the data line and the pixel electrode.

Owner:SAMSUNG DISPLAY CO LTD

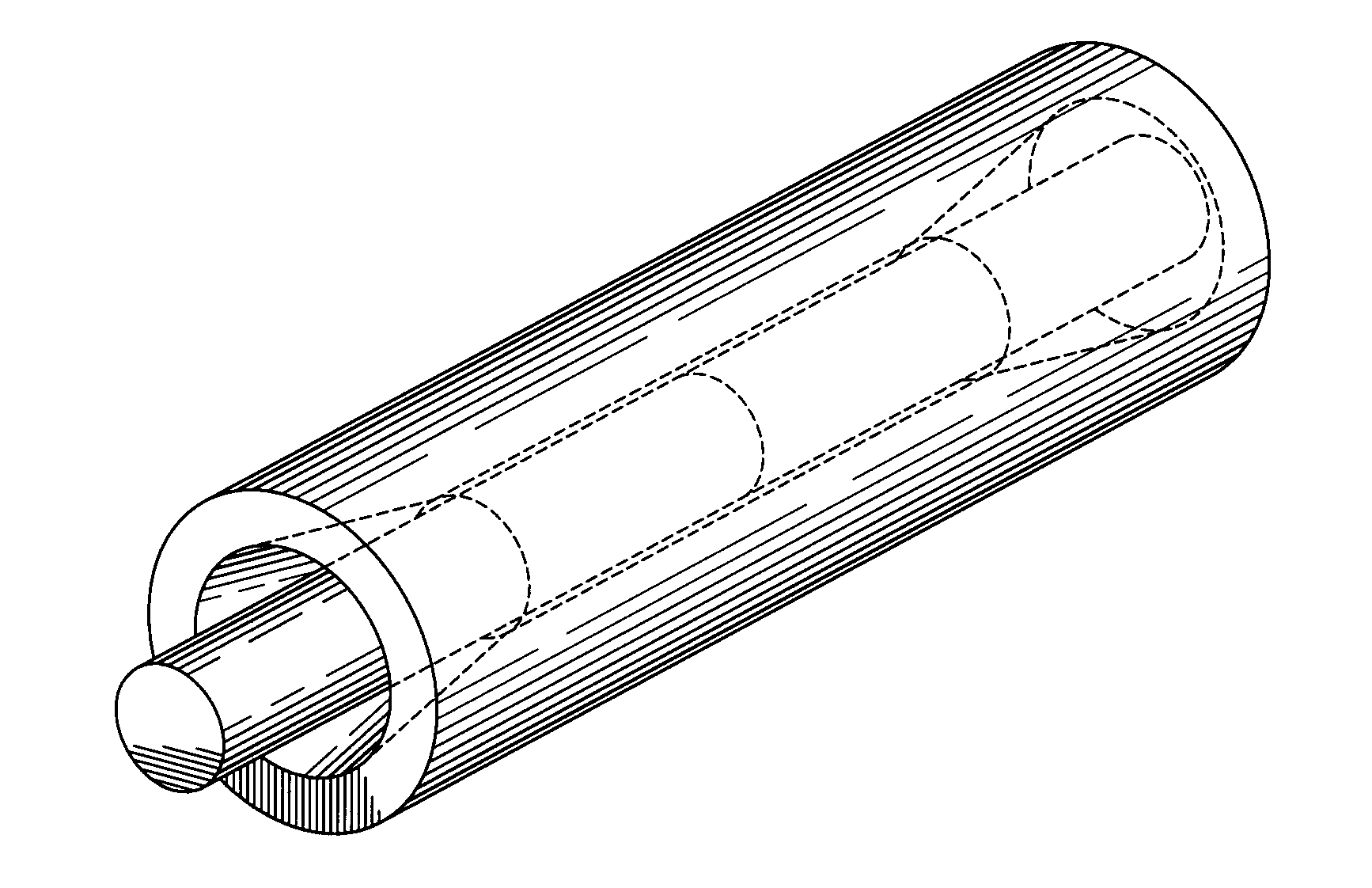

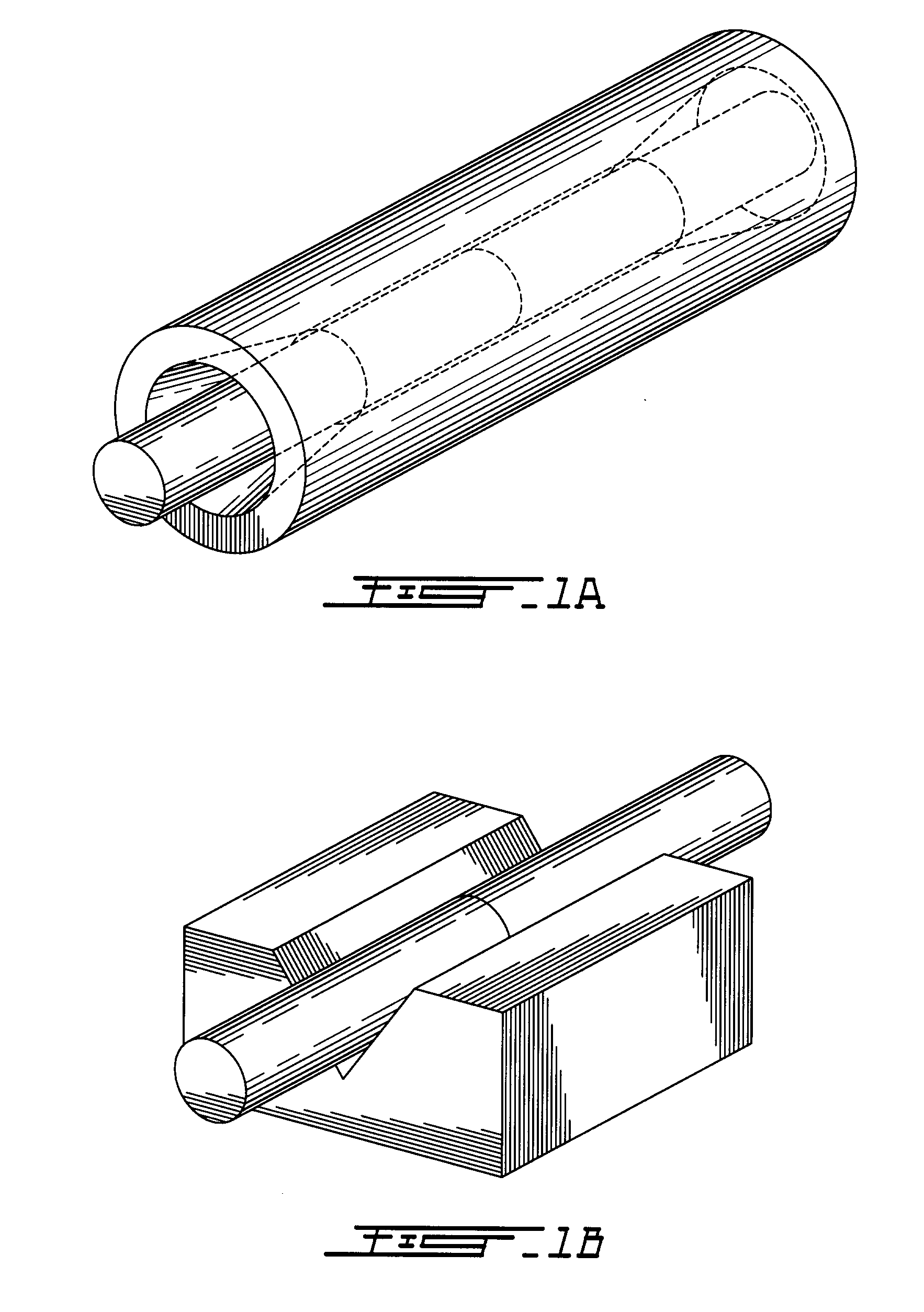

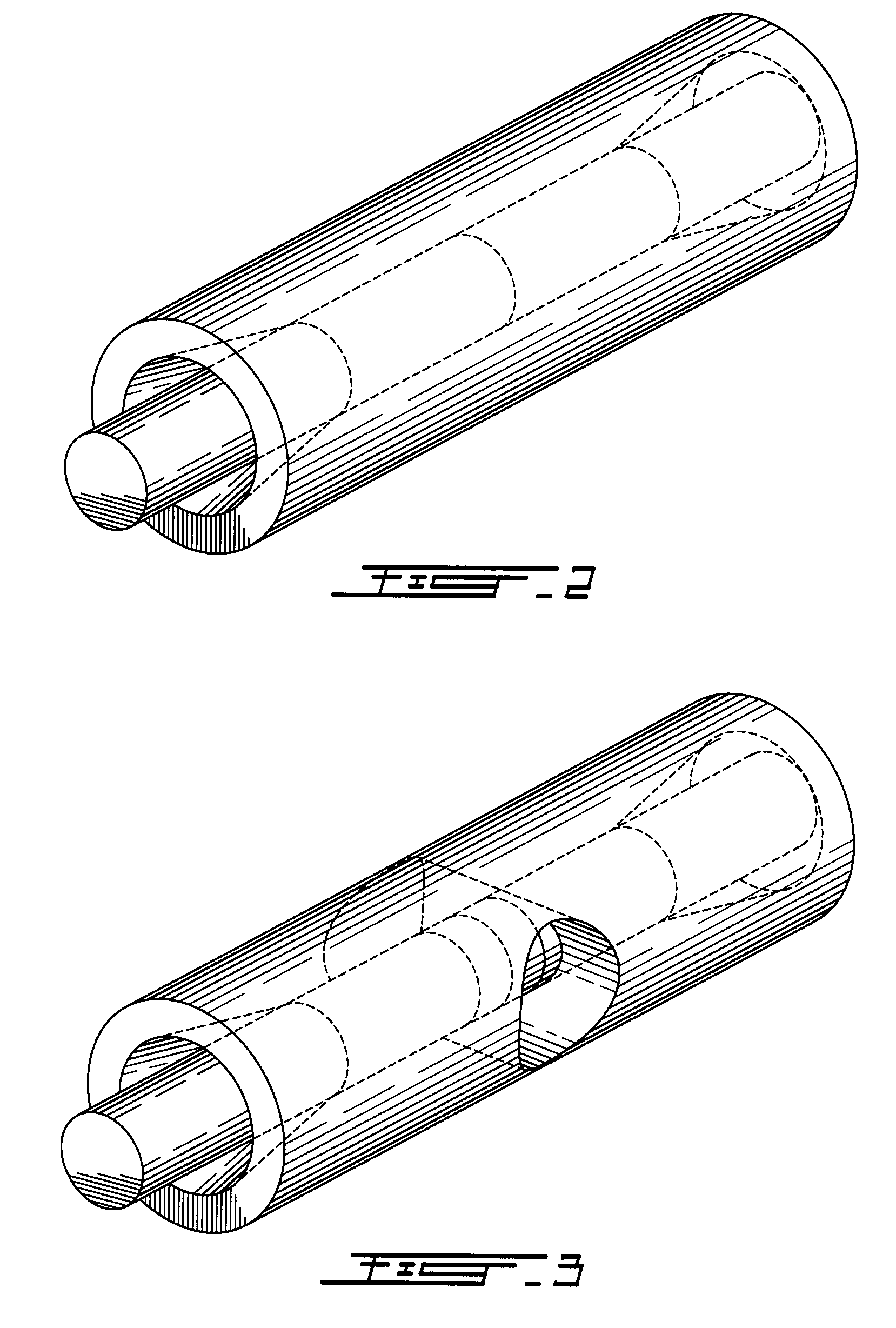

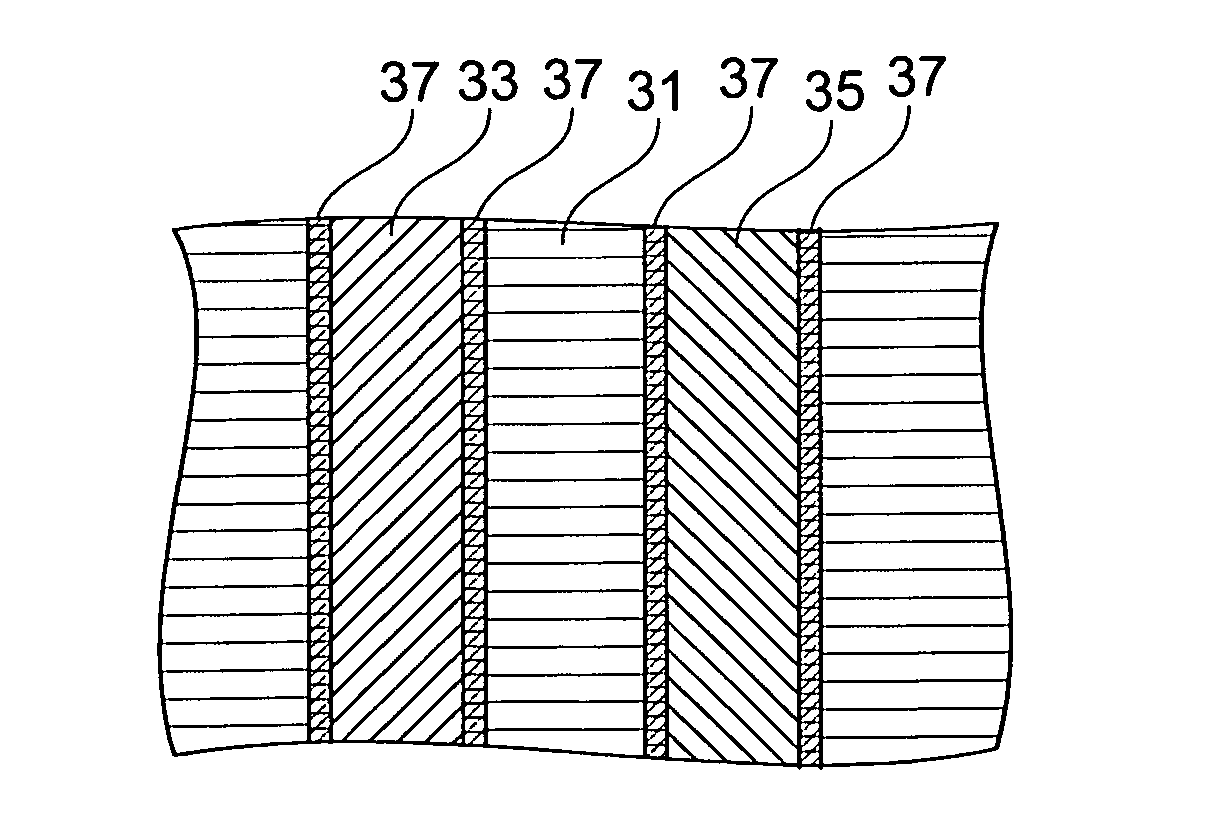

Method of fusing optical fibers within a splice package

InactiveUS20100101277A1Overcomes drawbackNot to damageGlass making apparatusOptical articlesFiberOptical fiber cable

The present invention relates to methods of connecting optical fibers. In a first aspect, the method proceeds by using a ferrule device having a passage adapted to apply radial pressure to optically align and hold in position opposed fiber ends, and fusing said fiber ends held by said ferrule device. In another aspect, the method of the present invention uses a ferrule device to optically align without mechanized adjustment and hold in position opposed fiber ends with a gap where said fiber ends meet, where the fibers have a temperature of fusion that is higher than a melting temperature of said ferrule device. The method then transmits radiation directly onto said fiber ends without significant direct transmission onto said ferrule device to generate heat in said fiber ends and fuse said fiber ends held by said ferrule device.

Owner:GONTHIER FRANCOIS +1

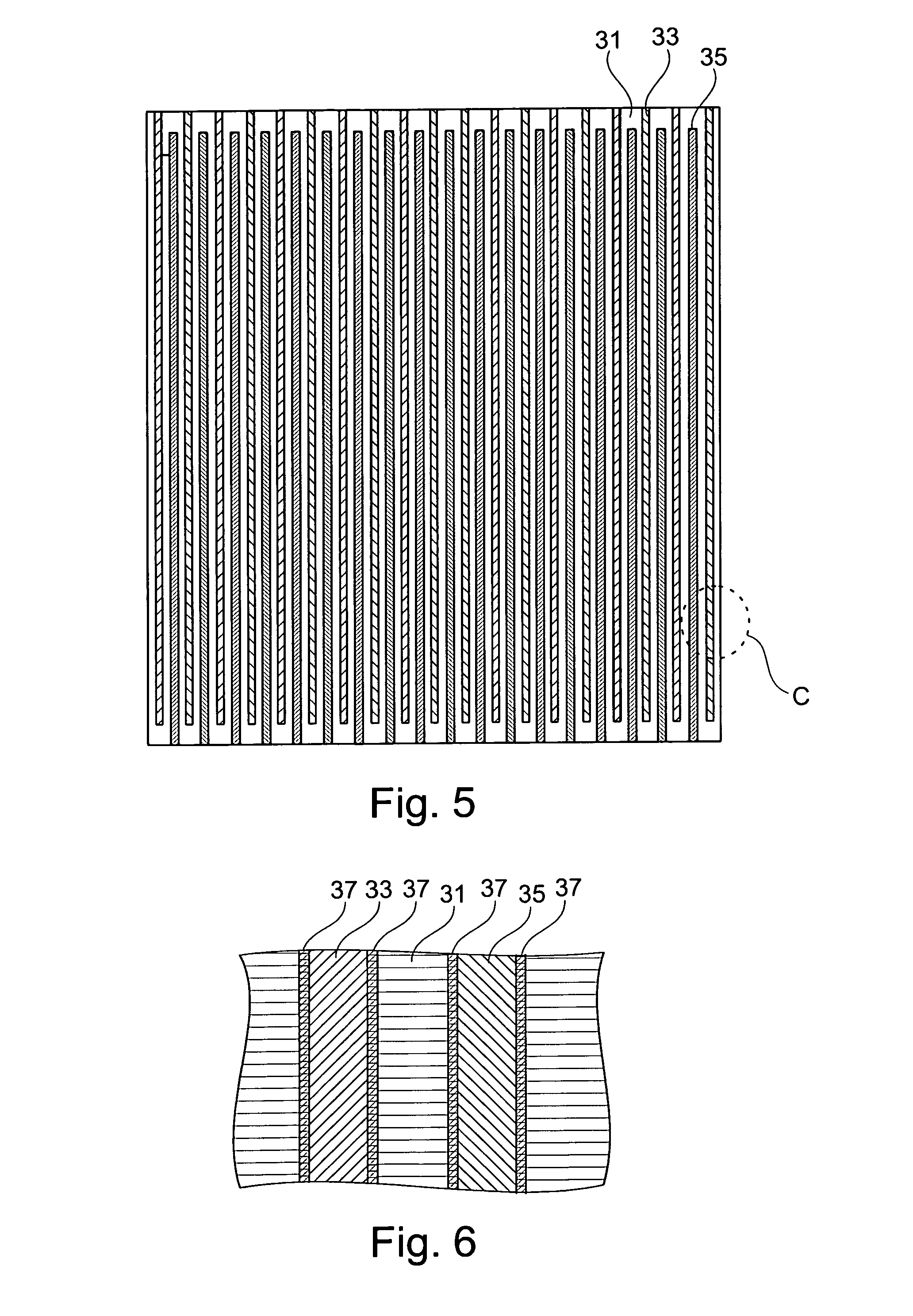

Solar cell and method for producing same

ActiveUS20140096819A1Minimize misalignmentImprove efficiencySemiconductor/solid-state device manufacturingPhotovoltaic energy generationHeterojunctionGas phase

A rear contact heterojunction solar cell and a fabricating method. The solar cell comprises a silicon substrate having a passivating layer and an intrinsic amorphous silicon layer. At a back side of the intrinsic amorphous silicon layer, an emitter layer and a base layer are provided. Interposed between these emitter and base layers is a separation layer comprising an electrically insulating material. This separation layer as well as the base layer and emitter layer may be generated by vapour deposition. Due to such processing, adjacent regions of the emitter layer and the separating layer and adjacent regions of the base layer and the separating layer partially laterally overlap in overlapping areas in such a way that at least a part of the separating layer is located closer to the substrate than an overlapping portion of the respective one of the emitter layer and the base layer.

Owner:REC SOLAR

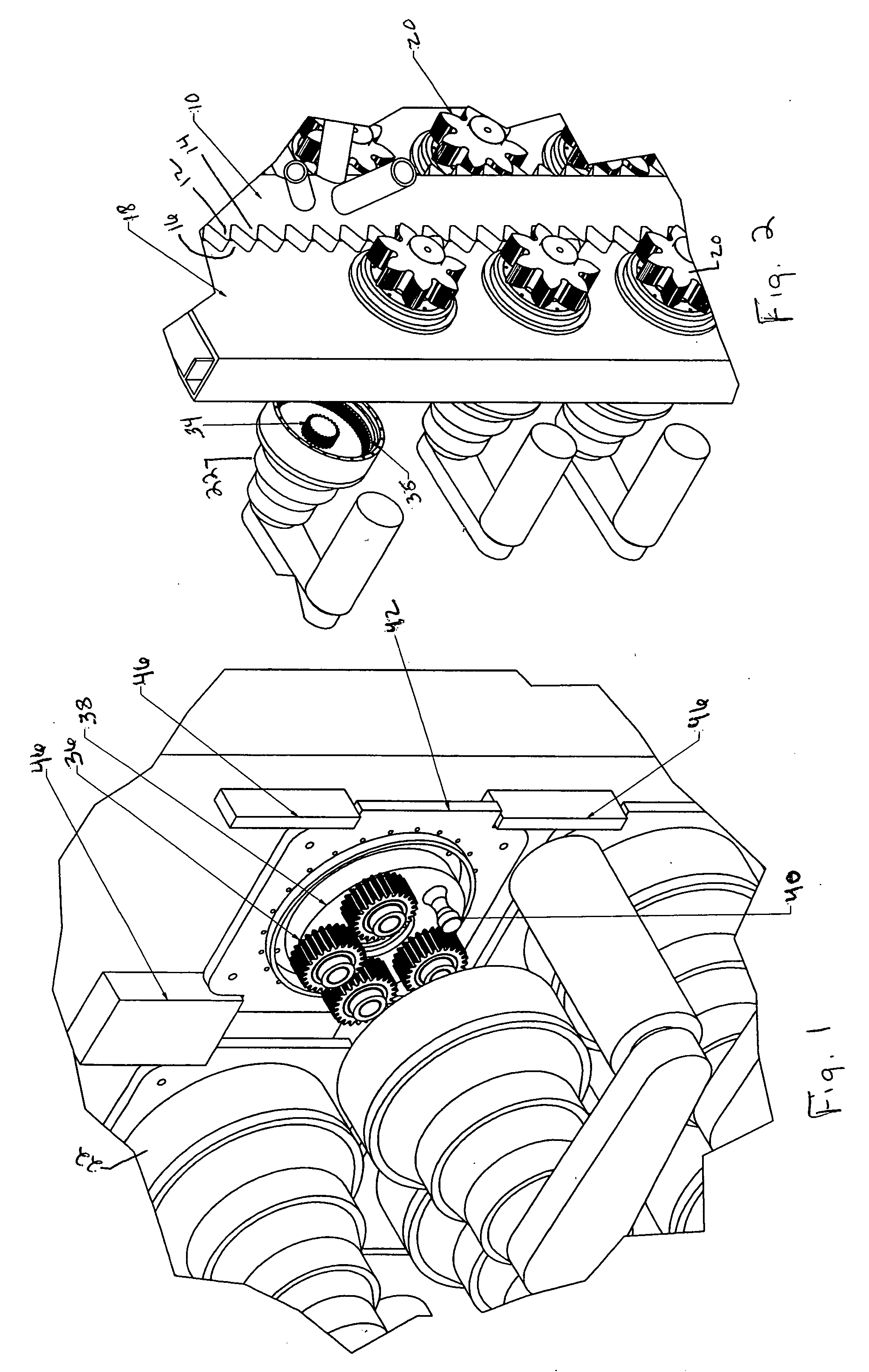

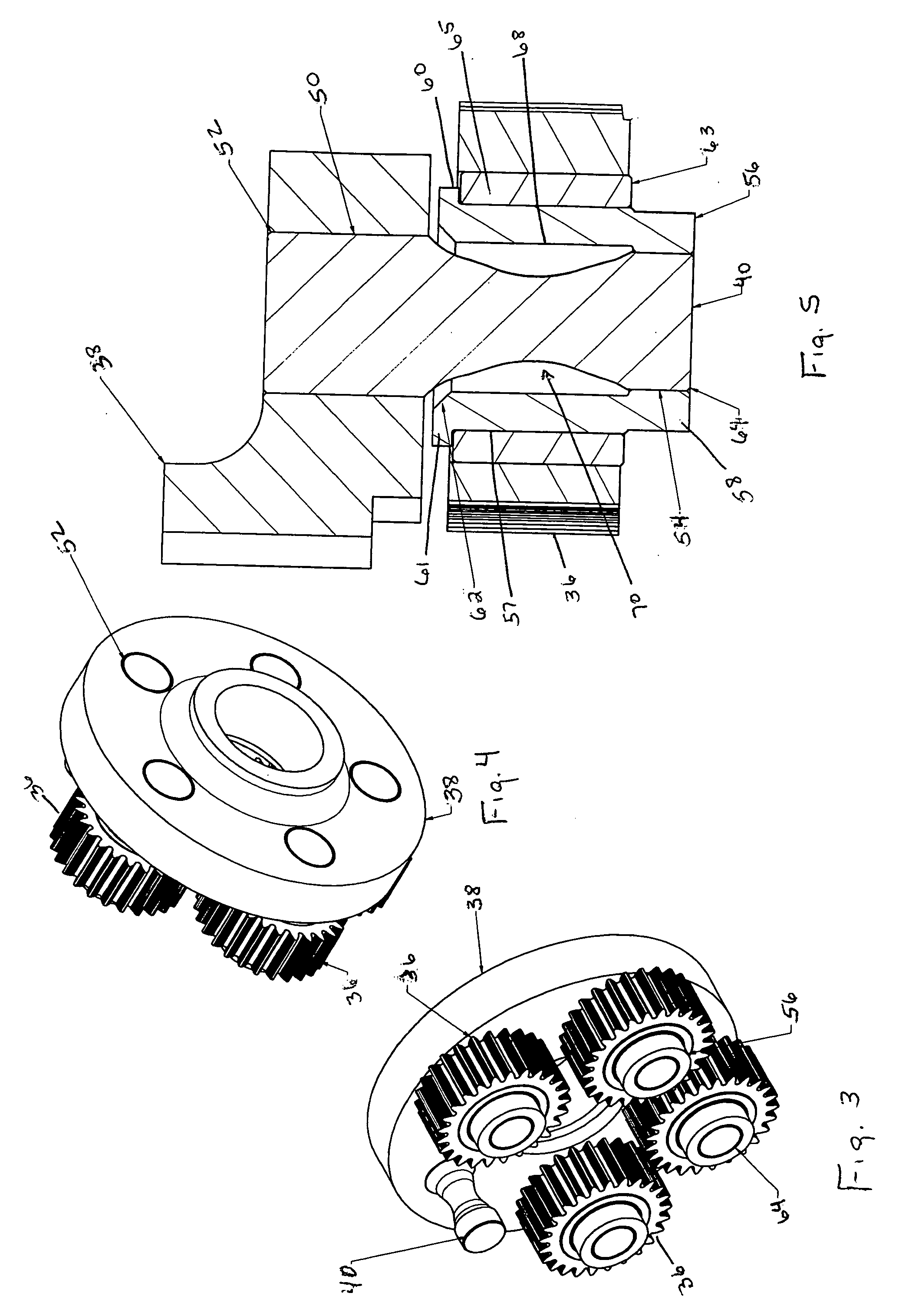

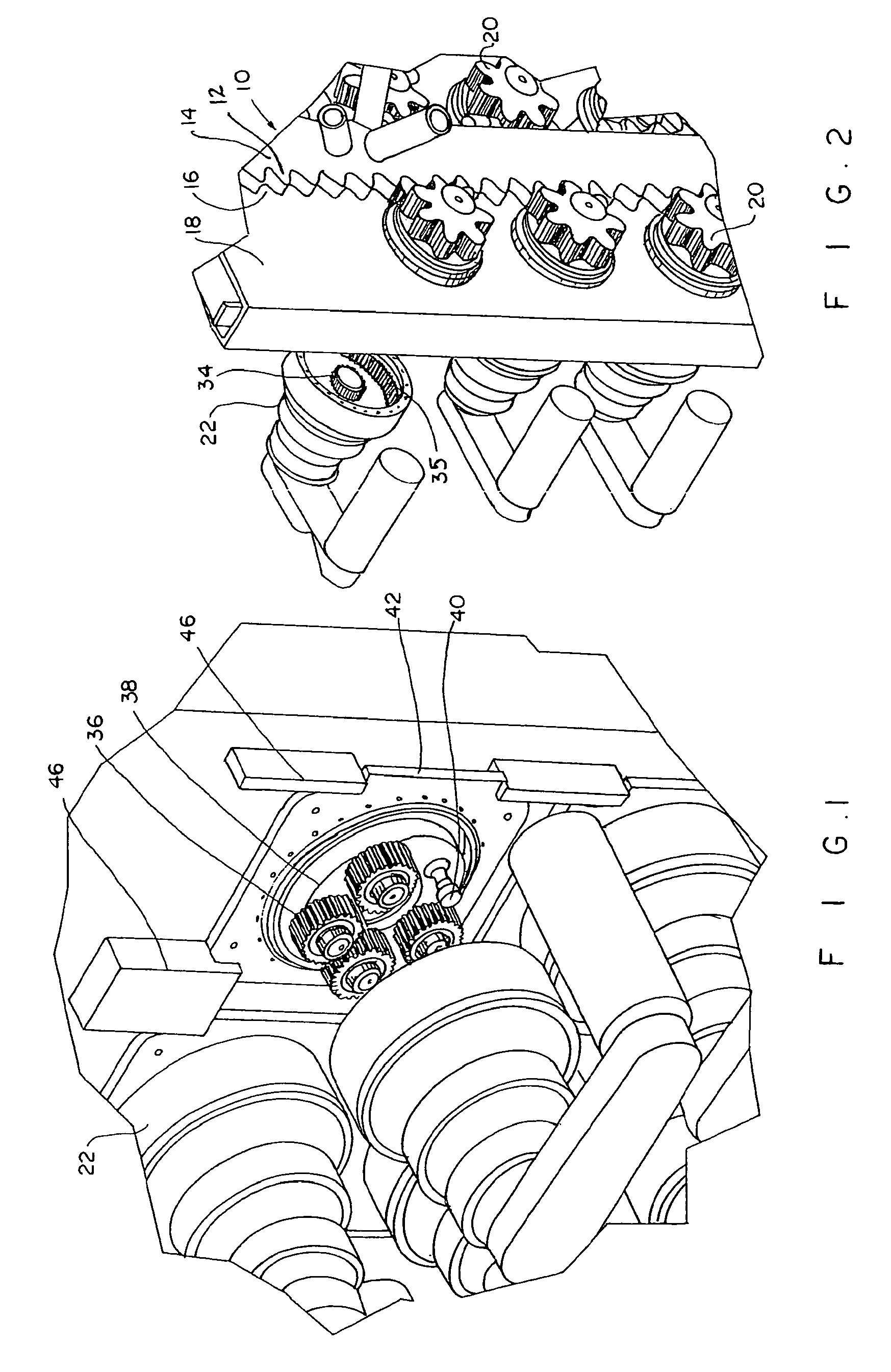

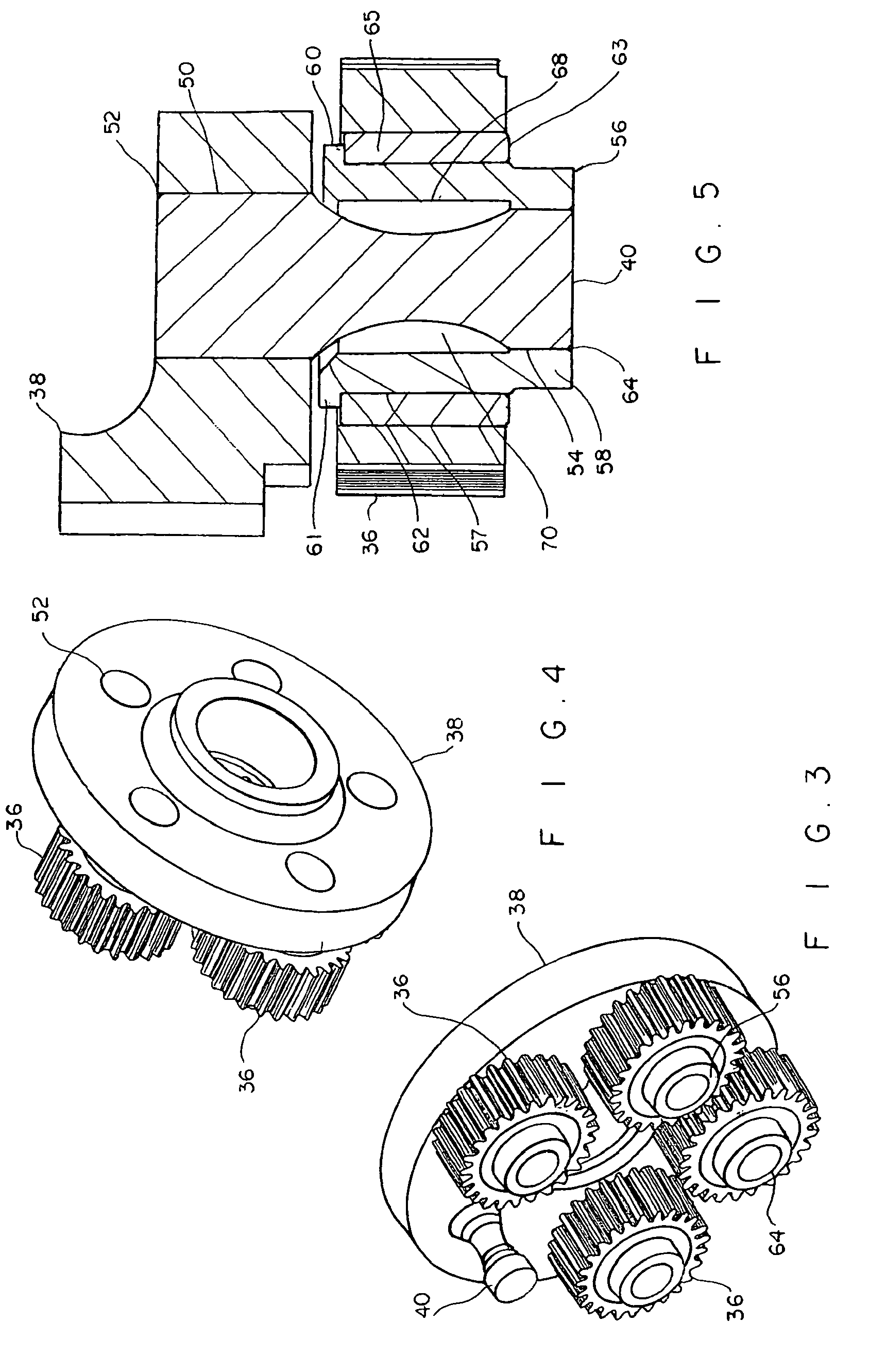

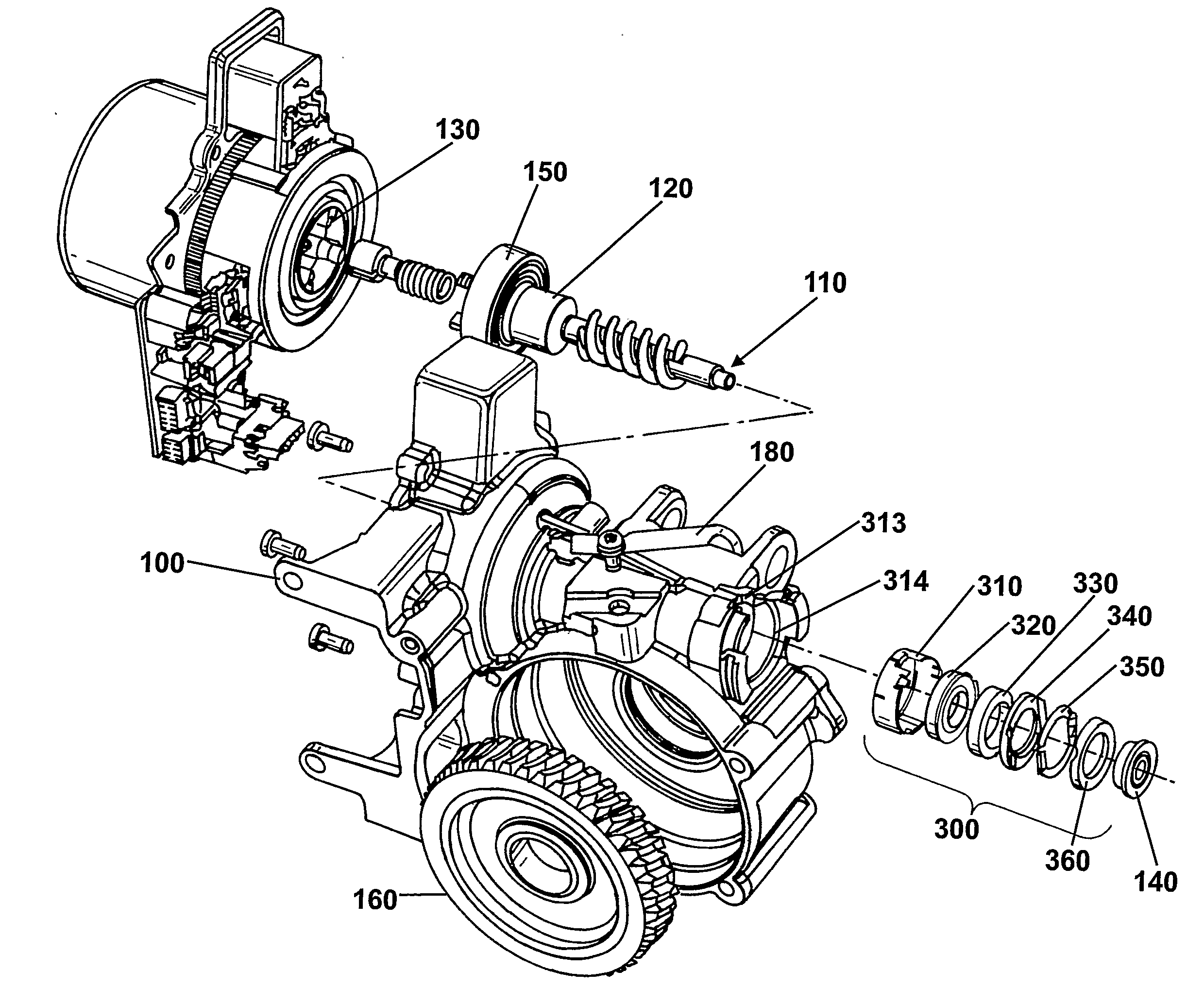

Gear assembly with tapered flex pin

ActiveUS20100197444A1Maximize deflectionMinimize misalignmentShaftsToothed gearingsEngineeringCantilever

An epicyclic gear assembly has a central toothed sun gear unit mounted on a carrier plate and plurality of planetary gear sets surrounding the central gear in torque-transmitting relationship. Each of said planetary gear sets has a toothed planet gear supported by a planet shaft, the first end of which is cantilevered from the carrier plate. A second end of the planet shaft supports the planet gear. A double-tapered concave middle portion of the planet shaft allows flexing of the shaft so as to facilitate elastic deflection of the planet shaft while distributing load between the planet gear sets. The outer circumference of the middle portion has a pair of spaced outwardly convex protrusions formed between the first end and the second end.

Owner:FRIEDE & GOLDMAN

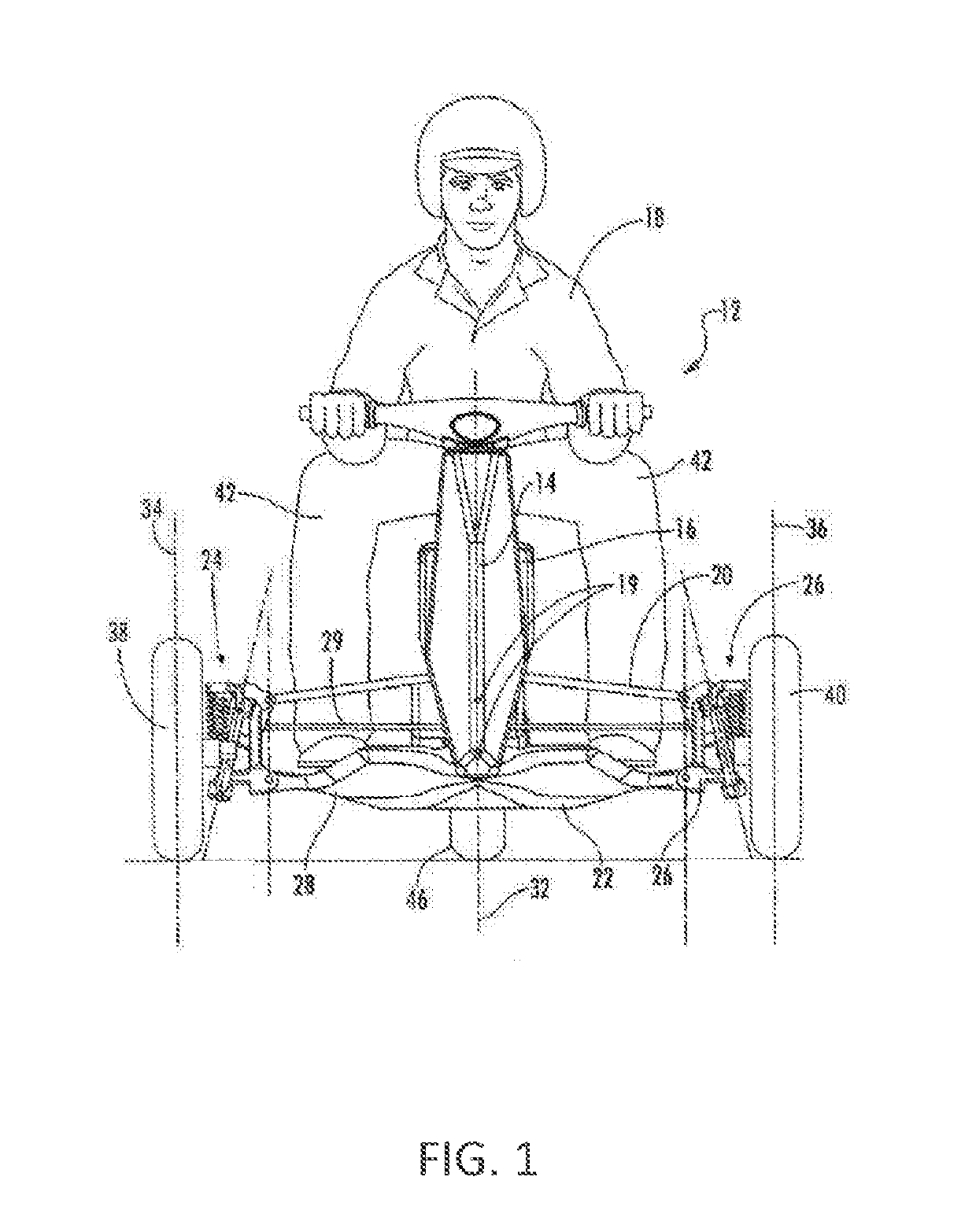

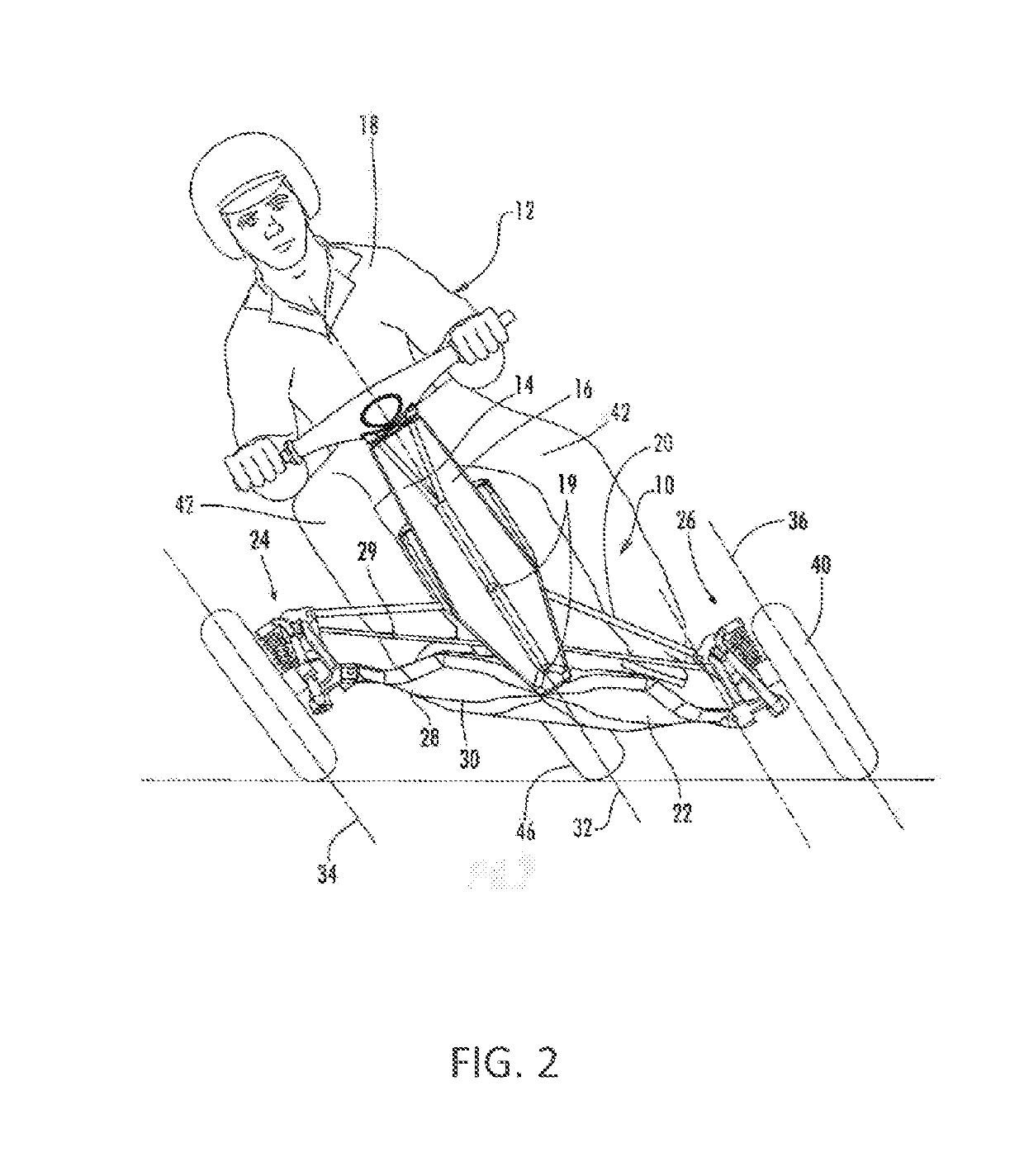

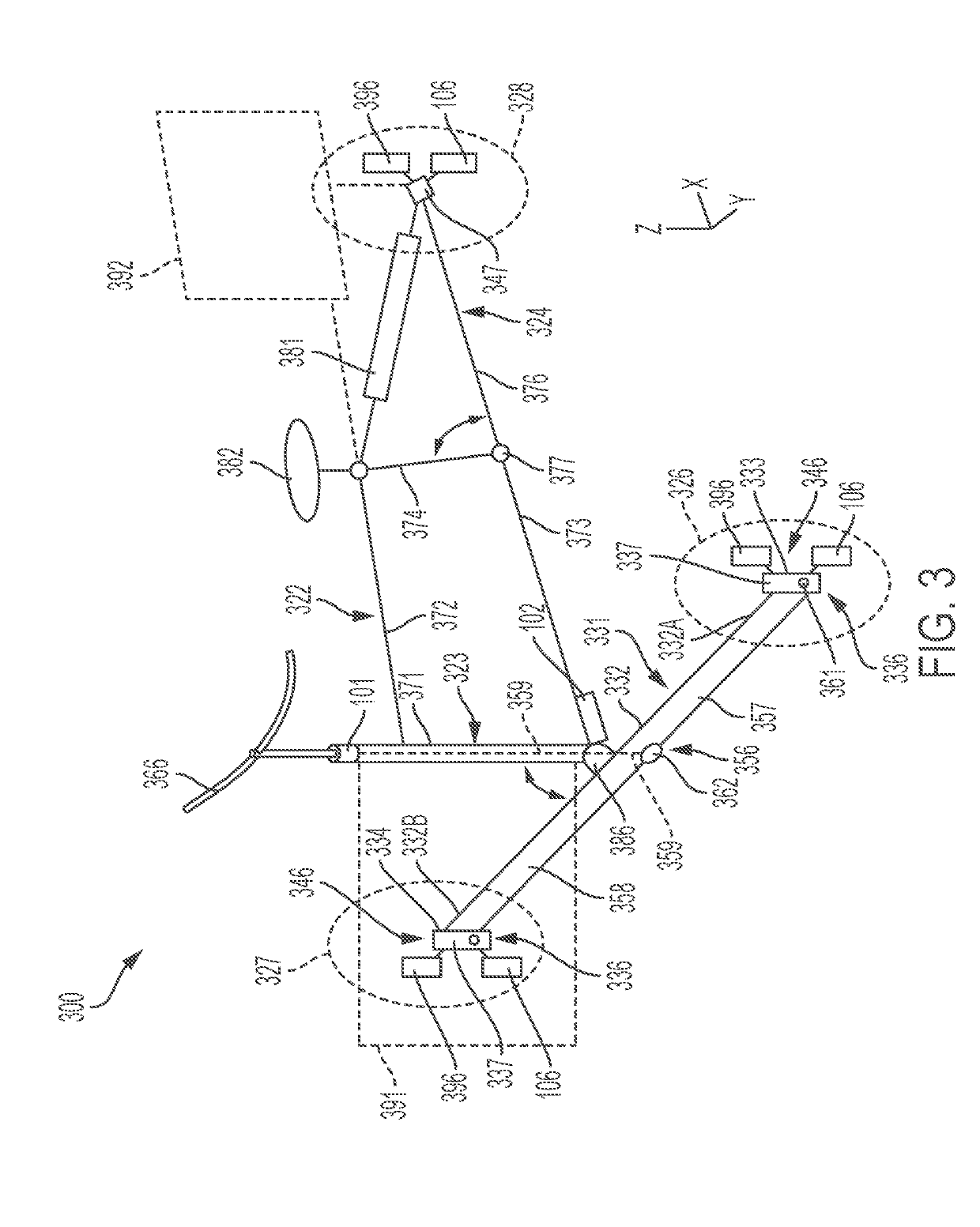

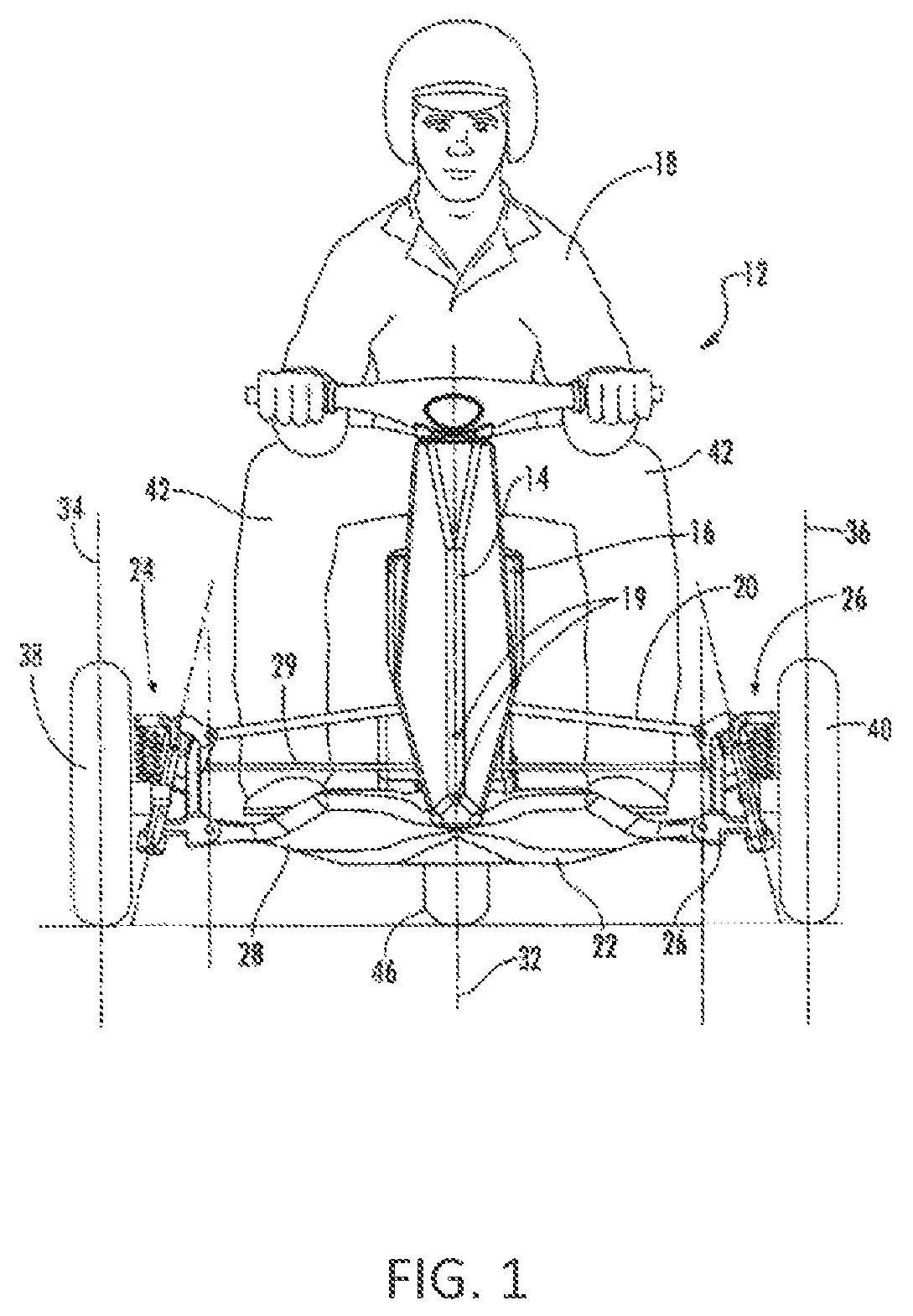

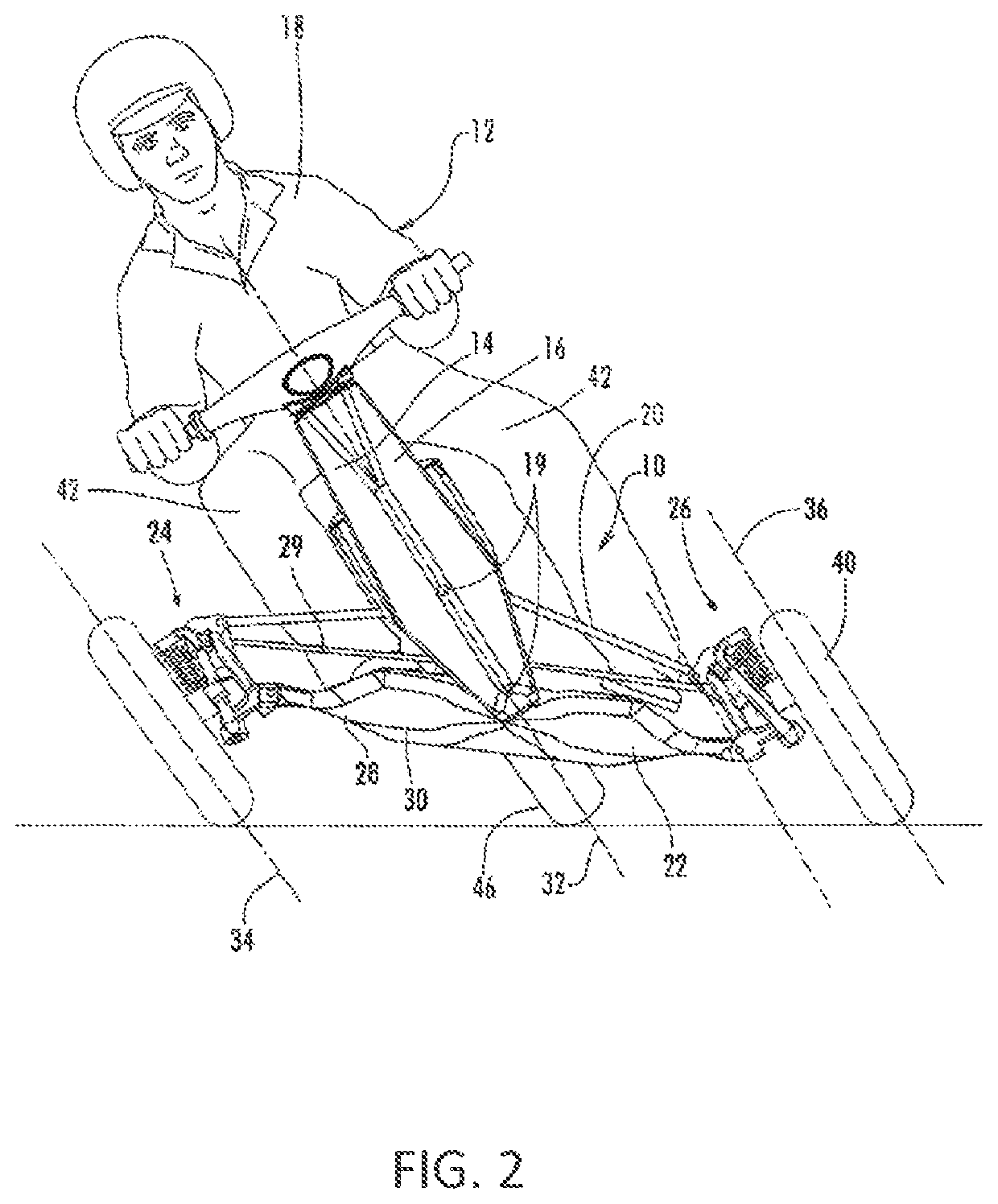

Control system for a tiltable vehicle

A vehicle of the present disclosure may include at least one pair of opposing wheels coupled to a tiltable central chassis by a four-bar linkage or the like, such that the wheels are configured to tilt in unison with the central chassis. A steering actuator and / or a tilting actuator may be discretely controllable by an electronic controller of the vehicle. The controller may include processing logic configured to maintain alignment between a median plane of the chassis and a net force vector caused by gravity and any induced centrifugal forces. Various control algorithms may be utilized to steer the vehicle along a desired path, either autonomously or semi-autonomously.

Owner:SWAY MOTORSPORTS LLC

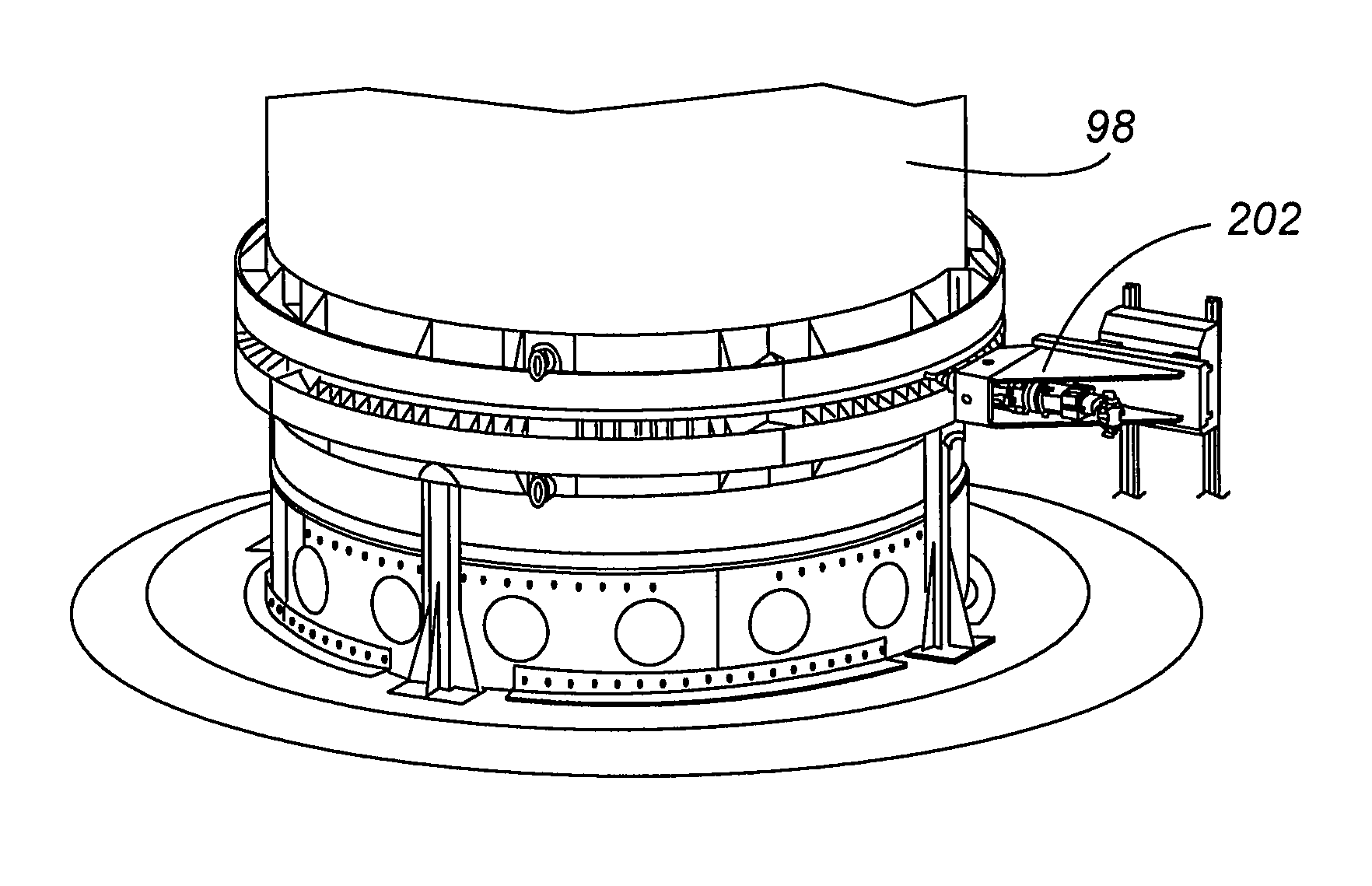

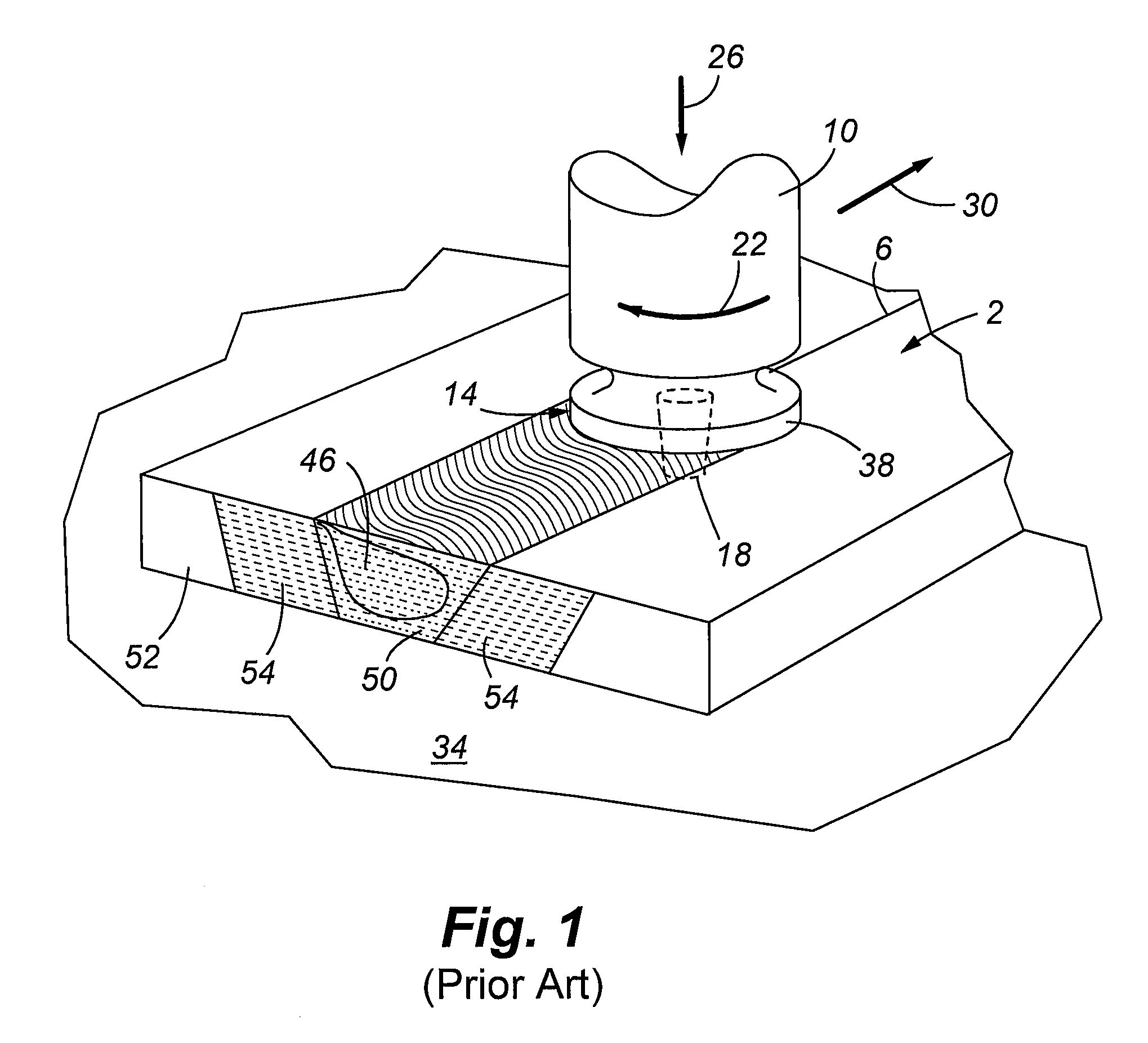

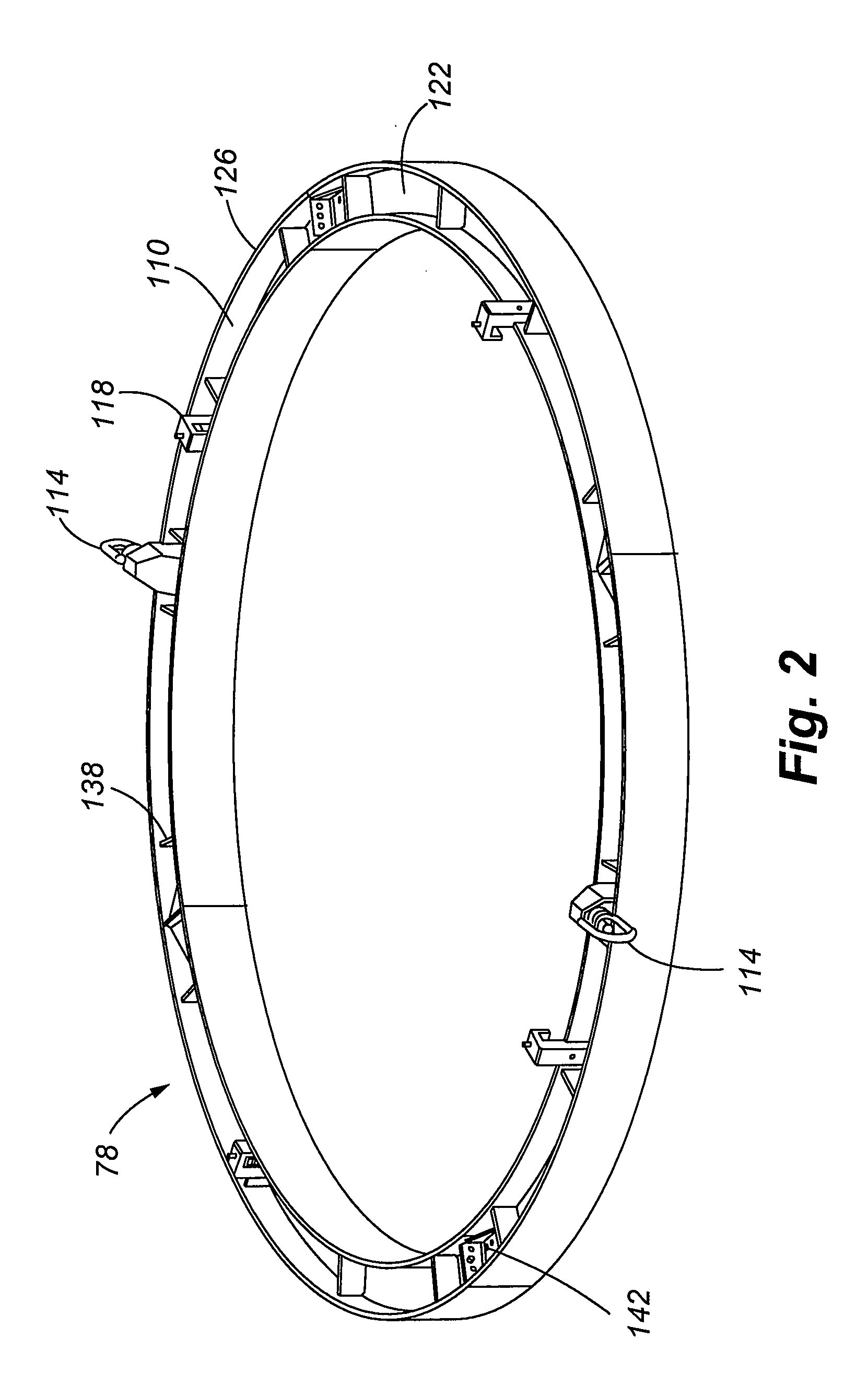

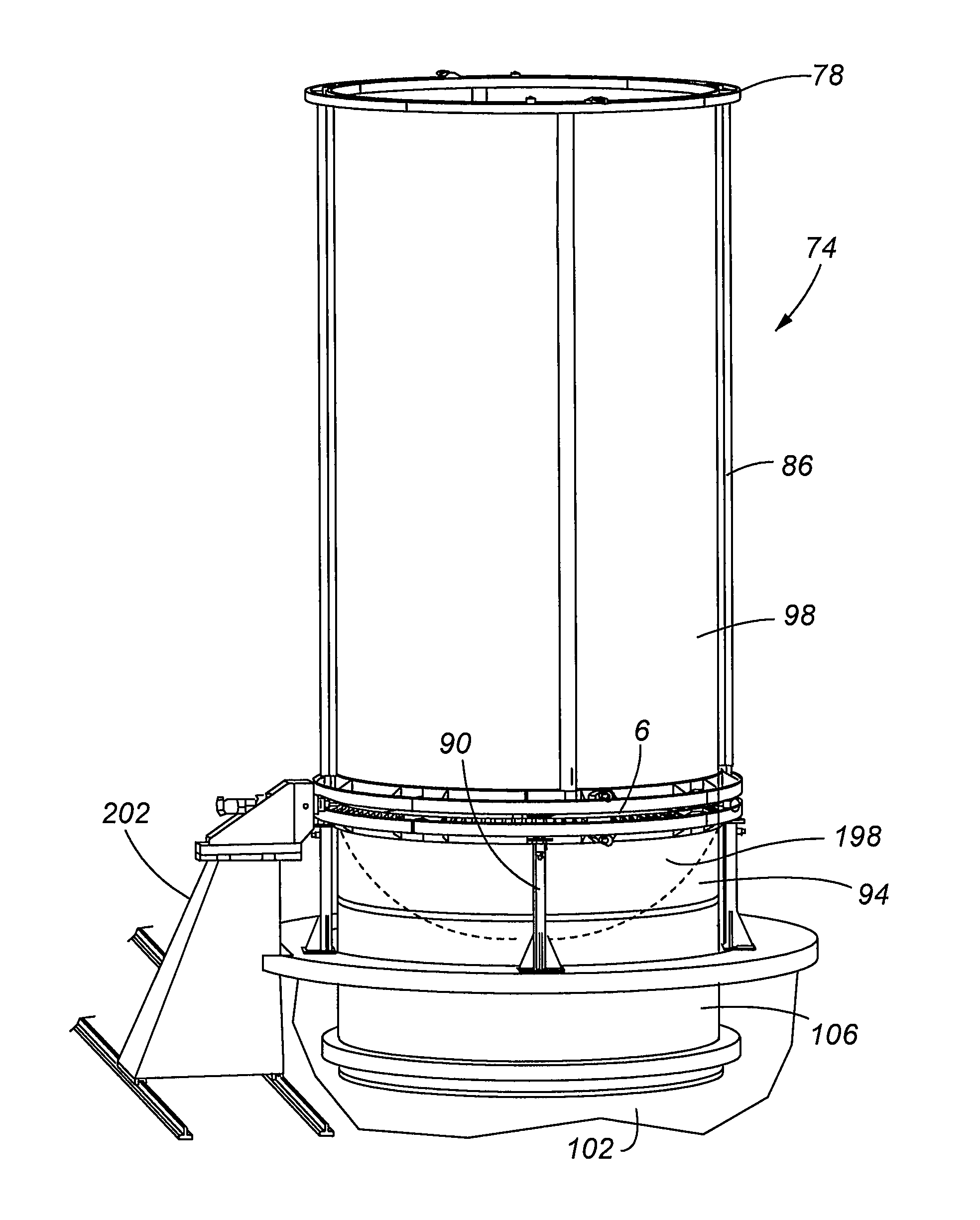

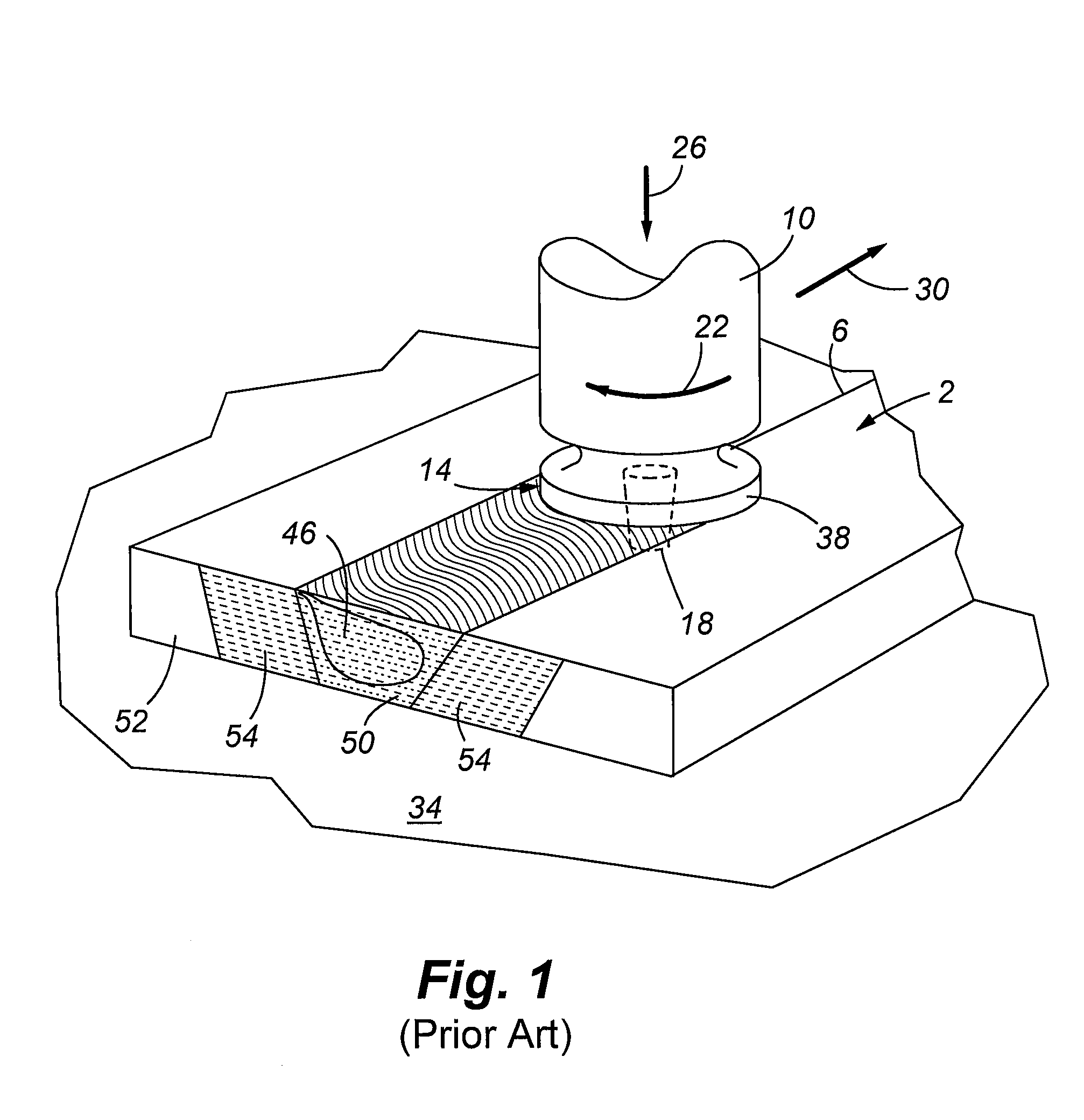

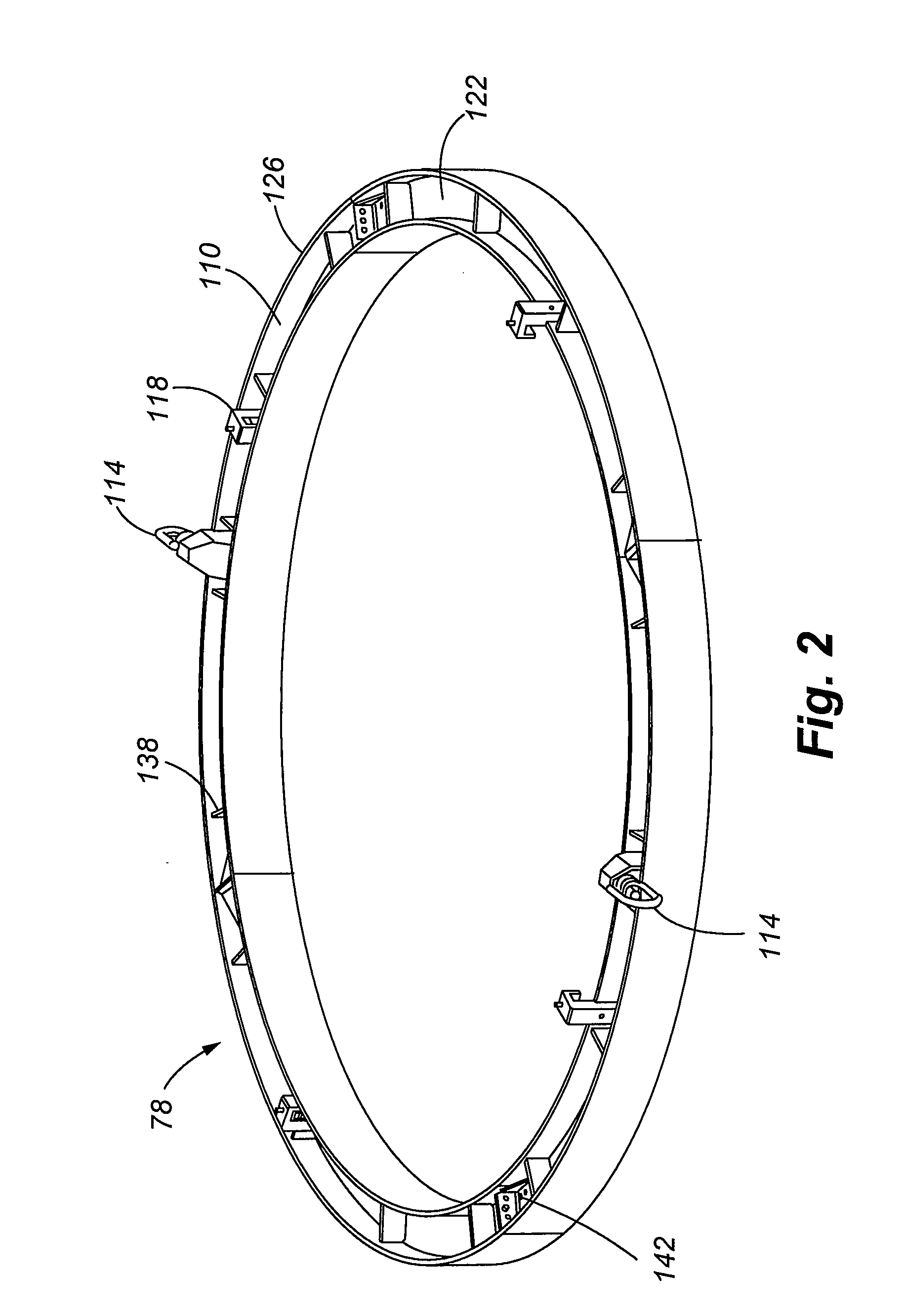

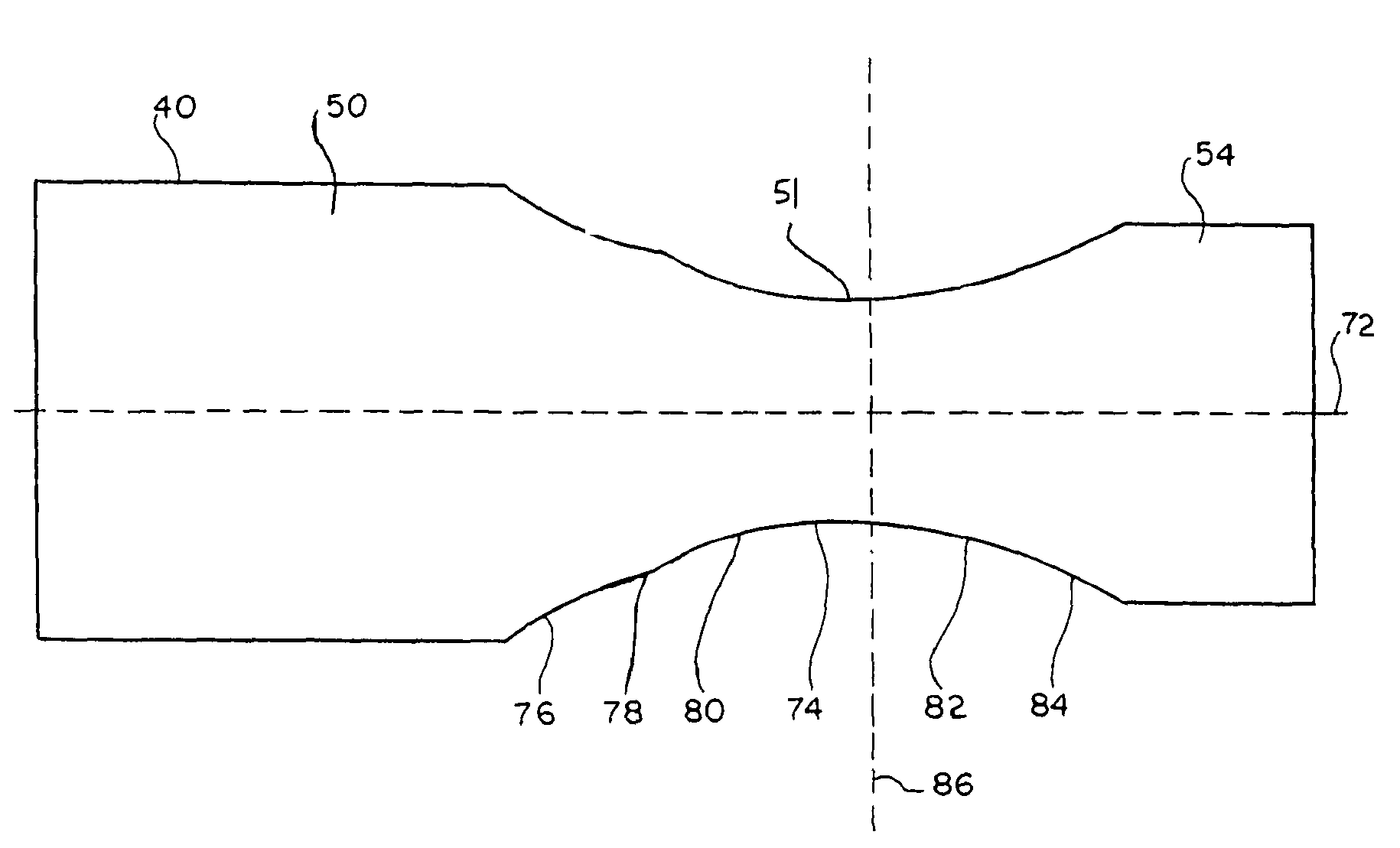

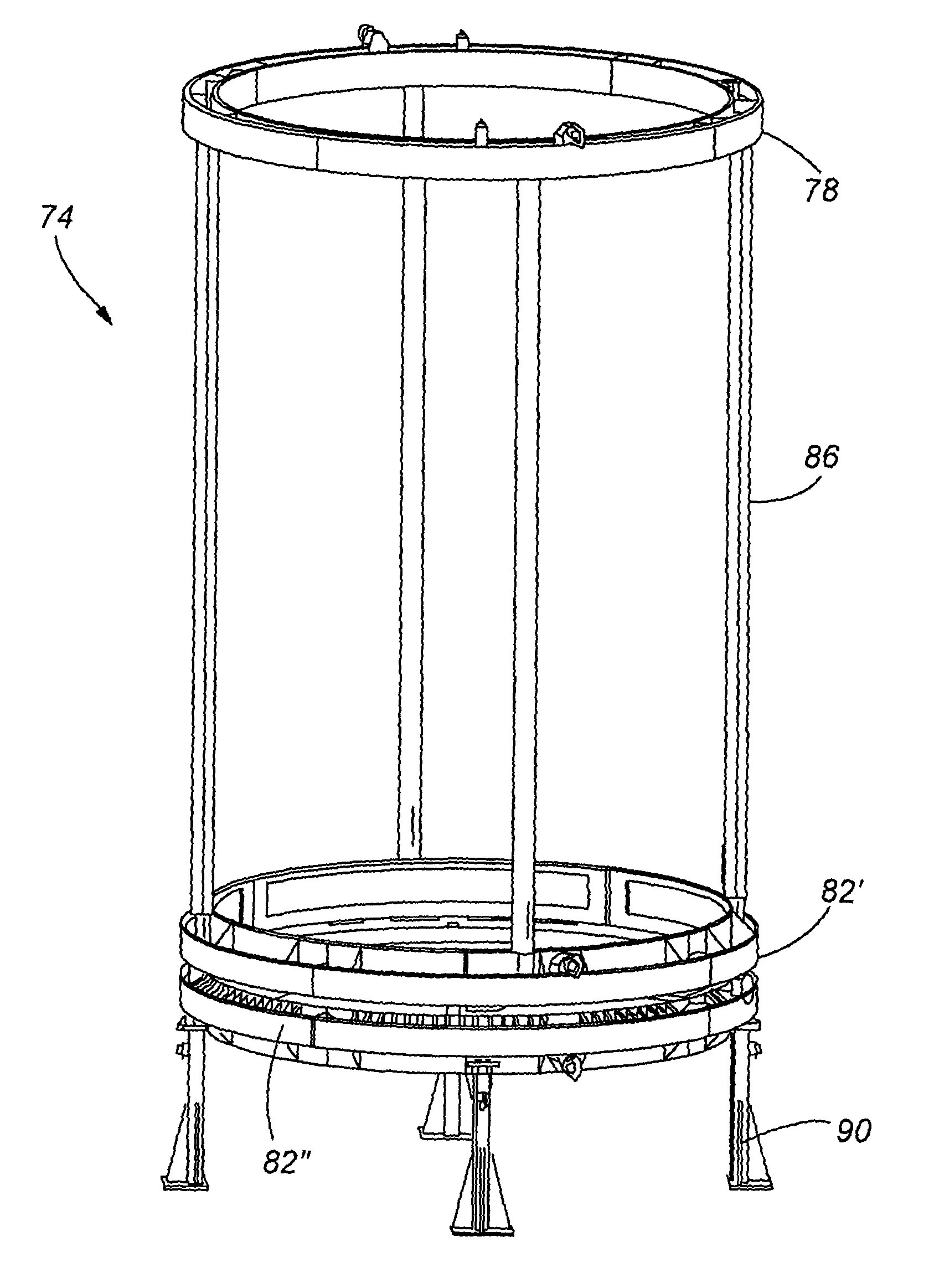

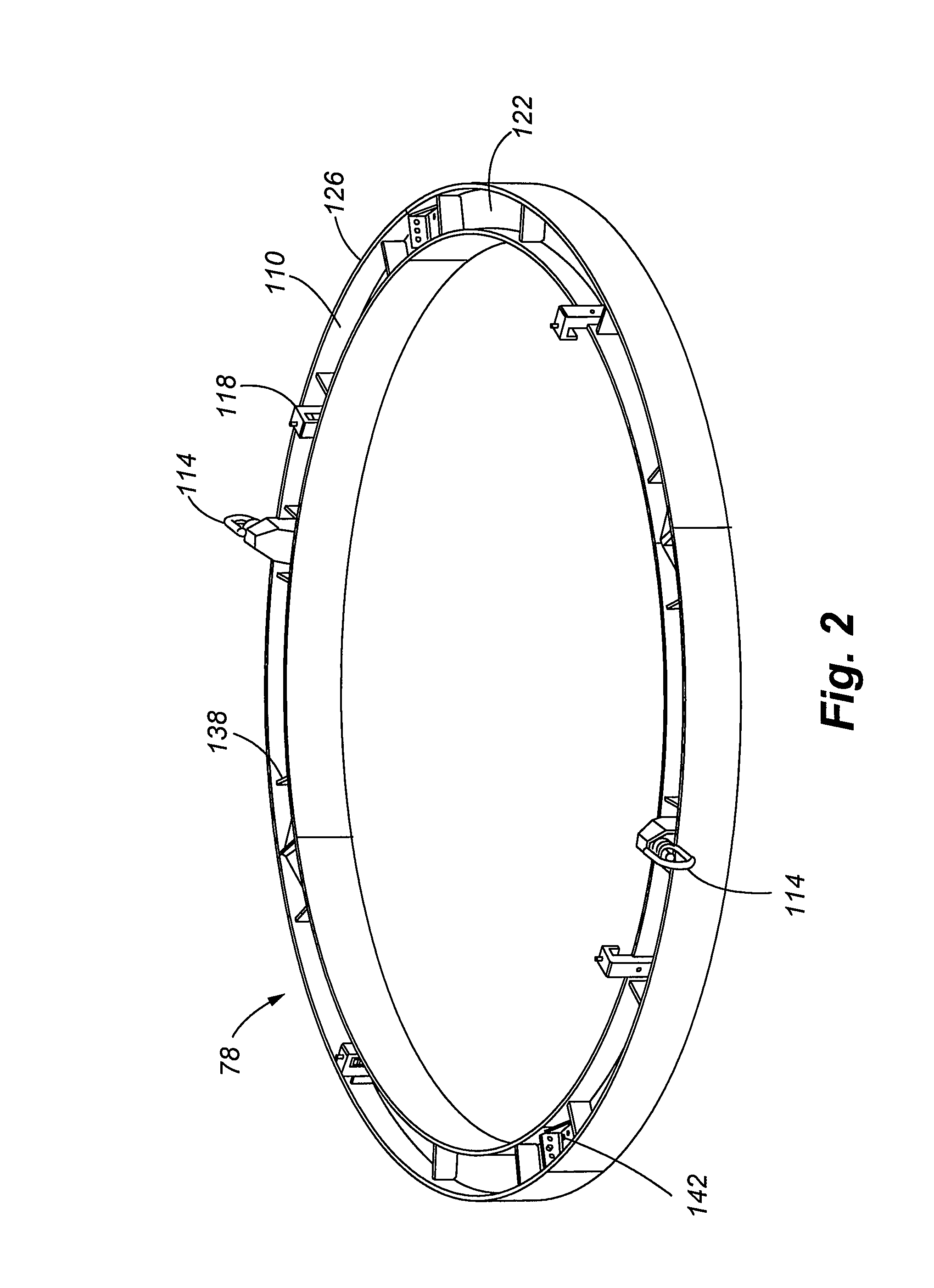

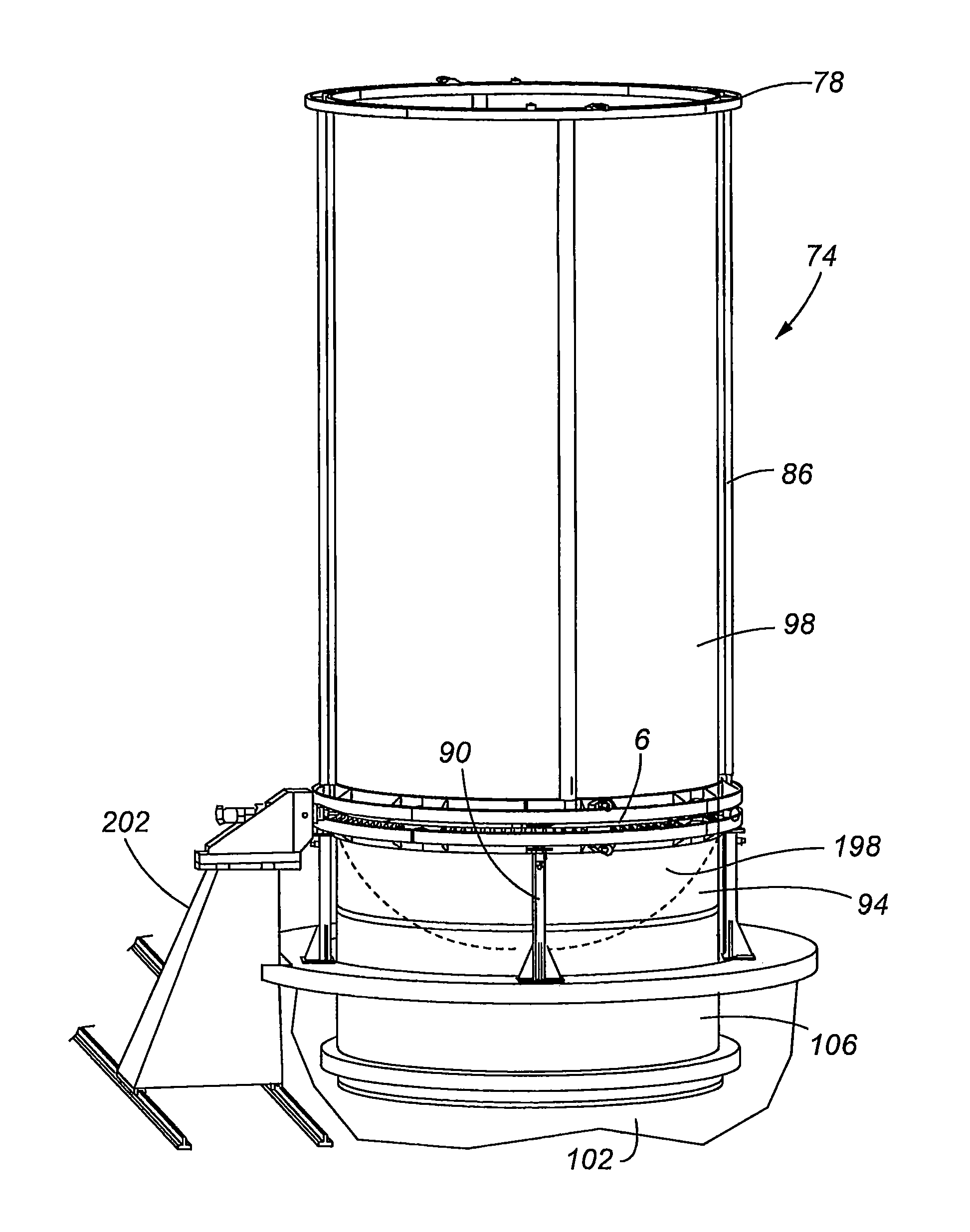

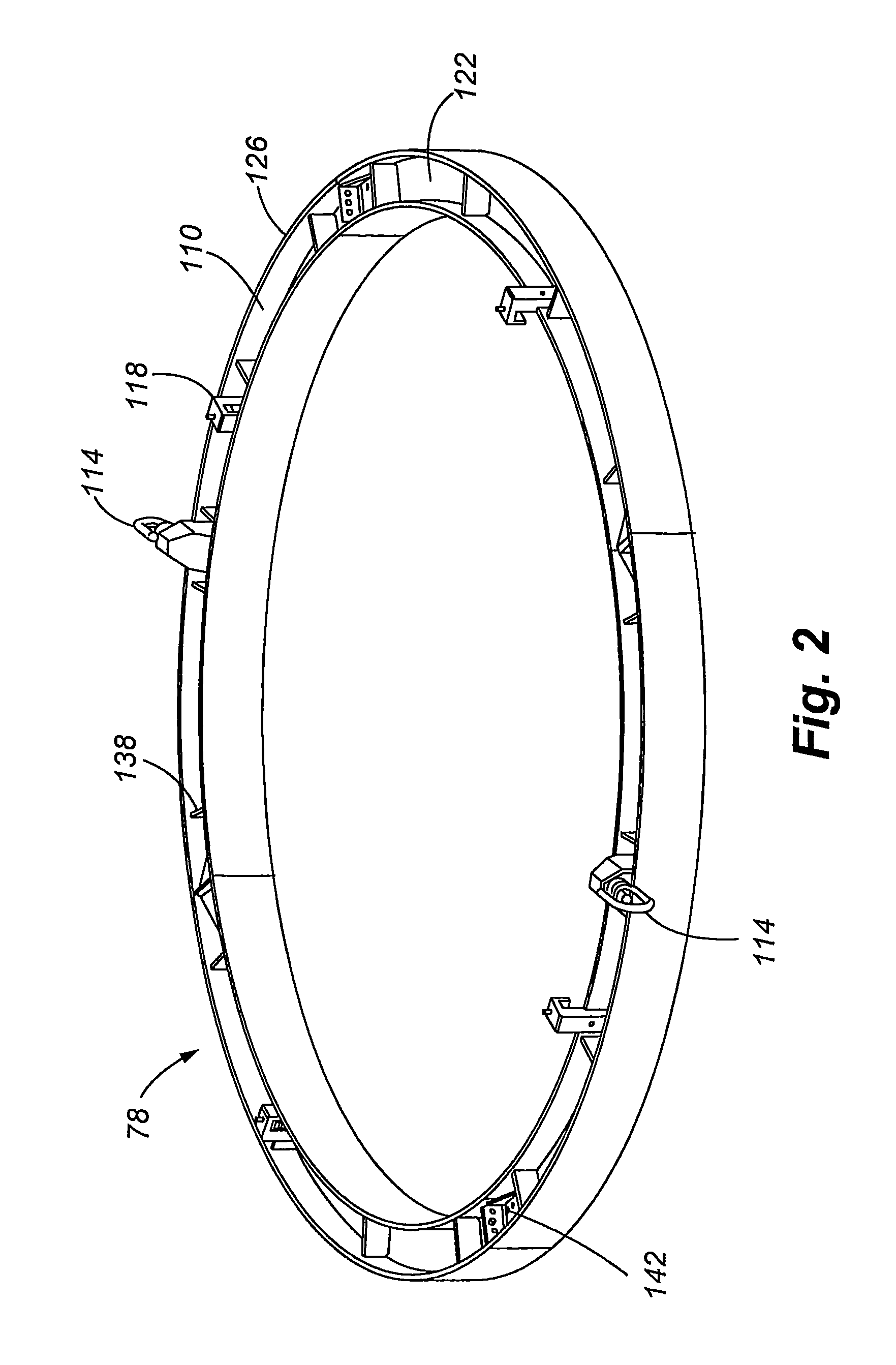

Friction welding apparatus, system and method

ActiveUS8123104B1Minimize misalignmentHighly creativeWelding/cutting auxillary devicesAuxillary welding devicesFriction weldingEngineering

A friction stir welding apparatus is provided herein. More specifically, traditional friction stir welding requires a rotatable head that is forced against a plurality of work pieces to bond the same. The rotational and normal forces generated by the friction stir welding tool are generally reacted by a backing plate, anvil, mandrel or other mechanisms, such hardware are subject to the applied forces and are often supported with additional internal supports. Conversely, an apparatus for performing a friction stir weld is described that omits the need for such a backing member and internal supports as it is performed using a self reacting pin tool.

Owner:UNITED LAUNCH ALLIANCE

Gear assembly with tapered flex pin

ActiveUS8216108B2Maximize deflectionMinimize misalignmentShaftsToothed gearingsCantileverMechanical engineering

Owner:FRIEDE & GOLDMAN

Friction stir welding apparatus, system and method

ActiveUS8141764B1Easy to useManpowerWelding/cutting auxillary devicesAuxillary welding devicesMechanical engineeringNormal force

A friction stir welding system is provided herein. More specifically, traditional friction stir welding requires a rotatable head that is forced against a plurality of work pieces to bond the same. The rotational and normal forces generated by the friction stir welding tool are generally reacted by a backing plate, anvil, mandrel or other mechanisms, such hardware are subject to the applied forces and are often supported with additional internal supports. Conversely, a friction stir weld system is described that omits the need for such a backing member and internal supports as it is performed using a self reacting pin tool.

Owner:UNITED LAUNCH ALLIANCE

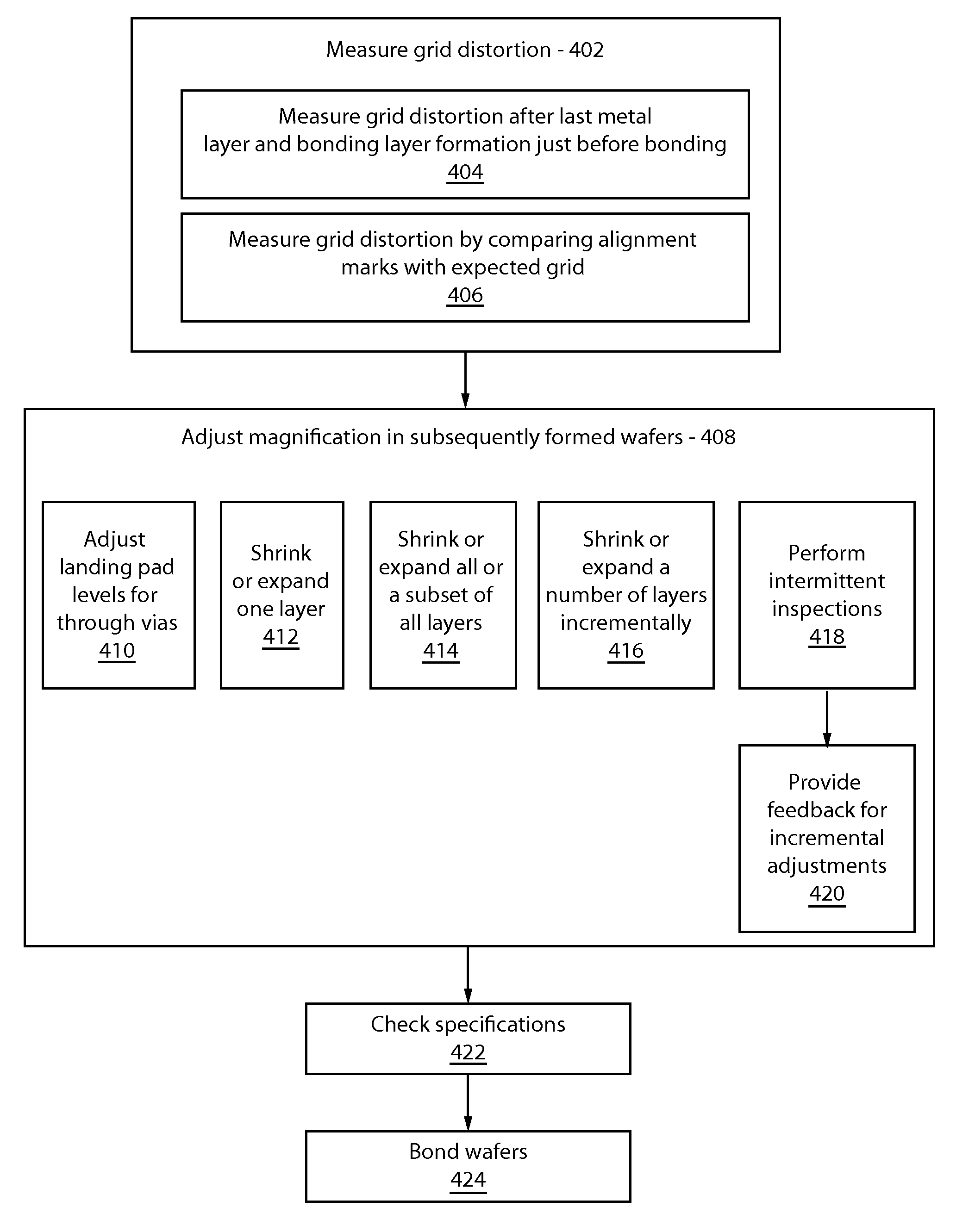

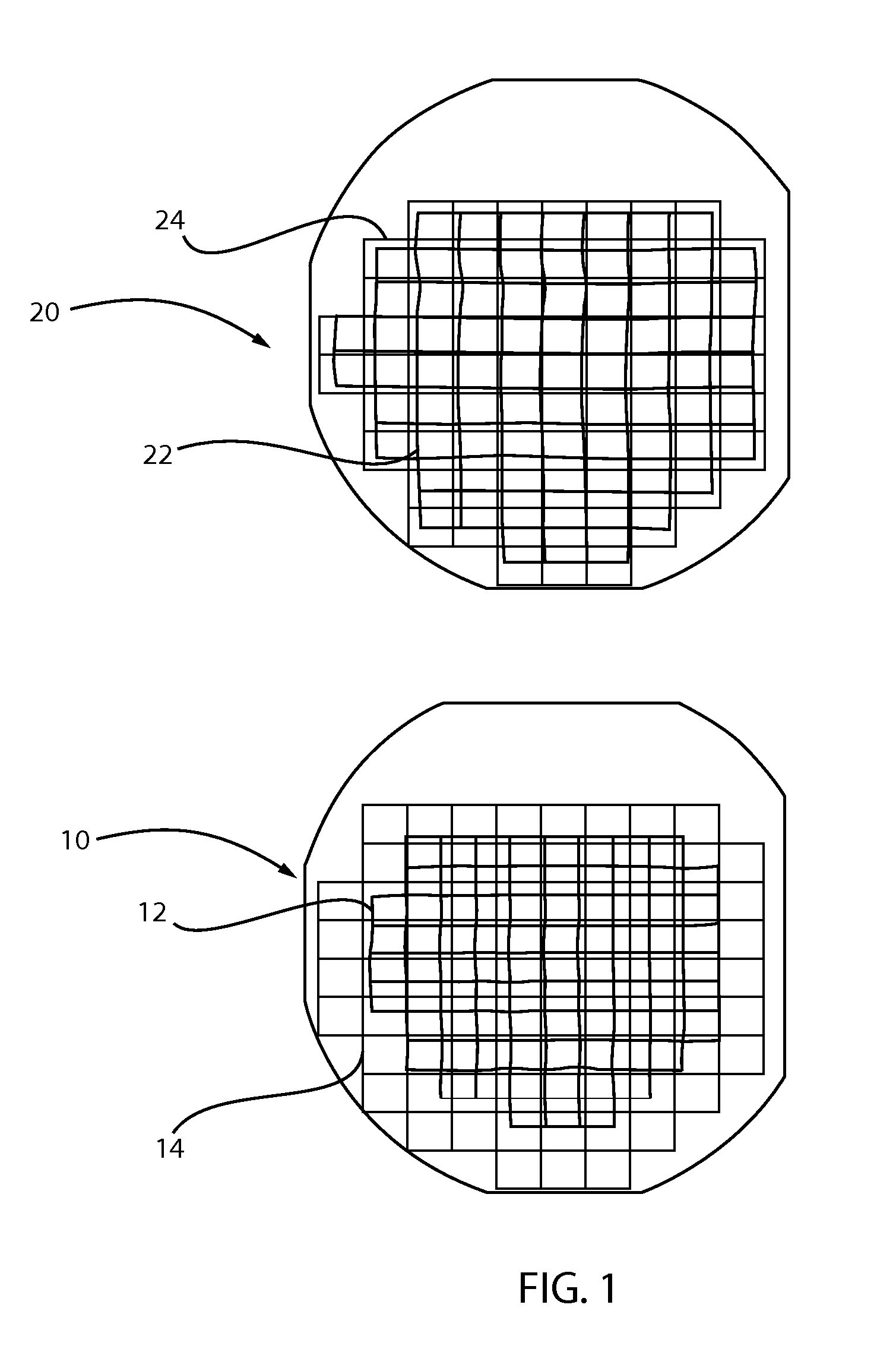

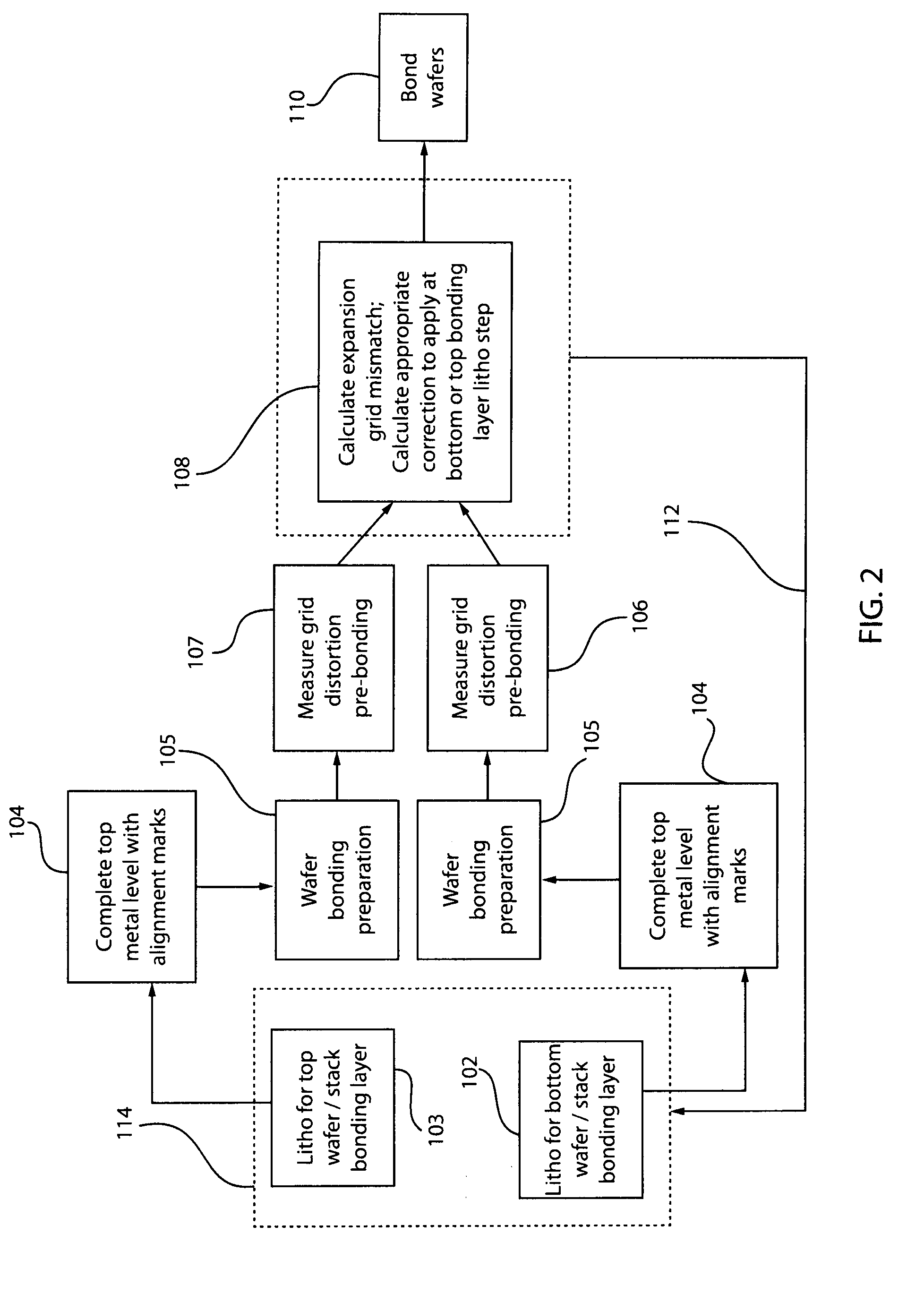

Wafer bonding misalignment reduction

InactiveUS8900885B1Minimize misalignmentSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsMagnificationWafer bonding

A method for wafer bonding includes measuring grid distortion for a mated pairing of wafers to be bonded to determine if misalignment exists between the wafers. During processing of subsequent wafers, magnification of one or more lithographic patterns is adjusted to account for the misalignment. The subsequent wafers are bonded with reduced misalignment.

Owner:GLOBALFOUNDRIES INC

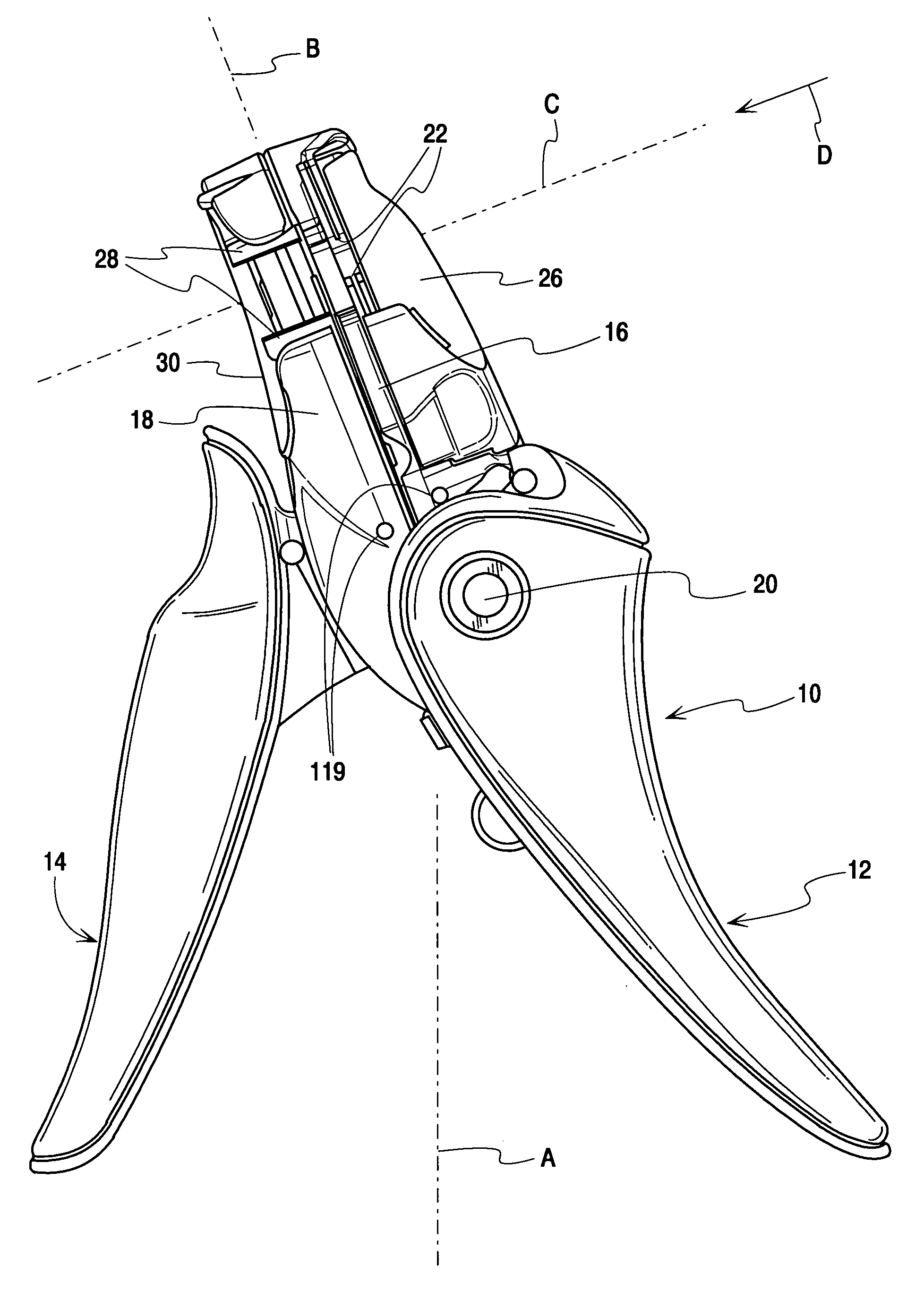

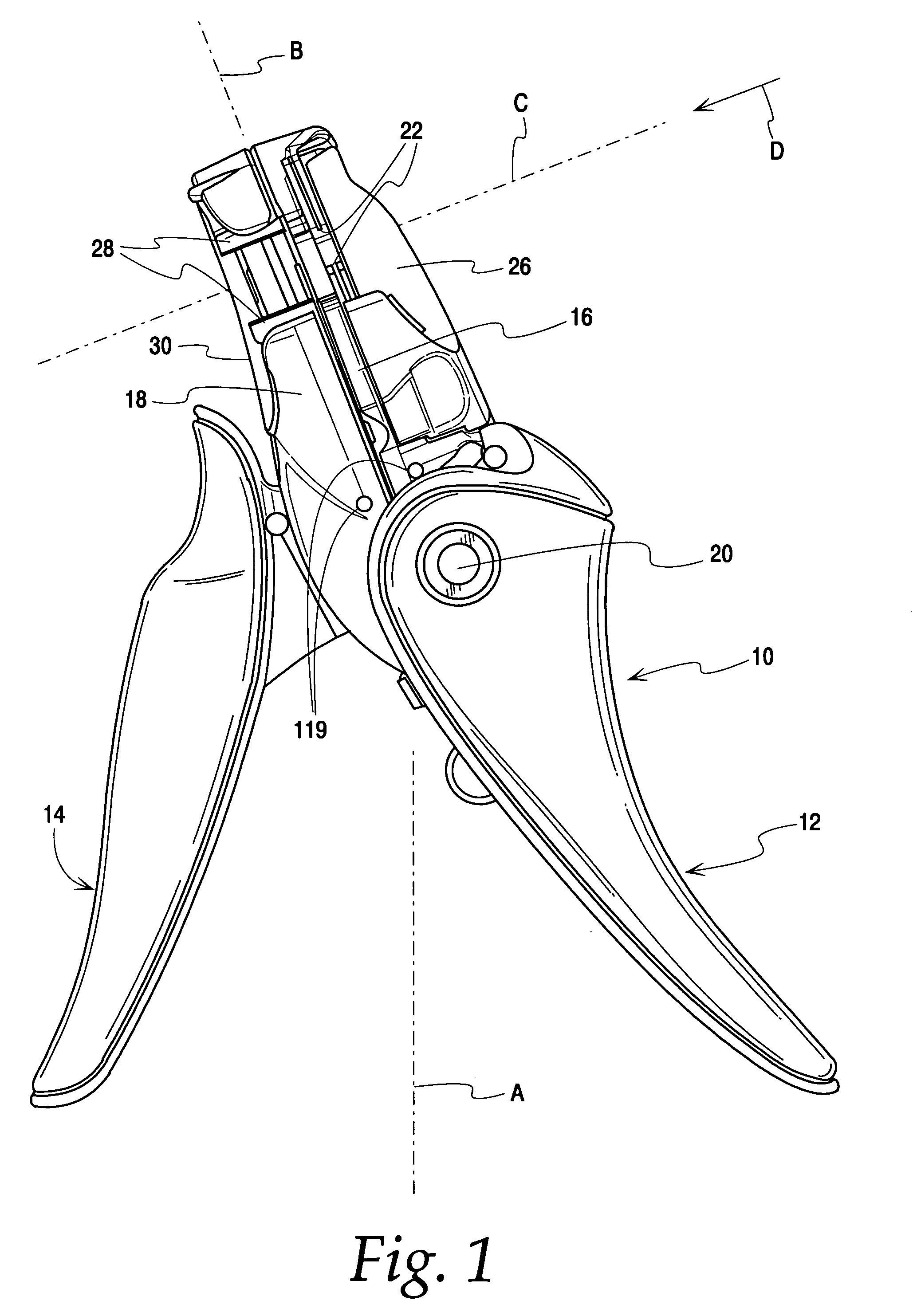

Precision hand-held wire stripper

ActiveUS20050235778A1Highly precise insulation cuttingAvoids nickingApparatus for removing/armouring cablesResistHand held

A wire stripper has a blade handle, a gripper handle, a blade jaw and a gripper jaw all pivotally connected at a main pivot pin that is offset from the mating faces of the jaws. Movable and floating cutting blades mounted on the blade jaw are self-aligning due to a floating connection of the blades that allows them to move respective gauge surfaces into engagement during closing. A blade hold down spring urges the blades into alignment. The jaws are angled with respect to the handle axis so the throat of the cutting blades aligns with a user's line of sight. Individual handle springs have differential springs rates and are arranged so that the handles springs do no resist opening of the jaws.

Owner:IDEAL IND INC

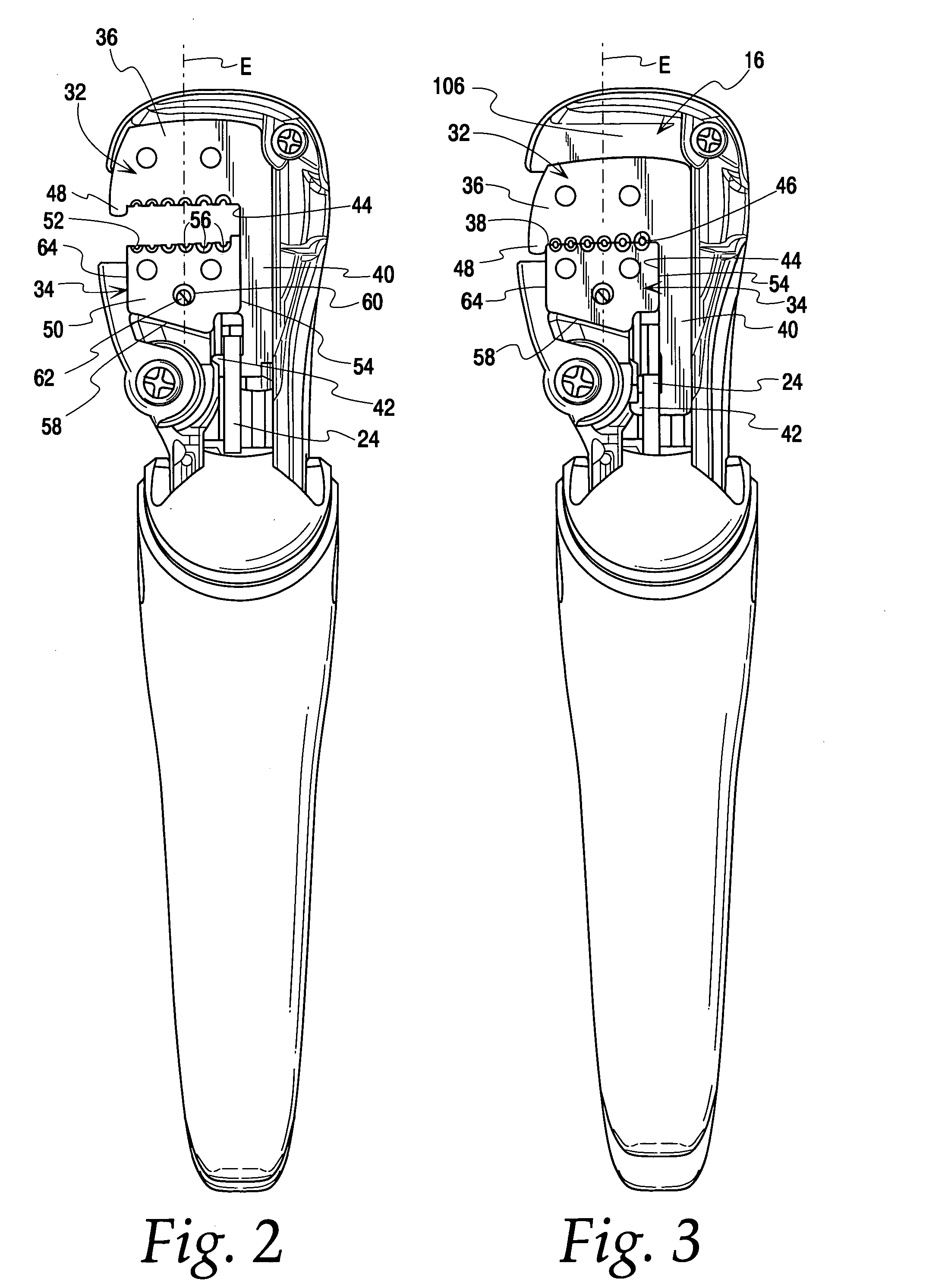

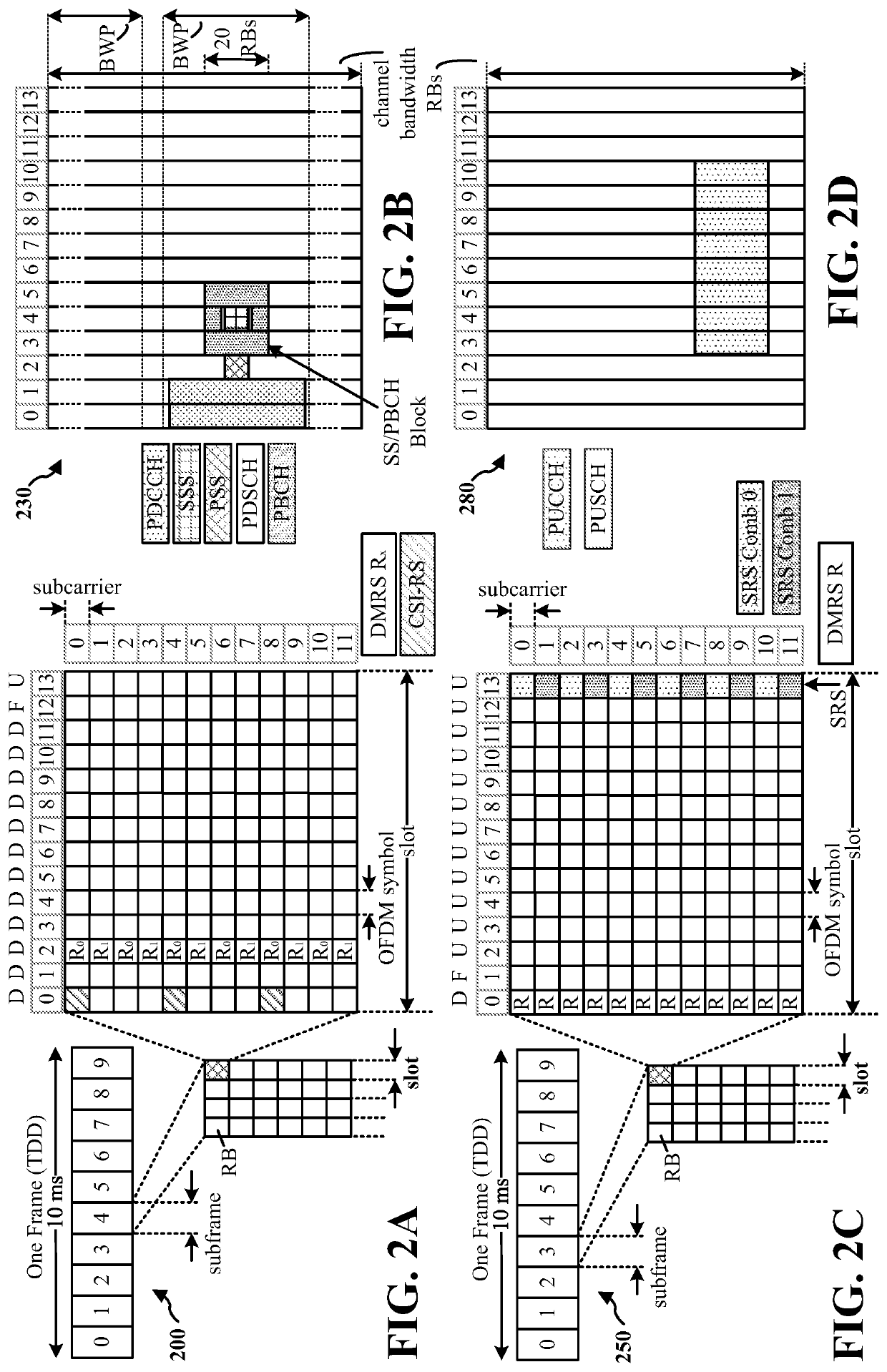

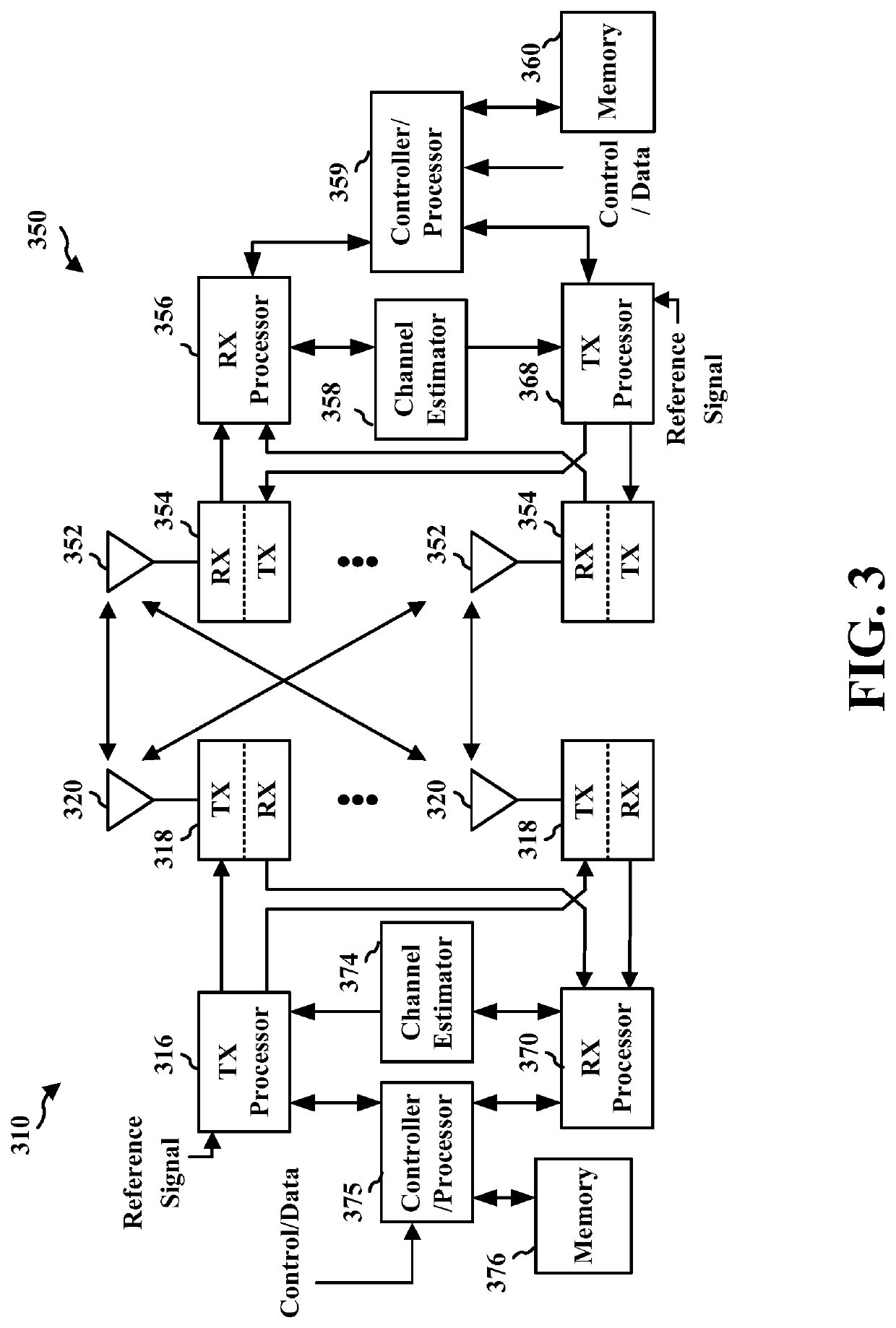

Methods and apparatus to selectively monitor uplink preemptive indication for supplementary uplink and non-supplementary uplink carriers

ActiveUS20200359447A1Save signaling overheadReducing uplink transmission powerTransmission path divisionSignal allocationCarrier signalReal-time computing

Aspects are provided allowing for selective monitoring of uplink cancellation indication (ULCI) occasions by UEs and allowing UEs to determine from ULCI whether canceled uplink transmission are carried on non-supplementary uplink (NUL) carriers or supplementary uplink (SUL) carriers. A UE may determine not to monitor a ULCI occasion if it does not have an uplink transmission which can be punctured by higher priority data. When the uplink transmission is dynamically scheduled, the UE may determine to monitor a ULCI occasion if the UE receives the uplink grant a certain number of symbols earlier than the ULCI occasion. The base station may configure blocks in downlink control information to indicate the UE should apply ULCI to SUL and / or NUL. The base station may configure the UE to perform different behaviors after receiving a ULCI depending on whether the portion of the uplink transmission to be canceled is on SUL or NUL.

Owner:QUALCOMM INC

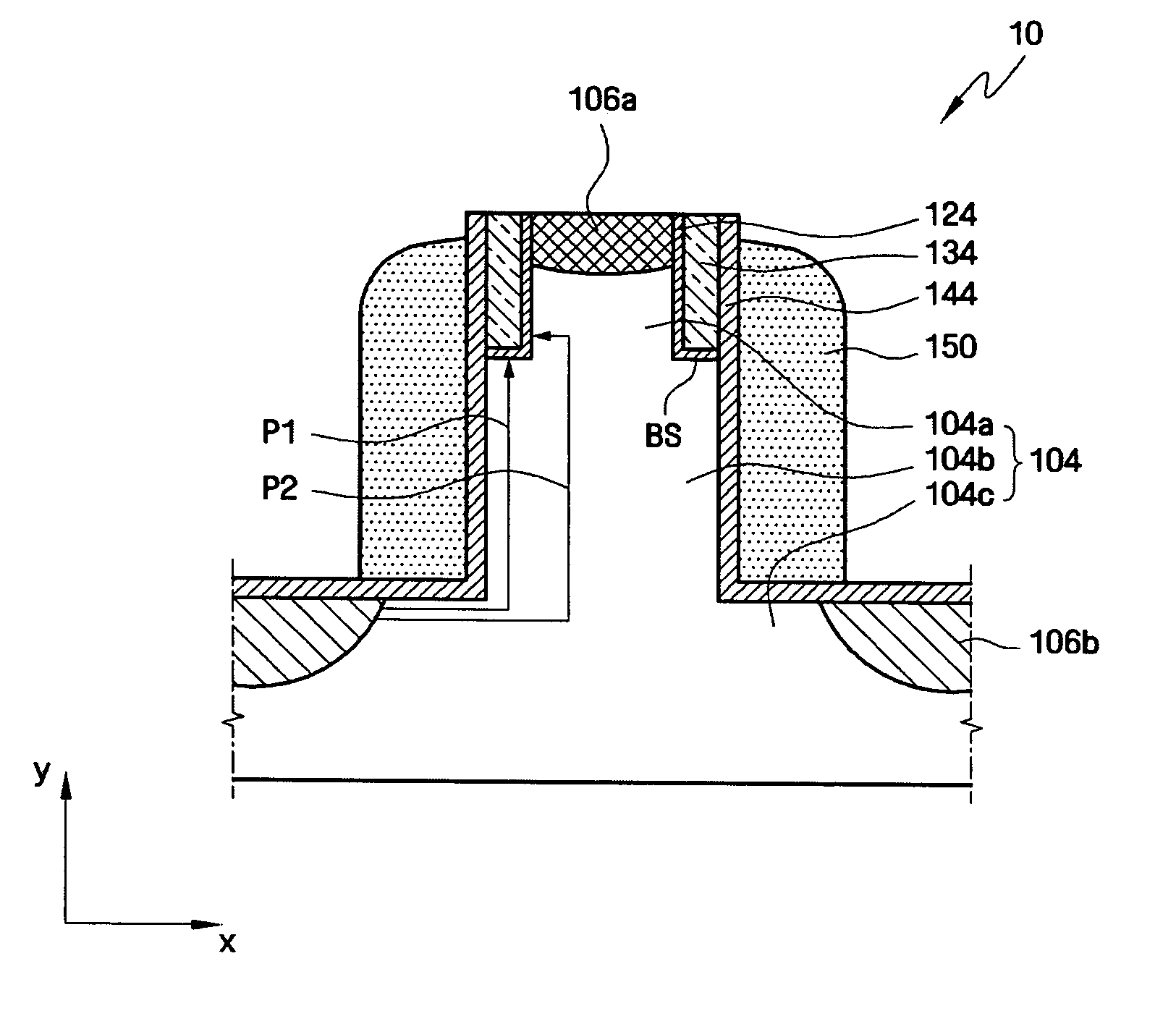

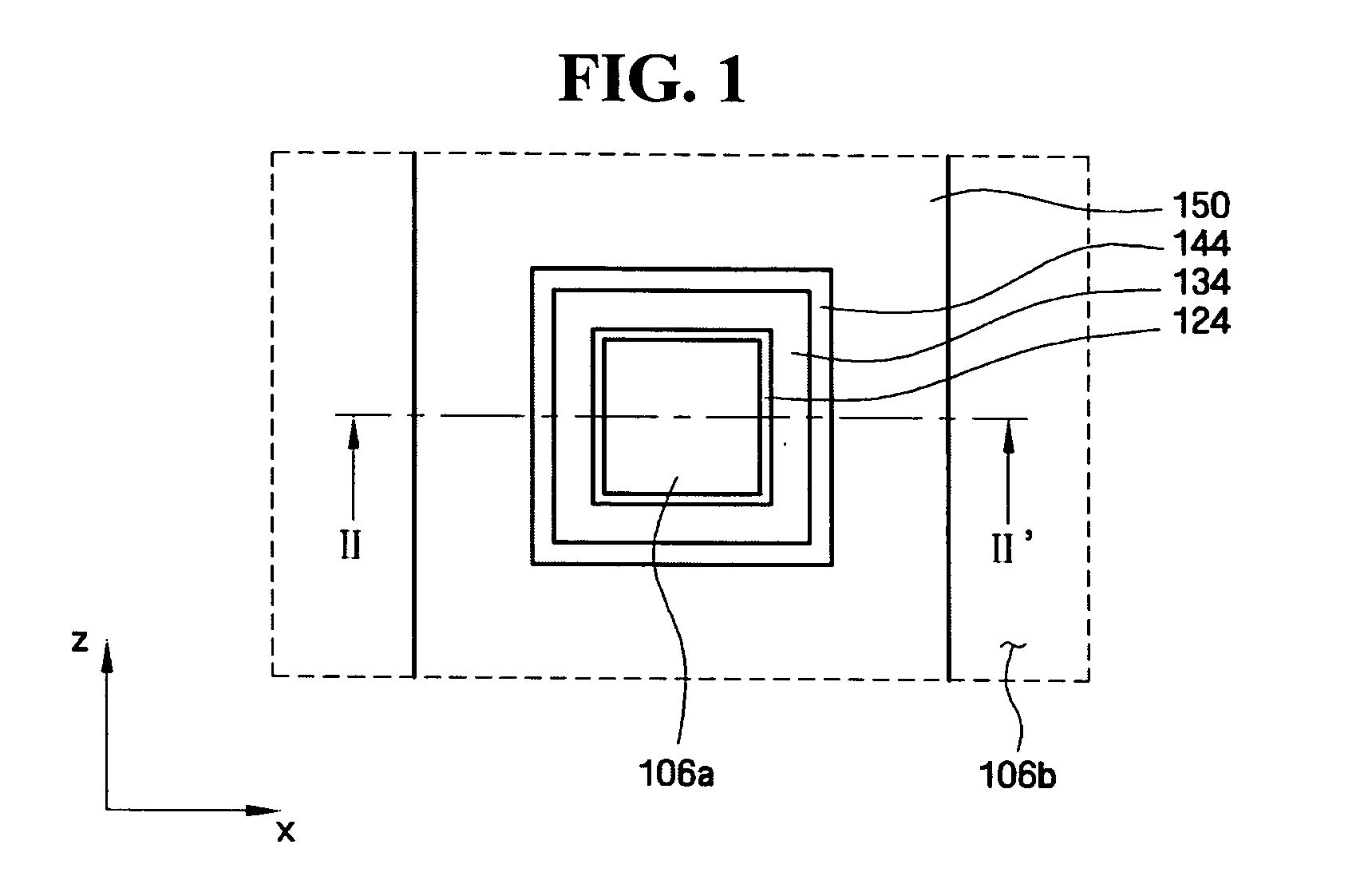

Nonvolatile memory device and method of fabricating the same

InactiveUS20080087940A1Improve electron injection efficiencyMinimize misalignmentSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSemiconductor

A nonvolatile memory device, includes a semiconductor substrate having a bottom part, a second vertical part positioned vertically on the bottom part, and a first vertical part having a width smaller than a width of the second vertical part and positioned on the second vertical part to have a boundary step therebetween; a charge trap layer disposed on a lateral surface of the first vertical part and on an upper surface of the boundary step; and a control gate electrode disposed on an upper surface of the bottom part and on lateral surfaces of the second vertical part and the charge trap layer.

Owner:SAMSUNG ELECTRONICS CO LTD +1

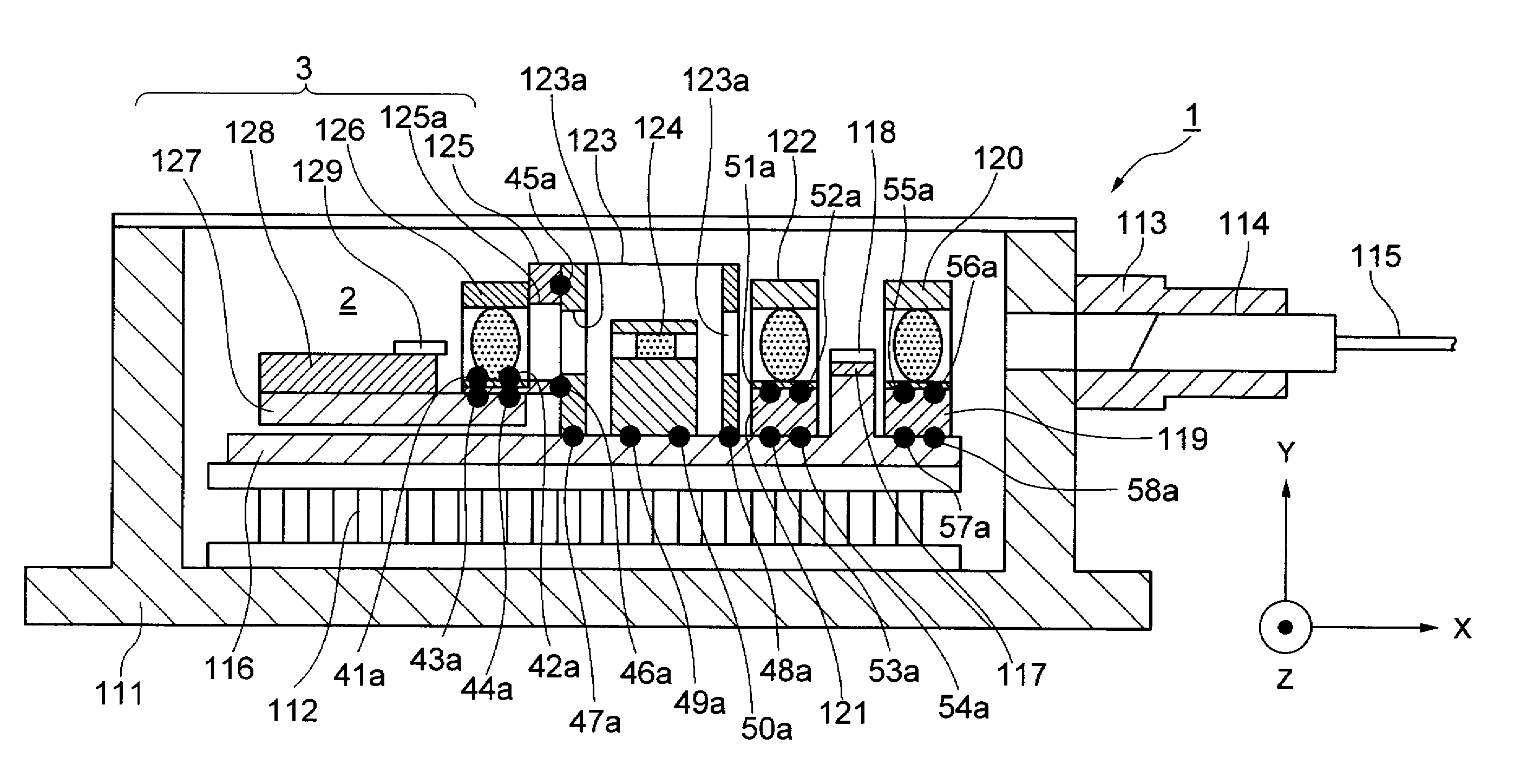

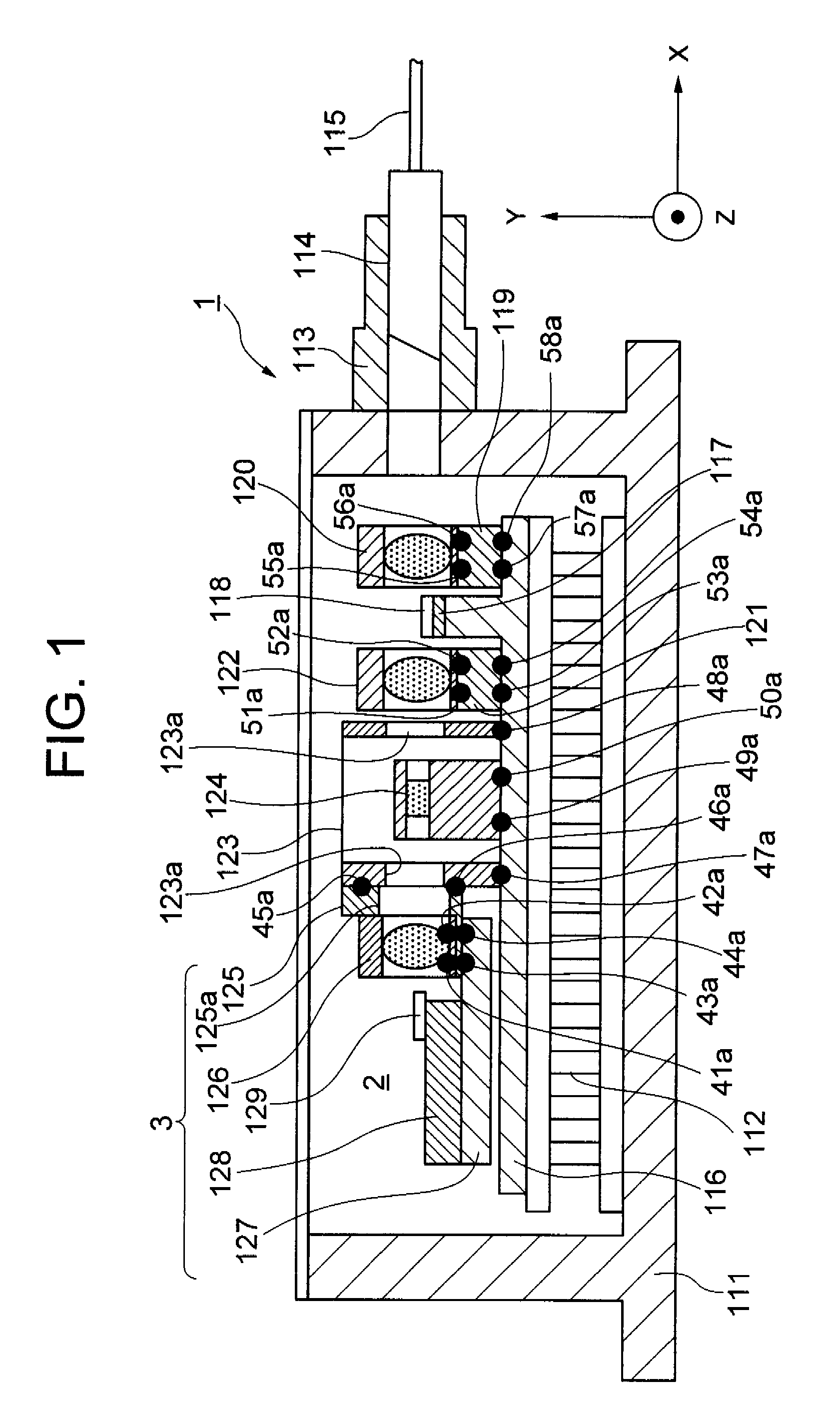

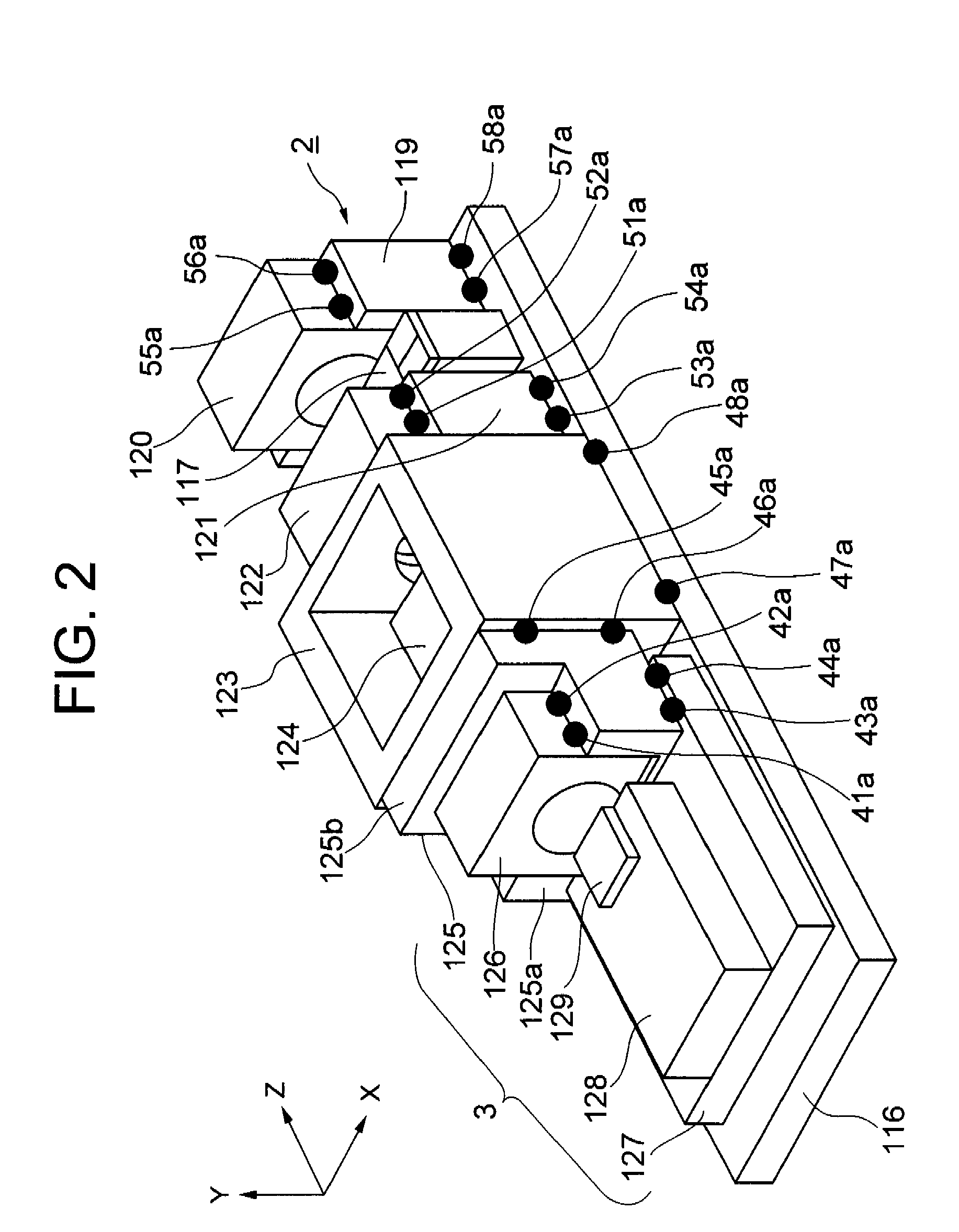

Optical transmission module and manufacturing method of the same

InactiveUS20090153949A1Minimize misalignmentQuality improvementLaser detailsSemiconductor/solid-state device manufacturingCarrier signalEngineering

[Problems] To accommodate a plurality of optical semiconductor elements in one package with their optical axes aligned highly precisely.[Means for Solving the Problems] An optical transmission module includes an optical transmission unit, a carrier to become a base, a semiconductor optical amplification element mounted on the carrier through a first sub-carrier, first and second lenses fixed on the carrier through first and second lens holders, an element supporting member and an optical isolator fixed on the carrier, a third lens holder supported by the element supporting member, a third lens and a small carrier individually fixed in the third lens holder, and a semiconductor laser element mounted on the small carrier through a second sub-carrier.

Owner:NEC CORP

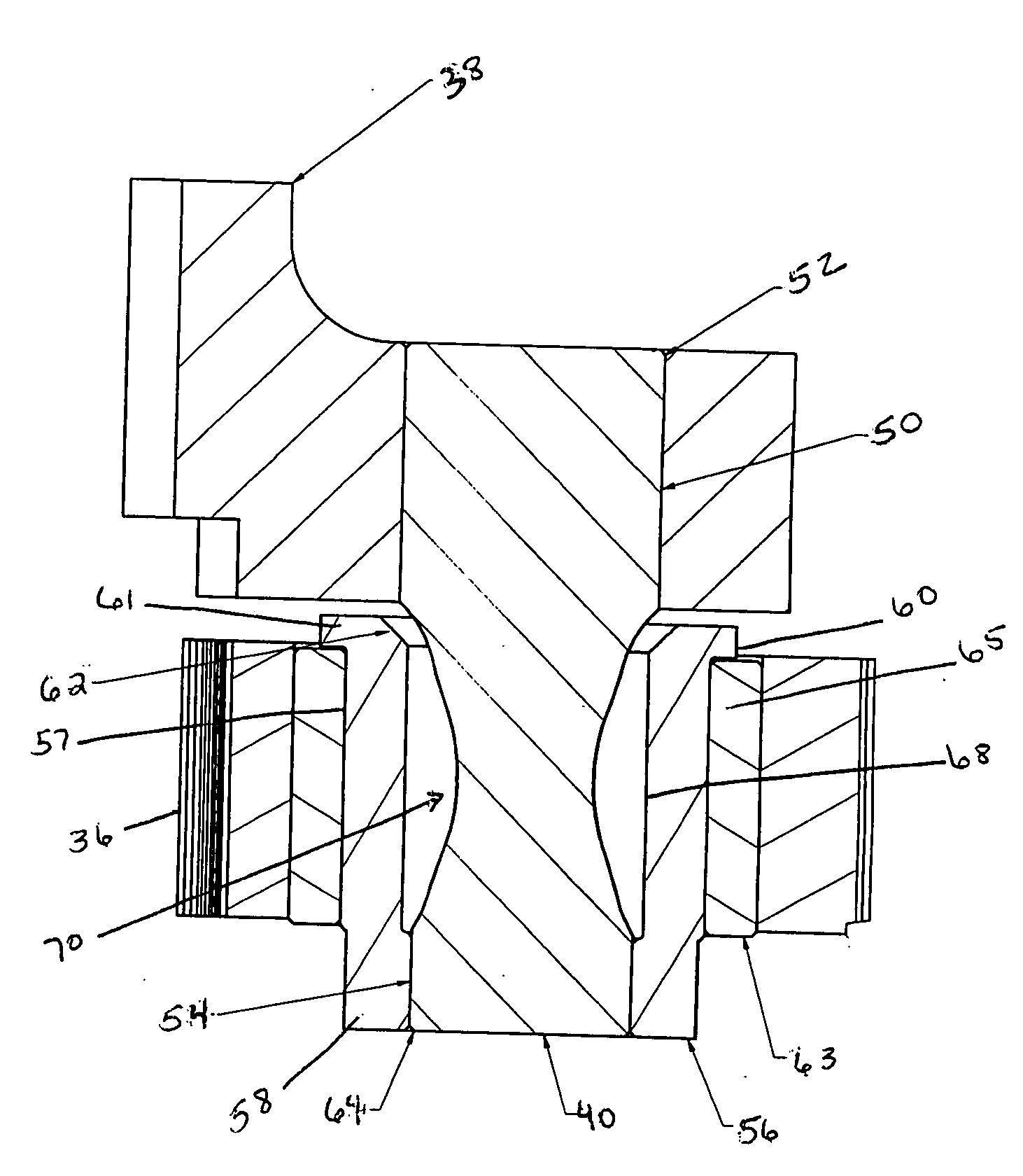

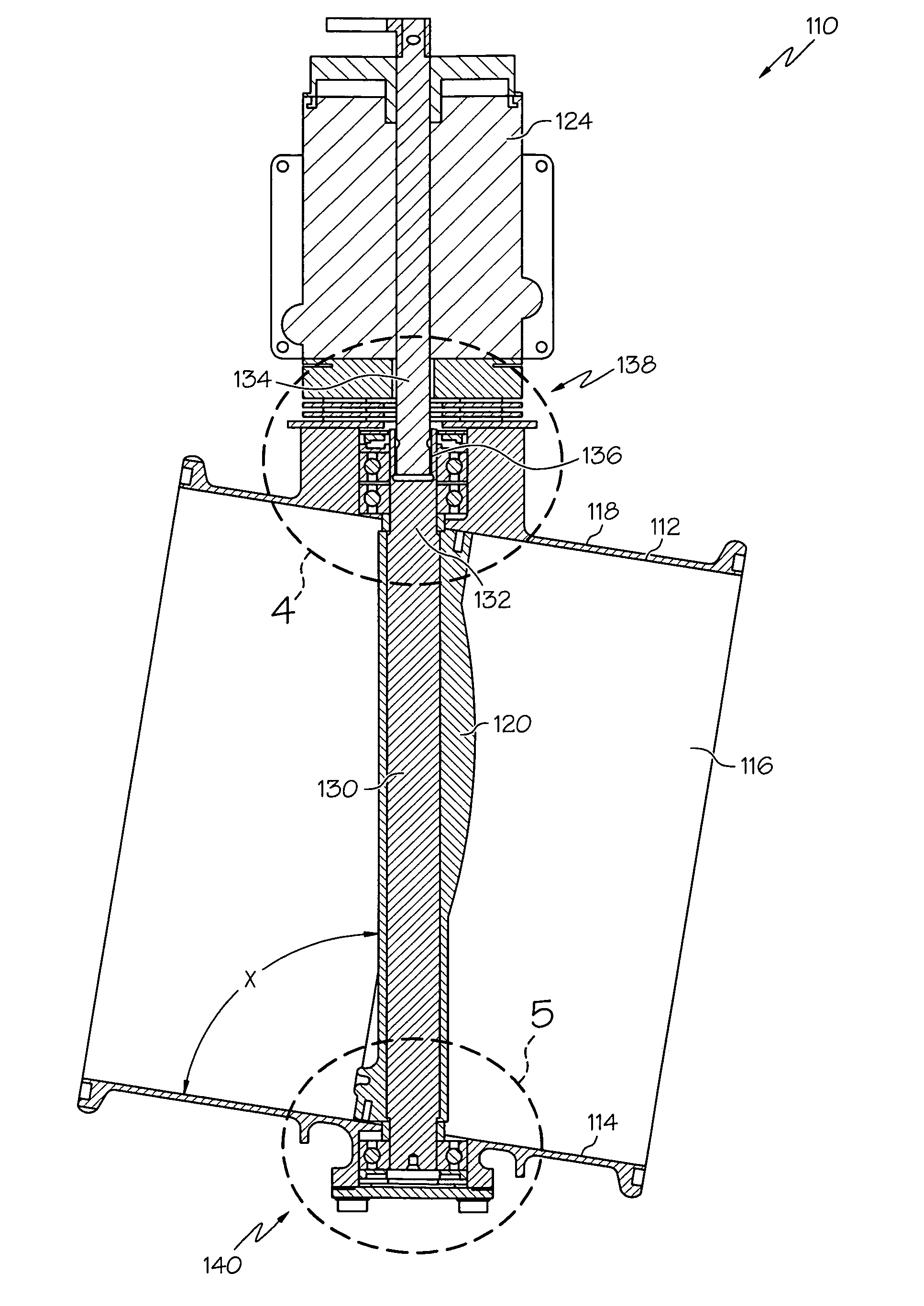

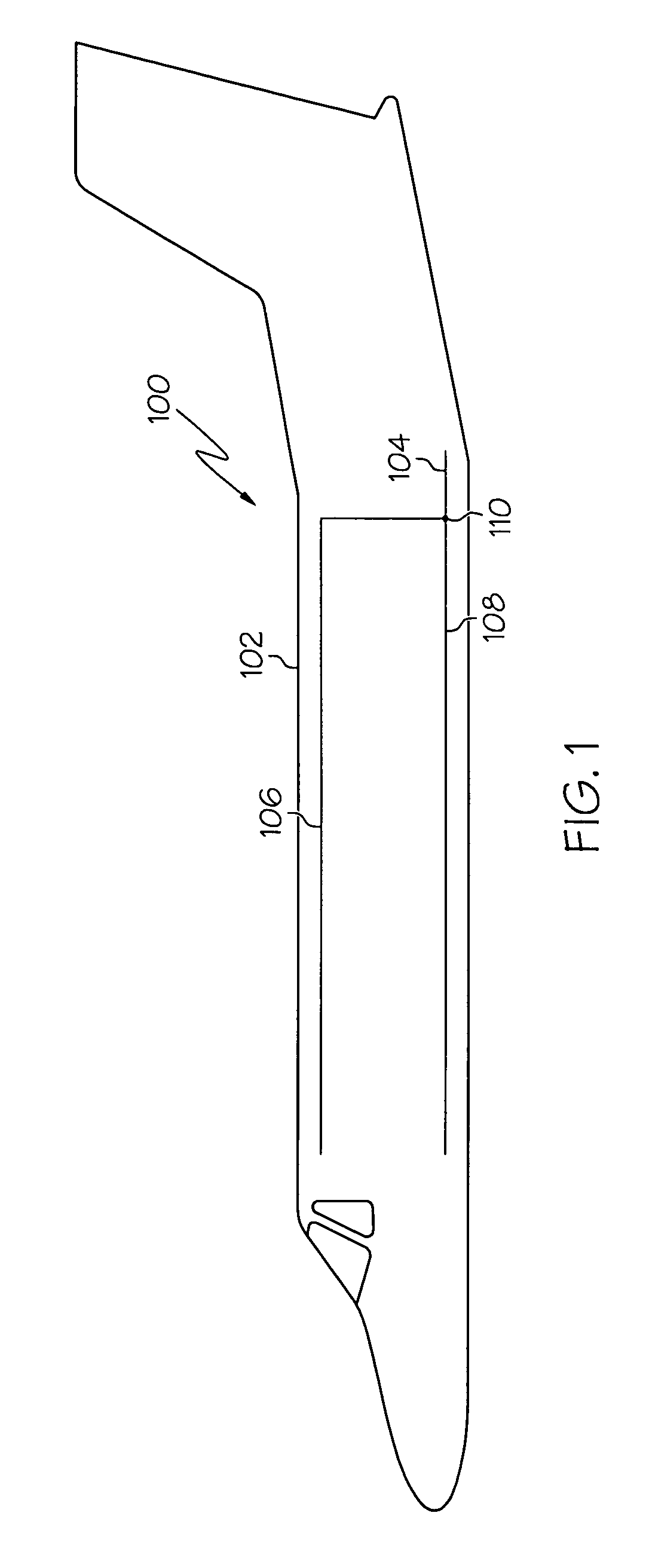

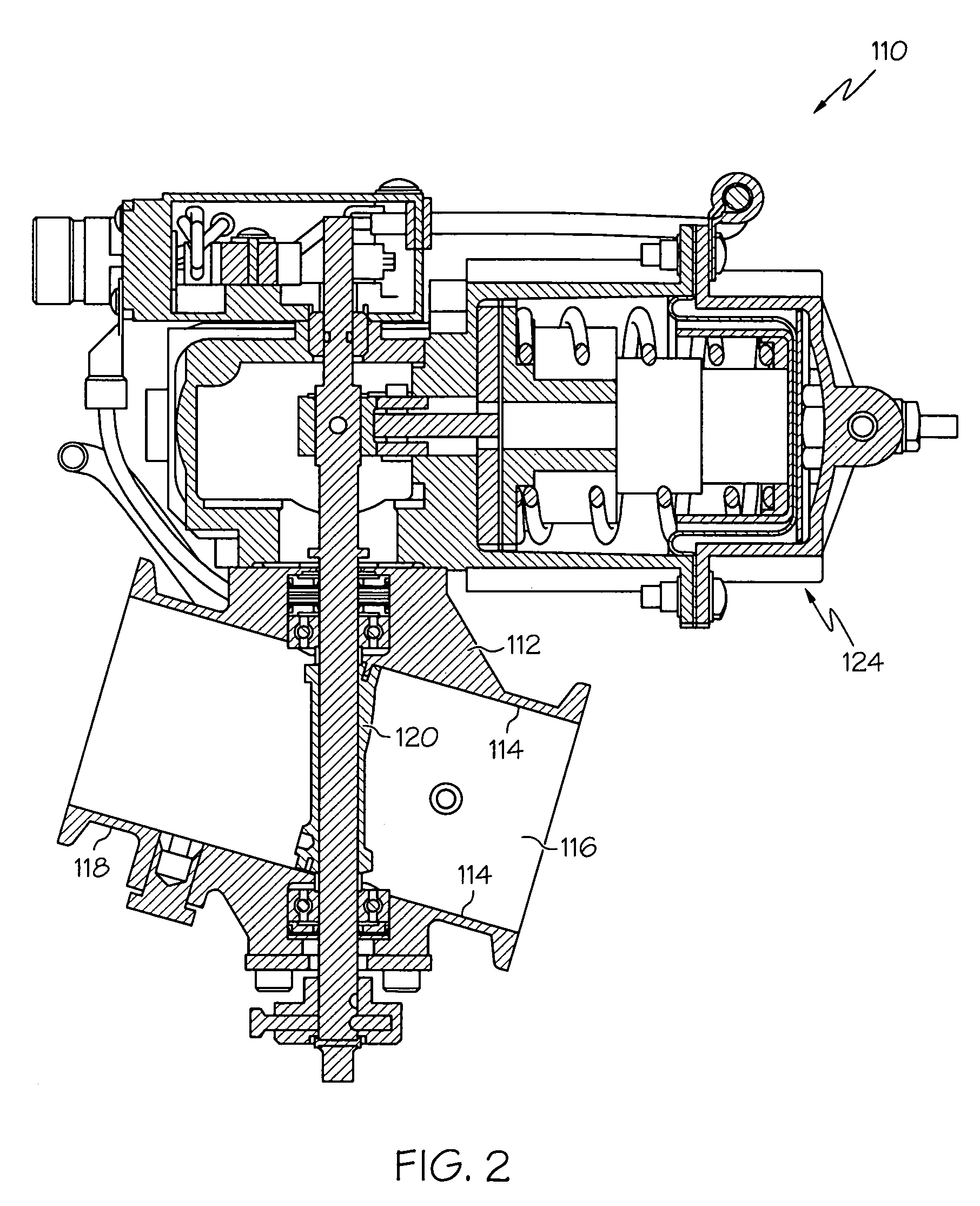

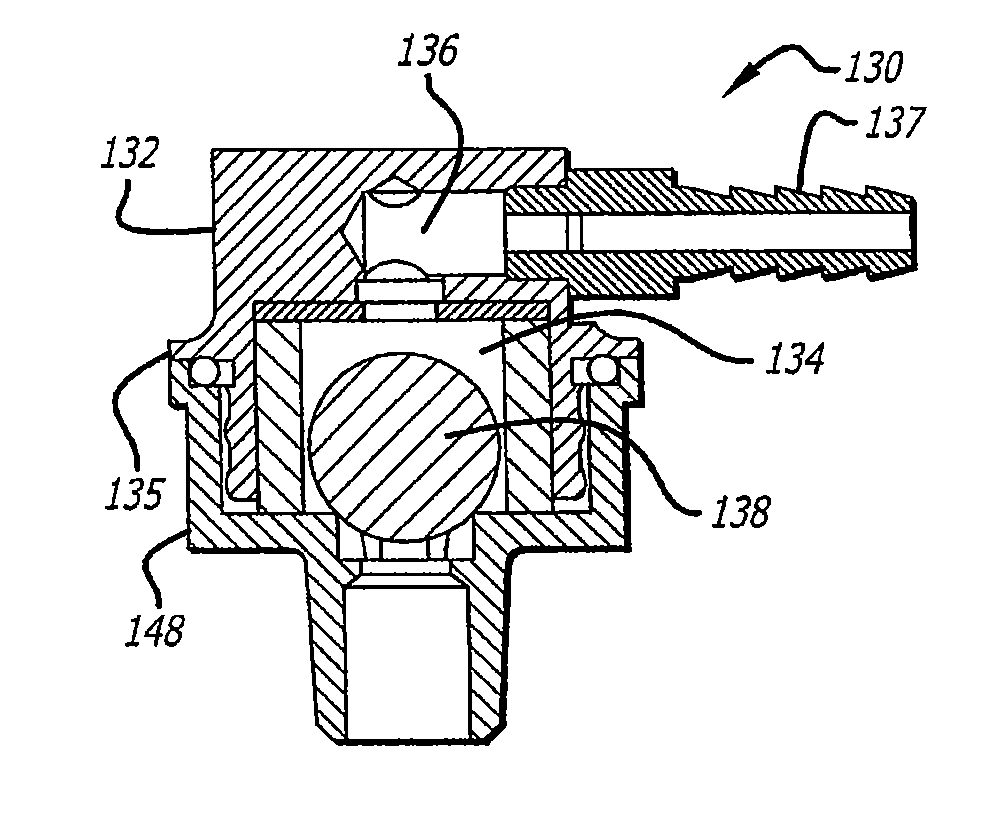

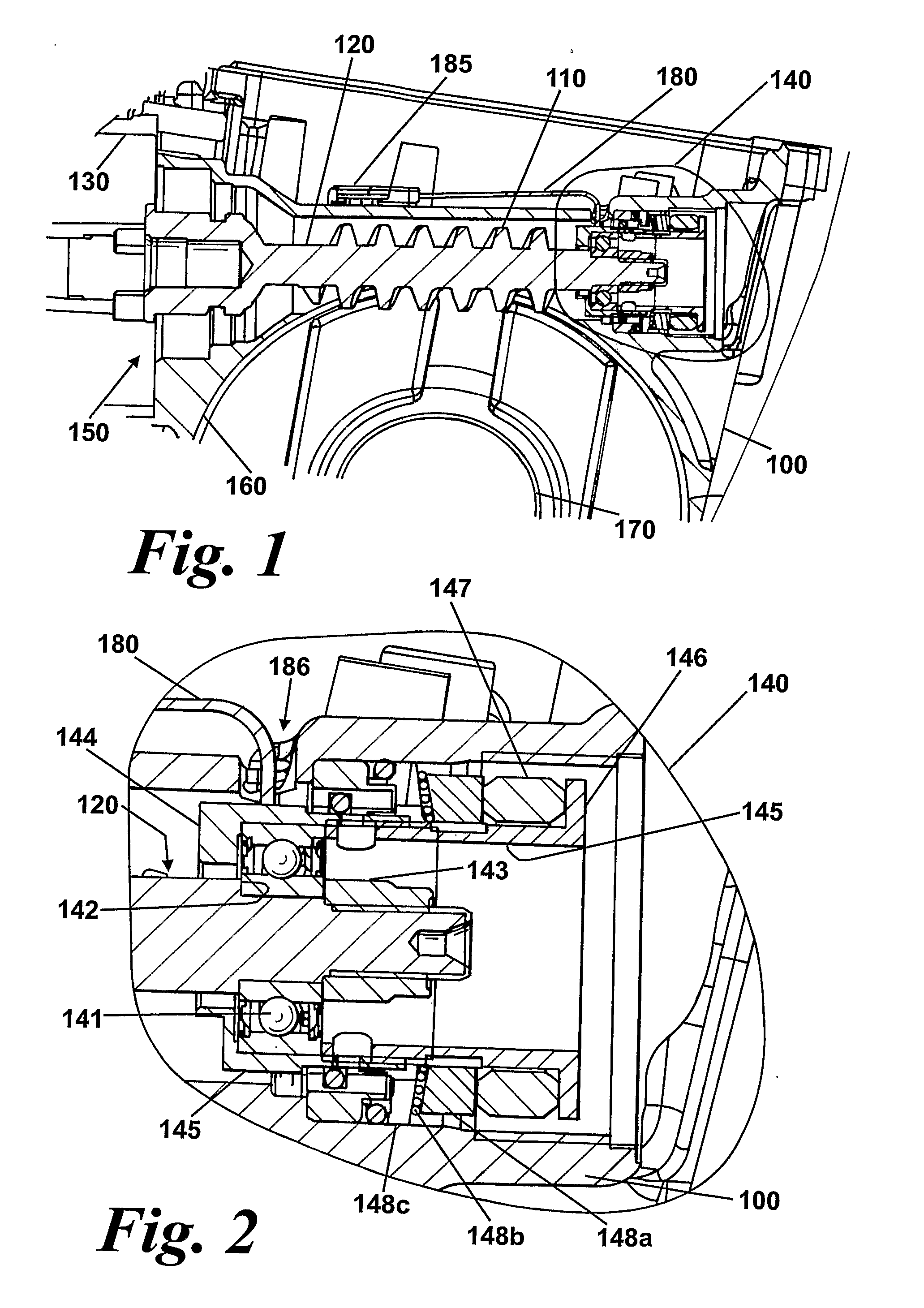

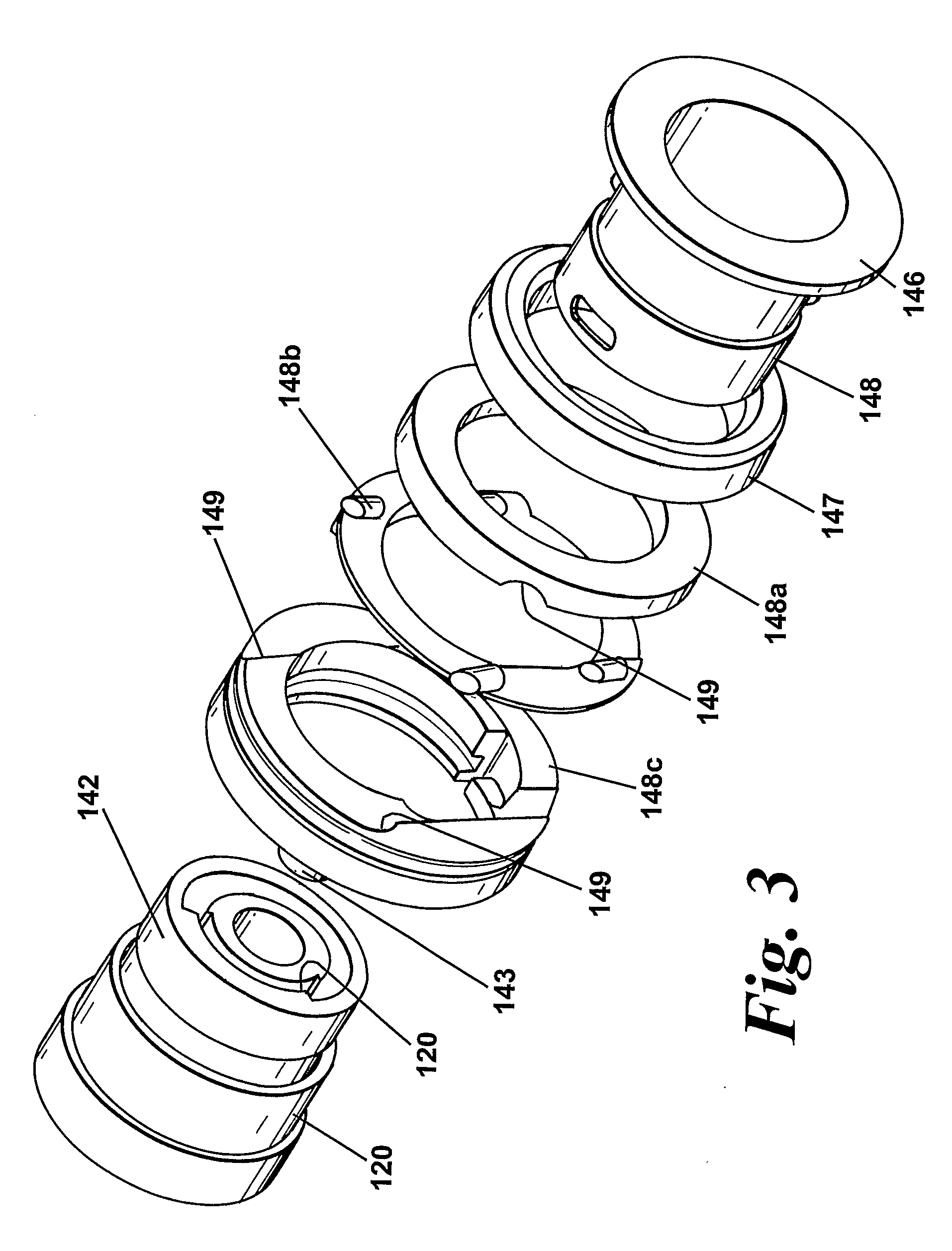

Butterfly valve assembly including a bearing assembly for serrated spline constraint

InactiveUS8172202B2Minimize misalignmentMinimize couplingBearing assemblyAir-treatment apparatus arrangementsCouplingEngineering

Butterfly valves assemblies are provided that include a flowbody, a butterfly plate, an actuator and an upper chimney and a lower chimney disposed within the flowbody. The flowbody has an inner surface defining a channel. The butterfly plate is disposed in the channel, is rotationally mounted to the flowbody, and has an outer periphery. The actuator has an actuator output shaft that is coupled to the valve shaft via a serrated spline coupling. The upper chimney and the lower chimney are configured to include bearing assemblies that constrain radial loads and thrust loads exerted upon the valve shaft and minimize misalignment of the serrated spline coupling.

Owner:HONEYWELL INT INC

Friction stir welding apparatus, system and method

ActiveUS8132708B1Minimize misalignmentHighly creativeWelding/cutting auxillary devicesAuxillary welding devicesEngineeringMechanical engineering

A method of performing friction stir welding is provided herein. More specifically, traditional friction stir welding requires a rotatable head that is forced against a plurality of work pieces to bond the same. The rotational and normal forces generated by the friction stir welding tool are generally reacted by a backing plate, anvil, mandrel or other mechanisms, such hardware are subject to the applied forces and are often supported with additional internal supports. Conversely, a method of performing a friction stir weld is described that omits the need for such a backing member and internal supports as it is performed using a self reacting pin tool.

Owner:UNITED LAUNCH ALLIANCE

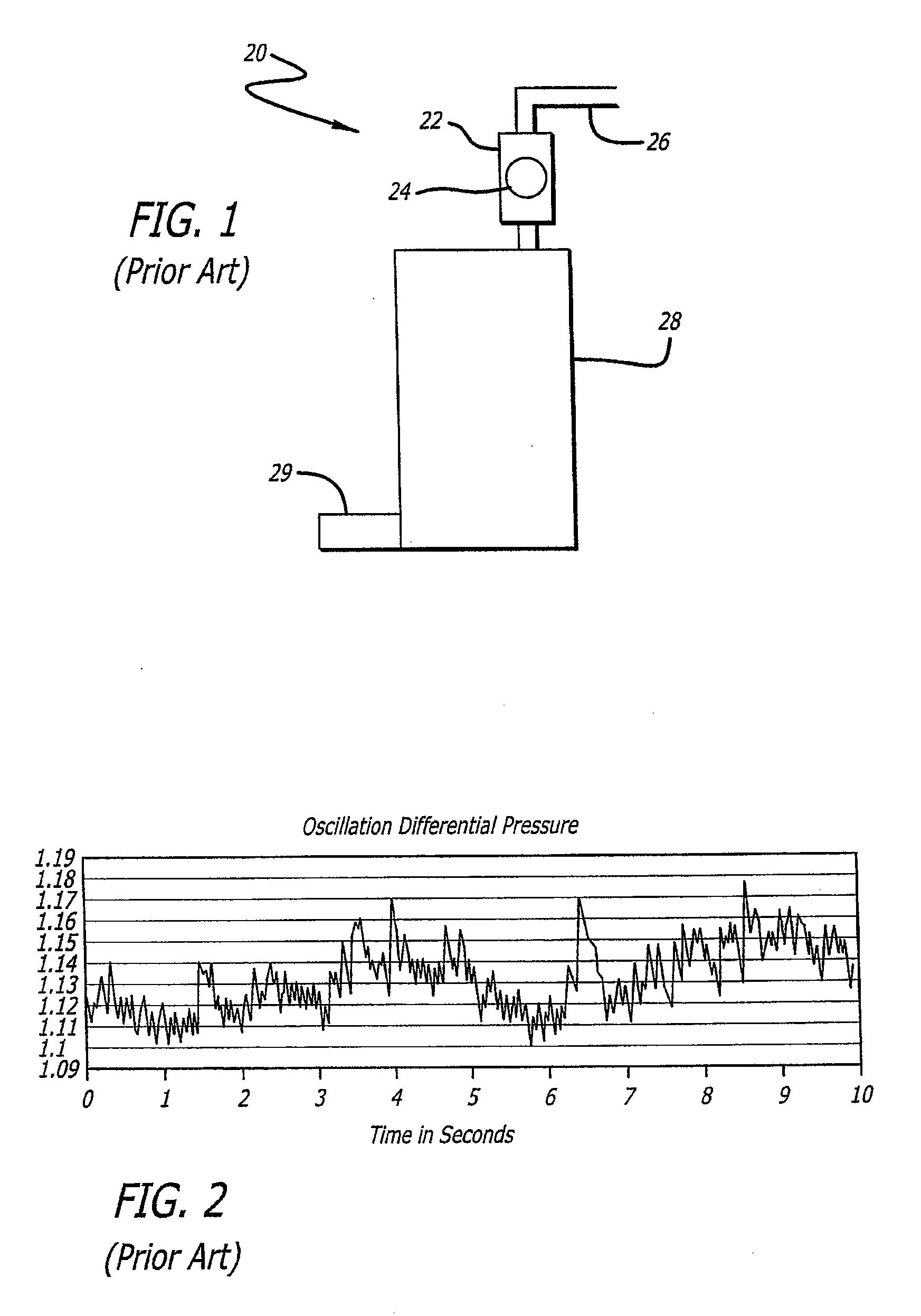

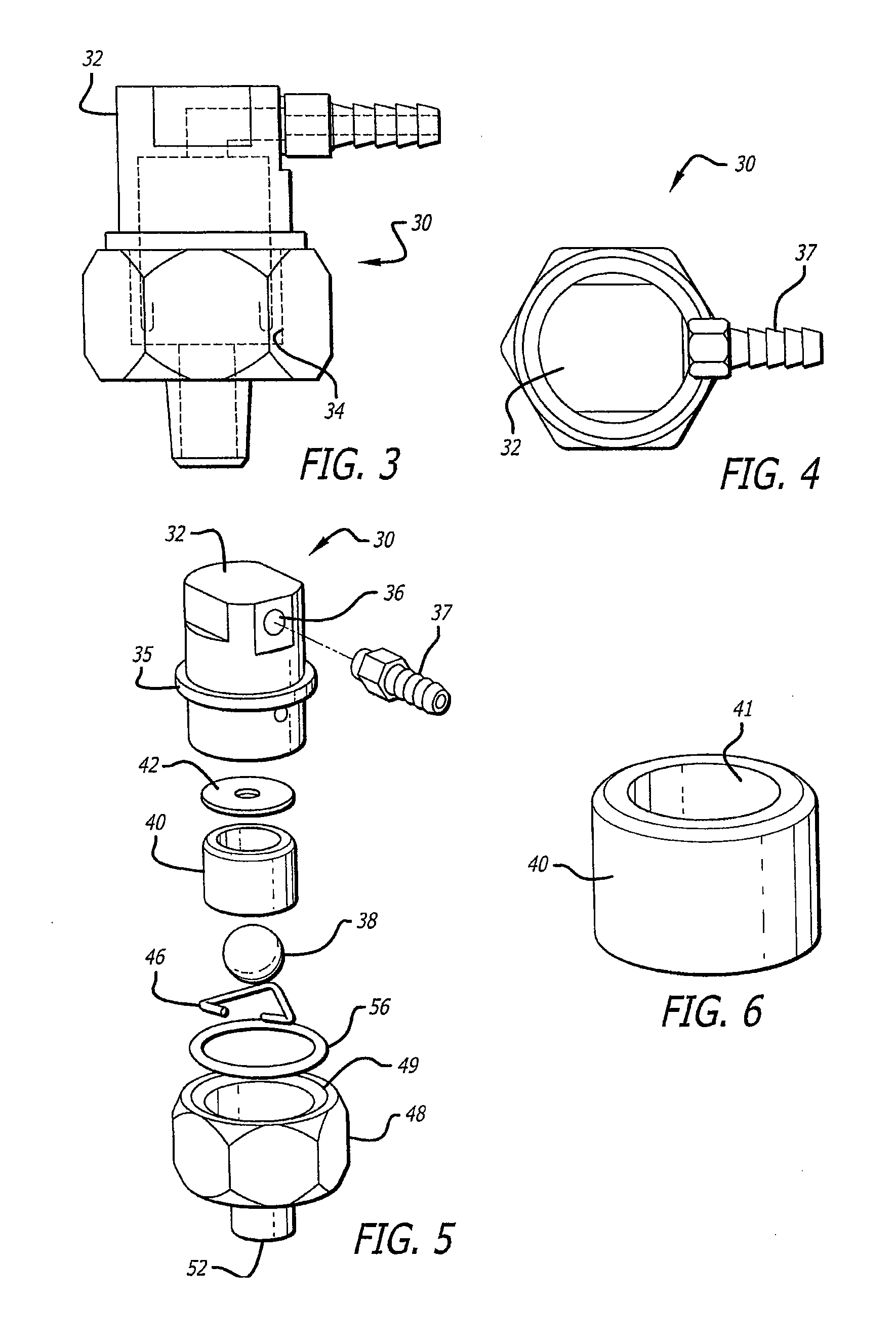

Air vent valve for beverage makers

InactiveUS20100132805A1Eliminate chatterImprove performanceVenting valvesAeration devicesEngineeringVALVE PORT

The air vent valve includes a vent valve body and a valve adapter that sealingly mate together. A vent outlet of the vent valve body and a fluid inlet of the valve adapter are connected through interior flow chambers of the vent valve body and valve adapter. A spherical ball float is constrained for longitudinal movement within a tubular collar in the interior chamber of the vent valve body, and a planar valve seat member with a central flow aperture is disposed within the vent valve body between the tubular collar and the outflow passage of the vent valve body.

Owner:BE INTPROP

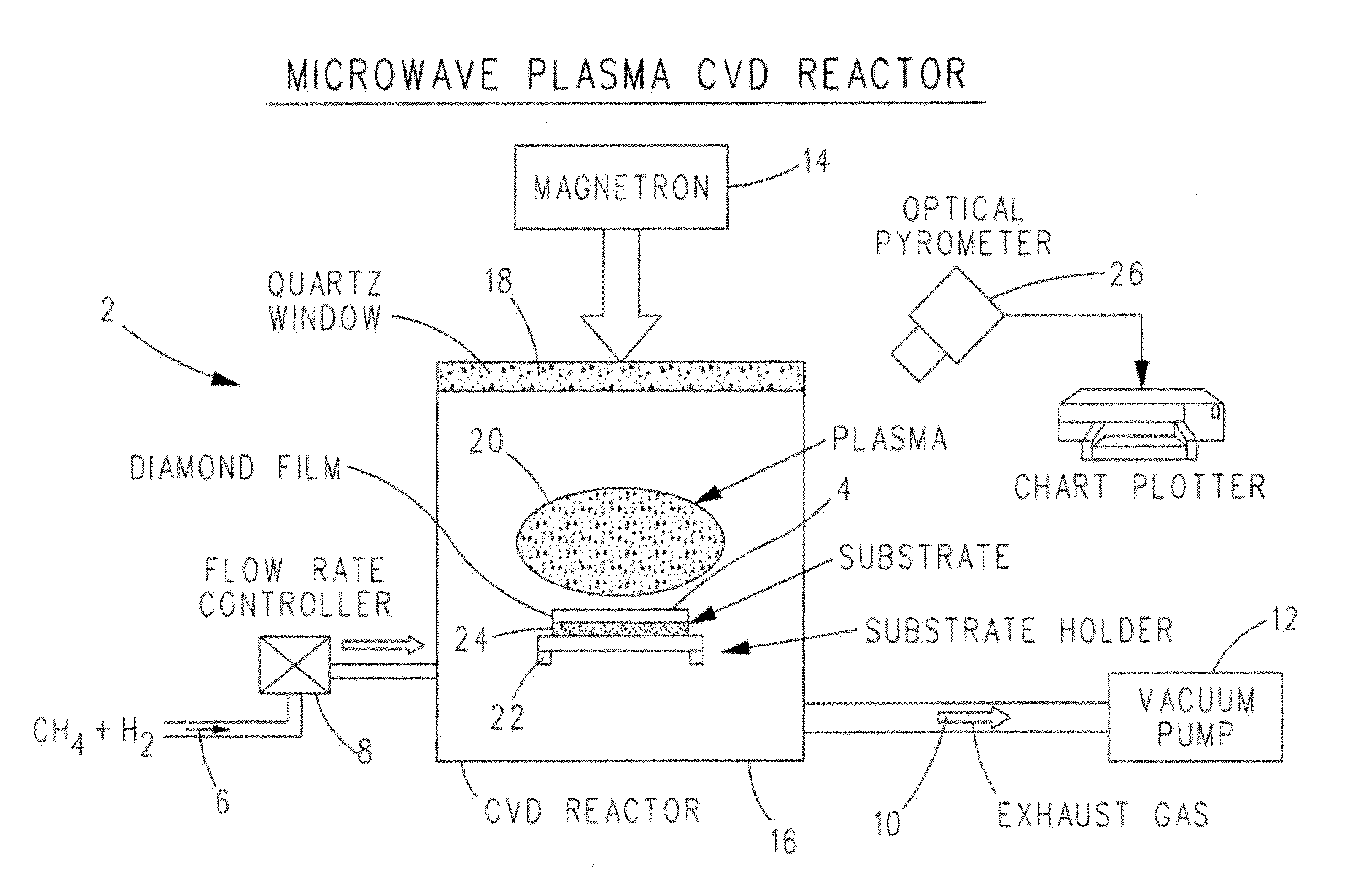

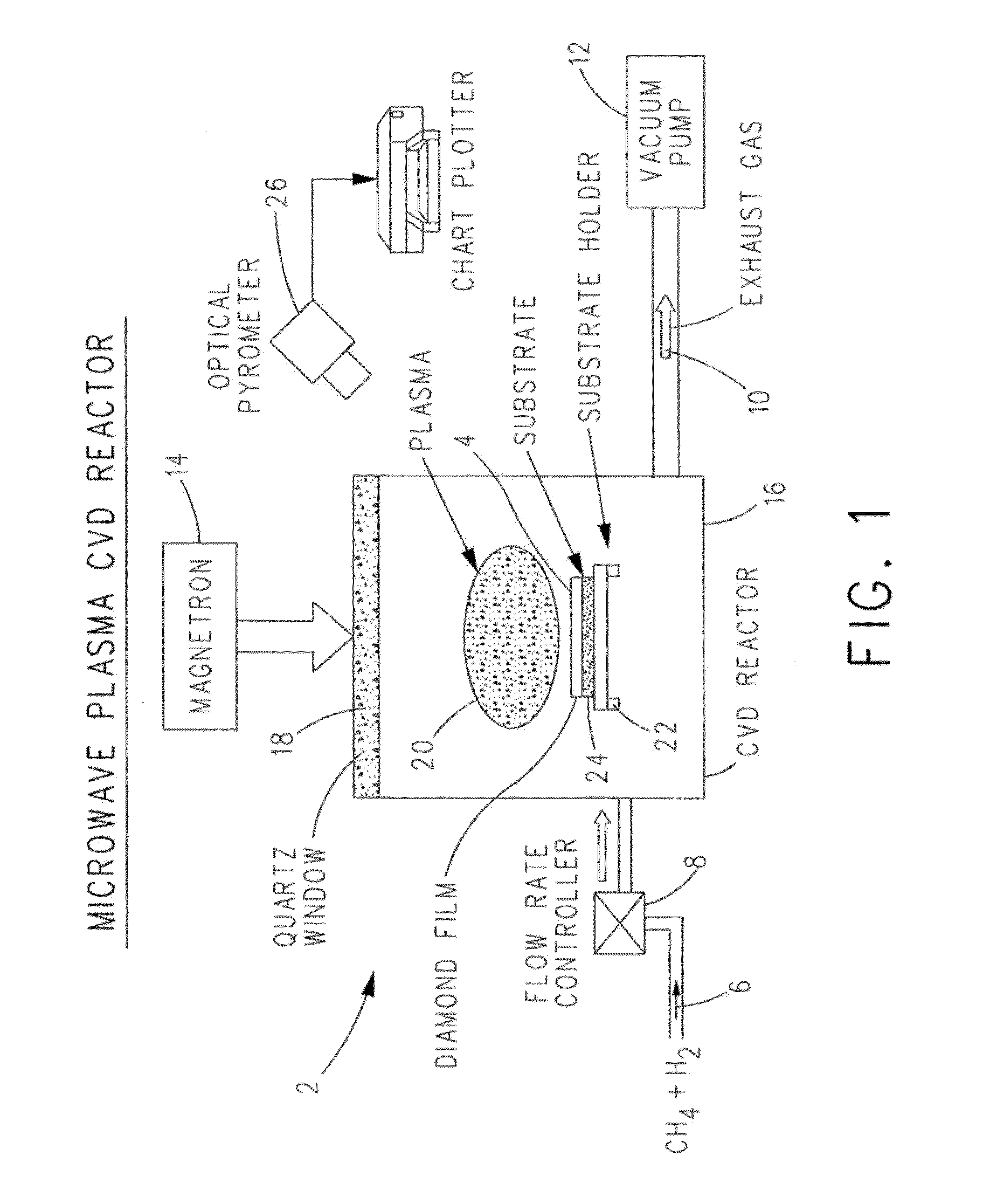

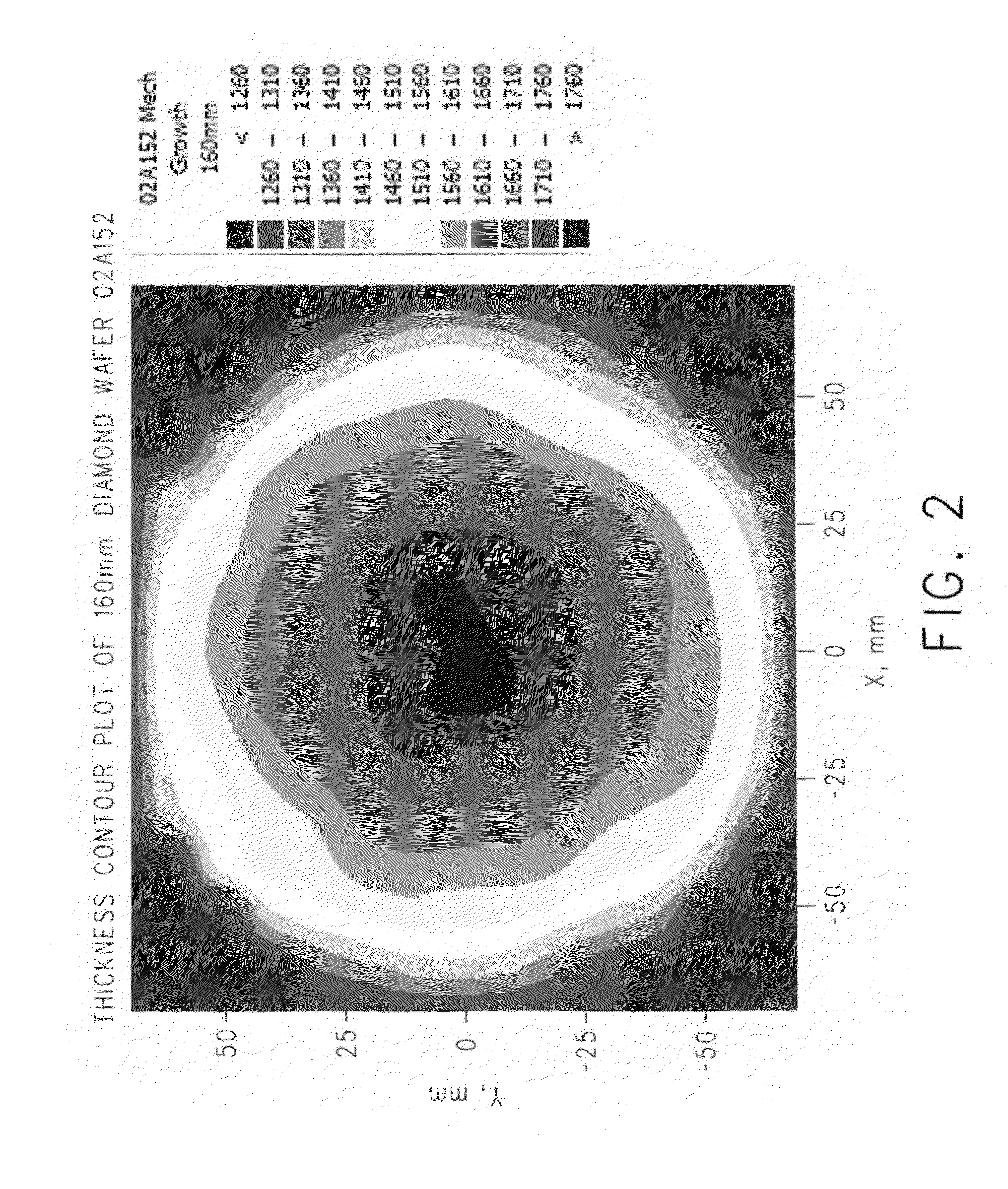

Highly Twinned, Oriented Polycrystalline Diamond Film and Method of Manufacture Thereof

ActiveUS20160130725A1High surface finishIncrease speedUltra-high pressure processesConductive materialGas phasePolycrystalline diamond

In a method of chemical vapor deposition (CVD) growth of a polycrystalline diamond film in a CVD reactor, a gas mixture of gaseous hydrogen and a gaseous hydrocarbon is introduced into the CVD reactor. A plasma formed from the gas mixture is maintained above a surface of a conductive substrate disposed in the CVD reactor and causes a polycrystalline diamond film to grow on the surface of the conductive substrate. A temperature T at the center of the polycrystalline diamond film is controlled during growth of the polycrystalline diamond film. The CVD grown polycrystalline diamond film includes diamond crystallites that can have a percentage of orientation along a [110] diamond lattice direction ≧70% of the total number of diamond crystallites forming the polycrystalline diamond film.

Owner:II VI DELAWARE INC

Gear assemblies

ActiveUS20090294205A1Easy accessMinimize misalignmentElectrical steeringGearing detailsElectric power steeringGear wheel

In a gearbox for use in an electric power assisted steering system comprises a housing, an input shaft located at least partially within the housing which carries a worm gear and includes means for coupling to a motor rotor at one end, an output shaft located at least partially within the housing which carries a wheel gear, and a first bearing means which supports the input shaft at a side of the worm distal from the end of the shaft which connects to the motor rotor and second bearing means which supports the input shaft at the other side of the worm, the invention comprises further providing a first biasing means adapted to apply an axial load to the input shaft to bias the axial clearance in the second bearing, the second biasing means acting upon a part of the first bearing means; and a second biasing means adapted to apply a radial load to the input shaft to bias the worm into engagement with the wheel gear, the second biasing means also acting upon a part of the first bearing means.

Owner:TRW LIMITED

Liquid crystal display structure

ActiveUS20030076286A1Minimize misalignmentMinimizing liquid crystal misalignmentStatic indicating devicesNon-linear opticsLiquid-crystal displayLiquid crystal

A liquid crystal display structure includes a first substrate panel, a second substrate panel, and a liquid crystal layer disposed between the first substrate panel and the second substrate panel. Pixel portions are formed by respective electrodes for applying a voltage to the liquid crystal layer. The pixel portions include a transparent substrate panel, an organic insulating layer, a patterned reflective layer, a dielectric layer, a transparent conductive layer and a thin film transistor. The organic insulating layer is formed over the transparent substrate panel. The patterned reflective layer is formed over the organic insulating layer exposing a portion of the organic insulating layer. The dielectric layer is formed over the patterned reflective layer. The dielectric layer has a smooth upper surface. The transparent conductive layer is over the dielectric layer. The transparent conductive layer is connected to the thin film transistor so that the thin film transistor can drive the transparent conductive electrode.

Owner:AU OPTRONICS CORP

Control system for a tiltable vehicle

A vehicle of the present disclosure may include at least one pair of opposing wheels coupled to a tiltable central chassis by a four-bar linkage or the like, such that the wheels are configured to tilt in unison with the central chassis. A steering actuator and / or a tilting actuator may be discretely controllable by an electronic controller of the vehicle. The controller may include processing logic configured to maintain alignment between a median plane of the chassis and a net force vector caused by gravity and any induced centrifugal forces. Various control algorithms may be utilized to steer the vehicle along a desired path, either autonomously or semi-autonomously.

Owner:SWAY MOTORSPORTS LLC

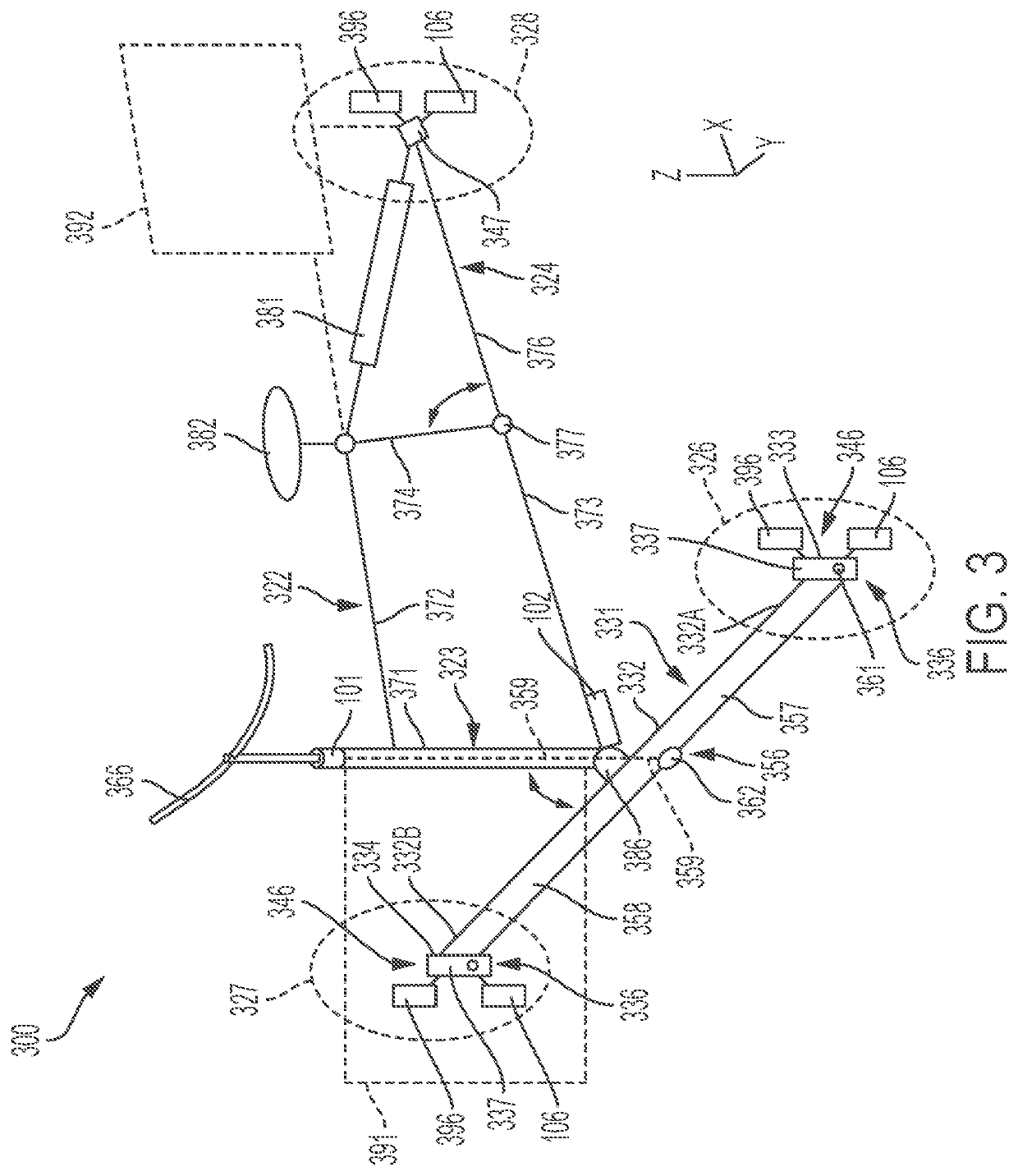

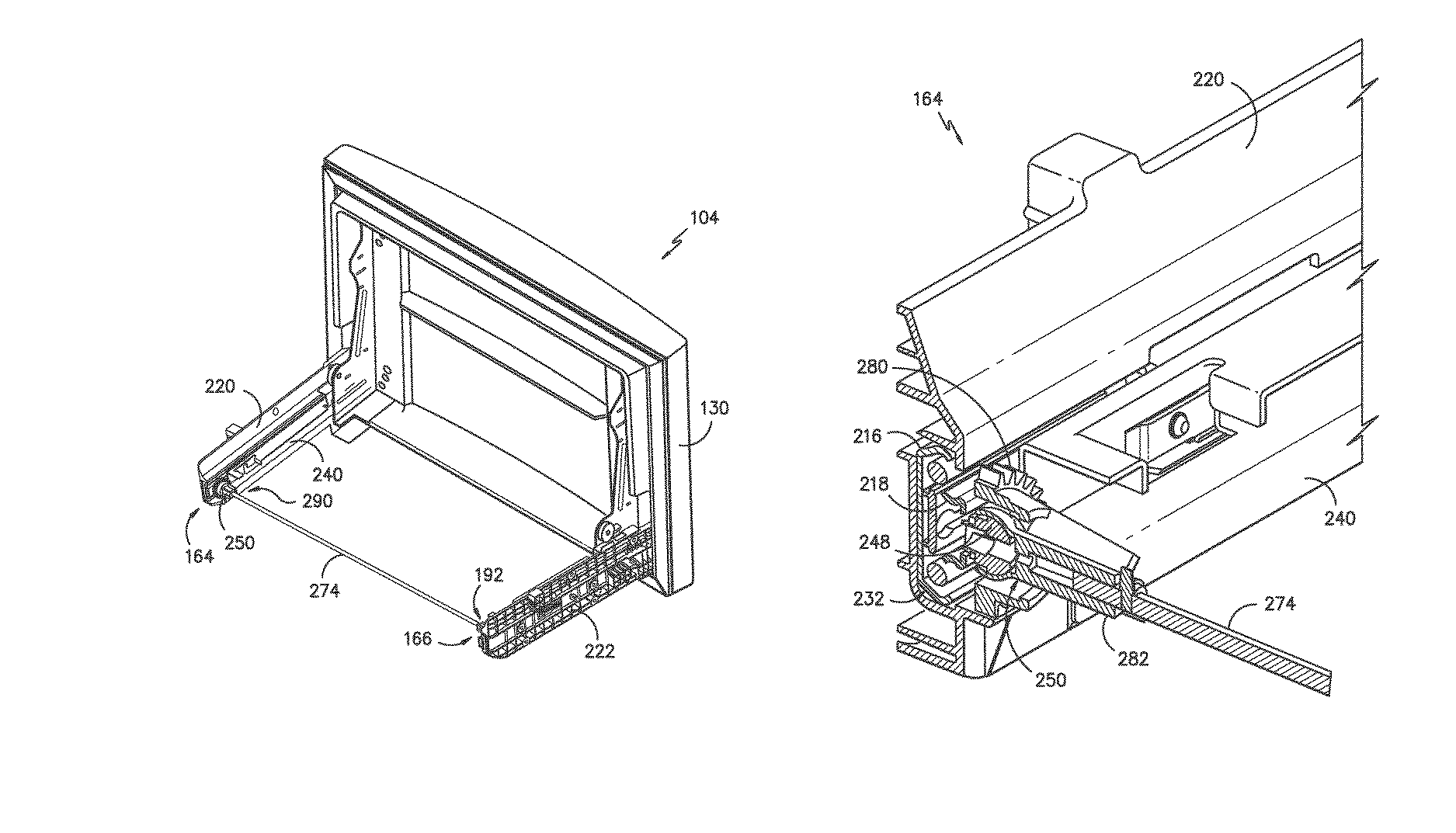

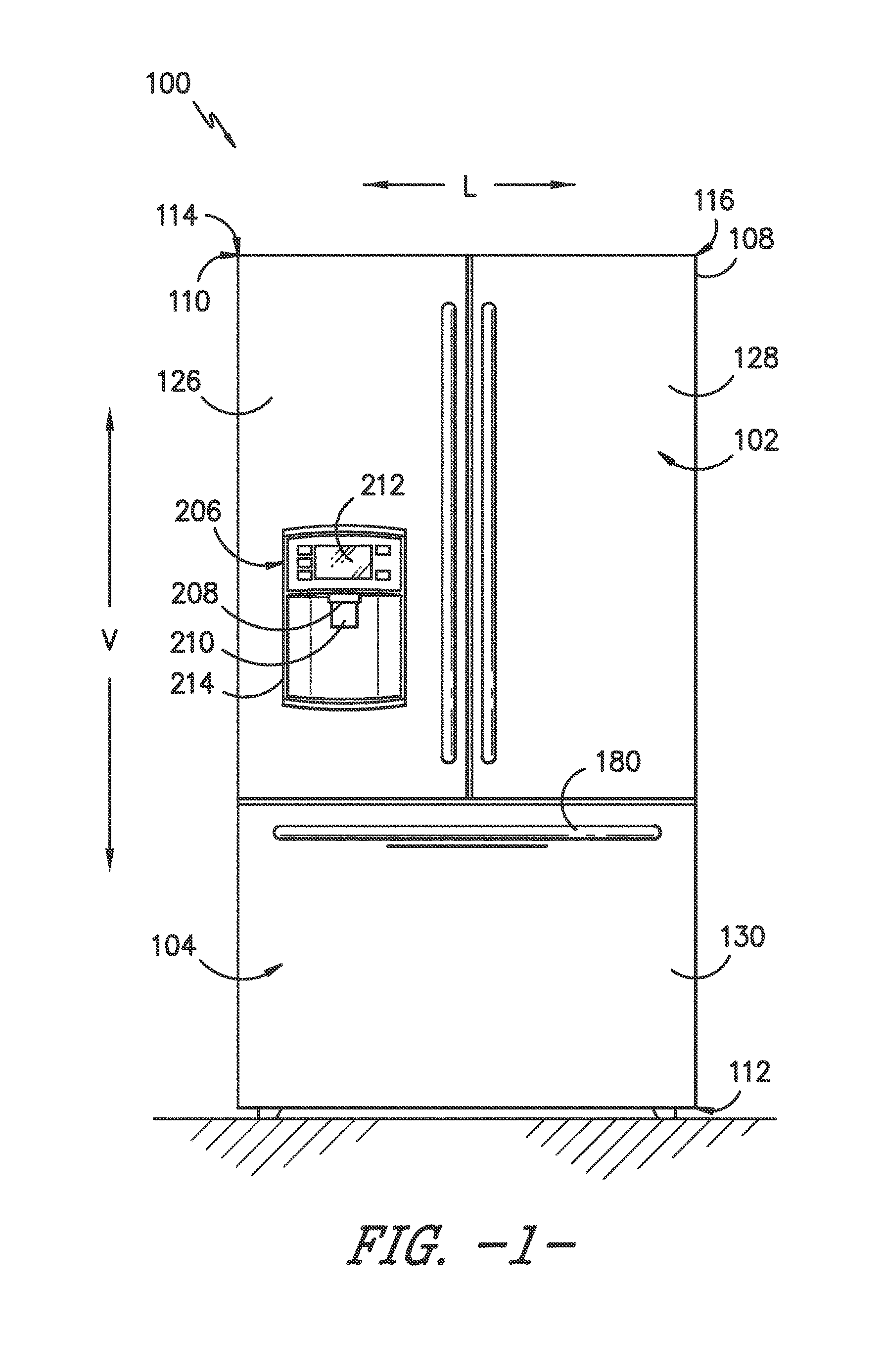

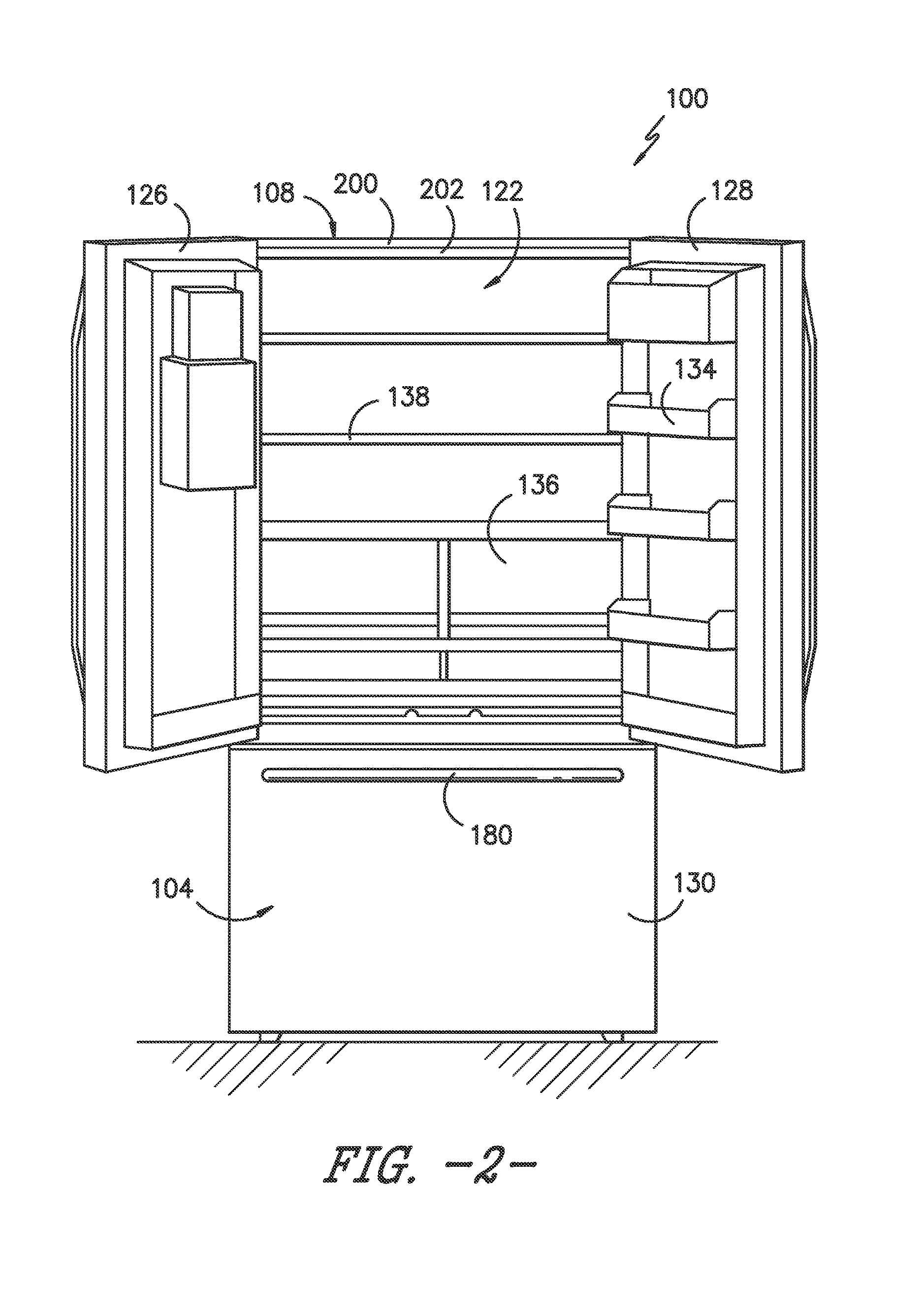

Ball joint pinion for a drawer slide assembly

ActiveUS9565937B1Minimize misalignmentMinimizes rackingLighting and heating apparatusDrawersSubject matterDegrees of freedom

A drawer assembly for a consumer appliance is provided. The drawer assembly includes an anti-racking system for minimizing misalignment of an appliance drawer. More particularly, the present subject matter provides a drawer slide assembly for a drawer having some horizontal flexibility. The drawer slide assembly may have a pinion gear and connecting rod assembly that minimizes racking of the appliance drawer as it is moved into and out an appliance chamber. The appliance drawer may be attached to the appliance chamber by a ball and joint pinion gear configuration that adds another degree of freedom to the anti-racking system in order to reduce stress on the pinion gear. By adding an additional degree of freedom to the pinion gear and reducing the imposed stresses applied to the pinion gear, the performance and lifetime of the drawer assembly may be improved.

Owner:HAIER US APPLIANCE SOLUTIONS INC

Ez key registration assembly

InactiveUS20080226408A1Reduce cutting vibrationStable positionWorkpiece holdersMilling machinesEngineeringMechanical engineering

A locating system and method for accurately positioning key blanks with respect to a key cutter where the key head is clamped between opposing jaws with the key blade working edges projecting therefrom, the key head is provided with shaped recesses having at least a partially specifically shaped edge wall and wherein at least one jaw member is provided with a projection having a correspondingly shaped sidewall, the pin being positioned with respect to the clamp such that when the key blank head is abutted against the pin with the key blank edge configuration mating to the pin sidewall configuration, the key blade will project from the jaw in a proper position for engagement by either the bitting follower or bitting cutter respectively.

Owner:KABA ILCO CORP

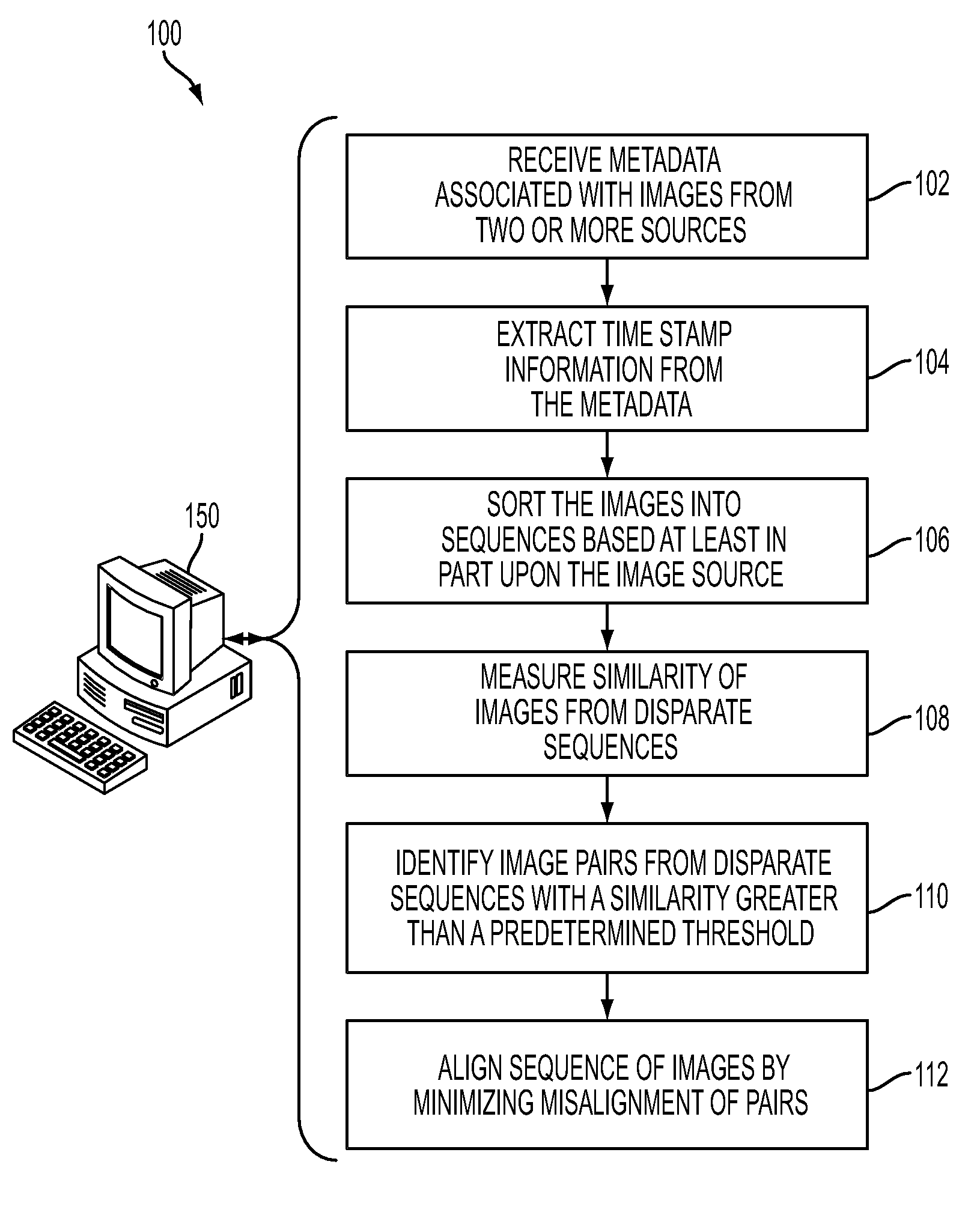

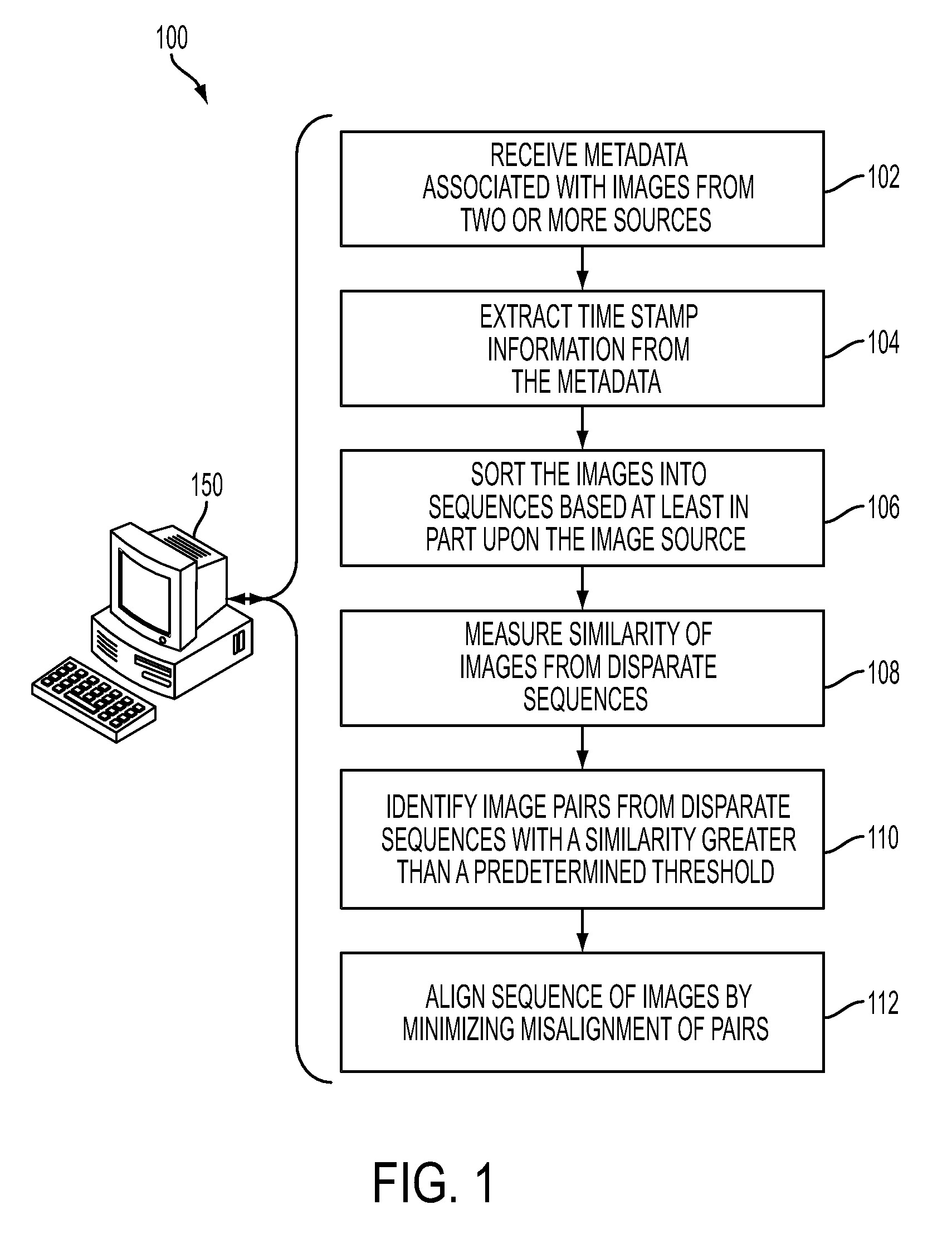

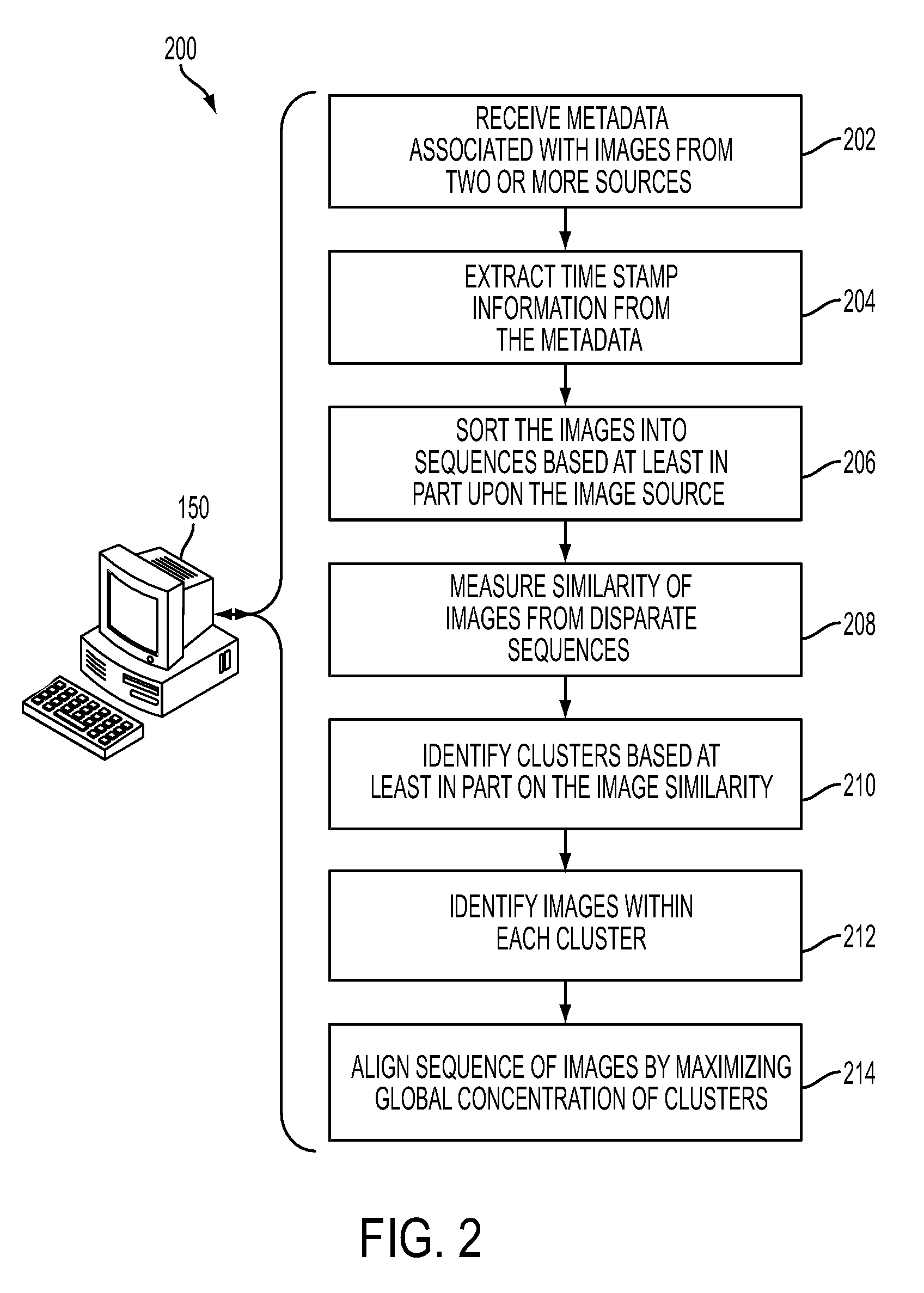

Synchronizing image sequences

InactiveUS8326087B2Minimize misalignmentConcentration maximizationCharacter and pattern recognitionMetadata still image retrievalPattern recognitionImage pair

As set forth herein, a computer-based method is employed to align a sequences of images. Metadata associated with images from two or more sources is received and a time stamp is extracted from the metadata. The images are sorted into sequences based at least in part upon the image source. The similarity of images from disparate sequences is measured and image pairs from disparate sequences with a similarity greater than a predetermined threshold are identified. A sequence of images is aligned by minimizing the misalignment of pairs.

Owner:XEROX CORP