Patents

Literature

50results about How to "Reduce trace width" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

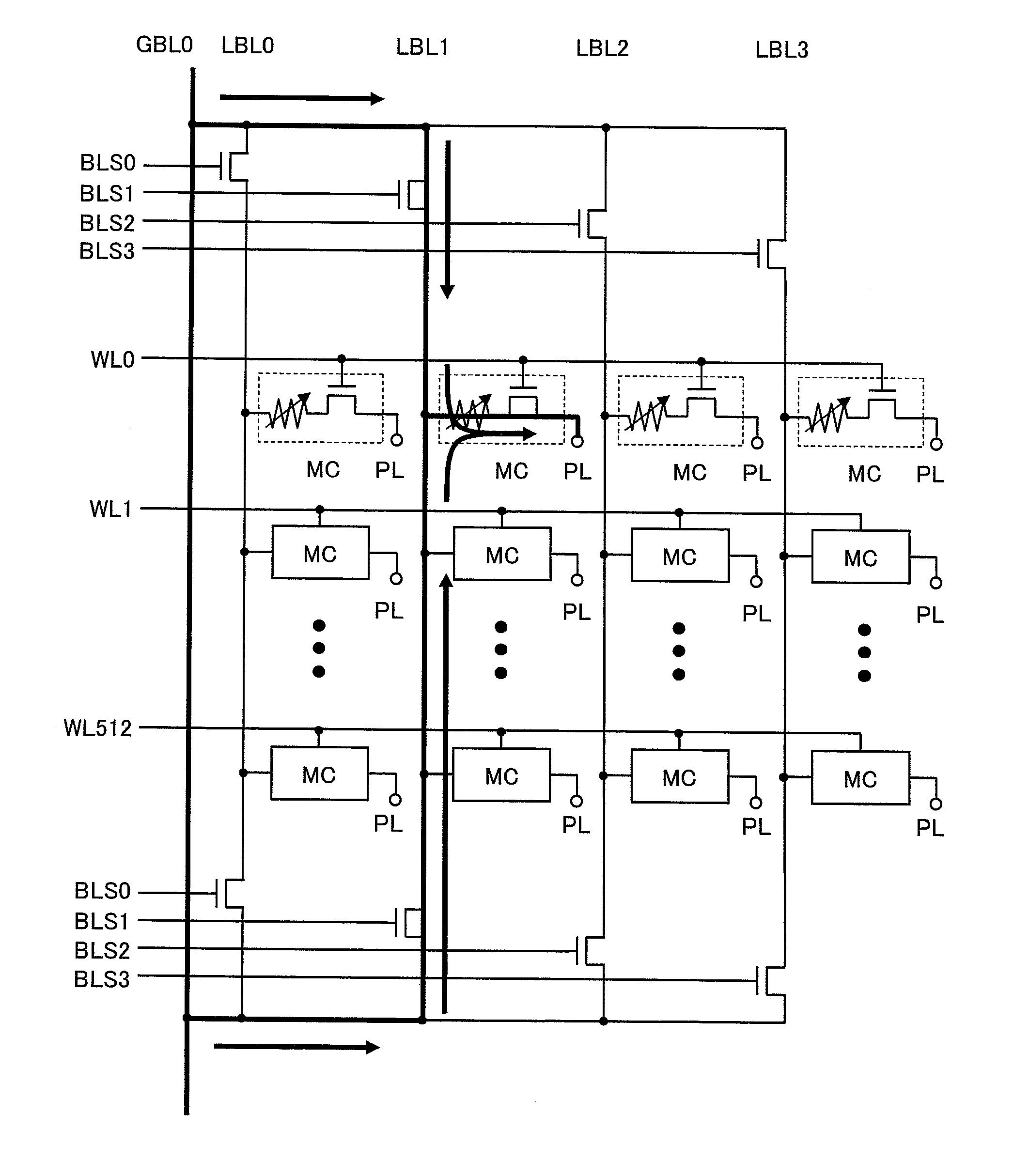

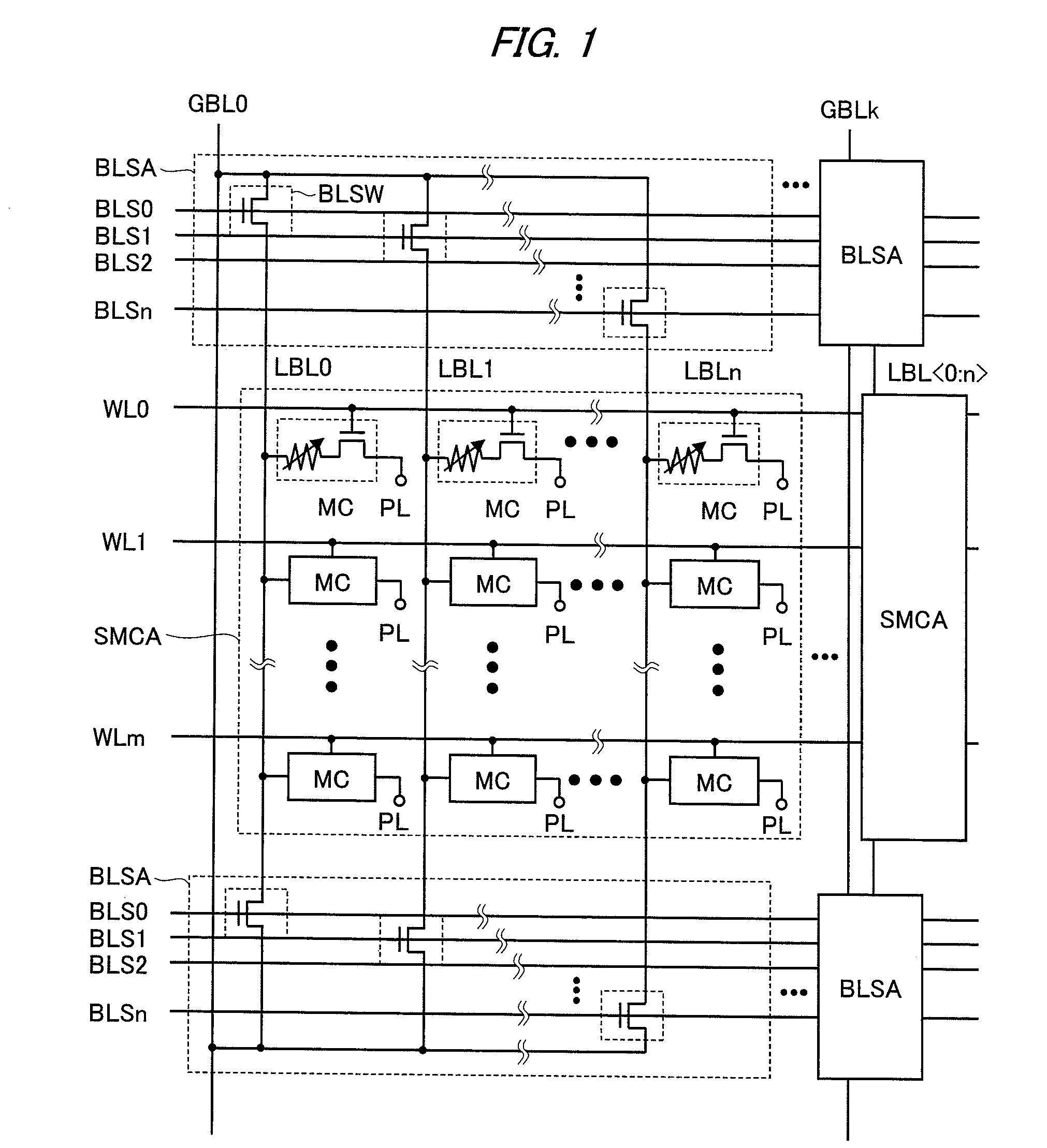

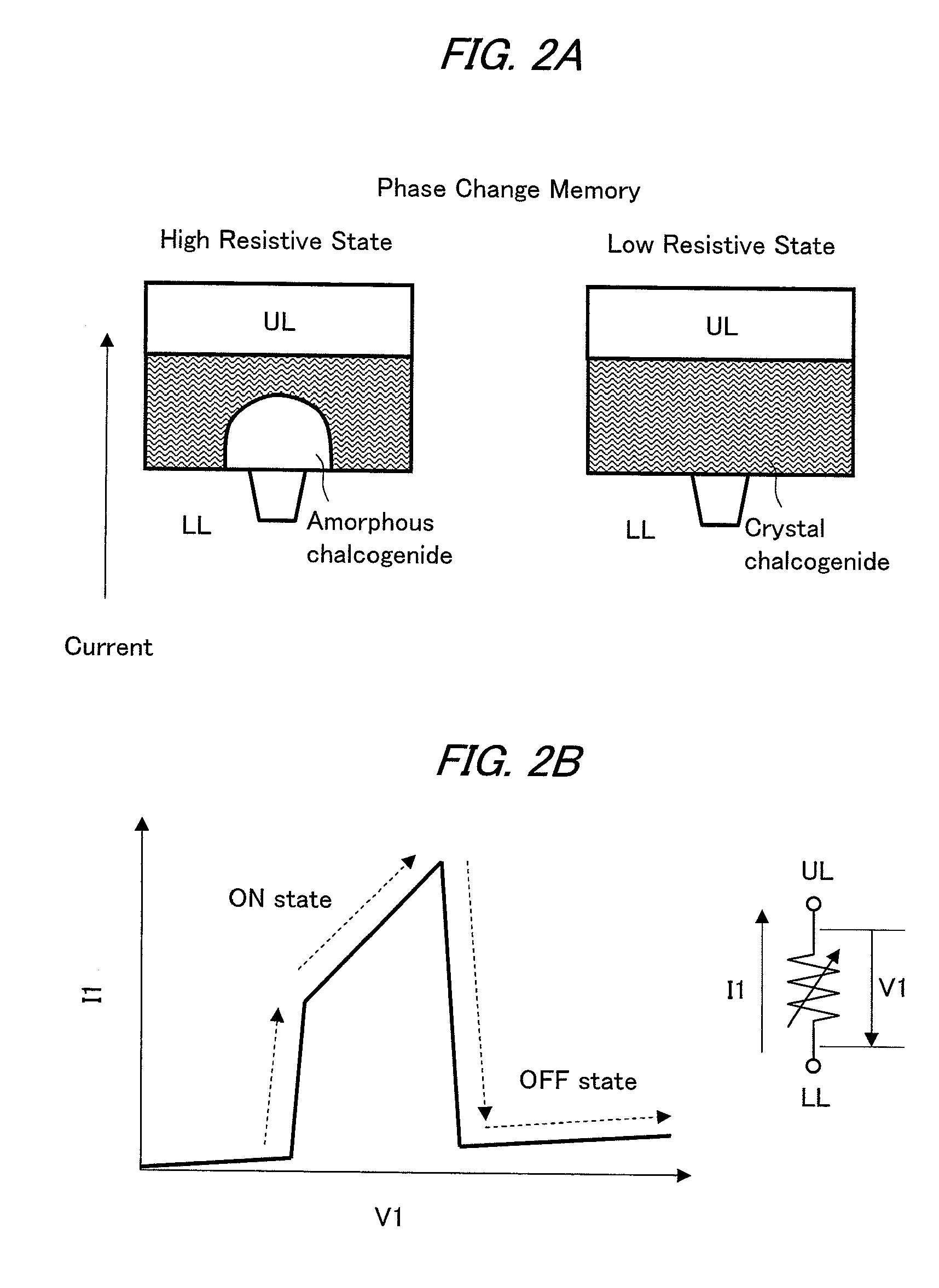

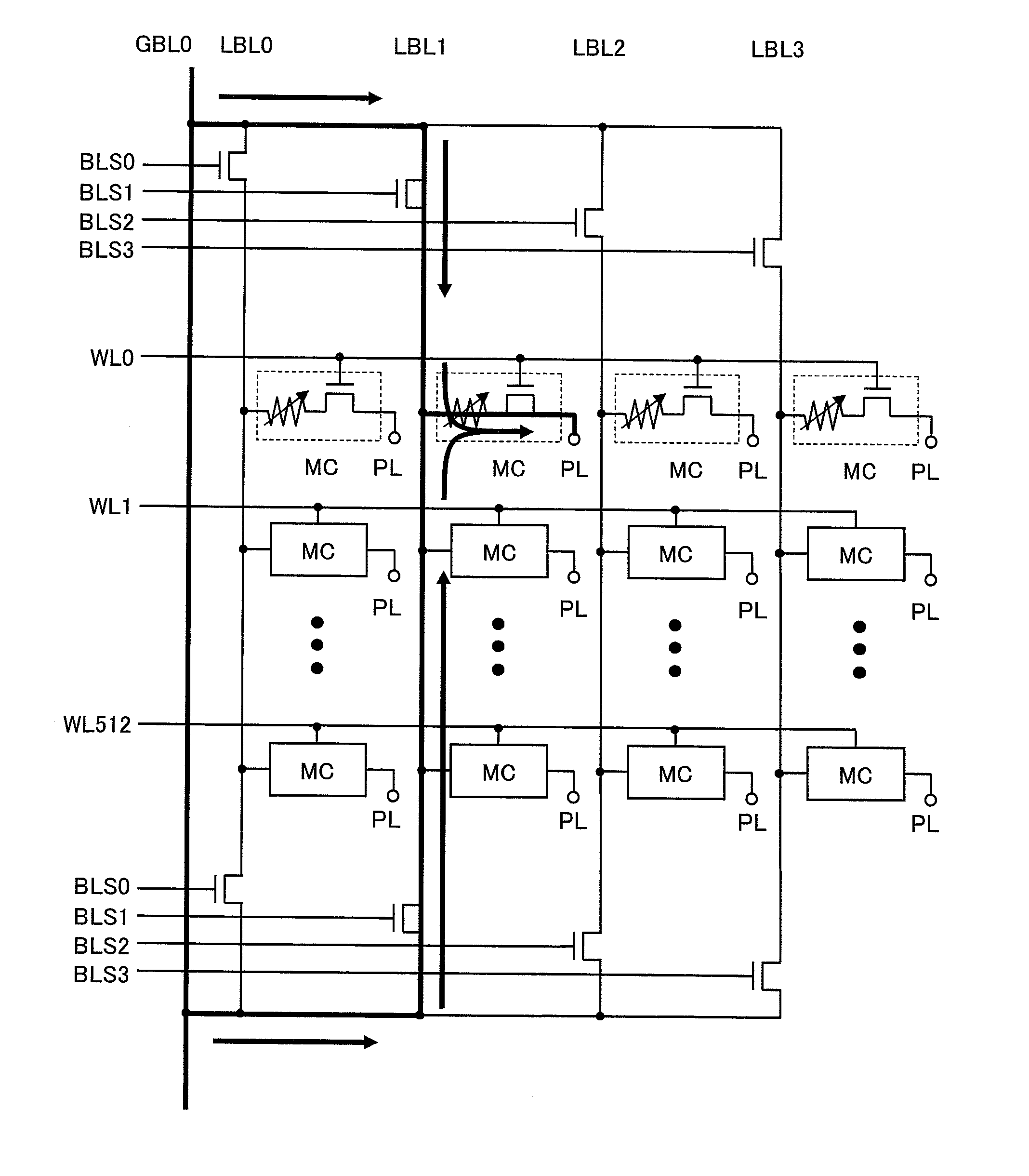

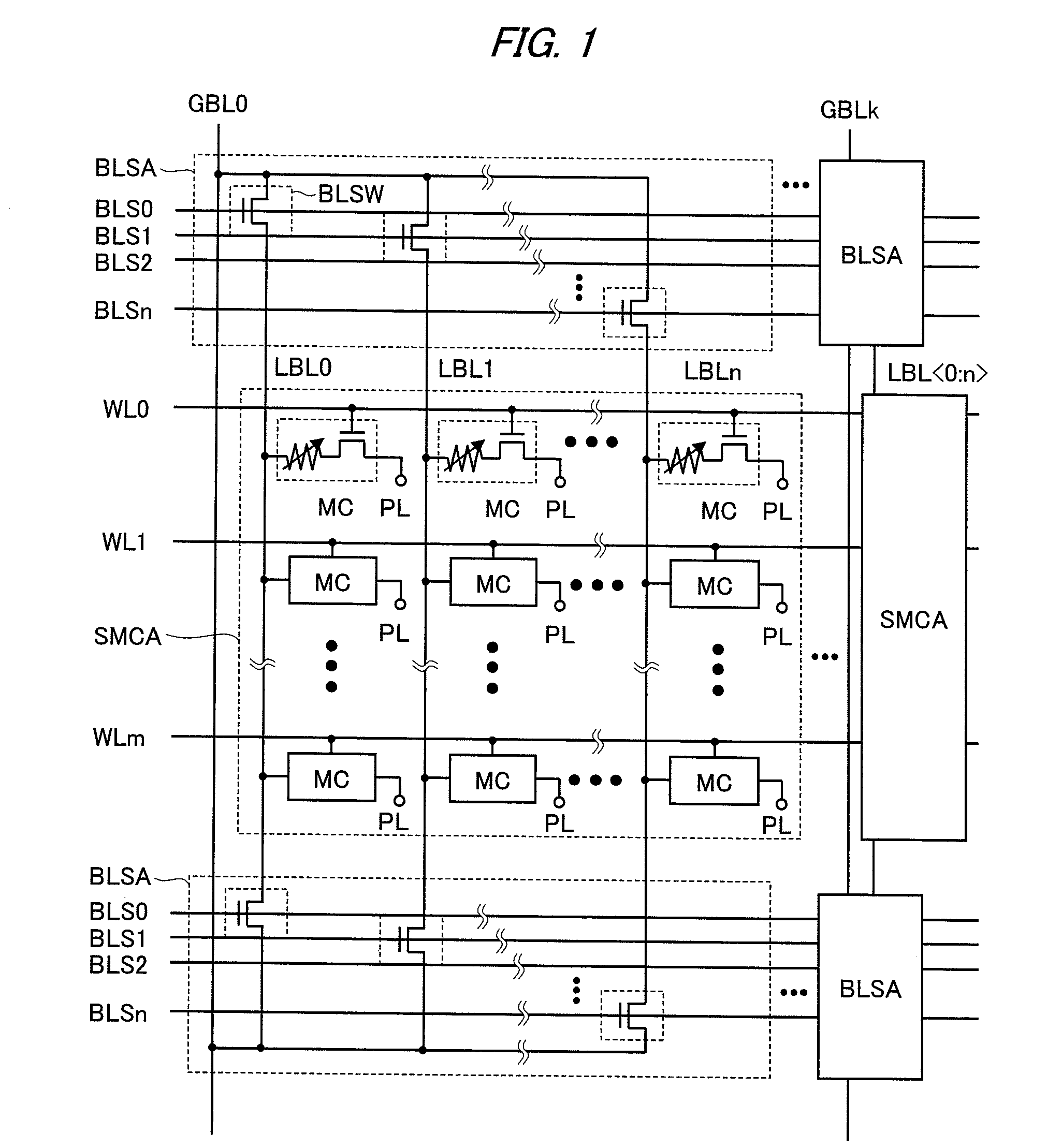

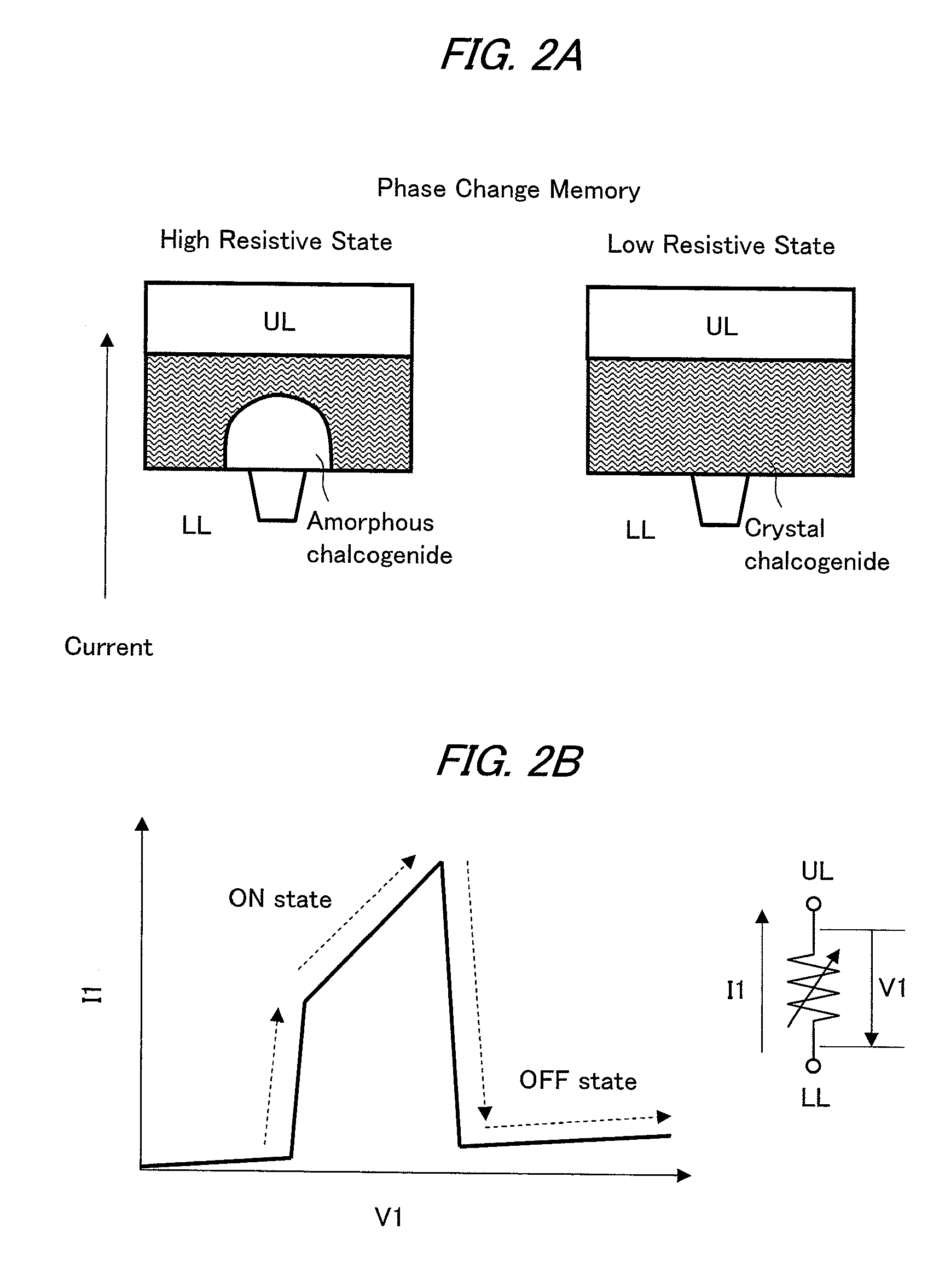

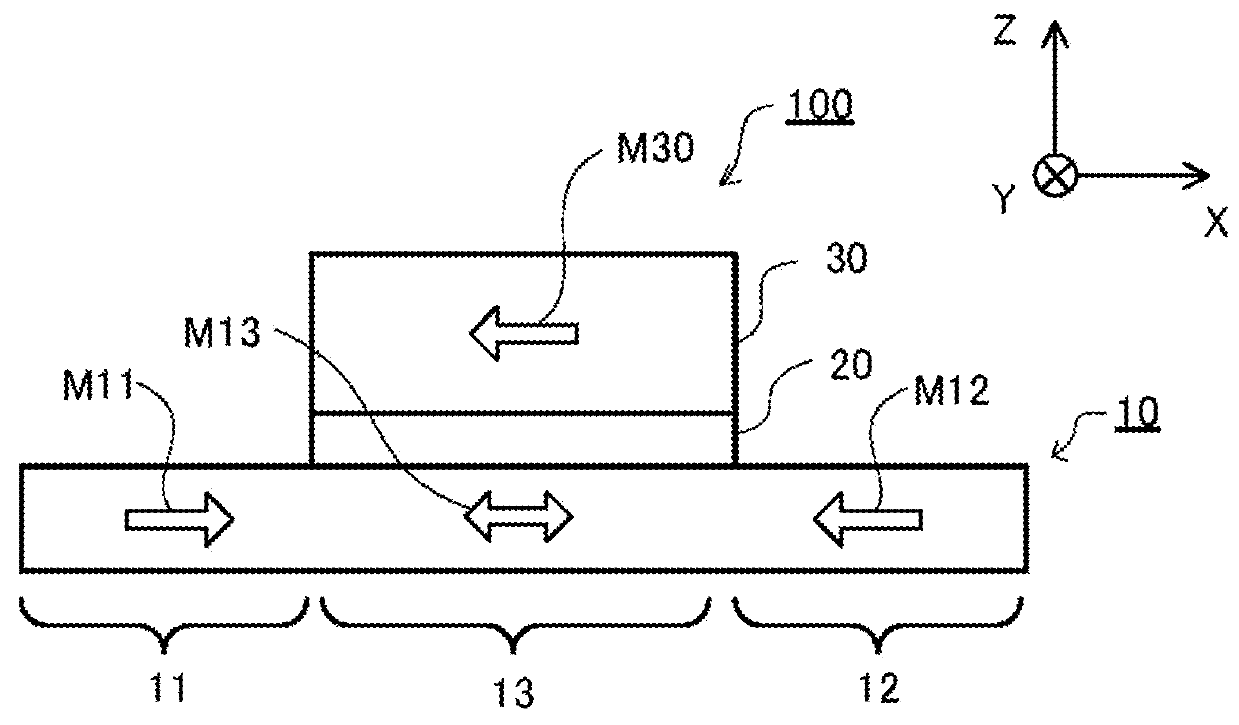

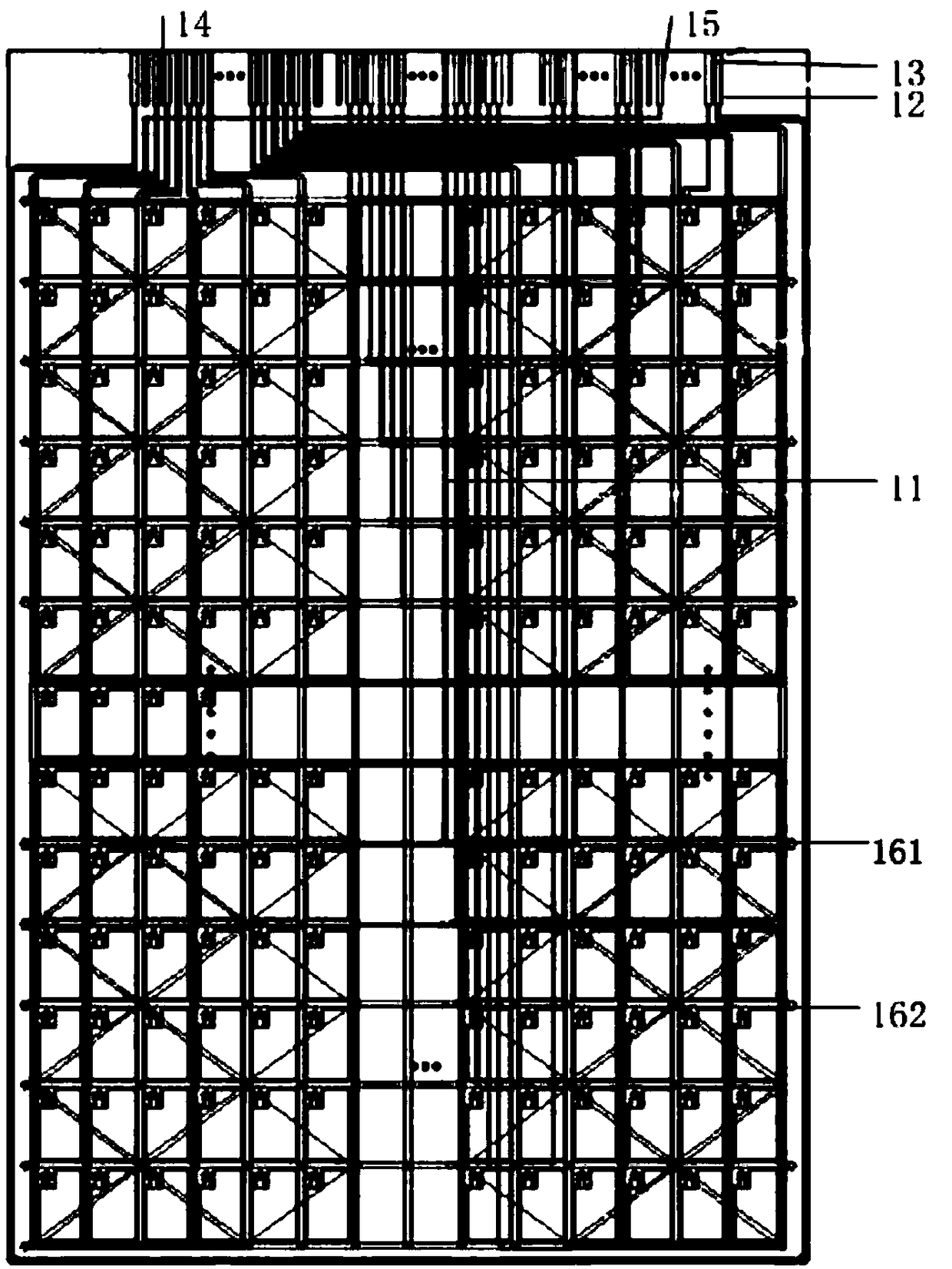

Semiconductor device

A technique for increasing rewriting current without increasing a power supply voltage and also reducing location dependency inside a memory array of a resistive state after the rewriting is provided in a resistance change memory in which the resistance value of a memory cell changes between logical values “1” and “0”. In the resistance change memory, bit lines are formed into a layered structure, the bit line select switches for connecting to the global bit line are provided at both ends of the local bit line, and a control method of the bit line select switches is changed in the writing and the reading, thereby realizing the optimum array configurations for each of them. More specifically, in the writing and the reading, two current paths are provided in parallel by turning ON the bit line select switches simultaneously.

Owner:HITACHI LTD

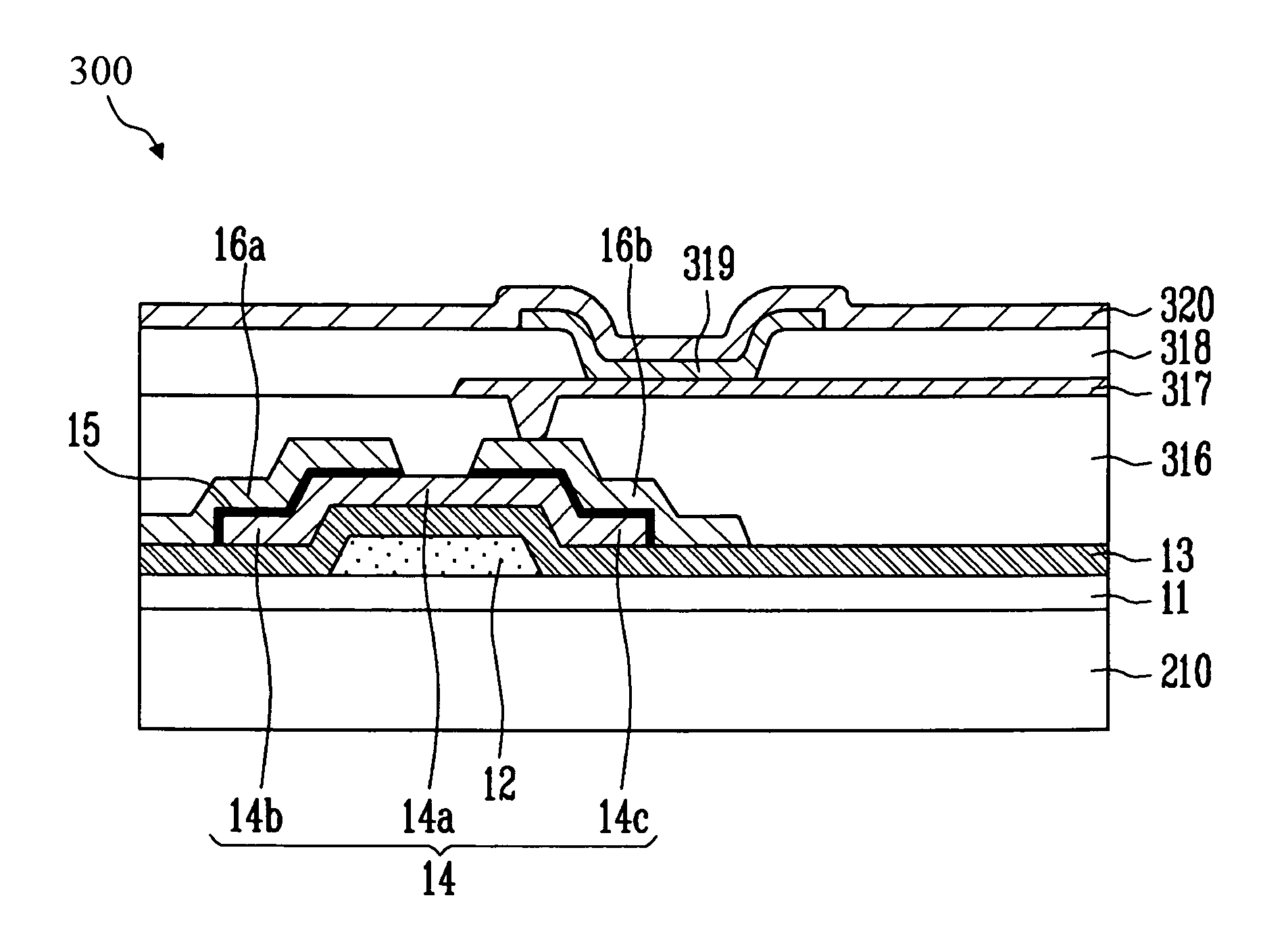

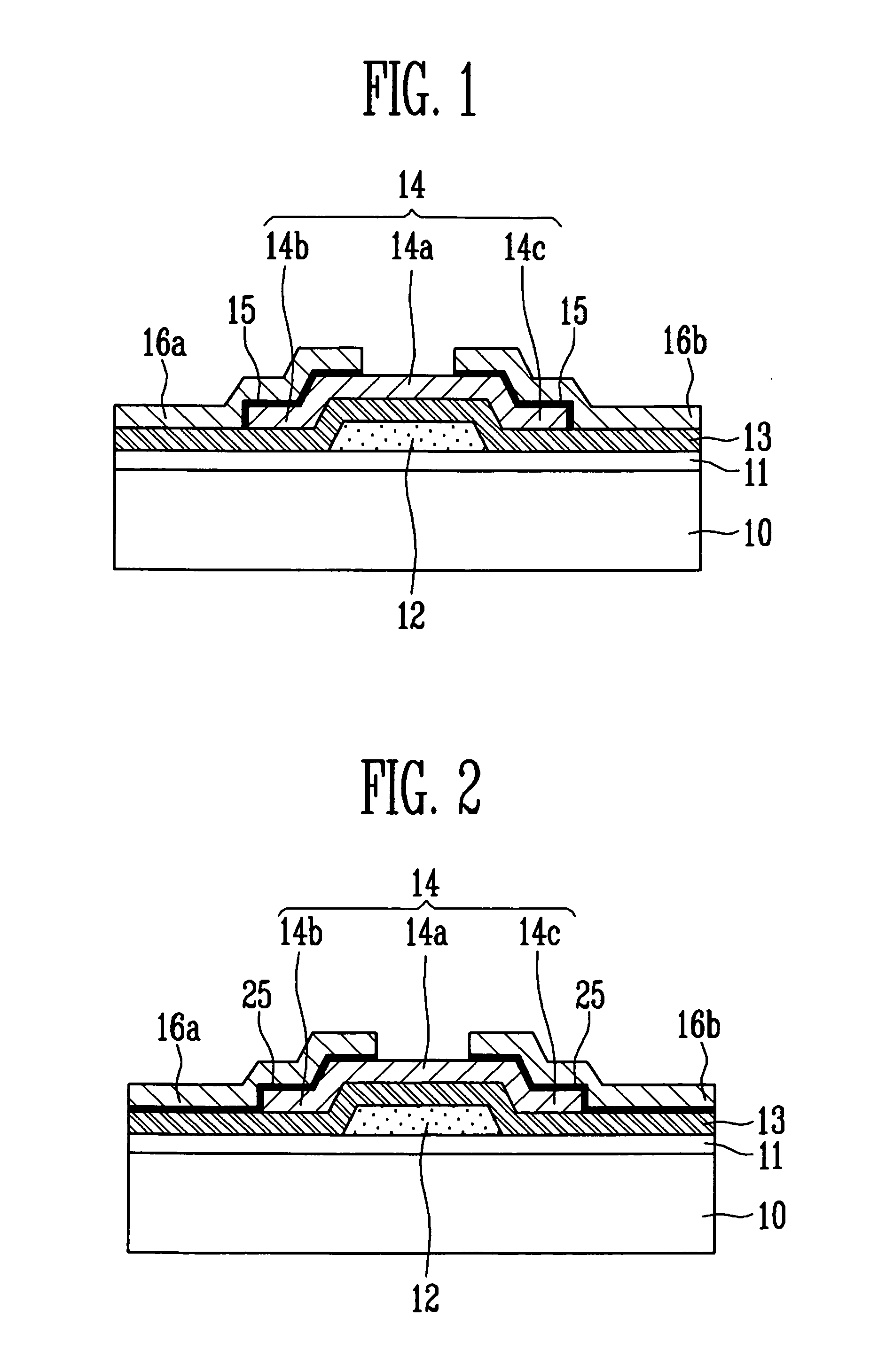

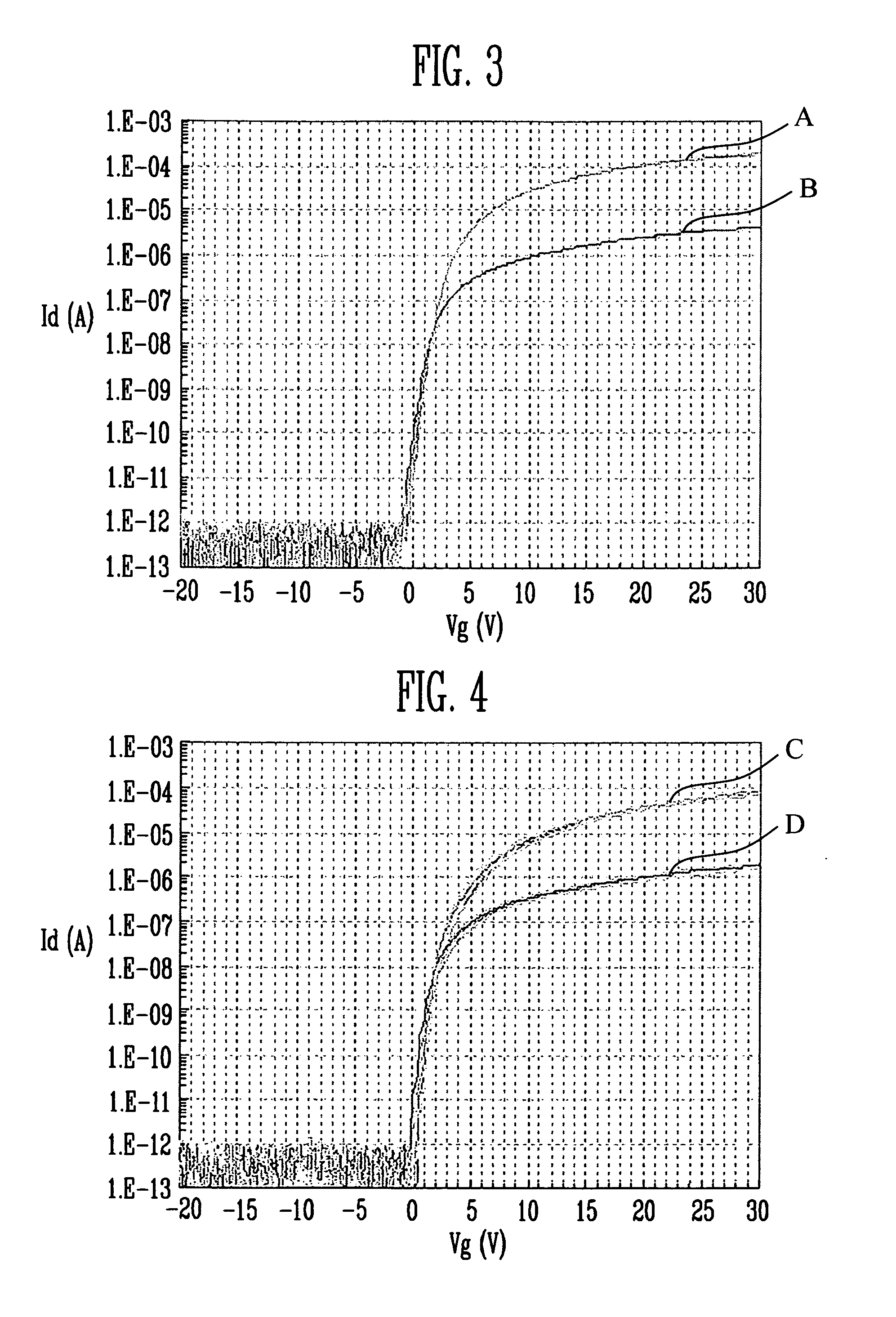

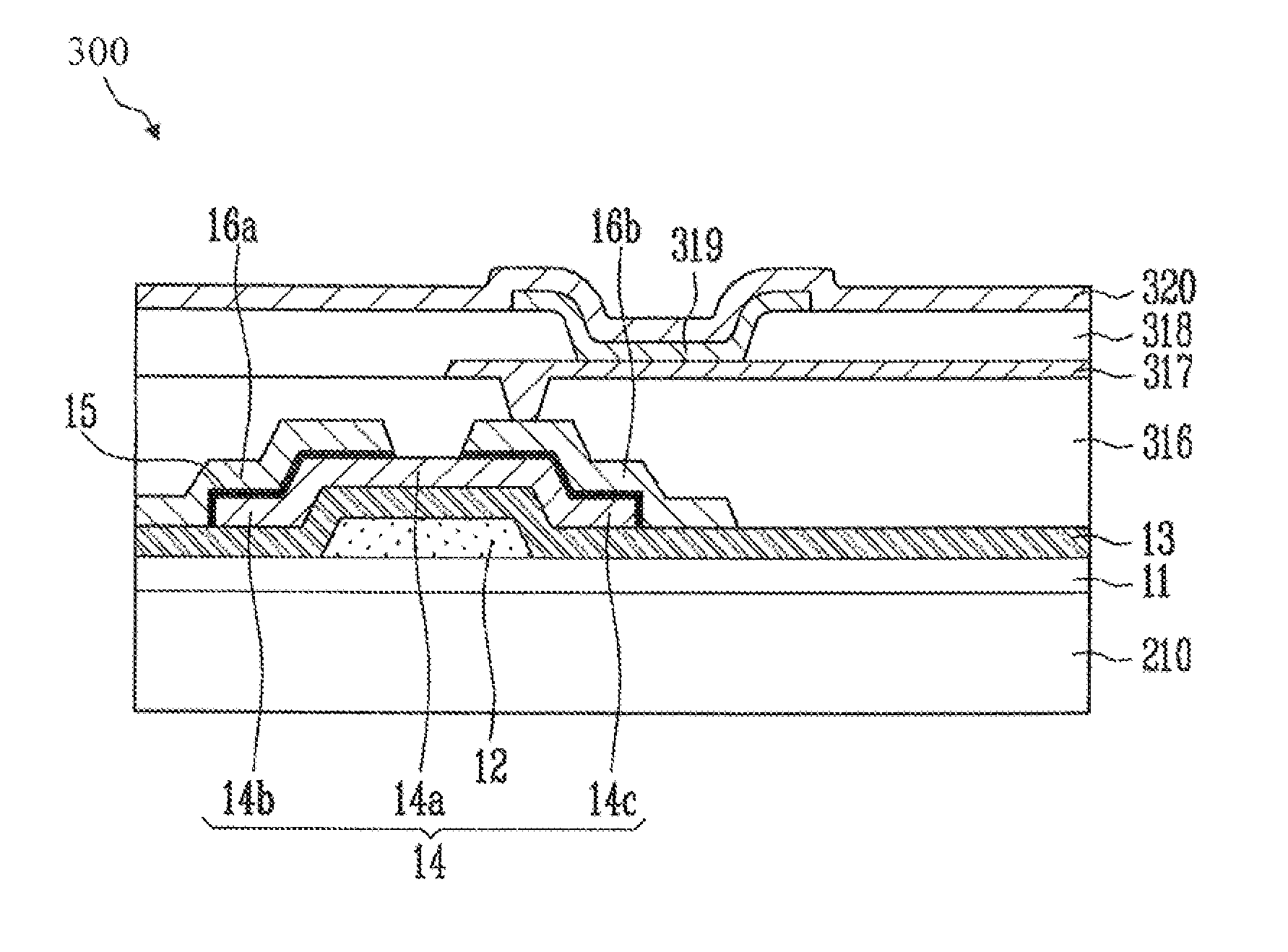

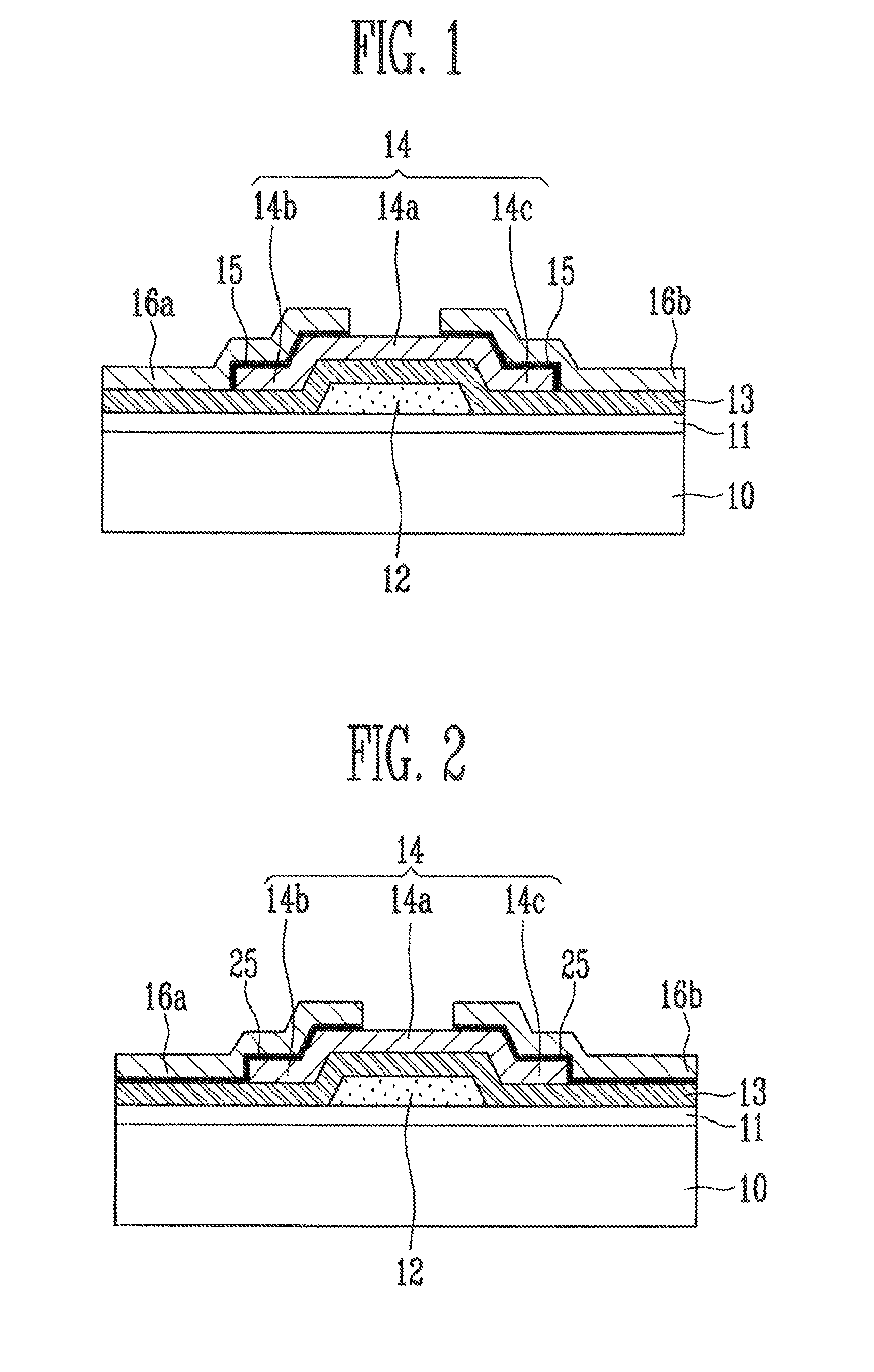

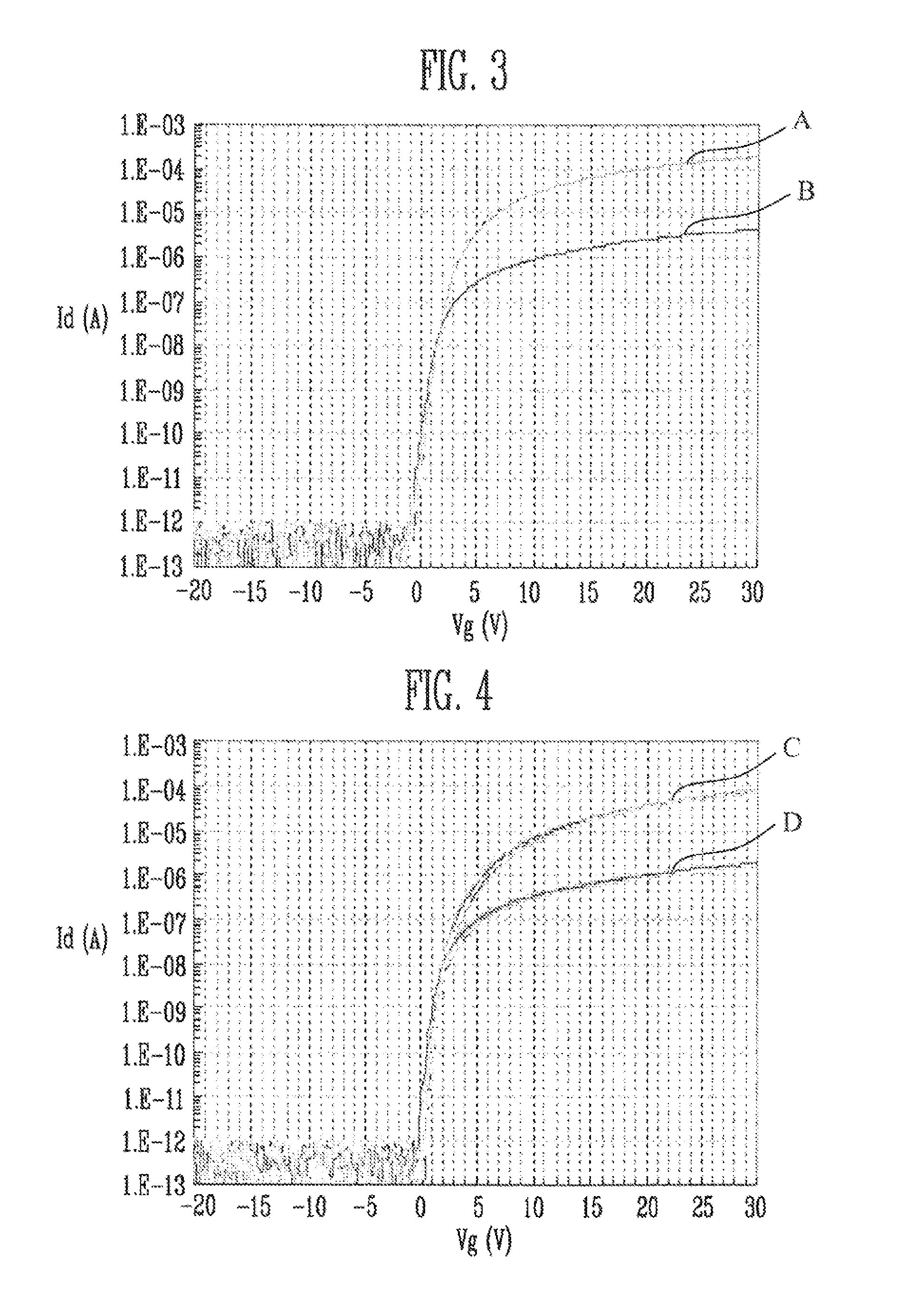

Thin film transistor and flat panel display device having the same

InactiveUS20100176394A1Avoid voltage dropReduce trace widthTransistorSolid-state devicesTitaniumFlat panel display

An oxide semiconductor thin film transistor and a flat panel display device incorporating the same oxide semiconductor thin film transistor. The thin film transistor includes a gate electrode formed on the substrate, a gate insulating layer formed on the substrate and covering the gate electrode, an oxide semiconductor layer formed on the gate insulating layer and covering the gate electrode, a titanium layer formed in a source region and a drain region of the oxide semiconductor layer, and source and drain electrodes respectively coupled to the source region and the drain region through the titanium layer and made of copper. The titanium layer reduces the contact resistance between the source and drain electrodes made of copper and the oxide semiconductor layer, forms a stable interface junction therebetween, and blocks a diffusion of copper.

Owner:SAMSUNG DISPLAY CO LTD

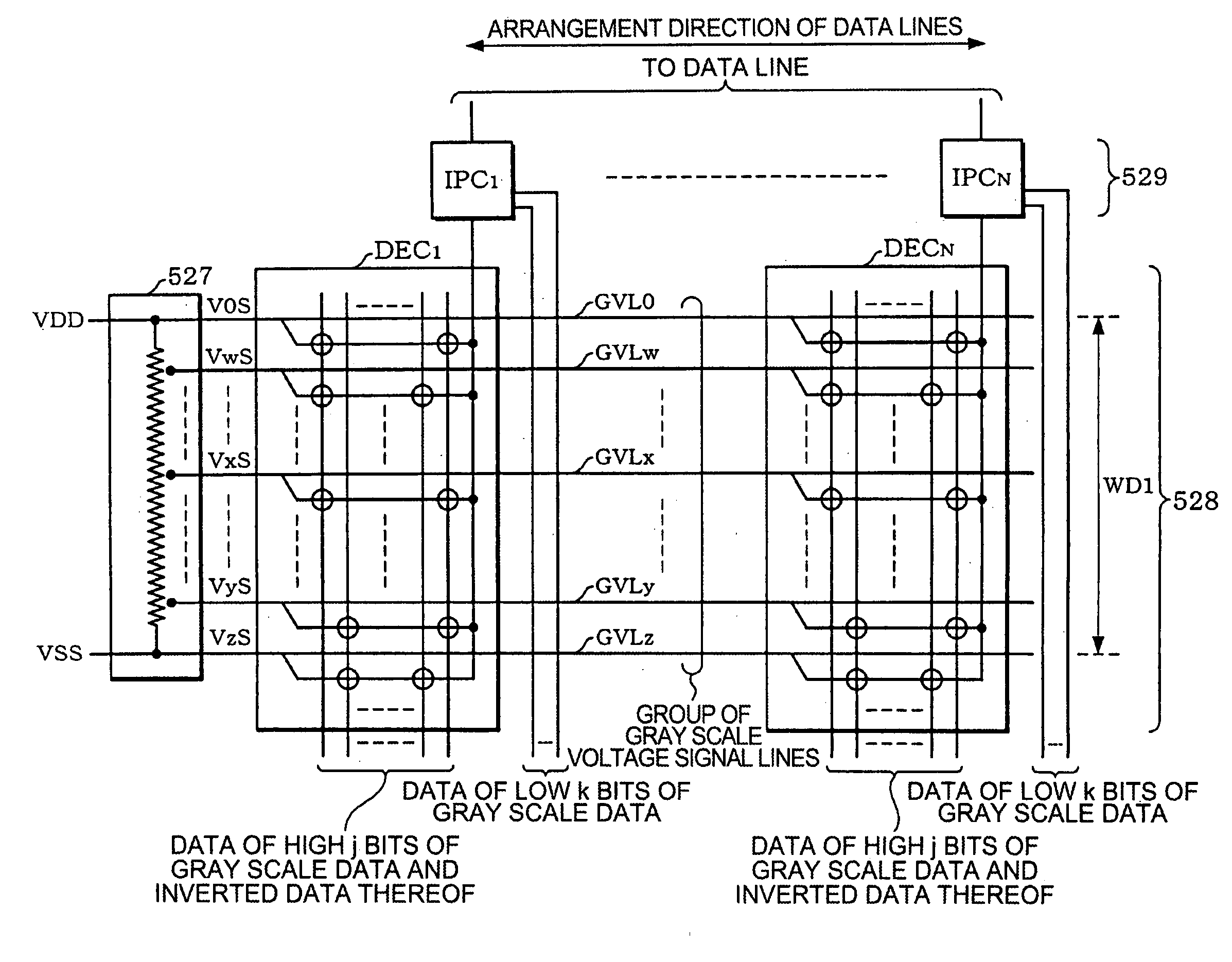

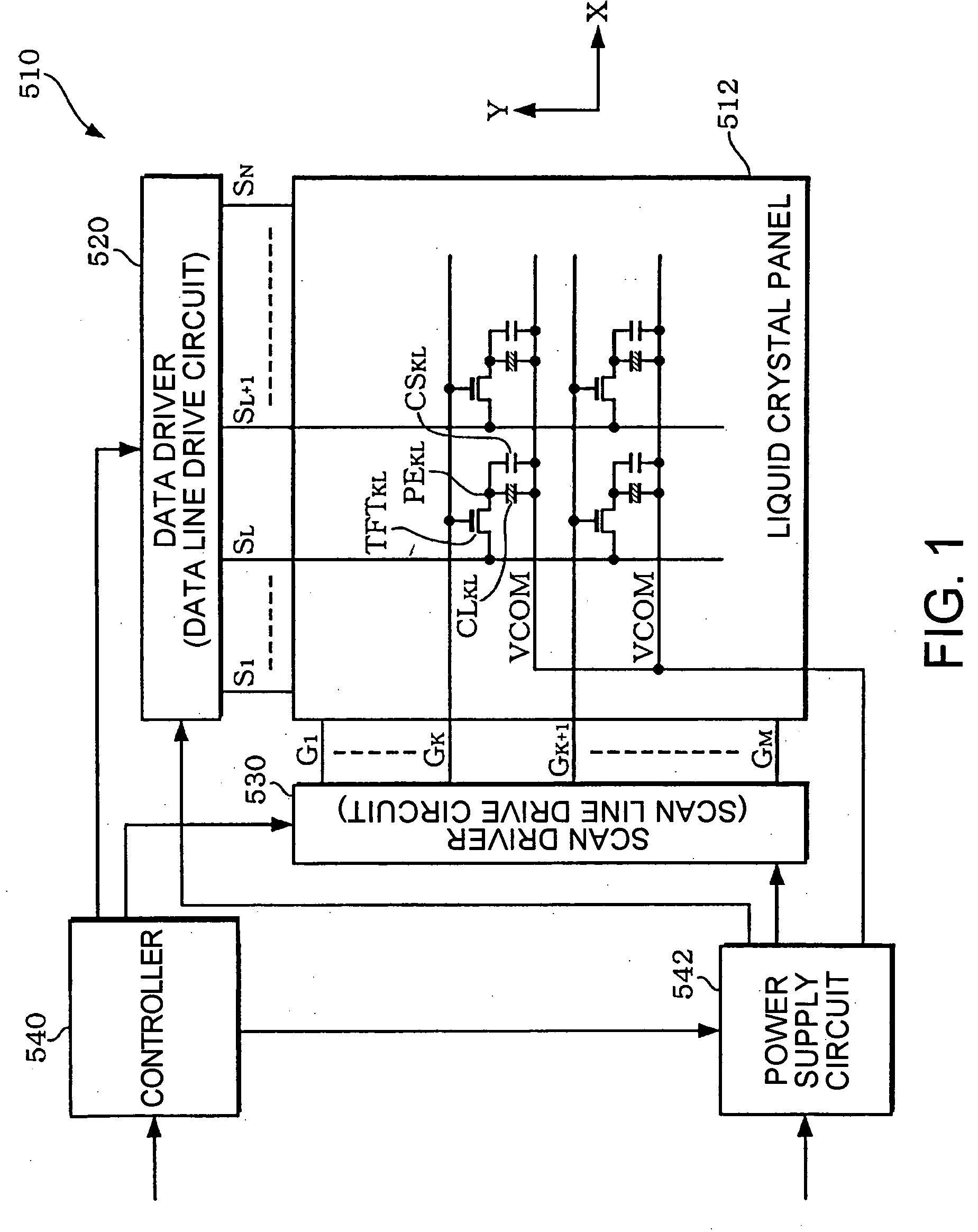

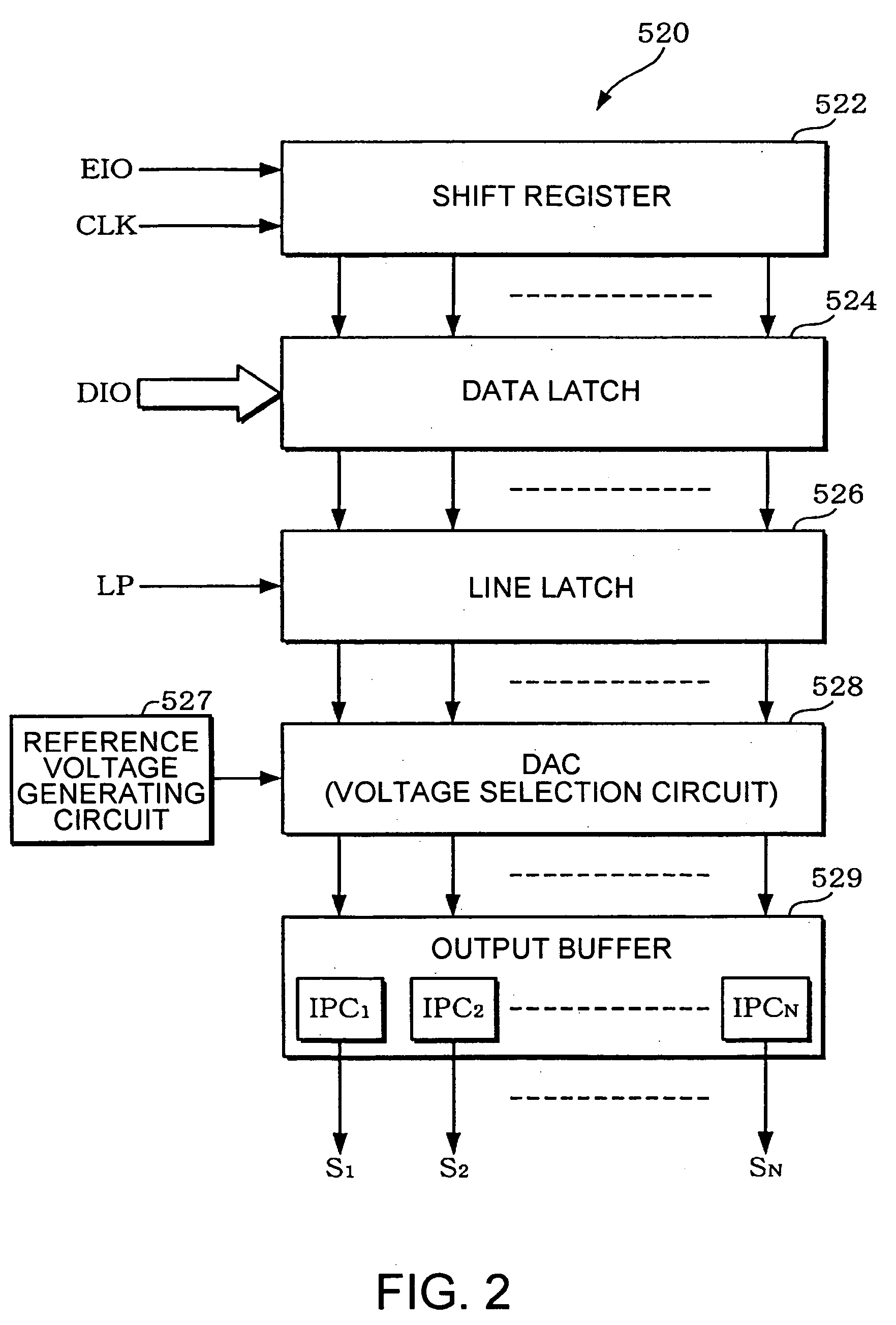

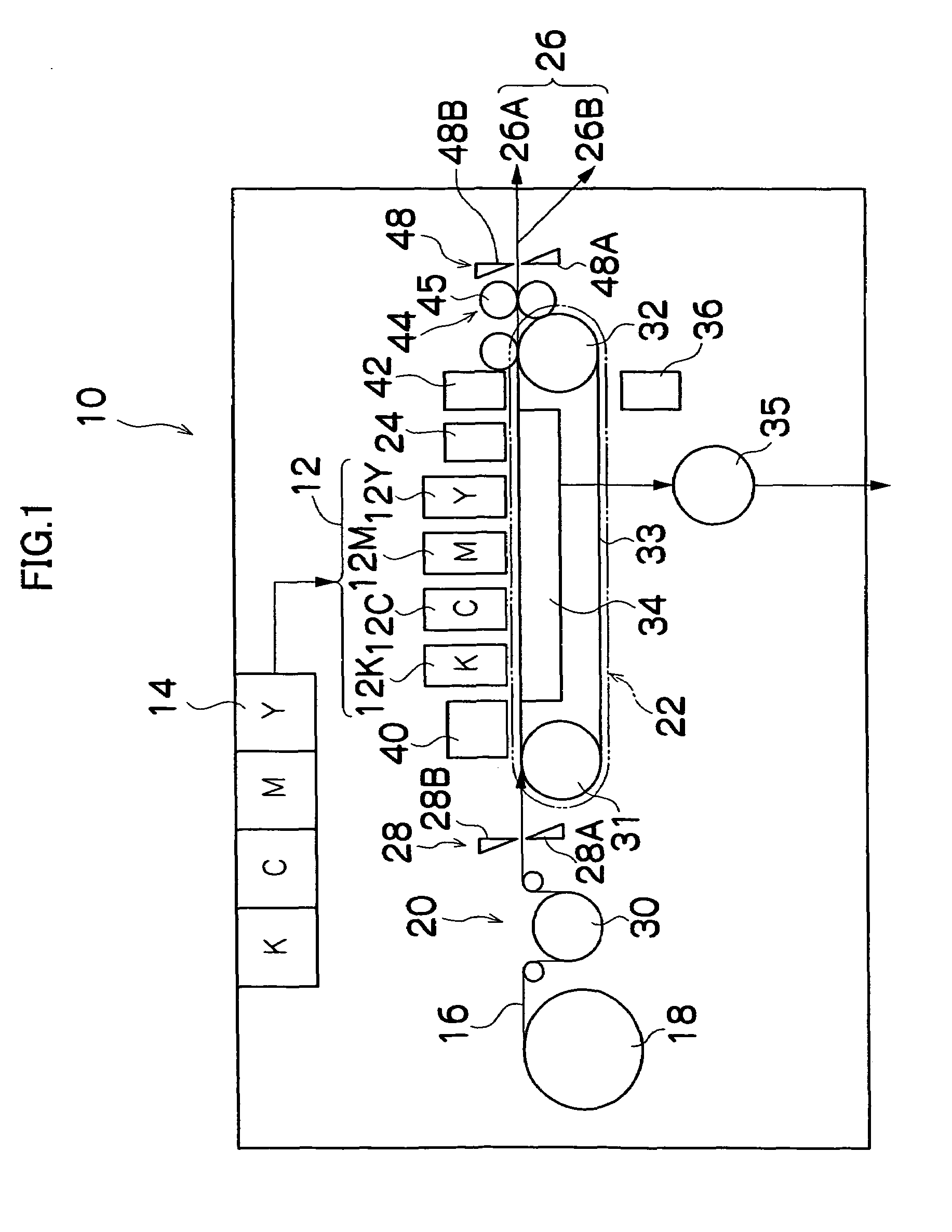

Impedance conversion circuit, drive circuit, and control method of impedance conversion circuit

InactiveUS20060050037A1Reduce in quantityVoltage is accurateStatic indicating devicesAudio power amplifierElectrical current

An impedance conversion circuit IPC1 including: an operational amplifier OP1 connected as a voltage follower and supplied with, as an input voltage Vin, a voltage selected from 2j levels of voltages (j is a positive integer) based on data of high j bits of the gray scale data; and an output voltage setting circuit OVS1 for precharging or discharging an output of the operational amplifier OP1 based on data of a most significant bit of low k bits (k is an integer more than 1) of the gray scale data. The operational amplifier OP1 outputs, as an output voltage, a voltage having a difference from the input voltage by a dead zone width after the output voltage setting circuit OVS1 precharges or discharges the output of the operational amplifier OP1. The dead zone width is determined by an operating current of the operational amplifier OP1. The operating current is varied based on data of low k bits of the gray scale data.

Owner:SEIKO EPSON CORP

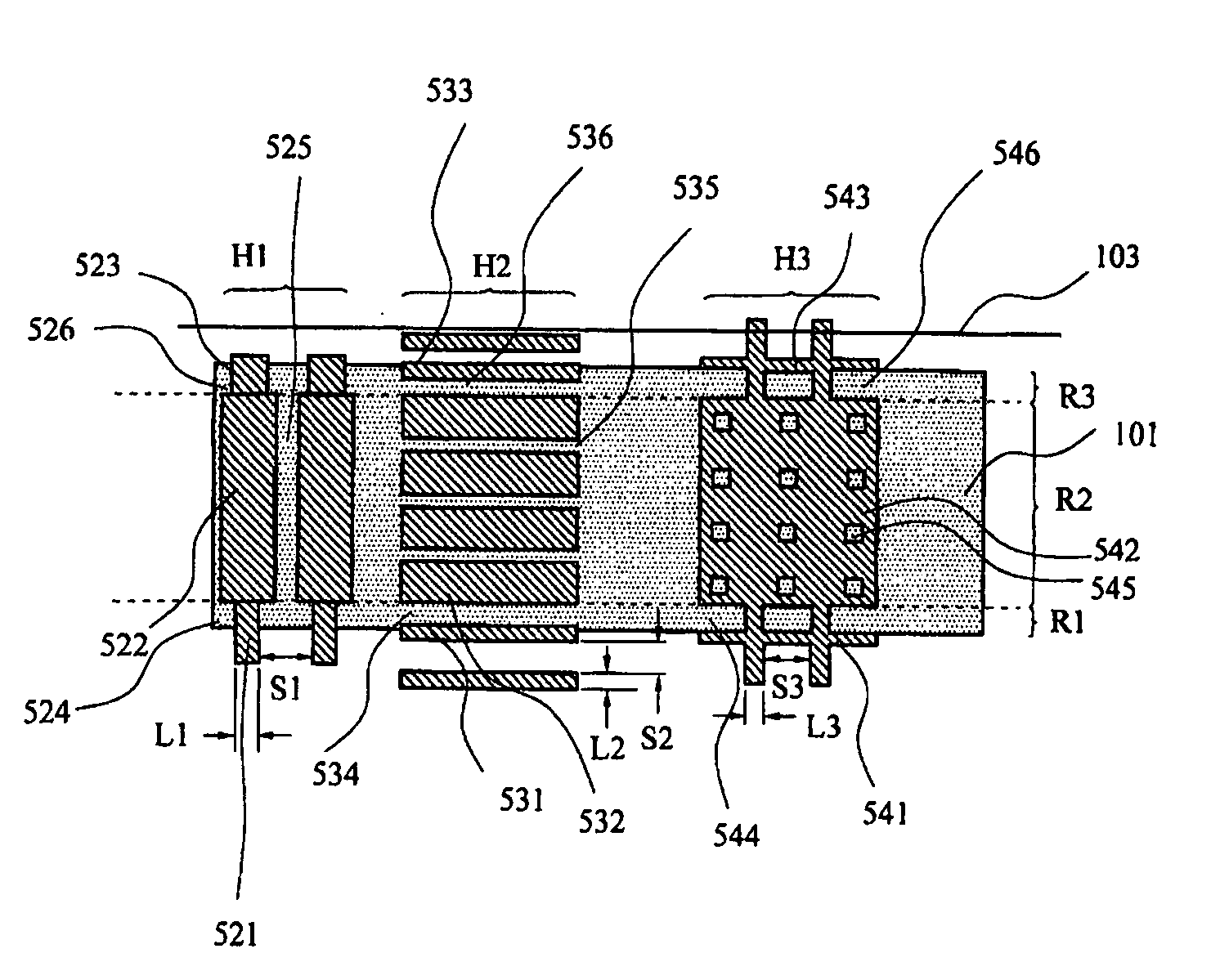

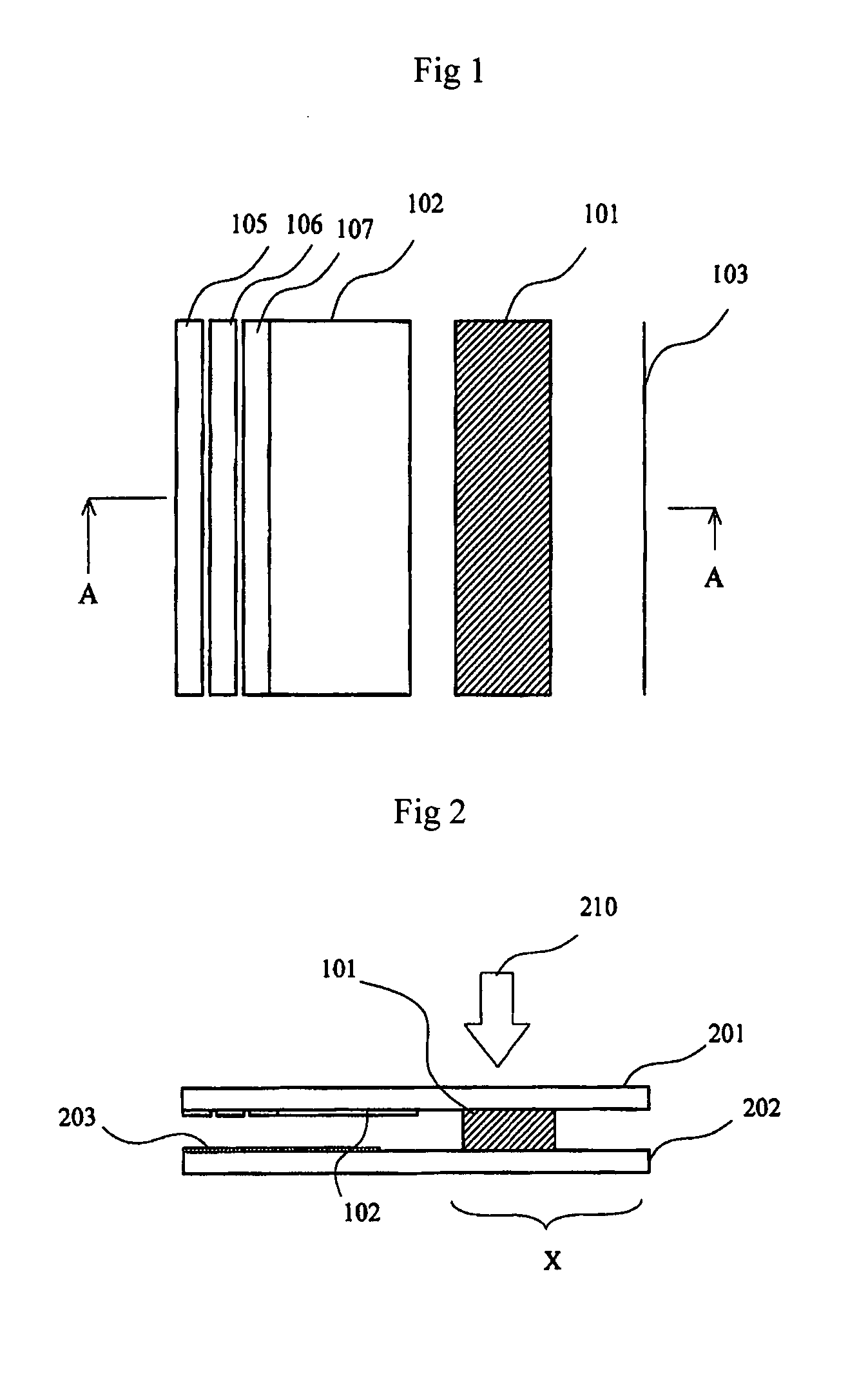

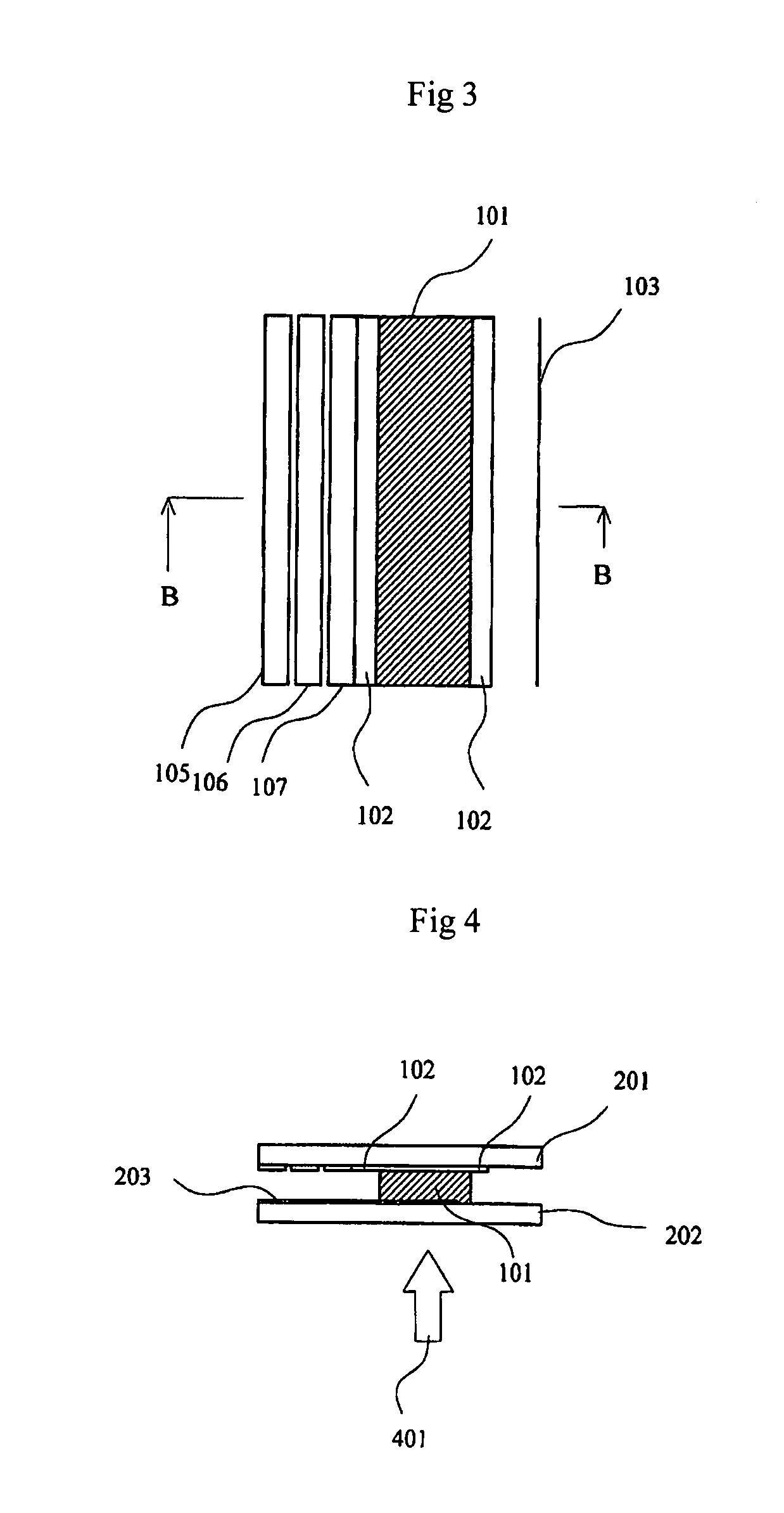

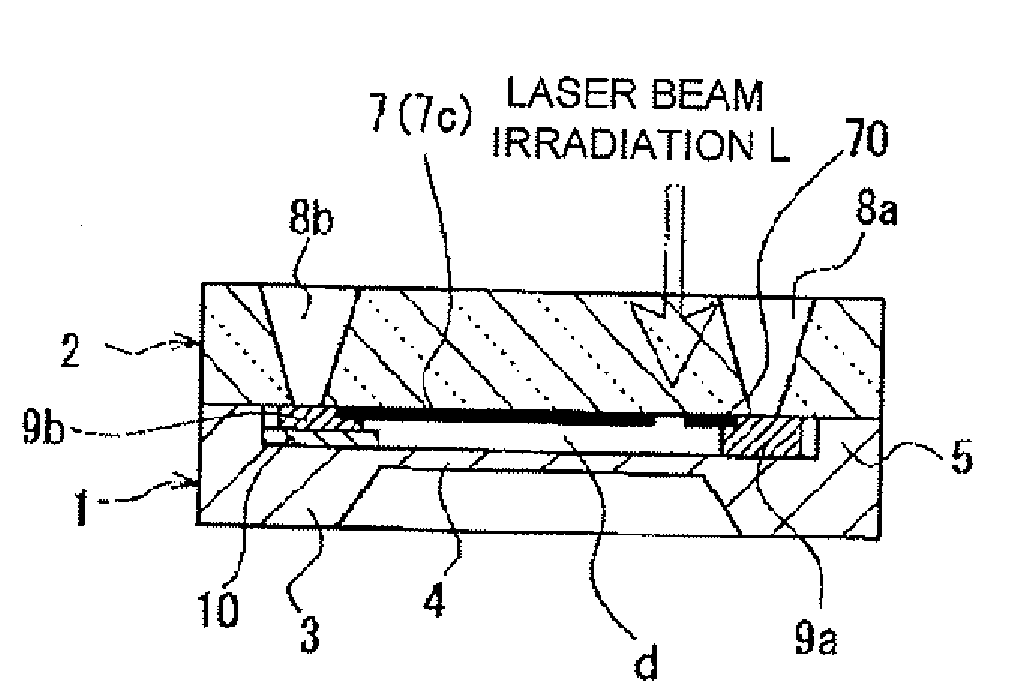

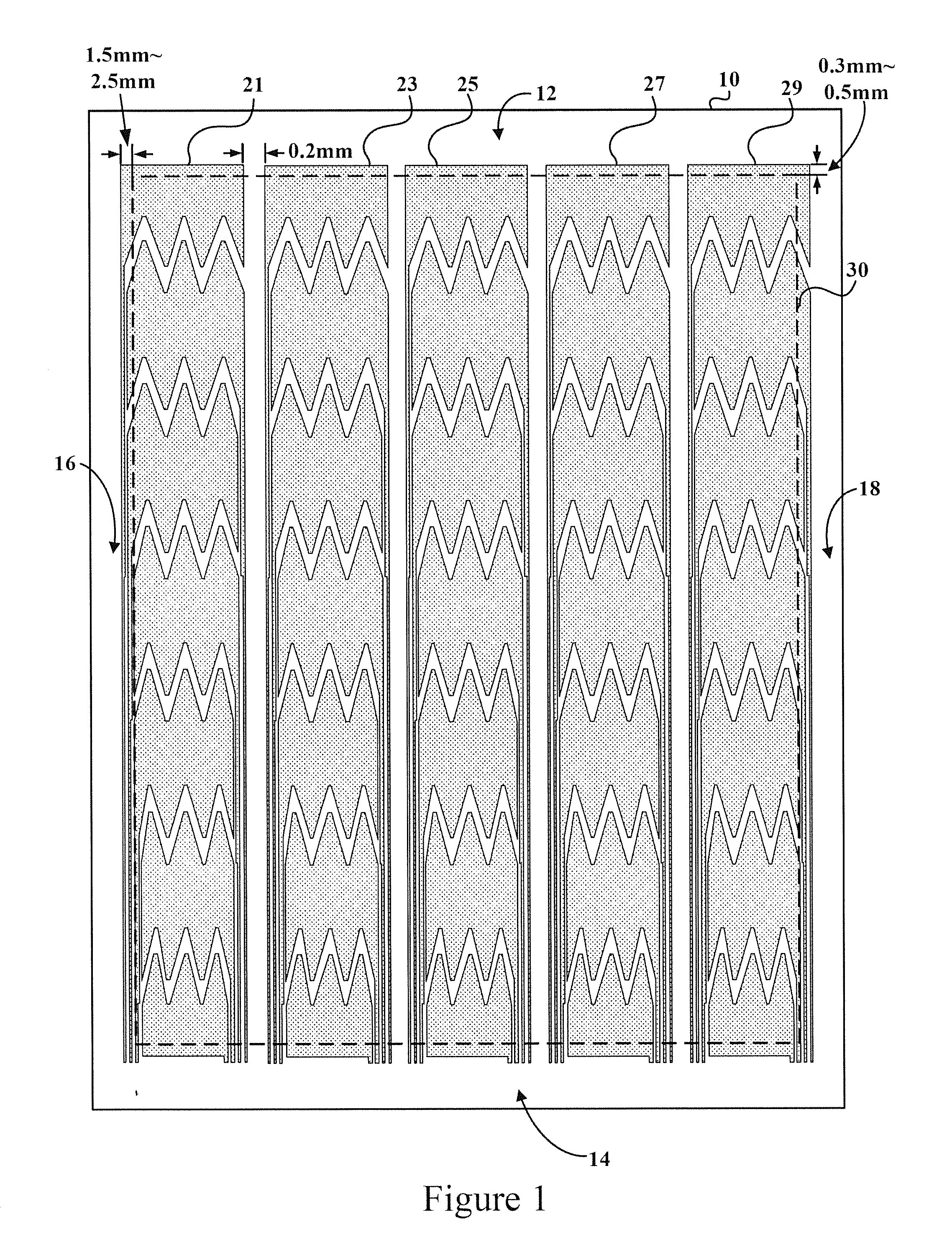

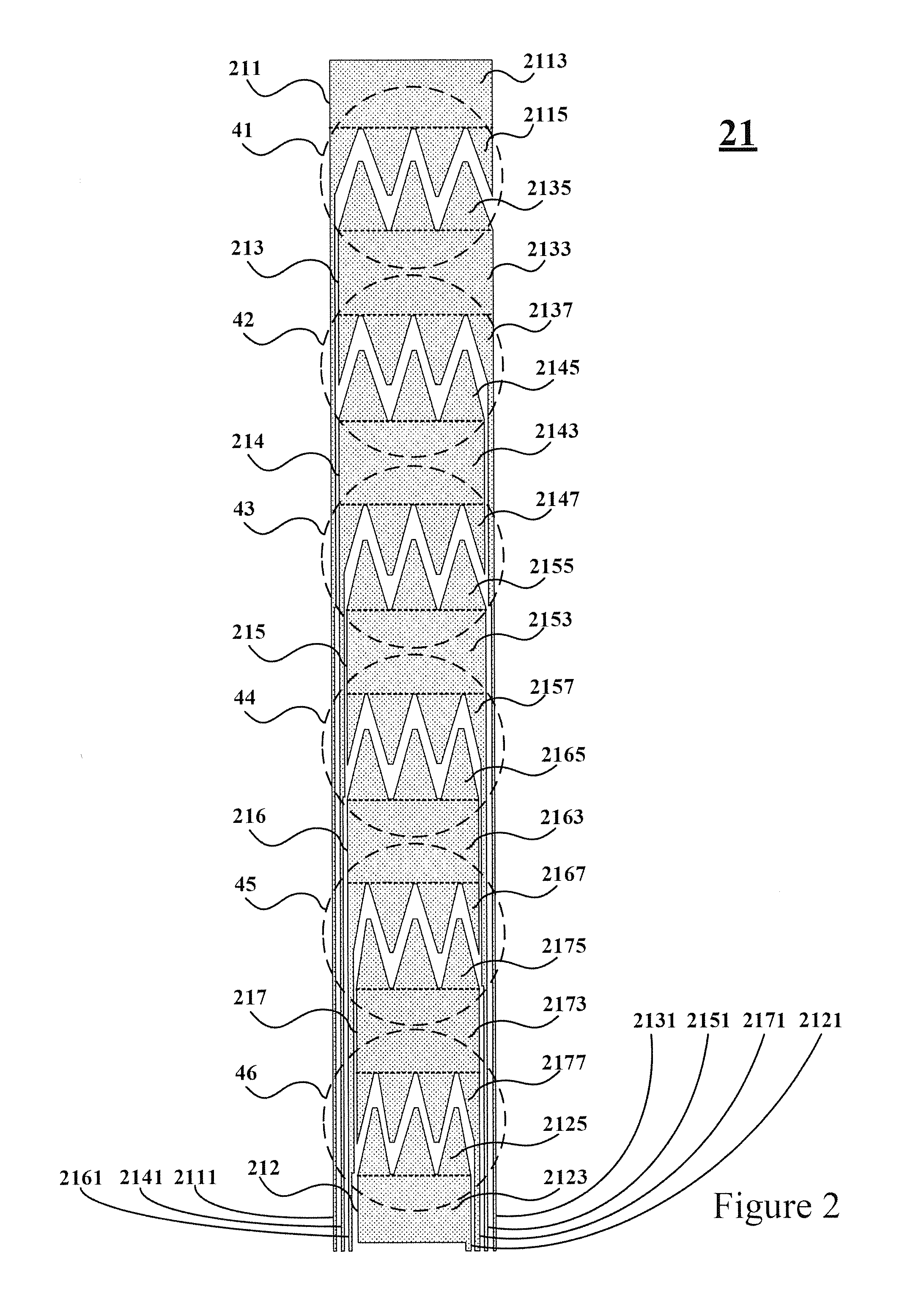

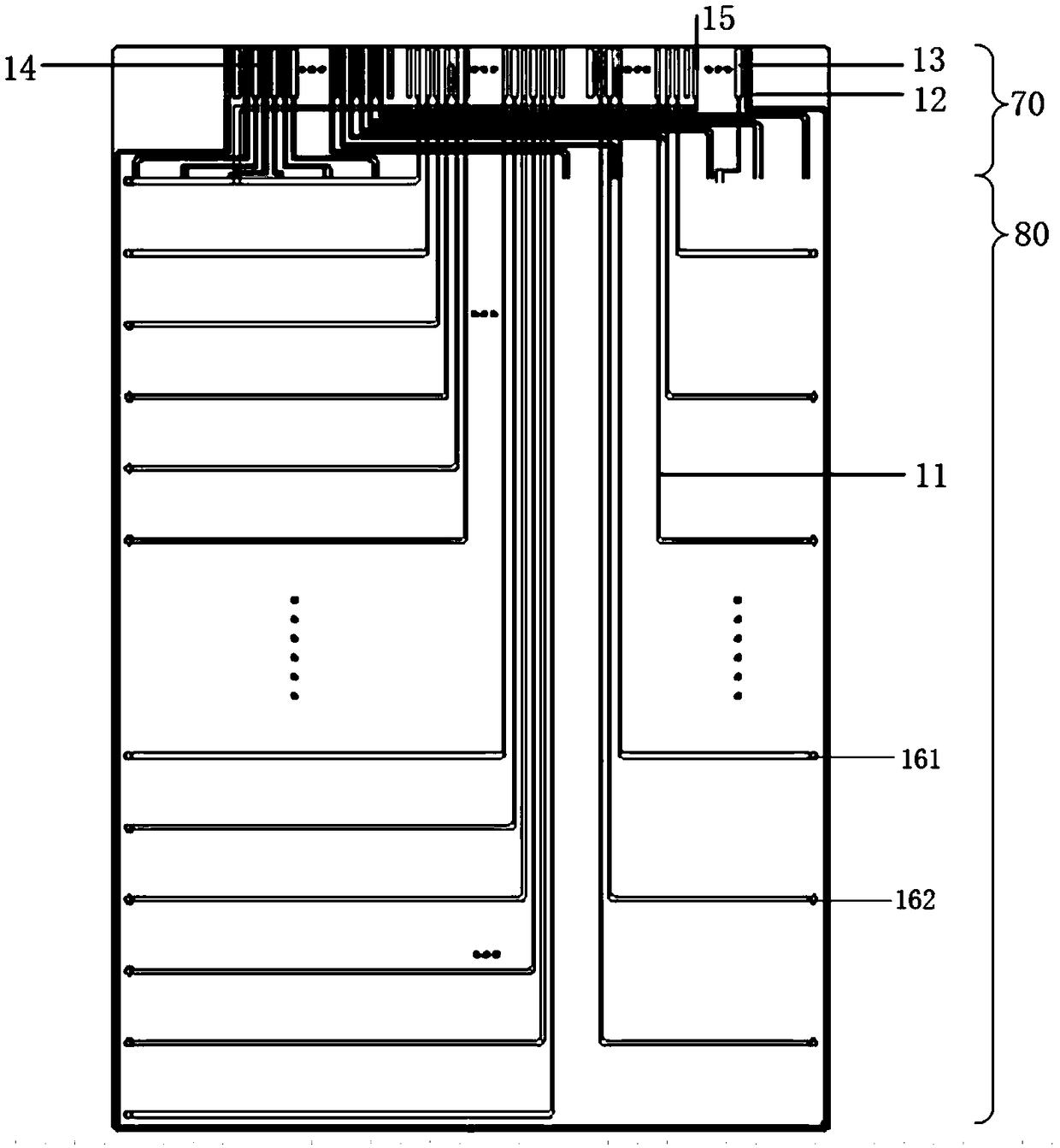

Liquid crystal panel for liquid crystal display device

ActiveUS20080284963A1Downsize frameIncrease widthNon-linear opticsElectrical resistance and conductanceLiquid-crystal display

To utilize effectively the panel space of the liquid crystal panel, this invention has provided a wiring structure, in which the seal material and BM are coated in a superposition and the UV light is irradiated from one side of the TFT substrate; this invention has also provided a wiring structure, in which the seal material can still be irradiated by the UV light with high efficiency, meanwhile, the drop of the resistance value of the metal wiring on the TFT substrate can be restricted to a specific range. The solution is: the liquid crystal dropped is sandwiched between the TFT substrate and the CF substrate, meanwhile the liquid crystal panel is formed by adhering the light cured seal material disposed at the peripheral area of two substrates. In the adhering-formed liquid crystal panel, for the wiring portion, which is the portion of wiring disposed on the TFT substrate superposing the light cured seal material, the wiring structure is formed as follows, that is, the region of the seal material is divided into three regions, an adjacent region, a middle region and an outer region. The function of the respective regions must be held, and the resistance of the metal wiring is minimized under the precondition that the respective function is satisfied sufficiently.

Owner:INFOVISION OPTOELECTRONICS HLDG LTD

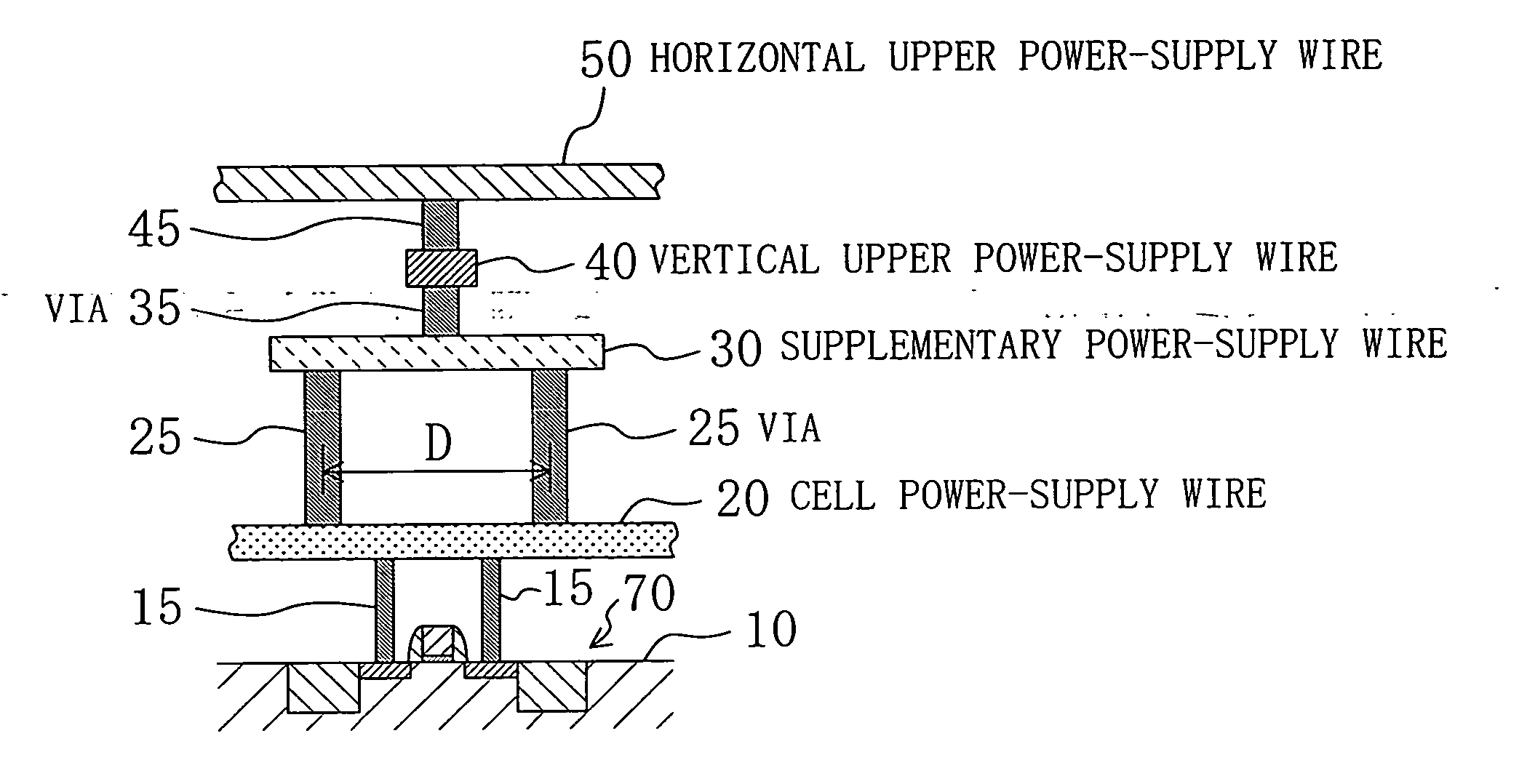

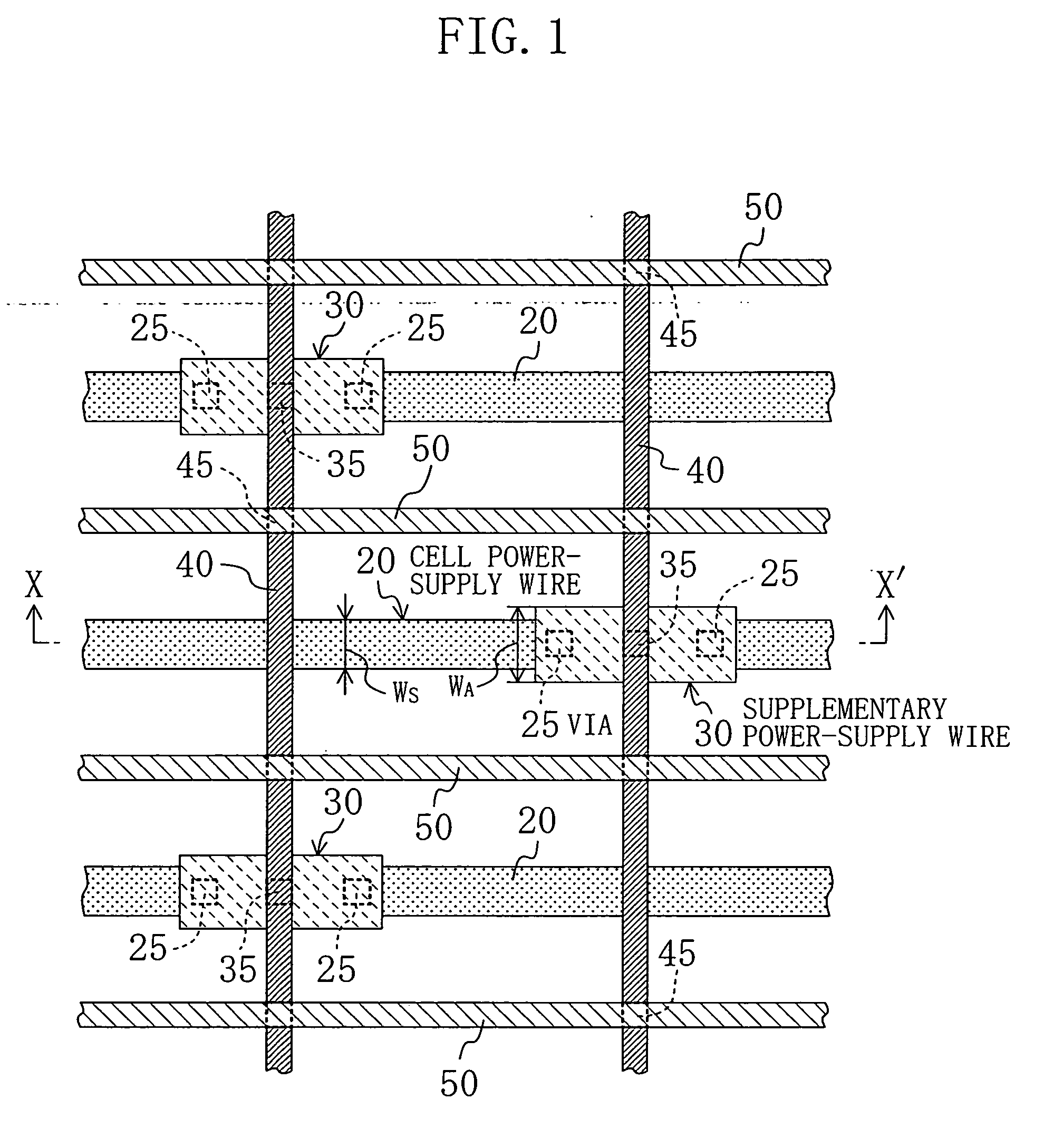

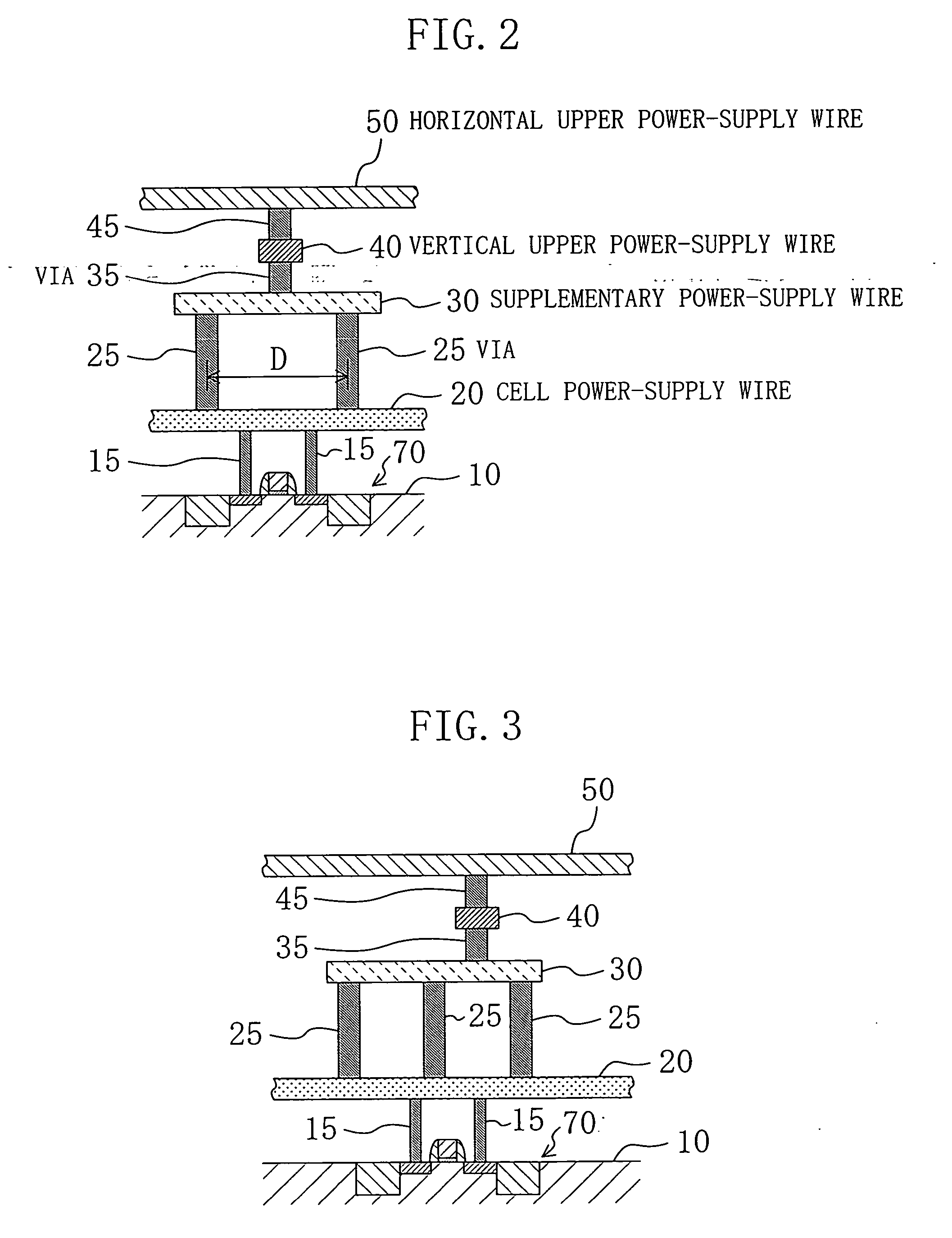

Semiconductor integrated circuit

ActiveUS20060071319A1Decreasing current concentrationLarge wire widthSemiconductor/solid-state device detailsSolid-state devicesSemiconductorIntegrated circuit

In a semiconductor integrated circuit including a plurality of cells, a supplementary power-supply wire is disposed between a lattice-shaped upper power-supply wire and a lower cell power-supply wire for cases in which power is supplied from the upper power-supply wire to the lower cell power-supply wire. The supplementary power-supply wire and the lower cell power-supply wire are connected by two vias. The supplementary power-supply wire and the upper power-supply wire are connected by a single via. Current from the supplementary power-supply wire is divided by the two vias and then supplied to the lower cell power-supply wire. Therefore, when power is supplied from the upper power-supply wire to the lower cell power-supply wire, current concentration at the connection points of the lower cell power-supply wire to the vias is decreased, thereby reducing wire breaks caused by EM (electro migration).

Owner:III HLDG 12 LLC

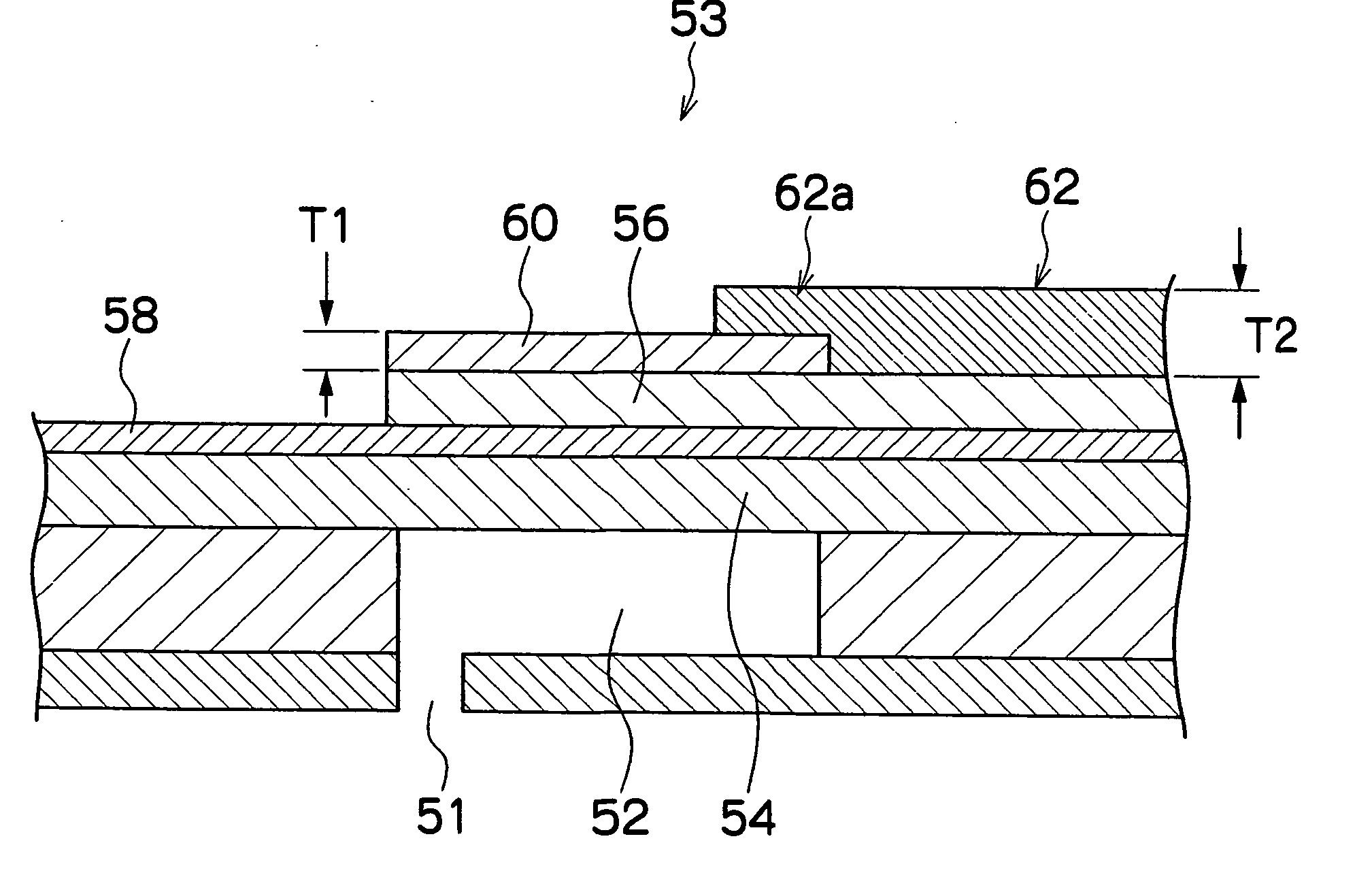

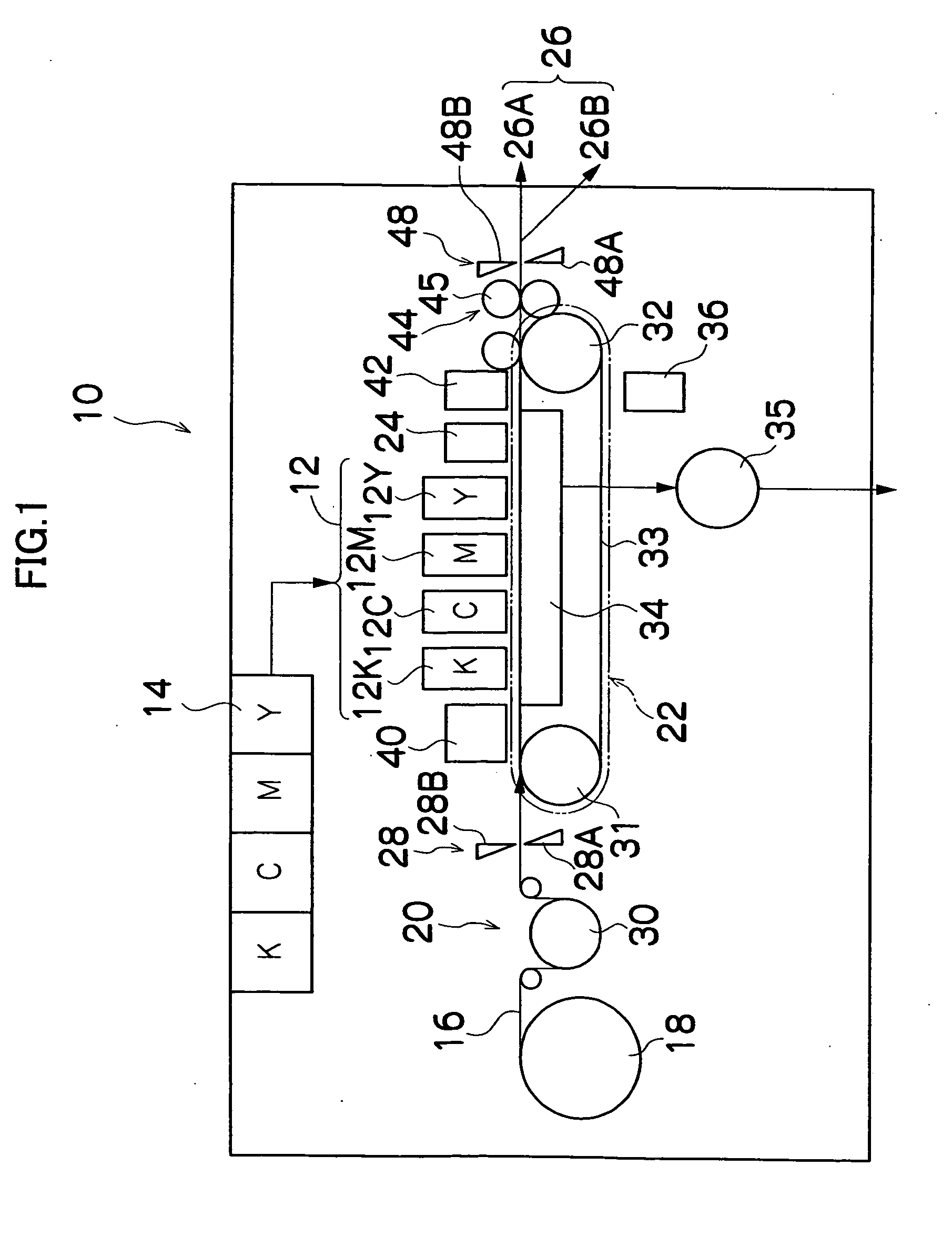

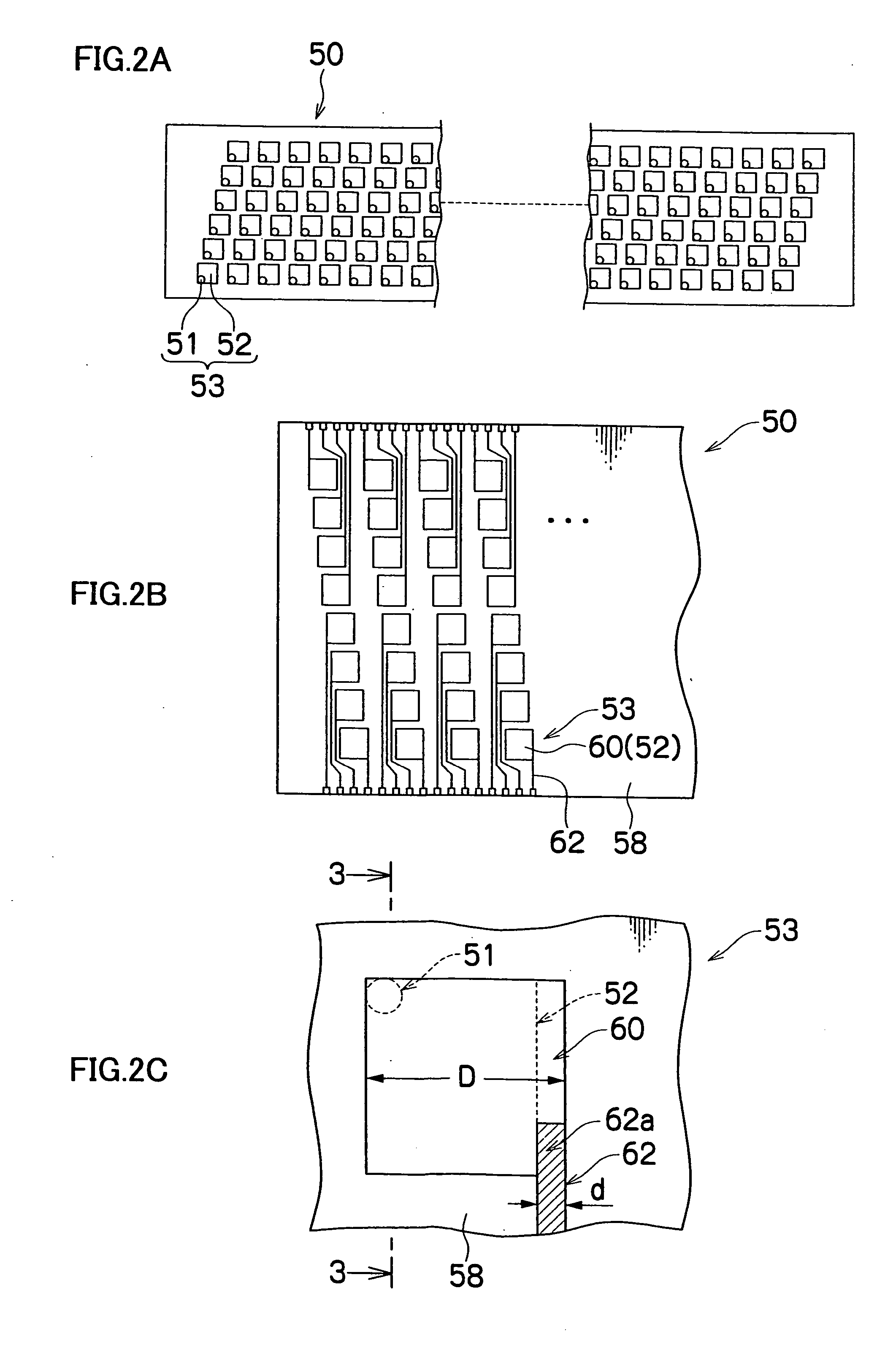

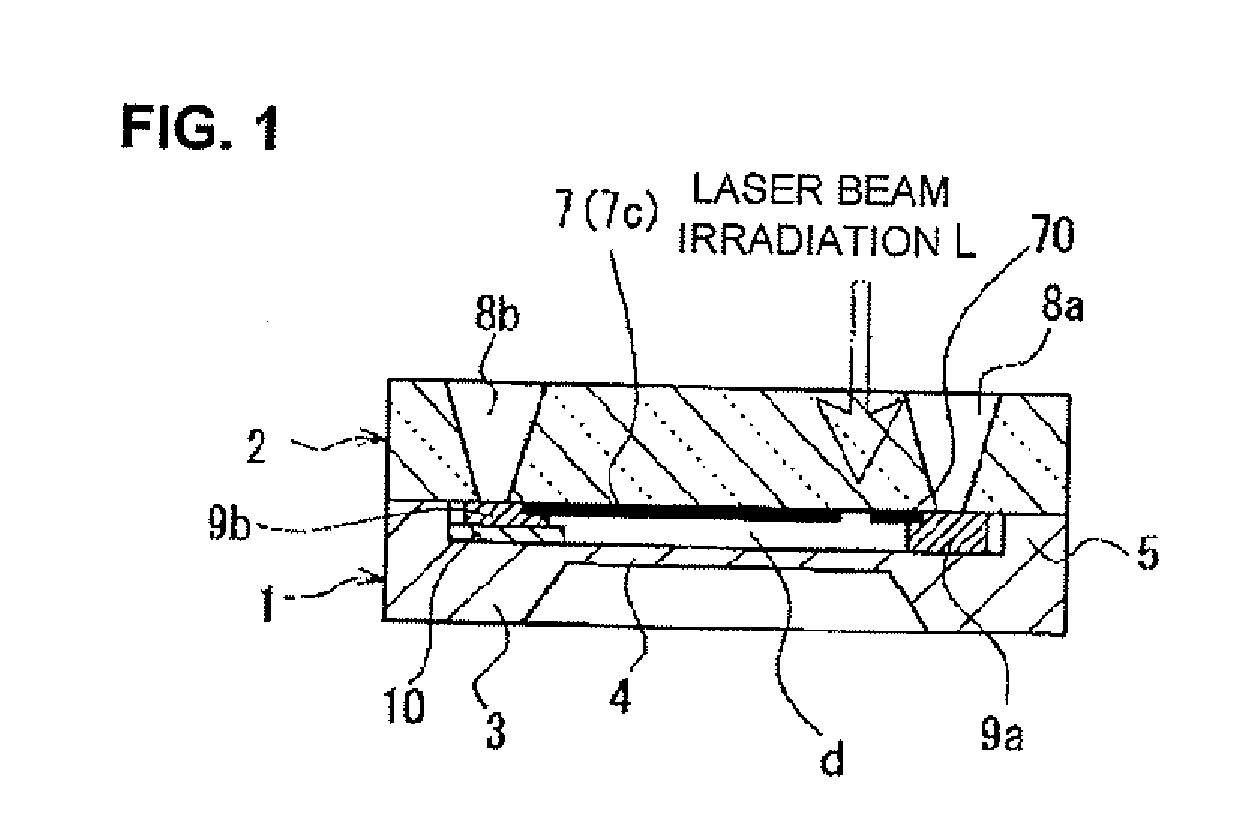

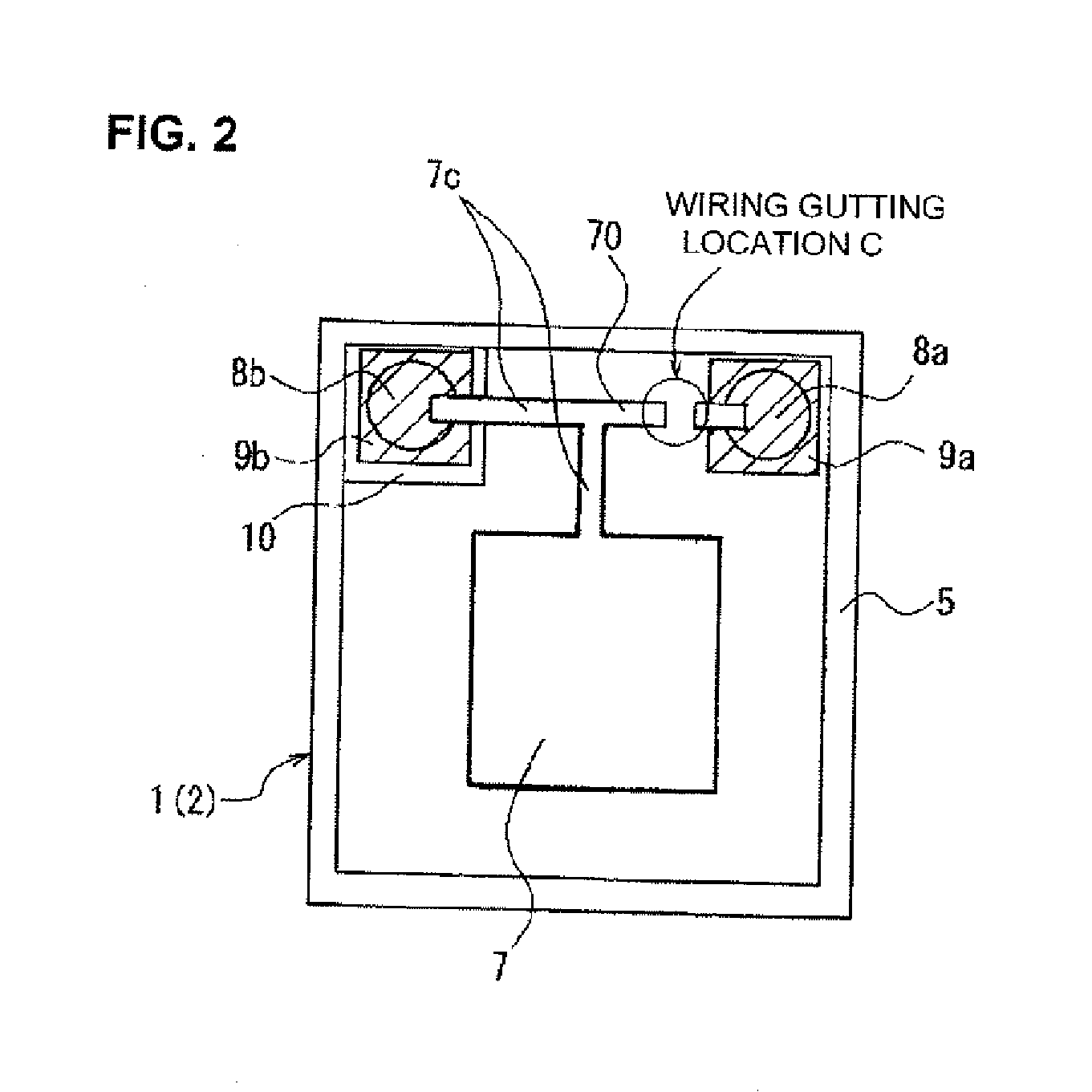

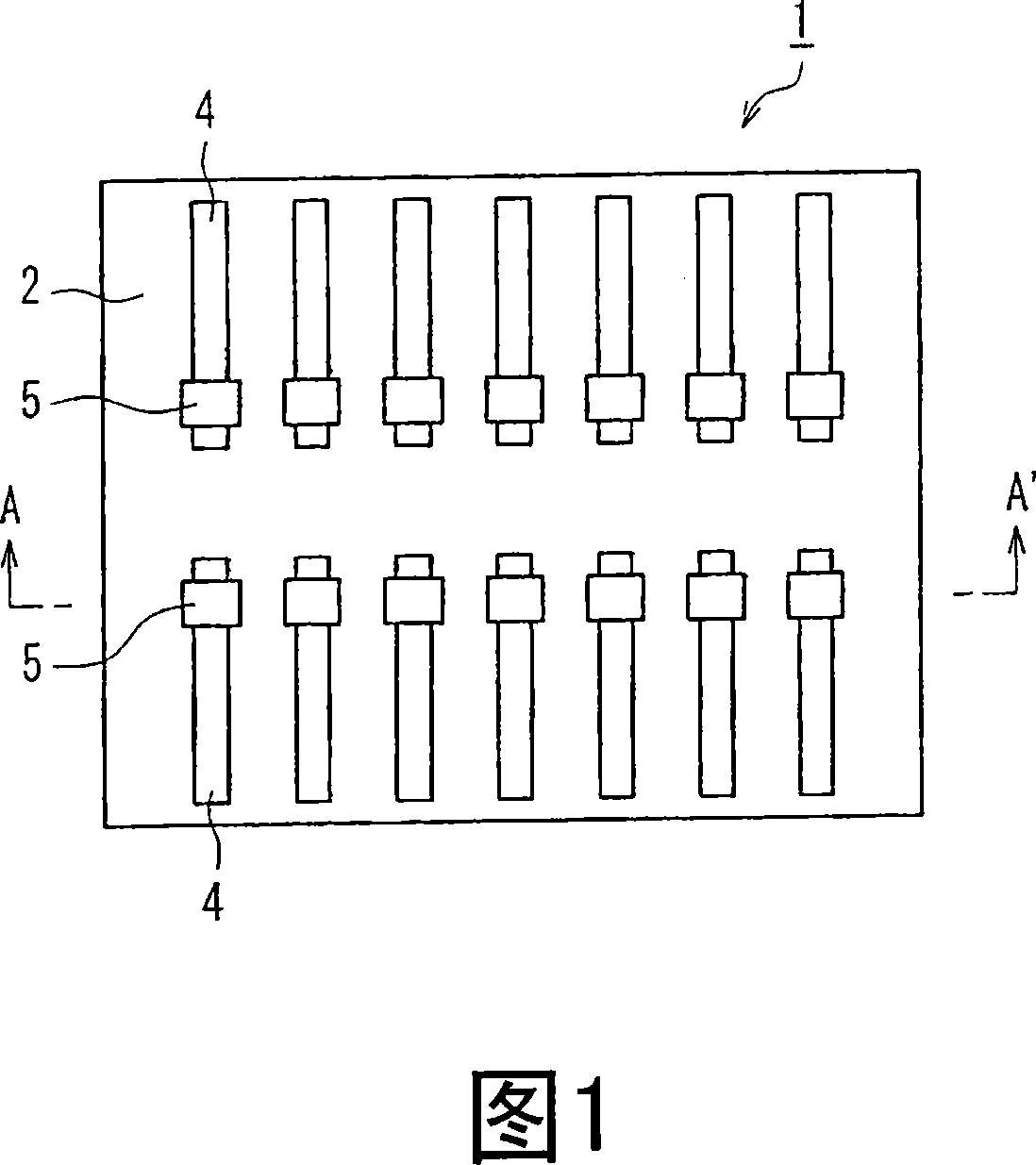

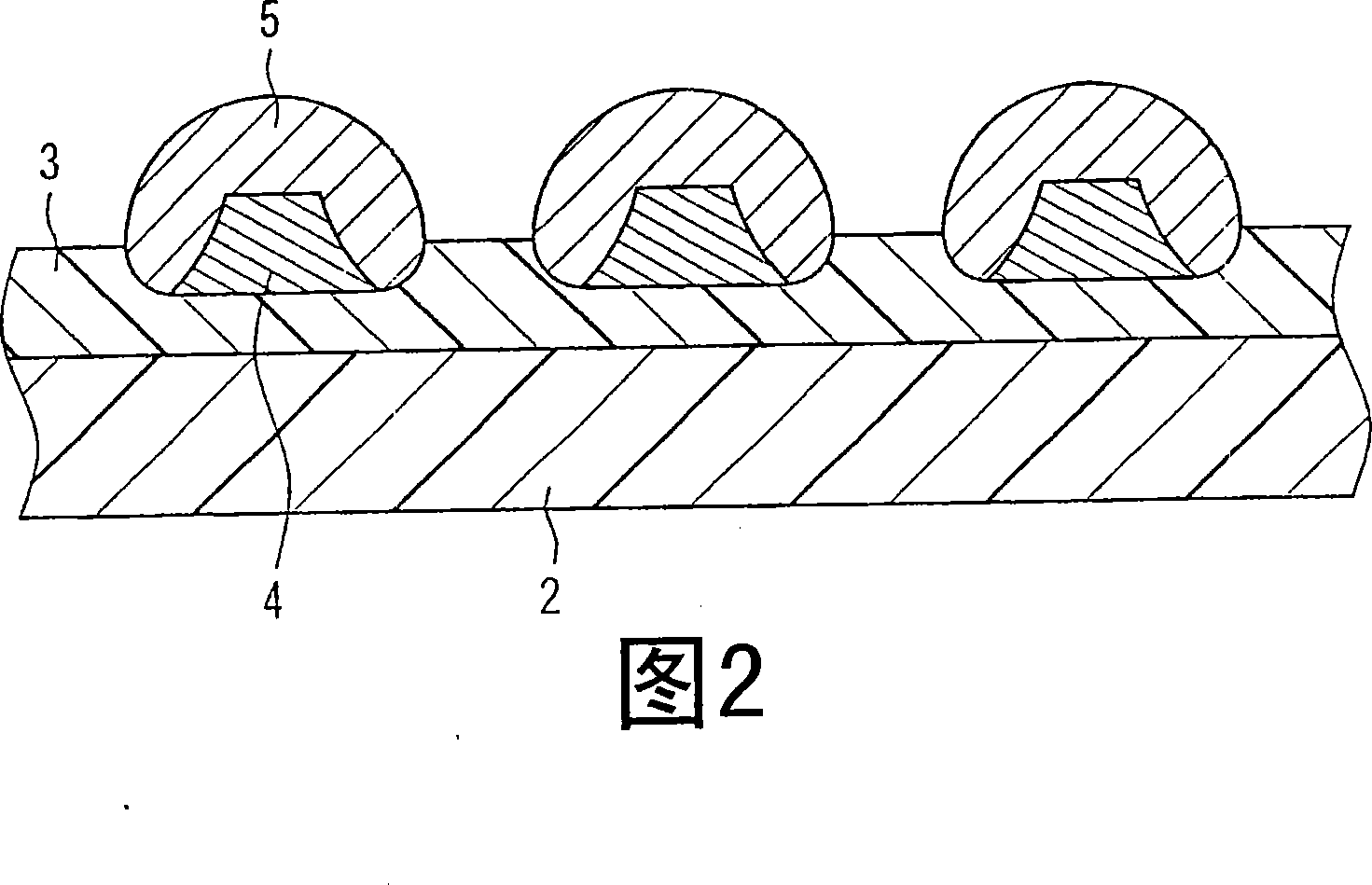

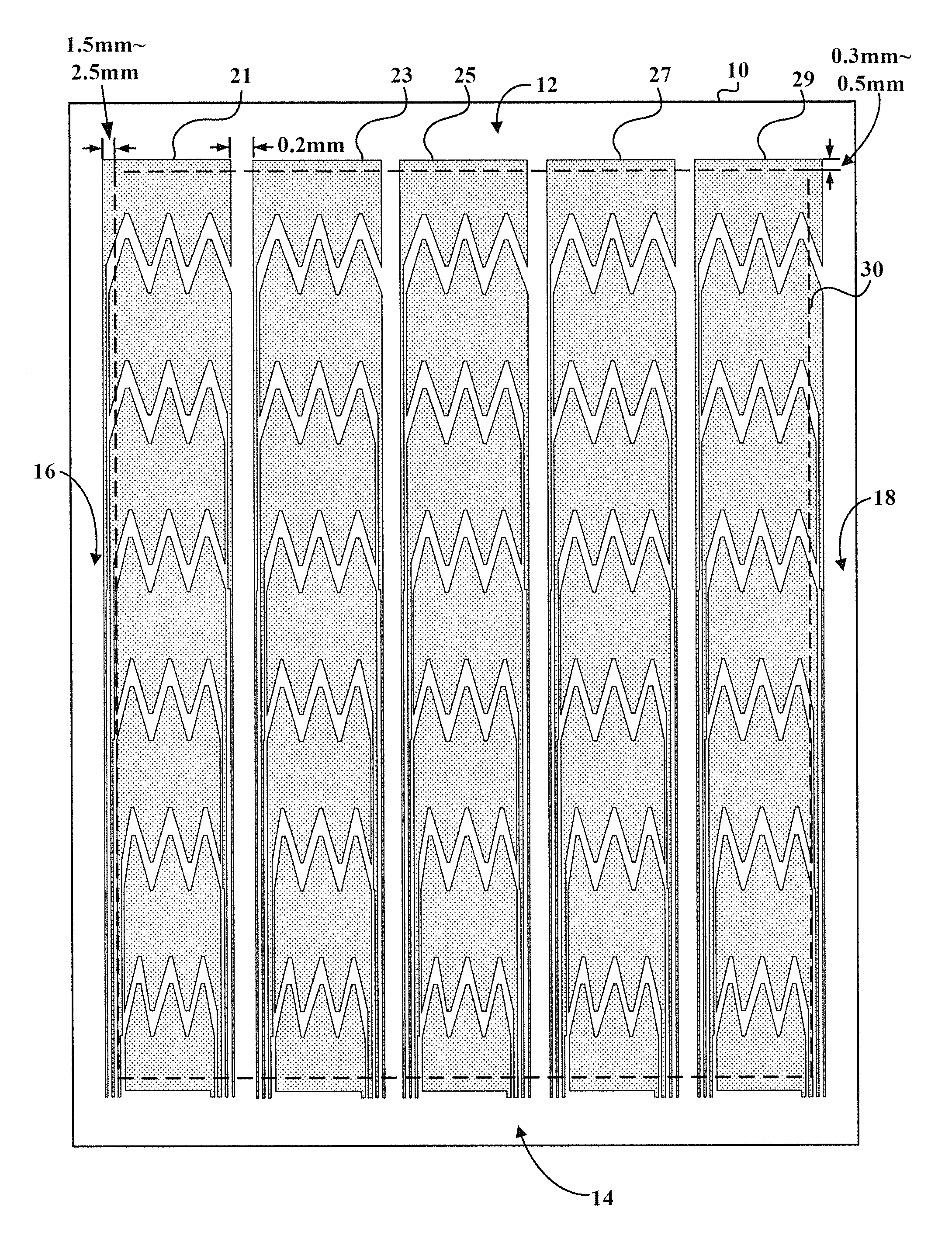

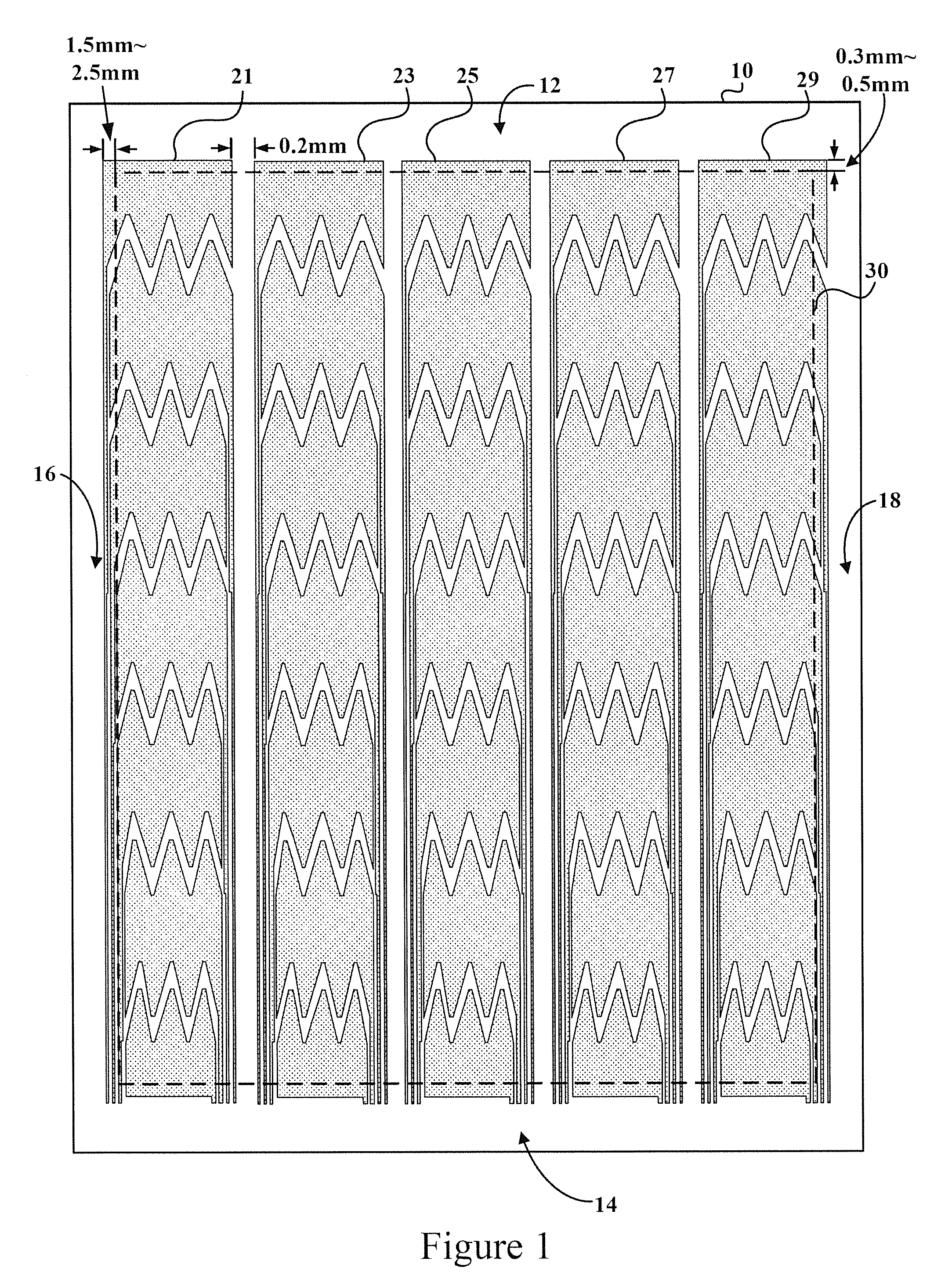

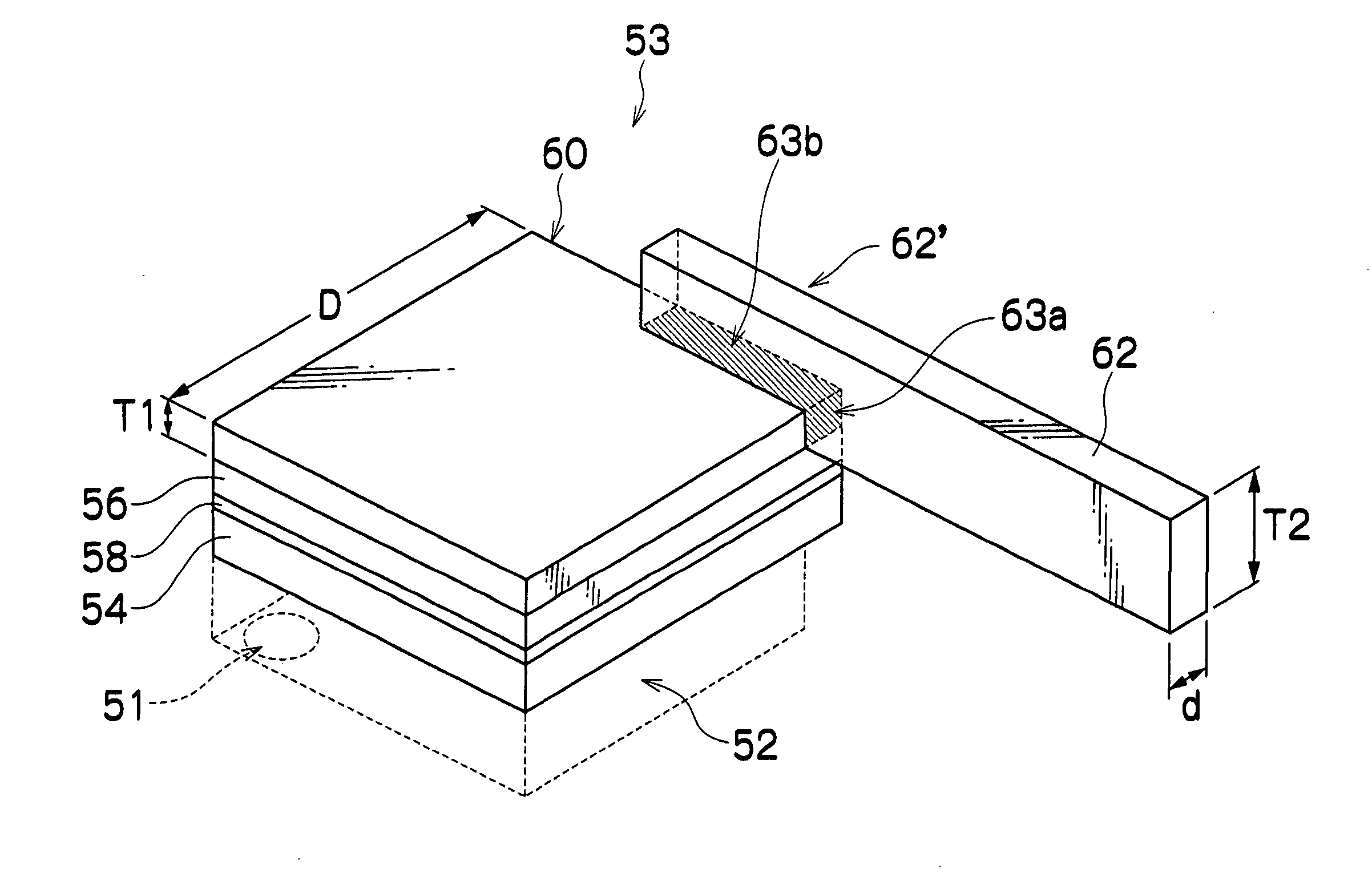

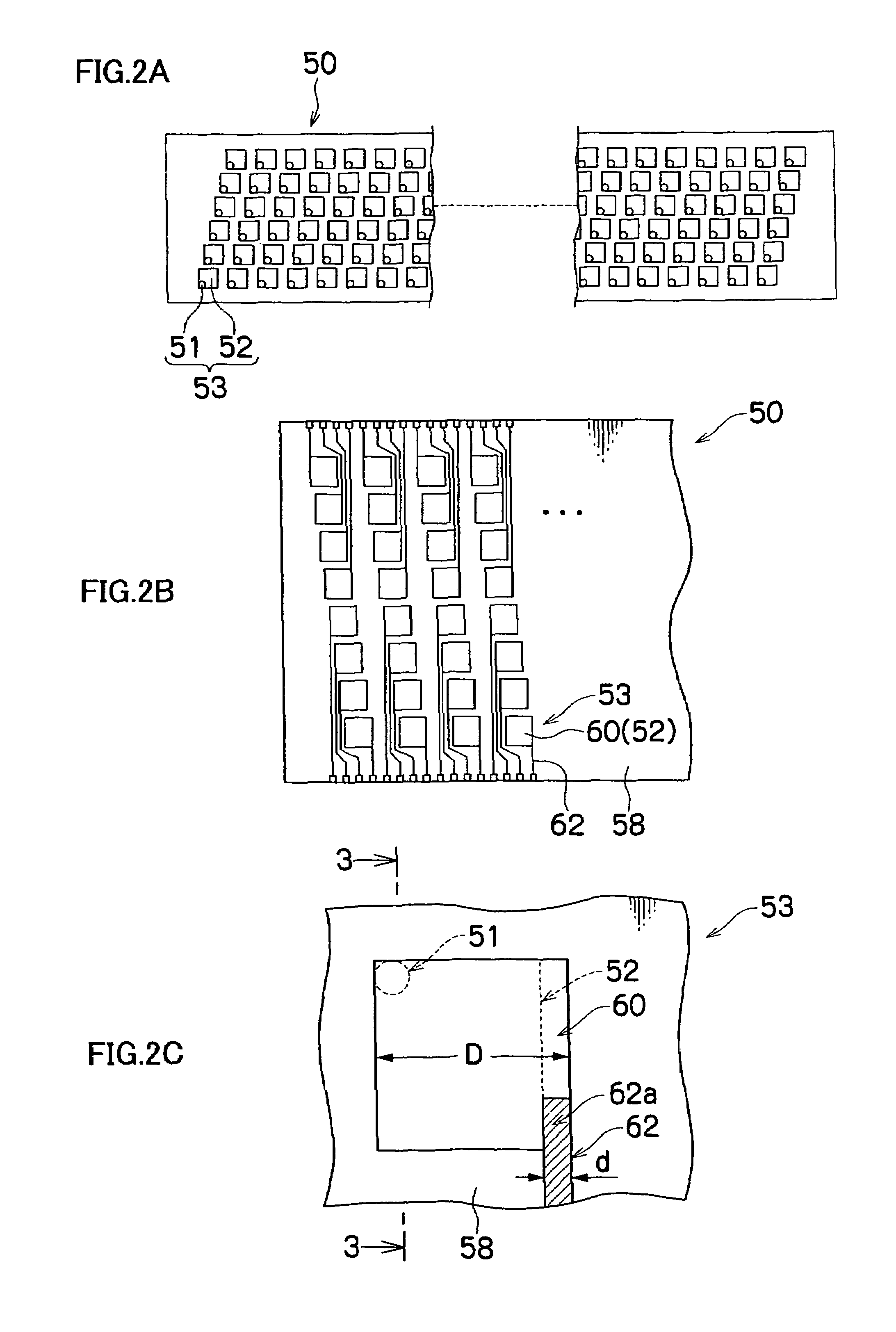

Inkjet head and manufacturing method thereof

The inkjet head comprises: a plurality of ink discharge nozzles which are arranged two-dimensionally; a plurality of pressure chambers which are in communication with the ink discharge nozzles so as to store ink, the pressure chambers being two-dimensionally arranged in correspondence with the ink discharge nozzles; a plurality of piezoelectric elements; a common electrode which is disposed on pressure chamber sides of the piezoelectric elements; a plurality of discrete electrodes which are disposed on sides of the piezoelectric elements opposite to the common electrode; and a plurality of discrete lead electrodes which feed electricity to the discrete electrodes, wherein: each of the piezoelectric elements is deformed by applying voltage to the common electrode and the discrete electrode so that a volume of the pressure chamber is varied to discharge a droplet of the ink from the ink discharge nozzle; and with respect to each pair of the discrete electrode and discrete lead electrode corresponding to each of the pressure chambers, when T1 is a thickness of the discrete electrode and T2 is a thickness of the discrete lead electrode which feed electricity to the discrete electrode, the discrete electrode and the discrete lead electrode are configured so that T1 and T2 satisfy the following formula: T1<T2.

Owner:FUJIFILM CORP

Semiconductor device

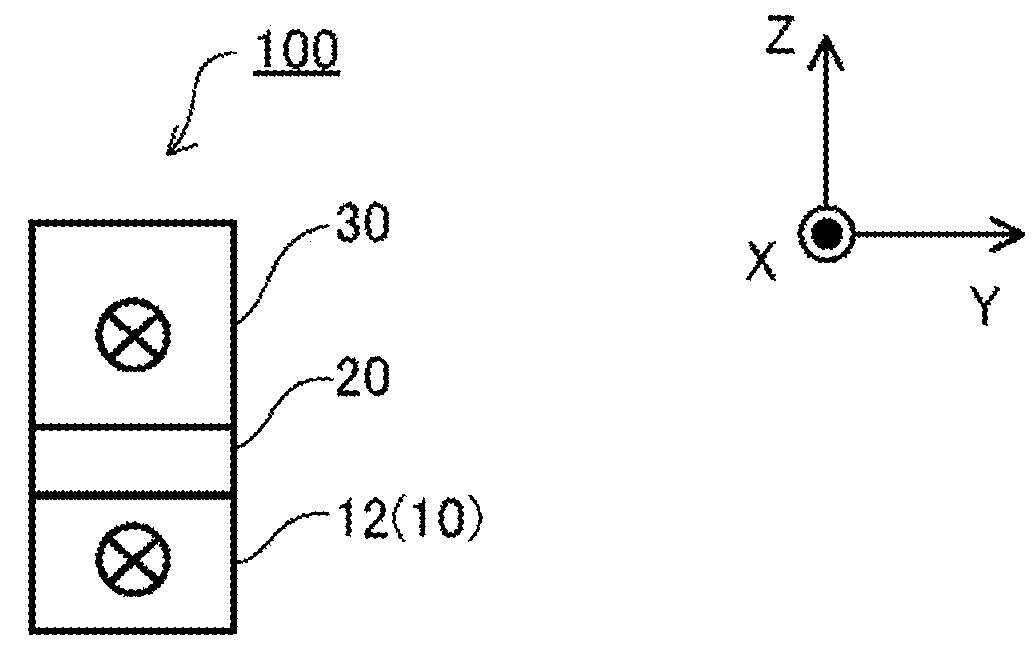

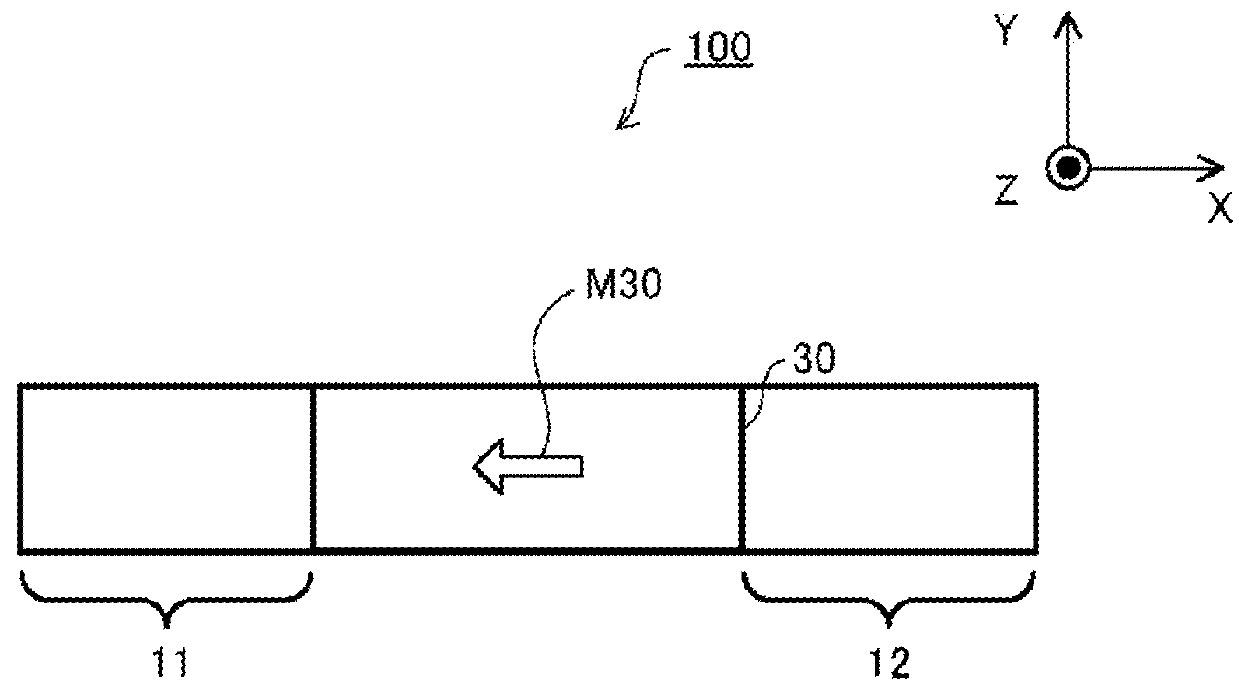

InactiveUS8102695B2Reduce loadReduce trace widthDigital storageBit lineElectrical resistance and conductance

A technique for increasing rewriting current without increasing a power supply voltage and also reducing location dependency inside a memory array of a resistive state after the rewriting is provided in a resistance change memory in which the resistance value of a memory cell changes between logical values “1” and “0”. In the resistance change memory, bit lines are formed into a layered structure, the bit line select switches for connecting to the global bit line are provided at both ends of the local bit line, and a control method of the bit line select switches is changed in the writing and the reading, thereby realizing the optimum array configurations for each of them. More specifically, in the writing and the reading, two current paths are provided in parallel by turning ON the bit line select switches simultaneously.

Owner:HITACHI LTD

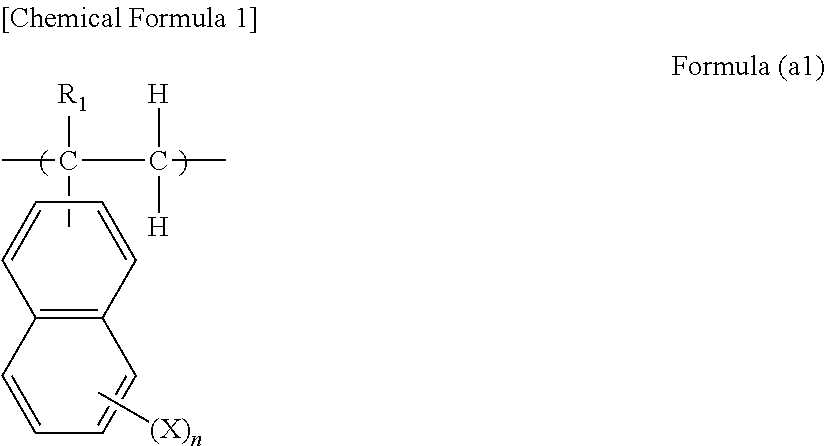

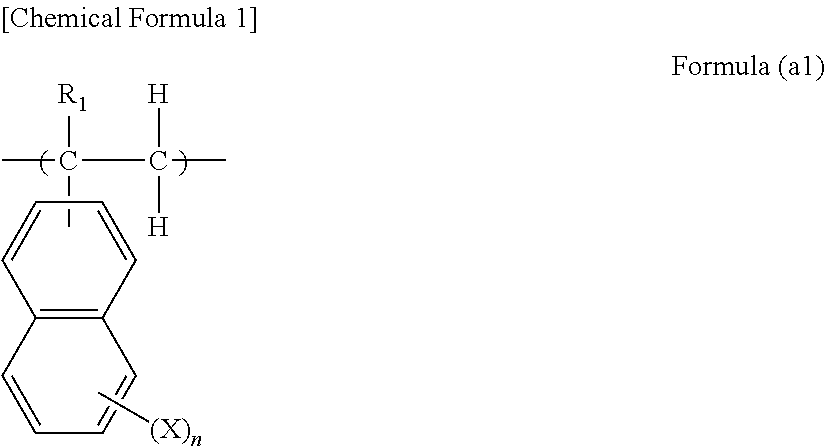

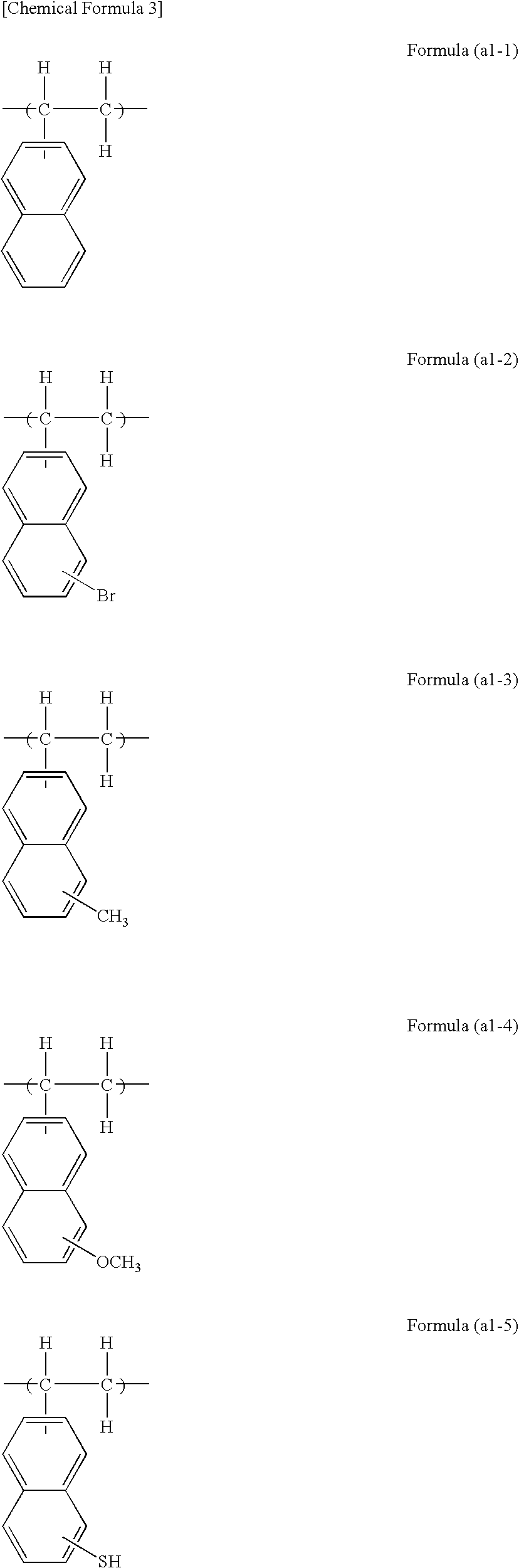

Method for manufacturing semiconductor device using quadruple-layer laminate

ActiveUS20100022089A1Increase depth of focusEliminate DiffusionPhotosensitive materialsSemiconductor/solid-state device manufacturingLithography processEngineering

There is provided a laminate used as an underlayer layer for a photoresist in a lithography process of a semiconductor device and a method for manufacturing a semiconductor device by using the laminate. The method comprising: laminating each layer of an organic underlayer film (layer A), a silicon-containing hard mask (layer B), an organic antireflective film (layer C) and a photoresist film (layer D) in this order on a semiconductor substrate. The method also comprises: forming a resist pattern in the photoresist film (layer D); etching the organic antireflective film (layer C) with the resist pattern; etching the silicon-containing hard mask (layer B) with the patterned organic antireflective film (layer C); etching the organic underlayer film (layer A) with the patterned silicon-containing hard mask (layer B); and processing the semiconductor substrate with the patterned organic underlayer film (layer A).

Owner:NISSAN CHEM IND LTD

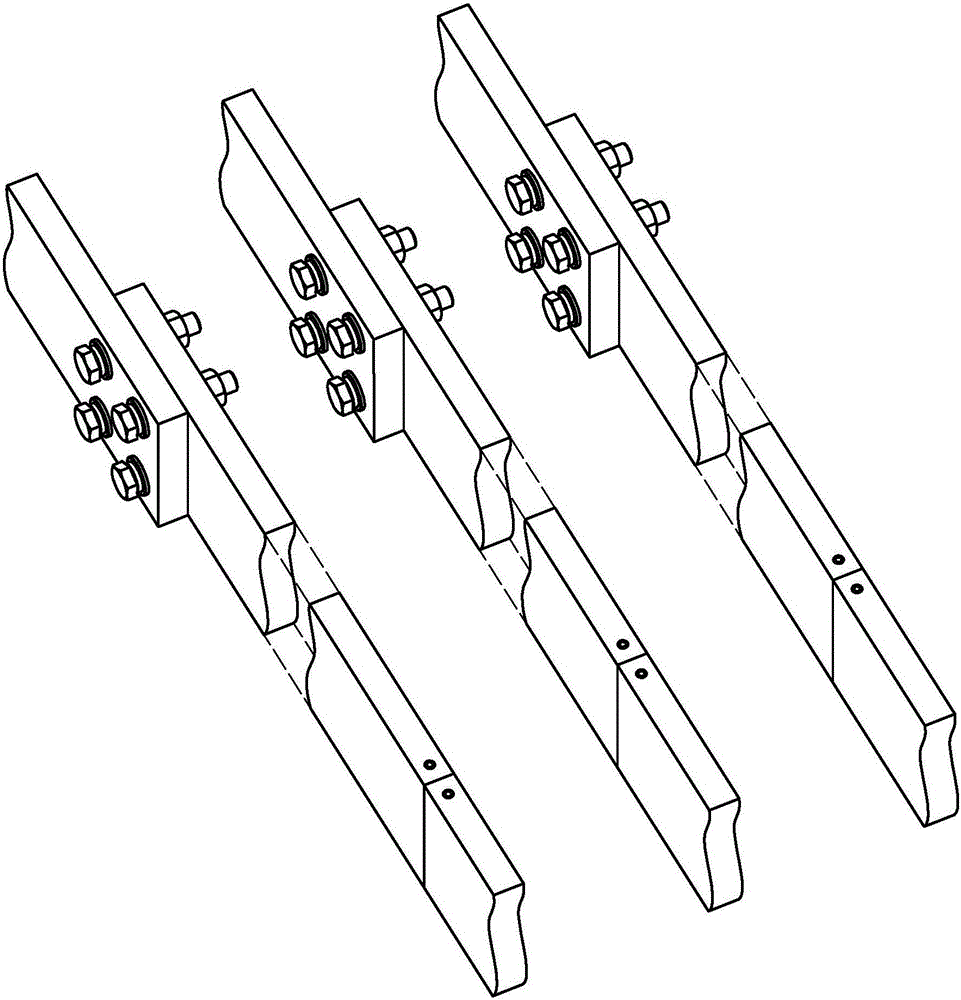

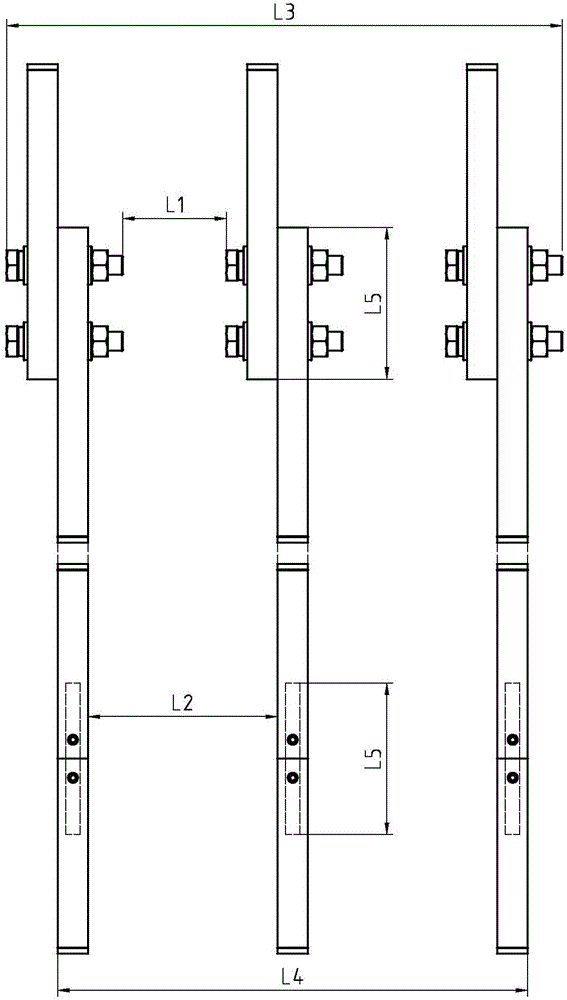

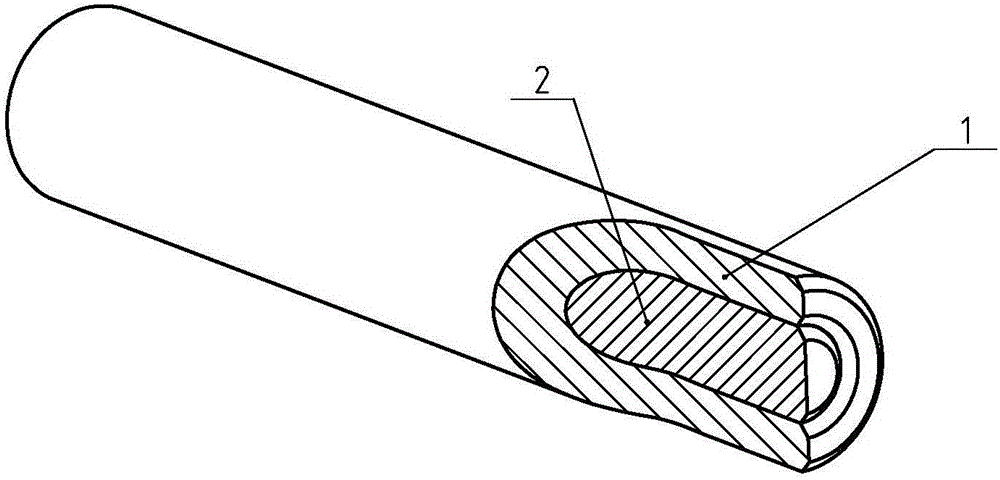

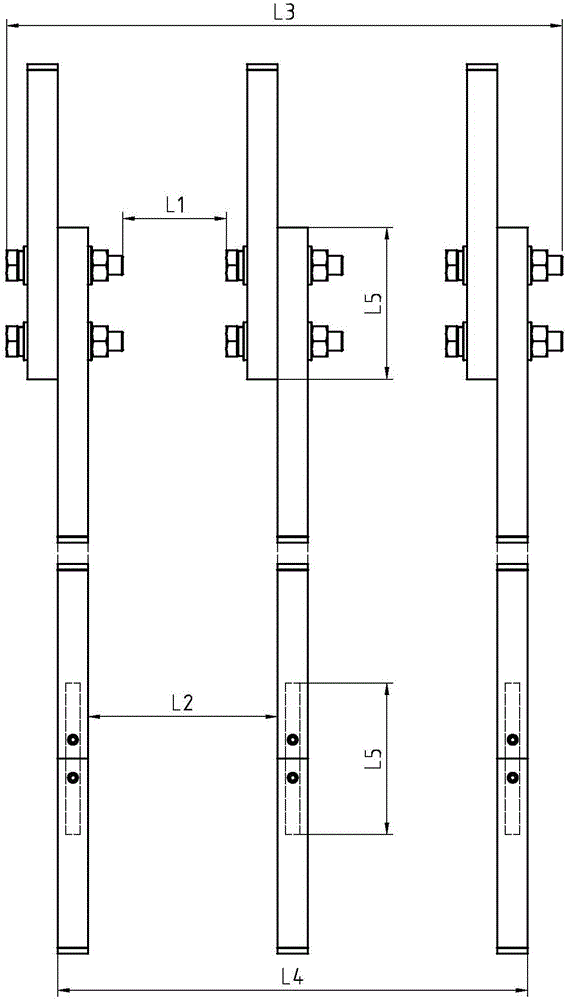

Construction method for reducing temperature rise at electrician busbar lap joint part

ActiveCN105896429AAchieve low temperature riseLarge conductive areaCooling bus-bar installationsInterference fitBusbar

The invention discloses a construction method for reducing temperature rise at an electrician busbar lap joint part, belonging to the field of electrical equipment, and specifically relates to construction and installation of an electrician busbar. The connection column is provided with a first cylindrical portion which is in interference fit with a pre-drilled hole in an electrician busbar, wherein the first cylindrical portion is provided with conductivity; a second cylindrical portion with conductivity is coaxially arranged in the first cylindrical portion; the first cylindrical portion is in interference fit with the second cylindrical portion; and the thermal expansion coefficient of the second cylindrical portion is greater than the thermal expansion coefficient of the first cylindrical portion. The connection column has the advantages that 1) the same lap joint length can generate larger conductive area, so that the current density can be reduced and the low temperature rise of the busbar can be realized; 2) the use level of the busbar is reduced so that the resource is saved; 3) the electric clearance or the phase spacing can be enlarged, so that the electrical safety of equipment is improved; and 4) the wiring width of the busbar is reduced, so that the occupied space of the busbar can be reduced.

Owner:国网甘肃省电力公司金昌供电公司

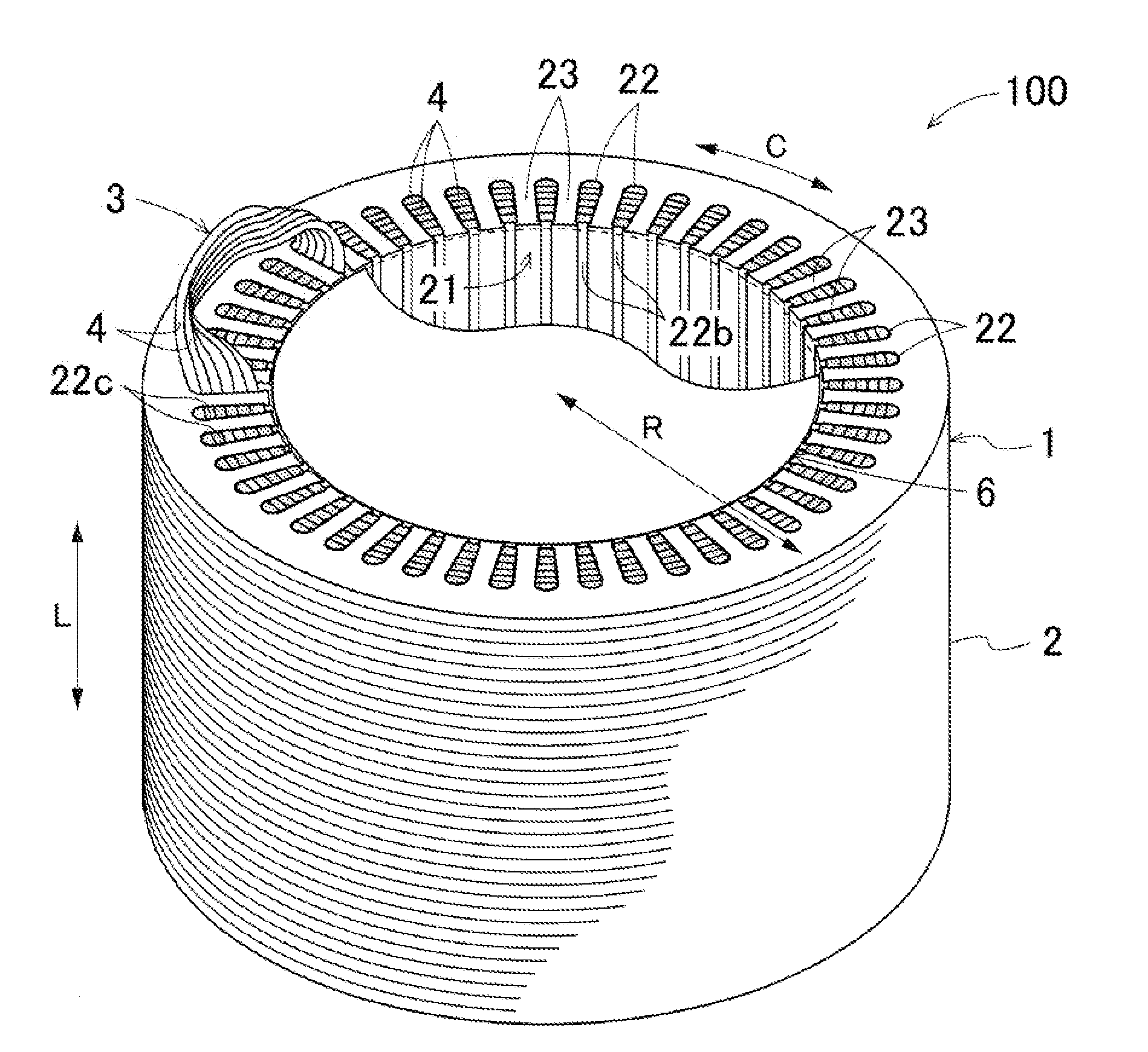

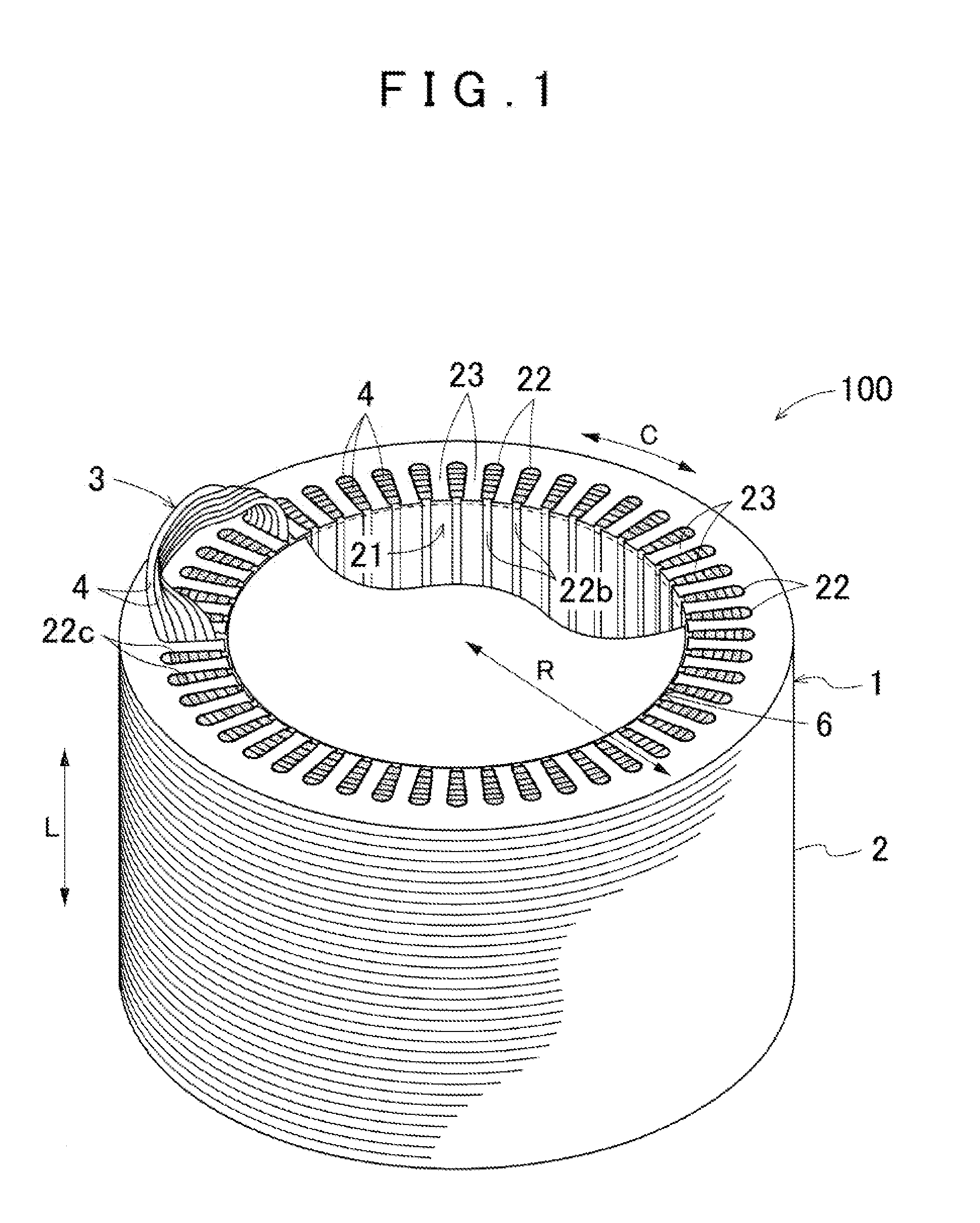

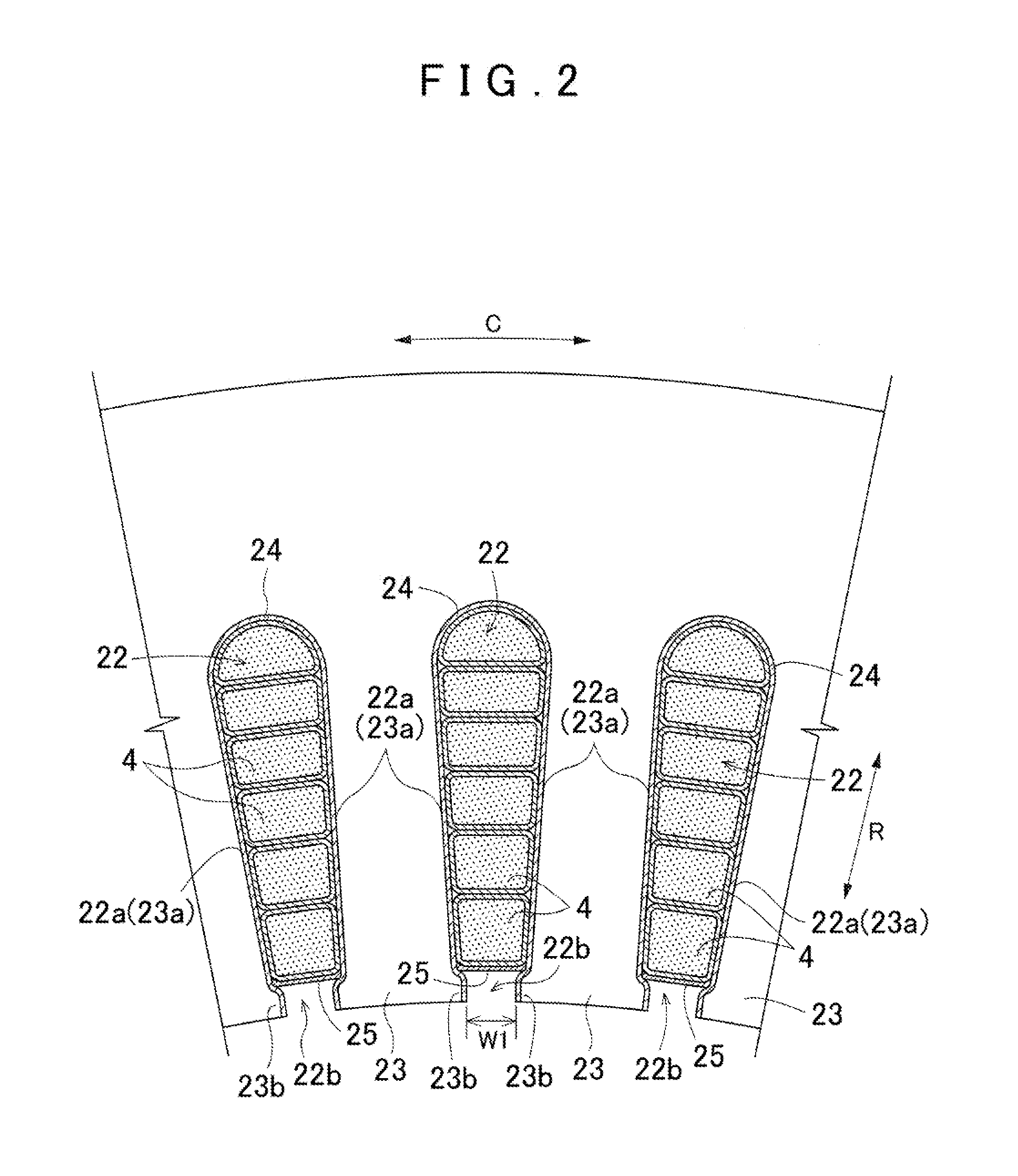

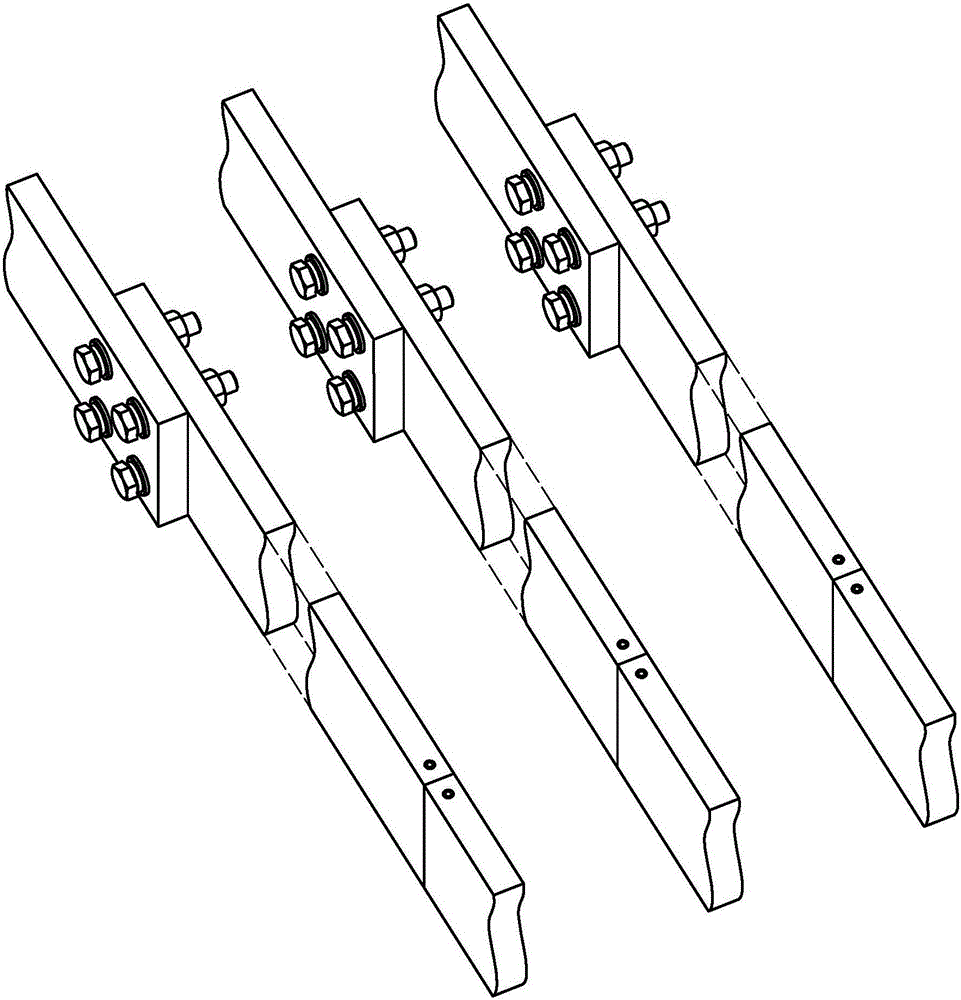

Manufacturing method for coil unit

InactiveUS20130192057A1Reduce amountIncrease spacingManufacturing dynamo-electric machinesWindings conductor shape/form/constructionWire widthDepth direction

A method for manufacturing a coil unit includes inserting a coil conductor wire into a slot from a slot opening portion with a circumferential wire width of the coil conductor wire equal to or less than a slot opening width, the slot opening width being a width of the slot opening portion in the circumferential direction, the circumferential wire width being a wire width of the coil conductor wire in a direction parallel with the slot opening width, the coil conductor wire being a conductor wire with a deformable cross-sectional shape, and a diameter of the coil conductor wire with a circular cross-sectional shape being larger than the slot opening width; and pressing the coil conductor wire inserted into the slot in a depth direction which is opposite to the opening direction to deform the cross-sectional shape of the coil conductor wire.

Owner:AISIN AW CO LTD

Design method of connecting column for reducing temperature rise at overlap position between electric bus bars

InactiveCN105720538AAchieve low temperature riseLarge conductive areaCooling bus-bar installationsInterference fitPower equipment

The invention discloses a design method of a connecting column for reducing temperature rise at an overlap position between electric bus bars, belongs to the field of power equipment, and particularly relates to a design method of a connecting column. The design method of the connecting column disclosed by the invention comprises the following steps: providing first columnar parts which are in interference fit with prefabricated holes in the electric bus bars, wherein the first columnar parts are electrically conductive; coaxially arranging second columnar parts which are electrically conductive in the first columnar parts; making the first columnar parts be in interference fit with the second columnar parts; and making thermal expansion coefficients of the second columnar parts be greater than the thermal expansion coefficients of the first columnar parts. The connecting column made by the design method disclosed by the invention has the beneficial effects that 1, more electric conduction area is formed at a same overlap length, so that the current density is lowered, and low temperature rise of the bus bars is realized; 2, a using quantity of the bus bars is reduced, and resources are saved; 3, electric clearances or space distances are increased, and the electrical safety of equipment is enhanced; and 4, arrangement widths of the bus bars are reduced, so that space occupied by the bus bars can be reduced.

Owner:龚柱

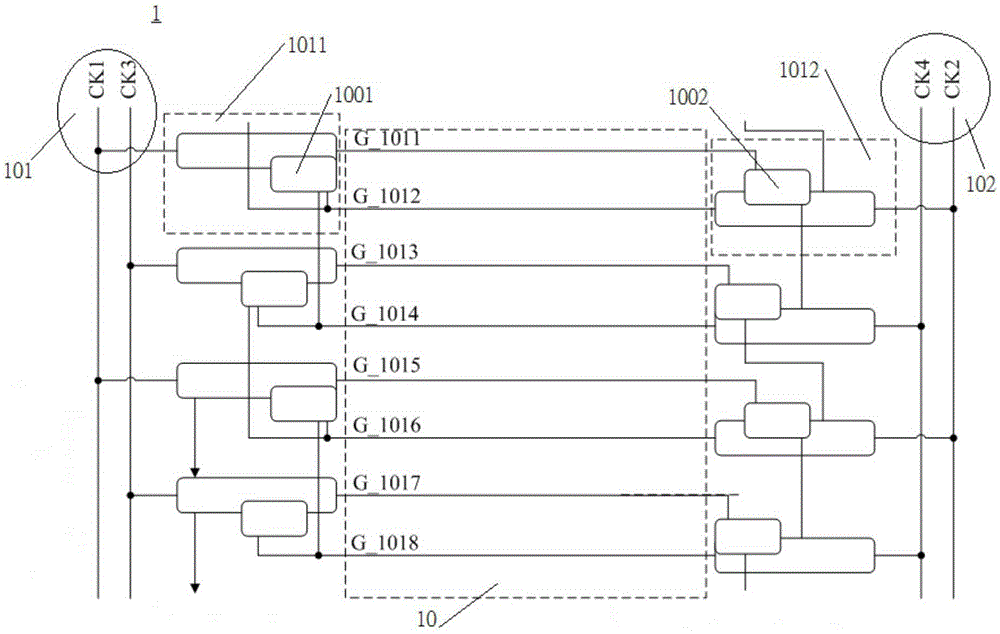

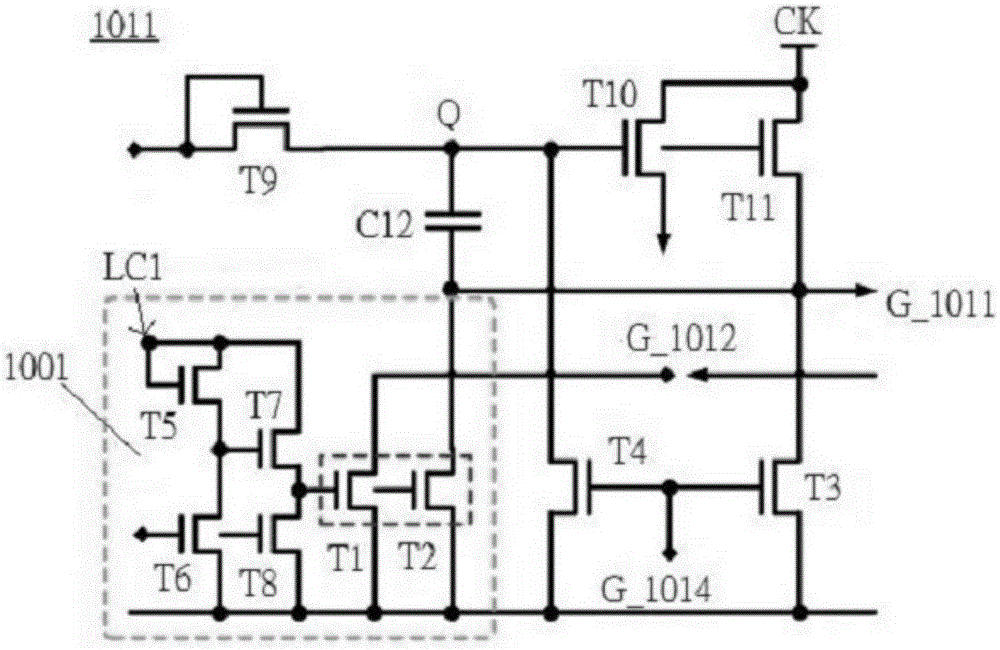

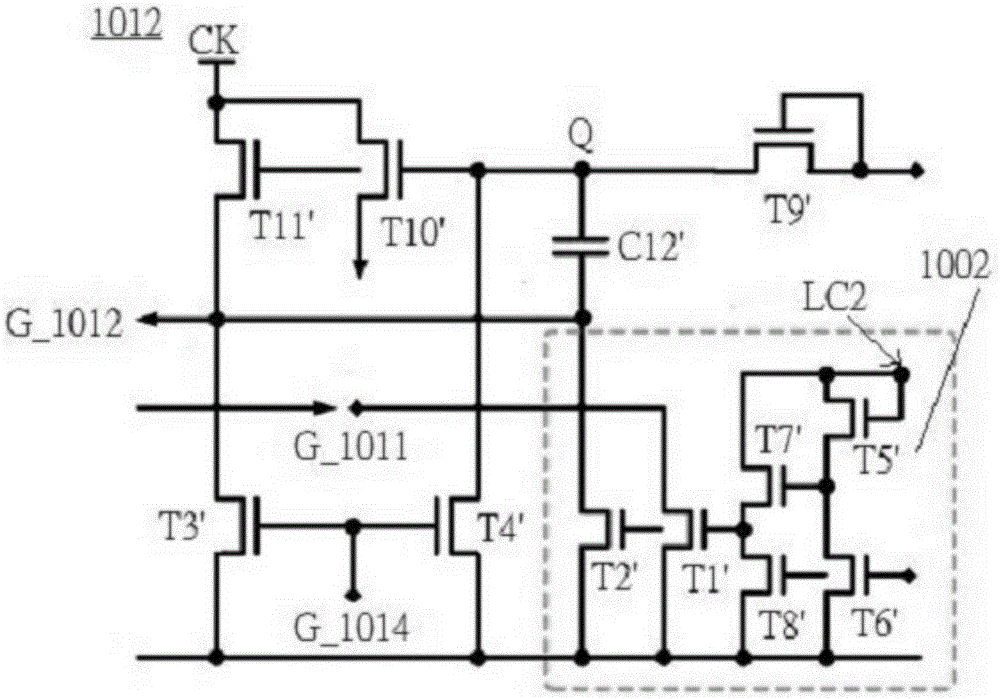

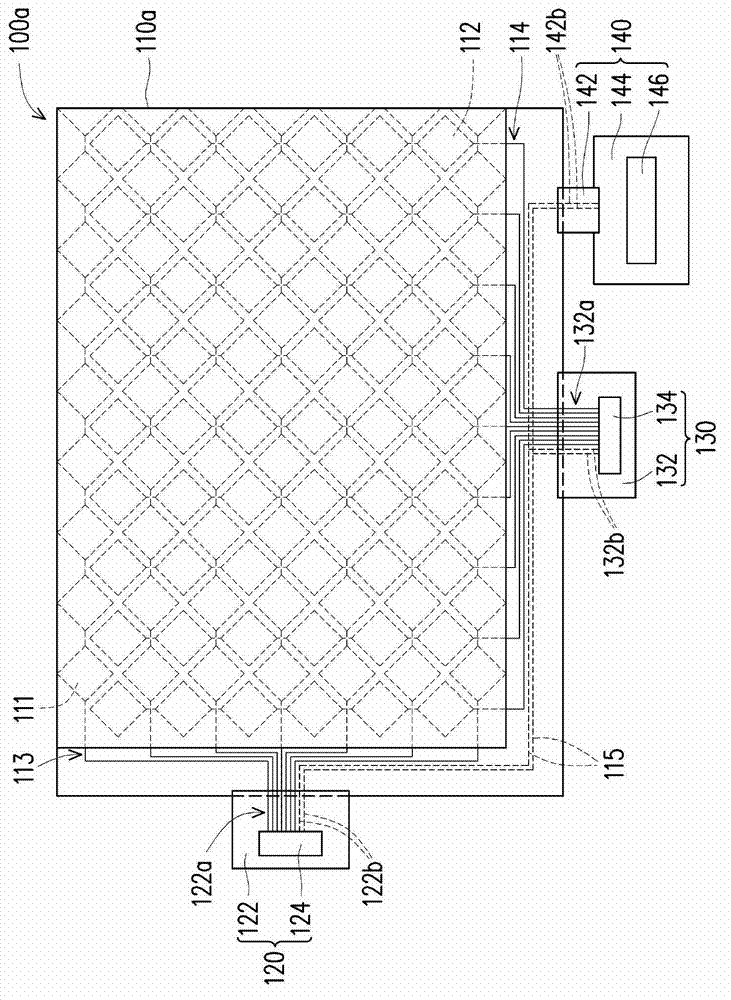

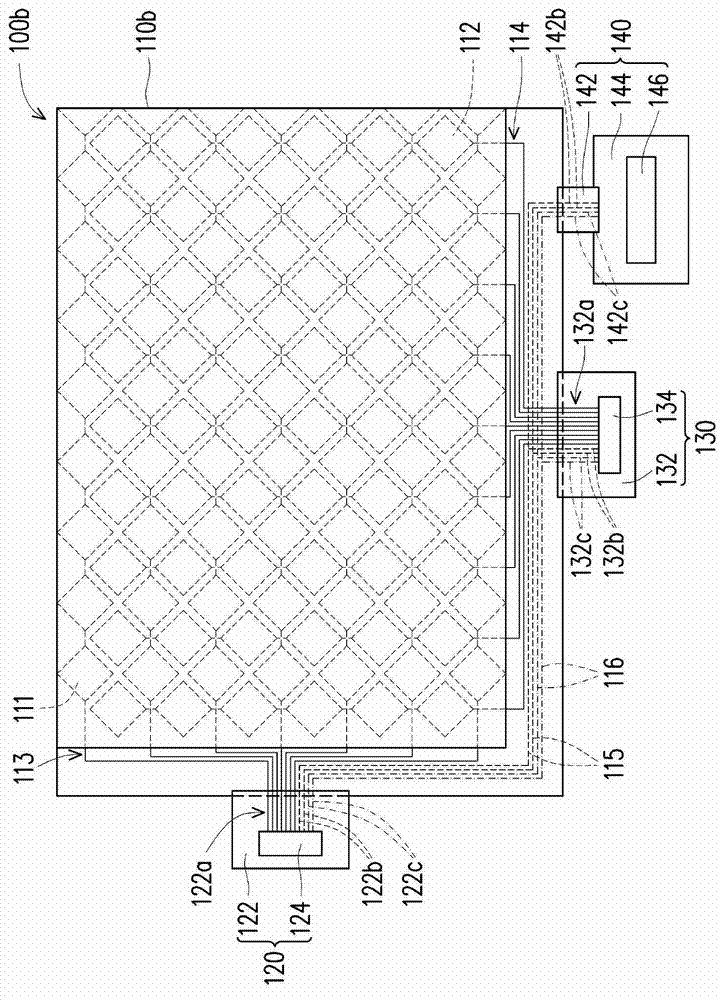

Liquid crystal drive circuit and gate drive panel

ActiveCN105355175ASmall footprintSimple designStatic indicating devicesDigital storageDisplay deviceEngineering

The invention relates to a liquid crystal drive display device which comprises a display region and a liquid crystal drive circuit. The liquid crystal drive circuit comprises a plurality of stages of GOA circuits. Each stage of GOA circuit comprises gate lines and an auxiliary pull-down circuit, wherein the gate lines comprise an odd group of grid lines and an even group of grid lines, and the auxiliary pull-down circuit comprises a first group of auxiliary pull-down circuit and a second group of auxiliary pull-down circuit. The odd group of grid lines and the even group of grid lines are arranged at the two sides of the display region separately and respectively; the first group of auxiliary pull-down circuit and the second group of auxiliary pull-down circuit are also arranged at the two sides of the display region separately and respectively; and any two stages of GOA circuits in the plurality of stages of GOA circuits share the first group of auxiliary pull-down circuit and the second group of auxiliary pull-down circuit.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

Semiconductor physical quantity sensor of electrostatic capacitance type and method for manufacturing the same

InactiveUS20070176249A1Reduce chip sizeAvoid bondingFluid pressure measurement by electric/magnetic elementsForce measurementCapacitanceCountermeasure

Owner:MATSUSHITA ELECTRIC WORKS LTD

Method for manufacturing semiconductor device using quadruple-layer laminate

ActiveUS7842620B2Reduce thicknessReduce trace widthPhotosensitive materialsSemiconductor/solid-state device manufacturingLithography processEngineering

There is provided a laminate used as an underlayer layer for a photoresist in a lithography process of a semiconductor device and a method for manufacturing a semiconductor device by using the laminate. The method comprising: laminating each layer of an organic underlayer film (layer A), a silicon-containing hard mask (layer B), an organic antireflective film (layer C) and a photoresist film (layer D) in this order on a semiconductor substrate. The method also comprises: forming a resist pattern in the photoresist film (layer D); etching the organic antireflective film (layer C) with the resist pattern; etching the silicon-containing hard mask (layer B) with the patterned organic antireflective film (layer C); etching the organic underlayer film (layer A) with the patterned silicon-containing hard mask (layer B); and processing the semiconductor substrate with the patterned organic underlayer film (layer A).

Owner:NISSAN CHEM IND LTD

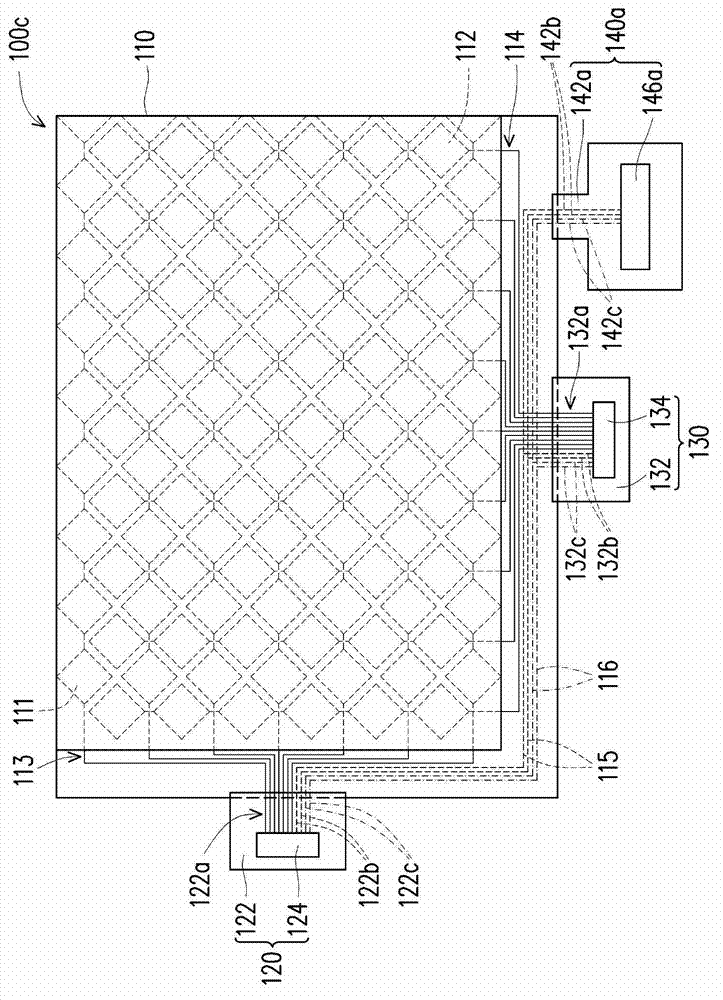

Touch panel, touch conducting film and manufacture method for conducting film

ActiveCN108170314AReduce trace widthInput/output processes for data processingFlexible circuitsTouch panel

The invention relates to a touch panel, a touch conducting film and a manufacture method for the conducting film. The touch film comprises a substrate and a main electric conduction layer, wherein thesubstrate comprises a main body part and a first auxiliary part, the main body part and the first auxiliary part are connected and are arranged along a first direction, the boundary of the main bodypart and the first auxiliary part is a first folding line, the first folding line extends along a second direction, and the second direction is vertical to the first direction; and the main electric conduction layer is arranged on the first auxiliary part, the free ends of first touch leads arranged along the first direction in the main electric conduction layer independently extend to a main binding area, which is far away from the first auxiliary part, of the main body part, and the first auxiliary part is far away from the first auxiliary binding area of the main body part. The above touchfilm and the touch lead of the touch panel extend along two opposite directions and are connected with a flexible circuit board through a folding way, and the routing width of a boarder is lowered.

Owner:INTERFACE TECH CHENGDU CO LTD +2

Magnetoresistance effect element and magnetic memory device

ActiveUS20180108390A1Unstable operationReduce adverse effectsNanomagnetismMagnetic measurementsIn planeNanowire

A magnetoresistance effect element includes a recording layer containing a ferromagnetic body, and including a first fixed and second magnetization regions having magnetization components fixed substantially in a direction antiparallel to the in-plane direction to each other, and a free magnetization region disposed between the first and second fixed magnetization regions and having a magnetization component invertible in the in-plane direction, a domain wall disposed between the first fixed magnetization region and the free magnetization region, and being movable within the free magnetization region, and a magnetic nanowire having a width of 40 nm or less. The thickness of the recording layer is 40 nm or less and at least half but no more than twofold the width of the magnetic nanowire. The element further includes a barrier layer disposed on the recording layer, and a reference layer disposed on the barrier layer and containing a ferromagnetic body.

Owner:TOHOKU UNIV

Wiring board, method for manufacturing the same, and semiconductor device

InactiveCN101079407AReduce trace widthPrinted circuit assemblingPrinted circuit detailsElectrical conductorEngineering

A wiring board includes an insulating base; an adhesive layer formed on the surface of the insulating base; a conductor wiring formed on the surface of the adhesive layer; and a bump formed crossing the longitudinal direction of the conductor wiring over regions on the adhesive layer on both sides of the conductor wiring, wherein the back face at a part of the conductor wiring where the bump is formed, and the back faces and parts of the side faces of the bump formed above the regions of the adhesive layer on both sides of the conductor wiring, are embedded in the surface of the adhesive layer so as to be adhered to the adhesive layer. Even when the wiring width of the conductor wiring is decreased, the conductor wiring can be adhered to the wiring board firmly.

Owner:PANASONIC CORP

Sensing structure of touch panel

ActiveUS20130234738A1High sensitivityImprove accuracyCapacitance measurementsNon-linear opticsTouch SensesTouchscreen

The present invention relates to a sensing structure of touch panel, which comprises a plurality of electrode groups disposed on a substrate. The substrate has a first side and a second side. Each electrode group comprises a first external electrode, a second external electrode, a plurality of internal electrodes, and a plurality of wires. The first external electrode is disposed on a first side; the second external electrode is disposed on the second side; the plurality of internal electrodes are disposed between the first external electrode and the second external electrode; and the plurality of wires are disposed on both sides of the electrode group alternately. Thereby, by disposing the first external electrode, the second external electrode, and the internal electrodes, all being zigzag, the disposable number of electrodes in each electrode group is increased. Accordingly, the sensitivity of touch sensing for the sensing structure of touch panel is enhanced.

Owner:HEFEI SITRONIX CO LTD

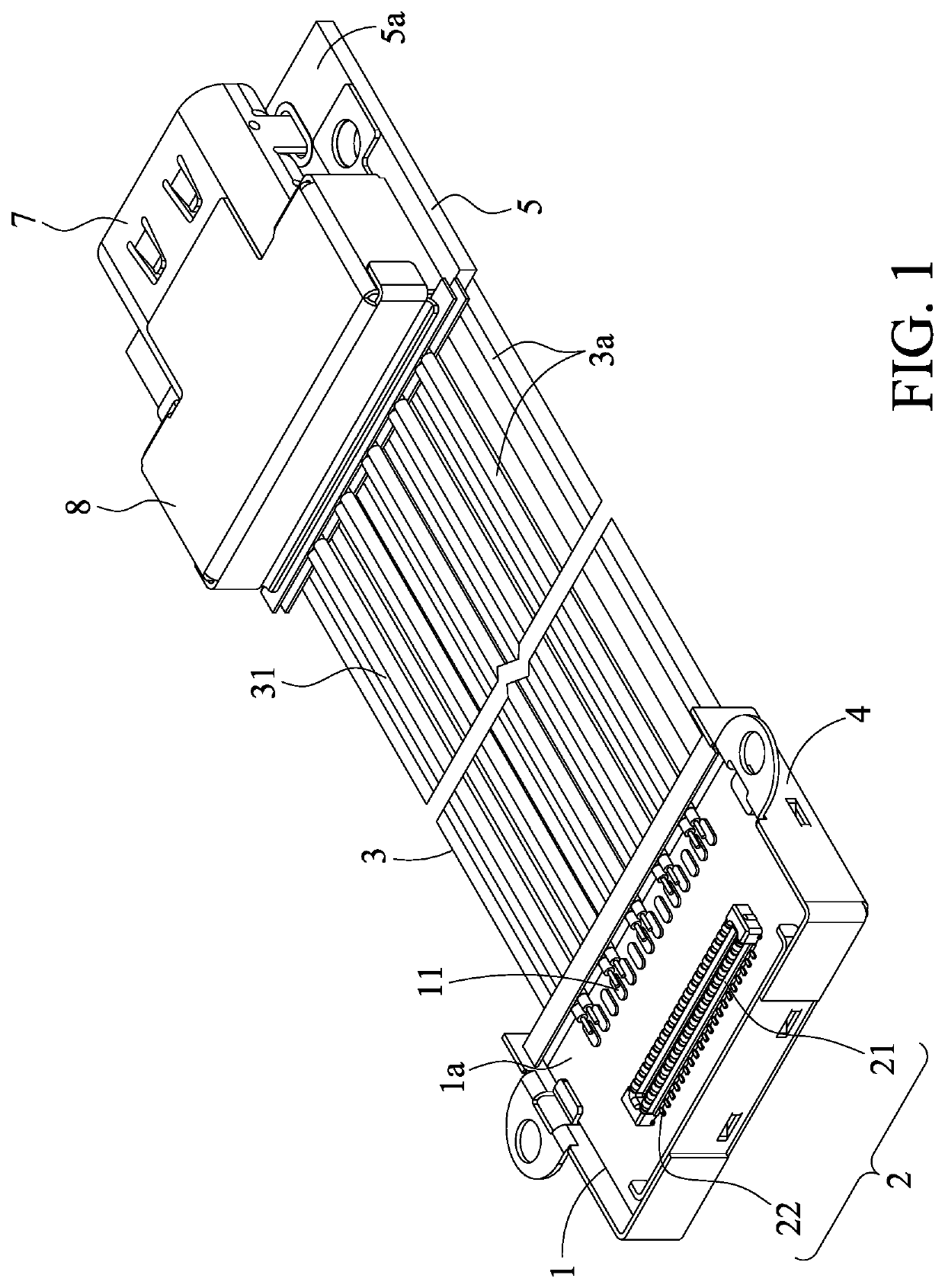

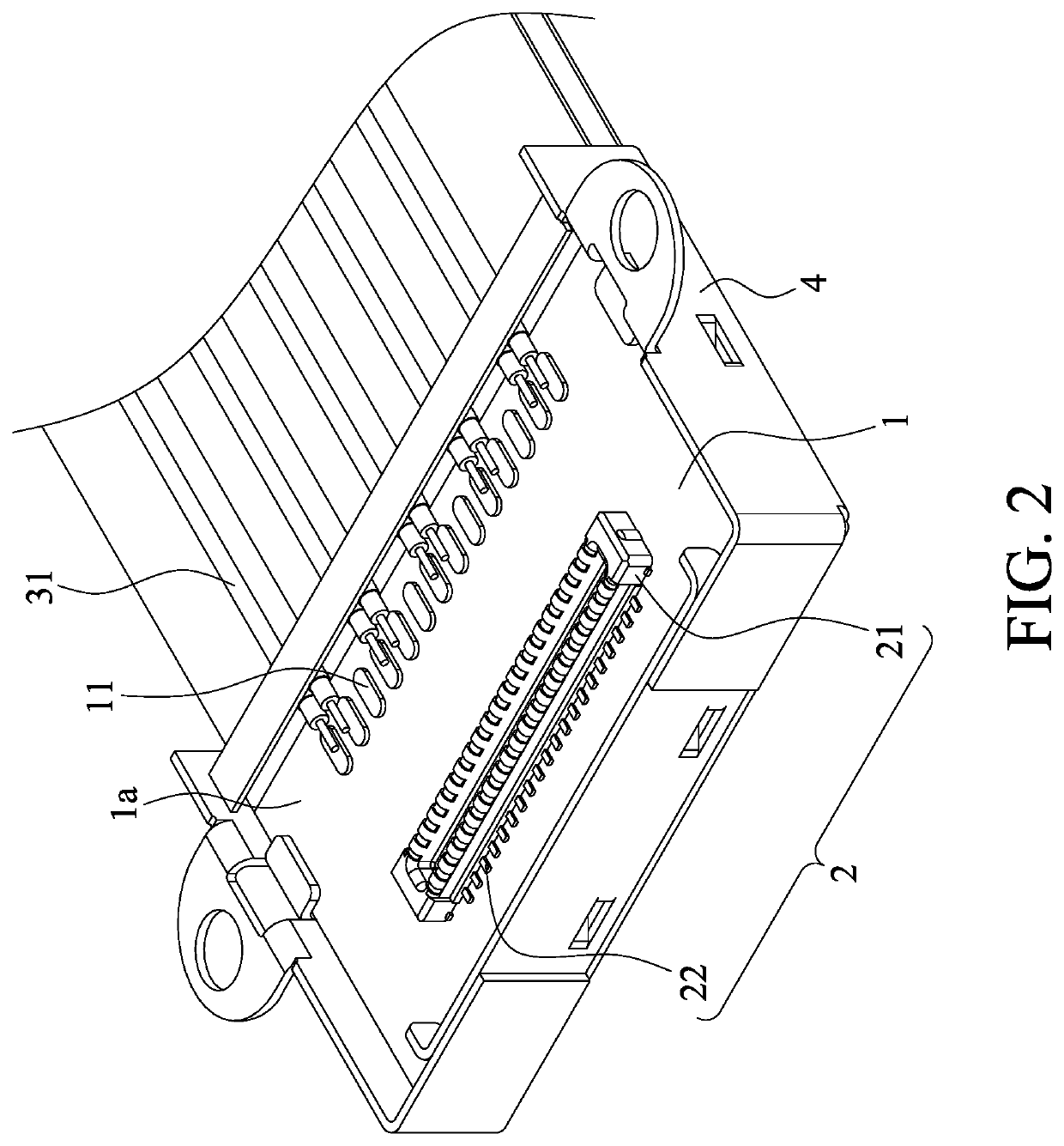

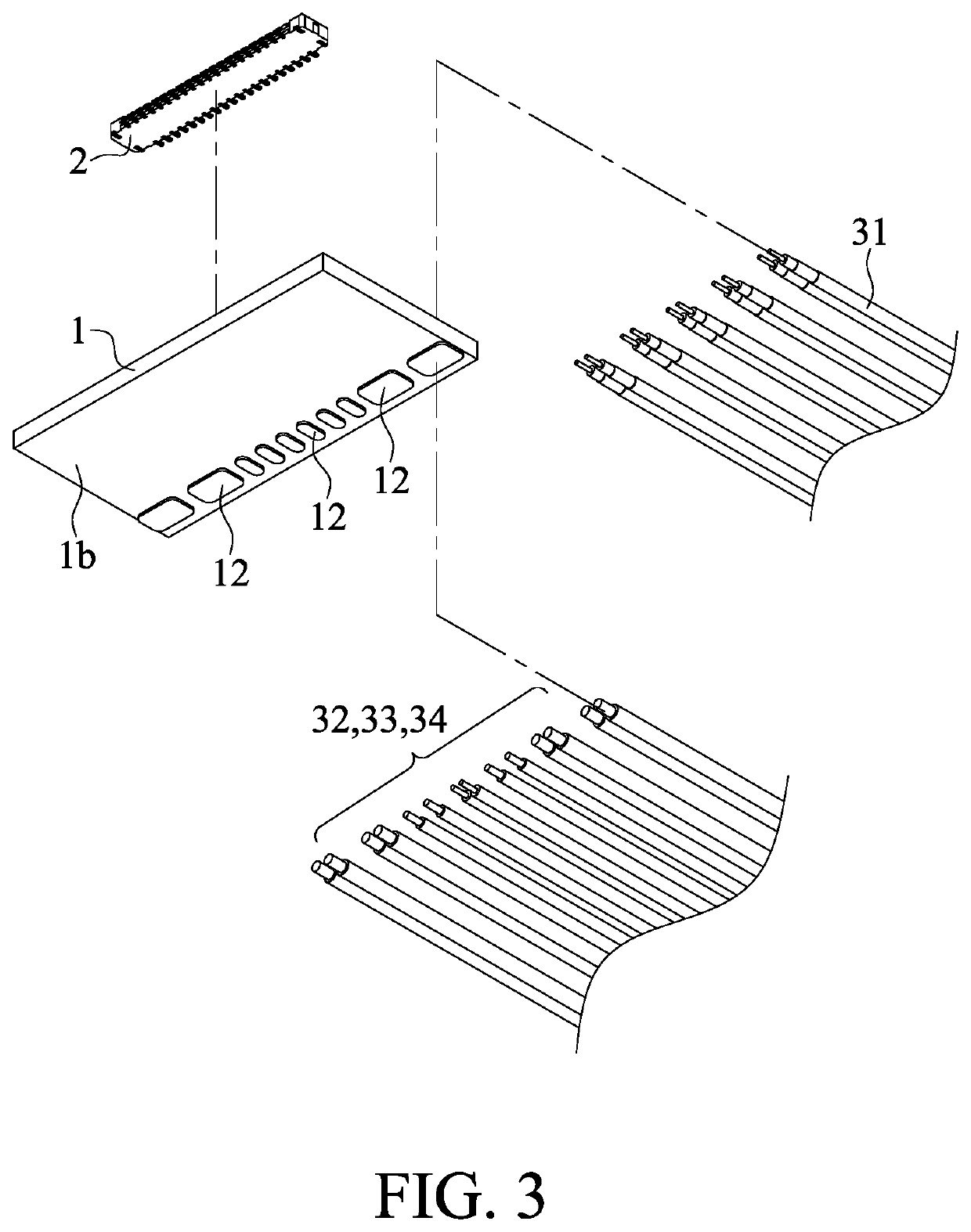

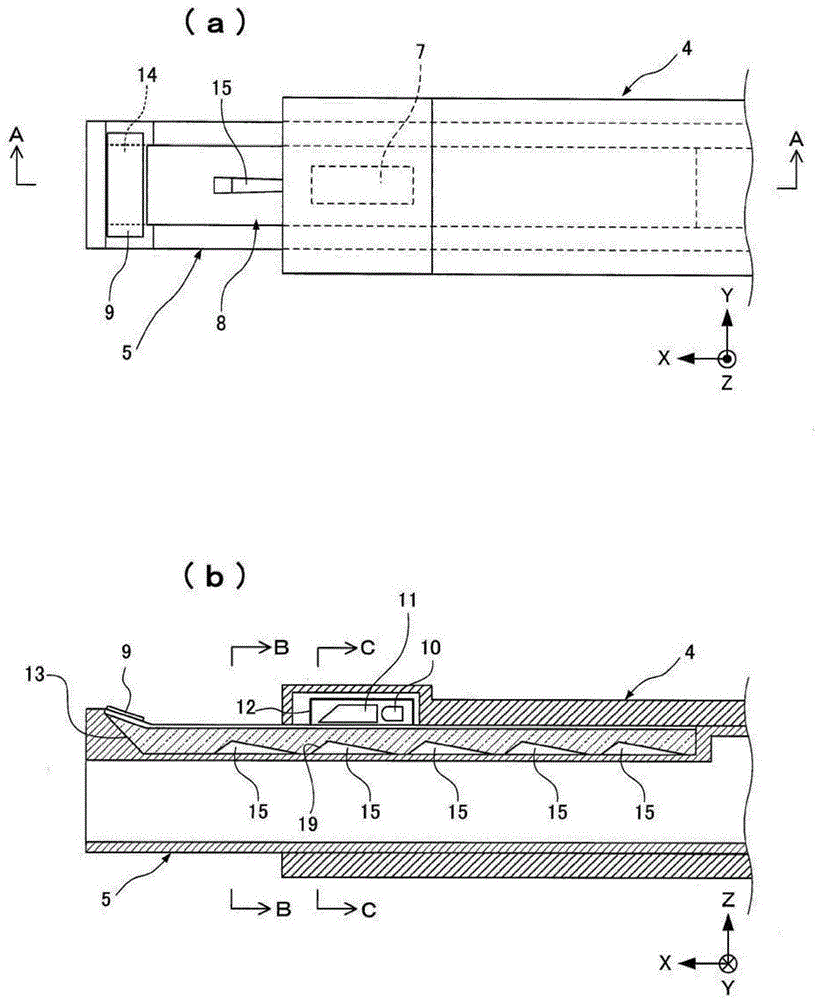

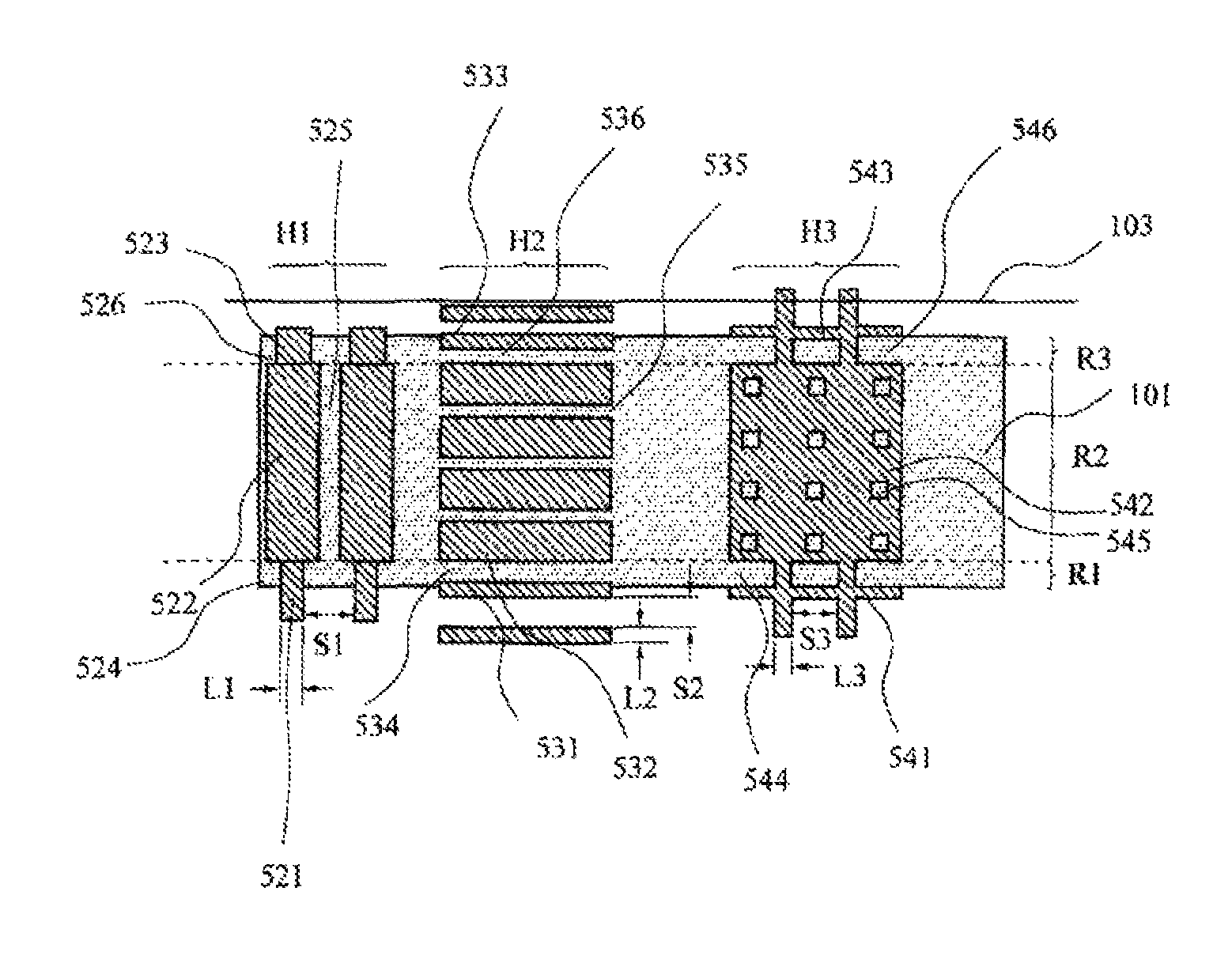

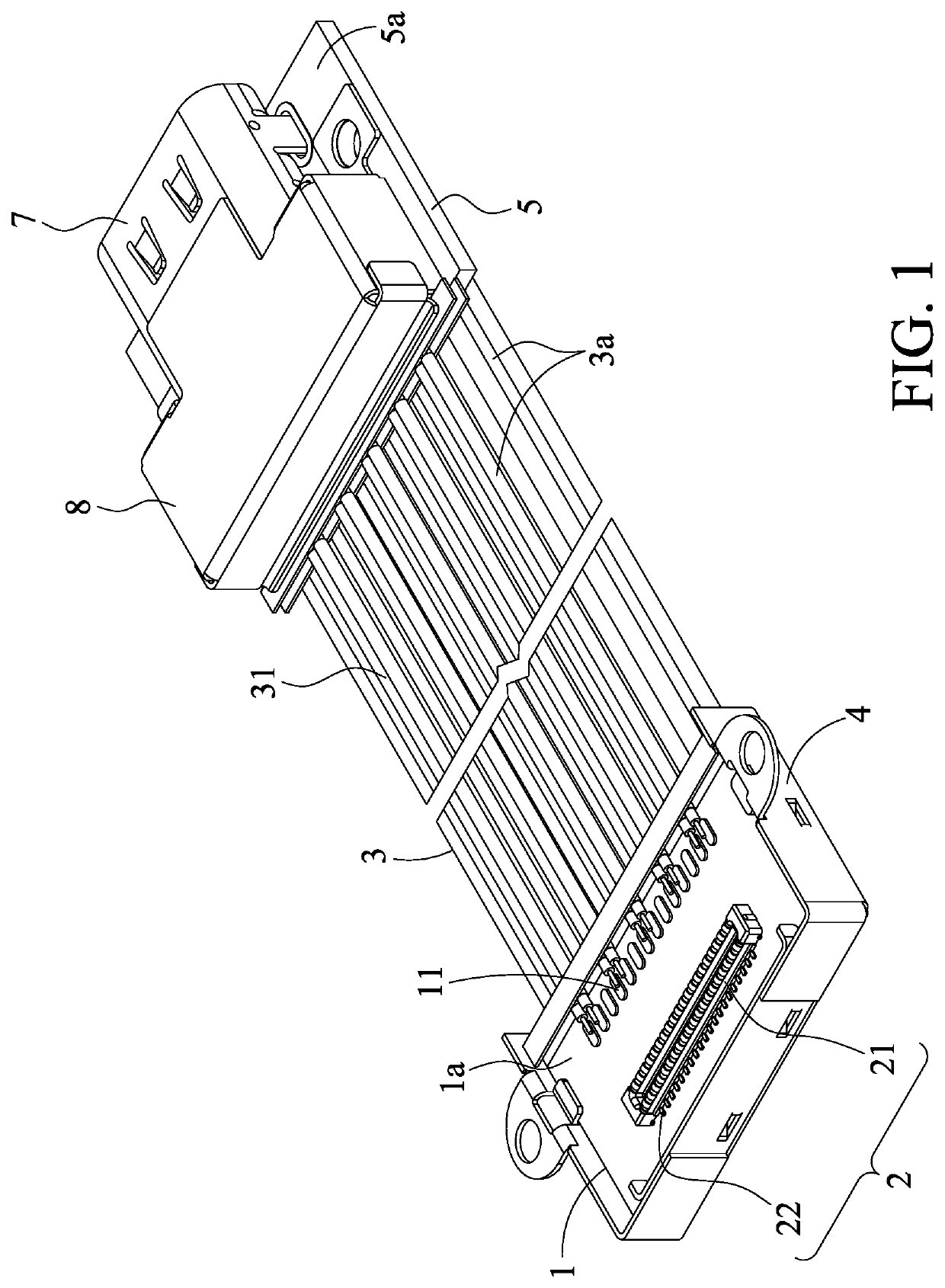

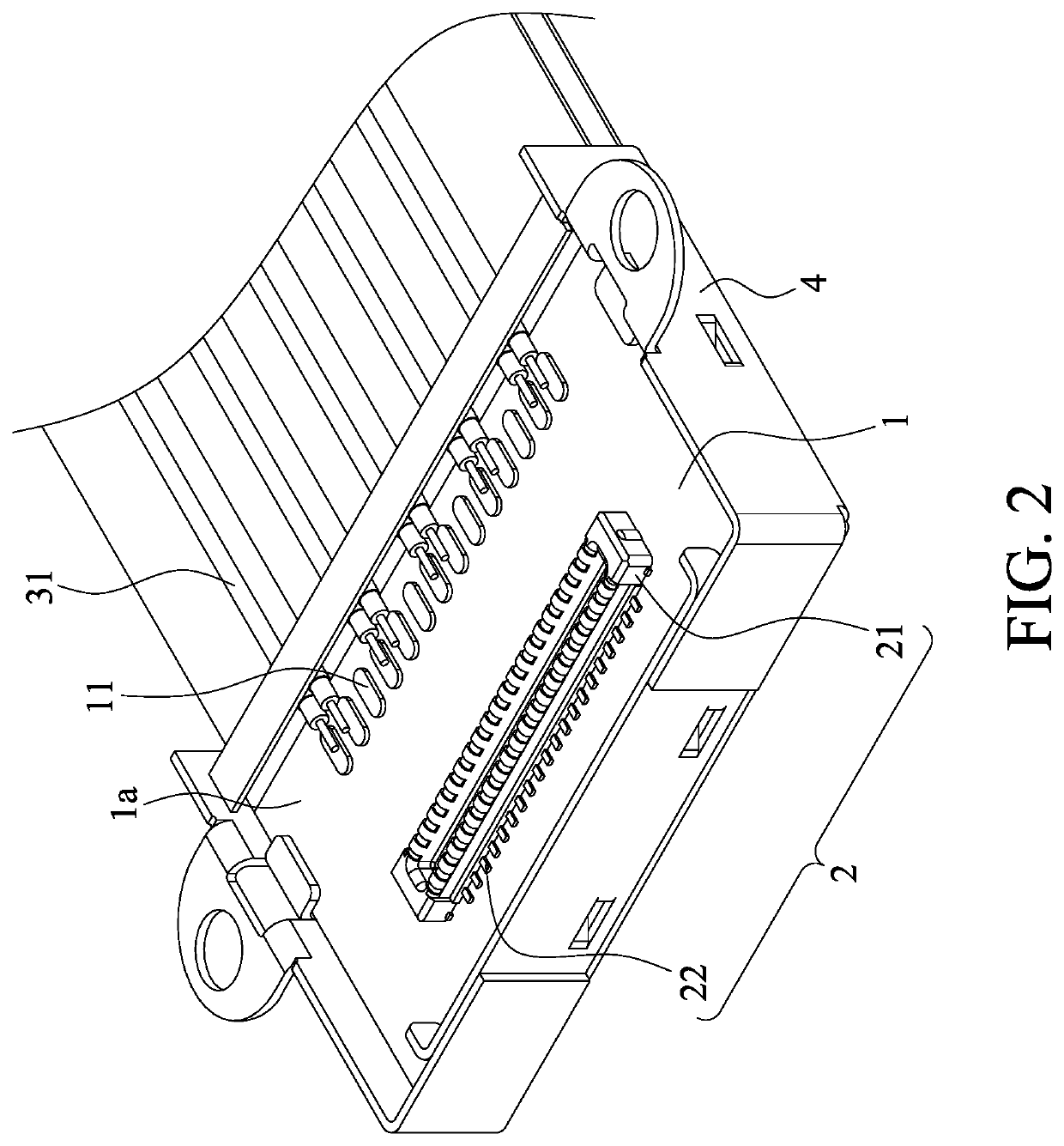

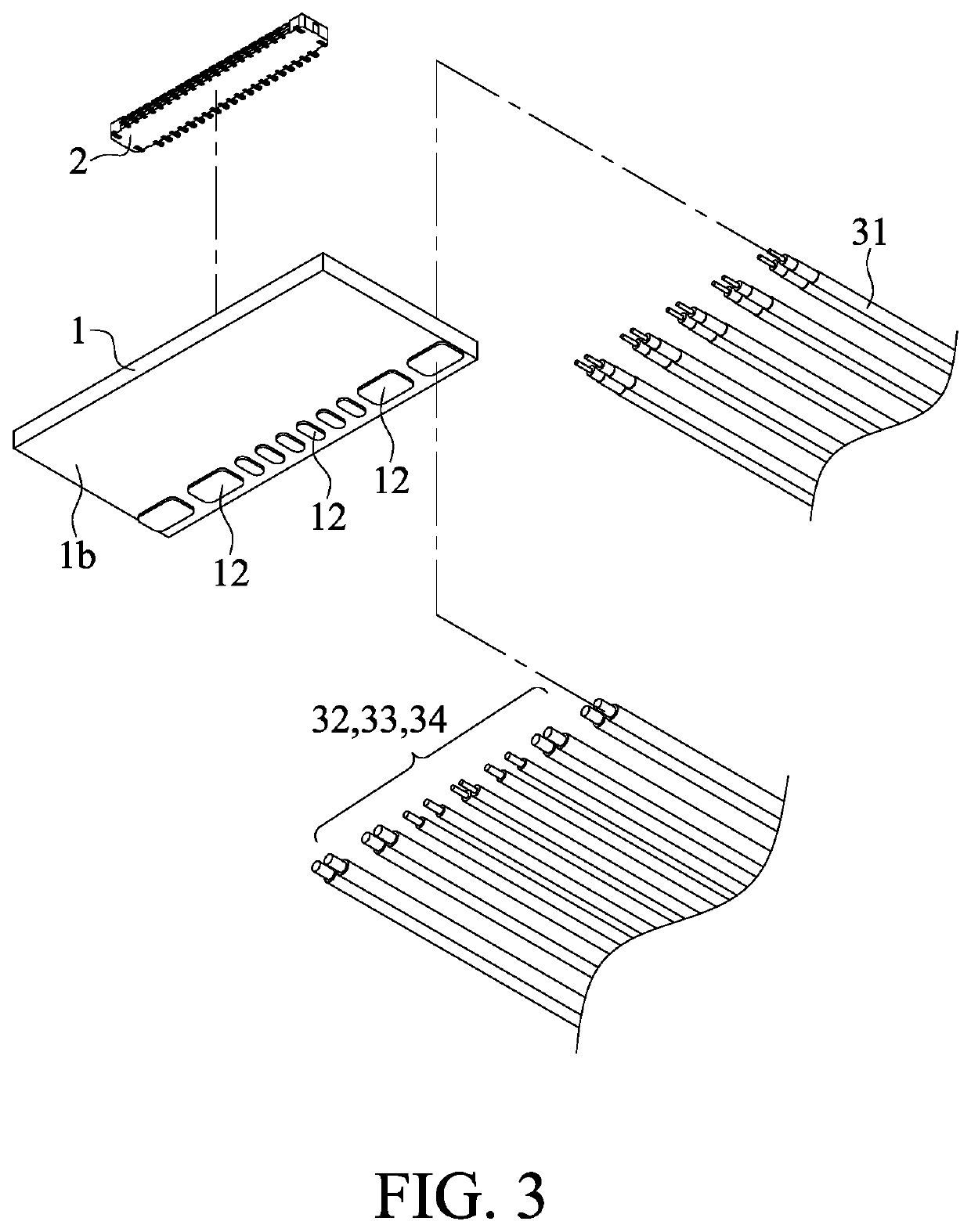

Dual-row cable structure

ActiveUS20210091491A1Reduce weld areaCost reductionTwo-part coupling devicesComputer periphery connectorsEngineeringElectrical connection

A dual-row cable structure is applied to a first circuit board and a second circuit board. A board-to-board connector is on the first circuit board, and the first circuit board includes a first group of contacts and a second group of contacts. An electrical connector is on the second circuit board. The second circuit board includes a third group of contacts and a fourth group of contacts. The dual-row cable structure includes a wire assembly including high-speed signal wires, low-speed signal wires, one or more power wires, and one or more ground wires. The high-speed signal wires are connected to the first group of contacts. The low-speed signal wires, the power wire, and the ground wire are respectively connected to the second group of contacts. The third group of contacts and the fourth group of contacts are respectively connected to the other end of the wire assembly.

Owner:ADVANCED CONNECTEK INC

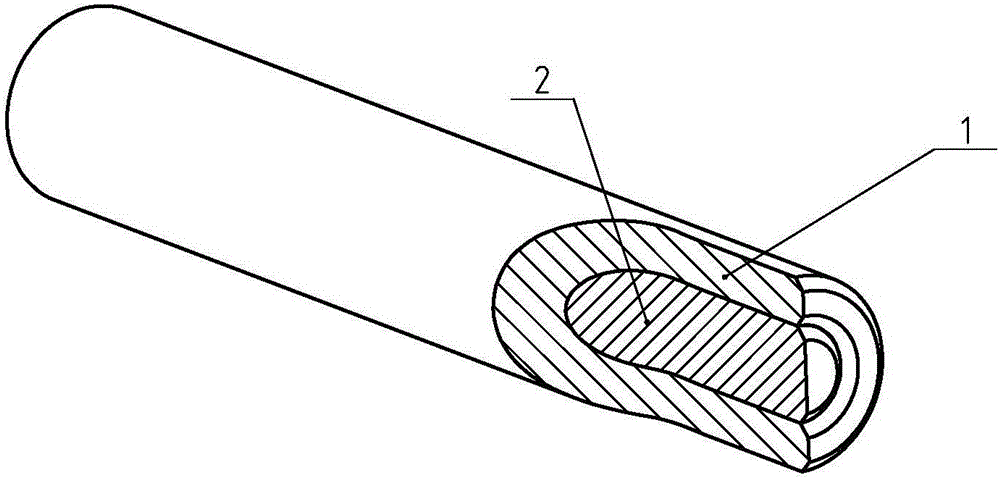

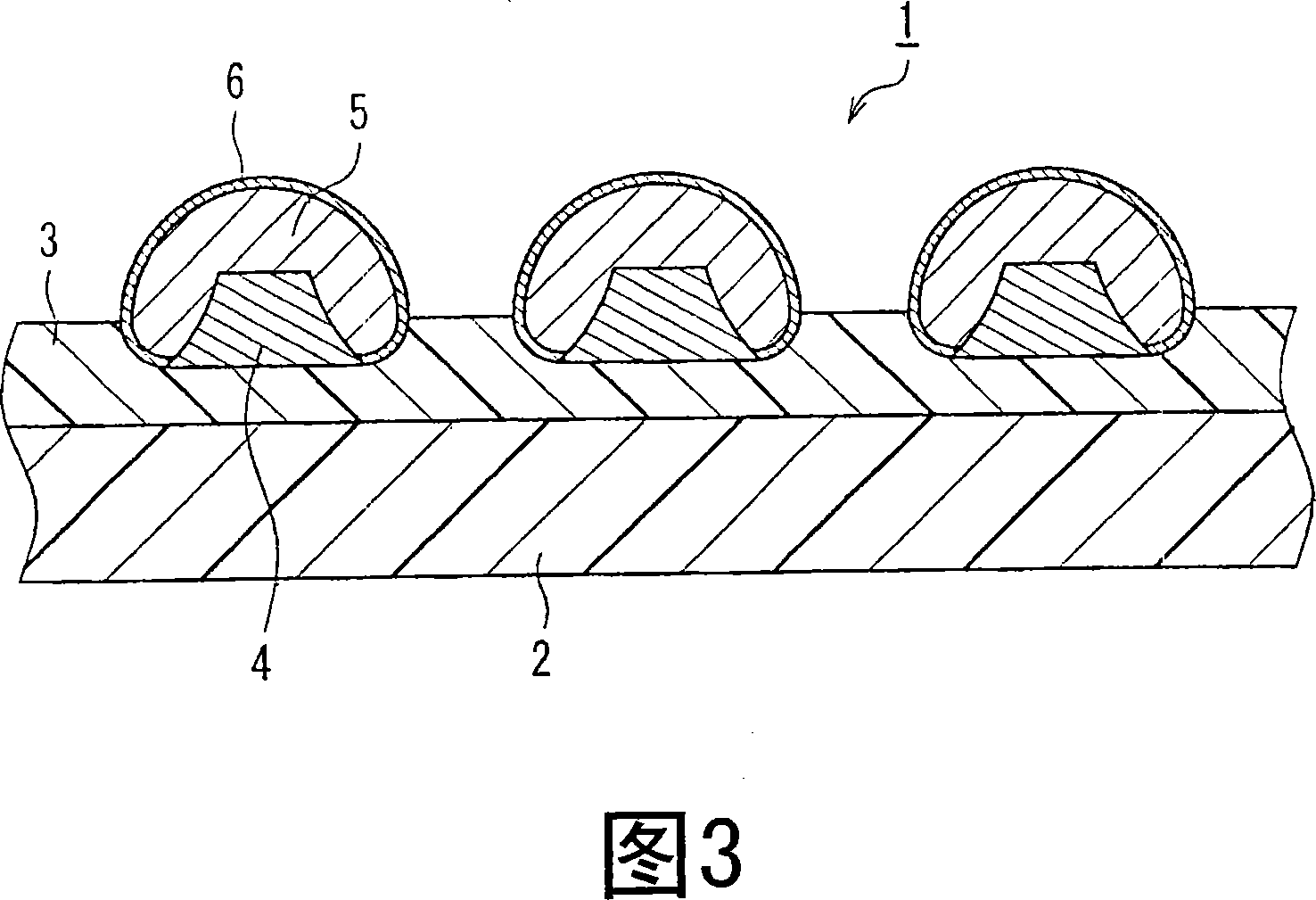

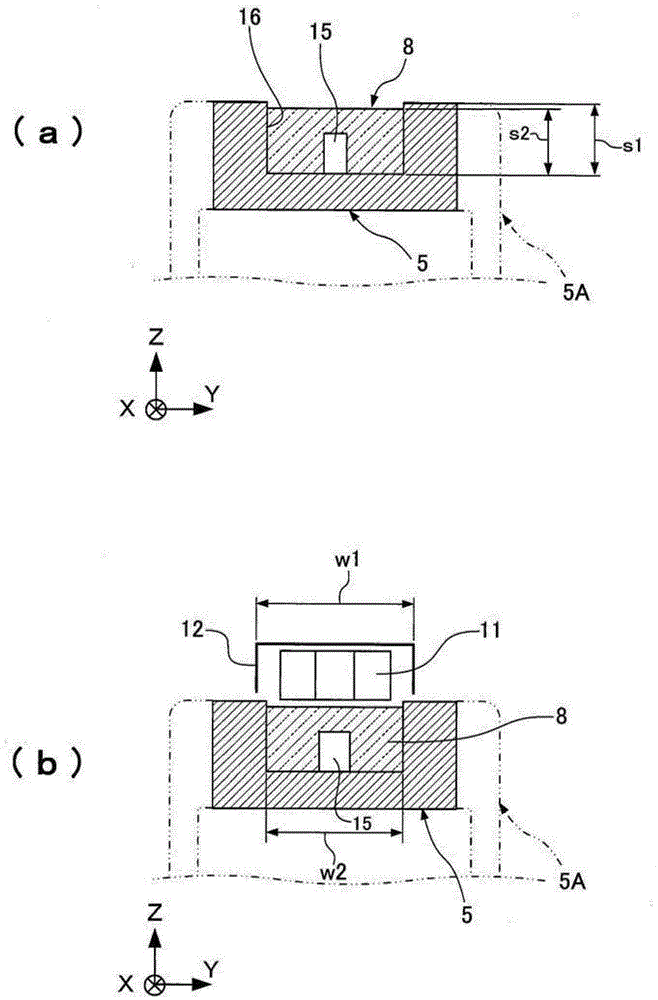

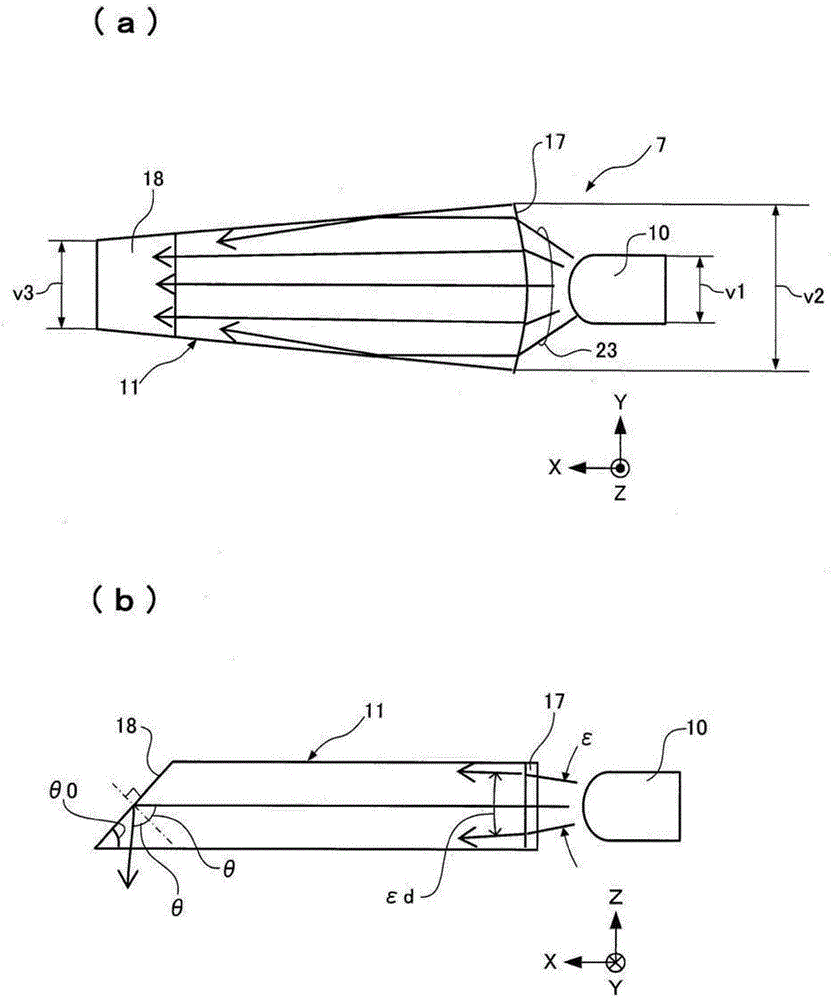

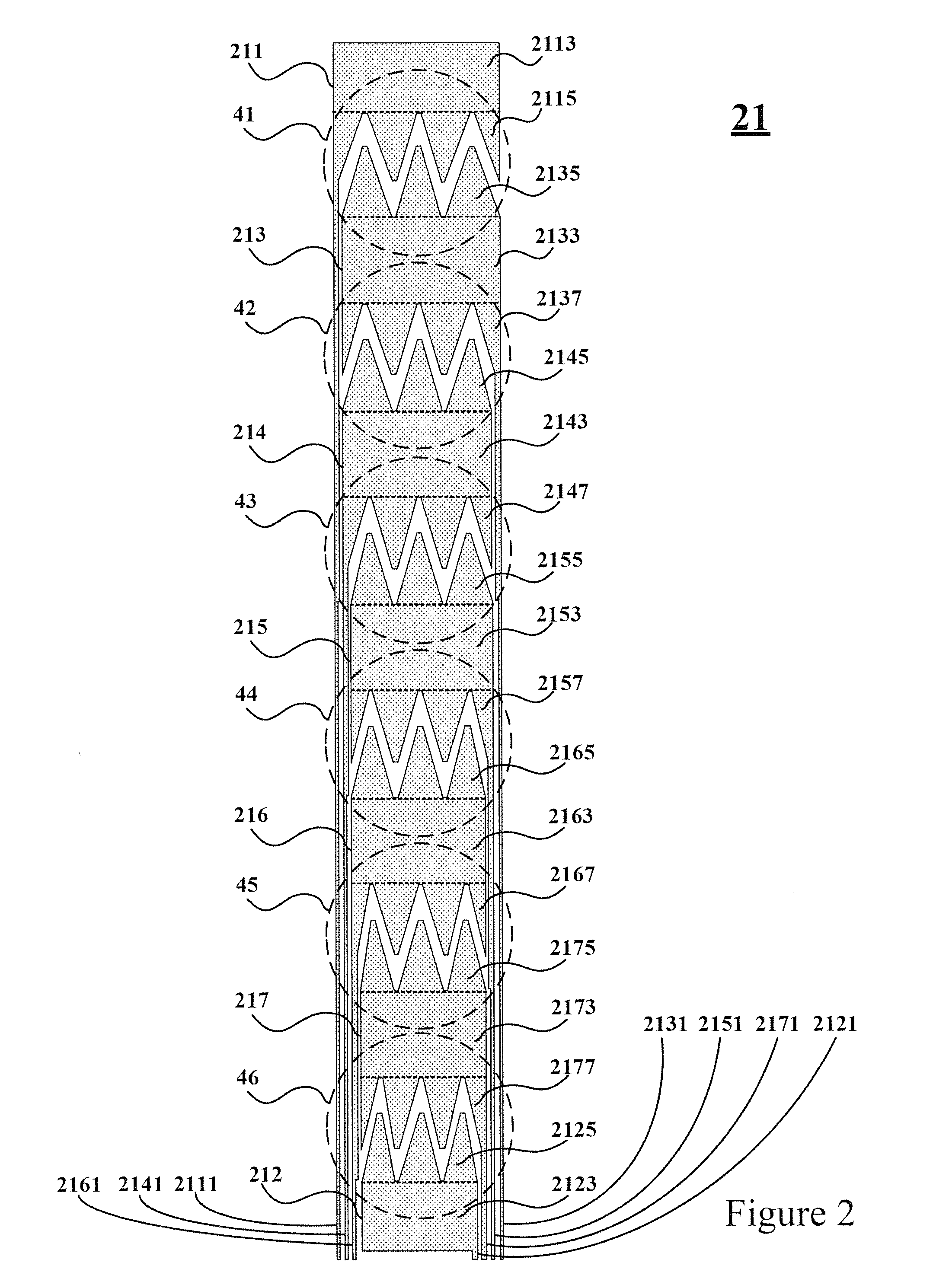

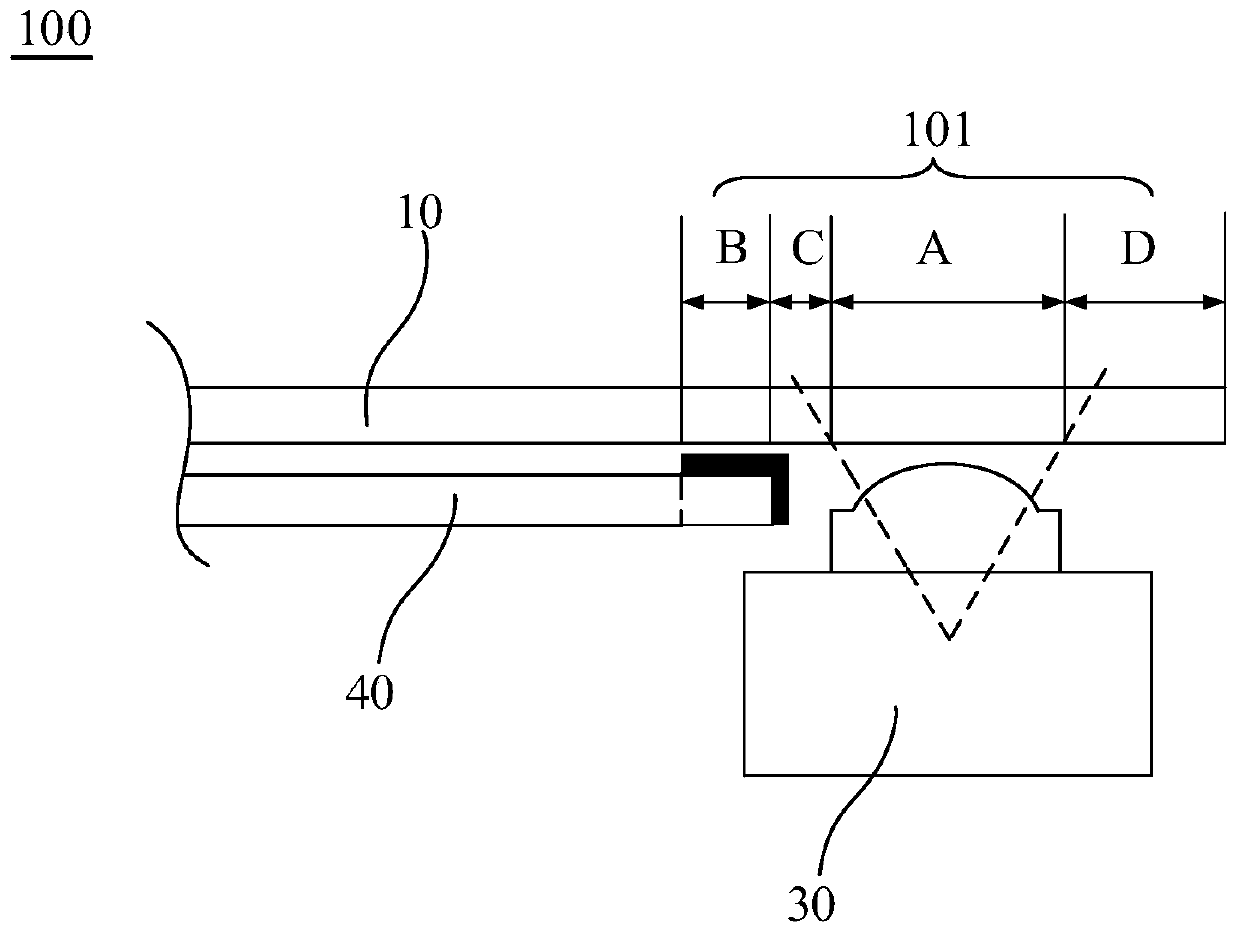

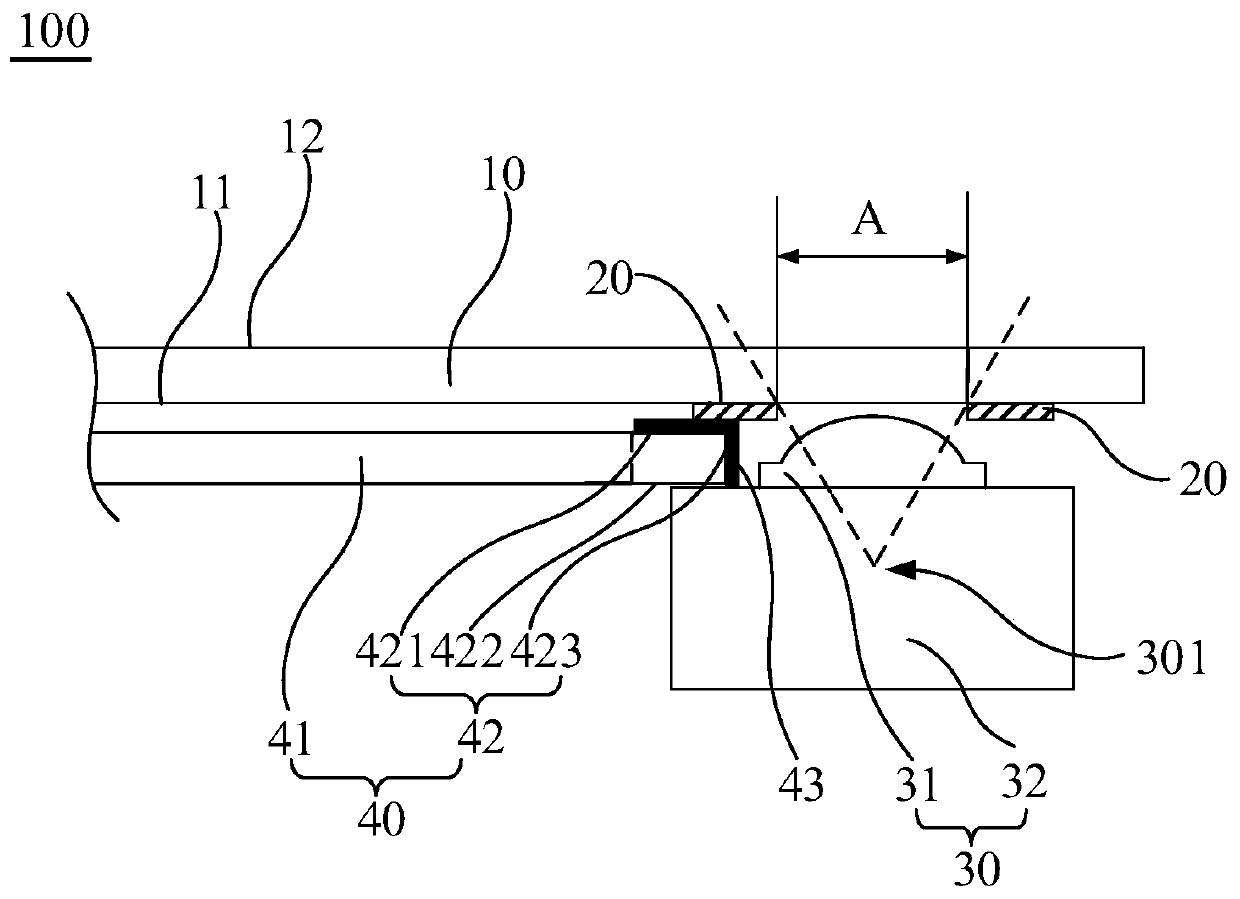

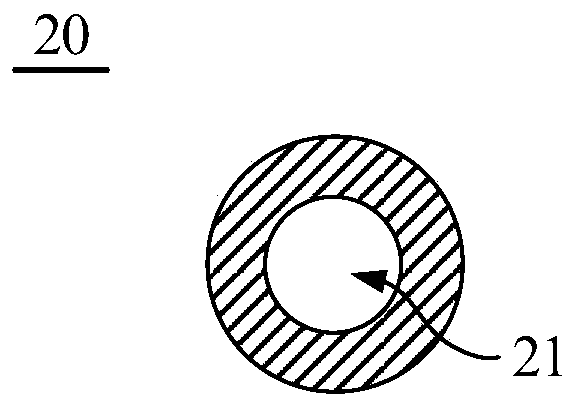

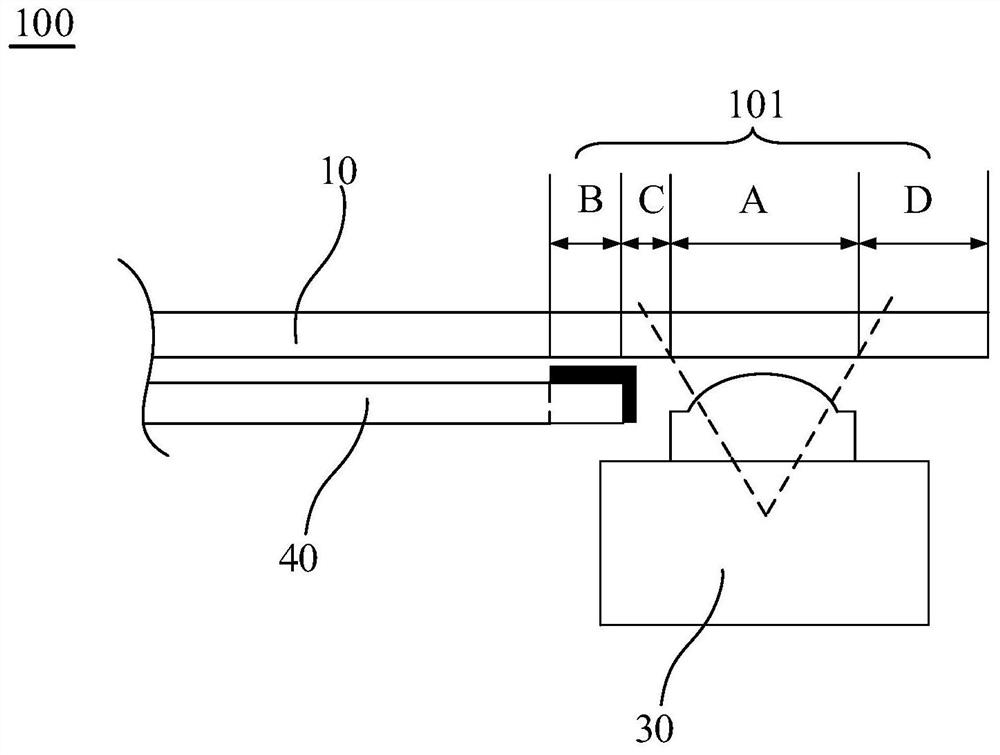

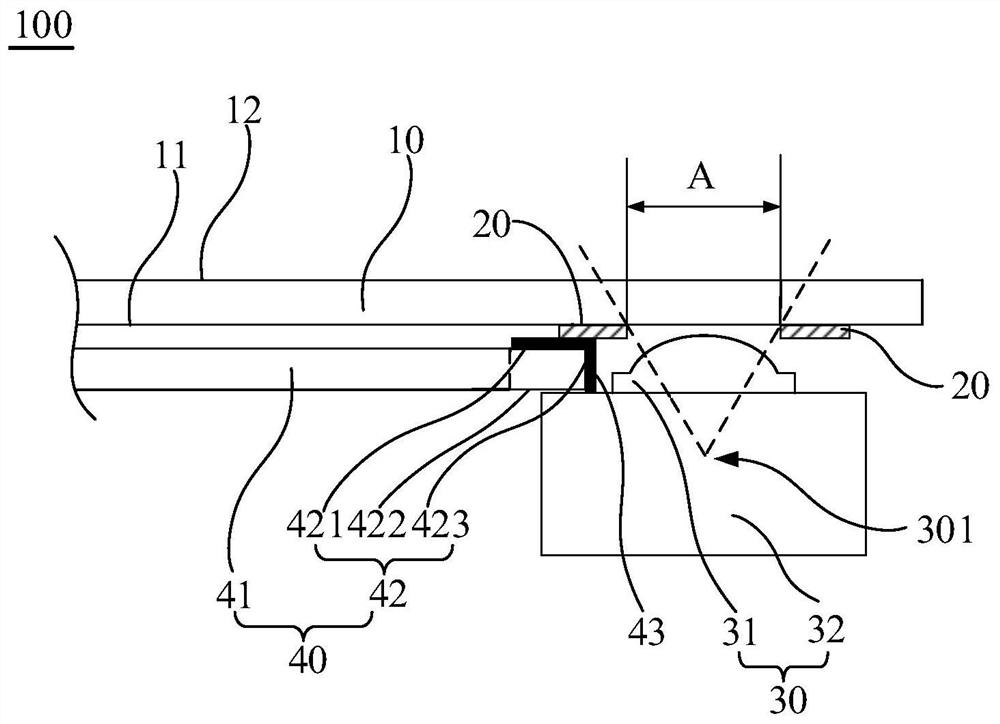

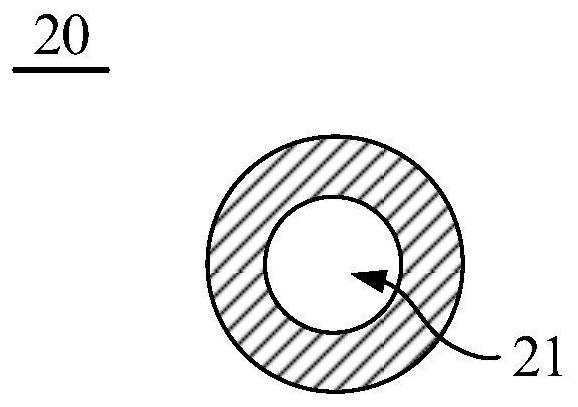

Indication lighting device and vacuum cleaner including the same

An indication lighting device provided is capable of reducing the number of electric wiring from a fixed, part to a moving part when an indication part is provided in the moving part's side. The indication lighting device makes indication by emitting light from a light source arranged in a fixed part to an optical waveguide arranged in a moving part, reflecting the light incident on the optical waveguide by reflection surfaces of prisms of the optical waveguide to an indication part provided in a tip side of the optical waveguide to be propagated, and emitting the light propagated inside the optical waveguide through the indication part.

Owner:PANASONIC INTELLECTUAL PROPERTY MANAGEMENT CO LTD

Sensing structure of touch panel

ActiveUS9194901B2High sensitivityImprove accuracyCapacitance measurementsNon-linear opticsTouch SensesTouchpad

The present invention relates to a sensing structure of touch panel, which comprises a plurality of electrode groups disposed on a substrate. The substrate has a first side and a second side. Each electrode group comprises a first external electrode, a second external electrode, a plurality of internal electrodes, and a plurality of wires. The first external electrode is disposed on a first side; the second external electrode is disposed on the second side; the plurality of internal electrodes are disposed between the first external electrode and the second external electrode; and the plurality of wires are disposed on both sides of the electrode group alternately. Thereby, by disposing the first external electrode, the second external electrode, and the internal electrodes, all being zigzag, the disposable number of electrodes in each electrode group is increased. Accordingly, the sensitivity of touch sensing for the sensing structure of touch panel is enhanced.

Owner:HEFEI SITRONIX CO LTD

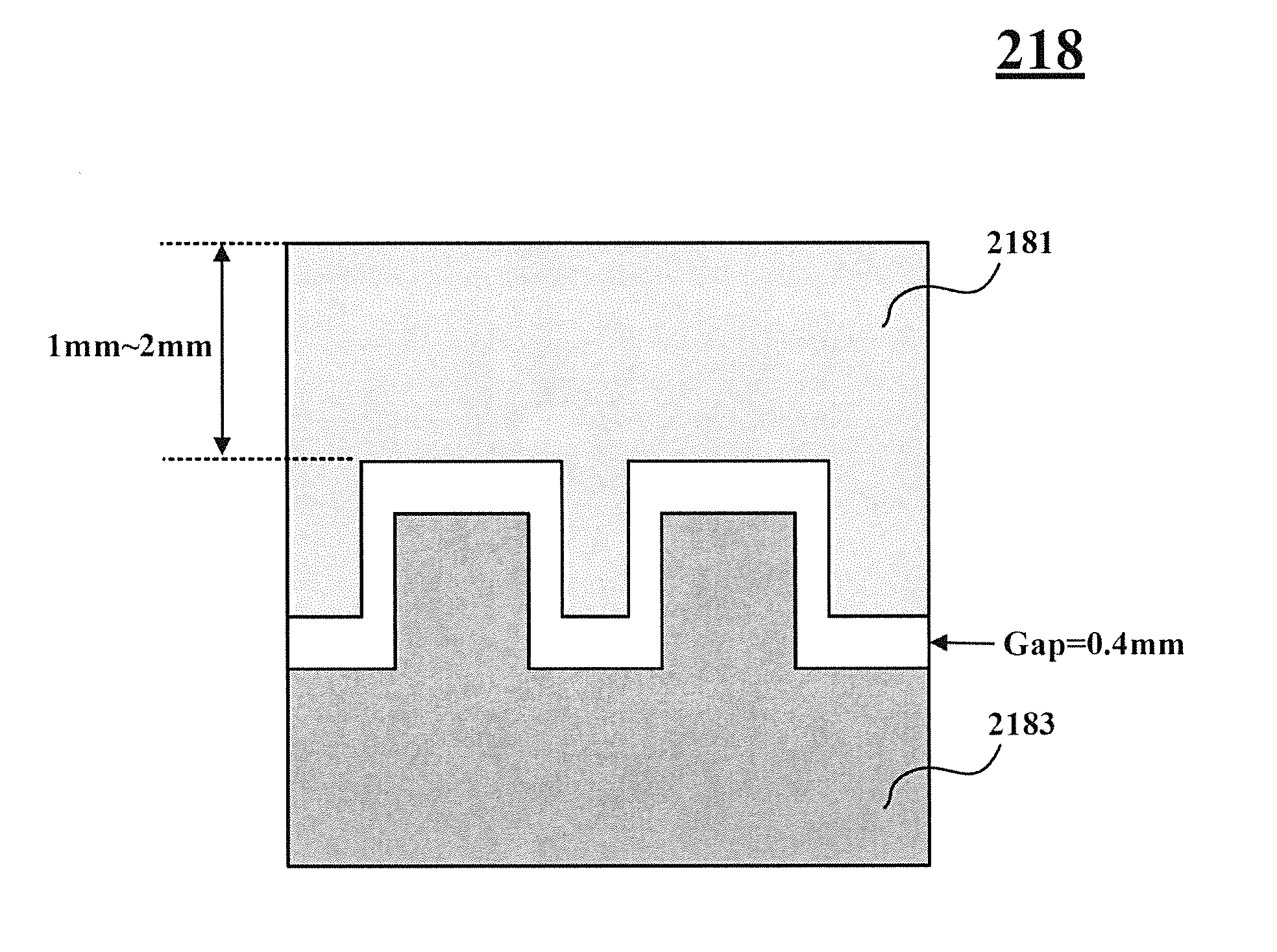

Liquid crystal panel for liquid crystal display device

ActiveUS7868987B2Improve the immunityEffective exposureNon-linear opticsLiquid-crystal displayEngineering

To utilize effectively the panel space of the liquid crystal panel, this invention has provided a wiring structure, in which the seal material and BM are coated in a superposition and the UV light is irradiated from one side of the TFT substrate; this invention has also provided a wiring structure, in which the seal material can still be irradiated by the UV light with high efficiency, meanwhile, the drop of the resistance value of the metal wiring on the TFT substrate can be restricted to a specific range. The solution is: the liquid crystal dropped is sandwiched between the TFT substrate and the CF substrate, meanwhile the liquid crystal panel is formed by adhering the light cured seal material disposed at the peripheral area of two substrates. In the adhering-formed liquid crystal panel, for the wiring portion, which is the portion of wiring disposed on the TFT substrate superposing the light cured seal material, the wiring structure is formed as follows, that is, the region of the seal material is divided into three regions, an adjacent region, a middle region and an outer region. The function of the respective regions must be held, and the resistance of the metal wiring is minimized under the precondition that the respective function is satisfied sufficiently.

Owner:INFOVISION OPTOELECTRONICS HLDG LTD

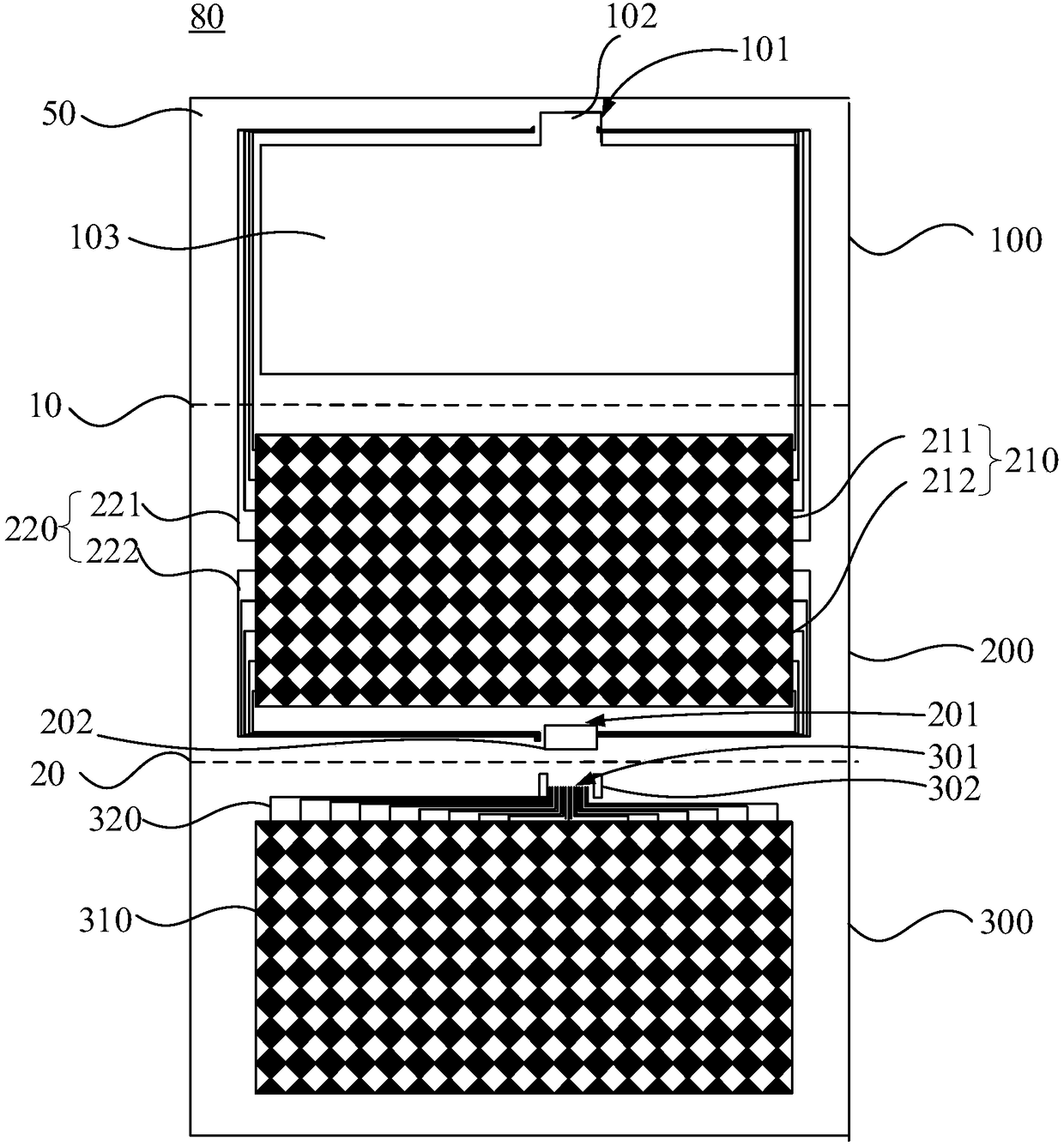

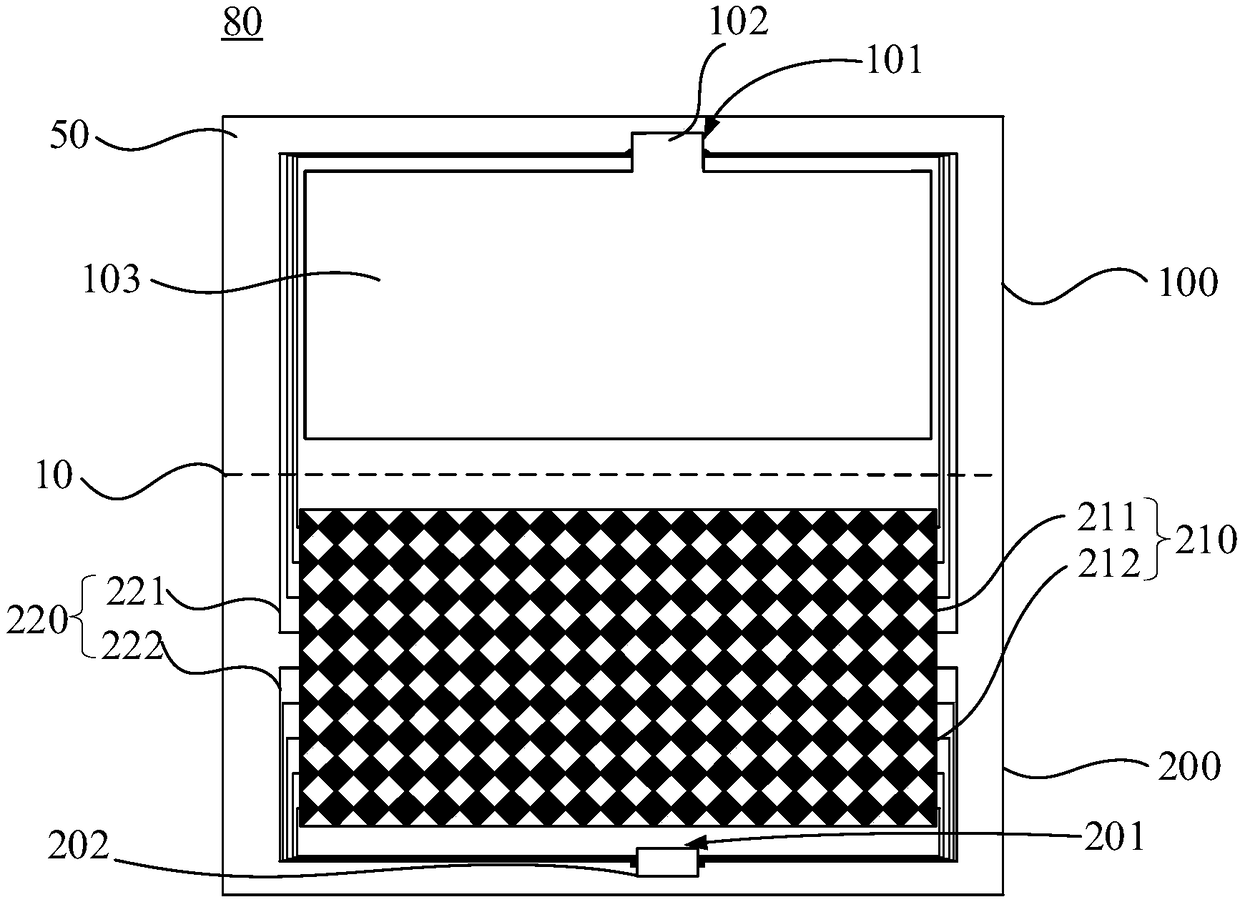

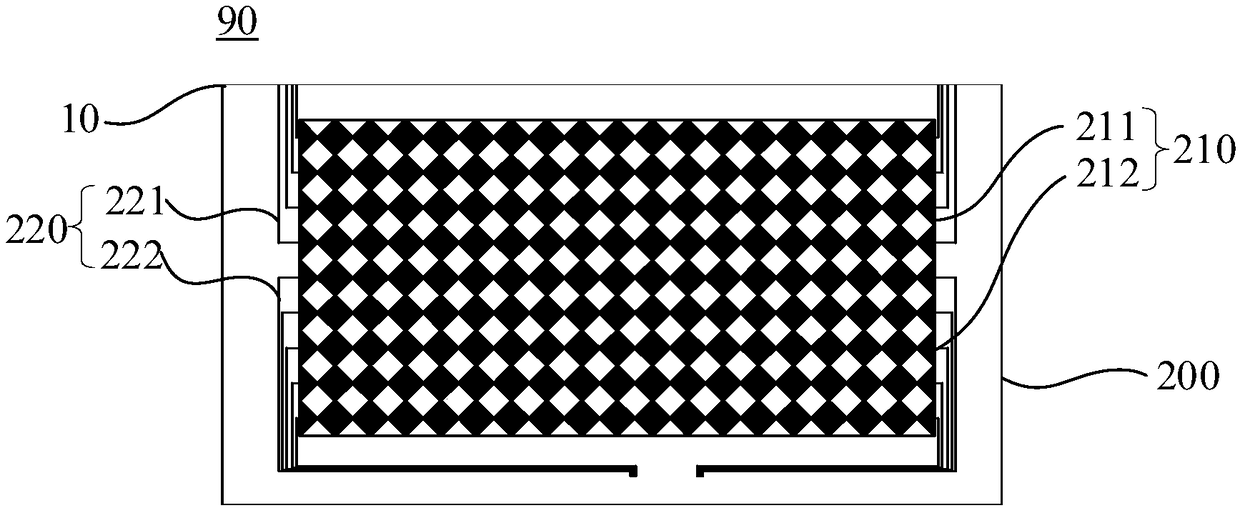

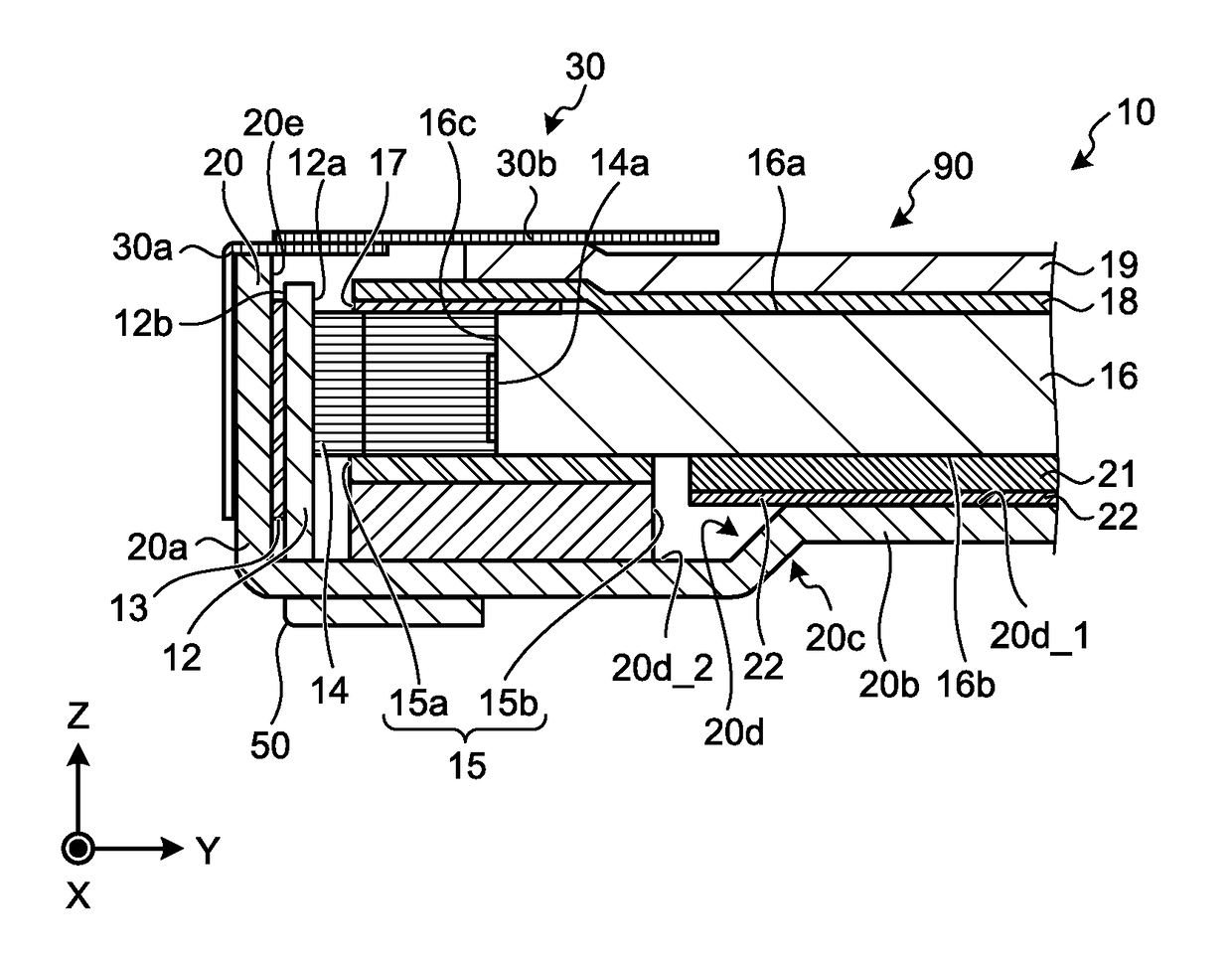

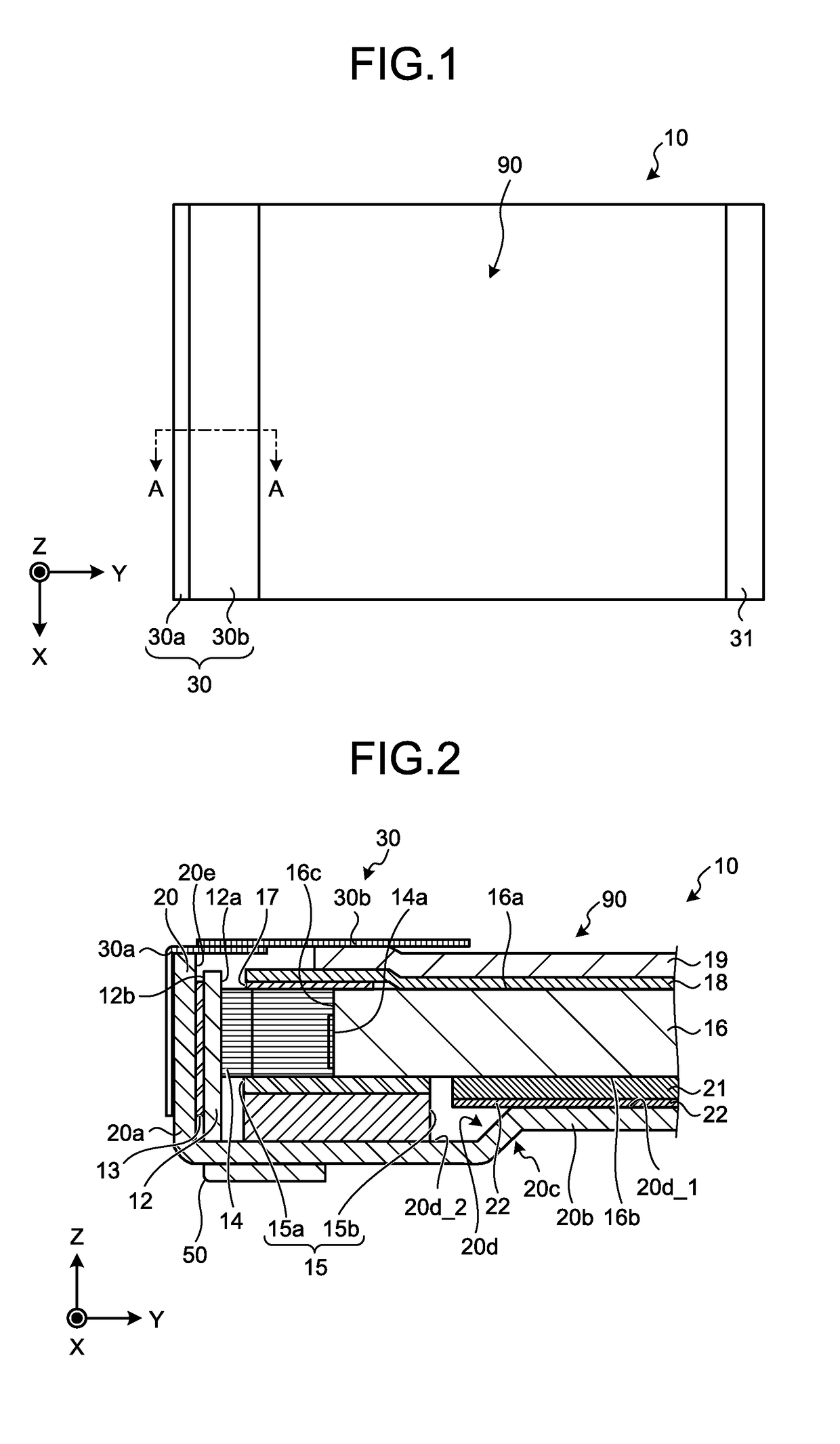

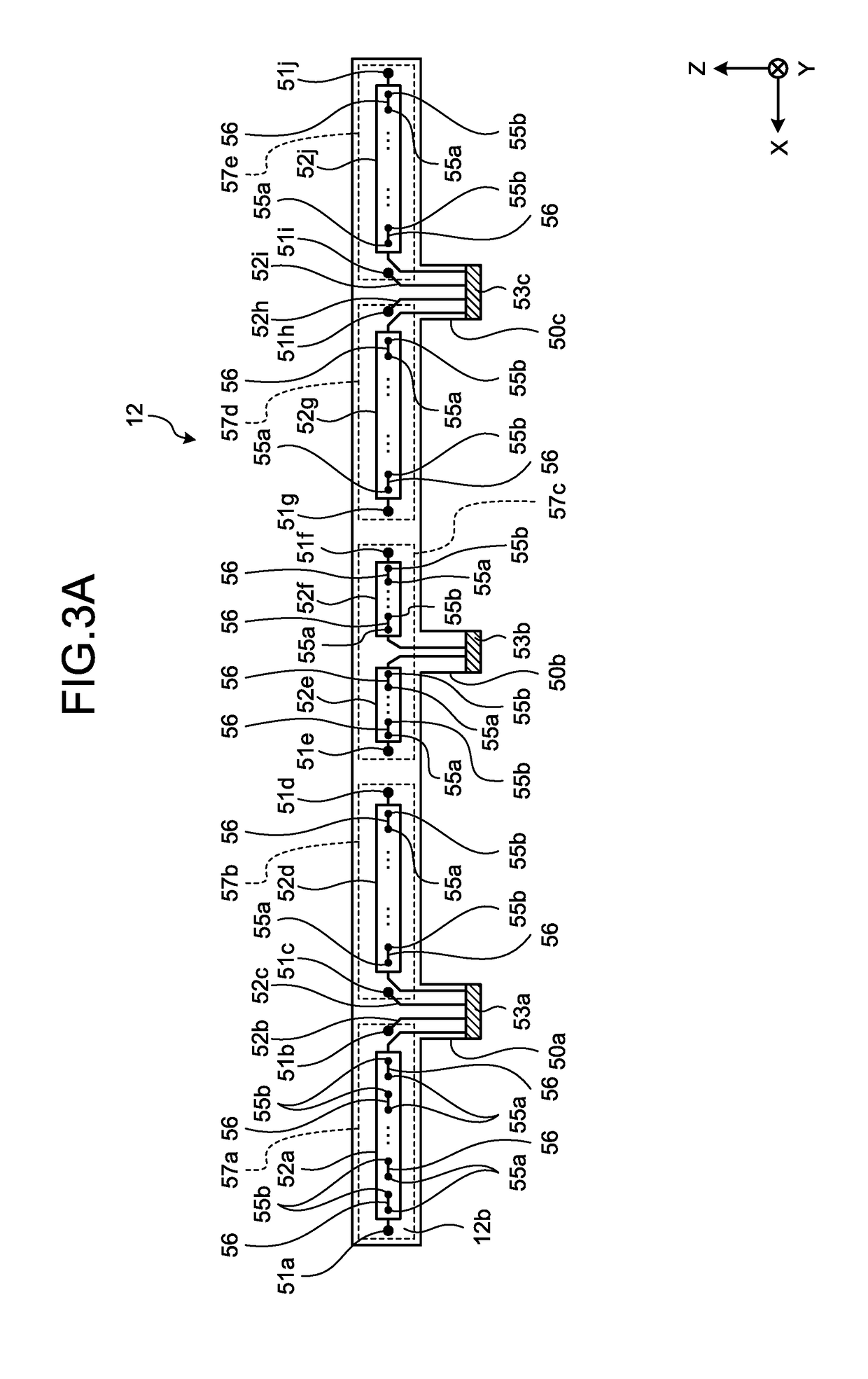

Planar illumination apparatus and substrate

ActiveUS20180059313A1Reduce trace widthMechanical apparatusElectric circuit arrangementsOptoelectronicsLight guide

A planar illumination apparatus according to an embodiment includes a light guide plate that outputs light entered into the light guide plate through a side face of the light guide plate, a plurality of light sources that are arranged on the side face side, and emit light to be entered into the side face, a substrate having a mounting surface where the light sources are mounted, and first wiring that is formed on an opposite surface opposite to the mounting surface of the substrate, and connects serially the light sources with each other.

Owner:MINEBEAMITSUMI INC

Dual-row cable structure

ActiveUS11355875B2Reduced soldering areaSpace neededTwo-part coupling devicesComputer periphery connectorsBoard-to-board connectorElectrical connection

A dual-row cable structure is applied to a first circuit board and a second circuit board. A board-to-board connector is on the first circuit board, and the first circuit board includes a first group of contacts and a second group of contacts. An electrical connector is on the second circuit board. The second circuit board includes a third group of contacts and a fourth group of contacts. The dual-row cable structure includes a wire assembly including high-speed signal wires, low-speed signal wires, one or more power wires, and one or more ground wires. The high-speed signal wires are connected to the first group of contacts. The low-speed signal wires, the power wire, and the ground wire are respectively connected to the second group of contacts. The third group of contacts and the fourth group of contacts are respectively connected to the other end of the wire assembly.

Owner:ADVANCED CONNECTEK INC

Flexible display panel and preparation method thereof

ActiveCN109448555AReduce trace widthReduce dead areaNon-linear opticsIdentification meansControl layerFlexible display

The invention discloses a flexible display panel and a preparation method thereof. According to the flexible display panel, a display area, a combination area and a frame area are defined; the flexible display panel includes a flexible substrate, a protection layer, a semiconductor layer and a touch control layer, wherein grid electrode lead wires, earth wires, touch control inductive pickup electrode lead wires and a display area liner are arranged on the portion, in the display area, of the flexible display panel; first through holes are formed in the protection layer in the frame area, thegrid electrode lead wires are electrically connected with grid electrodes in the semiconductor layer through the first through holes. The flexible display panel has the advantages that traditional wiring positions are changed, hidden wiring design is adopted, the wires and the display area are designed at the same positions, in this way, extra space cannot be occupied, the non-display area is reduced, and the panel edge wiring width is effectively reduced.

Owner:WUHAN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

Inkjet head and manufacturing method thereof

The inkjet head includes: a plurality of ink discharge nozzles which are arranged two-dimensionally; a plurality of pressure chambers which are in communication with the ink discharge nozzles so as to store ink, the pressure chambers being two-dimensionally arranged in correspondence with the ink discharge nozzles; a plurality of piezoelectric elements; a common electrode which is disposed on pressure chamber sides of the piezoelectric elements; a plurality of discrete electrodes which are disposed on sides of the piezoelectric elements opposite to the common electrode; and a plurality of discrete lead electrodes which feed electricity to the discrete electrodes, wherein: each of the piezoelectric elements is deformed by applying voltage to the common electrode and the discrete electrode so that a volume of the pressure chamber is varied to discharge a droplet of the ink from the ink discharge nozzle; and with respect to each pair of the discrete electrode and discrete lead electrode corresponding to each of the pressure chambers, when T1 is a thickness of the discrete electrode and T2 is a thickness of the discrete lead electrode which feed electricity to the discrete electrode, the discrete electrode and the discrete lead electrode are configured so that T1 and T2 satisfy the following formula: T1<T2.

Owner:FUJIFILM CORP

Electronic equipment

ActiveCN110266853AReduce trace widthIncrease the proportionTelevision system detailsColor television detailsBlack edgeCamera module

The invention provides electronic equipment which comprises a display screen, a camera module and a transparent cover plate, the display screen comprises a display area and a non-display area, the display area and the non-display area are adjacently arranged or at least part of the display area surrounds the non-display area, and the non-display area is of an arc-shaped structure; the camera module is arranged adjacent to the non-display area of the display screen, and comprises a lens part and a main body part, wherein the transparent cover plate comprises a first surface and a second surface which are arranged back to back; the display screen and the camera module are arranged on one side, close to the first surface, of the transparent cover plate; and the projection of the main body part of the camera module on the transparent cover plate is at least partially overlapped with the projection of the non-display area of the display screen on the transparent cover plate. The electronic equipment is small in screen black edge width and high in screen-to-body ratio.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

Thin film transistor and flat panel display device having the same

InactiveUS20130277660A1Avoid voltage dropReduce trace widthTransistorSolid-state devicesTitaniumFlat panel display

An oxide semiconductor thin film transistor and a flat panel display device incorporating the same oxide semiconductor thin film transistor. The thin film transistor includes a gate electrode formed on the substrate, a gate insulating layer formed on the substrate and covering the gate electrode, an oxide semiconductor layer formed on the gate insulating layer and covering the gate electrode, a titanium layer formed in a source region and a drain region of the oxide semiconductor layer, and source and drain electrodes respectively coupled to the source region and the drain region through the titanium layer and made of copper. The titanium layer reduces the contact resistance between the source and drain electrodes made of copper and the oxide semiconductor layer, forms a stable interface junction therebetween, and blocks a diffusion of copper.

Owner:PARK JIN SEONG +6

Touch device

InactiveCN103838420ASmall sizeImprove accuracyInput/output processes for data processingAnalog signal processingTouch panel

A touch device includes the following elements. A touch panel has two panel analog circuits and a panel digital circuit. Two inverting modules are assembled to two neighboring sides of the touch panel respectively, electrically coupled to the two panel analog circuits, and each electrically coupled to the panel digital circuit. A controlling module is assembled to the touch panel. The two inverting modules process analog signals transmitted from the two analog circuits into digital signals that are transmitted to the controlling module through the panel digital circuit. Therefore, the touch device may decrease a layout width that is occupied by the panel analog circuit.

Owner:CORETRONIC

Electronic equipment

ActiveCN110266853BReduce trace widthIncrease the proportionTelevision system detailsColor television detailsCamera moduleMechanical engineering

The present application provides an electronic device, the electronic device includes: a display screen, a camera module and a transparent cover, the display screen includes a display area and a non-display area, and the display area is adjacent to the non-display area Set or the display area at least partially surrounds the non-display area, the non-display area is an arc structure; the camera module is set adjacent to the non-display area of the display screen, and the camera module includes a lens part and the main body; the transparent cover includes a first surface and a second surface opposite to each other; the display screen and the camera module are arranged on a side of the transparent cover close to the first surface; the The projection of the main body of the camera module on the transparent cover at least partially overlaps the projection of the non-display area of the display screen on the transparent cover. The screen of the electronic device has a small width of black borders and a high screen-to-body ratio.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD