Patents

Literature

65 results about "Hardware Application" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The use of a piece of hardware with the requisite Parameters and ParameterValues. (caMAGE)

Intelligent hardware device control achieving method and device

ActiveCN104503688AReduce memory usageReduce battery consumptionProgramme controlComputer controlRelevant informationTerminal equipment

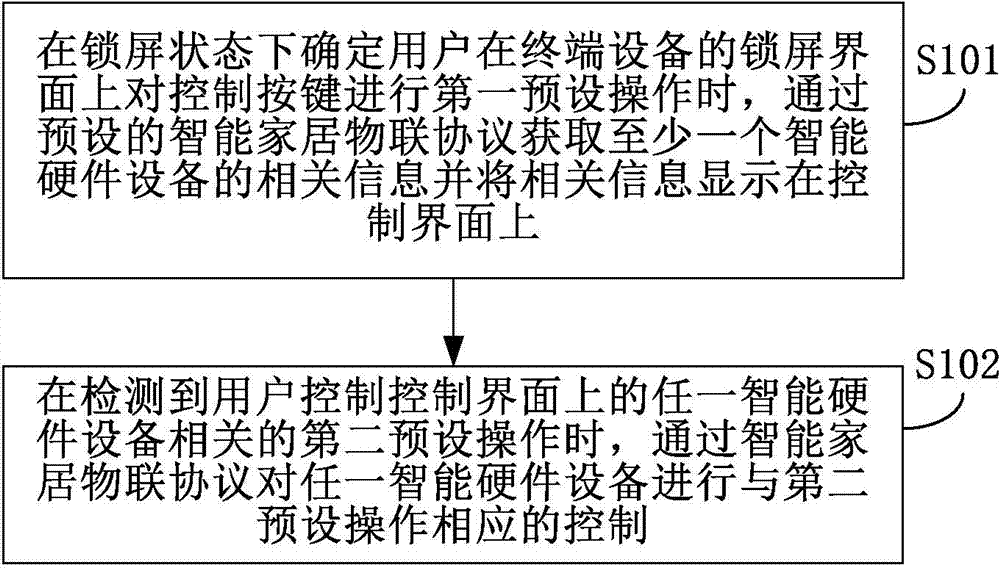

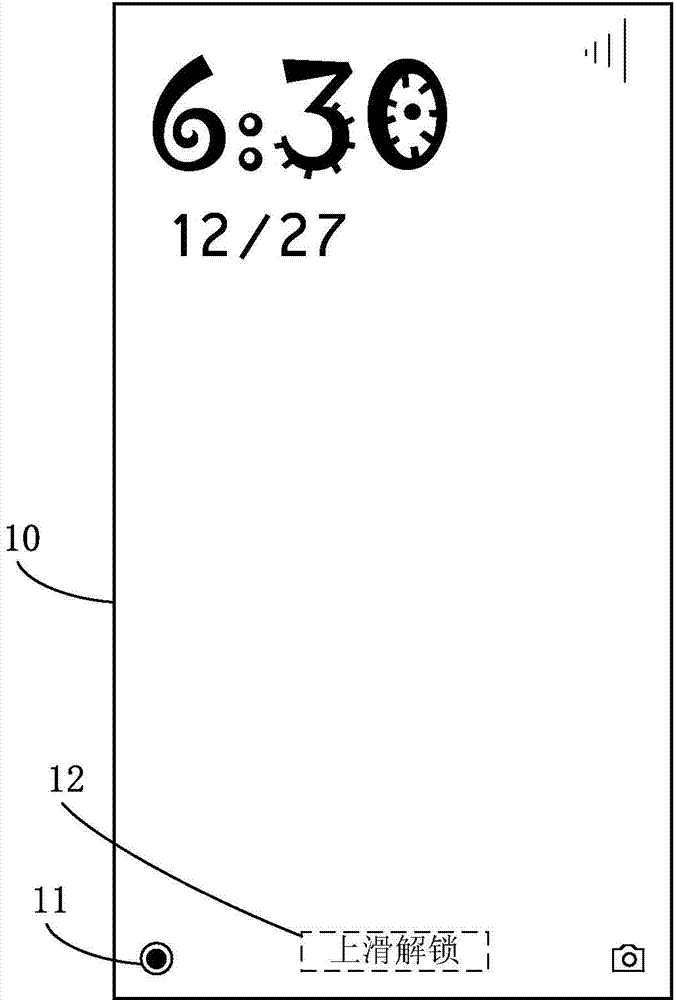

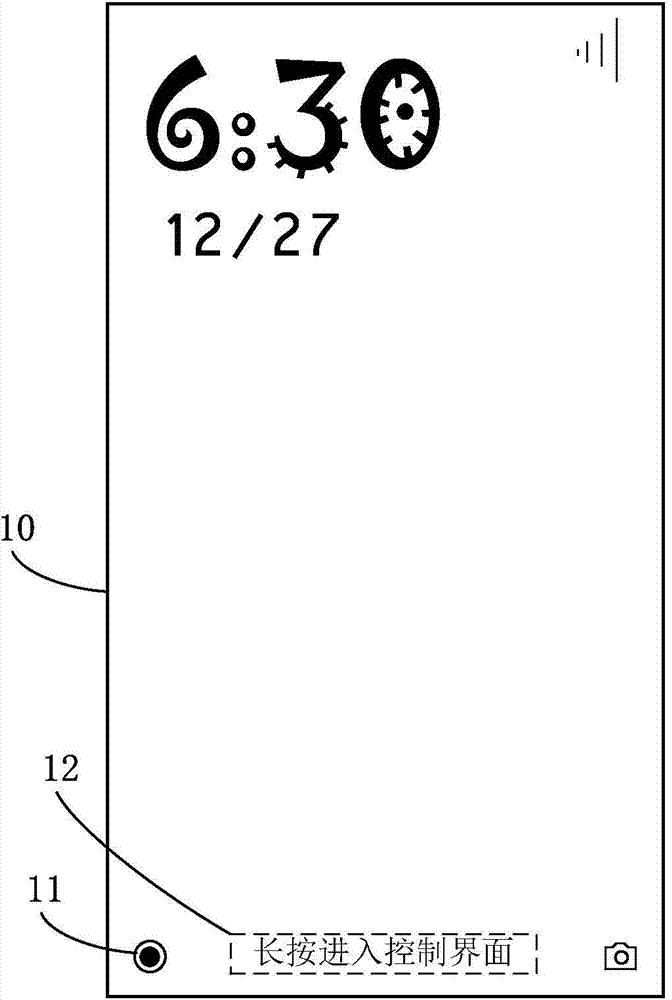

The invention relates to an intelligent hardware device control achieving method and device which aims at simplifying control operation of a user on an intelligent hardware device. The method includes acquiring relevant information of at least one intelligent hardware device through the preset intelligent home thing network protocol when determining that the user conducts first preset operation on a control key on a lock screen interface of a terminal device in the lock screen state and displaying the relevant information on the control interface; conducting controlling corresponding to second preset operation on the intelligent hardware device through the intelligent home thing network protocol when detecting that the user controls the second preset operation relevant to any intelligent hardware device on the control interface. By means of the method and device, the shortcoming that the user unlocks the terminal device and then enters the corresponding intelligent hardware applications to control the intelligent hardware device is overcome, the control operation process of the intelligent hardware device is simplified, and the intelligent hardware device can be controlled conveniently in the lock screen state of the terminal device.

Owner:XIAOMI INC

Multiprotocol data acquisition gateway

InactiveCN101626351ASolve problems such as multiple and complex interfacesFacilitate data exchangeNetwork connectionsProgramme total factory controlComputer hardwareData transformation

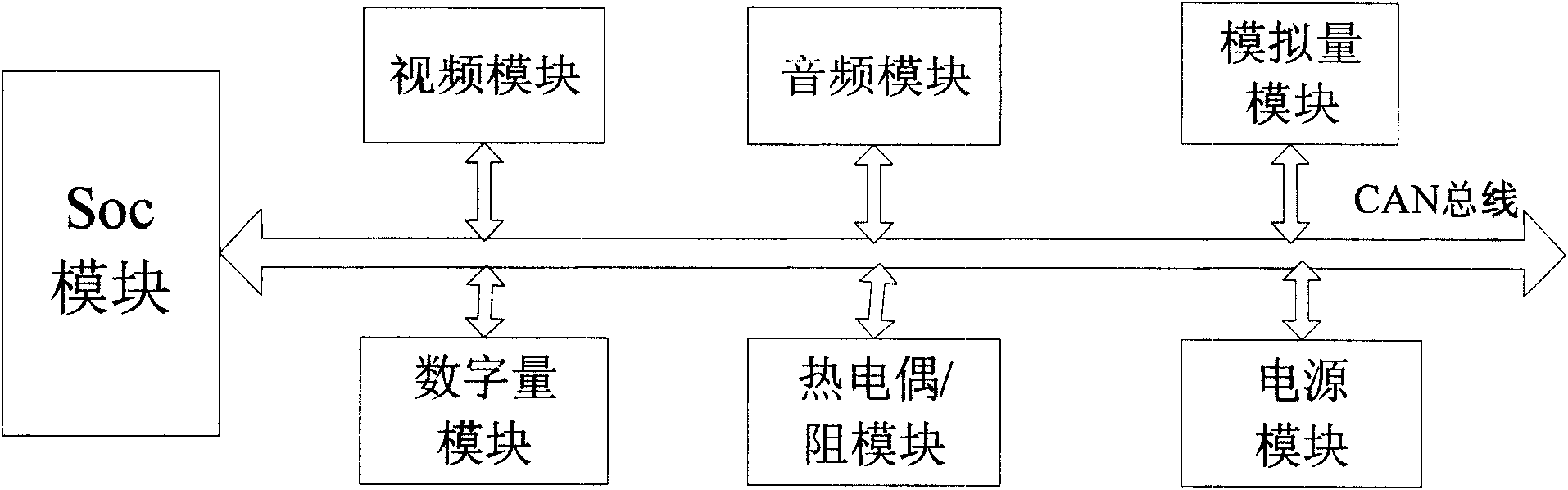

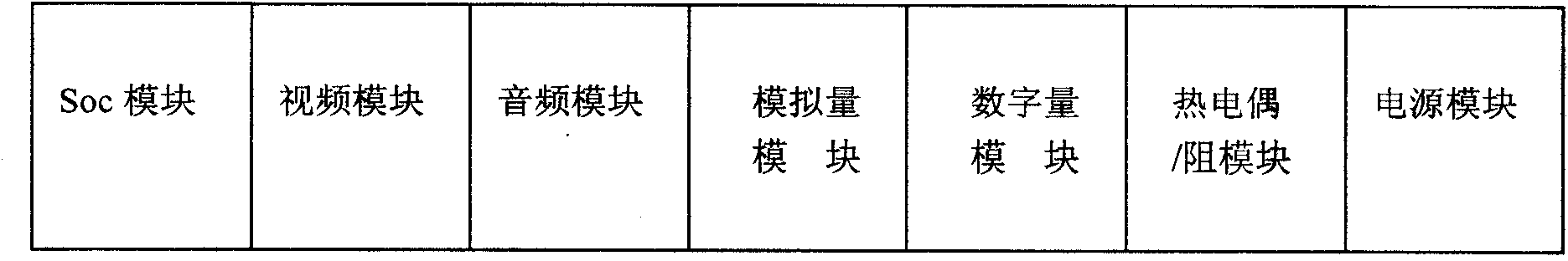

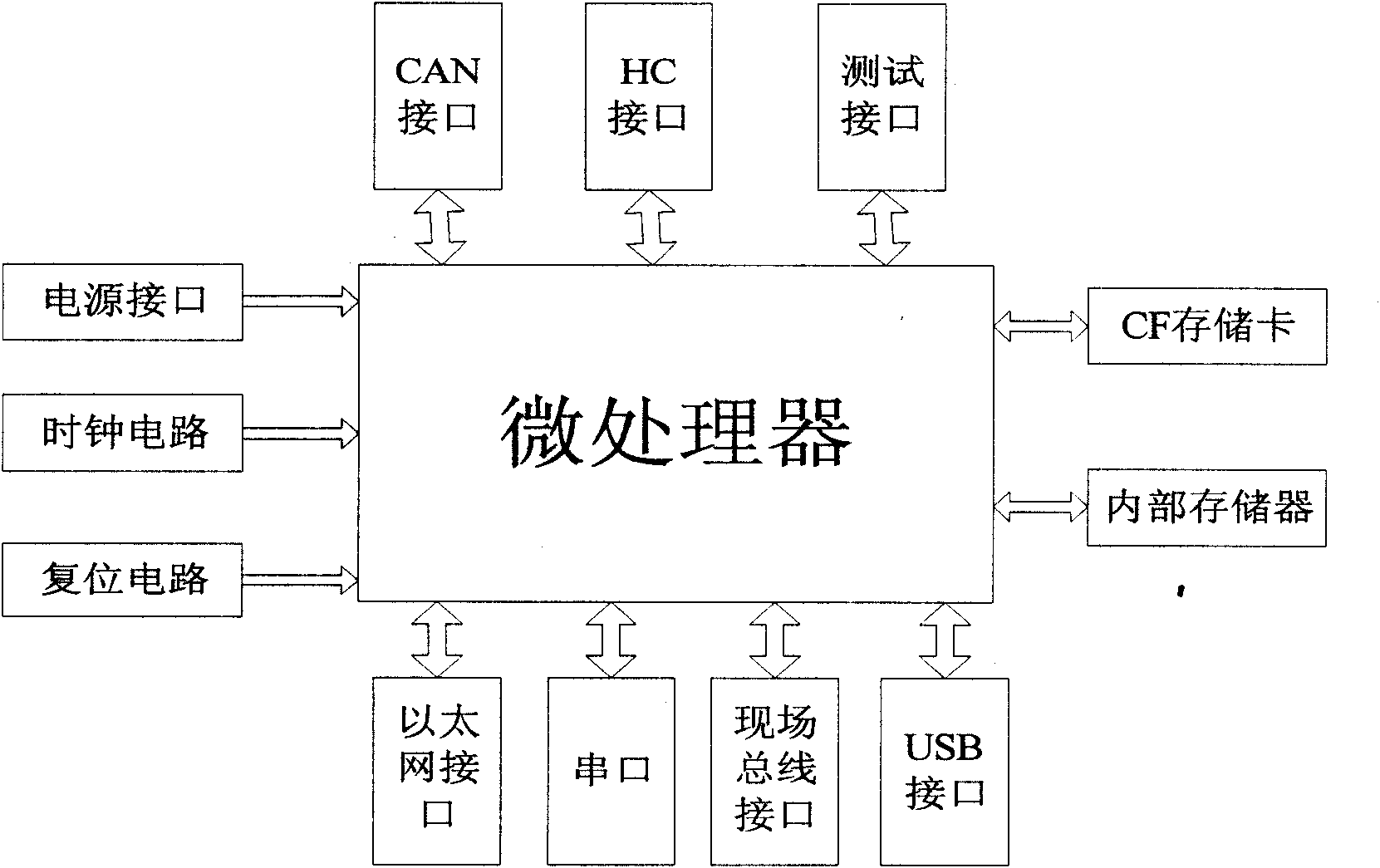

The invention relates to a device for connecting different types of exchanging system networks, in particular to a multiprotocol data acquisition gateway which adopts an ARM+DSP-based embedded system structure and comprises a hardware application platform, a system software platform and application software. A memory is used as a data server to set up a database; buses with different protocols access to the database to realize the protocol transformation, the data sharing and the communication among different networks with different protocols; the hardware application platform is provided with a universal interface so as to acquire standard and nonstandard current-voltage signals and audio-video signals in the industrial field or acquire the data of equipment with standard communication protocols in the industrial field and further realize the protocol transformation and provide a comprehensive data transformation scheme from a physical layer and a data link layer to an application layer, wherein the application layer is a single network protocol, which facilitates enterprise data intercommunication and reduces the application cost. The multiprotocol data acquisition gateway is applied to the electric power, the mine and the like to realize the remote centralized automatic data acquisition and is used for transforming different communication protocols of equipment in a system to the unified communication protocol.

Owner:QINGDAO GAOXIAO INFORMATION IND

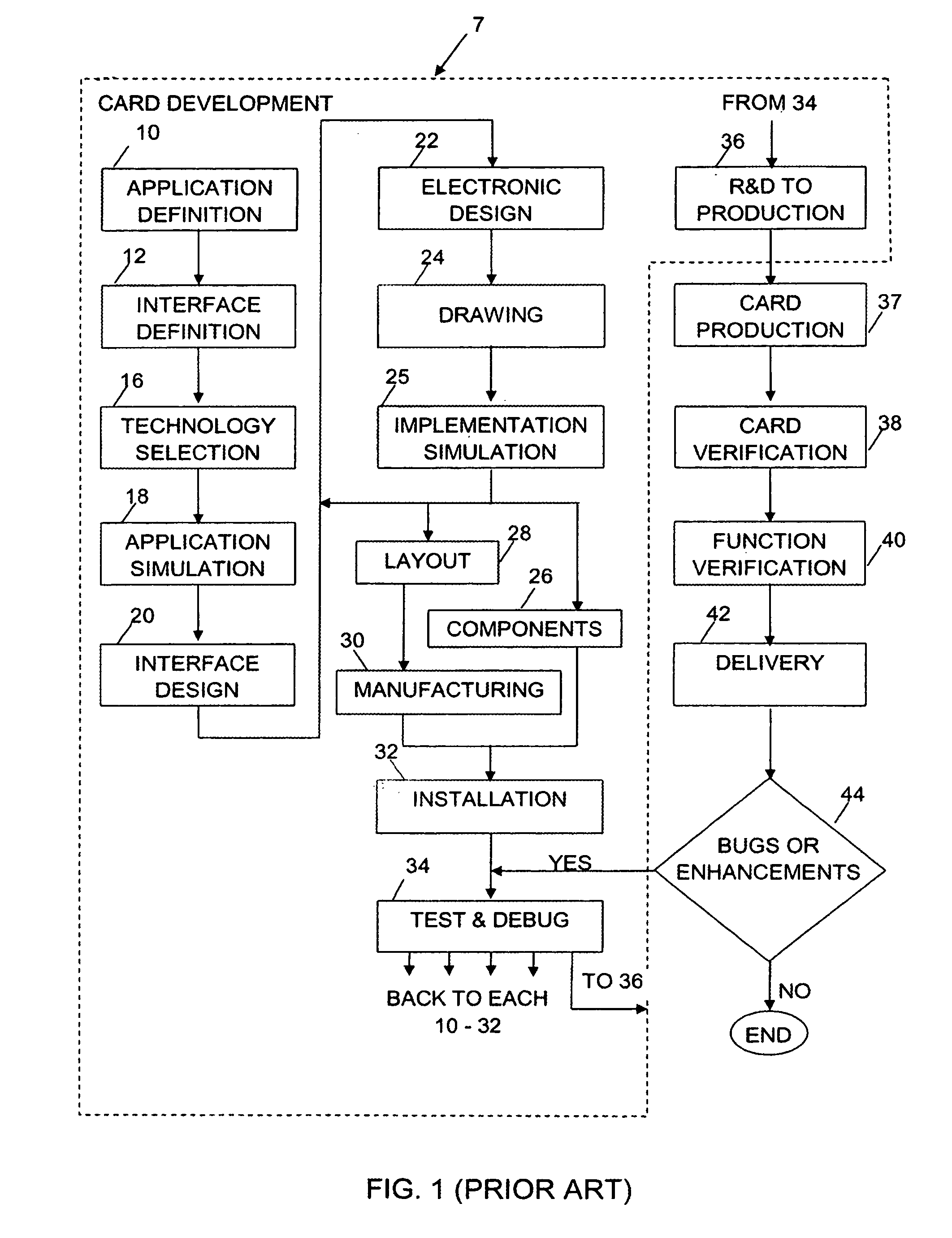

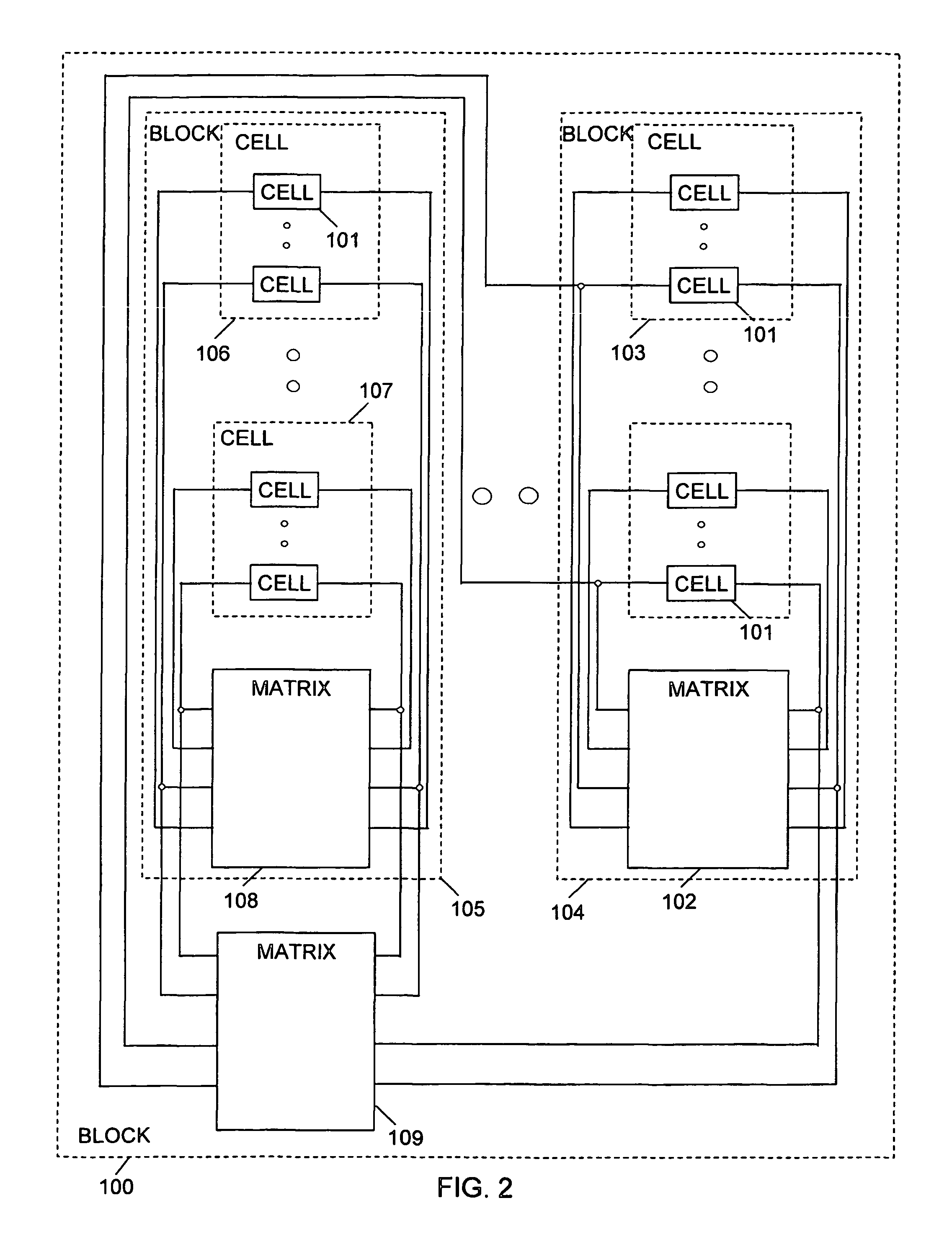

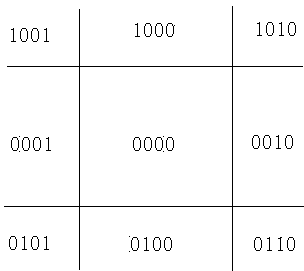

Universal hardware device and method and tools for use therewith

InactiveUS7185293B1Shorten the timeIncrease flexibilityCAD circuit designSpecial data processing applicationsComputer scienceHardware Application

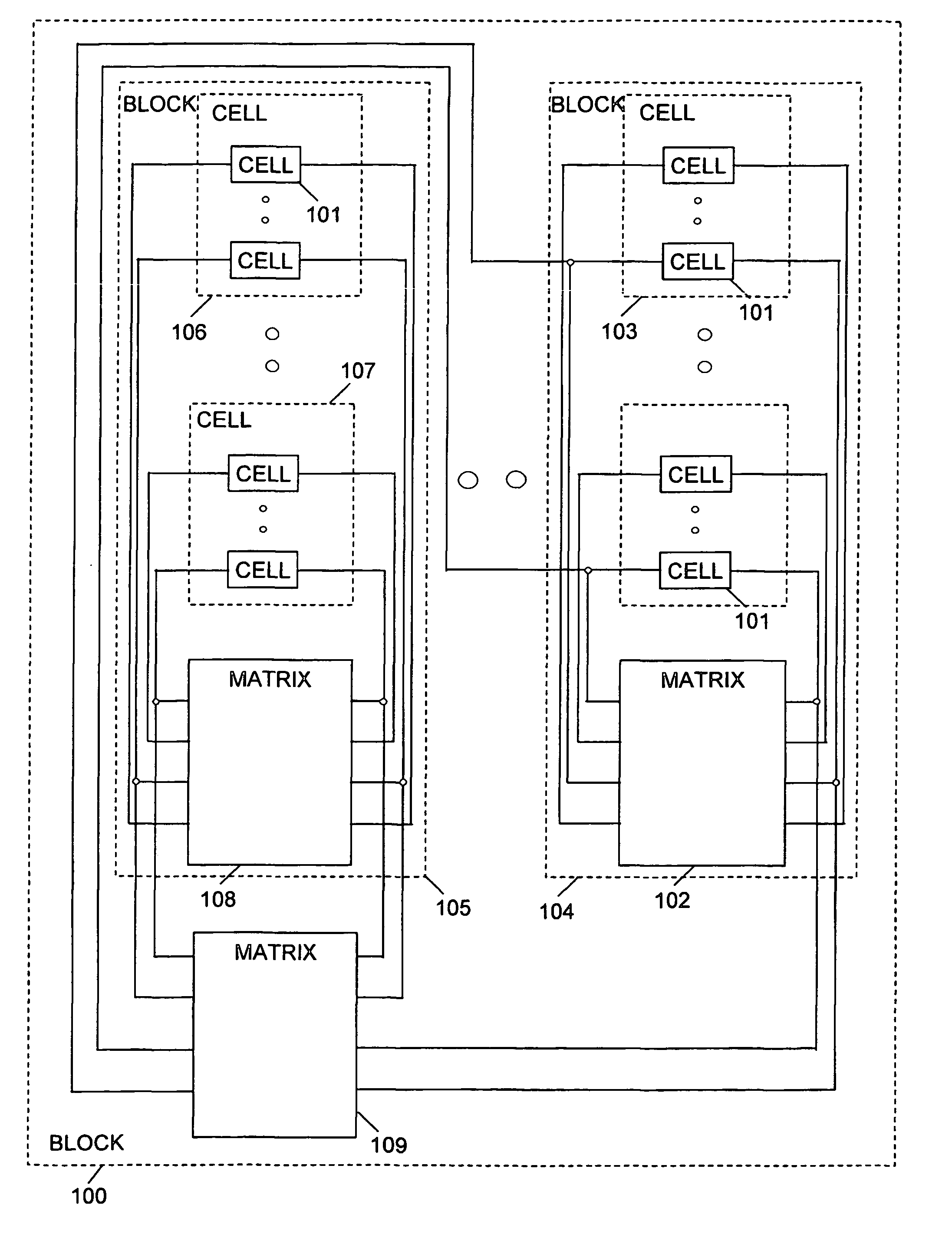

A universal hardware device including at least one plurality of cells for storing data; and at least one programmable matrix coupled to the at least one plurality of cells, whereby a plurality of hardware applications may be implemented by selectively storing data in the cells and selectively programming the matrix to connect at least one of the cells to at least one of the cells.

Owner:OFER MEGED

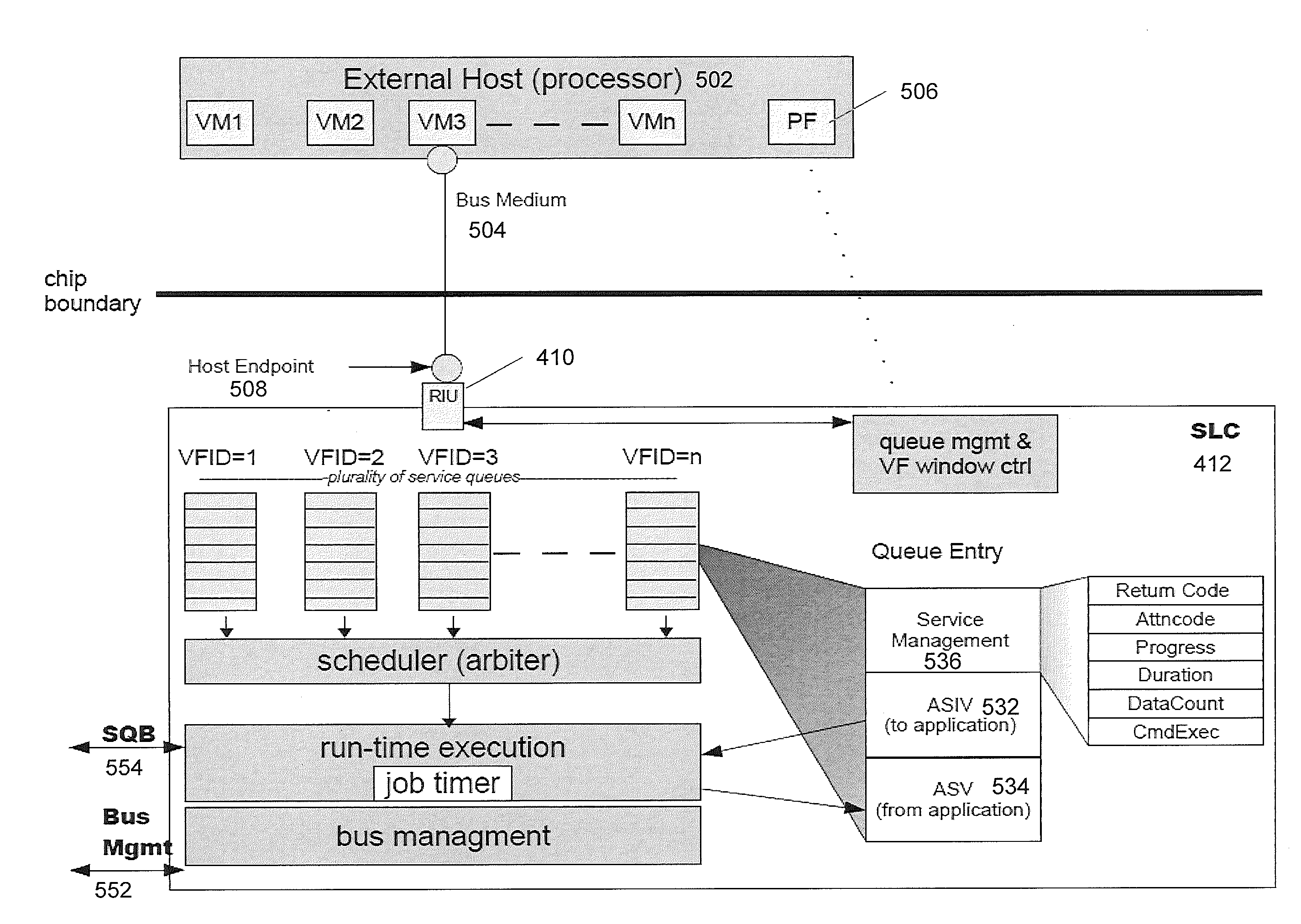

Encapsulation of an application for virtualization

InactiveUS20140282506A1Interprogram communicationSoftware simulation/interpretation/emulationVirtualizationComputerized system

Embodiments relate to a computer system comprising a service layer controller. The computer system comprises a ring interface unit configured to provide access to a host system that enables access to a plurality of virtual machines (VMs). The computer system comprises a hardware application configured to be encapsulated by the service layer controller such that the hardware application communicates to the host system via interfaces controlled by the ring interface unit and service layer controller.

Owner:IBM CORP

Commodity information recommending method and device

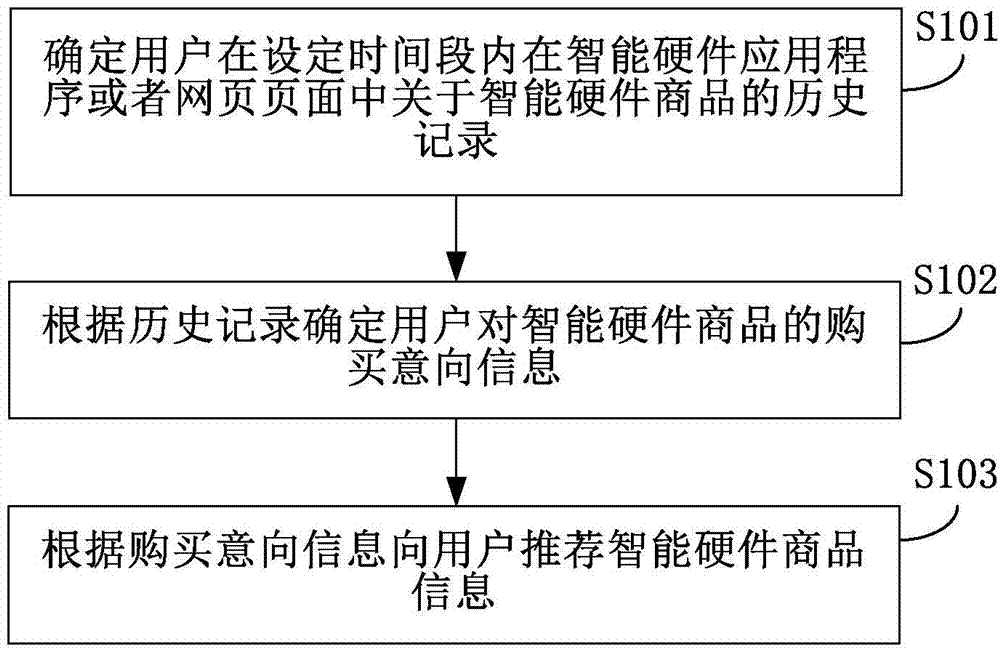

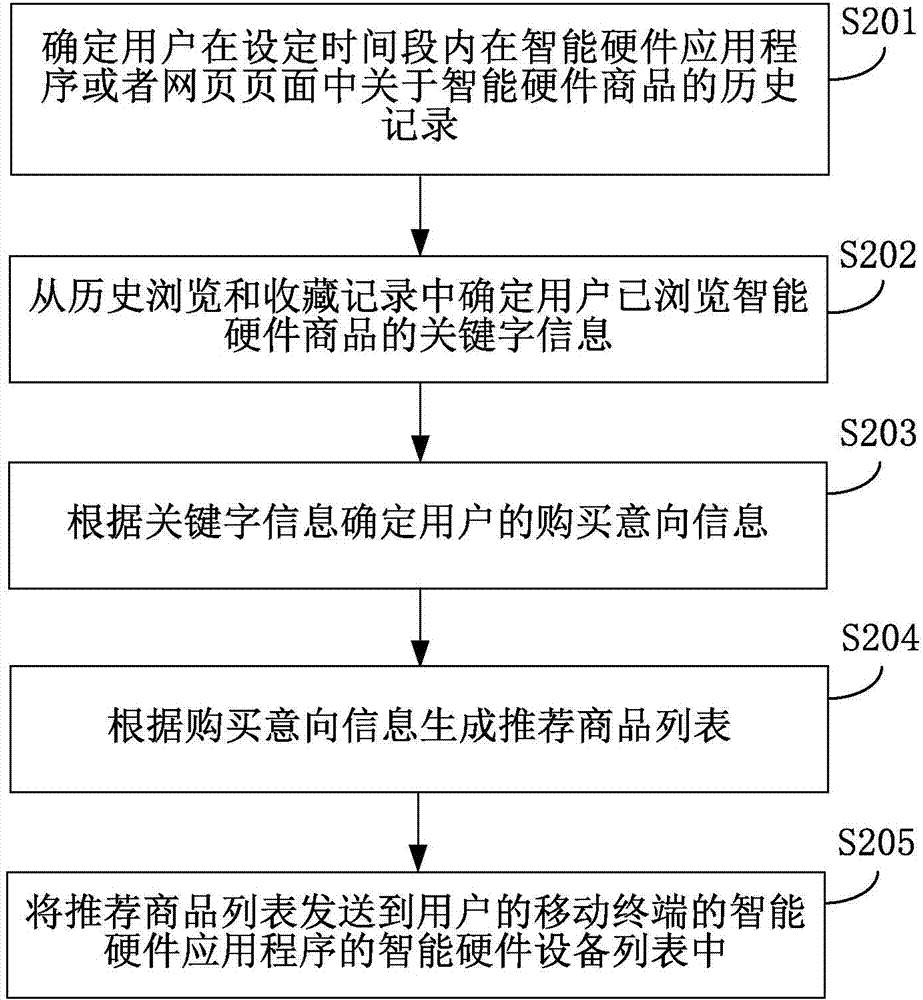

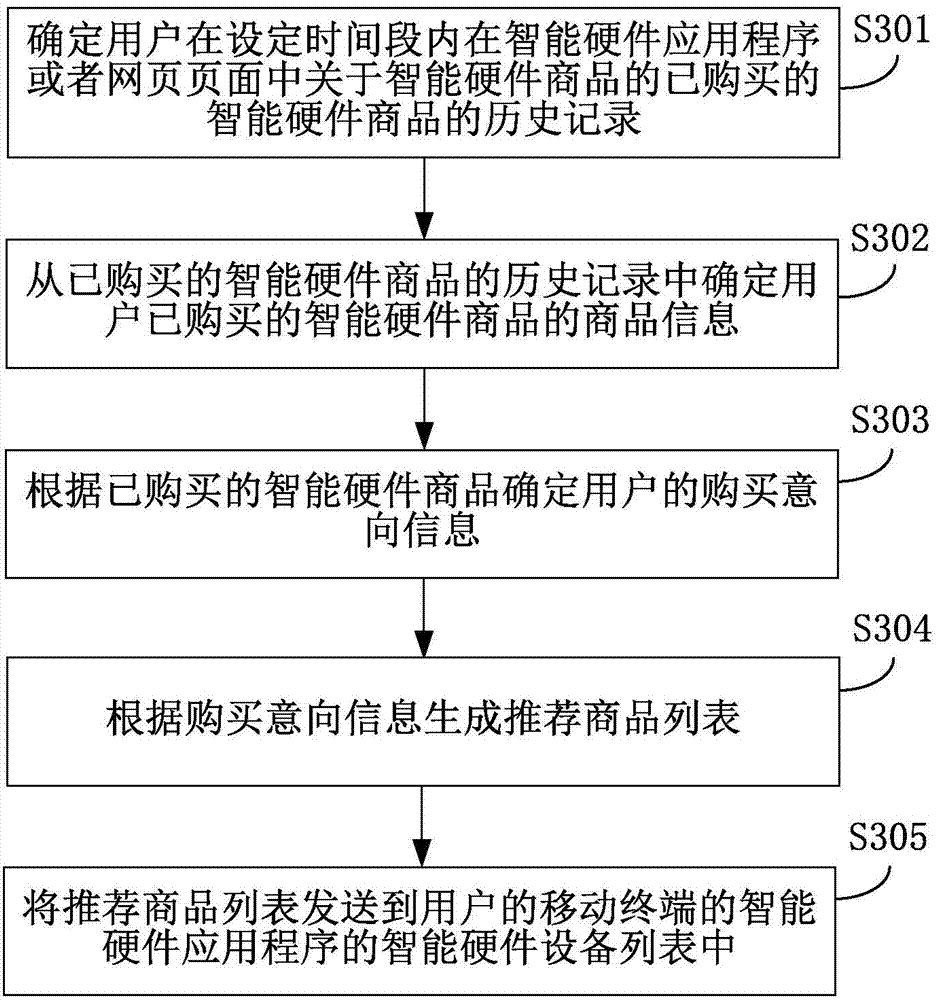

The invention relates to a commodity information recommending method and device and aims to provide better user experience of purchasing intelligent hardware commodities. The method includes: determining a user's historical record, about intelligent hardware commodities, in an intelligent hardware application or a webpage; according to the historical record, determining the user's intentional information about purchasing the intelligent hardware commodities; according to the intentional information, recommending the information of the intelligent hardware commodities to the user. The commodity information recommending method and device has the advantages that potential demands of users are acquired according to purchase intentional information of the users, the information of the intelligent hardware commodities which the users potentially demand is recommended to the users, and user experience of purchasing the intelligent hardware commodities is improved.

Owner:XIAOMI INC

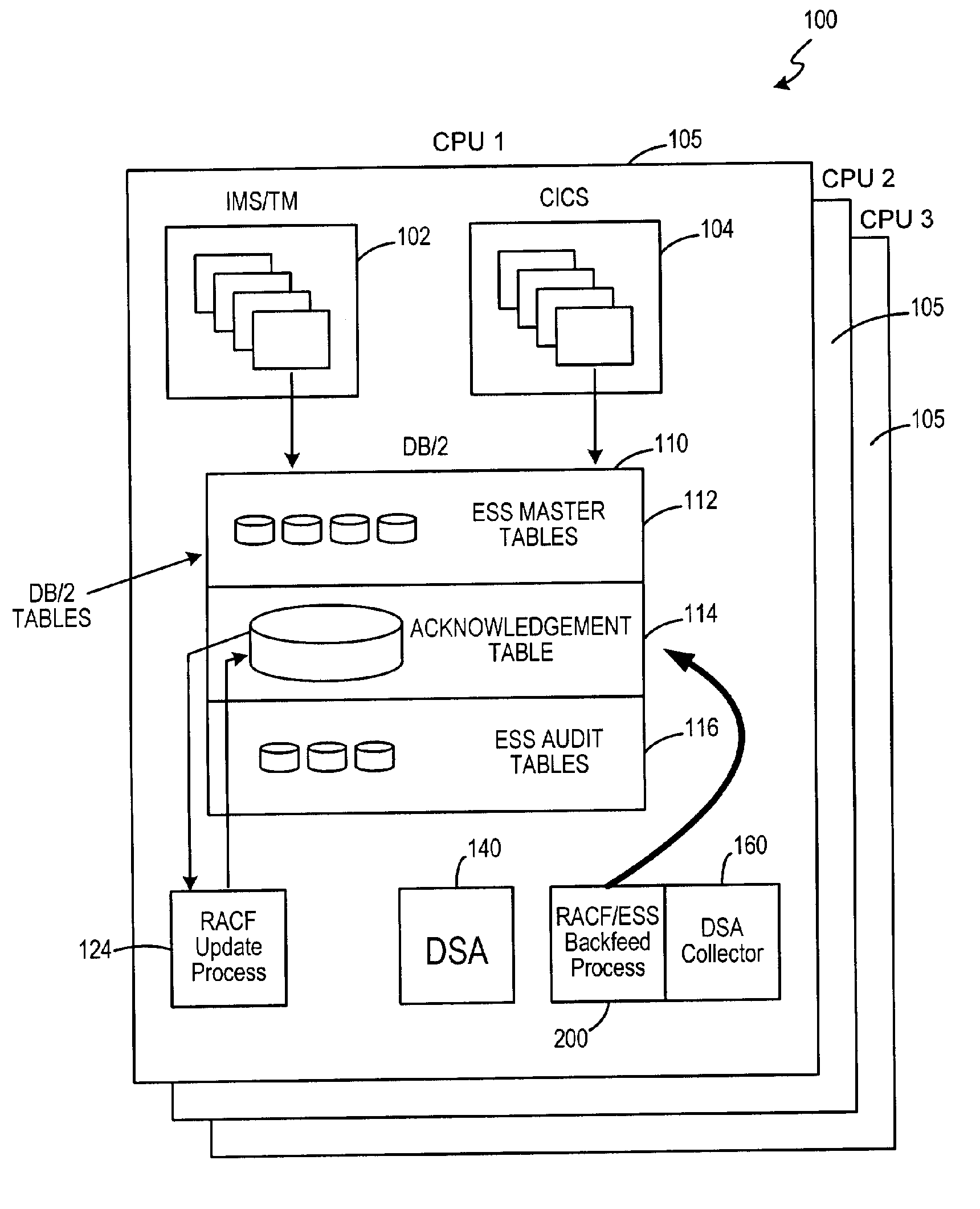

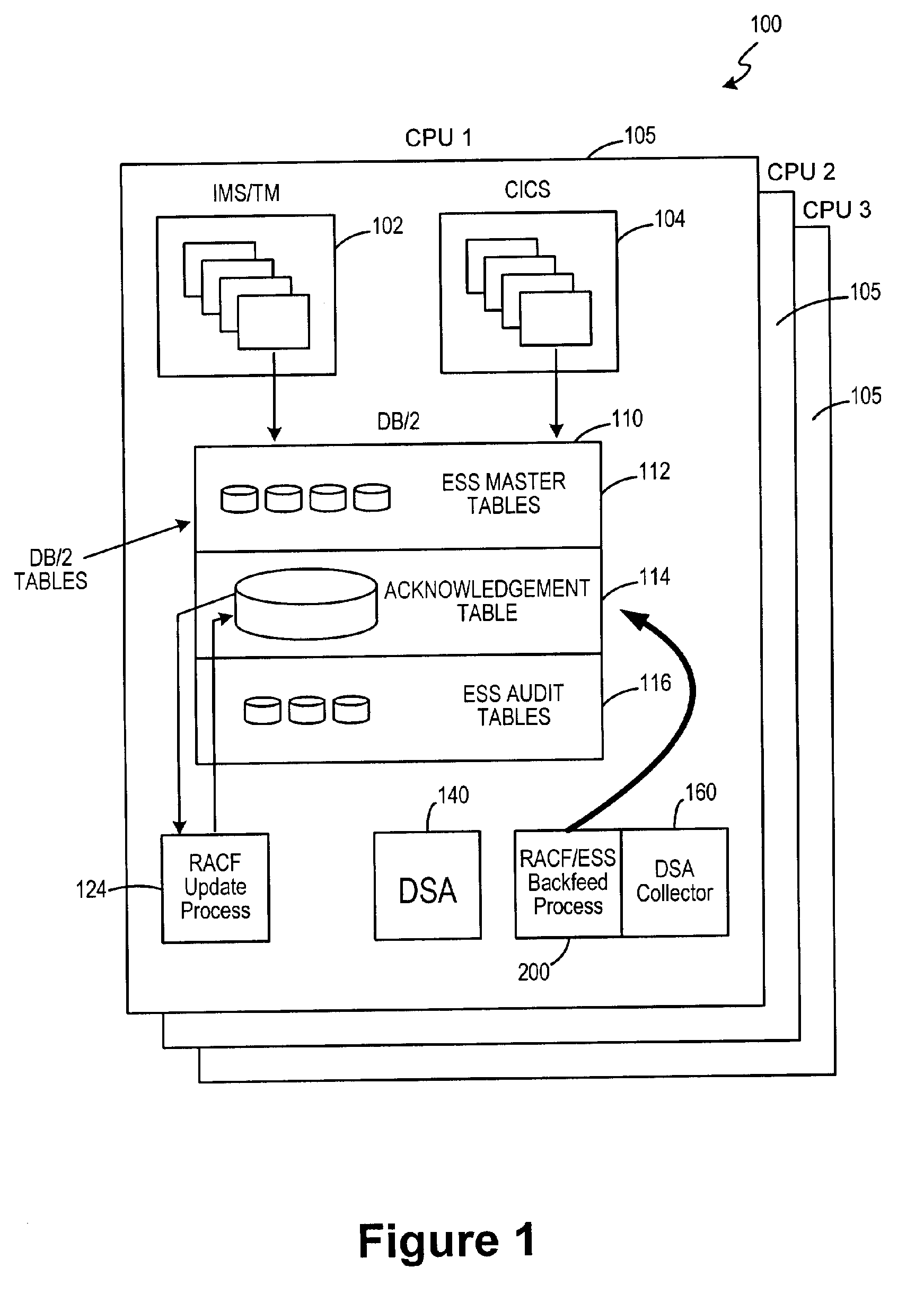

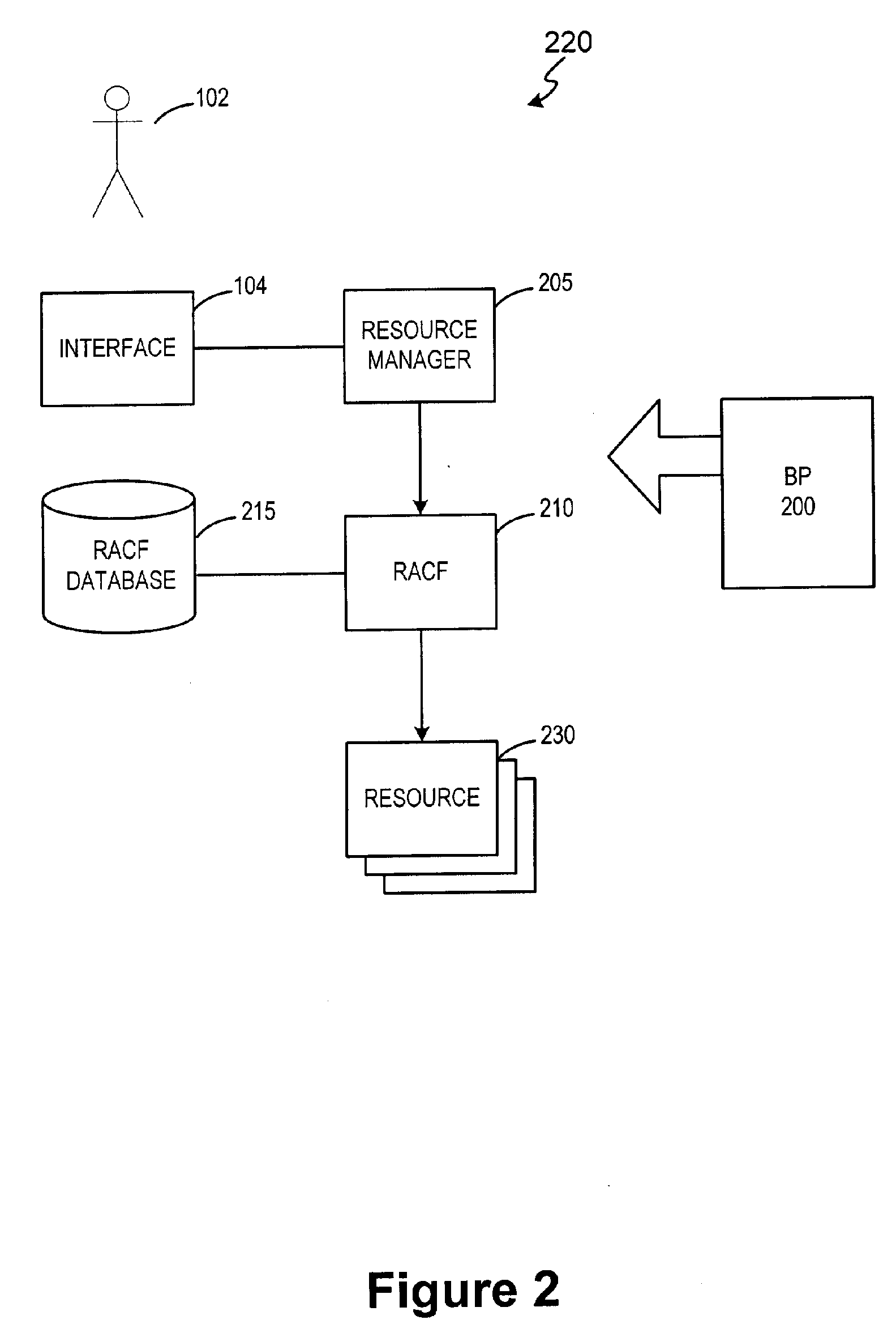

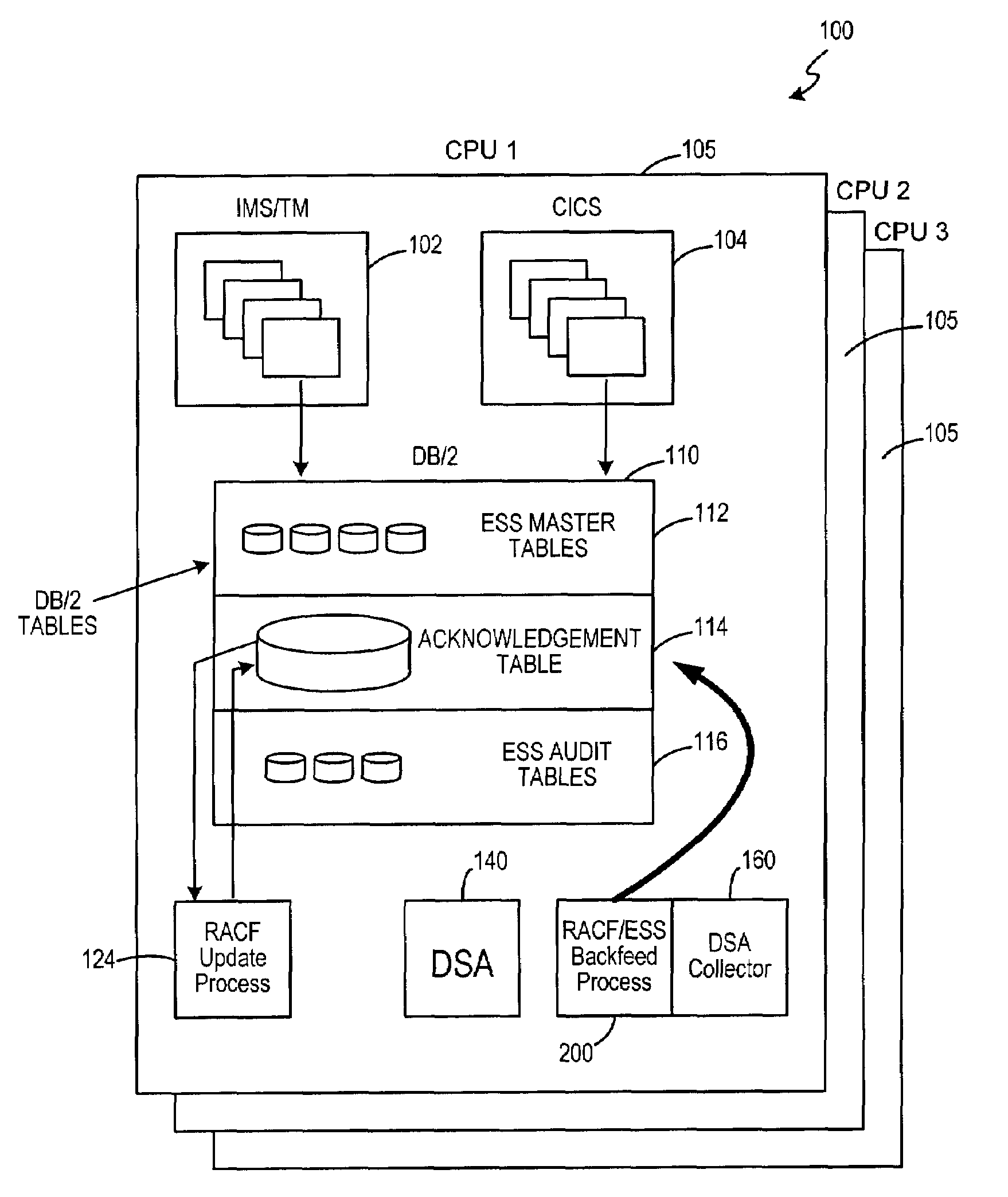

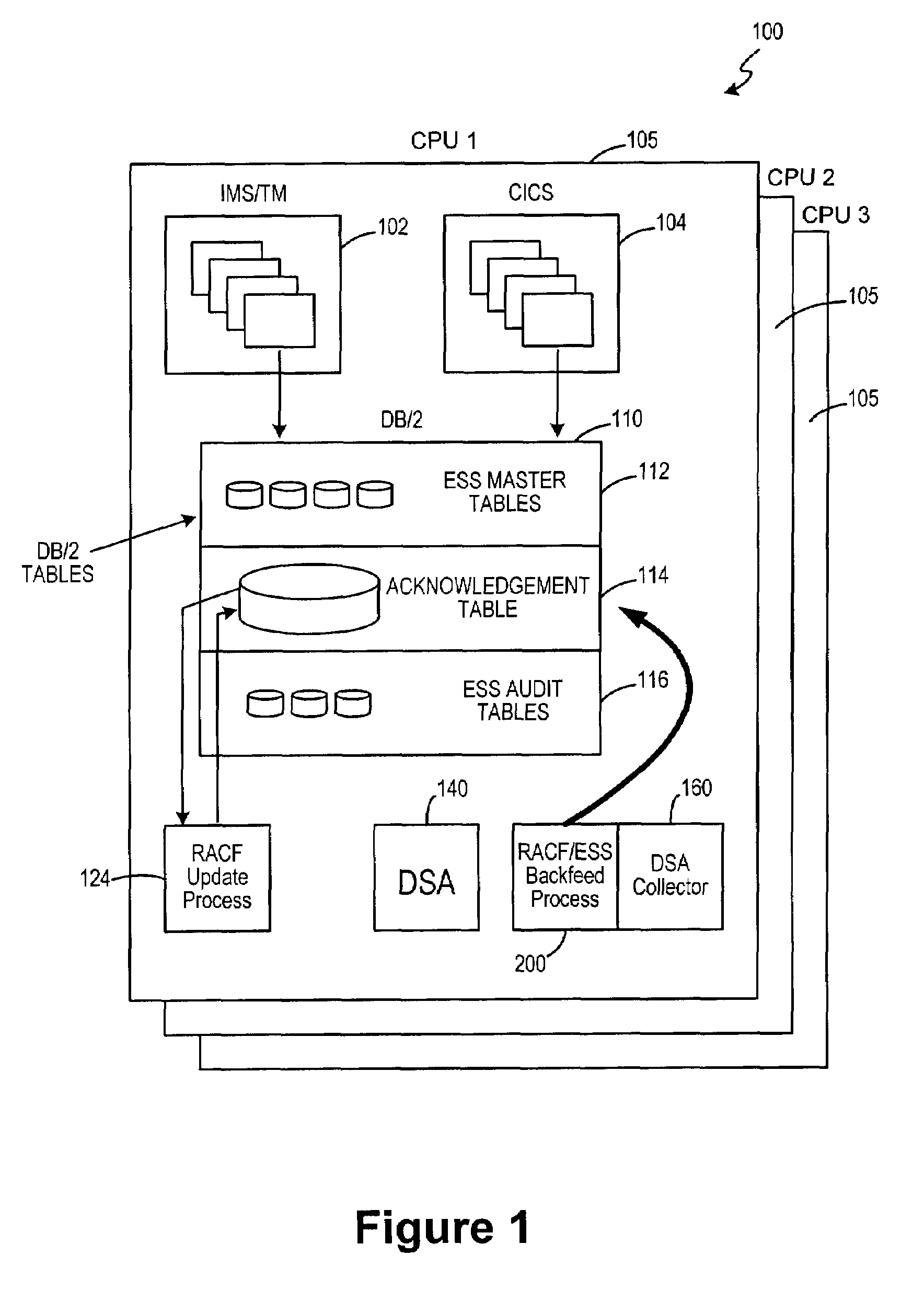

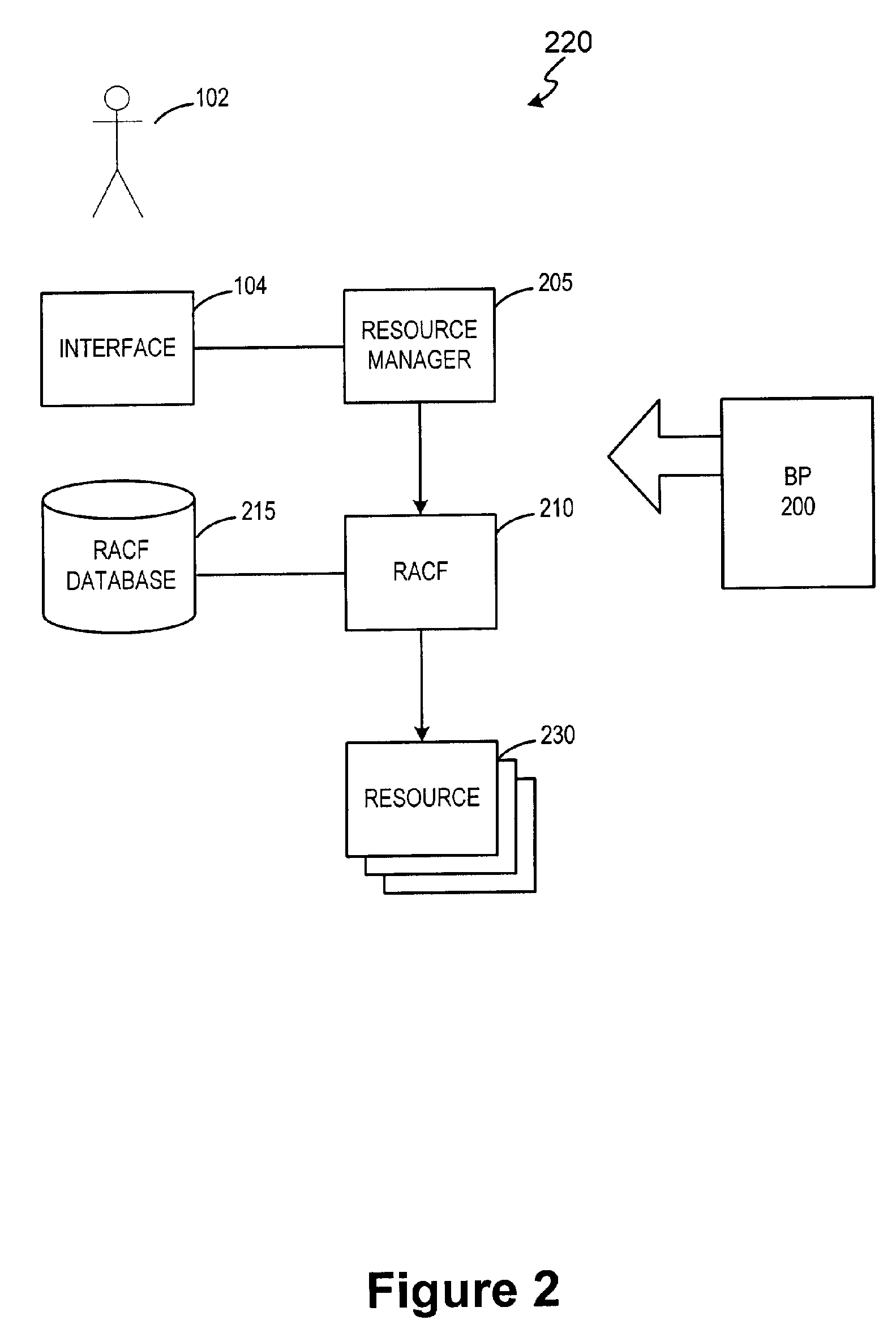

System and method for monitoring and ensuring data integrity in an enterprise security system

InactiveUS20060075488A1Memory loss protectionDigital data processing detailsThird partyData integrity

The invention facilitates monitoring and ensuring data security in security update information between software and hardware applications. The invention is achieved through an automated system that allows for substantial uniformity and substantially seamless security through a front-end system. The invention may use one or more third-party products to facilitate communication between computing platforms.

Owner:LIBERTY PEAK VENTURES LLC

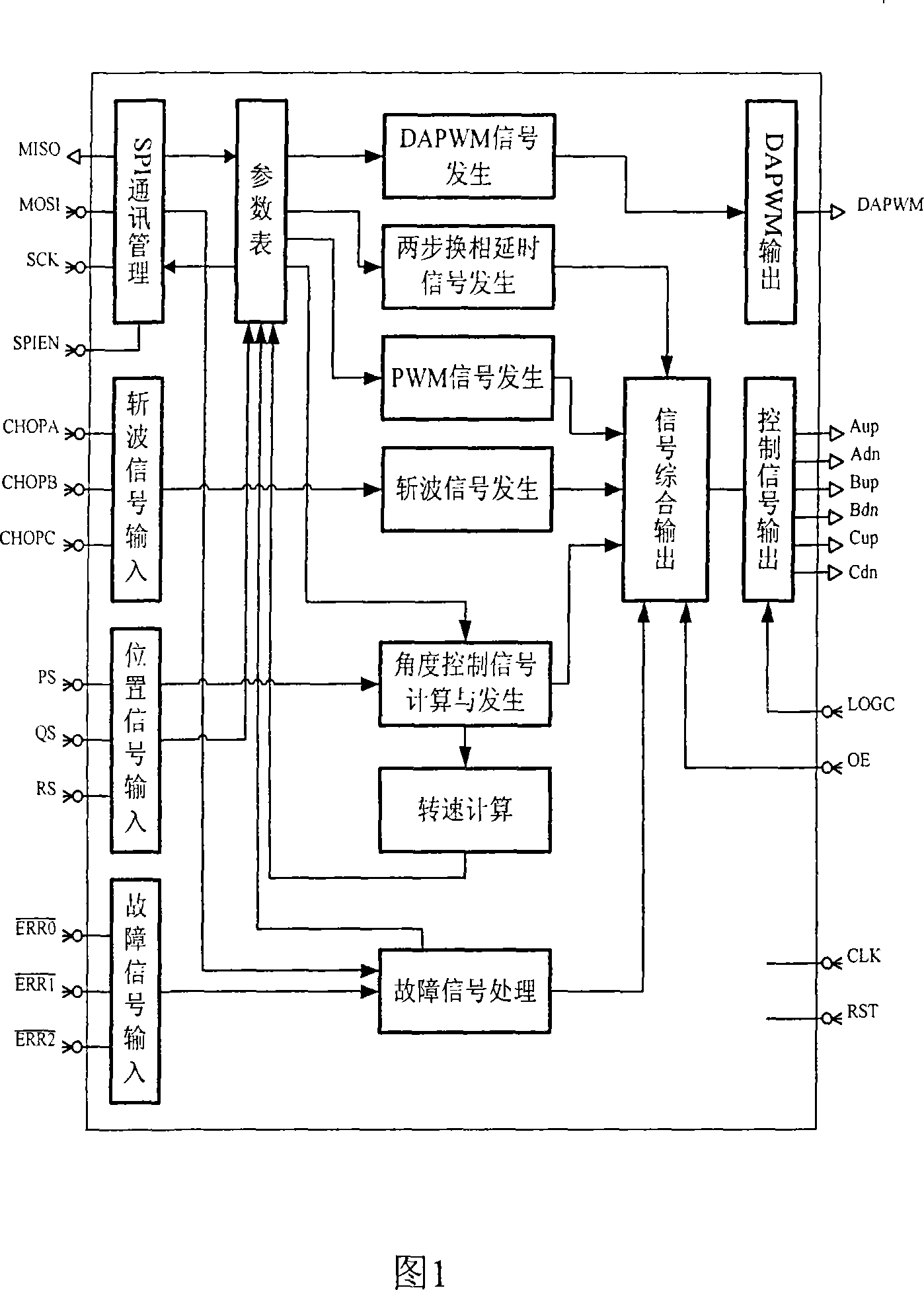

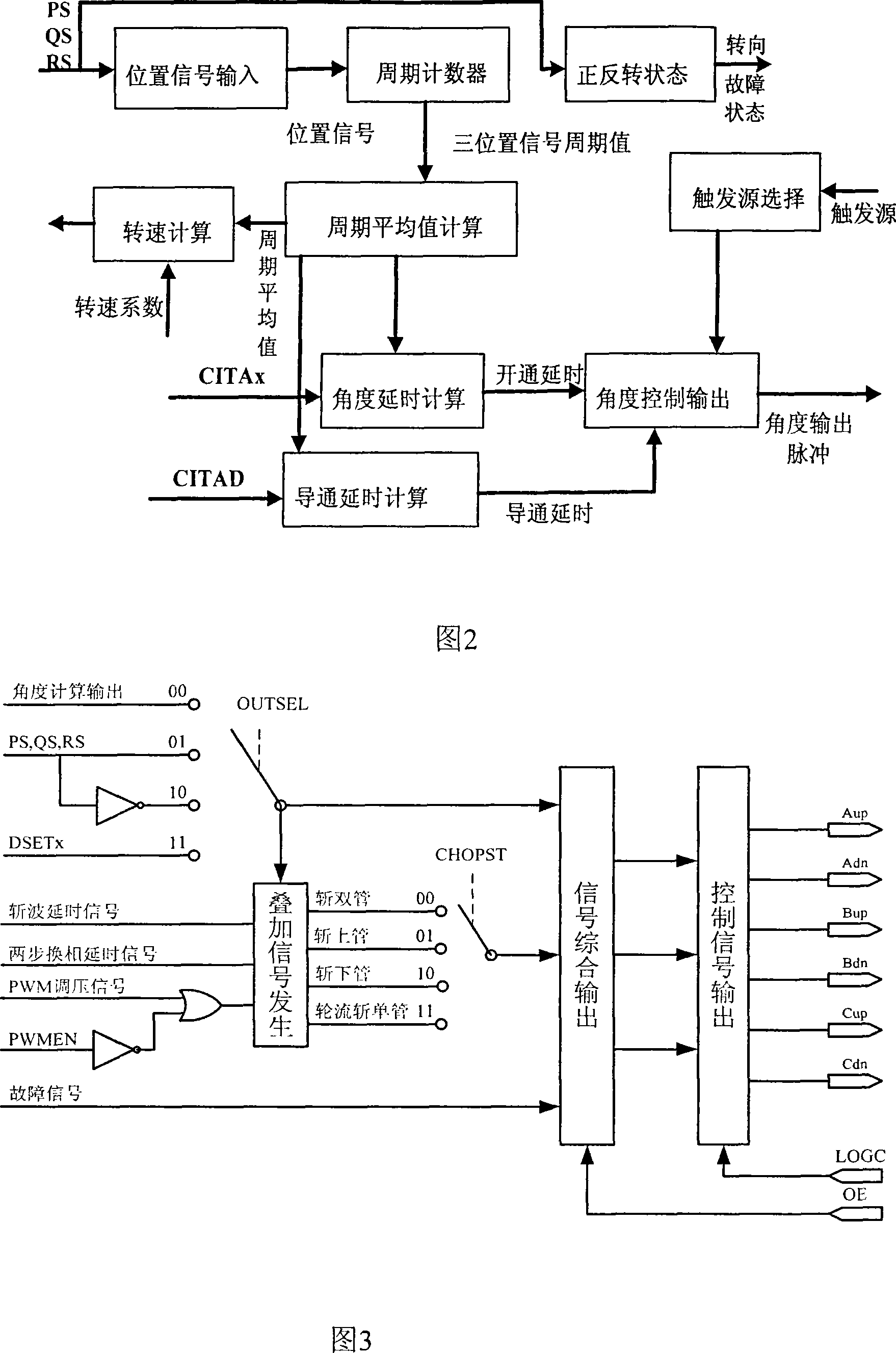

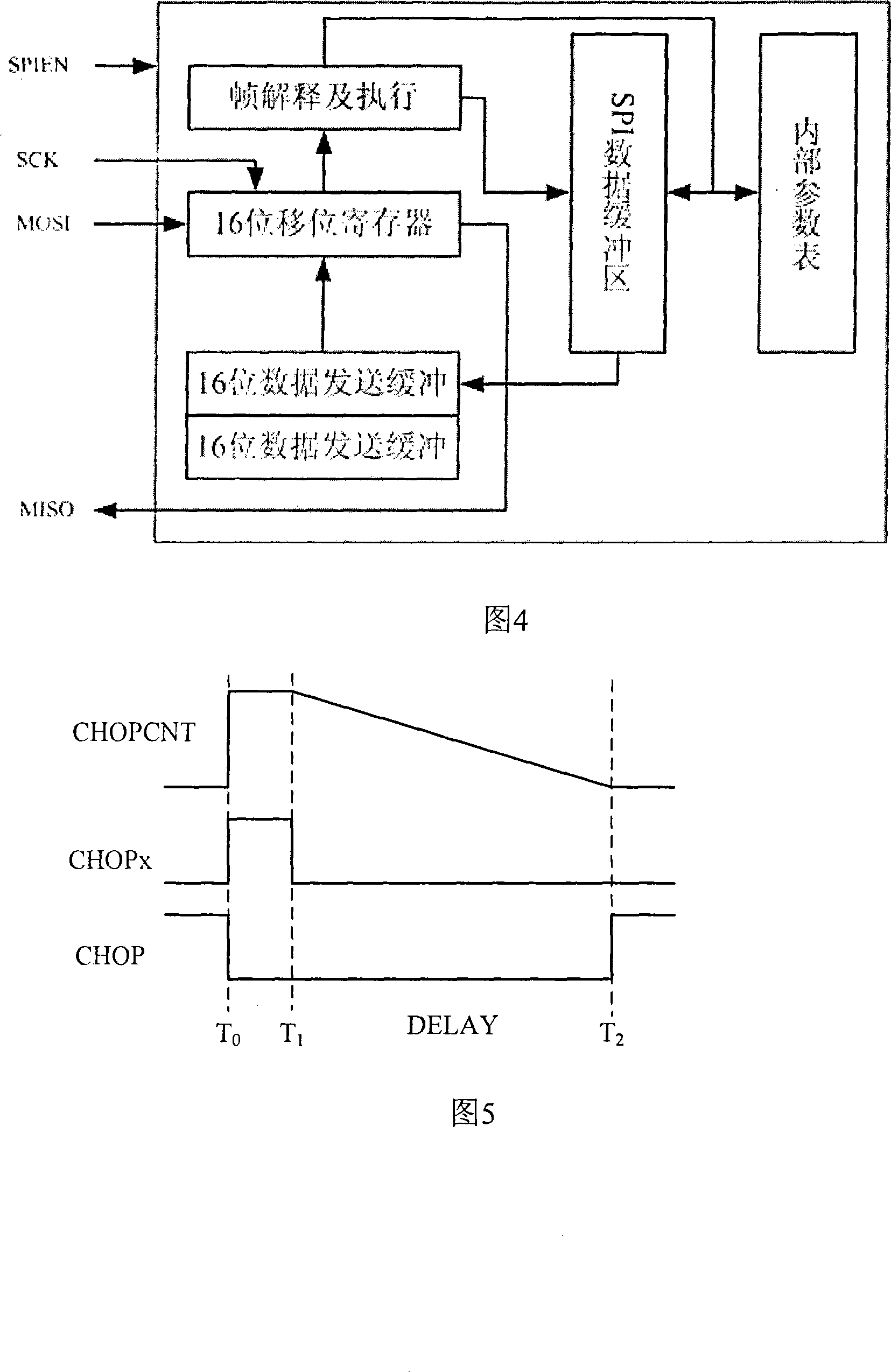

Integrated circuit special for controlling switch reluctance motor

InactiveCN101227161ALower performance requirementsAvoid writingCommutation monitoringAC motor controlControl signalTime delays

The invention relates to an application-specific integrated circuit which is controlled by a switch reluctance motor, wherein the structure mainly comprises a three-phase electric current chopped wave module which can change time delay length of chopped wave, a two-step commutating module which can change time delay length, two PWM generating modules which are respectively set for cycle and duty cycle and a counting and generating function module for positioning and angle controlling signals. The application-specific integrated circuit has the advantages that angle control of the switch reluctance motor can be finished through full hardware application-specific integrated circuits, concrete closed-loop control is still realized by a microprocessor, the property requirement of the microprocessor is led to greatly reduce, the application-specific integrated circuit can be applied to wide range of rotating speed, in particular to high speed and super high speed range, and has strong anti-interference property, avoid compiling position to calculate software, and the reliability of the system is increased. The integrated circuit also integrates common controlling modules such as error protection, electric current chopped wave, SPI communicating management and the like, and further reduces the hardware cost and development cost of the controlling device, simplifies complex degree of the switch reluctance motor controlling device, and increases working stability and reliability of the system.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

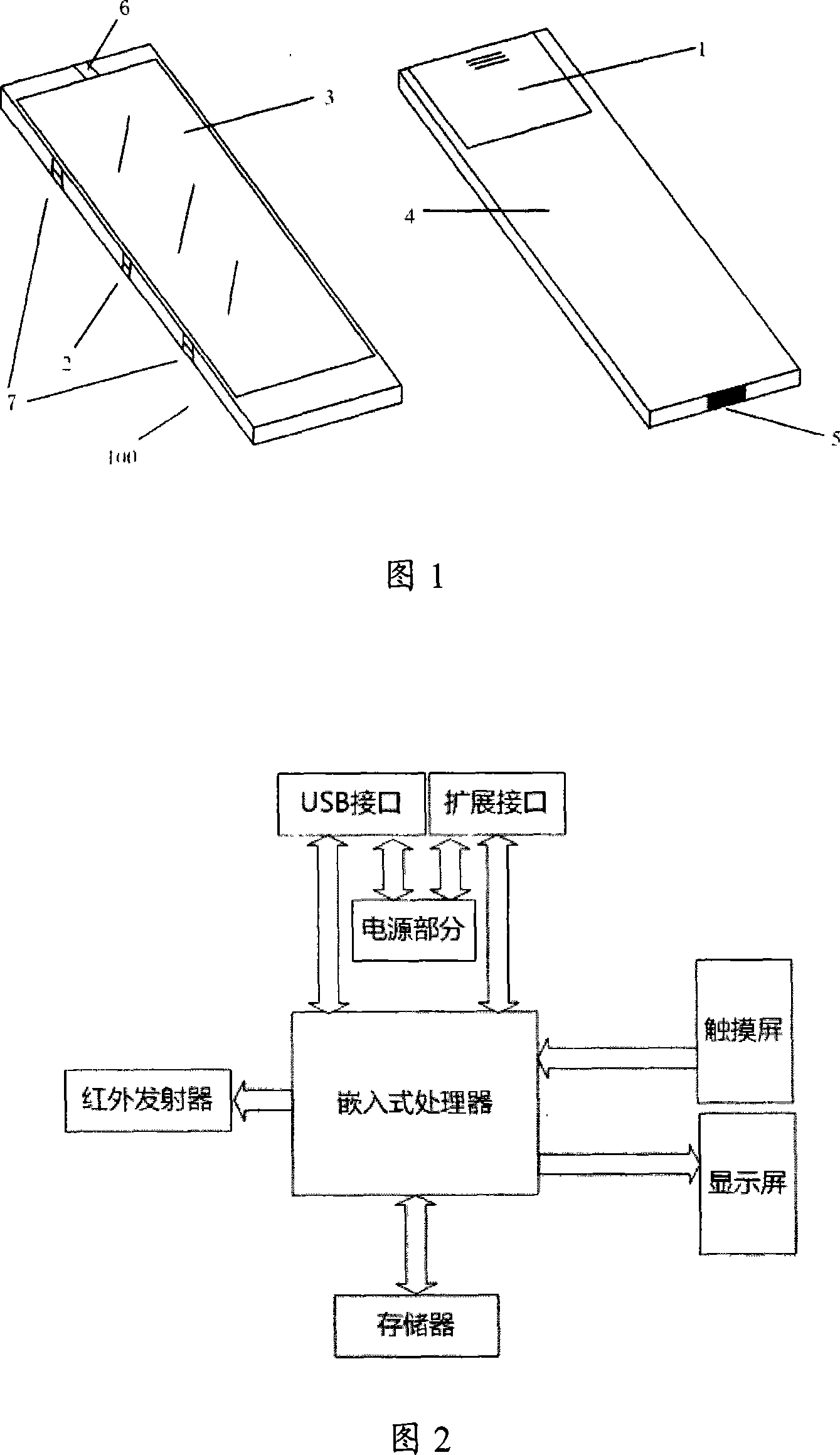

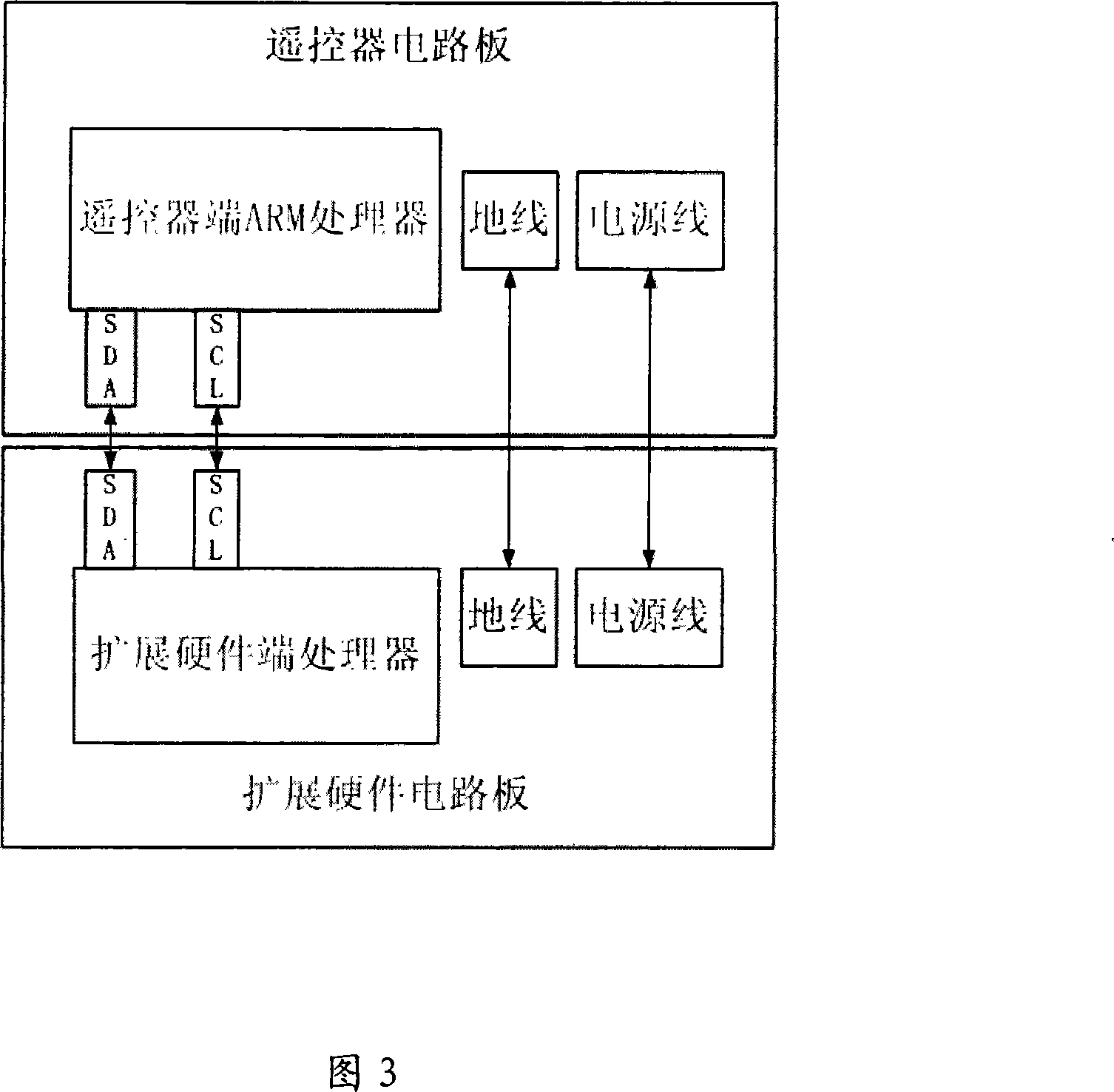

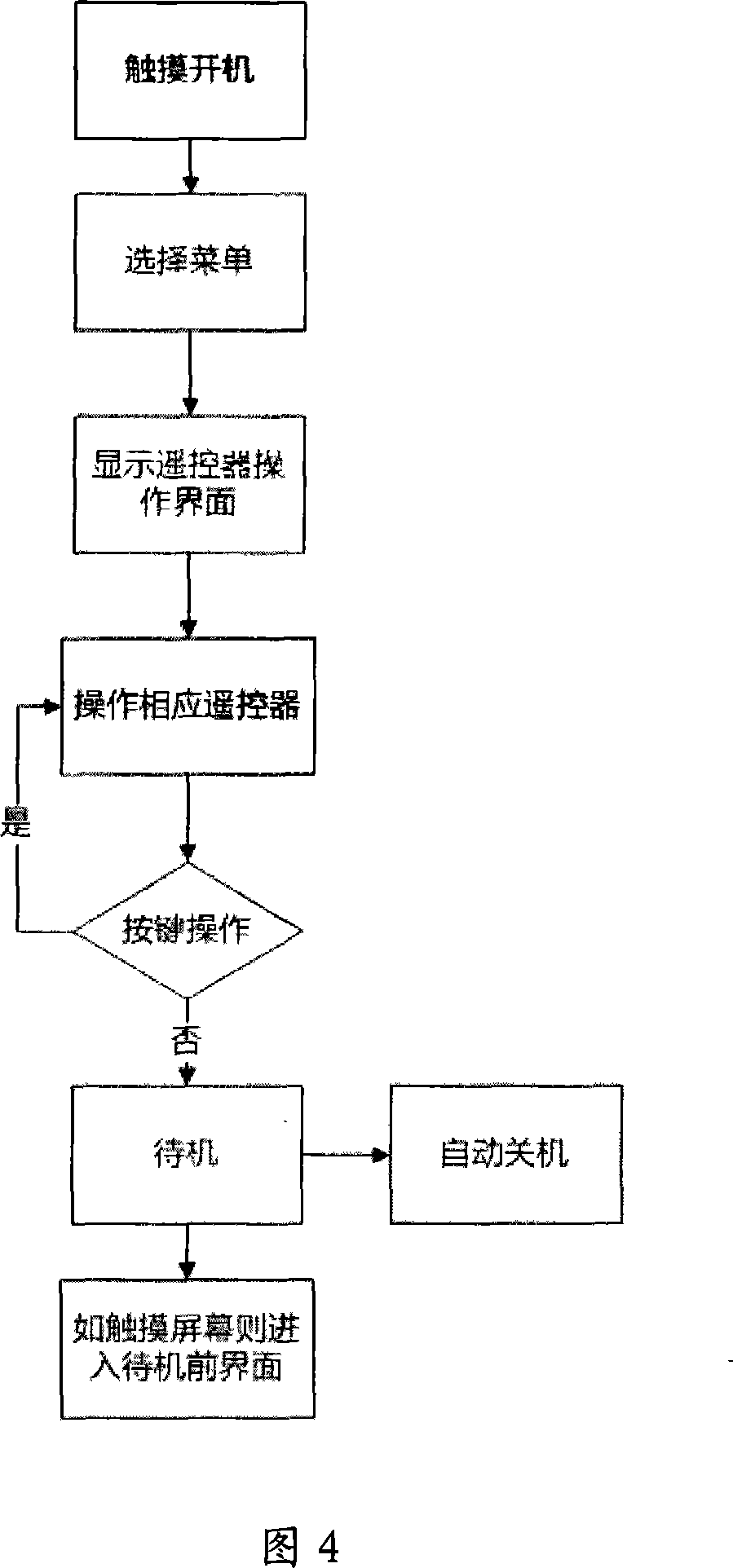

A household touch screen general multifunctional remote controller with extended functions

InactiveCN101216994AButtons are clearEasy to operateEnergy efficient ICTNon-electrical signal transmission systemsBus interfaceApplication software

The invention discloses a household touch-screen universal multifunctional remote controller with extension function, which is characterized in that the remote controller comprises a memory and an embedded processor, also includes a universal serial bus interface and an extension interface, and he universal serial bus interface can load data, and store the data in the memory to be called by the embedded processor; the extension interface includes a ground wire, a power wire and a data lines; the ground wire is used for grounding the remote controller; the power wire is connected with the power wire of the universal serial bus interface in parallel; the data lines are connected with the I2C bus of the embedded processor for exchanging data with extension hardware for realizing the extension function of the remote controller. The embedded processor can load and extend a hardware application program via the universal serial bus interface, and store the program into the memory to be called by the embedded processor. The invention can realize integrated control of household appliances, has strong extension and upgrade capability, and can greatly reduce circuit power consumption by using an ARM processor.

Owner:SOUTHEAST UNIV

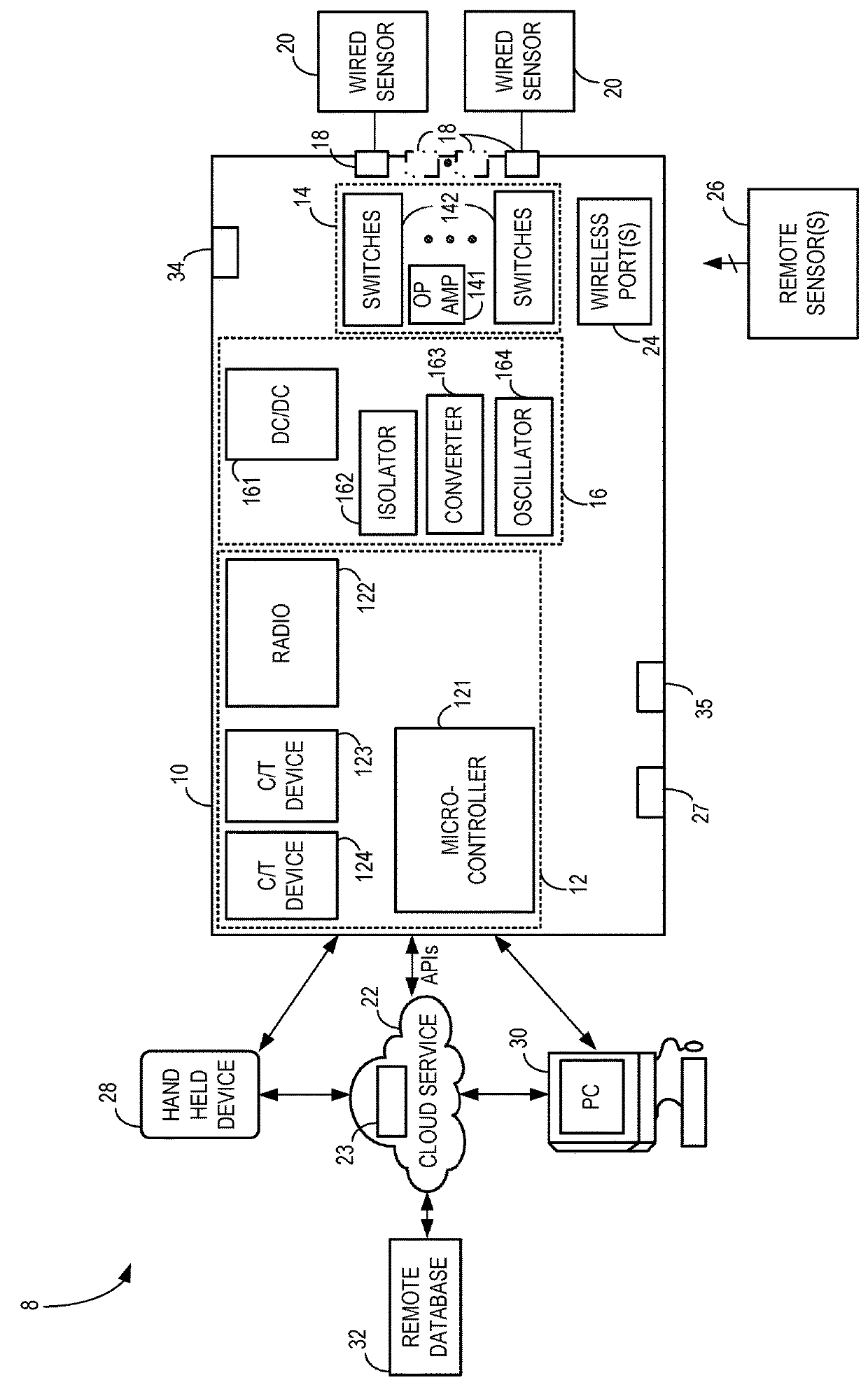

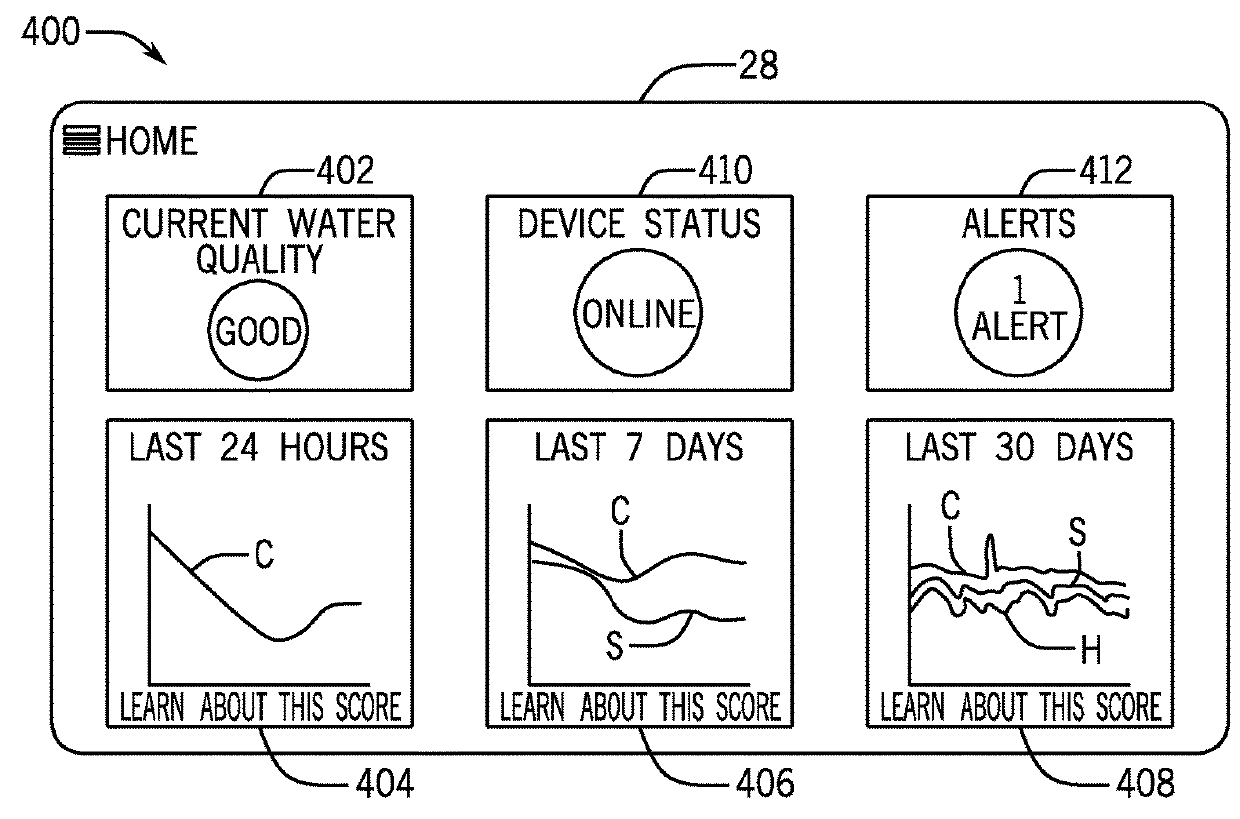

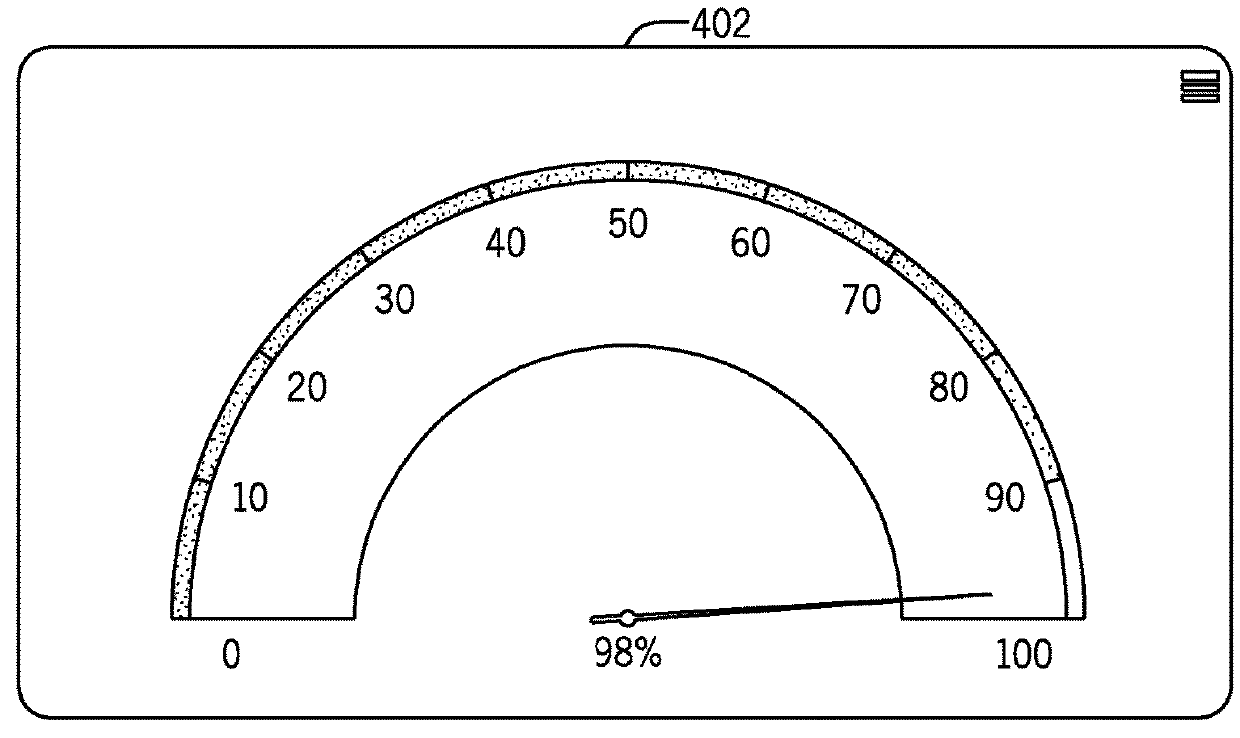

Water quality monitoring system and method

InactiveUS20180270548A1Low costSub-station arrangementsWireless architecture usageCommunication interfaceMonitoring system

A sensor system includes a sensing device that has a hardware application program interface (API) that is manipulated by a cloud service to measure certain parameters using a variety of attached sensors. The hardware API creates a communication interface between the sensing device and the cloud service that permits the cloud service to manipulate how the device's hardware components acquire raw data from one or more attached wired or wireless sensors. In certain embodiments data acquisition with the sensing device may be entirely cloud initiated permitting sensing device to be controlled to collect data using any type of sensor without the sensing device requiring any sensor-specific hardware or locally-stored programming specific to a particular type of sensor coupled to the device.

Owner:RICHTER CHRISTOPHER ROBERT

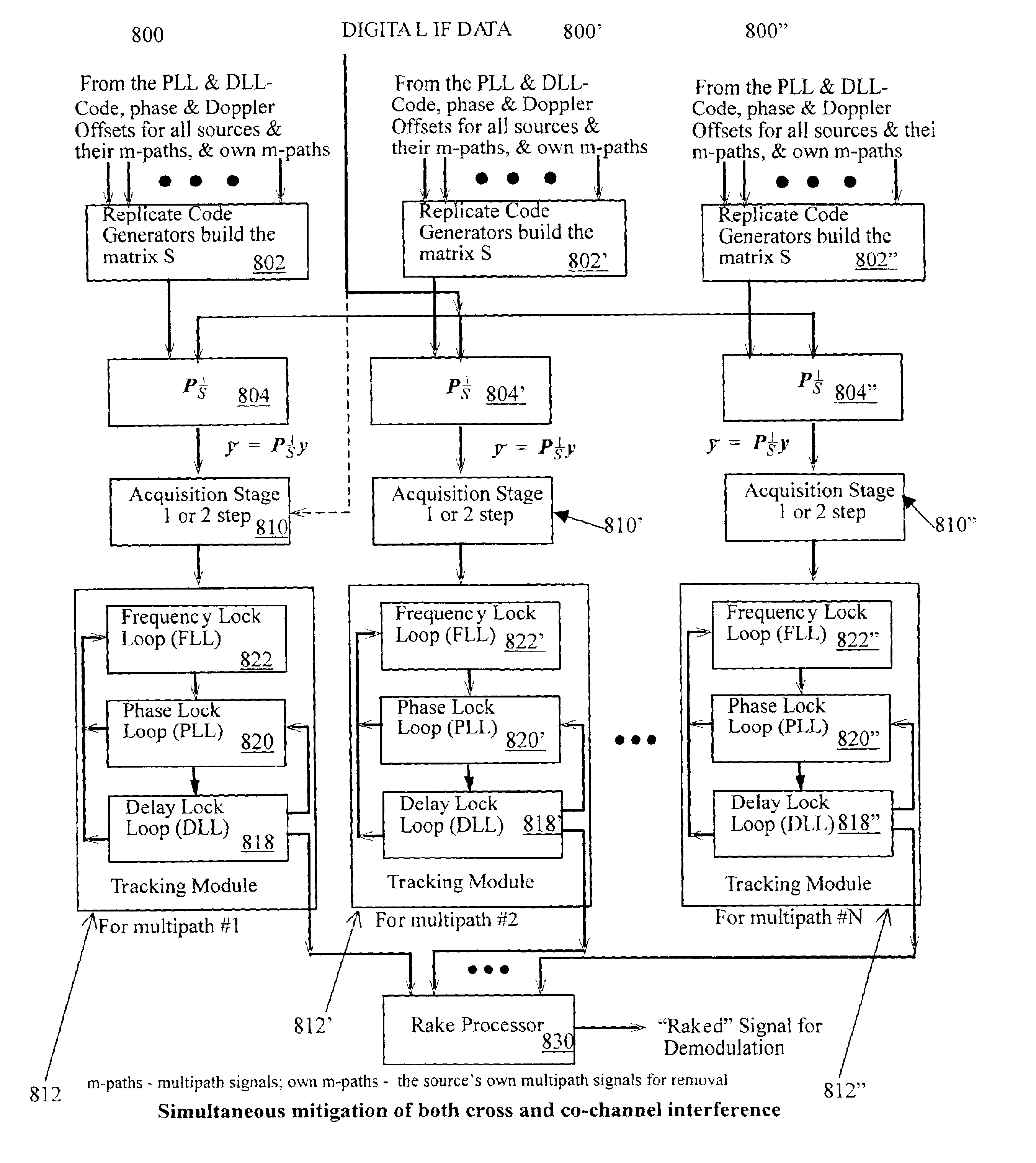

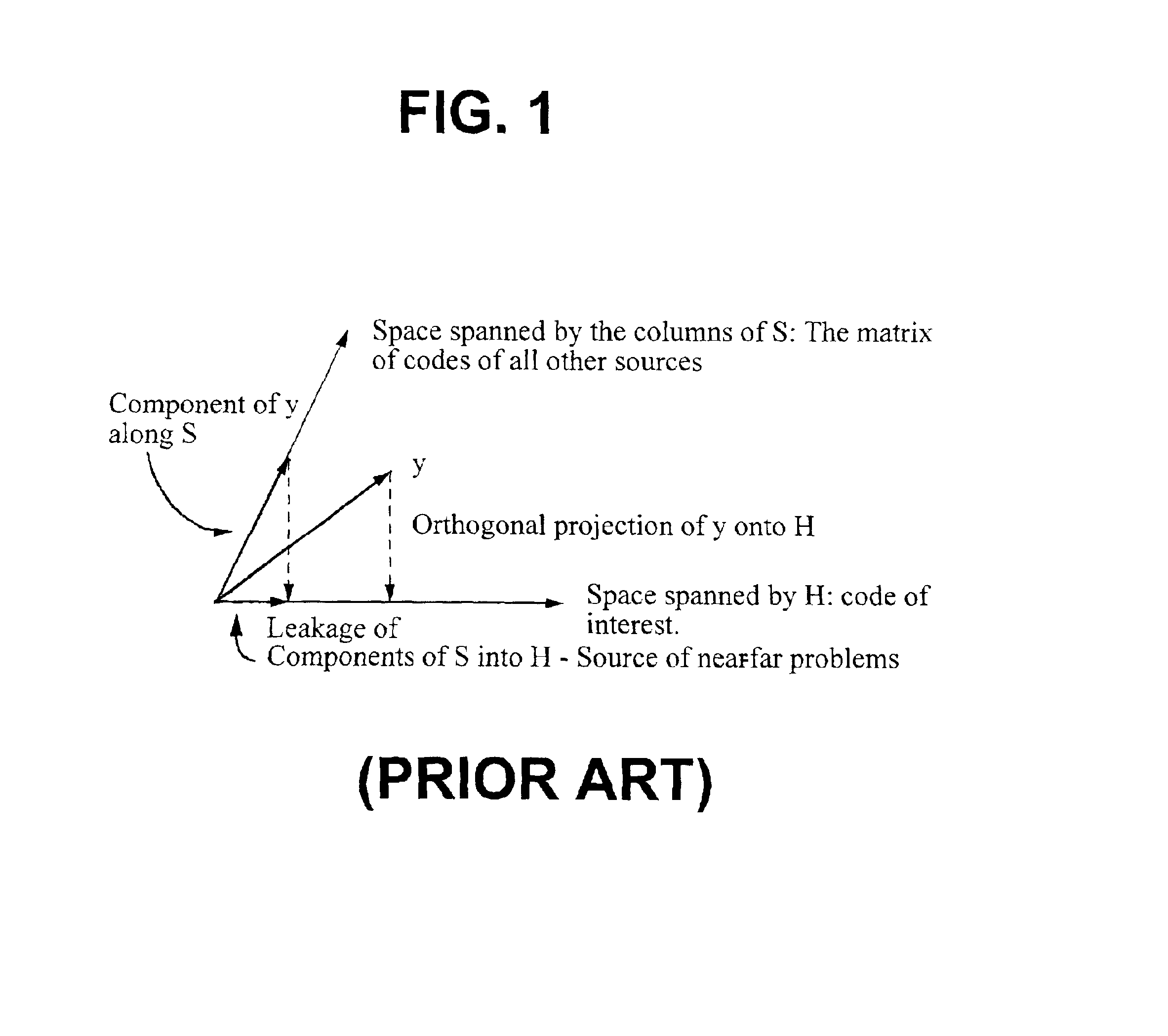

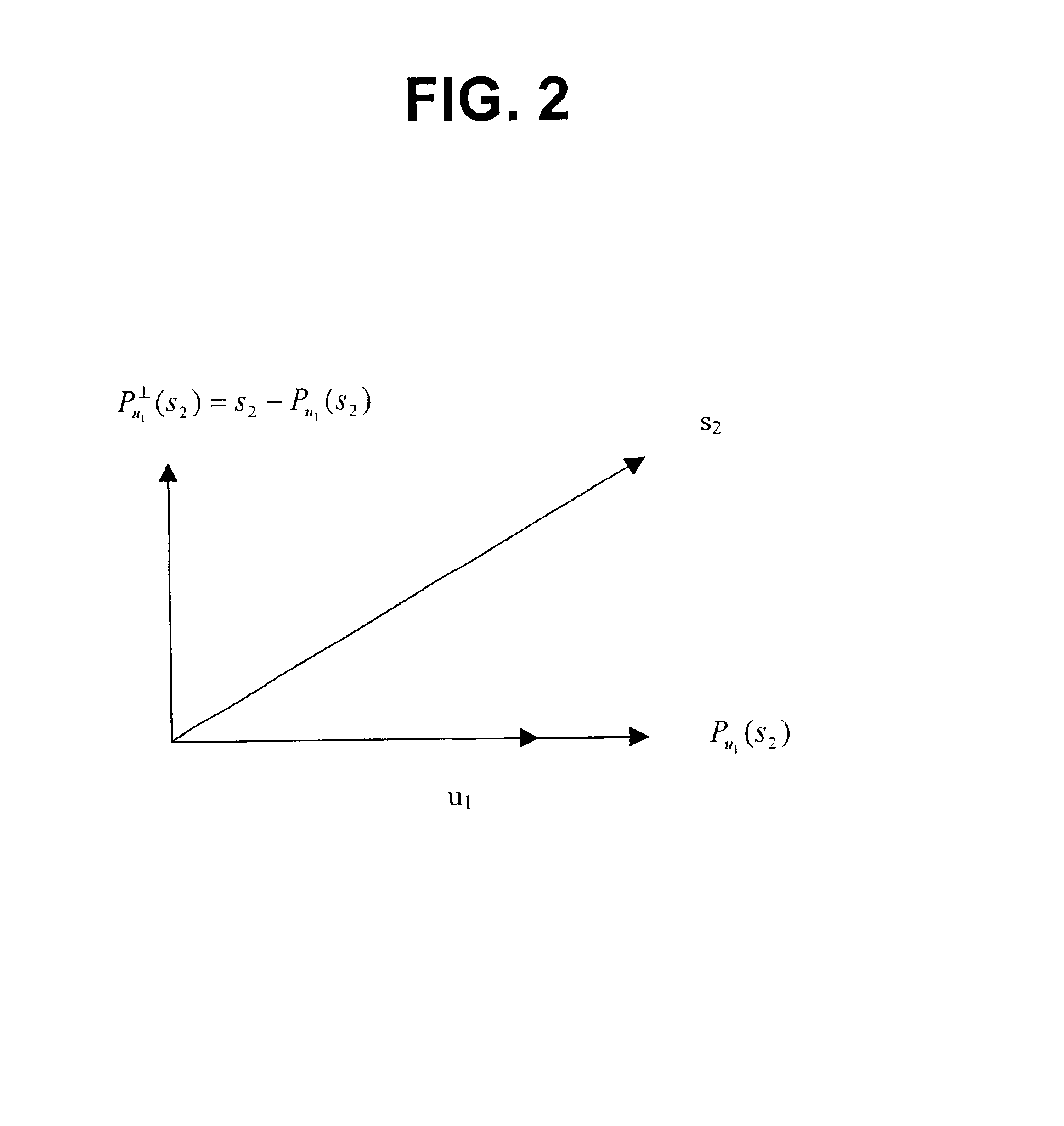

Method and apparatus for implementing projections in signal processing applications

InactiveUS6856945B2Amplifier modifications to reduce noise influenceDigital computer detailsOrthogonal basisComputer science

A novel method and apparatus is provided for enabling the computation of a signal in a certain subspace, its projection that lies outside the subspace, and the orthogonal basis for a given matrix. More particularly, the present invention relates to the use of such a method or apparatus for real-time hardware applications since the method and apparatus may be utilized without matrix inversions or square root computations.

Owner:III HLDG 1

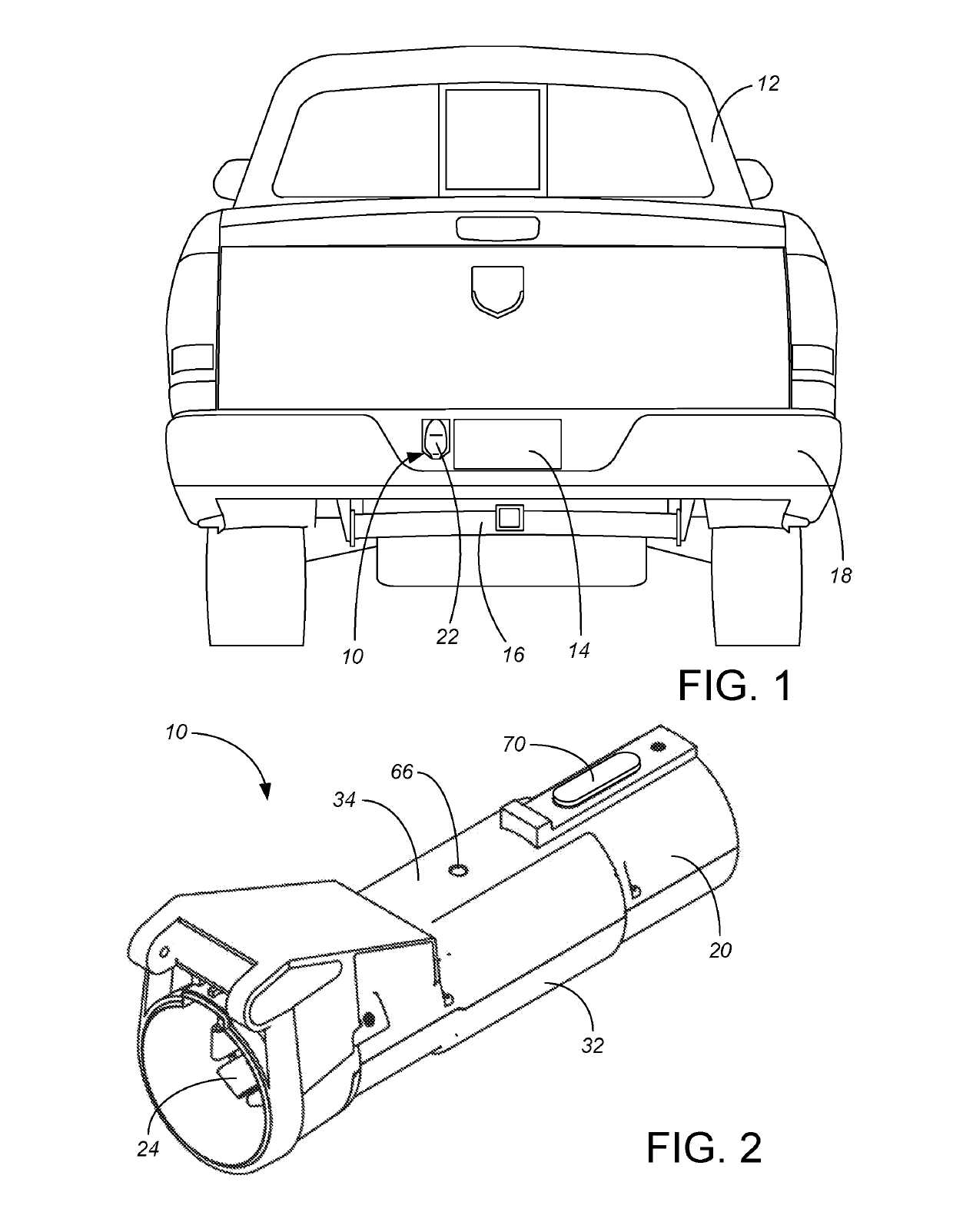

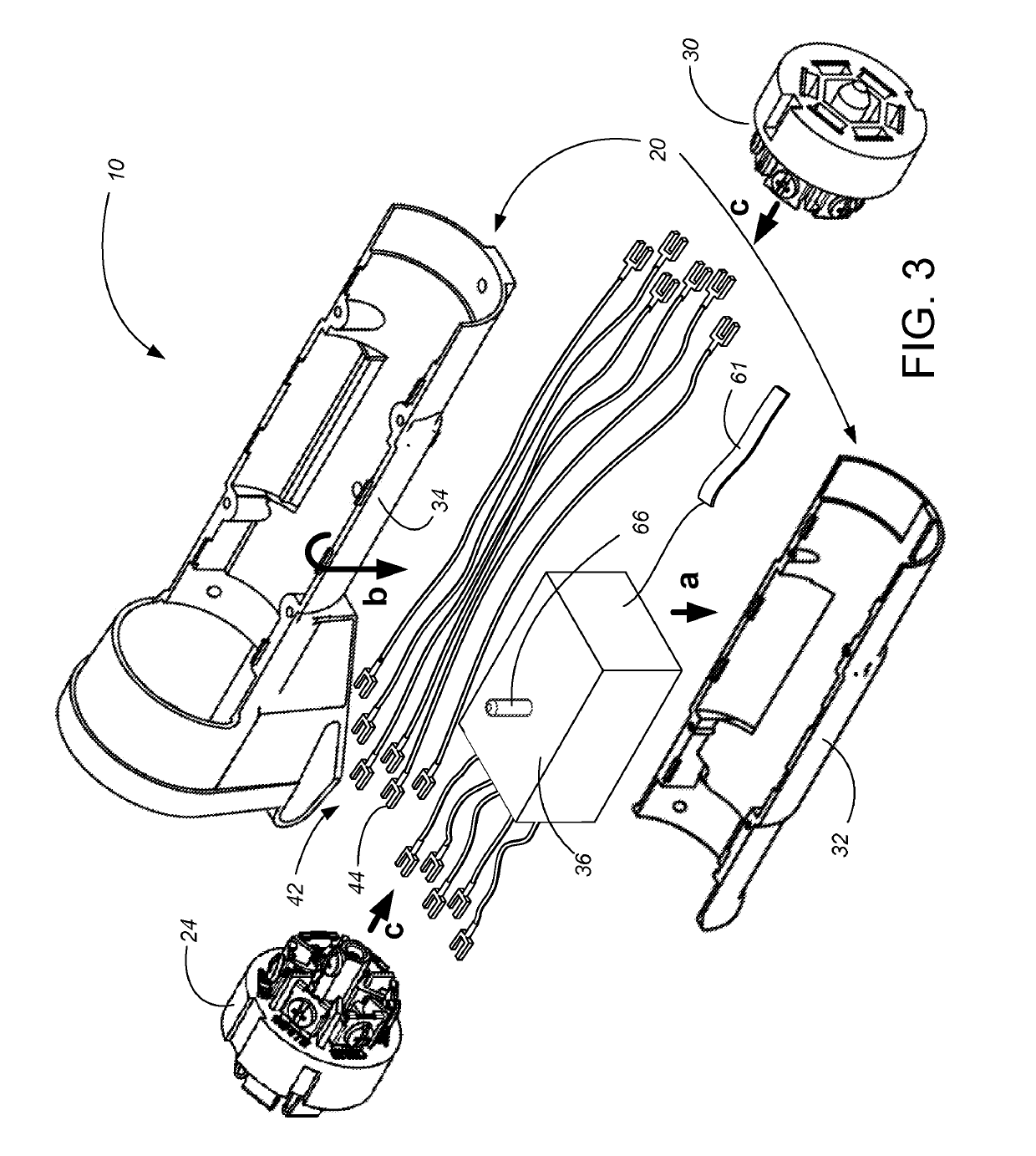

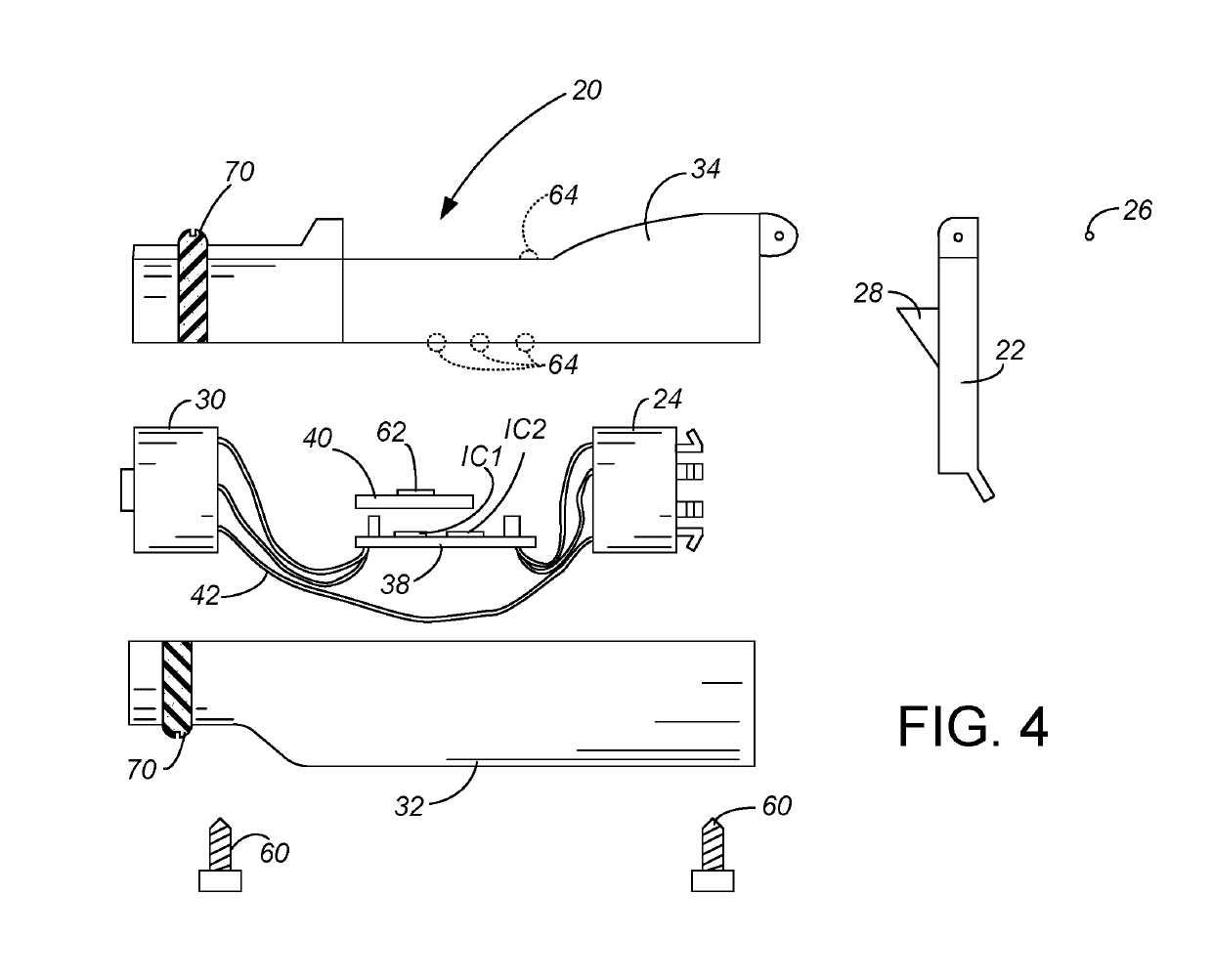

Portable Brake Controller With Wireless Control Interface

ActiveUS20190111899A1Weather resistantVehicle connectorsCoupling device detailsWireless controlAccelerometer

A brake controller is provided as an inline plug between the towing vehicle and the towed vehicle or trailer. The electronics including an accelerometer and wireless communication radio are potted within a brake controller housing package. There is no conventional display or input controls on the exterior of the brake controller package. Input settings, and possibly output messages, are communicated through a smartphone or similar software or hardware application. The brake controller can identify a hazard lighting condition and avoid braking the towed vehicle during the hazard lighting condition, and can also distinguish when braking during signaling a turn, using the turn signals of the towing vehicle.

Owner:CURT MFG

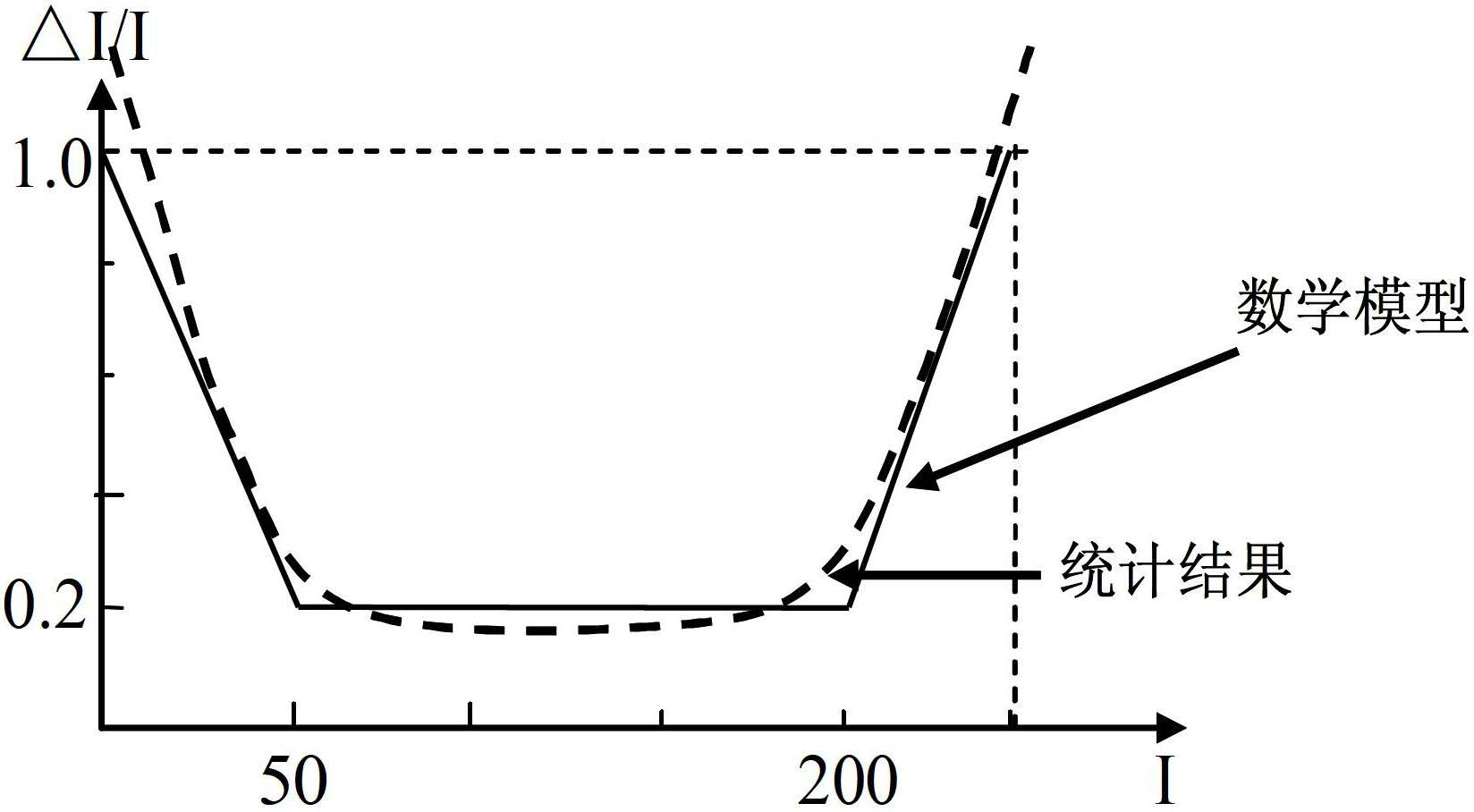

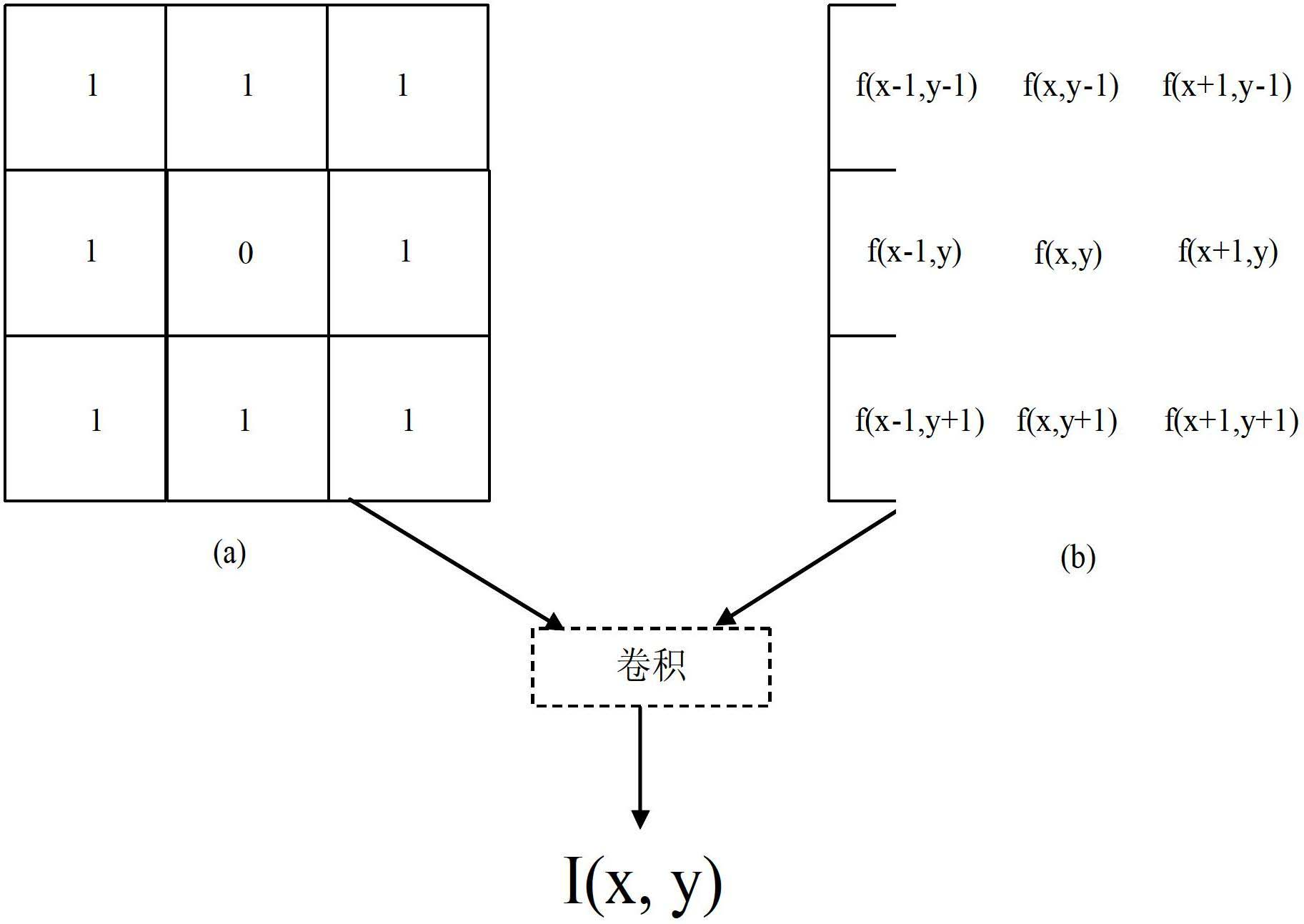

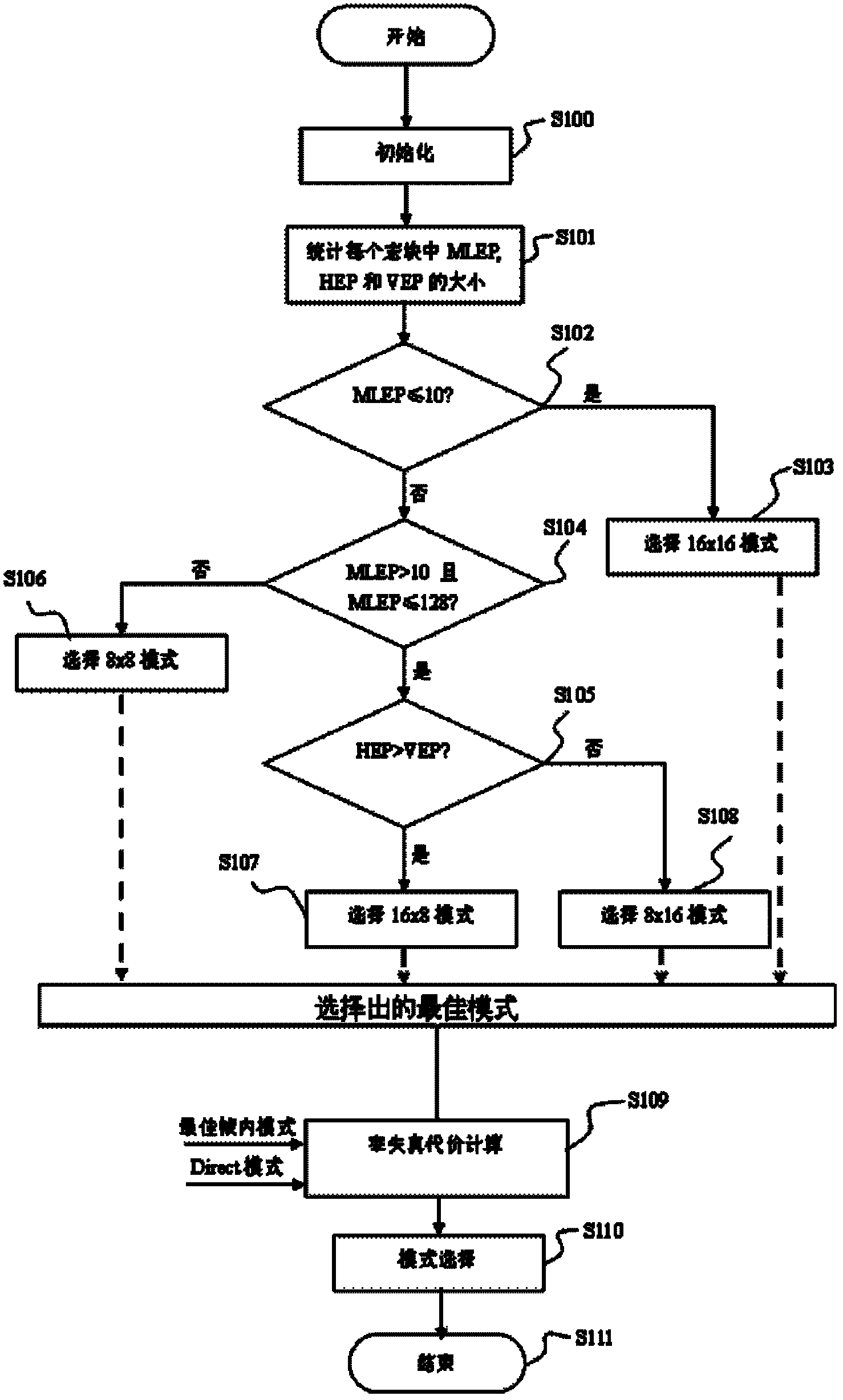

Rapid interframe mode selection method and device for AVS (Advanced Audio Video Coding Standard) coder

ActiveCN102685497AReduce complexityEasy to shareTelevision systemsDigital video signal modificationComputer hardwareRate distortion

The invention discloses a rapid inter-frame mode selection method for an AVS (Advanced Audio Video Coding Standard) coder. The method comprises the following steps of: preselecting an optimal mode from a 16*16 mode, a 16*8 mode, a 8*16 mode and a 8*8 mode by virtue of a vision perception judging model and pixel point edge information; breaking through the dependence on data of interframe mode selection by virtue of a rapid interframe mode selection algorithm facilitating the realization of hardware to ensure that the interframe mode selection does not need to wait the relevant reconstruction data and becomes the premise for realizing an efficient interruption-free mode selection stream line; designing 5-level stream algorithm which can be realized oriented at the hardware and is capable of efficiently calculating rate distortion cost values to allow the application and popularization of the practical hardware for the interframe mode selection on the basis of rate distortion cost values to be possible; and finally, determining an optimal mode according to cost values of three candidate modes including a preset optimal mode, a direct mode and an intra mode. The invention also discloses an AVS interframe mode selection device. According to the invention, the coding property of the hardware coder is remarkably improved.

Owner:PEKING UNIV

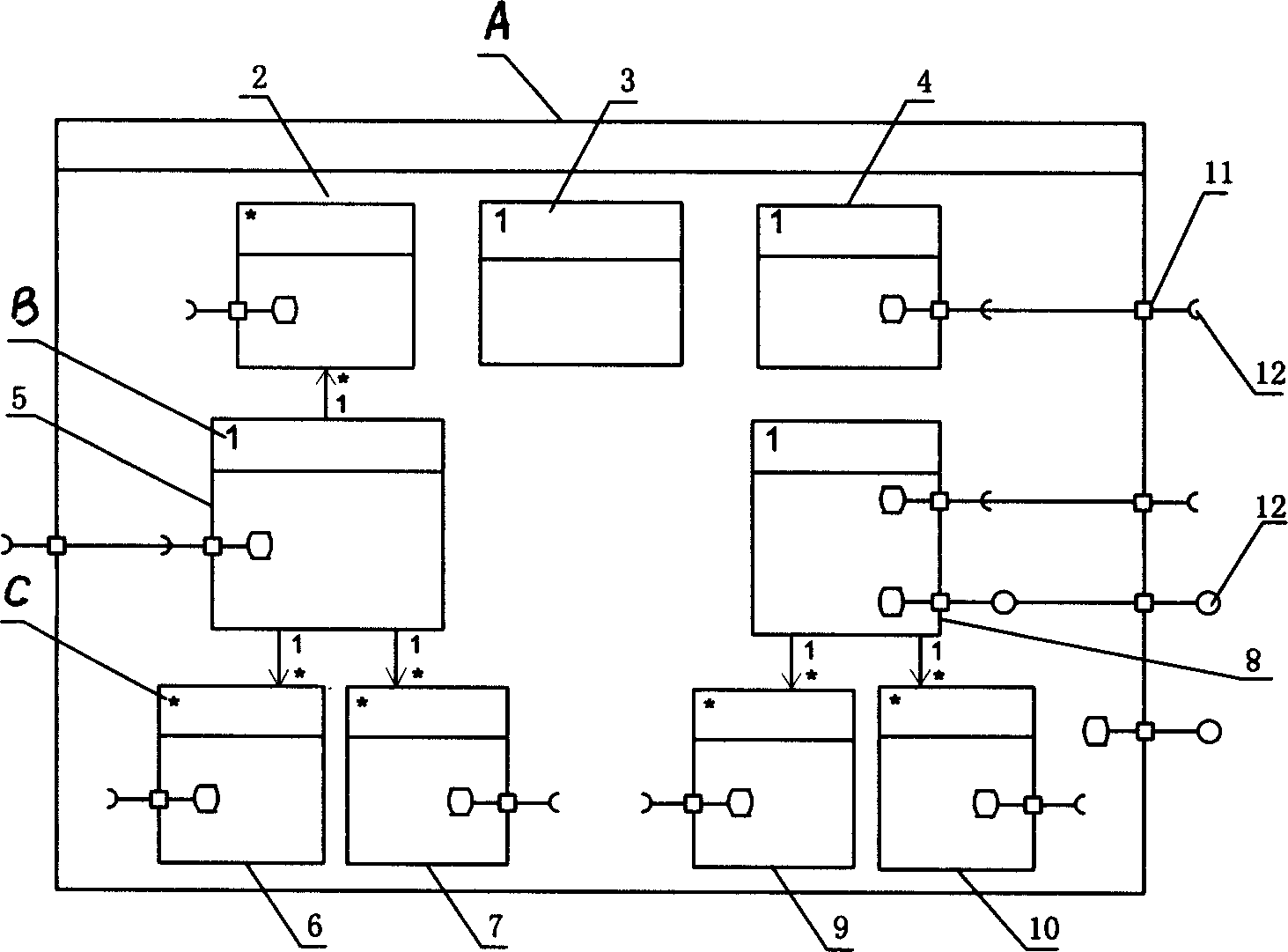

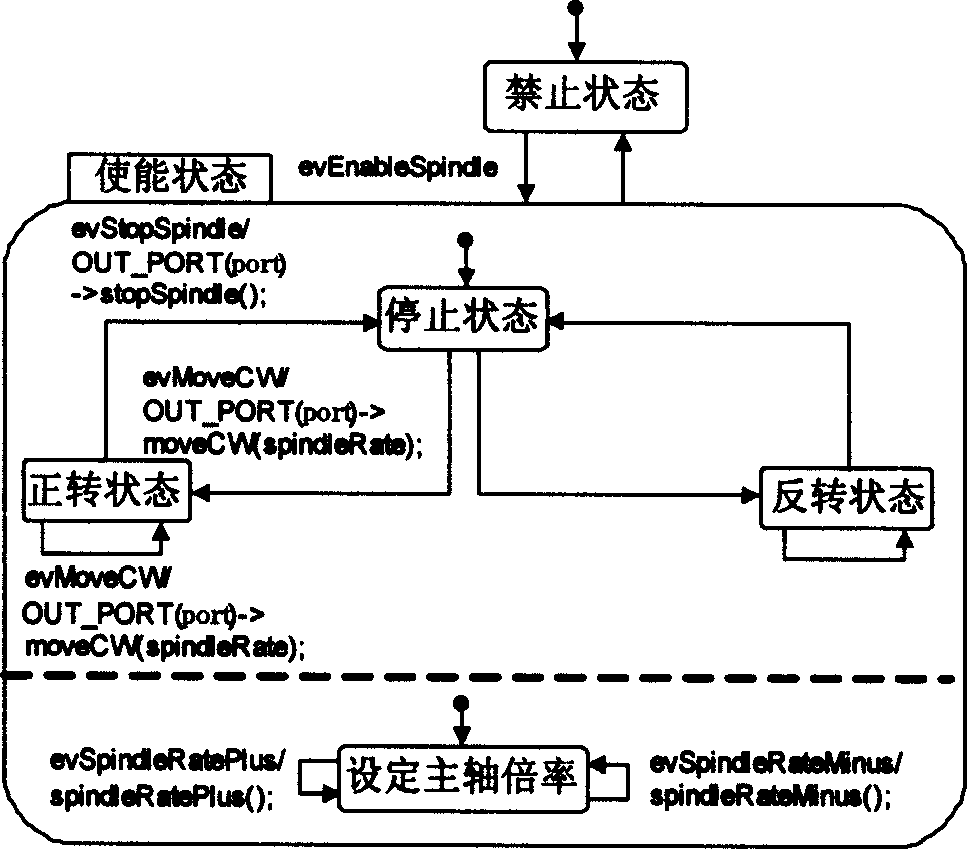

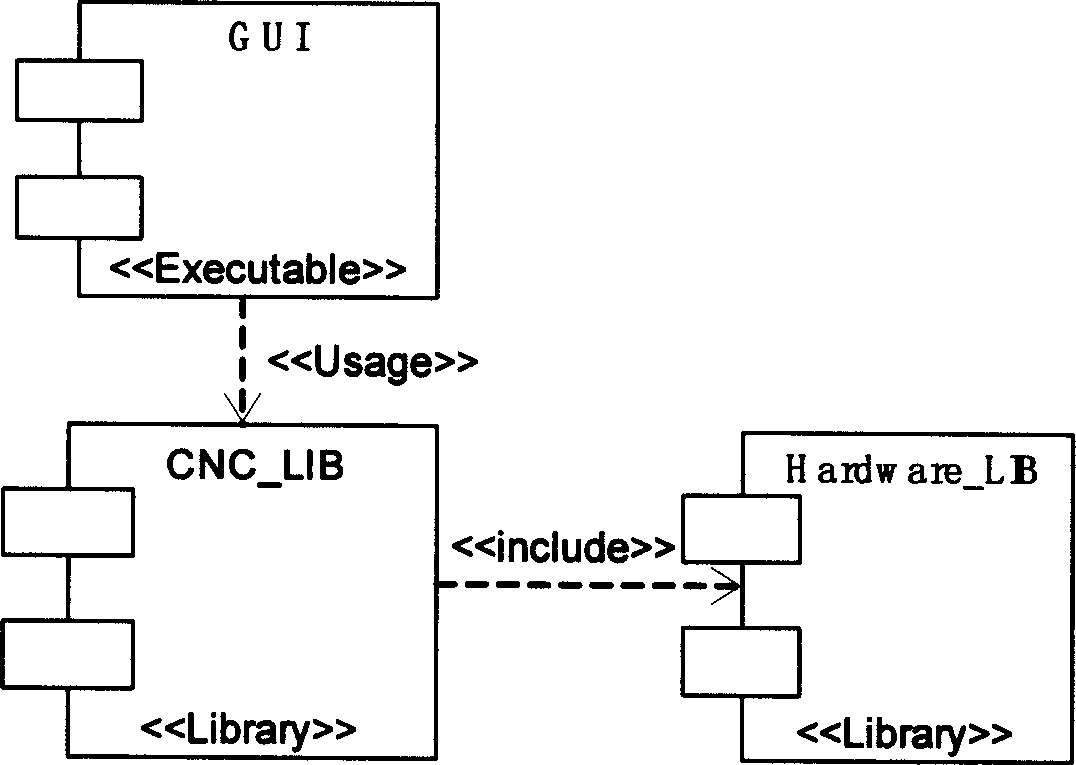

Opening structural computer digital control system able to re-configurate

InactiveCN1601416ARealize the control applicationGuaranteed robustnessComputer controlSimulator controlModel driven developmentHuman–machine interface

The invention is characterized by that making numerical system undergo the process of function module division, maknig model creation based on model drive development method, separating function of module from its behavious, utilizing change of state graph of correspondent module to despatch the the condition of its function execution so as to implement reuse of module function; using port to make communication between modules, said port can utilize its contract abstract interface to make interaction with man-machine interface and bottom layer hardware equipment so as to make related hardware application program meet the interface function requirement provided by system, and in the model layer increasing / reducing or replacing correspondent module so as to implement change of system functino. Said invention also provides the application of said numerical control system.

Owner:东莞市升力智能科技有限公司

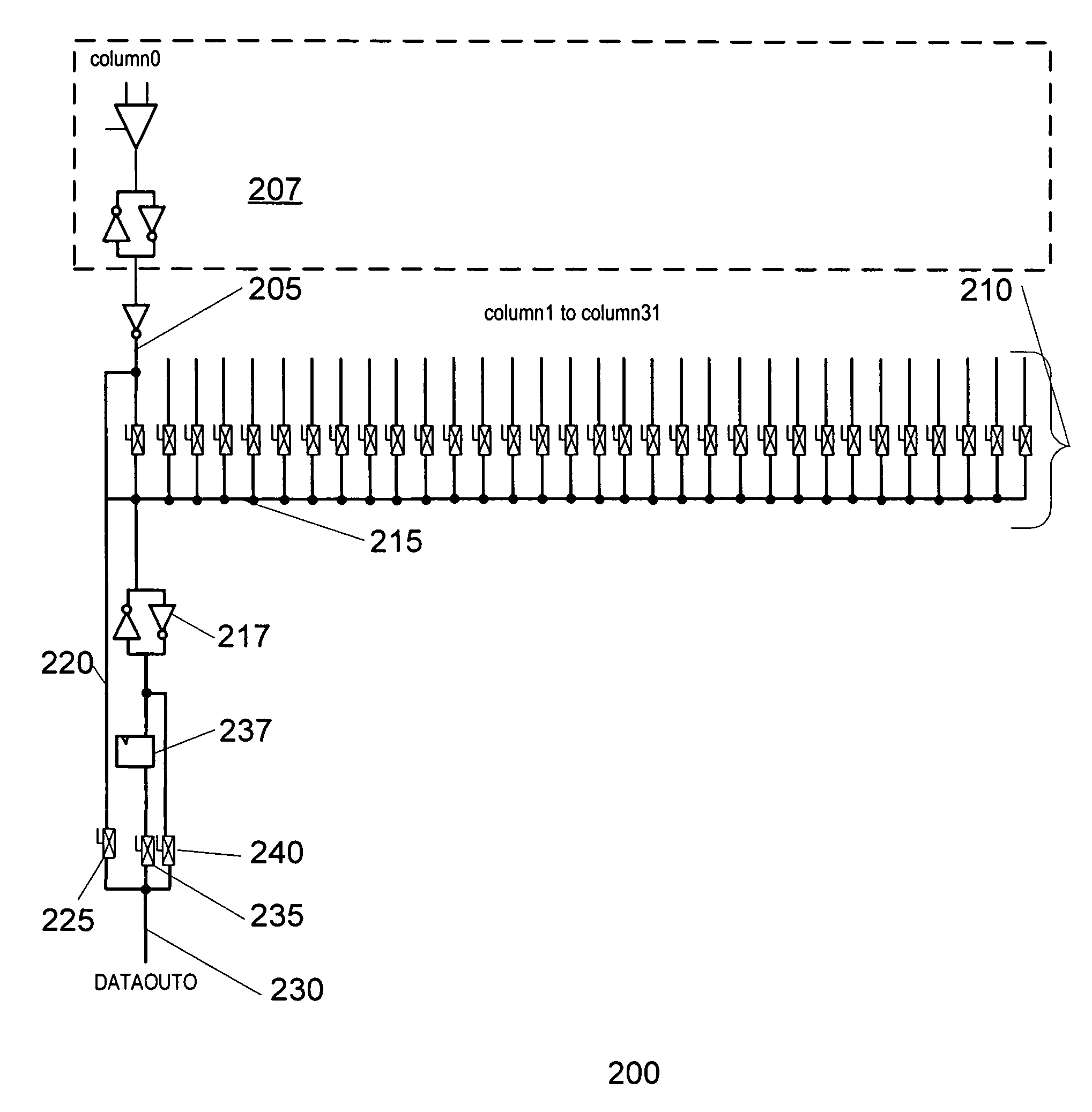

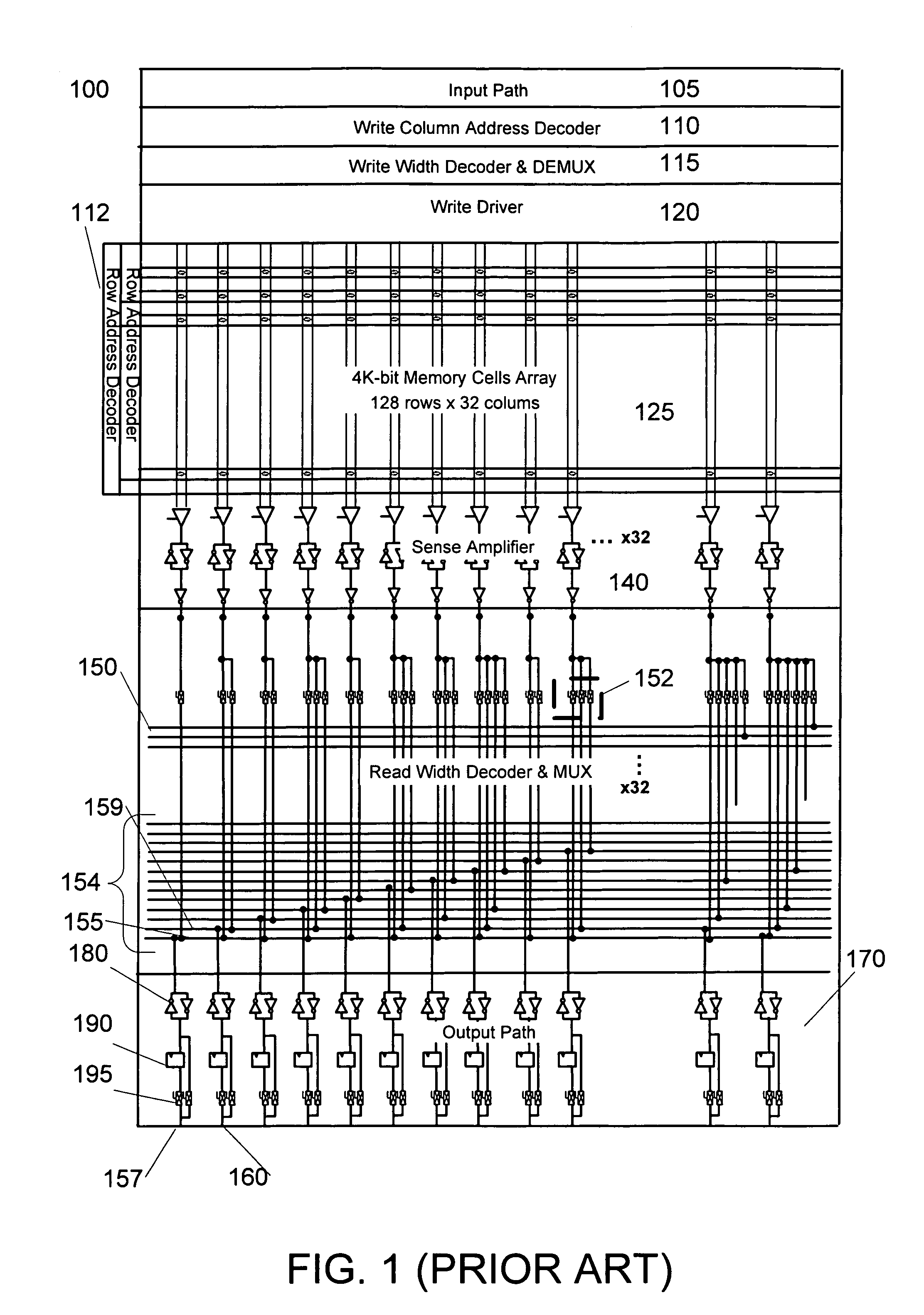

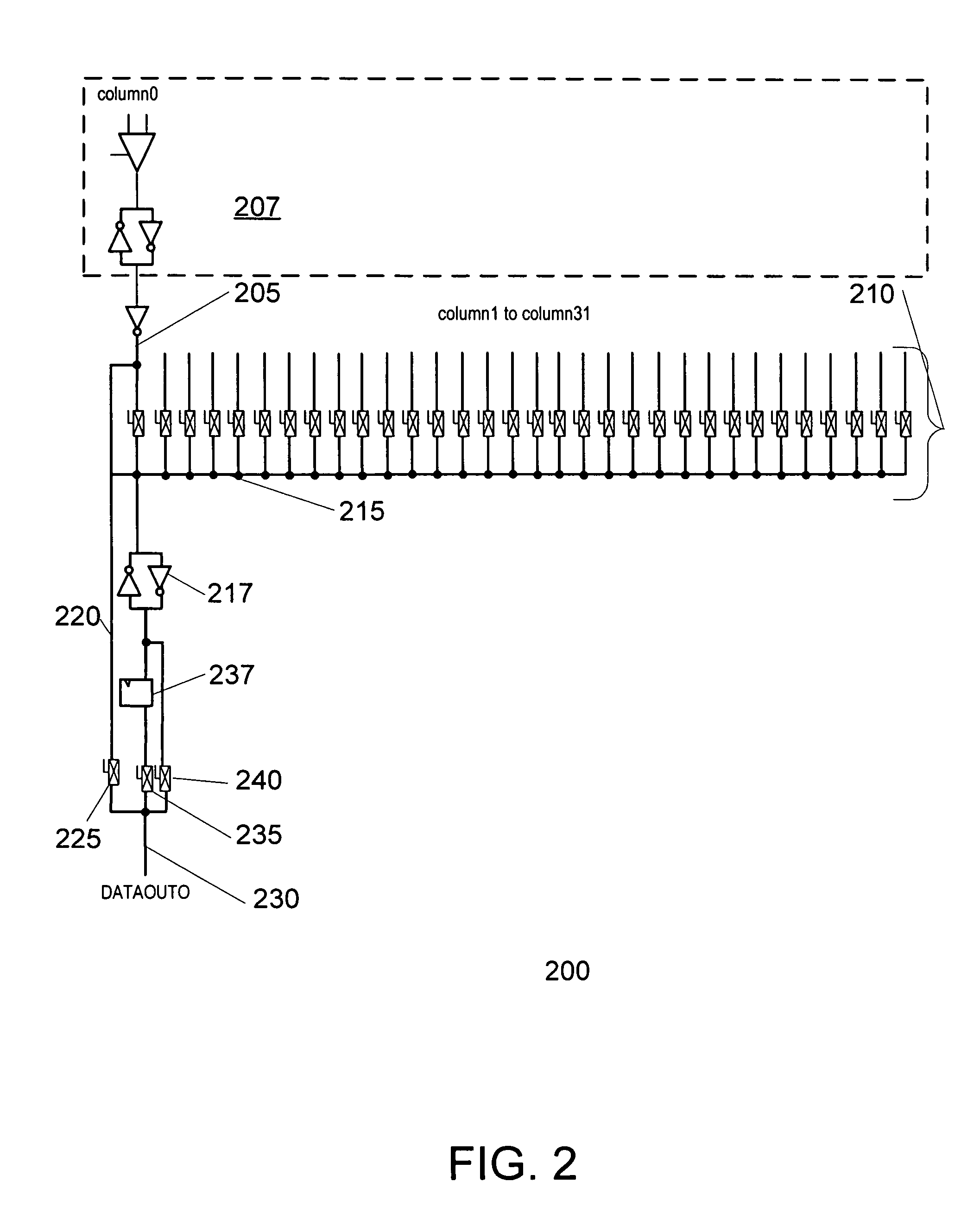

Using dedicated read output path to reduce unregistered read access time for FPGA embedded memory

ActiveUS7414916B1Increase speedImprove memory performanceDigital storageLogic circuitsAccess timeFull data

A memory unit includes width decoding logic enabling data to be accessed in a memory array at different data widths. To improve memory access speed, the memory unit also includes dedicated read output paths for accessing data at the full data width of the memory array. The dedicated read output paths bypass the width decoding logic and provide data from the memory array directly to a data bus, thereby providing improved memory performance when width decoding is not needed. The memory unit can be incorporated in programmable devices and a programmable device configuration can select either the read bypass paths or the width decoding logic. Hardware applications that require width decoding and improved memory access speed can utilize additional programmable device resources outside the memory unit to register the full width data from the memory unit and convert it to a different data width.

Owner:TAHOE RES LTD

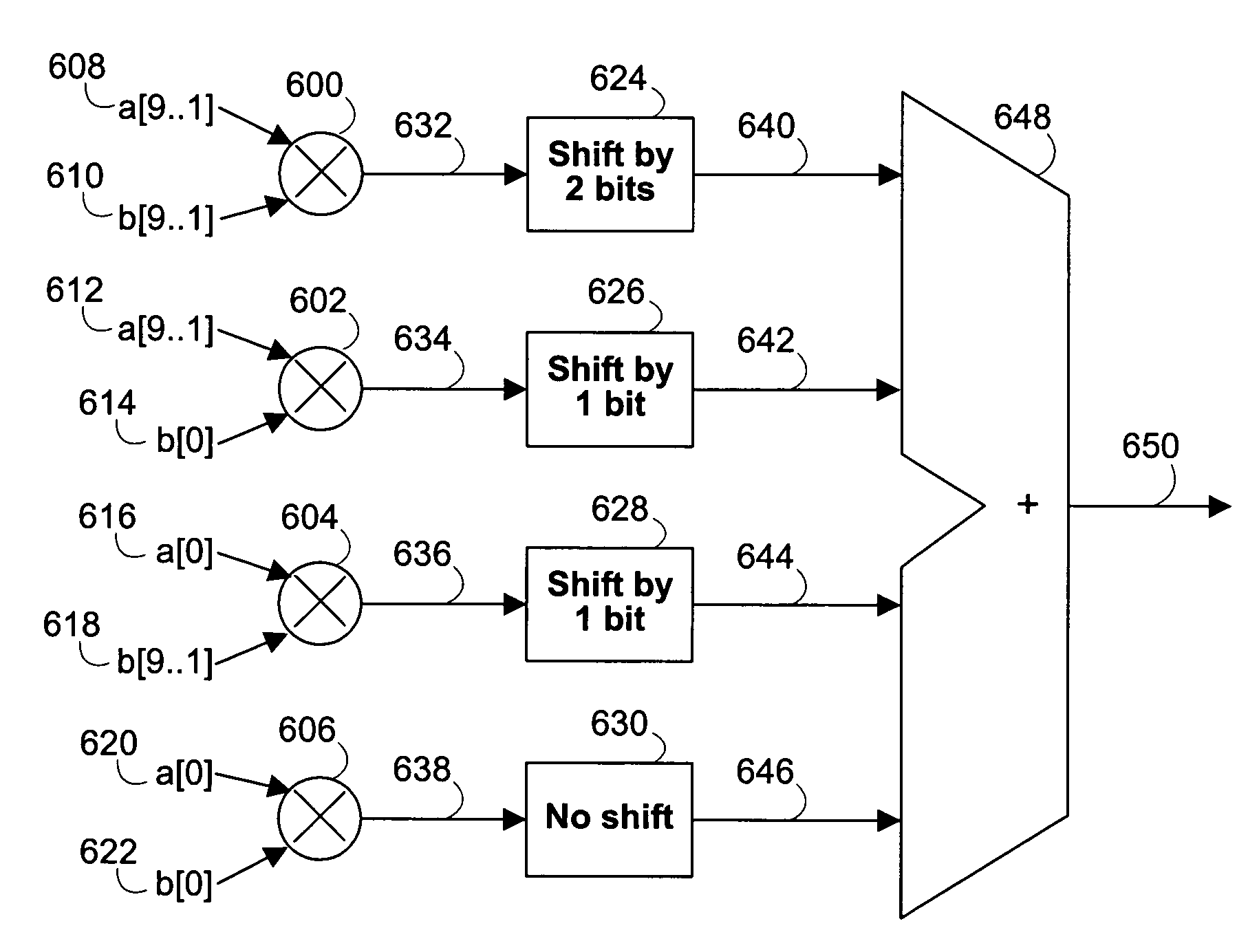

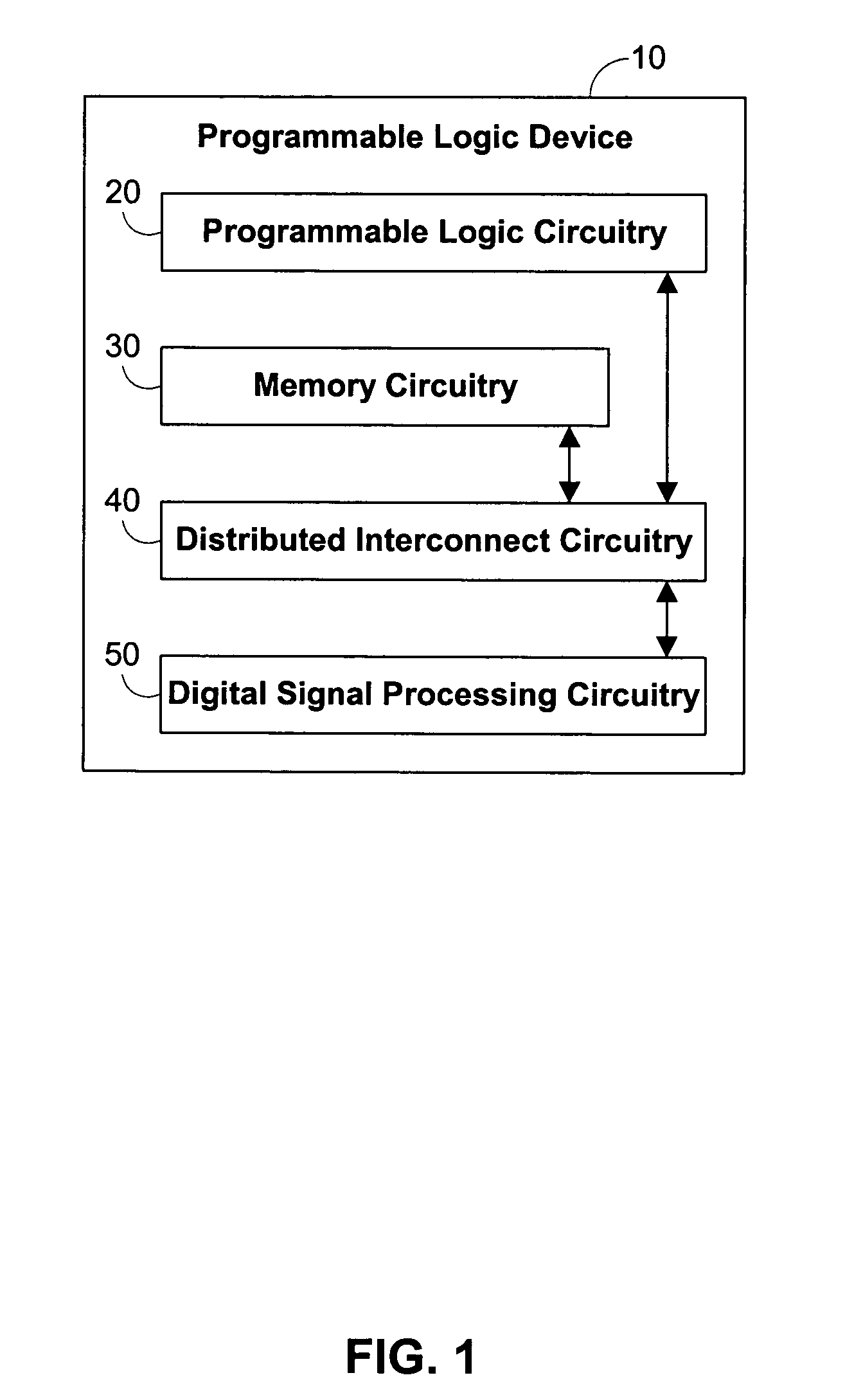

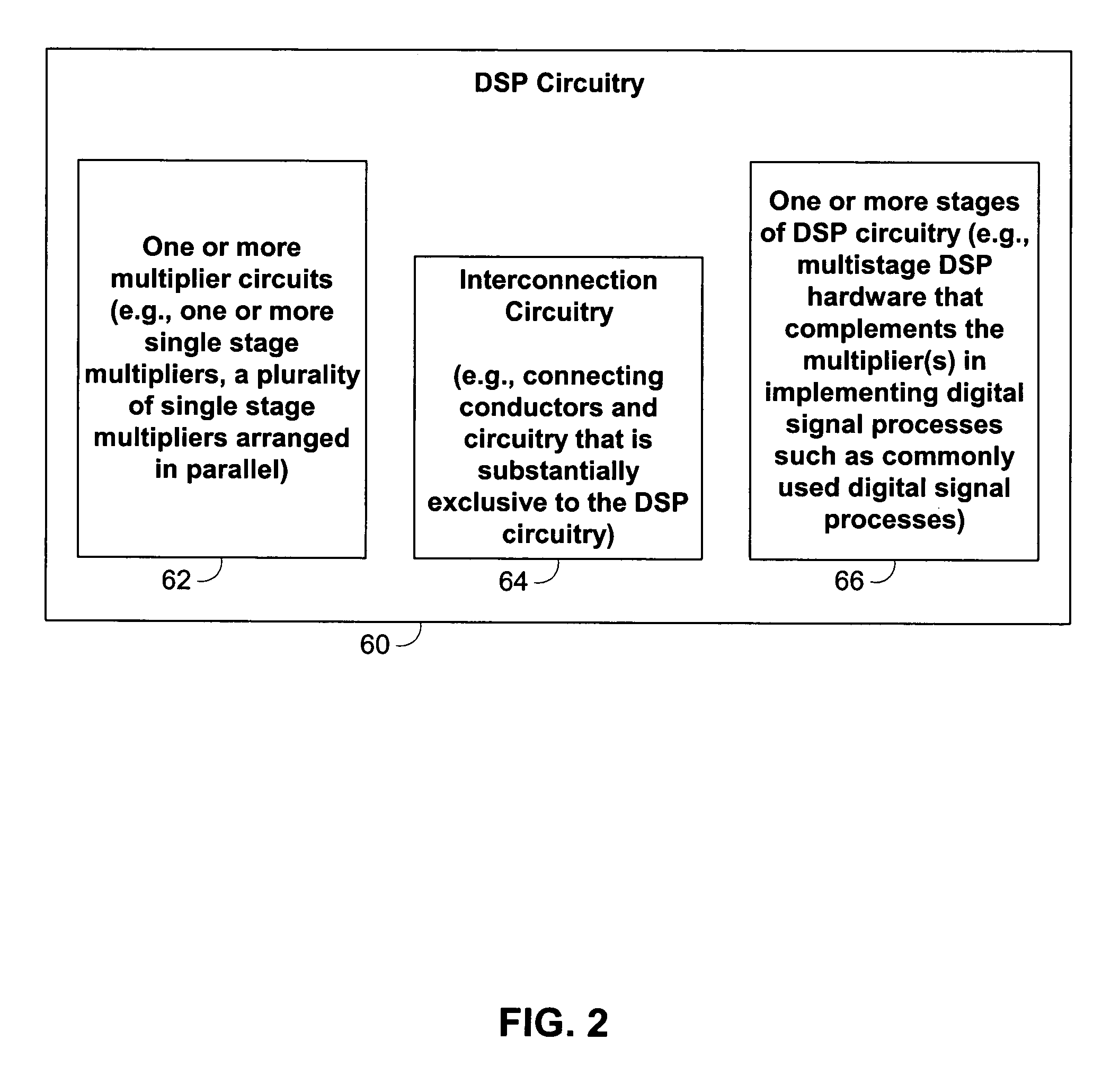

Hybrid multipliers implemented using DSP circuitry and programmable logic circuitry

ActiveUS7269617B1Efficient implementationComputation using non-contact making devicesLogic circuitsBinary multiplierPartial product

A user logic design to hardware application is provided that efficiently implements in a PLD a user logic design multiplier using both programmable logic circuitry and one or more multipliers embedded in DSP circuitry integrated in the PLD. A smaller DSP multiplier may be used by implementing the user logic design multiplier in a sum of partial product arrangement in which one of the partial products is generated using the smaller DSP multiplier with the remaining partial products being generated by multipliers implemented using programmable logic circuitry.

Owner:ALTERA CORP

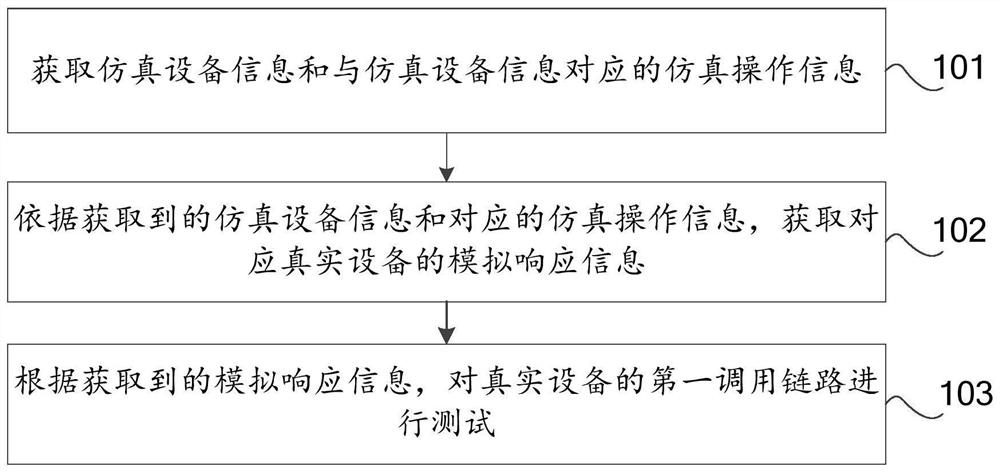

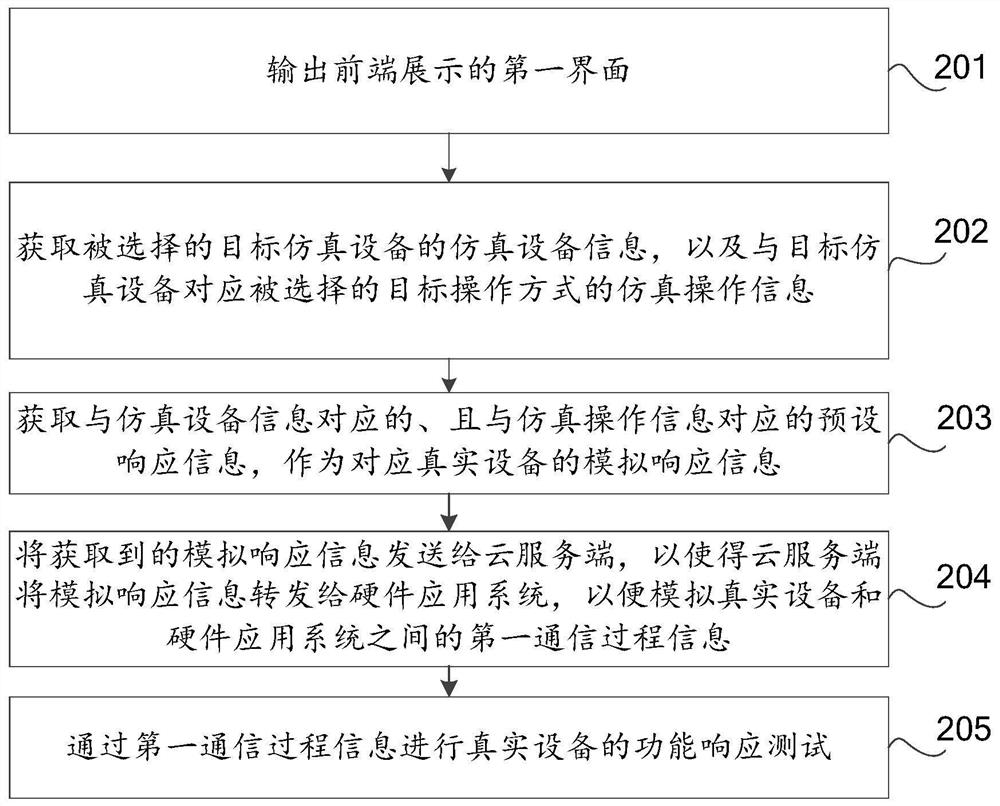

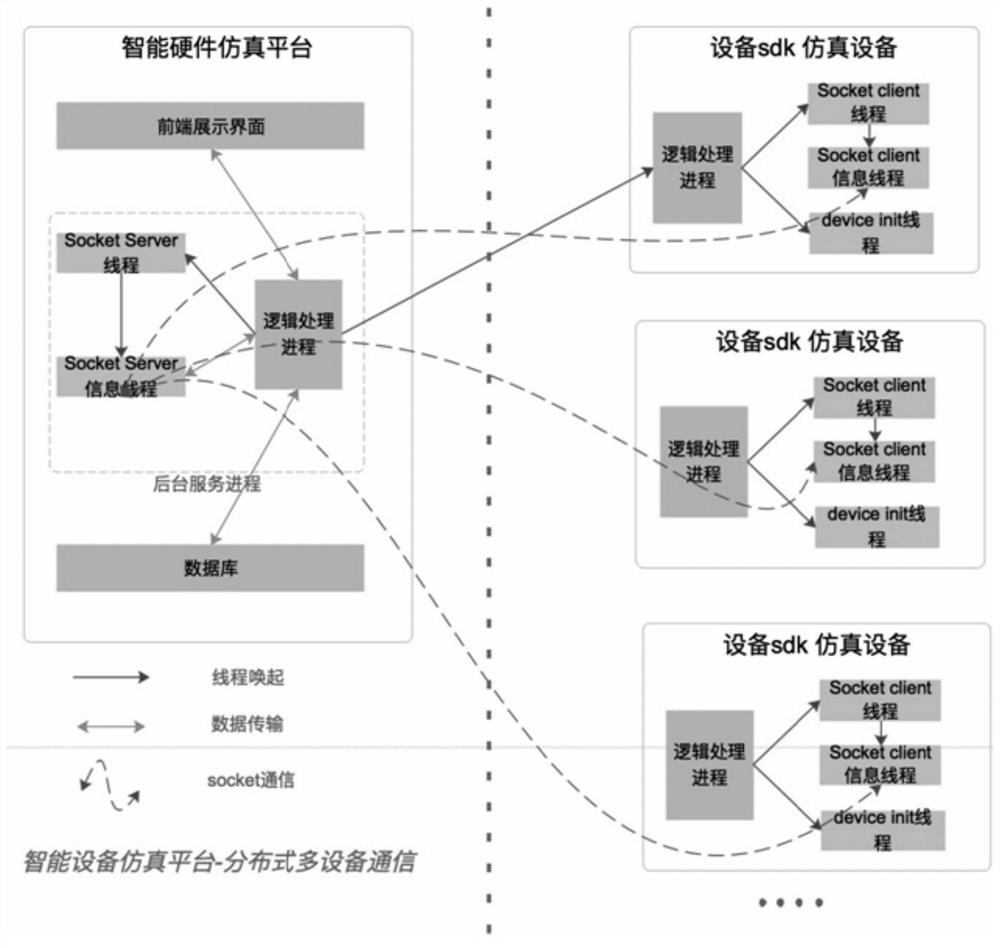

Hardware simulation test method, device and equipment

PendingCN111611121ASave offline development and testing costsHigh precisionFunctional testingComputer hardwareInformation acquisition

The invention discloses a hardware simulation testing method, device and equipment, and relates to the technical field of testing. The method comprises the following steps: firstly, acquiring simulation equipment information and simulation operation information corresponding to the simulation equipment information; acquiring simulation response information corresponding to real equipment accordingto the simulation equipment information and the simulation operation information; and finally, testing a first call link of the real device according to the simulation response information, the firstcall link being a call link that the real device responds to according to instruction information of a hardware application system. Real intelligent hardware equipment does not need to be purchased in the whole process, and the offline development and test cost is saved. In addition, simulation equipment meeting standards can be selected to replace real equipment of more types and styles for testing according to actual testing requirements, and the testing accuracy can be improved.

Owner:ZHEJIANG KOUBEI NETWORK TECH CO LTD

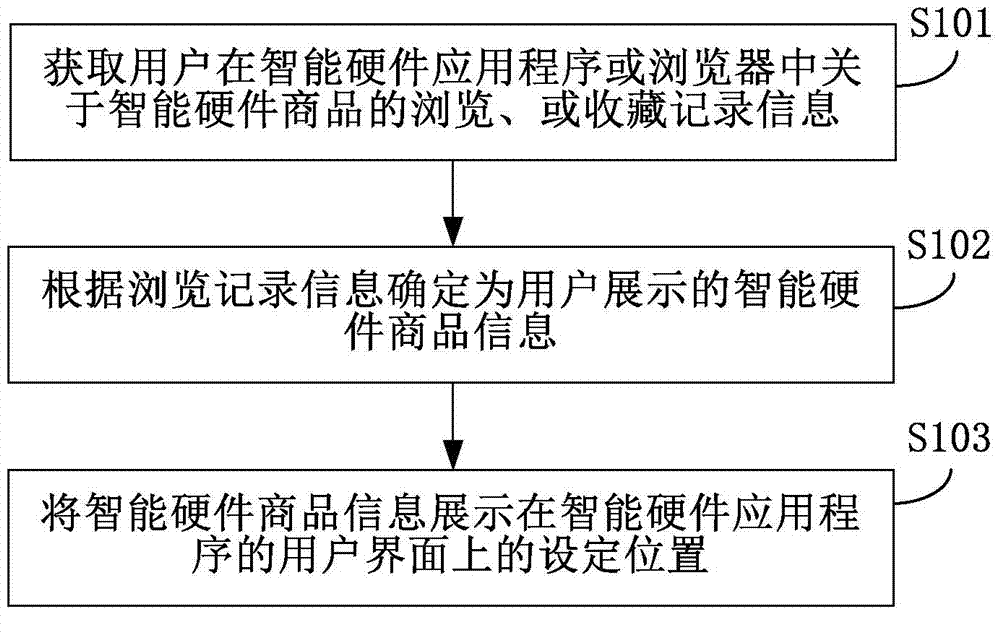

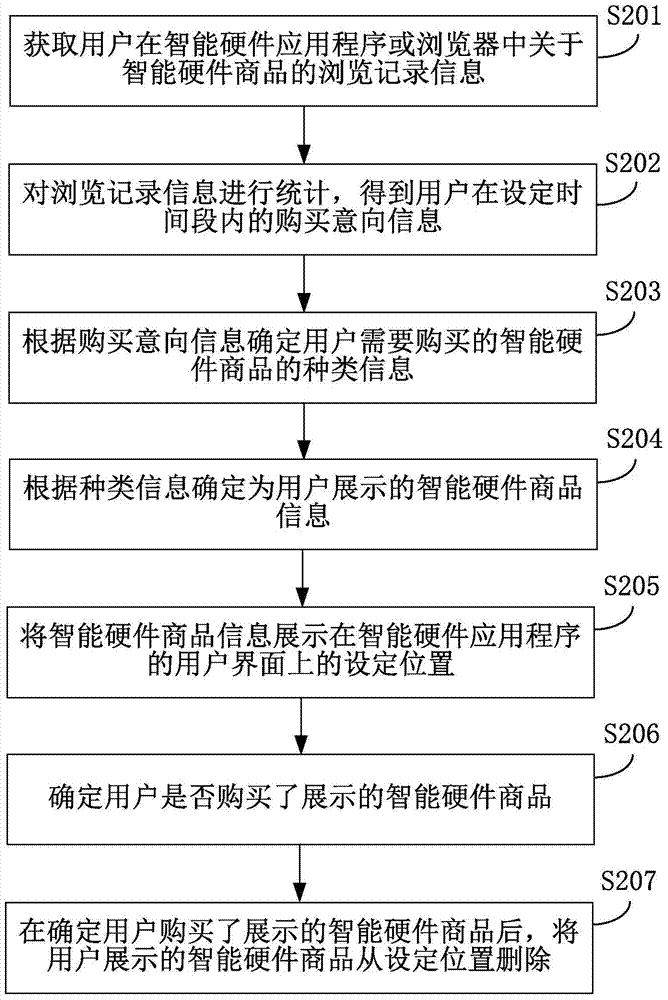

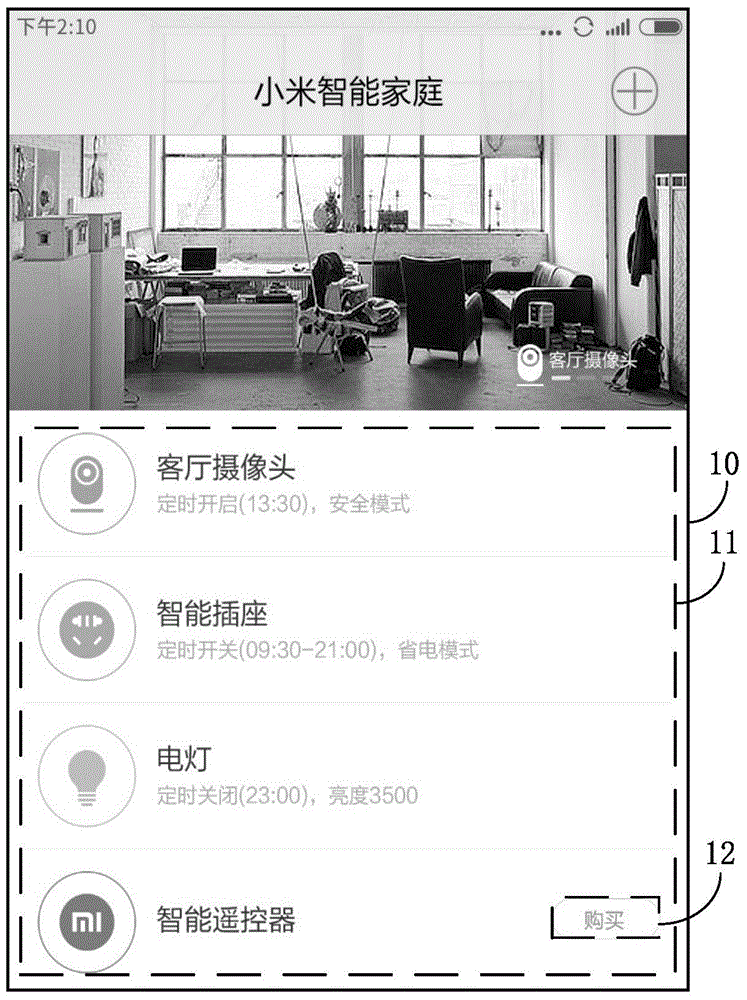

Method and device for setting intelligent hardware commodities on tops and displaying intelligent hardware commodities

InactiveCN104517222AImprove experienceFit the purchase needsMarketingComputer hardwareApplication software

The invention relates to a method and a device for setting intelligent hardware commodities on tops and displaying the intelligent hardware commodities. By the aid of the method and the device, the experience can be improved for users in intelligent hardware equipment purchasing procedures. The method includes acquiring browsing record information of the users; determining intelligent hardware commodity information to be displayed for the users according to the browsing record information; displaying the intelligent hardware commodity information at set positions of user interfaces of intelligent hardware application programs. The browsing record information of the users is stored in the intelligent hardware application programs or browsers and is related to the intelligent hardware commodities. According to the technical scheme, the method and the device have the advantages that the users can visually select the required-to-be-purchased intelligent hardware commodities according to the displayed intelligent hardware commodities, accordingly, the method and the device can bring convenience for the users when the users look up the intelligent hardware commodities, the probability that the users purchase the intelligent hardware commodities can be increased, and the experience can be improved for the users when the users are about to purchase the intelligent hardware commodities.

Owner:XIAOMI INC

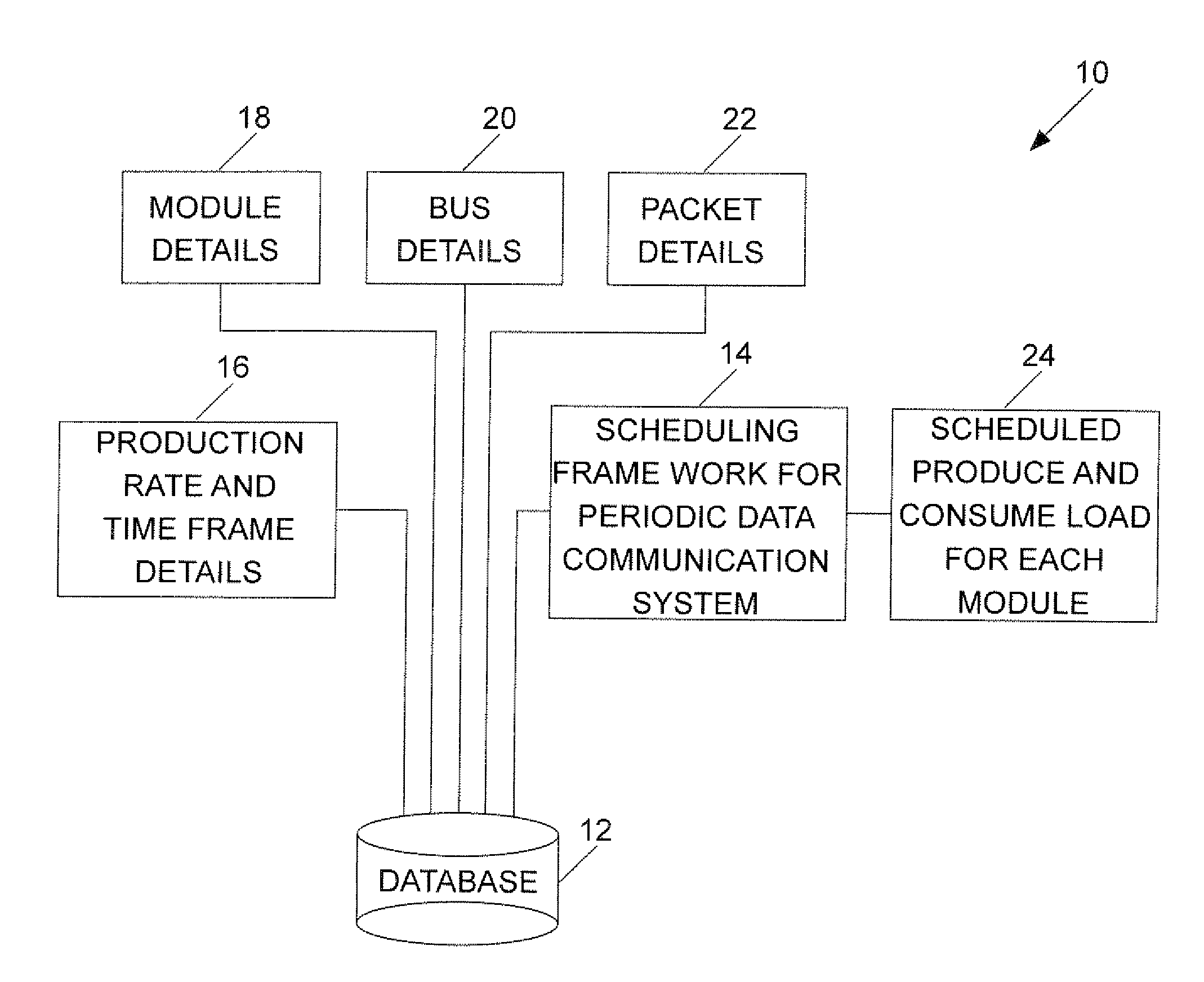

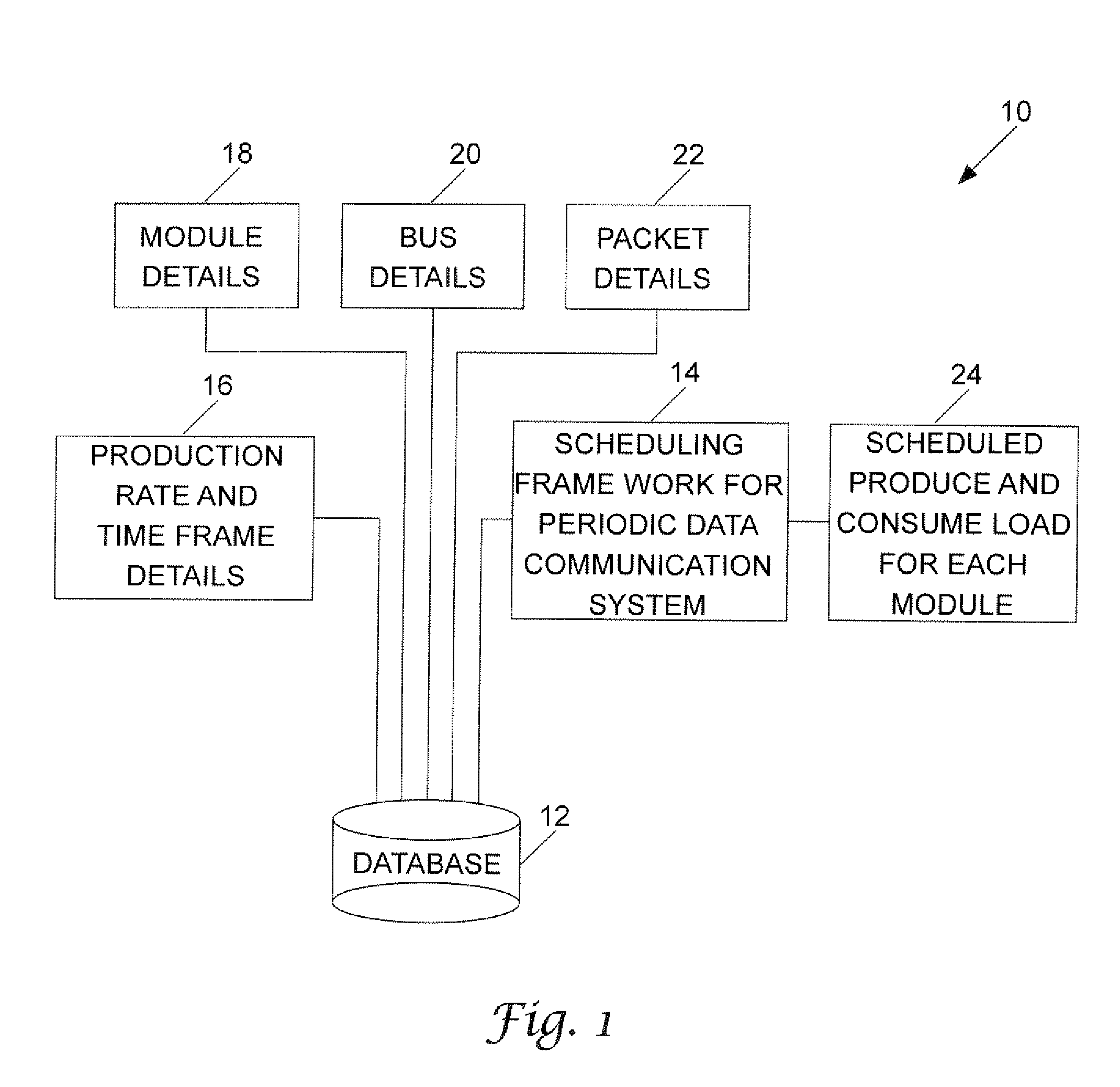

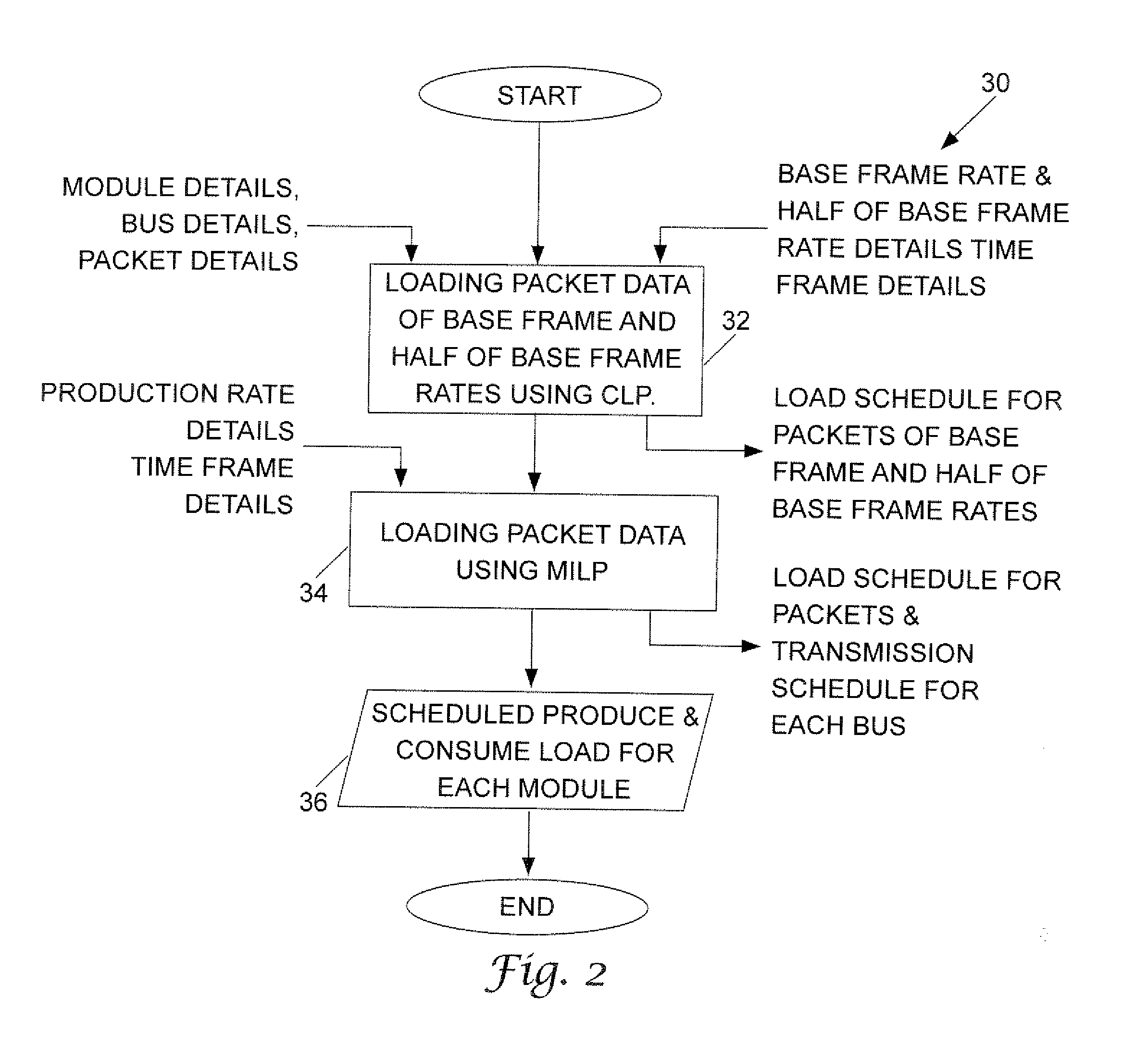

Optimization and/or scheduling framework for a periodic data communication system having multiple buses and hardware application modules

InactiveUS20080201717A1Interprogram communicationTransmissionCommunications systemApplication module

Periodic communication of data packets between modules in time frames having a plurality of frame rates including a base frame rate through a bus is schedule by determining a first load schedule for data packets of base frame and half base frame rates using constraint logic programming techniques, by determining a second load schedule for data packets of other frame rates using mixed integer linear programming techniques, and by scheduling produce and consume loads for each of the modules based on the first and second load schedules.

Owner:HONEYWELL INT INC

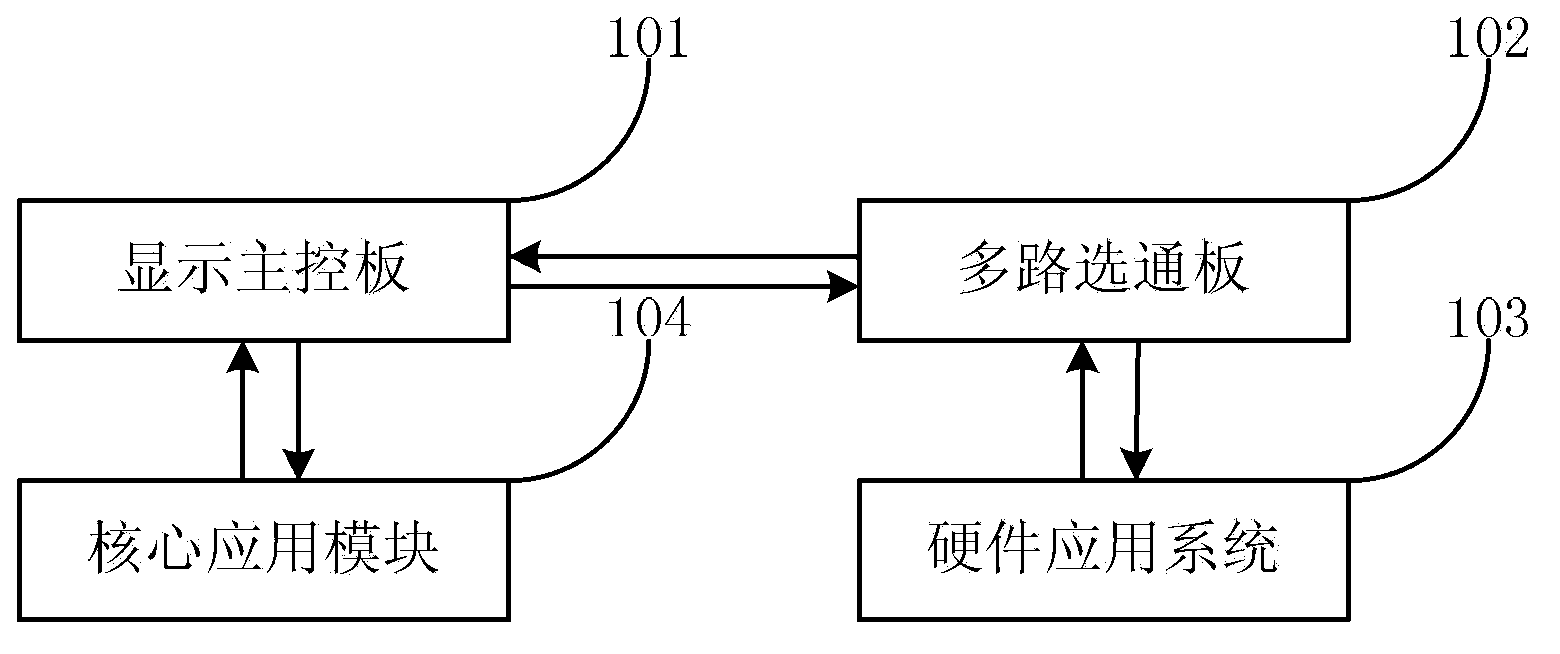

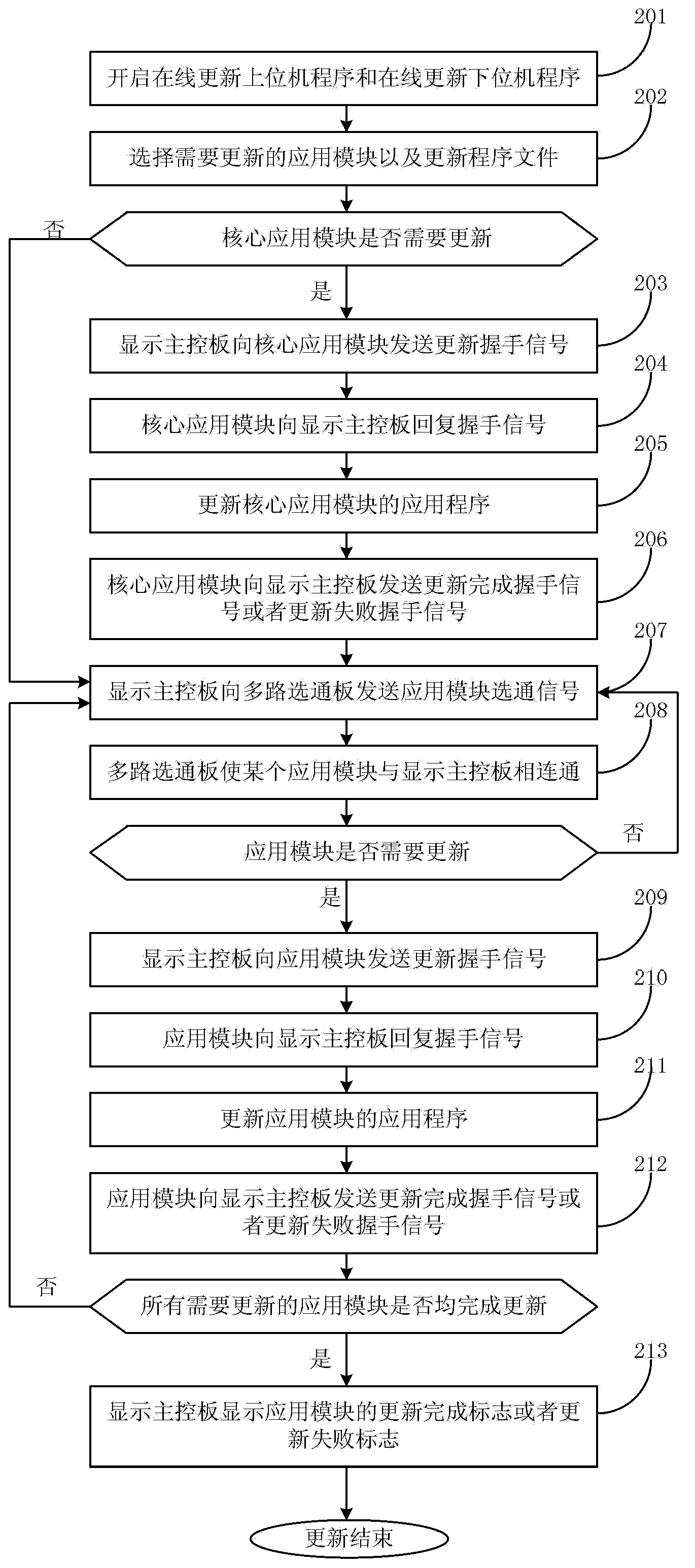

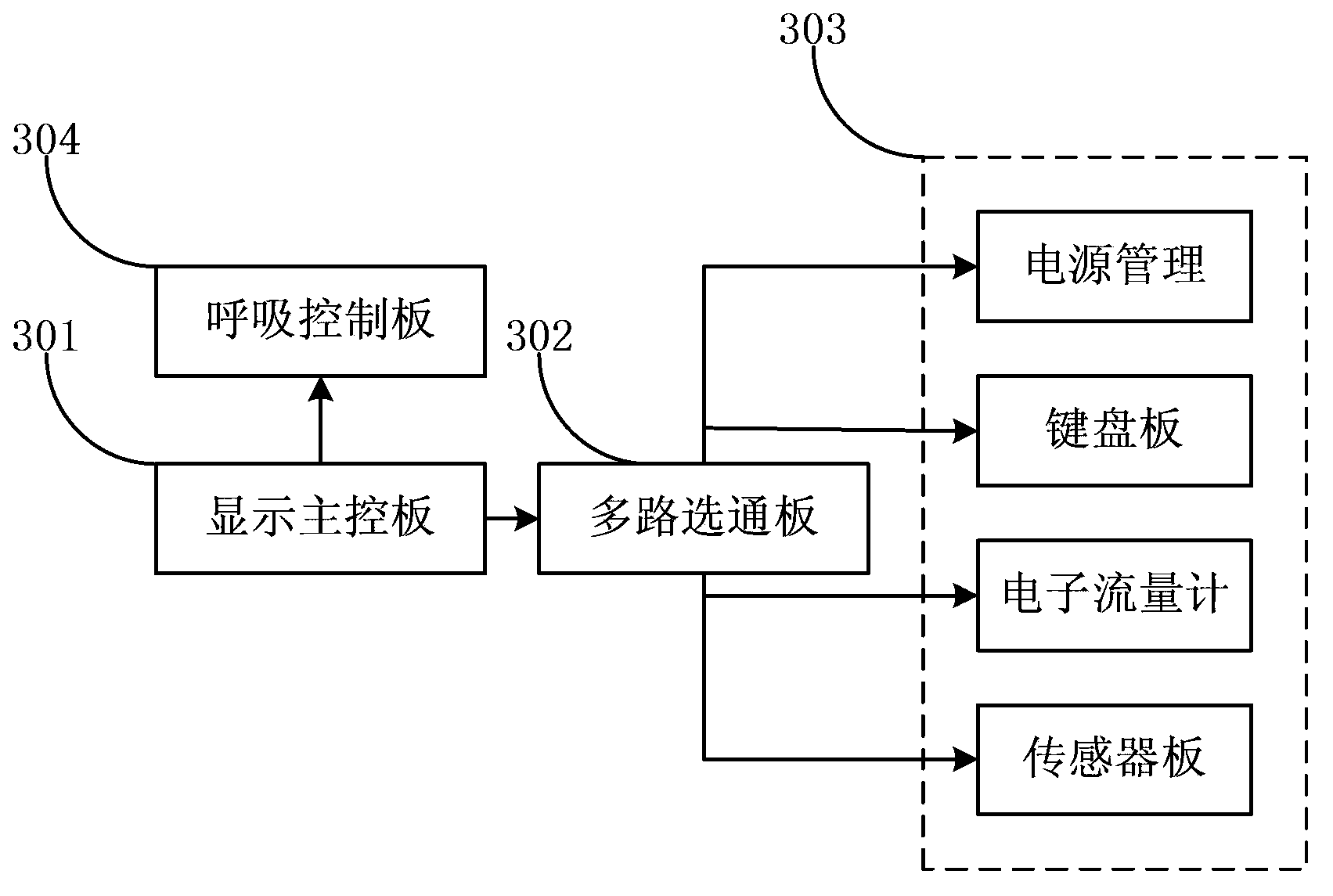

System and method for online updating of multiple board cards

InactiveCN103902315AFix update issuesRealize online updateProgram loading/initiatingComputer moduleApplication module

The invention provides a system and a method for online updating of multiple board cards. The system comprises a master display control board, a multichannel gating board, a hardware application system and a kernel application module. The master display control board is provided with an online updating upper computer program and used for updating application programs of application modules; the multichannel gating board is connected with the master display control board and used for communicating a certain application module in the hardware application system with the master display control board; the hardware application system is connected with the multichannel gating board and comprises a plurality of different application modules which are provided with different application programs; the kernel application module is directly connected with the master display control board and provided with a corresponding application program and an online updating lower computer program. According to the technical scheme, the multichannel gating board is additionally arranged between the master display control board and the hardware application system, and consequently the problem that batch updating of huge and complex application apparatus system hardware cannot be realized in the prior art is solved, and online batch updating of the multiple board cards can be realized at one time.

Owner:BEIJING AEONMED

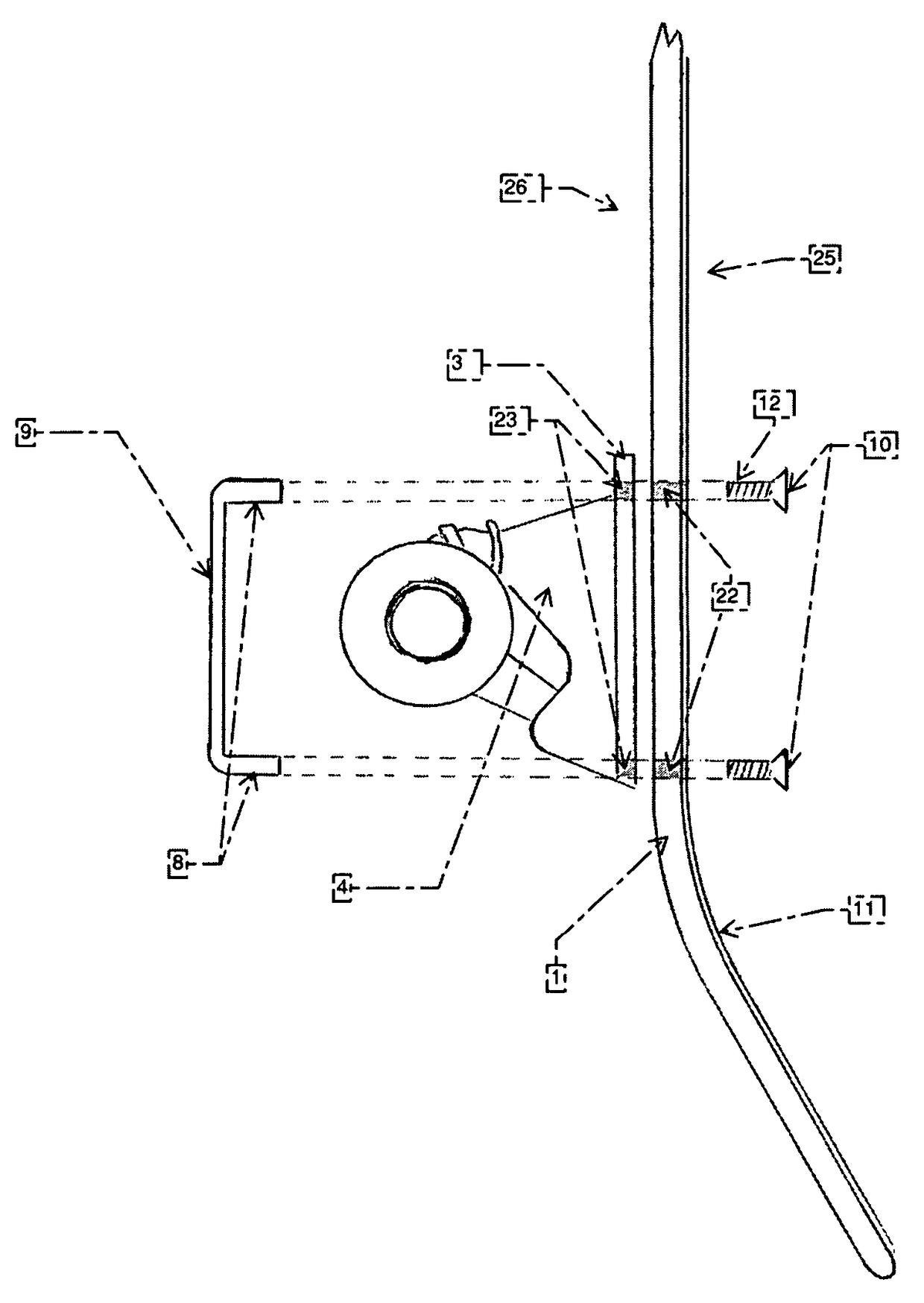

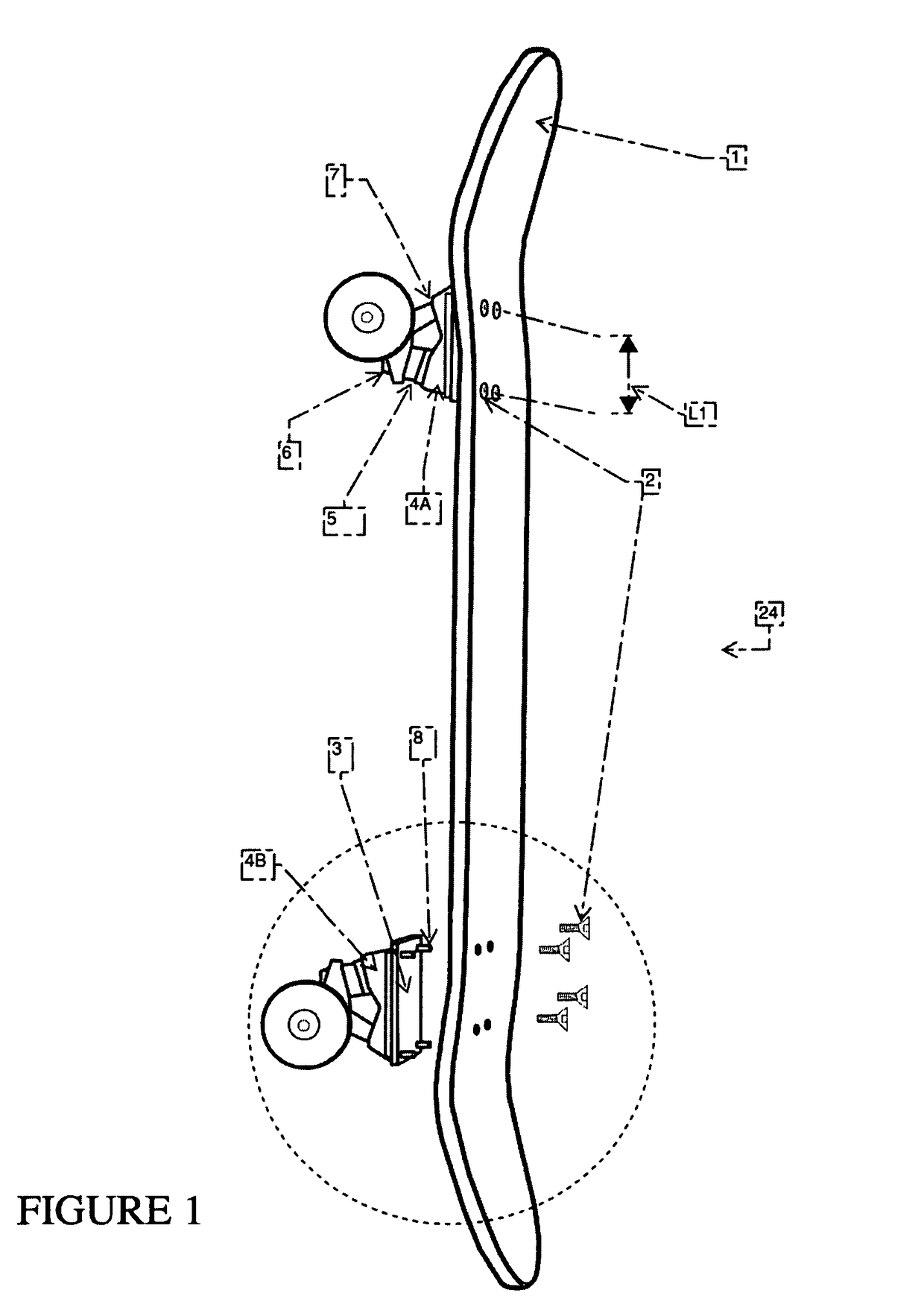

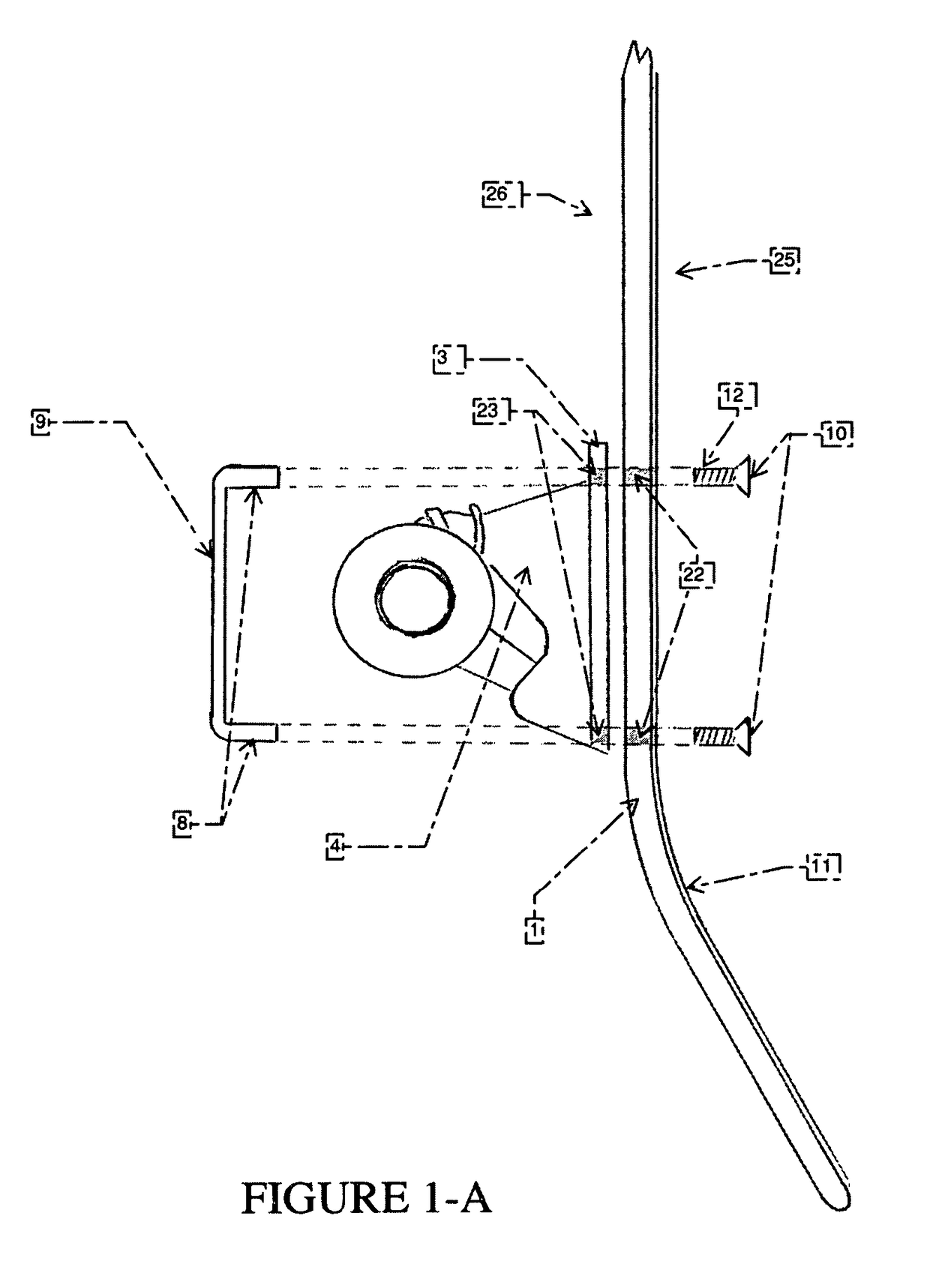

Double barrel truck mounting assembly

The Double Barrel Mounting Hardware invention is a hardware application for attaching skateboard trucks to the underside of a skateboard deck. The hardware is shaped like an elongated U (Harness) and mounts from the underside of the skateboard trucks through two corresponding holes on either the left or right side of the skateboard truck. The Double Barrel Mounting Hardware spans across these two corresponding holes in the skateboard truck along the underside of the skateboard truck baseplate and has two 90 degrees turned barrels at each end to pass through the holes in the skateboard truck baseplate and into the underside corresponding holes in the skateboard deck. The barrel of the harness that goes through the skateboard trucks and into the skateboard deck contains female threaded barrels. Male threaded mating bolts engage the harness barrels from the top side of the skateboard deck and when threaded together the mating bolt and harness bond the skateboard deck and skateboard trucks together. This hardware system securely attaches the skateboard trucks to the underside of the skateboard deck to be used in skateboard riding maneuvers.

Owner:ROLAND CHRISTOPHER DANIEL +1

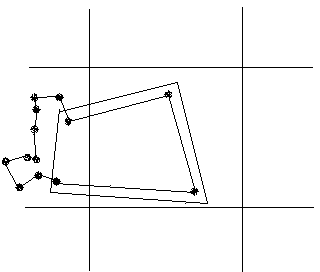

Quick polygon fill method of vectorgraph

InactiveCN104182928AIncrease display speedImprove processing efficiencyProcessor architectures/configurationTime delaysResource consumption

The invention discloses a quick polygon fill method of a vectorgraph. The quick polygon fill method of the vectorgraph has a specific technical scheme that the quick polygon fill method comprises the following steps: carrying out first preprocessing to a polygon, carrying out polygon cutting, and carrying out polygon filling, wherein the step of carrying out first preprocessing to the polygon comprises the following specific step: converting a point set list which represents a vector polygon in a file to be processed into a point minimum subset list which can represent the part, which is positioned in a screen display area, of the vector polygon. The quick polygon fill method of the vectorgraph overcomes a defect that a filling method in an original electronic chart engine has the disadvantages of big computing resource consumption, small hardware application range and non-ideal cooling, power consumption and system stability, greatly lowers the computing resource consumption of the display filling of a great quantity of vectorgraph elements in the electronic chart engine, reduces heat generated during the filling display processing of a great quantity of real-time graphs of a CPU or a graph display processing chip, effectively improves the time delay of real-time chart processing, and is especially suitable for low-configuration computers and mobile terminals of which the heat dissipating capacity and the operational performance are seriously restricted.

Owner:CHENGDUSCEON TECH

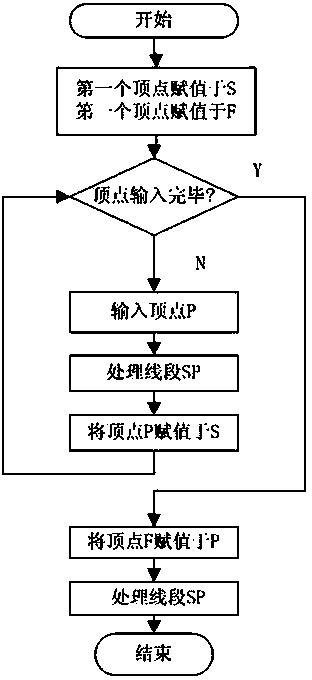

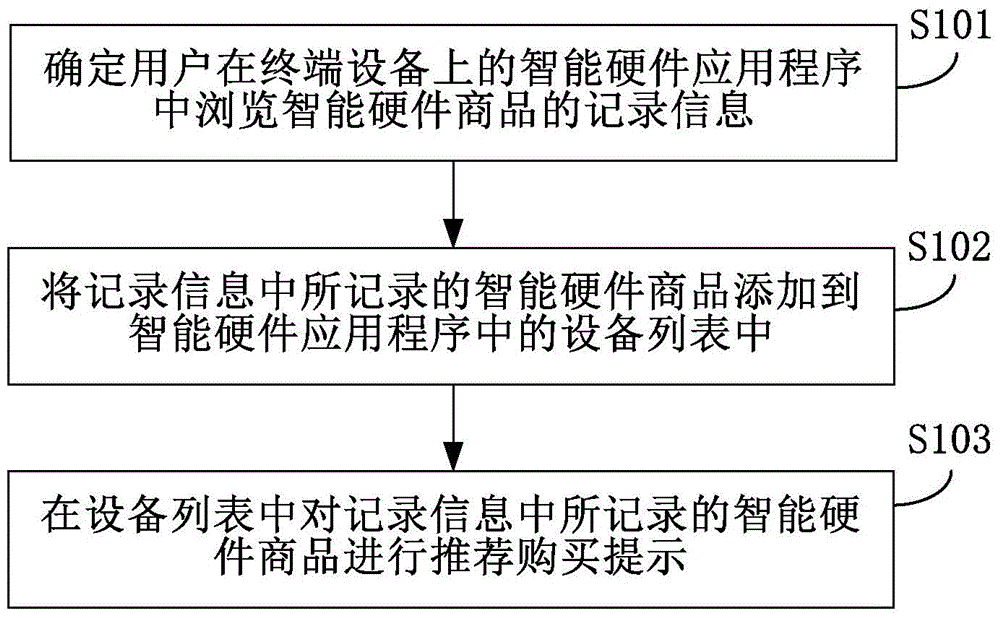

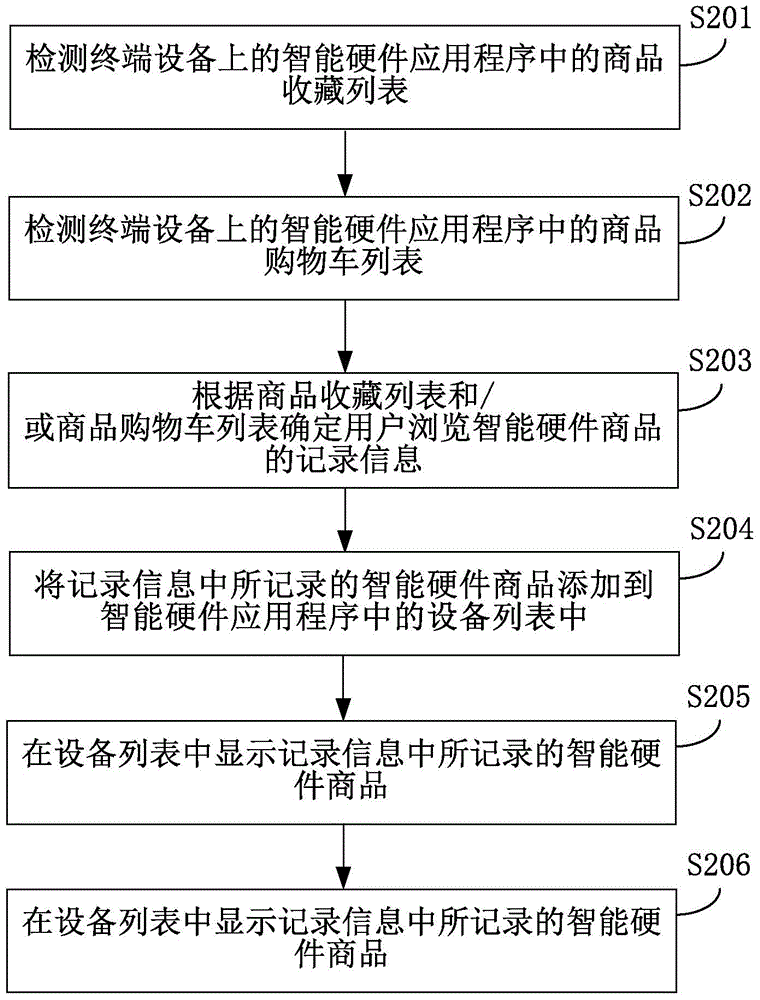

Recommendation display method and device for intelligent hardware commodities

ActiveCN104463640AImprove experienceEasy to determineBuying/selling/leasing transactionsMarketingComputer hardwareTerminal equipment

The invention discloses a recommendation display method and device for intelligent hardware commodities. The recommendation display method and device are used for improving the user experience in the intelligent hardware equipment purchasing process. The method comprises the steps of determining recording information of a user for browsing intelligent hardware commodities in an intelligent hardware application program on terminal equipment; adding the intelligent hardware commodities recoded in the recoding information to an equipment list in the intelligent hardware application program; purchase recommendation prompting is carried out on the intelligent hardware commodities recorded in the recording information in the equipment list. According to the technical scheme, the user can more conveniently determine whether to purchase the intelligent hardware commodities or not, and therefore the recommended intelligent hardware commodities have more pertinence for the user.

Owner:XIAOMI INC

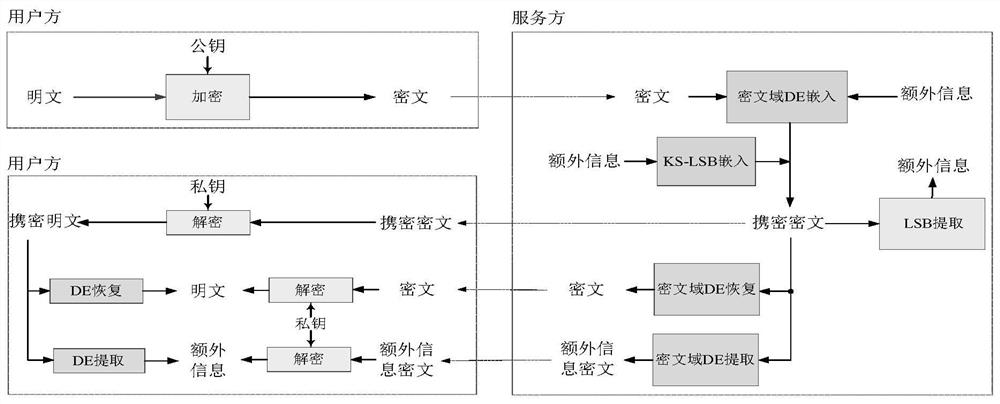

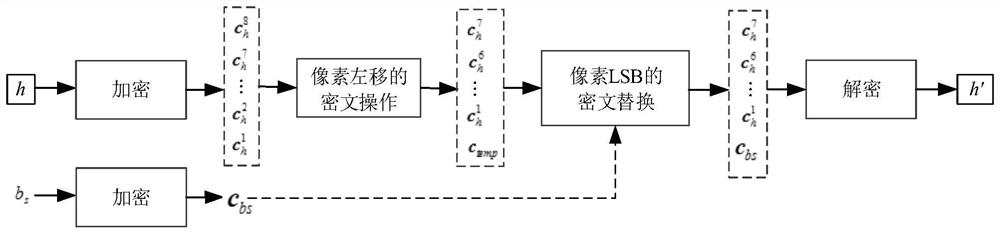

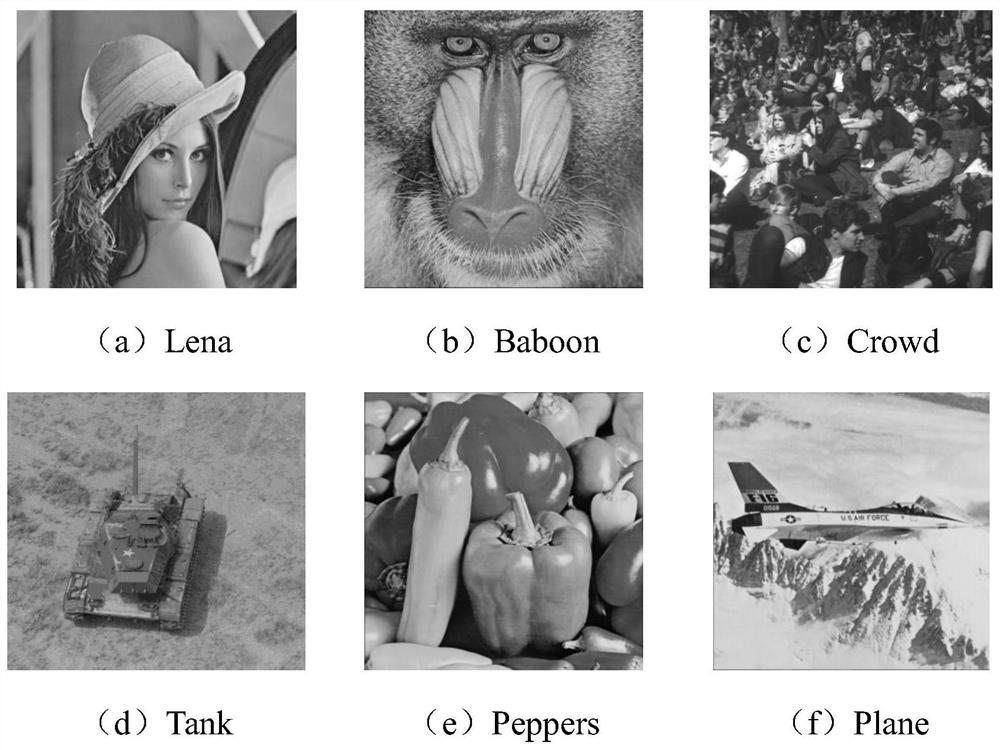

Ciphertext domain reversible information hiding method and software and hardware application system

PendingCN112054900AGuaranteed separation effectDoes not affect the decryption resultKey distribution for secure communicationPublic key for secure communicationComputer hardwarePlaintext

The invention discloses a ciphertext domain reversible information hiding method, which comprises the following steps of: (1) preprocessing and encrypting a plaintext to obtain a ciphertext; (2) embedding the encrypted additional information into a ciphertext to obtain a first secret-carrying ciphertext; (3) secondarily embedding ciphertext LSB information based on key replacement into the first secret-carrying ciphertext, and finally obtaining the secret-carrying ciphertext; wherein the ciphertext LSB information based on key replacement is data obtained by encrypting additional information;(4) carrying out LSB extraction on the secret-carrying ciphertext, and extracting secondary embedded additional information; and processing the secret-carrying ciphertext through ciphertext domain information extraction and carrier recovery or plaintext domain information extraction and carrier recovery to obtain an original plaintext and additional information embedded for the first time. The invention further discloses a ciphertext domain reversible information hiding system, computer equipment and a readable storage medium, and efficient and large-capacity embedding of data and reversible recovery of carrier data are guaranteed on the premise that separable ciphertext domain reversible information hiding is met.

Owner:ENG UNIV OF THE CHINESE PEOPLES ARMED POLICE FORCE

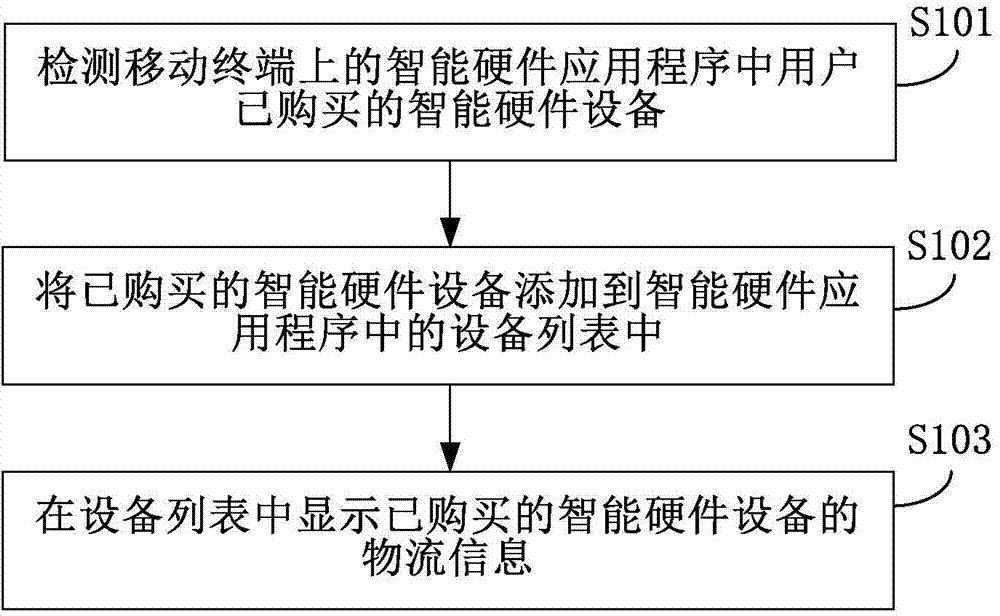

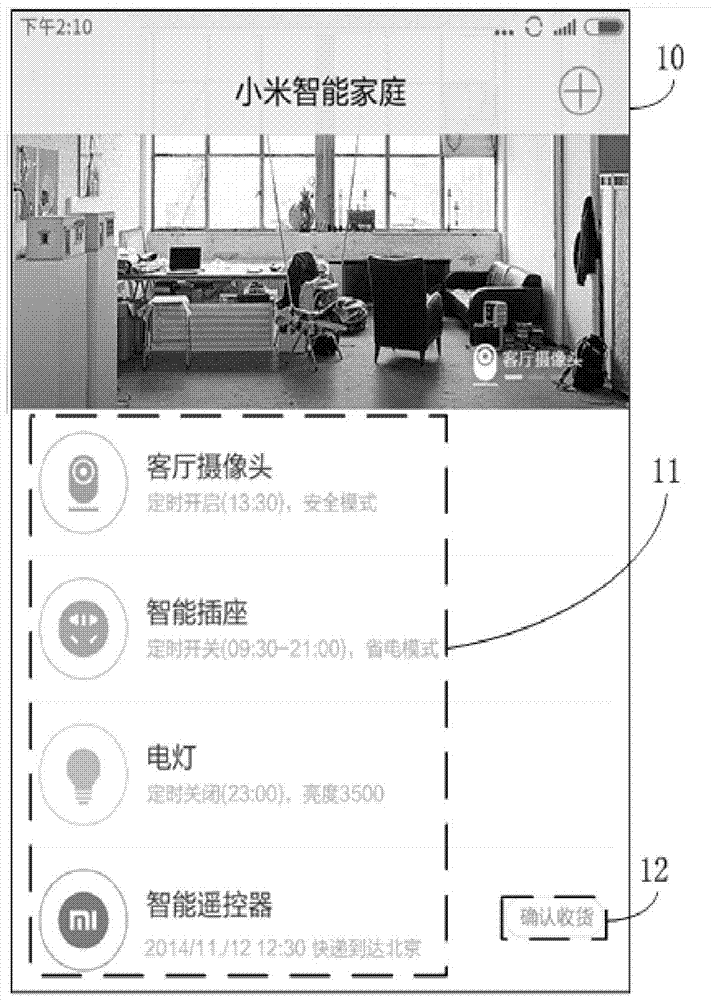

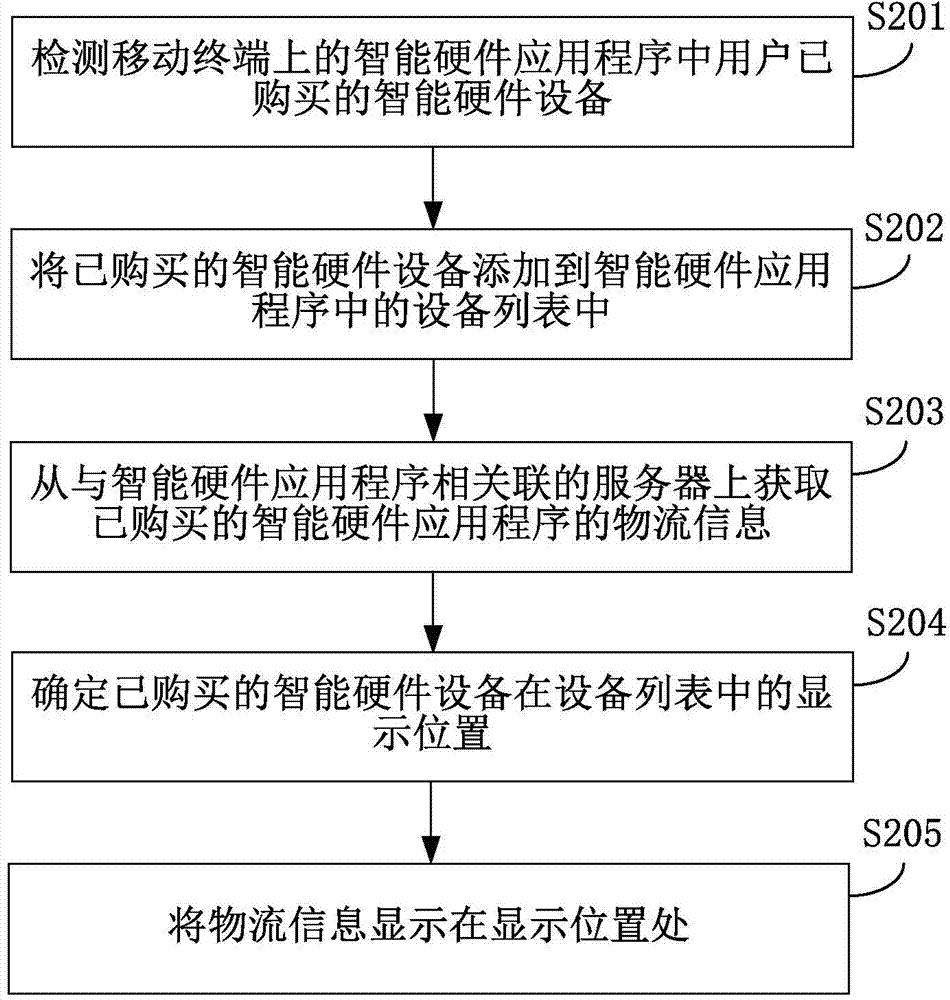

Logistics information display method and device of intelligent hardware equipment

ActiveCN104516634AEasy to understandImprove experienceLogisticsMarketingLogistics managementComputer terminal

The invention discloses a logistics information display method and a logistics information device of intelligent hardware equipment used for improving the experience in the course of purchasing the intelligent hardware equipment by a user. The method comprises the steps of detecting the intelligent hardware equipment purchased by the user in an intelligent hardware application program at a mobile terminal; adding the intelligent hardware equipment purchased to an equipment list in the intelligent hardware application program; and displaying the logistic information of the intelligent hardware equipment purchased in the equipment list. According to the technical scheme of the logistics information display method provided by the invention, the user can be more convenient to know the logistic state of the existing intelligent hardware equipment purchased, more pertinence to the logistics monitoring of the intelligent hardware equipment purchased by the user can be realized, and the experience on the intelligent hardware equipment purchased by the user can be improved.

Owner:XIAOMI INC

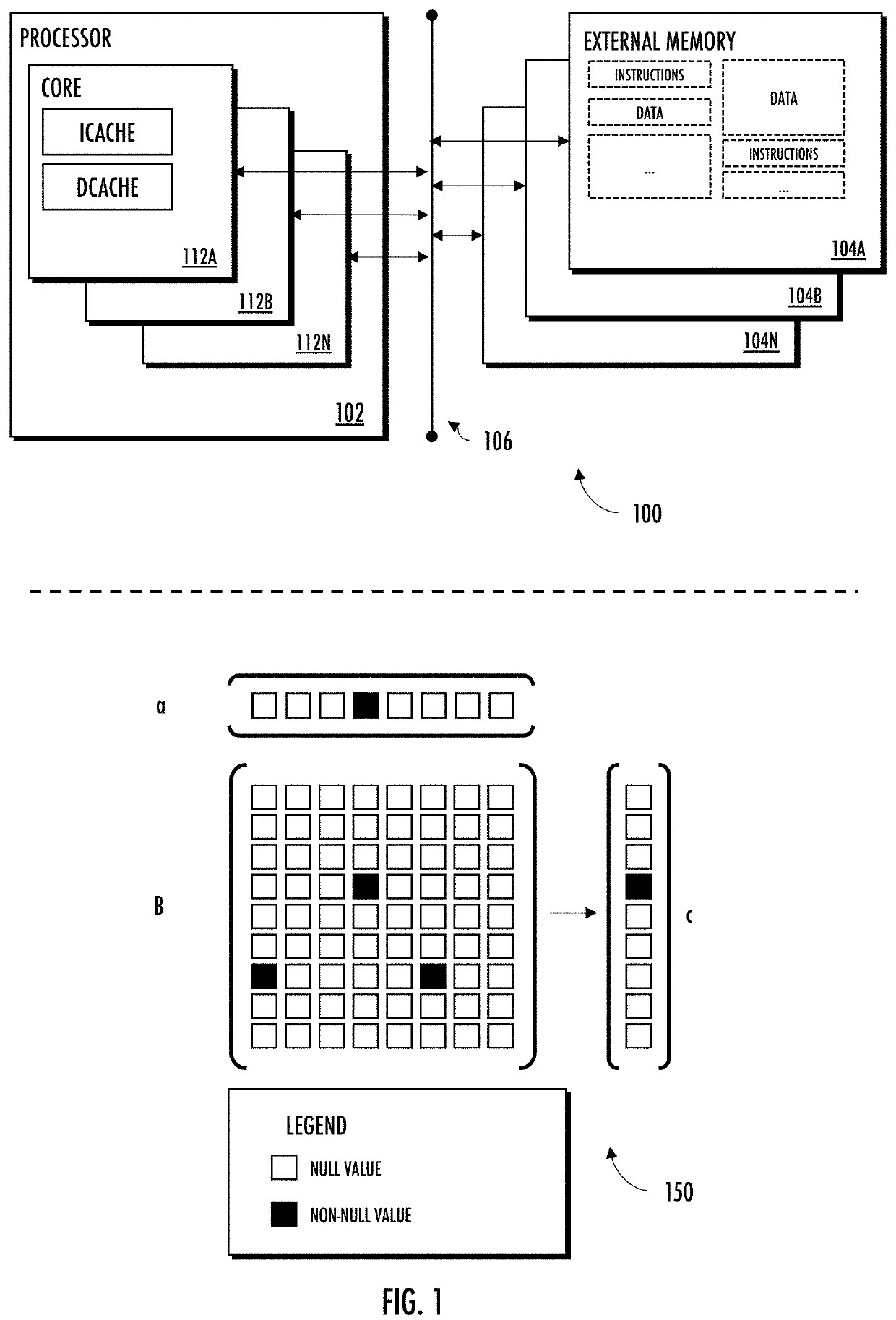

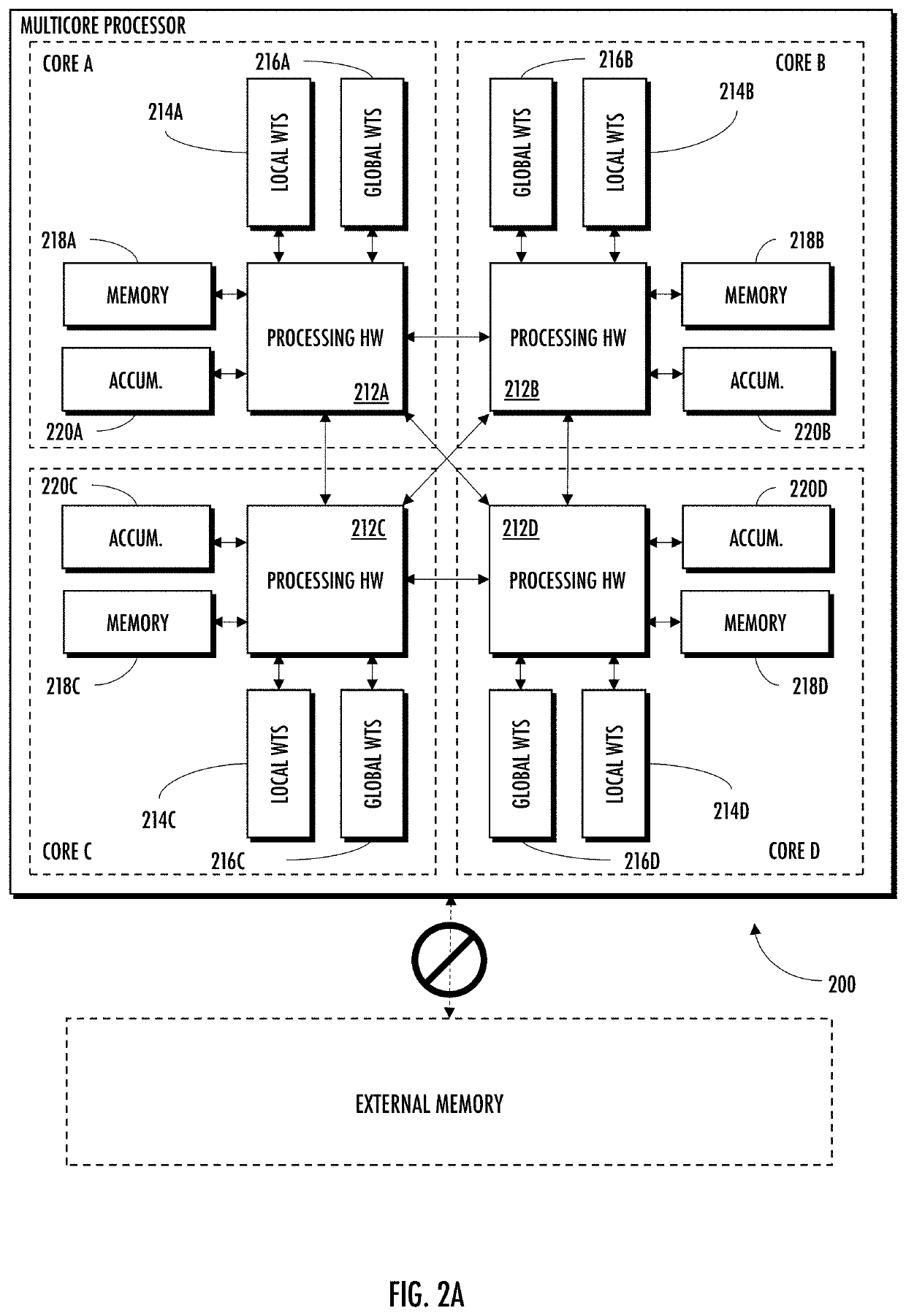

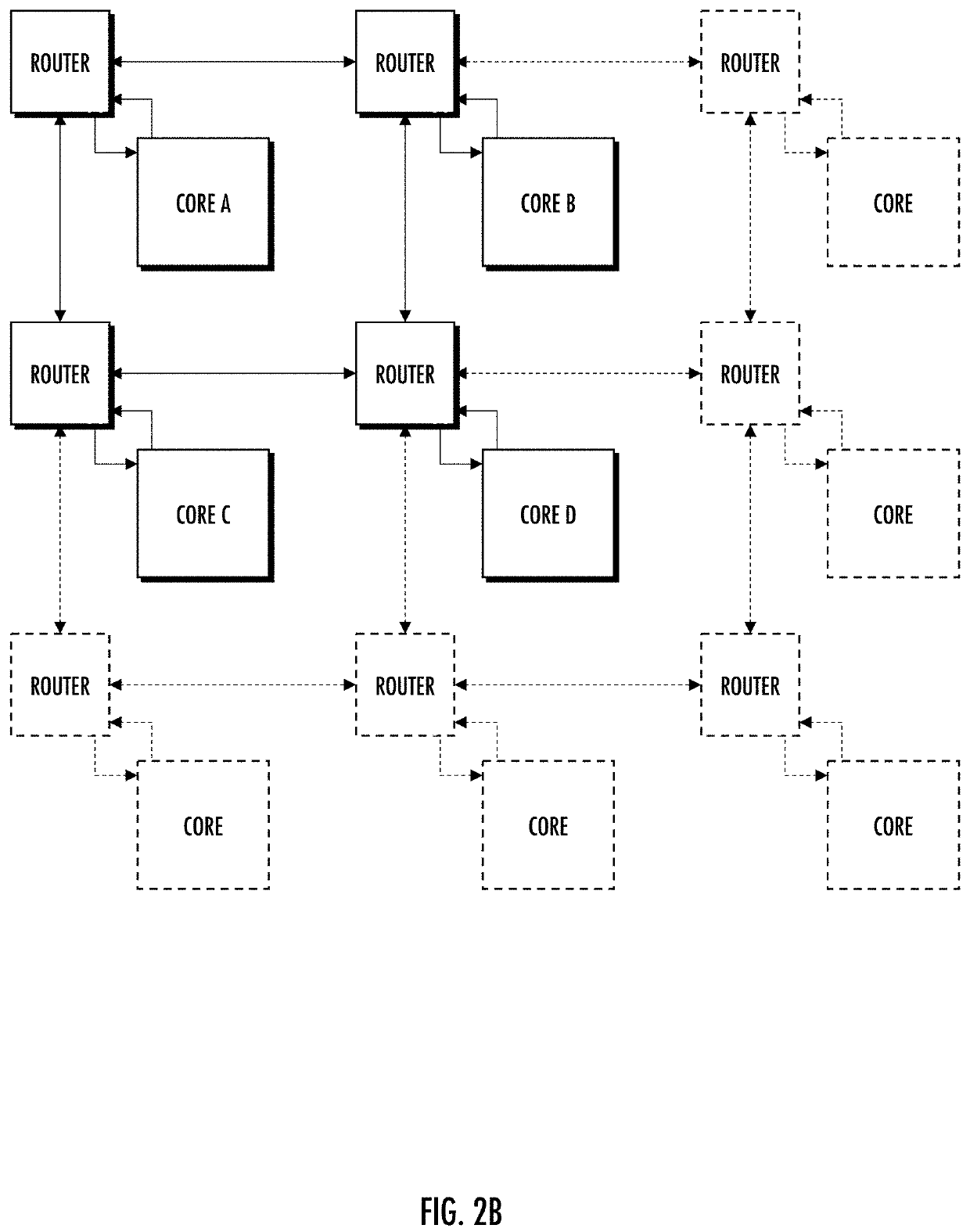

Methods and apparatus for localized processing within multicore neural networks

PendingUS20220012575A1Program initiation/switchingError detection/correctionComputer architectureBrute force

Methods and apparatus for localized processing within multicore neural networks. Unlike existing solutions that rely on commodity software and hardware to perform “brute force” large scale neural network processing the various techniques described herein map and partition a neural network into the hardware limitations of a target platform. Specifically, the various implementations described herein synergistically leverage localization, sparsity, and distributed scheduling, to enable neural network processing within embedded hardware applications. As described herein, hardware-aware mapping / partitioning enhances neural network performance by e.g., avoiding pin-limited memory accesses, processing data in compressed formats / skipping unnecessary operations, and decoupling scheduling between cores.

Owner:FEMTOSENSE INC

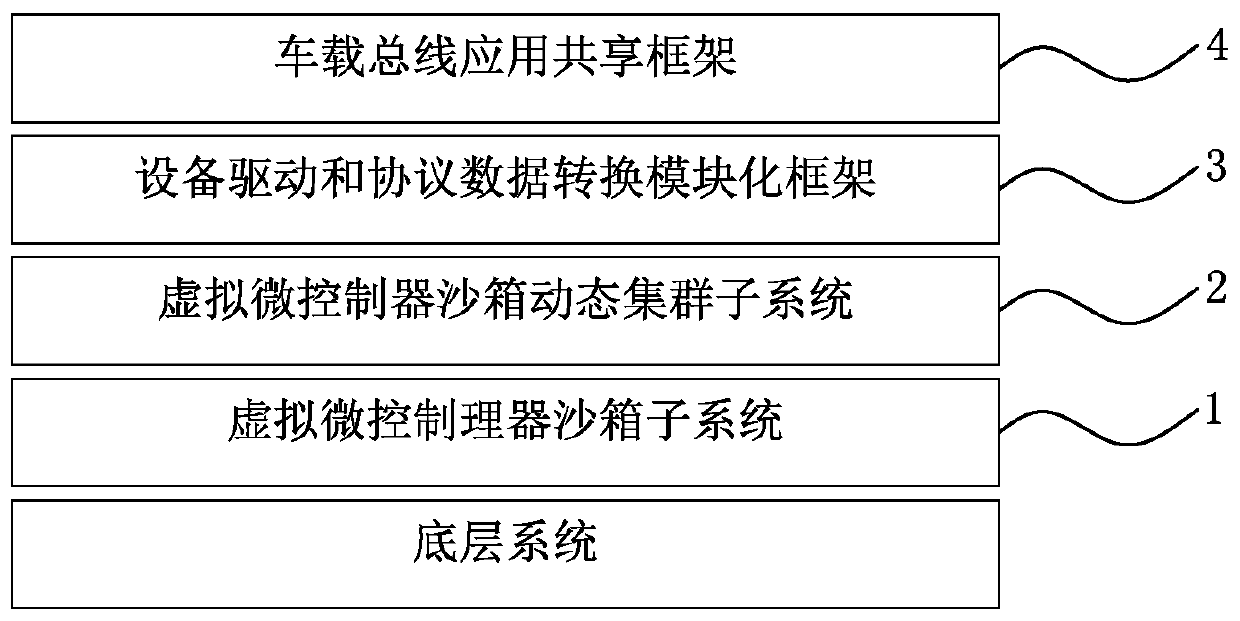

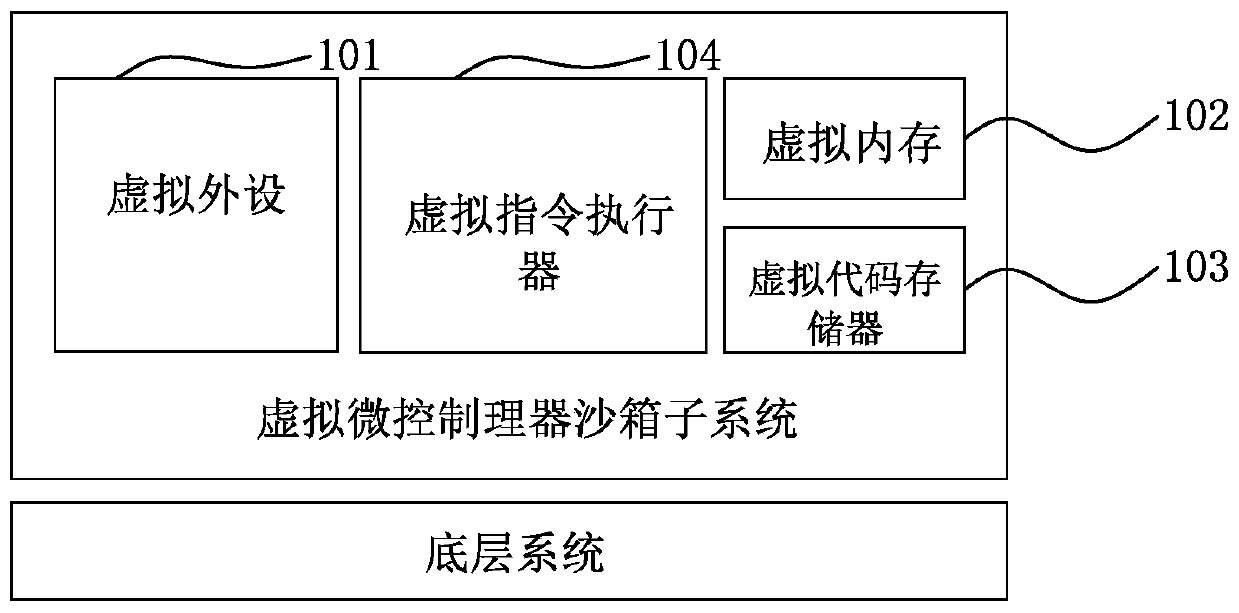

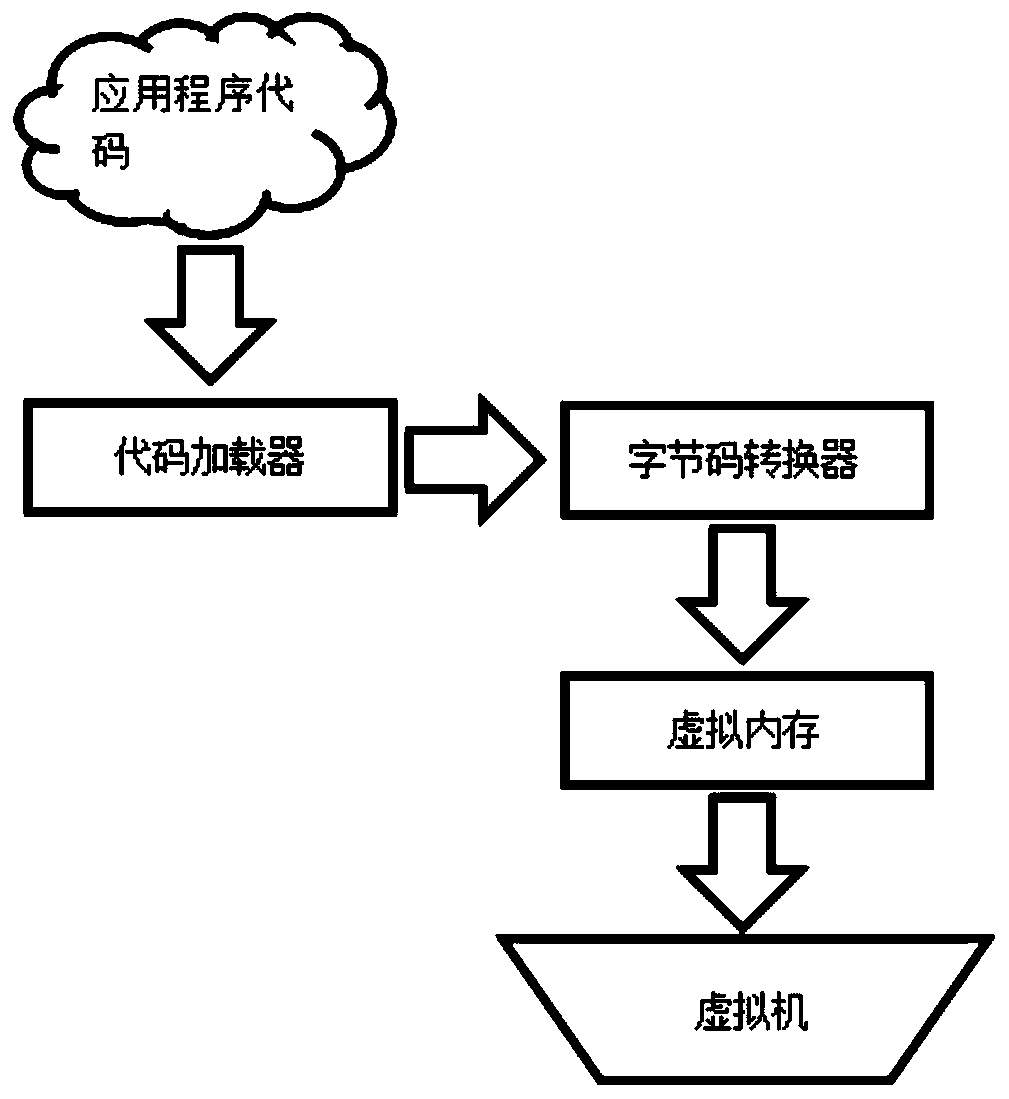

Vehicle-mounted application cross-hardware platform based on virtualization technology

ActiveCN111045646APromote software and hardware application innovationGuaranteed functionSoftware designEnergy efficient computingApplication softwareEmbedded system

The invention belongs to the technical field of virtual machines, and particularly relates to a vehicle-mounted application cross-hardware platform based on a virtualization technology. According to the new vehicle-mounted application cross-hardware platform based on the virtualization technology, the vehicle-mounted application cross-hardware platform based on the virtualization technology widelysupports various hardware platforms, so that complex software functions can be rapidly developed and deployed to buses; by means of standardized supporting system software structure design, competition barriers caused by specificity of the bus industry are removed, product functions and quality are powerfully guaranteed, meanwhile, operation and maintenance service complexity is greatly reduced,and the purposes of reduction and efficiency improvement are achieved. Through unifying a vehicle-mounted application software development language and a standardized vehicle-mounted hardware equipment software interface, the development of a vehicle-mounted application system is simplified, the software and hardware application innovation of the bus industry is promoted, and a solid foundation islaid for the interconnection and vehicle-road cooperative application of the bus industry.

Owner:BEIJING CE VANLINK TECH CO LTD +3

System and method for monitoring and ensuring data integrity in an enterprise security system

Owner:LIBERTY PEAK VENTURES LLC

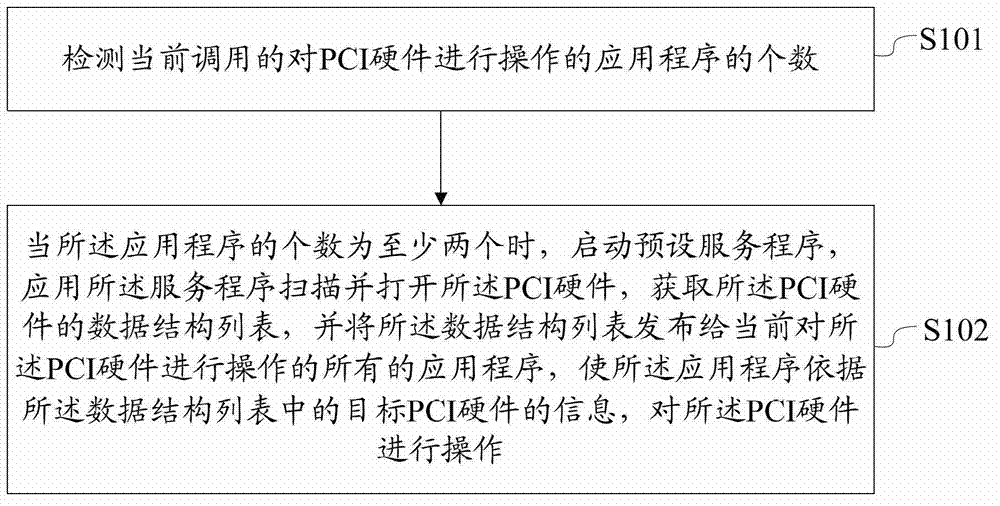

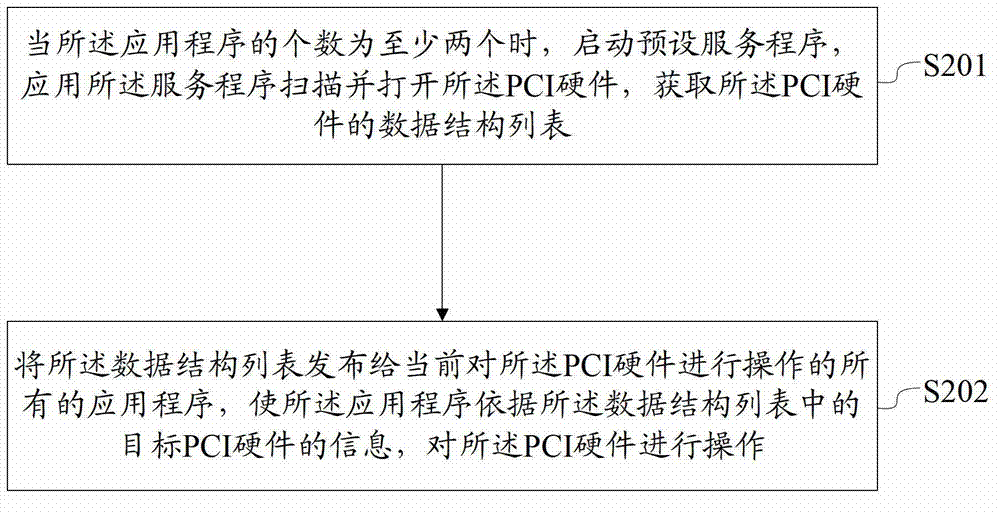

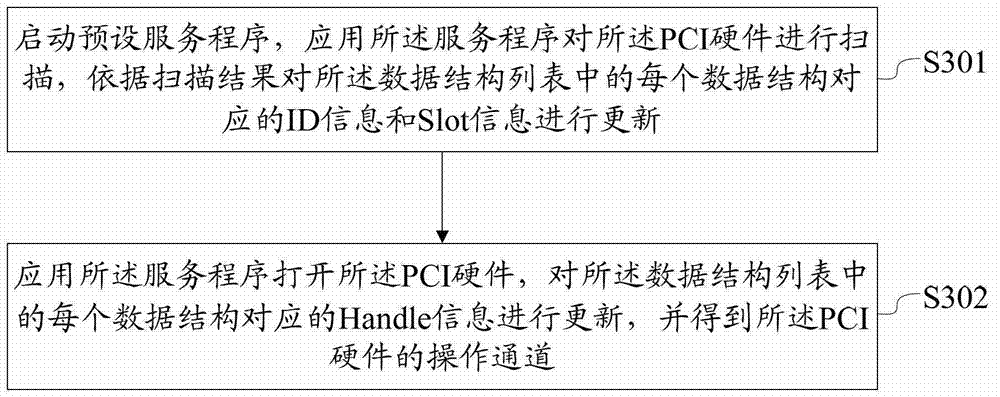

Method and device for compatible operation of PCI (peripheral component interconnection) hardware applications

The invention provides a method for compatible operation of PCI (peripheral component interconnection) hardware applications. The method includes: when PCI hardware is operated by at least two applications, starting a service program, applying the service program to obtain a data structural list of the PCI hardware, and releasing the data structural list to all applications operating the PCI hardware to enable the applications to operate the target PCI hardware according to target PCI hardware information in the data structural list. Using the method and the device for compatible operation of PCI hardware applications solves the problem of abnormality when the PCI hardware is simultaneously operated by multiple applications, and enables the applications to operate compatibly.

Owner:BEIJING RUNKE GENERAL TECH

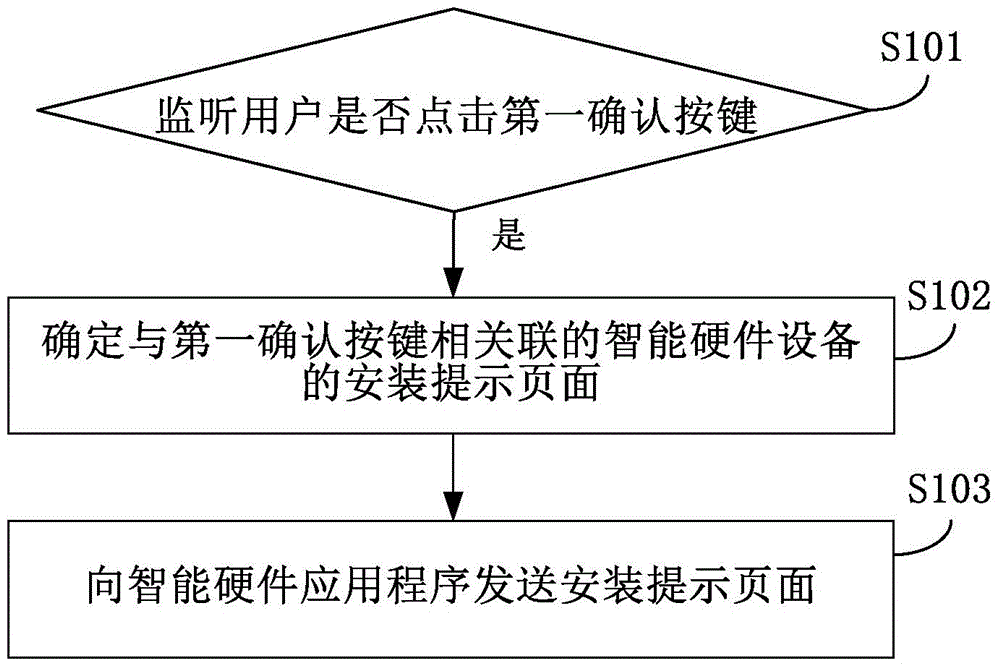

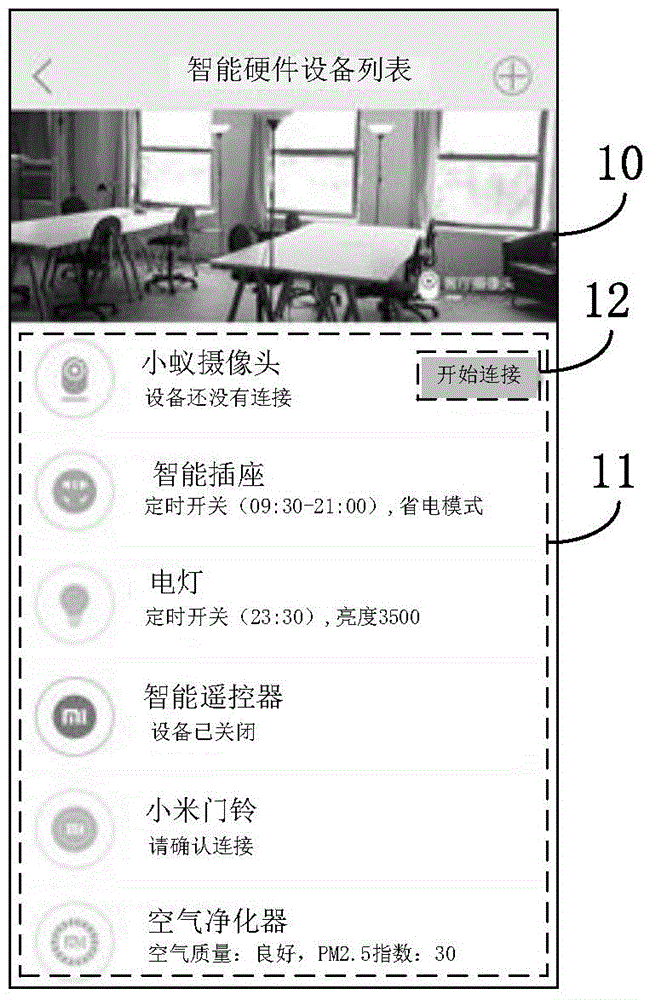

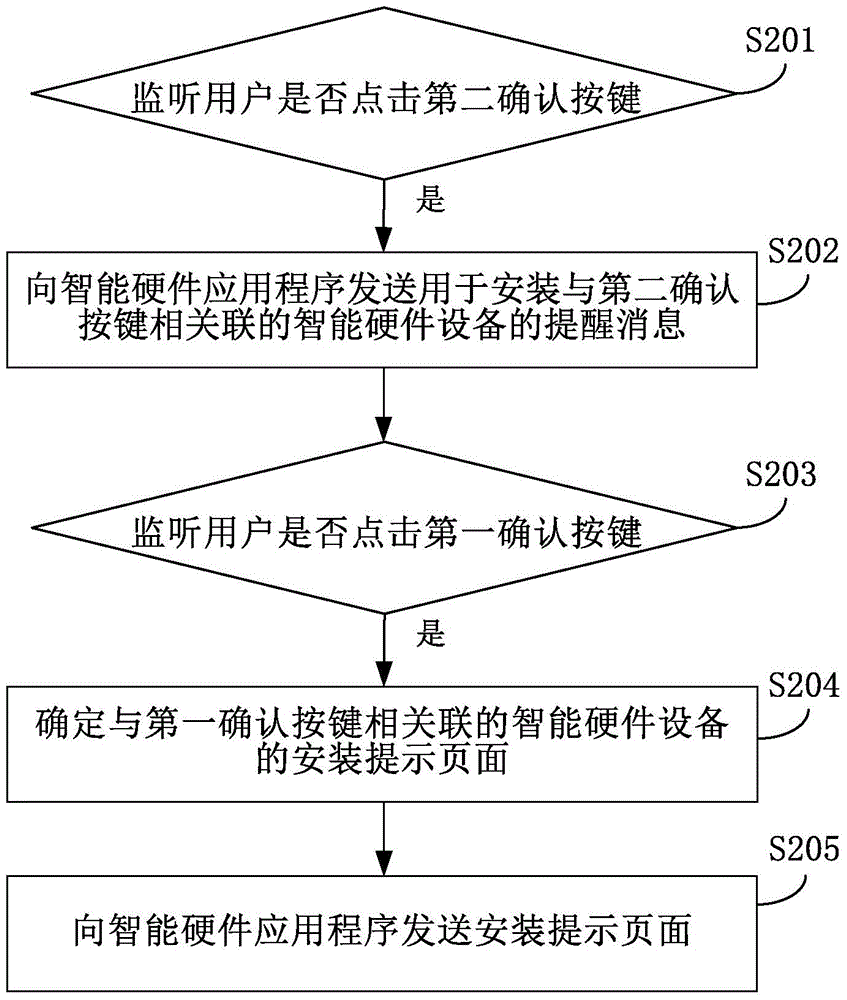

Installing implementation method and device of intelligent hardware equipment

ActiveCN104483865AImprove experienceSimplify the installation processExecution for user interfacesProgramme control in sequence/logic controllersKey pressingTerminal equipment

The invention relates to an installing implementation method and device of intelligent hardware equipment. The installing implementation method and device are used for simplifying the operation of a user for installing the intelligent hardware equipment. The method comprises the steps that whether a user clicks a first confirmation key through a user interface of an intelligent hardware application program on terminal equipment or not is monitored; when it is monitored that the user clicks the first confirmation key, an installing prompt page, associated with the first confirmation key, of the intelligent hardware equipment is determined; the installing prompt page is sent to the intelligent hardware application program. According to the technical scheme, the user can install the intelligent hardware equipment according to the installing prompt page, the user is prevented from reading a paper product instruction book, and the installing process of the intelligent hardware equipment is simplified.

Owner:XIAOMI INC

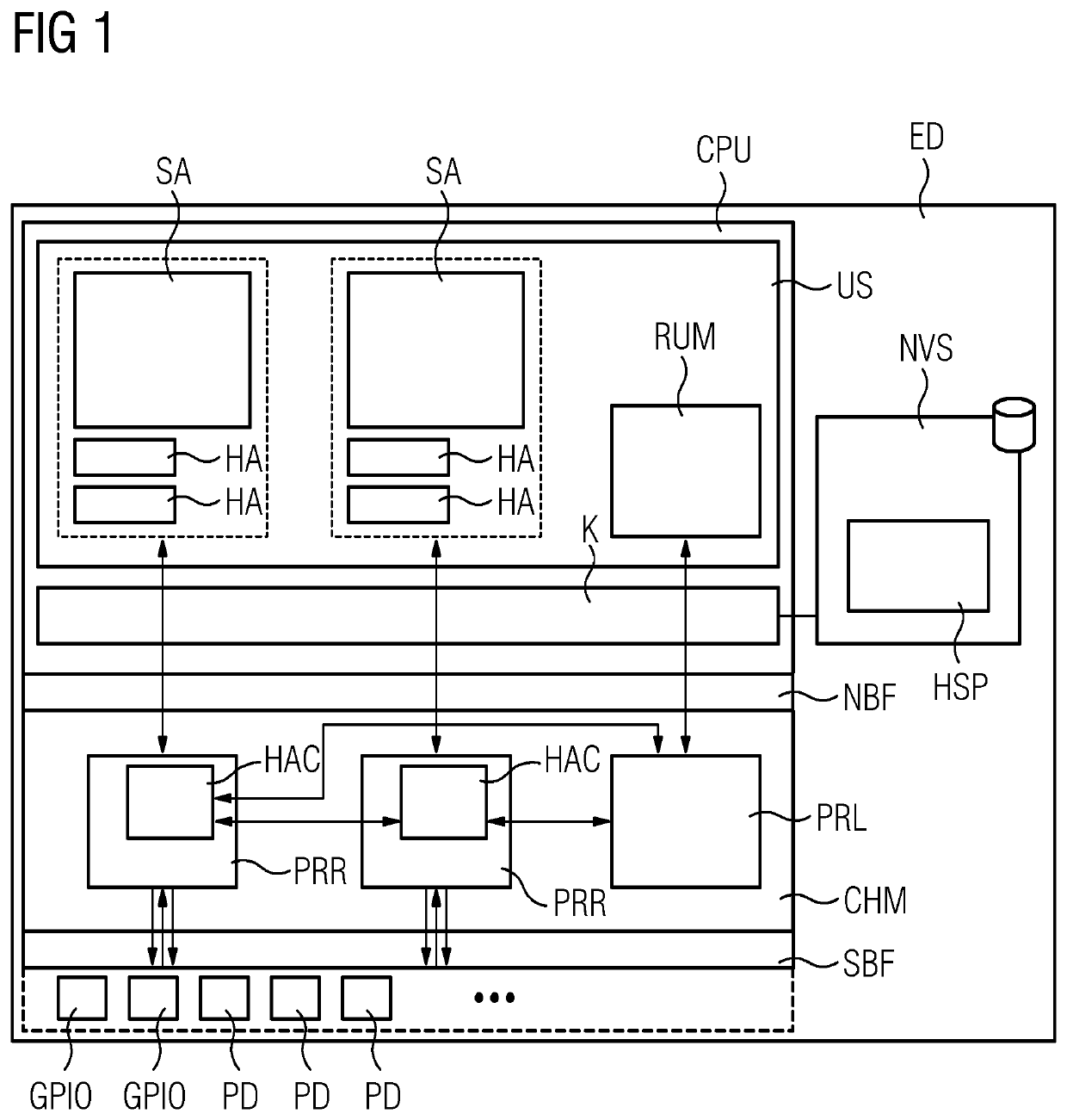

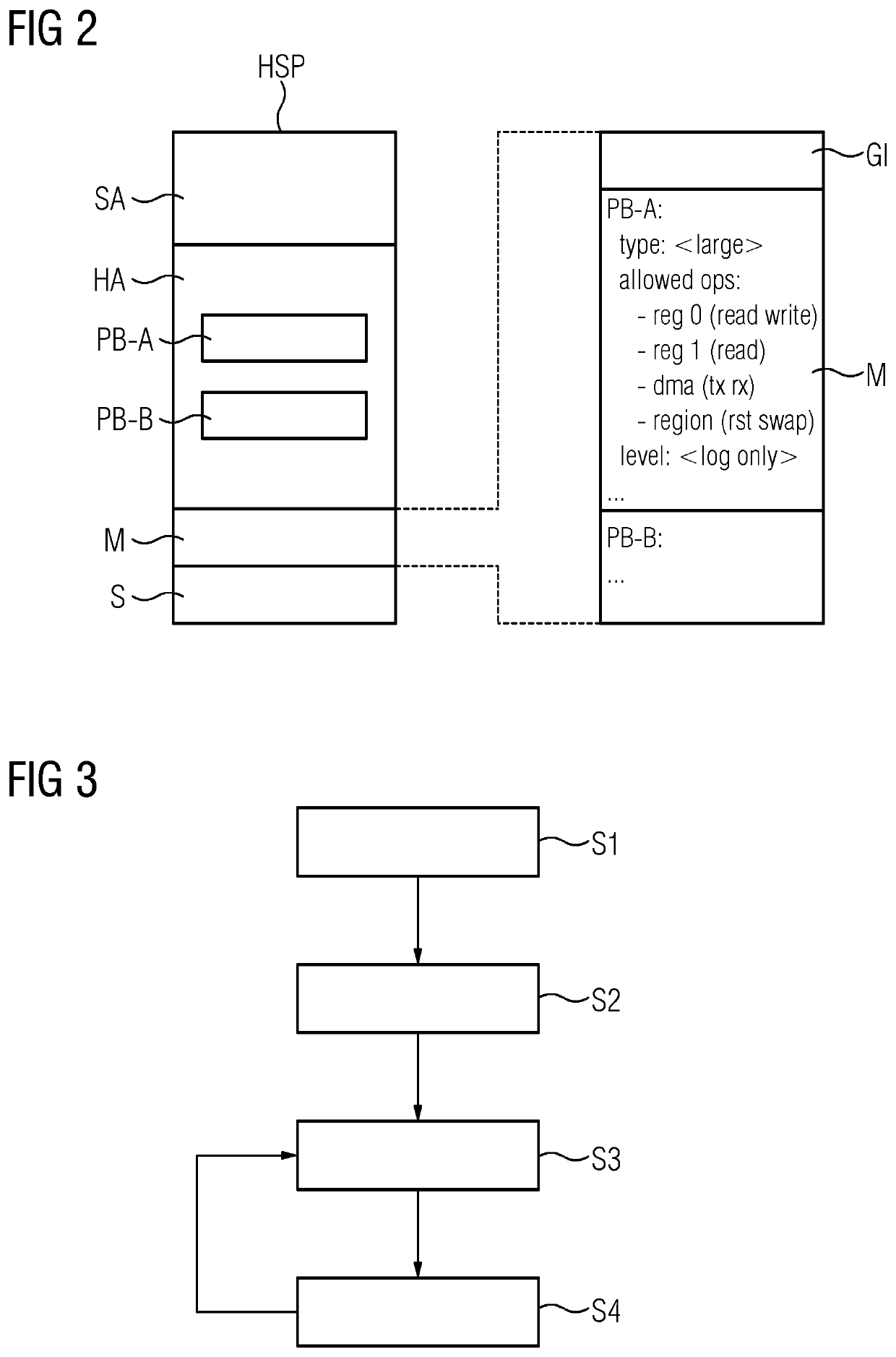

Method and configurable hardware module for monitoring a hardware-application

PendingUS20220164485A1Improve compromiseAuthentication is convenientDigital data protectionInternal/peripheral component protectionComputer hardwareThird party

Incoming and outgoing communication of a hardware-application component is monitored and controlled at runtime of the hardware-application component. In this way, a kind of firewall is provided for ensuring secure and un-altered operation of a hardware-application performing security-critical functionalities on a field-programmable gate array. The hardware-application component may interact with other components directly and / or via an on-chip bus. The monitoring of incoming and / or outgoing communication is particularly advantageous when using third party hardware-applications or software applications, i.e., applications developed by untrusted parties. Another advantage is the possibility of monitoring and controlling all the communication between hardware-applications, hardware- and software applications, hardware-applications and peripherals, IO controllers, etc. It is beneficial especially in case a hardware-application is compromised and tries to compromise the rest of the embedded device, or in case a corrupted software application tries to compromise the associated hardware-application at runtime.

Owner:SIEMENS AG