Patents

Literature

35results about How to "Excellent moisture resistance reliability" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

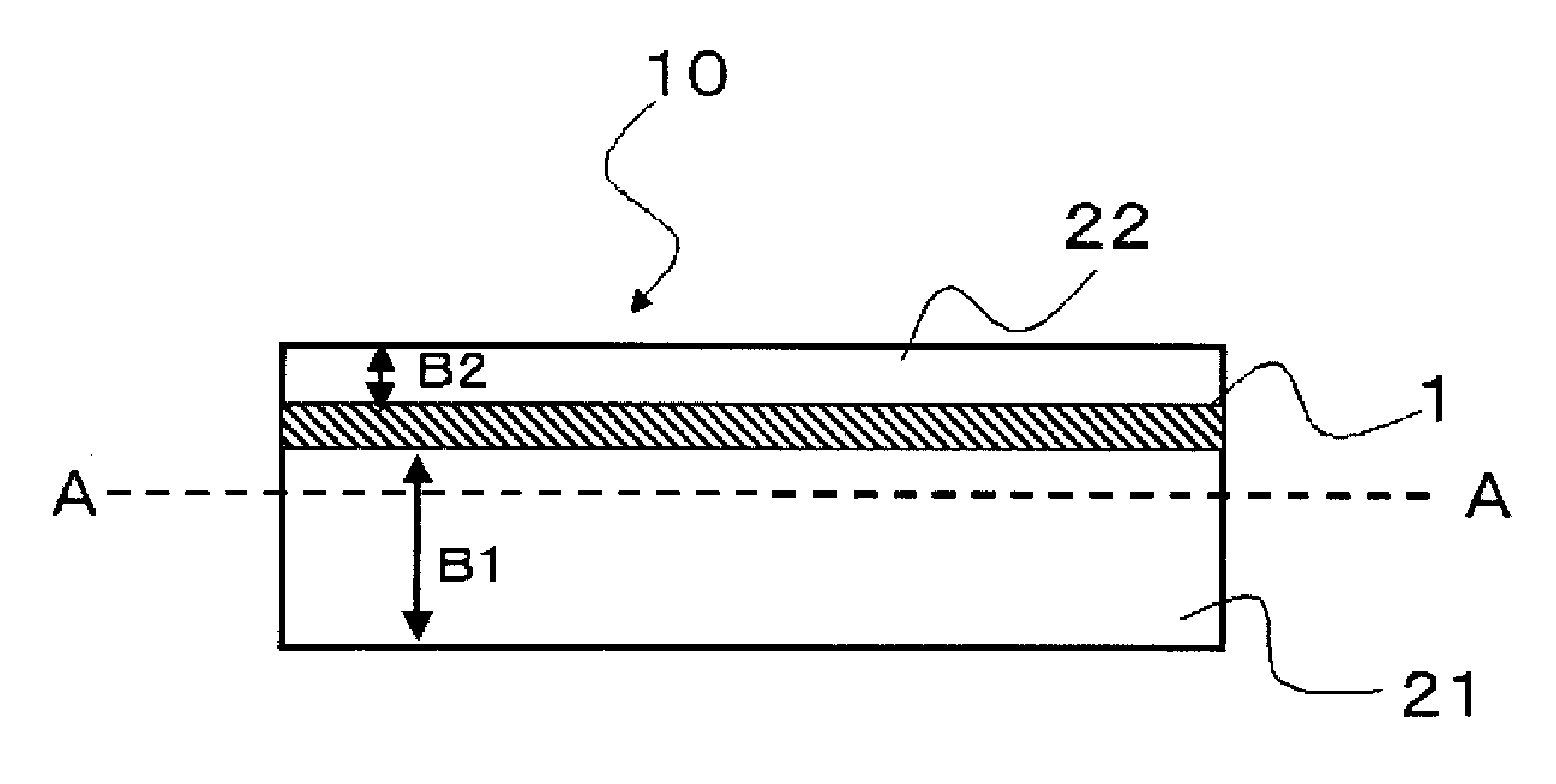

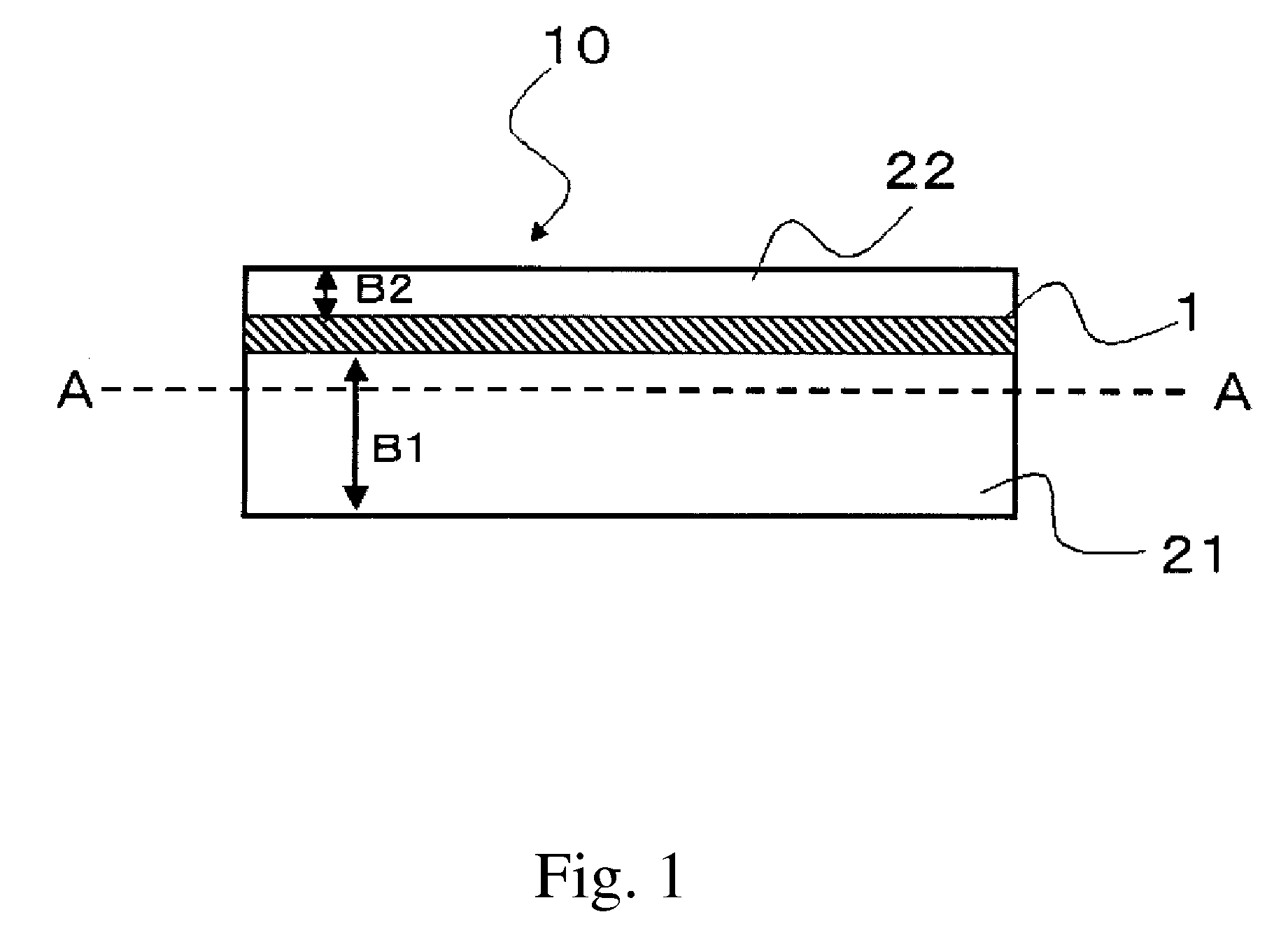

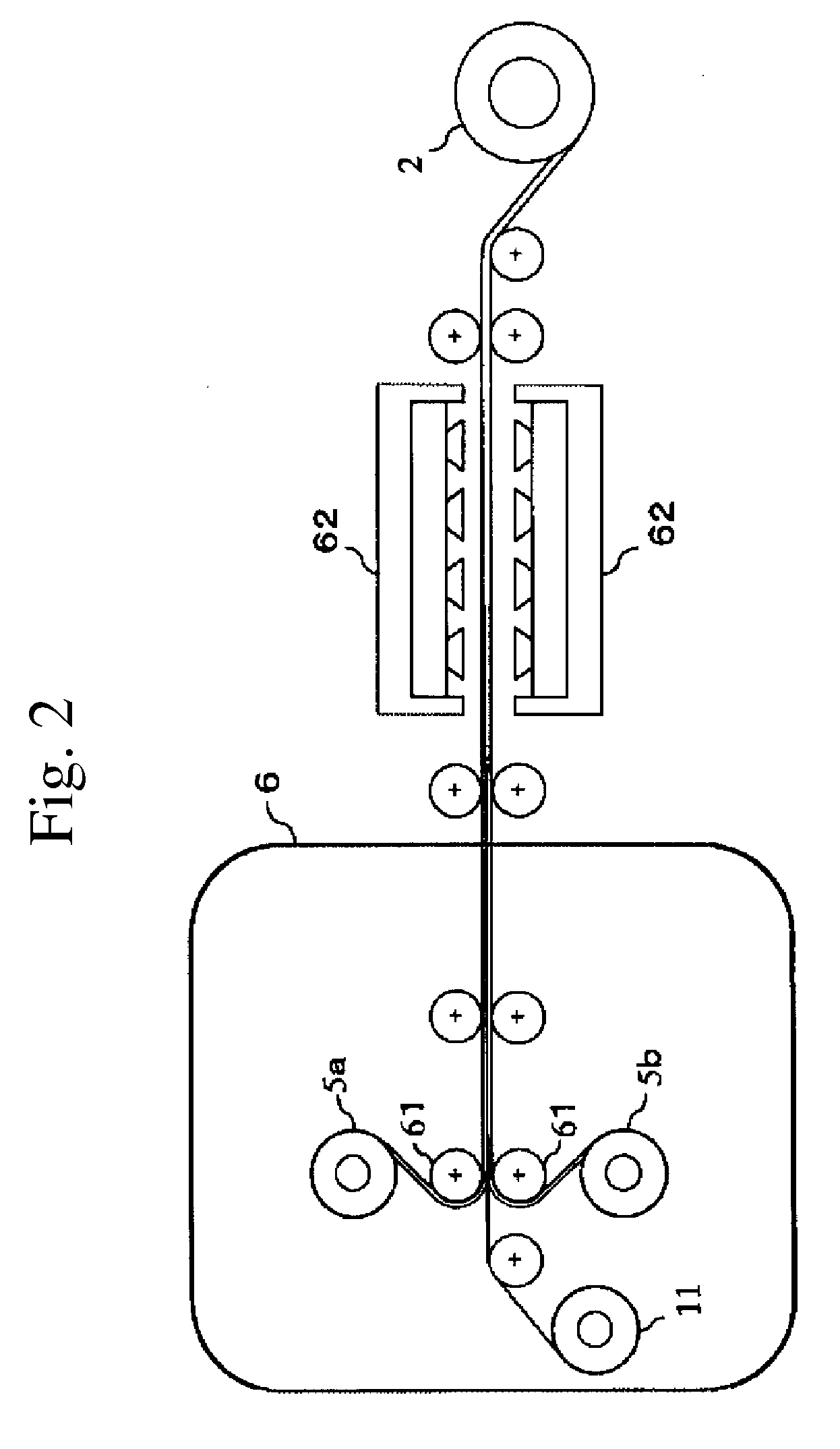

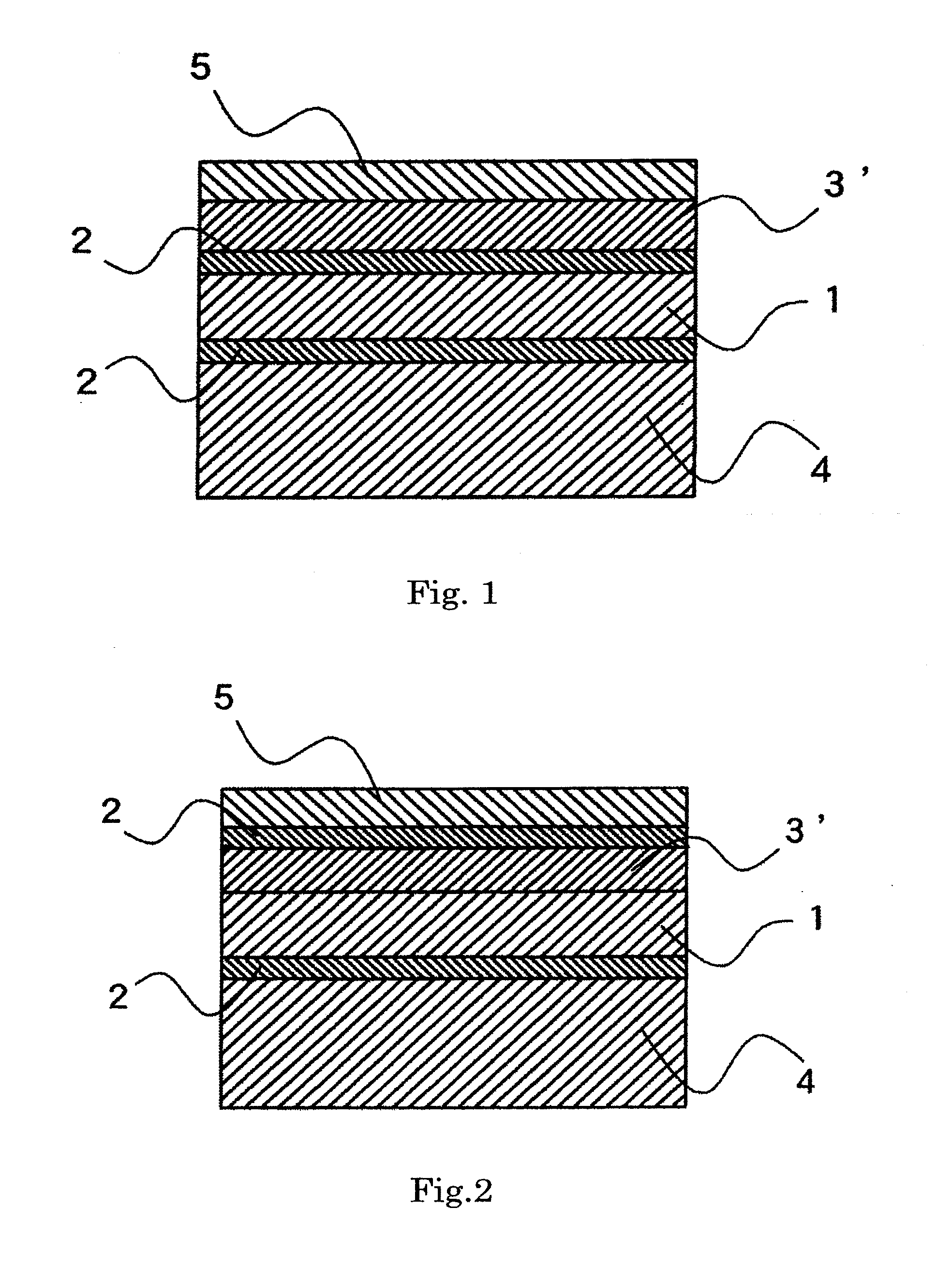

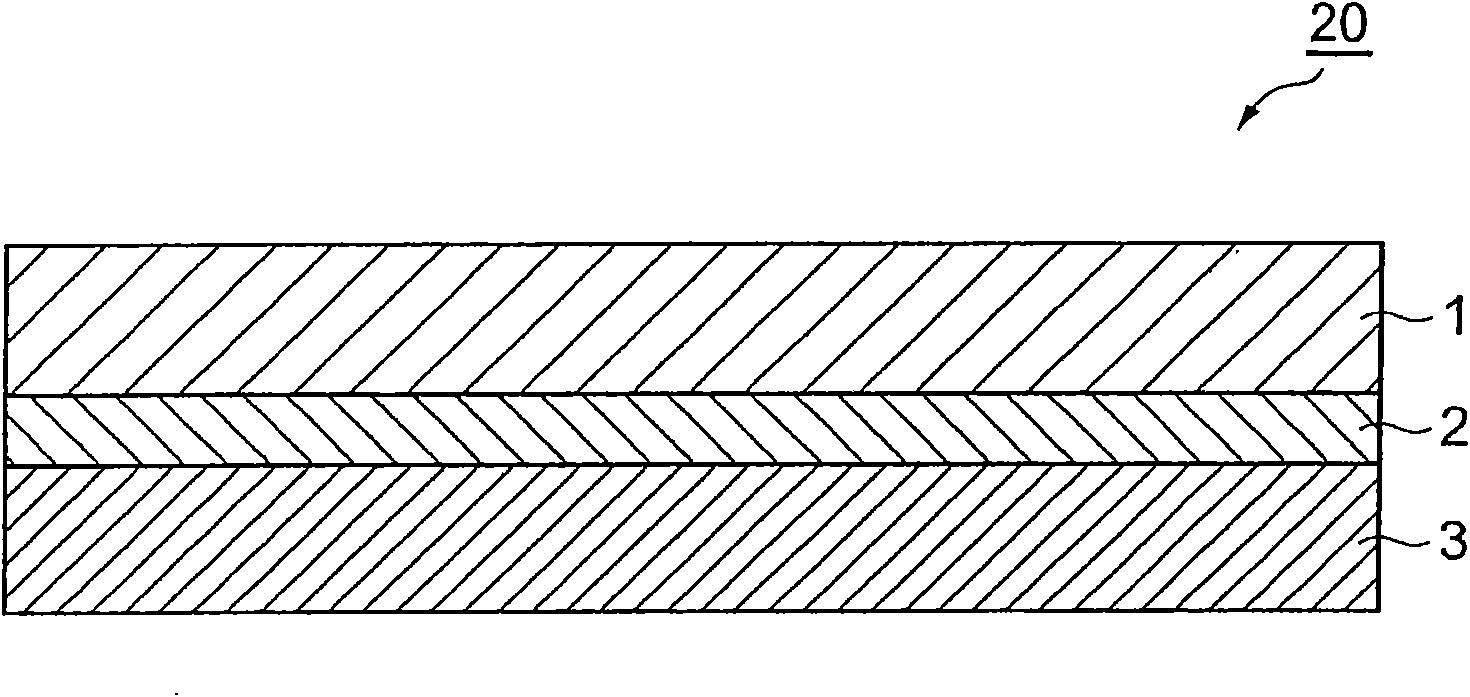

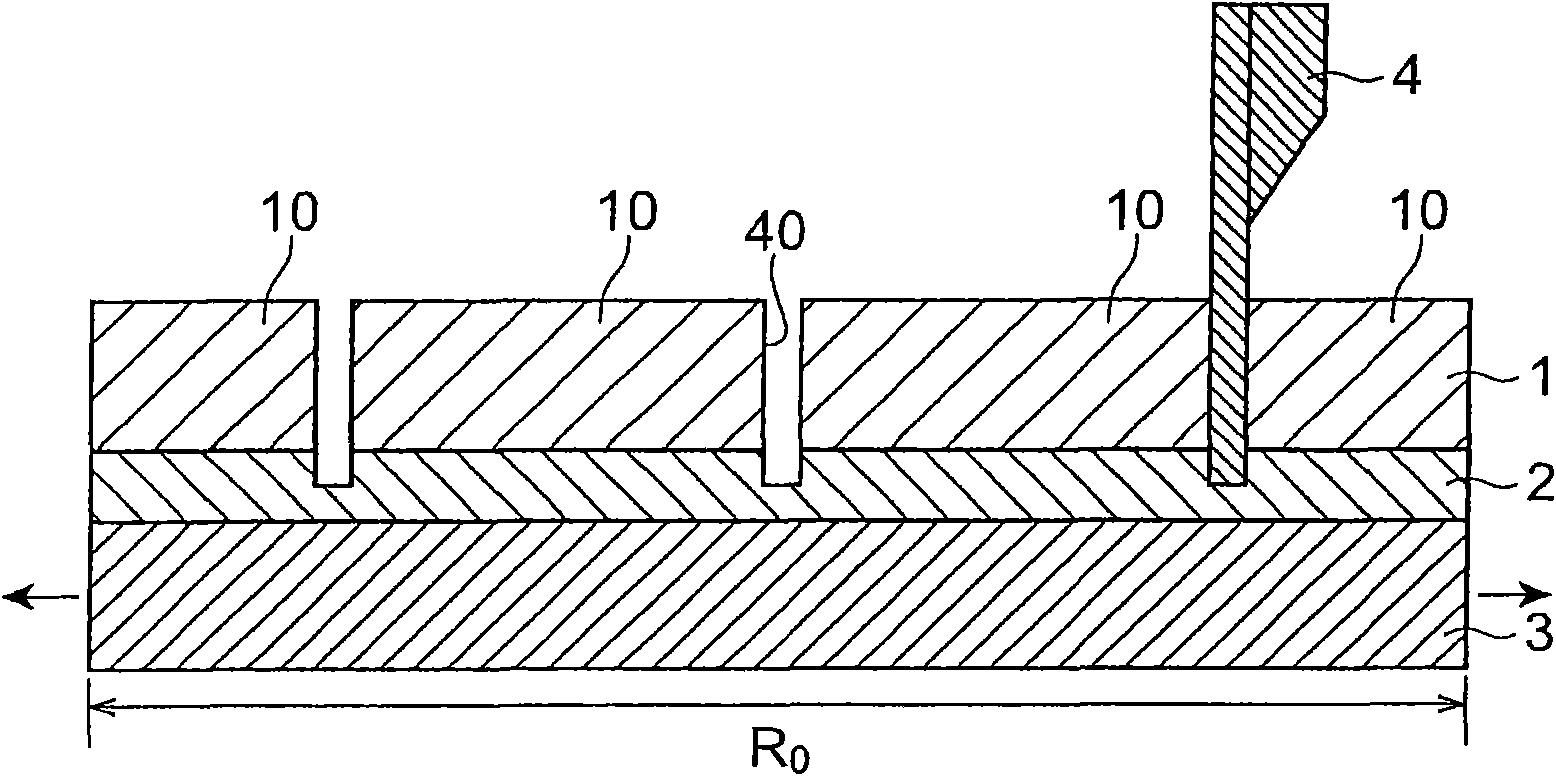

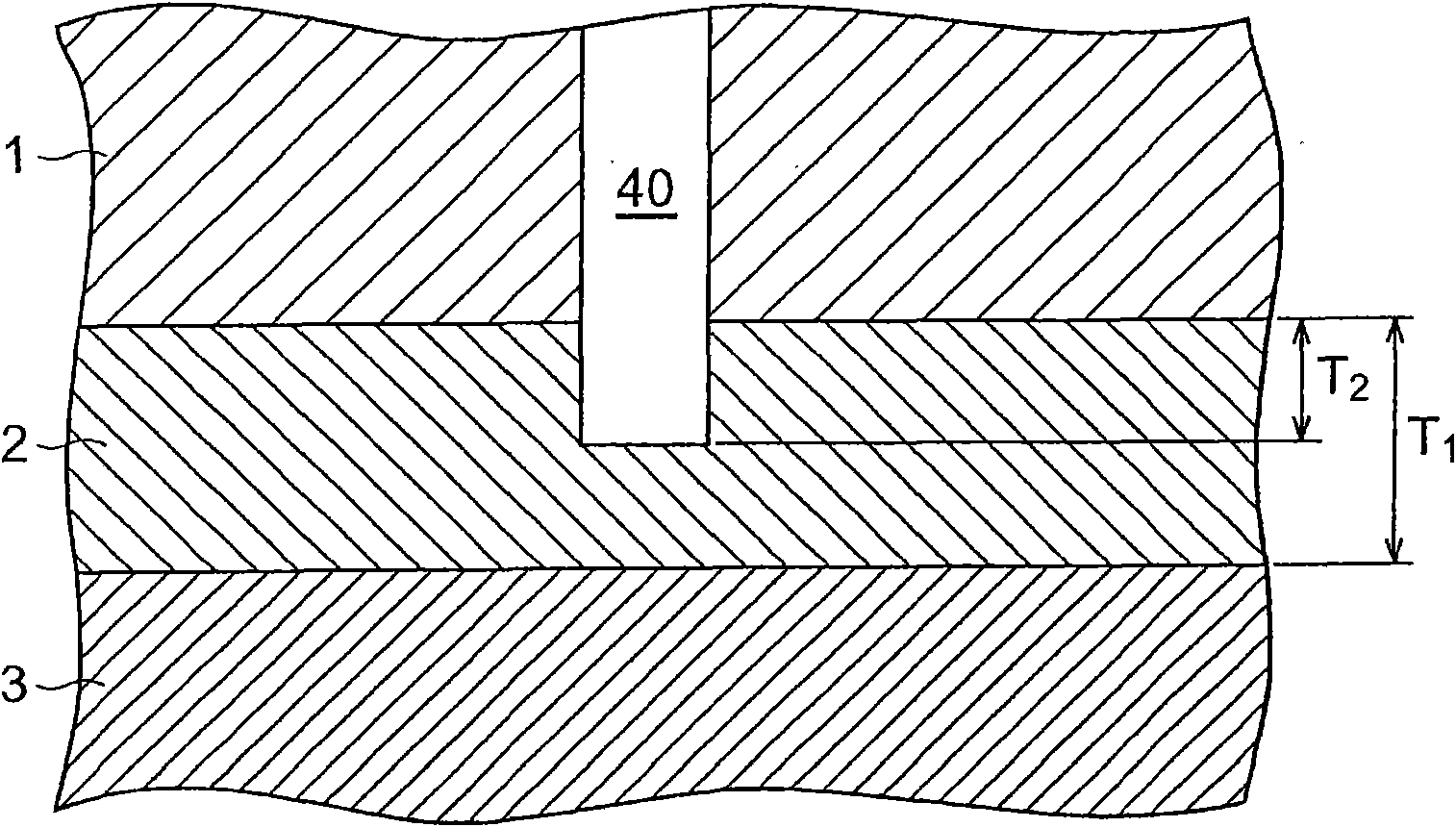

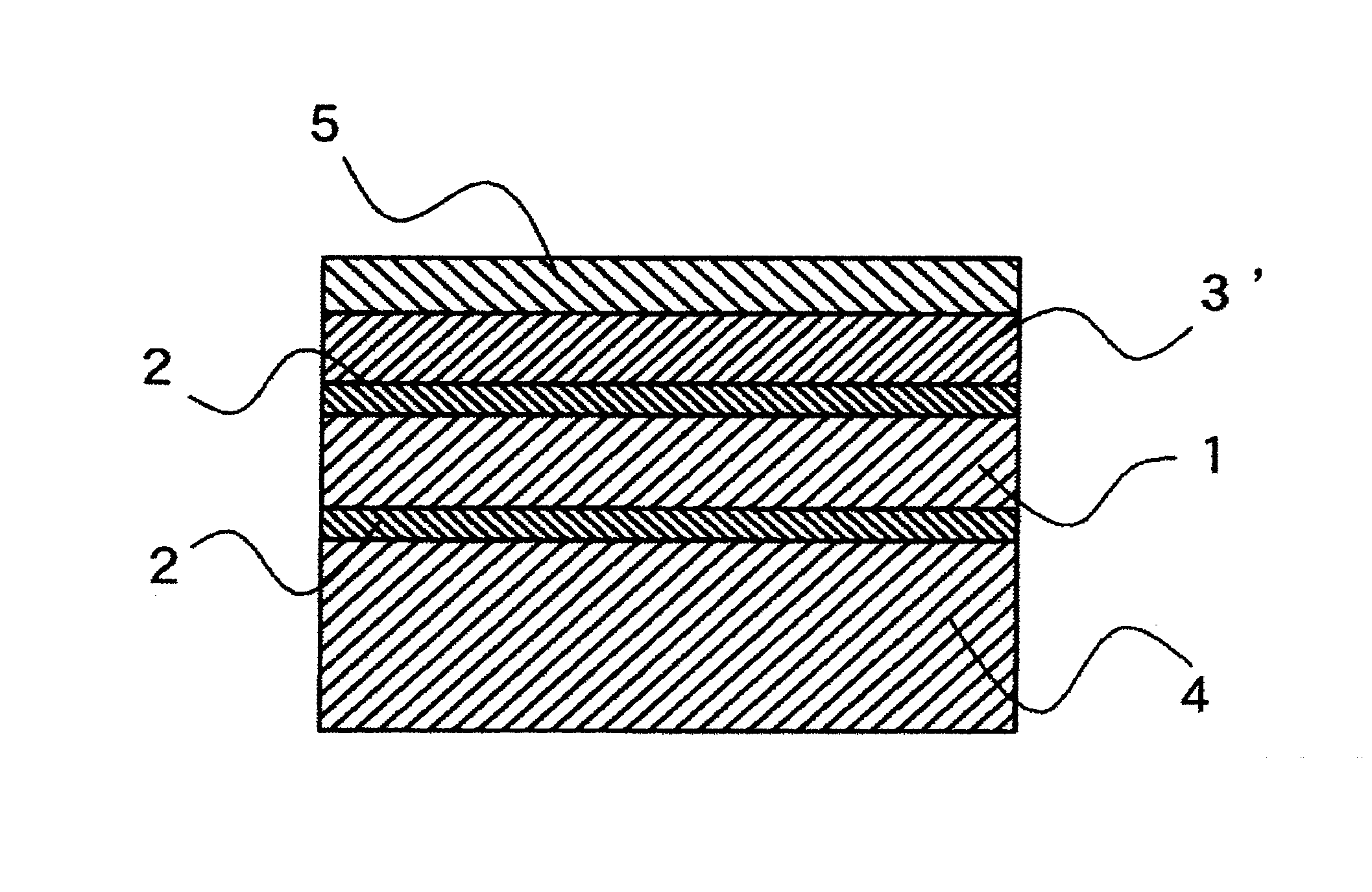

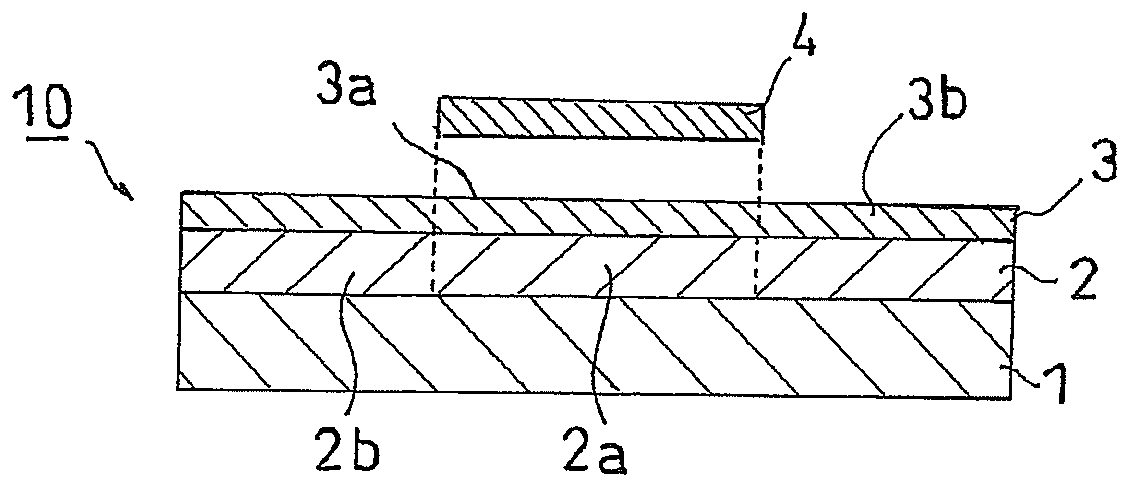

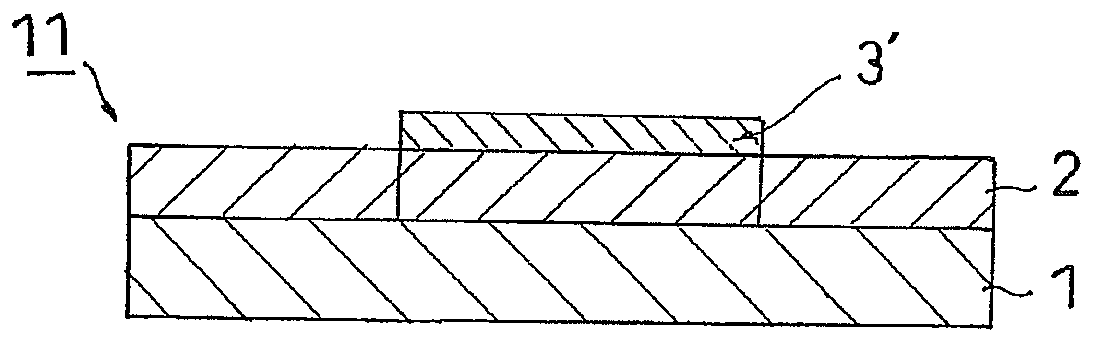

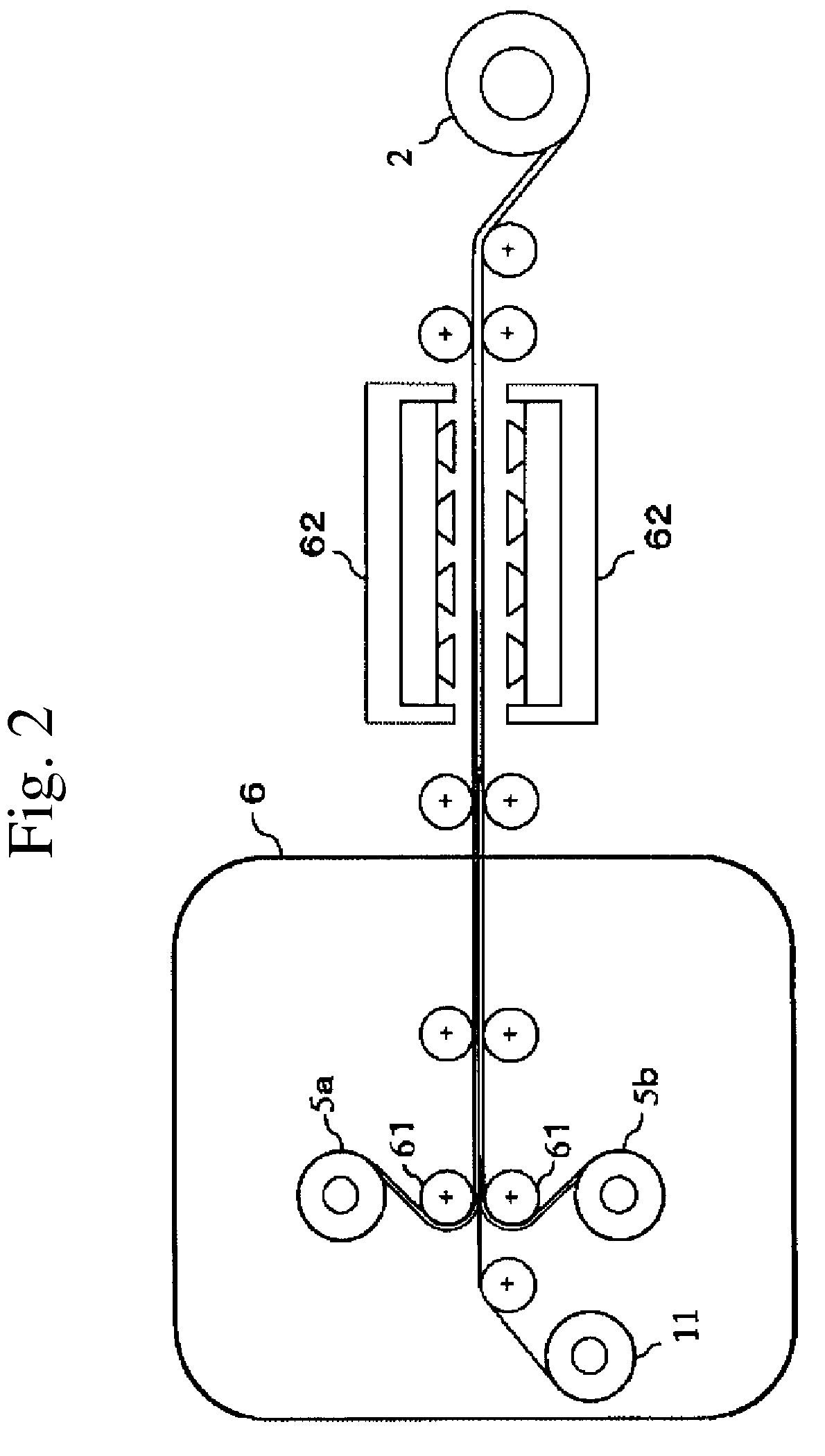

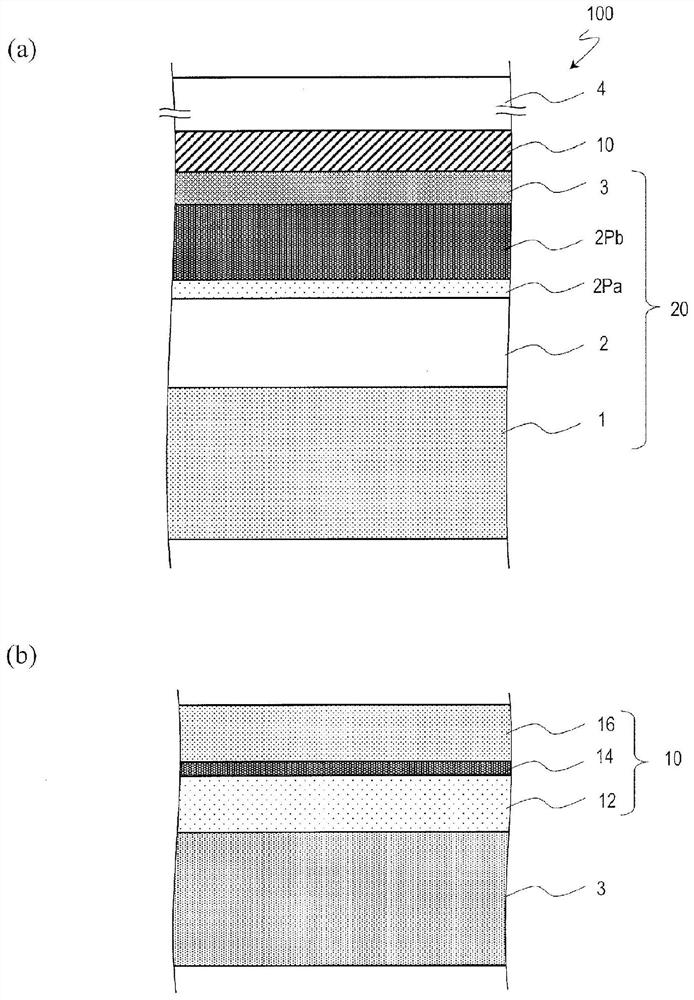

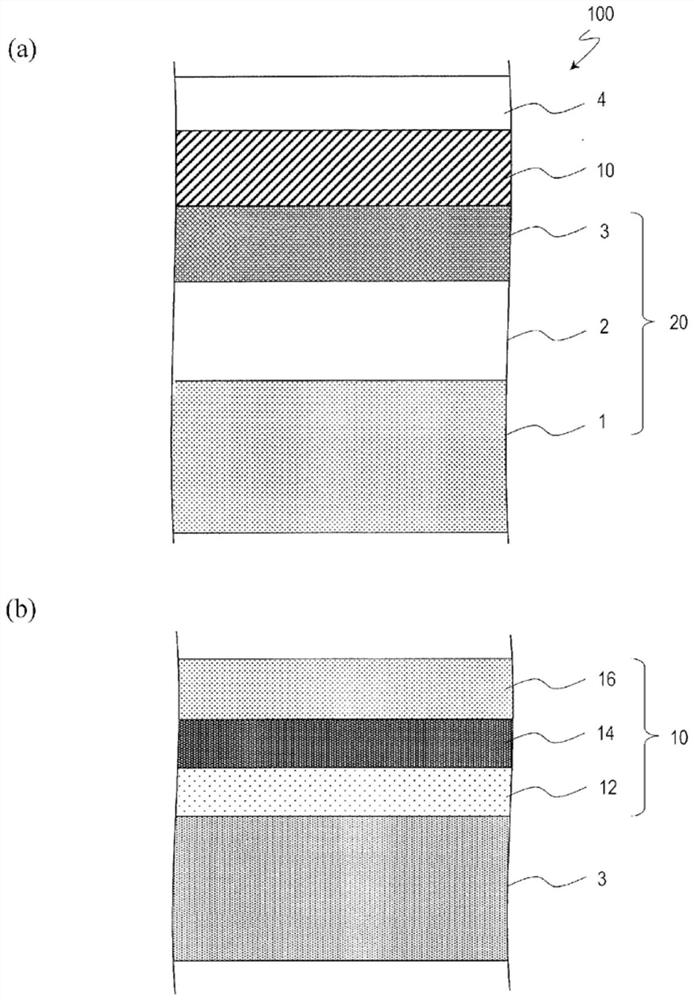

Solder resist material, wiring board using the solder resist material, and semiconductor package

InactiveUS20090218672A1Warpage suppressionReduction factorSemiconductor/solid-state device detailsPrinted circuit aspectsFiberResist

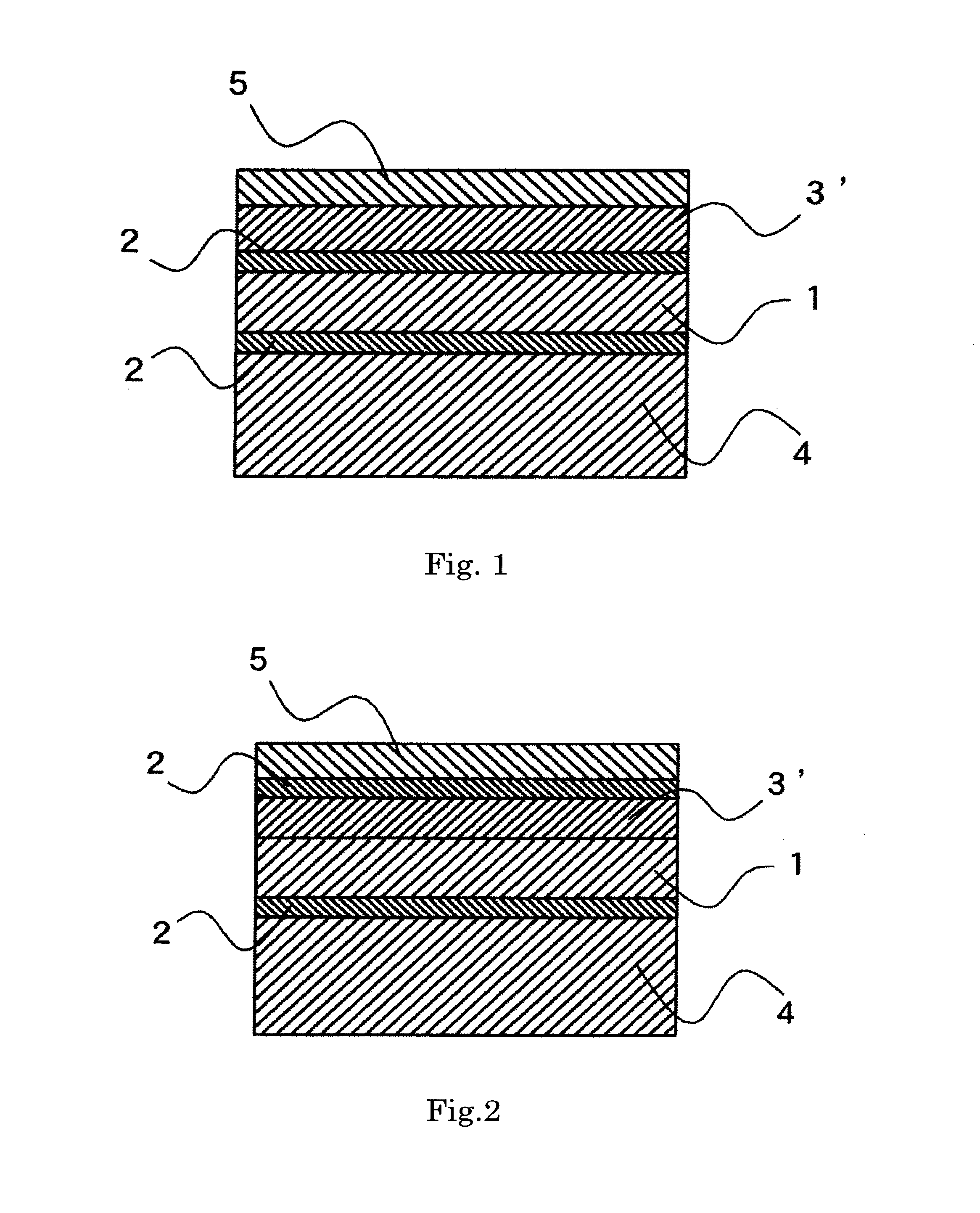

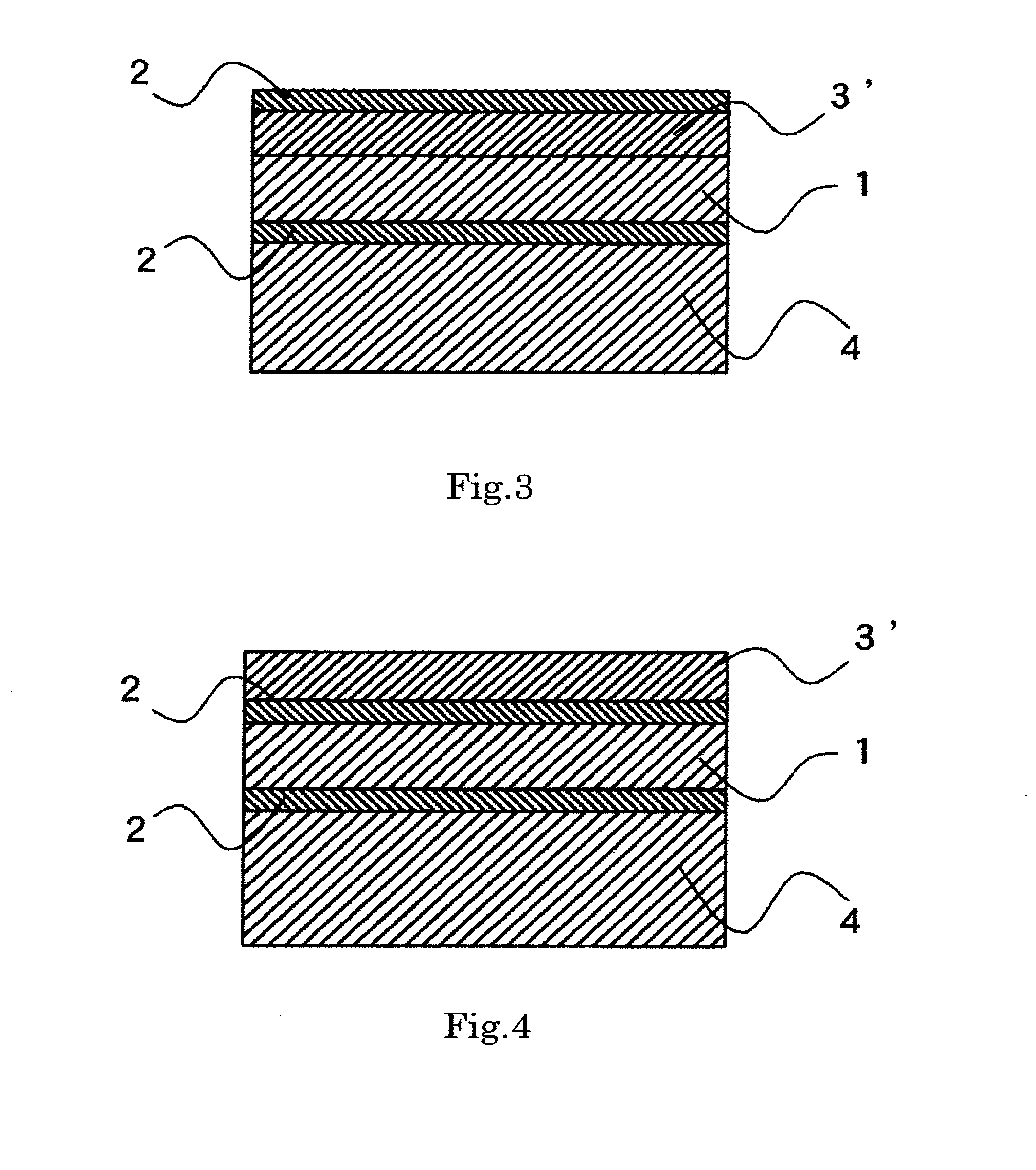

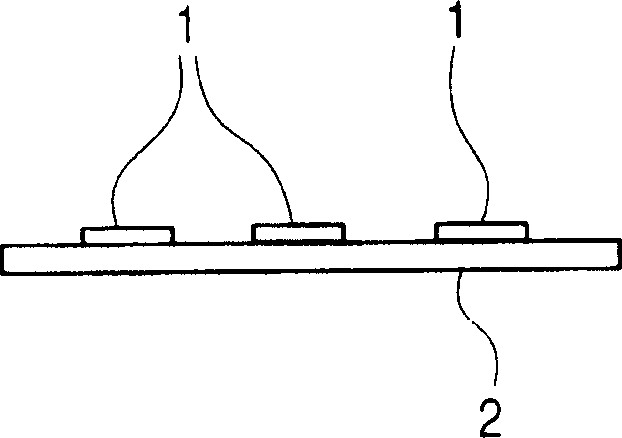

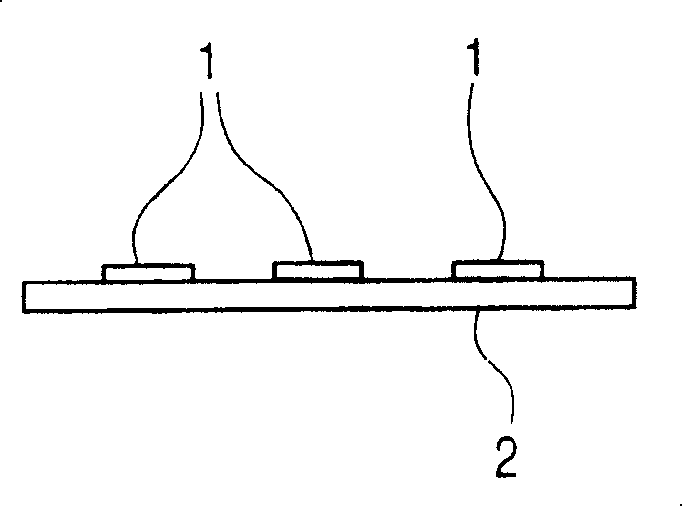

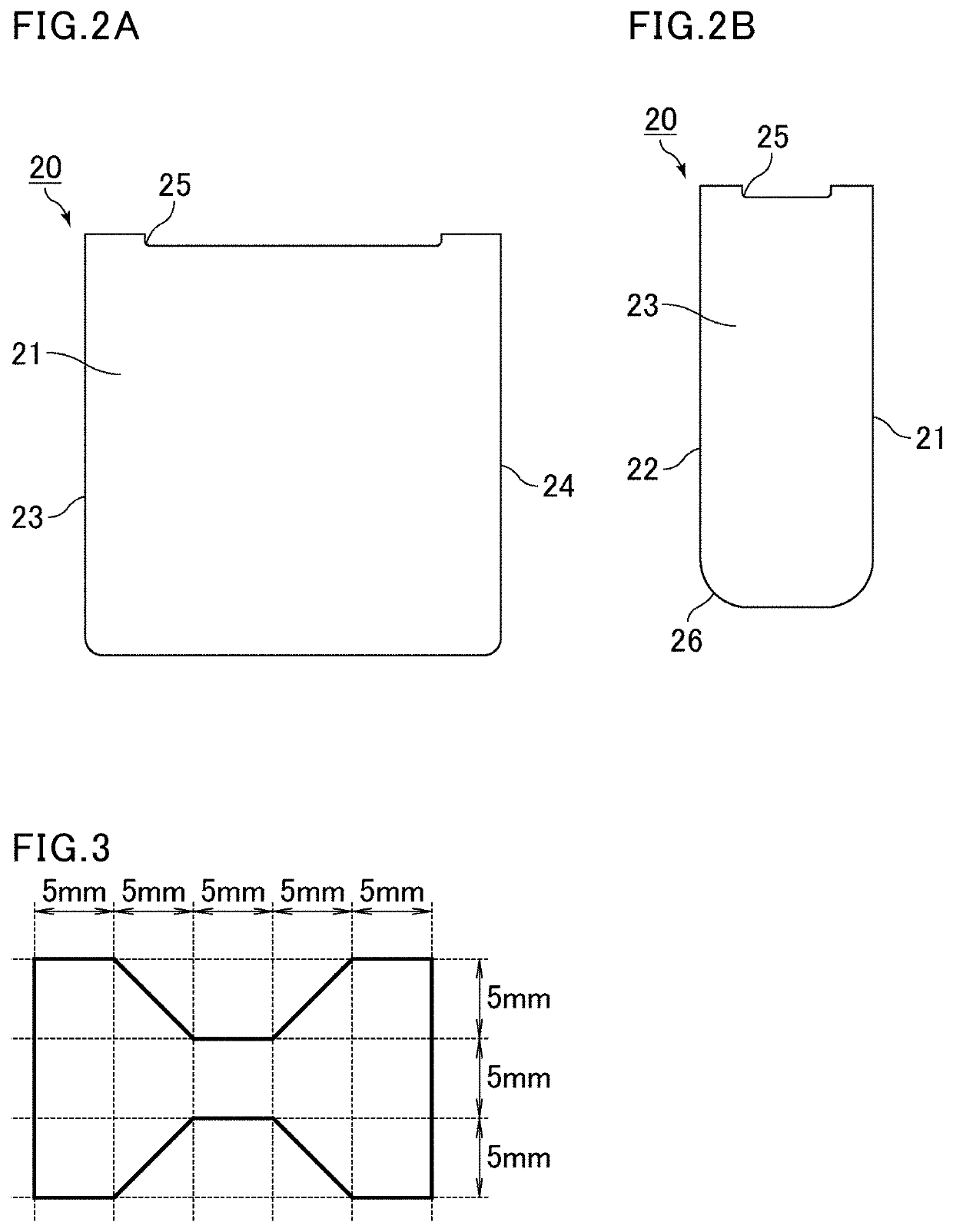

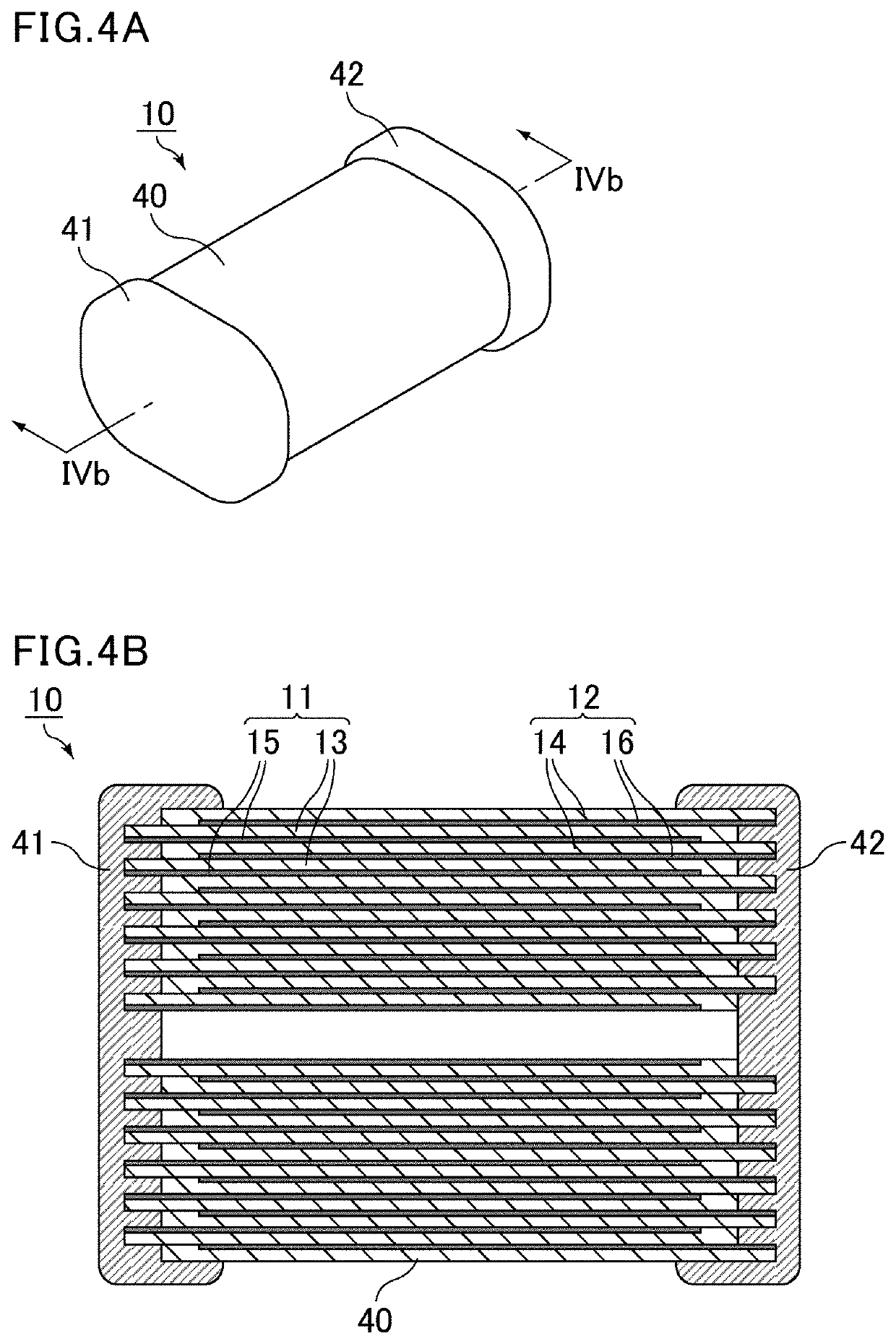

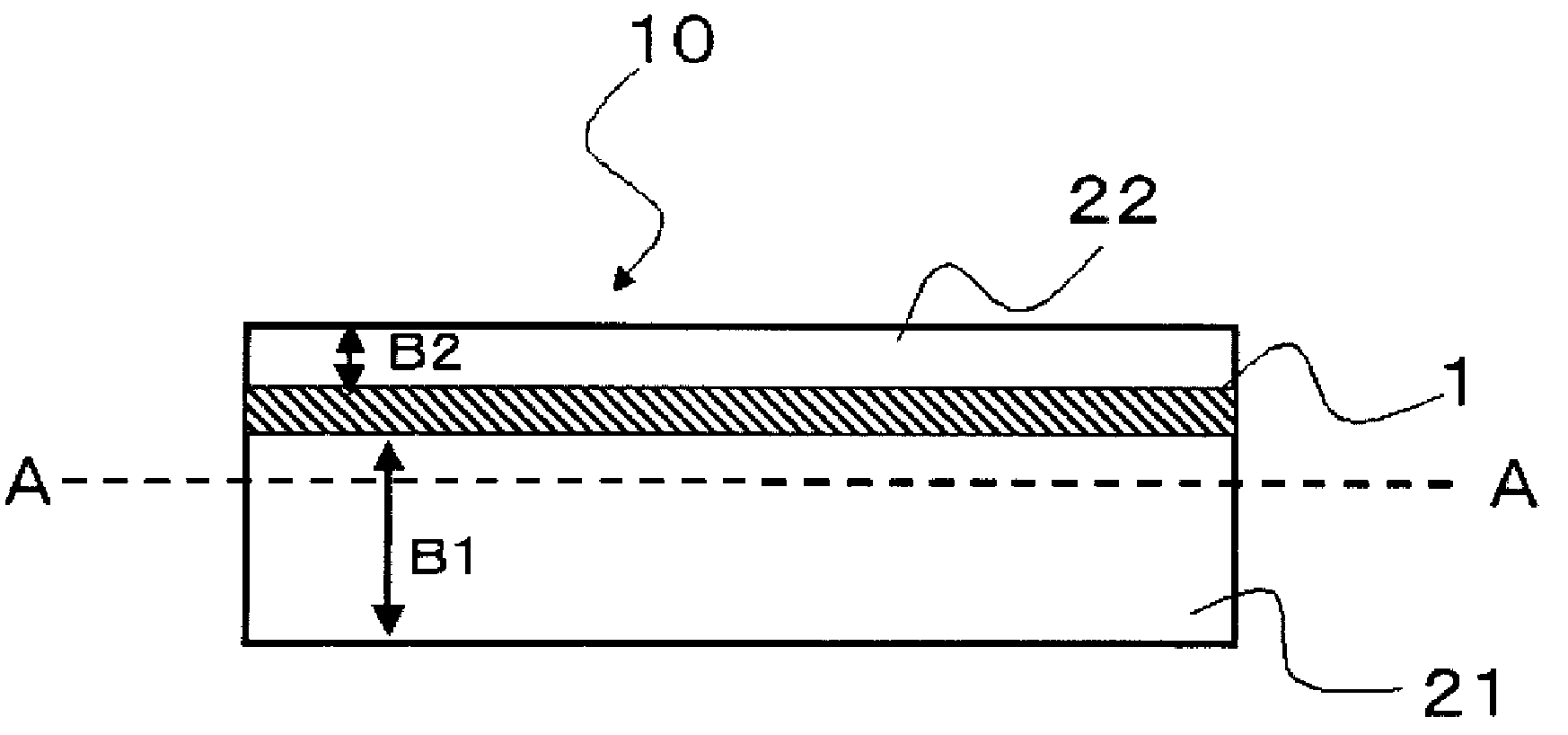

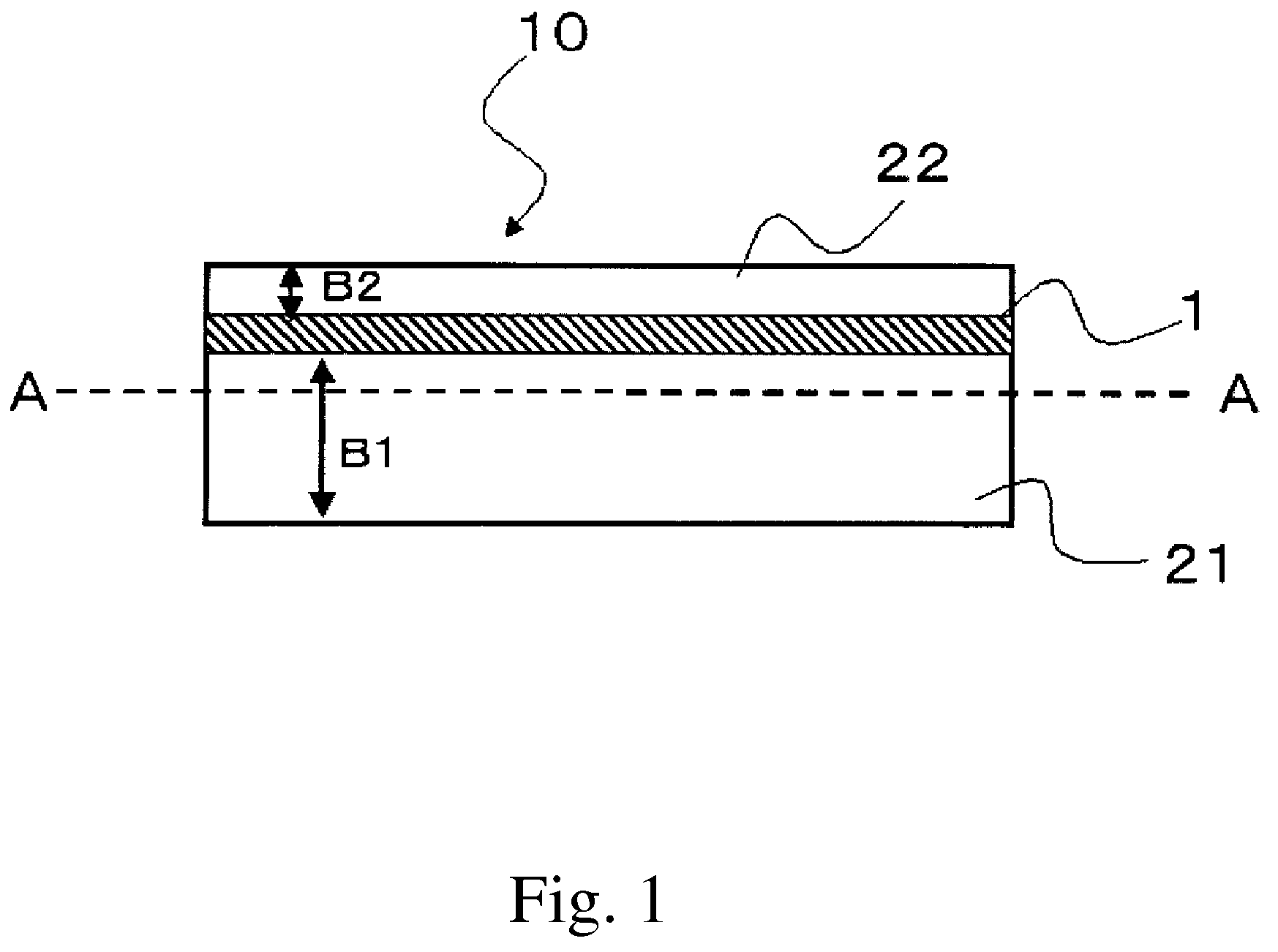

The present invention provides a solder resist material, which can suppress the warpage of a semiconductor package upon exposure to heat or impact even when used in a thin wiring board and meets a demand for size reduction in electronic devices and a higher level of integration, and a wiring board comprising the solder resist material and a semiconductor package. The solder resist material of the present invention can effectively suppress the warpage of a semiconductor package through a fiber base material-containing layer interposed between resin layers. The fiber base material-containing layer is preferably unevenly distributed in the thickness direction of the solder resist material.

Owner:SUMITOMO BAKELITE CO LTD

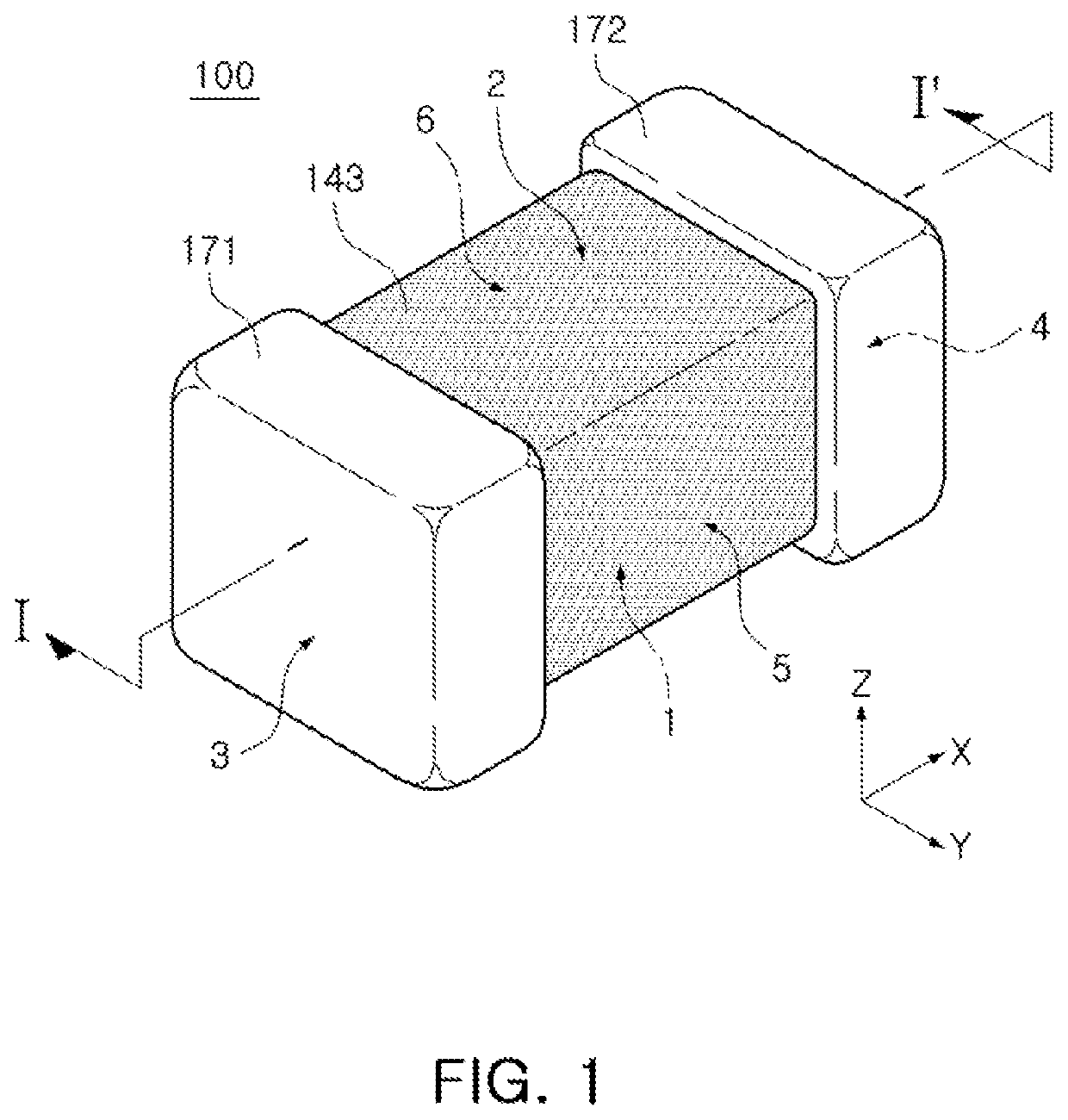

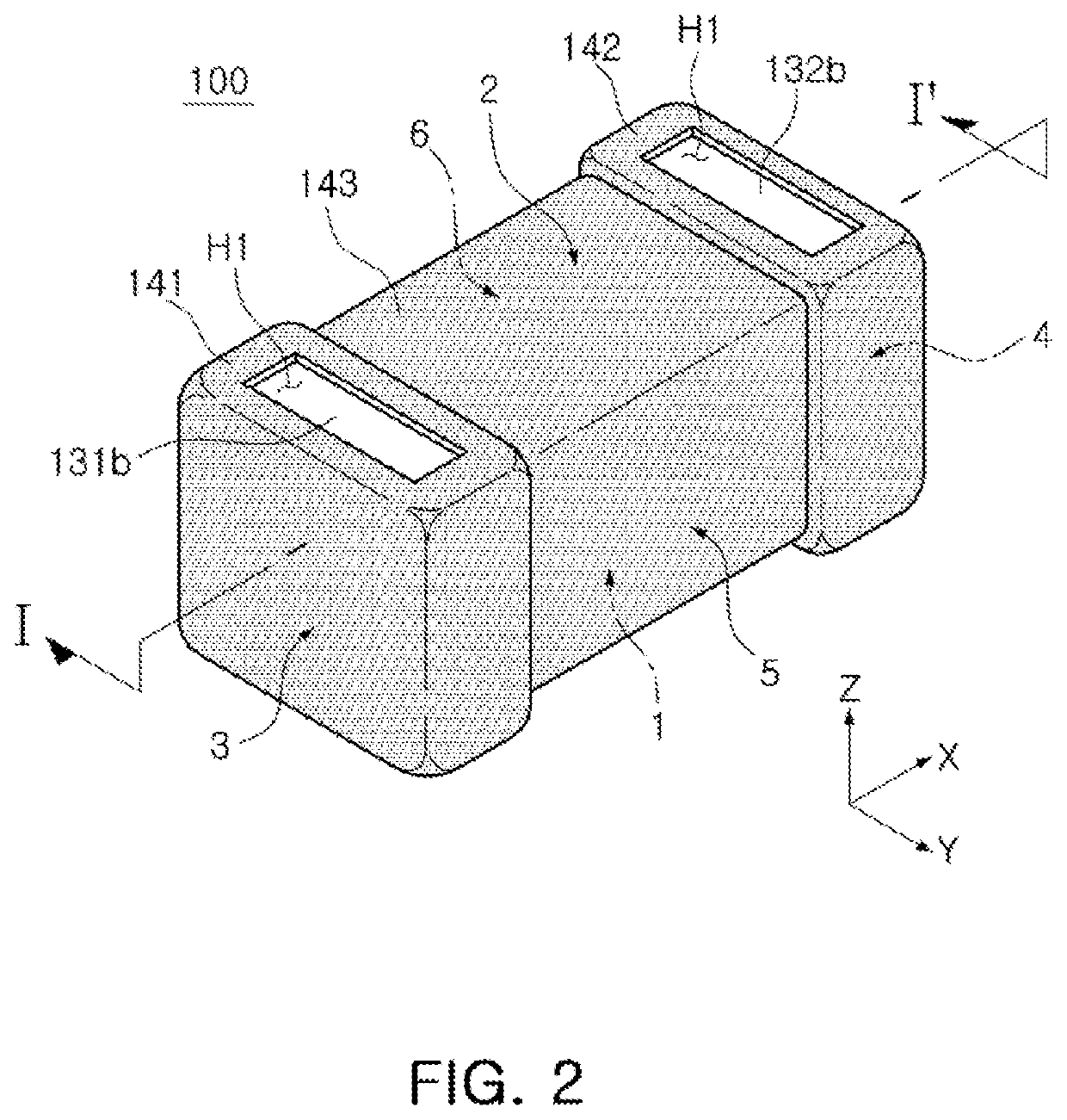

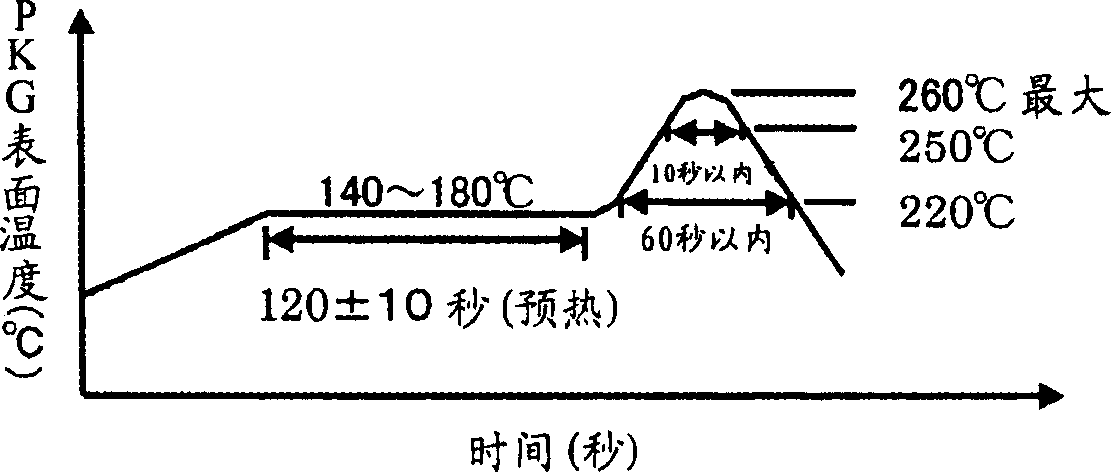

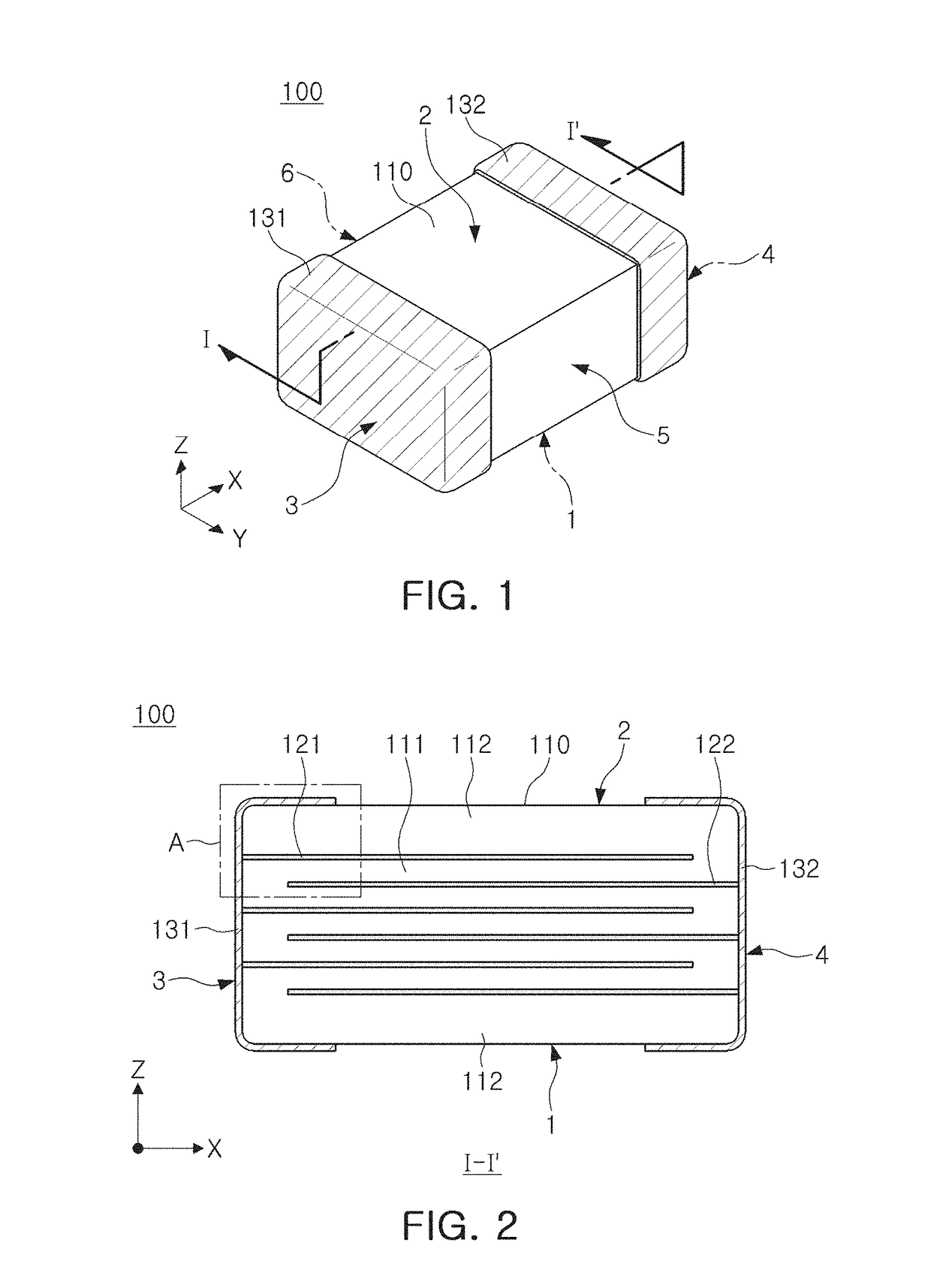

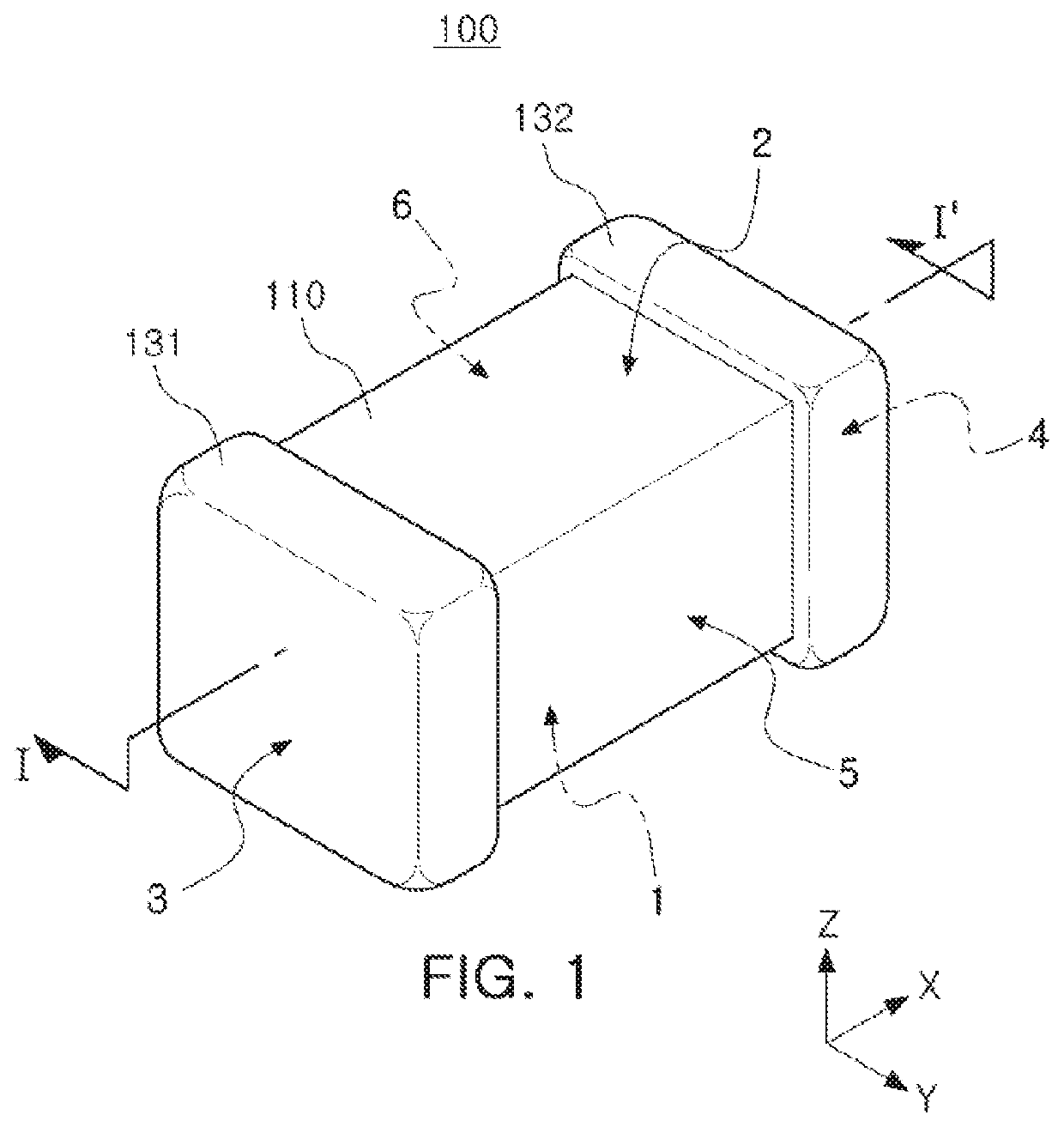

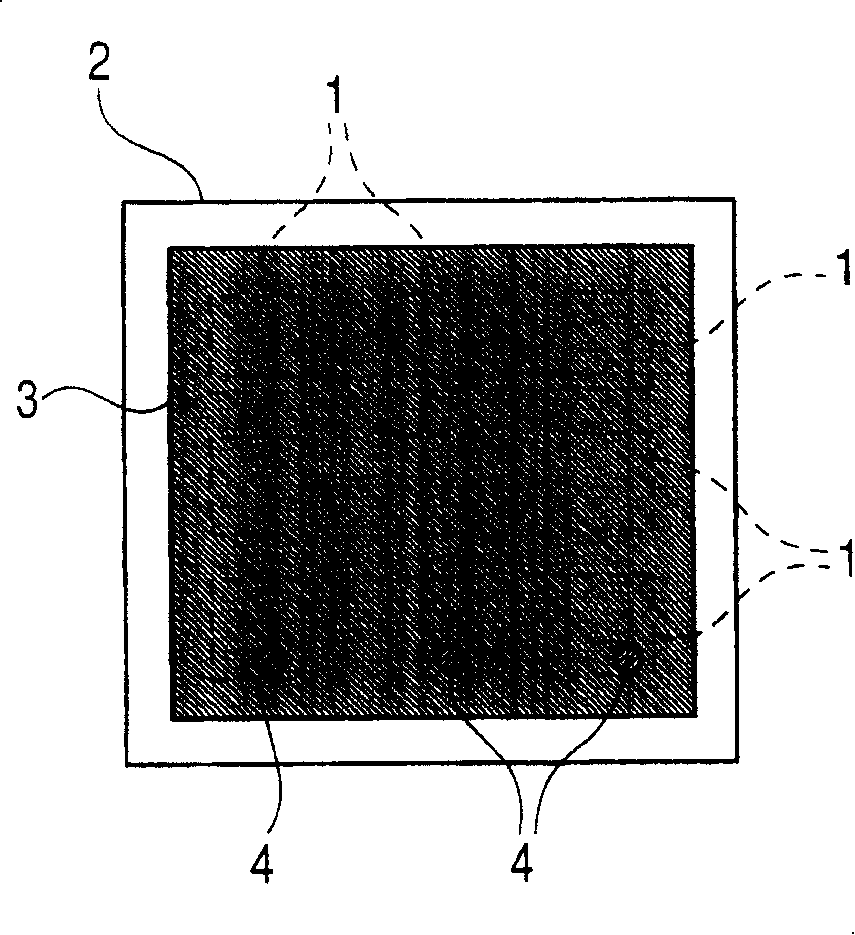

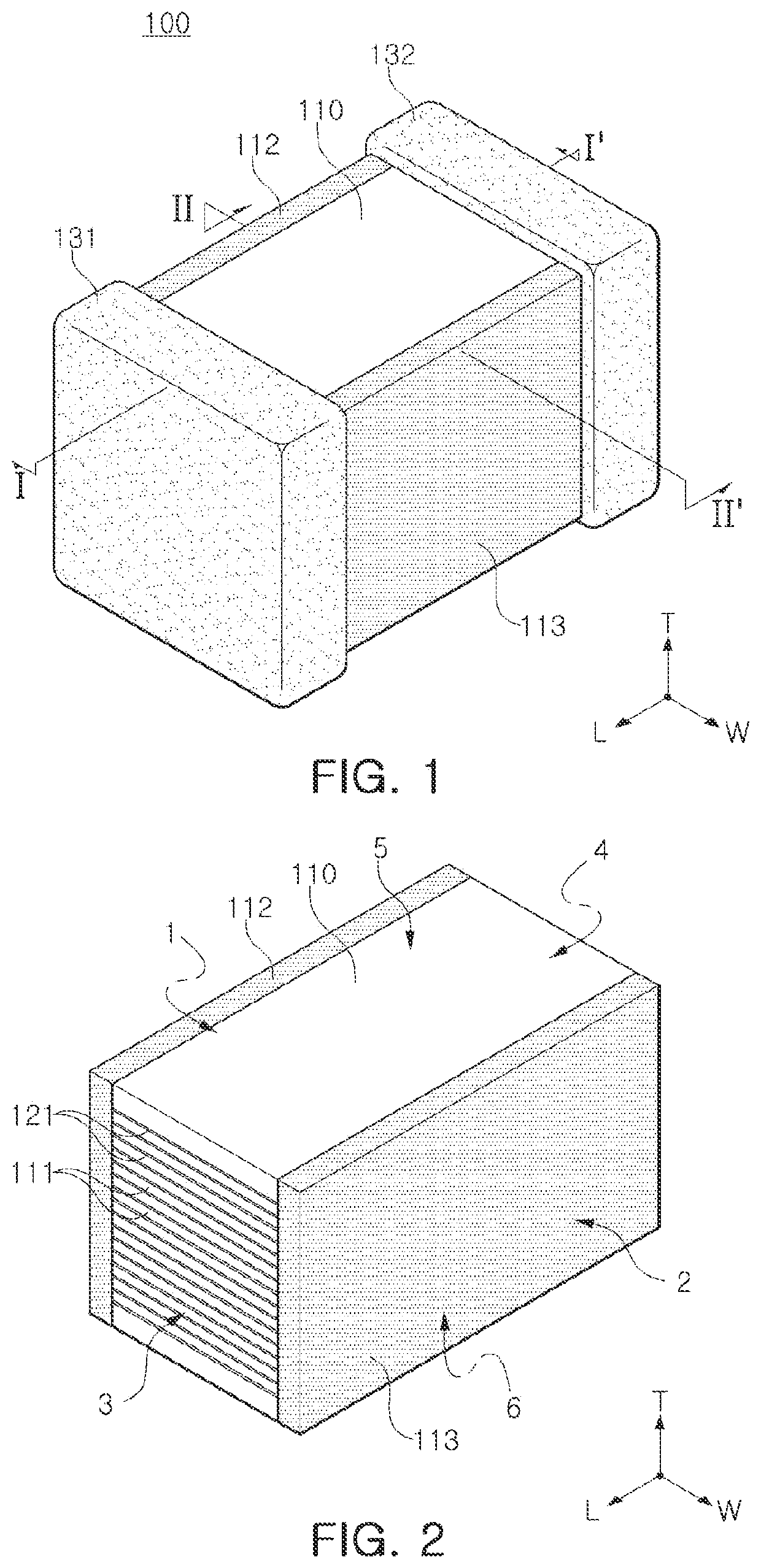

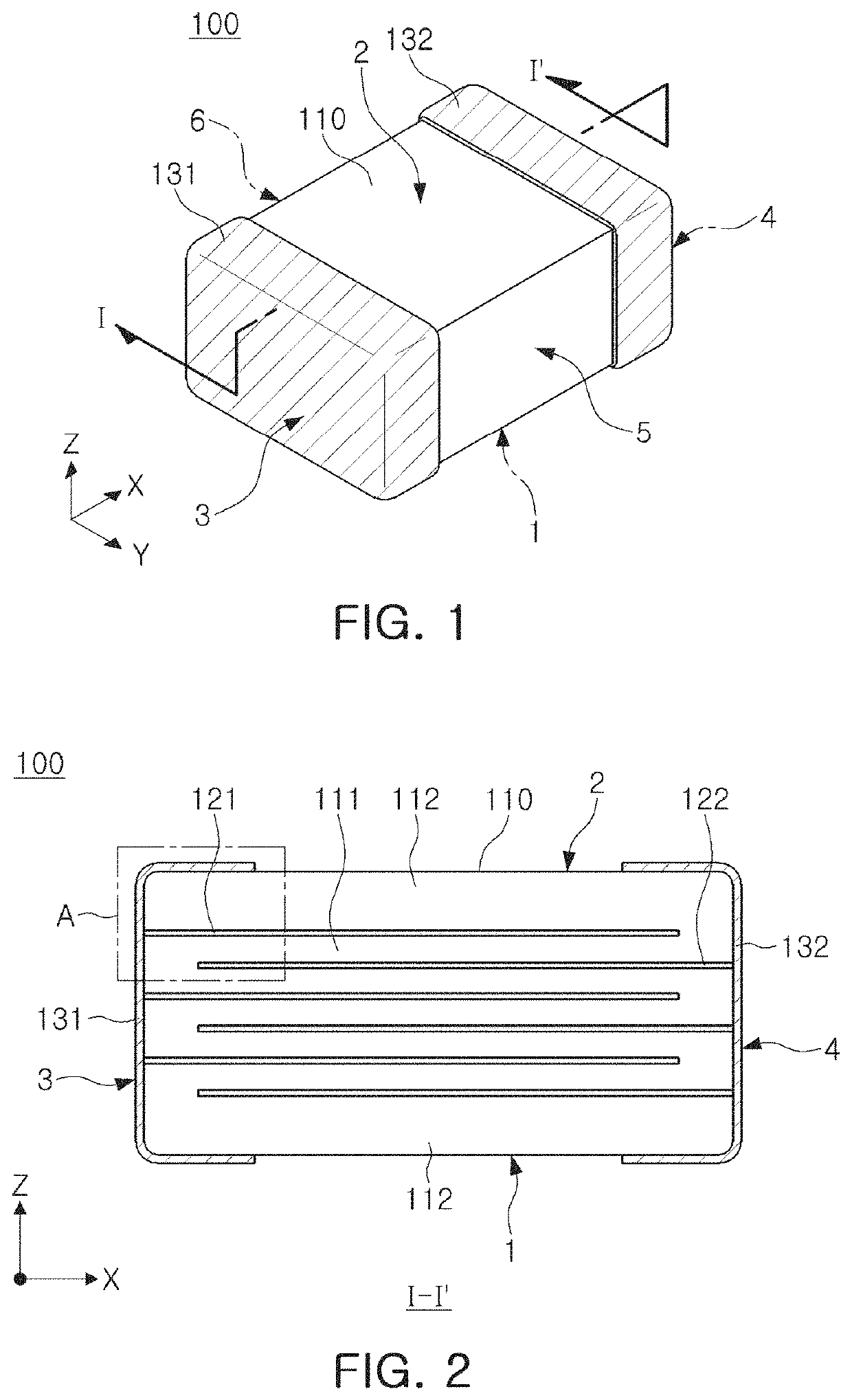

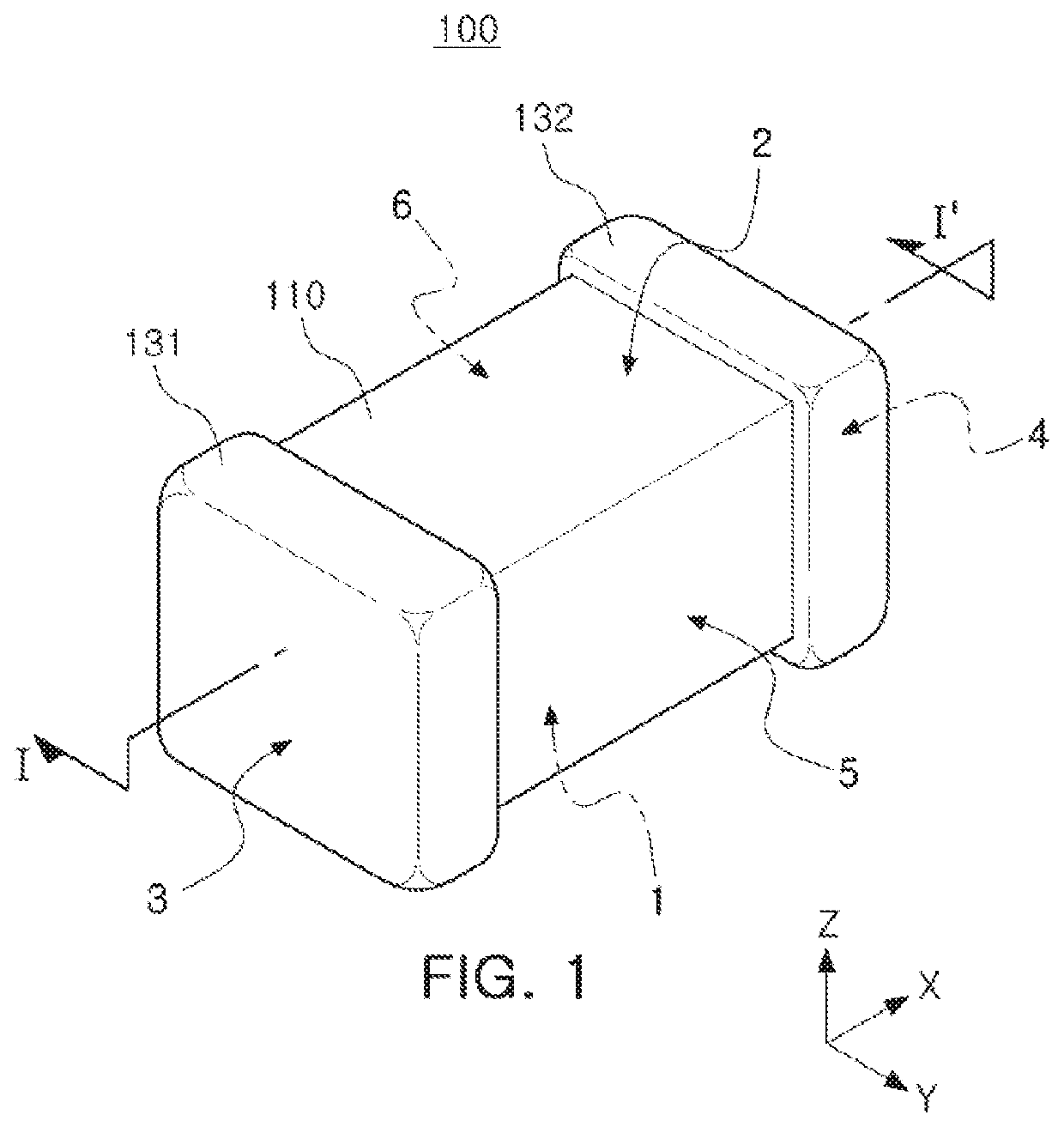

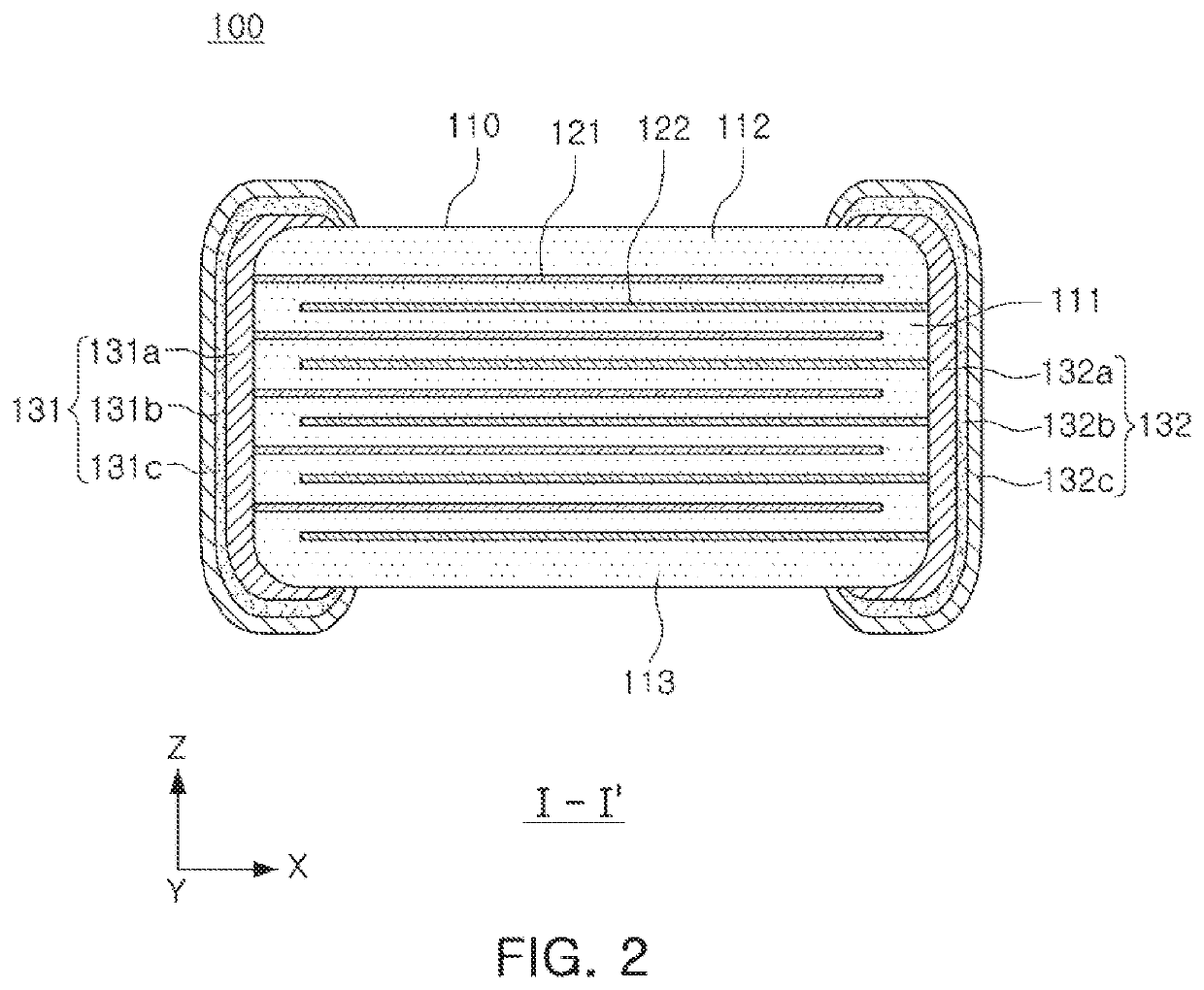

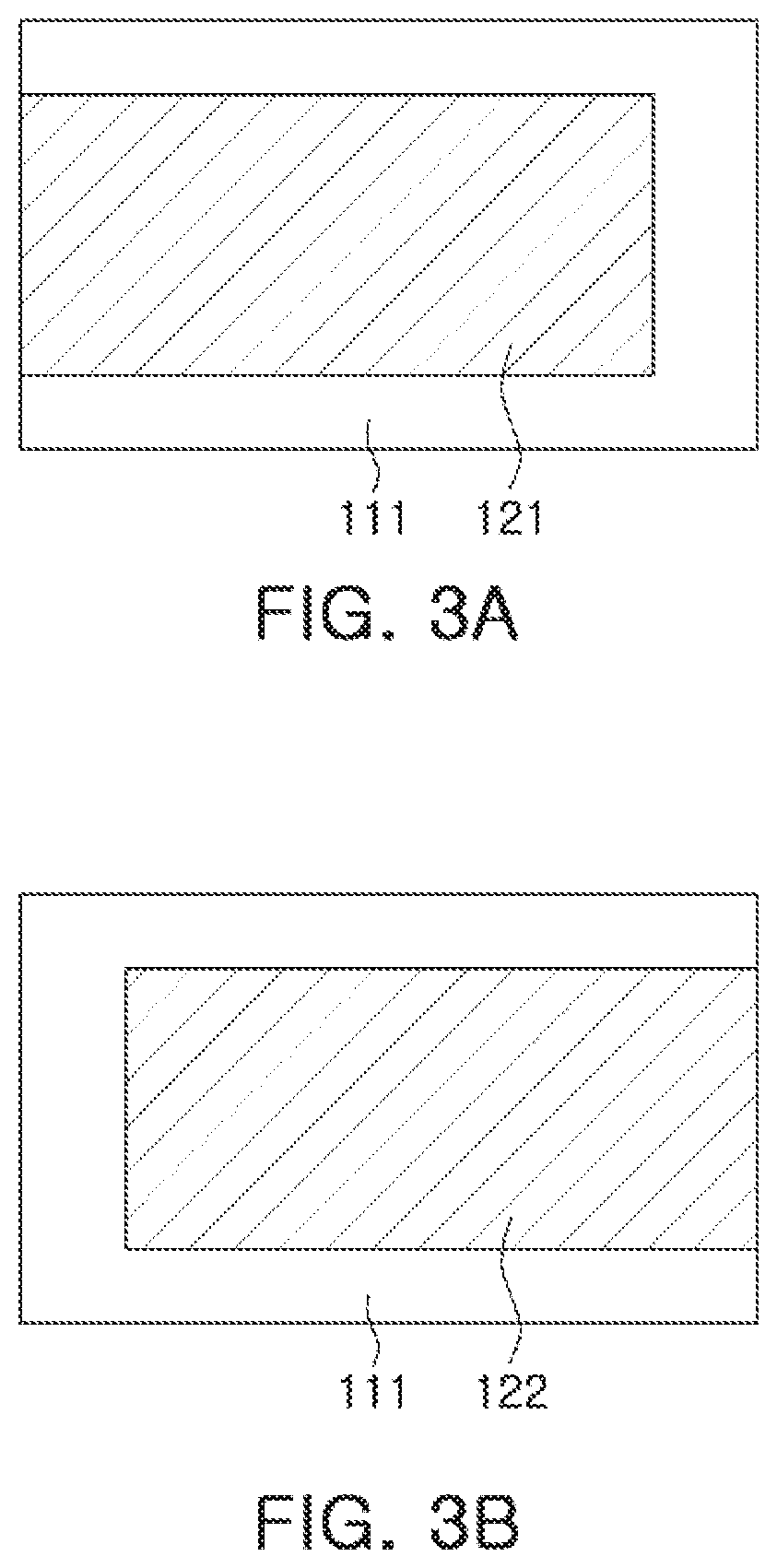

Capacitor component

ActiveUS20190385795A1Excellent moisture resistance reliabilityFixed capacitor dielectricStacked capacitorsElectrical connectionEngineering

A capacitor component includes a humidity resistant layer formed on a portion of the external surface of a body on which an external electrode is not formed, and further includes a humidity resistant layer disposed inside the external electrode, to improve humidity resistance reliability. The capacitor component includes an opening portion formed by removing a portion of the humidity resistant layer disposed inside the external electrode to improve electrical connection.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

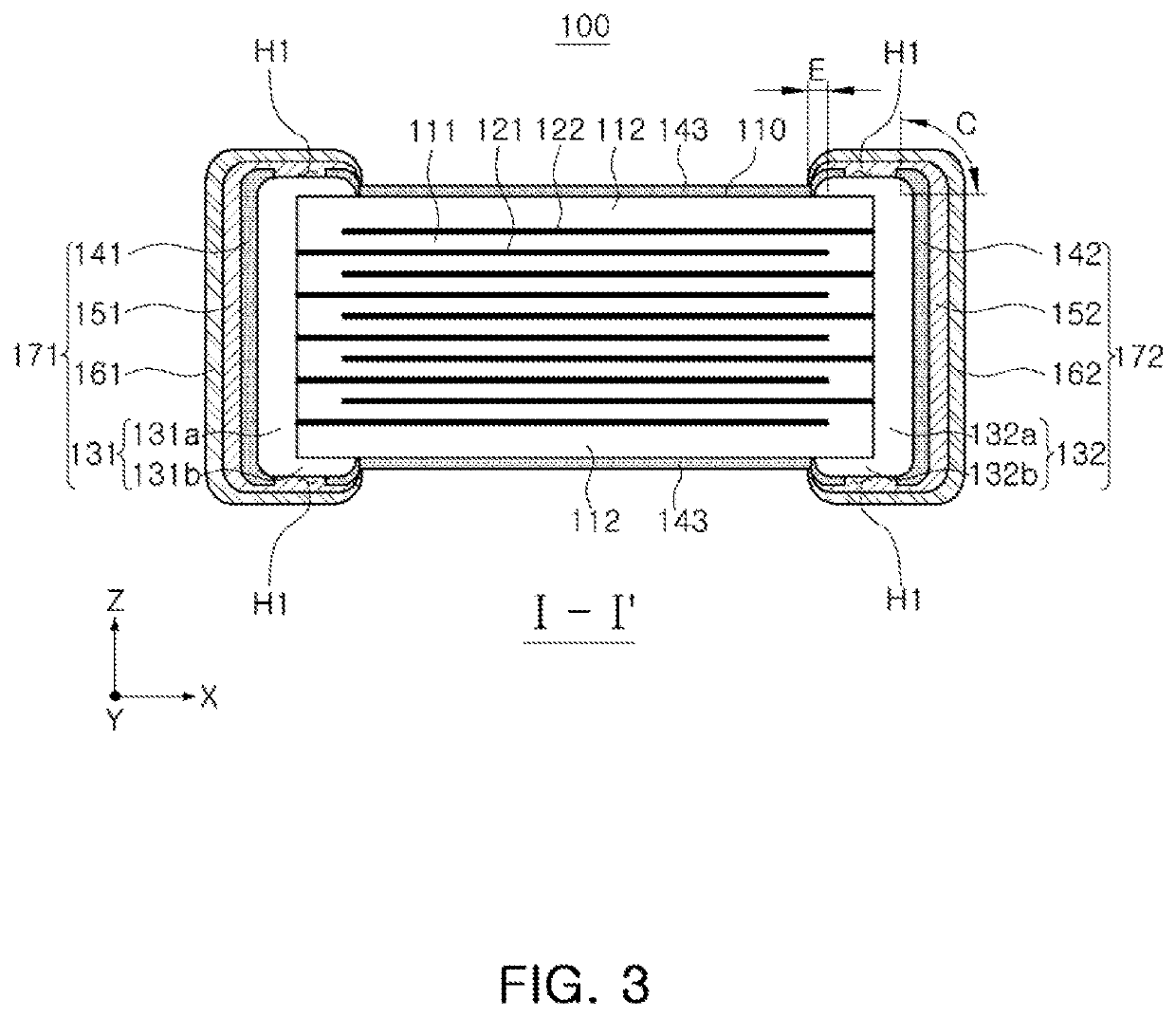

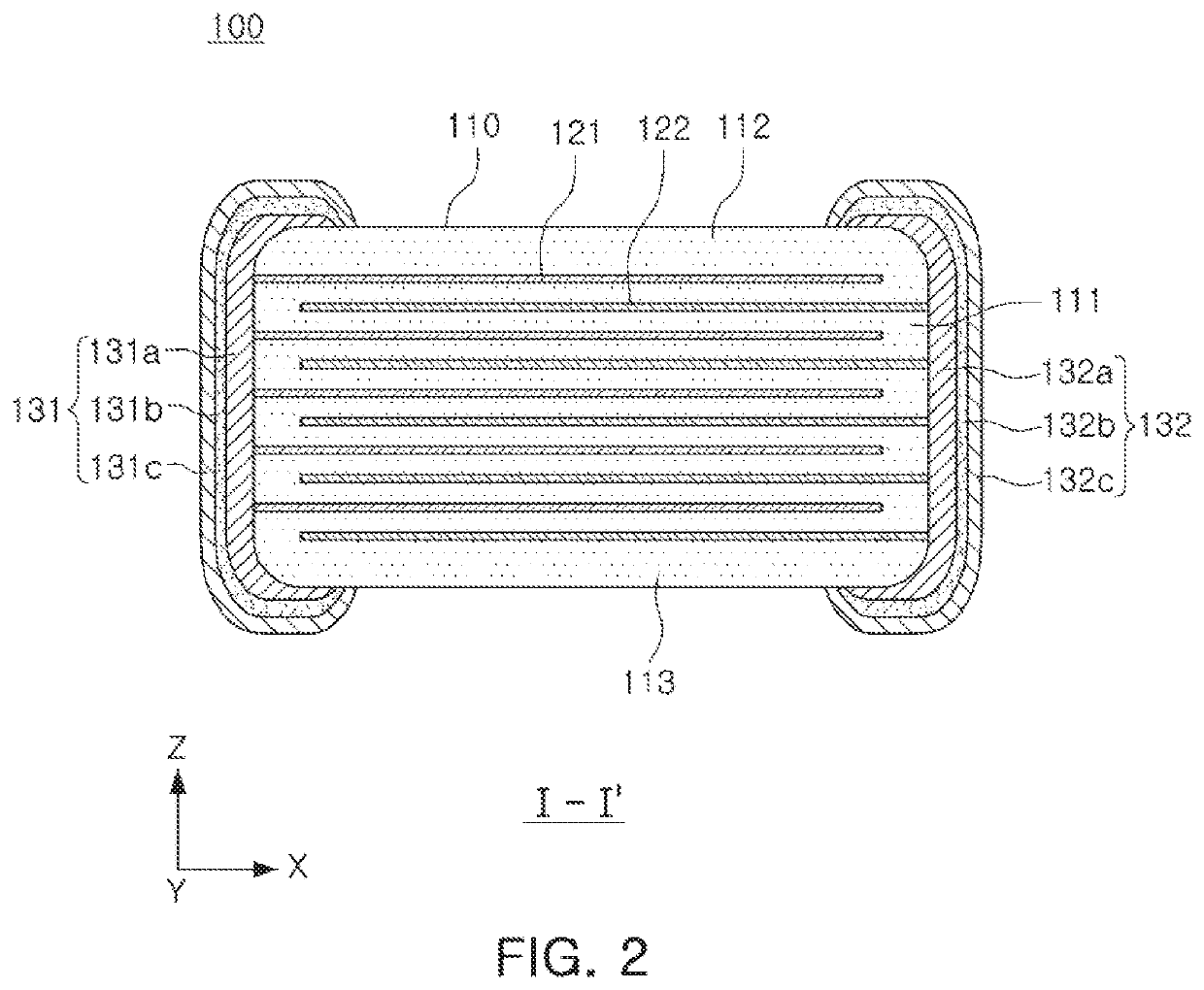

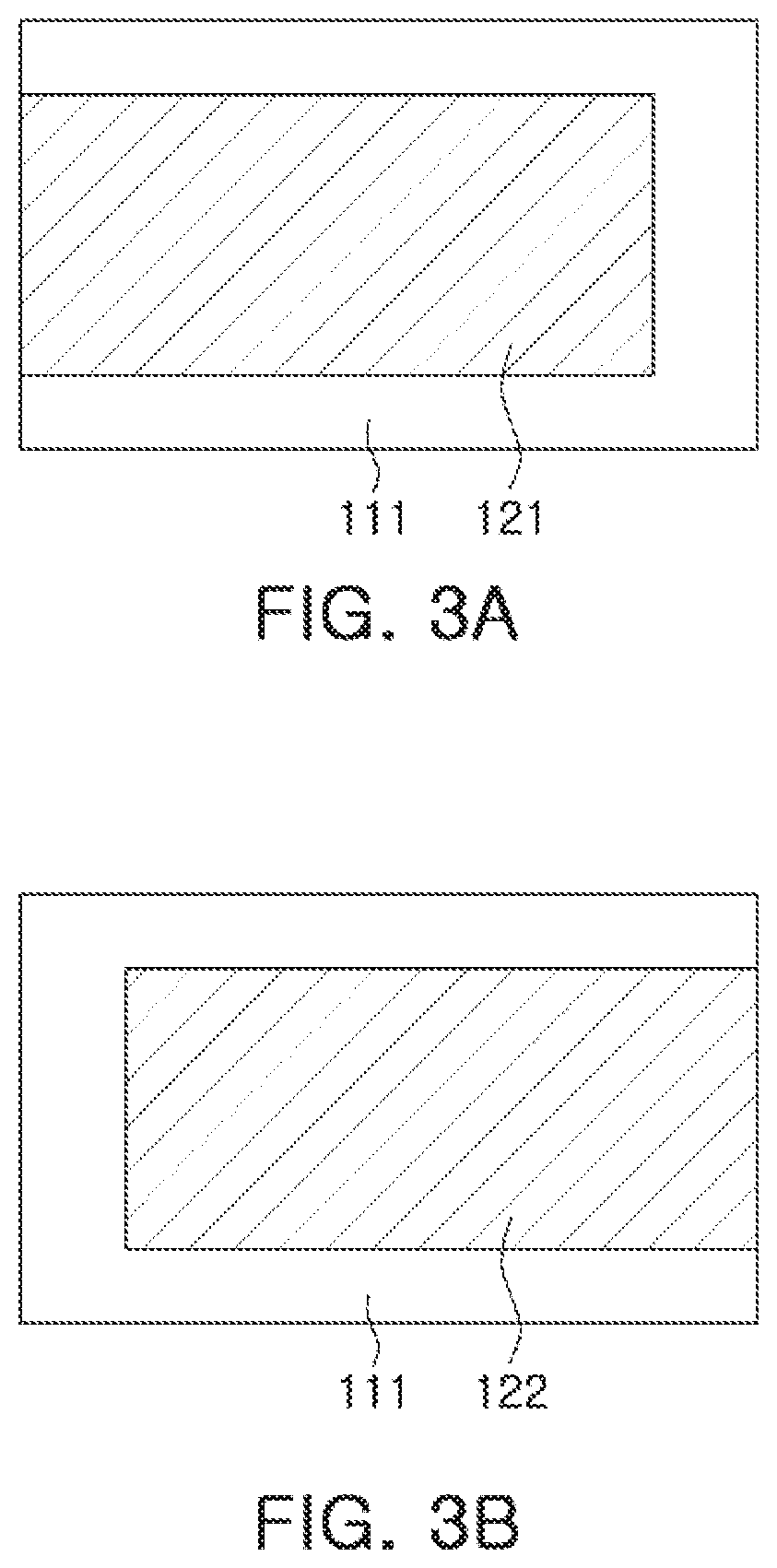

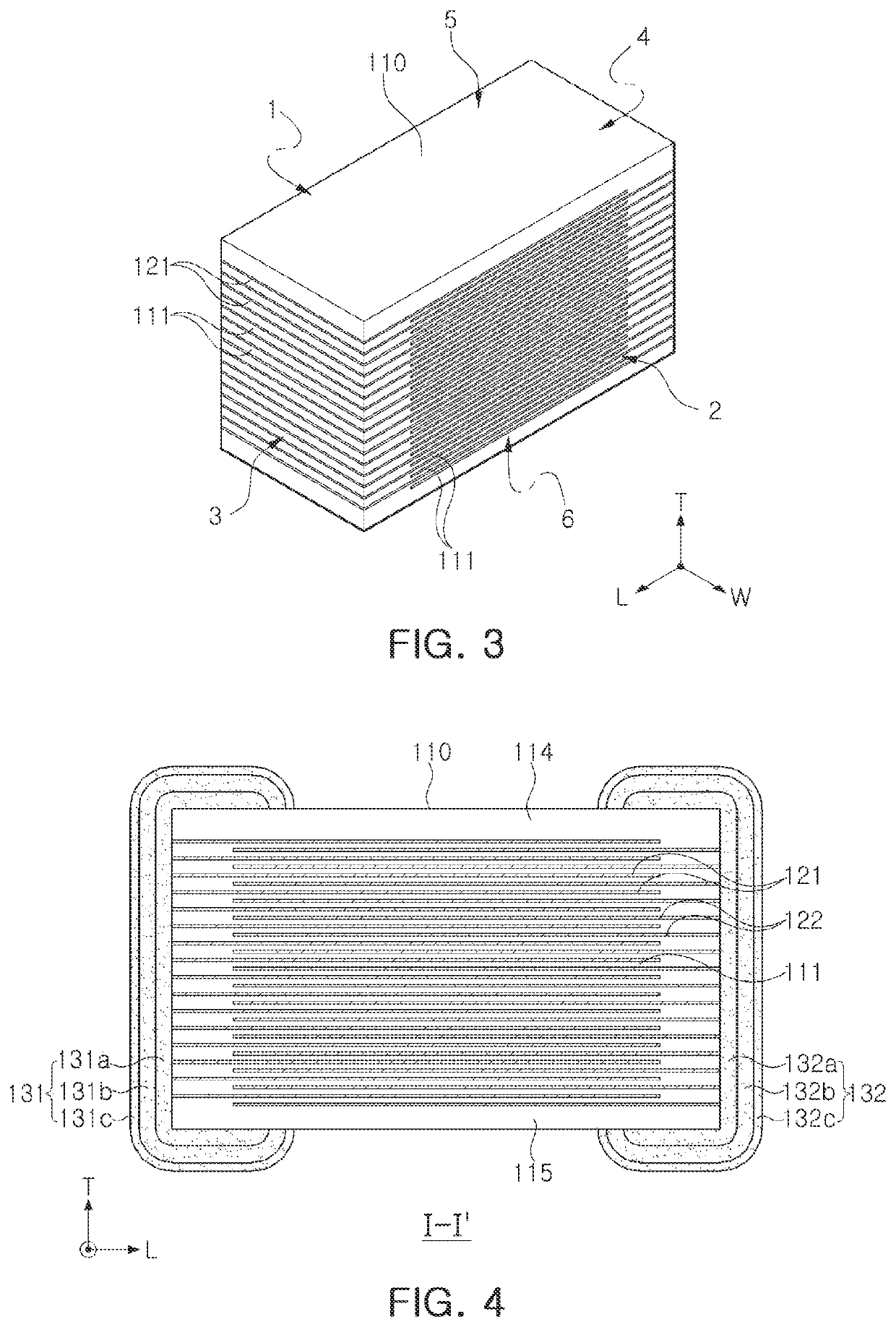

Ceramic electronic component

ActiveUS10366834B1Excellent moisture resistance reliabilityFixed capacitor electrodesFixed capacitor dielectricMaterials scienceDielectric layer

A ceramic electronic component includes a body including a dielectric layer and first and second internal electrodes, a first external electrode including a first electrode layer electrically connected to the first internal electrode, a first inorganic insulating layer disposed on the first electrode layer, and a first plating layer disposed on the first inorganic insulating layer, a second external electrode including a second electrode layer electrically connected to the second internal electrode, a second inorganic insulating layer disposed on the second electrode layer, and a second plating layer disposed on the second inorganic insulating layer, and a third inorganic insulating layer disposed on the body and connected to the first and second inorganic insulating layers. The first, second and third inorganic insulating layers comprise one or more of SiO2, Al2O3 and ZrO2, and the first, second and third inorganic insulating layers have a thickness within a range from 20 nm to 150 nm.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

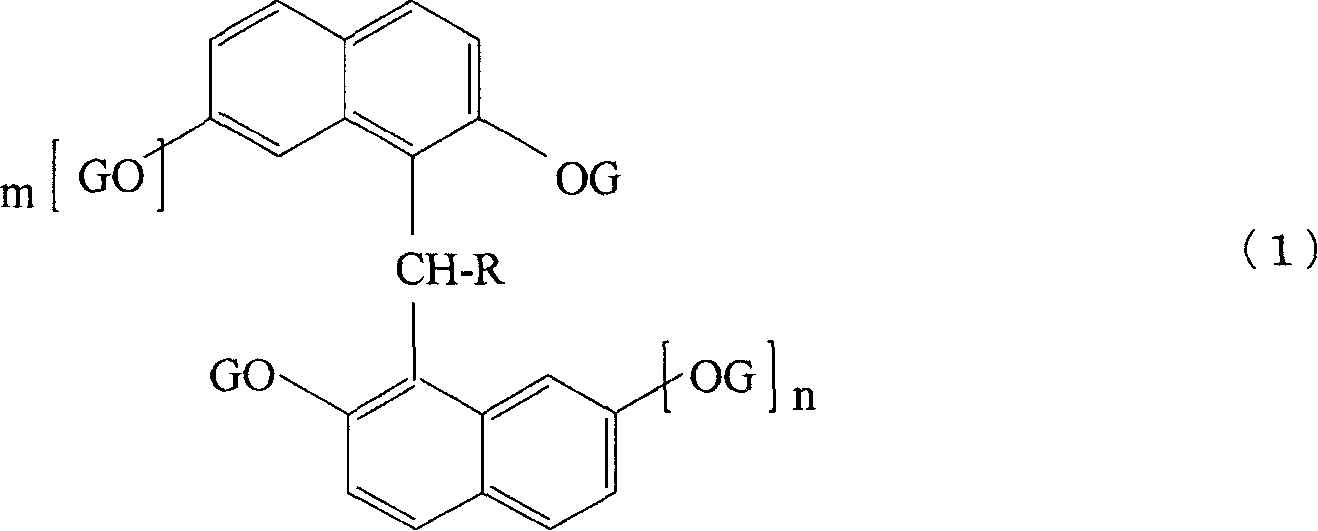

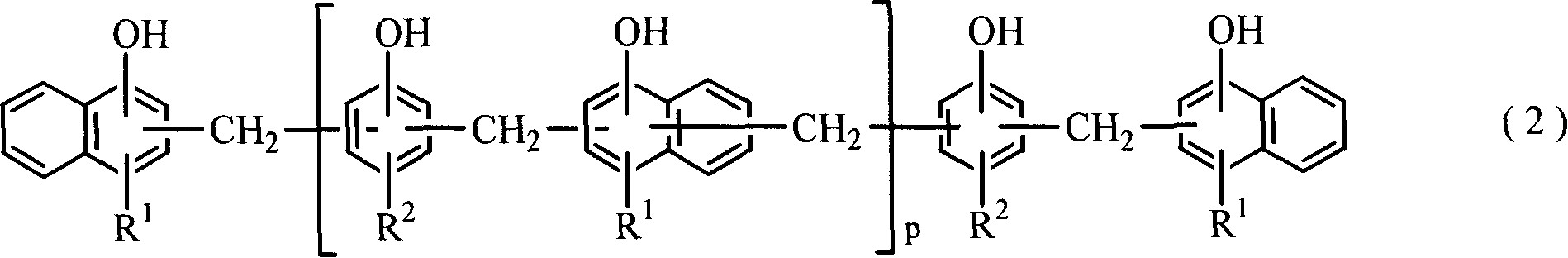

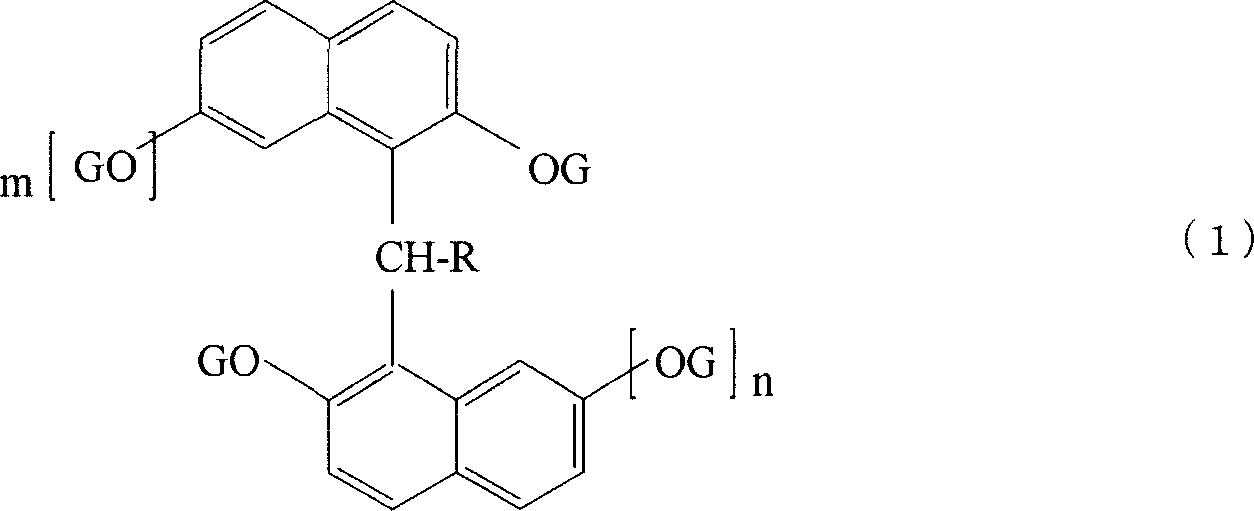

Semiconductor encapsulating epoxy resin composition and semiconductor device

ActiveCN1854186AImprove liquiditySmall coefficient of linear expansionOther chemical processesSemiconductor/solid-state device detailsEpoxyDevice material

The present invention provides an epoxy resin composition, which is characterized in that it contains: (A) a naphthalene type epoxy resin represented by the following general formula (1), (m, n represent 0 or 1, R represents a hydrogen atom , an alkyl or phenyl group with 1 to 4 carbon atoms, G represents an organic group containing a glycidyl group, but in 100 parts by mass of the above general formula (1), the compound containing m=0 and n=0 is 35~ 85 mass parts, m=1, n=1 compound is 1 to 35 mass parts); (B) a phenolic resin curing agent having at least one substituted or unsubstituted naphthalene ring in one molecule; (C) inorganic matter filling agent and (D) at least one compound selected from rare earth oxides or hydrotalcite compounds. The epoxy resin composition of the present invention has good fluidity, small coefficient of linear expansion, high glass transition temperature, low hygroscopicity, and excellent lead-free solder crack resistance.

Owner:SHIN ETSU CHEM CO LTD

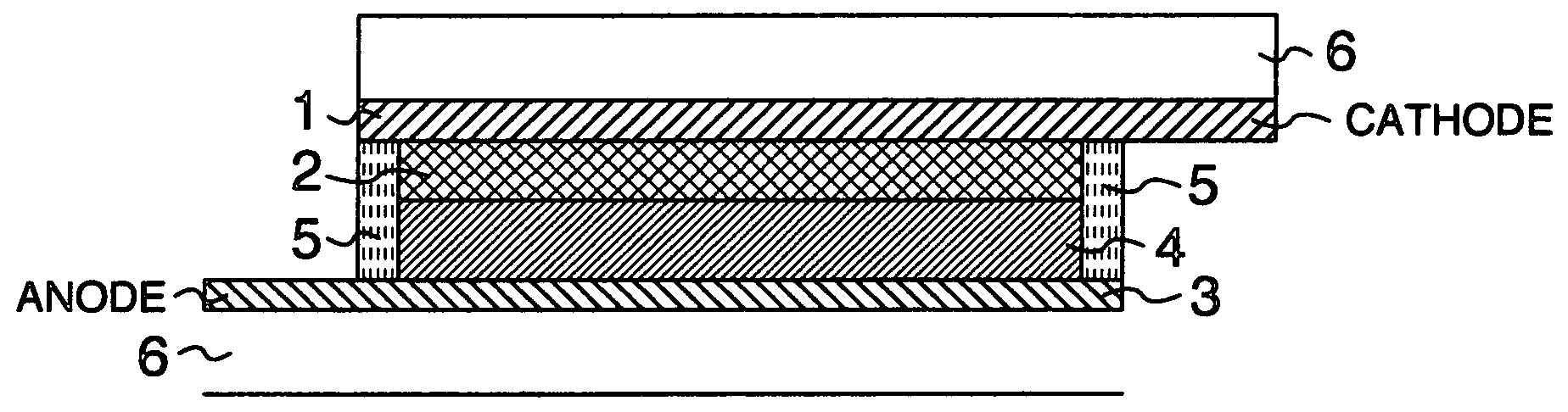

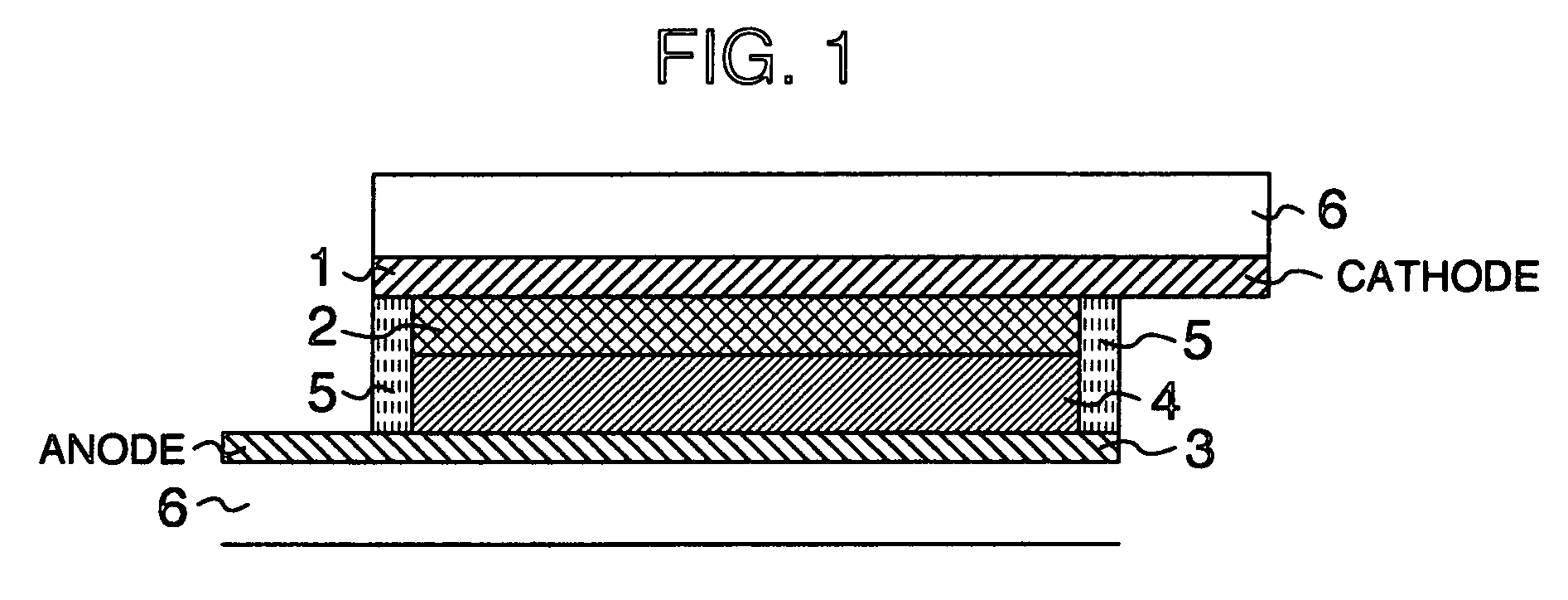

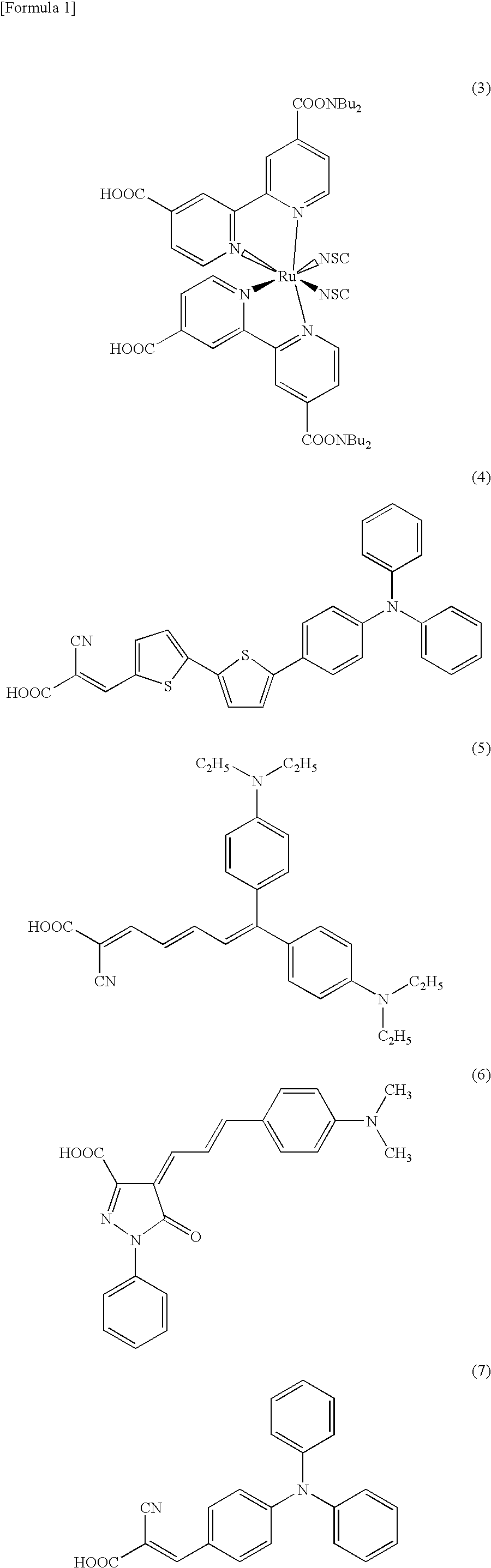

Sealing Agent for Photoelectric Converter and Photoelectric Converter Using Same

InactiveUS20090114272A1High yieldExcellent adhesive reliabilityOther chemical processesElectrolytic capacitorsEpoxyMeth-

Disclosed is a sealing agent for photoelectric converters which enables to easily bond upper and lower conductive supporting bodies during production of a photoelectric converter while forming a sealed portion having excellent adhesion strength, moisture resistance reliability, flexibility and the like. Specifically, a photocuring and thermosetting resin composition containing an epoxy resin (a), a thermosetting agent (b), an epoxy(meth)acrylate (c) and a photopolymerization initiator (d), and additionally if necessary, a filler (e), a silane coupling agent (f) and an ion capturing agent (g) is used as a sealing agent for photoelectric converters.

Owner:NIPPON KAYAKU CO LTD

Optical resin composition, optical resin material using the same, optical filter for image display device, and image display device

InactiveUS20120120347A1Improve impact absorption performanceHigh transparencyOptical filtersCoatingsDiacrylate esterBiopolymer

An optical resin composition that is transparent, has suitable adhesion and necessary impact absorption for protection of an image display device etc., not affecting constituent materials of a image display panel, and being excellent in reliability, can be used to provide an optical resin material using the same. The optical resin composition contains (A) a first acrylate derivative that is a compound having one polymerizable unsaturated bond in its molecule, (B) a second acrylate derivative that is a compound having two or more polymerizable unsaturated bonds in its molecule, and (C) an acrylate derivative polymer, and an optical resin material produced by curing reaction of the optical resin composition.

Owner:HITACHI CHEM CO LTD

Flame-retardant epoxy resin composition, and electronic device, laminated circuit board, multilayered circuit board and printed circuit board using the flame-retardant epoxy resin composition

ActiveUS20060217462A1Sufficient flame resistanceImprove crack resistanceSynthetic resin layered productsPrinted circuit aspectsEpoxyPrinted circuit board

A flame-retardant epoxy resin composition, as well as an electronic device, a laminated circuit board, a multilayered circuit board and a printed circuit board employing the flame-retardant epoxy resin composition are disclosed. The flame-retardant epoxy resin composition contains: an epoxy resin; an epoxy resin curing agent; and flame-retardant particles containing a metal hydrate. The flame-retardant particles are provided with a coating layer on the surfaces thereof and have a volume average particle diameter in a range from 1 to 500 nm.

Owner:FUJIFILM BUSINESS INNOVATION CORP

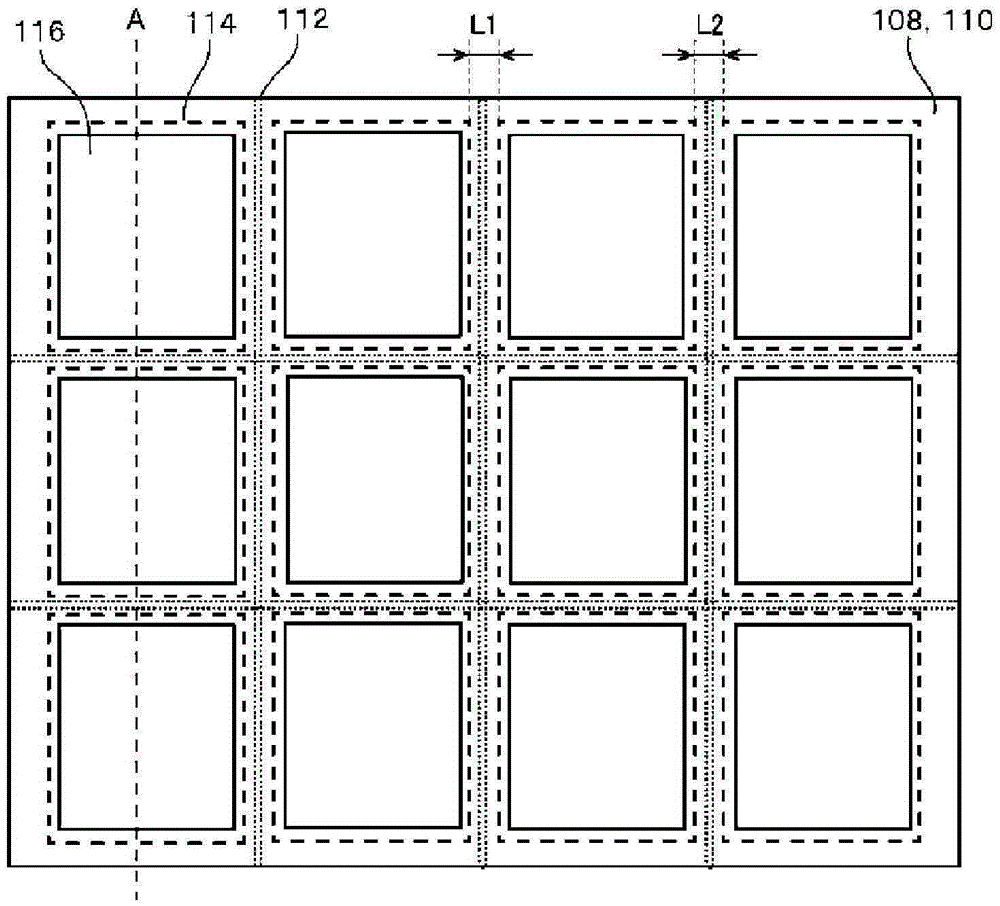

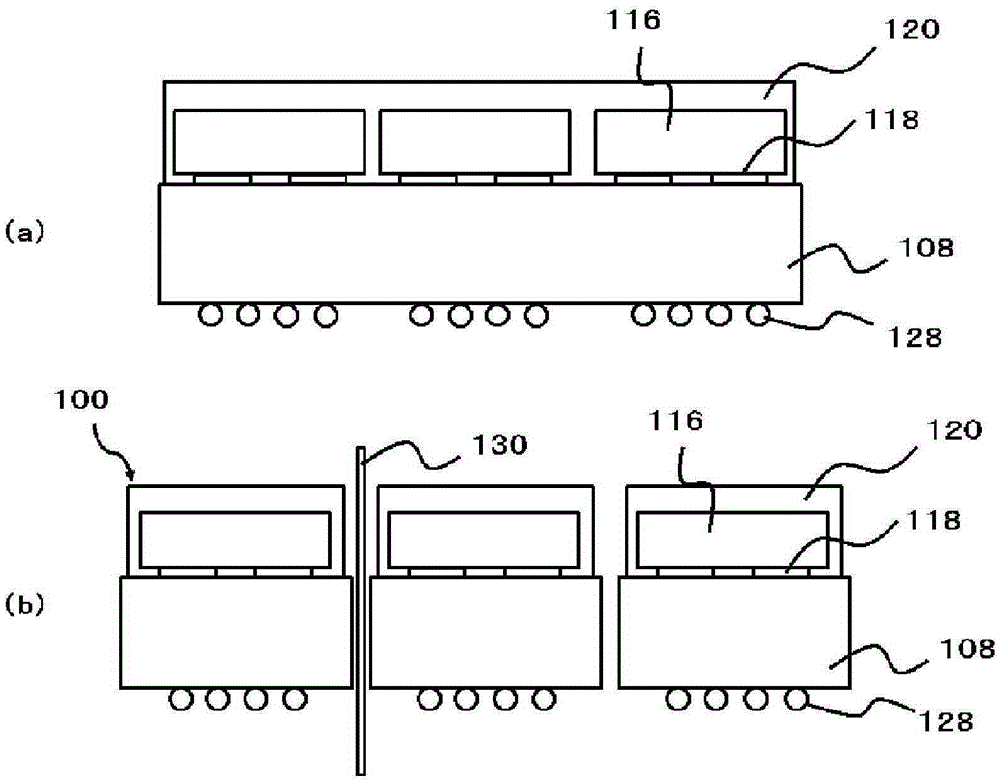

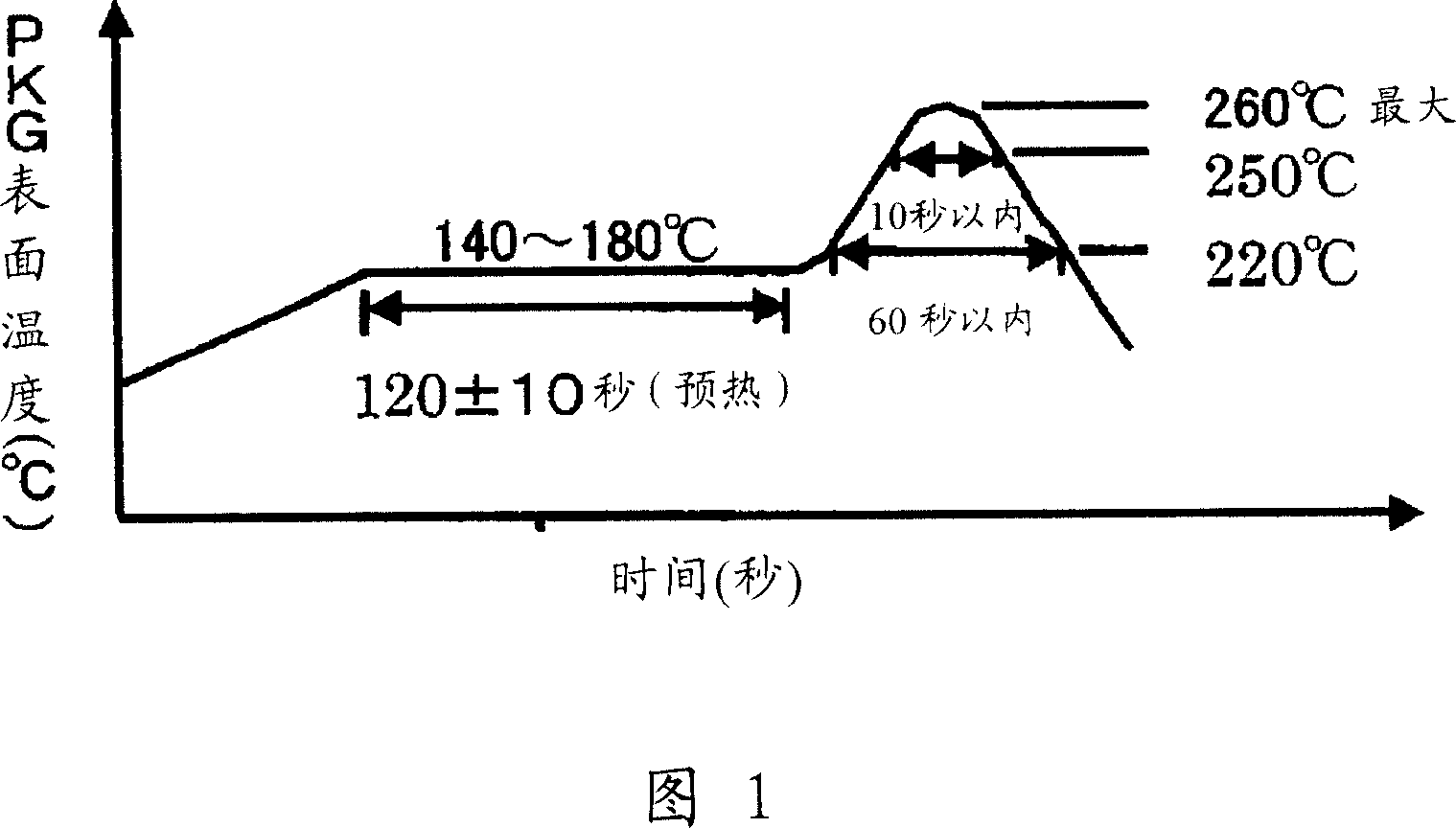

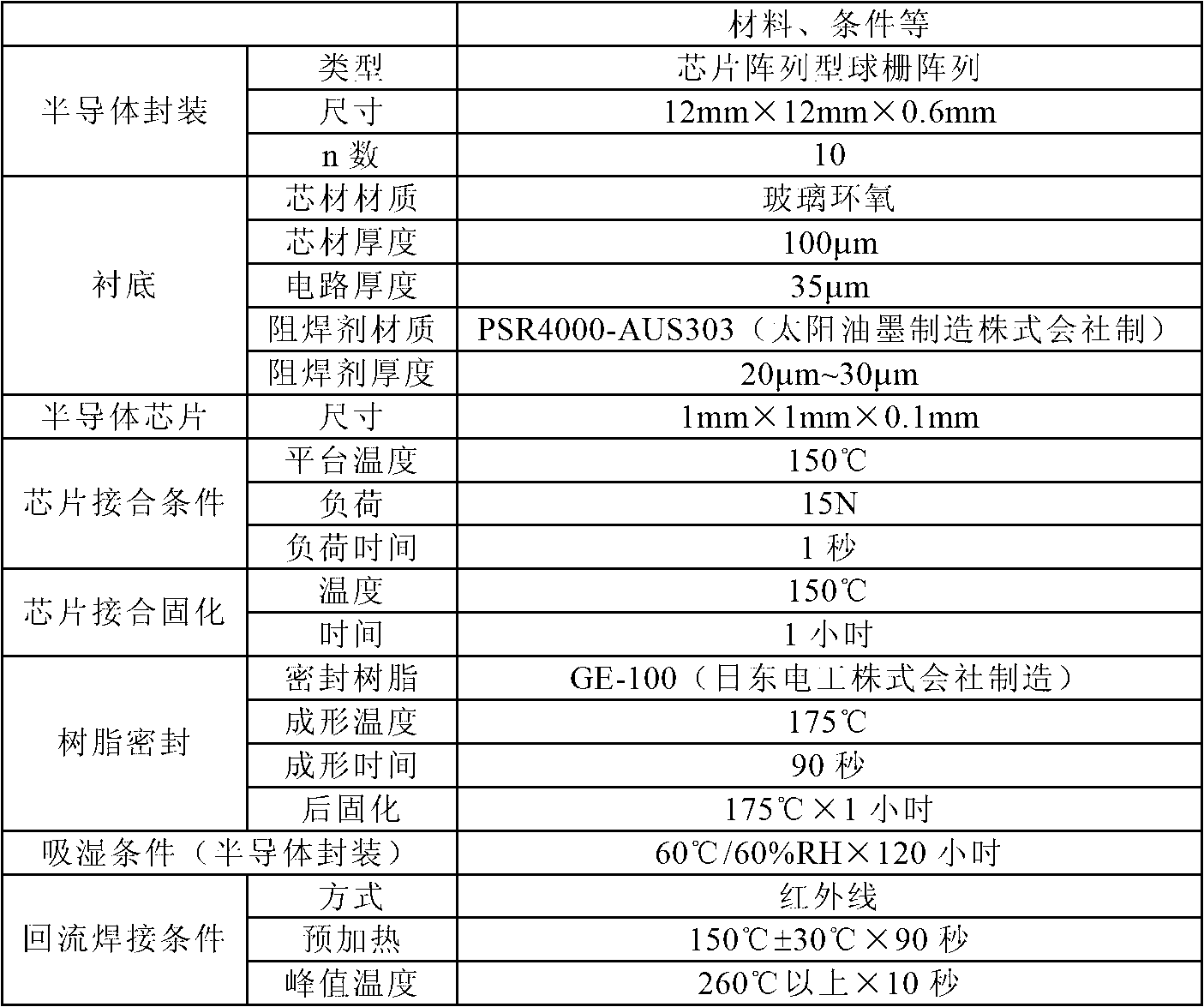

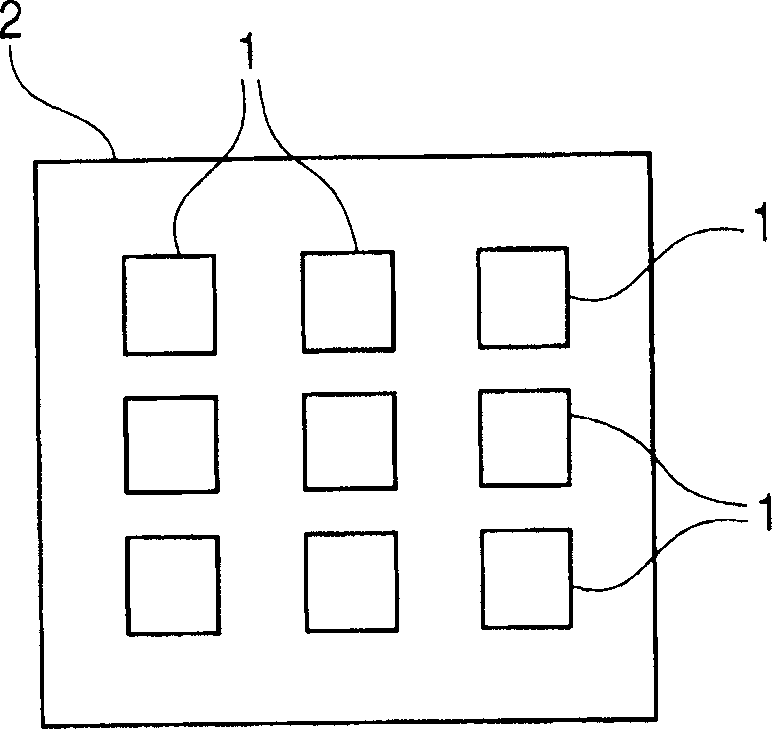

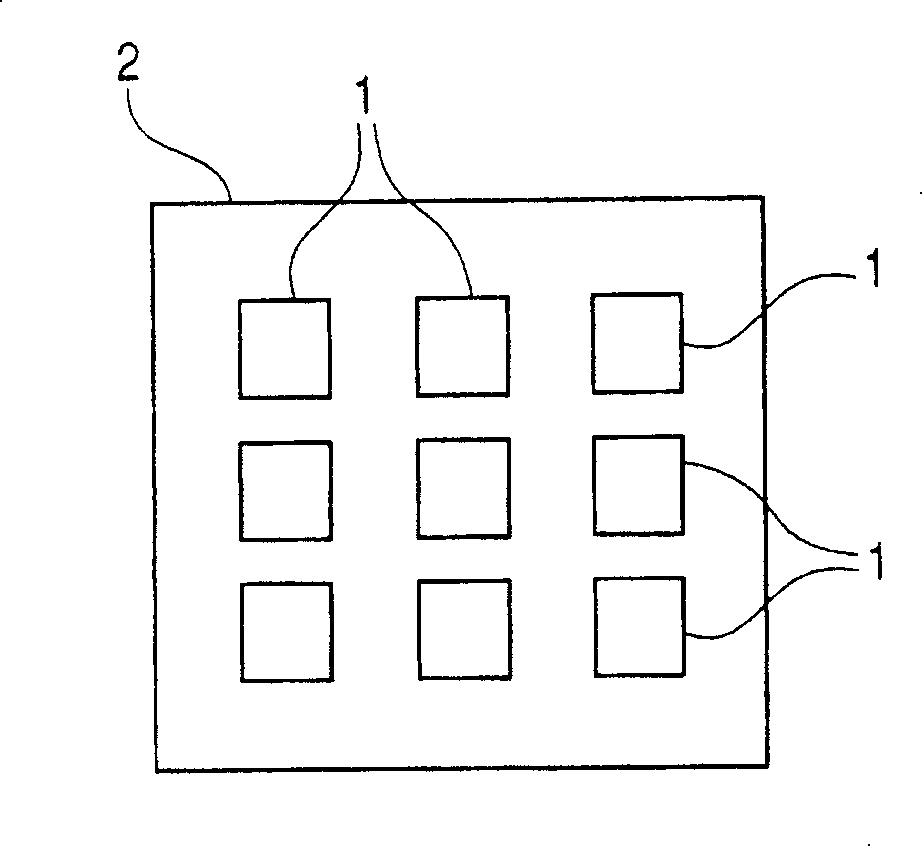

Process for producing semiconductor devices, and semiconductor device

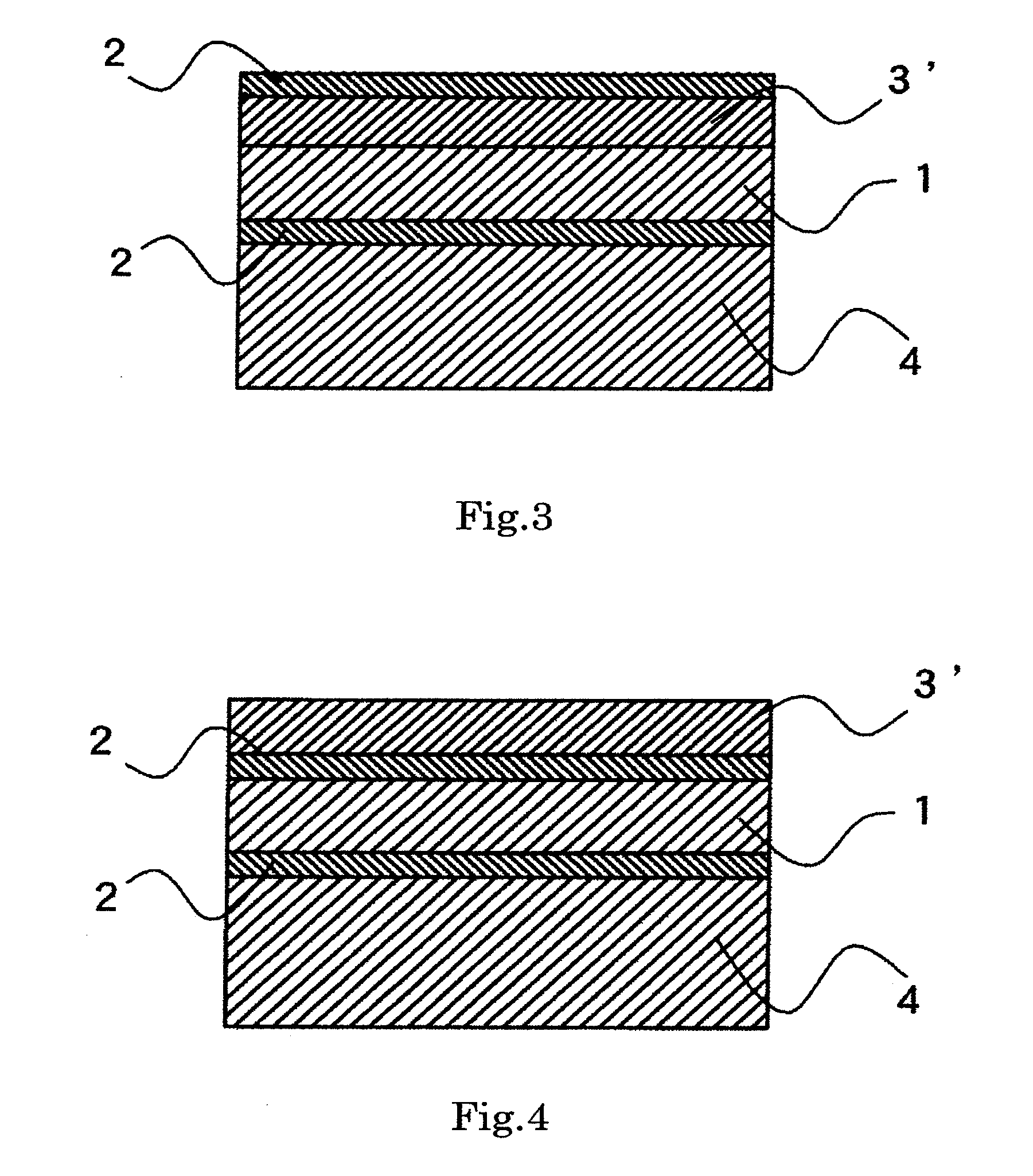

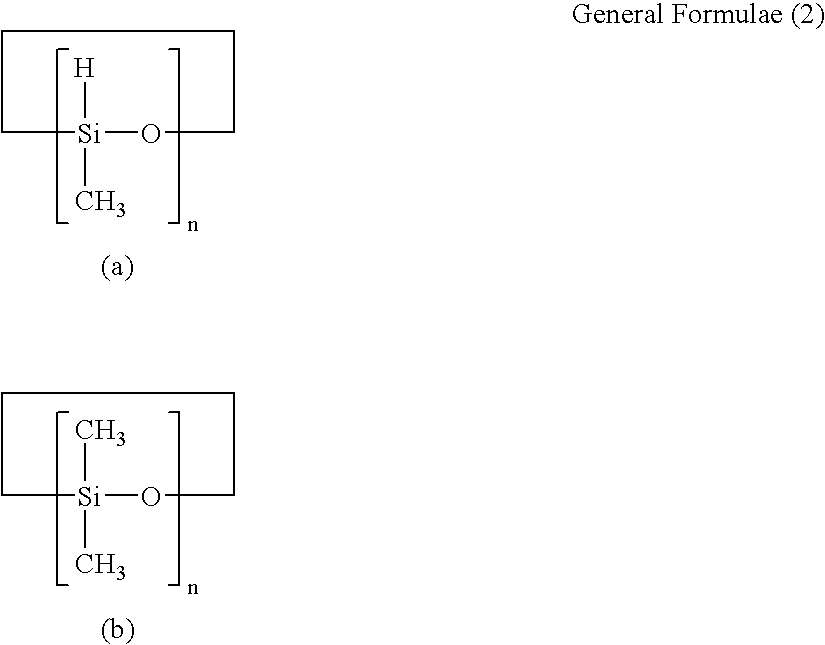

InactiveCN105377980AImprove heat resistanceExcellent resistance to temperature cyclingEpoxySemiconductor chip

A process for semiconductor device production which comprises: a preparation step in which a substrate for element mounting (108) equipped with a plurality of package areas (114) separated by dicing regions (112) is prepared; a mounting step in which semiconductor chips (116) are mounted respectively on the package areas (114) of the substrate for element mounting (108); a molding step in which the semiconductor chips (116) are simultaneously encapsulated by molding with an encapsulating epoxy resin composition; and a chip formation step in which the resultant structure is diced along the dicing regions (112) to separate the individual encapsulated semiconductor chips (116). The encapsulating epoxy resin composition comprises (A) an epoxy resin, (B) a hardener, (C) a silicone resin, (D) an inorganic filler, and (E) a hardening accelerator, wherein the silicone resin (C) is a branched silicone resin that is a methylphenyl-type thermoplastic silicone resin and has repeating structural units represented by general formulae (a), (b), (c), and (d). (In the formulae, symbol * indicates a bond with the Si atom contained in a repeating structural unit of another or the same kind; and R1a, R1b, R1c, and R1d are each a methyl or phenyl group and may be the same as or different from one another. The content of Si-bonded phenyl groups is 50 mass% or higher of the molecule, and the content of Si-bonded OH groups is less than 0.5 mass% of the molecule.) The formulae is shown in the specification.

Owner:SUMITOMO BAKELITE CO LTD

Semiconductor encapsulating epoxy resin composition and semiconductor device

InactiveCN1962802AExcellent temperature cyclingGood warping propertiesOther chemical processesSemiconductor/solid-state device detailsEpoxyAlkane

An epoxy resin composition comprising (A) a naphthalene type epoxy resin in which 35-85 parts by weight of 1,1-bis(2-glycidyloxy-1-naphthyl)alkane and 1-35 parts by weight of 1,1-bis(2,7-diglycidyloxy-1-naphthyl)alkane are included per 100 parts by weight of the resin, (B) a phenolic resin curing agent, (C) a copolymer obtained through addition reaction of alkenyl groups on an alkenyl-containing epoxy compound and SiH groups on an organohydrogenpolysiloxane of 20 to 50 silicon atoms, and (D) an inorganic filler is best suited for semiconductor encapsulation because the cured composition has good thermal cycling, anti-warping, reflow resistance, and moisture-proof reliability.

Owner:SHIN ETSU CHEM IND CO LTD

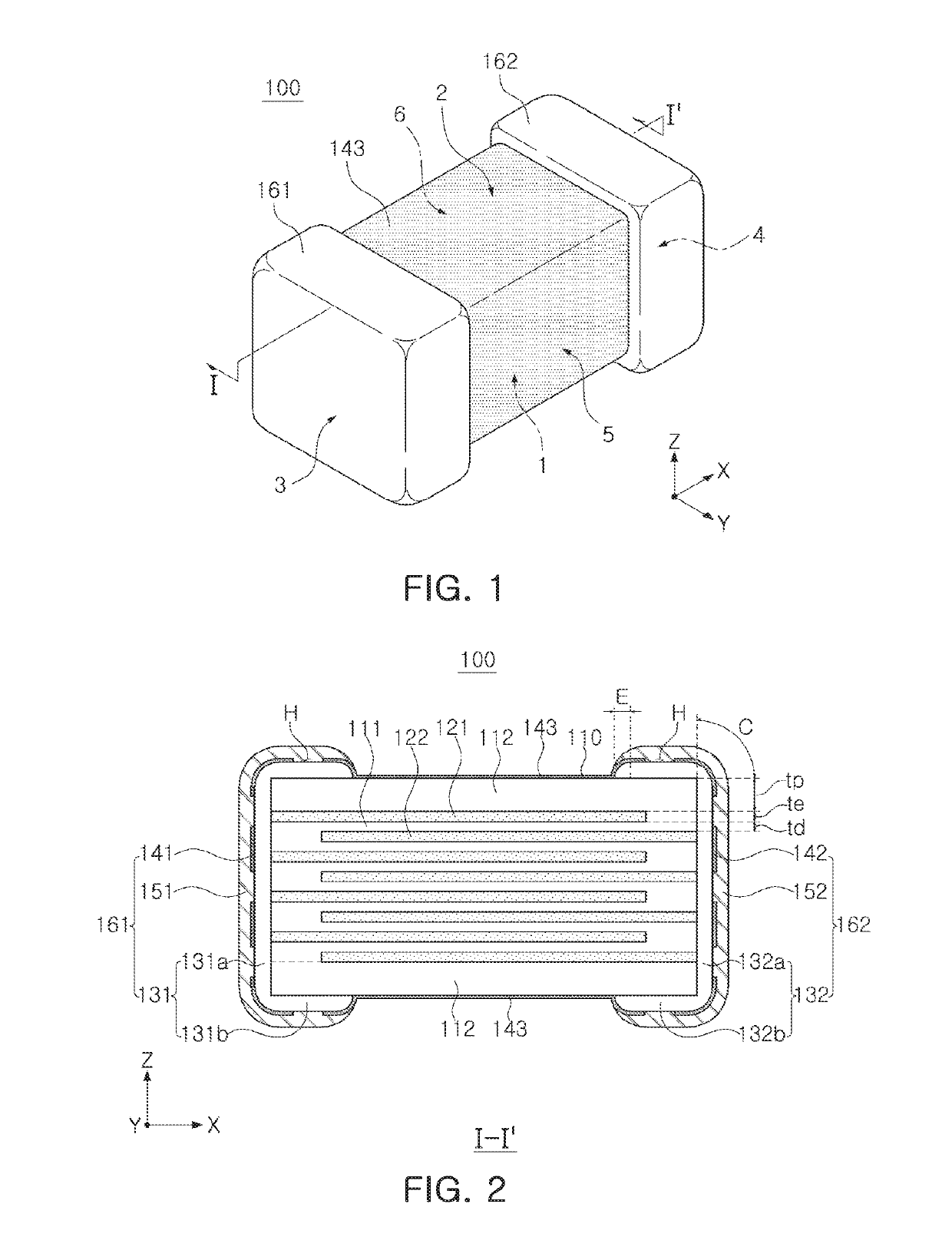

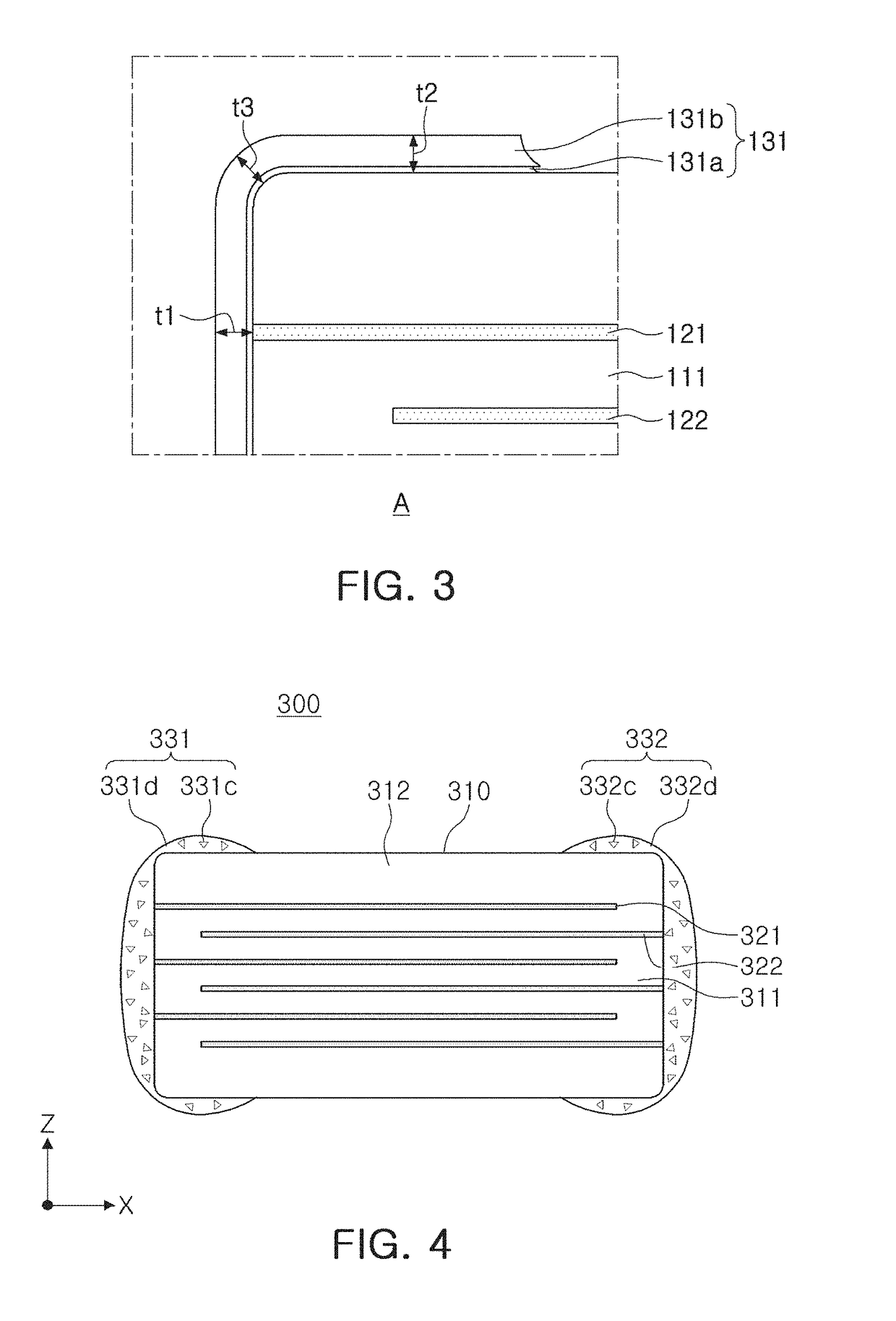

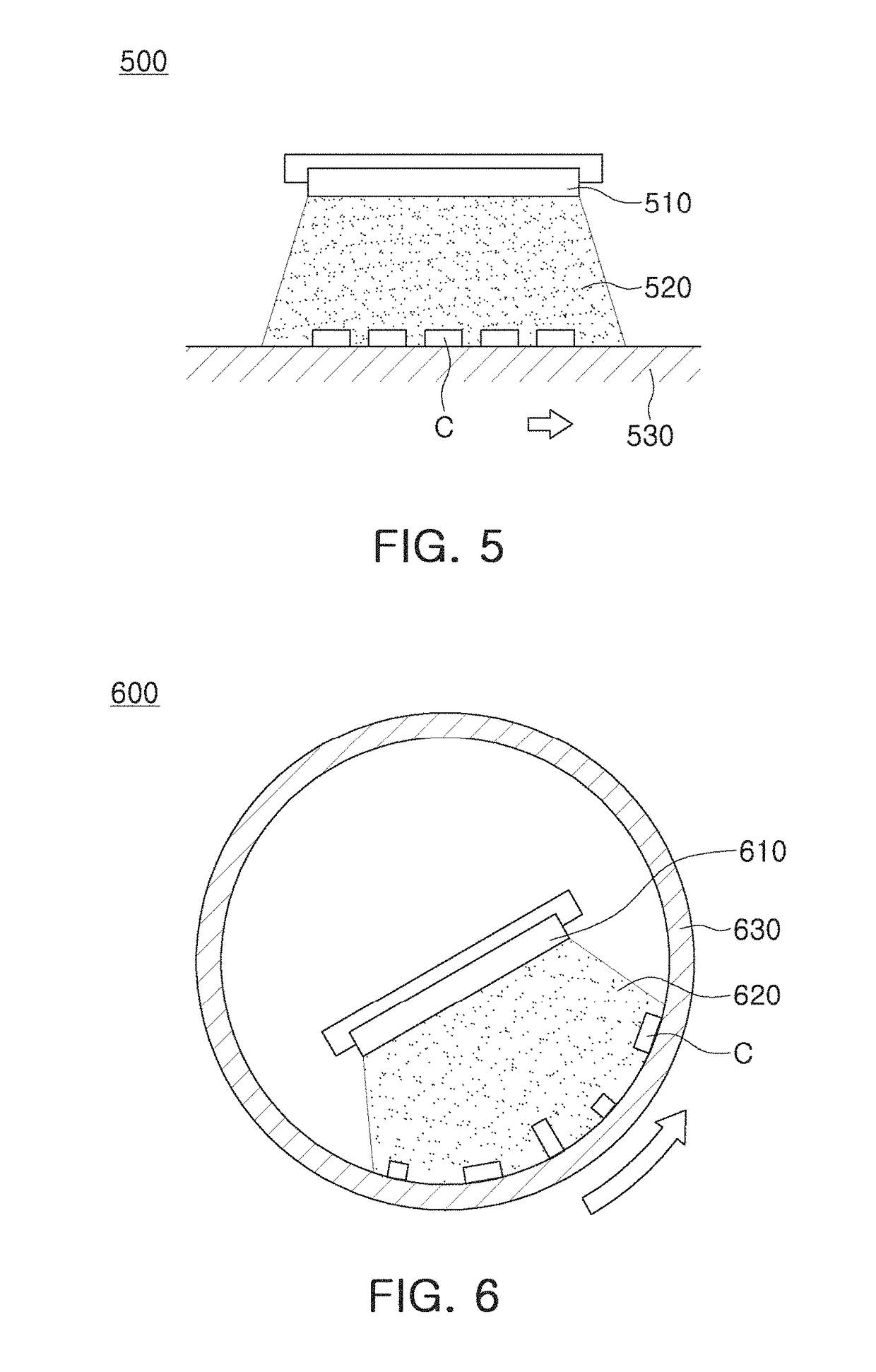

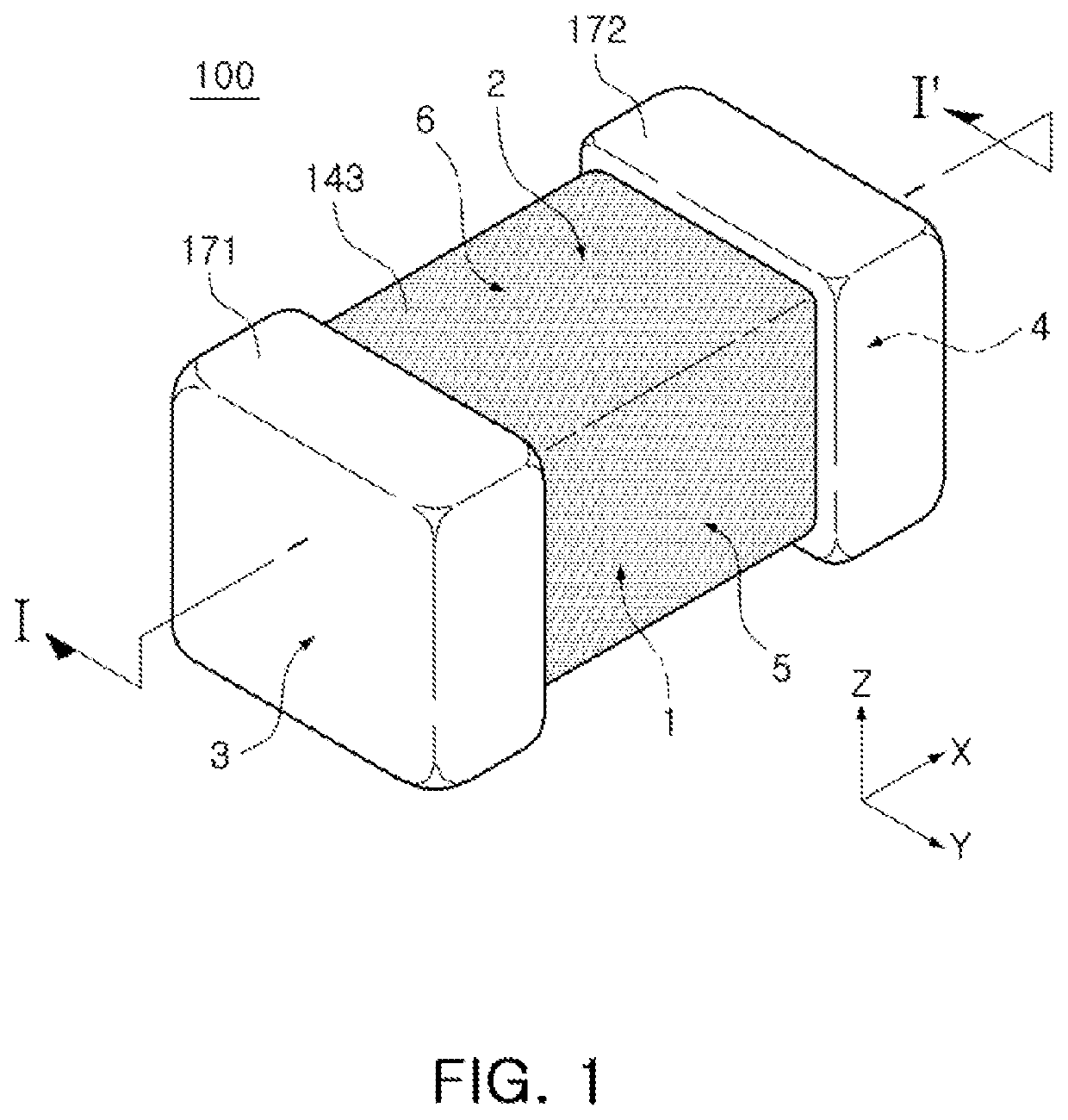

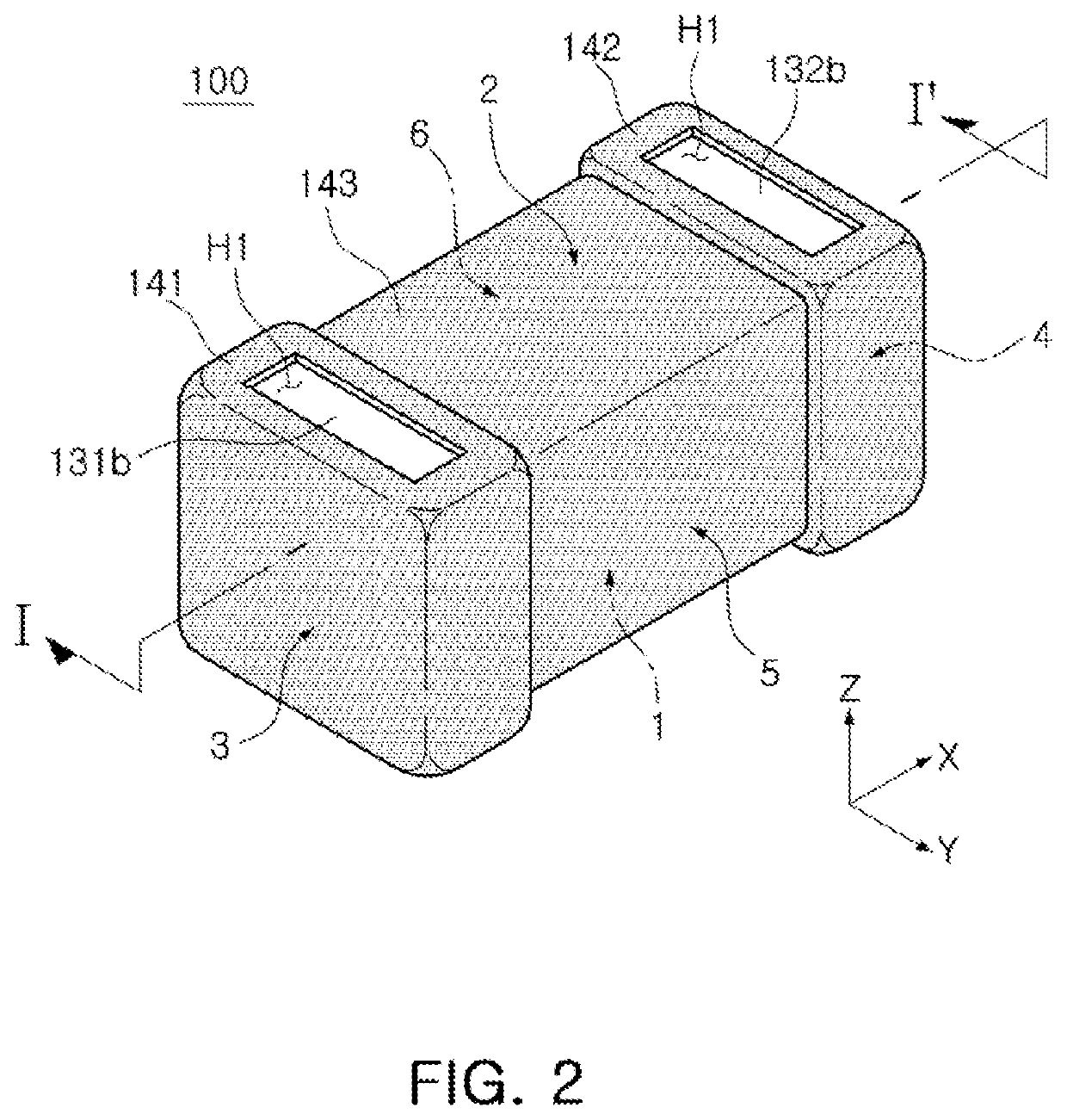

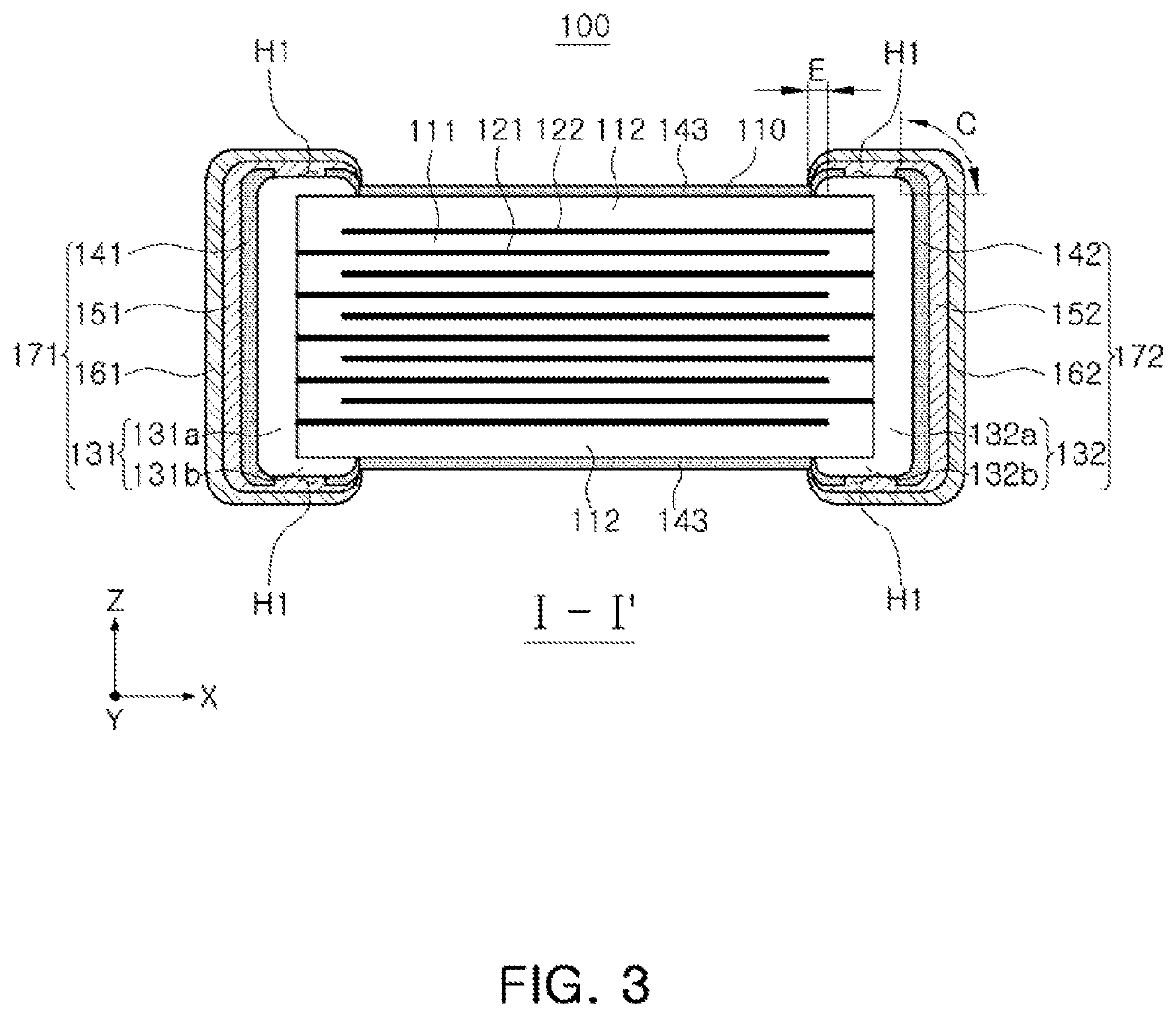

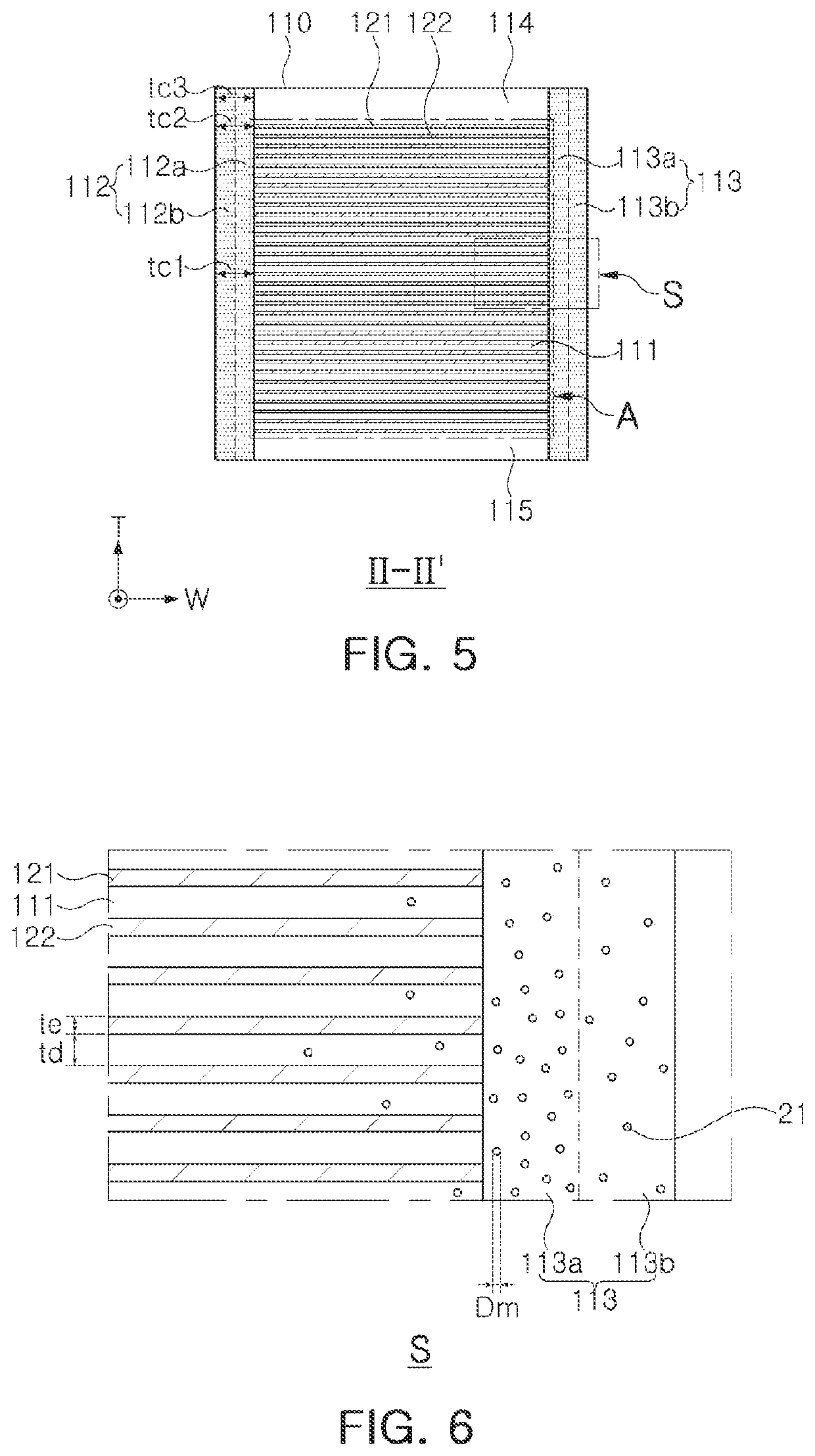

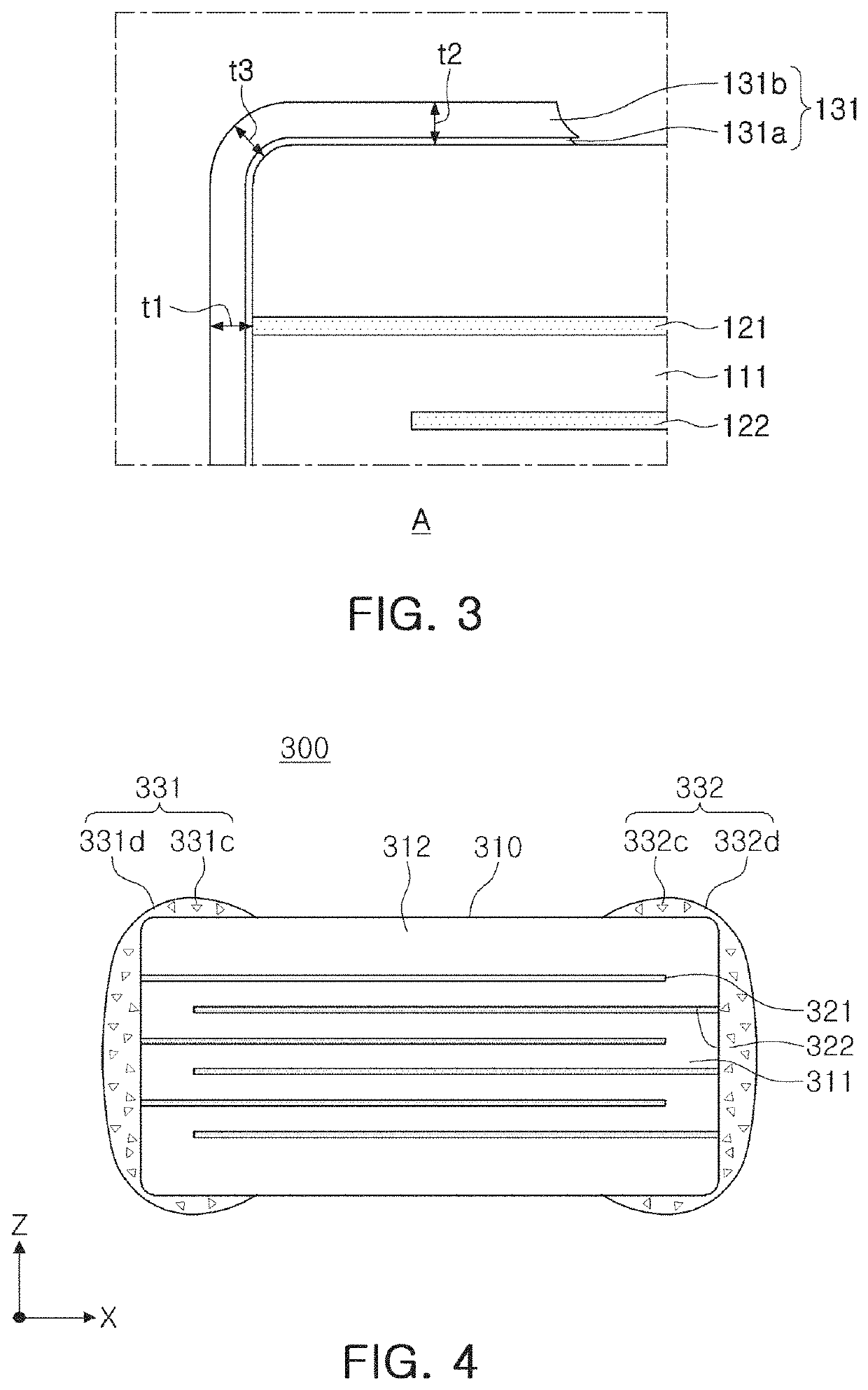

Multilayer ceramic capacitor and method of manufacturing the same

ActiveUS20190019624A1Increase in volume ratioExcellent moisture tolerance reliabilityFixed capacitor electrodesFixed capacitor dielectricMetallurgyDielectric layer

A multilayer ceramic capacitor includes a body having a dielectric layer and internal electrodes disposed to be alternately exposed to the third and fourth surfaces with the dielectric layer interposed therebetween. External electrodes include connection parts respectively formed on opposing surfaces of the body, band parts formed to extend from the connection parts to portions of side surfaces of the body, and corner parts in which the connection parts and the band parts are contiguous. A thickness of each of the external electrodes may be 50 nm to 2 μm. The external electrodes may be formed using a barrel-type sputtering method. A ratio t2 / t1 may satisfy 0.7 to 1.2, where t1 is a thickness of each connection part and t2 is a thickness of each band part. A ratio t3 / t1 may satisfy 0.7 to 1.0, where t3 is a thickness of each corner part.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

Adhesive film for semiconductor, composite sheet, and method for producing semiconductor chip using them

InactiveCN101641766AExcellent moisture resistance reliabilitySuppression of chip cracks or burrsFilm/foil adhesivesSolid-state devicesDiamineChemistry

There is provided an adhesive film for a semiconductor, which can be attached to a semiconductor wafer at low temperature and which allows semiconductor chips to be obtained at high yield from the semiconductor wafer while sufficiently inhibiting generation of chip cracks and burrs. The adhesive film for a semiconductor comprises a polyimide resin that can be obtained by reaction between a tetracarboxylic dianhydride containing 4,4'-oxydiphthalic dianhydride represented by chemical formula (I) below and a diamine containing a siloxanediamine represented by the following general formula (II) below, and that can be attached to a semiconductor wafer at 100 DEG C or below.

Owner:HITACHI CHEM CO LTD

Optical resin composition, optical resin material using the same, optical

InactiveUS20140023799A1Improve impact absorption performanceHigh transparencyLiquid crystal compositionsOptical filtersPolymer scienceAcrylate ester

The invention provides an optical resin composition being transparent, having suitable adhesion and necessary impact absorption for protection of an image display device etc., not affecting constituent materials of a image display panel, and being excellent in reliability, and an optical resin material using the same.Disclosed is an optical resin composition containing (A) a first acrylate derivative that is a compound having one polymerizable unsaturated bond in its molecule, (B) a second acrylate derivative that is a compound having two or more polymerizable unsaturated bonds in its molecule, and (C) an acrylate derivative polymer, and an optical resin material produced by curing reaction of the optical resin composition.

Owner:RESONAC CORP

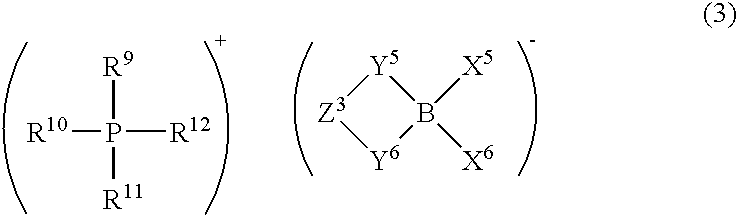

Latent catalyst

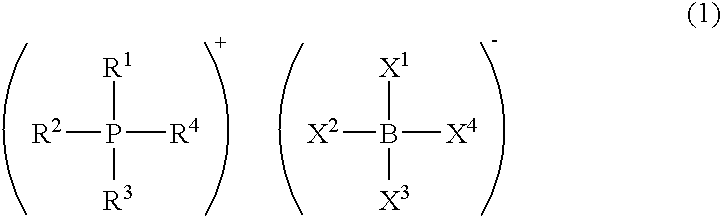

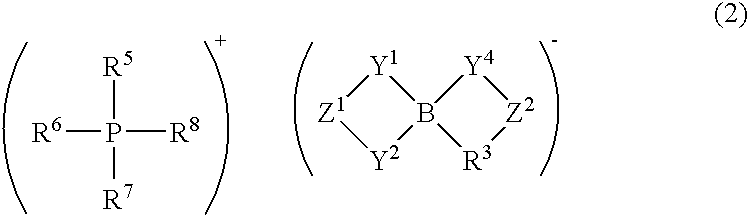

InactiveUS6946421B2Excellent curabilityImprove reliabilityOrganic-compounds/hydrides/coordination-complexes catalystsSemiconductor/solid-state device detailsEpoxyPhosphonium

This invention provides a latent catalyst having a structure of phosphonium borate consisting of a monovalent cation portion in which four specific groups are bonded to the phosphorus atom and a monovalent anion portion in which four specific groups are bonded to the boron atom, and a latent catalyst having a structure wherein the above phosphonium borate is the recurring unit and at least two of said recurring unit are connected through at least one of the four specific groups bonded to the boron atom. This invention also provides a thermo-setting resin composition comprising such a latent catalyst and an epoxy resin molding material comprising such a latent catalyst and further provides a semiconductor device in which a semiconductor is encapsulated with said epoxy resin molding material.

Owner:SUMITOMO BAKELITE CO LTD

Dicing die-bonding film

InactiveCN102911617AExcellent moisture resistance reliabilityPrevent Reflow Soldering CracksFilm/foil adhesivesSolid-state devicesProduction rateDie bonding

Provide is a dicing die-bonding film that prevents the occurrence of reflow cracking and that is capable of manufacturing a semiconductor device having excellent reliability with good productivity. The dicing die-bonding film of the present invention comprises at least: a dicing film in which a pressure-sensitive adhesive layer is provided on a support base material; and a die-bonding film that is provided on the pressure-sensitive adhesive layer, wherein the dicing die-bonding film has a water absorption rate of 1.5% by weight or less calculated from the following formula (1). [Numerical Formula 1] [(M2-M1) / M1]*100=Water absorption rate(% by weight) (1) (wherein, M1 represents the initial weight of the dicing die-bonding film, and M2 represents the weight after the dicing die-bonding film is left under an atmosphere of 85 DEG C and 85% RH for 120 hours to absorb moisture.)

Owner:NITTO DENKO CORP

Multilayer capacitor

ActiveUS20190341190A1Excellent moisture resistance reliabilityFixed capacitor electrodesFixed capacitor dielectricDielectric layerCapacitor

A multilayer capacitor includes a body including an internal electrode alternately disposed with a dielectric layer, and an external electrode disposed on the body. The external electrode includes a first electrode layer contacting the internal electrode, an oxide layer disposed on the first electrode layer and including a metal oxide and glass, and a second electrode layer disposed on the oxide layer.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

Epoxy resin composition for semiconductor encapsulation and semiconductor device using the same

InactiveCN1696169APrevent interfacial peelingImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesEpoxySemiconductor

PROBLEM TO BE SOLVED: To provide an epoxy resin composition for sealing a semiconductor excellent in fillability and void resistance, for example, in a flip chip package and capable of suppressing generation of warpage.

Owner:NITTO DENKO CORP

Epoxy resin composition for semiconductor encapsulation and semiconductor device using the same

InactiveCN100391995CPrevent interfacial peelingImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesEpoxySemiconductor

PROBLEM TO BE SOLVED: To provide an epoxy resin composition for sealing a semiconductor excellent in fillability and void resistance, for example, in a flip chip package and capable of suppressing generation of warpage.

Owner:NITTO DENKO CORP

Capacitor component

ActiveUS10910161B2Excellent moisture resistance reliabilityFixed capacitor dielectricStacked capacitorsCapacitanceElectrical connection

A capacitor component includes a humidity resistant layer formed on a portion of the external surface of a body on which an external electrode is not formed, and further includes a humidity resistant layer disposed inside the external electrode, to improve humidity resistance reliability. The capacitor component includes an opening portion formed by removing a portion of the humidity resistant layer disposed inside the external electrode to improve electrical connection.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

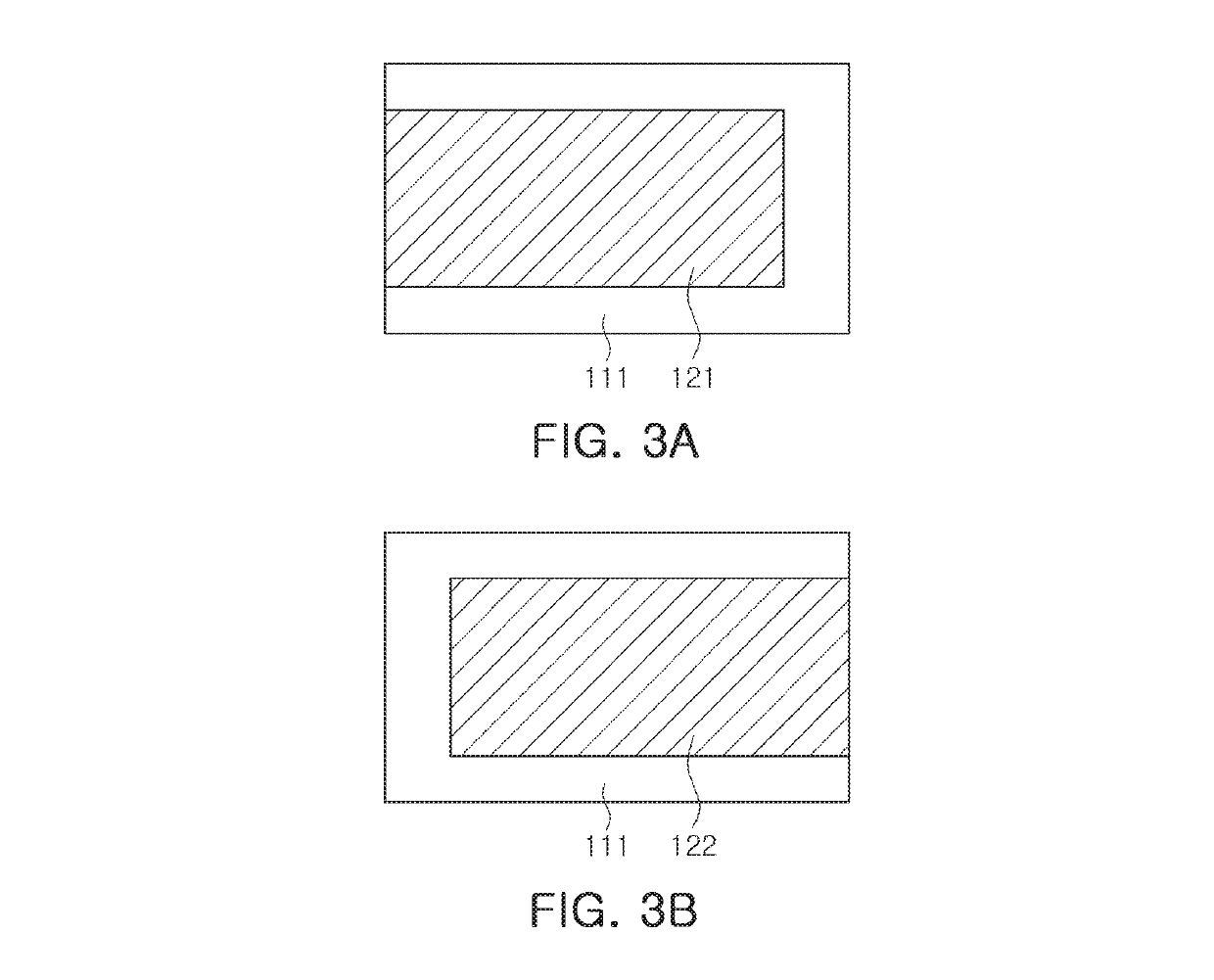

Multilayer electronic component and method of manufacturing the same

ActiveUS20220076891A1Excellent moisture resistance reliabilityExcellent internal electrode connectivityFixed capacitor electrodesFixed capacitor dielectricElectronic componentEngineering physics

A multilayer electronic component includes a body including a plurality of dielectric layers and having first and second surfaces opposing each other, third and fourth surfaces connected to the first surface and the second surface and opposing each other, and fifth and sixth surfaces connected to the first to fourth surfaces and opposing each other, a plurality of internal electrodes disposed inside of the body, exposed to the first surface and the second surface, and having one ends exposed to the third or fourth surfaces, side margin portions disposed on the first surface and the second surface, and external electrodes disposed on the third surface and the fourth surface. The side margin portions and the plurality of dielectric layers include a metal, and a total amount of the metal included in the side margin portions is greater than that of the plurality of dielectric layers.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

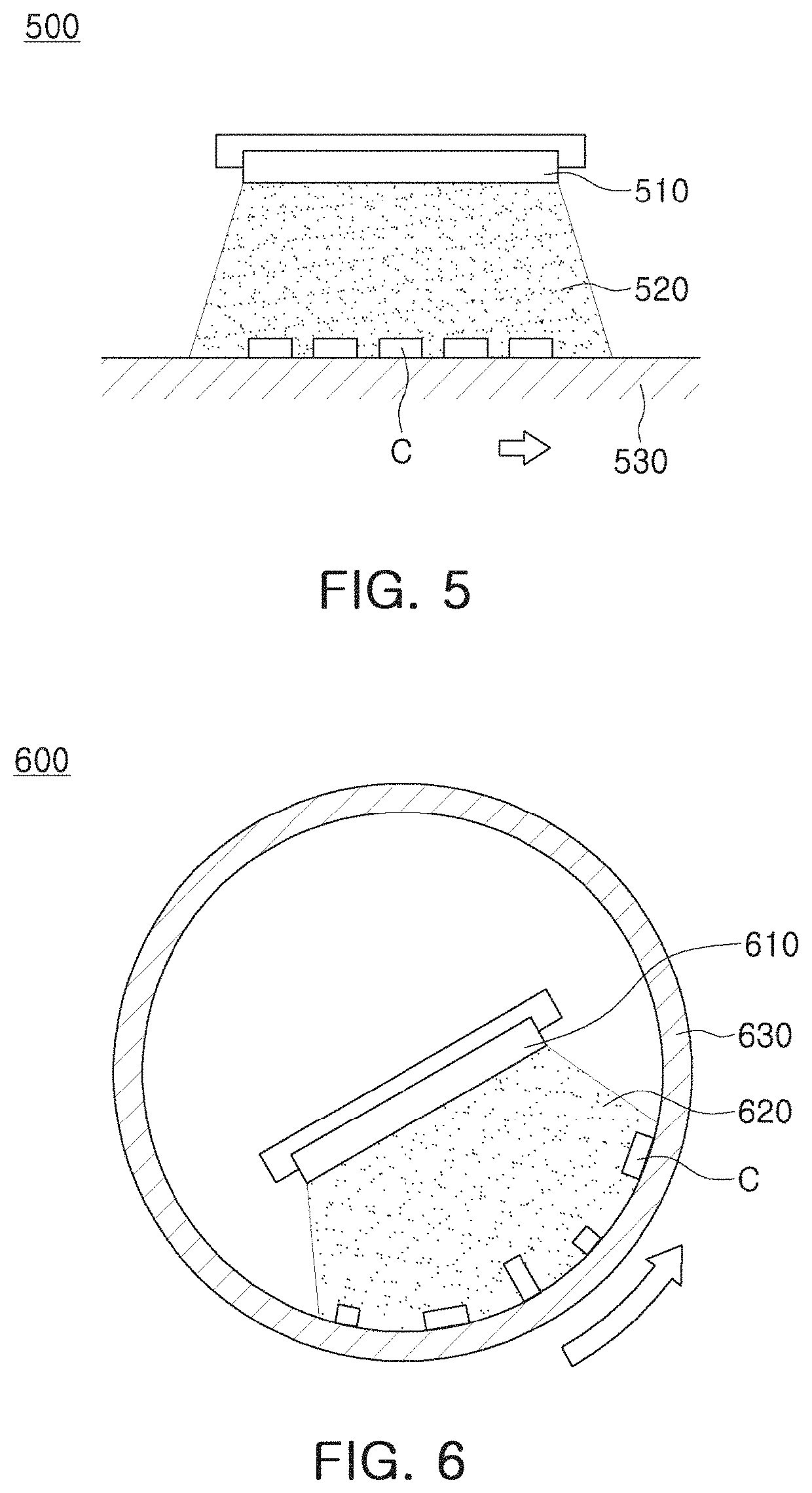

Film capacitor, and outer case for film capacitor

ActiveUS20200294717A1Workability is degradedExcellent moisture resistance reliabilityThin/thick film capacitorFixed capacitor electrodesPolymer scienceThin membrane

A film capacitor that includes a capacitor element including one or more wound or laminated metallized films, each metallized film including a resin film and a metal layer on a surface of the resin film; an outer case that houses the capacitor element; and a filling resin that fills a space between the capacitor element and the outer case, wherein the outer case is made of a resin composition containing a liquid crystal polymer and an inorganic filler.

Owner:MURATA MFG CO LTD +1

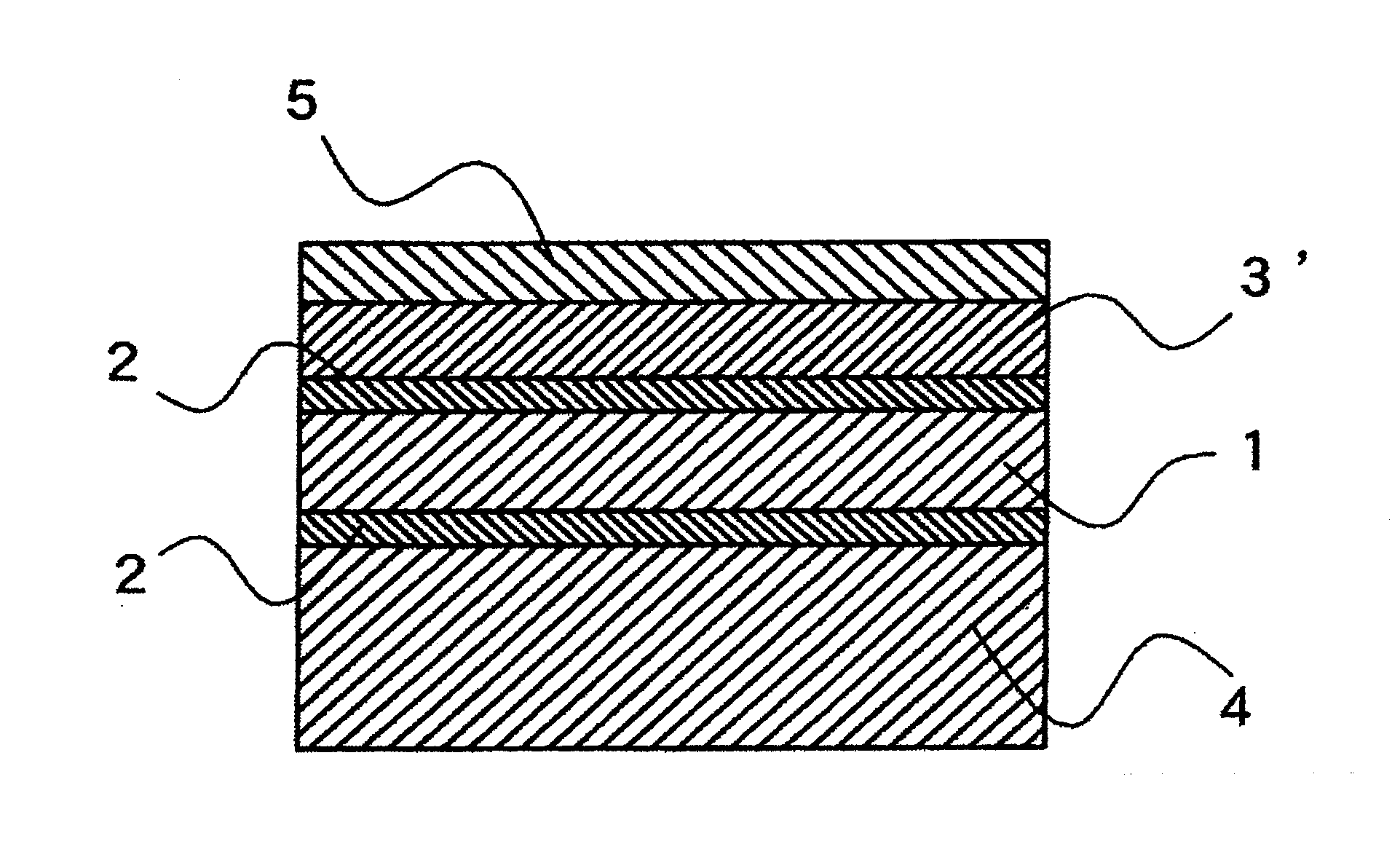

Solder resist material, wiring board using the solder resist material, and semiconductor package

InactiveUS7859110B2Warpage suppressionSmall sizeSemiconductor/solid-state device detailsSynthetic resin layered productsResistFiber

The present invention provides a solder resist material, which can suppress the warpage of a semiconductor package upon exposure to heat or impact even when used in a thin wiring board and meets a demand for size reduction in electronic devices and a higher level of integration, and a wiring board comprising the solder resist material and a semiconductor package. The solder resist material of the present invention can effectively suppress the warpage of a semiconductor package through a fiber base material-containing layer interposed between resin layers. The fiber base material-containing layer is preferably unevenly distributed in the thickness direction of the solder resist material.

Owner:SUMITOMO BAKELITE CO LTD

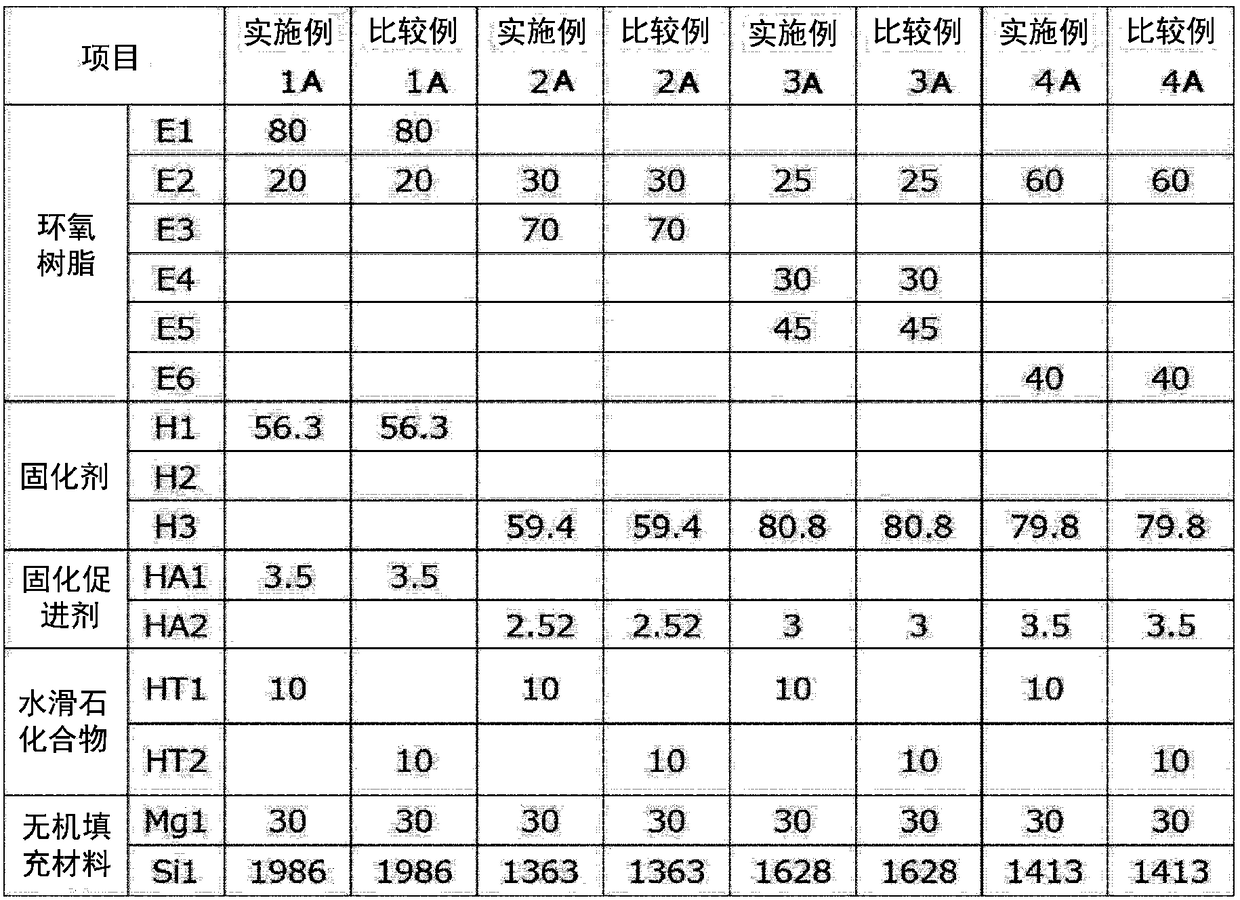

Sealing composition and semiconductor device

PendingUS20200335409A1Excellent moisture resistance reliabilitySemiconductor/solid-state device detailsSolid-state devicesDevice materialHydrotalcite

A first sealing composition includes an epoxy resin, a curing agent, an inorganic filler, and an unbaked hydrotalcite compound having a mole ratio of Mg ion to Al ion (Mg / Al) of 2.4 or more. A second sealing composition includes an epoxy resin, a curing agent, a hydrotalcite compound represented by Formula (1): Mg1-xAlx(OH)2(CO3)x / 2.mH2O, in which each of x and m independently represents a positive number, and a magnesium-containing compound that is different from the hydrotalcite compound. A third sealing composition includes an epoxy resin, a curing agent, a hydrotalcite compound represented by Formula (I), and a magnesium oxide, and a content of the magnesium oxide is from 1 part by mass to 50 parts by mass parts with respect to 100 mass parts of the epoxy resin.

Owner:RESONAC CORP

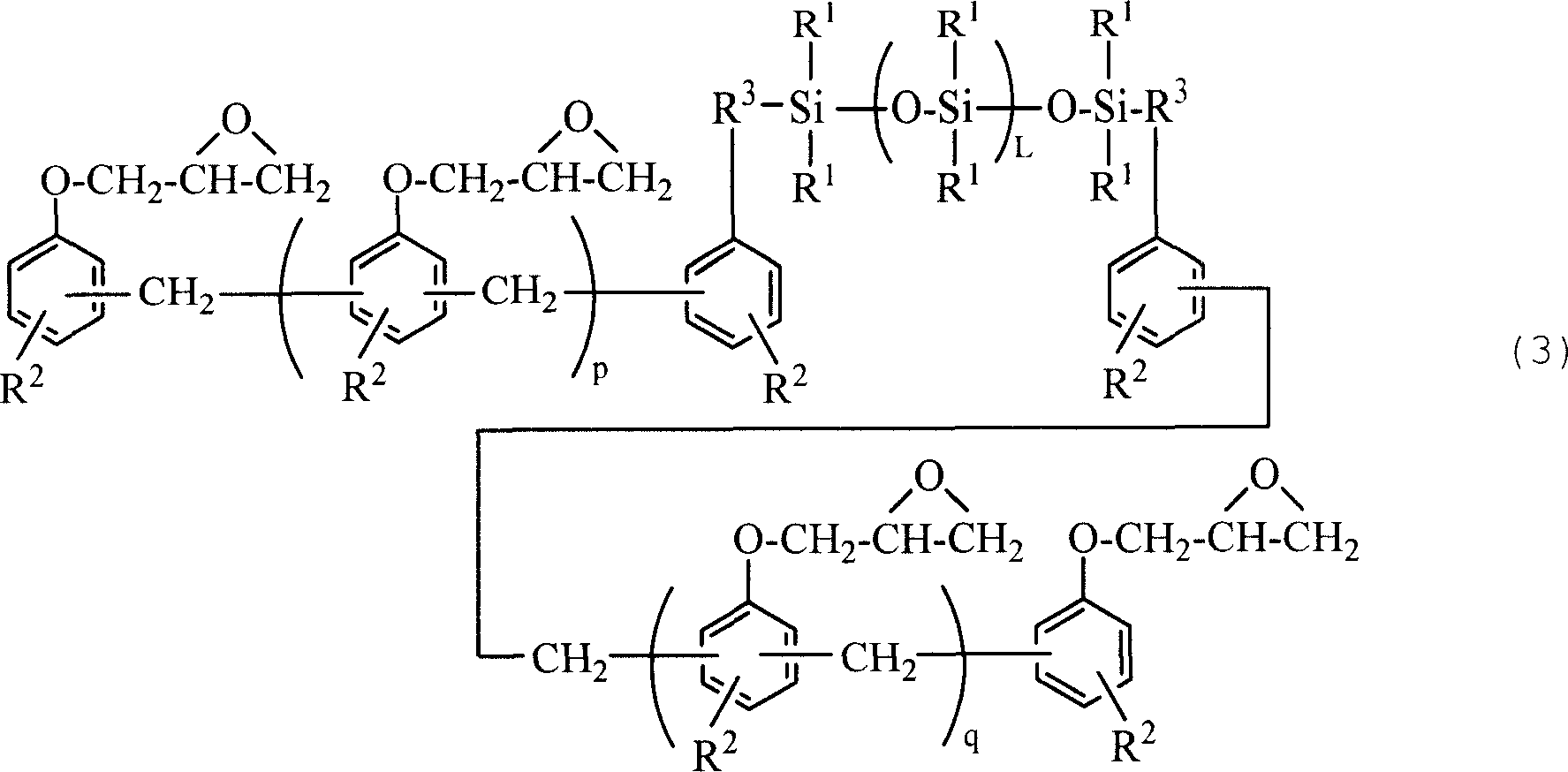

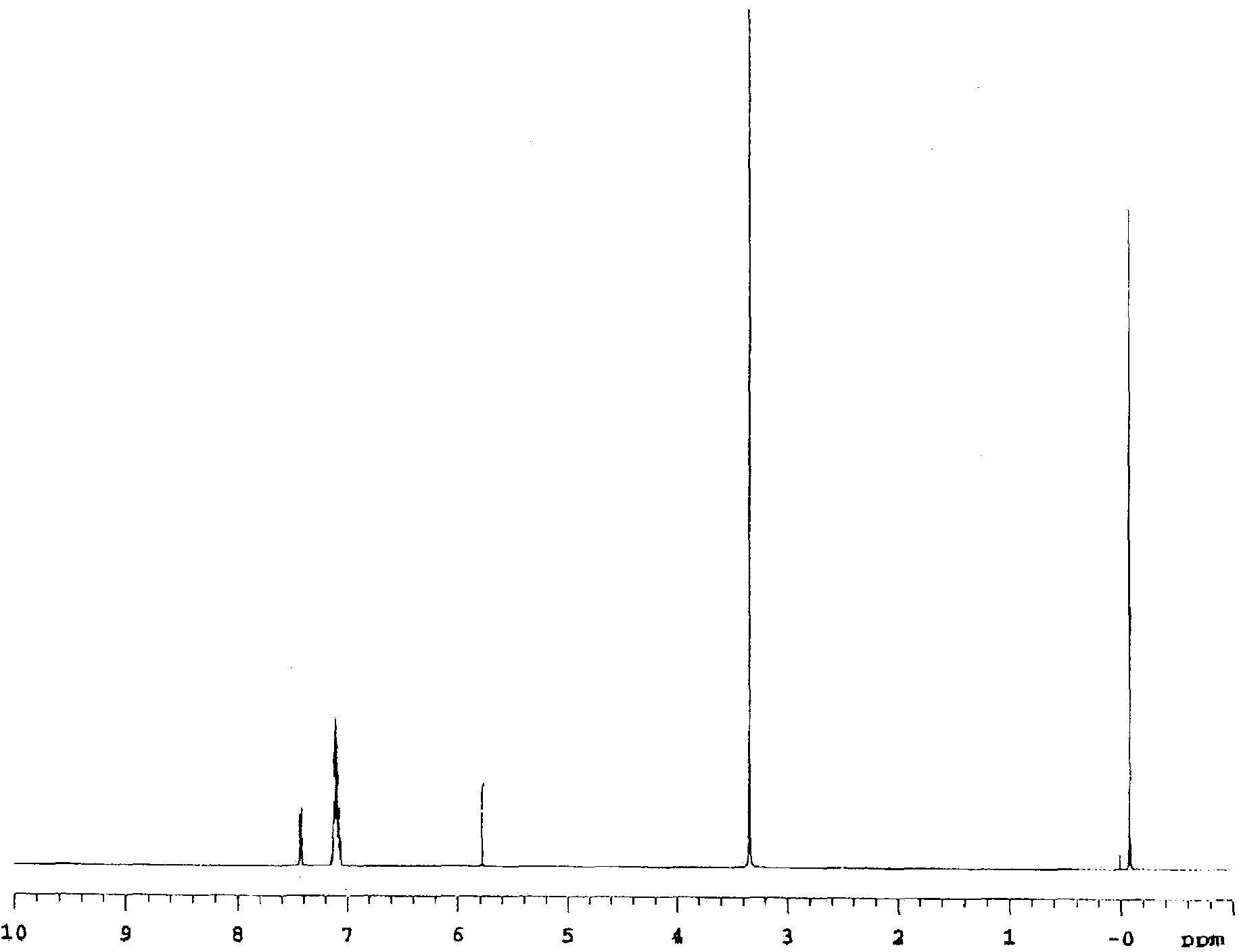

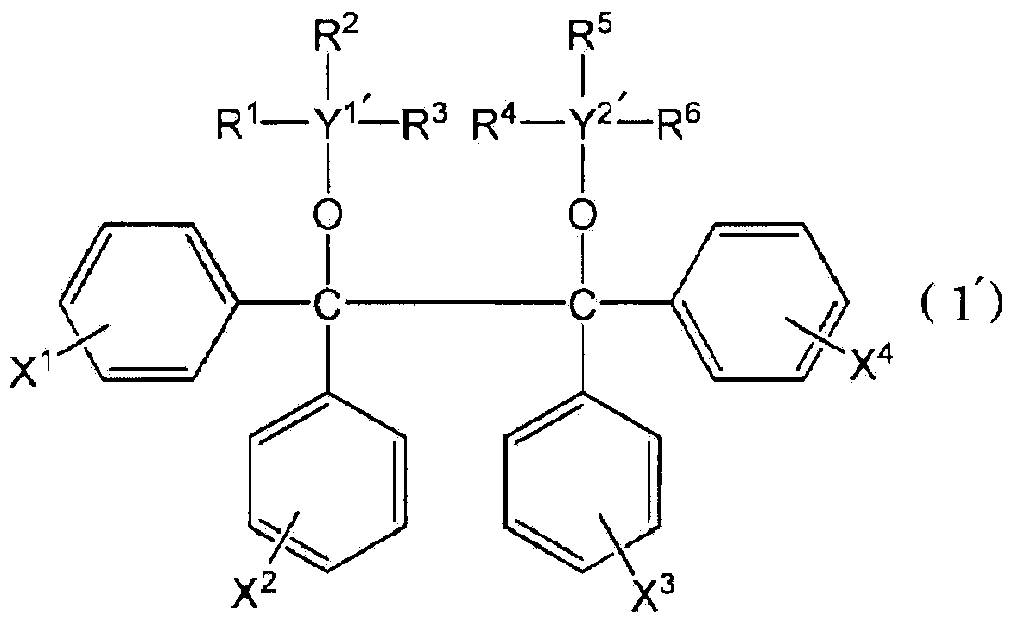

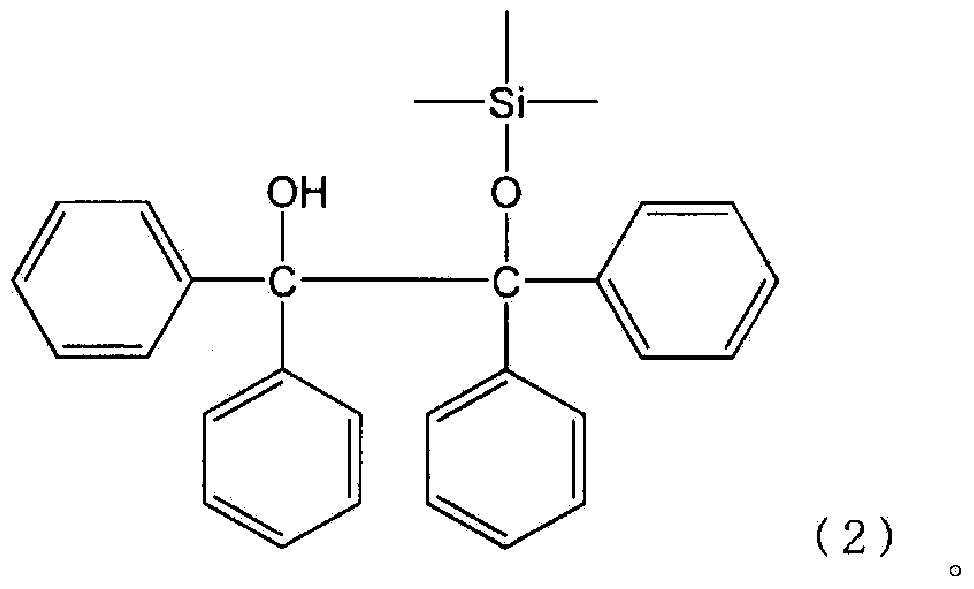

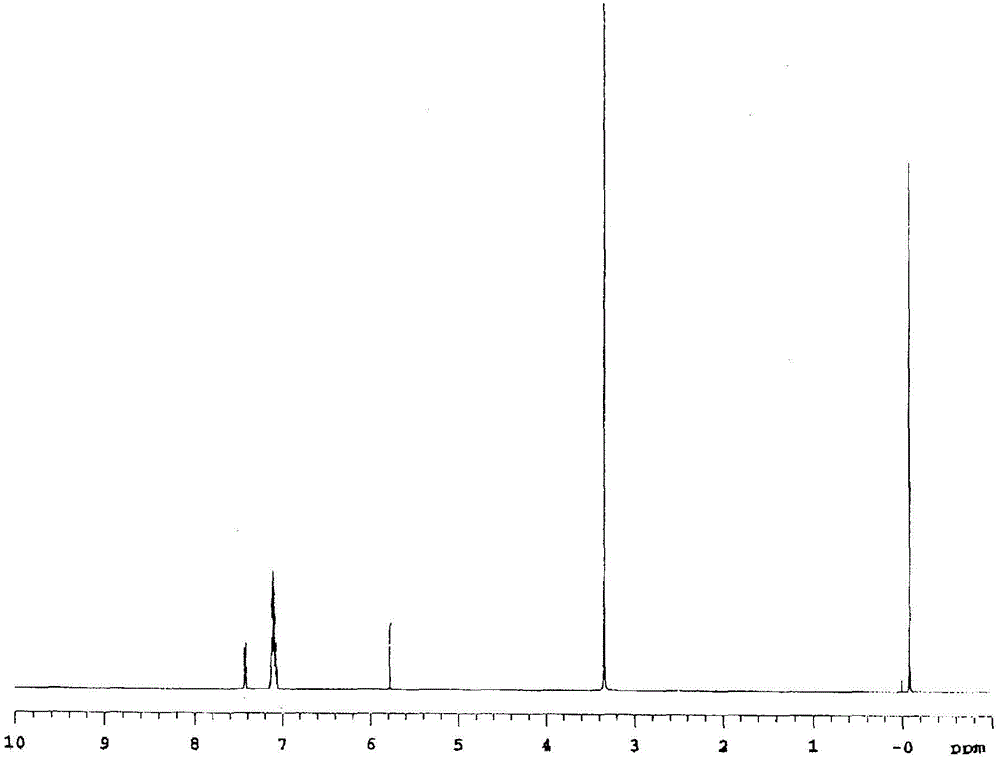

Novel thermal radical generator, method for producing the same, liquid crystal sealing agent, and liquid crystal display cell

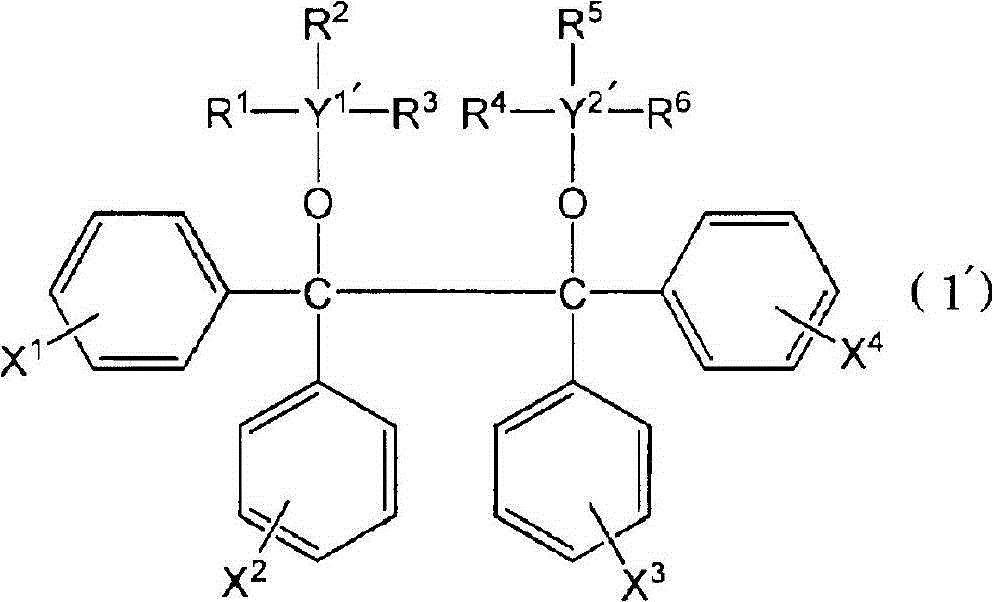

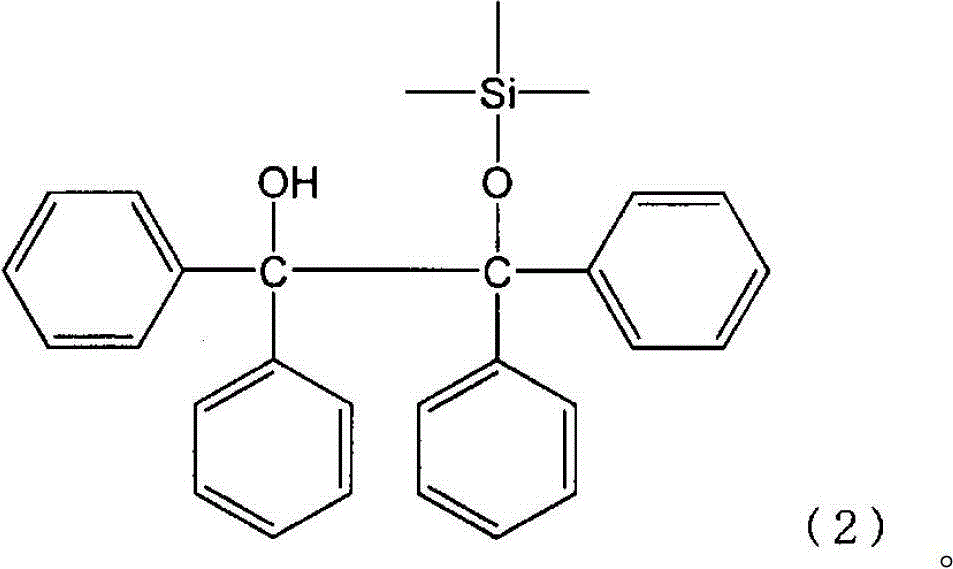

InactiveCN104031082AGood physical propertiesImproved shape stabilityGroup 4/14 element organic compoundsHydrogenLiquid-crystal display

Provided are a tetraphenylethane derivative represented by general formula (1), a method for producing the same, the use of the tetraphenylethane derivative as a radical generator, a liquid crystal sealing agent containing the tetraphenylethane derivative, and a thermosetting liquid crystal sealing agent for the one-drop fill process in particular. The radical generator does not foam and has excellent thermal radical generating performance, and, when used with a liquid crystal sealing agent, the resulting liquid crystal sealing agent does not contaminate liquid crystals, has a long pot life, and performs well in terms of forming a seal and forming a cell gap. (1) Y1 and Y2 in general formula (1) are each independently a hydrogen atom, phenyl, or silicon atom, R1 through R6 are each independently a hydrogen atom or C1-4 linear or branched alkyl group, and X1 through X4 are each independently a hydrogen atom, methyl group, ethyl group, methoxy group, ethoxy group, phenoxy group, or halogen group. R1 through R3 or R4 through R6 that bond with Y1 or Y2, respectively, are not present when Y1 or Y2 is a hydrogen atom, and Y1 and Y2 are not both hydrogen atoms.

Owner:NIPPON KAYAKU CO LTD

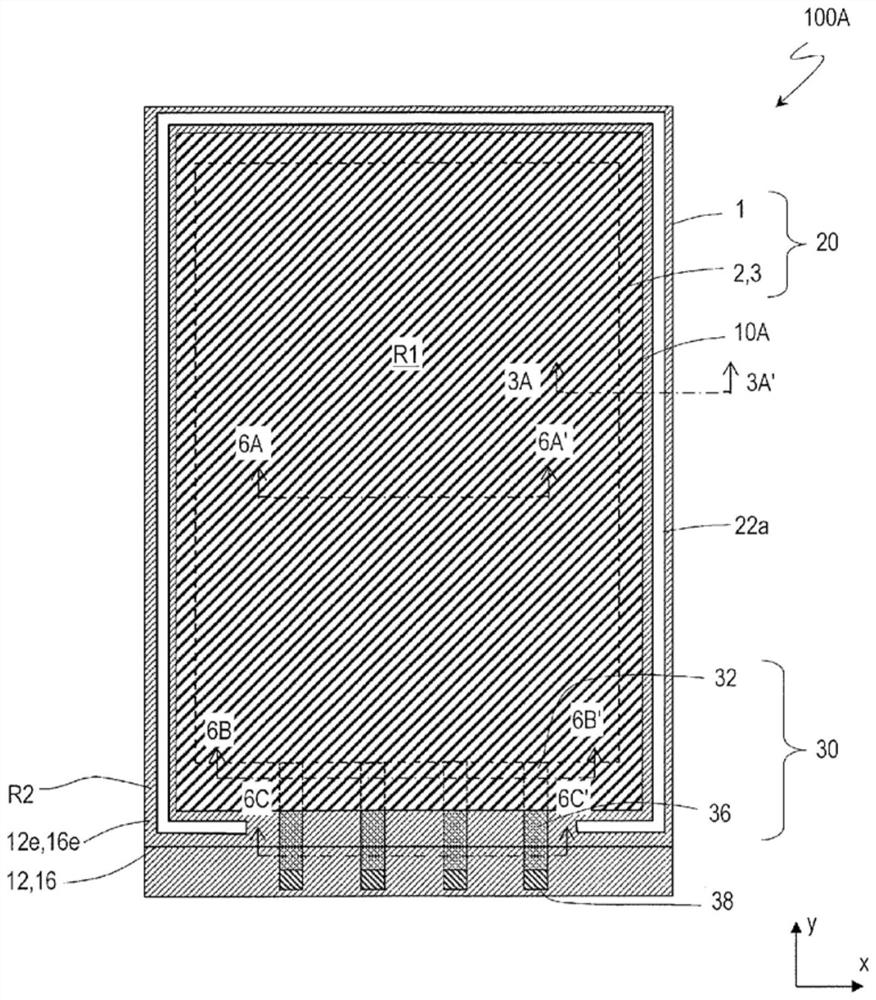

Organic el device and production method therefor

ActiveCN111937490AExcellent moisture resistance reliabilityElectroluminescent light sourcesSolid-state devicesOrganic devicesHemt circuits

Owner:SAKAI DISPLAY PROD

Novel thermal radical generator, method for producing same, liquid crystal sealing agent, and liquid crystal display unit

ActiveCN102612521BGood physical propertiesImproved shape stabilityGroup 4/14 element organic compoundsOther chemical processesHydrogenHalogen

Provided are a tetraphenylethane derivative represented by general formula (1), a method for producing the same, the use of the tetraphenylethane derivative as a radical generator, a liquid crystal sealing agent containing the tetraphenylethane derivative, and a thermosetting liquid crystal sealing agent for the one-drop fill process in particular. The radical generator does not foam and has excellent thermal radical generating performance, and, when used with a liquid crystal sealing agent, the resulting liquid crystal sealing agent does not contaminate liquid crystals, has a long pot life, and performs well in terms of forming a seal and forming a cell gap. (1) Y1 and Y2 in general formula (1) are each independently a hydrogen atom, phenyl, or silicon atom, R1 through R6 are each independently a hydrogen atom or C1-4 linear or branched alkyl group, and X1 through X4 are each independently a hydrogen atom, methyl group, ethyl group, methoxy group, ethoxy group, phenoxy group, or halogen group. R1 through R3 or R4 through R6 that bond with Y1 or Y2, respectively, are not present when Y1 or Y2 is a hydrogen atom, and Y1 and Y2 are not both hydrogen atoms.

Owner:NIPPON KAYAKU CO LTD

Sealing composition and semiconductor device

ActiveCN109219637AExcellent moisture resistance reliabilityImprove thermal conductivitySemiconductor/solid-state device detailsSolid-state devicesDevice materialHydrotalcite

A first sealing composition according to the present invention contains an epoxy resin, a curing agent, an inorganic filler and an uncalcined hydrotalcite compound having a molar ratio of Mg ions to Al ions (Mg / Al) of 2.4 or more. A second sealing composition according to the present invention contains an epoxy resin, a curing agent, a hydrotalcite compound represented by general formula (1) Mg1-xAlx(OH)2(CO3)x / 2mH2O (wherein each of x and m independently represents a positive number), and a magnesium-containing compound that is different from the hydrotalcite compound. A third sealing composition according to the present invention contains an epoxy resin, a curing agent, a hydrotalcite compound represented by general formula (1), and magnesium oxide; and the content of the magnesium oxideis from 1 part by mass to 50 parts by mass relative to 100 parts by mass of the epoxy resin.

Owner:RESONAC CORP

Multilayer ceramic capacitor

ActiveUS11011313B2Excellent moisture resistance reliabilityEffective volume ratioFixed capacitor dielectricStacked capacitorsSputteringCeramic capacitor

A multilayer ceramic capacitor includes a body having a dielectric layer and internal electrodes disposed to be alternately exposed to the third and fourth surfaces with the dielectric layer interposed therebetween. External electrodes include connection parts respectively formed on opposing surfaces of the body, band parts formed to extend from the connection parts to portions of side surfaces of the body, and corner parts in which the connection parts and the band parts are contiguous. A thickness of each of the external electrodes may be 50 nm to 2 μm. The external electrodes may be formed using a barrel-type sputtering method. A ratio t2 / t1 may satisfy 0.7 to 1.2, where t1 is a thickness of each connection part and t2 is a thickness of each band part. A ratio t3 / t1 may satisfy 0.7 to 1.0, where t3 is a thickness of each corner part.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

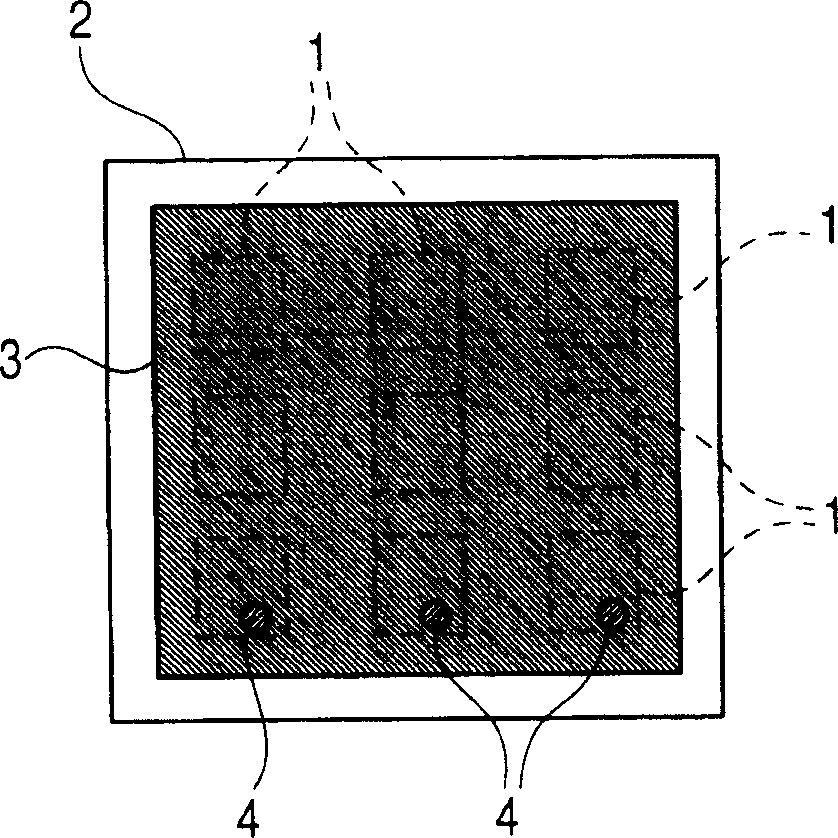

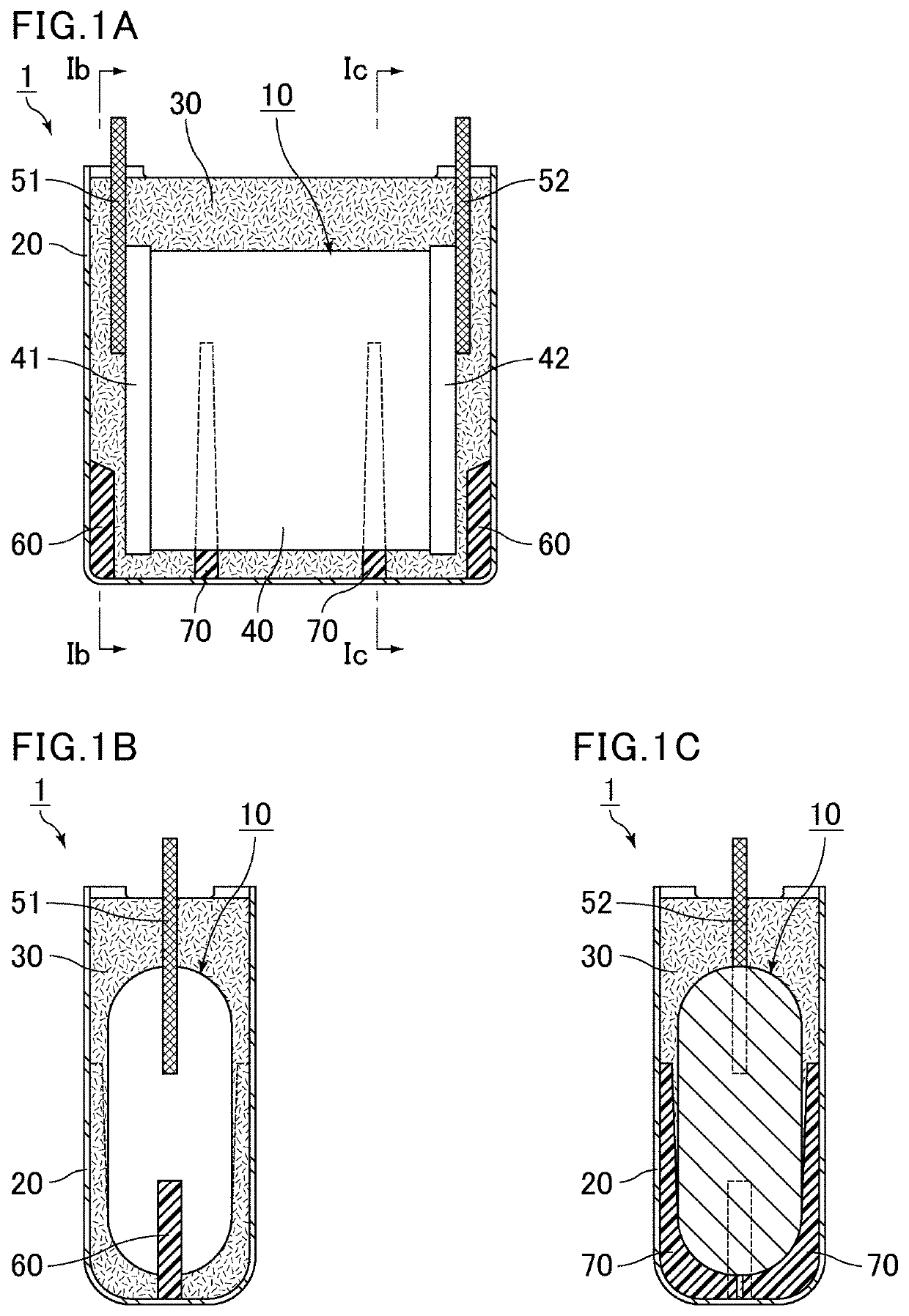

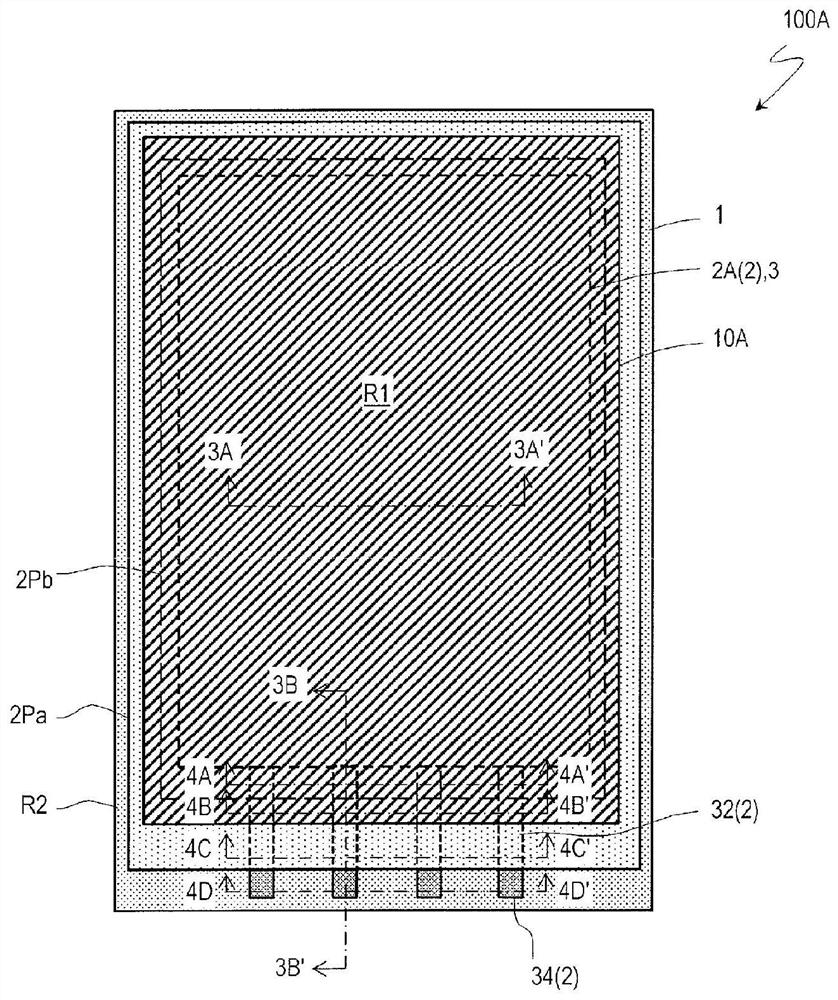

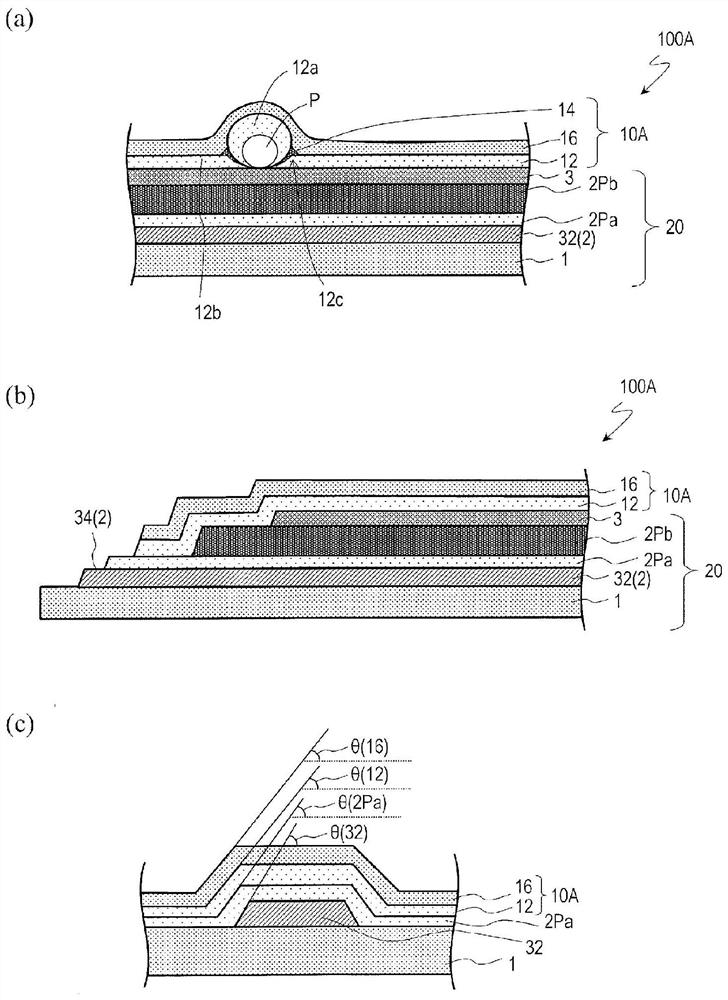

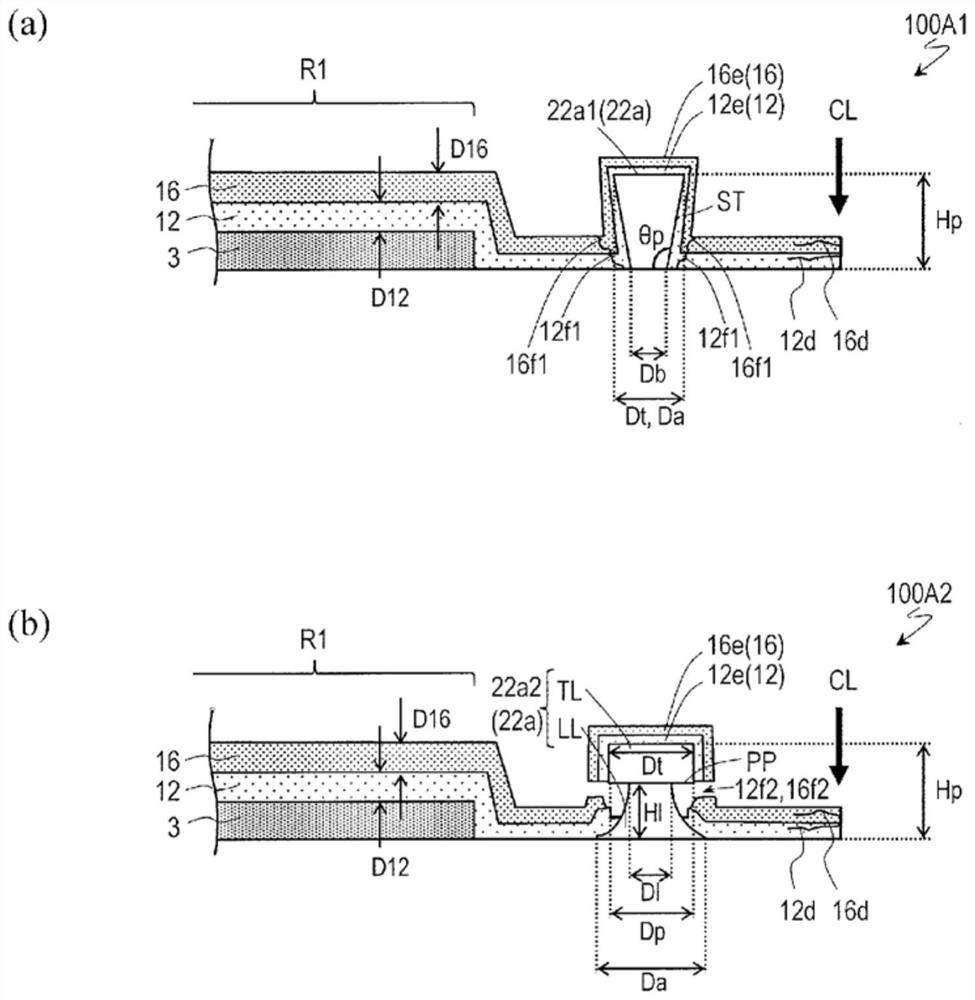

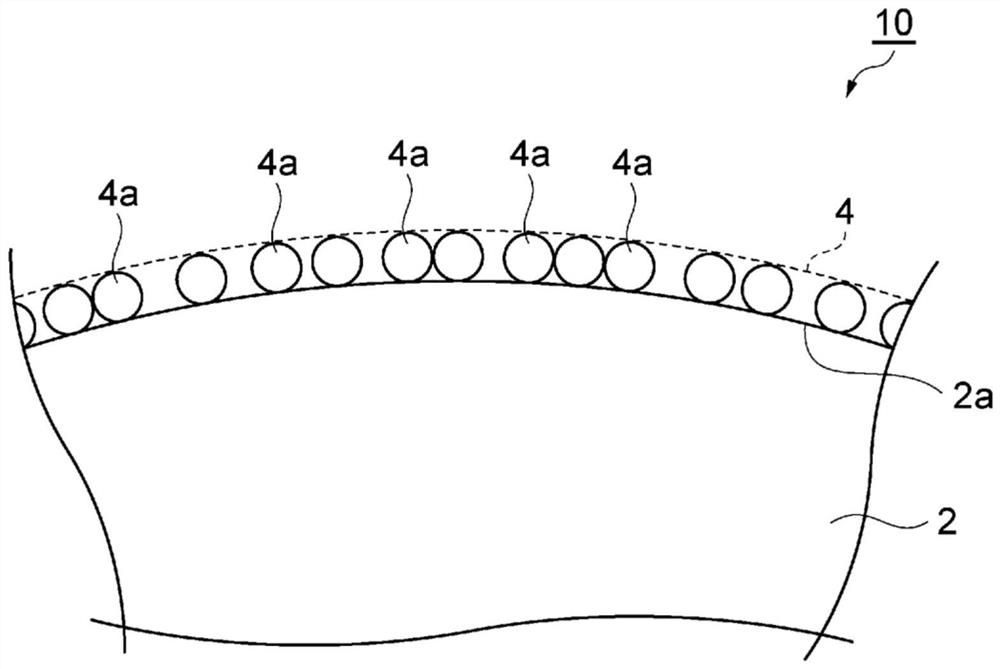

Organic el device and production method therefor

InactiveCN111788863AExcellent moisture resistance reliabilityElectroluminescent light sourcesSolid-state devicesThin membraneMaterials science

An organic EL device (100A) comprises a peripheral region (R2) and an active region (R1) containing a plurality of organic EL elements (3), and includes an element substrate (20) having a plurality oforganic EL elements, and a thin film seal structure (10A) covering the plurality of organic EL elements. The thin film seal structure comprises a first inorganic barrier layer (12), an organic barrier layer (14) in contact with the upper surface of the first inorganic barrier layer, and a second inorganic barrier layer (16) in contact with the upper surface of the first inorganic barrier layer and the upper surface of the organic barrier layer. The peripheral region comprises a first protruding structure (22a) containing a section extending along at least one edge of the active region, and anextending section (12e) of the first inorganic barrier layer extending over the first protruding structure. The first protruding structure includes a first part and second part. The first part is closer to the top portion of the first protruding structure than the second part and, as observed from the normal direction to the base board, a cross section parallel to the substrate surface of the first part includes a part that does not overlap with the cross section parallel to the substrate surface of the second part.

Owner:SAKAI DISPLAY PROD

Multilayer capacitor

ActiveUS10861651B2Excellent moisture resistance reliabilityFixed capacitor electrodesFixed capacitor dielectricElectrode ContactDielectric layer

A multilayer capacitor includes a body including an internal electrode alternately disposed with a dielectric layer, and an external electrode disposed on the body. The external electrode includes a first electrode layer contacting the internal electrode, an oxide layer disposed on the first electrode layer and including a metal oxide and glass, and a second electrode layer disposed on the oxide layer.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com