Patents

Literature

31 results about "Threshold voltage degradation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

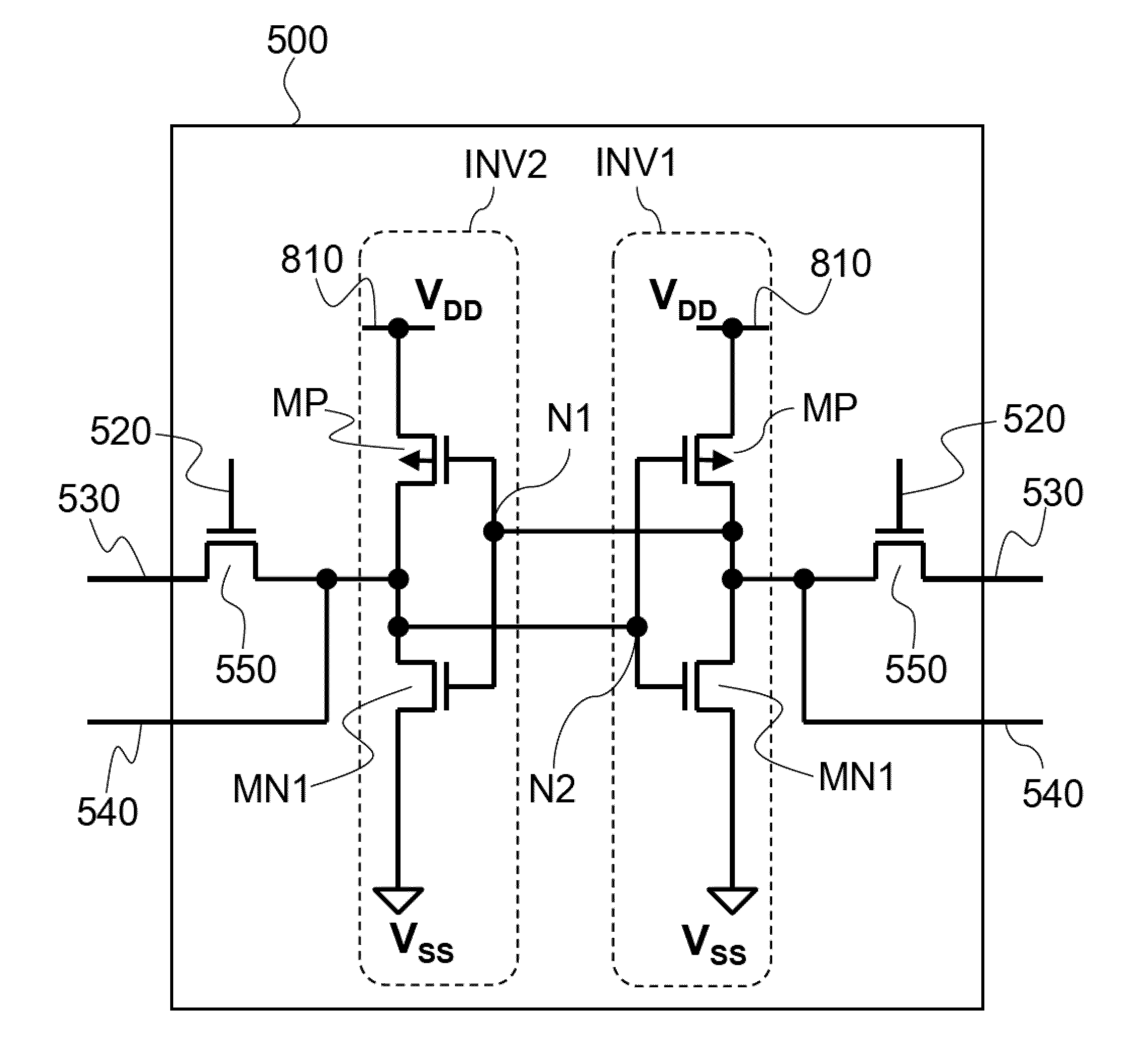

Semiconductor device

ActiveUS20160118106A1Easy to manufactureDigital data processing detailsDigital storageLow voltageEngineering

It is an object of the present invention to provide a device which can be easily manufactured and obtain a ground state of an arbitrary Ising model. A semiconductor device includes a first memory cell and a second memory cell that interacts with the first memory cell, in which storage content of the first memory cell and the second memory cell is stochastically inverted. The storage content is stochastically inverted by dropping threshold voltages of the first memory cell and the second memory cell. The threshold voltages of the first and second memory cells are dropping by controlling substrate biases, power voltages, or trip points of the first and second memory cells.

Owner:HITACHI LTD

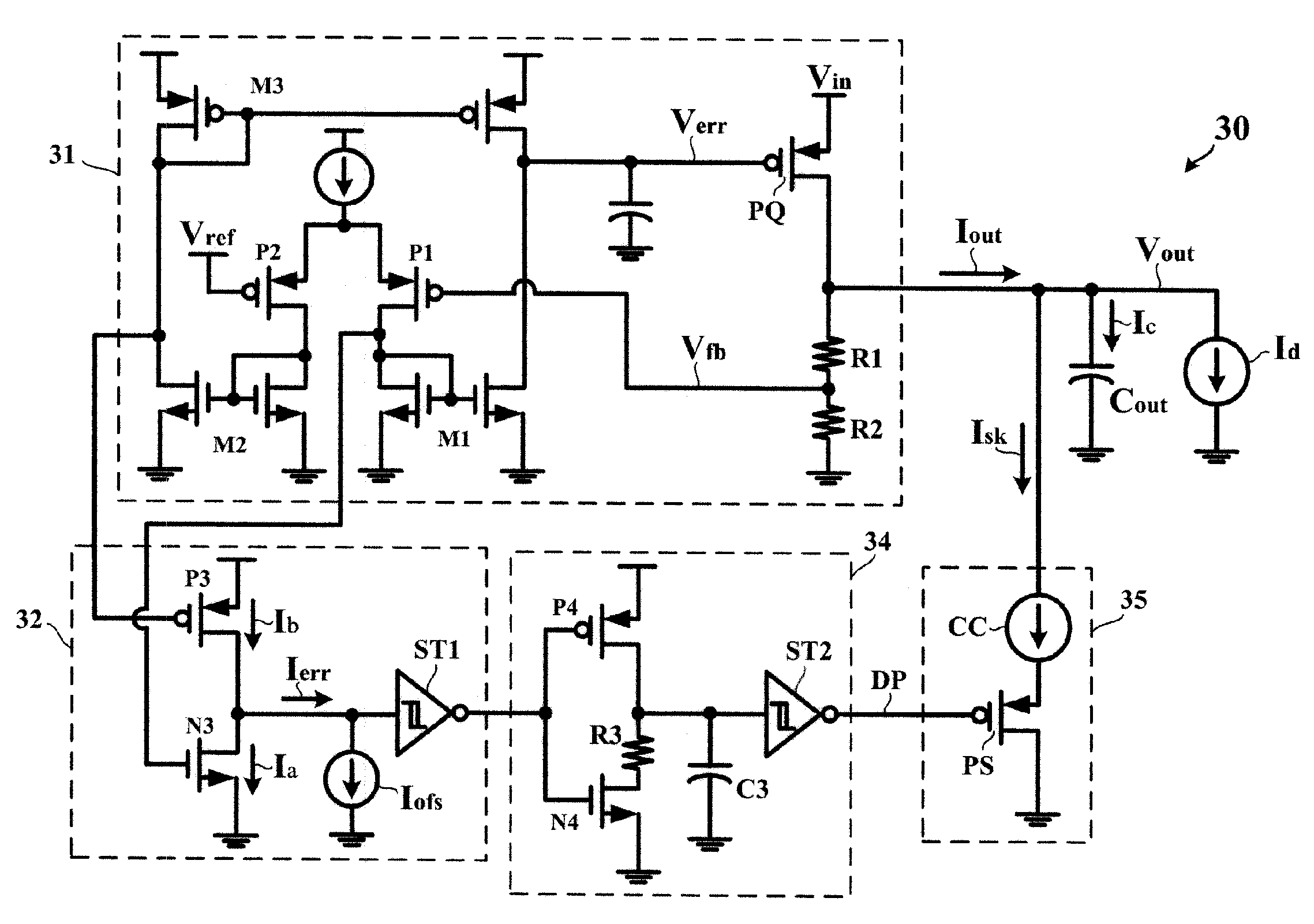

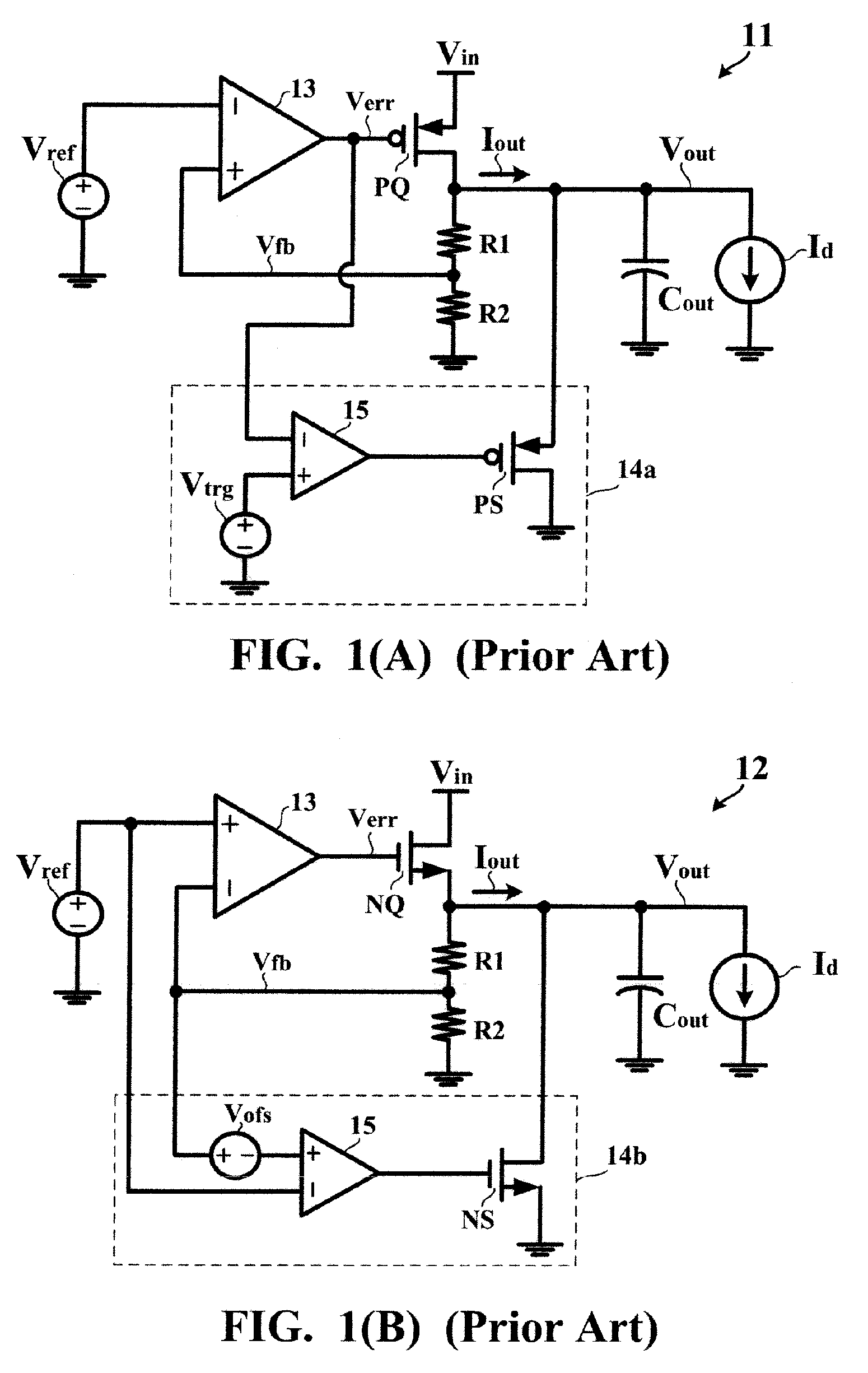

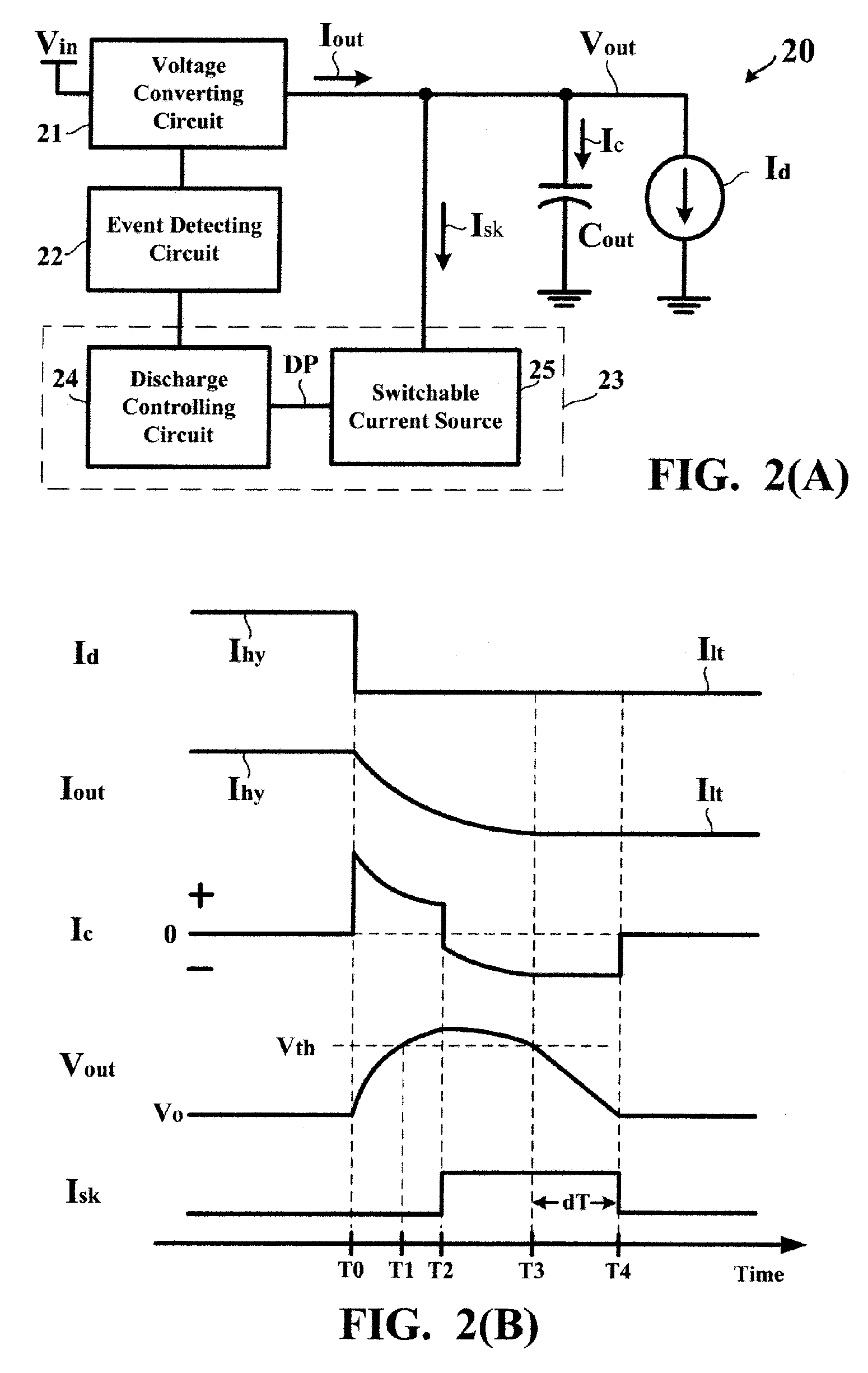

Voltage regulator with prevention from overvoltage at load transients

InactiveUS20070030054A1Stable output voltageElectric variable regulationOvervoltageVoltage regulation

A voltage converting circuit has an output terminal for supplying an output current at an output voltage to a load. In response to a transient of the load, a current sinking circuit allows a current source to provide a sink current flowing from the output terminal of the voltage converting circuit into a ground potential. The sink current is finite and stable. When the output voltage decreases below a threshold voltage, the current sinking circuit allows the current source to keep providing the finite and stable sink current for an extension time, causing the output voltage to decrease from the threshold voltage to a regulated value.

Owner:GLOBAL MIXED MODE TECH

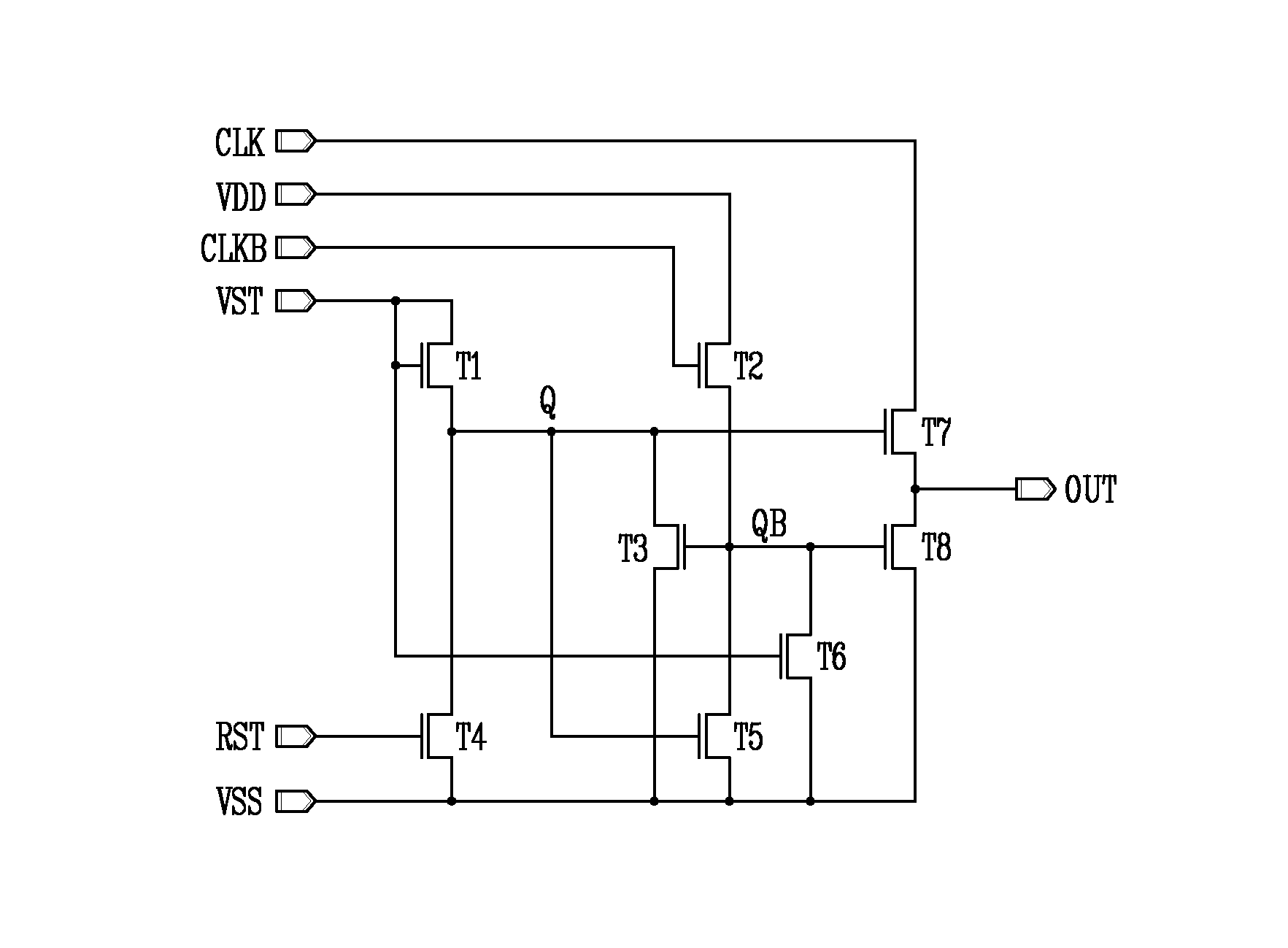

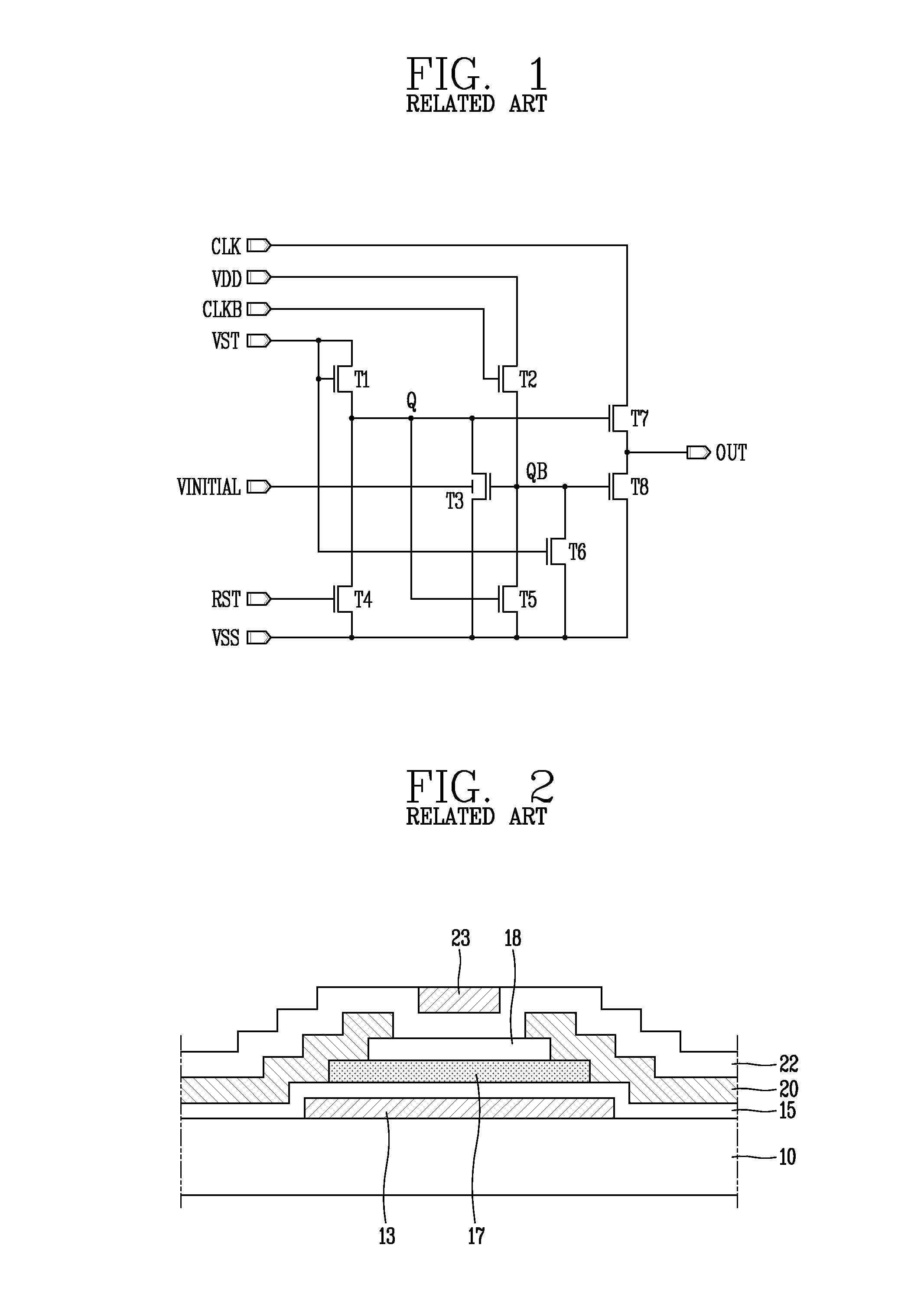

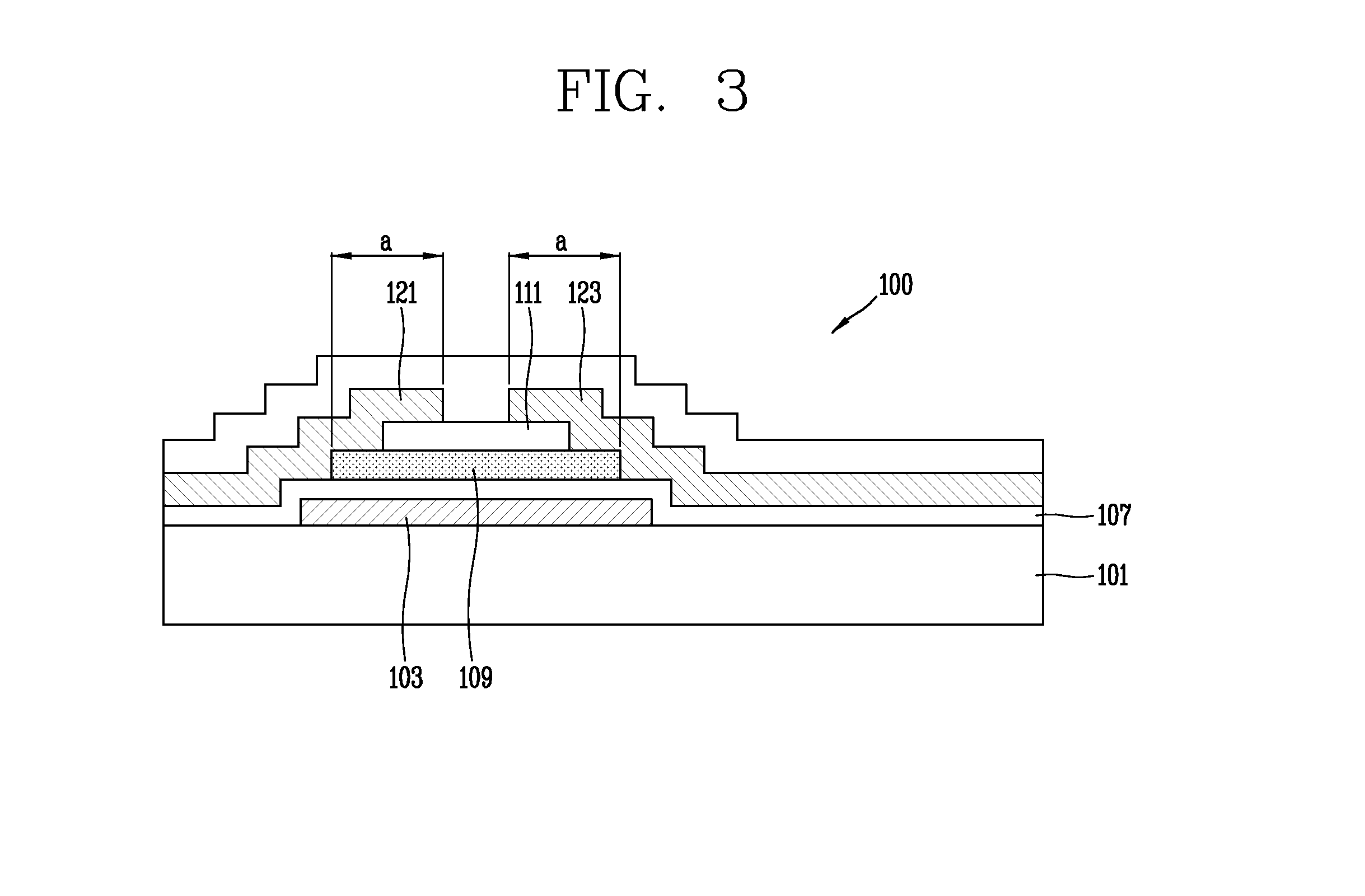

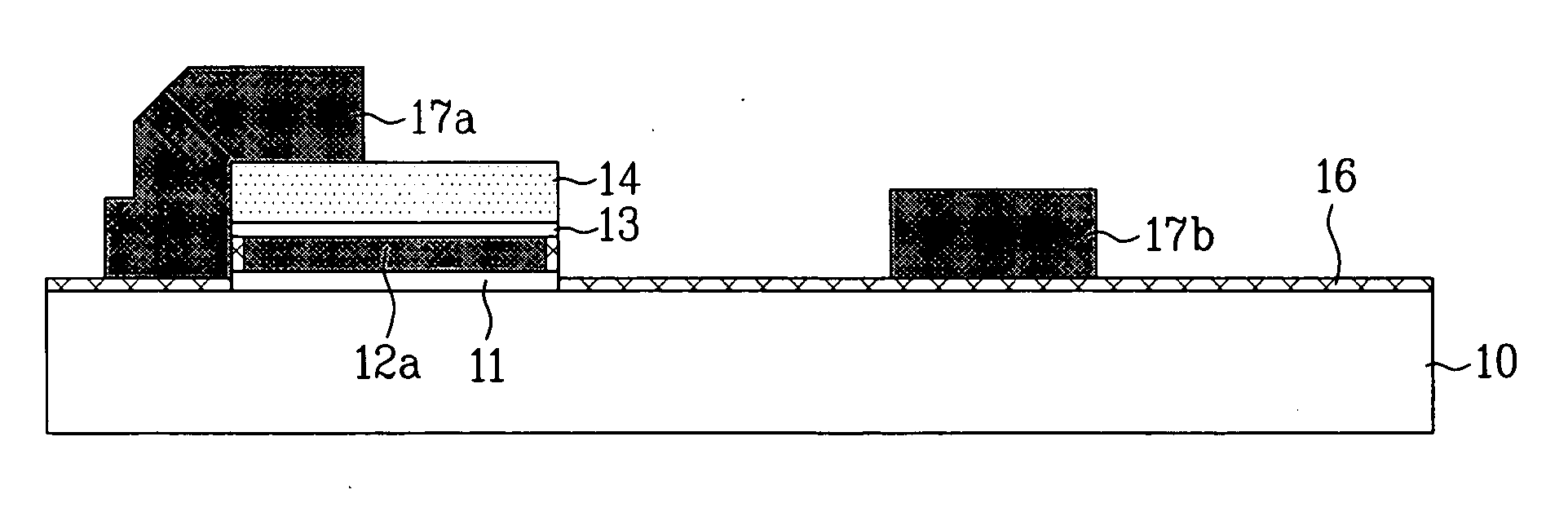

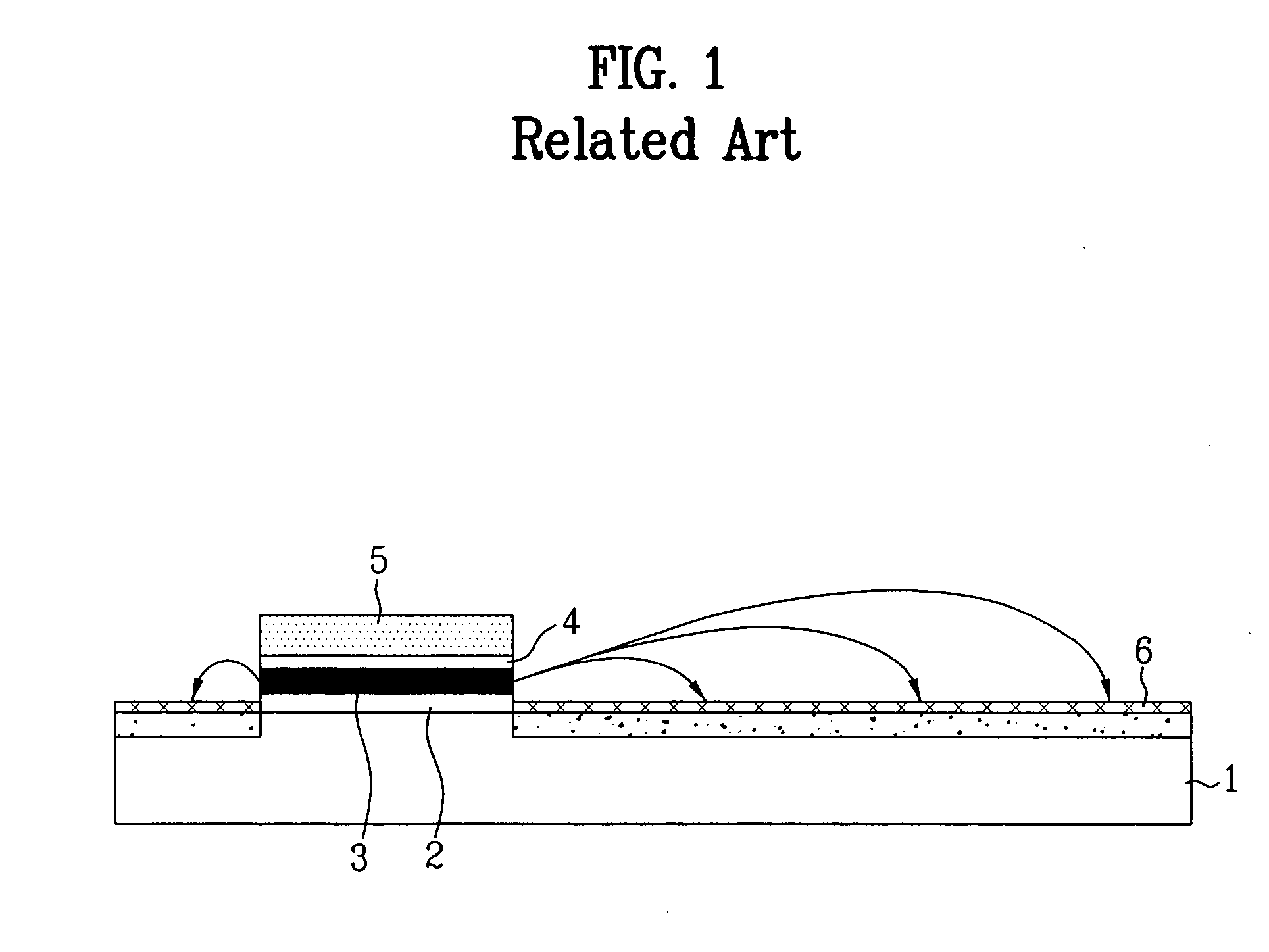

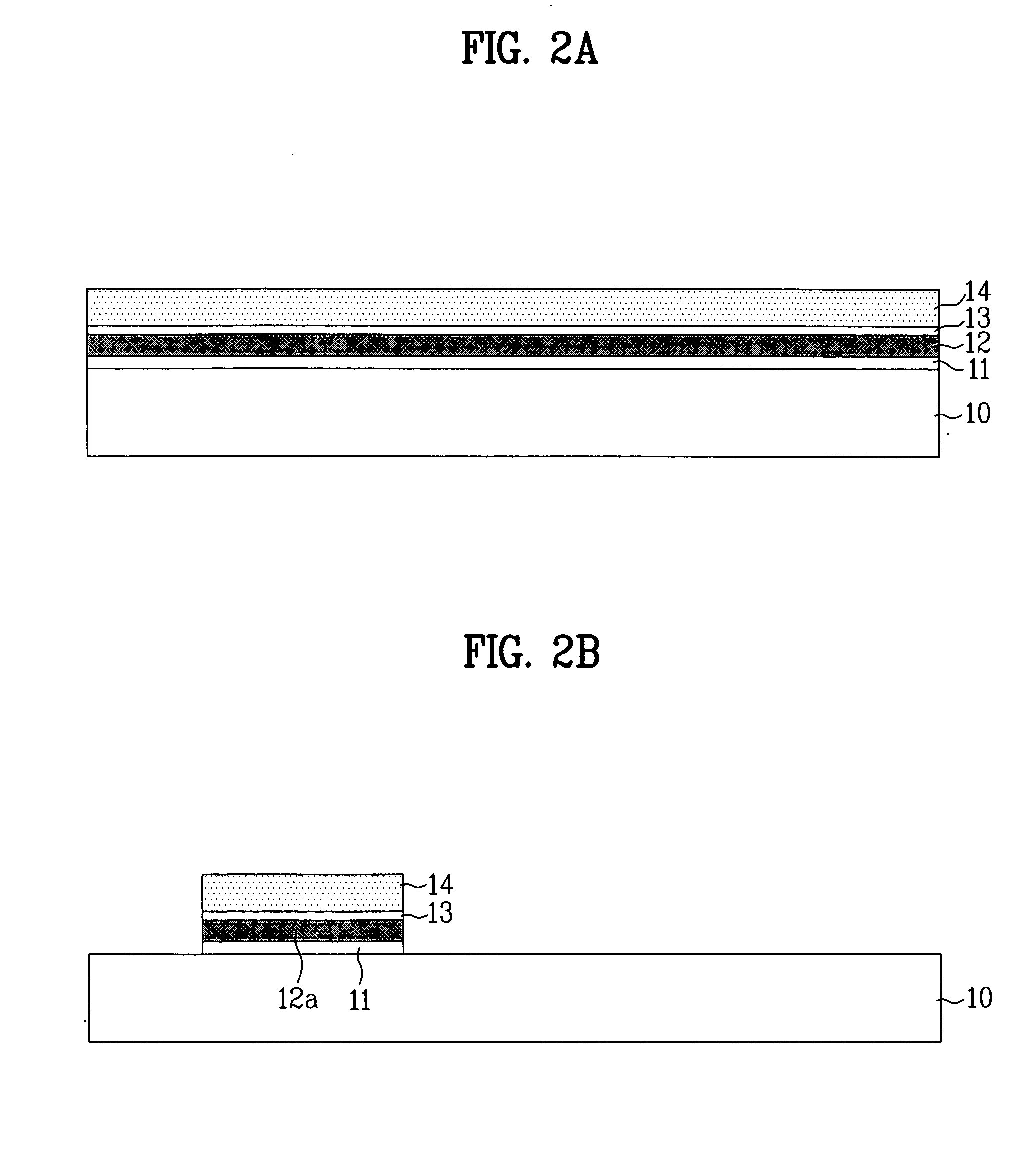

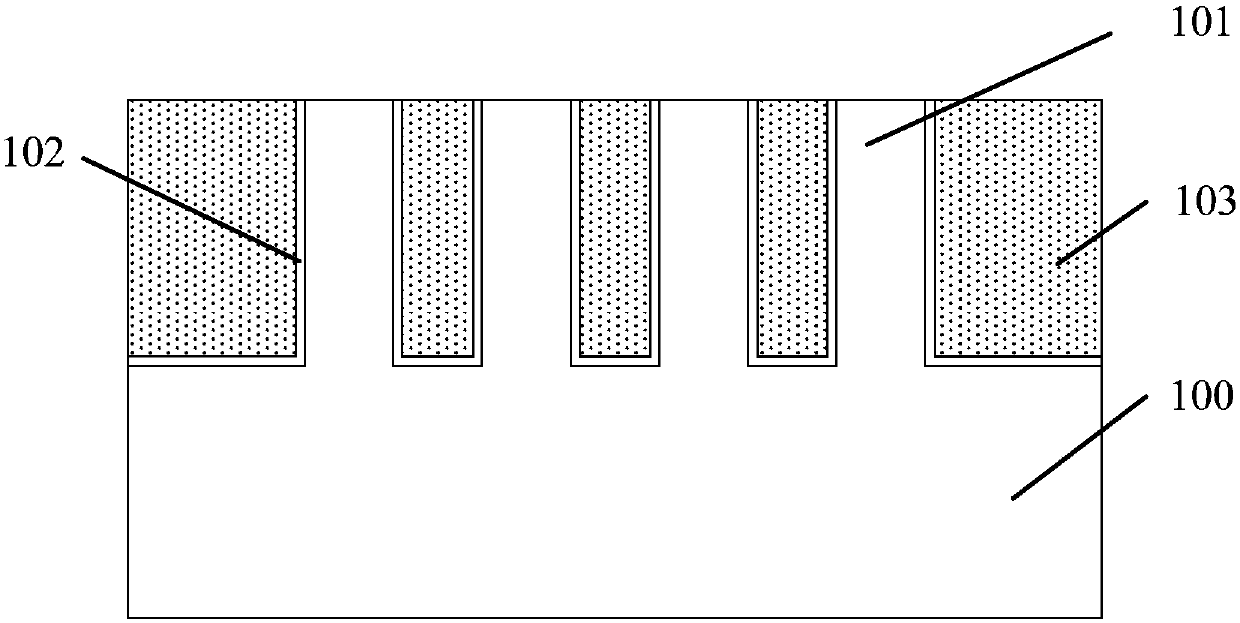

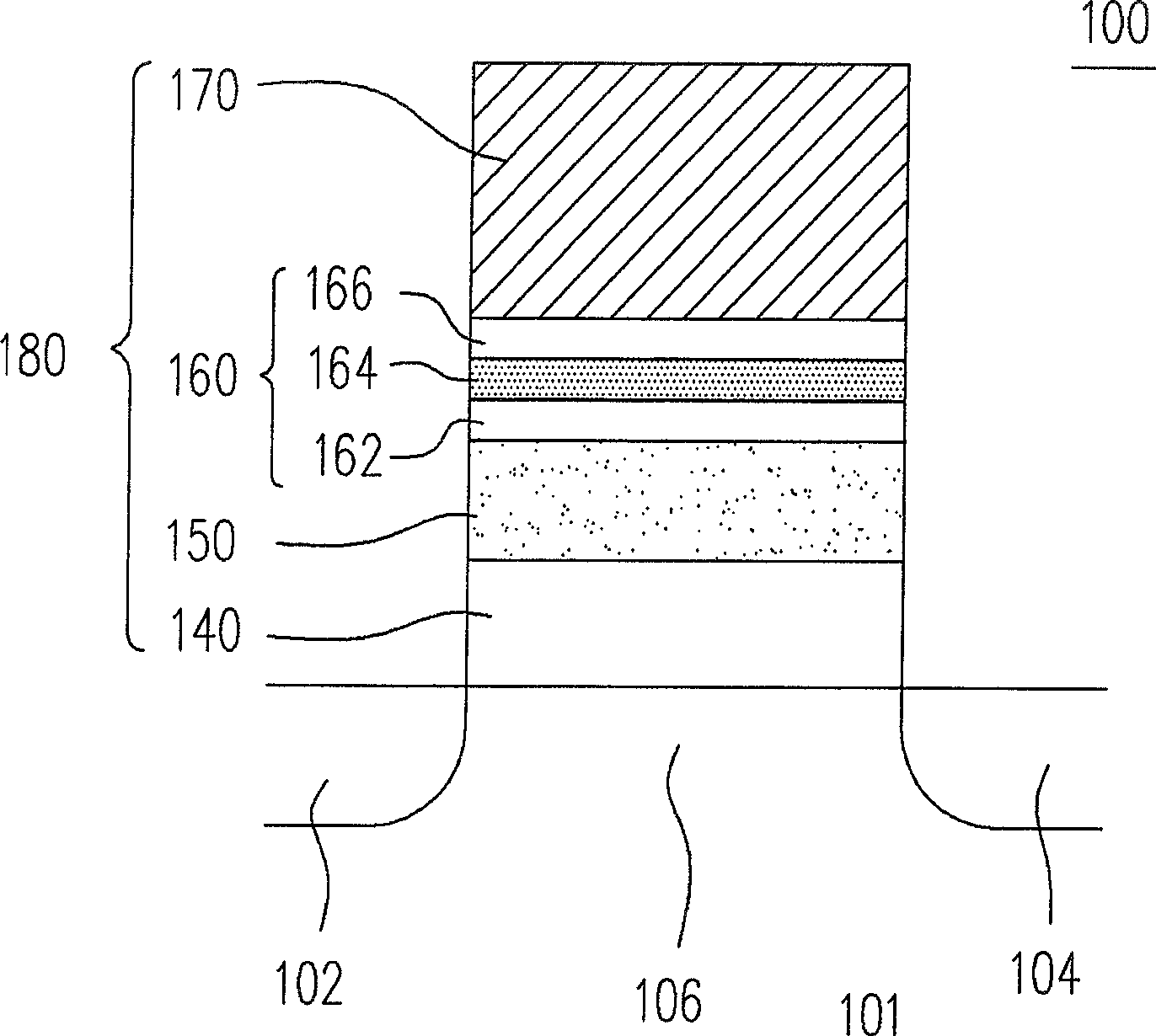

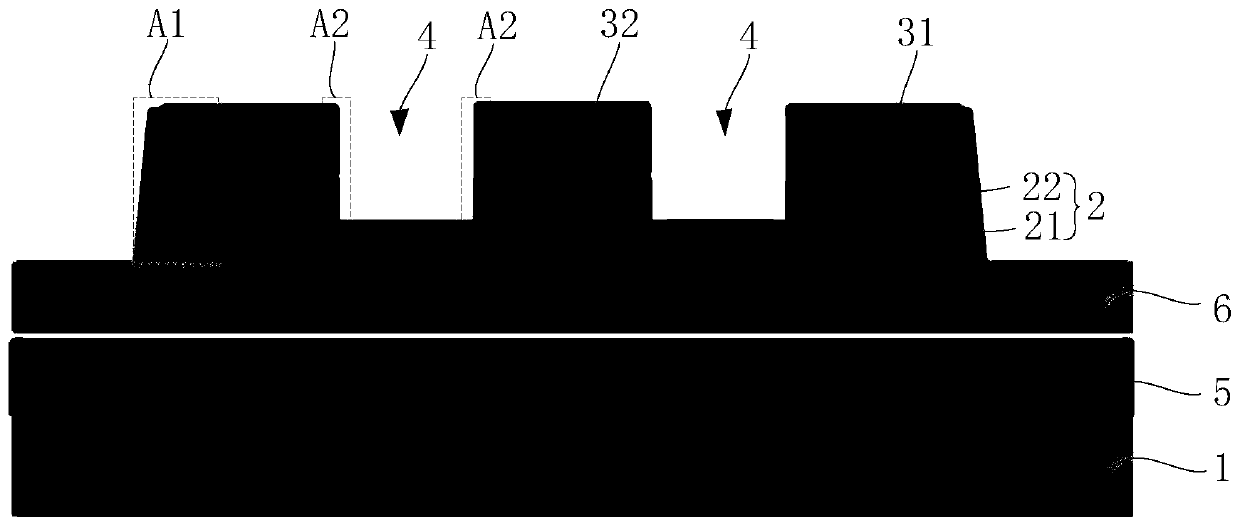

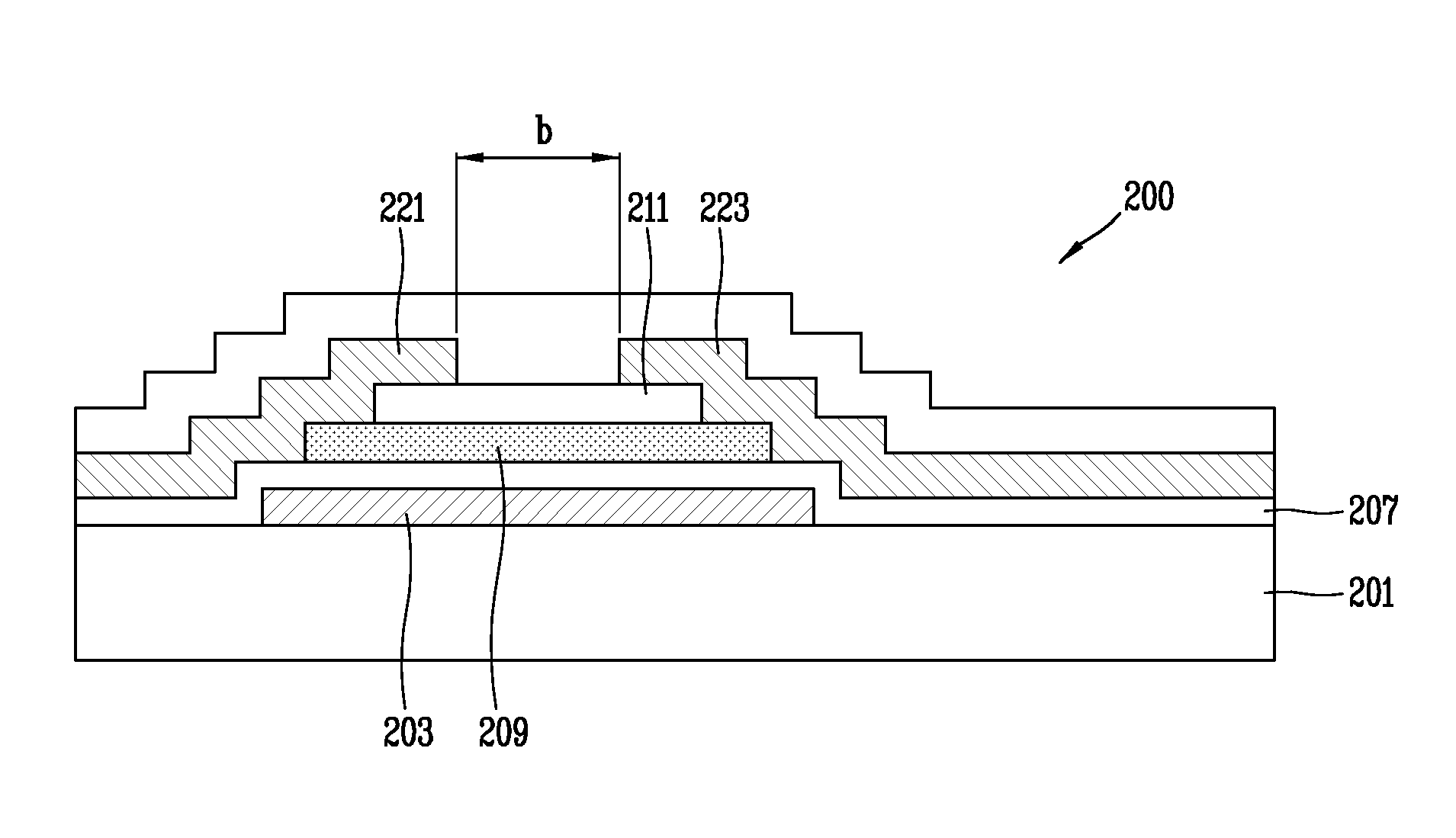

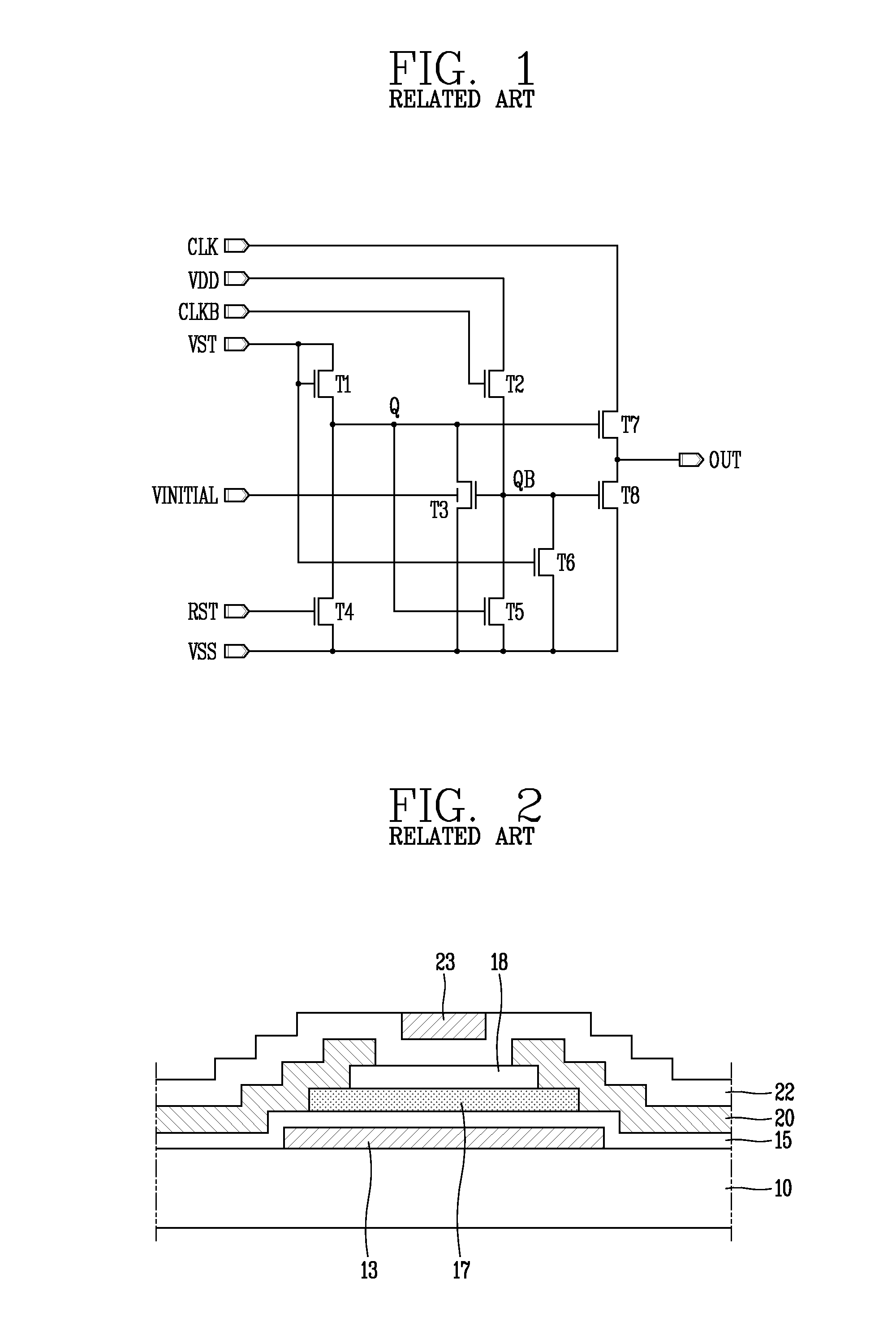

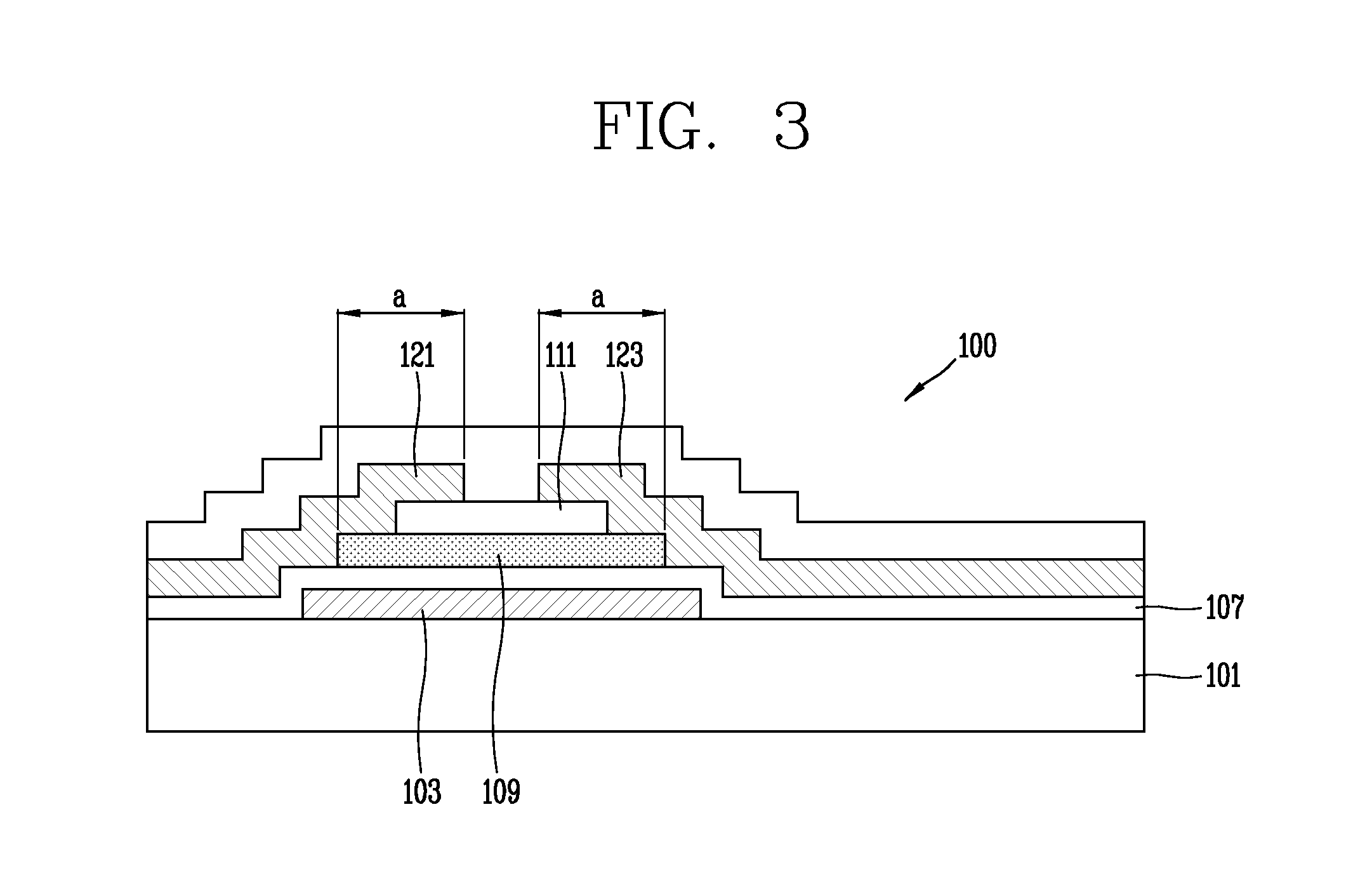

Substrate including oxide thin film transistor, method for fabricating the same, and driving circuit for liquid crystal display device using the same

ActiveUS20140061653A1Increase incidenceTransistorStatic indicating devicesLiquid-crystal displayOxide thin-film transistor

There are provided a substrate including an oxide TFT having improved initial threshold voltage degradation characteristics included in a driving circuit of a liquid crystal display (LCD) device, a method for fabricating the same, and a driving circuit for an LCD device using the same. The substrate including an oxide thin film transistor (TFT) includes: a base substrate divided into a pixel region and a driving circuit region; and a plurality of TFTs formed on the base substrate, wherein an initial threshold voltage of at least one of the plurality of TFTs formed in the driving circuit region is positive-shifted to have a predetermined level.

Owner:LG DISPLAY CO LTD

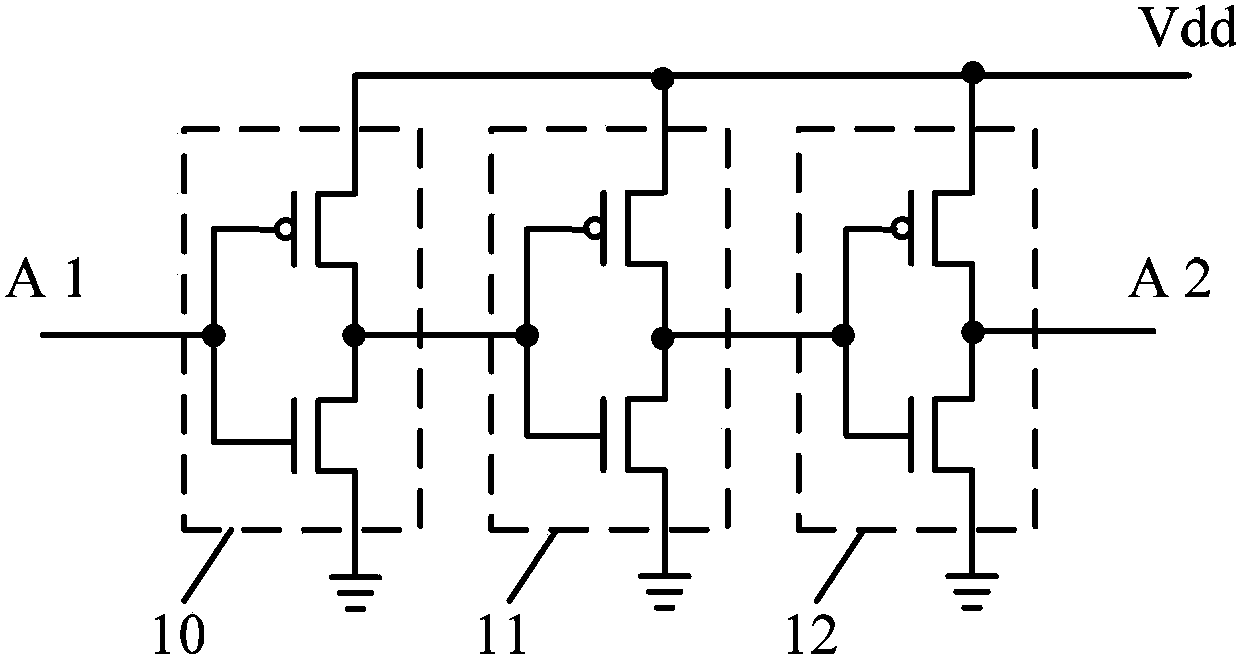

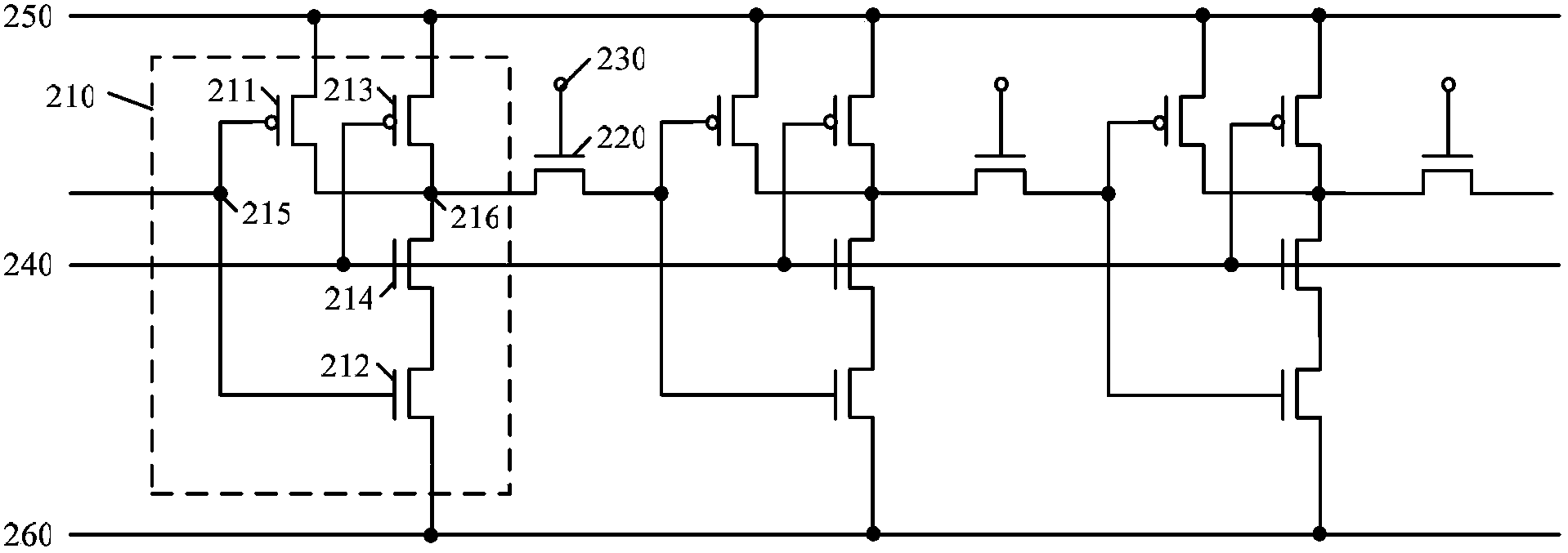

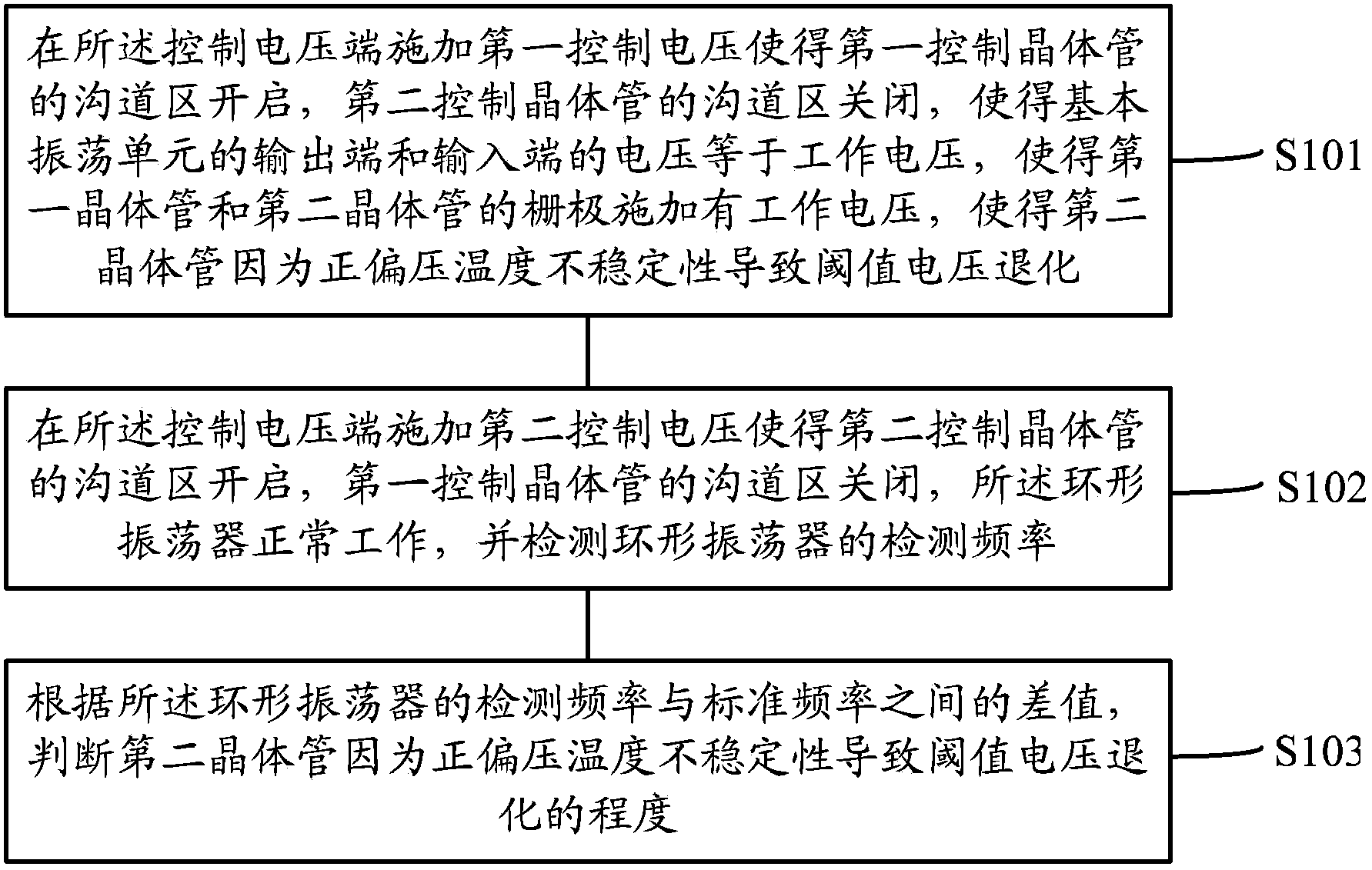

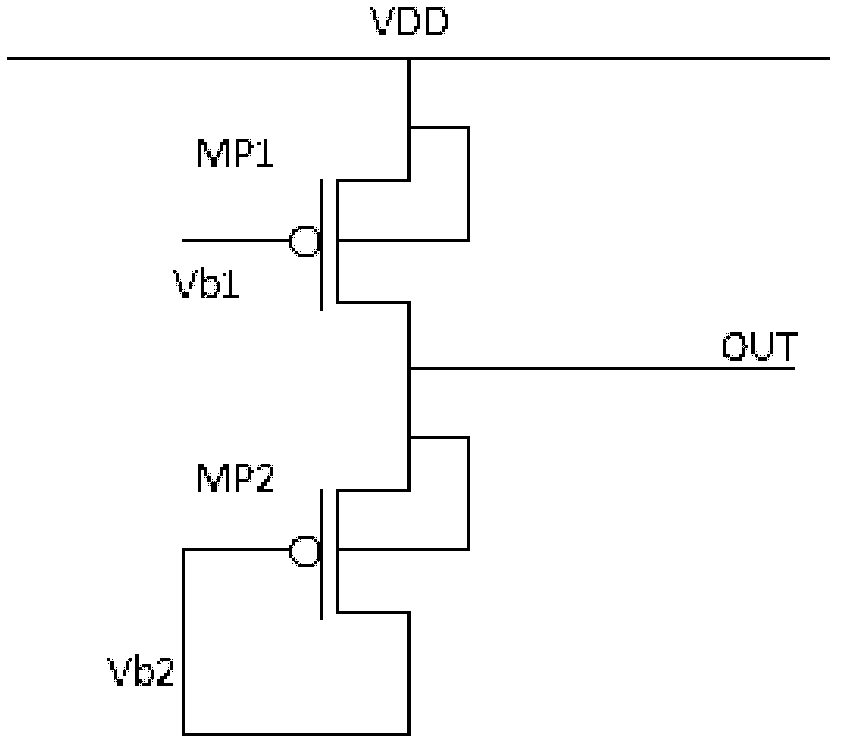

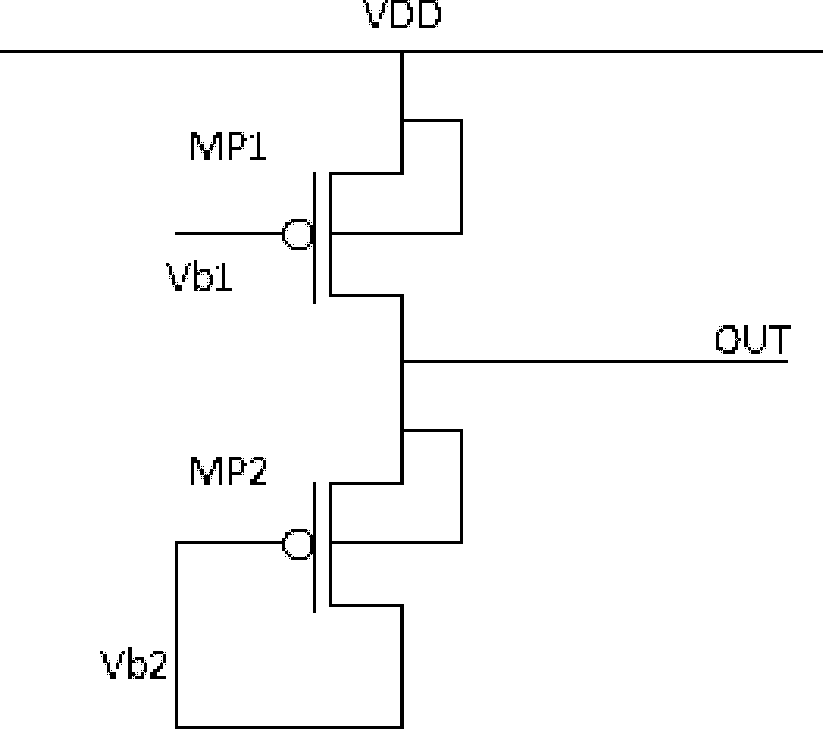

Bias voltage temperature instability detection circuit and detection method

ActiveCN103424684AZoom in on test resultsHigh precisionElectronic circuit testingEngineeringNegative bias

The invention provides bias voltage temperature instability detection circuit and detection method. The bias voltage temperature instability detection circuit comprises an odd number of fundamental oscillation units. Each fundamental oscillation unit comprises a first transistor, a second transistor, a first control transistor, a second control transistor, an input end and an output end. The detection circuit further comprises third transistors which are located between adjacent fundamental oscillation units. The fundamental oscillation units and the third transistors are connected in series to form an annular oscillator. According to the embodiment of the invention, the bias voltage temperature instability detection circuit can respectively detect the degree of threshold voltage degradation, which is caused by negative bias voltage temperature instability, of a PMOS transistor and the degree of threshold voltage degradation, which is caused by positive bias voltage temperature instability, of an NMOS transistor; by using the third transistors, the degree of threshold voltage degradation, which is caused by bias voltage temperature instability, of an MOS transistor can be amplified; and the final detection result is sensitive and the detection precision is high.

Owner:SEMICON MFG INT (SHANGHAI) CORP

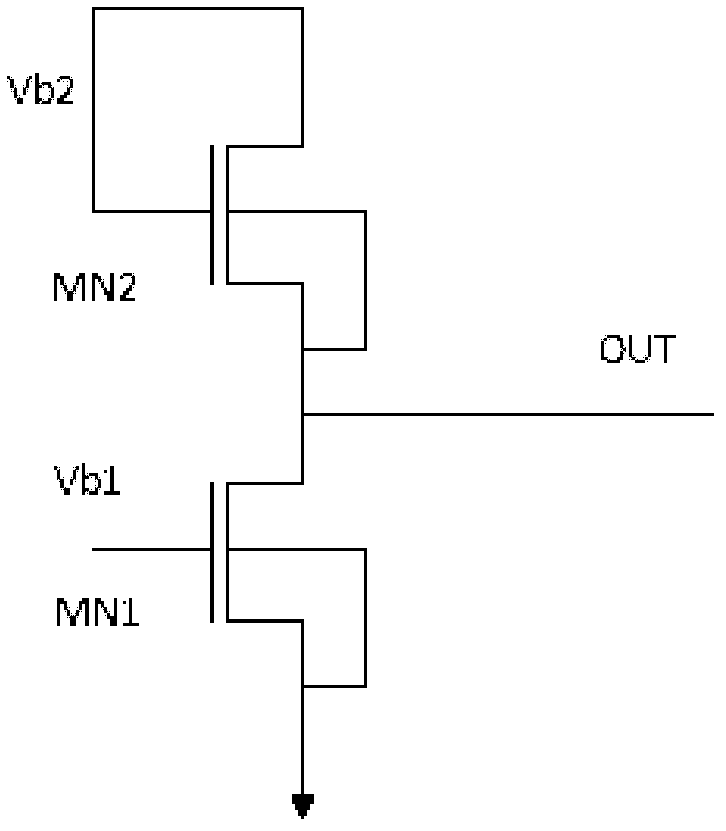

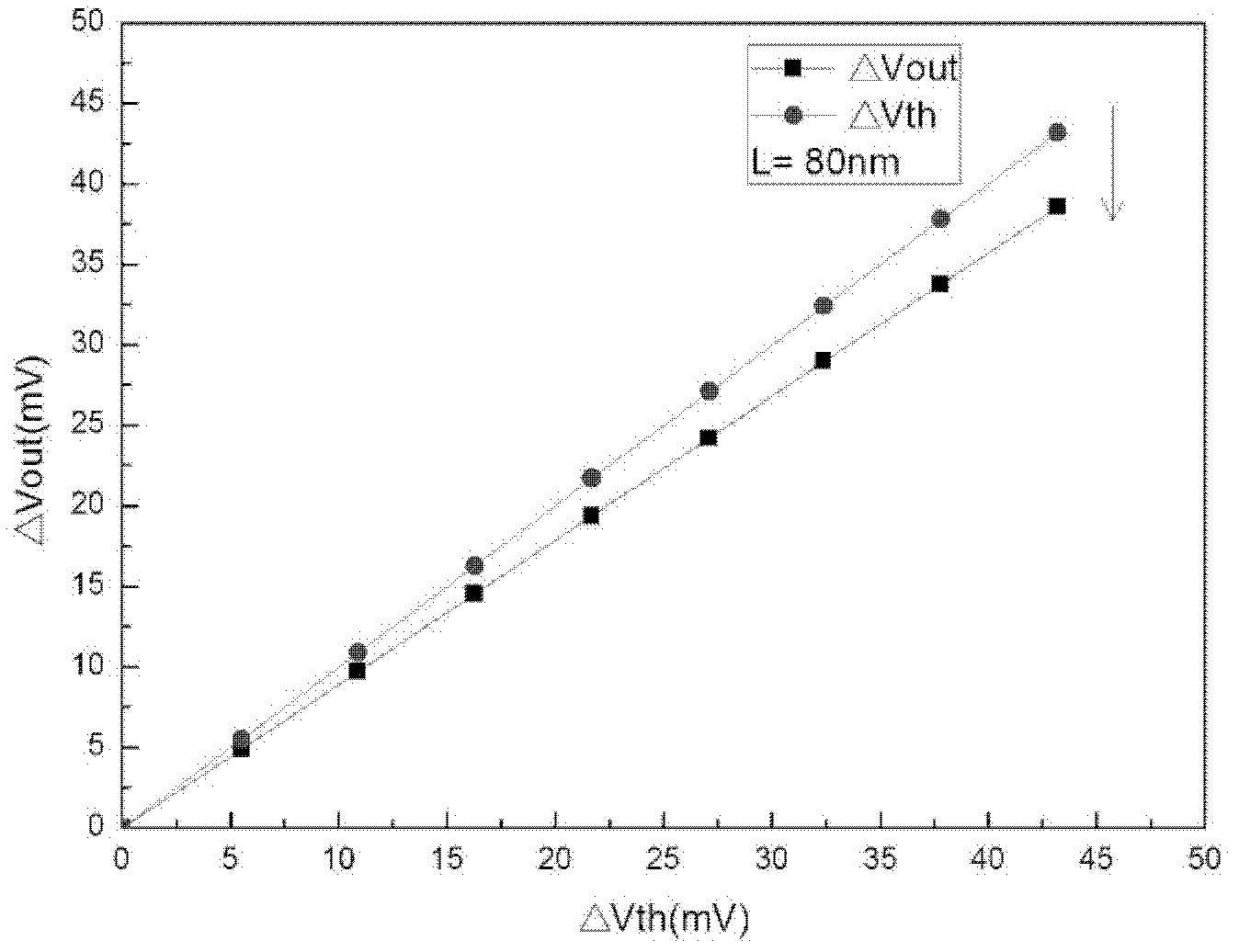

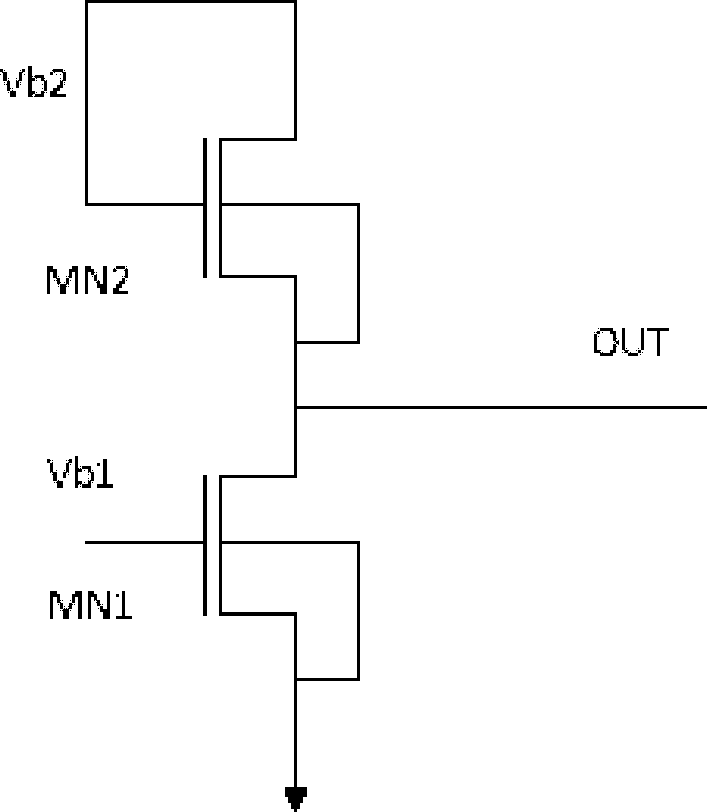

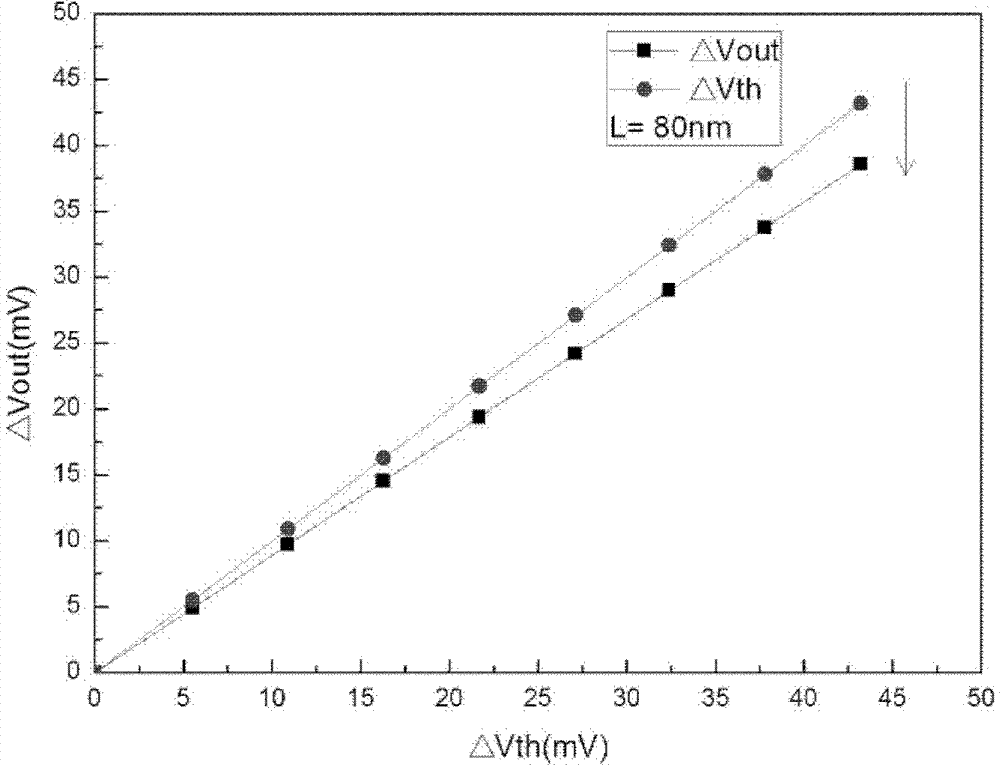

Threshold voltage degradation measuring circuit

ActiveCN102636678ASimple structureEasy to operateCurrent/voltage measurementVoltage variationDirect current

The invention relates to the technical field of integrated circuits and provides a threshold voltage degradation measuring circuit. The circuit comprises two MOS (Metal Oxide Semiconductor) tubes which are connected in series, wherein the first MOS tube is a detected tube; a grid electrode of the first MOS tube is connected with first direct-current voltage, a source electrode and a substrate of the first MOS tube are simultaneously connected with source electrode voltage, and a drain electrode of the first MOS tube is connected with an output end; a grid electrode and a drain electrode of the second MOS tube are simultaneously connected with second direct-current voltage, and a source electrode and a substrate of the second MOS tube are simultaneously connected with the output end. According to the scheme disclosed by the invention, the threshold voltage degradation measuring circuit with a simple structure is provided; the circuit only comprises the two MOS tubes which are connected in series and the threshold voltage degradation condition of the tube to be detected can be directly measured by only measuring the voltage change of the output end; and the circuit only relates to the obtaining of one physical amount and does not need to carry out secondary process and analysis, so that the technical scheme has the advantages of simple structure, convenience for operation, time-saving property, accurate and direct results and easiness in implementation.

Owner:PEKING UNIV

Method for fabricating semiconductor device

Method for fabricating a semiconductor device, including the steps of providing a first conductive type semiconductor substrate having a cell region and a logic region defined thereon, forming a first insulating film, second conductive type polysilicon, and a second insulating film in succession on the semiconductor substrate, selectively removing the first insulating film, the polysilicon, and the second insulating film, to form a floating gate pattern at the cell region, elevating a temperature initially in a state O2 gas is injected, maintaining a fix temperature, and dropping the temperature in a state N2 gas is injected, to form a gate oxide film on a surface of the semiconductor substrate at the logic region, and forming a gate electrode pattern at each of the cell region and the logic region, whereby preventing a threshold voltage of a semiconductor device from dropping due to infiltration of impurities from doped polysilicon at the cell region to the active channel region.

Owner:COLUMBA TECH INC

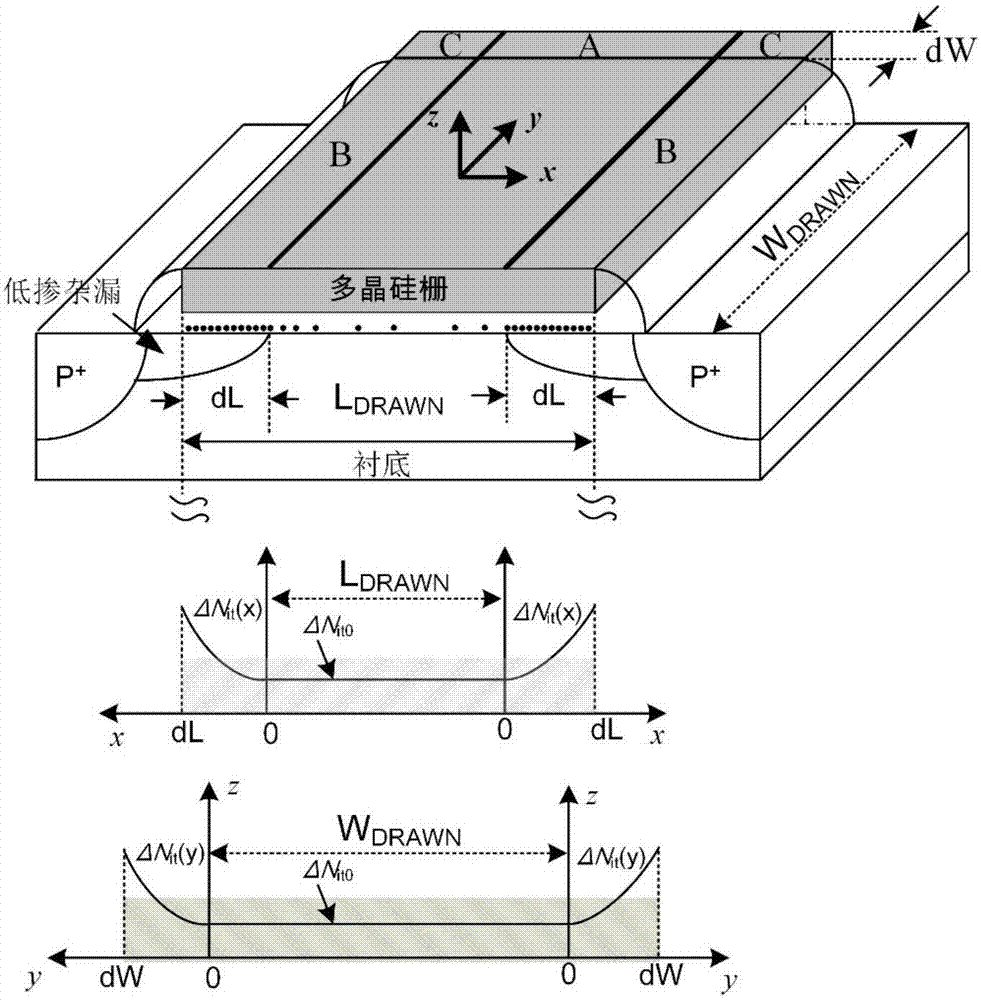

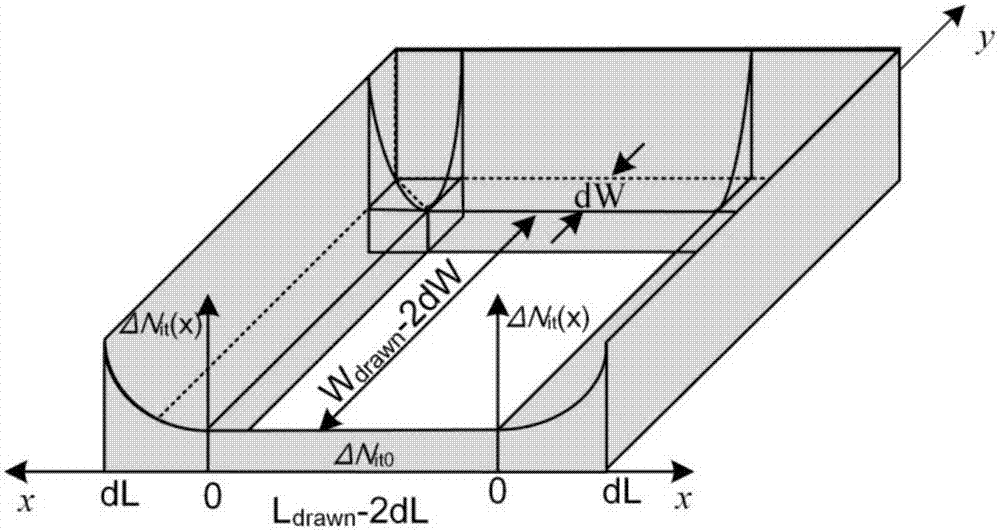

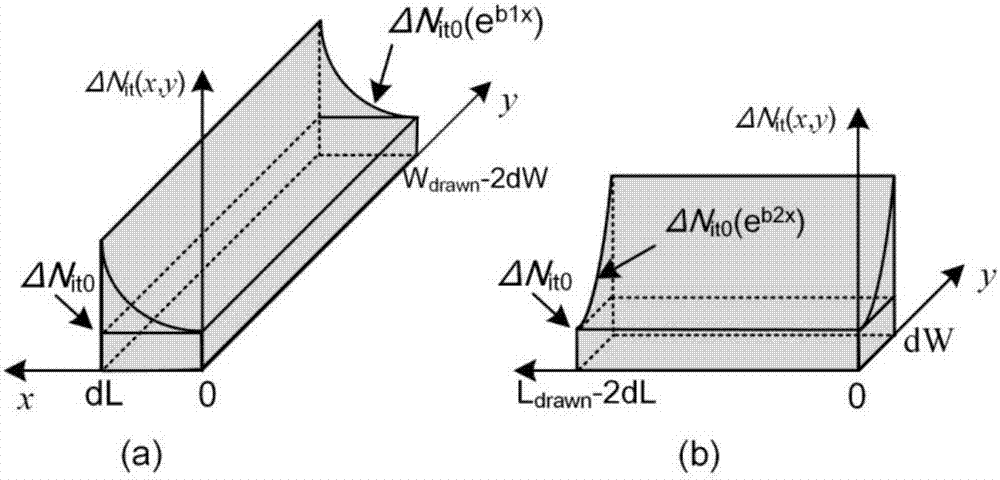

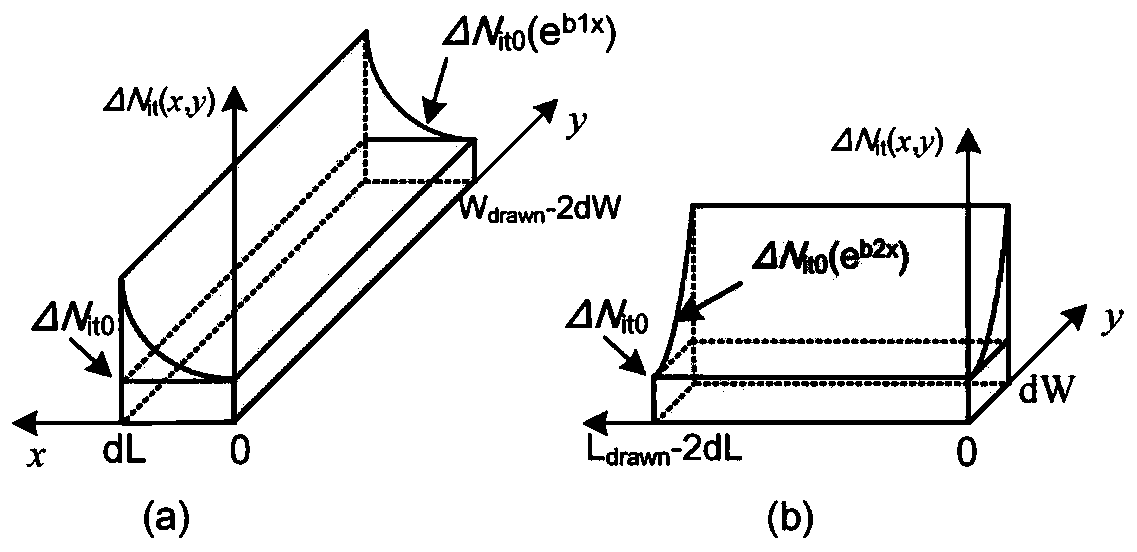

NBTI degradation model obtaining method based on nonuniform distribution interface traps

ActiveCN107220477AFew fitting parametersWide applicabilitySpecial data processing applicationsInformaticsDistribution frameComputer science

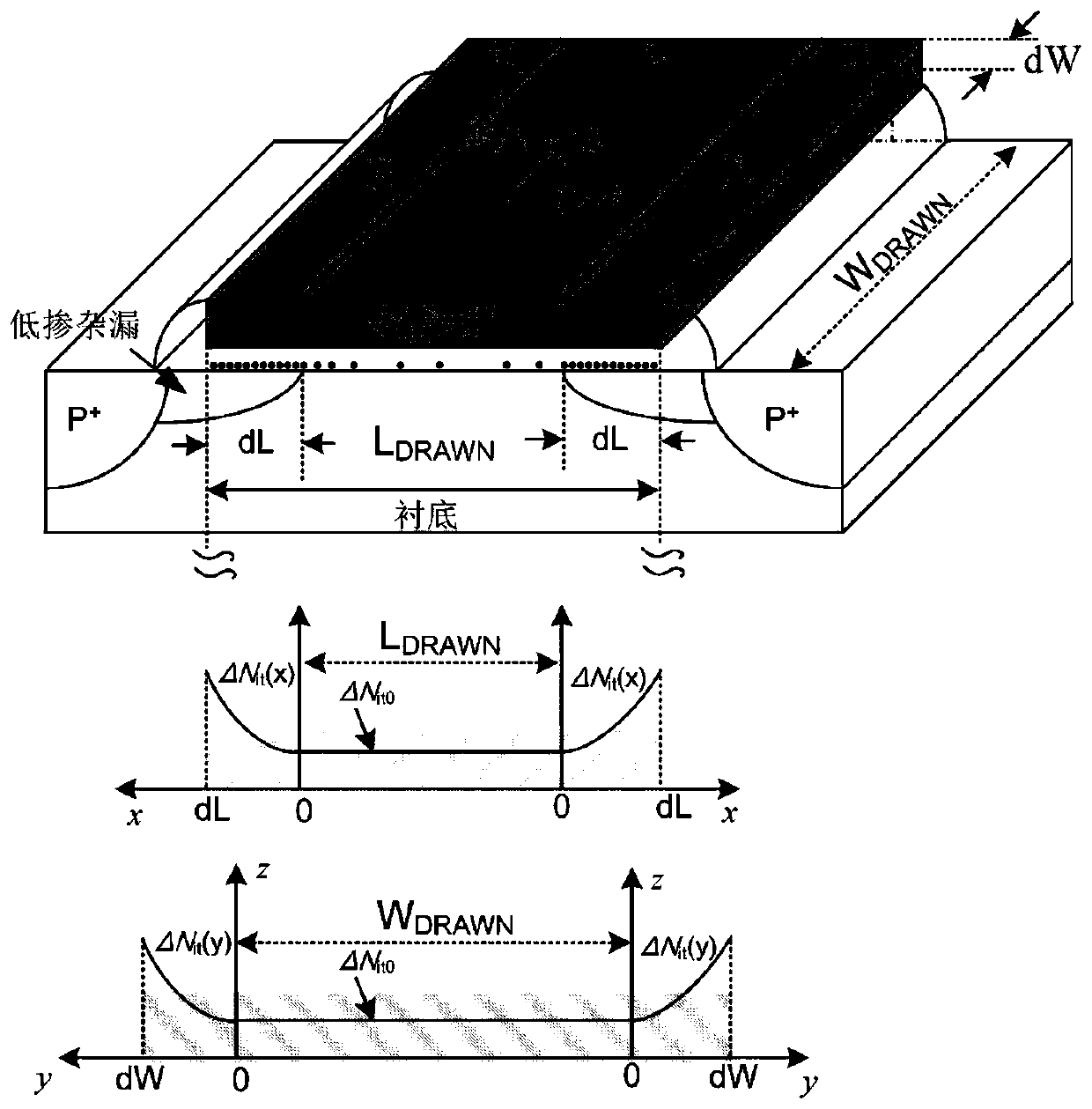

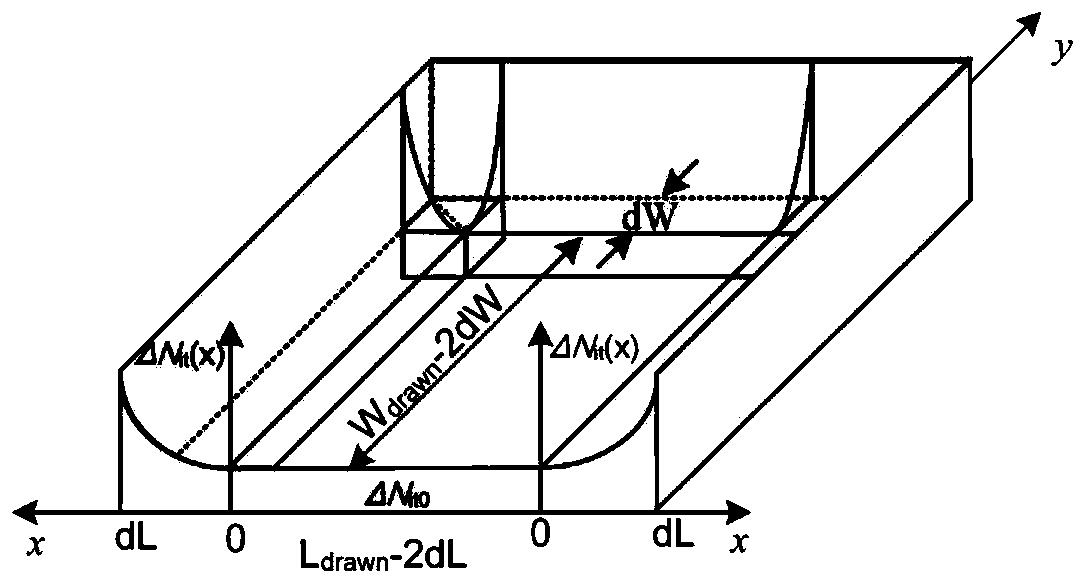

The invention discloses an NBTI degradation model obtaining method based on nonuniform distribution interface traps. The method comprises the steps that 1, interface trap distributions in different zone of an MOS device are divided to obtain total distribution frame of the interface traps; 2, according to geometric construction, the interface trap distribution density in each zone is calculated, and the total density of the nonuniform distribution interface traps is obtained; 3, threshold voltage deviation caused by NBTI is obtained according to the deltaNIT total density, and an NBTI degradation model based on geometric construction analysis is obtained. The actual distribution situation of the interface traps produced by an NBTI effect is incorporated in the model, accordingly the total density of interface trap charges produced in the MOS device can be accurately calculated, thus a threshold voltage degradation model is obtained, few fitting parameters are required, the applicability is wide, and the model provides more accurate precision for device reliability.

Owner:EAST CHINA NORMAL UNIV +1

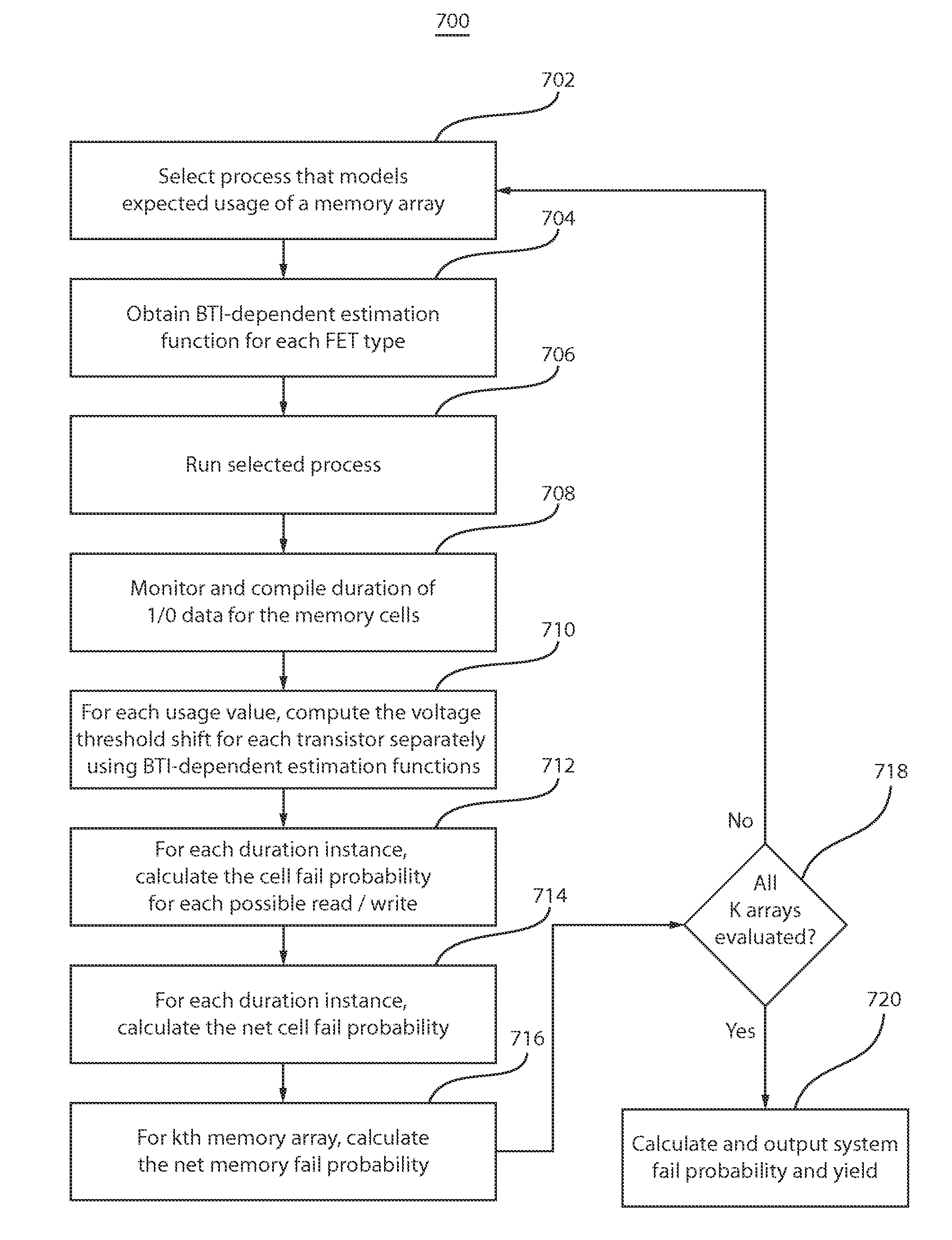

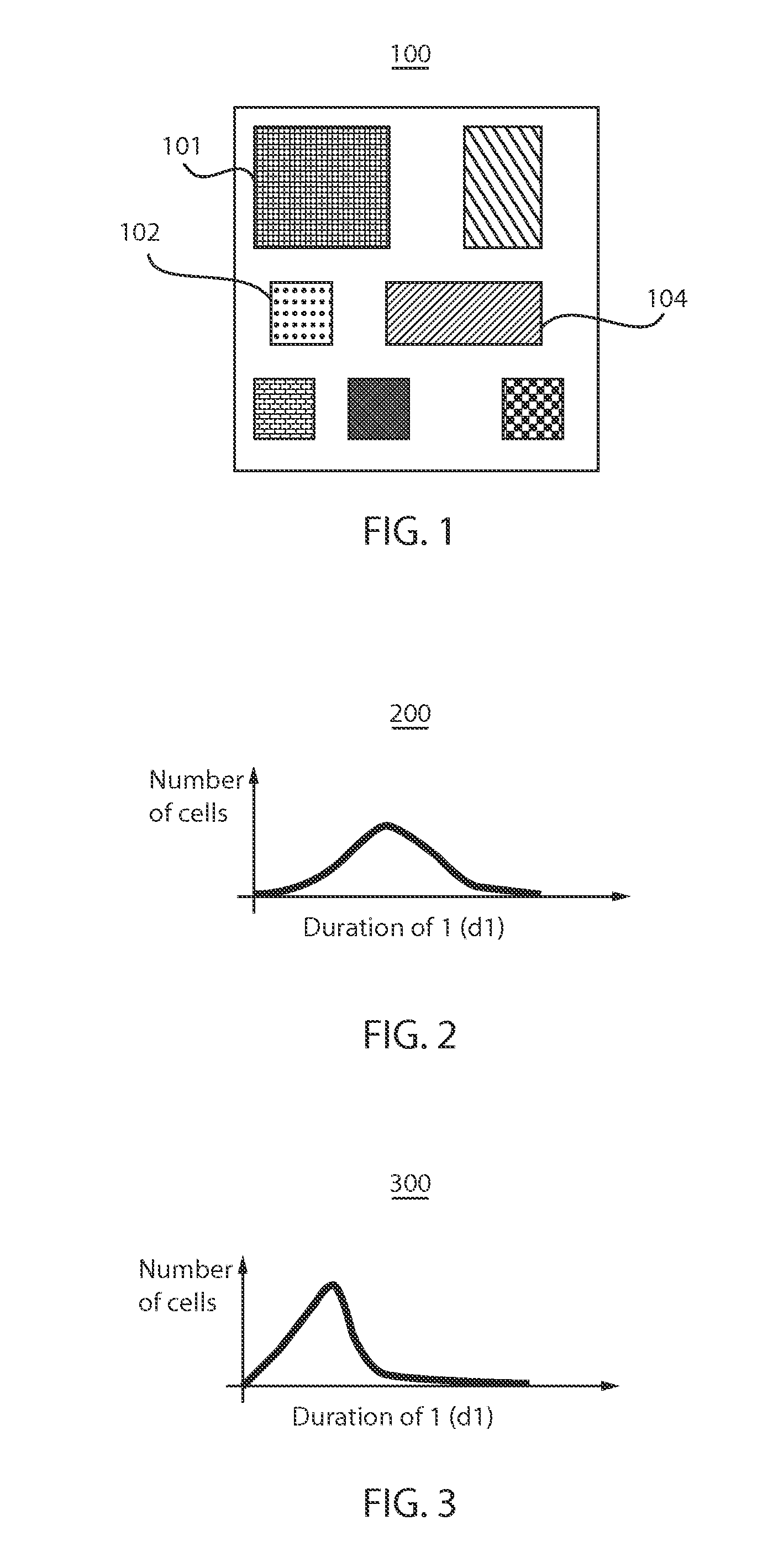

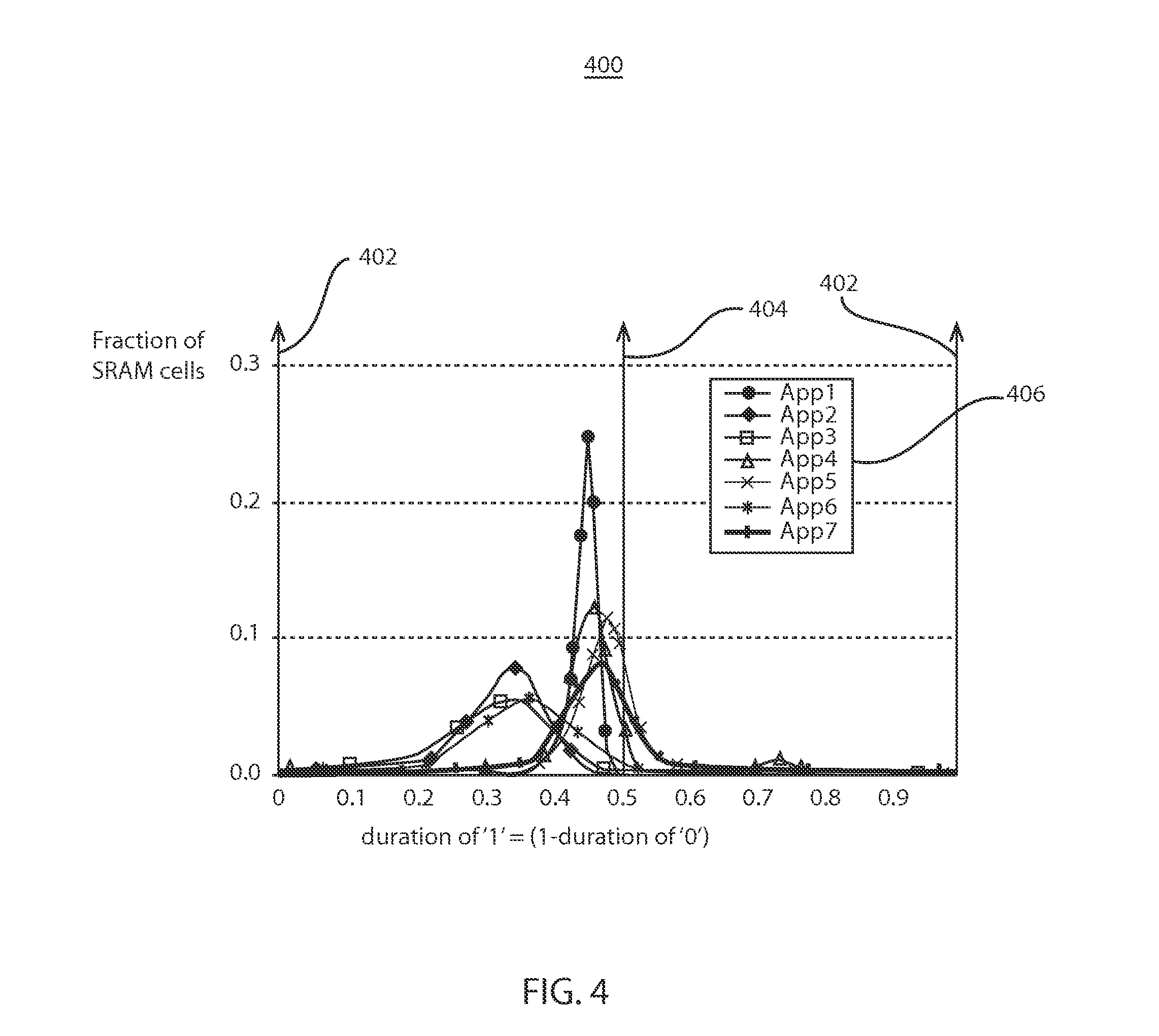

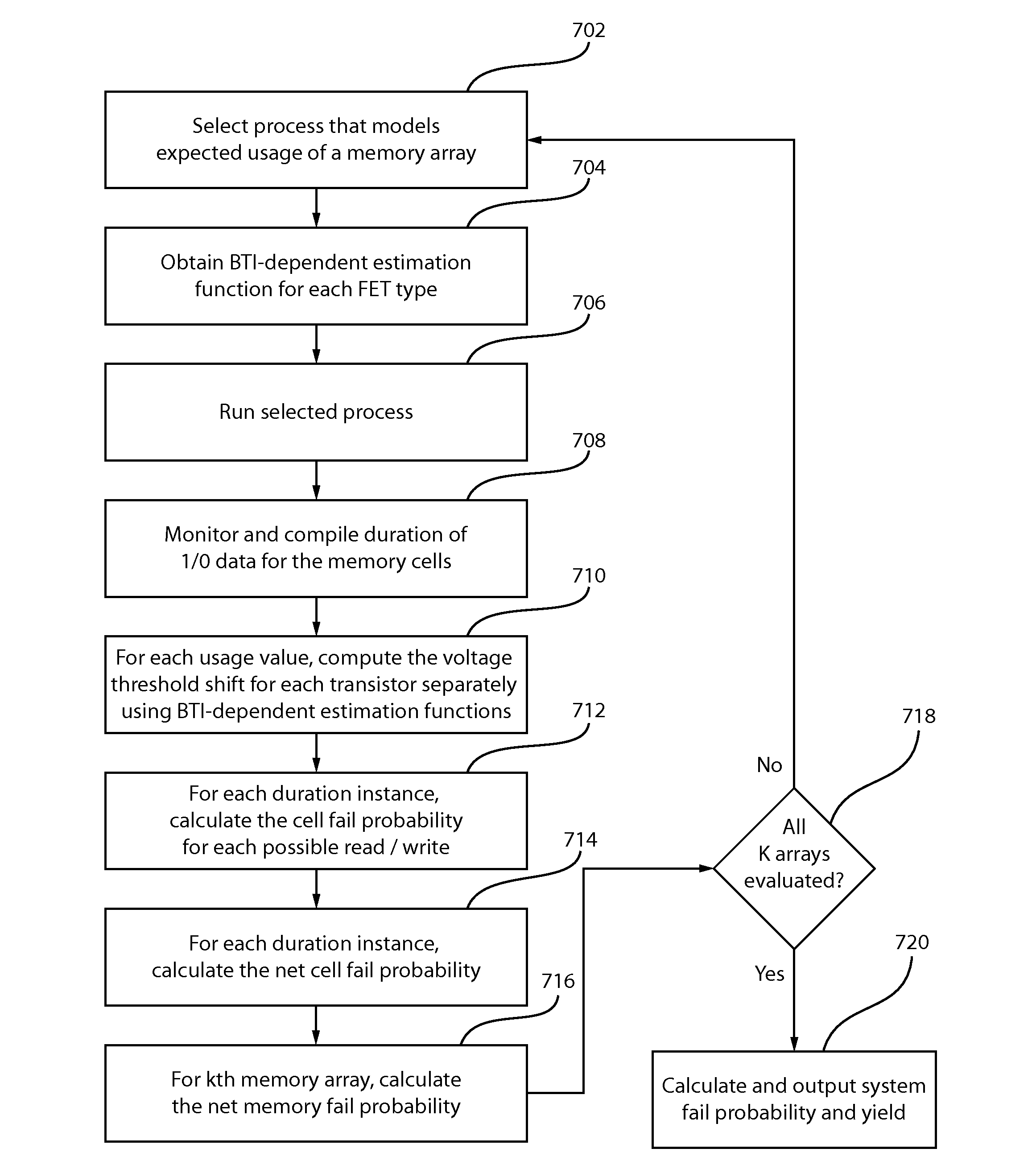

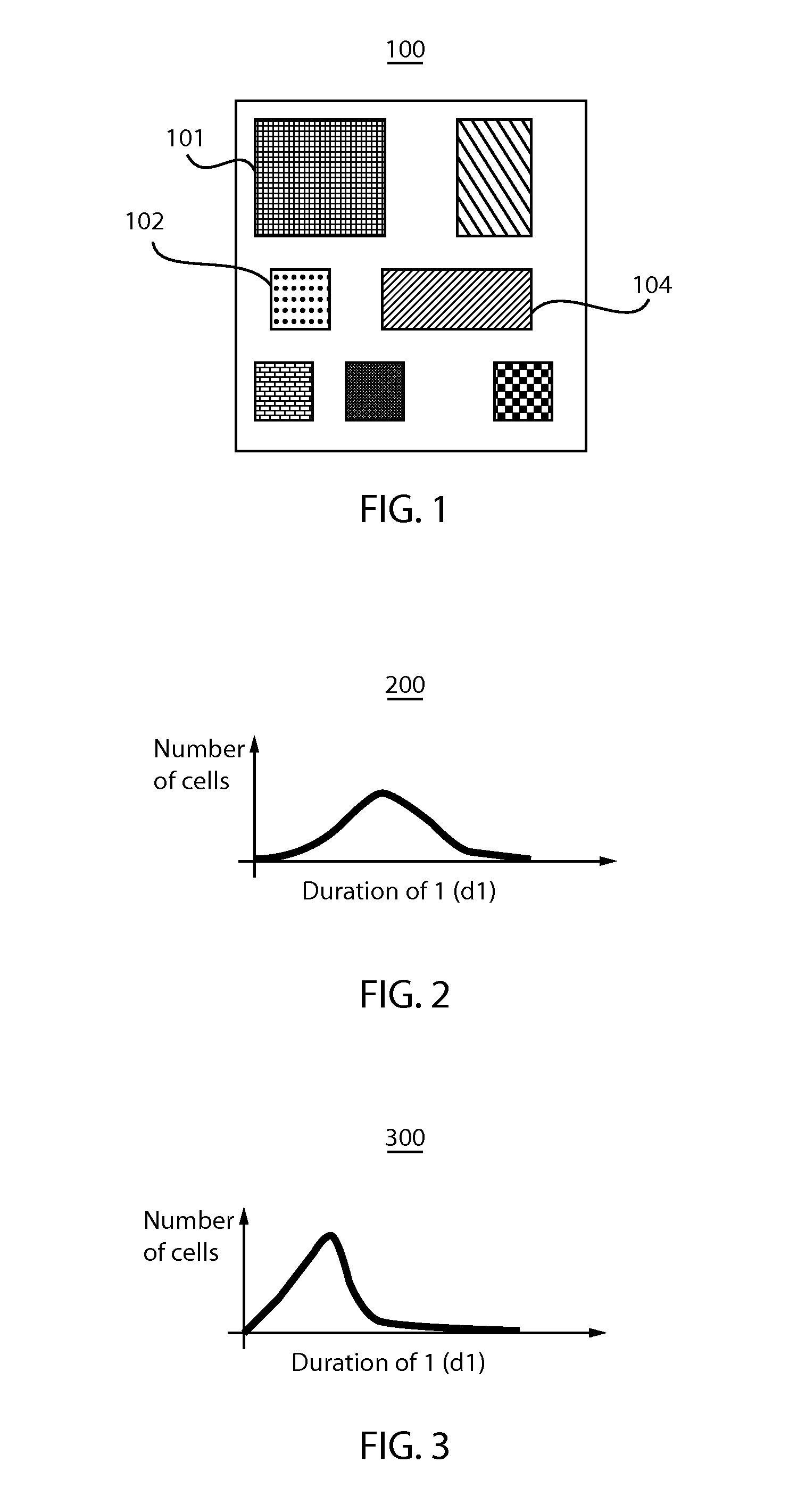

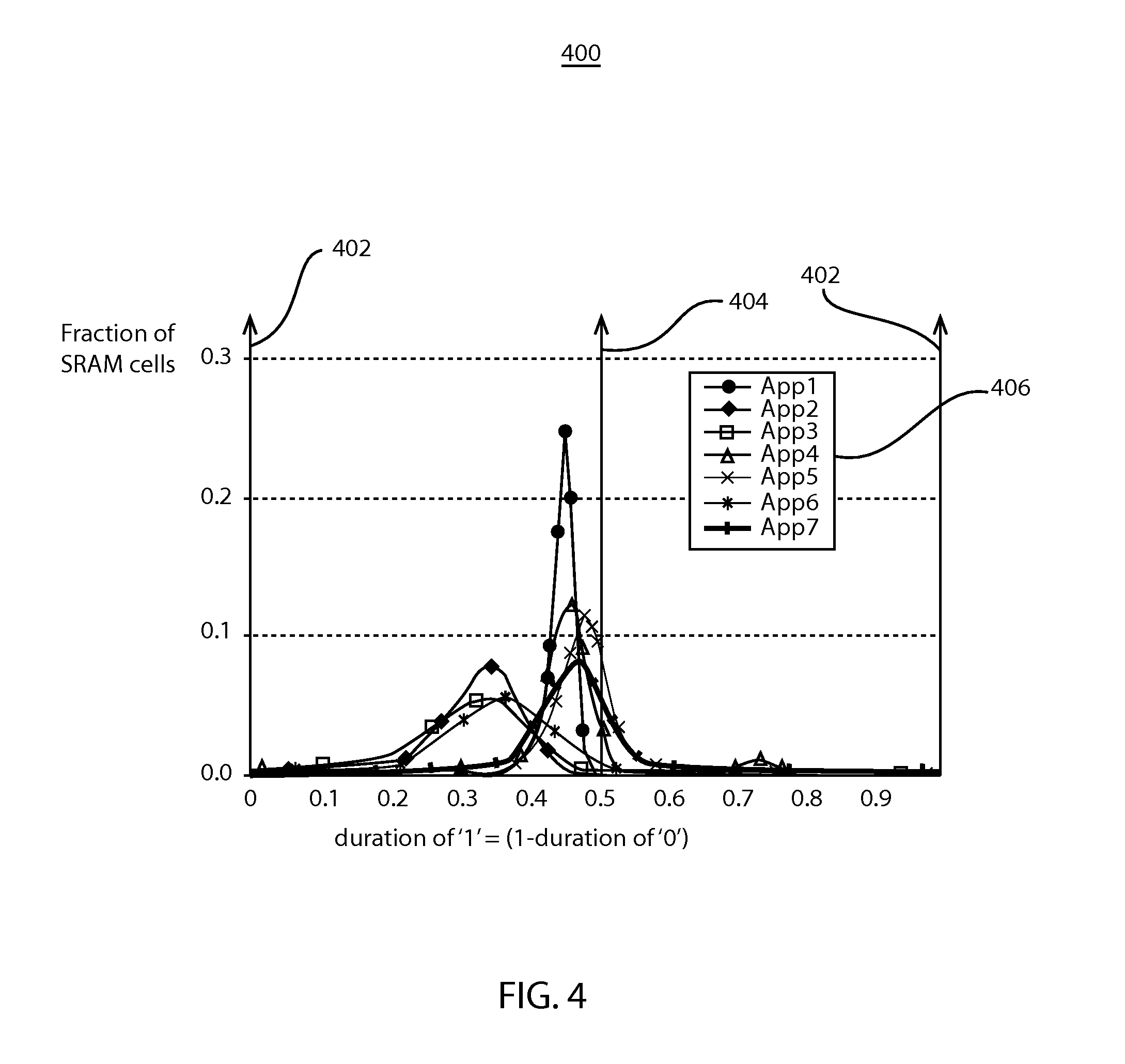

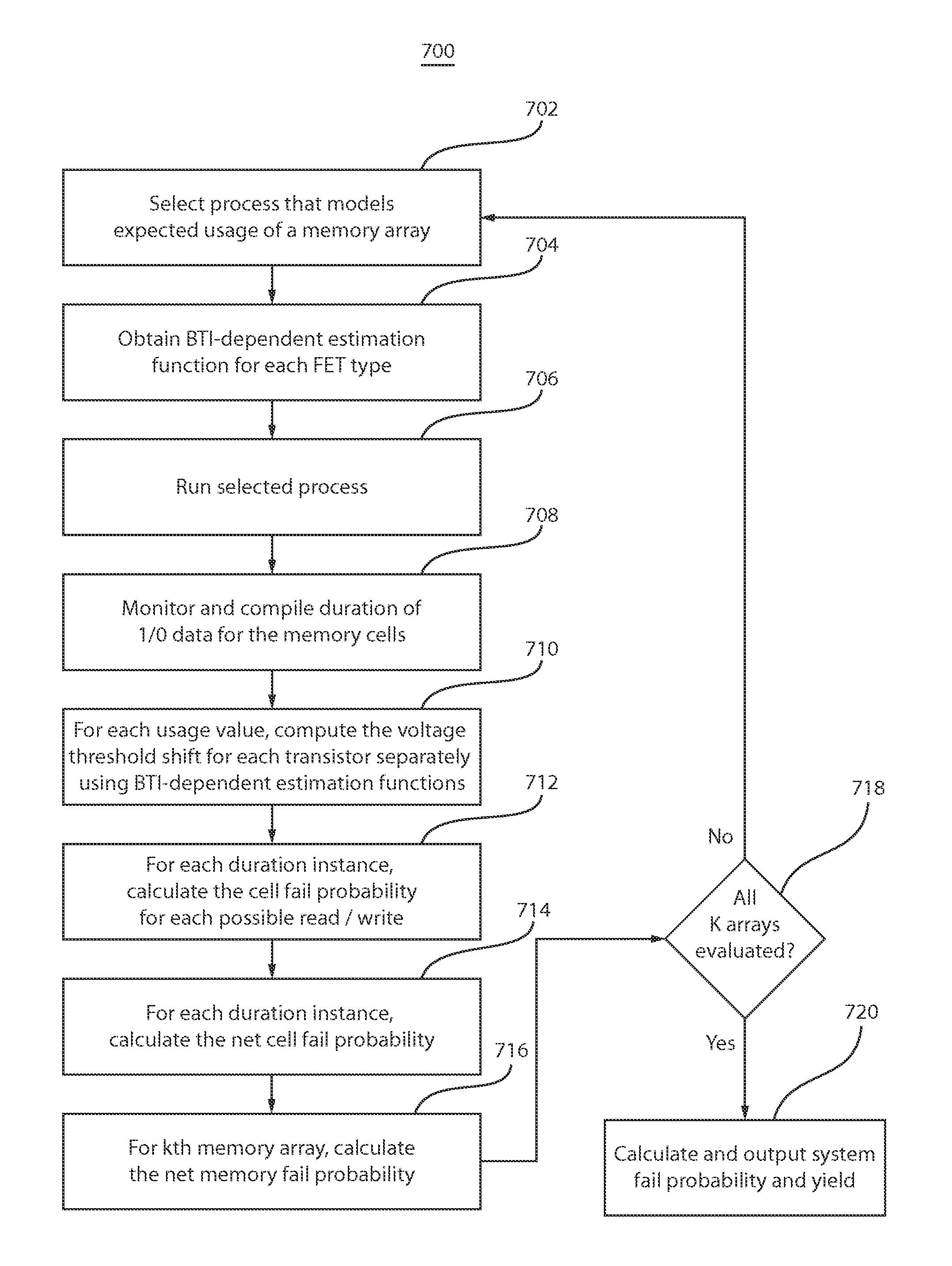

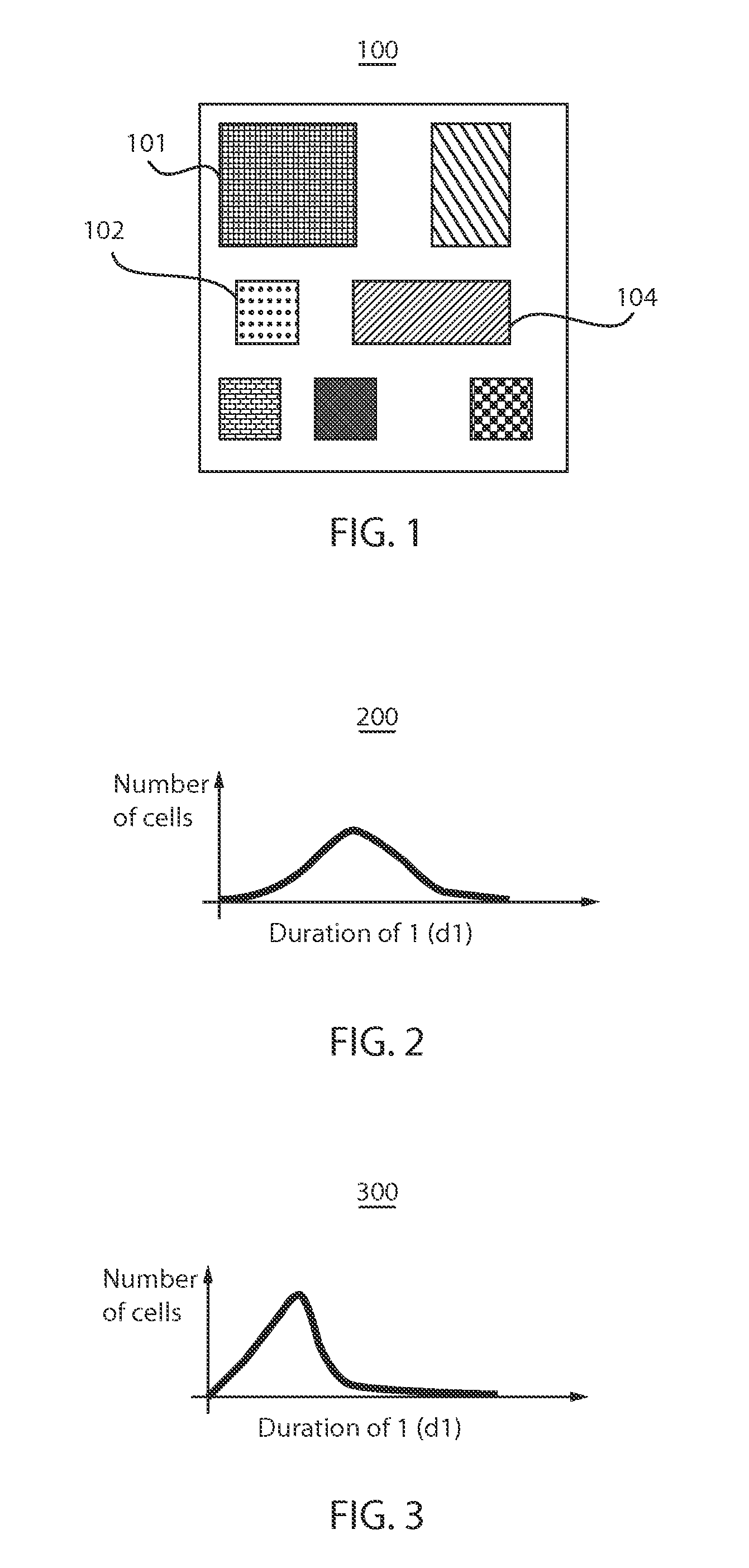

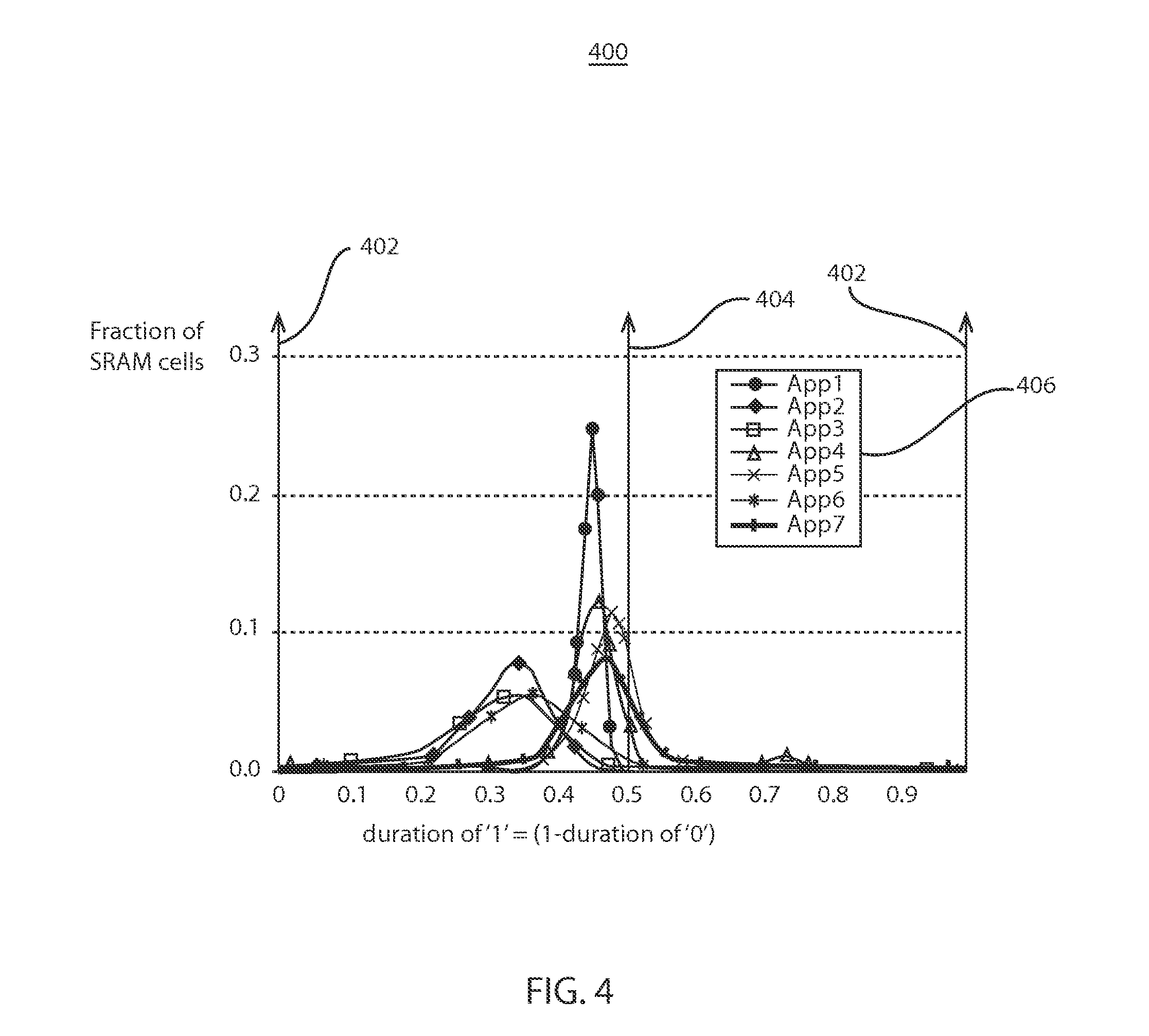

Usage-based temporal degradation estimation for memory elements

InactiveUS20130138407A1Analogue computers for electric apparatusComputation using non-denominational number representationInstabilityCell based

Methods and systems for computing threshold voltage degradation of transistors in an array of memory cells are disclosed. In accordance with one method, a process that models an expected usage of the array is selected. In addition, a hardware processor can run the process to populate the array with data over time to simulate the expected usage of the array. The method further includes compiling data that detail different durations at which each of the memory cells in the array stores 1 or at which each of the memory cells in the array stores 0. For each separate grouping of memory cells that share a common duration of the different compiled durations, a threshold voltage degradation is determined for each transistor in the corresponding grouping of cells based on at least one biased temperature instability model.

Owner:GLOBALFOUNDRIES INC

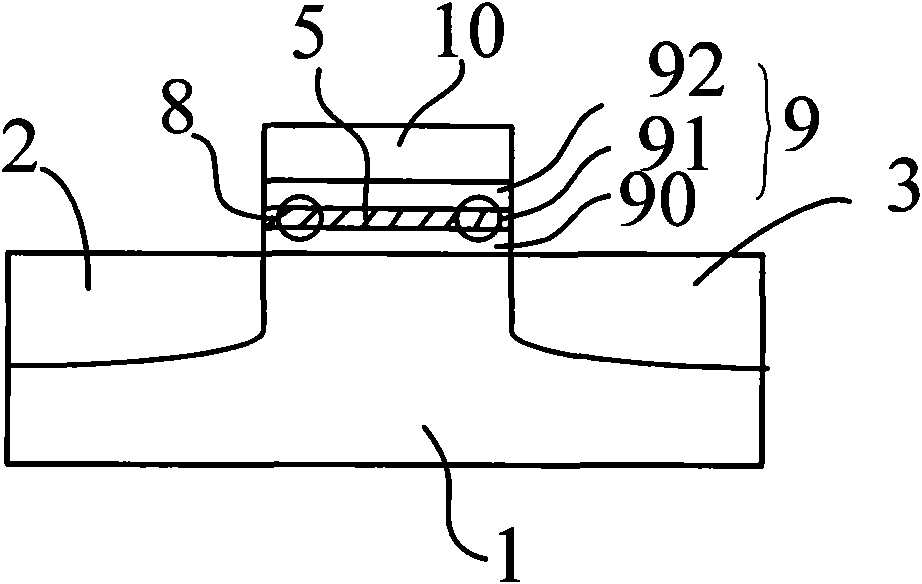

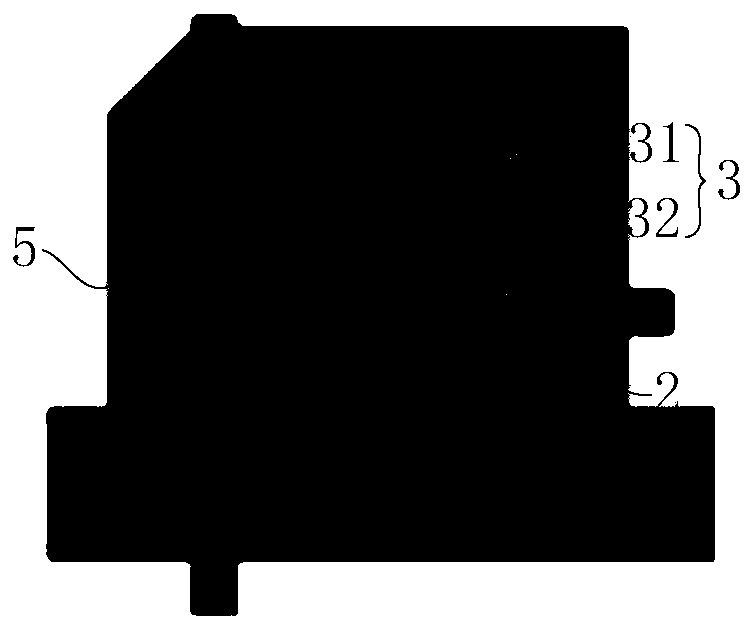

MOS field effective pipe and its production

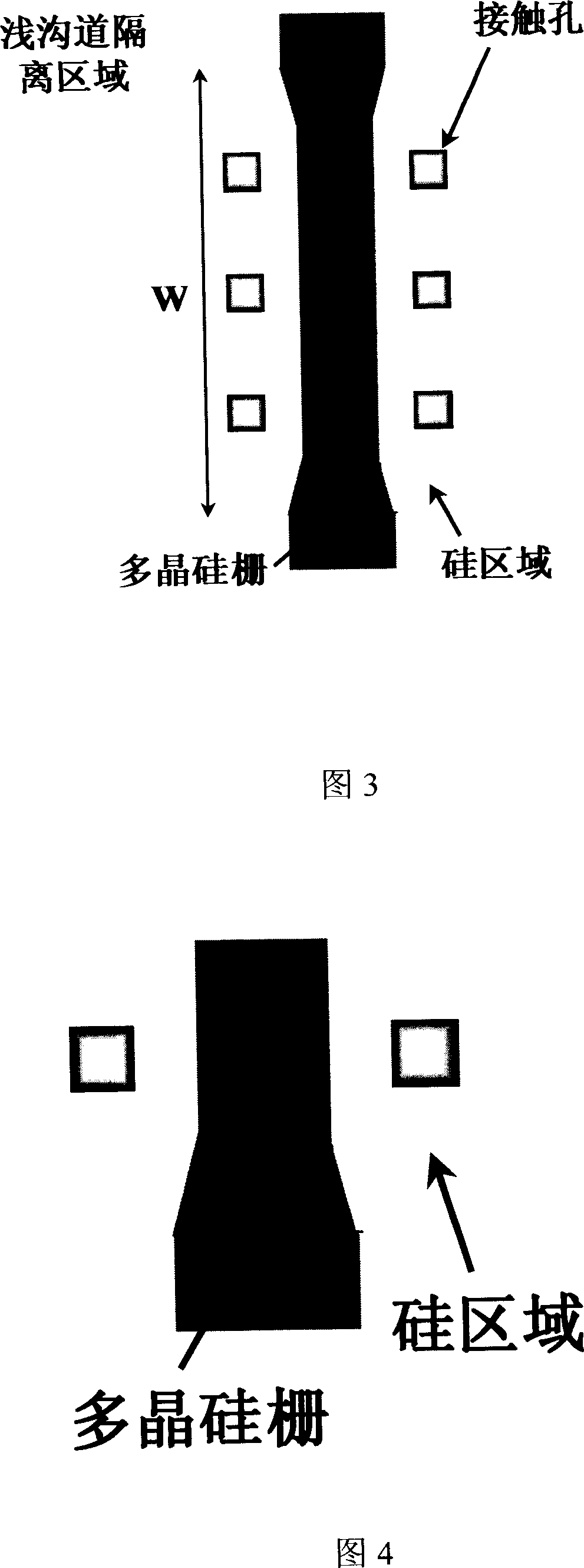

InactiveCN1983631AIncrease widthRaise the threshold voltageSemiconductor/solid-state device manufacturingSemiconductor devicesShape changeEngineering

The invention is concerned with a kind of MOS field-effect transistor. The breadth of the poly gate to MOS field-effect transistor adds in linearity from the someplace of the simple channel insulated area closed to both sides of breadth and the silicon area on boundary of silicon area. The invention is also concerned with the production method of MOS field-effect transistor. At first, define the geometry parameter of the shape change to this poly gate, according to the degree of anti-narrow channel effect and the general characteristic of MOS field-effect transistor. Then, change domain according to the decided geometry parameter. It adds the breadth of the poly gate on the rim of field-effect transistor in linearity, and this is equal to add the length of channel to parasitical transistor and reduces its leakage current to advance the threshold voltage of parasitical transistor. Then the result is to reduce the leakage current of main and advance its threshold voltage and solve the problem that the descendant of threshold voltage caused from the improvement of anti-narrow channel effect of MOS field-effect transistor.

Owner:SHANGHAI HUA HONG NEC ELECTRONICS

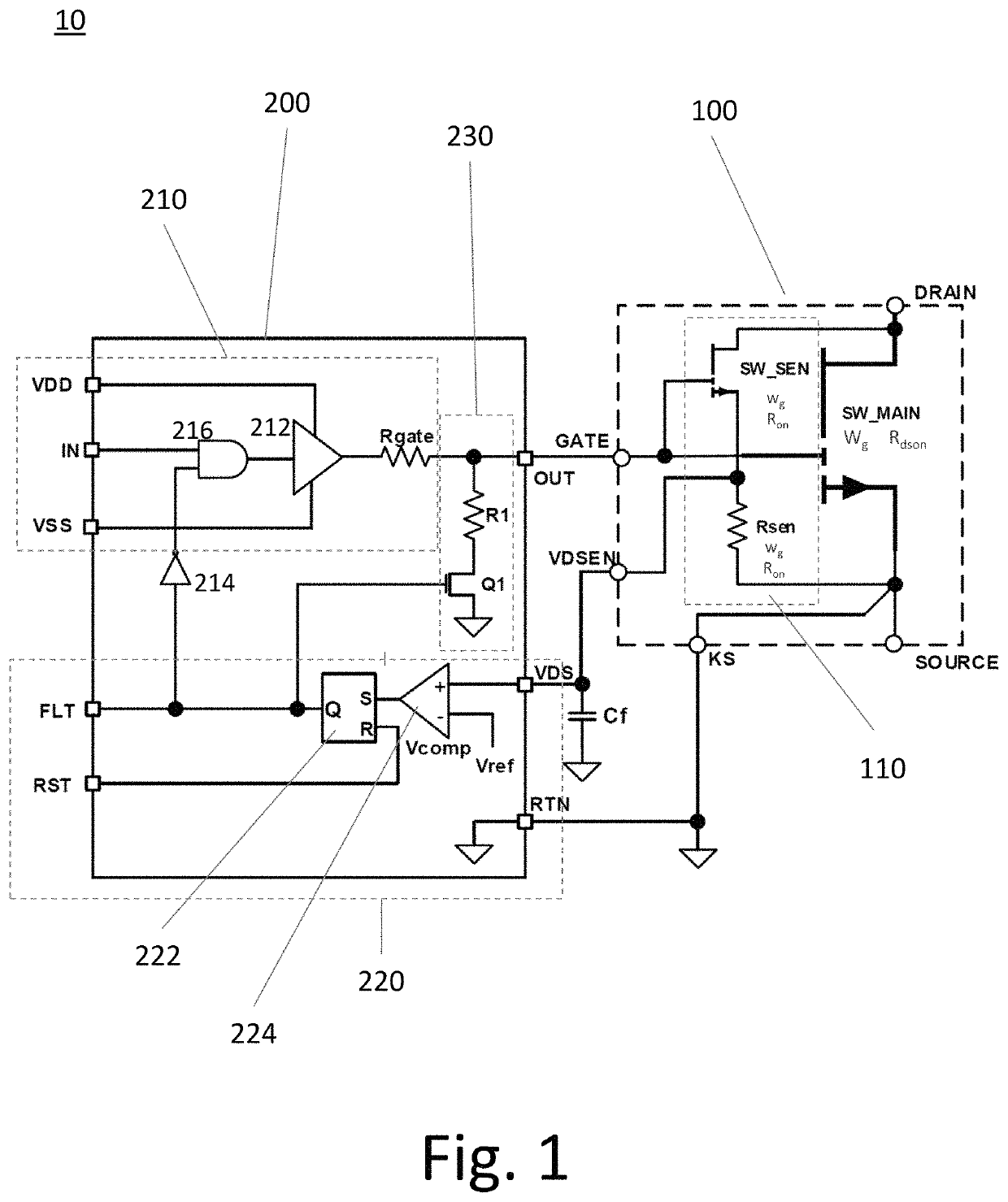

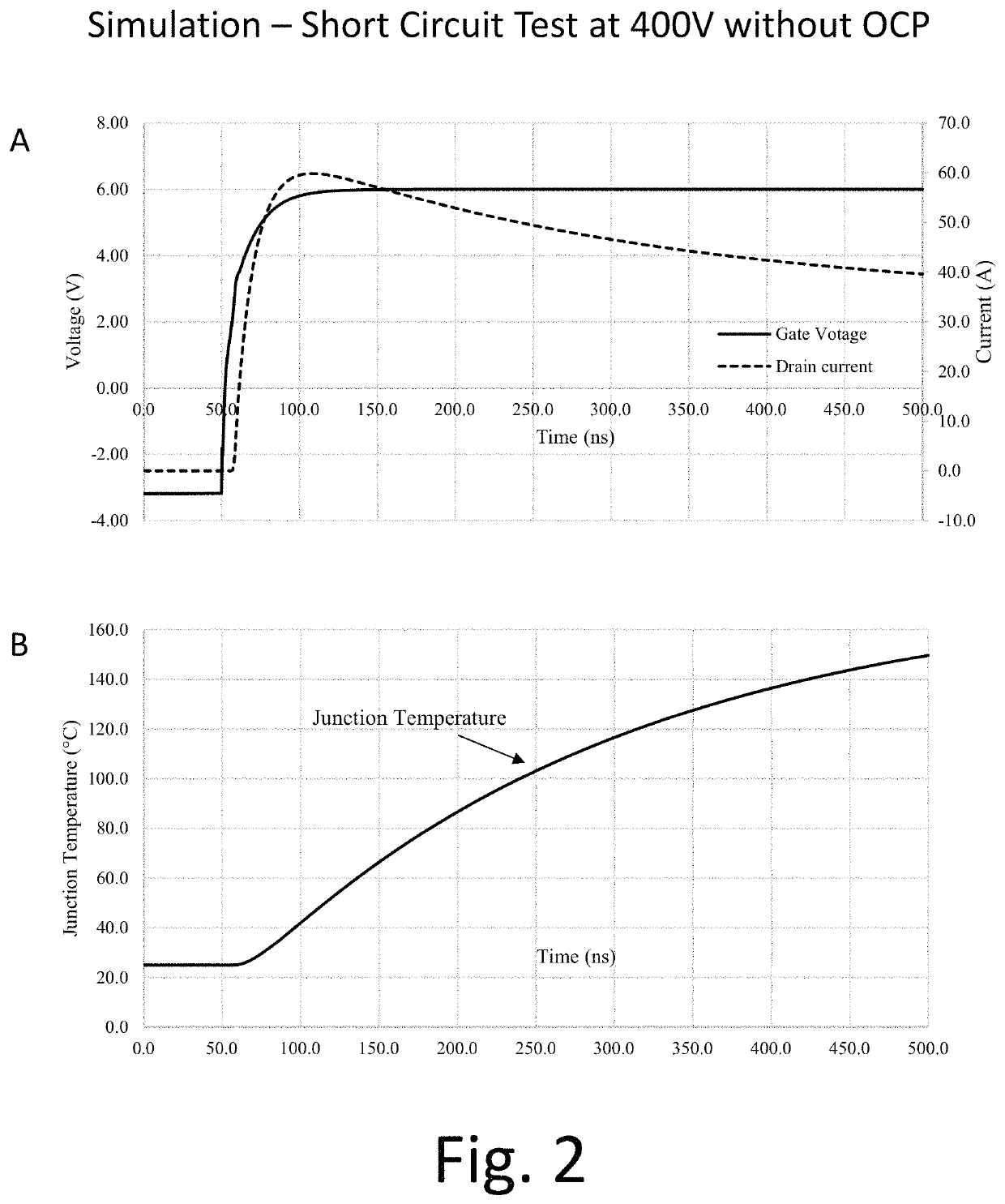

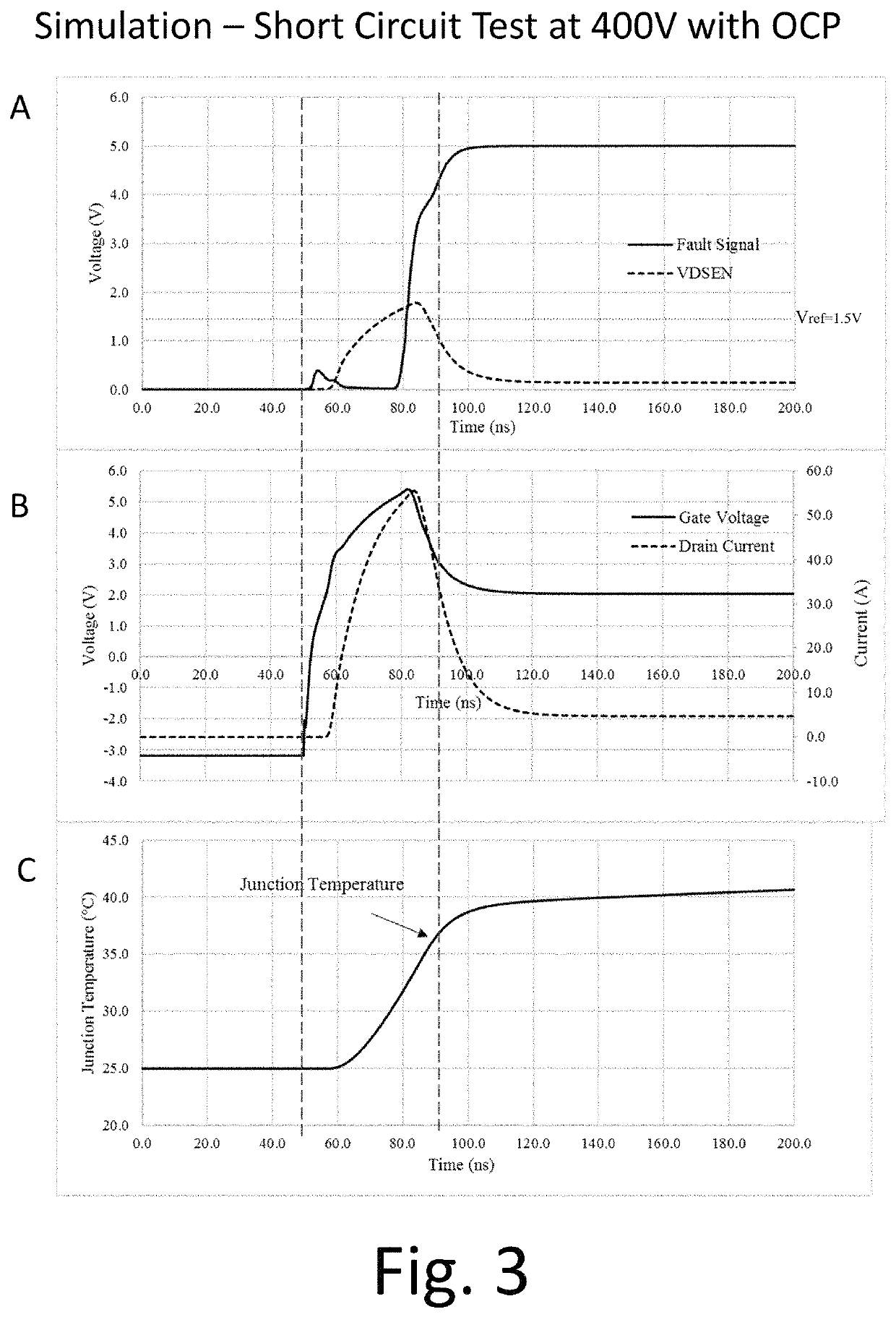

GaN transistor with integrated drain voltage sense for fast overcurrent and short circuit protection

A GaN power switching device comprises a GaN transistor switch SW_MAIN has an integrated drain voltage sense circuit, which comprises GaN sense transistor SW_SEN and GaN sense resistor RSEN, which at turn-on form a resistive divider for sensing the drain voltage of SW_MAIN to provide a drain voltage sense output VDSEN. Fault detection logic circuitry of a driver circuit generates a fault signal FLT when VDSEN reaches or exceeds a reference voltage Vref, which triggers fast turn-off of the gate of SW_MAIN, e.g. within less than 100 ns of an overcurrent or short circuit condition. During turn-off, RSEN resets VDSEN to zero. For two stage turn-off, the driver circuit further comprises fast soft turn-off circuitry which is triggered first by the fault signal to pull-down the gate voltage to the threshold voltage, followed by a delay before full turn-off of the gate of SW_MAIN by the gate driver.

Owner:GAN SYST

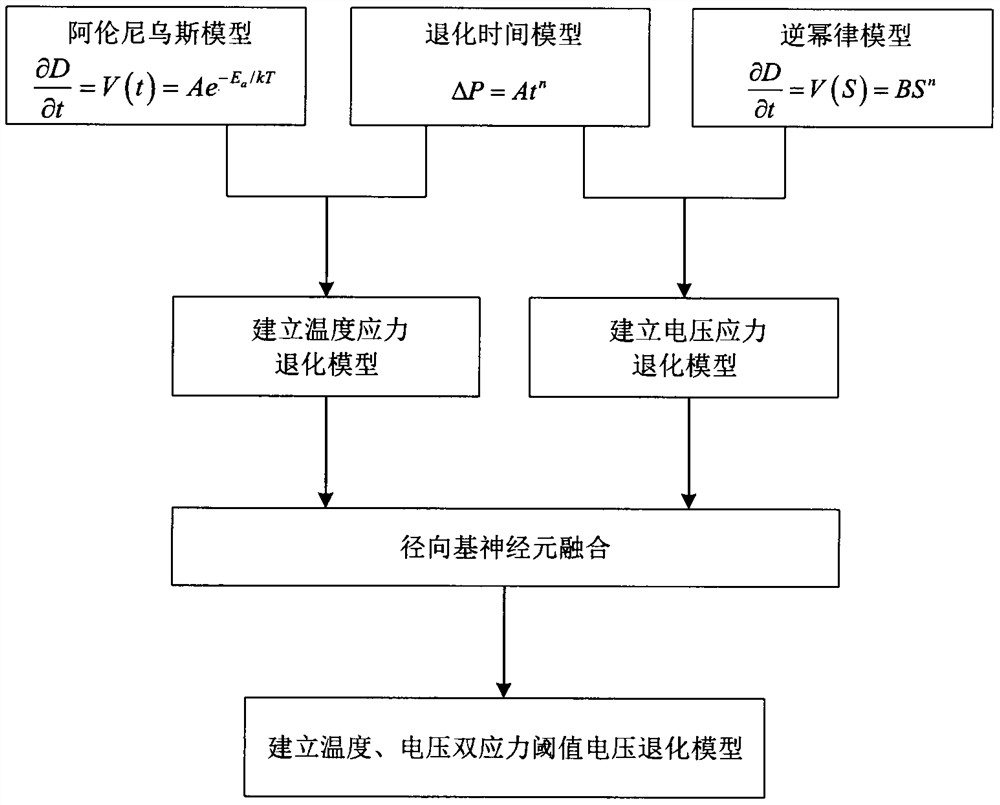

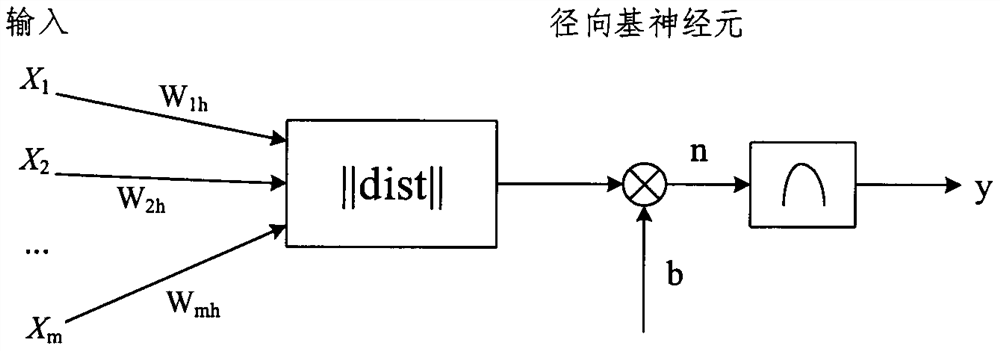

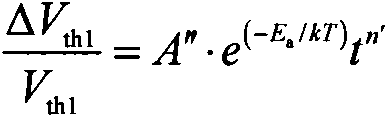

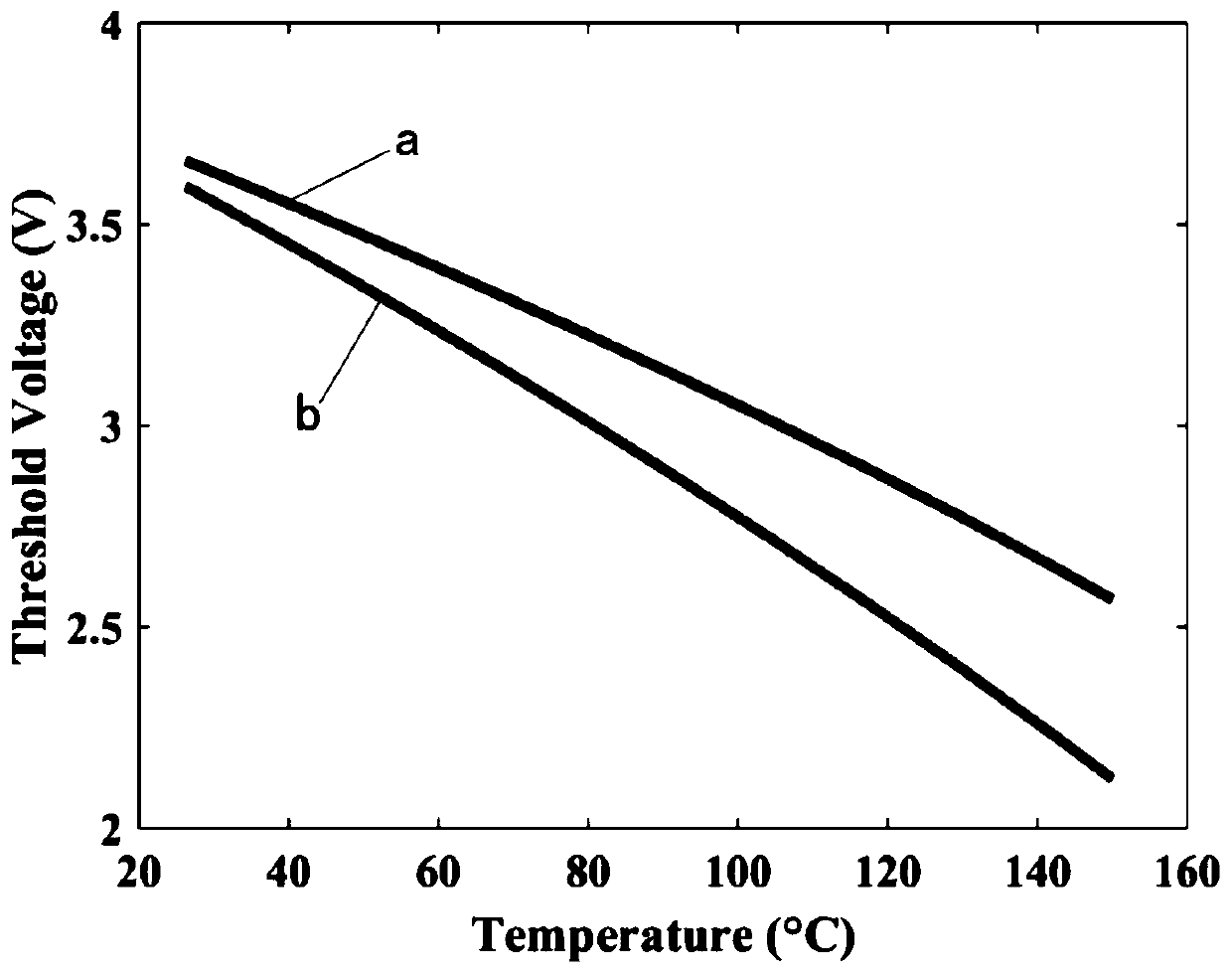

SiC power tube threshold voltage degradation model under temperature and voltage stress

PendingCN112100914AReduce complexityImprove versatilityDesign optimisation/simulationSpecial data processing applicationsComputational physicsPower MOSFET

The invention discloses a SiC power tube threshold voltage degradation model under temperature and voltage stress. The SiC power tube threshold voltage degradation model under temperature and voltagestress comprises the specific steps: firstly, establishing a single stress degradation model of SiC power MOSFET threshold voltage under temperature stress and voltage stress according to an Arrheniusmodel, an inverse power law model and a degradation time model; and then fusing the obtained two single-stress threshold voltage degradation models into a threshold voltage degradation model of the SiC power MOSFET under temperature and voltage coupling dual stress by using three radial basis neurons. According to the method, the single-stress physical degradation model of the threshold voltage of the SiC power MOSFET is combined with the radial basis neurons, and the threshold voltage degradation model with higher universality under the working condition of considering both temperature and voltage is established, so that the degradation trend of the SiC power MOSFET can be accurately evaluated.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

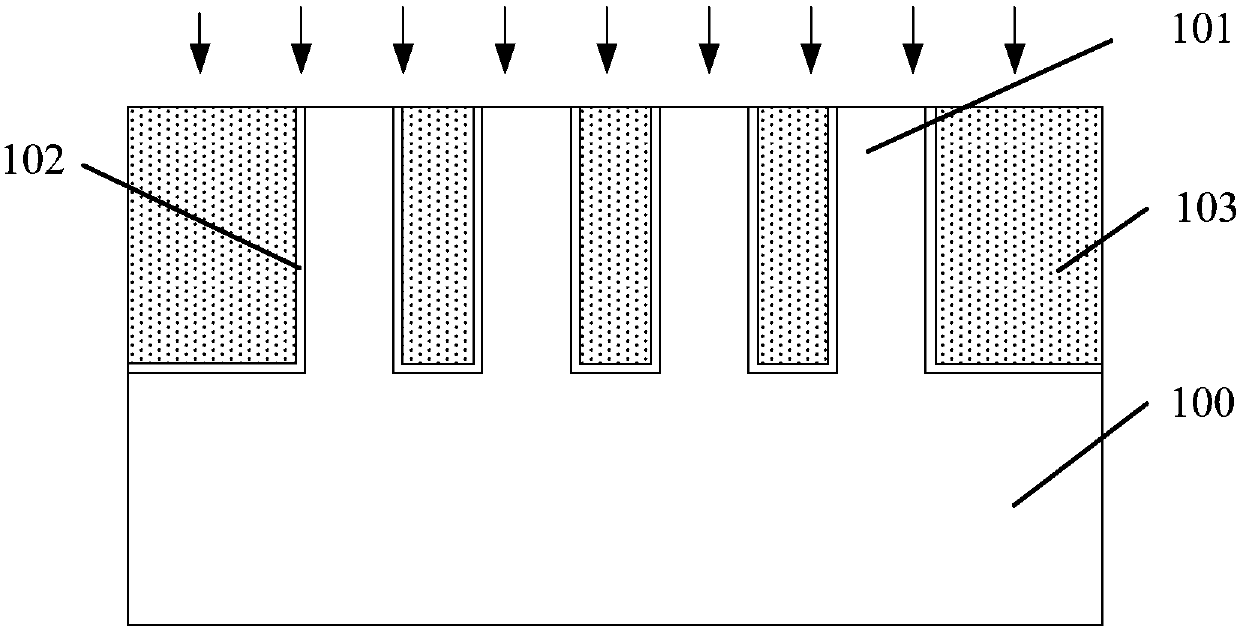

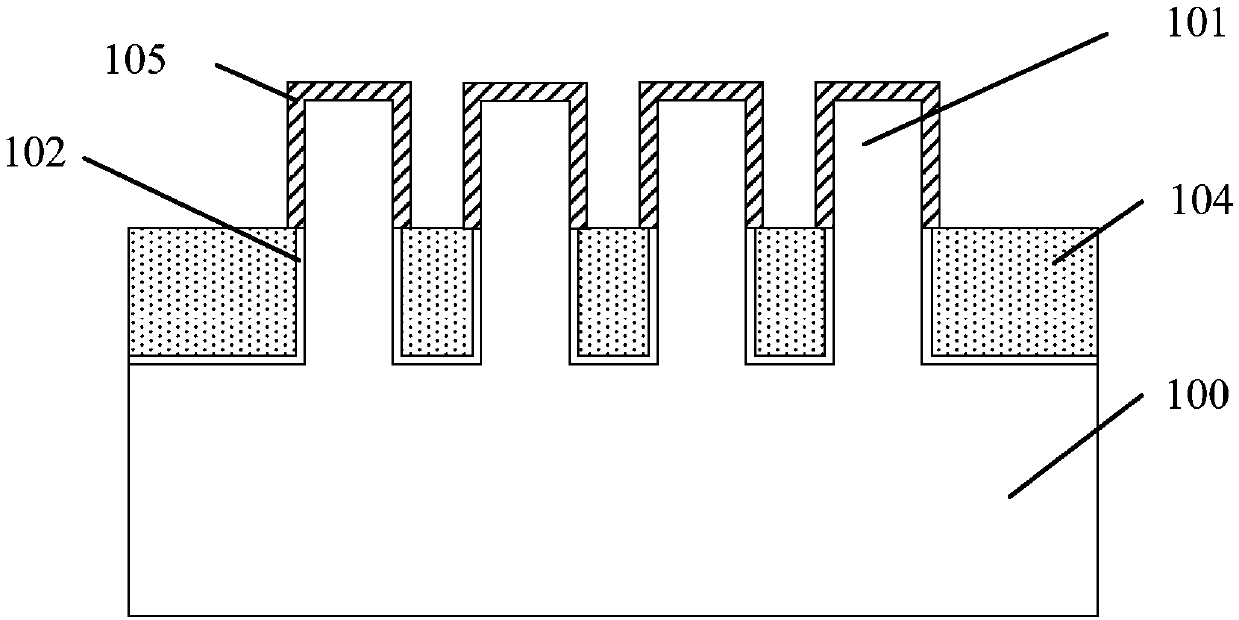

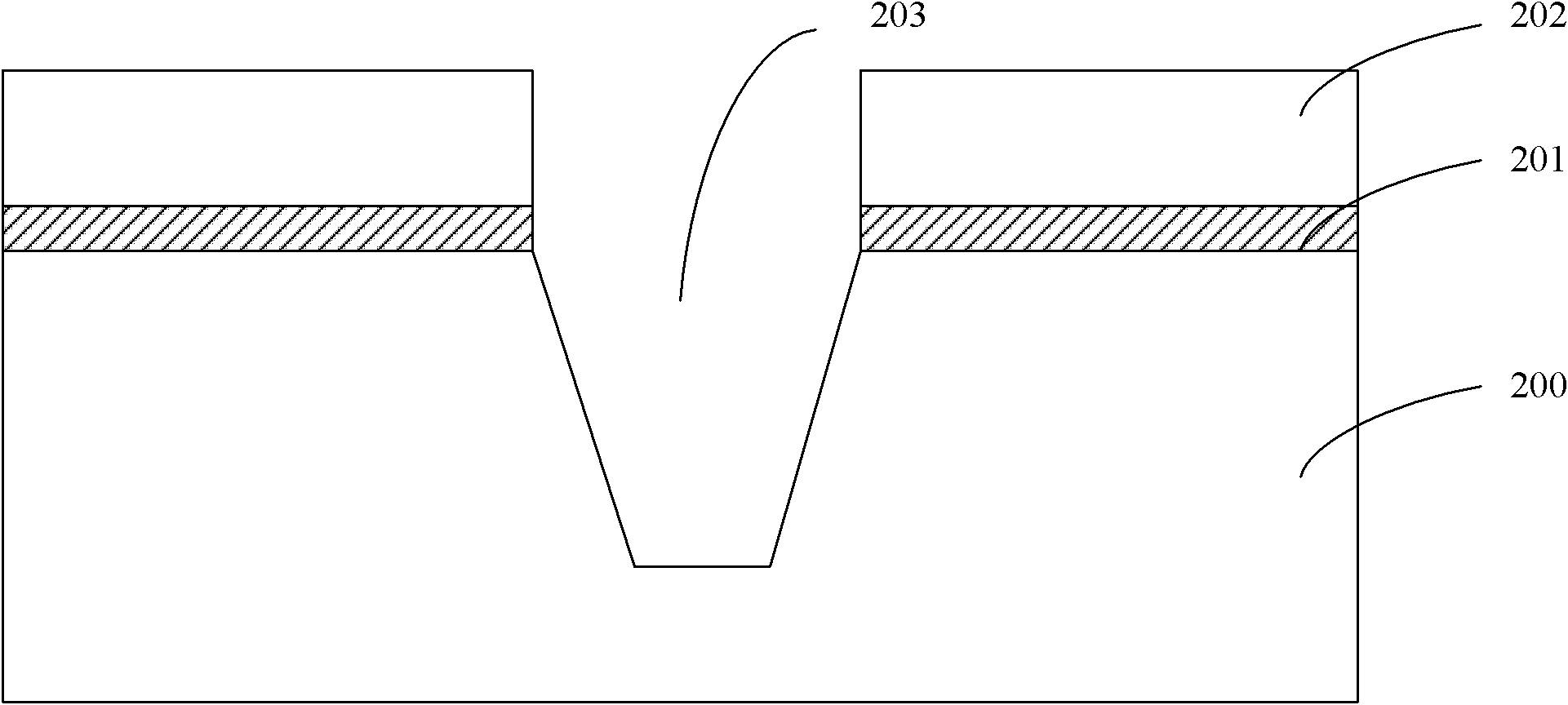

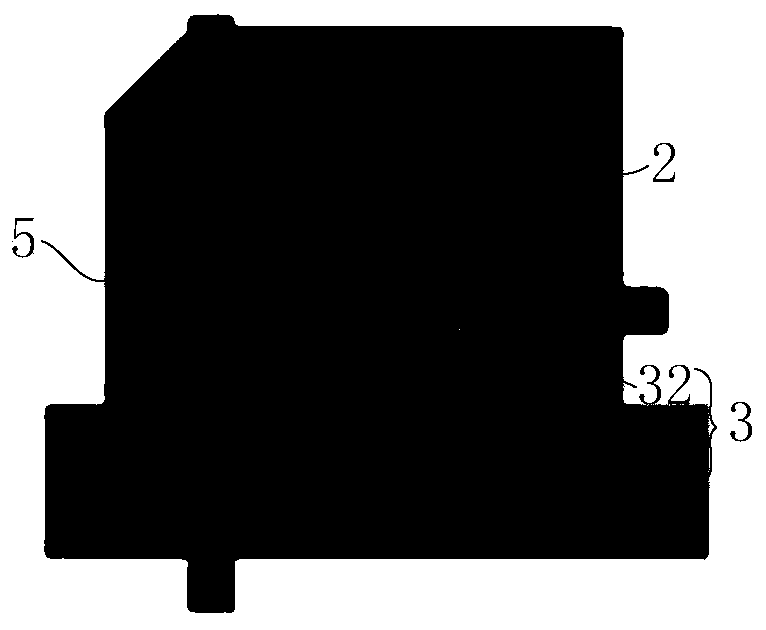

Method of forming semiconductor device

The present invention provides a method of forming a semiconductor device. The method comprises the steps of: providing a substrate having a fin thereon; forming a dummy gate oxide layer at the side wall and the top portion of the fin; forming a protection layer on the dummy gate oxide layer; forming an isolation layer on the substrate, wherein the isolation layer is located on the protection layer and covers the side wall of the fin; performing ion doping for the fin after the isolation layer is formed; and removing the part of the isolation layer to form an isolation structure covering partof the side wall of the fin, wherein the isolation structure exposes part of the protection layer. The method of forming a semiconductor device forms the dummy gate oxide layer prior to ion doping toavoid the thermal effect in the process of forming the dummy gate oxide layer through thermal treatment, the thermal effect can allow the doped ions doped in the fin to be diffused, the diffusion of the doped ions can reduce the ion doping dosage in the fin to cause the threshold voltage drop and influence the device performance.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Usage-based temporal degradation estimation for memory elements

InactiveUS20130138403A1Analogue computers for electric apparatusComputation using non-denominational number representationInstabilityData filling

Methods and systems for computing threshold voltage degradation of transistors in an array of memory cells are disclosed. In accordance with one method, a process that models an expected usage of the array is selected. In addition, a hardware processor can run the process to populate the array with data over time to simulate the expected usage of the array. The method further includes compiling data that detail different durations at which each of the memory cells in the array stores 1 or at which each of the memory cells in the array stores 0. For each separate grouping of memory cells that share a common duration of the different compiled durations, a threshold voltage degradation is determined for each transistor in the corresponding grouping of cells based on at least one biased temperature instability model.

Owner:GLOBALFOUNDRIES INC

Threshold voltage degradation measuring circuit

ActiveCN102636678BSimple structureEasy to operateCurrent/voltage measurementVoltage variationDirect current

Owner:PEKING UNIV

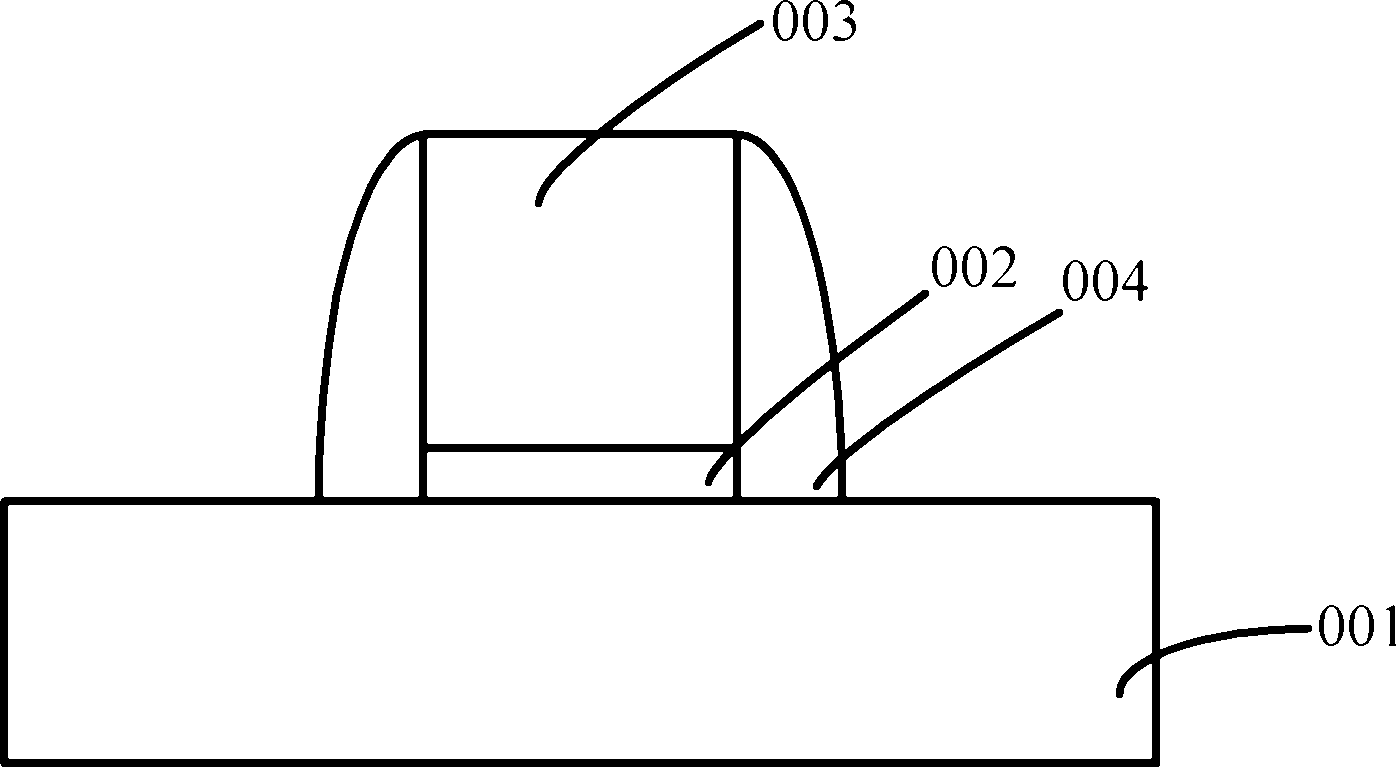

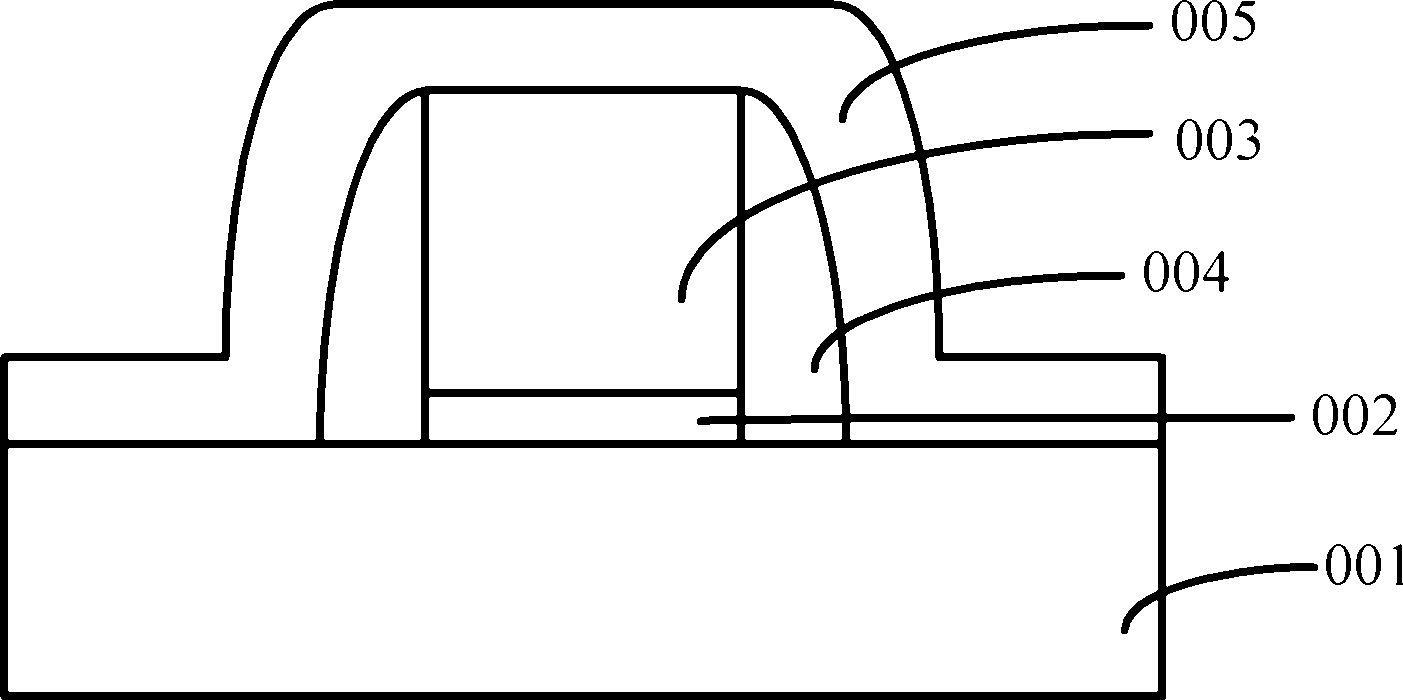

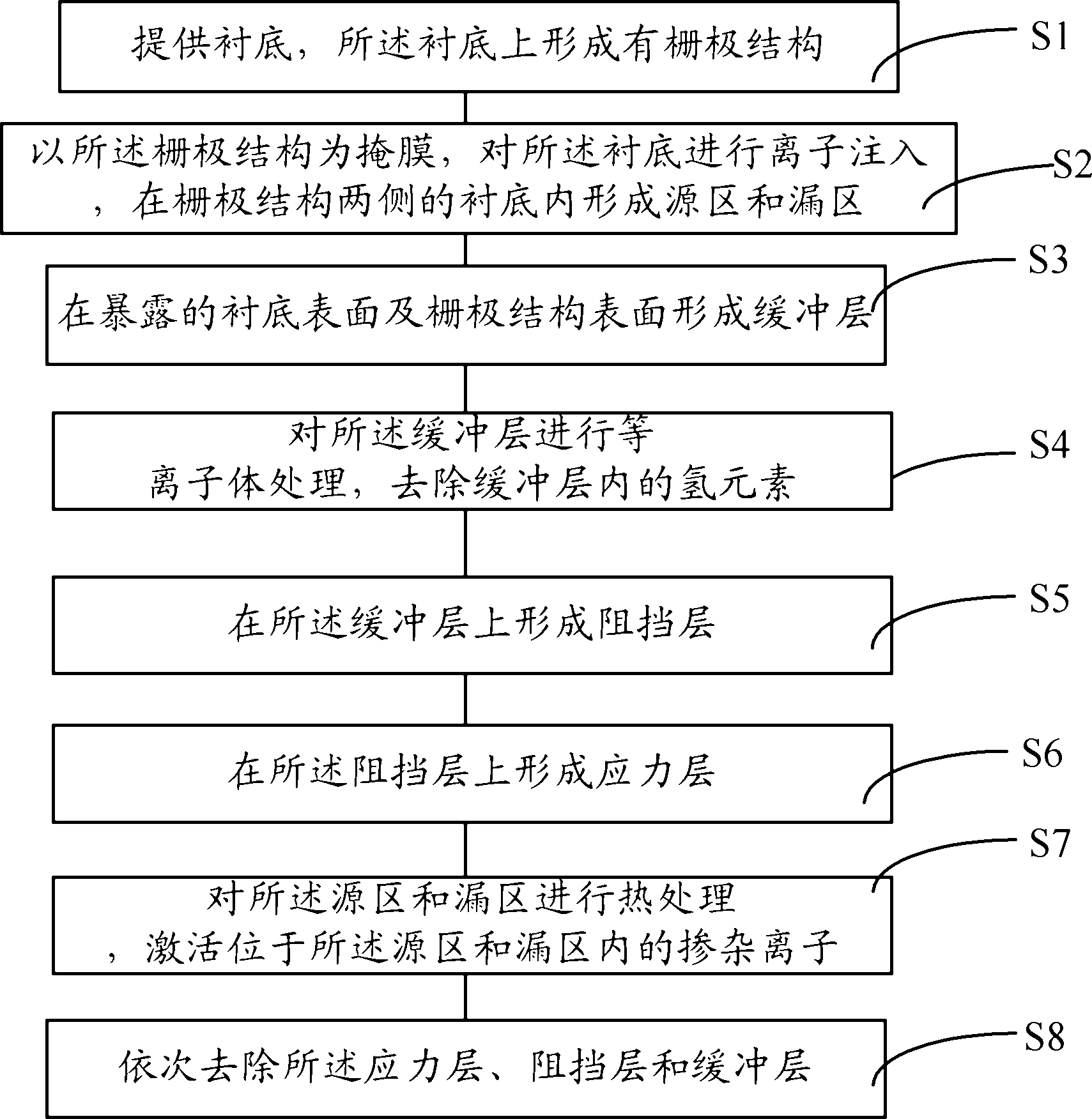

Method for forming NMOS (N-channel Metal Oxide Semiconductor) transistor

ActiveCN102569090BHigh densityImprove reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesHydrogenOptoelectronics

The invention provides a method for forming an NMOS (N-channel Metal Oxide Semiconductor) transistor. The method comprises the following steps of: providing a substrate and a grid structure located on the substrate; taking the grid structure as a mask to carry out ion implantation on the substrate, and forming a source area and a drain area in the substrate at the both sides of the grid structure; forming a stopping layer on the exposed surfaces of the substrate and the grid structure; forming a stress layer on the stopping layer, wherein the stopping layer is used for preventing hydrogen elements used in the forming environment of the stress layer from entering the source area and the drain area; carrying out heat treatment on the source area and the drain area; and removing the stopping layer and the strain layer. According to the method disclosed by the invention, the compact stopping layer is formed on the surfaces of the substrate and the grid structure before the stress layer is formed, so as to prevent the hydrogen elements used in the forming environment of the stress layer from entering the source area / drain area in the substrate. Therefore, the problem of descending of threshold voltage, caused when the diffusion of doped ions in the source area / drain area is enhanced by the hydrogen elements, is solved, the reliability of the threshold voltage is improved, and the property reliability of the NMOS transistor is further improved.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP

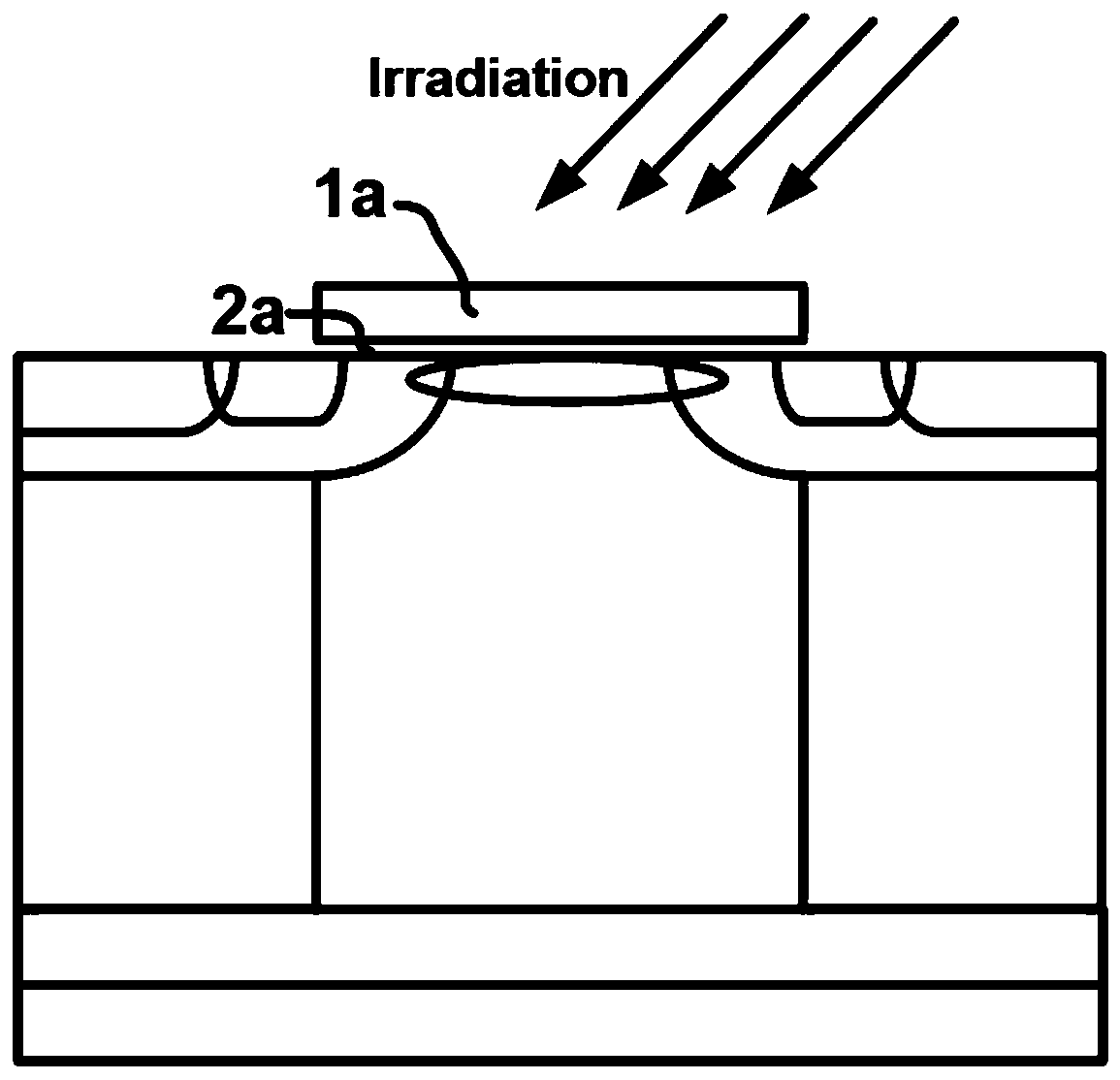

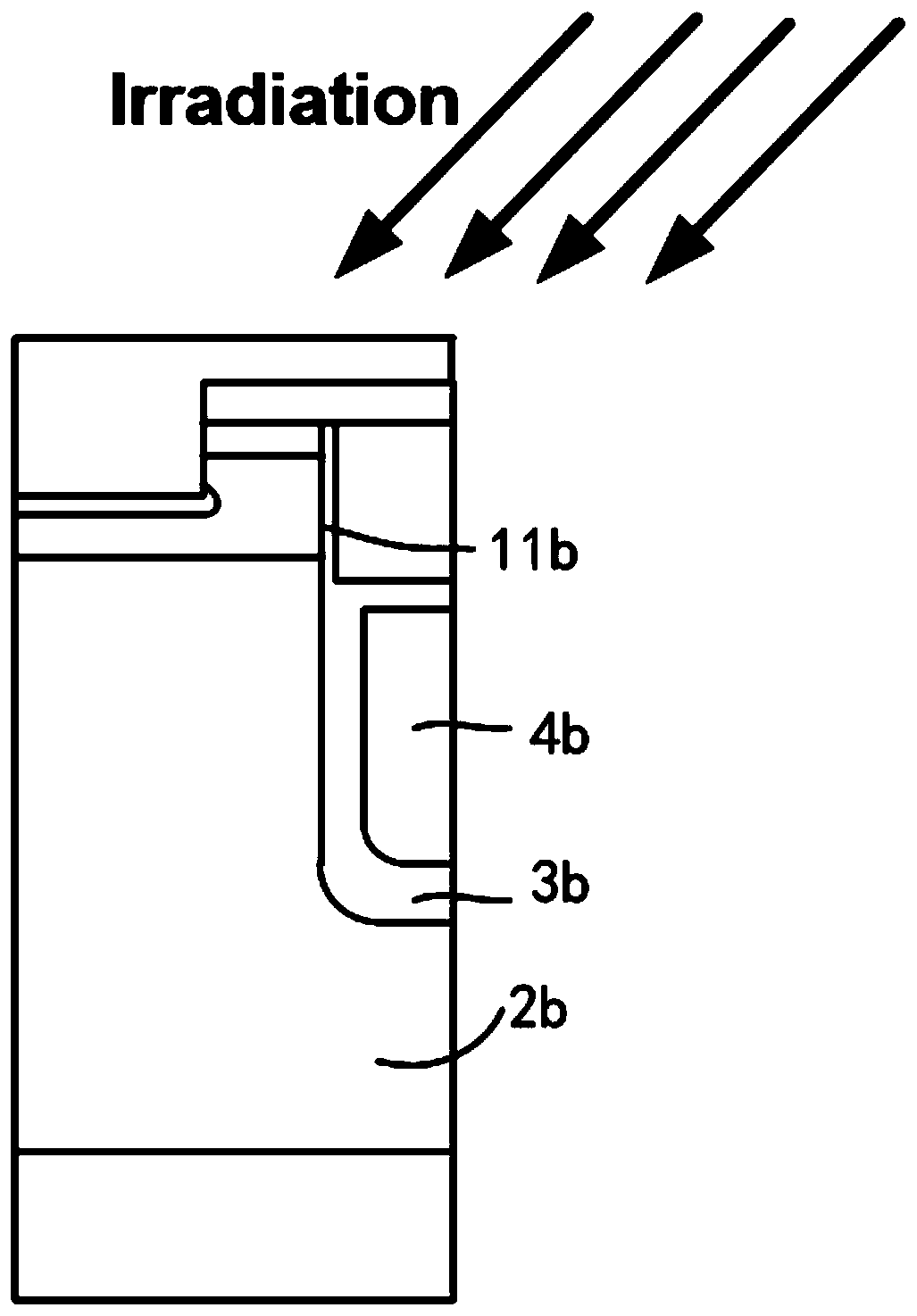

Method for recovering threshold voltage reduction of MOSFET after irradiation

PendingCN110783203AAlleviate the problem of severe threshold voltage dropRecovery Threshold VoltageSemiconductor/solid-state device manufacturingSemiconductor devicesElectron holeEngineering

The invention discloses a method for recovering the threshold voltage reduction of a MOSFET after irradiation. The method comprises the following steps: step 1, providing the MOSFET, wherein the MOSFET is irradiated; and step 2: applying a voltage of a certain value to the gate or the drain of the MOSFET for a period of time so that a part of electrons enter the oxide layer of the gate of the MOSFET and are recombined with the trapped holes. The voltage is applied to the gate or the drain of the irradiated MOSFET so that the electrons enter the oxide layer of the gate and are recombined with trapped holes, the threshold voltage of the device can be recovered and the problem of severe threshold voltage reduction of the MOSFET at high temperature can be alleviated.

Owner:SHENZHEN SANRISE TECH CO LTD

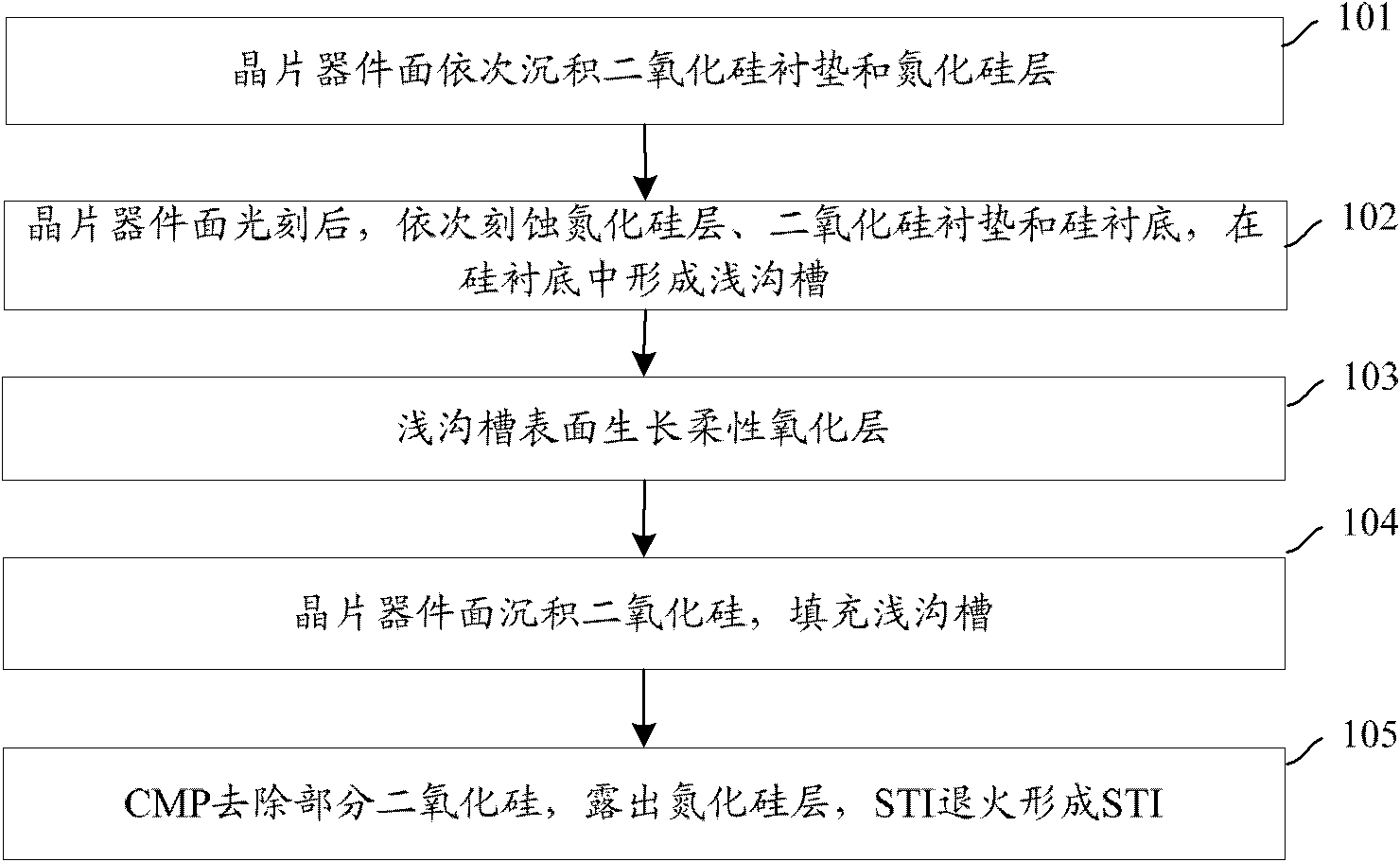

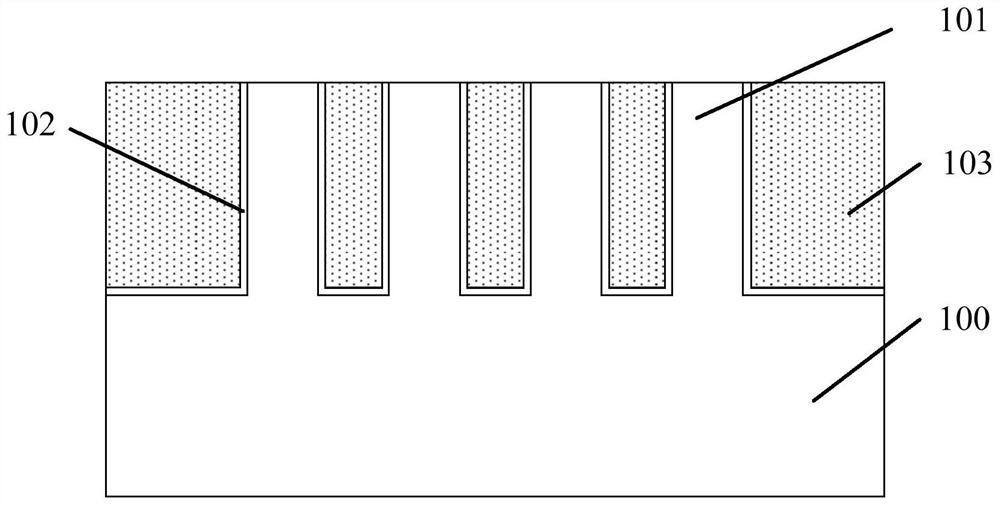

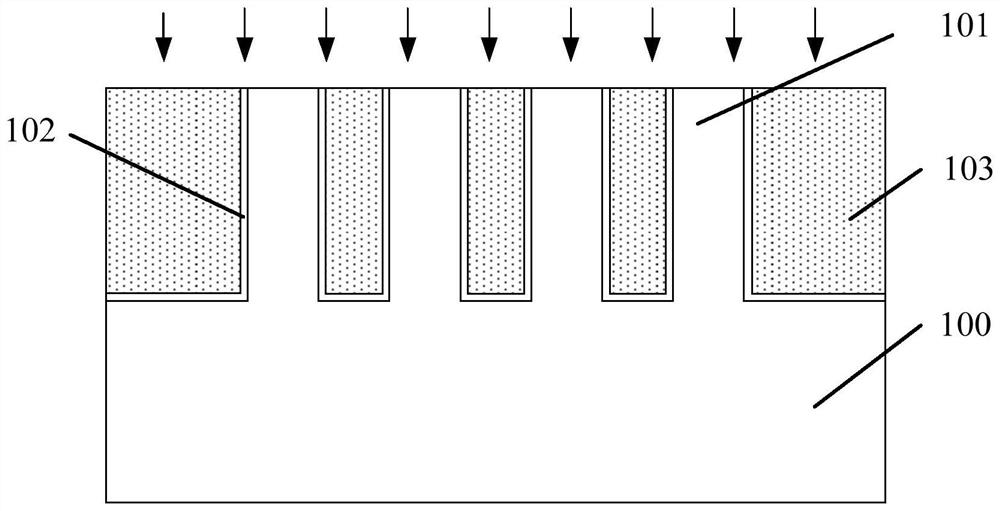

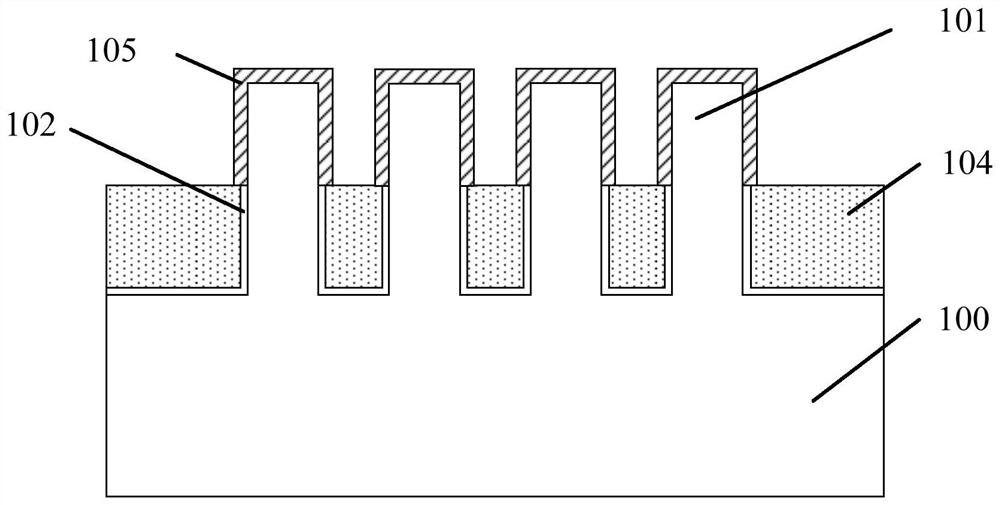

Manufacturing method of STI (shallow trench insulation)

ActiveCN102543824BGuaranteed concentrationLower threshold voltageSemiconductor/solid-state device manufacturingEtchingSilicon oxide

The invention provides a manufacturing method of STI (shallow trench insulation). The method comprises the following steps: firstly growing an LO (lining oxide) on the surface of a shallow trench which is formed in a substrate through etching, and then carrying out primary boron element doping and secondary nitrogen element doping on the LO; forming a first barrier layer with boron ion concentration which is 1-2 orders of magnitude higher than a P well at the part, adjacent to the substrate region, of the LO; forming a second barrier layer above the first barrier layer; and finally, depositing silicon oxide in the shallow trench, carrying out CMP(chemical mechanical polishing) and STI annealing, thus forming the STI. The manufacturing method provided by the invention utilizes the second barrier layer to block boron ions in the first barrier layer so as to keep the concentration of the boron ions in the first barrier layer; the concentration of the boron ions in the first barrier layer is higher than the P well, in a follow-up P well annealing process, and the first barrier layer can be used for effectively preventing the boron ions in the P well from passing through the LO so as to diffuse into the STI; and the concentration of the boron ions injected into the P well is kept, and the performance of an NMOS (N-channel mental-oxide-semiconductor) device is prevented from being influenced by the degression of a threshold voltage caused by the reduction of the concentration of the boron ions.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

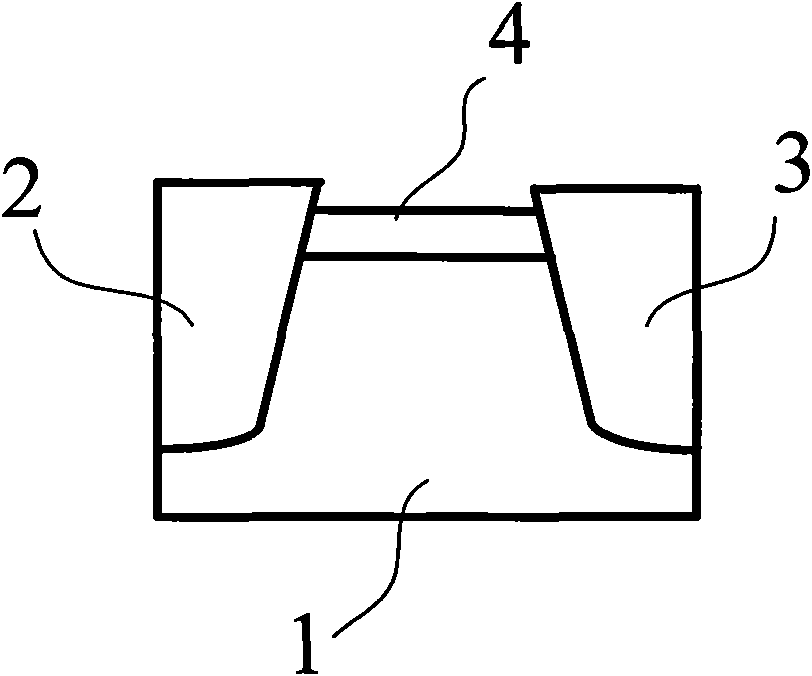

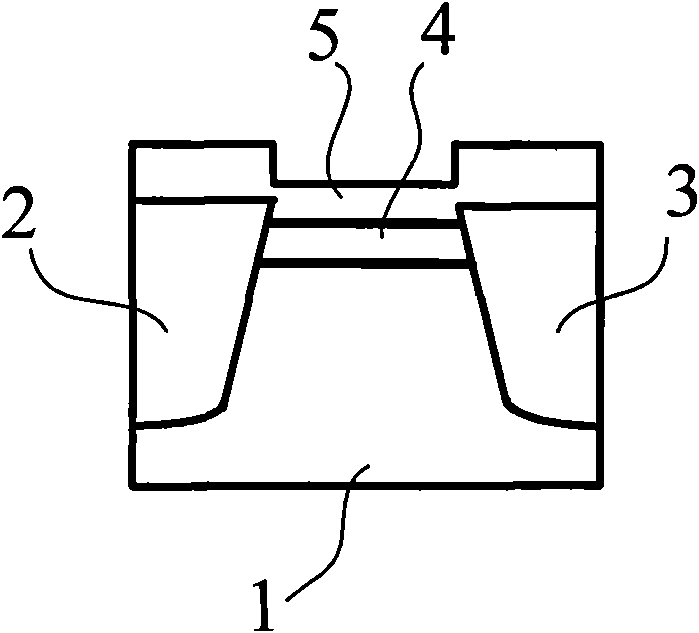

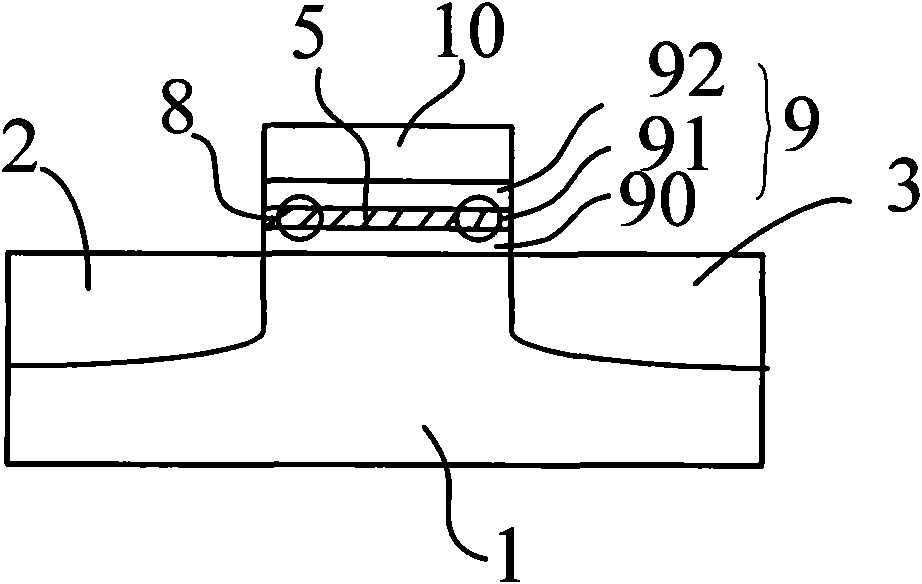

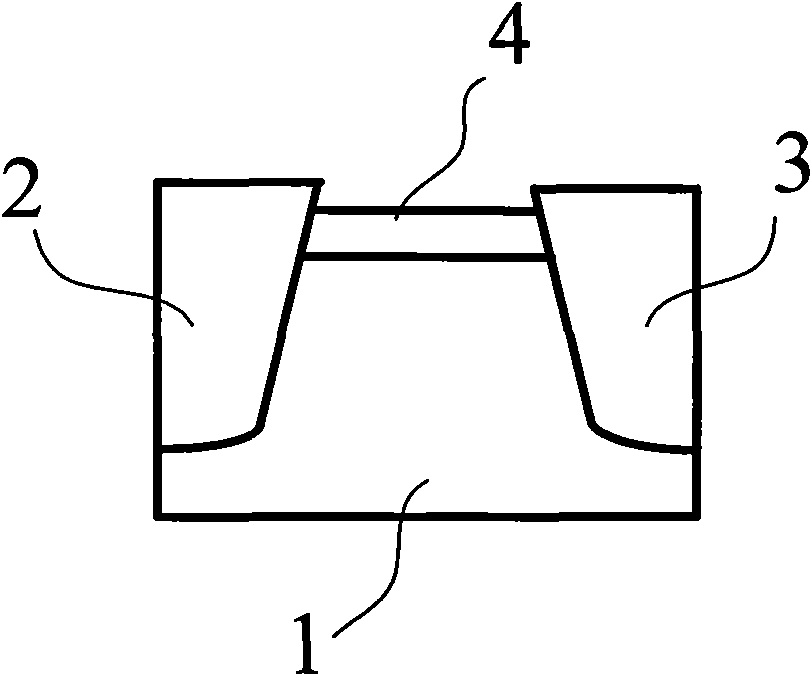

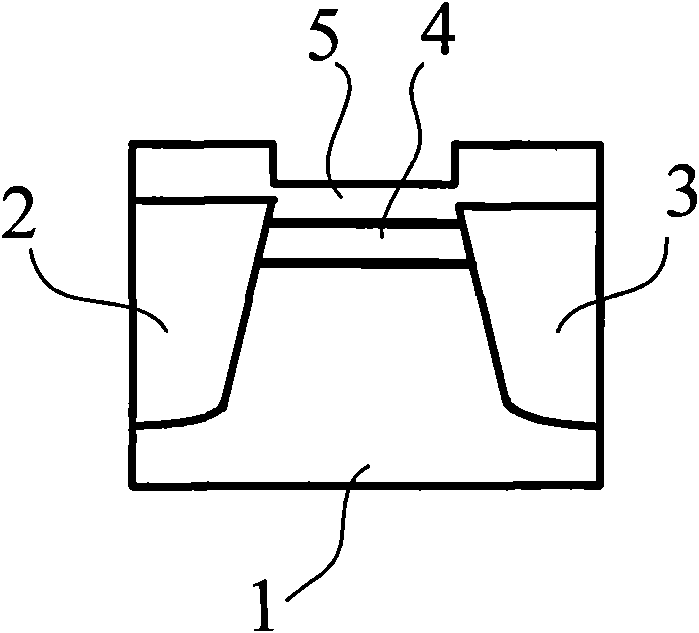

Manufacturing method of NROM and device thereof

InactiveCN101894801ALower threshold voltageImprove leakage currentSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerSemiconductor

The invention discloses a manufacturing method of an NROM and a device thereof. The method comprises the following steps of: forming a source electrode and a drain electrode below a working surface of a semiconductor substrate; etching a chute on the semiconductor substrate between the source electrode and the drain electrode, and infusing silicon ion on the chute section of the semiconductor substrate so as to ensure non-crystallization of the semiconductor substrate on the surface of the chute; forming an ONO insulation layer on the surfaces of the semiconductor substrate, the source electrode and the drain electrode, wherein the ONO insulation layer is projected corresponding to the section of the chute and is inlayed in the chute of the semiconductor substrate; and forming a control grid on the surface of the ONO insulation layer between the source electrode and the drain electrode. Compared with the NROM device with reduced size in equal proportion, the NROM device during operation relatively lengthens the effective chute and solves all kinds of problems resulting from reducing the length of the chute, such as declination of the threshold voltage of the device, higher leakage current and interference generated between two locations.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Method of forming semiconductor device

ActiveCN109560047BAvoid damageReduce lossTransistorSolid-state devicesDevice materialPhysical chemistry

The present invention provides a method of forming a semiconductor device. The method comprises the steps of: providing a substrate having a fin thereon; forming a dummy gate oxide layer at the side wall and the top portion of the fin; forming a protection layer on the dummy gate oxide layer; forming an isolation layer on the substrate, wherein the isolation layer is located on the protection layer and covers the side wall of the fin; performing ion doping for the fin after the isolation layer is formed; and removing the part of the isolation layer to form an isolation structure covering partof the side wall of the fin, wherein the isolation structure exposes part of the protection layer. The method of forming a semiconductor device forms the dummy gate oxide layer prior to ion doping toavoid the thermal effect in the process of forming the dummy gate oxide layer through thermal treatment, the thermal effect can allow the doped ions doped in the fin to be diffused, the diffusion of the doped ions can reduce the ion doping dosage in the fin to cause the threshold voltage drop and influence the device performance.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

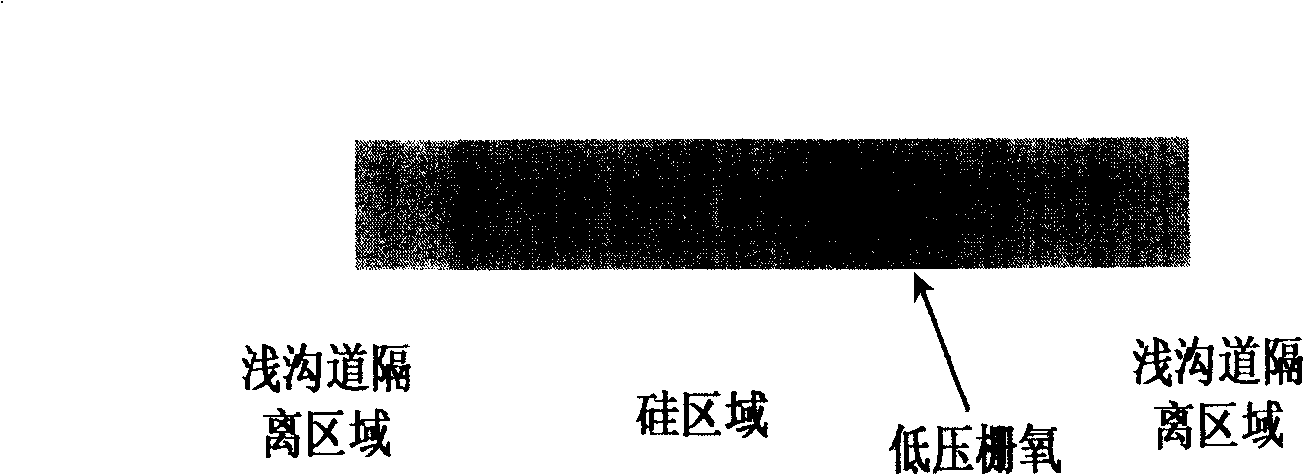

MOS field effect pipe and its production

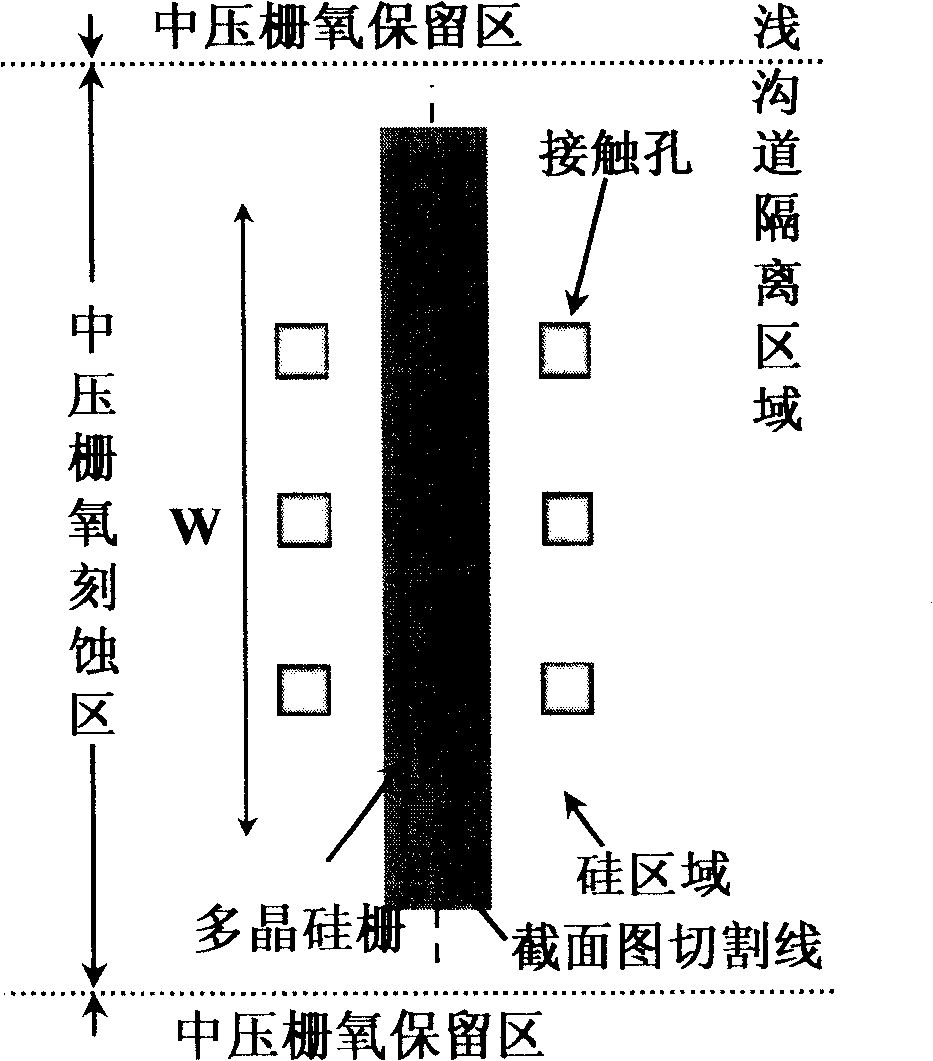

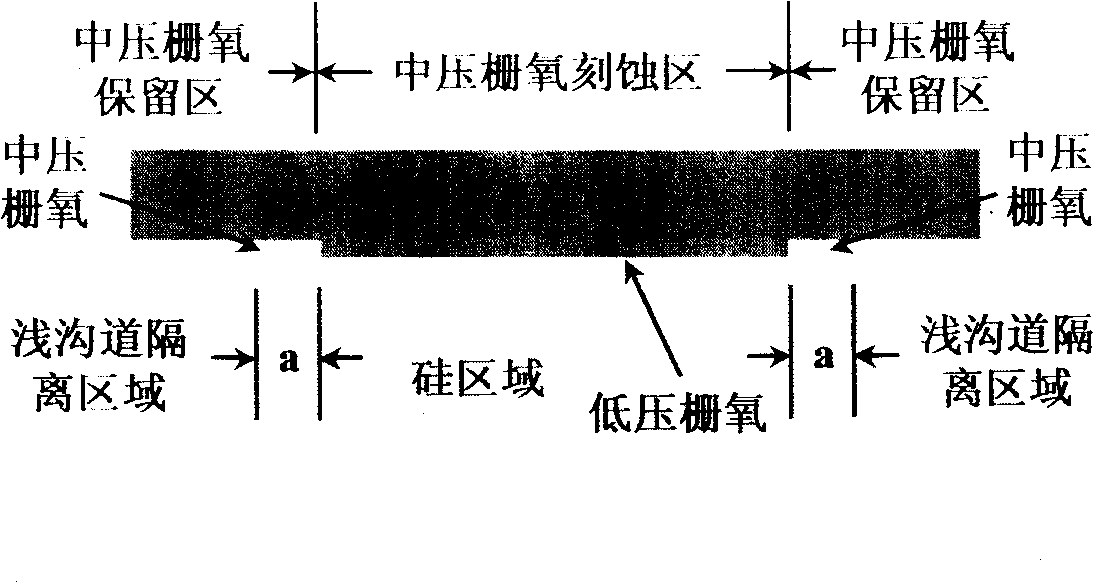

ActiveCN100446273CRaise the threshold voltageImproved anti-narrow channel effectSemiconductor/solid-state device manufacturingSemiconductor devicesLow voltageEngineering

The invention discloses a method for manufacturing a MOS field effect transistor. In the double gate oxide etching step, only the medium-voltage thick gate oxide in the middle part of the silicon region of the low-voltage MOS tube is etched away, and the two ends in the width direction of the MOS tube are kept close to the From somewhere within the silicon region at the junction of the shallow trench isolation region and the silicon region to a medium voltage thick gate oxide at the junction of the shallow trench isolation region and the silicon region. The invention improves the threshold voltage of the total transistor of the low-voltage MOS field effect transistor by retaining the medium-voltage thick gate oxide at the edge of the silicon region of the low-voltage MOS transistor, and improves the problem of threshold voltage drop caused by the reverse narrow channel effect of the MOS field effect transistor.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

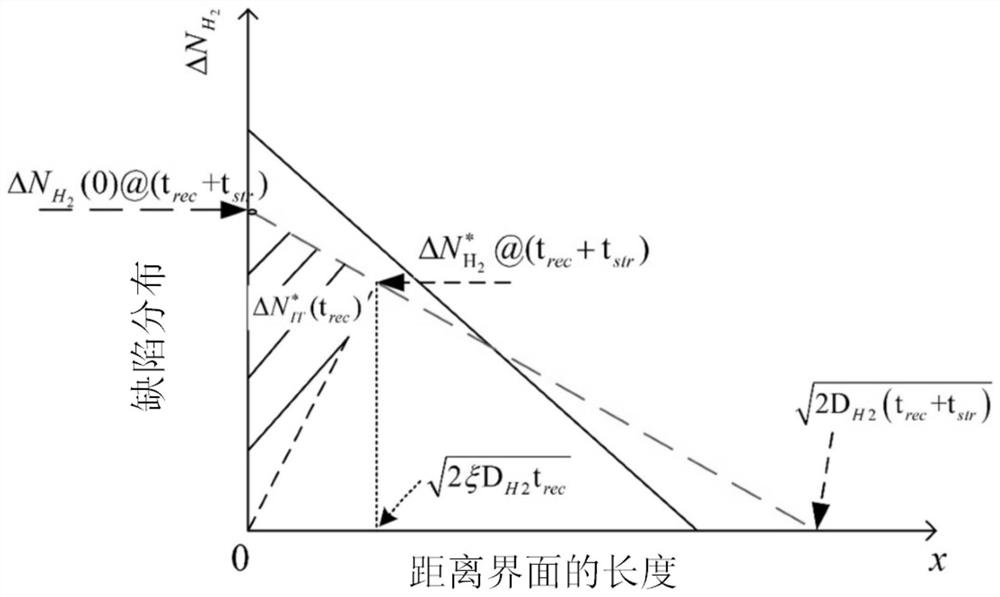

A method for obtaining nbti degradation model based on non-uniform distribution of interface traps

ActiveCN107220477BFew fitting parametersWide applicabilityDesign optimisation/simulationInformaticsDistribution frameComputational physics

The invention discloses an NBTI degradation model obtaining method based on nonuniform distribution interface traps. The method comprises the steps that 1, interface trap distributions in different zone of an MOS device are divided to obtain total distribution frame of the interface traps; 2, according to geometric construction, the interface trap distribution density in each zone is calculated, and the total density of the nonuniform distribution interface traps is obtained; 3, threshold voltage deviation caused by NBTI is obtained according to the deltaNIT total density, and an NBTI degradation model based on geometric construction analysis is obtained. The actual distribution situation of the interface traps produced by an NBTI effect is incorporated in the model, accordingly the total density of interface trap charges produced in the MOS device can be accurately calculated, thus a threshold voltage degradation model is obtained, few fitting parameters are required, the applicability is wide, and the model provides more accurate precision for device reliability.

Owner:EAST CHINA NORMAL UNIV +1

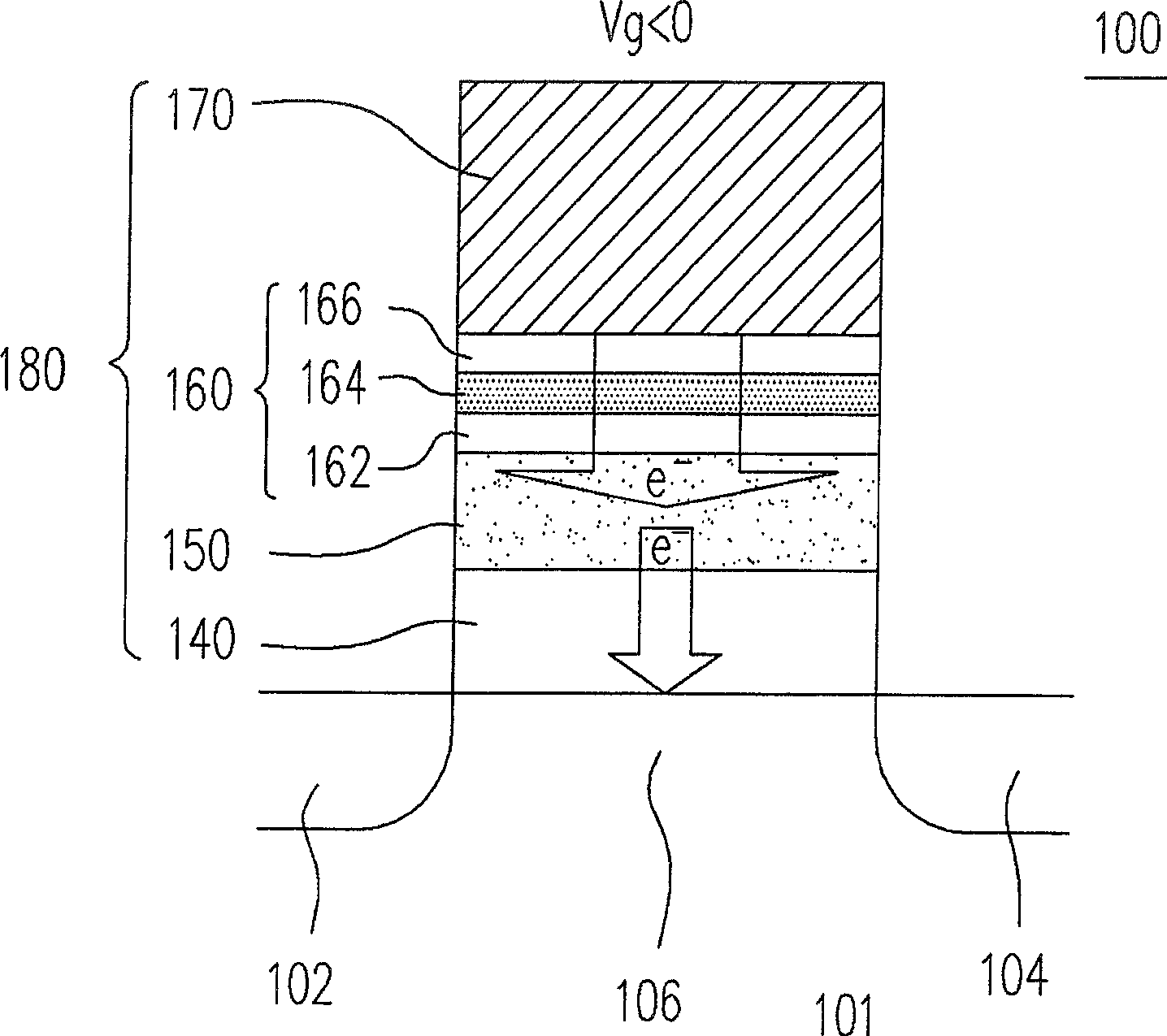

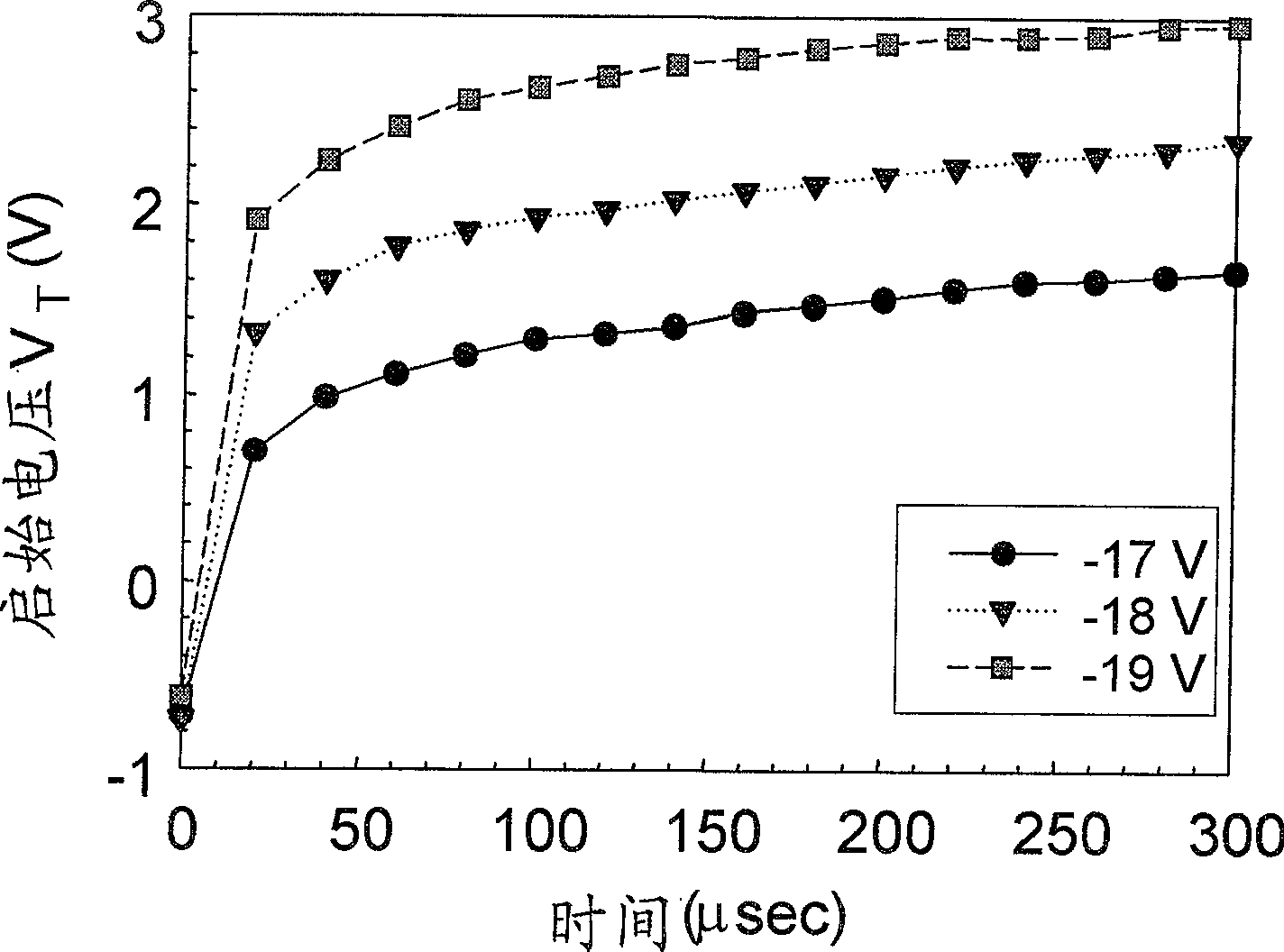

Method for operating non-volatile memory element

A method for operating nonvolatile memory element includes exerting negative bias at gate electrode, utilizing-FN tunneling mechanism to make electron inject into electric charge storage layer from gate electrode of memory unit and via multiplayer tunneling dielectric structure for causing initial voltage-rise of memory unit, exerting a positive bias on gate electrode, utilizing + FN tunneling mechanism to make electric cavity inject into said electric charge layer from said gate electrode of memory unit and via said tunneling dielectric structure for causing initial voltage-drop of memory unit.

Owner:MACRONIX INT CO LTD

Manufacturing method of NROM and device thereof

InactiveCN101894801BLower threshold voltageImprove leakage currentSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerReduced size

The invention discloses a manufacturing method of an NROM and a device thereof. The method comprises the following steps of: forming a source electrode and a drain electrode below a working surface of a semiconductor substrate; etching a chute on the semiconductor substrate between the source electrode and the drain electrode, and infusing silicon ion on the chute section of the semiconductor substrate so as to ensure non-crystallization of the semiconductor substrate on the surface of the chute; forming an ONO insulation layer on the surfaces of the semiconductor substrate, the source electrode and the drain electrode, wherein the ONO insulation layer is projected corresponding to the section of the chute and is inlayed in the chute of the semiconductor substrate; and forming a control grid on the surface of the ONO insulation layer between the source electrode and the drain electrode. Compared with the NROM device with reduced size in equal proportion, the NROM device during operation relatively lengthens the effective chute and solves all kinds of problems resulting from reducing the length of the chute, such as declination of the threshold voltage of the device, higher leakagecurrent and interference generated between two locations.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Thin film transistor, preparation method thereof, array substrate, display panel and device

PendingCN110620154AReduce generationReduce concentrationTransistorSolid-state devicesWork performanceDisplay device

The invention belongs to the technical field of display and discloses a thin film transistor, a preparation method thereof, an array substrate, a display panel and a display device. The thin film transistor comprises a substrate, as well as an active layer and a source-drain electrode which are sequentially stacked on the substrate; and the projection of a source electrode in the source-drain electrode on the substrate is overlapped with the projection of part of the edge of the active layer on the substrate. According to the thin film transistor, the illumination-receiving area of the activelayer is small, so that the generation of holes can be effectively reduced, the concentration of photon-generated carriers under an illumination condition is reduced, and therefore, the defect statessuch as hole capture probability increase and threshold voltage reduction, of the TFT working in a high-temperature illumination environment are avoided, and the performance of the TFT device in the high-temperature illumination environment is improved. When the thin film transistor is applied to the display panel, the working performance of the display product in a high-temperature environment can be improved, and the reliability of the display product is enhanced.

Owner:HEFEI XINSHENG OPTOELECTRONICS TECH CO LTD +1

Usage-based temporal degradation estimation for memory elements

InactiveUS9058448B2Analogue computers for electric apparatusComputation using non-denominational number representationInstabilityCell based

Owner:GLOBALFOUNDRIES INC

Substrate including oxide thin film transistor, method for fabricating the same, and driving circuit for liquid crystal display device using the same

ActiveUS8847294B2Increase incidenceTransistorStatic indicating devicesLiquid-crystal displayOxide thin-film transistor

There are provided a substrate including an oxide TFT having improved initial threshold voltage degradation characteristics included in a driving circuit of a liquid crystal display (LCD) device, a method for fabricating the same, and a driving circuit for an LCD device using the same. The substrate including an oxide thin film transistor (TFT) includes: a base substrate divided into a pixel region and a driving circuit region; and a plurality of TFTs formed on the base substrate, wherein an initial threshold voltage of at least one of the plurality of TFTs formed in the driving circuit region is positive-shifted to have a predetermined level.

Owner:LG DISPLAY CO LTD

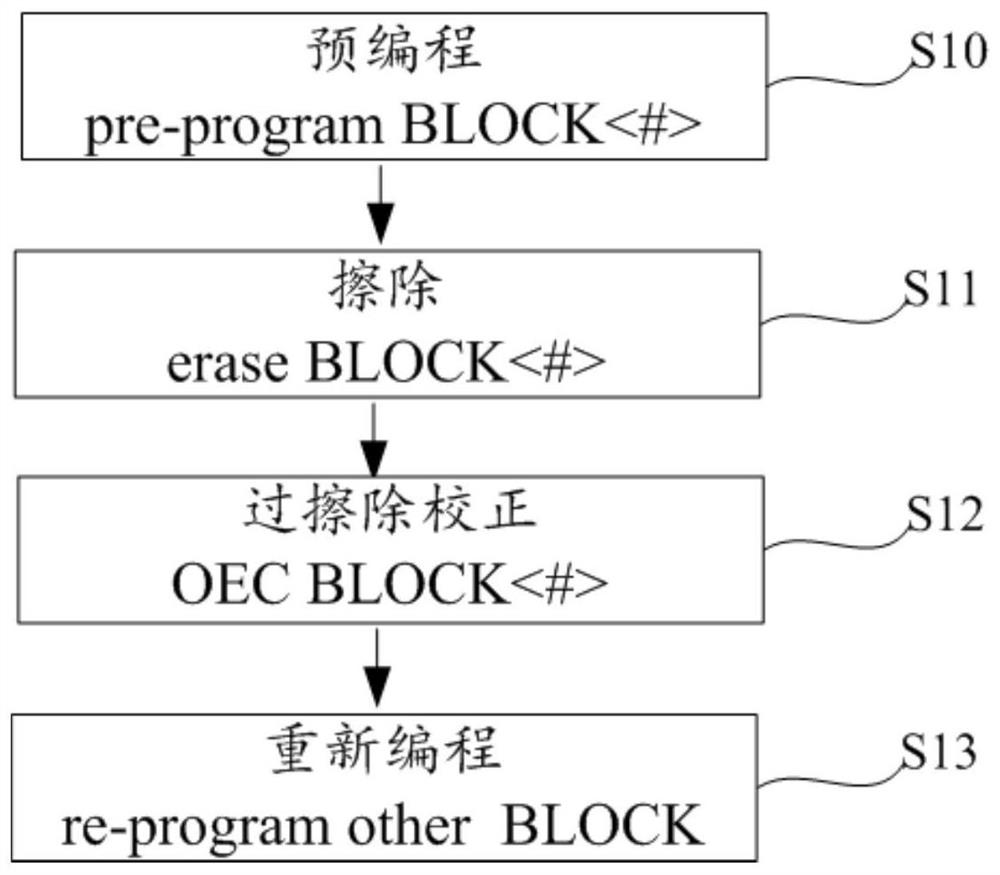

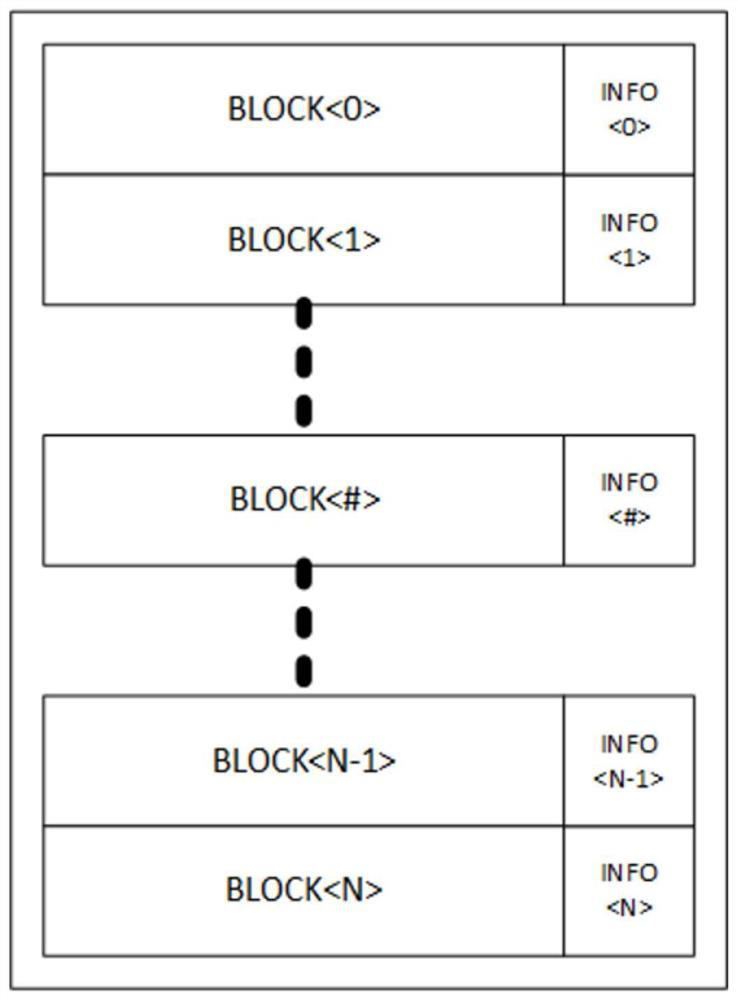

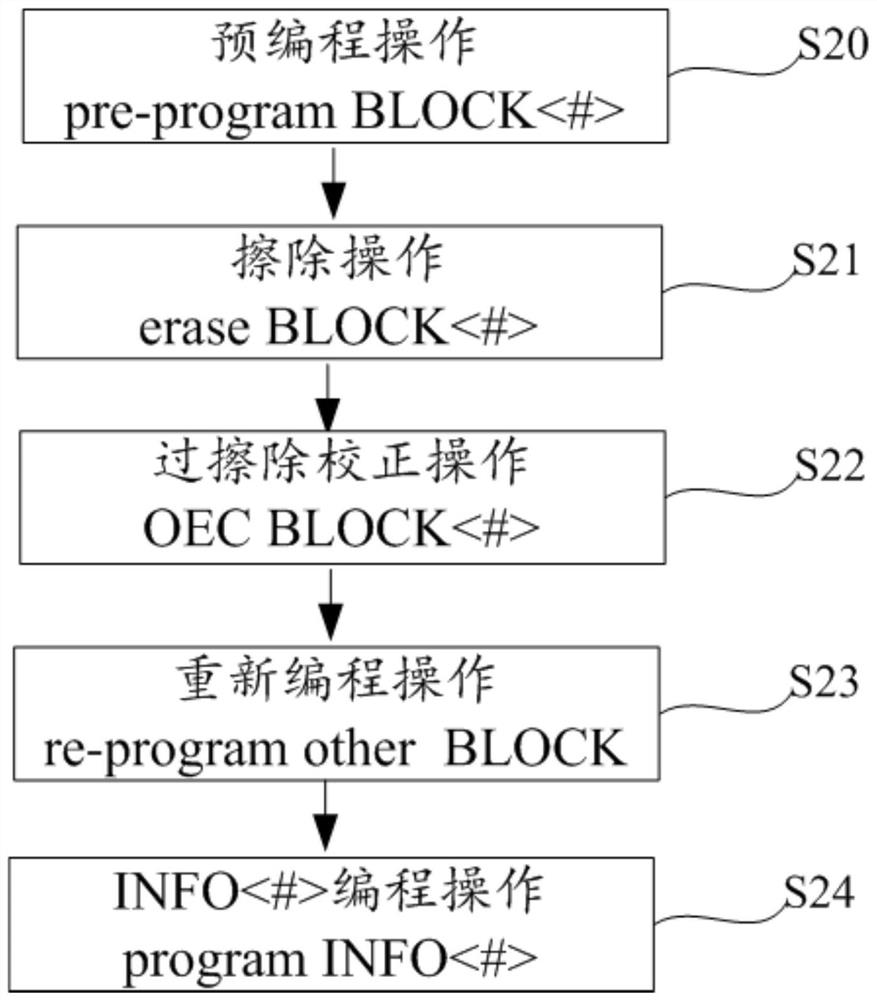

Flash memory and erasing method thereof, electronic system and computer storage medium

ActiveCN113327638AAvoid the problem of read failure (fail)Read-only memoriesElectronic systemsReading (computer)

The invention provides a flash memory and an erasing method thereof, an electronic system and a computer storage medium. The flash memory adds a corresponding information bit for each storage block so as to indicate whether the storage block is erased or not before power failure, which memory block in a flash memory is performing erasing operation can be easily known through the information bits before power failure, and after the flash memory is powered on next time, whether the memory block in the flash memory is not erased before power failure or not can be checked by reading the information stored in the information bits corresponding to the memory block, and further reprogramming operation is performed on each storage block in the power-on process of the flash memory, so that the problems that the threshold voltage VT of some storage units is reduced and data reading of the storage units is failed due to erasing stress of erasing a certain storage block by block in the flash memory can be avoided.

Owner:WUHAN XINXIN SEMICON MFG CO LTD

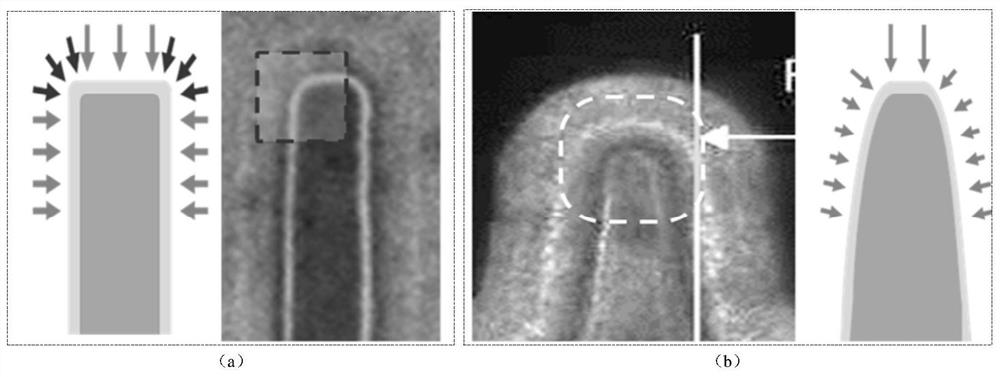

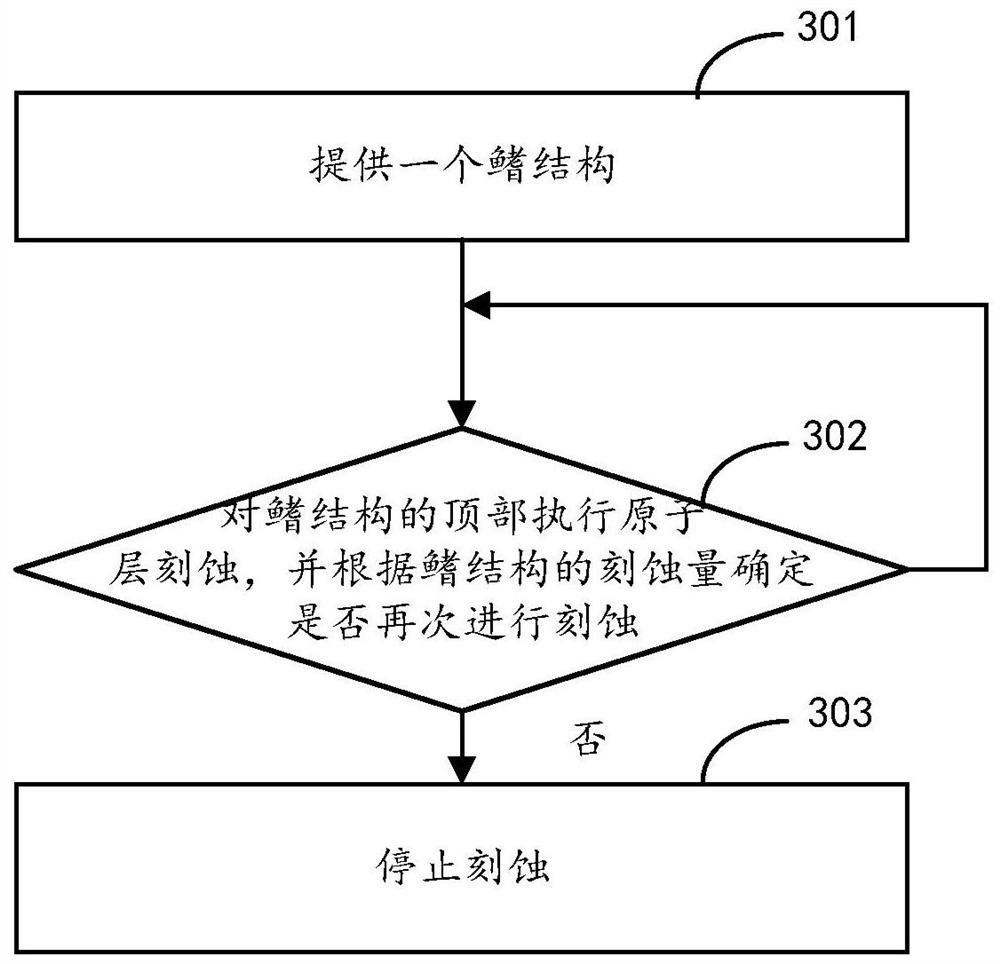

Arc-shaped fin top forming method and fin field effect transistor

PendingCN113808931AMiniaturizationAffect electrical characteristicsTransistorSemiconductor/solid-state device manufacturingEngineeringField effect

The invention discloses an arc-shaped fin top forming method and a fin field effect transistor. The method comprises the following steps that: a fin structure is provided; atomic layer etching is carried out on the top of the fin structure, and whether etching is carried out again is determined according to the etching amount of the fin structure; if yes, atomic layer etching on the top of the fin structure continues to be executed, and whether the etching process is conducted again or not is determined according to the etching amount of the fin structure; and if not, etching is stopped. The atomic layer etching process is circularly executed on the top of the fin structure to form the arc-shaped fin top, although the etching rate of the circulating process is lower than that of an existing mode, the circulating process does not damage the surface, and the pattern size and the loading density can be minimized. As the surface is not damaged, charge trapping is not formed, and the electrical characteristics of the device are not influenced by the reduction of the gate threshold voltage of the device.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI +1

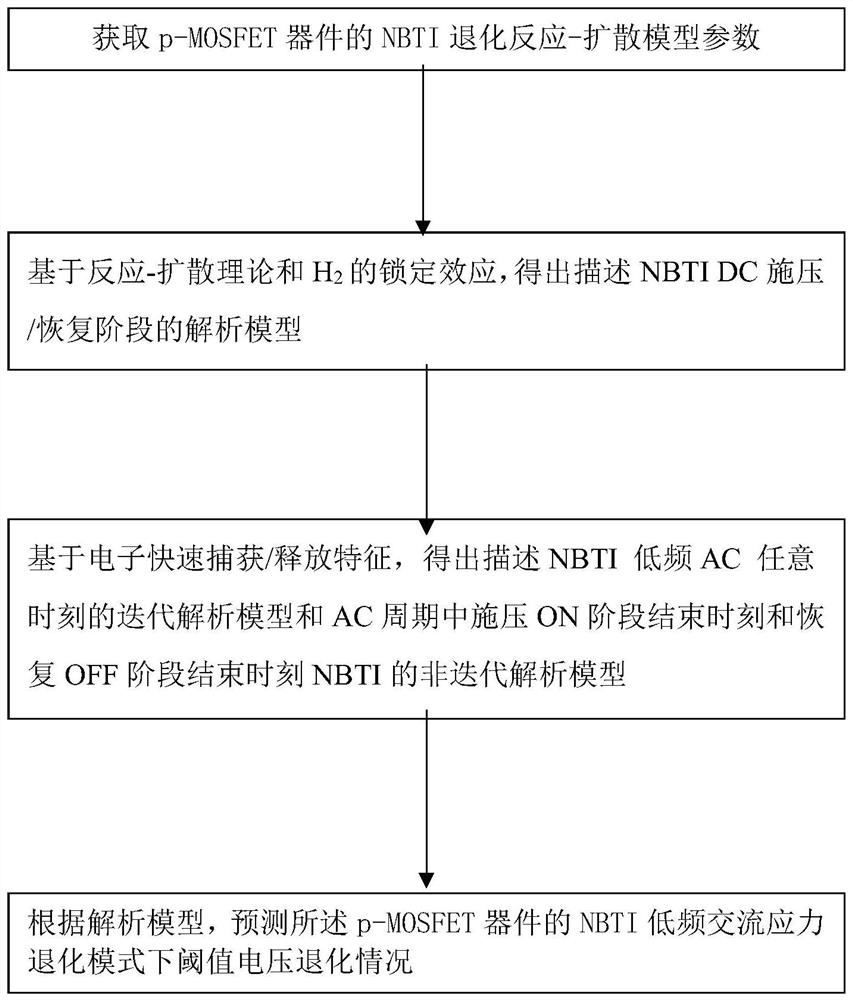

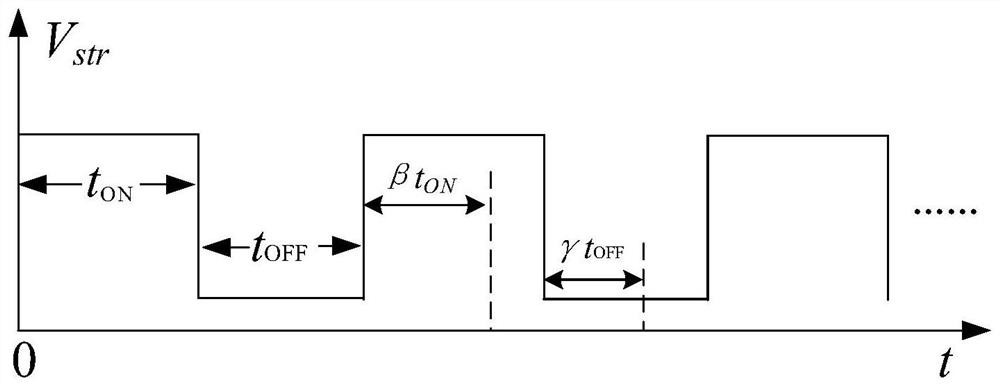

An analytical method and analytical system for nbti degradation prediction under low-frequency AC stress mode

ActiveCN108363861BFew parametersWide applicabilityForecastingComputer aided designChemical physicsPhysical chemistry

The present invention proposes an analytical method for NBTI degradation prediction under a low-frequency AC stress mode, comprising the following steps: Step 1: Obtain the NBTI degradation reaction-diffusion model parameters of p-MOSFET devices; Step 2: Based on the basic reaction-diffusion theory and H 2 The locking effect of the NBTI DC stress / recovery phase is obtained; Step 3: Based on the fast capture / release of electrons, an iterative analytical model is obtained to describe the low-frequency AC stress mode of the NBTI at any moment and the pressure in the AC cycle The non-iterative analytical model of NBTI at the end of the ON phase and the end of the recovery OFF phase; Step 4: According to the analytical model, predict the threshold voltage degradation of the NBTI low-frequency AC stress degradation mode of the p-MOSFET device.

Owner:EAST CHINA NORMAL UNIV