Patents

Literature

110results about "Double resist layers" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

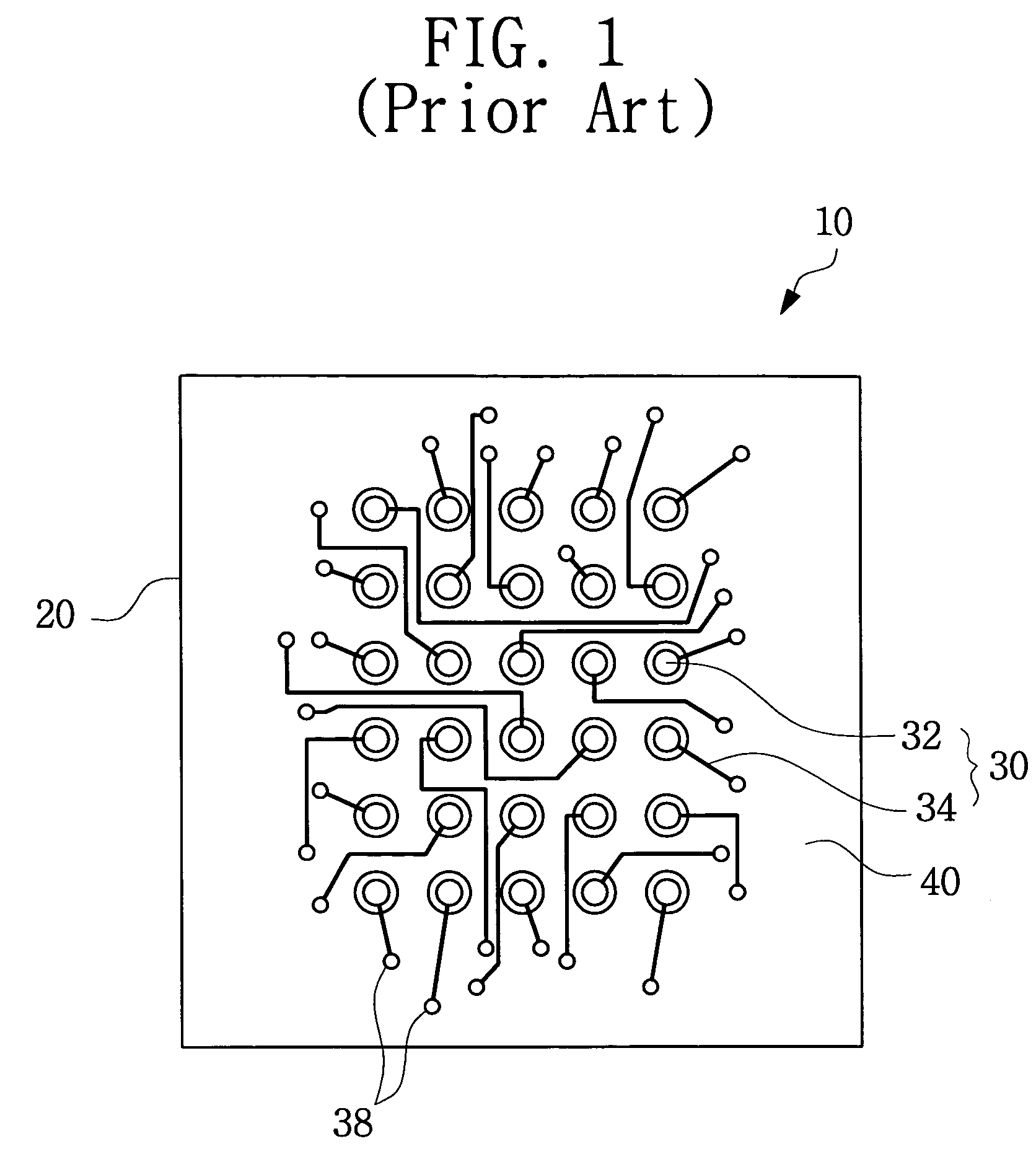

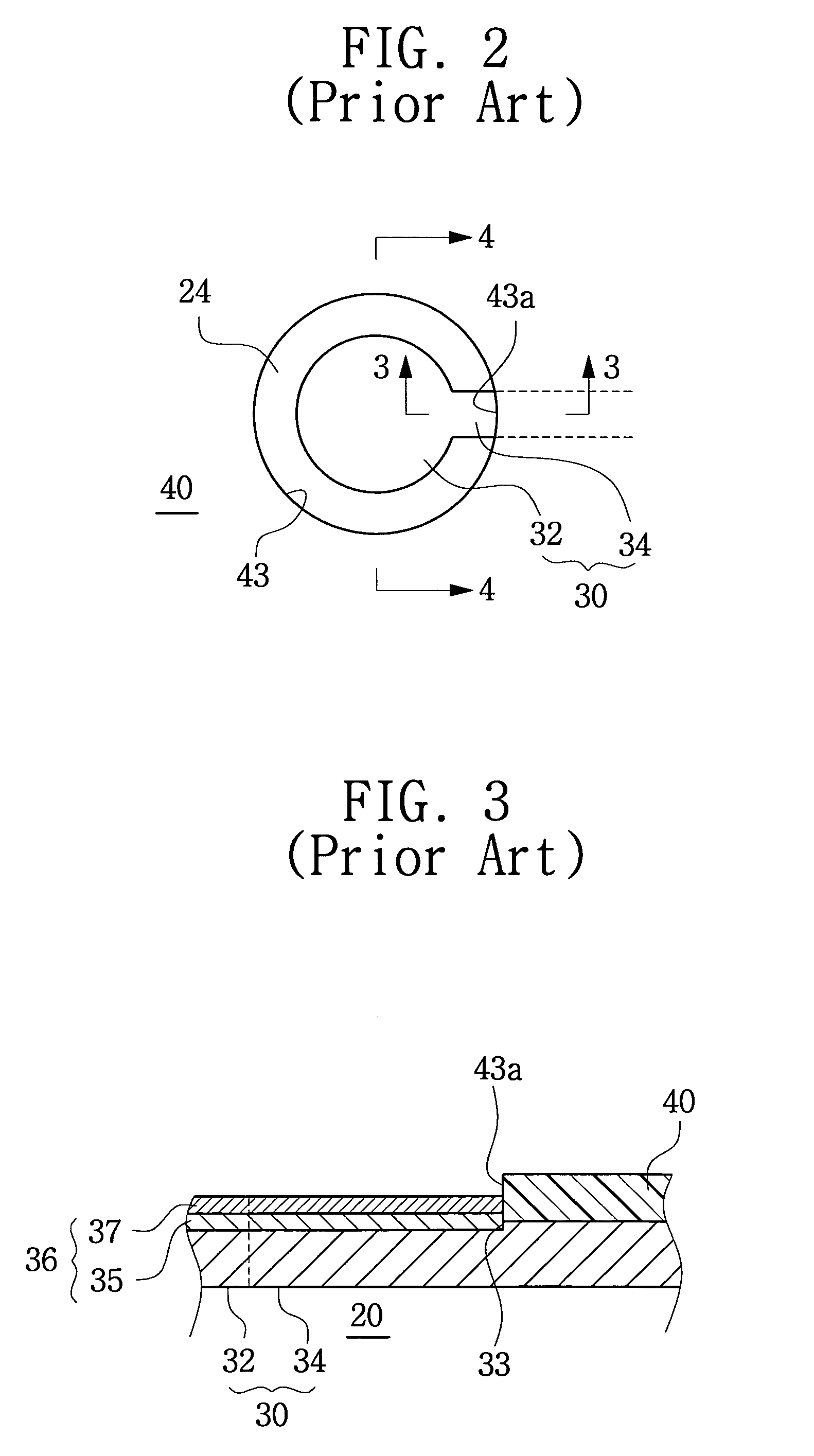

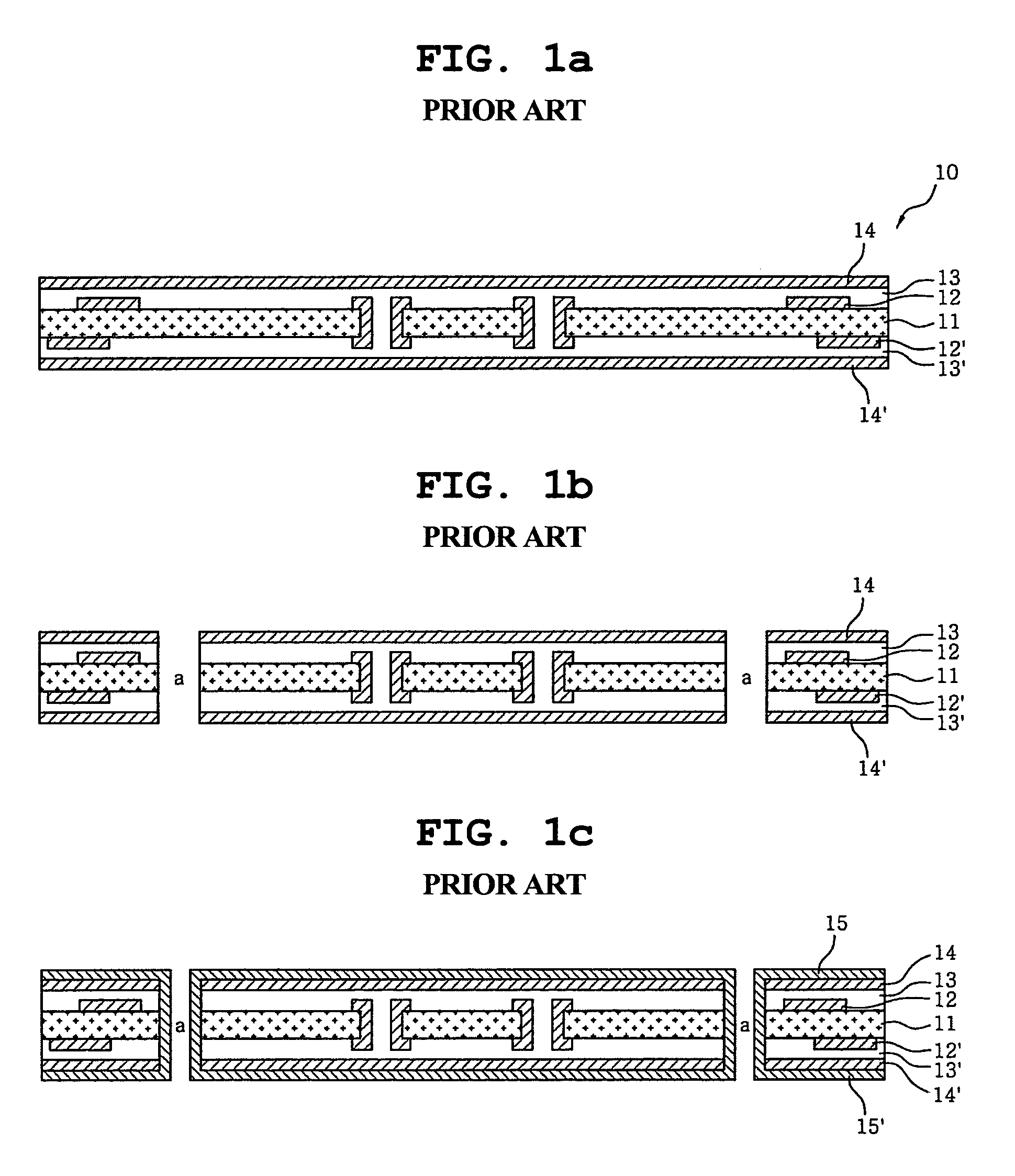

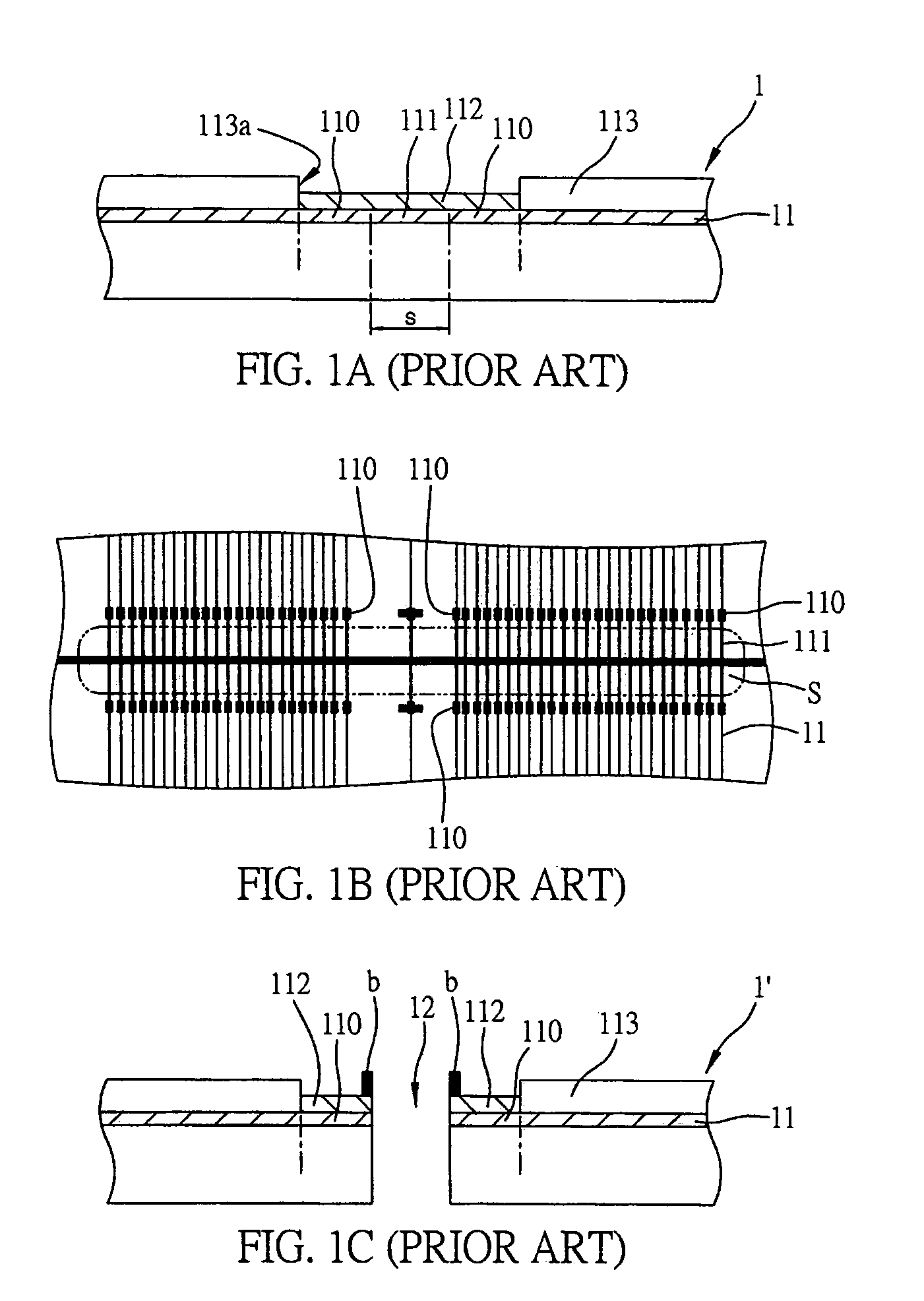

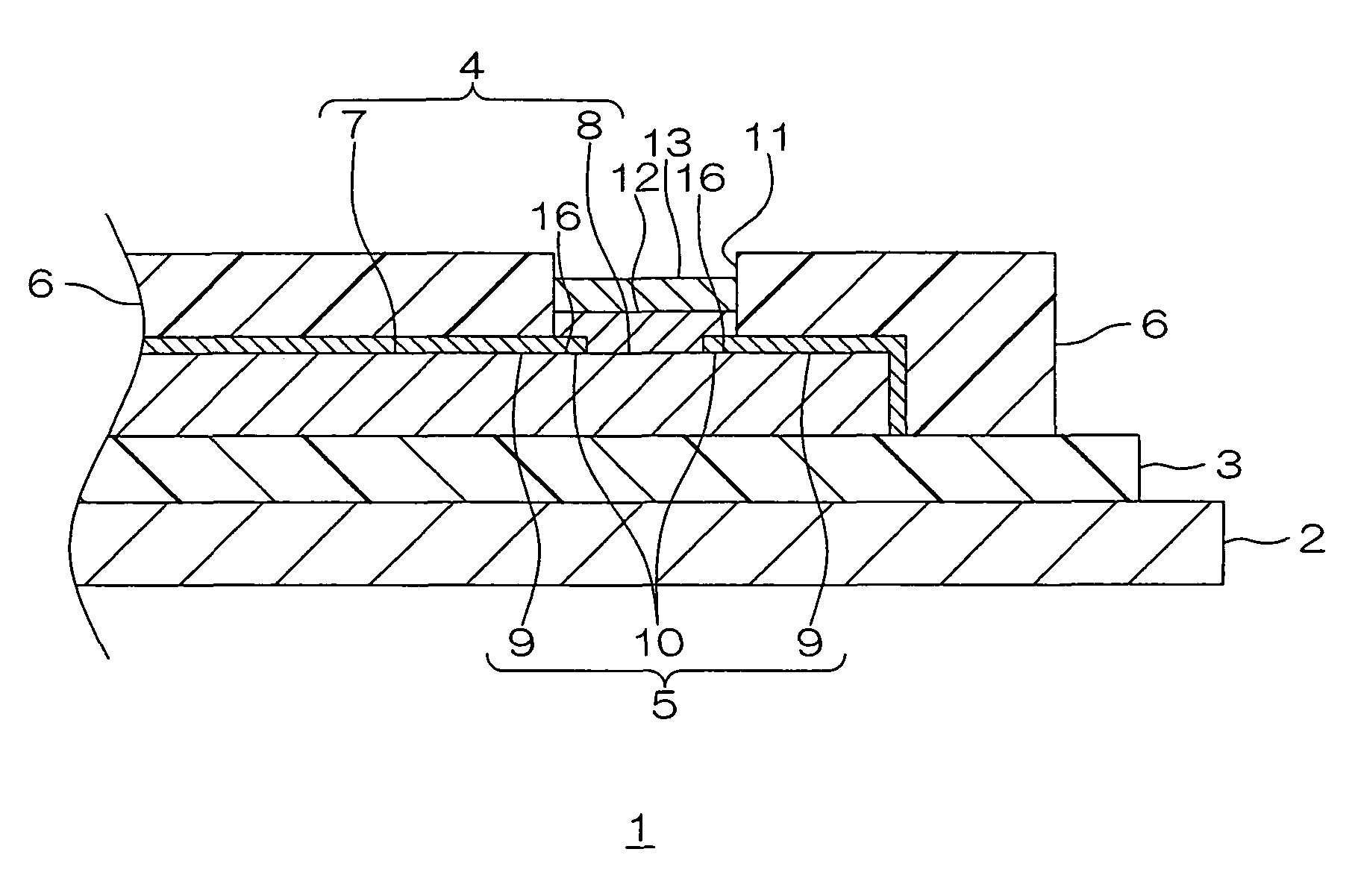

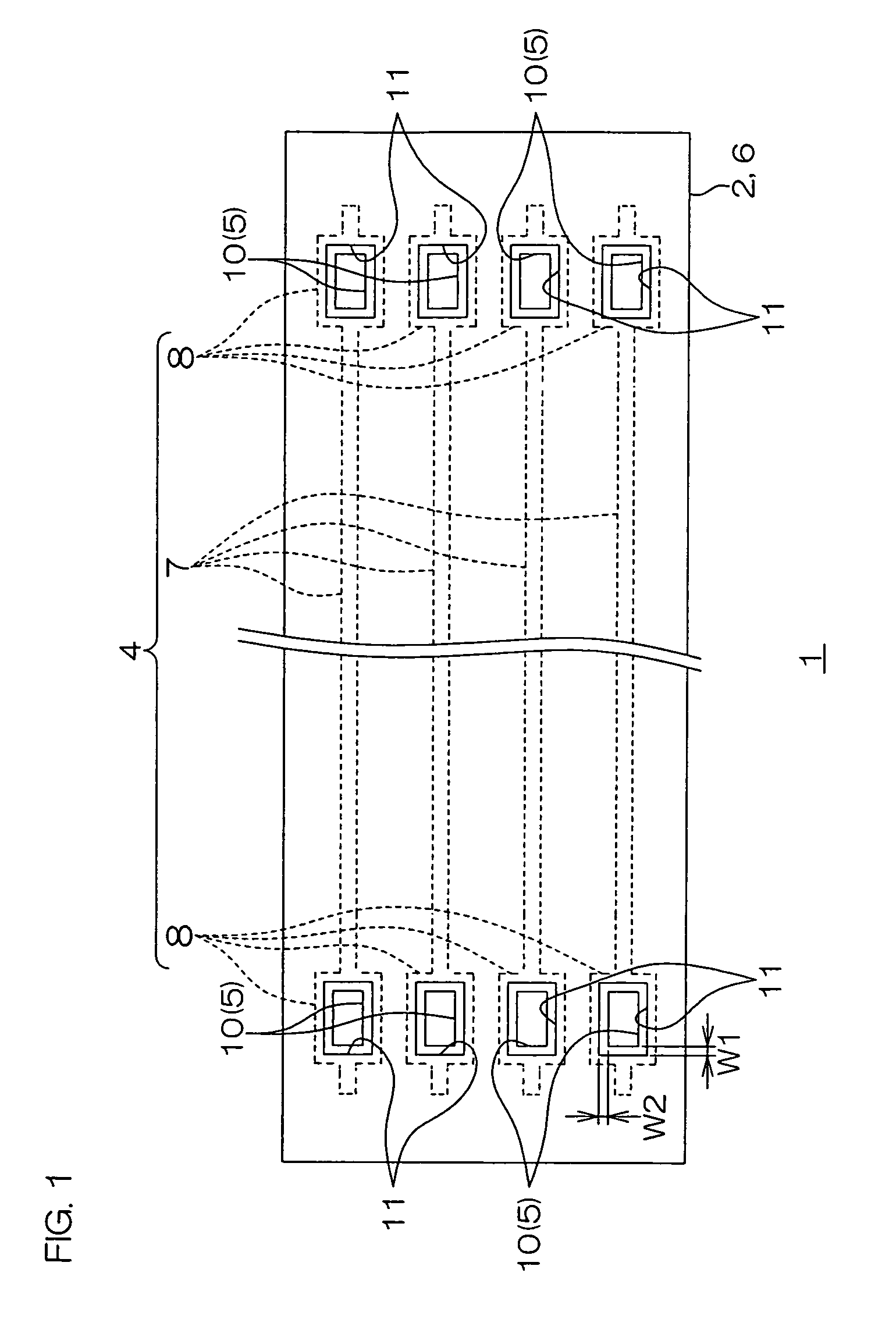

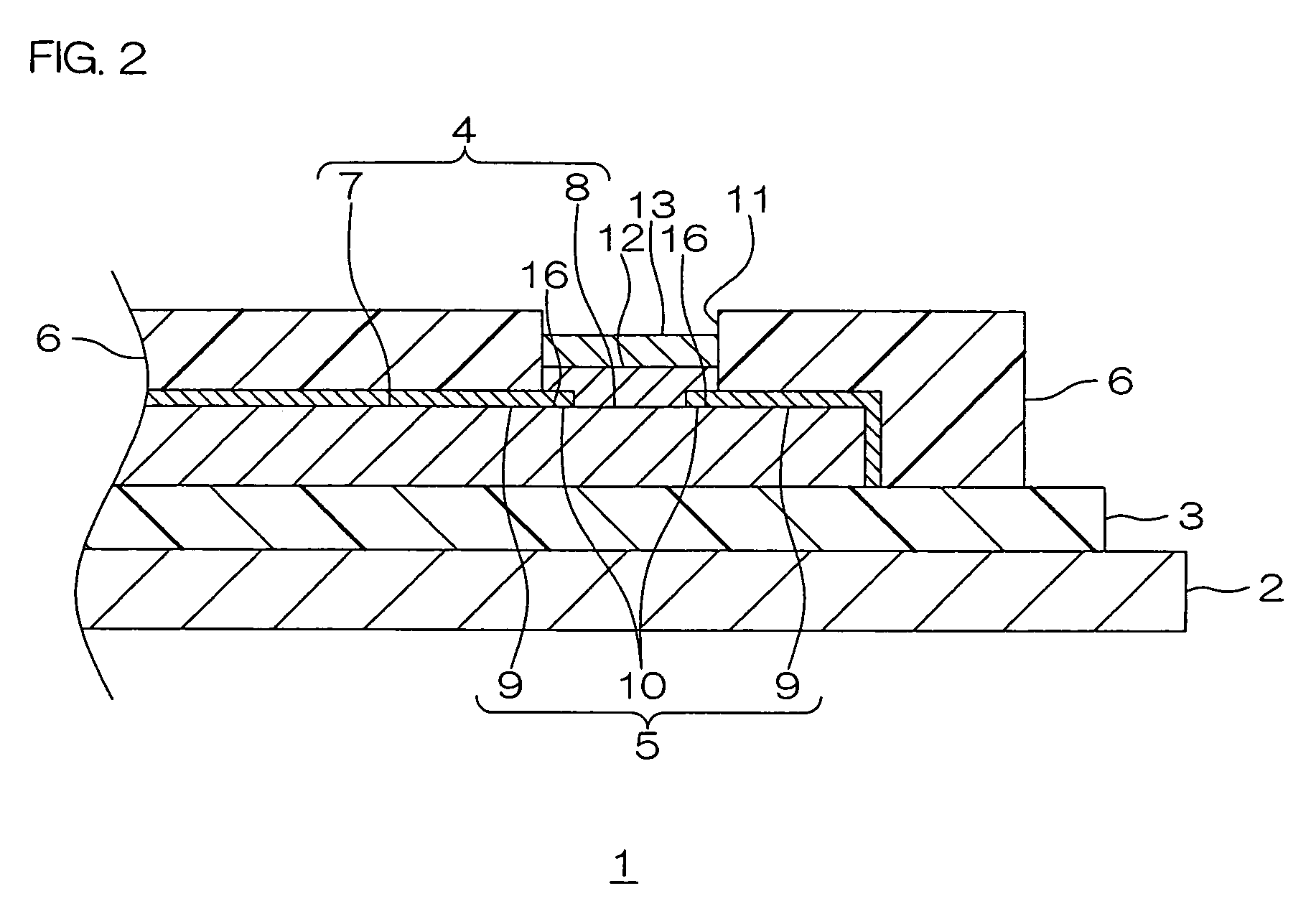

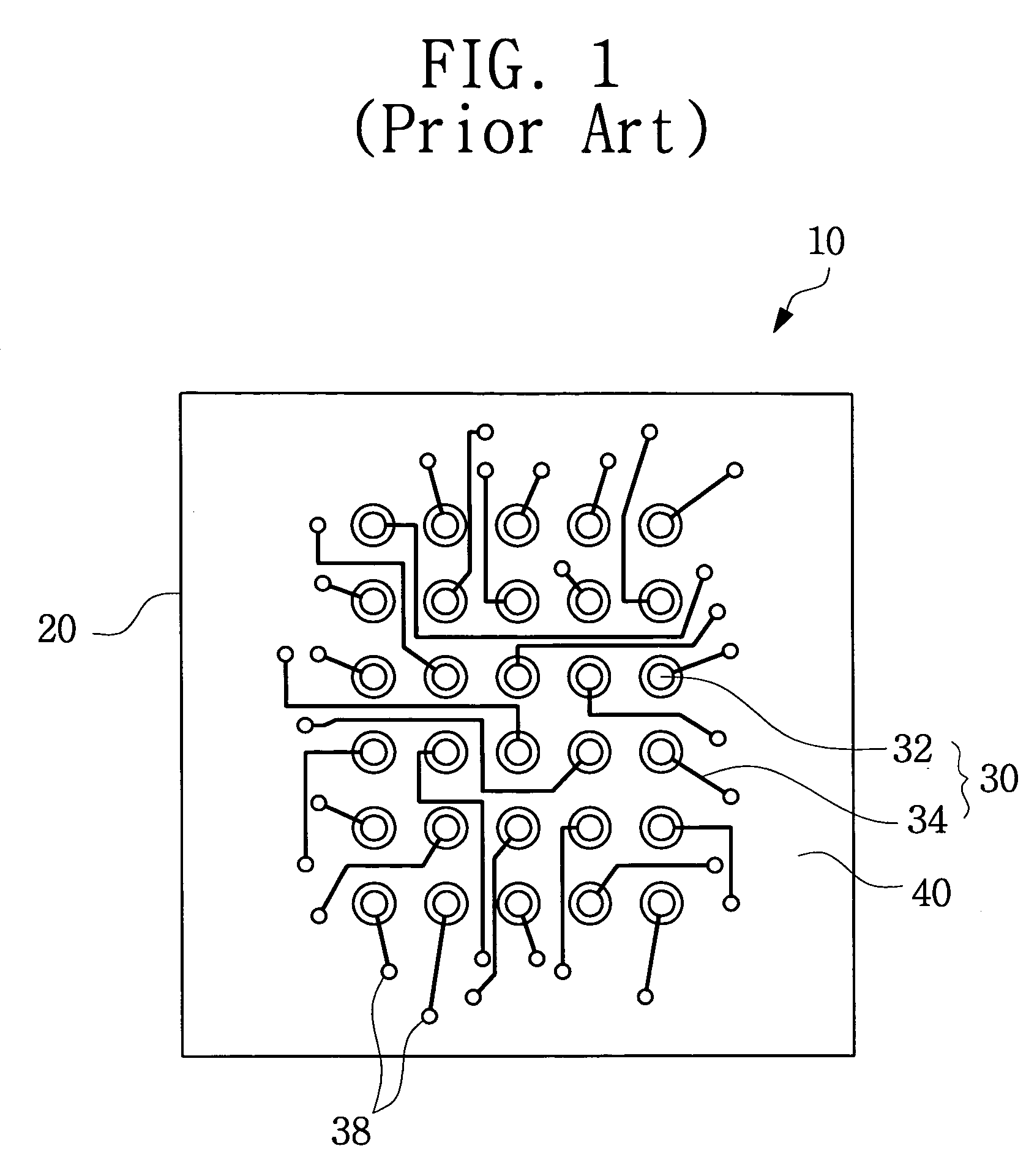

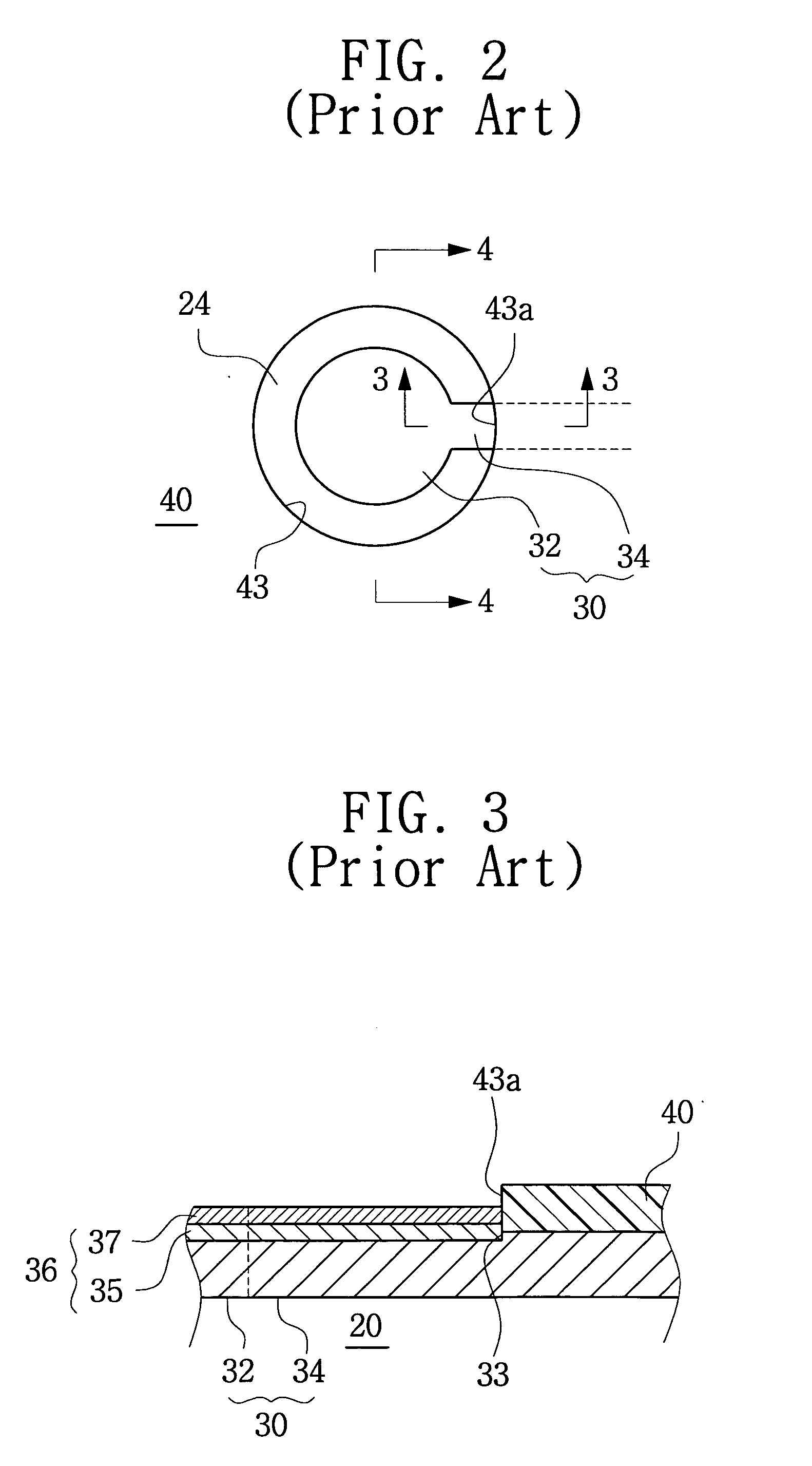

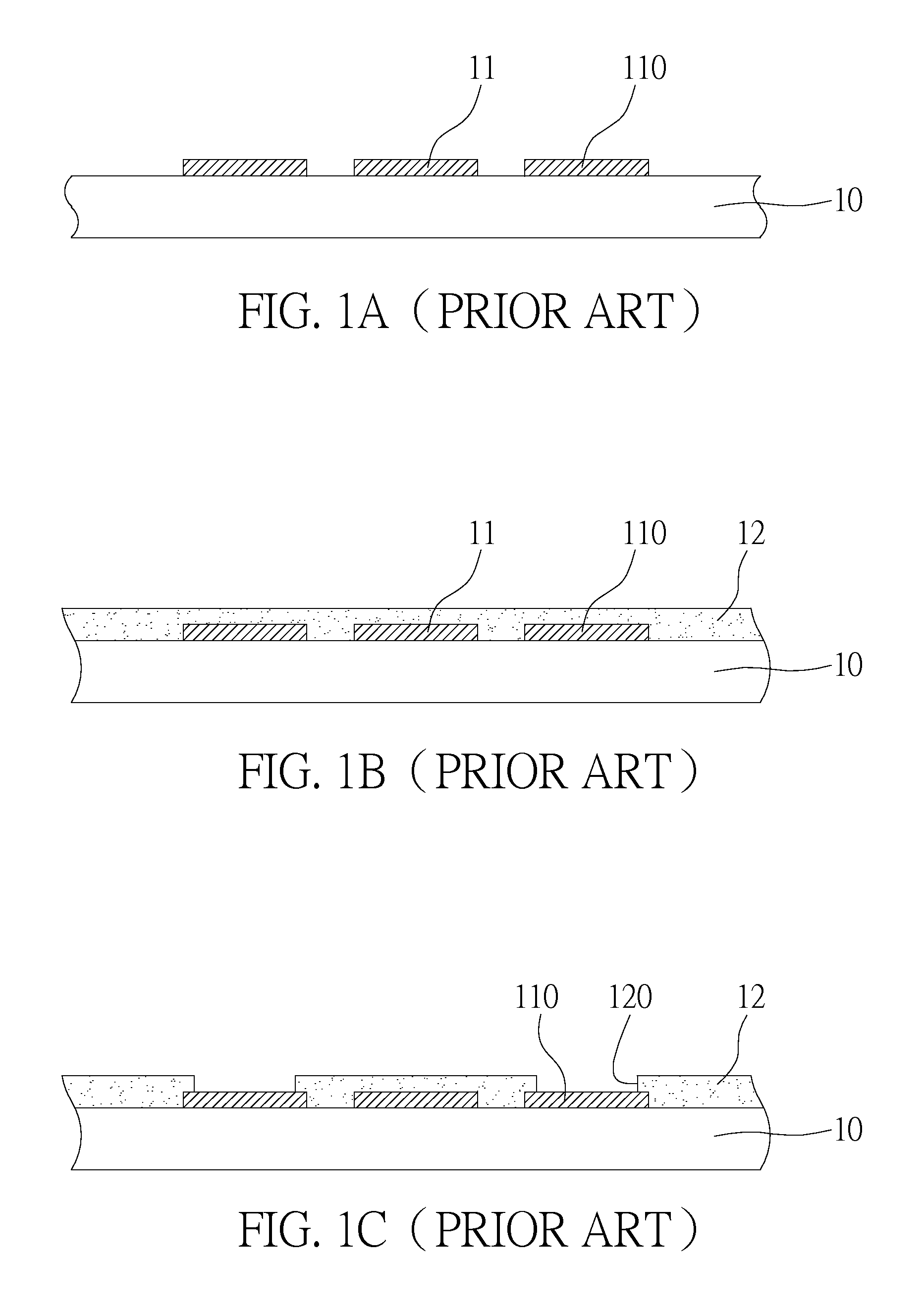

Non-solder mask defined (NSMD) type wiring substrate for ball grid array (BGA) package and method for manufacturing such a wiring substrate

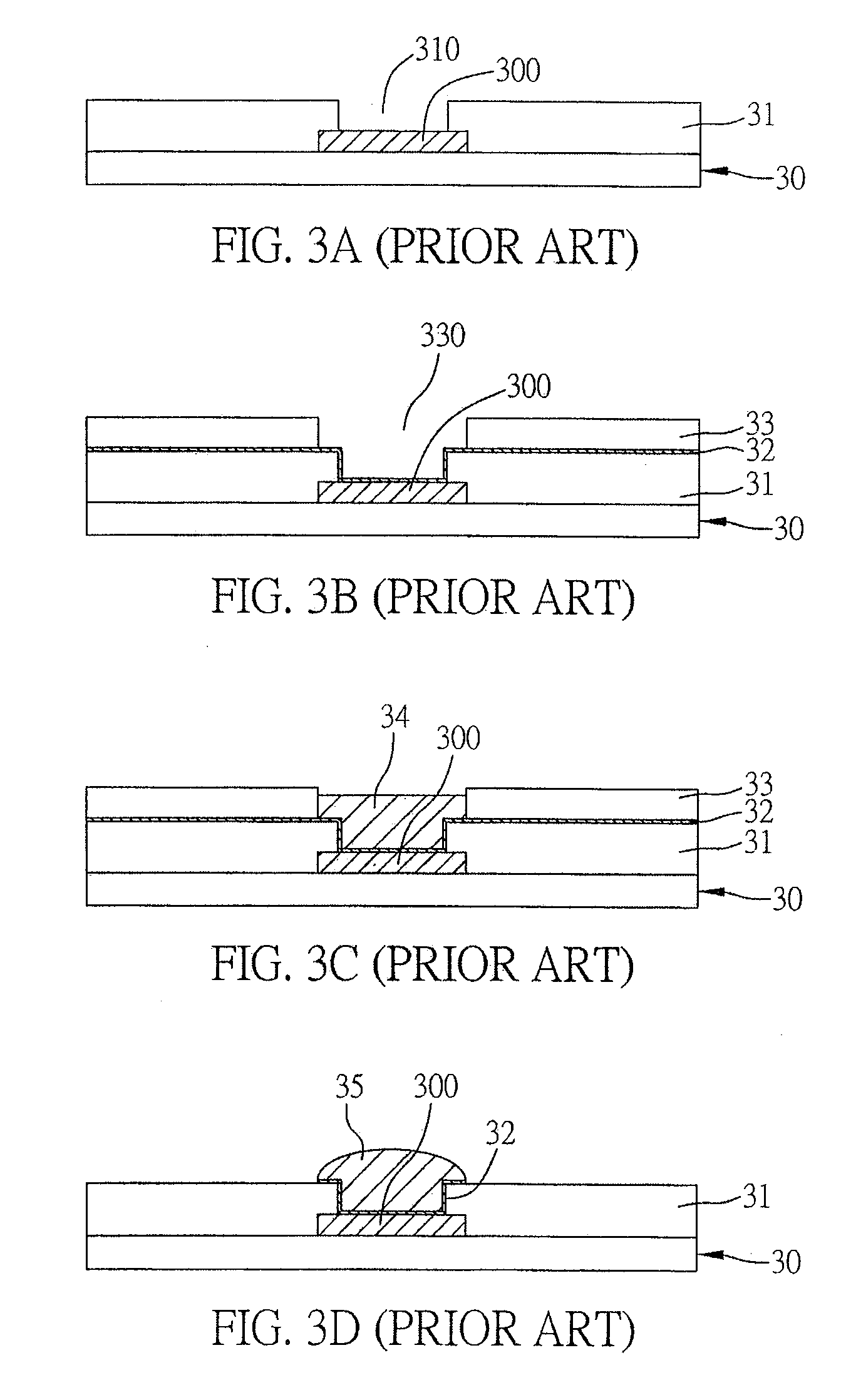

ActiveUS7098407B2Reduce crackingReduce stress concentrationPrinted circuit assemblingSemiconductor/solid-state device detailsStress concentrationSolder mask

In one embodiment, a pad is formed on a substrate surface. The pad is connected with a connecting pattern. A first mask is formed on the substrate. The first mask has a first opening exposing at least a portion of the pad and a portion of the connecting pattern. A second mask is formed on the first mask. The second mask has a second opening exposing at least a portion of the pad and a portion of the connecting pattern. A boundary surface or sidewall of the first opening is not coplanar with a boundary surface or sidewall of the second opening. Therefore, stresses may be prevented from concentrating on the boundary surface of the first opening, thereby allowing dispersion of the stresses and restraining pattern cracks.

Owner:SAMSUNG ELECTRONICS CO LTD

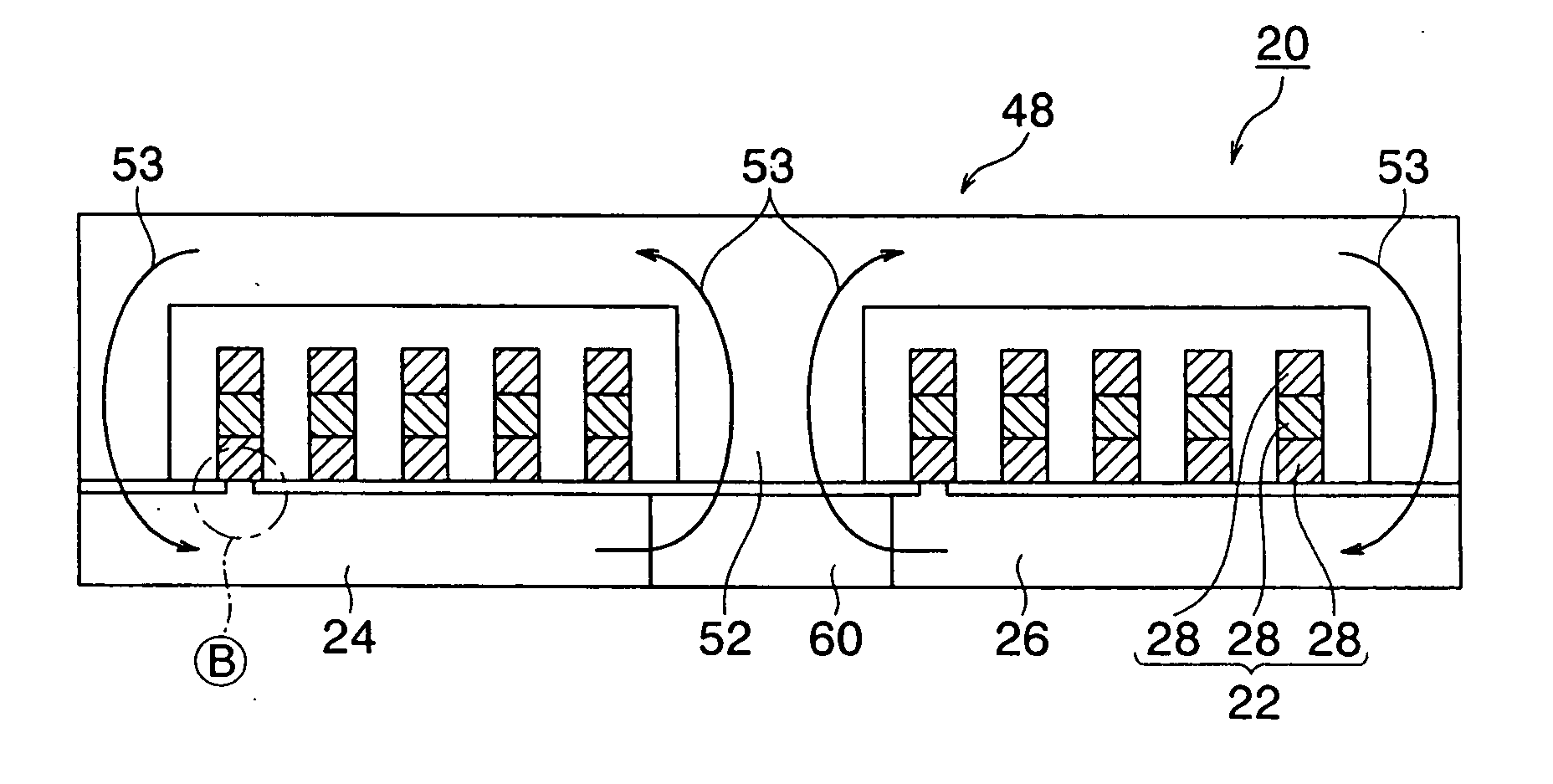

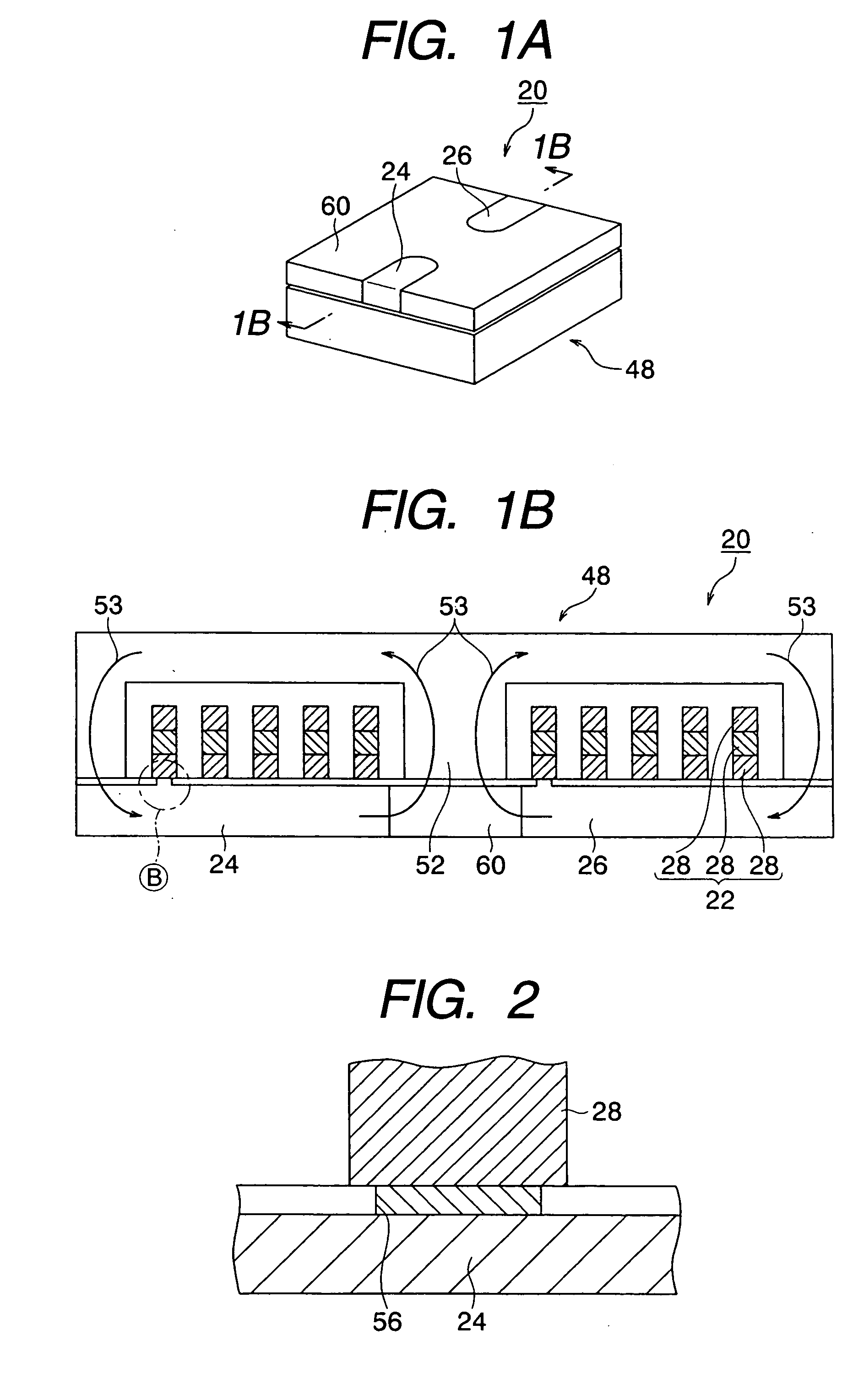

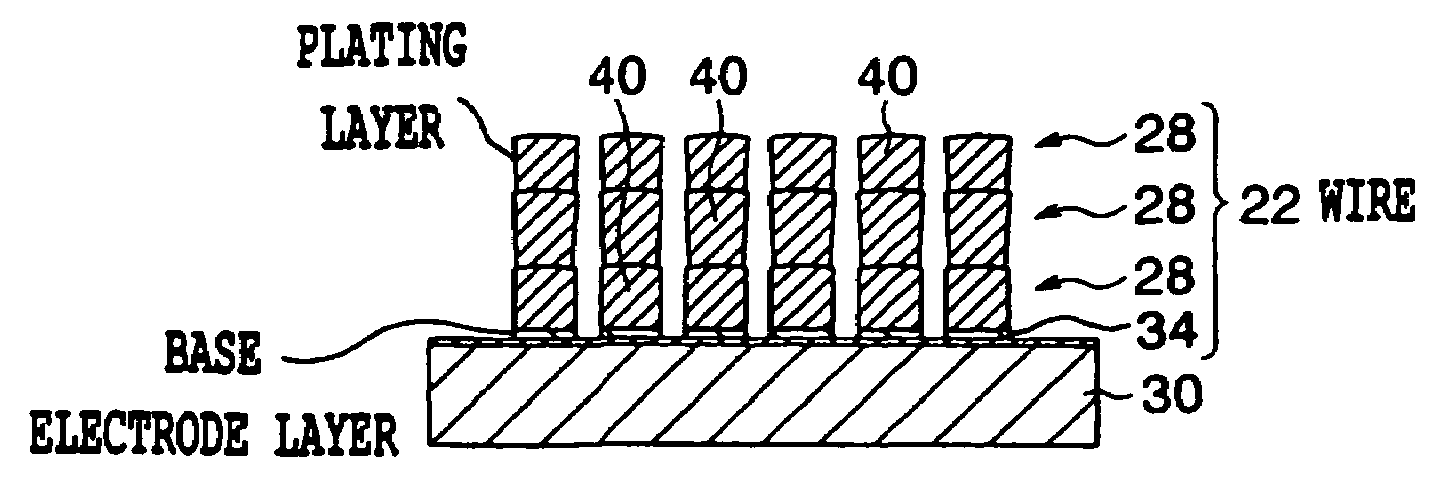

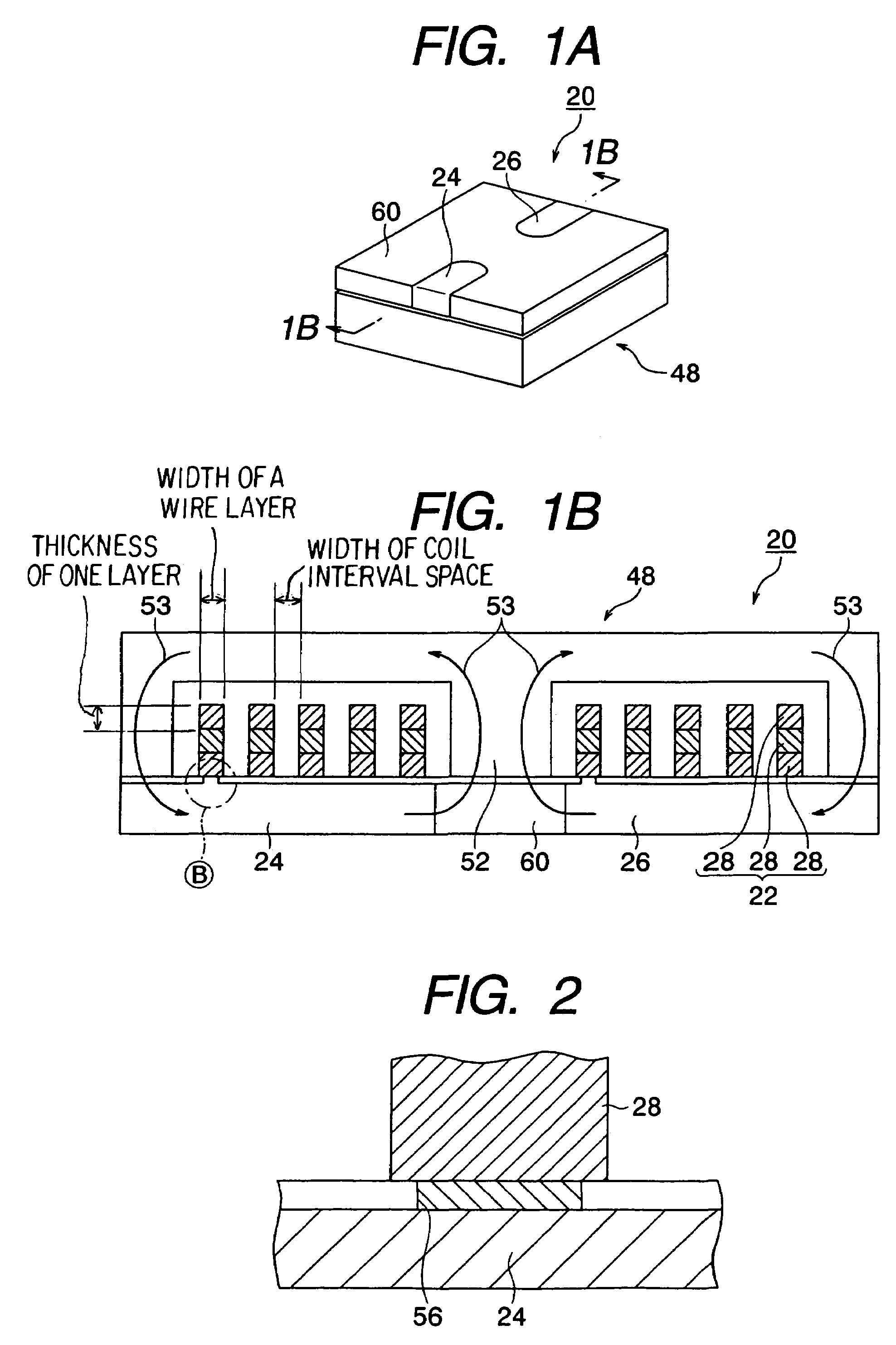

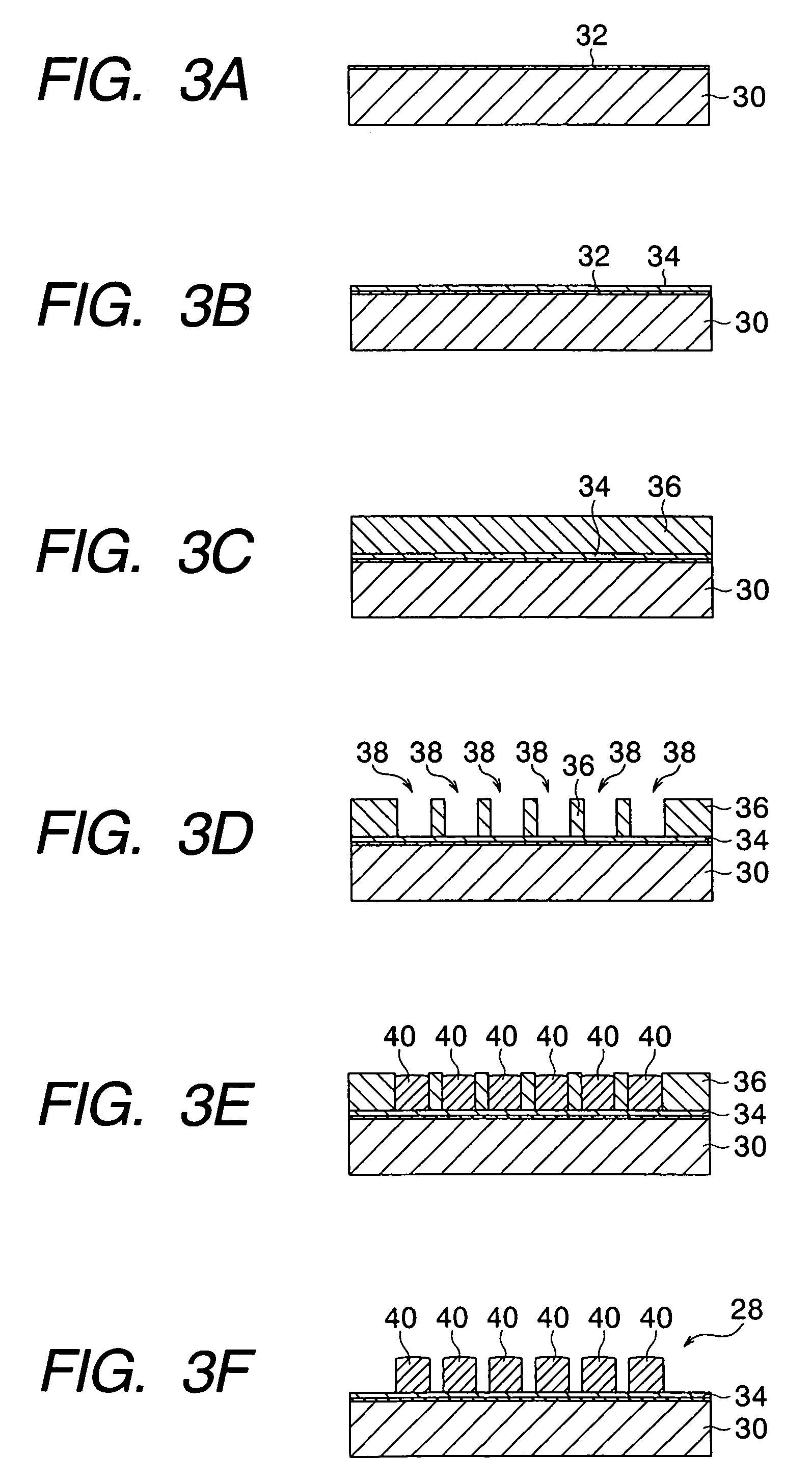

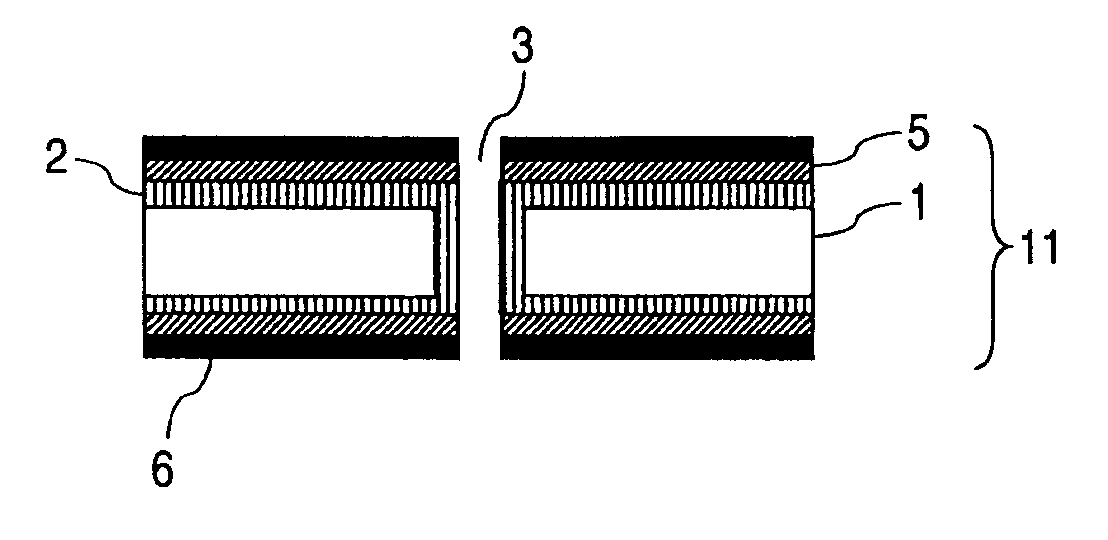

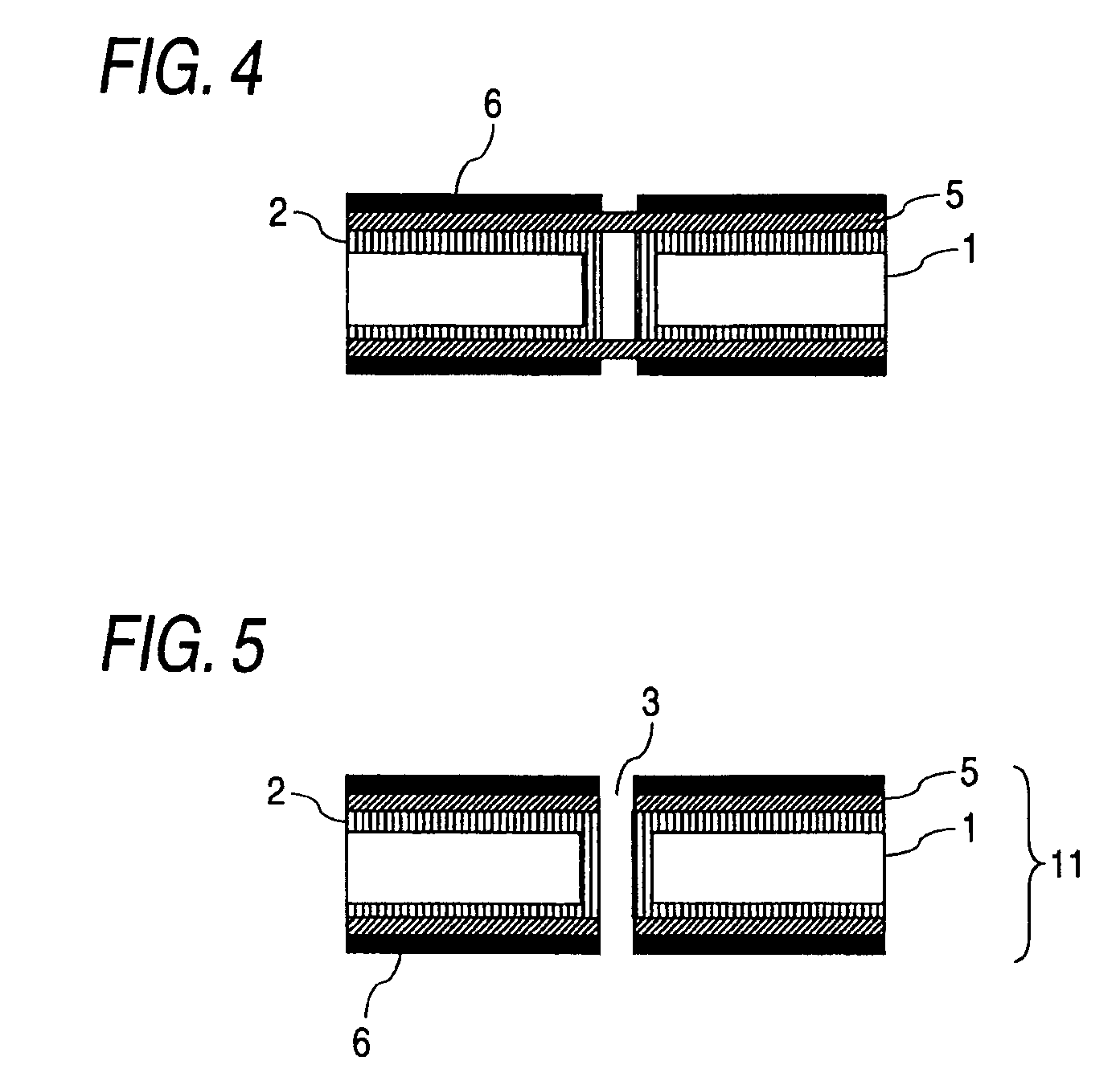

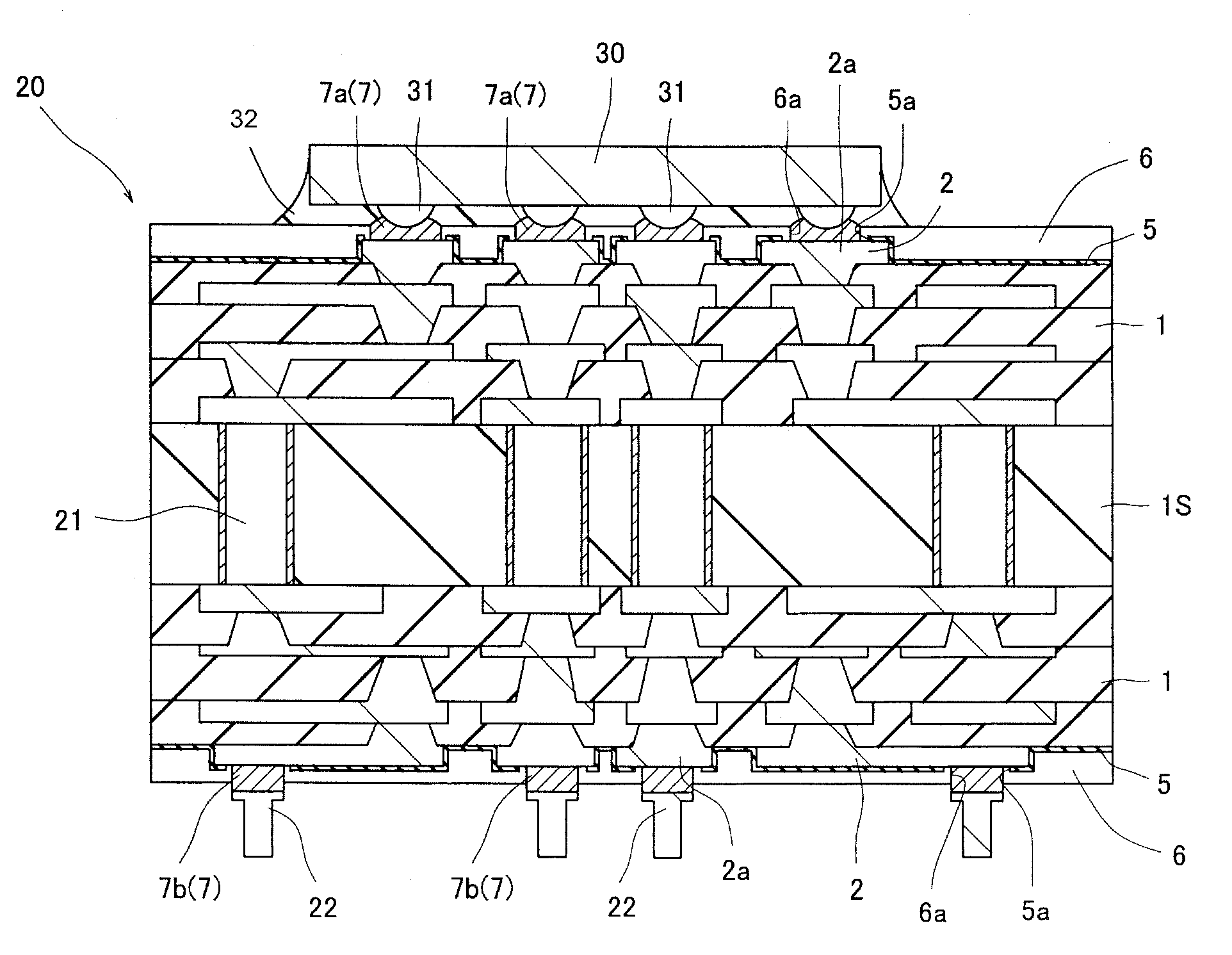

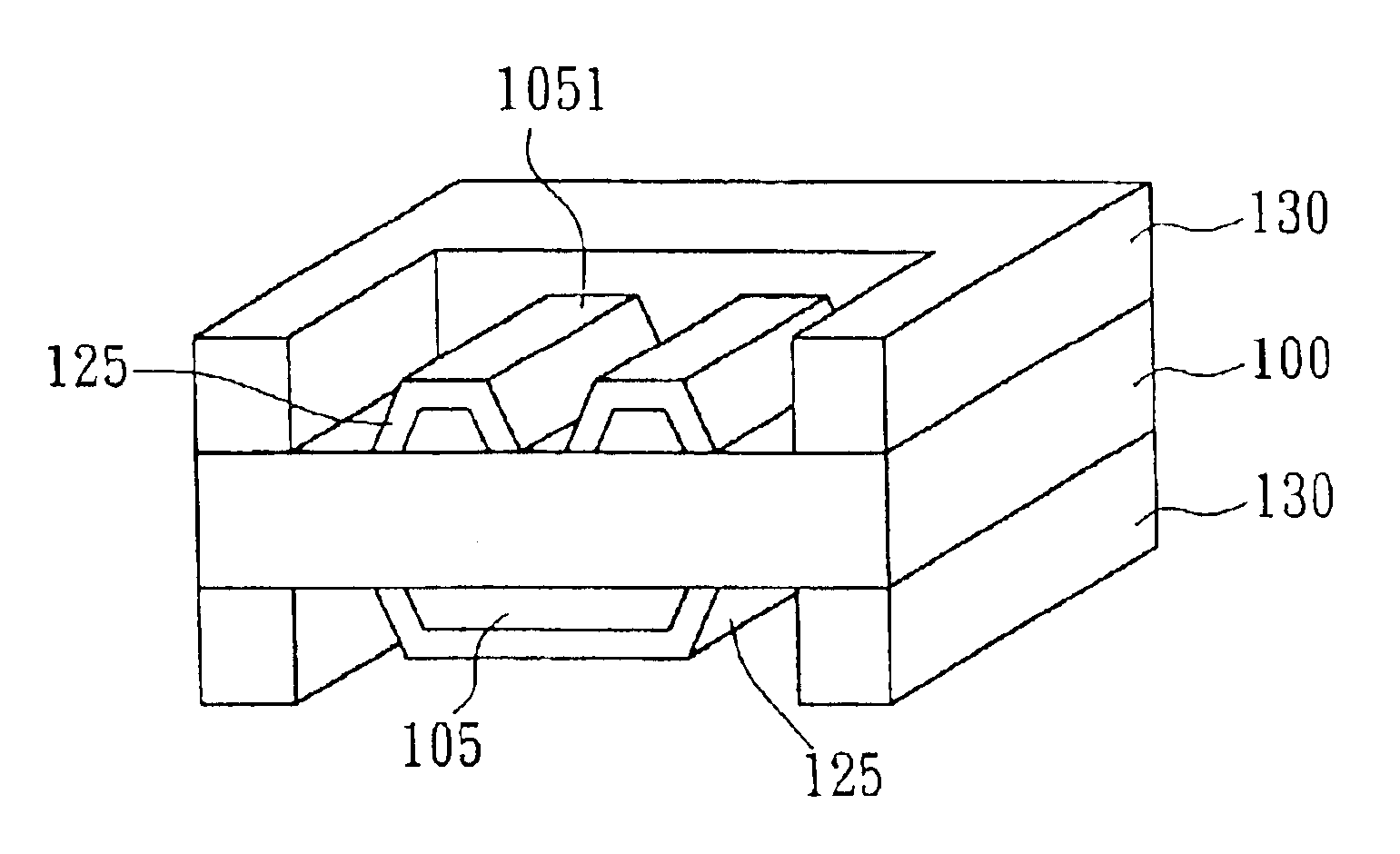

High density inductor and method for producing same

InactiveUS20040164835A1Reduce core sizeAccurate shapeTransformers/inductances coils/windings/connectionsSolid-state devicesHigh densityInductor

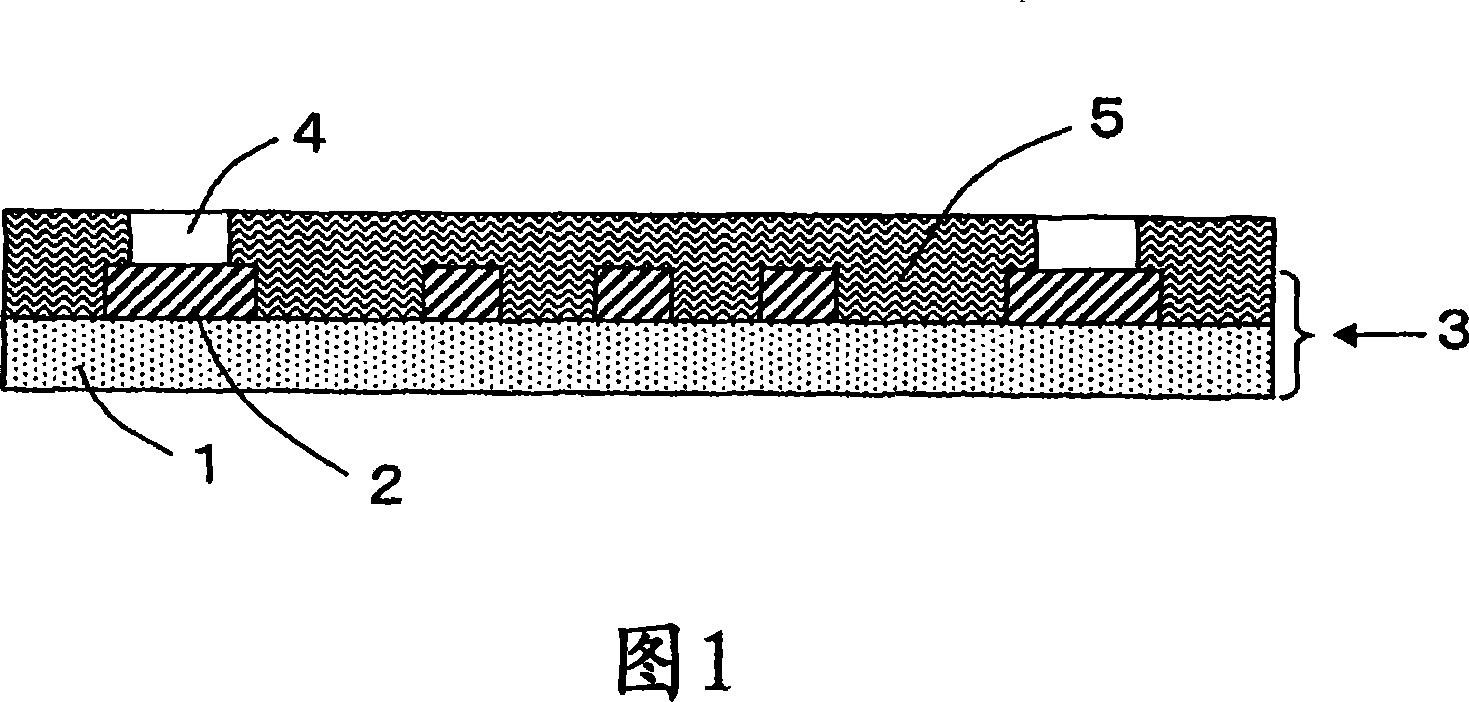

A method for producing a high density inductor includes the steps of forming a coil having a spiral shape, sealing the coil in the interior of a core member, and forming a terminal electrode for allowing electric conduction to said coil on the outside of said core member. In this method, the coil is formed by repeating a process of forming a wire layer by means of a thin film forming process and a process of forming an additional wire layer on top of the wire layer by means of the thin film forming process to pile up the wire layers. With this production method, it is possible to form a coil with a high aspect ratio. In addition, the inductor is designed in such a way that the core member envelopes only the coil. With that design, it is possible to make the inductor compact.

Owner:TDK CORPARATION

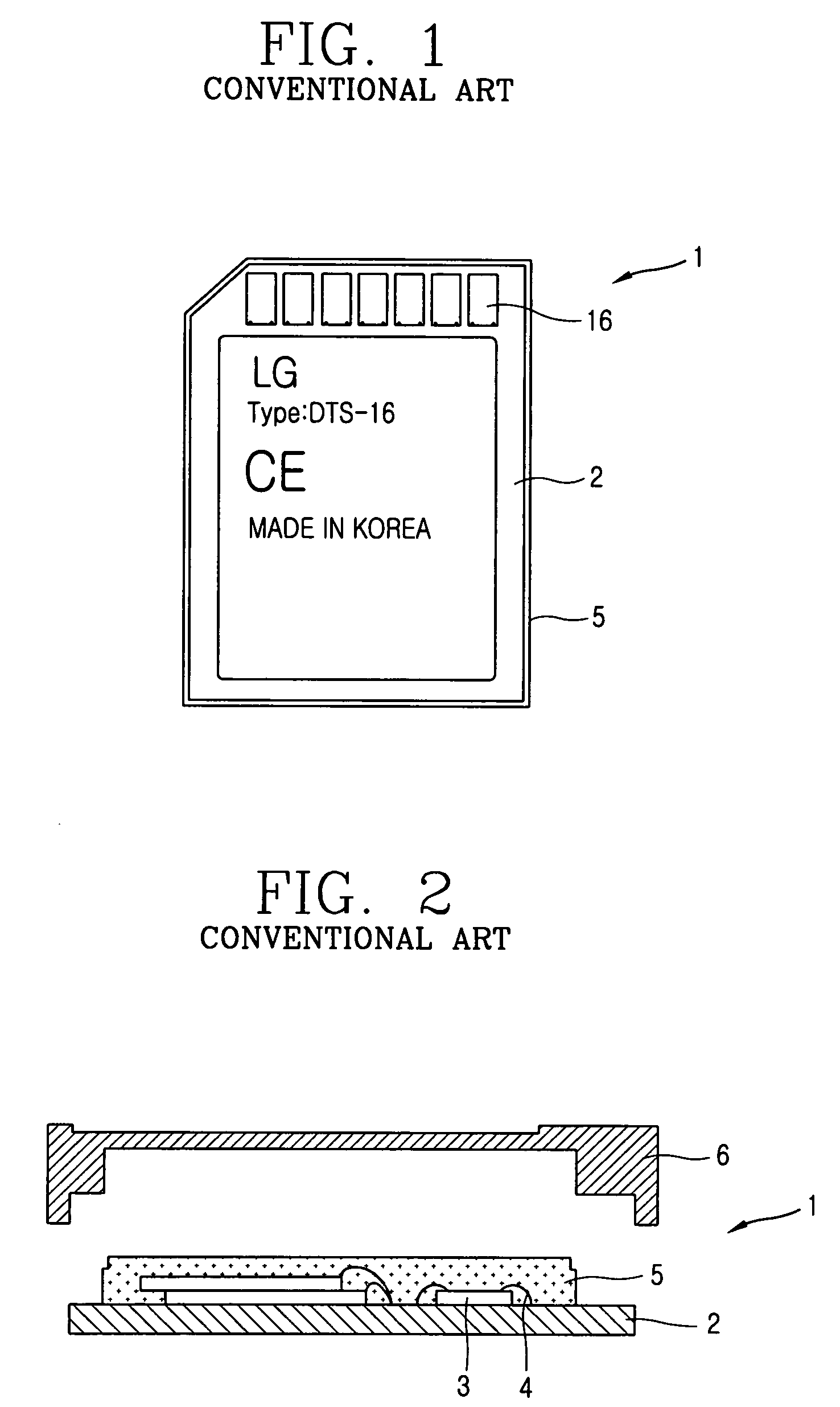

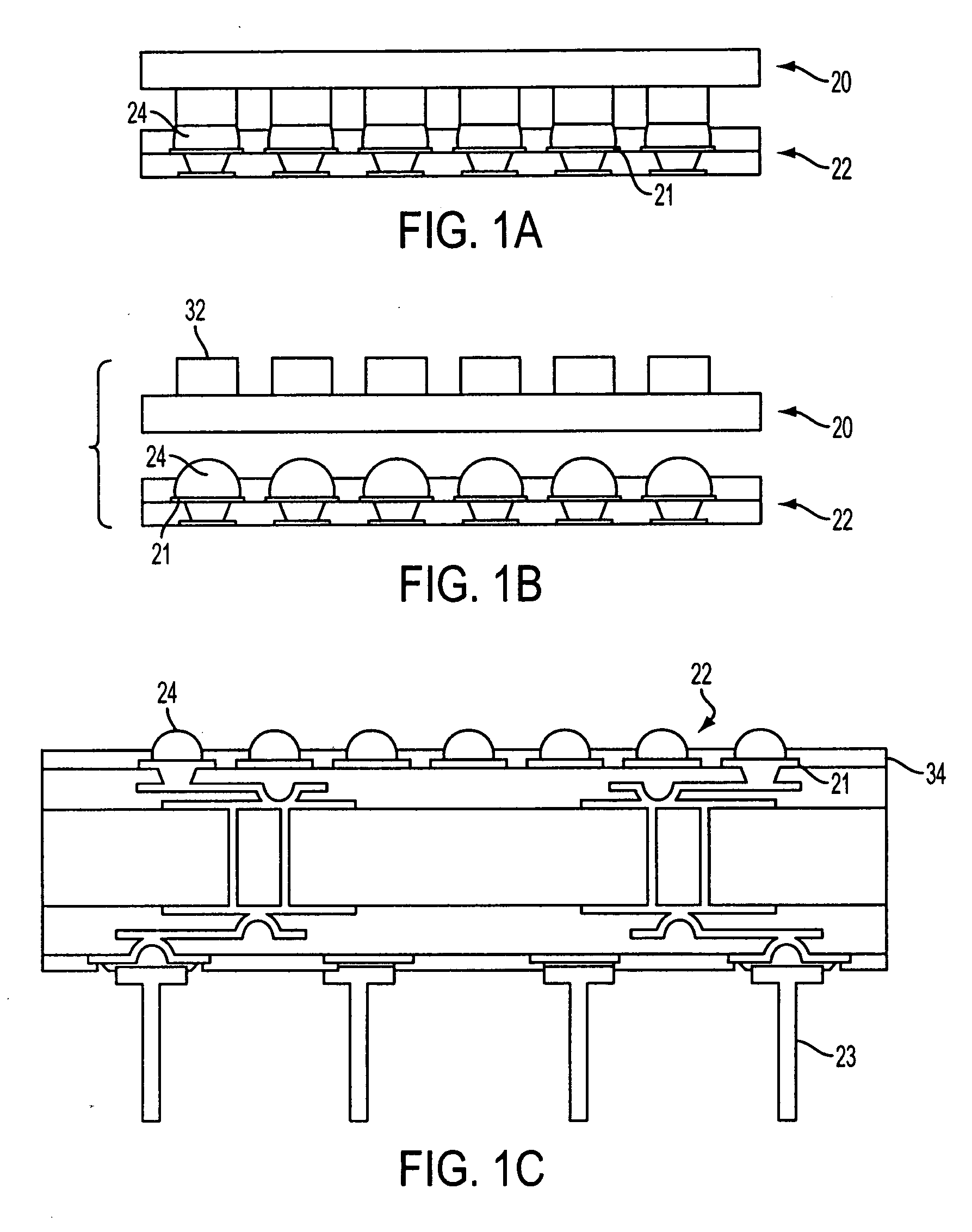

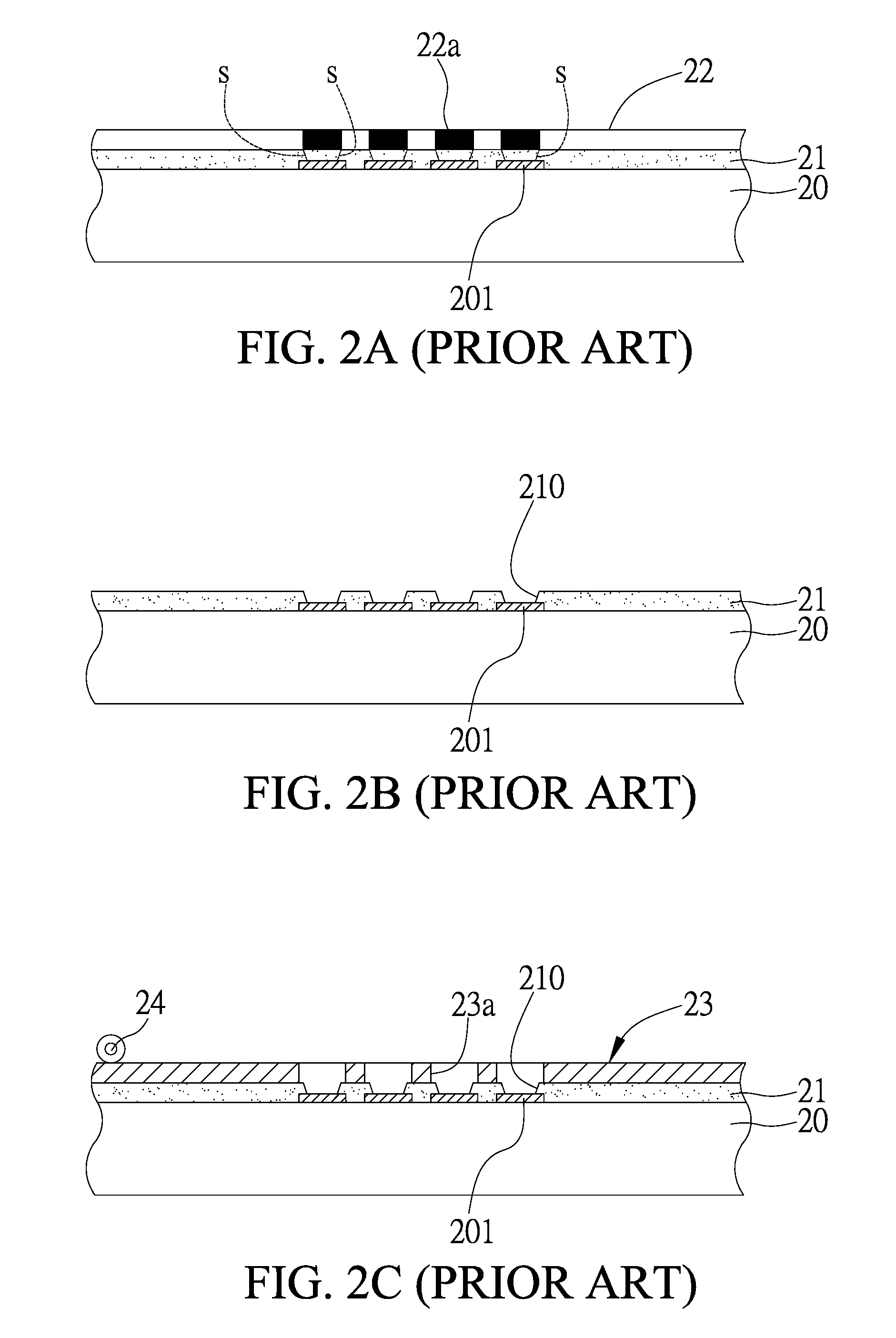

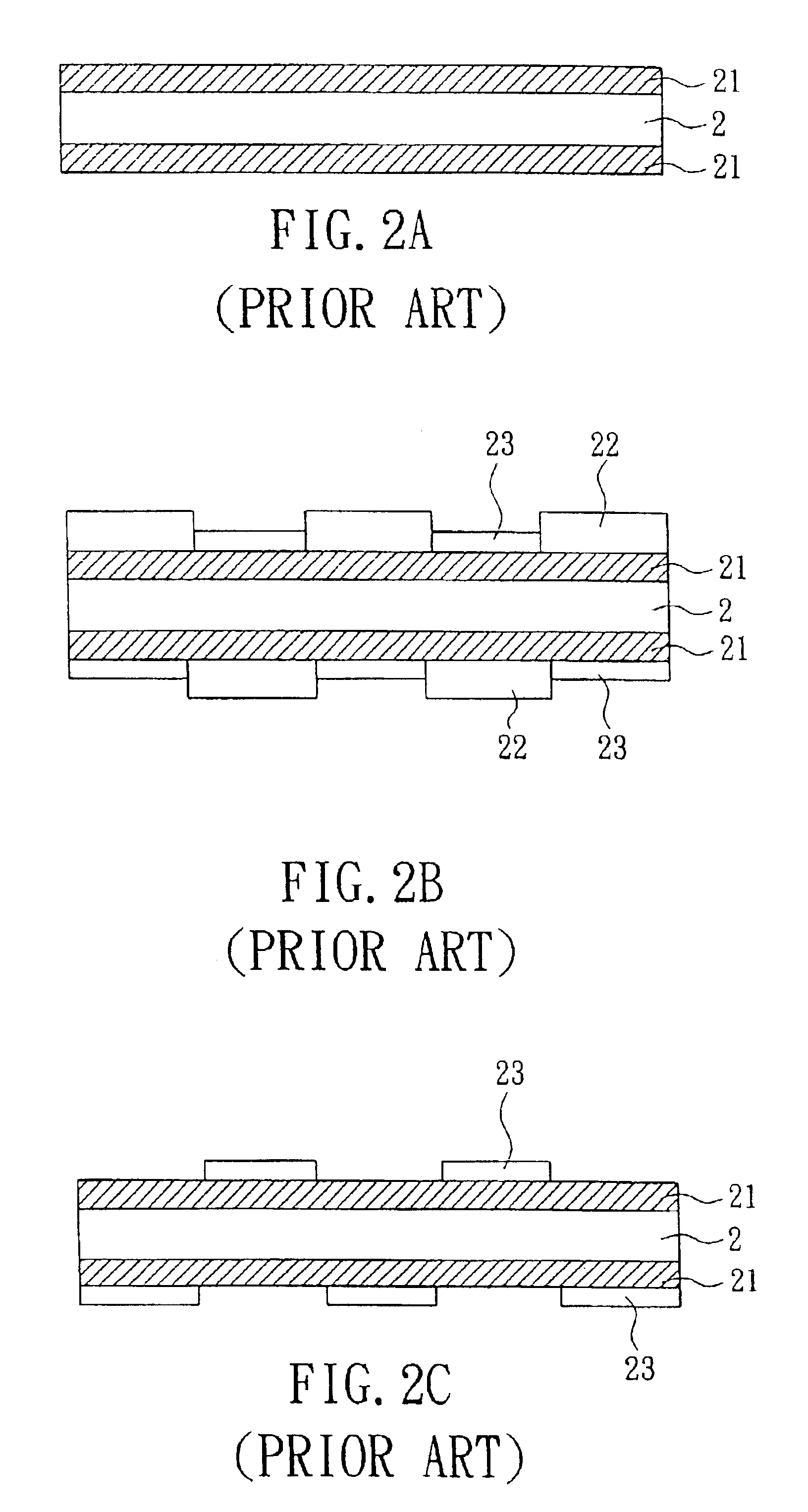

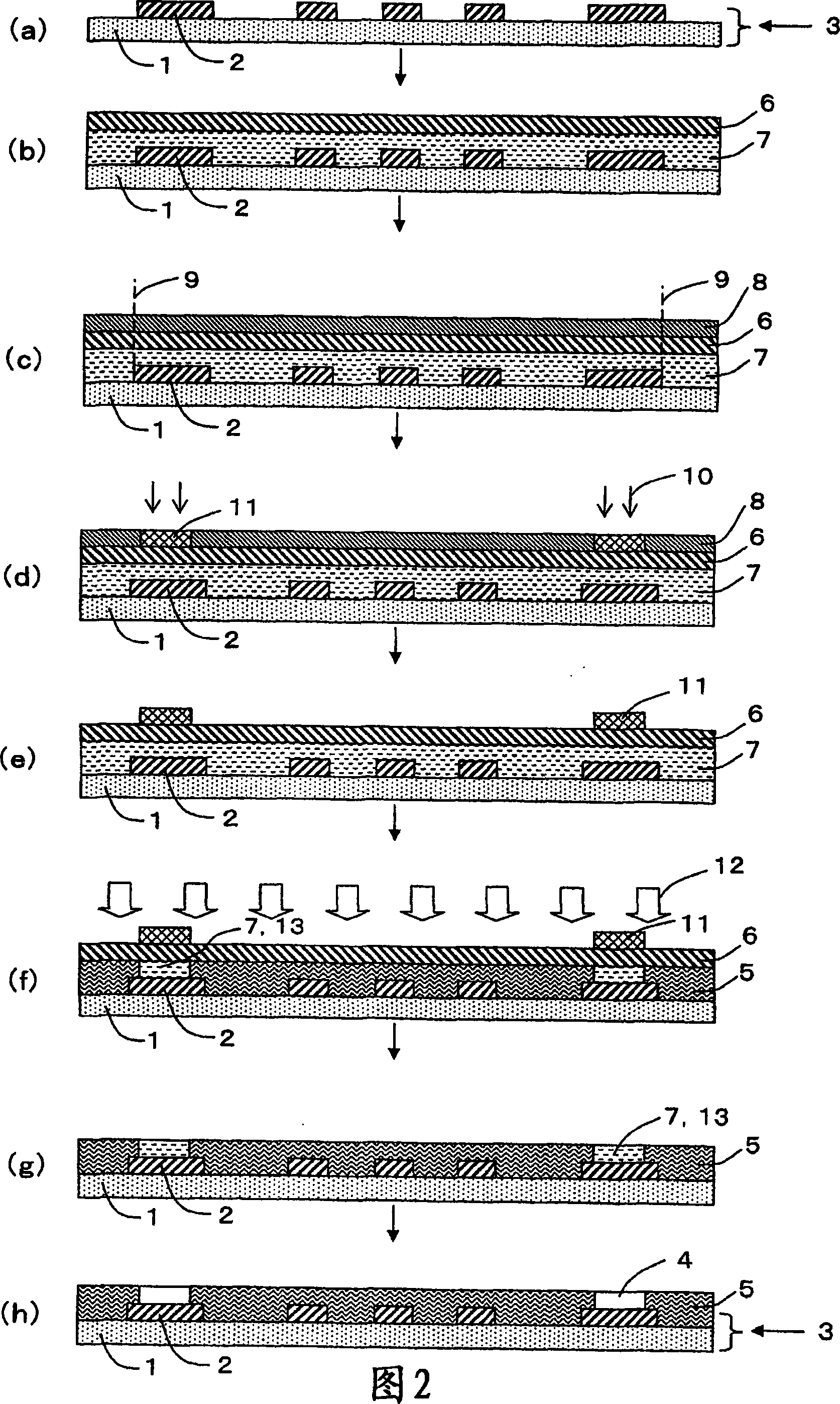

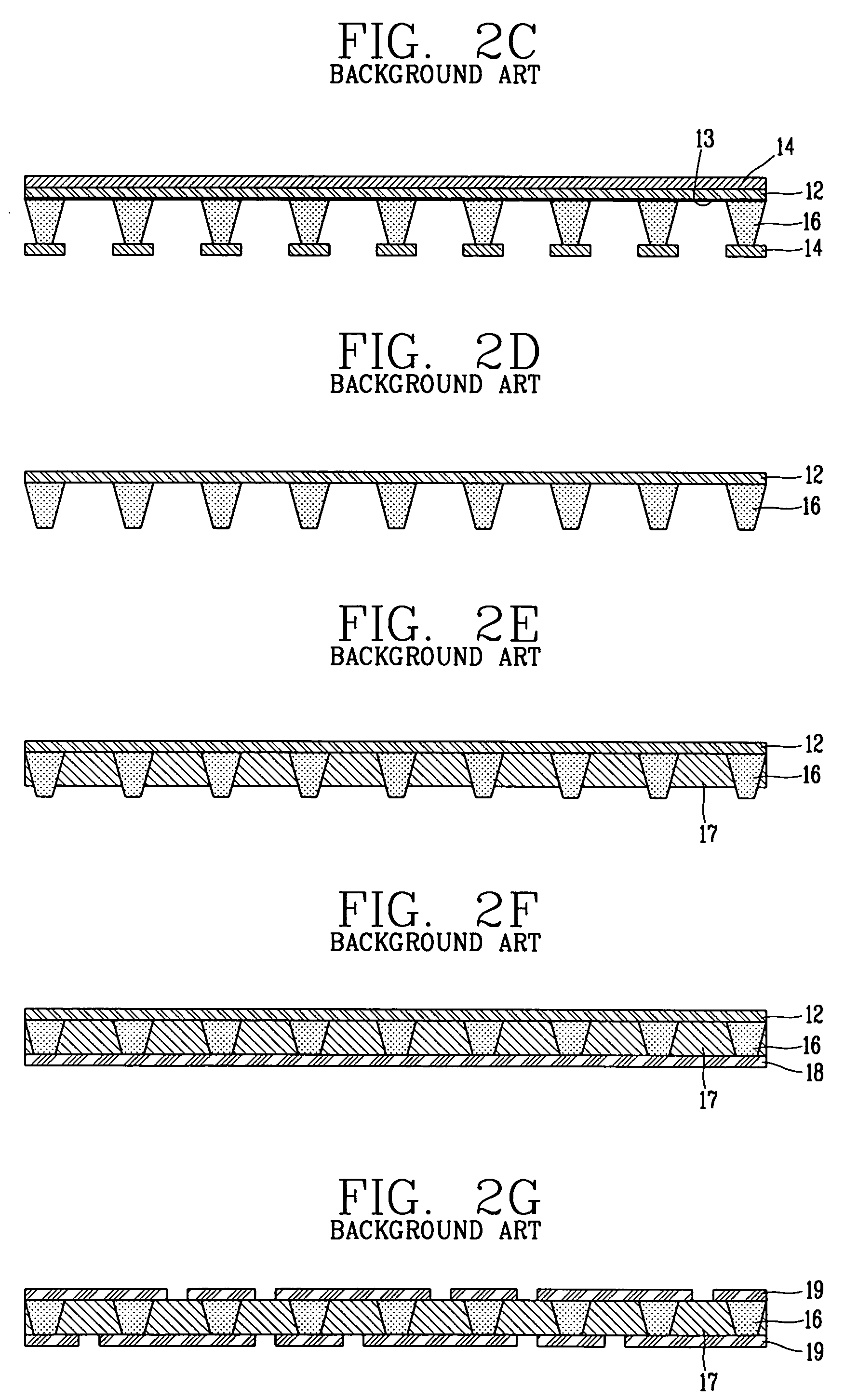

Method for manufacturing printed circuit board

InactiveUS7208341B2Improve efficiencyHigh yieldPrinted circuit aspectsSemiconductor/solid-state device manufacturingResistPrinted circuit board

A method for manufacturing a printed circuit board includes: forming inner circuit patterns in an insulating material in multi-layers, forming a plurality of through holes at certain portions of the insulating material, and forming an outer circuit pattern which is electrically connected to the inner circuit pattern, at an inner circumferential surface of the through hole and the surface of the insulating material, and a terminal portion; forming a first photo solder resist layer at an entire surface of the insulating material and an entire surface of the outer circuit pattern, and exposing the terminal portion by removing a specific portion of the first photo solder resist layer; abrading the surface of the first photo solder resist layer; printing a second photo solder resist layer at the surface of the first photo solder resist layer, and exposing the terminal portion to the outside by removing a specific portion of the second photo solder resist layer; and forming a pad portion by plating the surface of the exposed terminal portion with gold, and electrically connecting the pad portion and the terminal portion.

Owner:LG INNOTEK CO LTD +1

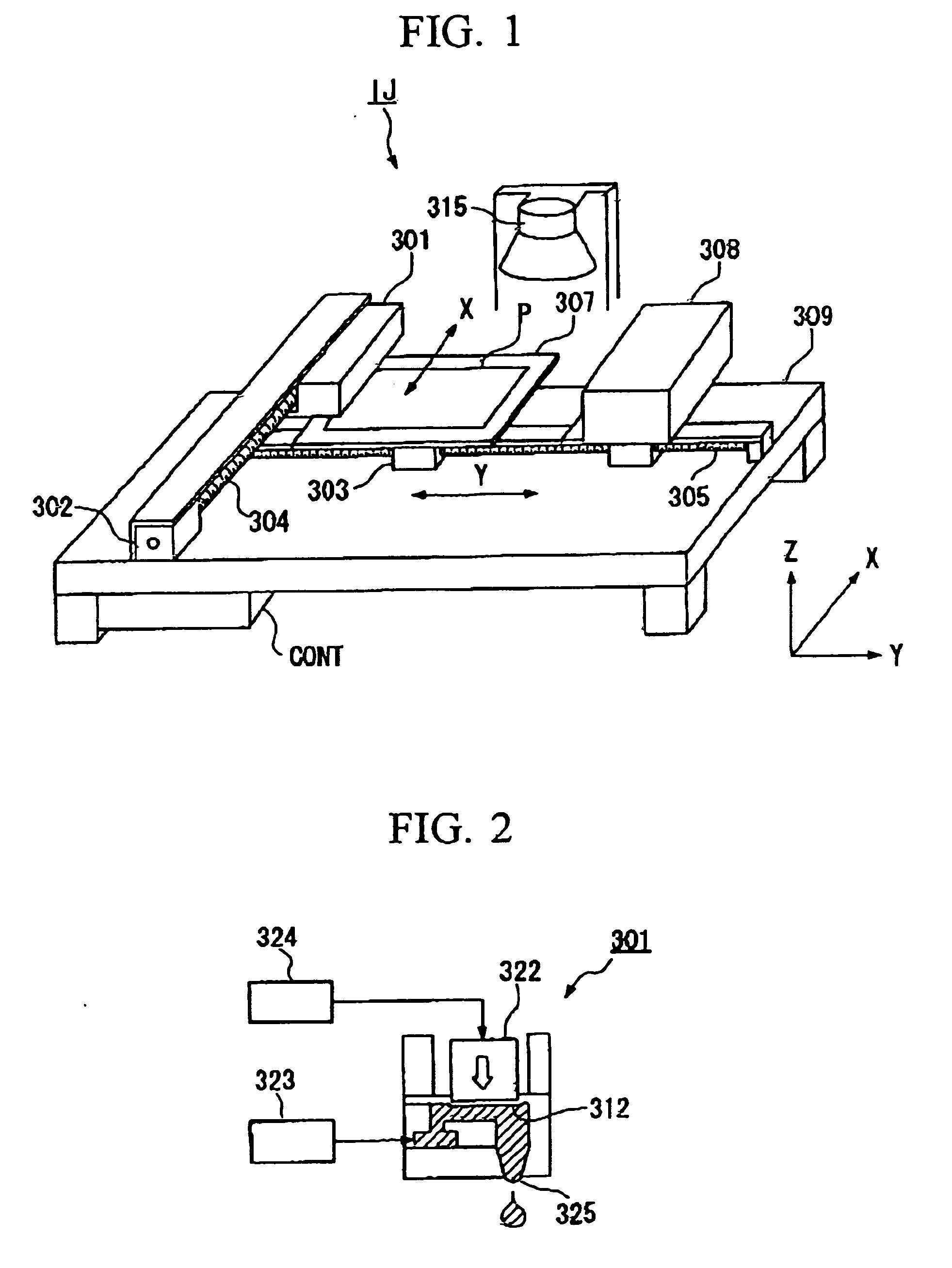

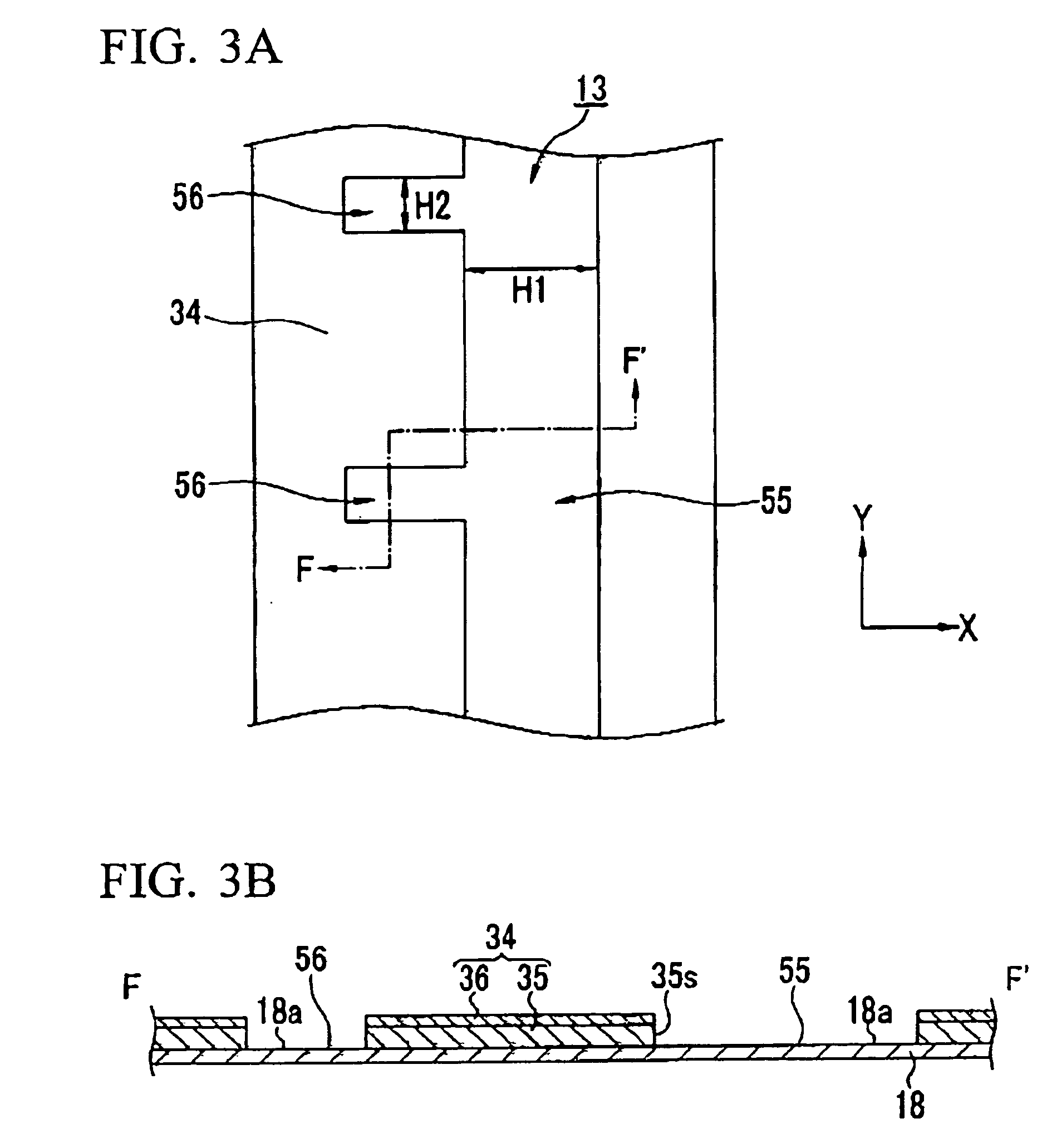

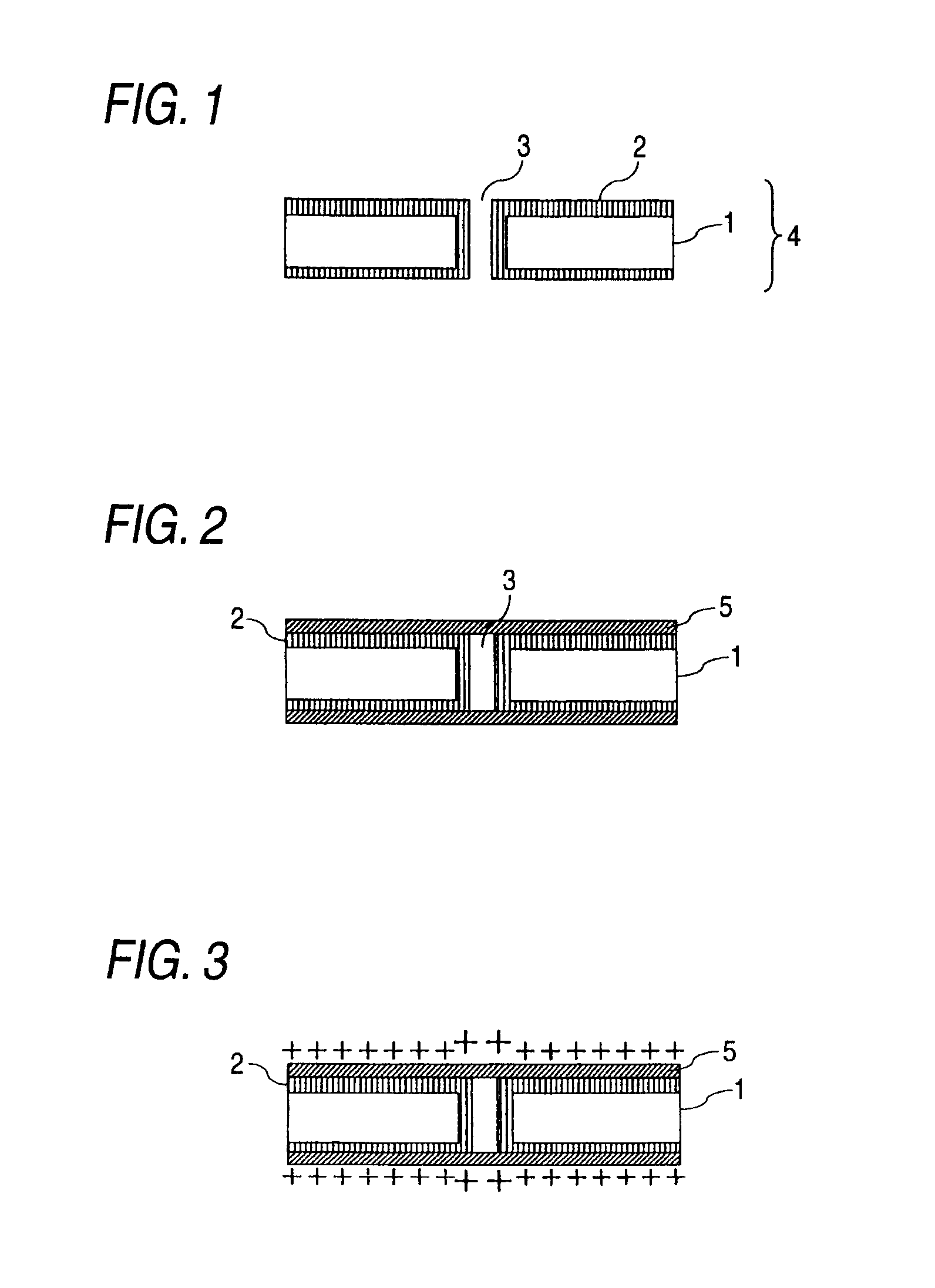

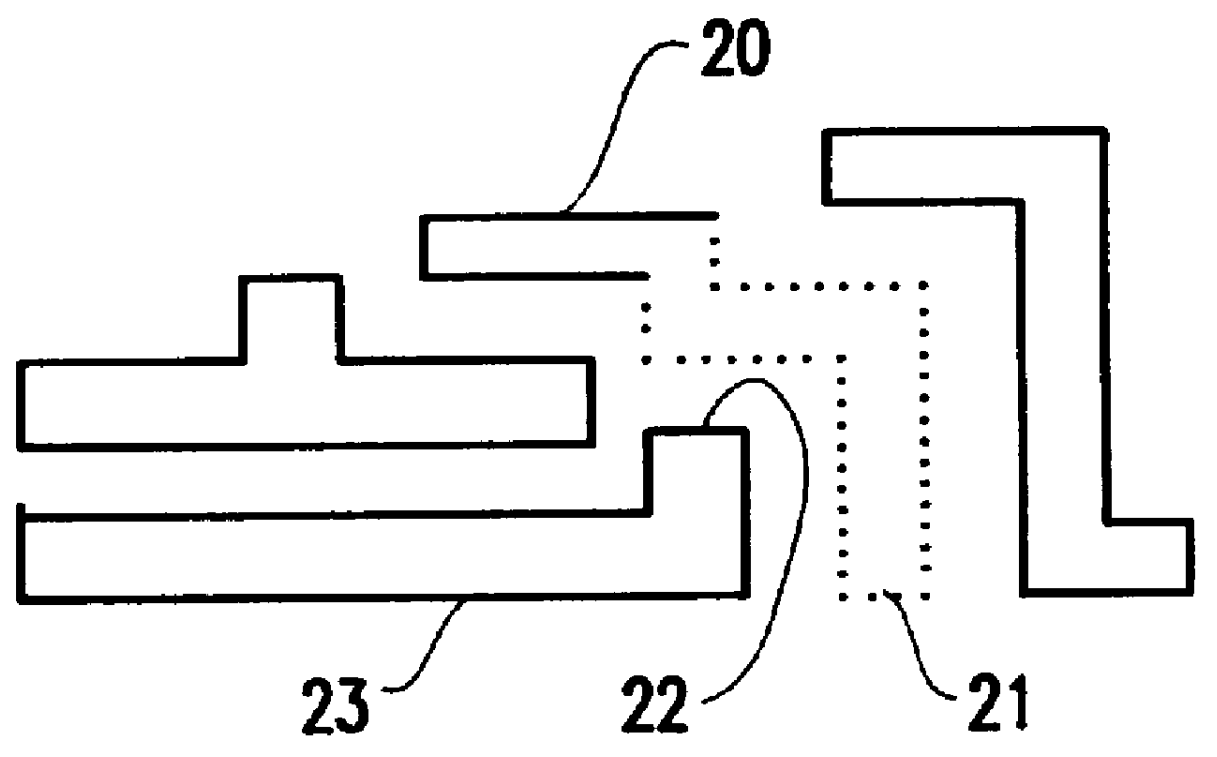

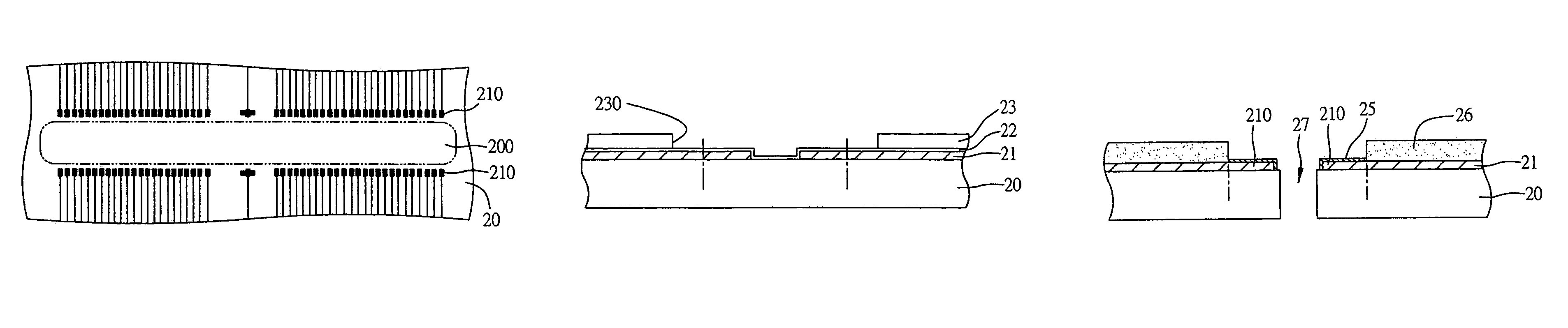

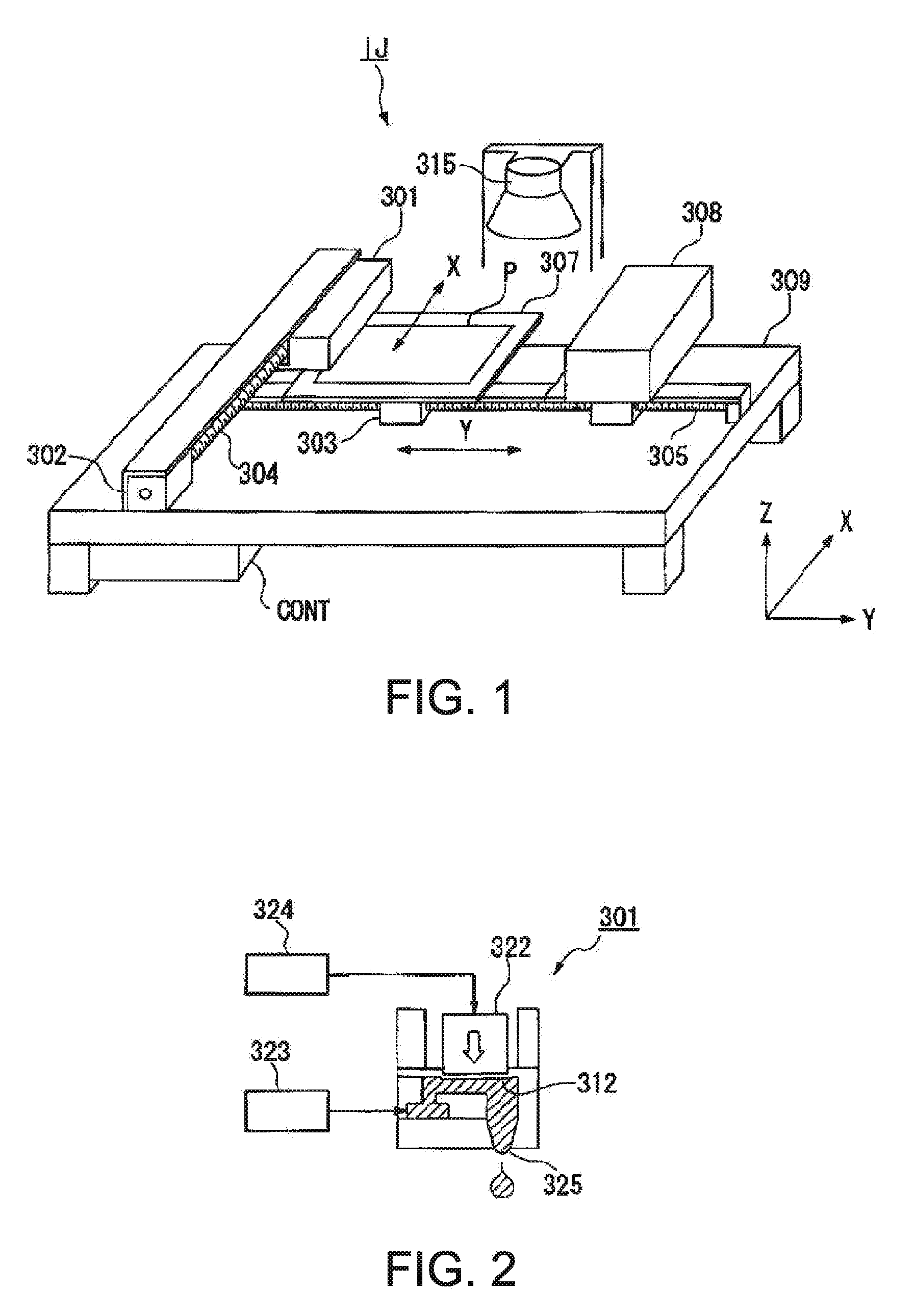

Forming method for film pattern, device, electro-optical apparatus, electronic apparatus, and manufacturing method for active matrix substrate

InactiveUS20070020899A1Solid-state devicesSemiconductor/solid-state device manufacturingActive matrixSide chain

A forming method for a film pattern, includes: forming a first bank layer on a substrate; forming a second bank layer on the first bank layer; patterning the first bank layer and the second bank layer thereby forming a bank having a pattern formation region including a first pattern formation region and a second pattern formation region which is connected to the first pattern formation region and has a width which is wider than that of the first pattern formation region; and forming the film pattern by depositing a functional liquid onto the pattern formation region which has been demarcated by the bank, wherein a first bank formation material and a second bank formation material are both materials including a siloxane bonds as a main chain, and the second bank formation material is a material including a fluorine bonds as a side chain.

Owner:SEIKO EPSON CORP

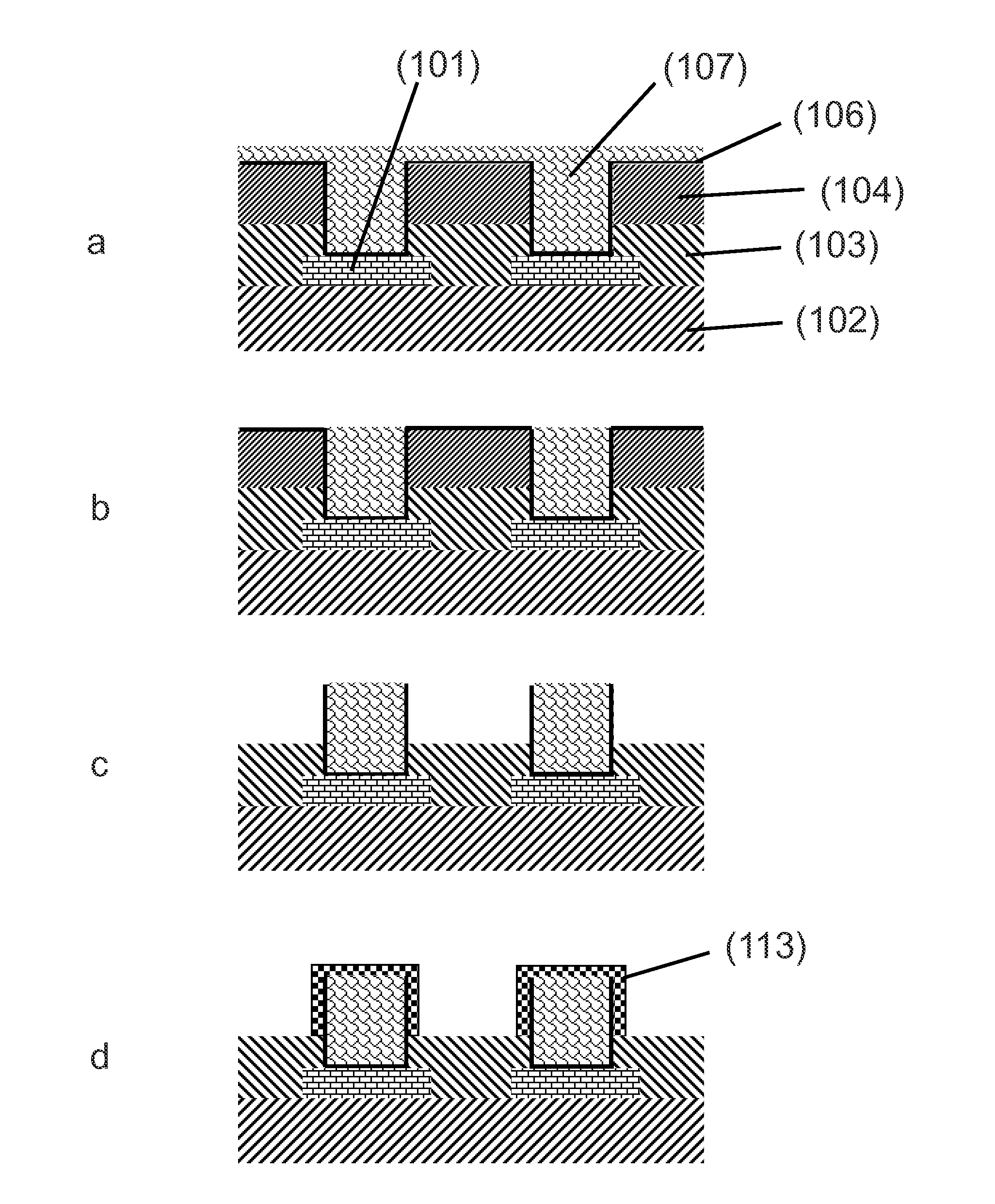

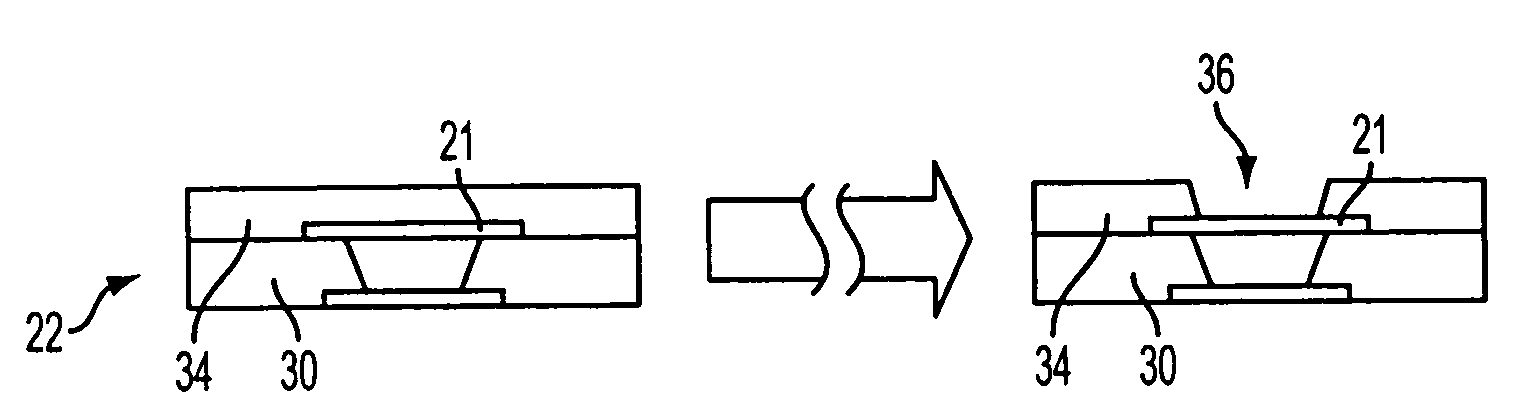

Method to form solder deposits and non-melting bump structures on substrates

InactiveUS20130105329A1Uniform layersReduce in quantitySemiconductor/solid-state device detailsSolid-state devicesMetal alloySubstrate surface

Described is a method of forming a metal or metal alloy layer onto a substrate comprising the following steps i) provide a substrate including a permanent resin layer on top of at least one contact area and a temporary resin layer on top of the permanent resin layer, ii) contact the entire substrate area including the at least one contact area with a solution suitable to provide a conductive layer on the substrate surface and i) electroplate a metal or metal alloy layer onto the conductive layer.

Owner:ATOTECH DEUT GMBH

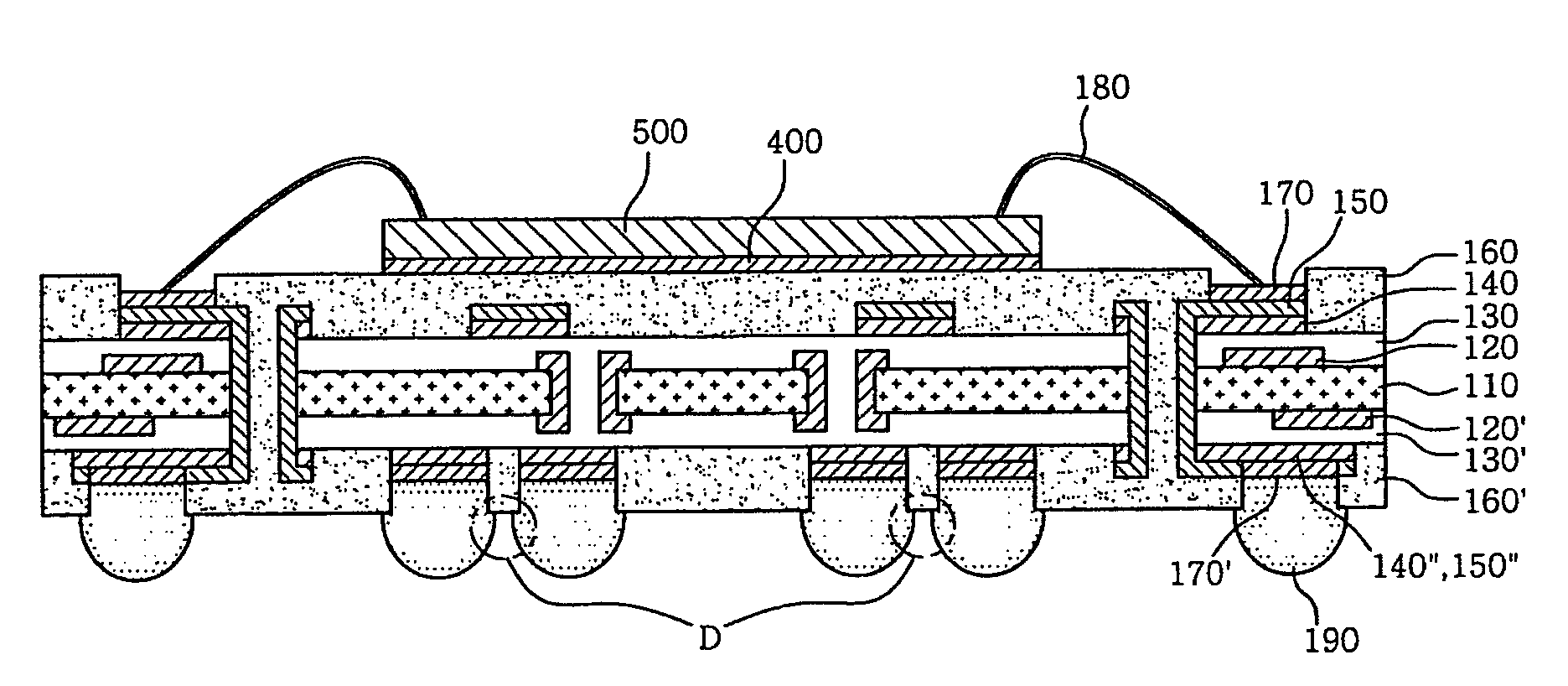

BGA package board and method for manufacturing the same

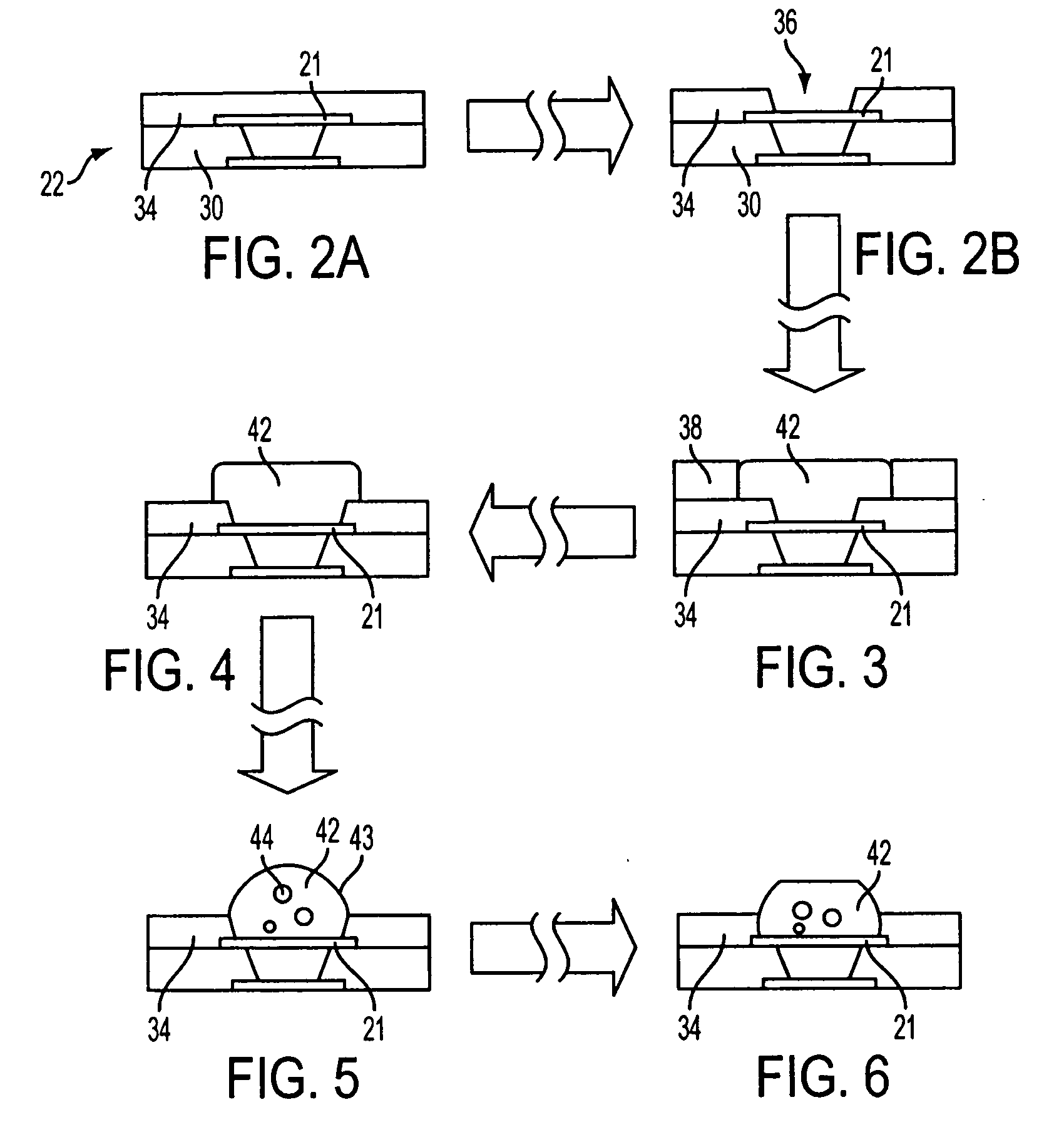

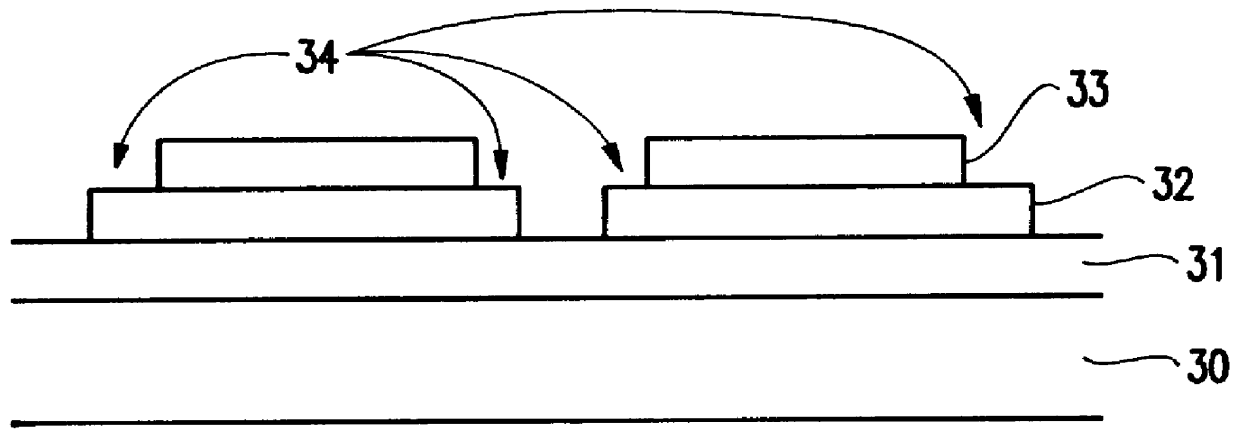

ActiveUS7408261B2Avoid stickingAdapt effectivelySemiconductor/solid-state device detailsStacked resist layersResistLead bonding

Disclosed herein is a Ball Grid Array (BGA) package board. The BGA package board includes a first external layer on which a pattern comprising a circuit pattern and a wire bonding pad pattern is formed, a second external layer on which a pattern comprising a circuit pattern and a solder ball pad pattern is formed, an insulating layer formed between the first and second external layers, a first outer via hole to electrically connect the first and second external layers to each other, and a solder resist layer formed on each of the first and second external layers, with portions of the solder resist layer corresponding to the wire bonding pad pattern and the solder ball pad pattern being opened. The solder ball pad pattern is thinner than the circuit pattern of the second external layer.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

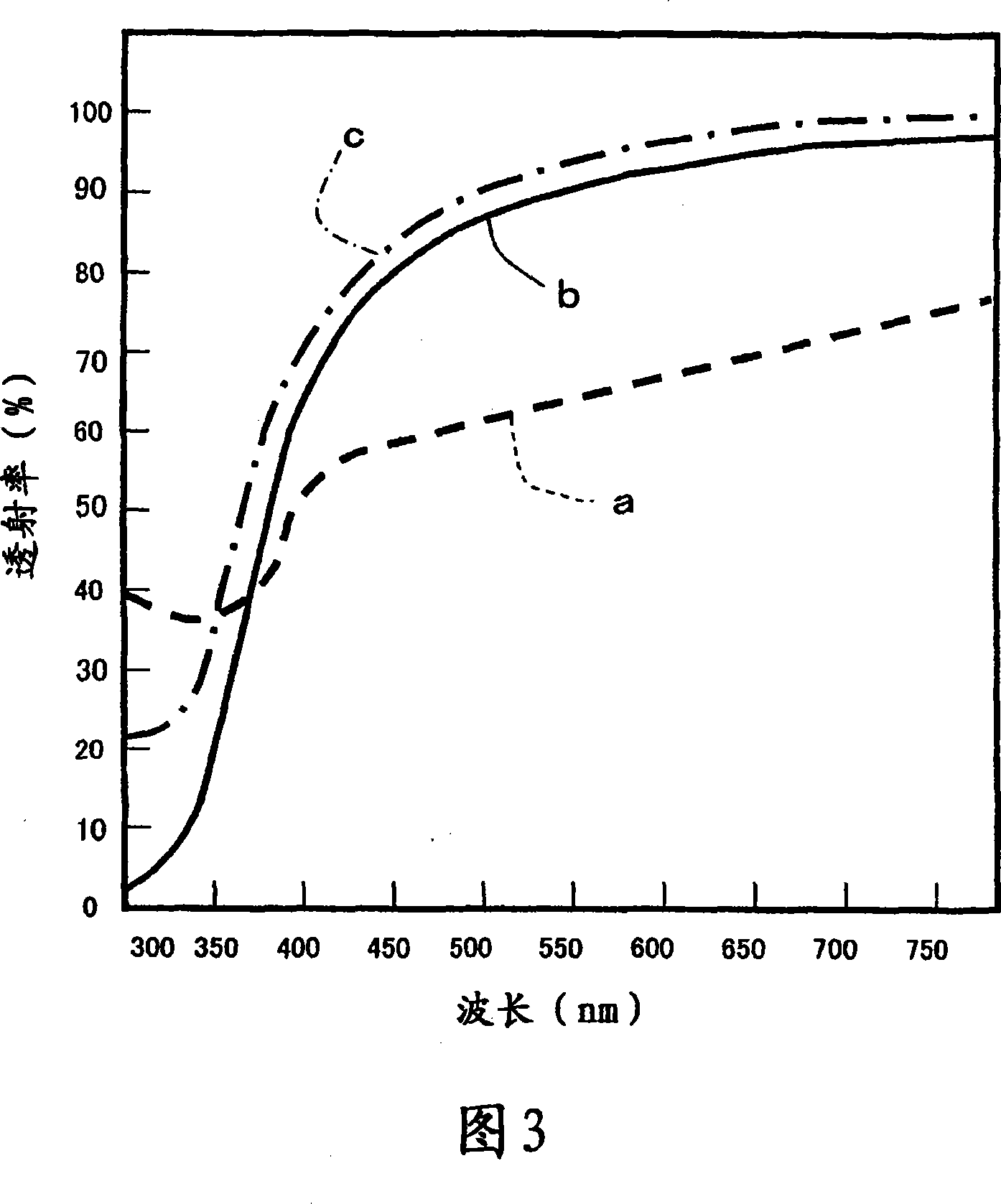

Light-sensitive sheet comprising support, first and second light-sensitive layers and barrier layer

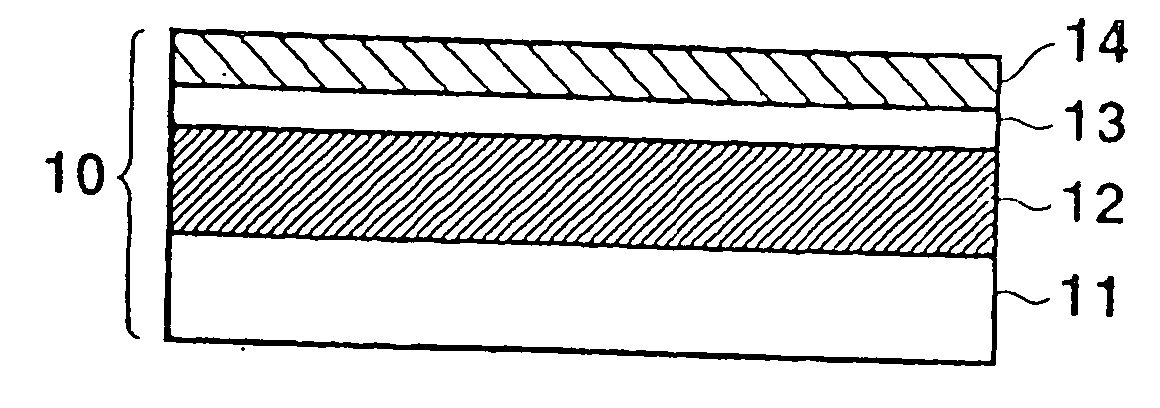

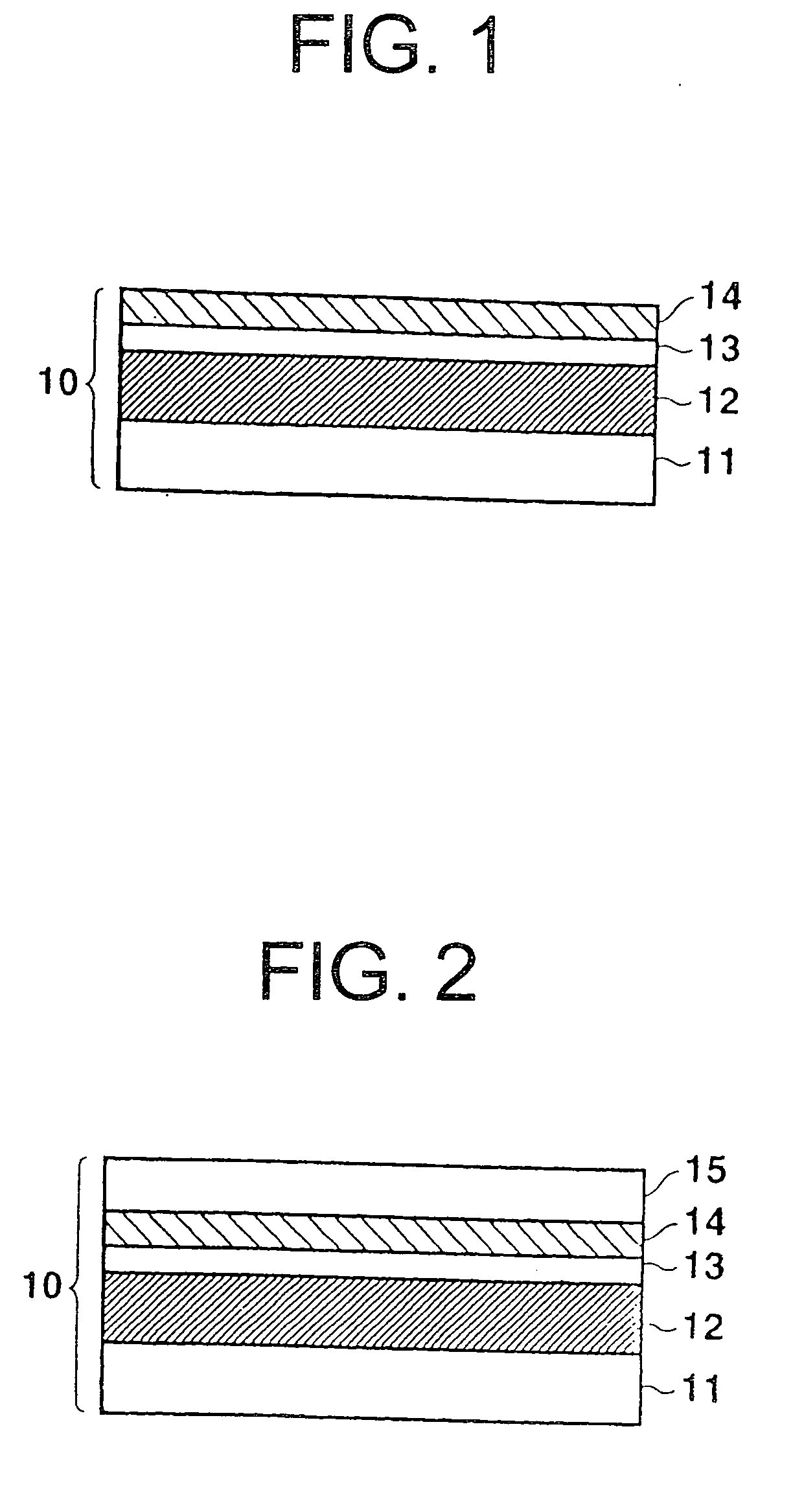

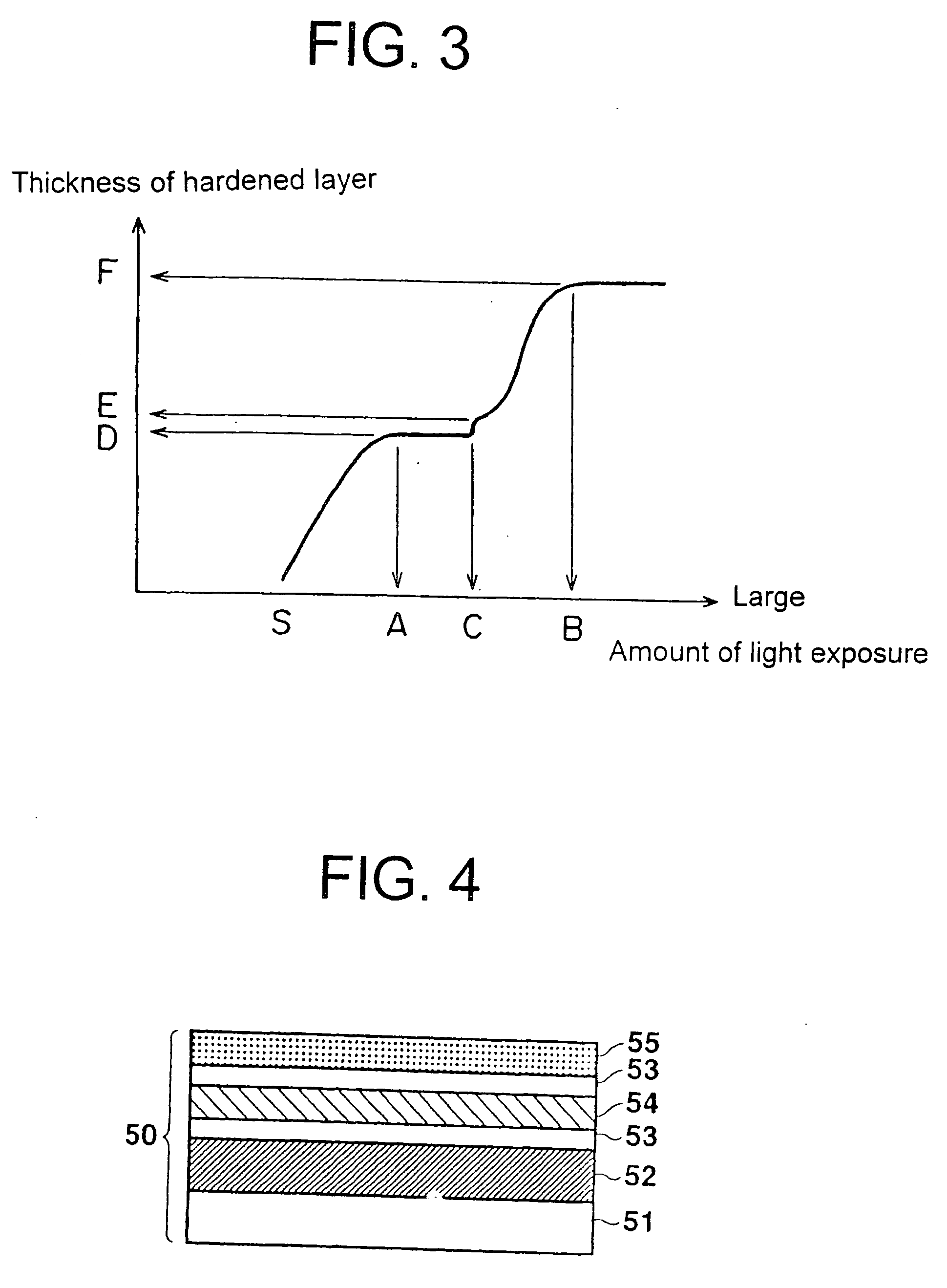

ActiveUS20050037281A1High film strengthHigh resolutionRadiation applicationsSemiconductor/solid-state device manufacturingPolymerizationChemistry

A light-sensitive sheet comprises a support, a first light-sensitive layer, a barrier layer and a second light-sensitive layer in this order. Each of the first and second light sensitive layers independently contains a binder, a polymerizable compound and a photo-polymerization initiator. The second light-sensitive layer is more sensitive to light than the first light-sensitive layer. A light-sensitive laminate comprises a substrate, the second light-sensitive layer, the barrier layer and the first light-sensitive layer in this order.

Owner:FUJIFILM CORP +1

High density inductor and method for producing same

InactiveUS7176773B2Reduce core sizeAccurate shapeTransformers/inductances casingsTransformers/inductances coils/windings/connectionsHigh densityInductor

Owner:TDK CORPARATION

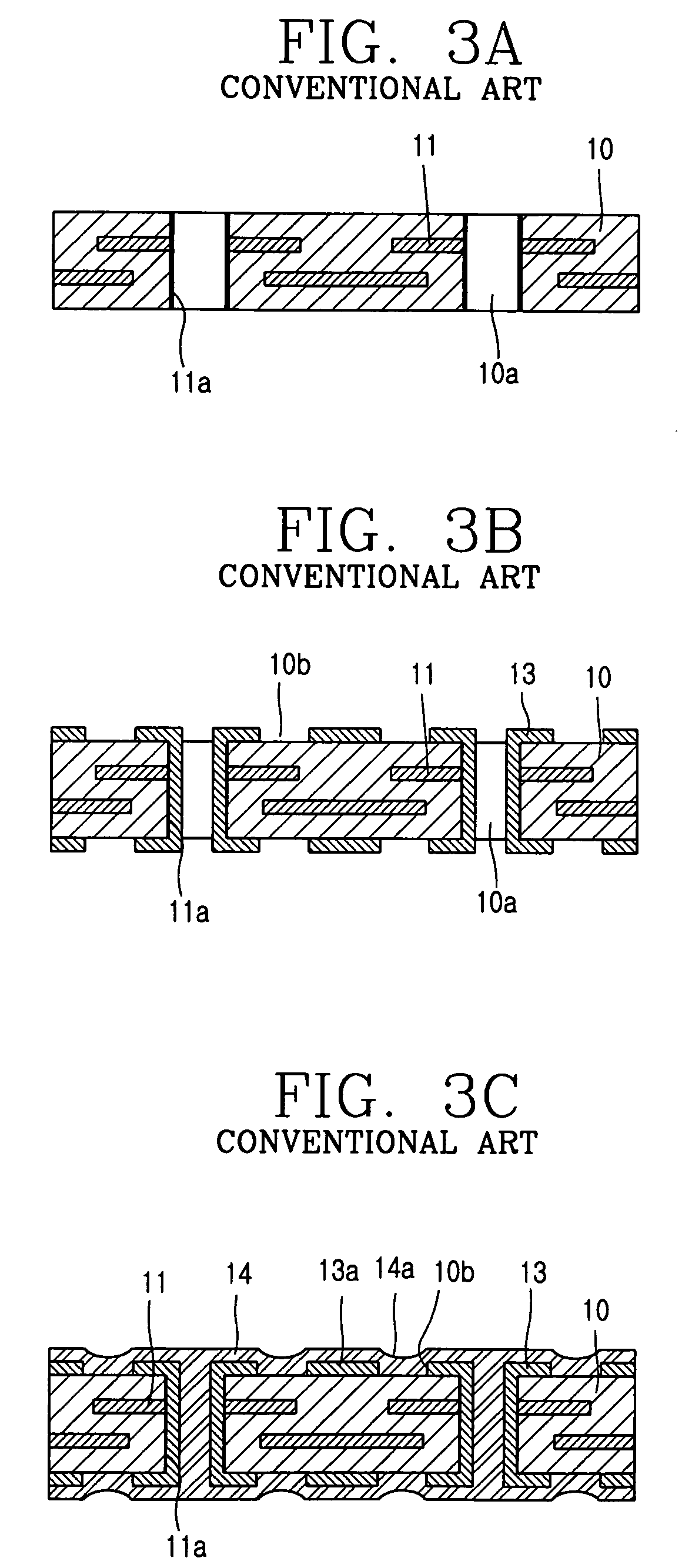

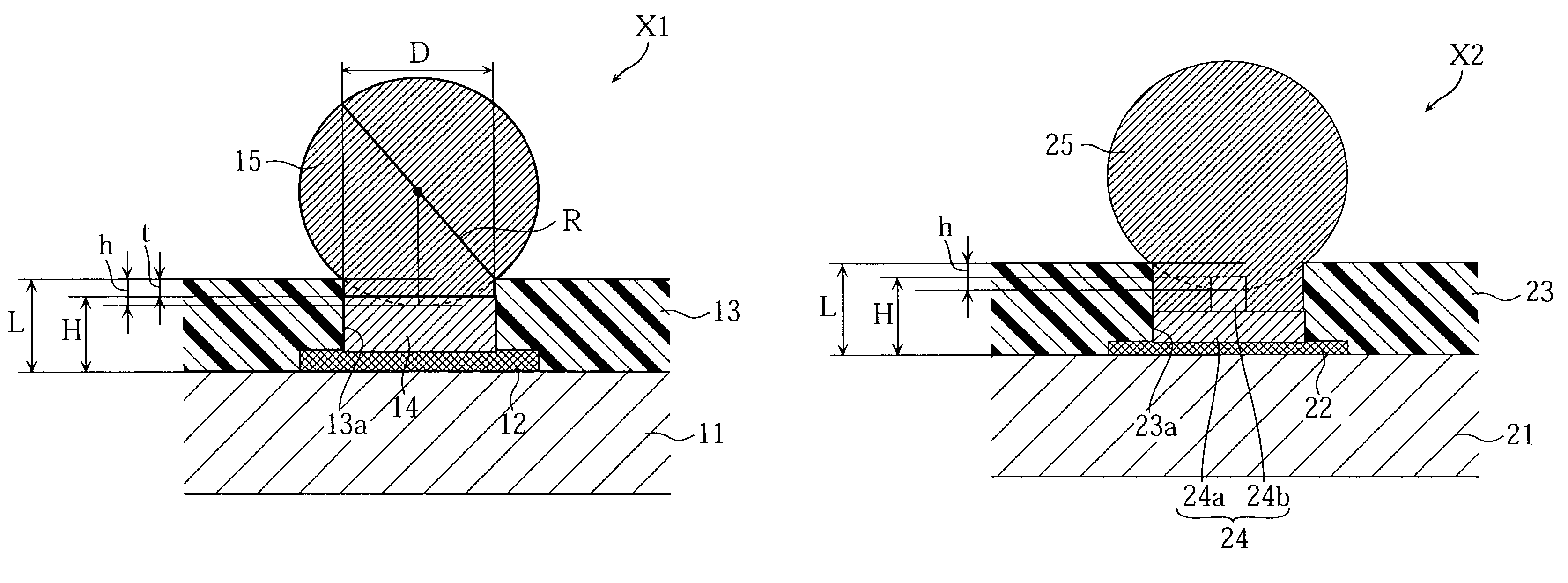

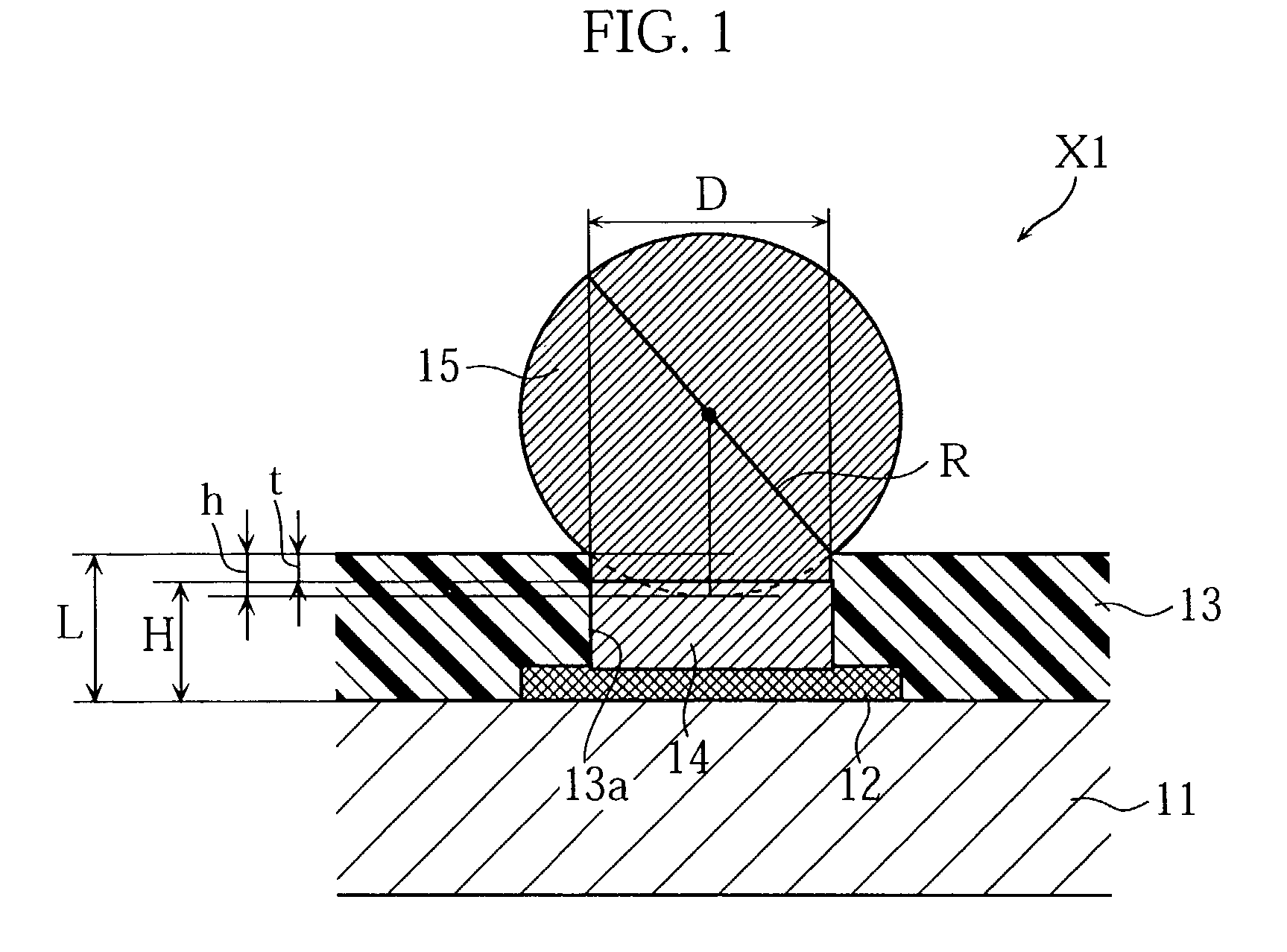

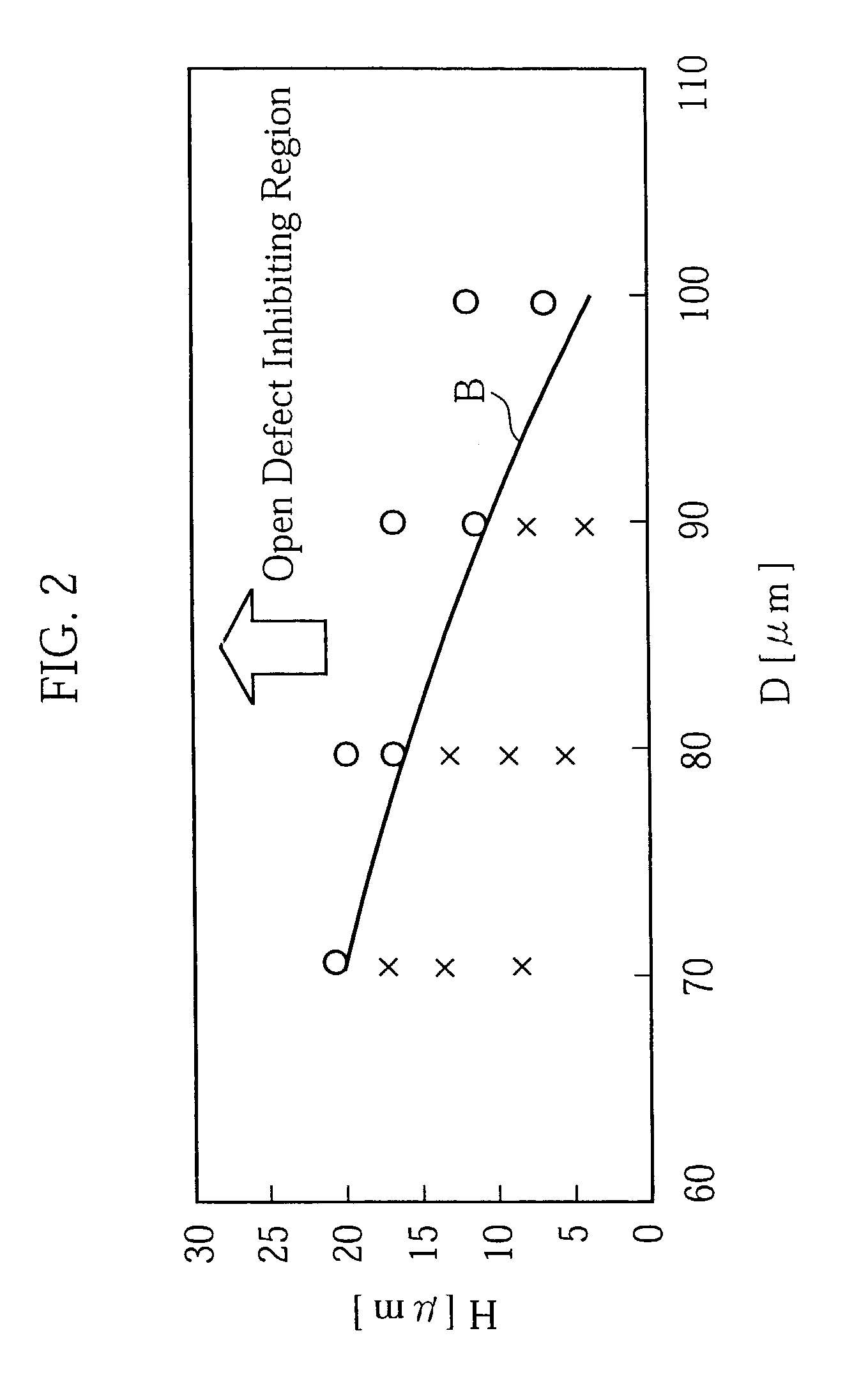

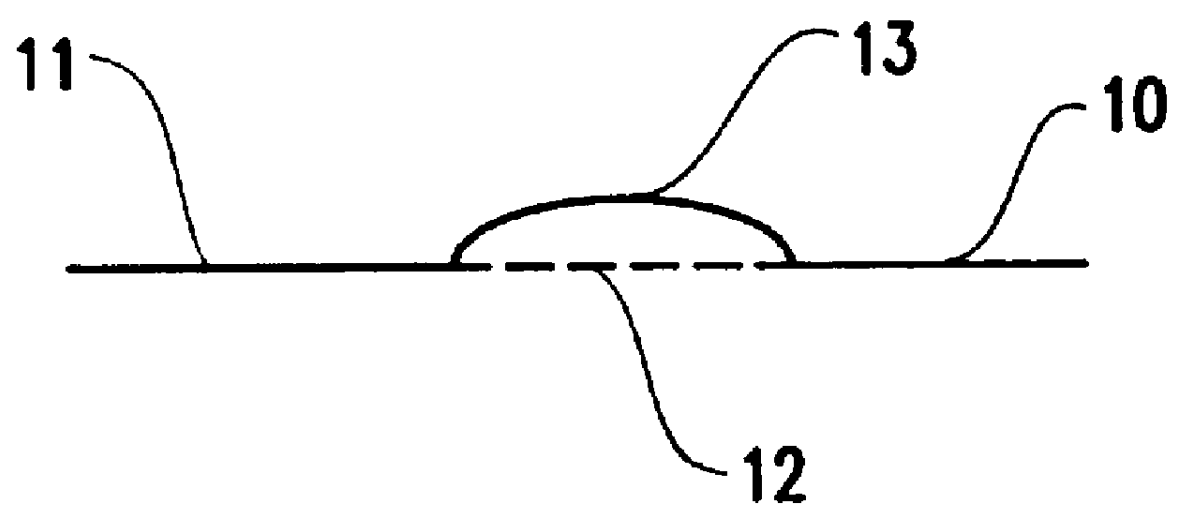

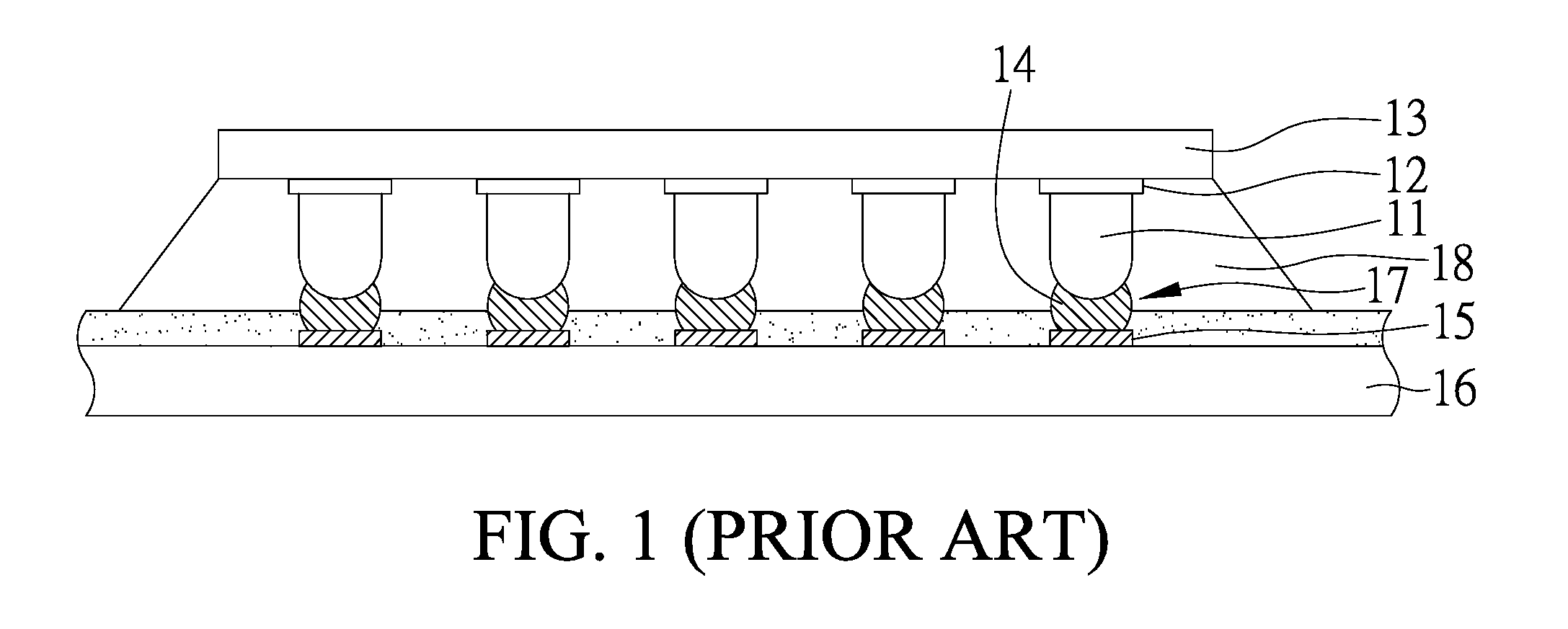

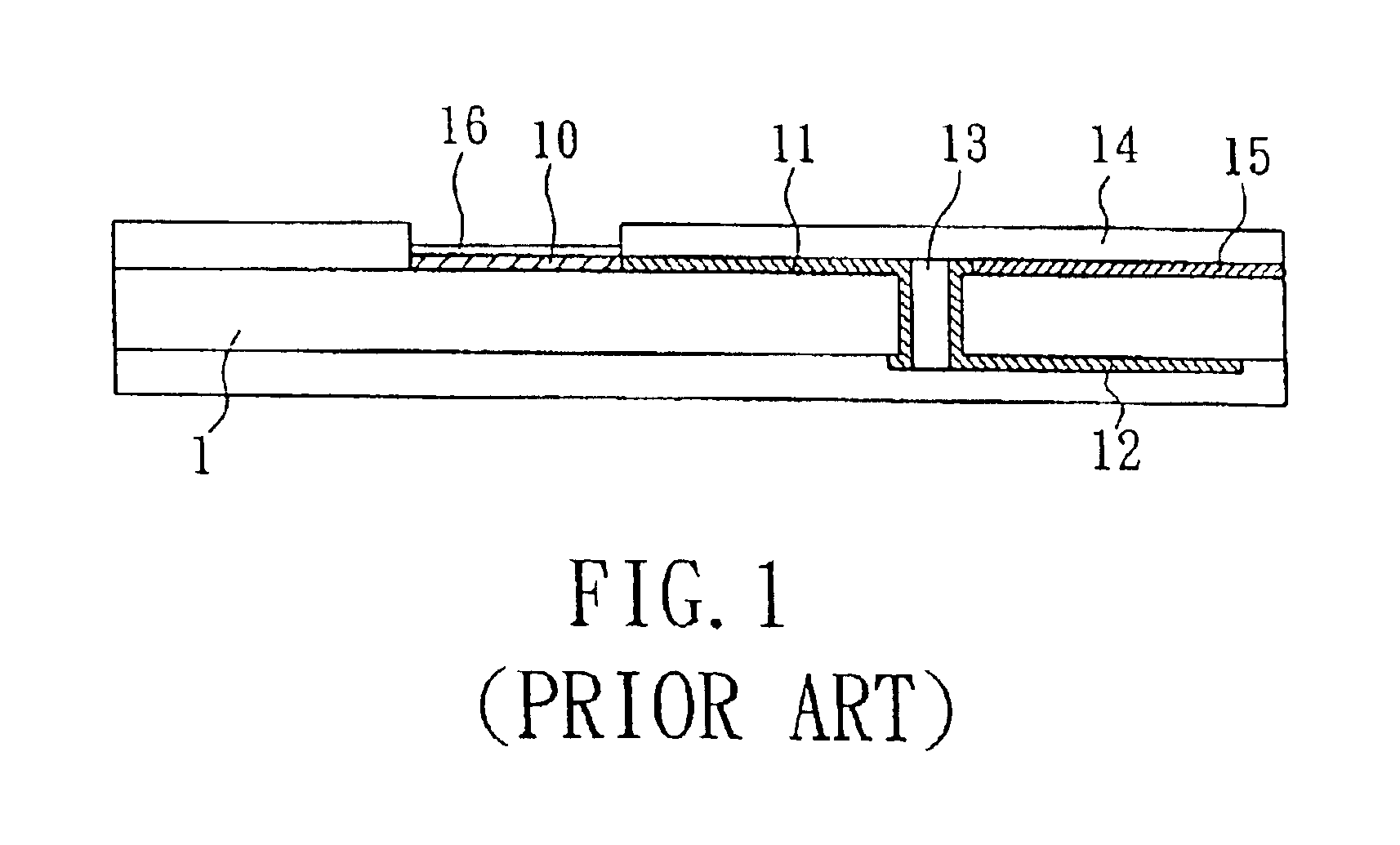

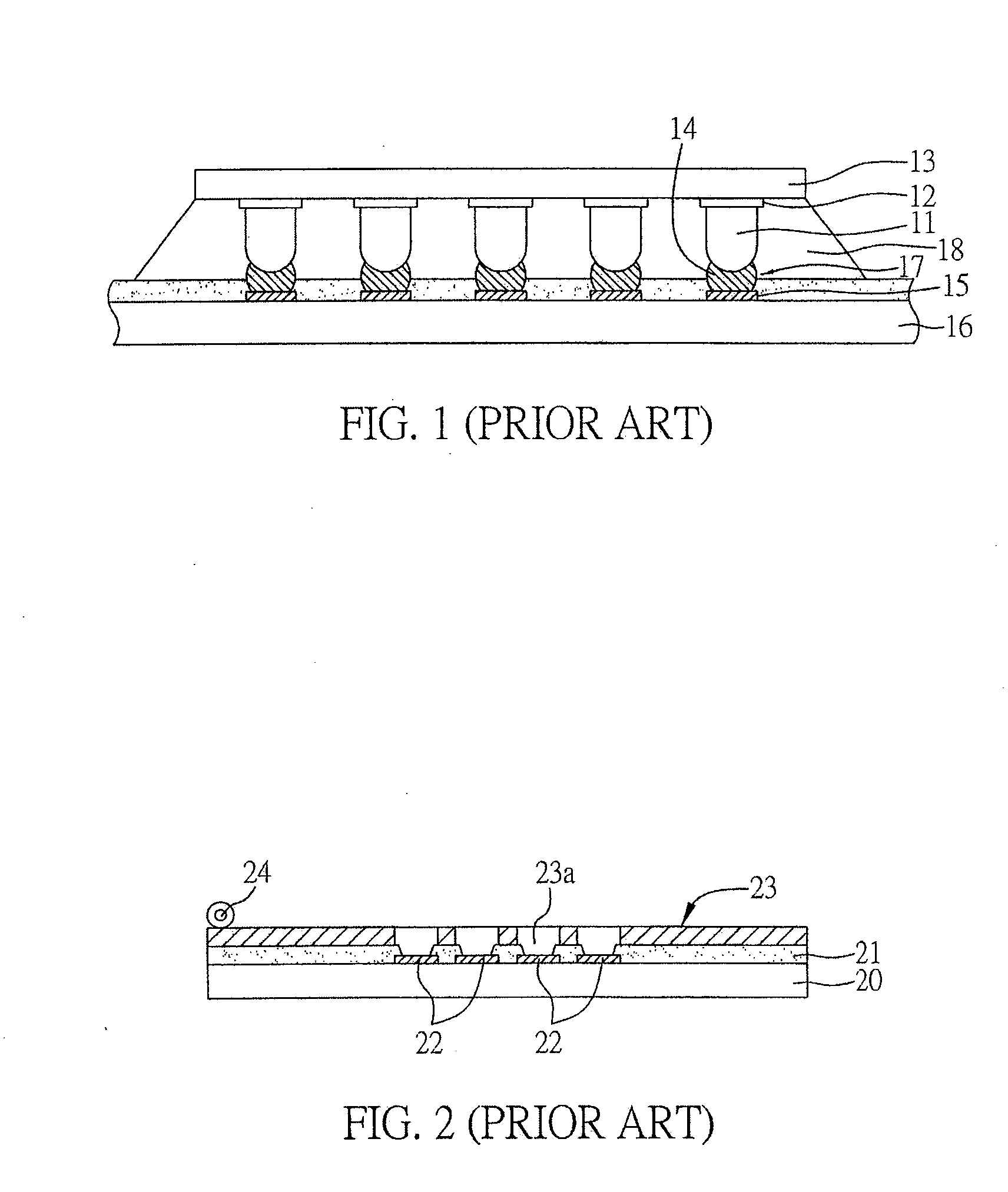

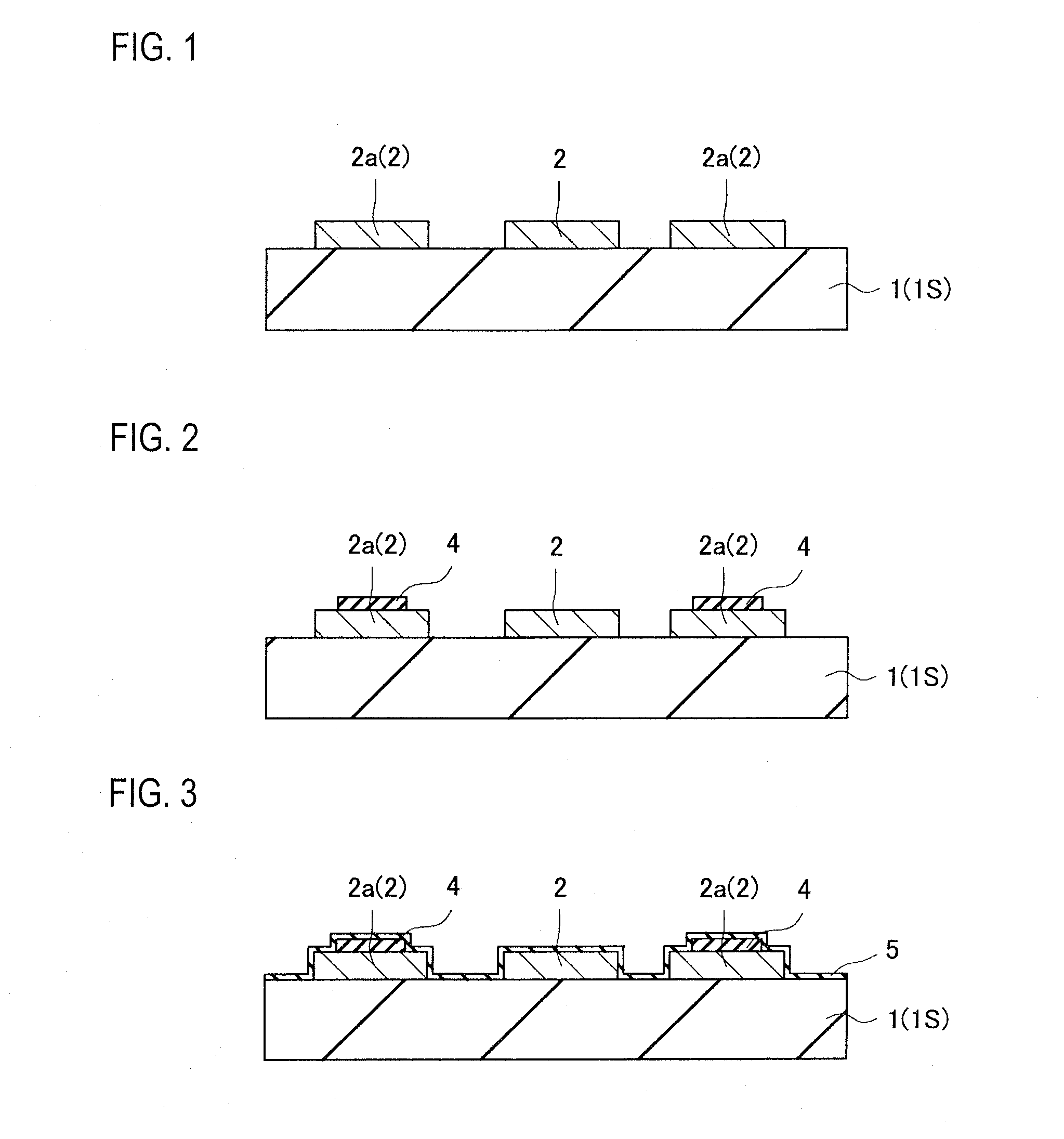

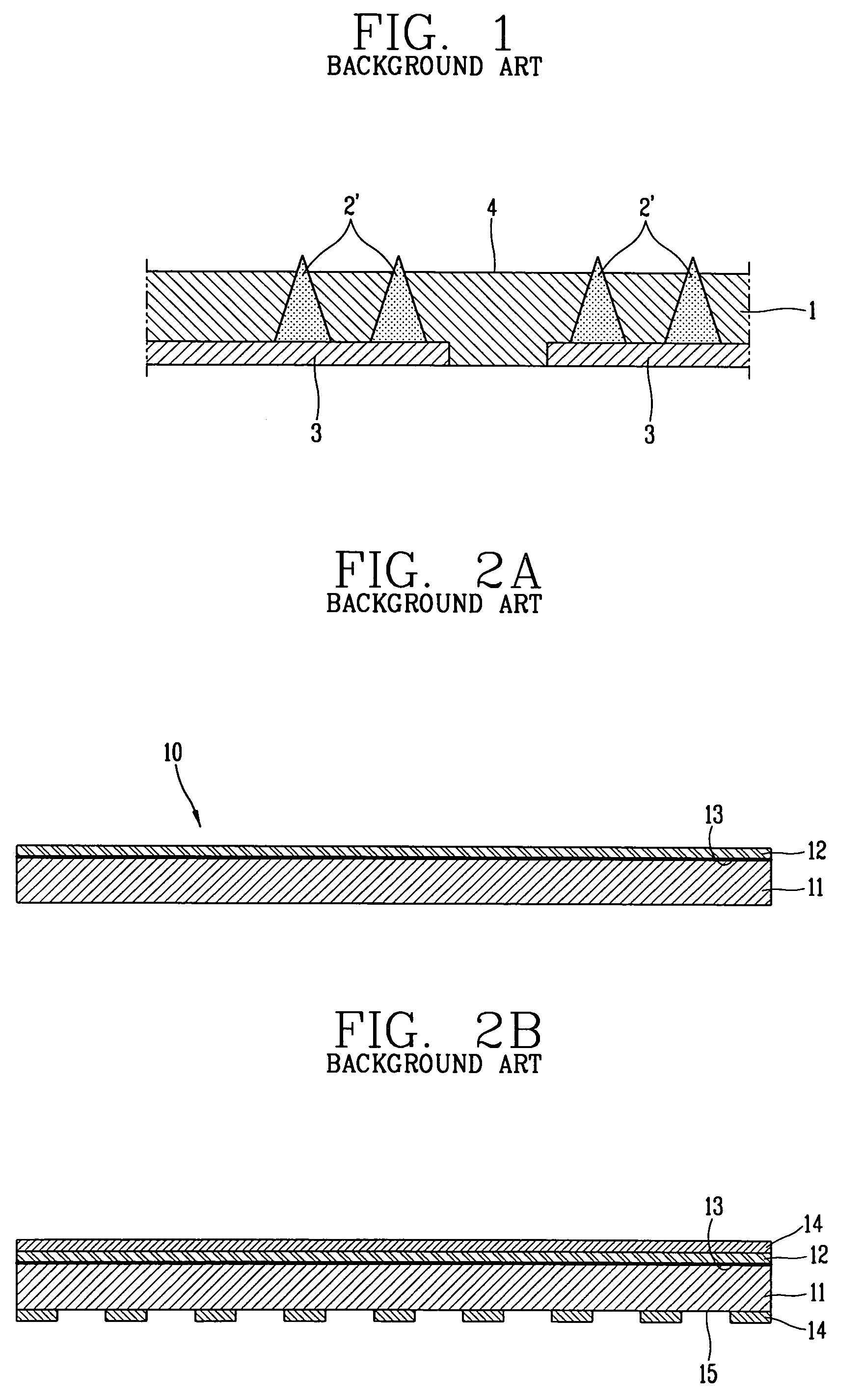

Electronic component with bump electrodes, and manufacturing method thereof

InactiveUS7189927B2Reduce generationAvoid insufficient thicknessFinal product manufactureSemiconductor/solid-state device detailsEngineeringElectronic component

An electronic component with bump electrodes includes a surface-protecting insulating film of adequate thickness and bump elements of adequate height, and allows the occurrence of open defects in the manufacturing process to be appropriately reduced. An electronic component with bump electrodes (X1) includes a substrate (11), electrode pads (12) provided on the substrate (11), an insulating film (13) that has openings (13a) in correspondence with the electrode pads (12) and is laminated and formed on the substrate (11), electroconductive connecting elements (14) provided on the electrode pads (12) in the openings (13a), and bump elements (15) that are in direct contact with the electroconductive connecting elements (14) and project from the openings (13a).

Owner:FUJITSU LTD

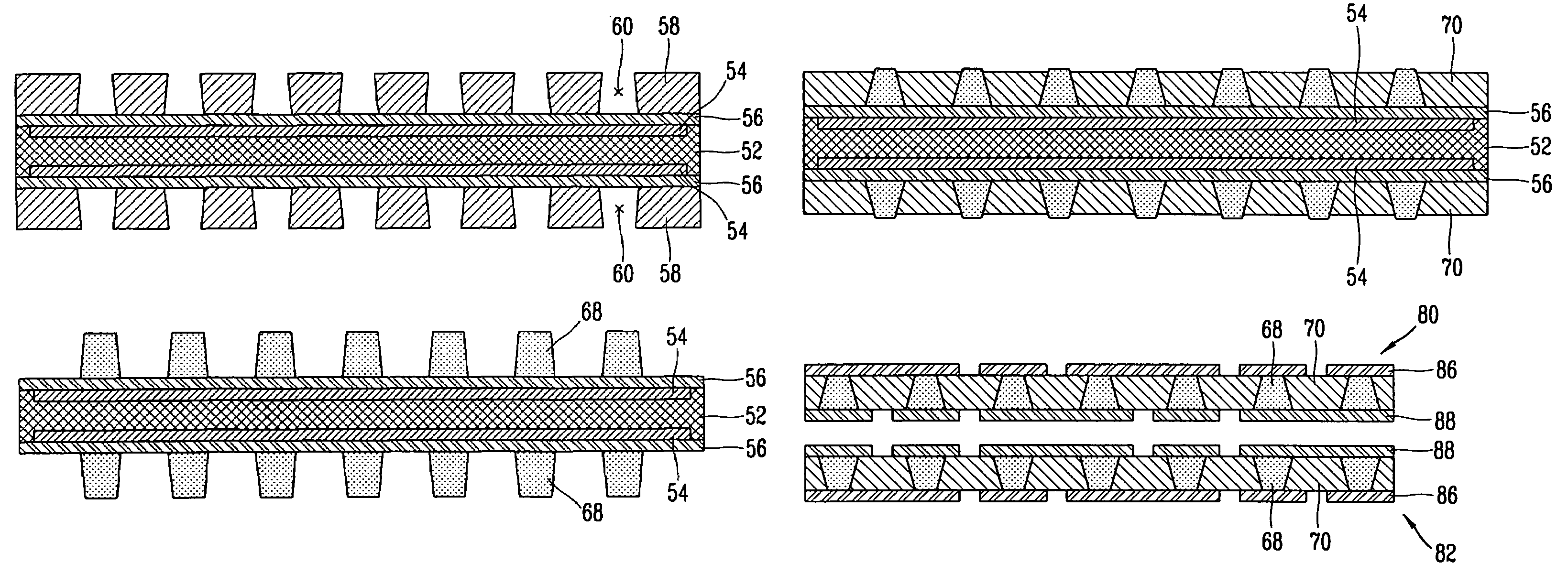

Circuit board manufacturing method and circuit board

InactiveUS20070181994A1Easy to manufactureSemiconductor/solid-state device detailsSolid-state devicesResistPotential difference

As means for solving a problem of a positional shift of a land and a hole which is caused by an alignment in the formation of an etching resist layer and a plated resist layer in a method of manufacturing a circuit board, there are provided a method of manufacturing a circuit board including the steps of forming a first resin layer on a surface of an insulating substrate having a conductive layer on the surface and an internal wall of a through hole or / and a non-through hole, forming a second resin layer which is insoluble or slightly soluble in a developing solution for the first resin layer on the first resin layer provided on the surface conductive layer, and removing the first resin layer provided over the hole with the developing solution for the first resin layer, and a method of manufacturing a circuit board including the step of uniformly charging a surface of the first resin layer to induce a potential difference to the first resin layer provided over the hole and the first resin layer provided on the surface conductive layer before forming the second resin layer. Moreover, there is provided a circuit board having a hole with a small positional shift and high precision.

Owner:SHINKO ELECTRIC IND CO LTD +1

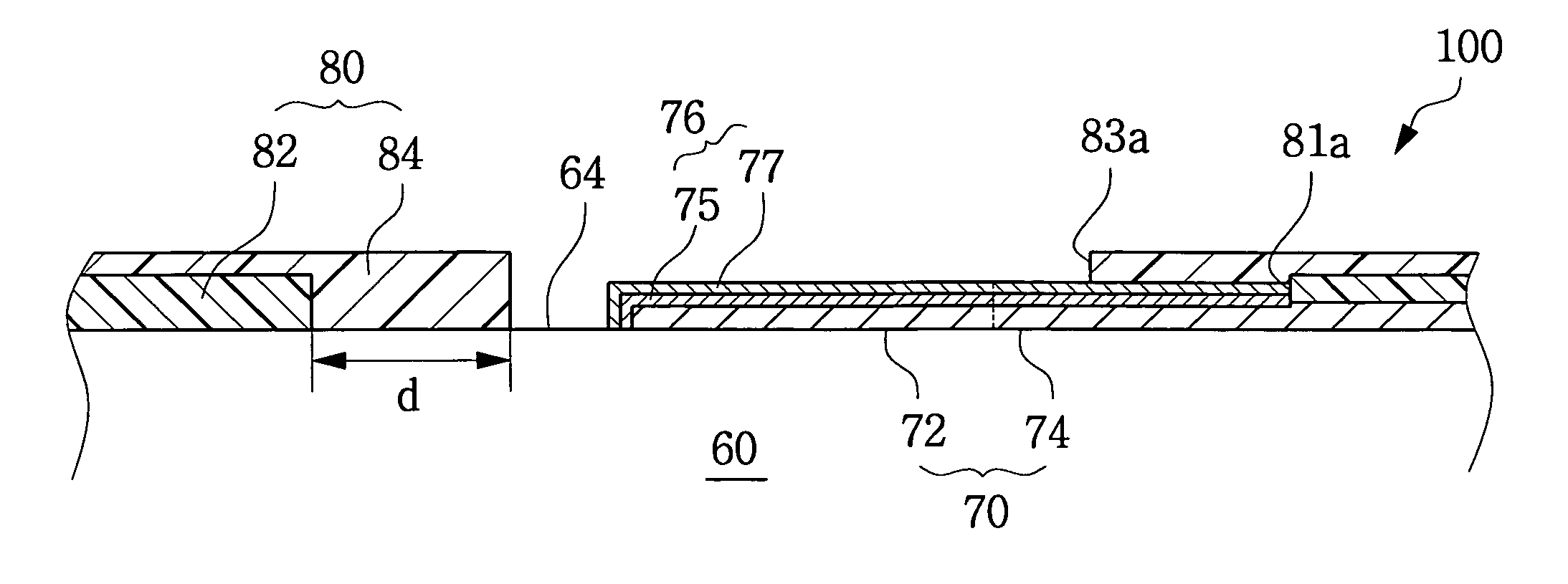

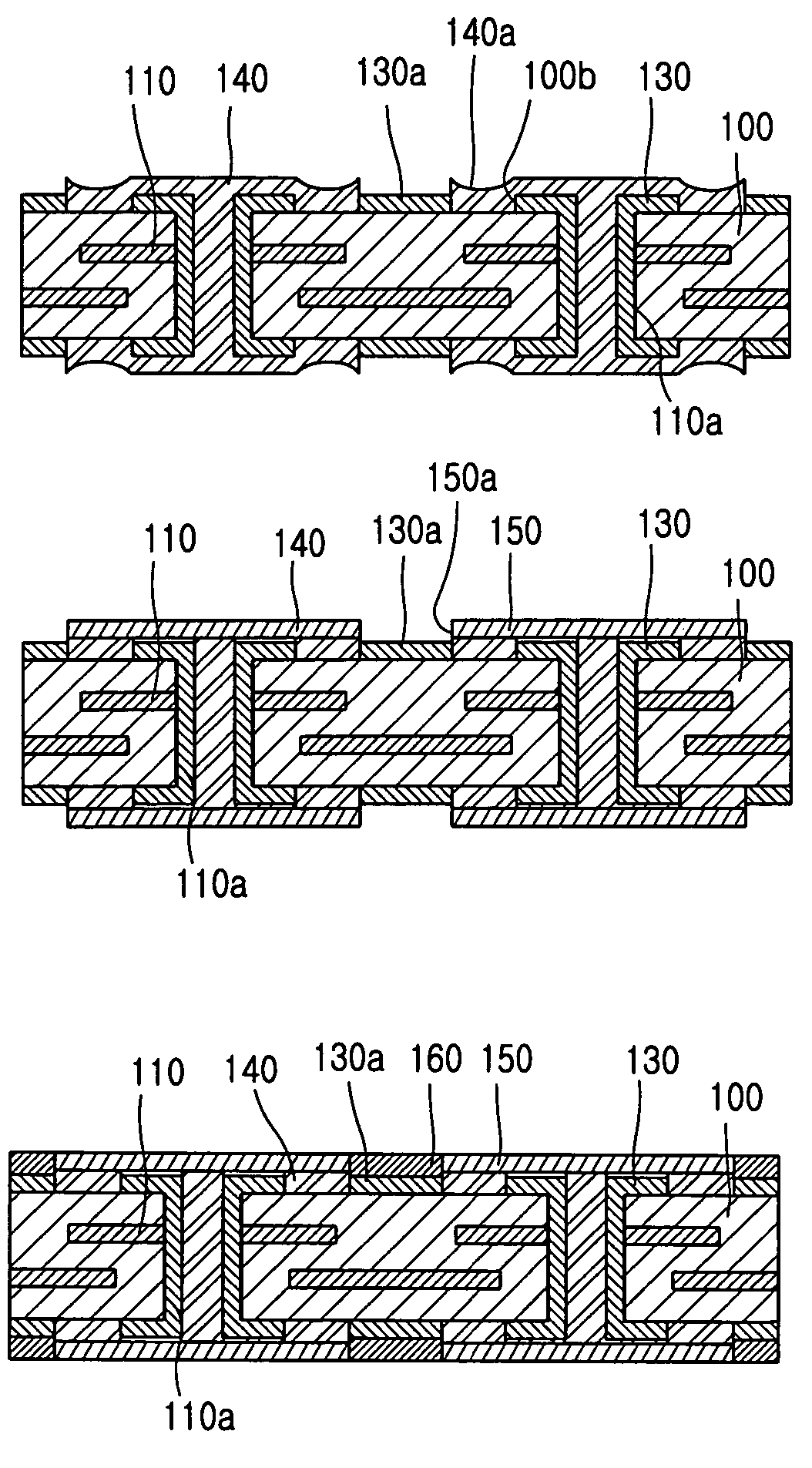

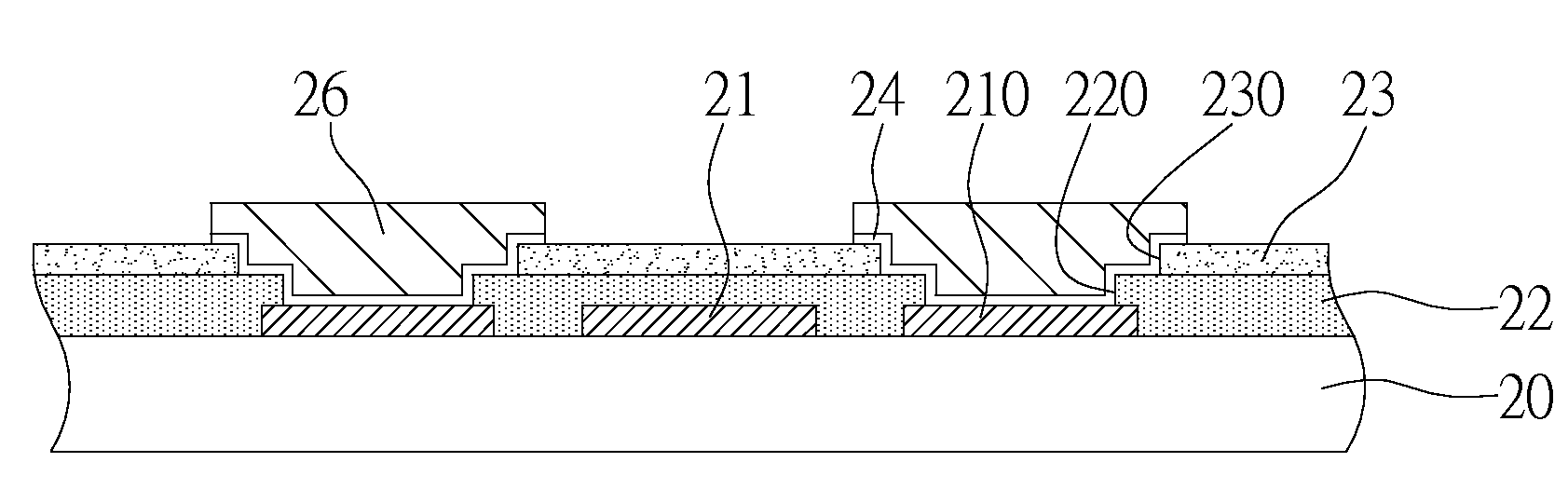

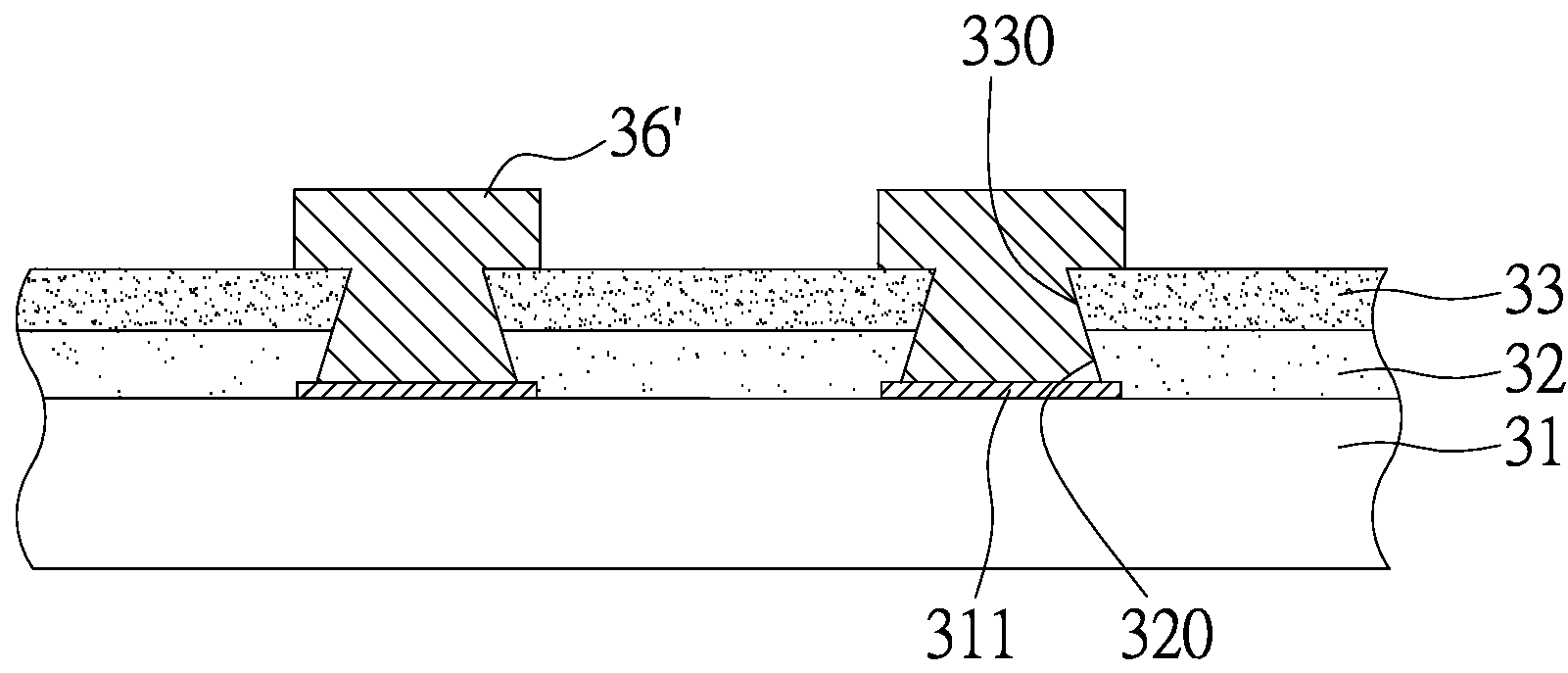

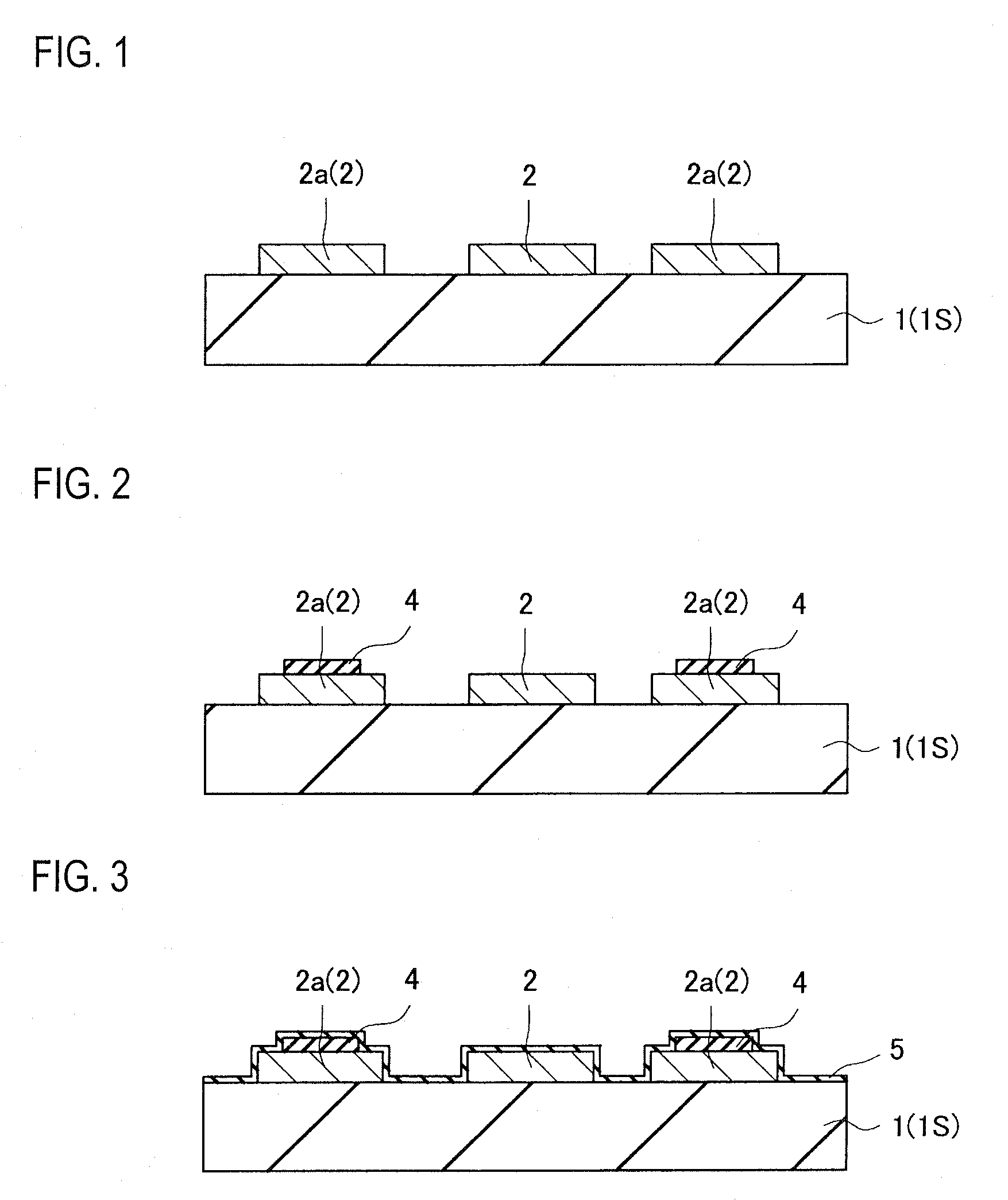

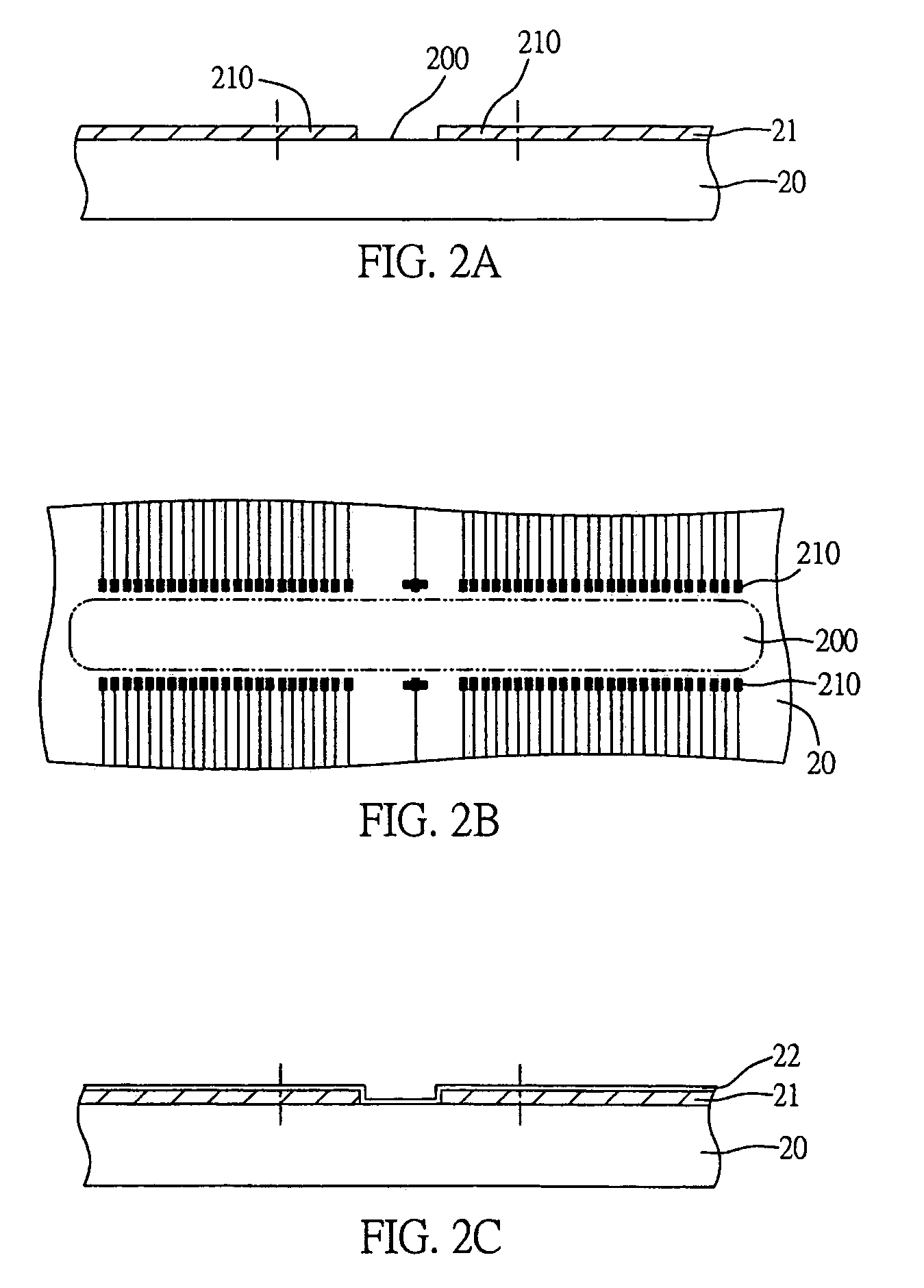

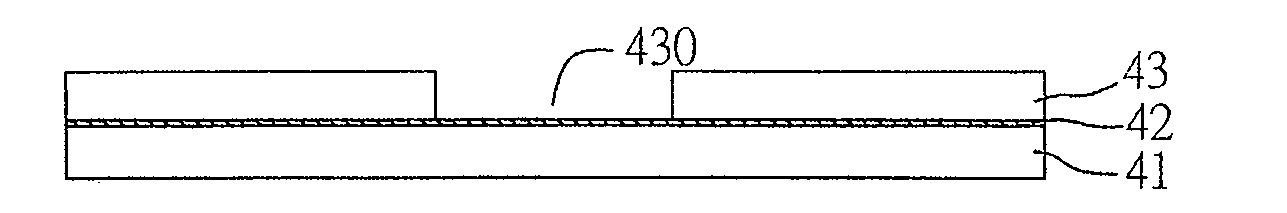

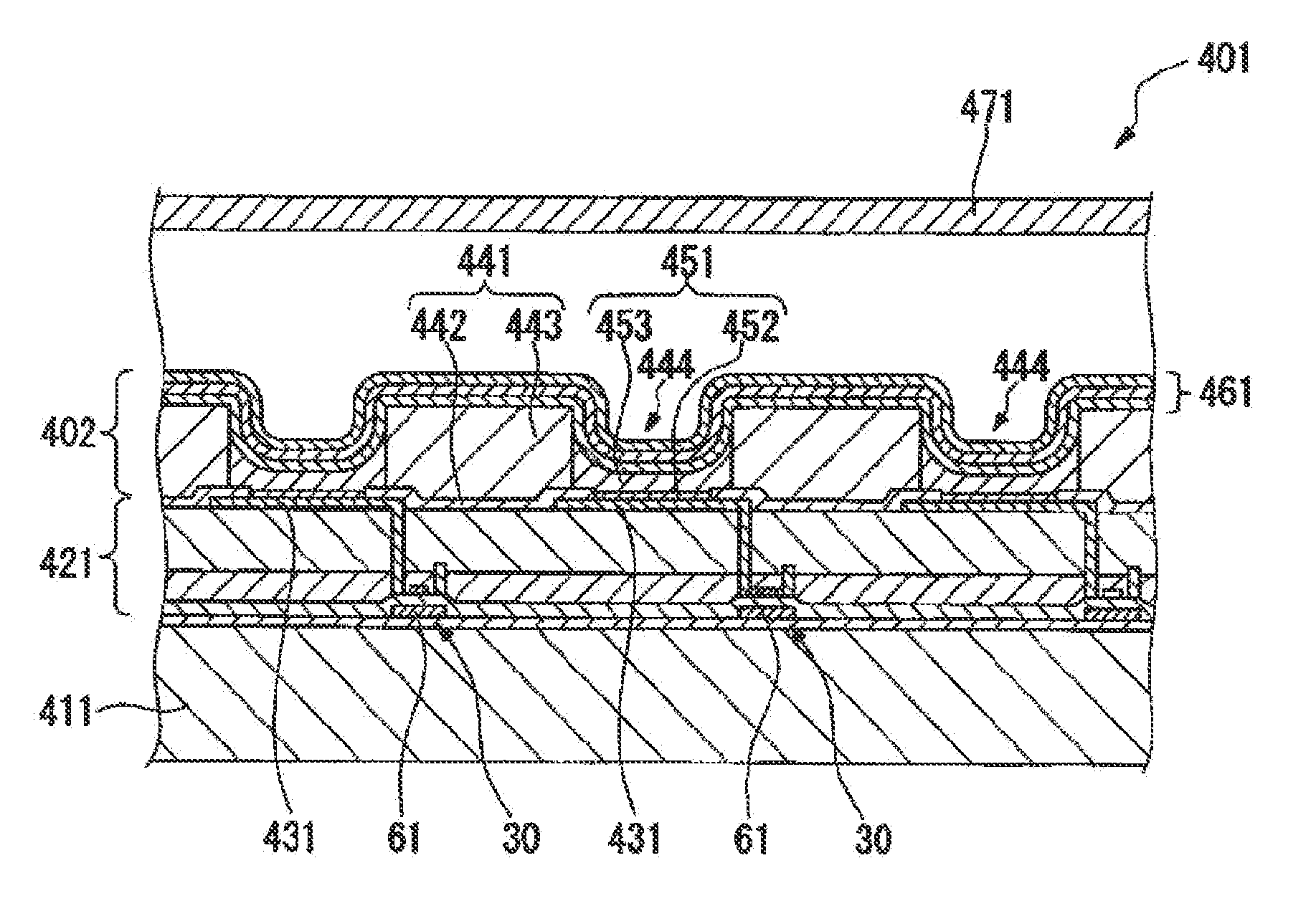

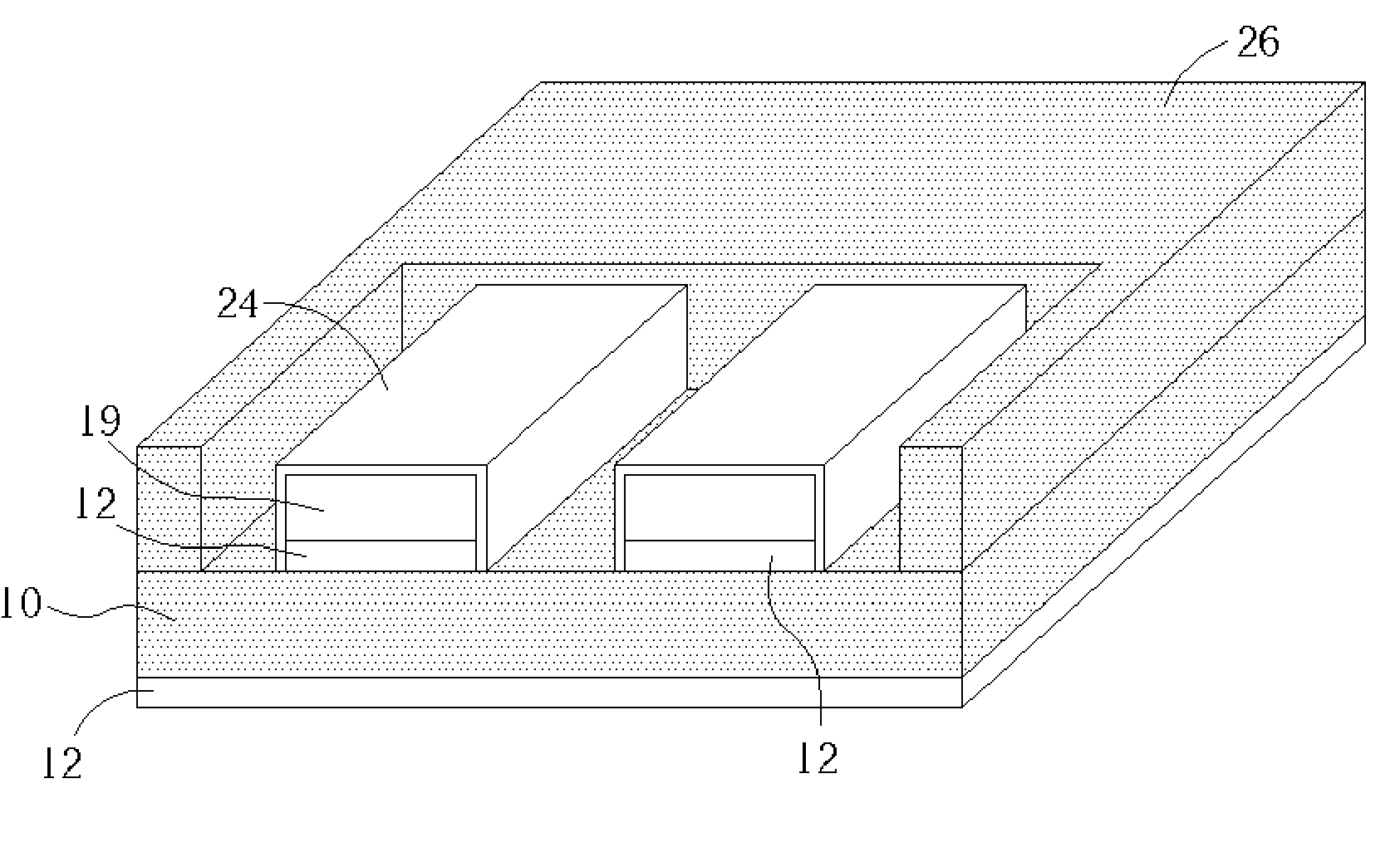

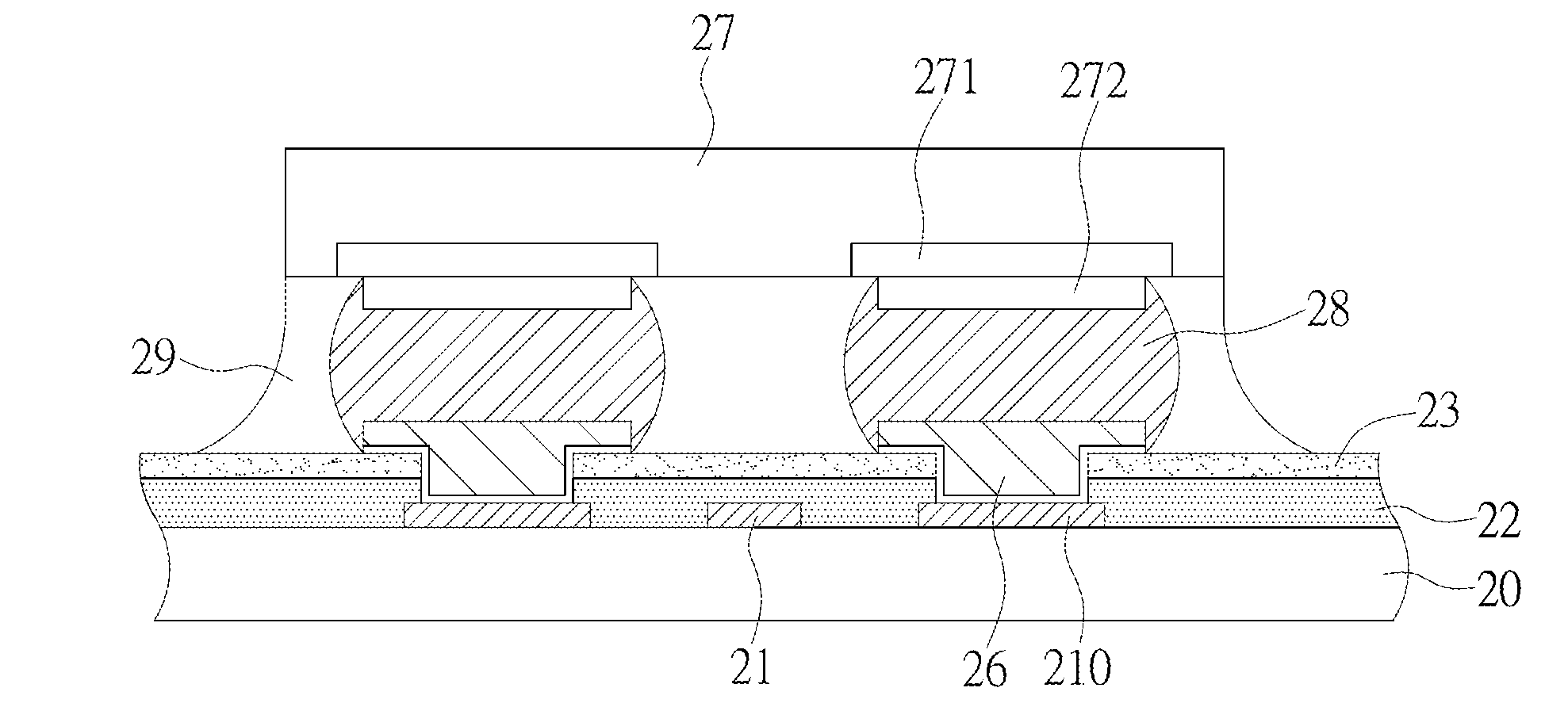

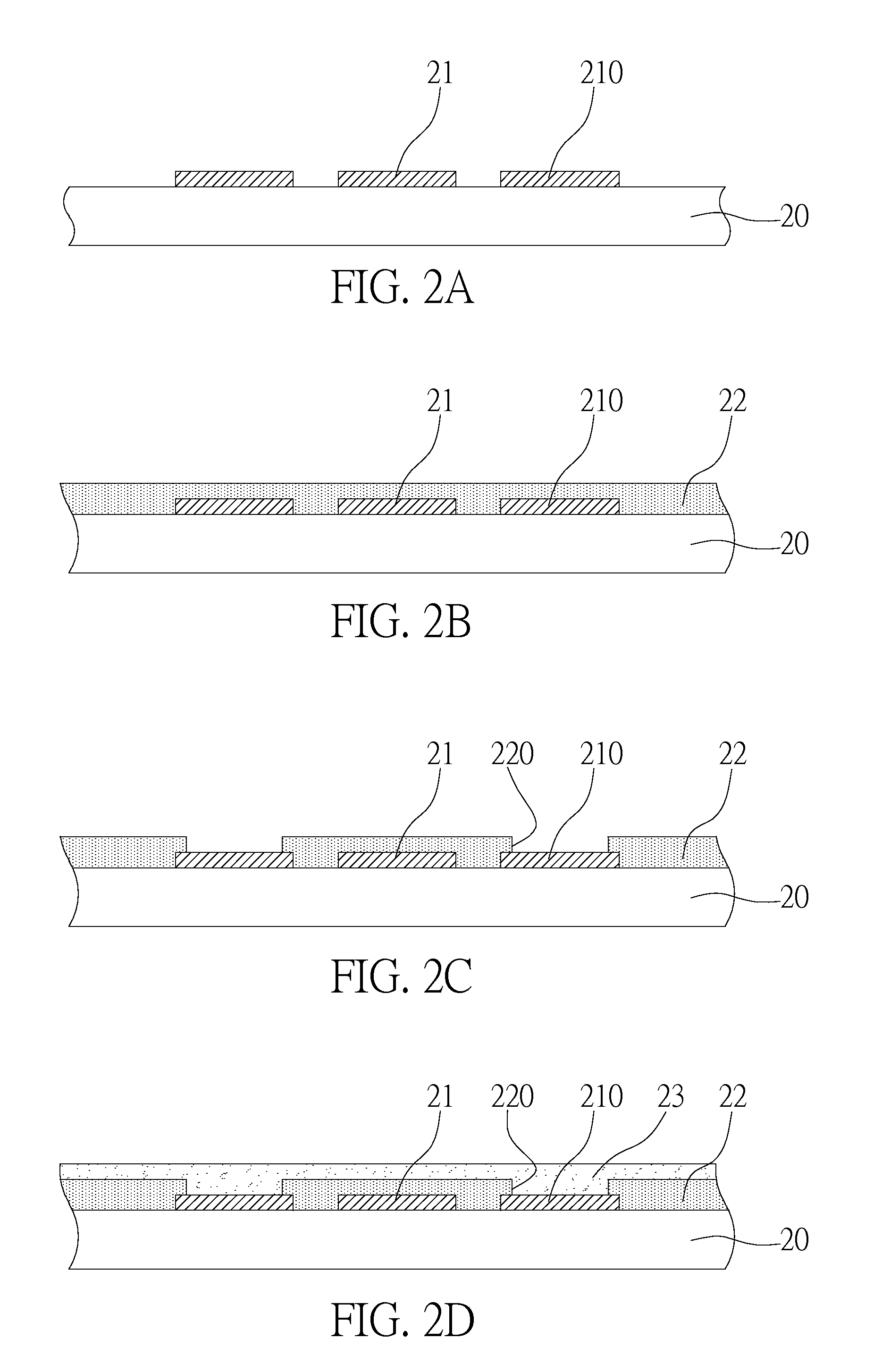

Circuit board structure and fabrication method of the same

ActiveUS20080176035A1Improve insulation performanceImprove liquidityLayered productsSemiconductor/solid-state device detailsEngineeringMicroparticle

A circuit board structure and a fabrication method of the same are disclosed according to the present invention. The circuit board structure includes: a carrier board with at least one surface formed with a circuit layer having electrically connecting pads; a first solder mask formed on the carrier board and the circuit layer and formed with first openings for exposing the electrically connecting pads; and a second solder mask formed on the first solder mask and formed with second openings for exposing the first openings and the electrically connecting pads. The first solder mask is made of a high-insulation photosensitive material characterized by presence or absence of impurities, such as microparticles, to have enhanced fluidity for being filled in the circuit layer, thereby preventing metal ions migration and subsequent metal hypha electricity discharge which might otherwise affect electrical performance, therefore the present invention is applicable to fine circuit fabrication.

Owner:UNIMICRON TECH CORP

Multiple polarity mask exposure method

A patterned mask and method of forming a patterned mask over a substrate, comprising forming a first resist layer over the substrate, forming a second resist layer over the first resist layer, patterning the first resist using energy selective to the first resist layer to form a first patterned resist, and patterning the second resist using energy selective to the second resist layer to form a second patterned resist, wherein the first patterned resist and the second patterned resist form the patterned mask.

Owner:IBM CORP

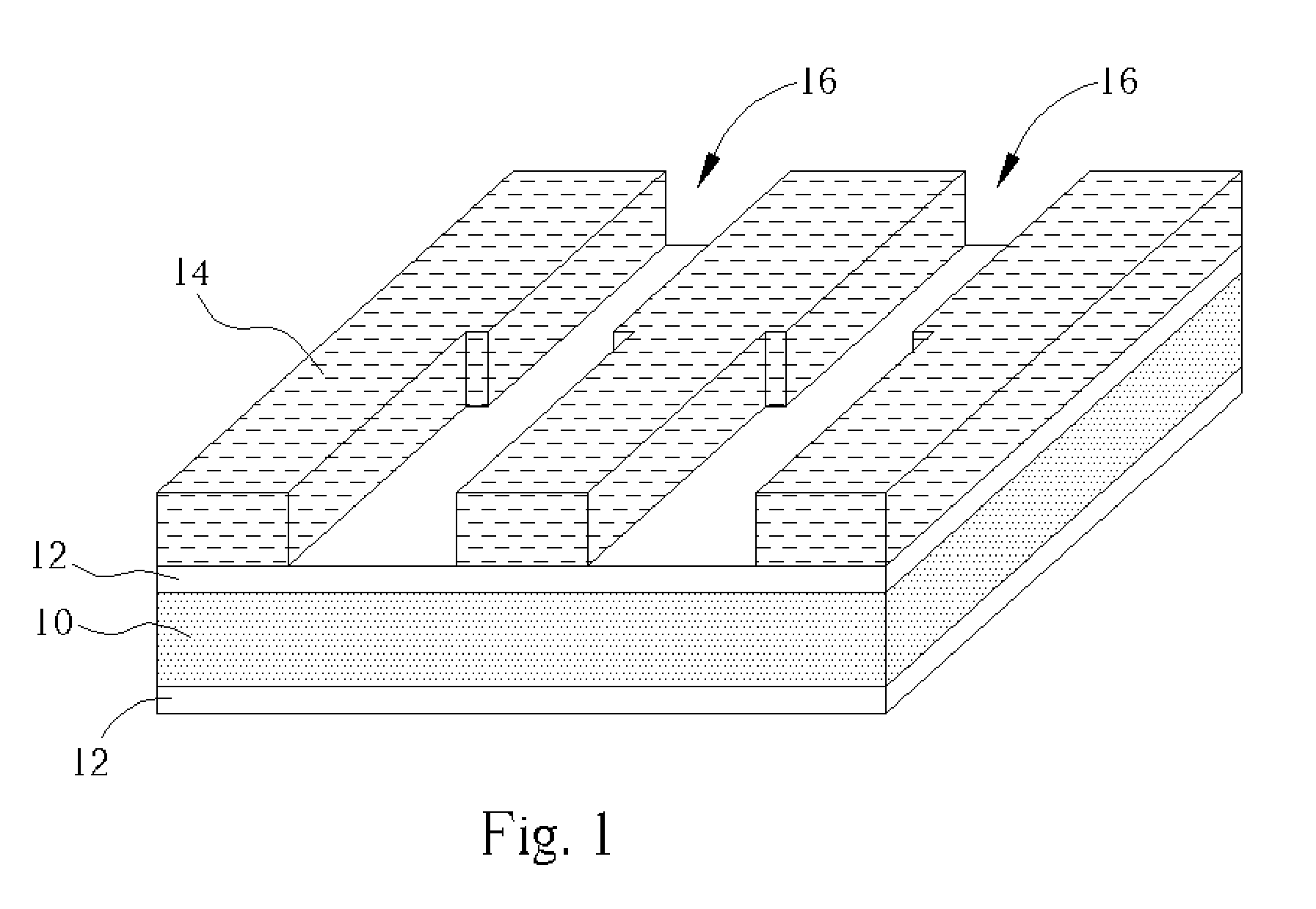

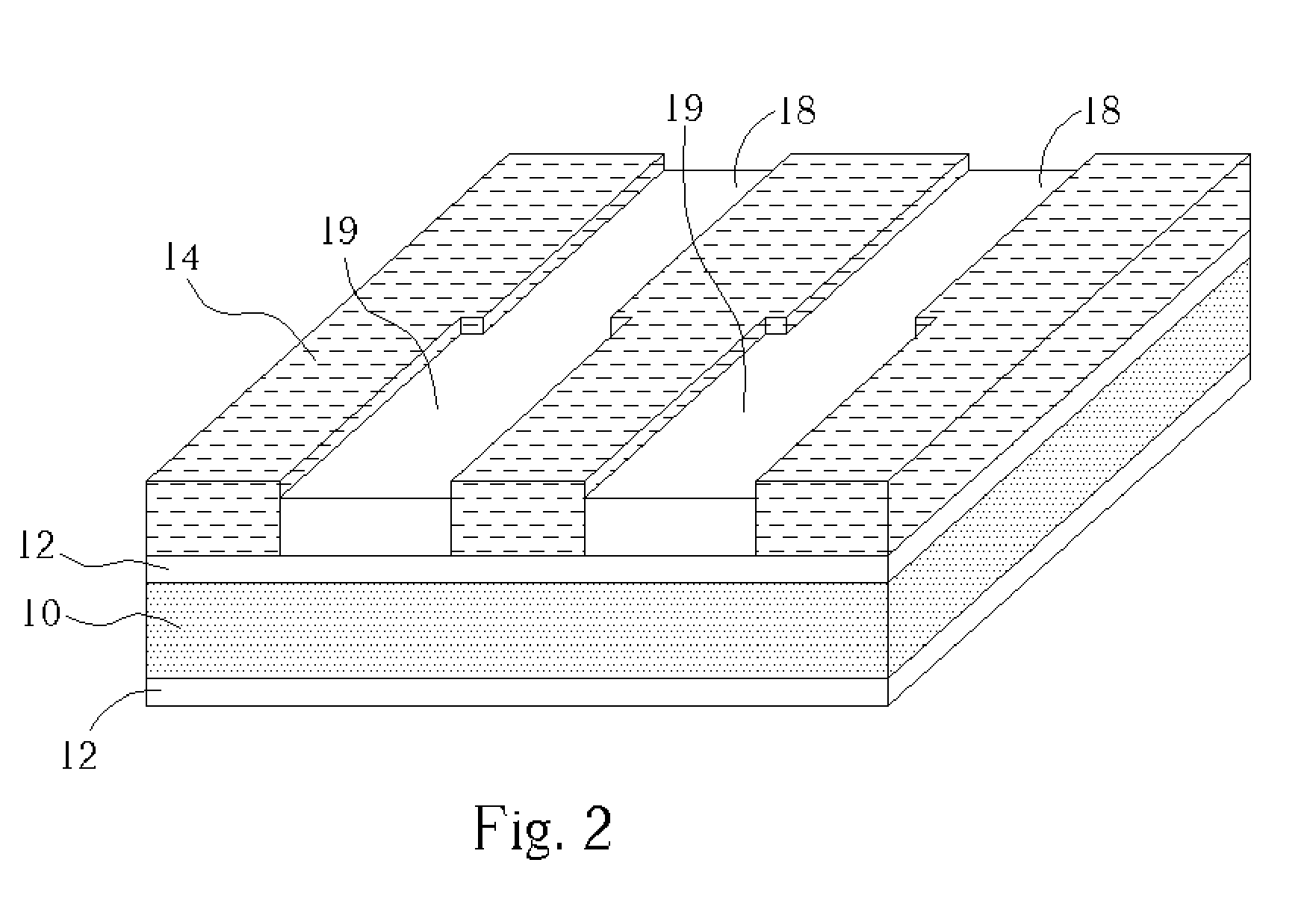

Circuit board surface structure and fabrication method thereof

ActiveUS20080217046A1Improve bindingGood adhesionSemiconductor/solid-state device detailsPrinted circuit aspectsEngineeringSurface structure

A circuit board surface structure and a fabrication method thereof are proposed. The circuit board surface structure includes: a circuit board having a plurality of electrically connecting pads formed on at least one surface thereof; a first and a second insulating protective layers formed on the surface of the circuit board in sequence; first and a second openings respectively formed in the first and second insulating protective layers to expose the electrically connecting pads on the surface of the circuit board, wherein the first and second openings have narrow top and wide bottom and the diameter of the first openings is bigger than that of the second openings; and conductive elements formed in the first and second openings on surfaces of the electrically connecting pads. The present structure facilitates to strengthen the bonding between the conductive elements and the corresponding electrically connecting pads.

Owner:UNIMICRON TECH CORP

Method of manufacturing a semiconductor package and semiconductor package having an electrode pad with a small pitch

ActiveUS8288875B2Improve reliabilitySemiconductor/solid-state device detailsPrinted circuit aspectsResistSemiconductor package

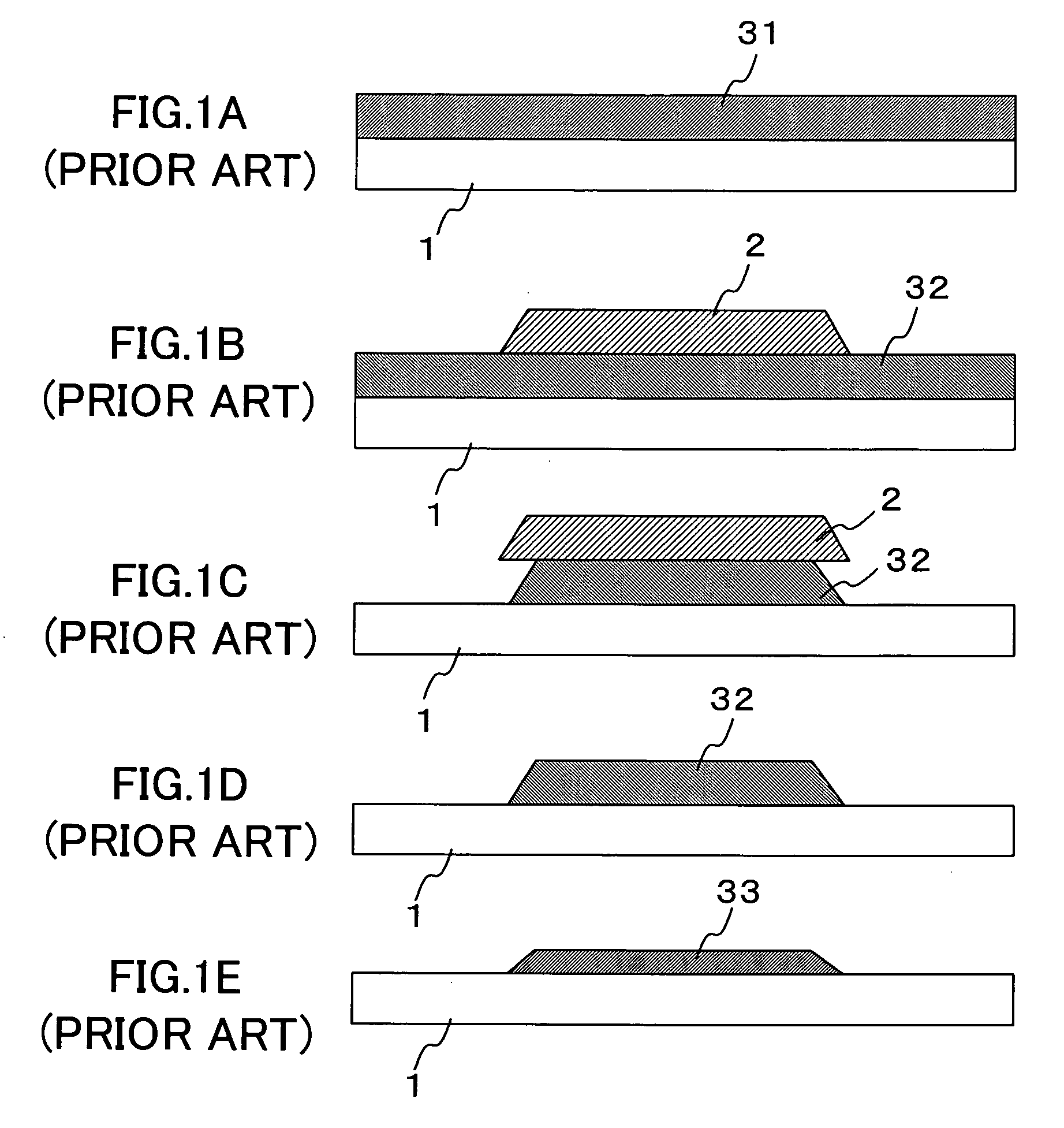

A board on which a wiring having an electrode pad is formed is prepared. A resist film is formed on the board in order to cover the wiring and then the resist film is left on the electrode pad through patterning. An inorganic insulating film is formed on the board in order to cover the wiring and then the resist film is removed, thereby removing the inorganic insulating film provided on the resist film to leave the inorganic insulating film between the wirings. A solder resist layer is formed on the board in order to cover the wiring and then the electrode pad is exposed.

Owner:SHINKO ELECTRIC IND CO LTD

Method for manufacturing semiconductor package substrate

ActiveUS7399399B2Eliminate burrsIncrease productionSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageElectroplating

A method for manufacturing a semiconductor package is proposed. A circuit board with a circuit layer on at least one surface thereof is provided. The circuit board has at least one free area, and the circuit layer has a plurality of electrically connecting pads distributed on the periphery of the free area. A metal protecting layer is plated on the electrically connecting pads by non-plating line. The free area is removed, to form a cavity penetrating the circuit board. The present invention prevents burrs which may otherwise form on the periphery of a cavity, to increase the yield and throughput.

Owner:PHONEIX PRECISION TECH

Wired circuit board with interposed metal thin film and producing method thereof

InactiveUS8030576B2Avoid conductionPrevents corrosion and discolorationDisposition/mounting of recording headsPrinted circuit aspectsPrinted circuit boardMetal thin film

A wired circuit board includes an insulating base layer, a conductive pattern formed on the insulating base layer and including a wire and a terminal portion, an insulating cover layer formed on the insulating base layer and having an opening portion to expose the terminal portion, and a metal thin film including a protecting portion interposed between the wire and the insulating cover layer, and an exposed portion formed continuously from the protecting portion on a peripheral end portion of the terminal portion exposed from the opening portion.

Owner:NITTO DENKO CORP

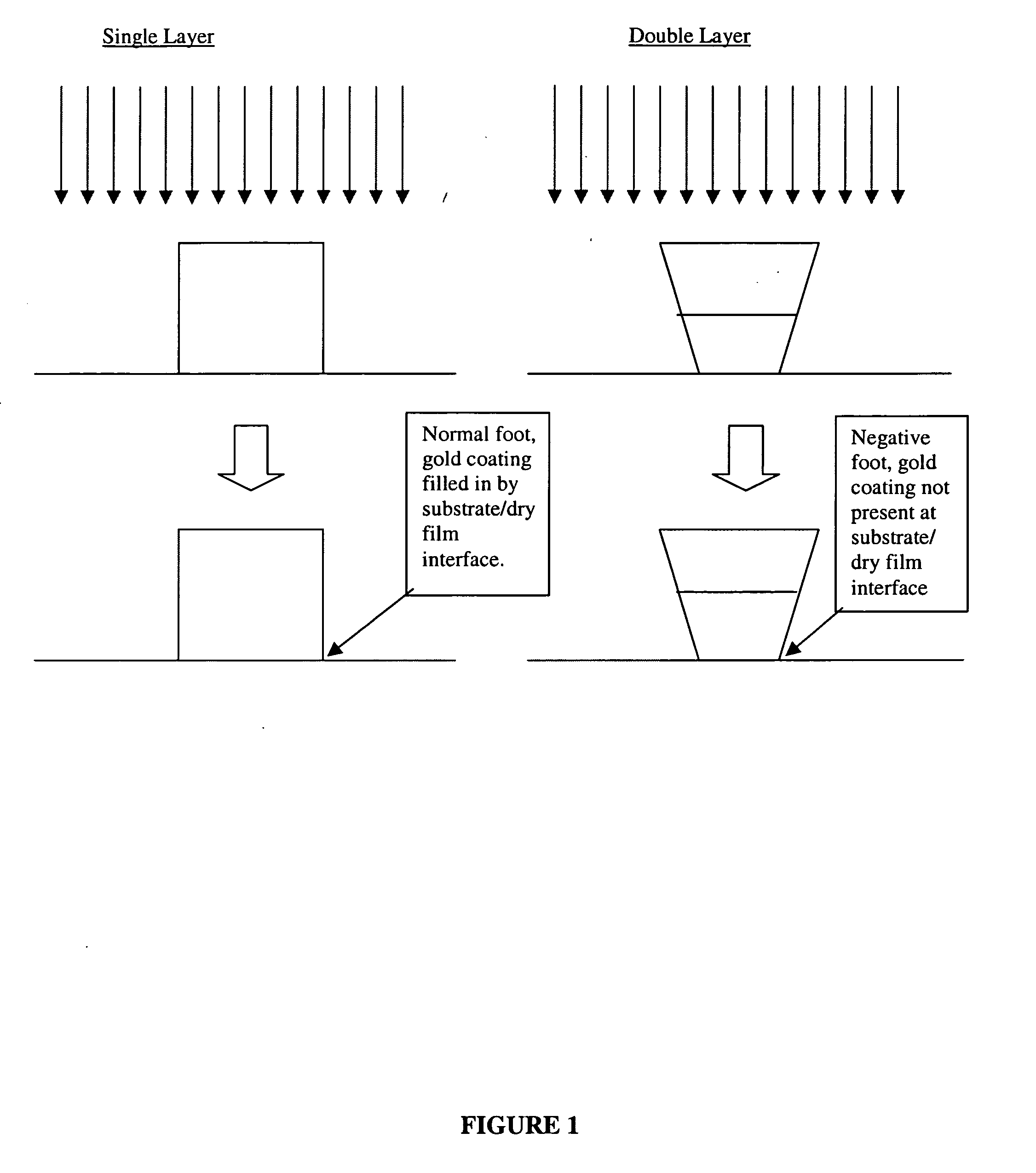

Method of forming a metal pattern on a substrate

ActiveUS20050221232A1Slow curingCures to a higher cross link density more quicklyPhotomechanical apparatusSemiconductor/solid-state device manufacturingMetalChemistry

The invention relates to a method of providing two distinct photoimageable film compositions, in particular, two distinct dry film compositions, on a substrate. Each of the two photoimageable film compositions is selected to have a different developing speed and / or curing speed so that, after development, the top layer of photoimageable film overhangs the bottom layer of photoimageable film. A metal layer is subsequently deposited over the surface of the substrate. The overhang allows for the clean removal of the photoimageable film layers, without damage to the subsequently applied metal layer, because the overhang prevents the metal layer from making intimate contact with the photoimageable film layers along the interface of the substrate with the photoimageable film layers.

Owner:MACDERMID ACUMEN INC

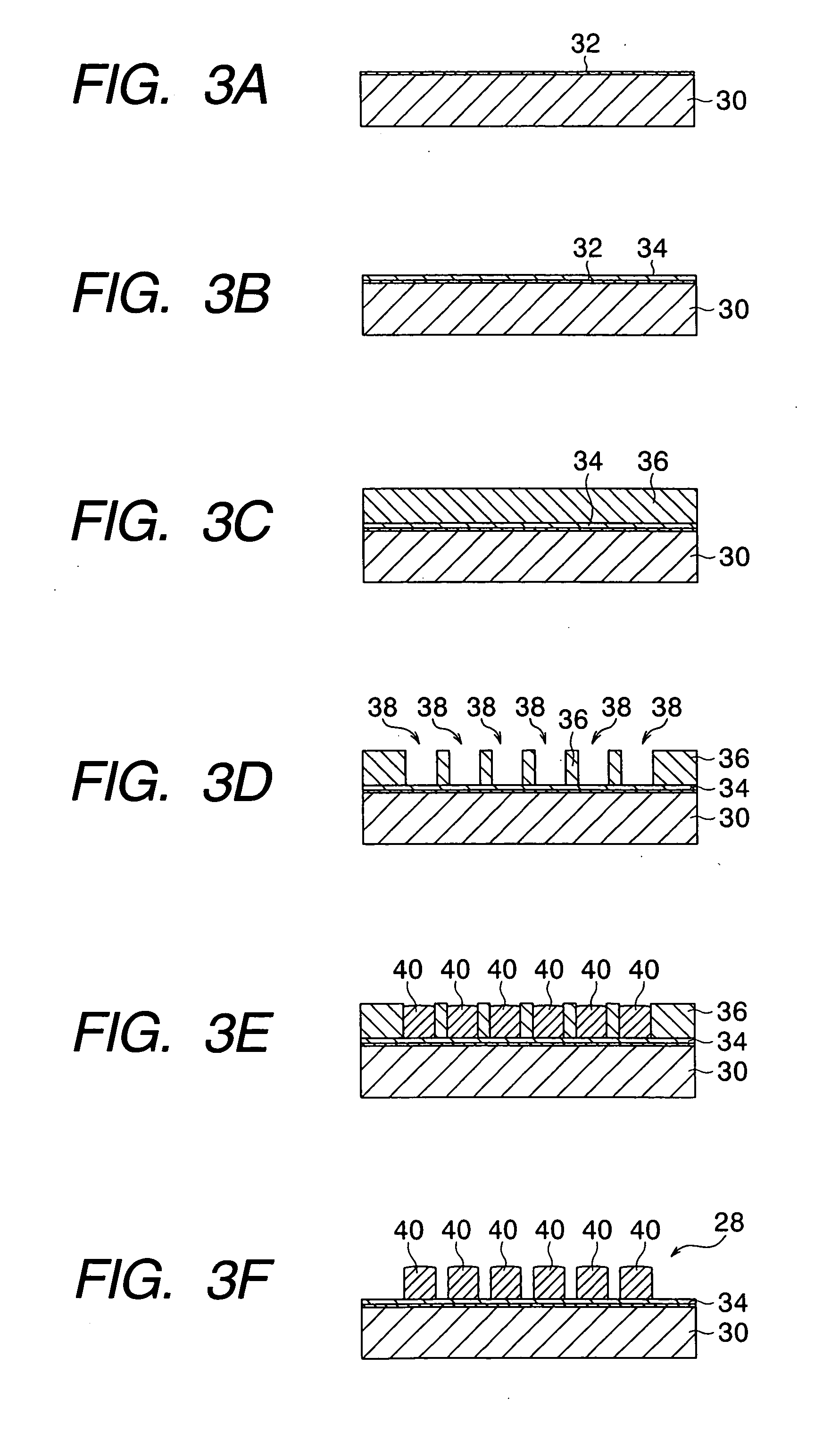

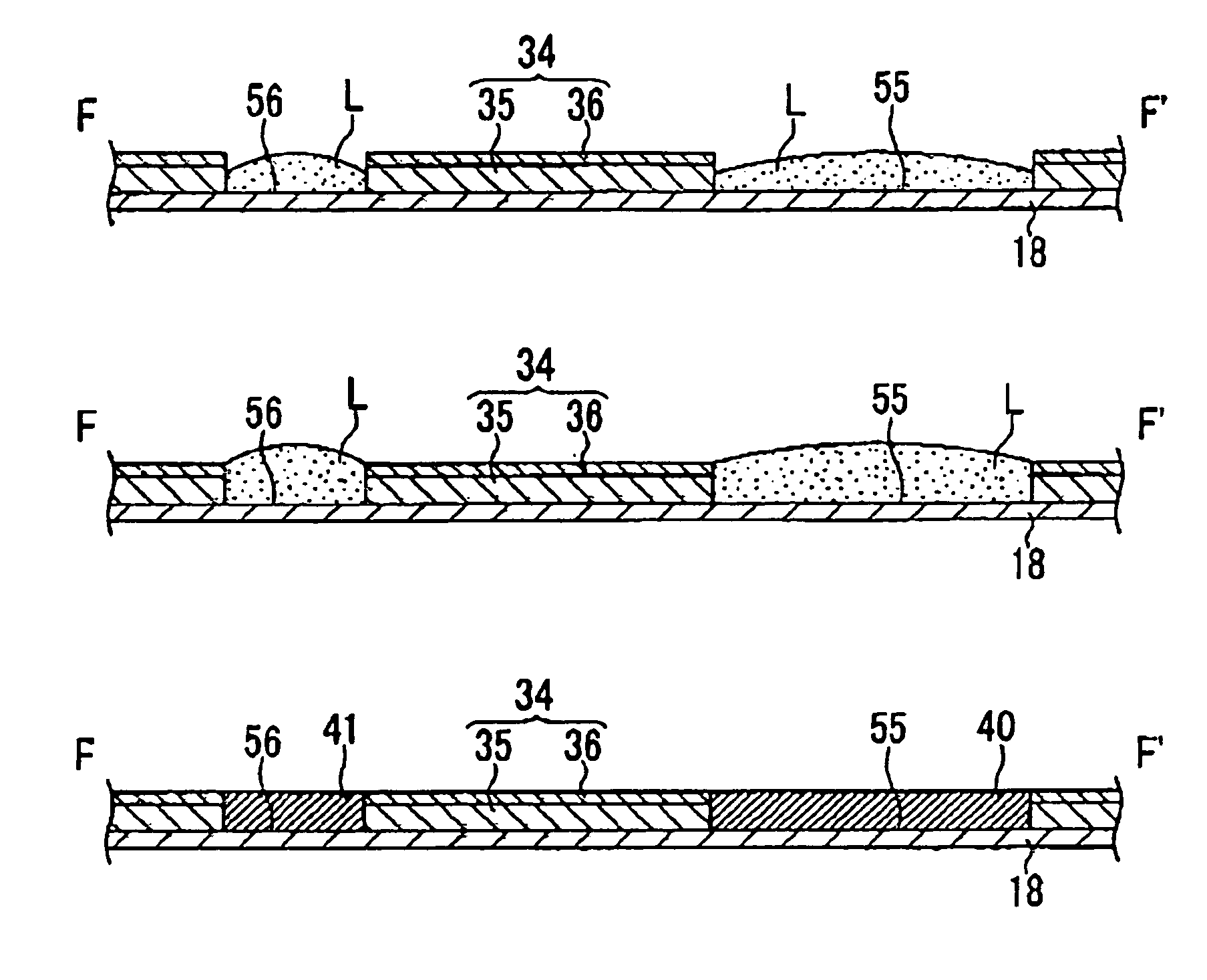

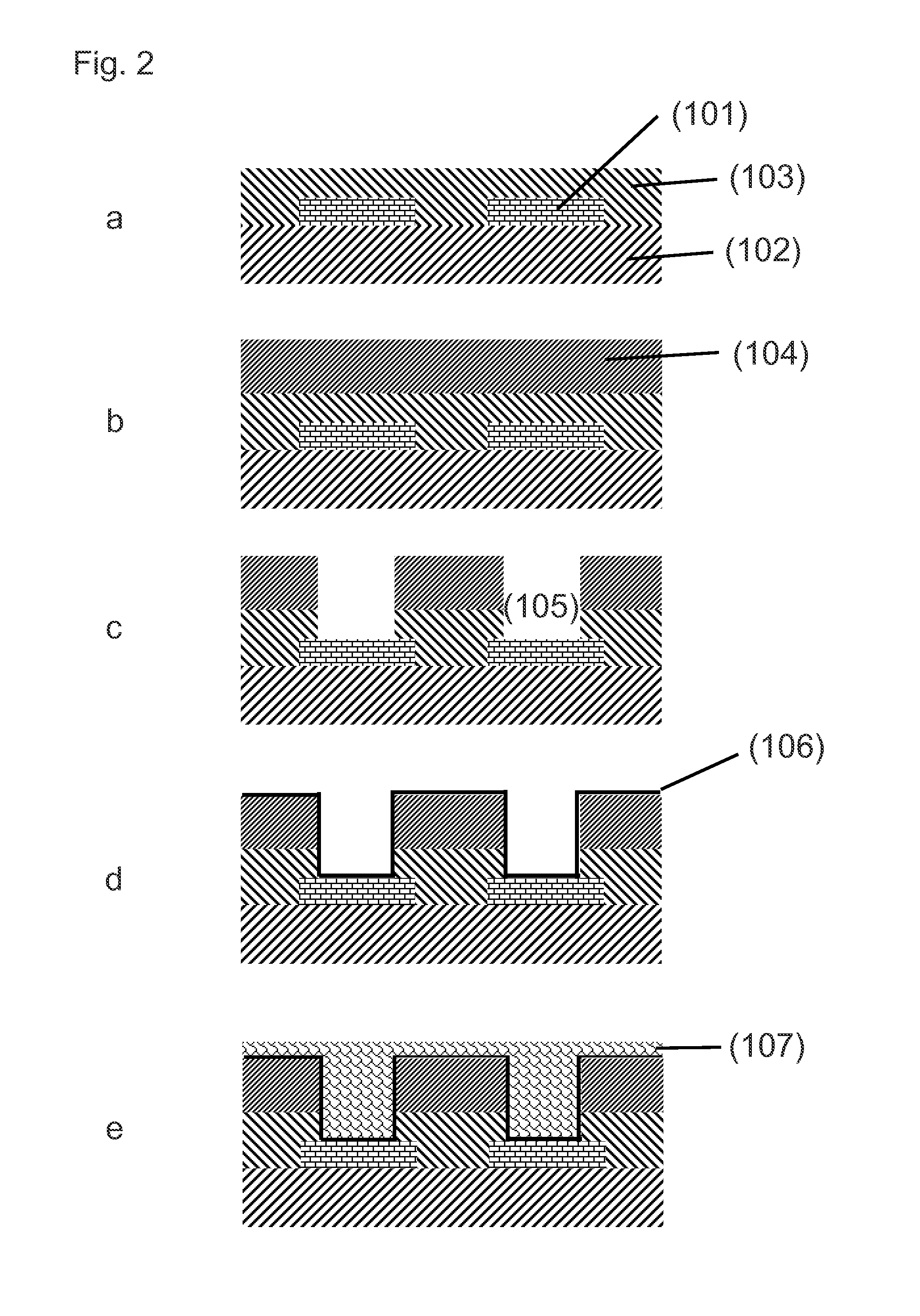

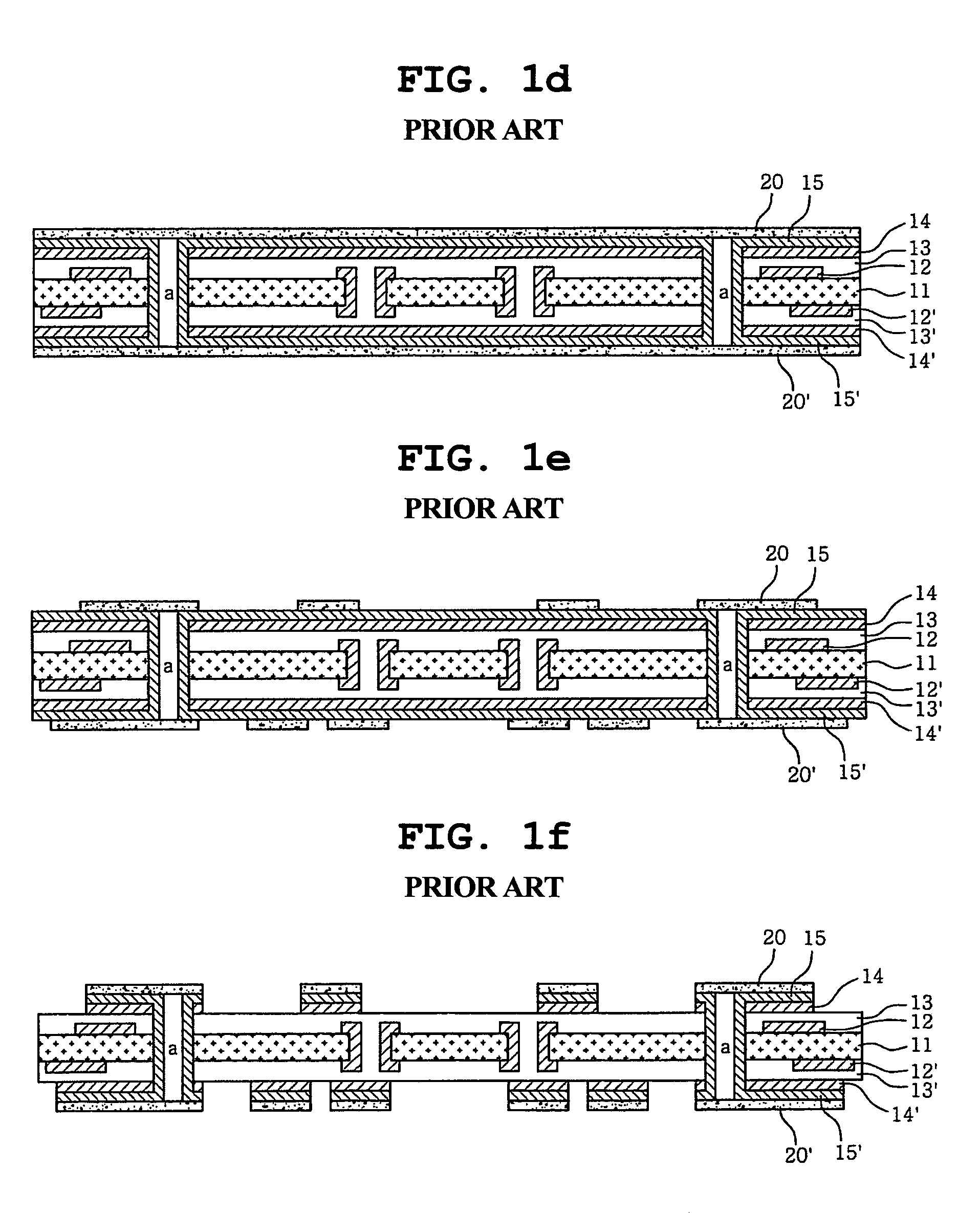

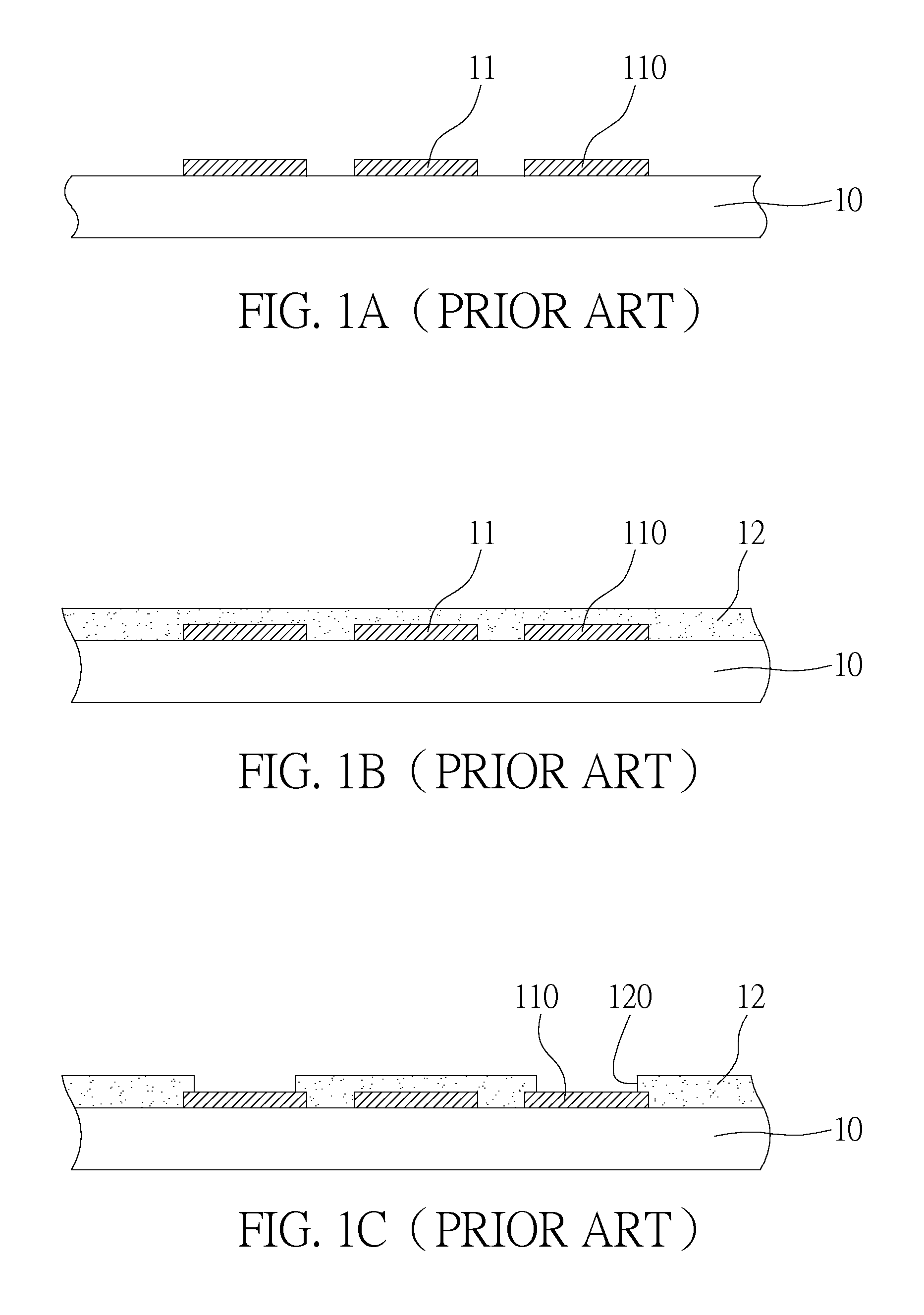

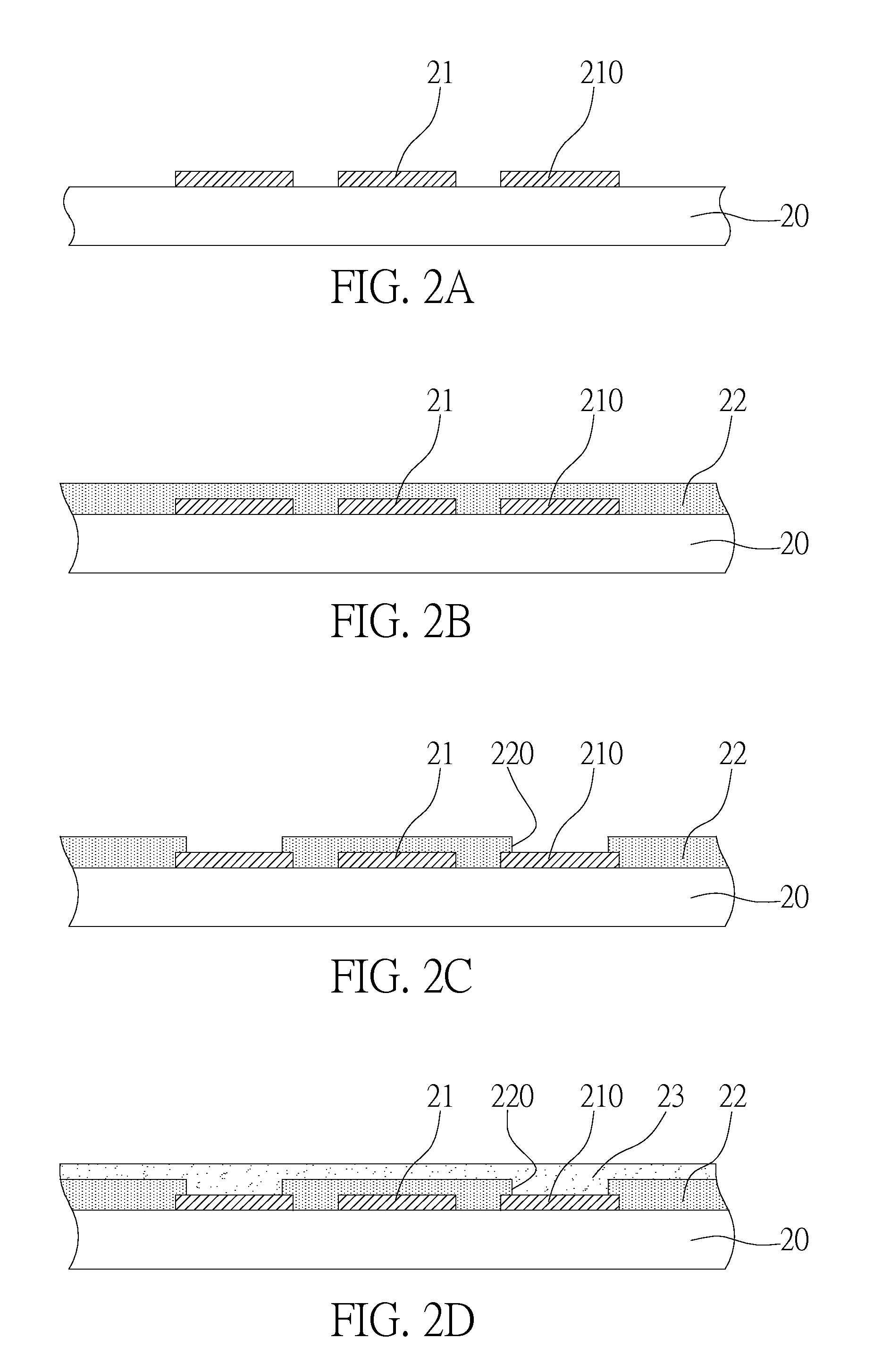

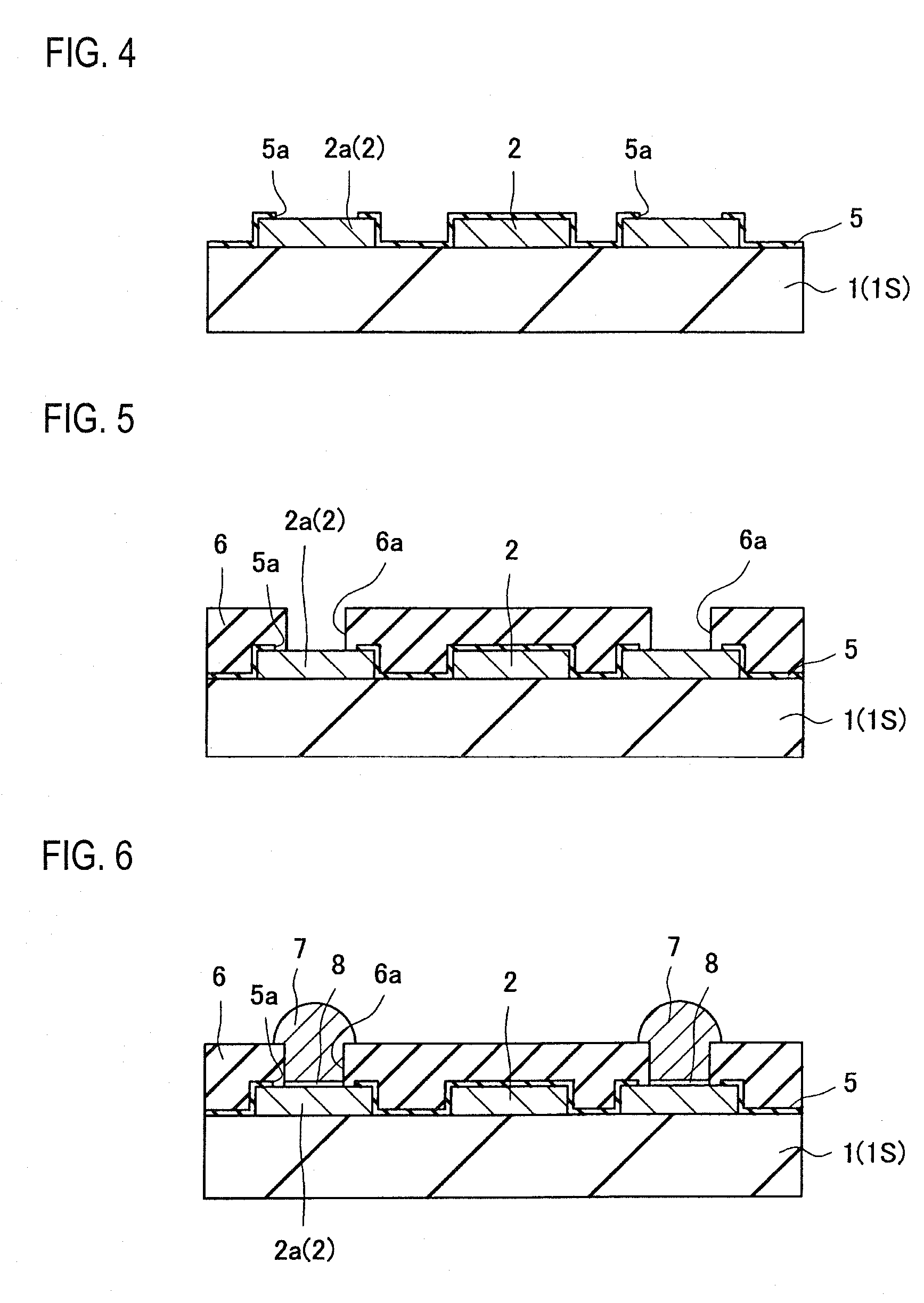

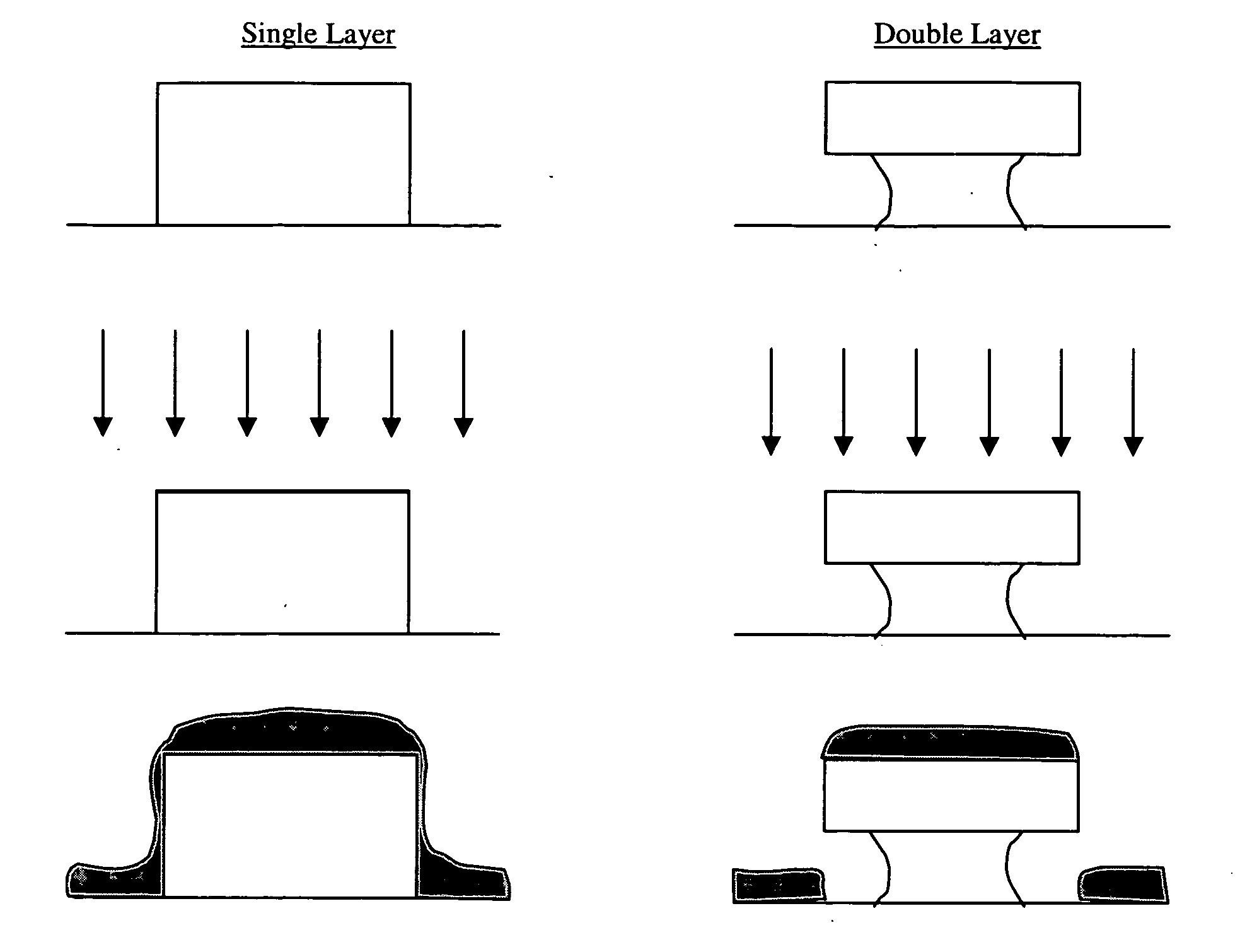

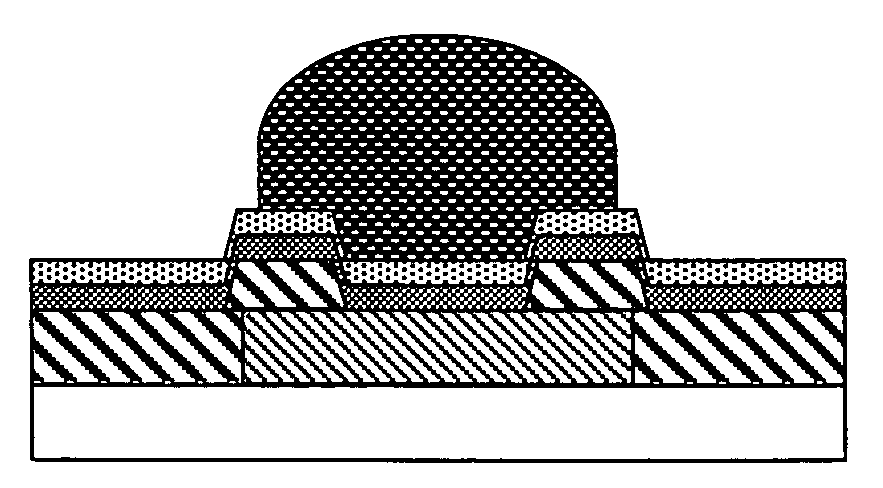

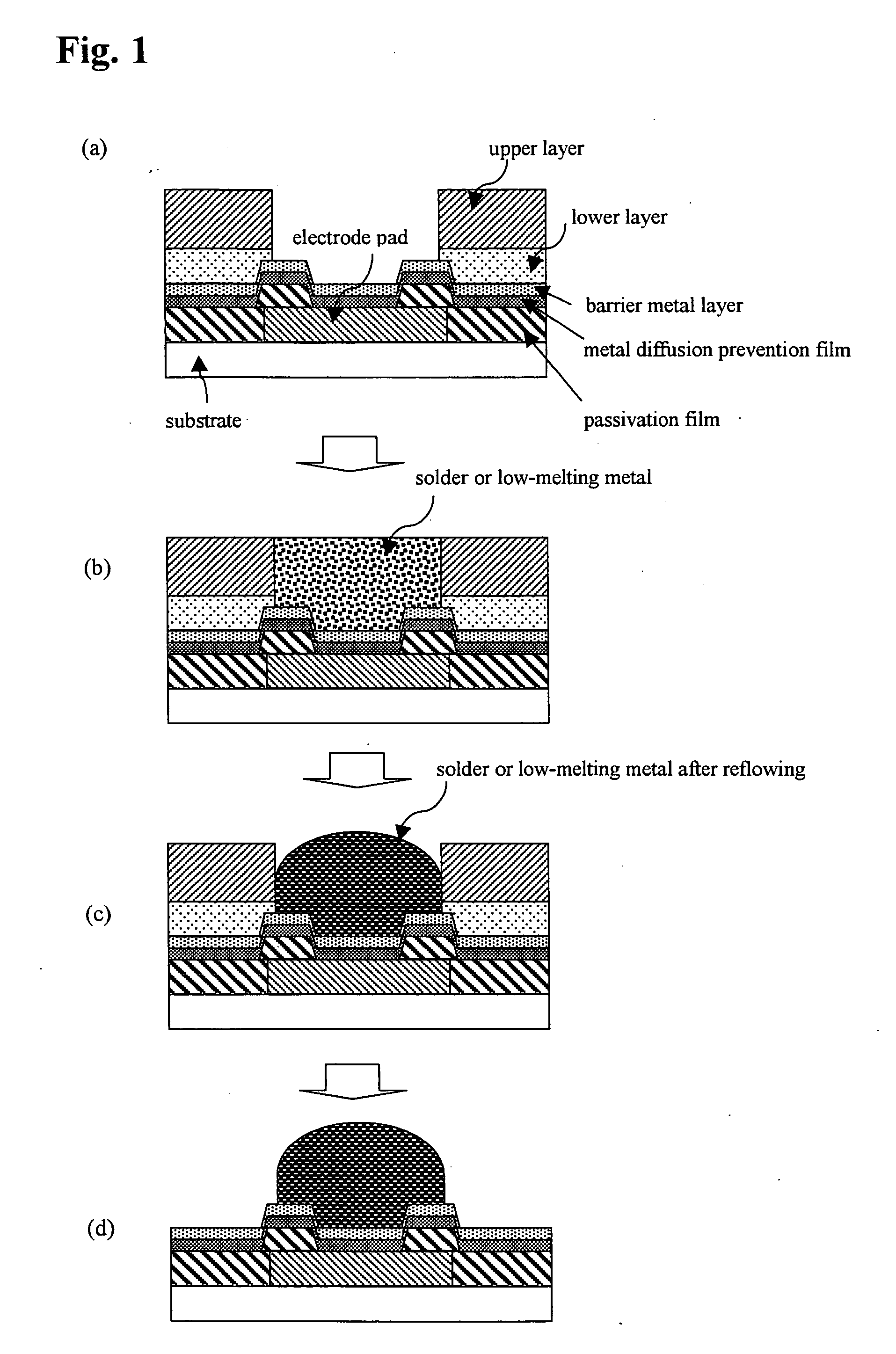

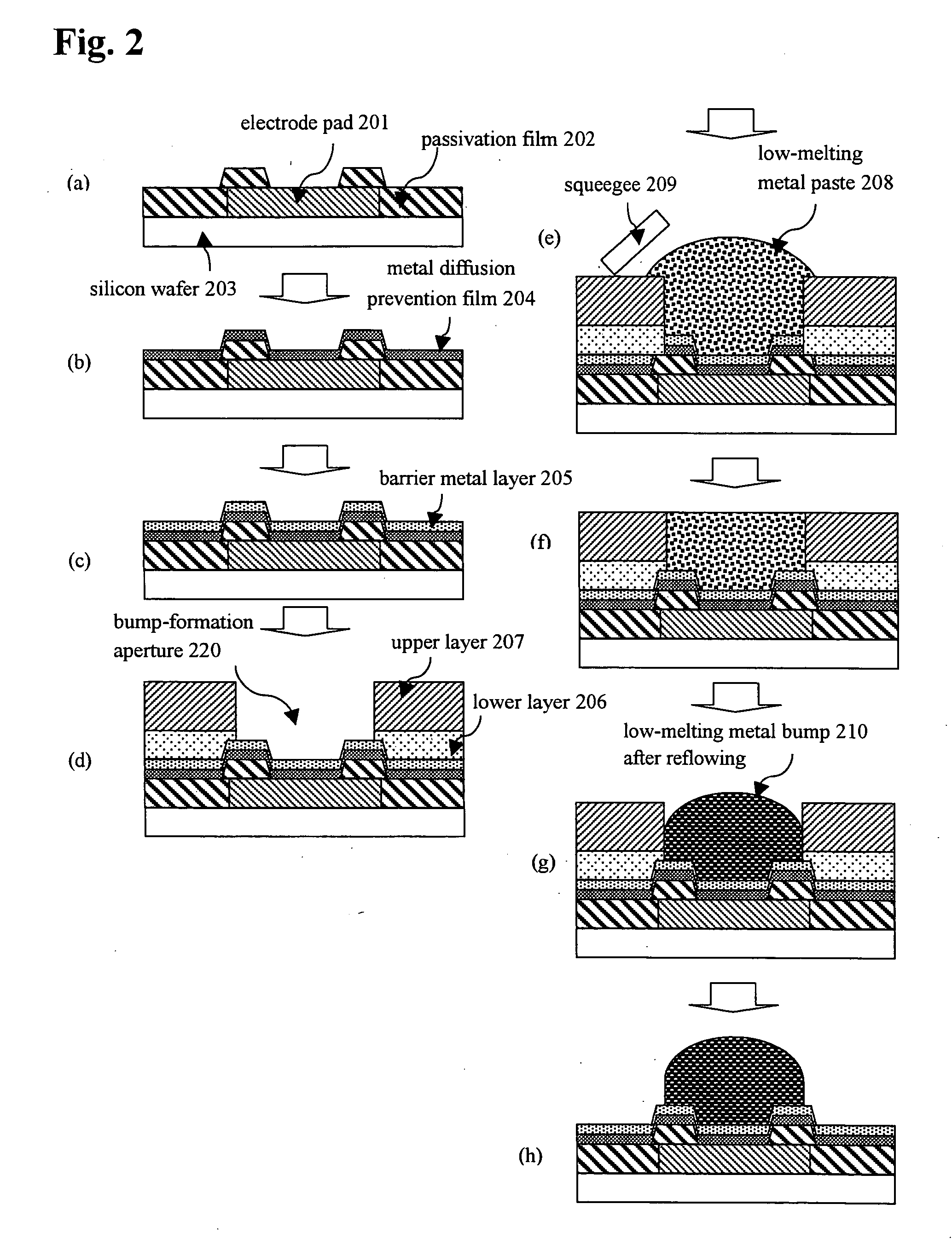

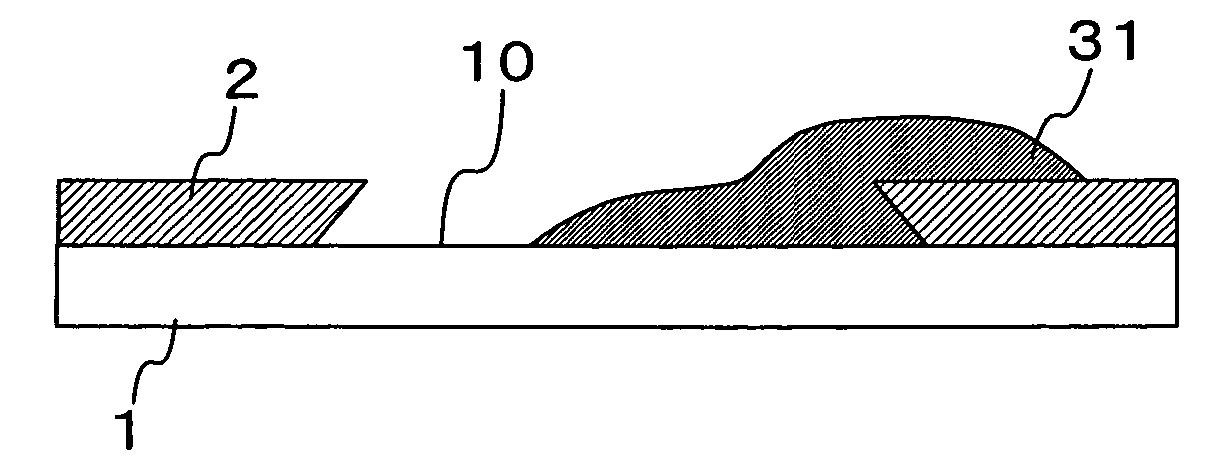

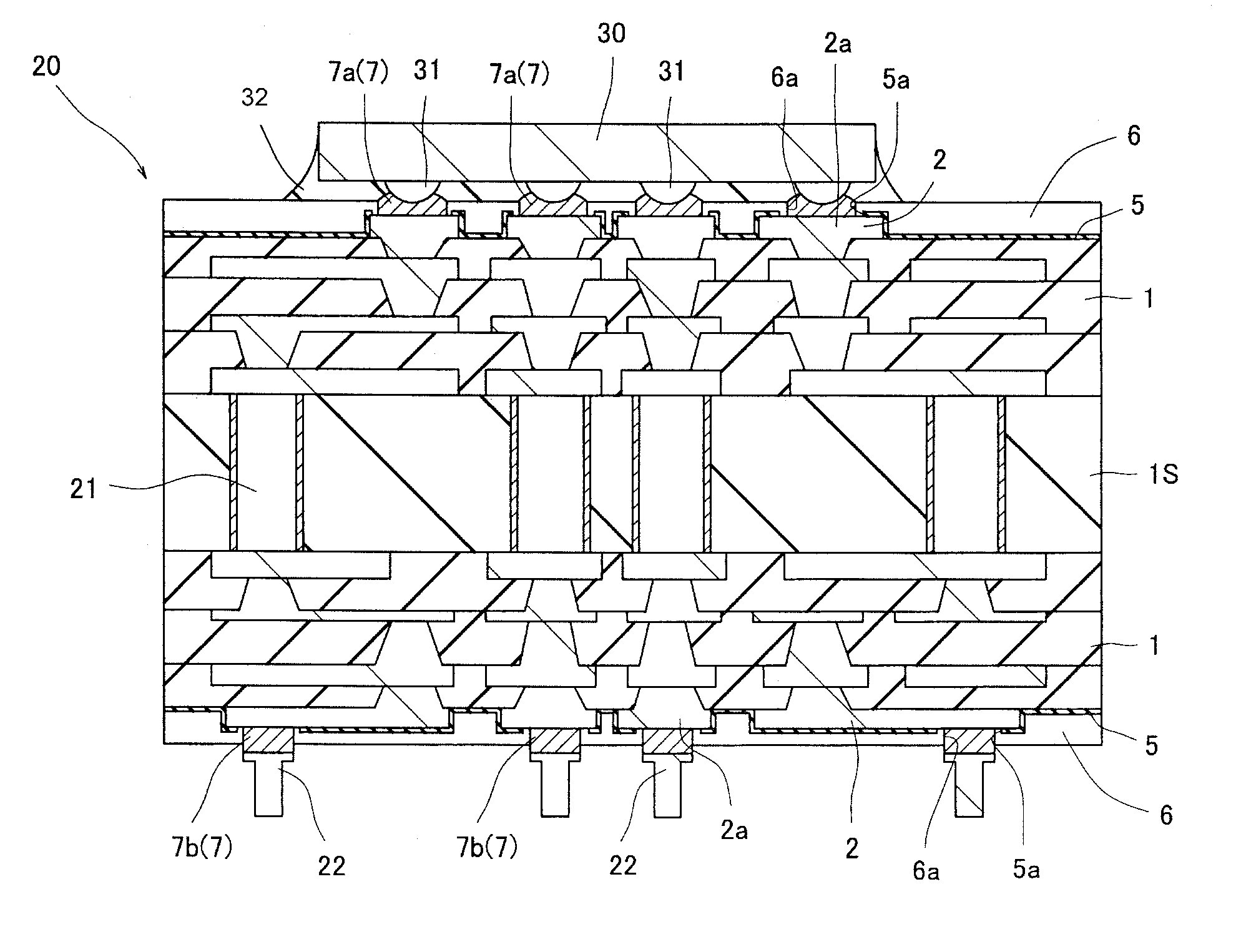

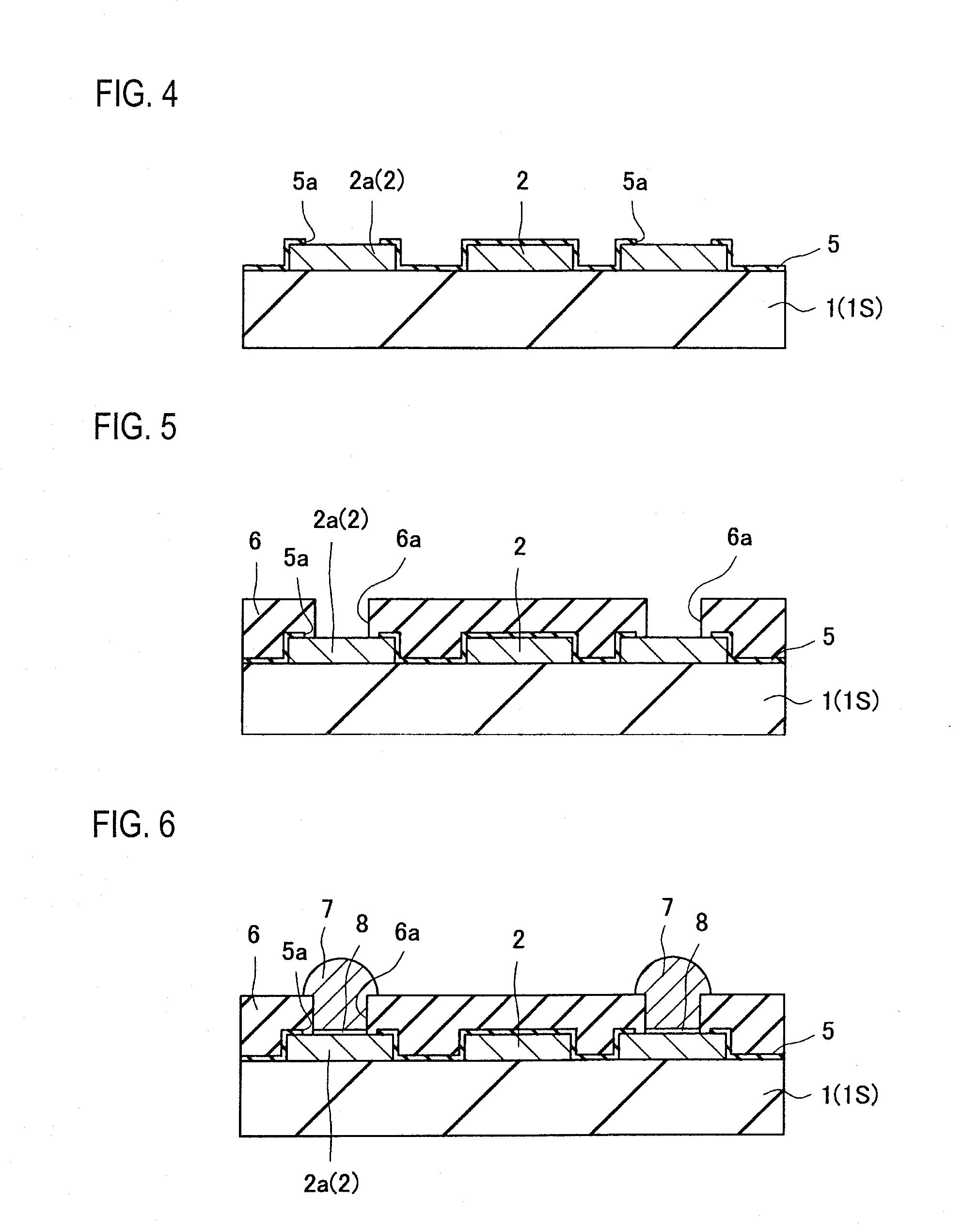

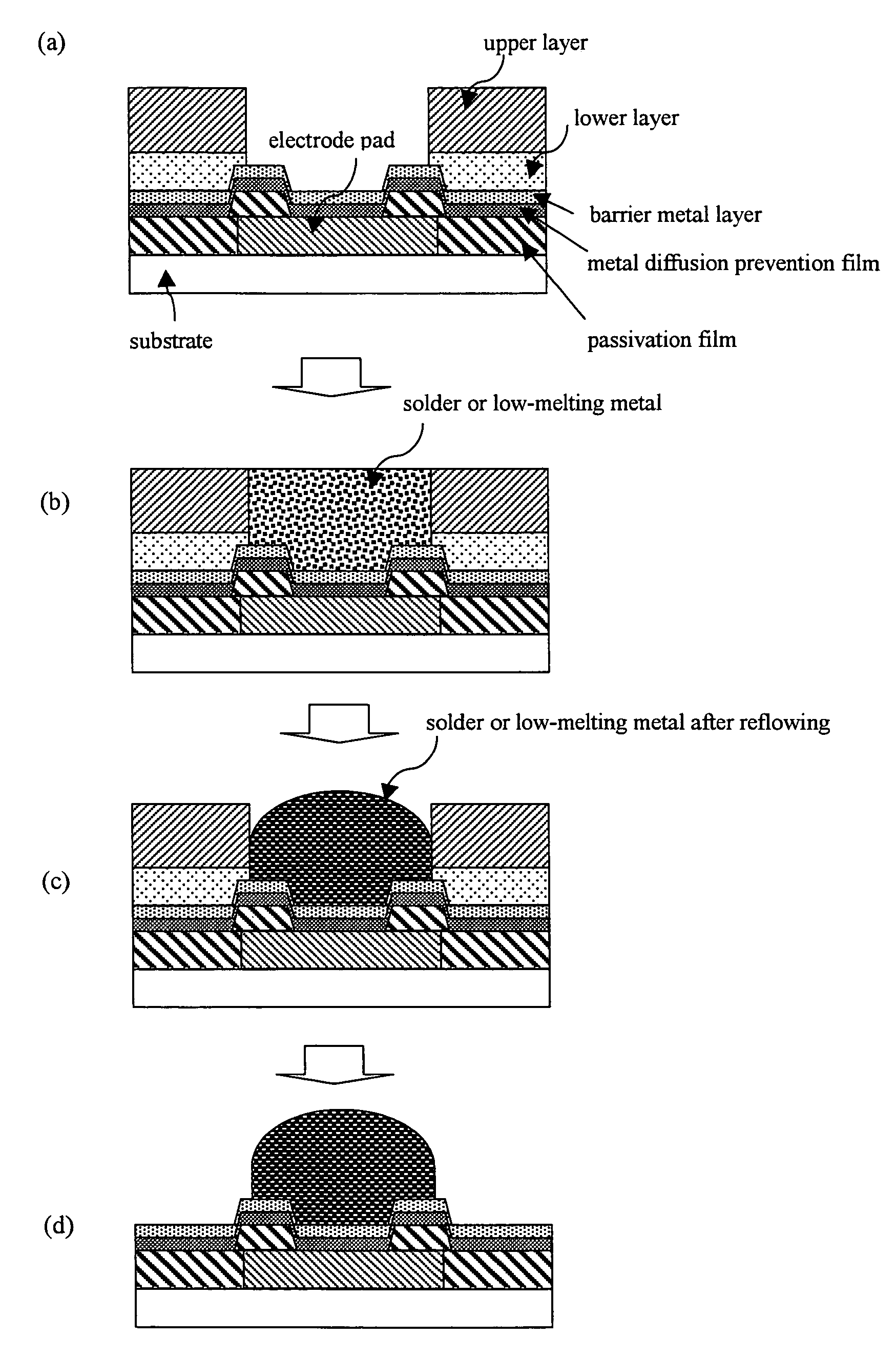

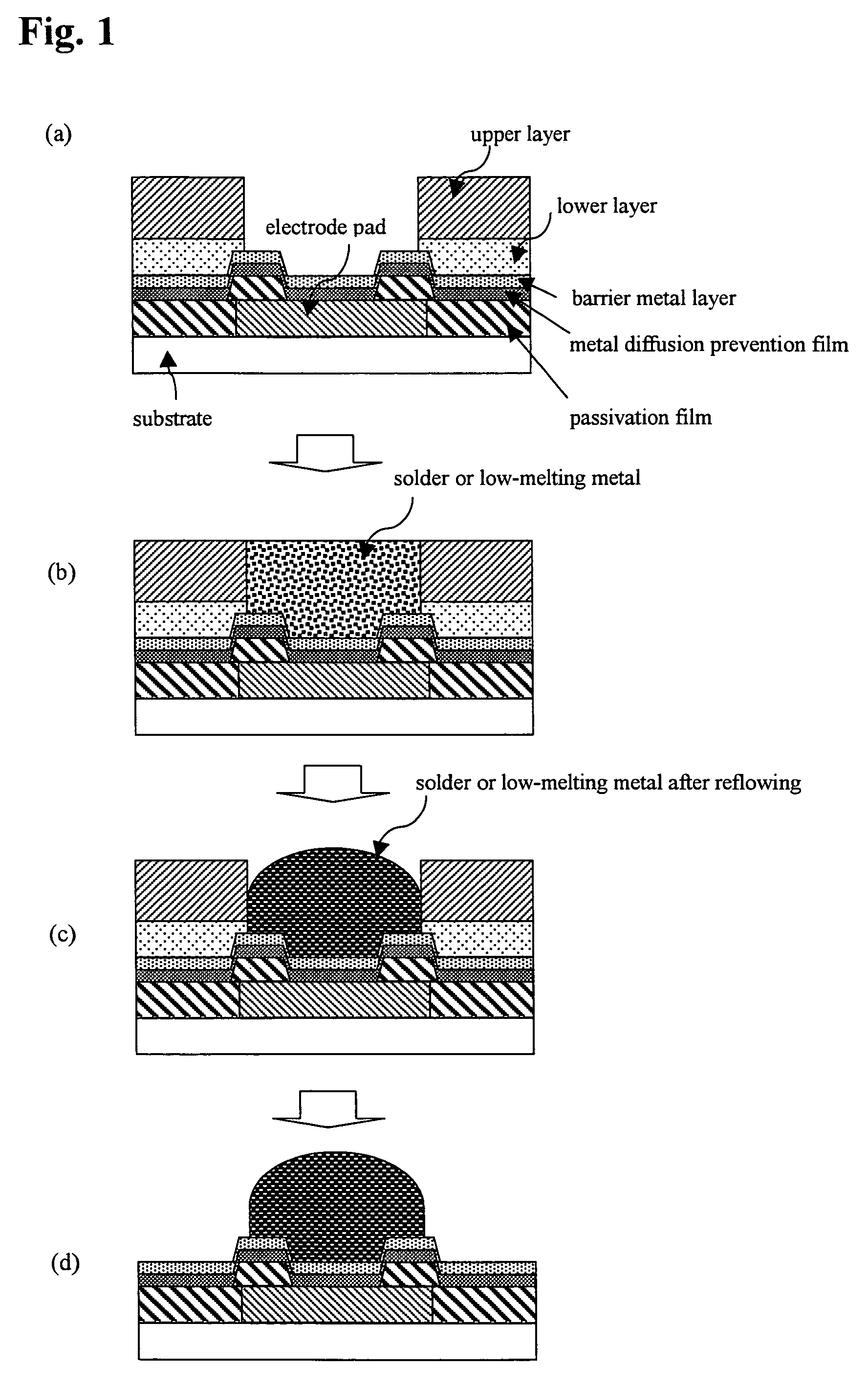

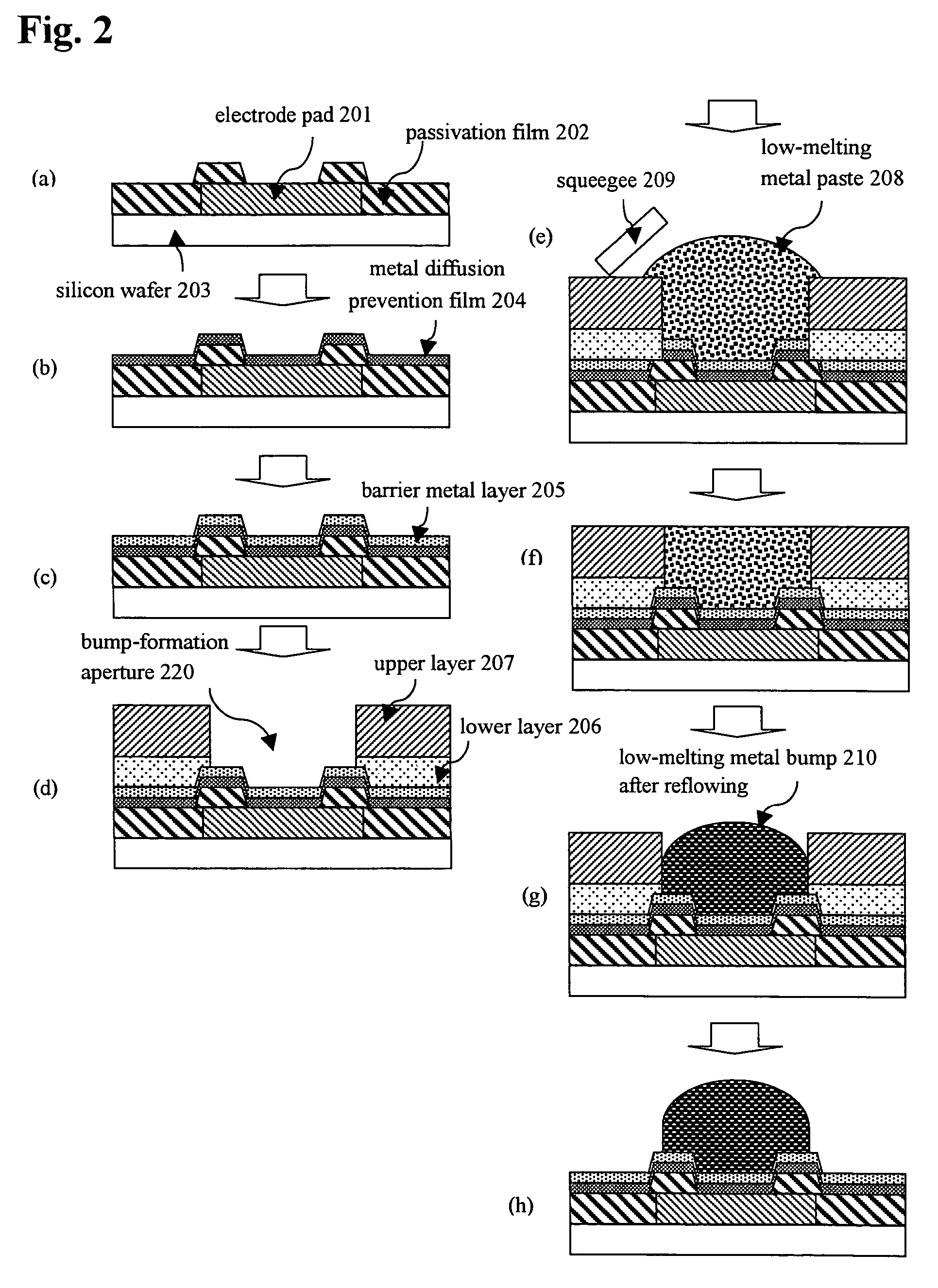

Method for forming bump on electrode pad with use of double-layered film

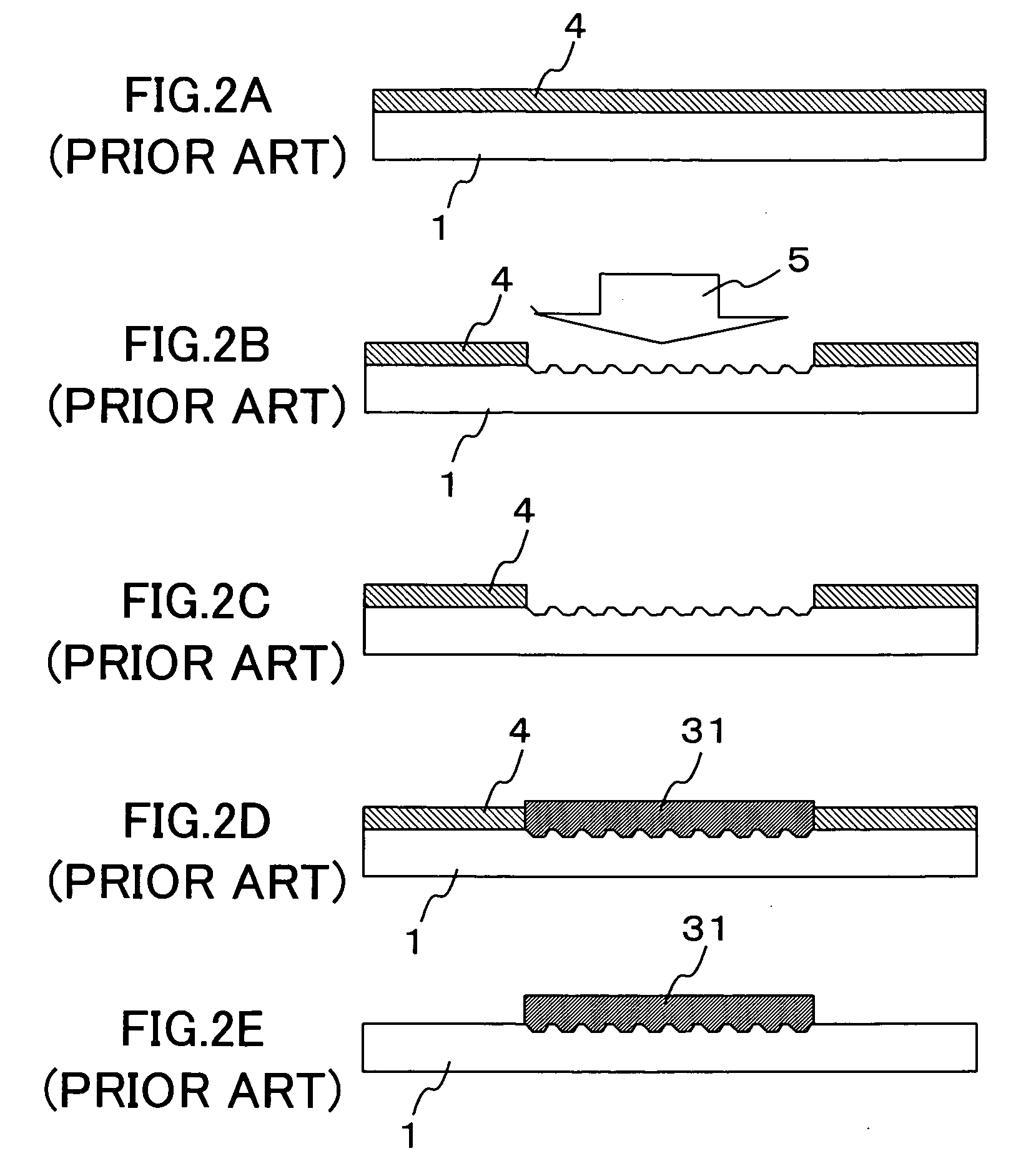

ActiveUS20050277245A1High resolutionEasy peel propertyPrinted circuit assemblingSemiconductor/solid-state device detailsEngineeringMetal

A process for forming bumps on electrode pads for a wiring board including a substrate and a plurality of electrode pads. The process (a) forms a laminated two-layer film on the wiring board and forms a pattern of apertures at positions corresponding to the electrode pads, the laminated two-layer film including a lower layer containing an alkali-soluble radiation-nonsensitive resin composition and an upper layer containing a negative radiation-sensitive resin composition; (b) fills a low-melting metal in the aperture pattern; (c) reflows the low-melting metal by pressing or heating to form bumps; and (d) peels and removes the laminated two-layer film from the board. The laminated film including two layers with different properties permits high resolution and easy peeling.

Owner:JSR CORPORATIOON

Substrate within a Ni/Au structure electroplated on electrical contact pads and method for fabricating the same

InactiveUS6853084B2Increase the effective areaReduce noiseSemiconductor/solid-state device detailsSolid-state devicesSolder maskCoupling

The present invention discloses a substrate within a Ni / Au structure electroplated on electrical contact pads and a method for fabricating the same. The method comprises: providing a substrate with a circuit layout pattern and forming a conducting film on the surface of the substrate; depositing a first photoresist layer within an opening on said electrical conducting film surface to expose a portion of said circuit layout pattern to be electrical contact pads; removing the exposed conducting film uncovered by the first photoresist layer; depositing a second photoresist layer, covering the conducting film exposed in the openings of the first photoresist layer; electroplating Ni / Au covering the surface of the electrical contact pads; removing the first and second photoresists, and the conducting film covered by the photoresists; depositing solder mask on the substrate within an opening to expose said electrical contact pads. It improves the electrical coupling between gold wires and the electrical contact pads of the substrate, prevents the electrical contact pads from oxidation, and insurances the electrical interconnection performance.

Owner:PHOENIX PRECISION TECH CORP

Method of forming wiring pattern

ActiveUS20060009020A1Reduce the impactMaterial efficiencyMaterial nanotechnologySemiconductor/solid-state device manufacturingResistCooking & baking

A photoresist pattern is formed on an insulating substrate so that it has a reverse tapered cross section and a reverse pattern of a wiring pattern to be formed. Next, a nanoparticles-containing ink is injected on a wiring region using an inkjet system, followed by a leveling process, a drying process, a resist separation process and a baking process. Thus a wiring pattern is formed.

Owner:HANNSTAR DISPLAY CORPORATION

Method for fabrication of a conductive bump structure of a circuit board

ActiveUS20080179190A1Avoid problemsEnsure reliabilitySemiconductor/solid-state device detailsPrinted circuit aspectsResistElectrical connection

A method for fabricating a conductive bump structure of a circuit board is disclosed. The circuit board with a plurality of electrical connection pads is provided. An insulating protective layer and a resist layer are successively applied on the circuit board, wherein openings are formed in the layers at positions corresponding to the pads to expose the pads. Then, a conductive layer is formed on surfaces of the resist layer and openings, and a metal layer is formed on the conductive layer via electroplating and filled in the openings. Subsequently, the metal layer and conductive layer formed on the resist layer are removed via thinning, so as to form metal bumps on the pads. After the resist layer is removed, the metal bumps are covered by an adhesive layer to form a conductive bump structure for electrically connecting the circuit board to the external electronic component.

Owner:PHOENIX PRECISION TECH CORP

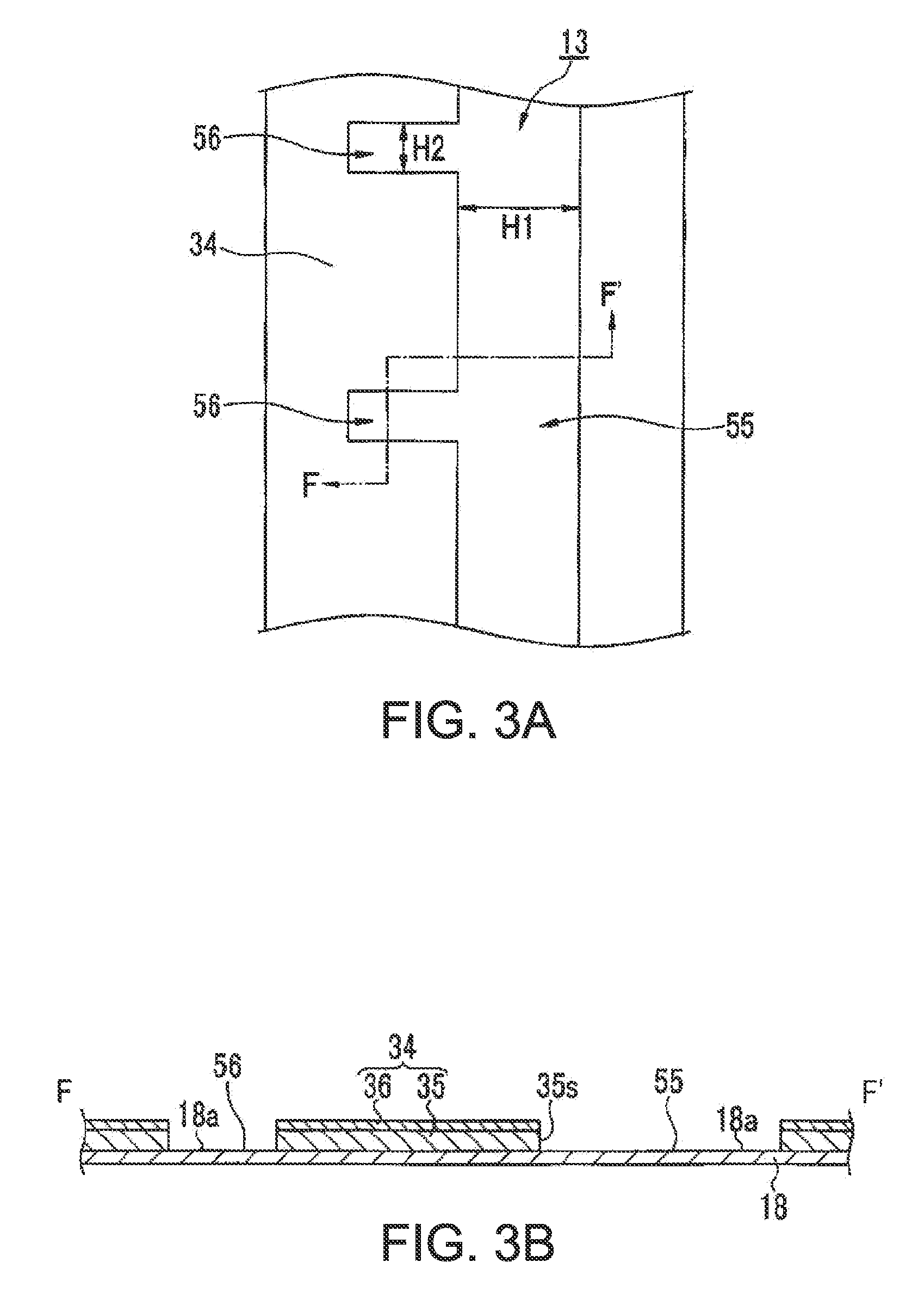

Forming method for protecting image

ActiveCN101126893ANo position deviationNo protection position deviationSemiconductor/solid-state device manufacturingDouble resist layersResistSemiconductor chip

Production of a resist pattern involves applying first then second photohardenable resist films (F1, F2), sensitive to light in first and second wavelength regions (WL1, WL2) respectively, to a semiconductor chip or a circuit board, where film F2 blocks light of WLR1. Laser light in WL2 is applied through a screen onto part of F2 followed by applying a developer solution, to form a mask pattern. F1 is illuminated with light in WL1 through a membrane mask, and finally F1 is developed.

Owner:SANEI KAGAKU KK

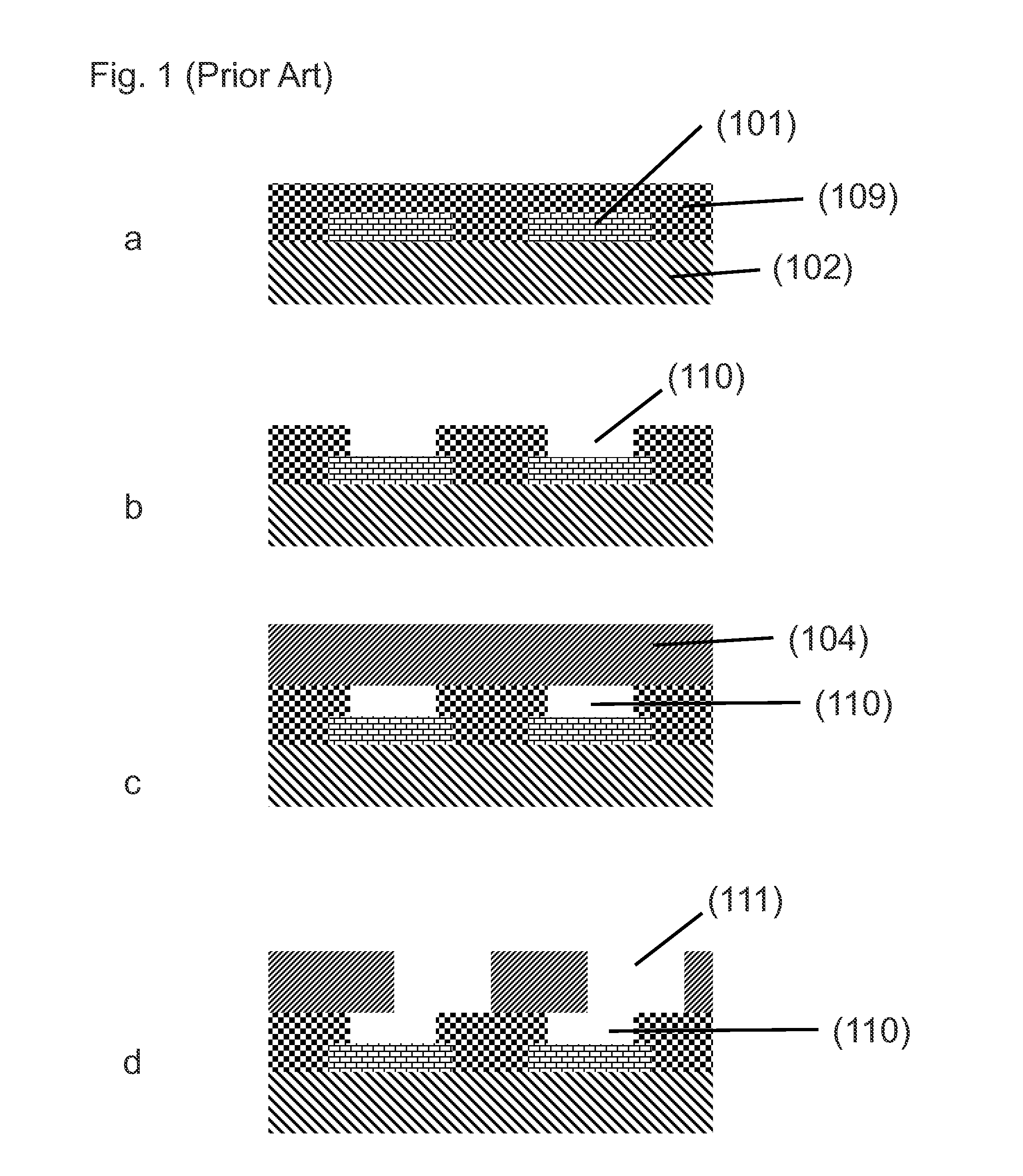

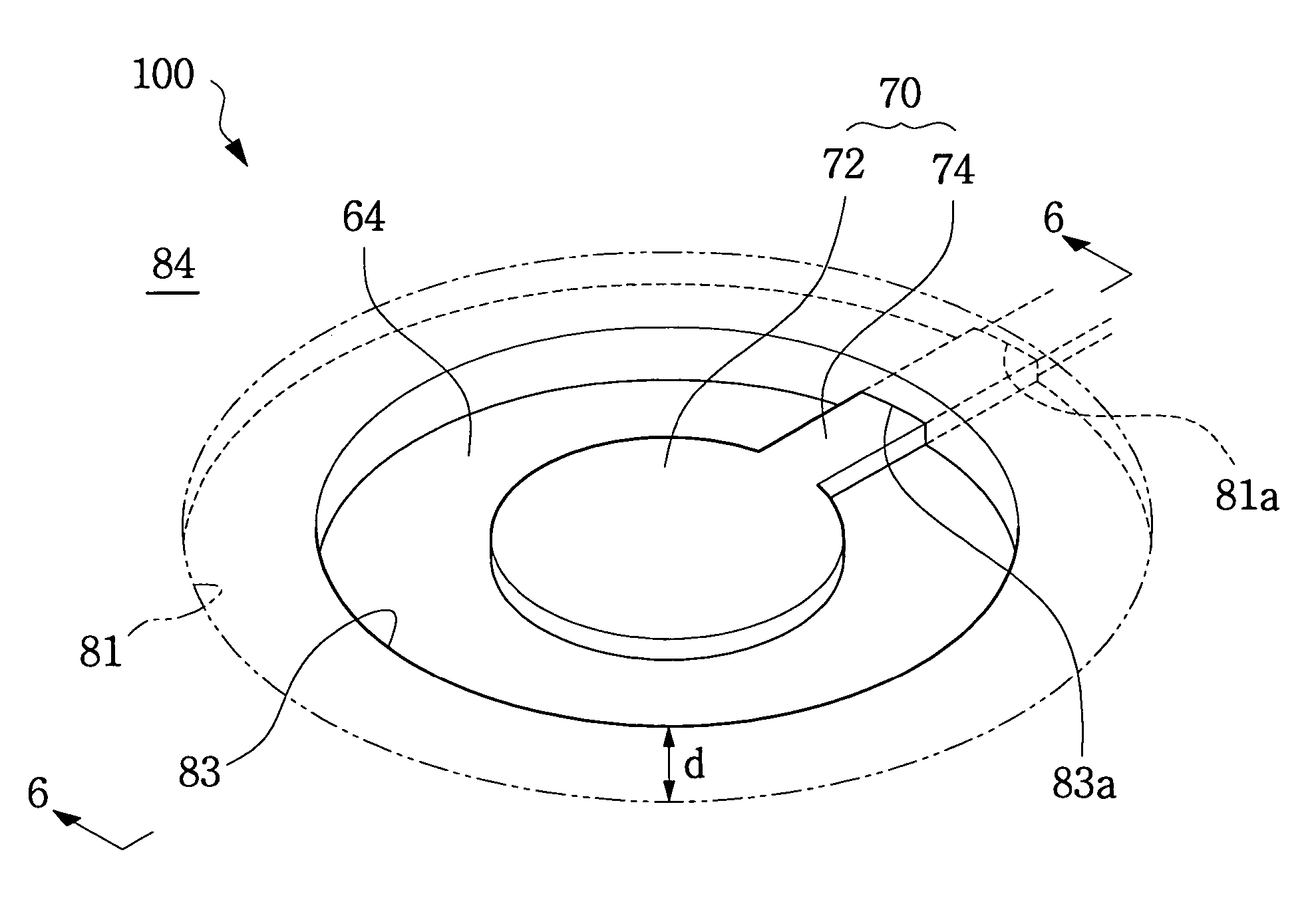

Non-solder mask defined (NSMD) type wiring substrate for ball grid array (BGA) package and method for manufacturing such a wiring substrate

ActiveUS20050039944A1Reduce crackingReduce stress concentrationPrinted circuit assemblingSemiconductor/solid-state device detailsStress concentrationSolder mask

In one embodiment, a pad is formed on a substrate surface. The pad is connected with a connecting pattern. A first mask is formed on the substrate. The first mask has a first opening exposing at least a portion of the pad and a portion of the connecting pattern. A second mask is formed on the first mask. The second mask has a second opening exposing at least a portion of the pad and a portion of the connecting pattern. A boundary surface or sidewall of the first opening is not coplanar with a boundary surface or sidewall of the second opening. Therefore, stresses may be prevented from concentrating on the boundary surface of the first opening, thereby allowing dispersion of the stresses and restraining pattern cracks.

Owner:SAMSUNG ELECTRONICS CO LTD

Method for forming film pattern, and method for manufacturing device, electro-optical device, electronic apparatus and active matrix substrate

InactiveUS20070020834A1Large widthShort timePrinted circuit aspectsSolid-state devicesActive matrixBiomedical engineering

A method for forming a film pattern, comprises: disposing a first bank forming material to a substrate so as to form a first bank layer; disposing a second bank forming material on the first bank layer so as to form a second bank layer; and pattering the first bank layer and the second bank layer so as to form a bank including a pattern forming region having a first pattern forming region and a second pattern forming region, the second pattern forming region having a width larger than a width of the first pattern forming region, and being continuously formed from the first pattern forming region, wherein the first bank layer has a sidewall facing the pattern forming region and a first contact angle of less than 50 degrees with respect to a functional liquid containing H2O on the sidewall, and the second bank layer has a second contact angle larger than the first contact angle with respect to the functional liquid.

Owner:SEIKO EPSON CORP

Method of manufacturing semiconductor package and semiconductor package

ActiveUS20100244280A1Improve reliabilitySemiconductor/solid-state device detailsPrinted circuit aspectsResistSemiconductor package

A board on which a wiring having an electrode pad is formed is prepared. A resist film is formed on the board in order to cover the wiring and then the resist film is left on the electrode pad through patterning. An inorganic insulating film is formed on the board in order to cover the wiring and then the resist film is removed, thereby removing the inorganic insulating film provided on the resist film to leave the inorganic insulating film between the wirings. A solder resist layer is formed on the board in order to cover the wiring and then the electrode pad is exposed.

Owner:SHINKO ELECTRIC IND CO LTD

Method for fabricating a packaging substrate

ActiveUS6930044B1Low costAvoid damageSemiconductor/solid-state device manufacturingDual purpose resistResistCopper plating

A method for making a packaging substrate is provided. A thin copper seed layer is formed on a carrier plate. A first resist layer is coated on the thin copper seed layer. The first resist layer defines a wire layout of copper plating area. A layer of copper is then electroplated on the copper plating area to form the wire layout. After this, the first resist layer is stripped to expose the wire layout and the thin copper seed layer. A patterned second resist layer is formed on the wire layout. The patterned second resist layer defines the Ni / Au plating area of the wire layout. The copper seed layer that is not covered by the second resist layer is etched away. A third resist layer is stacked on the second resist layer and defines an Au-plating area of the I / O fingers. Using the third resist layer as a plating hard mask, a layer of Ni / Au layer is plated on the exposed area of the wires. After this step, the second and third resist layers are removed.

Owner:NAN YA PRINTED CIRCUIT BOARD CORPORATION

Circuit board structure

ActiveUS7948085B2Avoid insulating propertiesImprove insulation performanceLayered productsSemiconductor/solid-state device detailsElectricitySolder mask

A circuit board structure and a fabrication method of the same are disclosed according to the present invention. The circuit board structure includes: a carrier board with at least one surface formed with a circuit layer having electrically connecting pads; a first solder mask formed on the carrier board and the circuit layer and formed with first openings for exposing the electrically connecting pads; and a second solder mask formed on the first solder mask and formed with second openings for exposing the first openings and the electrically connecting pads. The first solder mask is made of a high-insulation photosensitive material characterized by presence or absence of impurities, such as microparticles, to have enhanced fluidity for being filled in the circuit layer, thereby preventing metal ions migration and subsequent metal hypha electricity discharge which might otherwise affect electrical performance, therefore the present invention is applicable to fine circuit fabrication.

Owner:UNIMICRON TECH CORP

Method for forming bump on electrode pad with use of double-layered film

ActiveUS7265044B2High resolutionEasy peel propertyPrinted circuit assemblingSemiconductor/solid-state device detailsEngineeringMetal

A process for forming bumps on electrode pads for a wiring board including a substrate and a plurality of electrode pads. The process (a) forms a laminated two-layer film on the wiring board and forms a pattern of apertures at positions corresponding to the electrode pads, the laminated two-layer film including a lower layer containing an alkali-soluble radiation-nonsensitive resin composition and an upper layer containing a negative radiation-sensitive resin composition; (b) fills a low-melting metal in the aperture pattern; (c) reflows the low-melting metal by pressing or heating to form bumps; and (d) peels and removes the laminated two-layer film from the board. The laminated film including two layers with different properties permits high resolution and easy peeling.

Owner:JSR CORPORATIOON

Method for interconnecting multi-layer printed circuit board

InactiveUS7320173B2Reduce lossesImprove connection strengthElectrical connection printed elementsSurface layering apparatusResistProduction rate

A method for fabricating a multi-layer printed circuit board can include forming an etching resist layer on a first metal layer having plating grooves that selectively expose the first metal layer, forming a plated layer at the surface of the first metal layer exposed by the plating groove through a plating process to form connection protrusion, removing the etching resist layer, forming an insulation layer at the first metal layer and positioning a second metal layer at the surface of the insulation layer coupled to an end portion of the connection protrusion. By forming the connection protrusion through the plating process, a loss of material can be reduced and a strength of the connection protrusion can be increased. Further, a complexity of the fabrication process is reduced to reduce costs and increase productivity.

Owner:LG INNOTEK CO LTD +1