Patents

Literature

65results about How to "Significant performance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

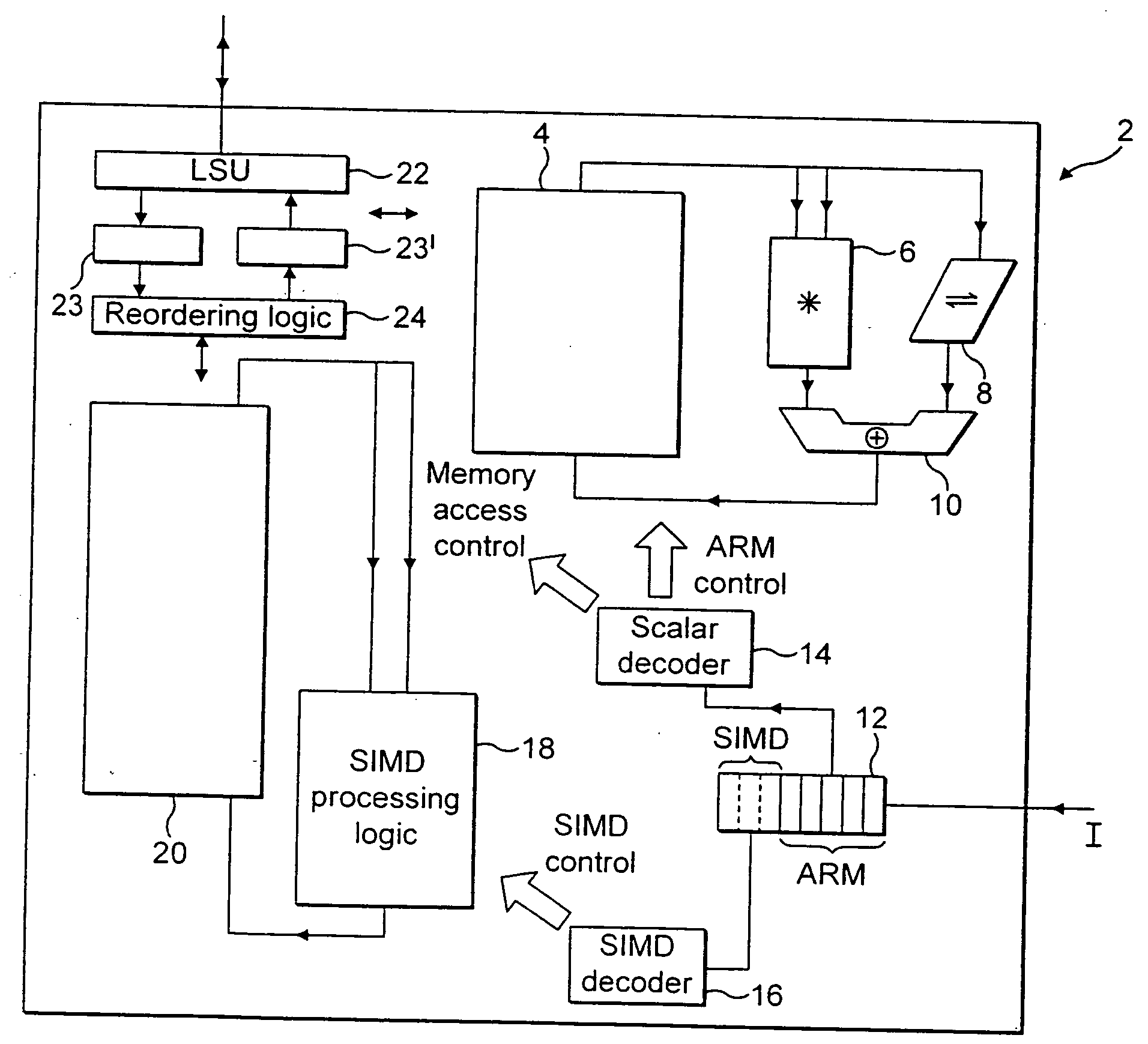

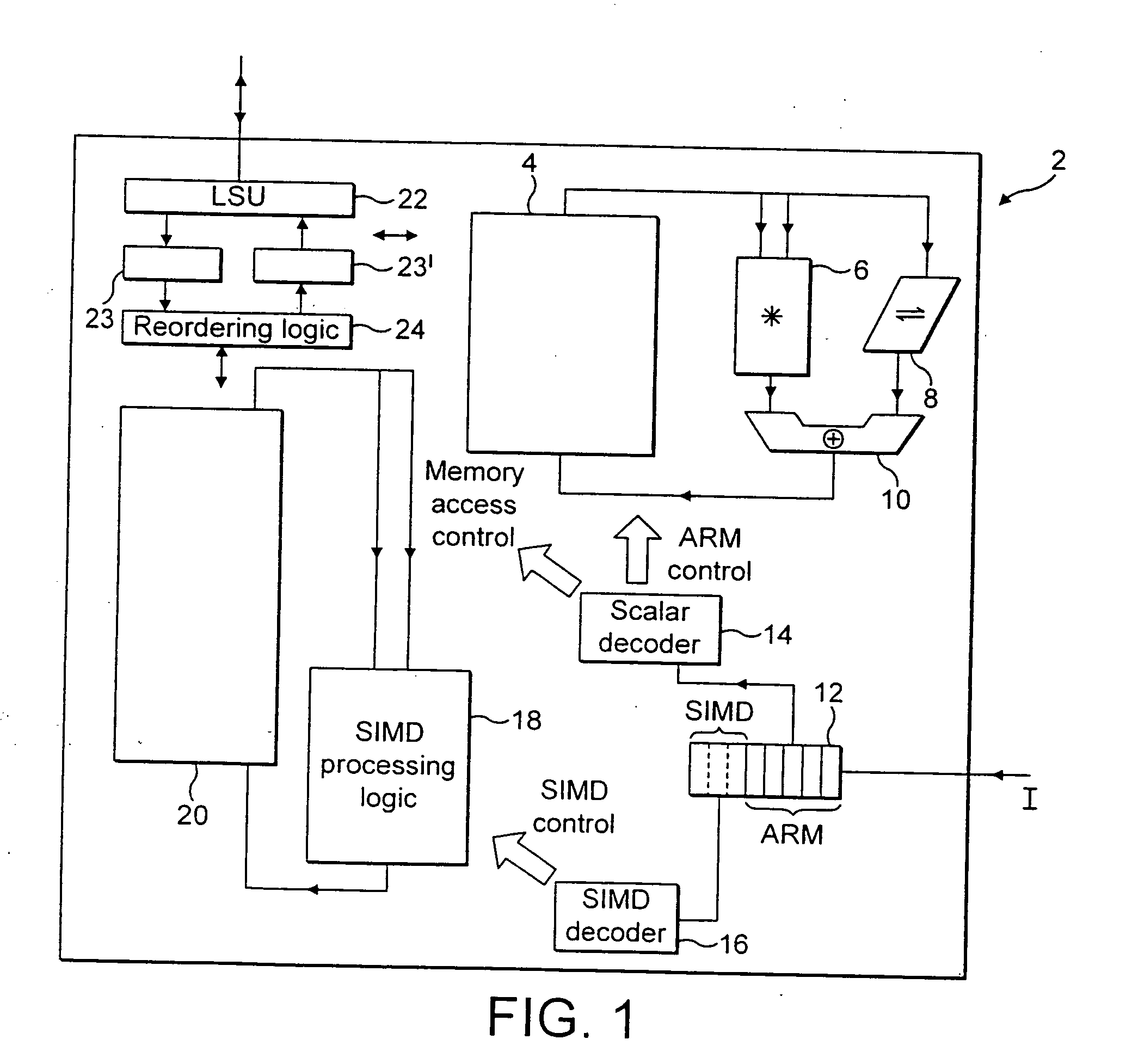

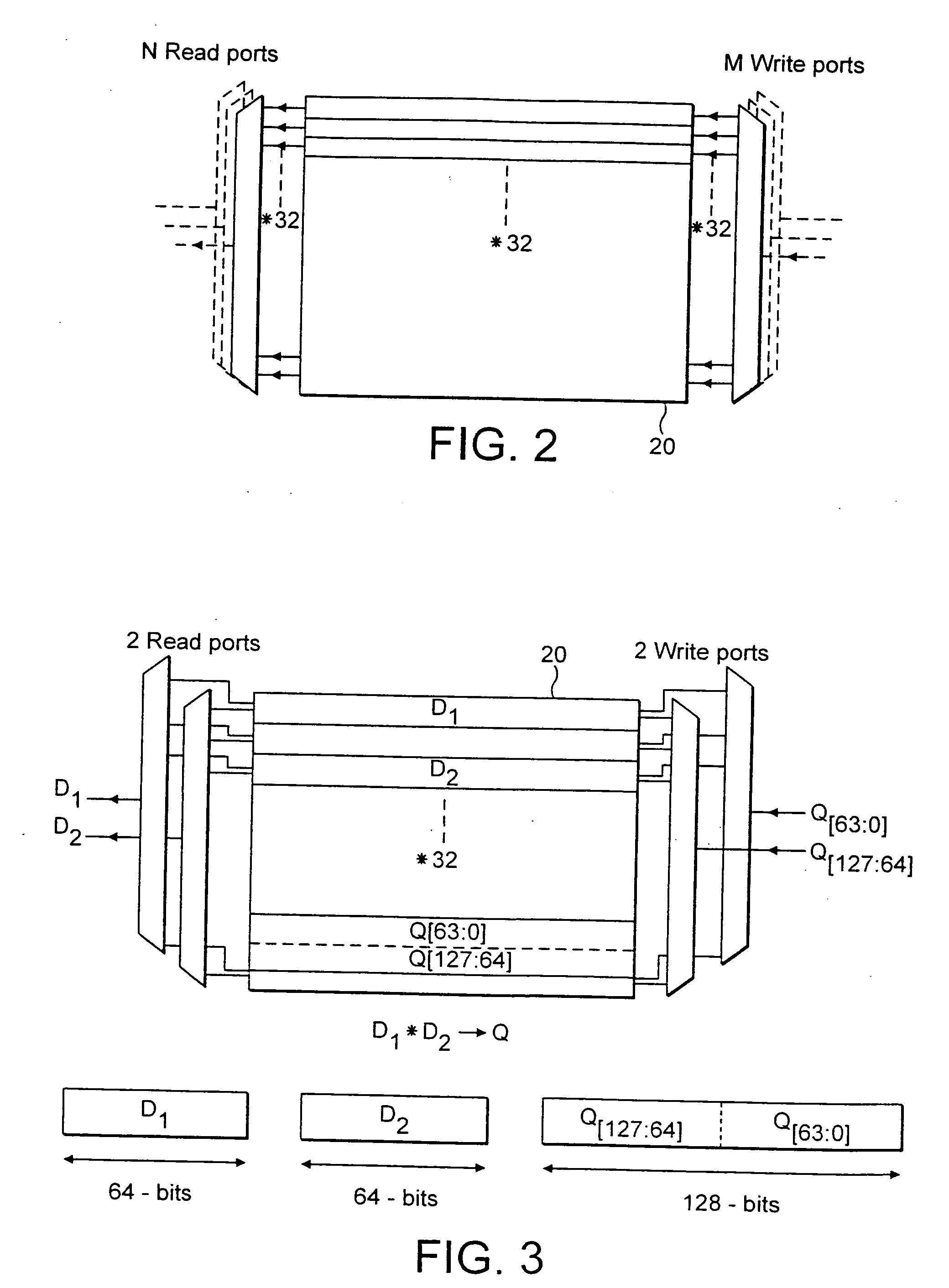

Data processing apparatus and method for performing rearrangement operations

ActiveUS20100106944A1Further flexibilityReduce energy consumptionDigital data processing detailsInstruction analysisControl signalProcessor register

A data processing apparatus and method are provided for performing rearrangement operations. The data processing apparatus has a register data store with a plurality of registers, each register storing a plurality of data elements. Processing circuitry is responsive to control signals to perform processing operations on the data elements. An instruction decoder is responsive to at least one but no more than N rearrangement instructions, where N is an odd plural number, to generate control signals to control the processing circuitry to perform a rearrangement process at least equivalent to: obtaining as source data elements the data elements stored in N registers of said register data store as identified by the at least one re-arrangement instruction; performing a rearrangement operation to rearrange the source data elements between a regular N-way interleaved order and a de-interleaved order in order to produce a sequence of result data elements; and outputting the sequence of result data elements for storing in the register data store. This provides a particularly efficient technique for performing N-way interleave and de-interleave operations, where N is an odd number, resulting in high performance, low energy consumption, and reduced register use when compared with known prior art techniques.

Owner:ARM LTD

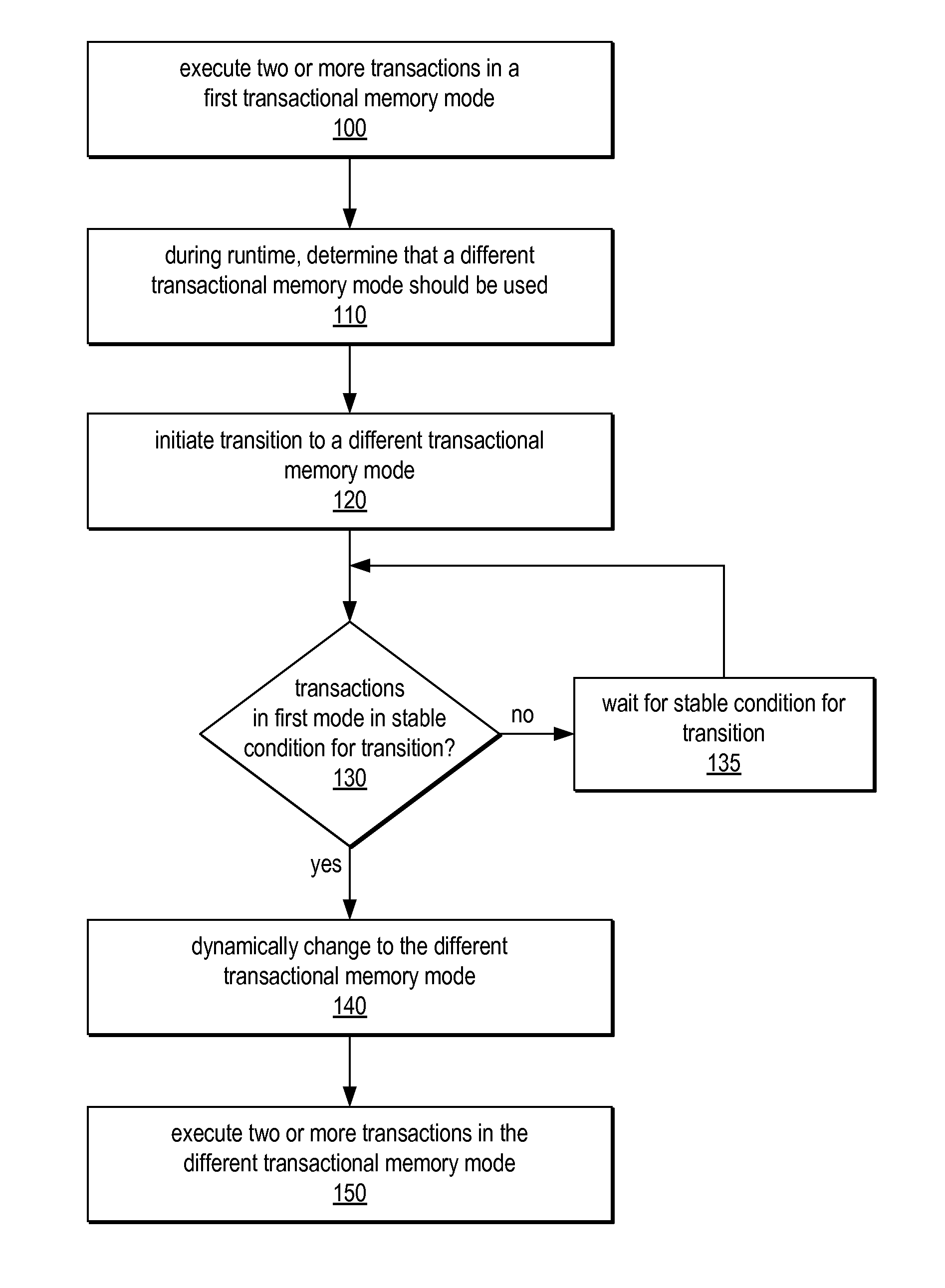

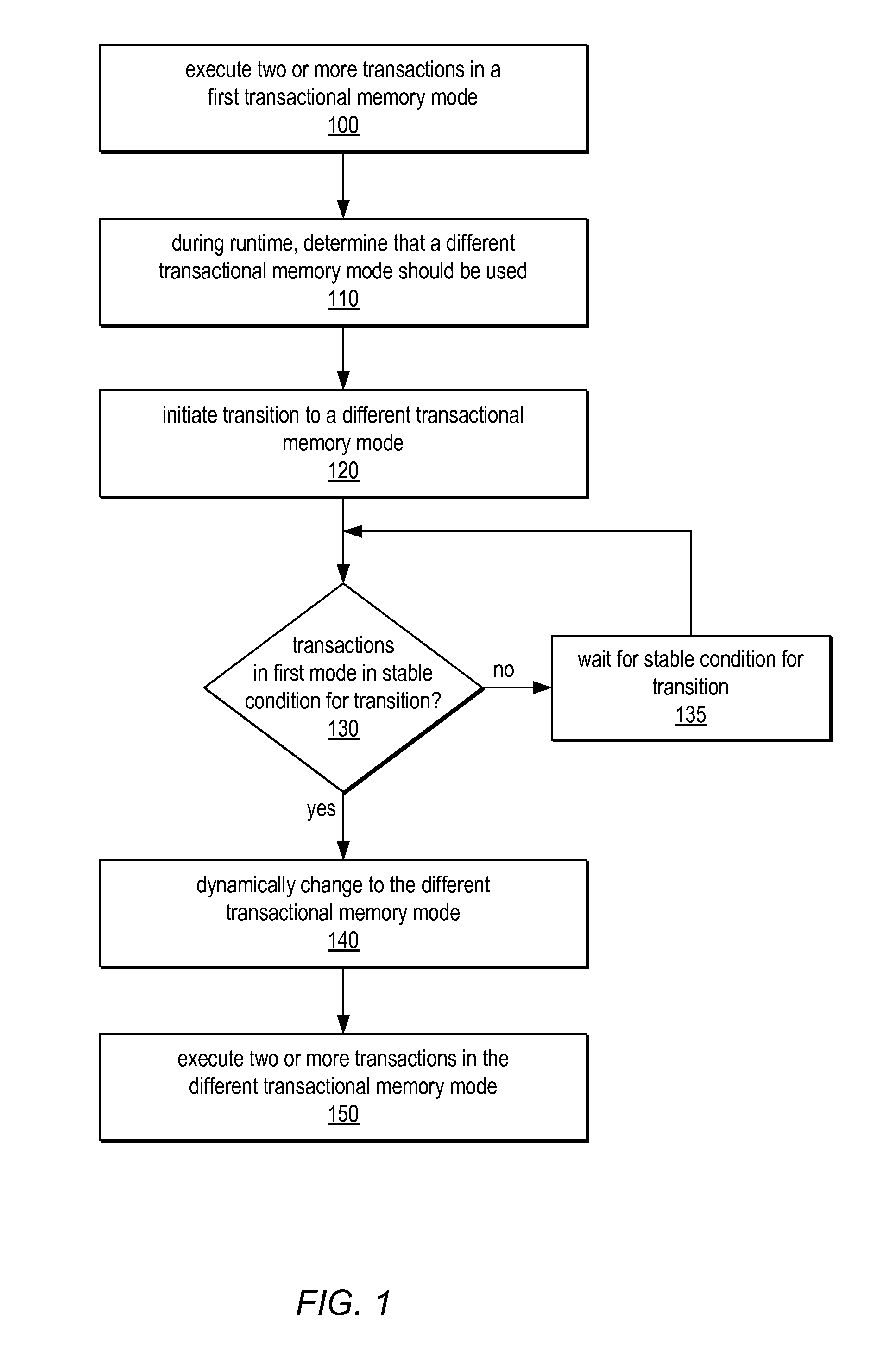

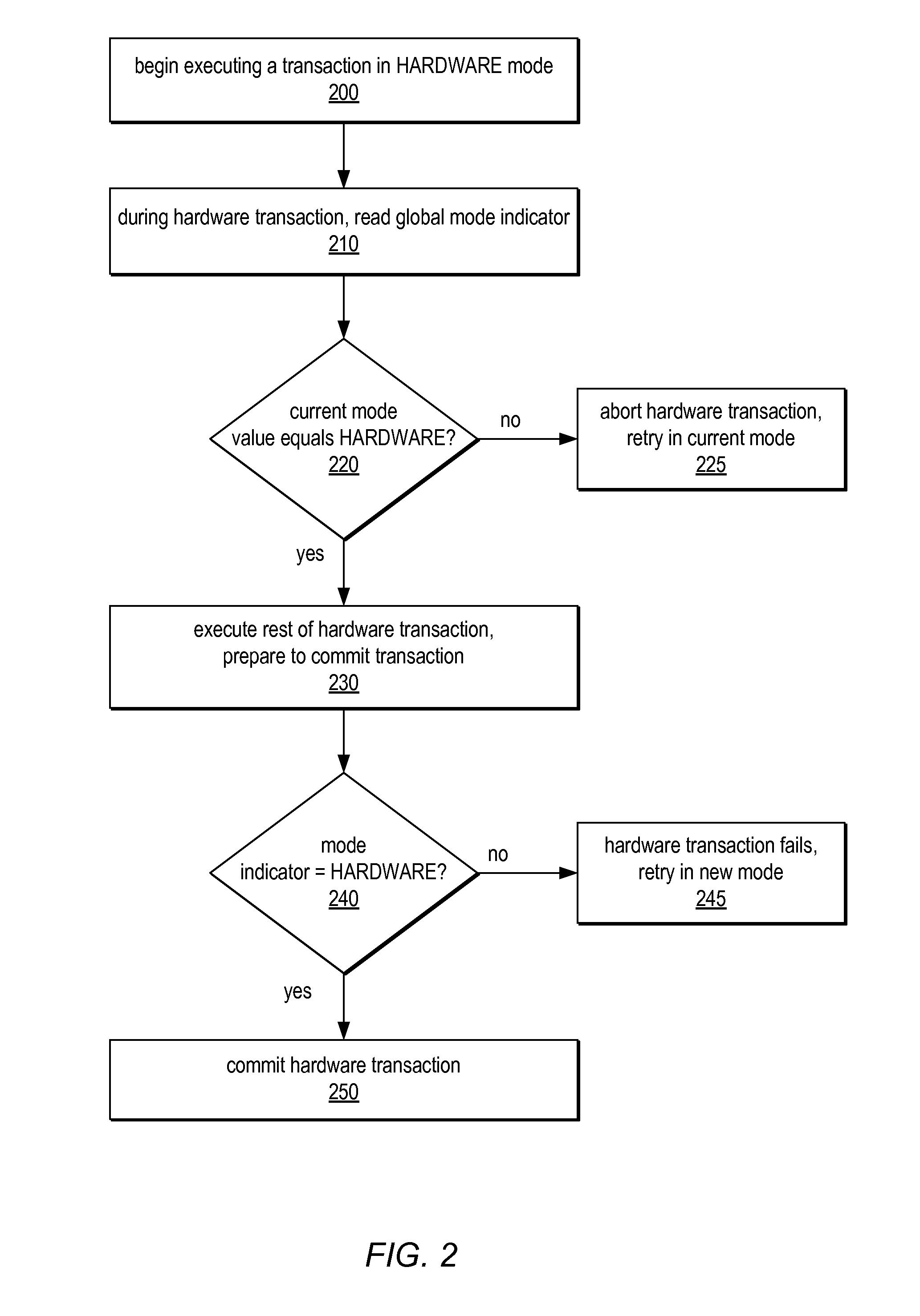

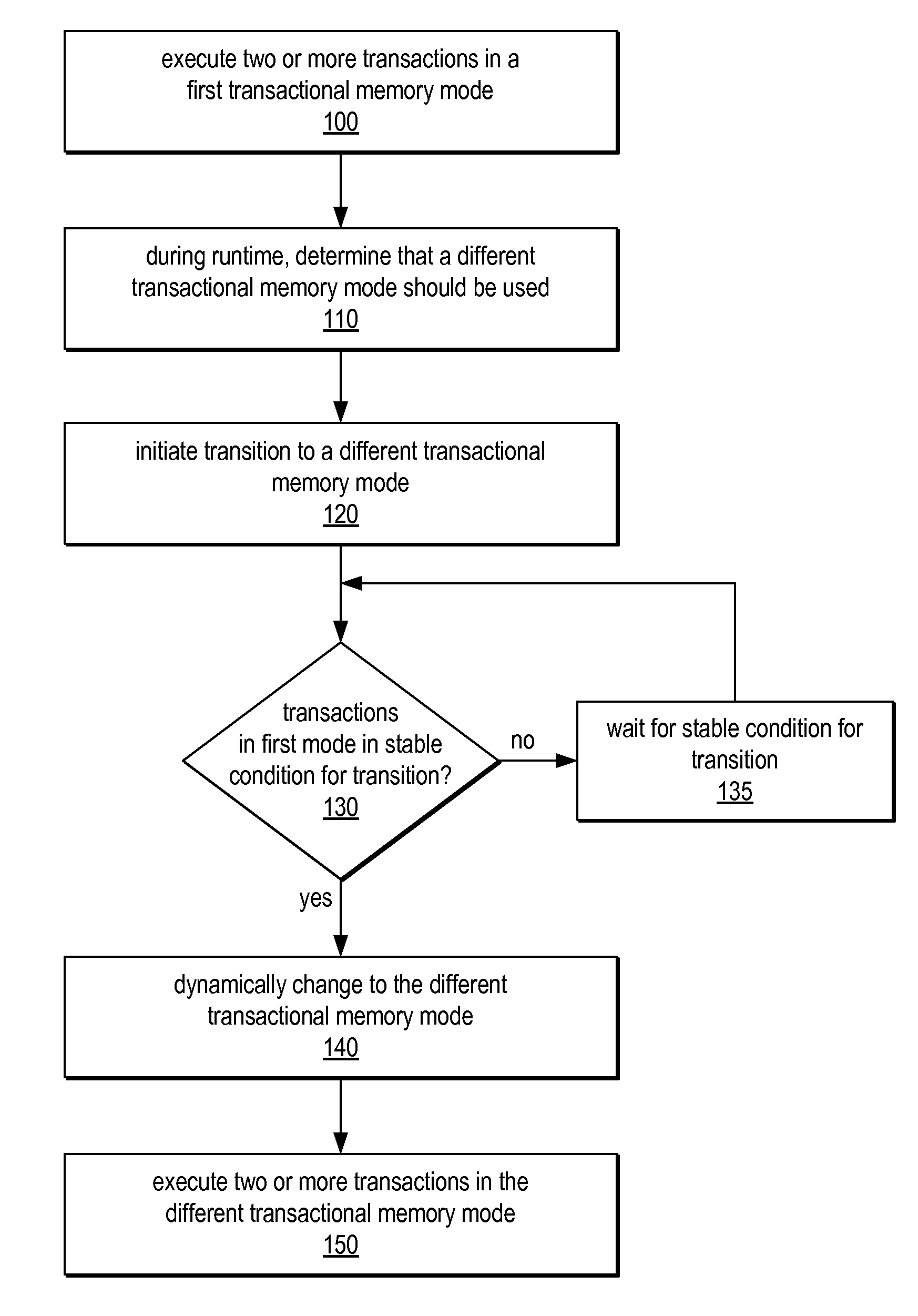

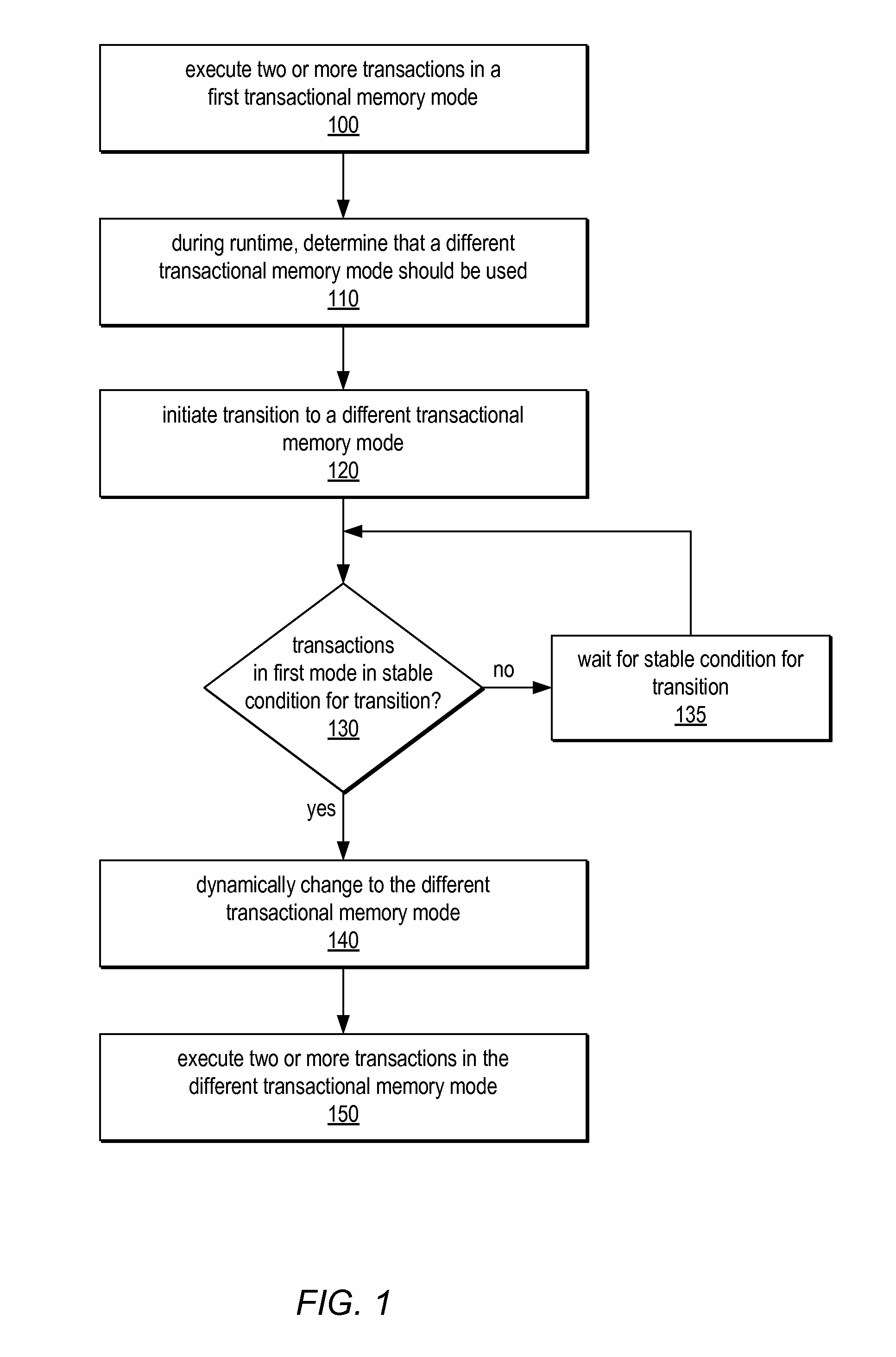

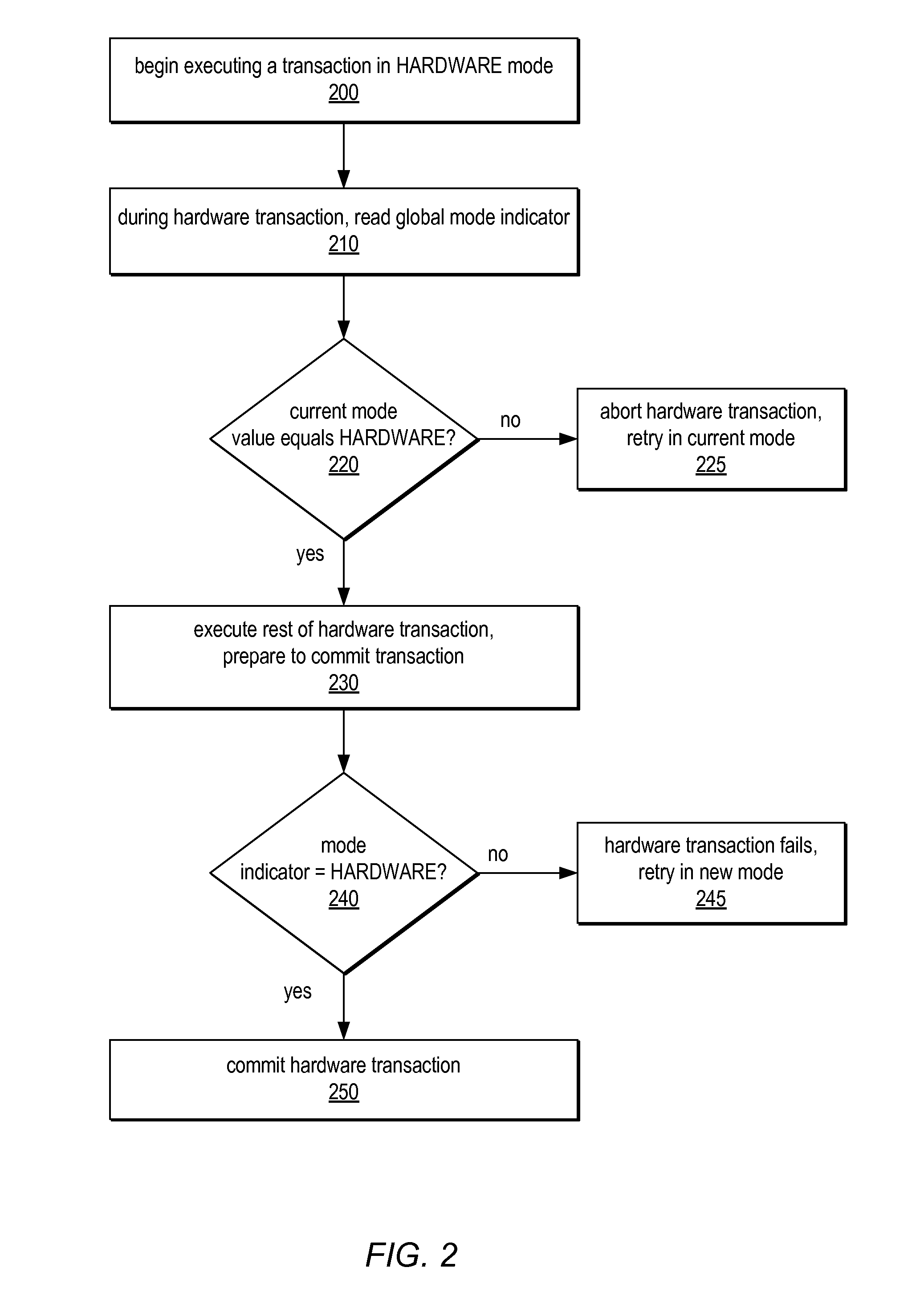

System and Method for Supporting Phased Transactional Memory Modes

ActiveUS20090172306A1Reduce difficultyMaximum flexibilityProgram control using stored programsDigital computer detailsParallel computingTransactional memory

A phased transactional memory (PhTM) may support a plurality of transactional memory implementations, including software, hardware, and hybrid implementations, and may provide mechanisms for dynamically transitioning between transactional memory modes in response to changing workload characteristics; upon discovering that the current mode does not perform well, is not suitable, or does not support functionality required for particular transactions; or according to scheduled phases. A system providing PhTM may be configured to transition from a first transactional memory mode to a second transactional memory mode while ensuring that transactions executing in the first transactional memory mode do not interfere with correct execution of transactions in the second transactional memory mode. The system may be configured to abort transactions in progress or to wait for transactions to complete, be aborted, or reach a safe transition point before transitioning to a new mode, and may use a global mode indicator in coordinating transitions.

Owner:ORACLE INT CORP

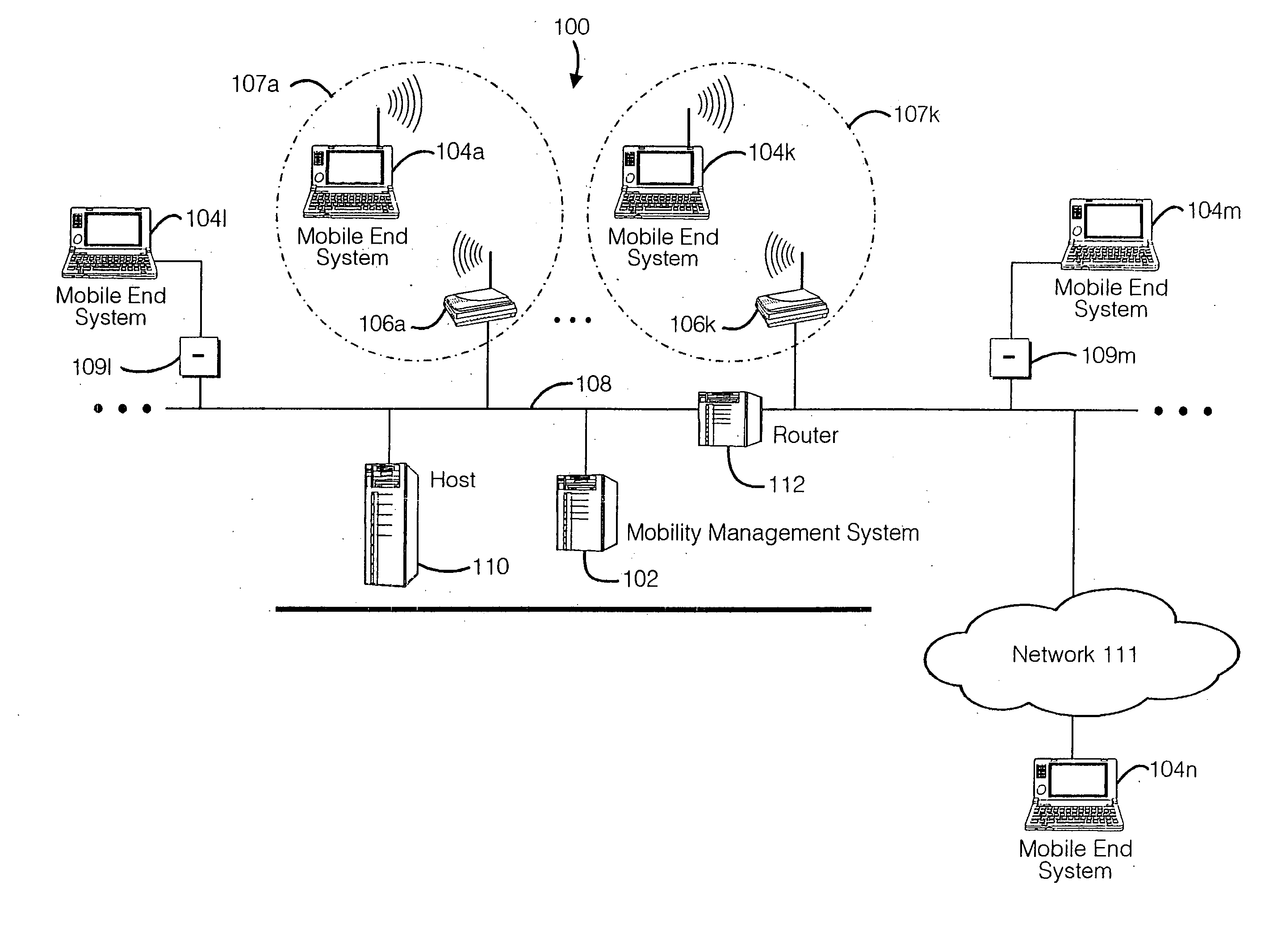

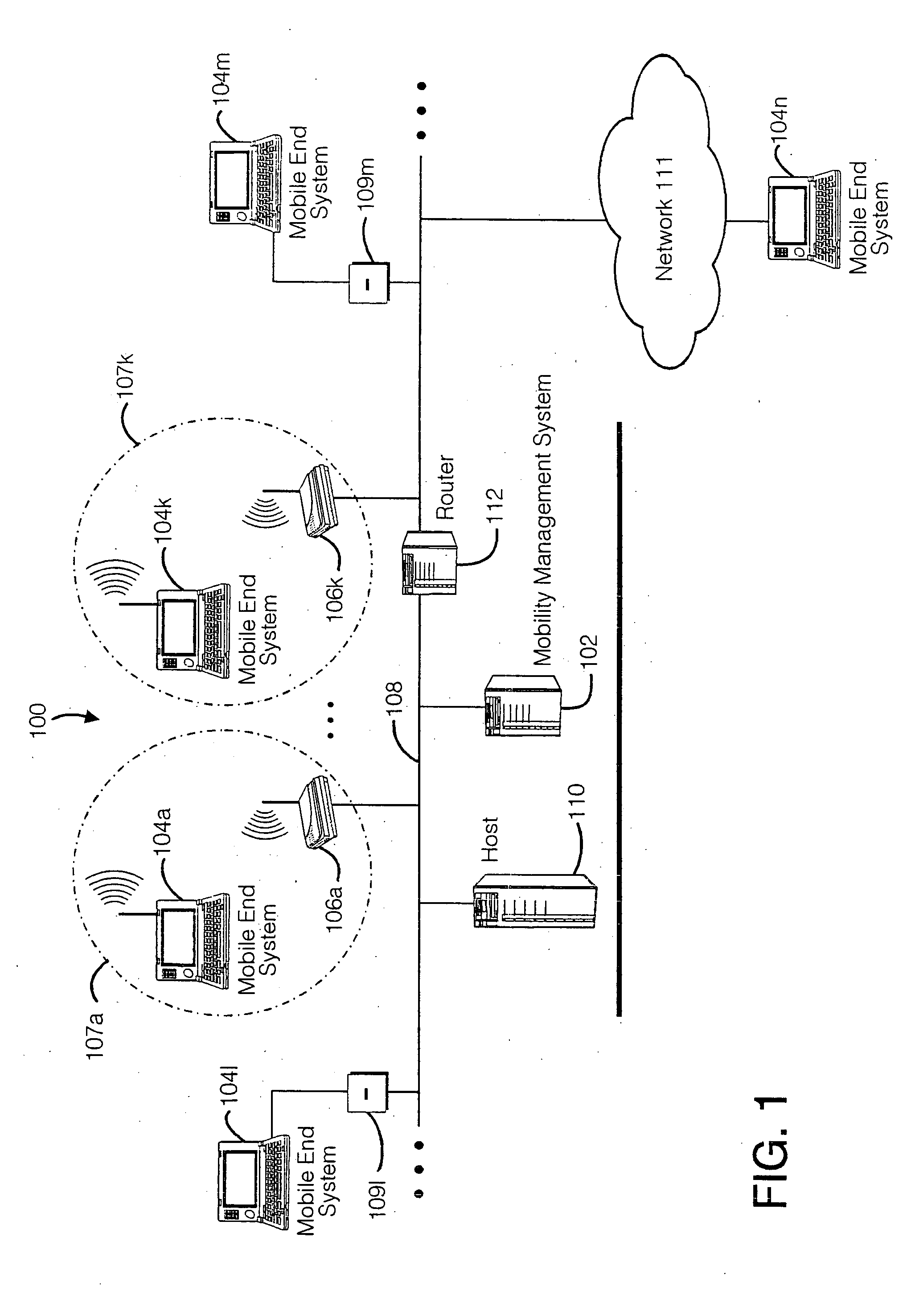

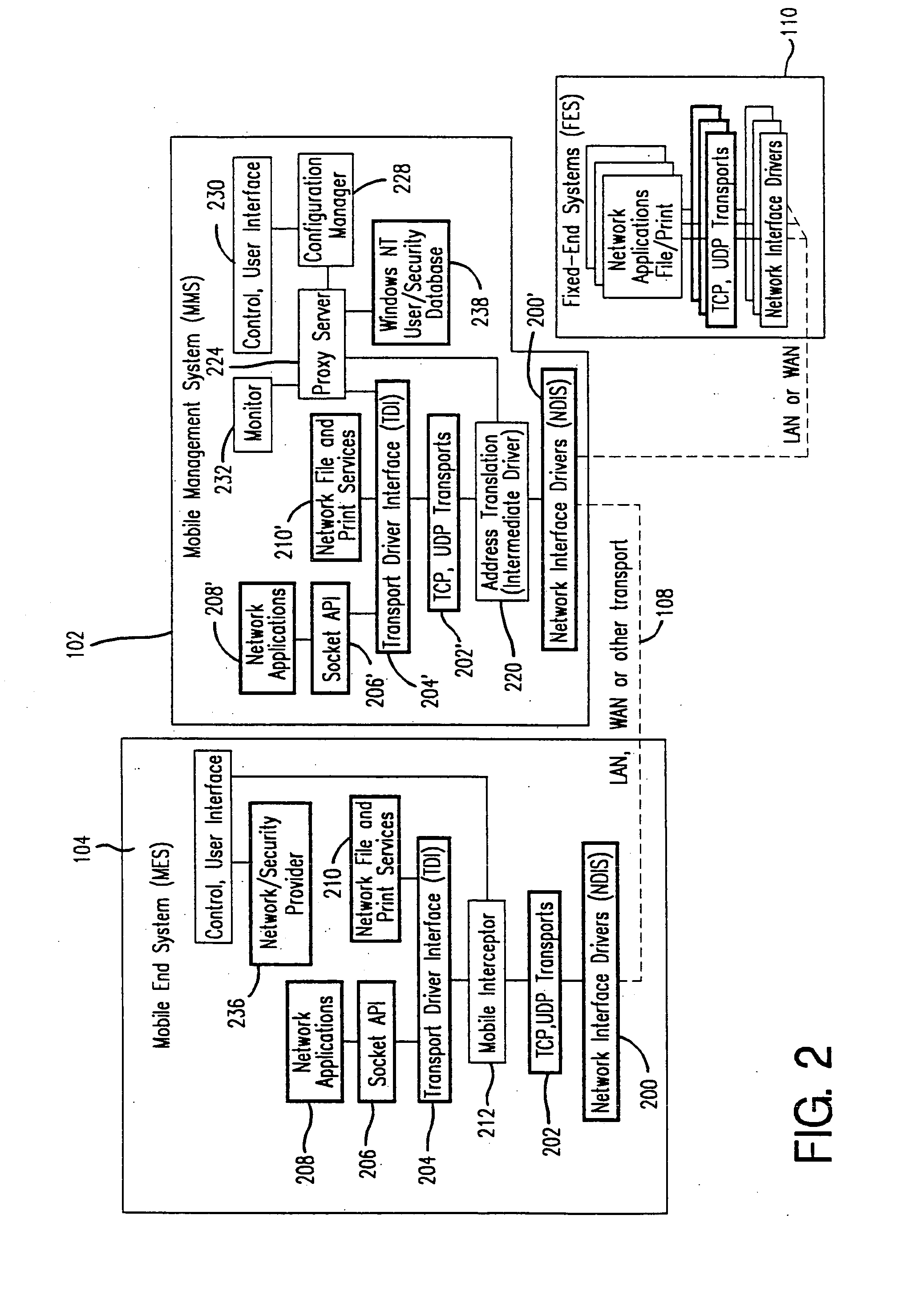

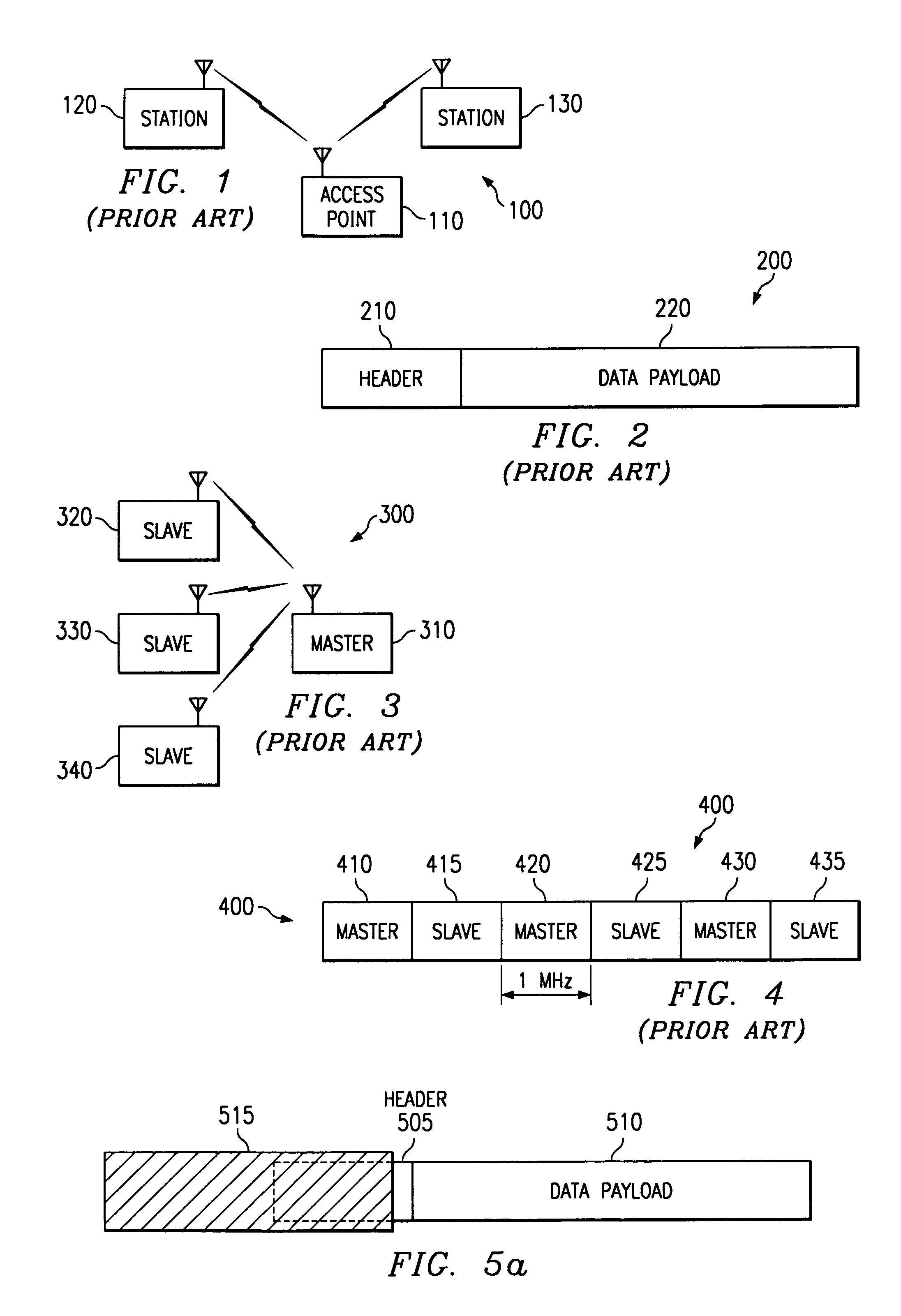

Method and apparatus for providing mobile and other intermittent connectivity in a computing environment

InactiveUS20050223114A1Reduce network trafficSignificant performanceConnection managementData switching by path configurationCable networkNetwork address

A seamless solution transparently addresses the characteristics of nomadic systems, and enables existing network applications to run reliably in mobile environments. The solution extends the enterprise network, letting network managers provide mobile users with easy access to the same applications as stationary users without sacrificing reliability or centralized management. The solution combines advantages of existing wire-line network standards with emerging mobile standards to create a solution that works with existing network applications. A Mobility Management Server coupled to the mobile network maintains the state of each of any number of Mobile End Systems and handles the complex session management required to maintain persistent connections to the network and to other peer processes. If a Mobile End System becomes unreachable, suspends, or changes network address (e.g., due to roaming from one network interconnect to another), the Mobility Management Server maintains the connection to the associated peer task—allowing the Mobile End System to maintain a continuous connection even though it may temporarily lose contact with its network medium. In one example, Mobility Management Server communicates with Mobile End Systems using Remote Procedure Call and Internet Mobility Protocols.

Owner:MOBILE SONIC INC

System and method for supporting phased transactional memory modes

ActiveUS7966459B2Reduce difficultyMaximum flexibilityDigital computer detailsSpecific program execution arrangementsParallel computingTransactional memory

A phased transactional memory (PhTM) may support a plurality of transactional memory implementations, including software, hardware, and hybrid implementations, and may provide mechanisms for dynamically transitioning between transactional memory modes in response to changing workload characteristics; upon discovering that the current mode does not perform well, is not suitable, or does not support functionality required for particular transactions; or according to scheduled phases. A system providing PhTM may be configured to transition from a first transactional memory mode to a second transactional memory mode while ensuring that transactions executing in the first transactional memory mode do not interfere with correct execution of transactions in the second transactional memory mode. The system may be configured to abort transactions in progress or to wait for transactions to complete, be aborted, or reach a safe transition point before transitioning to a new mode, and may use a global mode indicator in coordinating transitions.

Owner:ORACLE INT CORP

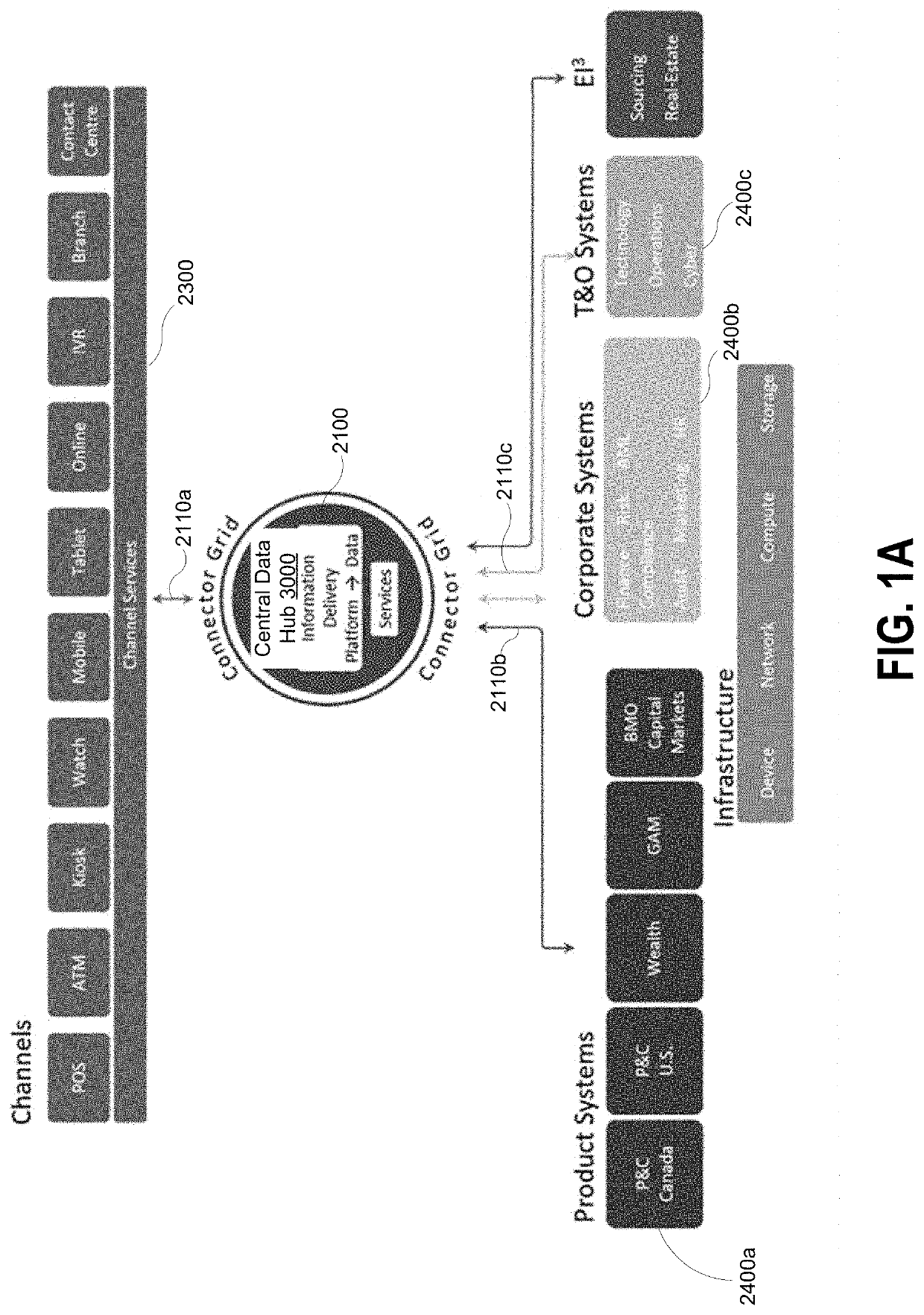

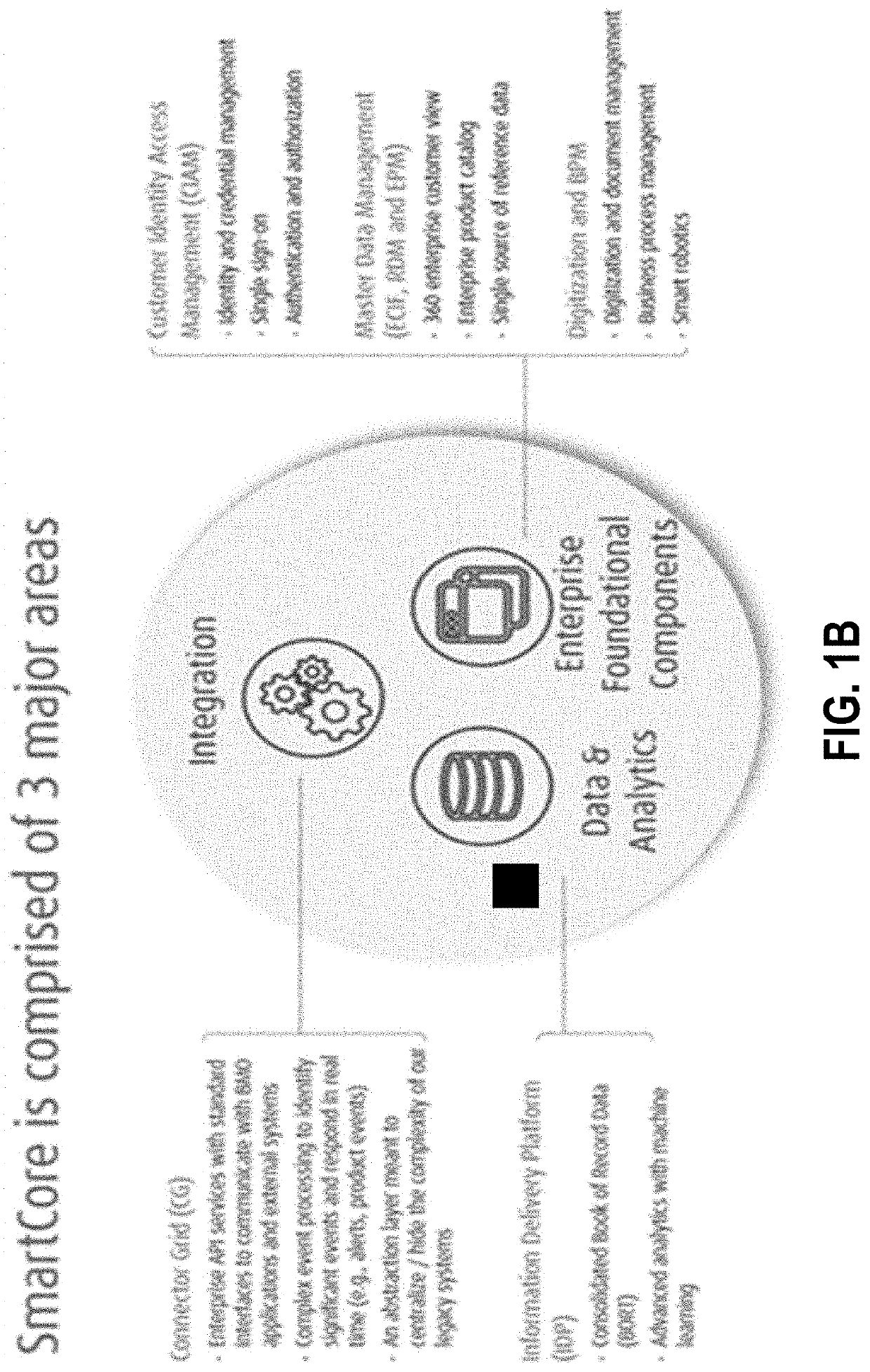

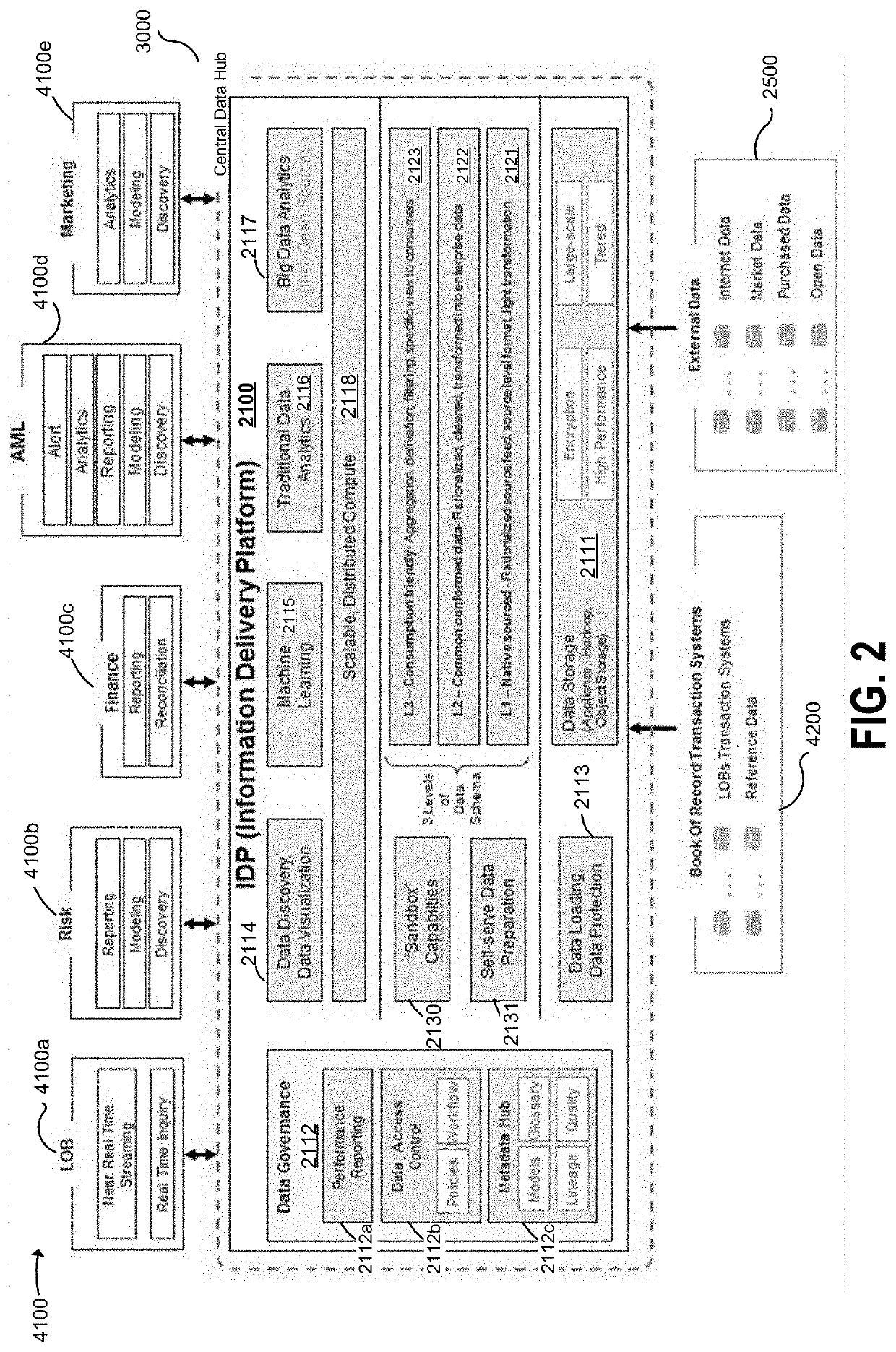

Systems and methods for data storage and processing

ActiveUS20200026710A1Easy to useMaximum efficiencyDatabase management systemsMachine learningData setData graph

Systems and methods for processing data are provided. The system may include at least a processor and a non-transient data memory storage, the data memory storage containing machine-readable instructions for execution by the processor, the machine-readable instructions configured to, when executed by the processor, provide an information delivery platform configured to: extract raw data from a plurality of source systems; load and store the raw data at a non-transient data store; receive a request to generate data for consumption for a specific purpose; in response to the request, select a set of data from the raw data based on a data map; transform the selected set of data into a curated set of data based on the data map; and transmit the curated set of data to a channel for consumption.

Owner:BANK OF MONTREAL

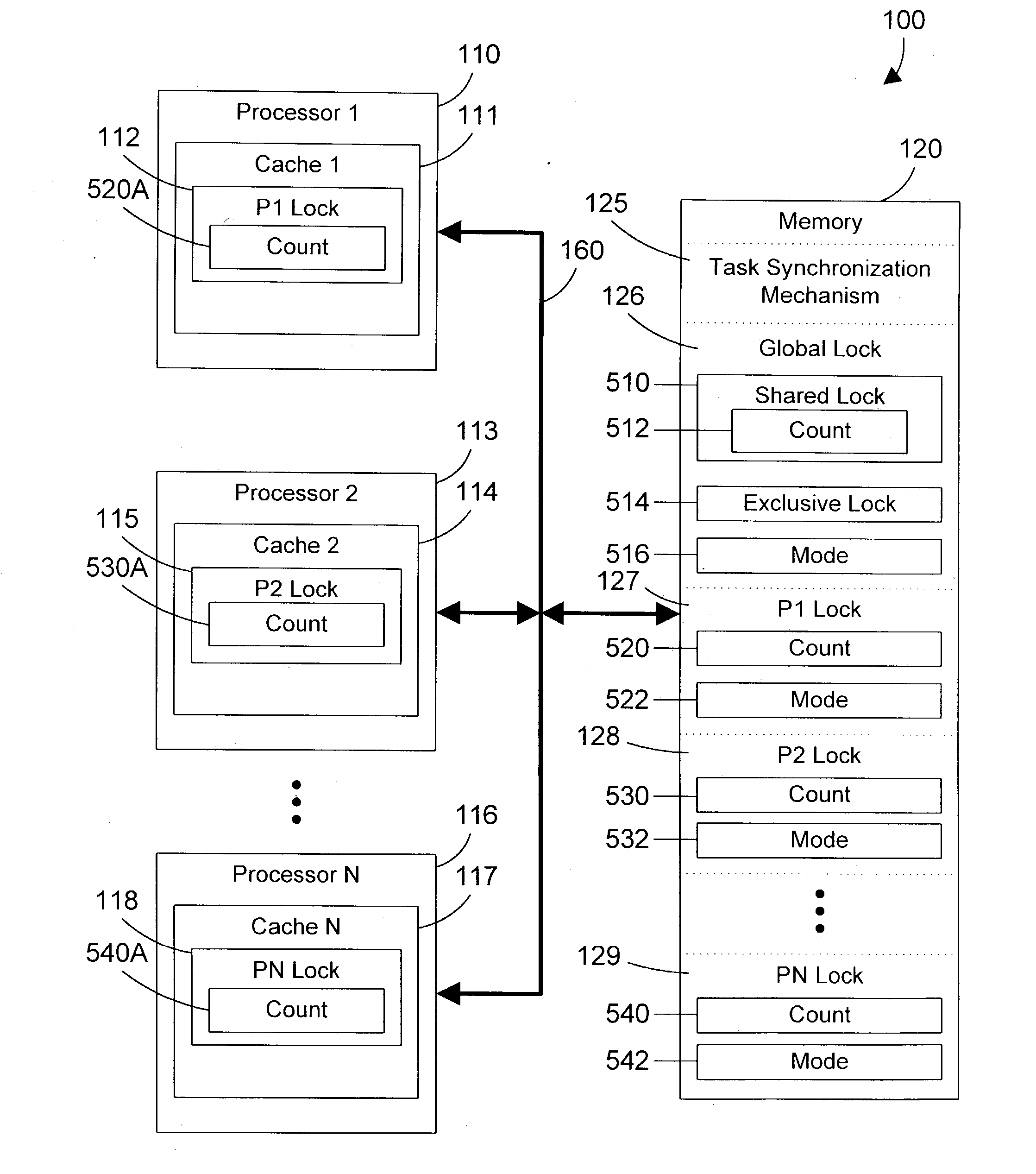

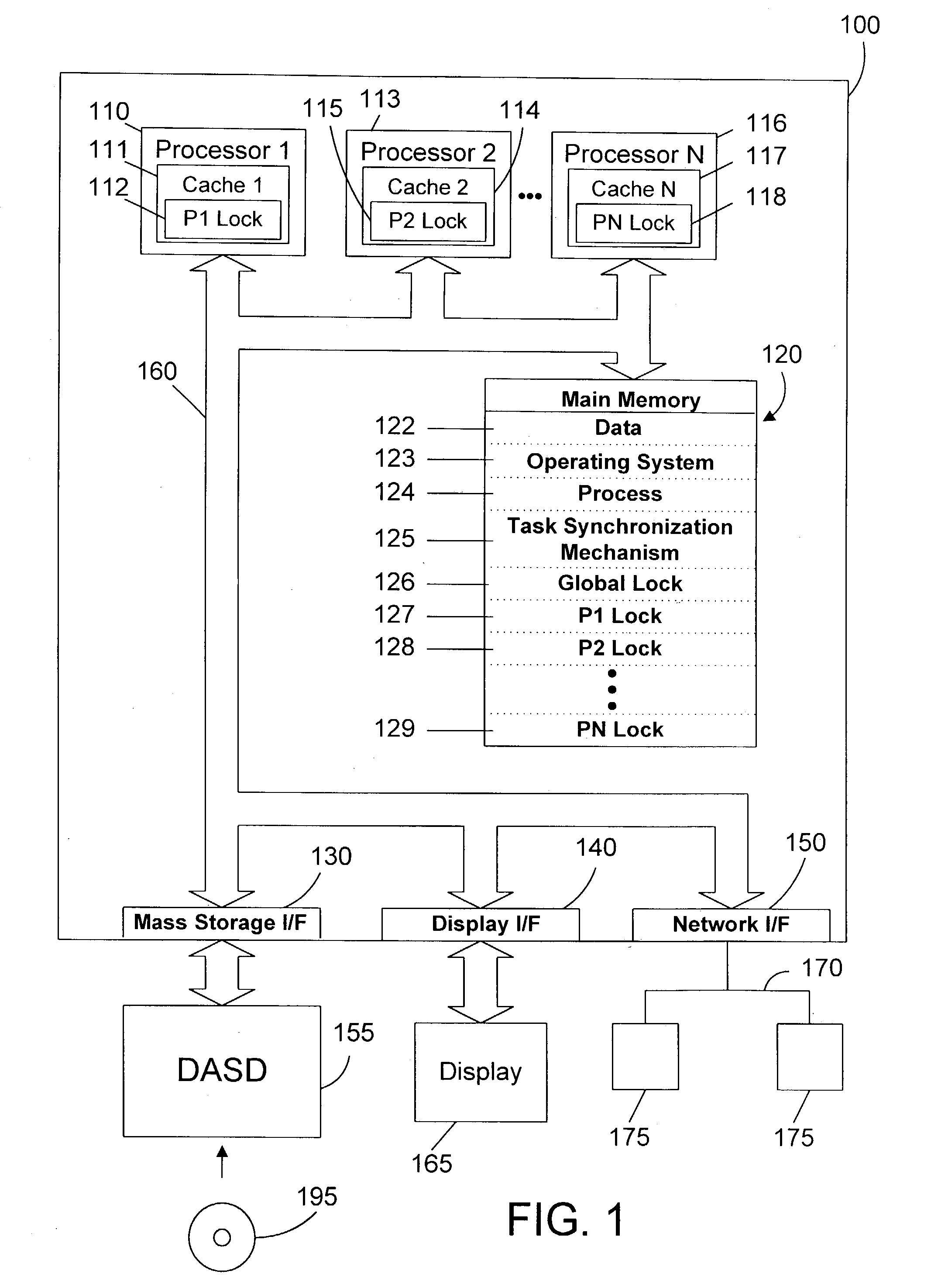

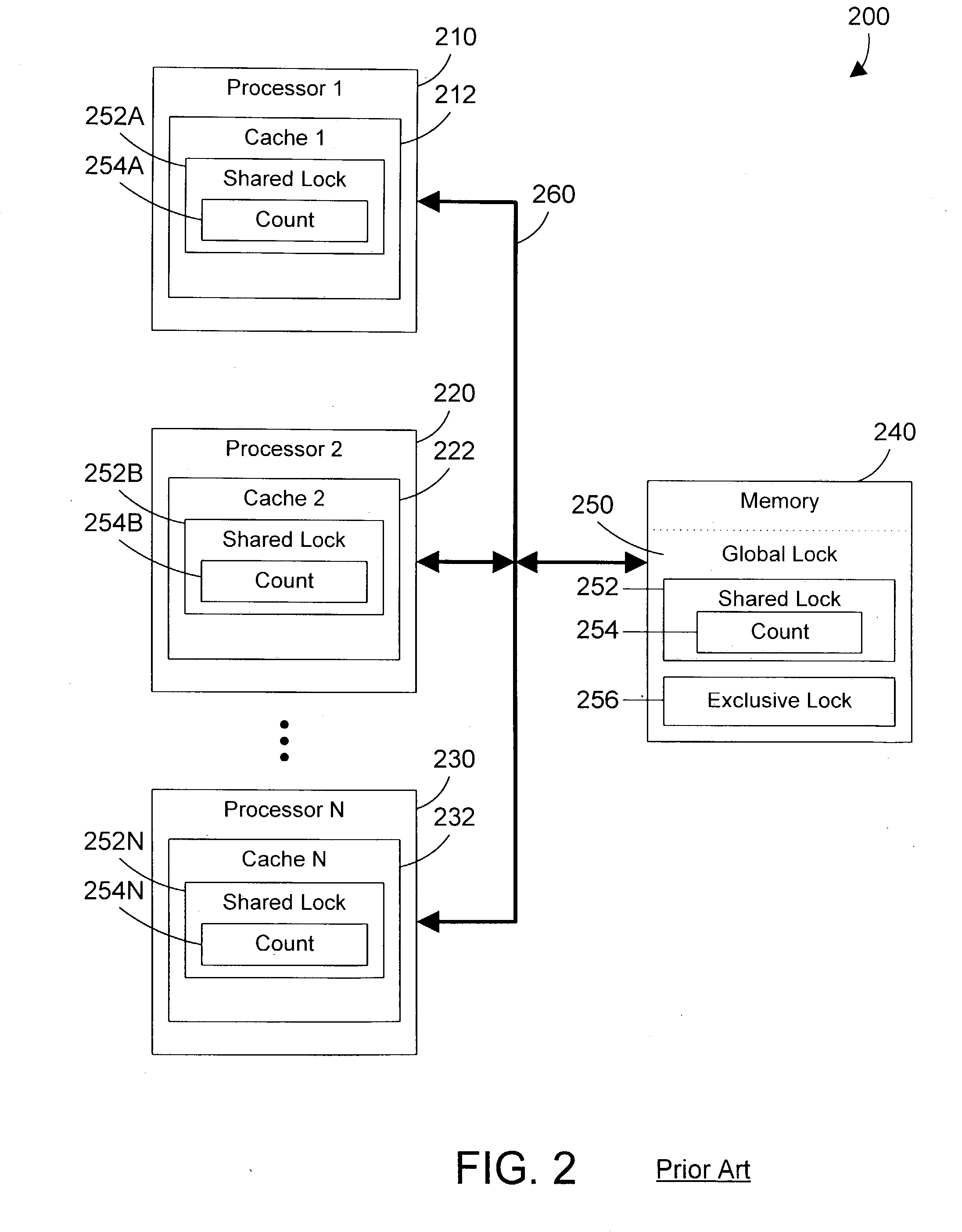

Task synchronization mechanism and method

ActiveUS20040143712A1Significant overheadSignificant performanceUnauthorized memory use protectionMultiprogramming arrangementsComputer architectureMemory bus

A task synchronization mechanism operates on a global lock that is shared between processors an on local locks that are not shared between processors. The local locks are processor-specific locks. Each processor-specific lock is dedicated to a particular processor in the system. When shared access to a resource is required, a processor updates its processor-specific lock to indicate the processor is sharing the resource. Because each processor-specific lock is dedicated to a particular processor, this eliminates a significant portion of the memory bus traffic associated with all processors reading and updating the same lock. When exclusive access to a resource is required, the requesting processor waits until the count of all processor-specific locks indicate that none of these processors have a lock on the resource. Once no processor has a lock on the resource, exclusive access to the resource may be granted. By changing from a single lock to multiple processor-specific locks, significant performance benefits are achieved by eliminating the memory bus traffic associated with caching a single lock to multiple processors.

Owner:IBM CORP

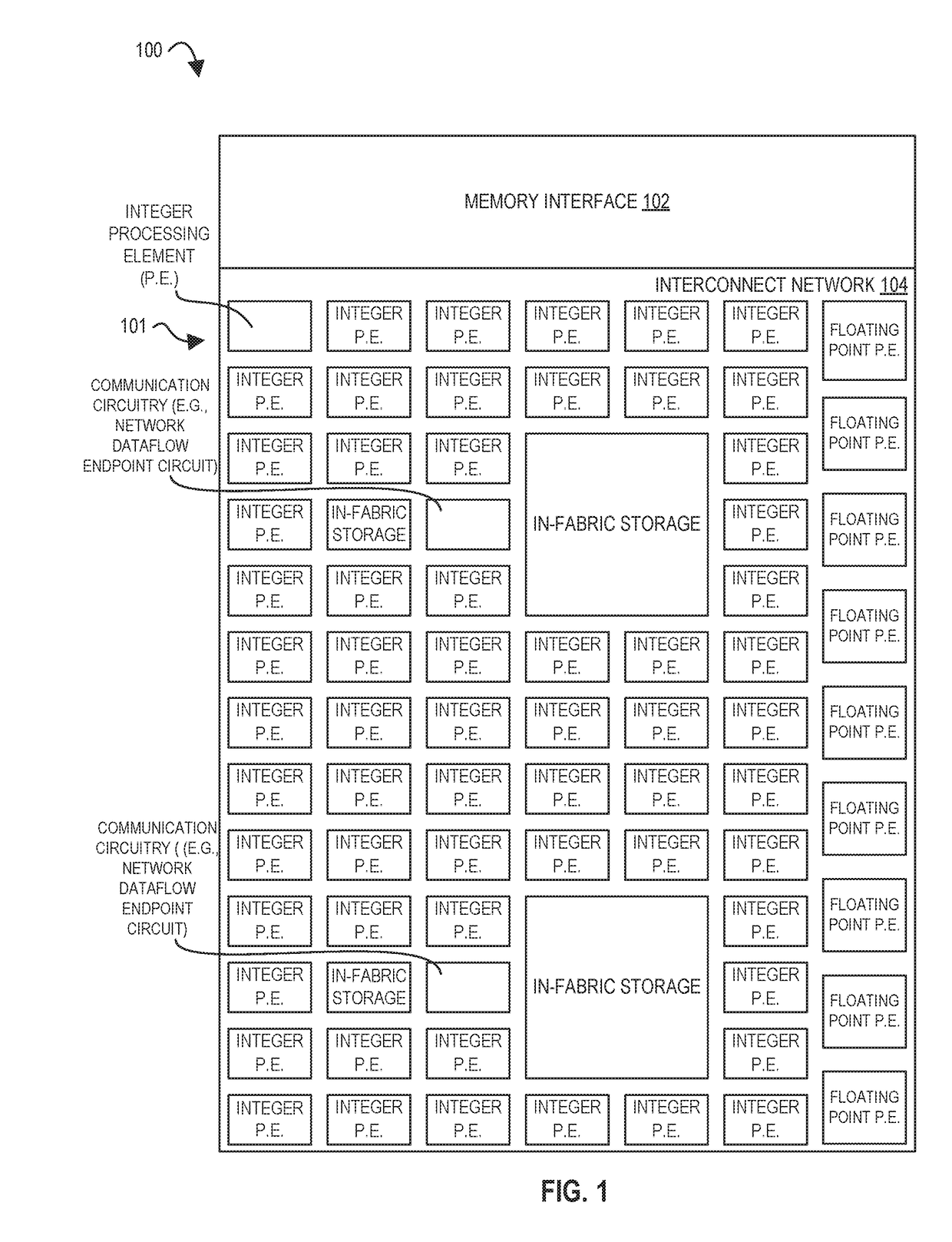

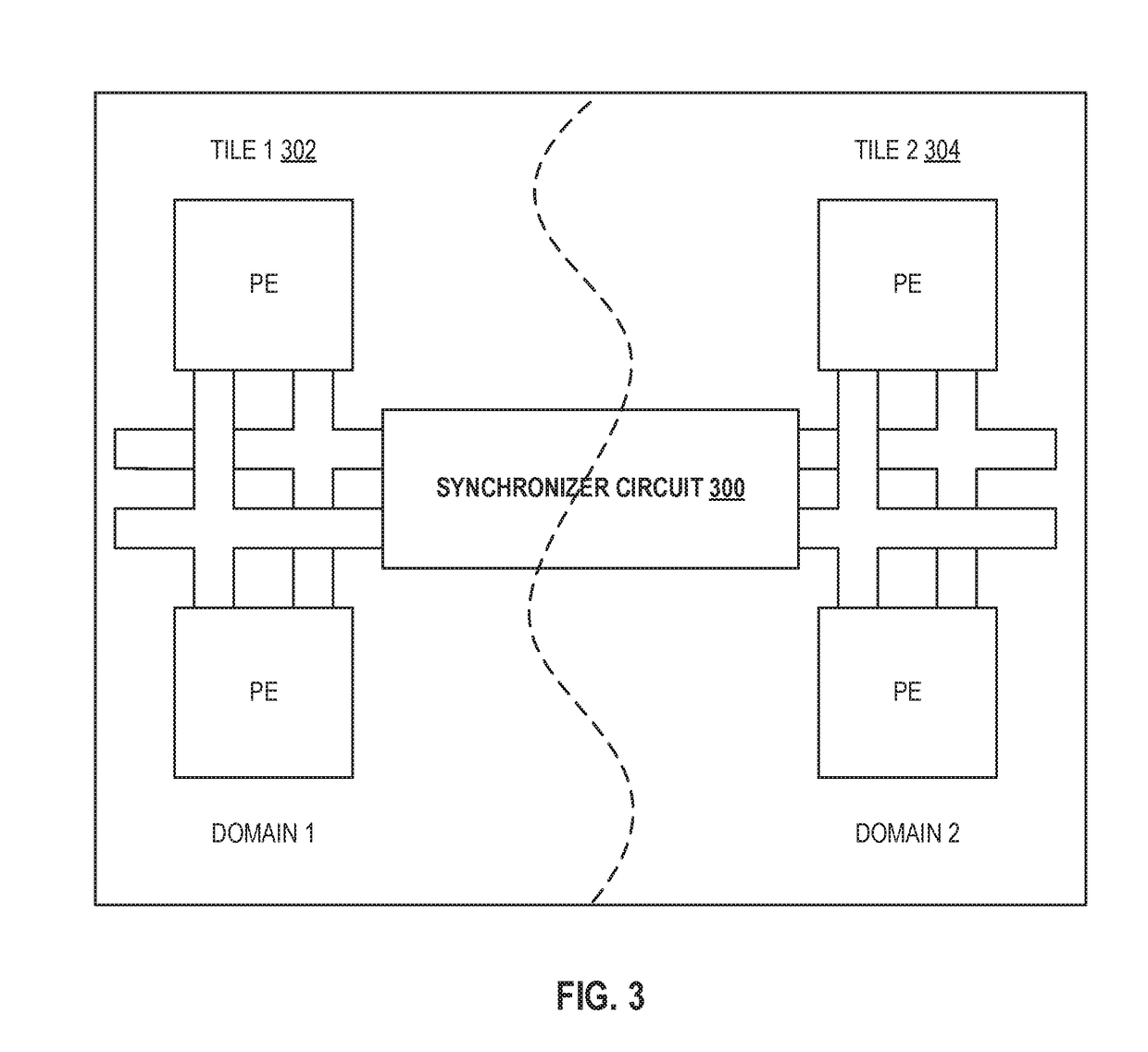

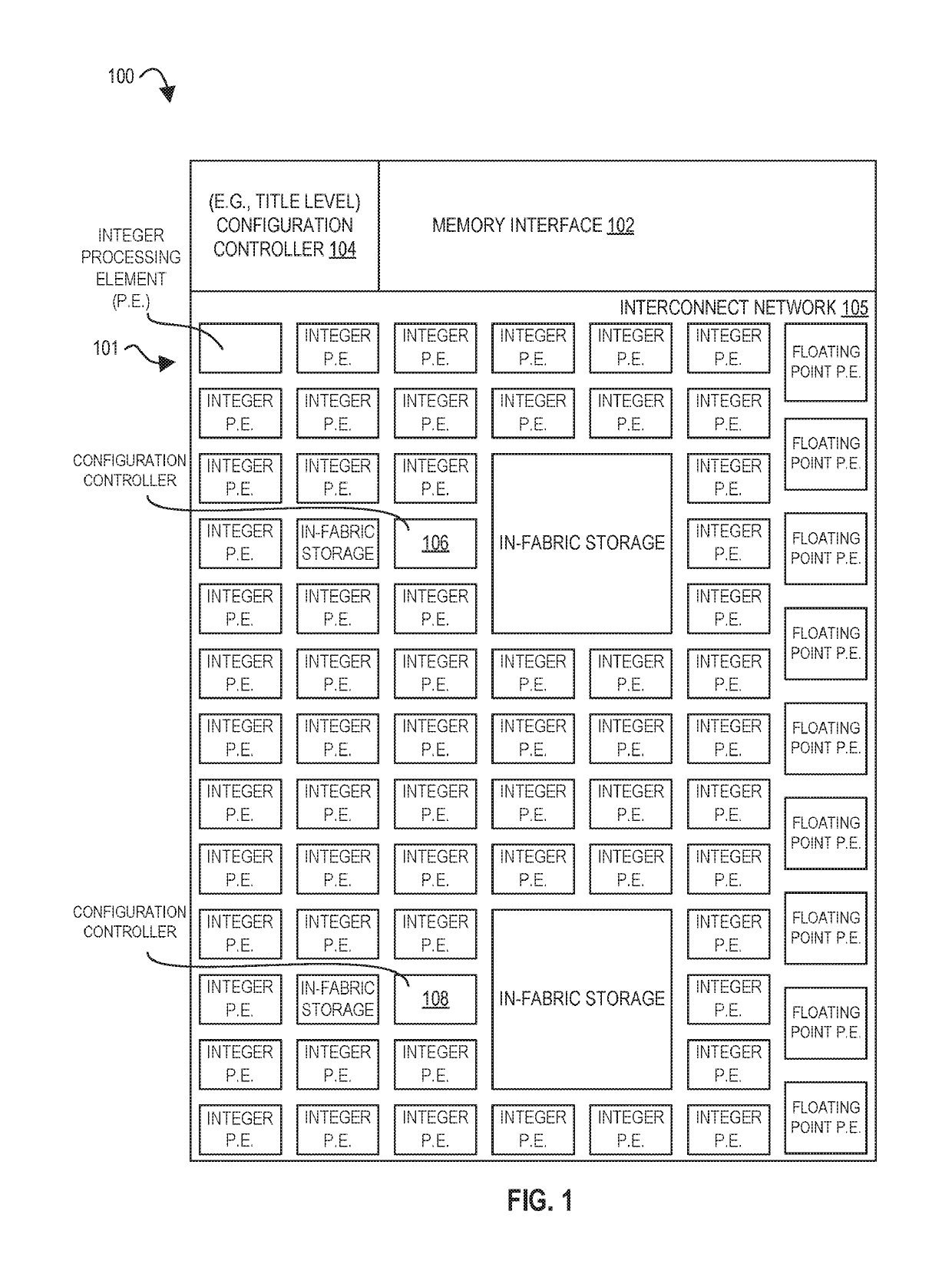

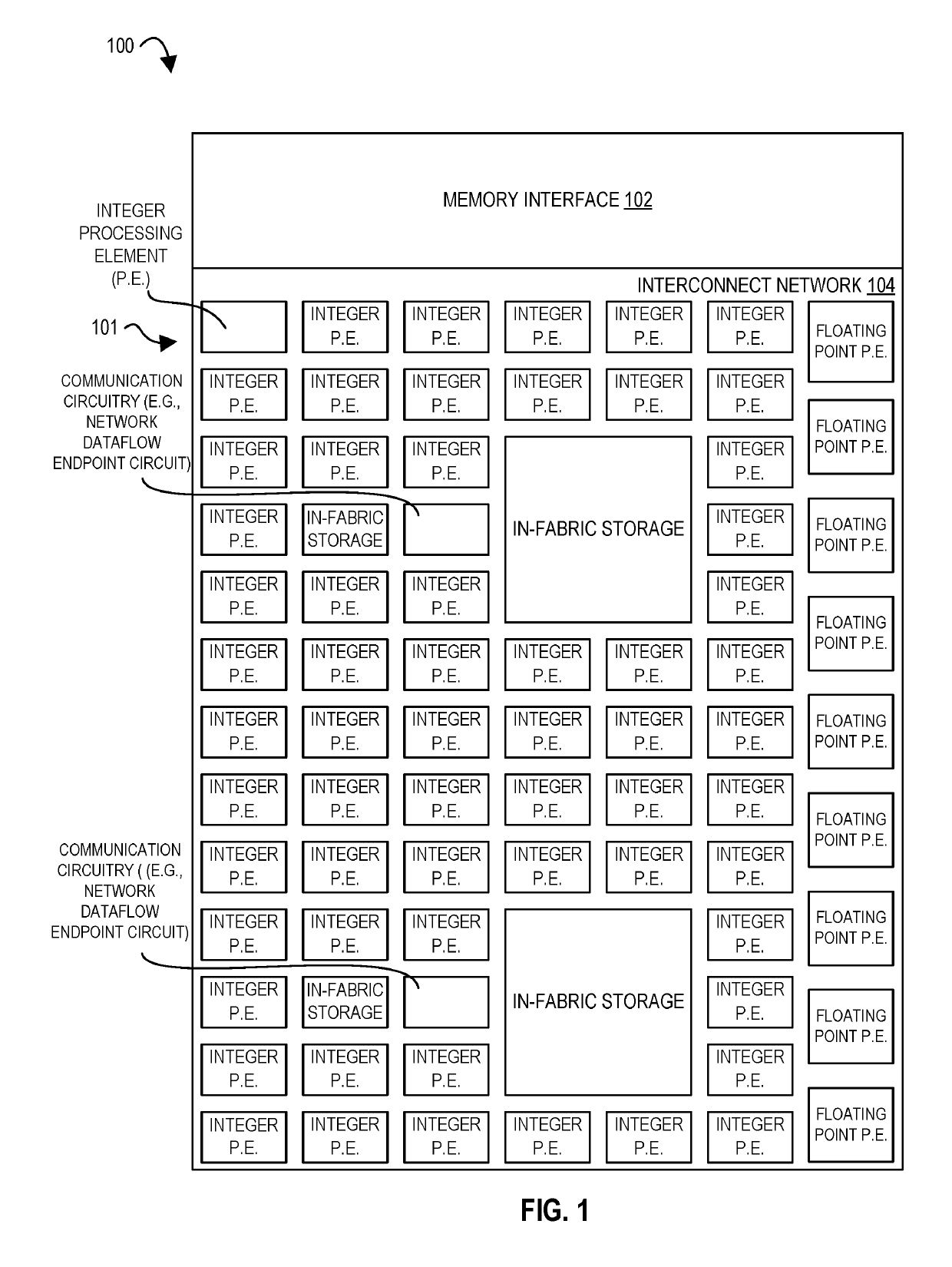

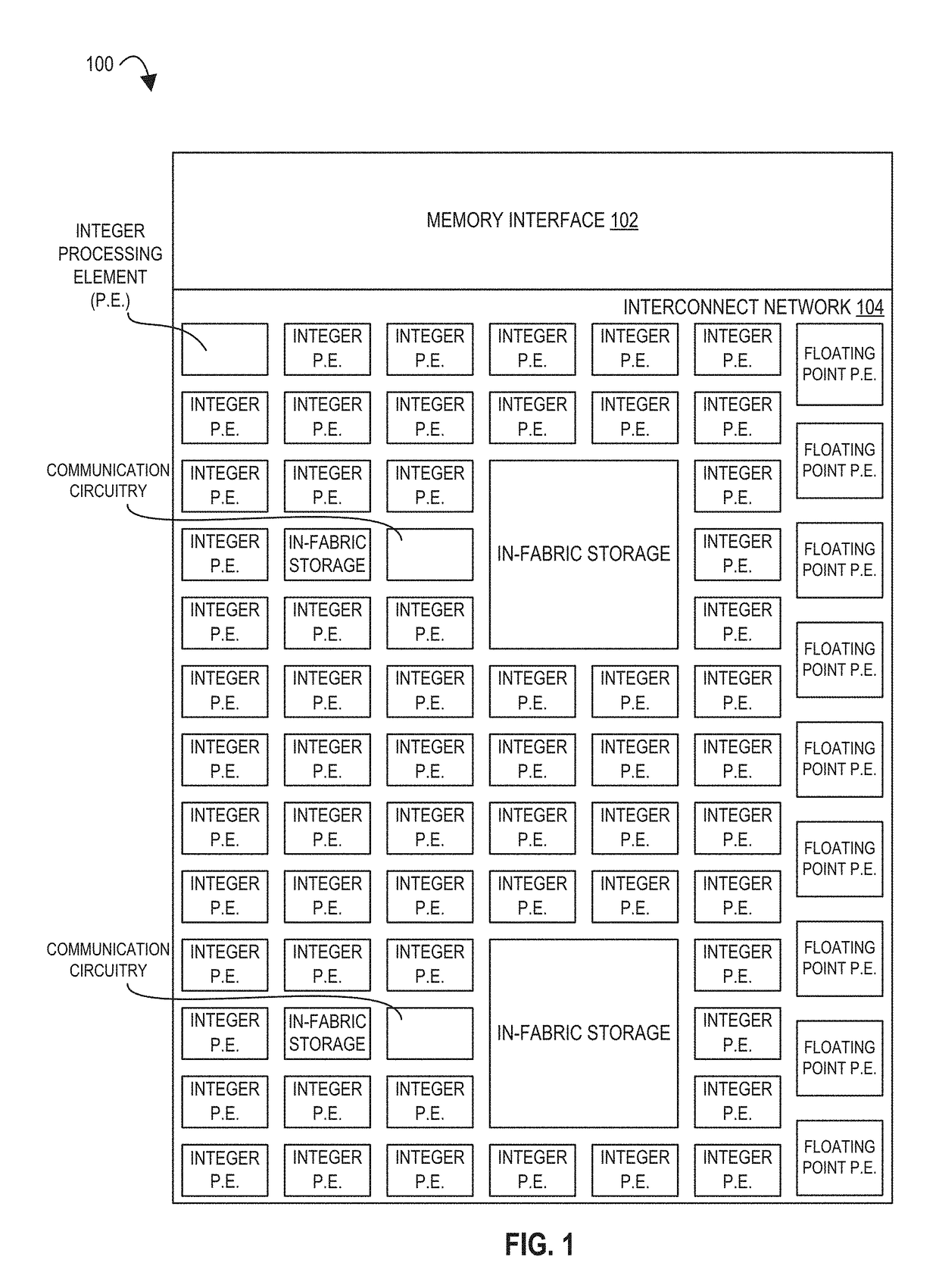

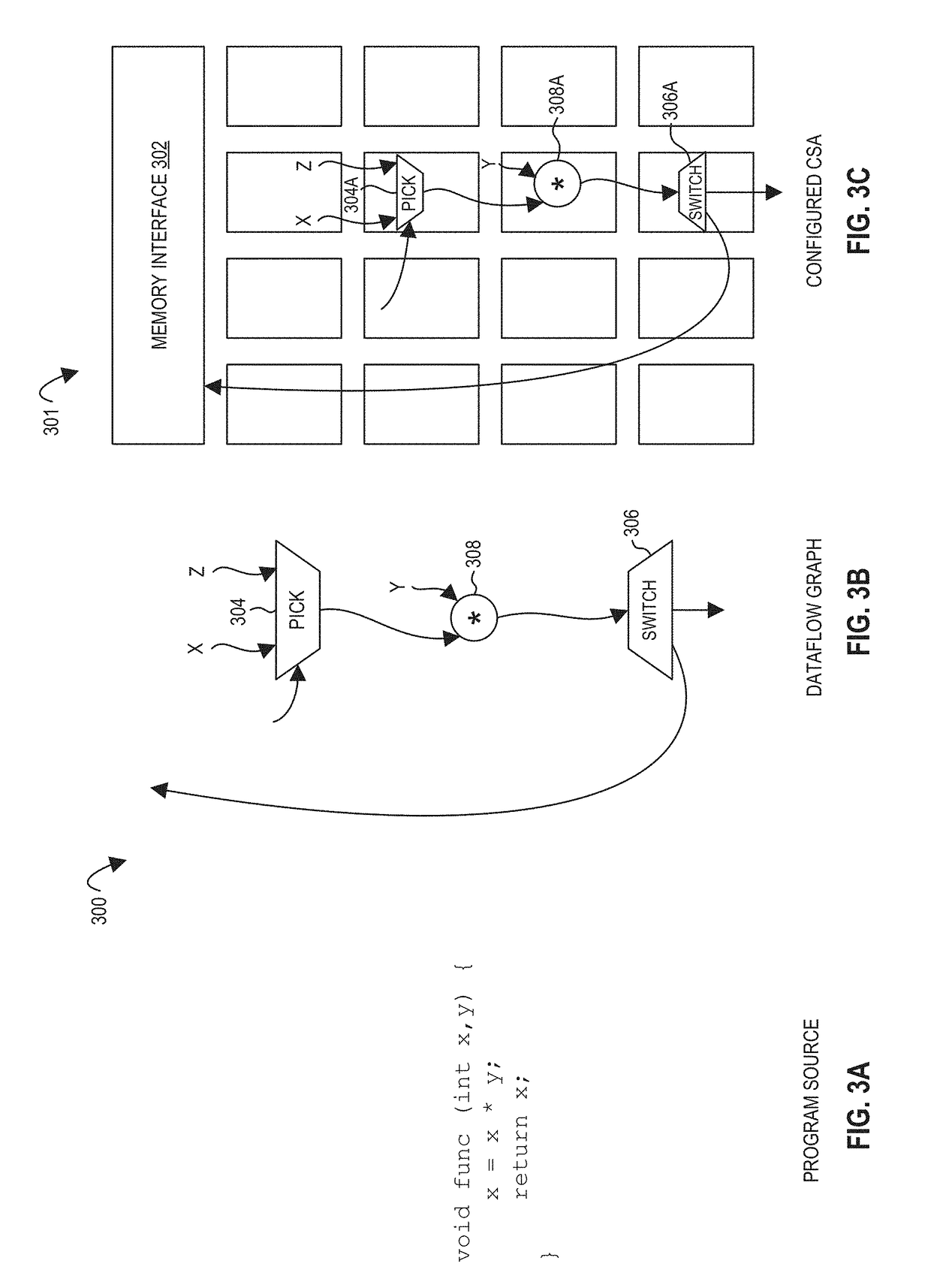

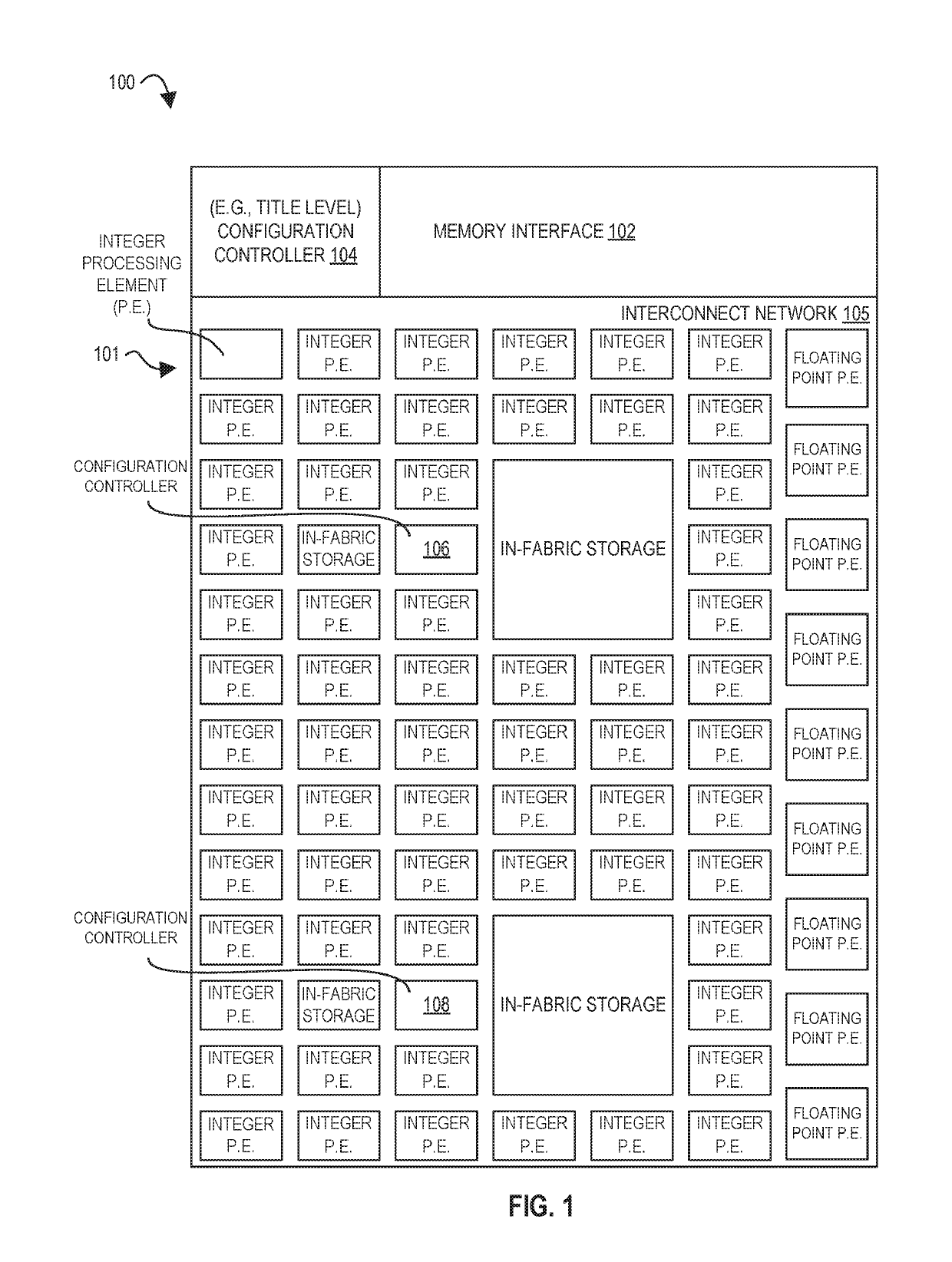

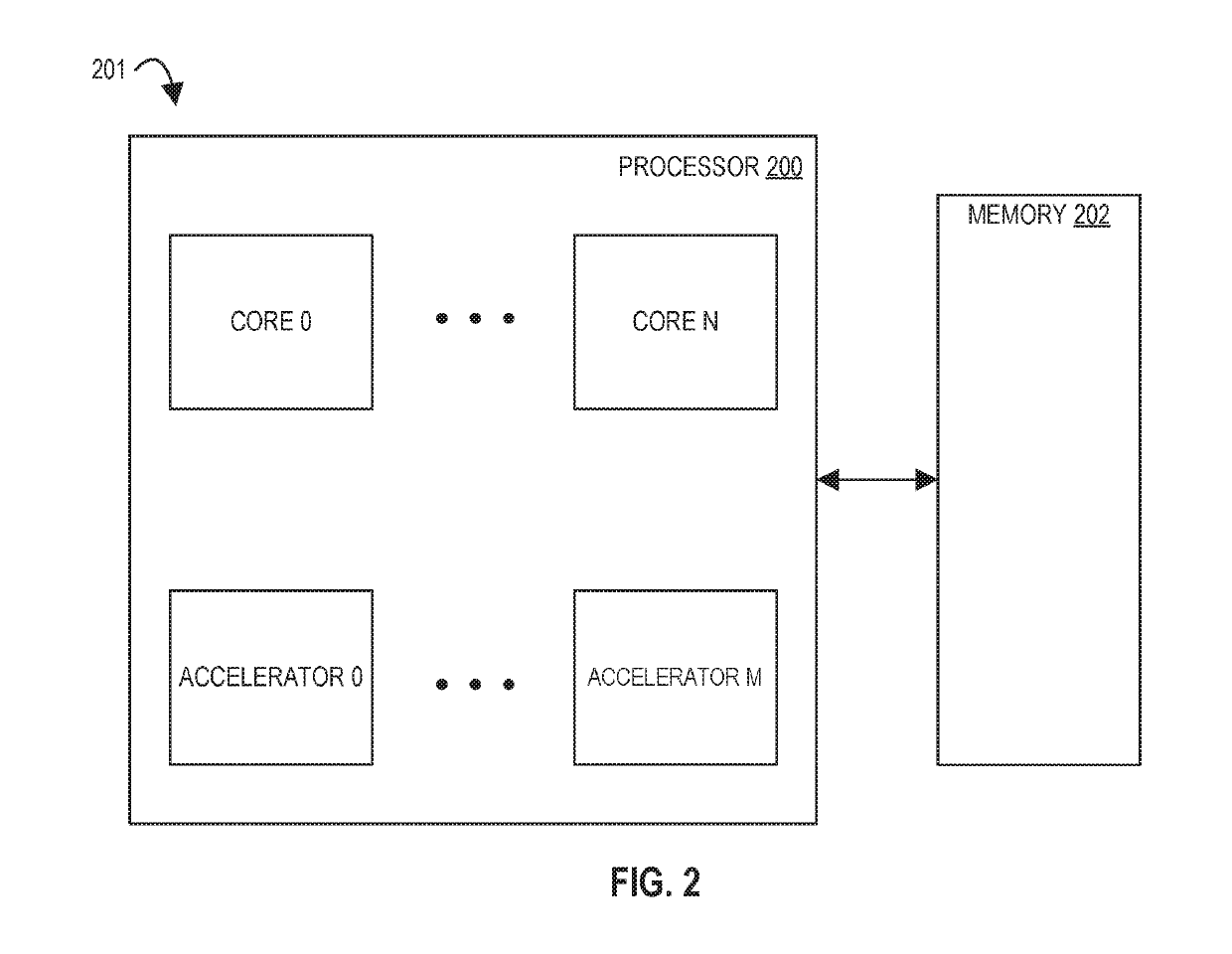

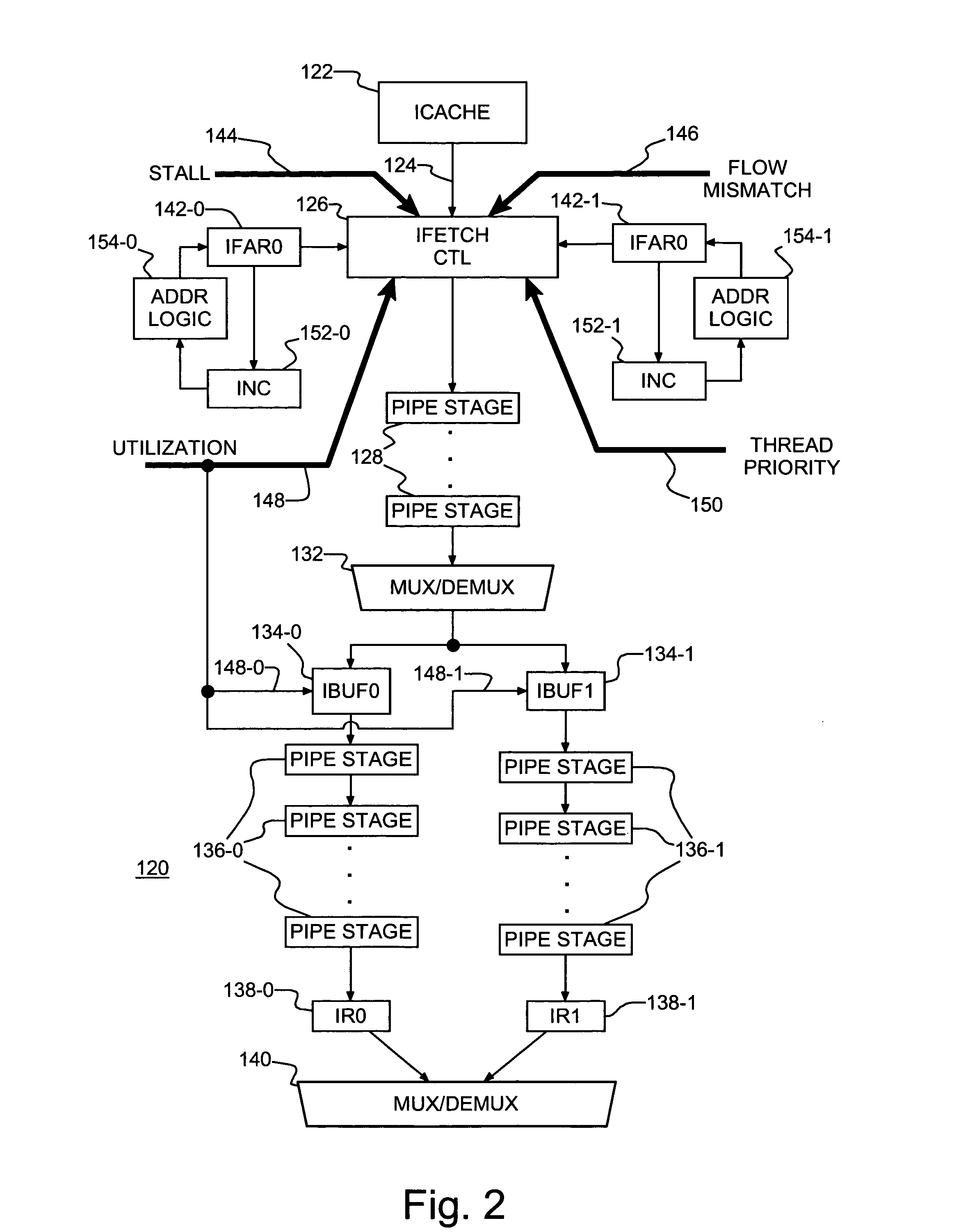

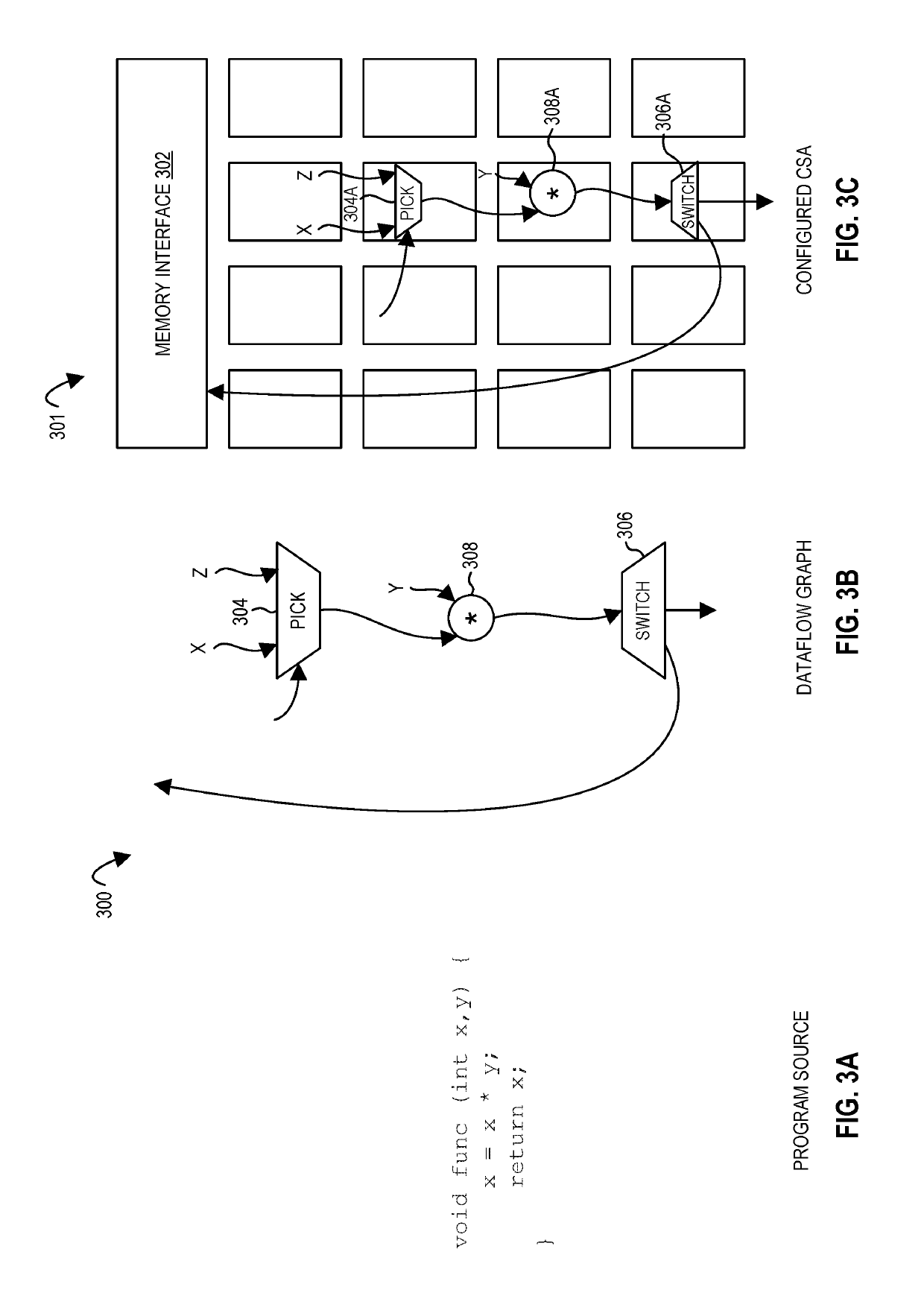

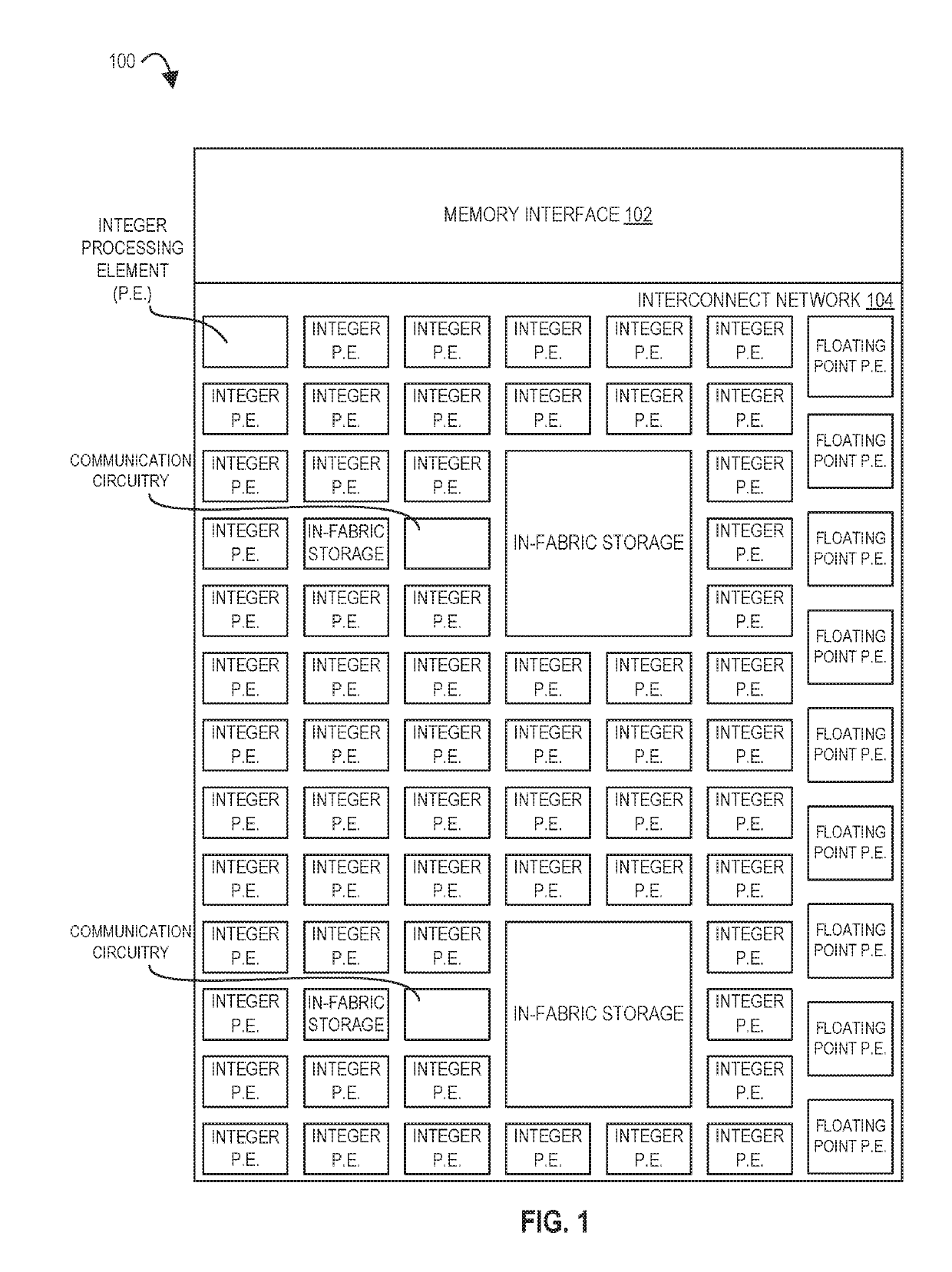

Processors, methods, and systems with a configurable spatial accelerator

ActiveUS20190018815A1Easy to adaptImprove performanceDataflow computersResource allocationComputer scienceVoltage

Systems, methods, and apparatuses relating to a configurable spatial accelerator are described. In one embodiment, a processor includes a synchronizer circuit coupled between an interconnect network of a first tile and an interconnect network of a second tile and comprising storage to store data to be sent between the interconnect network of the first tile and the interconnect network of the second tile, the synchronizer circuit to convert the data from the storage between a first voltage or a first frequency of the first tile and a second voltage or a second frequency of the second tile to generate converted data, and send the converted data between the interconnect network of the first tile and the interconnect network of the second tile

Owner:INTEL CORP

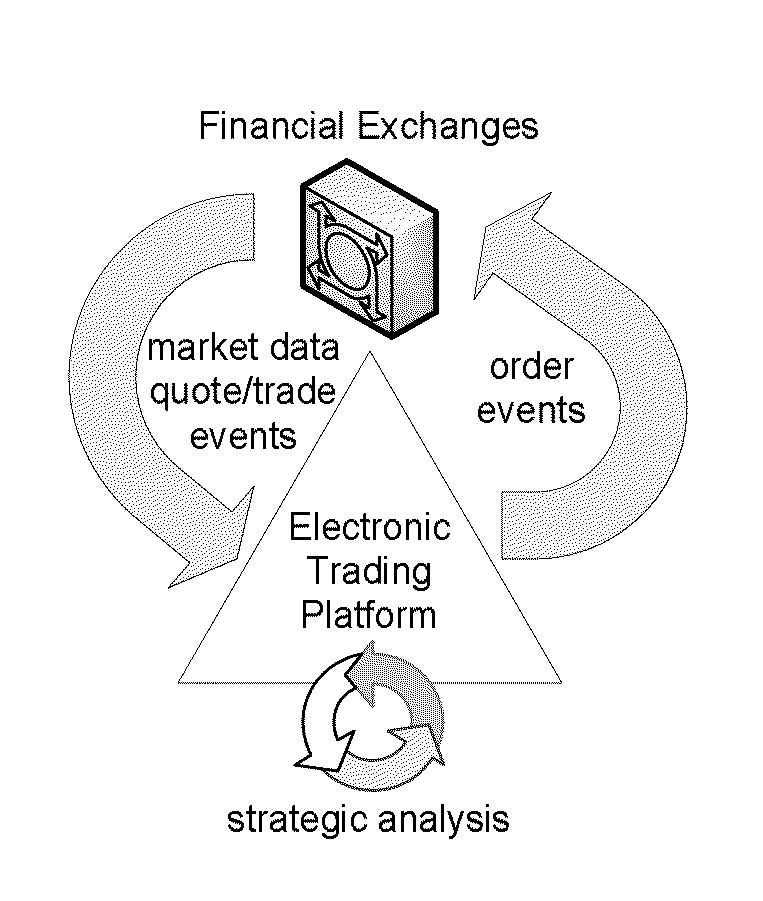

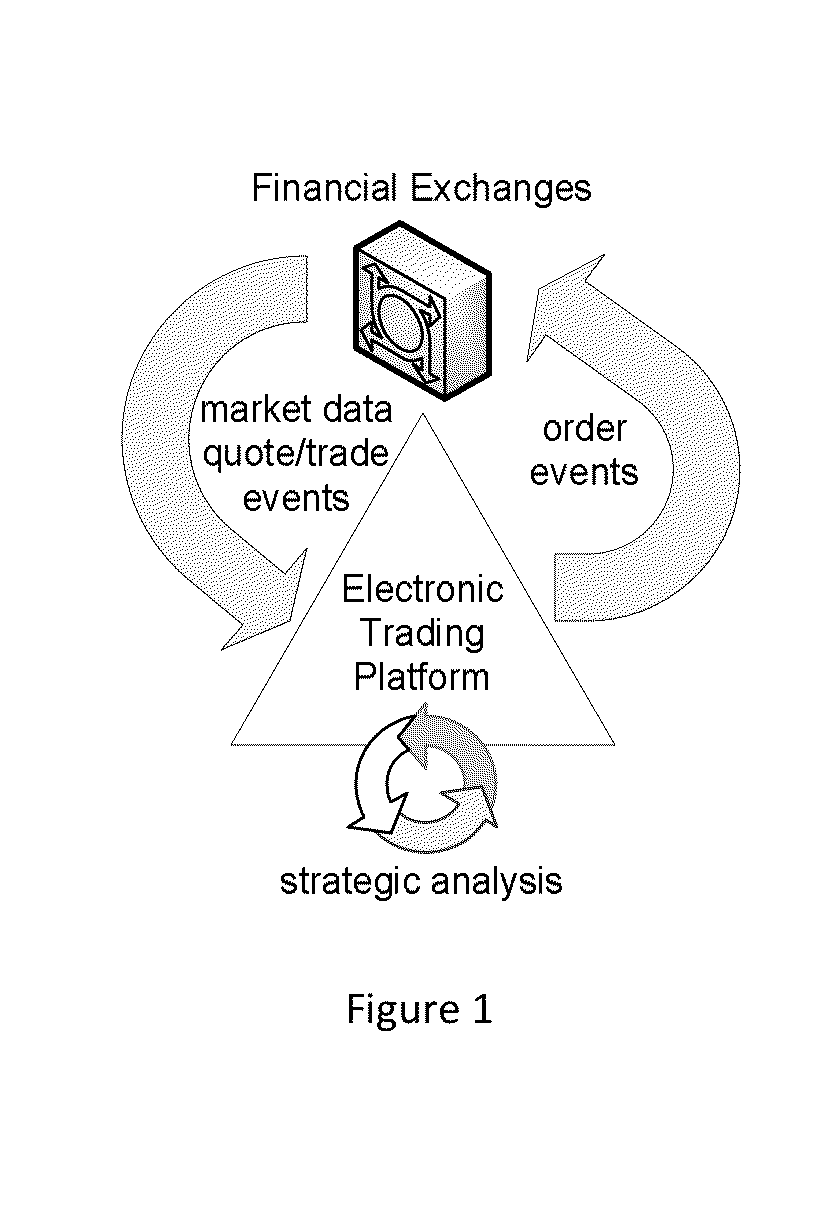

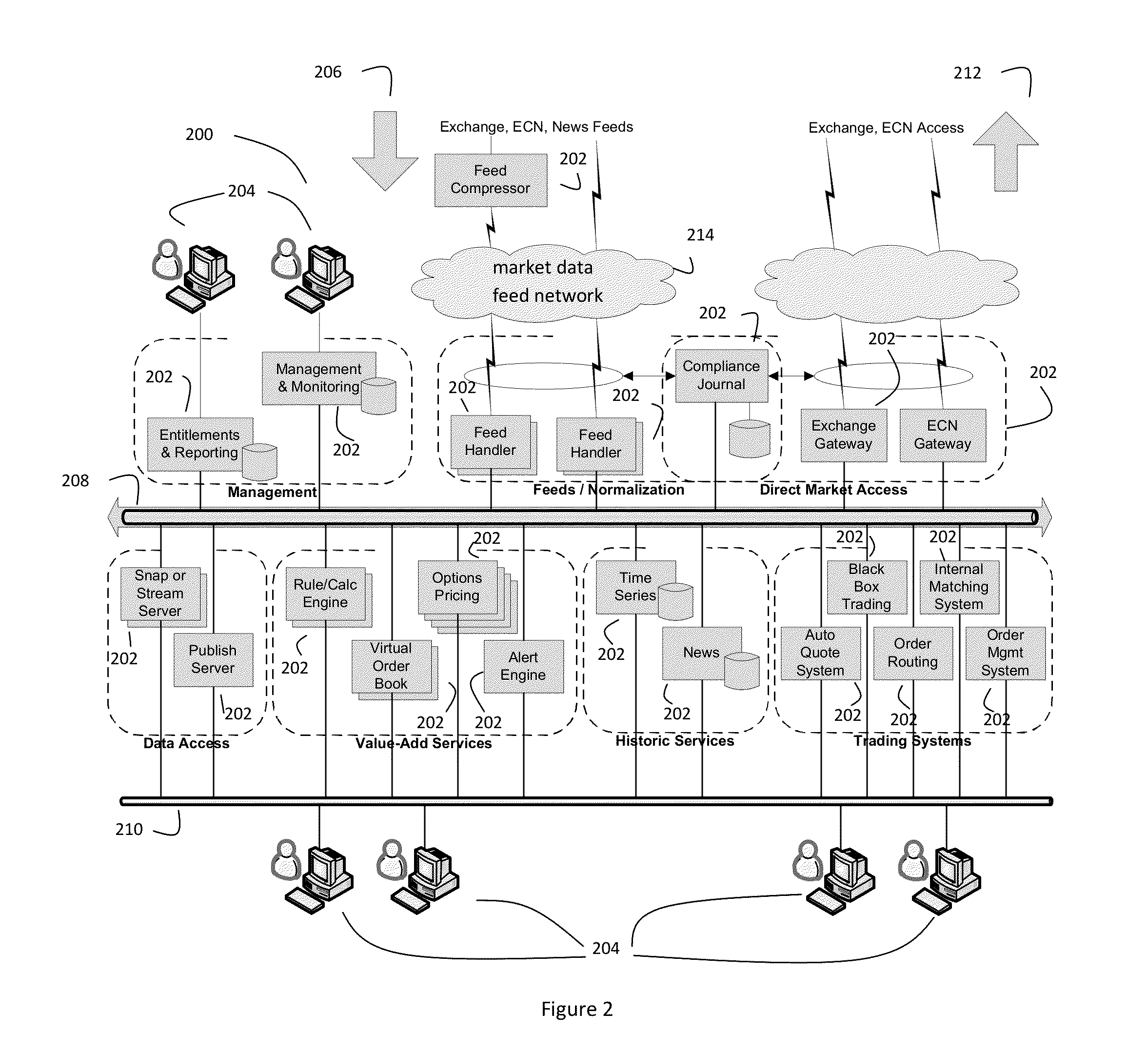

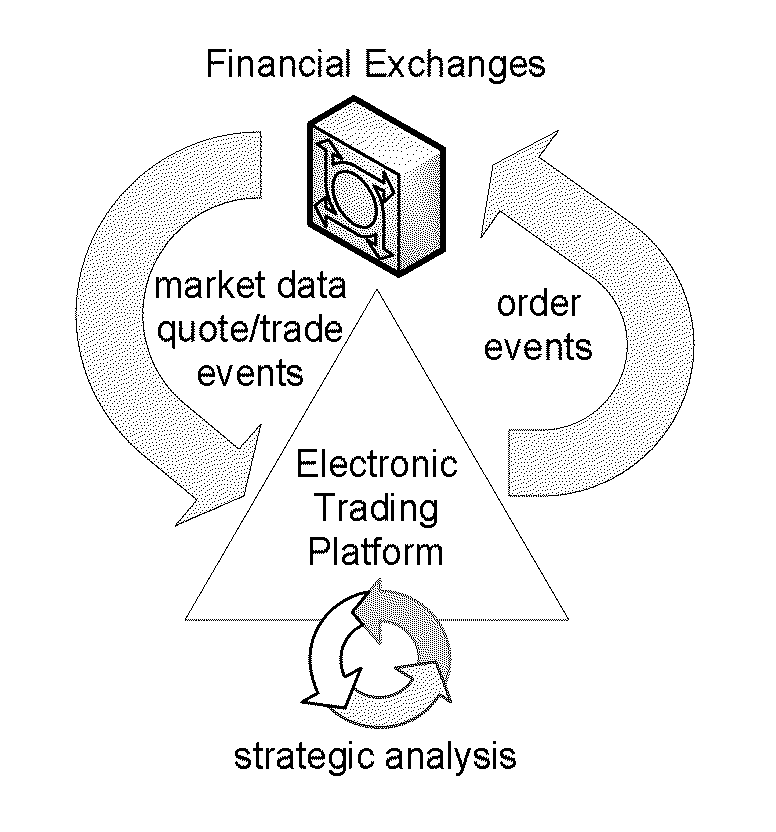

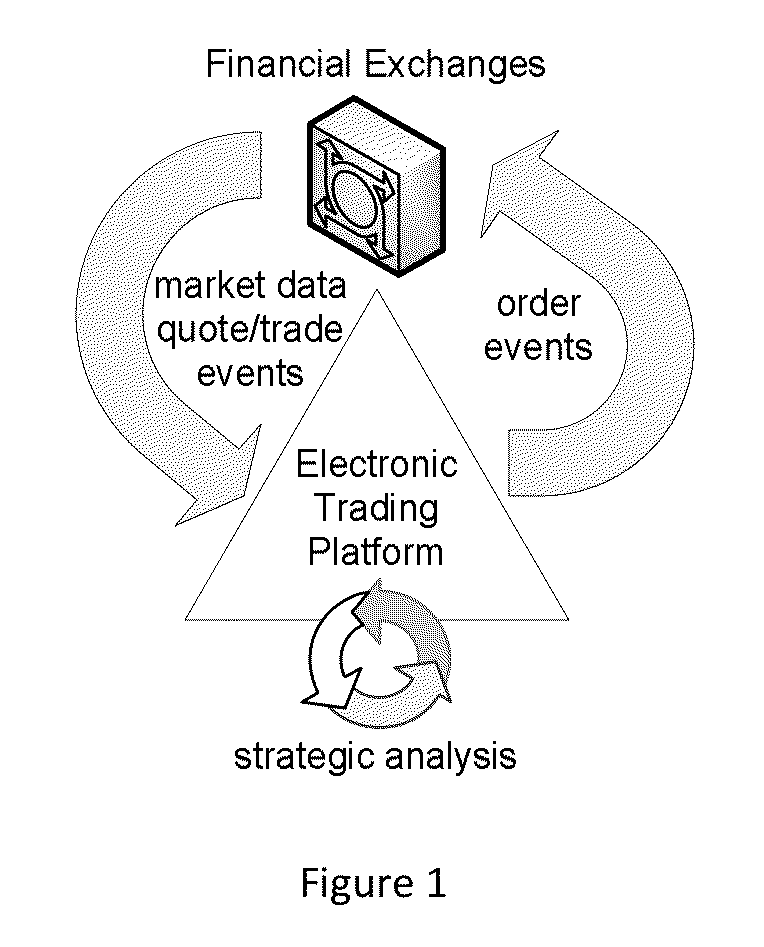

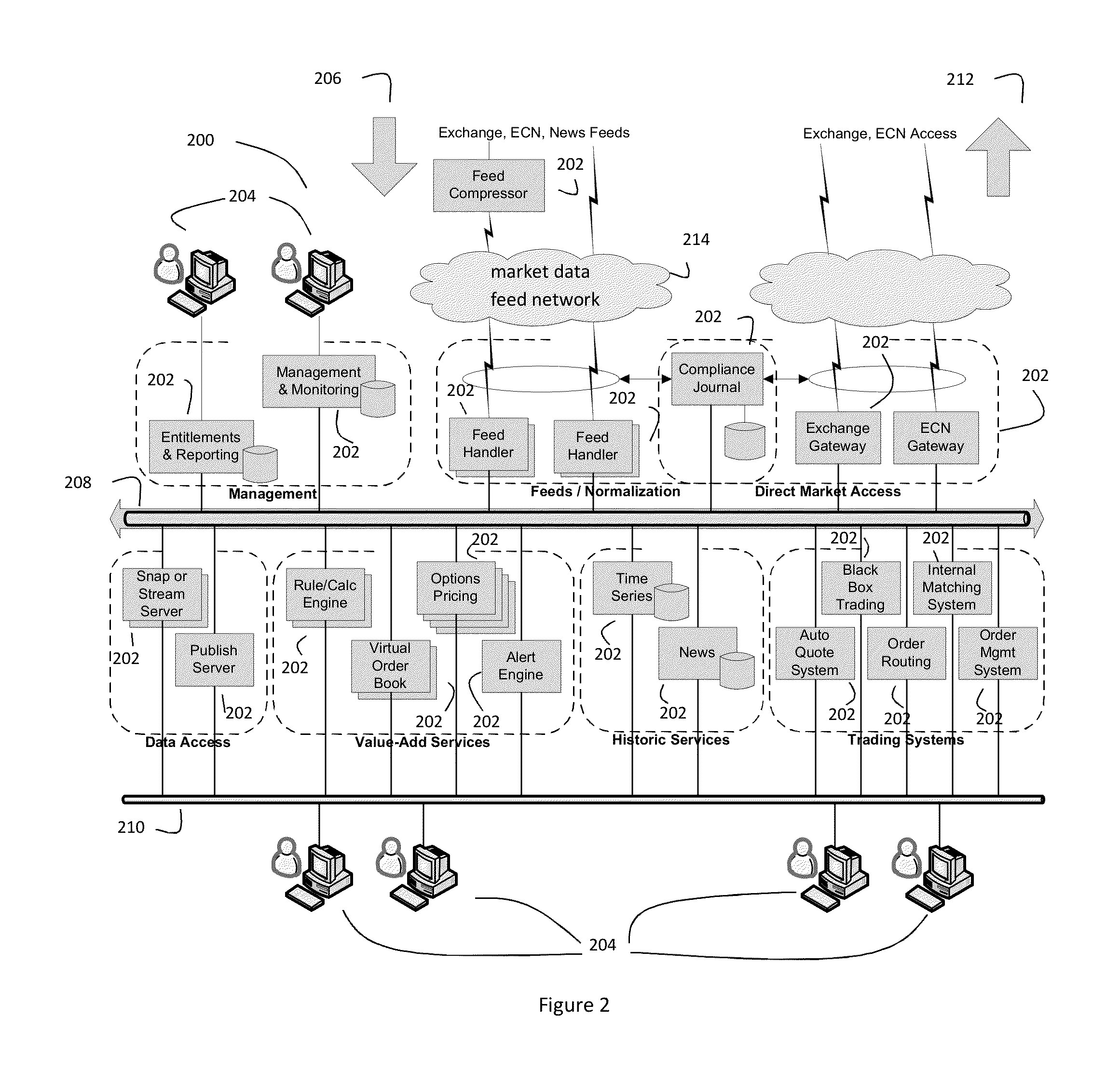

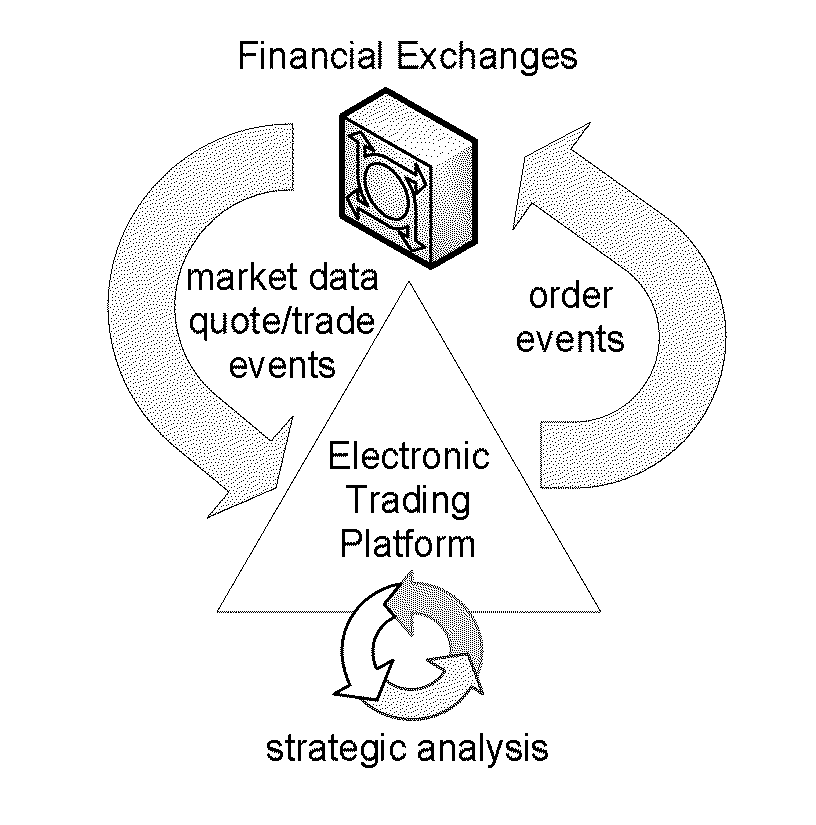

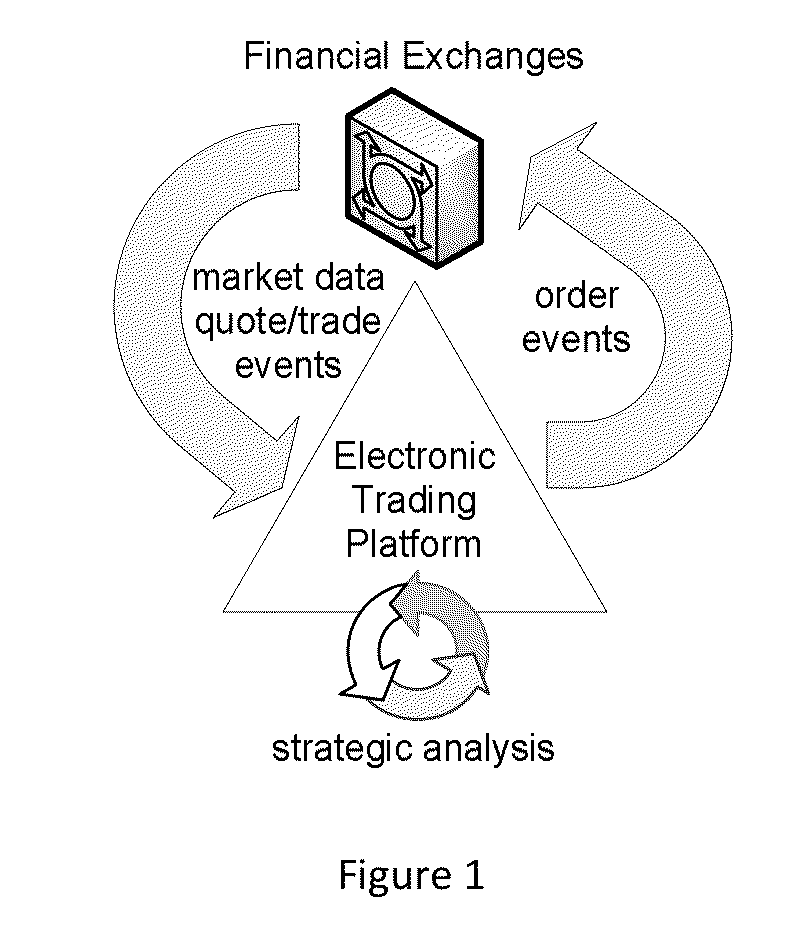

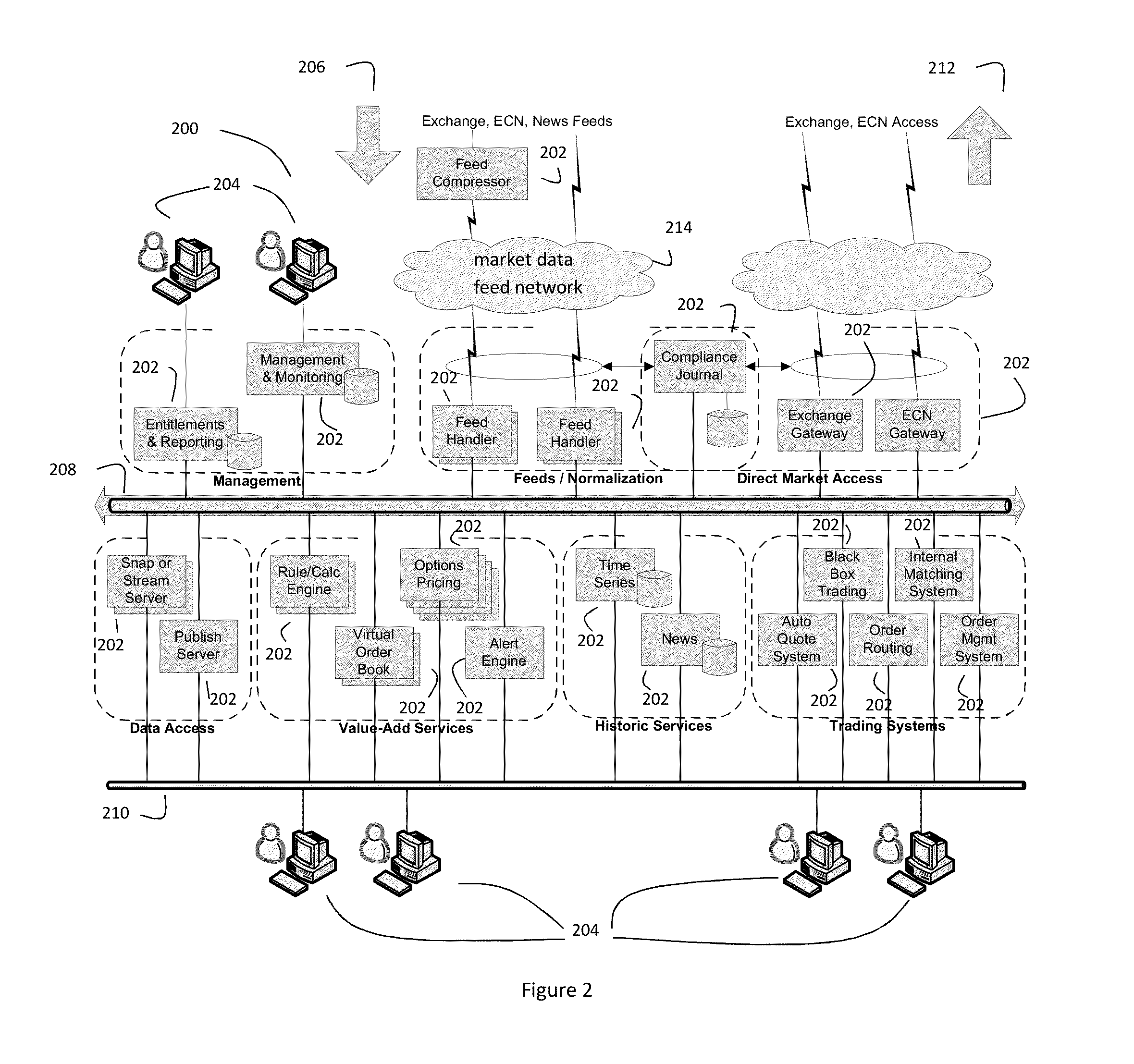

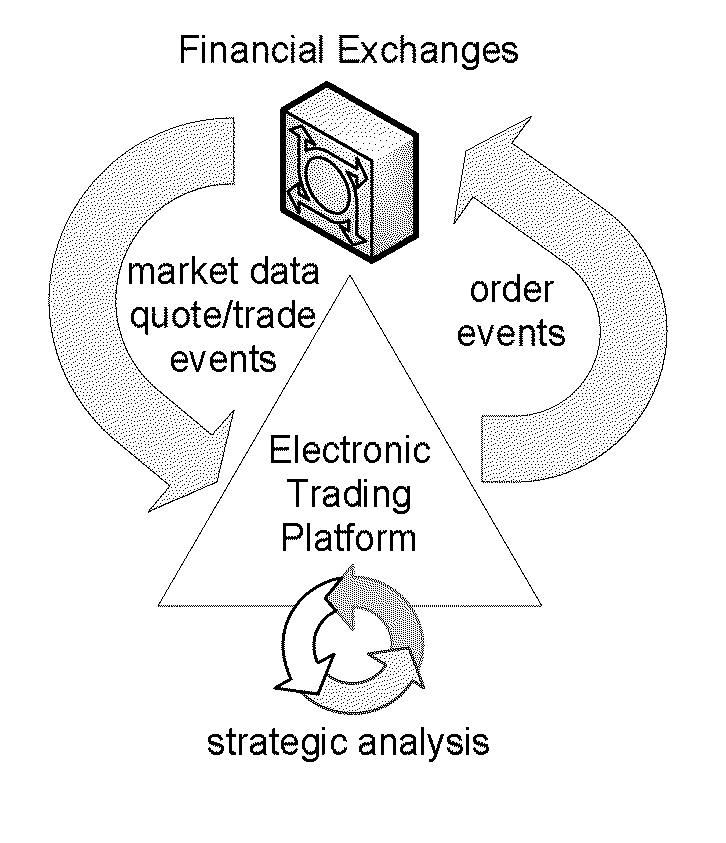

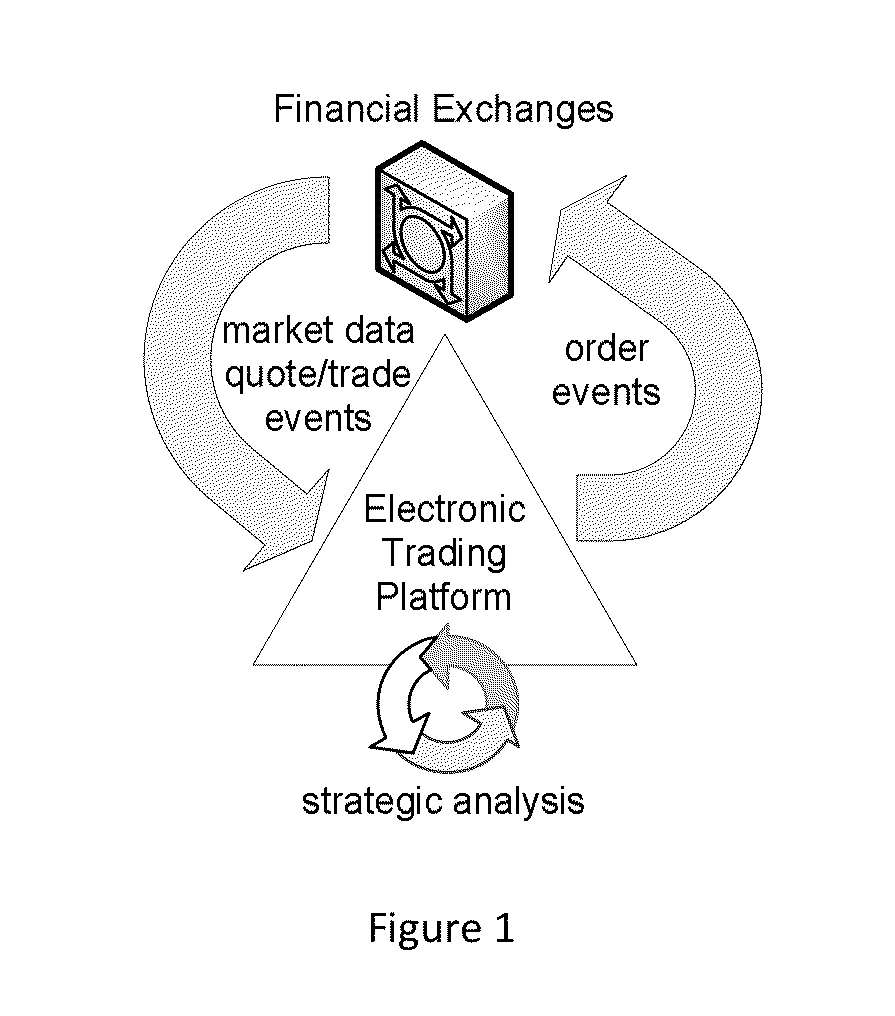

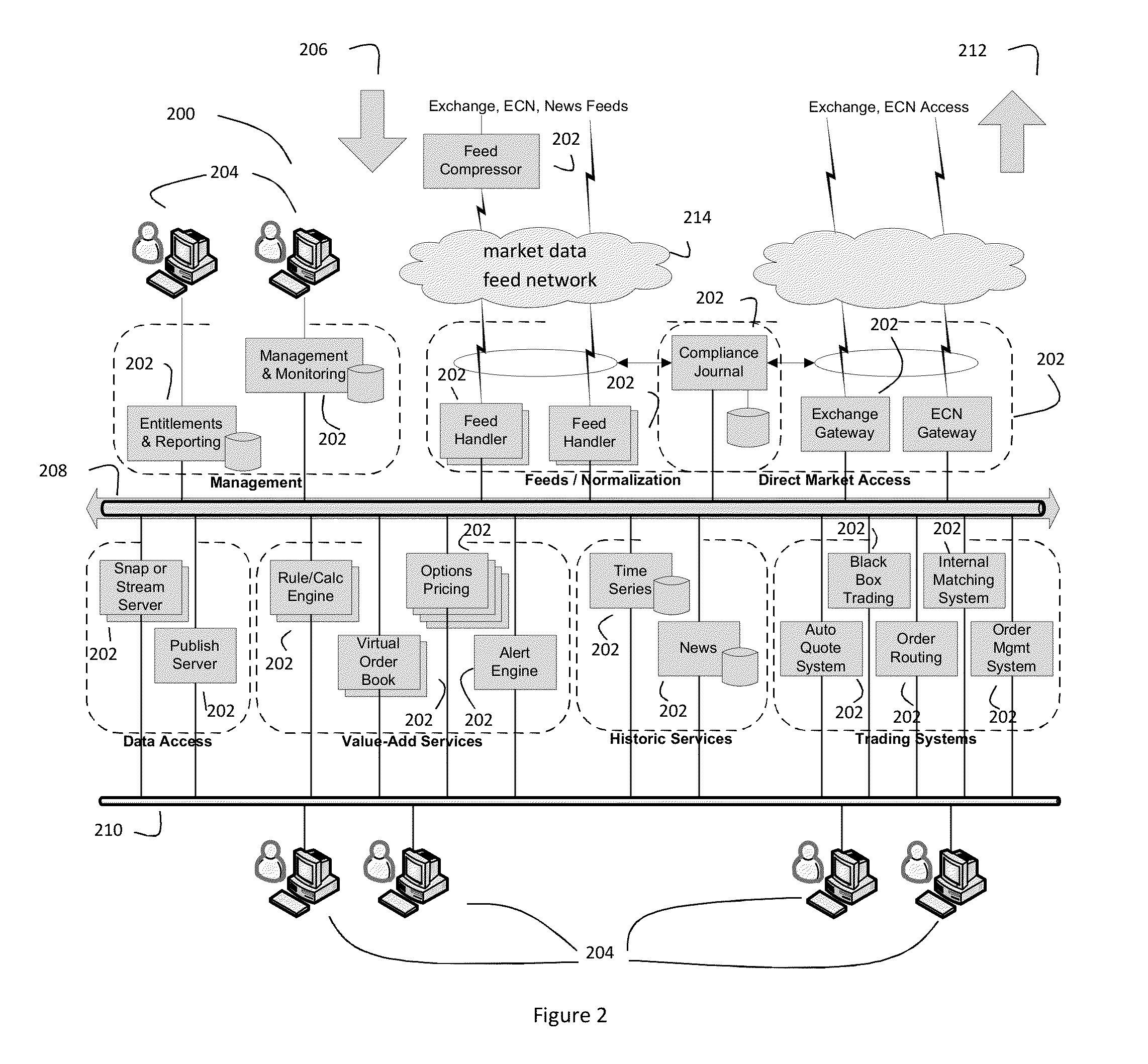

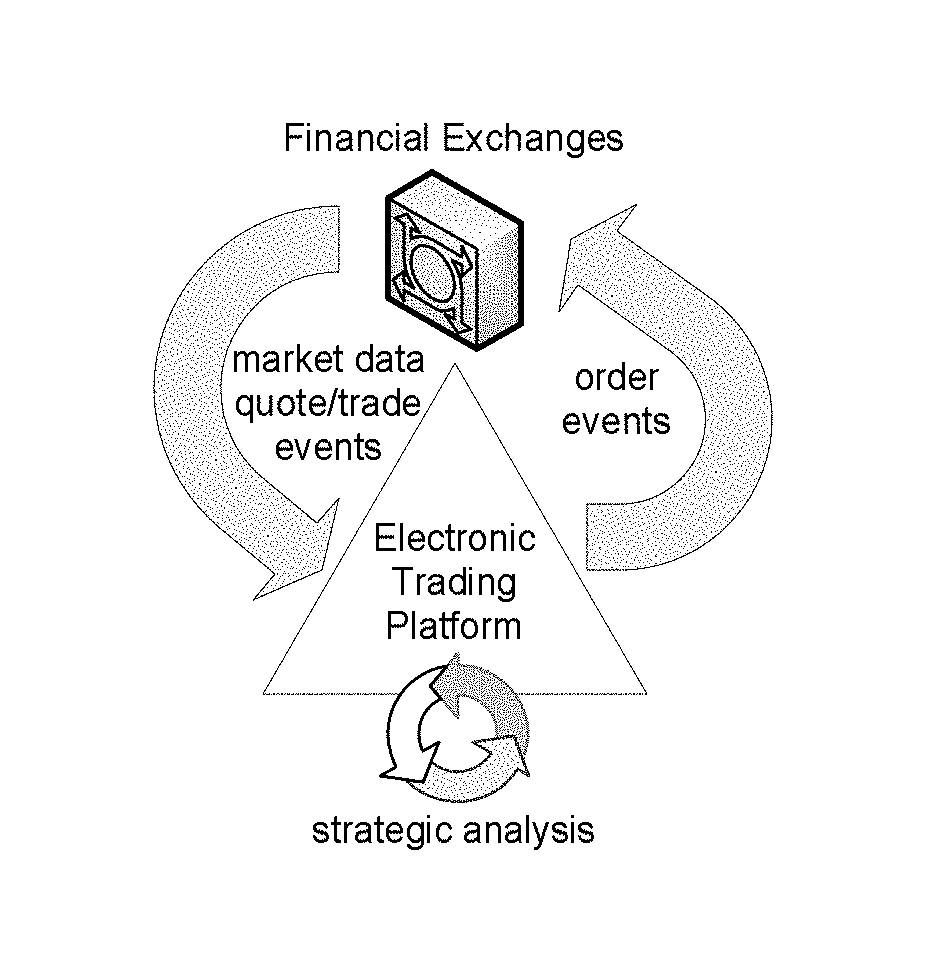

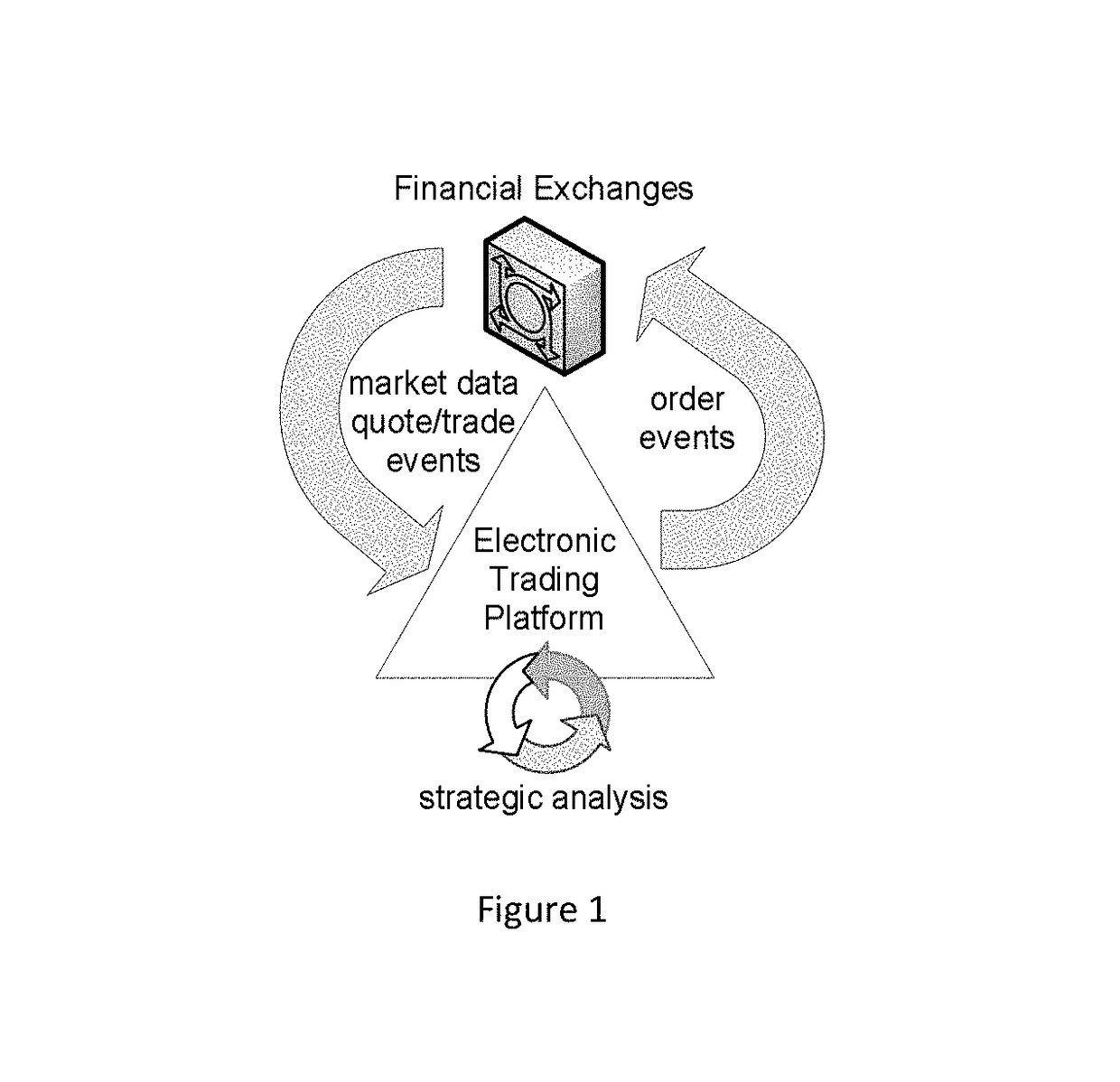

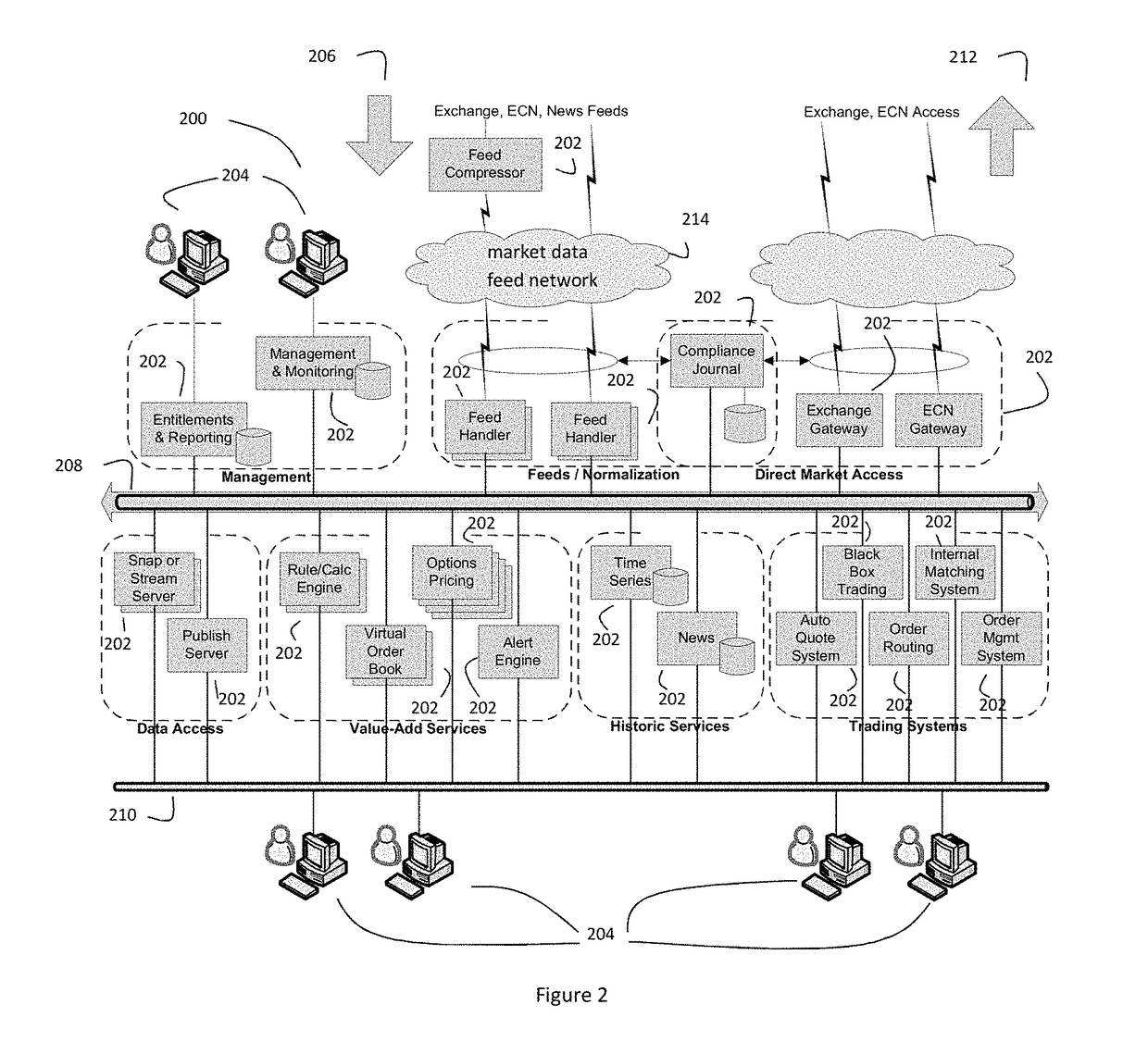

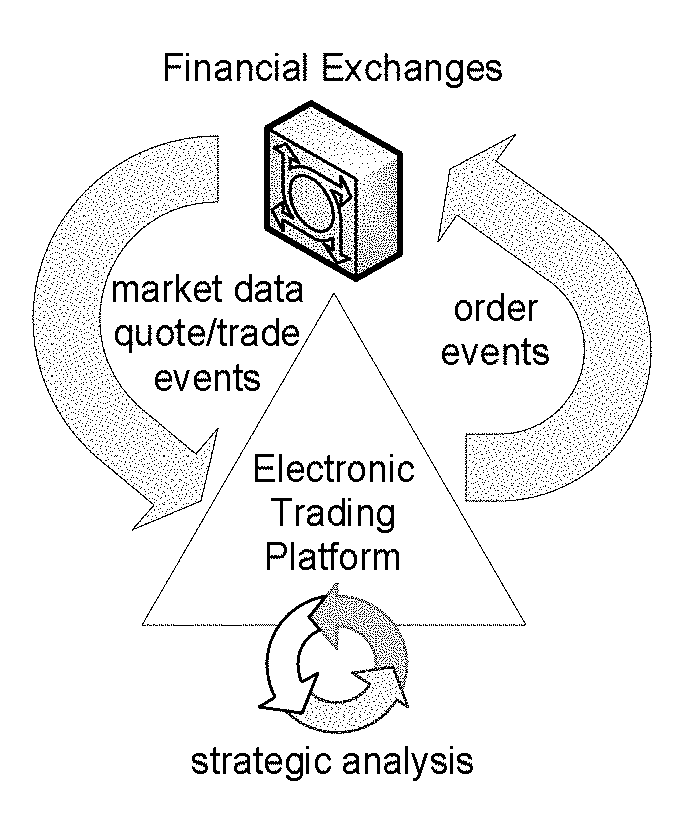

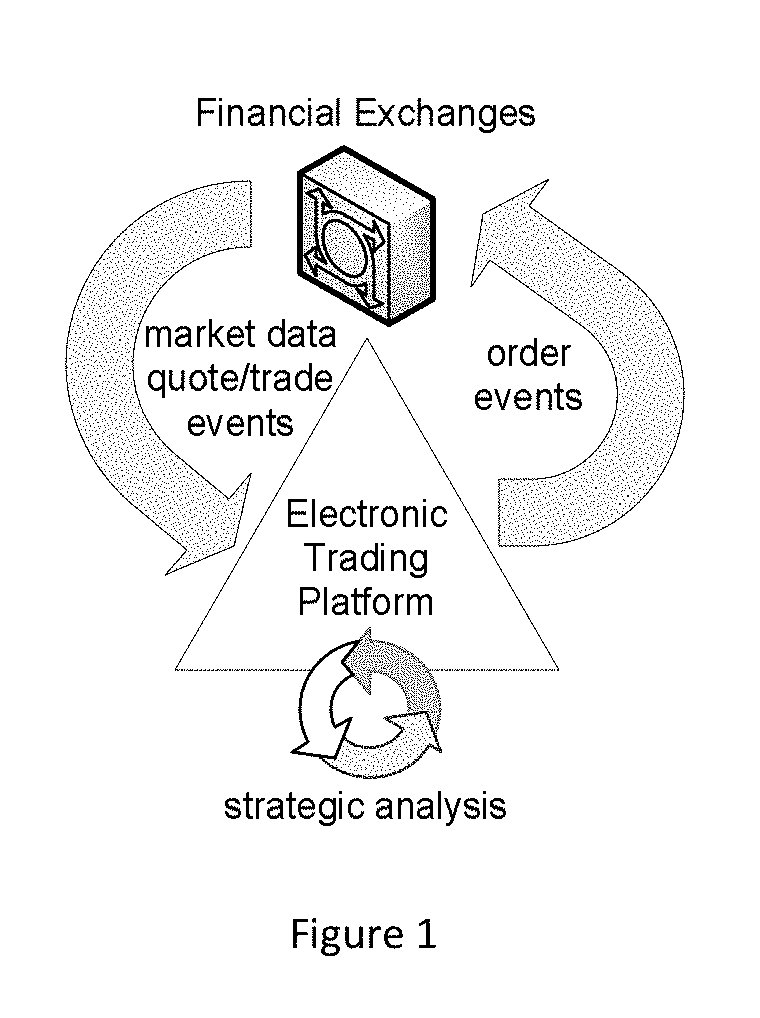

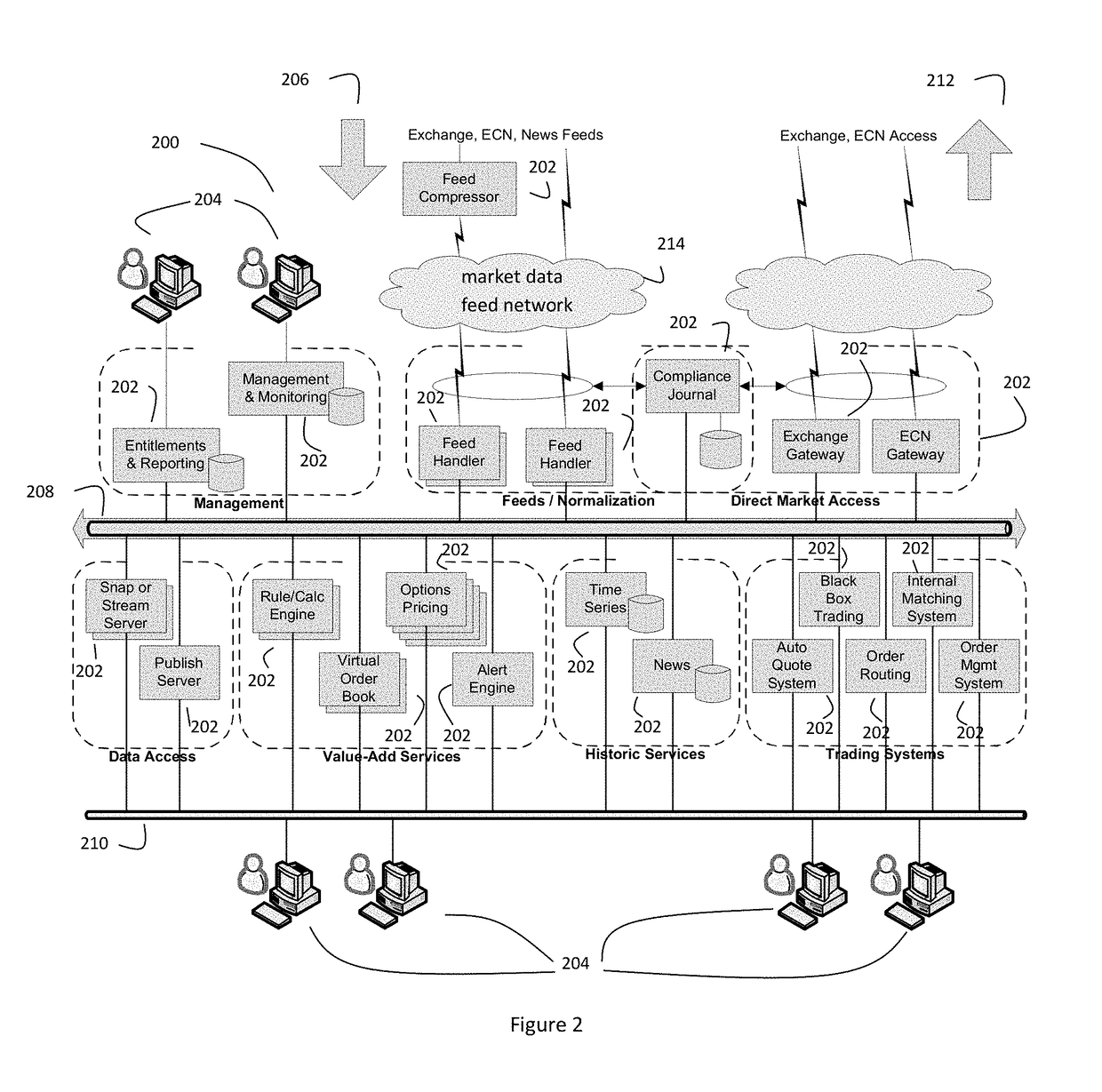

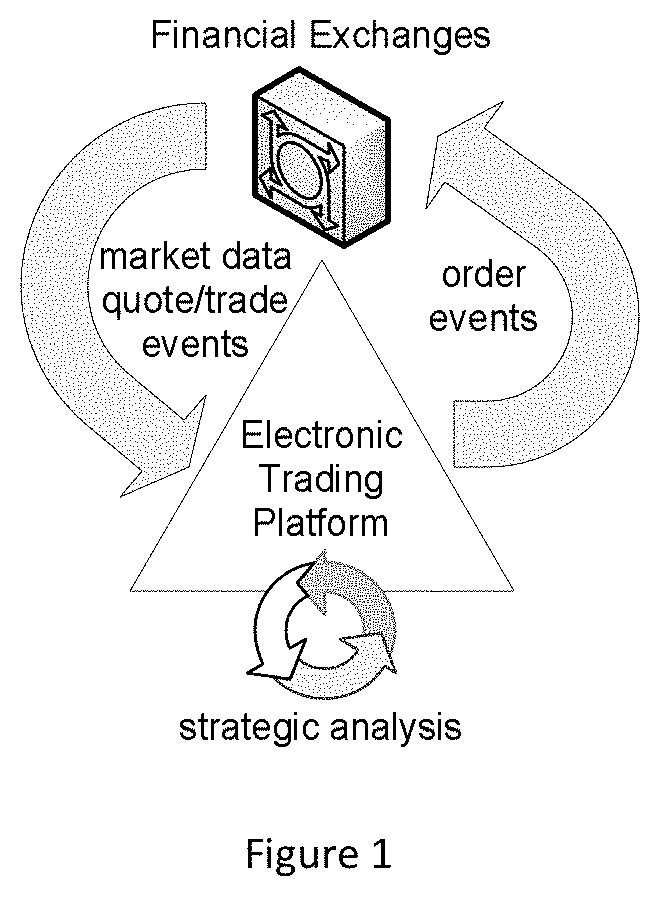

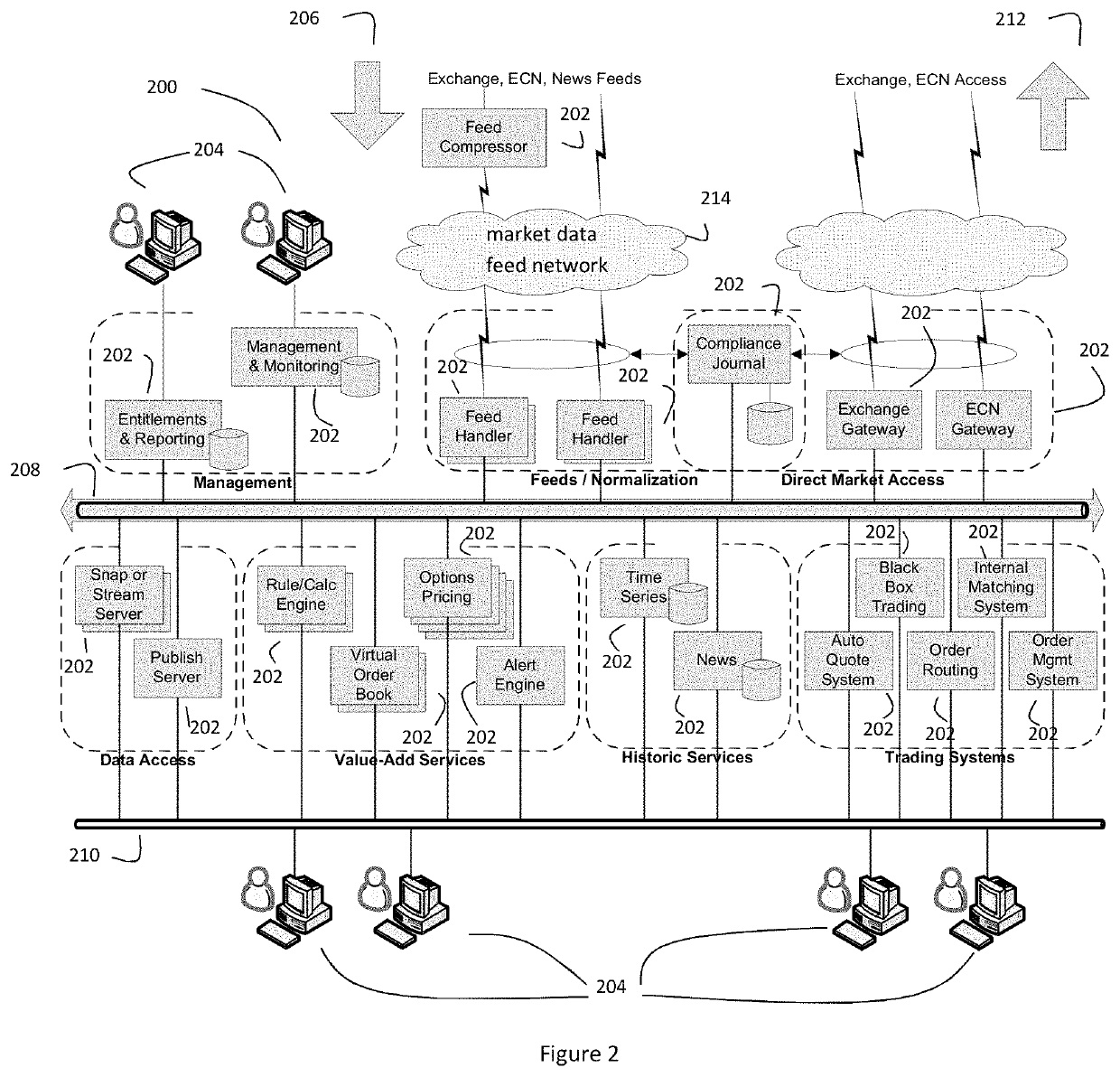

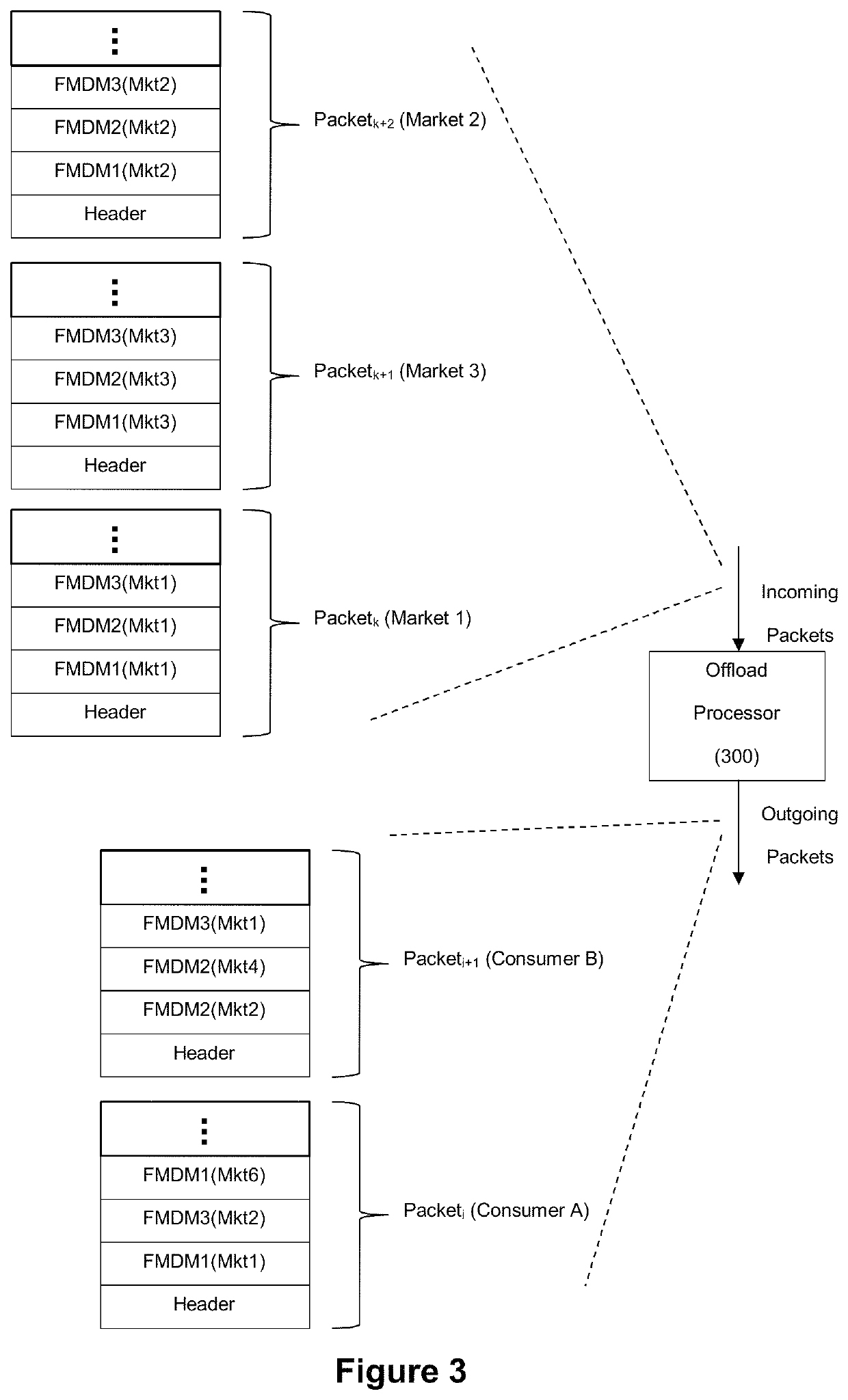

Offload Processing of Data Packets Containing Financial Market Data

Various techniques are disclosed for offloading the processing of data packets that contain financial market data. For example, incoming data packets can be processed through an offload processor to generate a new stream of outgoing data packets that organize financial market data in a manner different than the incoming data packets. Furthermore, in an exemplary embodiment, the offloaded processing can be resident in an intelligent switch, such as an intelligent switch upstream or downstream from an electronic trading platform.

Owner:IP RESERVOIR

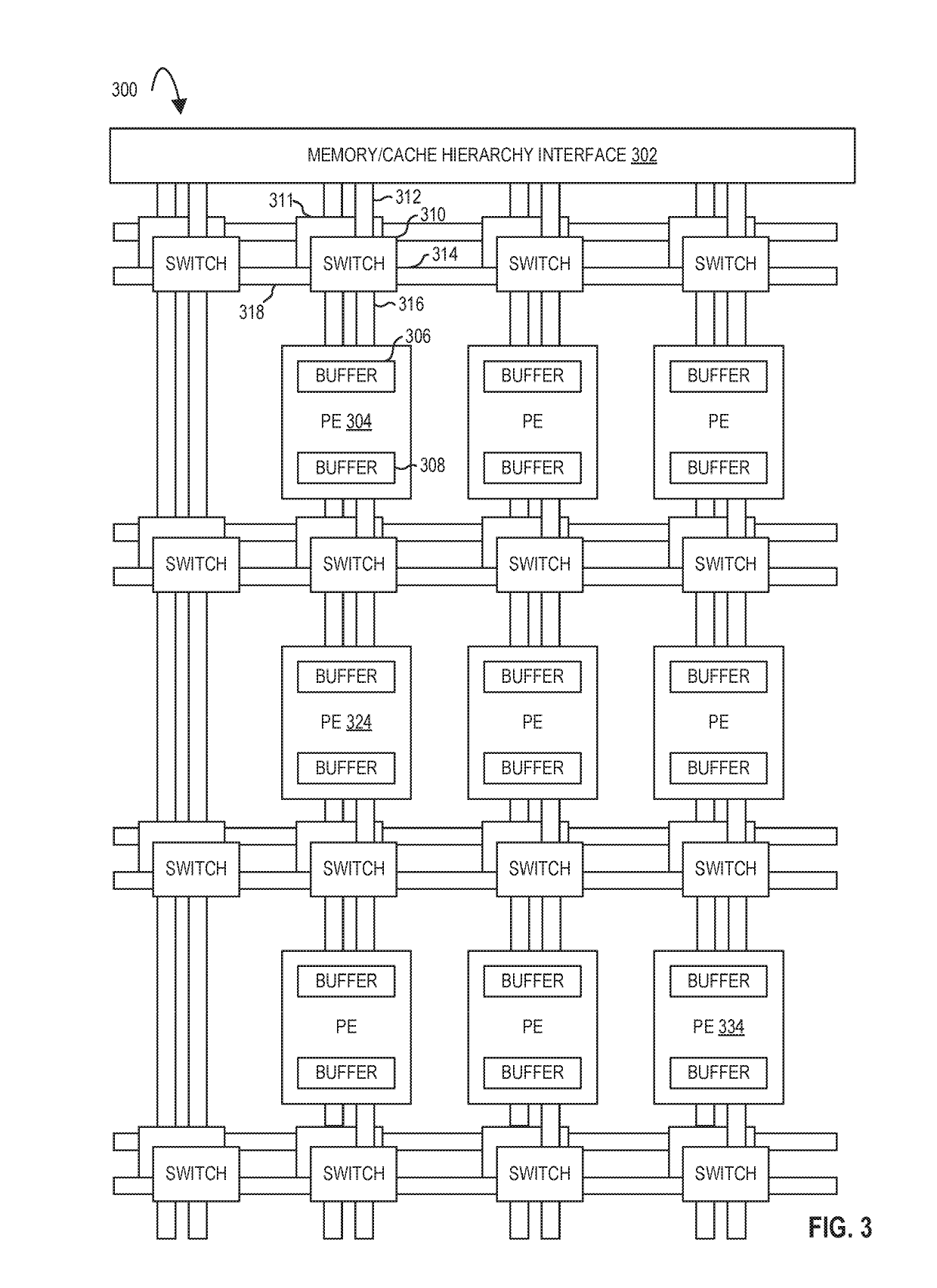

Processors and methods for privileged configuration in a spatial array

ActiveUS20190102179A1Easy to adaptImprove performanceResource allocationRuntime instruction translationArray data structureProcessing element

Methods and apparatuses relating to privileged configuration in spatial arrays are described. In one embodiment, a processor includes processing elements; an interconnect network between the processing elements; and a configuration controller coupled to a first subset and a second, different subset of the plurality of processing elements, the first subset having an output coupled to an input of the second, different subset, wherein the configuration controller is to configure the interconnect network between the first subset and the second, different subset of the plurality of processing elements to not allow communication on the interconnect network between the first subset and the second, different subset when a privilege bit is set to a first value and to allow communication on the interconnect network between the first subset and the second, different subset of the plurality of processing elements when the privilege bit is set to a second value.

Owner:INTEL CORP

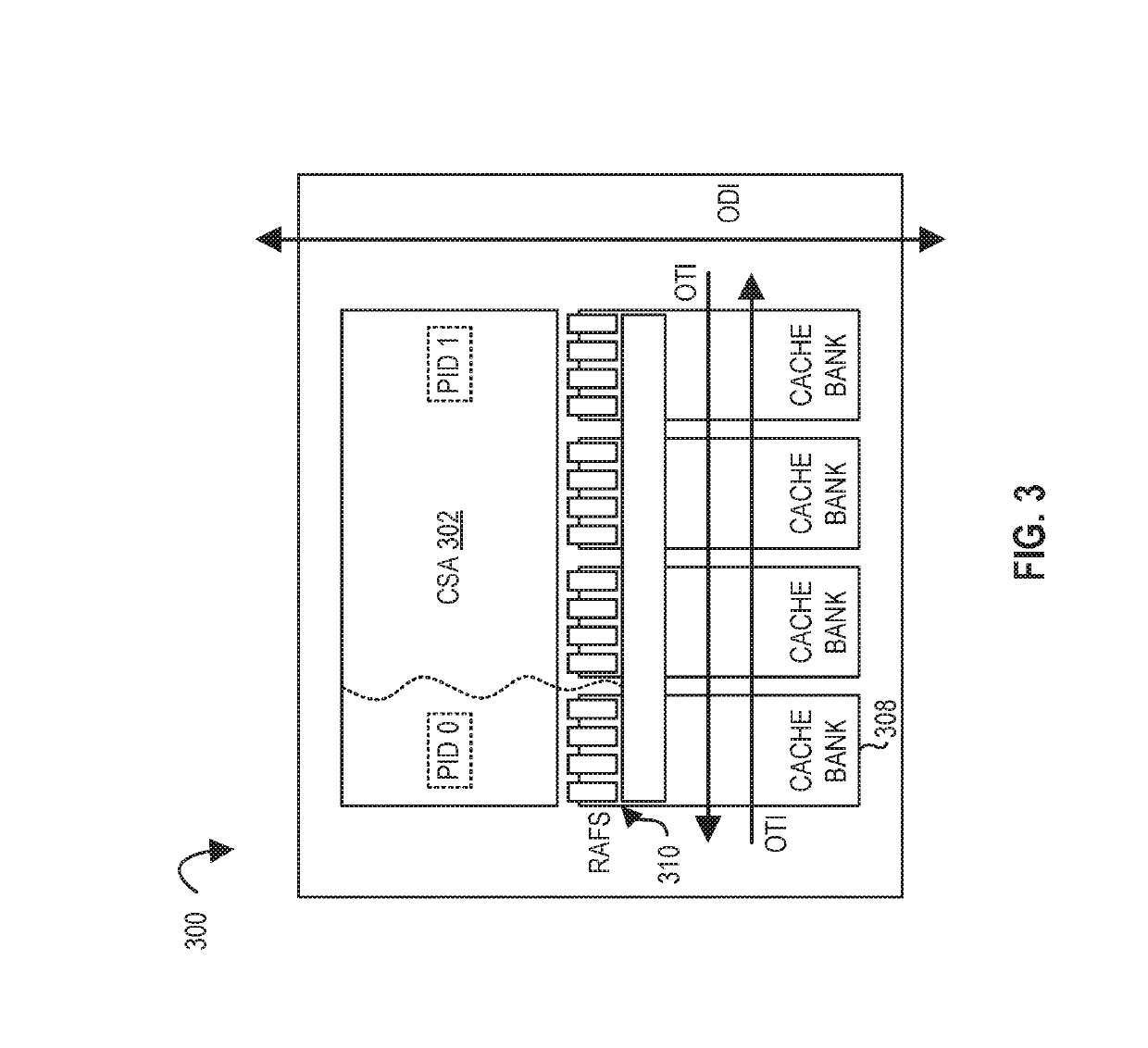

Apparatus, methods, and systems for remote memory access in a configurable spatial accelerator

InactiveUS20190303297A1Easy to adaptImprove performanceMemory architecture accessing/allocationDigital computer detailsDirect memory accessRemote memory access

Systems, methods, and apparatuses relating to remote memory access in a configurable spatial accelerator are described. In one embodiment, a configurable spatial accelerator includes a first memory interface circuit coupled to a first processing element and a cache, the first memory interface circuit to issue a memory request to the cache, the memory request comprising a field to identify a second memory interface circuit as a receiver of data for the memory request; and the second memory interface circuit coupled to a second processing element and the cache, the second memory interface circuit to send a credit return value to the first memory interface circuit, to cause the first memory interface circuit to mark the memory request as complete, when the data for the memory request arrives at the second memory interface circuit and a completion configuration register of the second memory interface circuit is set to a remote response value.

Owner:INTEL CORP

Processors, methods, and systems for a configurable spatial accelerator with security, power reduction, and performace features

InactiveUS20190004878A1Easy to adaptImprove performanceInterprogram communicationDigital computer detailsArray data structurePower consumption

Systems, methods, and apparatuses relating to a configurable spatial accelerator are described. In one embodiment, a processor includes a plurality of processing elements; and an interconnect network between the plurality of processing elements to receive an input of two dataflow graphs each comprising a plurality of nodes, wherein a first dataflow graph and a second dataflow graph are be overlaid into a first and second portion, respectively, of the interconnect network and a first and second subset, respectively, of the plurality of processing elements with each node represented as a dataflow operator in the plurality of processing elements, and the first and second subsets of the plurality of processing elements are to perform a first and second operation, respectively, when incoming first and second, respectively, operand sets arrive at the plurality of processing elements.

Owner:INTEL CORP

Offload Processing of Data Packets Containing Financial Market Data

Various techniques are disclosed for offloading the processing of data packets. For example, incoming data packets can be processed through an offload processor to generate a new stream of outgoing data packets that organize data from the data packets in a manner different than the incoming data packets. Furthermore, in an exemplary embodiment, the offloaded processing can be resident in an intelligent switch, such as an intelligent switch upstream or downstream from an electronic trading platform.

Owner:IP RESERVOIR

Intelligent Feed Switch

ActiveUS20140181133A1Minimize of data processingMinimize powerDatabase queryingFinanceData packOnline trading

Various techniques are disclosed for offloading the processing of data packets. For example, incoming data packets can be processed through an offload processor to generate a new stream of outgoing data packets that organize data from the data packets in a manner different than the incoming data packets. Furthermore, in an exemplary embodiment, the offloaded processing can be resident in an intelligent switch, such as an intelligent switch upstream or downstream from an electronic trading platform.

Owner:IP RESERVOIR

Processors and methods for configurable clock gating in a spatial array

InactiveUS20190101952A1Easy to adaptImprove performanceDataflow computersSingle instruction multiple data multiprocessorsSignal onParallel computing

Methods and apparatuses relating to configurable clock gating in spatial arrays are described. In one embodiment, a processor includes processing elements; an interconnect network between the processing elements; and a configuration controller, coupled to a first processing element and a second processing element of the plurality of processing elements and the first processing element having an output coupled to an input of the second processing element, to configure the second processing element to clock gate at least one clocked component of the second processing element, and configure the first processing element to send a reenable signal on the interconnect network to the second processing element to reenable the at least one clocked component of the second processing element when data is to be sent from the first processing element to the second processing element.

Owner:INTEL CORP

Offload Processing of Data Packets

Various techniques are disclosed for offloading the processing of data packets. For example, incoming data packets can be processed through an offload processor to generate a new stream of outgoing data packets that organize data from the data packets in a manner different than the incoming data packets. Furthermore, in an exemplary embodiment, the offloaded processing can be resident in an intelligent switch, such as an intelligent switch upstream or downstream from an electronic trading platform.

Owner:IP RESERVOIR

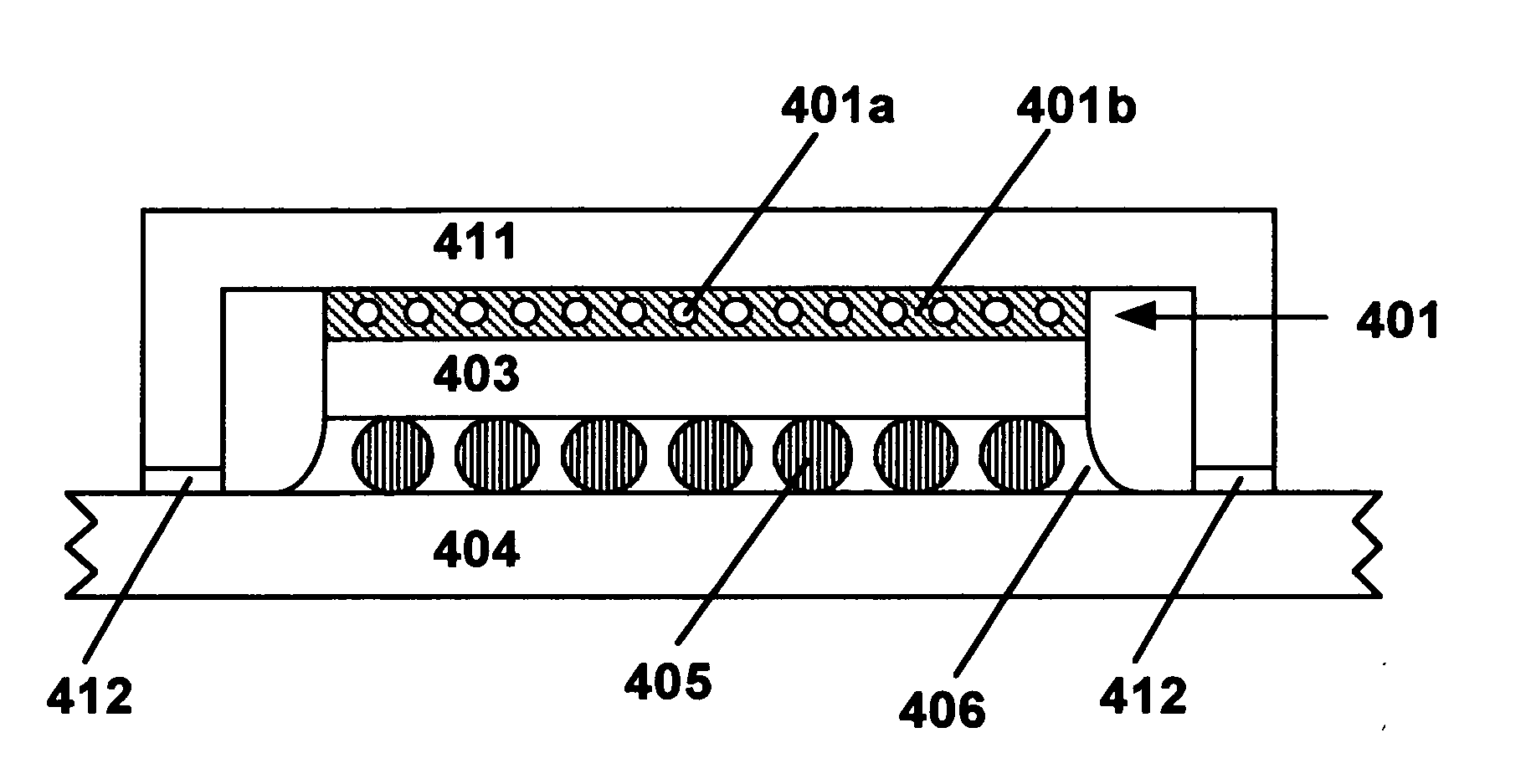

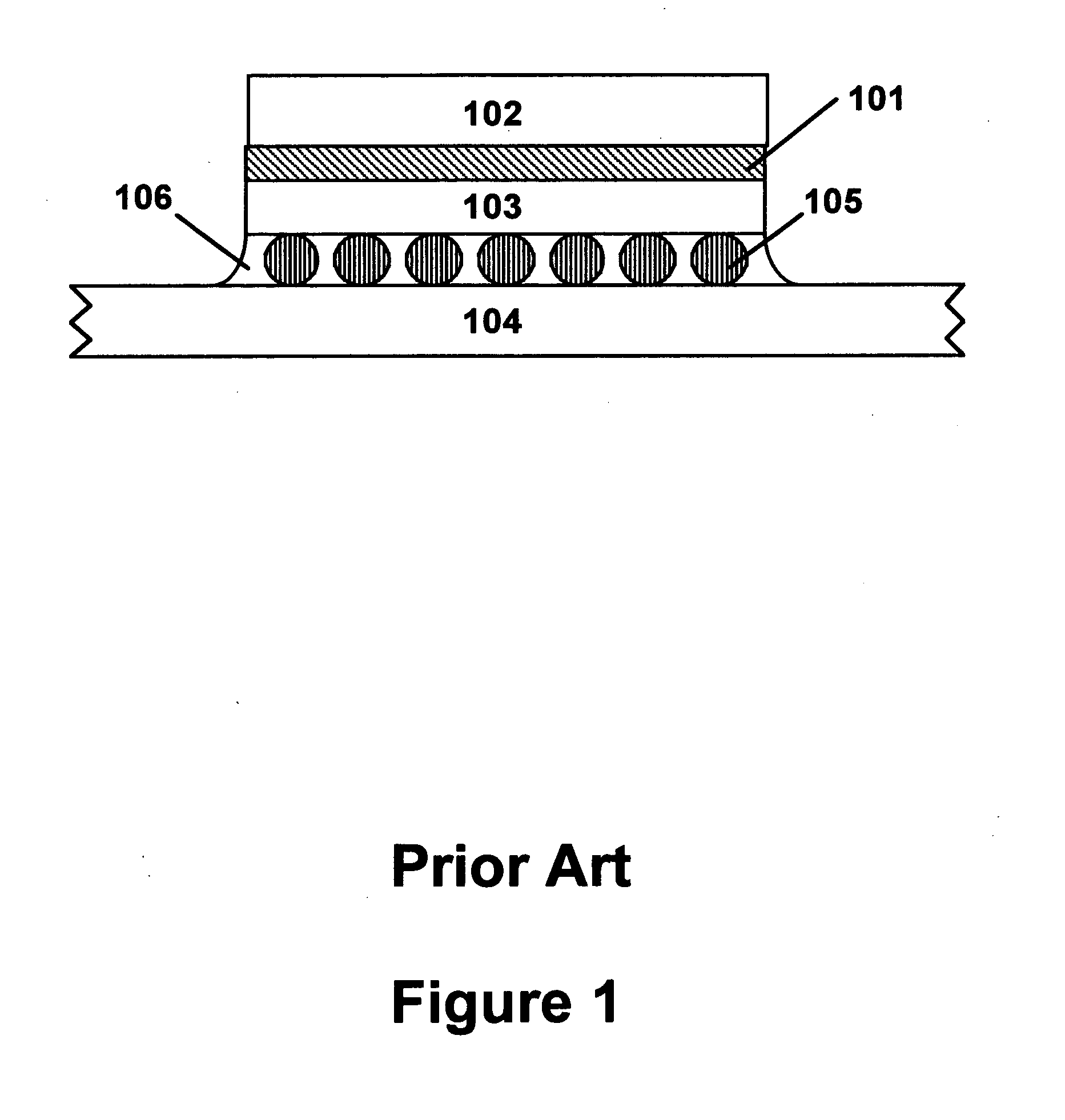

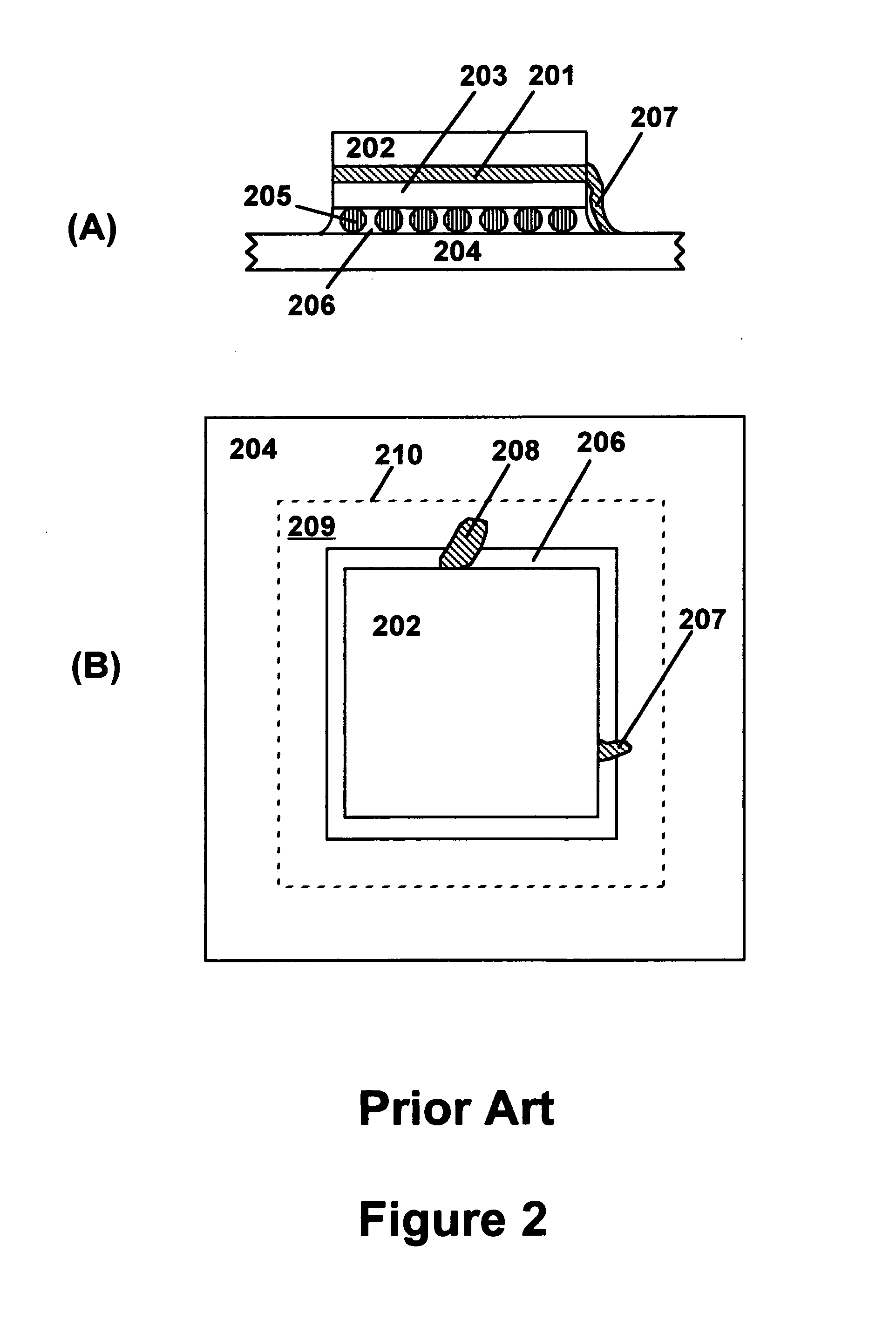

Microelectronic thermal interface

InactiveUS20110096507A1Improve thermal conductivityReduce the temperatureSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipCopper

An improved thermal interface between an integrated circuit chip and a heat sink comprises a copper grid embedded in a layer of a solder material that has a fusion temperature higher than the maximum operating temperature of the semiconductor chip, and bonds to the semiconductor chip and the heat sink when heated to the fusion temperature of the solder material in the presence of a soldering flux. The copper grid has high thermal conductivity so that the amount of solder material needed for an efficient thermal interface is reduced and solder materials with less expensive components may be used. The copper grid also tends to mitigate local hot spots by enhancing lateral heat transfer, and inhibits solder spreading during formation of the thermal interface.

Owner:KESTER

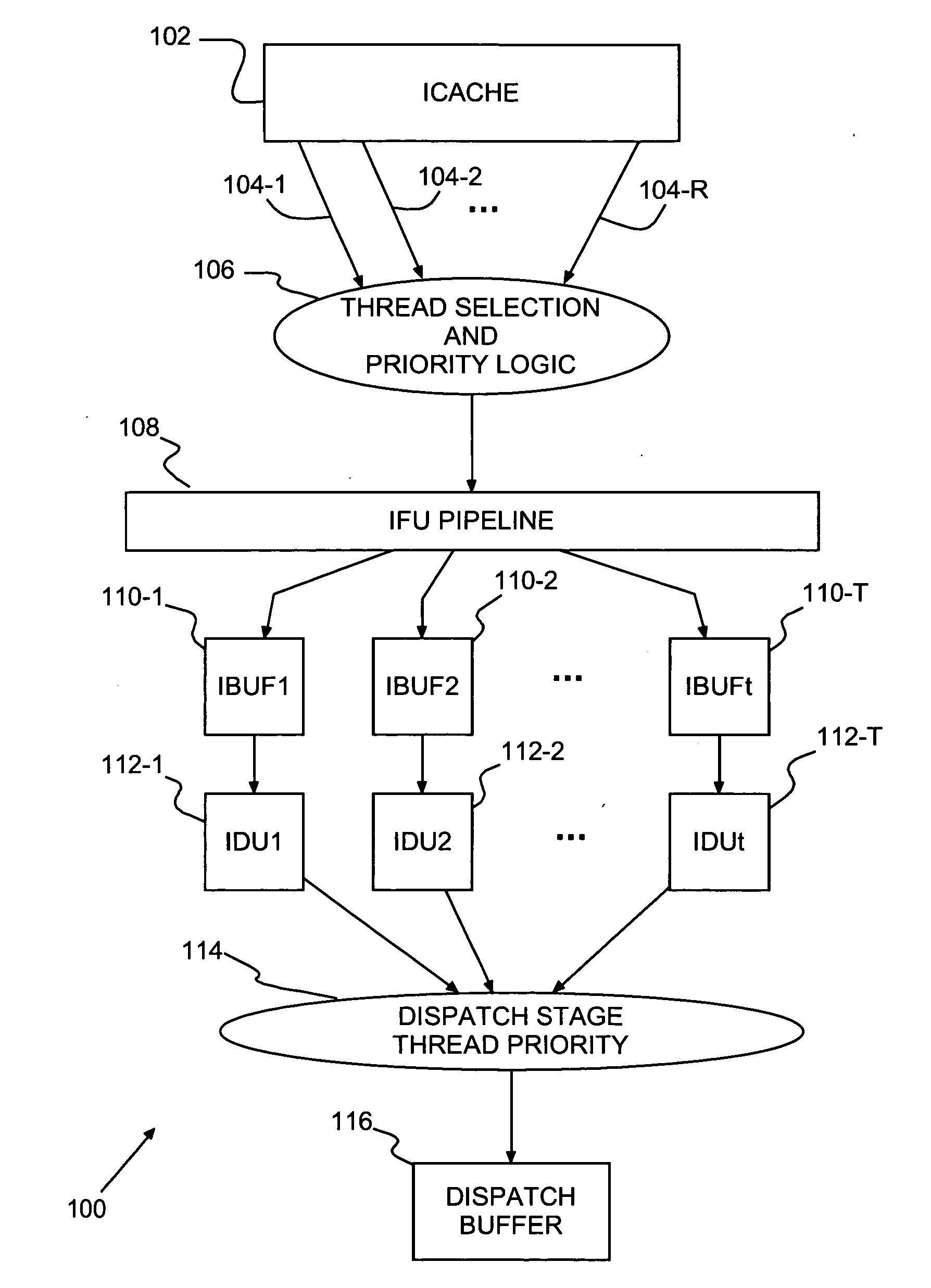

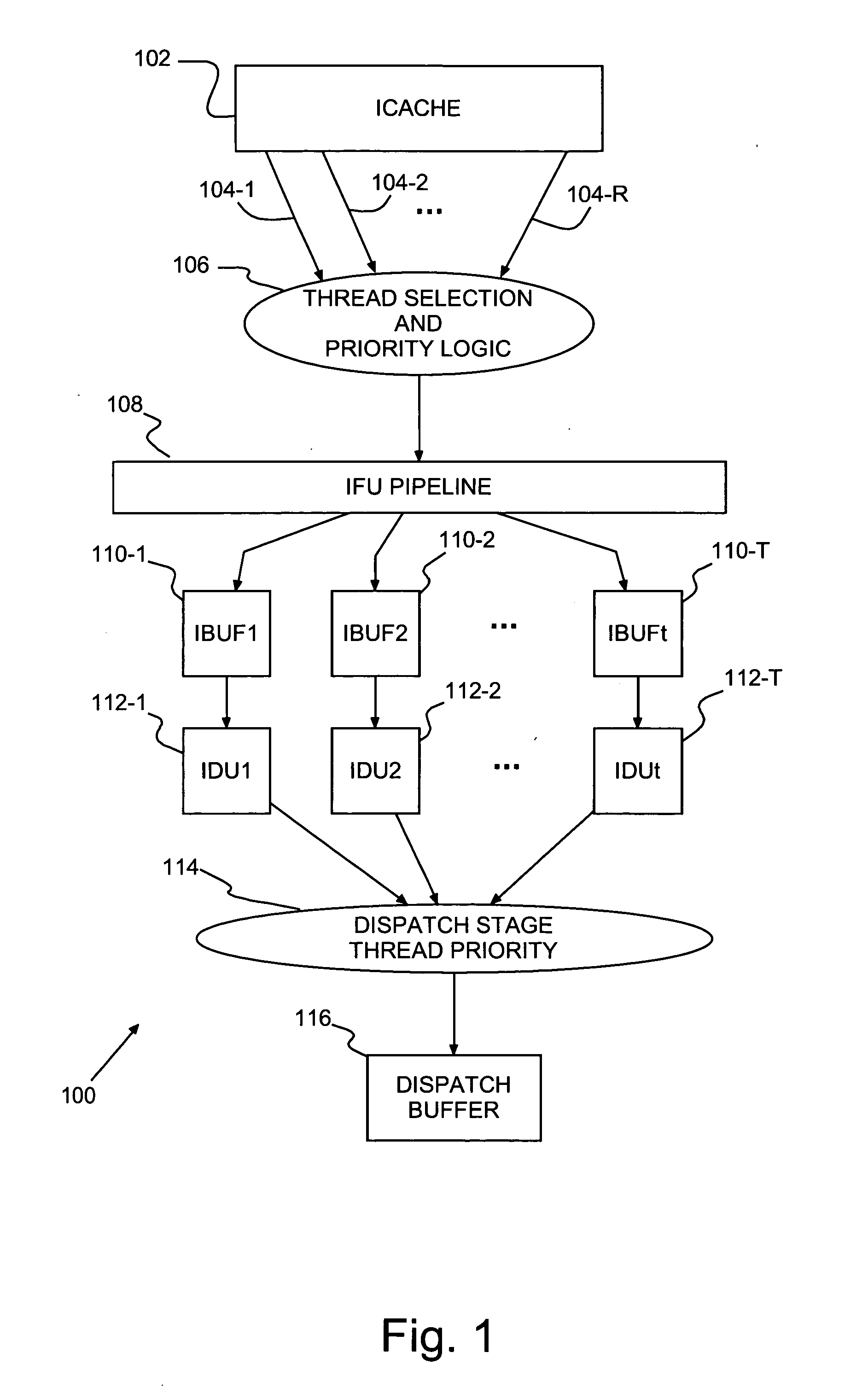

Adaptive fetch gating in multithreaded processors, fetch control and method of controlling fetches

ActiveUS20060101238A1Minimize processor power consumptionMinimize Simultaneous MultiThreaded (SMT) processor power consumptionDigital computer detailsMemory systemsComputer architectureParallel computing

A multithreaded processor, fetch control for a multithreaded processor and a method of fetching in the multithreaded processor. Processor event and use (EU) signs are monitored for downstream pipeline conditions indicating pipeline execution thread states. Instruction cache fetches are skipped for any thread that is incapable of receiving fetched cache contents, e.g., because the thread is full or stalled. Also, consecutive fetches may be selected for the same thread, e.g., on a branch mis-predict. Thus, the processor avoids wasting power on unnecessary or place keeper fetches.

Owner:META PLATFORMS INC

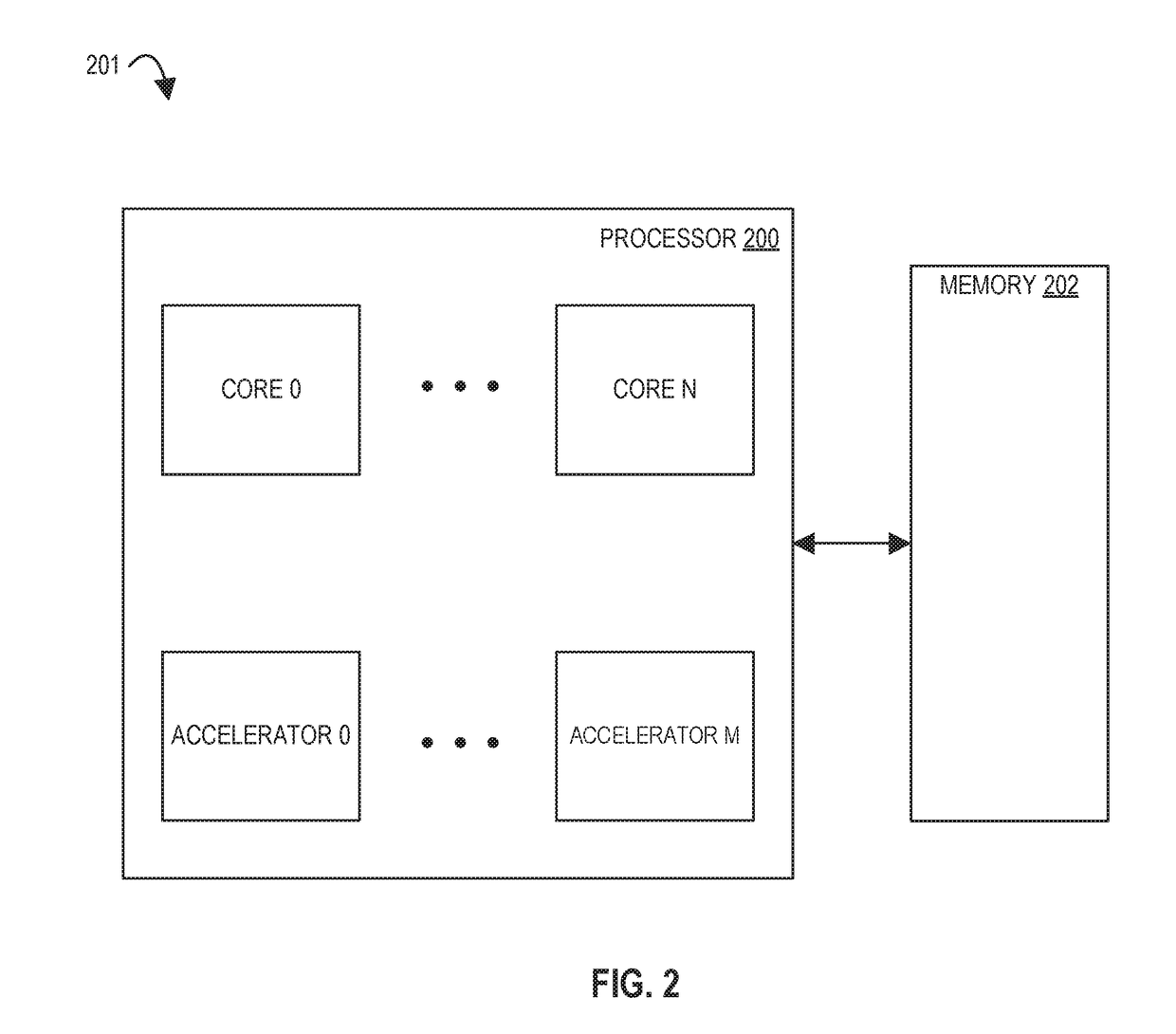

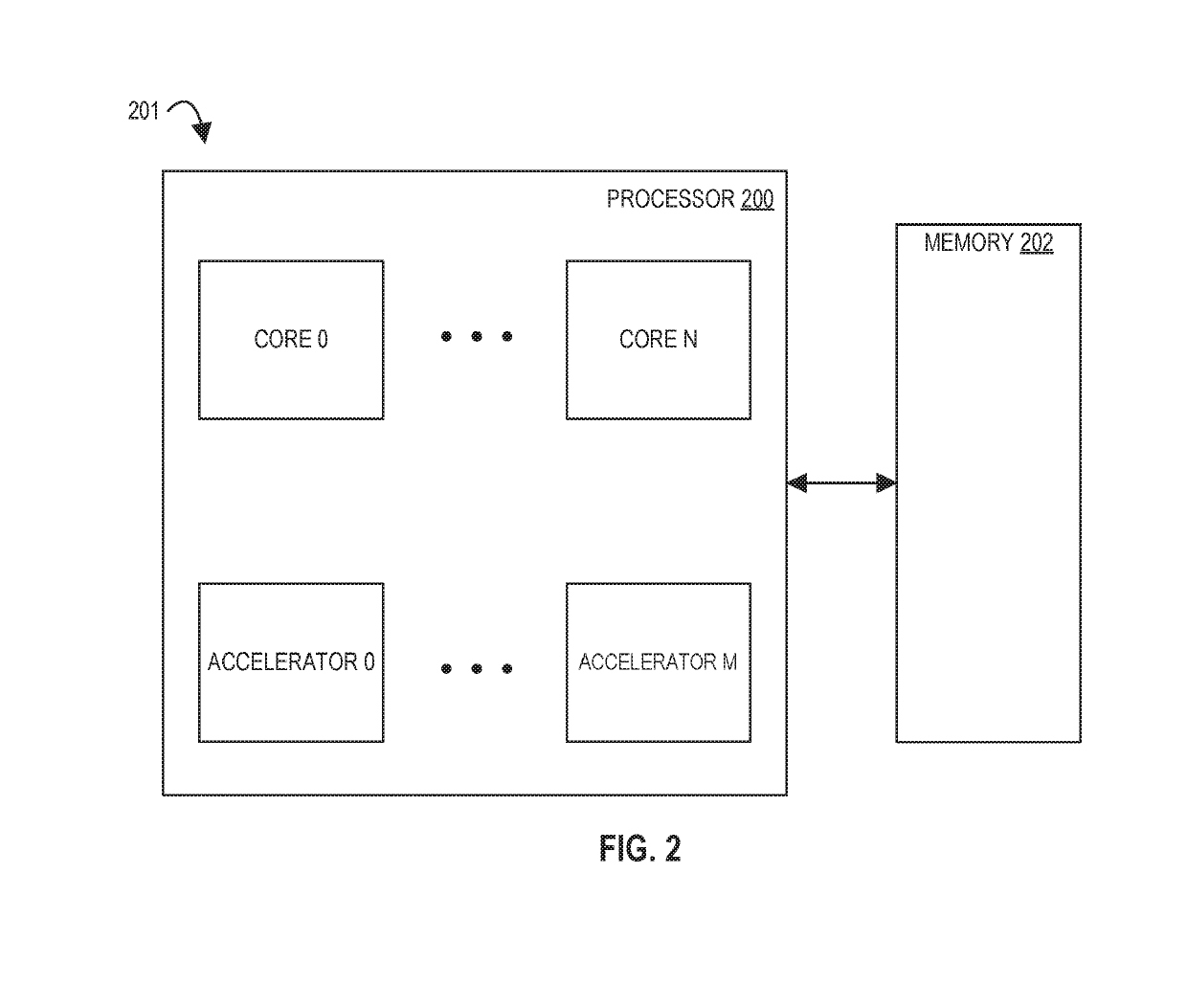

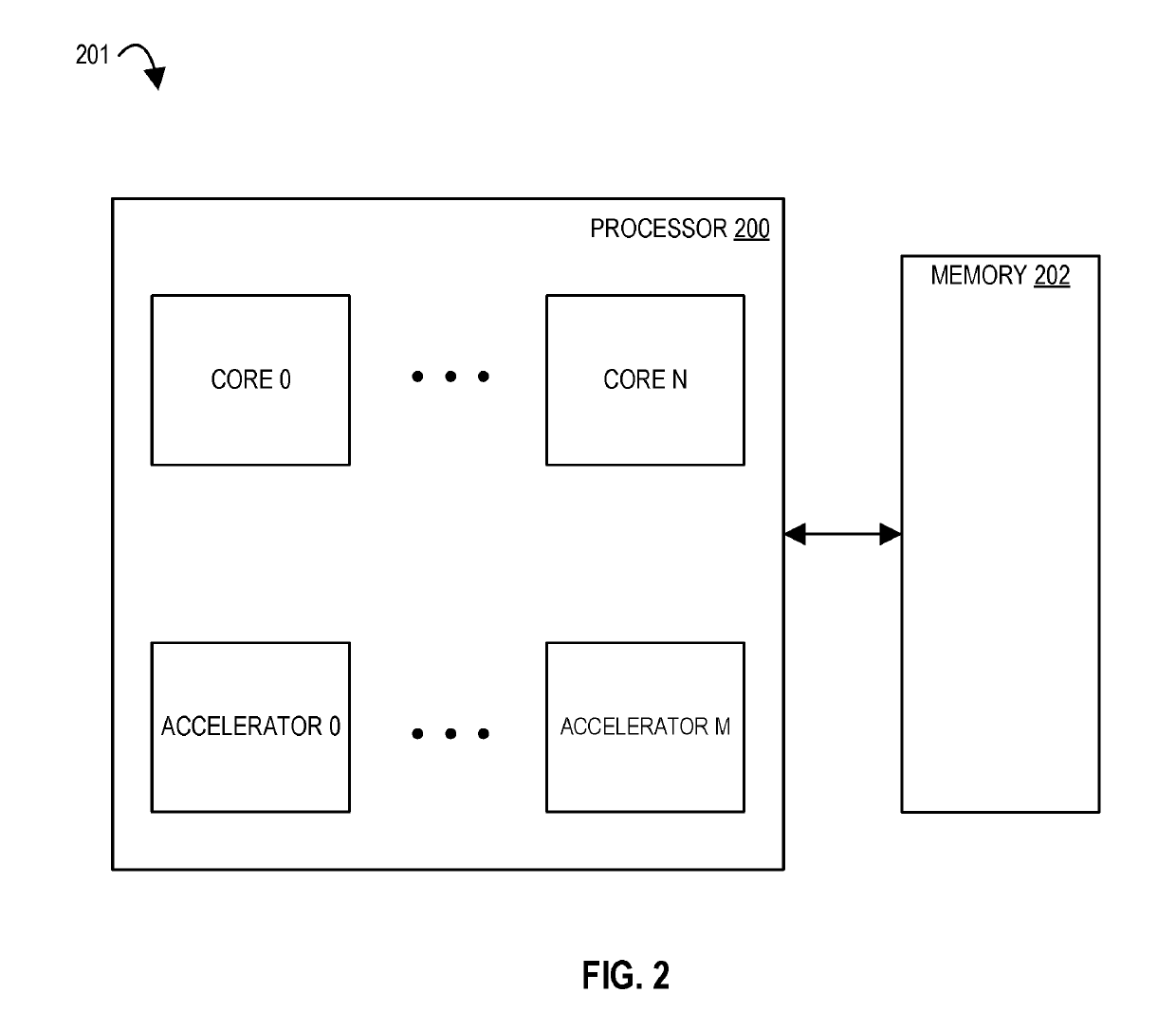

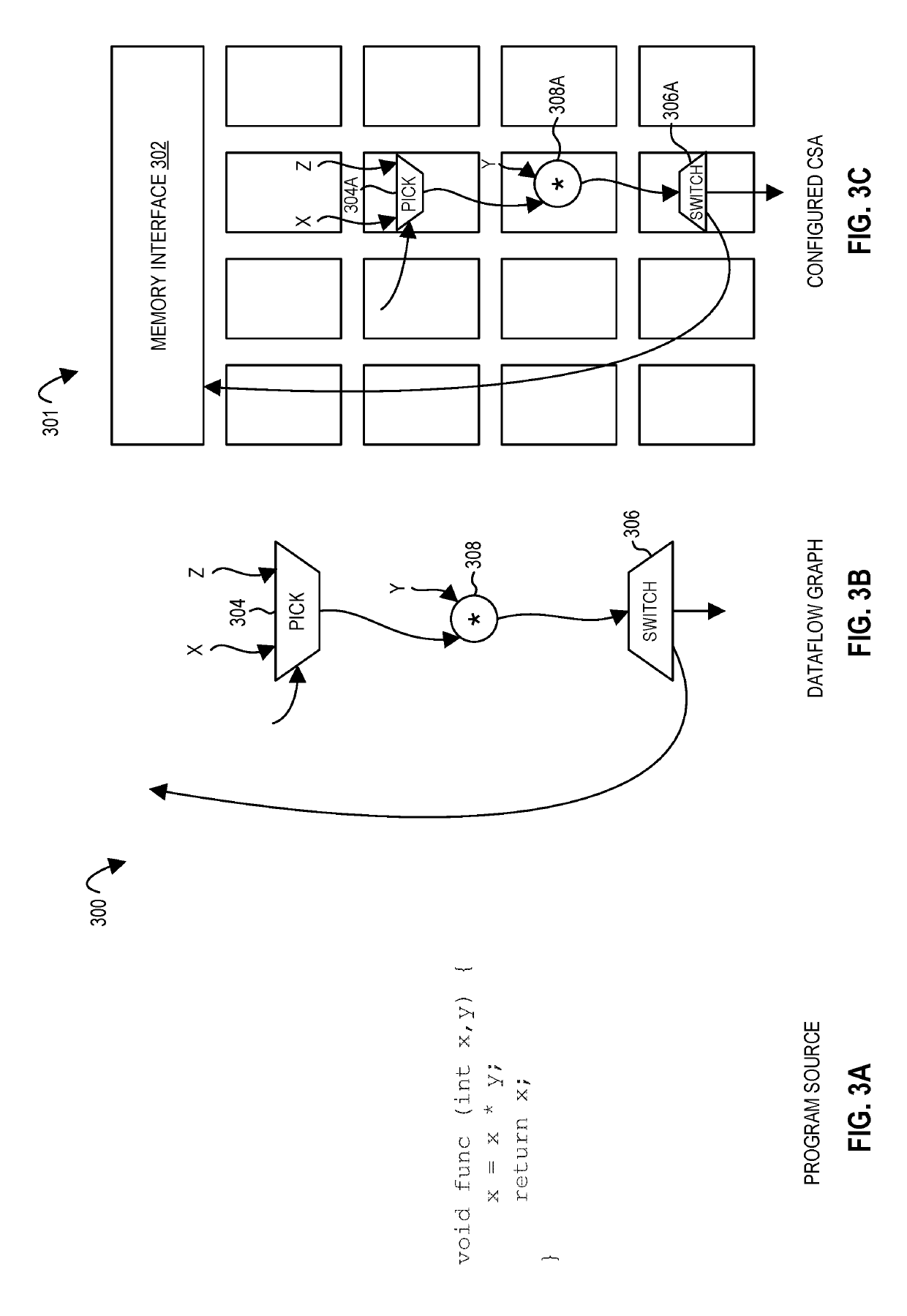

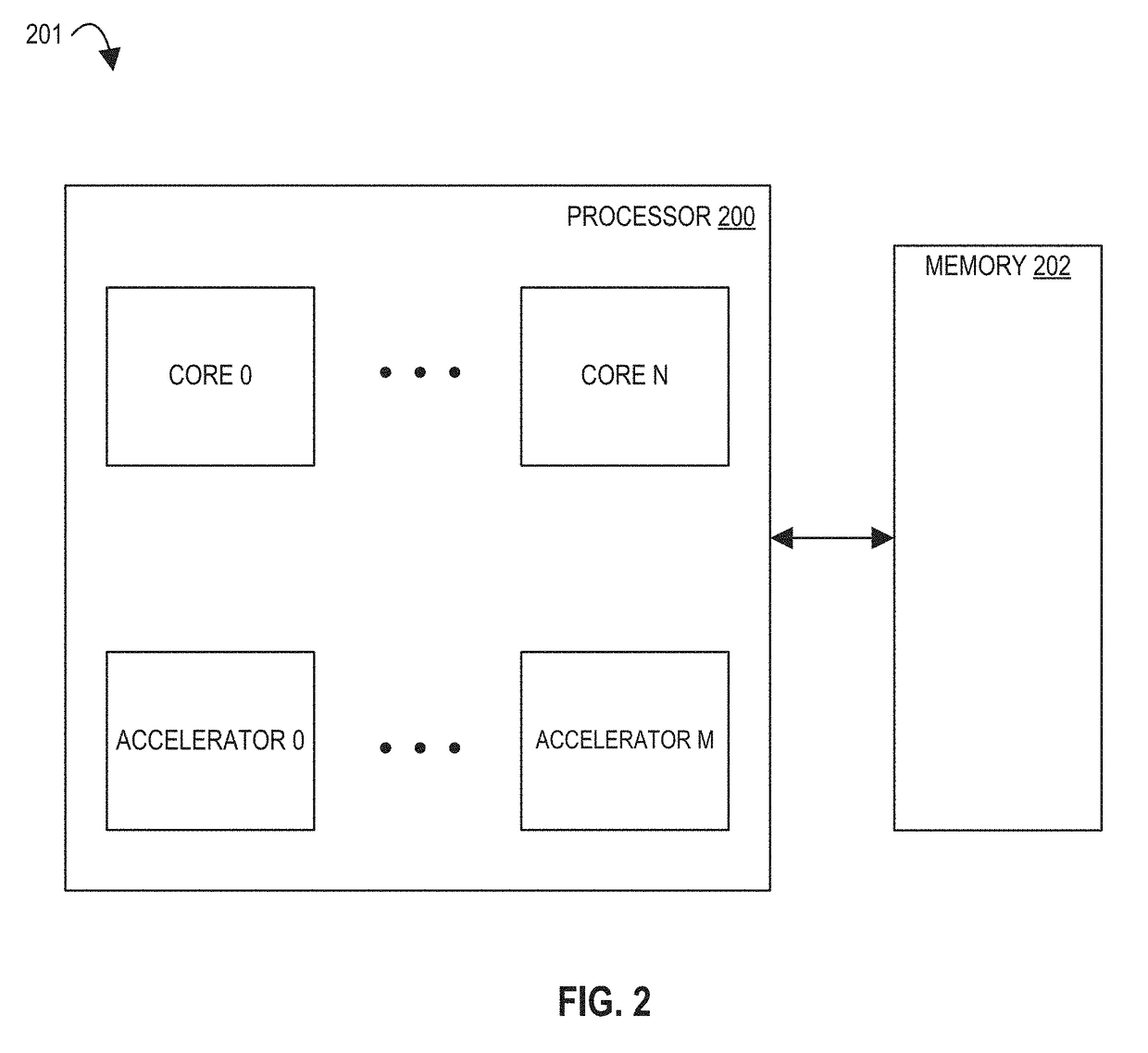

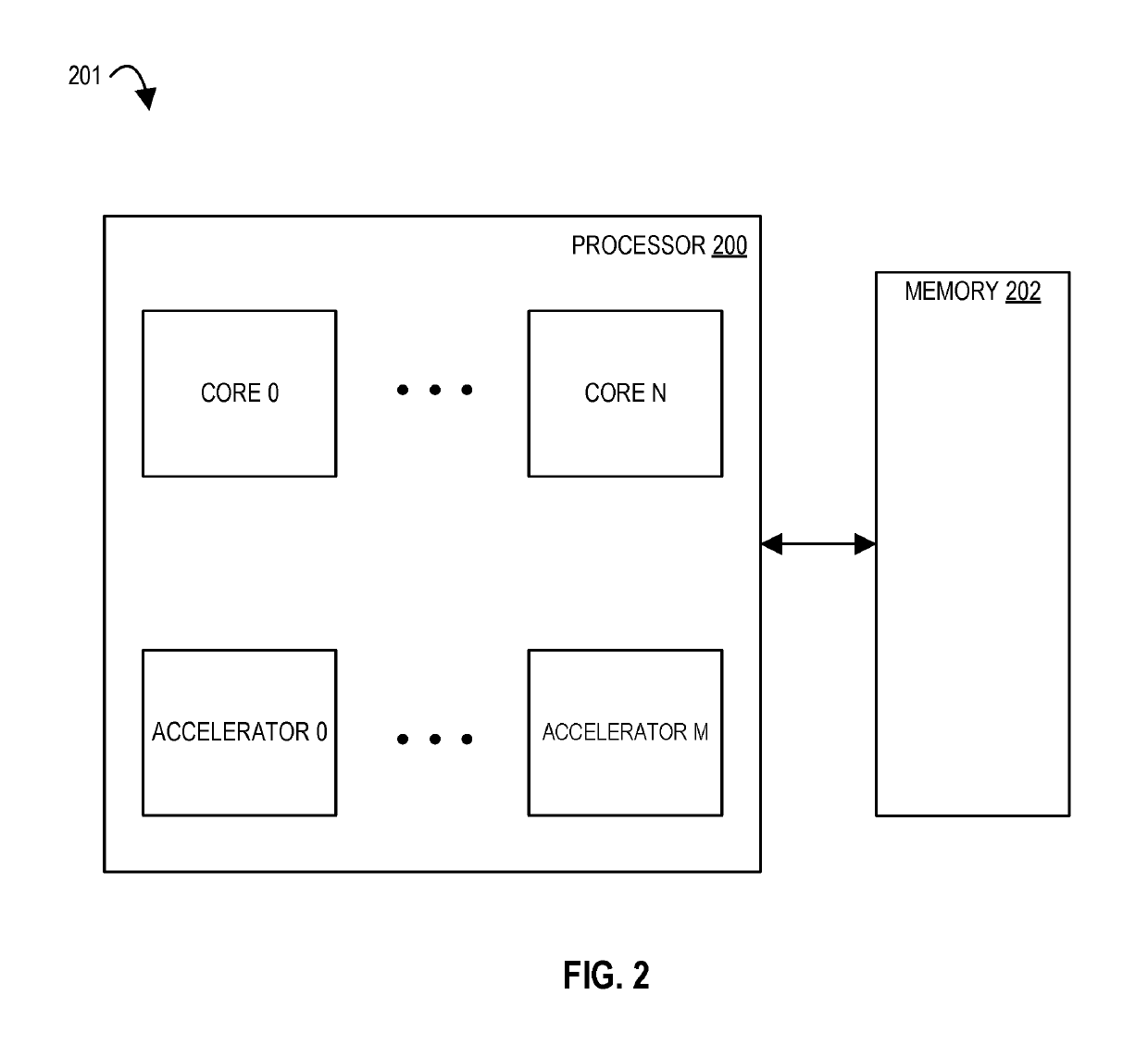

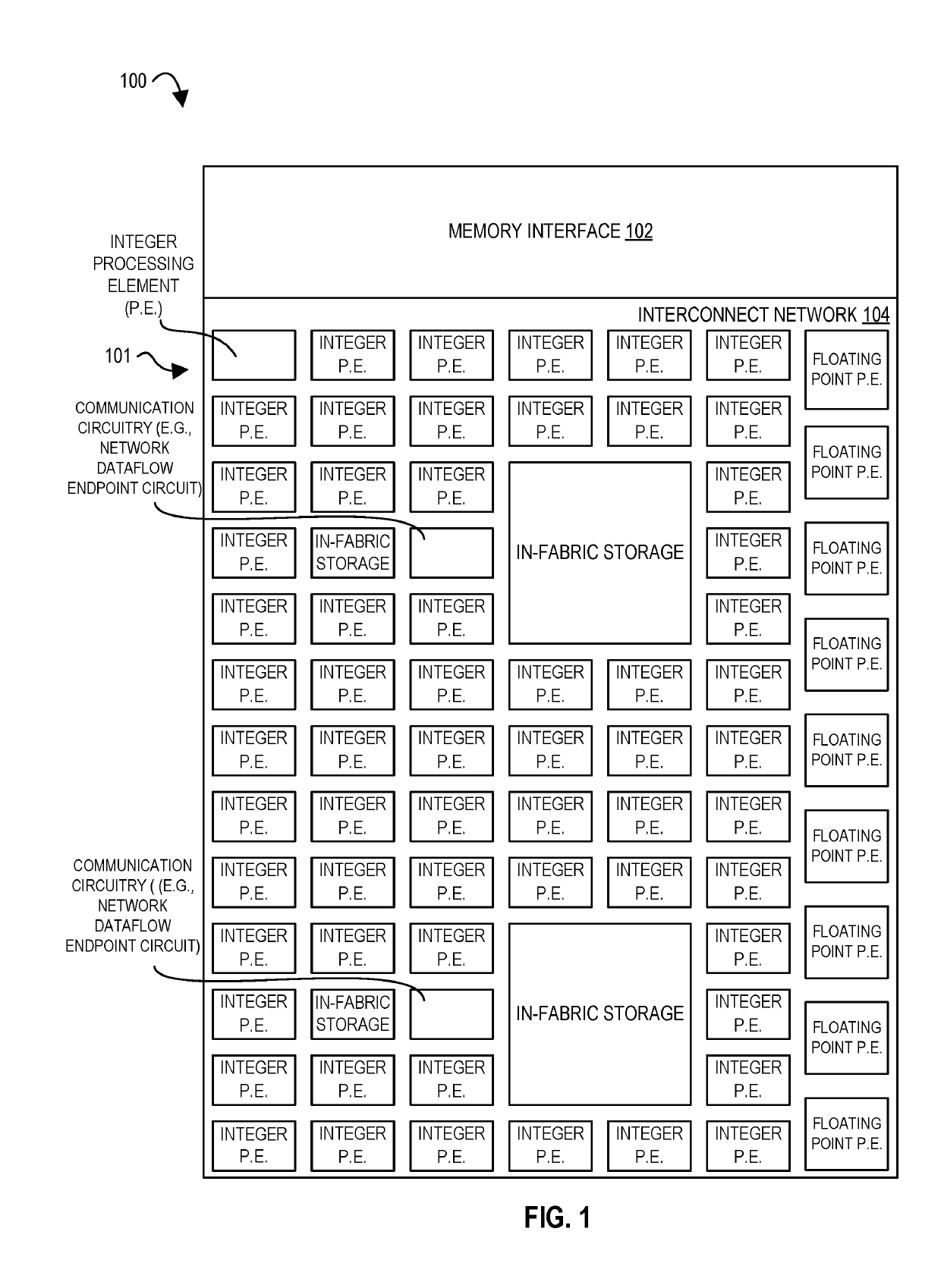

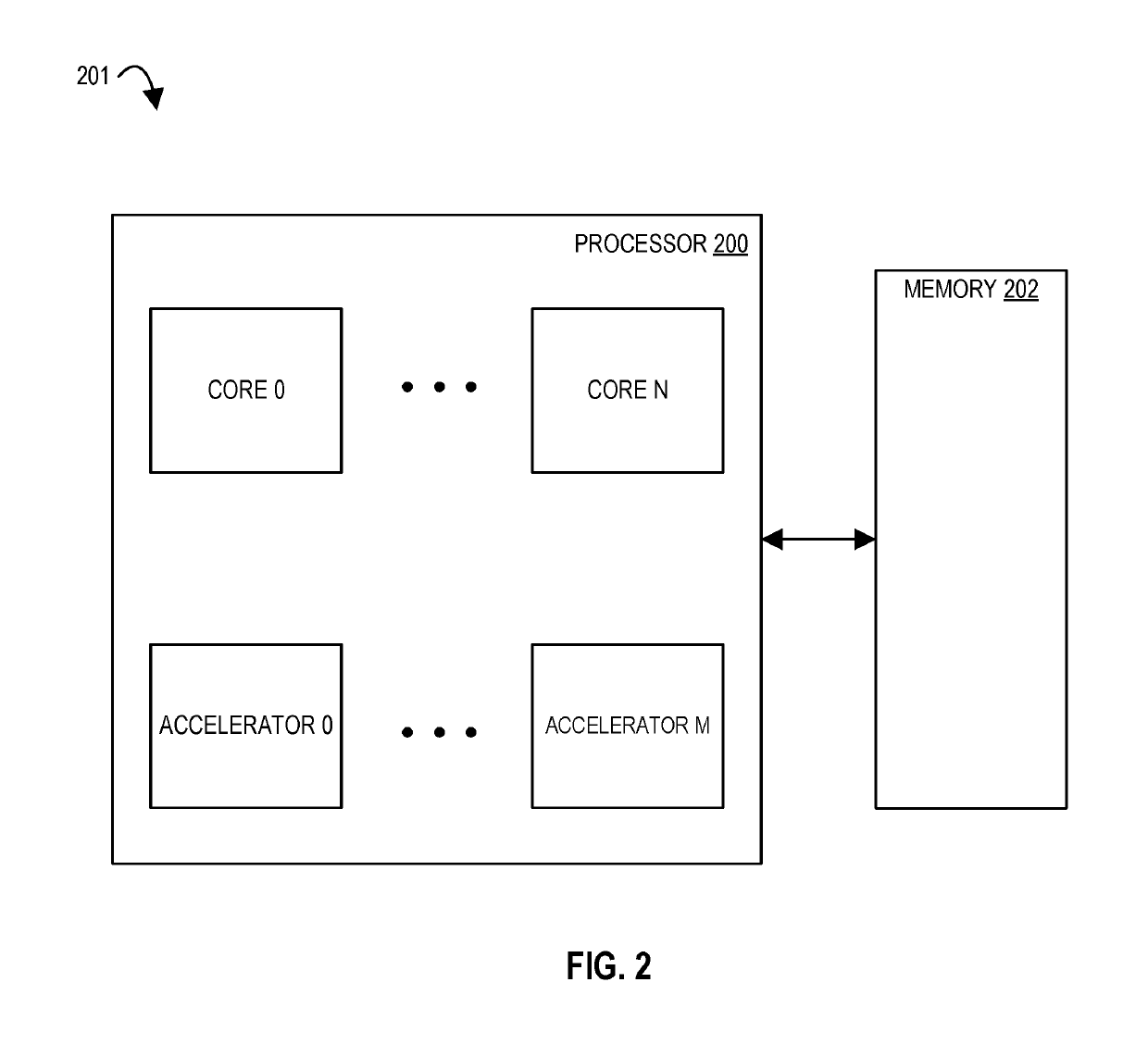

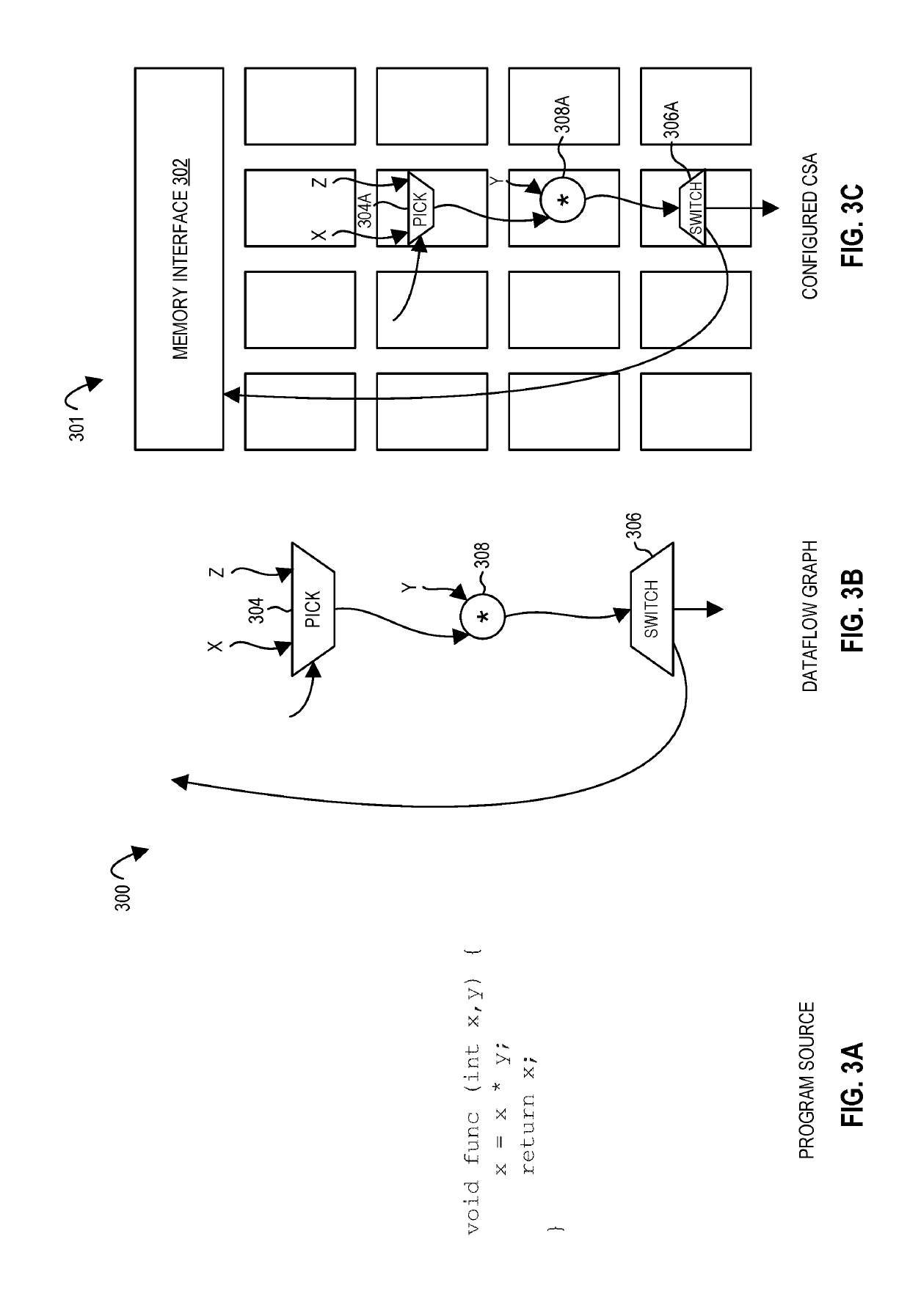

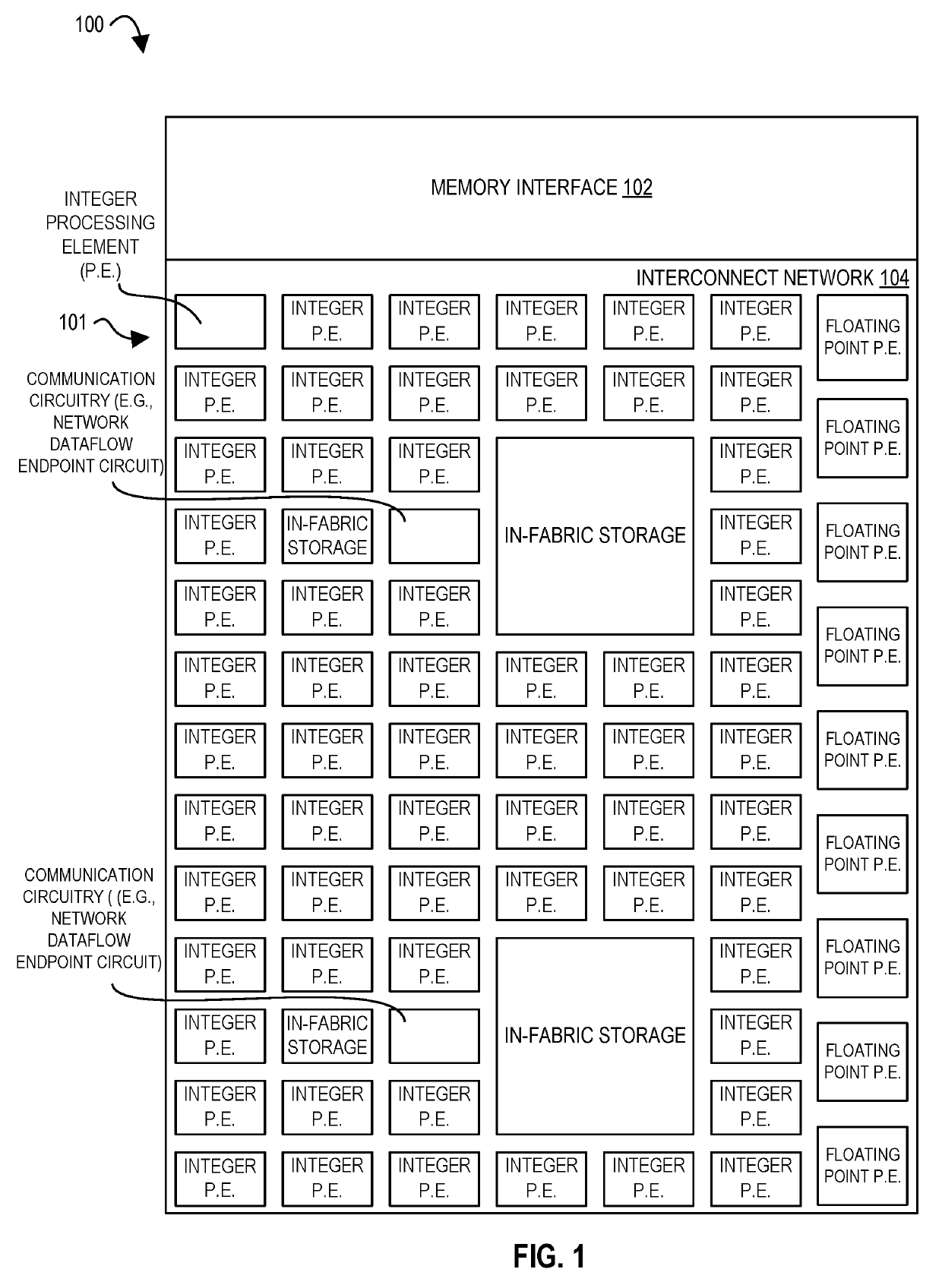

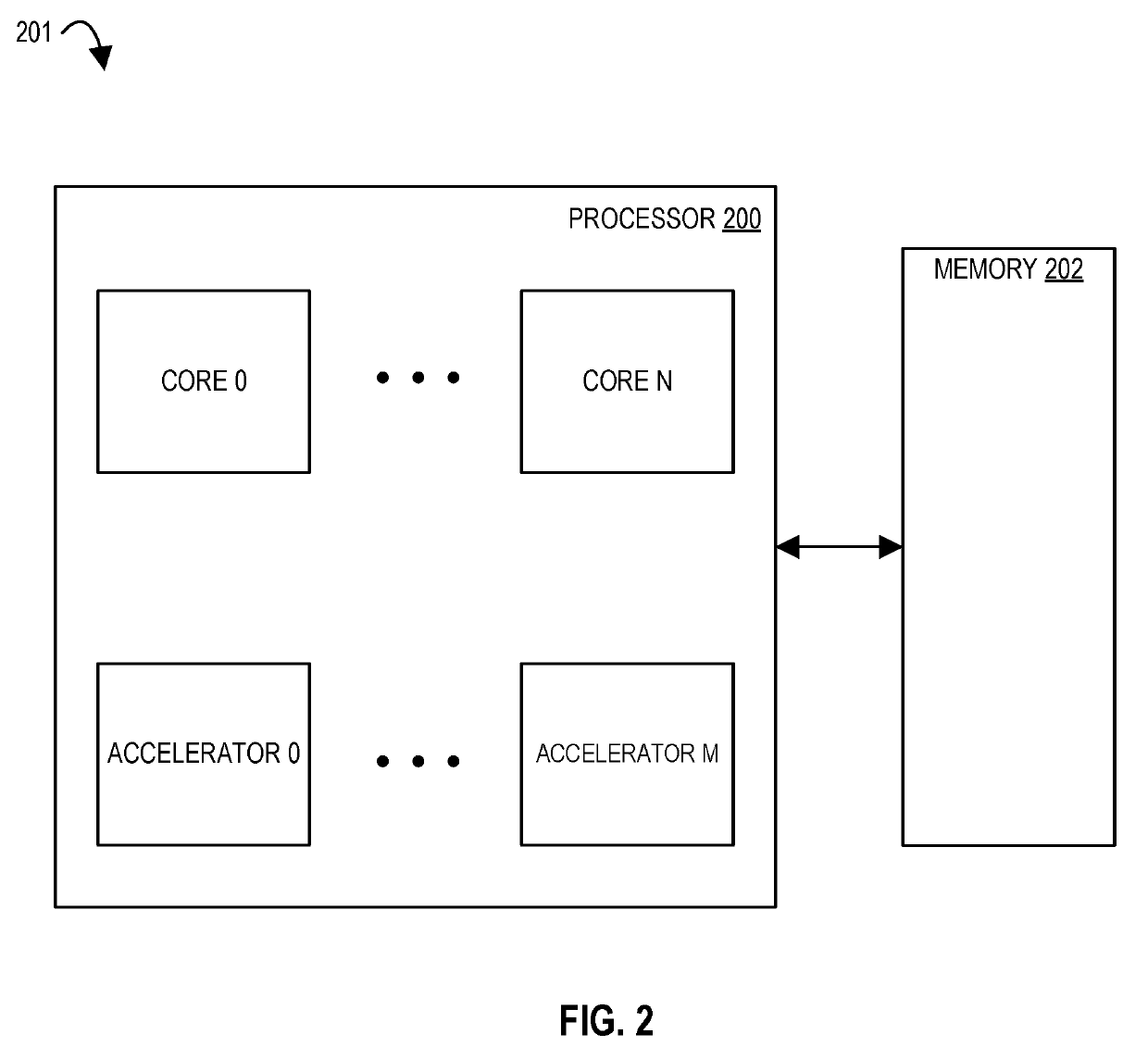

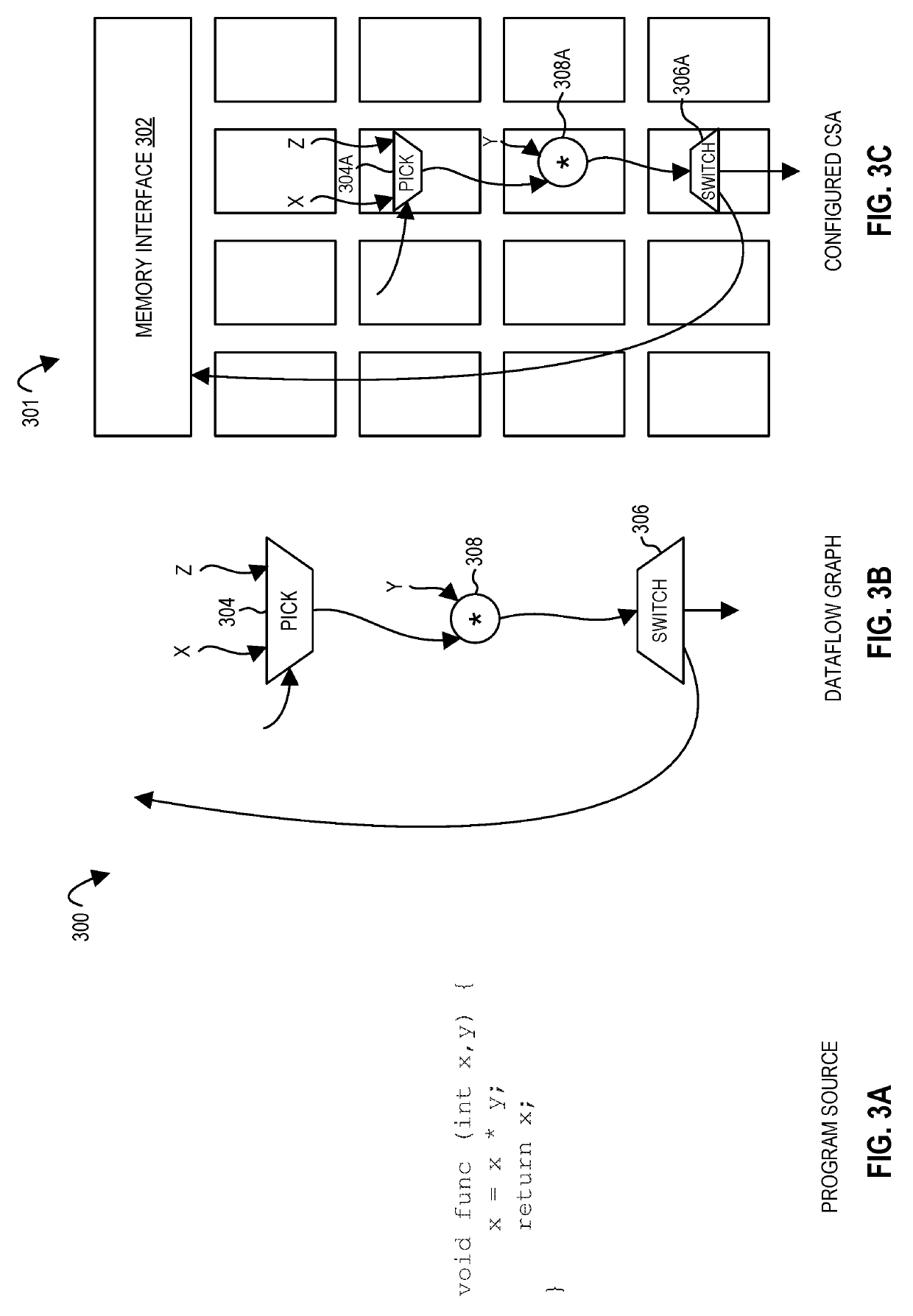

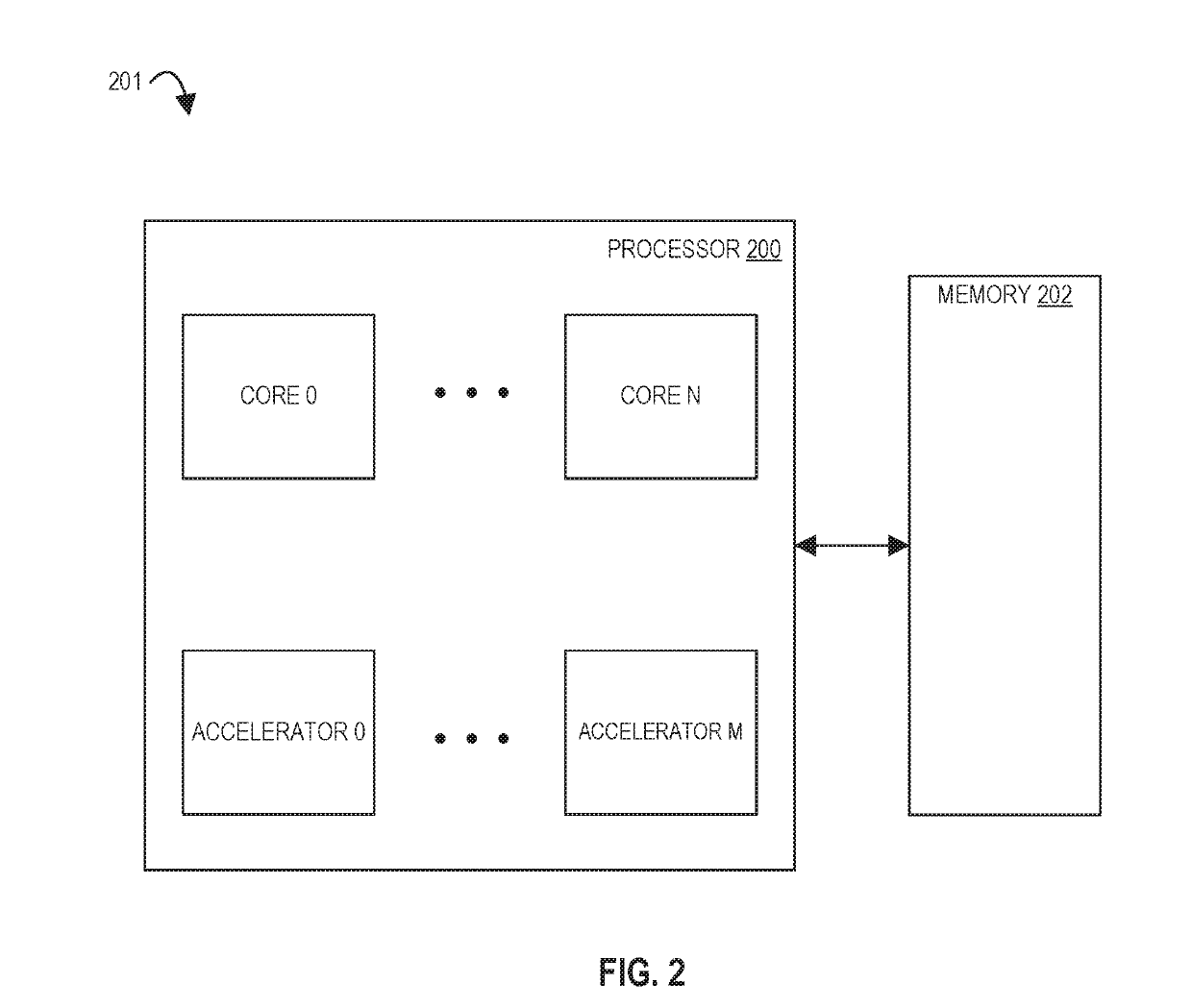

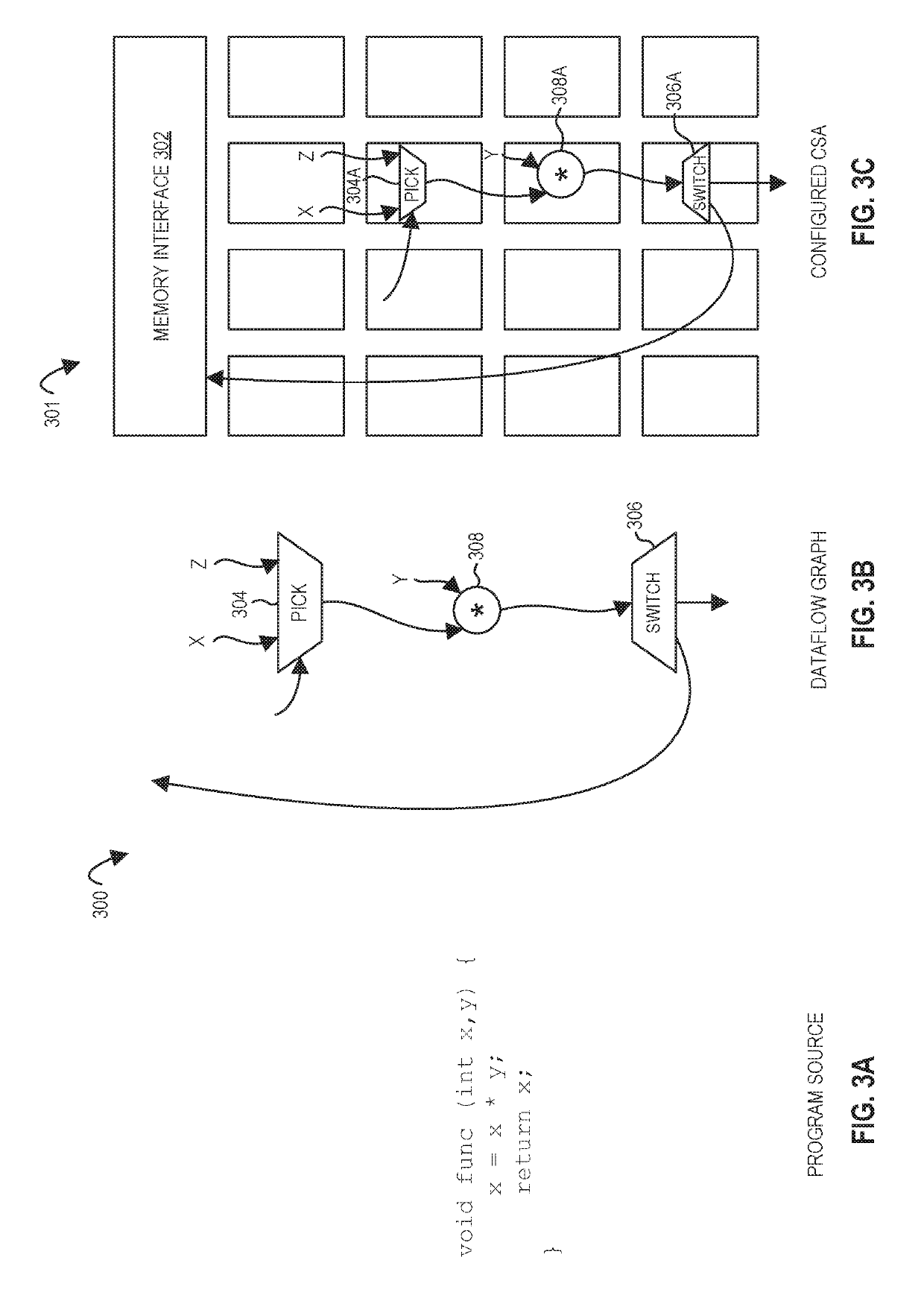

Apparatus, methods, and systems with a configurable spatial accelerator

ActiveUS20190205263A1Easy to adaptImprove performanceMemory architecture accessing/allocationEnergy efficient computingSystems approachesDataflow

Systems, methods, and apparatuses relating to a configurable spatial accelerator are described. In one embodiment, a processor includes a core with a decoder to decode an instruction into a decoded instruction and an execution unit to execute the decoded instruction to perform a first operation; a plurality of processing elements; and an interconnect network between the plurality of processing elements to receive an input of a dataflow graph comprising a plurality of nodes, wherein the dataflow graph is to be overlaid into the interconnect network and the plurality of processing elements with each node represented as a dataflow operator in the plurality of processing elements, and the plurality of processing elements are to perform a second operation by a respective, incoming operand set arriving at each of the dataflow operators of the plurality of processing elements.

Owner:INTEL CORP

Apparatus, methods, and systems for conditional queues in a configurable spatial accelerator

ActiveUS20190303168A1Easy to adaptImprove performanceSingle instruction multiple data multiprocessorsConcurrent instruction executionDataflowDatapath

Systems, methods, and apparatuses relating to conditional queues in a configurable spatial accelerator are described. In one embodiment, a configurable spatial accelerator includes a first output buffer of a first processing element coupled to a first input buffer of a second processing element and a second input buffer of a third processing element via a data path that is to send a dataflow token to the first input buffer of the second processing element and the second input buffer of the third processing element when the dataflow token is received in the first output buffer of the first processing element; a first backpressure path from the first input buffer of the second processing element to the first processing element to indicate to the first processing element when storage is not available in the first input buffer of the second processing element; a second backpressure path from the second input buffer of the third processing element to the first processing element to indicate to the first processing element when storage is not available in the second input buffer of the third processing element; and a scheduler of the second processing element to cause storage of the dataflow token from the data path into the first input buffer of the second processing element when both the first backpressure path indicates storage is available in the first input buffer of the second processing element and a conditional token received in a conditional queue of the second processing element from another processing element is a true conditional token.

Owner:INTEL CORP

Apparatus, methods, and systems for memory consistency in a configurable spatial accelerator

ActiveUS20190205284A1Easy to adaptImprove performanceInterprogram communicationDigital computer detailsComputer scienceProcedure sequence

Owner:INTEL CORP

Processors, methods, and systems for debugging a configurable spatial accelerator

ActiveUS20190095383A1Easy to adaptImprove performanceAssociative processorsDataflow computersProcessing elementOperand

Systems, methods, and apparatuses relating to debugging a configurable spatial accelerator are described. In one embodiment, a processor includes a plurality of processing elements and an interconnect network between the plurality of processing elements to receive an input of a dataflow graph comprising a plurality of nodes, wherein the dataflow graph is to be overlaid into the interconnect network and the plurality of processing elements with each node represented as a dataflow operator in the plurality of processing elements, and the plurality of processing elements are to perform an operation by a respective, incoming operand set arriving at each of the dataflow operators of the plurality of processing elements. At least a first of the plurality of processing elements is to enter a halted state in response to being represented as a first of the plurality of dataflow operators.

Owner:INTEL CORP

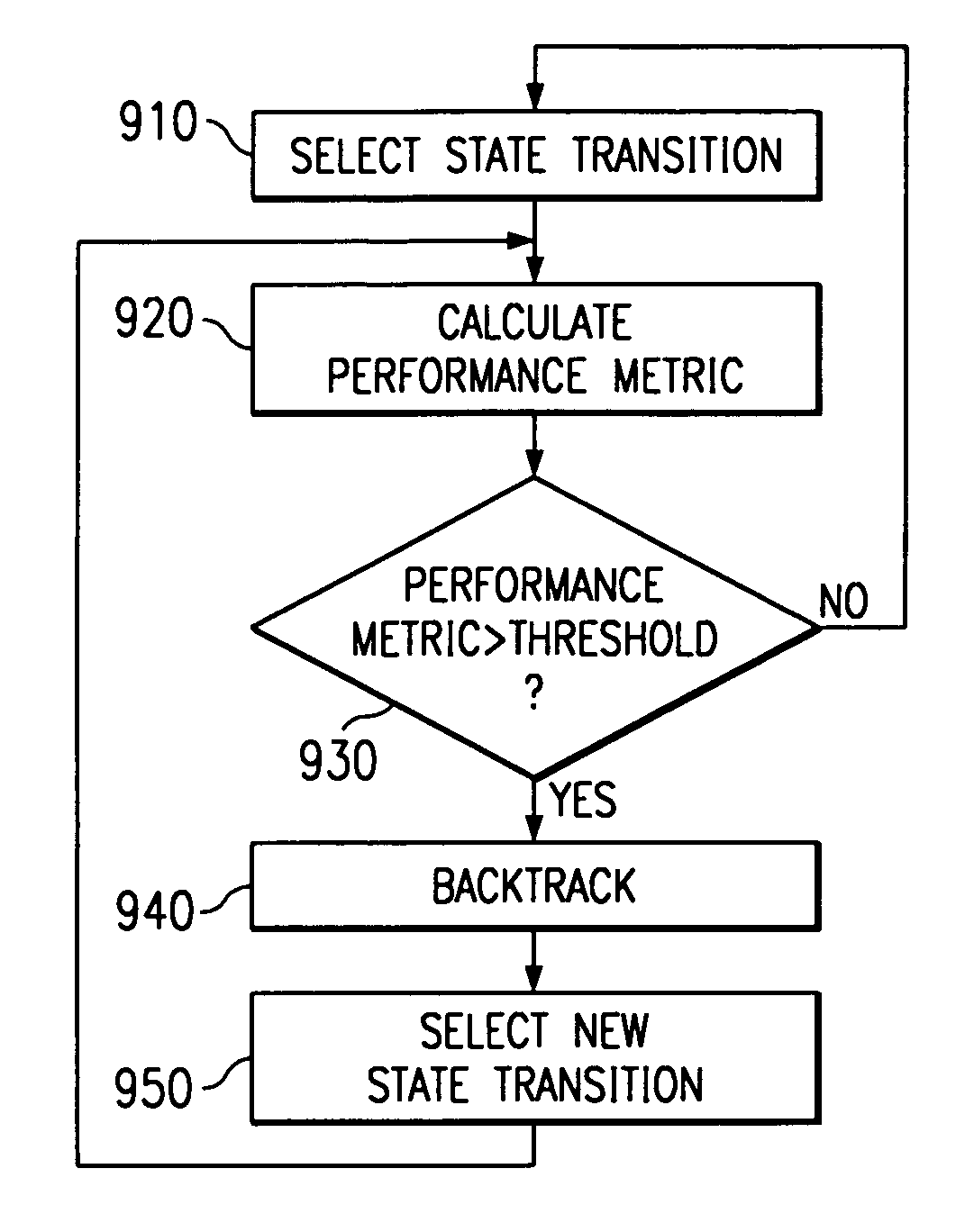

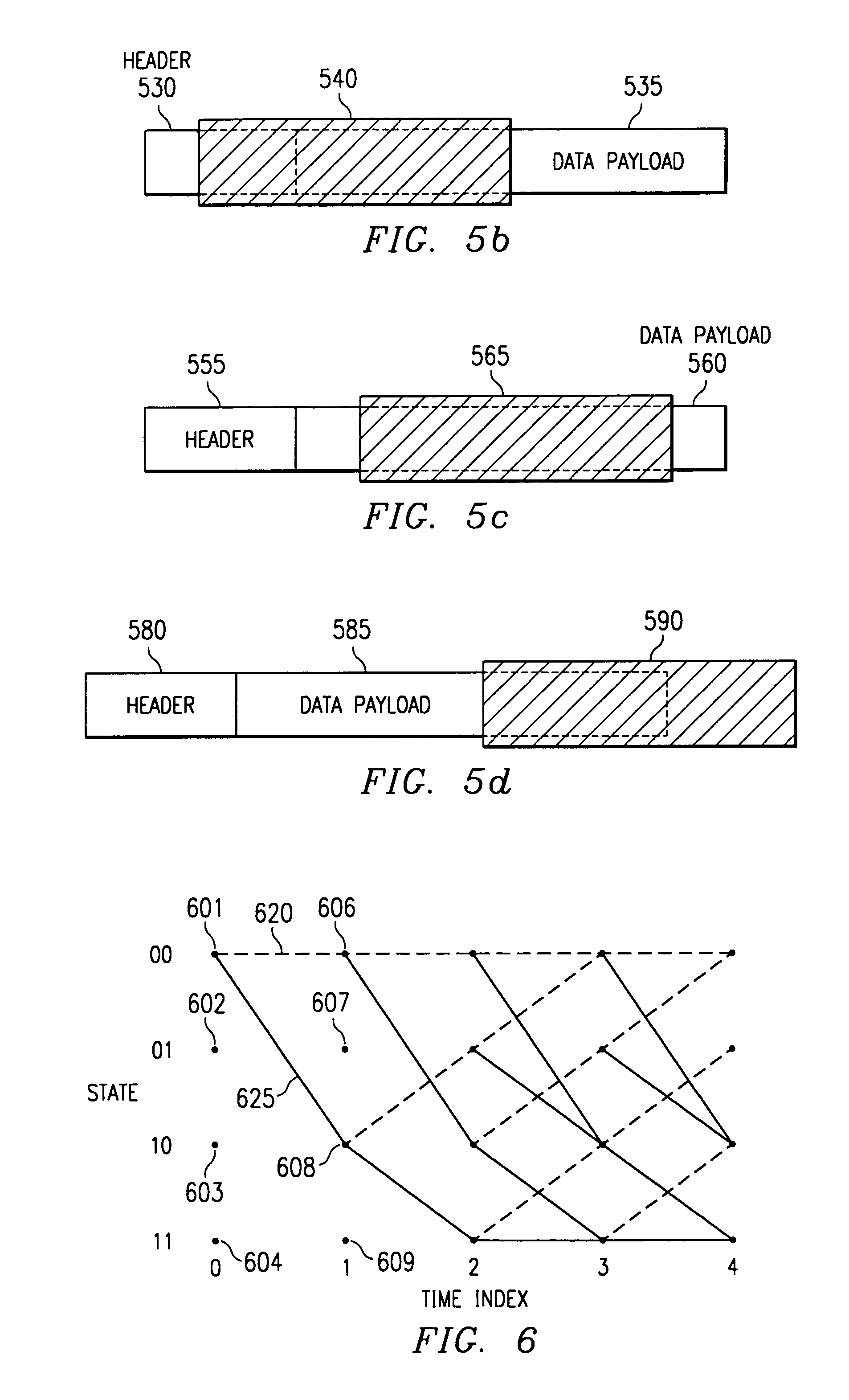

Sequential decoding with backtracking and adaptive equalization to combat narrowband interference

ActiveUS7099412B2Significant performanceError preventionAmplitude-modulated carrier systemsSignal-to-noise ratio (imaging)Narrowband interference

Narrowband interference can seriously degrade the overall performance of a communications network without significantly damaging a large percentage of the communications network's transmissions. In a single tone communications network, narrowband interference can reduce the overall signal-to-noise ratio to a level such that a receiver can no longer accurately decode the received transmission. However, the receiver's filters and equalizers often can filter out the effects of the narrowband interference and the receiver can accurately decode the received transmission if the receiver can restart the decoding at the point when the narrowband interference began interfering with the transmission. A technique using sequential decoding with backtracking and adaptive equalization permits the receiver to adapt to the presence of the narrowband interference and backtrack the decoding to a point prior to the interference.

Owner:TEXAS INSTR INC

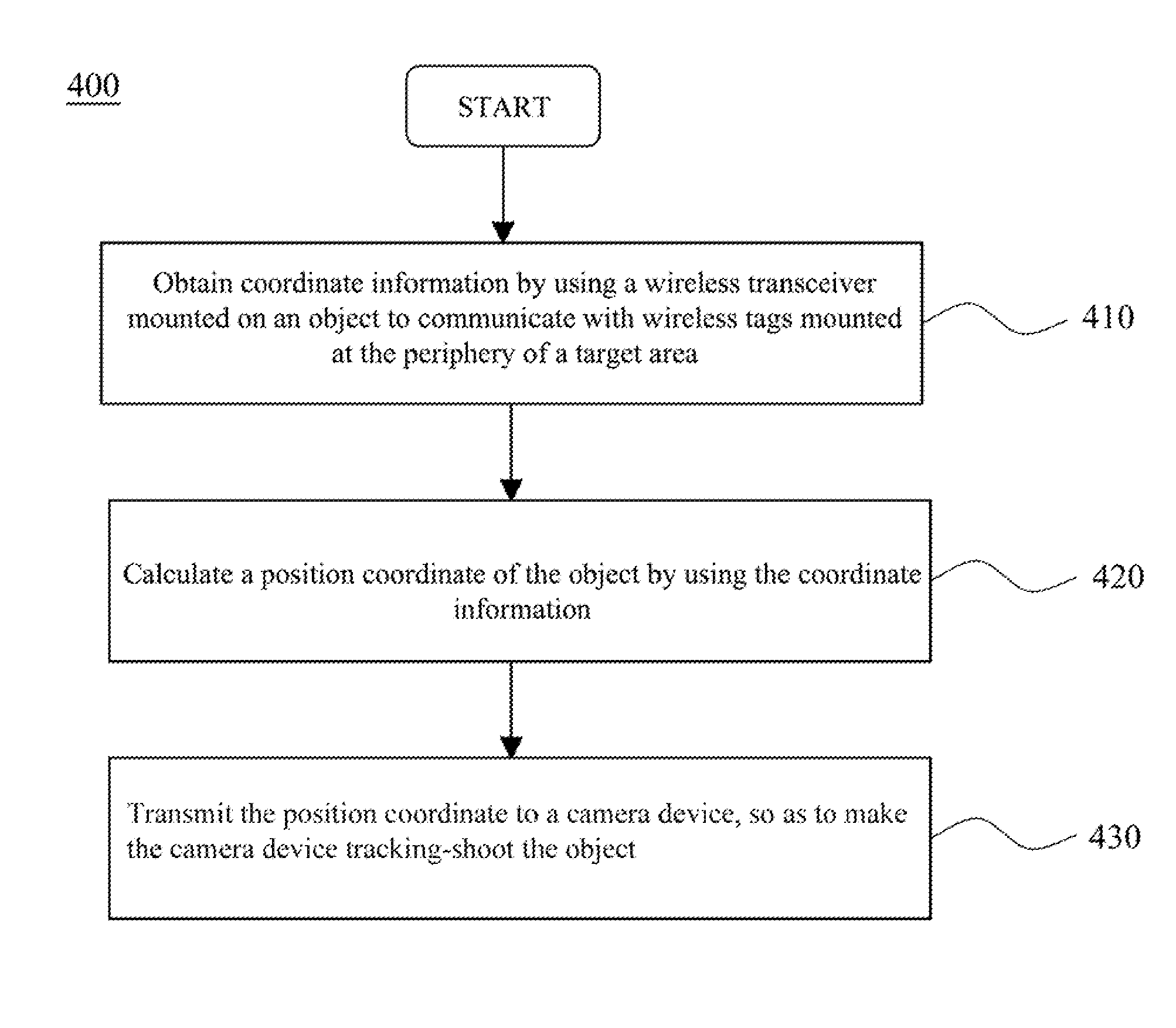

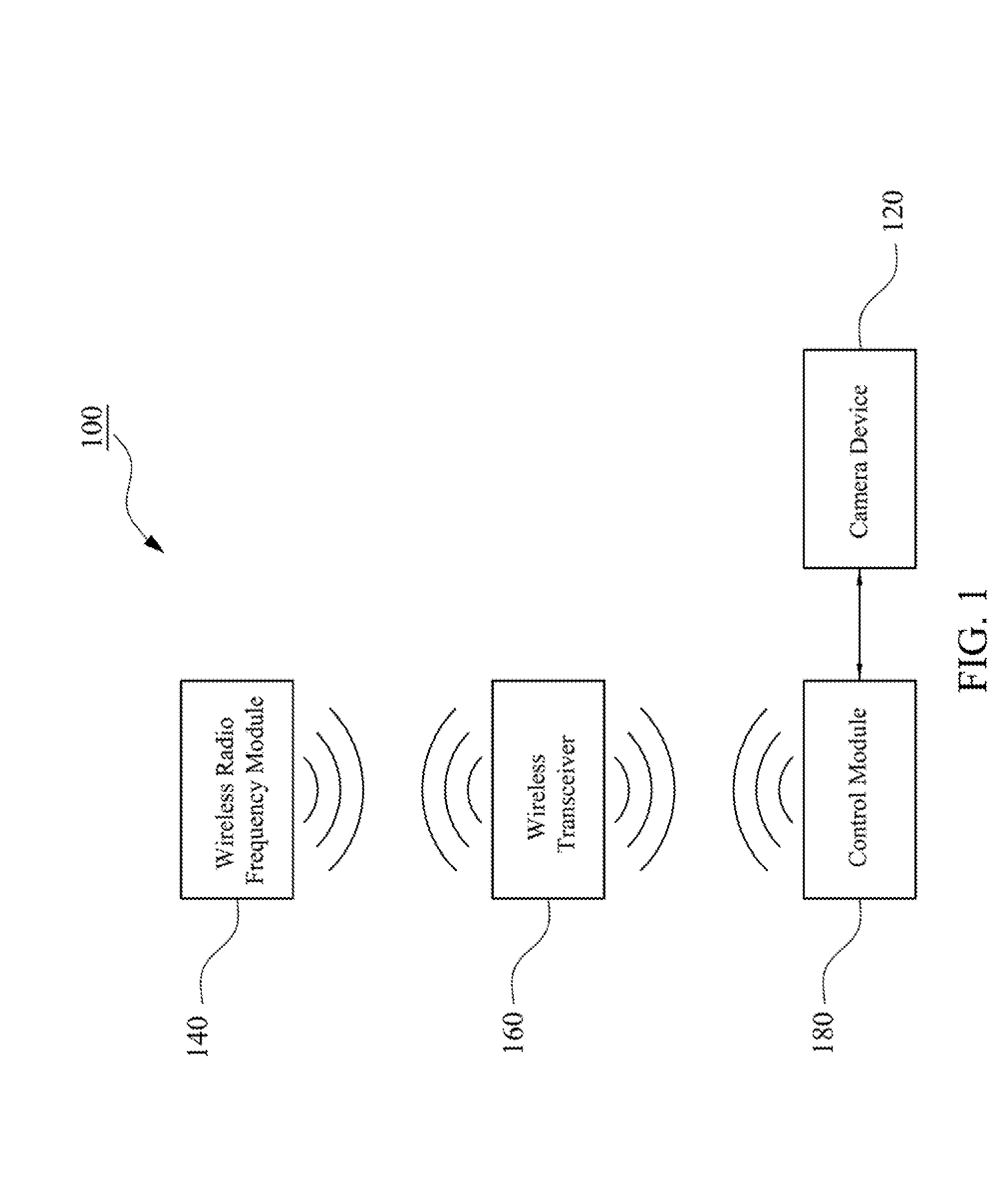

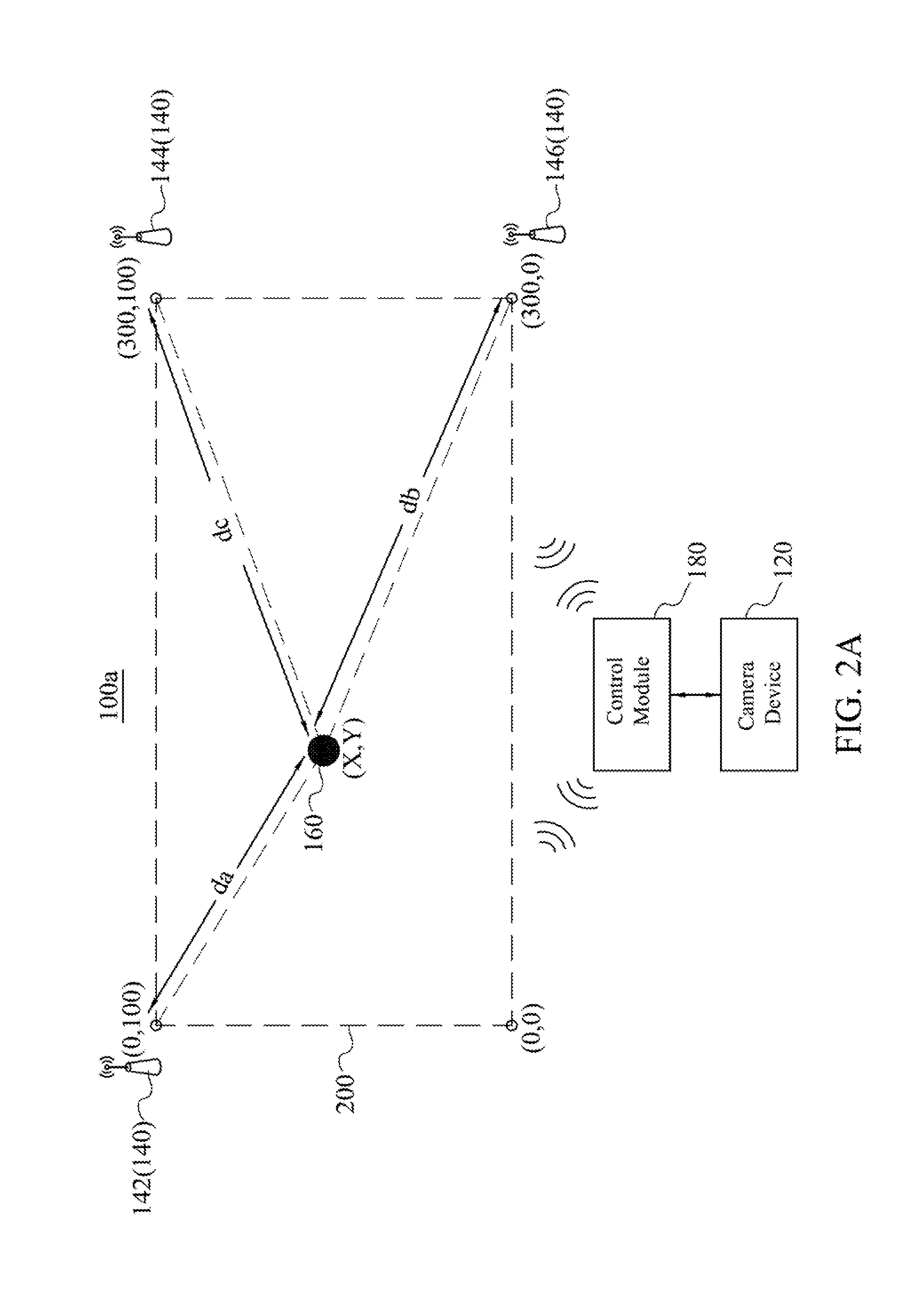

Tracking shooting system and method

InactiveUS20140313346A1High accuracy of trackingBig advantageTelevision system detailsColor television detailsComputer hardwareInformation control

A tracking shooting system and method are disclosed herein. The tracking shooting system includes a camera device, a wireless radio frequency module, a wireless transceiver and a control module. The wireless radio frequency module is mounted beside a target area. The wireless transceiver is disposed on an object, and is configured to communicate with the wireless radio frequency module to obtain coordinate information. The control module is configured to receive the coordinate information transmitted from the wireless transceiver, and to calculate a position coordinate of the object in accordance with the coordinate information. The control module controls the camera device in accordance with the position coordinate, so as to tracking-shoot the object.

Owner:AVER INFORMATION INC

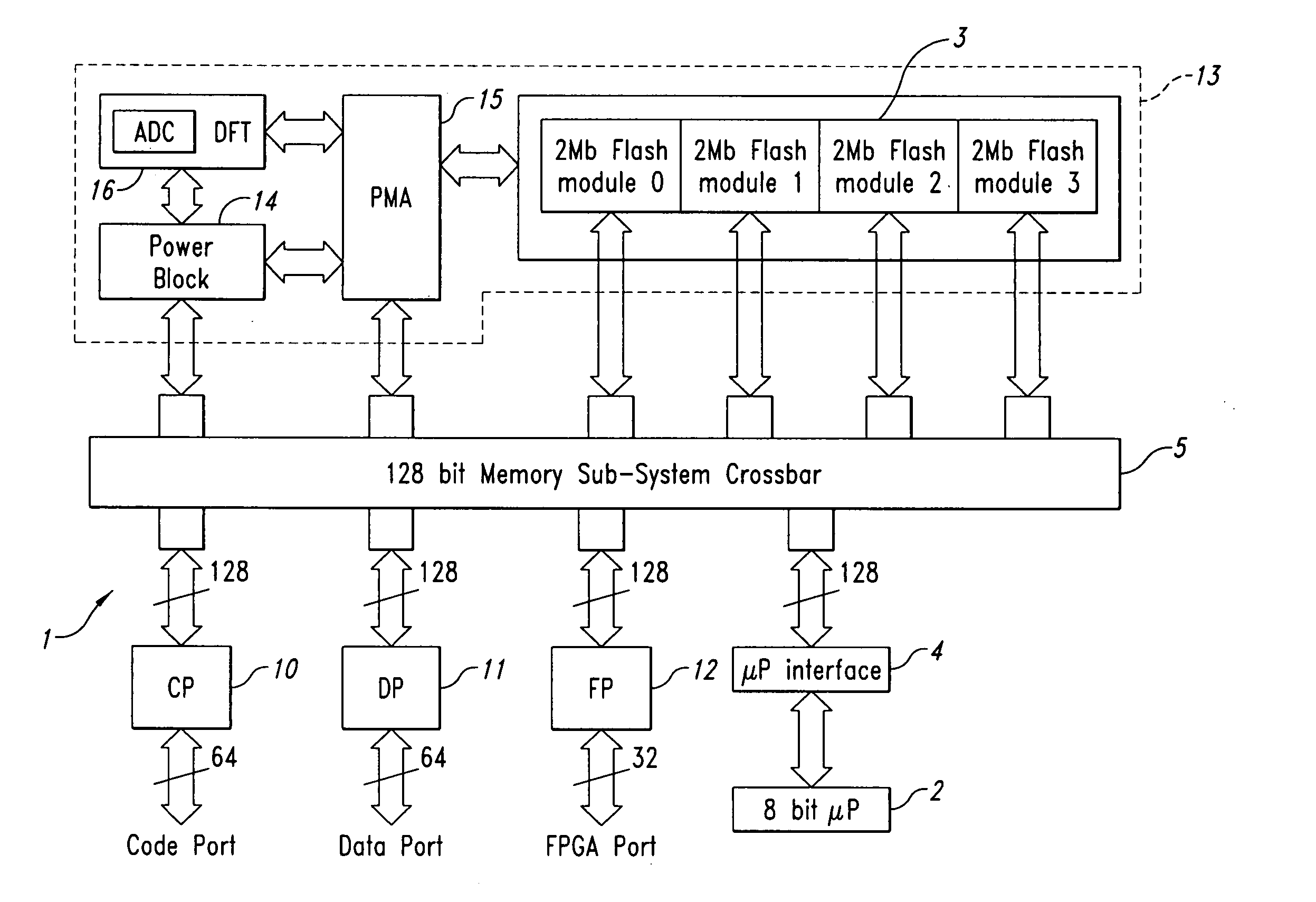

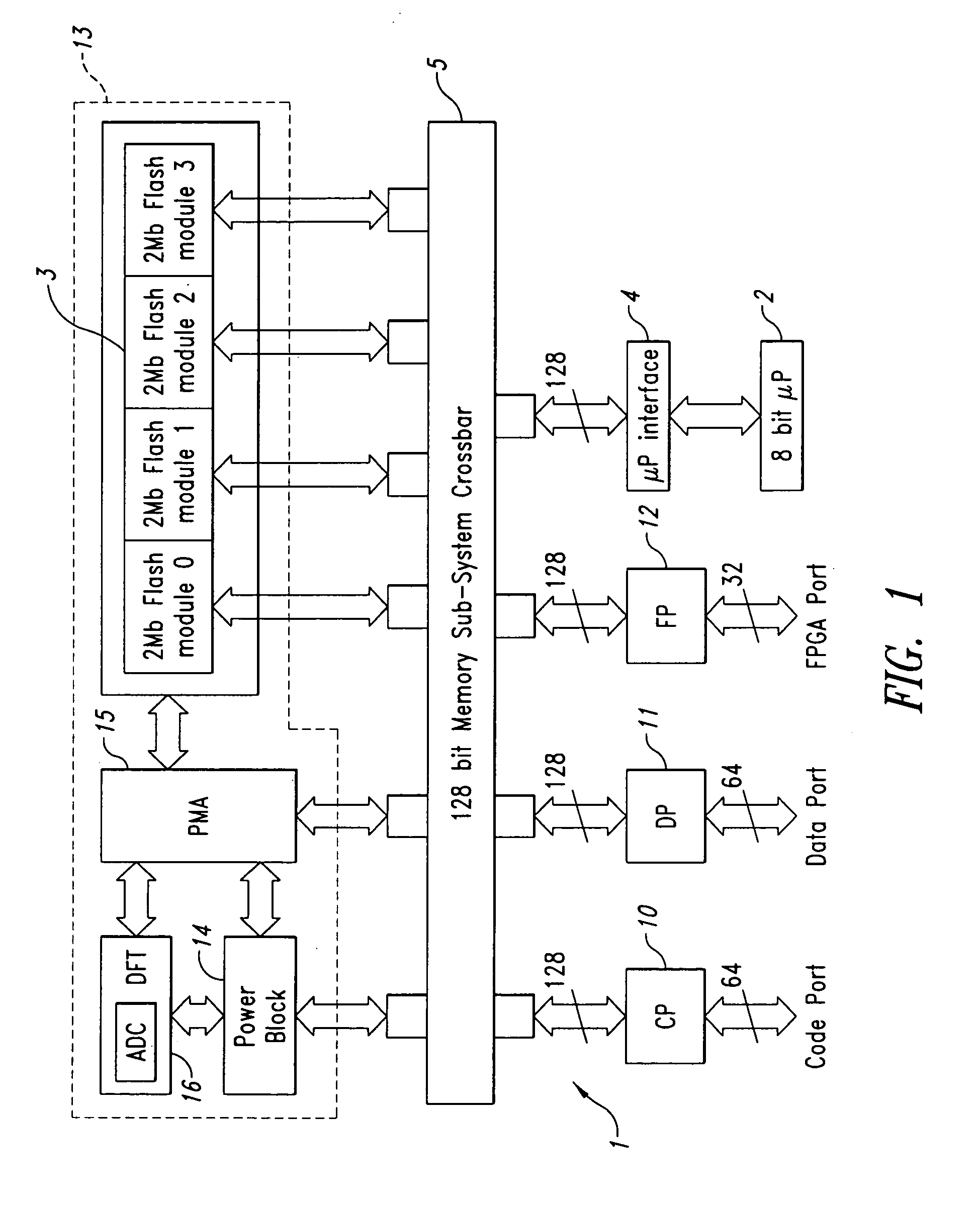

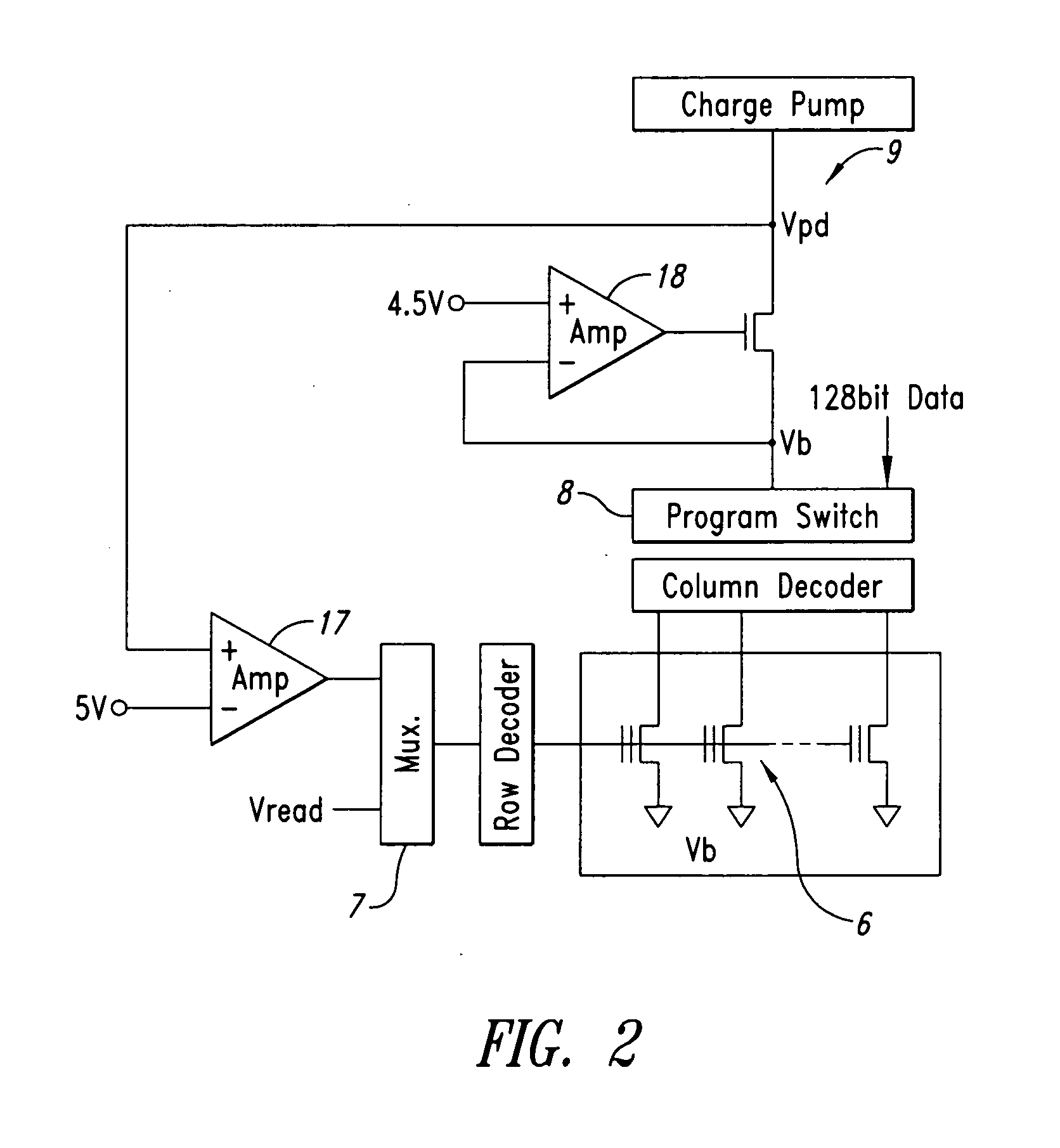

Embeddable flash memory system for non-volatile storage of code, data and bit-streams for embedded FPGA configurations

InactiveUS20050005055A1Significant energySignificant performanceMemory adressing/allocation/relocationRead-only memoriesEmbedded technologyApplication specific

An application-specific embeddable flash memory having three content-specific I / O ports and delivering a peak read throughput of 1.2 GB / s. The memory is combined with a special automatic programming gate voltage ramp generator circuit having a programming rate of 1 Mbyte / s for non-volatile storage of code, data, and embedded FPGA bit stream configurations. The test chip uses a NOR-type 0.18 μm flash embedded technology with 1.8V power supply, two poly, six metal and memory cell size of 0.35 μm2.

Owner:STMICROELECTRONICS SRL

Intelligent feed switch

ActiveUS9990393B2Minimize of data processingMinimize powerDatabase queryingFinanceOnline tradingElectronic trading

Various techniques are disclosed for offloading the processing of data packets. For example, incoming data packets can be processed through an offload processor to generate a new stream of outgoing data packets that organize data from the data packets in a manner different than the incoming data packets. Furthermore, in an exemplary embodiment, the offloaded processing can be resident in an intelligent switch, such as an intelligent switch upstream or downstream from an electronic trading platform.

Owner:IP RESERVOIR

Offload processing of data packets containing financial market data

Various techniques are disclosed for offloading the processing of data packets that contain financial market data. For example, incoming data packets can be processed through an offload processor to generate a new stream of outgoing data packets that organize financial market data in a manner different than the incoming data packets. Furthermore, in an exemplary embodiment, the offloaded processing can be resident in an intelligent switch, such as an intelligent switch upstream or downstream from an electronic trading platform.

Owner:IP RESERVOIR

Offload processing of data packets

Various techniques are disclosed for offloading the processing of data packets. For example, incoming data packets can be processed through an offload processor to generate a new stream of outgoing data packets that organize data from the data packets in a manner different than the incoming data packets. Furthermore, in an exemplary embodiment, the offloaded processing can be resident in an intelligent switch, such as an intelligent switch upstream or downstream from an electronic trading platform.

Owner:IP RESERVOIR

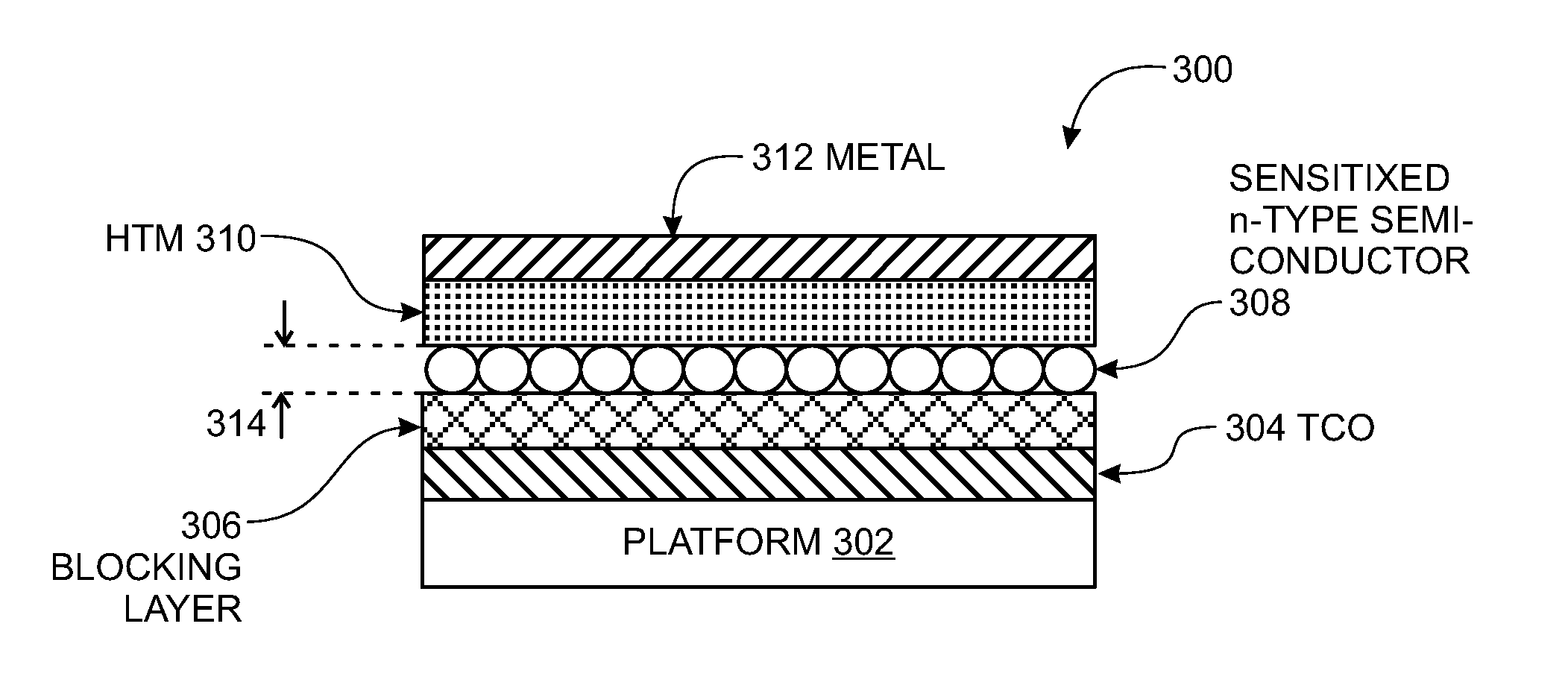

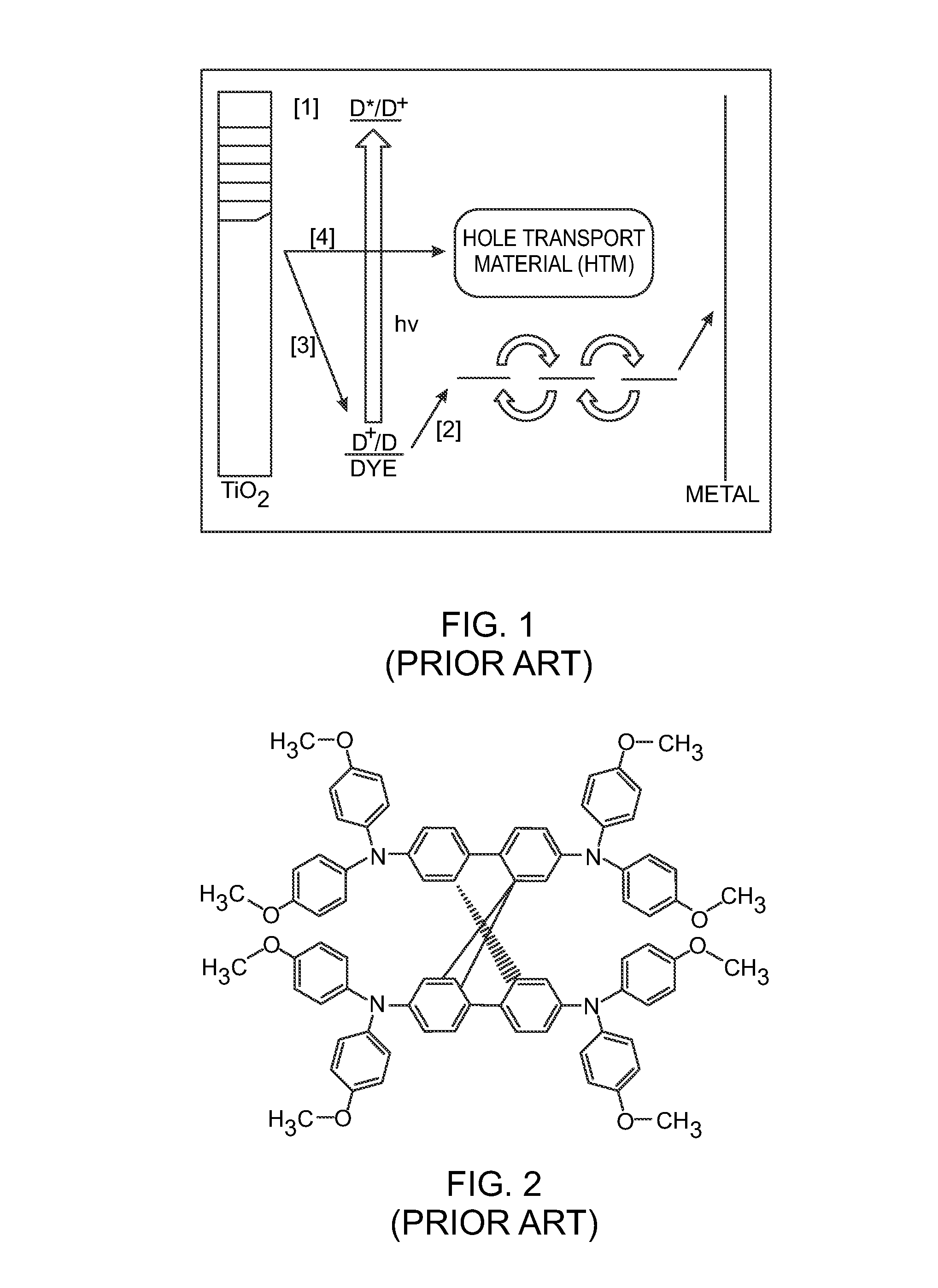

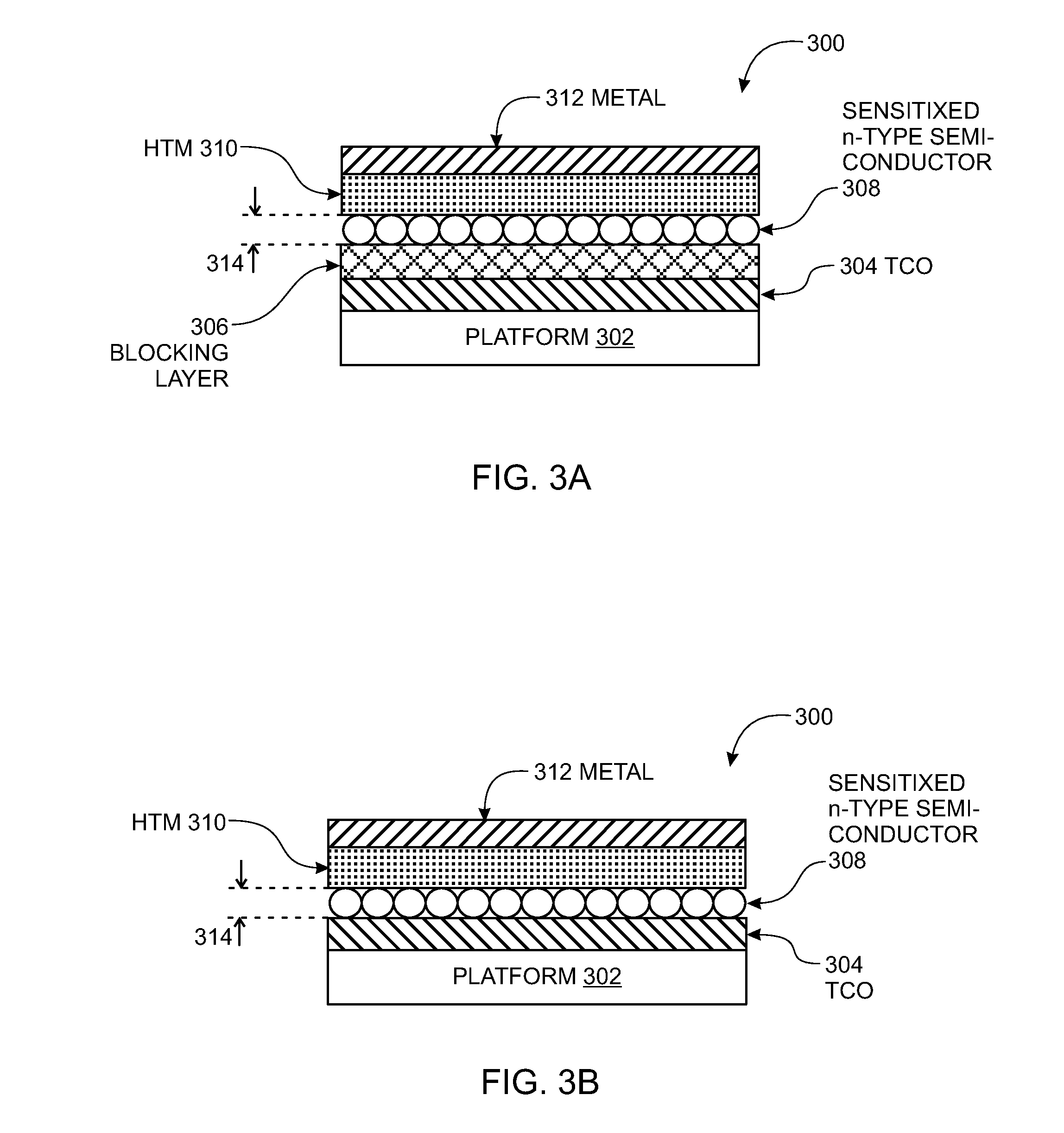

Solid-State Dye-Sensitized Solar Cell Using Oxidative Dopant

InactiveUS20140116509A1Improve performanceSignificant performanceConductive materialSolid-state devicesNeutral ChargeOrganic semiconductor

A solid-state hole transport composite material (ssHTM) is provided. The ssHTM is made from a neutral charge first p-type organic semiconductor, and a chemically oxidized first p-type semiconductor, where the dopants are silver(I) containing materials. A reduced form of the silver(I) containing material is also retained as functional component in the ssHTM. In one aspect, the silver(I) containing material is silver bis(trifluoromethanesulfonyl)imide (TFSI). In another aspect, the first p-type organic semiconductor is 2,2′,7,7′-tetrakis(N,N-di-p-methoxyphenylamine)-9,9′-spirobifluorene (Spiro-OMeTAD). In one variation, the ssHTM additionally includes a first p-type organic semiconductor doped with an ionic dopant such as lithium (Li+), sodium (Na+), potassium (K+), or combinations of the above-mentioned materials. Also provided are a method for synthesizing the above-described ssHTM, and a solid-state dye solar cell (ssDSC) fabricated from the ssHTM.

Owner:SHARP LAB OF AMERICA INC SLA

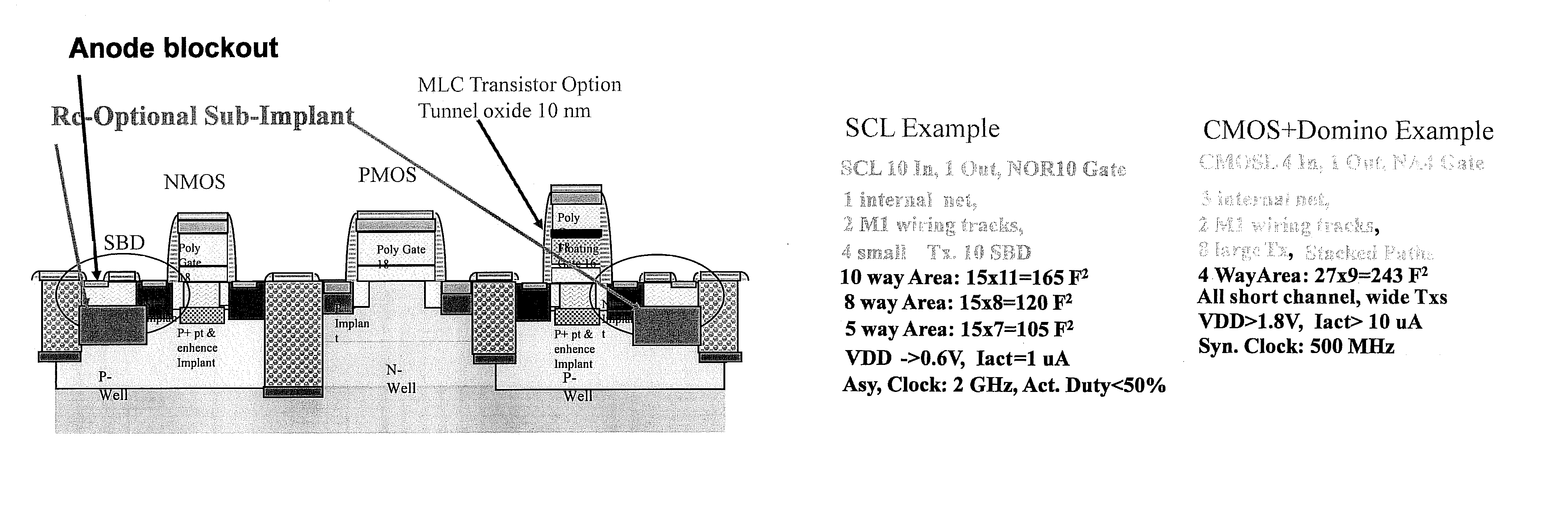

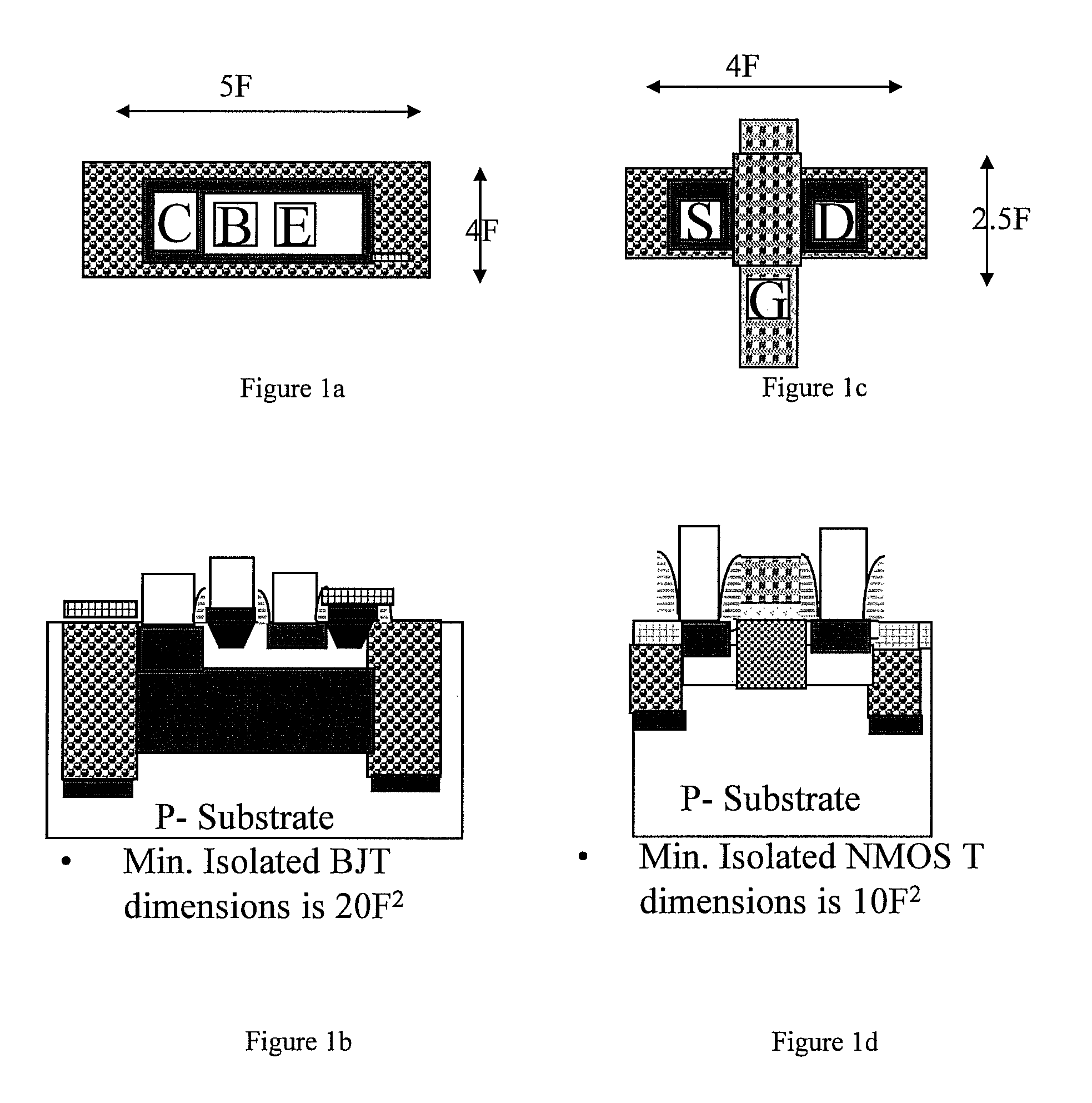

Super CMOS devices on a microelectronics system

ActiveUS8476689B2Significant costSignificant performanceTransistorSolid-state devicesCMOSSchottky barrier

A low cost IC solution is disclosed in accordance with an embodiment to provide Super CMOS microelectronics macros. Hereinafter, the Super CMOS or Schottky CMOS all refer to SCMOS. The SCMOS device solutions with a niche circuit element, the complementary low threshold Schottky barrier diode pairs (SBD) made by selected metal barrier contacts (Co / Ti) to P- and N- Si beds of the CMOS transistors. A DTL like new circuit topology and designed wide contents of broad product libraries, which used the integrated SBD and transistors (BJT, CMOS, and Flash versions) as basic components. The macros are composed of diodes that are selectively attached to the diffusion bed of the transistors, configuring them to form generic logic gates, memory cores, and analog functional blocks from simple to the complicated, from discrete components to all grades of VLSI chips. Solar photon voltaic electricity conversion and bio-lab-on-a-chip are two newly extended fields of the SCMOS IC applications.

Owner:SCHOTTKY LSI

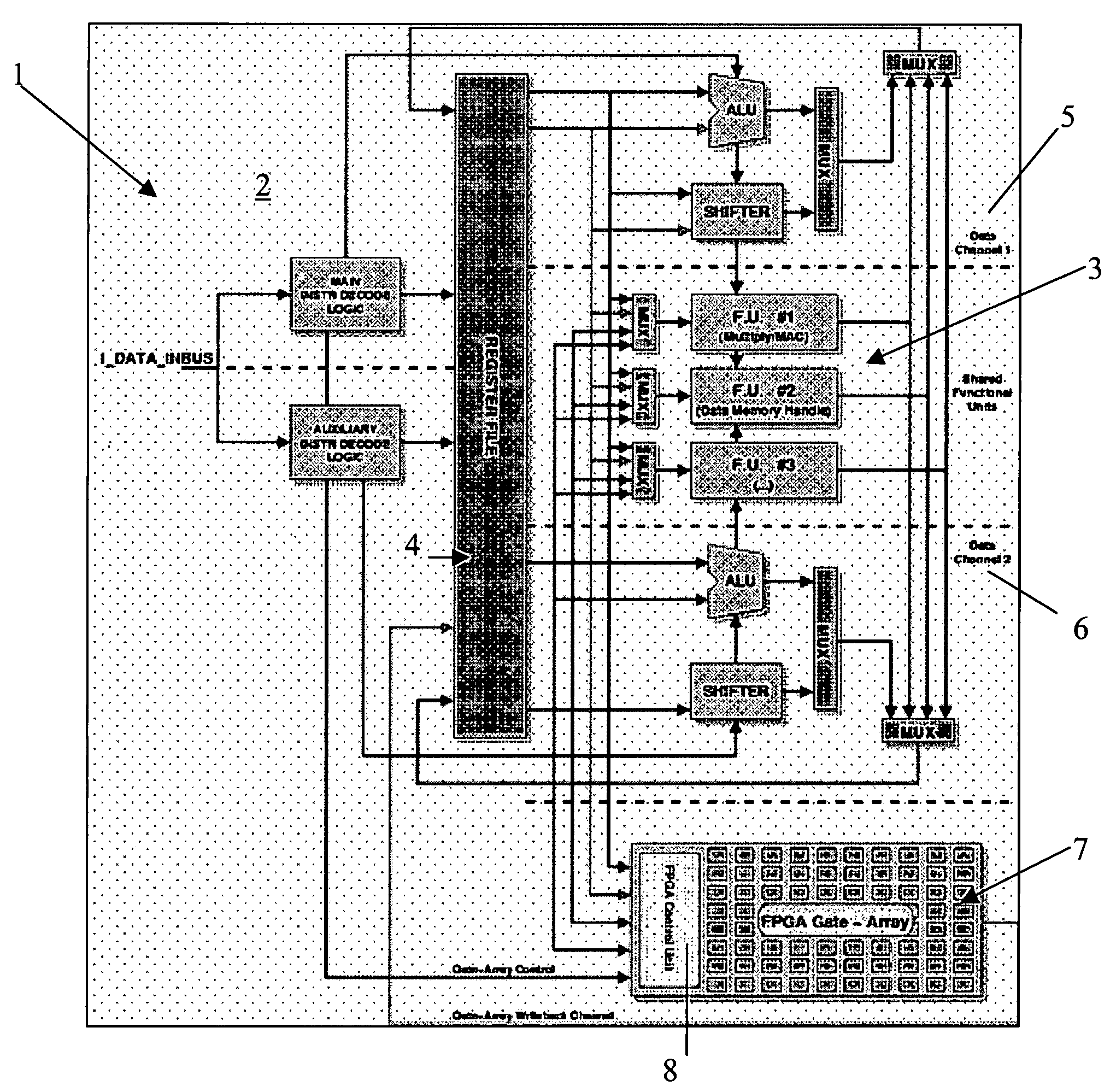

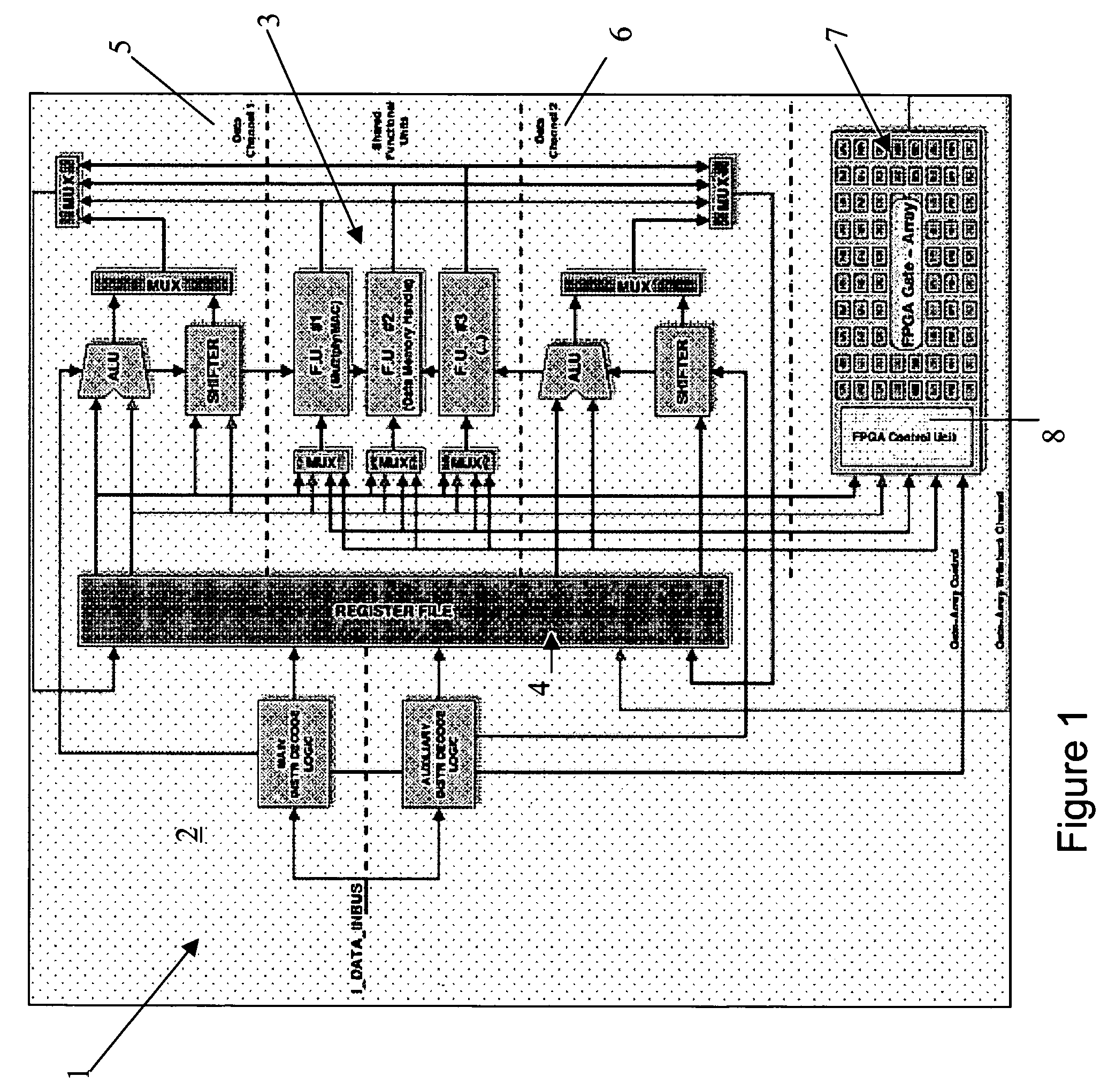

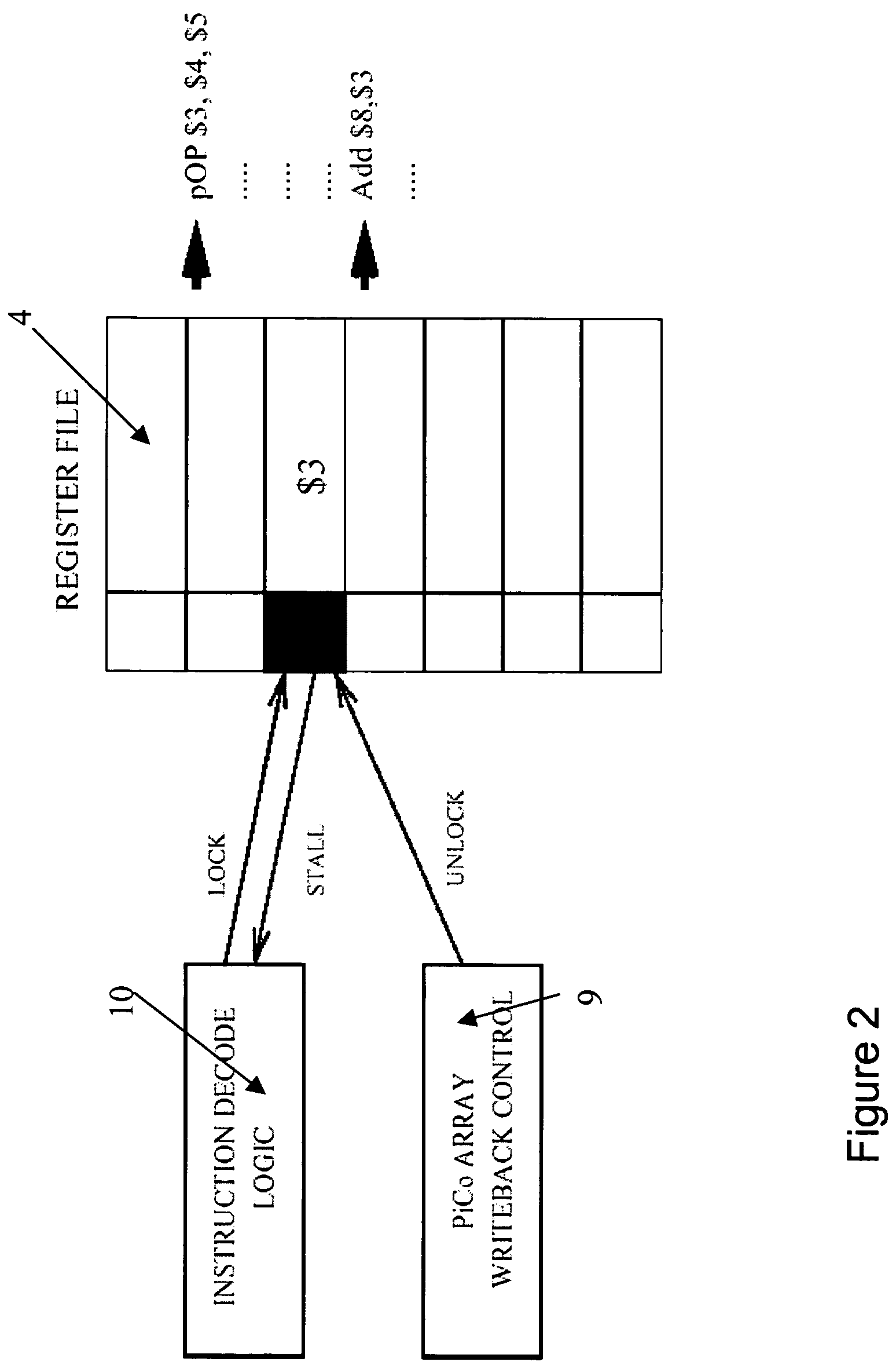

Digital architecture for reconfigurable computing in digital signal processing

ActiveUS7225319B2Significant energySignificant performanceConcurrent instruction executionArchitecture with single central processing unitMicrocontrollerDigital signal processing

A digital embedded architecture, includes a microcontroller and a memory device, suitable for reconfigurable computing in digital signal processing and comprising: a processor, structured to implement a Very Long Instruction Word elaboration mode by a general purpose hardwired computational logic, and an additional data elaboration channel comprising a reconfigurable function unit based on a pipelined array of configurable look-up table based cells controlled by a special purpose control unit, thus easing the elaboration of critical kernels algorithms.

Owner:STMICROELECTRONICS SRL