Patents

Literature

48 results about "Postsynapse" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The part of a synapse that is part of the post-synaptic cell. [GOC:dos]

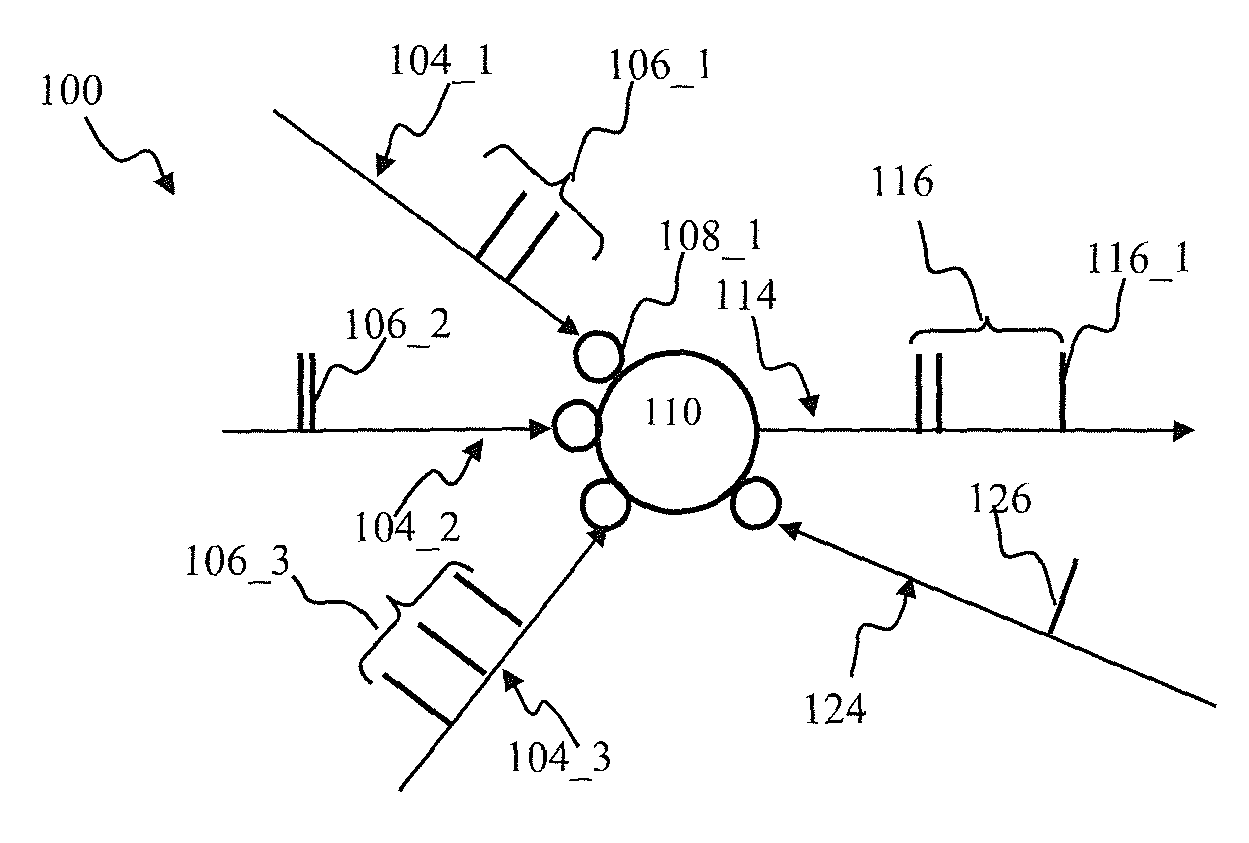

Neural network learning and collaboration apparatus and methods

ActiveUS20140089232A1Reinforce similar learning experienceIncrease macroNeural architecturesSpecial data processing applicationsNeural network learningArtificial intelligence

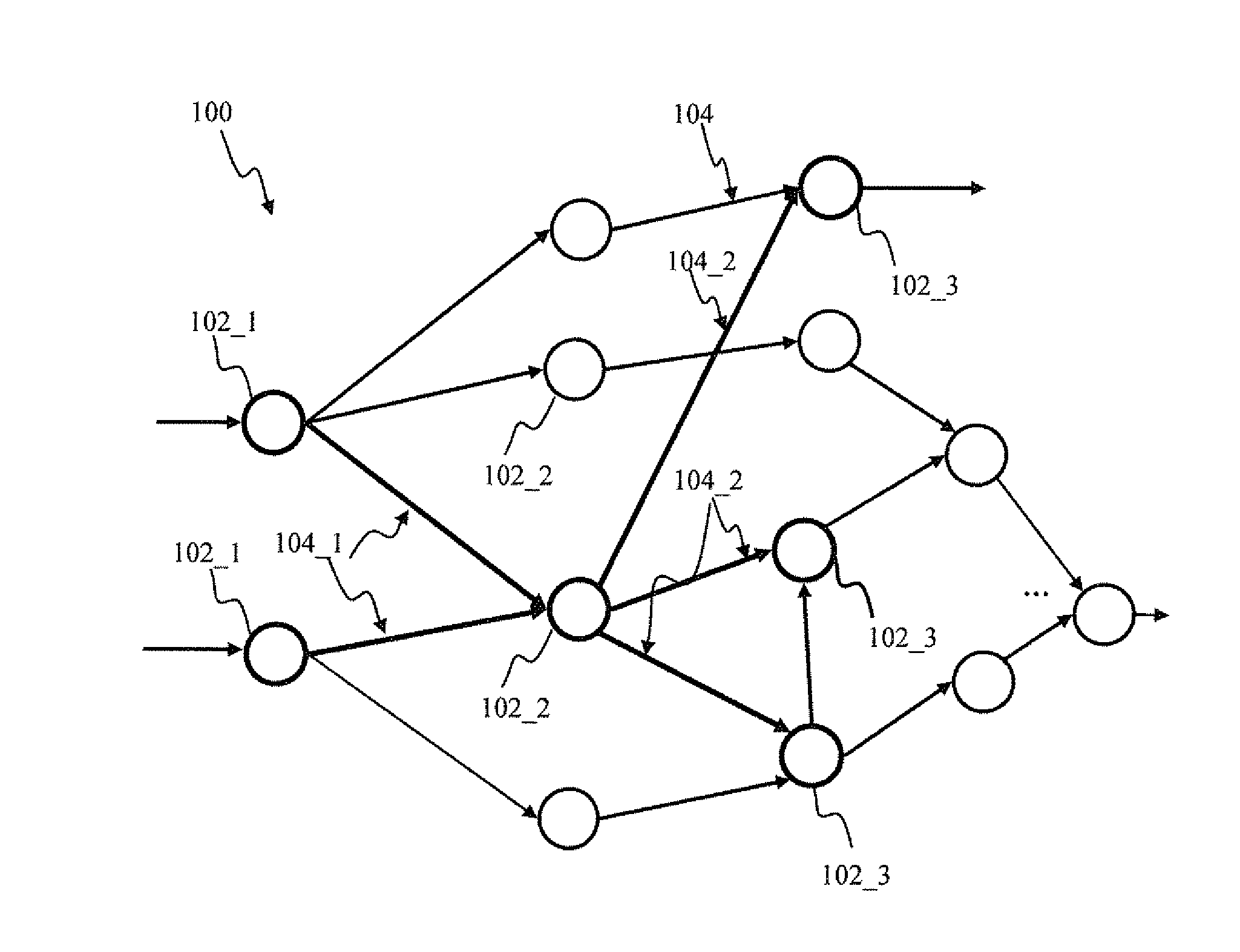

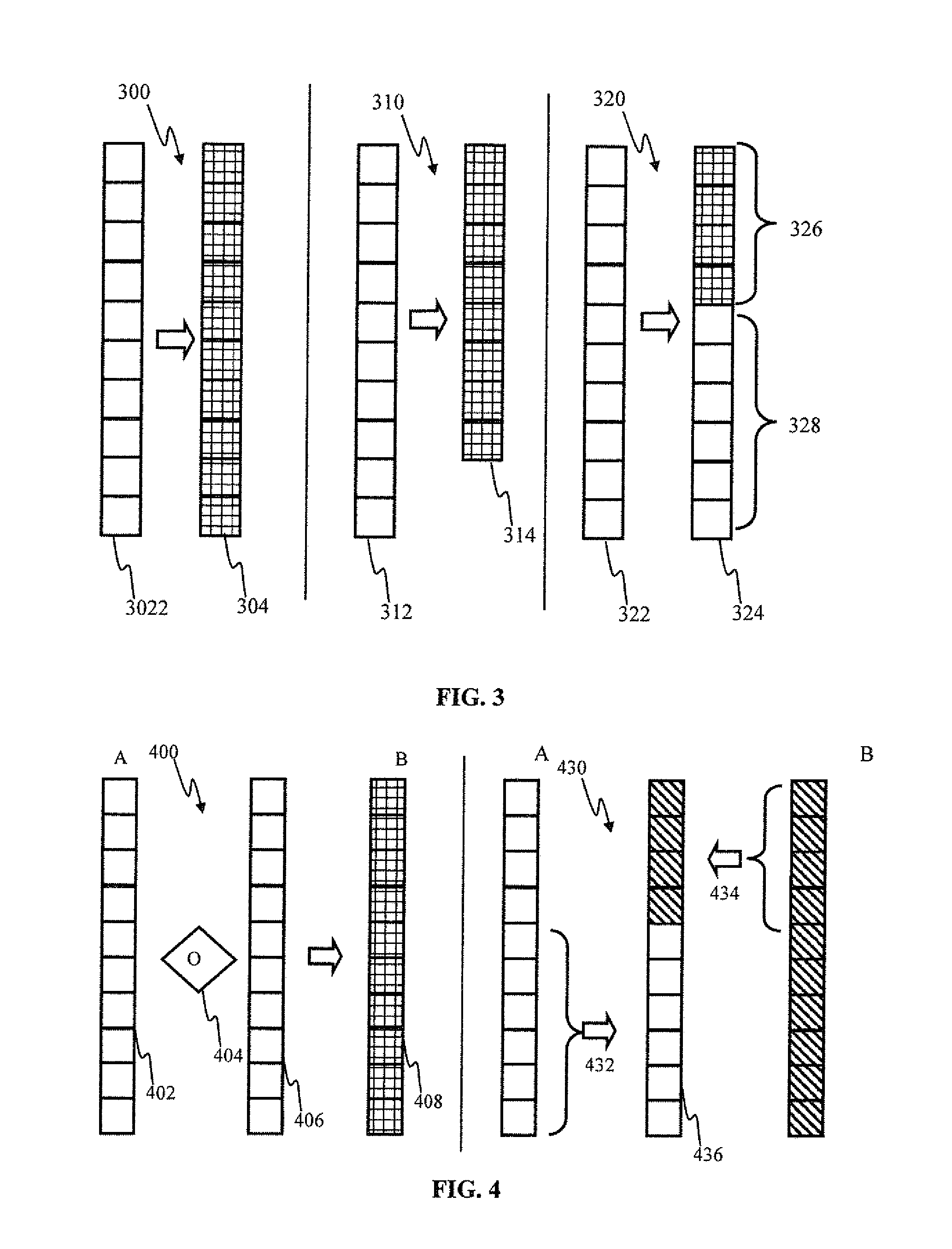

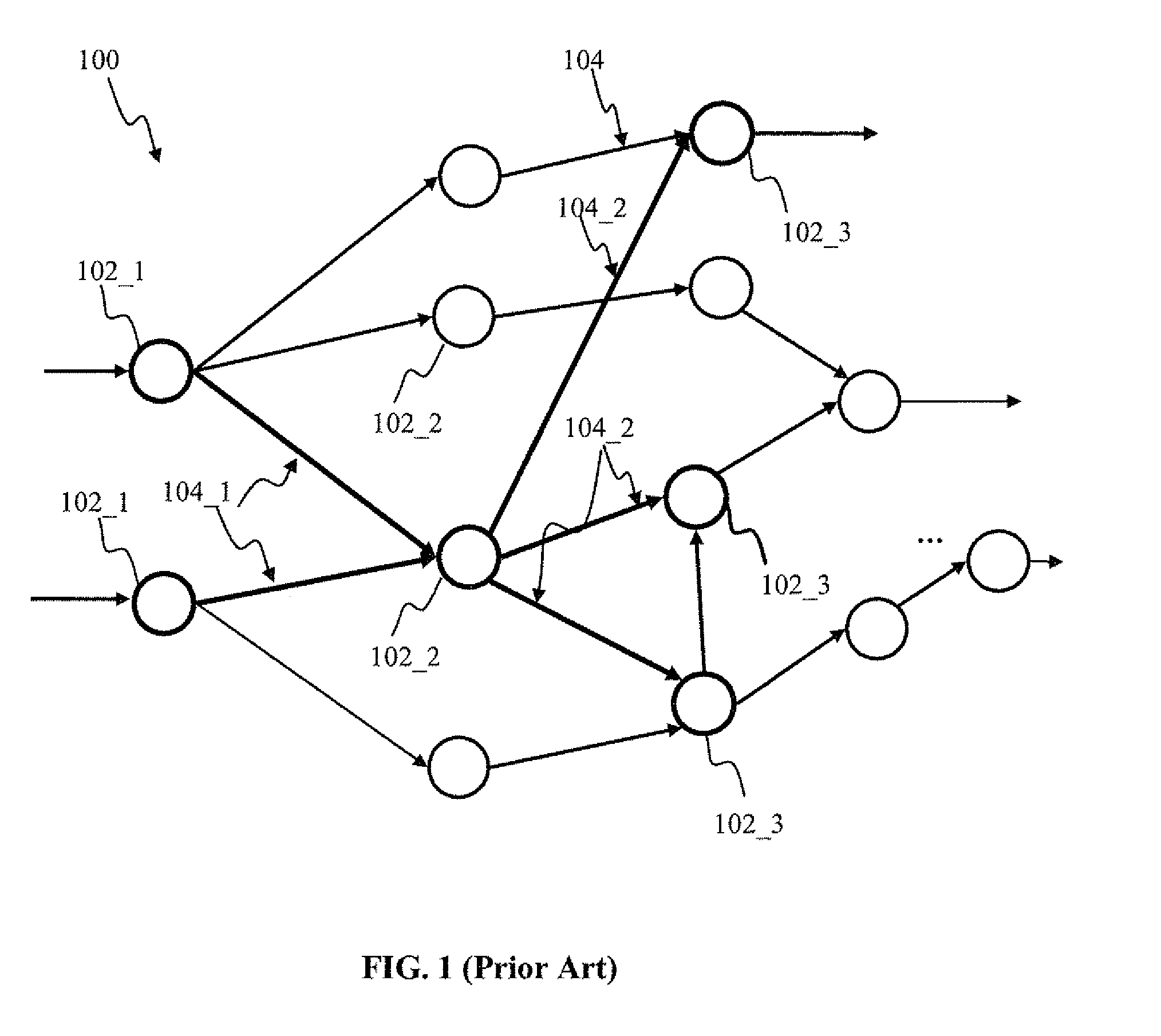

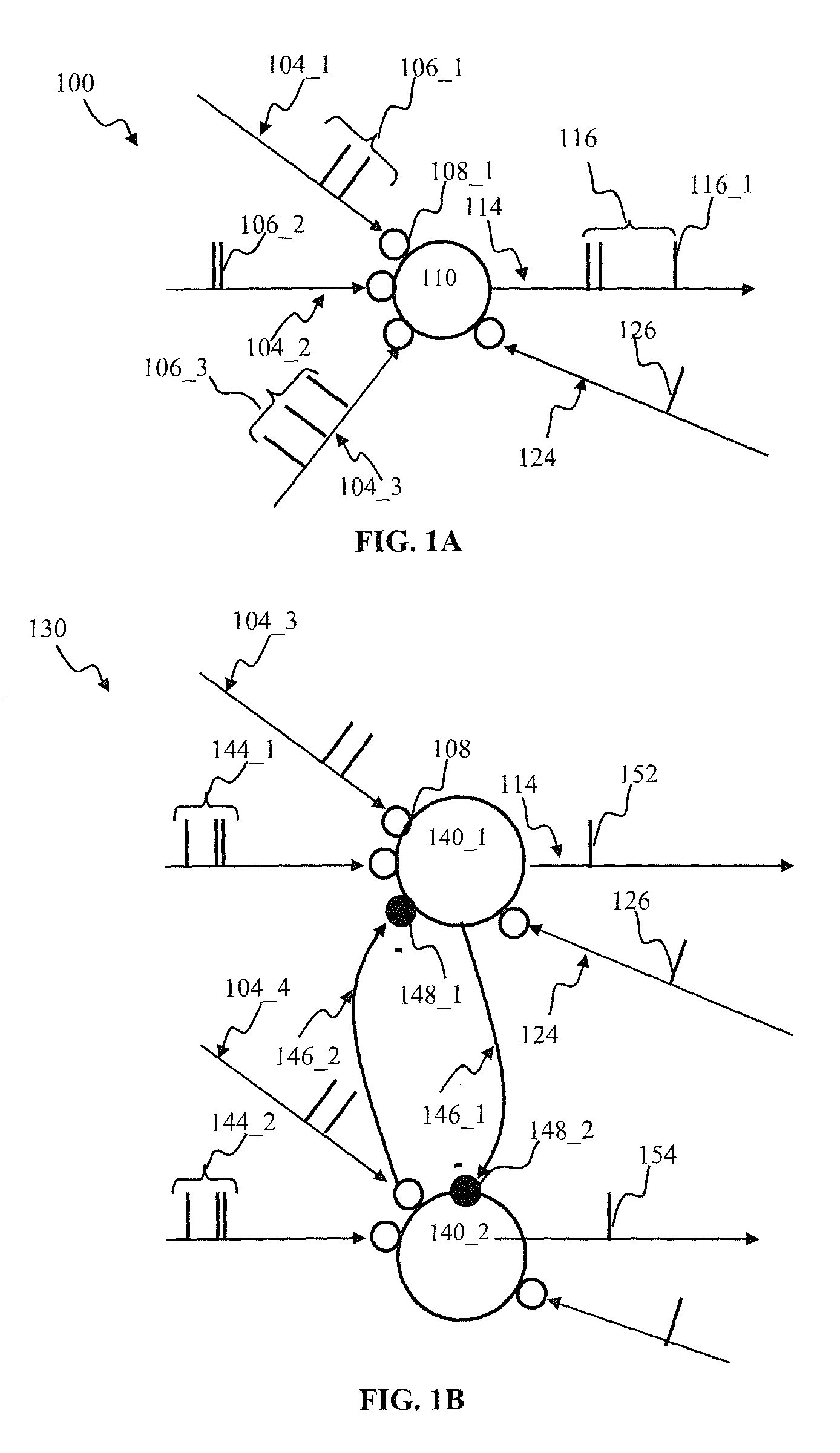

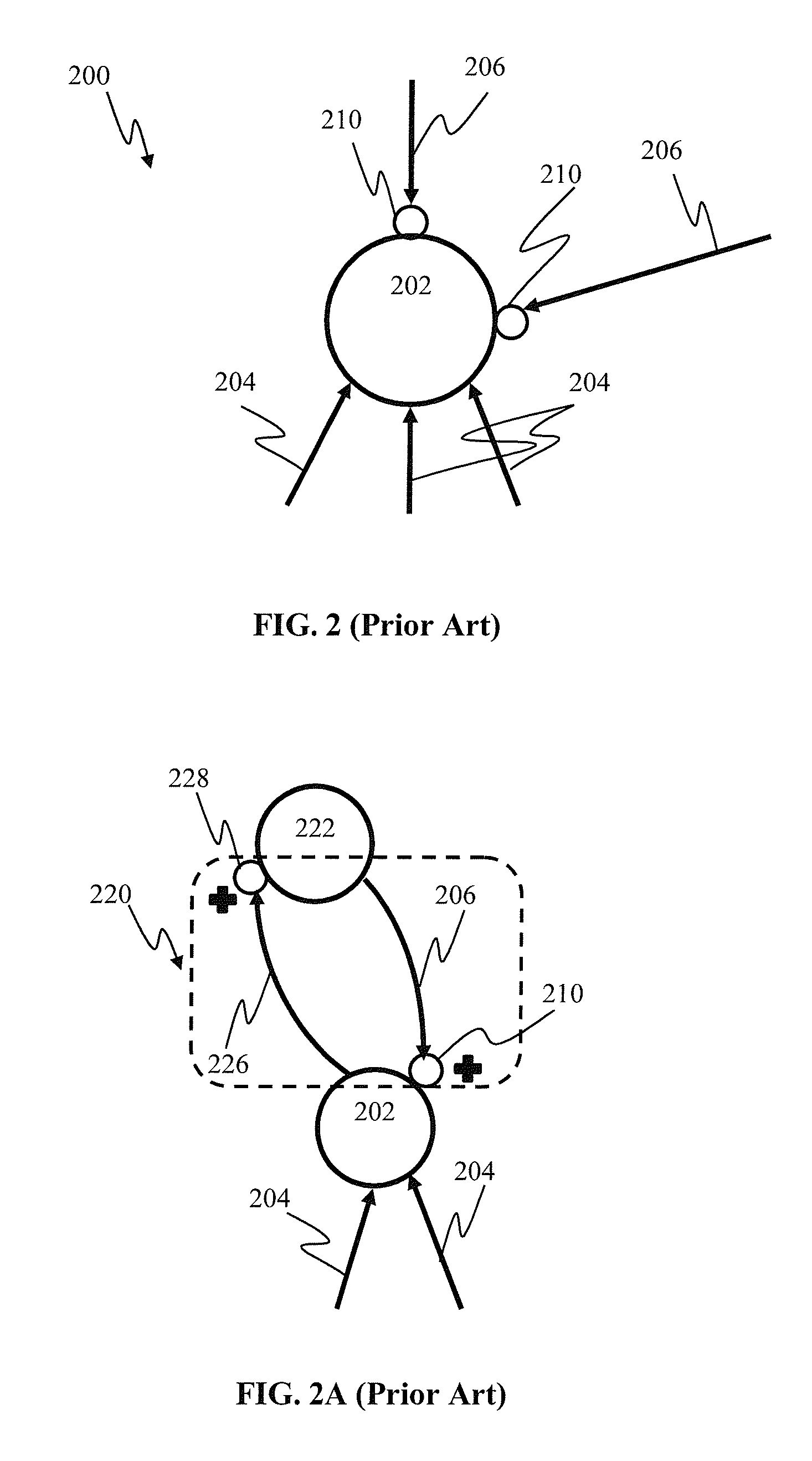

Apparatus and methods for learning and training in neural network-based devices. In one implementation, the devices each comprise multiple spiking neurons, configured to process sensory input. In one approach, alternate heterosynaptic plasticity mechanisms are used to enhance learning and field diversity within the devices. The selection of alternate plasticity rules is based on recent post-synaptic activity of neighboring neurons. Apparatus and methods for simplifying training of the devices are also disclosed, including a computer-based application. A data representation of the neural network may be imaged and transferred to another computational environment, effectively copying the brain. Techniques and architectures for achieve this training, storing, and distributing these data representations are also disclosed.

Owner:BRAIN CORP

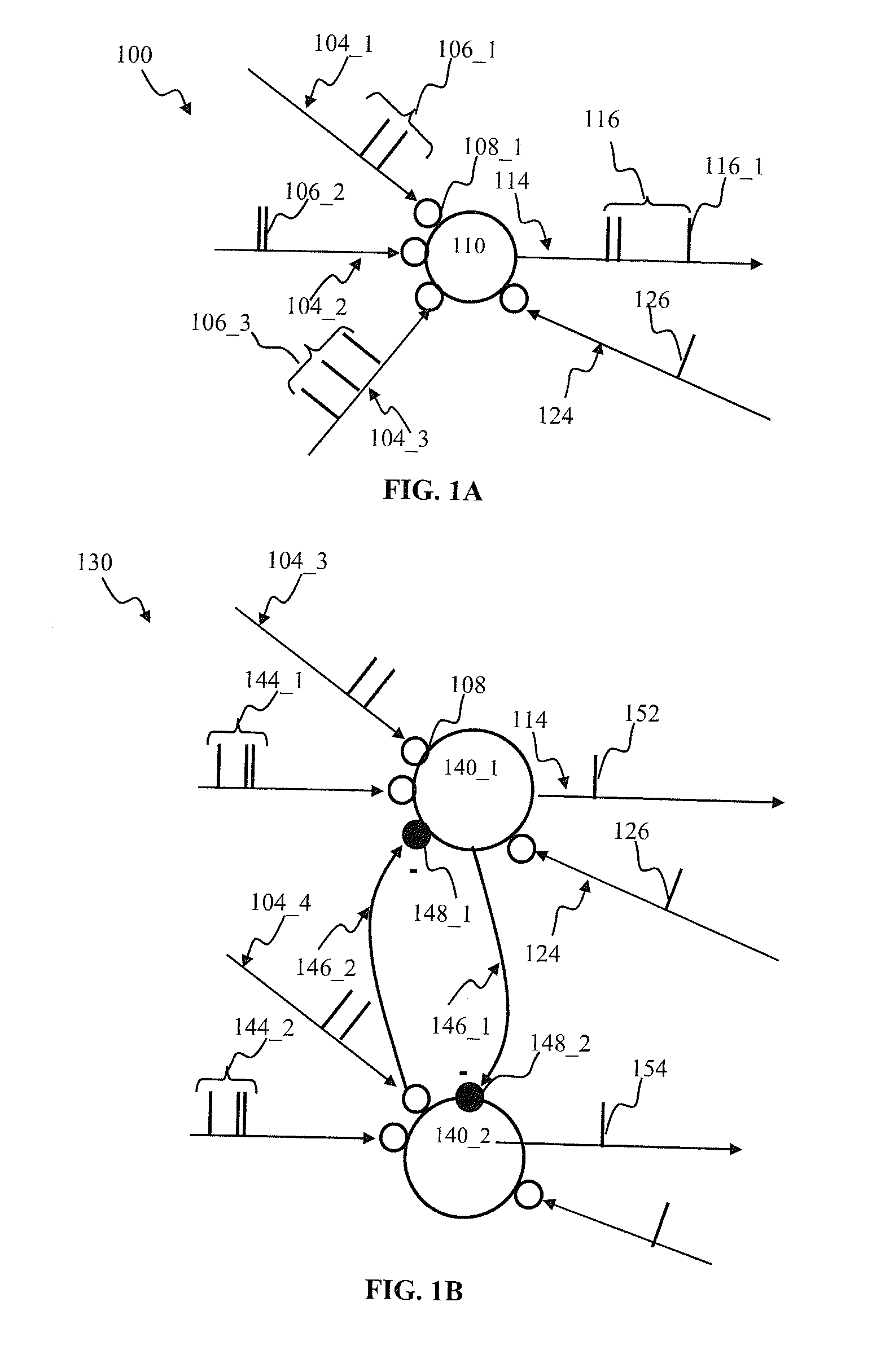

Sensory input processing apparatus in a spiking neural network

ActiveUS20130297542A1Reduce formationDigital computer detailsDigital dataSpiking neural networkSpike-timing-dependent plasticity

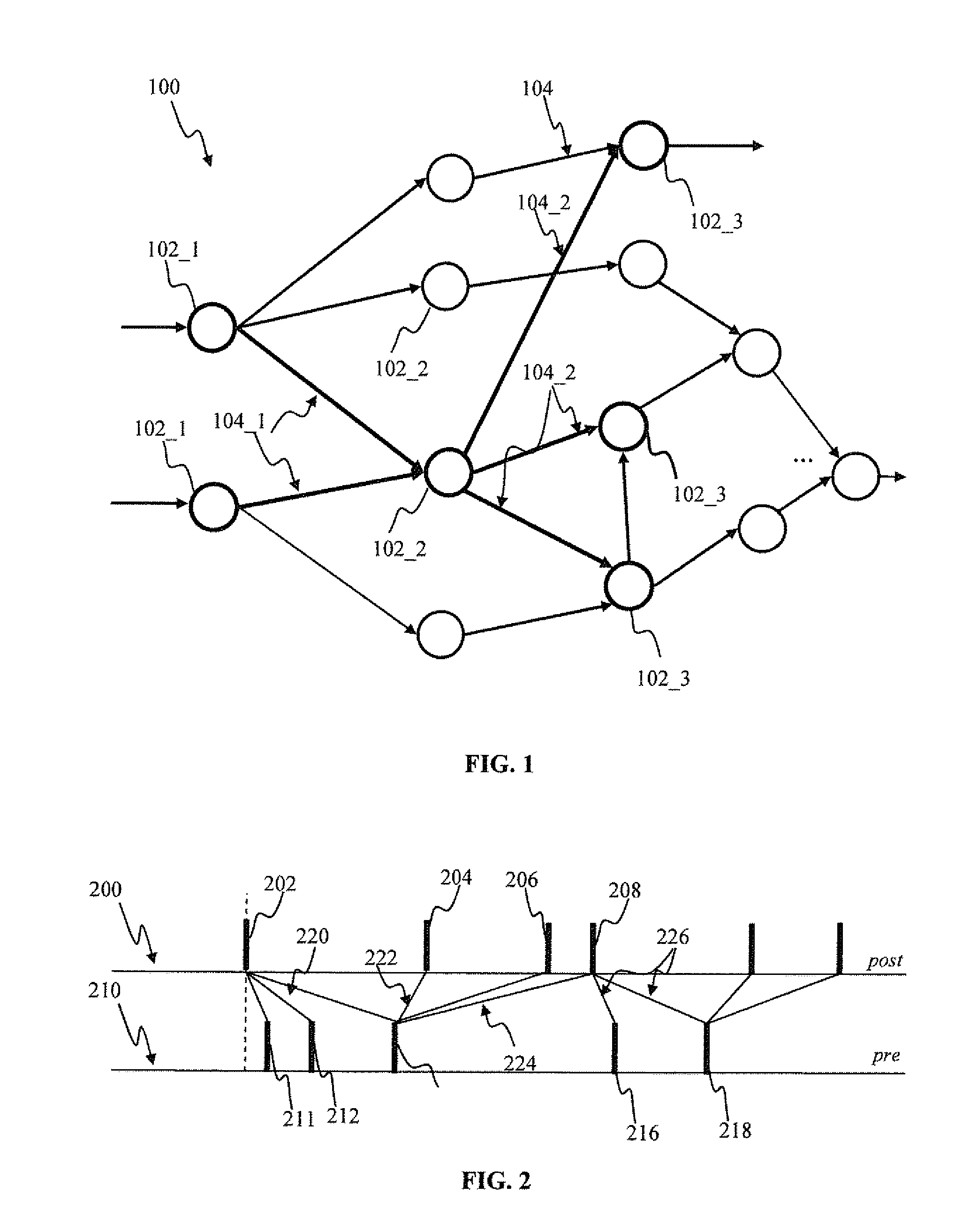

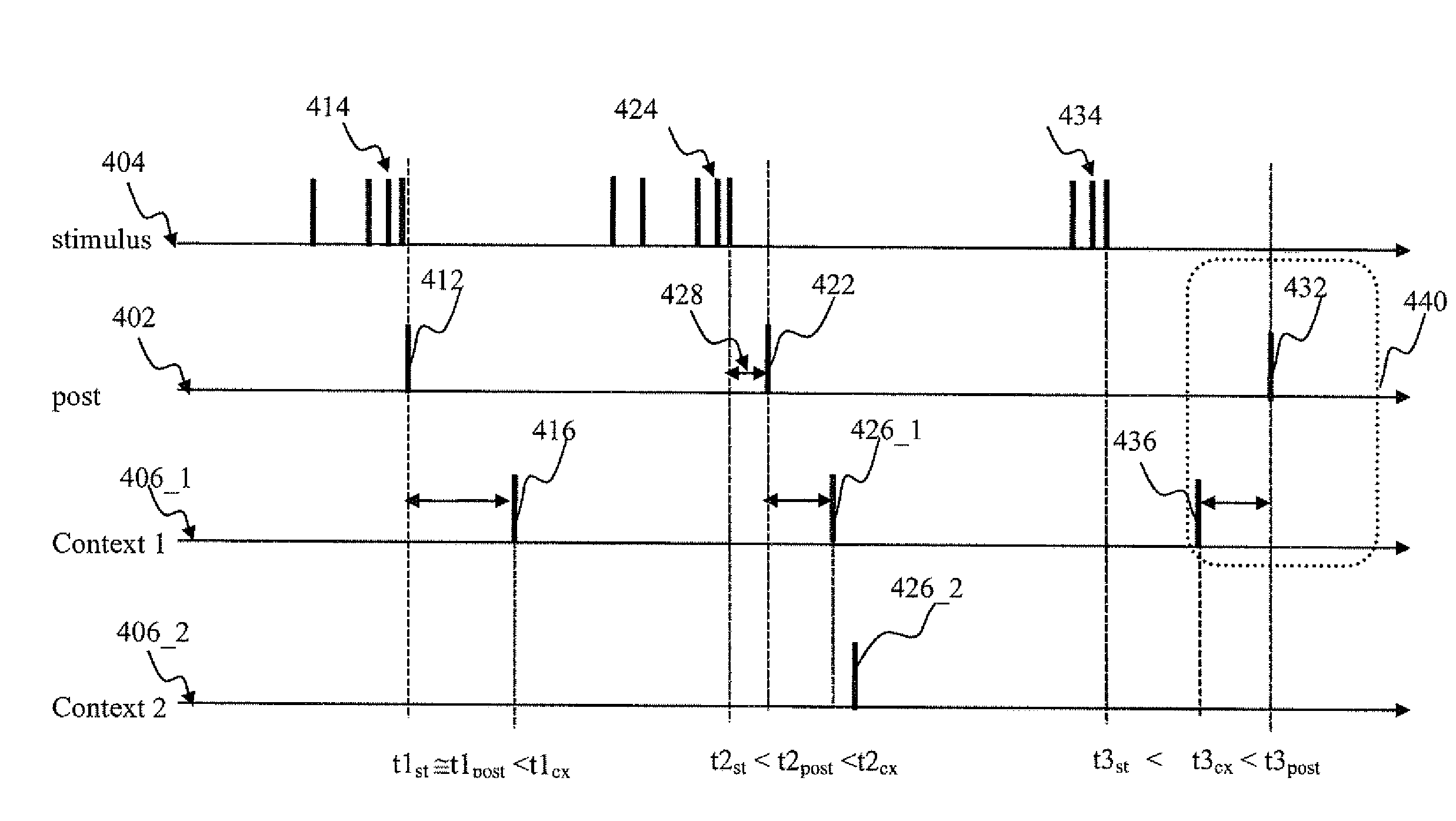

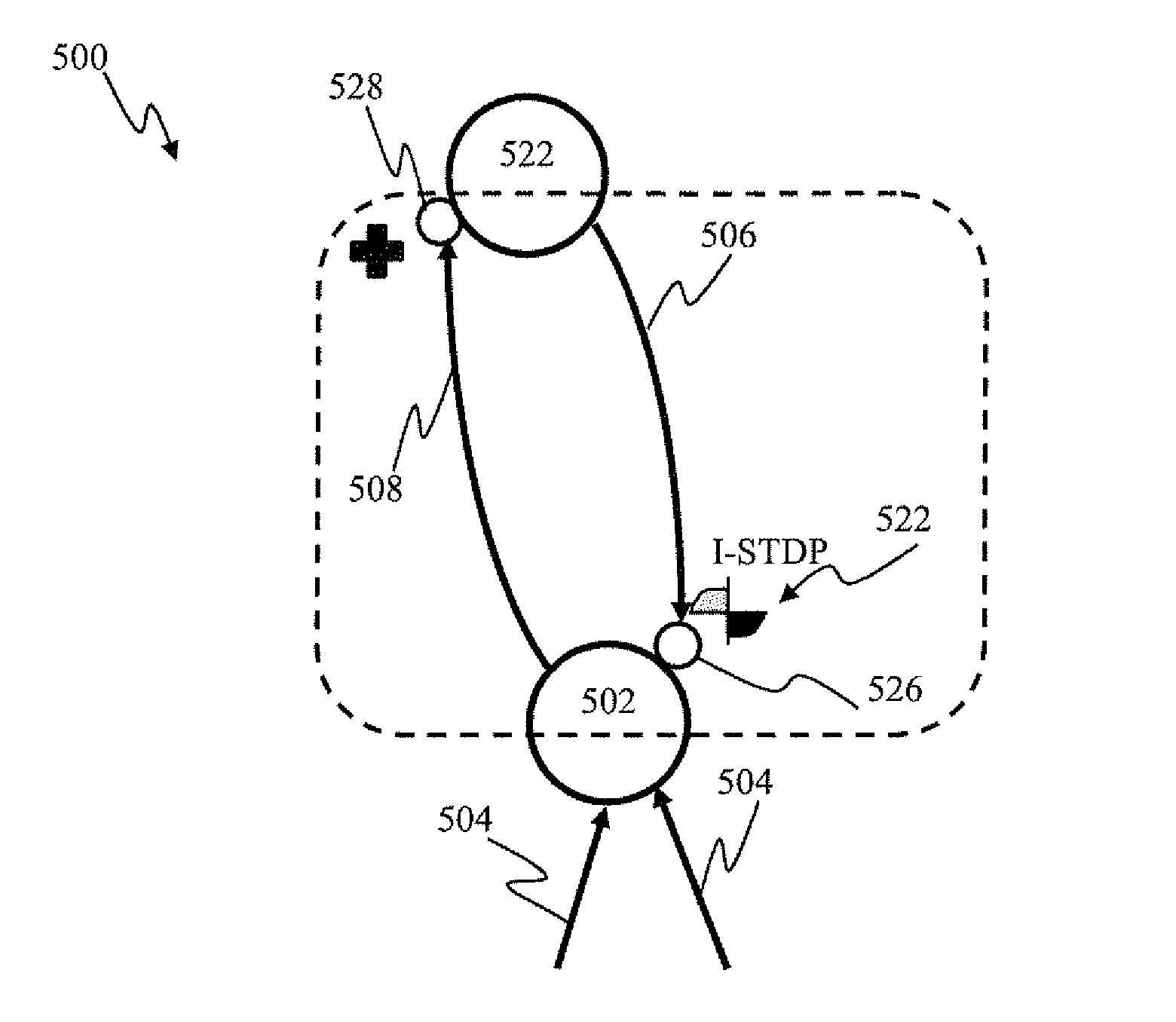

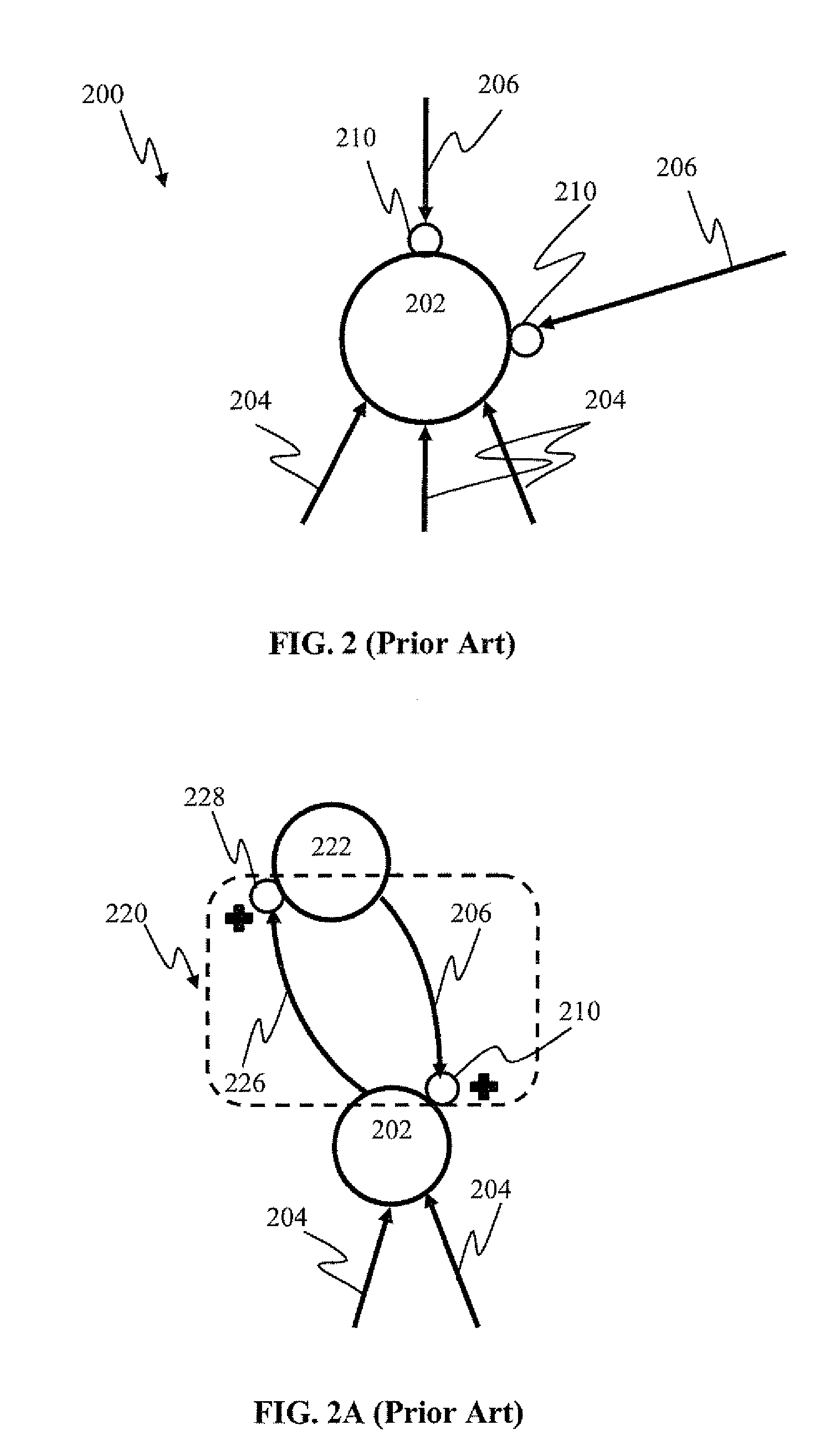

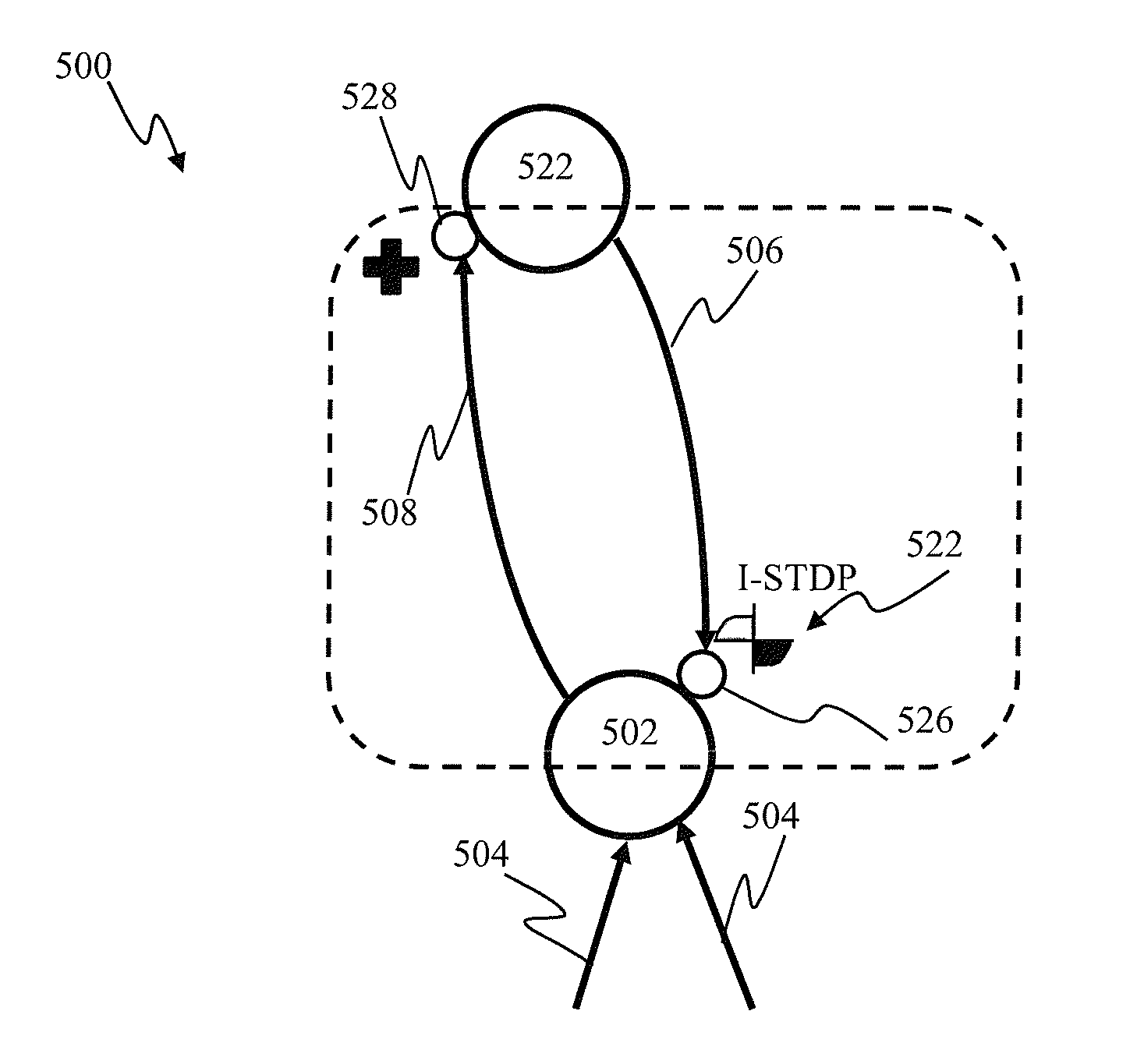

Apparatus and methods for feedback in a spiking neural network. In one approach, spiking neurons receive sensory stimulus and context signal that correspond to the same context. When the stimulus provides sufficient excitation, neurons generate response. Context connections are adjusted according to inverse spike-timing dependent plasticity. When the context signal precedes the post synaptic spike, context synaptic connections are depressed. Conversely, whenever the context signal follows the post synaptic spike, the connections are potentiated. The inverse STDP connection adjustment ensures precise control of feedback-induced firing, eliminates runaway positive feedback loops, enables self-stabilizing network operation. In another aspect of the invention, the connection adjustment methodology facilitates robust context switching when processing visual information. When a context (such an object) becomes intermittently absent, prior context connection potentiation enables firing for a period of time. If the object remains absent, the connection becomes depressed thereby preventing further firing.

Owner:BRAIN CORP

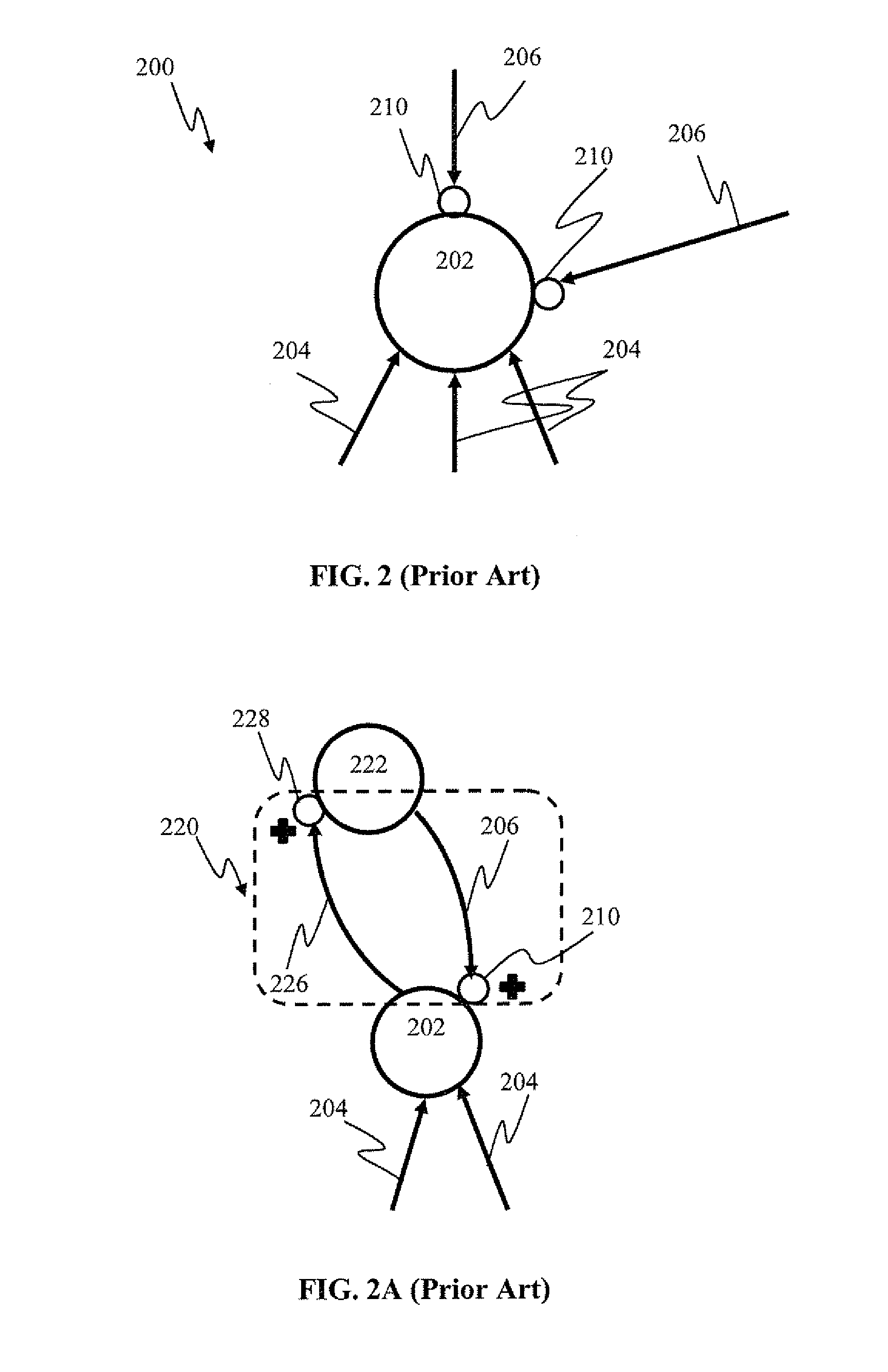

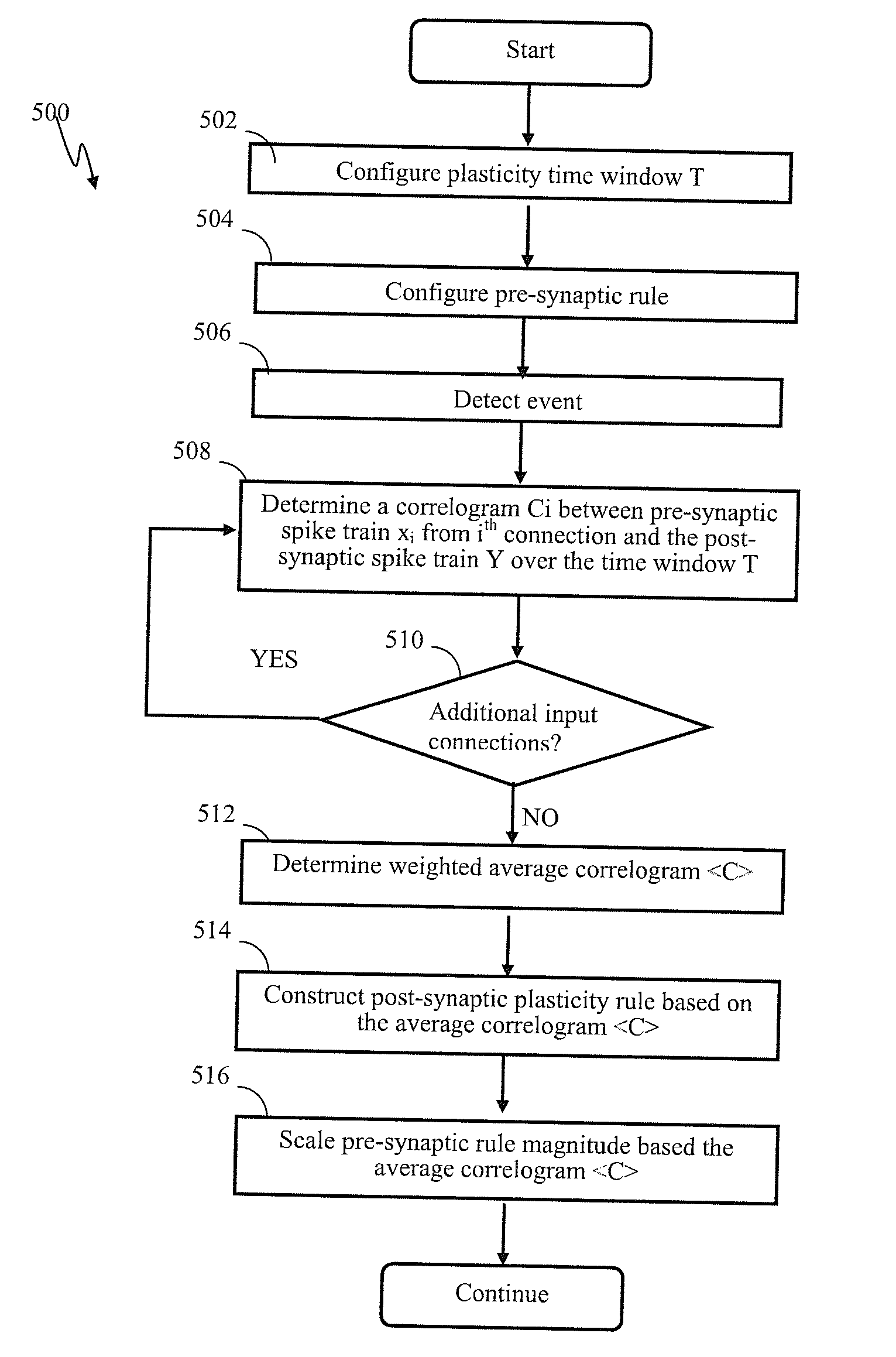

Modulated plasticity apparatus and methods for spiking neuron network

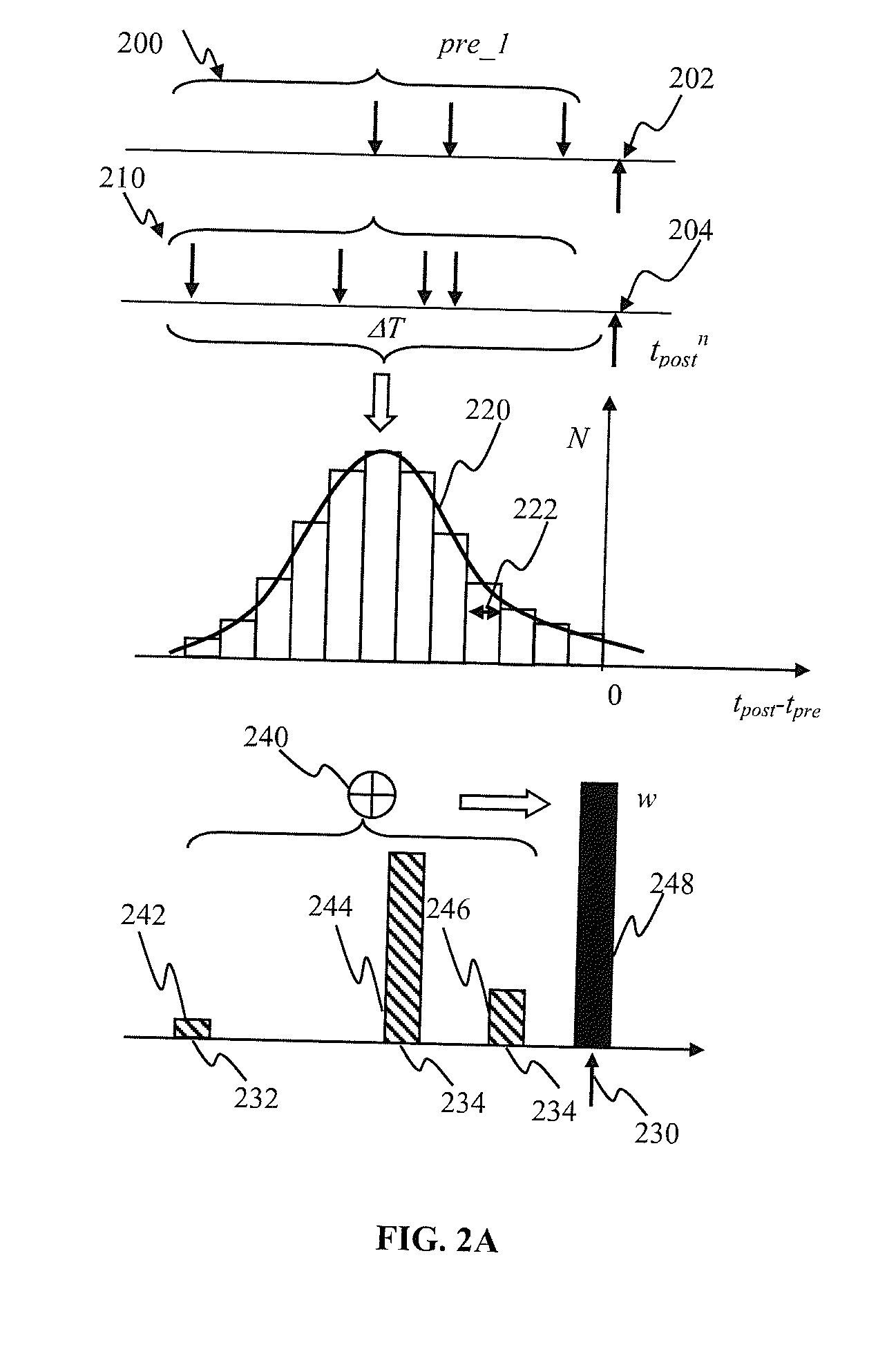

Apparatus and methods for modulated plasticity in a spiking neuron network. A plasticity mechanism may be configured for example based on a similarity measure between post-synaptic activities of two or more neurons that may be receiving the same feed-forward input. The similarity measure may comprise a dynamically determined cross-correlogram between the output spike trains of two neurons. An a priori configured similarity measure may be used during network operation in order to update efficacy of inhibitory connections between neighboring neurons. Correlated output activity may cause one neuron to inhibit output generation by another neuron thereby hindering responses by multiple neurons to the same input stimuli. The inhibition may be based on an increased efficacy of inhibitory lateral connection. The inhibition may comprise modulation of the pre synaptic portion the plasticity rule based on efficacies of feed-forward connection and inhibitory connections and a statistical parameter associated with the post-synaptic rule.

Owner:BRAIN CORP

Spiking neural network object recognition apparatus and methods

InactiveUS20130297539A1Reduce probabilityDigital computer detailsDigital dataSynapseSpiking neural network

Apparatus and methods for feedback in a spiking neural network. In one approach, spiking neurons receive sensory stimulus and context signal that correspond to the same context. When the stimulus provides sufficient excitation, neurons generate response. Context connections are adjusted according to inverse spike-timing dependent plasticity. When the context signal precedes the post synaptic spike, context synaptic connections are depressed. Conversely, whenever the context signal follows the post synaptic spike, the connections are potentiated. The inverse STDP connection adjustment ensures precise control of feedback-induced firing, eliminates runaway positive feedback loops, enables self-stabilizing network operation. In another aspect of the invention, the connection adjustment methodology facilitates robust context switching when processing visual information. When a context (such an object) becomes intermittently absent, prior context connection potentiation enables firing for a period of time. If the object remains absent, the connection becomes depressed thereby preventing further firing.

Owner:BRAIN CORP

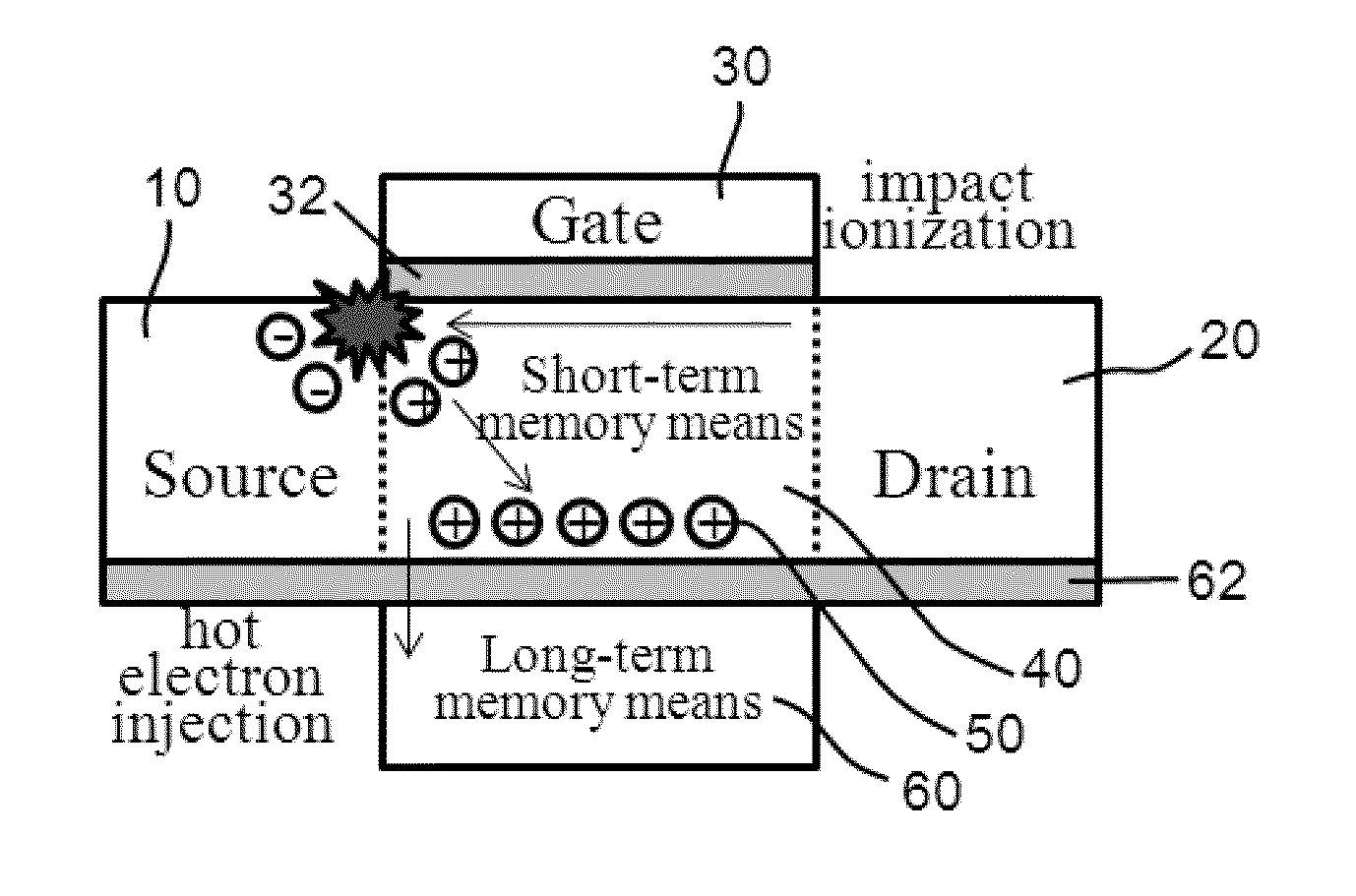

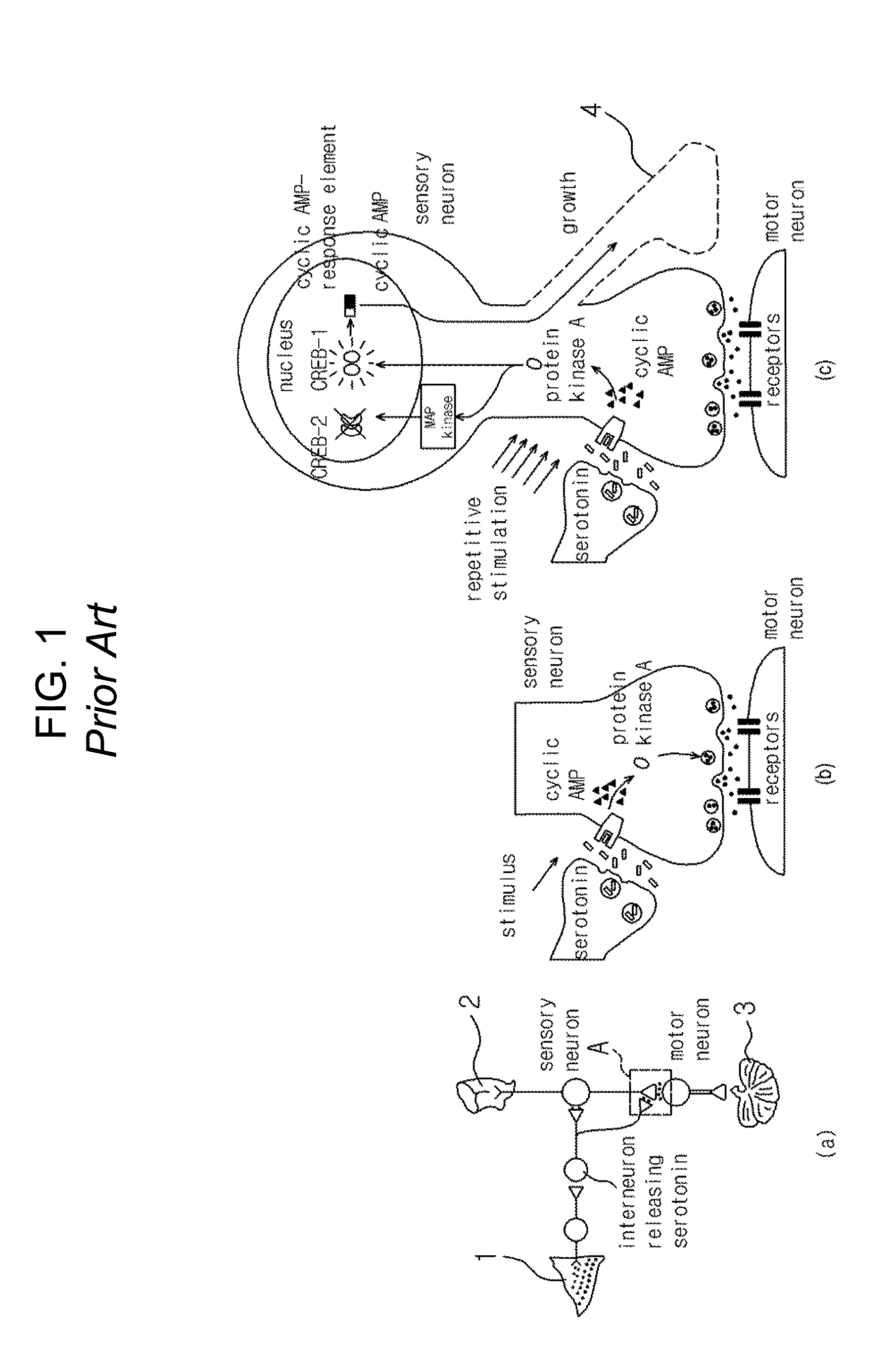

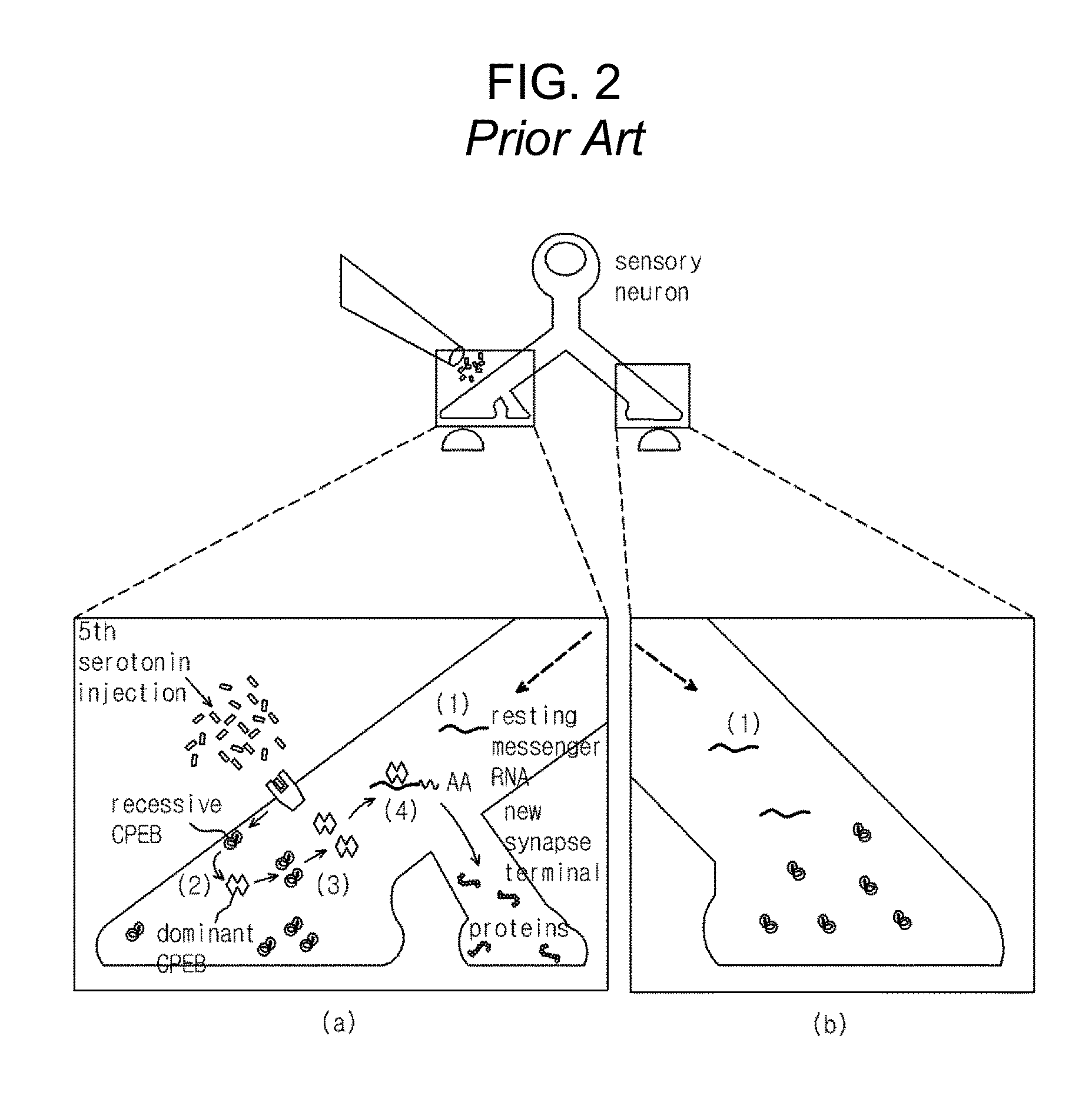

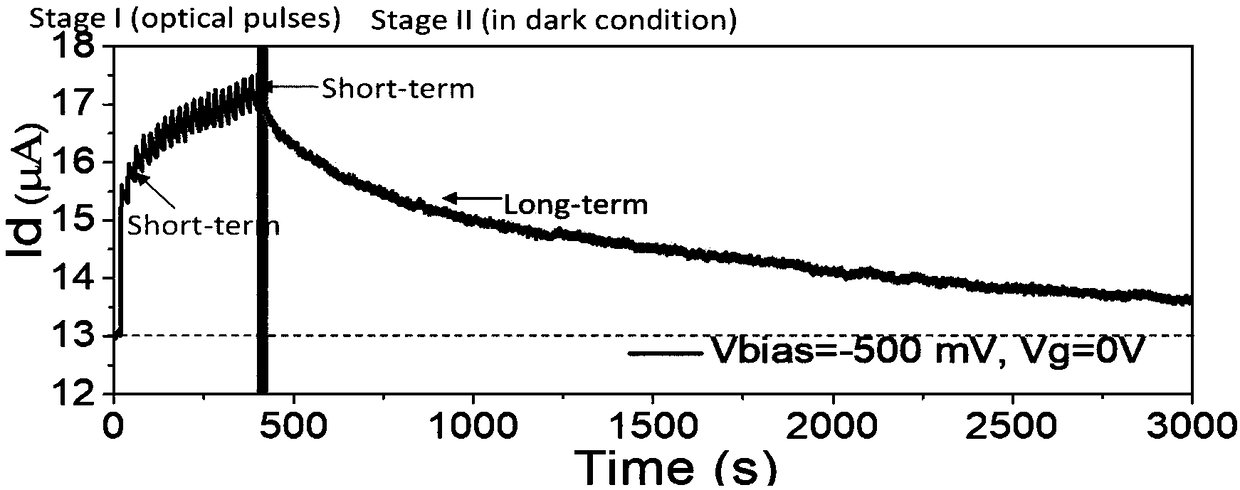

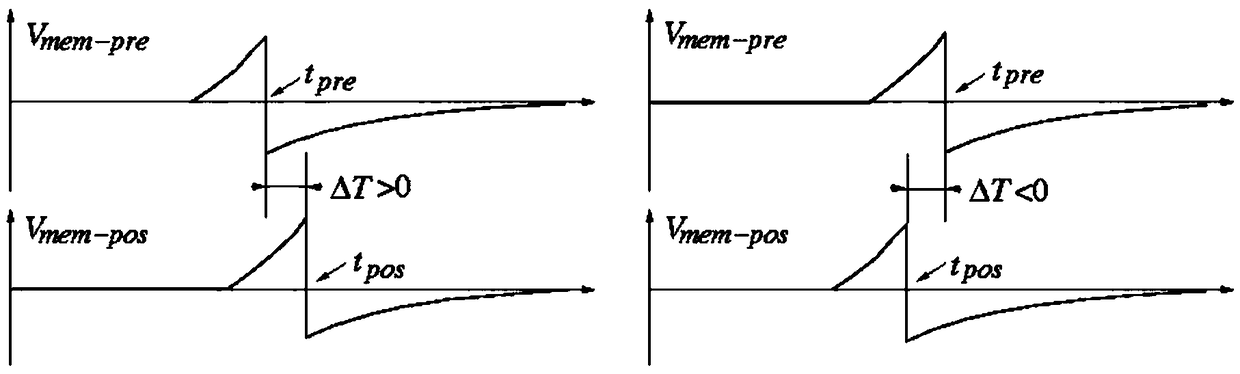

Synaptic semiconductor device and operation method thereof

Disclosed is a semiconductor device used to embody a neuromorphic computation system and operation method thereof. By comprising a floating body as a short-term memory means electrically isolated from the surroundings and a long-term memory means formed at one side of the floating body not formed of a source, a drain and a gate, a low power synaptic semiconductor device is provided, which can be mimic not only the short-term memory in a nervous system of a living body by an impact ionization, but also the short- and long-term memory transition property and the causal inference property of a living body due to the time difference of signals of the pre- and post-synaptic neurons.

Owner:SEOUL NAT UNIV R&DB FOUND

Modulated plasticity apparatus and methods for spiking neuron network

Apparatus and methods for modulated plasticity in a spiking neuron network. A plasticity mechanism may be configured for example based on a similarity measure between post-synaptic activities of two or more neurons that may be receiving the same feed-forward input. The similarity measure may comprise a dynamically determined cross-correlogram between the output spike trains of two neurons. An a priori configured similarity measure may be used during network operation in order to update efficacy of inhibitory connections between neighboring neurons. Correlated output activity may cause one neuron to inhibit output generation by another neuron thereby hindering responses by multiple neurons to the same input stimuli. The inhibition may be based on an increased efficacy of inhibitory lateral connection. The inhibition may comprise modulation of the pre synaptic portion the plasticity rule based on efficacies of feed-forward connection and inhibitory connections and a statistical parameter associated with the post-synaptic rule.

Owner:BRAIN CORP

Spiking neural network feedback apparatus and methods

InactiveUS9129221B2Low efficacyGood curative effectDigital computer detailsDigital dataSpiking neural networkArtificial intelligence

In one approach, spiking neurons receive sensory stimulus and context signal that correspond to the same context. When the stimulus provides sufficient excitation, neurons generate response. Context connections are adjusted according to inverse spike-timing dependent plasticity. When the context signal precedes the post synaptic spike, context synaptic connections are depressed. Conversely, whenever the context signal follows the post synaptic spike, the connections are potentiated. The inverse STDP connection adjustment ensures precise control of feedback-induced firing, eliminates runaway positive feedback loops, and enables self-stabilizing network operation. In another aspect, the connection adjustment methodology facilitates robust context switching when processing visual information. When a context (such an object) becomes intermittently absent, prior context connection potentiation enables firing for a period of time. If the object remains absent, the connection becomes depressed thereby preventing further firing.

Owner:BRAIN CORP

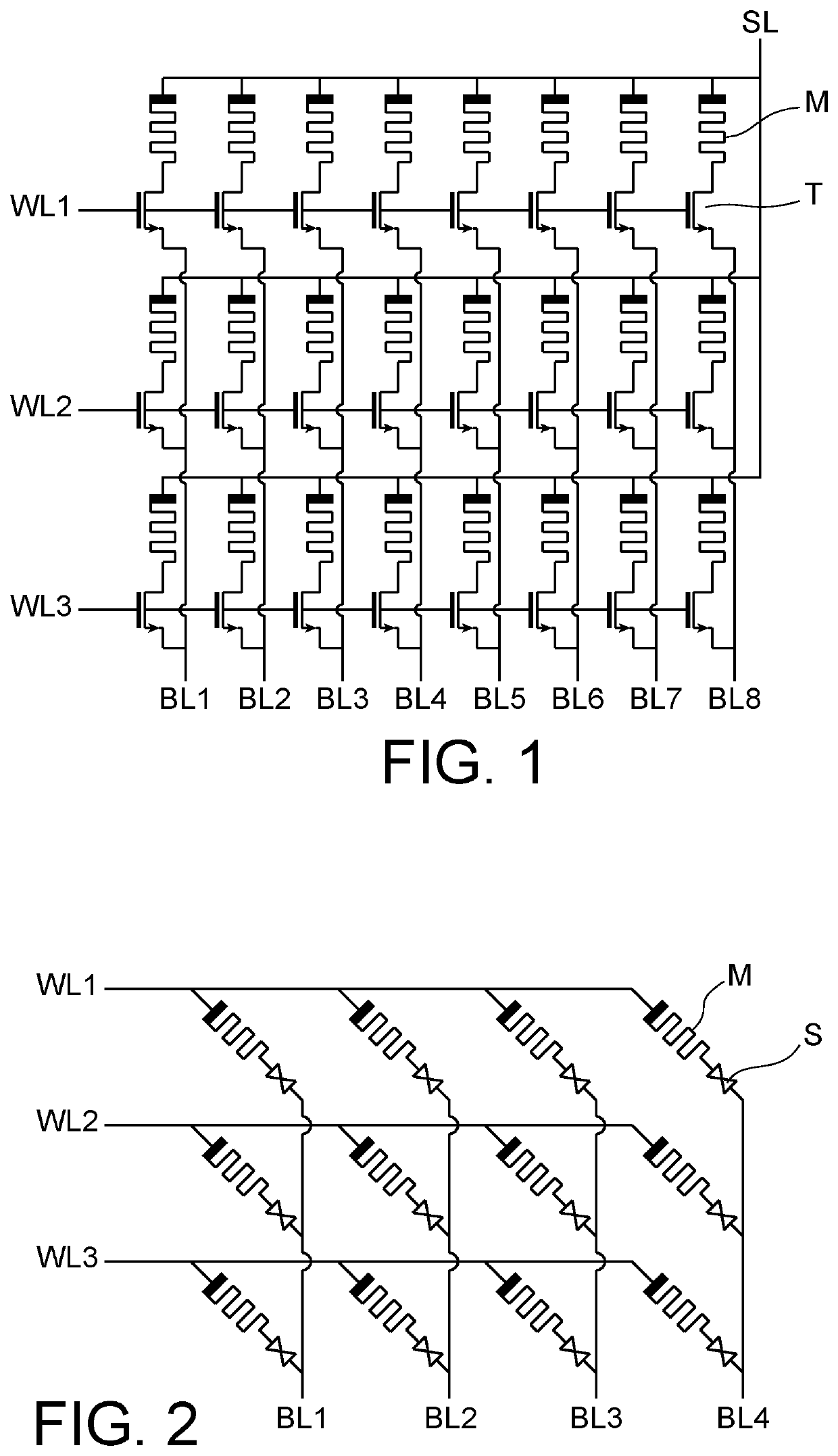

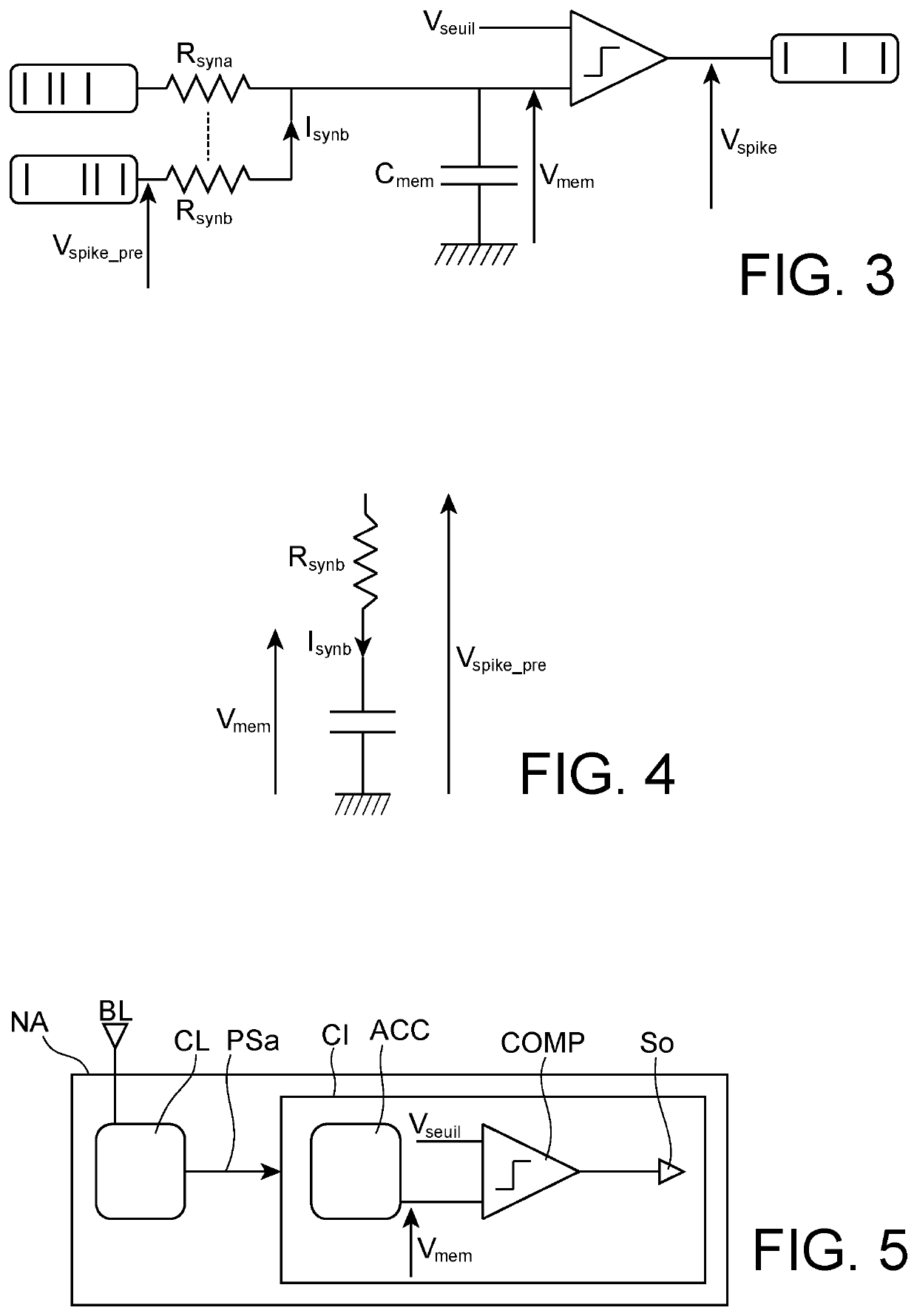

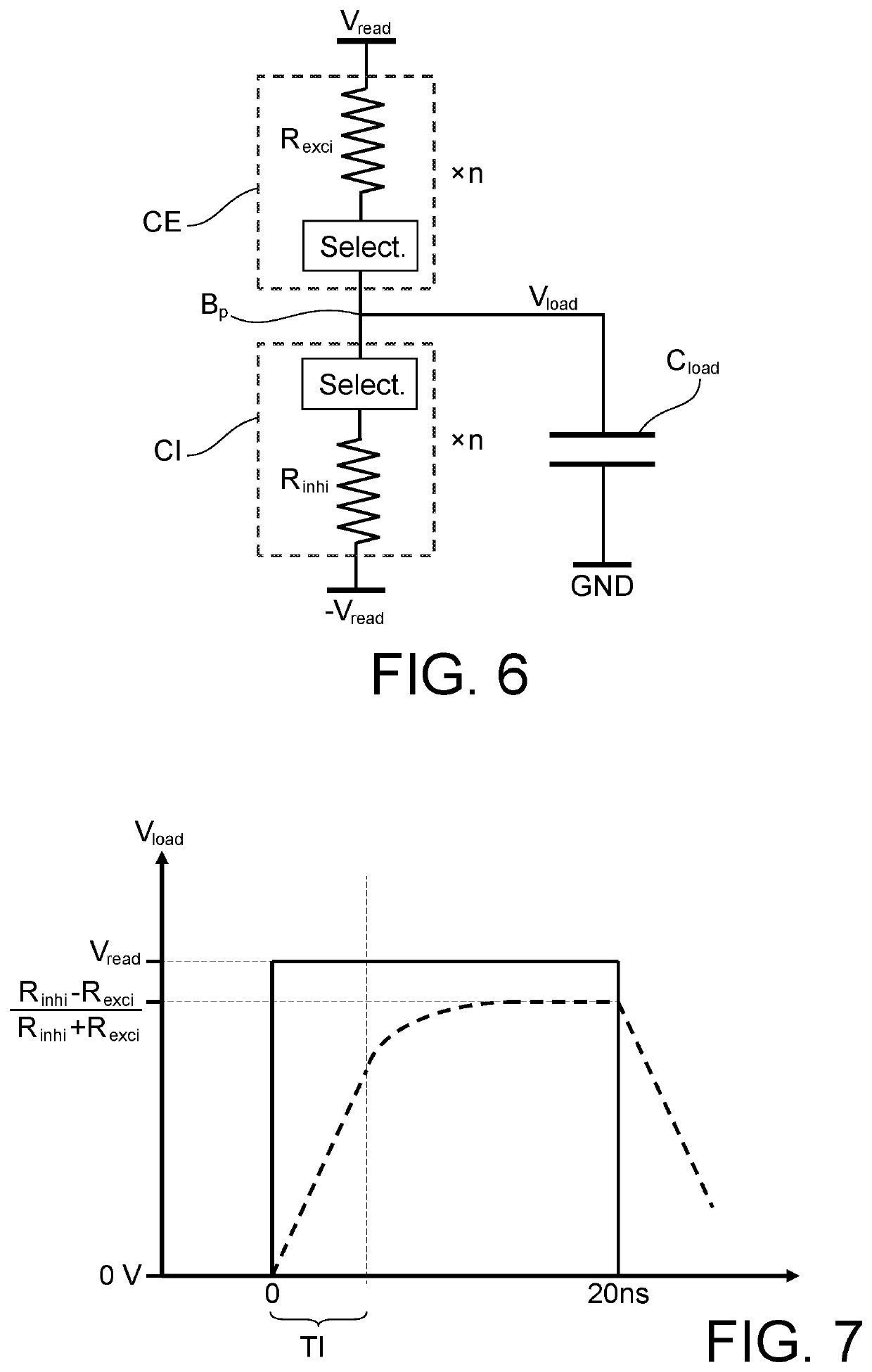

Artificial neuron for neuromorphic chip with resistive synapses

An artificial neuron for a neuromorphic chip comprises a synapse with resistive memory representative of a synaptic weight. The artificial neuron comprises a read circuit, an integration circuit and a logic circuit interposed between the read circuit and the integration circuit. The read circuit is configured to impose on the synapse a read voltage independent of the membrane voltage and to provide an analogue value representative of the synaptic weight. The logic circuit is configured to generate from the analogue value a pulse having a duration. The integration circuit comprises an accumulator of synaptic weights at the terminals of which a membrane voltage is established and a comparator configured to emit a postsynaptic pulse if a threshold is exceeded by the membrane voltage. Moreover, it comprises a source of current controlled by the pulse to inject a current into the accumulator of synaptic weights during this duration.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

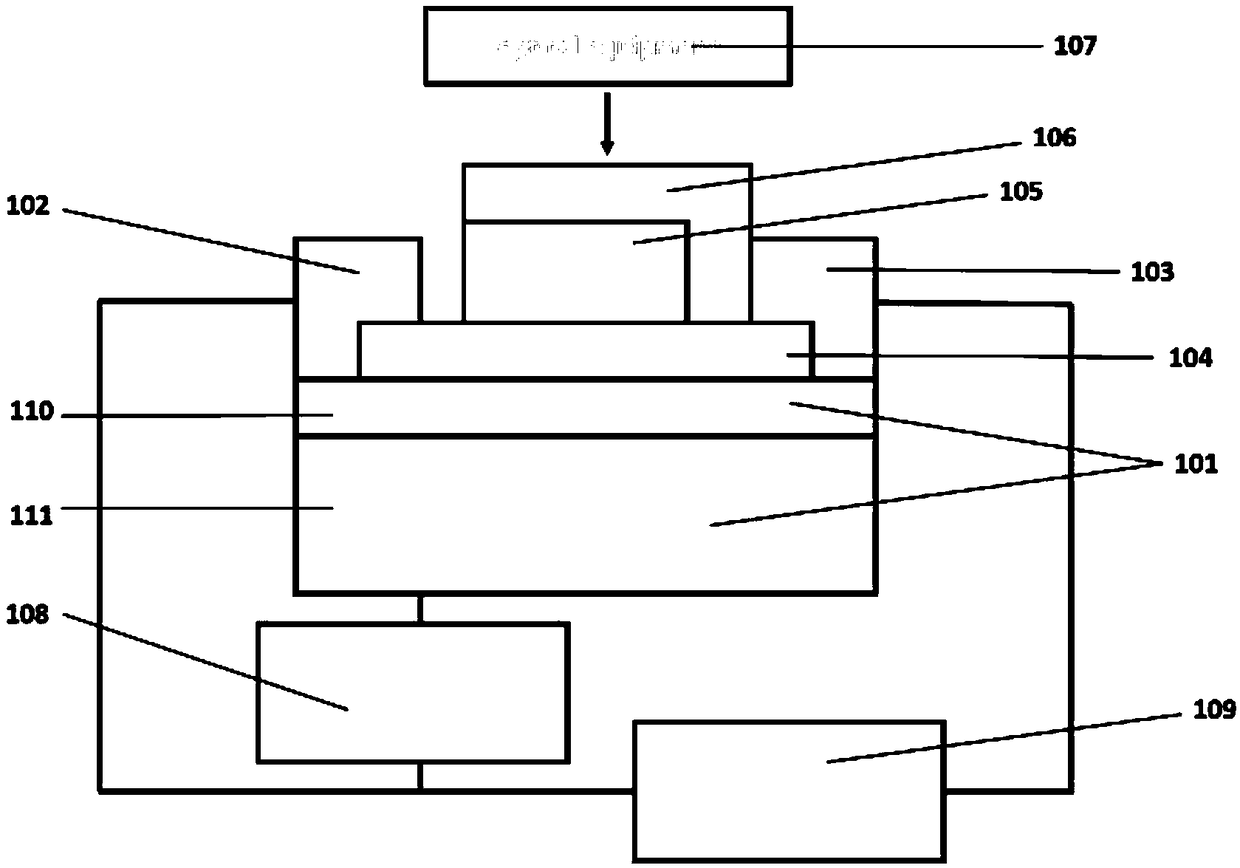

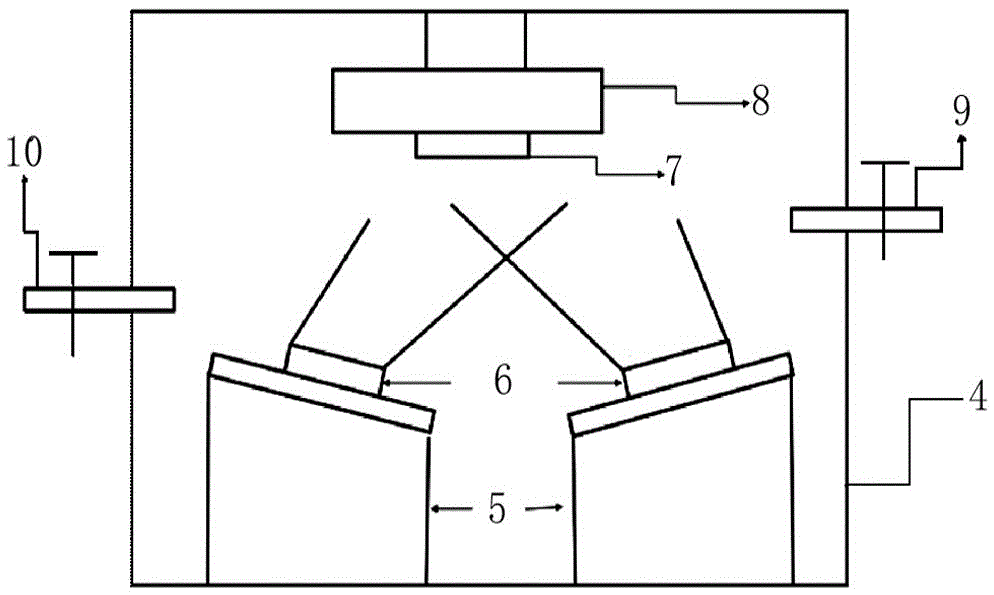

A method and device for simulate an optical synapse of an organism

ActiveCN109460819AChange the size of the currentEnables full parallel connectionPhysical realisationSynaptic weightOrganism

The invention discloses a method and a device for simulating the optical synapse of an organism, belonging to the technical field of biomimetic synapse. The method comprises steps of generating an optical signal for simulating an action potential of a synaptic front end in an organism, using a hole electron pair generated by the semiconductor photosensitive material responsive to the optical signal to carry out directional movement under an electric field, thereby changing the concentration of carriers in the postsynaptic end, thereby increasing or decreasing the current passing through the postsynaptic end to simulate the basic performance of the biological synapse stimulated by the optical signal. The device includes a substrate, a first electrode, a second electrode, a postsynaptic layer, a semiconductor photosensitive layer, a presynaptic layer, a light source signal input device, a backgate signal input device, and a source / drain signal input device. The invention realizes the basic performance of the simulated biological synapse under the stimulation of the optical signal, can greatly reduce the power consumption caused by the existence of the bus, and makes it possible to directly convert the optical image into the synapse weight and bring the optical image into the artificial neural network for image recognition.

Owner:TSINGHUA UNIV

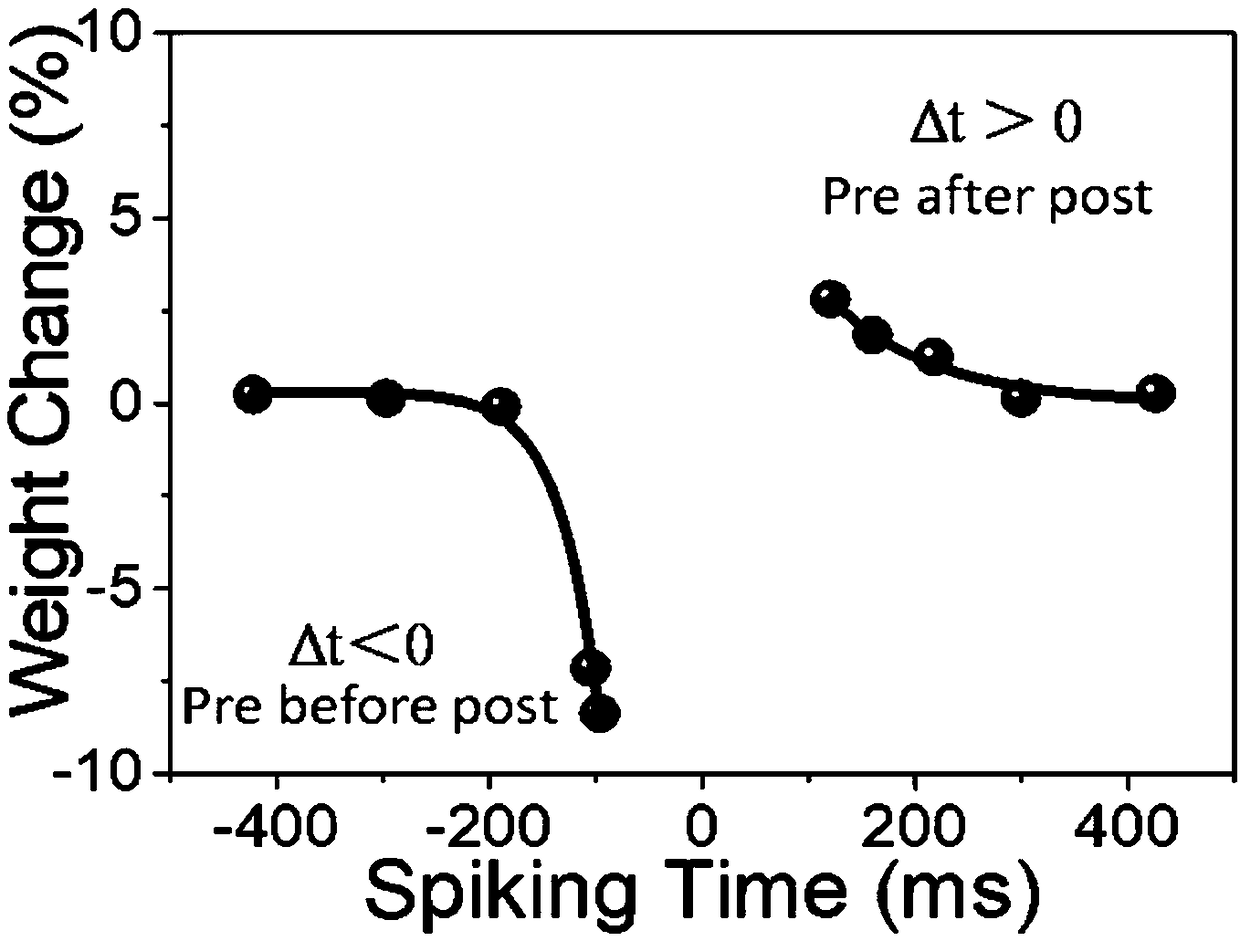

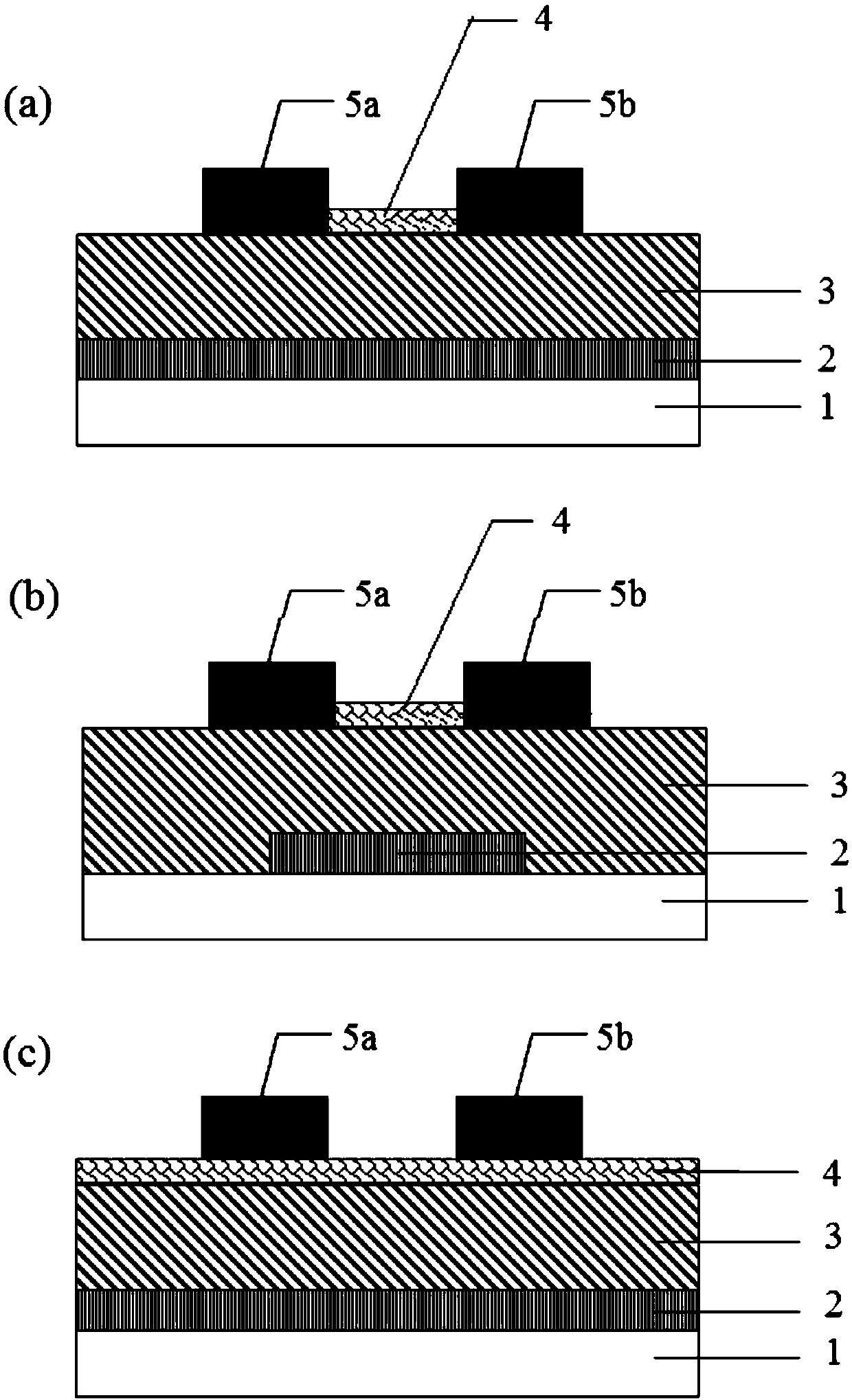

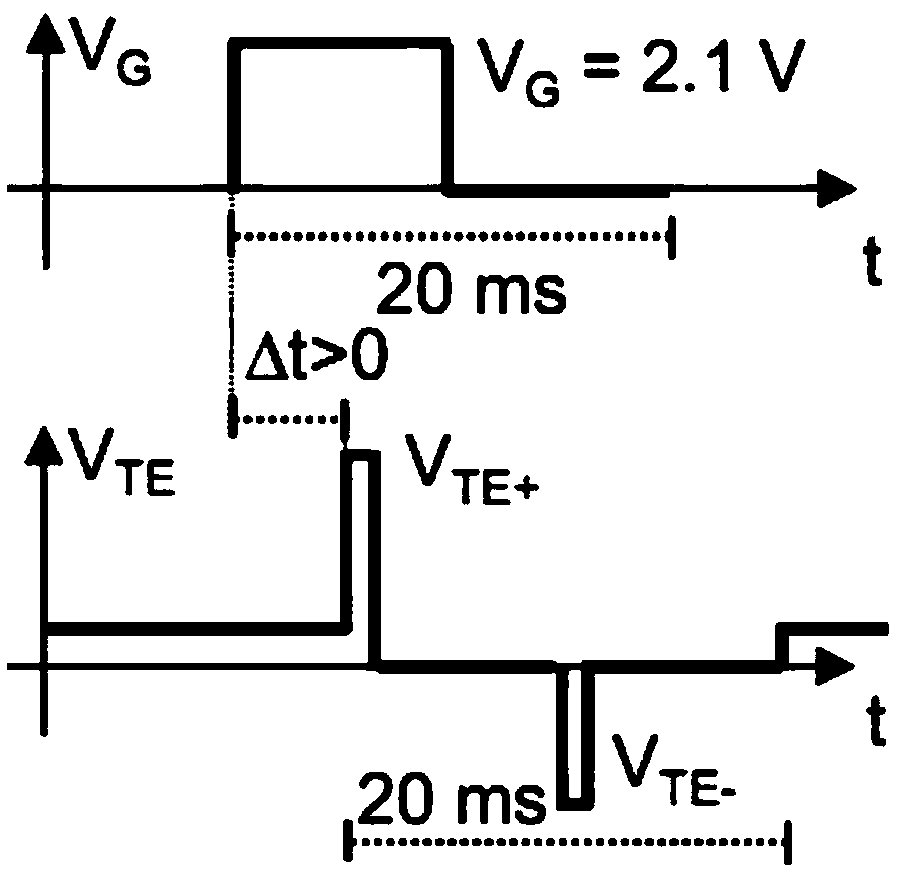

Bionic synaptic device, manufacturing method and application thereof

The invention discloses a bionic synaptic device and a manufacturing method and application thereof. Specifically, the invention relates to the bionic synaptic device with spike-time-dependent plasticity learning behaviors. The bionic synaptic device includes a gate electrode (2), wherein the square resistance of the gate electrode is 30 to 800 omega. The gate electrode is used as the synaptic front end of the bionic synaptic device. The device further includes a gate dielectric layer (3) which comprises a solid electrolyte with a proton conductive property, a channel (4), wherein the channellayer is used as the synaptic rear end of the bionic synaptic device. The device further includes a source (5a) and a drain (5b). According to the bionic synaptic device, different linear spike-time-dependent plasticity learning behaviors can be realized on a single device; the circuit design is greatly simplified; and the device has important application prospects in the fields of neuromorphic devices, artificial intelligence and the like.

Owner:NINGBO INST OF MATERIALS TECH & ENG CHINESE ACADEMY OF SCI

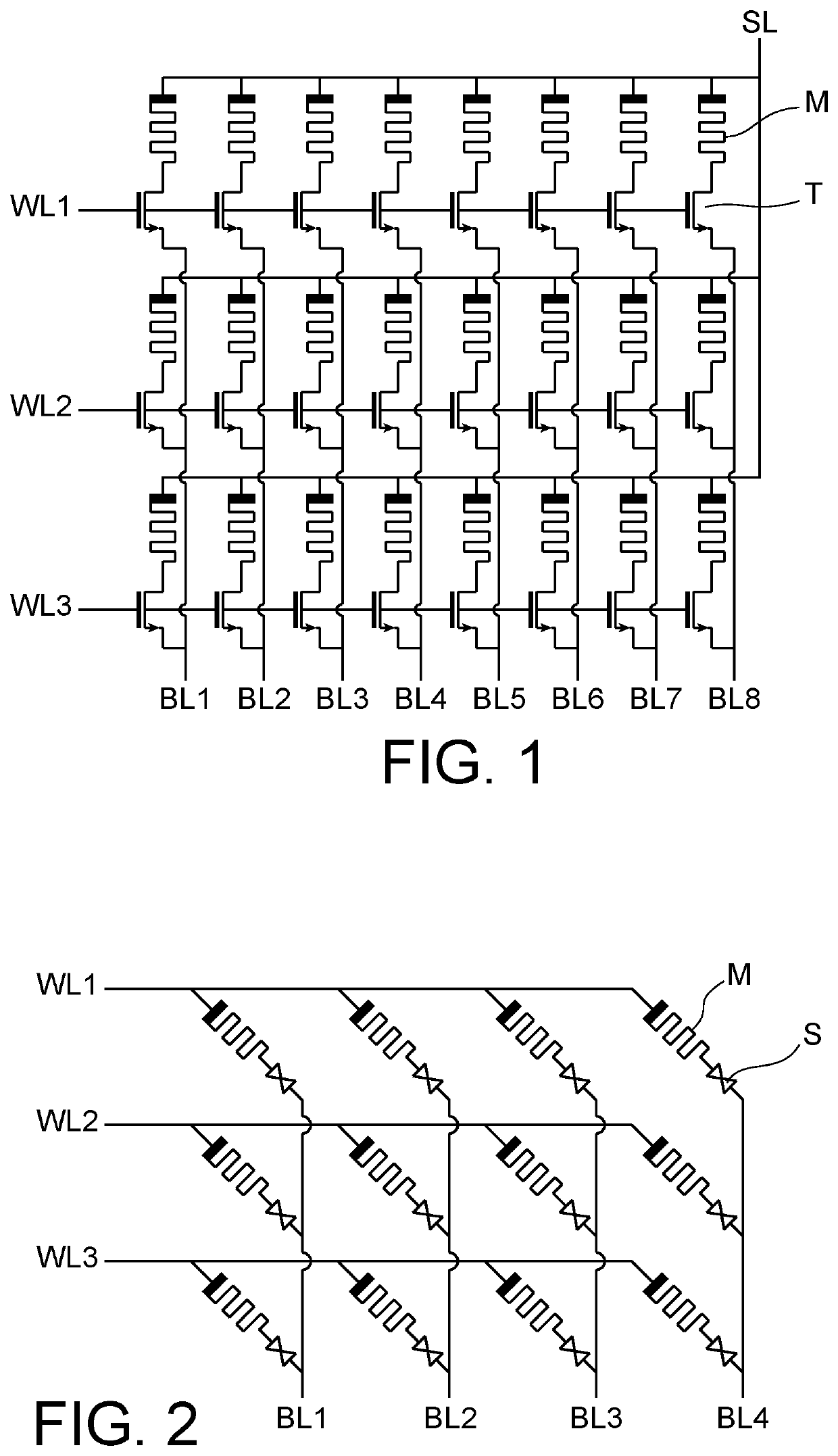

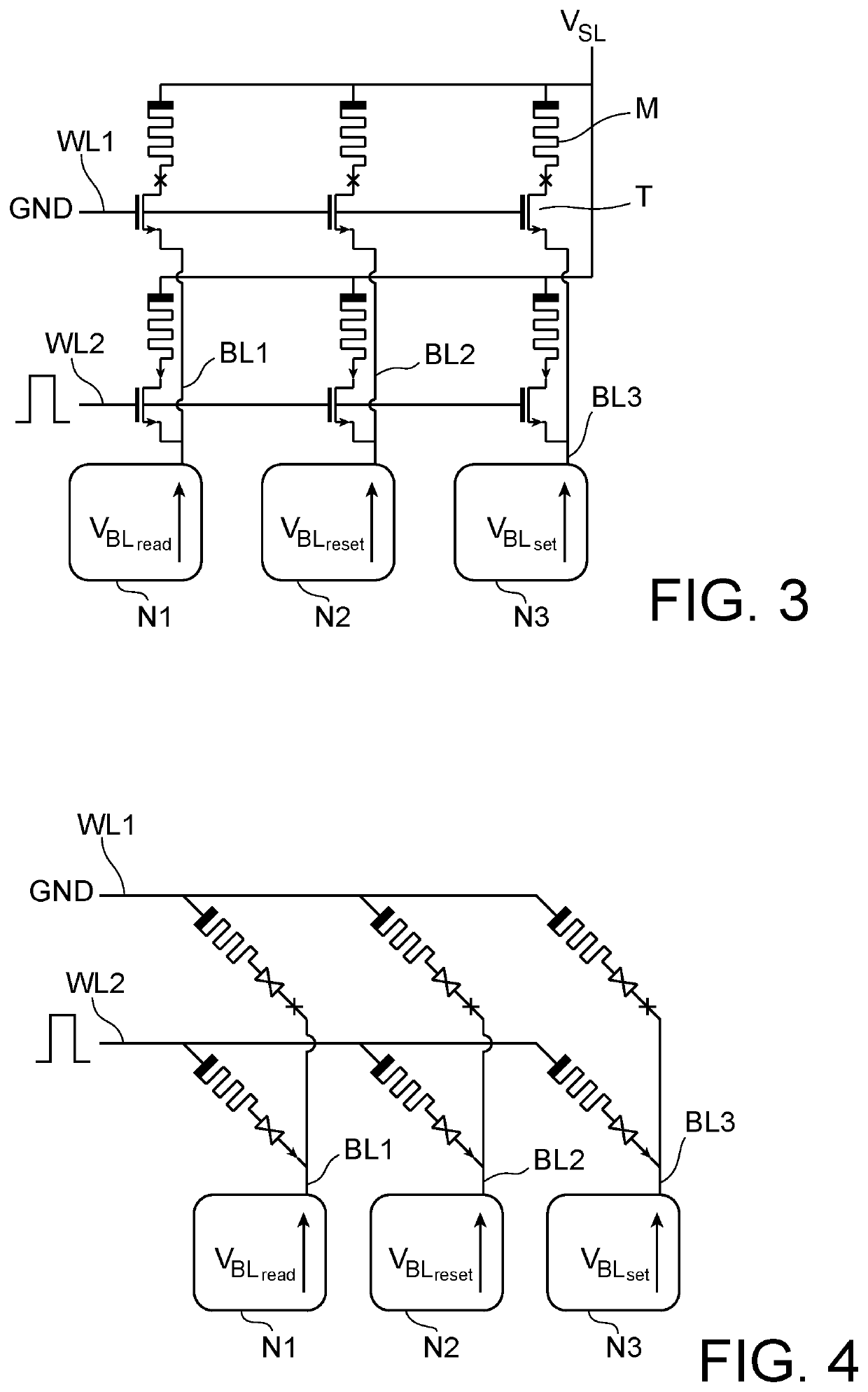

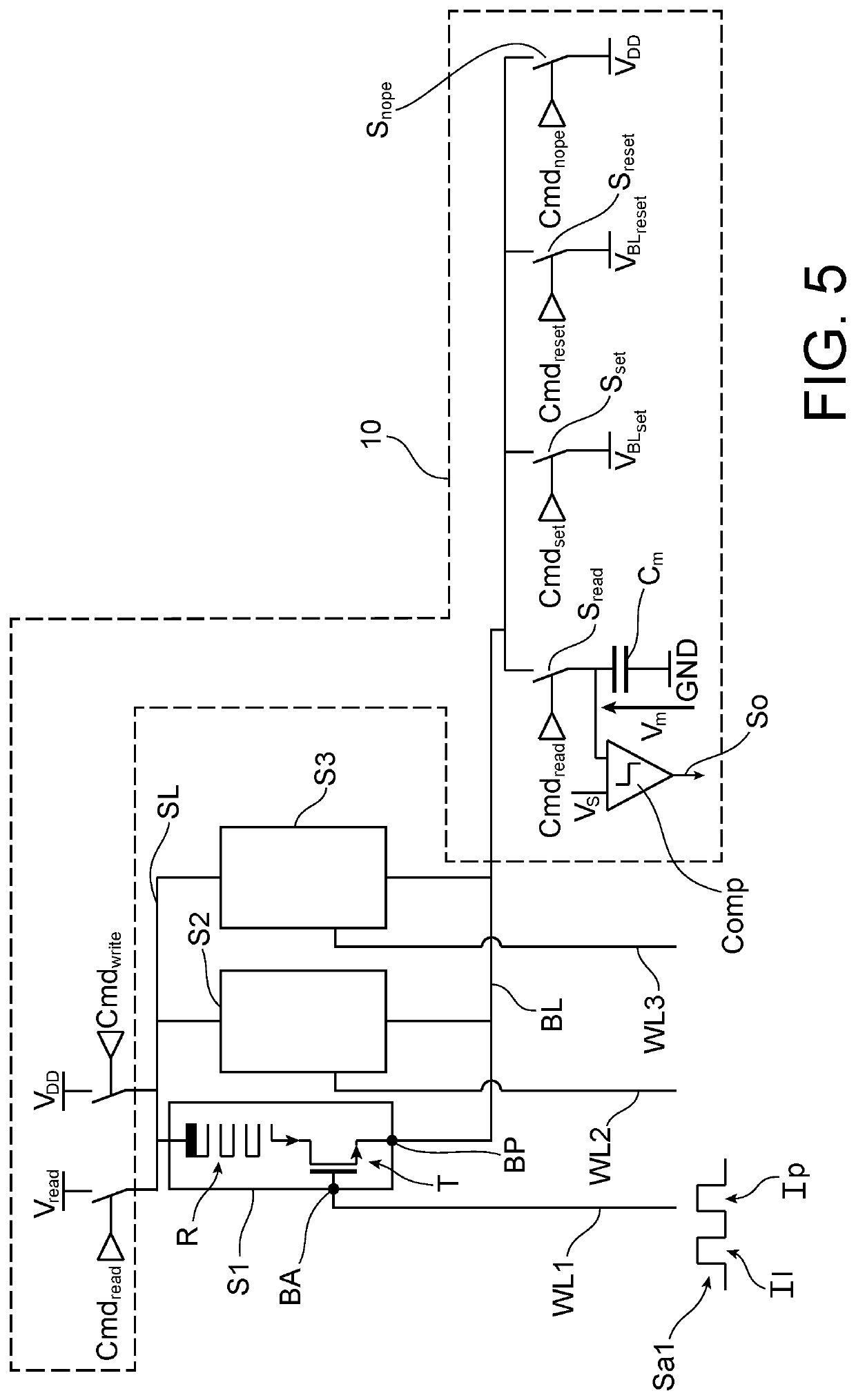

Circuit neuronal apte à mettre en oeuvre un apprentissage synaptique

A synaptic integration circuit for a neuromorphic chip comprising a resistive memory synapse which has an activation terminal to receive a presynaptic action signal and a propagation terminal intended to be connected to the circuit for transmitting a synaptic output signal which depends on the resistance of the memory. The circuit comprises an accumulator of the synaptic output signal, a comparator configured to emit a postsynaptic spike in case of the crossing of a threshold (Vm) by the accumulated output signal. It further comprises a control unit configured, when a presynaptic action signal is applied on the activation terminal, to impose a conductance modification voltage on the synapse by controlling the application of a postsynaptic action signal (VBL<sub2>set< / sub2>, VBL<sub2>reset< / sub2>) on the propagation terminal.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

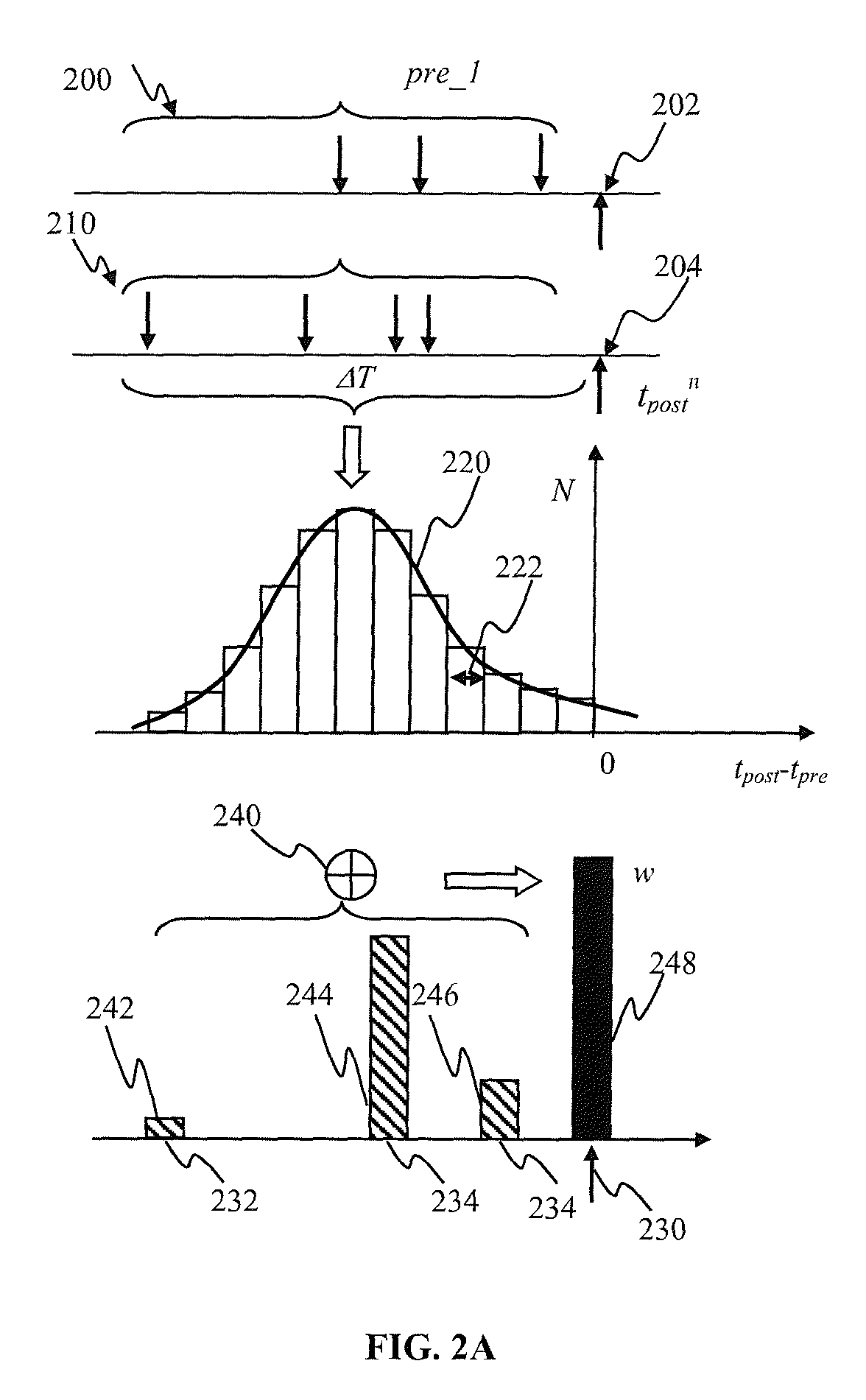

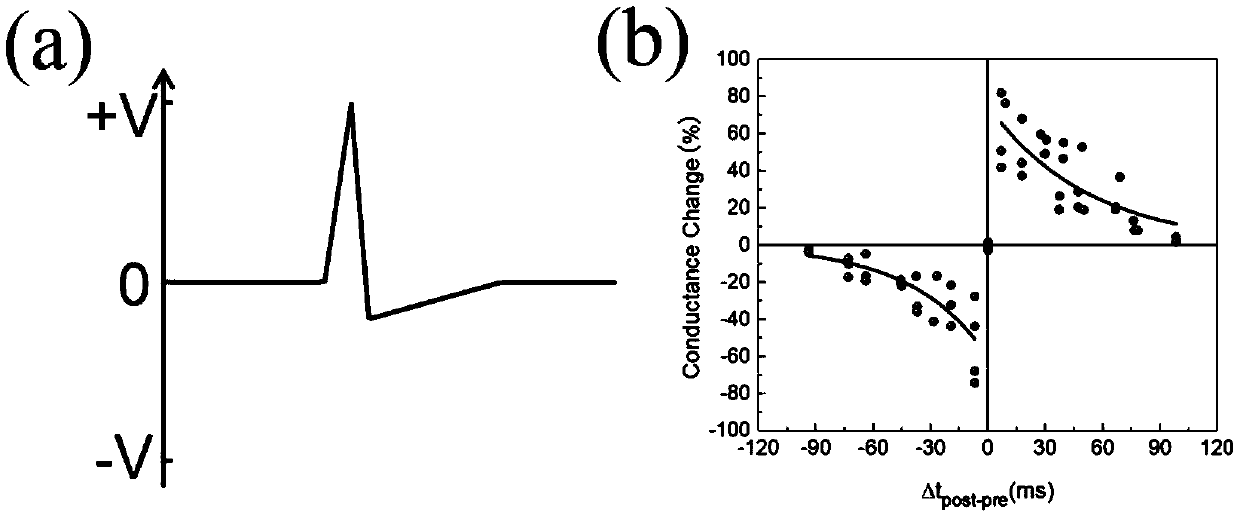

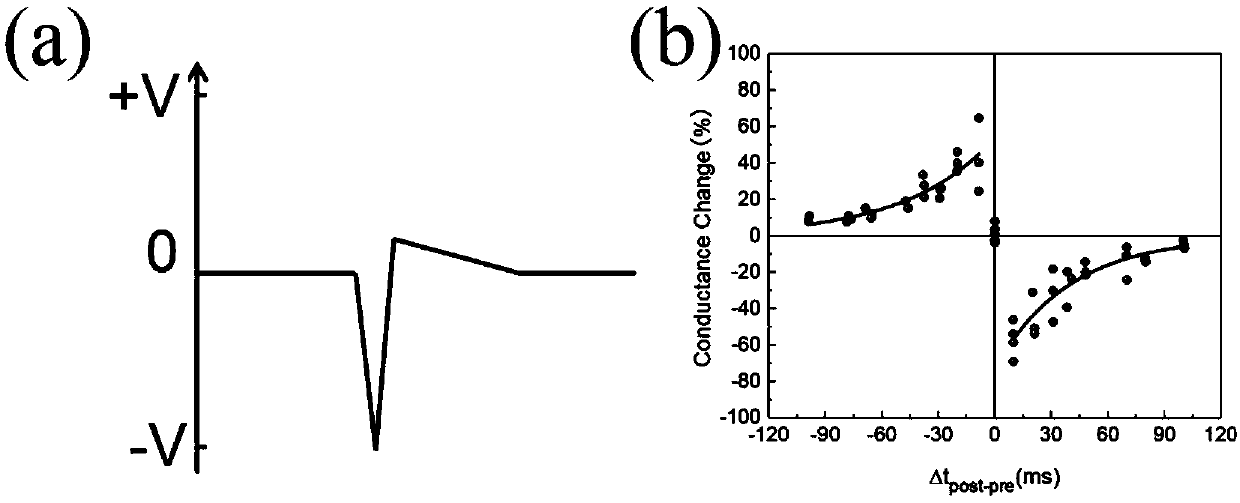

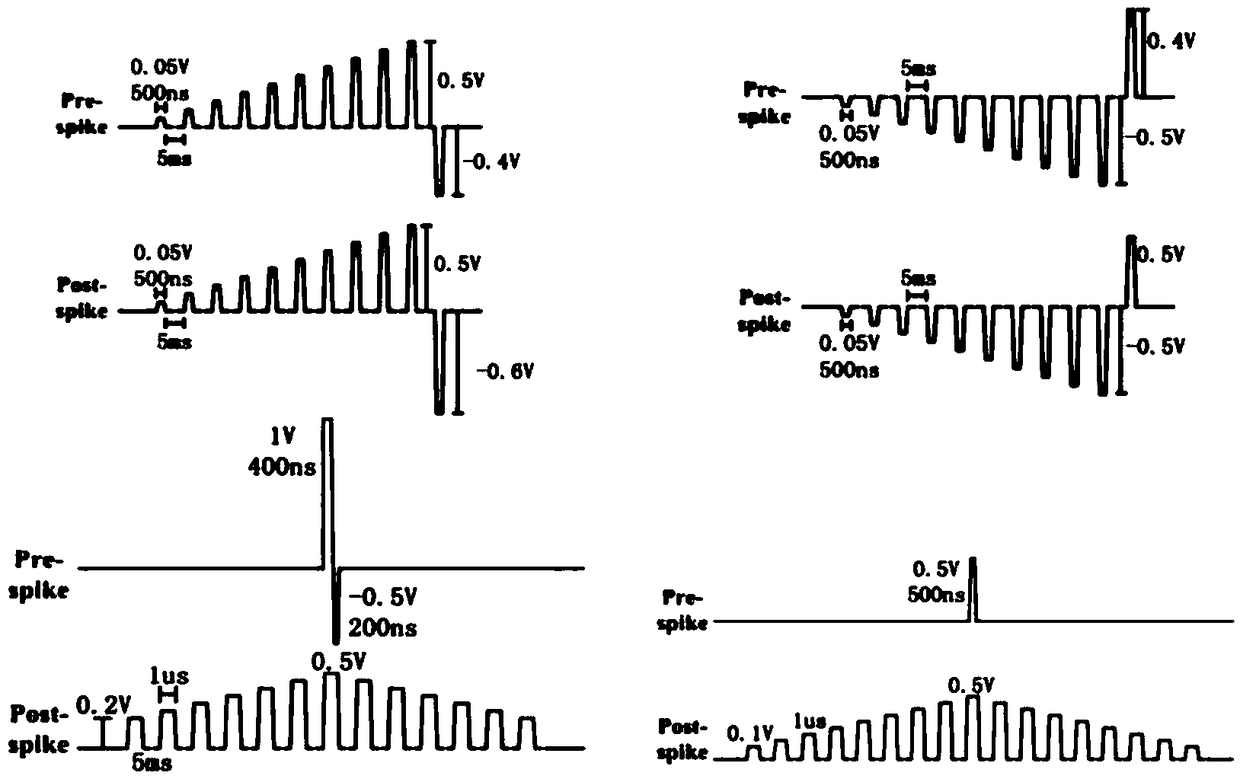

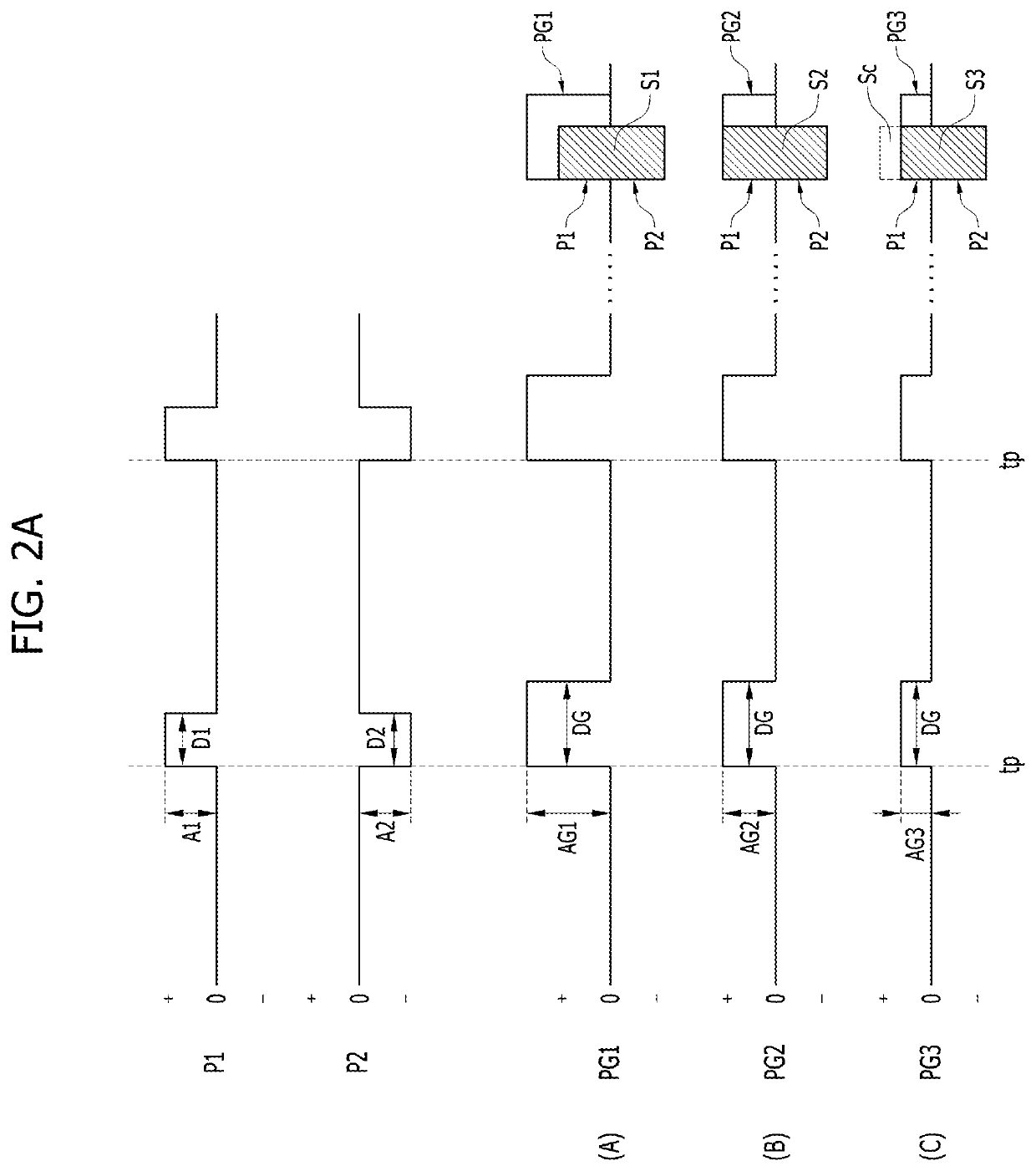

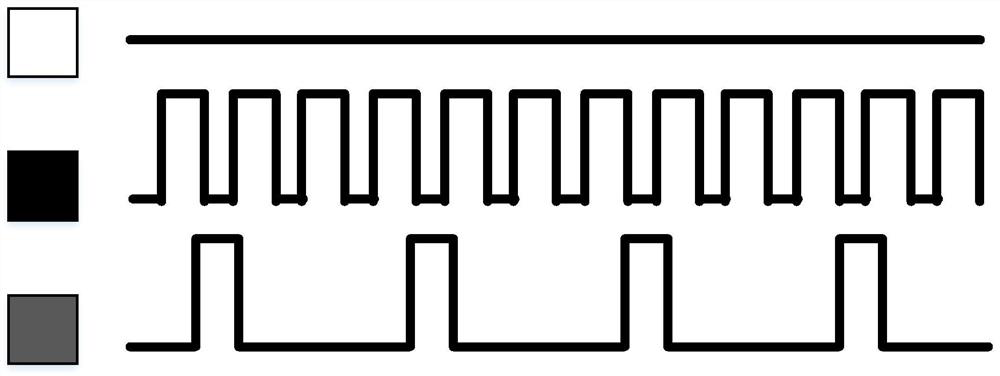

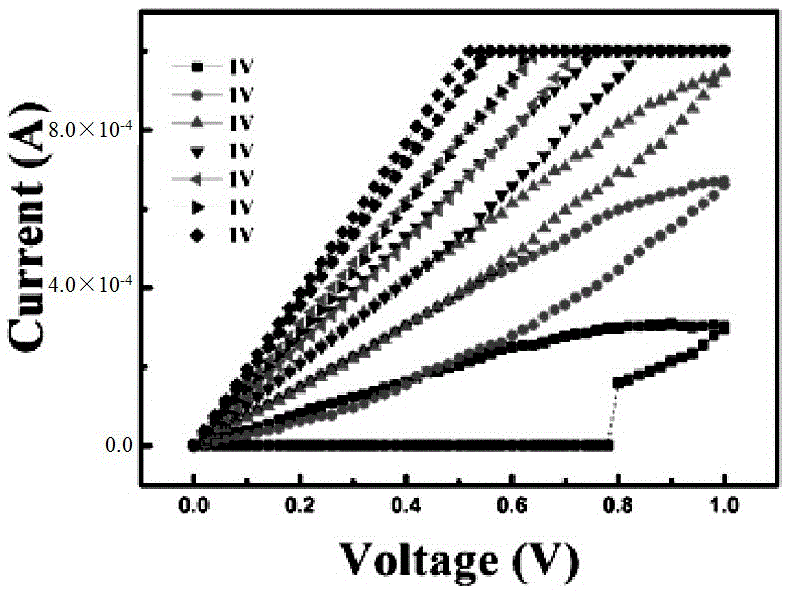

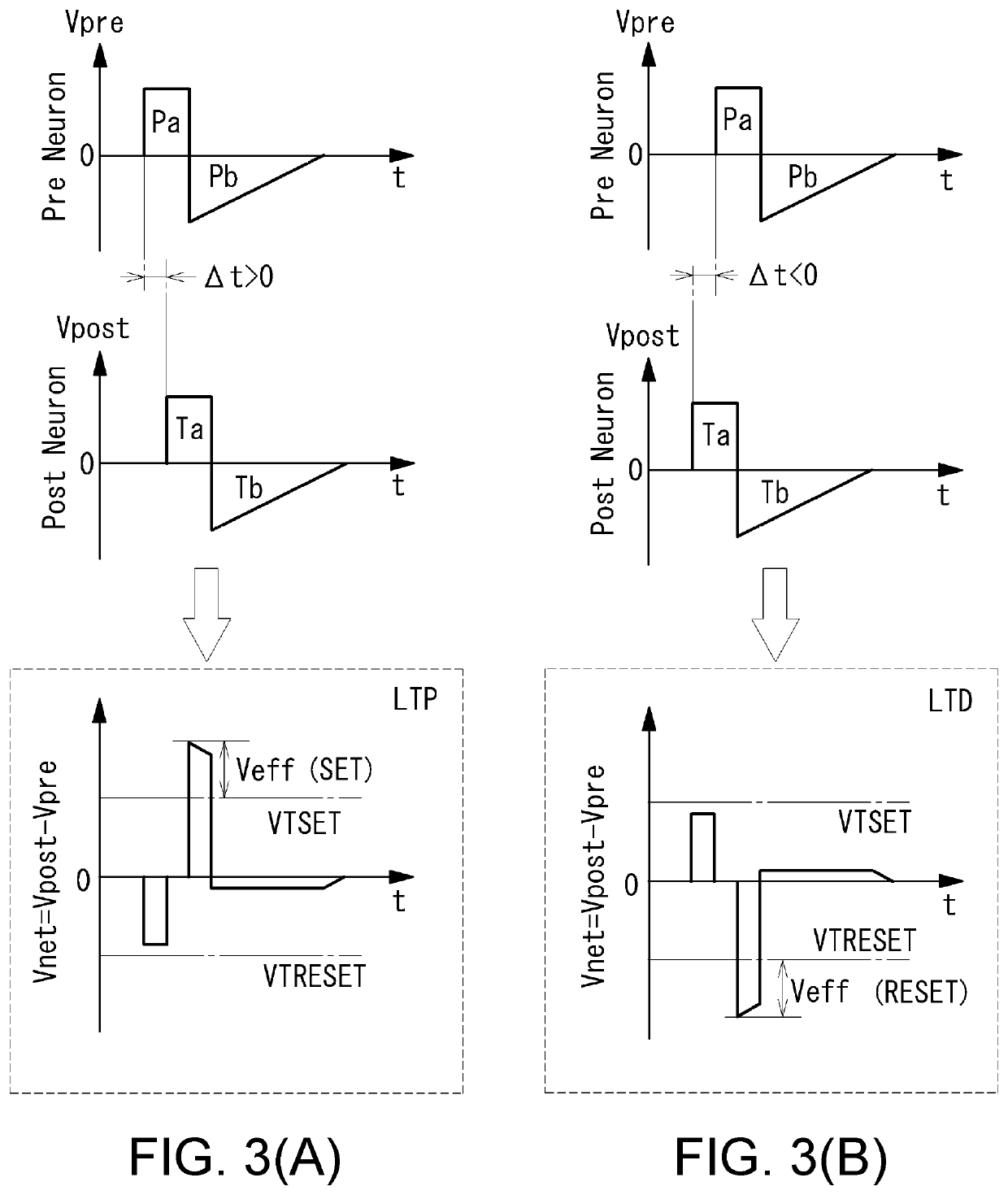

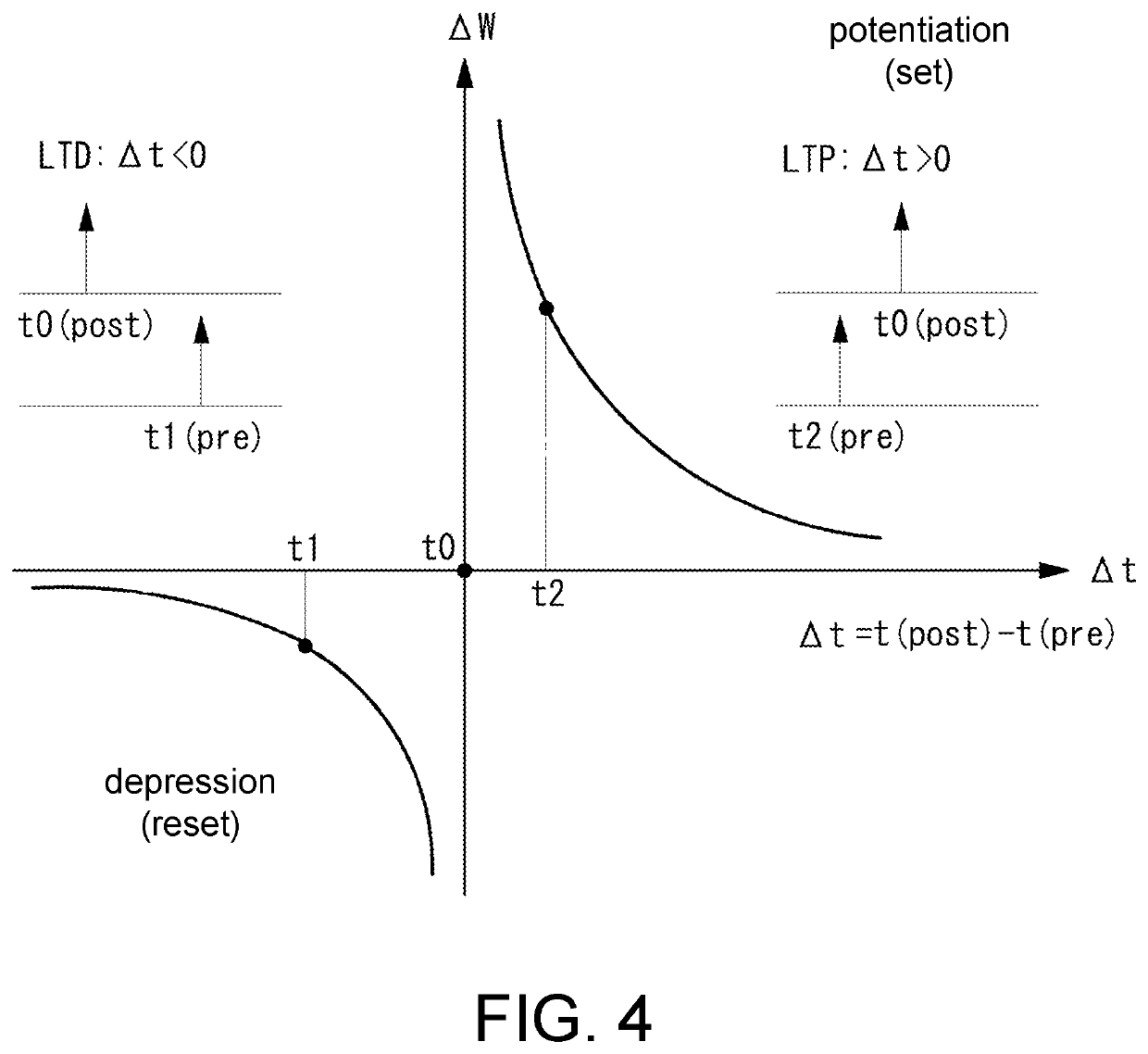

STDP pulse design method based on multi-value memristor and implementation method of diversified STDPs

ActiveCN108664735AMeet electrical characteristicsCAD circuit designPhysical realisationMulti valuedPhysics

The invention discloses a STDP pulse design method based on a multi-value memristor and an implementation method of diversified STDPs. According to the pulse design method, a synaptic pre-pulse and asynaptic post-pulse are designed into triangular waves with the same waveform, the selecting of the amplitude values of the triangular waves and the time interval of the front and rear triangular waves is determined by the amplitude value of the tested pulse and the pulse width threshold response range, and the pulse design of the STDP synaptic plasticity is simplified. According to the implementation method of the diversified STDP synaptic plasticity, different resistance states are selected as initial resistance states, and the design pulses are superposed on and applied to the memristor, sothat the STDP synaptic plasticity of the biological index attenuation type and the STDP synaptic plasticity different from the biological index attenuation type are realized, thereby realizing diversification of STDP synaptic plasticity. The method is expected to be applied to any kind of multi-value memristor and further expands the application of the memristor in the calculation of artificial synapse and nerve morphology.

Owner:HUAZHONG UNIV OF SCI & TECH

A health-protective pharmaceutical for activating and improving intellect and its preparation method

InactiveCN1943751AIncrease mobilityEasy to passPowder deliveryOrganic active ingredientsCranial nervesAlpha-Lipoic Acid

A brain activating and intelligence-promoting health care medicament and preparation method, selecting radix notoginseng, radix angelicae sinensis , radix paeoniae rubra, cortex moutan, fructus alpiniae oxyphyllae, radix polygalae, day lily ,semen juglandis, semen cuscutae, semen ziziphi spinosae, herba menthae, bulbus allii, semen platycladi, radix glycyrrhizae ,ginkgo extract, alpha-lipoic acid, phosphatidyl choline, pyroglutamic acid ester as raw manufacturing materials. The present invention can increase cerebral blood flow, add nutrient substances needed by cerebral memory, inoxidize and remove harmful free radicals, promote metabolism, increase the permeabilitythe membrane of the cranial nerves and presynapses and postsynapses supplemented with mind- tranquilizing and intelligence-promoting Chinese traditional medicine, make nutrient substances easy to pass through the blood-brain barrier, supplement oxygen , nutrient substances and energy to the brain on every side, has the noticeable effect of enhancing the activity of brain cells thereby exert the brain's potential, activate the brain, promoting intelligence and anti-fatigue. It mainly applied to increase the cerebral blood flow, add cerebral energy, and relieve the brain fatigue, in order to achieve significant increase in memory, enhancement of intelligence of middle school students or pupils and young adults.

Owner:刘良韡 +1

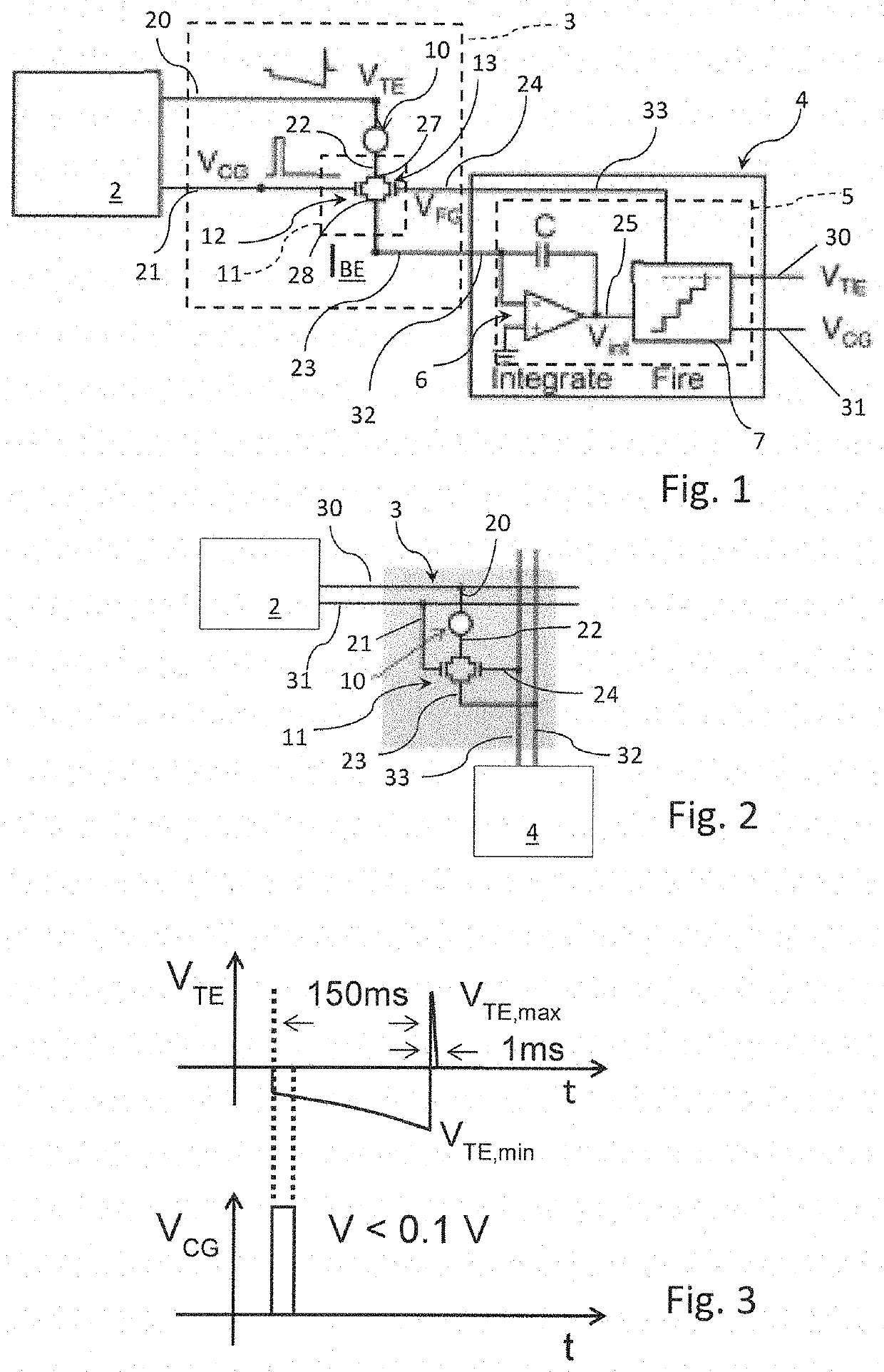

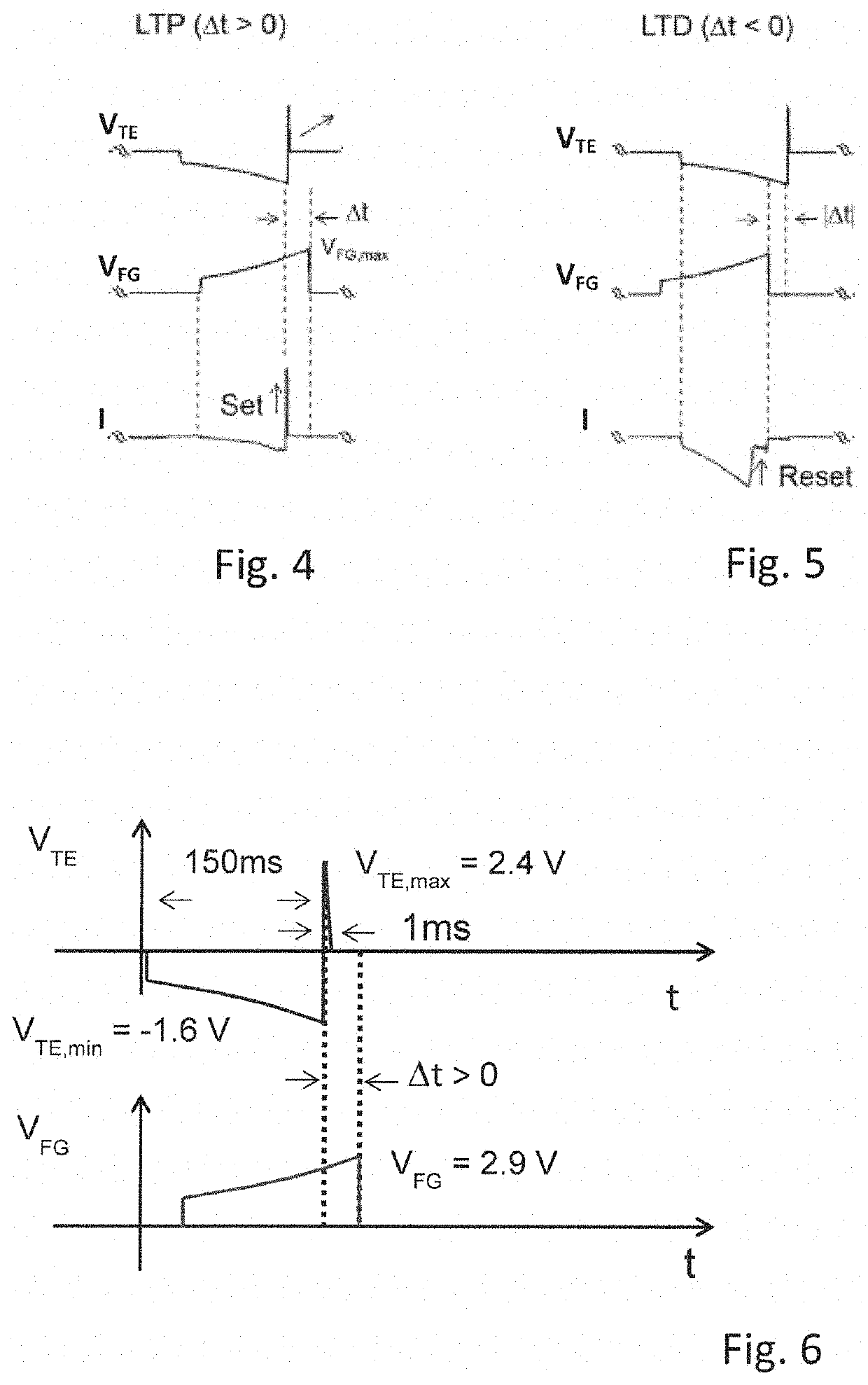

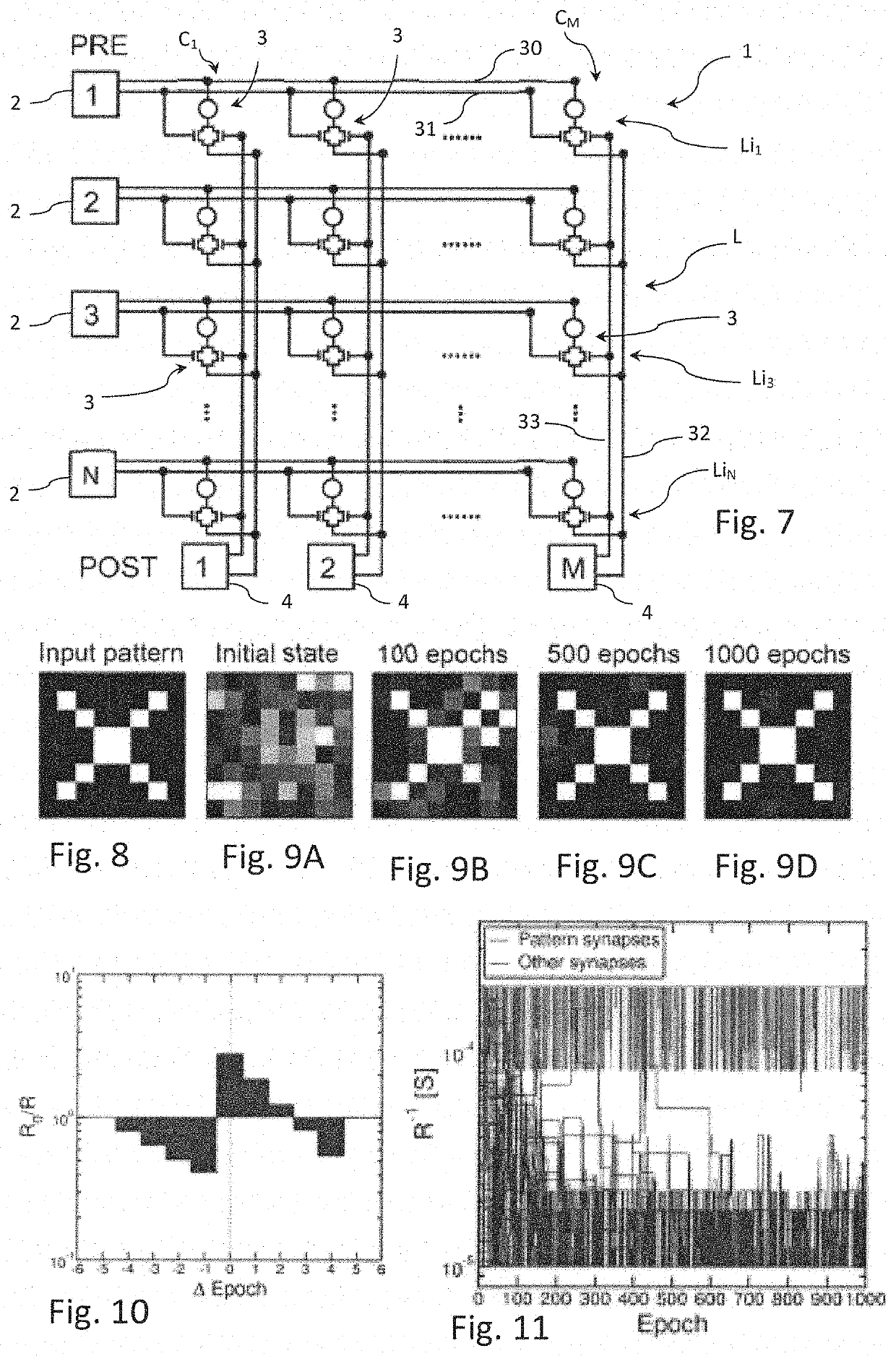

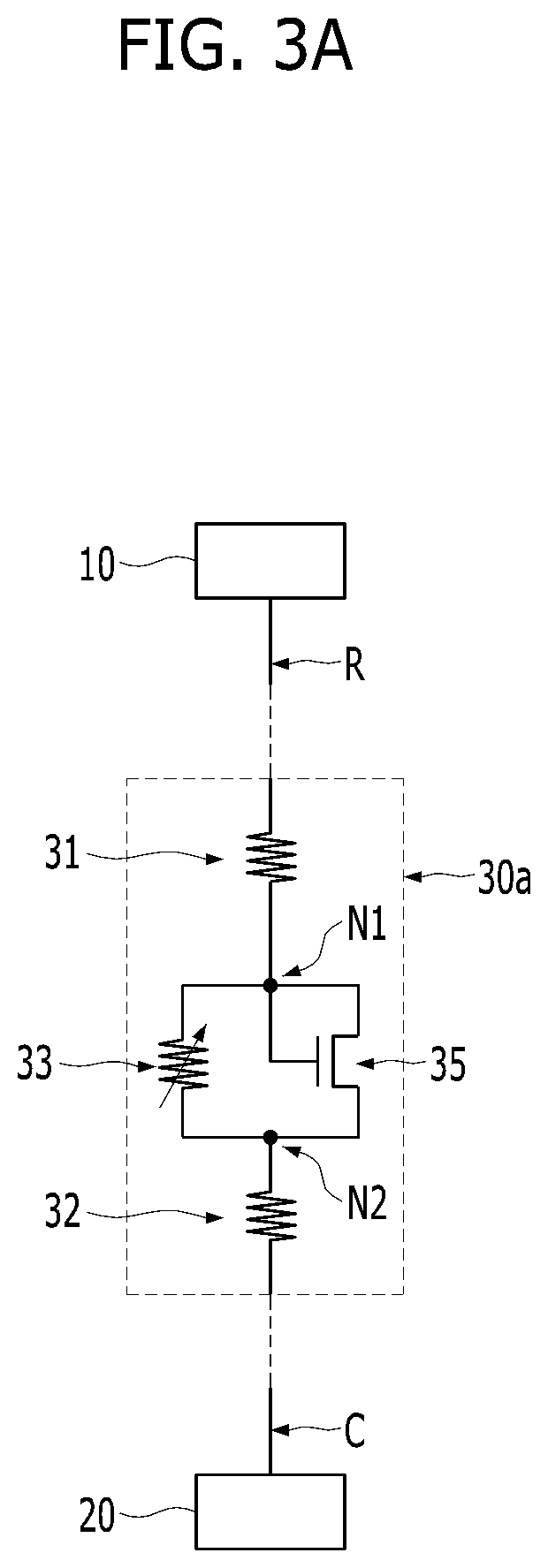

Electronic neuromorphic system, synaptic circuit with resistive switching memory and method of performing spike-timing dependent plasticity

ActiveUS10650308B2Neural architecturesPhysical realisationSpike-timing-dependent plasticityArtificial intelligence

A synaptic circuit performing spike-timing dependent plasticity STDP interposed between a pre-synaptic neuron and a post-synapse neuron includes a memristor having a variable resistance value configured to receive a first signal from the pre-synaptic neuron. The circuit has an intermediate unit connected in series with the memristor for receiving a second signal from the pre-synaptic neuron and provides an output signal to the post-synaptic neuron. The intermediate unit receives a retroaction signal generated from the post-synaptic neuron and the memristor modifies the resistance value based on a delay between two at least partially overlapped input pulses, a spike event of the first signal and a pulse of the retroaction signal, in order to induct a potentiated state STP or a depressed state STD at the memristor. An electronic neuromorphic system having synaptic circuits and a method of performing spike timing dependent plasticity STDP by a synaptic circuit are also provided.

Owner:POLITECNICO DI MILANO

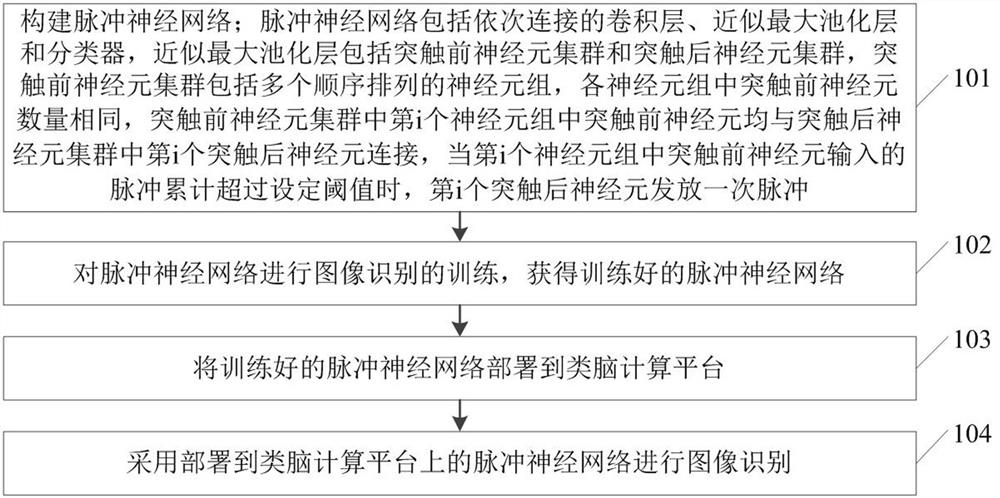

Image recognition method and system based on brain-like computing platform

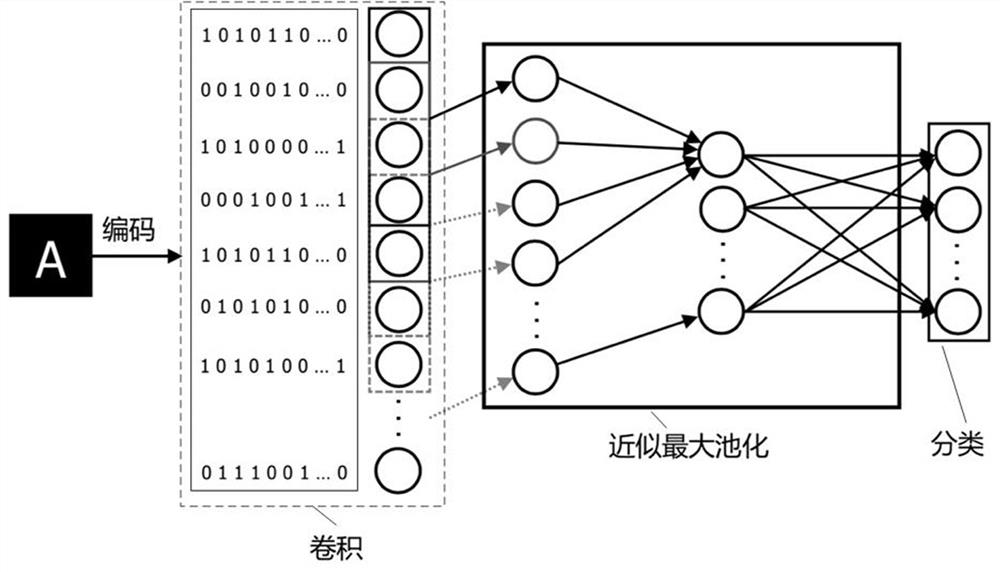

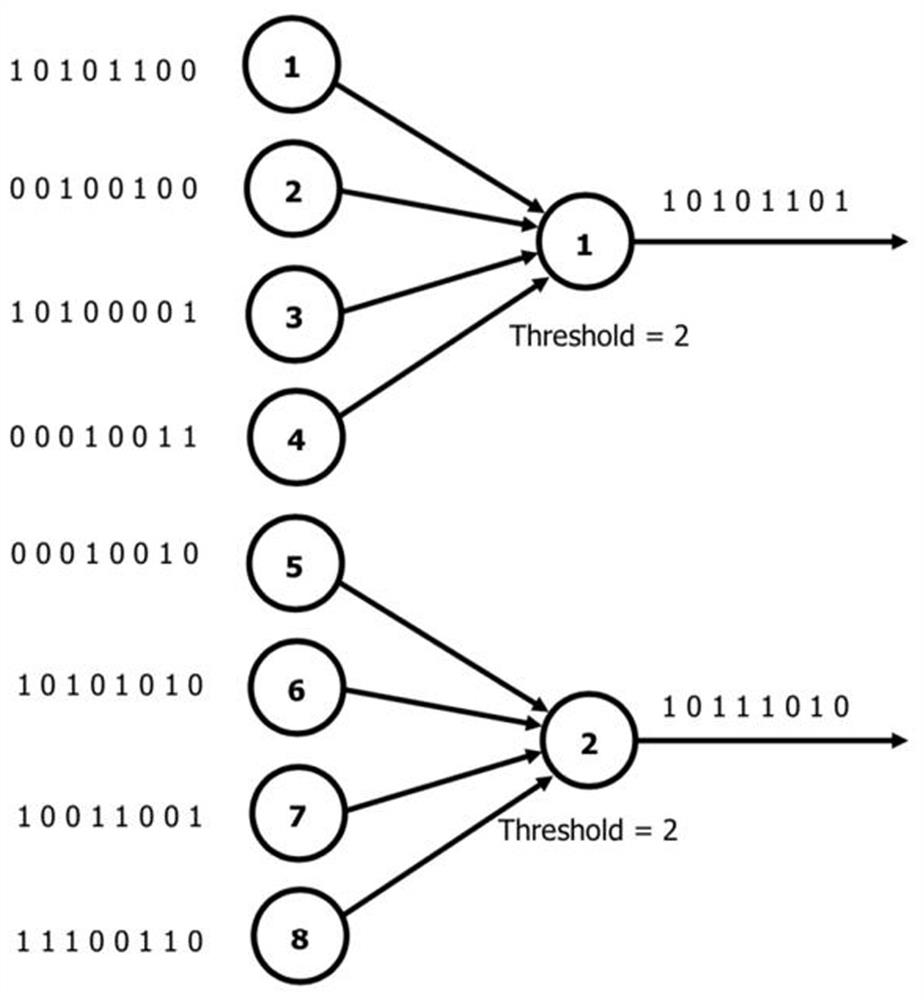

ActiveCN113962371AReduce energy consumptionReduce computationNeural architecturesPhysical realisationSpiking neural networkThresholding

The invention relates to an image recognition method and system based on a brain-like computing platform. The method comprises the following steps: constructing a spiking neural network, wherein the spiking neural network comprises an approximate maximum pooling layer, the approximate maximum pooling layer comprises a pre-synaptic neuron cluster and a post-synaptic neuron cluster, the pre-synaptic neuron cluster comprises a plurality of neuron groups which are arranged in sequence, the number of pre-synaptic neurons in each neuron group is the same, the pre-synaptic neurons in the ith neuron group in the pre-synaptic neuron cluster are all connected with the ith post-synaptic neuron in the post-synaptic neuron cluster, and when spiking input by the pre-synaptic neurons in the ith neuron group exceeds a set threshold value in an accumulated manner, the ith post-synaptic neuron gives out spiking once; deploying the trained spiking neural network to a brain-like computing platform; and carrying out image recognition by adopting the spiking neural network deployed on a brain-like computing platform. According to the invention, the energy consumption of image recognition during hardware platform calculation is reduced.

Owner:中科南京智能技术研究院

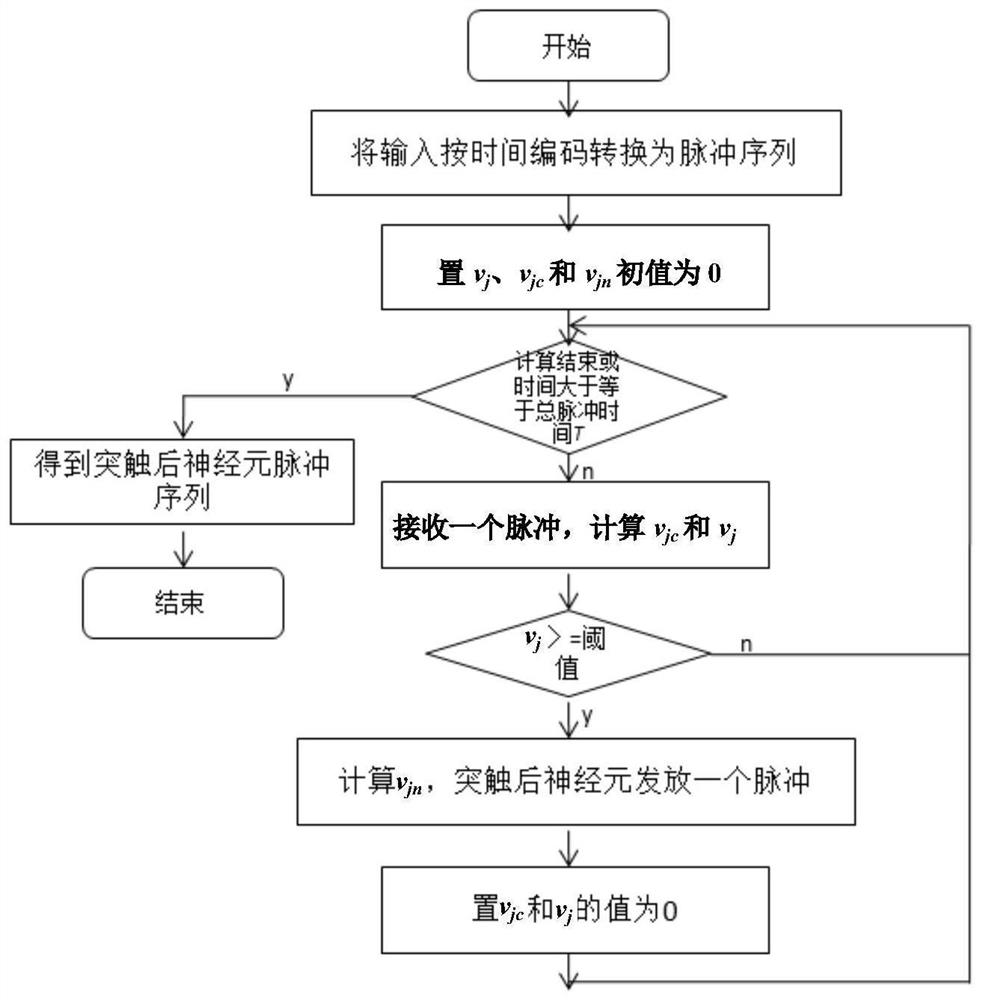

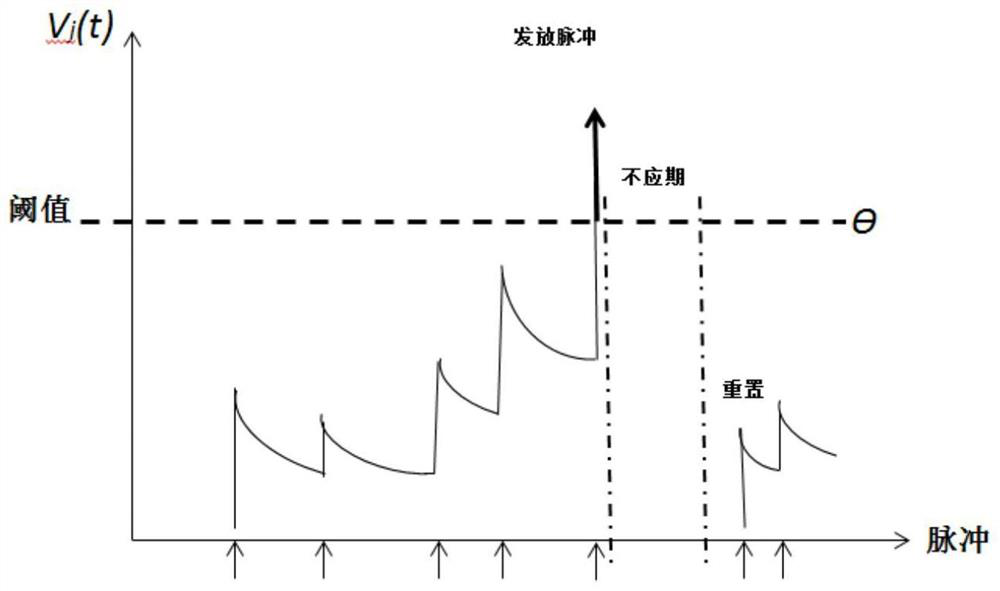

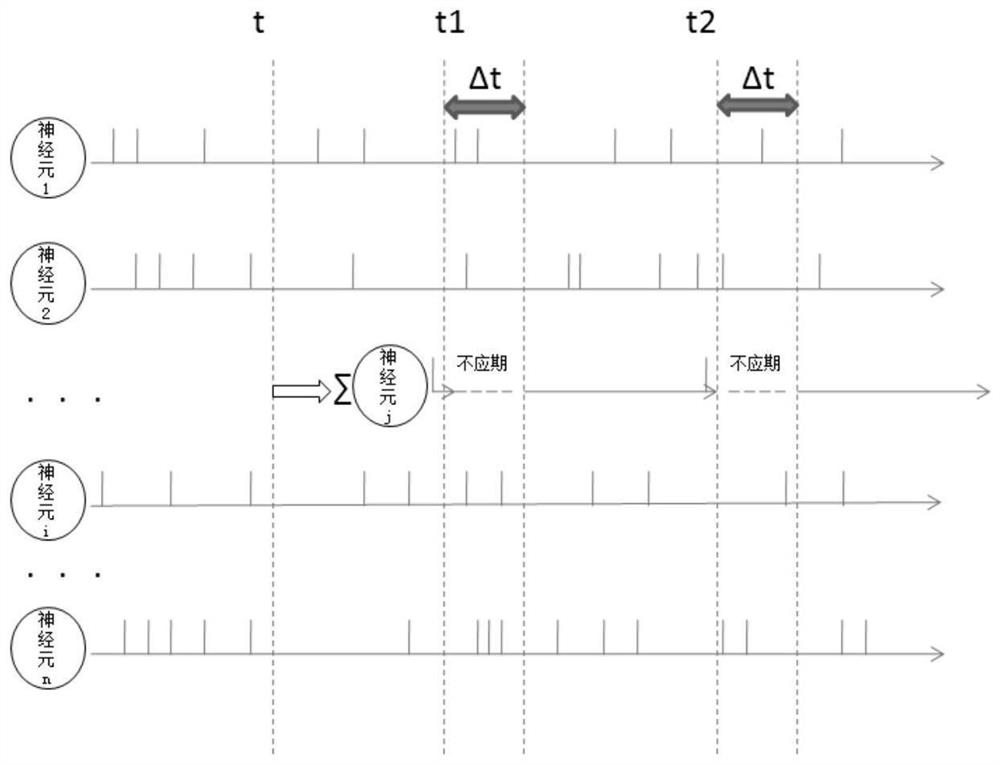

Pulse neural network neuron membrane voltage calculation method

PendingCN114239405ASolve the lossMake up for the lossDesign optimisation/simulationImaging processingImage manipulation

The invention provides a method for calculating neuron membrane voltage of a spiking neural network, and relates to the technical field of spiking neural networks, and the method comprises the steps: firstly, converting an input signal into a pulse sequence through employing a time coding method, selecting a Spike Response Model neuron model as a membrane voltage calculation model of a neuron non-nonstress time period of the spiking neural network, and carrying out the calculation of the membrane voltage of the spiking neural network; then establishing a membrane voltage model generated by pulse accumulation of the pre-synaptic neurons in the post-synaptic neuron non-stress period, and finally establishing a pulse neural network neuron membrane voltage calculation model to realize calculation of the post-synaptic neuron membrane voltage; according to the method, the accumulation of neuron input pulses before the non-stress period highlights is calculated, the loss of input information is made up, the method is applied to image processing, the loss of information is reduced, and the utilization rate of the input information is improved.

Owner:NORTHEASTERN UNIV

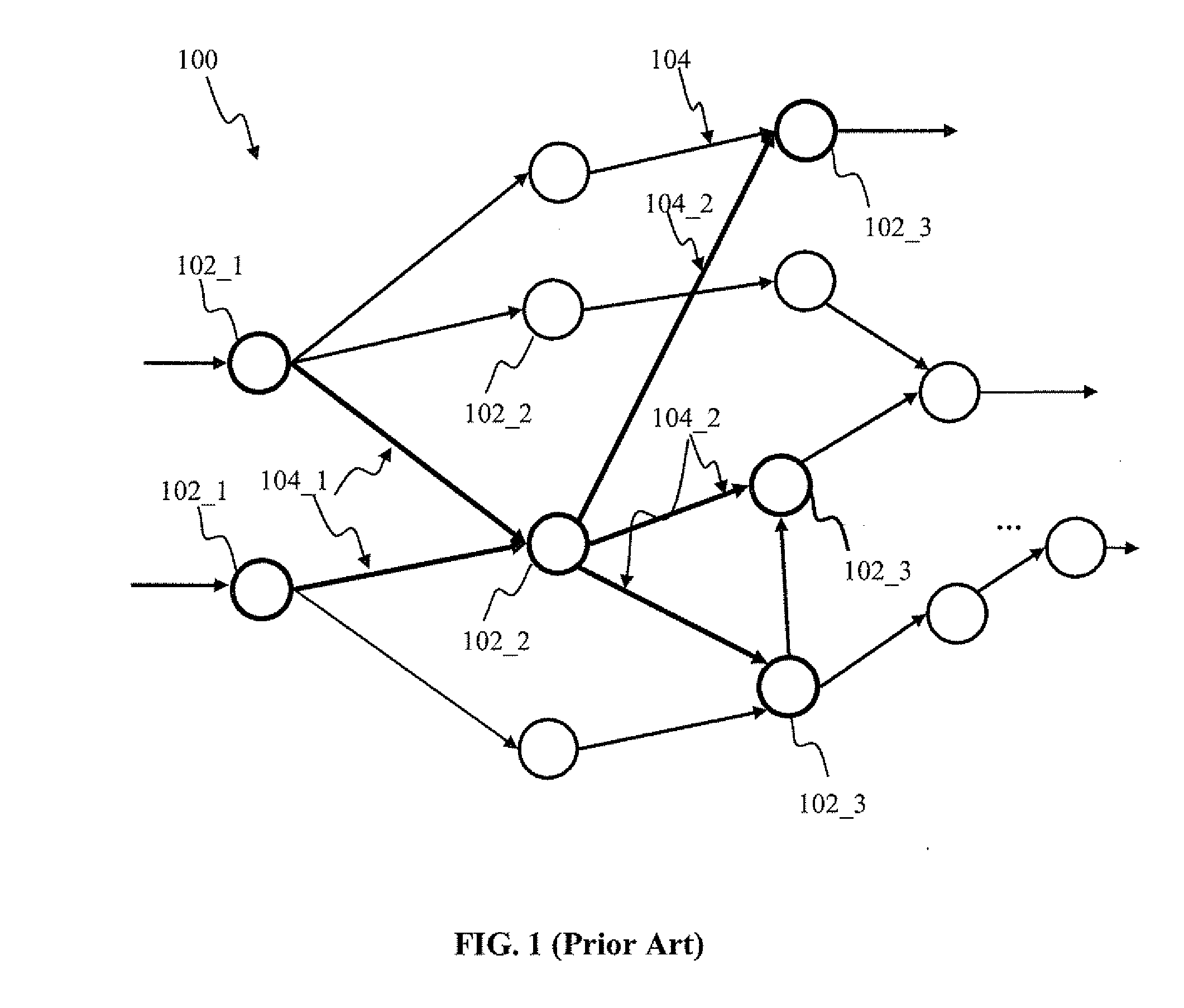

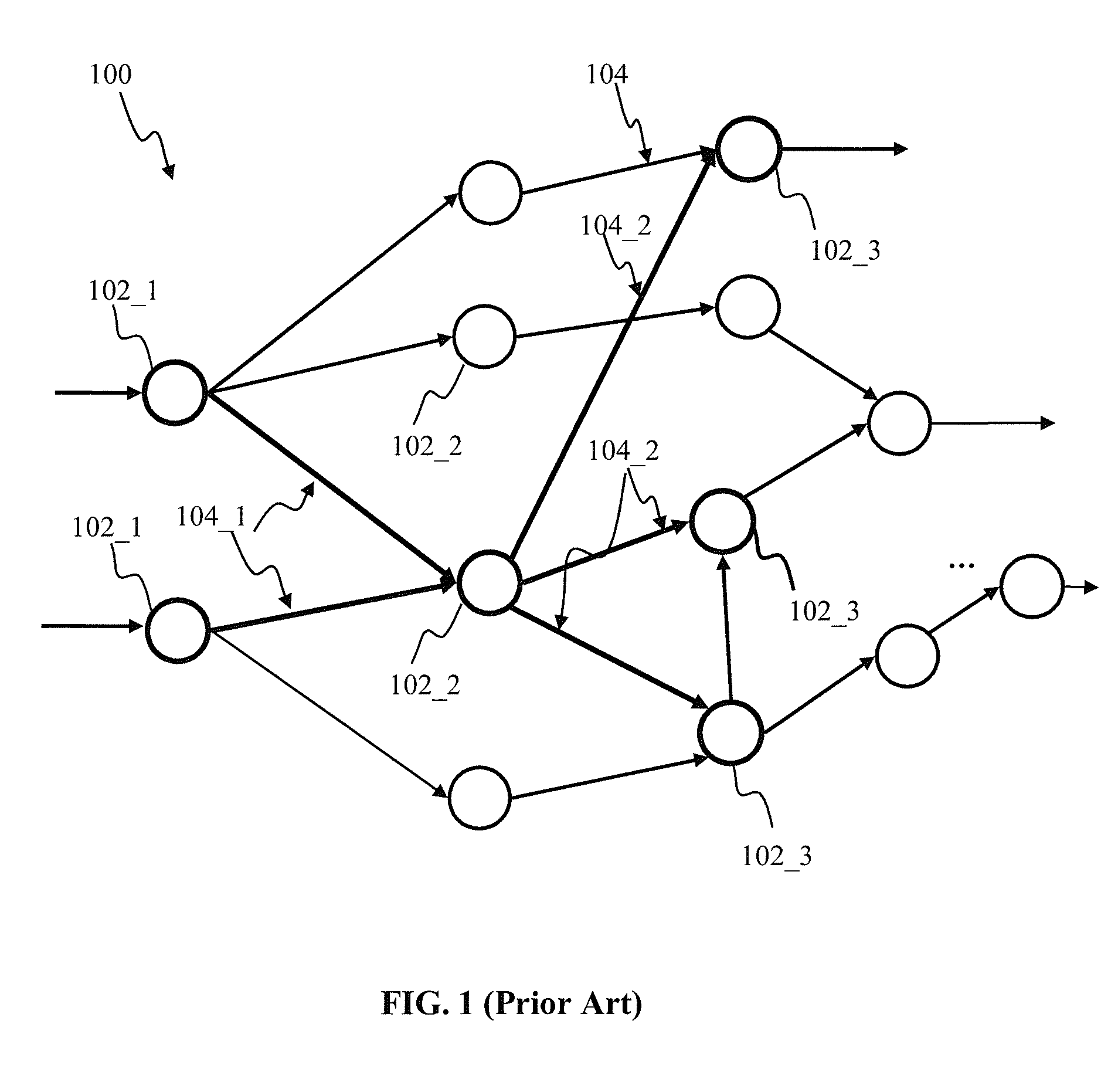

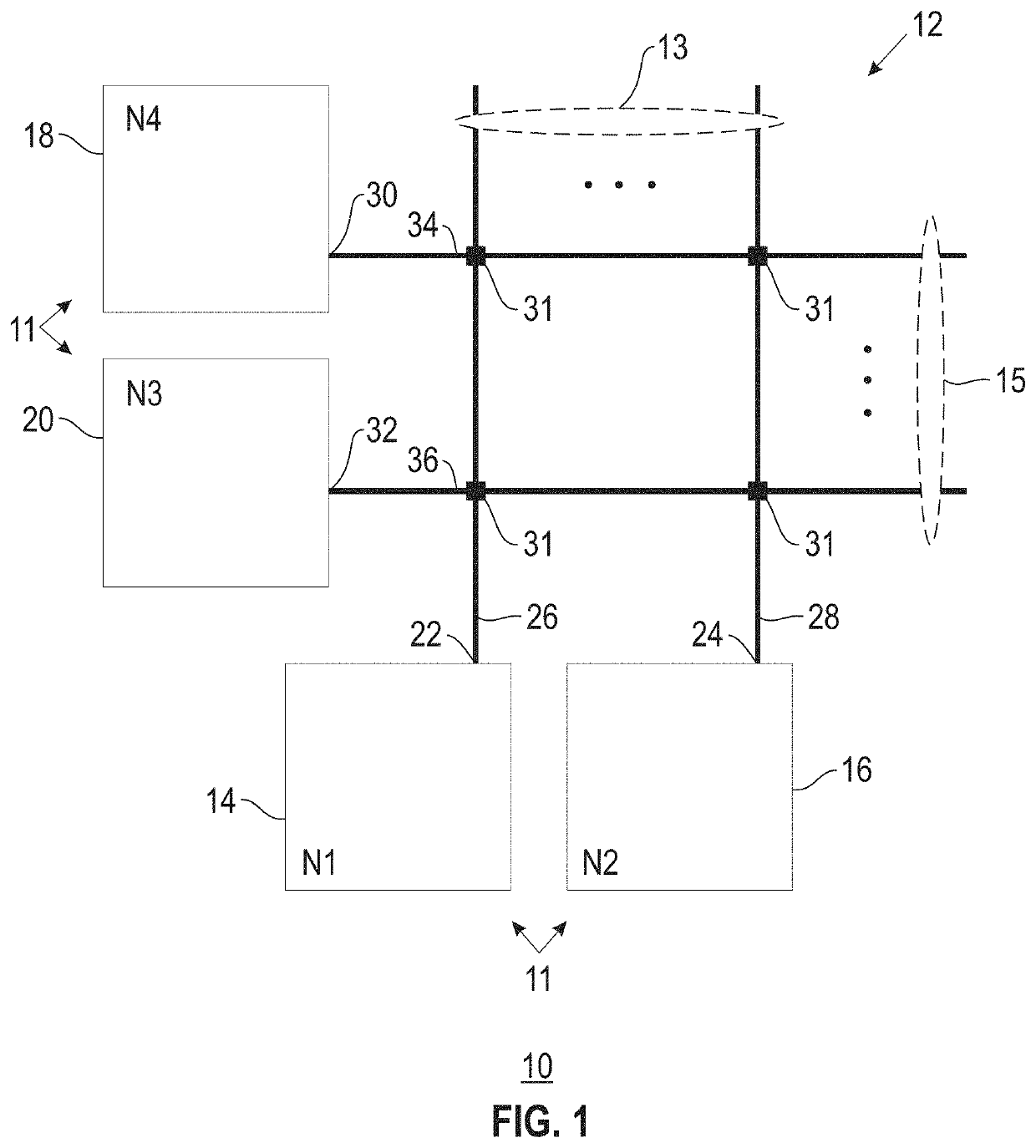

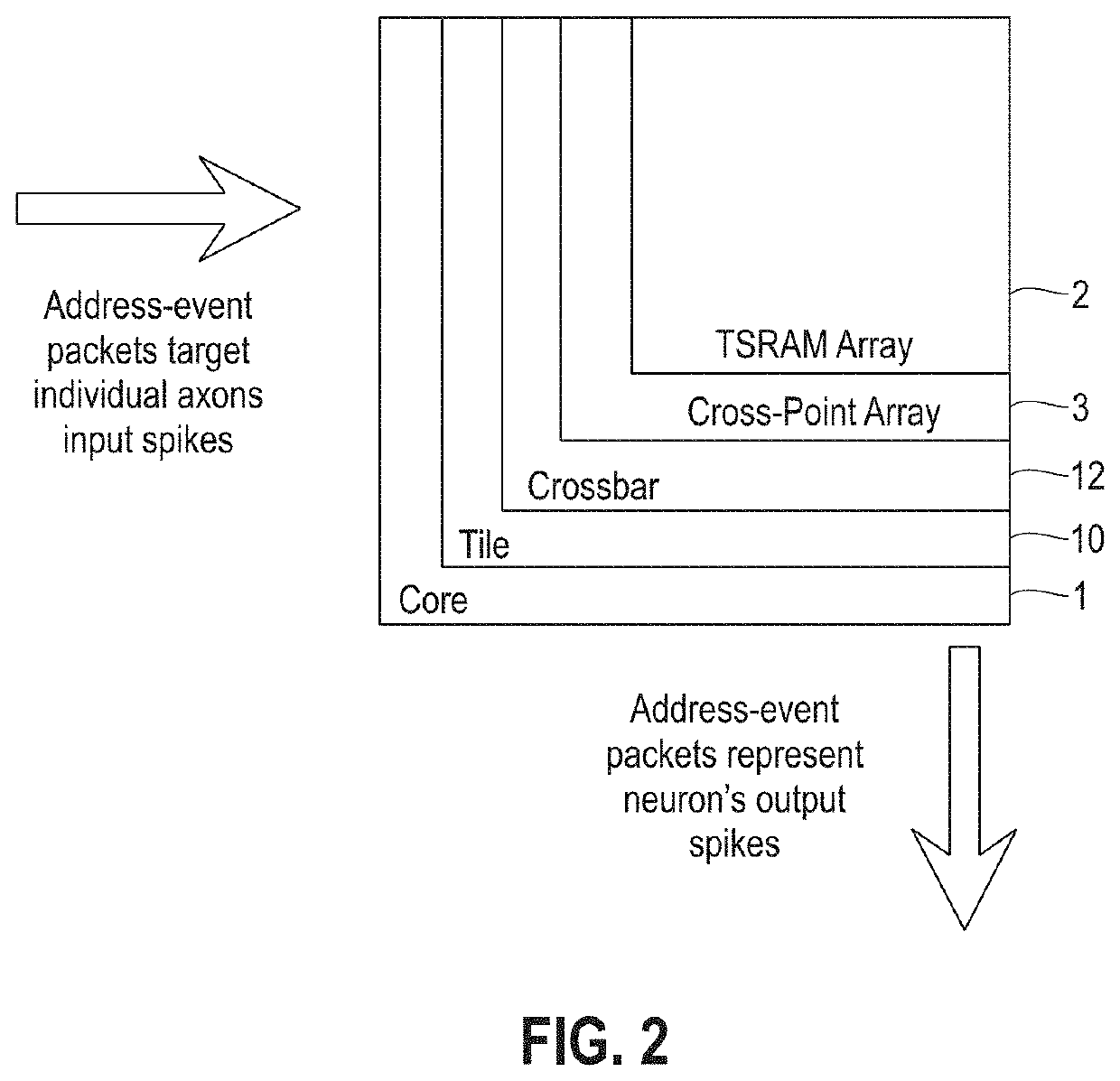

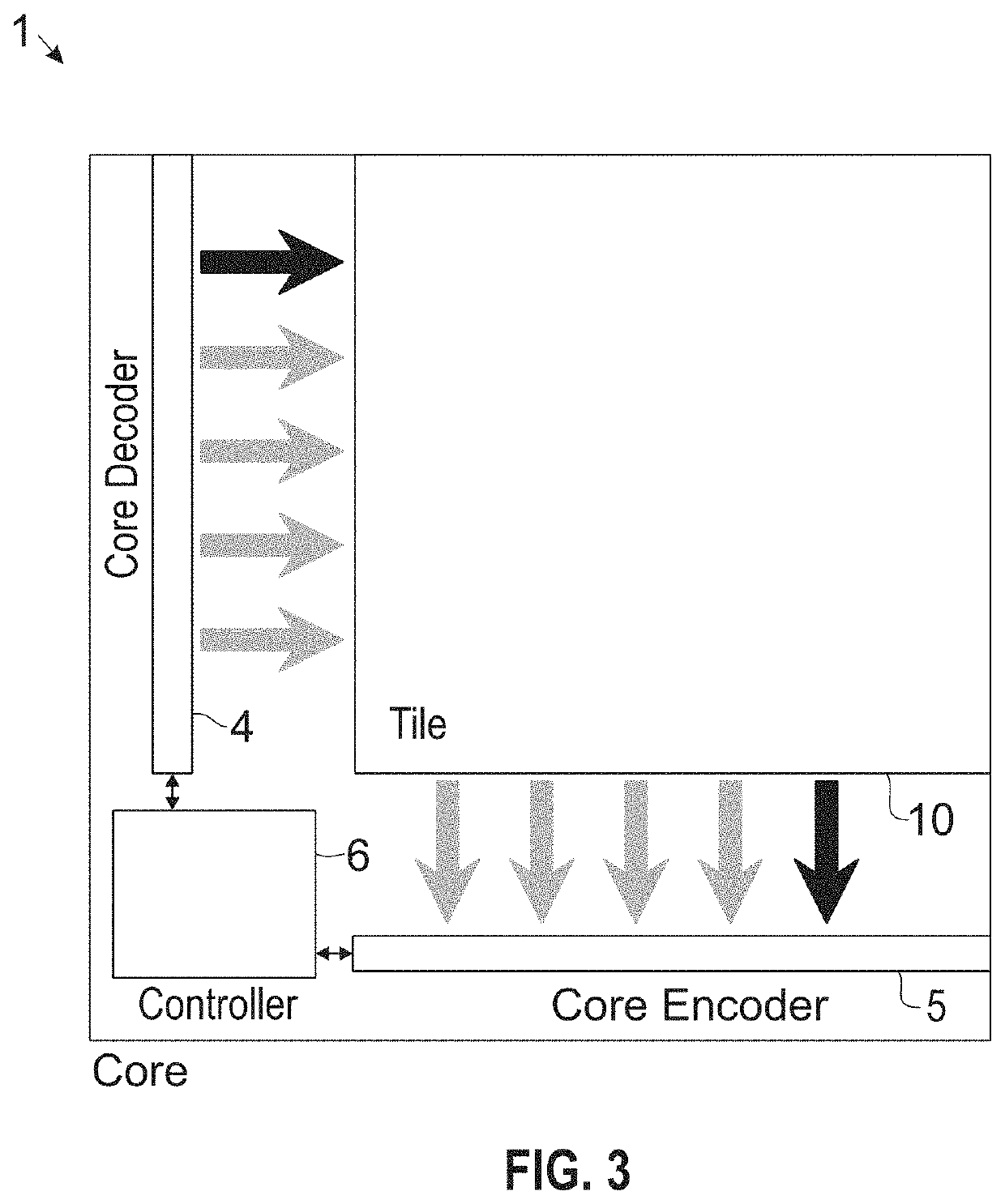

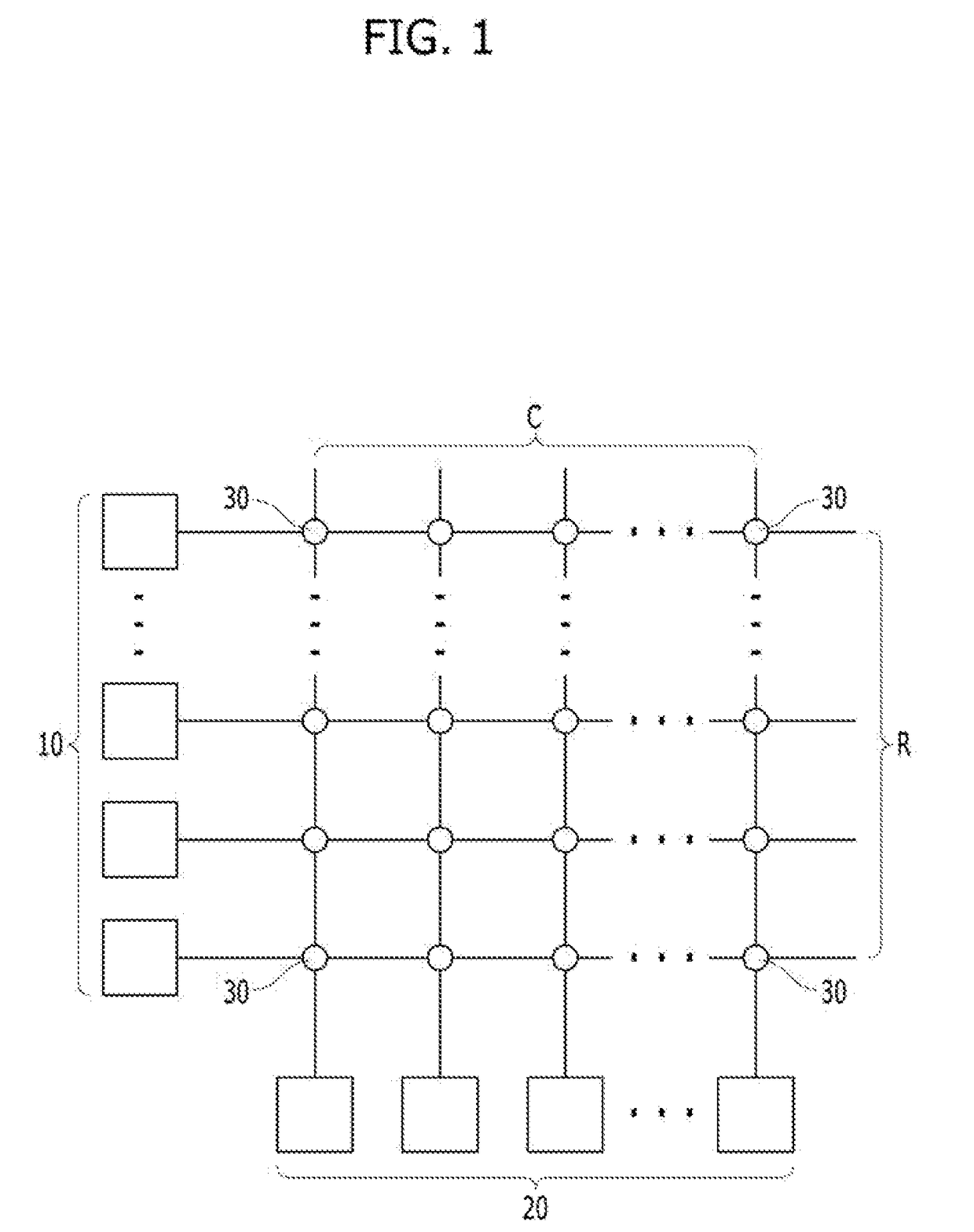

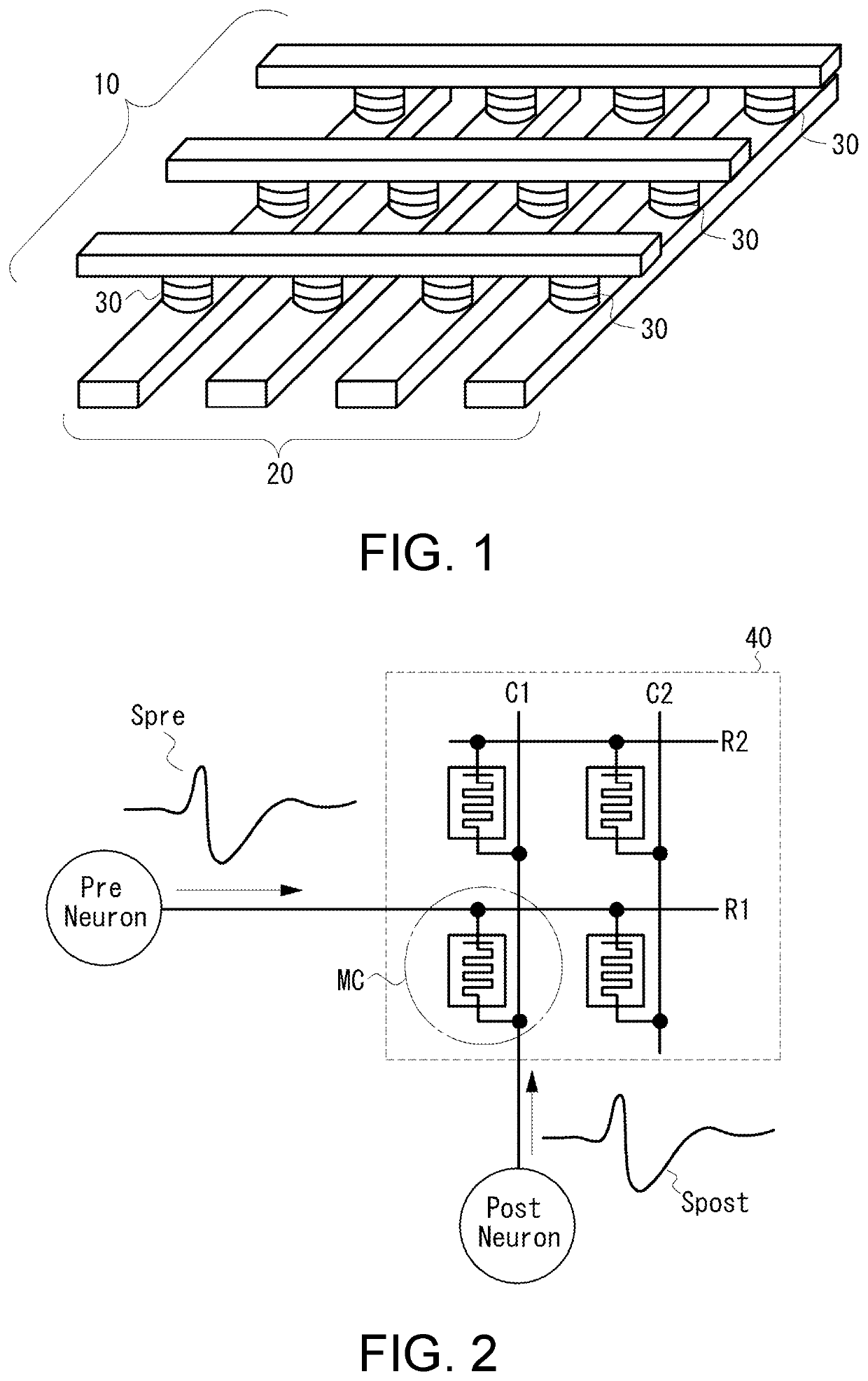

Neuromorphic event-driven neural computing architecture in a scalable neural network

An event-driven neural network includes a plurality of interconnected core circuits is provided. Each core circuit includes an electronic synapse array has multiple digital synapses interconnecting a plurality of digital electronic neurons. A synapse interconnects an axon of a pre-synaptic neuron with a dendrite of a post-synaptic neuron. A neuron integrates input spikes and generates a spike event in response to the integrated input spikes exceeding a threshold. Each core circuit also has a scheduler that receives a spike event and delivers the spike event to a selected axon in the synapse array based on a schedule for deterministic event delivery.

Owner:IBM CORP +1

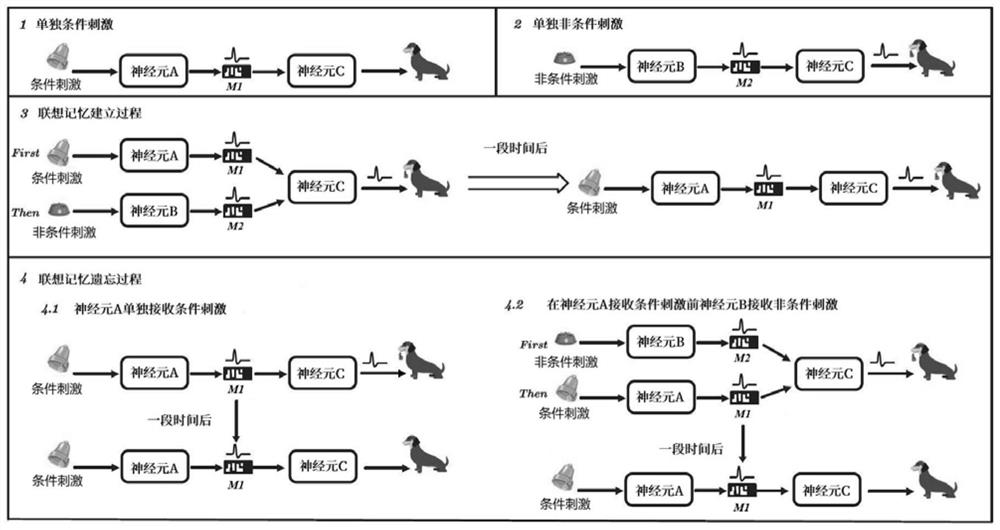

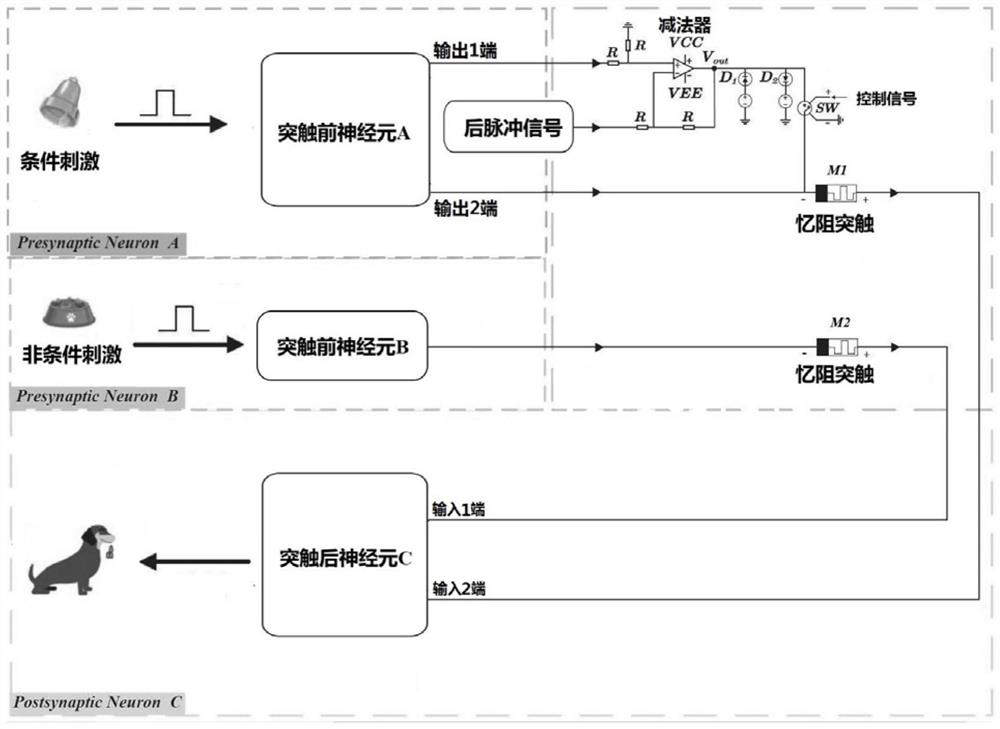

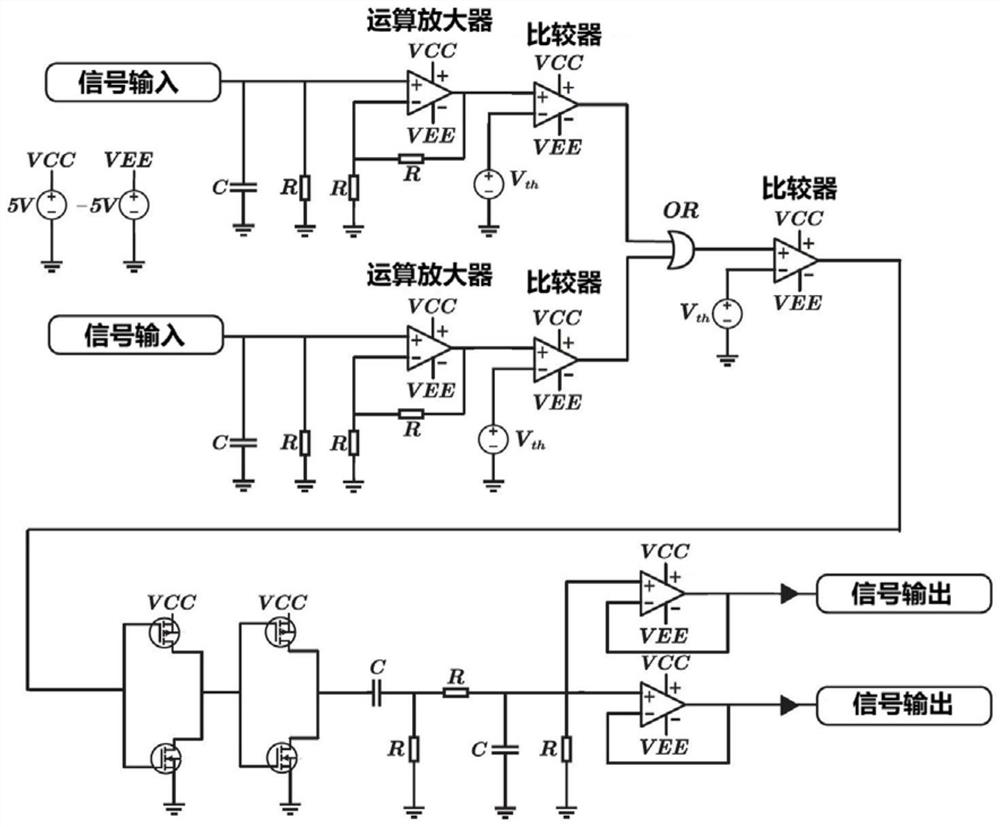

Associative memory circuit and method based on physical memristor

PendingCN114169511AHigh similaritySimulation results are accuratePhysical realisationSynapseMemory circuits

The invention provides an associative memory circuit and memory method based on a physical memristor. The circuit comprises a synaptic unit and a spiking neuron unit, the synapse unit comprises a memristive synapse M1 and a memristive synapse M2; the pulse neuron unit comprises a pre-synaptic neuron A, a pre-synaptic neuron B and a post-synaptic neuron C. The pre-synaptic neuron A and the pre-synaptic neuron B receive conditional stimulation signals and non-conditional stimulation signals respectively. The synaptic units and the spiking neuron units form a basic associative memory unit, and a plurality of basic associative memory units can form a biological neural network. The synaptic unit is based on a physical memristor, the defects that a traditional synaptic circuit is large in size and high in energy consumption are overcome, the integration level of the artificial neural network is improved, and the possibility is provided for an artificial neural network hardware circuit to simulate a large-scale biological neural network.

Owner:SHANDONG UNIV OF SCI & TECH

Application of postsynaptic neurotoxin, cardiotoxin, cytotoxin, phospholipase A2 and crude venom of cobra in resisting virus infection

The invention relates to application of a postsynaptic neurotoxin, a cardiotoxin, a cytotoxin, a phospholipase A2 and a crude venom of a cobra in resisting virus infection. A respiratory tract is easily invaded and infected by viruses due to an open anatomical structure to the outside, and viral influenza and pneumonia are relatively common cases in daily life; and in addition, hepatitis B virusesand AIDS viruses can infect human beings to cause diseases through various ways. The current treatment means of respiratory diseases caused by viruses is not ideal in vaccine or drug effect, and thetreatment effect of viral hepatitis and AIDS needs to be further improved, so that a product which has broad-spectrum inhibition capacity on viruses and has small side effect is developed to become aclinical urgent need. The postsynaptic neurotoxin, the cardiotoxin, the cytotoxin, the phospholipase A2 and the crude venom of the cobra show the effectiveness in resisting virus infection, and possibly become a candidate of a new antiviral product.

Owner:沈喆景

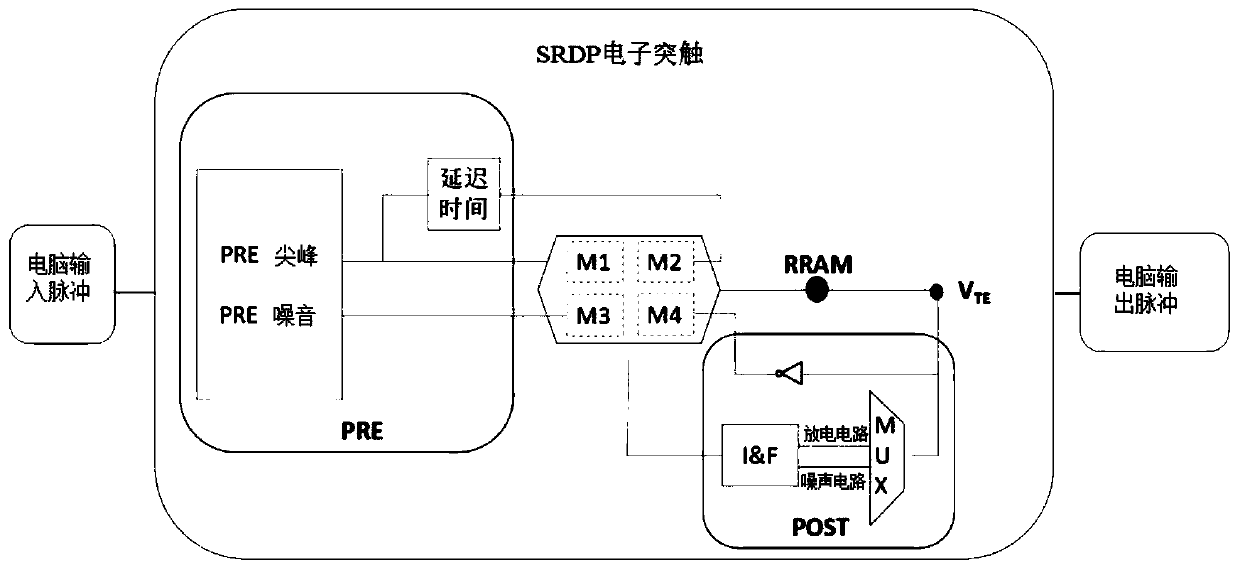

Discharge rate dependent plasticity structure and implementation method

InactiveCN110766149ASupport feasibilityImprove plasticityPhysical realisationElectronic synapseNeural network nn

The invention provides a discharge rate dependent plasticity structure and an implementation method, the discharge rate dependent plasticity structure comprises a pre-synaptic neuron PRE, a post-synaptic neuron POST and an SRDP electronic synapse, and the SRDP electronic synapse comprises four MOS transistors and a bipolar switch RRAM; wherein the four MOS transistors are respectively representedas M1, M2, M3 and M4 by using symbols, M1 and M2 form a group to form M1 / M2 branches, M3 and M4 form a group to form M3 / M4 branches, and M1 / M2 and M3 / M4 are connected in parallel; and the M1 / M2, the M3 / M4, the post-synaptic neuron POST and the bipolar switch RRAM are mutually connected in series. According to the structure and the method, plasticity of discharge time can be realized; unsupervisedlearning can be demonstrated on the neural network level, and the feasibility of a hybrid CMOS / RRAM integrated circuit supporting human brain learning ability matching is proved.

Owner:BEIJING INFORMATION SCI & TECH UNIV

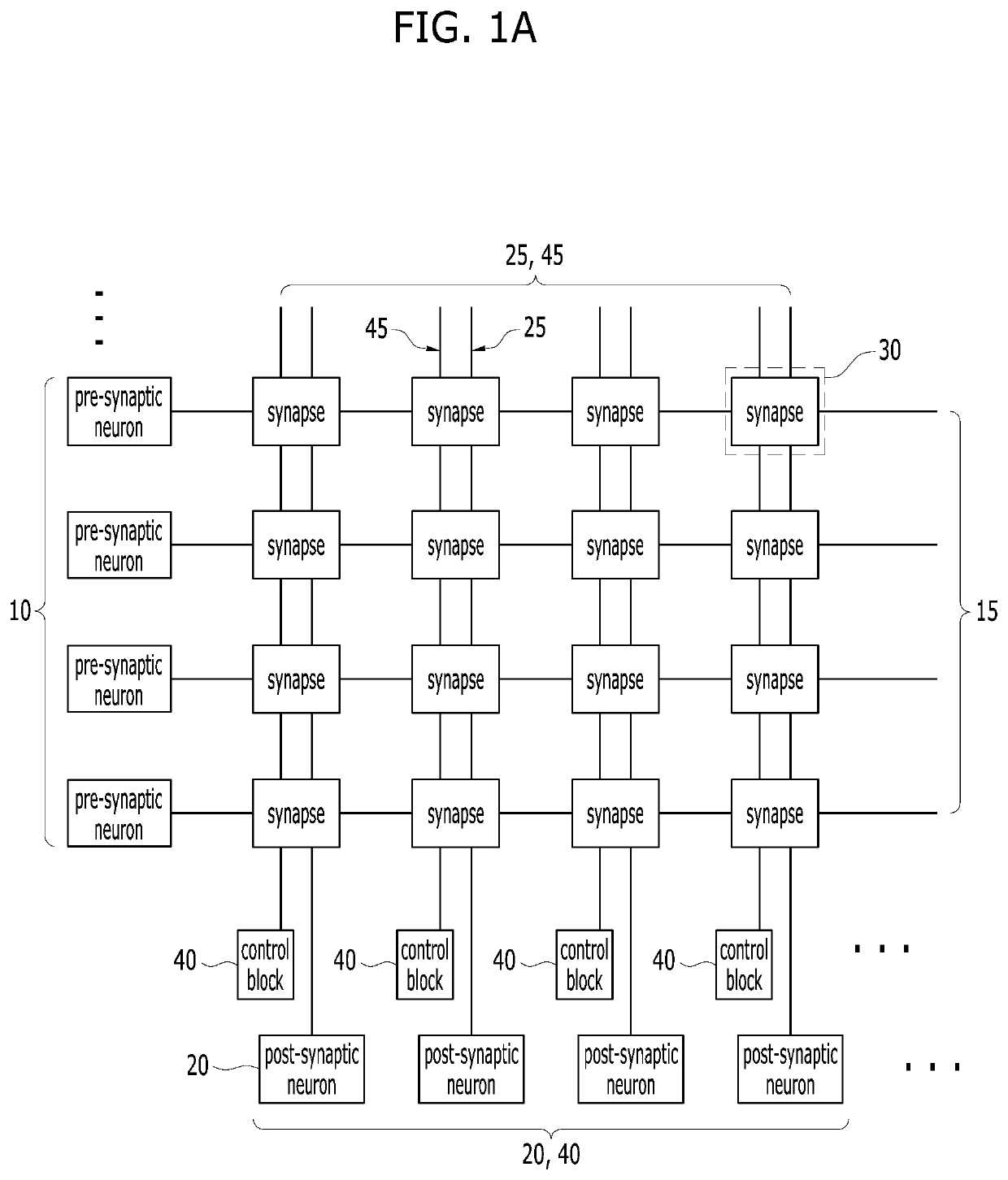

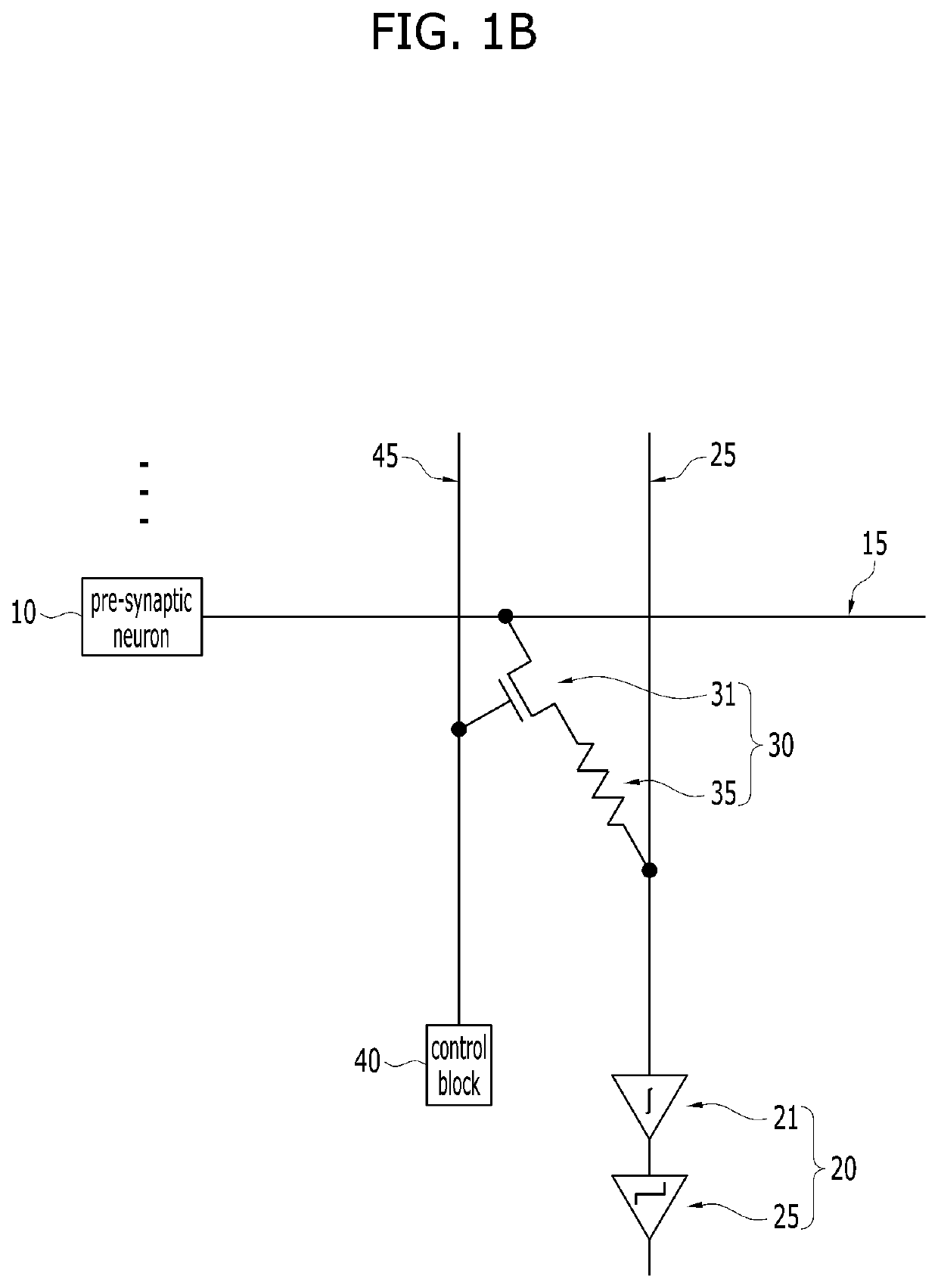

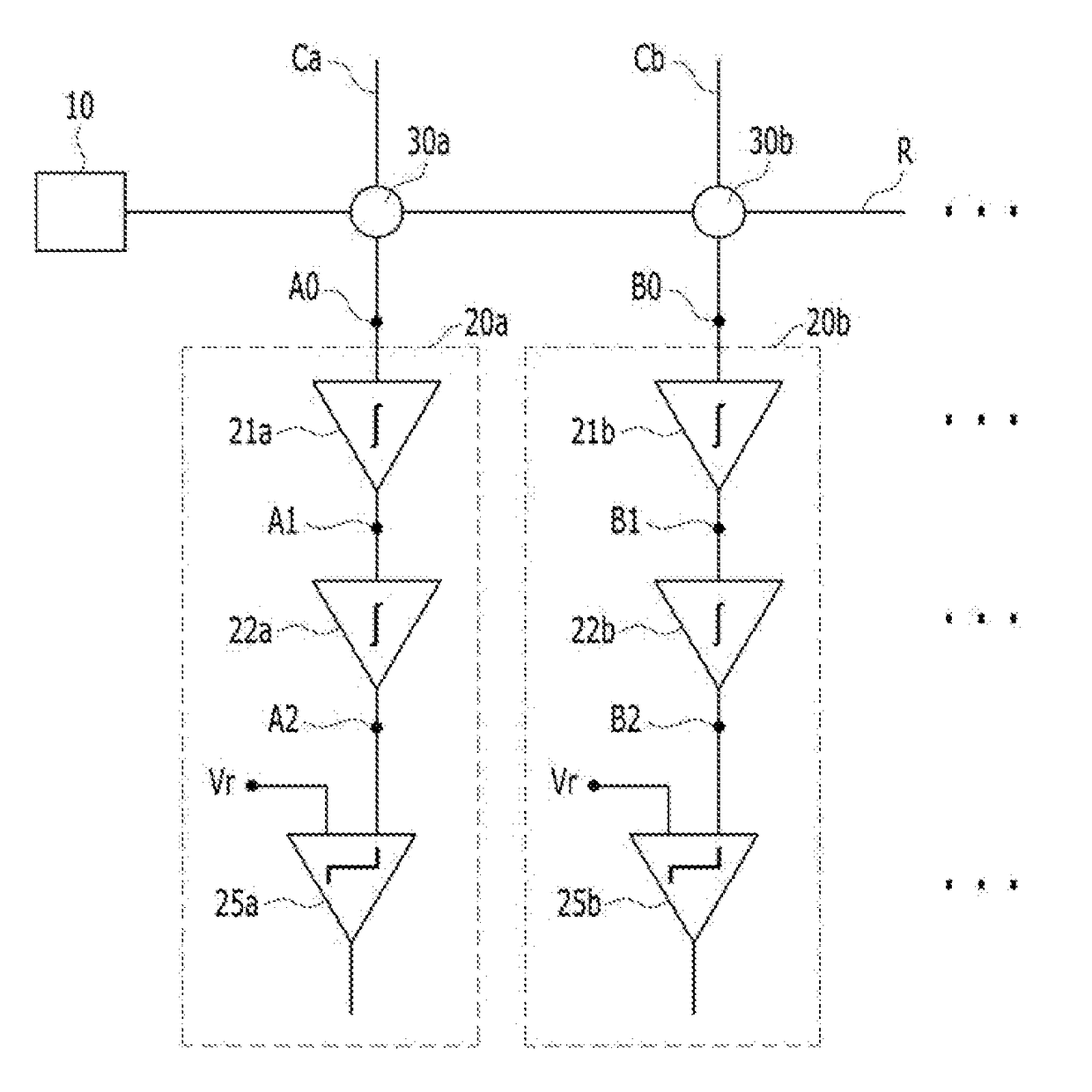

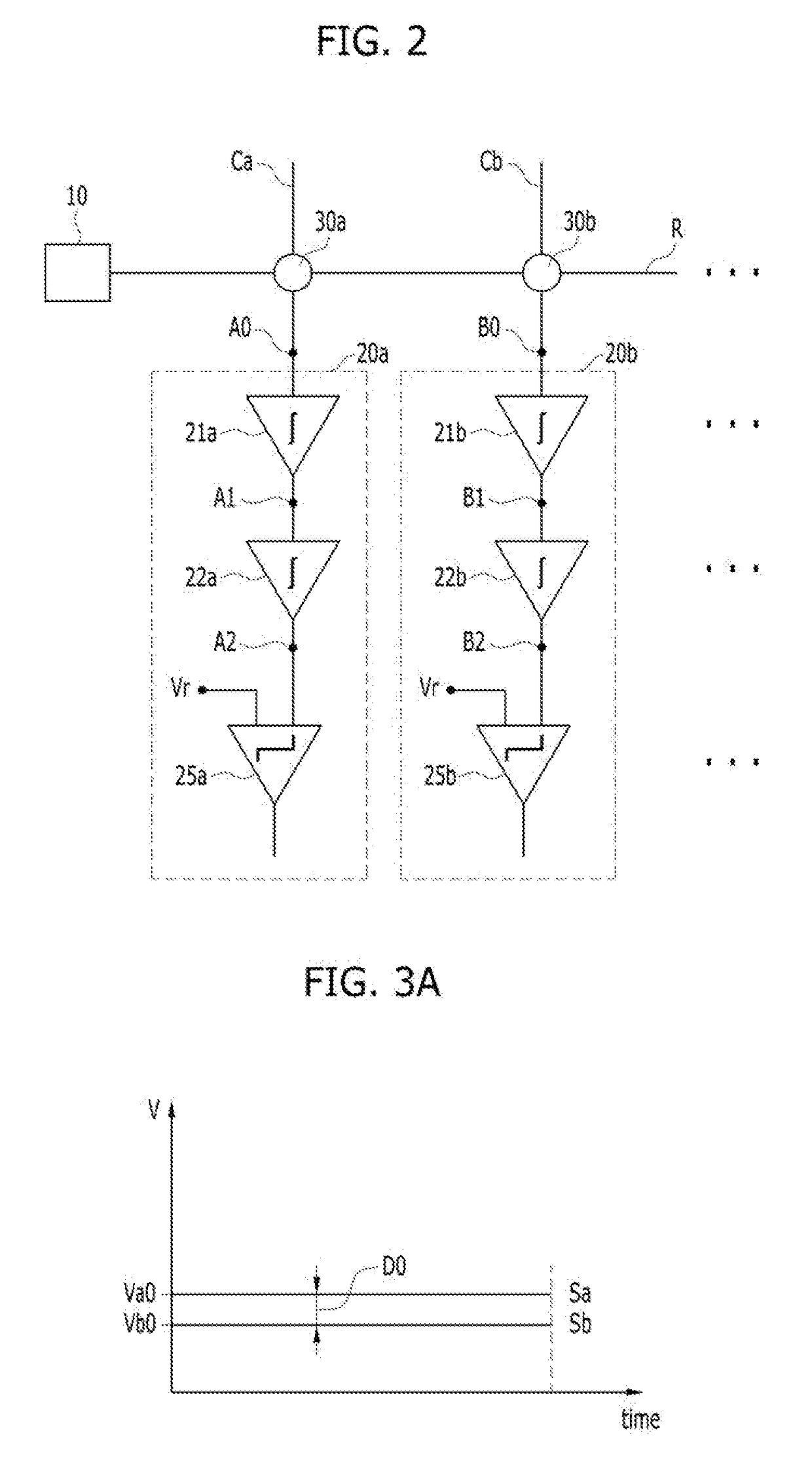

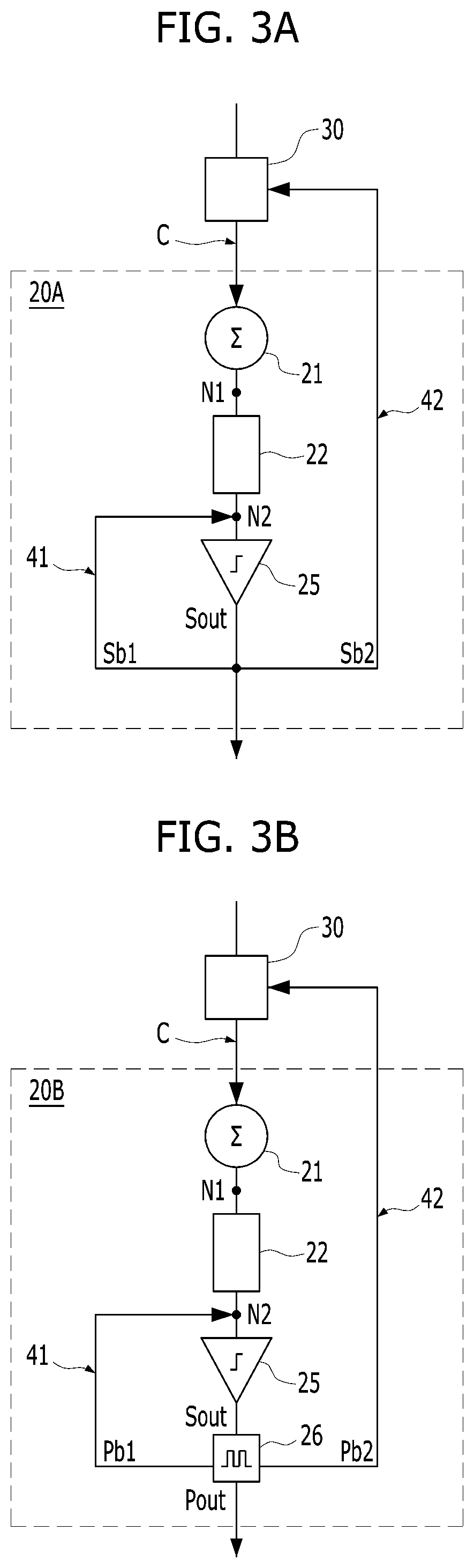

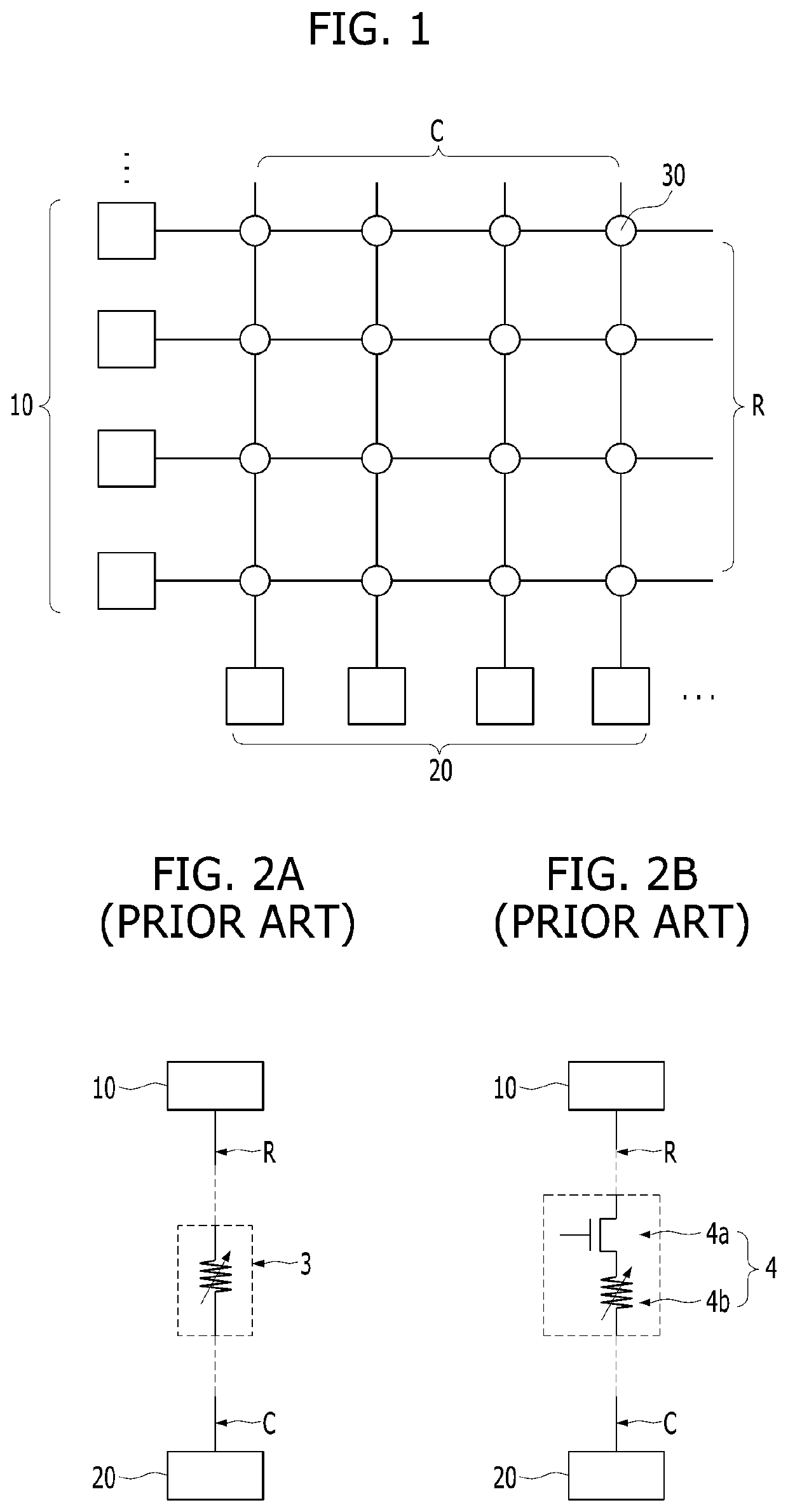

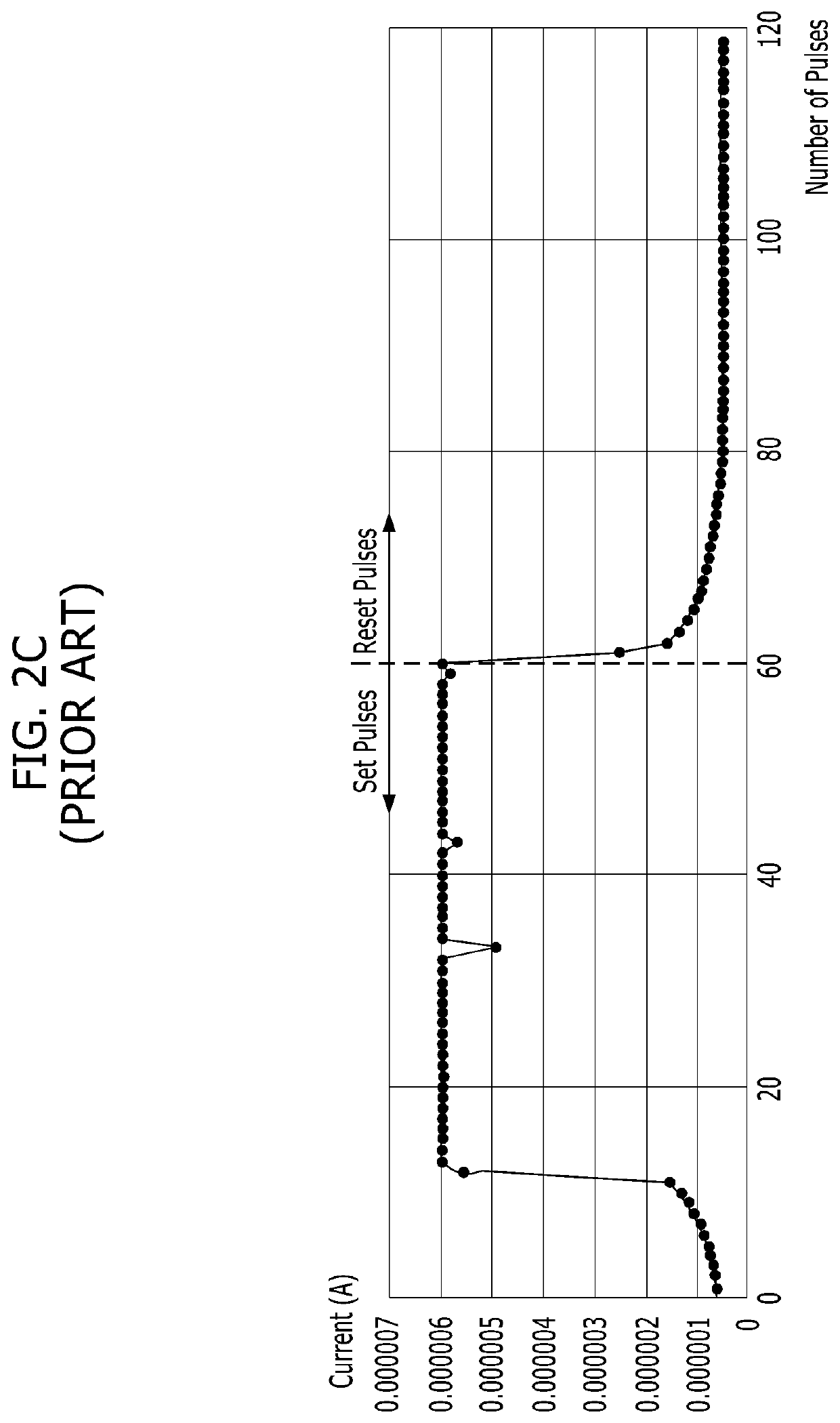

Neuromorphic devices including post-synaptic neurons having at least one of integrators, amplifiers, or sampling elements

InactiveUS20170193358A1Prevent and minimize occurrenceNeural architecturesPhysical realisationSynapseNeuron

A neuromorphic device may include: a pre-synaptic neuron; a row line electrically coupled to the pre-synaptic neuron; a post-synaptic neuron; a column line electrically coupled to the post-synaptic neuron; and a synapse disposed at a cross point between the row line and the column line. The post-synaptic neuron may include: a first integrator electrically coupled to the synapse; a second integrator electrically coupled to the first integrator; and a comparator electrically coupled to the second integrator.

Owner:SK HYNIX INC

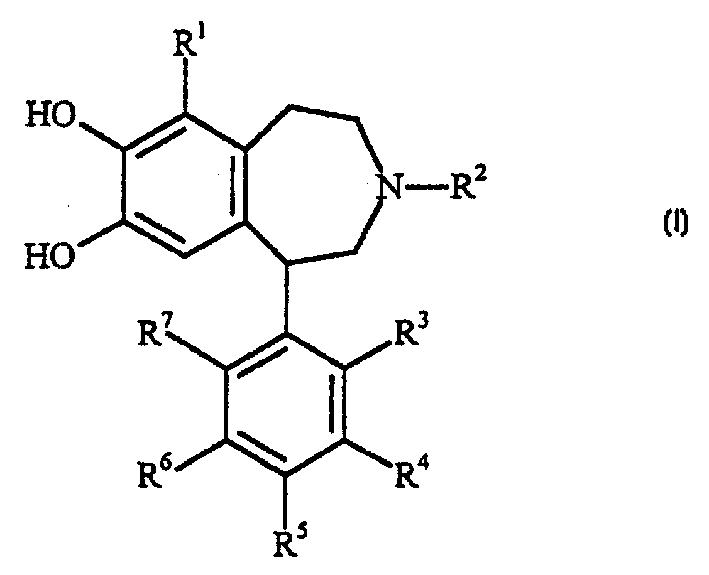

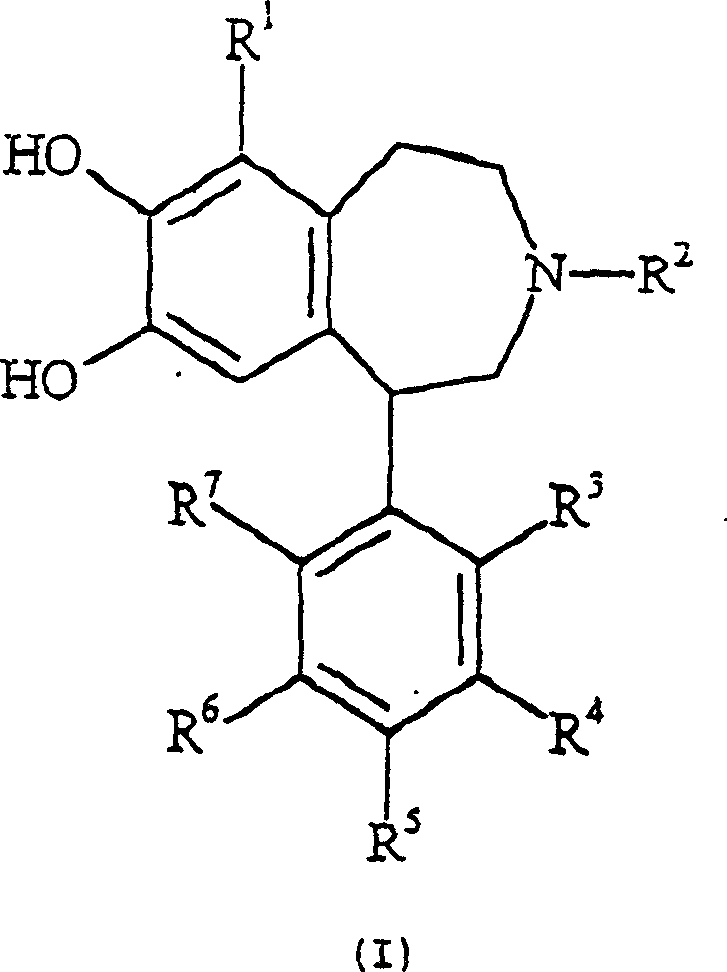

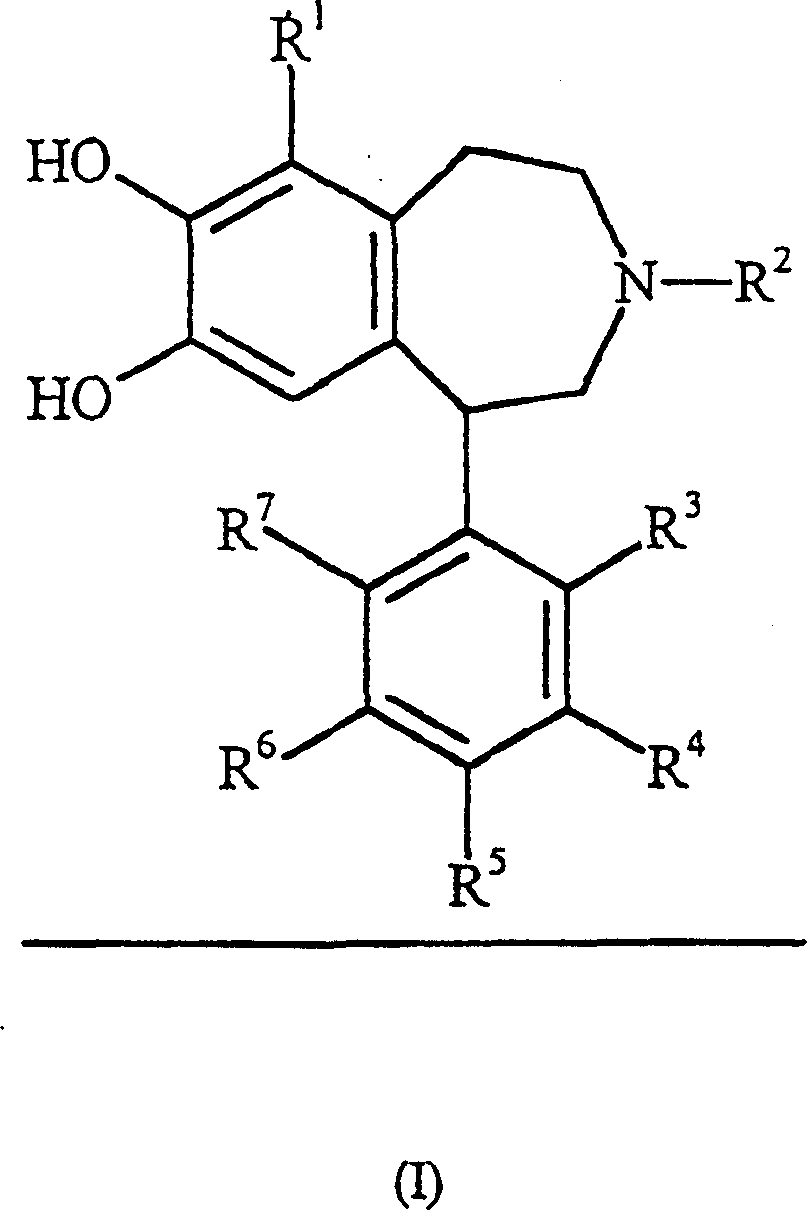

Dopamine D1 receptor agonist compounds

The invention provides 2,3,4,5-tetrahydro-1H-3-benzazepines of general formula (I) wherein: R<1> is hydrogen, halogen, C1-C4 alkyl, or CF3; R<2> is hydrogen, methyl, or lower alkenyl of 3-5 carbon atoms; R<3> and R<4> together form a furan, dihydrofuran, thiophene, dihydrothiophene, cyclopentane or cyclohexane ring and R<5> is hydrogen or R<4> and R<5> together form a furan, dihydrofuran, thiophene, dihydrothiophene, cyclopentane or cyclohexane ring and R<3> is hydrogen; R<6> is hydrogen, halogen, CF3, CN, NO2 or NH2; R<7> is hydrogen, halogen, CF3, CN, NO2 or NH2. The specific combination of substituents: R1 = H, R2 = H and R4 and R5 together forming a cyclohexane ring is excluded, namely 1-(5,6,7,8-tetrahydronaphthalen-2-yl)-2,3,4,5-tetrahydro-1H-benzol[d]azepine-7,8-diol. The compounds of the invention provide therapeutic agents that selectively interact positively with postsynaptic dopamine D1 receptors in the striatum, directly or in-directly (termed dopamine D1 agonists) and are particularly valuable as anti-Parkinsonian agents.

Owner:SHIRE PHARMA DEV

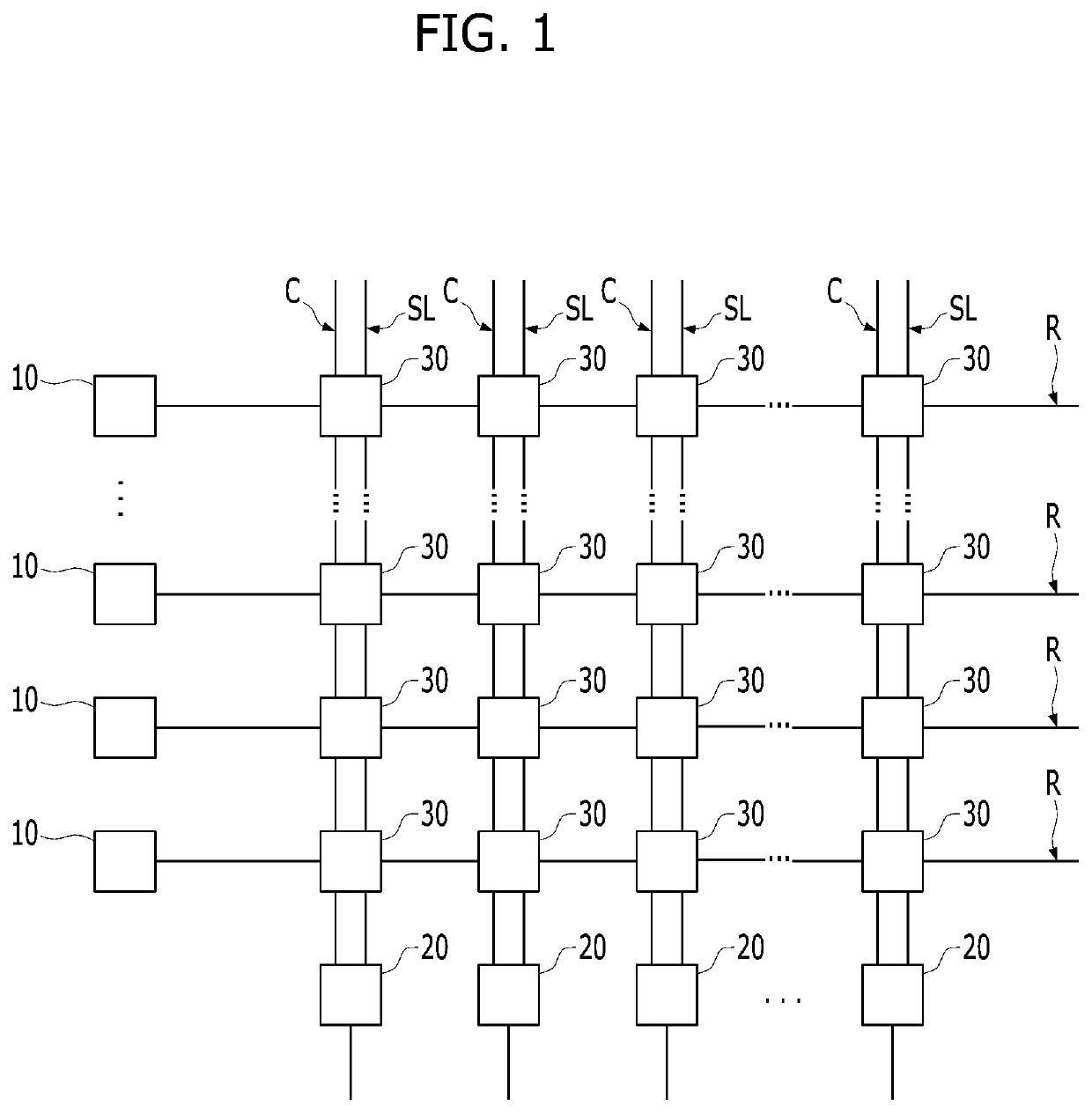

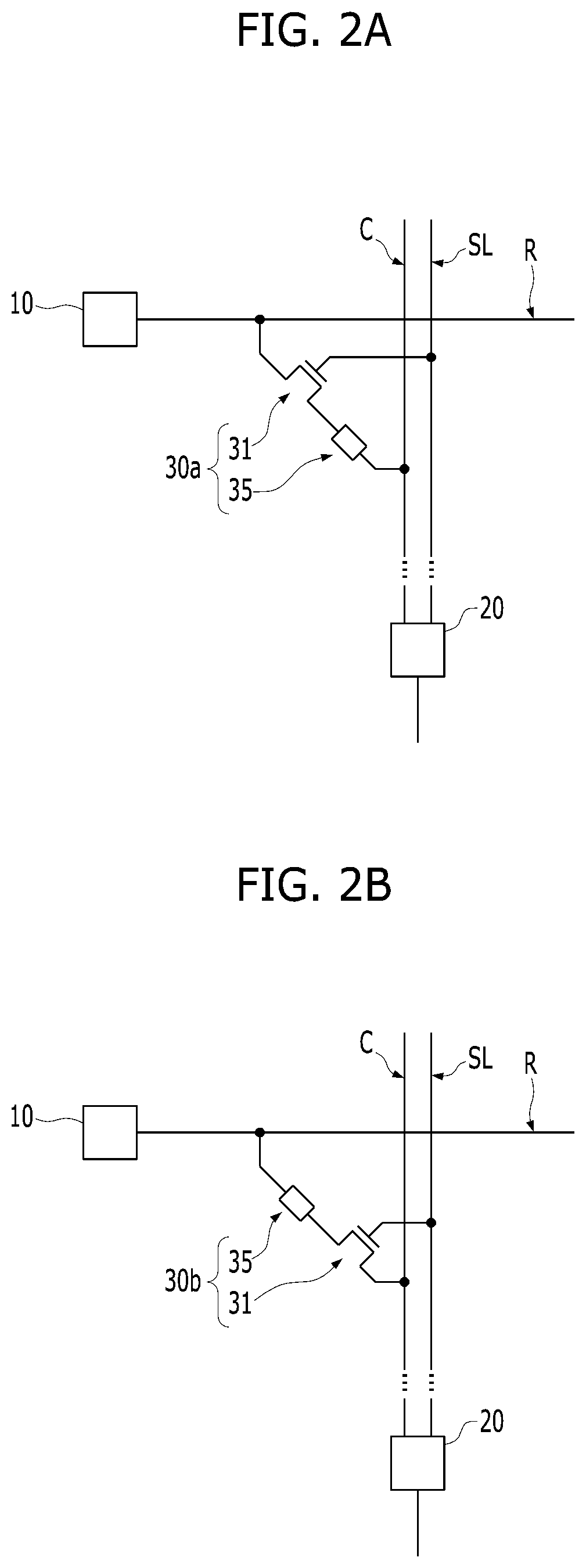

Neuromorphic device including a synapse having a variable resistor and a transistor connected in parallel with each other

A neuromorphic device is provided. The neuromorphic device may include a pre-synaptic neuron, a row line extending from the pre-synaptic neuron in a row direction, a post-synaptic neuron, a column line extending from the post-synaptic neuron in a column direction, and a synapse at an intersection region between the row line and the column line. The synapse may include a switching device and a memristor electrically connected with each other in series. The post-synaptic neuron may include a summation circuit, a variable resistor, and a comparator.

Owner:SK HYNIX INC

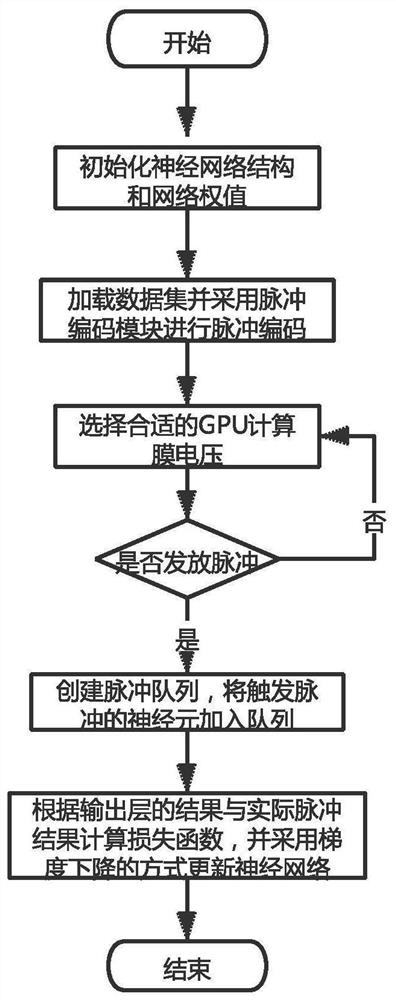

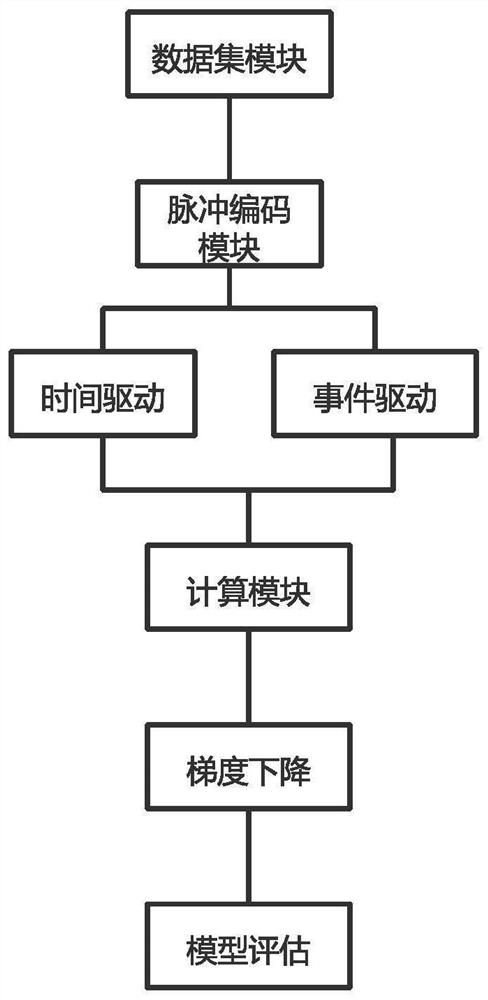

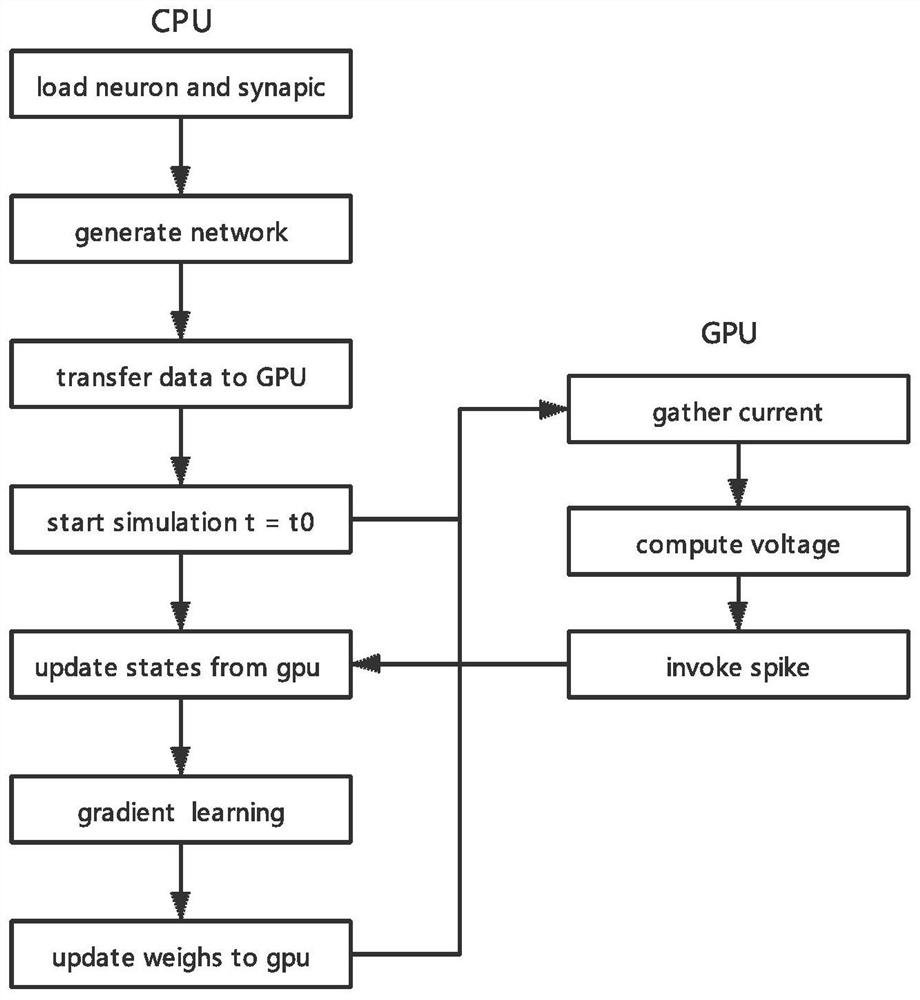

Pulse neural network simulation method based on GPU

PendingCN114186665ASave time and costPrevent invalid operationResource allocationNeural architecturesVideo memoryData set

The invention discloses a GPU-based spiking neural network simulation method. The method comprises the steps of initializing a neural network structure and a network weight; loading a data set and carrying out pulse coding by adopting a pulse coding module; calling a GPU calculation module to select a proper GPU to calculate the pulse neuron membrane voltage according to the data volume, the calculation amount and the priority of the calculation task, comparing whether the pulse neuron membrane voltage exceeds a threshold value or not, and issuing a pulse; creating a pulse queue, and adding neurons of a trigger pulse into the pulse queue; if the pulse queue is not empty, finding out a post-synaptic neuron corresponding to the next layer according to the network structure, and repeating the steps S3-S5 until an output layer is reached; and calculating a loss function according to the result of the output layer and the actual pulse result, and updating the neural network by adopting a gradient descent mode until the iteration is completed. According to the invention, the training speed of the spiking neural network is accelerated, the advantages of the spiking neural network in the aspects of low power consumption and low time delay are exerted, and the conditions of overlarge data set, insufficient video memory and incapability of training are avoided.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

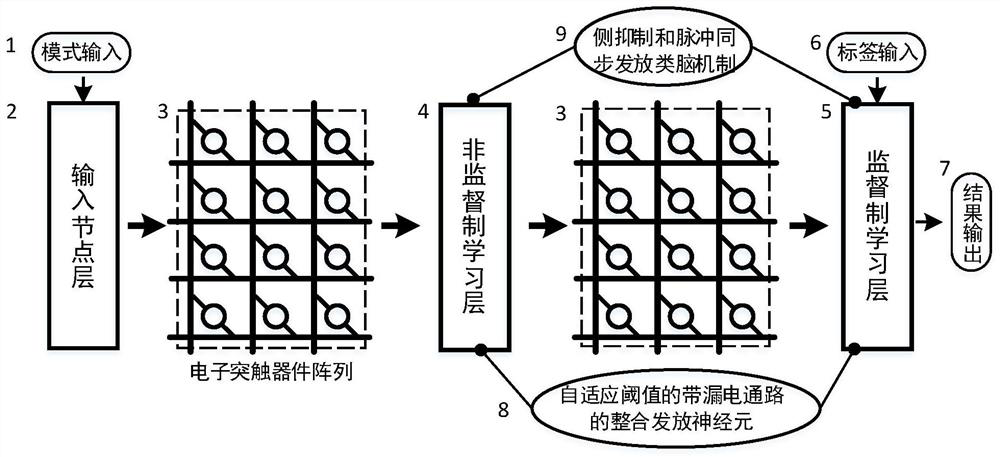

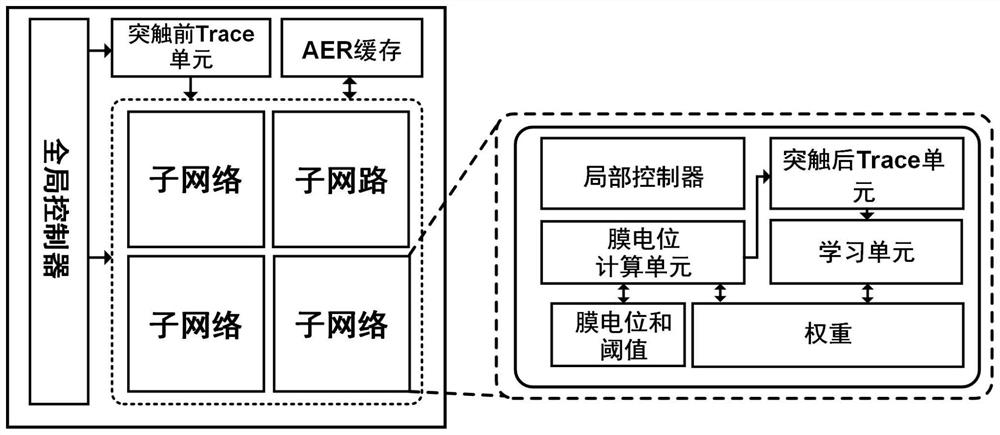

A hardware spiking neural network system

ActiveCN108985447BEasy to identifyImprove robustnessPhysical realisationNeural network systemSynaptic weight

The invention discloses a hardware pulse neural network system, comprising: the input node layer and the unsupervised learning layer are connected through a synaptic connection unit through a neuron full connection mode, and the unsupervised learning layer and the supervised learning layer are connected by a neuron full connection The method is connected through another synaptic connection unit; the input node layer realizes the information input under different encoding methods, the unsupervised learning layer adopts the unsupervised learning method, and the supervised learning layer adopts the supervised learning method; the synaptic connection unit is composed of electronic The synaptic device is implemented so that the synaptic connection unit has pulse timing-dependent plasticity STDP, and the synaptic array unit receives the stimulus signal carrying information from the previous layer of neurons as a presynaptic pulse, combined with the actions excited by the subsequent layer of neurons The potential pulse acts as a post-synaptic pulse, and the time difference between the pre-synaptic pulse and the post-synaptic pulse determines the amount of synaptic weight adjustment of the synaptic connection unit. The neural network system provided by the invention has wide application value.

Owner:HUAZHONG UNIV OF SCI & TECH

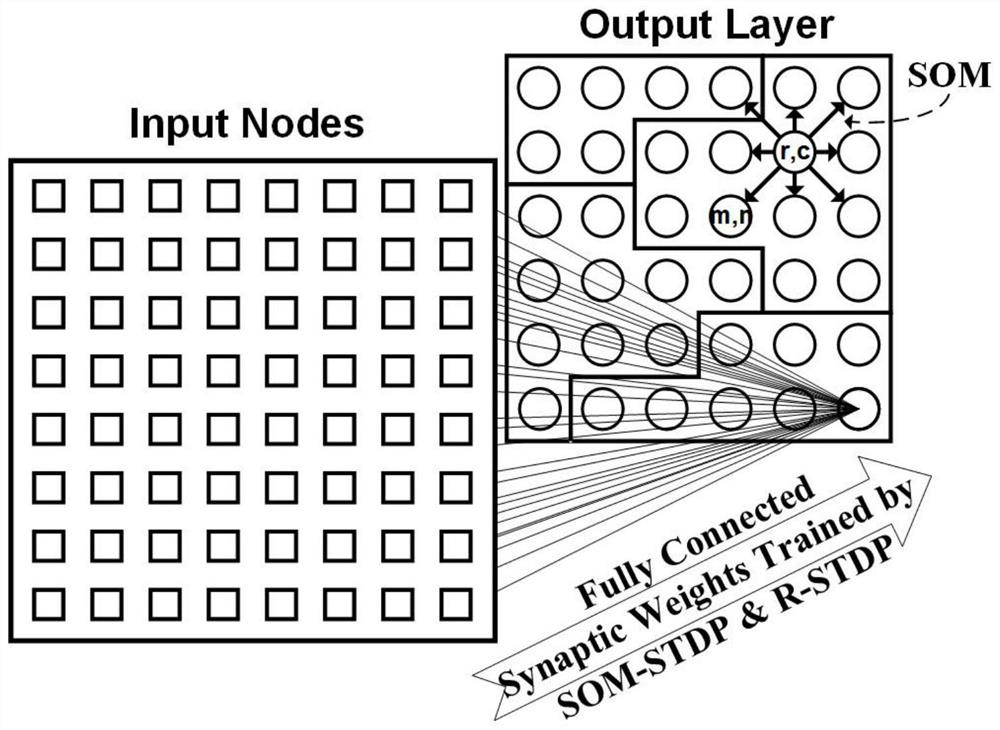

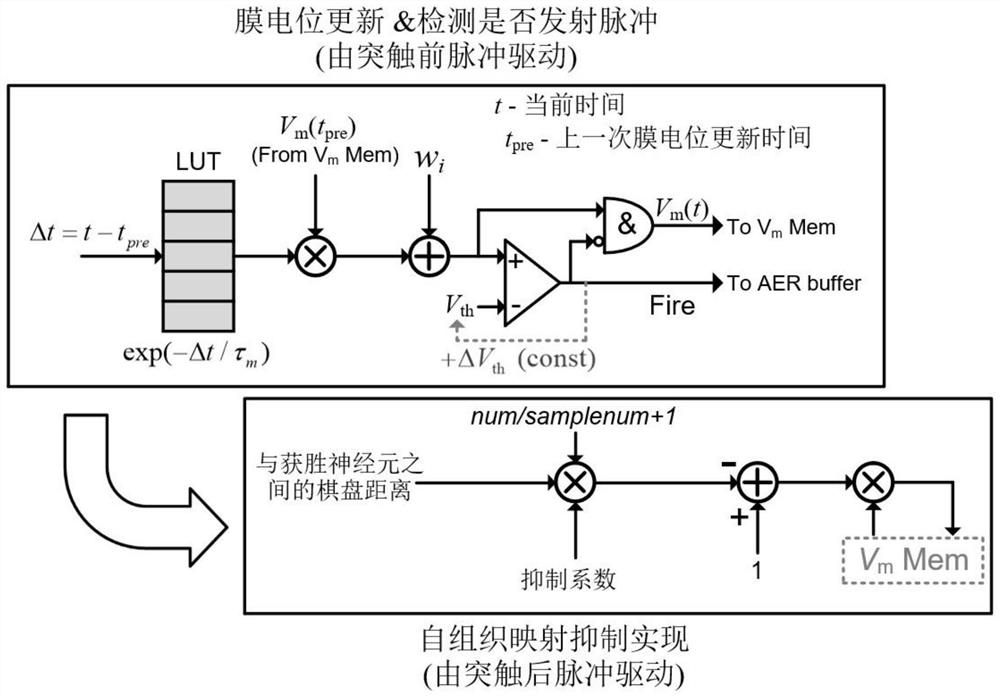

Lightweight on-chip learning method and system based on spiking neural network, and processor

PendingCN114091663AGuaranteed performanceImprove recognition rateNeural architecturesArchitecture with single central processing unitSpiking neural networkLearning rule

The invention belongs to the technical field of microprocessors, and particularly discloses a lightweight on-chip learning method based on a spiking neural network. The method comprises the steps: carrying out the rate coding of an input image, converting a static frame image into a pulse form, taking each pixel point as a presynaptic neuron, and enabling an output layer of the spiking neural network to be composed of LIF neuron, wherein each neuron is a post-synaptic neuron, the pre-synaptic neuron and the post-synaptic neuron are connected in a full connection mode, and in the training of the spiking neural network, the weight of each synaptic is updated according to an STDP weight updating learning rule; when the post-synaptic neurons emit pulses, the neurons are winning neurons, the winning neurons are taken as centers, membrane potentials of other post-synaptic neurons are inhibited according to the chessboard distances of the post-synaptic neurons, and finally the self-organizing pulse neural network is obtained. The problem that the shallow pulse network recognition rate is low is solved.

Owner:CHONGQING UNIV

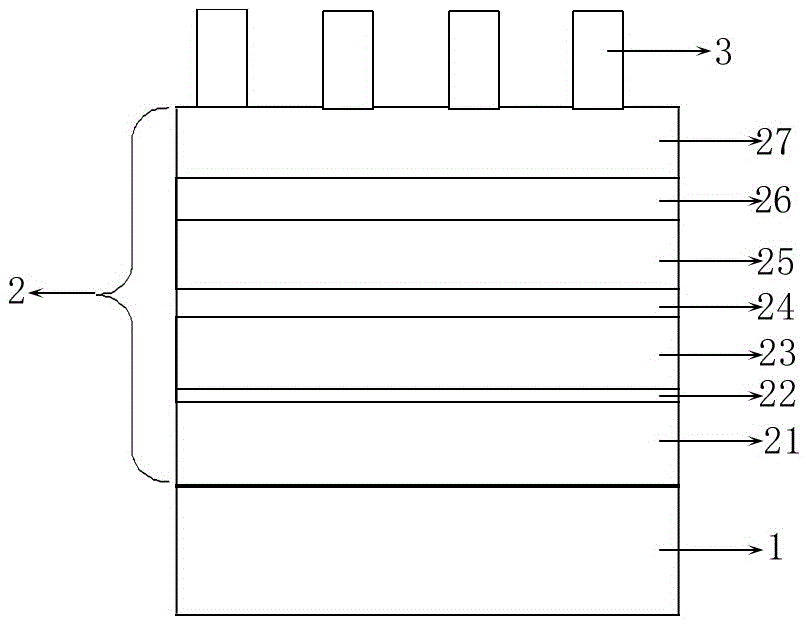

Ga2O3 nerve bionic layer-based nerve bionic device and preparation method thereof

ActiveCN106531885AStable characteristicsStable high and low resistance state and maintain good characteristicsElectrical apparatusAnatomyElectrical impulse

The invention discloses a Ga2O3 nerve bionic layer-based nerve bionic device, which comprises a Pt / Ti / SiO2 / Si substrate, a nerve bionic layer and an Ag electrode layer, wherein the nerve bionic layer and the Ag electrode layer are sequentially formed on a Pt film of the Pt / Ti / SiO2 / Si substrate; and the nerve bionic layer sequentially comprises a first Ga2O3 film, a first Ag film, a second Ga2O3 film, a second Ag film, a third Ga2O3 film, a third Ag film and a fourth Ga2O3 film from bottom to top. Meanwhile, the invention further discloses a preparation method of the nerve bionic device. According to the prepared device, the resistance can be changed according to a time difference between a presynaptic stimulus and a postsynaptic stimulus, the characteristic of a biological synapse can be simulated, high-and-low resistance states slowly change and the range is stable; multiple stable resistance states appear, the nerve bionic device has a good retention characteristic, the resistance can keep relatively high repeatability of high-and-low resistance transformation under the condition of repeatedly exerting electric pulse stimuli; and the nerve bionic device is the nerve bionic device which is more stable in performance and wider in application prospect.

Owner:HEBEI UNIVERSITY

Neuromorphic device including a synapse having a variable resistor and a transistor connected in parallel with each other

A neuromorphic device may include a pre-synaptic neuron, a row line extending in a row direction from the pre-synaptic neuron, a post-synaptic neuron, a column line extending in a column direction from the post-synaptic neuron, and a synapse disposed at an intersection region between the row line and the column line. The synapse may include a first node electrically connected with the row line, a second node electrically connected with the column line, and a variable resistor and a first transistor electrically coupled between the first node and the second node. The variable resistor and the first transistor may be electrically connected with each other in parallel.

Owner:SK HYNIX INC

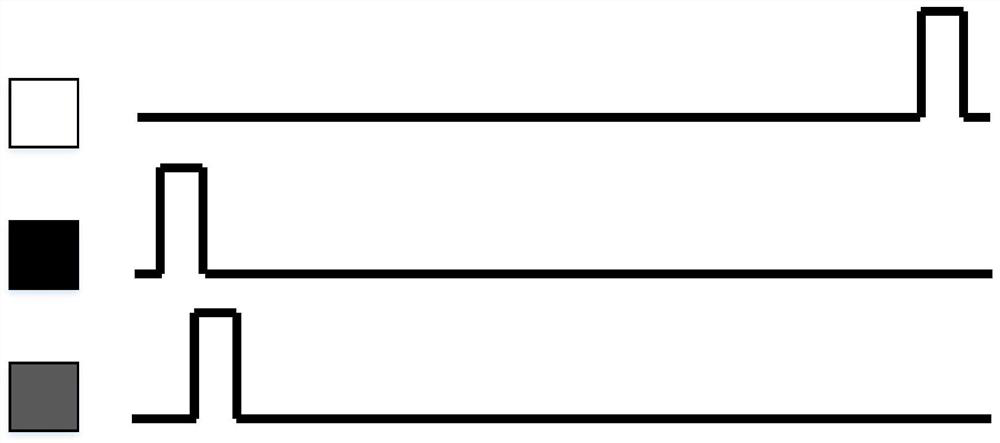

Spike timing dependent plasticity write method and synapse array apparatus

A resistance variable type synapse array apparatus that can perform STDP writing using a positive potential is provided. The synapse array apparatus includes a writing unit writing to a selected resistance variable type memory element in a crossbar array. The writing unit includes a driver generating a positive pulse signal corresponding to a positive part of a spike signal generated by a presynaptic neuron, a driver generating a positive pulse signal corresponding to a negative part of a spike signal generated by a postsynaptic neuron, a driver generating a positive pulse signal corresponding to a positive part of the spike signal generated by the postsynaptic neuron, and a driver generating a positive pulse signal corresponding to a negative part of the spike signal generated by the presynaptic neuron.

Owner:WINBOND ELECTRONICS CORP