Patents

Literature

44results about How to "Optimal performance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

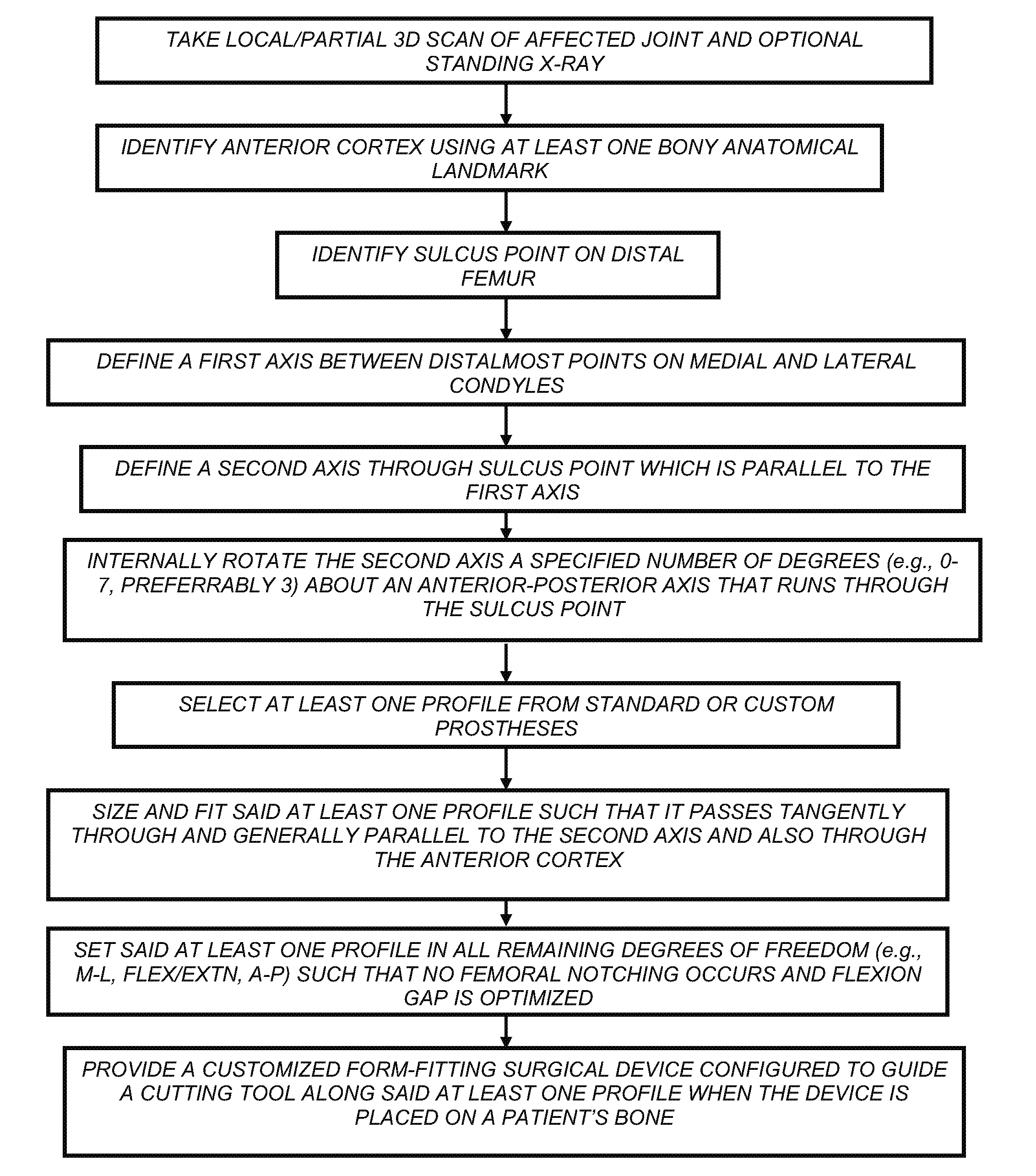

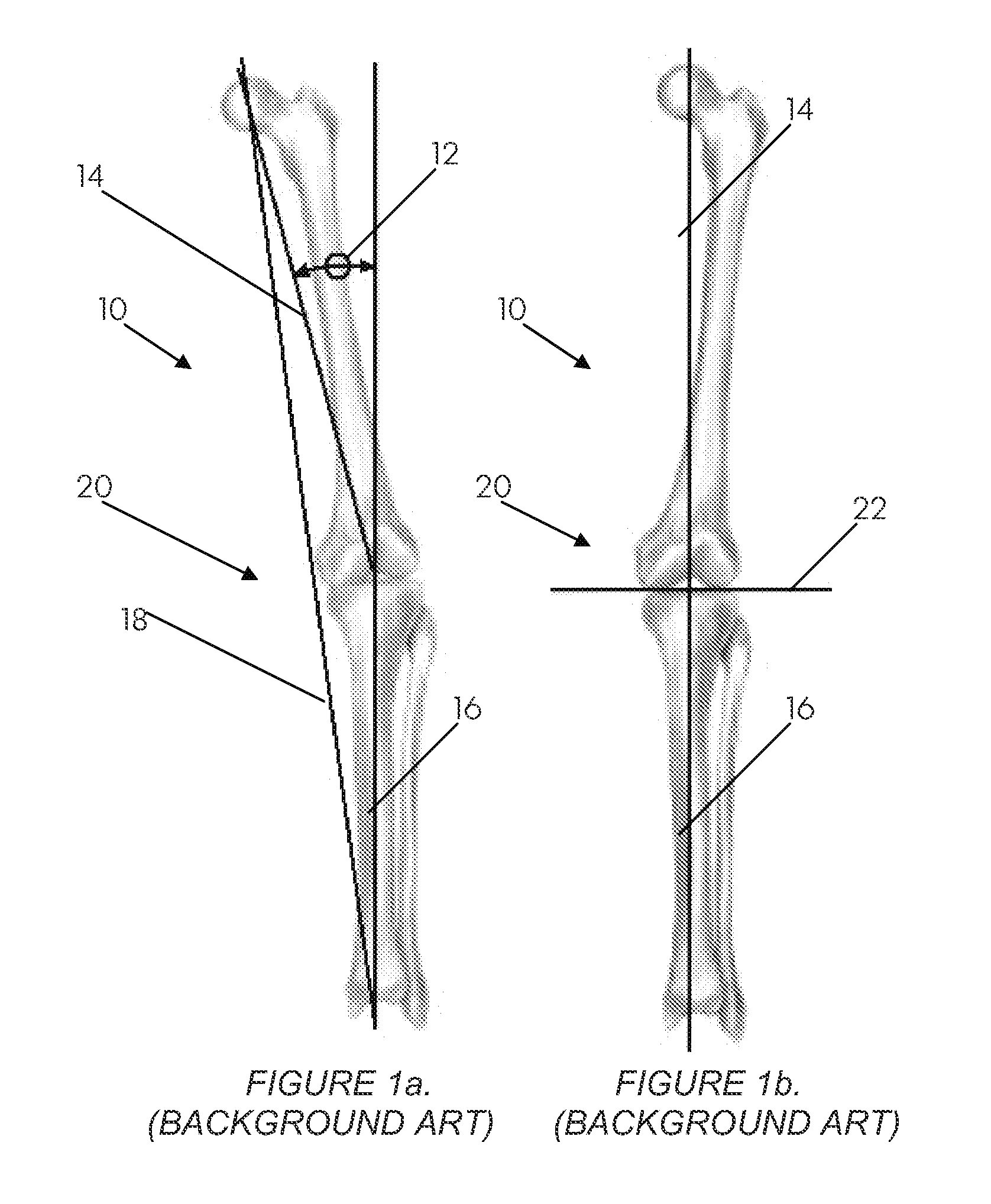

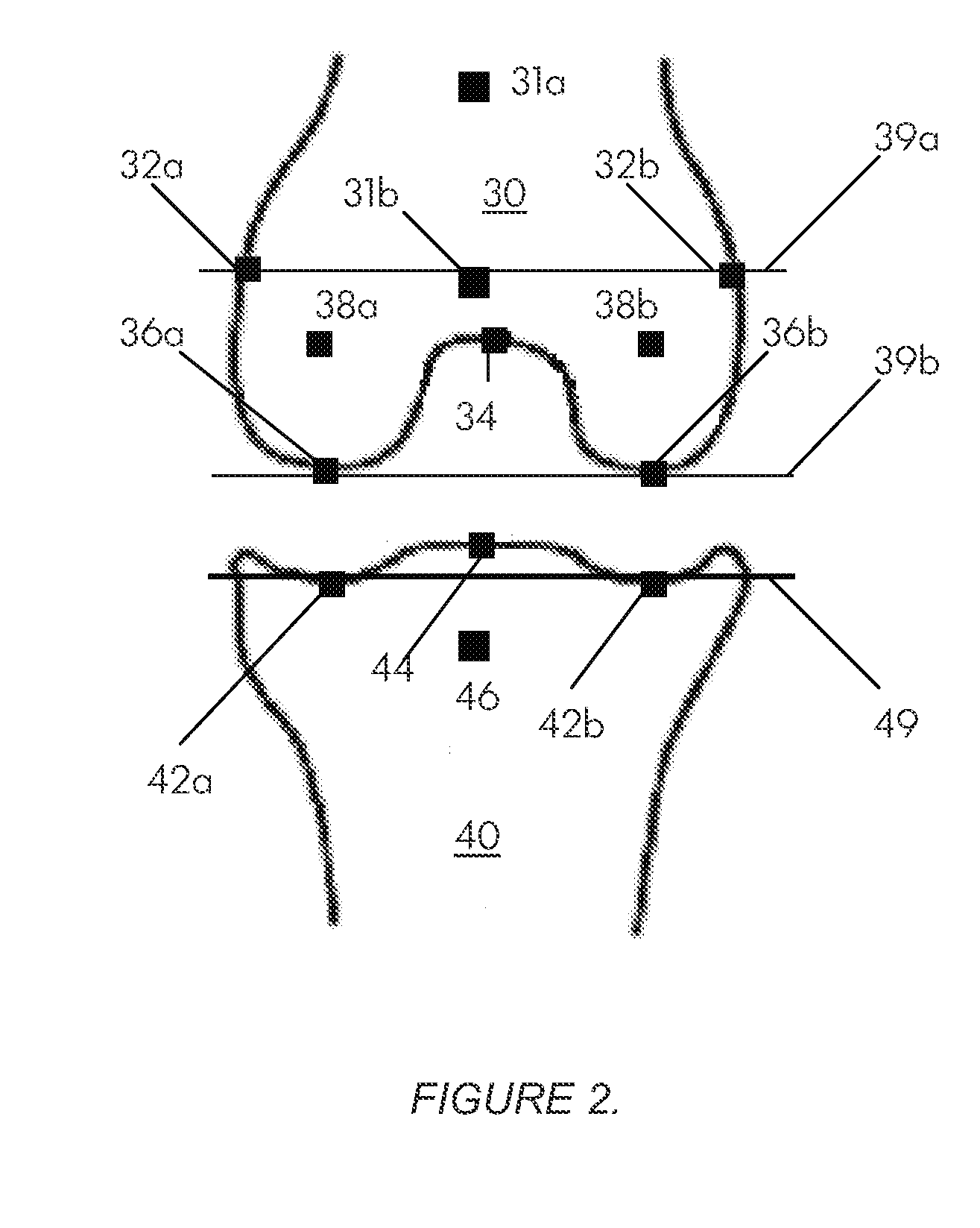

Systems and methods for determining the mechanical axis of a femur

ActiveUS20110029116A1Optimal performanceImprove performanceDiagnosticsData visualisationThree dimensional modelPatient specific

A method positions a profile of a prosthetic component on the three-dimensional model of a limb. Patient-specific anatomical data of the limb is gathered. First and second anatomical landmarks are identified to determine a first spatial relationship. A third anatomical landmark is identified to determine a second spatial relationship with respect to the first spatial relationship. The profile of the prosthetic component is positioned in all but one degree of freedom. A fourth anatomical landmark is identified to position the profile of the prosthetic component in the one remaining degree of freedom.

Owner:SMITH & NEPHEW INC

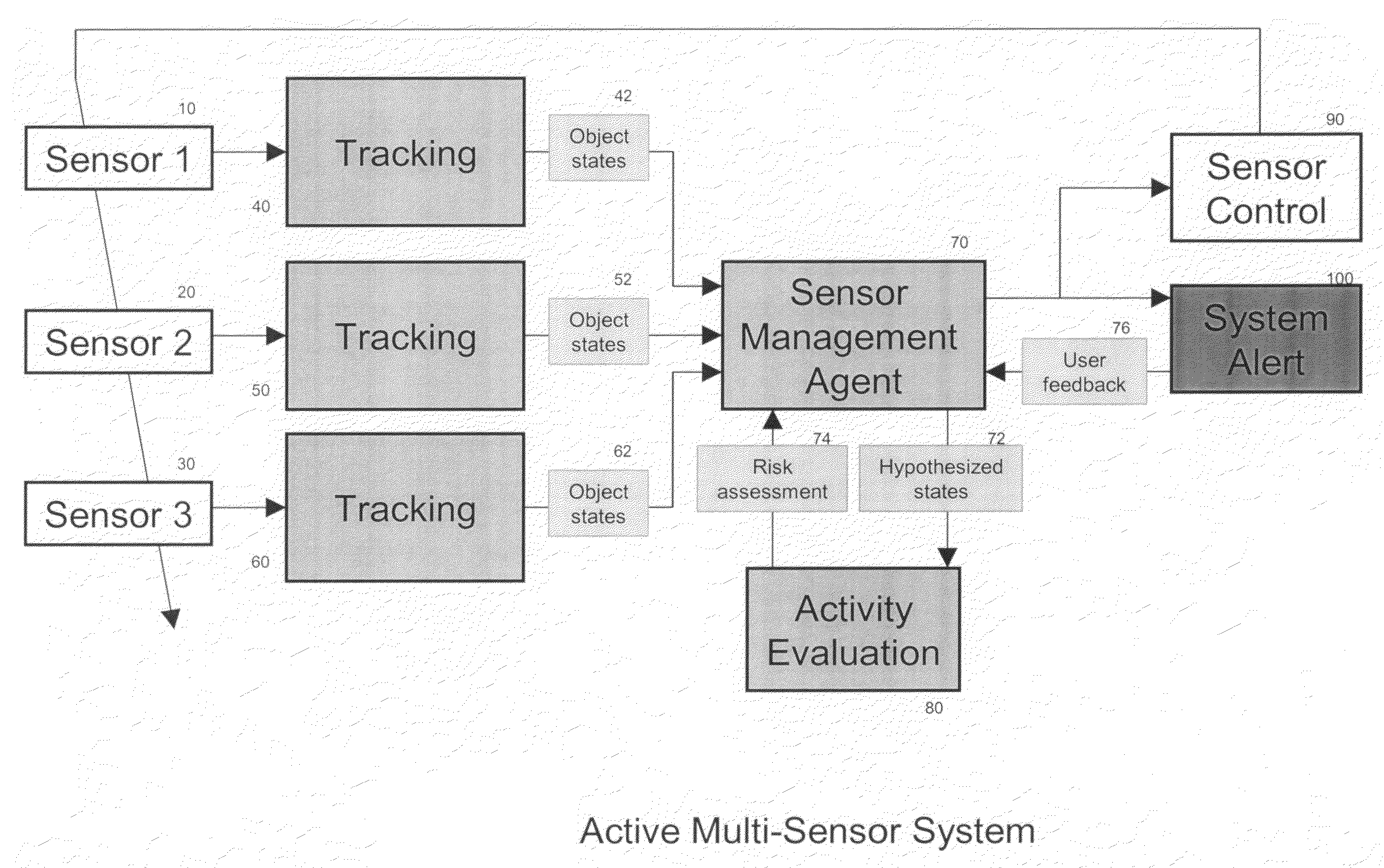

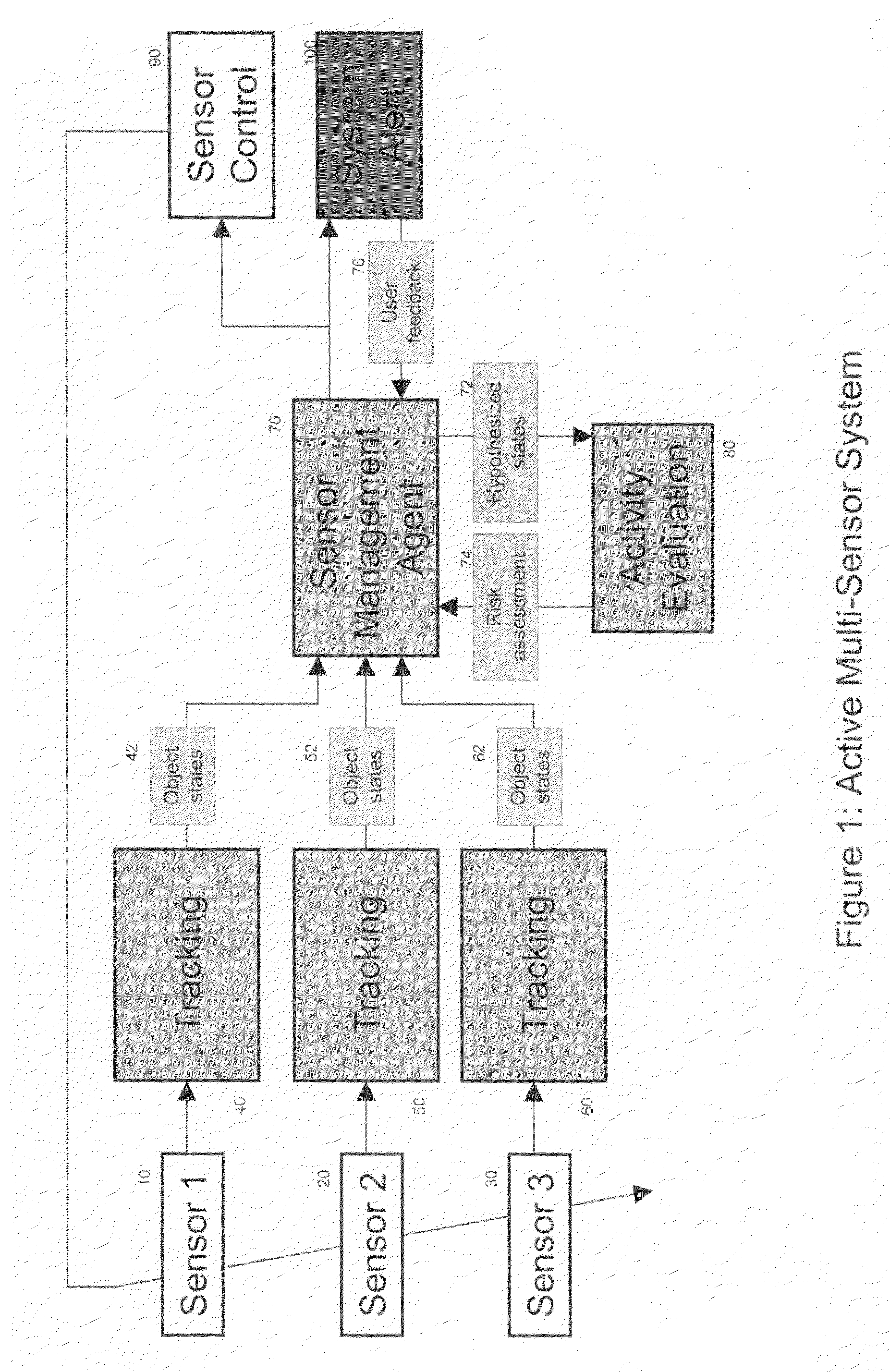

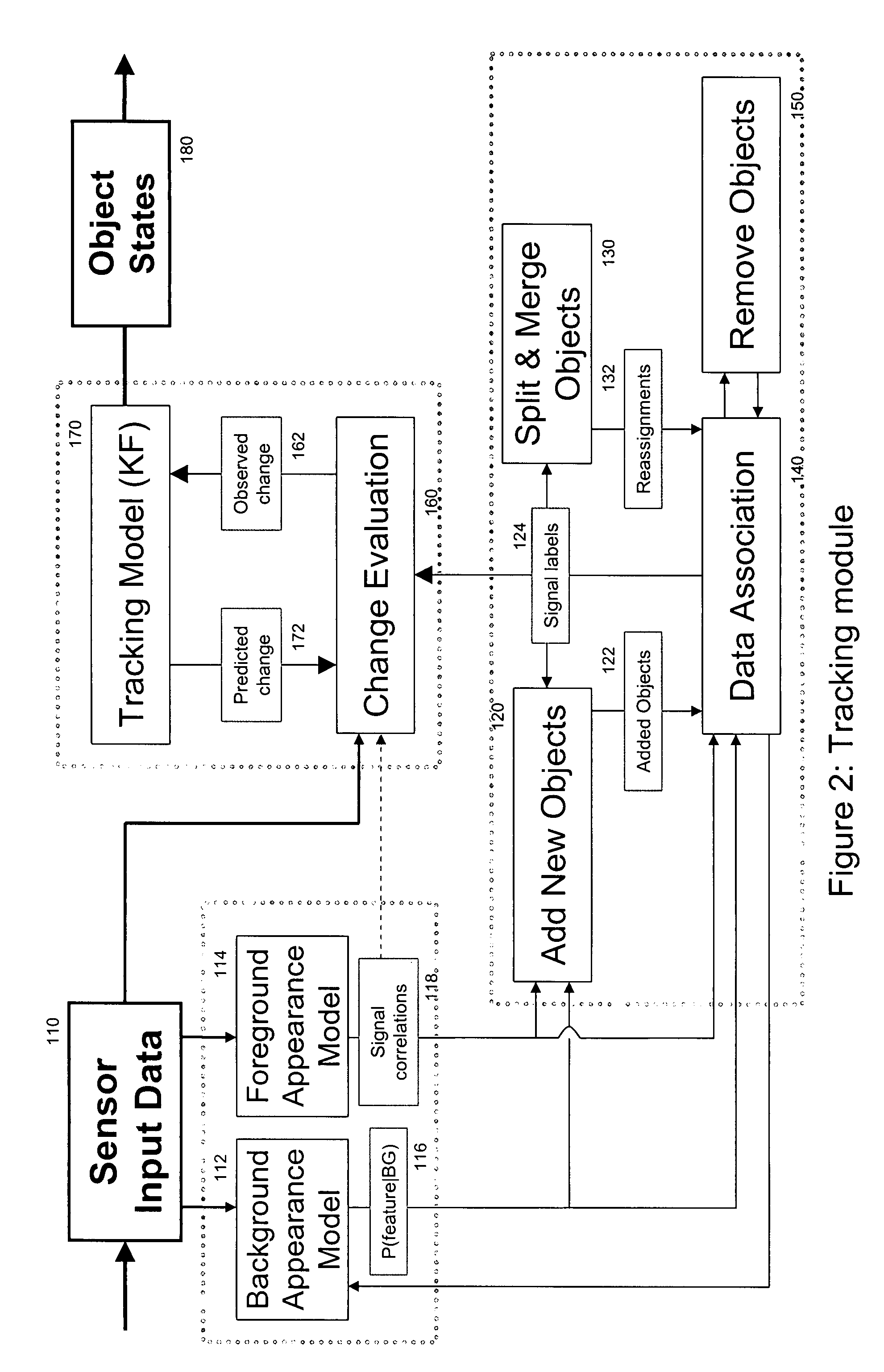

Sensor exploration and management through adaptive sensing framework

InactiveUS20080243439A1Improve system performanceOptimal performanceImage enhancementImage analysisPolicy decisionRelative cost

The identification and tracking of objects from captured sensor data relies upon statistical modeling methods to sift through large data sets and identify items of interest to users of the system. Statistical modeling methods such as Hidden Markov Models in combination with particle analysis and Bayesian statistical analysis produce items of interest, identify them as objects, and present them to users of the system for identification feedback. The integration of a training component based upon the relative cost of sampling sensors for additional parameters, provides a system that can formulate and present policy decisions on what objects should be tracked, leading to an improvement in continuous data collection and tracking of identified objects within the sensor data set.

Owner:SIGNAL INNOVATIONS GRP

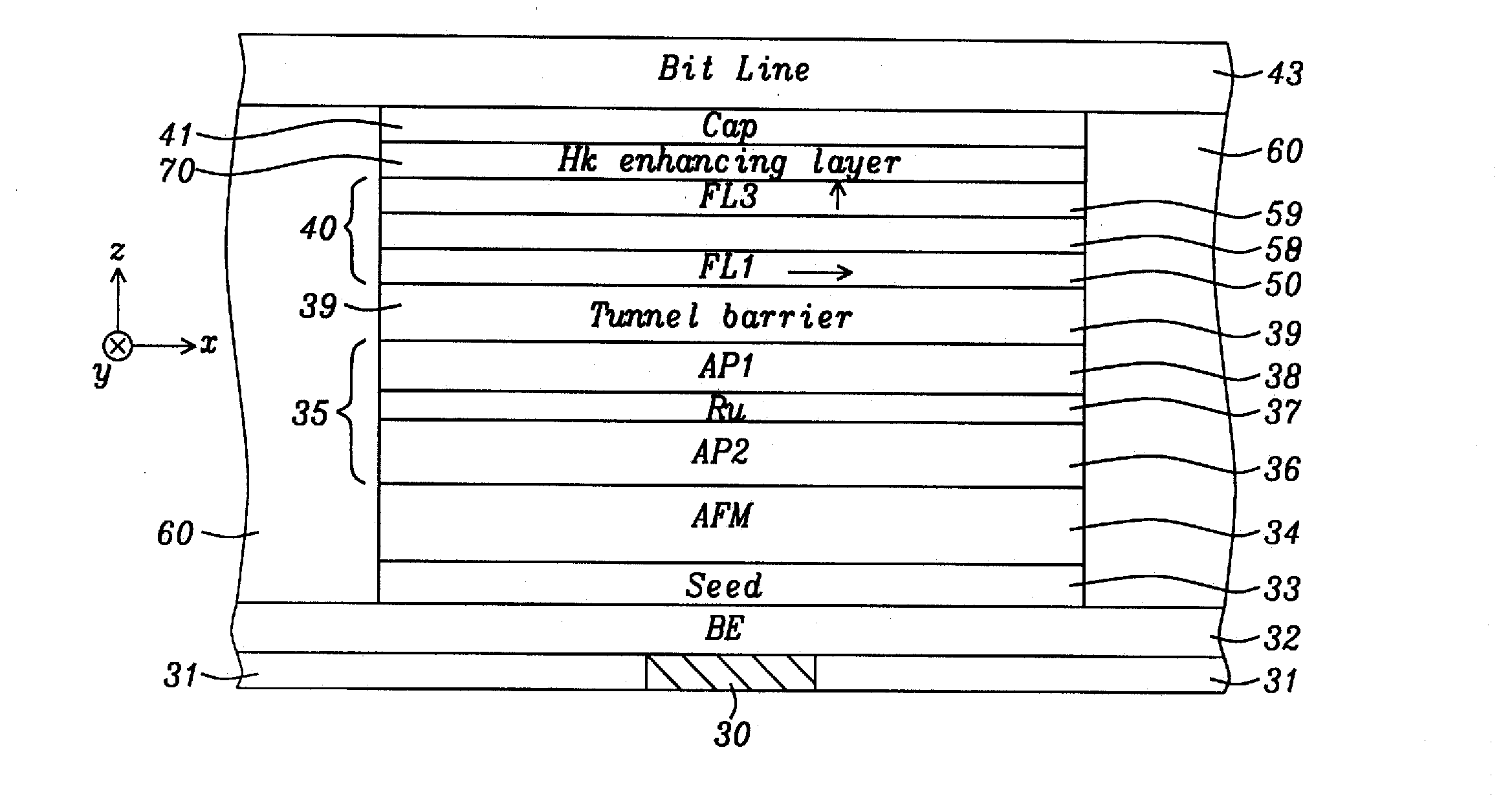

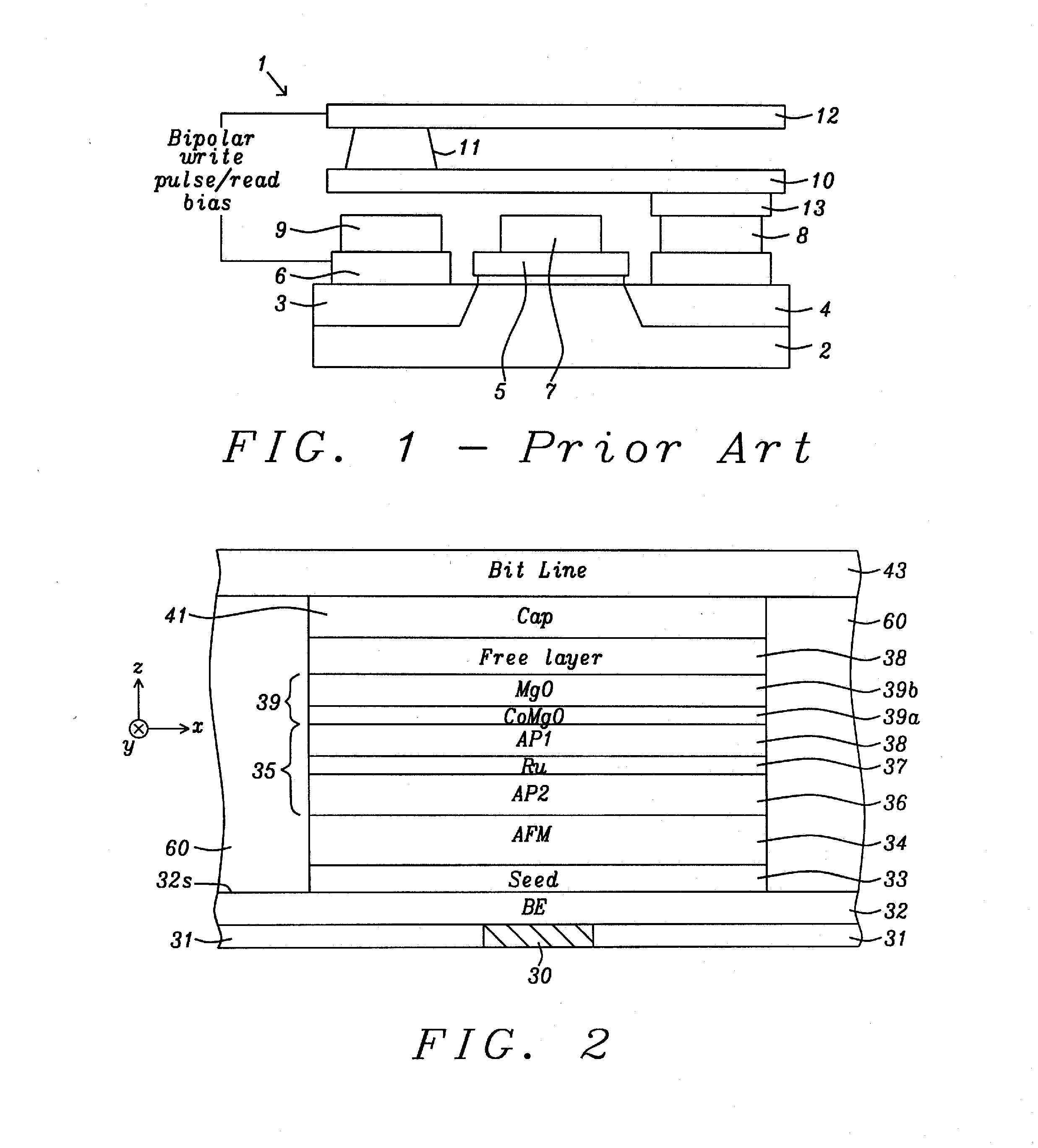

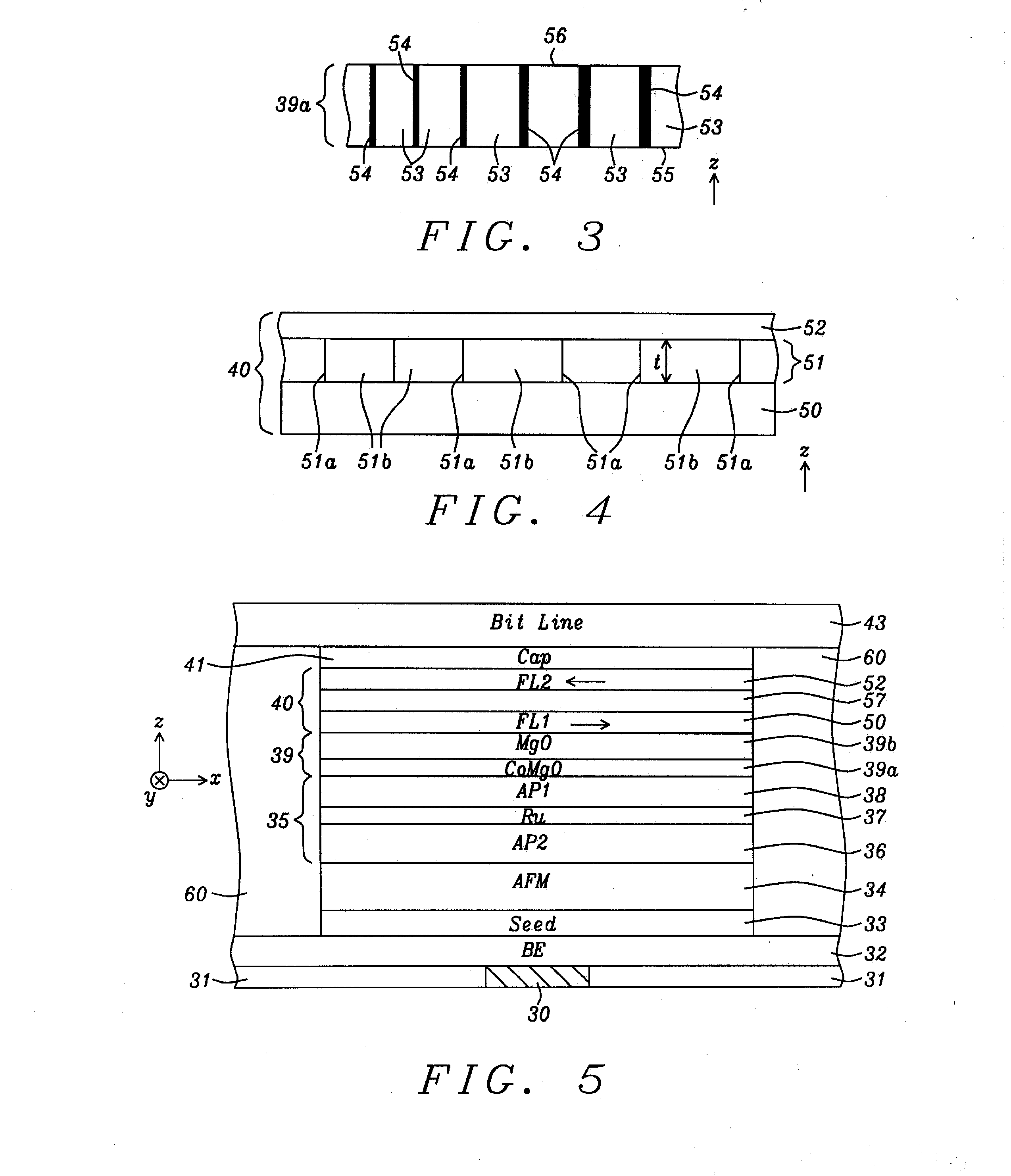

Spin Torque Transfer Magnetic Tunnel Junction Fabricated with a Composite Tunneling Barrier Layer

ActiveUS20130175644A1High pattern densityOptimal performanceMagnetic-field-controlled resistorsSolid-state devicesPhysicsElectromigration

A STT-RAM MTJ is disclosed with a composite tunnel barrier comprised of a CoMgO layer that contacts a pinned layer and a MgO layer which contacts a free layer. A CoMg layer with a Co content between 20 and 40 atomic % is deposited on the pinned layer and is then oxidized to produce Co nanoconstrictions within a MgO insulator matrix. The nanoconstrictions control electromigration of Co into an adjoining MgO layer. The free layer may comprise a nanocurrent channel (NCC) layer such as FeSiO or a moment dilution layer such as Ta between two ferromagnetic layers. Furthermore, a second CoMgO layer or a CoMgO / MgO composite may serve as a perpendicular Hk enhancing layer formed between the free layer and a cap layer. One or both of the pinned layer and free layer may exhibit in-plane anisotropy or perpendicular magnetic anisotropy.

Owner:TAIWAN SEMICON MFG CO LTD

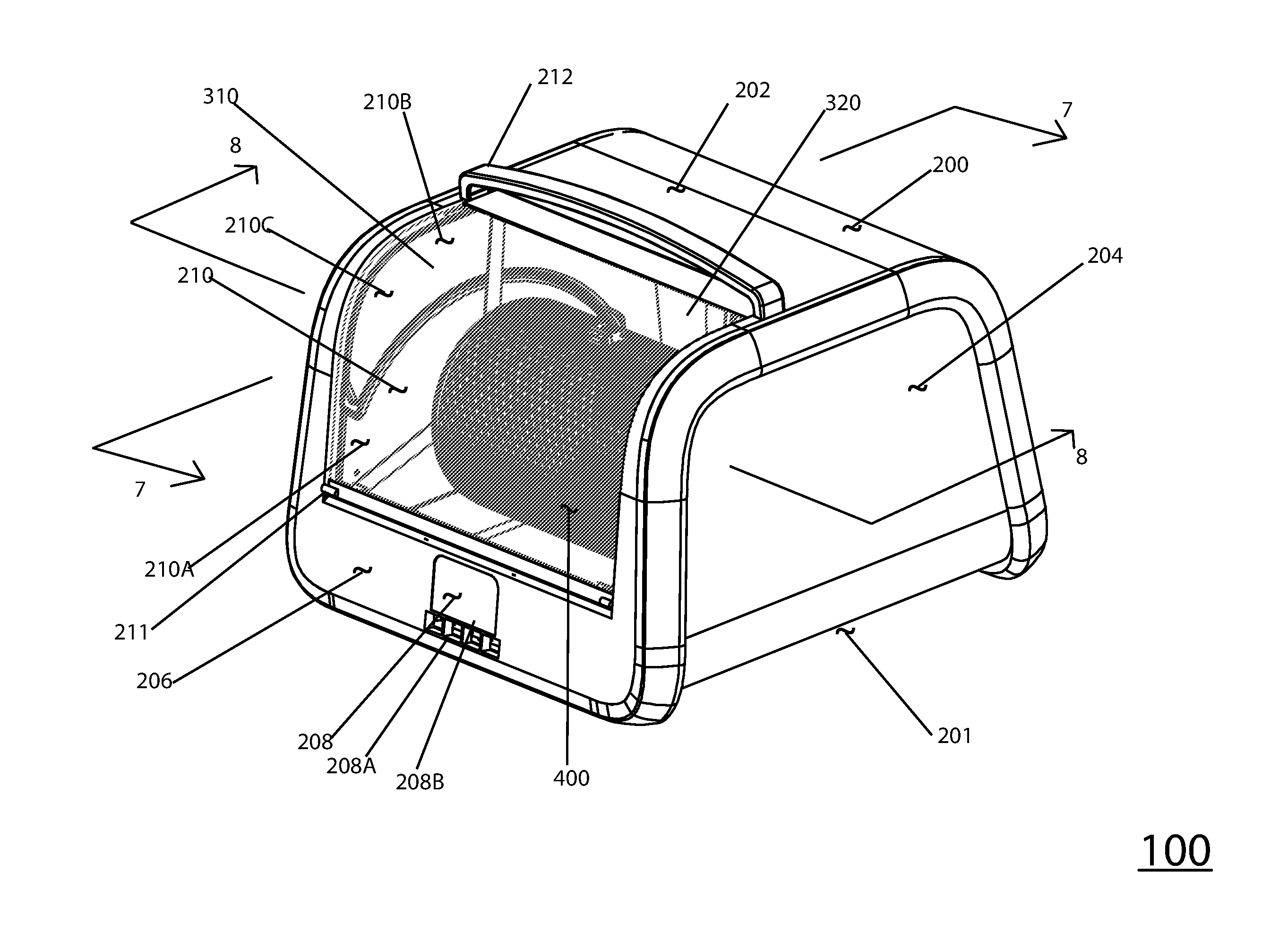

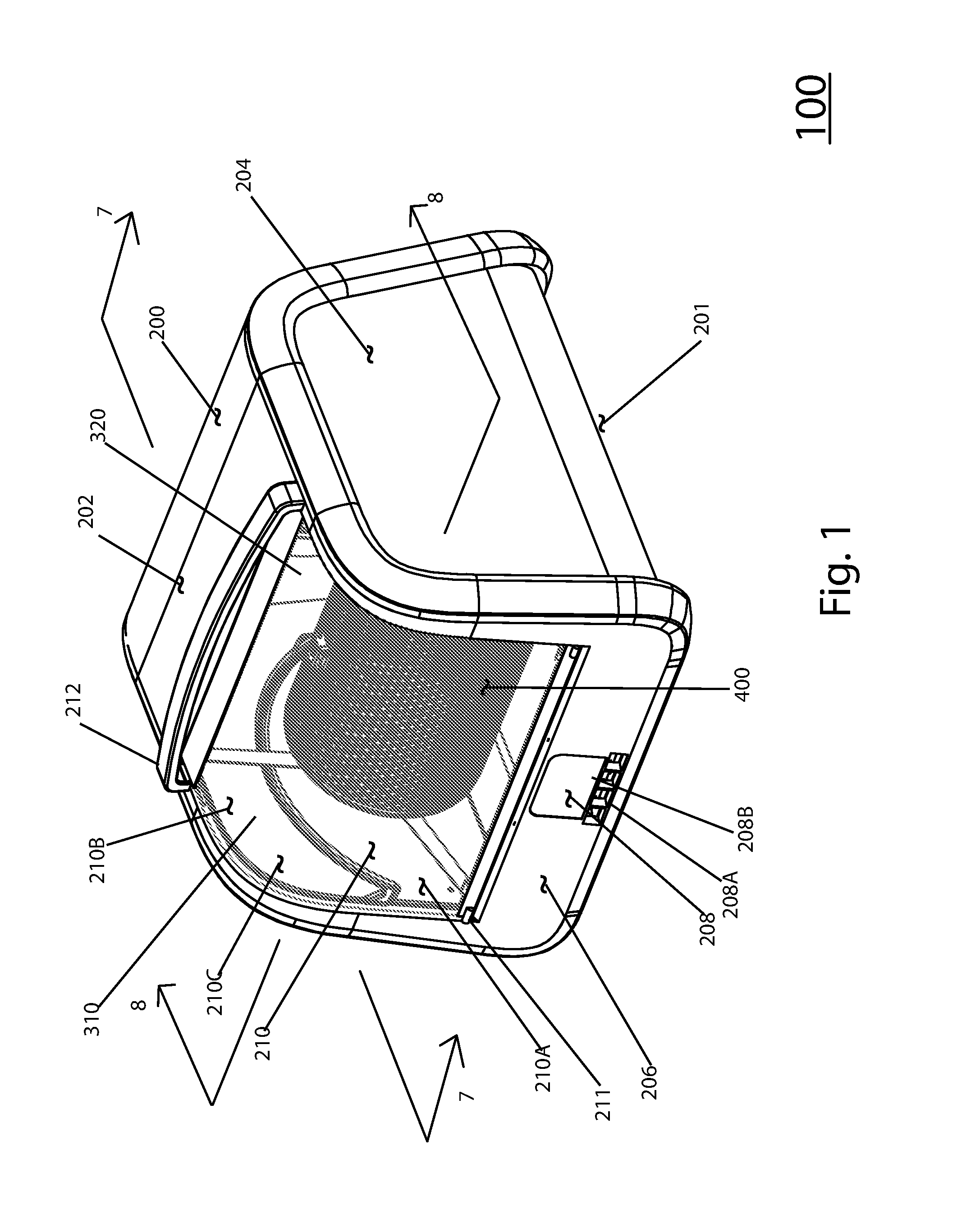

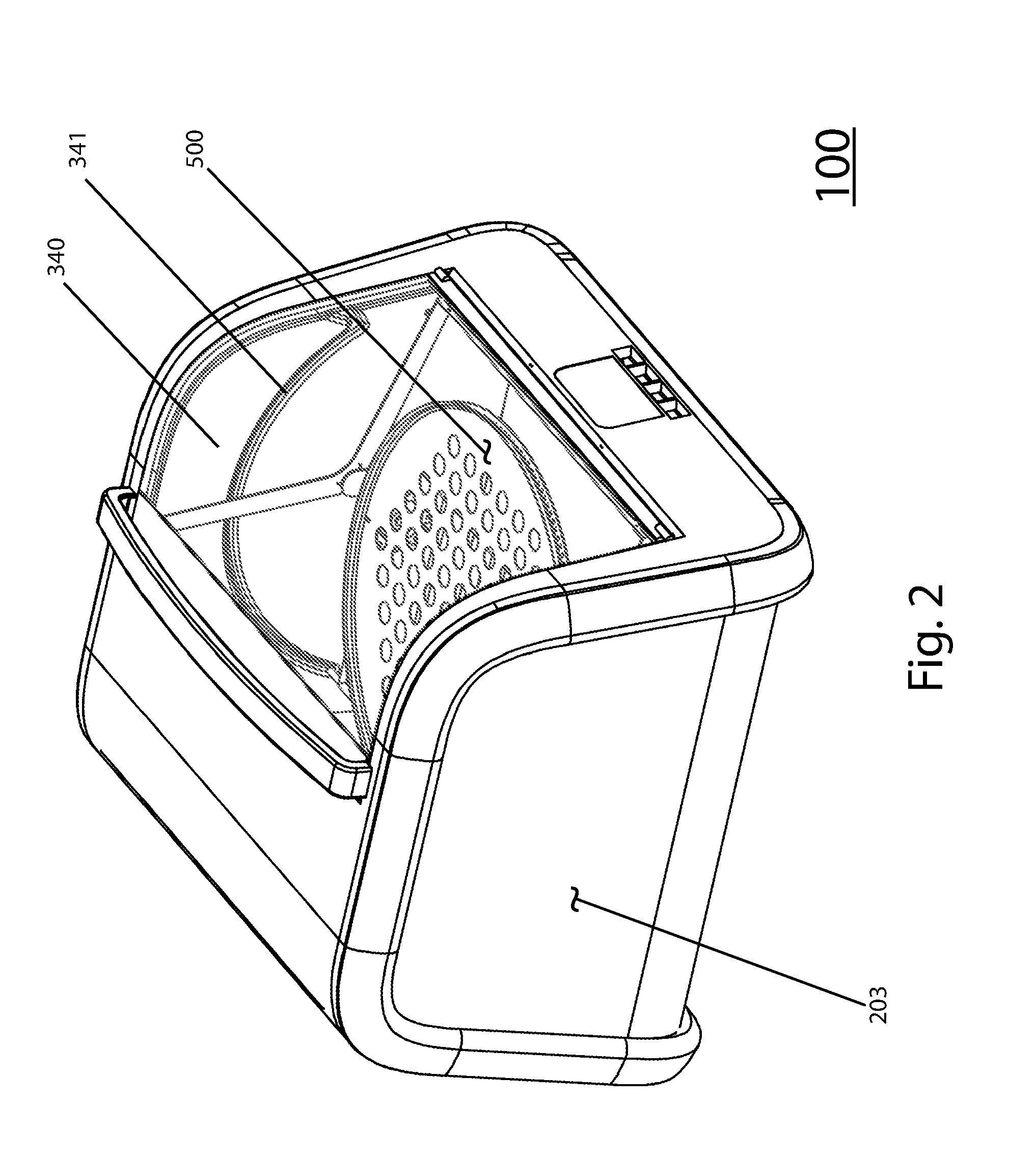

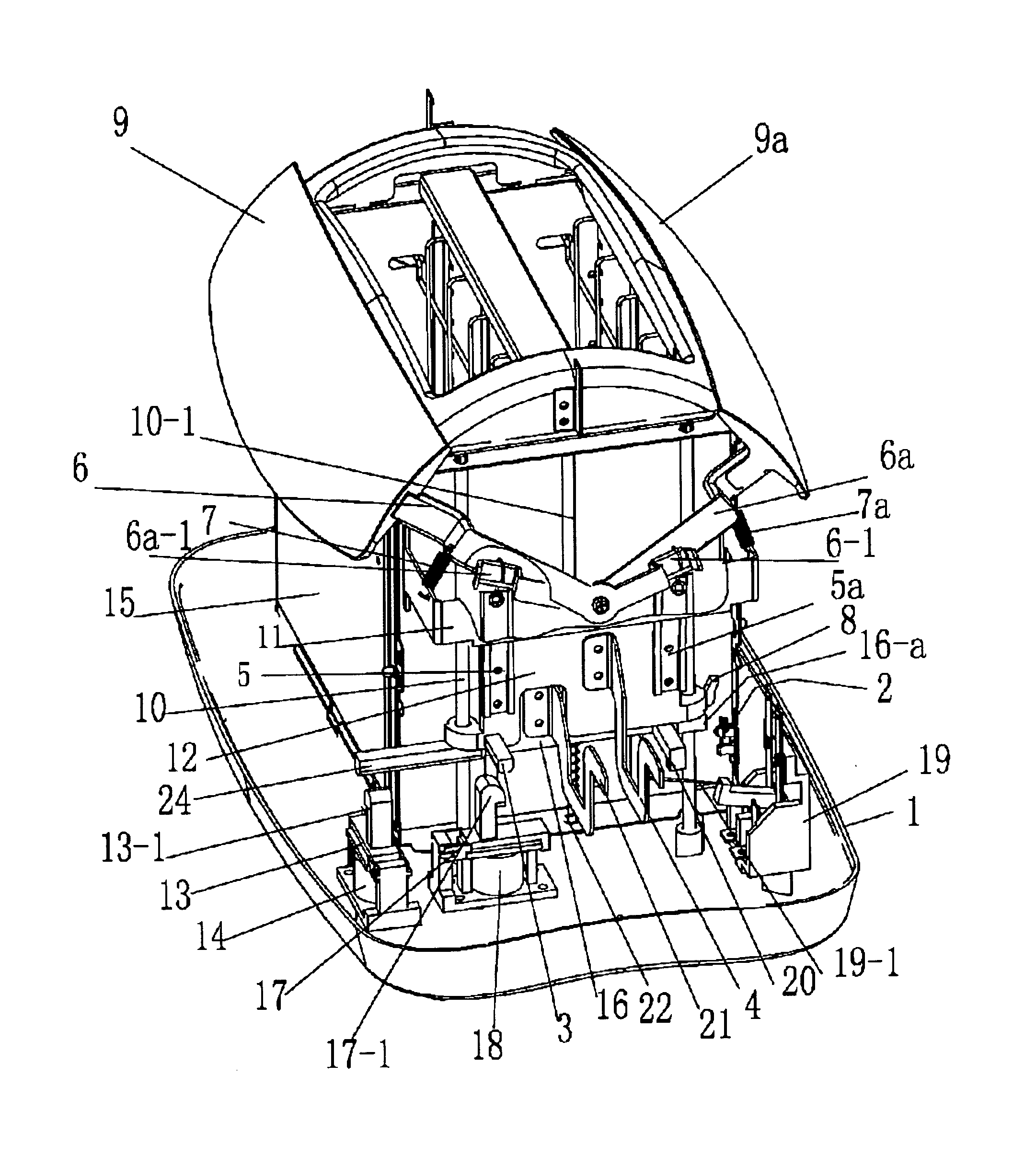

Counter top cooking appliance

ActiveUS20160309956A1Optimal performanceUniform exposureDomestic stoves or rangesStoves/ranges shelves or racksDriver/operatorCooker

A counter top electric appliance optimally performs a variety of cooking modes with both radiant and convective heat sources as well as control means for controlling the timing and intensity of the heat sources. A driver turns food about either a horizontal or a vertical axis of rotation suitable for the specific food and recipe. A hinged door supports the food to be cooked so that in one location the food is caused to be turned by the drive means and in another location the food is loaded into or removed the appliance, external of the cooking compartment, to be easily handled by the operator.

Owner:GLUCKSMAN DOV Z

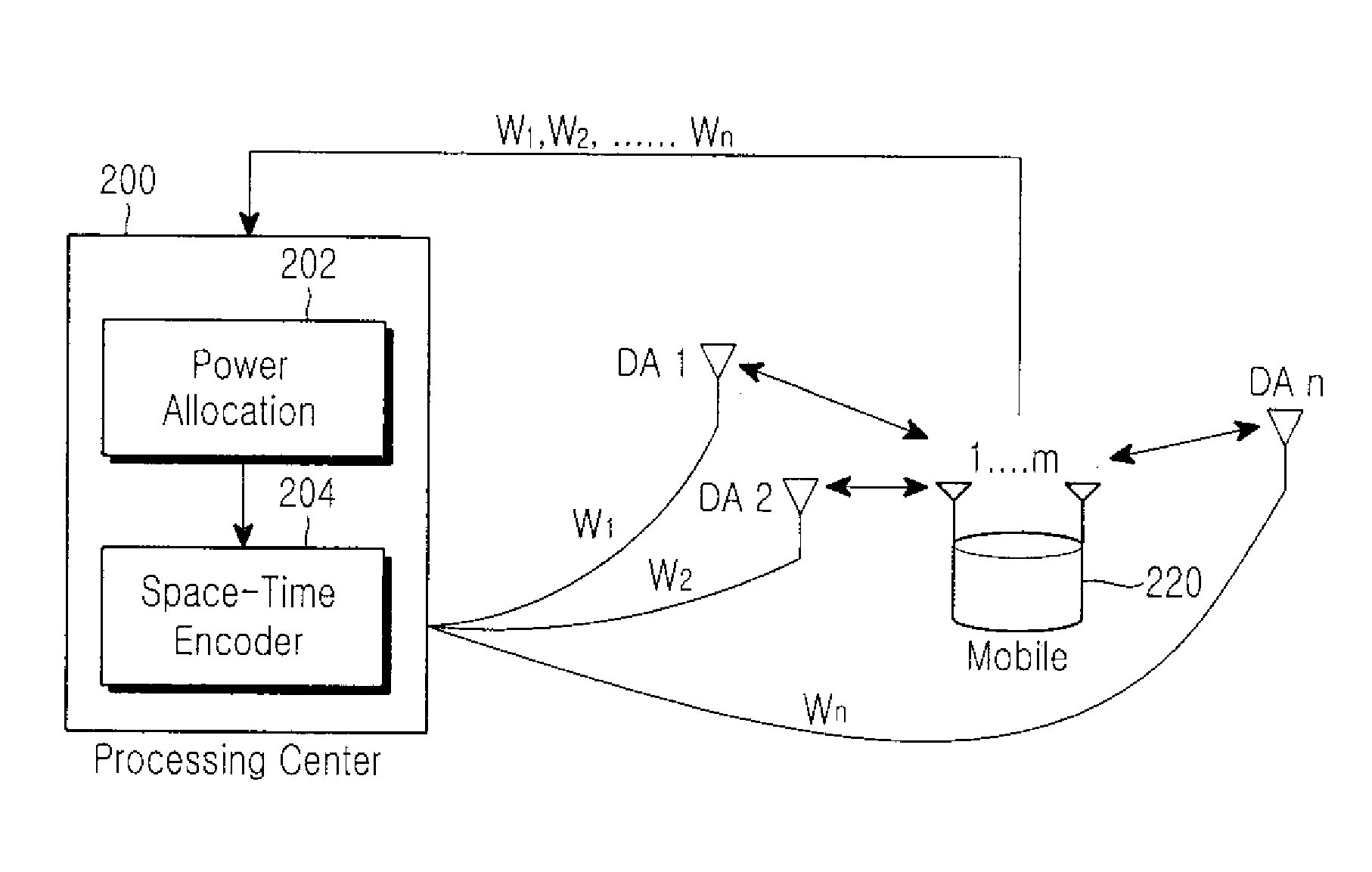

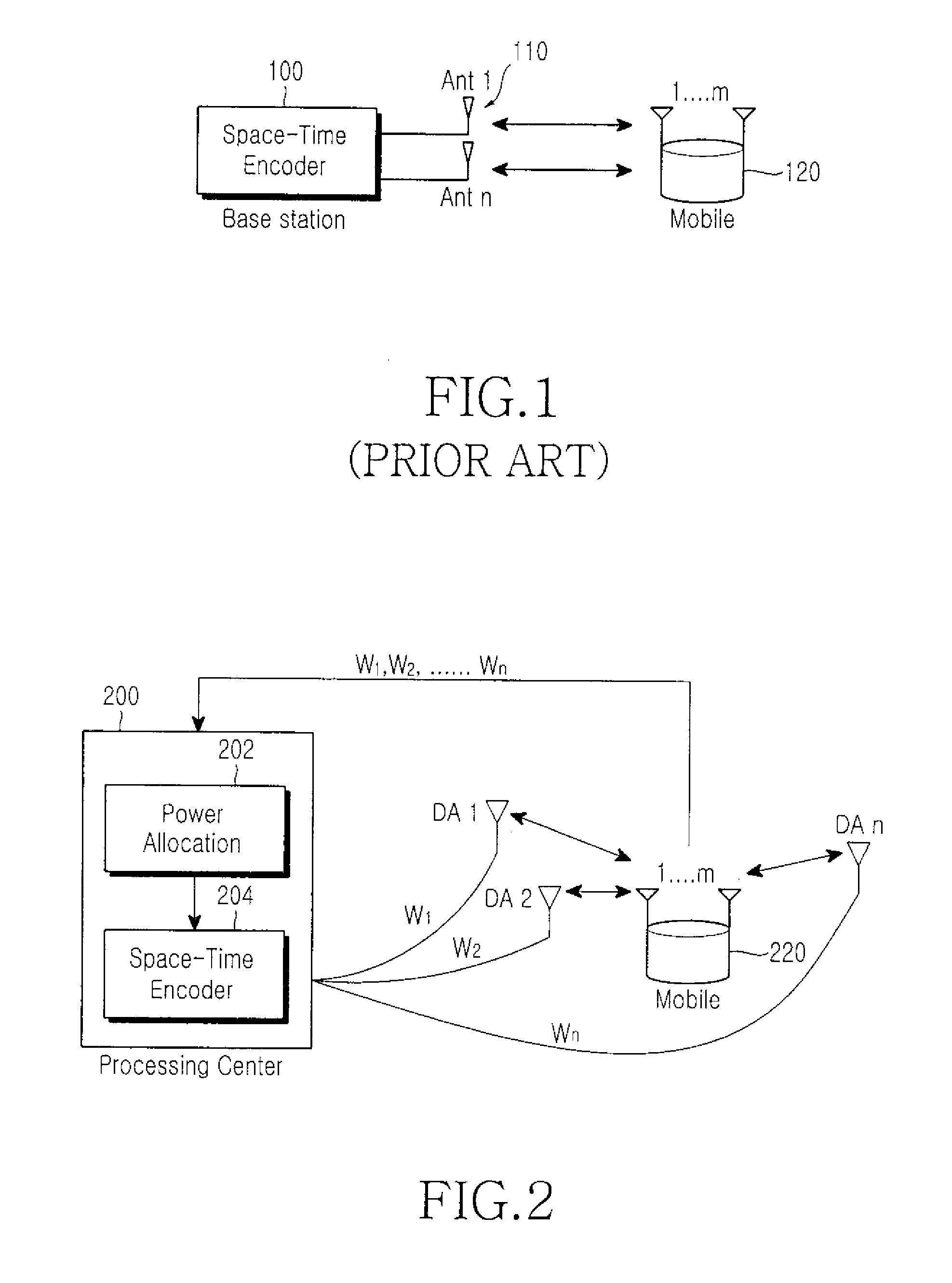

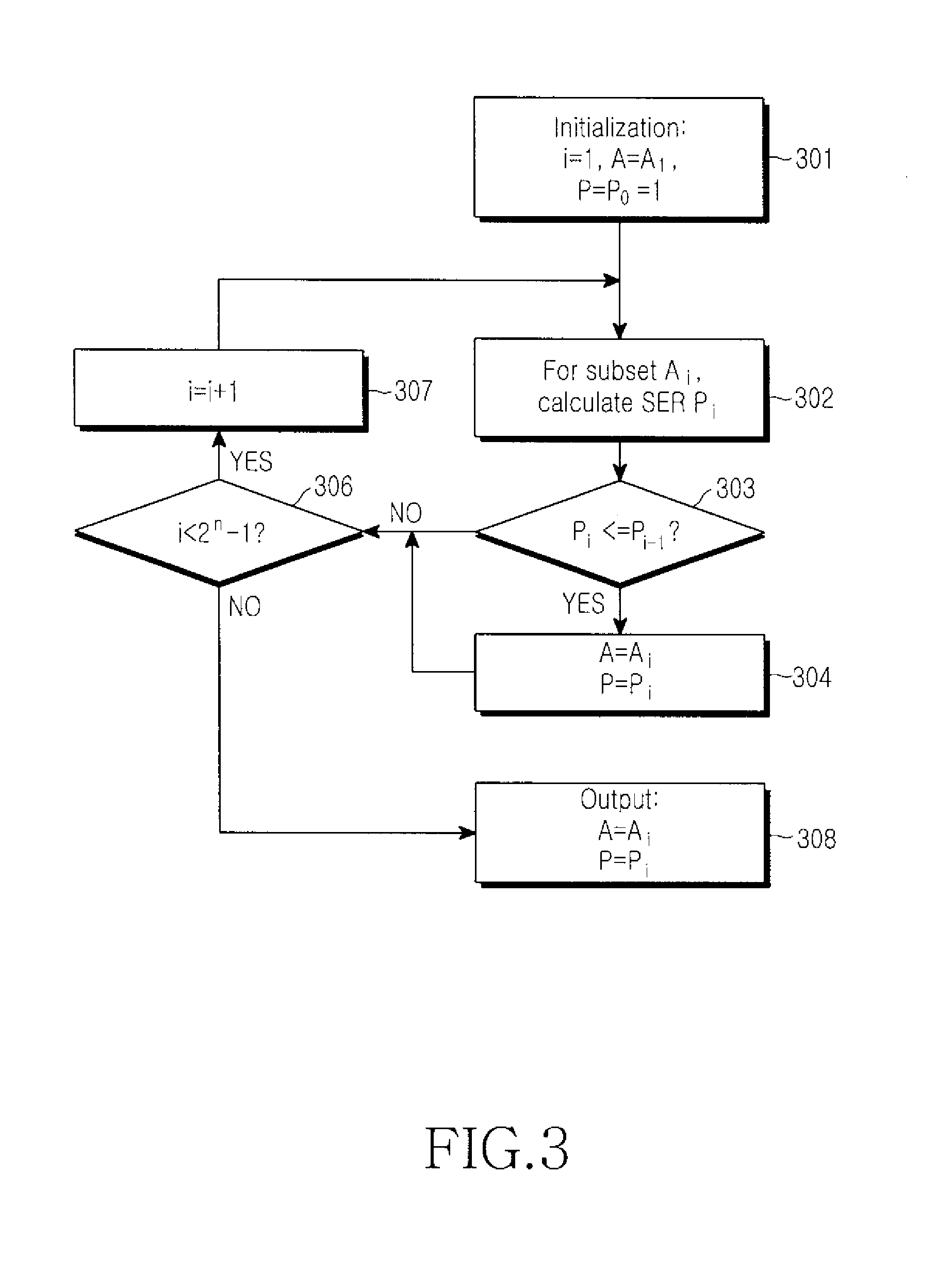

Method for ser approximation for ostbc in distributed wire communication systems

InactiveUS20080205538A1Optimal performanceError detection/prevention using signal quality detectorFrequency diversitySignal-to-noise ratio (imaging)Multiple antenna

A method for Symbol Error Rate (SER) approximation of an SER-based transmission power allocation operation for an Orthogonal Space Time Block Code in a DWCS equipped with multiple transmission Distributed Antennas (DA) geographically dispersed at random. The method for SER approximation includes the steps of: setting multiple combinable antenna subsets from the multiple DAs; selecting a quasi-optimal antenna subset Ag (1≦g≦2n−1) having a quasi-optimal power allocation weight wg based on predetermined power allocation, for each of the set multiple antenna subsets; and calculating an SER approximation value of the selected quasi-optimal antenna subset by applying a Probability Density Function (PDF) of a Signal-to-Noise Ratio (SNR) to the OSTBC SER having symbol constellation of a predetermined modulation scheme. The output of the SER approximation value can be output to a transmitter, or to a space-time encoder of a central processor for optimal power transmission.

Owner:SAMSUNG ELECTRONICS CO LTD

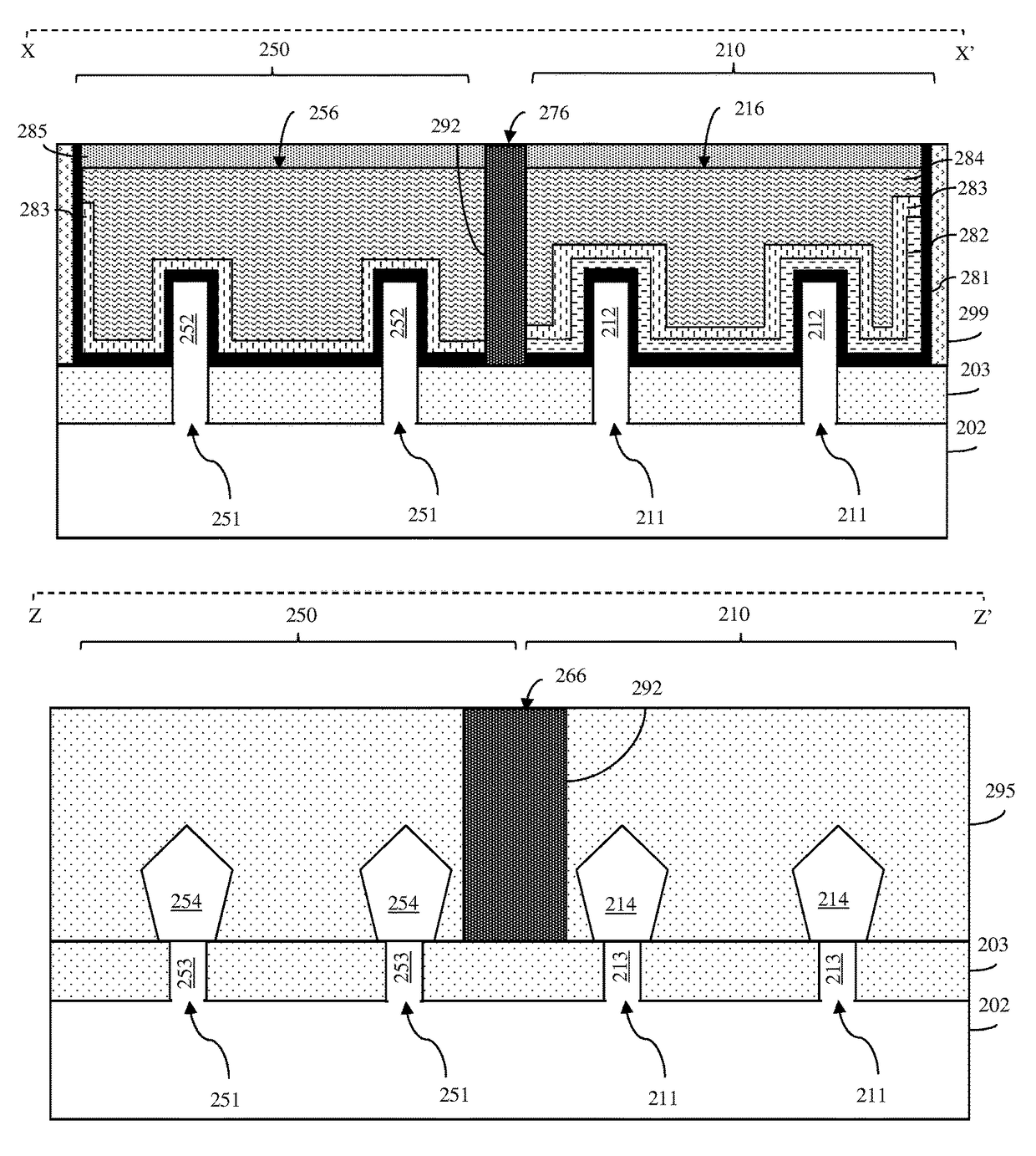

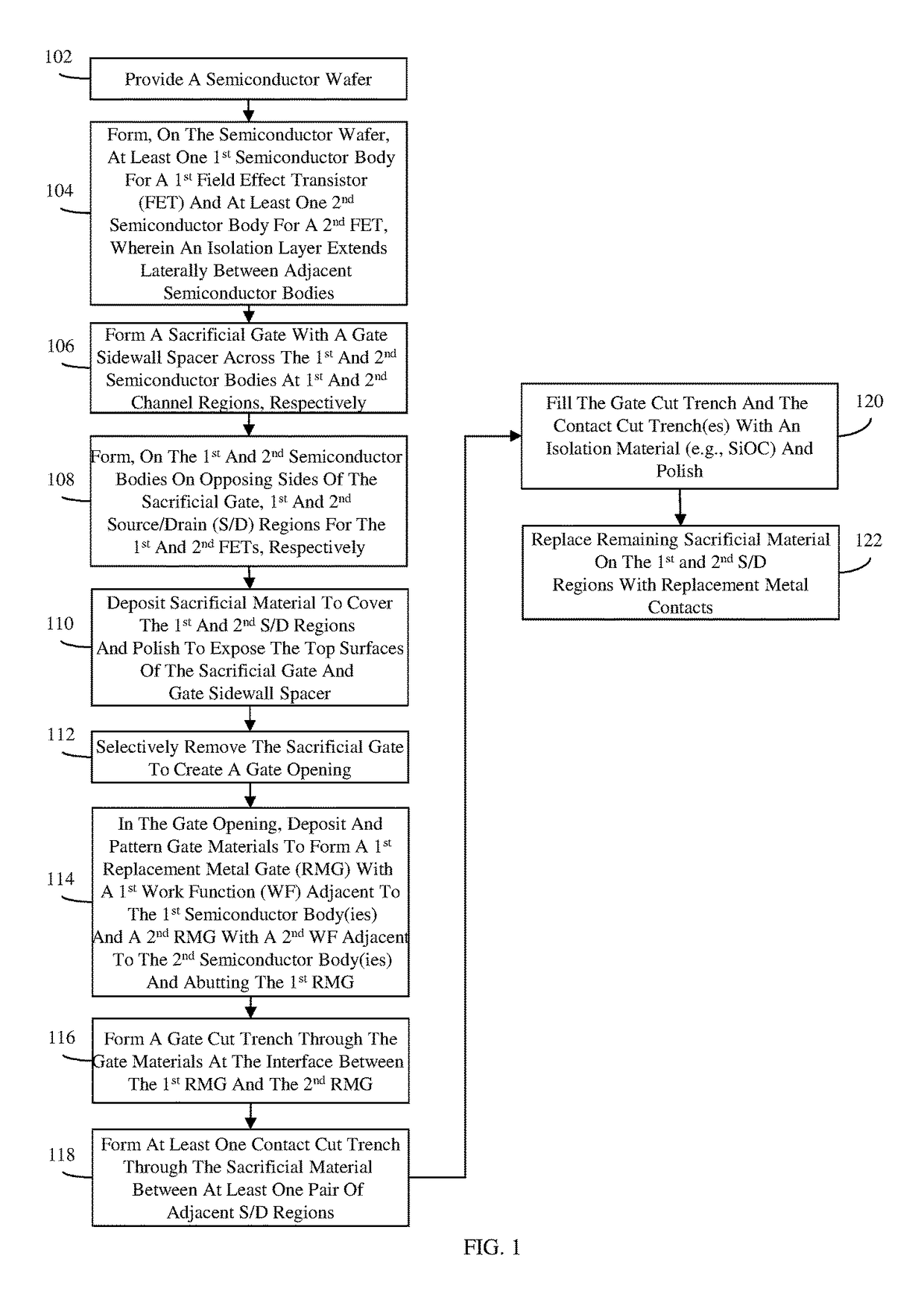

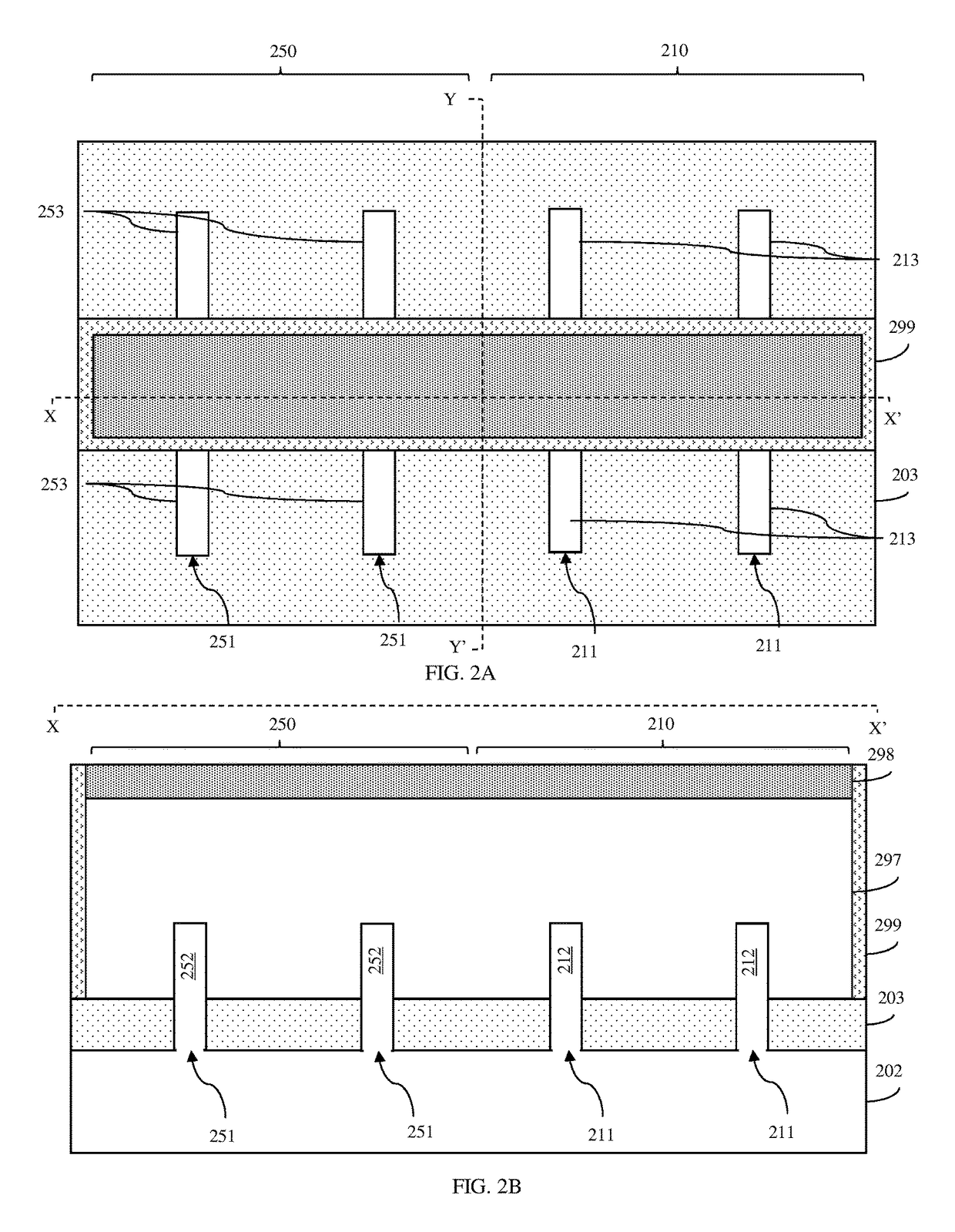

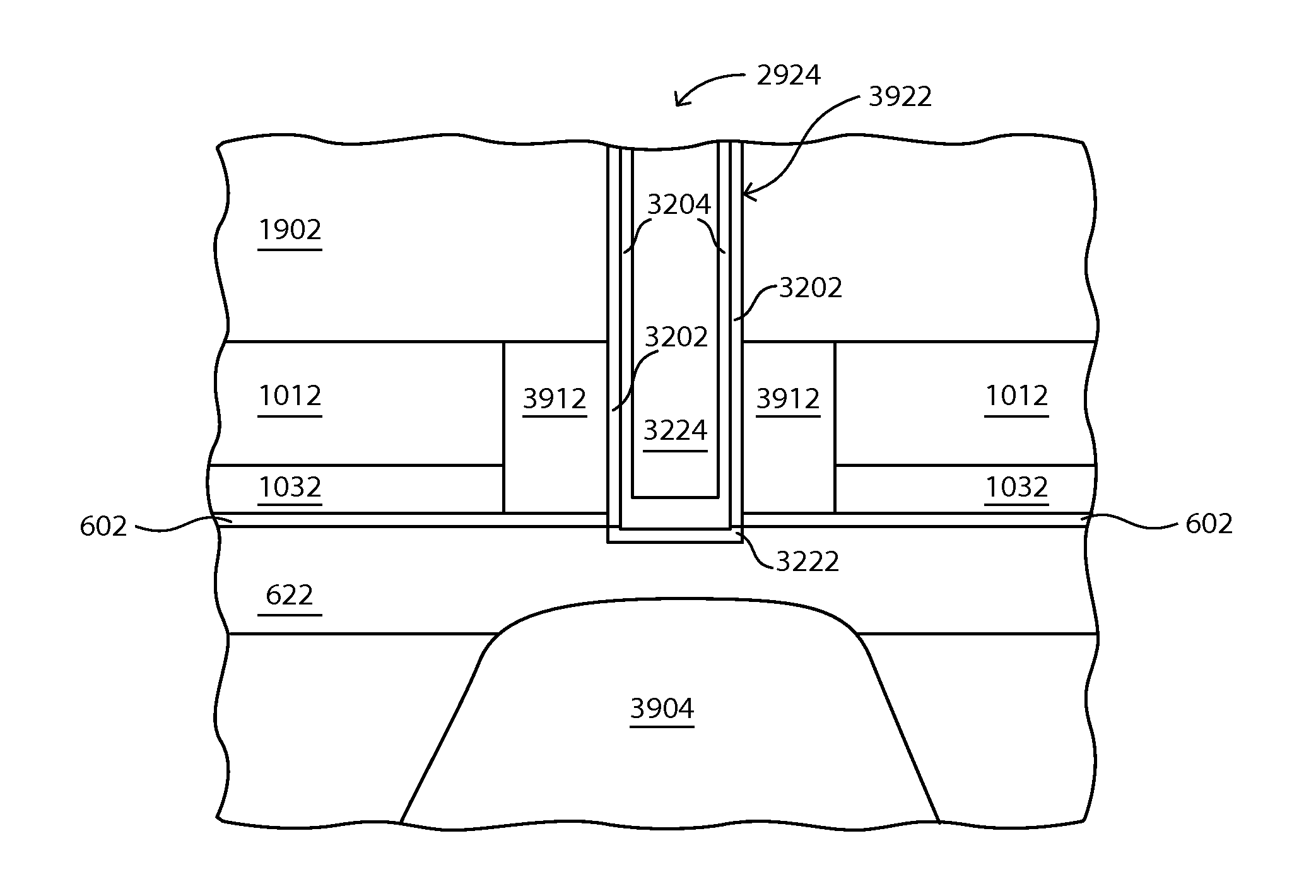

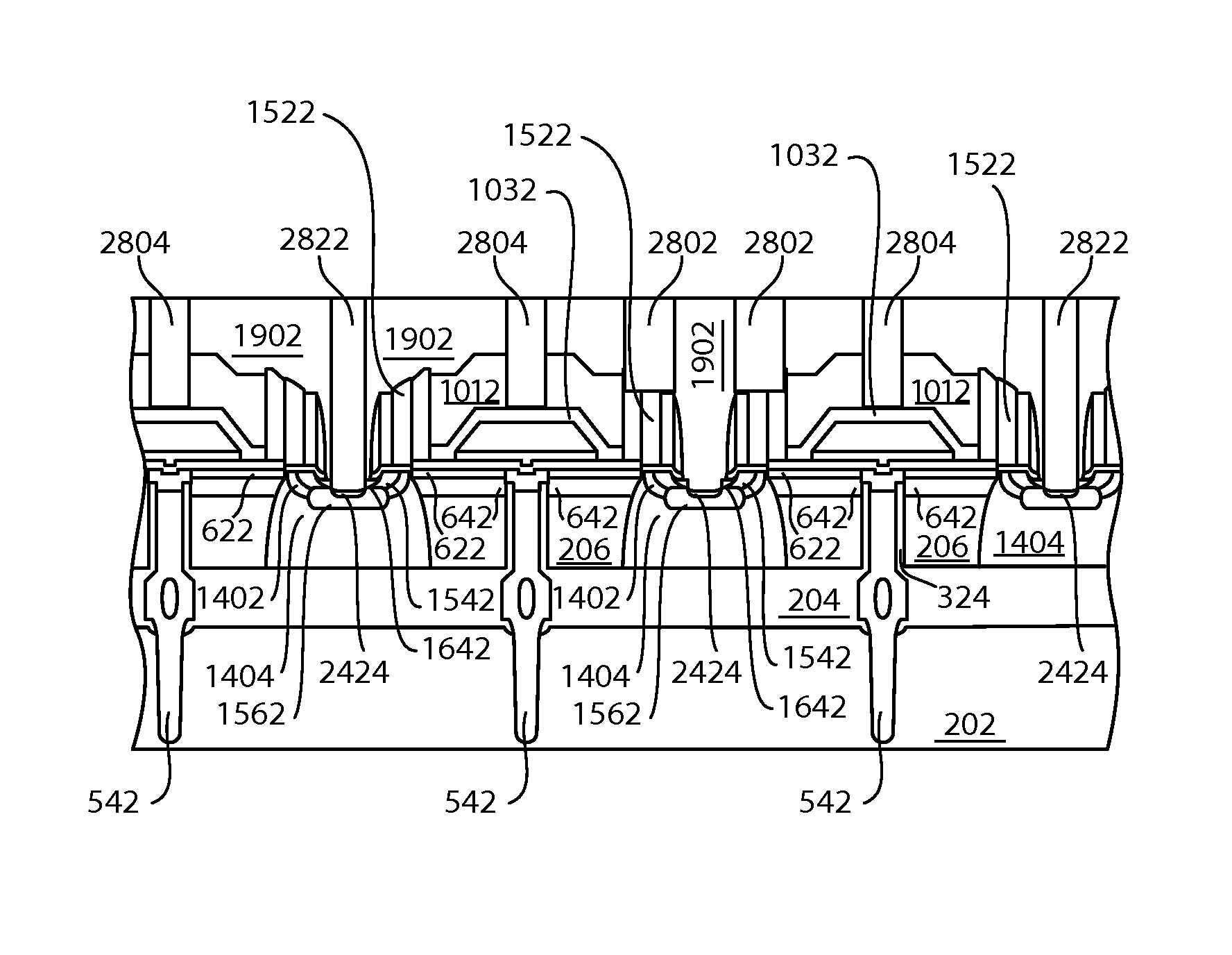

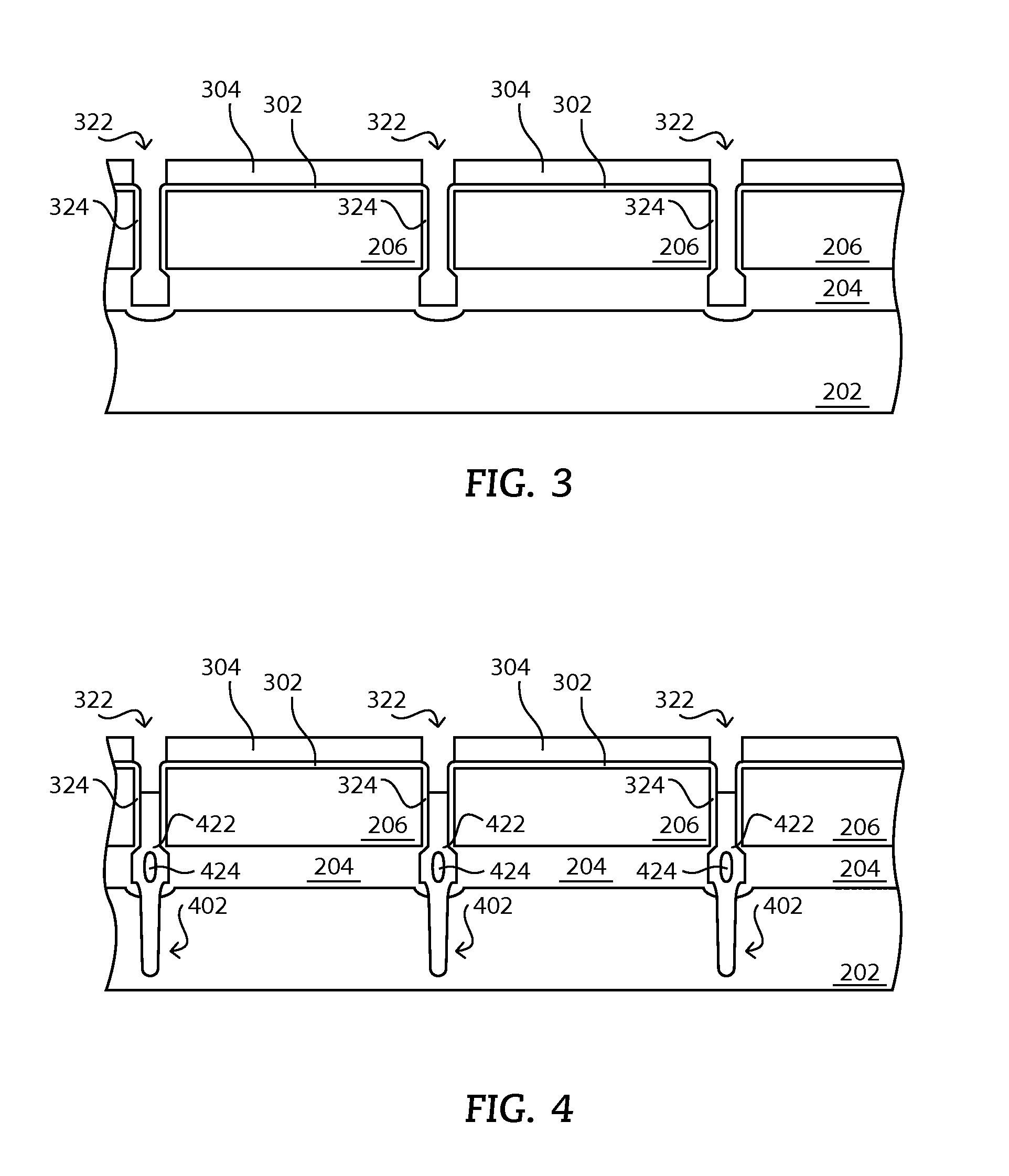

Method of forming field effect transistors with replacement metal gates and contacts and resulting structure

ActiveUS9911736B1Optimal performanceImprove performanceTransistorSolid-state devicesIntegrated circuitCompound (substance)

In a method for forming an integrated circuit (IC) structure, which incorporates multiple field effect transistors (FETs) with discrete replacement metal gates (RMGs) and replacement metal contacts (RMCs), gate cut trench(es) and contact cut trench(es) are formed at the same process level. These trench(es) are then filled at the same time with the same isolation material to form gate cut isolation region(s) for electrically isolating adjacent RMGs and contact cut isolation region(s) for electrically isolating adjacent RMCs, respectively. The selected isolation material can be a low-K isolation material for optimal performance. Furthermore, since the same process step is used to fill both types of trenches, only a single chemical mechanical polishing (CMP) process is needed to remove the isolation material from above the gate level, thereby minimizing gate height loss and process variation. Also disclosed herein is an IC structure formed according to the method.

Owner:GLOBALFOUNDRIES US INC

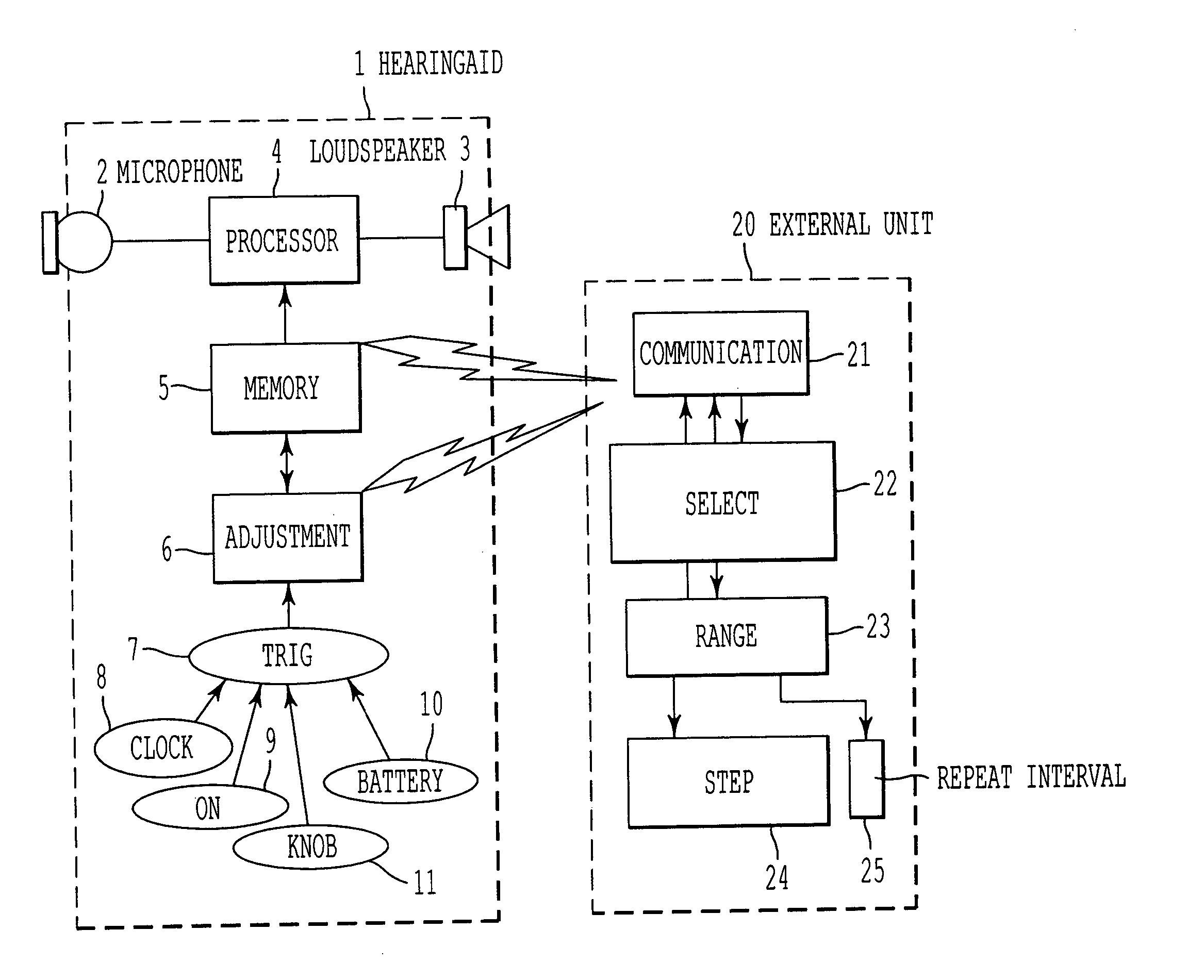

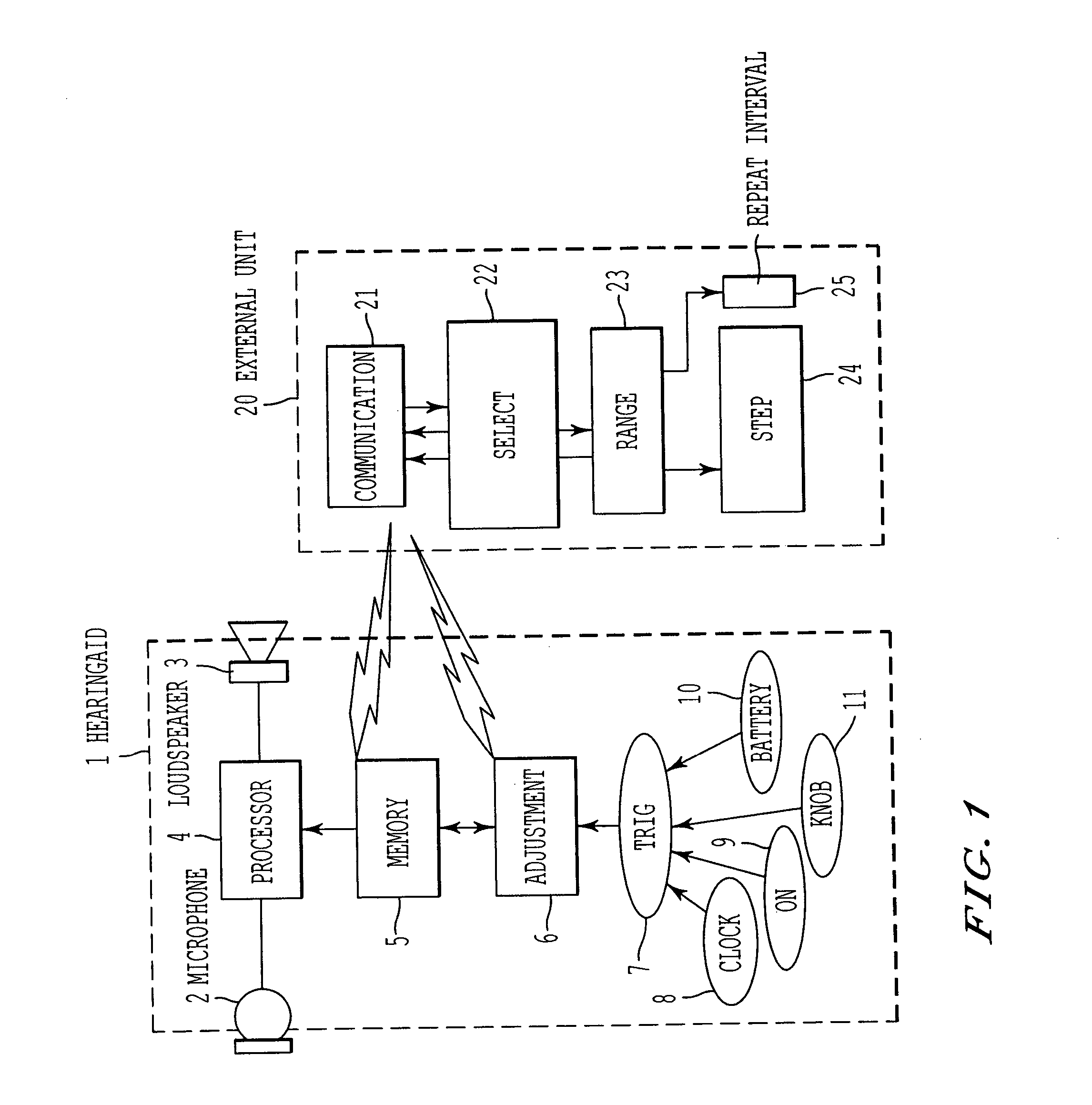

Automatic adjusting hearing aid

InactiveUS20050036637A1Optimal performanceImprove performanceDeaf aid adaptationEngineeringTerminal point

A hearing aid that stores preset signal processing parameters, and performs stepwise adjustment of one or more of the stored signal processing parameters from a starting point of a predetermined range to an end point of the range is provided. Examples of signal processing parameters to be adjusted are high tone amplification, maximum output level and noise suppression threshold value. Examples of trigger signal supplying means include a time clock, the power state of the hearing aid, battery replacement, and a switch. The hearing aid may be arranged for mutual communication with an external unit. The external unit may select the one or more parameters to be adjusted, set the range of the one or more parameters to be adjusted, set a step magnitude to be used in the stepwise adjustment, and set the repeat interval of the successive trigger signals in the time clock. The hearing aid carries out the adjustment autonomously.

Owner:BELTONE NETHERLANDS

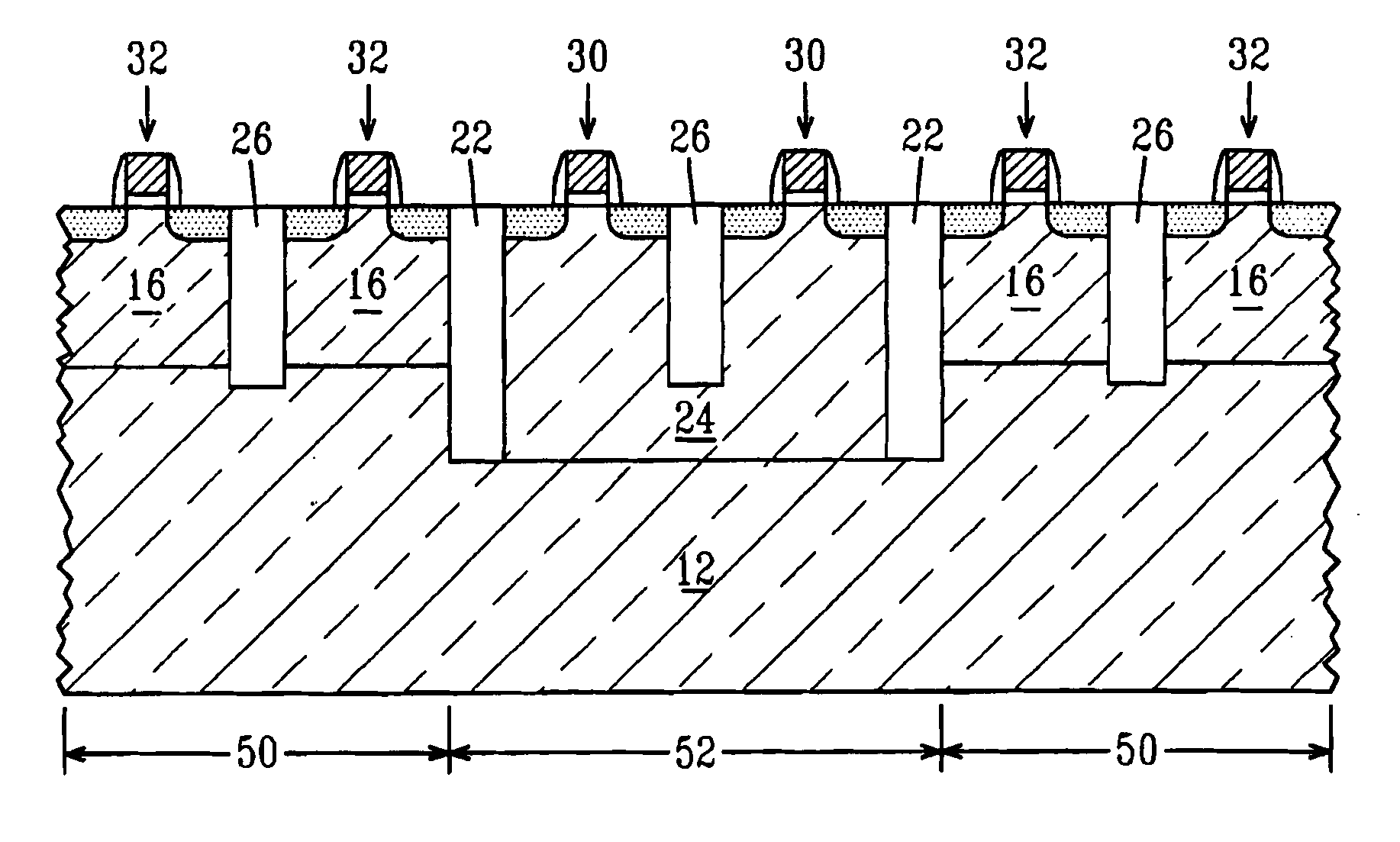

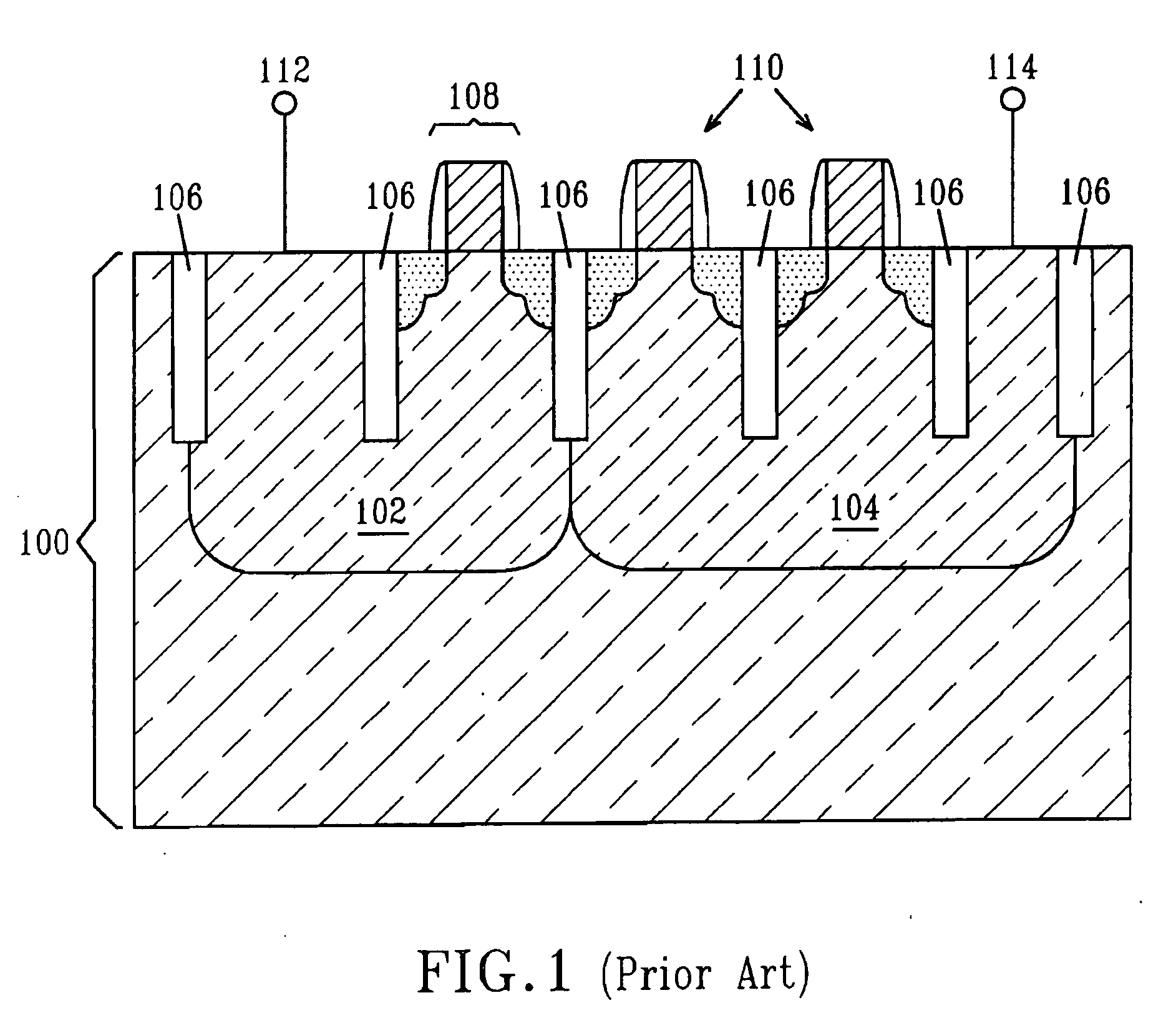

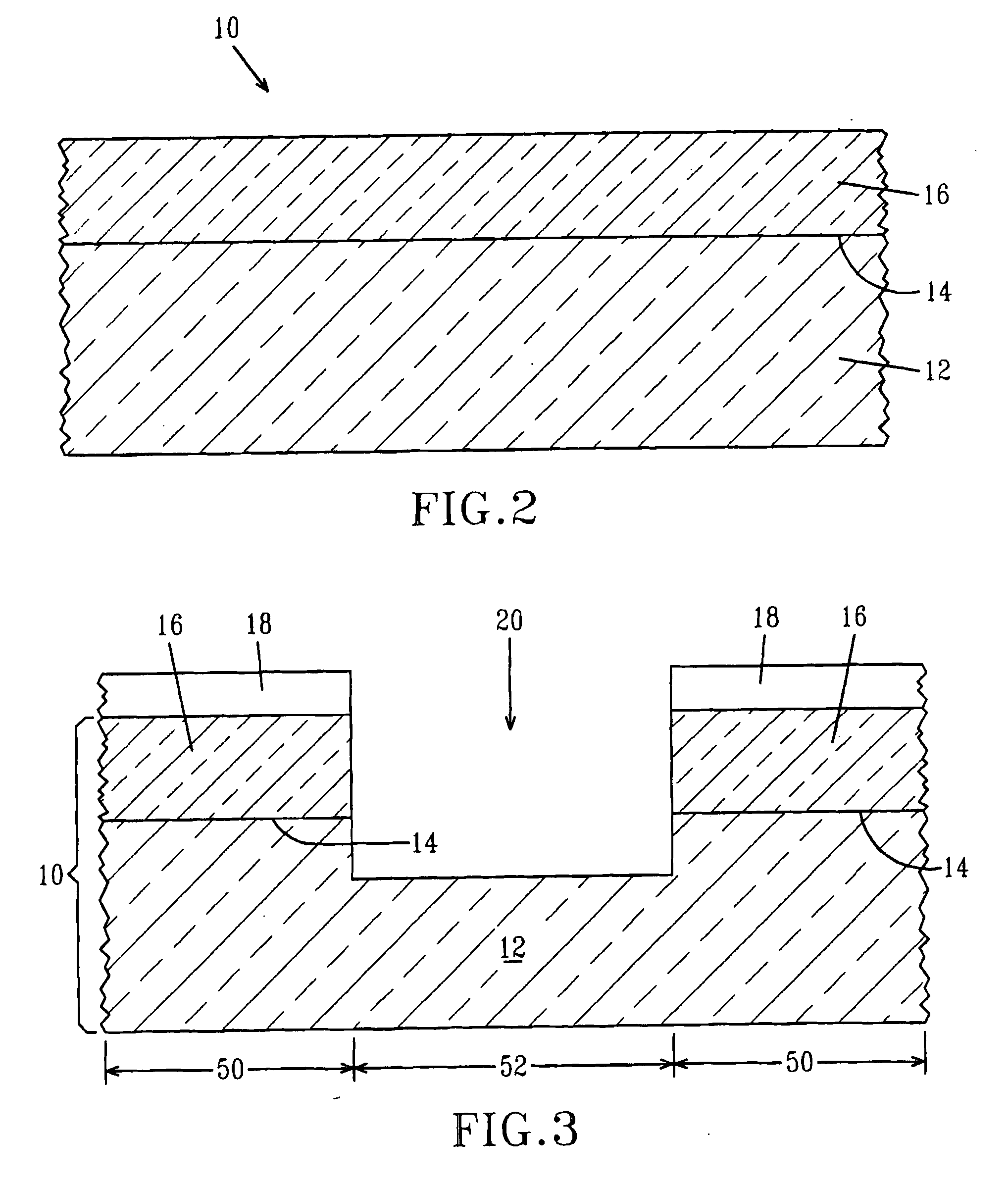

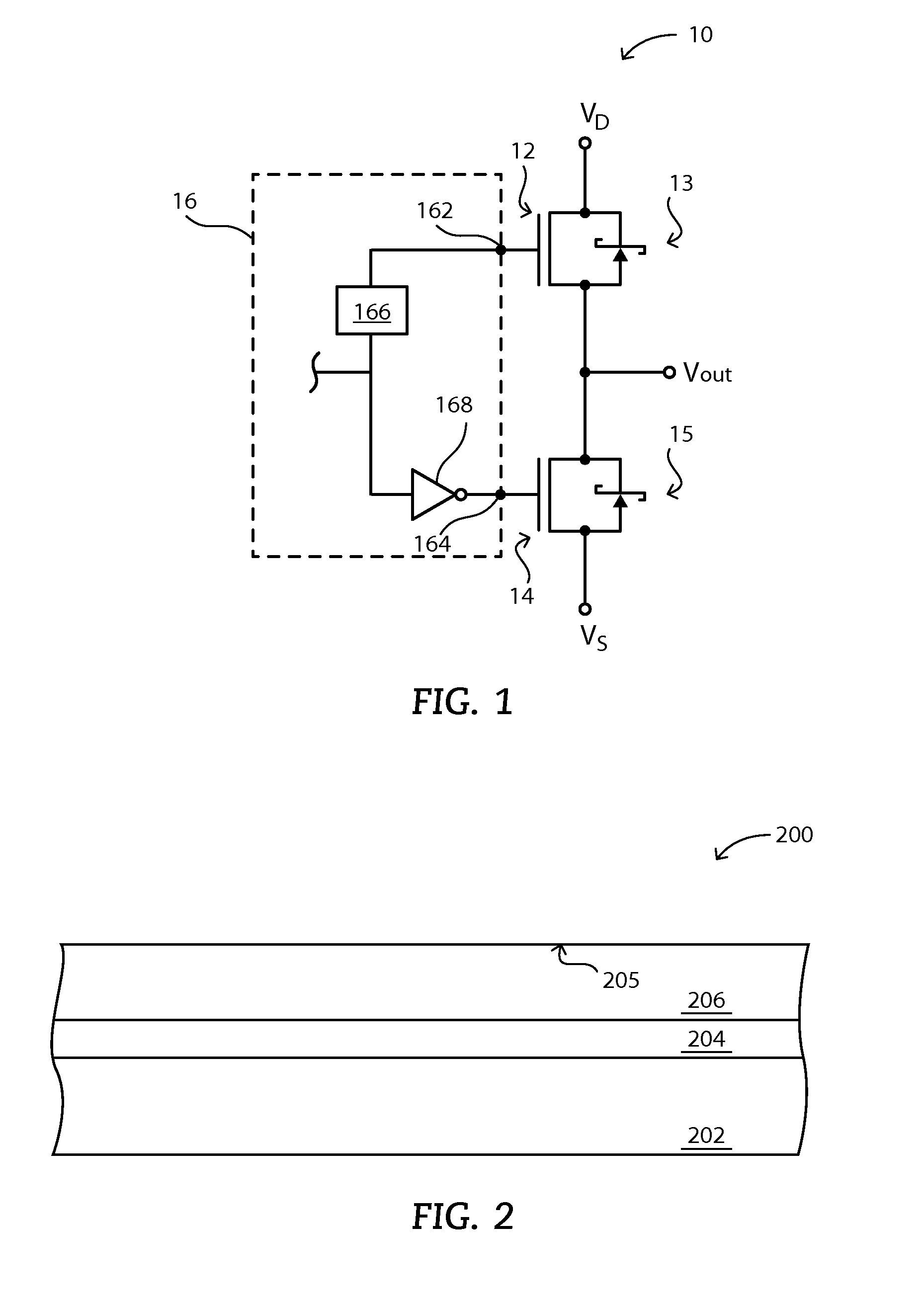

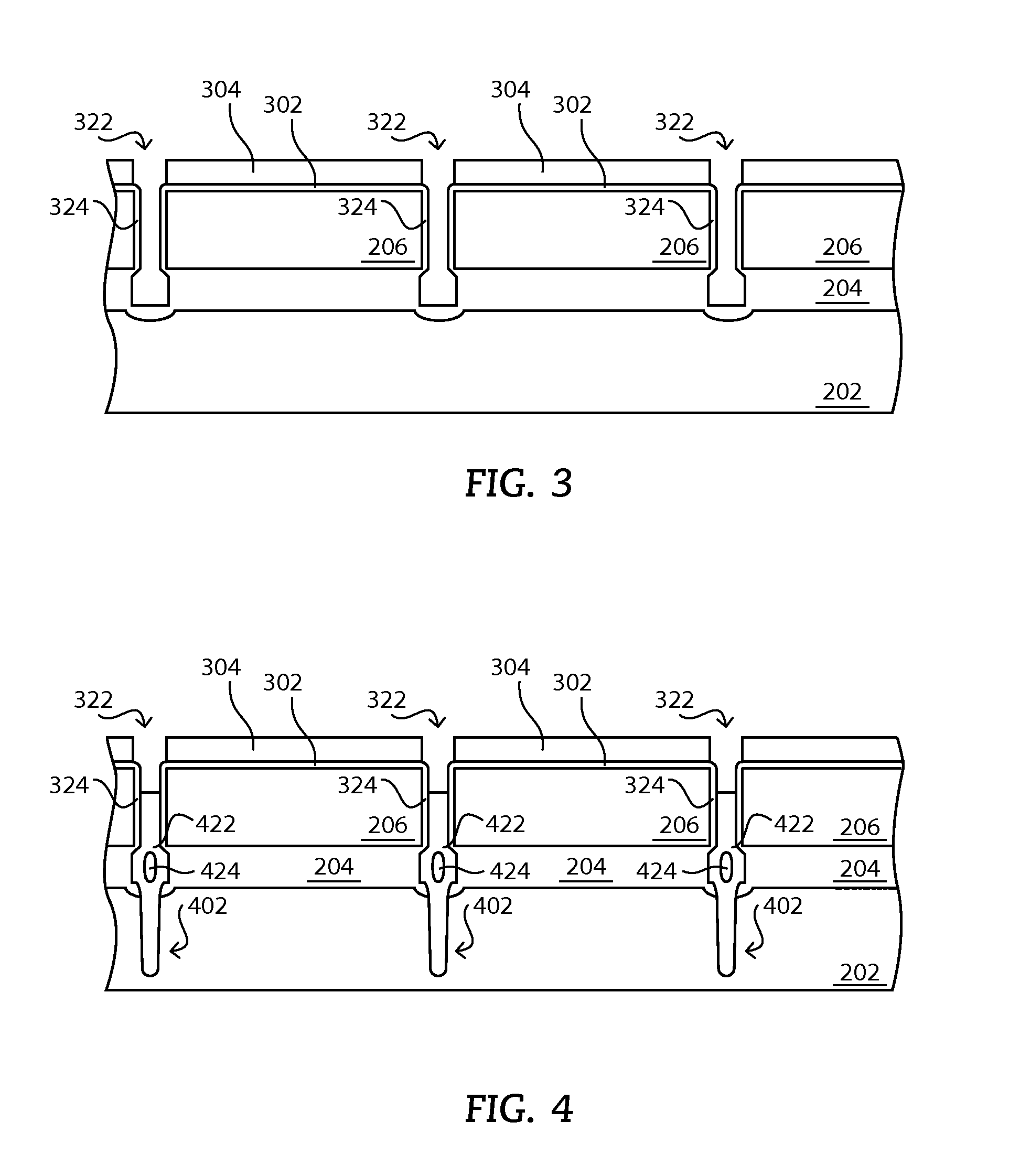

Dual trench isolation for CMOS with hybrid orientations

InactiveUS20070040235A1Optimal performanceImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesCMOSEngineering

The present invention provides a semiconductor structure in which different types of devices are located upon a specific crystal orientation of a hybrid substrate that enhances the performance of each type of device. In the semiconductor structure of the present invention, a dual trench isolation scheme is employed whereby a first trench isolation region of a first depth isolates devices of different polarity from each other, while second trench isolation regions of a second depth, which is shallower than the first depth, are used to isolate devices of the same polarity from each other. The present invention further provides a dual trench semiconductor structure in which pFETs are located on a (110) crystallographic plane, while nFETs are located on a (100) crystallographic plane. In accordance with the present invention, the devices of different polarity, i.e., nFETs and pFETs, are bulk-like devices.

Owner:GLOBALFOUNDRIES INC

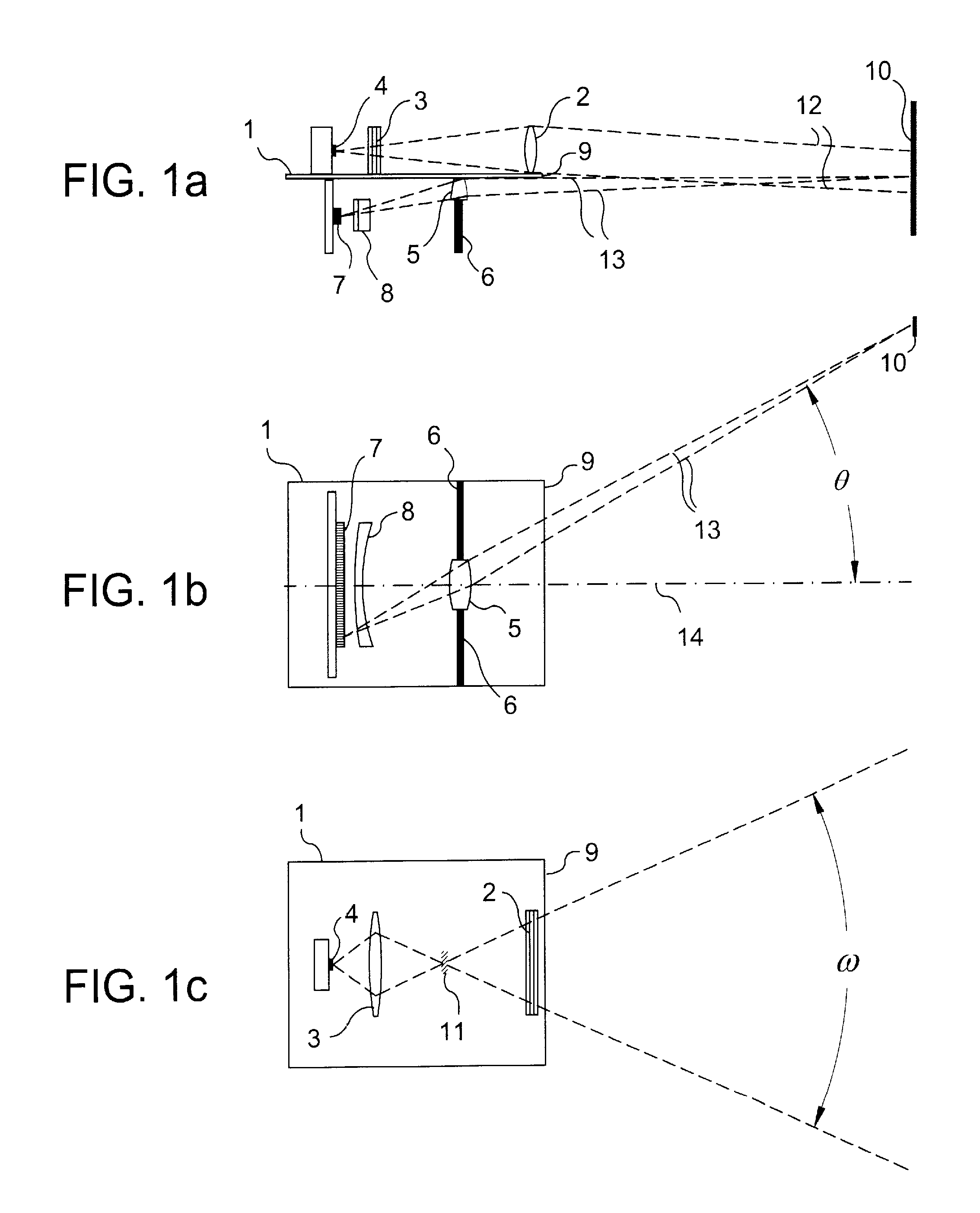

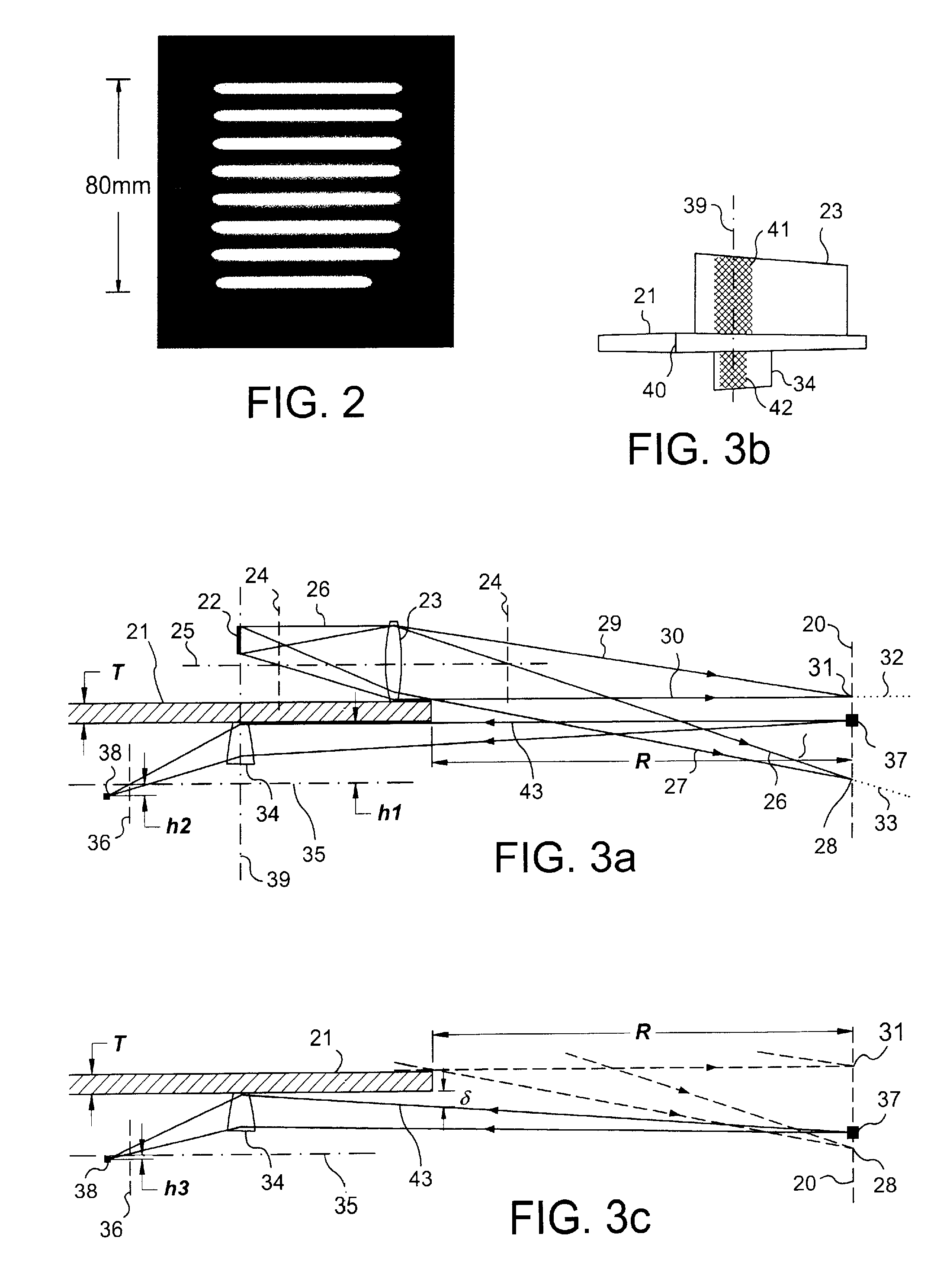

Electro-optical sensors

InactiveUS20100133424A1Optimal performanceEnsures performancePhotometryMaterial analysis by optical meansOpto electronicPixel array

An electro-optical sensor for use with a retro-reflective target (10). The light-emitting assembly involves a LED (4) and collimating and parallel lenses (2, 4), and the sensing assembly involves a collecting lens (5), an aperture plate (6) and a photodiode array (7) with optional field-curvature correcting lens (8). The lens (5) abut the substrate (1) within the aperture of plate (6) so that the entrance pupil and the exit pupil, when viewed from the target (10), abut opposite, parallel straight-edges of the substrate (1). The photodiode array (7) may be a linear pixel array parallel to the substrate-surface, or may be replaced by a single, large-area photodiode with aperture-limitation of its field of view to a narrow fan-shape parallel to the substrate-surface. A plurality of light-emitters (77) may be used with photo-detectors (71) that have individual light-collection optics (72, 73) with merged fields of view. The sensor can sense golf club-head (100) movement and vehicle speed and plate number (116).

Owner:LINDSAY LTD

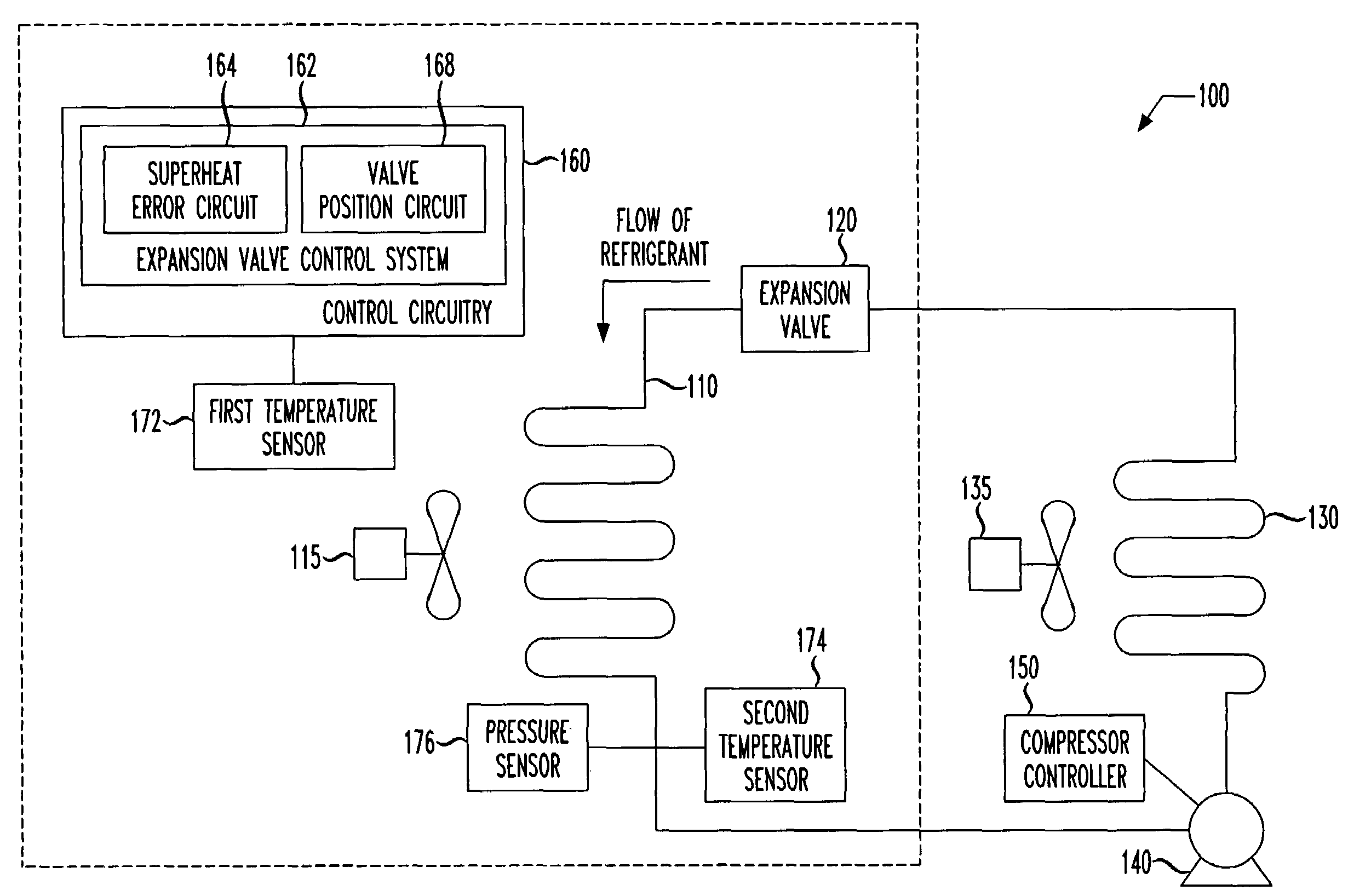

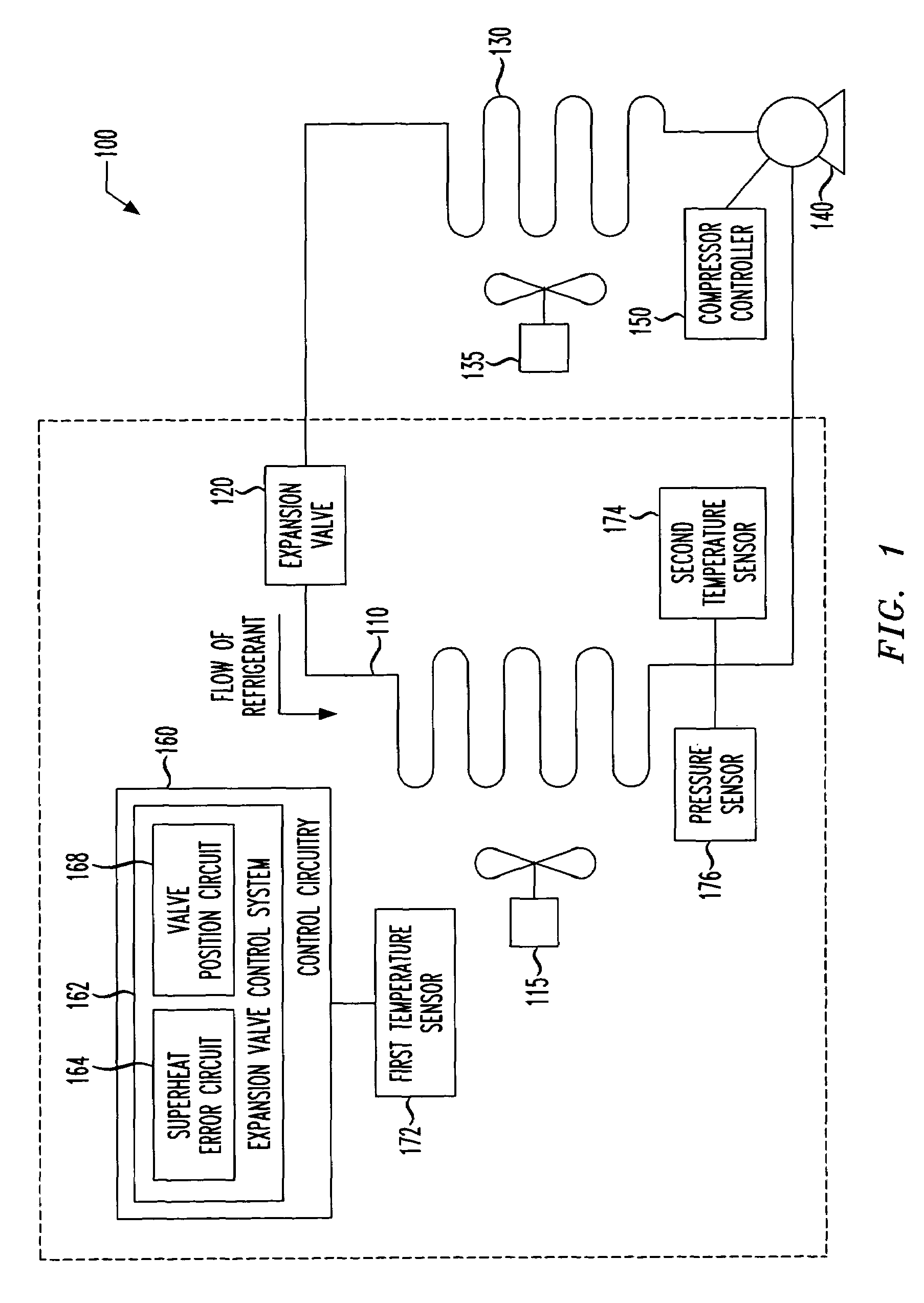

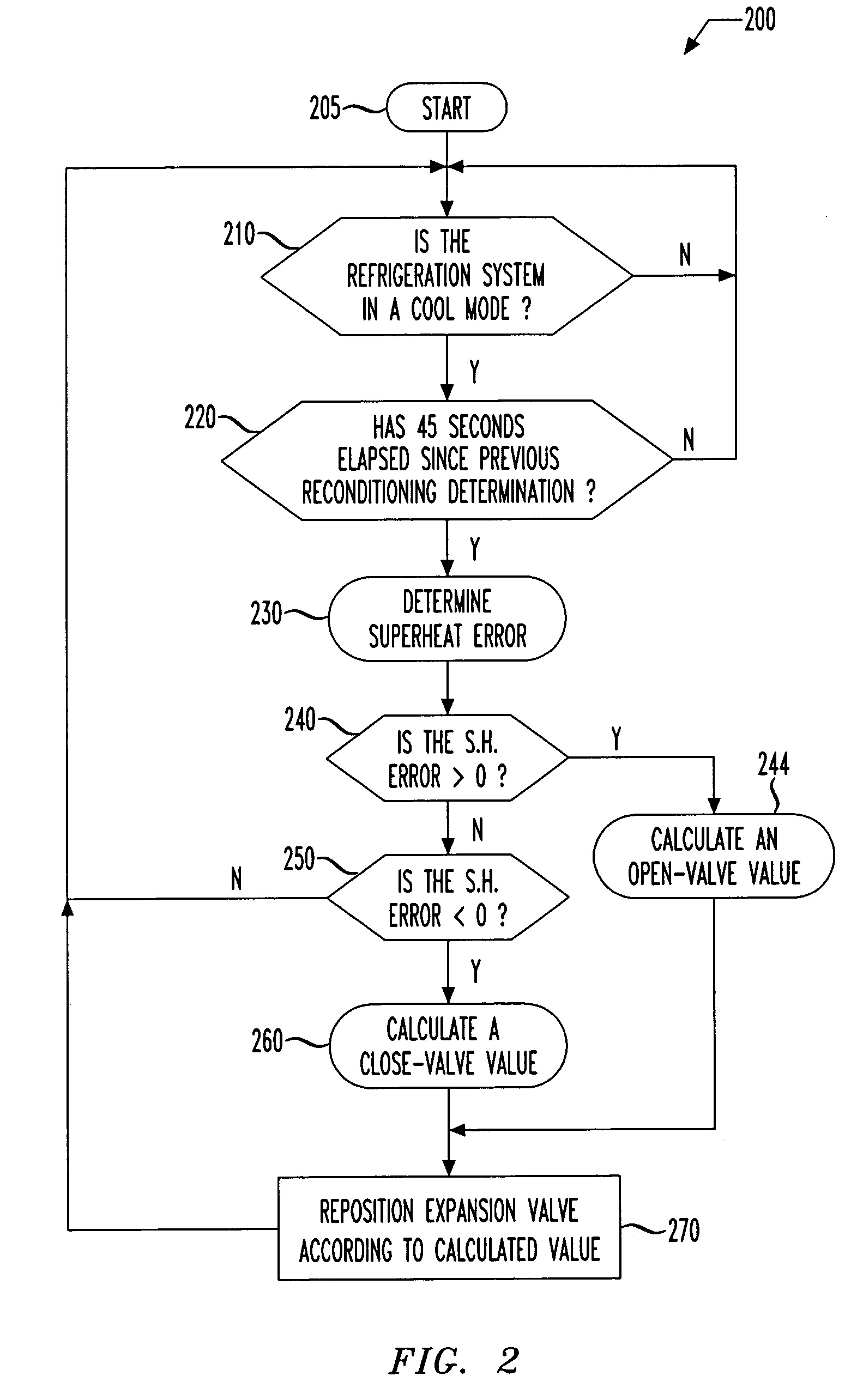

Expansion valve control system and method and refrigeration unit employing the same

ActiveUS7290402B1Increase measurementOptimal performanceTemperature control without auxillary powerMechanical apparatusControl systemRefrigeration

An expansion valve control system, a method of controlling an expansion valve and a refrigeration unit incorporating the same. In one embodiment, the expansion valve control system includes (1) a superheat error circuit configured to derive a superheat error for a fluid associated with the expansion valve and (2) a valve position circuit, associated with the superheat error circuit, configured to reposition the expansion valve proportionally based on both a current position thereof and the superheat error.

Owner:HEATCRAFT REFRIGERATION PRODS

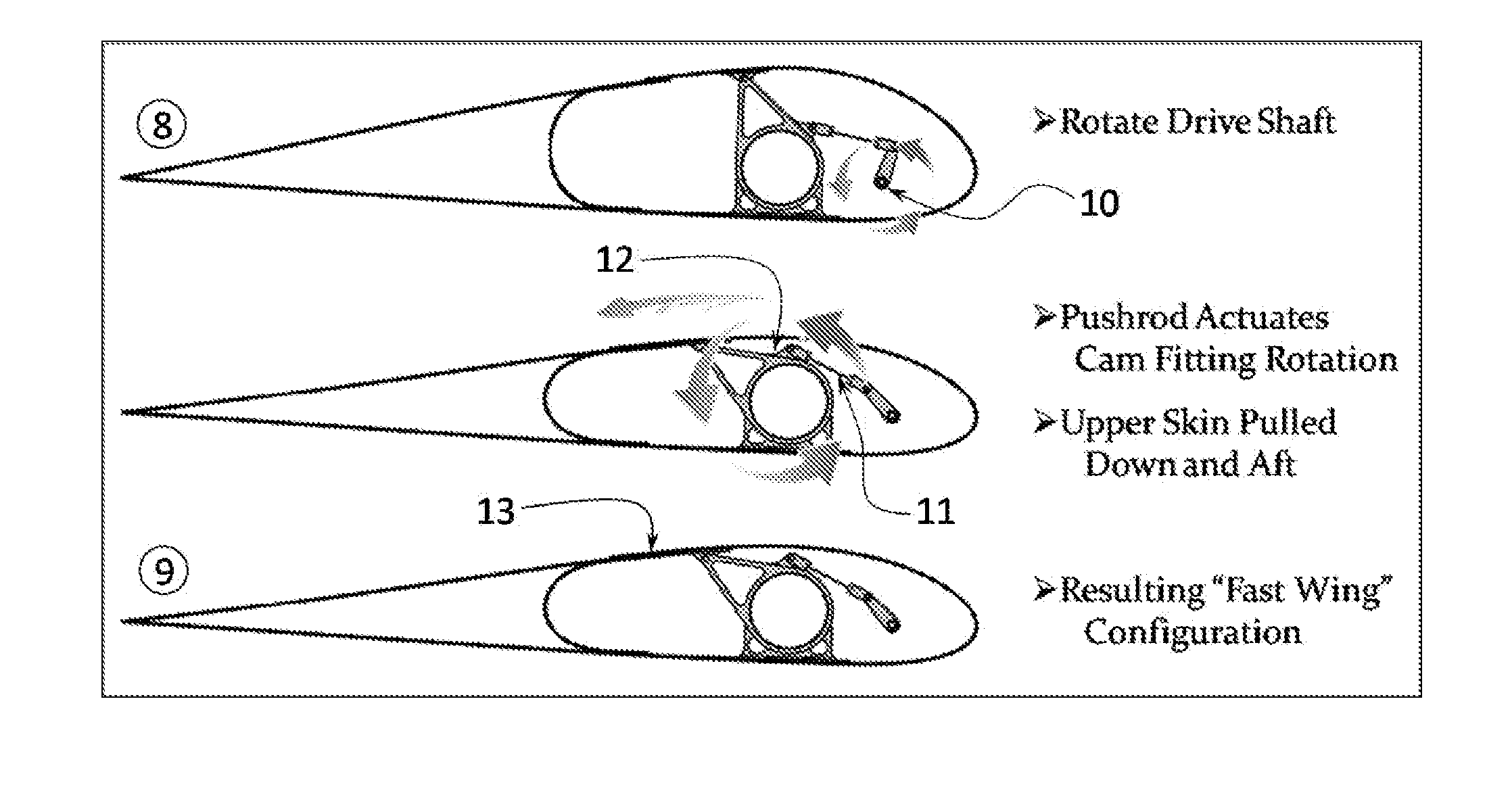

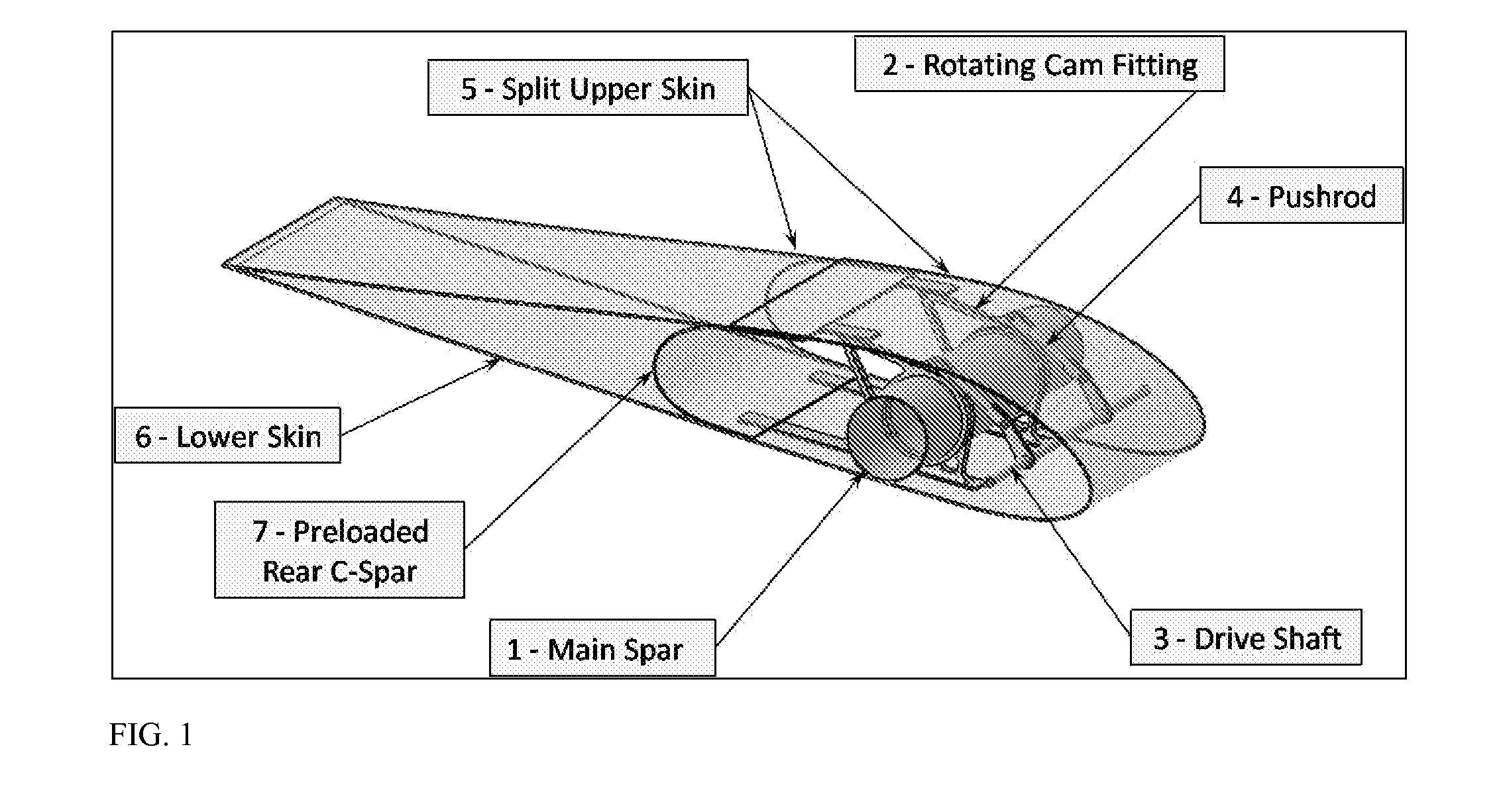

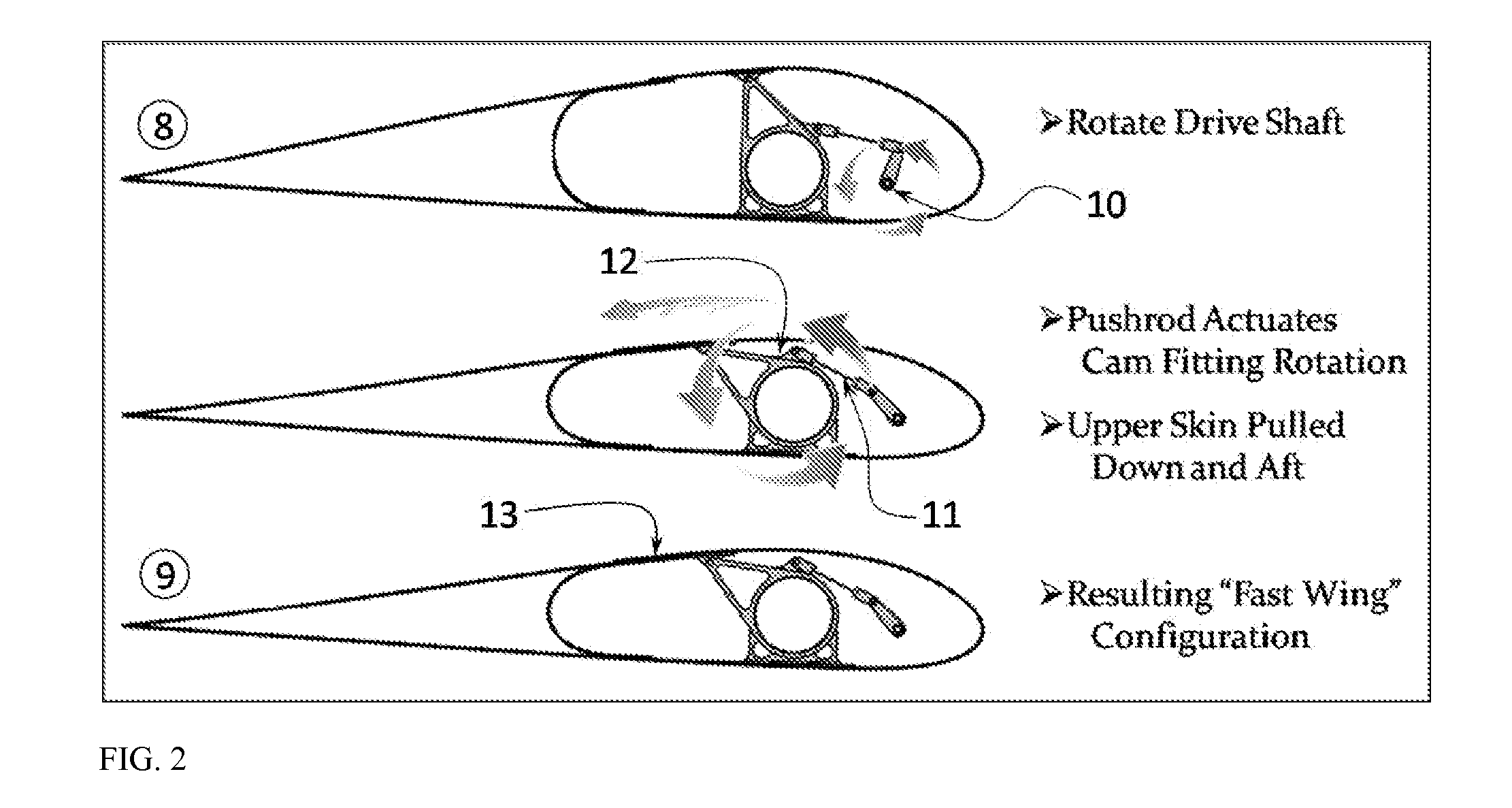

Cross-Sectionally Morphing Airfoil

InactiveUS20120104181A1Low weightOptimal performanceEfficient propulsion technologiesWing adjustmentsEngineeringLow speed

The present invention provides an apparatus, system, and method for morphing the cross-sectional shape of an airfoil between a high-speed, low-lift airfoil and a low-speed, high-lift airfoil, including interim airfoil configurations, to allow for optimal performance. This is done by inputting a control command into the system that alters the shape of the split or elastic upper and / or lower skin surface to allow the airfoil camber and chord to vary.

Owner:RIX MATTHEW BOYD

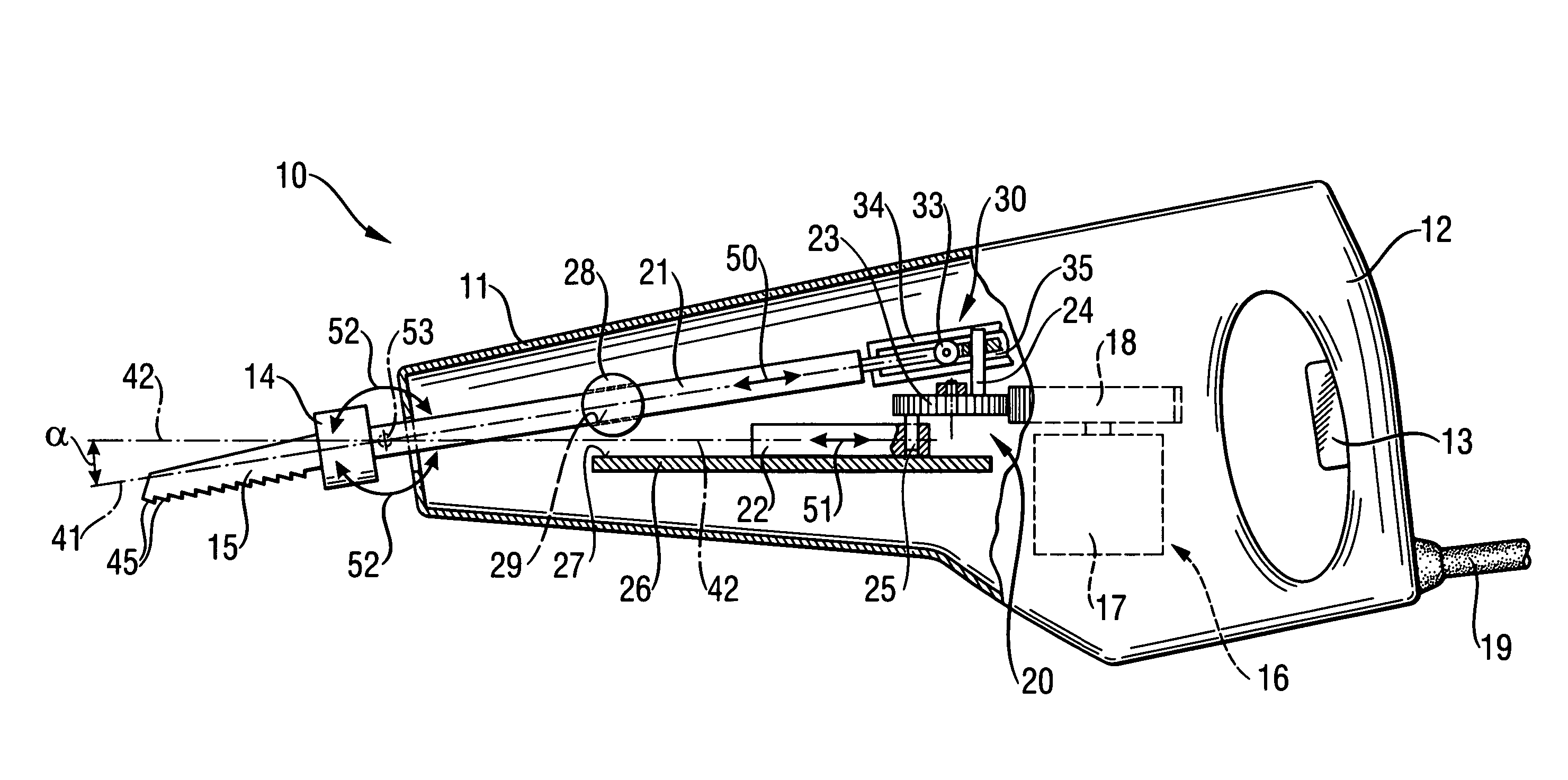

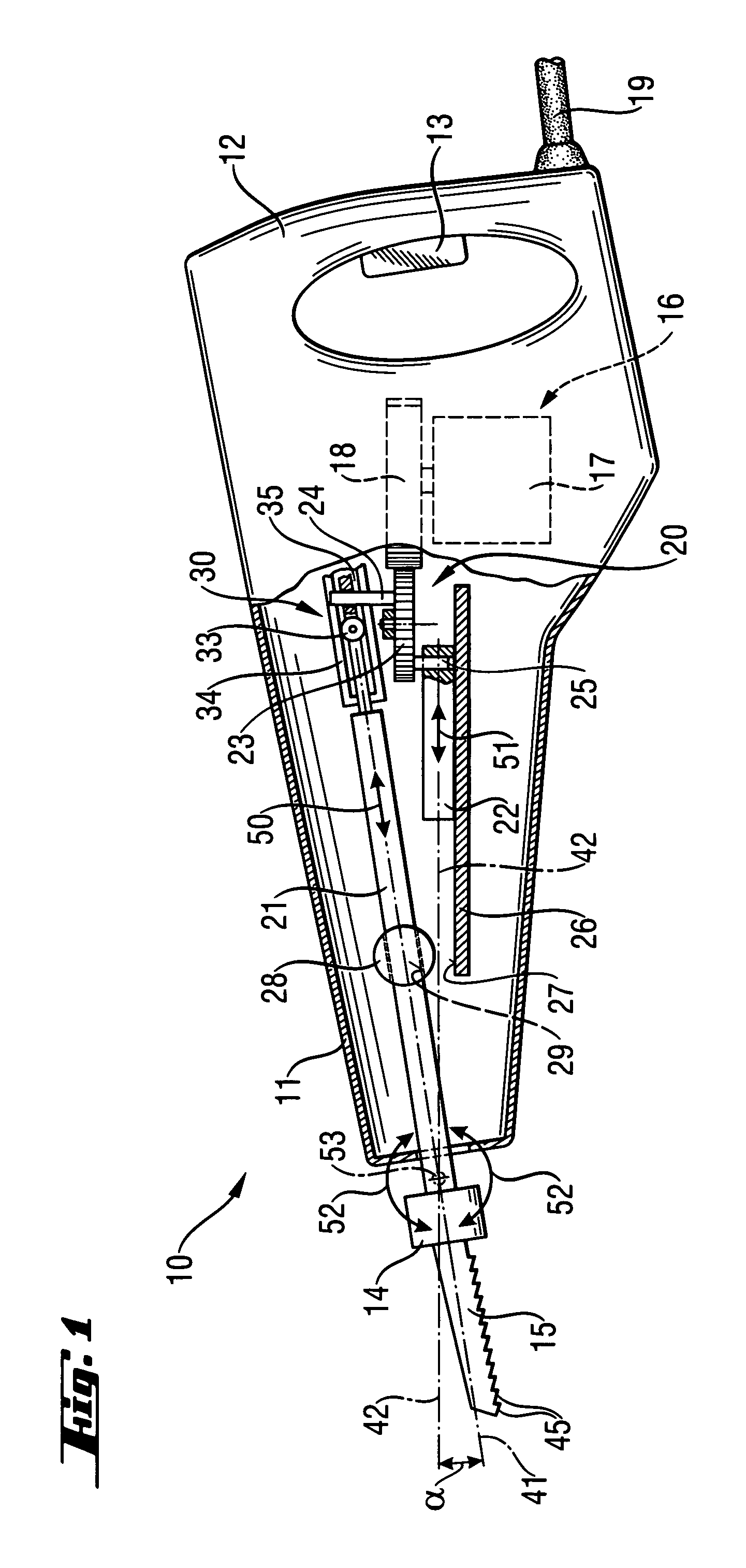

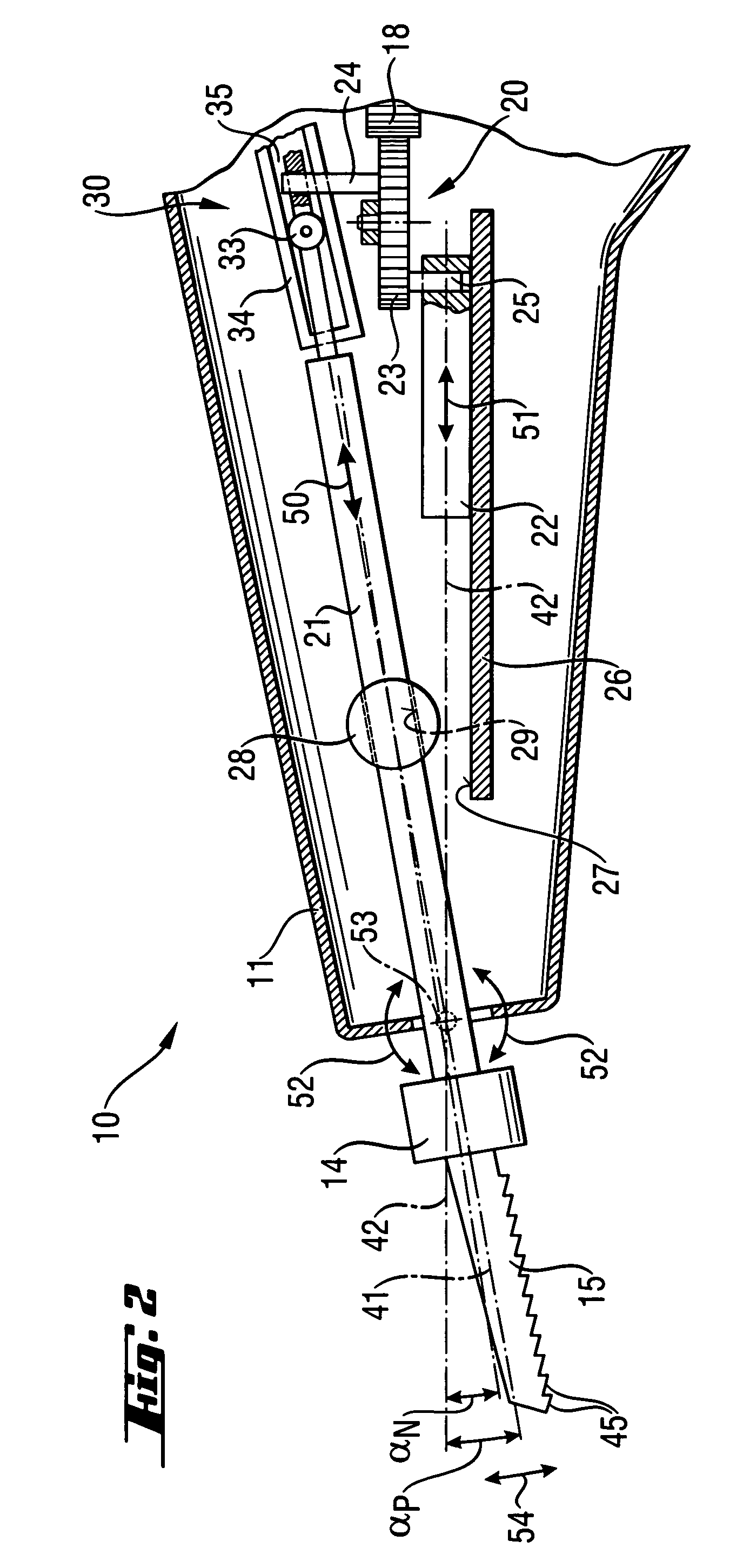

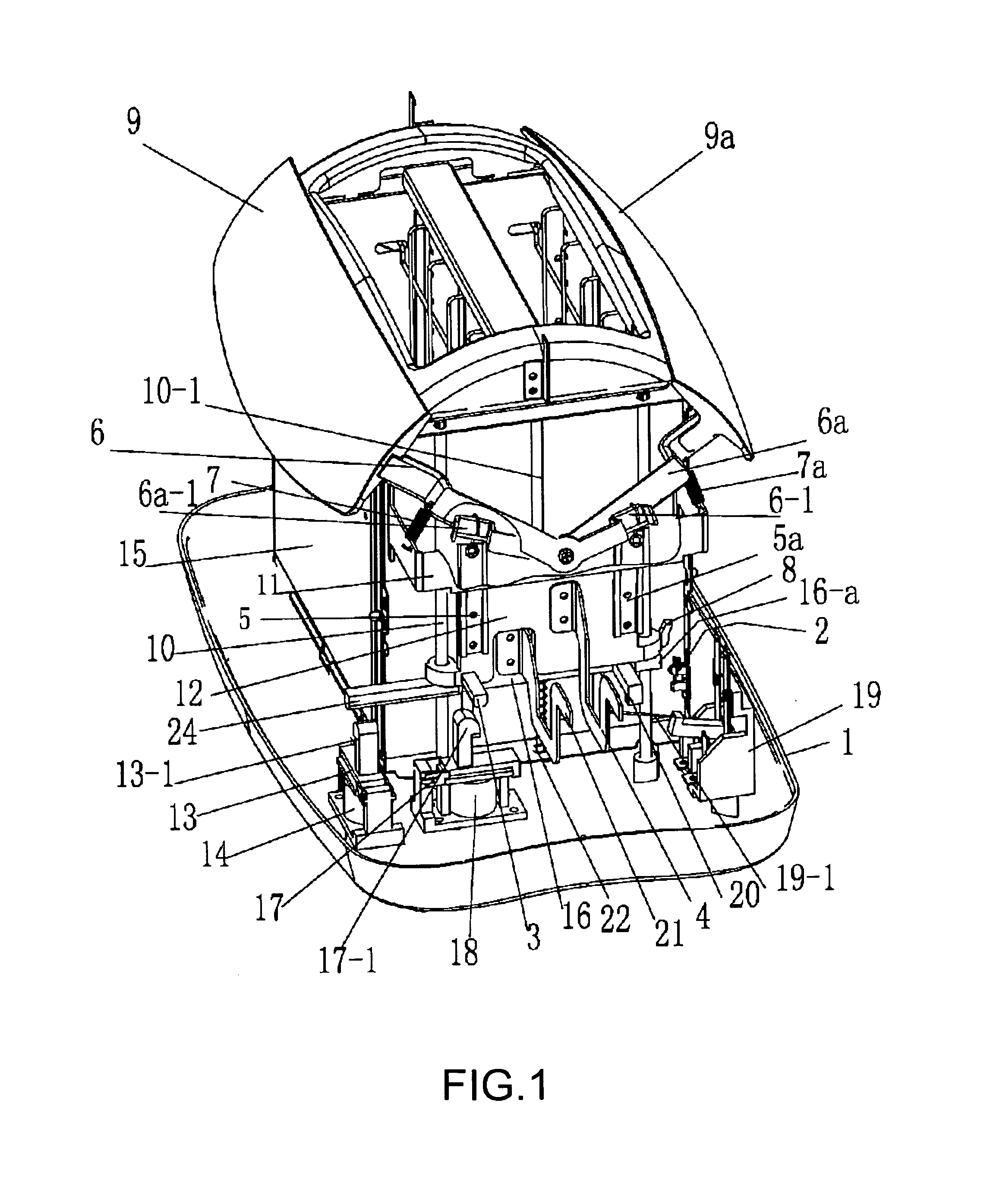

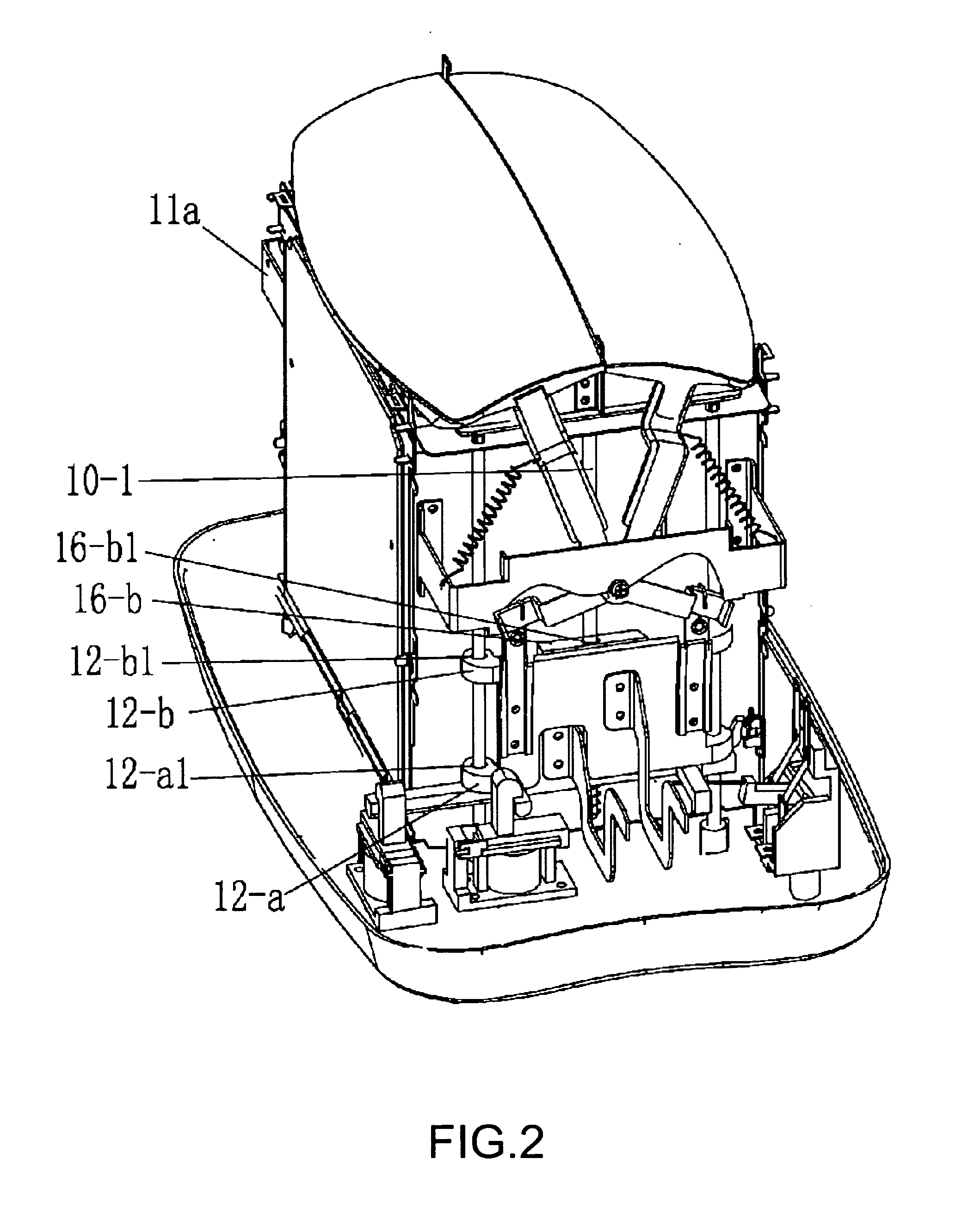

Saber saw tool

ActiveUS20050262708A1Minimize influenceOptimal performanceMetal sawing devicesCross-cut reciprocating sawsEngineeringMotor drive

The present invention relates to a reciprocating saw tool (10) having a motor drive (17) with a reciprocating driver (21) for a tool (15) and having a mass equilibrating body (22). In addition, a device (20) is provided, which serves to convert a rotary movement of the motor drive (17) into a reciprocating movement of the reciprocating driver (21) along a first movement axis (41) and an opposite reciprocating movement of the mass equilibrating body (22) along a second movement axis (42). For improving the sawing performance, the mass equilibrating body (22) is guided at an angle α to the reciprocating driver (21) so that its movement axis (42) is constantly at an angle to the movement axis (41) of the reciprocating driver (21).

Owner:HILTI AG

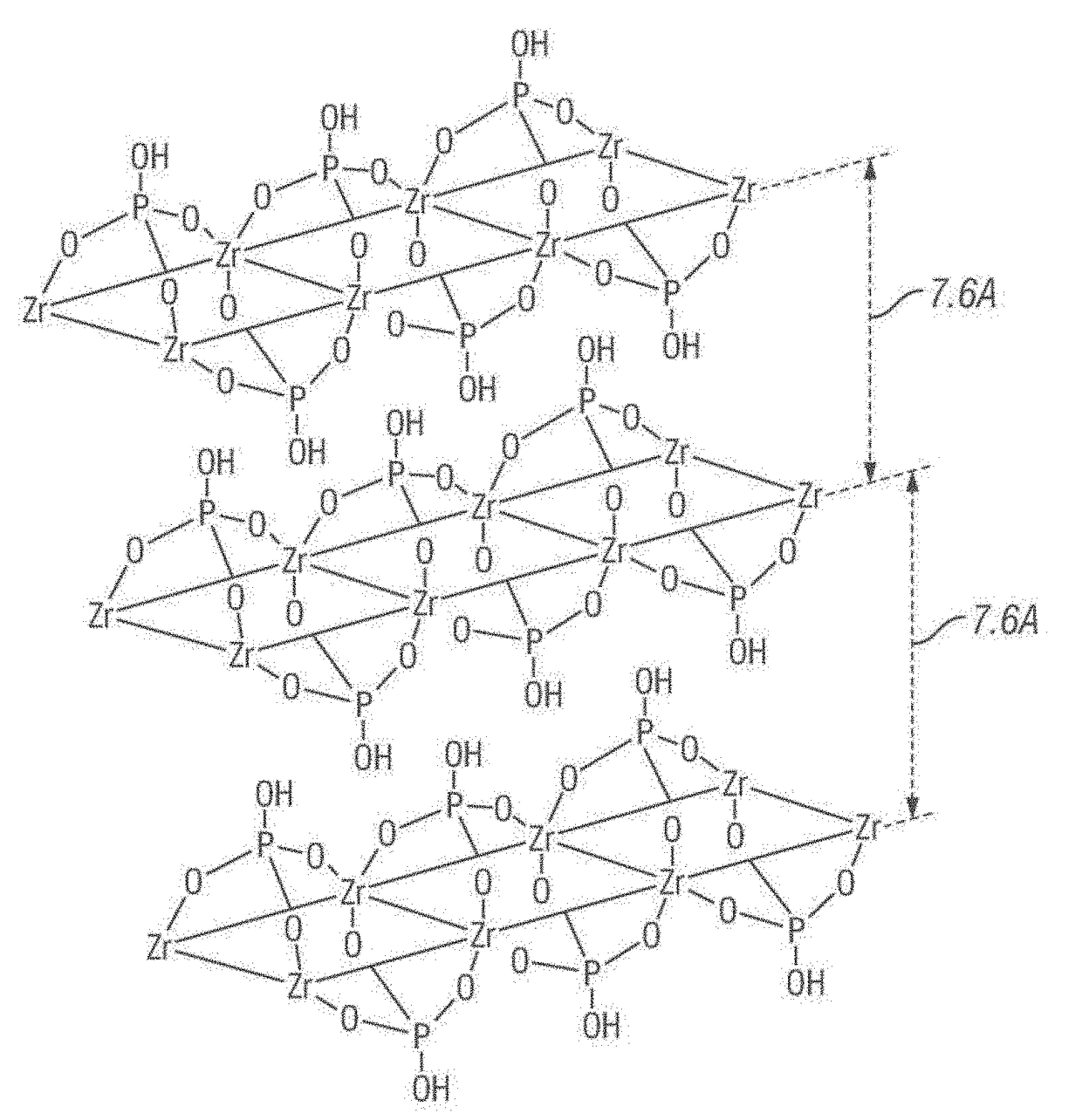

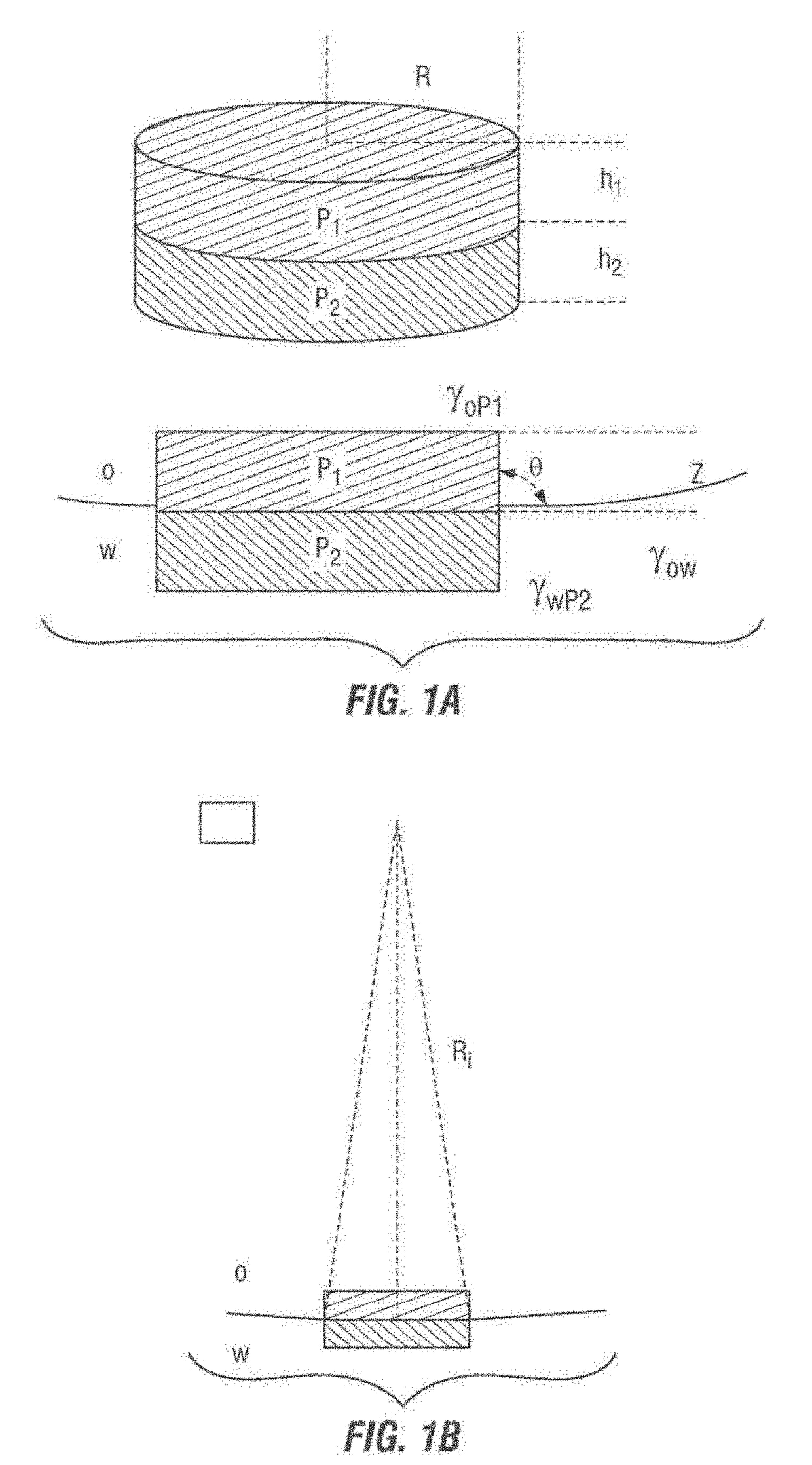

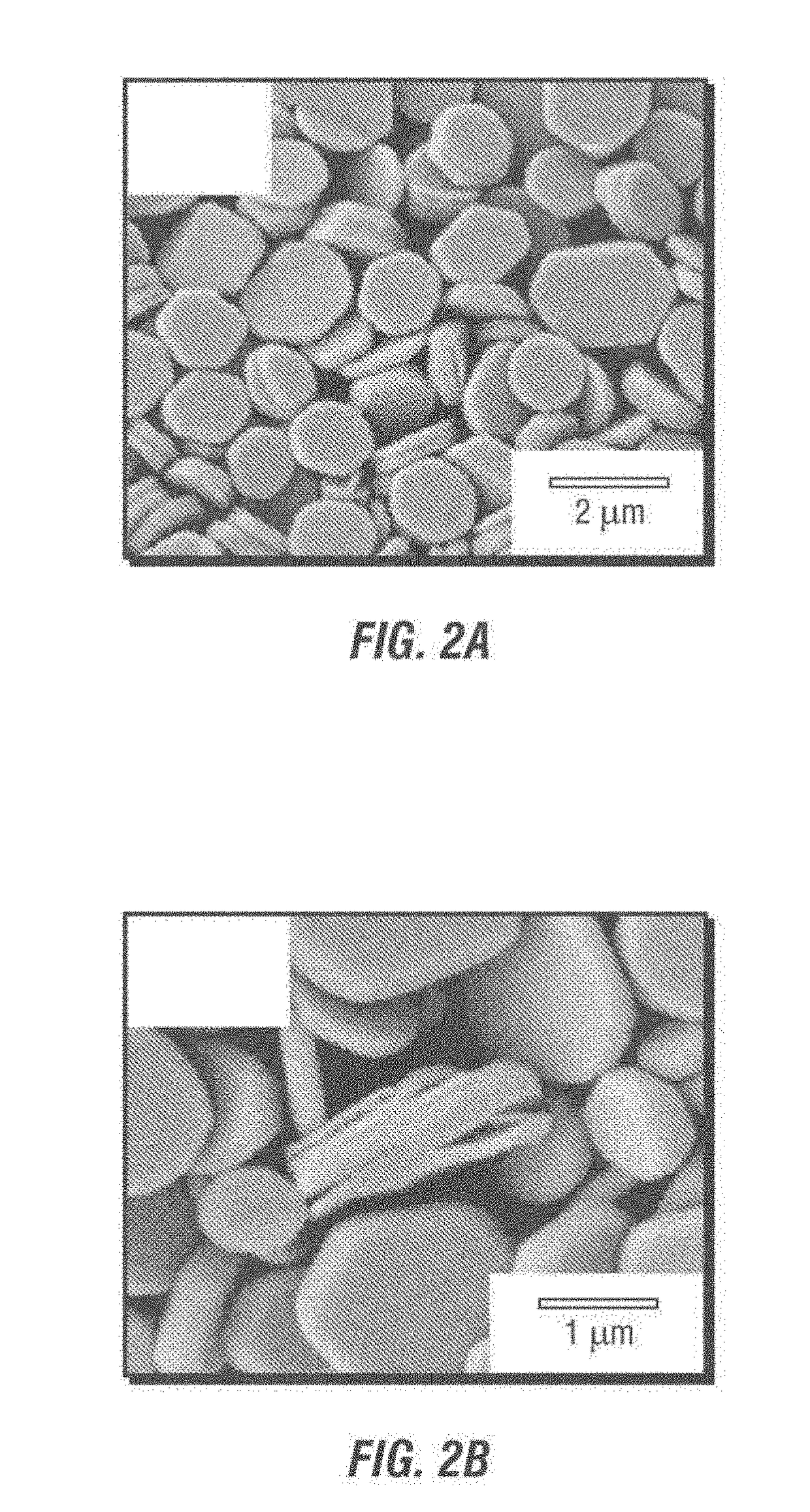

Amphiphilic nanosheets and methods of making the same

InactiveUS20170173546A1Good emulsion stabilizerOptimal performanceMaterial nanotechnologyPhosphatesZirconium phosphateLamellar crystals

In some embodiments, the present invention provides amphiphilic nanosheets that comprise lamellar crystals with at least two regions: a first hydrophilic region and a second hydrophobic region. In some embodiments, the amphiphilic nanosheets of the present invention also comprise a plurality of functional groups that are appended to the lamellar crystals. In some embodiments the functional groups are hydrophobic functional groups that are appended to the second region of the lamellar crystals. In some embodiments, the lamellar crystals comprise α-zirconium phosphates. Additional embodiments of the present invention pertain to methods of making the aforementioned amphiphilic nanosheets. Such methods generally comprise appending one or more functional groups to a stack of lamellar crystals; and exfoliating the stack of lamellar crystals for form the amphiphilic nanosheets.

Owner:TEXAS A&M UNIVERSITY

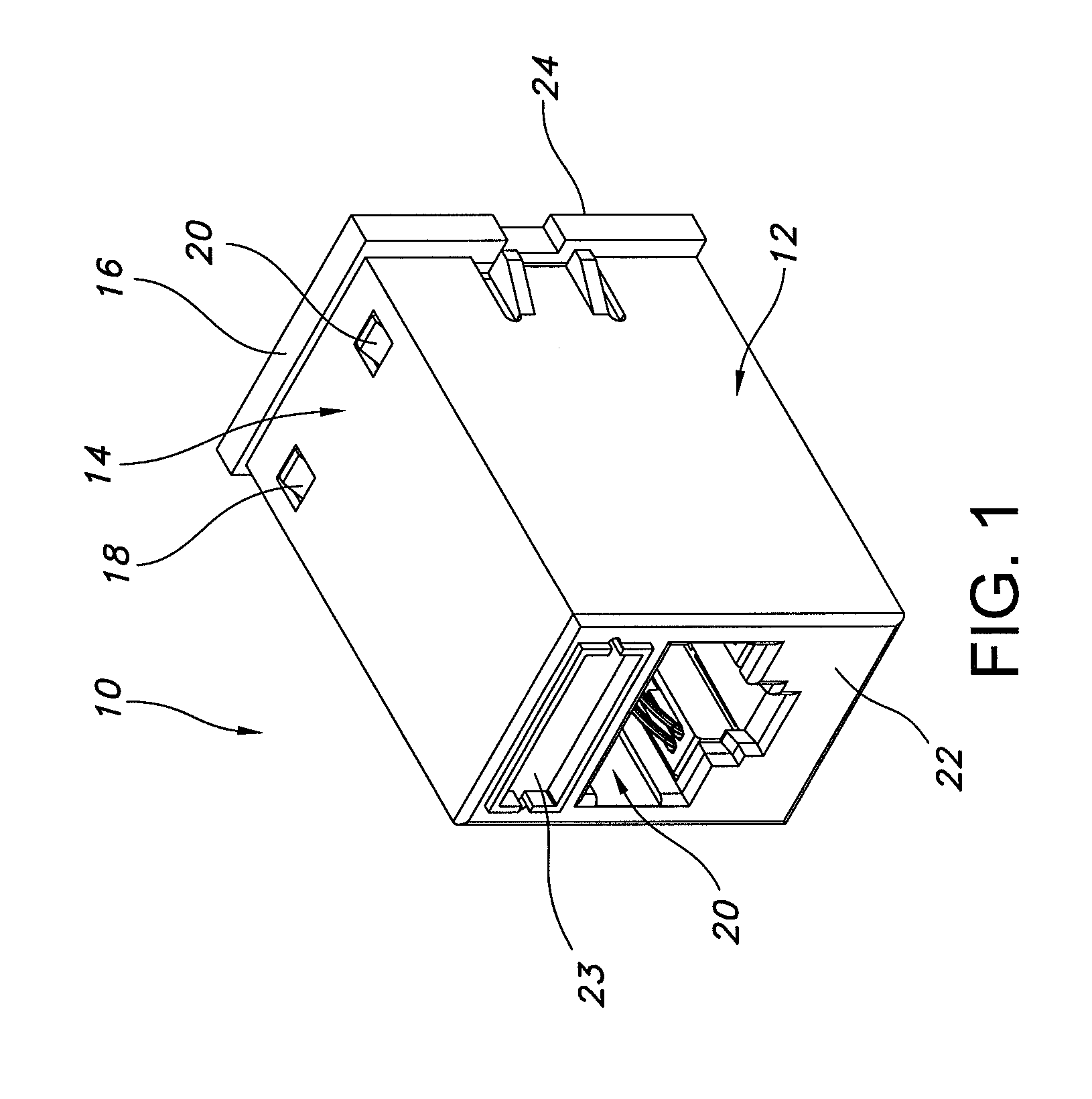

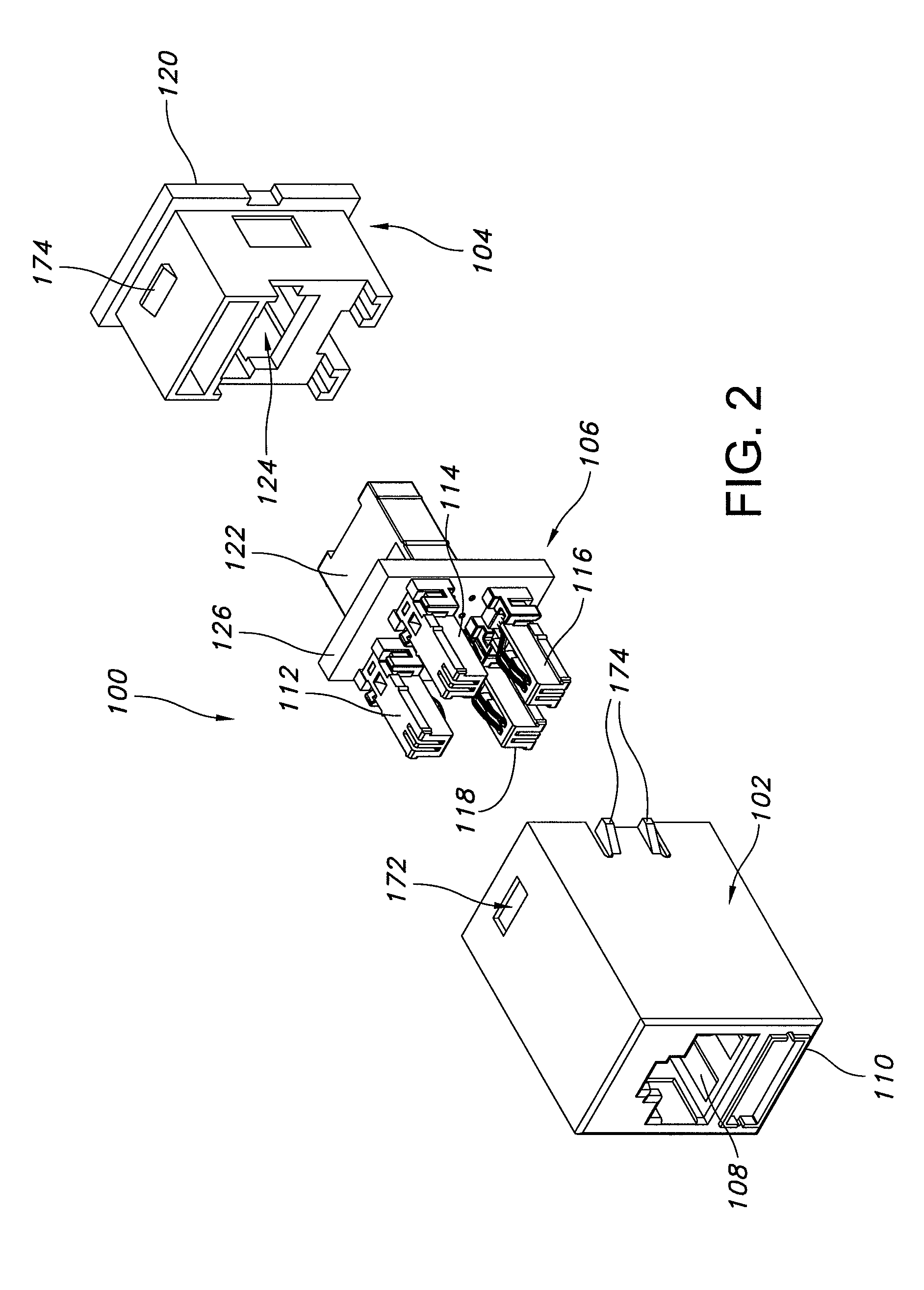

Connector Assembly And Related Methods of Use

ActiveUS20100173528A1Optimal performanceFacilitate interactionElectrically conductive connectionsElectric discharge tubesTwisted pairElectrical contacts

Connector assemblies for use in wiring / cabling applications are disclosed. The connector assemblies include first and second jack openings that facilitate interaction between plugs that feature contact layouts according to the IEC 60603-7-7 standard. Cable / plug combinations are also provided wherein the cable features shielded twisted pair (STP) fully shielded twisted pair (FTP) and unshielded twisted pair (UTP) wires. The cable / plug interface includes a housing wherein individual wires are brought into electrical communication with electrical contacts that are exposed relative to the exterior of the housing. The electrical contacts are positioned in quadrants of the plug housing, when viewed in cross-section, such that the plug complies with the contact geometry set forth in the IEC 60603-7-7 standard. The cable / plug is generally a preterminated assembly, whereby the plug is pre-mounted to the cable before shipment to an installation location or distribution channel. A pulling eye assembly may be provided that defines a cavity sized and configured to receive the plug housing and a portion of the cable.

Owner:ORTRONICS INC

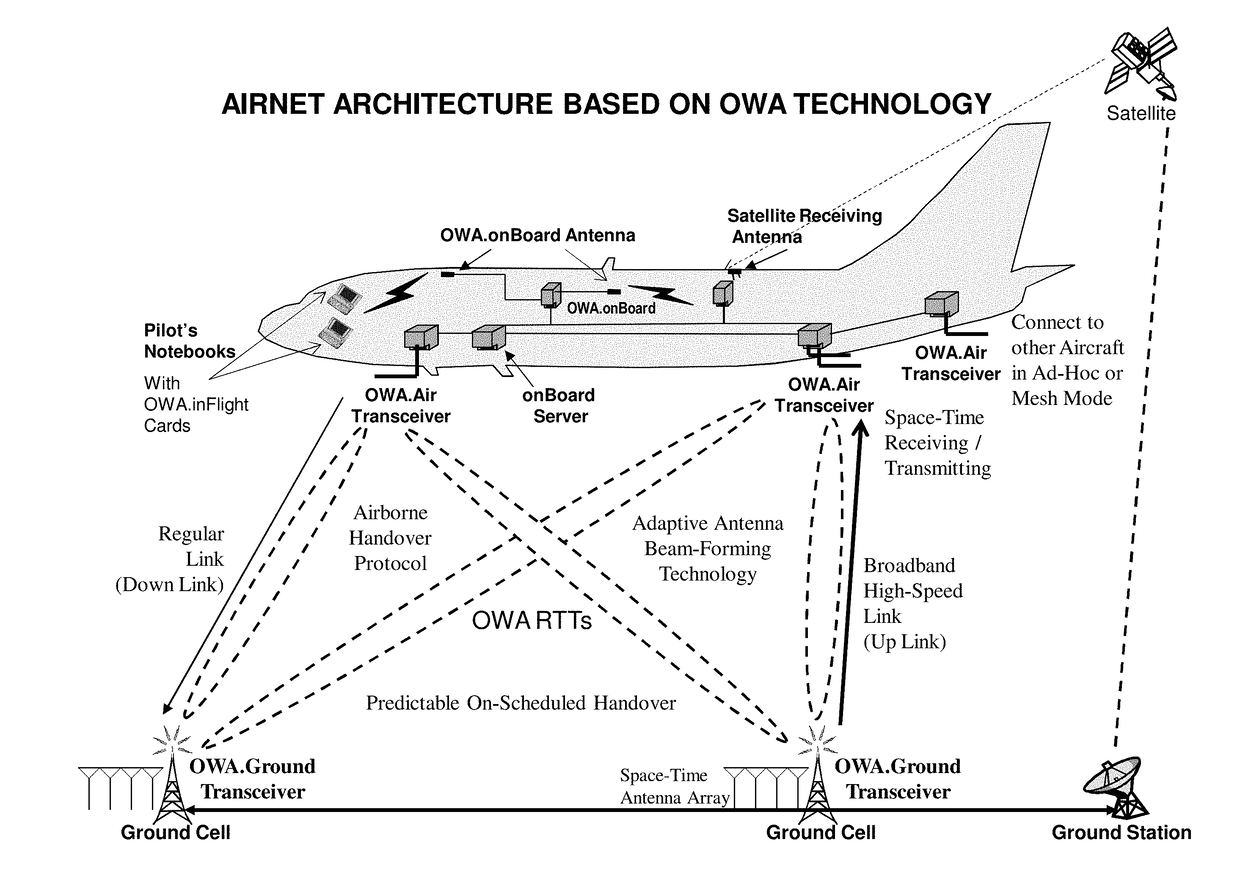

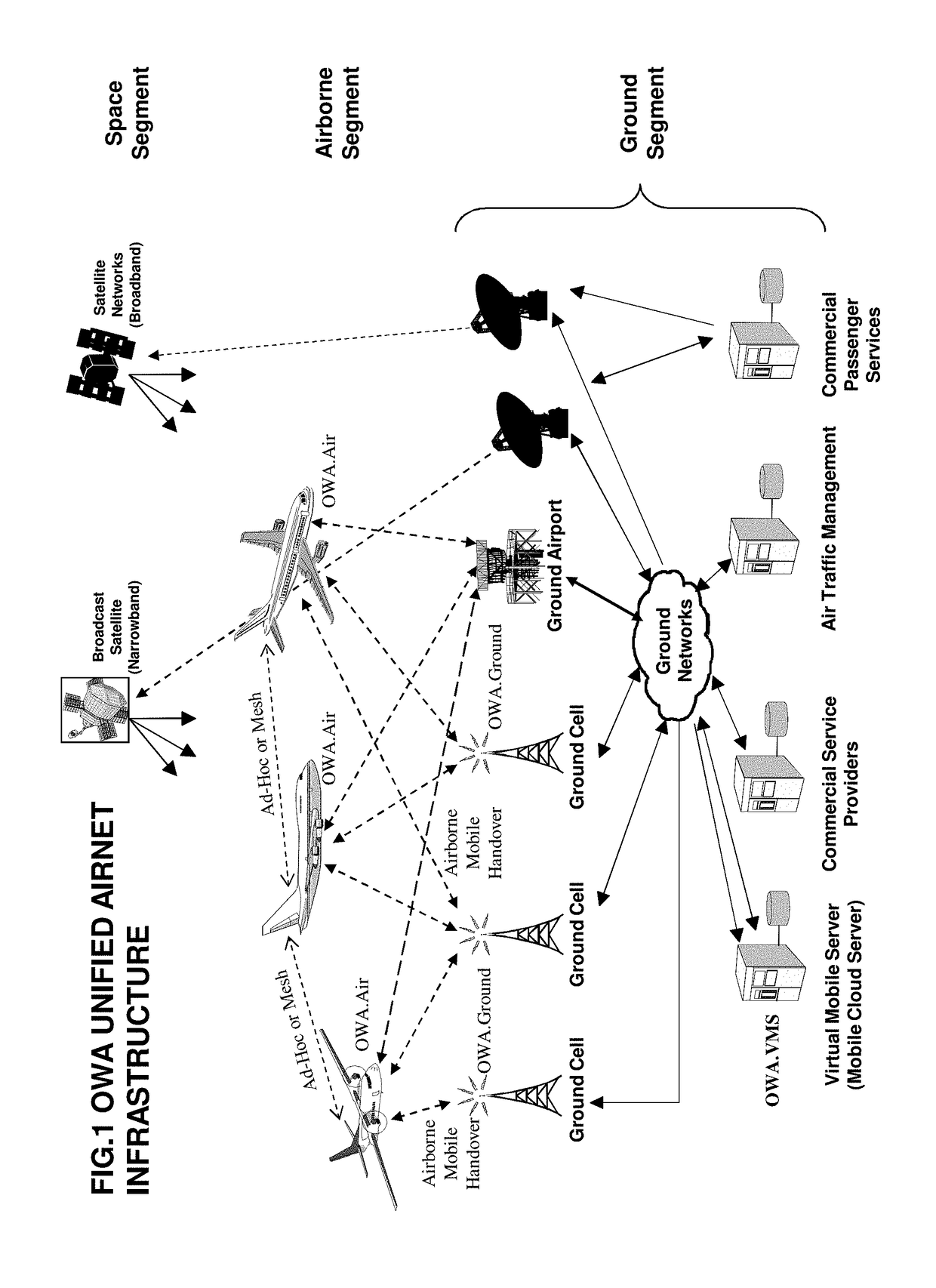

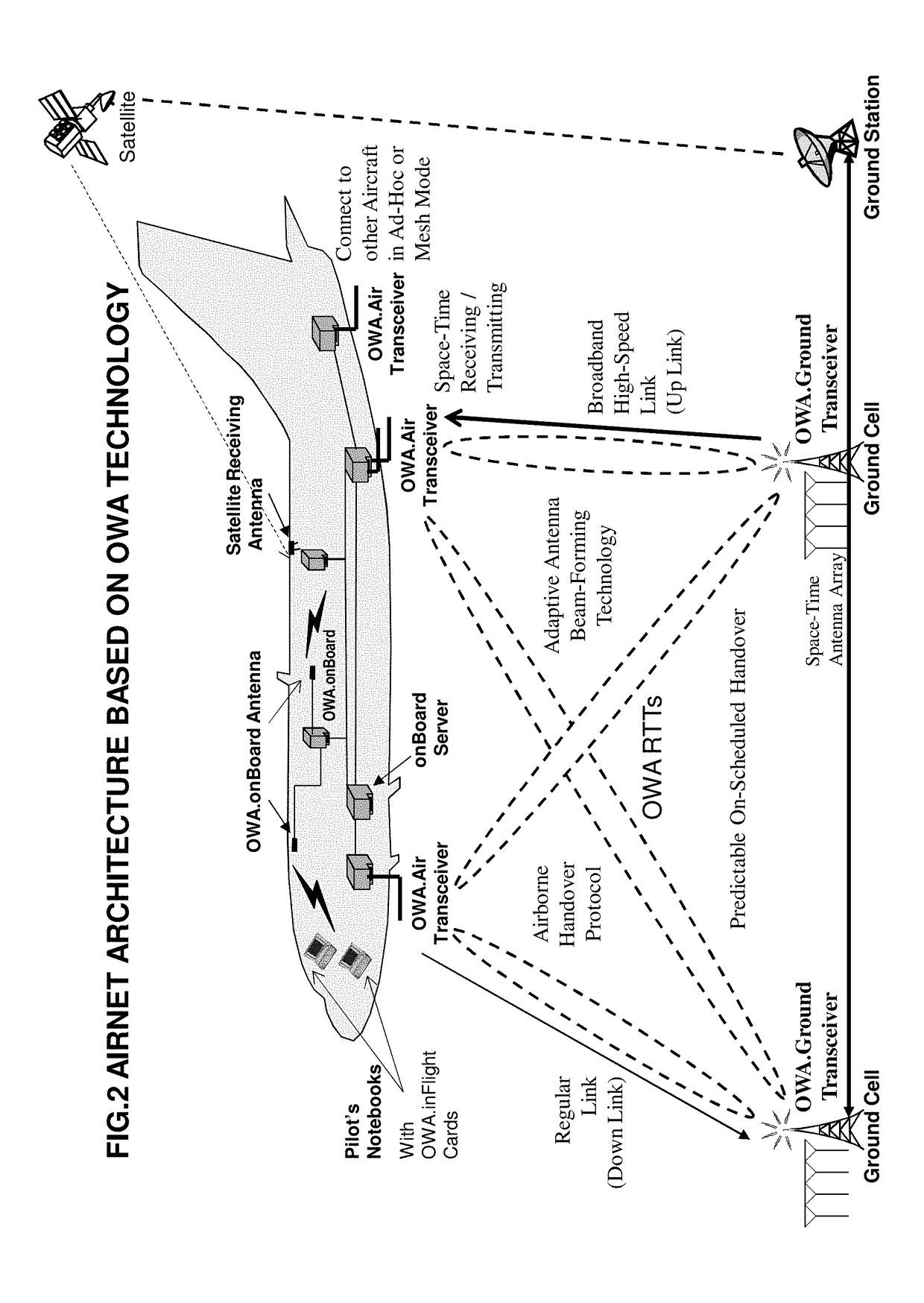

Open wireless architecture (OWA) unified airborne and terrestrial communications architecture

ActiveUS20180241463A1Current be improveOptimal performanceNetwork topologiesRadio transmissionAirplaneMultiple dimension

Owner:LU WEI +1

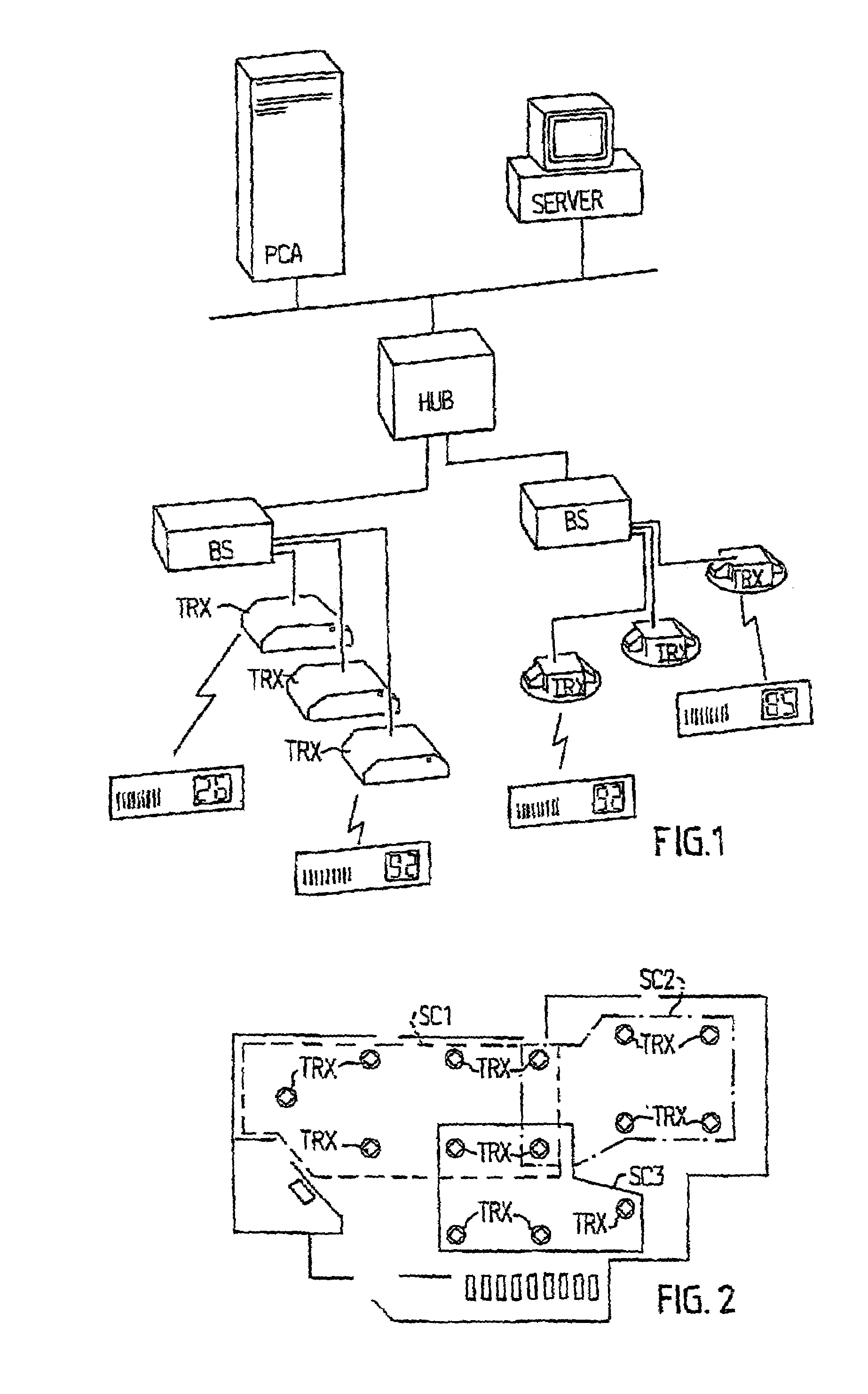

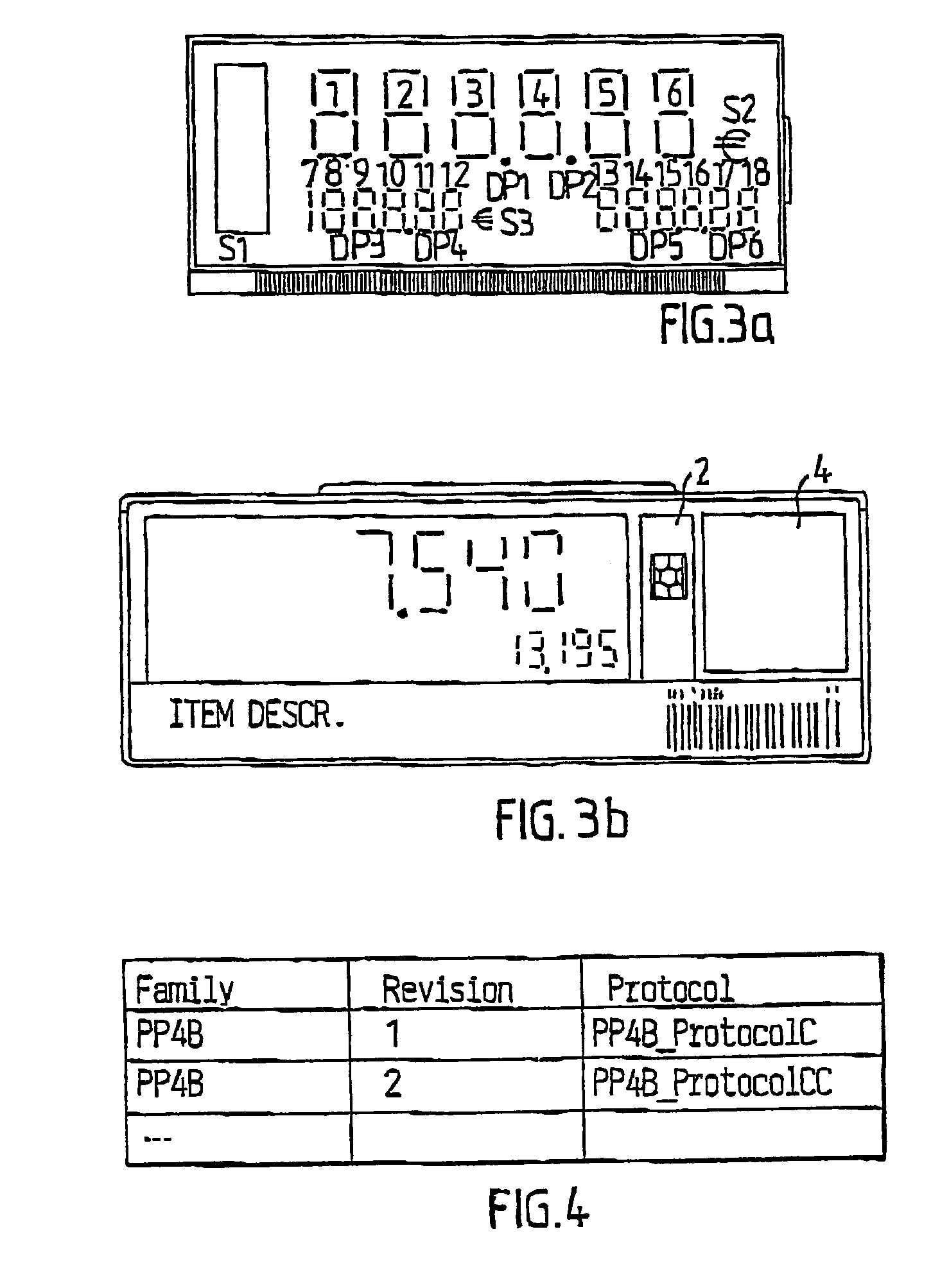

Price label communication system

InactiveUS7005962B2Optimal performanceImprove performanceElectric signal transmission systemsDigital data processing detailsSystem serviceTransceiver

Price label system comprising a price label system server connected to transceivers adapted to communicate price label information to price labels using a communication protocol. A predetermined number of transceivers defines a sub-cell and each sub-cell is associated with a communication profile that defines communication protocols to be used when communicating with the price labels in that sub-cell.

Owner:PRICER NORDEN AB

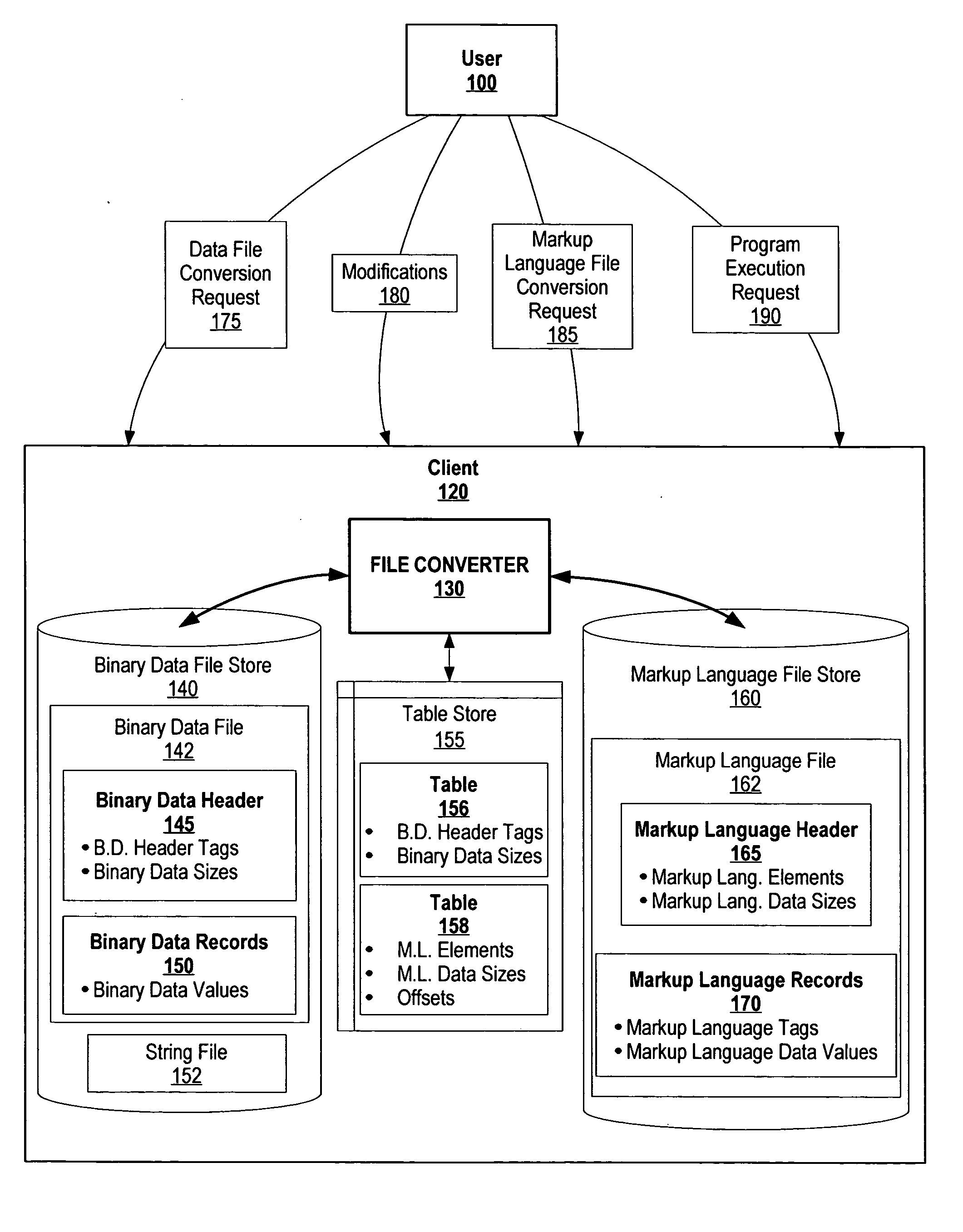

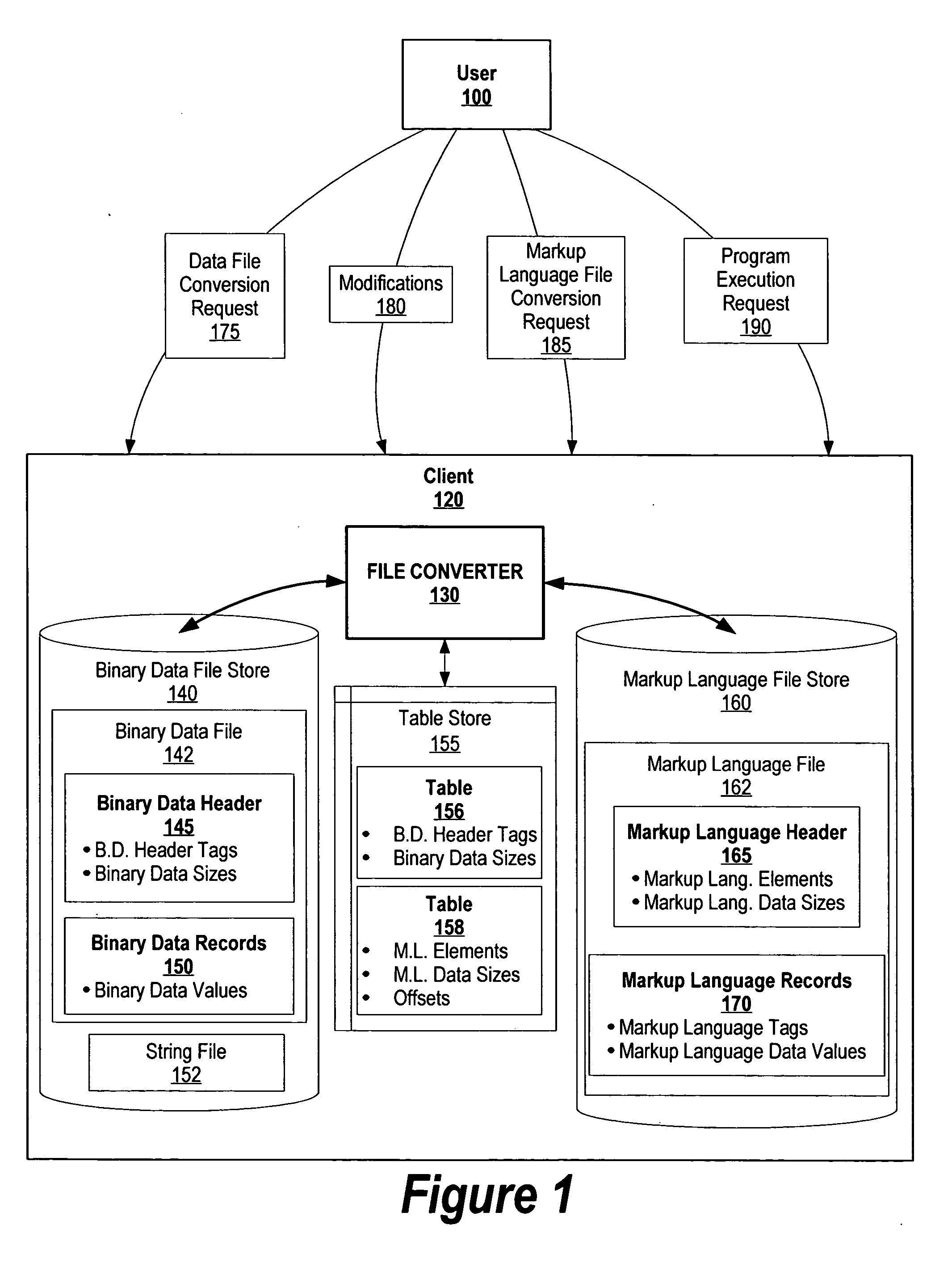

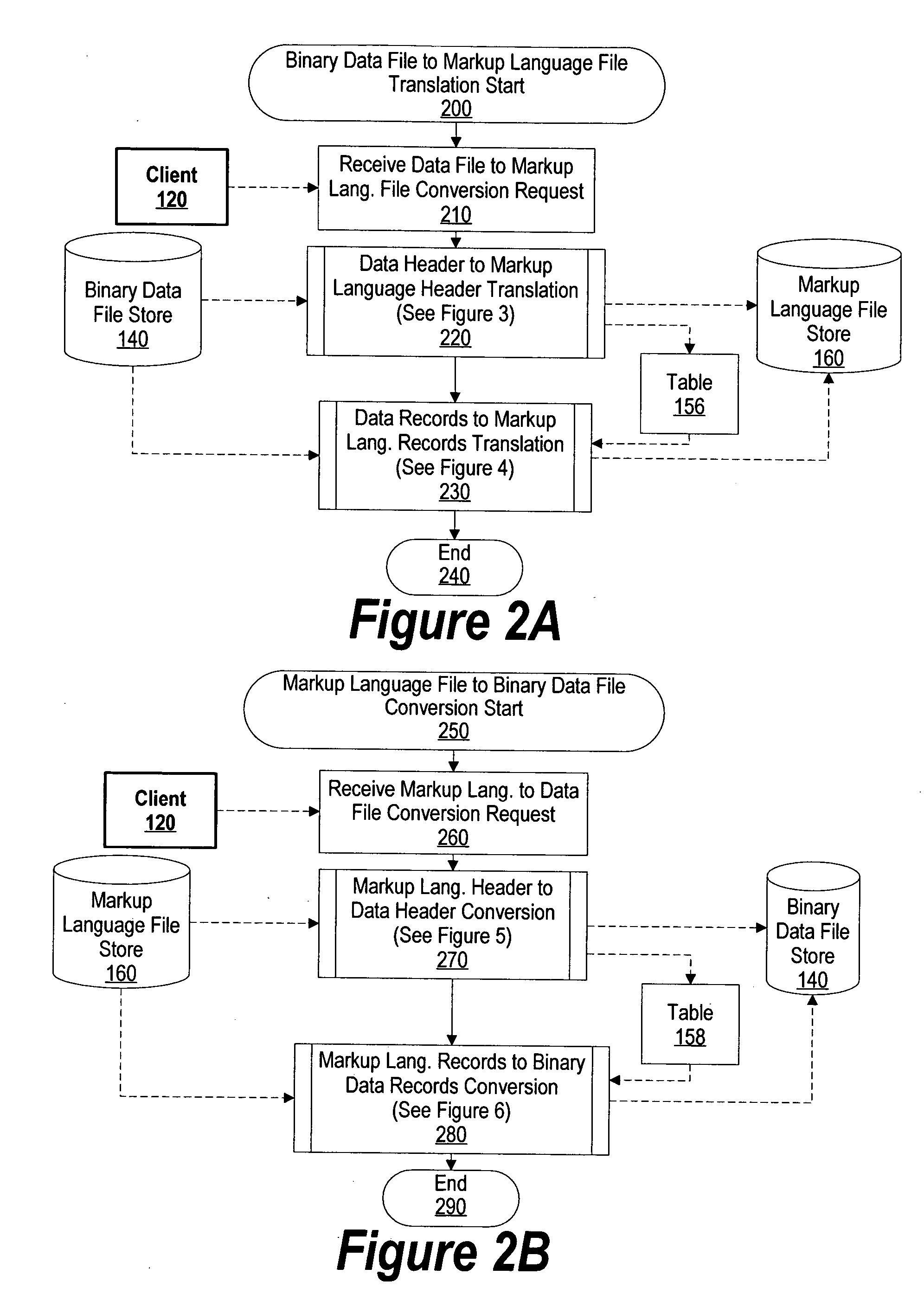

System and method for high performance pre-parsed markup language

InactiveUS20060230339A1Optimal performanceNatural language data processingSpecial data processing applicationsData fileData records

A system and method for high performance pre-parsed markup language is presented. A file converter performs translation between a binary data file and a markup language file. When translating a binary data file, the file converter translates binary data header tags and binary data sizes to markup language elements and markup language data sizes, respectively, and stores them in a markup language header. The file converter then translates the binary data file's records to markup language records. When a user is finished modifying the markup language file, the file converter translates the markup language file back to a binary data file by translating the markup language header tags and markup language data sizes to binary data header tags and binary data sizes, respectively, and stores them in a binary data header. The file converter then translates the markup language file's records to binary data records.

Owner:IBM CORP

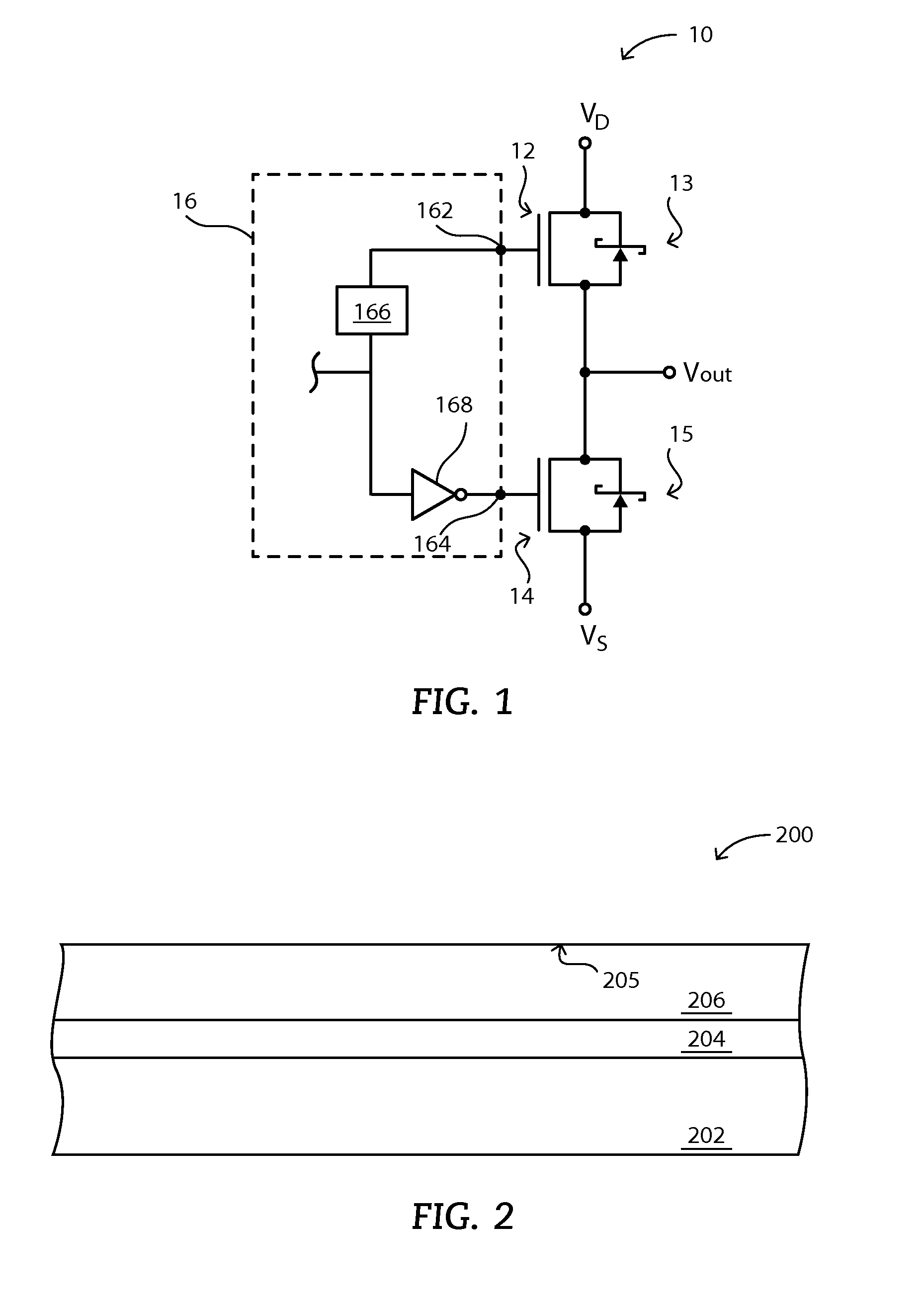

Electronic Device Including a Schottky Contact

ActiveUS20140252484A1Reduce the possibilityOptimal performanceSemiconductor/solid-state device detailsSolid-state devicesVoltage regulatorMetal

An electronic device can include a semiconductor layer having a primary surface, and a Schottky contact comprising a metal-containing member in contact with a horizontally-oriented lightly doped region within the semiconductor layer and lying adjacent to the primary surface. In an embodiment, the metal-containing member lies within a recess in the semiconductor layer and contacts the horizontally-oriented lightly doped region along a sidewall of the recess. In other embodiment, the Schottky contact may not be formed within a recess, and a doped region may be formed within the semiconductor layer under the horizontally-oriented lightly doped region and have a conductivity type opposite the horizontally-oriented lightly doped region. The Schottky contacts can be used in conjunction with power transistors in a switching circuit, such as a high-frequency voltage regulator.

Owner:SEMICON COMPONENTS IND LLC

Bread-toaster

InactiveUS20110185918A1Great convenienceOptimal performanceDomestic stoves or rangesElectrical heating fuelEngineeringMechanical engineering

Owner:SHENZHEN CRASTAL TECH CO LTD

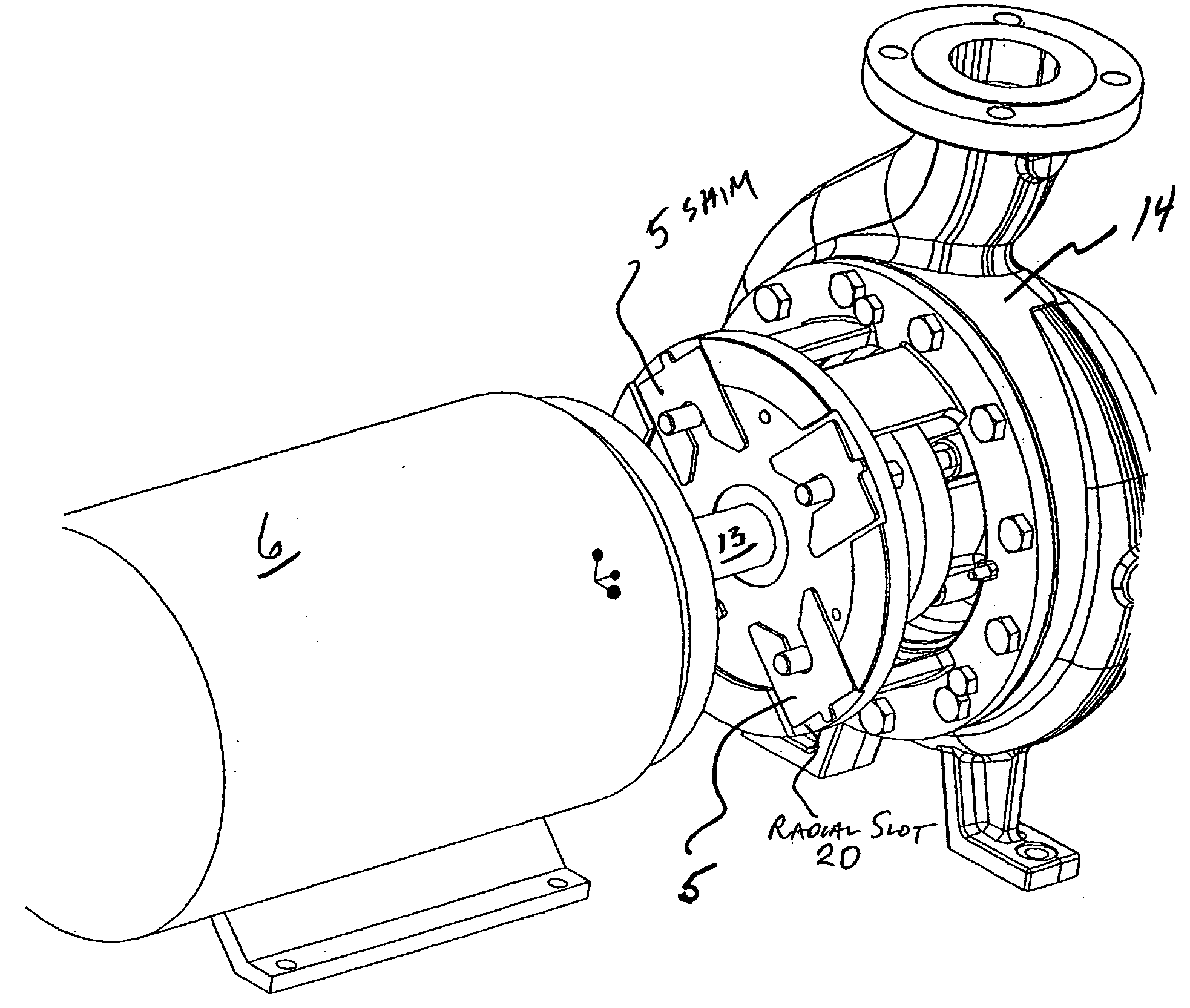

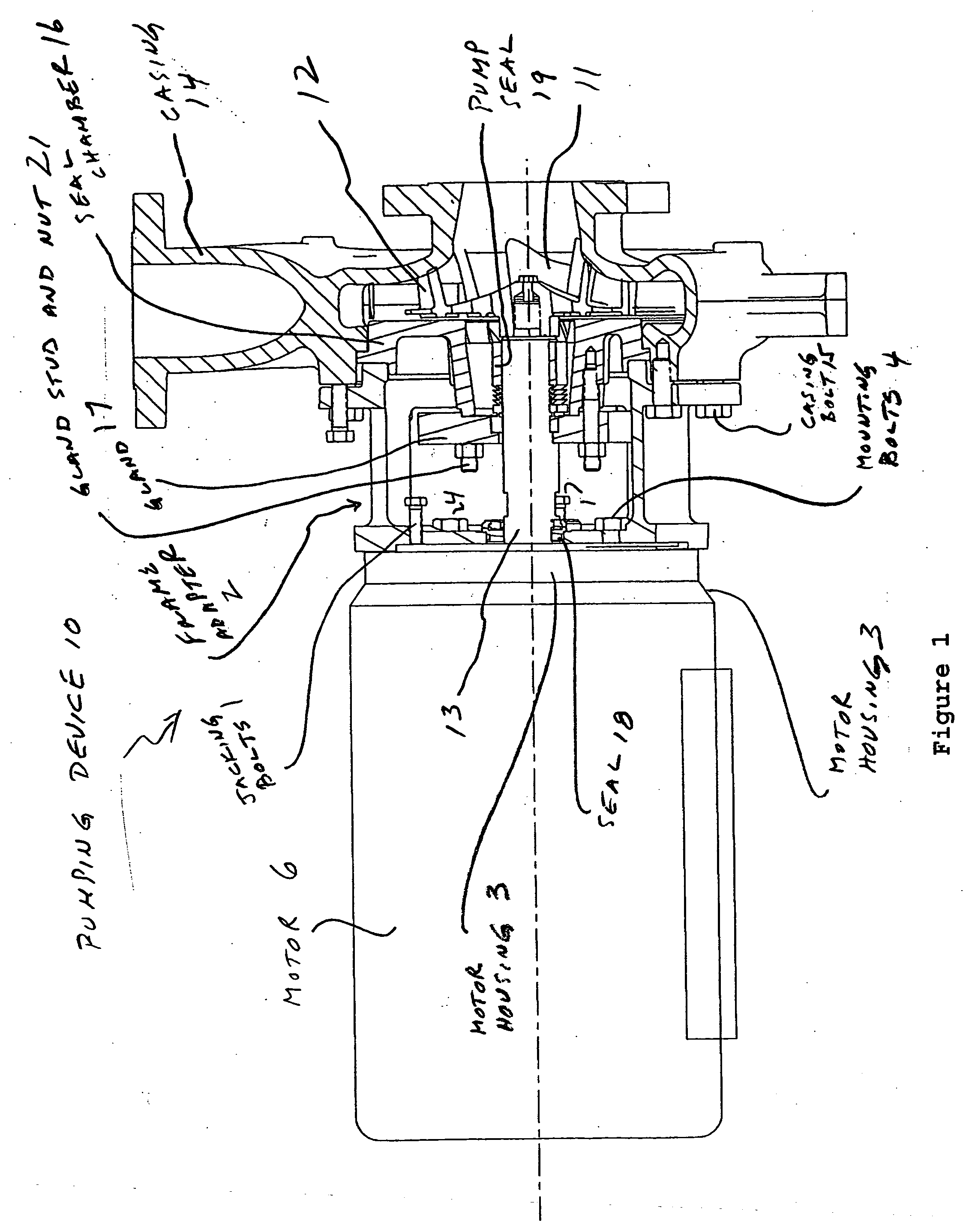

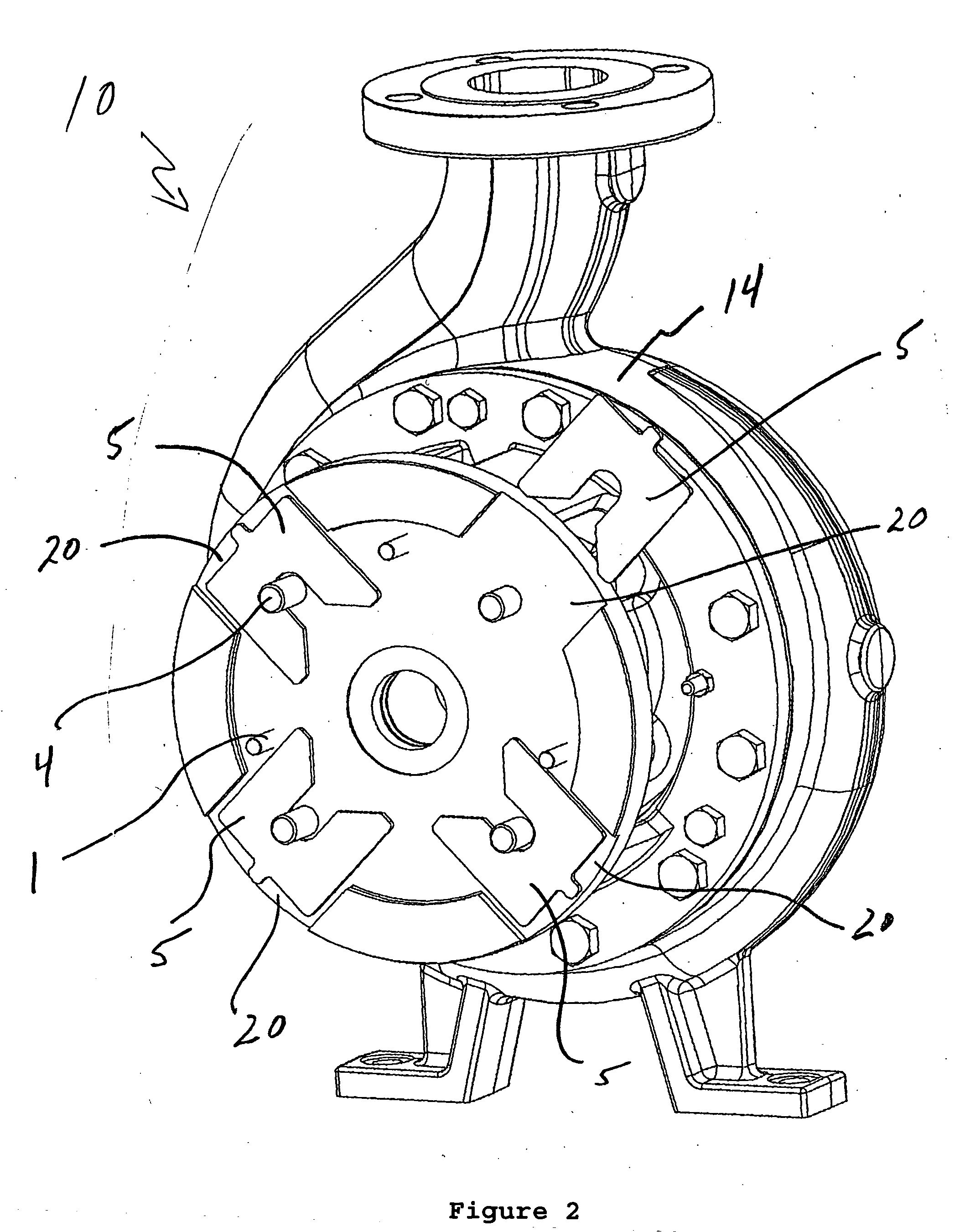

Impeller adjustment device and method for doing the same for close coupled pumps

ActiveUS20050169783A1Low operating costOptimal performancePump componentsBlade accessoriesImpellerEngineering

A method and apparatus are provided for adjusting an impeller in a motor and impeller assembly of a pumping device. The method features steps of: tightening mounting bolts so as to move the motor and impeller assembly of the pumping device forward until the impeller touches a casing; inserting a feeler gauge in radial slots in a frame adapter and measuring a gap between a housing of the motor and the frame adapter; determining a desired impeller adjustment distance based on the gap and the desired impeller running clearance; selecting at least one shim having a thickness that corresponds to the desired impeller adjustment distance; loosening the mounting bolts and threading jacking bolts arranged in the rear of the pump frame adapter so that the jacking bolts push against the housing of the motor, and the shims can then be inserted into the radial slots; inserting the shims into the radial slots; backing out the jacking bolts; and securing the mounting bolts locking the motor and impeller assembly in position so that the impeller is at the desired impeller adjustment distance in relation to the casing. The frame adapter assembly features a frame adapter having four radial slots to enable access to the gap for measurement with a feeler gauge and for insertion of the shim to accurately set the impeller clearance.

Owner:ITT MFG ENTERPRISES LLC

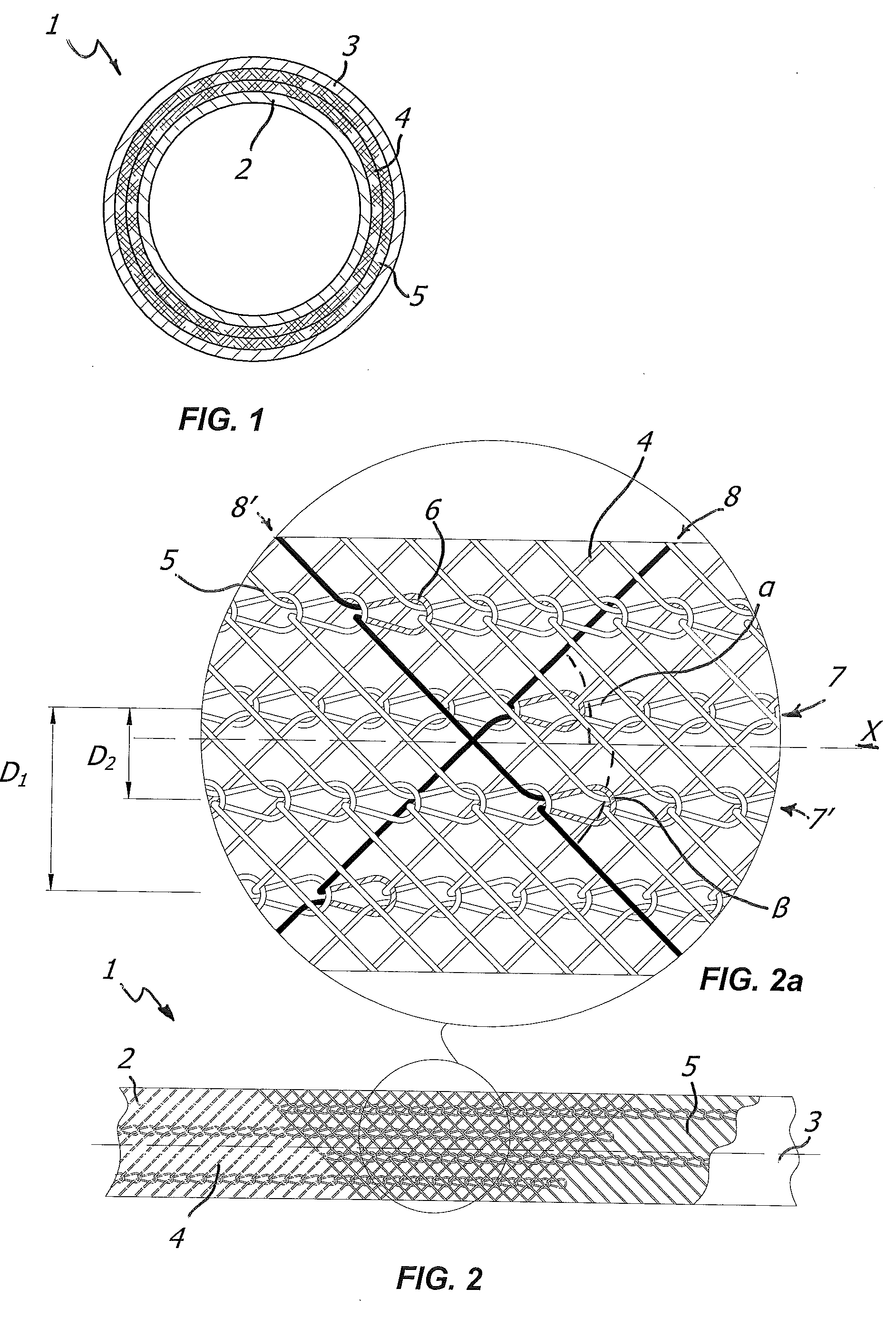

Multilayer Flexible Irrigating Hose

InactiveUS20110209791A1Simple and quick mannerOptimal performanceFlexible pipesCircular knitting machinesIrrigationEngineering

A multilayer flexible irrigation hose includes an inner layer made of a first thermoplastic polymer material, an outer layer made of a second thermoplastic polymer material, and a first textile reinforcement layer and a second textile reinforcement layer in mutually overlapping relation. The first and second textile reinforcement layers are knitted with stitches of the tricot type, having wales of stitches and lines of stitches. The lines of stitches of said first and second textile layers have opposite inclinations to the longitudinal axis of the hose, and the wales of stitches of at least one of said first and second textile layers are substantially parallel to said longitudinal axis. A method of making said hose, a line for manufacturing same and a knitting apparatus for making such hose are also disclosed.

Owner:FITT

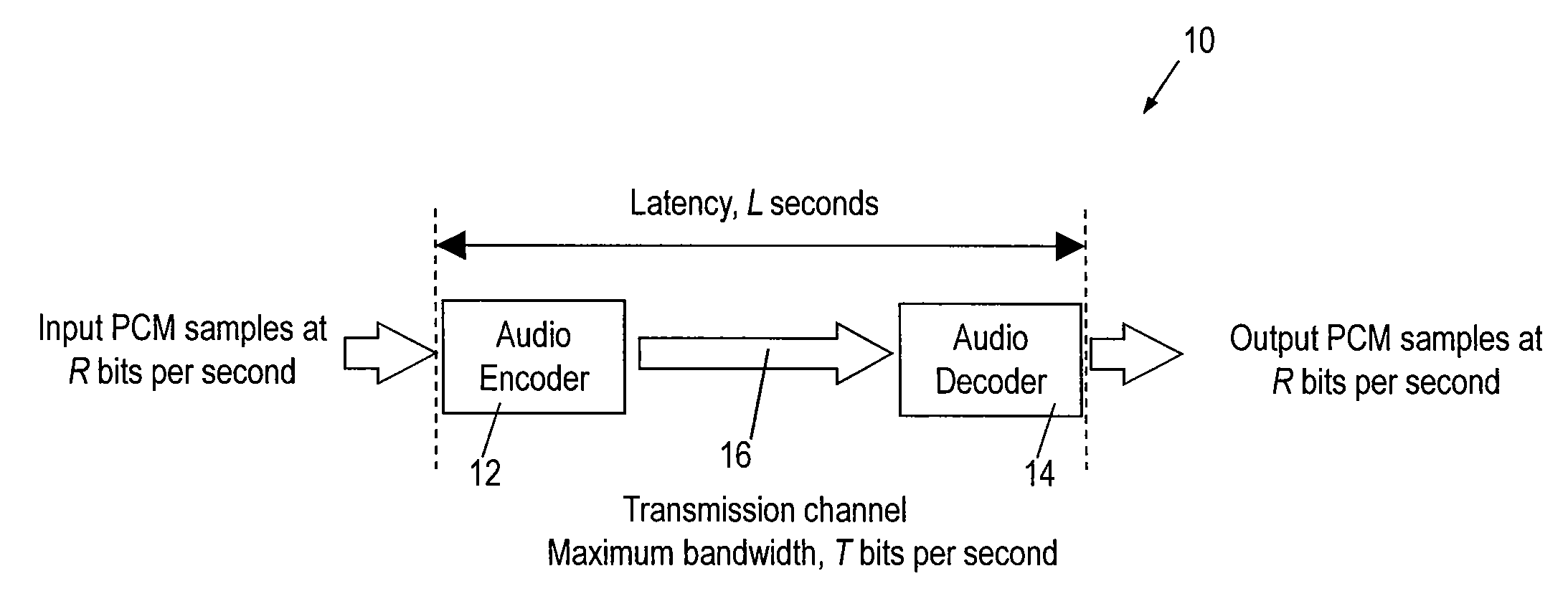

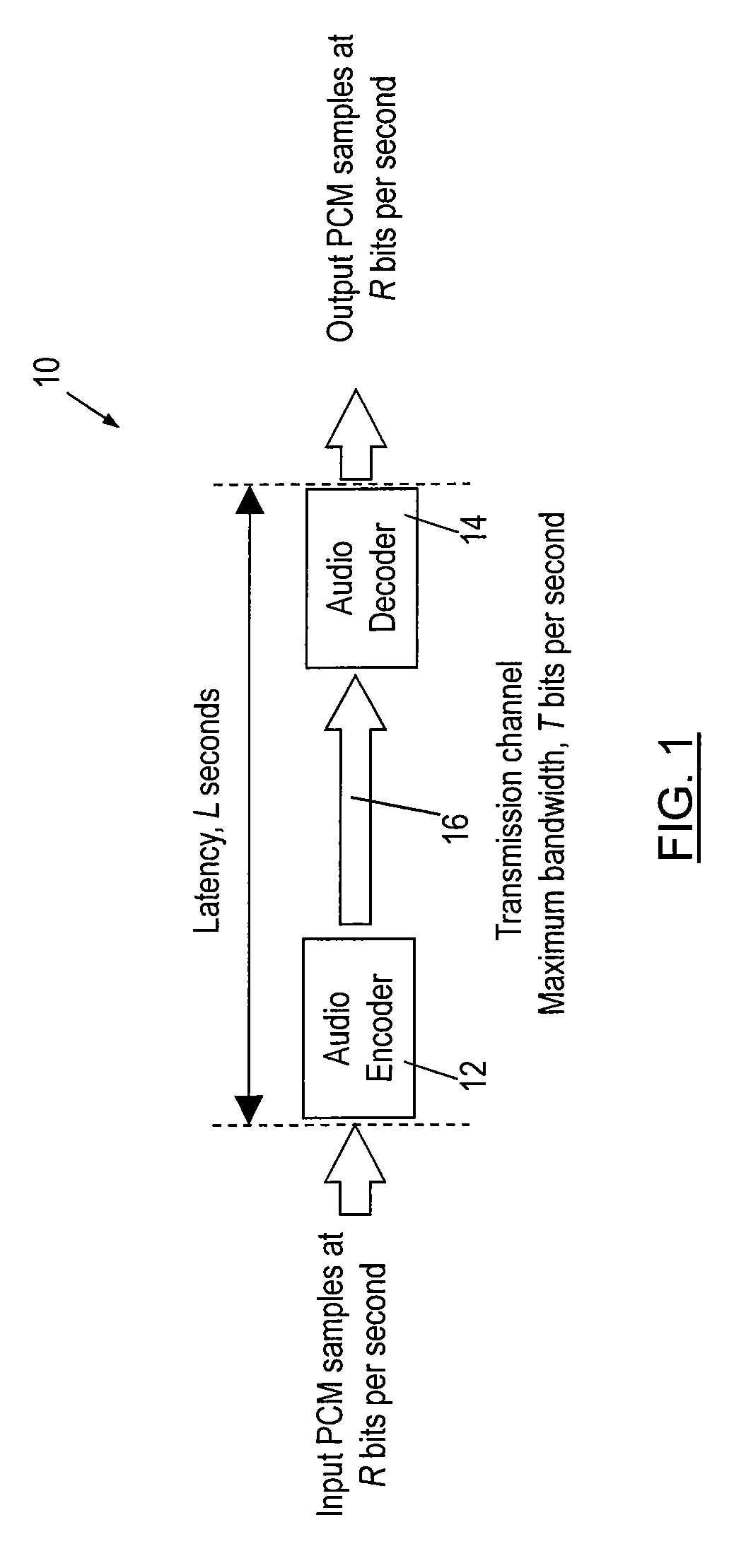

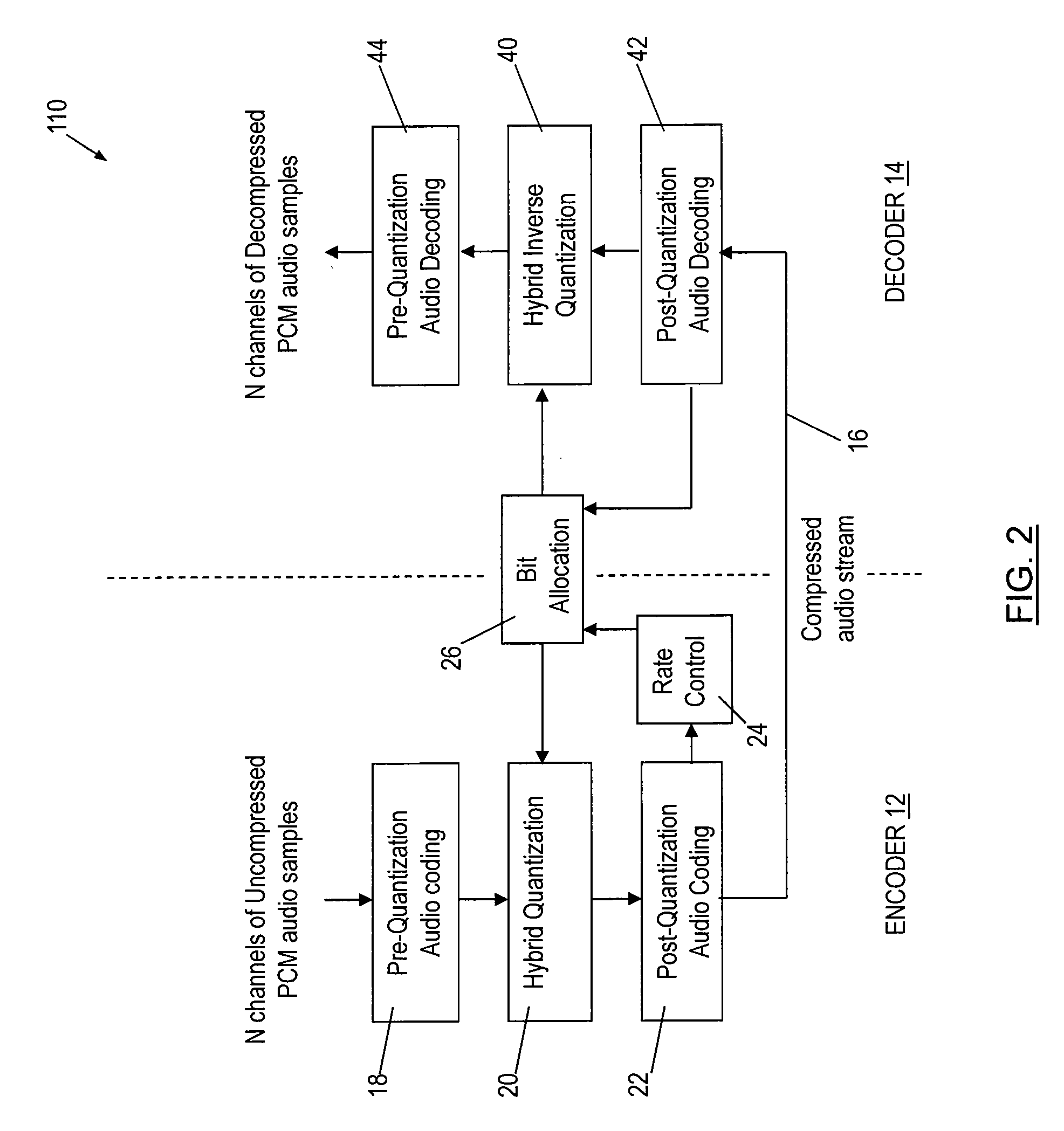

Hybrid coded audio data streaming apparatus and method

ActiveUS20120290306A1Optimal performanceImprove performanceSpeech analysisCode conversionFrame sizeVIT signals

Owner:QUALCOMM TECH INT

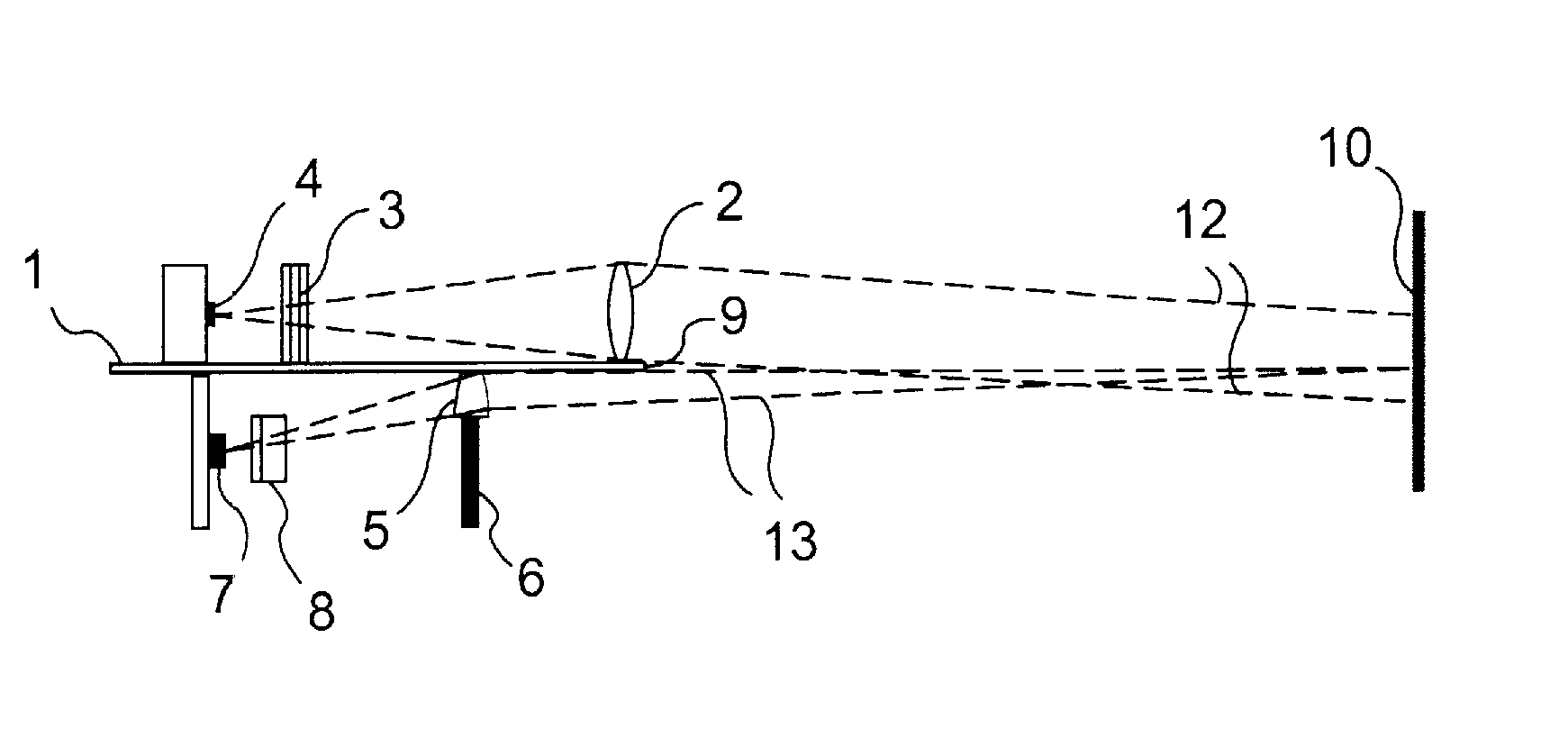

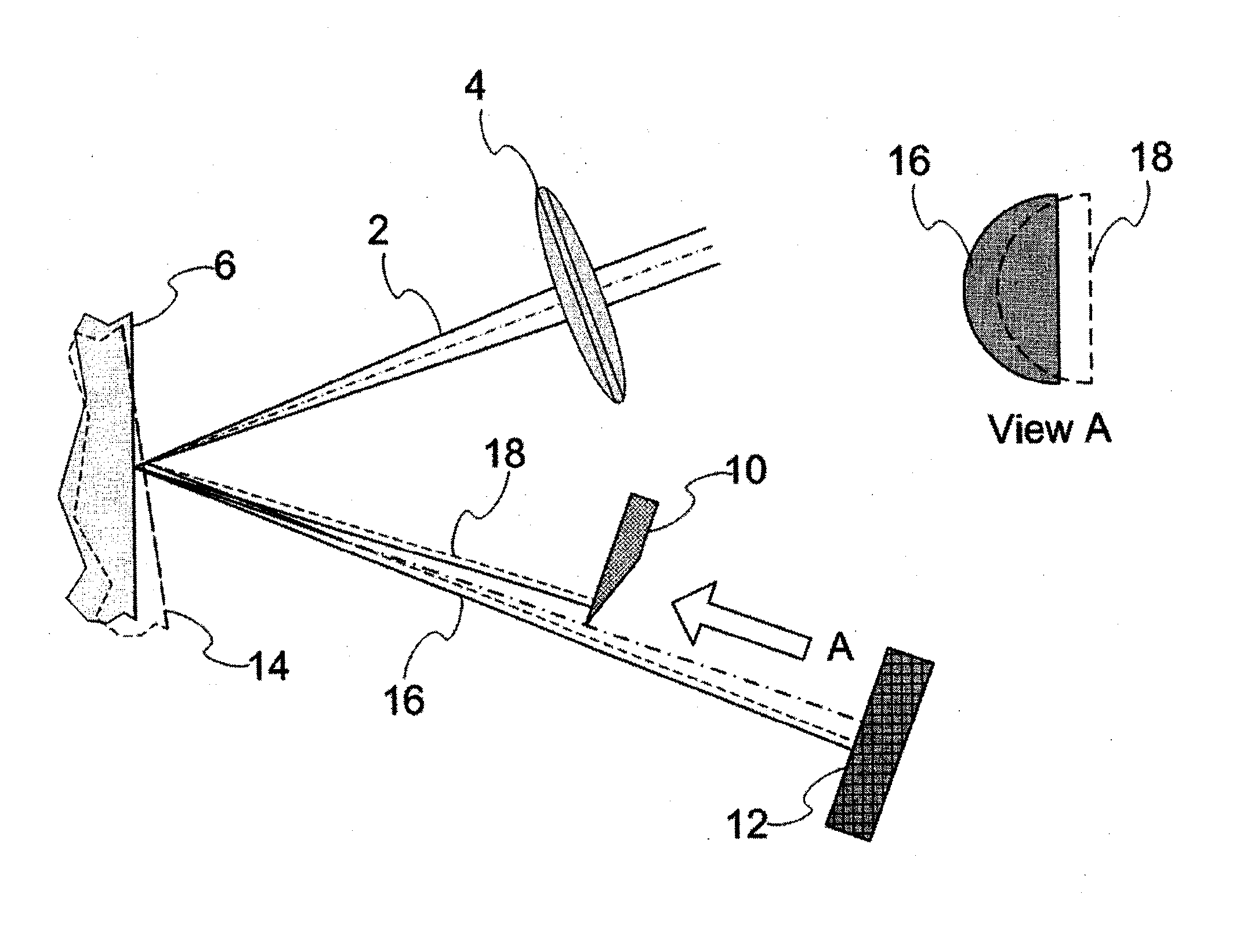

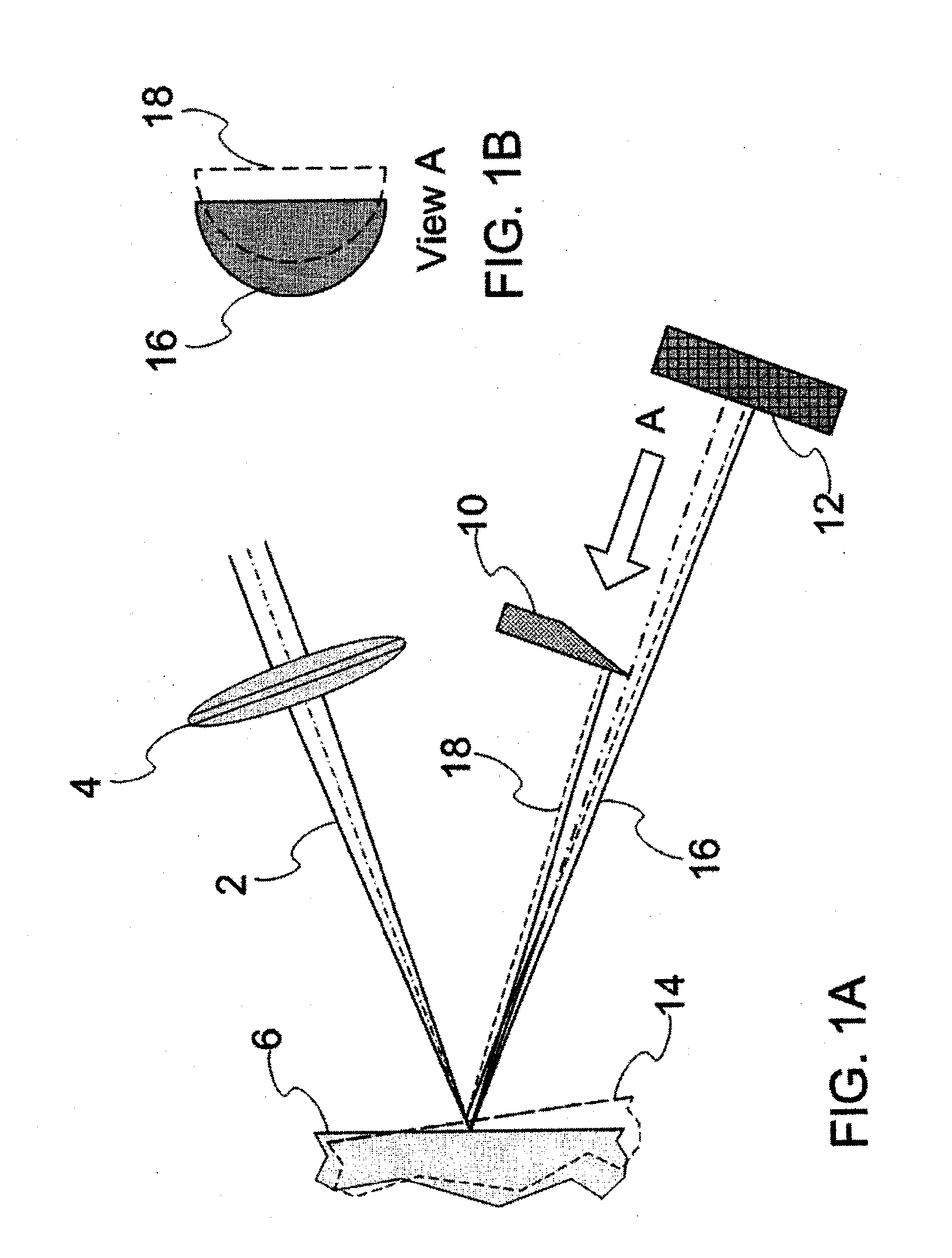

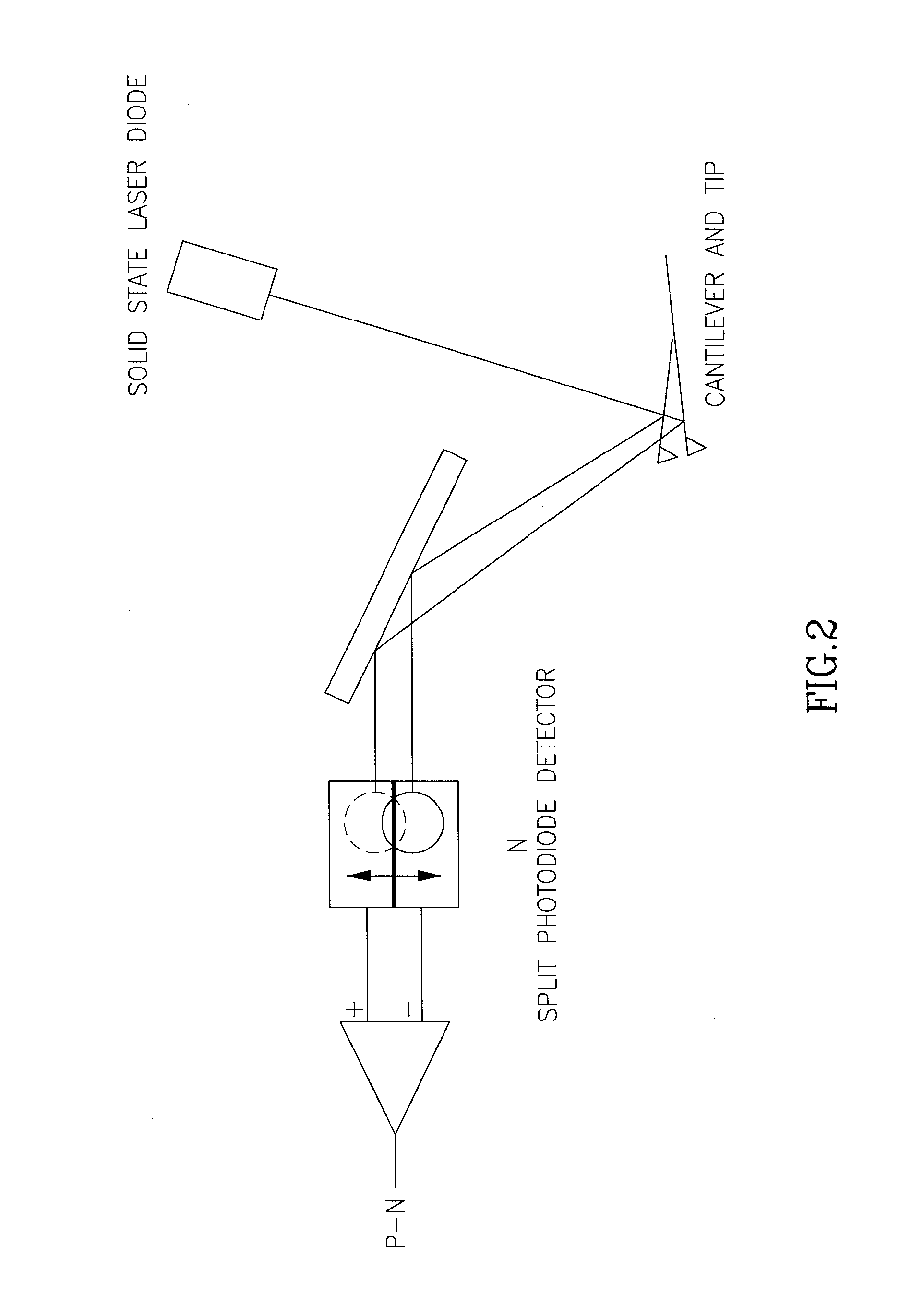

Optical knife-edge detector with large dynamic range

ActiveUS20160238631A1Maximize powerOptimal performanceSubsonic/sonic/ultrasonic wave measurementScanning probe techniquesLarge dynamic rangeEdge detector

A detection arrangement and method for directing the sensitivity of an optical knife-edge detection system to its optimal operating point. This is referred to as an increase in the detection dynamic range of the system with advantageous applications for detecting motion of a surface such as for Atomic Force Microscopy as well as detecting acoustic vibrations on unstable surfaces. A pair of parallel reflecting surfaces, such as an optical slab waveguide, serve to reflect the sensing beam back onto the knife-edge detector once it is shifted off its sensing range. Allowing multiple reflections, the sensing beam is maintained on the knife-edge detector even at large angular offsets from the optimal operating point of the basic knife-edge detector. Use of a modified arrangement, with two knife-edge detectors at quadrature ensures near-optimal sensitivity at a detection dynamic range up to forty-fold larger than that of the basic knife-edge system.

Owner:TECHNION RES & DEV FOUND LTD

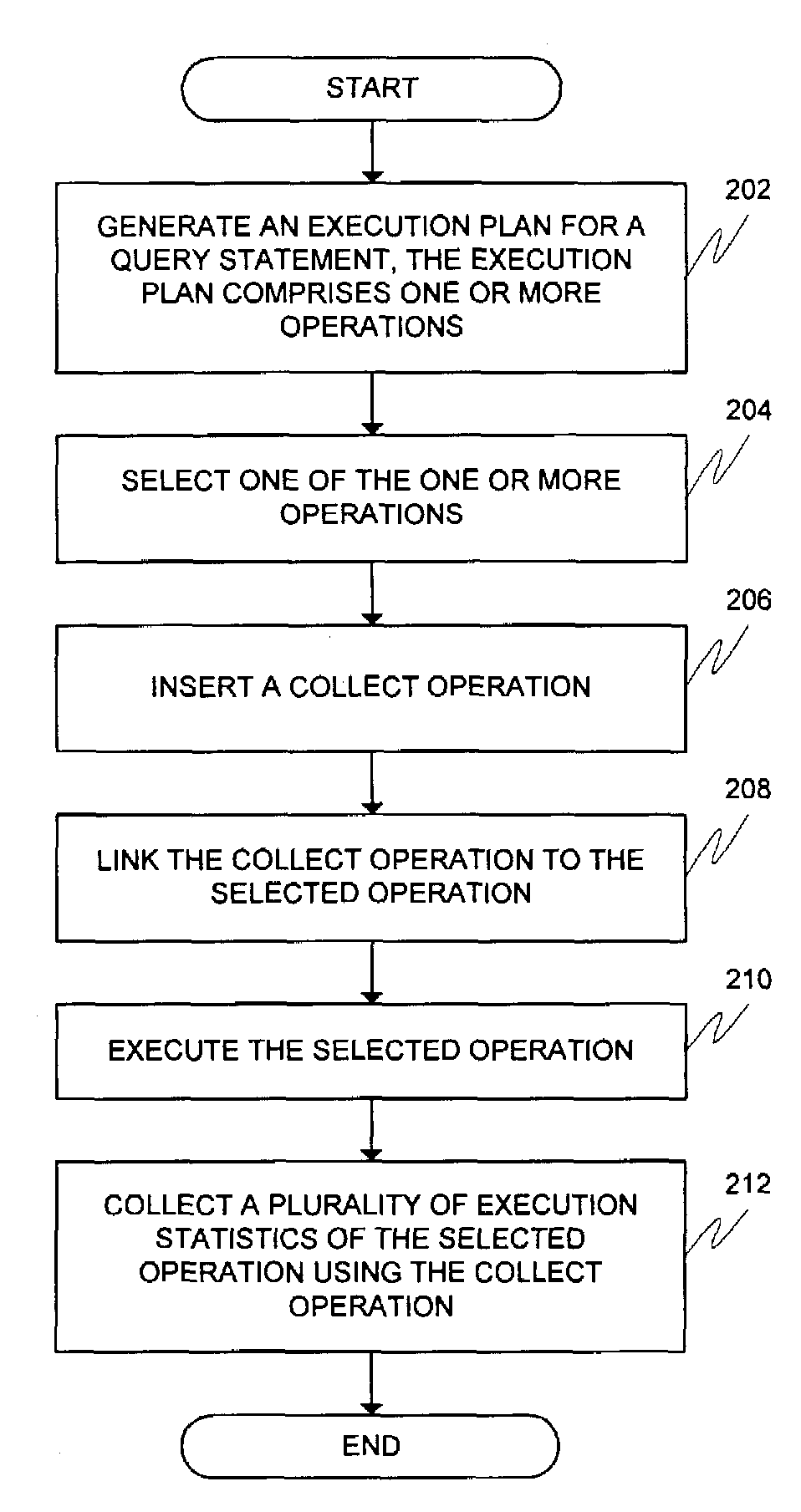

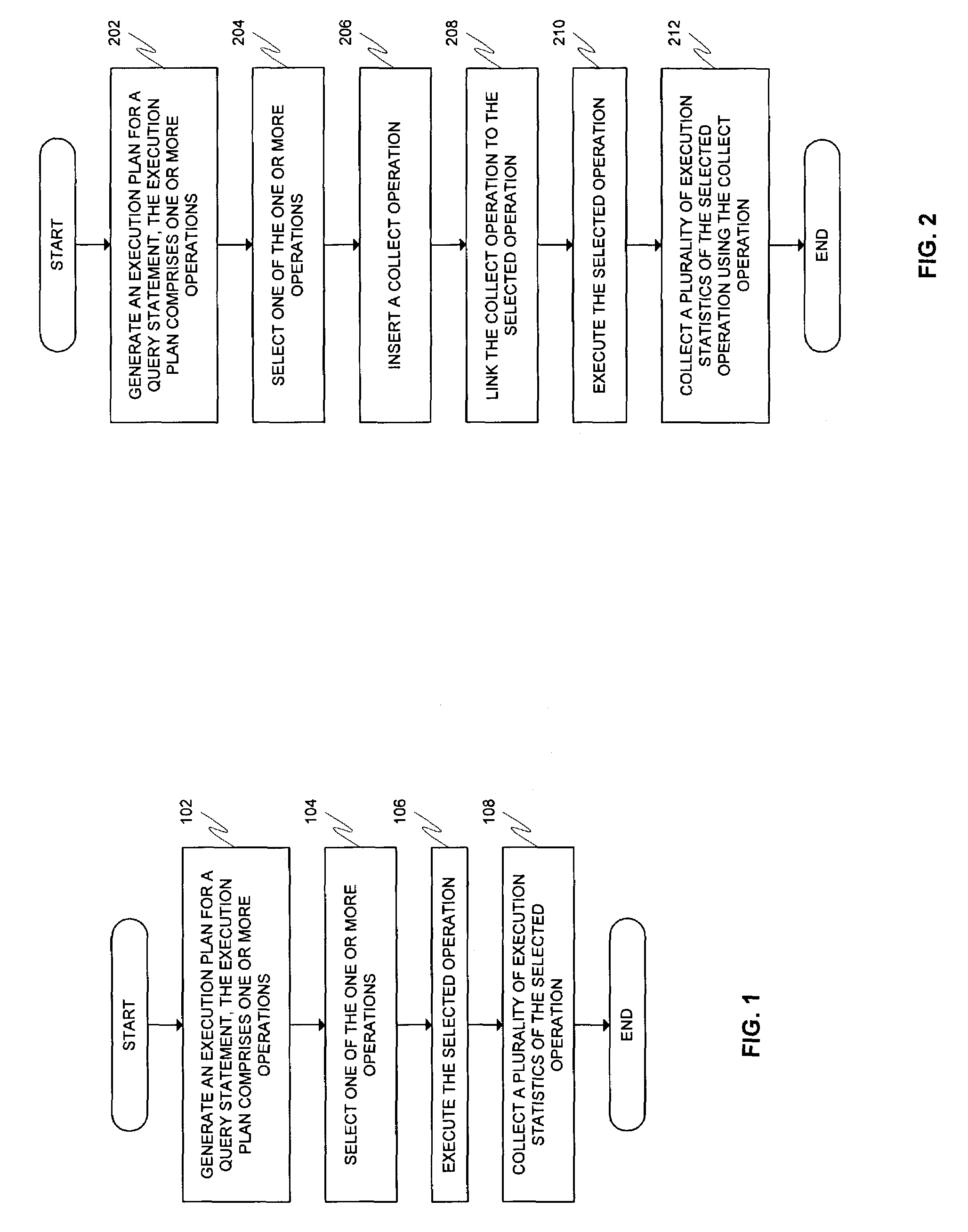

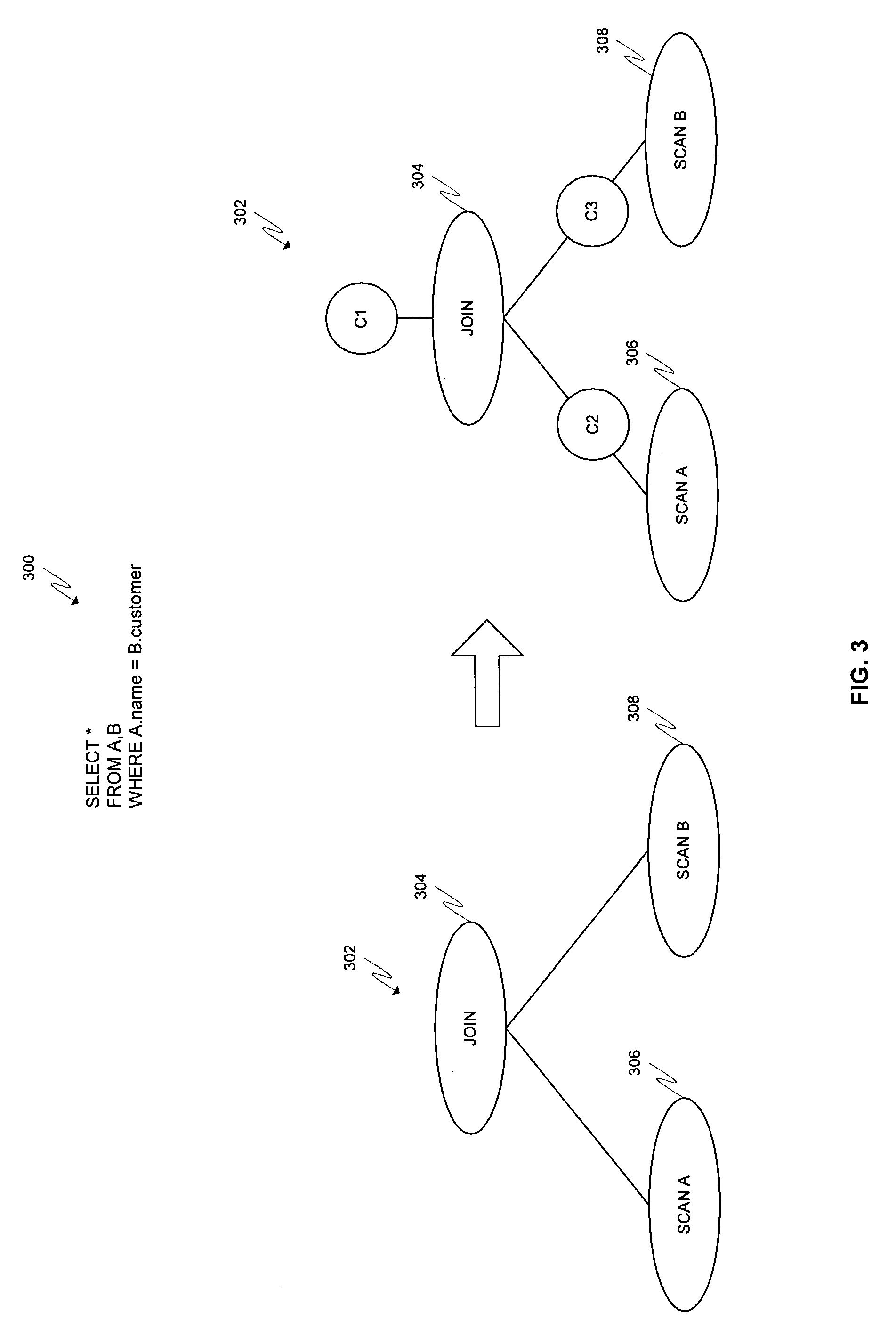

Method and system of collecting execution statistics of query statements

ActiveUS7447676B2Not possibleOptimal performanceData processing applicationsGeneral purpose stored program computerProgram planningExecution plan

A method and system of collecting execution statistics of query statements is disclosed. An execution plan is generated for a query statement in one embodiment of the invention. The execution plan includes one or more operations. One of the one or more operations is selected. The selected execution plan is then executed and a plurality of execution statistics of the selected operation is collected.

Owner:ORACLE INT CORP

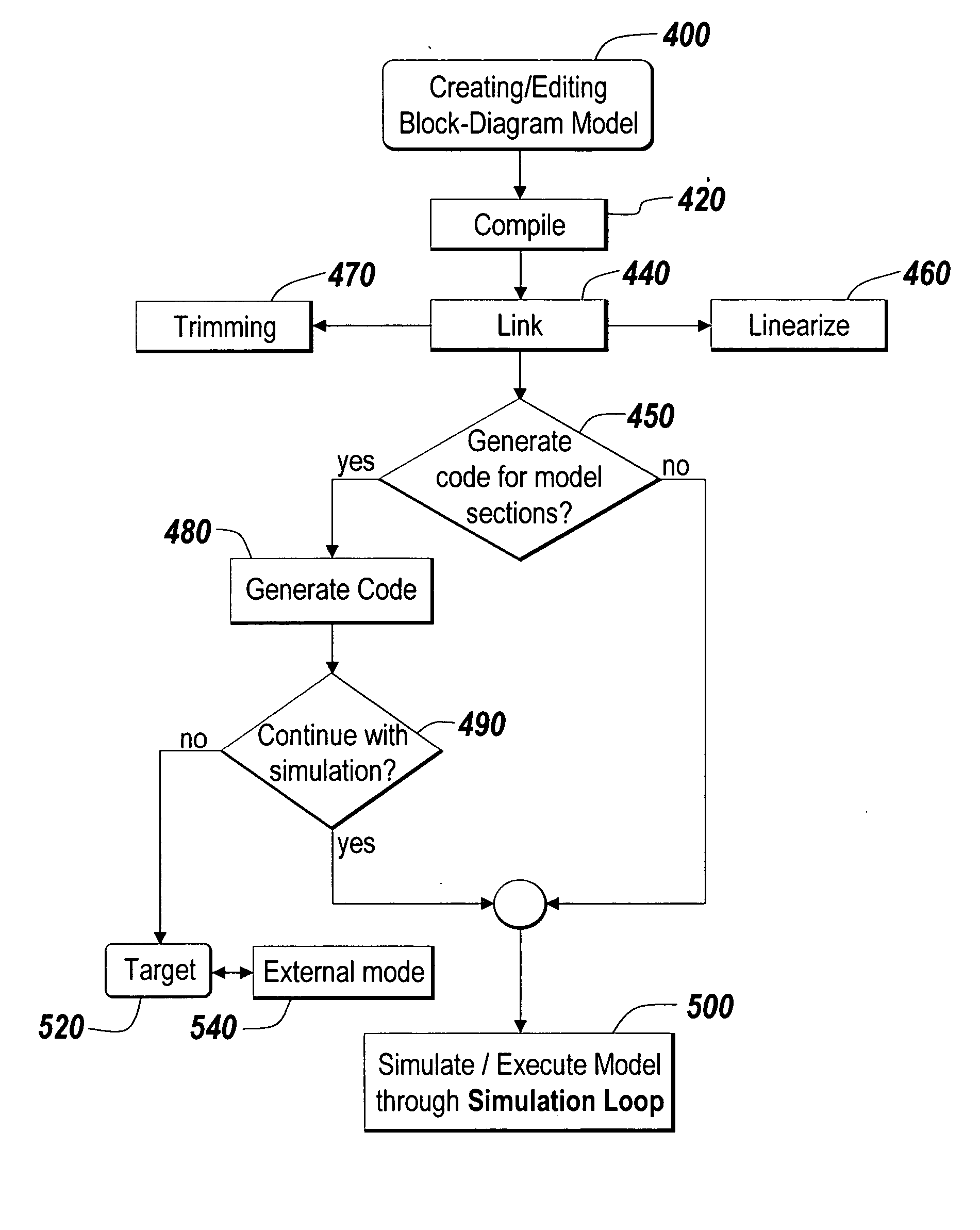

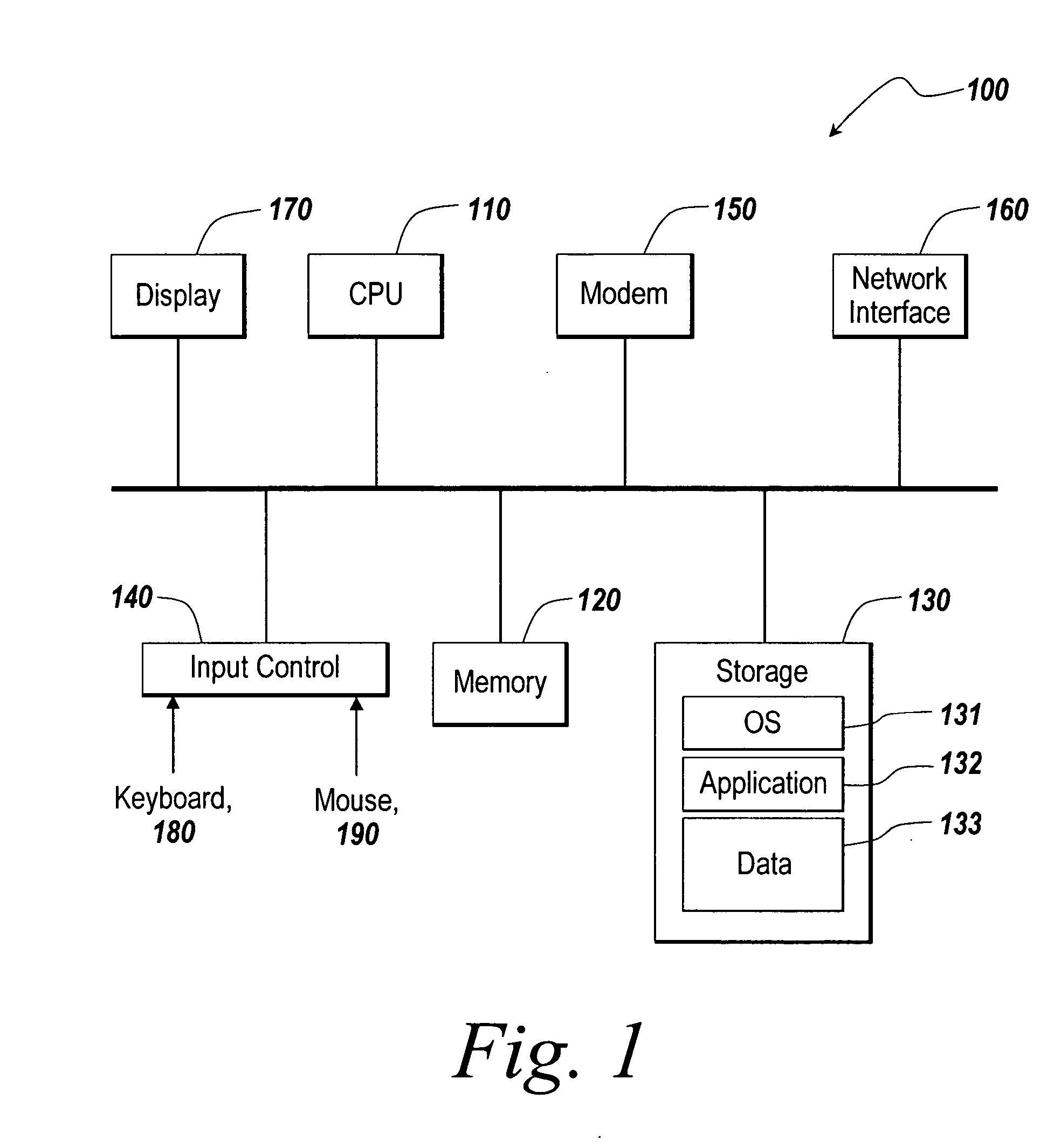

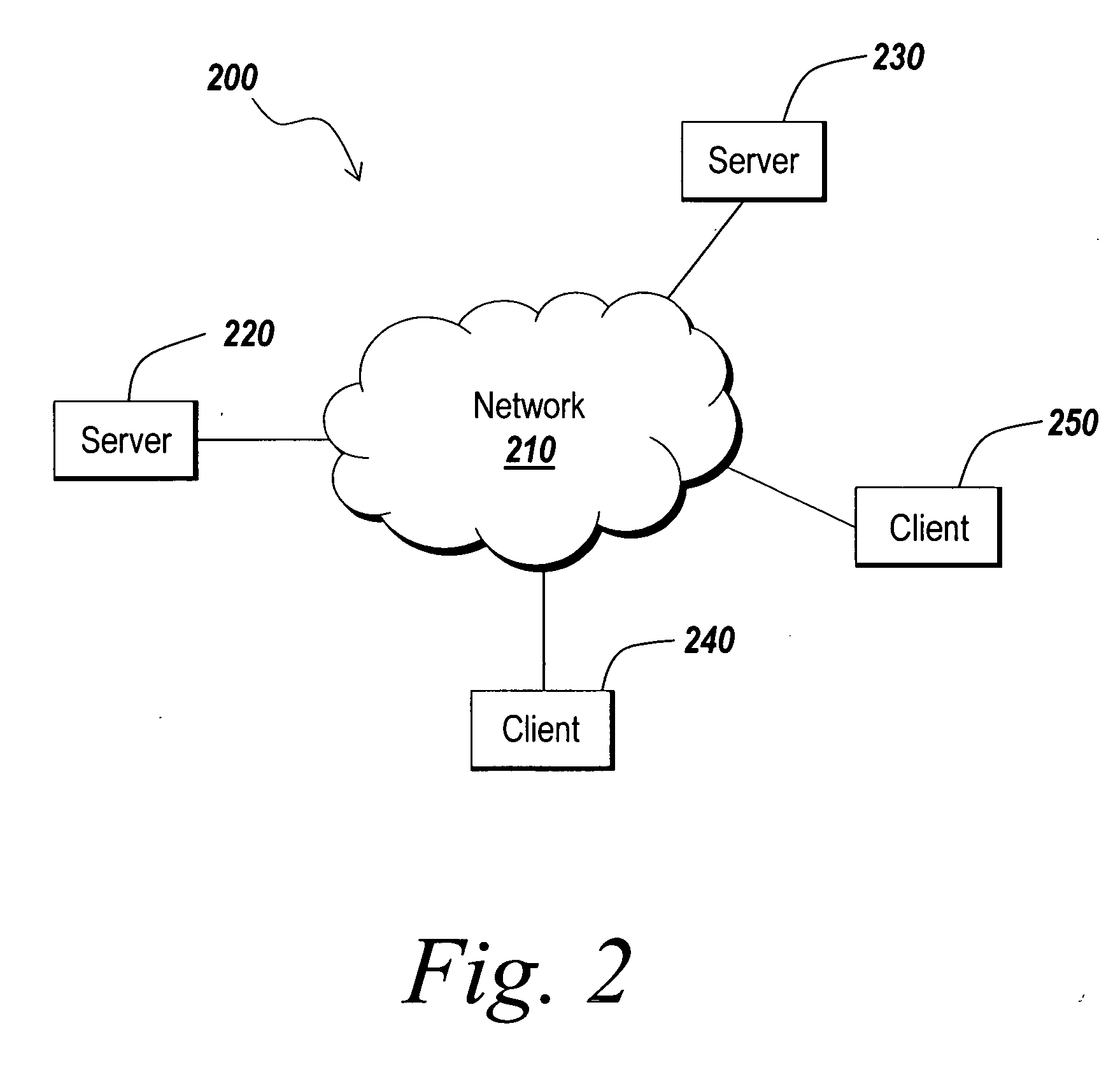

Run-time tunable sample time in programming or modeling environments

ActiveUS20070143095A1Optimal performanceEasy loadingComputation using non-denominational number representationDesign optimisation/simulationMockupRunning time

Programming or modeling environments in which programs or models are simulated or executed with tunable sample times are disclosed. The tunable sample times can be changed during the simulation or execution of the programs or models without recompiling the programs or models. The sample times are parameterized and the value of the sample times is changed during the simulation or execution of the programs or models. The sample times may be changed manually by a user. Alternatively, the sample times may be automatically changed by programmatically defining when and how the sample times are determined.

Owner:THE MATHWORKS INC

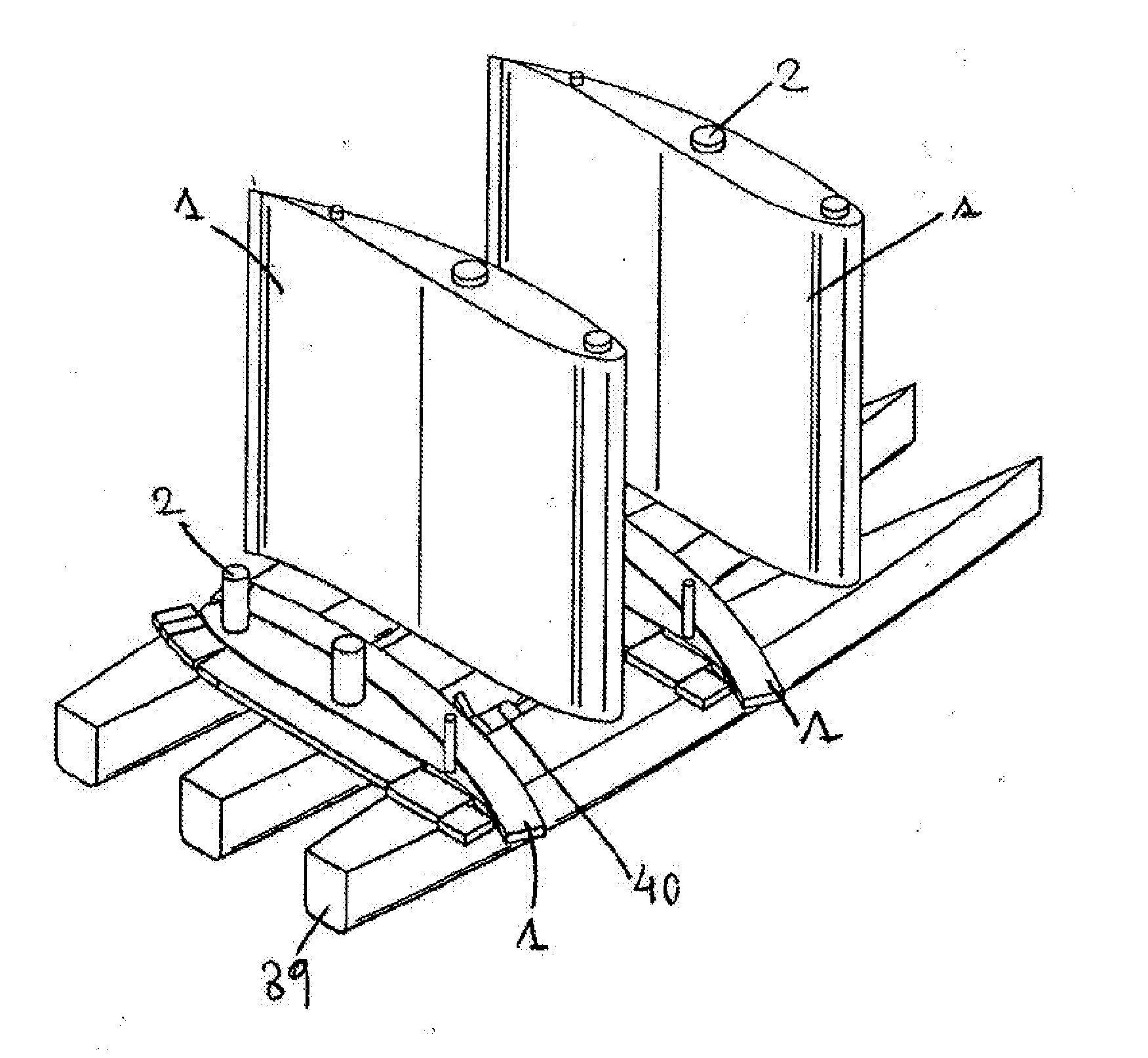

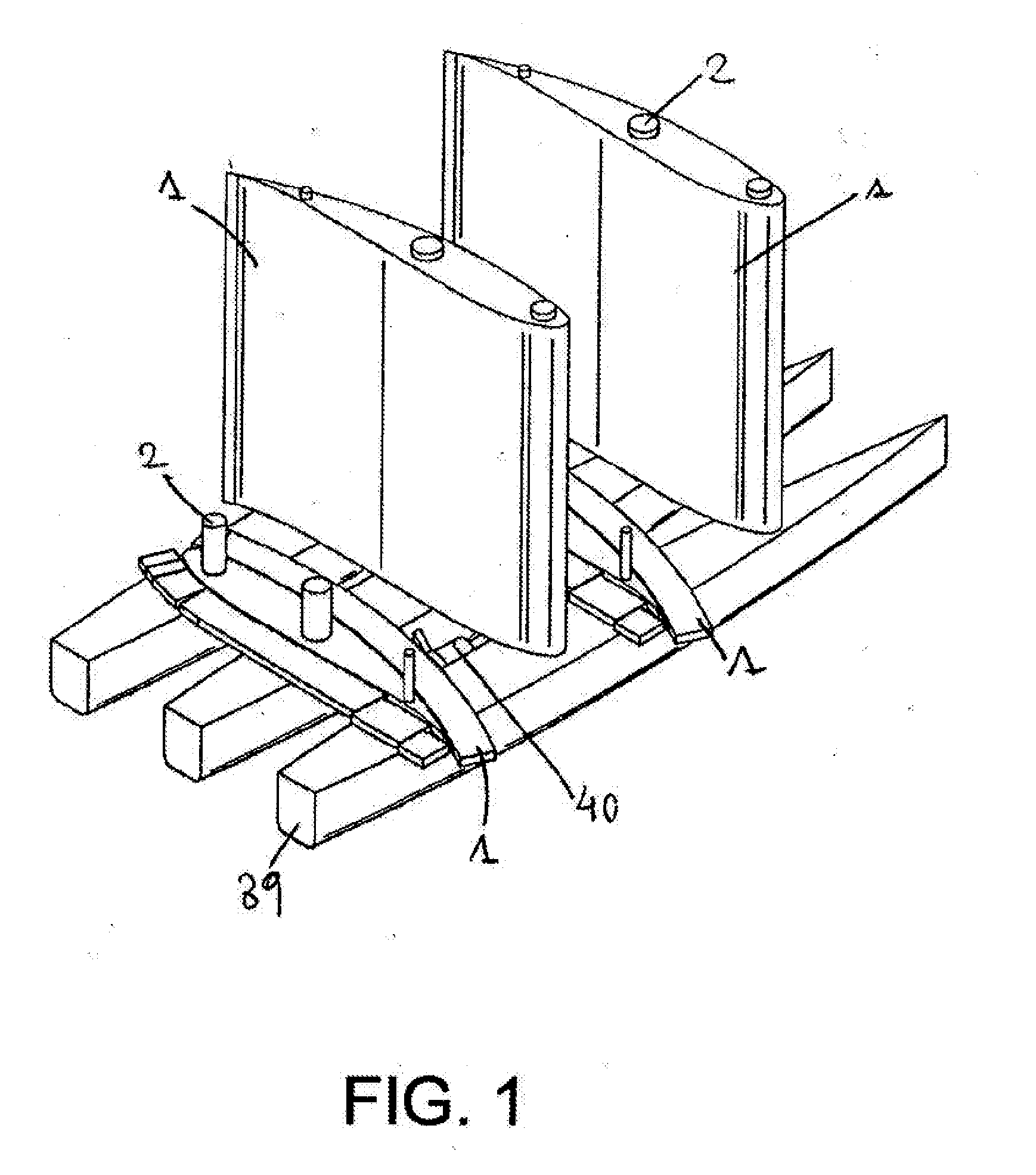

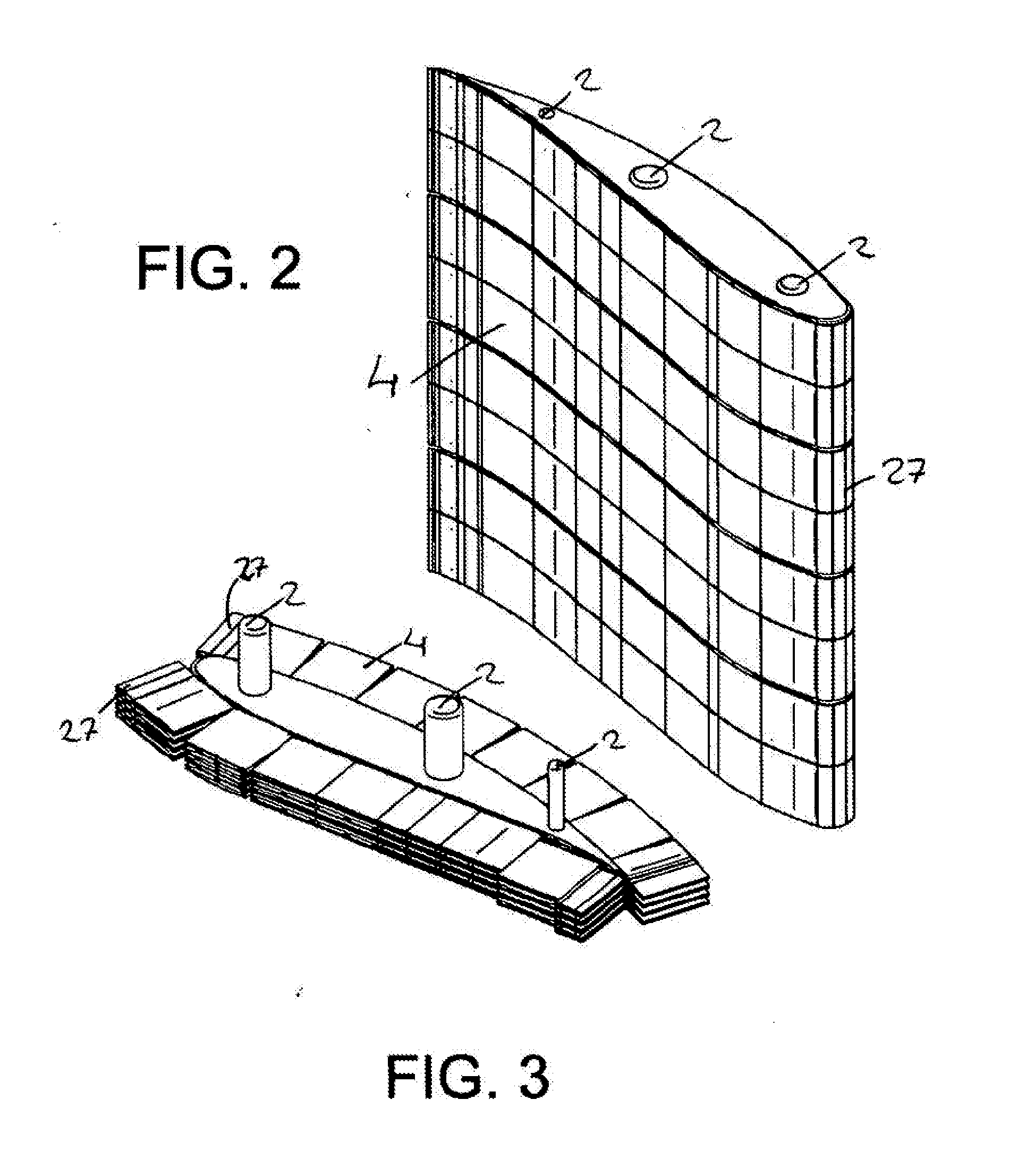

Set of stowable rigid sails

Owner:BERMUDEZ MIQUEL JOSE +1

Electronic device including a schottky contact

ActiveUS8928050B2Reduce the possibilityOptimal performanceSolid-state devicesDiodeEngineeringElectron

An electronic device can include a semiconductor layer having a primary surface, and a Schottky contact comprising a metal-containing member in contact with a horizontally-oriented lightly doped region within the semiconductor layer and lying adjacent to the primary surface. In an embodiment, the metal-containing member lies within a recess in the semiconductor layer and contacts the horizontally-oriented lightly doped region along a sidewall of the recess. In other embodiment, the Schottky contact may not be formed within a recess, and a doped region may be formed within the semiconductor layer under the horizontally-oriented lightly doped region and have a conductivity type opposite the horizontally-oriented lightly doped region. The Schottky contacts can be used in conjunction with power transistors in a switching circuit, such as a high-frequency voltage regulator.

Owner:SEMICON COMPONENTS IND LLC

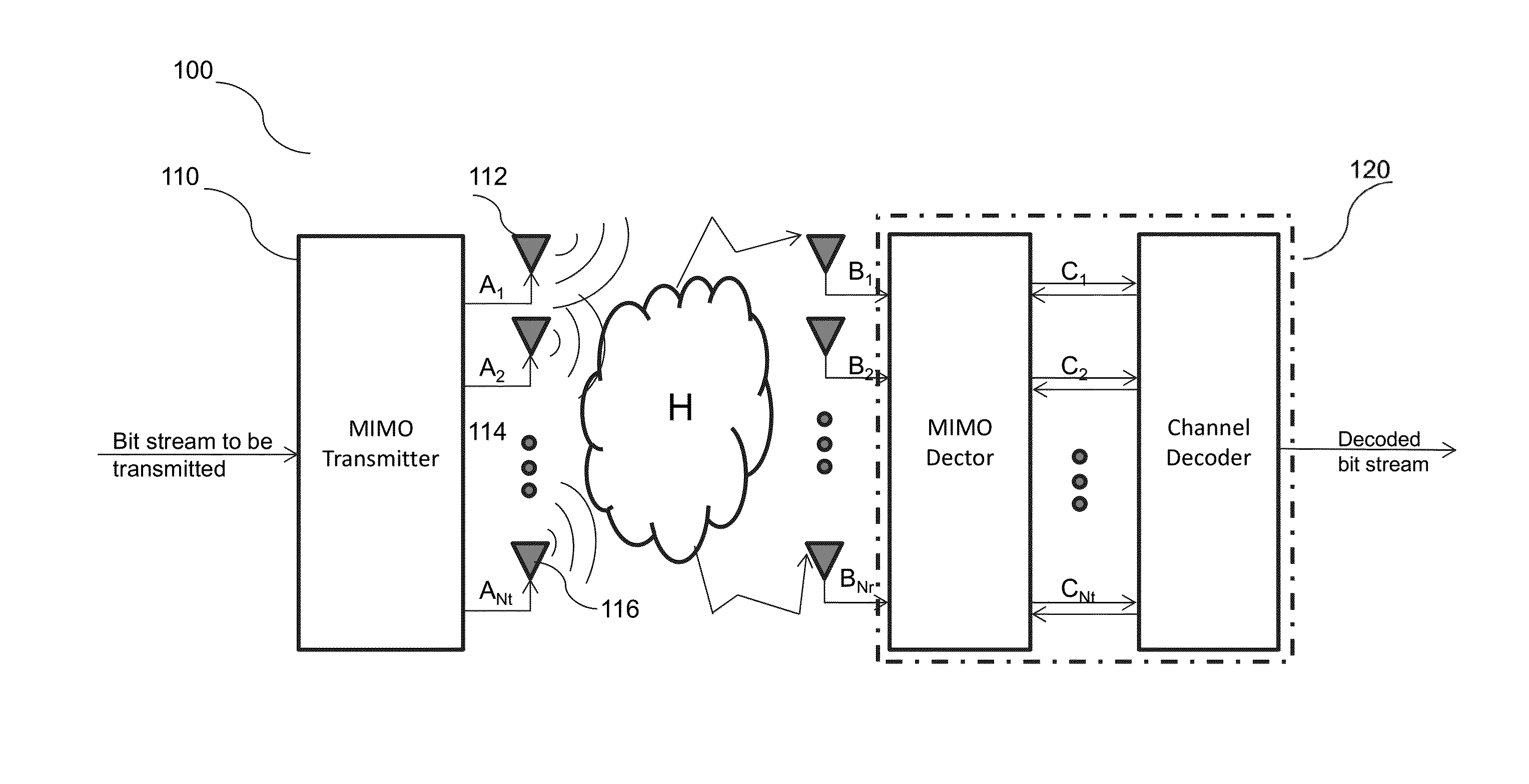

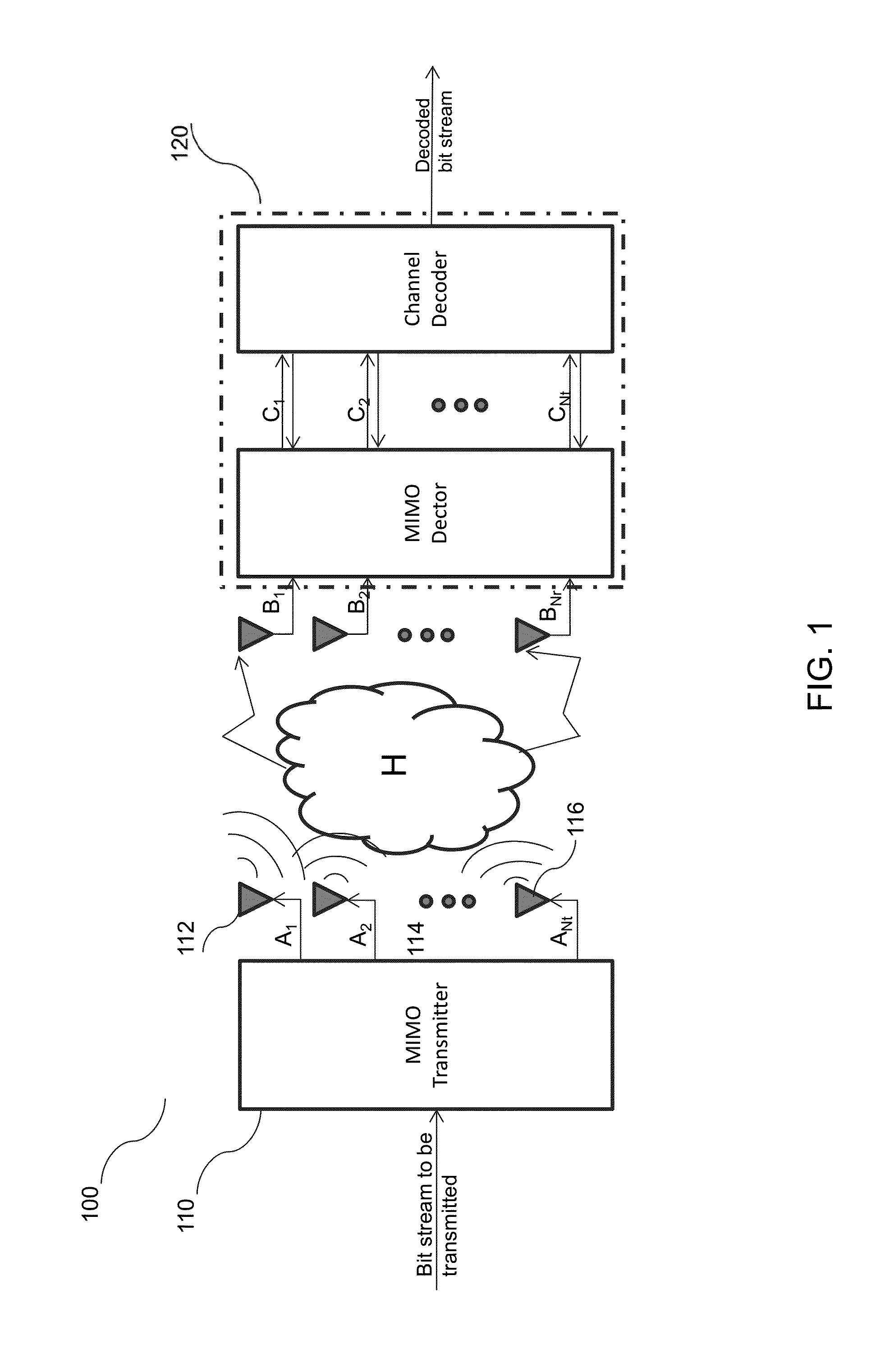

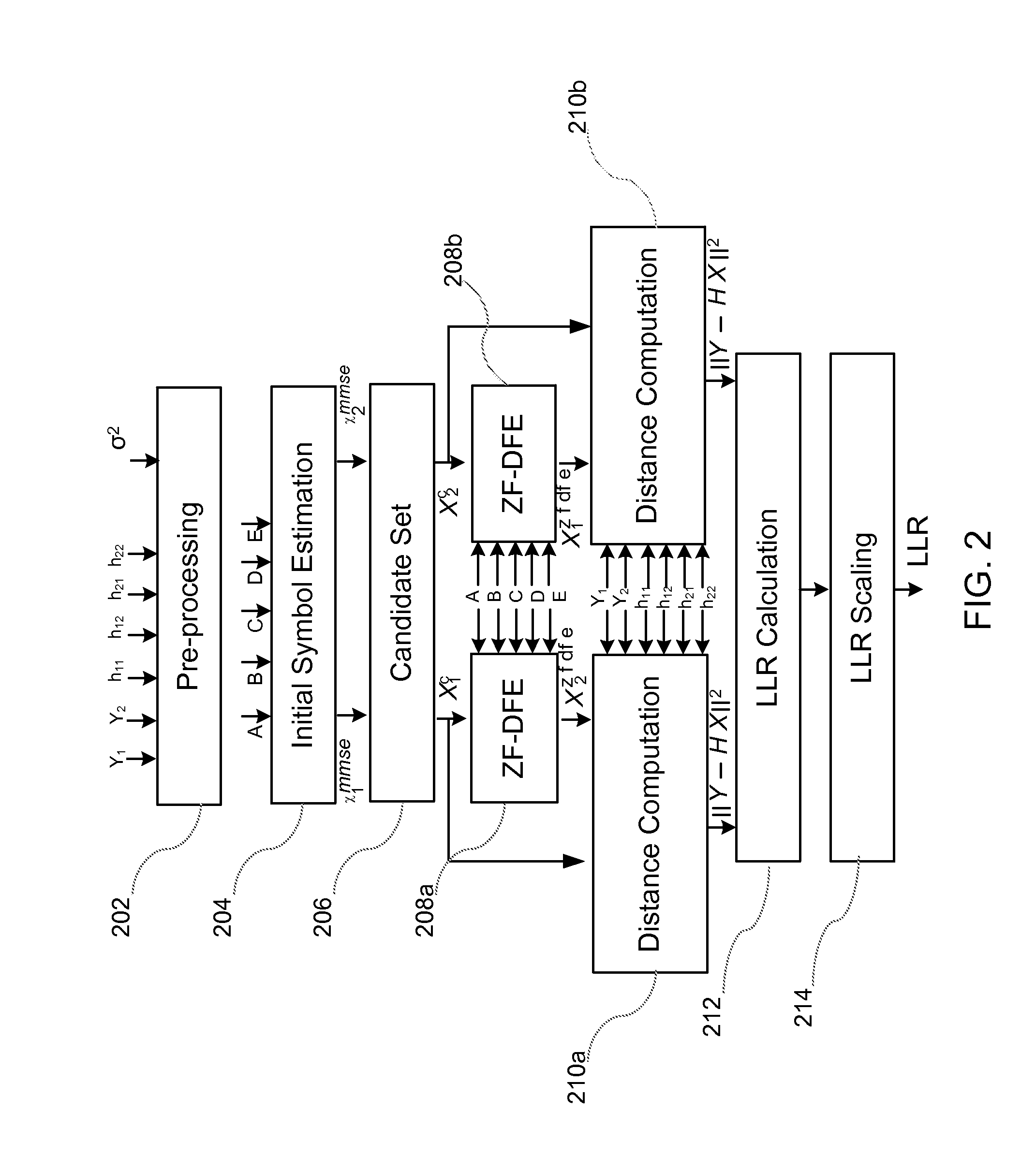

Decision feedback solution for channels with low signal to noise ratio

ActiveUS20150188667A1Cost reductionOptimal performanceSpatial transmit diversityError preventionRound complexitySignal-to-noise ratio (imaging)

This invention is related to a low-complexity MIMO detector in a wireless communication system with near optimal performance. Initial symbol estimation is performed for a transmitted symbol vector. The soft information of the transmitted symbol vector can be more accurately calculated by deemphasizing the LLRs associated with symbols belonging to weak channels that may suffer from poor initial estimation. By combining aspects of both the linear detection and the ML detection, the complexity of the proposed detector becomes orders of magnitude lower than that of a ML detector, but the performance is very close to that of an ML detector.

Owner:QUALCOMM TECH INT

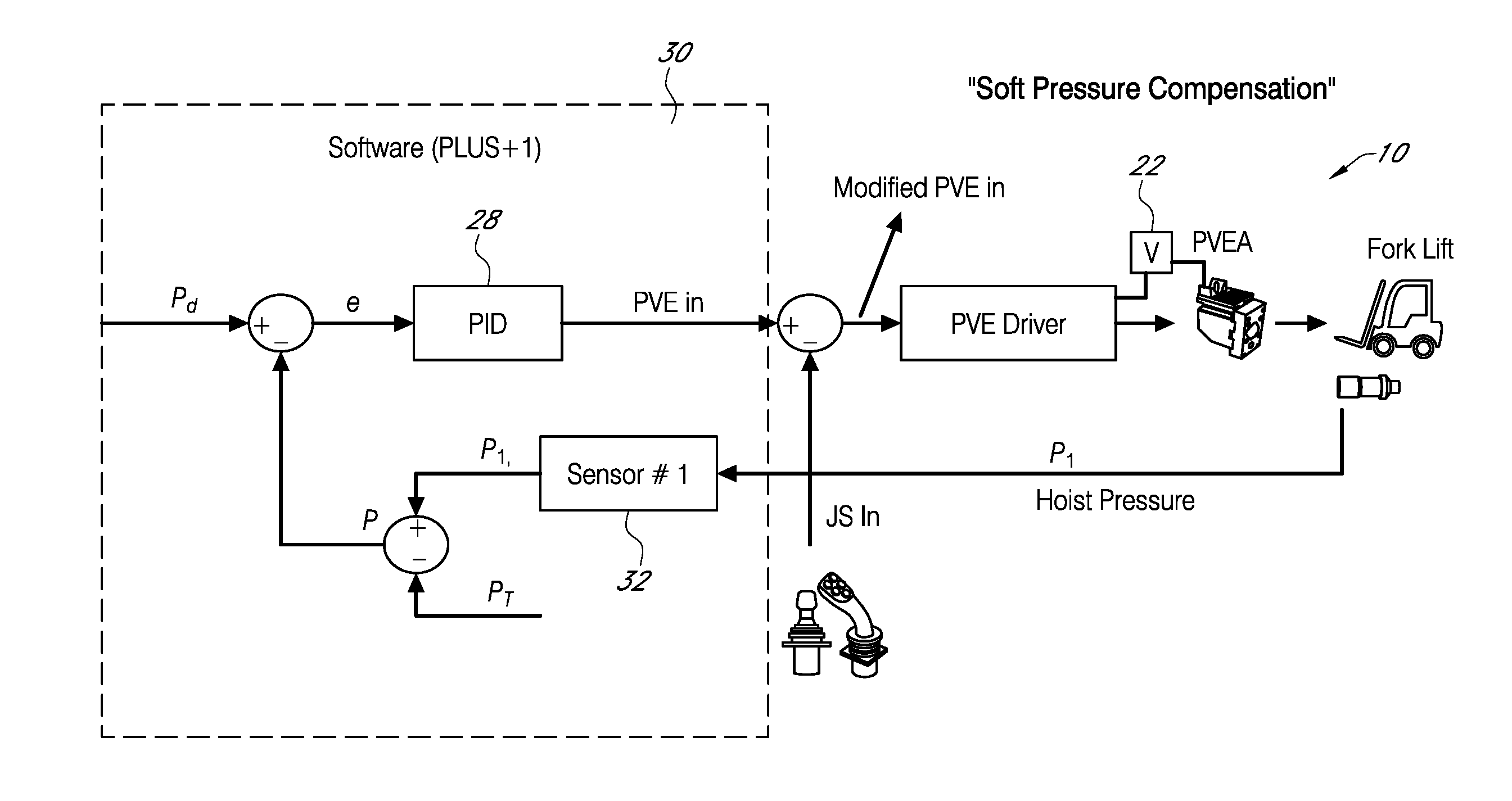

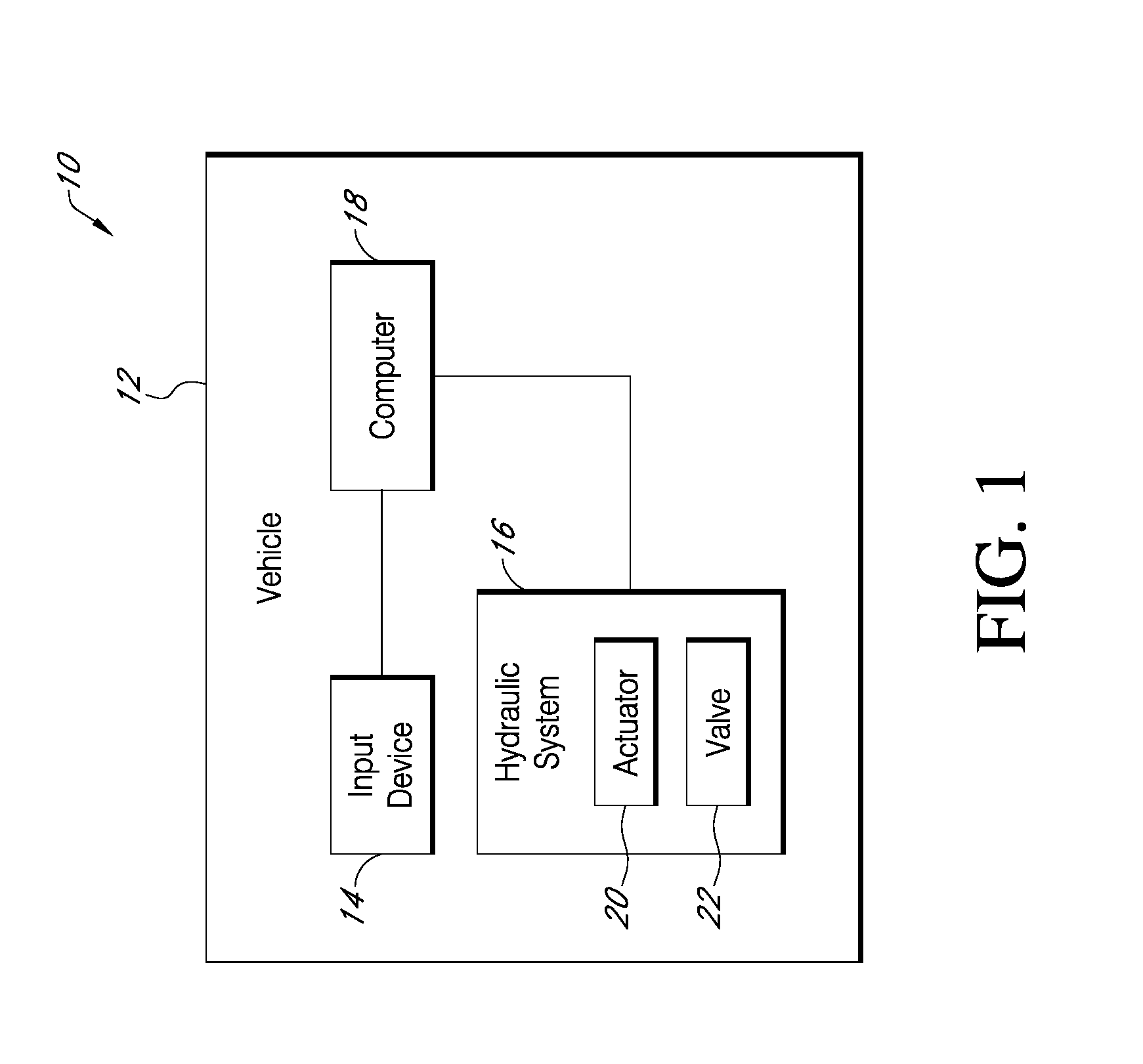

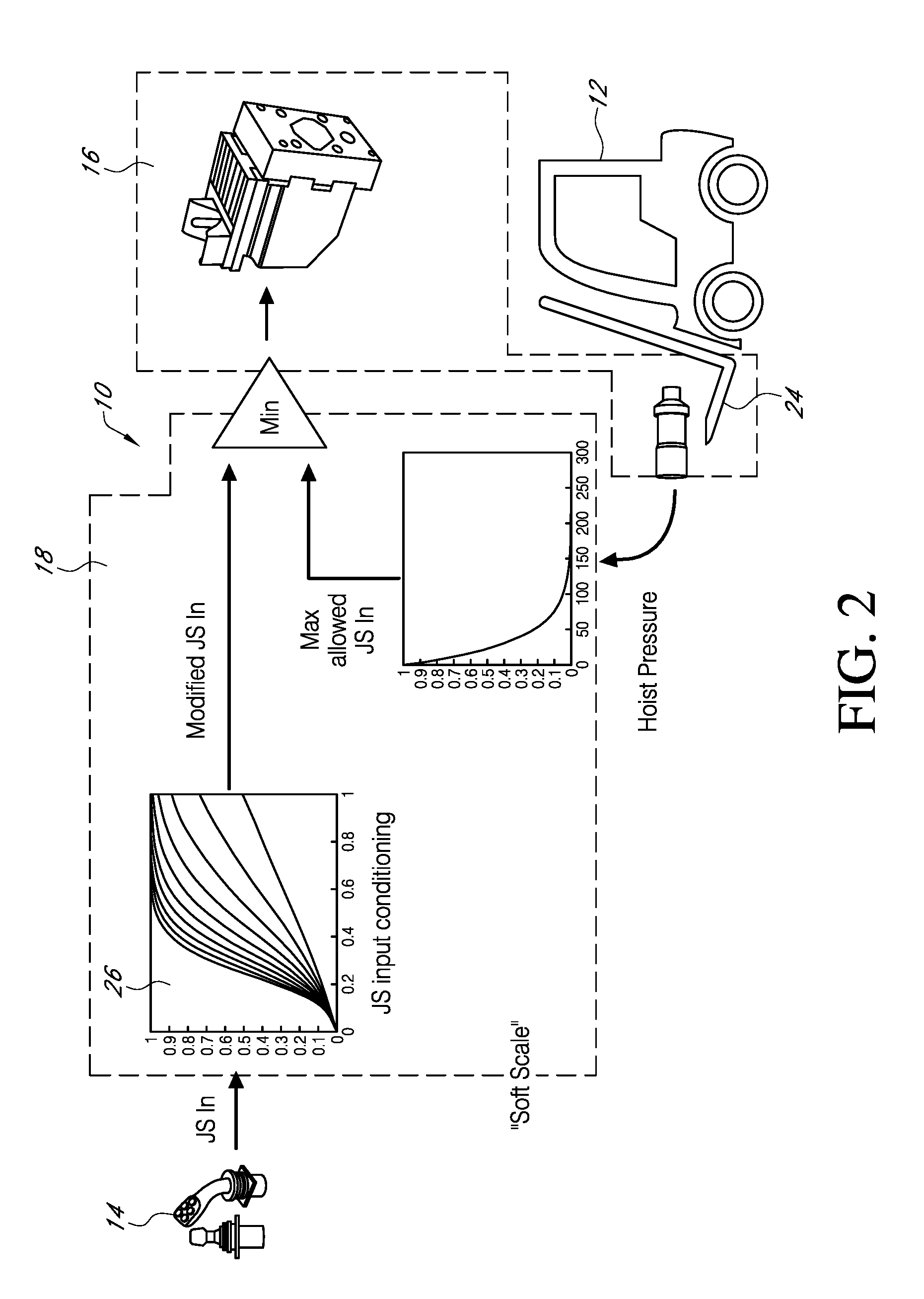

Load dependent electronic valve actuator regulation and pressure compensation

ActiveUS20170029256A1Cost reductionOptimal performanceFluid-pressure actuator testingOperating means/releasing devices for valvesSystem pressureHydraulic control

A hydraulic control system that uses system pressure information and a rescaled operator input to command valve spool area to control actuator speed. The system uses soft sealing and / or soft pressure compensation.

Owner:DANFOSS POWER SOLUTIONS GMBH & CO

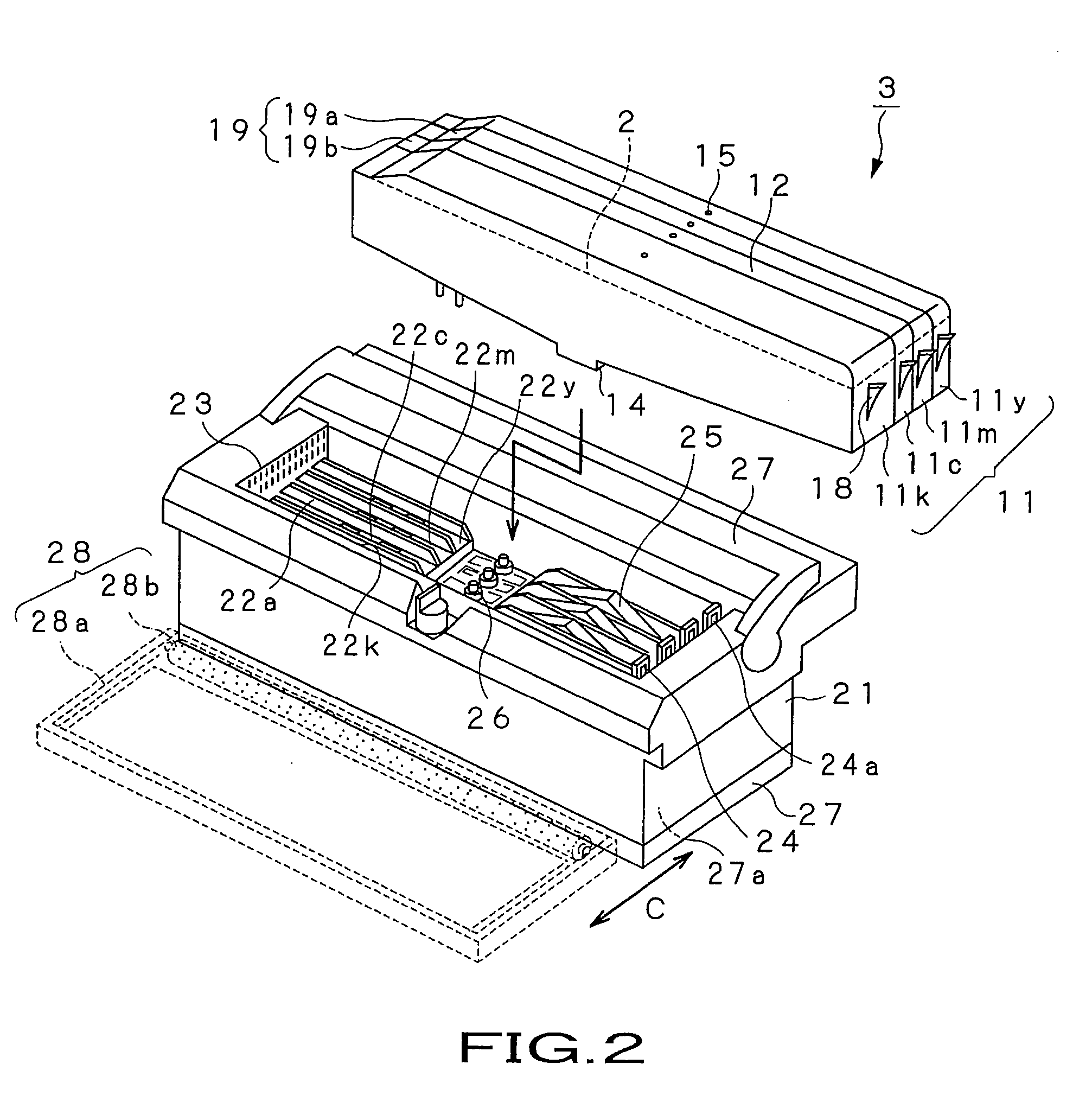

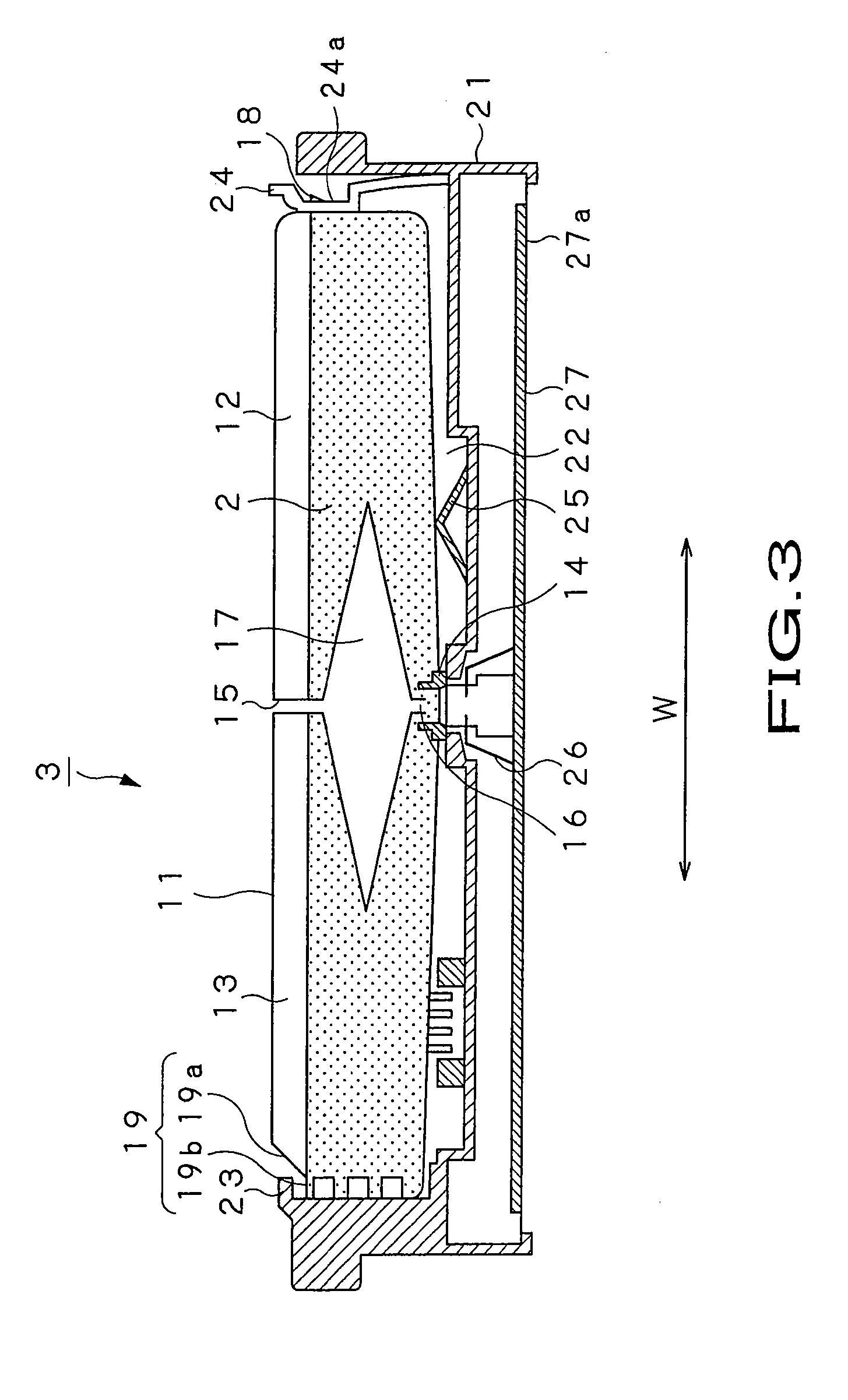

Recording liquid, liquid cartridge emitting device and liquid emitting method

InactiveUS20070209551A1Assure optimum wettabilityOptimal performanceMeasurement apparatus componentsDuplicating/marking methodsSimple Organic CompoundsOrganic compound

Disclosed is an ink liquid used in a printer device of the ink jet system for recording an image or letters / characters. A surfactant containing an organic compound represented by the following chemical formula 1: where m and n are integers not less than 1, is contained in an ink 2 to prevent blurring or bleeding from being produced at a point of deposition of an ink liquid droplet i.

Owner:SONY CORP