Patents

Literature

54results about How to "Minimize influence" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

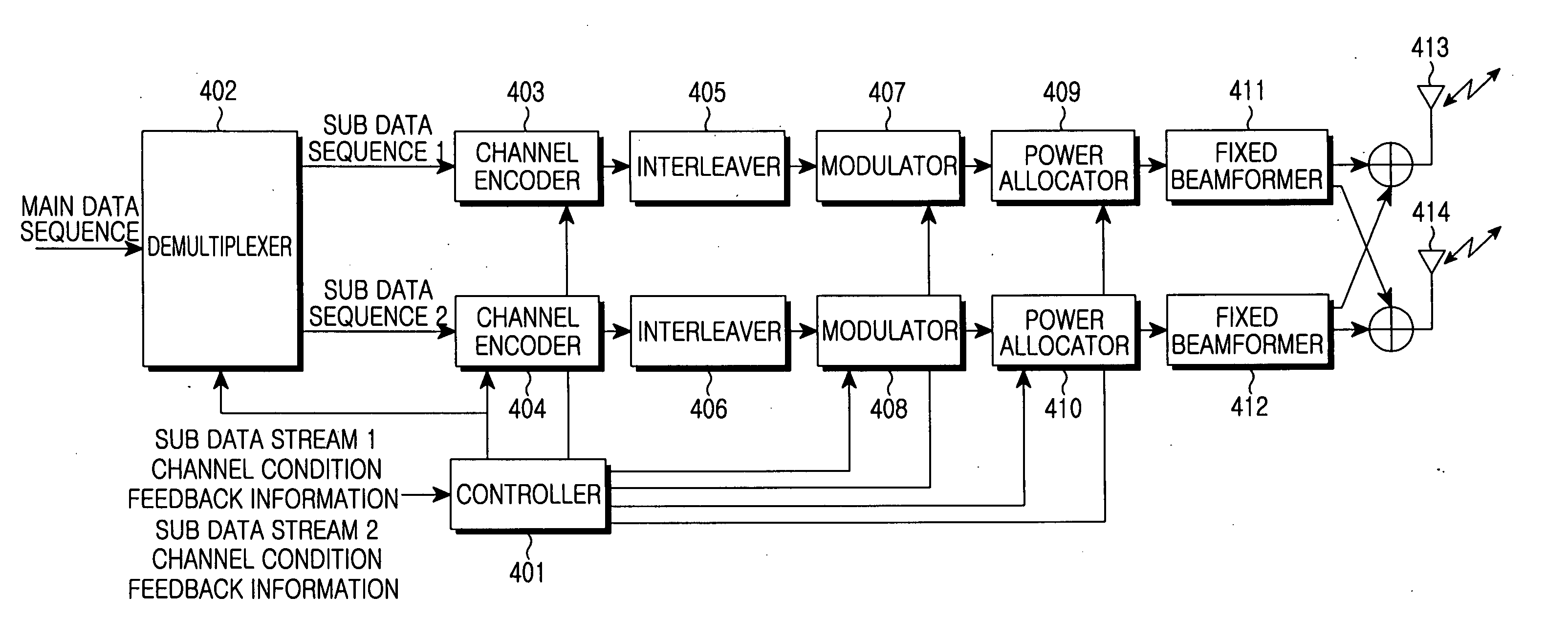

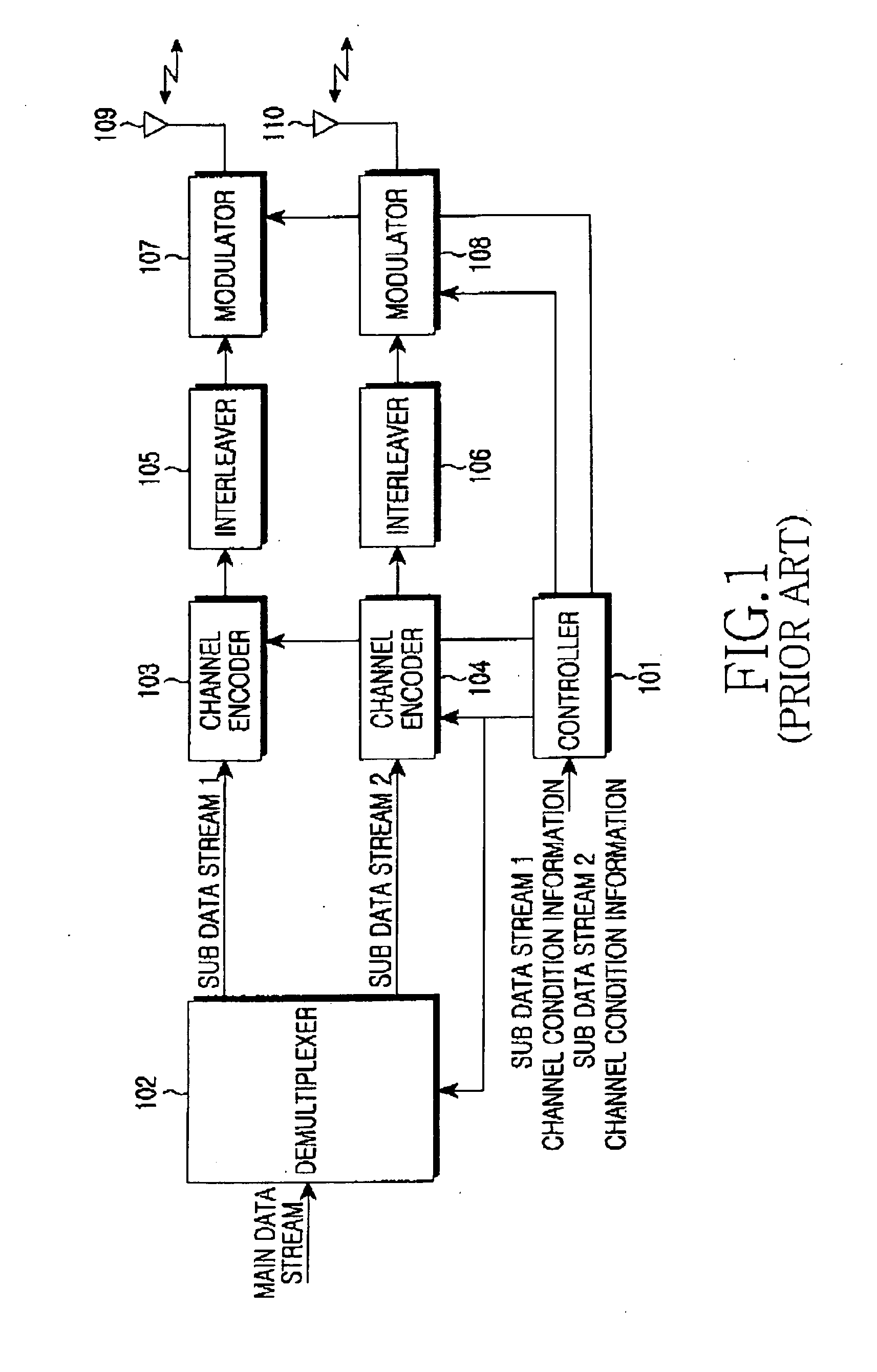

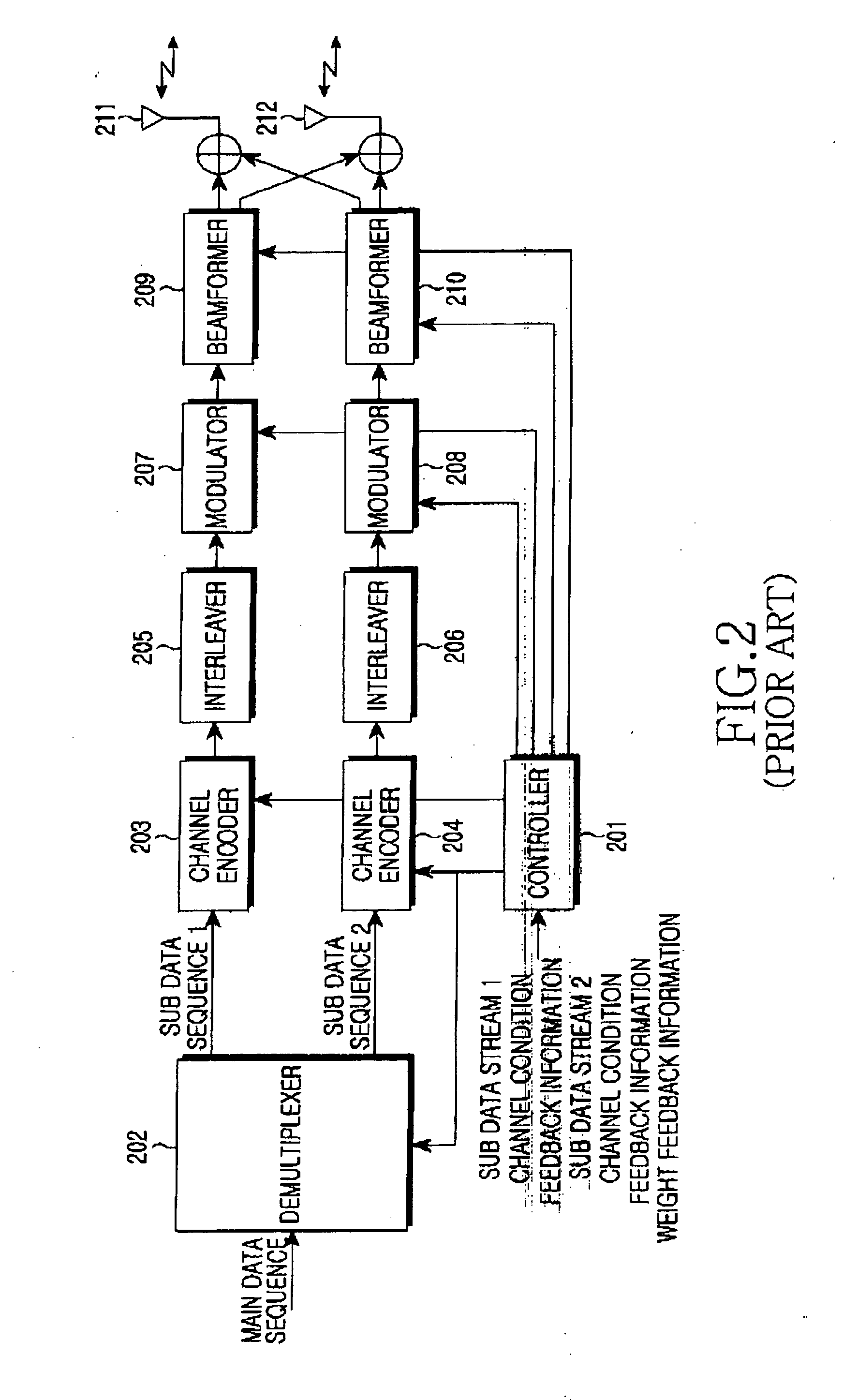

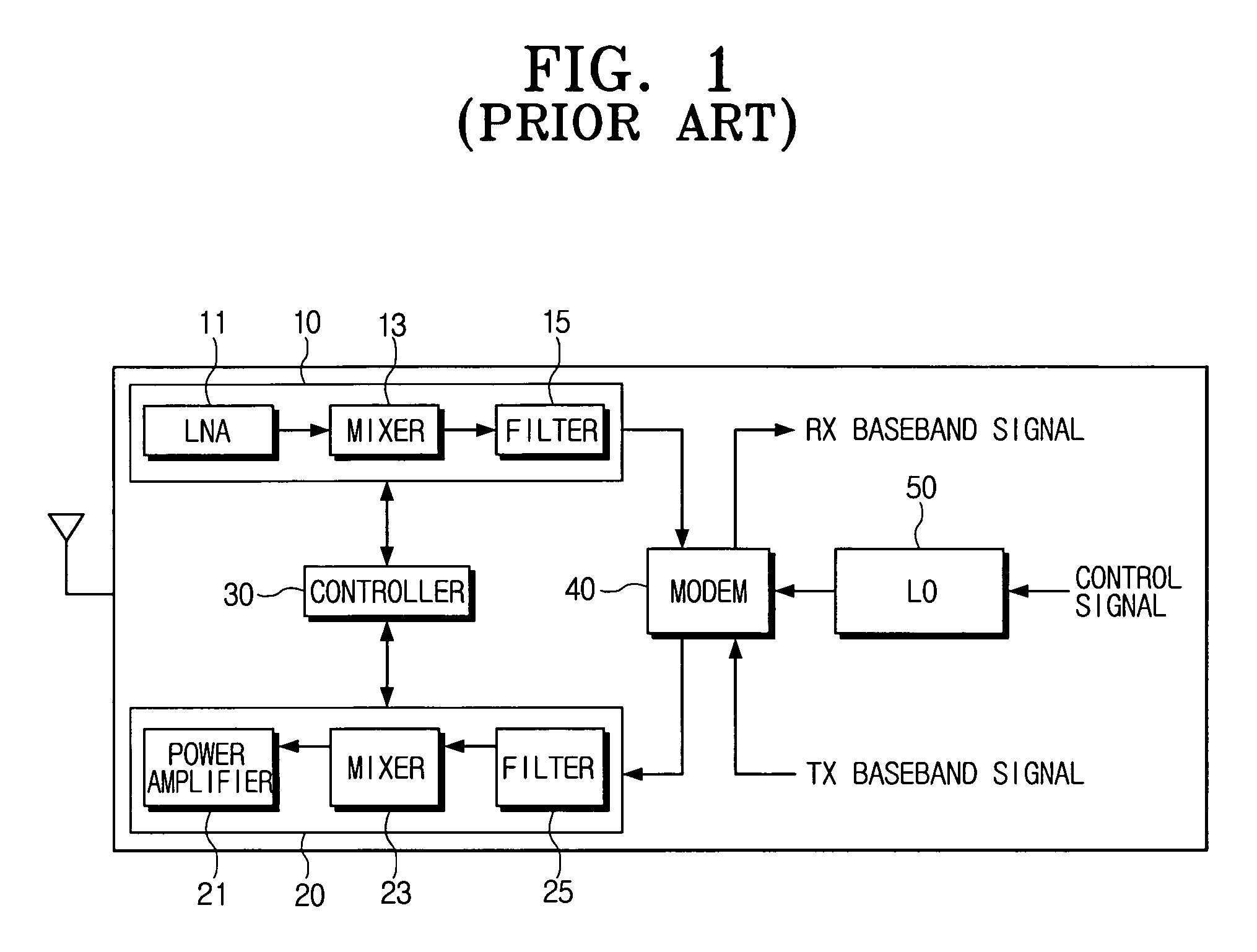

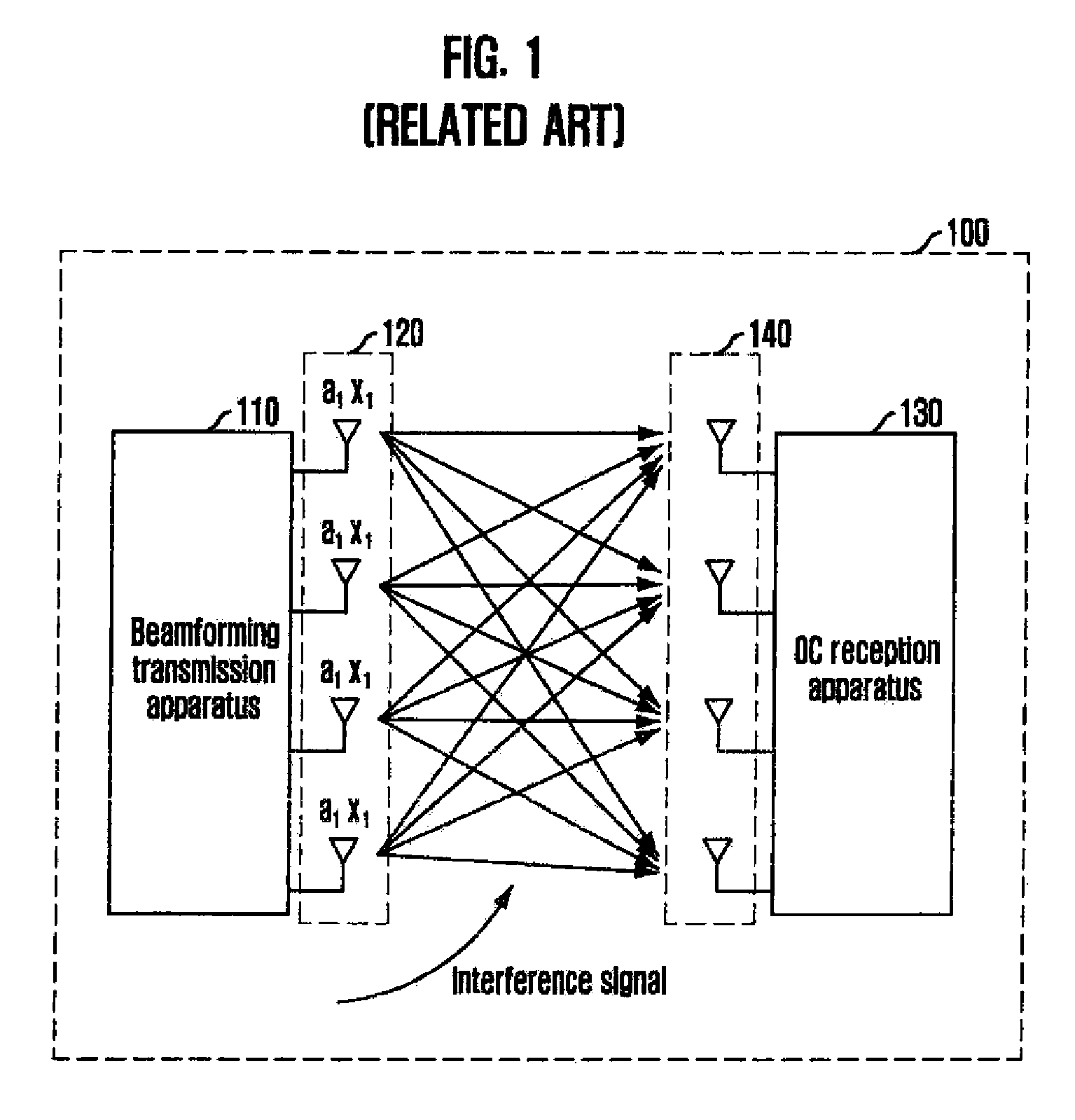

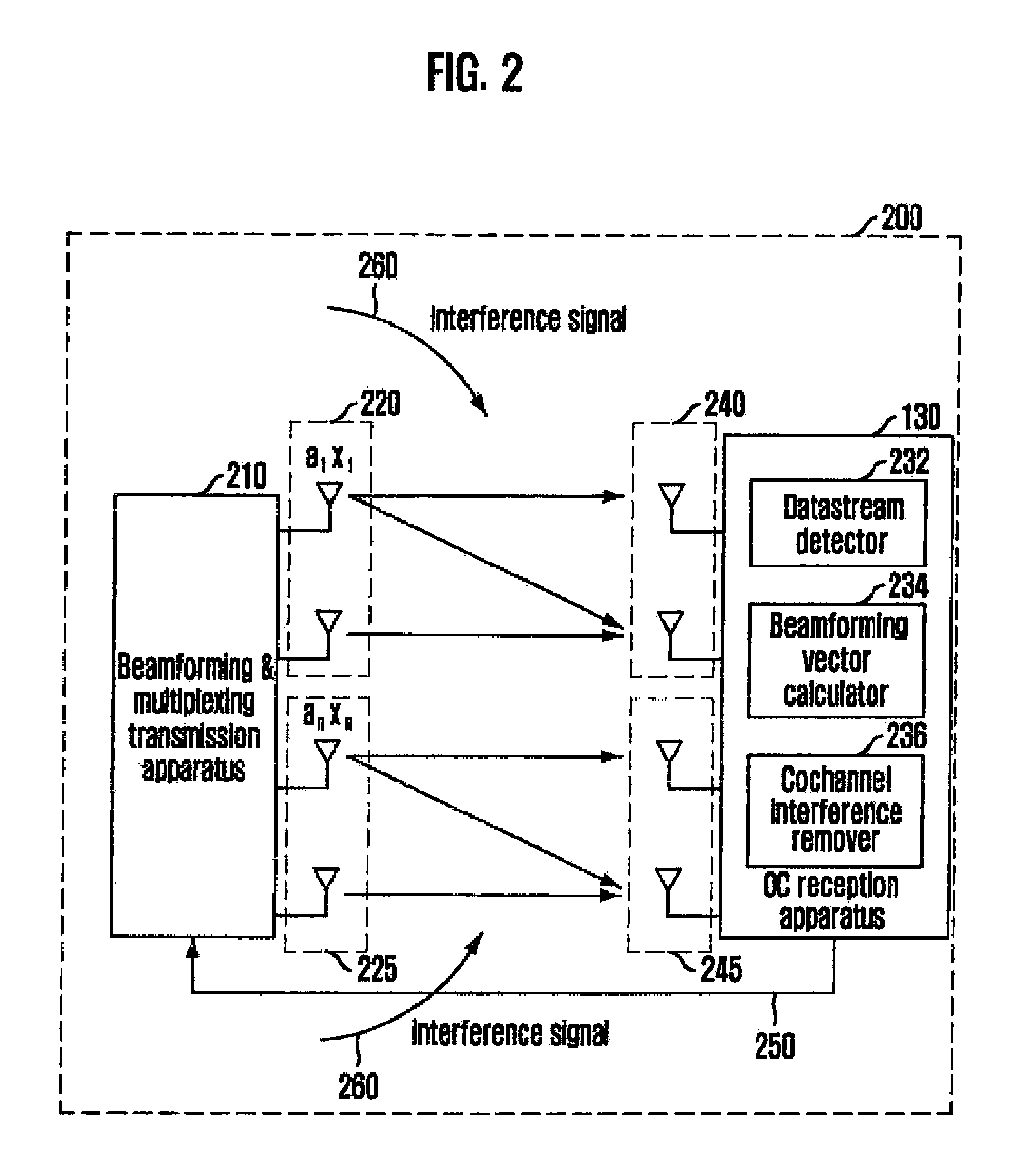

Apparatus and method for transmitting and receiving data in a mobile communication system using an array antenna

InactiveUS20050213682A1Maximize capacityMinimize influencePower managementSpatial transmit diversityData conversionTransmitted power

An apparatus and a method for transmitting and receiving data in a mobile communication system including an array antenna. The method includes the steps of transmitting pilot channels through a transmission antenna while aligning the pilot channels orthogonally to each other, receiving feedback information related to the pilot channels from a mobile station capable of receiving the data, dividing the data to be transmitted into sub-data streams by using the feedback information, and determining a coding rate and a transmit power for the sub-data streams, and converting the sub-data streams into symbol arrays to be transmitted according to the coding rate and the transmit power and transmitting data by converting the data into fixed beams.

Owner:SAMSUNG ELECTRONICS CO LTD

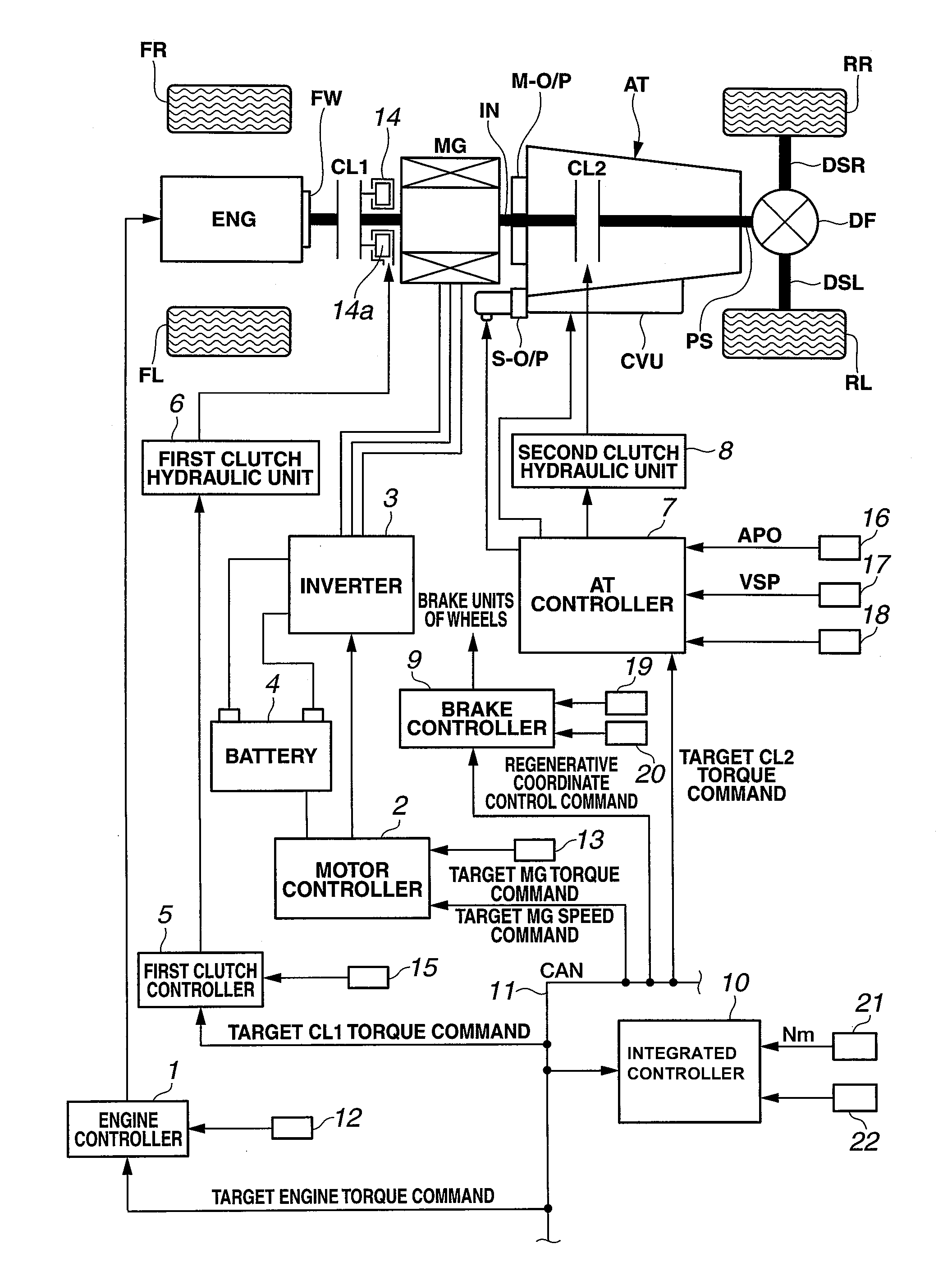

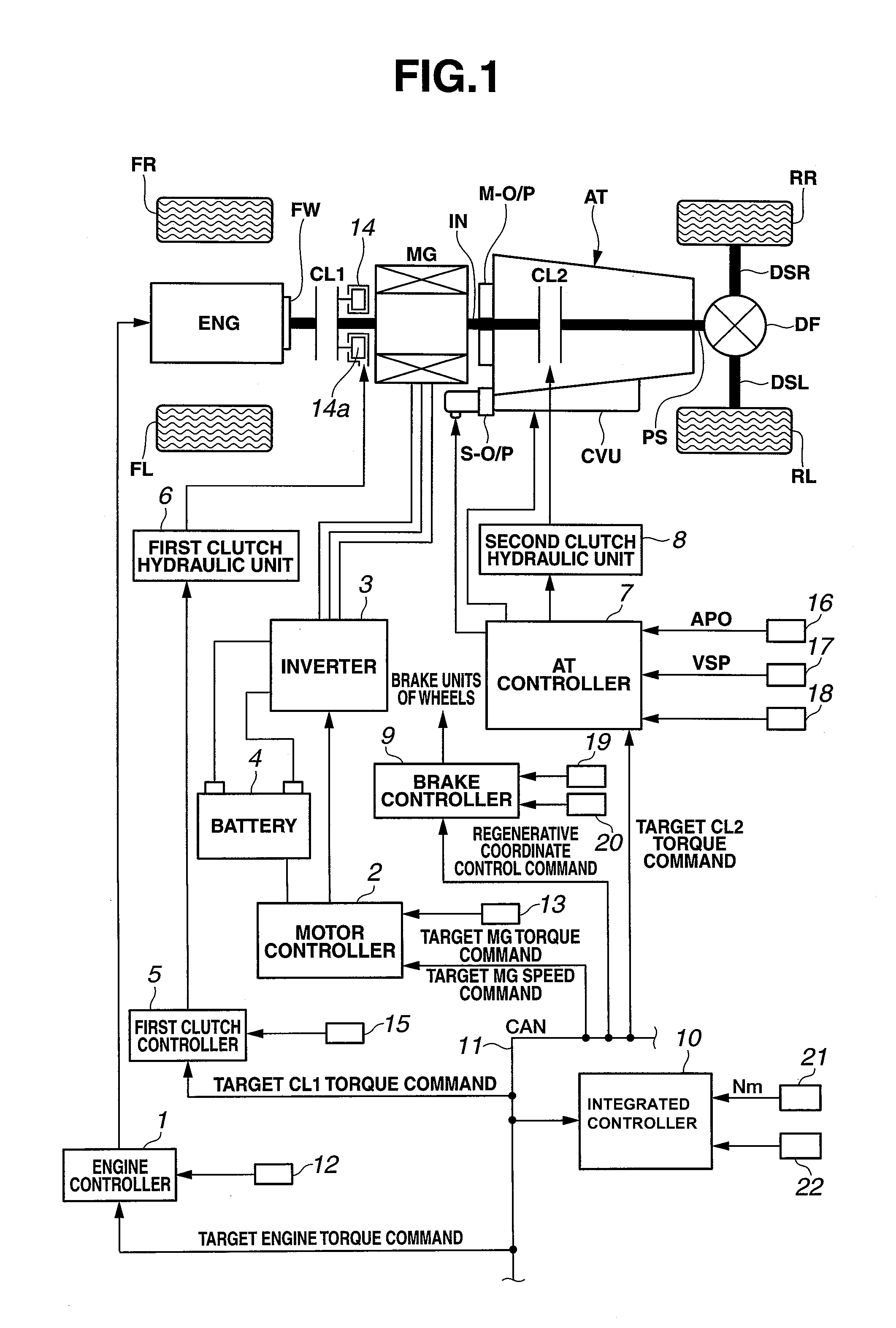

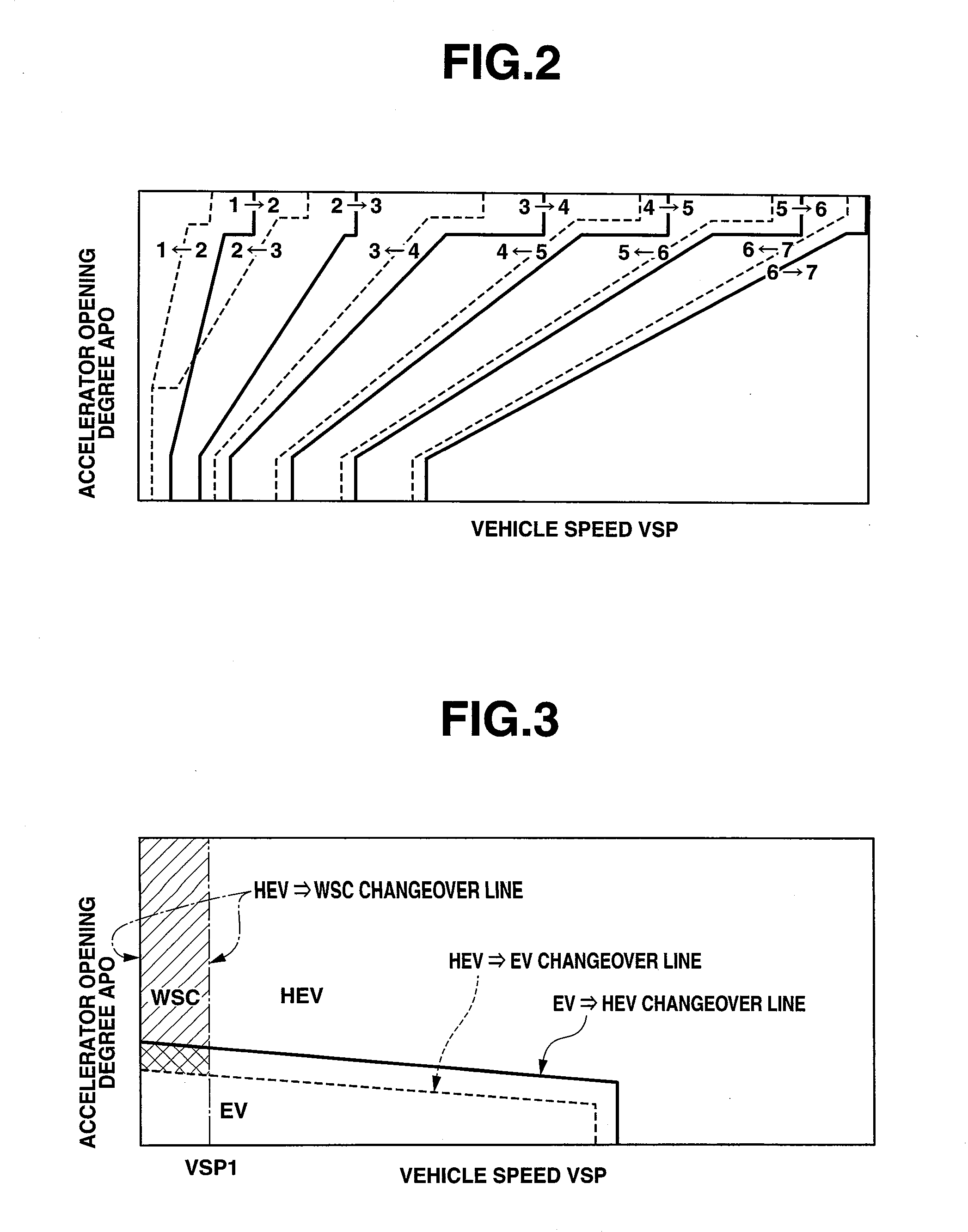

Control apparatus and method for hybrid vehicle

ActiveUS20130124027A1Improve responsivenessReduce adverse effectsDigital data processing detailsPropulsion using engine-driven generatorsAutomatic transmissionLag

A control apparatus and method for controlling a hybrid vehicle is arranged to prevent shock and to minimize adverse influence on lag and fuel consumption when one of a start / stop control of an engine and a shift control of an automatic transmission is requested while the other control is occurring. The control apparatus includes an engine, a motor / generator, a first clutch, an automatic transmission, an integrated controller, an AT controller and an engine / transmission coordinate controlling section. When a second control request is generated during the first control, the engine / transmission coordinate controlling section starts the second control at a request timing when a condition does not exist such that a shock does not exceed an acceptable level and starts the second control at a later timing when the condition exists such that the shock would exceed the acceptable level if the second control is started at the request timing.

Owner:NISSAN MOTOR CO LTD

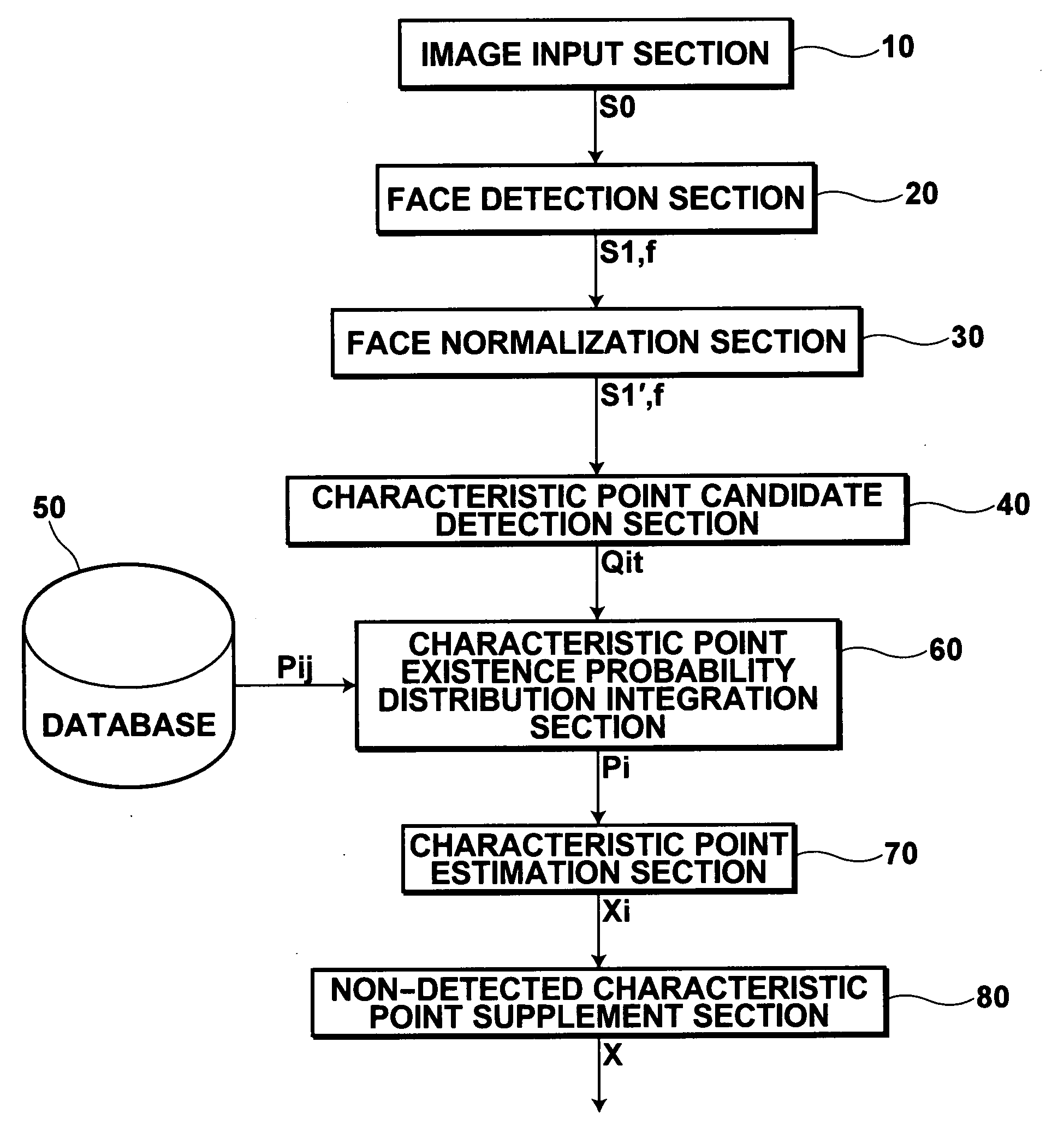

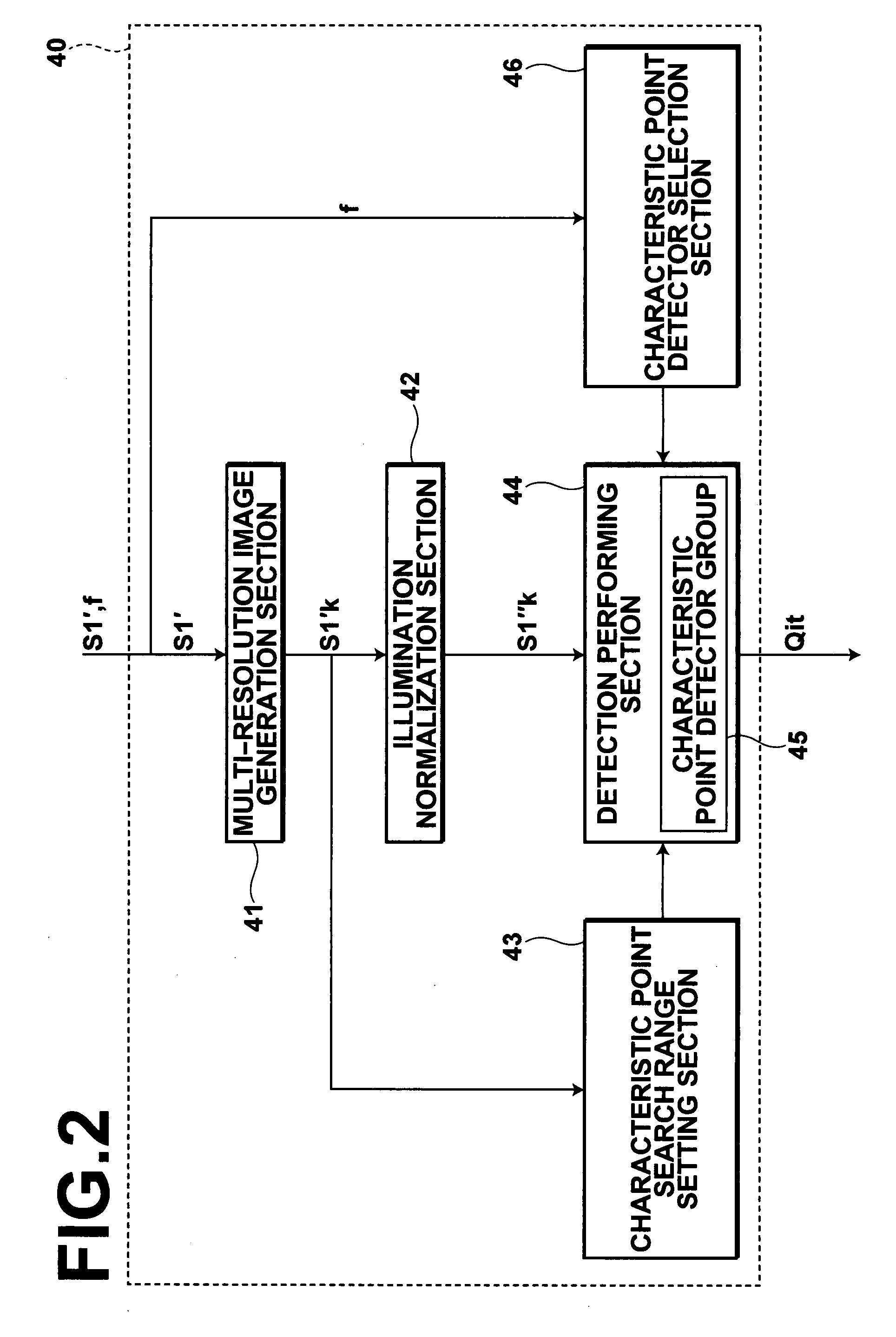

Characteristic point detection method, apparatus, and program

ActiveUS20070195996A1Minimize influenceAccurate and reliable detectionCharacter and pattern recognitionCharacteristic pointAlgorithm

A characteristic point detection method, including the steps of: detecting a candidate of each of a plurality of characteristic points of a predetermined object from a detection target image; obtaining an existence probability distribution for a target characteristic point with respect to each of the detected candidates of the other characteristic points, which is an existence probability distribution of the target characteristic point when the position of the detected candidate of another characteristic point is taken as a reference, using an existence probability distribution statistically obtained for each combination of two different characteristic points of the plurality of characteristic points; integrating the obtained existence probability distributions by weighting according to the positional relationship between the reference characteristic point and target characteristic point; and estimating the true point of the target characteristic point based on the magnitude of the existence probabilities in the integrated existence probability distribution thereof.

Owner:FUJIFILM CORP

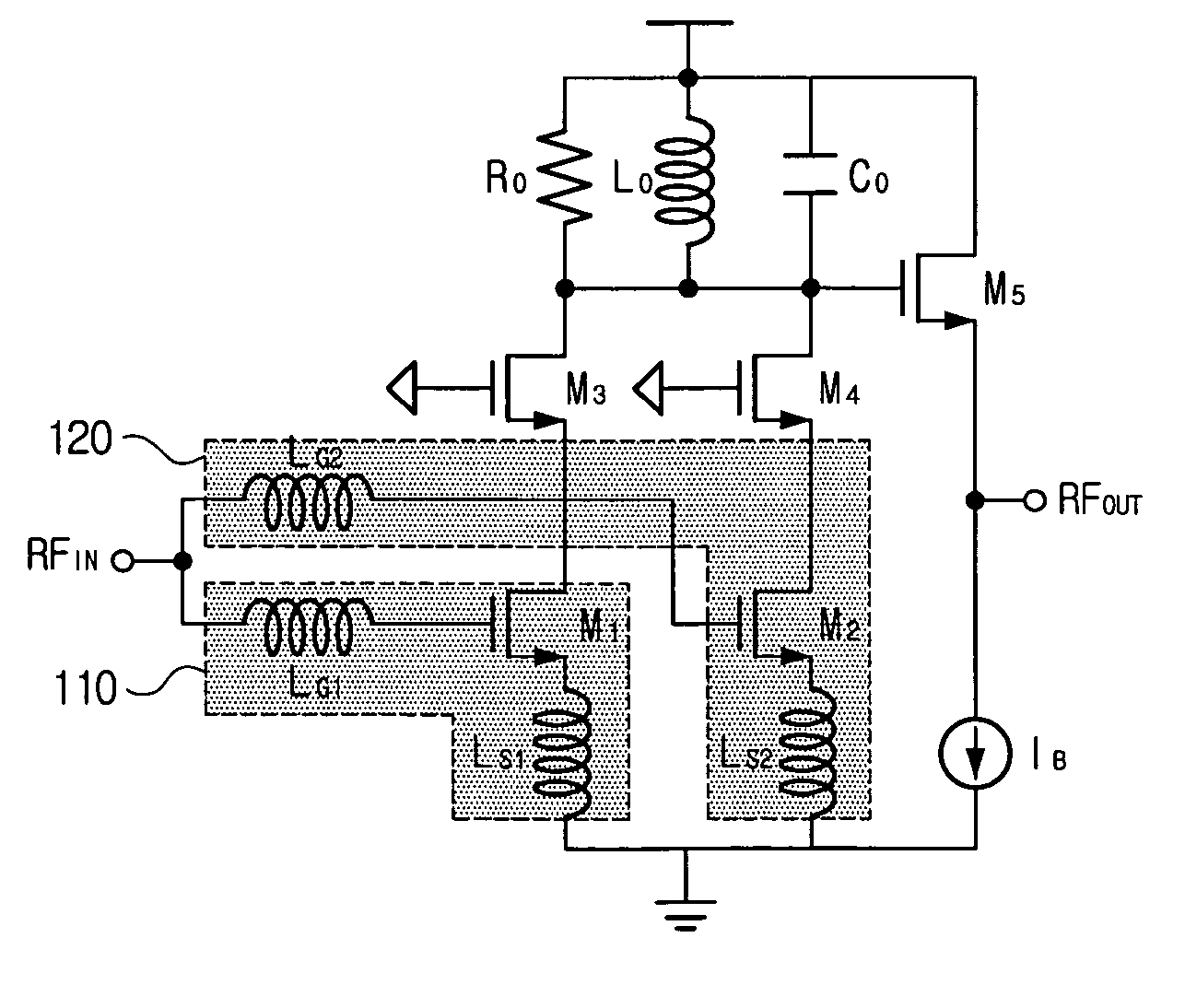

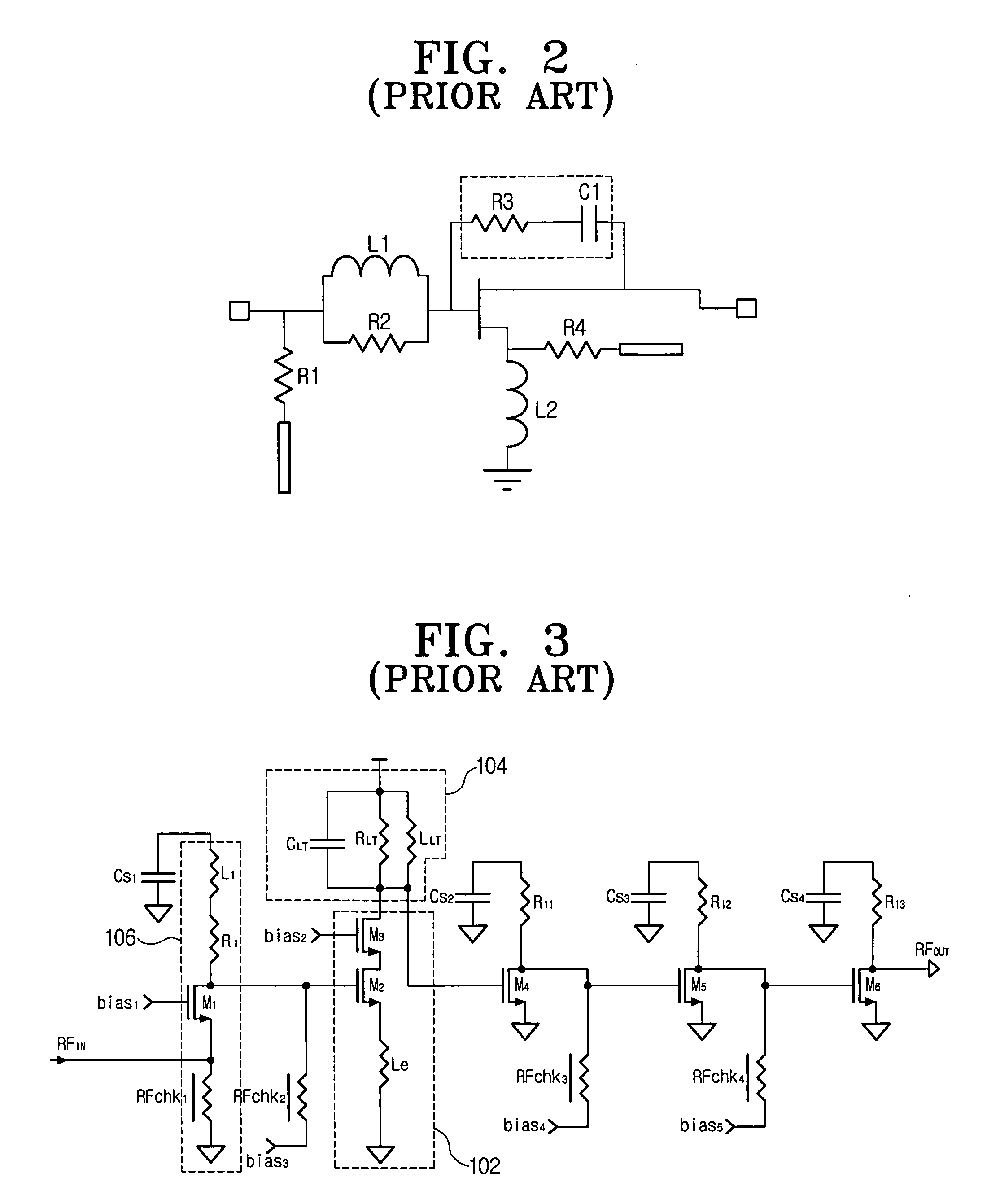

Low noise amplifier for ultra wide band

ActiveUS20060170502A1Minimize influenceMinimize impactOperating means/releasing devices for valvesAmplifier modifications to reduce noise influenceFrequency bandLoad circuit

A low noise amplifier (LNA) for ultra wide band recives and amplifies identical RF signals in different frequency bands, and includes more than one pair of narrow band LNAs coupled in parallel, and a load circuit which increases load impedance of the entire circuit of the narrow band LNAs. The LNA can not only amplify the RF signal in the UWB but also obtain the low noise and the high gain that are features of the conventional narrow band LNA.

Owner:SAMSUNG ELECTRONICS CO LTD

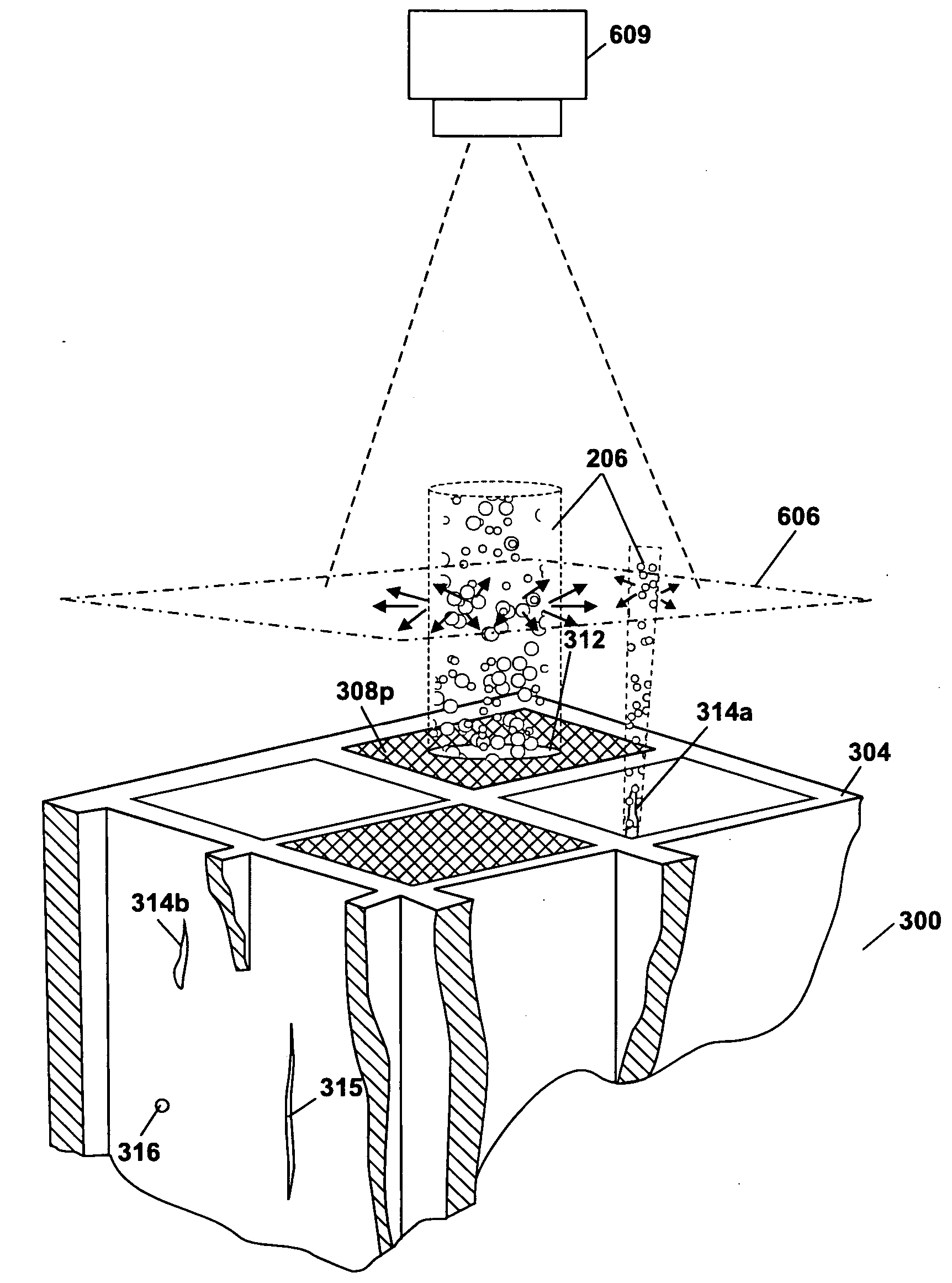

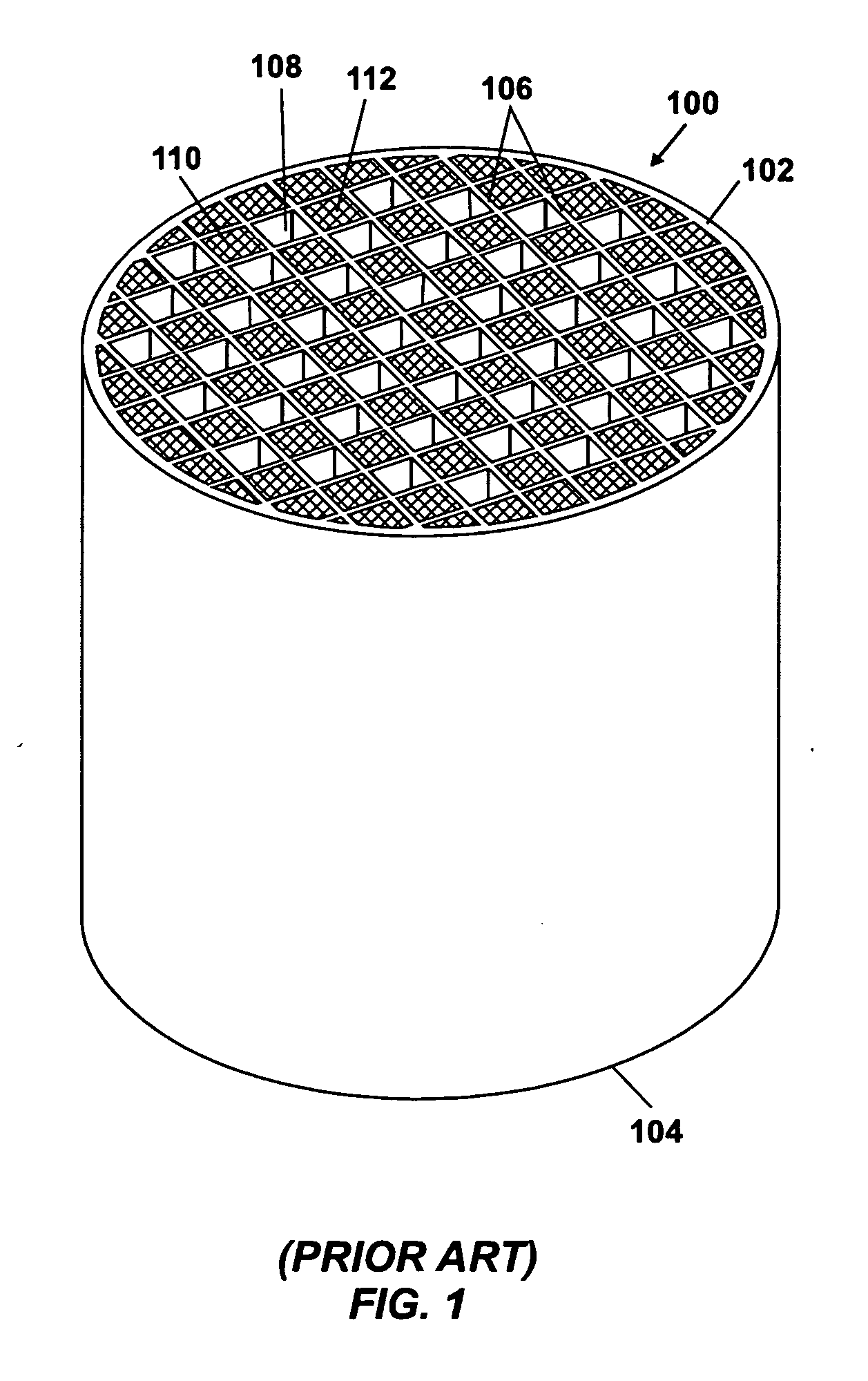

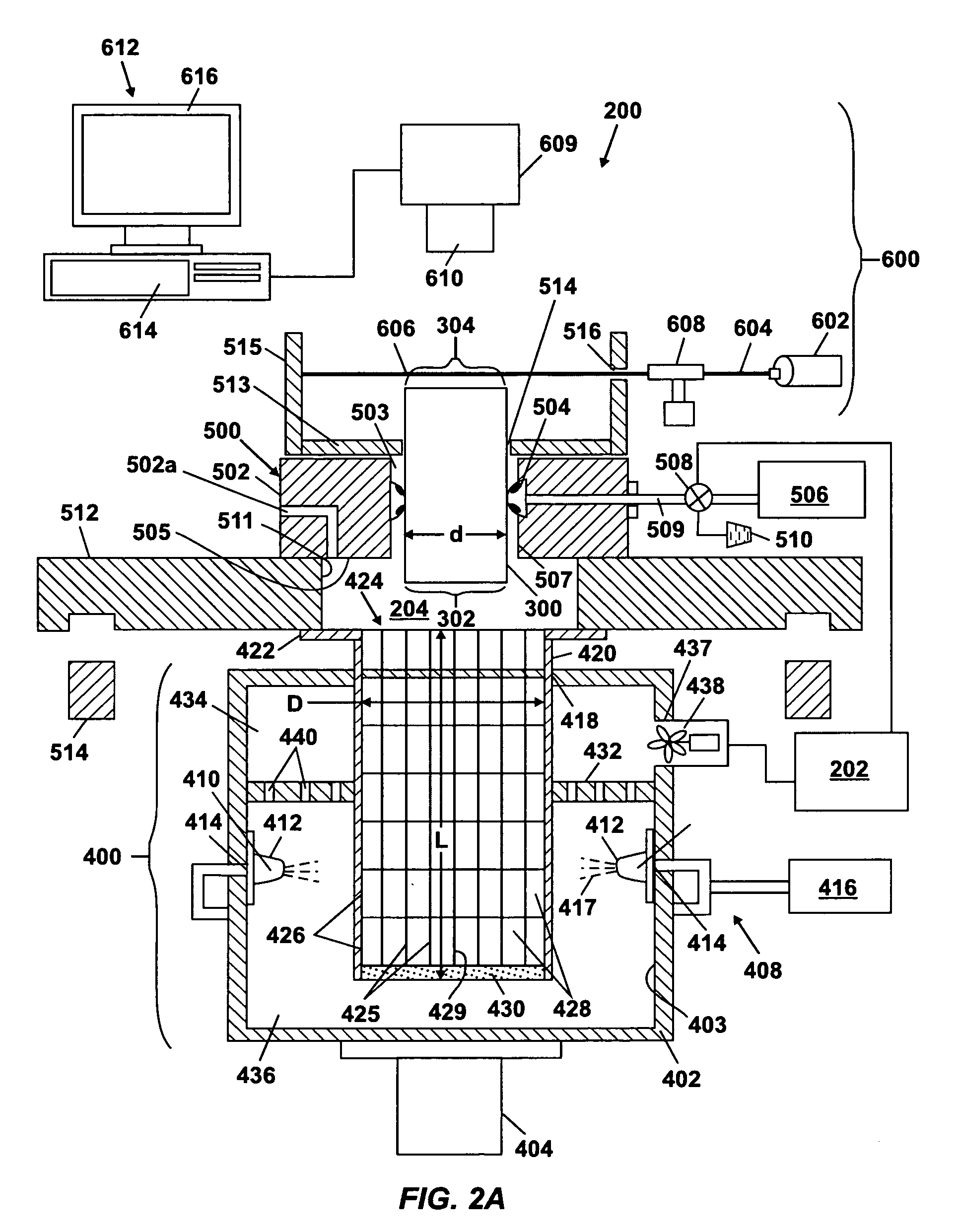

Method, system and apparatus for detecting defects in a honeycomb body using a particulate fluid

ActiveUS20070022724A1Minimize influenceMinimizes boundary layer influenceCombination devicesDispersed particle filtrationHoneycombEngineering

A system, apparatus and method for detecting defects in a honeycomb body. The system and apparatus include a fixture adapted to hold the honeycomb body, a particulate fluid source, a pipe which defines a flow path between the particulate fluid source and a first end face of the honeycomb body thereby allowing particulate fluid to flow from the particulate fluid source to the first end face of the honeycomb body. The particulate fluid emerges at a second end face of the honeycomb body through defects, if any, in the honeycomb body where the positions of such defects may be monitored. The system and apparatus includes a flow straightener disposed in the flow path to minimize boundary layer influence of the pipe on the flow of the particulate fluid. A substantially uniform velocity flow profile is provided to the first end face of the honeycomb body.

Owner:CORNING INC

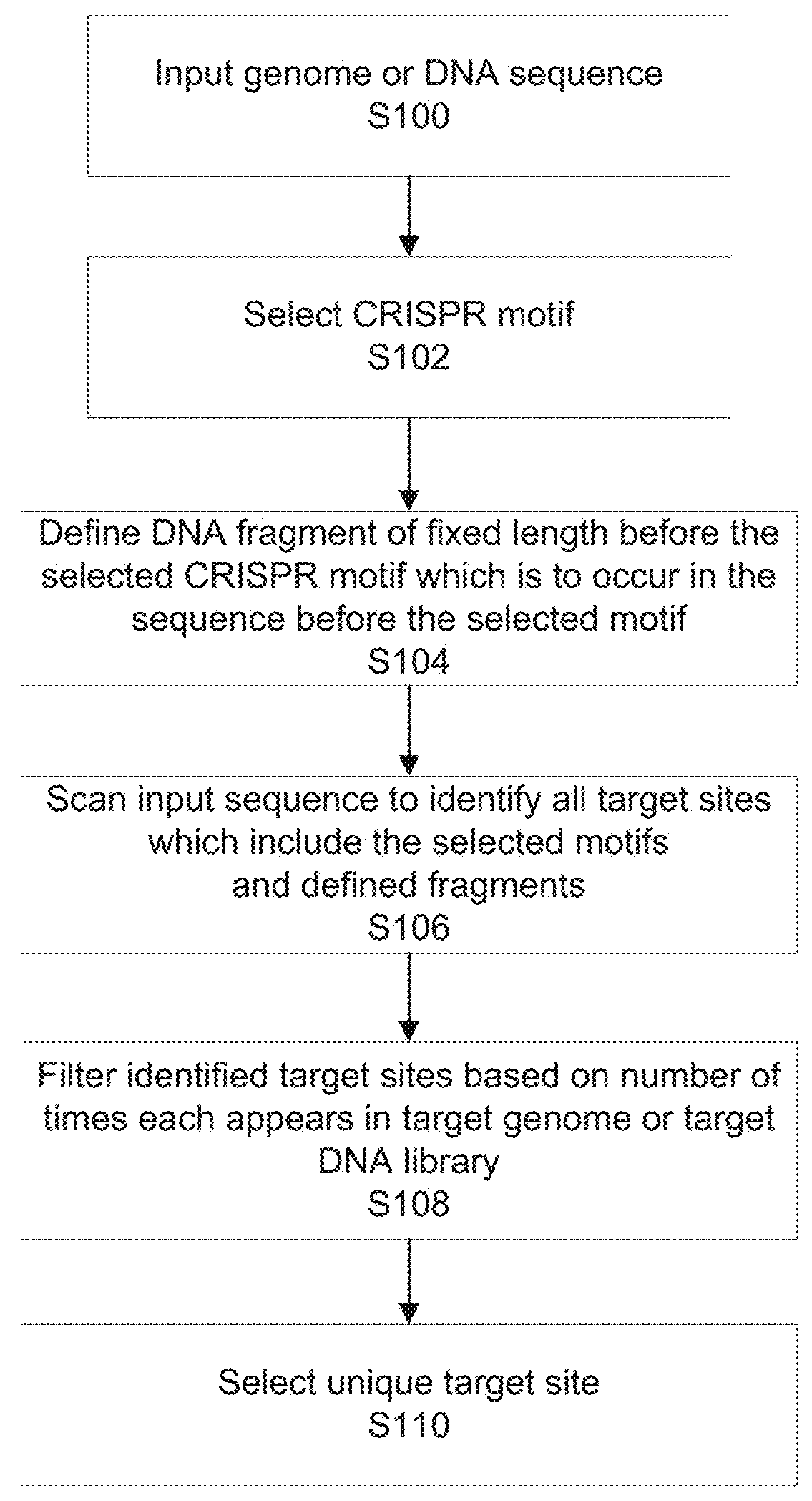

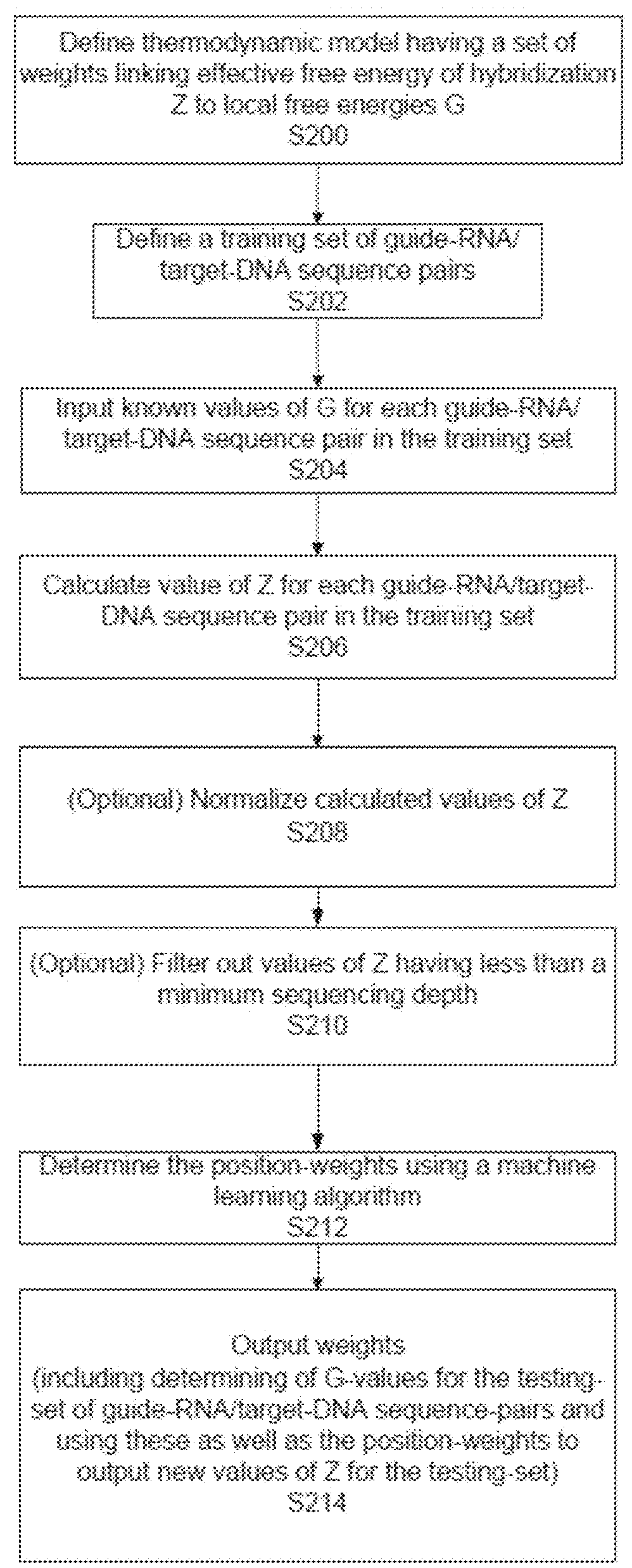

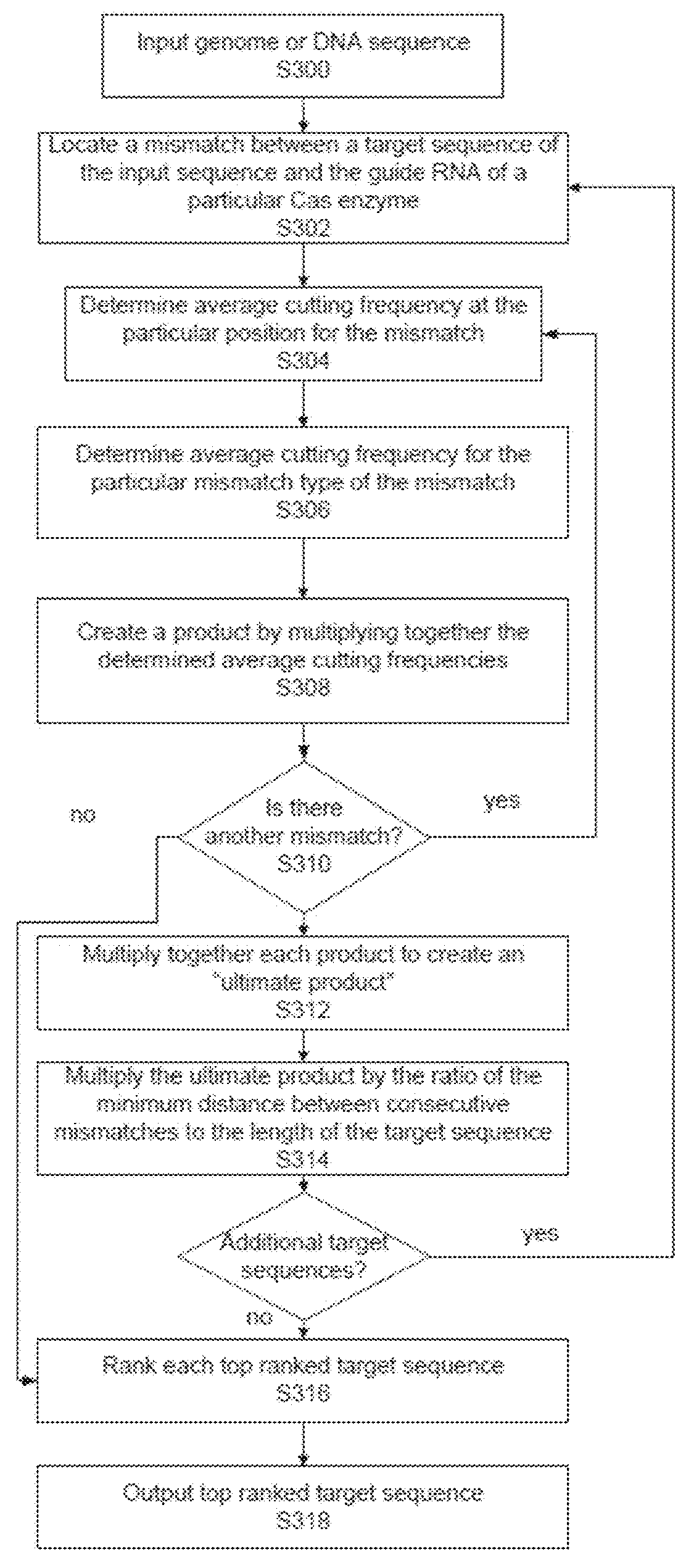

Unbiased identification of double-strand breaks and genomic rearrangement by genome-wide insert capture sequencing

ActiveUS20180163265A1Avoid biasMinimize influenceHydrolasesMicrobiological testing/measurementOff targetsDisease

Owner:THE BROAD INST INC +1

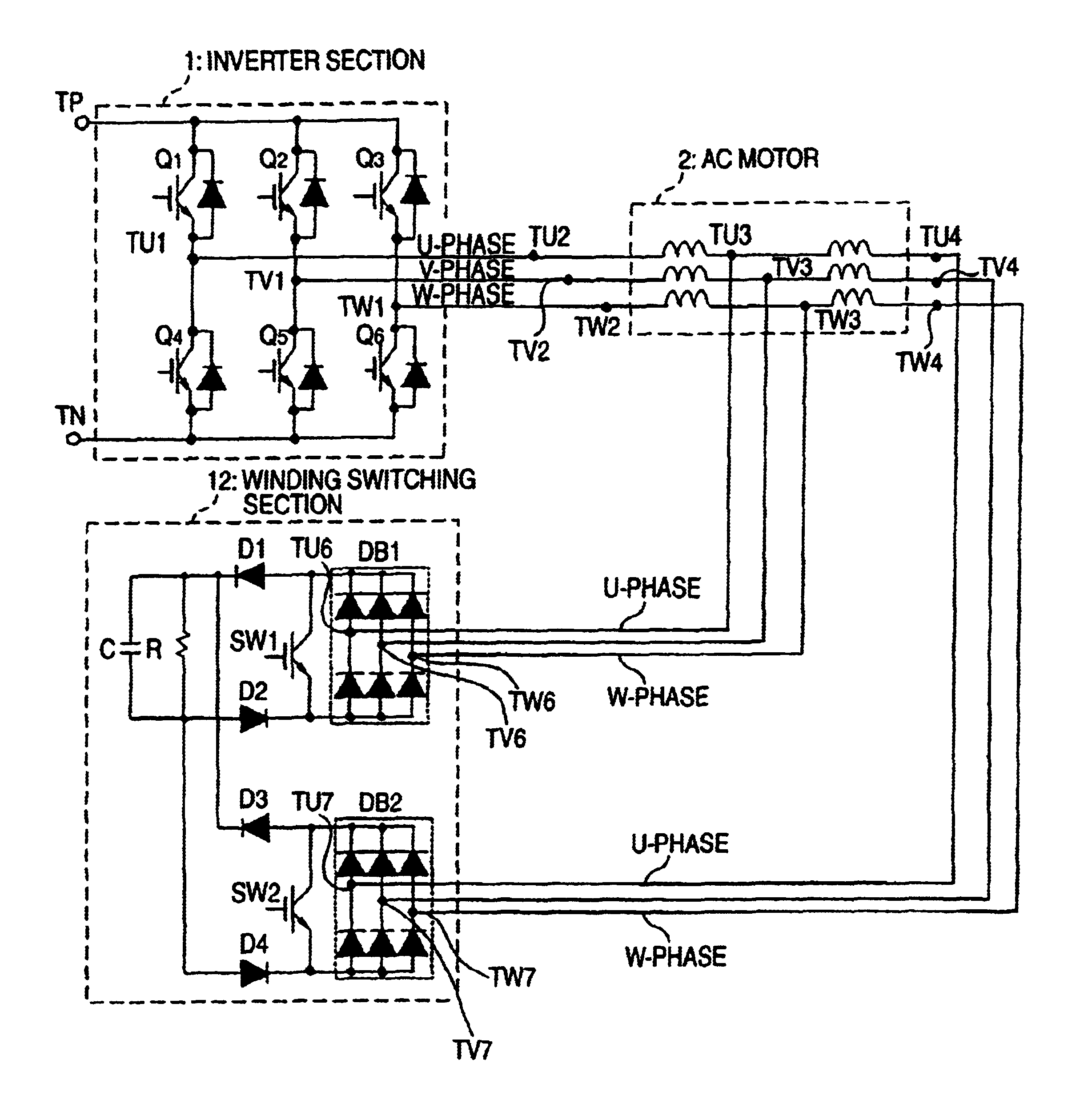

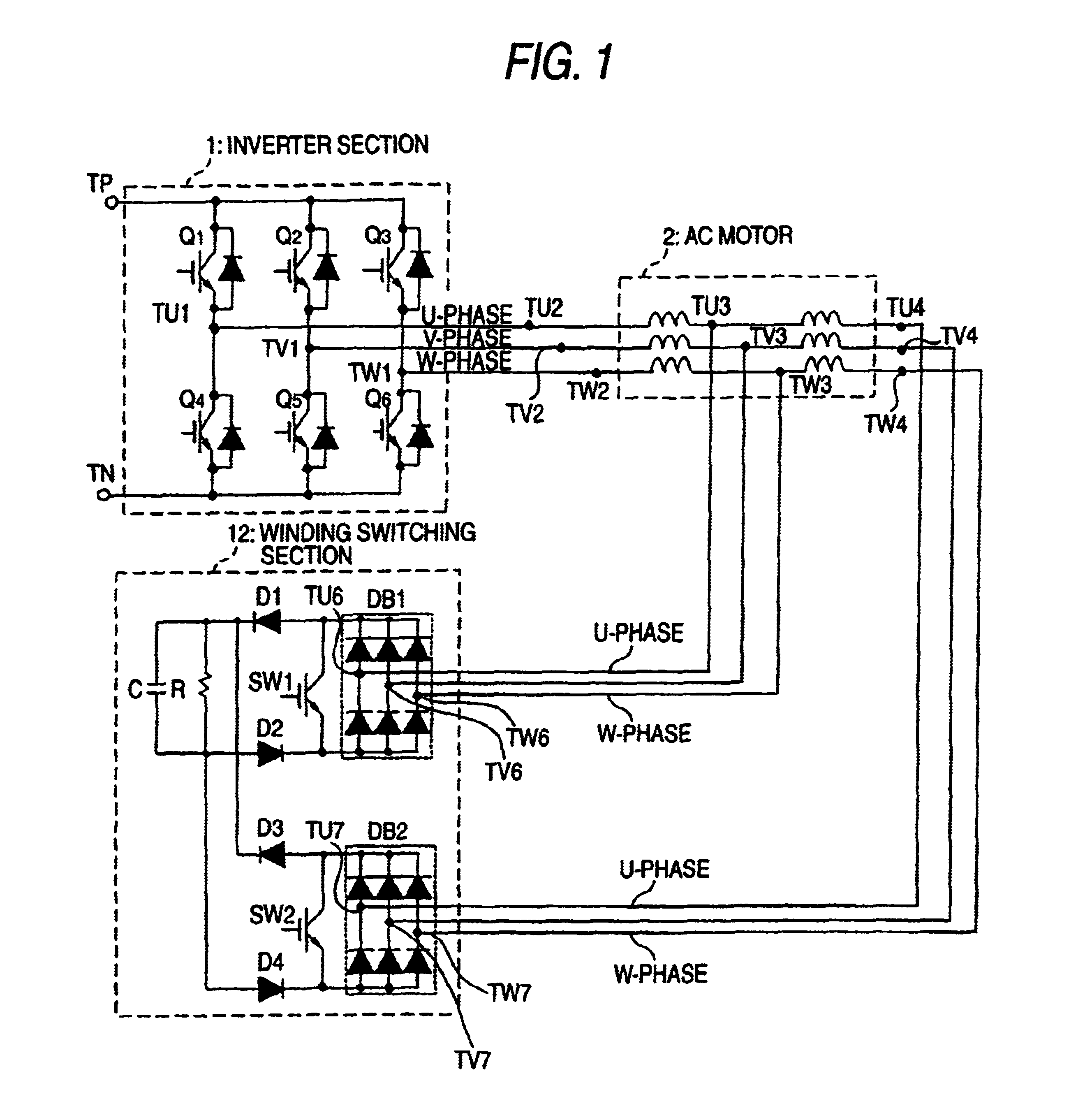

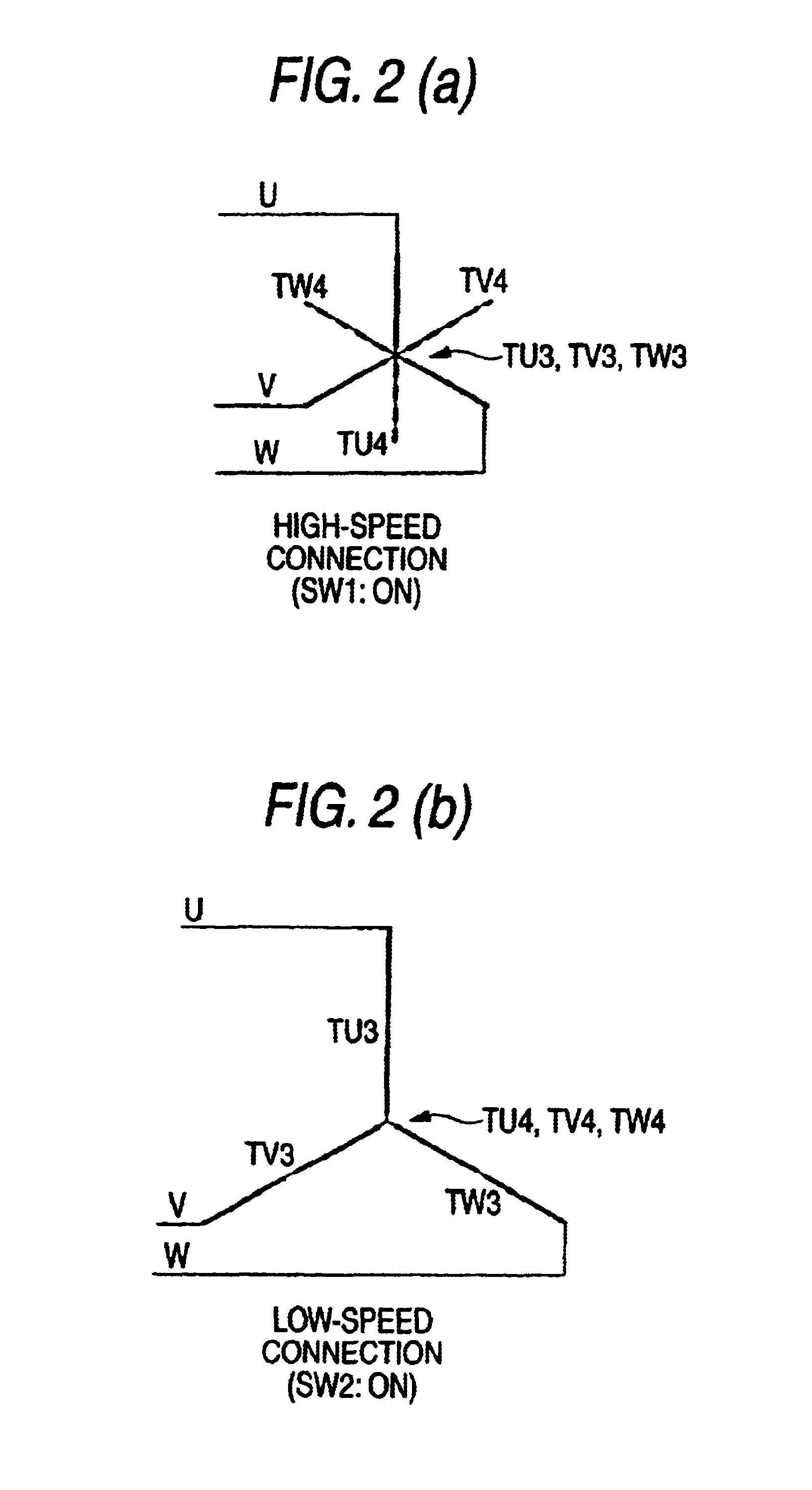

Apparatus for switching windings of AC three-phase motor

InactiveUS6847185B2No longer be switchedShorten the timeSingle-phase induction motor startersMotor/generator/converter stoppersThree-phaseEngineering

It is an object to provide a winding switching device of a three-phase AC motor having a small size at a low cost in which a time required for switching a winding is shortened and the number of semiconductor switch units is decreased as much as possible. In a winding switching device of a three-phase AC motor including an AC motor in which a winding having each phase is formed by a plurality of windings and a connecting terminal connecting the windings to each other and both terminals of the winding having the phase are provided on an outside of a motor, winding switching means for properly switching the connecting terminal, and a variable frequency power source for supplying a variable voltage having a variable frequency to the AC motor, the winding switching means is constituted by a plurality of three-phase rectifying means connecting one of ends of the winding having the phase to the variable frequency power source and connecting the other end and the connecting terminal to an input terminal on an AC side of the three-phase rectifying means for each phase, and a semiconductor switch provided to open and close both ends on a DC output side of the three-phase rectifying means.

Owner:YASKAWA DENKI KK

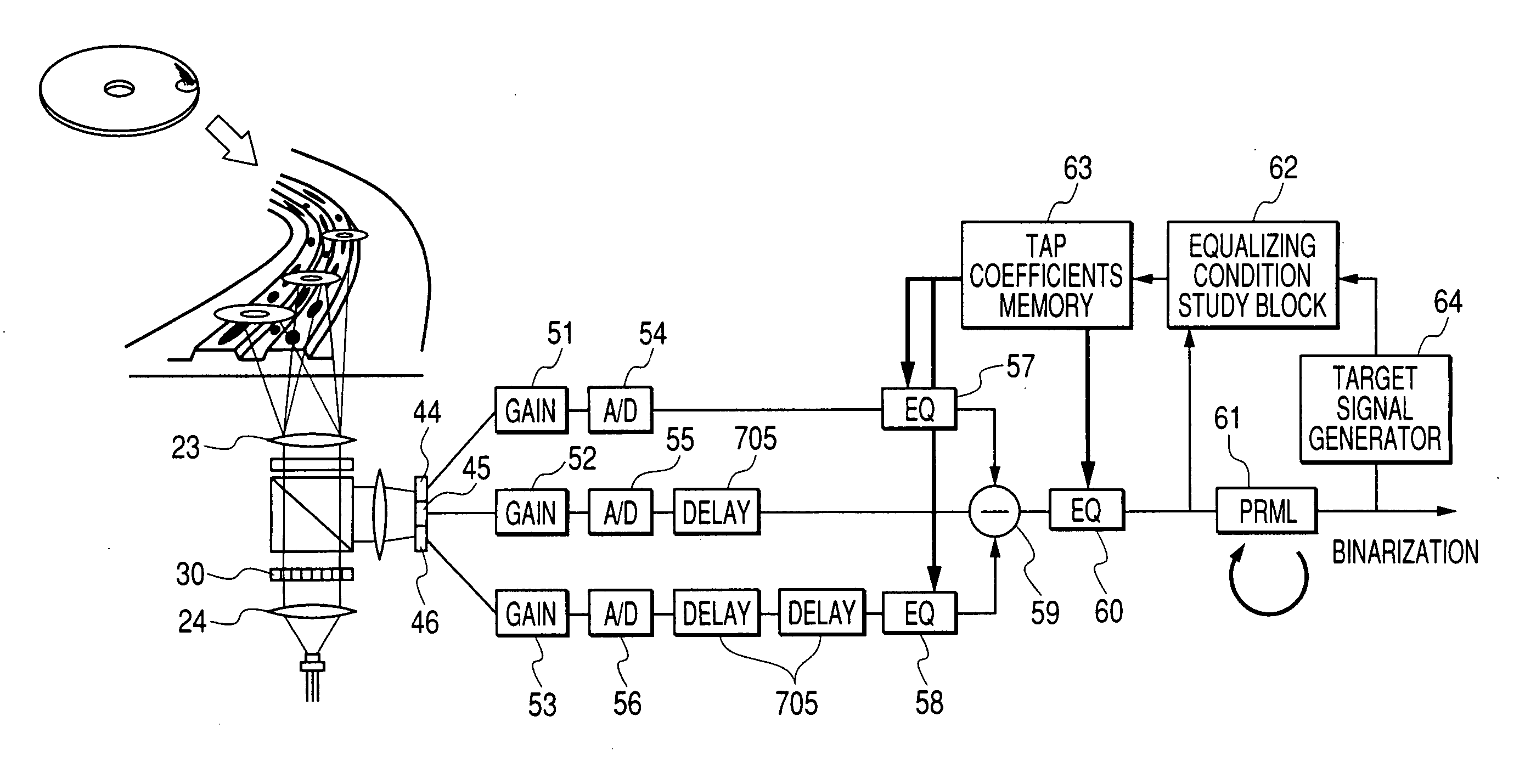

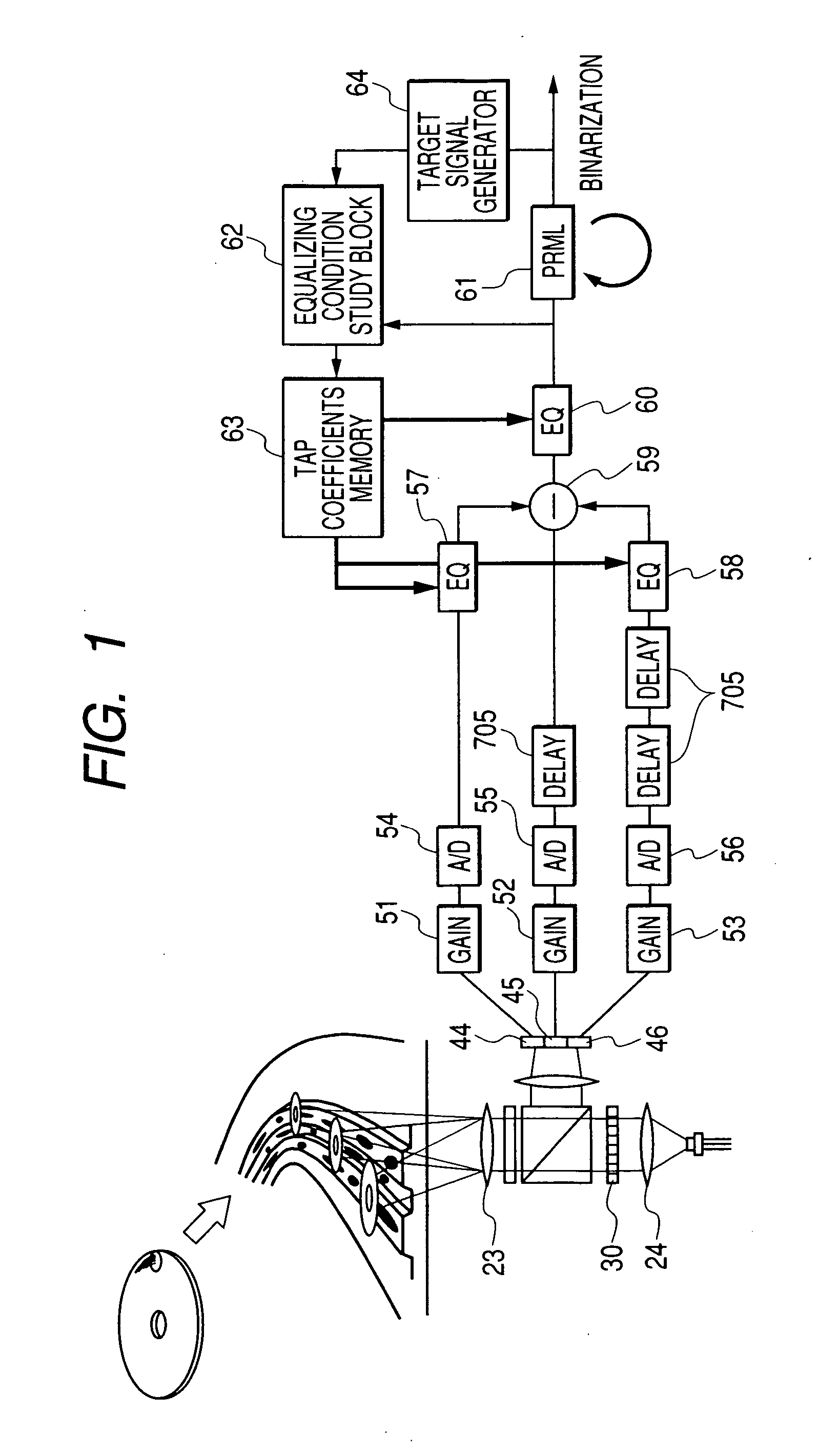

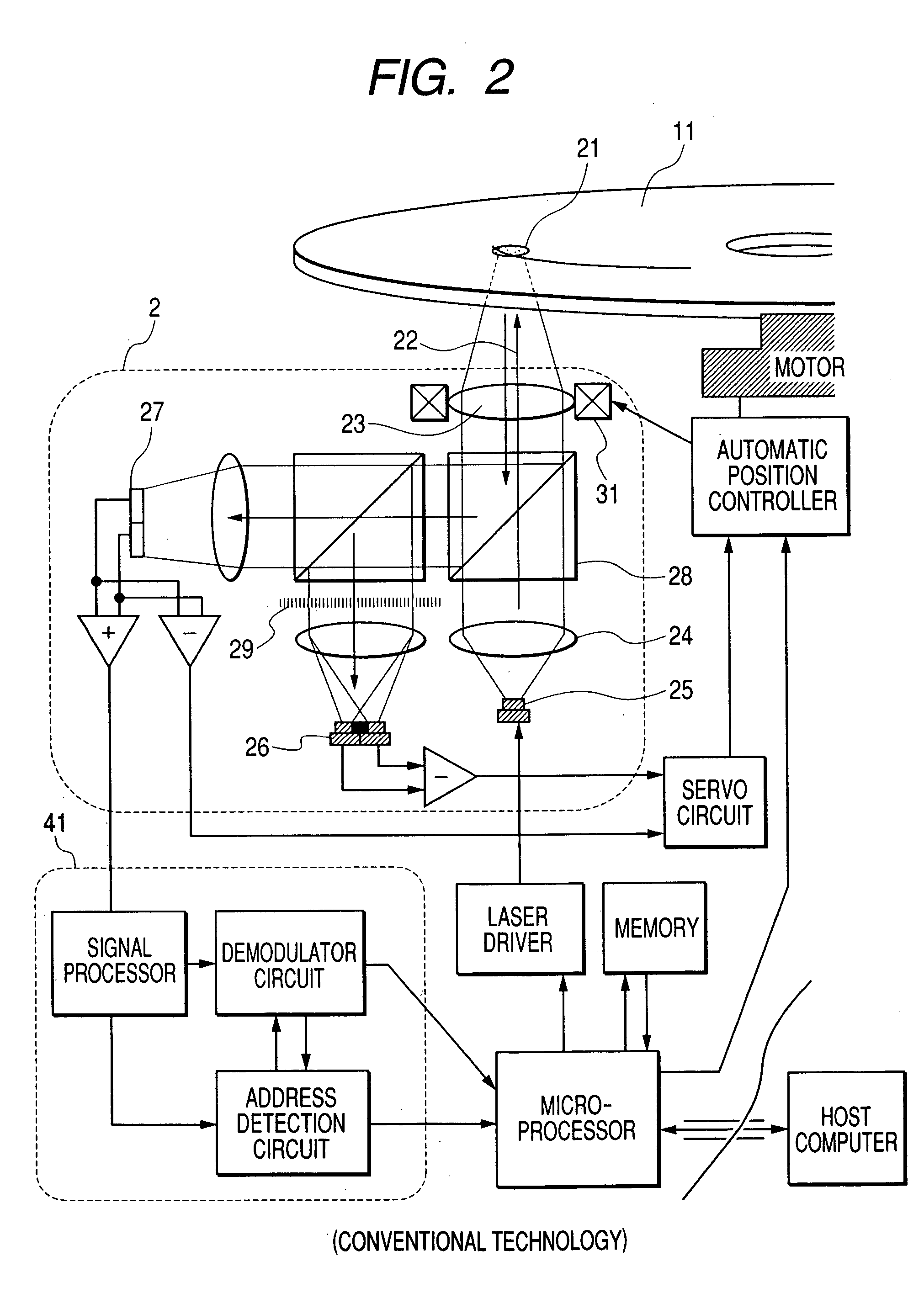

Information reproduction apparatus and information reproduction method

InactiveUS20050259551A1Minimize influenceLower error rateTelevision system detailsRecord information storageEngineeringElectrical and Electronics engineering

Disclosed here is an apparatus and method for realizing write / read of mass information by reducing cross-talk components that are apt to increase in narrow tracks when various disturbances and variations are recognized. In order to achieve the above object, the apparatus is provided with a plurality of equalizers for correcting frequency characteristics of signals reproduced from a plurality of spots, then outputs from those equalizers are subjected to a computing process to correct tap coefficients of the equalizers sequentially so as to minimize the influence of the subject cross-talk, thereby realizing stable reduction of the cross-talk components.

Owner:HITACHI LTD

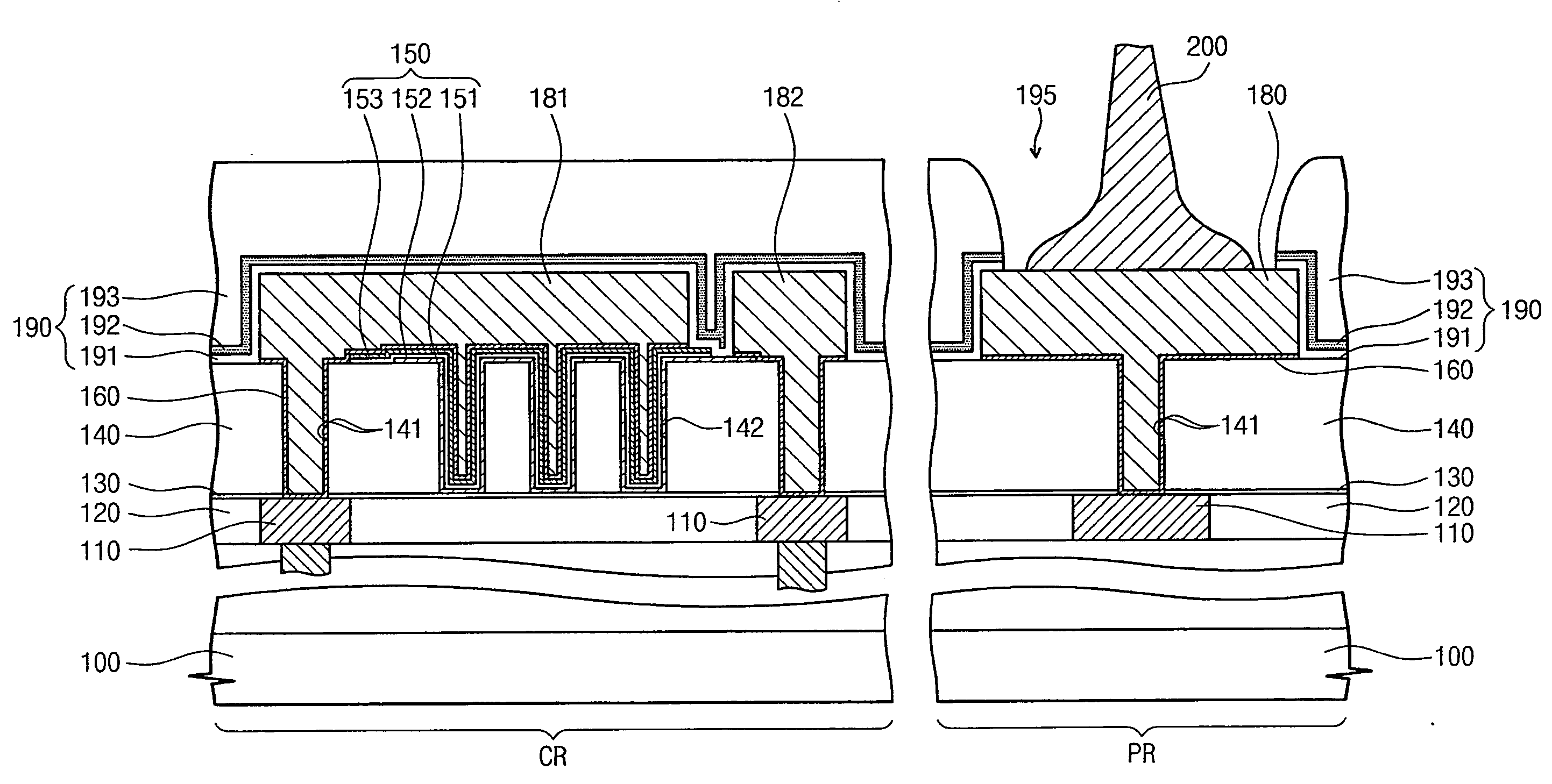

Capacitor structure of semiconductor device and method of fabricating the same

ActiveUS20070235790A1Minimize influenceMinimize impactTransistorSemiconductor/solid-state device detailsCapacitanceSemiconductor

A semiconductor device having superior capacitance may include interconnections formed on a semiconductor substrate, an interlayer insulation layer on the interconnections and having vias exposing a portion of the top surface of the interconnections, a capacitor which may be on the interlayer insulation layer and having a bottom electrode, a dielectric layer pattern, and a top electrode which may be sequentially stacked, and a pad structure may be connected to the interconnections through the vias. The pad structure may include pads for bonding with external electronic devices and a first upper interconnection connected to the top electrode of the capacitor.

Owner:SAMSUNG ELECTRONICS CO LTD

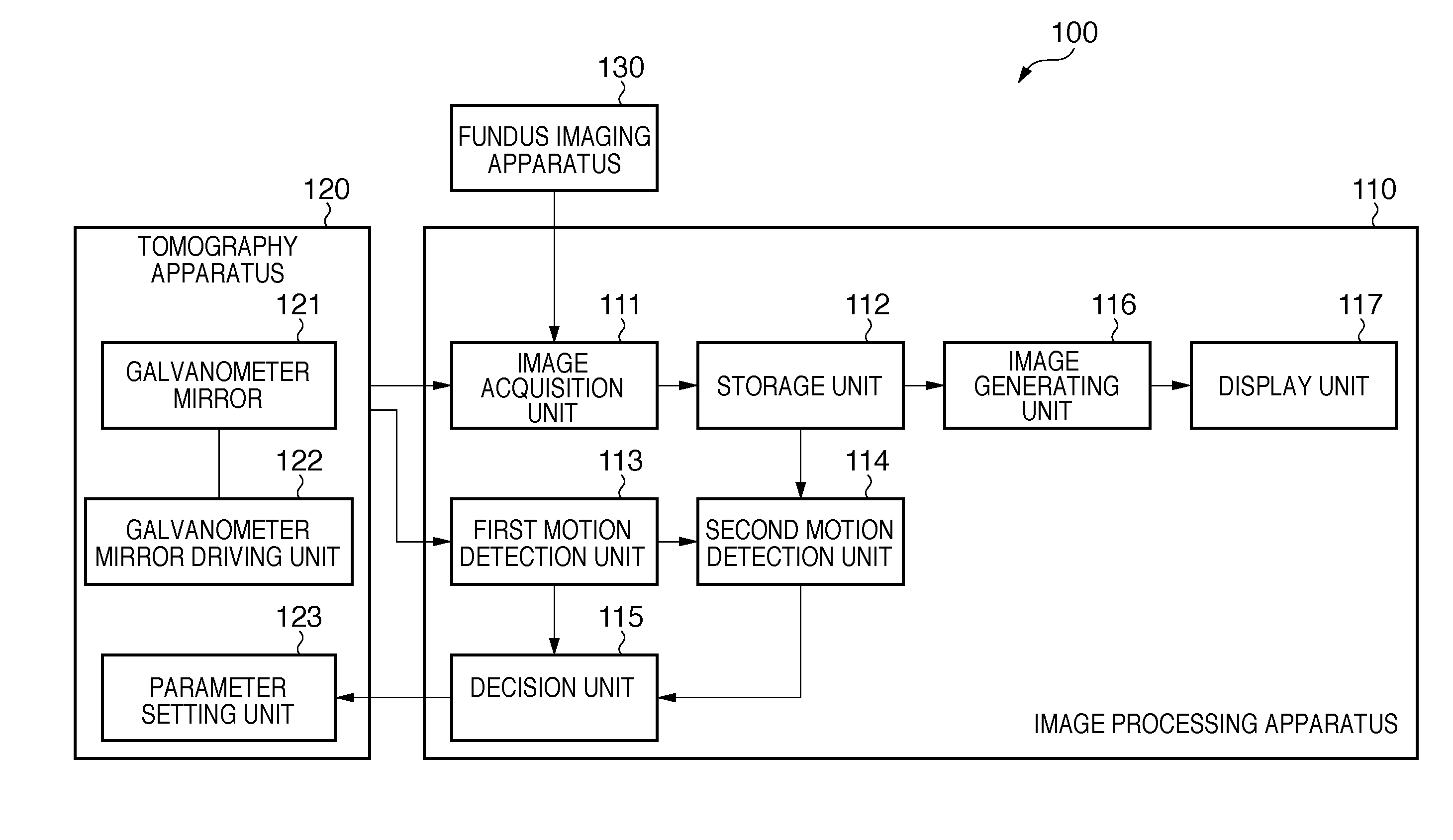

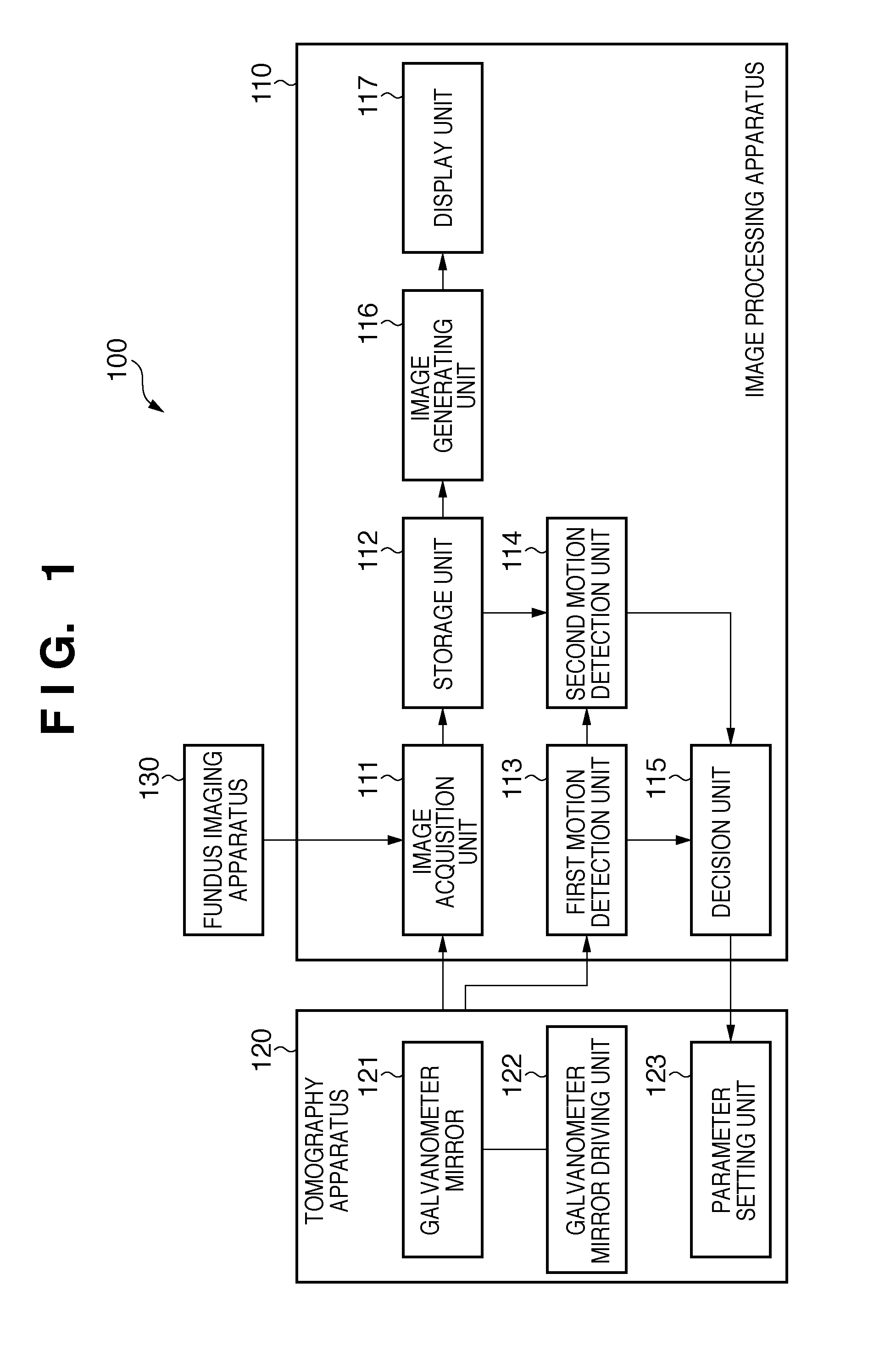

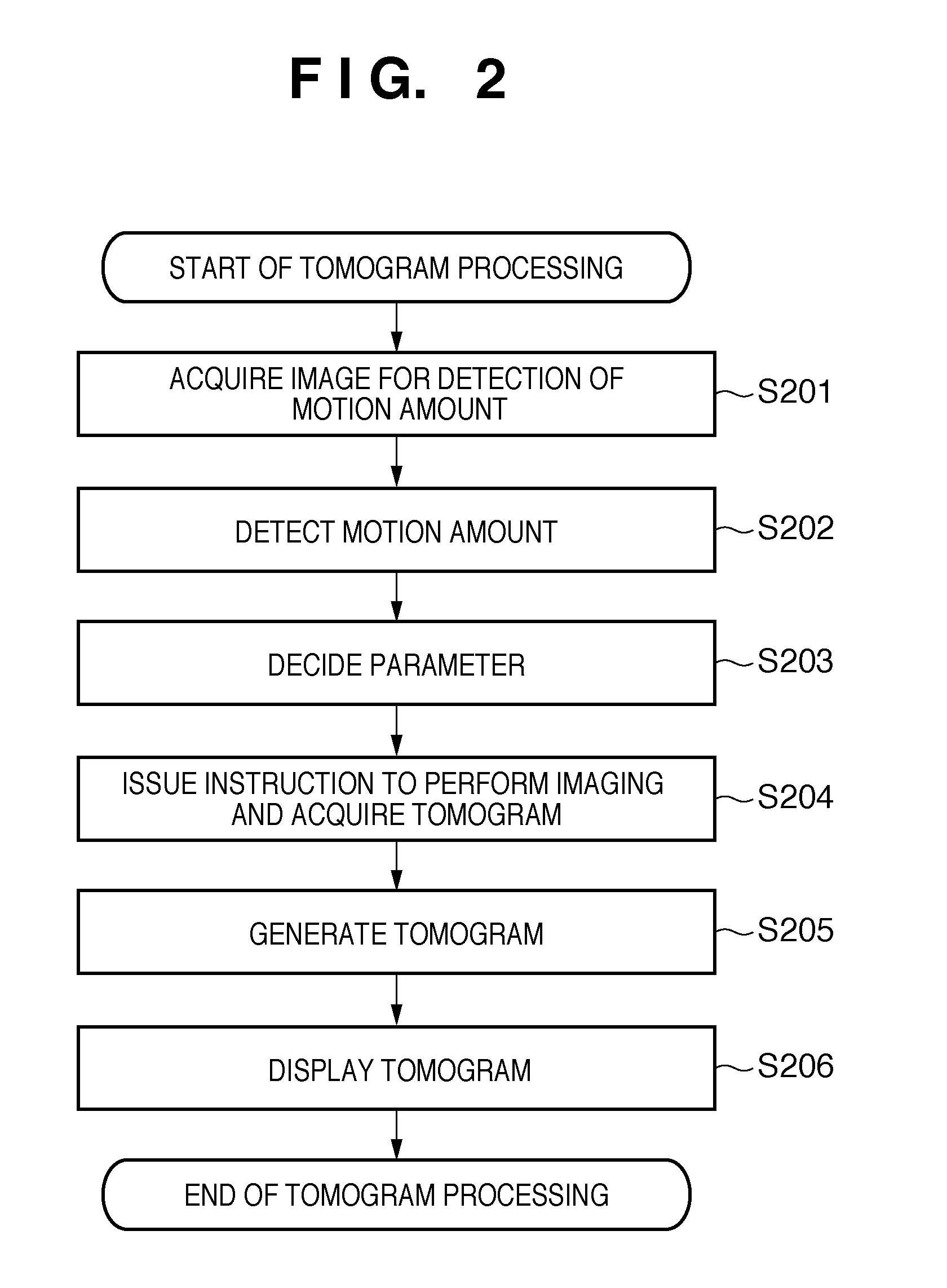

Image processing apparatus and image processing method

InactiveUS20110134392A1Minimize influenceMinimize impactImage enhancementImage analysisHead partsHigh resolution

This invention can generate a high-resolution, low-noise tomogram while minimizing the influences of the flicks of the eyeballs, the movement of the head, and the like. The invention is an image processing apparatus which processes a tomogram of an eye to be examined and includes detection units to detect the motion amount of the eye by using a signal obtained by capturing the tomogram, and a decision unit to decide the number of scanning lines for capturing of the tomogram based on the motion amount detected by the detection units.

Owner:CANON KK

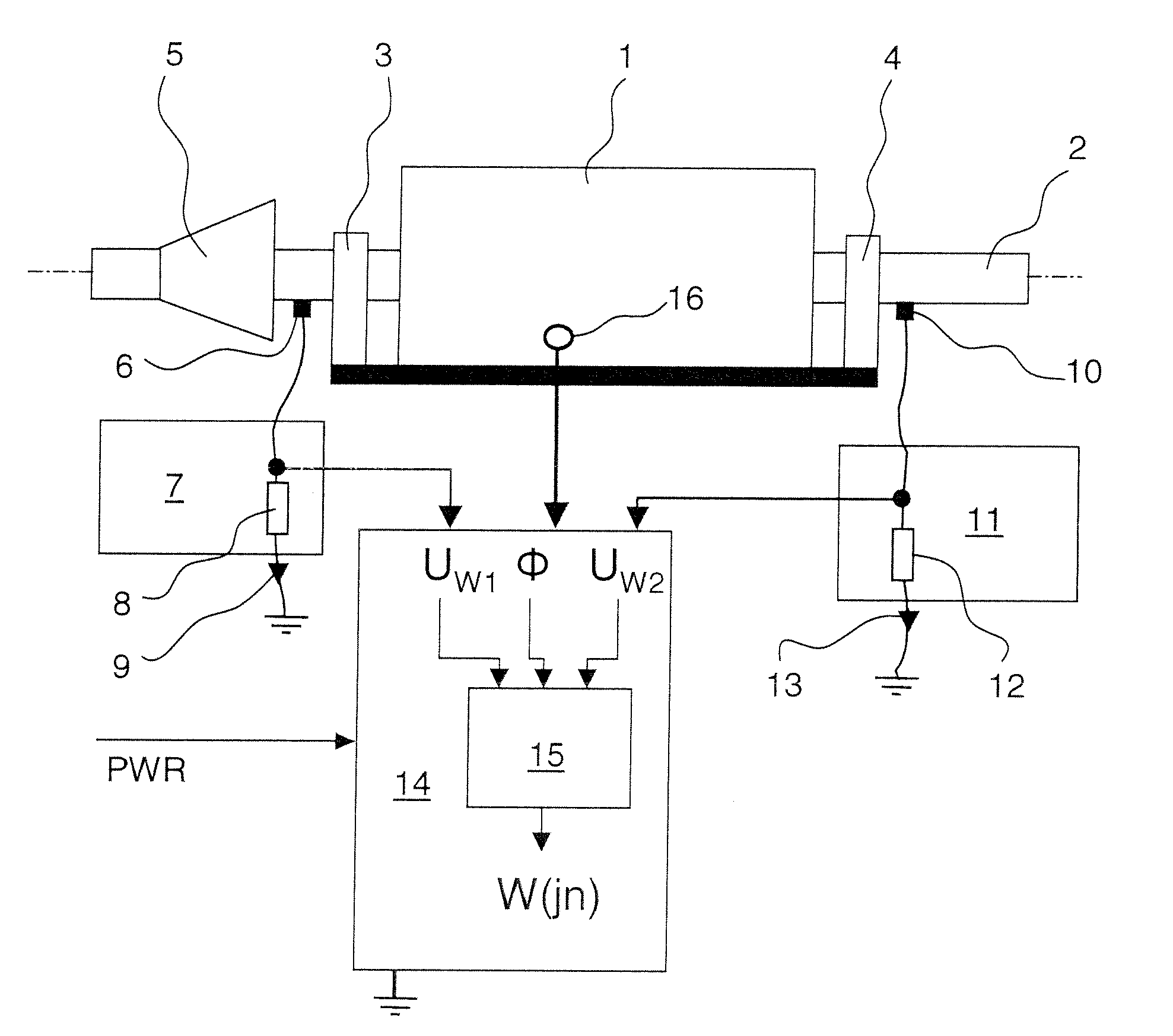

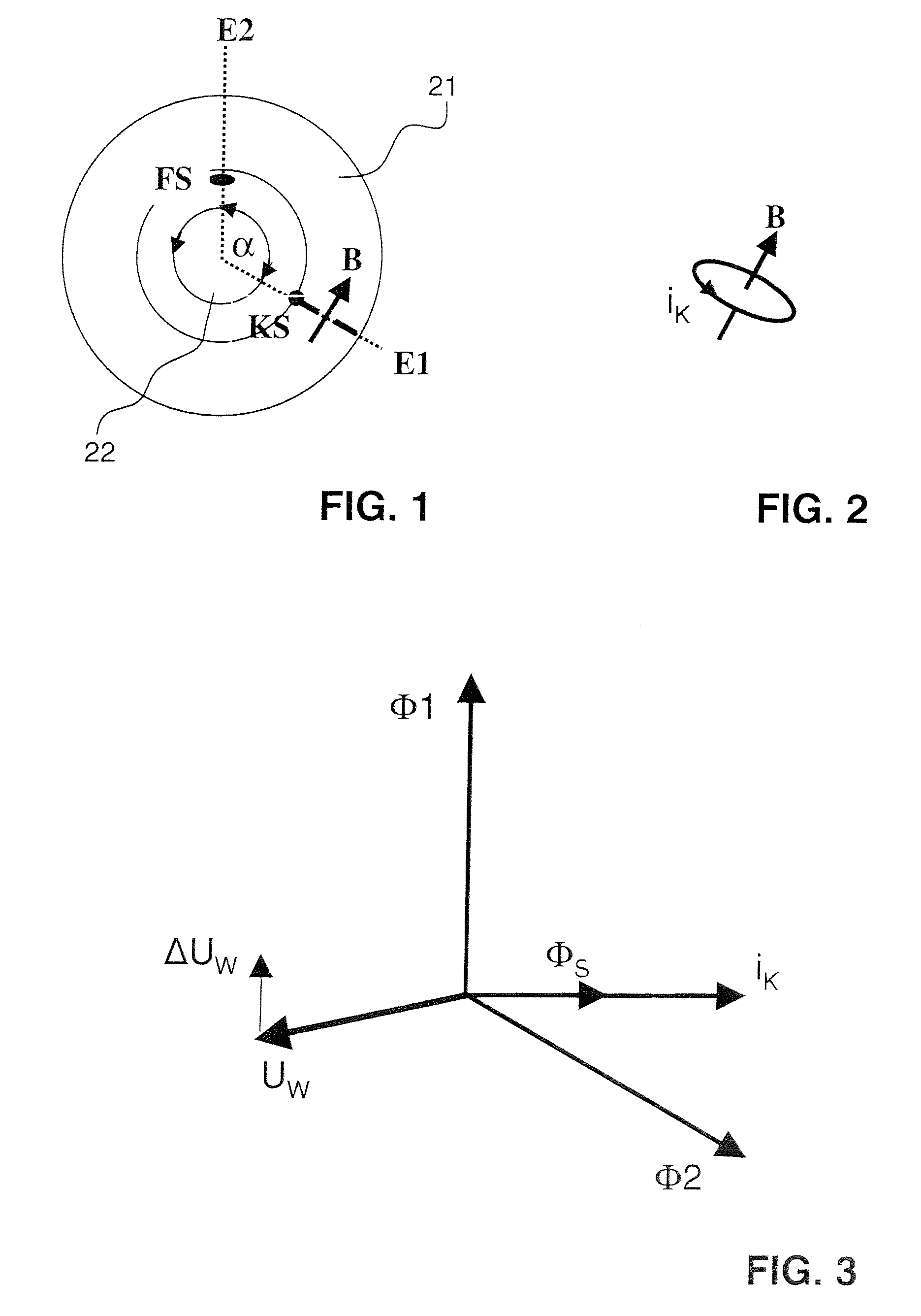

Method and device for detecting interlaminar short circuits

A method for determining a short circuit between at least two stator laminates in an electrical machine having a rotor mounted on a shaft and a stator, includes rotating the rotor on the shaft relative to the stator so to pass a magnetic stator flux, varying over time, through the stator, determining, during the rotation, a measurement variable sensitive to a short-circuit current caused by the magnetic stator flux between the at least two stator laminates, and determining the magnetic stator flux. In addition, a theoretical model is provided describing a relationship between the magnetic stator flux and the measurement value or an auxiliary variable derived from the measurement value, and the measurement variable or the auxiliary variable is compared with the theoretical model. A device for carrying out a method for determining a short circuit is also provided.

Owner:GENERAL ELECTRIC TECH GMBH

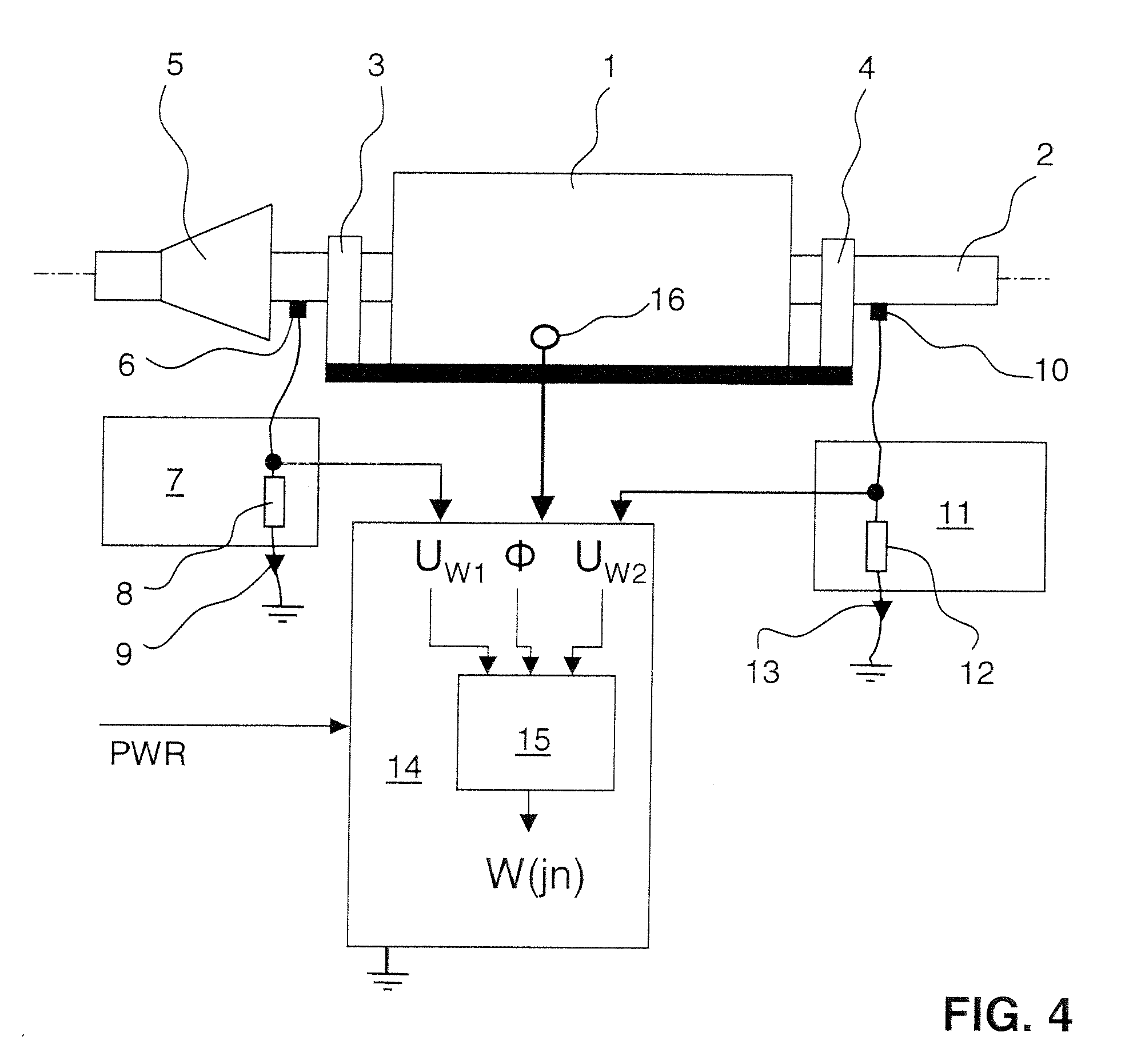

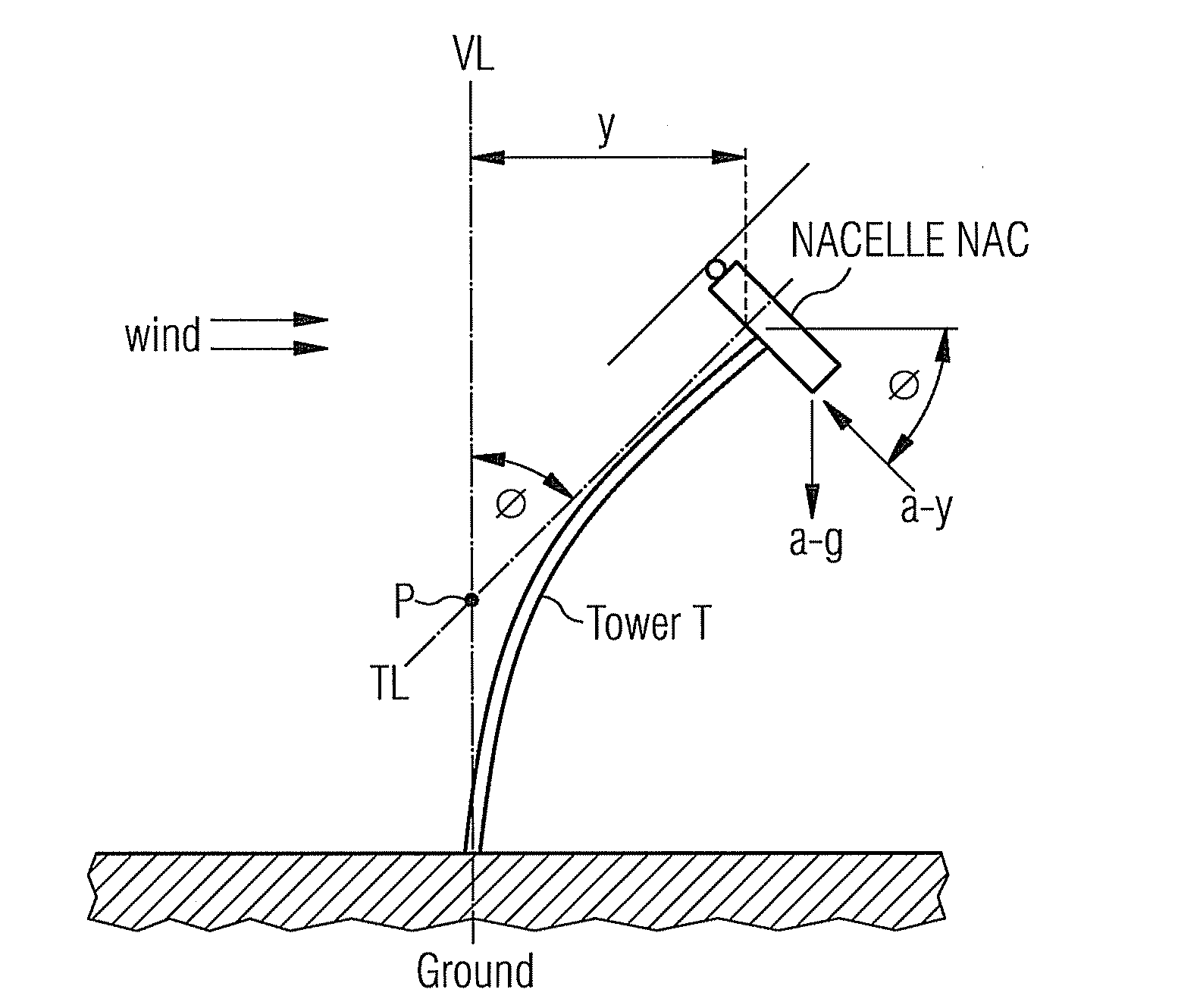

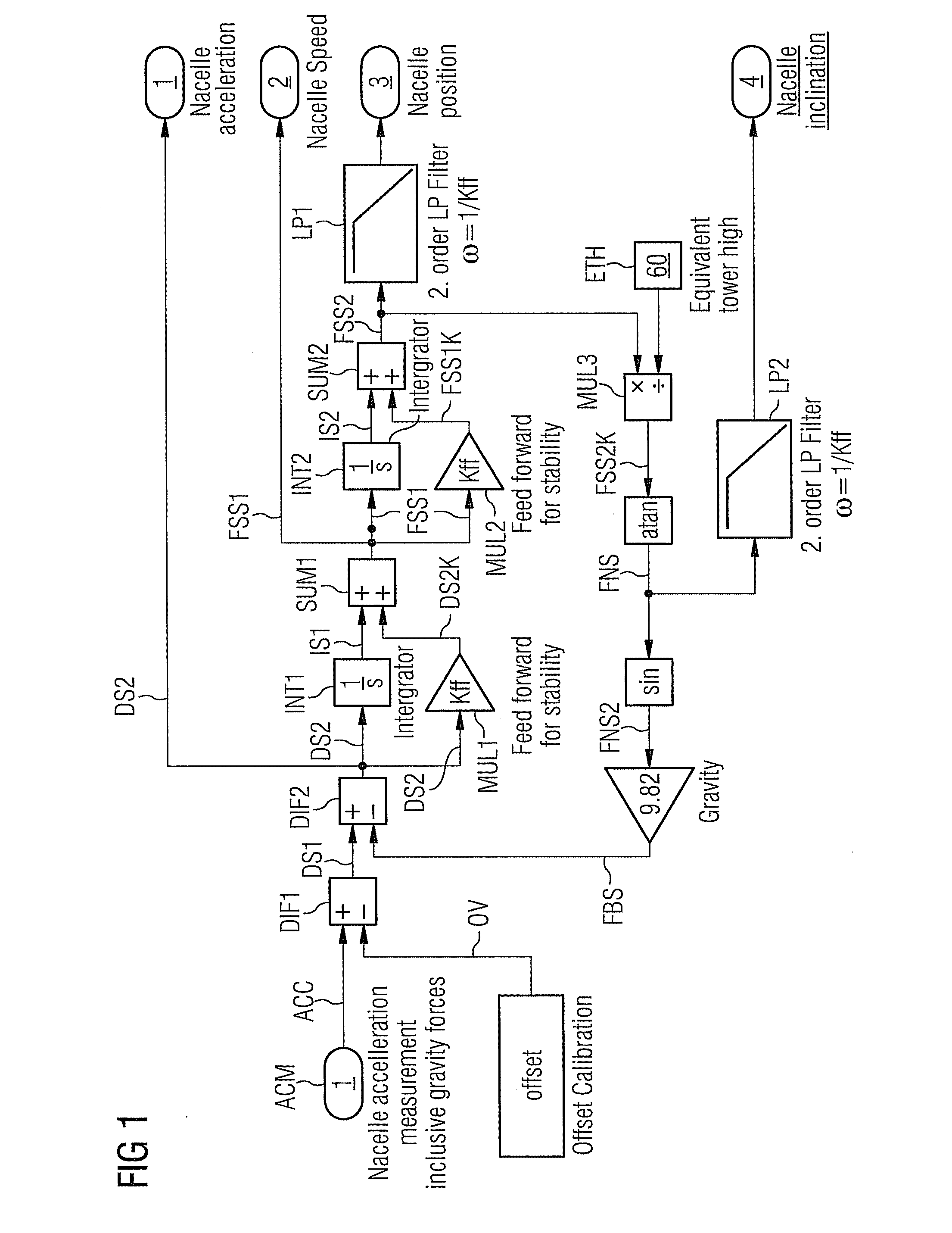

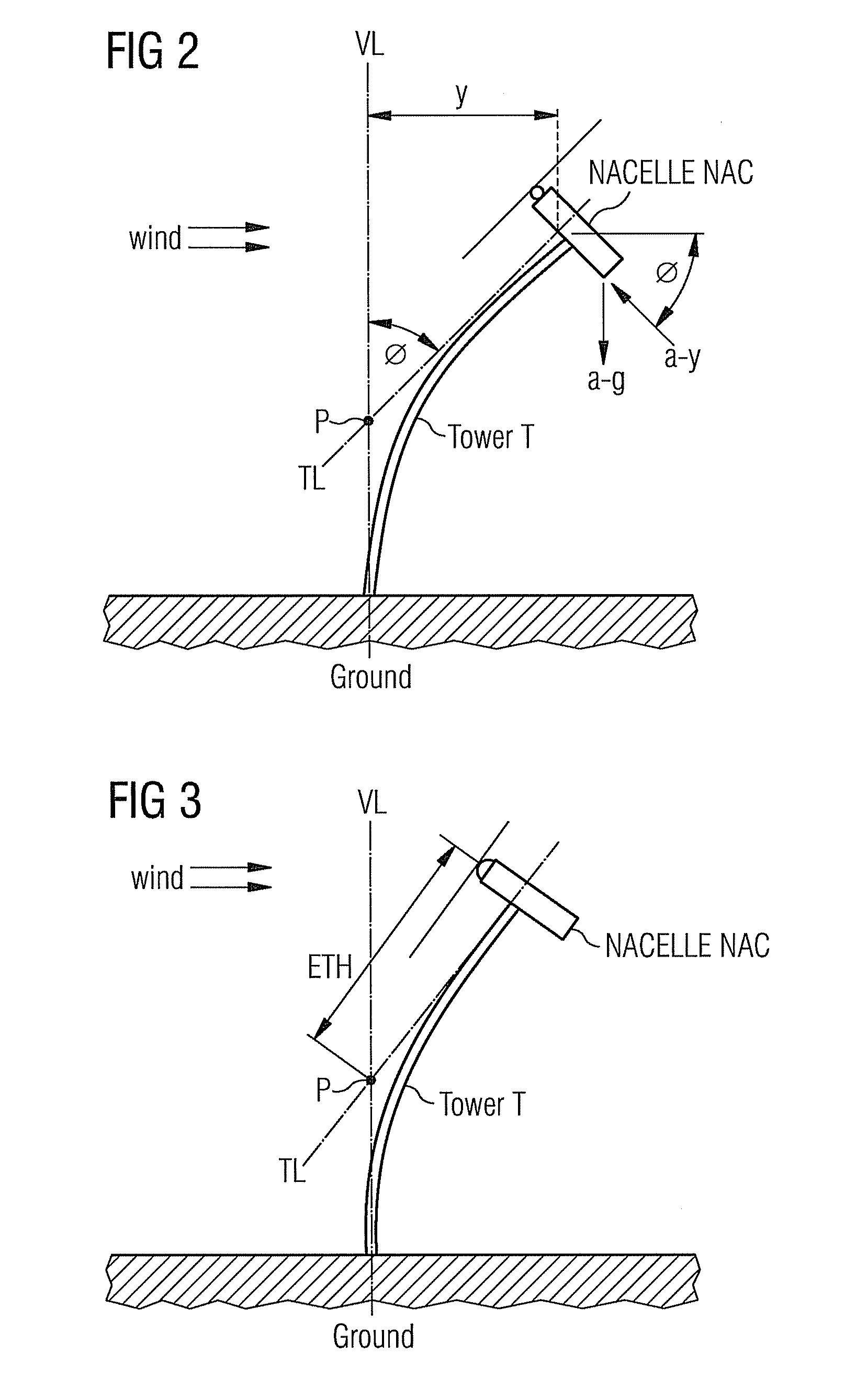

Method for the determination of a nacelle-inclination

InactiveUS20100063769A1Improve determinationMinimize influenceWind motor controlDigital data processing detailsNacelleEngineering

In one aspect, a method for the determination of a nacelle-inclination is provided. A first difference-signal is formed from the difference of a measured nacelle acceleration and an offset-value from a calibration. A second difference-signal is formed from a difference of the first difference-signal and a feedback signal. A first sum-signal is formed from adding an integrated second difference-signal with the product of the second difference signal and a factor. A second sum signal is formed from adding an integrated first sum-signal with the product of the first-sum-signal and the factor. A corrected signal is formed by a product of the second sum-signal and an equivalent tower height. A first nacelle-signal is formed by the arc-tangent of the corrected signal. A nacelle inclination is obtained from filtering the first nacelle-signal by a low-pass-filter. The feedback-signal is formed by multiplying the acceleration of gravity with the sine of the first nacelle-signal.

Owner:SIEMENS AG

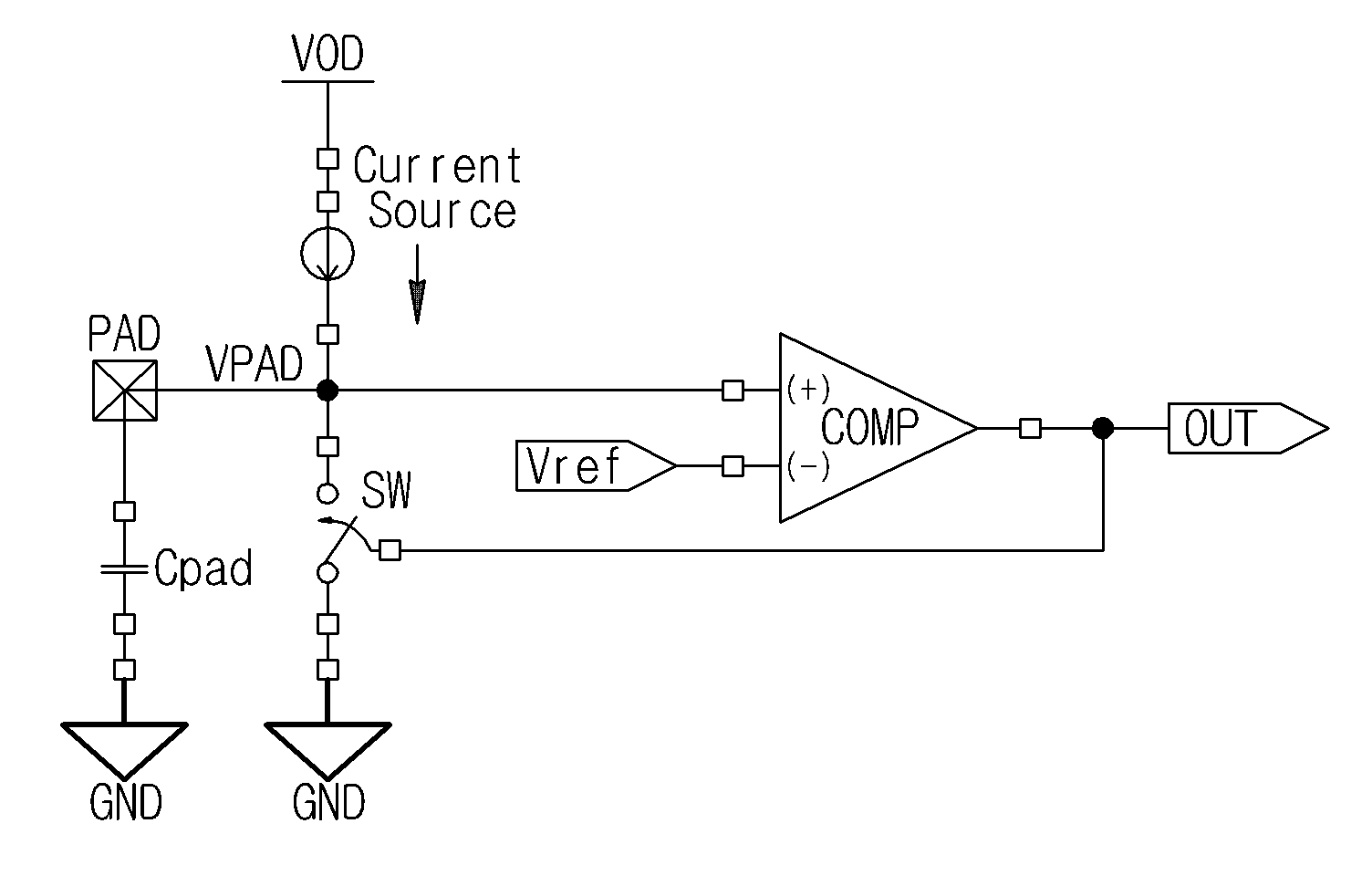

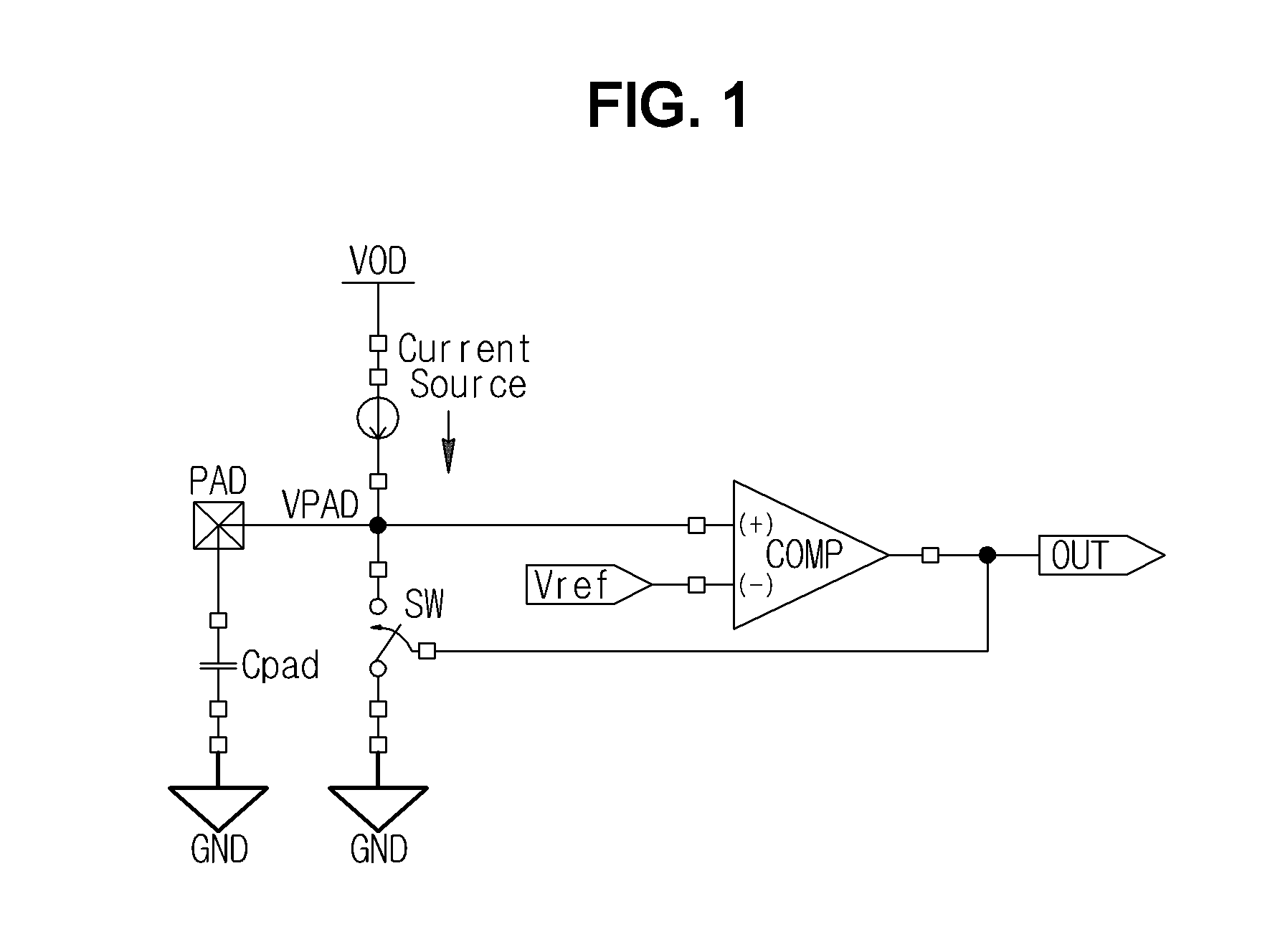

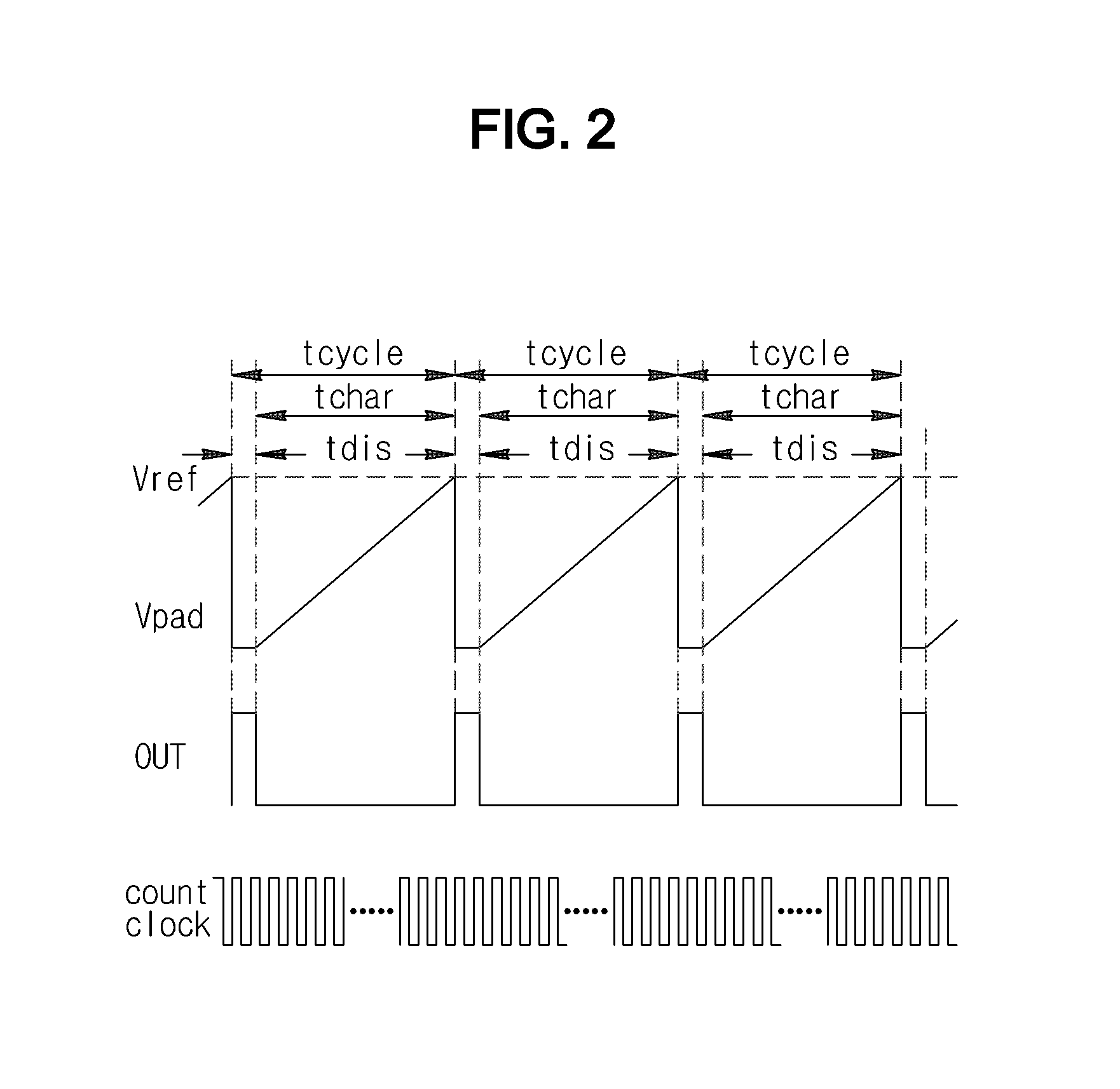

Capacitance measuring circuit for touch sensor

InactiveUS20110187389A1Measure accurately and stablyMinimize influenceResistance/reactance/impedenceElectronic switchingVoltage referenceEngineering

Disclosed herein is a capacitance measuring circuit for a touch sensor. The capacitance measuring circuit includes a reference voltage generation unit for generating a first reference voltage and a second reference voltage, a MUX unit for selecting one from among electrode voltages, a voltage comparator for comparing a voltage generated by the reference voltage generation unit with the electrode voltage, a charging / discharging circuit unit for performing charging of the input electrode voltage from the first reference voltage to the second reference voltage or performing discharging of the input electrode voltage from the second reference voltage to the first reference voltage, a timer unit for receiving an external control signal, measuring charging time and discharging time of the charging / discharging circuit unit, measuring entire charging time and entire discharging time, and outputting corresponding output signals, and a control unit for receiving an output signal of the voltage comparator and the external control signal, and controlling the charging / discharging circuit unit and the timer unit.

Owner:POINTCHIPS CO LTD

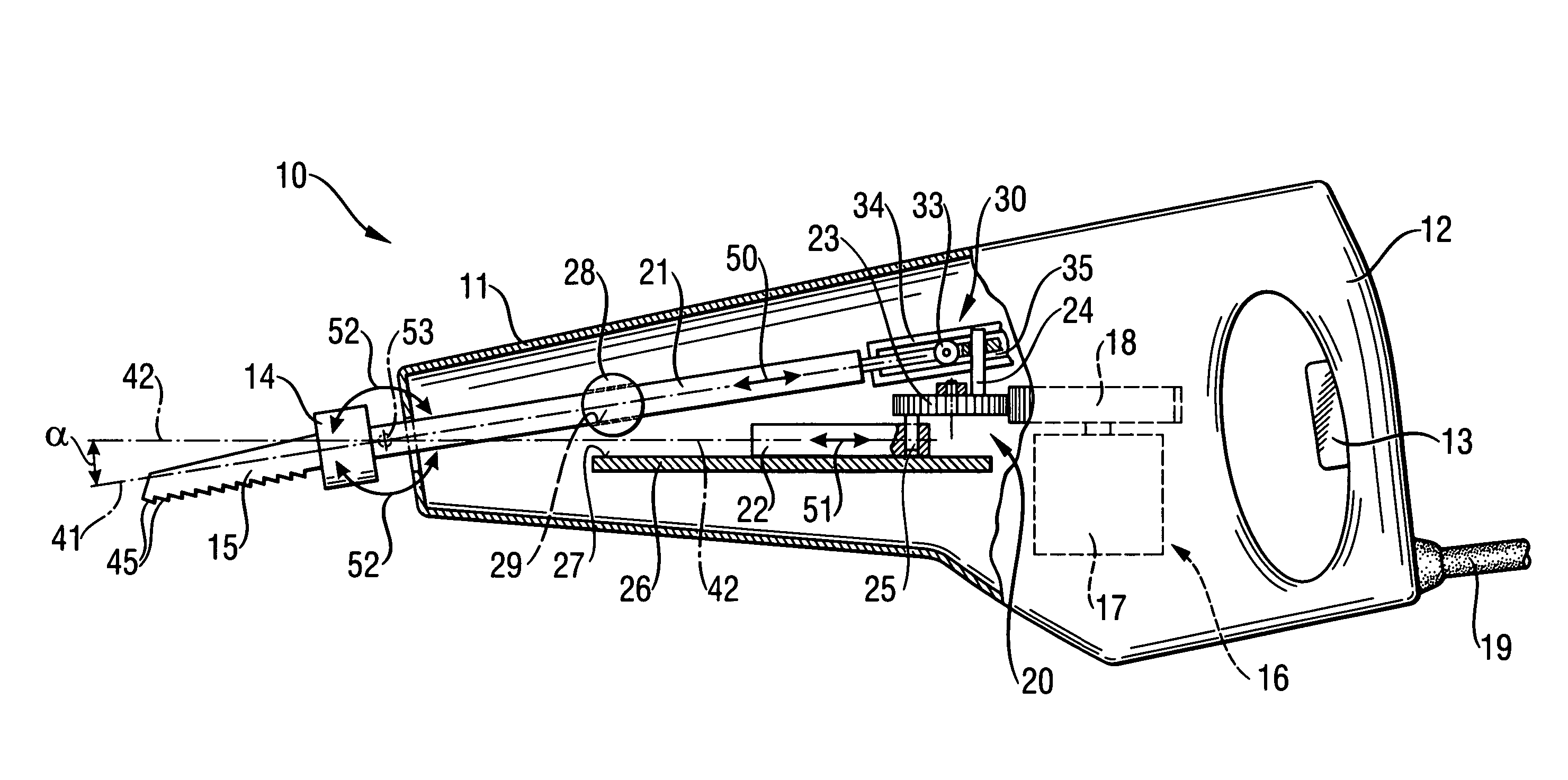

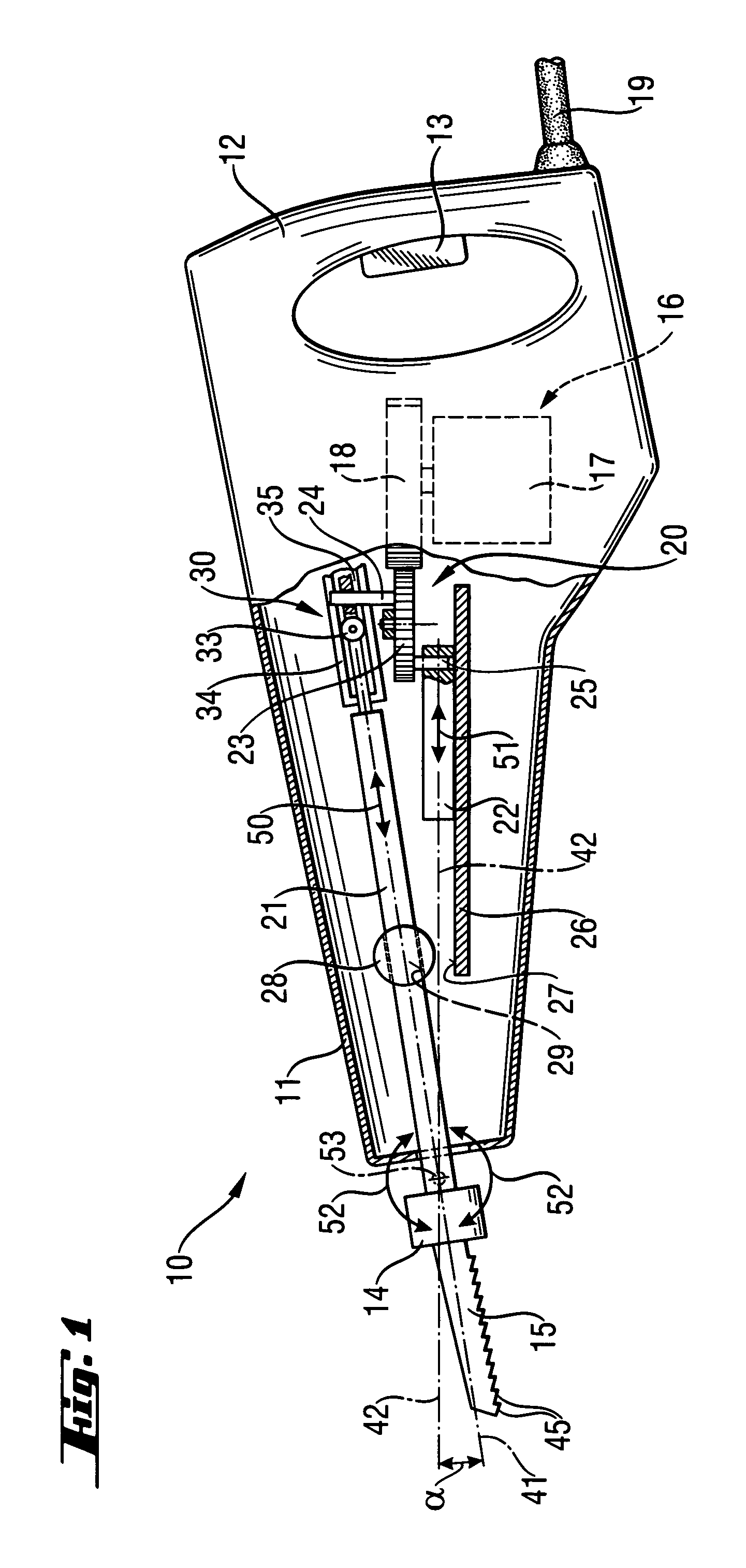

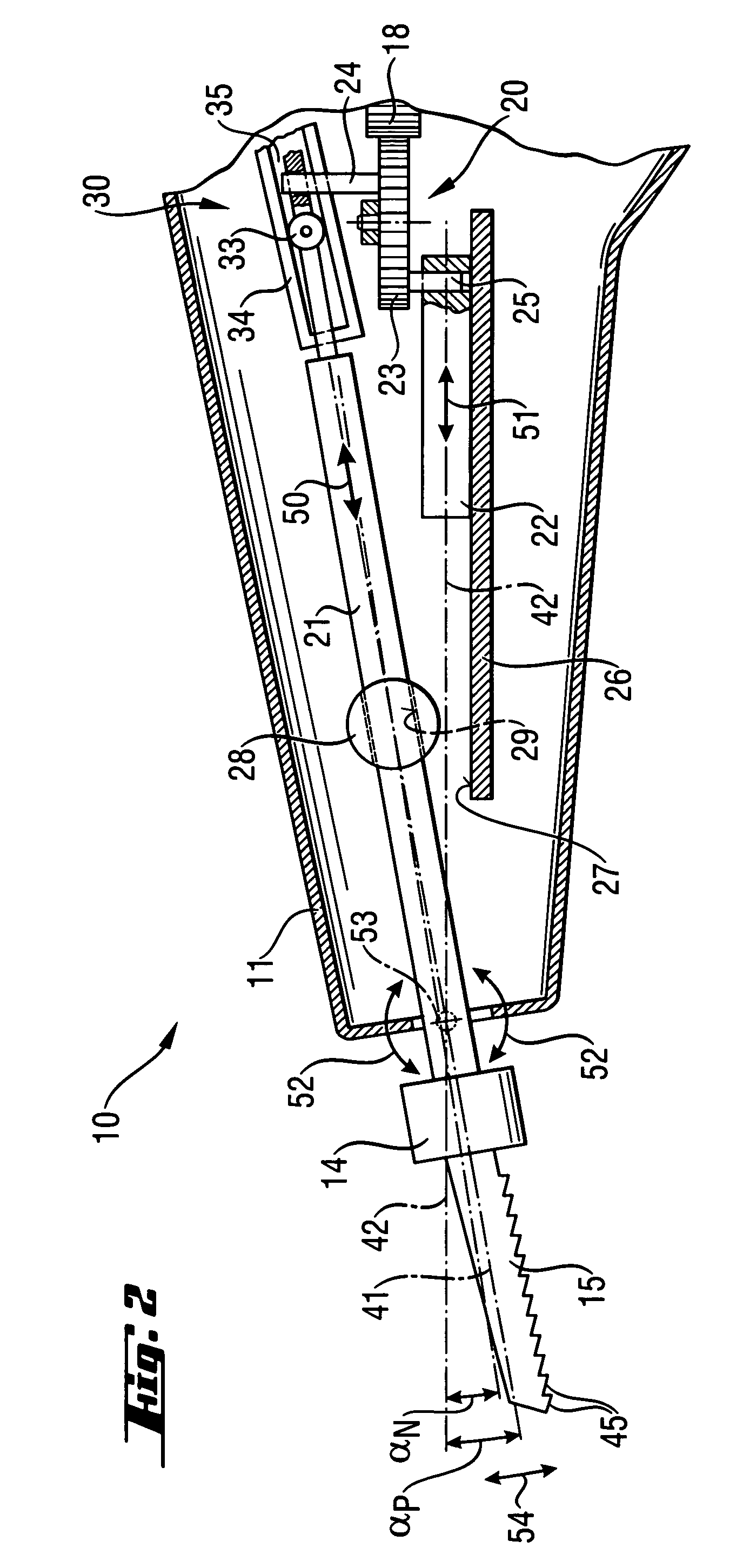

Saber saw tool

ActiveUS20050262708A1Minimize influenceOptimal performanceMetal sawing devicesCross-cut reciprocating sawsEngineeringMotor drive

The present invention relates to a reciprocating saw tool (10) having a motor drive (17) with a reciprocating driver (21) for a tool (15) and having a mass equilibrating body (22). In addition, a device (20) is provided, which serves to convert a rotary movement of the motor drive (17) into a reciprocating movement of the reciprocating driver (21) along a first movement axis (41) and an opposite reciprocating movement of the mass equilibrating body (22) along a second movement axis (42). For improving the sawing performance, the mass equilibrating body (22) is guided at an angle α to the reciprocating driver (21) so that its movement axis (42) is constantly at an angle to the movement axis (41) of the reciprocating driver (21).

Owner:HILTI AG

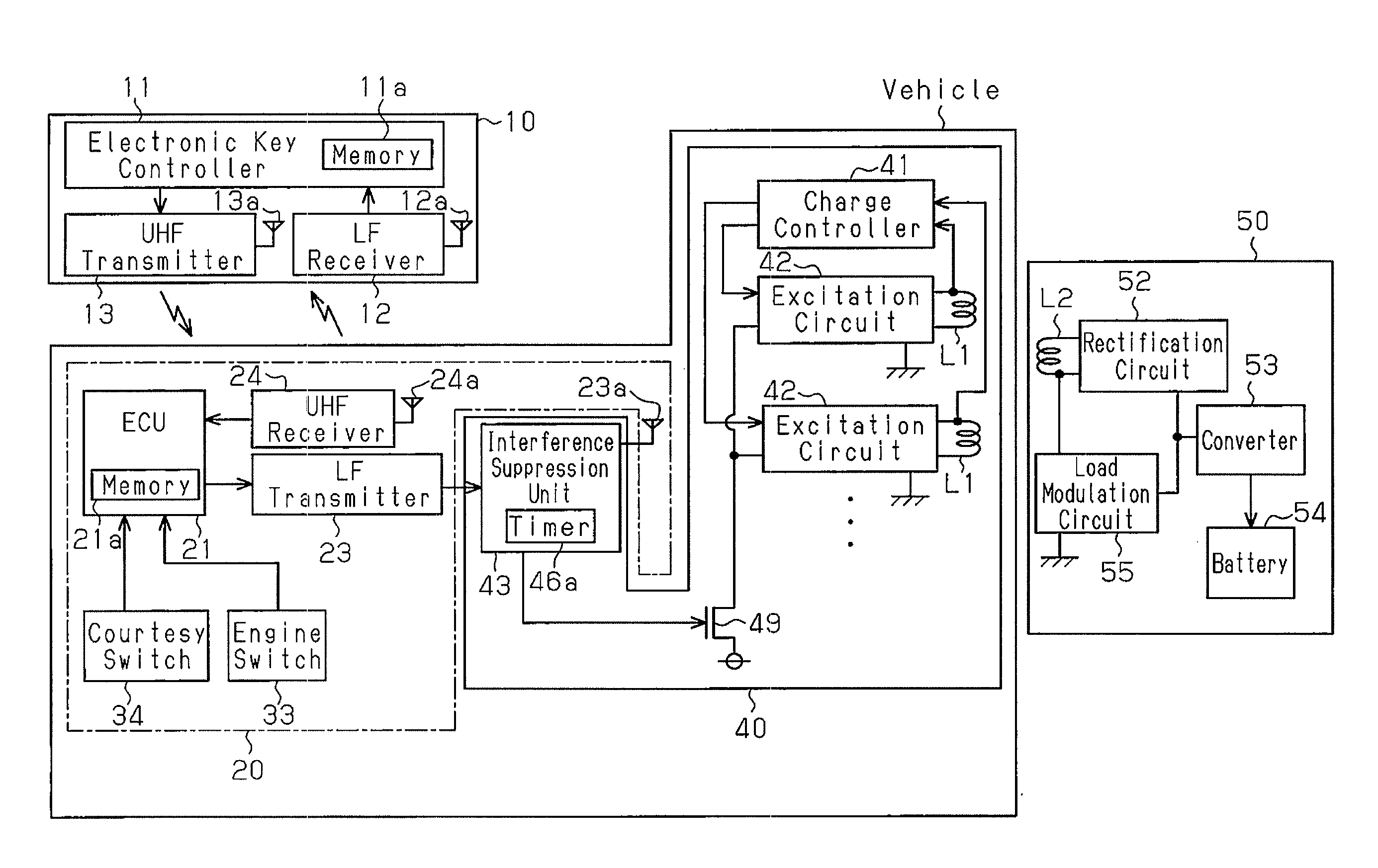

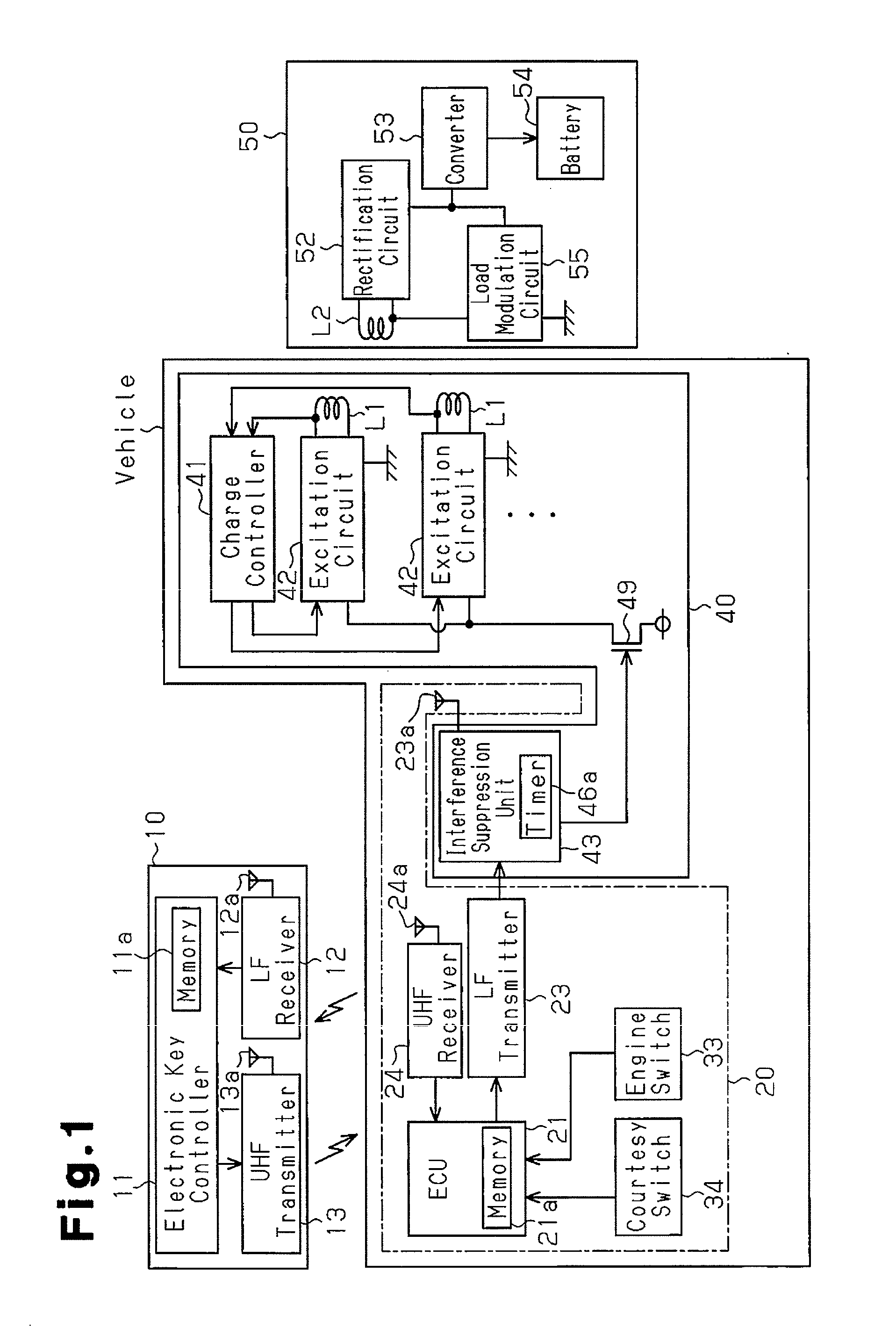

Wireless charging device and method for controlling wireless charging

InactiveUS20150015198A1Minimize influenceMinimize impactCircuit authenticationAnti-theft devicesElectric power transmissionIn vehicle

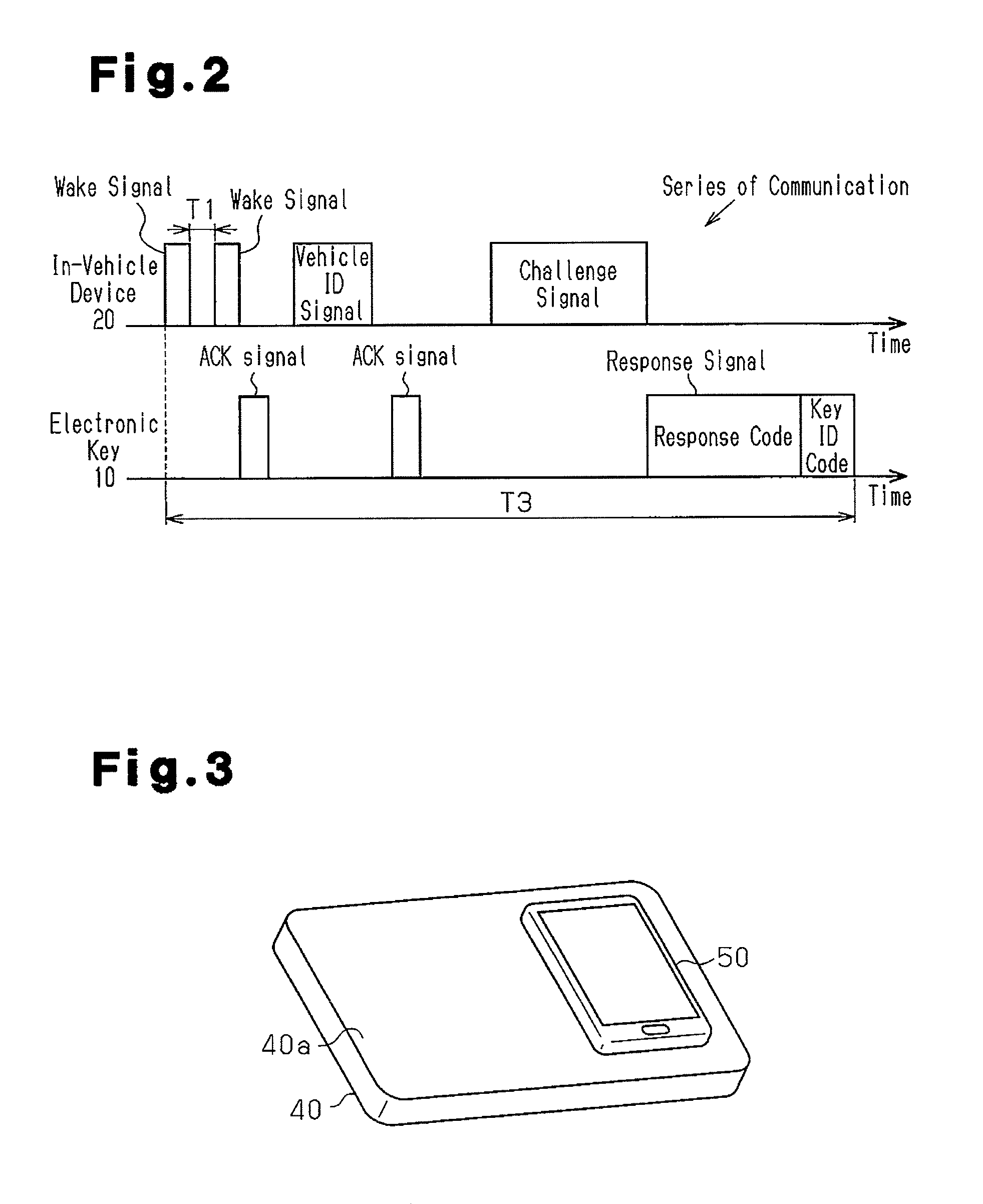

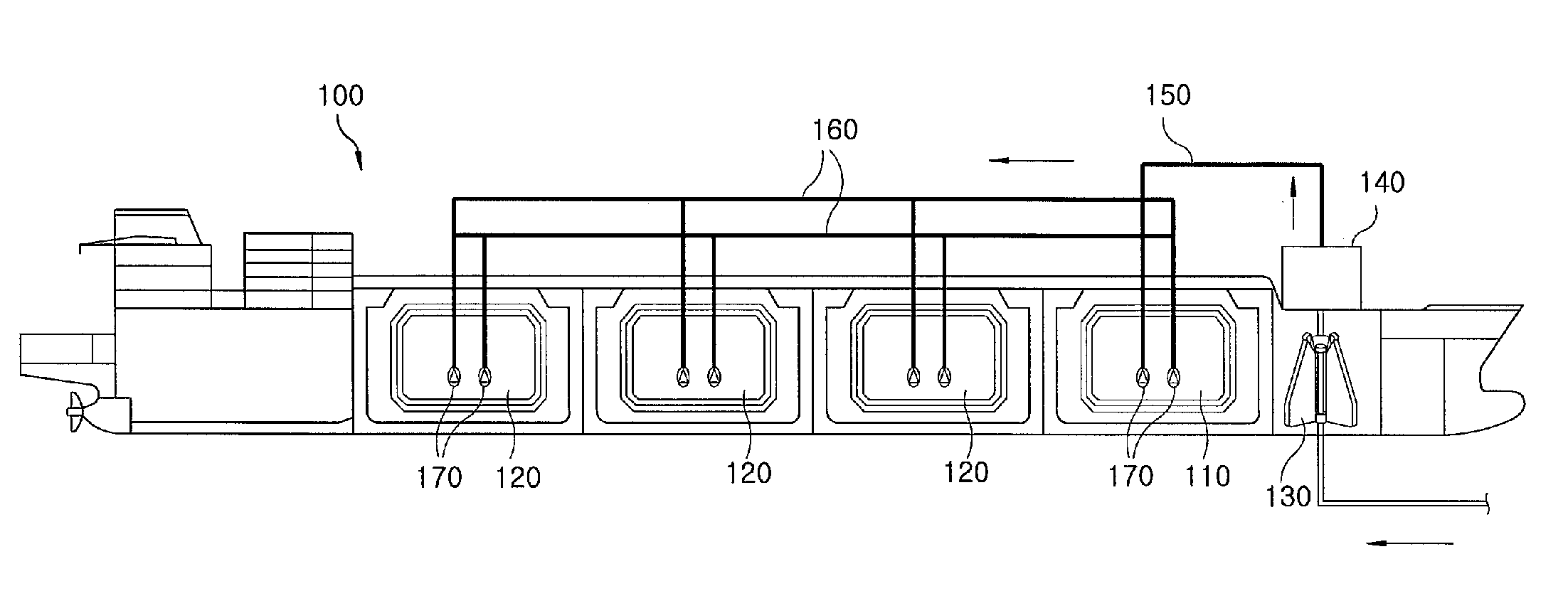

A wireless charging device (40) arranged in a vehicle including an in-vehicle device (20). The in-vehicle device transmits a wake signal in intervals until receiving a response from an electronic key (10) and communicates with the electronic key when receiving the response to determine whether the electronic key is authentic. The wireless charging device includes a primary coil (L1) that transmits power to a charged device (50) when supplied with alternating current. A detection unit (43) uses the wake signal to detect when communication starts between the in-vehicle device and the electronic key. A power supplying suppression unit (43) reduces the alternating current supplied to the primary coil over a certain time from when the communication starts. The power supplying suppression time includes the time required for a series of communication to be performed between the in-vehicle device and the electronic key for the verification.

Owner:KK TOKAI RIKA DENKI SEISAKUSHO +1

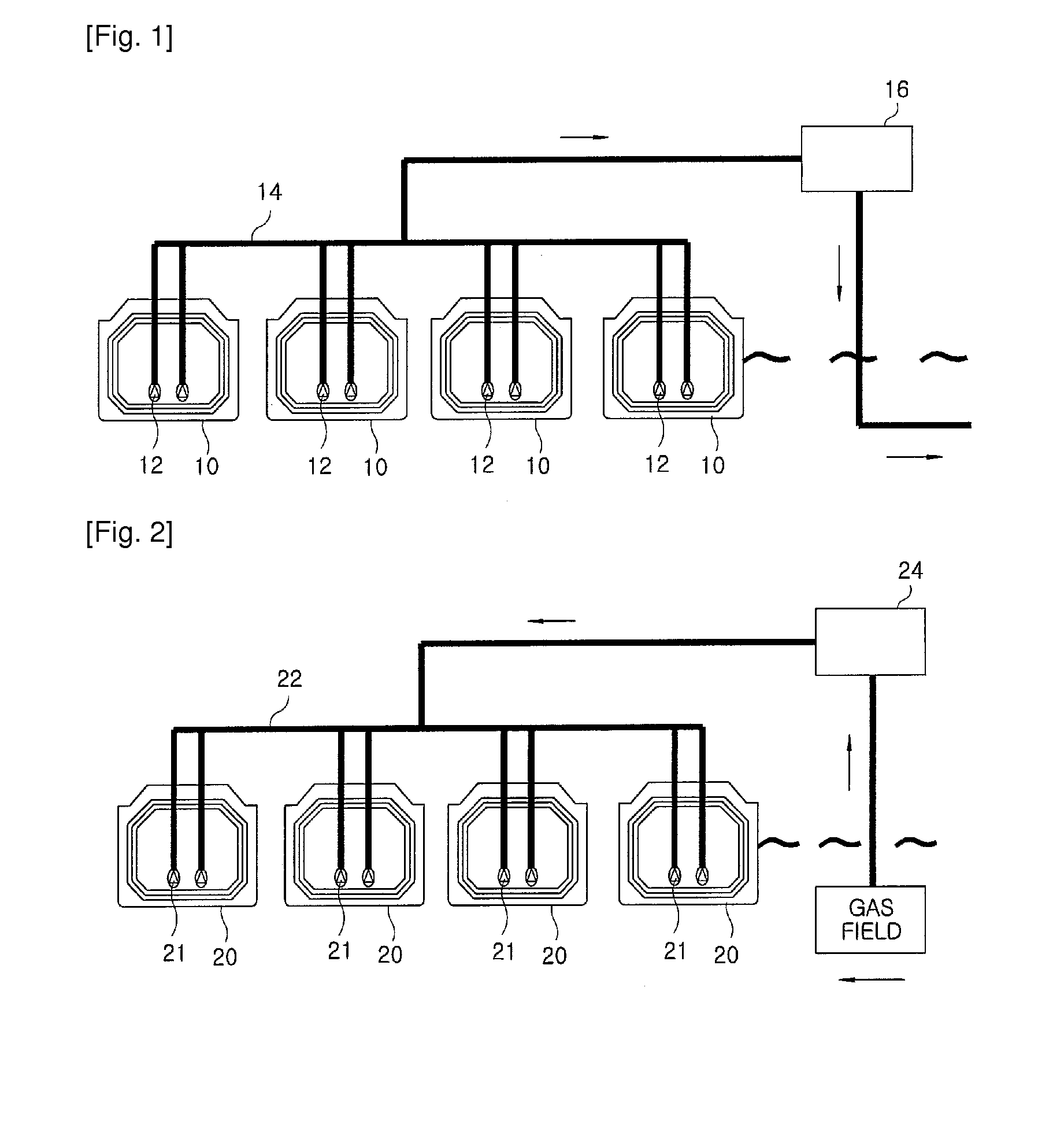

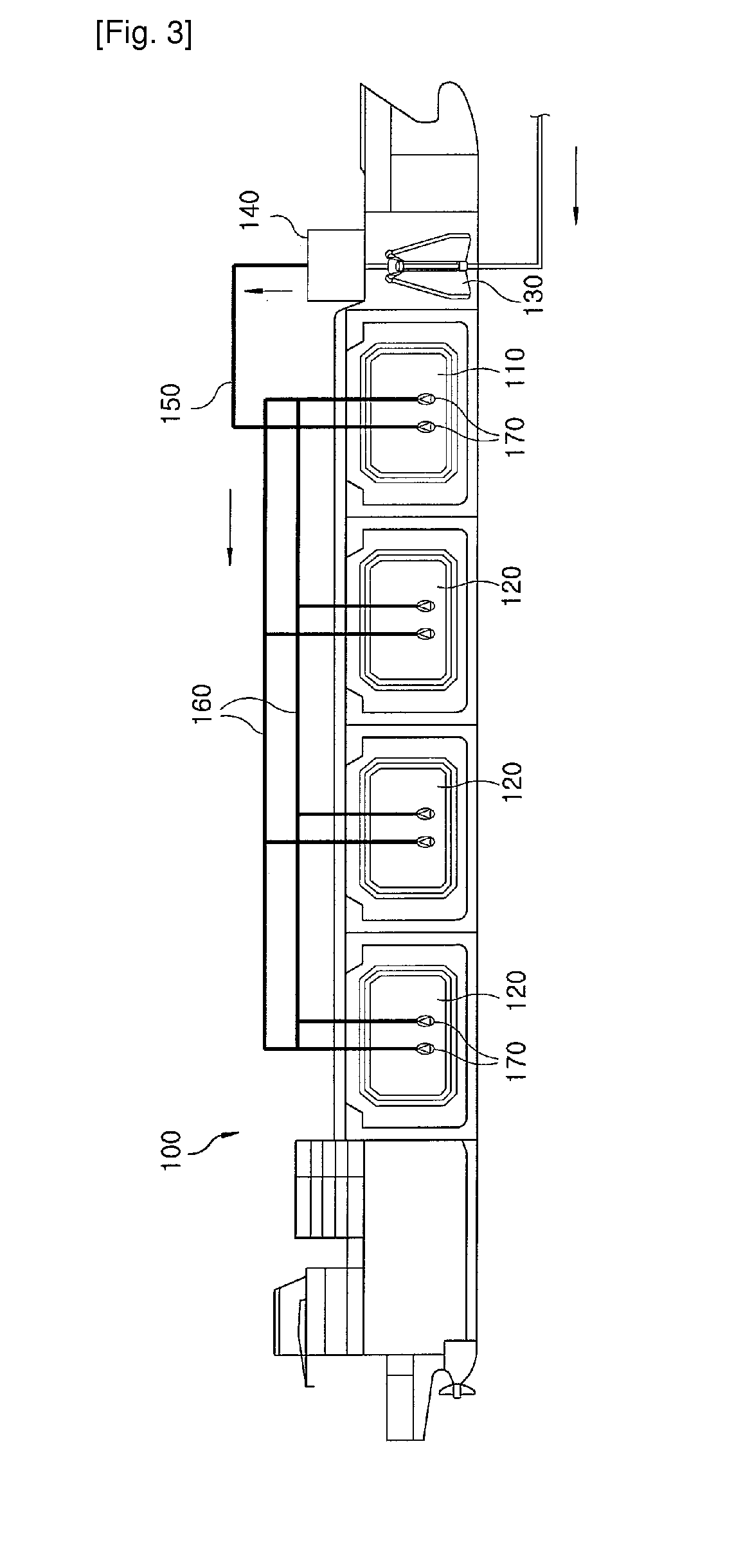

LNG carrier having an LNG loading and unloading system

ActiveUS20110011329A1Minimize influenceEliminate riskSolidificationLiquefactionProcess engineeringLiquefaction

An LNG carrier having an LNG loading and unloading system includes a submerged turret loading (STL) system for introducing and discharging a natural gas; a liquefaction plant for liquefying the natural gas introduced through the submerged turret loading system into a cryogenic liquefied natural gas; at least one self-supporting storage tank installed in the LNG carrier for storing the liquefied natural gas, the self-supporting storage tank arranged in such a manner that the liquefied natural gas is loaded to and unloaded from the LNG carrier through the self-supporting storage tank; and at least one membrane type storage tank arranged in a neighboring relationship with the self-supporting storage tank, the membrane type storage tank kept in fluid communication with the self-supporting storage tank. The LNG carrier further includes a regasification plant for regasifying the liquefied natural gas stored in the self-supporting storage tank.

Owner:SAMSUNG HEAVY IND CO LTD

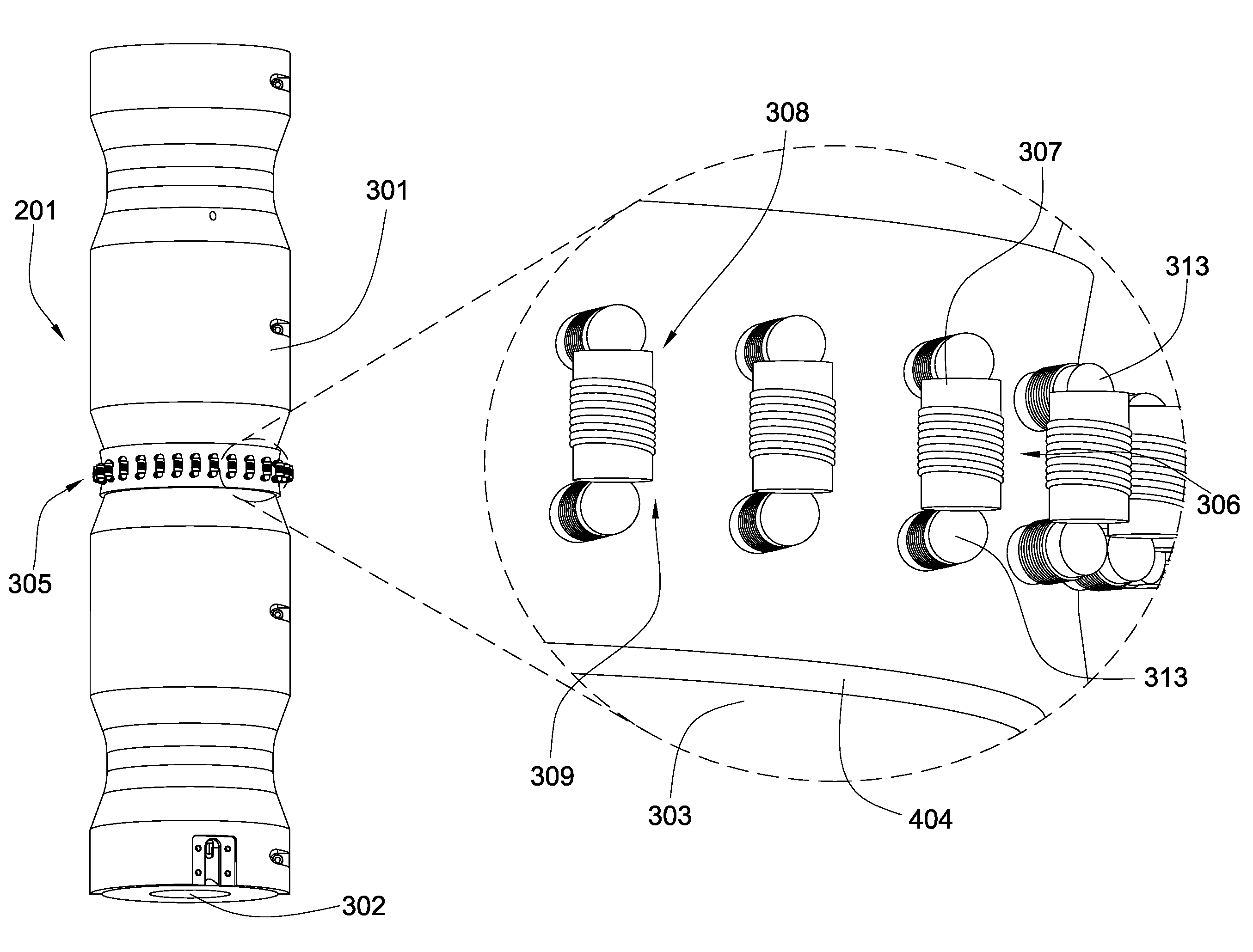

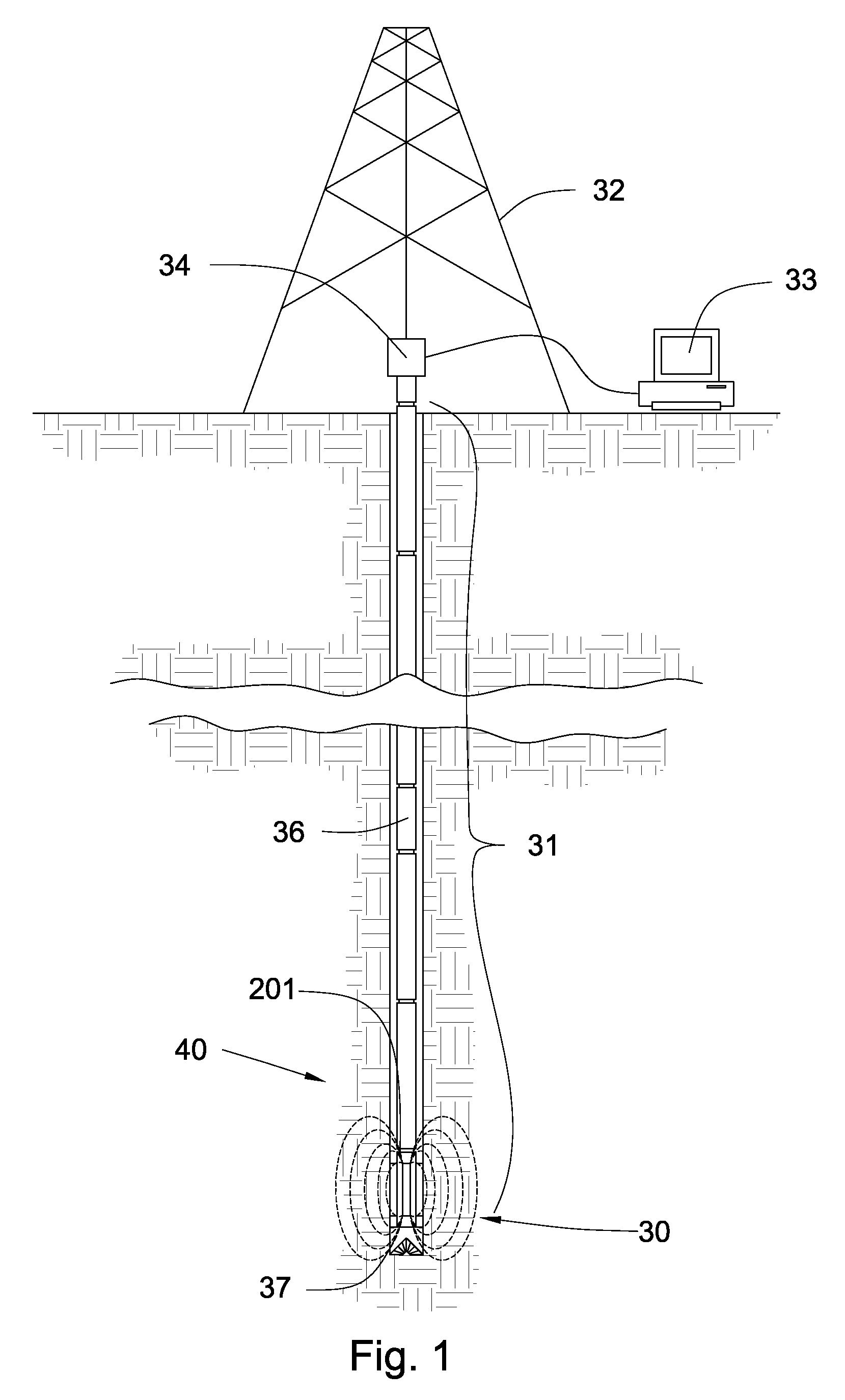

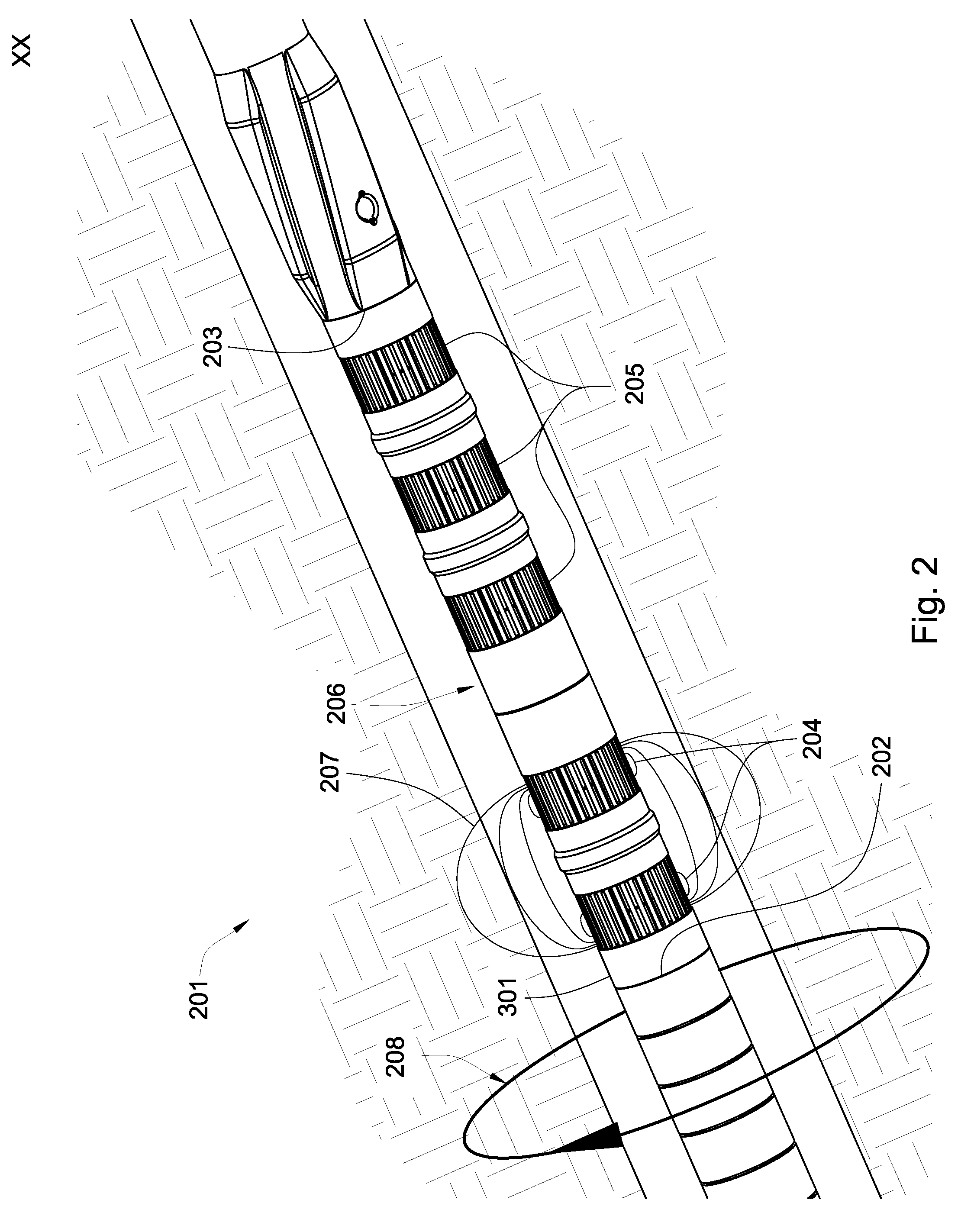

Externally Guided and Directed Field Induction Resistivity Tool

InactiveUS20080265893A1Minimize influenceMinimal influenceElectric/magnetic detection for well-loggingTransformers/inductances coils/windings/connectionsInductive ResistanceEngineering

In one aspect an induction resistivity tool incorporated into a downhole tool string comprises an outer wall of a downhole component comprising an outer diameter and at least one induction transmitter assembly disposed along the outer diameter. The at least one transmitter assembly comprises at least one induction transmitter coil wound about at least one core. The at least one transmitter coil is adapted to project an induction signal outward from the outer wall when the at least one transmitter coil is carrying an electrical current. The transmitter assembly is adapted to create electromagnetic fields that originate the induction signal from outside the outer wall and substantially prevent the signal from entering the outer wall.

Owner:SCHLUMBERGER TECH CORP

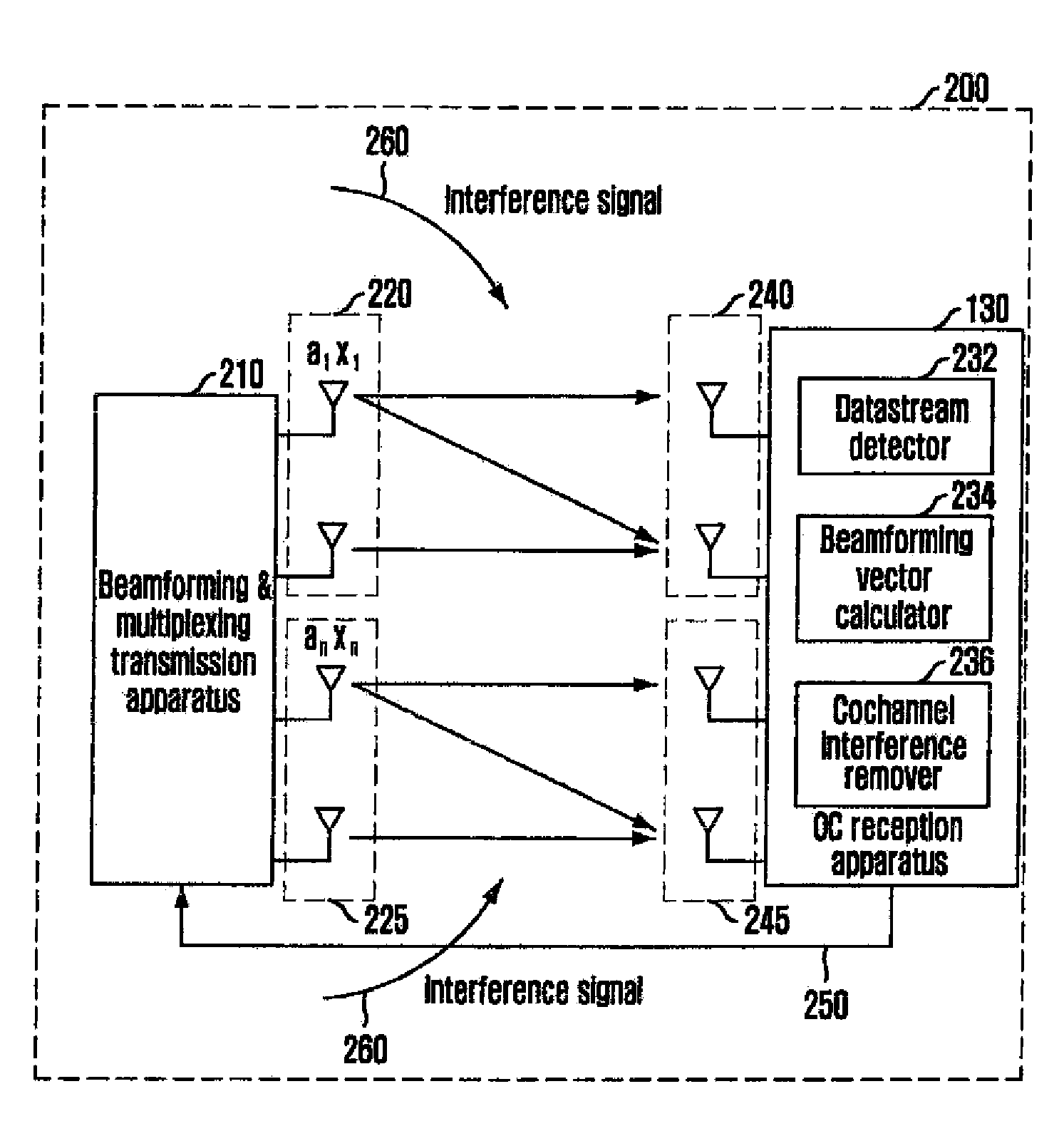

MIMO antenna receiving apparatus and receiving method

InactiveUS20090154587A1Secure high data transmission rateMinimize influencePolarisation/directional diversityTime-division multiplexChannel capacityMultiple input

Provided is a reception apparatus and method of a Multiple Input Multiple Output (MIMO) system that receives a plurality of different data streams in a multiple cell environment. The reception apparatus for receiving a plurality of different data streams in a multiple input multiple output (MIMO) antenna system includes a data stream detector for detecting each data stream by removing interference between the different data streams while maintaining channel information; and a cochannel interference (CCI) remover for removing cochannel interference from each data stream detected in the data stream detector. The present invention can remove cochannel interference and increase channel capacity to thereby acquire both diversity gain and multiplexing gain.

Owner:ELECTRONICS & TELECOMM RES INST

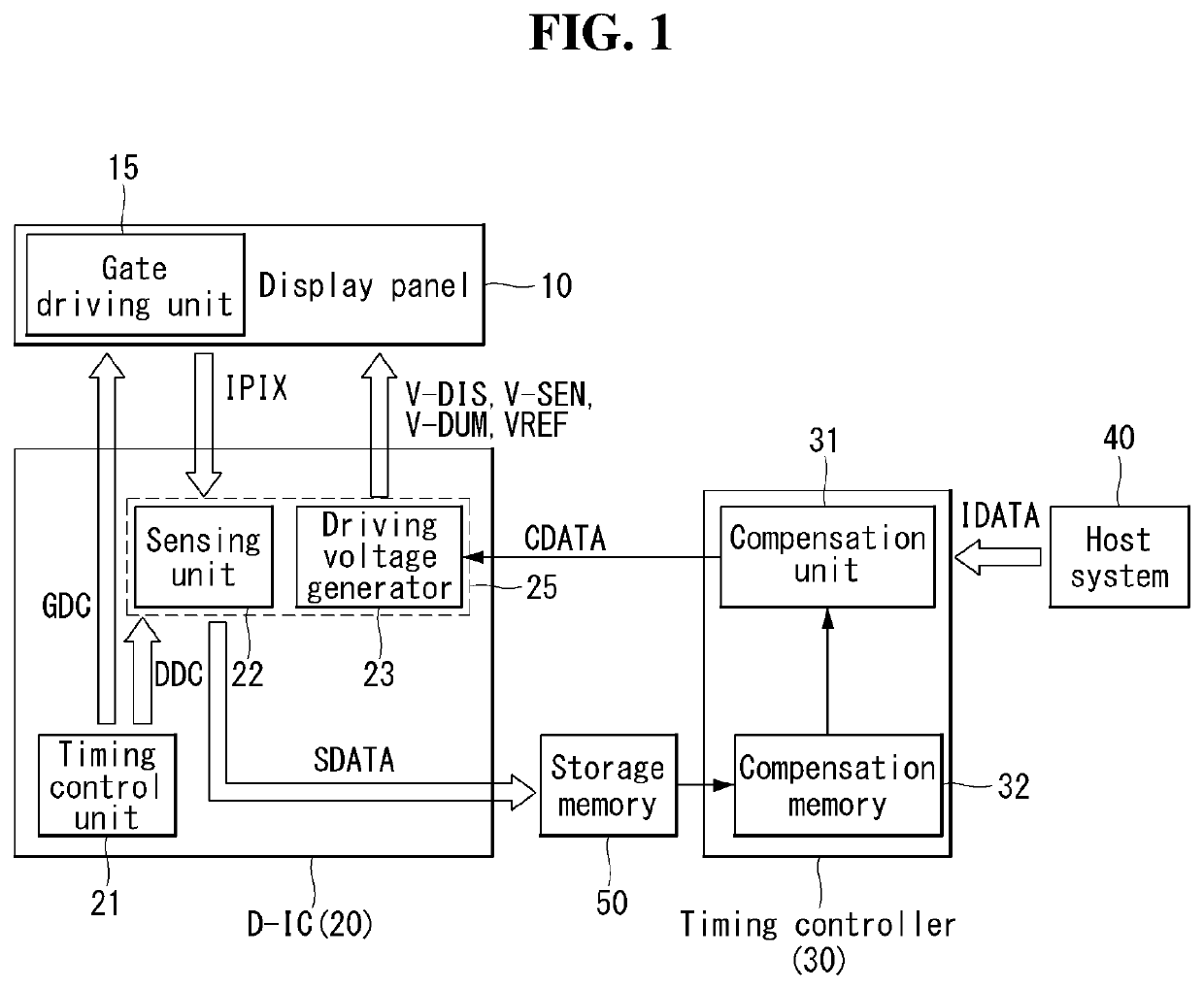

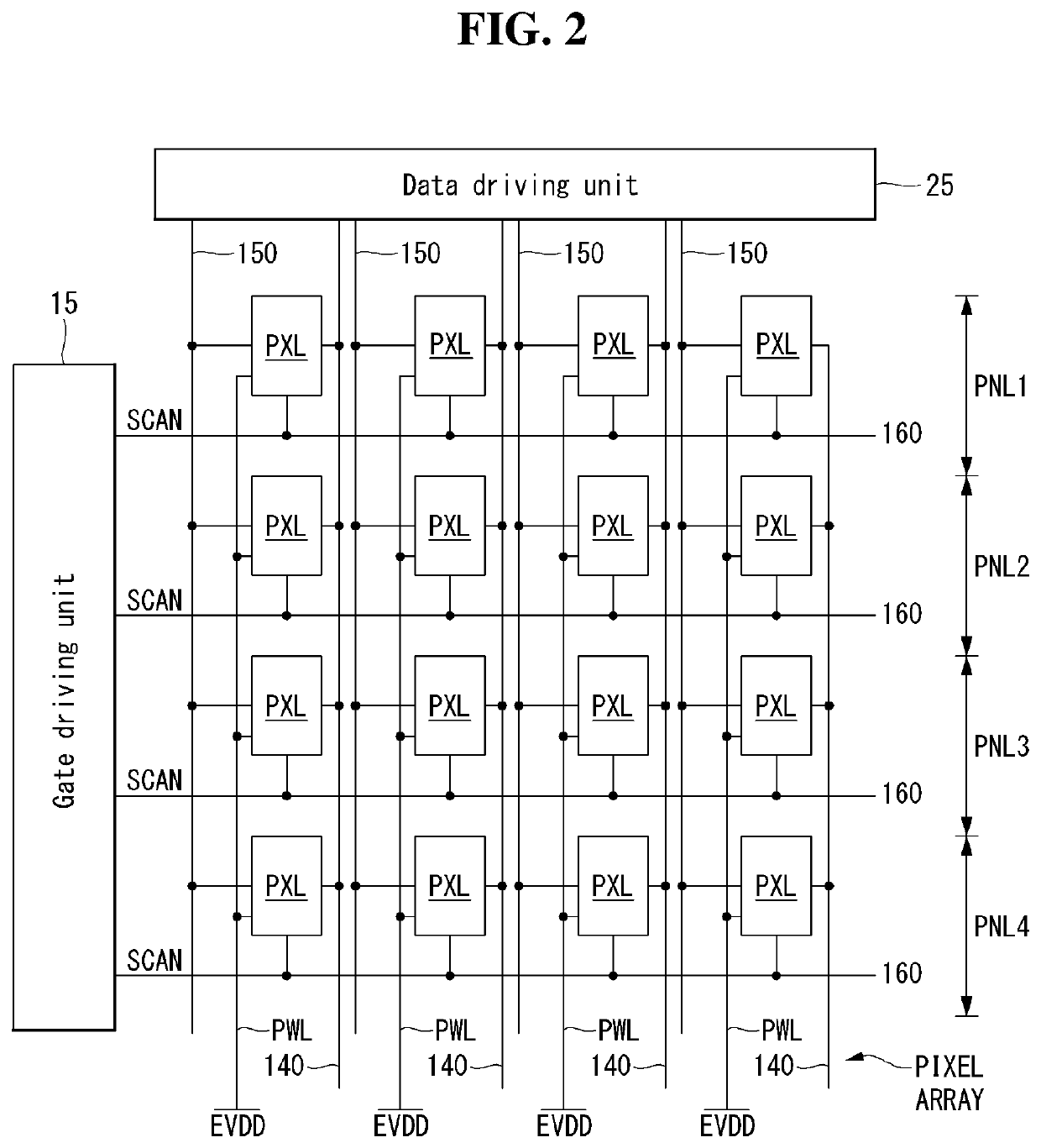

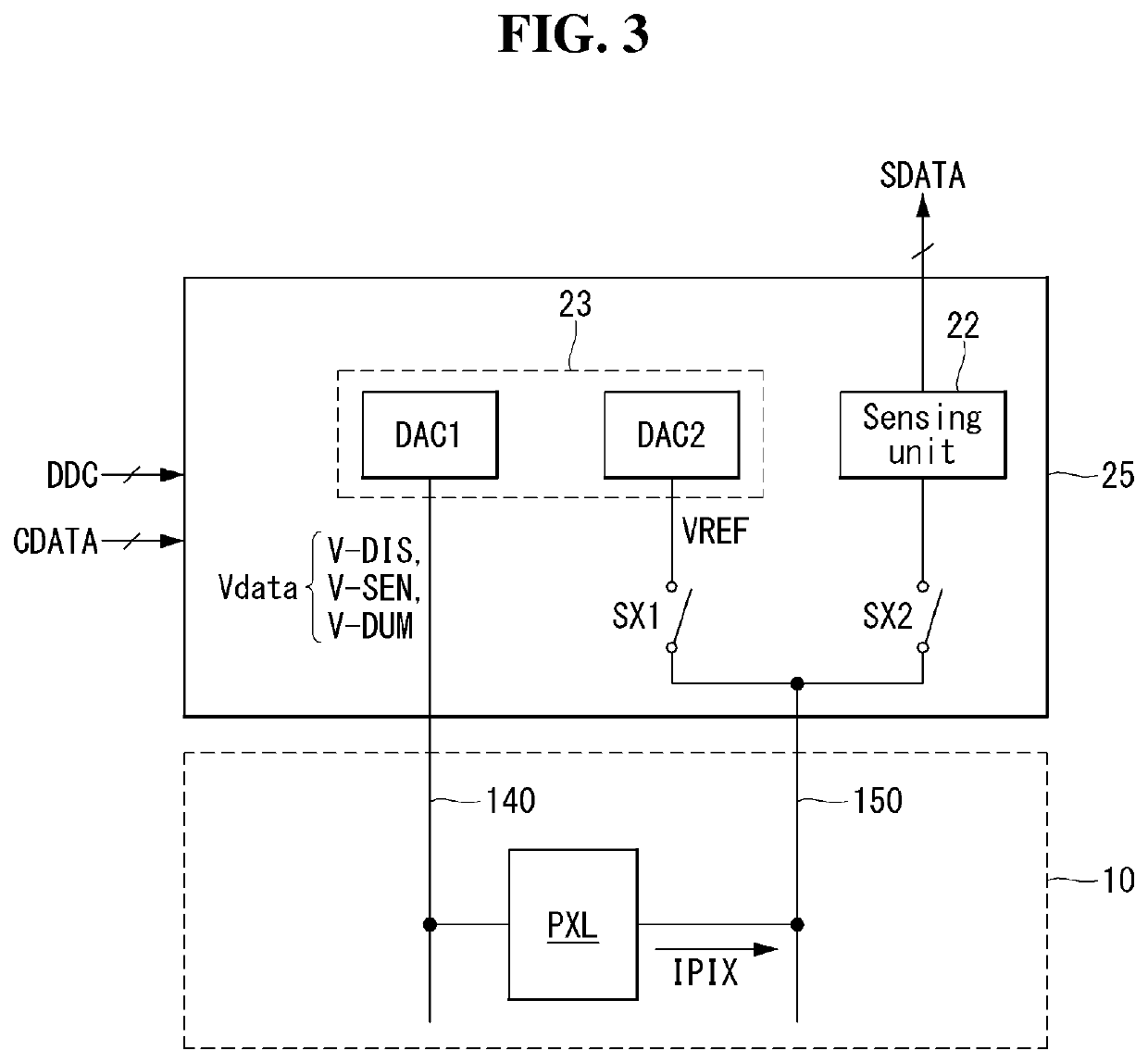

Organic Light Emitting Display Device and Pixel Sensing Method of the Same

ActiveUS20200202787A1Improve sense accuracy and sensing reliabilityMinimize influenceStatic indicating devicesEngineeringHemt circuits

A display device includes a display panel, a driving circuit, a sensing circuit, and a compensation circuit. The display panel includes a first pixel and a second pixel. The driving circuit provides a preset sensing voltage to the first pixel of the display panel, and provides a dummy voltage to the second pixel of the display panel. A first channel of a sensing circuit generates a first integrated voltage signal indicative of a magnitude of a first pixel current generated by the first pixel. A second channel of the sensing circuit generates a second integrated voltage signal indicative of a magnitude of a first dummy current generated by the second pixel. The compensation circuit determines a compensation amount from a difference between an output of the first and second channels of the sensing circuit, and compensates a display voltage of the first pixel by the compensation amount.

Owner:LG DISPLAY CO LTD

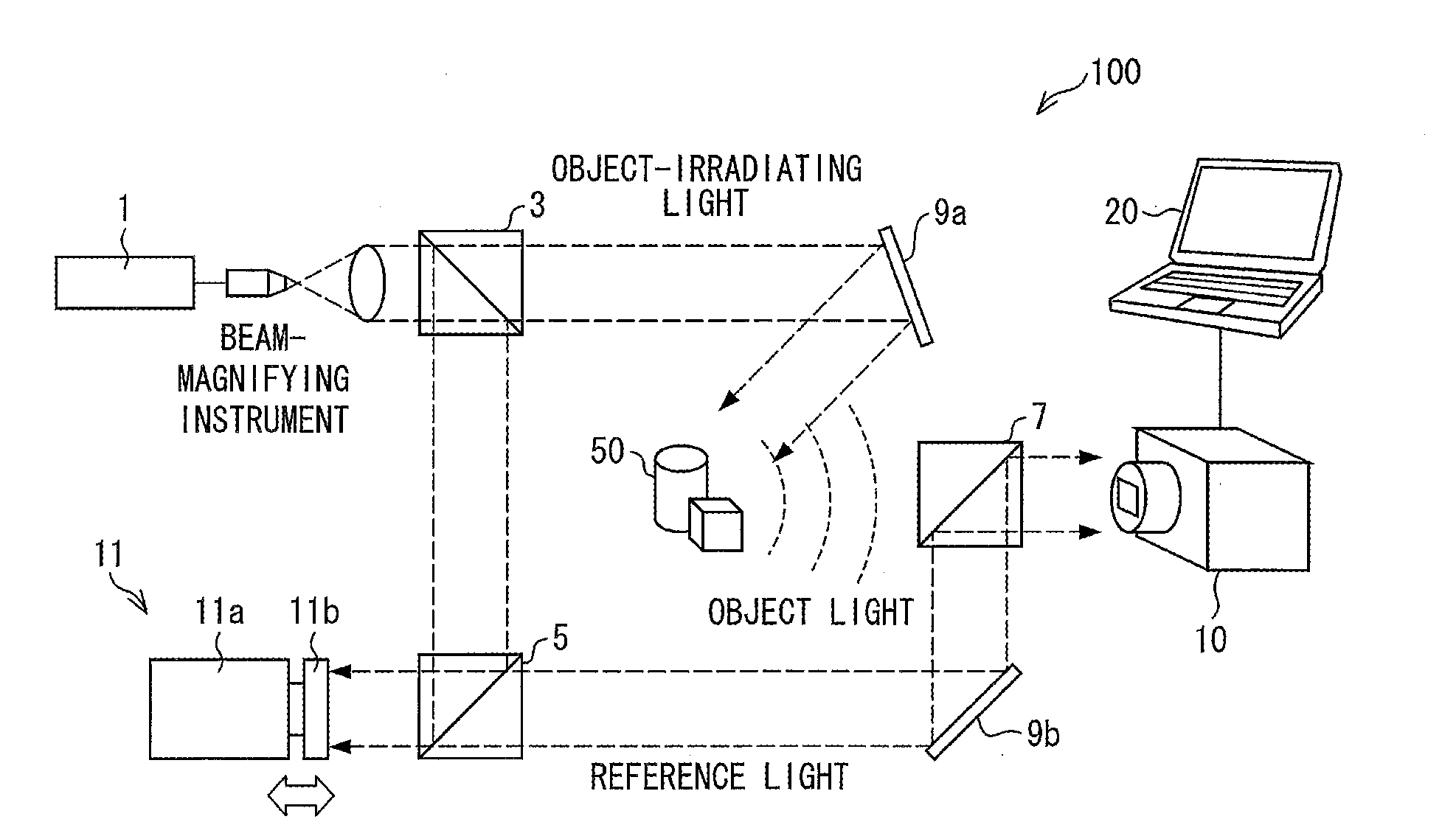

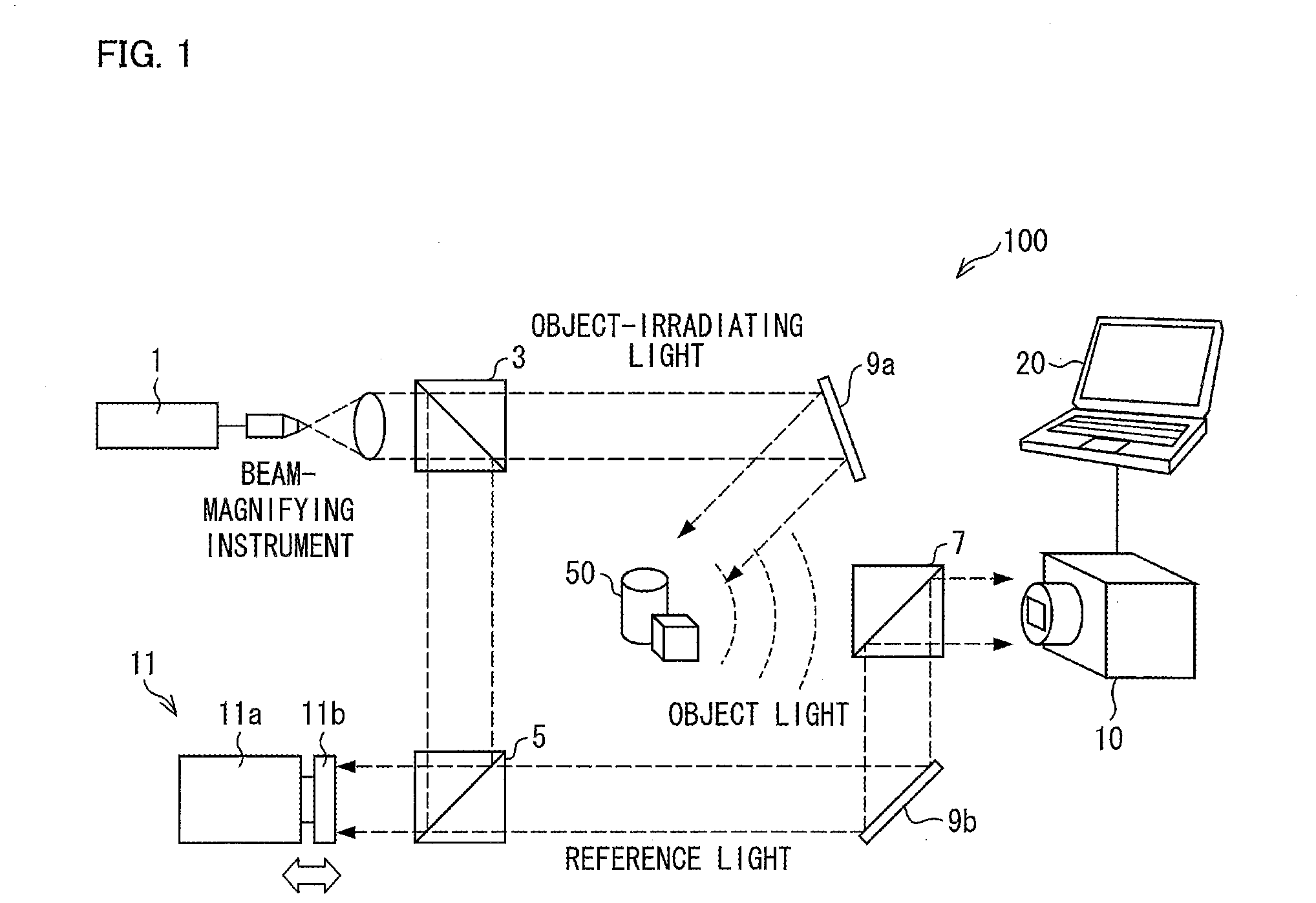

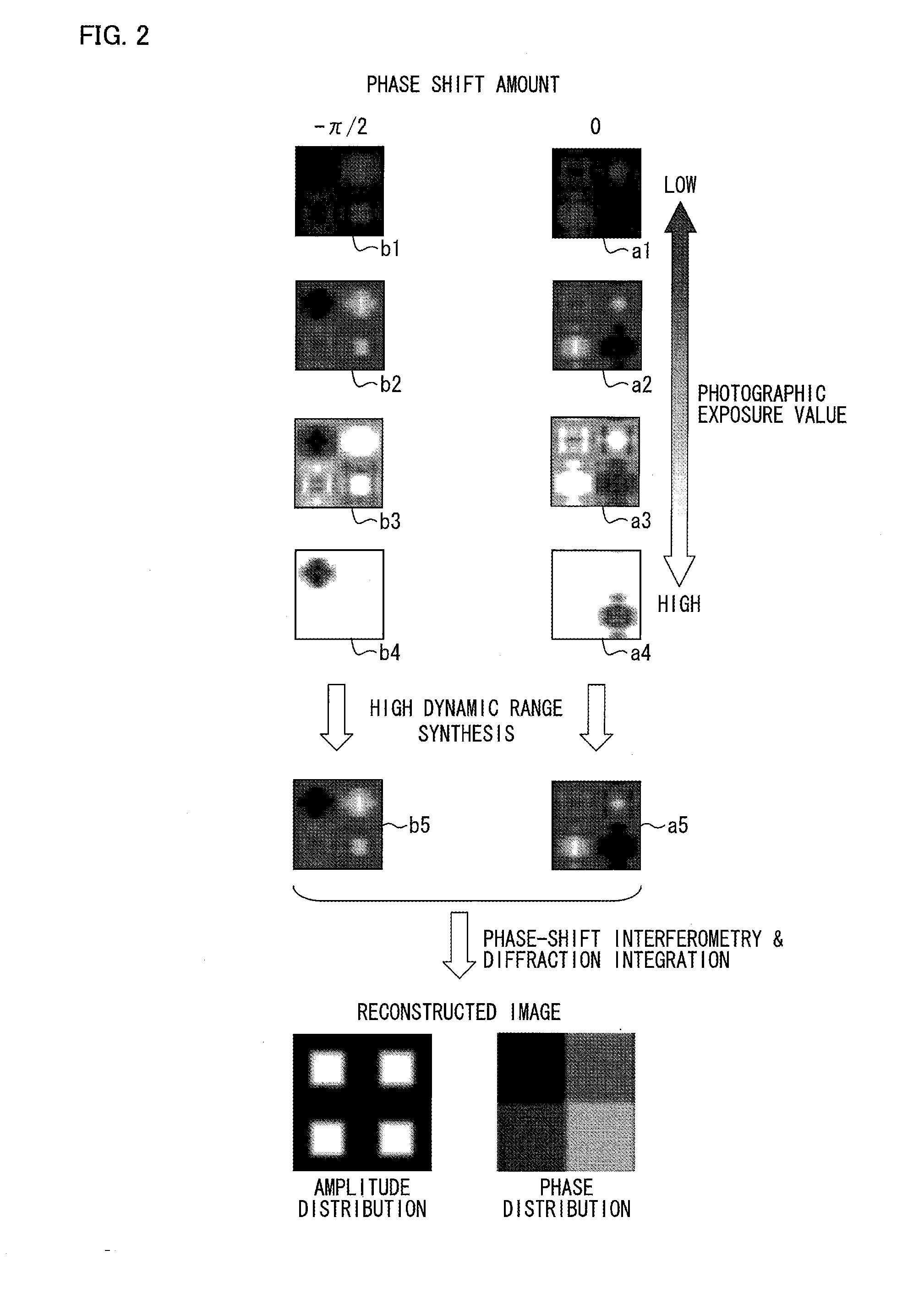

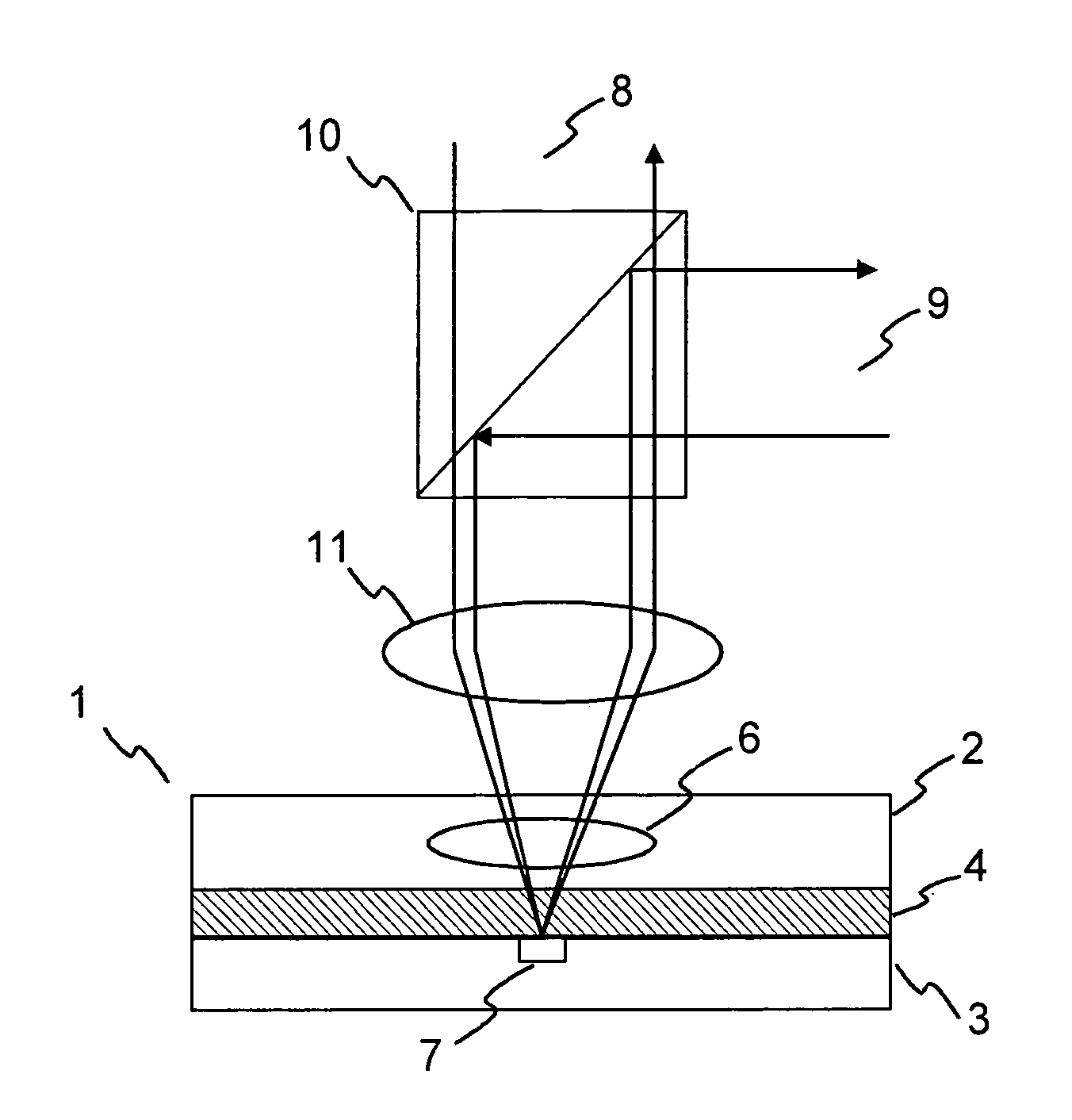

Digital holography device and digital holography play method

InactiveUS20150205260A1Minimize influenceHigh dynamic rangeTelevision system detailsHolographic light sources/light beam propertiesImage sensorHigh luminance

A digital holography device of an embodiment of the present invention includes: an image sensing device which records, in an image sensor and on the basis of an object, a plurality of holograms that correspond to respective different photographic exposure values; and a computer which (i) generates a high dynamic range hologram, which includes pieces of information ranging from low luminance information to high luminance information, by synthesizing the plurality of holograms recorded and (ii) generates a reconstructed image of the object by performing arithmetic processing of phase-shift interferometry, diffraction calculation, and / or the like on the basis of the high dynamic range hologram.

Owner:NAT UNIV KYOTO INST OF TECH

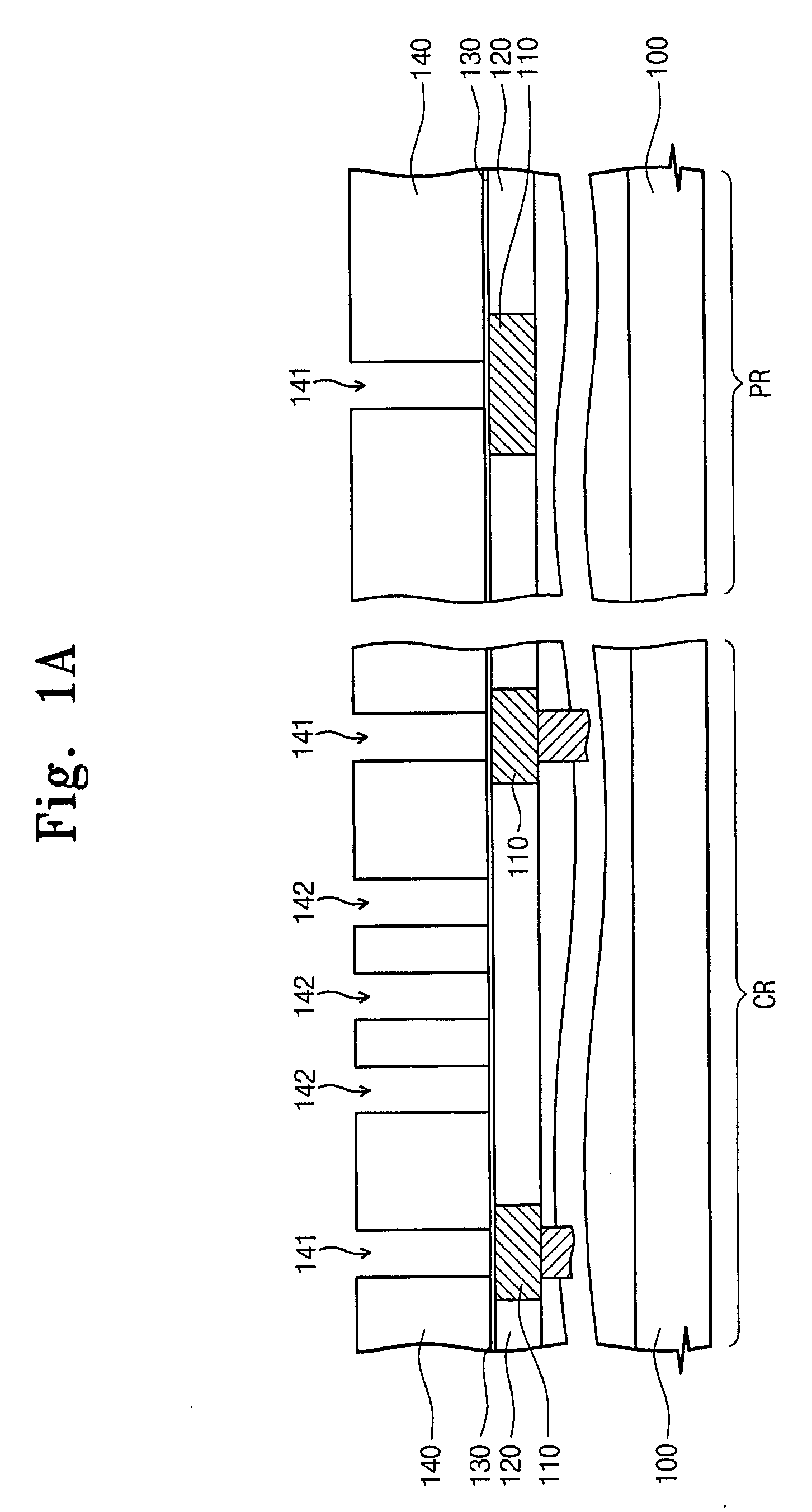

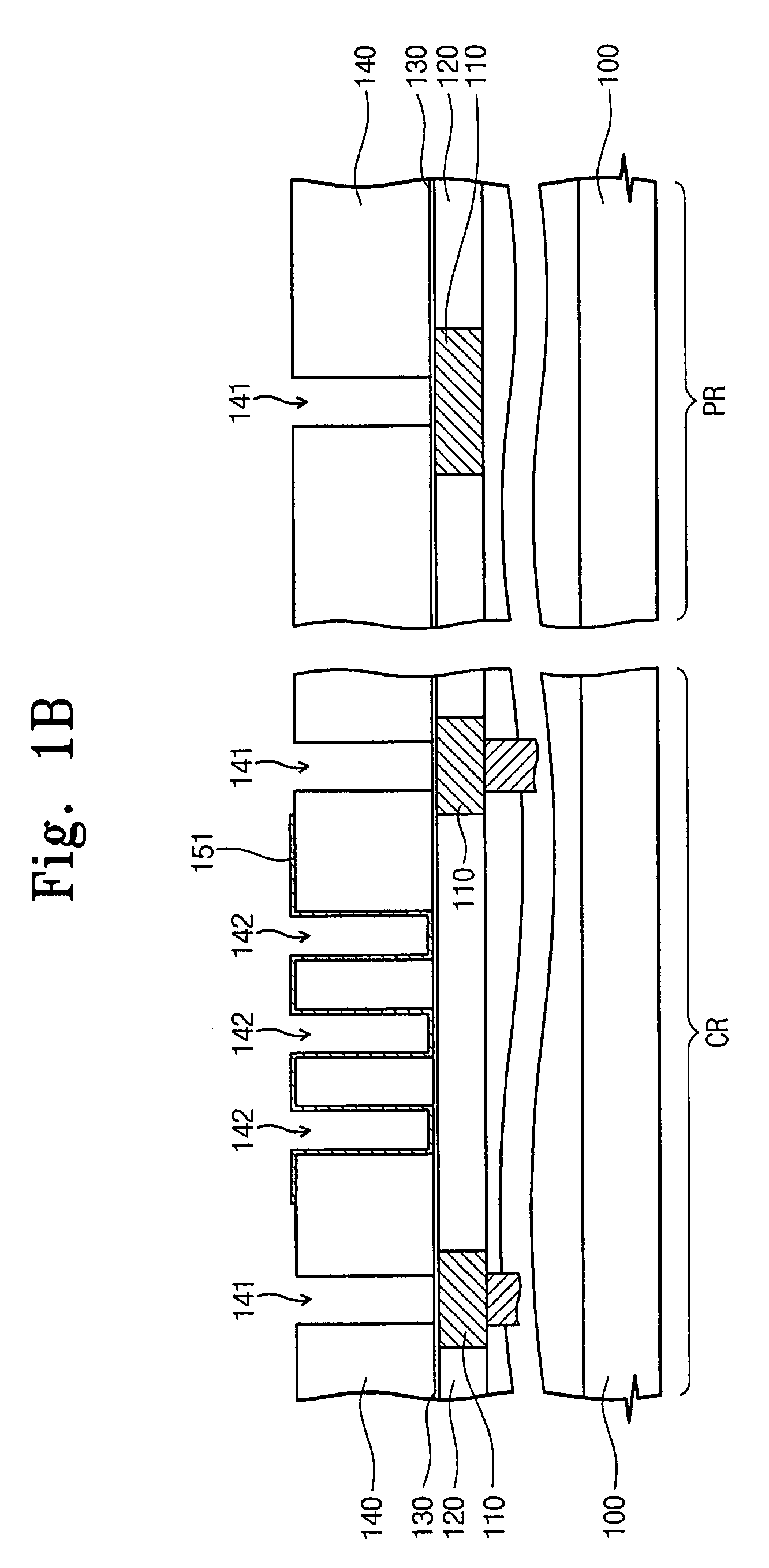

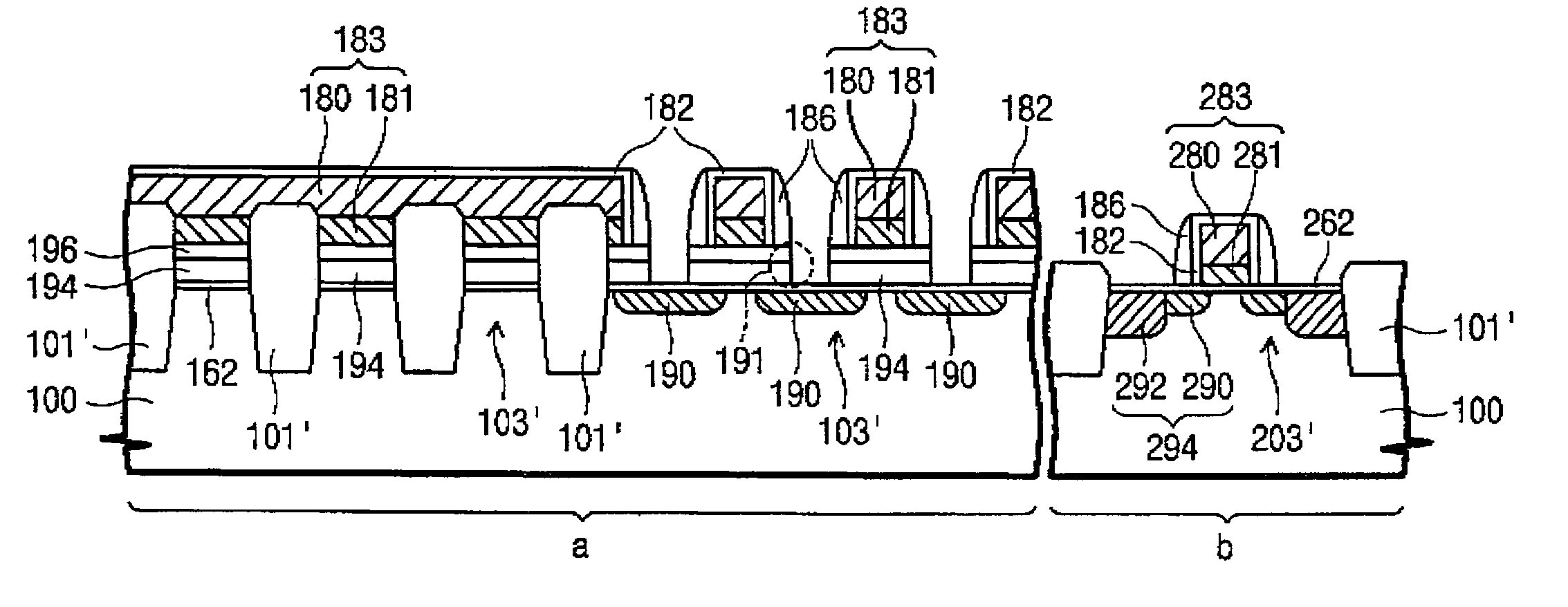

Non-volatile memory device with protruding charge storage layer and method of fabricating the same

InactiveUS7081651B2Minimize influenceMinimize impactTransistorSolid-state devicesImpurity diffusionEngineering

A non-volatile memory device includes a tunnel oxide layer, a charge storage layer, a blocking insulating layer, and a gate electrode that are sequentially stacked, as well as an impurity diffusion layer in an active region at both sides of the gate electrode. The gate electrode crosses active regions between device isolation layers formed in a predetermined area of a semiconductor substrate, and an edge of the charge storage layer is extended to have a protruding part that protrudes from the gate electrode. In order to form a charge storage layer having a protruding part, a stack insulating layer including first to third insulating layers is formed in an active region between the device isolation layers formed in the substrate. A plurality of gate electrodes crossing the active region are formed on the stack insulating layer, and a sidewall spacer is formed on both sidewalls of the gate electrode. Using the sidewall spacer and the gate electrode, the stack insulating layer is etched to form a charge storage layer that protrudes from the sidewall of the gate electrode.

Owner:SAMSUNG ELECTRONICS CO LTD

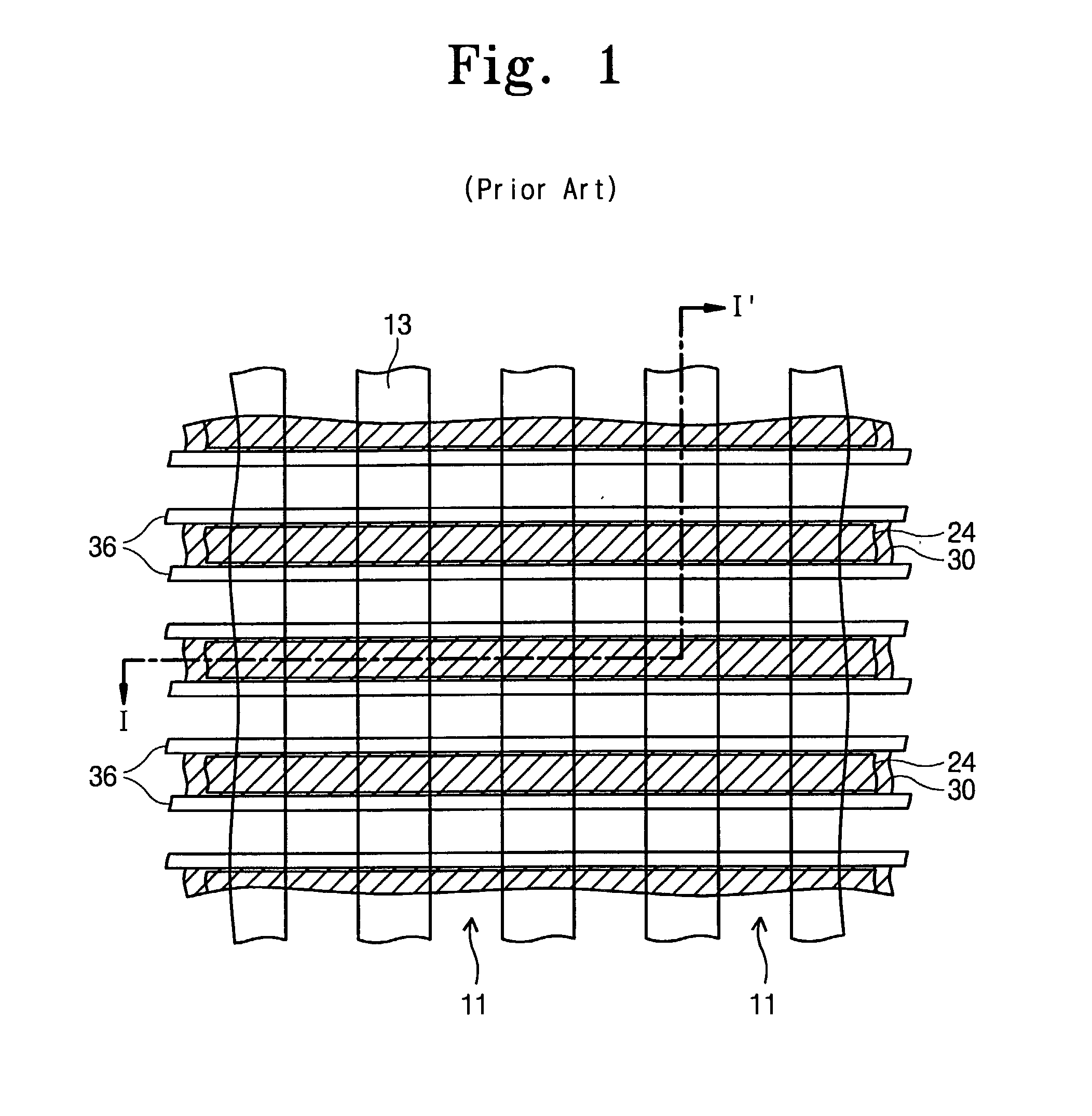

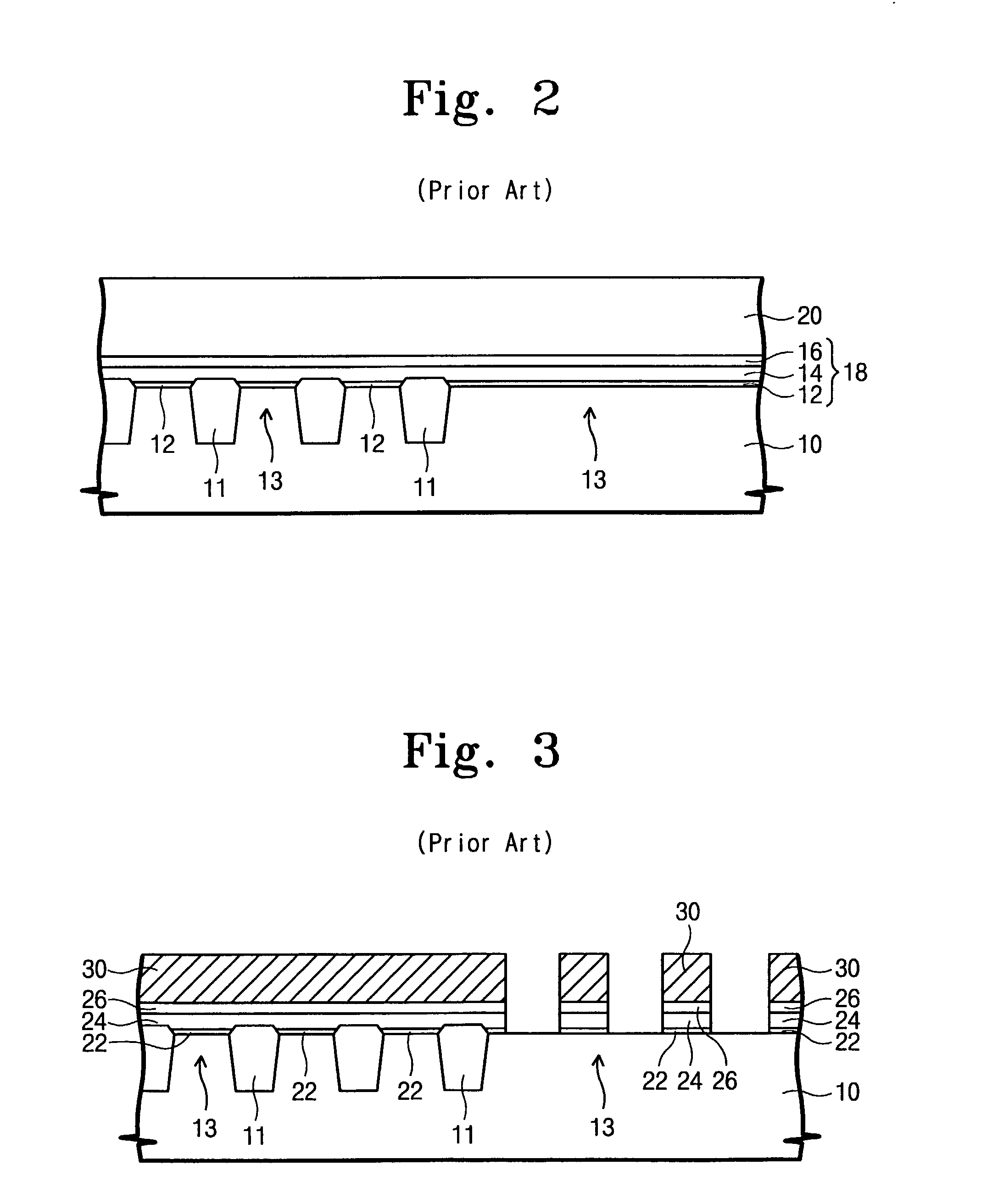

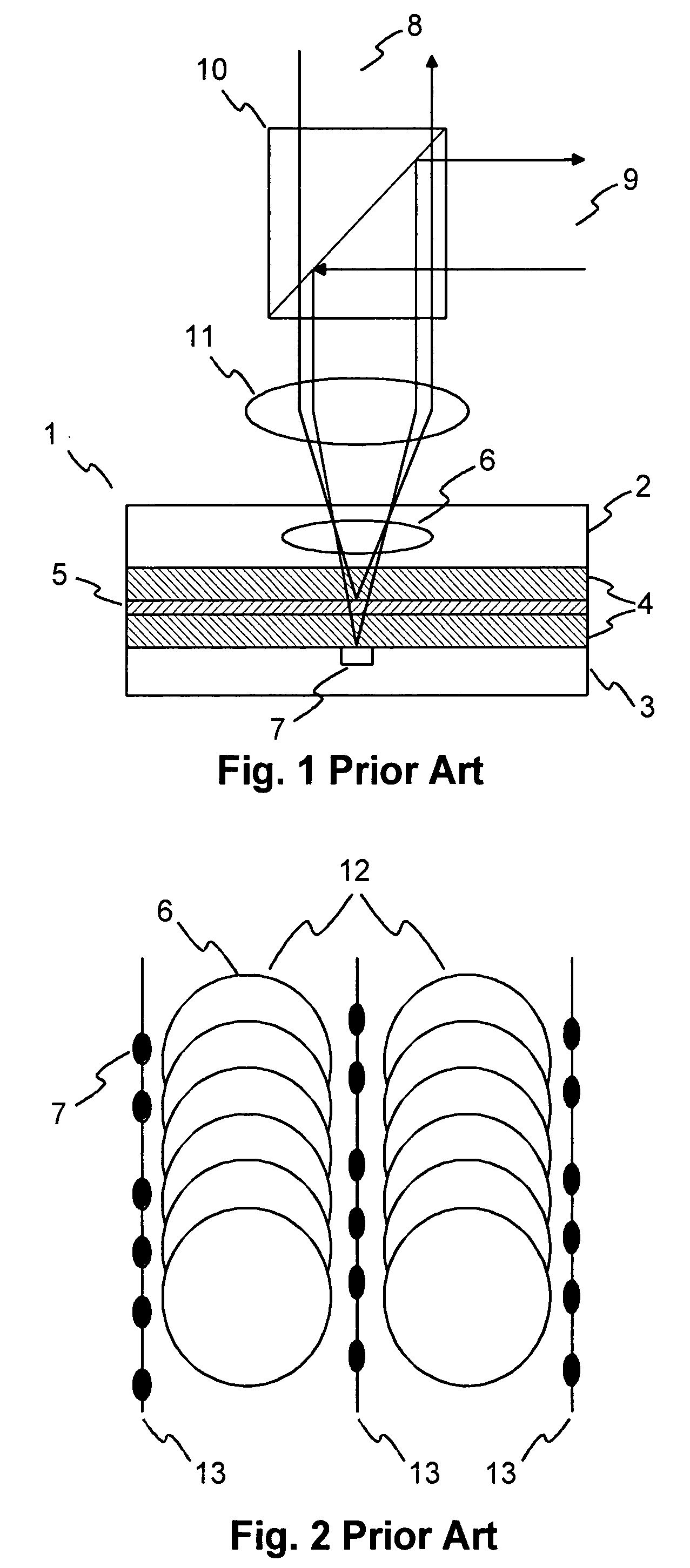

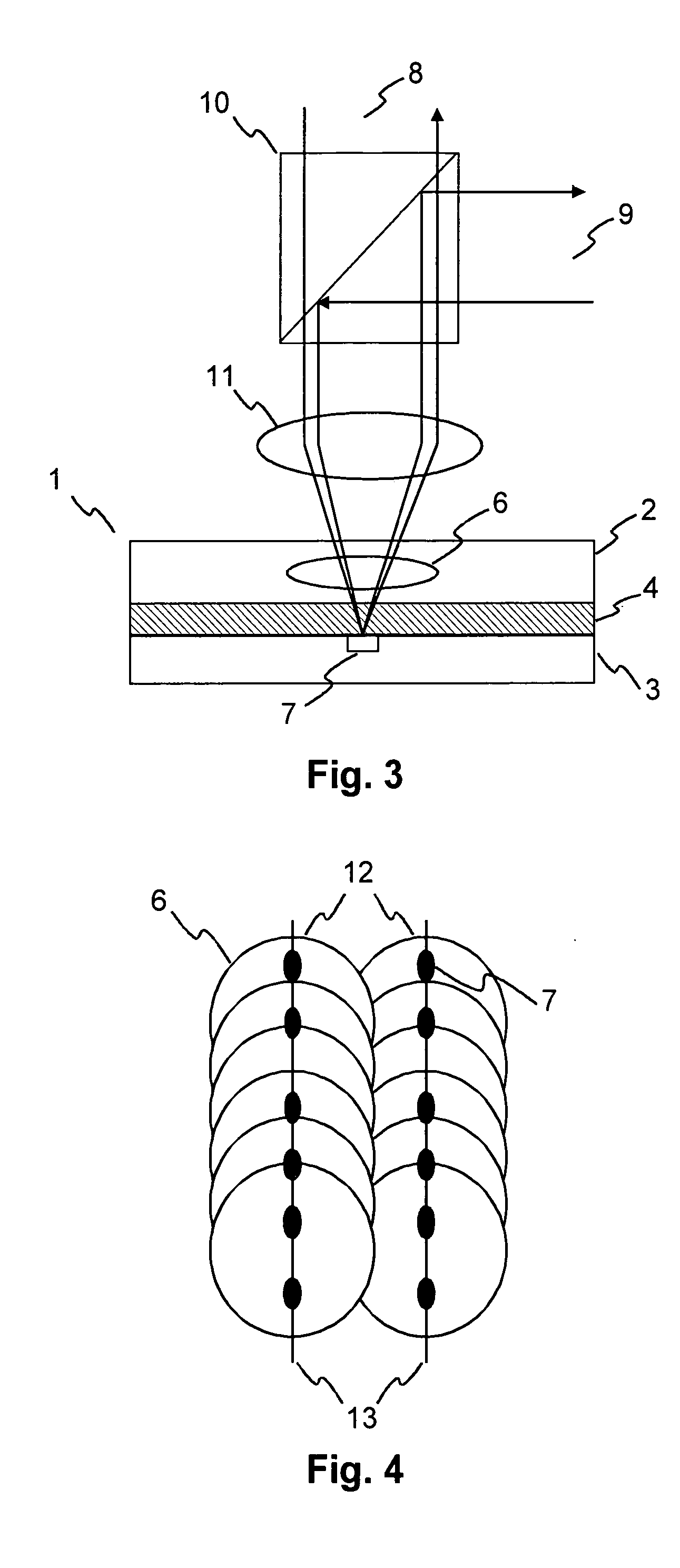

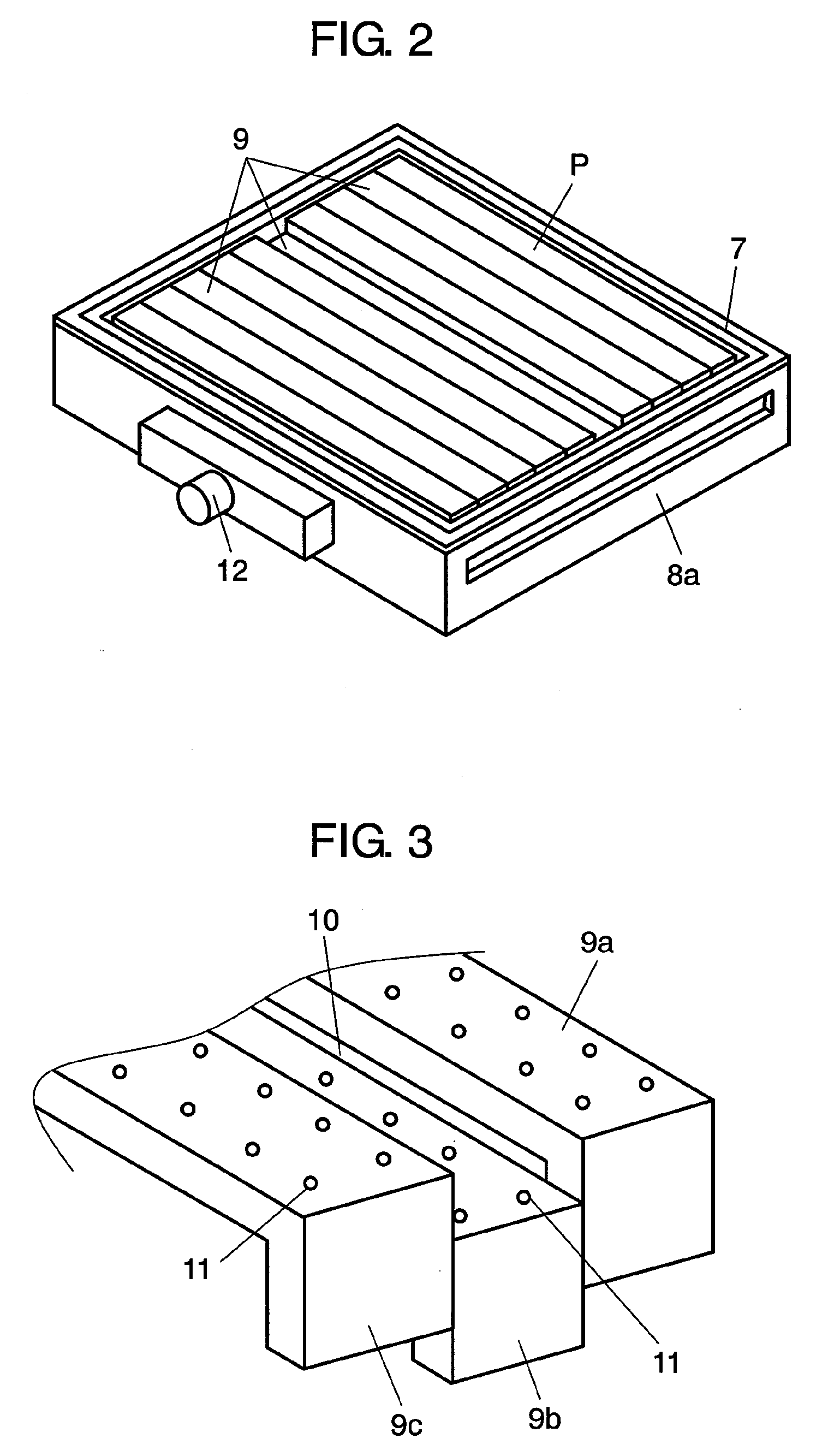

Holographic disk medium with servo marks

InactiveUS20060181999A1Minimize influenceServo beamMechanical record carriersRecord information storageEngineeringReference beam

The present invention relates to a holographic disk medium (1) with servo marks (7), and more specifically to a holographic disk medium (1) having a common reflective layer (3) for reflecting a servo beam (9) and object and reference beams (8). According to the invention, a holographic disk medium (1) with a recording layer (2) for recording holograms (6) and a reflective layer (3) for reflecting a servo beam (9) and object and reference beams (8), includes servo marks (7) which are located in the reflective layer (3) at least partly below the holograms (6), wherein the servo marks (7) are designed such that their influence on the object and reference beams (8) is minimized.

Owner:THOMSON LICENSING SA

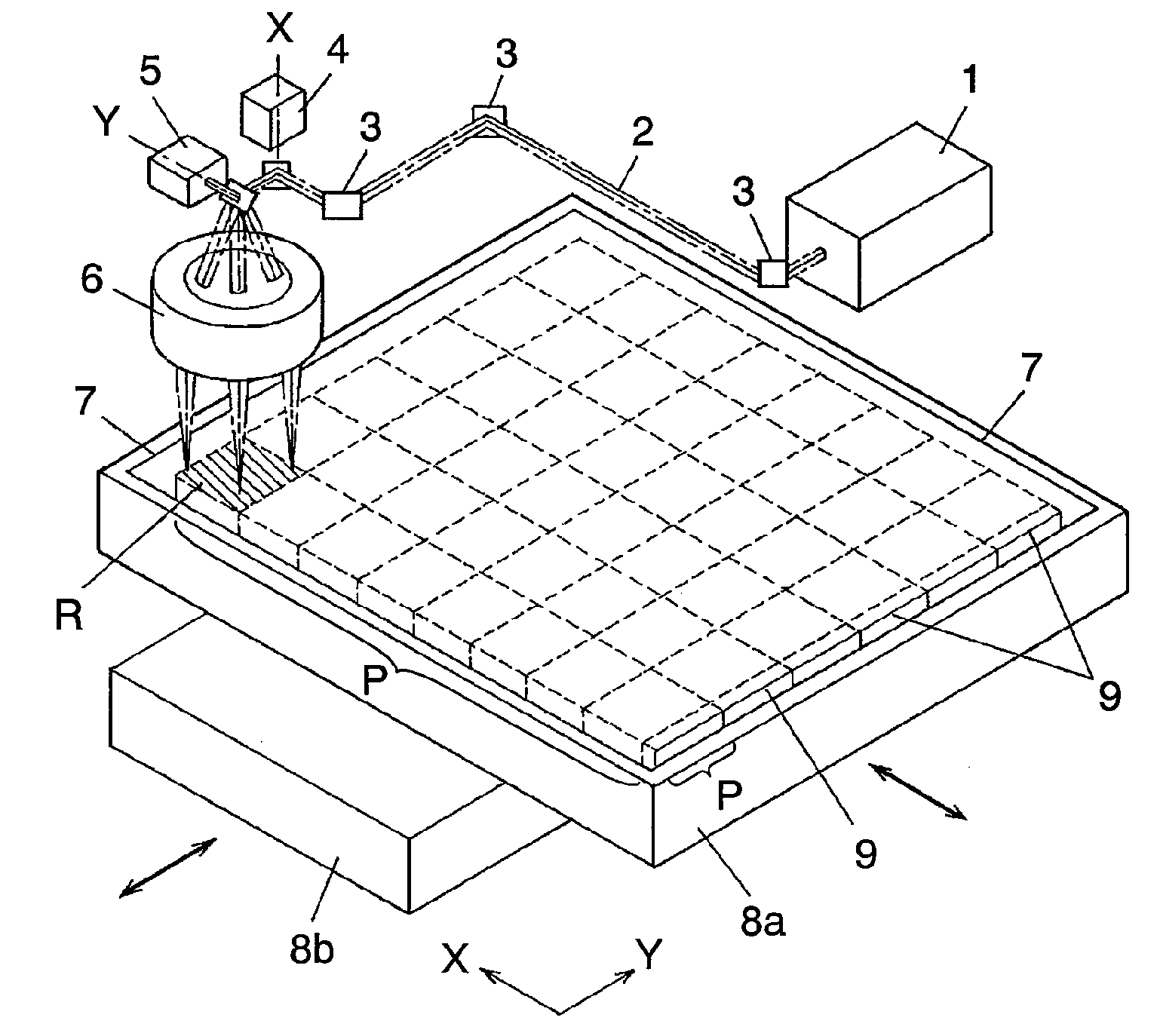

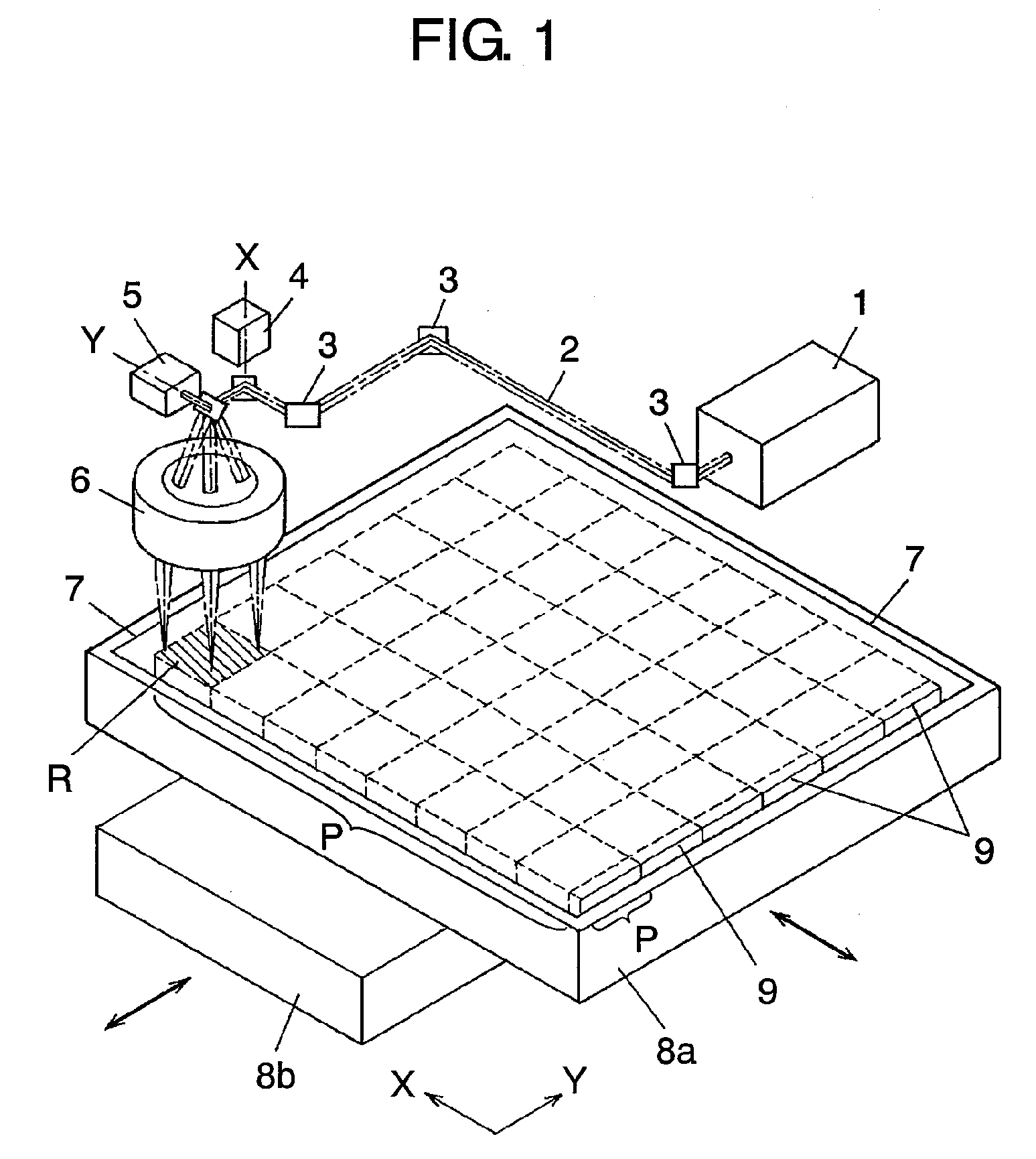

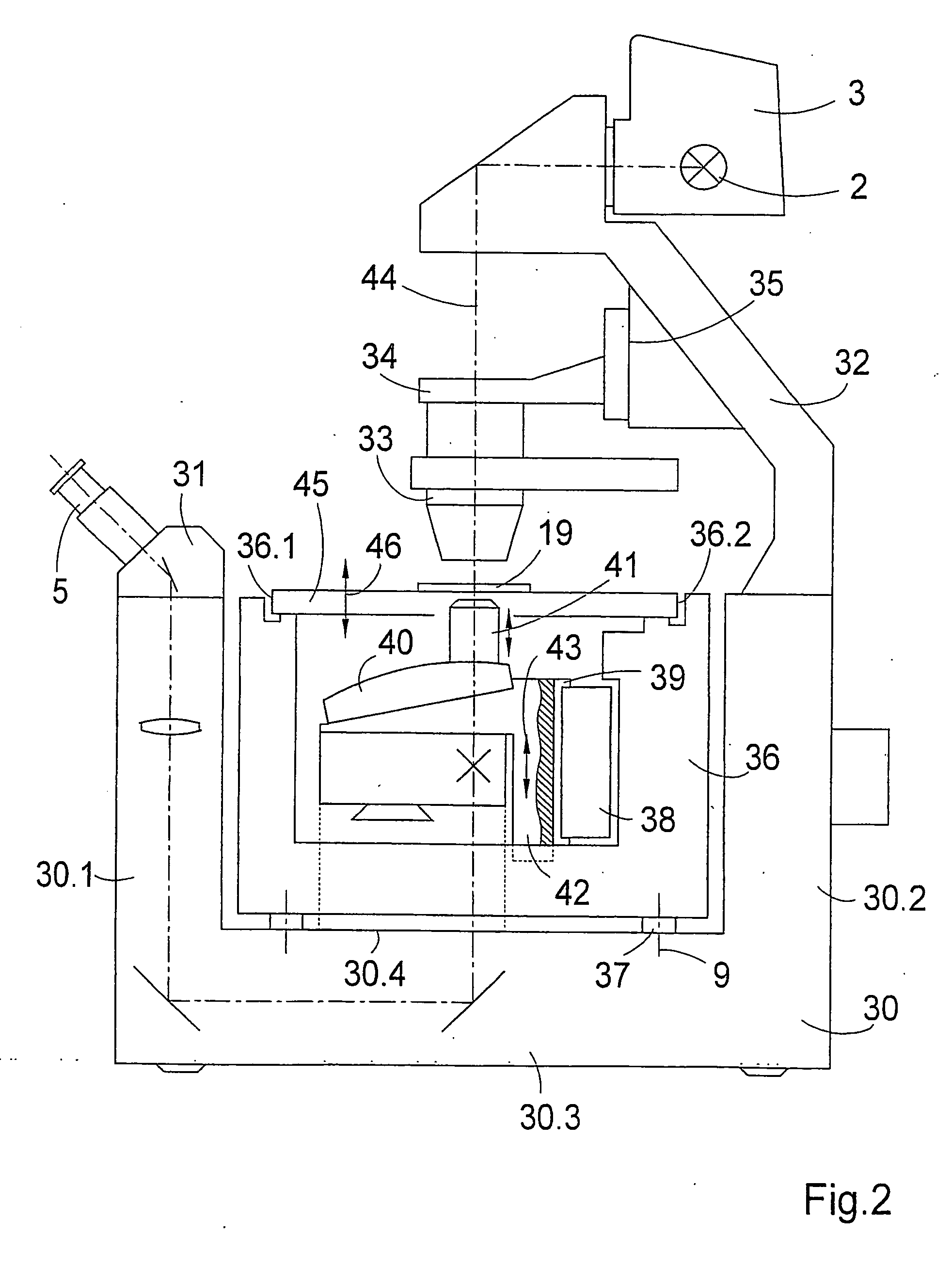

Laser processing apparatus and laser processing method using the same technical field

ActiveUS20090173723A1Increase productivityMinimize influenceWelding/cutting auxillary devicesAuxillary welding devicesOptoelectronicsLaser processing

A laser processing apparatus is provided in which its XY table is composed of plural divided blocks vertically movable, at least one divided block is stopped while it is moving down, and a through hole is formed by irradiating a workpiece in an area corresponding to a position directly above the divided block with a laser beam.

Owner:PANASONIC INTELLECTUAL PROPERTY MANAGEMENT CO LTD

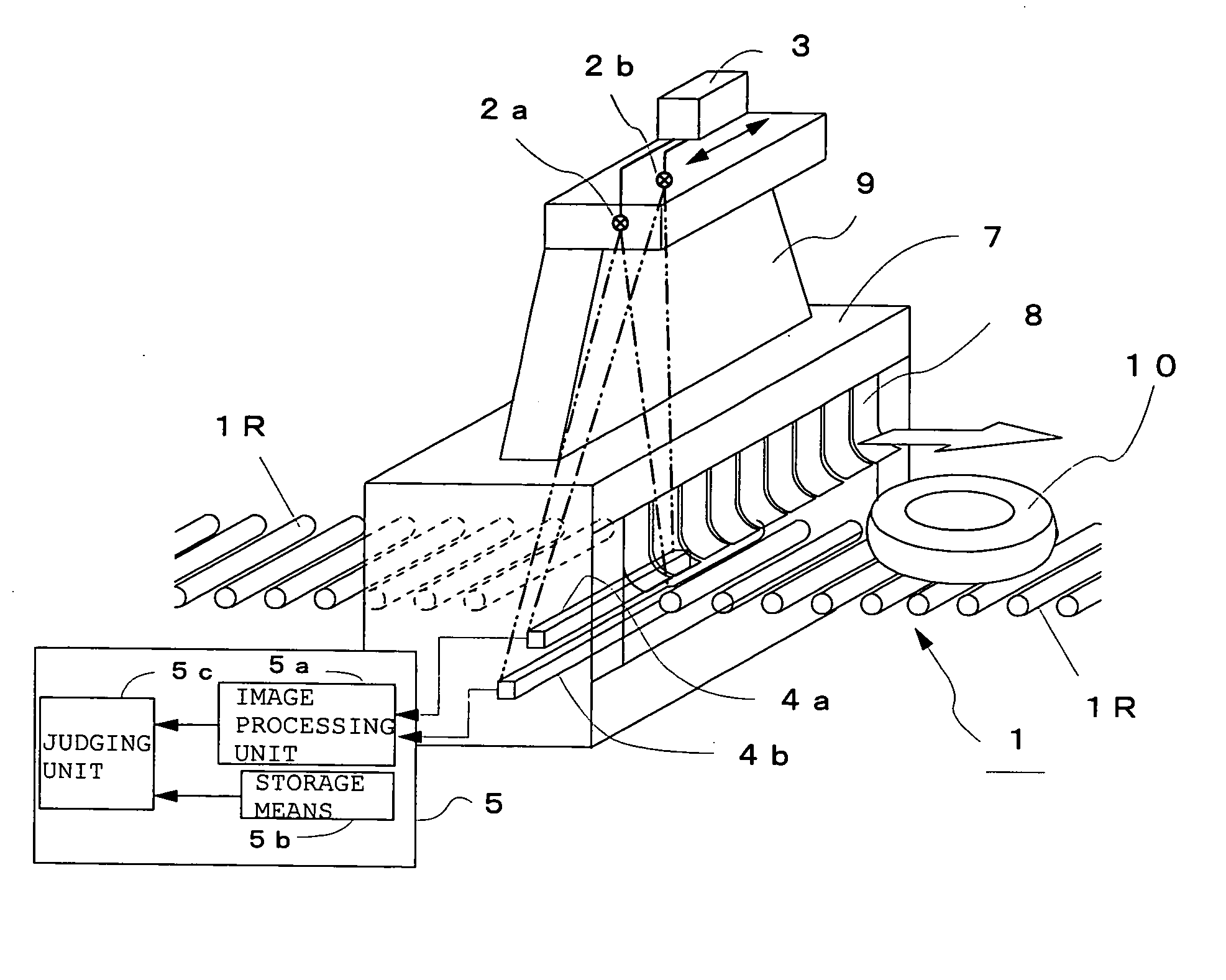

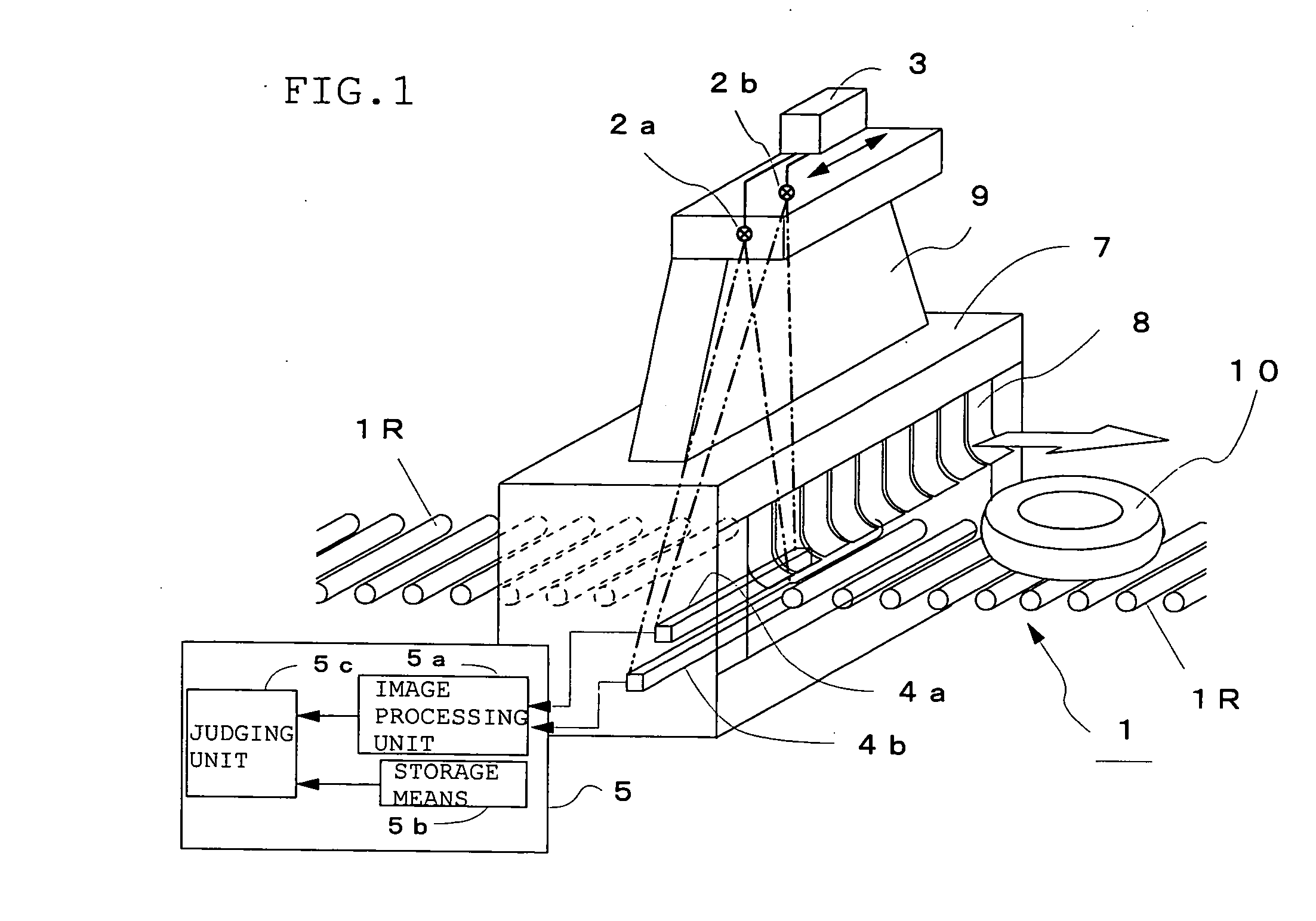

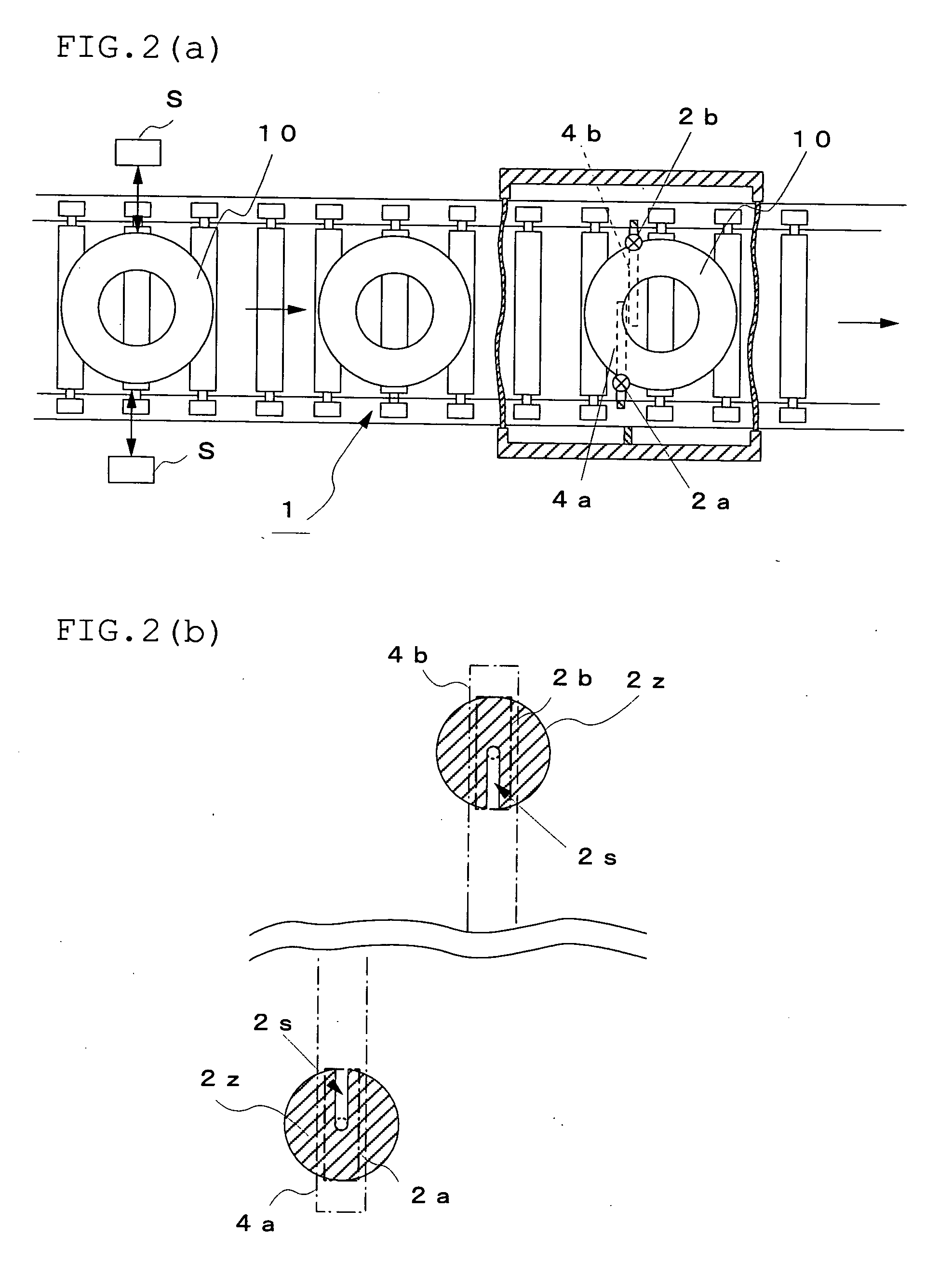

Method and device for x-ray inspection of tire

ActiveUS20050175146A1Minimize influenceAccurate imageVehicle endless-track testingUsing wave/particle radiation meansX ray imageLine sensor

An X-ray tire inspection apparatus comprising X-ray tubes 2a and 2b for applying an X-ray to a tire 10, installed right above the opposite ends of the tire 10 conveyed by a roll conveyor 1, and X-ray line sensors 4a and 4b arranged in the space between adjacent rolls 1R and 1R below the above roll conveyor 1 at positions corresponding to the above X-ray tubes 2a and 2b, respectively, wherein transmission X-ray images of left half and right half portions of the tire 10 are taken by the X-ray line sensors 4a and 4b and combined by tire internal image inspection means 5 to obtain a transmission X-ray composite image of the whole tire 10. Therefore, even a tire having a low aspect ratio can be internally inspected accurately and efficiently.

Owner:BRIDGESTONE CORP

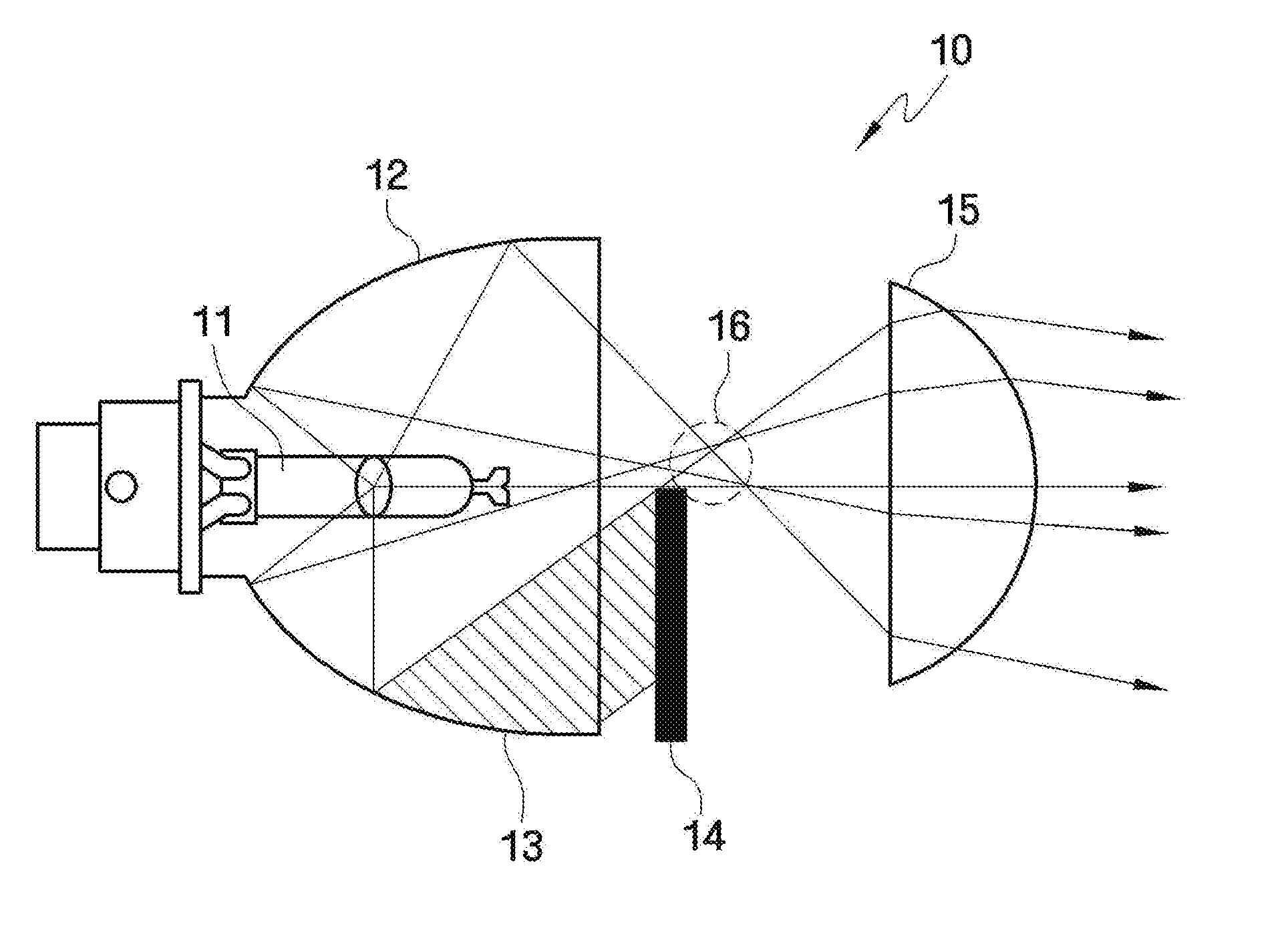

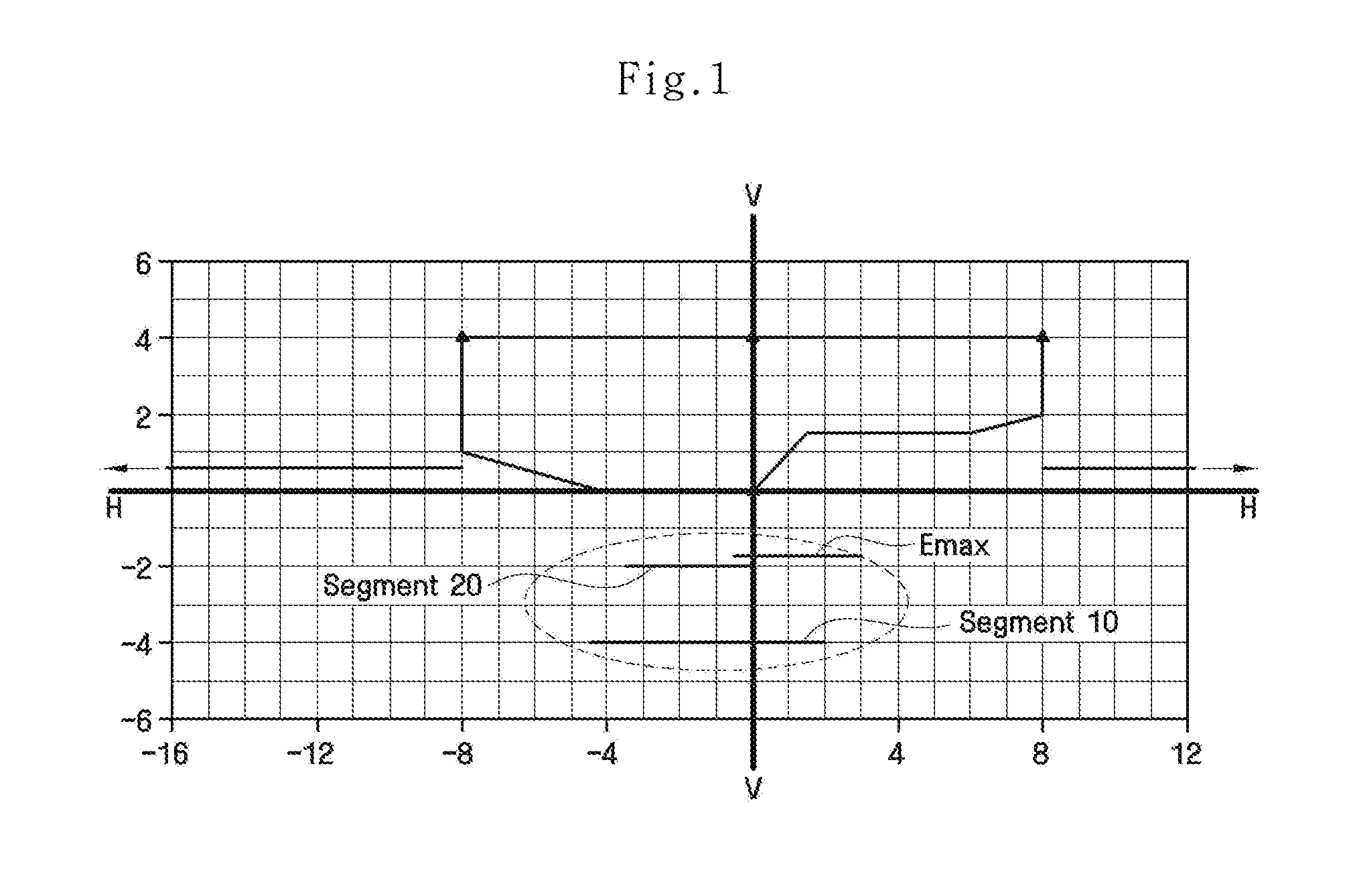

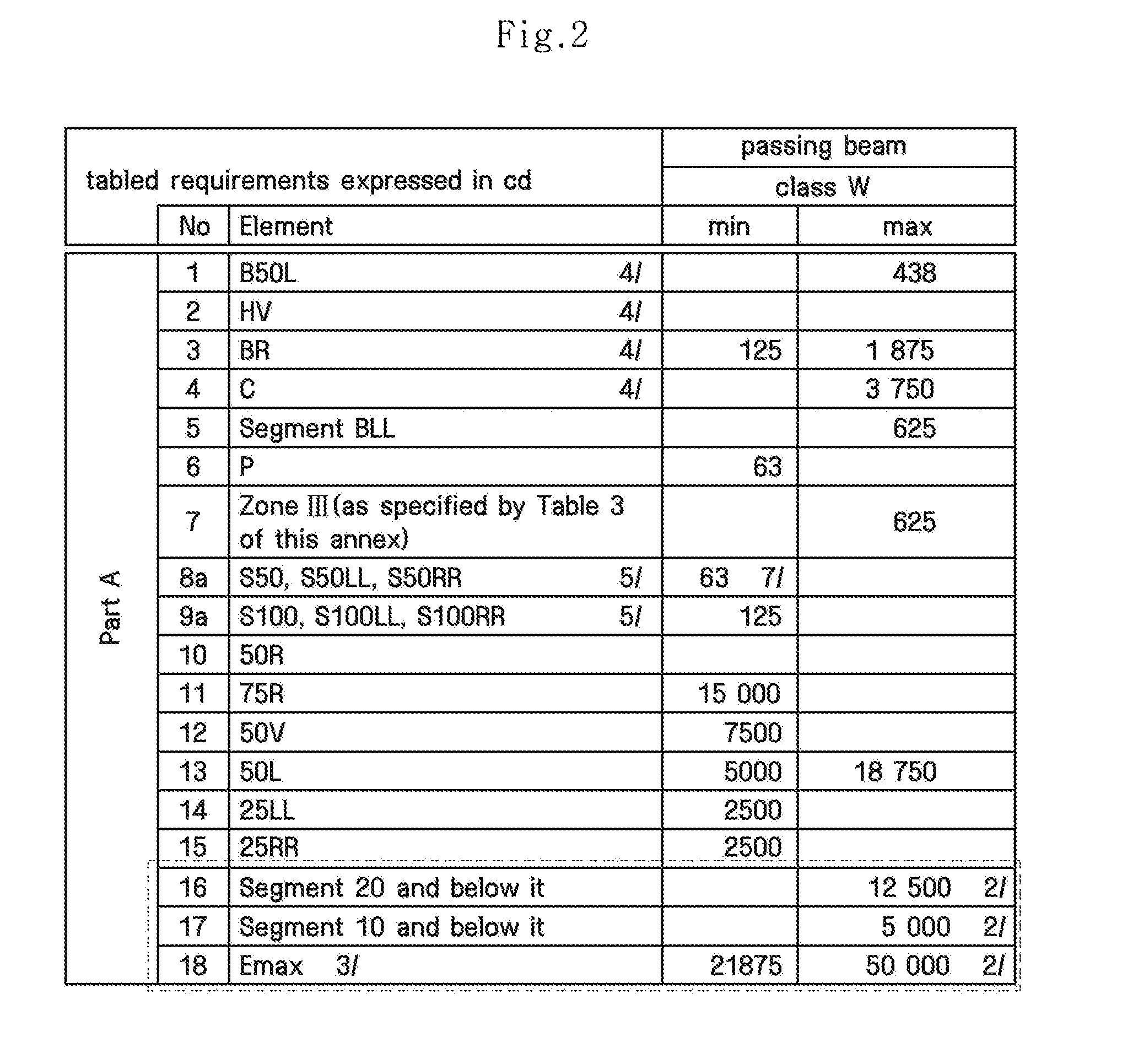

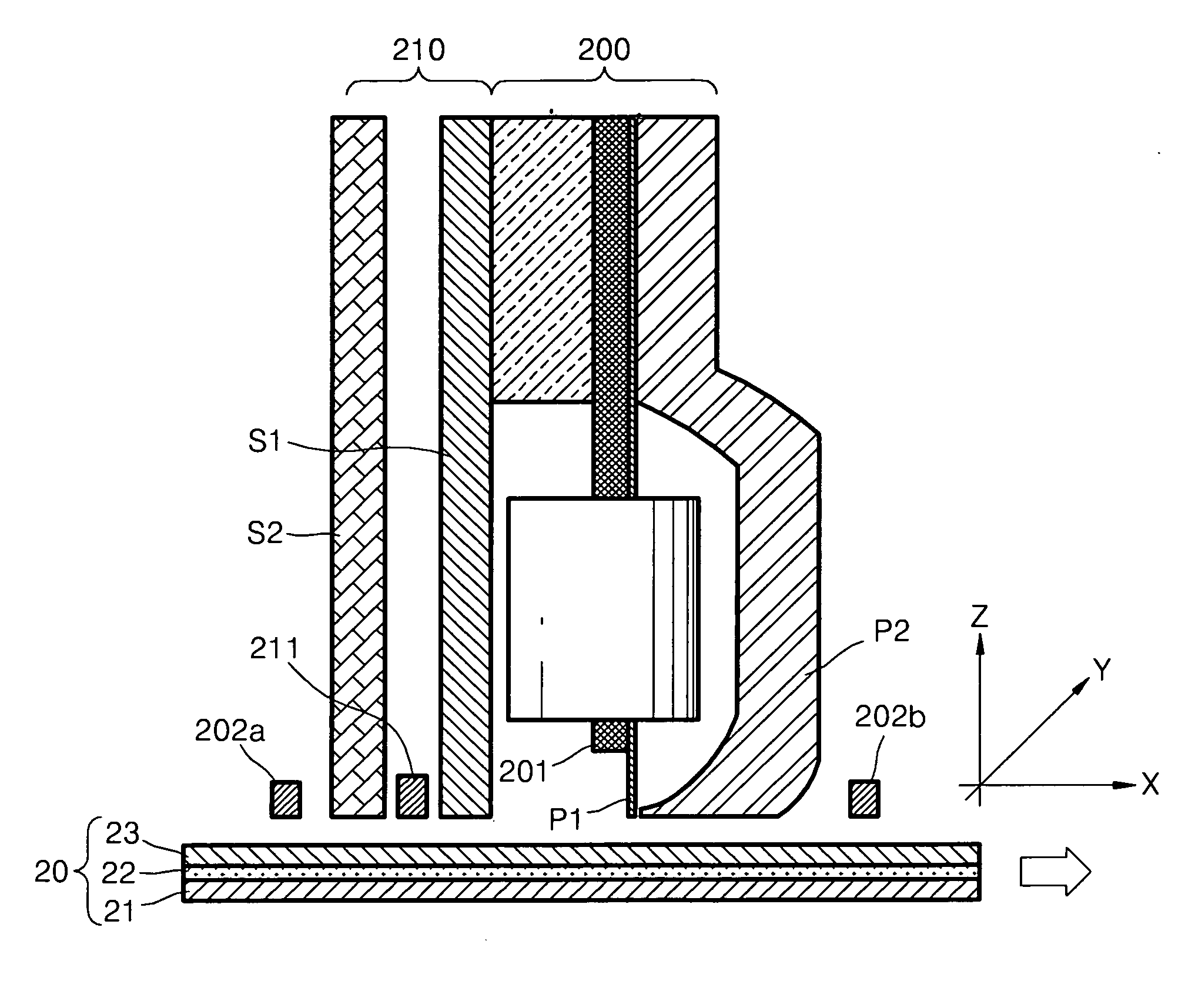

Head Lamp Assembly and Method for Controlling the Same

InactiveUS20120286662A1Minimize influenceReduce riskVehicle headlampsOptical signallingRotation controlEffect light

Provided are a head lamp assembly and a method for controlling the same. A head lamp assembly according to the present disclosure includes: a rotation control unit for rotating a head lamp to determine an irradiating direction of the head lamp; a lighting unit provided in the head unit to generate light; a shield unit located at the front of the lighting unit and having a cylindrical shape to be rotatable on a rotary shaft, the shield unit having a plurality of shield protrusions provided on the circumference thereof to partially intercept the light; and a shield operating unit for activating a selected shield protrusion, wherein the plurality of shield protrusions have different shapes from each other, wherein the plurality of shield protrusions include first and second shield protrusions having the same height and having steps which protrude upward and whose starting locations are different from each other.

Owner:GM GLOBAL TECH OPERATIONS LLC +1

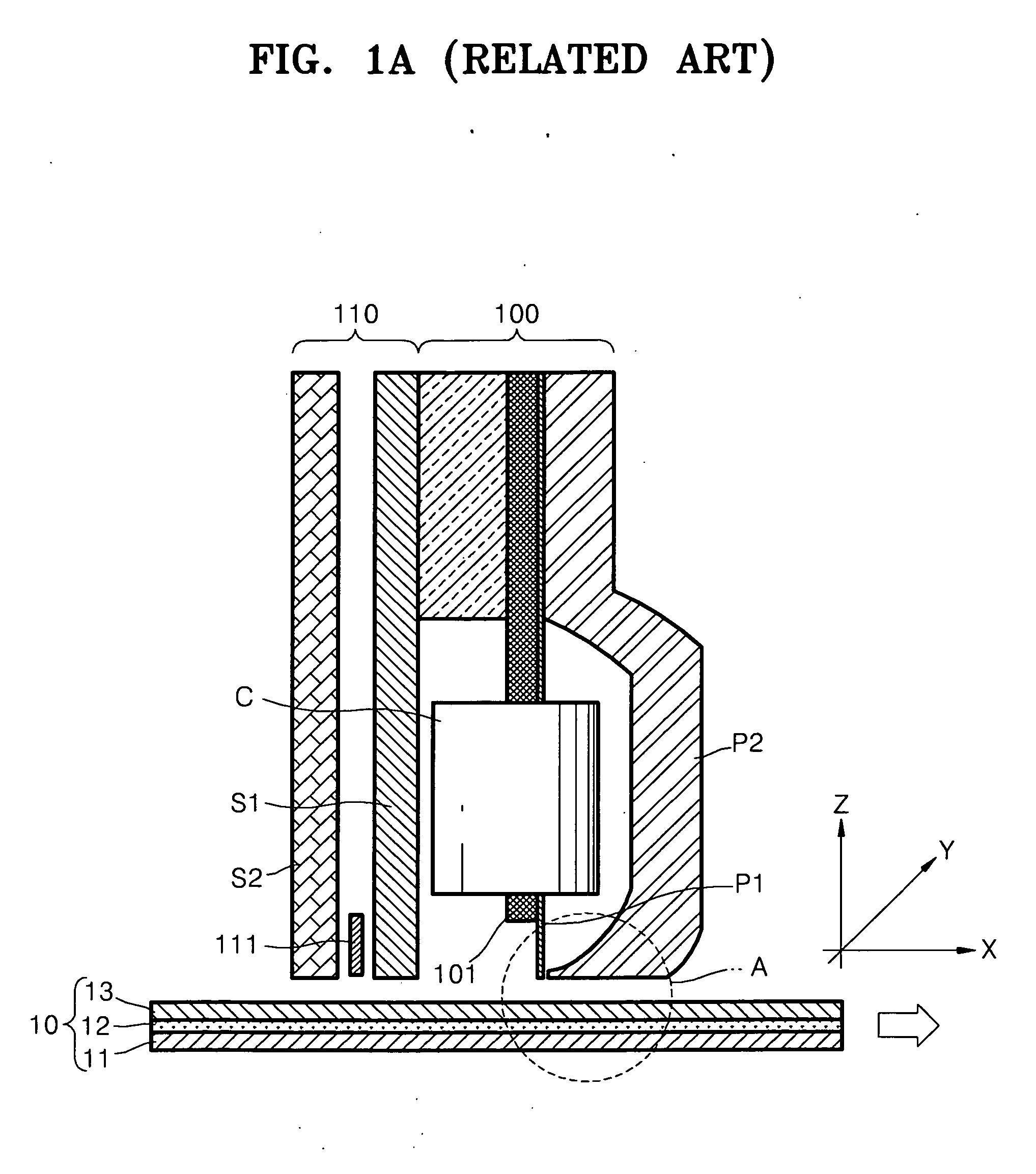

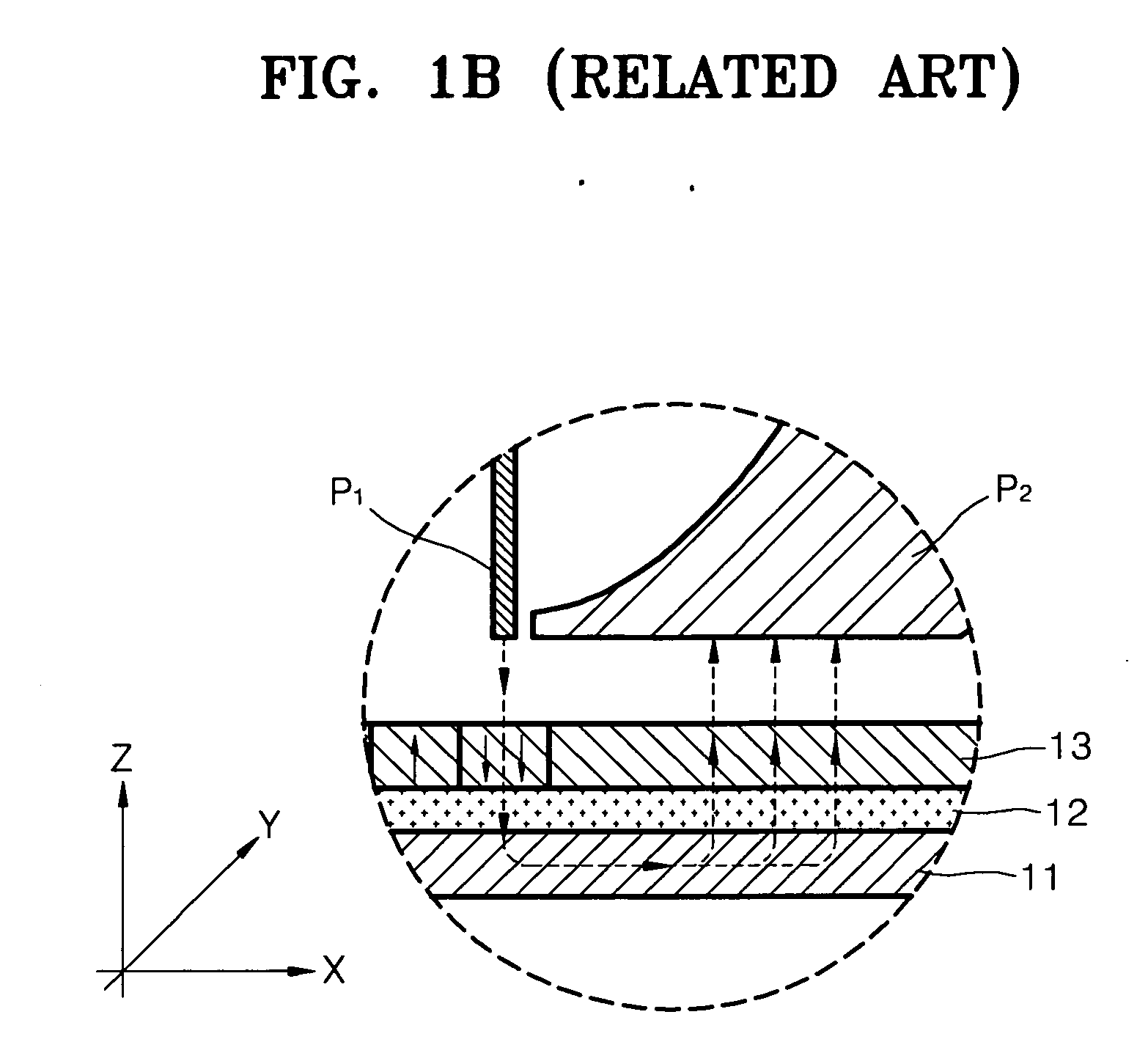

Perpendicular magnetic recording head

InactiveUS20070035884A1Minimize influenceMinimize impactManufacture head surfaceHeads using thin filmsRecording headAir bearing surface

A perpendicular magnetic recording head which moves in a track direction of a recording layer of a perpendicular magnetic recording medium to write information on the recording layer or read information from the recording layer. The perpendicular magnetic recording head includes: the perpendicular magnetic recording medium including a soft magnetic underlayer and the recording layer; a write head including a main pole that applies a magnetic field to, and writes information to, the recording layer and a return pole having a first end which is connected to the main pole and having a second end which is spaced apart from the main pole over an air bearing surface (ABS) of the perpendicular magnetic recording head which is adjacent to the recording layer; and a permanent magnet formed on at least one side of the write head.

Owner:SAMSUNG ELECTRONICS CO LTD

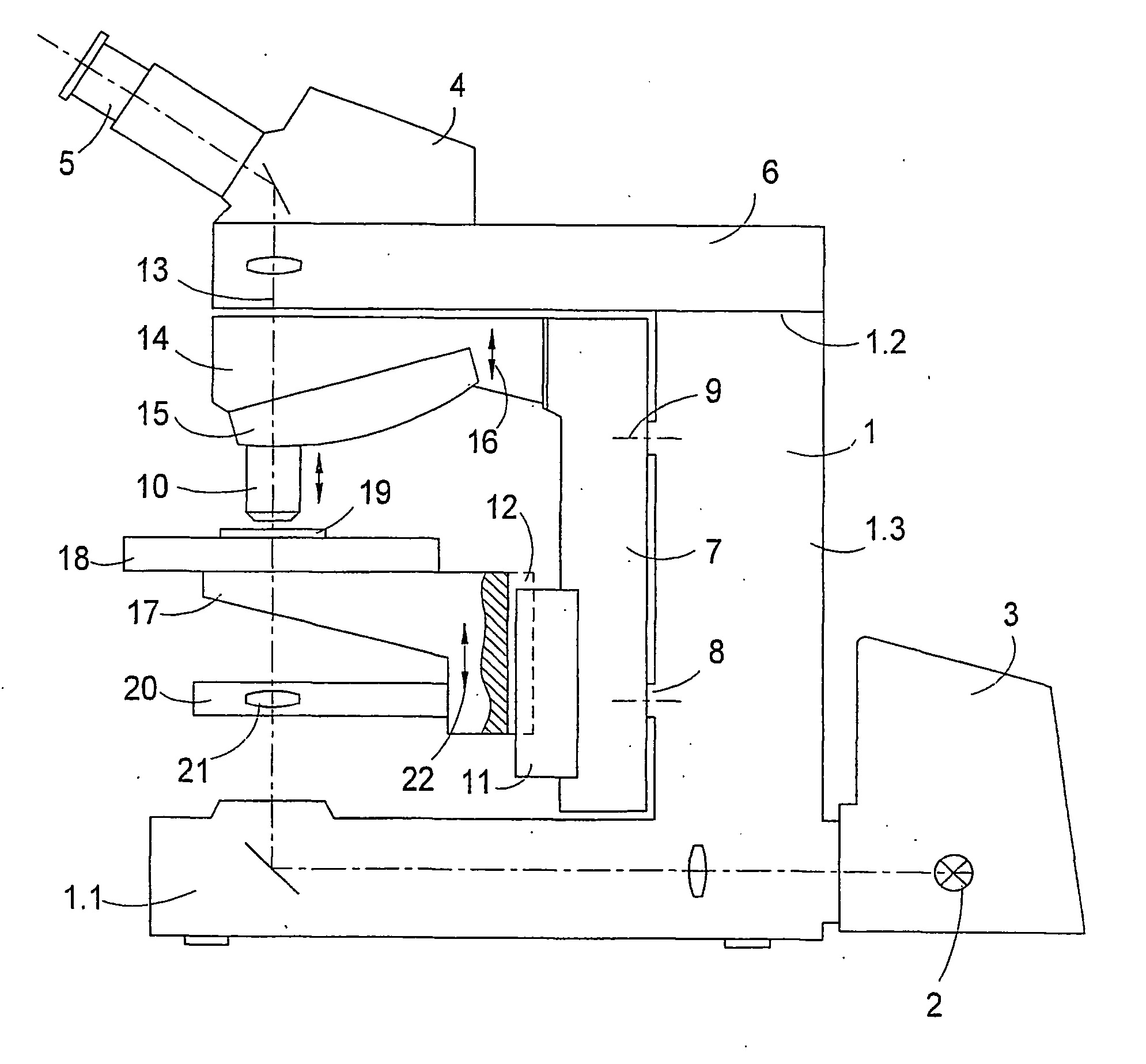

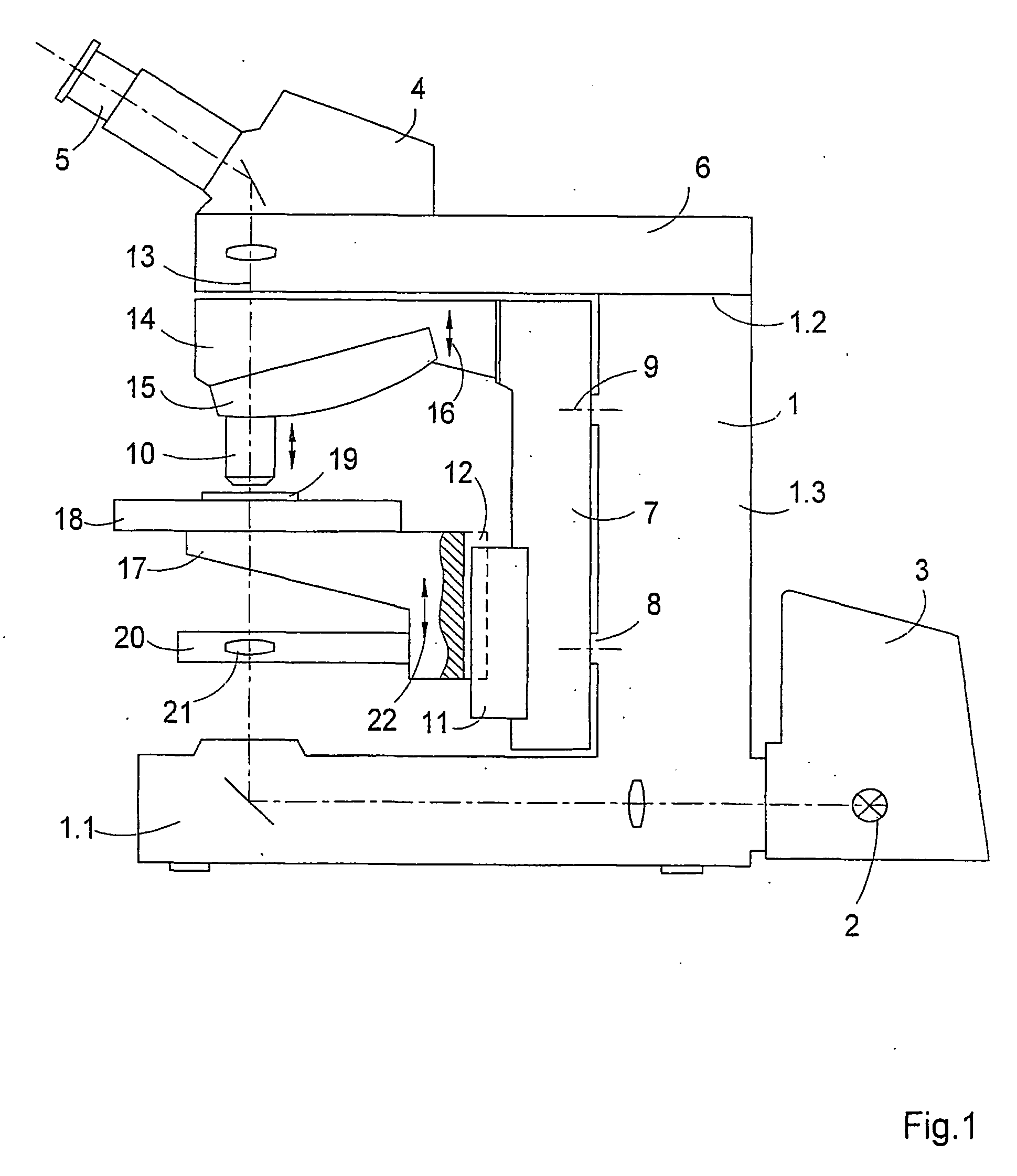

Microscope

InactiveUS20060139747A1Minimize influenceImprove dynamic behaviorMicroscopesSupporting cellMicroscope

The invention is directed to a microscope comprising a base body or stand, a stage support, a guide for adjusting the stage support or an objective changer device with inserted objectives, and a stage for holding the object or specimen. In the microscope, a supporting cell is provided which is optimized with respect to material and rigidity and is connected to the stand rigidly but so as to be exchangeable. First assemblies for receiving, holding and adjusting the objective and second assemblies for positioning the object or specimen relative to the objective are arranged at the supporting cell. The first assemblies are designed as an objective changer device and / or as an objective focusing device, and the second assemblies comprise a stage support, a stage guide, and a stage.

Owner:CARL ZEISS JENA GMBH

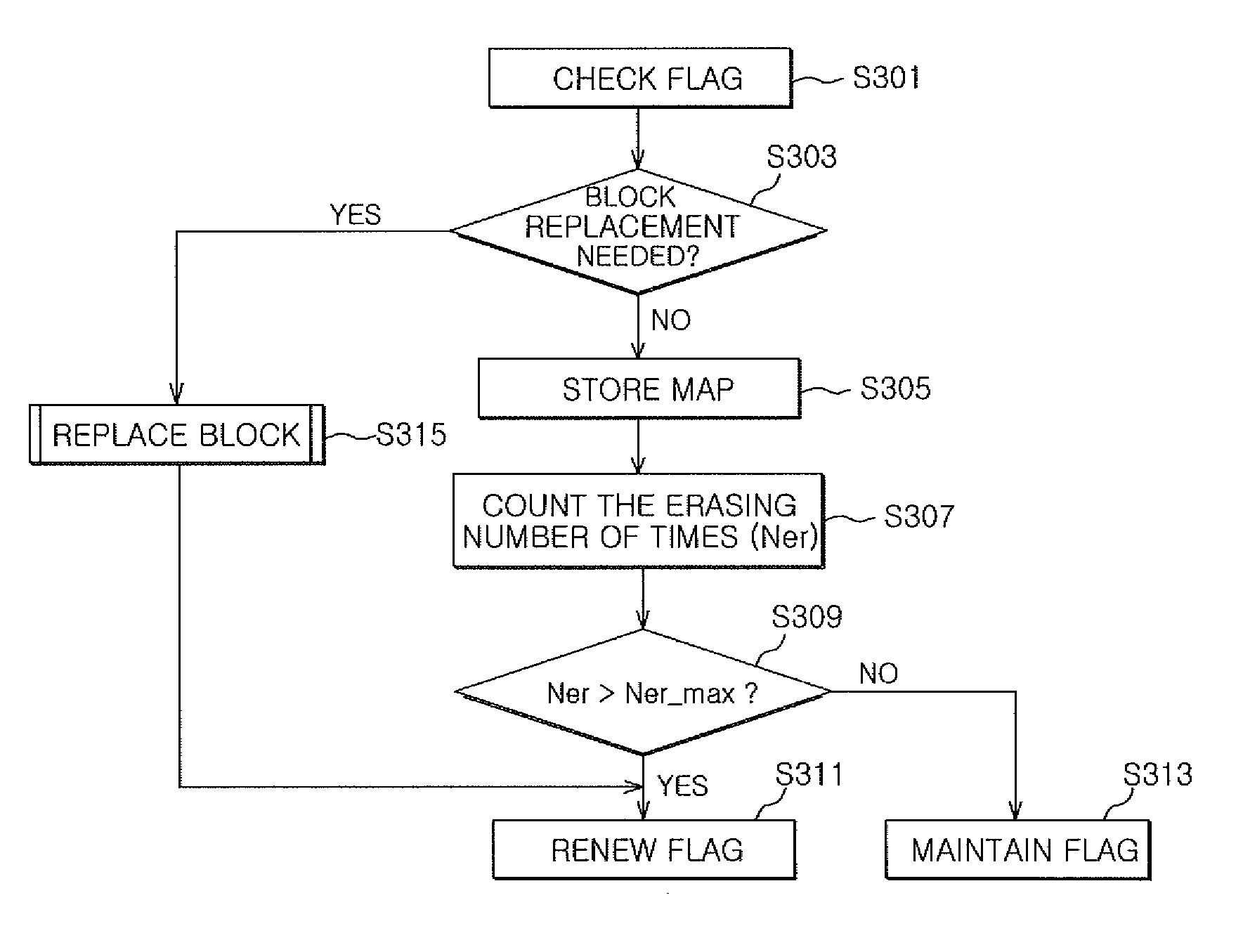

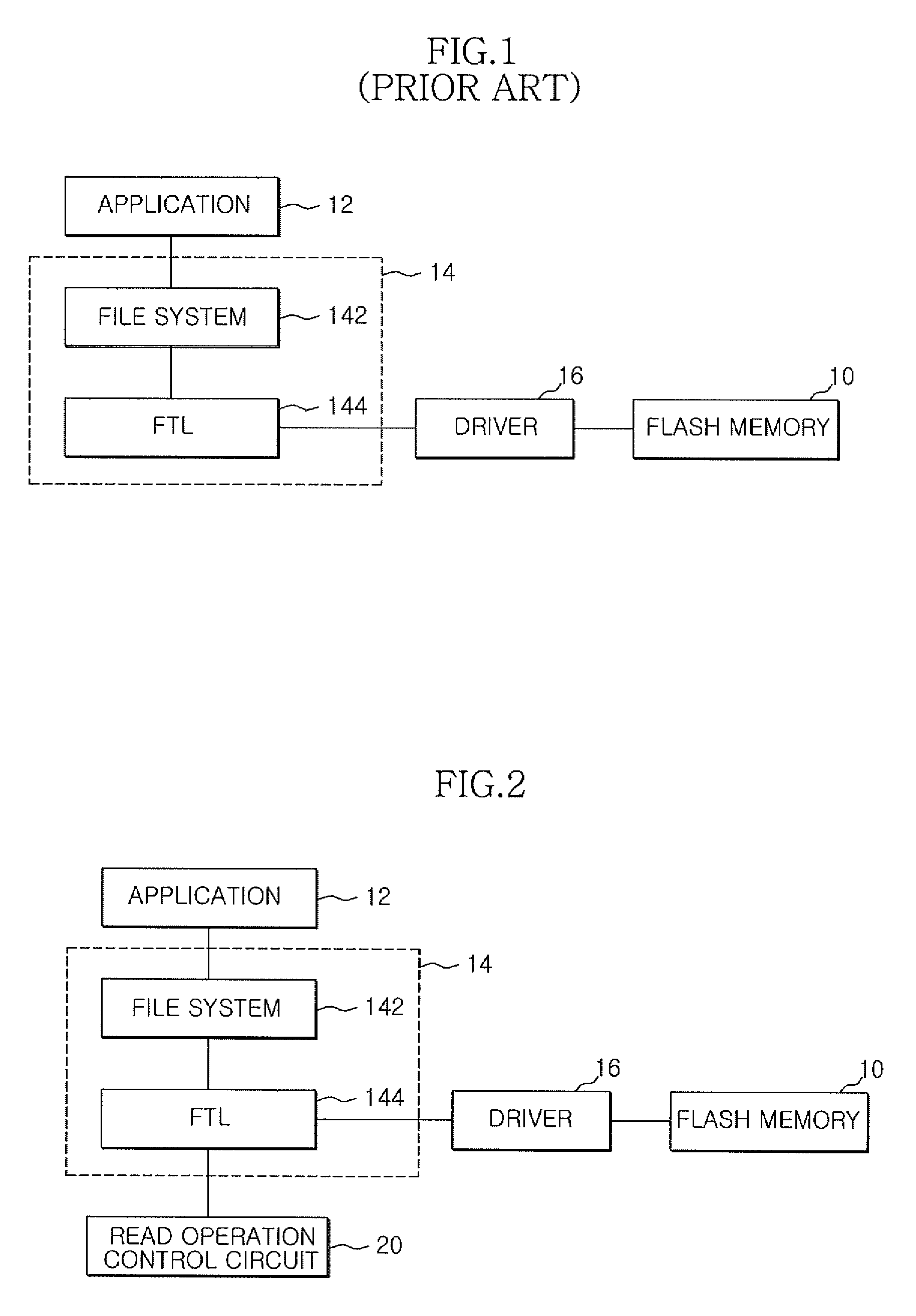

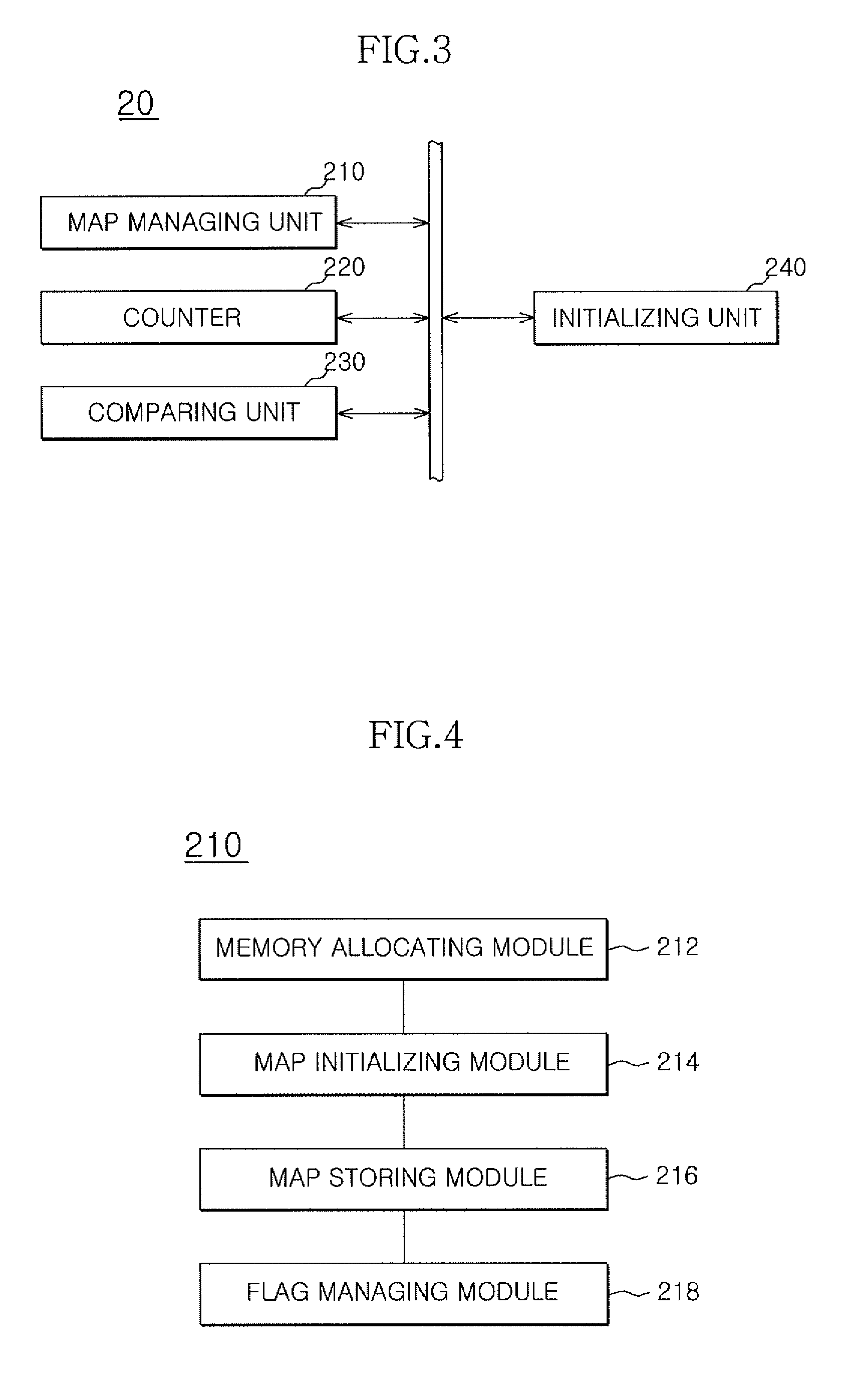

Flash memory apparatus and read operation control method therefor

ActiveUS20100165732A1Minimize influenceMinimize impactMemory architecture accessing/allocationRead-only memoriesControl circuitFlash memory

A flash memory apparatus of an embodiment is configured to include a flash memory including a plurality of blocks and a read operation control circuit determining whether to replace a block in accordance with the number of times a read process is performed for each block of the plurality of blocks.

Owner:SK HYNIX INC

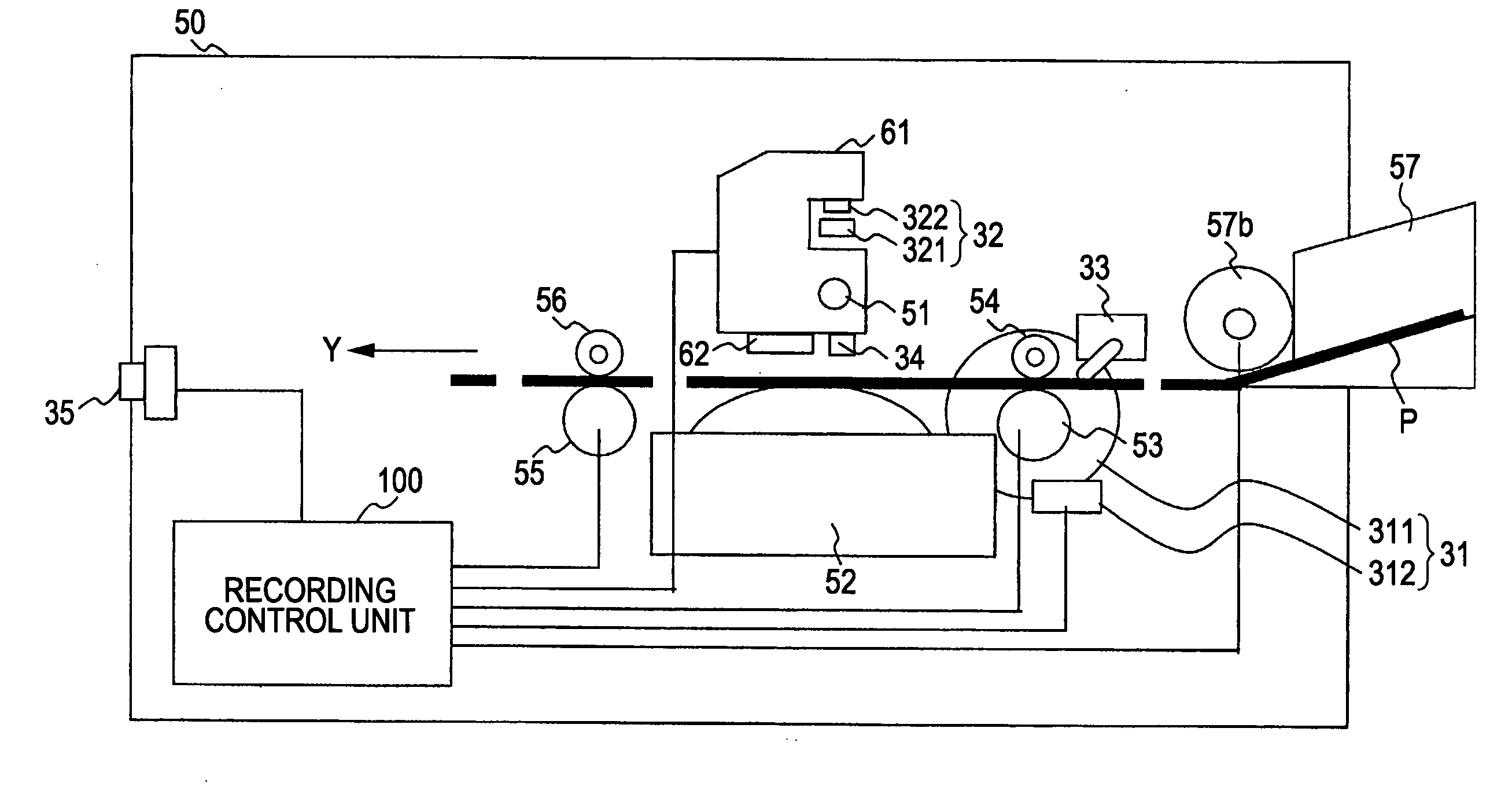

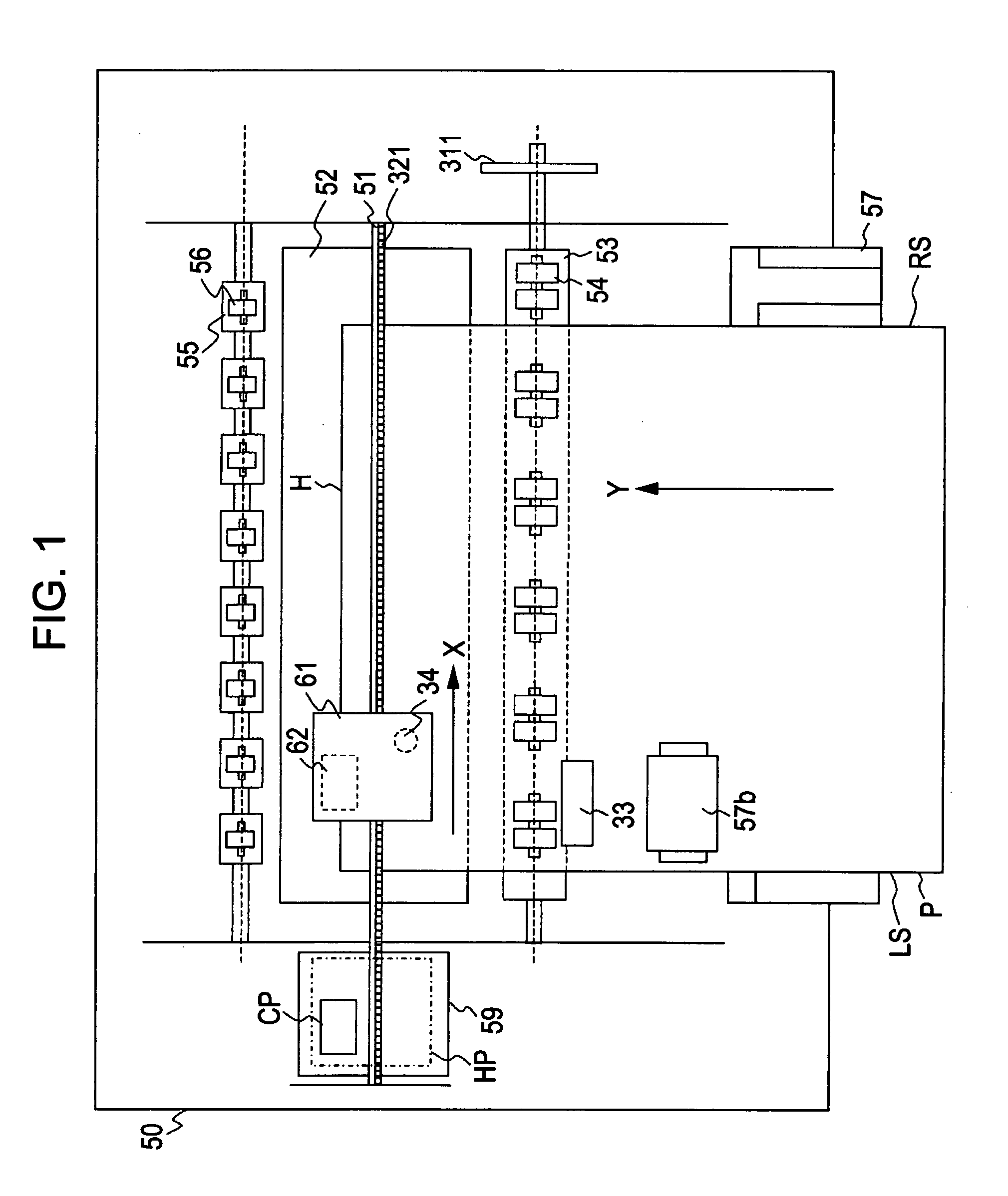

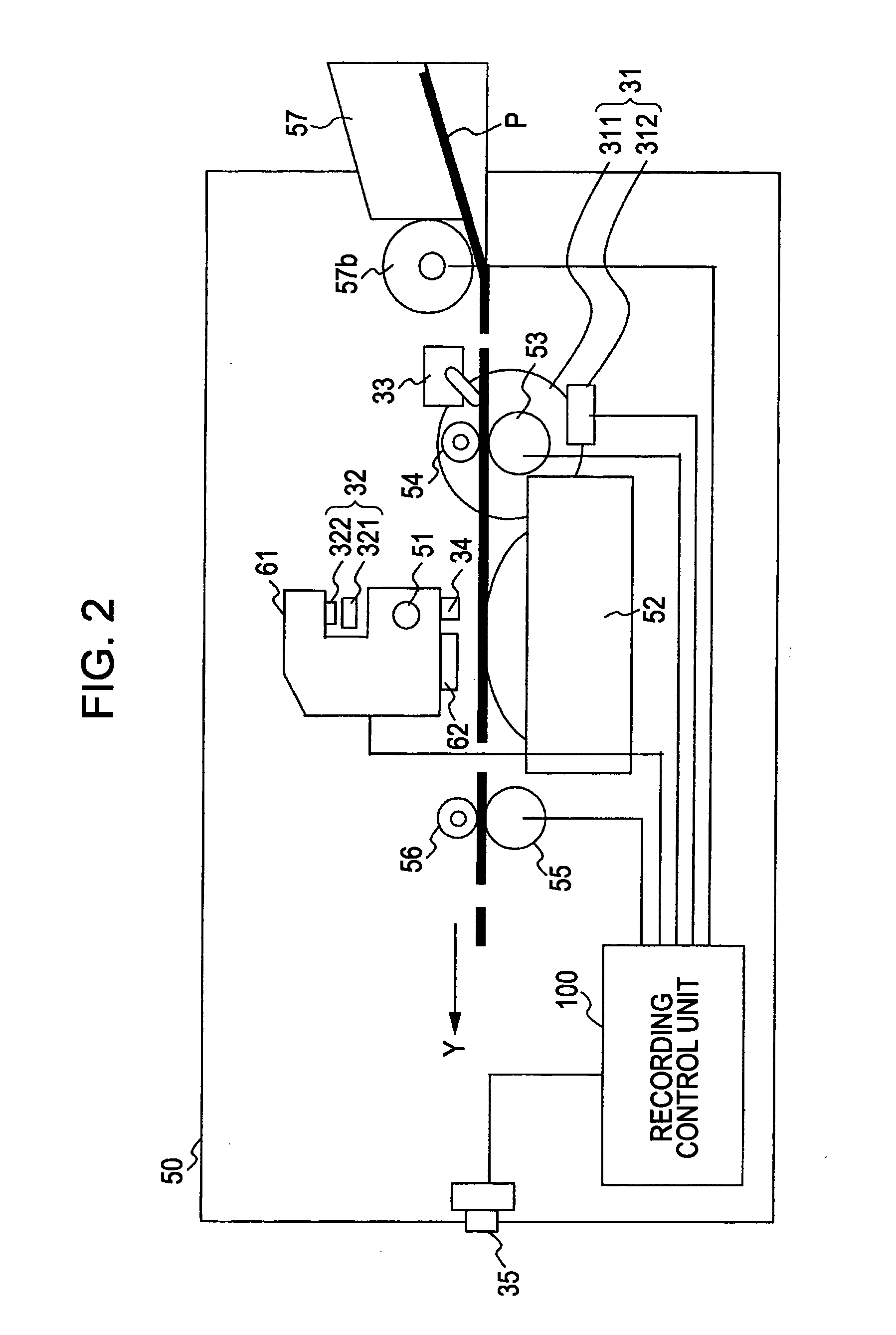

Recording apparatus and method

InactiveUS20070216718A1Minimize influenceMinimize changesOther printing apparatusComputer scienceLeading edge

A recording apparatus detects a leading edge of a recording material to be transported in a sub-scanning direction, and performs recording on a recording region of the recording material with reference to the leading edge. When a margin is formed at least at a leading end of the recording material, recording is performed on the recording region with reference to a center leading edge of the recording material. When a margin is not formed at least at the leading end of the recording material, recording is performed on the recording region with reference to one of right and left leading edges of the recording material that precedes in the sub-scanning direction.

Owner:SEIKO EPSON CORP

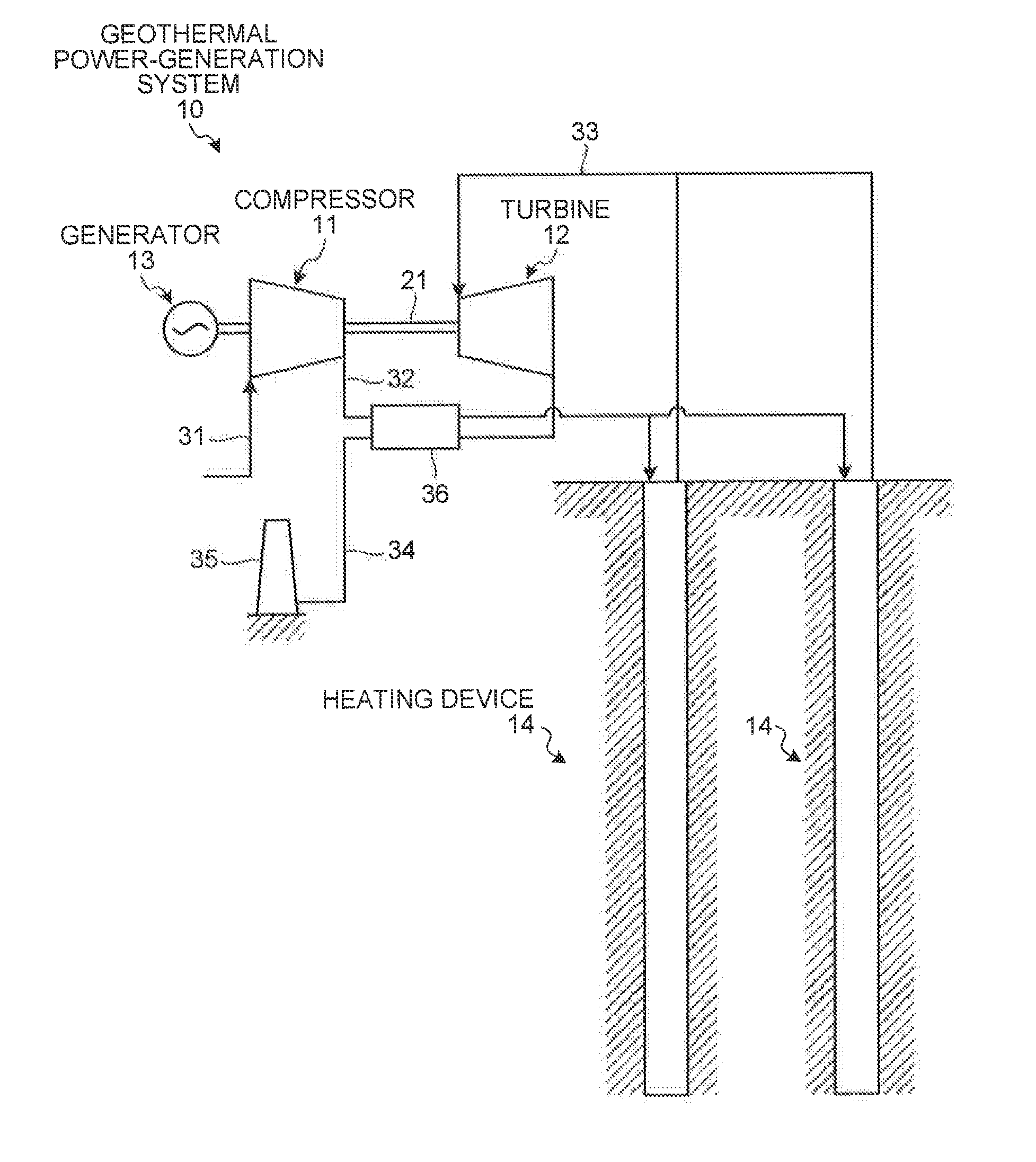

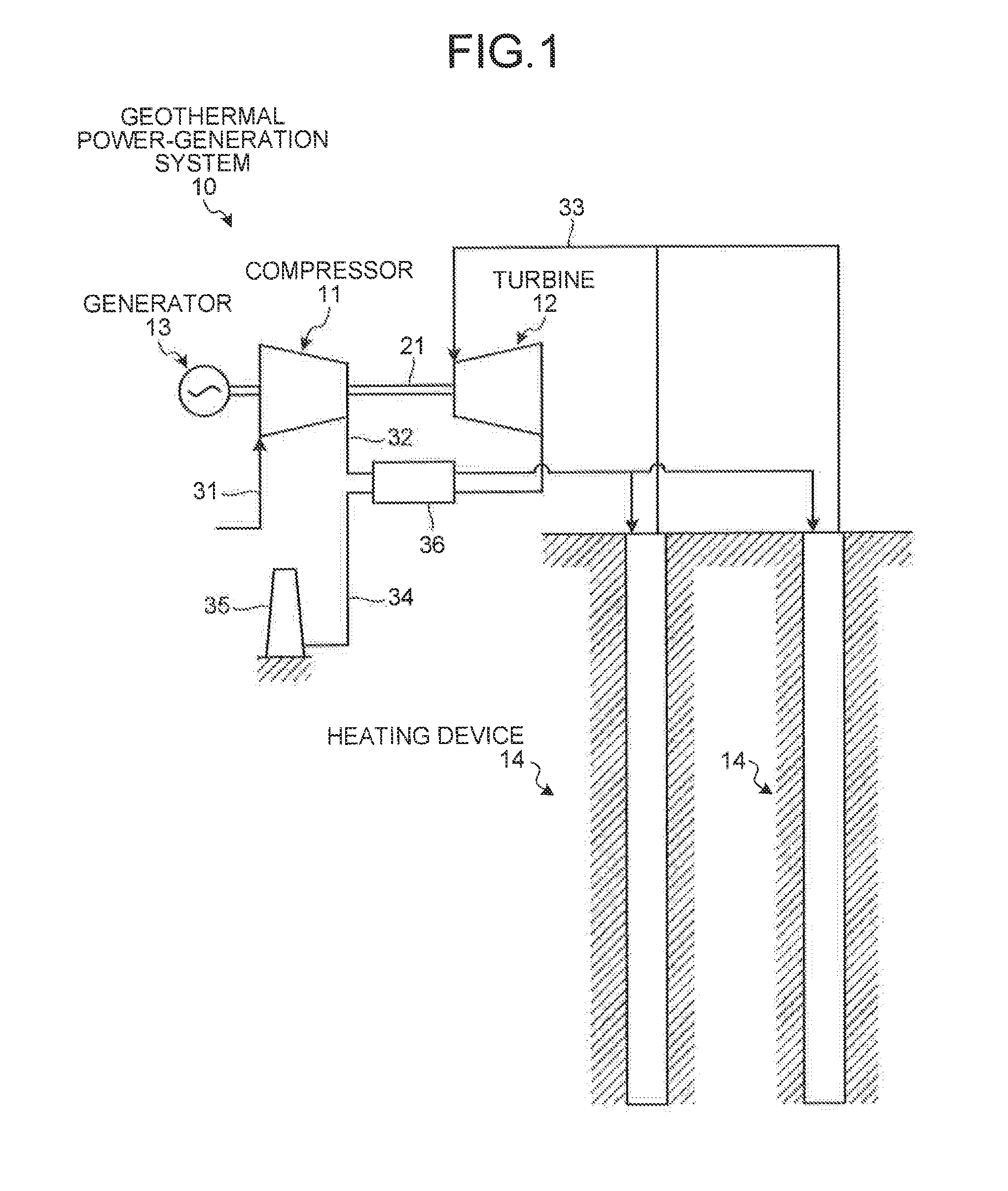

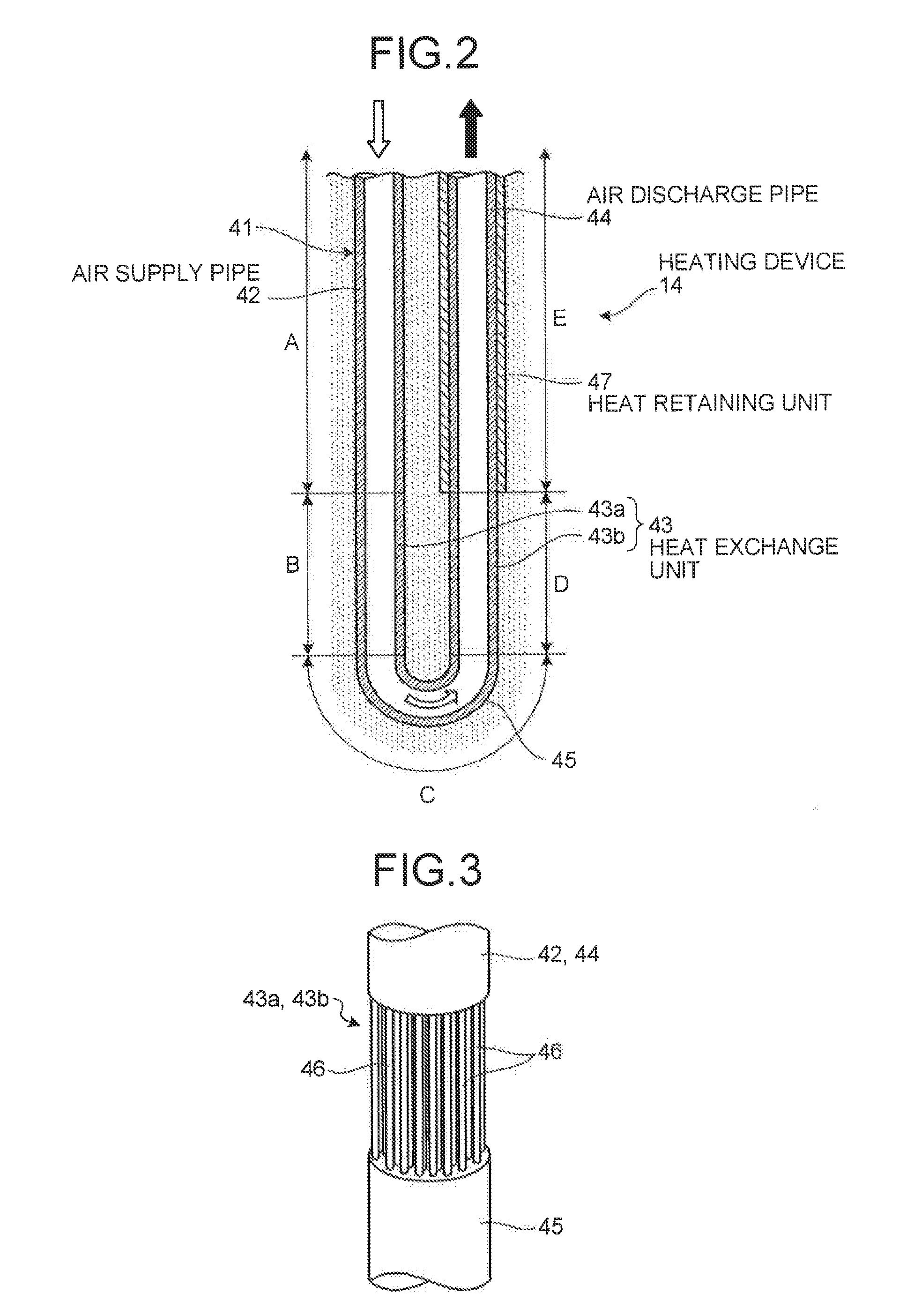

Geothermal power-generation system

InactiveUS20120000198A1Minimize influenceIncrease usage rateOther heat production devicesGeothermal energy generationGeothermal power generationElectric generator

[Problem to be solved] To achieve a reduction in facility costs in a geothermal power-generation system.[Solution] To provide a compressor 11 that compresses air, a heating device 14 that heats compressed air compressed by the compressor 11 by geothermal heat, a turbine 12 that obtains a rotational force by heated compressed air heated by the heating device 14, and a generator 13 that generates power by the rotational force inputted from the turbine 12. [Chosen Drawing] FIG. 1

Owner:MITSUBISHI HITACHIPOWER SYST LTD