Patents

Literature

35results about How to "Performance degradation can be prevented" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

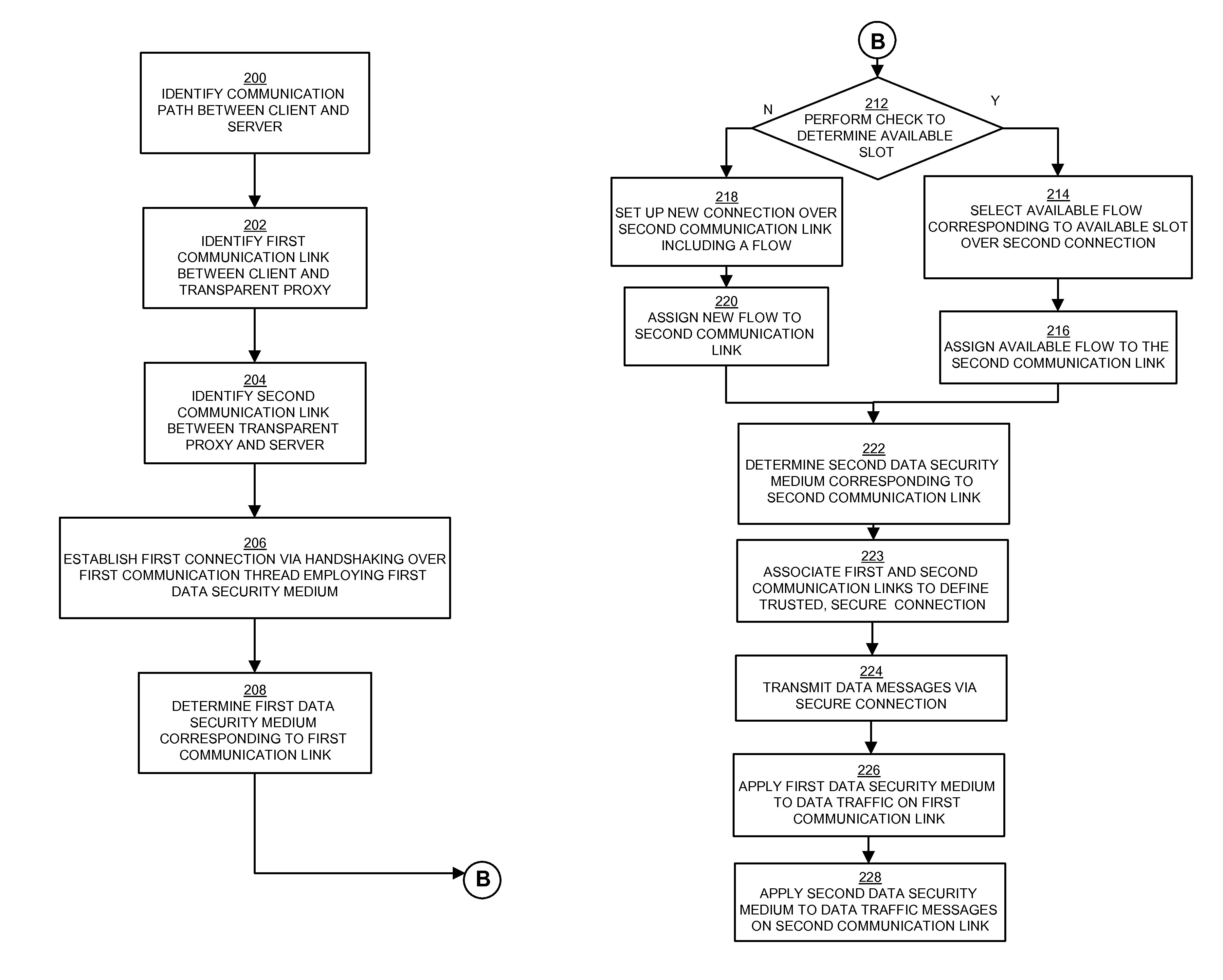

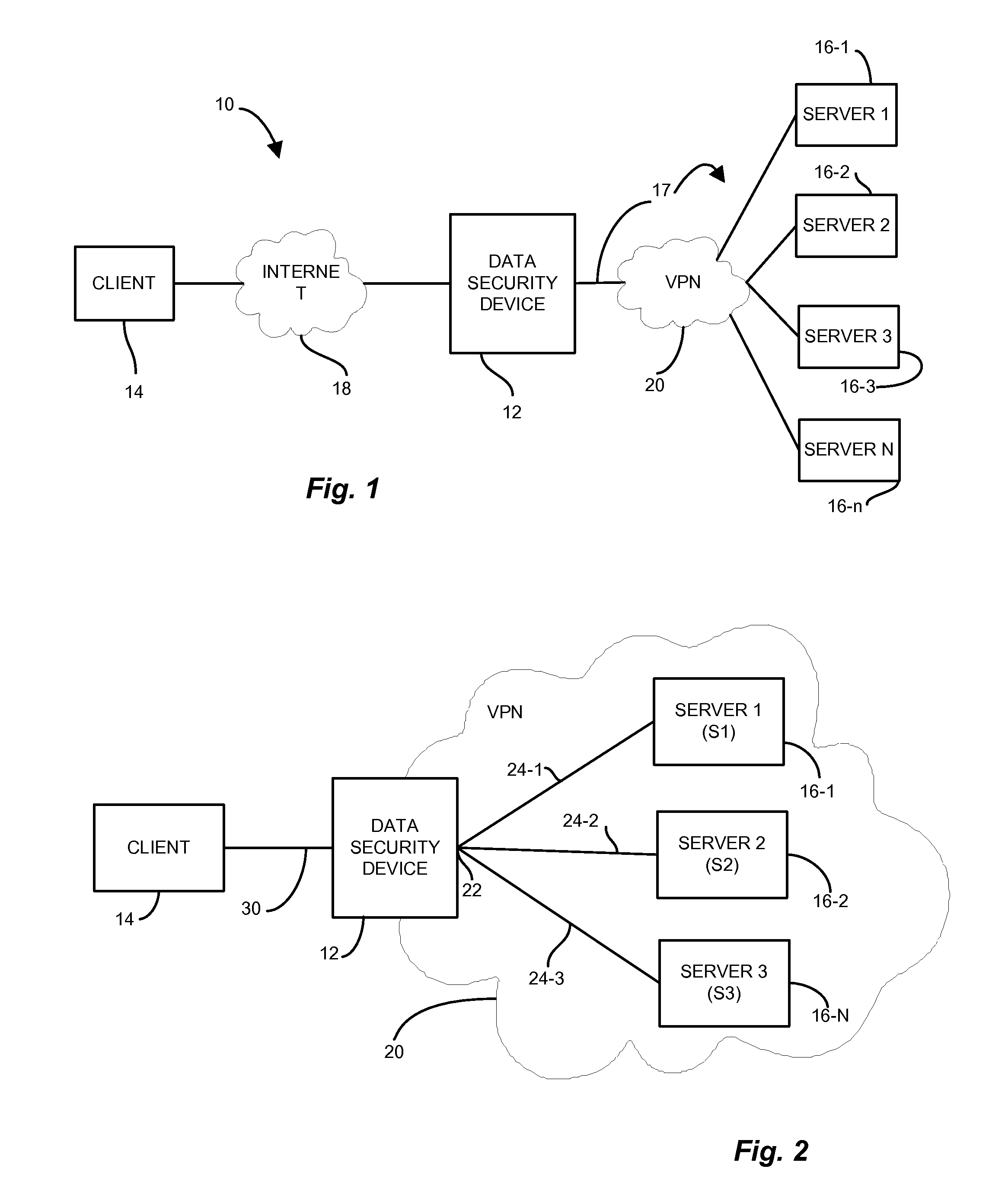

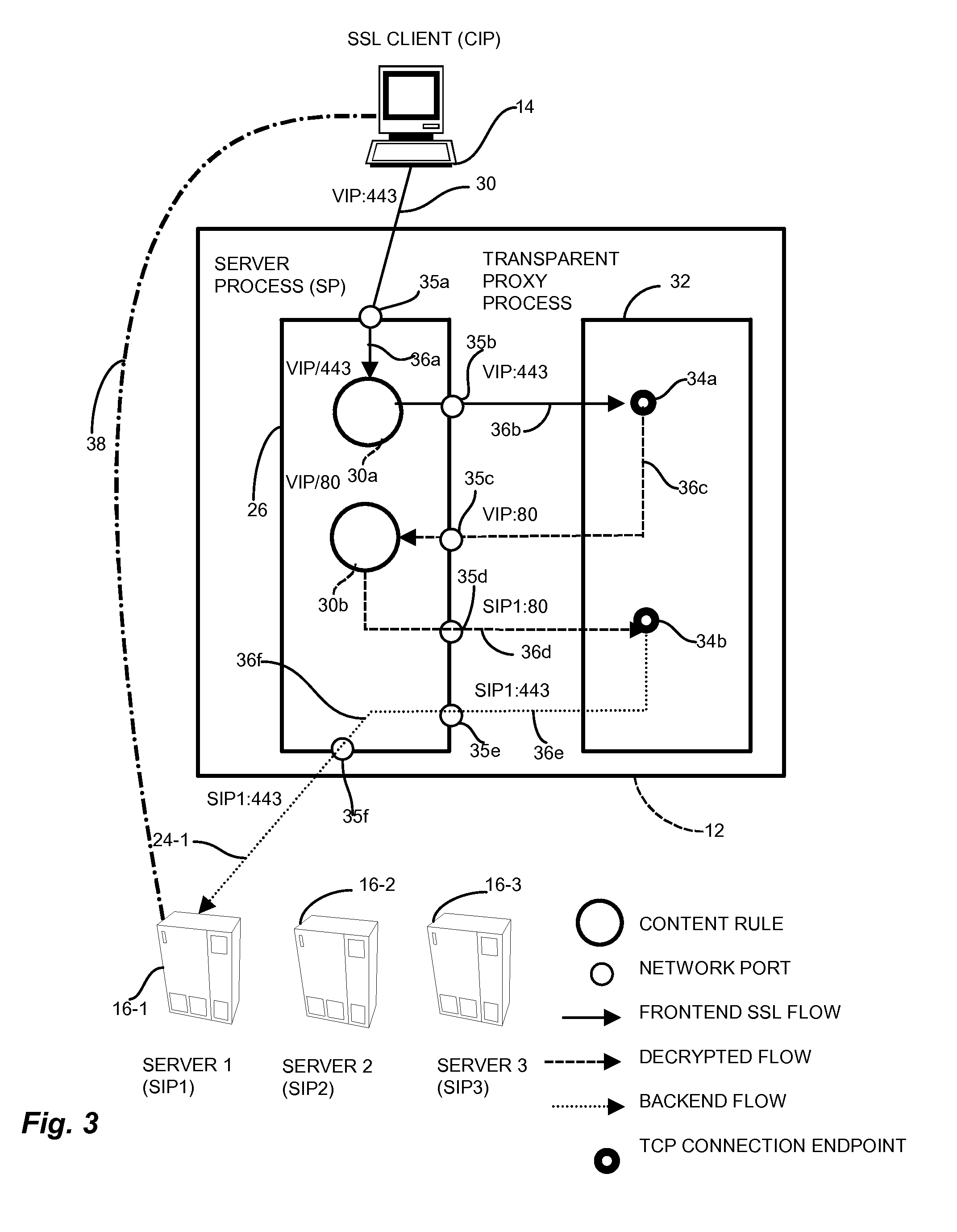

Methods and apparatus for network communications via a transparent security proxy

ActiveUS8452956B1Performance degradation can be preventedLess expensiveMultiple keys/algorithms usageUser identity/authority verificationSecure communicationNetwork communication

Owner:CISCO TECH INC

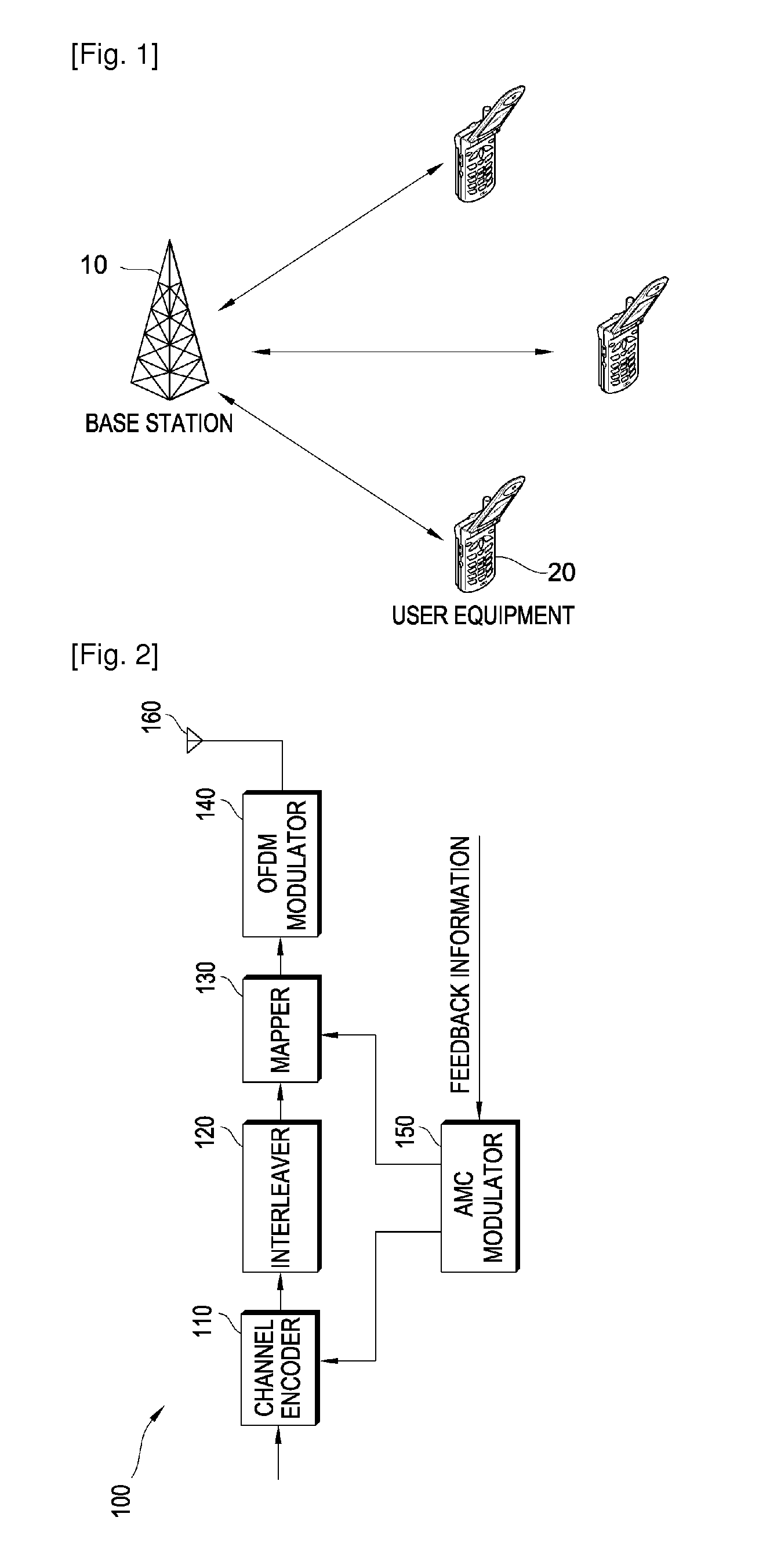

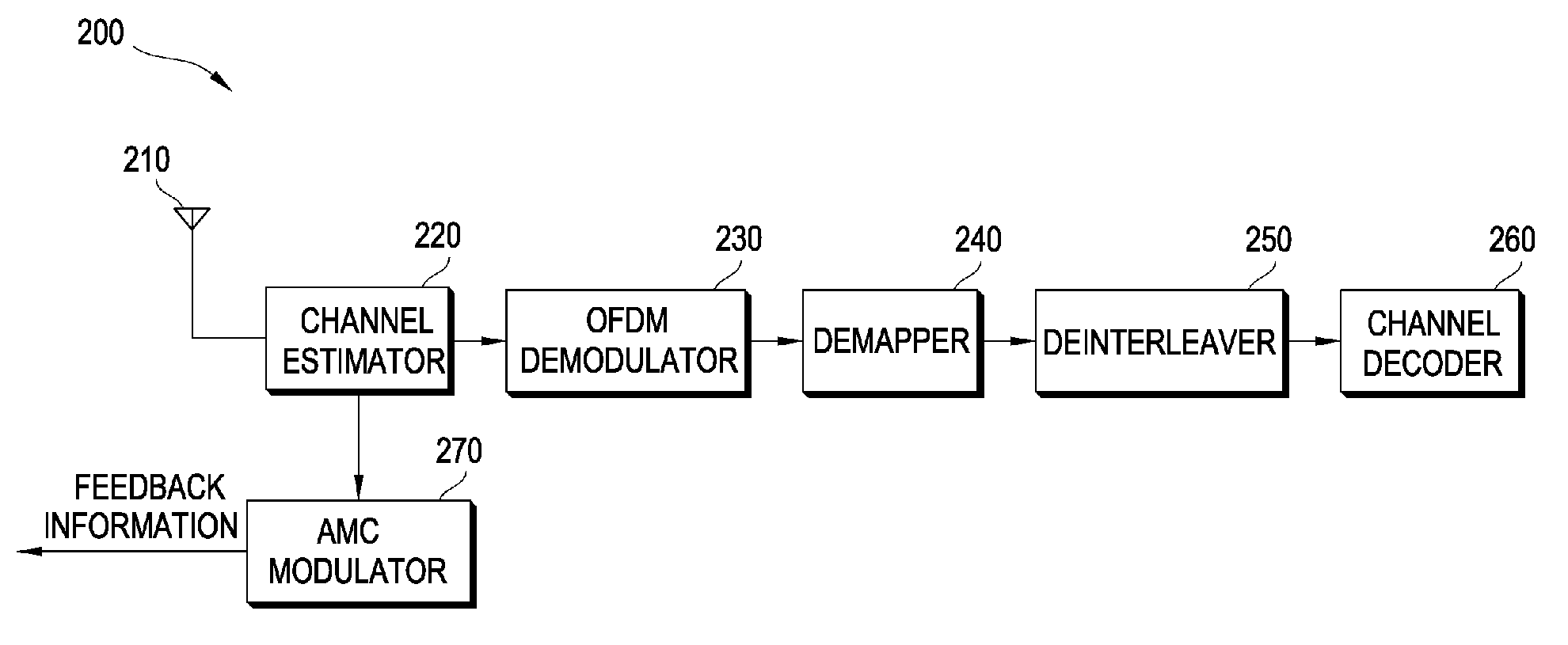

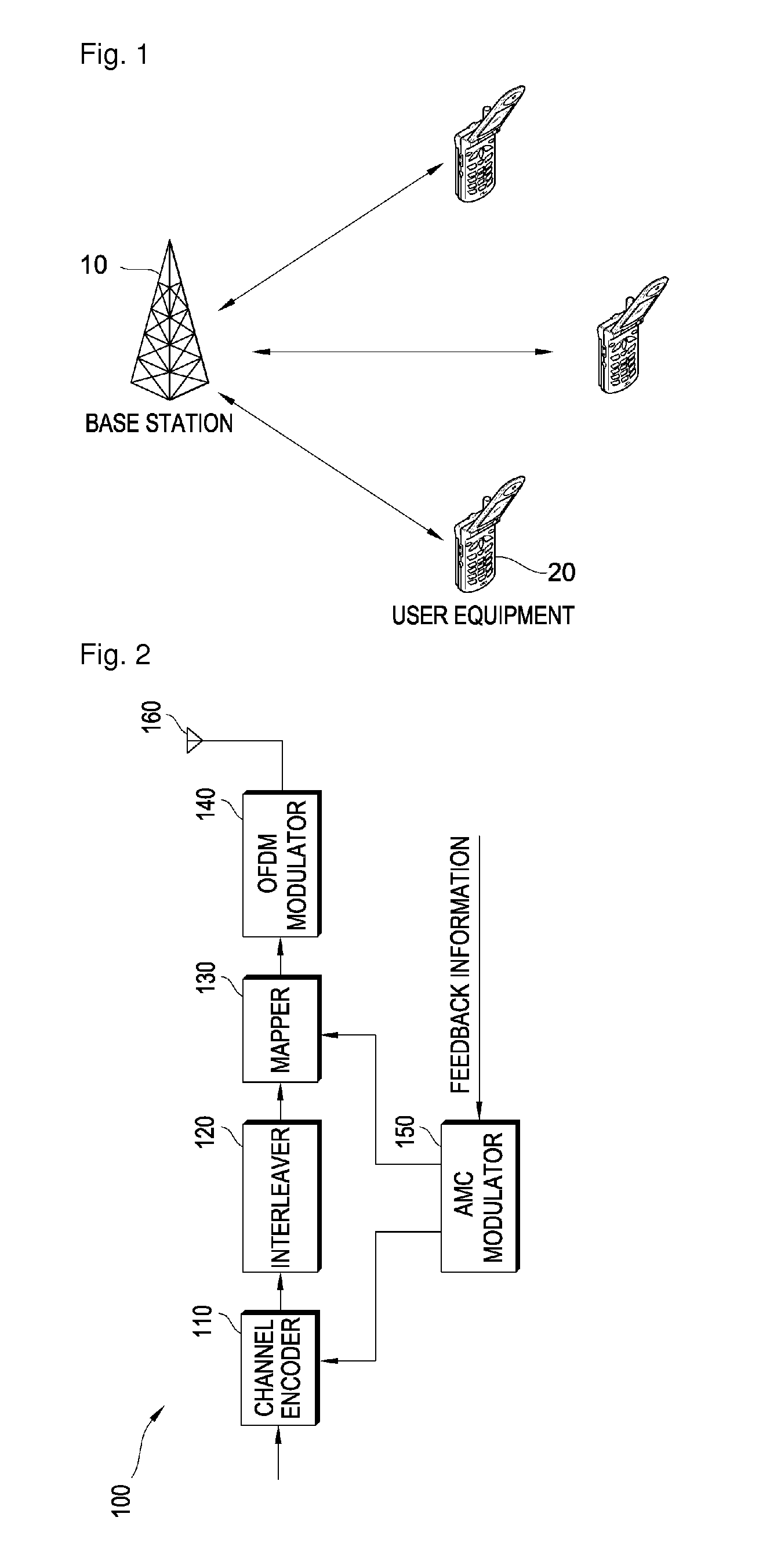

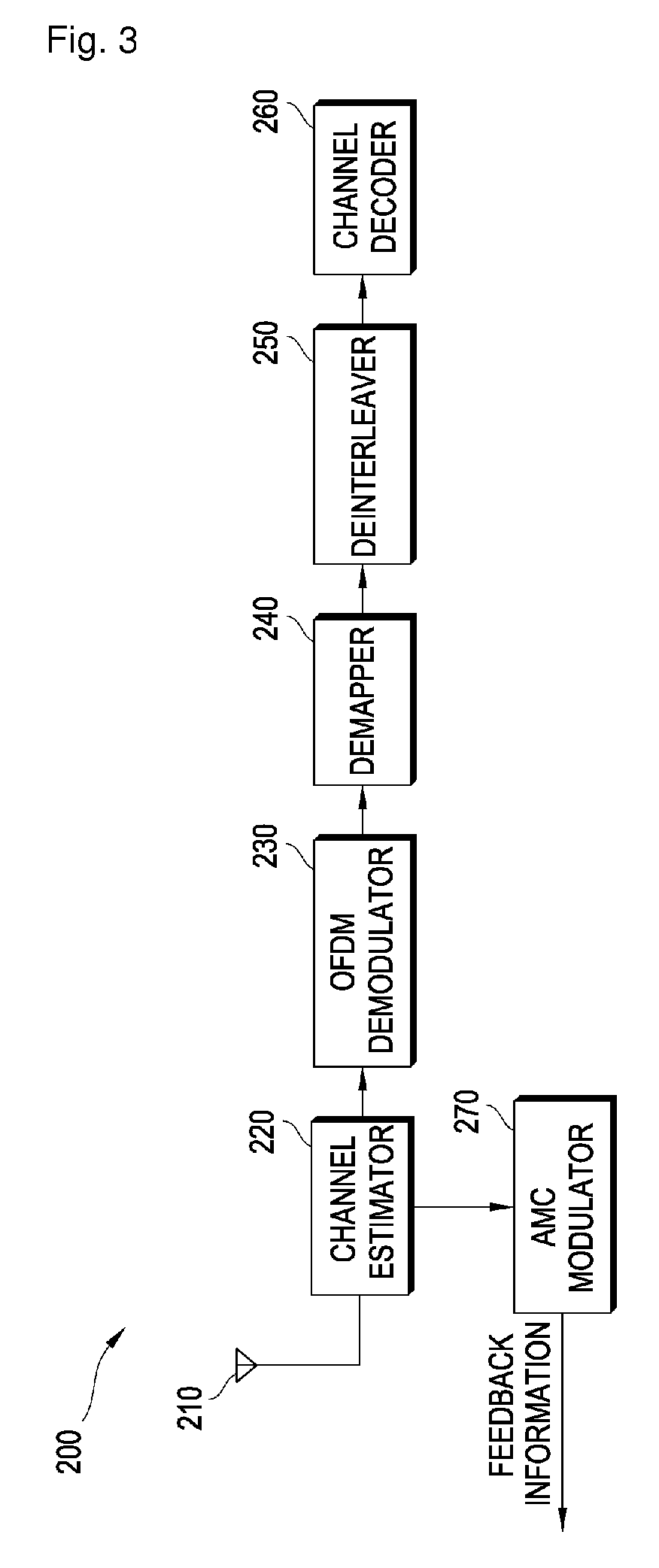

Method for determining modulation and coding scheme

InactiveUS20100278225A1Performance degradation can be preventedImprove spectral efficiencyModulated-carrier systemsPolarisation/directional diversityComputer scienceDiversity gain

There is provided a method of determining a Modulation and Coding Scheme (MCS). The method includes predicting an error rate of a symbol and determining a MCS of the symbol using the error rate. Since a MCS level is determined using an estimated error rate and user data is scheduled, multi-user diversity gain can be obtained and the transmission rate can be improved.

Owner:LG ELECTRONICS INC

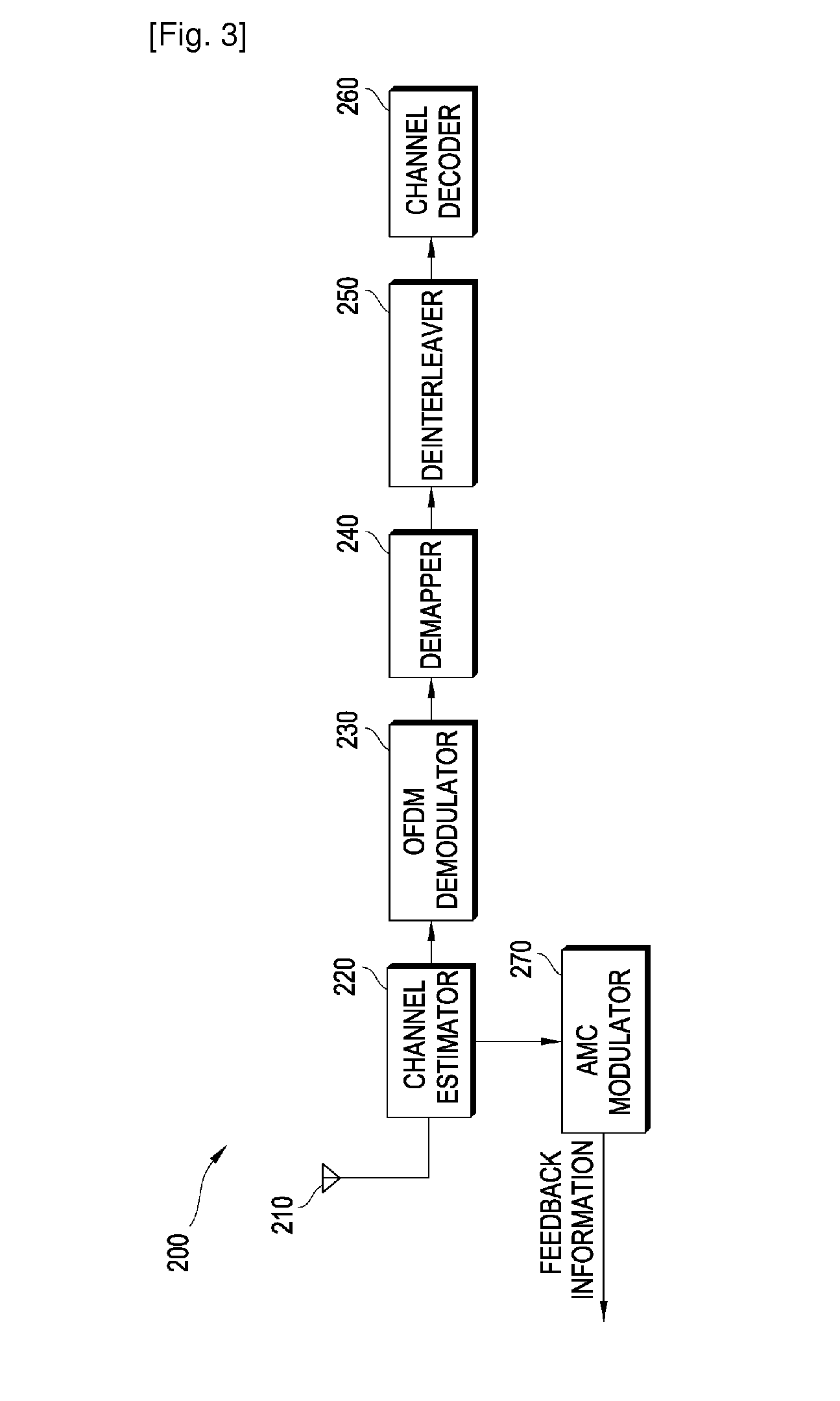

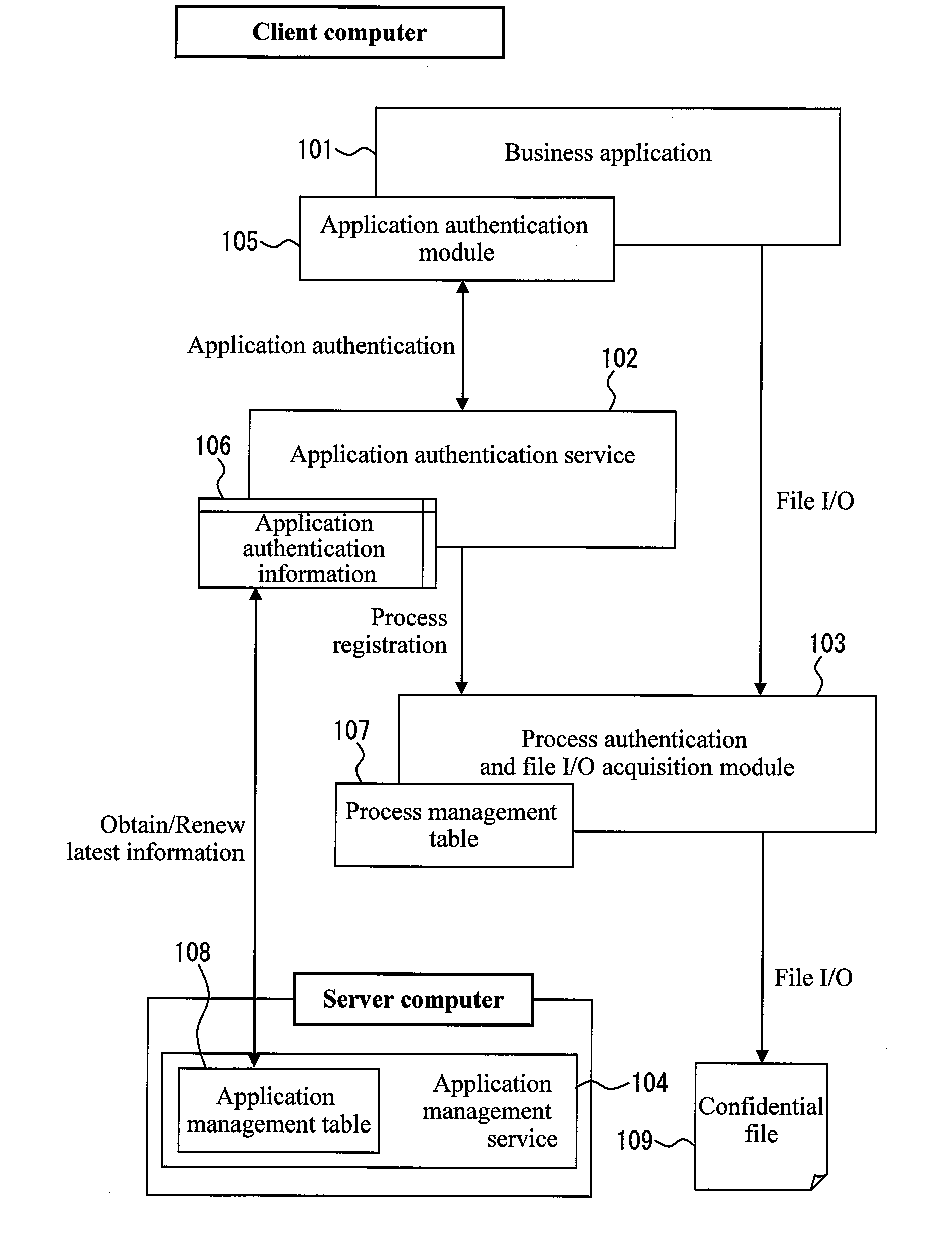

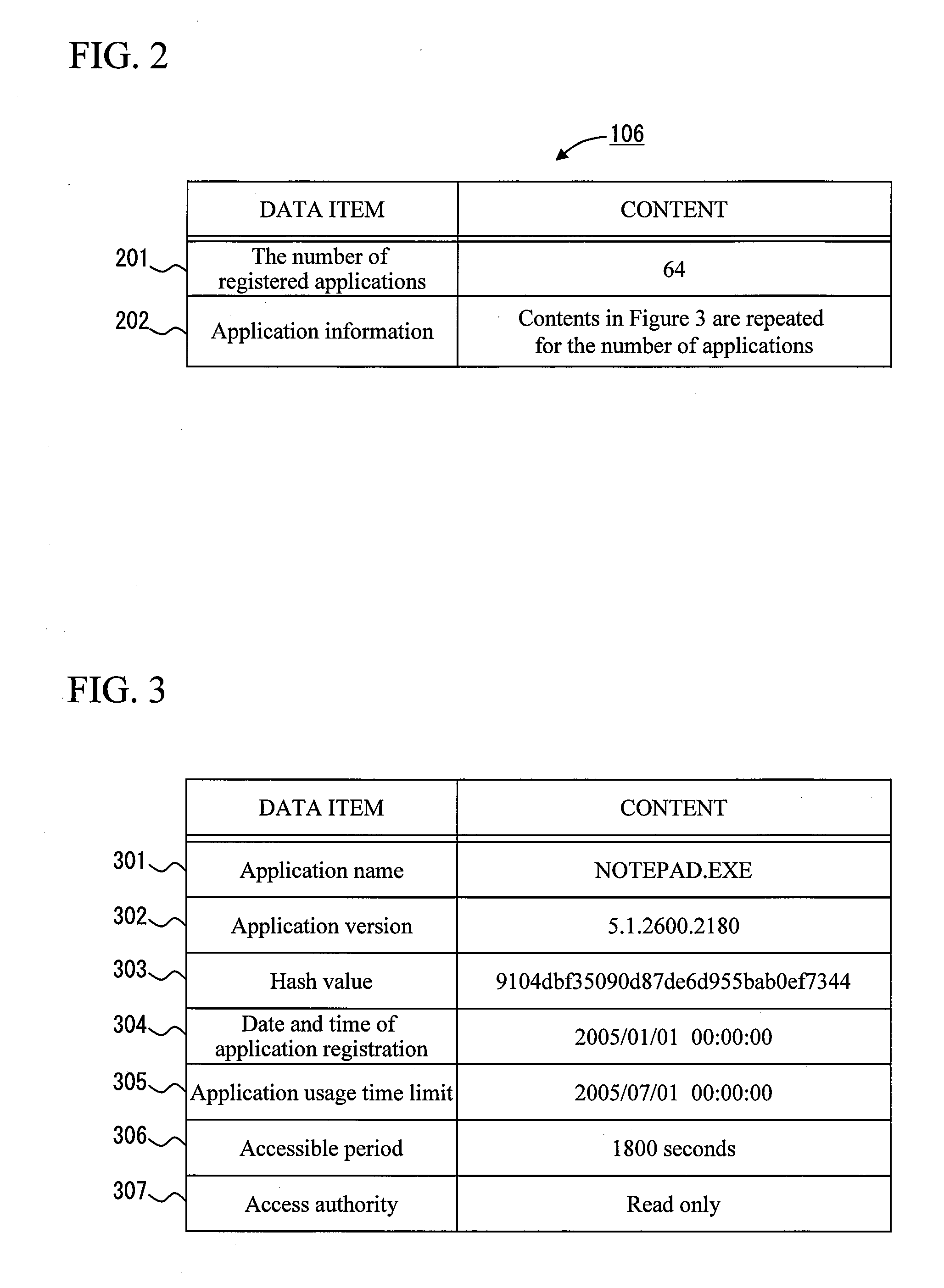

Method of protecting confidential file and confidential file protecting system

InactiveUS20090276860A1Performance degradation can be preventedReduce frequencyDigital data processing detailsAnalogue secracy/subscription systemsInternet privacyClient-side

There is provided a method of protecting confidential files to securely protect business confidential files in accordance with a security policy. In the method of protecting confidential files according to the present invention, information of a business application which is allowed to access confidential files is registered in a management server in advance and the registered application information is distributed to each client as needed. When the business application references confidential files, it is judged (application is authenticated) at the time of starting up the business application whether the business application is the application registered in advance in the server. Only when the application authentication is allowed, process information of the business application is registered in an I / O acquisition module. The I / O acquisition module allows only the process which is consistent with the registered process information to access confidential information, and rejects other processes.

Owner:HITACHI SOFTWARE ENG

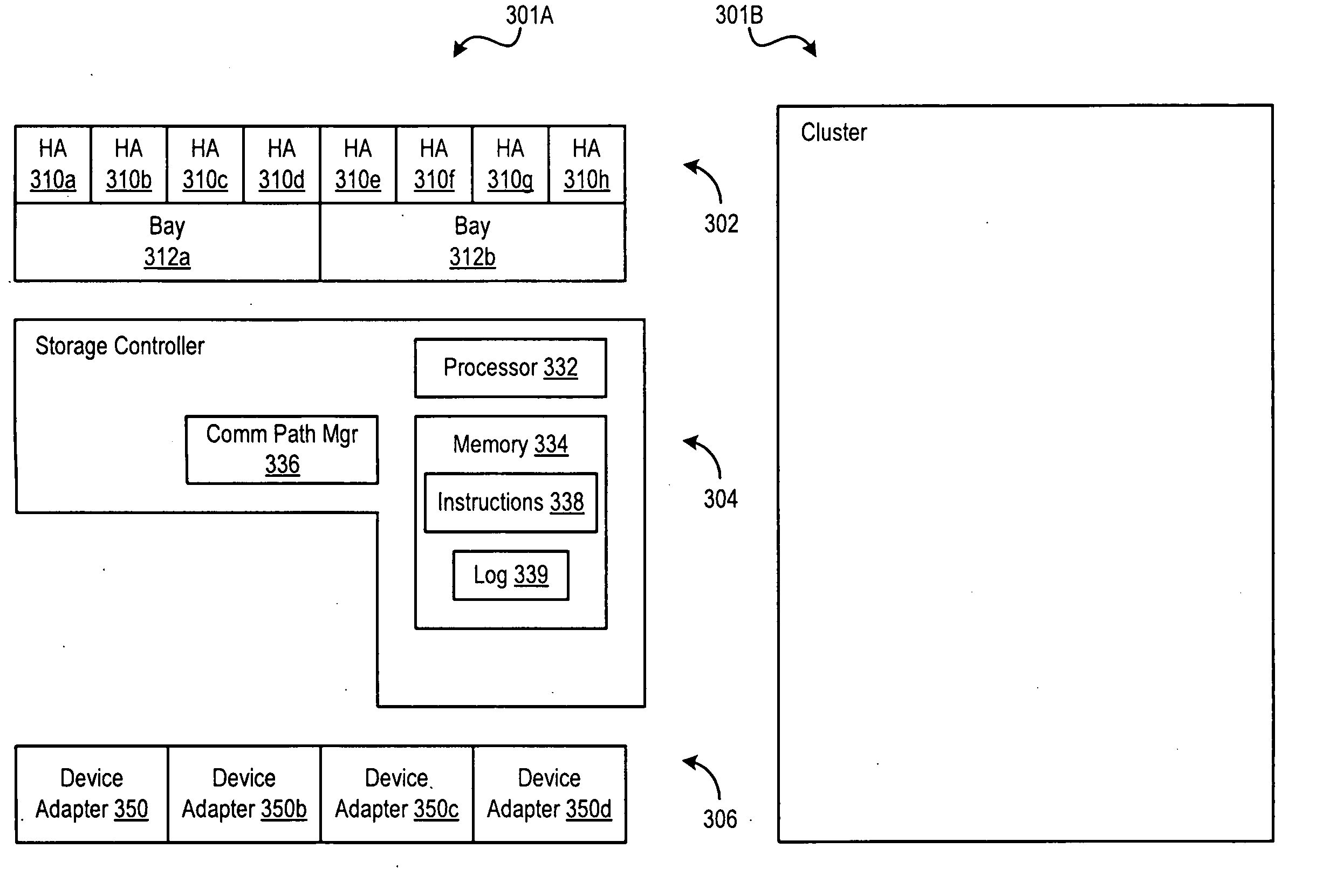

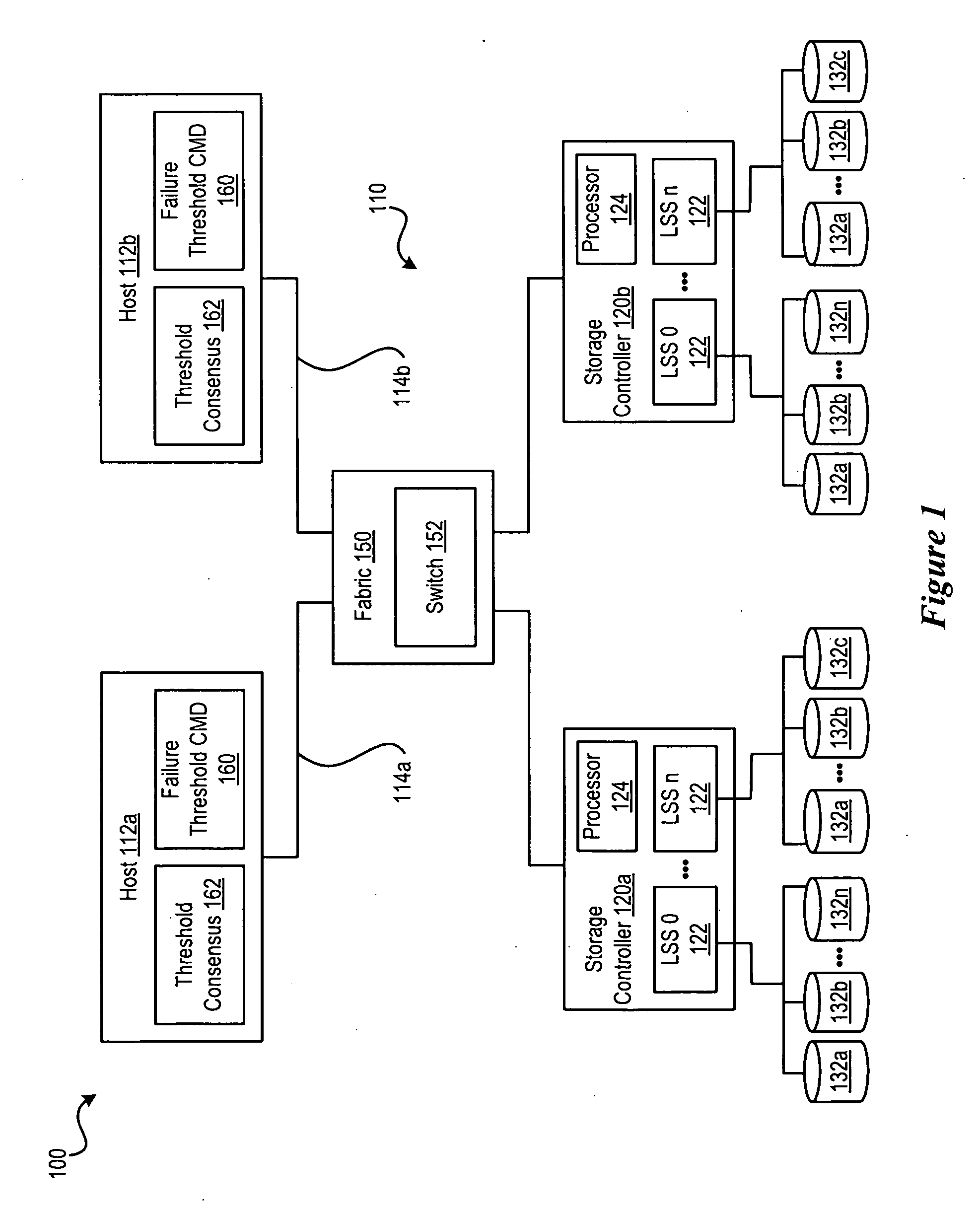

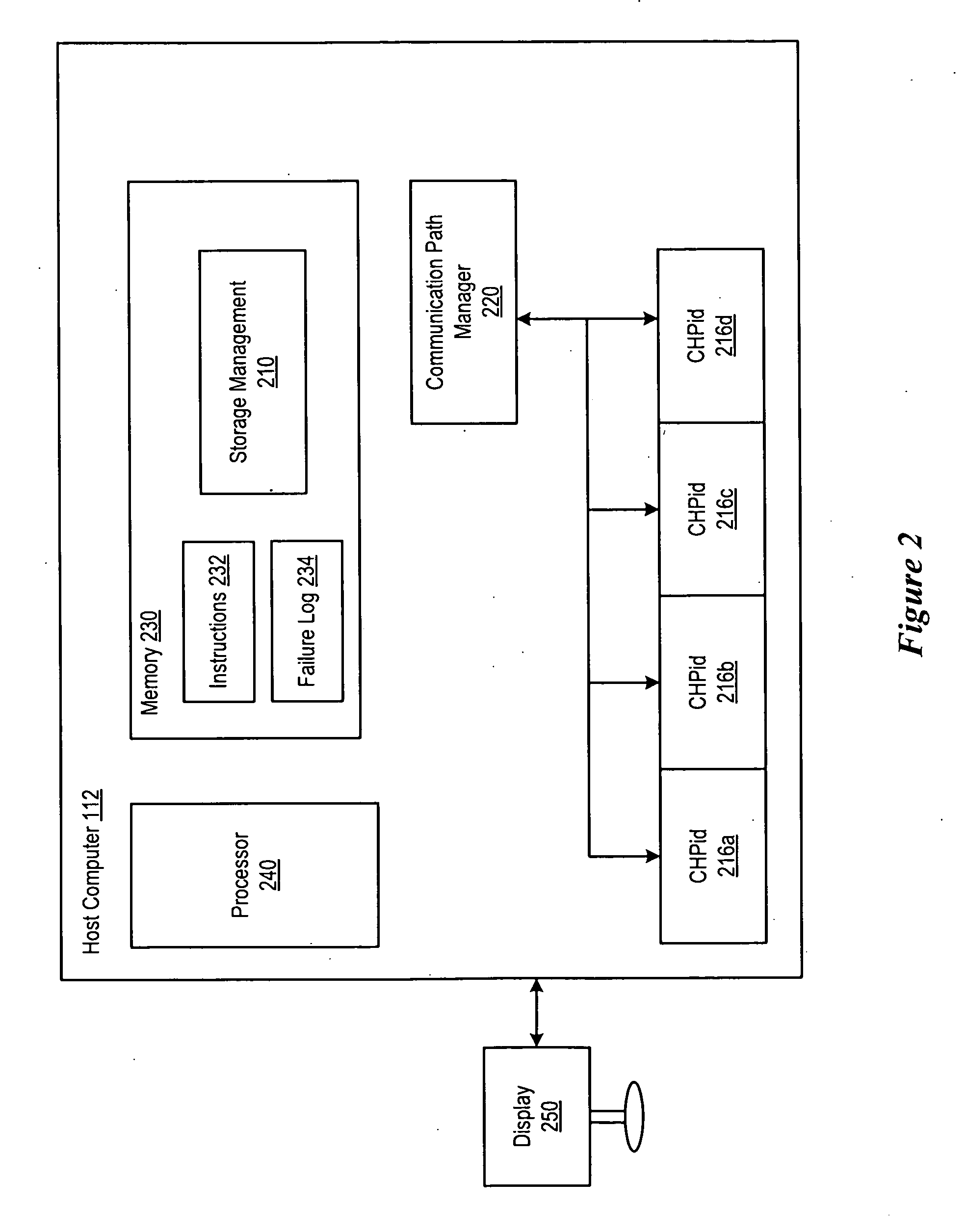

Method to Manage Path Failure Threshold Consensus

InactiveUS20100080117A1Performance degradation can be preventedPerformance degradation can be minimizedError preventionTransmission systemsControl storeDistributed computing

A system for providing hosts with a capability to determine which threshold rule of a plurality of threshold rules to use based upon threshold consensus. For example, the system would address a configuration case of several hosts sharing an output port of a fabric via zoning and that port being connected to a single port of a storage controller. If one host is executing lower priority jobs and its threshold is much higher than another host with higher priority jobs and a lower threshold, and the storage controller recognizes that several hosts are sharing the same storage controller port, the consensus will be to ignore the threshold of the first host and to use the threshold of the second host to prevent performance degradation in the system.

Owner:IBM CORP

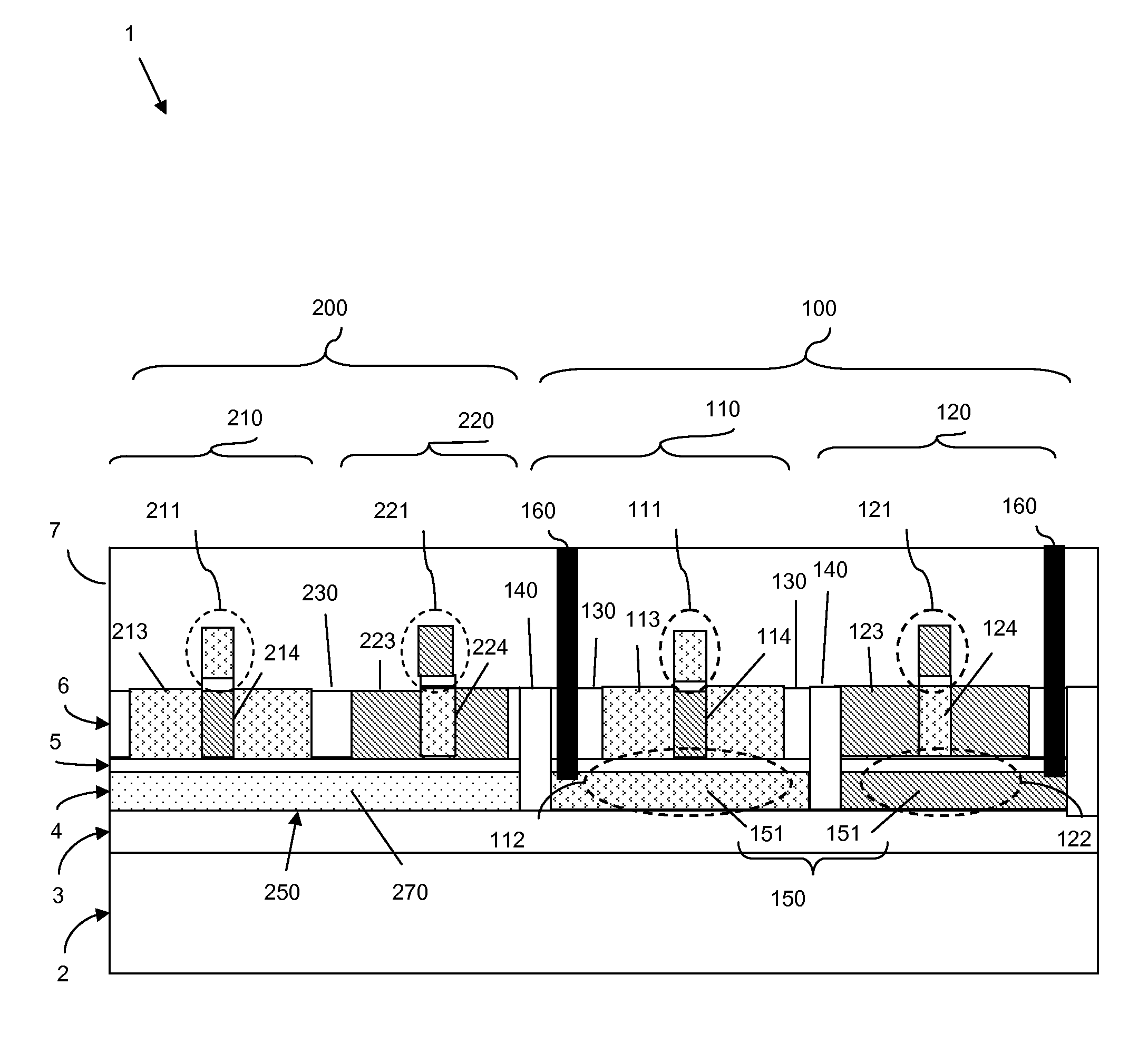

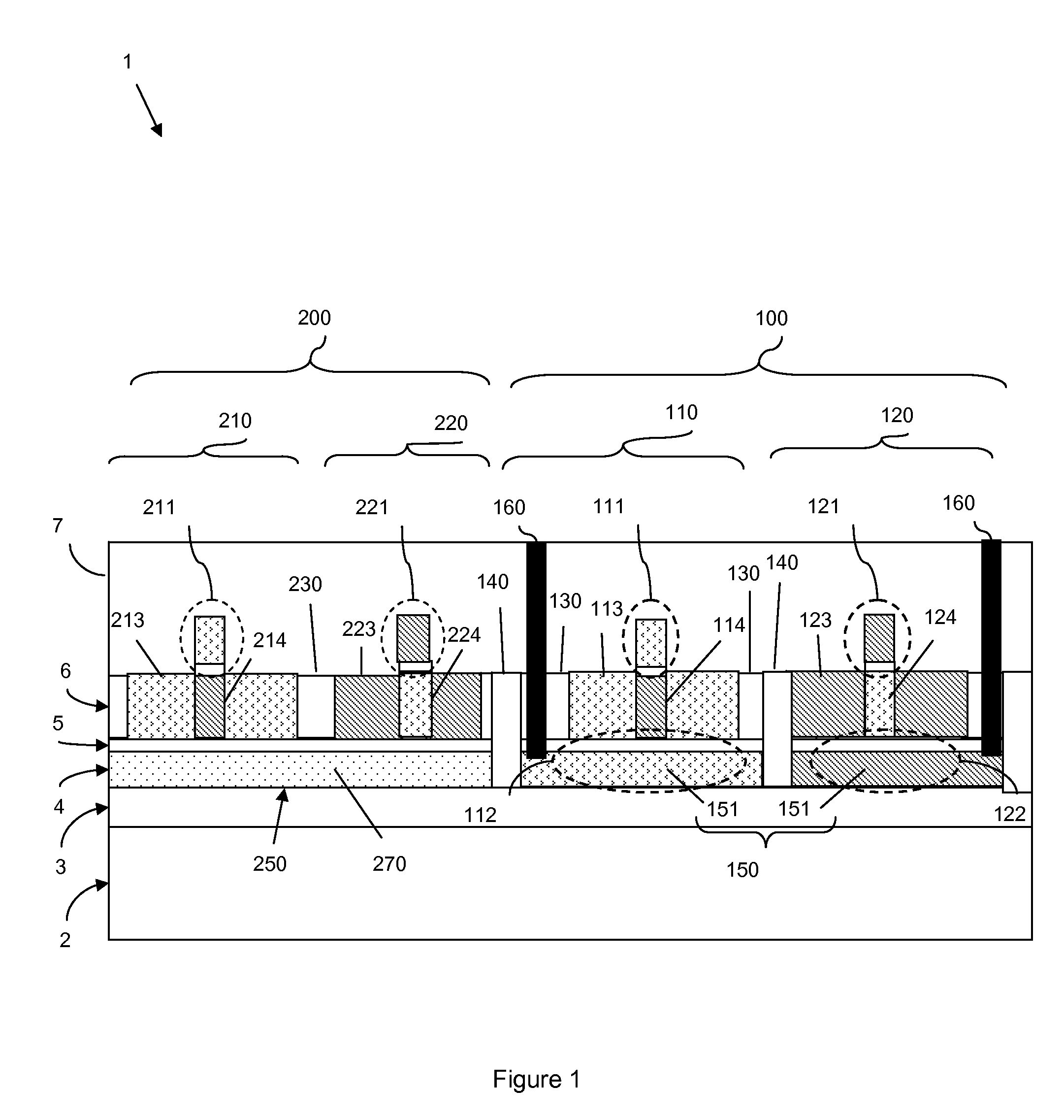

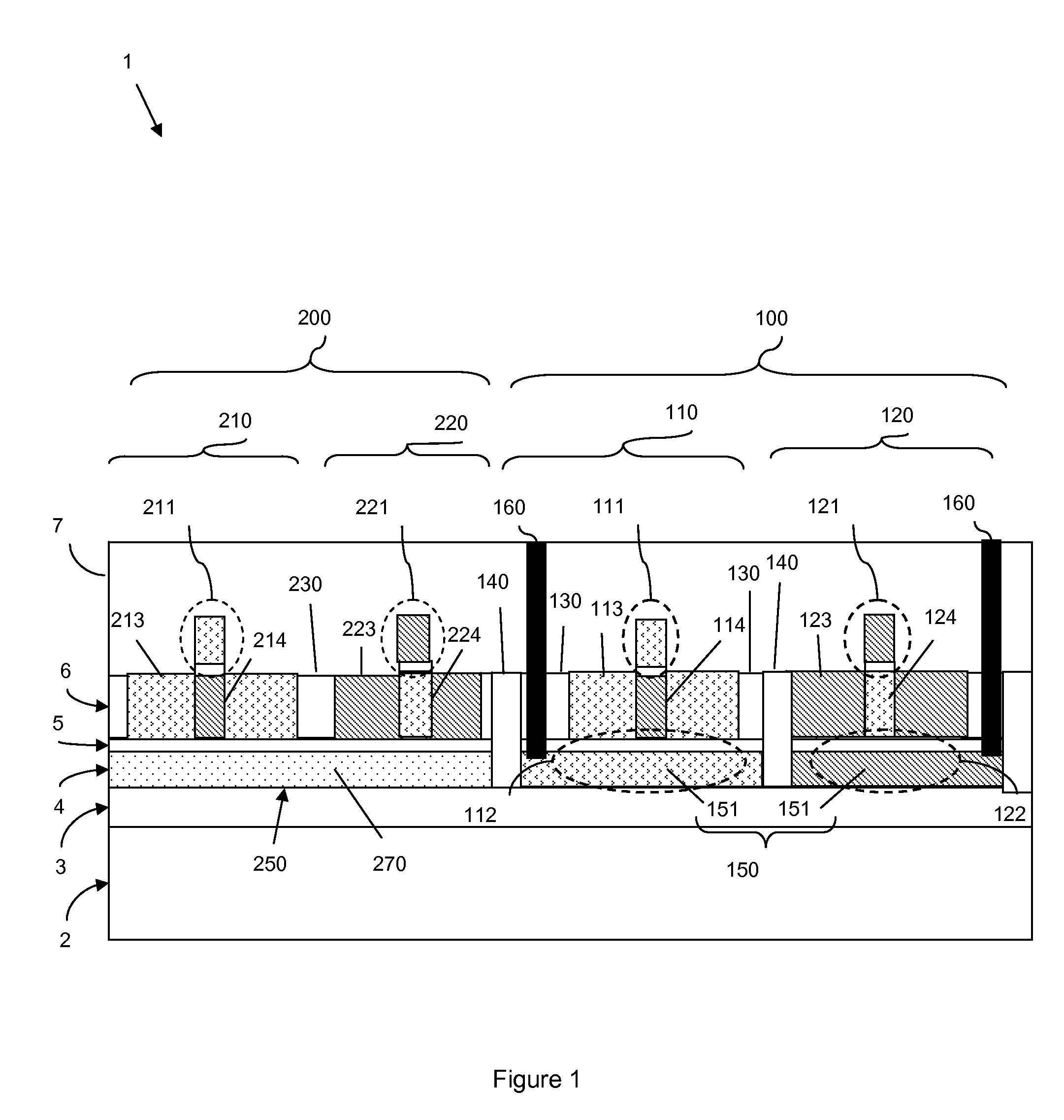

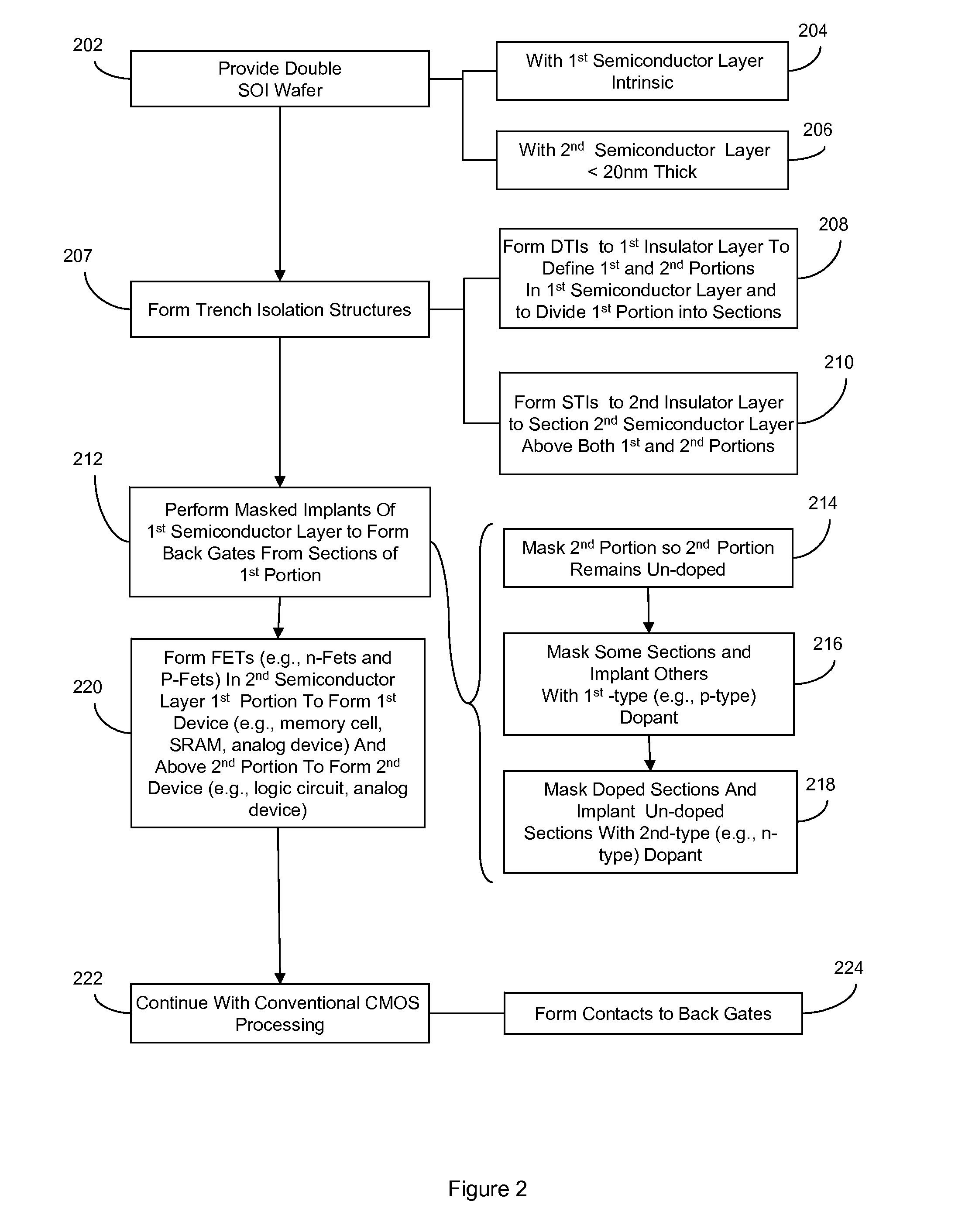

Ultra-thin logic and backgated ultra-thin SRAM

InactiveUS20070187769A1Fast switching speedPerformance degradation can be preventedSolid-state devicesSemiconductor/solid-state device manufacturingGate capacitanceSram cell

Disclosed are embodiments of a structure that comprises a first device, having multiple FETs, and a second device, having at least one FET. Sections of a first portion of a semiconductor layer below the first device are doped and contacted to form back gates. A second portion of the semiconductor layer below the second device remains un-doped and un-contacted and, thus, functions as an insulator. Despite the performance degradation of the first device due to back gate capacitance, the back gates result in a net gain for devices such as, SRAM cells, which require precise Vt control. Contrarily, despite marginal Vt control in the second device due to the absence of back gates, the lack of capacitance loading and the added insulation result in a net gain for high performance devices such as, logic circuits.

Owner:IBM CORP

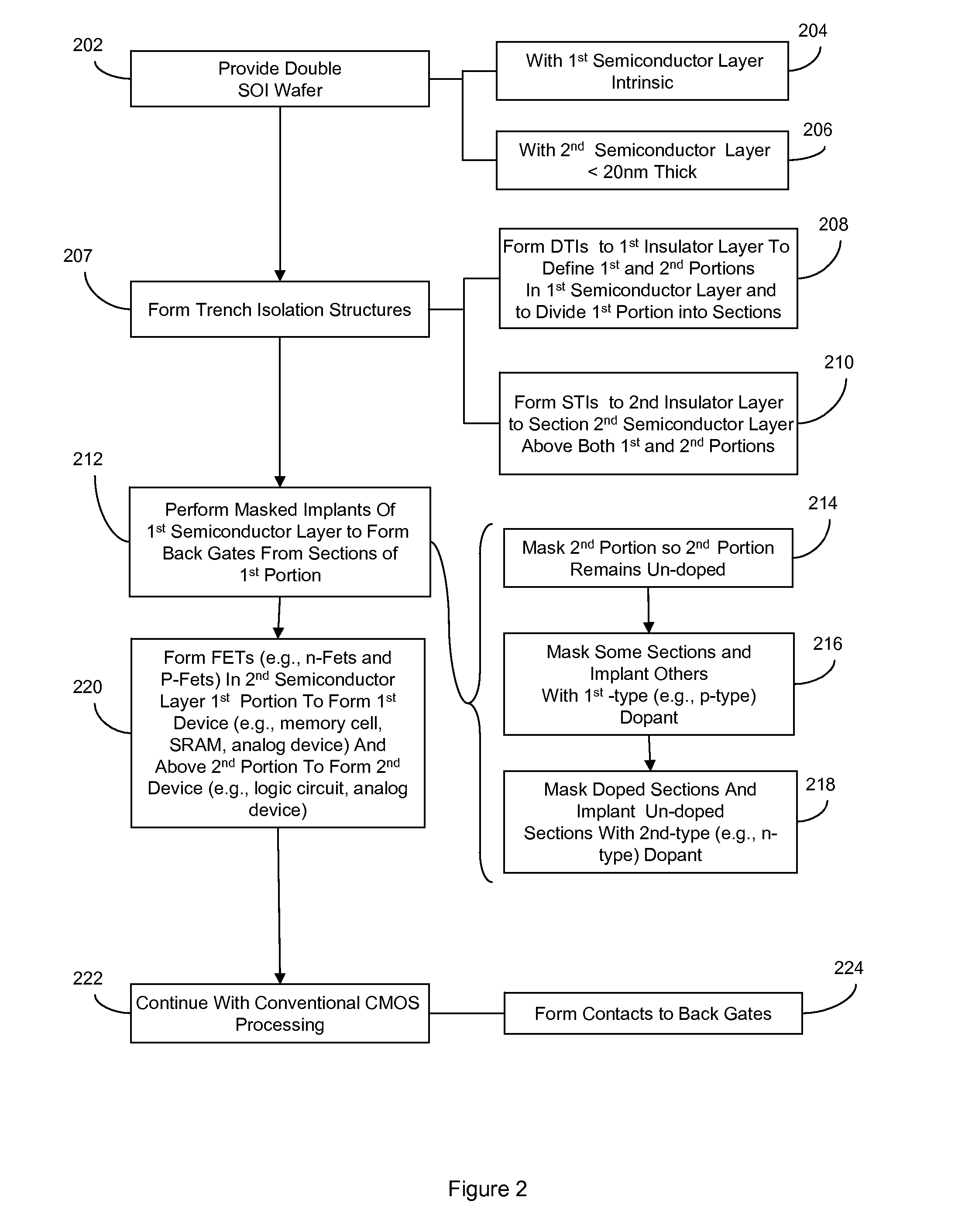

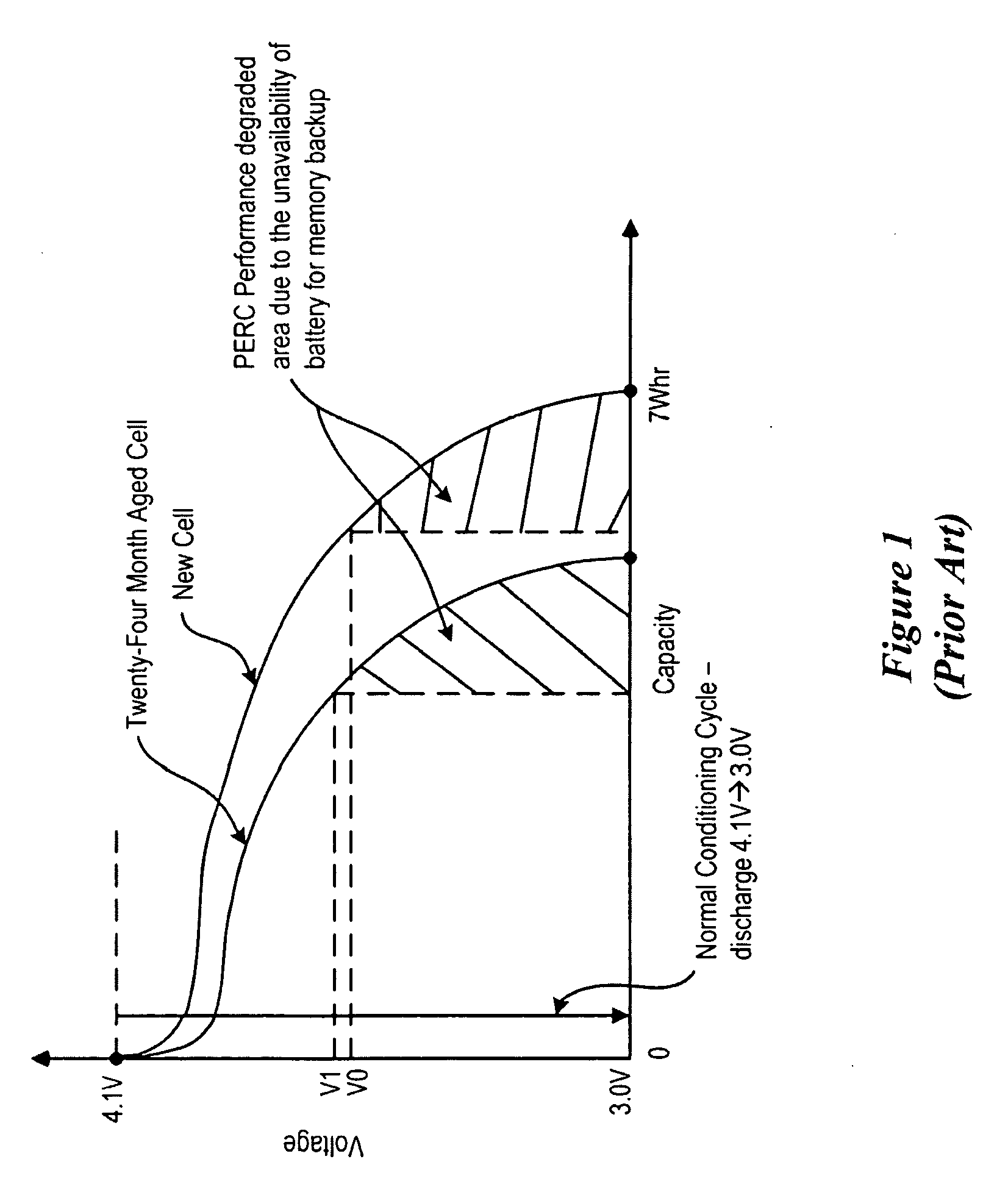

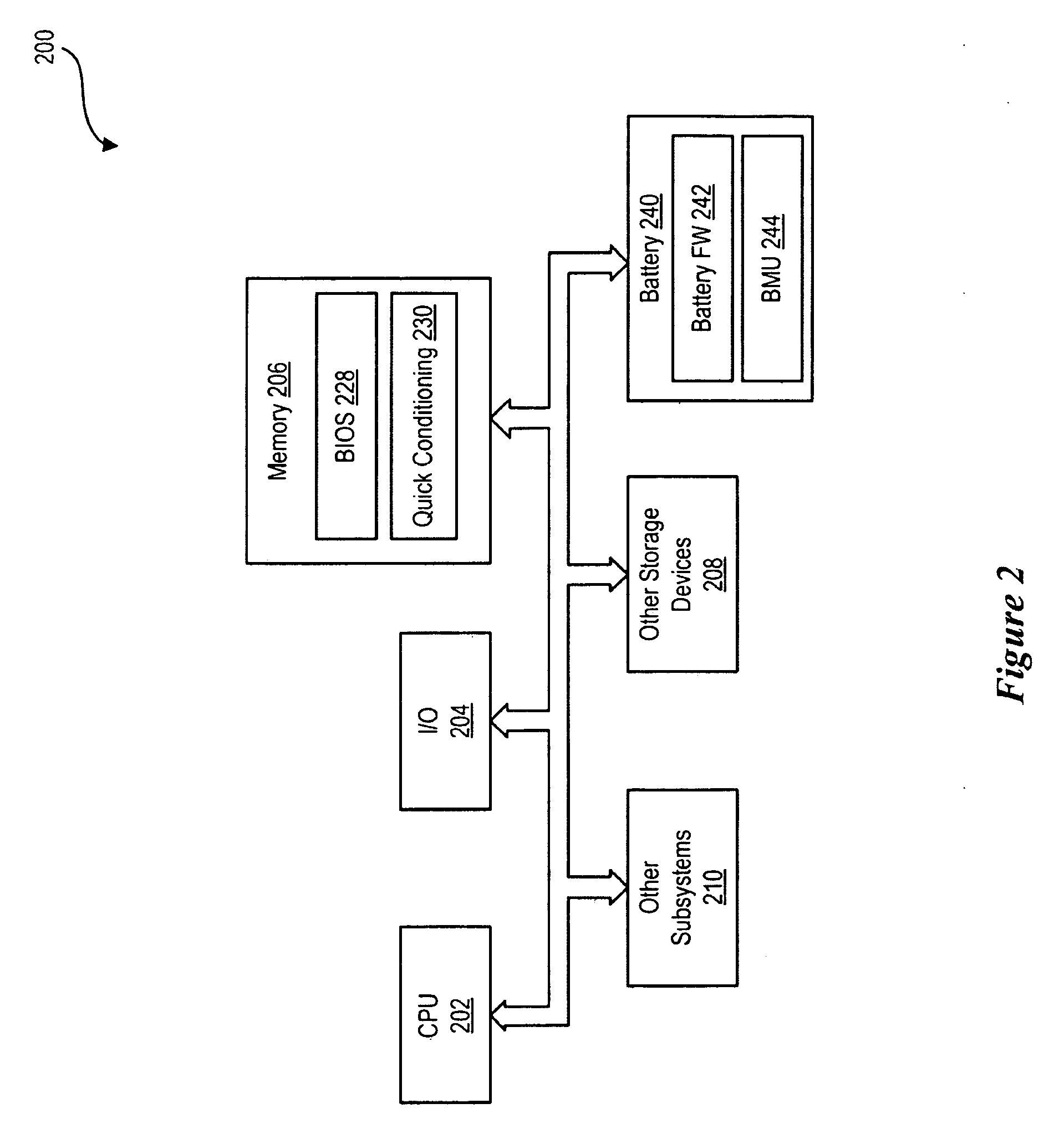

Quick Conditioning Memory Backup Battery

ActiveUS20090160402A1Performance degradation can be preventedAvoid performanceBatteries circuit arrangementsSecondary cells testingQuick conditionTime segment

A quick conditioning cycle system to avoid performance degradation at the end of calibrating cycle. The quick conditioning cycle system discharges a battery to a level where battery remaining capacity is still high enough to backup memory at a guaranteed period of time. During the quick learning cycle, the battery pack is discharged from a full charge. If measured capacity exceeds a predetermined threshold (Cpc), calibration stops. Otherwise, the quick conditioning cycle system reports a defected battery when measured capacity is less than Cpc and continues discharging to a full conditioning cycle, if desired.

Owner:DELL PROD LP

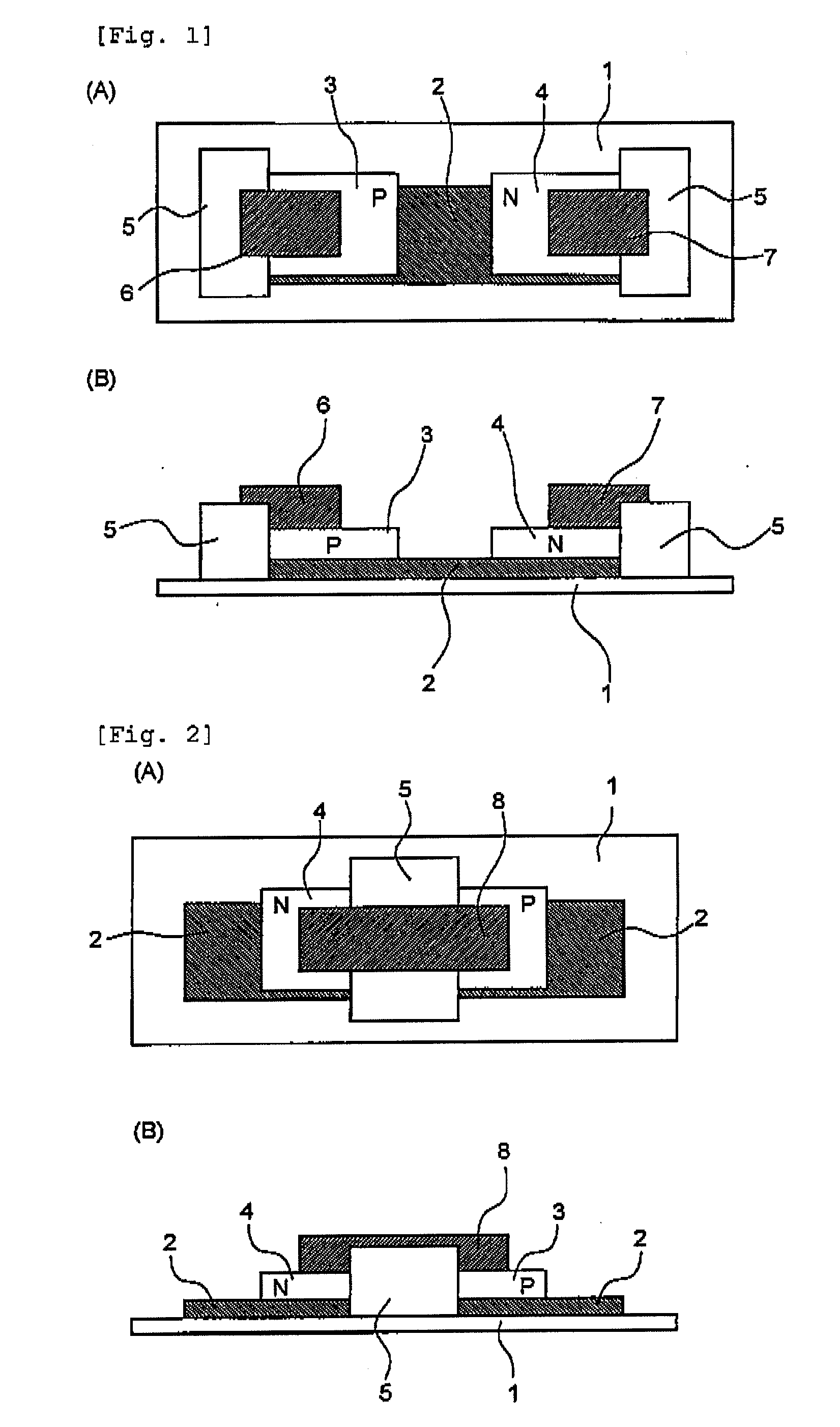

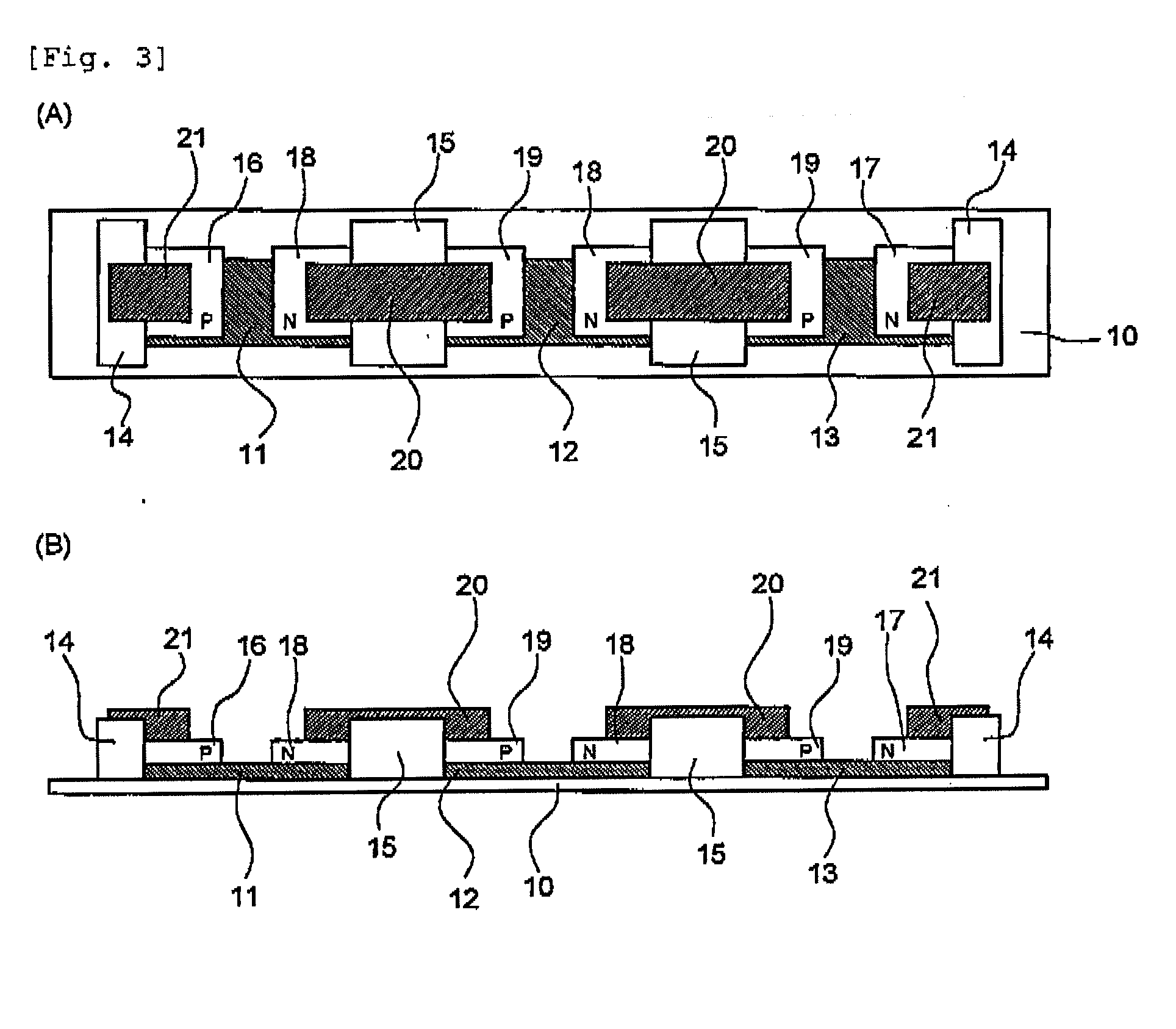

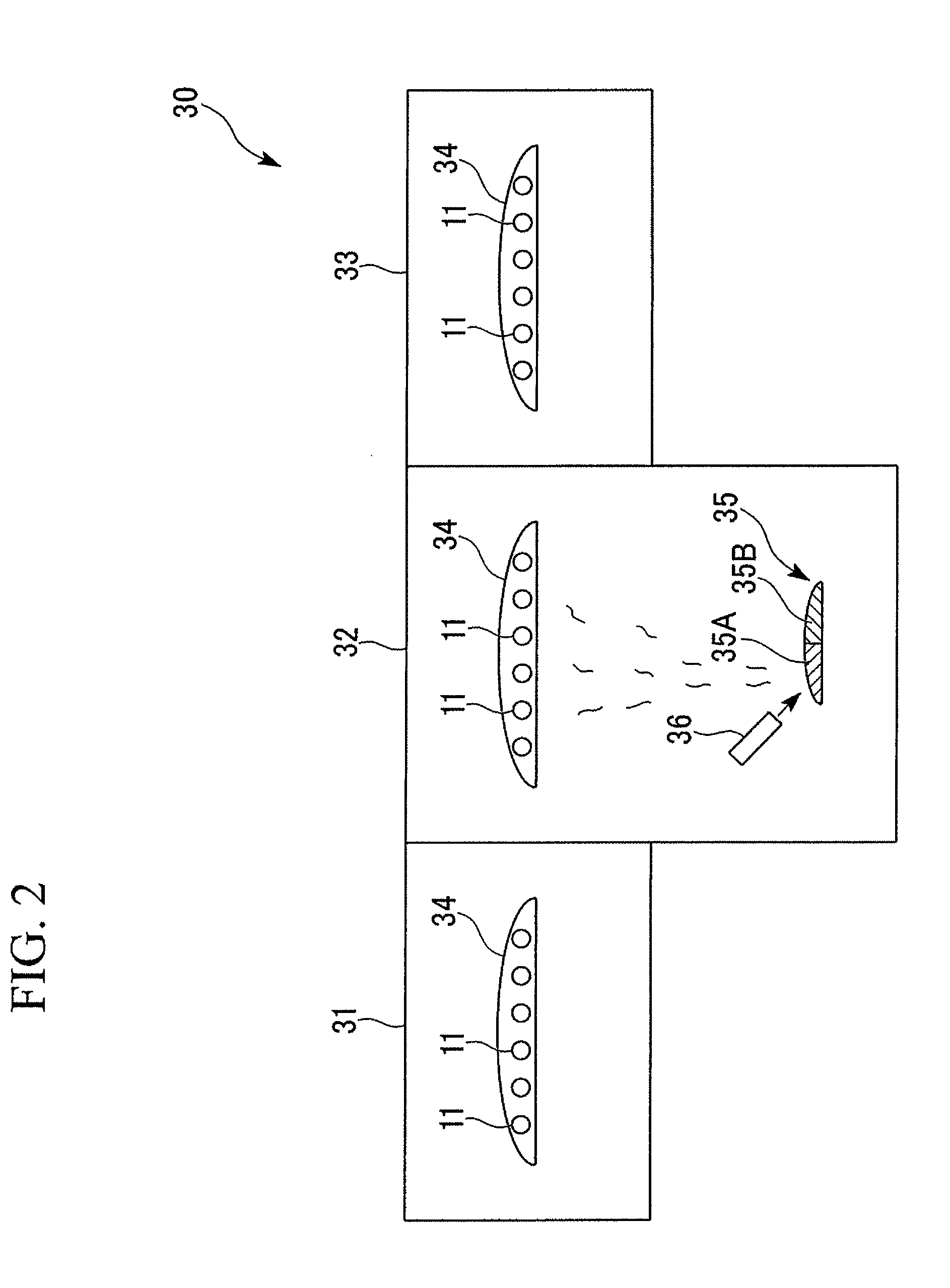

Thermoelectric conversion elements, thermoelectric conversion modules and a production method of the thermoelectric conversion modules

InactiveUS20100095995A1Improve conductivityImprove thermal conductivityThermoelectric device with peltier/seeback effectThermoelectric device manufacture/treatmentEngineeringThermal stability

The present invention provides a thermoelectric conversion module, comprising plural first electrode films (11, 12, 13) formed apart from each other on the top surface of an insulating body (10), plural p- and n-type thermoelectric semiconductor element films (16, 19) and (17, 18) formed thereon, which are arranged apart from each other so that p- and n-type thermoelectric semiconductor element films alternate with each other, and second electrode films (20) connecting p-type thermoelectric semiconductor element film (19) and n-type thermoelectric semiconductor element film (18) over the gaps between the first electrode films; and a terminal electrode is connected to each of the p-and n-type thermoelectric semiconductor element film (16, 17) at the end; and a production method thereof. The thermoelectric conversion module of the present invention, which can be produced at a low cost using thermoelectric conversion elements having a thin-film structure, is excellent in thermal stability and chemical durability and enables to secure high thermoelectric conversion efficiency.

Owner:ISHIKAWA PREFECTURAL GOVERNMENT +2

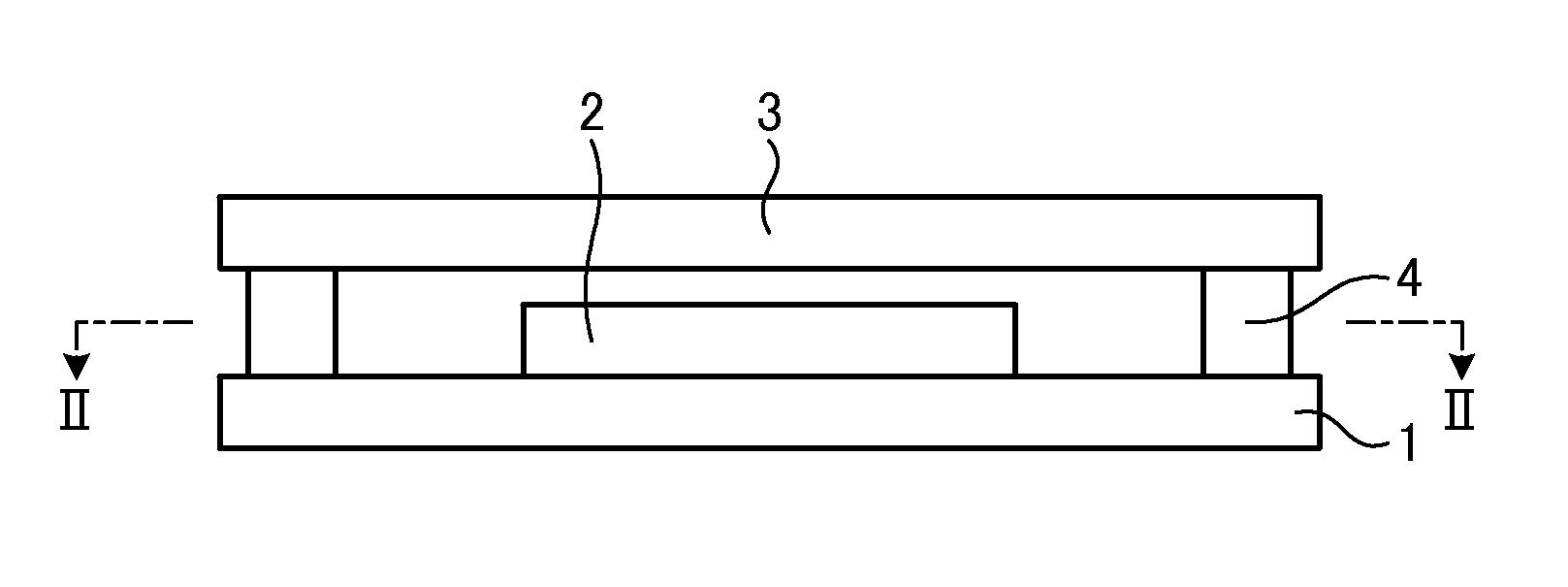

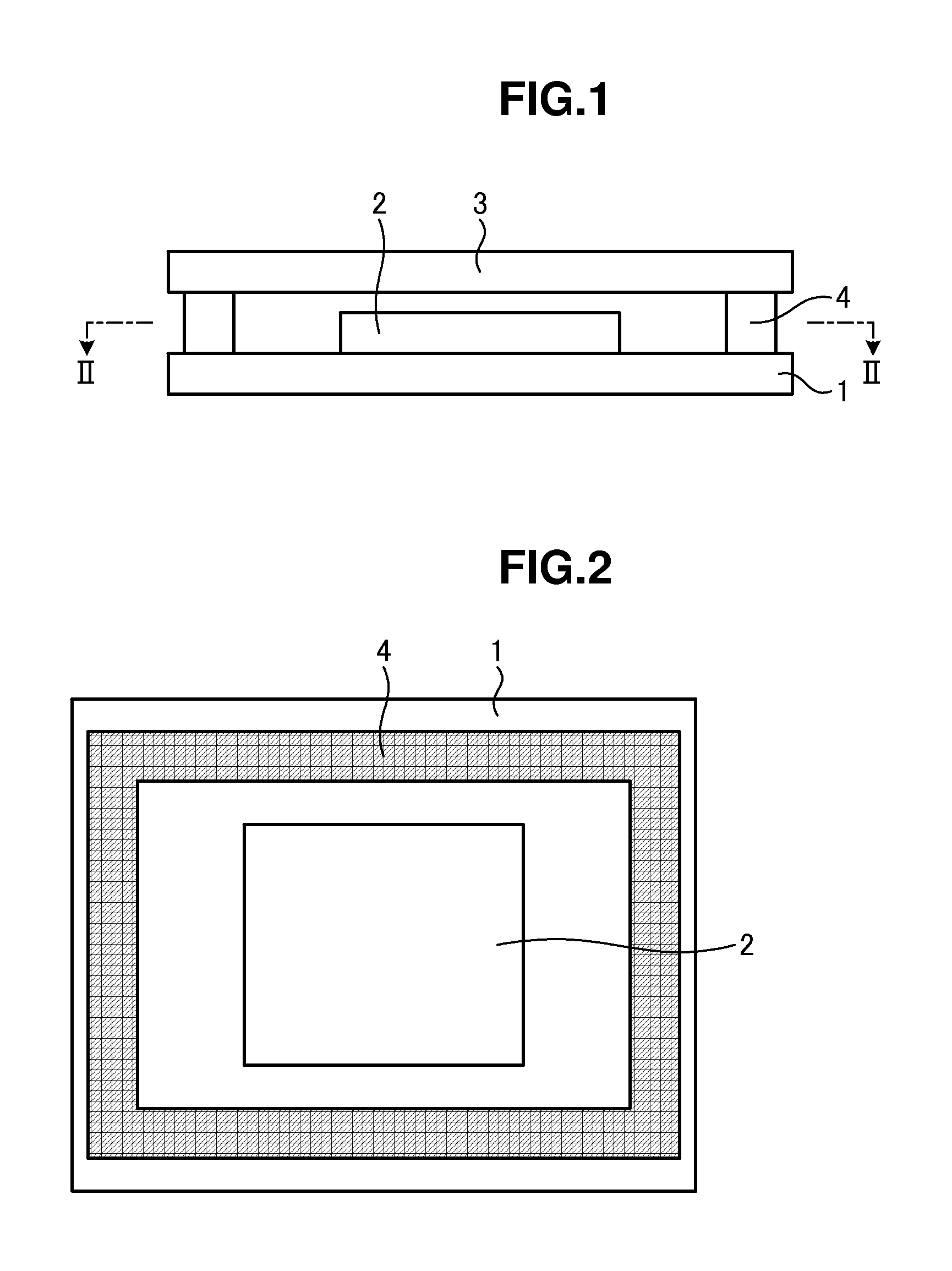

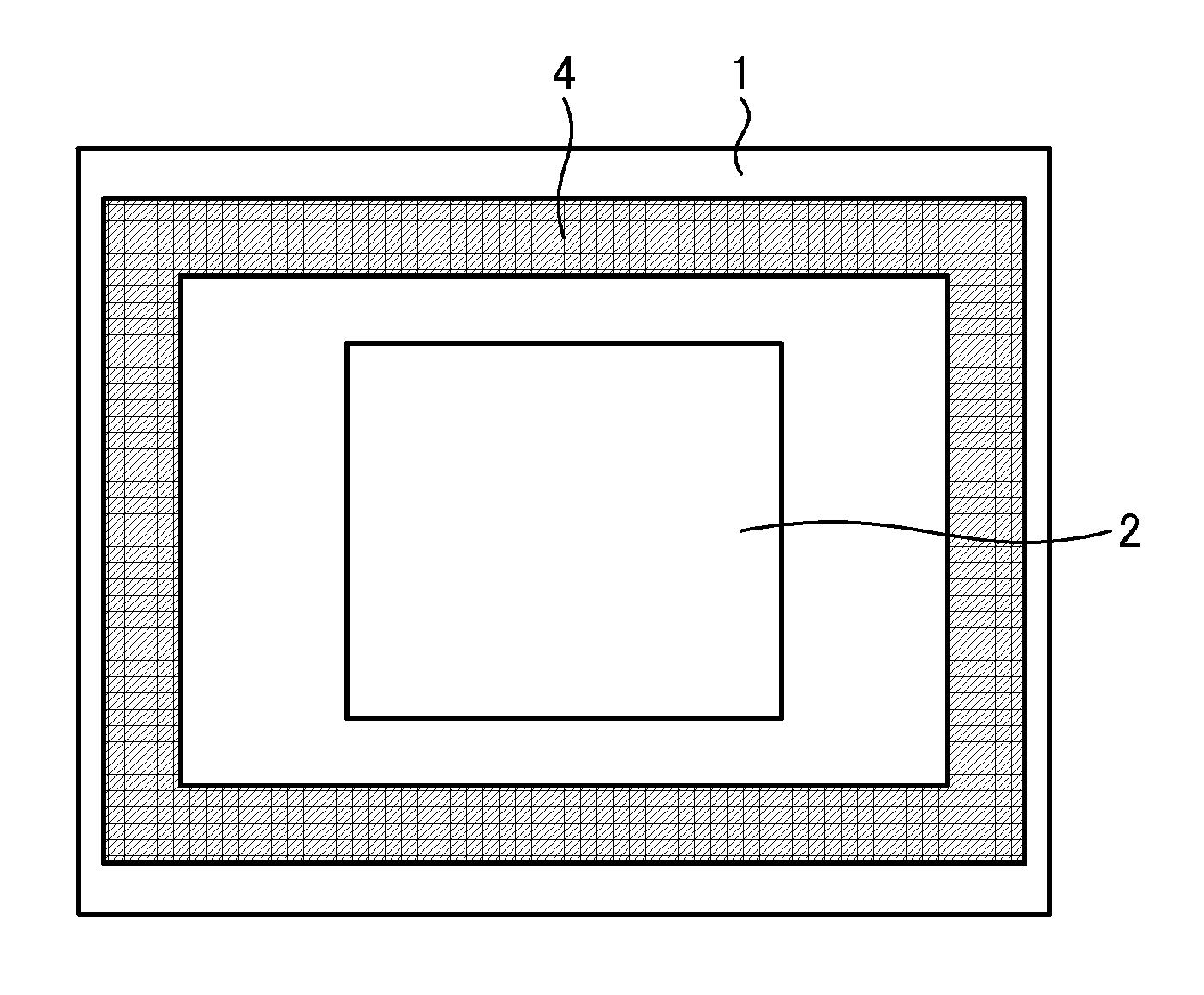

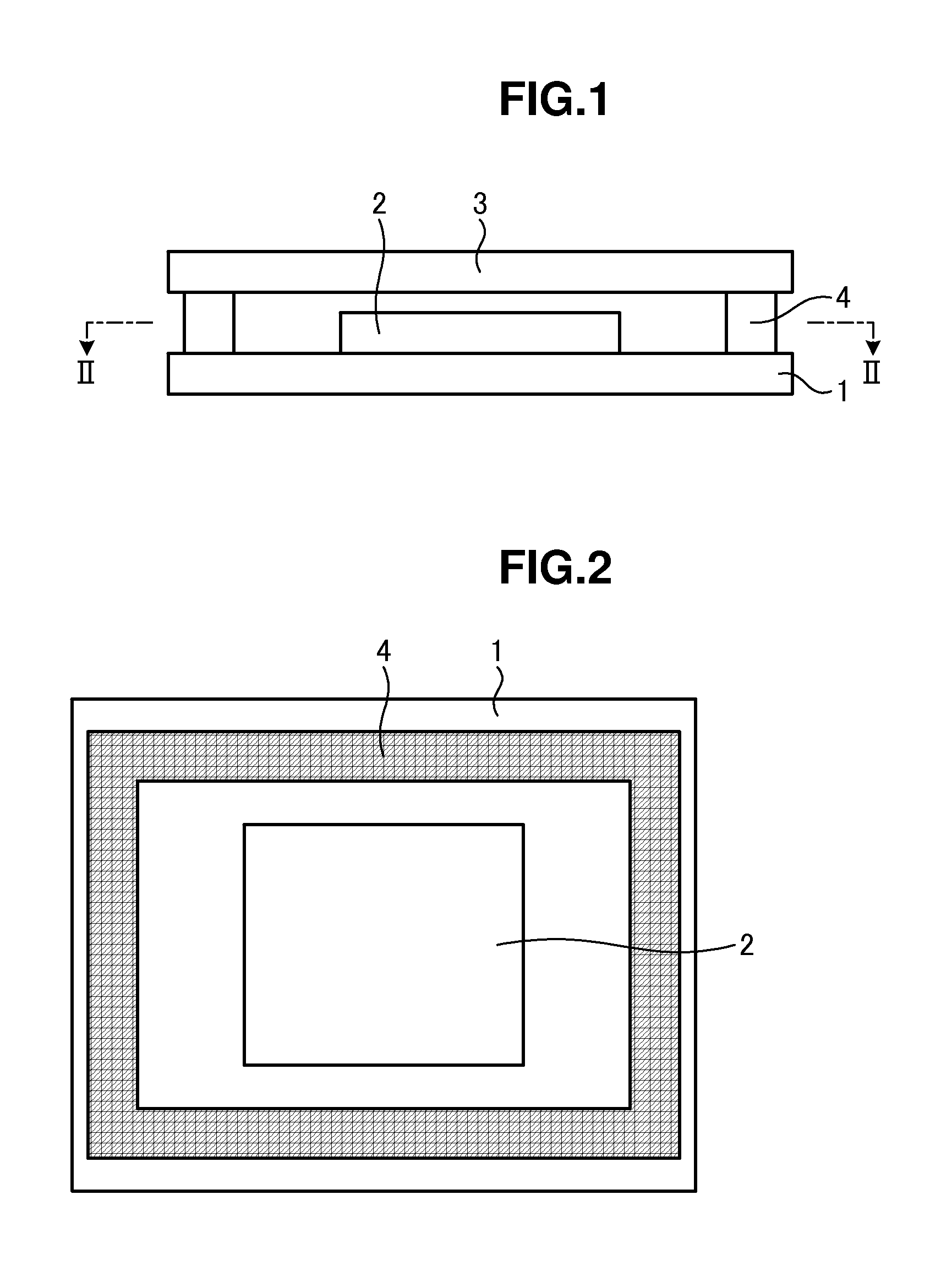

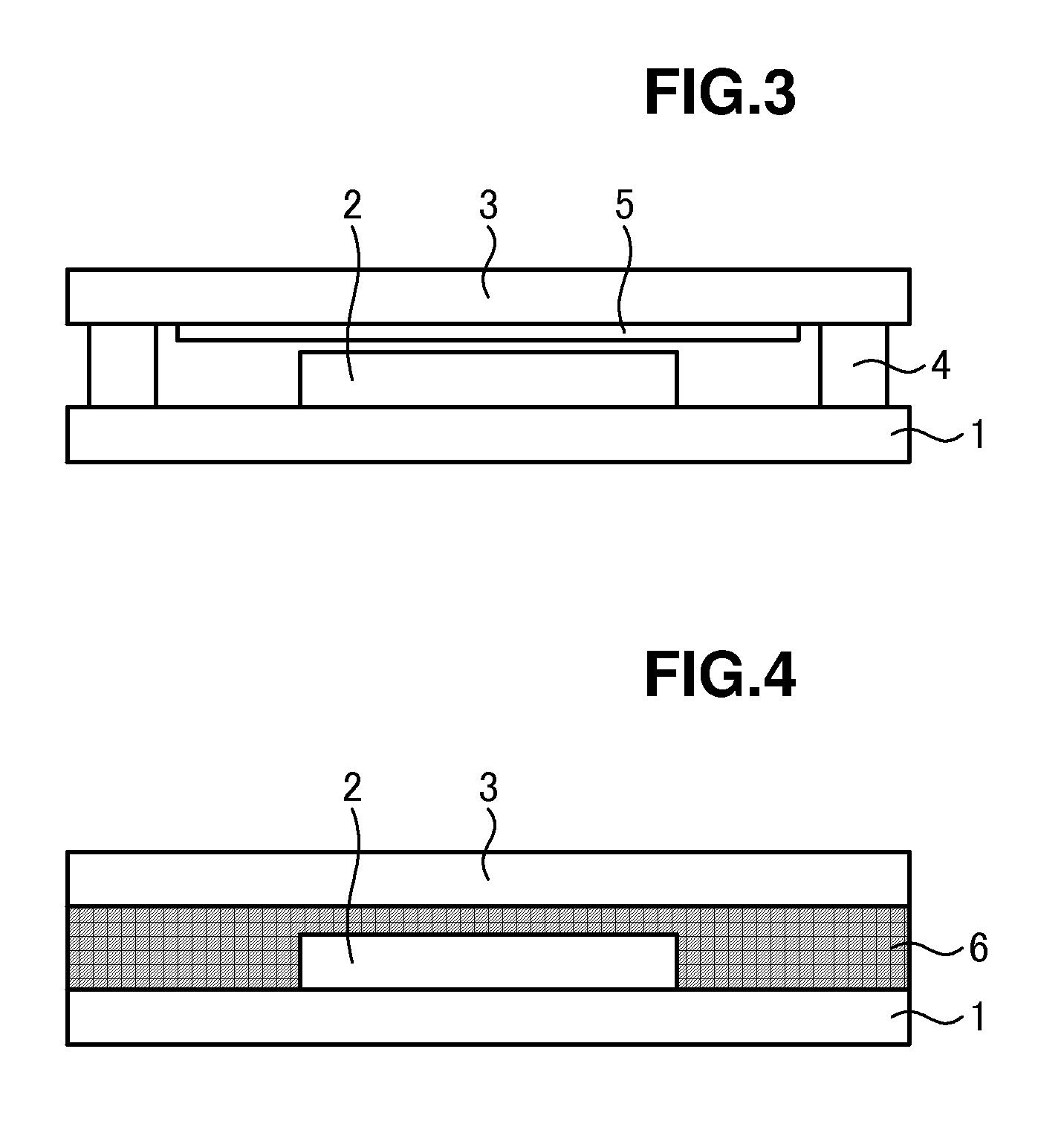

Method for manufacturing organic light-emitting device and organic light-emitting device

ActiveUS20130112966A1Reduce manufacturing costAvoid performance degradationFinal product manufactureSolid-state devicesEngineeringLight emitting device

The present invention provides a method for manufacturing an organic light-emitting device capable of simply manufacturing the organic light-emitting device without requiring a vacuum atmosphere. The manufacturing method of the present invention includes: a step of preparing a supporting substrate having an organic electroluminescent element formed thereon, the organic electroluminescent element containing an anode, a light-emitting layer, an electron injection layer made by forming a film with a solution containing an ionic polymer, and a cathode; and a step of laminating the supporting substrate and a sealing member to one another so as to seal the organic electroluminescent element.

Owner:SUMITOMO CHEM CO LTD

Method for determining modulation and coding scheme

InactiveUS8553818B2Performance degradation can be preventedImprove spectral efficiencyModulated-carrier systemsPolarisation/directional diversityModulation codingComputer science

Owner:LG ELECTRONICS INC

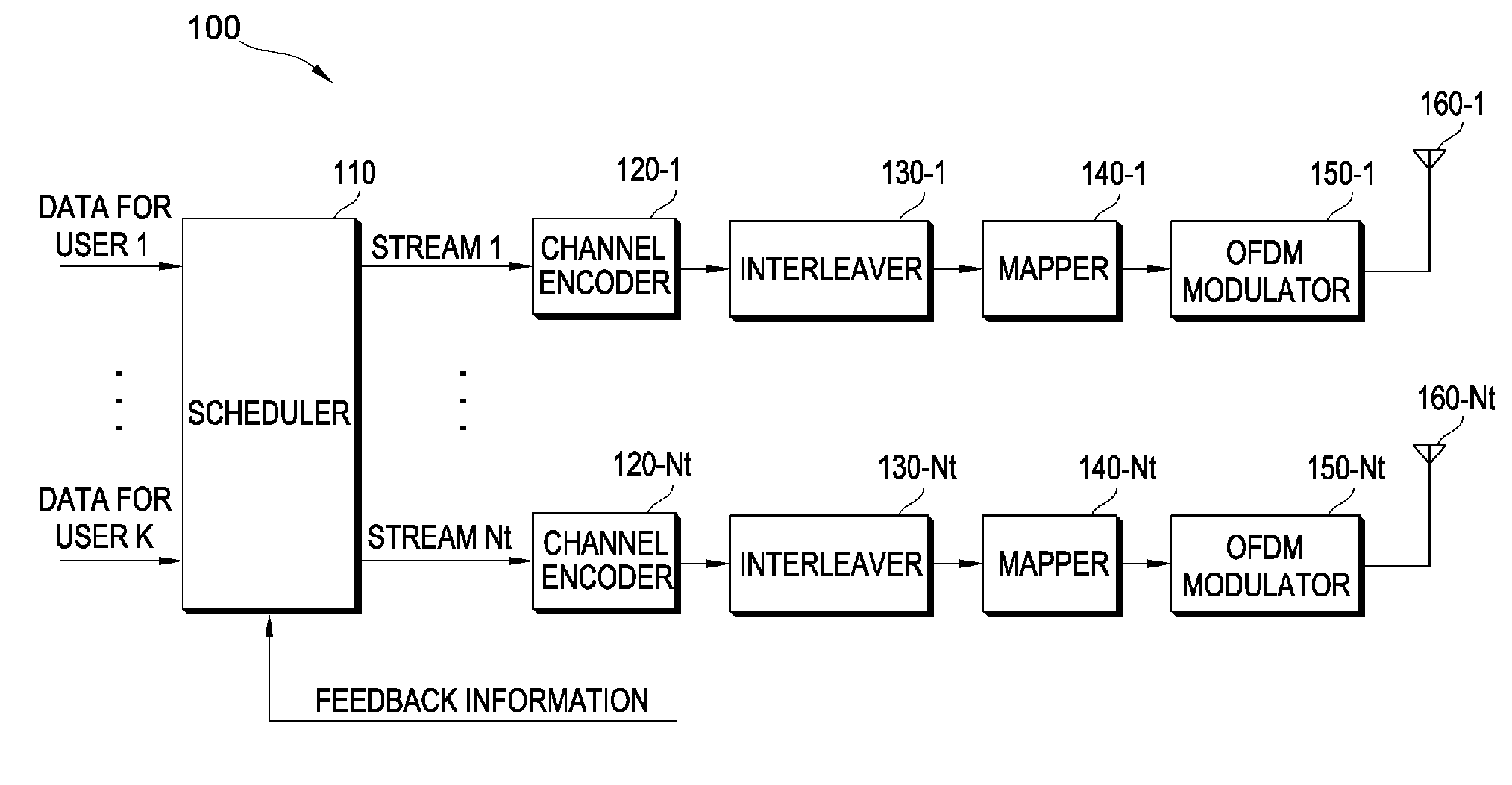

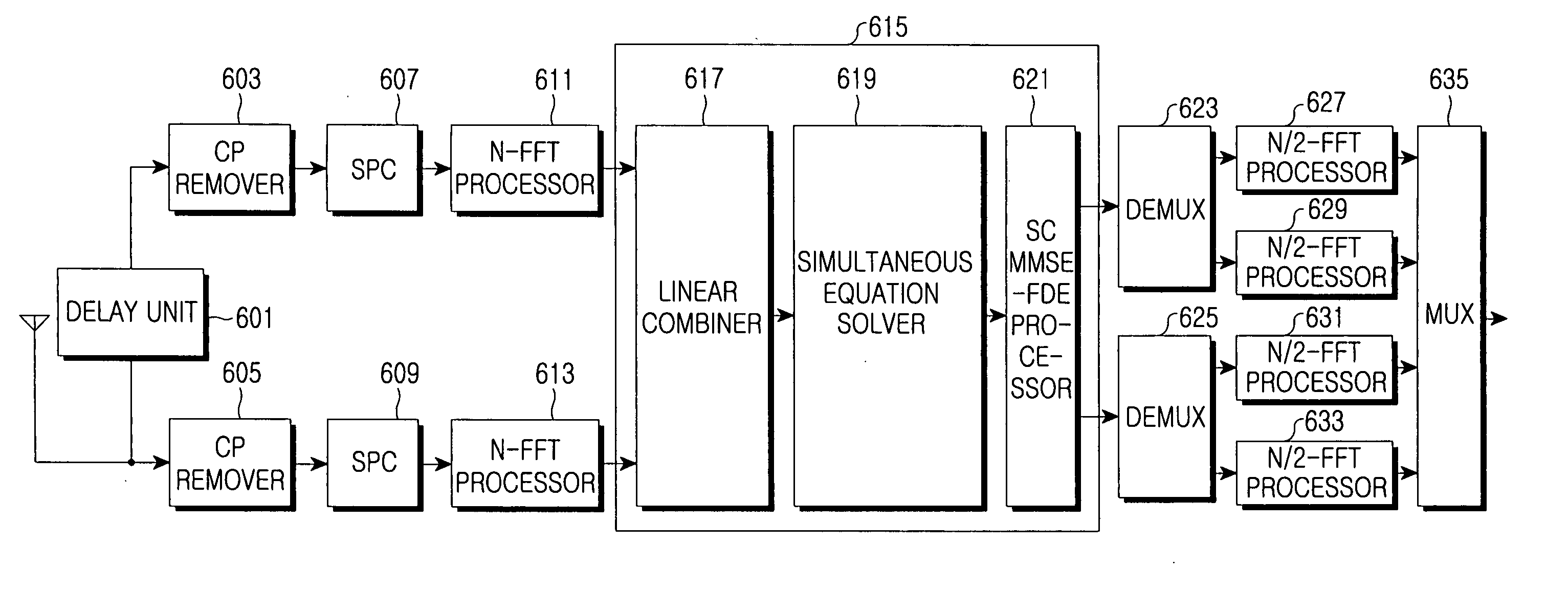

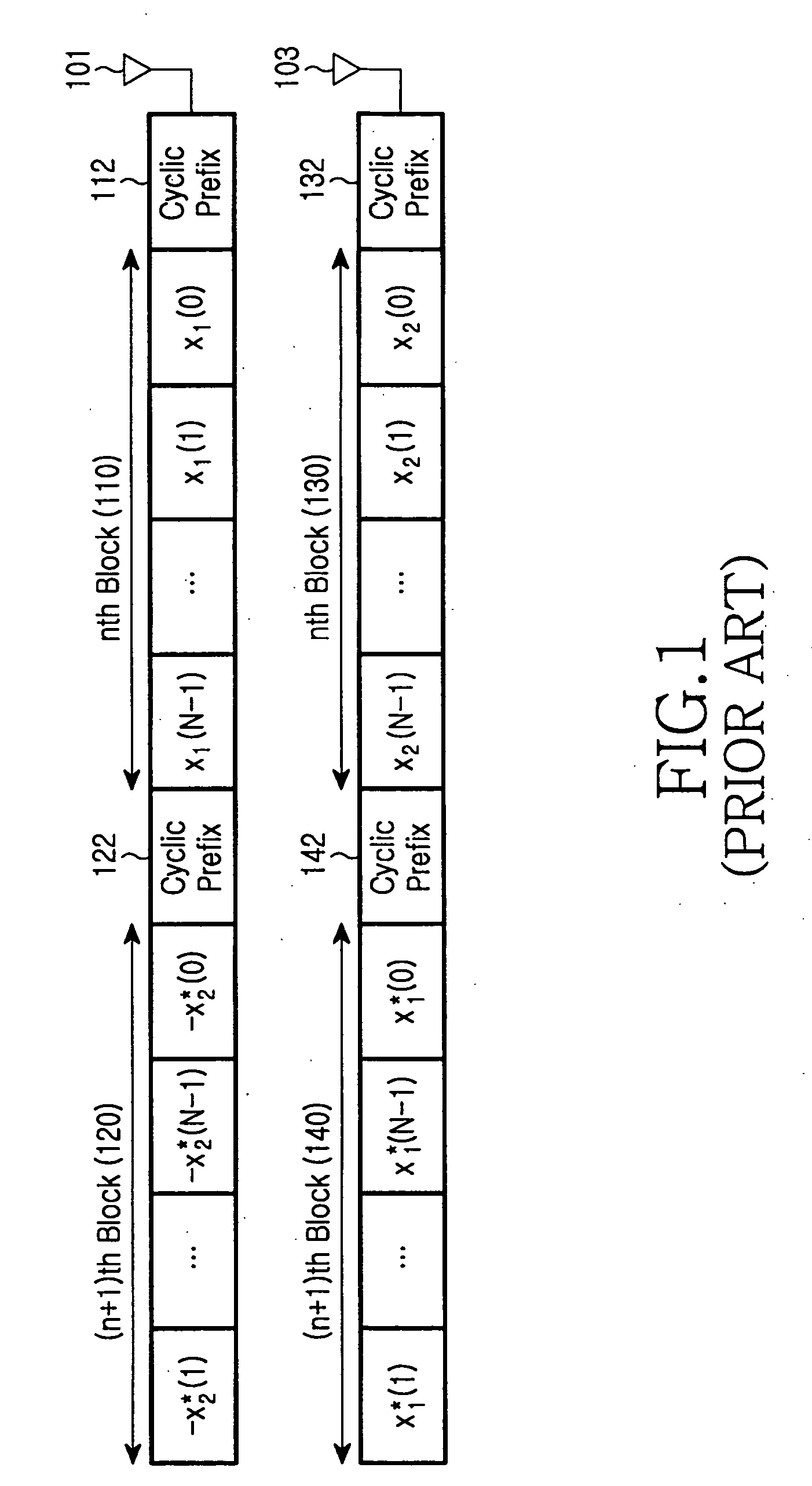

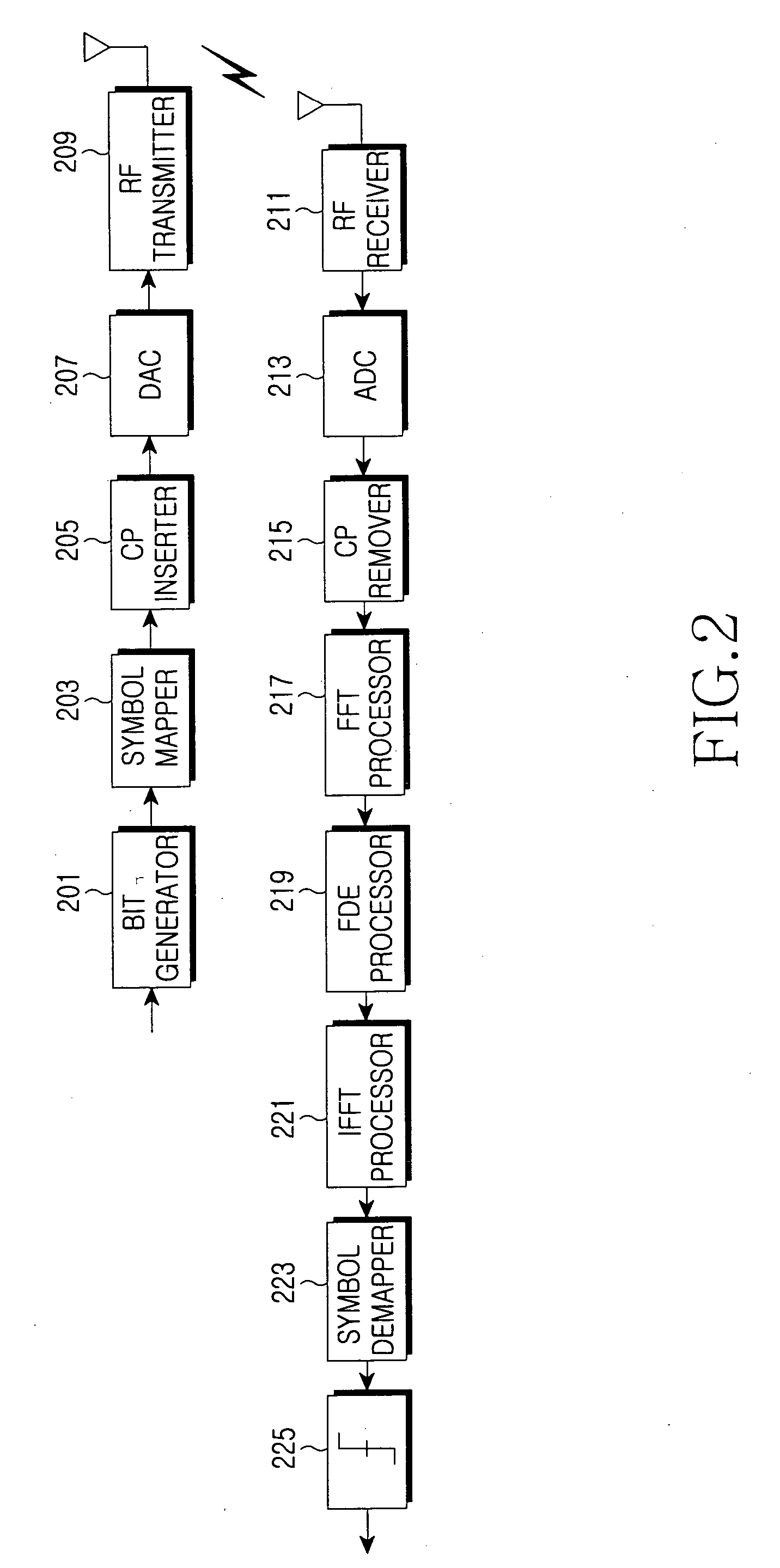

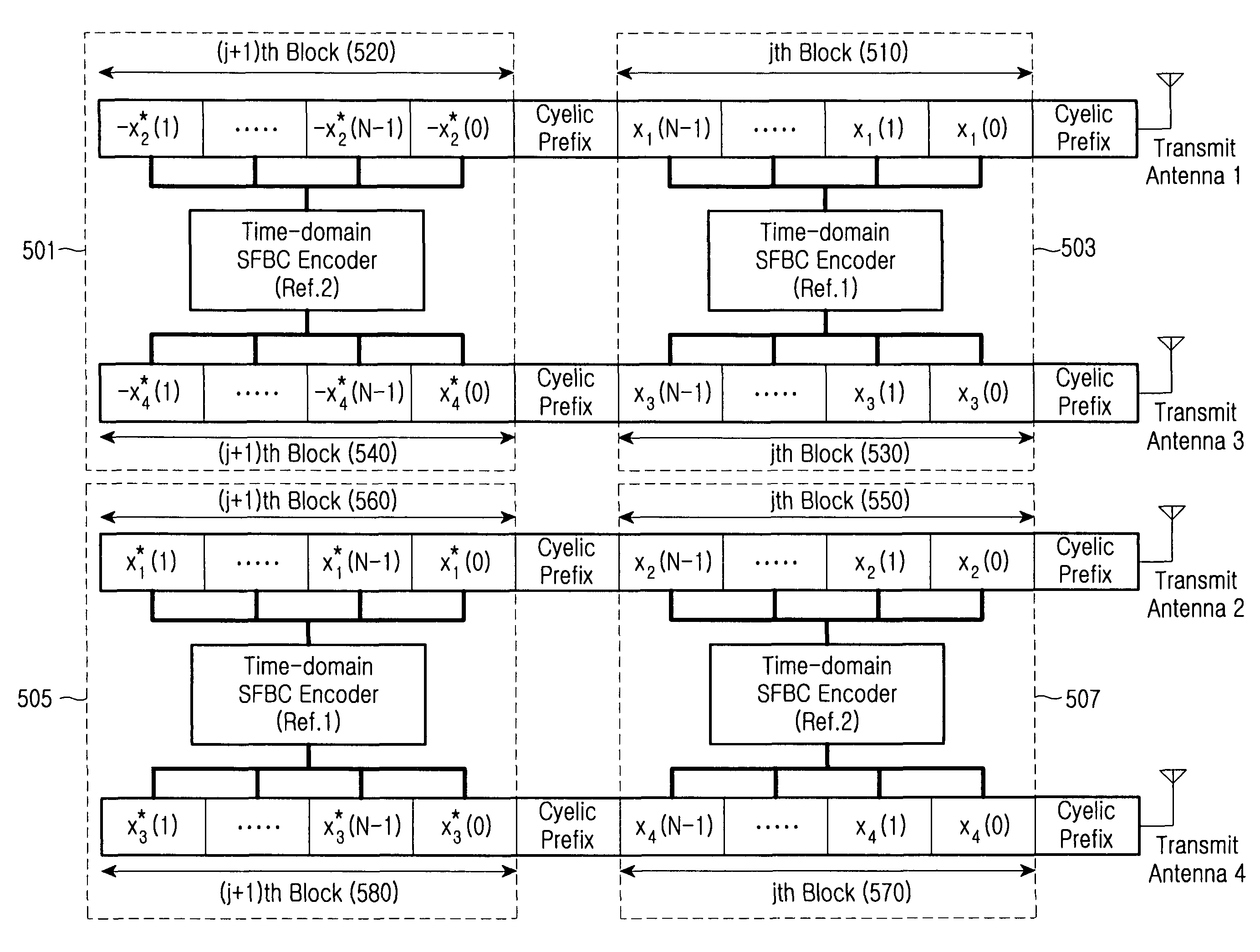

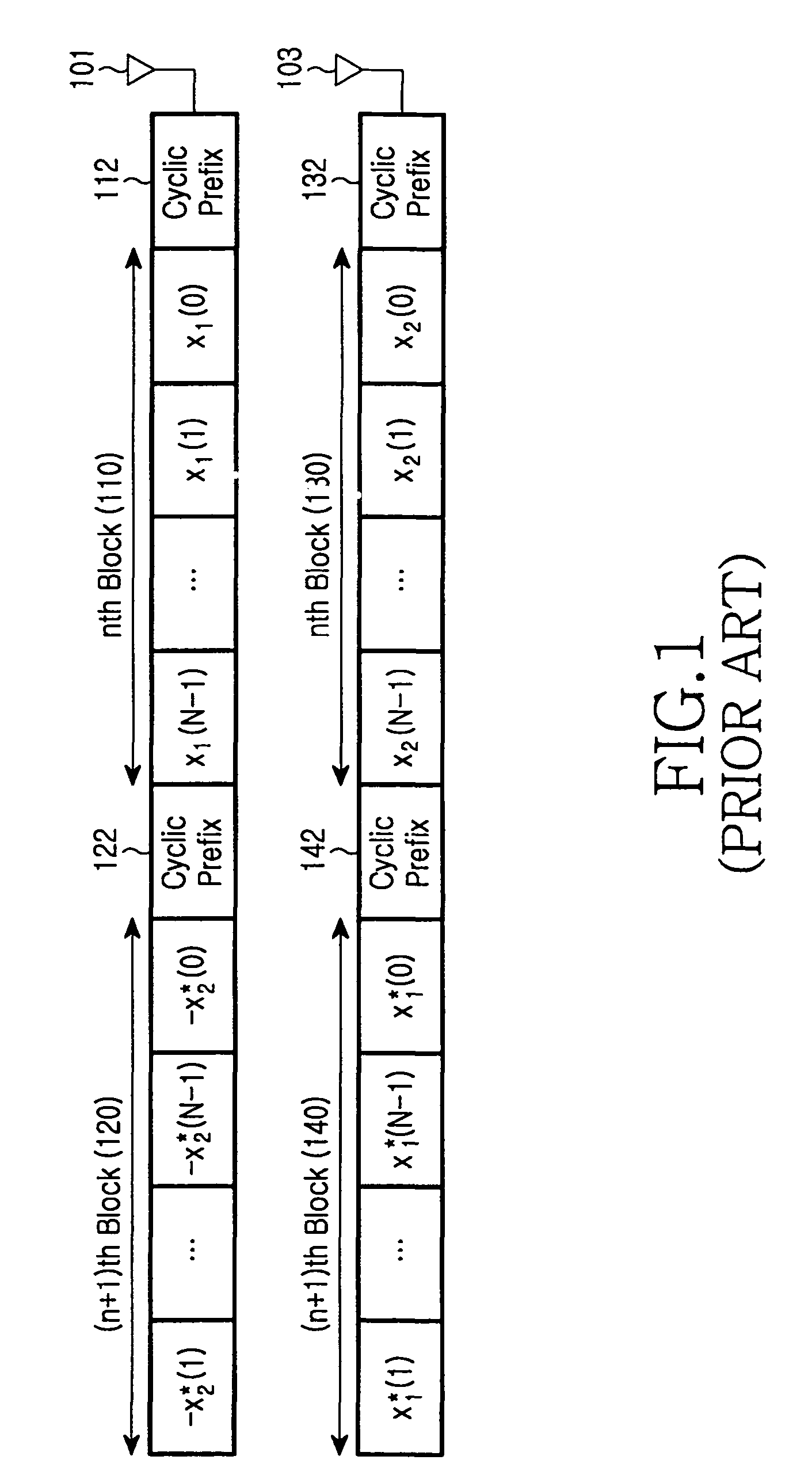

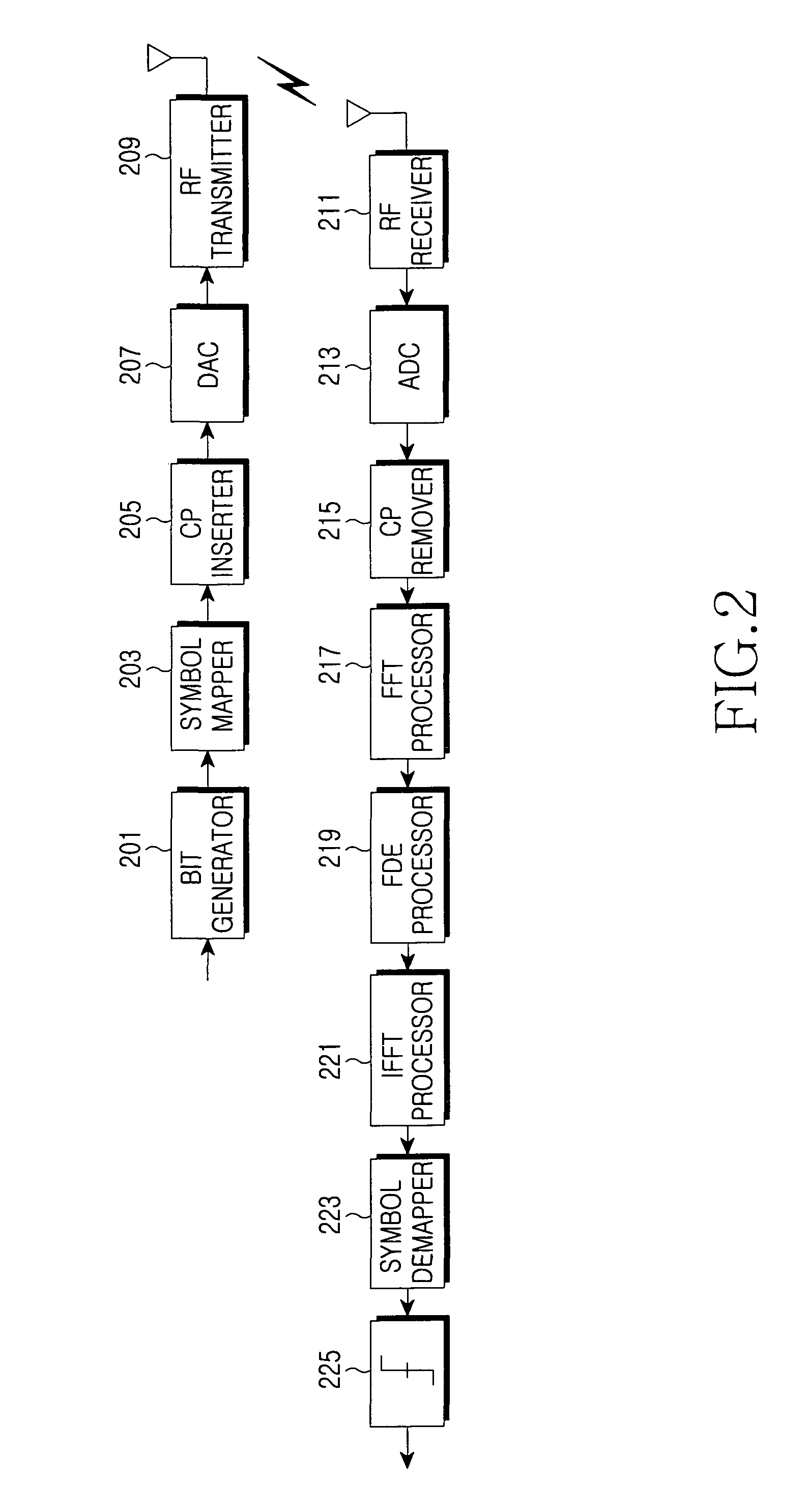

Apparatus and method for transmitting and receiving a signal in a wireless communication system

ActiveUS20070230383A1Performance degradation can be preventedError preventionMultiplex communicationCommunications systemSignal on

A method and apparatus for transmitting and receiving a signal in a wireless communication system. The wireless communication system includes a transmitter with at least four transmit antennas and a receiver with at least one receive antenna. Space Frequency Block Coding (SFBC) processes are performed for input signals on a basis of two antenna pairs. Signal blocks whose number corresponds to the number of transmit antennas are output. A Space Time Block Coding (STBC) process is performed for the signal blocks generated according to the antenna pairs. Signals carried by single carriers are transmitted through the at least four transmit antennas mapped to the signal blocks.

Owner:SAMSUNG ELECTRONICS CO LTD +1

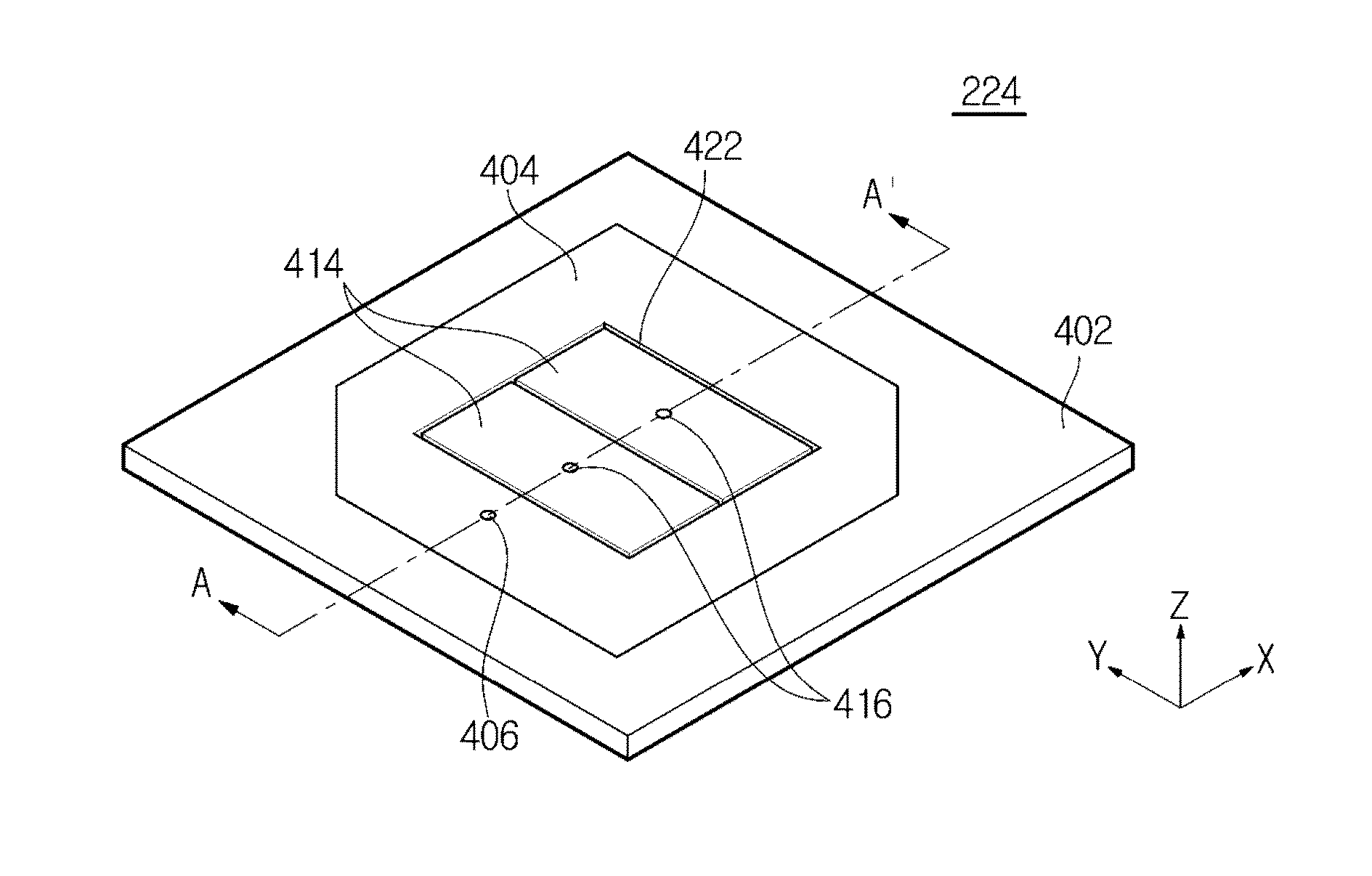

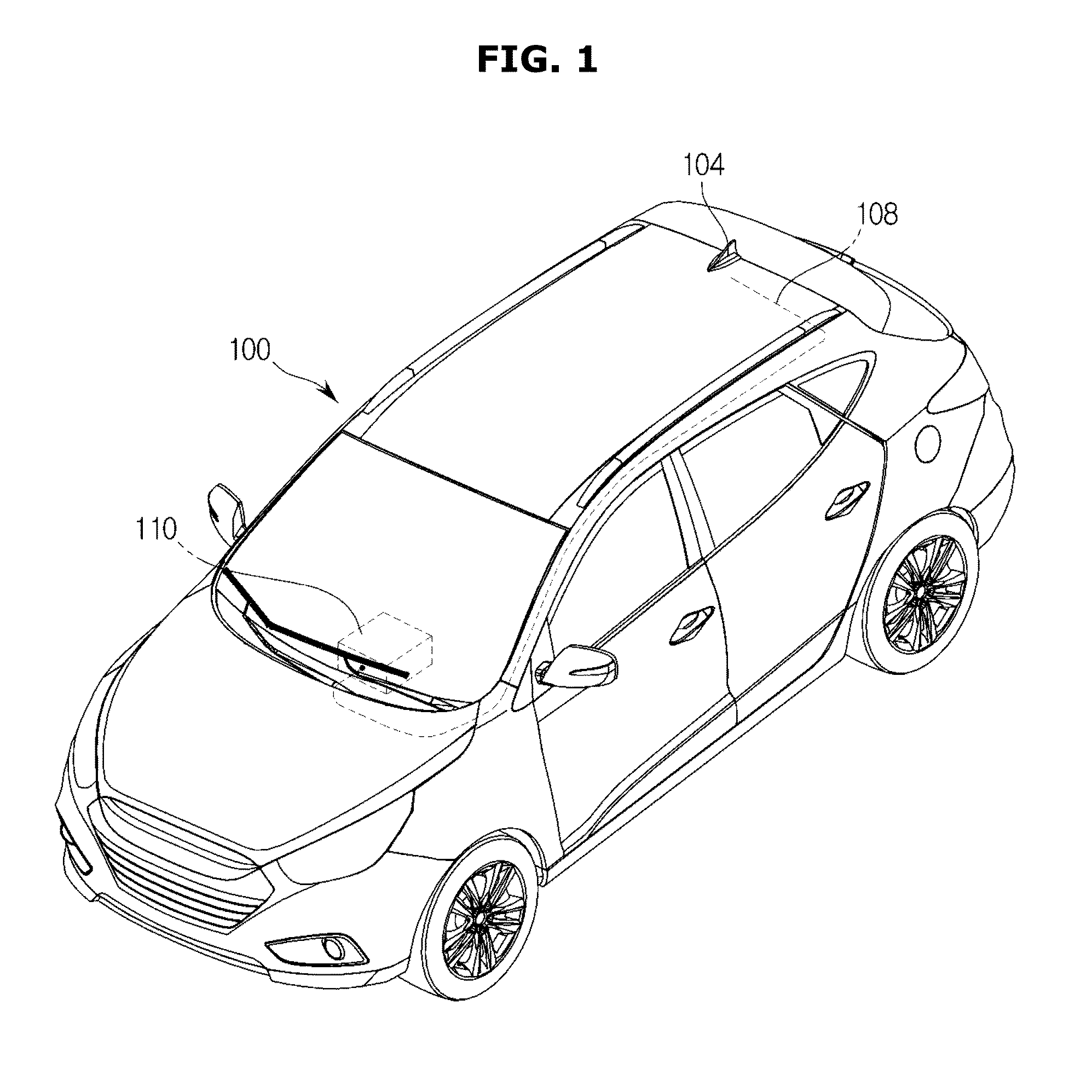

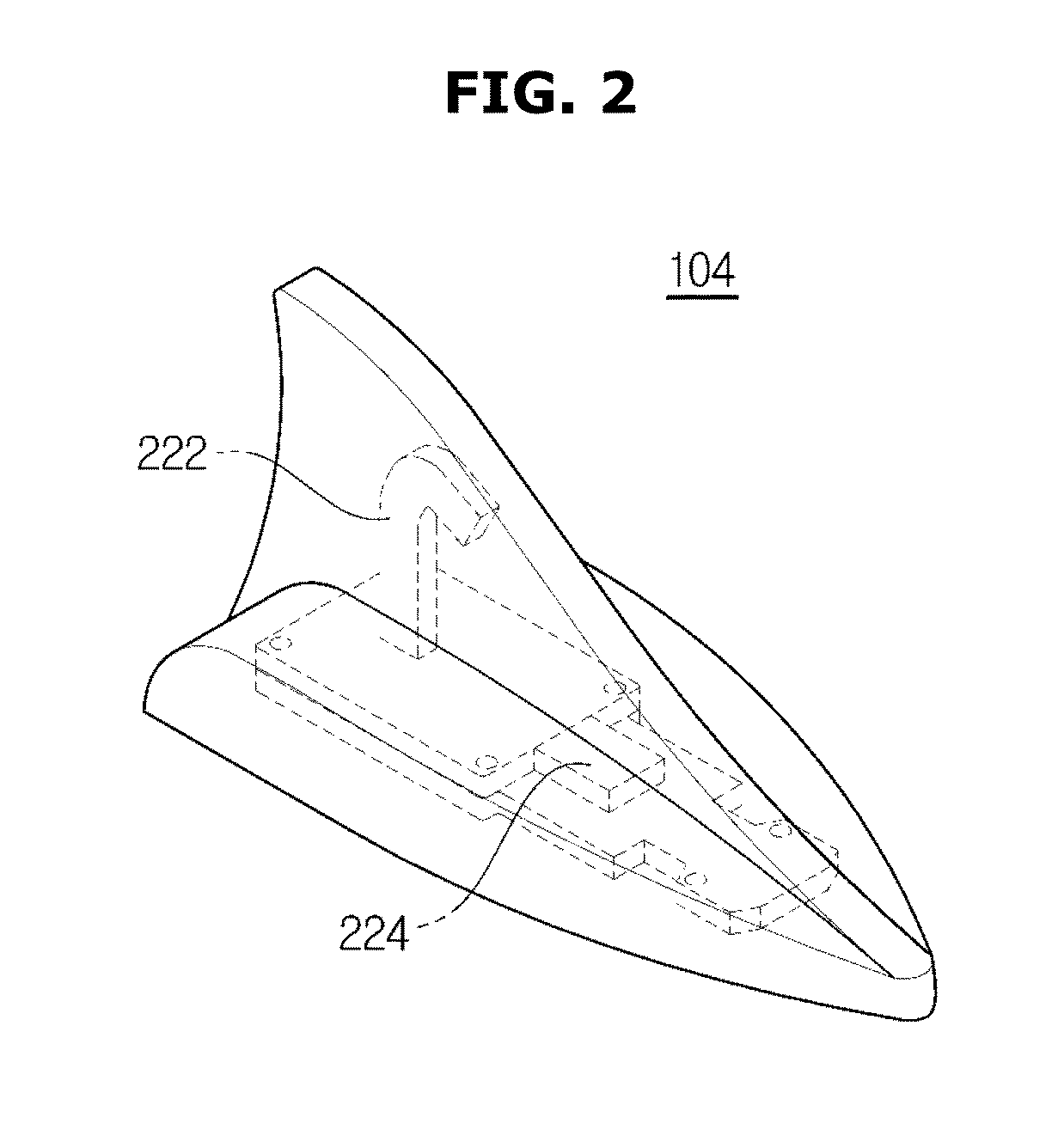

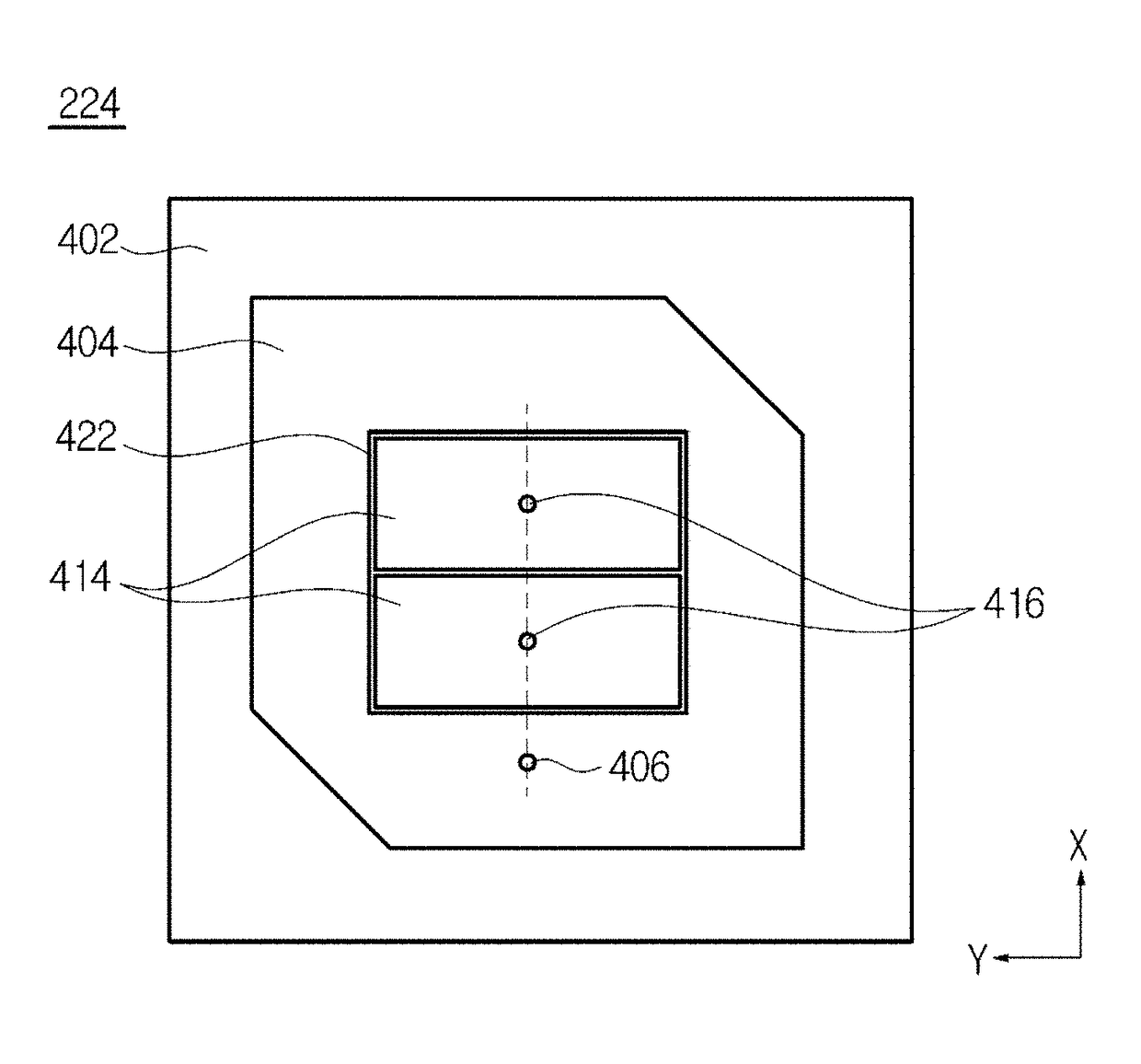

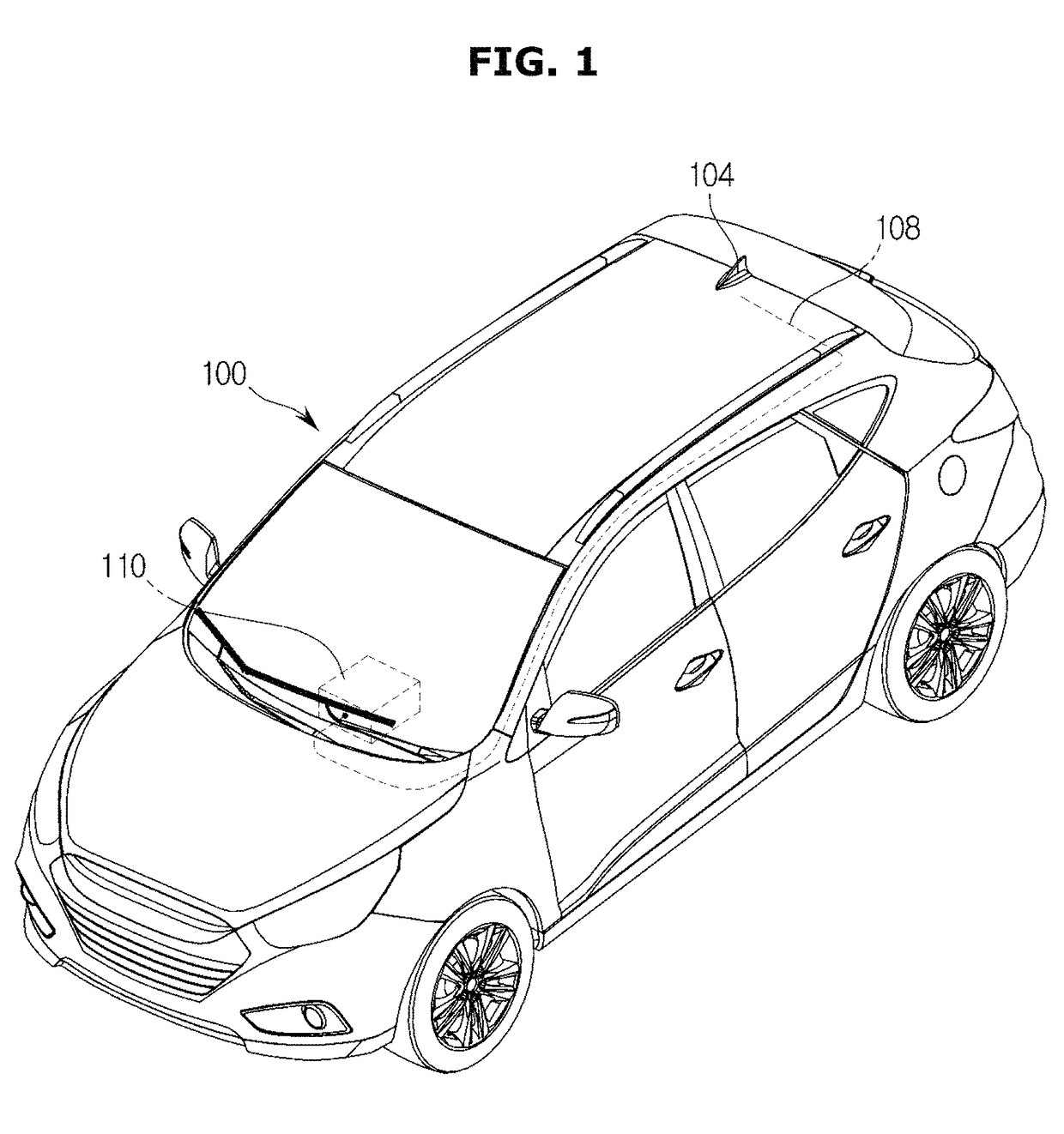

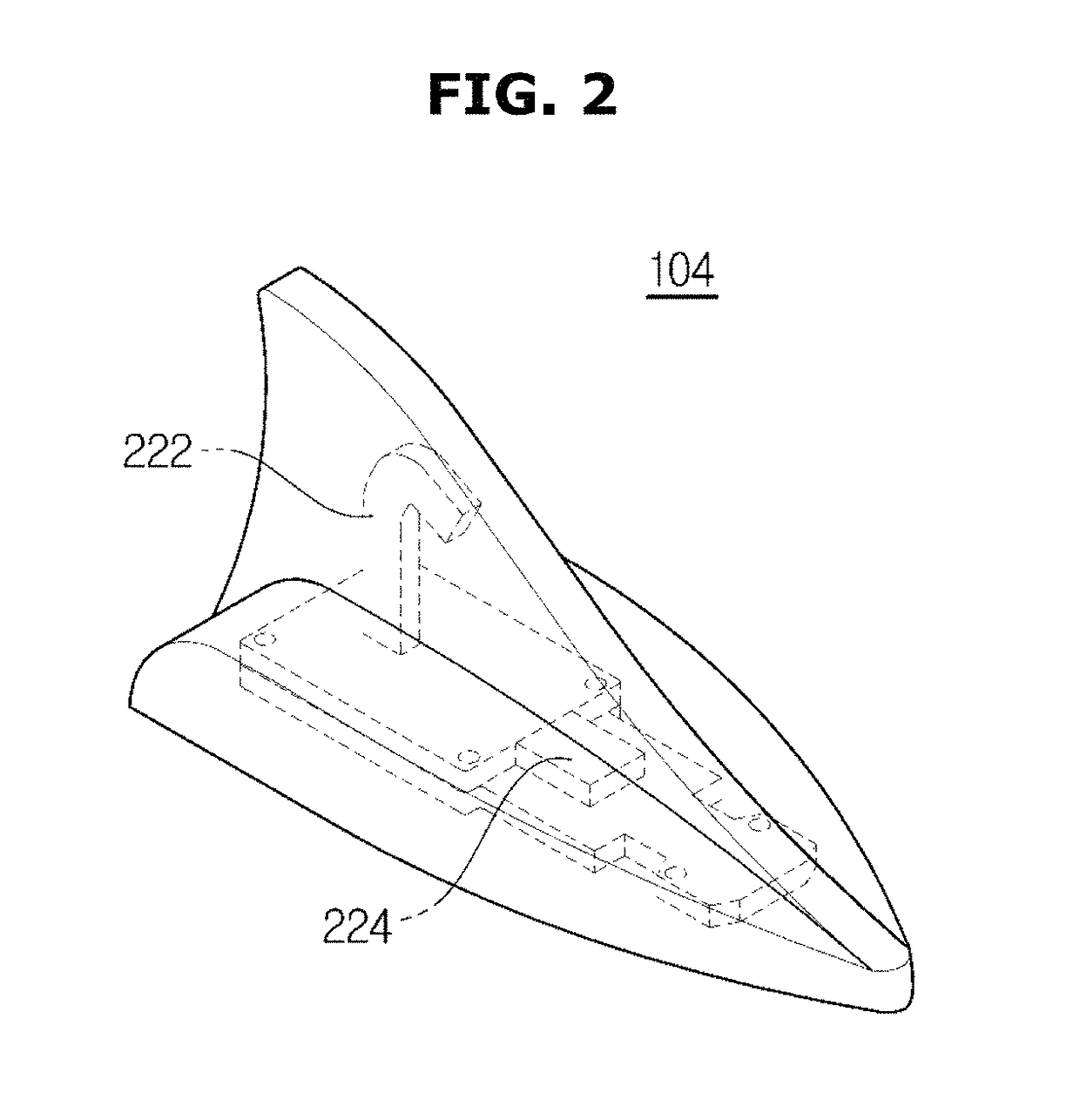

Antenna, circular polarized patch antenna, and vehicle having the same

ActiveUS20160118720A1Reduce size (volume)Performance degradation can be preventedSimultaneous aerial operationsAntenna adaptation in movable bodiesCouplingEngineering

An antenna, a circular polarized patch antenna, and a vehicle having the same are provided. The antenna includes a substrate, a ground portion formed on a first surface of the substrate, and a second radiator having a plurality of patches and formed on a second surface of the substrate. In addition, a first radiator is formed in a periphery of the second radiator with a gap from the second radiator and a feeding probe is disposed on the first radiator to enable power to be fed directly fed to the first radiator and to enable power to be fed to the second radiator through coupling.

Owner:HYUNDAI MOTOR CO LTD

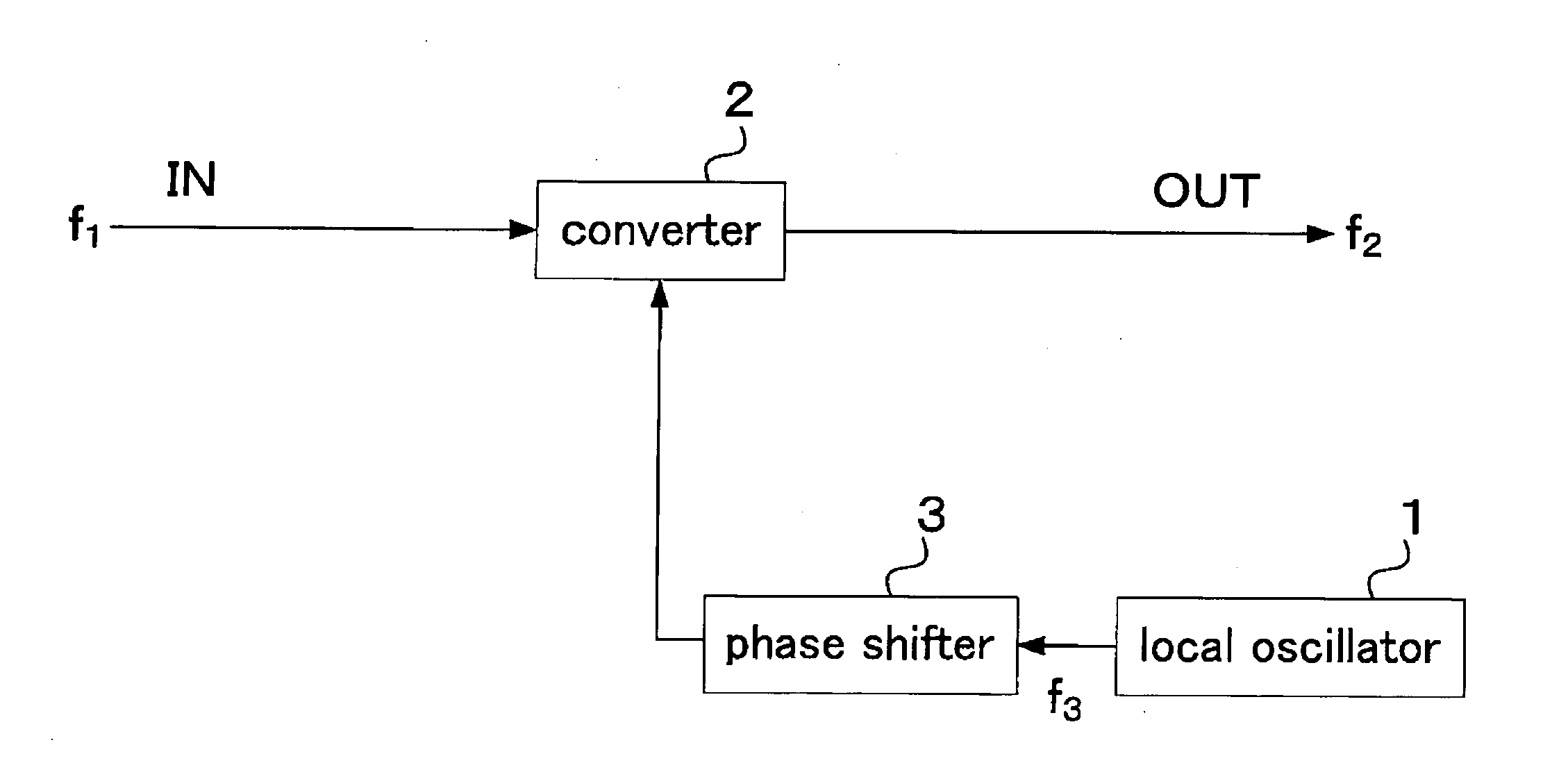

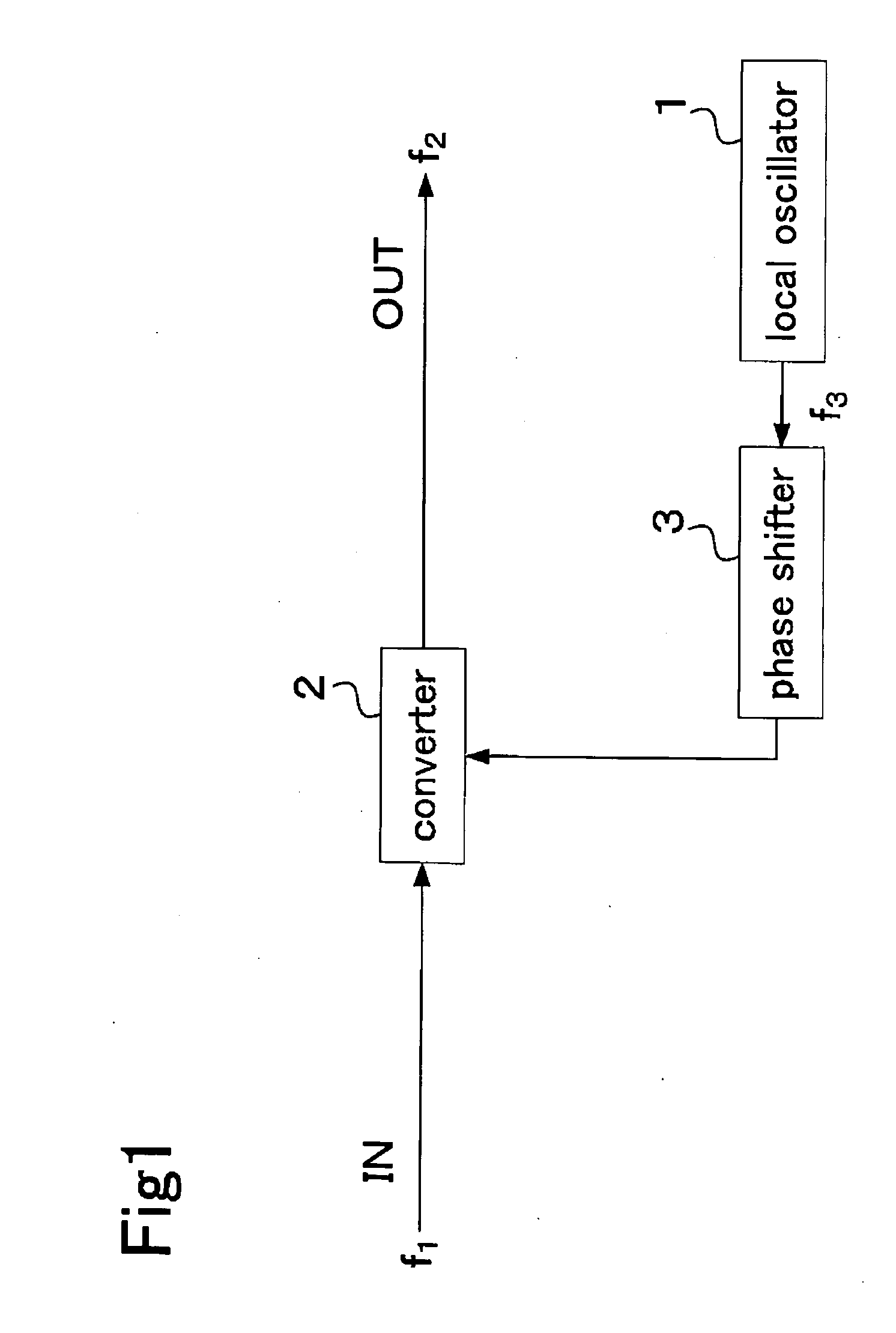

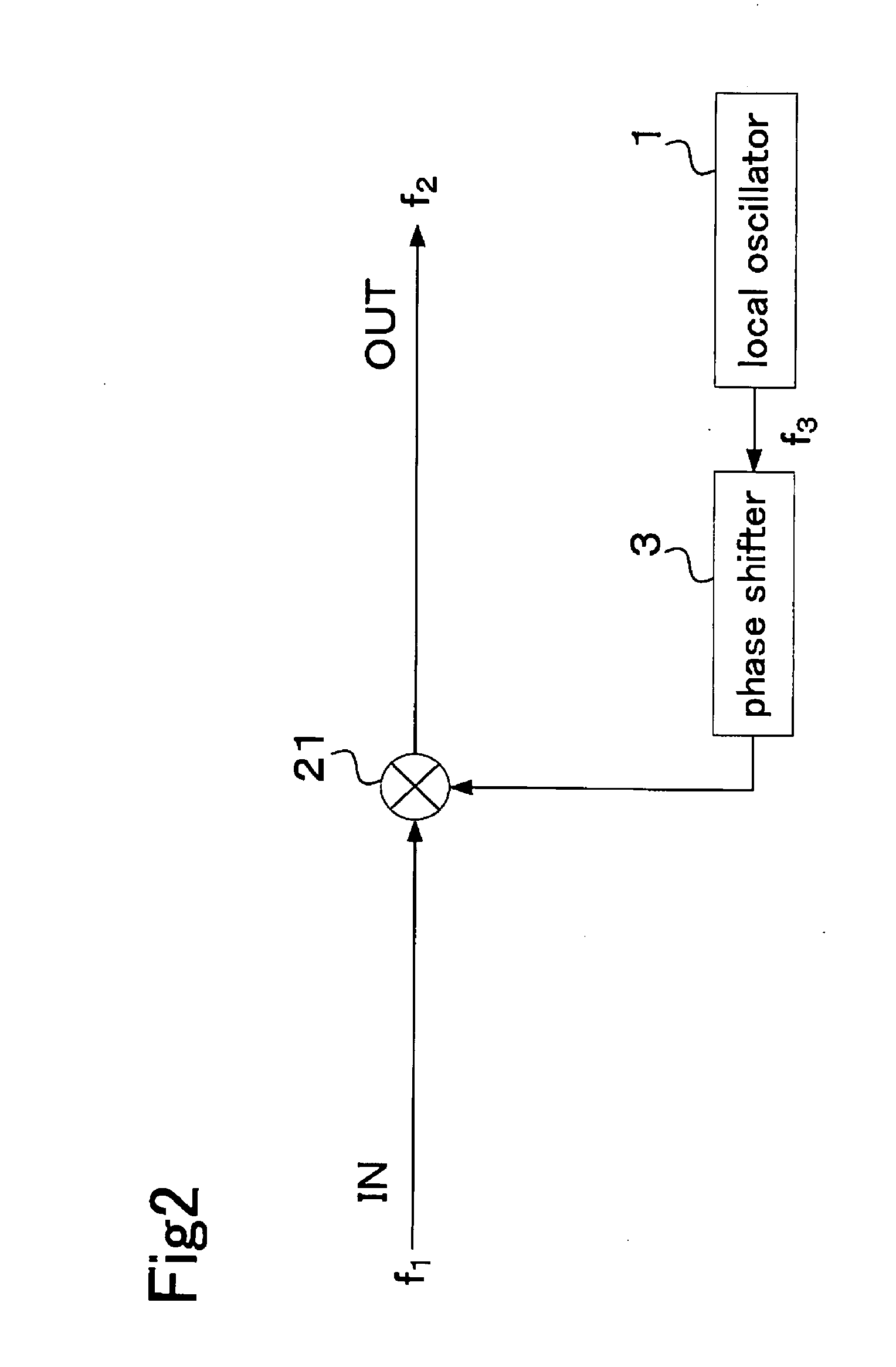

Signal conversion apparatus and signal conversion method

InactiveUS20070015481A1Simple processPerformance degradation can be preventedAngle modulation by variable impedenceResonant long antennasPhase shiftedLocal oscillator

A signal conversion apparatus includes a local oscillator for locally generating a signal having a frequency, a phase shifter for shifting the phase of the locally generated signal output from the local oscillator by an amount determined based on a relationship between the amount of phase shift and the amount of frequency pulling, and a converter for converting an input signal by using the phase-shifted locally generated signal output from the phase shifter. The phase shifter varies impedance between the local oscillator and the converter so that the oscillating frequency of the locally generated signal output from the local oscillator remains unchanged.

Owner:FURUNO ELECTRIC CO LTD

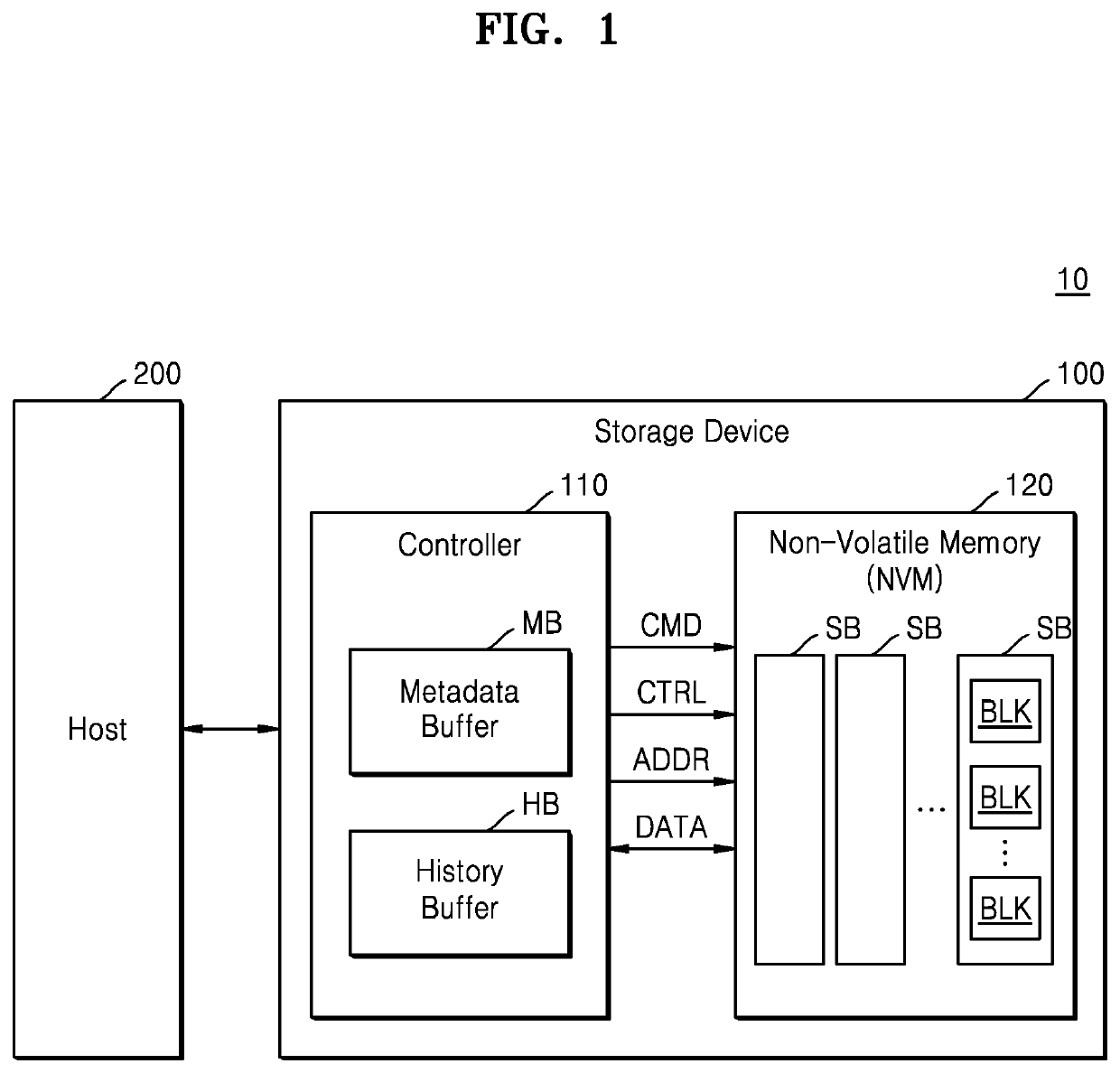

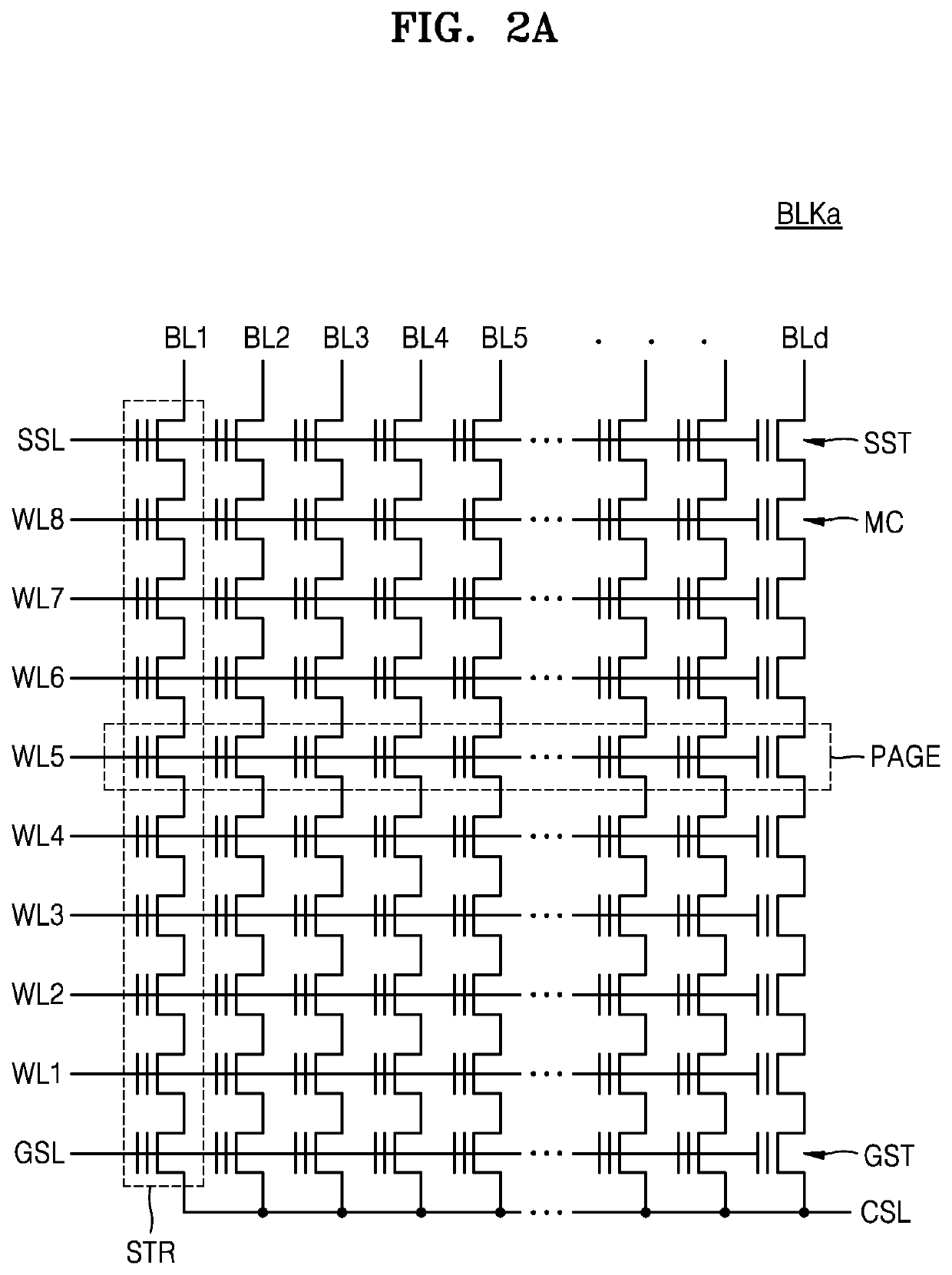

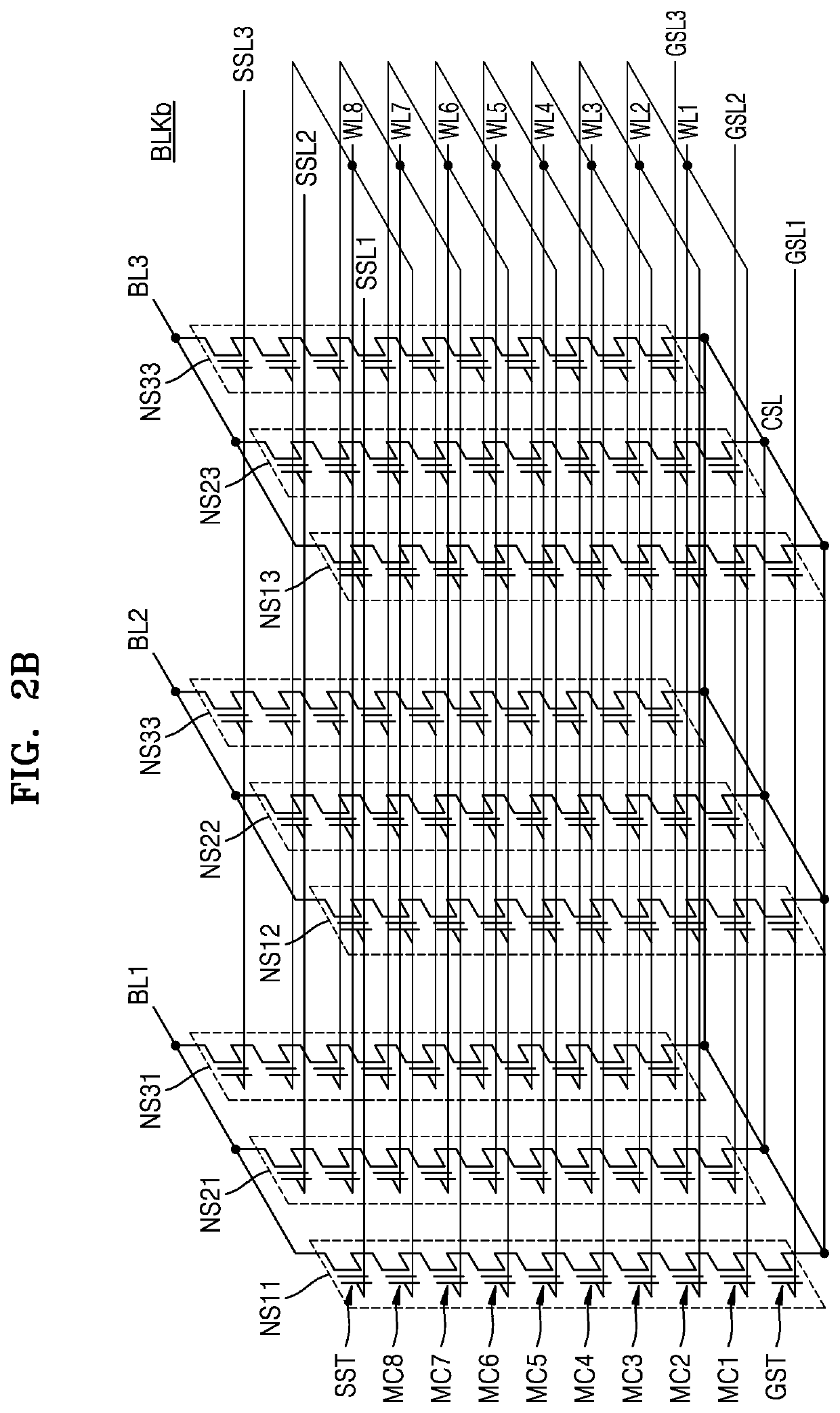

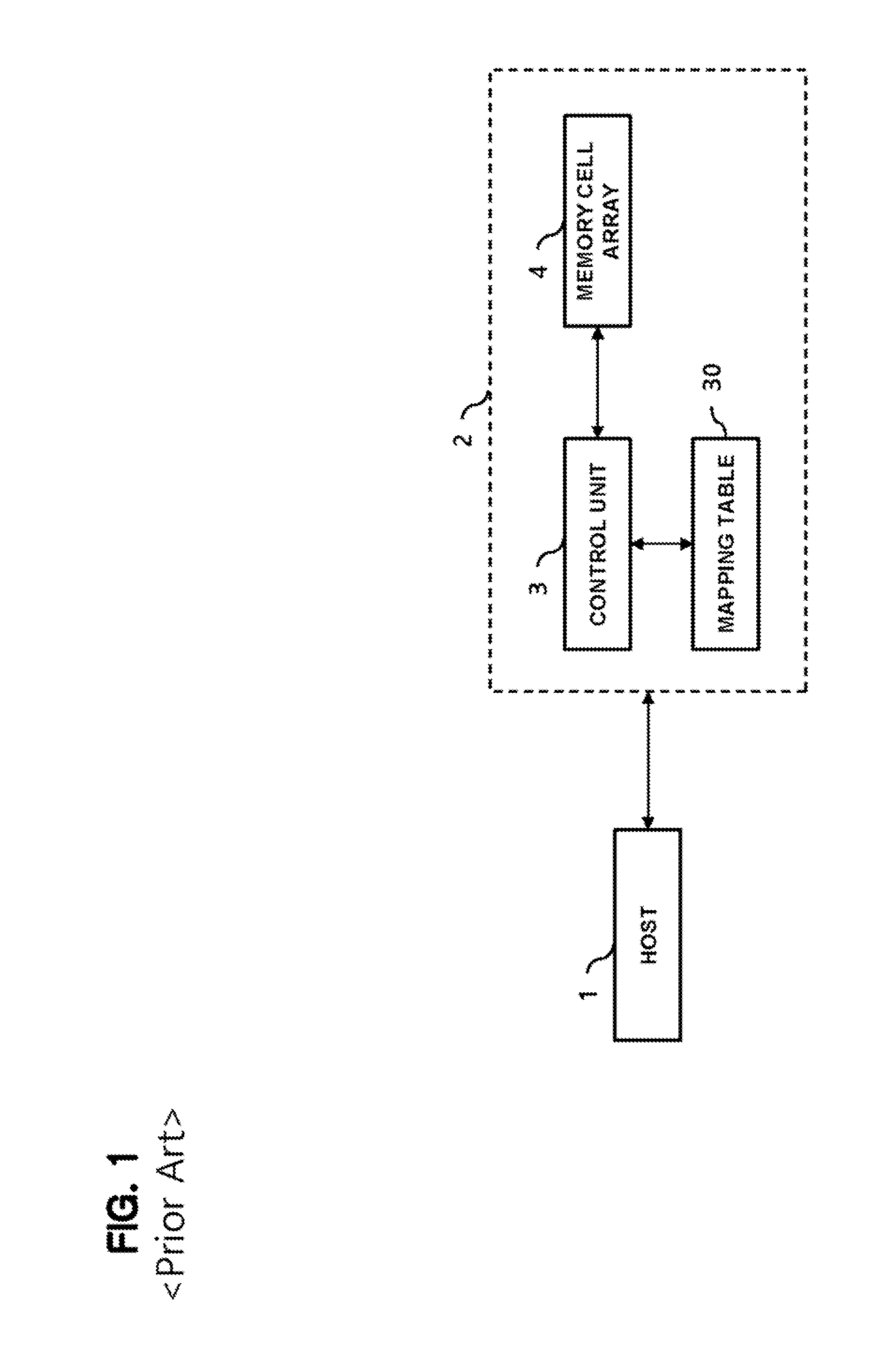

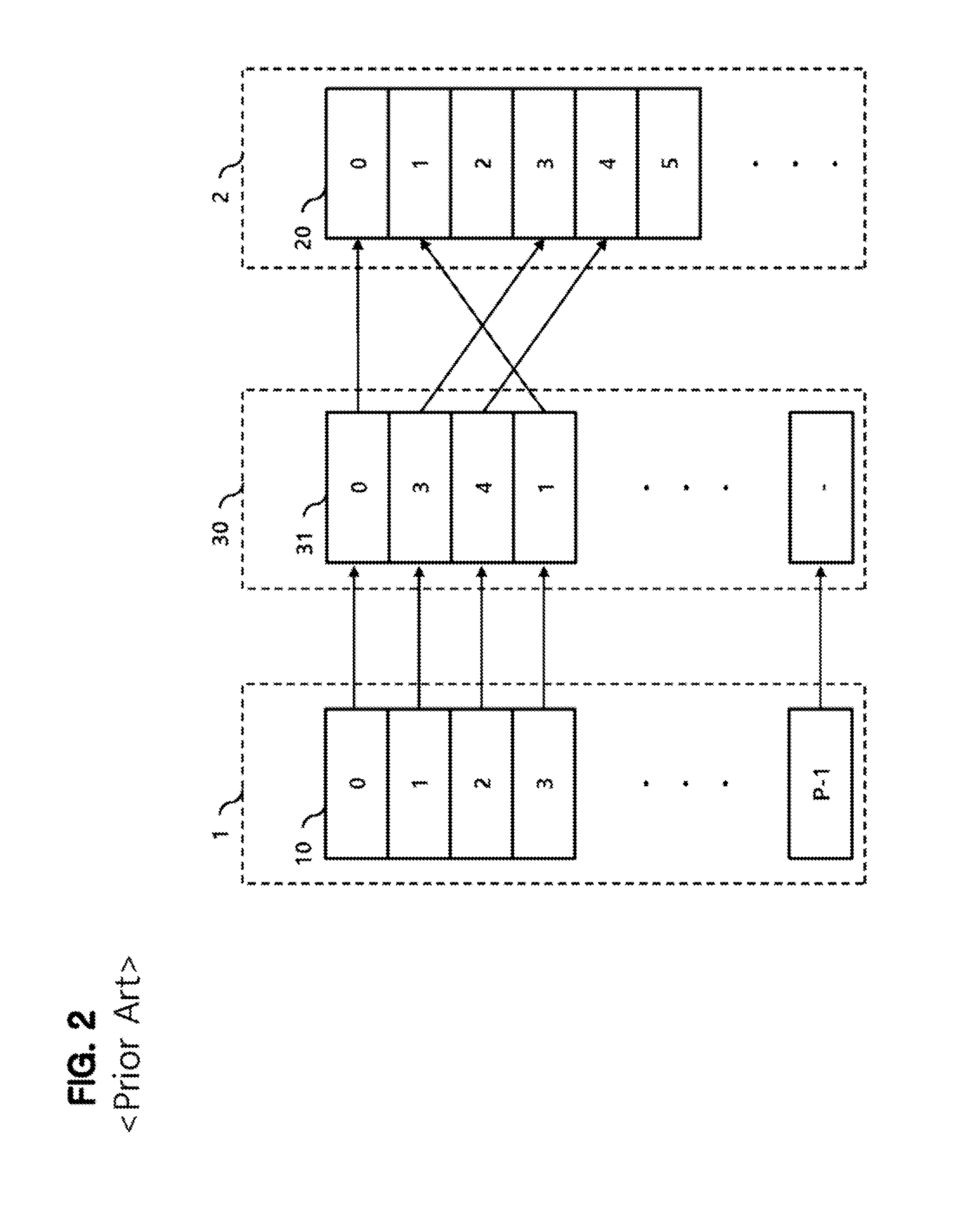

Storage device and method of operating the same

ActiveUS20210166774A1Less read retry operationCapacity history bufferRead-only memoriesMemory systemsEngineeringMetadata

A method of operating a storage device including a non-volatile memory includes storing program and erase counts of the non-volatile memory as metadata in units of super blocks, wherein each of the super blocks includes a pre-defined number of blocks of the non-volatile memory, performing a read operation on a first block included in a first super block based on a first read level, storing the first read level as a history read level of the first super block in a history buffer when the read operation on the first block is successful, receiving a read request for a second block of the first super block and an address of the second block from a host, and performing a read operation on the second block based on the history read level stored in the history buffer. The pre-defined number is at least two.

Owner:SAMSUNG ELECTRONICS CO LTD

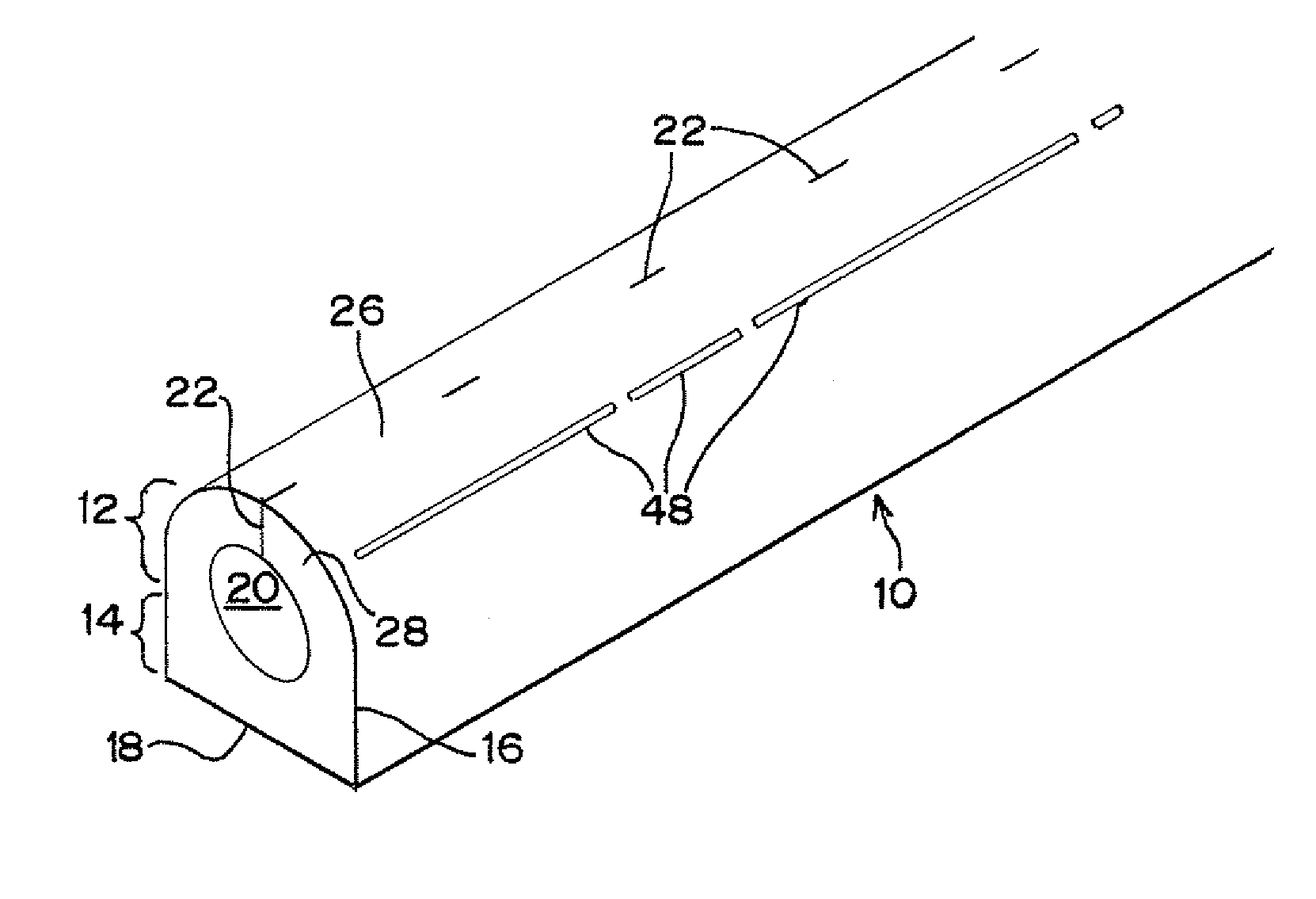

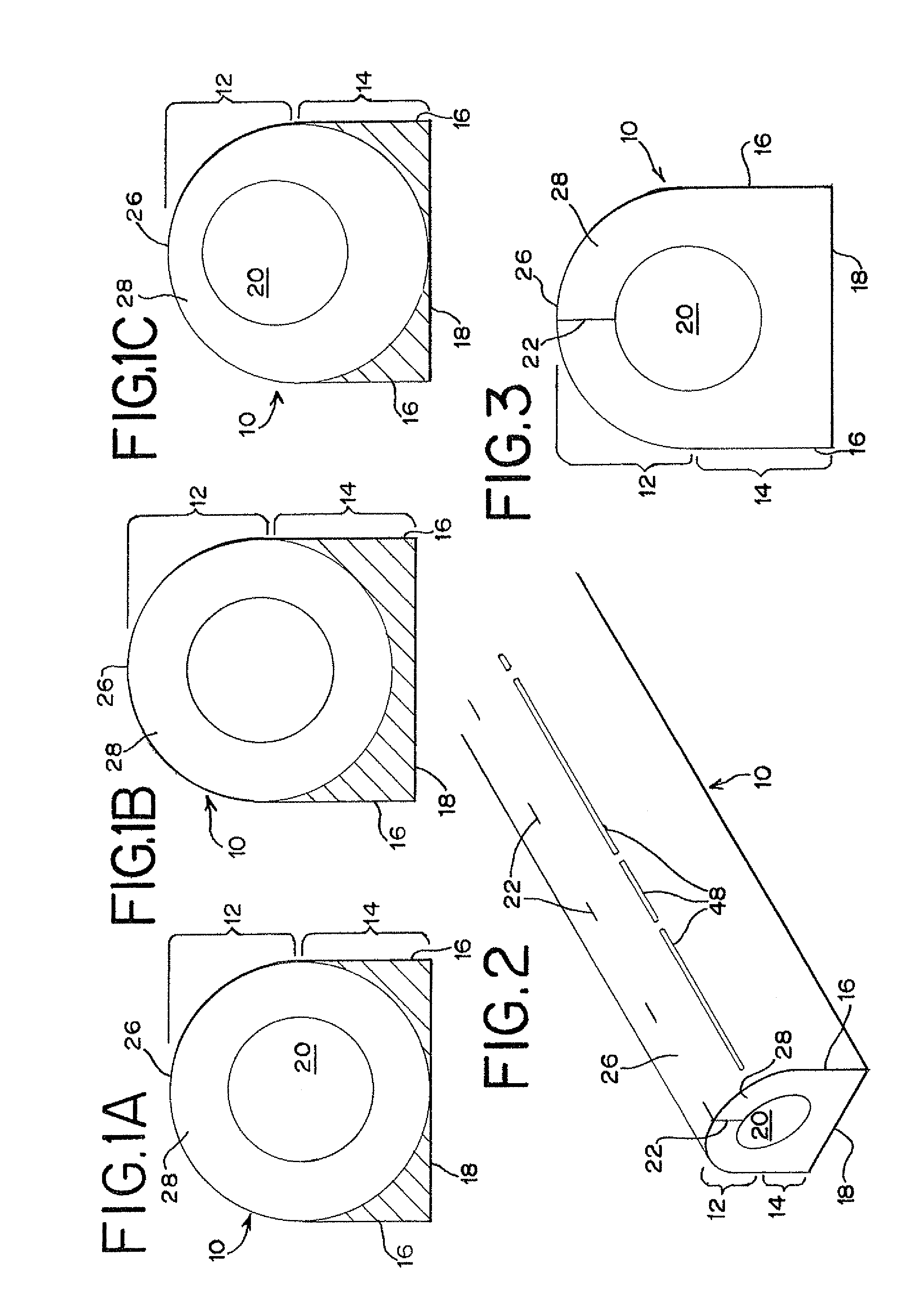

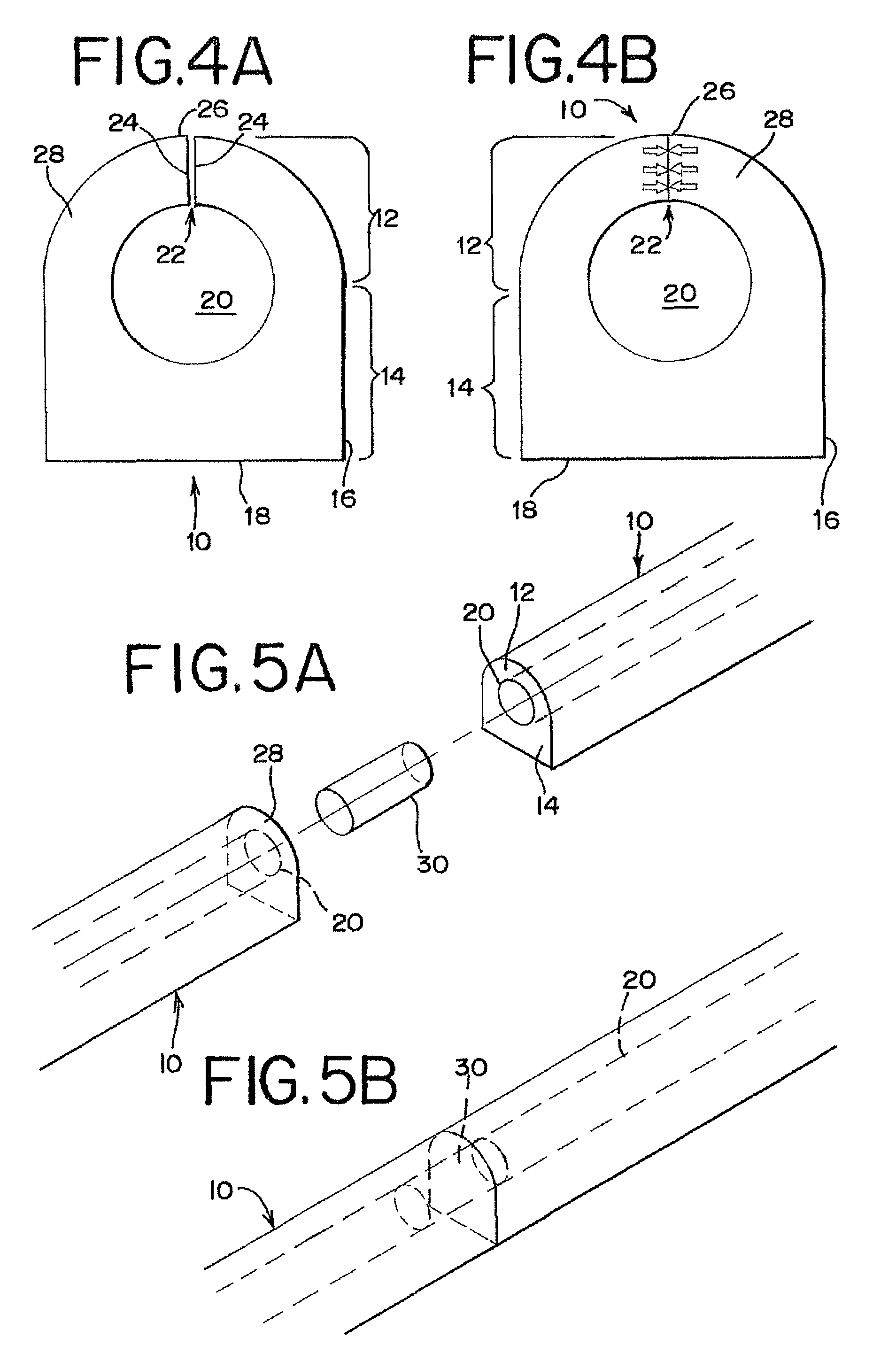

Fine bubble delivery for potable water, wastewater, and clean water treatment

ActiveUS8132794B2Overcome buoyancyDurable and resistant to deformationLighting and heating apparatusMixing methodsProduction linePotable water

Owner:AIR DIFFUSION SYST

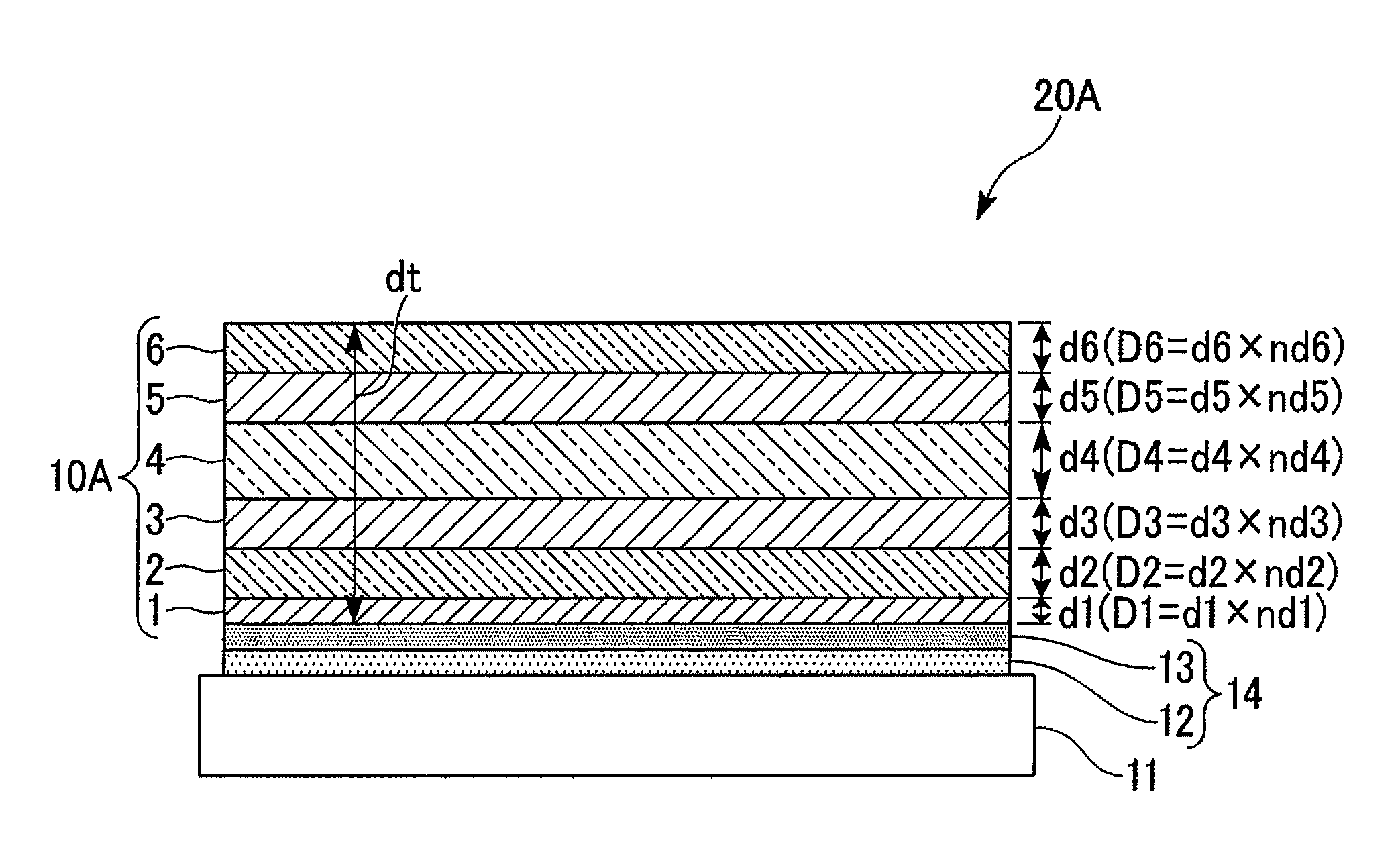

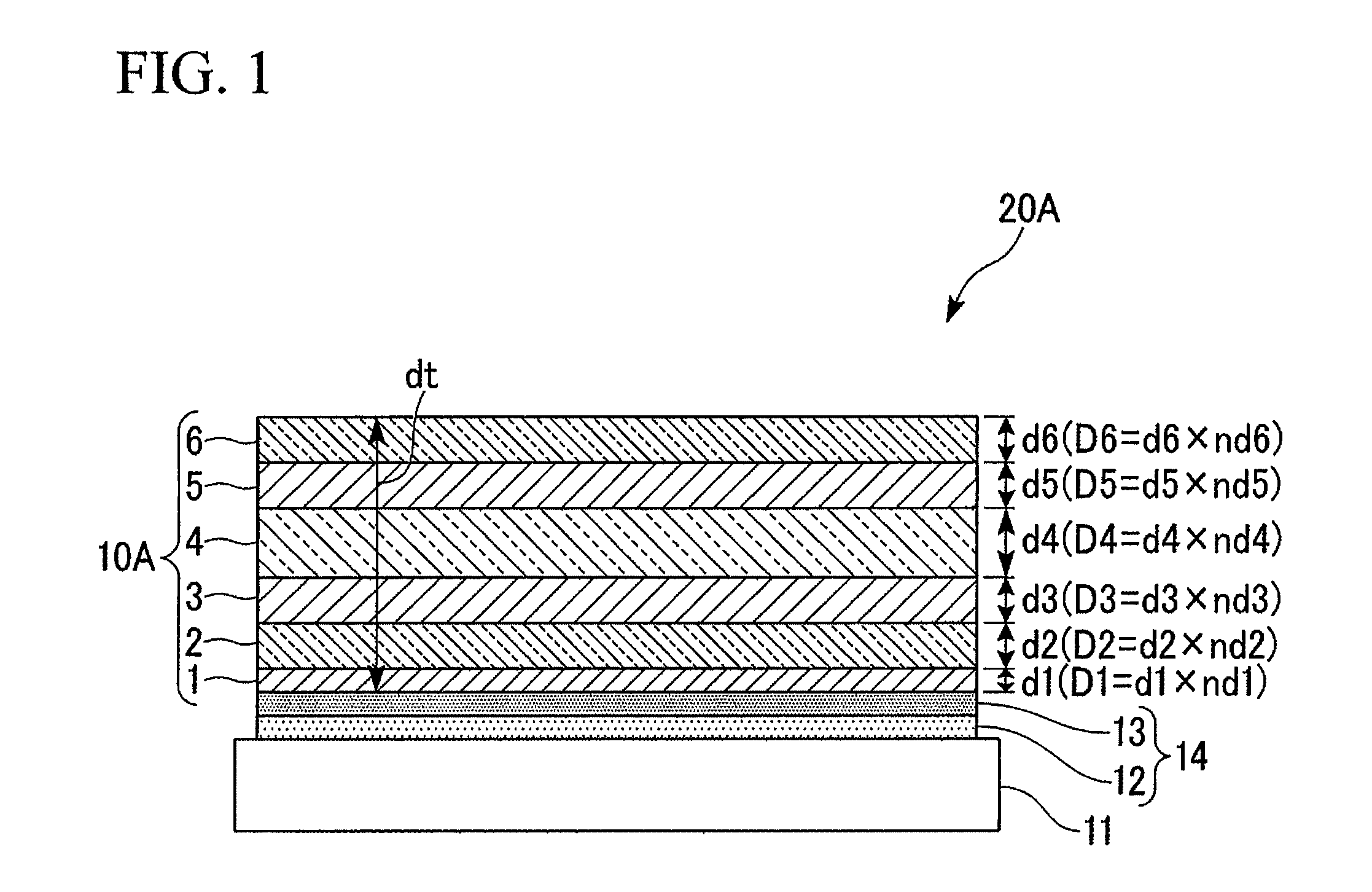

Optical component and method for manufacturing the same

ActiveUS8189261B2Performance degradation can be preventedLaminationLamination apparatusRefractive indexLength wave

An optical component includes an antireflection film that is a multilayer film having alternately-laminated six or more layers including high refractive index layers and low refractive index layers; wherein a first layer of the antireflection film deposited closest to the substrate is a high refractive index layer; λ satisfies 480 nm≦λ≦530 nm where λ is the wavelength of light incident into the antireflection film; an optical thickness D1 of the first layer satisfies 0.02λ≦D1≦0.04λ; an optical thickness Dm of a layer of the antireflection film that is located fifth from an outermost layer deposited furthest from the substrate satisfies 0.19λ≦Dm≦0.75λ; a total physical thickness dt of the entire antireflection film satisfies 350 nm≦dt≦480 nm; and a total physical thickness da of the low refractive index layers satisfies 0.65 dt≦da≦0.80 dt.

Owner:NIKON ESSILOR

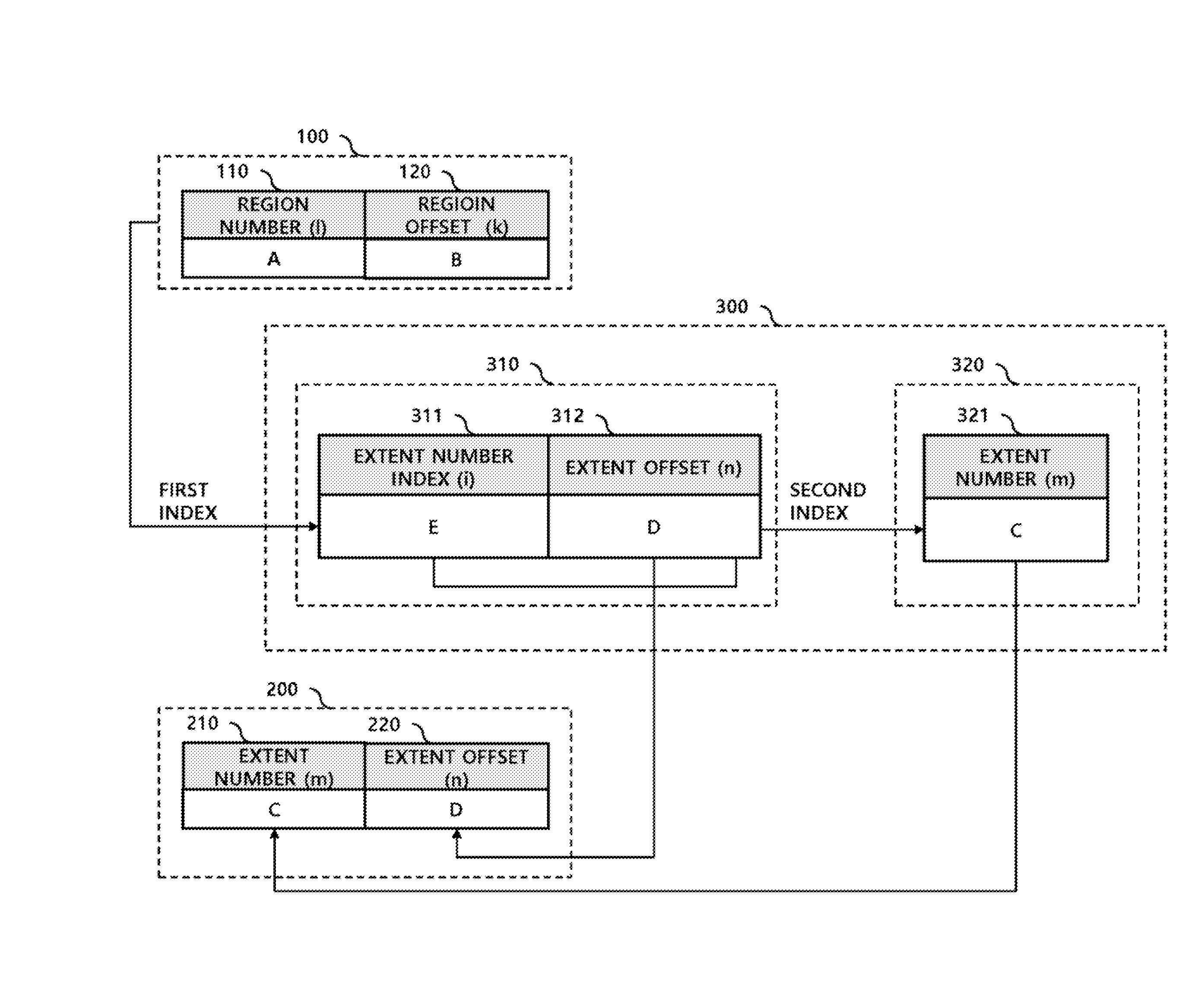

Semiconductor device and operating method thereof

ActiveUS20160259723A1Small sizeReduce erase operationsMemory architecture accessing/allocationMemory adressing/allocation/relocationComputer hardwarePower semiconductor device

A semiconductor device includes a mapping table that stores a corresponding relation between a logical address defined on a basis of regions and a physical address defined on a basis of extents, wherein one or more extents are dynamically allocated to one region.

Owner:SK HYNIX INC +1

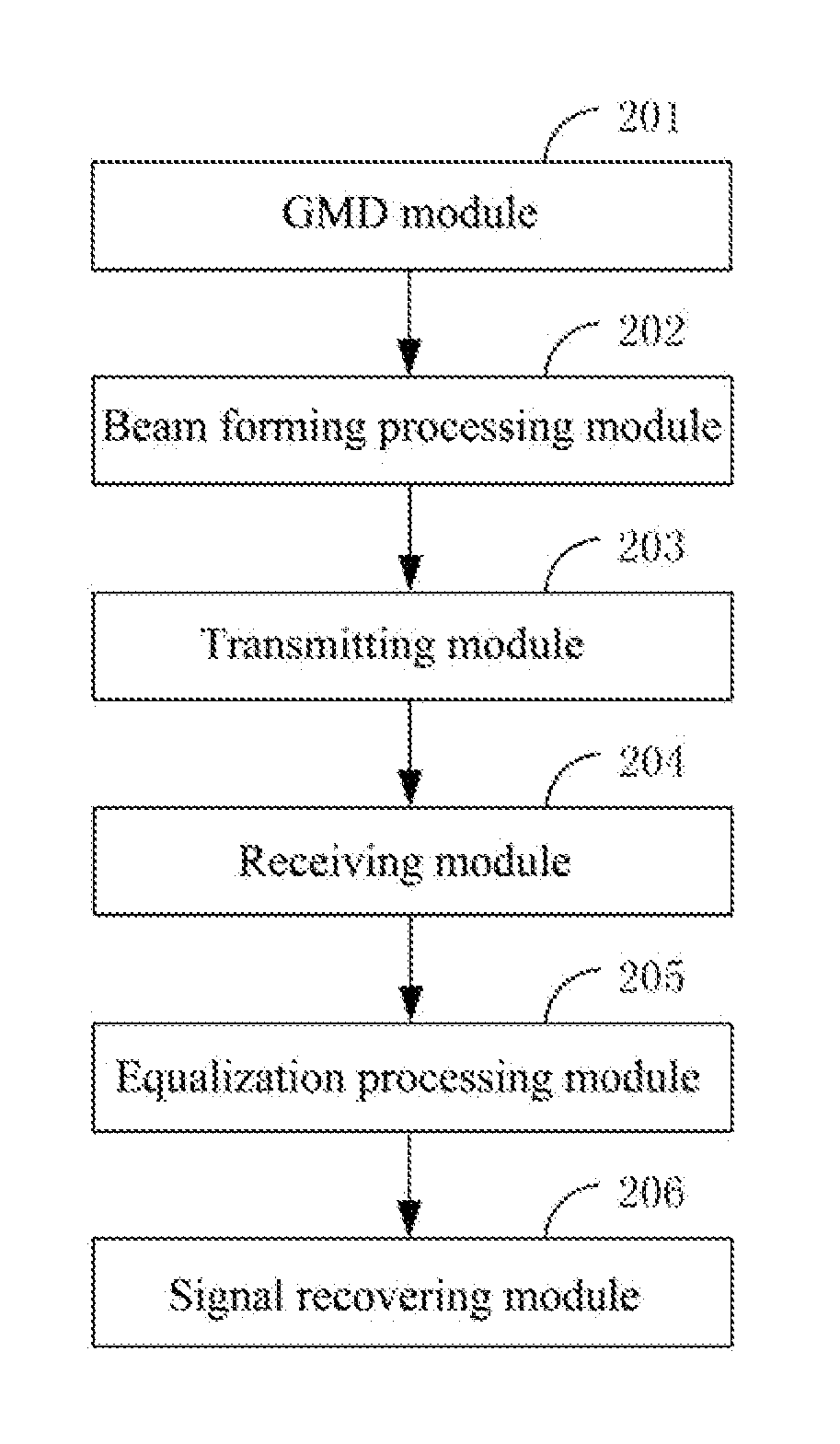

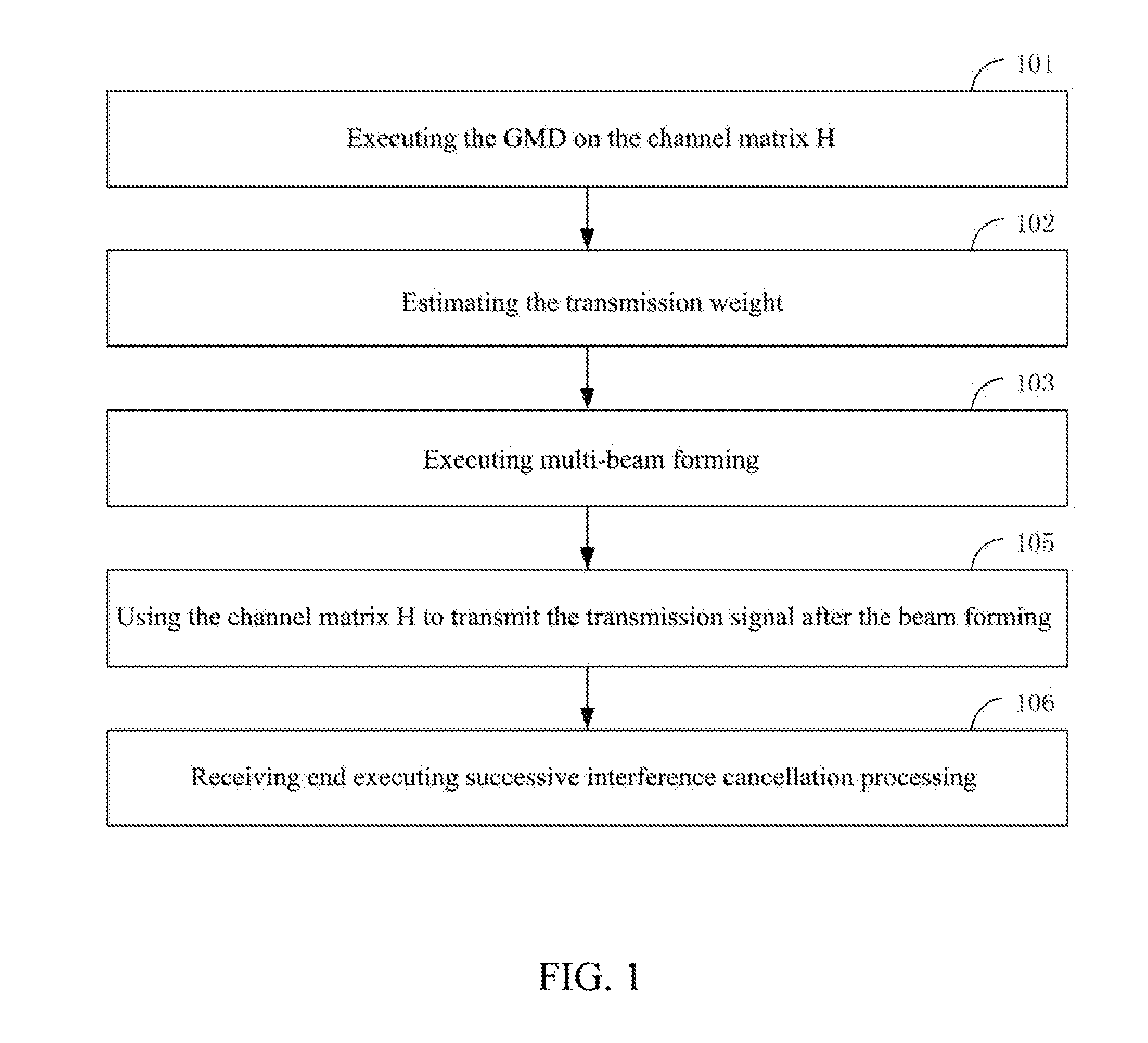

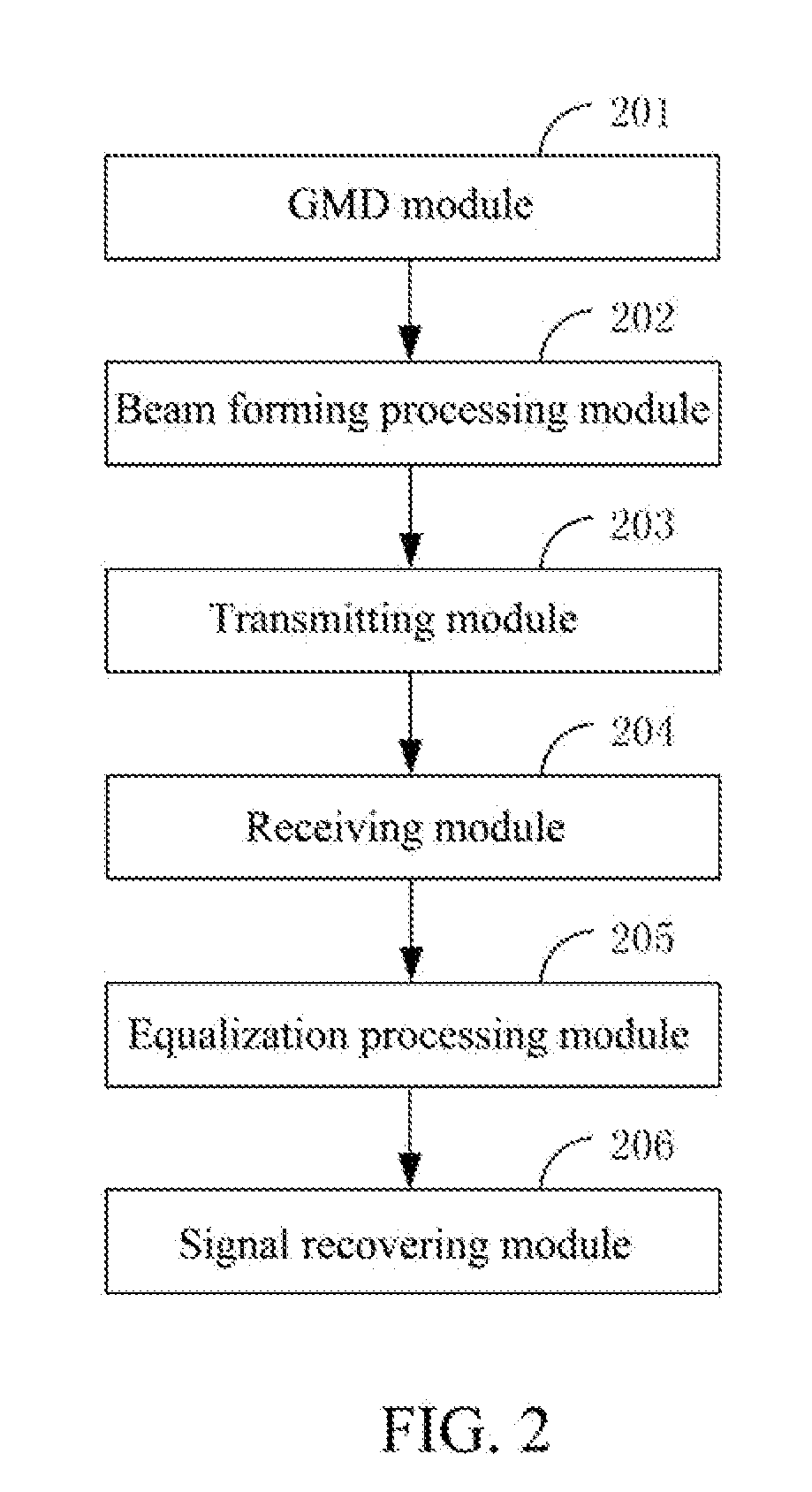

Method and System for Multi-Beam Forming Based on Joint Transceiver Information

ActiveUS20120164951A1Performance degradation can be preventedAvoid performanceSpatial transmit diversityTransmission noise suppressionInformation supportTransceiver

A method for multi-beam forming based on joint receiving and transmitting end information is provided. The method includes: a transmitting end decomposing a channel matrix H using a geometric mean decomposition (GMD) way to obtain a unitary matrix P; the transmitting end using the unitary matrix P as a weight matrix of GMD beam forming and executing multi-beam forming processing on an original transmission signal x. The present invention also provides a system for multi-beam forming based on joint receiving and transmitting end information, and a transmitting device and receiving device for supporting multi-beam forming based on joint receiving and transmitting end information. By using geometric mean decomposition way to decompose the channel matrix H, the sub channels corresponding to various beams obtain the equal gain. When the channel is ill-conditioned, the channel equalization will not interfere with searching the perturbation vector, thereby avoiding the performance degradation.

Owner:ZTE CORP

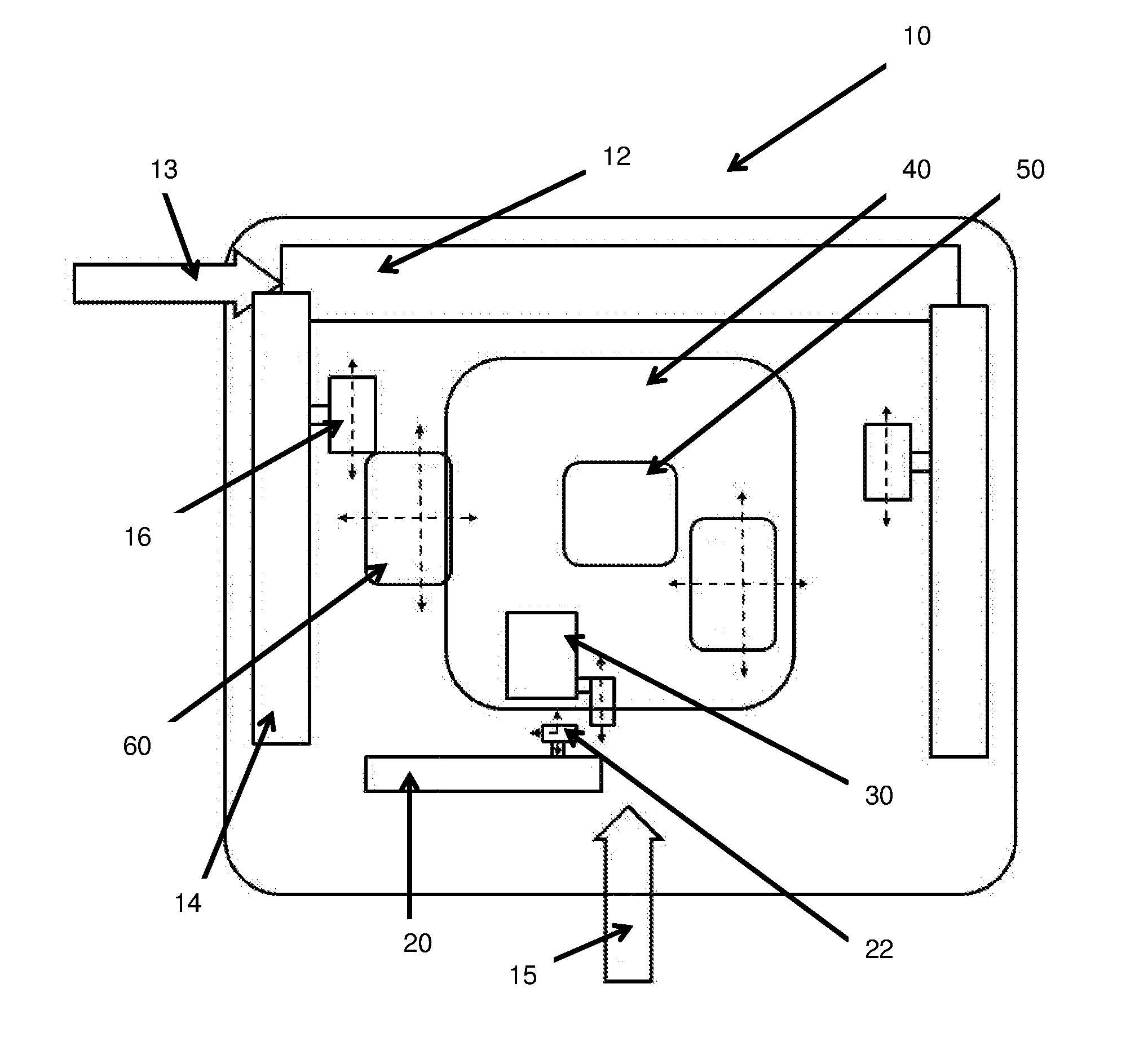

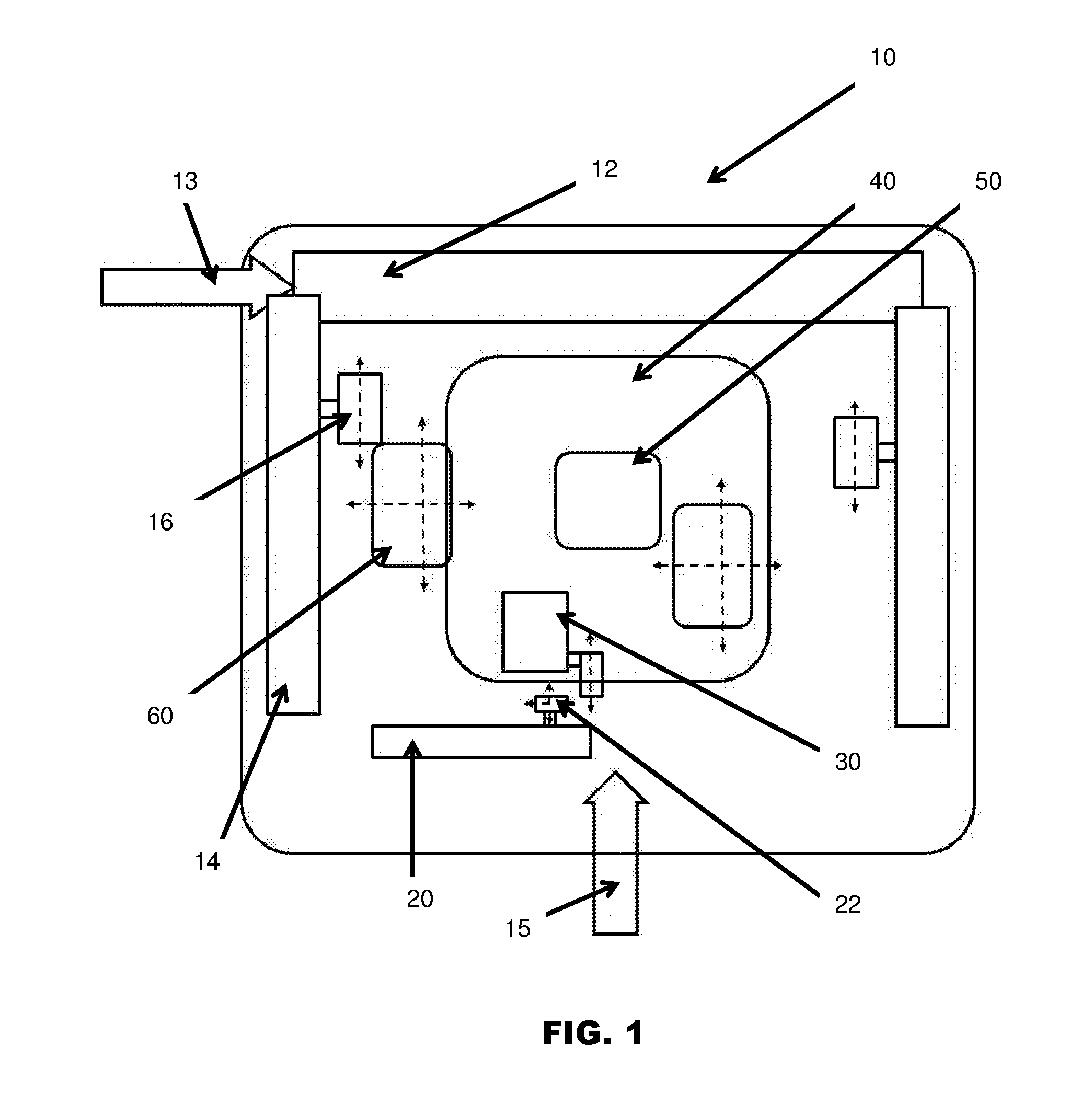

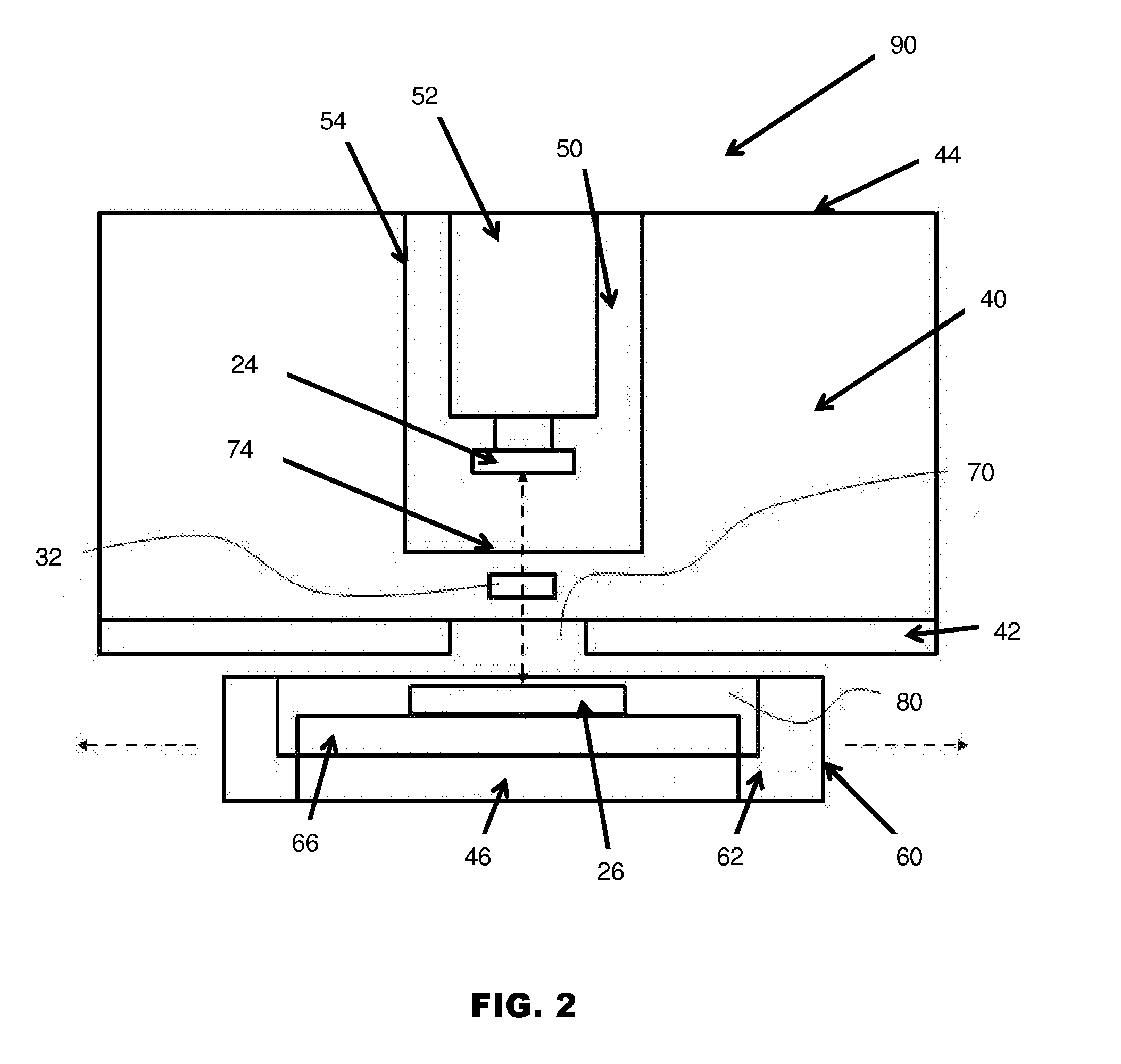

Die bonding apparatus comprising an inert gas environment

ActiveUS20160351527A1Reduce the amount requiredPerformance degradation can be preventedSemiconductor/solid-state device detailsSolid-state devicesDie bondingGas concentration

A die bonding apparatus comprising a first inert gas container having a first inert gas concentration, and a second inert gas container having a second inert gas concentration enclosed within the first inert gas container. The second inert gas concentration is higher than the first inert gas concentration. The die bonding apparatus further comprises a bond head located in the second inert gas container for receiving a die for bonding, and a third inert gas container having an inert gas environment that is separate from the first and second inert gas containers and where a substrate is locatable for die bonding. The bond head is operative to move the die between a first position within the second inert container and a second position within the third inert gas container to bond the die onto the substrate located in the third inert gas container.

Owner:ASMPT SINGAPORE PTE LTD

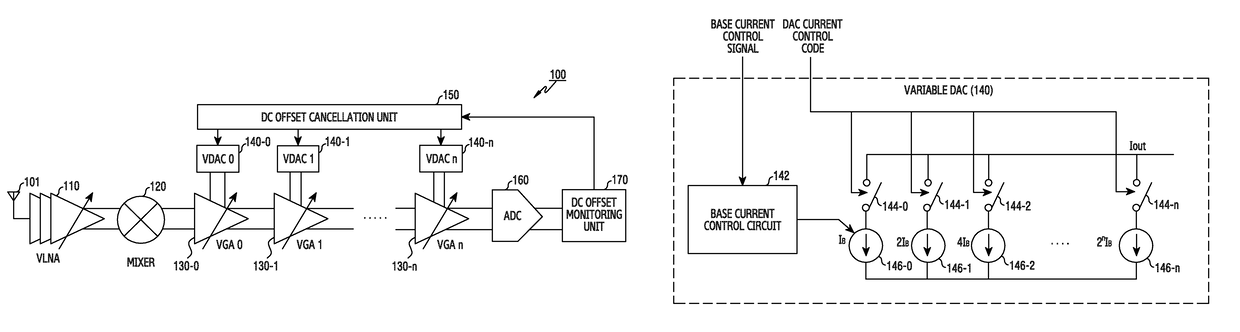

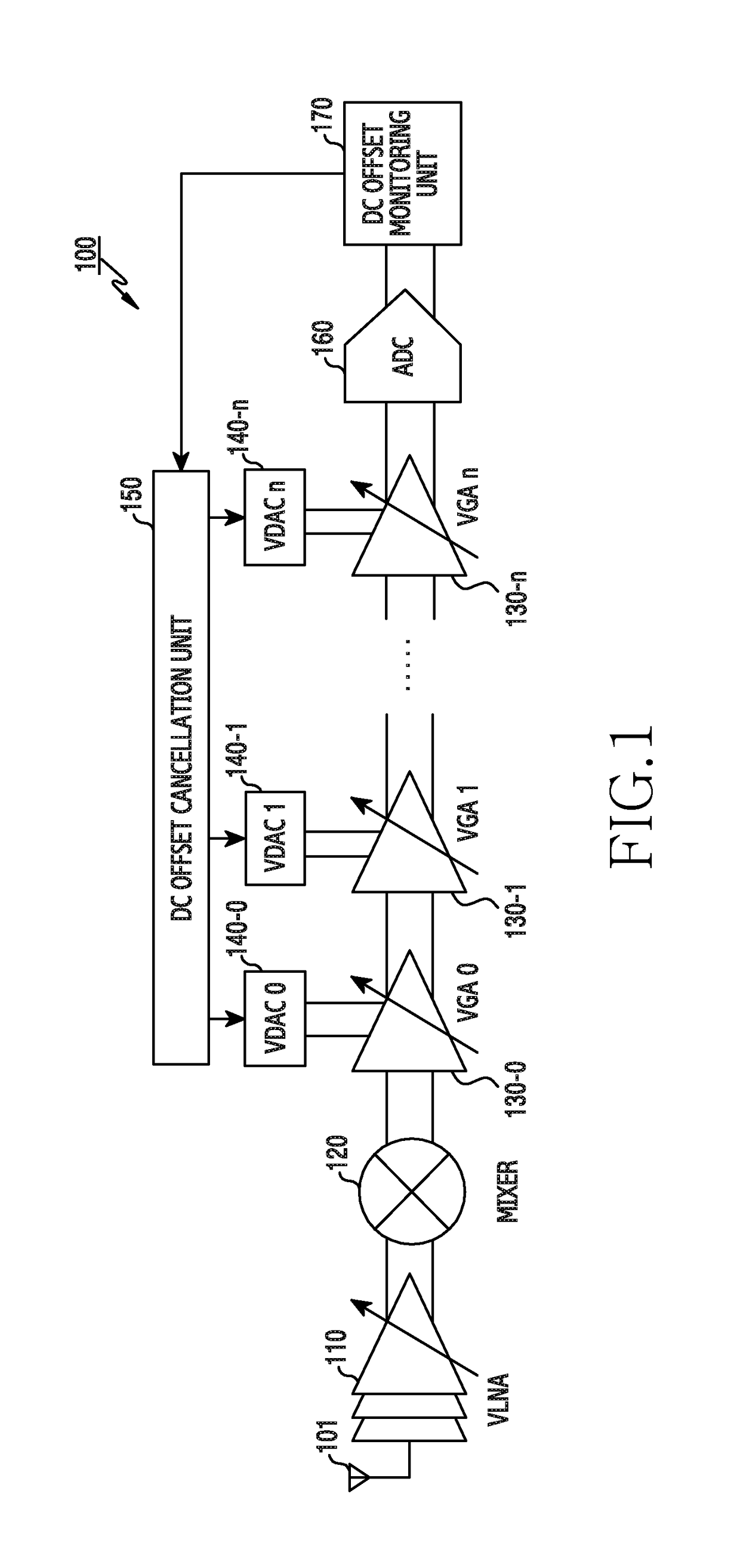

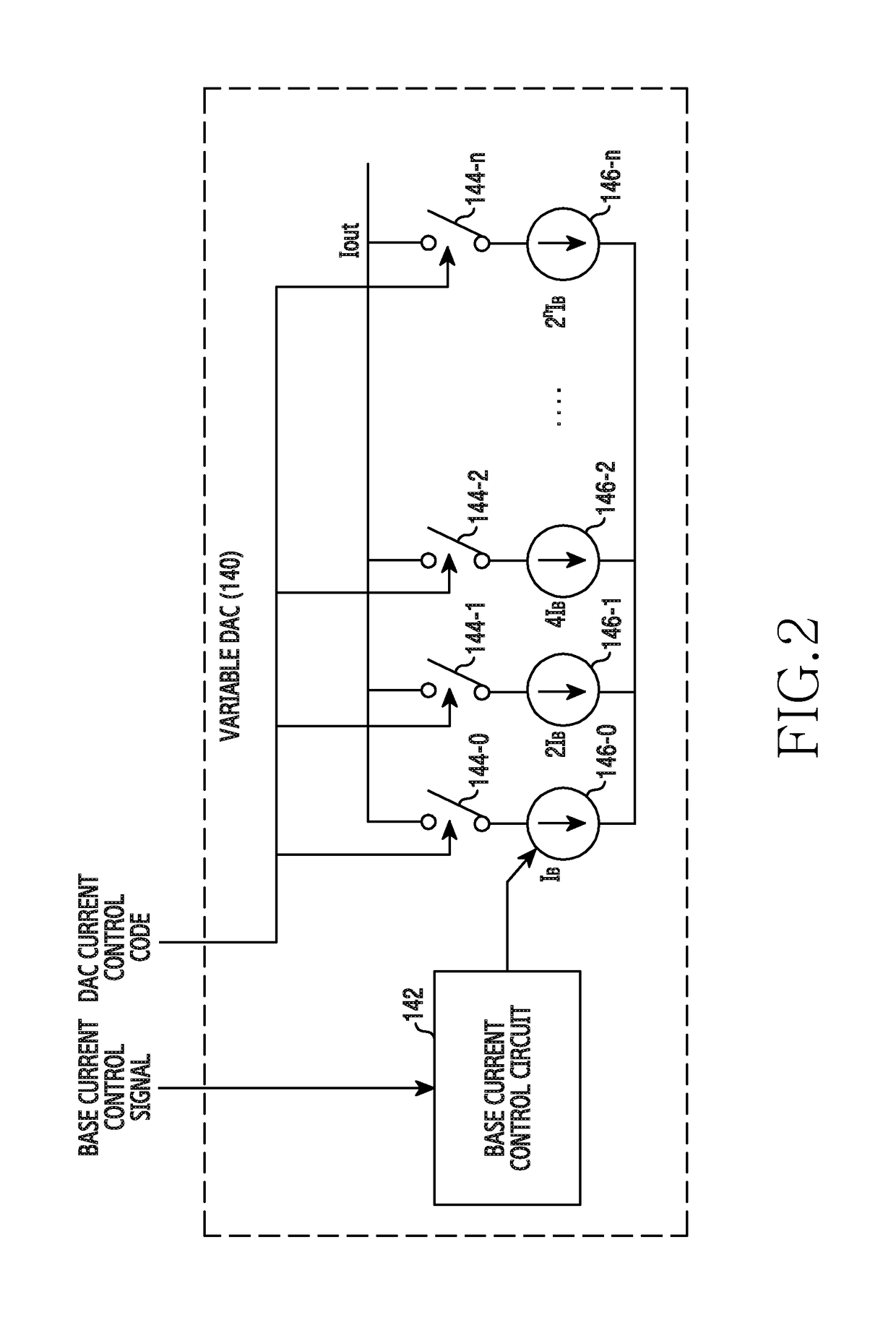

Method and apparatus for direct conversion receiver correcting direct current offset

ActiveUS9948484B2Performance degradation can be preventedMinimise currentDc level restoring means or bias distort correctionLine balance variation compensationAudio power amplifierVariable-gain amplifier

The present invention relates to a method and an apparatus for direct current offset calibration of a direct conversion receiver, a Direct Current (DC) offset calibration apparatus of a direct conversion receiver includes a plurality of variable gain amplifiers for amplifying an input signal based on a gain control value, a DC offset monitoring unit for monitoring a DC offset for an output signal of the plurality of variable gain amplifiers, a plurality of variable Digital to Analog Converters (DACs) for controlling a current applied to each of the plurality of variable gain amplifiers according to a current control code, and a DC offset cancellation unit for determining a current control code set which minimizes the DC offset value per preset gain control value, and thus the DC offset can be precisely cancelled without being affected by external factors such as a signal modulation method and heat and performance degradation of the receiver can be prevented.

Owner:SAMSUNG ELECTRONICS CO LTD

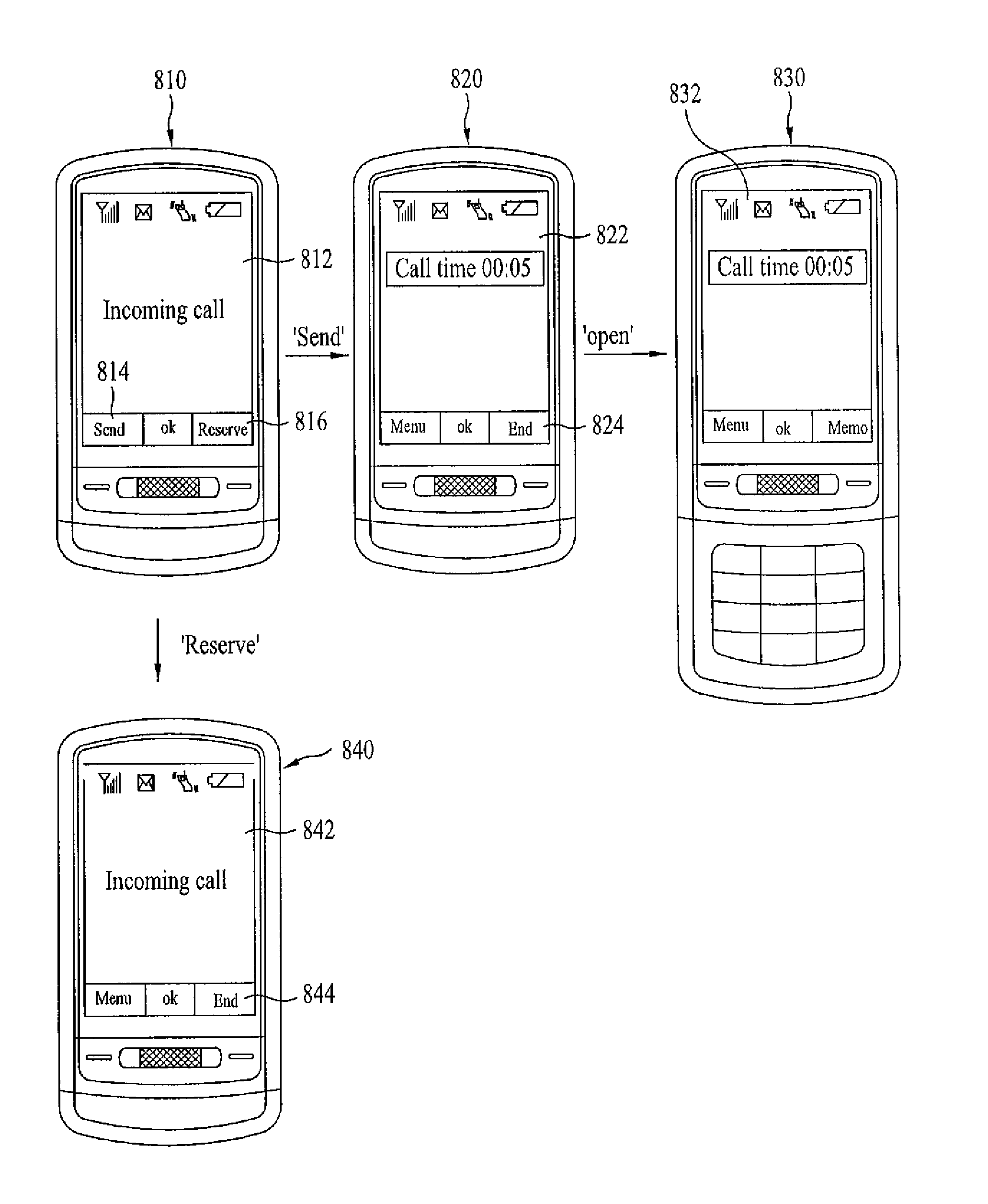

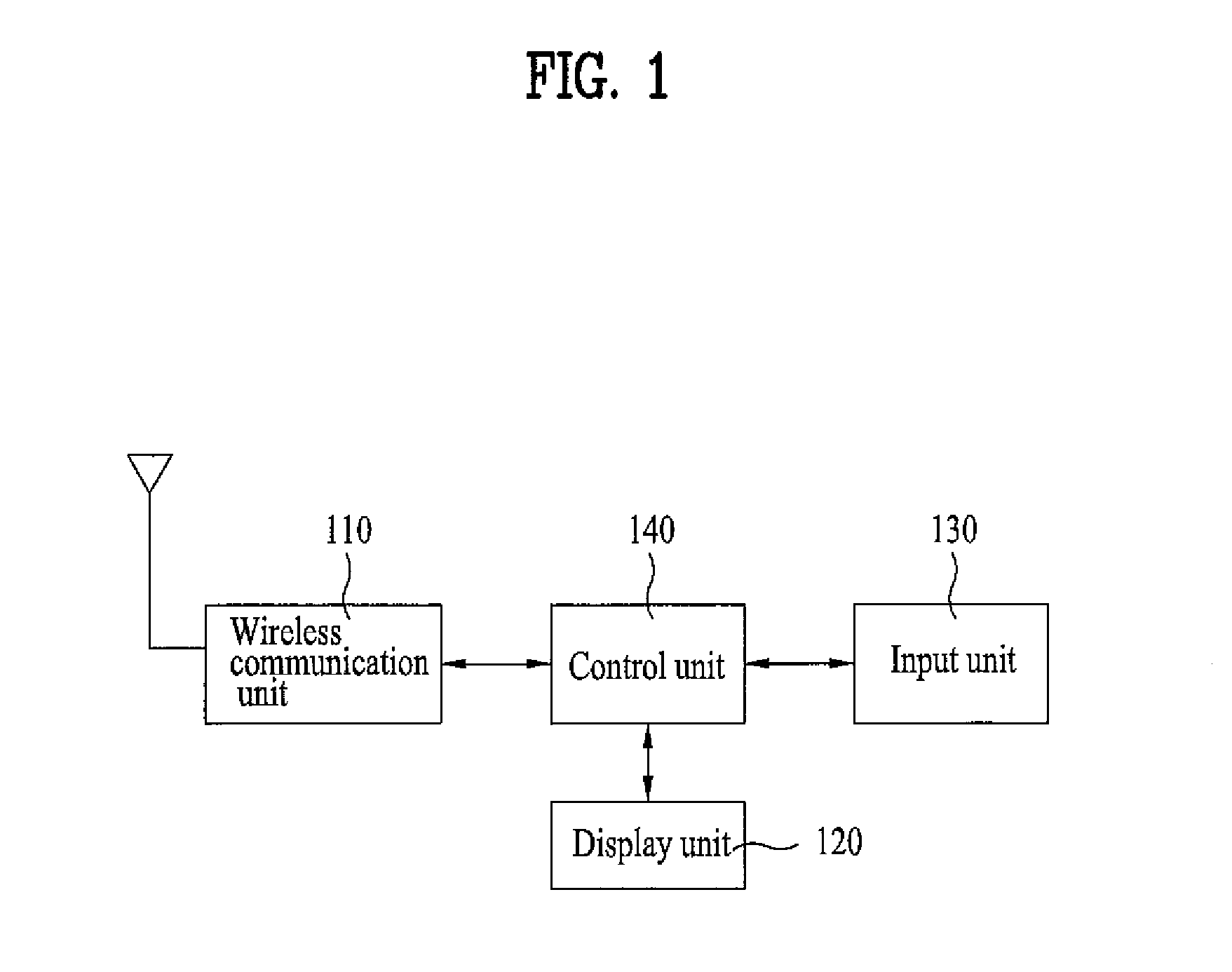

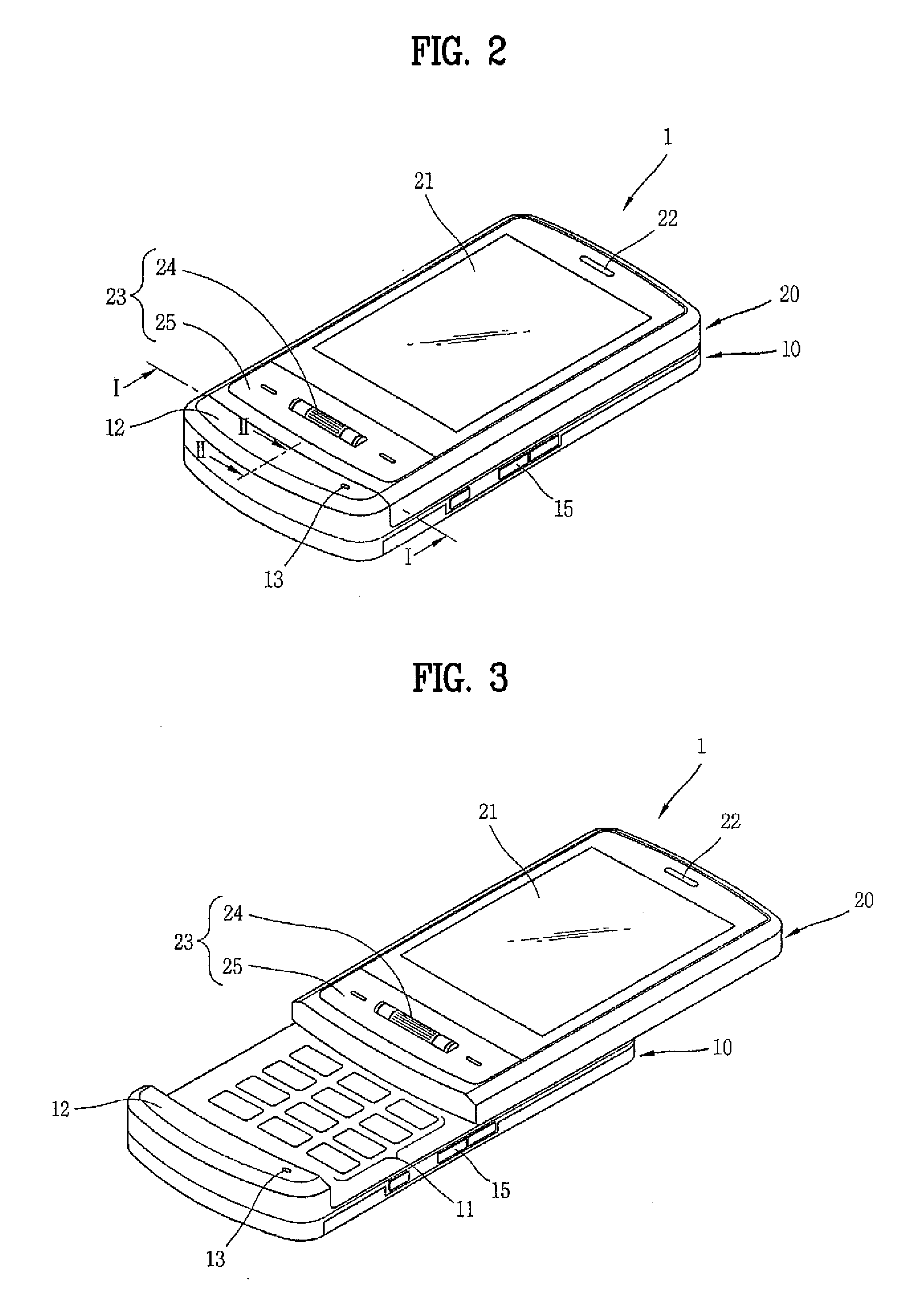

Mobile communication terminal and method of connecting call thereof

ActiveUS8032186B2Performance degradation can be preventedEfficient arrangementCommunication jammingTransmissionTelecommunicationsCommunication unit

A mobile communication terminal and method of connecting a call thereof are discussed. The mobile communication terminal according to an embodiment includes a wireless communication unit configured to receive a call, a display unit configured to display that the call is received and to output an image for selecting either a first item or a second item, if the call is received by the wireless communication unit, an input unit having a key for selecting either the first or second item, and a control unit configured to connect the received call if the first item is selected and to control the display unit to output an image for displaying that the call is received if the second is selected, when the upper body is closed against the lower body. Accordingly, a call is connected or a message is transceived even if the terminal is in the closed status.

Owner:LG ELECTRONICS INC

Fine Bubble Delivery For Potable Water, Wastewater, And Clean Water Treatment

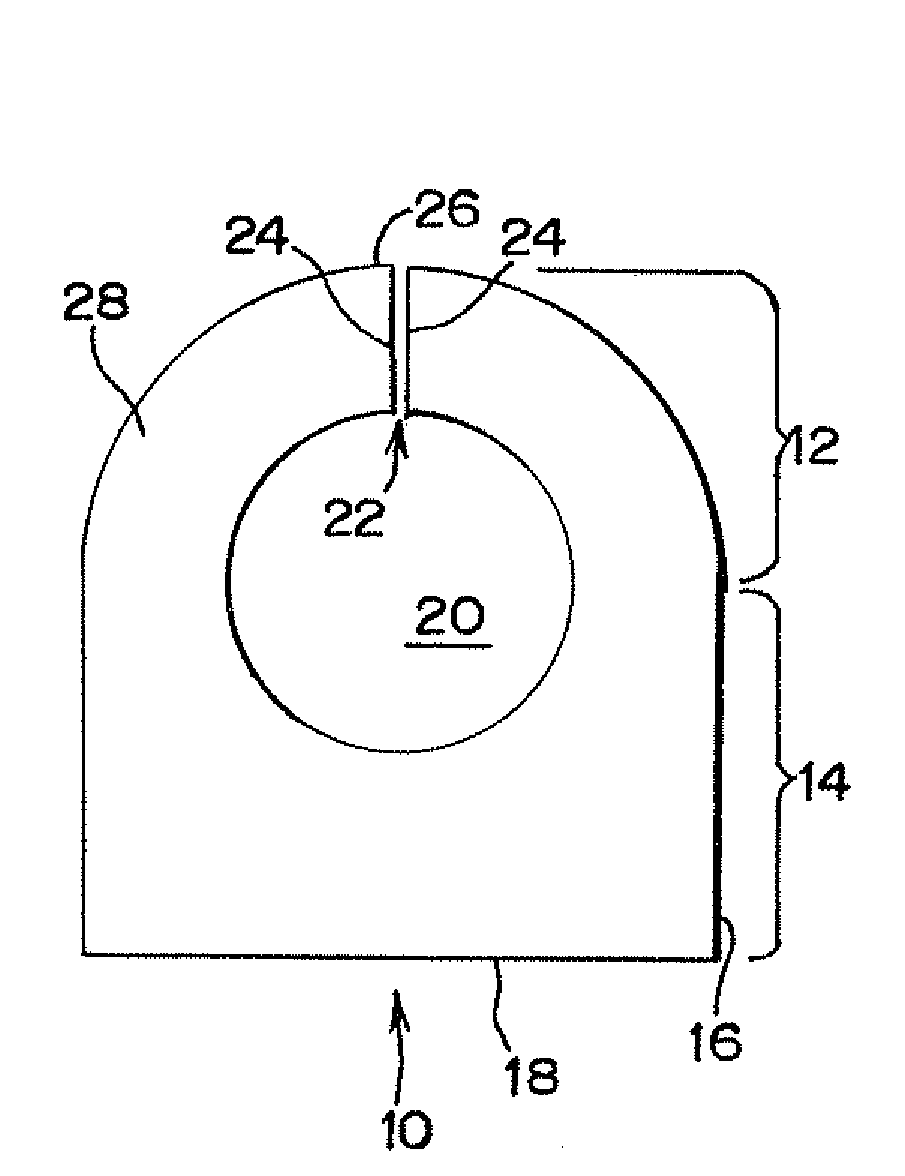

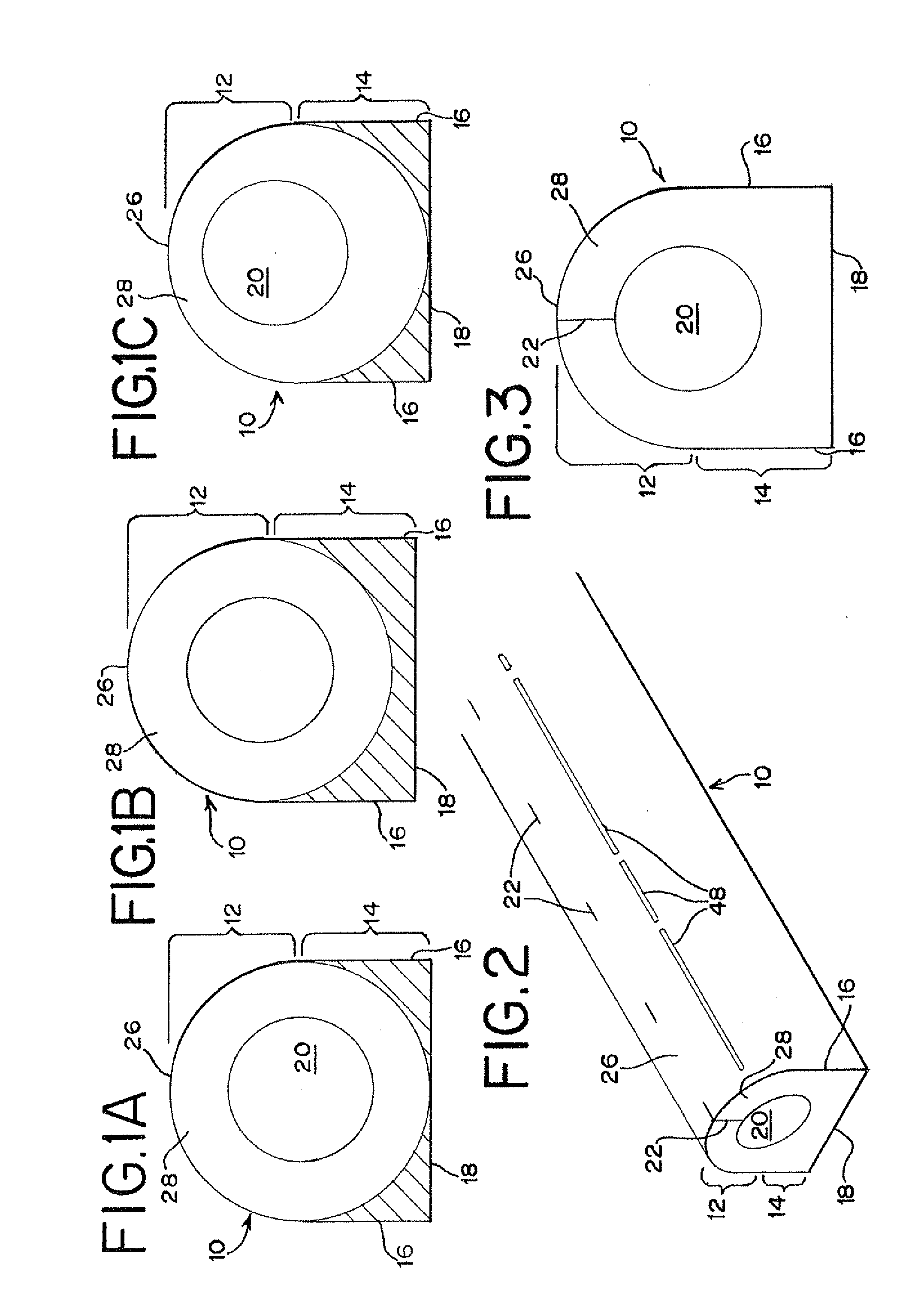

ActiveUS20080296789A1Avoid deformationAvoid degradationLighting and heating apparatusUsing liquid separation agentPotable waterWastewater

A flexible tubing for fine bubble aeration is provided with an air passageway defined in part by an upper portion and a lower portion. The tubing can be made of a uniform weighted material with more material in the lower portion than in the upper portion. This makes the tubing self-orienting, in that it will tend to orient itself with micro-slits along the upper portion facing upward and the lower portion facing downward when submerged in a body of water. An automated, one-stage production line converts raw tubing material to a finished tubing product without the need for separate processing. A method of coiling the tubing places the micro-slits approximately 90° away from the surface of a spool hub, thereby avoiding a longitudinal arch in the tubing and ultimately preventing roll-over and improper slit orientation after installation in a water body.

Owner:AIR DIFFUSION SYST

Ultra-thin logic and backgated ultra-thin SRAM

InactiveUS7494850B2Performance degradation can be preventedSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceEngineering

Disclosed are embodiments of a structure that comprises a first device, having multiple FETs, and a second device, having at least one FET. Sections of a first portion of a semiconductor layer below the first device are doped and contacted to form back gates. A second portion of the semiconductor layer below the second device remains un-doped and un-contacted and, thus, functions as an insulator. Despite the performance degradation of the first device due to back gate capacitance, the back gates result in a net gain for devices such as, SRAM cells, which require precise Vt control. Contrarily, despite marginal Vt control in the second device due to the absence of back gates, the lack of capacitance loading and the added insulation result in a net gain for high performance devices such as, logic circuits.

Owner:IBM CORP

Antenna, circular polarized patch antenna, and vehicle having the same

ActiveUS9941577B2Reduce size (volume)Low costAntenna adaptation in movable bodiesRadiating elements structural formsCouplingEngineering

An antenna, a circular polarized patch antenna, and a vehicle having the same are provided. The antenna includes a substrate, a ground portion formed on a first surface of the substrate, and a second radiator having a plurality of patches and formed on a second surface of the substrate. In addition, a first radiator is formed in a periphery of the second radiator with a gap from the second radiator and a feeding probe is disposed on the first radiator to enable power to be fed directly fed to the first radiator and to enable power to be fed to the second radiator through coupling.

Owner:HYUNDAI MOTOR CO LTD

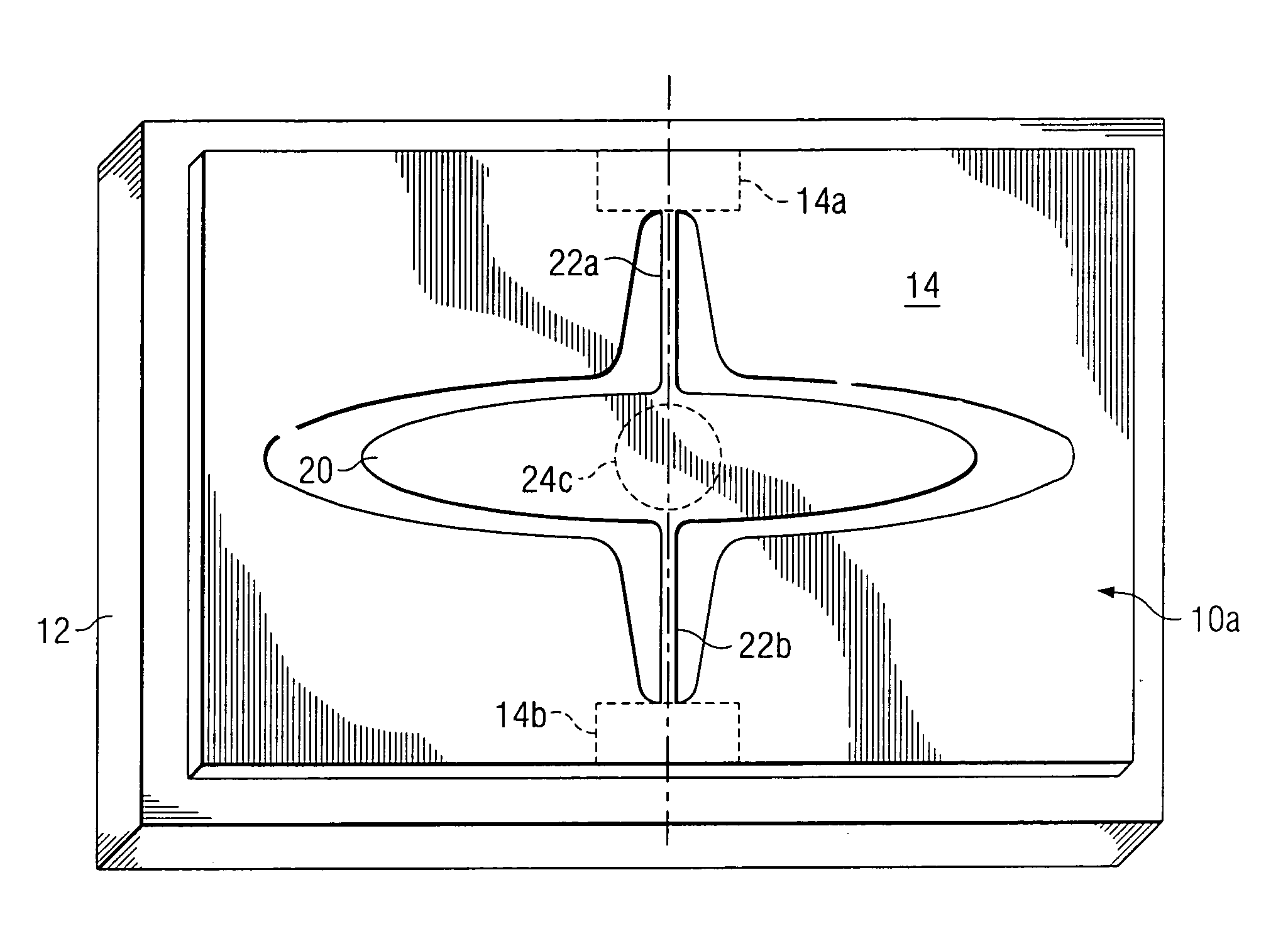

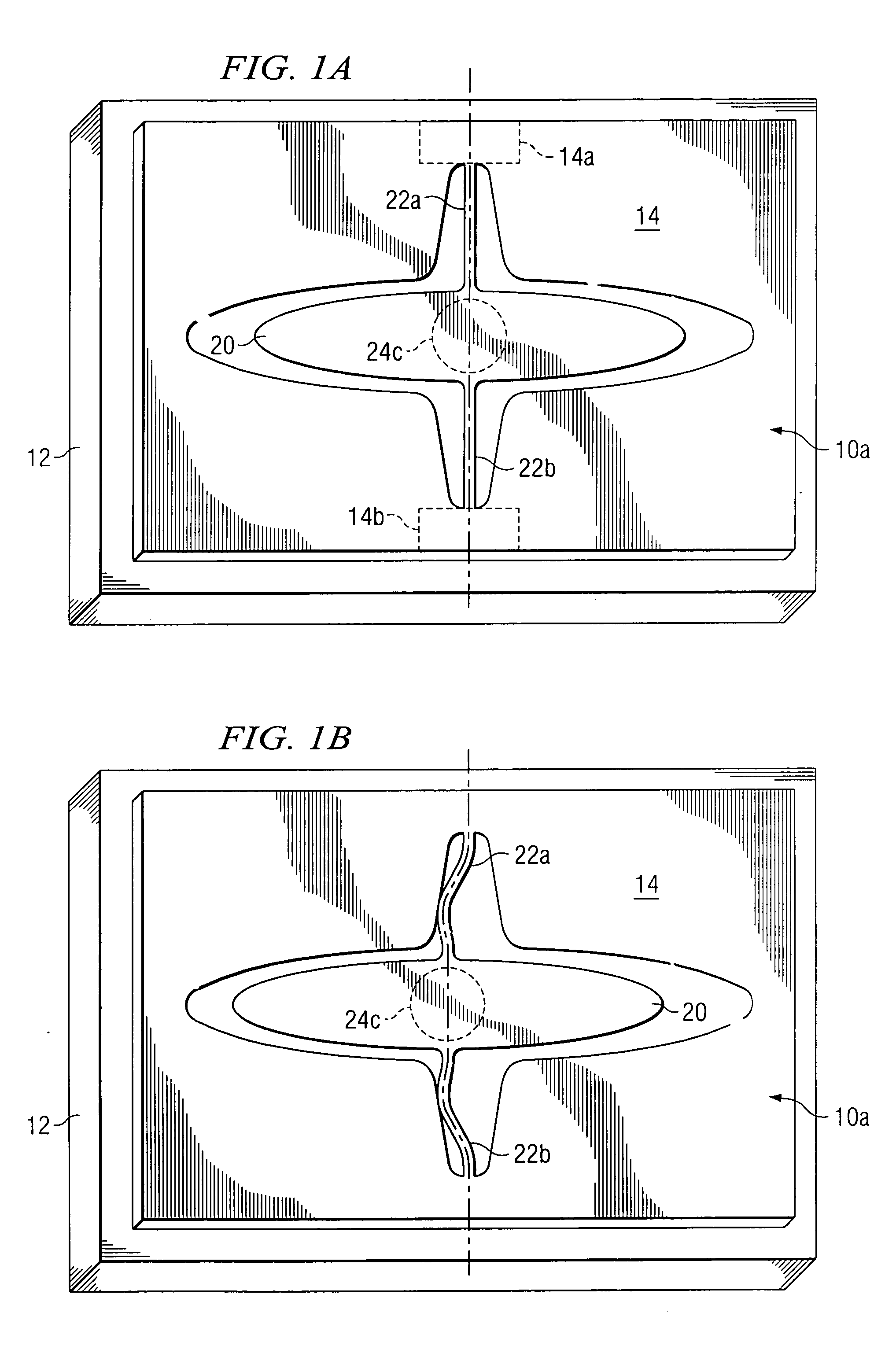

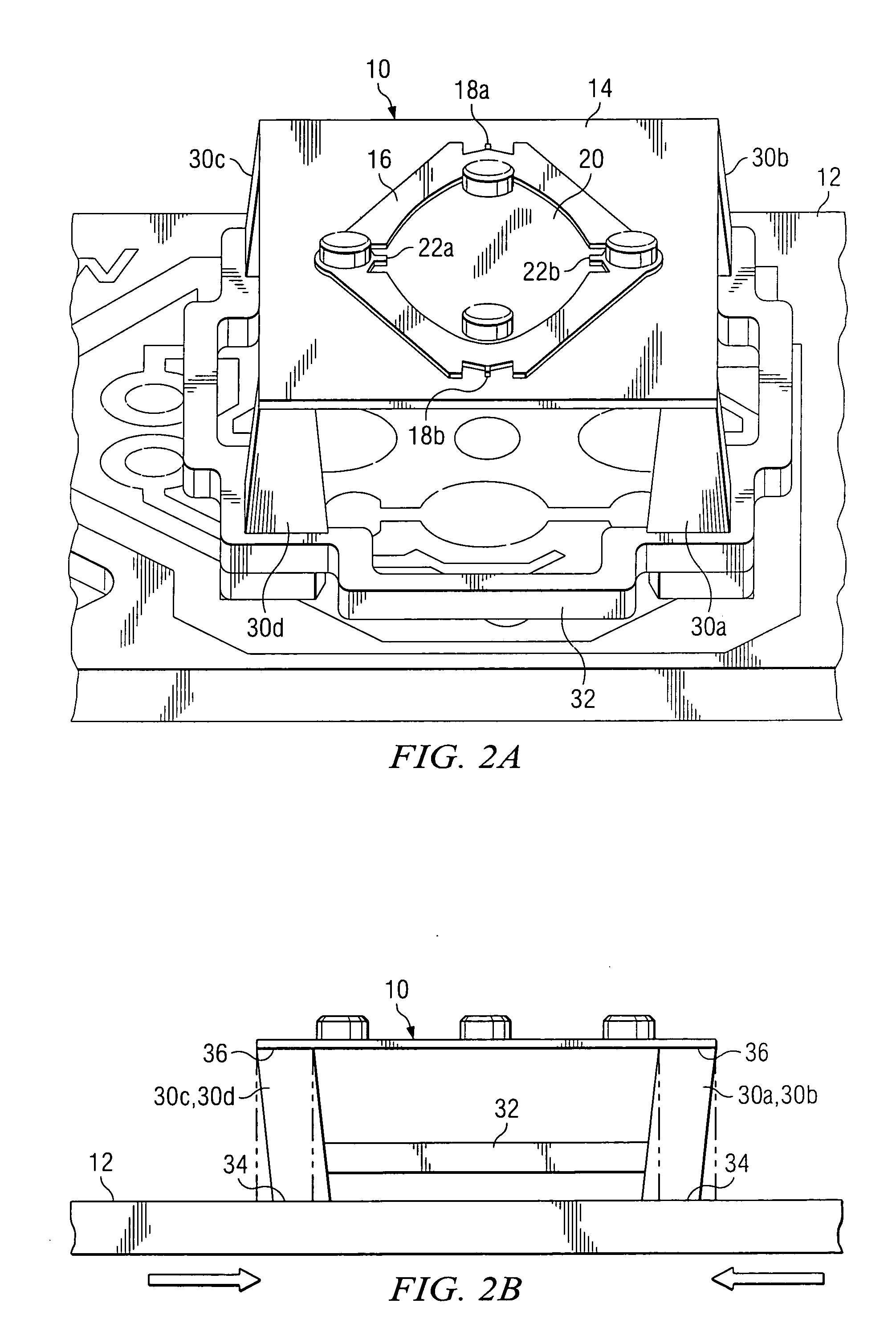

Structure and method for reducing thermal stresses on a torsional hinged device

ActiveUS20060132898A1Excessive compressive stress can be avoidedExcessive compressive stressNon-linear opticsFlexible microstructural devicesThermal coefficientEngineering

Method and structure for mounting a torsional hinged device, such as a mirror, having a first TCE (thermal coefficient of expansion) on a substrate having a second TCE different than said first TCE. The structure comprising a plurality of compliant support posts between the substrate and the torsional hinged device that deform when the contraction and / or expansion of the torsional hinged device is different than the corresponding contraction and expansion of the substrate.

Owner:TEXAS INSTR INC

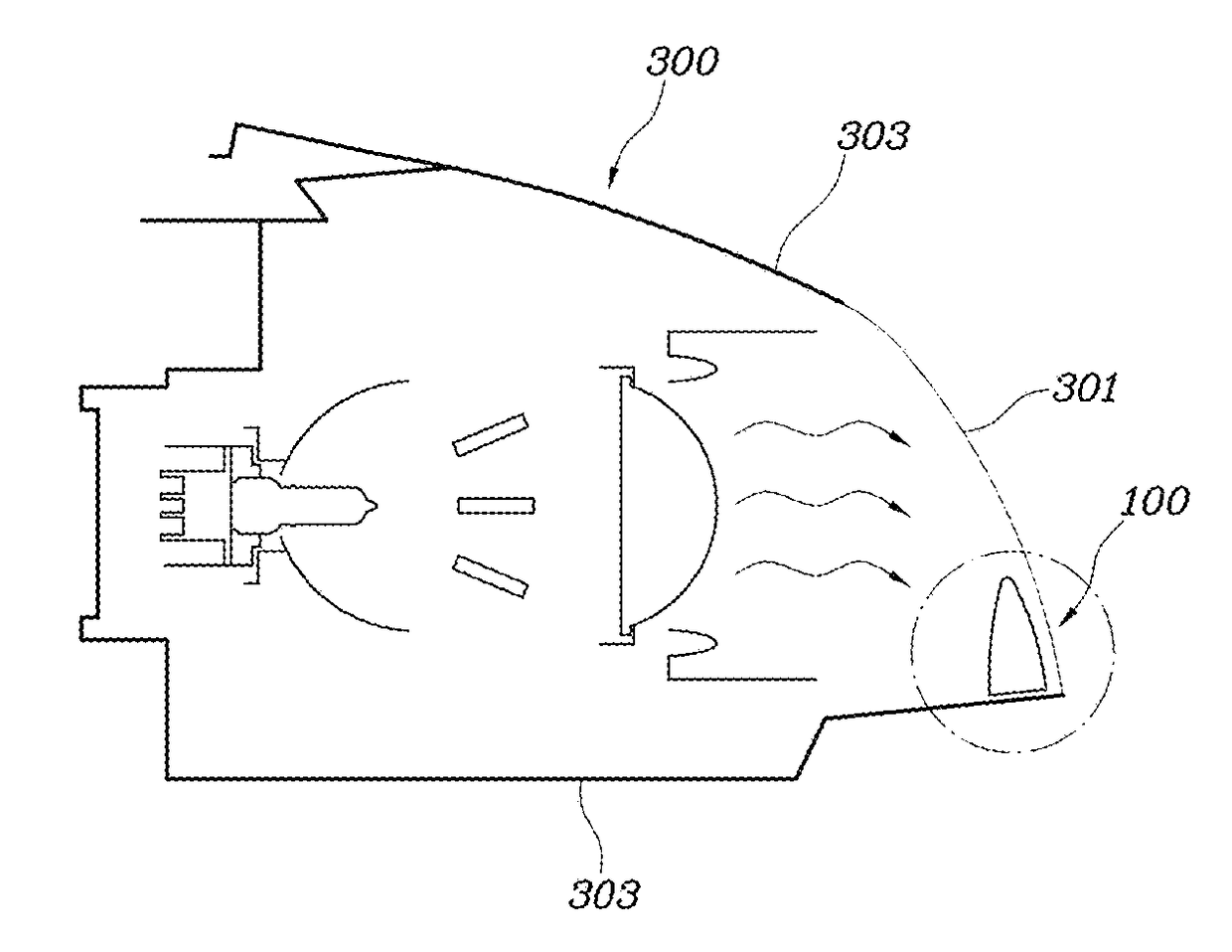

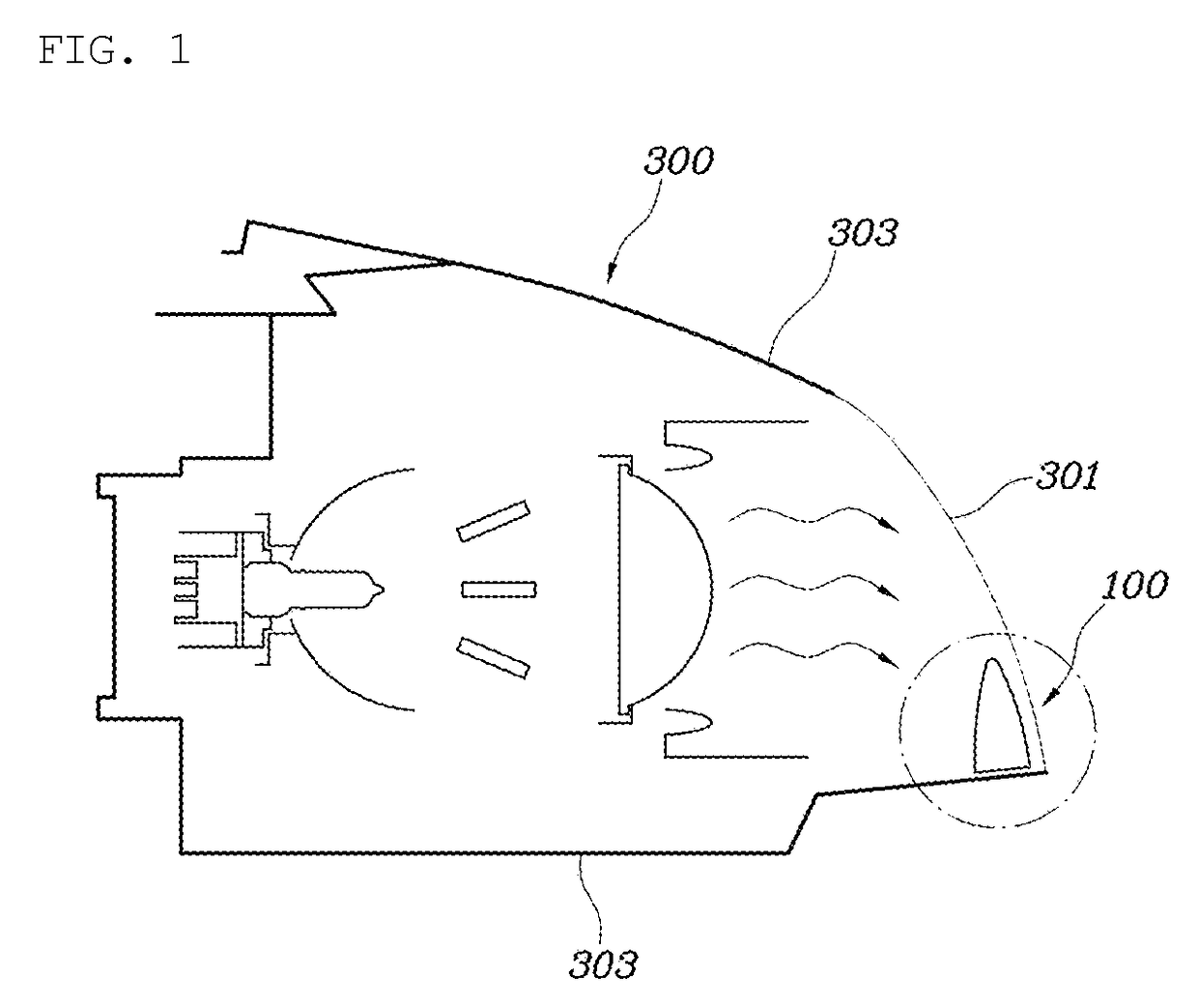

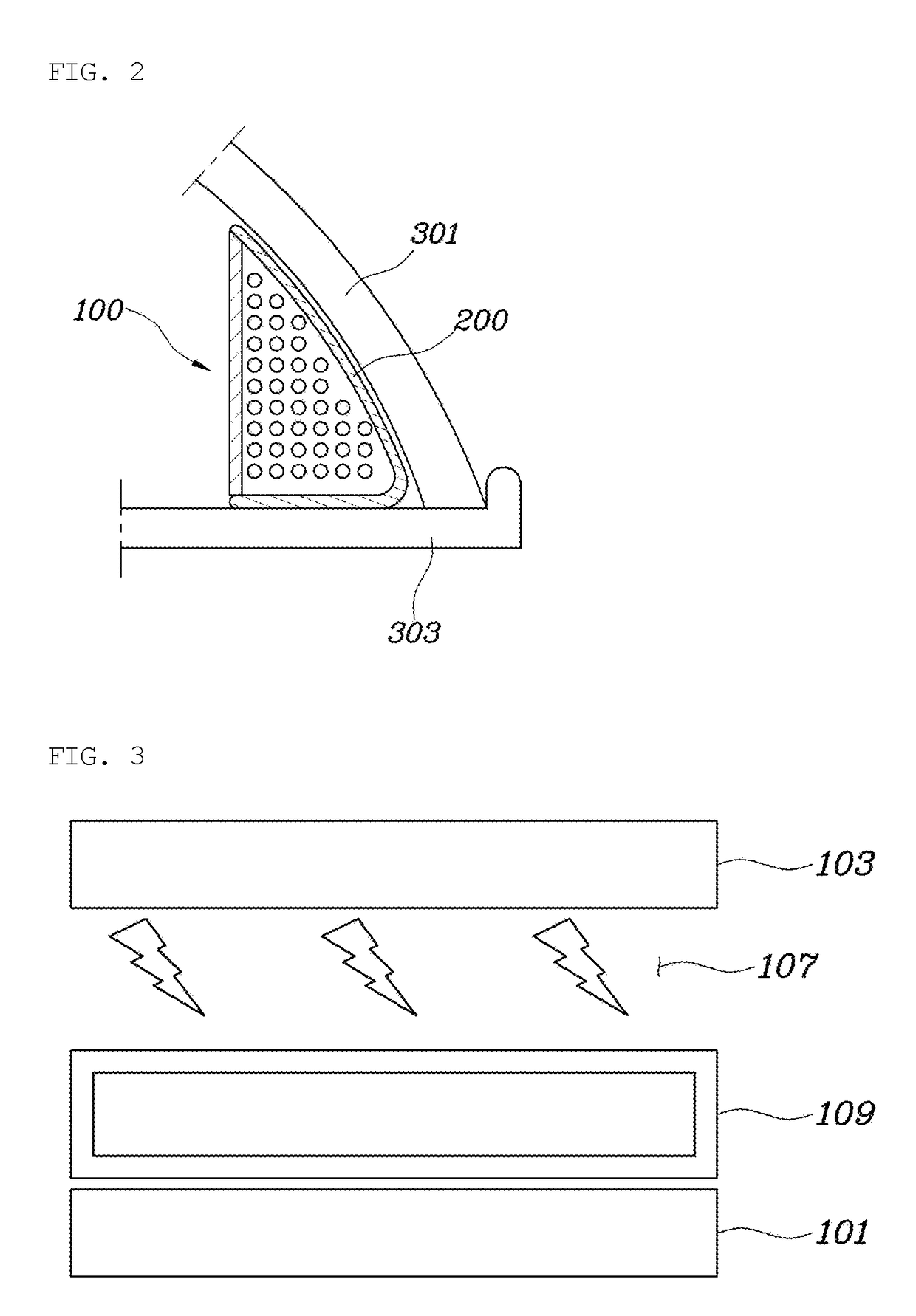

Moisture removing apparatus for headlight

ActiveUS20180128445A1Avoid performance degradationPerformance degradation can be preventedCellsGas-tight/water-tight arrangementsElectric dischargeMoisture

Disclosed is a moisture-removing apparatus for a headlight, the apparatus comprising: a moisture decomposition module having a first electrode that is exposed inside a headlight housing and is connected to a first electrode of a power source; a second electrode that is connected to a second electrode of the power source; and an electric discharge air path in the space between the surface of the first electrode and the surface of the second electrode; and a moisture-absorbing layer; wherein the first electrode of the moisture decomposition module is coated with a dielectric material on a surface thereof; and wherein the moisture-absorbing layer is configured to correspond to a shape of one of the first and second electrodes of the moisture decomposition module, and to come into surface contact with one of the first and second electrodes of the moisture decomposition module.

Owner:HYUNDAI MOTOR CO LTD

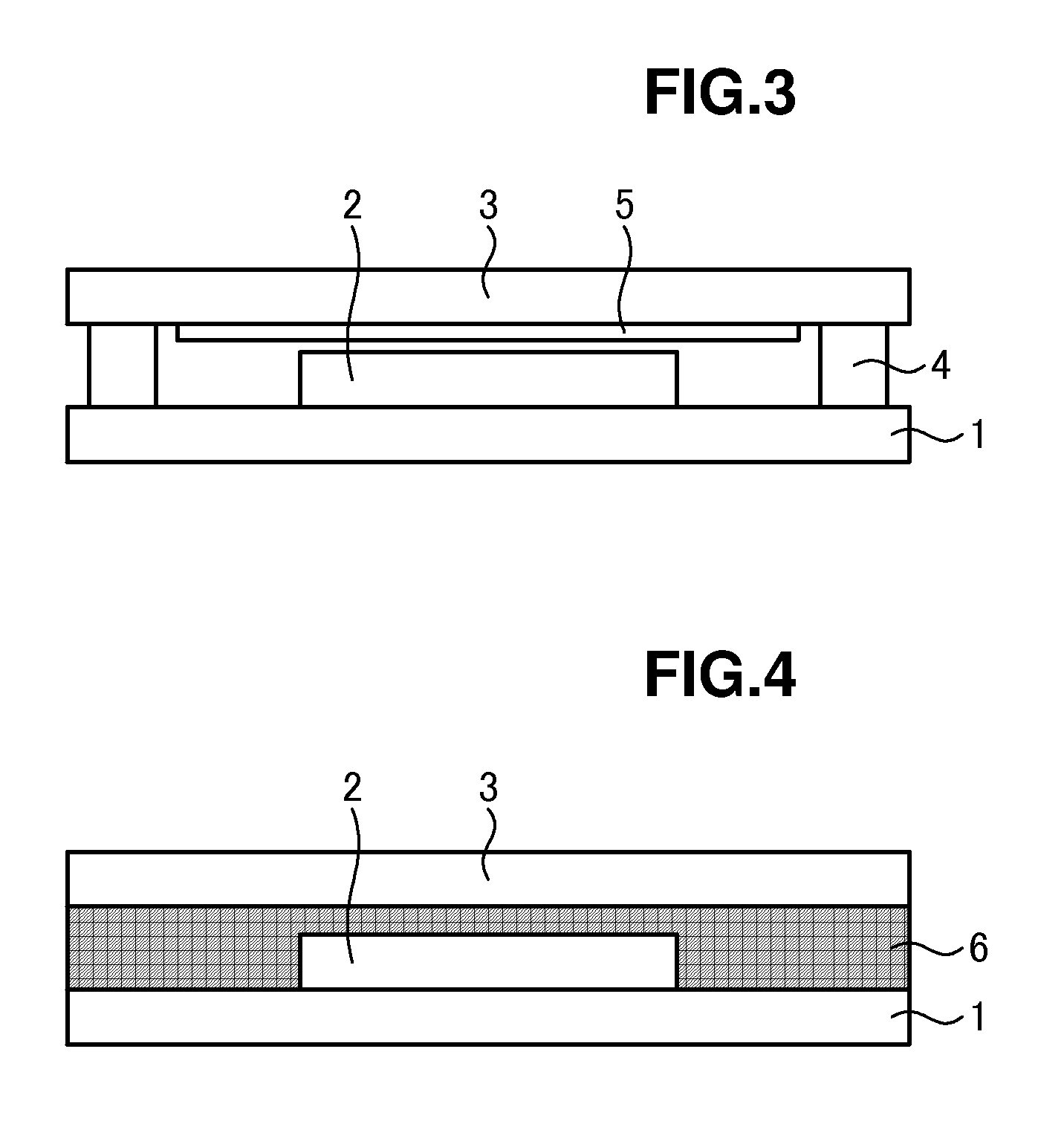

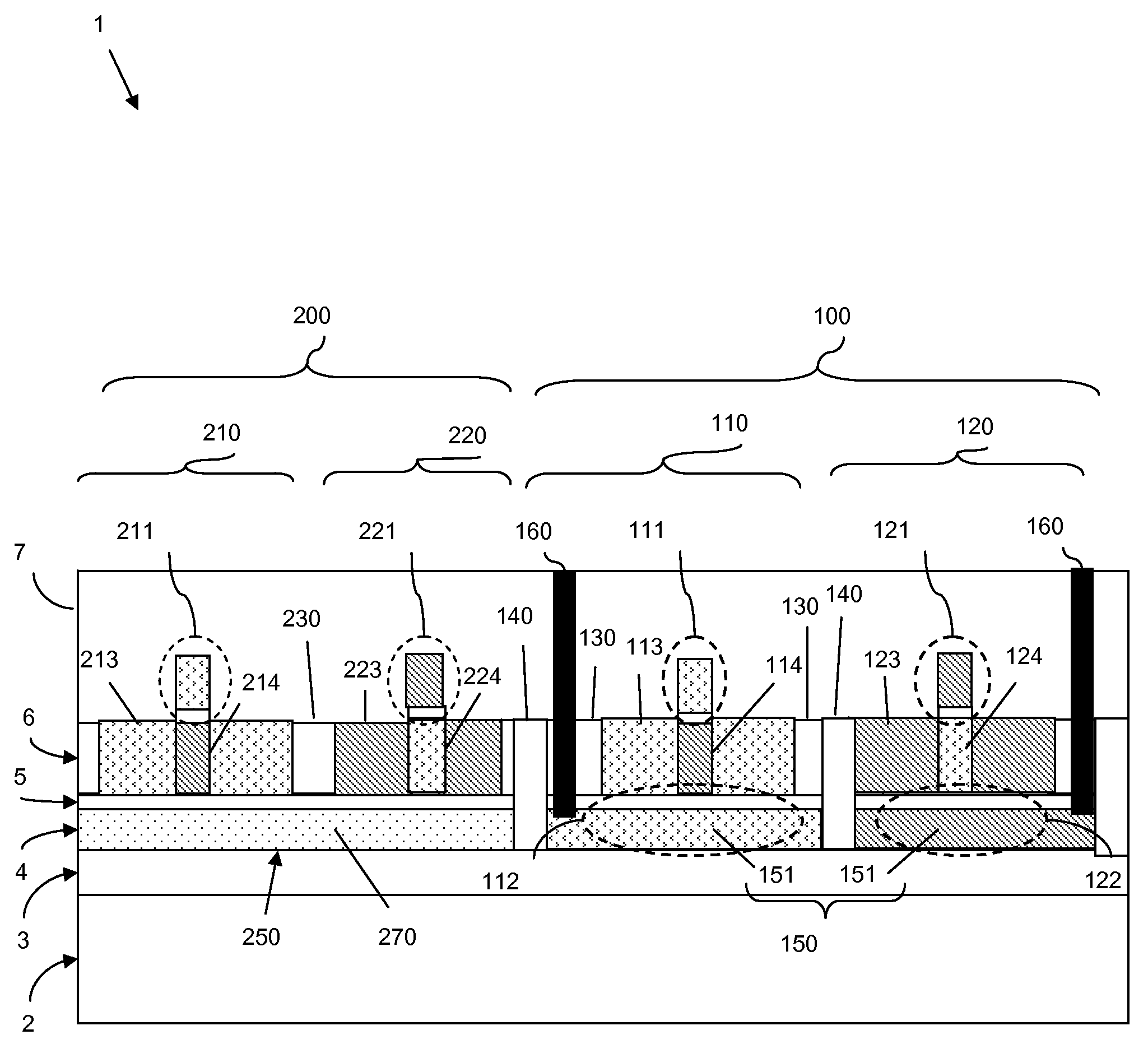

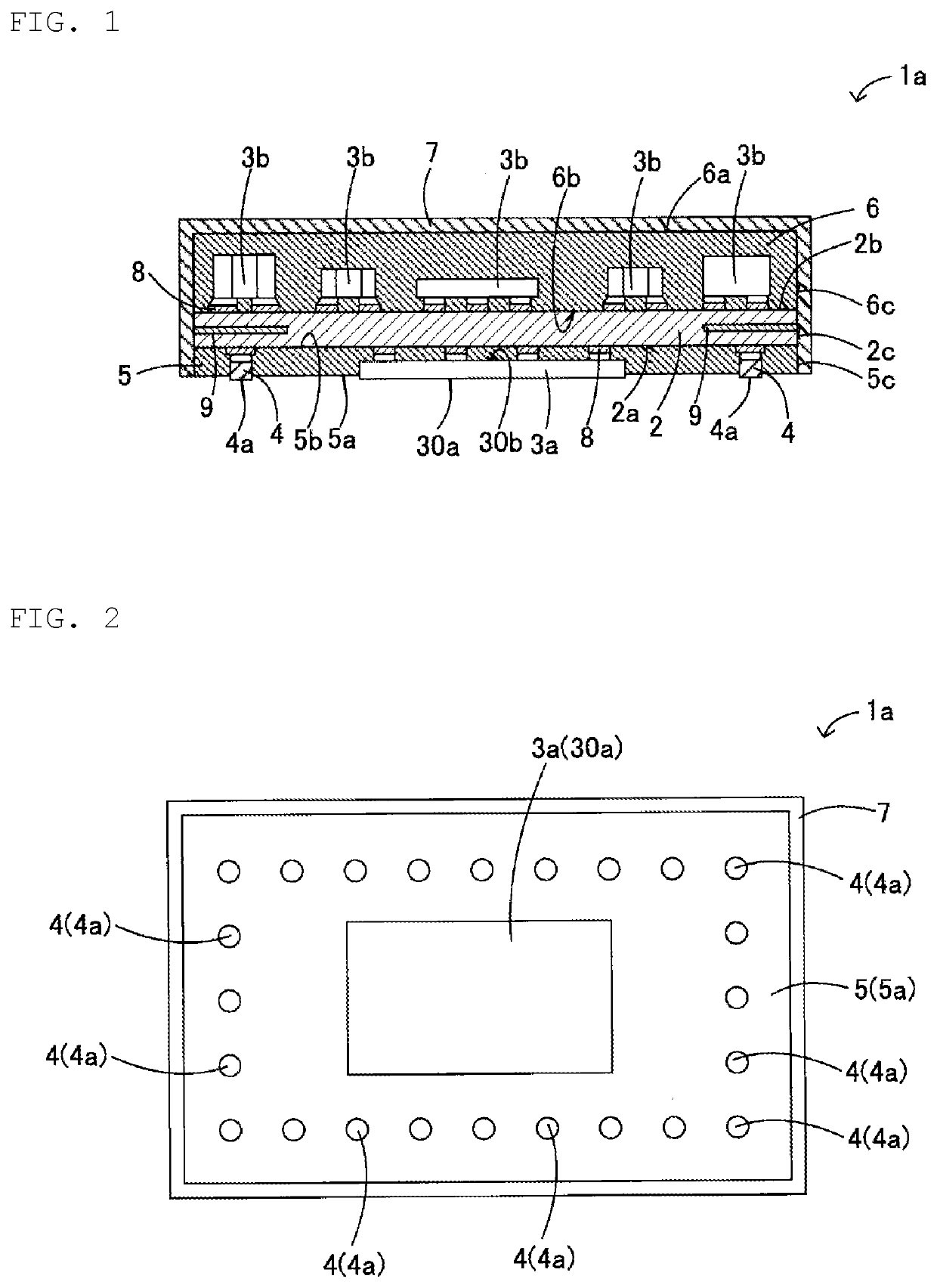

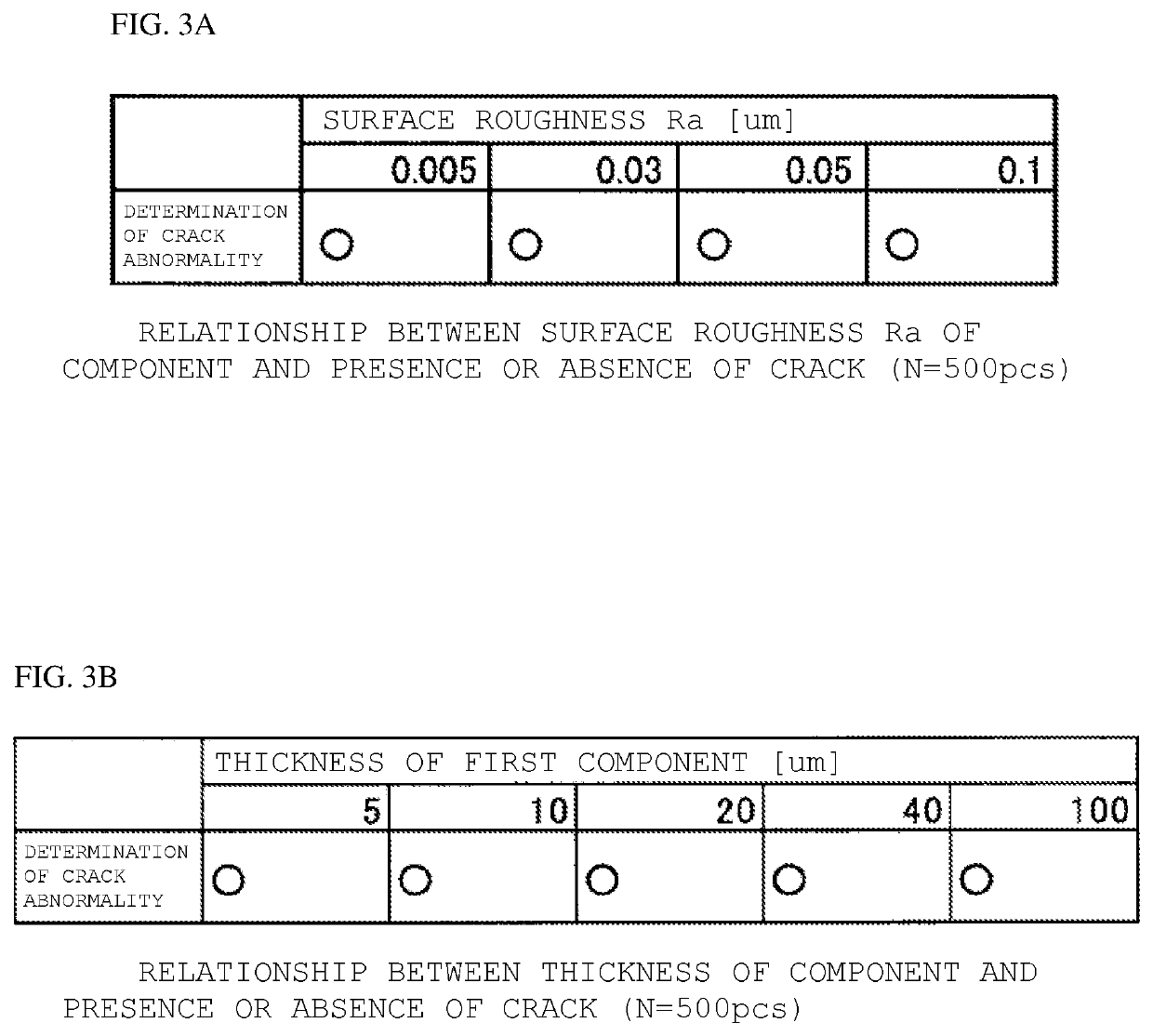

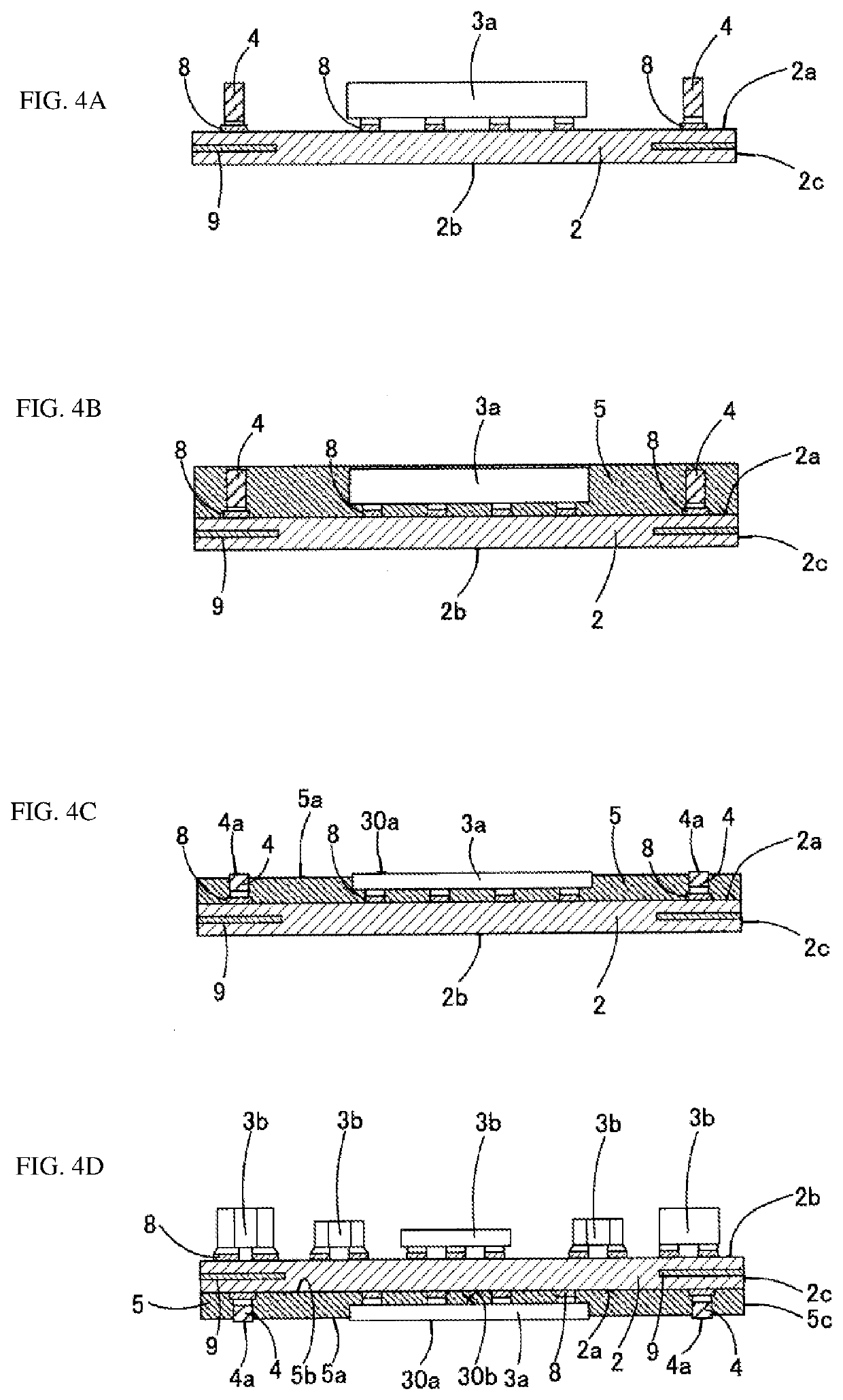

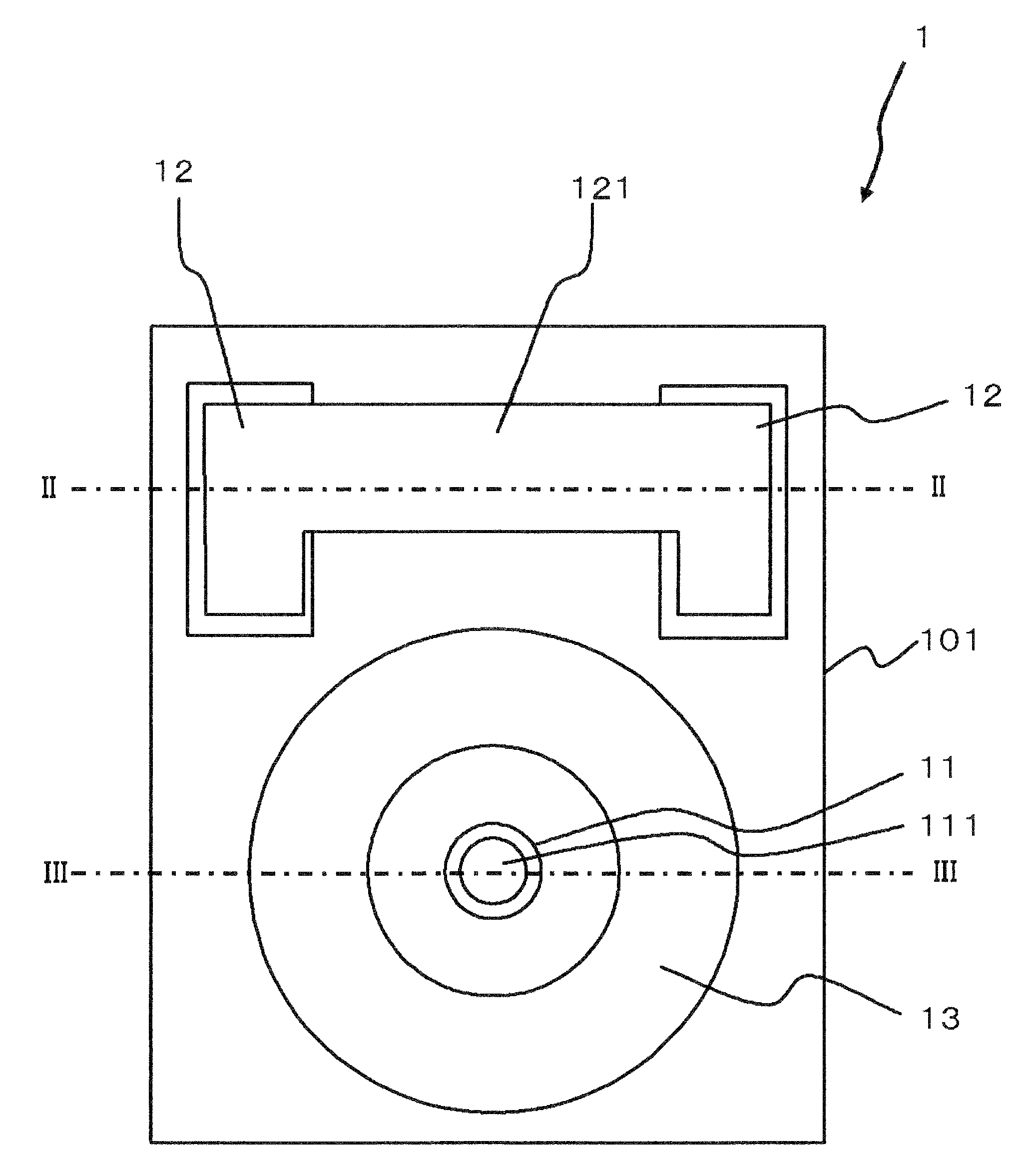

Radio-frequency module

ActiveUS20200395262A1Function increaseSuppress noiseSemiconductor/solid-state device detailsSolid-state devicesCrazingSurface roughness

A radio-frequency module 1a includes a wiring board 2, a first component 3a mounted on a lower surface 2a of the wiring board 2, a plurality of connection terminals 4, a first sealing resin layer 5 that covers the first component 3a and the connection terminals 4, a plurality of second components 3b mounted on an upper surface 2b of the wiring board 2, a second sealing resin layer 6 that covers the second components 3b, and a shield film 7. By adjusting surface roughness of a lower surface 5a of the first sealing resin layer 5, surface roughness of a lower surface 30a of the first component 3a, and surface roughness of a lower surface 4a of the connection terminal 4, it is possible to prevent abnormal deposition of plating and a crack in the first component 3a, and to prevent malfunction of the radio-frequency module 1a.

Owner:MURATA MFG CO LTD

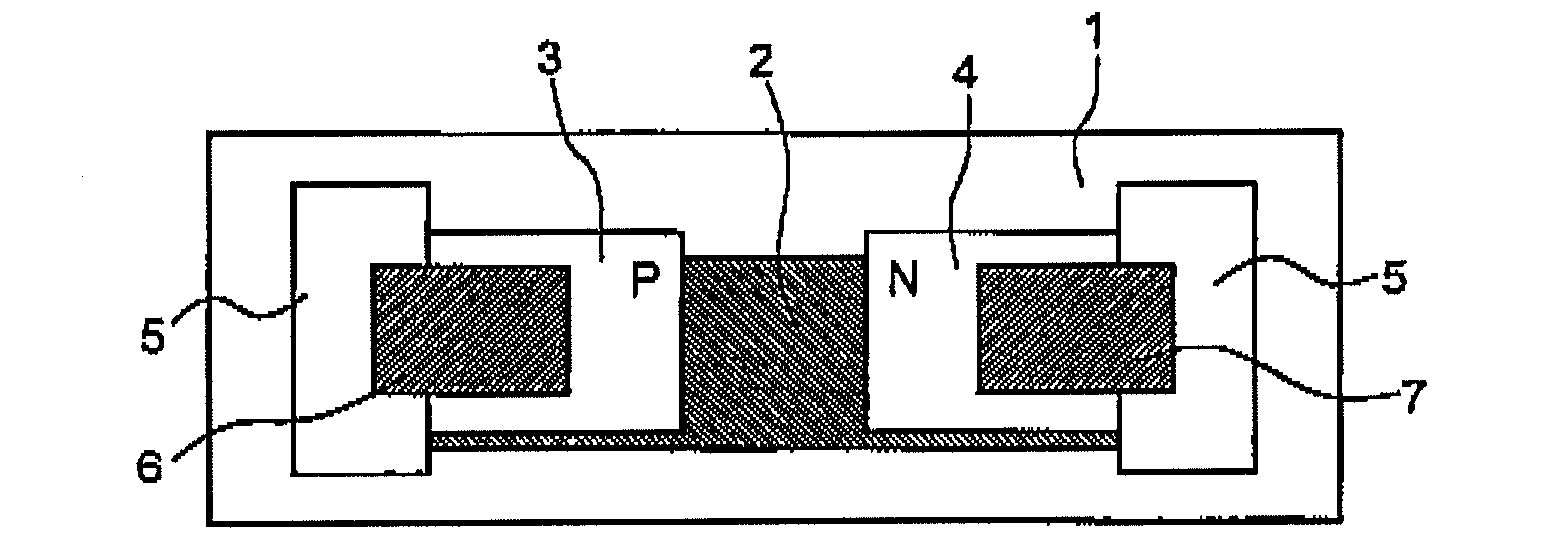

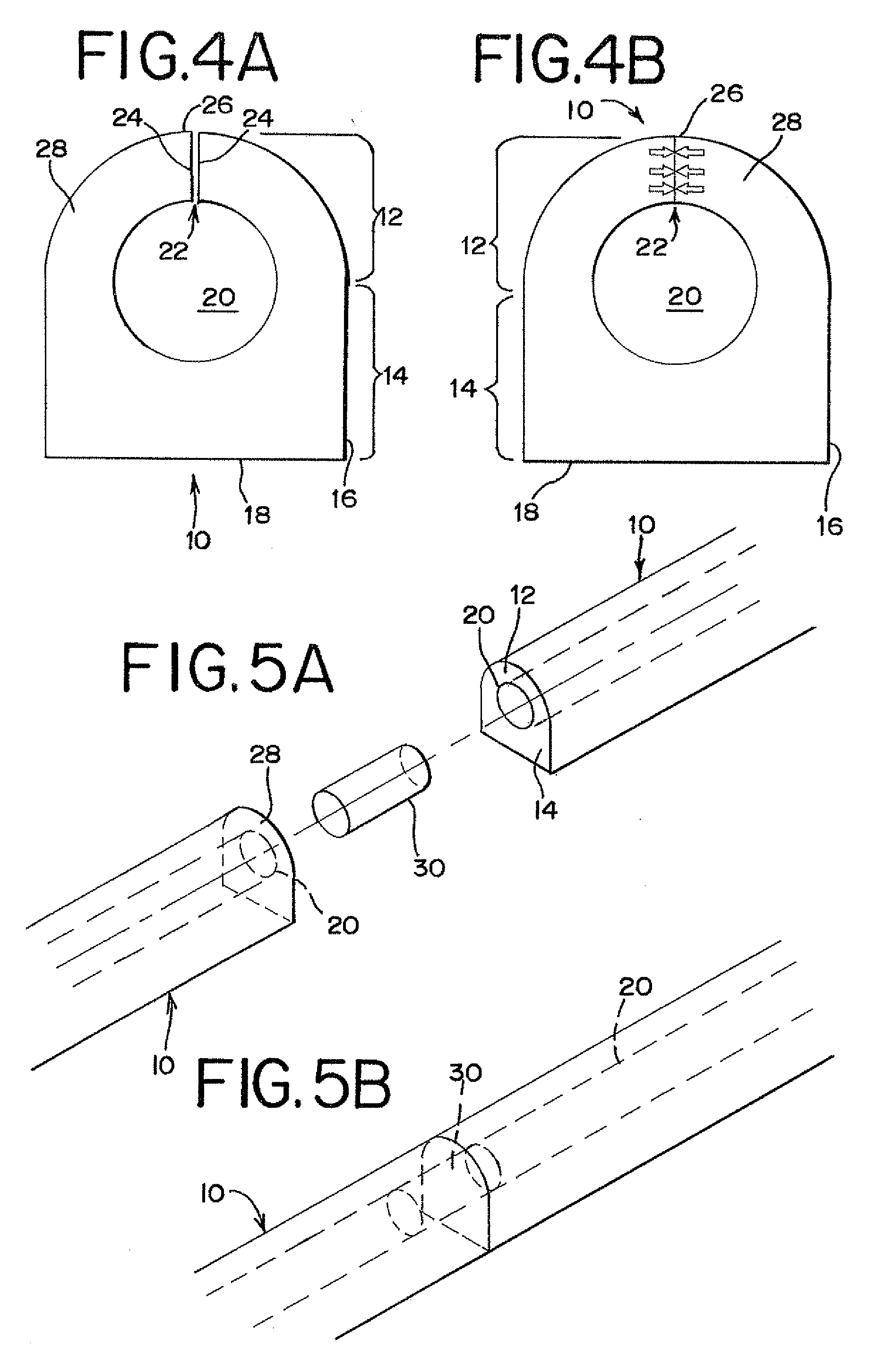

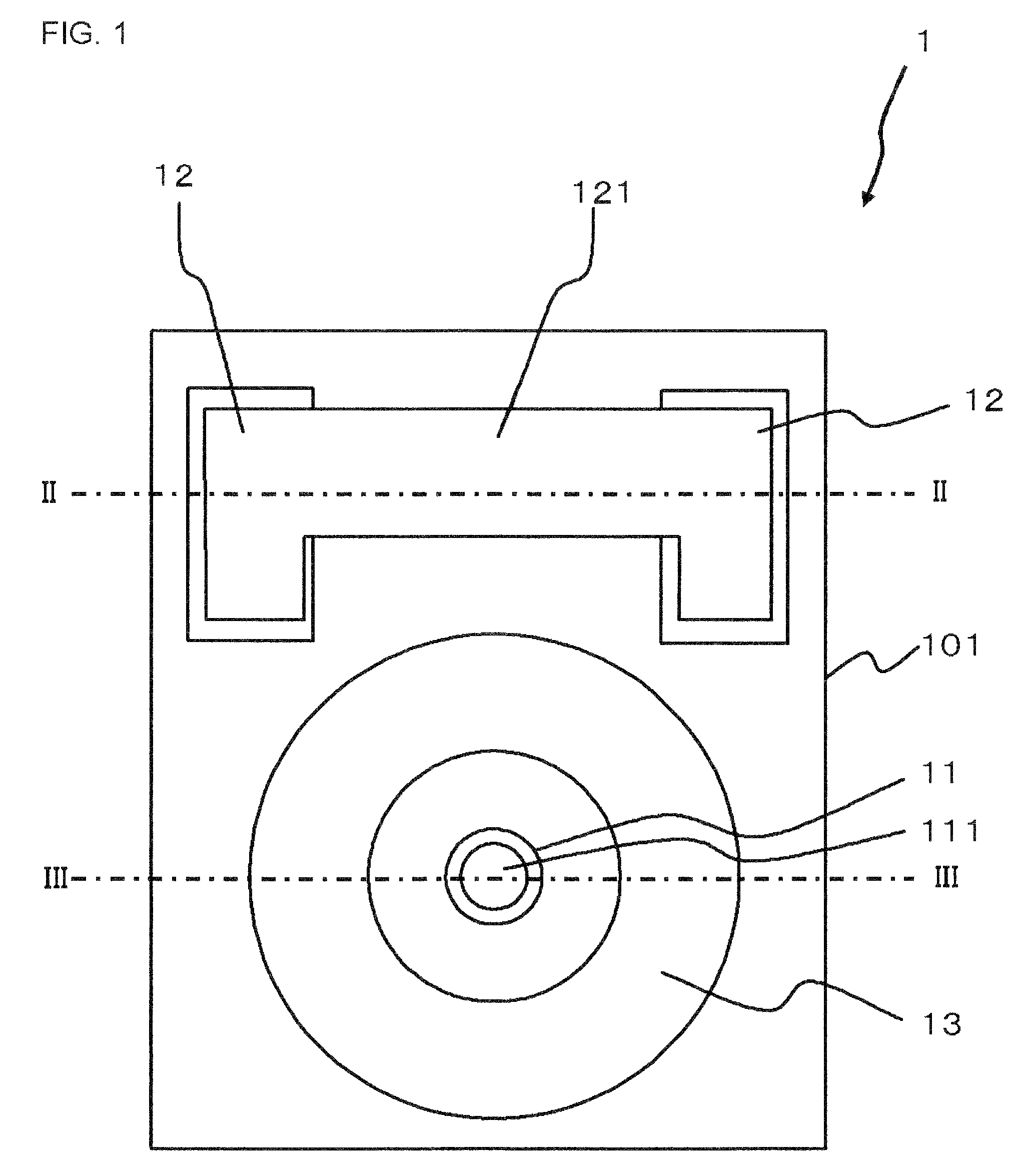

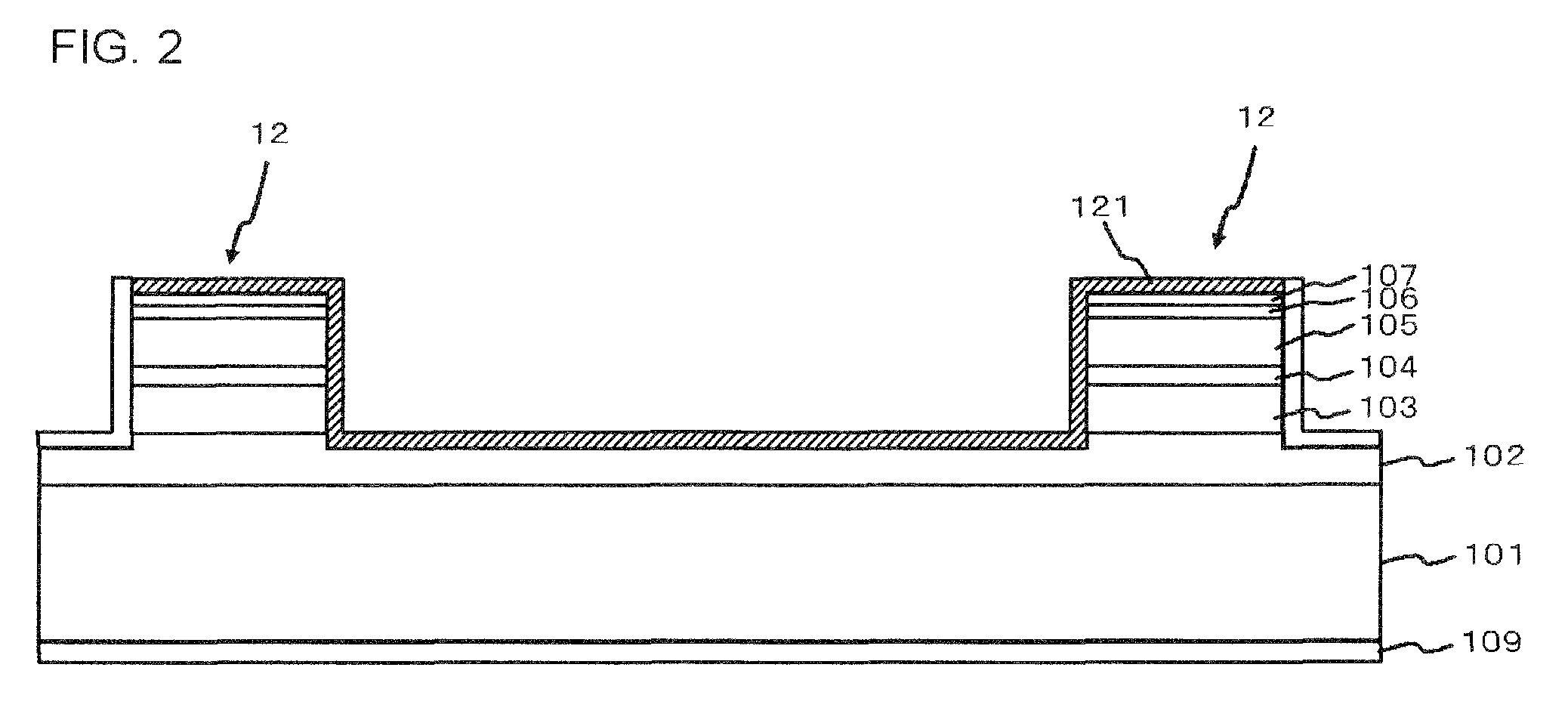

Semiconductor optical element

InactiveUS7952172B2Performance degradation can be preventedSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor packagePhysics

A light receiving element 1 has a semiconductor substrate 101; a first mesa 11 provided over the semiconductor substrate 101, and having an active region and a first electrode (p-side electrode 111) provided over the active region; a second mesa 12 provided over the semiconductor substrate 101, and having a semiconductor layer and a second electrode (n-side electrode 121) provided over the semiconductor layer; and a third mesa 13 provided over the semiconductor substrate 101, and having a semiconductor layer, wherein the third mesa 13 is arranged so as to surround the first mesa 11.

Owner:NEC CORP

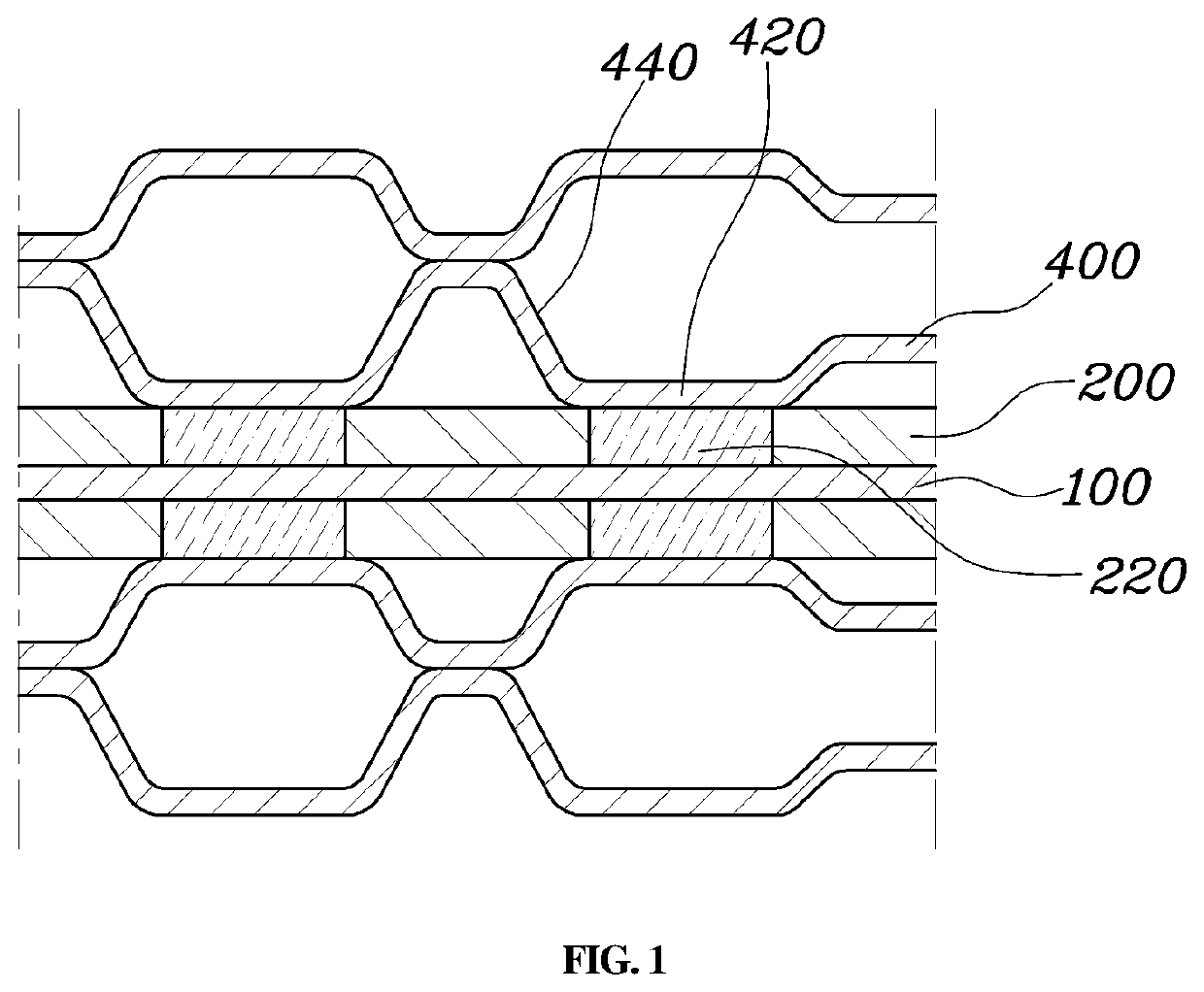

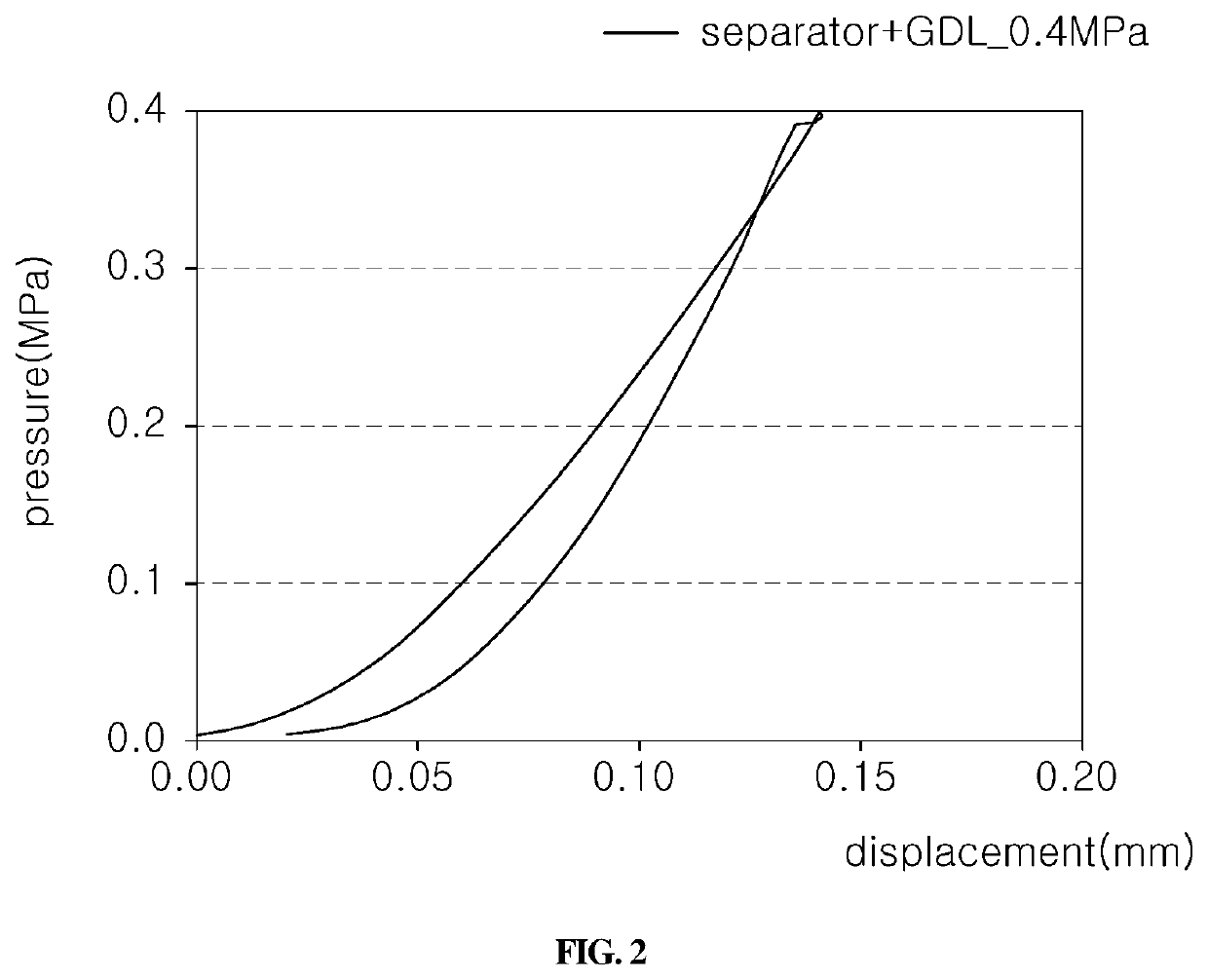

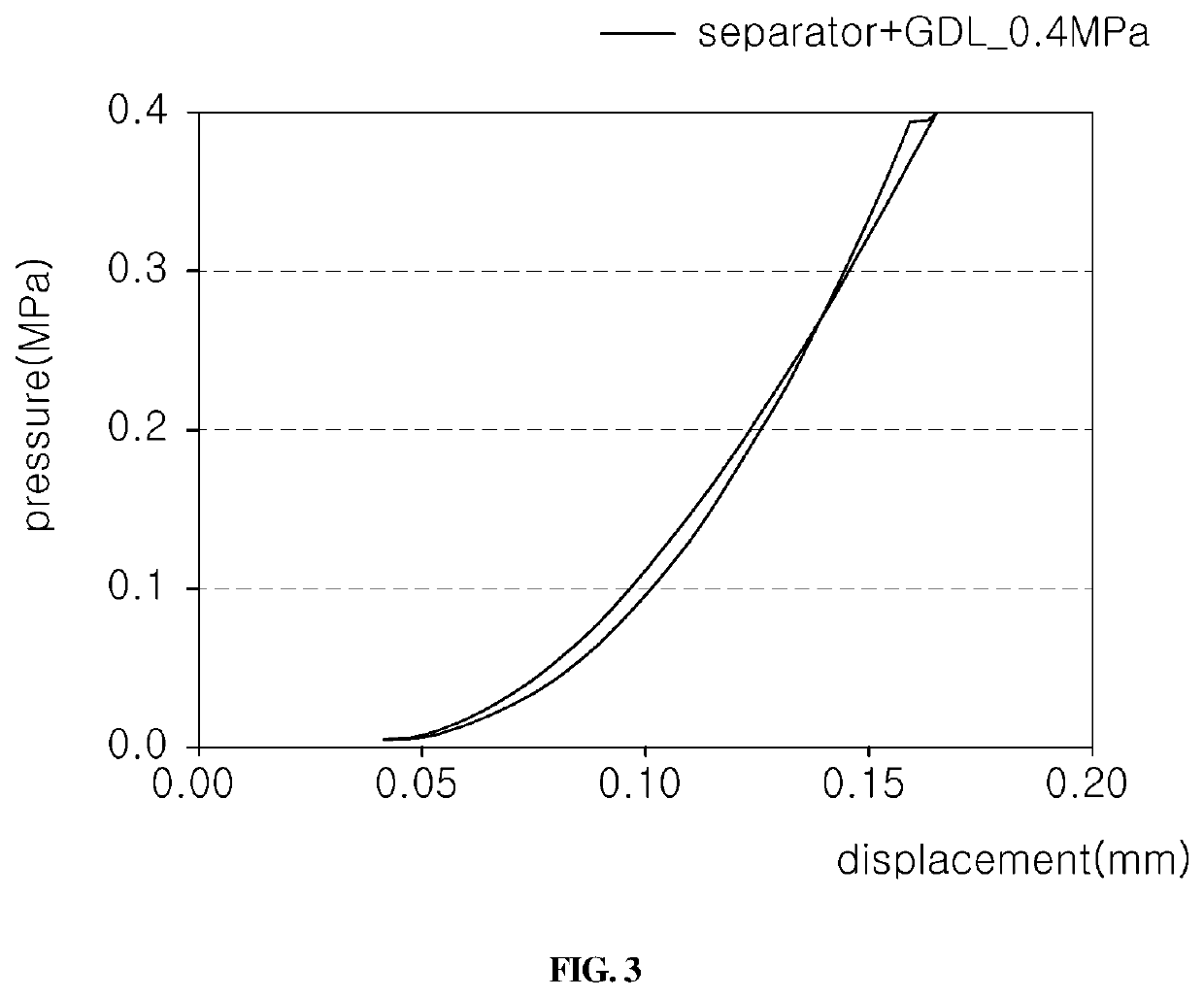

Fuel cell and method for producing the same

ActiveUS10826082B2Performance degradation can be preventedFinal product manufactureFuel cellsFuel cellsEngineering

A fuel cell and a method for producing the same are provided. The fuel cell includes a membrane electrode assembly and a gas diffusion layer that is disposed at each of opposite surfaces of the membrane electrode assembly, and includes a plurality of compressed parts that are formed by pressure at positions spaced out at predetermined intervals on the gas diffusion layer. The fuel cell further includes a separator that is in contact with an outer surface of the gas diffusion layer, and has a plurality of land parts that protrude toward the gas diffusion layer, and a plurality of channel parts that form flow paths between the land parts. The land parts respectively protrude toward the compressed parts of the gas diffusion layer to come in contact with the compressed parts.

Owner:HYUNDAI MOTOR CO LTD

Method for manufacturing organic light-emitting device and organic light-emitting device

ActiveUS8963422B2Performance degradation can be preventedReduce manufacturing costDischarge tube luminescnet screensFinal product manufactureOrganic light emitting deviceIonic polymerization

The present invention provides a method for manufacturing an organic light-emitting device capable of simply manufacturing the organic light-emitting device without requiring a vacuum atmosphere. The manufacturing method of the present invention includes: a step of preparing a supporting substrate having an organic electroluminescent element formed thereon, the organic electroluminescent element containing an anode, a light-emitting layer, an electron injection layer made by forming a film with a solution containing an ionic polymer, and a cathode; and a step of laminating the supporting substrate and a sealing member to one another so as to seal the organic electroluminescent element.

Owner:SUMITOMO CHEM CO LTD

Apparatus and method for transmitting and receiving a signal in a wireless communication system

ActiveUS8005031B2Performance degradation can be preventedError preventionMultiplex communicationCommunications systemSignal on

A method and apparatus for transmitting and receiving a signal in a wireless communication system. The wireless communication system includes a transmitter with at least four transmit antennas and a receiver with at least one receive antenna. Space Frequency Block Coding (SFBC) processes are performed for input signals on a basis of two antenna pairs. Signal blocks whose number corresponds to the number of transmit antennas are output. A Space Time Block Coding (STBC) process is performed for the signal blocks generated according to the antenna pairs. Signals carried by single carriers are transmitted through the at least four transmit antennas mapped to the signal blocks.

Owner:SAMSUNG ELECTRONICS CO LTD +1