Patents

Literature

74results about How to "Reduce write operations" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

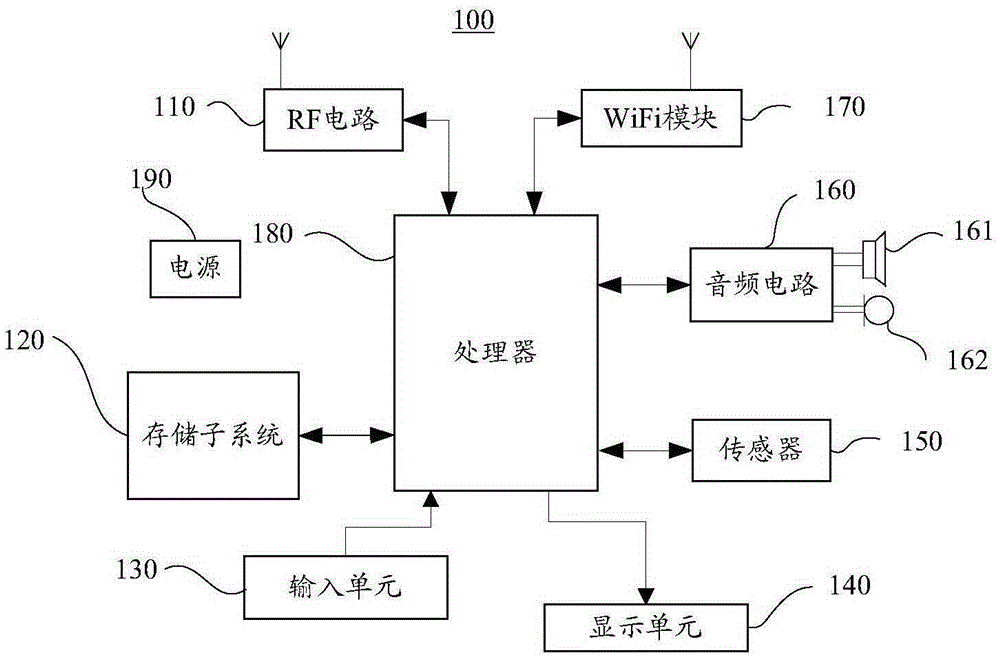

SSD-based (Solid State Disk) cache management method and system

ActiveCN102760101AReduce cache pollutionReduce write operationsMemory adressing/allocation/relocationWhole bodyGranularity

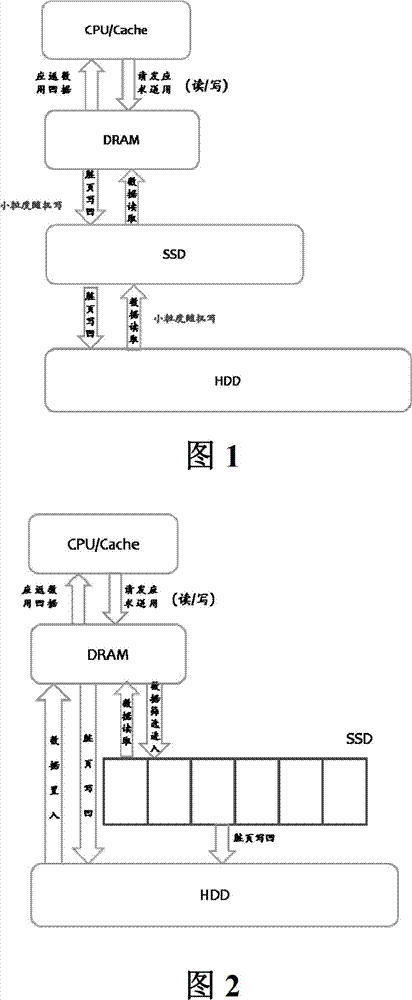

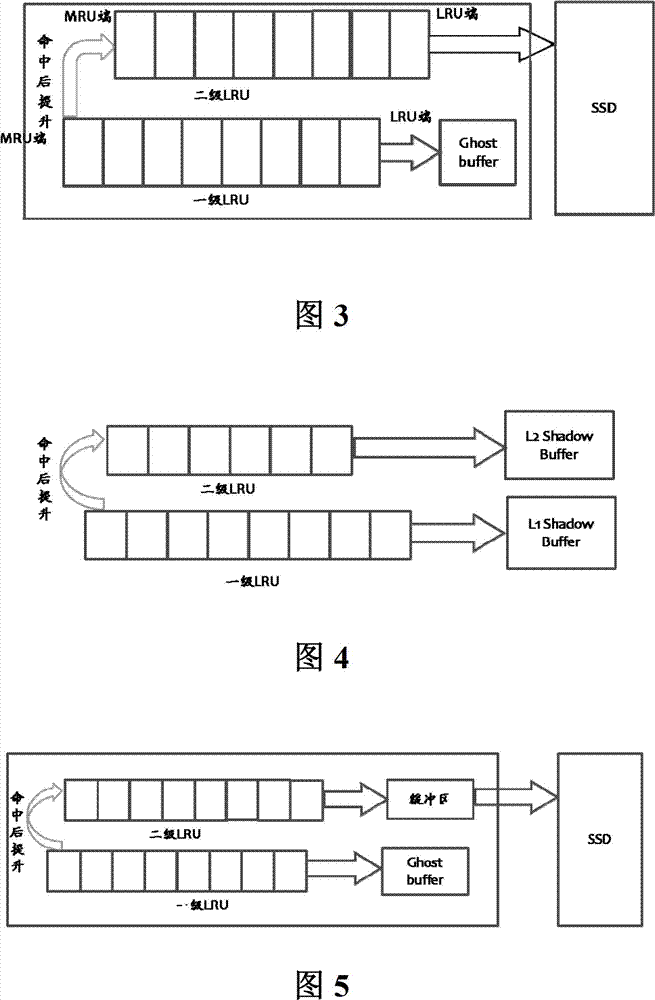

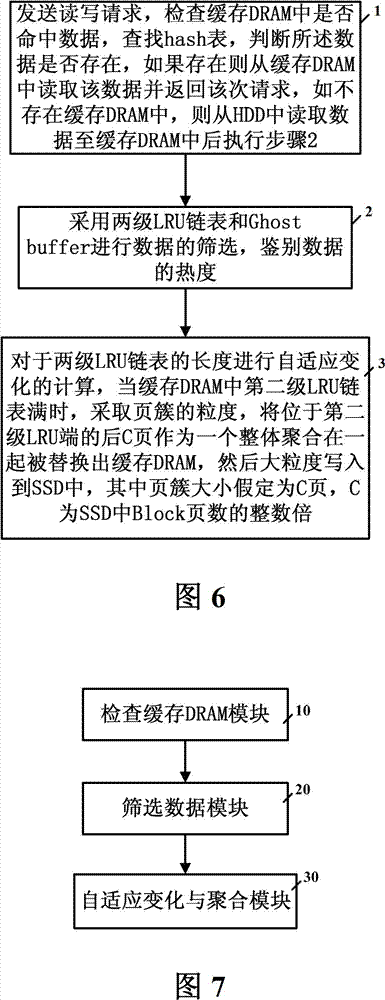

The invention discloses an SSD-based (Solid State Disk) cache management method and system. The SSD-based cache management method comprises the following steps: step 1, sending a read-write request, checking whether a cached DRAM (Dynamic Random Access Memory) hits data, searching a hash list, judging whether the data is existent, reading the data from the cached DRAM and returning the request if the data is existent, and reading data to the cached DRAM from a HDD (Hard Disk Drive) and carrying out step 2 if the data is nonexistent in the cached DRAM; step 2, carrying out data screening by using a two-level LRU (least recently used) linked list and a Ghost buffer, and identifying data heat; and step 3, carrying out self-adaptive change calculation on the length of the two-level LRU linked list, acquiring the granularity of a page cluster when the second-level LRU linked list of the cached DRAM is full, taking C pages behind the second-level LRU end as a whole body to replace the cached DRAM, and writing the C pages into an SSD in a large granularity, wherein the page cluster size is C pages, and C is an integral multiple of Block page number in the SSD.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI +1

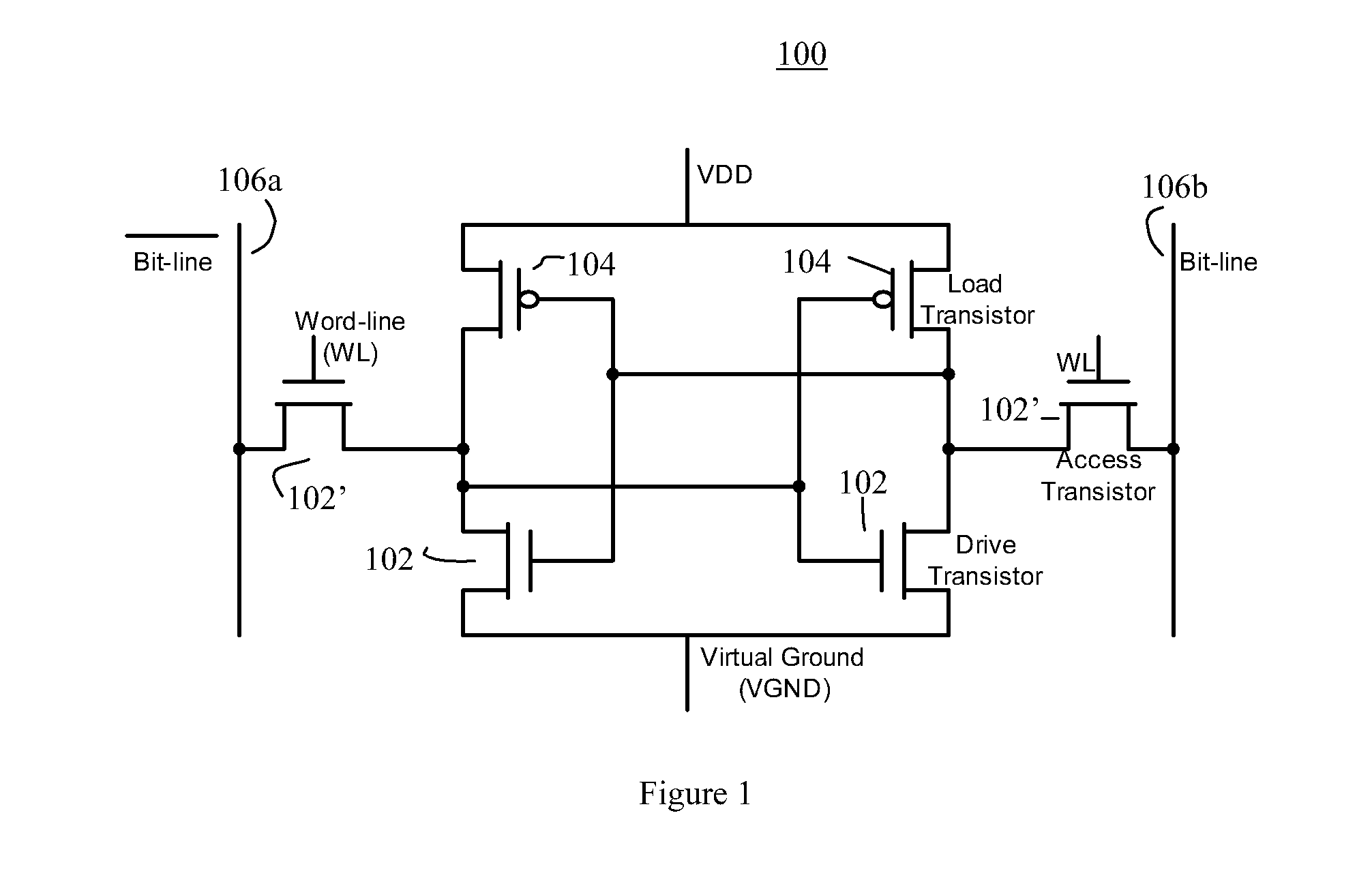

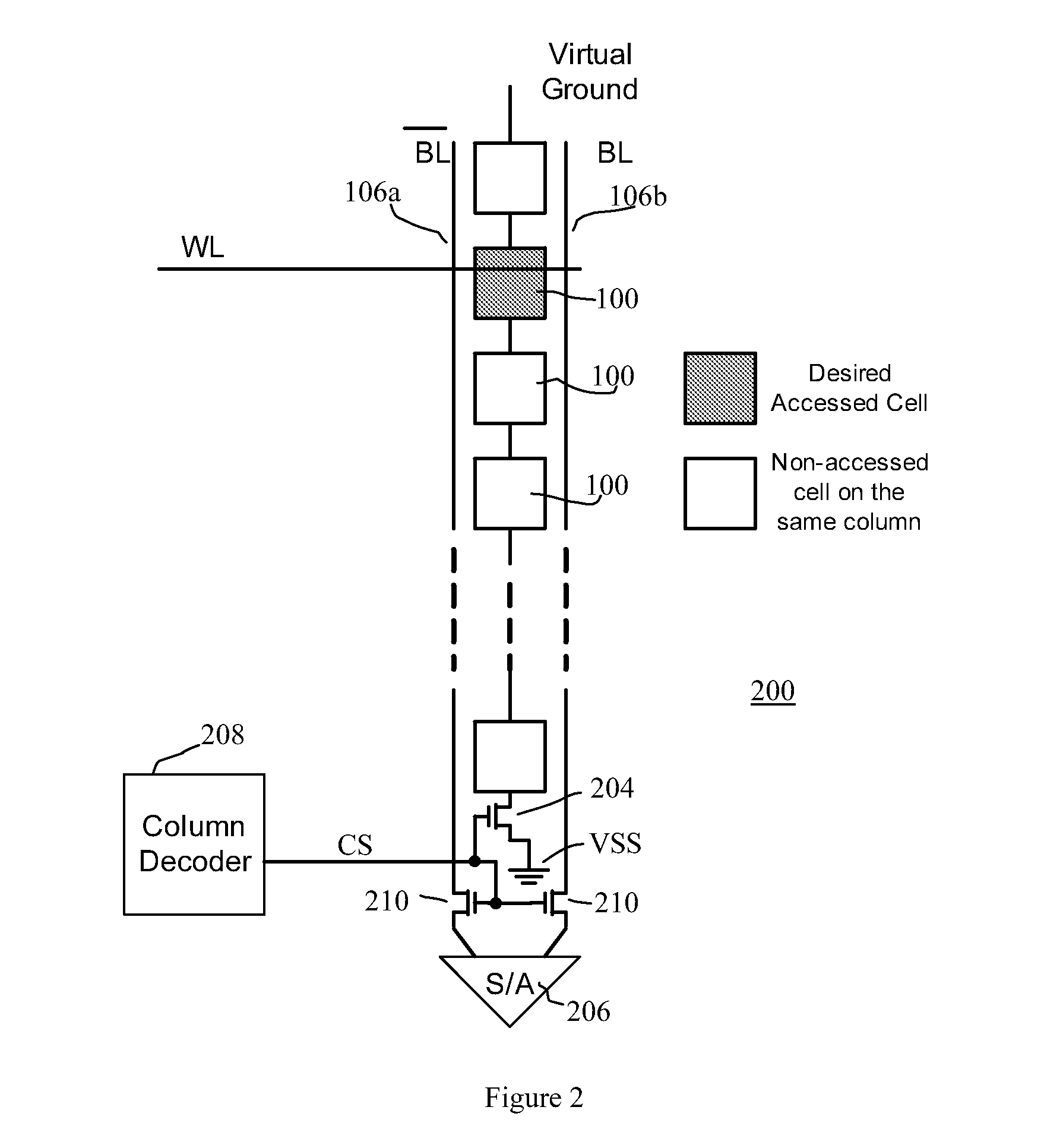

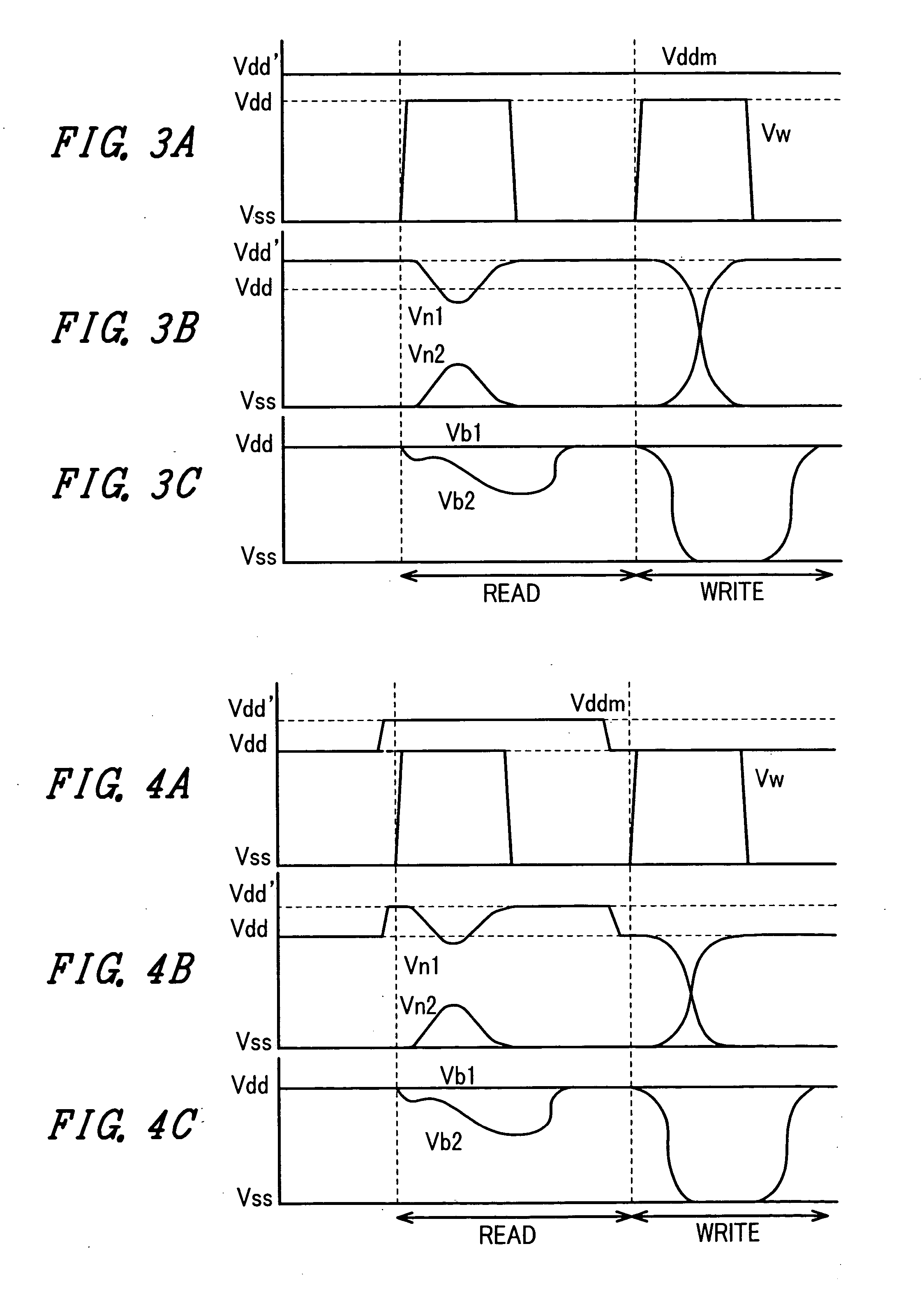

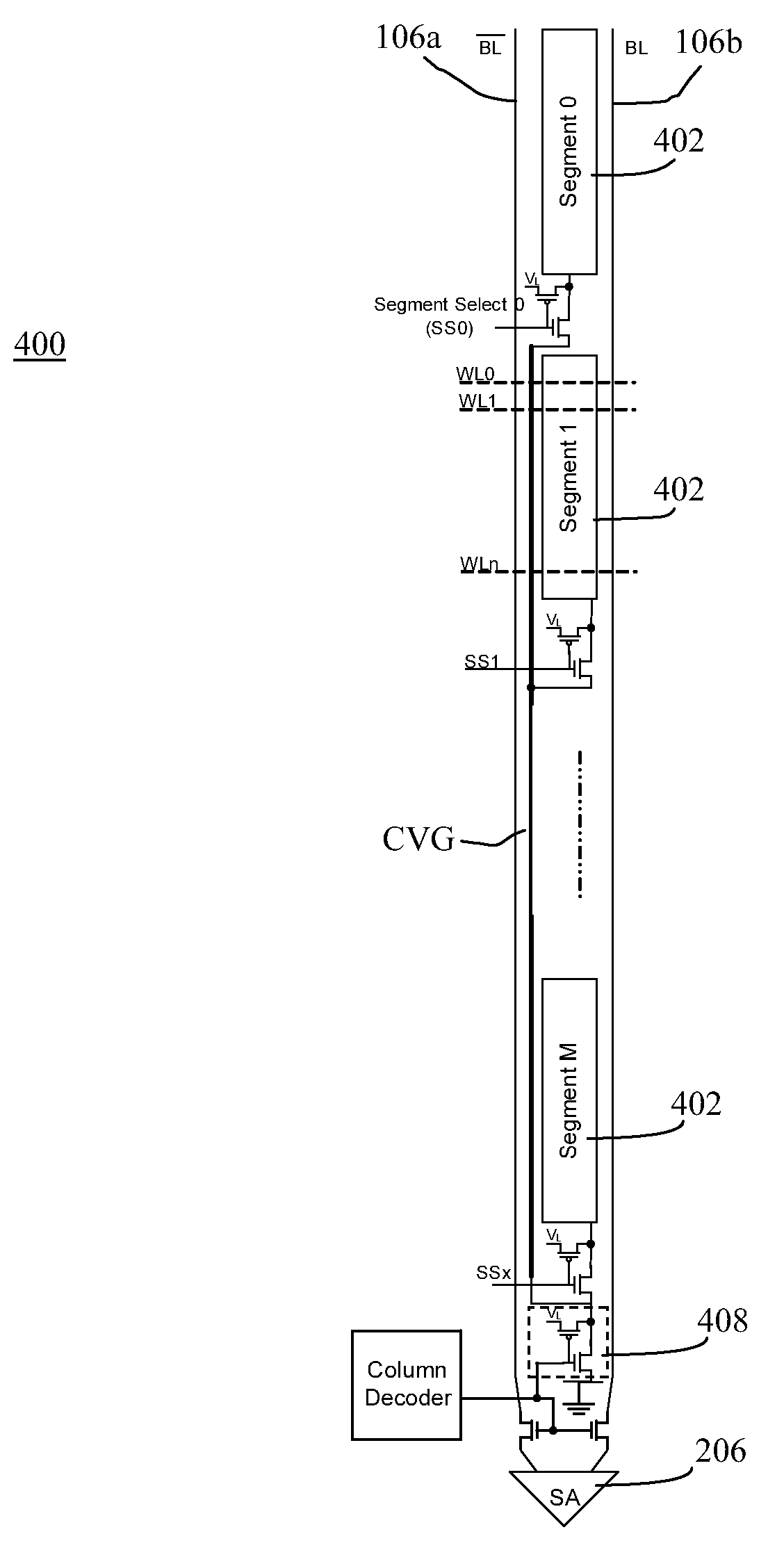

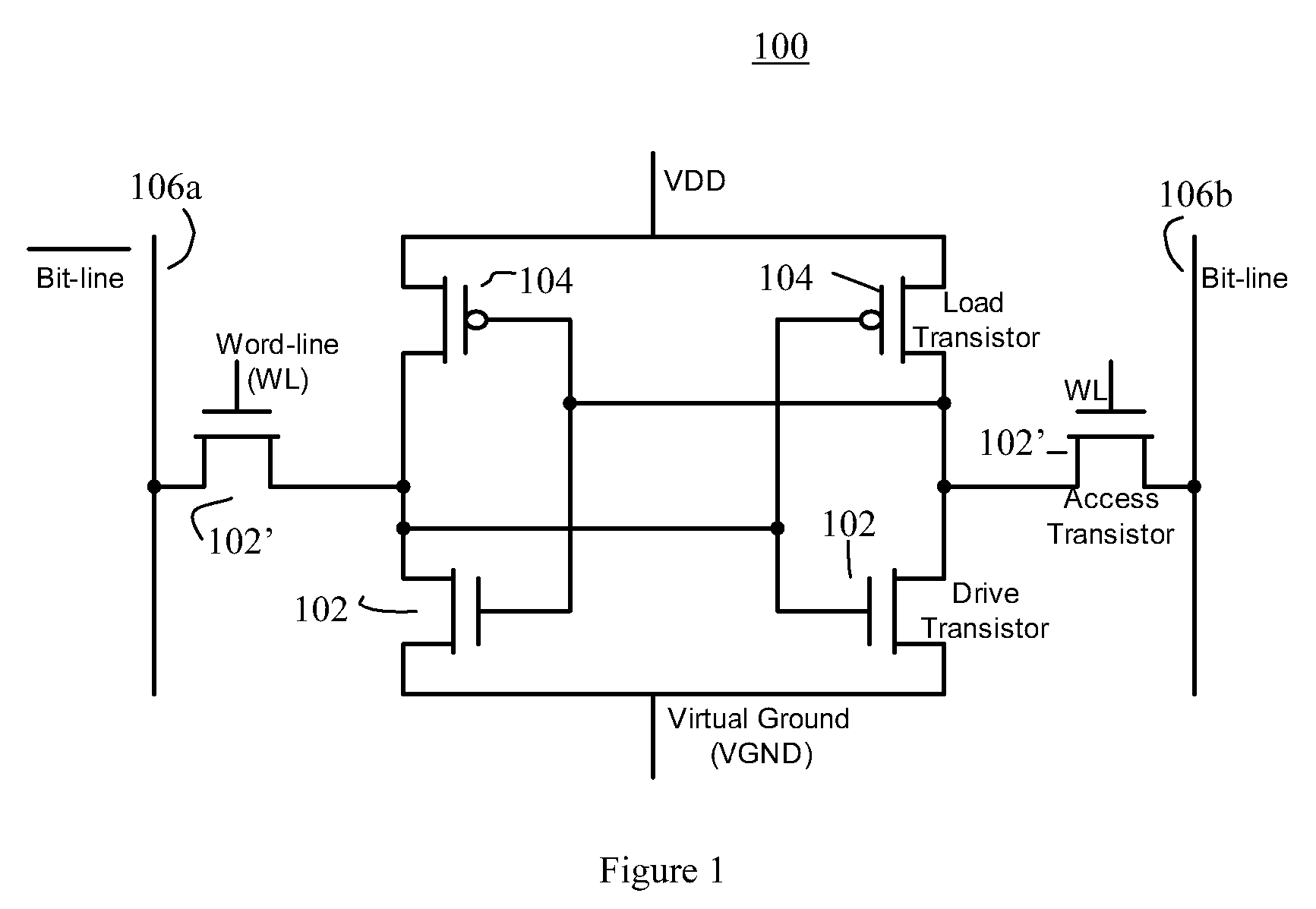

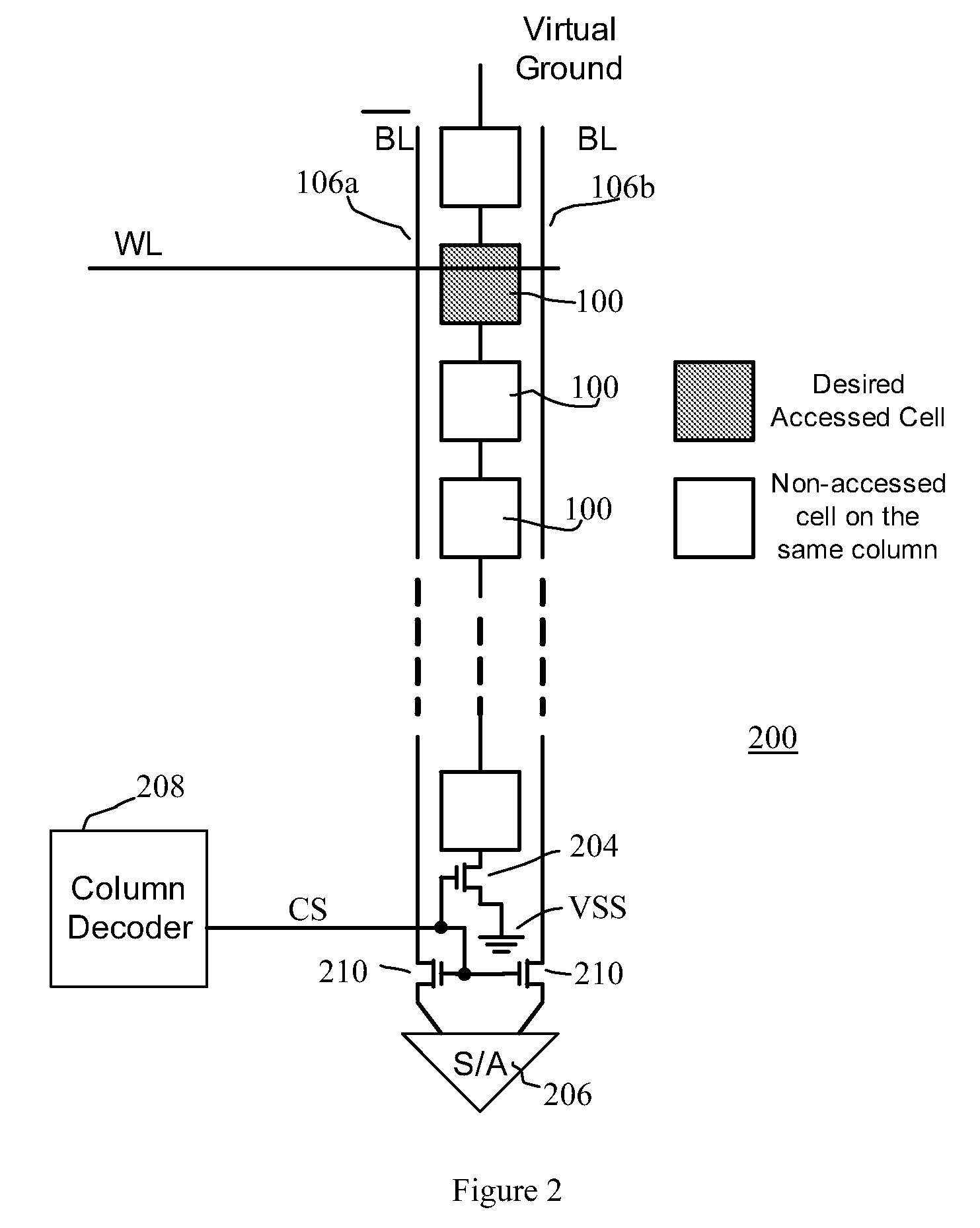

Segmented Column Virtual Ground Scheme In A Static Random Access Memory (SRAM) Circuit

InactiveUS20070217262A1Power write operationTotal current dropRead-only memoriesDigital storageStatic random-access memoryLow voltage

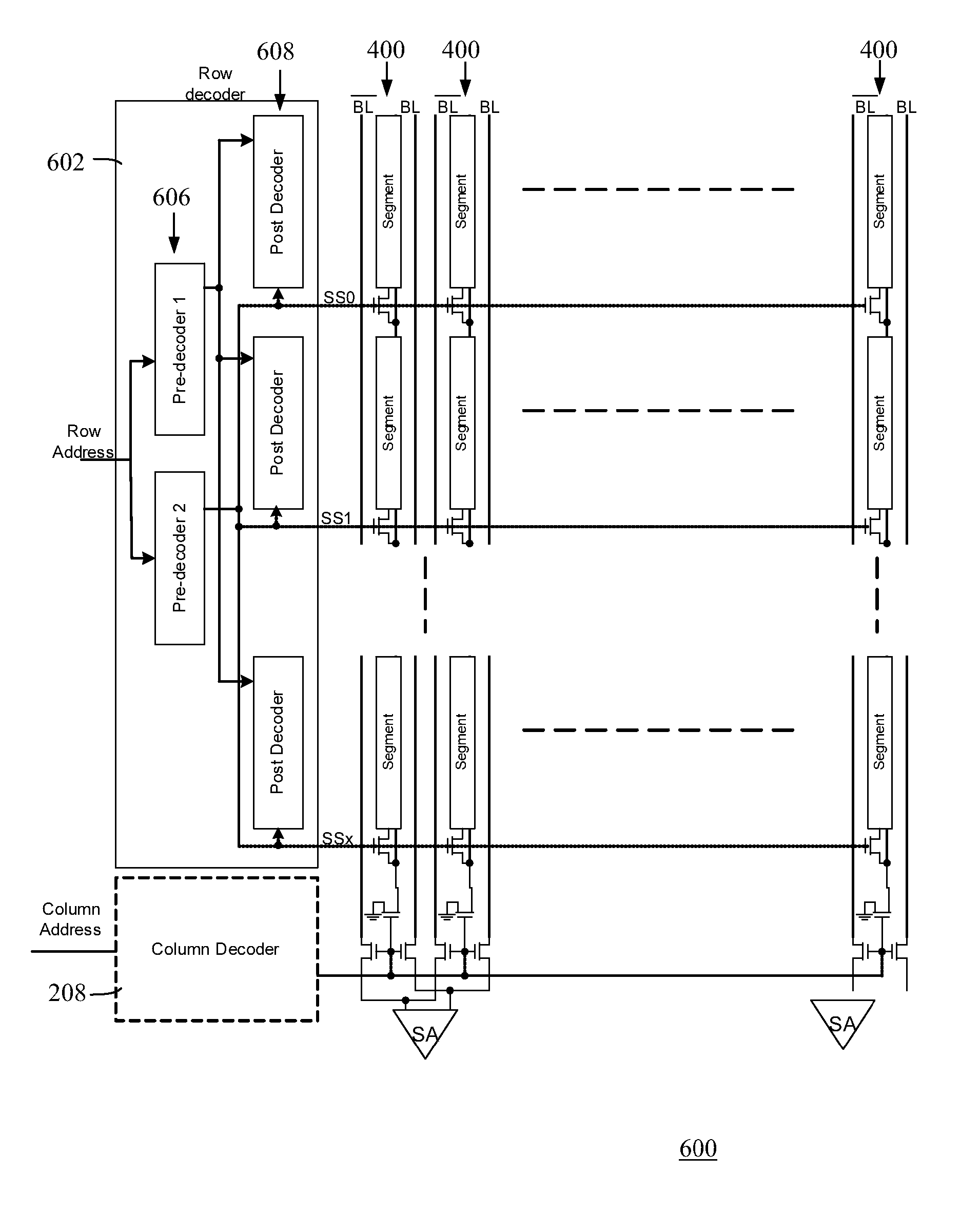

A static random access memory (SRAM) cell array is provided that reduces leakage current. The SRAM cell array is configured in a plurality of columns. Each of the columns comprises: a column virtual ground node; a column switch for selectively coupling the column virtual ground node to one of a ground or a nominal low voltage; and a plurality of segments. Each of the segments comprises: a segment virtual ground node; a plurality of SRAM cells including a virtual ground signal coupled to the segment virtual ground node; and a virtual ground switch for selectively coupling the segment virtual ground node to one of either a nominal low voltage or the column virtual ground node. A method for operating the SRAM cell array is also described.

Owner:SACHDEV MANOJ +1

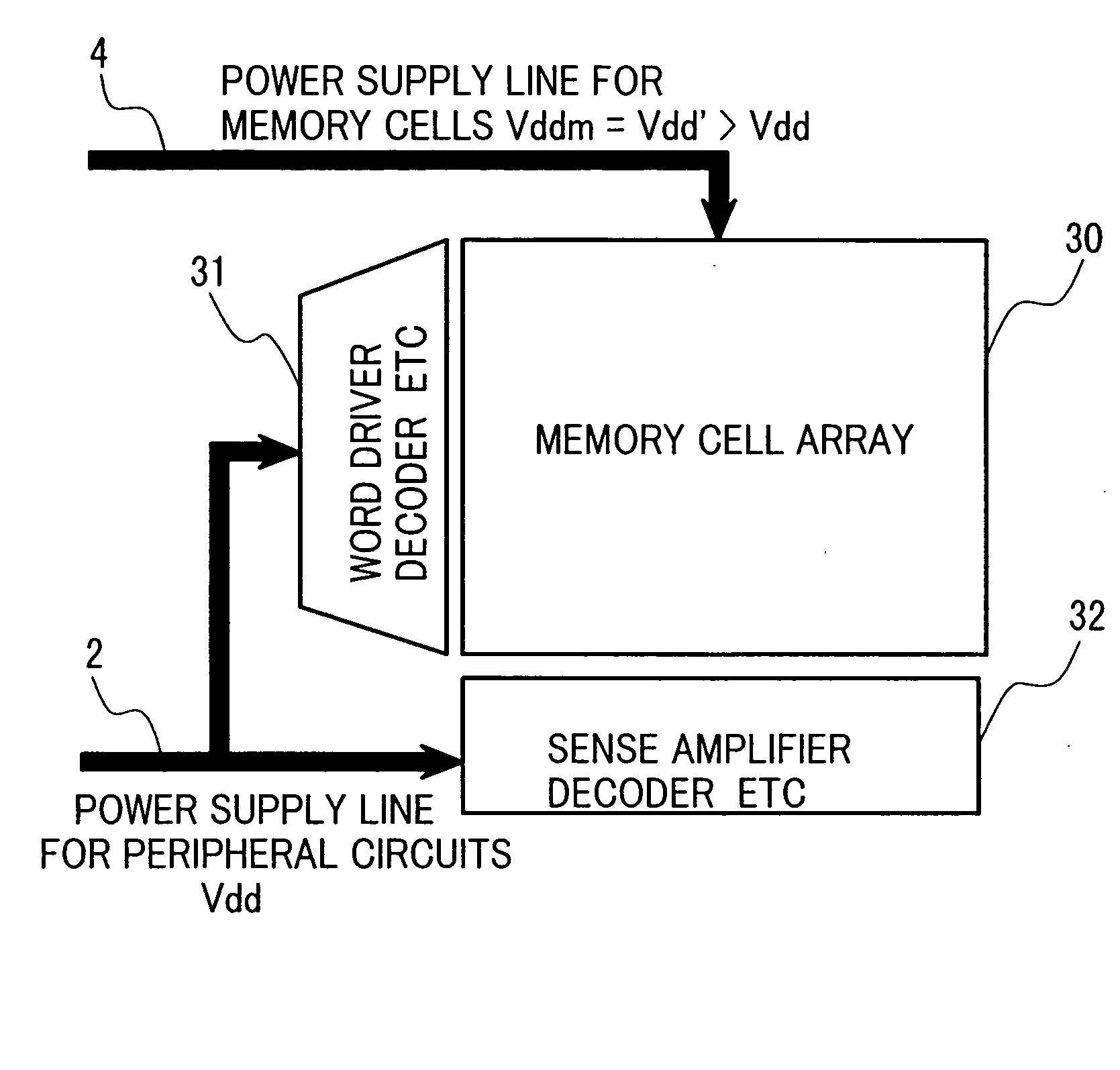

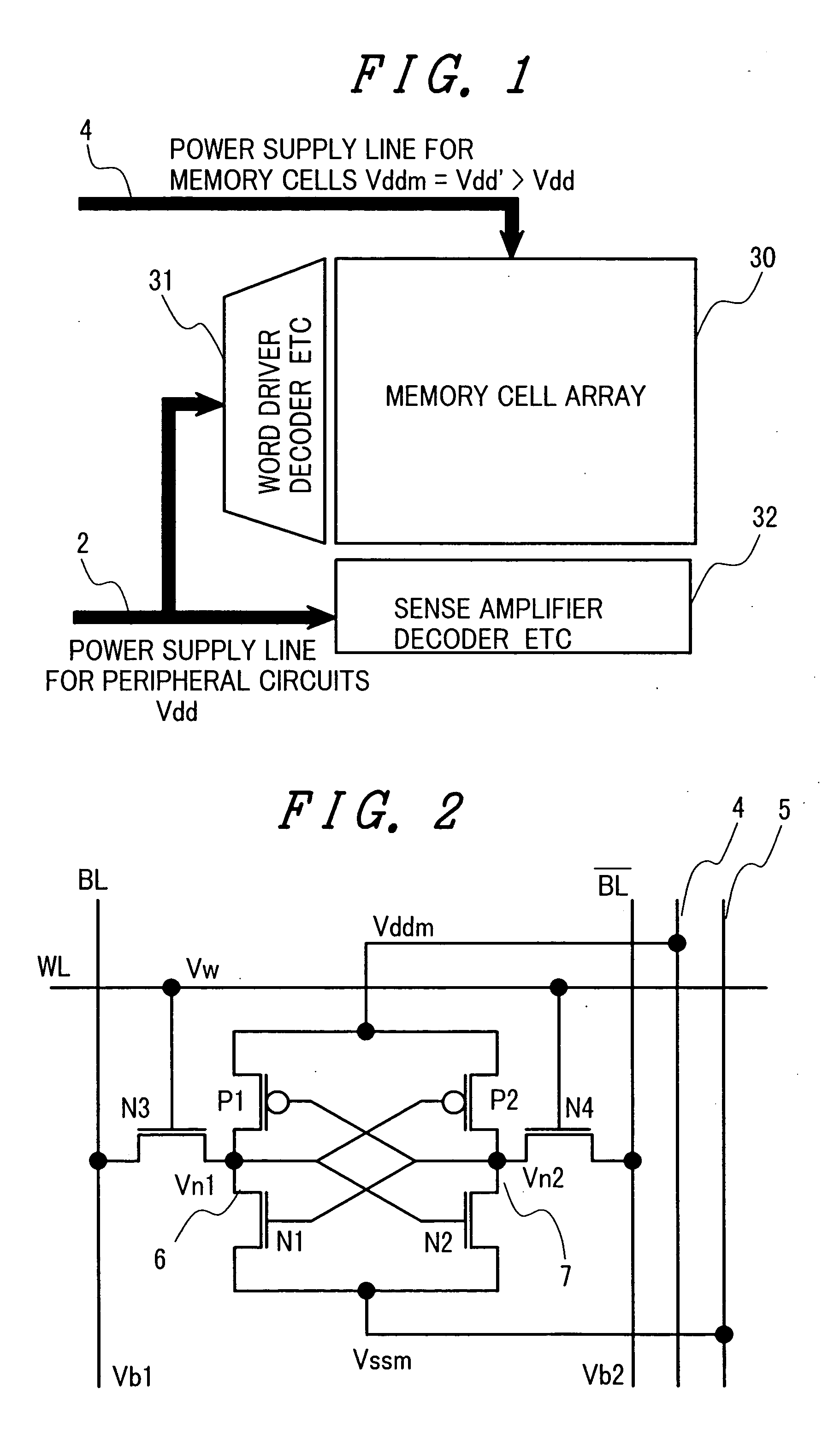

Semiconductor memory device with memory cells operated by boosted voltage

InactiveUS20050024917A1Reduced operating requirementsStatic noise marginSolid-state devicesSemiconductor/solid-state device manufacturingLow voltageEngineering

A memory using an SRAM memory cell intended for low-voltage operation is designed to decrease the threshold value of MOS transistors constituting the memory cell without substantial decrease in the static noise margin, which is the operational margin of the memory cell. To this end, a voltage Vdd′ higher than a power supply voltage Vdd of a power supply line for peripheral circuits is supplied from a power supply line for memory cells as a power supply voltage for memory cells. Since the conductance of driver MOS transistors is increased, the threshold voltage of the MOS transistors within the memory cells can be reduced without reducing the static noise margin. Further the ratio of width between the driver MOS transistor and a transfer MOS transistor can be set to 1, thereby allowing a reduction in the memory cell area.

Owner:RENESAS ELECTRONICS CORP

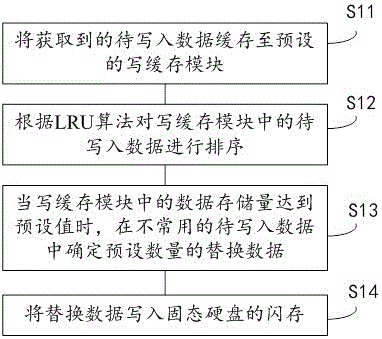

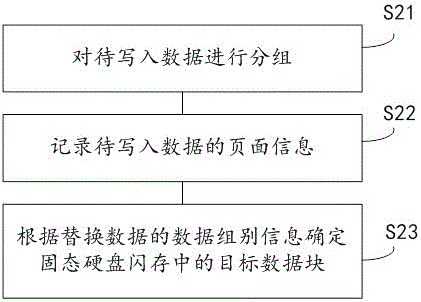

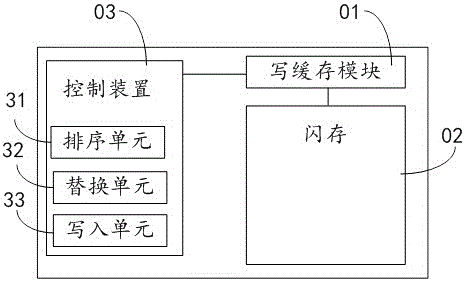

Solid state drive and data access method applied to solid state drive

InactiveCN106227471AReduce write amplification problemsReduce the number of rewritesMemory architecture accessing/allocationInput/output to record carriersWrite amplificationAccess method

The invention discloses a solid state drive and a data access method applied to the solid state drive. The data access method includes caching acquired to-be-written data in a preset write cache module; sorting the to-be-written data in the write cache module according to least recently used (LRU) page algorithms; determining preset quantities of replacement data among the not commonly used to-be-written data according to preset cache replacement algorithms when data memory spaces in the write cache module reach preset values; writing the replacement data in a flash memory of the solid state drive. The solid state drive and the data access method in an embodiment of the invention have the advantages that the rewriting frequencies of the flash memory in the solid state drive can be effectively reduced, and the problem of writing amplification of an existing solid state drive in data access procedures can be effectively solved.

Owner:SHENZHEN DAPU MICROELECTRONICS CO LTD

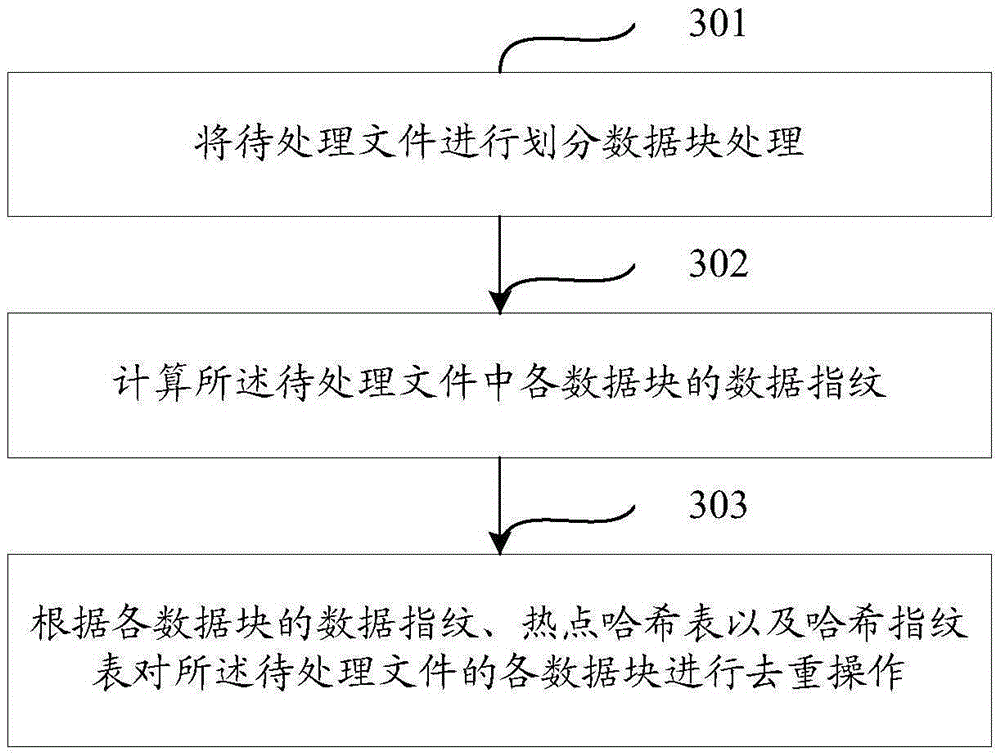

Repeated data deleting method and device

ActiveCN106610790ASmall amount of dataReduce occupancyInput/output to record carriersTheoretical computer scienceHash table

The invention discloses a repeated data deleting method and device, and improves system reliability of a mobile intelligent terminal. The method comprises the steps of: carrying out matching on a data fingerprint of a current data block and data fingerprints in a hotspot hash table, and if a matching result is that the data fingerprint of the current data block is consistent with one data fingerprint in the hotspot hash table, determining the current data block as repeated data; and if a matching result is that the data fingerprint of the current data block is inconsistent with the data fingerprints in the hotspot hash table, carrying out matching on the data fingerprint of the current data block and data fingerprints in a hash fingerprint table, and when a matching result is that the data fingerprint of the current data block is consistent with one data fingerprint in the hash fingerprint table, determining the current data block as the repeated data, wherein the data fingerprint of each harsh table item in the hotspot hash table is a data fingerprint of which repeated times in at least one file reach a set threshold value, and the data fingerprints of the hash fingerprint table are stored data fingerprints of all the data blocks.

Owner:HONOR DEVICE CO LTD

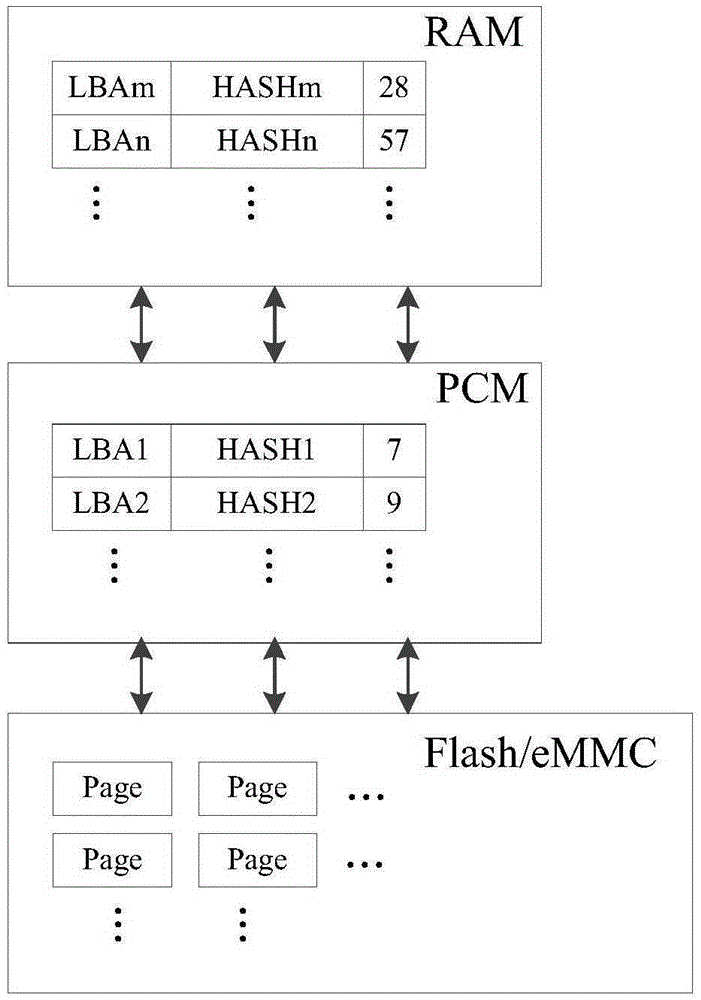

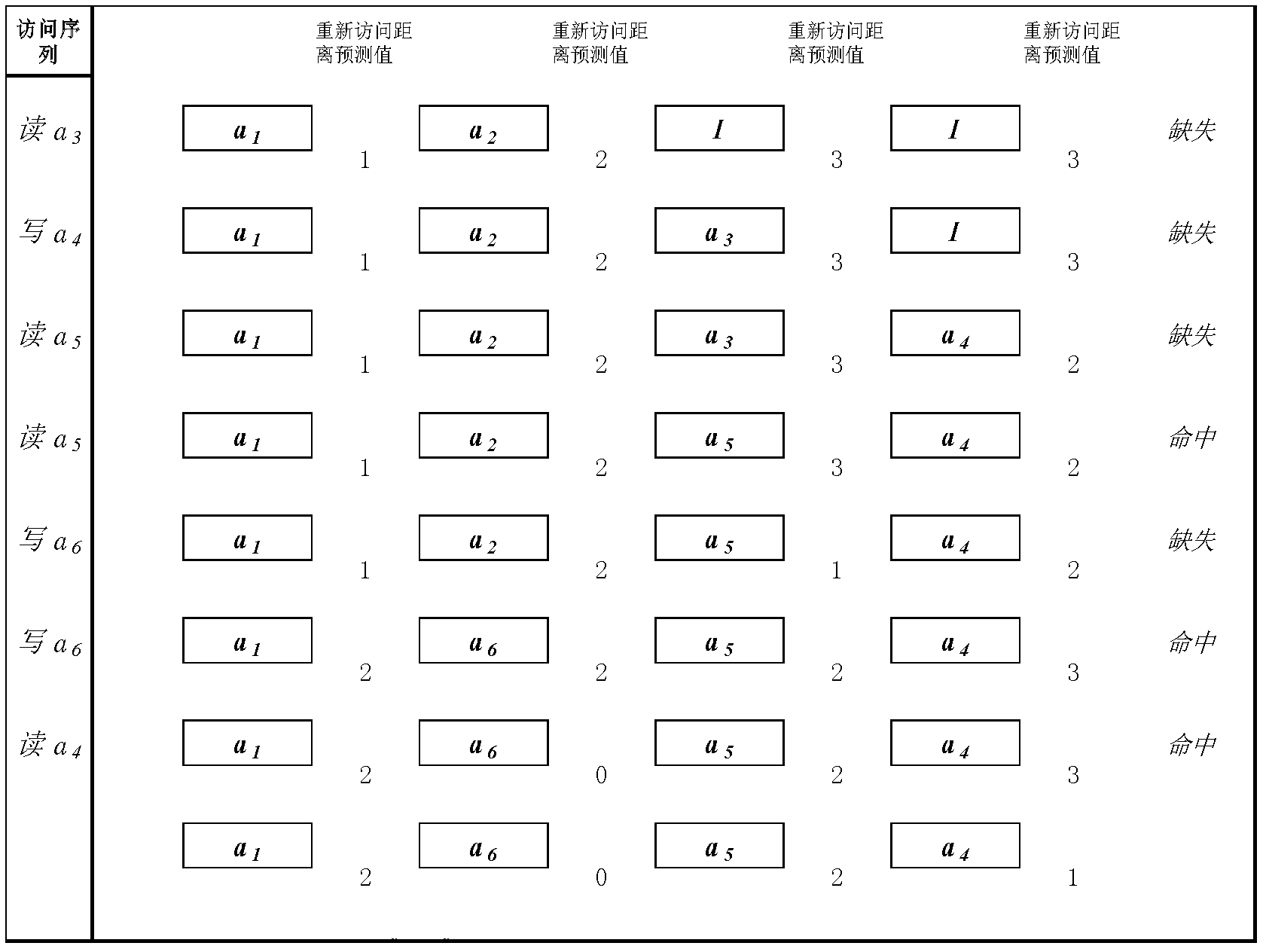

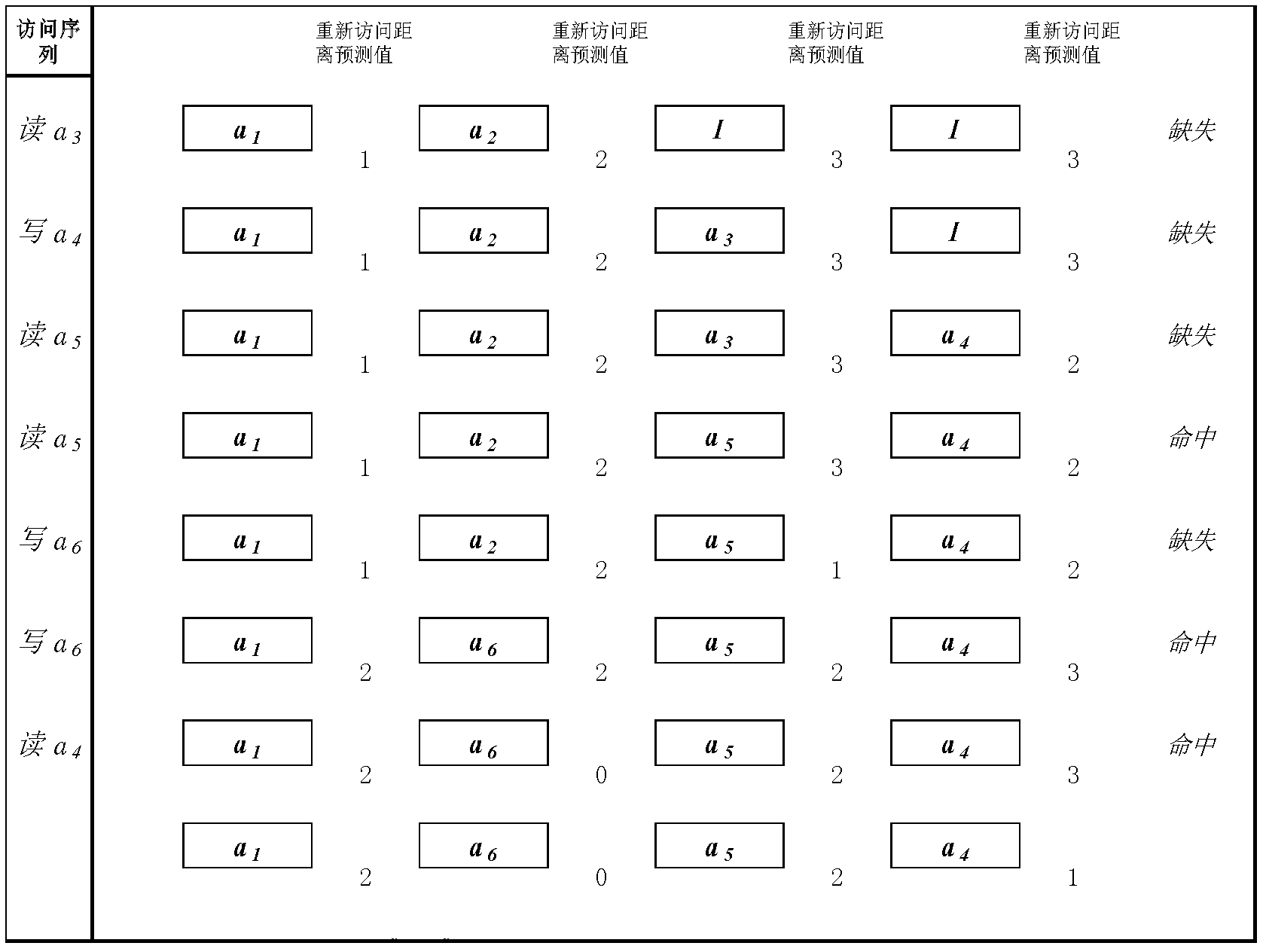

Read/write distinguished data storage replacing method based on phase change memory

ActiveCN102253901AReduce write operationsExtended service lifeMemory adressing/allocation/relocationMemory hierarchyPhase-change memory

The invention relates to read / write distinguished data storage replacing method based on a phase change memory and belongs to the technical field of computer system structures. The method provided by the invention comprises the following steps: defining the mark value of the M (M=2 or 3) bit width of each cache block as a re-access distance predicted value; in the case of data block replacement, selecting the block with the greatest re-access distance predicted value to replace; when a new data block is inserted and hit, setting the re-access distance predicted value as a different value according to the difference in read / write types. As the re-access distance predicted value assigned to the write access data is relatively small, the write access data is protected preferably in a cache region, and the frequency of replacing the write access data into the phase change memory is reduced. The method provided by the invention is applied to the superior storage layer of the phase change memory, and can be used for effectively reducing write operations on the phase change memory and prolonging the service life of the phase change main memory on the premise of ensuring the overall performance. The method provided by the invention has the characteristics of small storage cost and simplicity in realization.

Owner:TSINGHUA UNIV

Segmented column virtual ground scheme in a static random access memory (SRAM) circuit

InactiveUS7372721B2Total current dropReduce voltageRead-only memoriesDigital storageStatic random-access memoryRandom access memory

A static random access memory (SRAM) cell array is provided that reduces leakage current. The SRAM cell array is configured in a plurality of columns. Each of the columns comprises: a column virtual ground node; a column switch for selectively coupling the column virtual ground node to one of a ground or a nominal low voltage; and a plurality of segments. Each of the segments comprises: a segment virtual ground node; a plurality of SRAM cells including a virtual ground signal coupled to the segment virtual ground node; and a virtual ground switch for selectively coupling the segment virtual ground node to one of either a nominal low voltage or the column virtual ground node. A method for operating the SRAM cell array is also described.

Owner:SACHDEV MANOJ +1

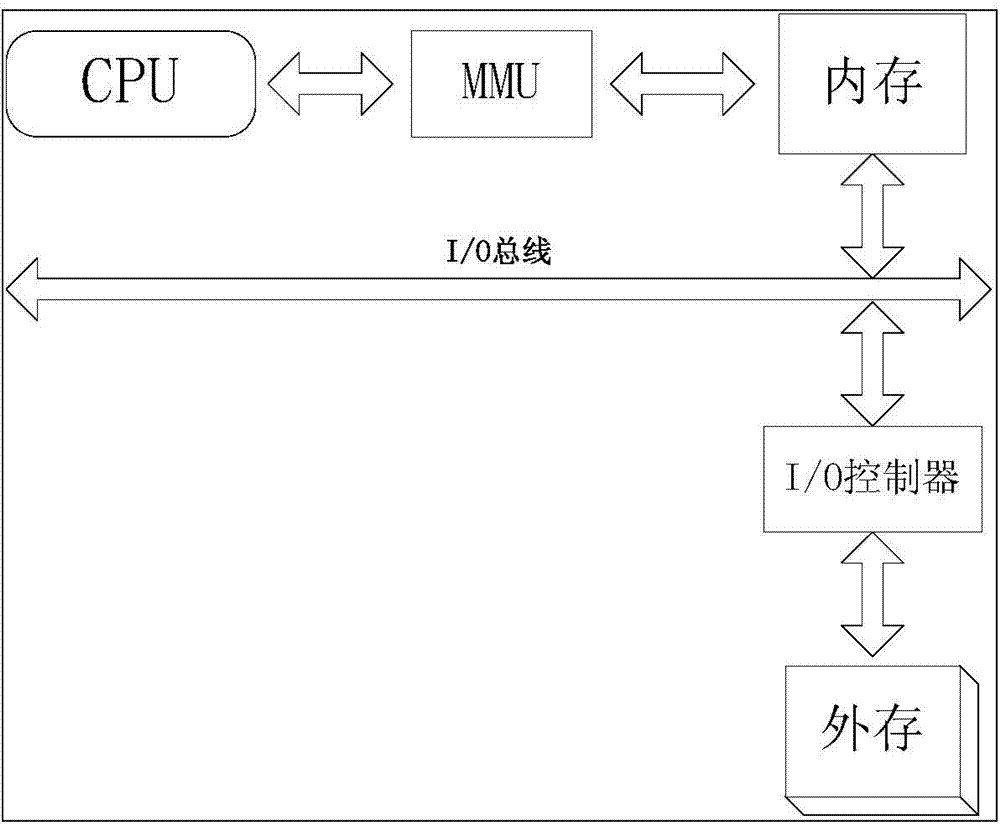

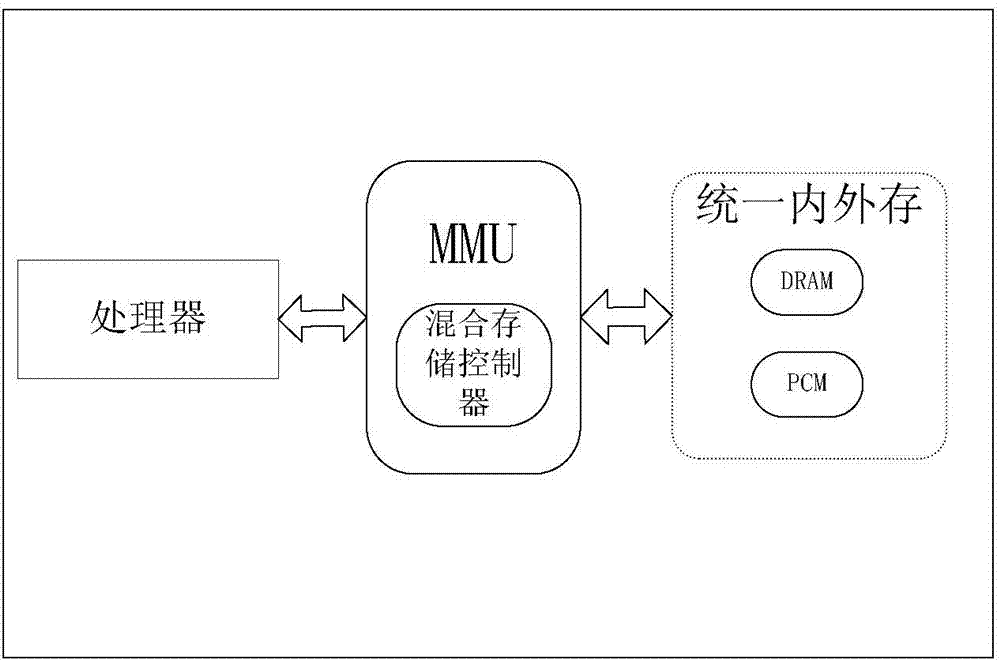

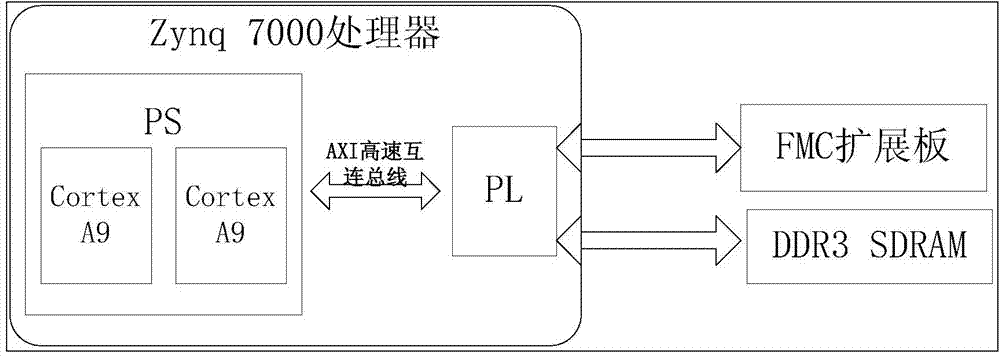

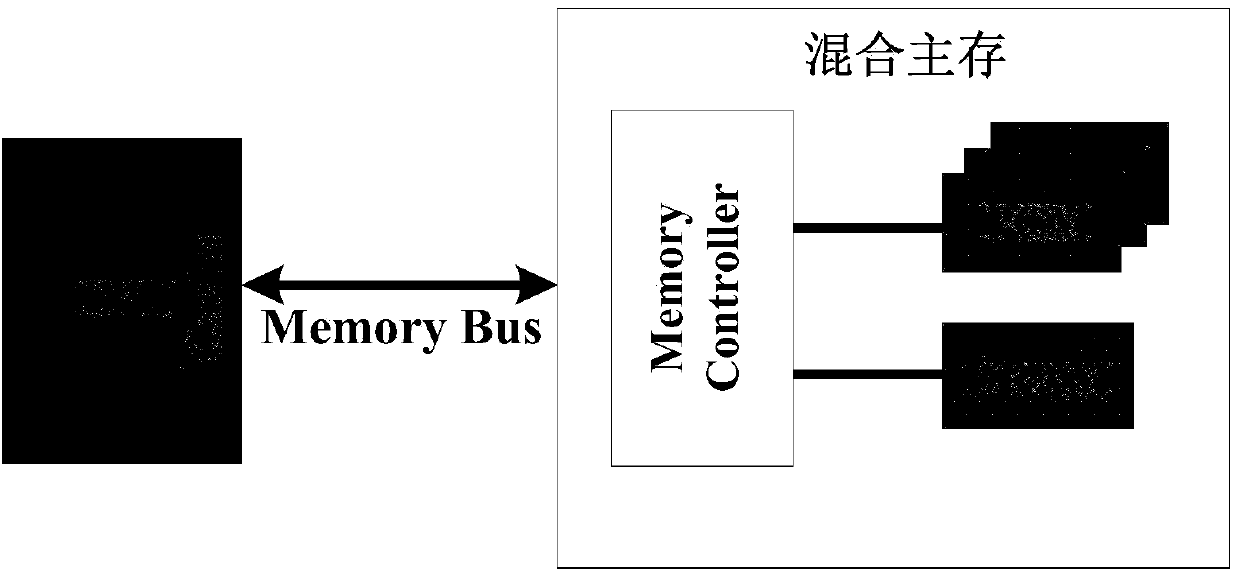

Uniform internal and external memory architecture based on MMU (memory management unit)

InactiveCN103927130AAvoid accessProtection securityInput/output to record carriersEnergy efficient computingInternal memoryAddress mapping

The invention discloses uniform internal and external memory architecture based on an MMU (memory management unit). The uniform internal and external memory architecture comprises a processor which is communicated with the MMU. The MMU is communicated with external equipment. The MMU comprises a management module and a memory control module. The external equipment comprises a DDR3SDRAM and a PCM. The management module comprises an internal memory mapping module, an internal memory protecting module and a dynamic data management module. The internal memory mapping module comprises an address mapping module and a mapping table which are communicated. The internal memory protecting module and the dynamic data management module receive data transmitted by the address mapping module. The uniform internal and external memory architecture has the advantages that various types of memories are used as mixed memories under the uniform internal and external memory architecture and used for storing data and executing programs, and a storage function good in performance and low in energy consumption is provided for a system by using the characteristics of different memories.

Owner:SHANDONG UNIV

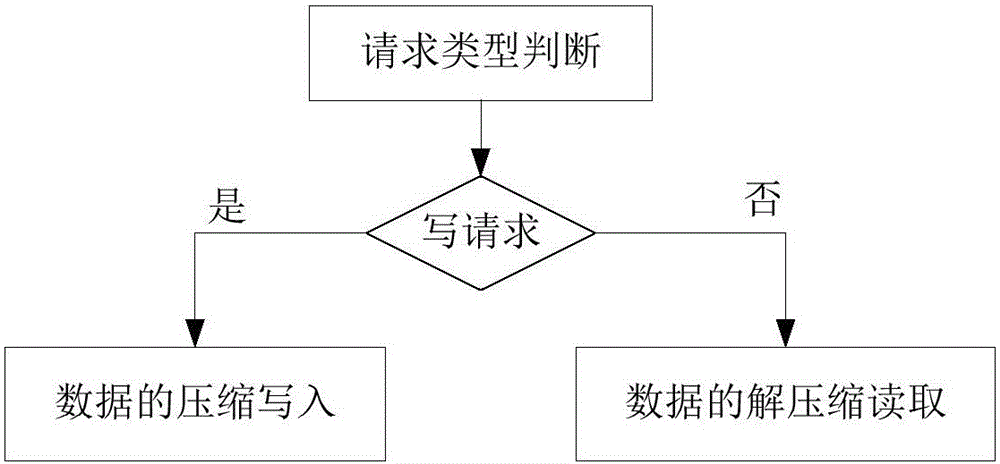

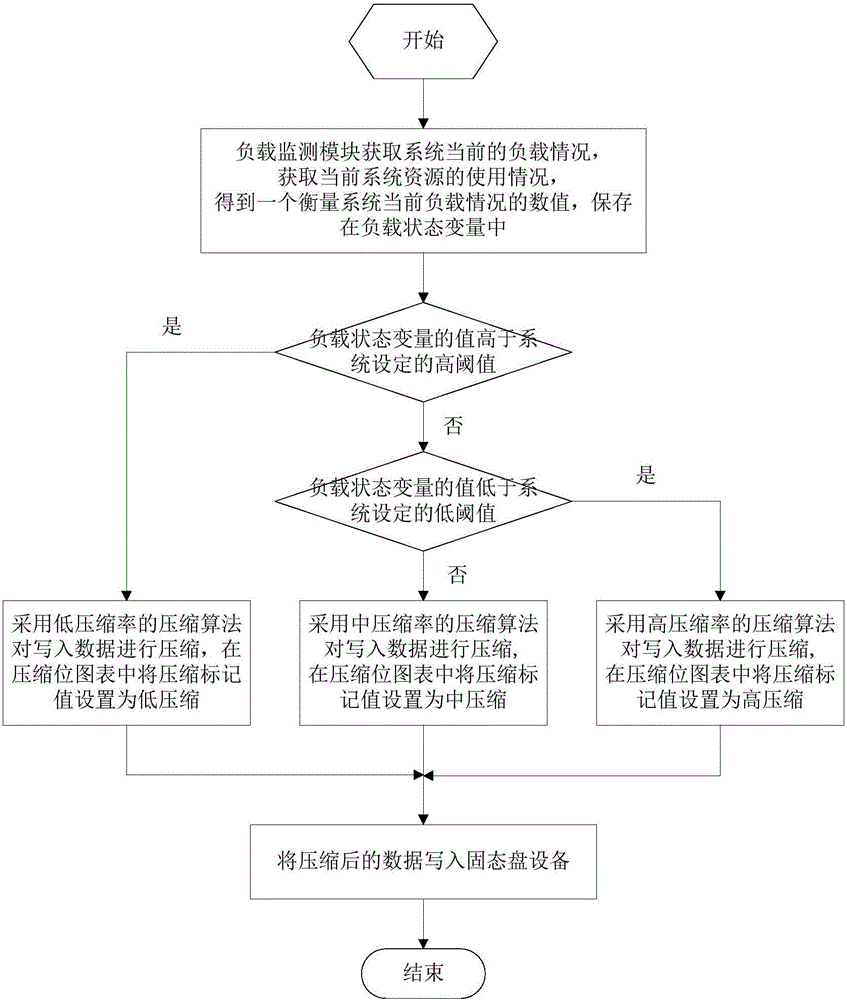

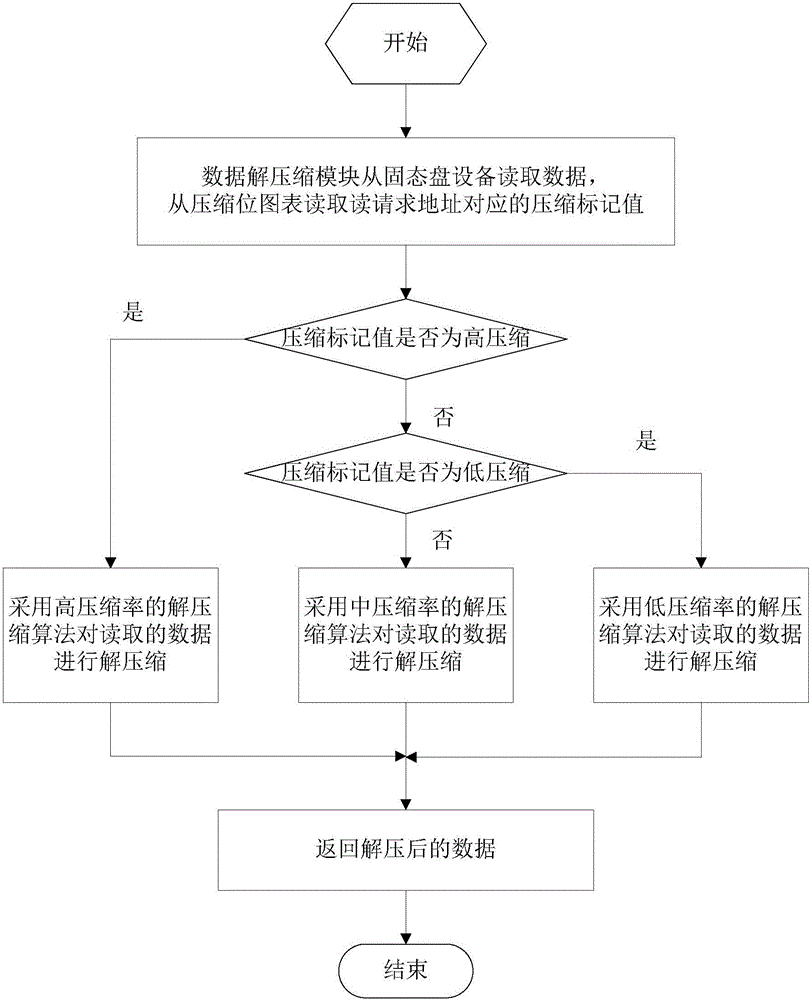

Dynamic data compression method for solid-state disc storage system

InactiveCN105094709AImprove performance and reliabilityReduce write operationsInput/output to record carriersSolid-stateData compression

The invention discloses a dynamic data compression method for a solid-state disc storage system and relates to the field of computer storage. The redundancy characteristic of data in the storage system is fully utilized, and through a dynamic data compression technology, the redundant information is reduced and the written data quantity is reduced, so that a problem of asymmetry of read-write performance of a solid-state disc is relieved while the space utilization and reliability of the solid-state disc are improved. A compression bit chart and three function modules, namely a load monitoring module, a data compression module and a data decompression module, are arranged on the solid-state disc storage system; and the method comprises a request type judging step, a data compression and writing step and a data decompression reading step. According to the current load state of the system, the written data is dynamically compressed, so that the service ability of the system is unaffected, the written data is fully compressed, more written data is reduced, and the performance and the reliability of a solid-state disc storage device are improved.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD +1

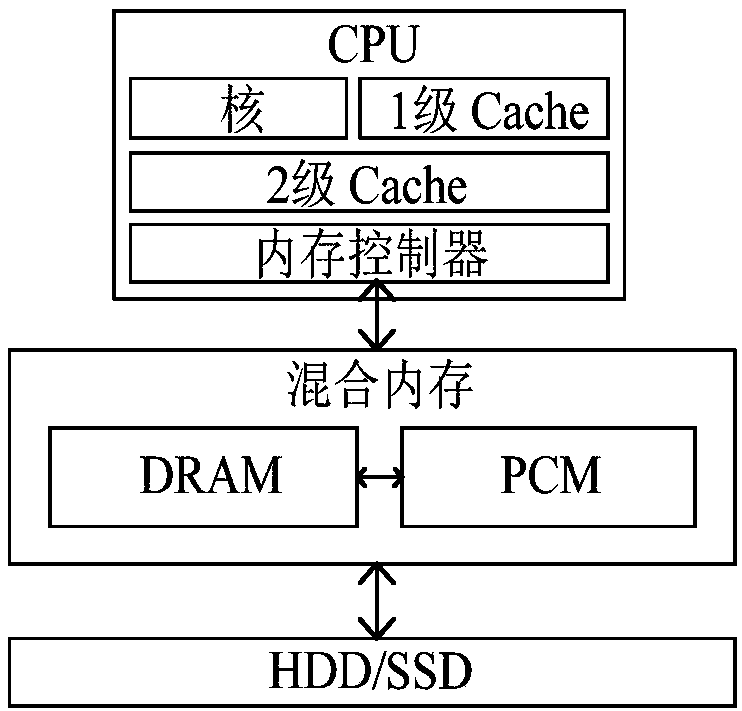

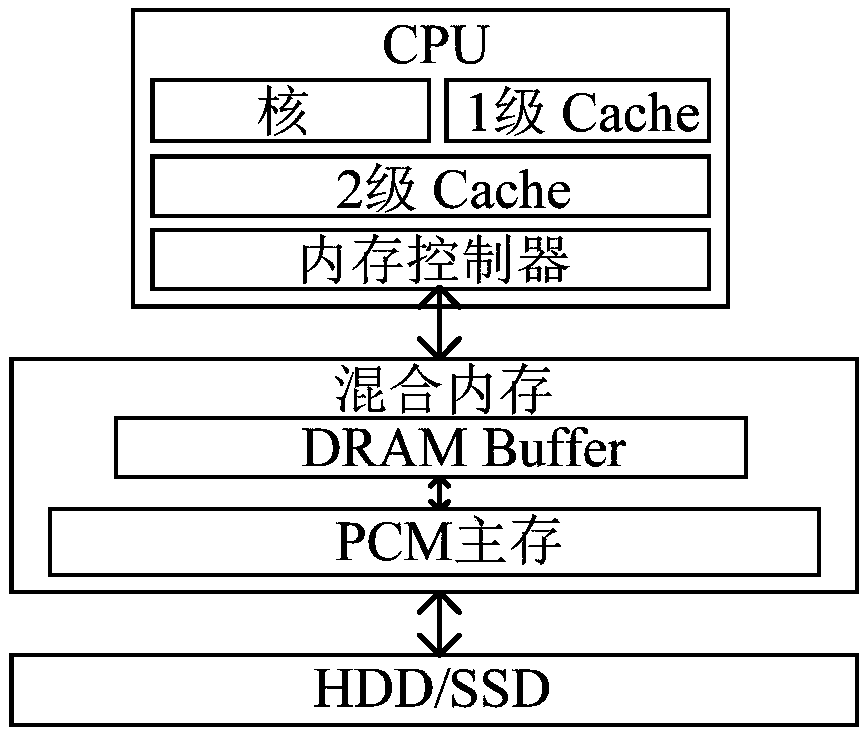

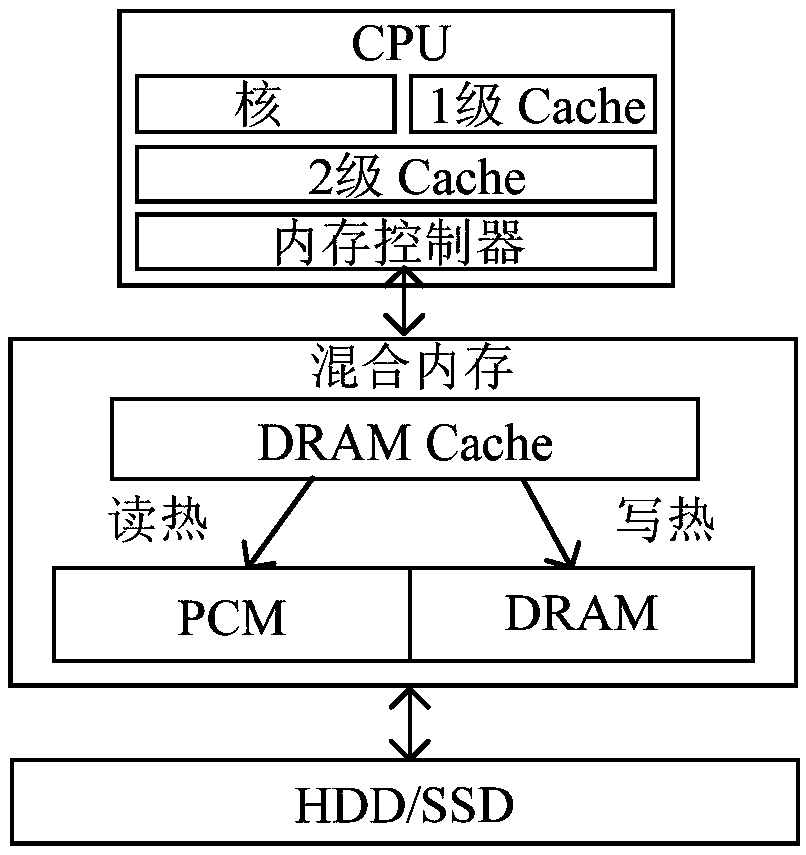

PCM and DRAM-based hybrid memory system and management method thereof

InactiveCN108762671AImprove I/O access performanceImprove access performanceInput/output to record carriersEnergy efficient computingDram cachePhase change

The invention discloses a PCM and DRAM-based hybrid memory system and a management method thereof. The hybrid memory system comprises an MB level small capacity DRAM as a cache, a GB level large capacity DRAM and GB level non-volatile phase change storage medium PCM as master memories. The management method comprises the steps of (10) small capacity DRAM cache: managing based on improved two-levelcache algorithms of LRU and LFU-Aging; (20) large capacity DRAM as master memory: managing a write oriented data page by using an LRU replacement algorithm; and (30) the phase change storage medium PC as master memory: managing a read oriented data page by using an inter-group abrasion balance method and an LRU replacement algorithm. The hybrid memory system and management method have advantagesof high performance and low energy consumption of the hybrid memory I / O, and write load balance and long service life of PCM.

Owner:ARMY ENG UNIV OF PLA

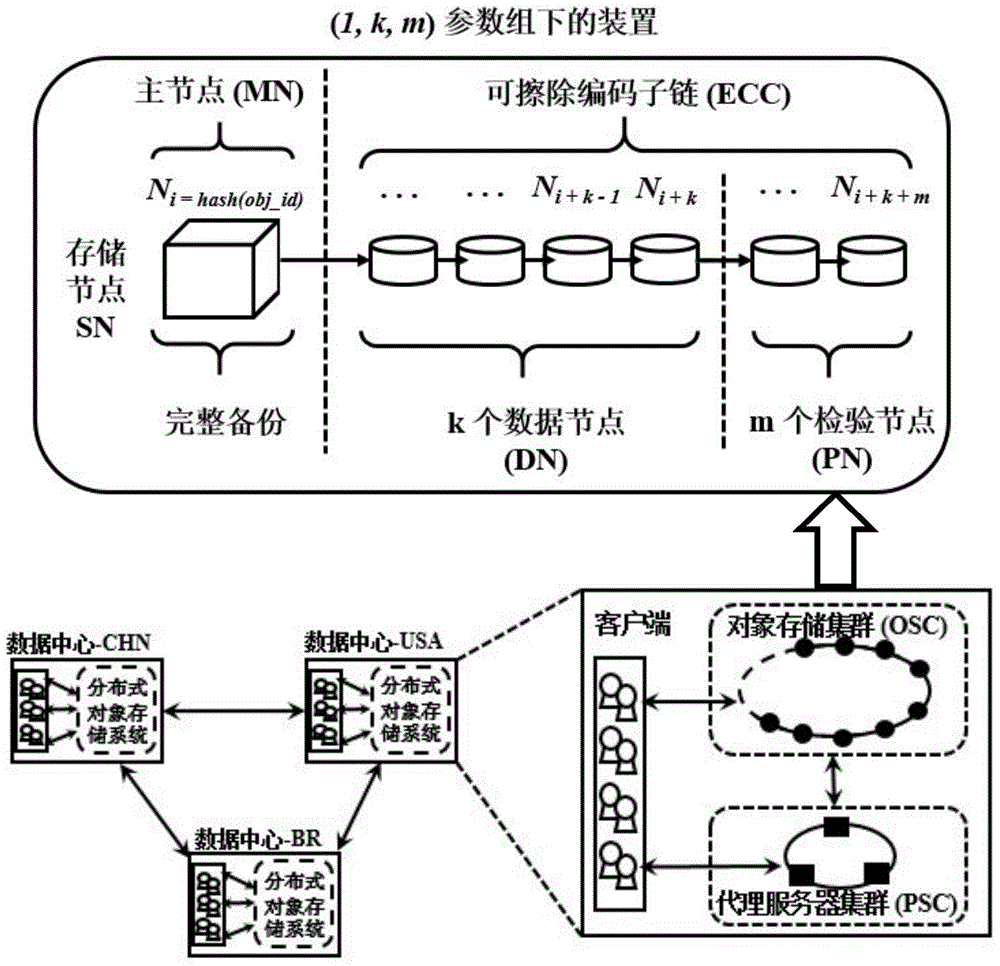

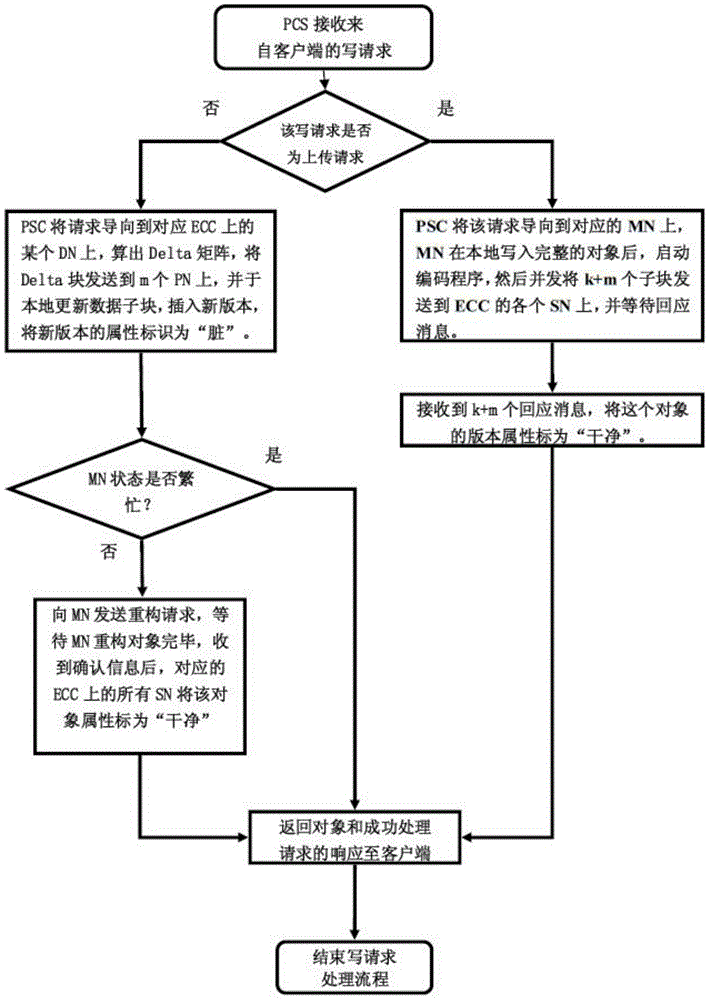

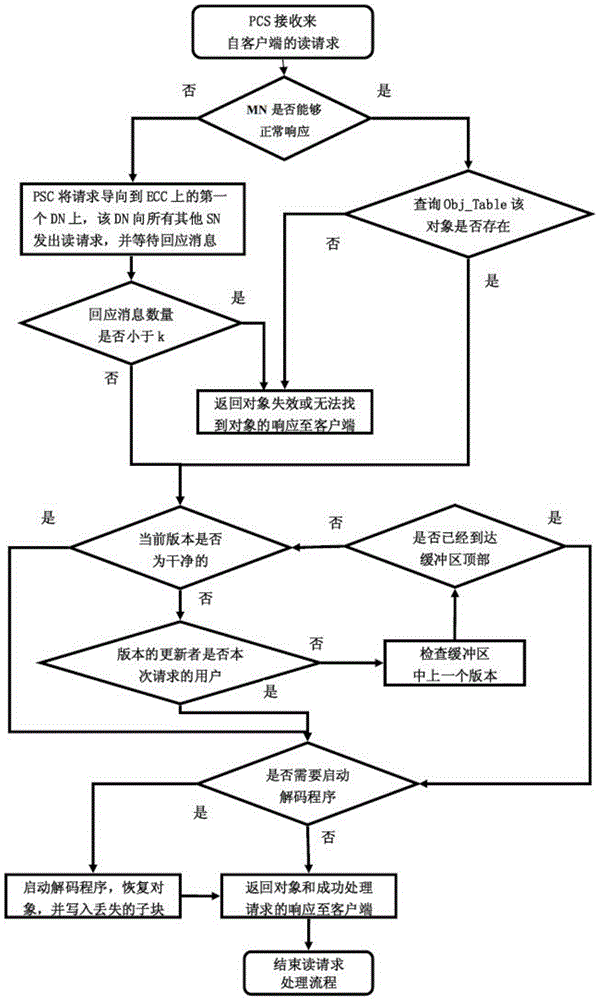

Erasable encoding and chained type backup-based distributed storage system

ActiveCN104902009AReduce overheadReduce transmission overheadDatabase distribution/replicationTransmissionProxy serverObject storage

The invention discloses an erasable encoding and chained type backup-based distributed storage system. The erasable encoding and chained backup-based distributed storage system includes a proxy server cluster composed of a plurality of proxy servers and an object storage cluster composed of a plurality of physical storage nodes. According to the devices, a traditional chained type backup method and encoding erasable storage method which are applied to the distributed storage system are combined together, so that excellent balance between reading and writing performance and storage space efficiency can be realized. Compared with a traditional multi-duplicate backup method, the devices of the invention can greatly reduce storage cost and maintain equally efficient reading and writing response performance; and compared with a pure encoding erasable storage scheme, the devices of the invention greatly improve the reading and writing efficiency of data objects and enhance the availability of the distributed storage system.

Owner:ZHEJIANG UNIV

Method and apparatus for search

ActiveUS20160275178A1Memory occupancyReduce readWeb data indexingSpecial data processing applicationsReverse indexLow frequency

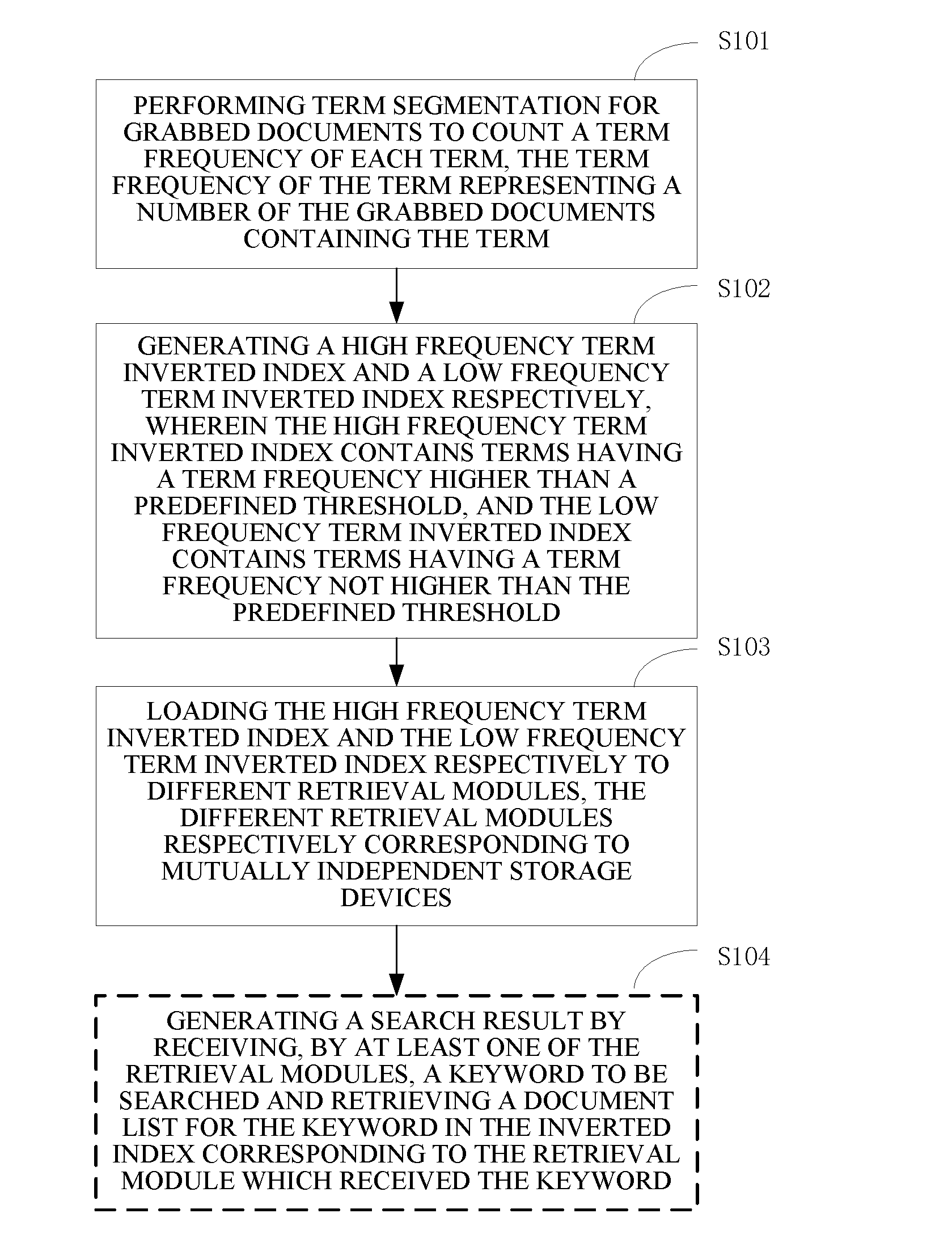

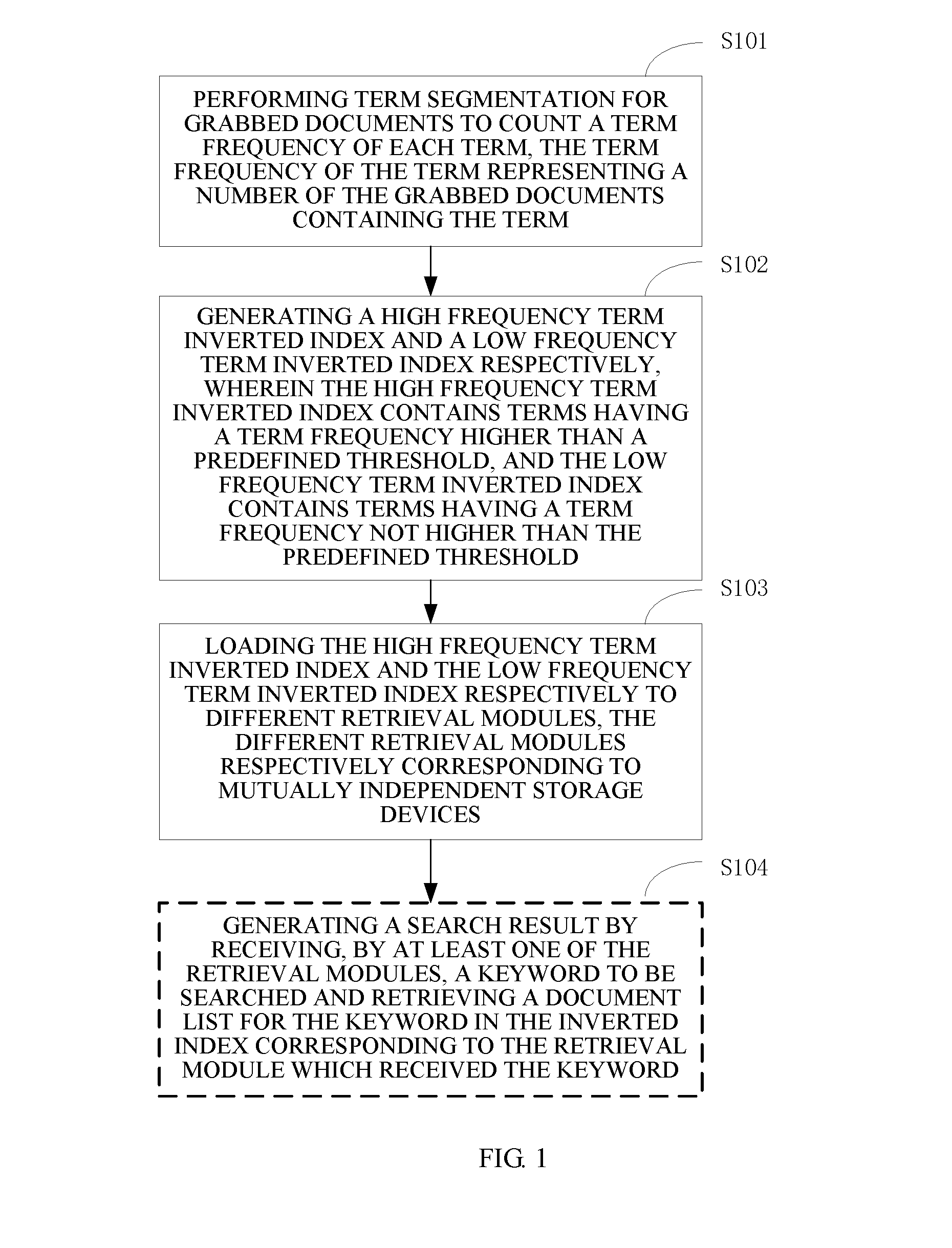

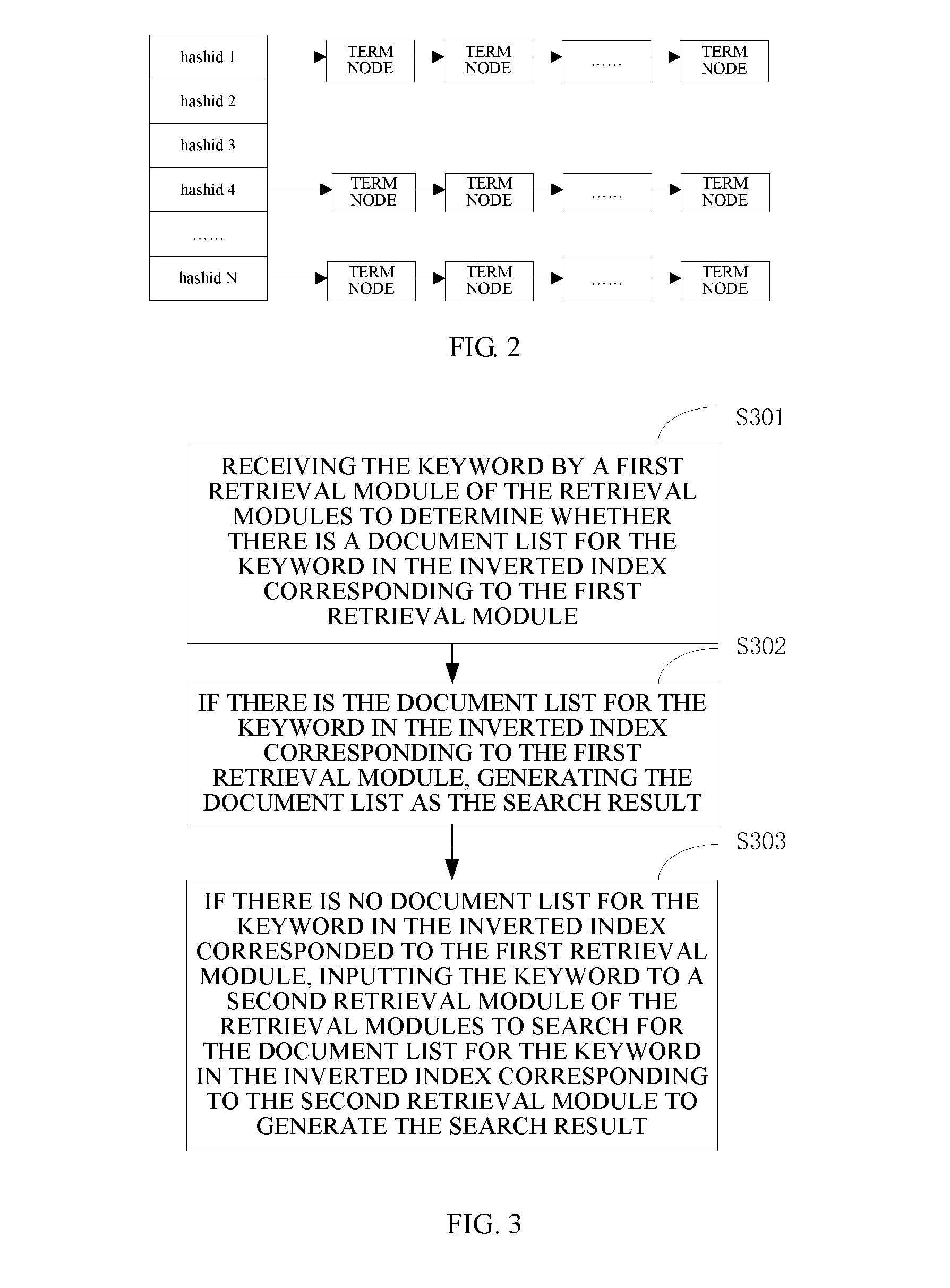

Methods and apparatuses for search are provided and related to the field of search technology. A method may include: performing term segmentation for grabbed documents to count a term frequency of each term, the term frequency of the term representing a number of the grabbed documents containing the term; generating a high frequency term inverted index and a low frequency term inverted index respectively, wherein the high frequency term inverted index contains terms having a term frequency higher than a predefined threshold, and the low frequency term inverted index contains terms having a term frequency not higher than the predefined threshold; and loading the high frequency term inverted index and the low frequency term inverted index respectively to different retrieval modules, the different retrieval modules respectively corresponding to mutually independent storage devices.

Owner:TENCENT TECH (SHENZHEN) CO LTD

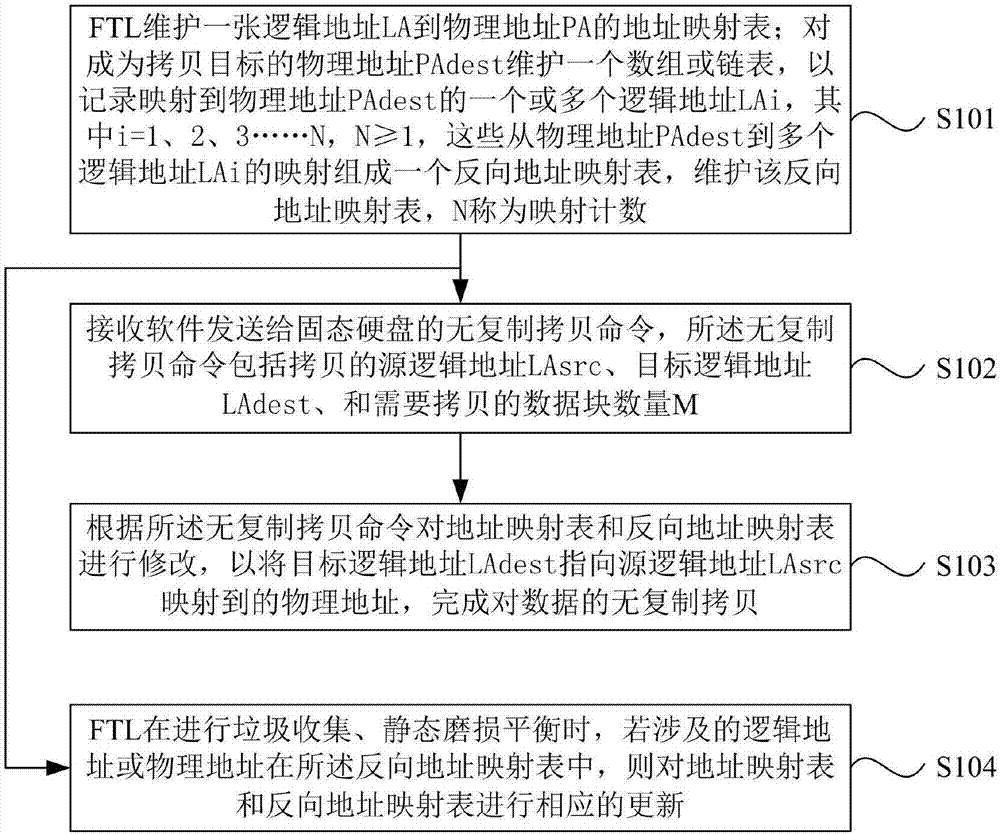

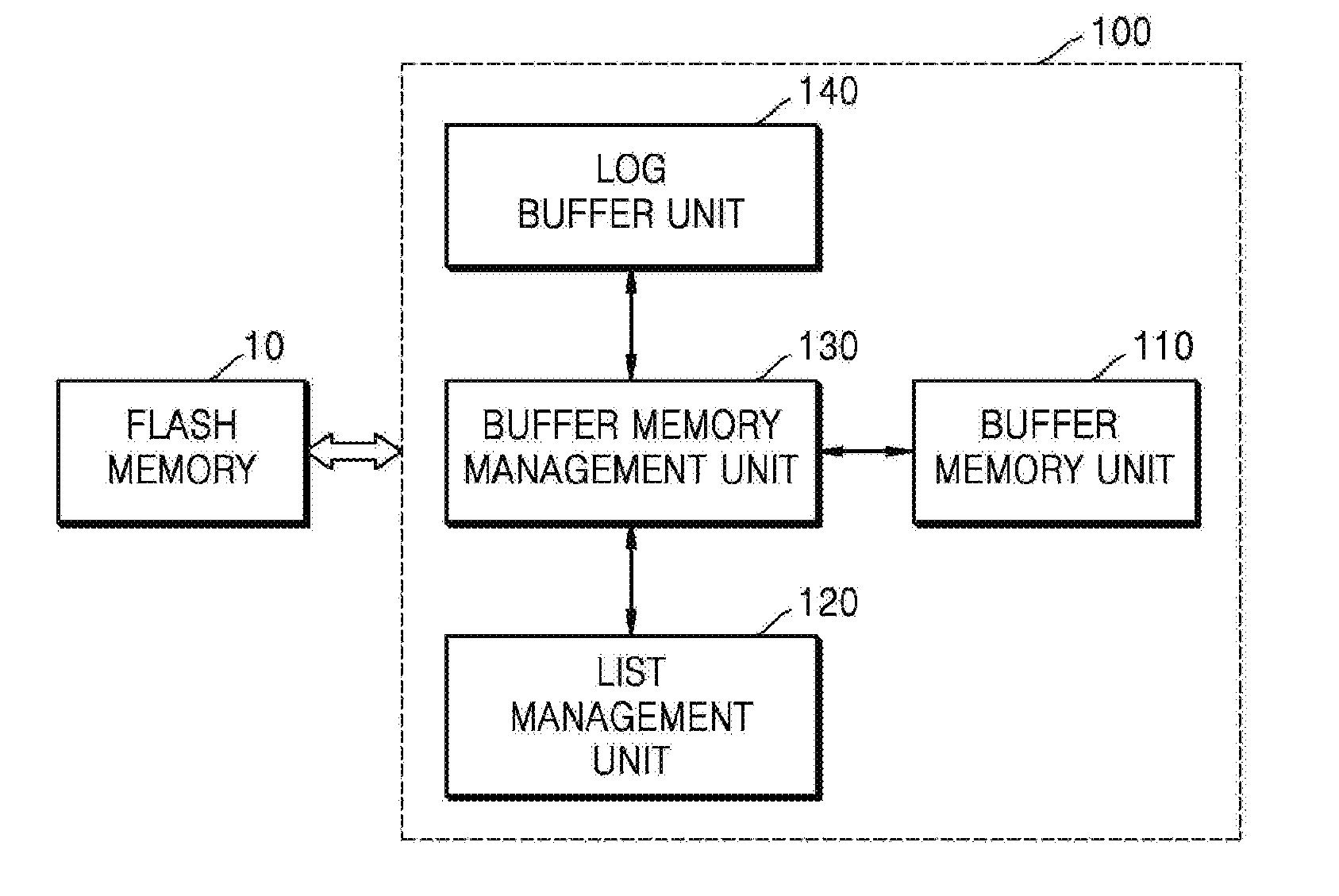

Method and system of achieving data copying of solid-state hard disk FTL and solid-state hard disk

ActiveCN107391391AReduce write operationsExtended service lifeMemory architecture accessing/allocationMemory adressing/allocation/relocationData reliabilityAddress mapping

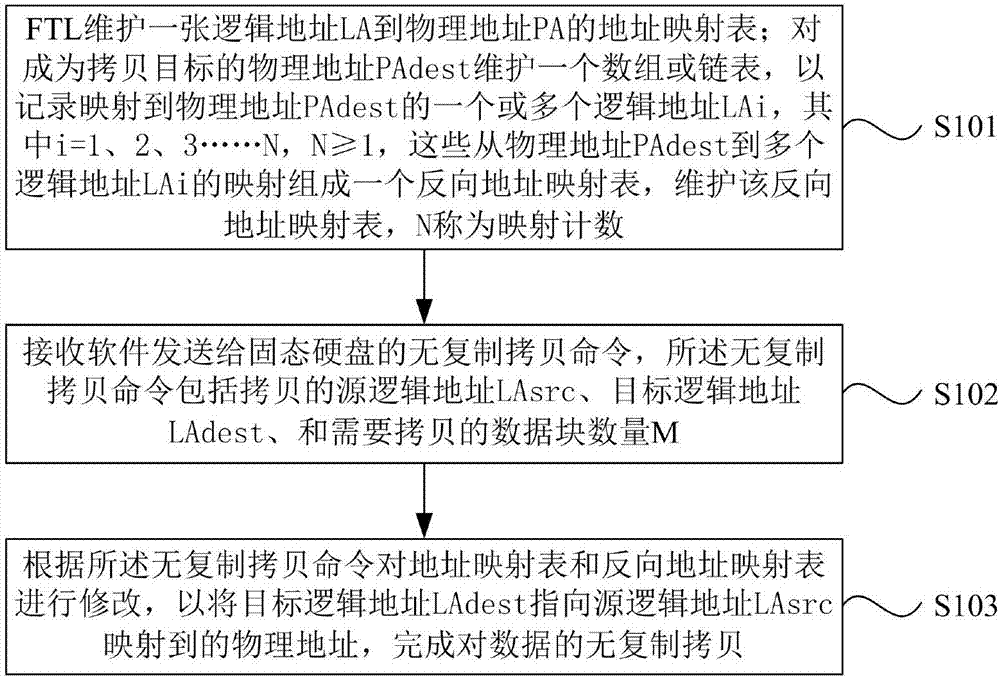

The invention discloses a method and system of achieving data copying of solid-state hard disk FTL and a solid-state hard disk. The method comprises the steps of maintaining an address mapping list from a logical address LA to a physical address PA; maintaining an array or linked list of the physical address PAdest which becomes a destination of a copy, forming a reverse address mapping list from the mapping of the physical address PAdest to multiple logical address LAi, and maintaining the reverse address mapping list; receiving a copy-free copy command sent by a software to the solid-state hard disk, wherein the copy-free copy command includes a source logical address LAsrc of the copy, a destination logical address LAdest, and the number of data blocks which need to be copied; modifying the address mapping list and the reverse address mapping list based on a copy-free command, directing the destination logical address LAdest to the physical address to which the source logical address LAsrc is mapped, and completing the copy-free copying of the data. According to the method and system of achieving the data copying of solid-state hard disk FTL, unnecessary writing operations in the solid-state hard disk can be greatly reduced, the copying time is reduced, the service life of the solid-state hard disk is prolonged, and data reliability is improved.

Owner:SHENZHEN DAPU MICROELECTRONICS CO LTD

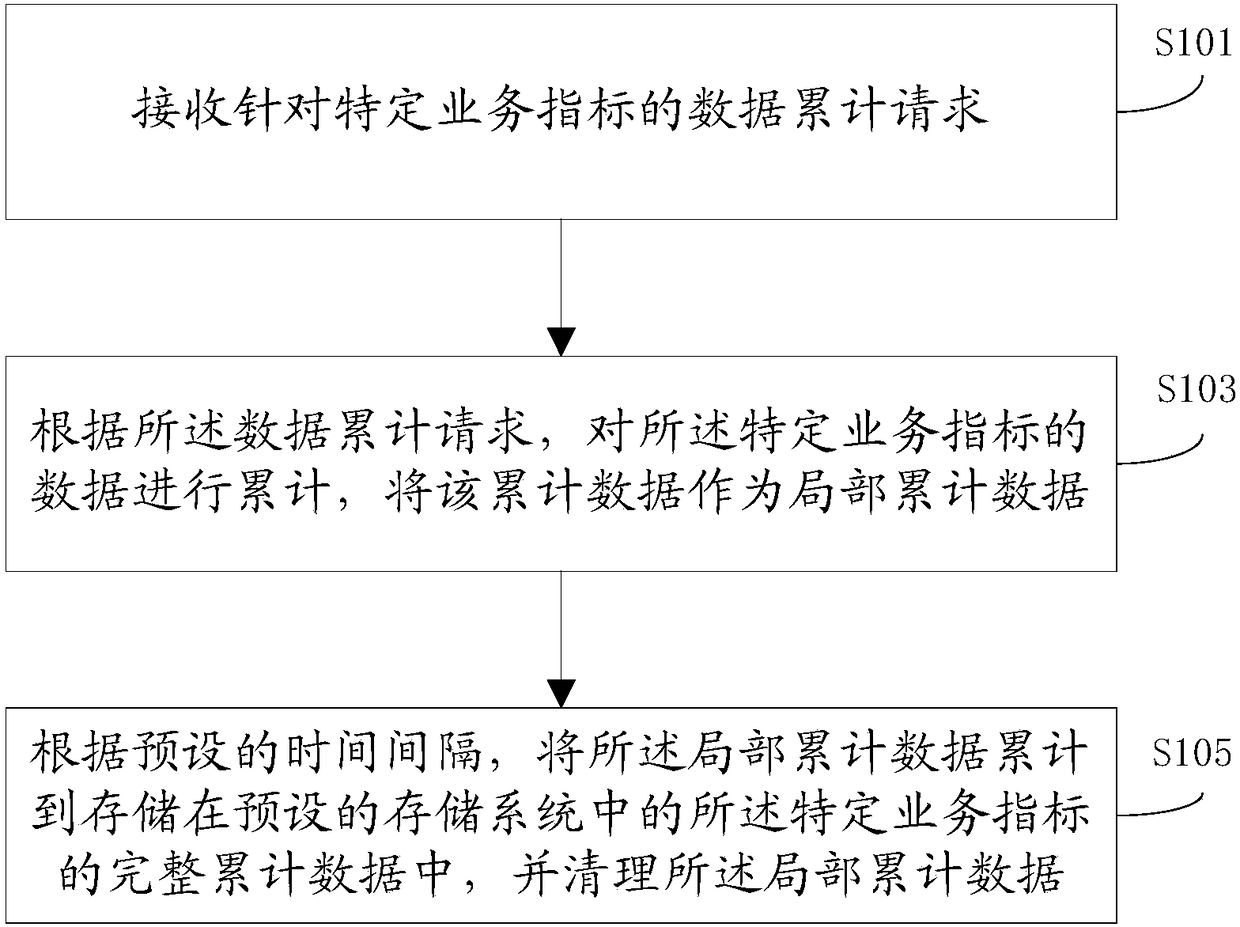

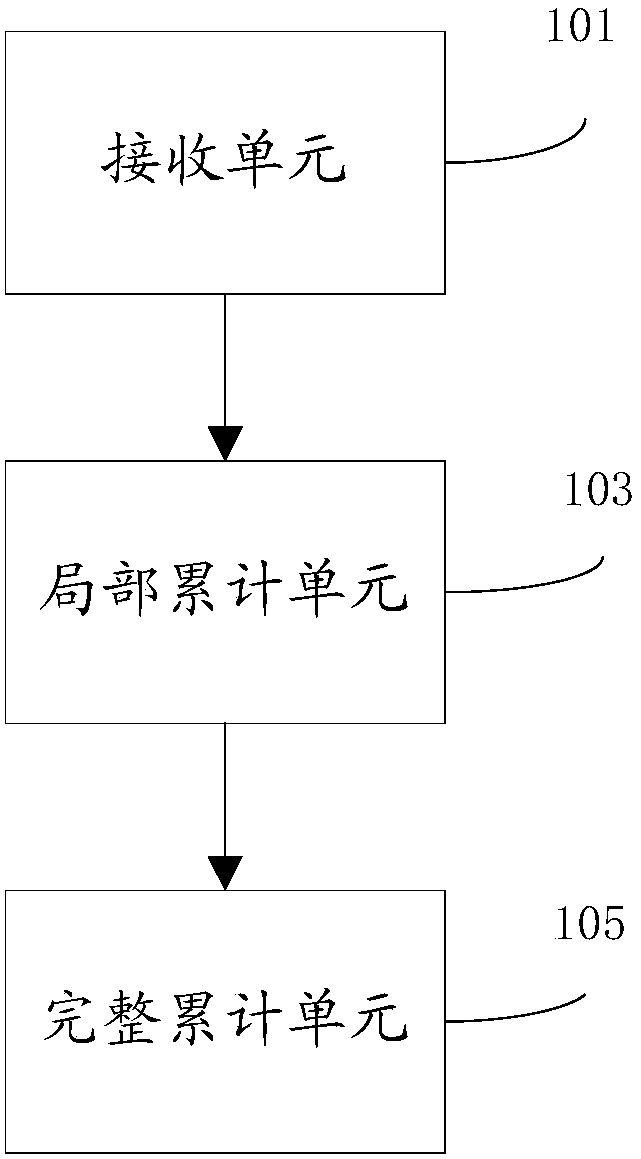

Data accumulation methods and devices and electronic equipment

InactiveCN108153758AReduce dependency costsReduce write operationsSpecial data processing applicationsLevel dataDatabase

The application discloses data accumulation methods. One of the methods includes: receiving a data accumulation request for a specific service index; accumulating data of the specific service index according to the data accumulation request, and using the accumulated data as local accumulated data; and accumulating and storing the local accumulated data into complete accumulated data of the specific service index in a preset storage system according to a preset time interval, and clearing the local accumulated data. According to the processing manner, a timeout reporting strategy is adopted, user-level data counting is regularized and merged into service-level data counting, and millions of service request writing operations can be reduced to be below a thousand-to-hundred level; and thuscosts of relying on writing performance of the data storage system can be effectively reduced.

Owner:ALIBABA GRP HLDG LTD

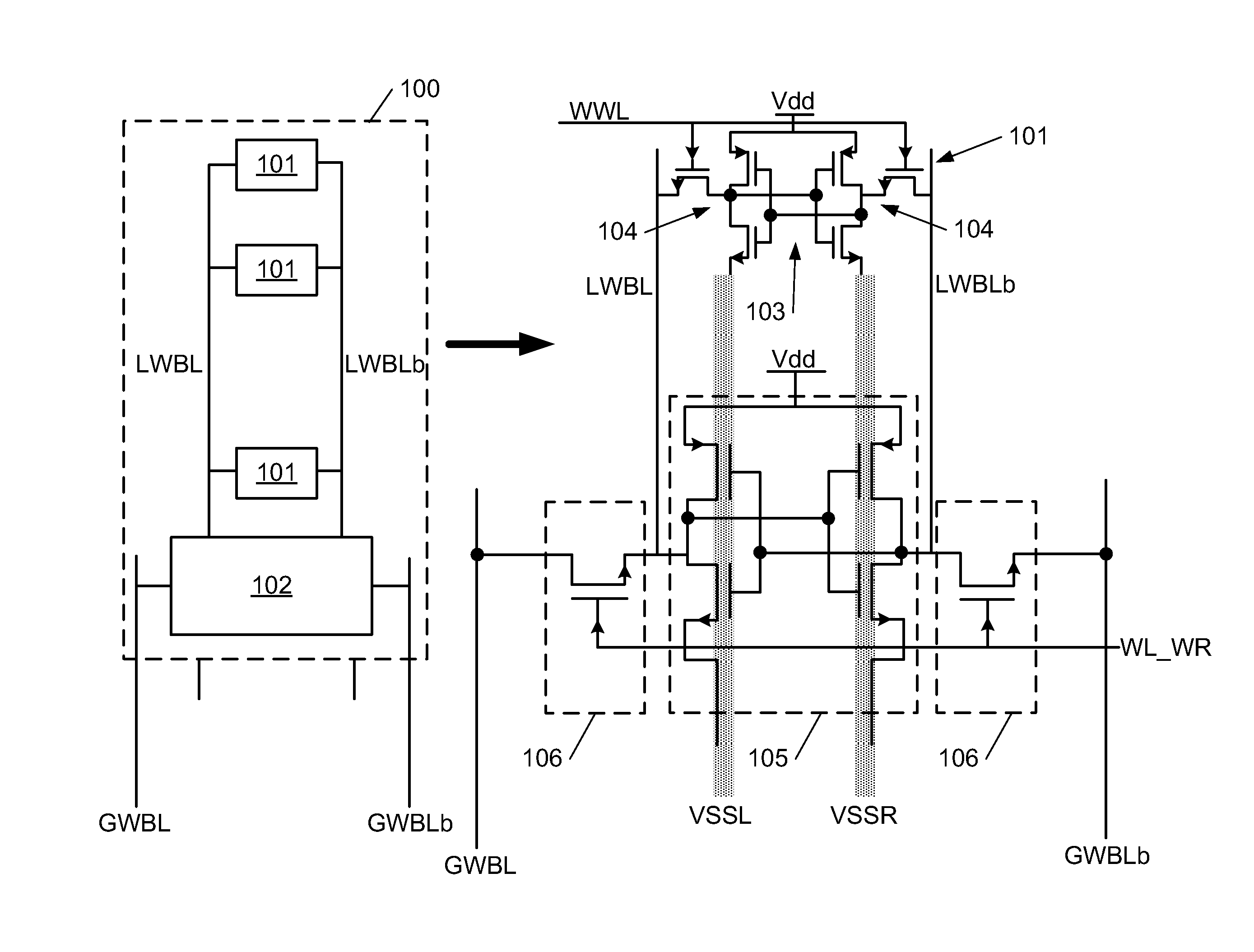

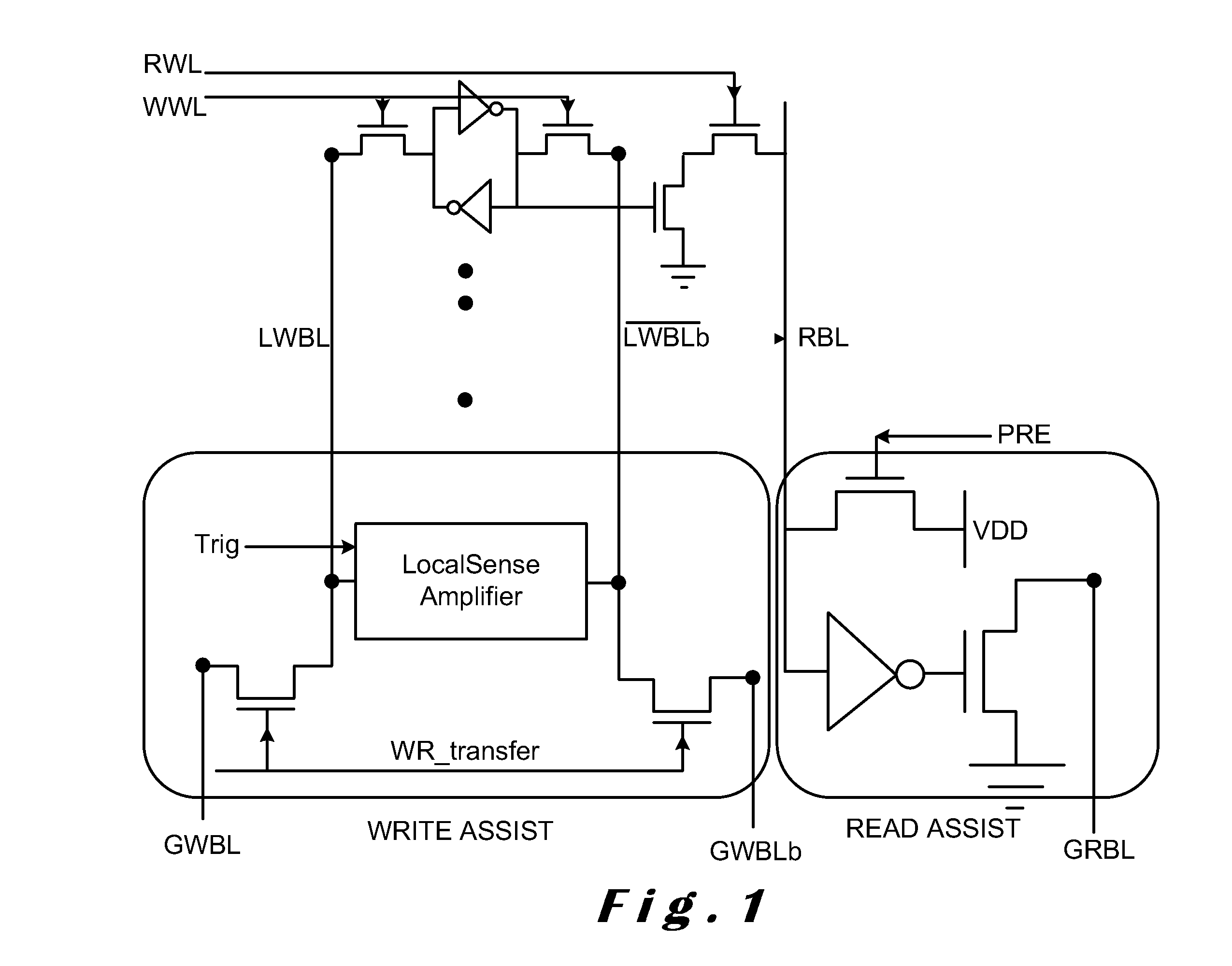

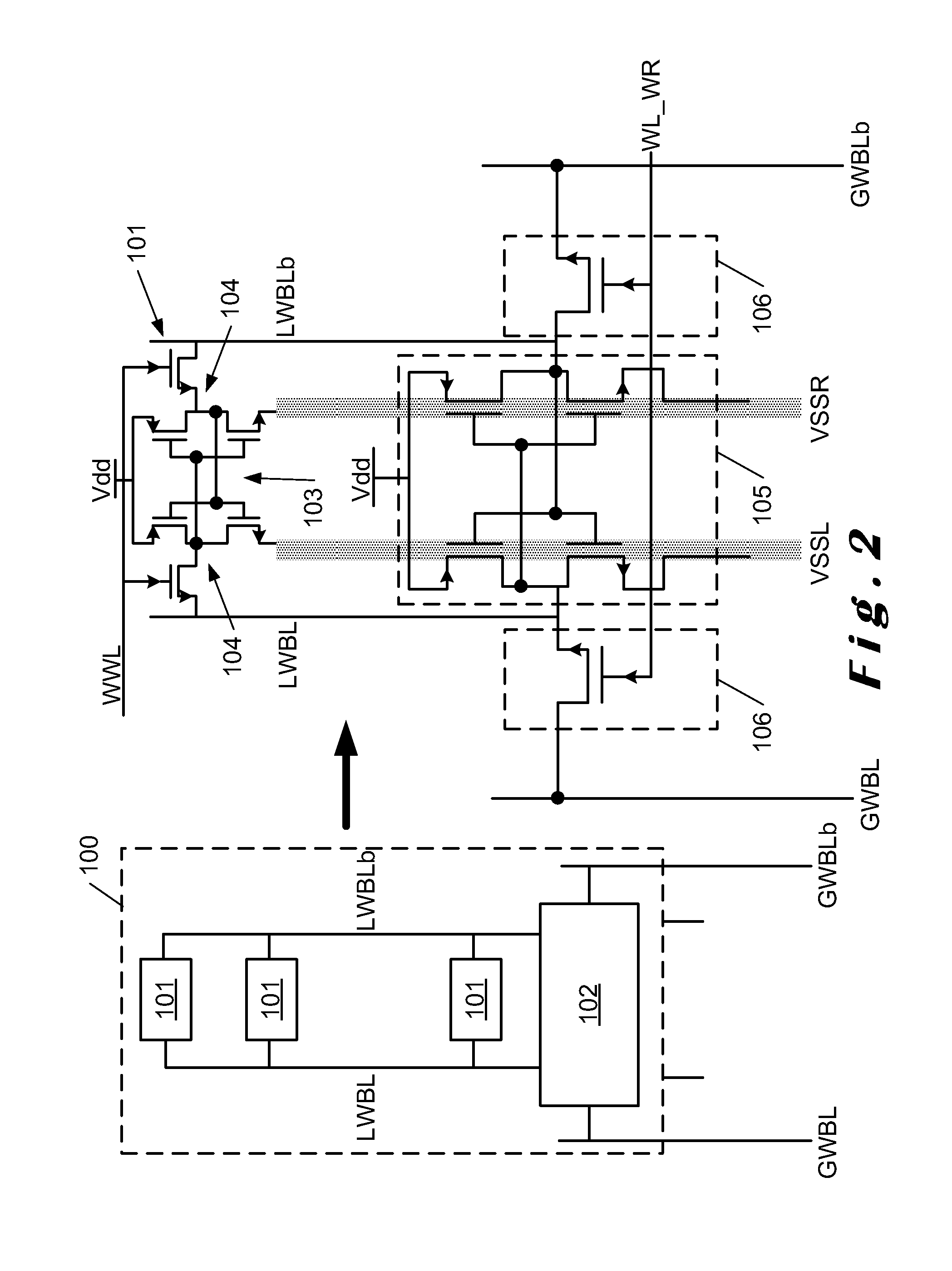

Local write and read assist circuitry for memory device

ActiveUS20140071737A1Reduce write operationsReduce power consumptionDigital storageBit lineHemt circuits

A memory device having complementary global and local bit-lines, the complementary local bit-lines being connectable to the complementary global bit-lines by means of a local write receiver which is configured for creating a full voltage swing on the complementary local bit lines from a reduced voltage swing on the complementary global bit lines. The local write receiver comprises a connection mechanism for connecting the local to the global bit-lines and a pair of cross-coupled inverters directly connected to the complementary local bit lines for converting the reduced voltage swing to the full voltage swing on the complementary local bit lines.

Owner:STICHTING IMEC NEDERLAND +1

Semiconductor device and operating method thereof

ActiveUS20160259723A1Small sizeReduce erase operationsMemory architecture accessing/allocationMemory adressing/allocation/relocationComputer hardwarePower semiconductor device

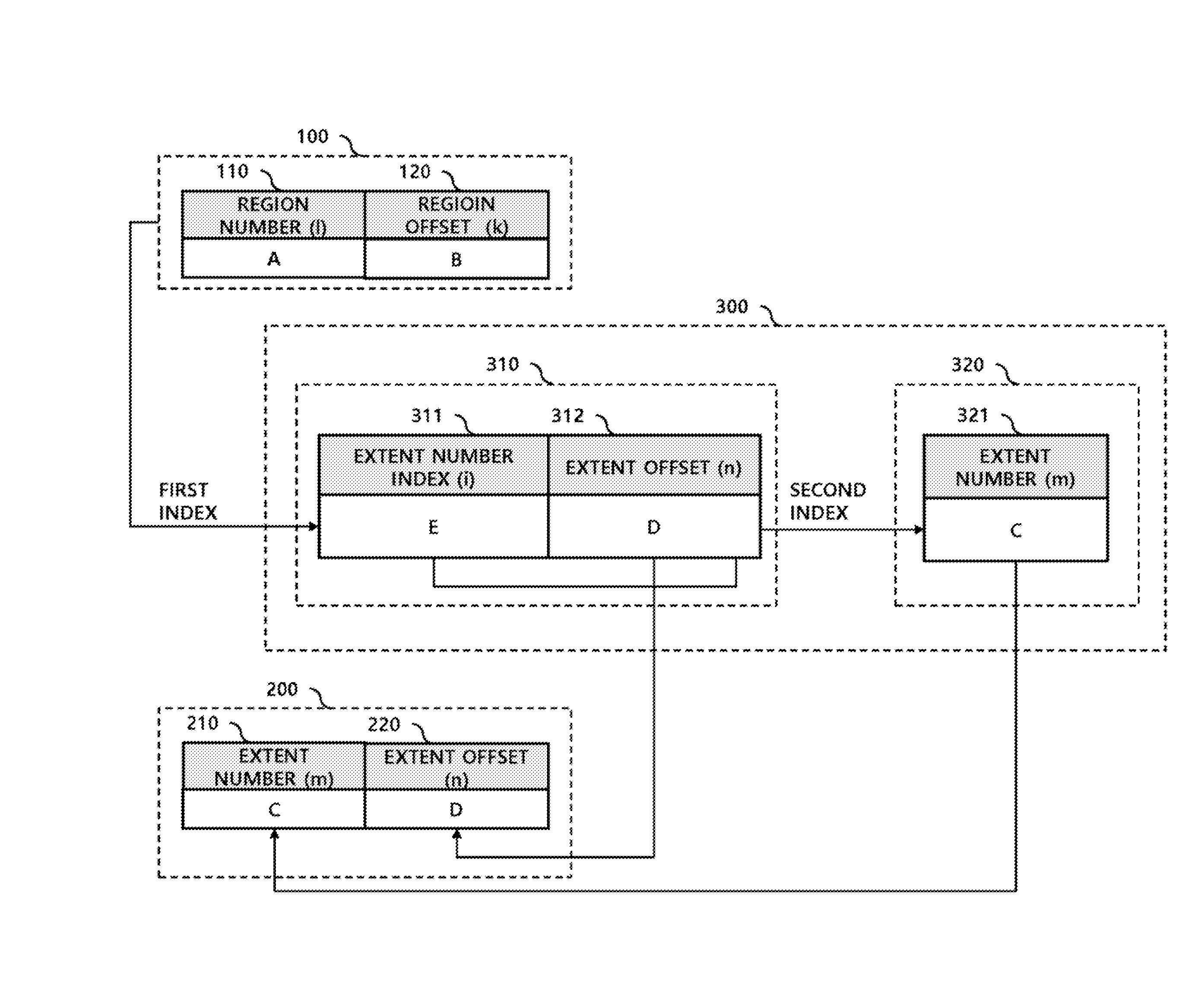

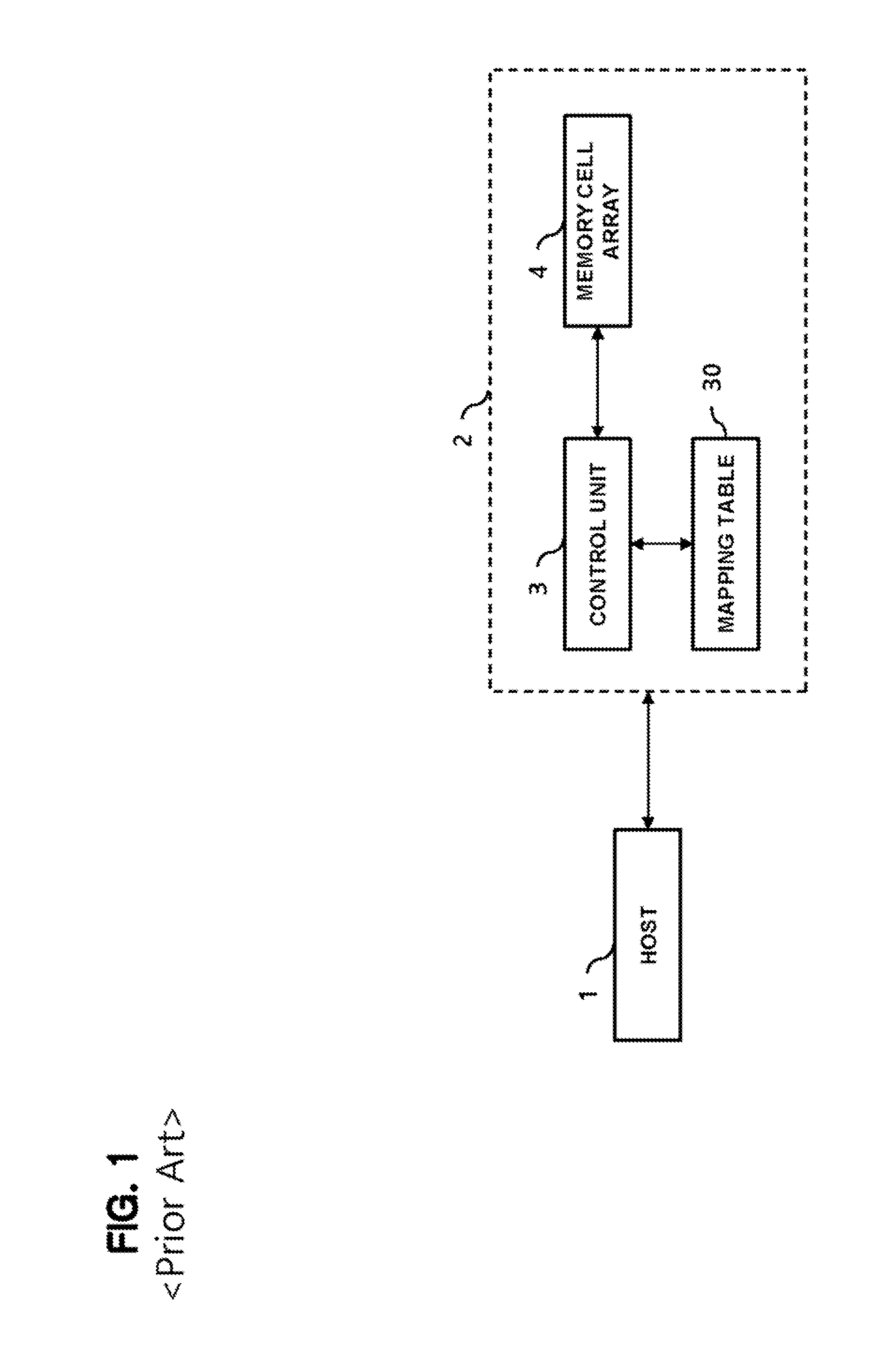

A semiconductor device includes a mapping table that stores a corresponding relation between a logical address defined on a basis of regions and a physical address defined on a basis of extents, wherein one or more extents are dynamically allocated to one region.

Owner:SK HYNIX INC +1

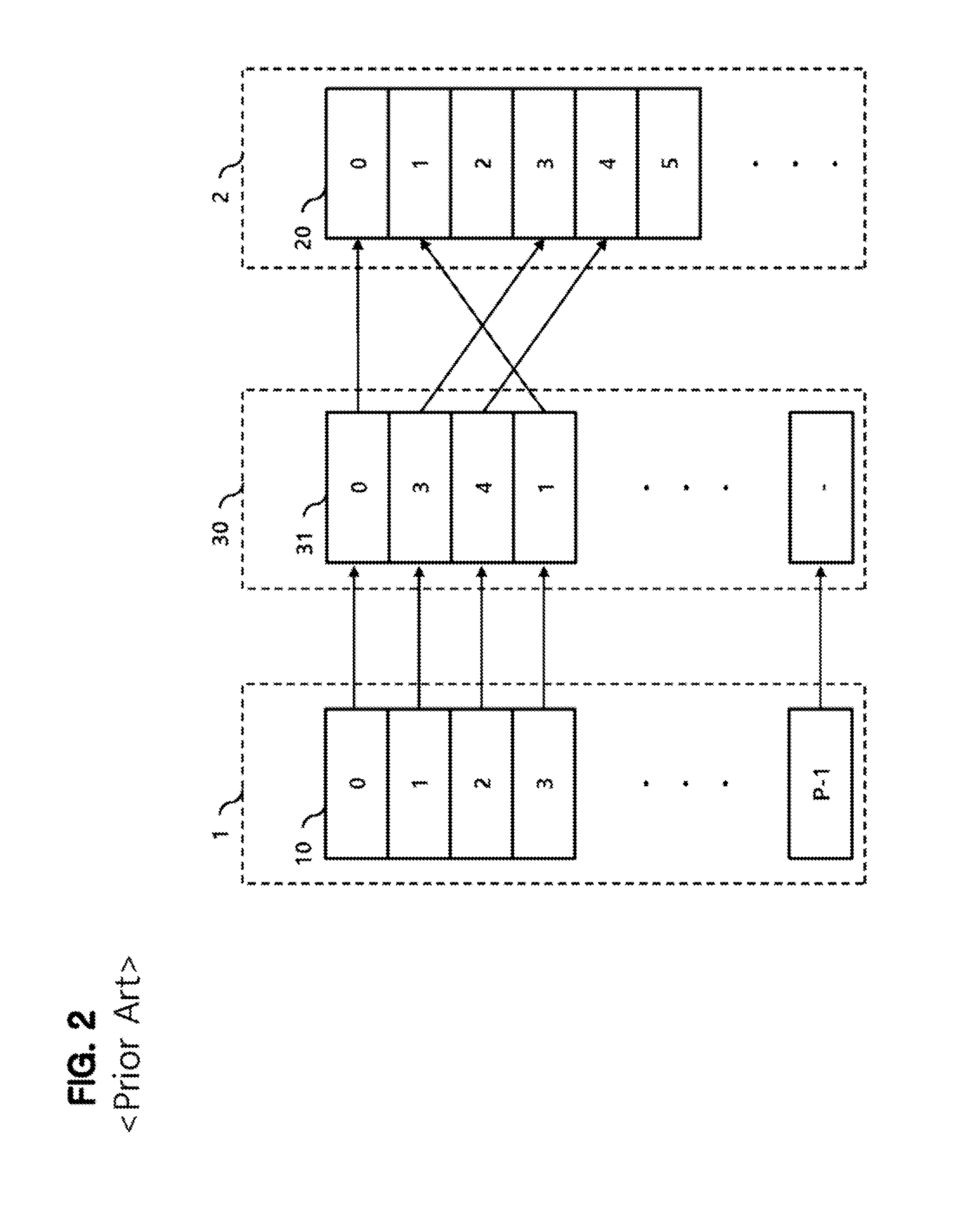

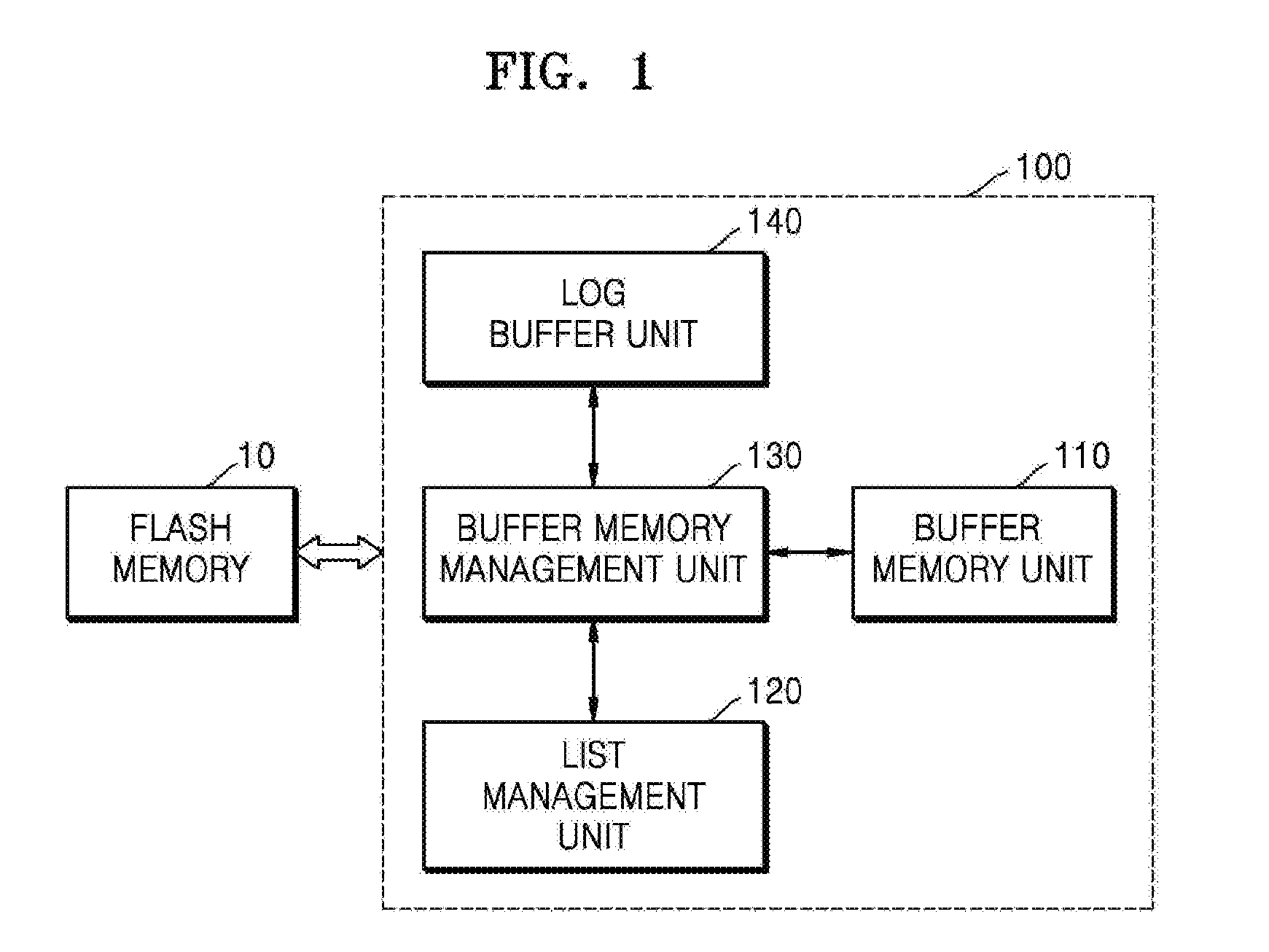

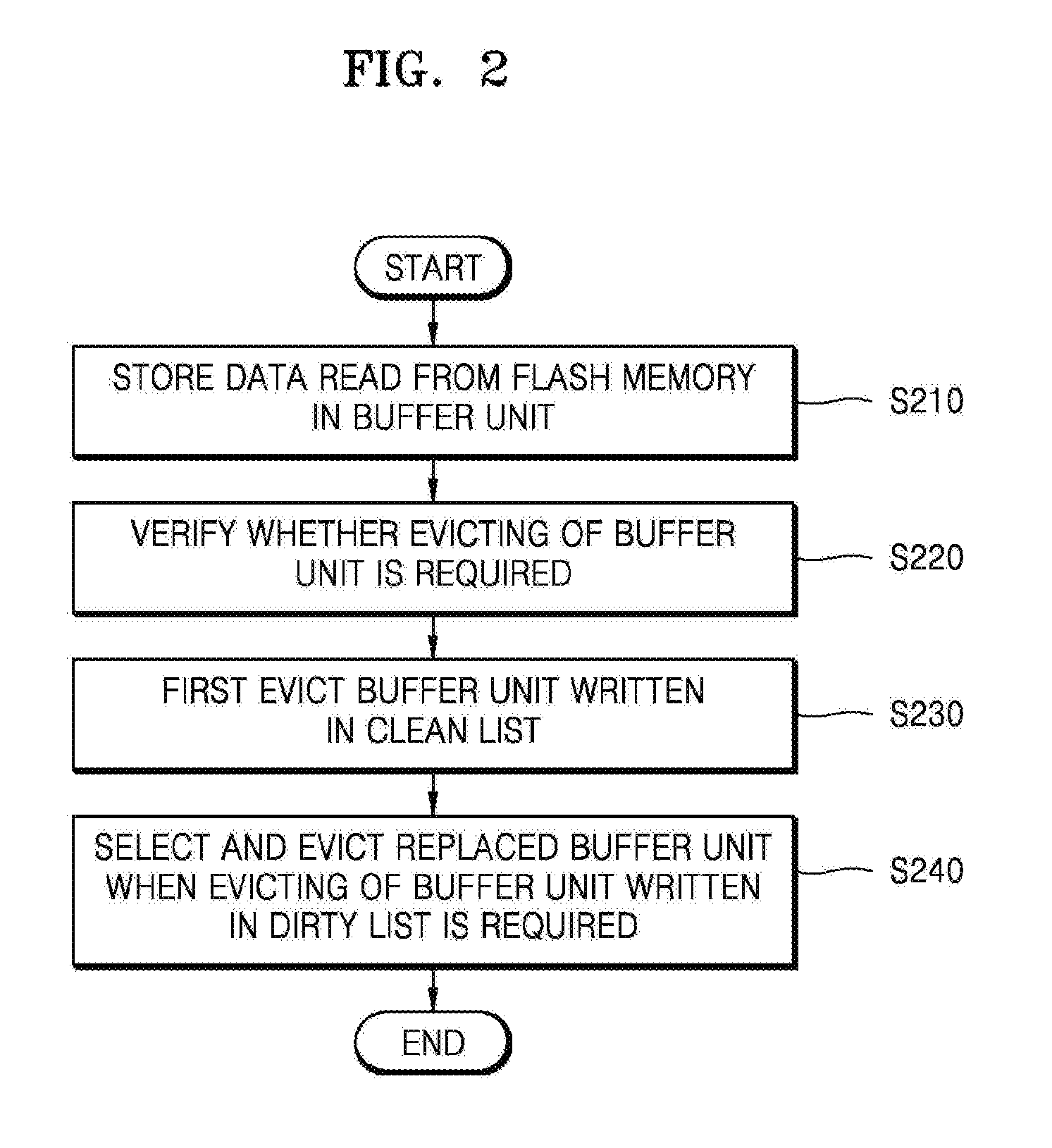

Apparatus and method for managing buffer having three states on the basis of flash memory

ActiveUS20160196063A1Reduce write operationsImprove performanceMemory architecture accessing/allocationInput/output to record carriersManagement unitInode

The present invention relates to an apparatus and a method for managing a buffer having three states on the basis of a flash memory and, more specifically, to an apparatus and a method for improving the performance of a database management system (DBMS) on the basis of the flash memory and a use life span of a storage device by reducing a writing operation for a flash memory device in which the writing operation is very slow in comparison with a reading operation, through an efficient buffer managing method and a new index node split policy. To this end, the buffer management device having three states on the basis of the flash memory according to an embodiment of the present invention comprises: a buffer memory unit; a list management unit; a buffer memory management unit; and a log buffer unit.

Owner:AJOU UNIV IND ACADEMIC COOP FOUND

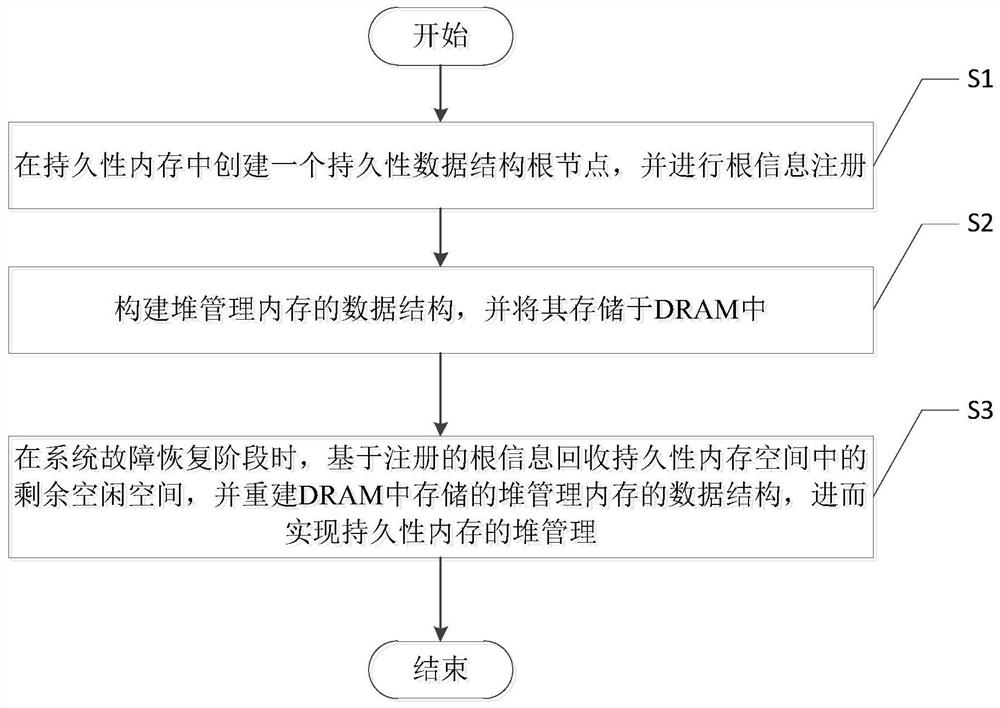

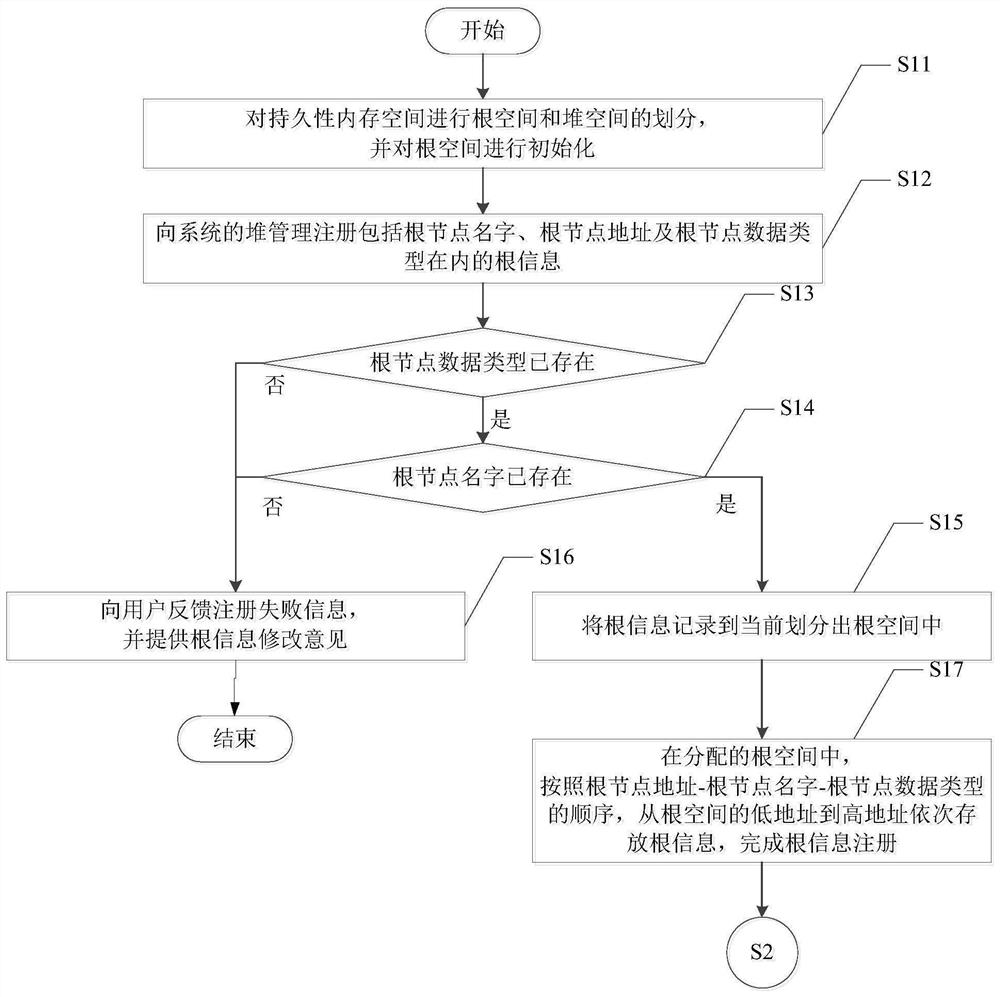

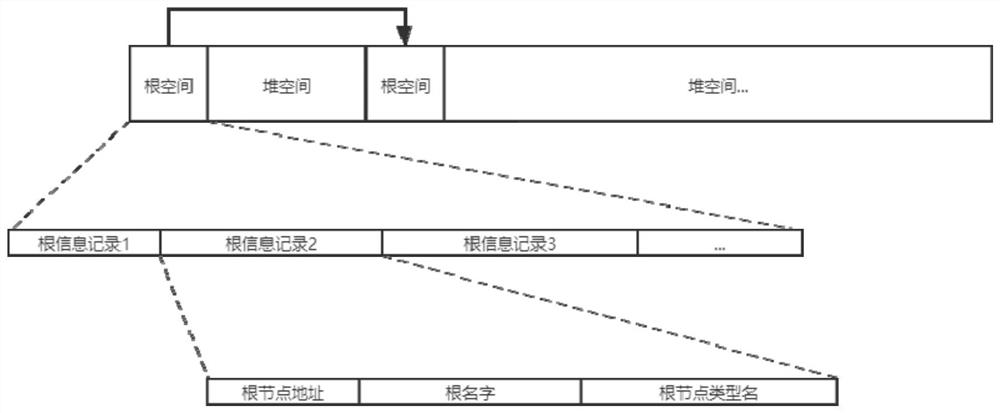

Write-optimized persistent memory heap management method

ActiveCN112084032AReduce write operationsExtend your lifeResource allocationEnergy efficient computingHeap (data structure)Parallel computing

The invention discloses a write-optimized persistent memory management method. The method comprises the steps of S1, performing root information registration in a persistent memory; s2, constructing adata structure of a heap management memory, and storing the data structure in a DRAM; and S3, in a system fault recovery stage, recovering residual free space in the persistent memory space based onthe registered root information, and reconstructing a data structure of the heap management memory stored in the DRAM to achieve heap management of the persistent memory. According to the method, allmetadata structures allocated to the management memory can be stored in the DRAM, and extra write operation on the persistent memory cannot be caused by allocation or release operation of any persistent memory space; in addition, in the fault recovery process, the reference count of the object can be accurately restored through the number of times of searching the same object while the allocated space is searched, so that the reference count of the object can be stored in the DRAM without worrying about the reference count error or loss caused by the fault.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

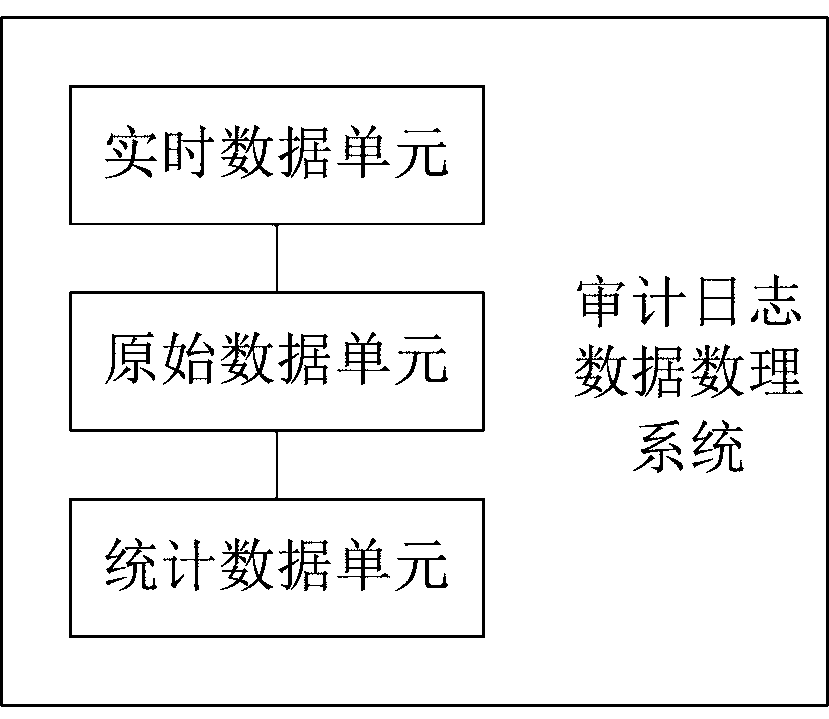

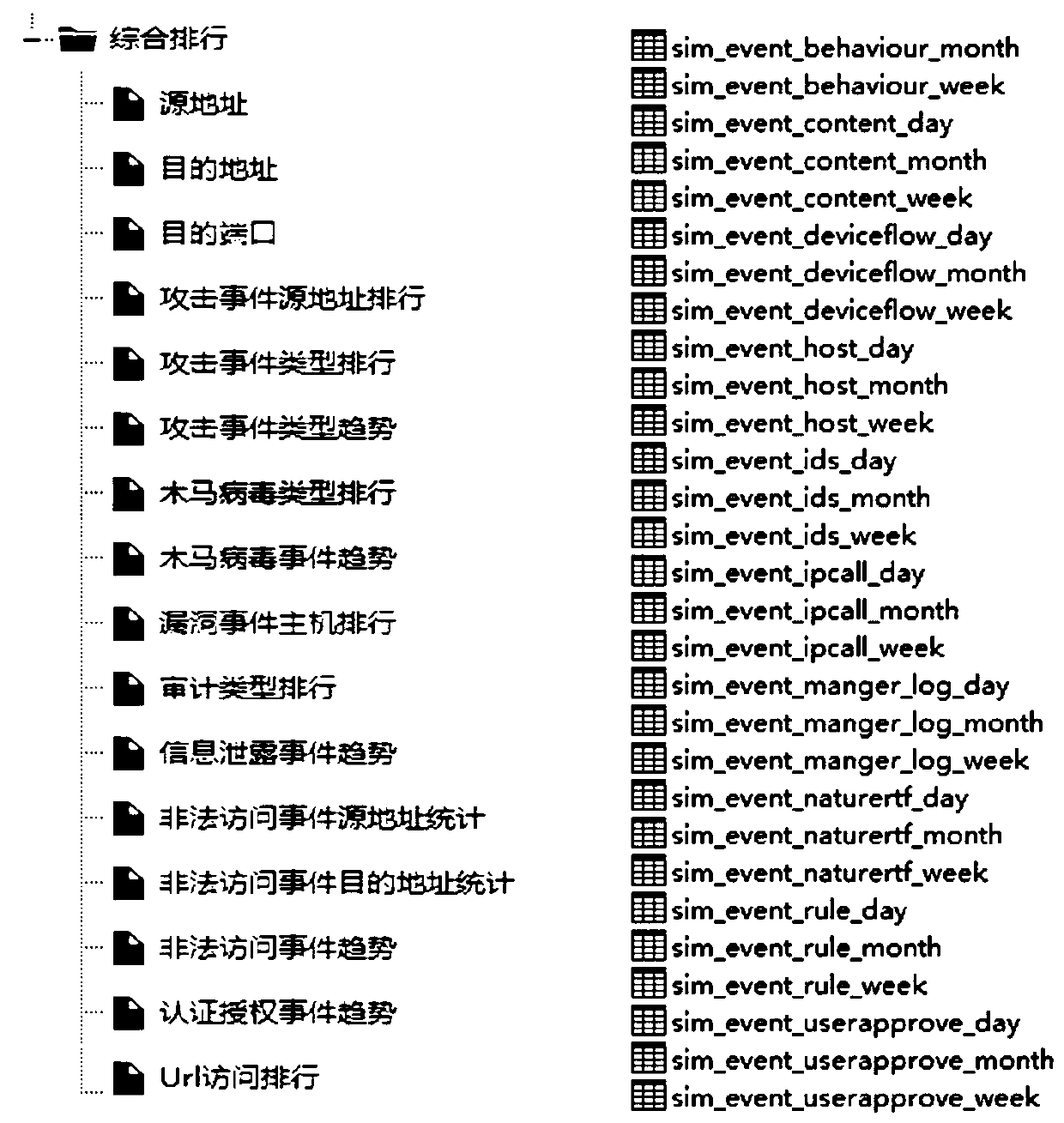

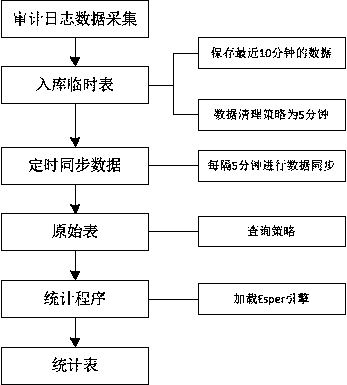

Audit log data processing method and system

InactiveCN110399351AReduce write operationsImprove read efficiency, that is, query efficiencyDatabase distribution/replicationSpecial data processing applicationsData queryComputer science

The invention aims to provide an audit log data processing method and system, and the method comprises the steps: building a temporary table, and enabling the writing operation of the temporary tableto be executed by a MyISAM engine; after auditing log data is collected, only storing the auditing log data in a temporary table, and only storing the data of the first duration in the temporary table; setting a data cleaning strategy of a second duration by the temporary table; adding a trigger to the temporary table, and executing synchronization operation of the temporary table and the originaltable regularly; and cancelling statistics of all operations of the temporary table. According to the technical scheme of combining the Esper engine and the Memcached, read-write separation of the original table is indirectly achieved, the data query efficiency is improved, and meanwhile data statistics is improved.

Owner:西安交大捷普网络科技有限公司

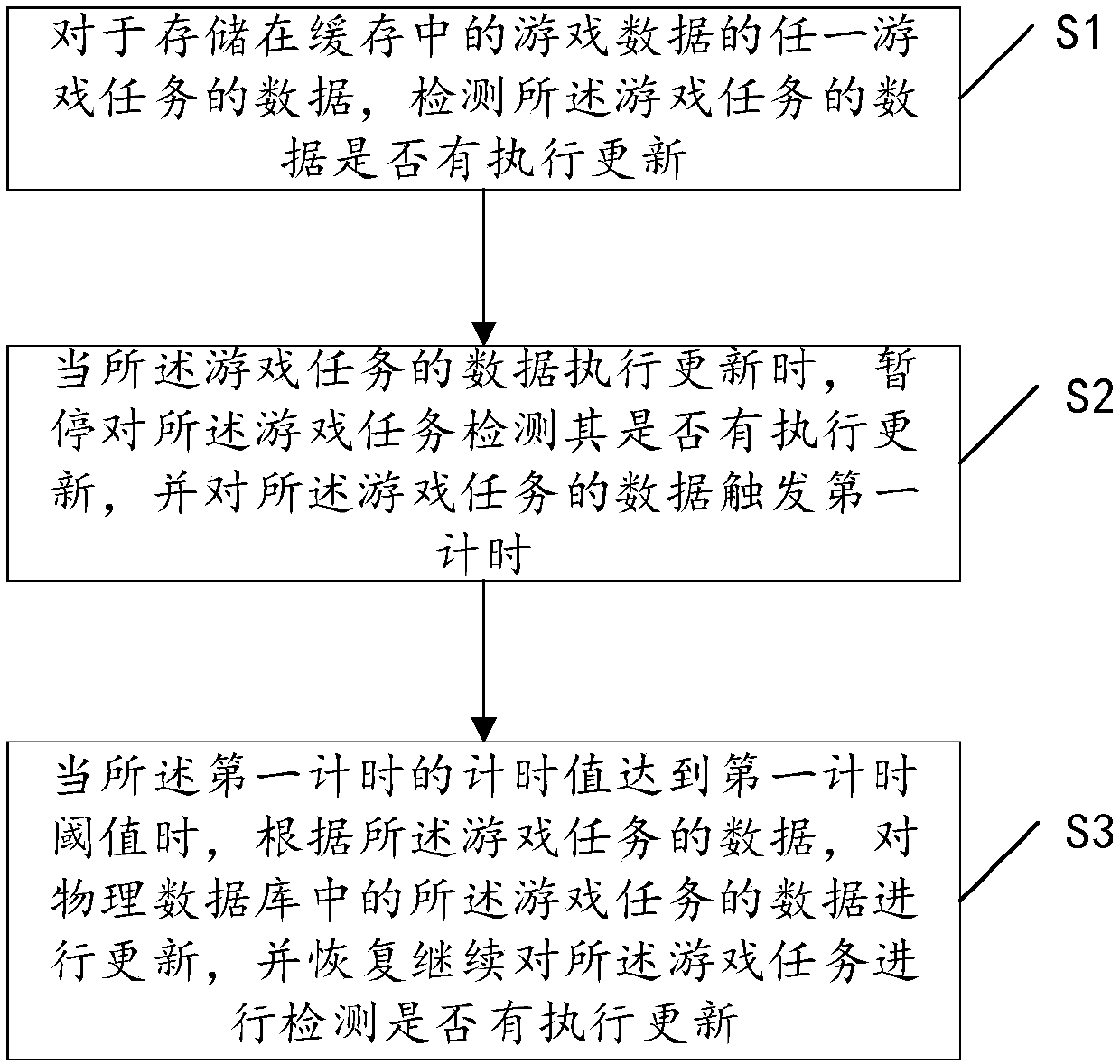

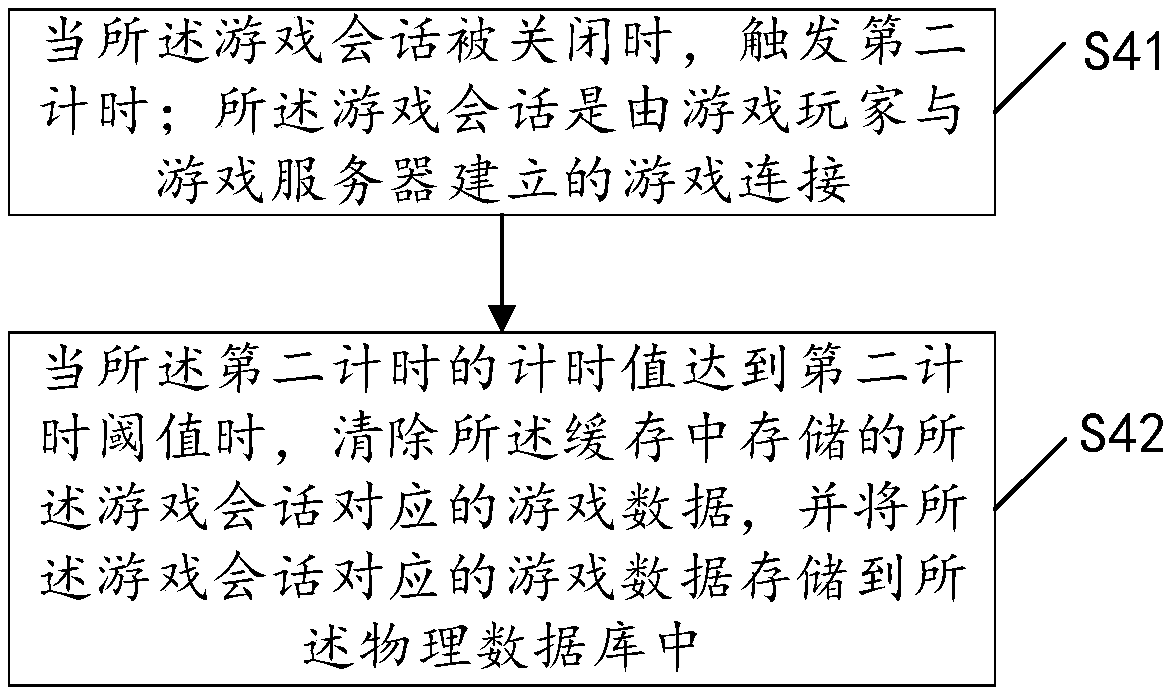

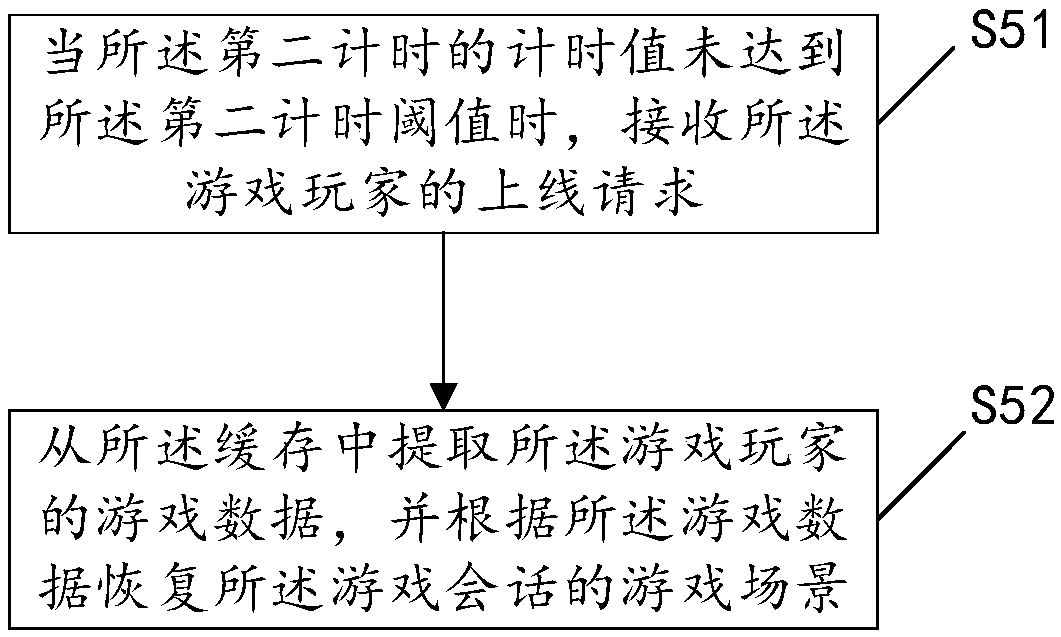

Data updating method, apparatus and device, and storage medium

ActiveCN107682356AReduce read and write operationsImprove performanceVideo gamesTransmissionGame playerData storing

The invention discloses a data updating method, apparatus and device, and a storage medium. The data updating method comprises the following steps: detecting whether game data stored in a cache are updated, wherein the game data are data generated in a game session in real time, the game data at least comprise the data of at least one game task, and the data of the game task are used for describing at least one attribute parameter of the game task; when the data of one game task in the game data are executed, triggering first timing of the data of the game task; and when the timing value of the first timing reaches a first timing threshold, updating the data of the game task in a physical database according to the data of the game task stored in the cache at present. By implementation of the data updating method, apparatus and device in the embodiment of the invention, the read-write operations of the database caused by data updating in a game process can be reduced, and the performance of a game server and the game experience of game players are improved.

Owner:广州市雷军游乐设备有限公司

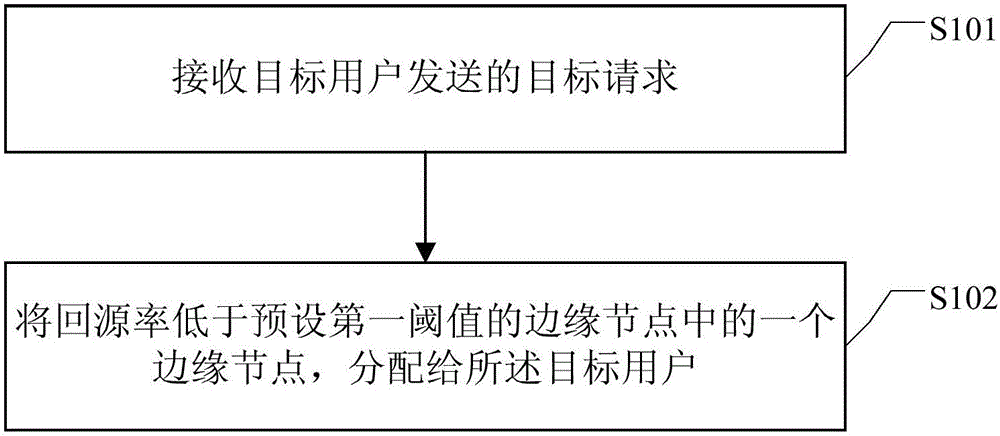

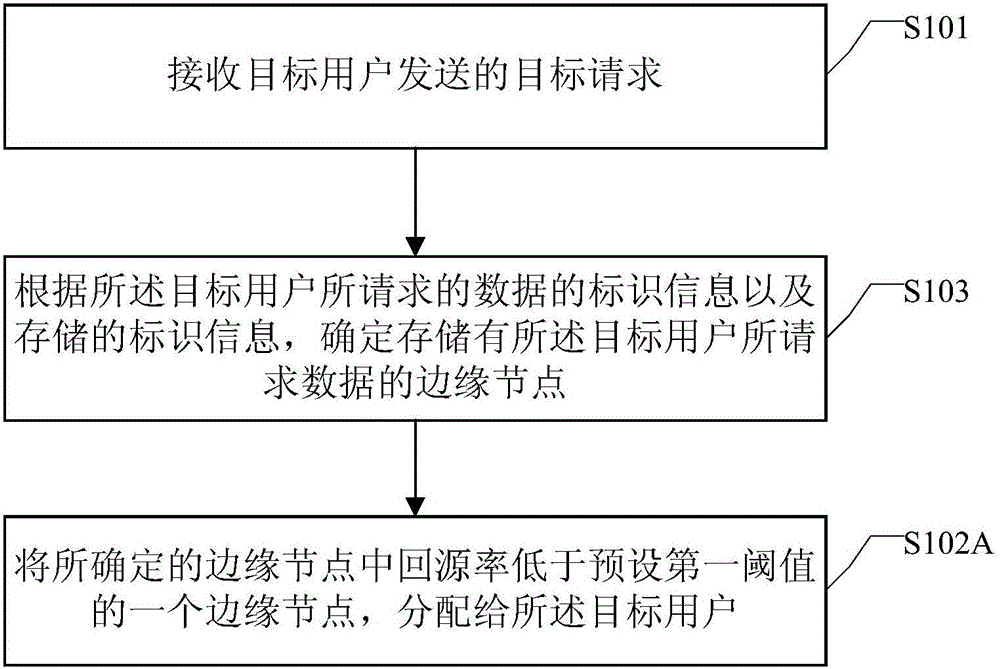

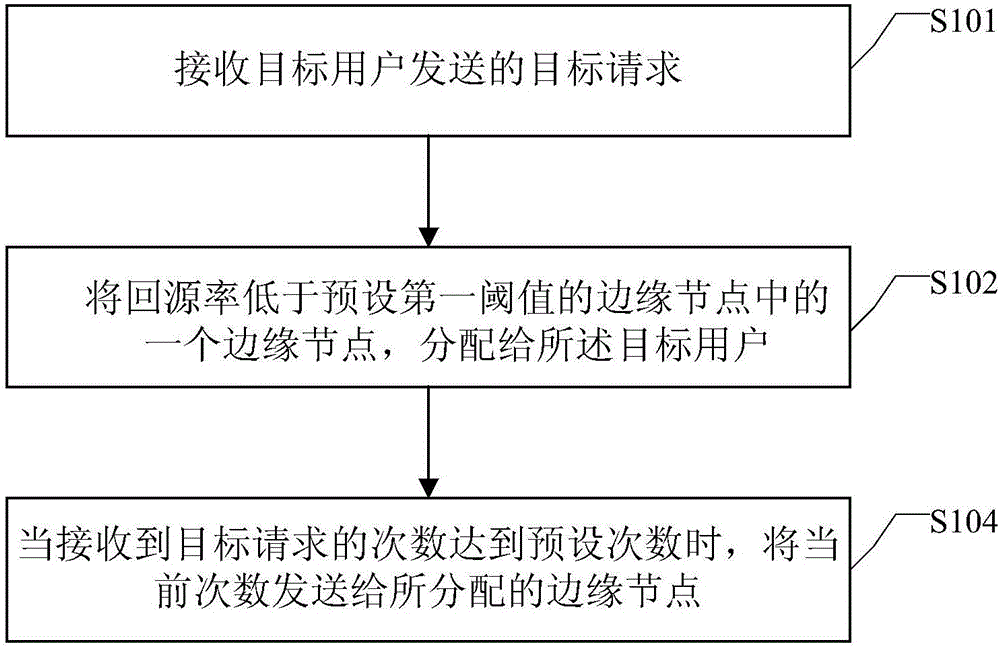

Method and device for distributing edge nodes

ActiveCN106357783AReduce write operationsGuaranteed stabilityTransmissionContent distributionContent delivery network

The embodiment of the invention discloses a method and a device for distributing edge nodes. The method and the device are applied to a dispatcher in a content distribution network system. The content distribution network system comprises at least one edge node and the dispatcher. The method comprises the following steps of receiving a target request sent by a target user, wherein the target request at least comprises identification information of data requested by the target user; distributing one edge node with source return rate lower than a preset first threshold value to the target user. The method disclosed by the embodiment has the advantages that the source return rate of the edge node distributed to the user is lower; compared with the edge node with higher source return rate, the writing operation of a magnetic disc of the edge node with low source return rate is relatively less, the reading operation efficiency is relatively higher, and the stability of the whole content distribution network system is further guaranteed.

Owner:BEIJING QIYI CENTURY SCI & TECH CO LTD

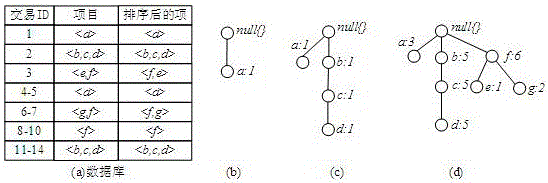

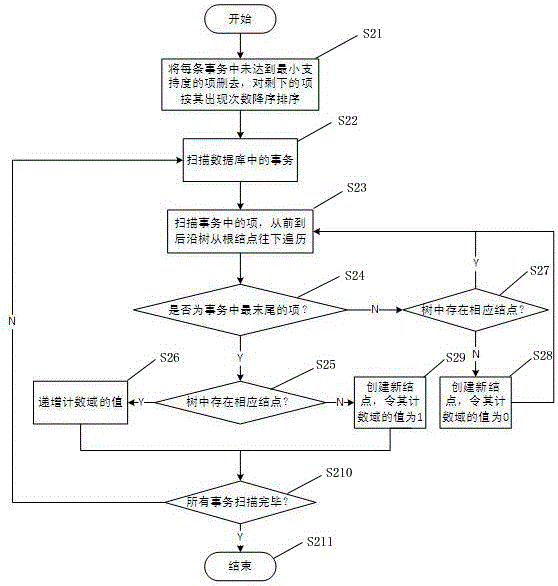

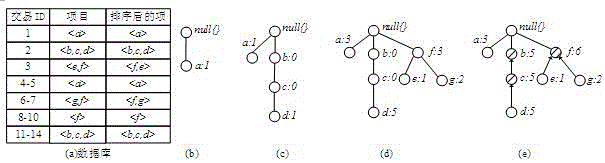

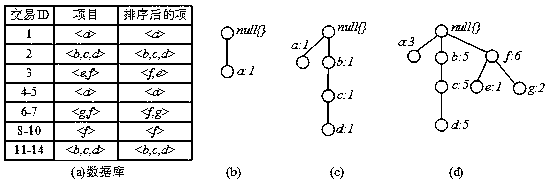

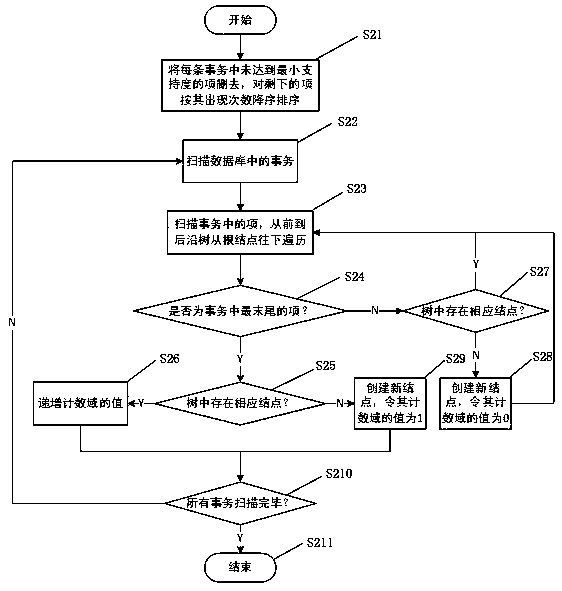

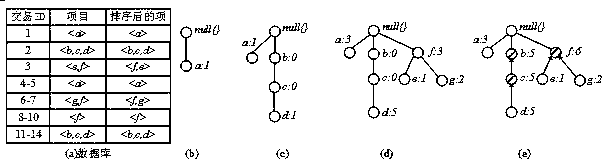

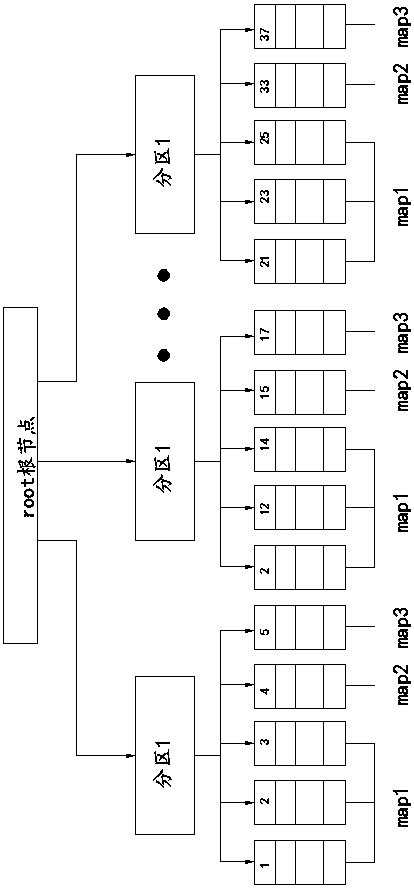

Memory-based frequent pattern mining method

ActiveCN106250549AQuick buildReduce write operationsSpecial data processing applicationsDepth-first searchNode count

The invention discloses a memory-based frequent pattern mining method. The method comprises the following steps of 1, creating an initial frequent pattern tree, creating a root node T of the frequent pattern tree, and marking the root node with ''null''; scanning a database again, selecting out frequent items in each read transaction, and sorting the frequent items according to an order in L; creating a path of the frequent pattern tree by taking null as the root node after sorting, adding 1 to a count of only a final node on the path, and keeping counts of other nodes on the path unchanged; scanning all transactions in the whole database in sequence and obtaining the initial frequent pattern tree; and 2, traversing the initial frequent pattern tree in sequence by using a depth-first search algorithm, wherein a counter value of a traversed node is the sum of the value of the node and the values of all child nodes of the node. The method has the technical effects that the write operation of an NVM (Non-Volatile Memory) can be reduced, so that the frequent pattern tree can be quickly established; and a large amount of dense write operations on a node counting domain close to the root node can be reduced, so that the service life of the NVM is prolonged.

Owner:CHONGQING UNIV

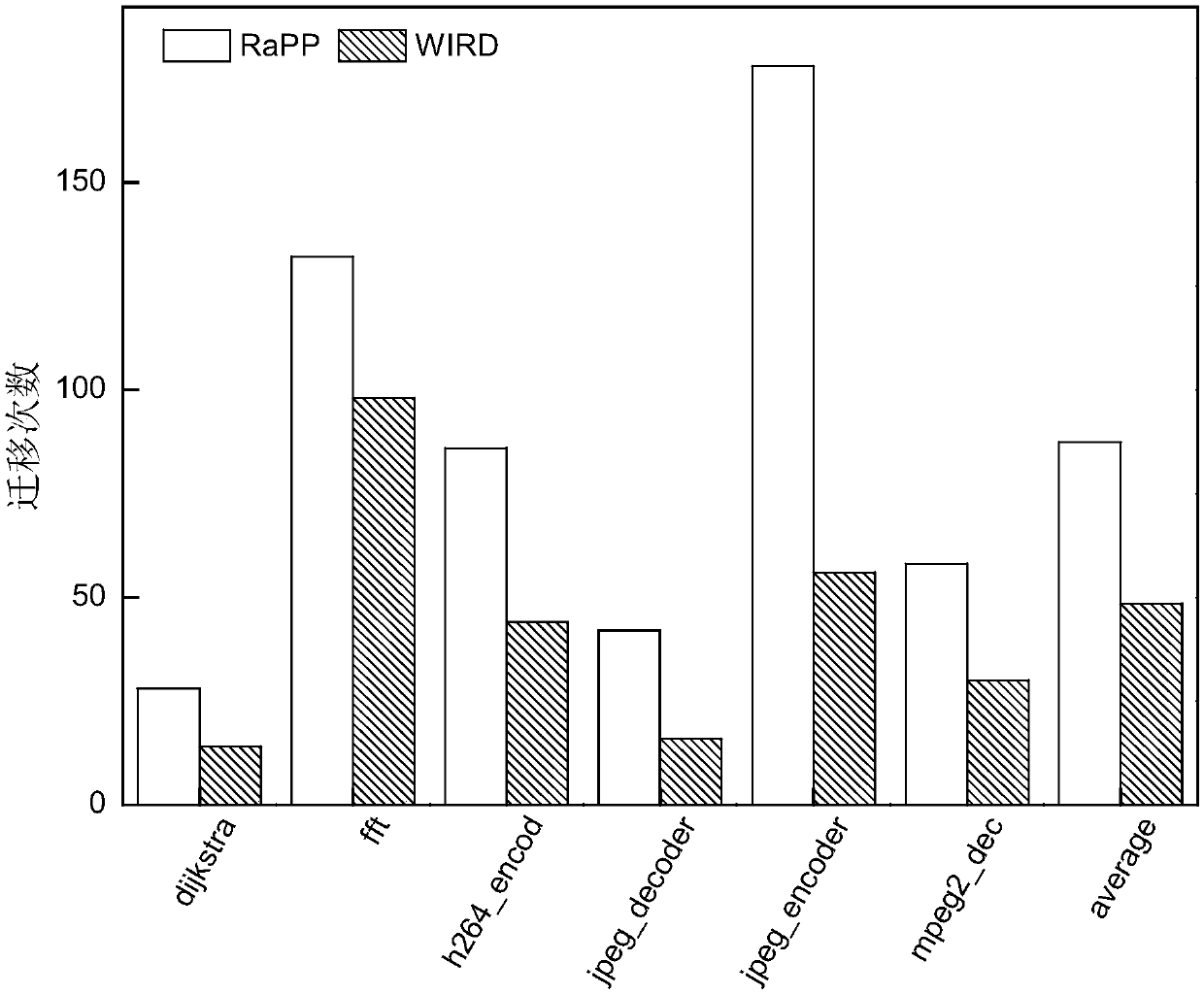

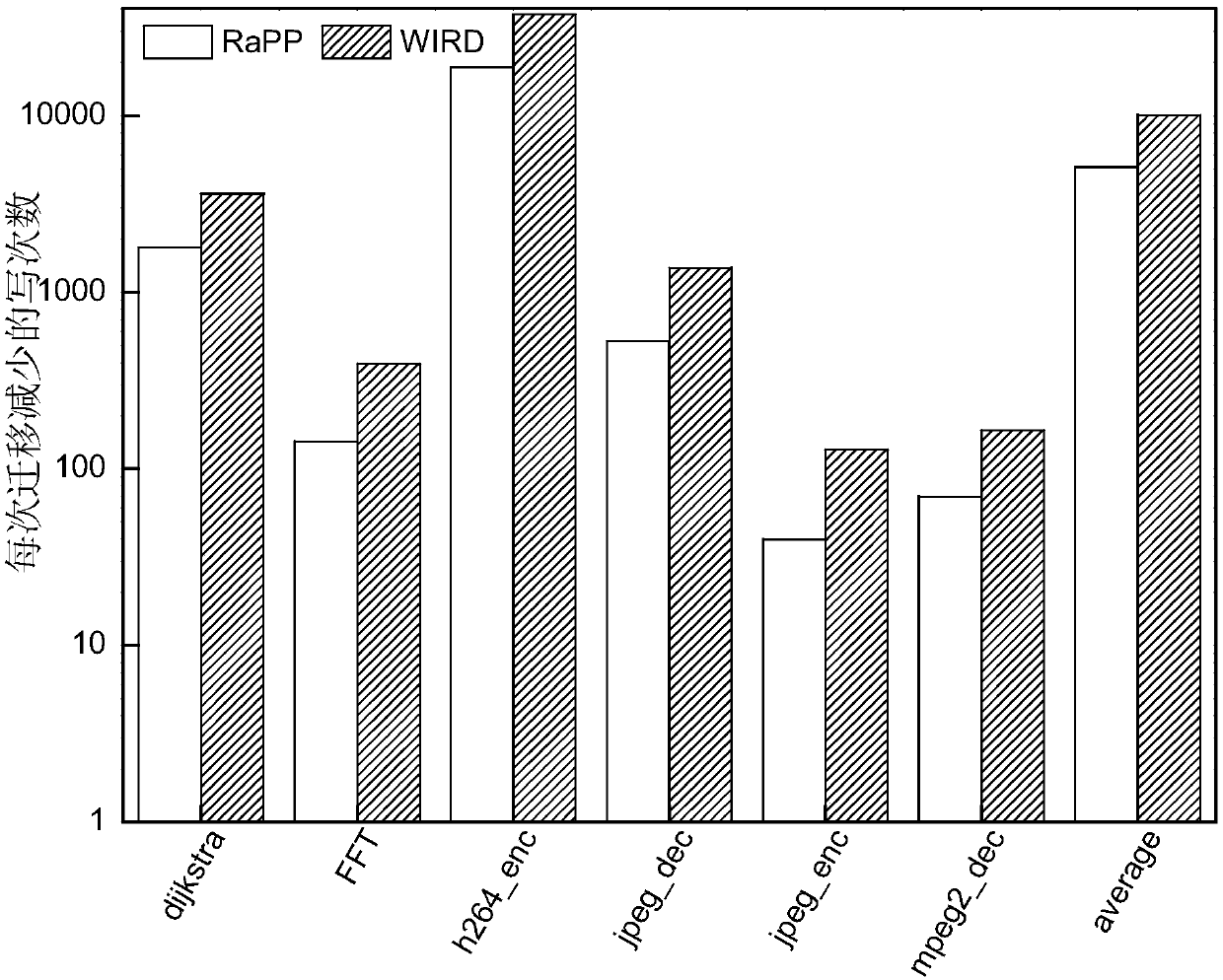

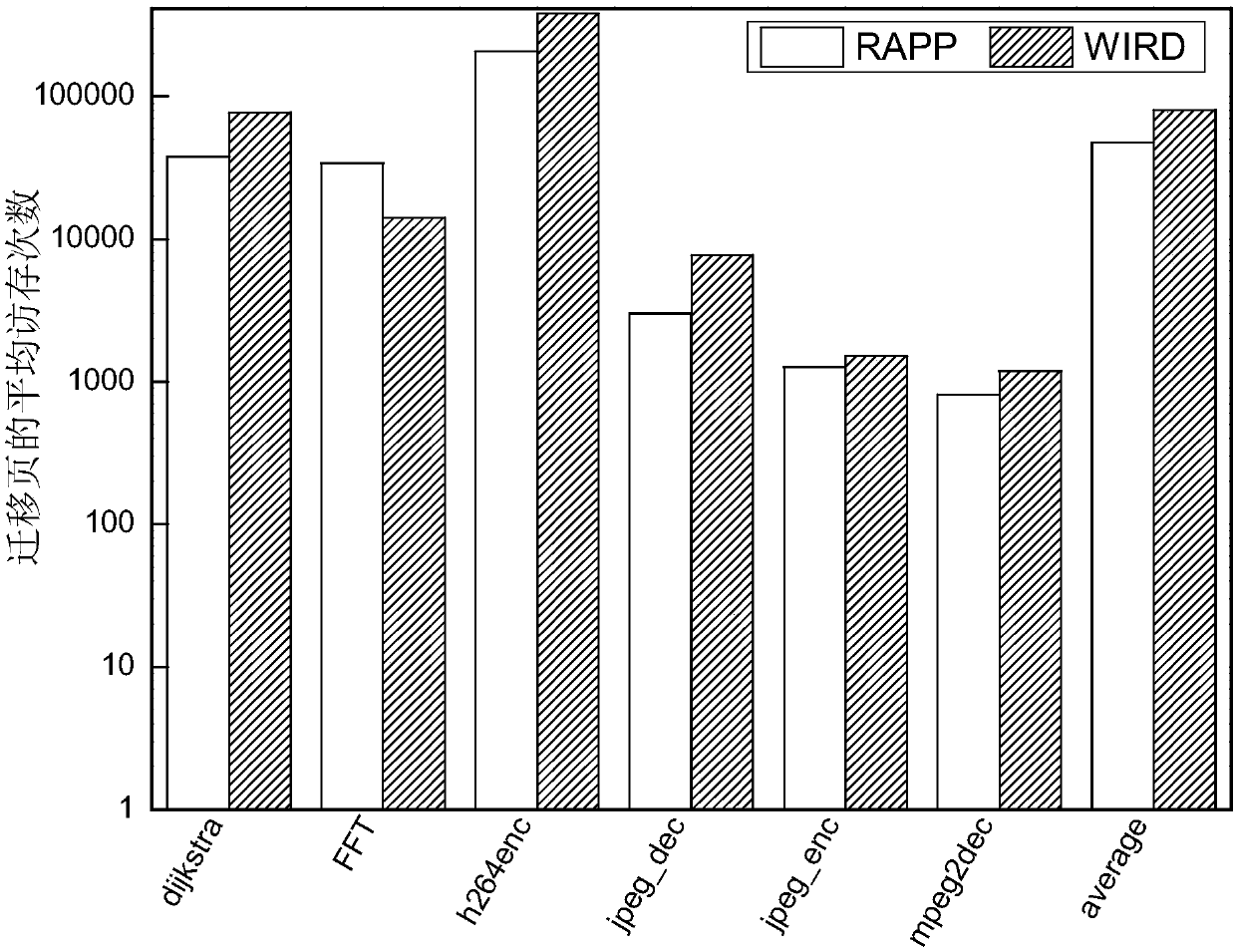

A hybrid memory page migration method for an image processing type load

ActiveCN109558093AReduce the number of write operationsExtended service lifeInput/output to record carriersDirty bitImaging processing

The invention discloses a hybrid memory page migration method for an image processing type load, and relates to a hybrid memory page migration method. The invention aims to solve the problems of shortservice life and damaged performance of the existing hybrid memory. And at the moment t, when a write operation occurs in the PCM page and the number of times of the write operation of the page is greater than or equal to n and the dirty bit of the page is 1, searching for a replacement page in a DRAM or a DRAM cache, starting migration, and requesting a counter to add 1. Requesting the counter to restart counting every integer multiple of the memory reference distance, and setting all dirty bits of the page in the PCM cache to be zero. And then enabling t to be equal to t + 1, and executingthe above steps again. The method is applied to the field of hybrid memory page migration of image processing type loads.

Owner:HARBIN INST OF TECH

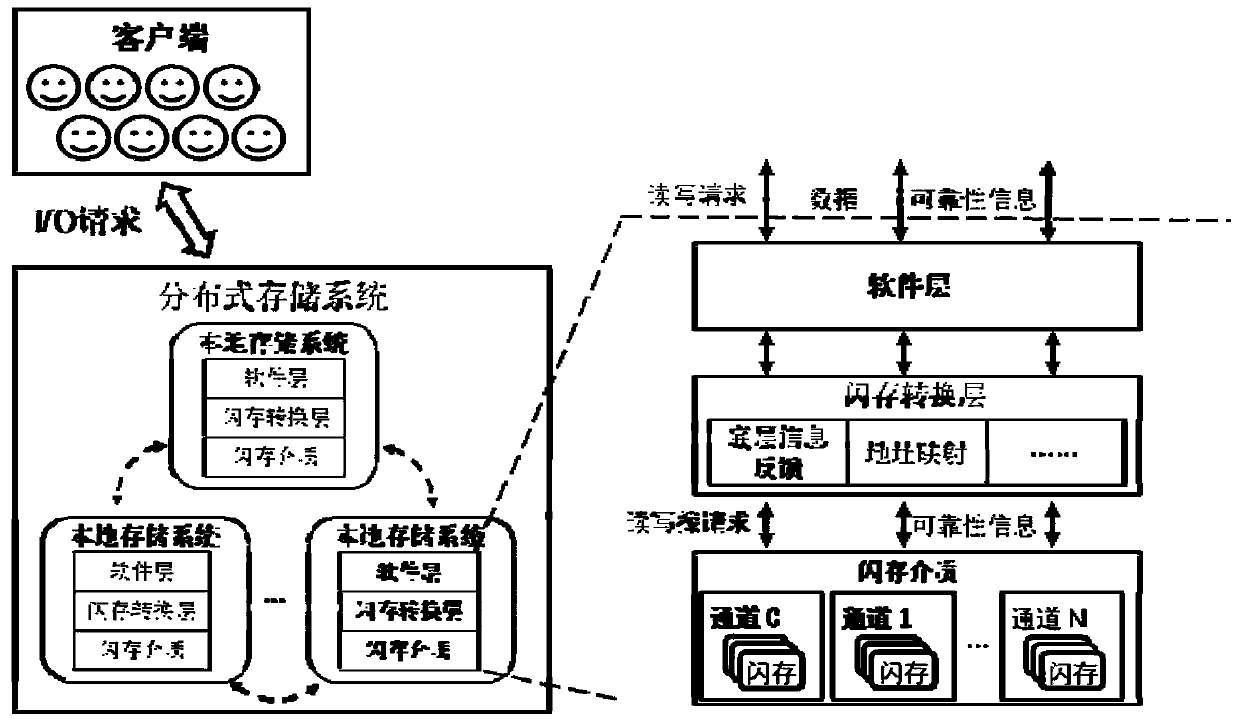

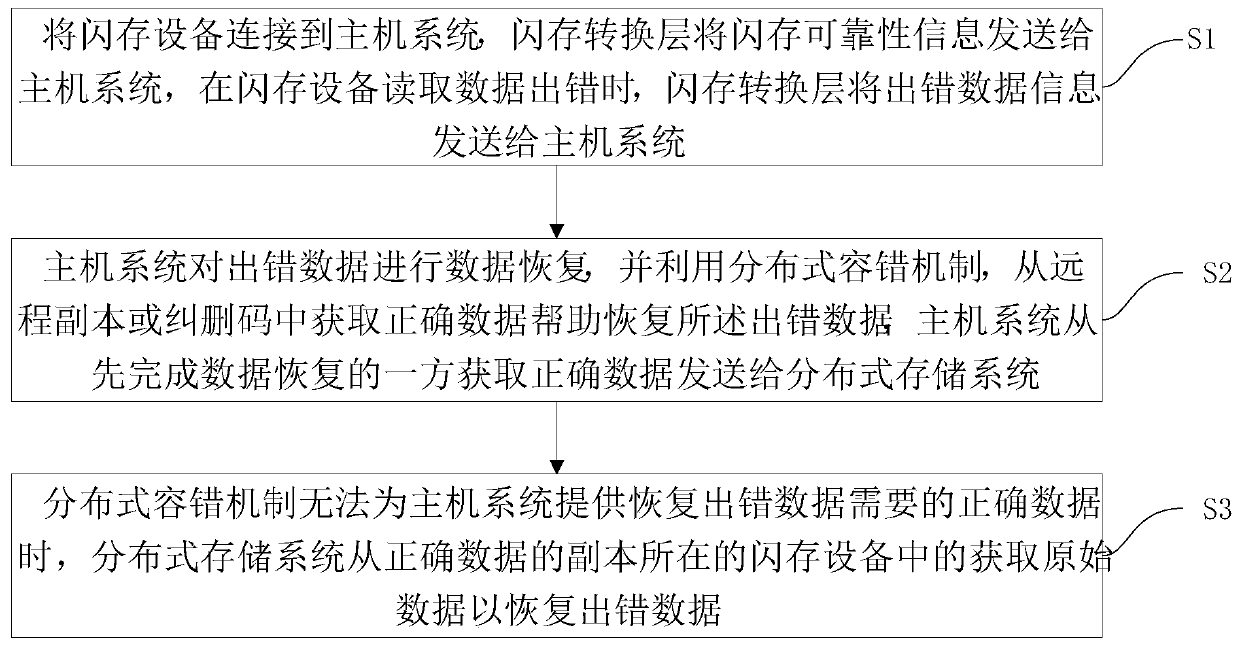

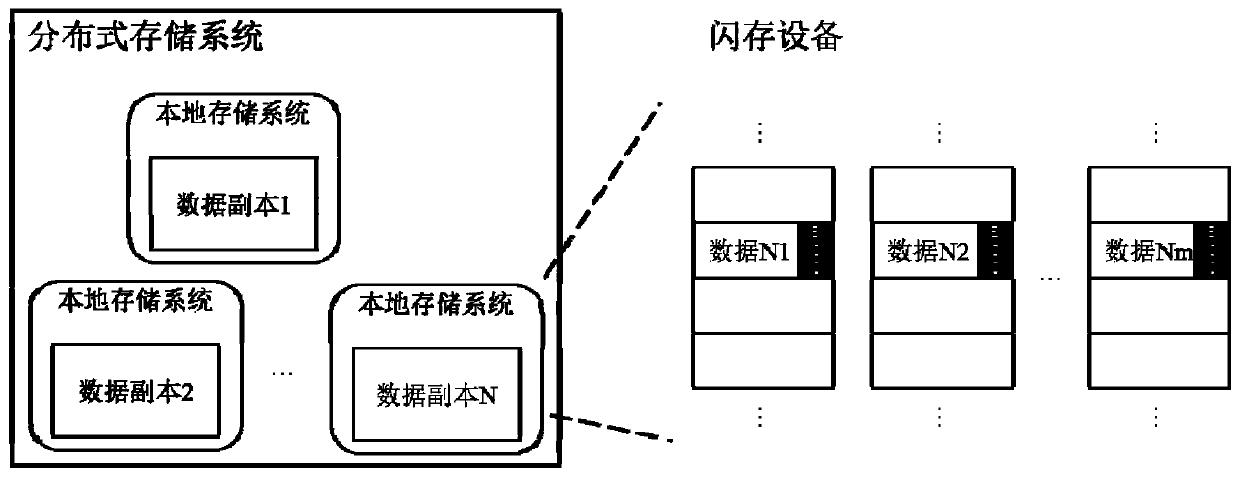

A reliable flash memory storage method and system based on local and distributed collaborative design

ActiveCN109739777AReduce redundancyImprove reliabilityMemory adressing/allocation/relocationRedundant data error correctionData informationOriginal data

The invention discloses a local and distributed collaborative design reliable flash memory storage method and system, and the method comprises the steps: enabling a flash memory conversion layer to send flash memory reliability information to a host when flash memory equipment is connected to a host system, and enabling error data information to be sent to the host when the flash memory equipmentreads data errors; the host carries out data recovery on the error data, obtains correct data from a remote copy or an erasure code by utilizing a distributed fault-tolerant mechanism to help recoverthe error data, obtains the correct data from a party completing data recovery first, and sends the correct data to the distributed storage system; and when the distributed fault-tolerant mechanism cannot provide the correct data required for recovering the error data, the distributed storage system obtains the original data from the flash memory device where the correct data copy is located so asto recover the error data. The method can comprehensively manage the reliability mechanism of the distributed storage system and the local flash memory device, reduces the read operation delay of thesystem, improves the local data recovery efficiency of the flash memory device, and enhances the reliability of the storage system.

Owner:TSINGHUA UNIV

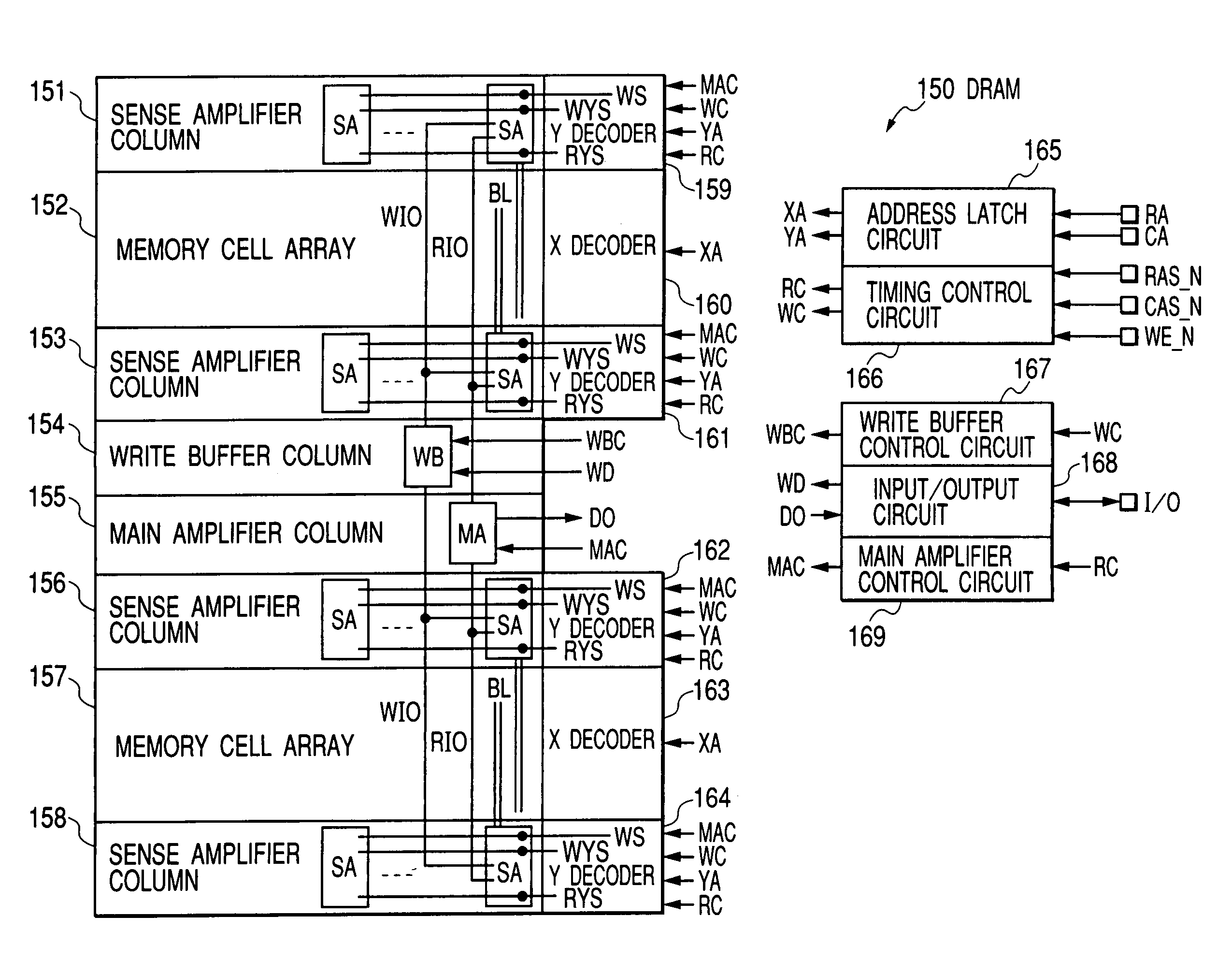

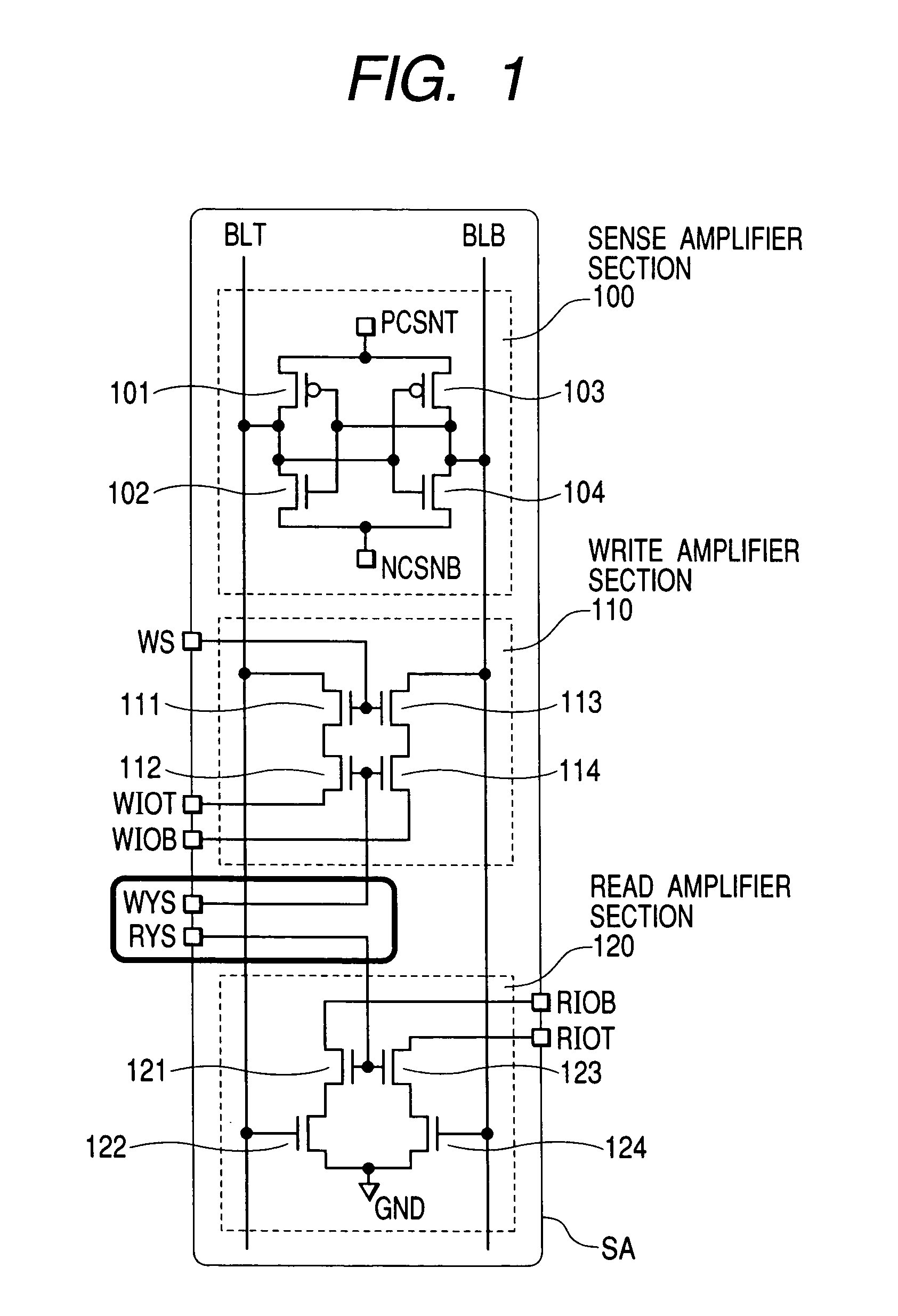

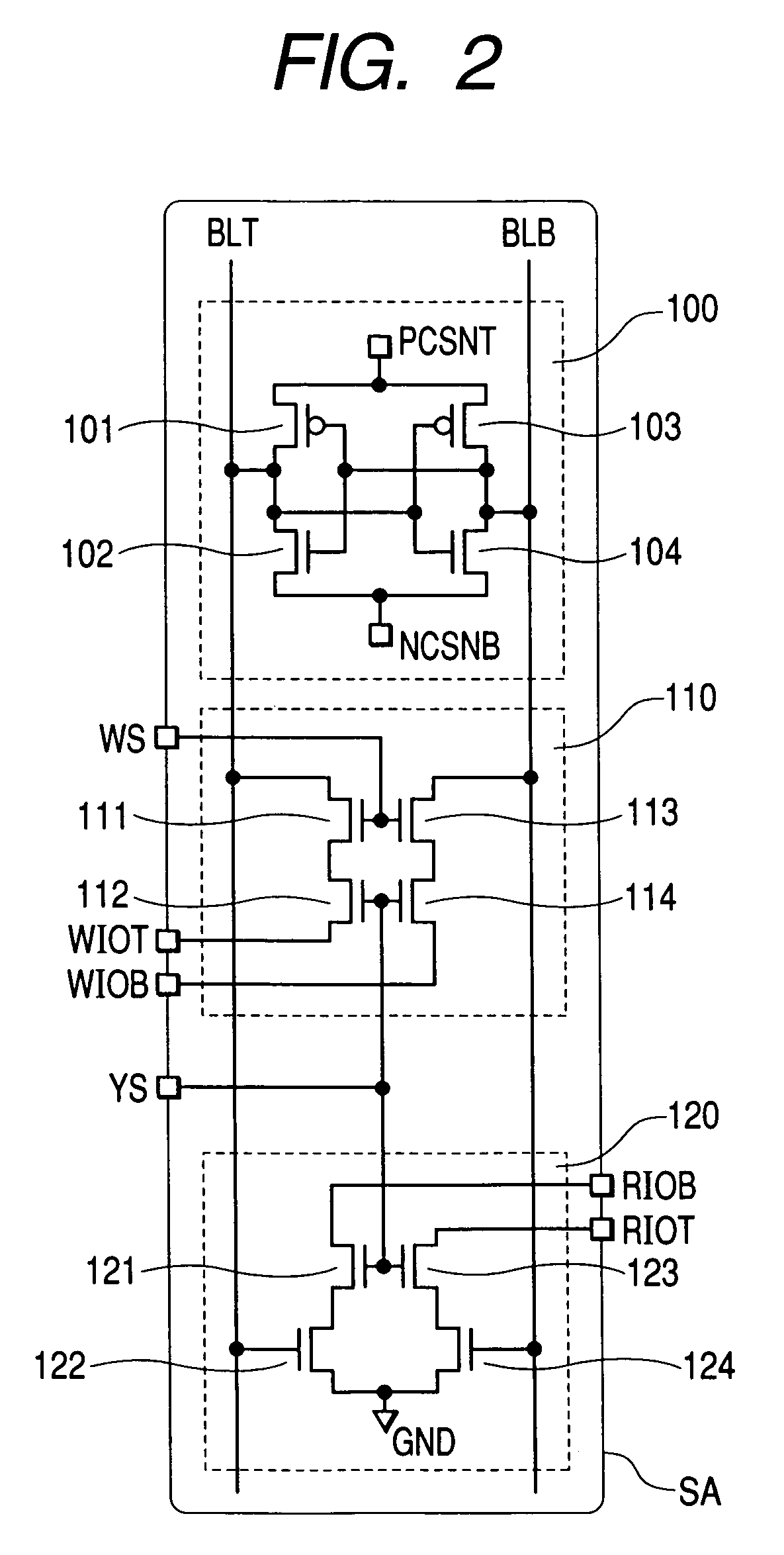

Semiconductor memory device provided with a write column selection switch and a read column selection switch separately

InactiveUS7251149B2Reduce the passing currentEasy to optimizeTransistorSemiconductor/solid-state device manufacturingAudio power amplifierComputer science

A Y selection line for write for controlling operations of a column selection switch within a write amplifier and a Y selection line for read for controlling operations of a column selection switch within a read amplifier are provided individually and the column selection switch within the read amplifier is set to the non-operating condition during the write operation. Accordingly, a through-current during the write operation may be reduced. In this case, the write IO line and read IO line are allocated crossing sense amplifier columns, while the column selection line for write and column selection line for read are allocated in parallel to the sense amplifier columns.

Owner:HITACHI LTD

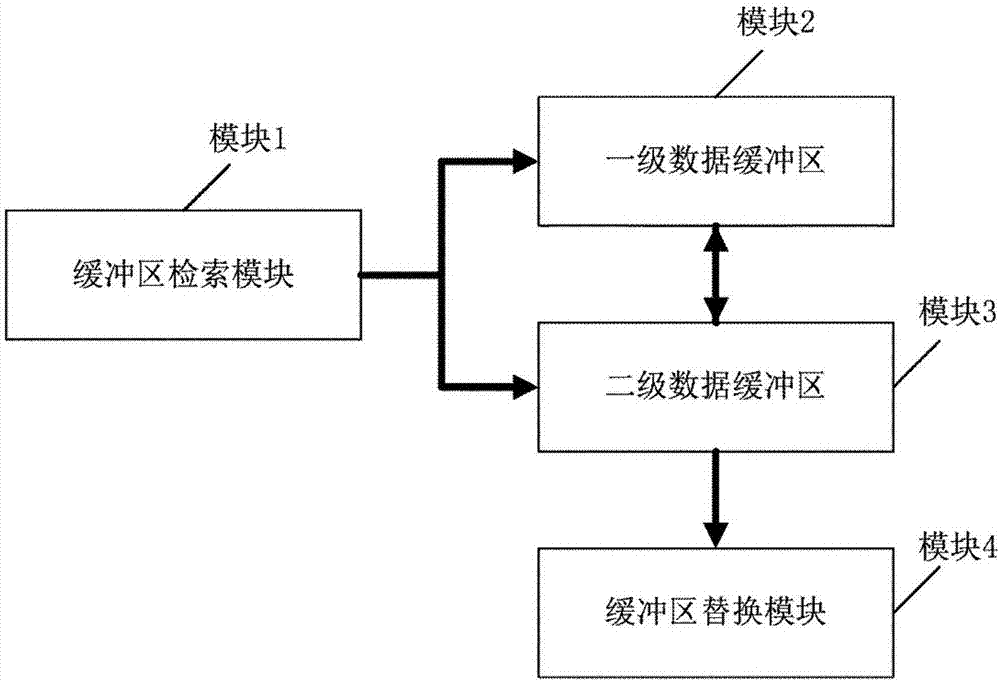

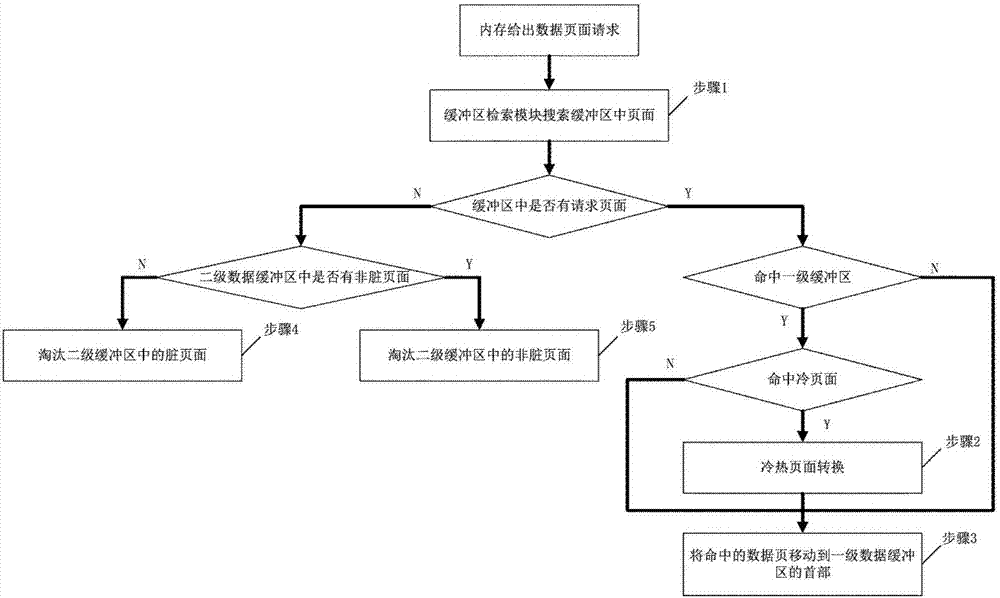

Flash memory data buffer area replacement method based on page access interval

InactiveCN107341112AGuaranteed hit rateReduce write operationsMemory architecture accessing/allocationMemory adressing/allocation/relocationDirty dataReplacement method

The invention discloses a flash memory data buffer area replacement method based on a page access interval. In the method, all data pages cached in the data buffer area are divided into hot dirty data pages, cold dirty data pages, hot clean data pages and cold clean data pages according to access interval characteristics and reading / writing characteristics of the data pages in the buffer area, and all the data pages are managed by using a primary data buffer area and a secondary data buffer area. When the cold data page access interval is less than the last hot data page in an LRU queue of the buffer area, conversion between cold and hot data pages is performed, and meanwhile, the cold data page in the LRU queue of the primary buffer area is moved into the secondary data buffer area. When the data buffer area page needs to be replaced, the cold clean data pages in the secondary buffer area are preferentially shifted out according to an LRU rule, and the influence on performance and service life of a flash memory due to too many times of write-back operations of the dirty data pages of the data buffer area is reduced under the premise of ensuring a hit rate.

Owner:XI AN JIAOTONG UNIV

A Memory-based Frequent Pattern Mining Method

ActiveCN106250549BQuick buildReduce write operationsOther databases indexingDepth-first searchNode count

Owner:CHONGQING UNIV

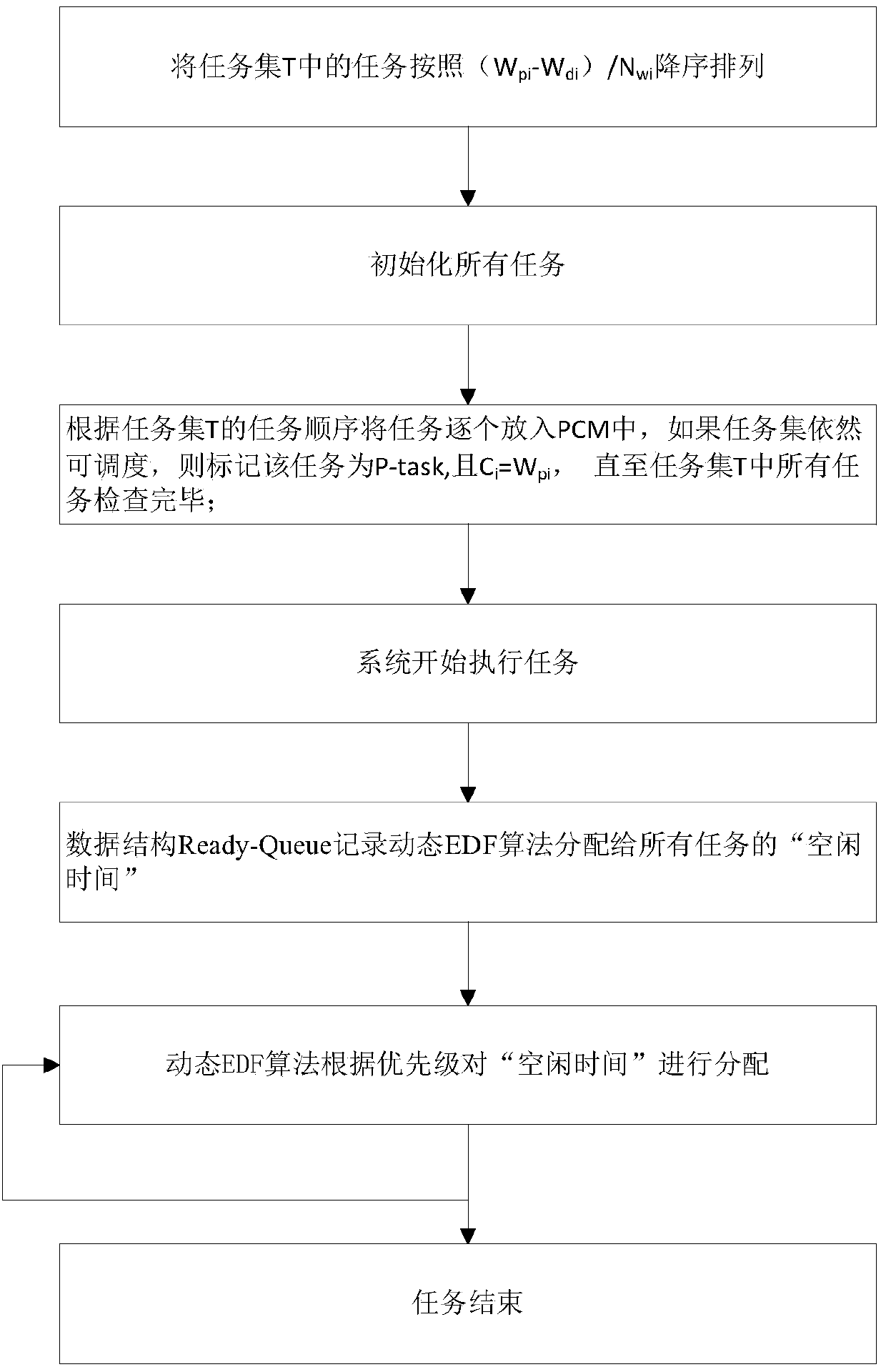

Low-energy EDF (earliest deadline first) real-time task scheduling method for mixed main memory embedded system

InactiveCN104182180AReduce power consumptionGuaranteed real-time constraintsInput/output to record carriersMultiprogramming arrangementsPhase-change memoryReal-time computing

The invention discloses a low-energy EDF (earliest deadline first) real-time task scheduling method for a mixed main memory embedded system. With the adoption of advantages that a PCM (phase-change memory) is non-volatile, low in energy and high in performance and in combination of a dynamic EDF algorithm, real-time constraint of the whole task set is guaranteed, accordingly, power consumption of the whole system is reduced, and the real-time constraint of tasks is not influenced. The method comprises the steps as follows: 1), tasks in the task set T are arranged according to a (Wpi-Wdi)Nwi descending order; 2), all the tasks are initialized; 3), the tasks are placed in the PCM one by one according to a task sequence of the task set T, if the task set still can be scheduled, the task is marked as P-task, Ci is equal to Wpi, and operation is performed until all the tasks in the task set T are checked; 4), the system starts to execute the tasks; 5), free time which is assigned to all the tasks with the dynamic EDF algorithm is calculated; 6), the free time is assigned with the dynamic EDF algorithm according to priority; and 7), the step 6 is repeated until the whole task set T is finished.

Owner:SHANDONG UNIV

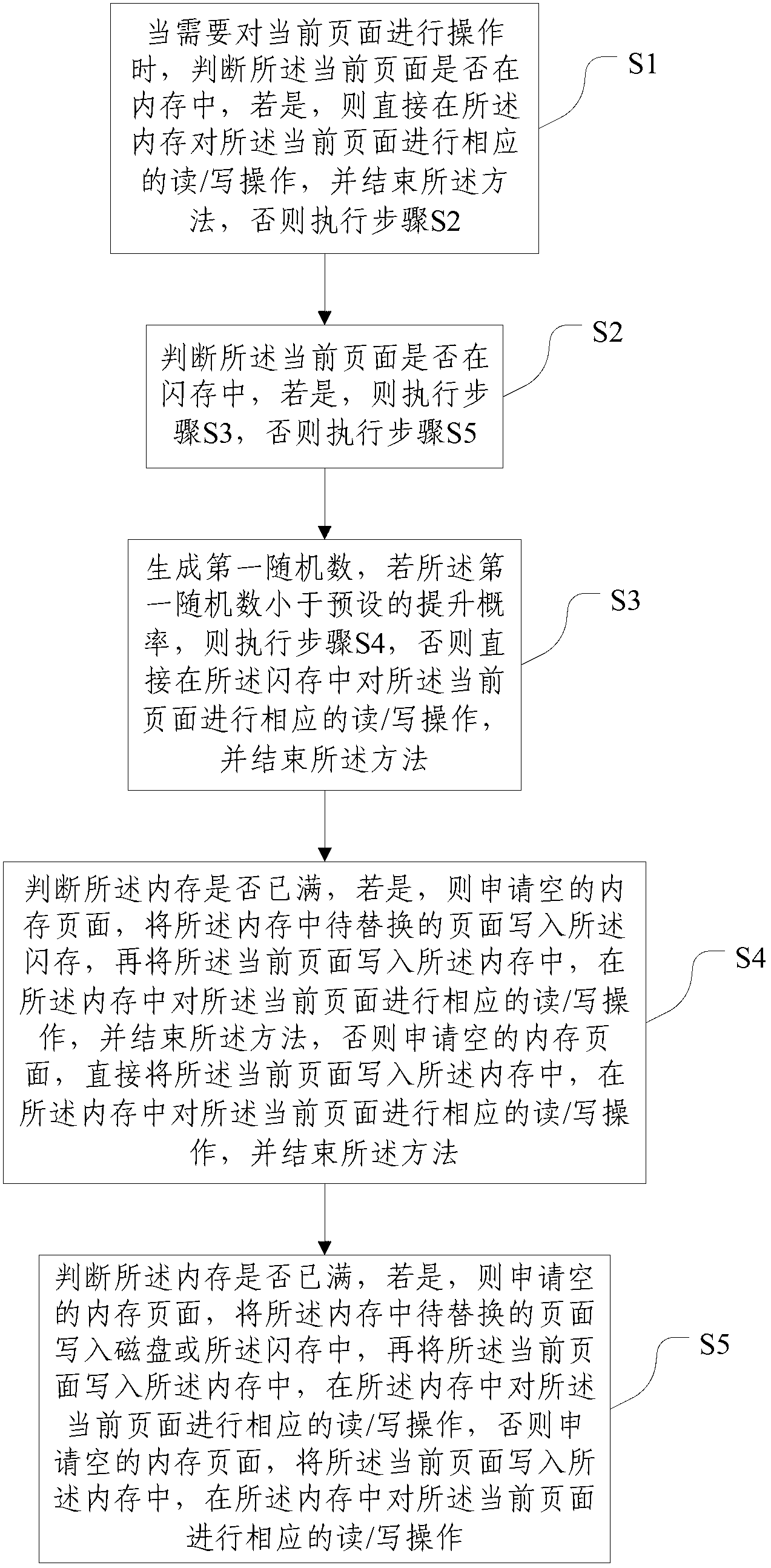

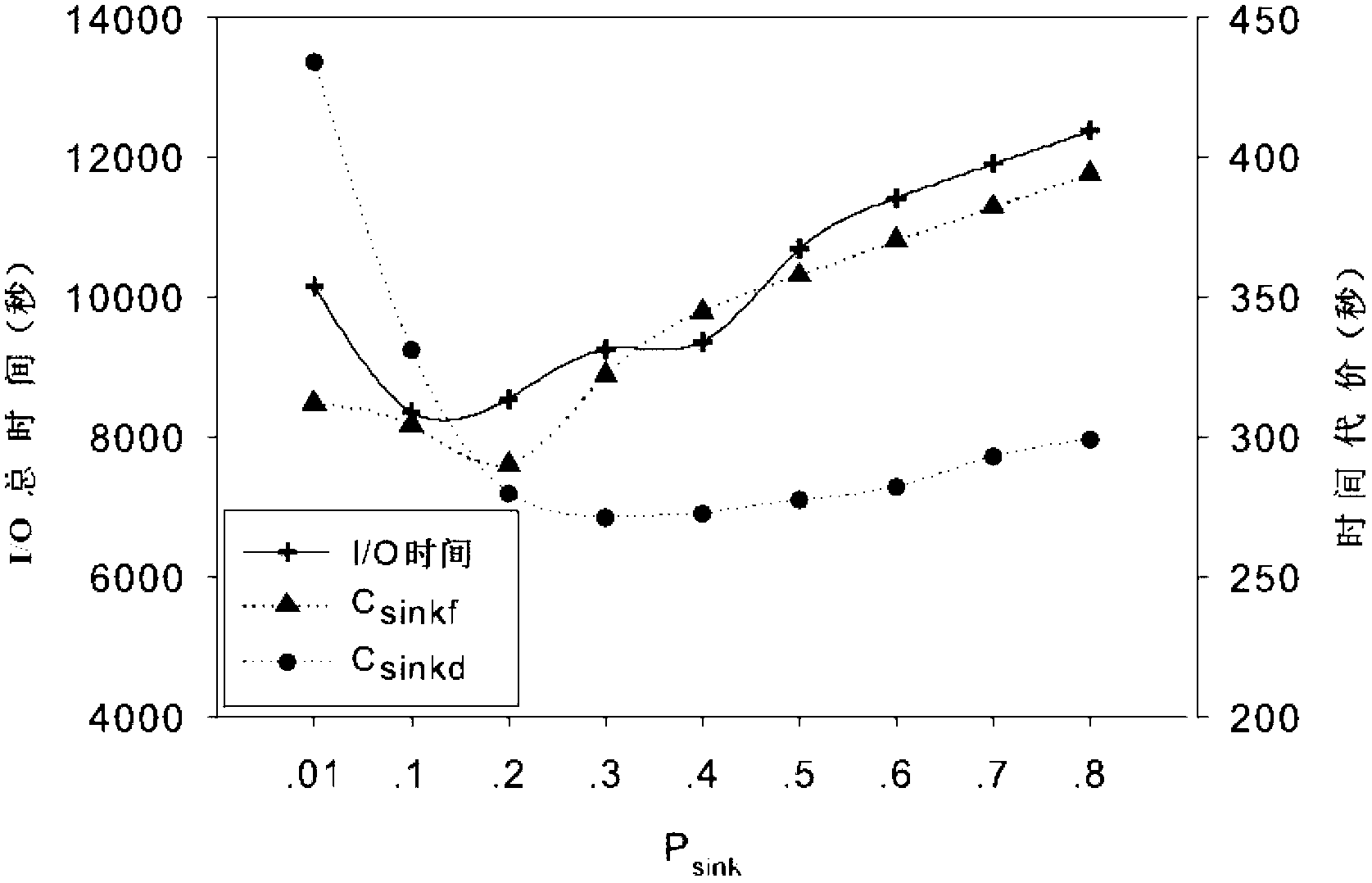

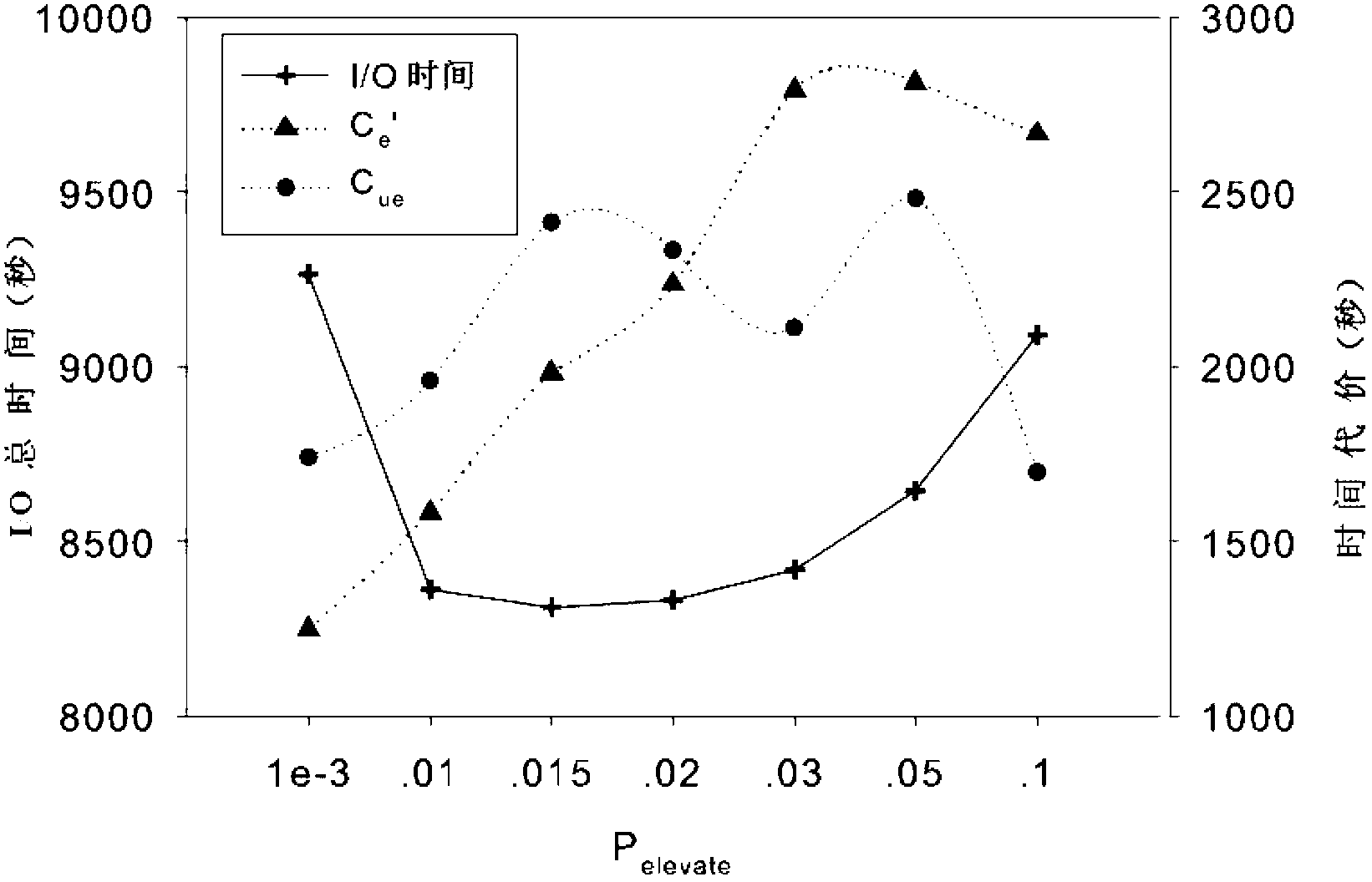

Data management method and system in mixed storage structure of flash disk

InactiveCN102707904ASave flash spaceReduce write operationsInput/output to record carriersMemory adressing/allocation/relocationStorage structureData management

The invention discloses a data management method and system in a mixed storage structure of a flash disk, and relates to the technical field of data management. According to the invention, the operation of the page is controlled by probability, so that the flash storage space is saved, the write operation of flash storage is reduced and the data management performance is improved.

Owner:PEKING UNIV

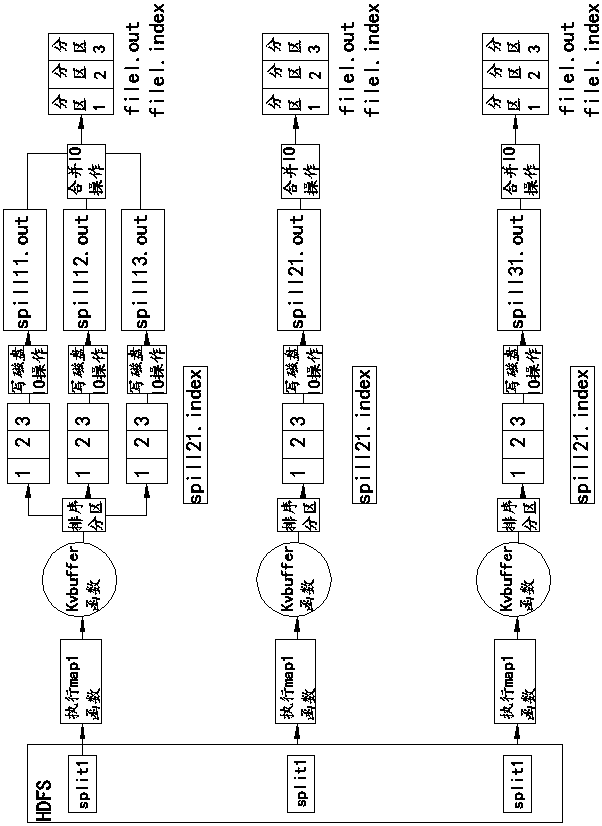

MapReduce calculation process optimization method based on B-tree data structure

ActiveCN110377601AReduce write operationsReduce stepsResource allocationSpecial data processing applicationsProcess optimizationComputer science

The invention discloses a MapReduce calculation process optimization method based on a B-tree data structure. The MapReduce calculation process optimization method comprises the following steps: 1) executing a Map task on data input into a district; 2) after executing the Map task, outputting a result which comprises an index file *. Index and a data file *. Out; 3) storing the index file *. Indexand the data file *. Out in an annular memory buffer area; 4) when the annular memory buffer area is about to overflow, judging whether the task is the last Map task or not; (5) if not, the data files *. Out are sorted and merged and then written into a disk, and the index files *. Index are left in an annular memory buffer area; and if so, directly inputting the data file *. Out into the reducefunction. According to the method, the disk read-write frequency is reduced, the calculation time is shortened, the calculation time is remarkably shortened, the calculation efficiency is improved, and the working efficiency can be effectively improved.

Owner:HENAN PROVINCIAL COMM PLANNING & DESIGN INST CO LTD