Patents

Literature

57results about How to "Rotational speed" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

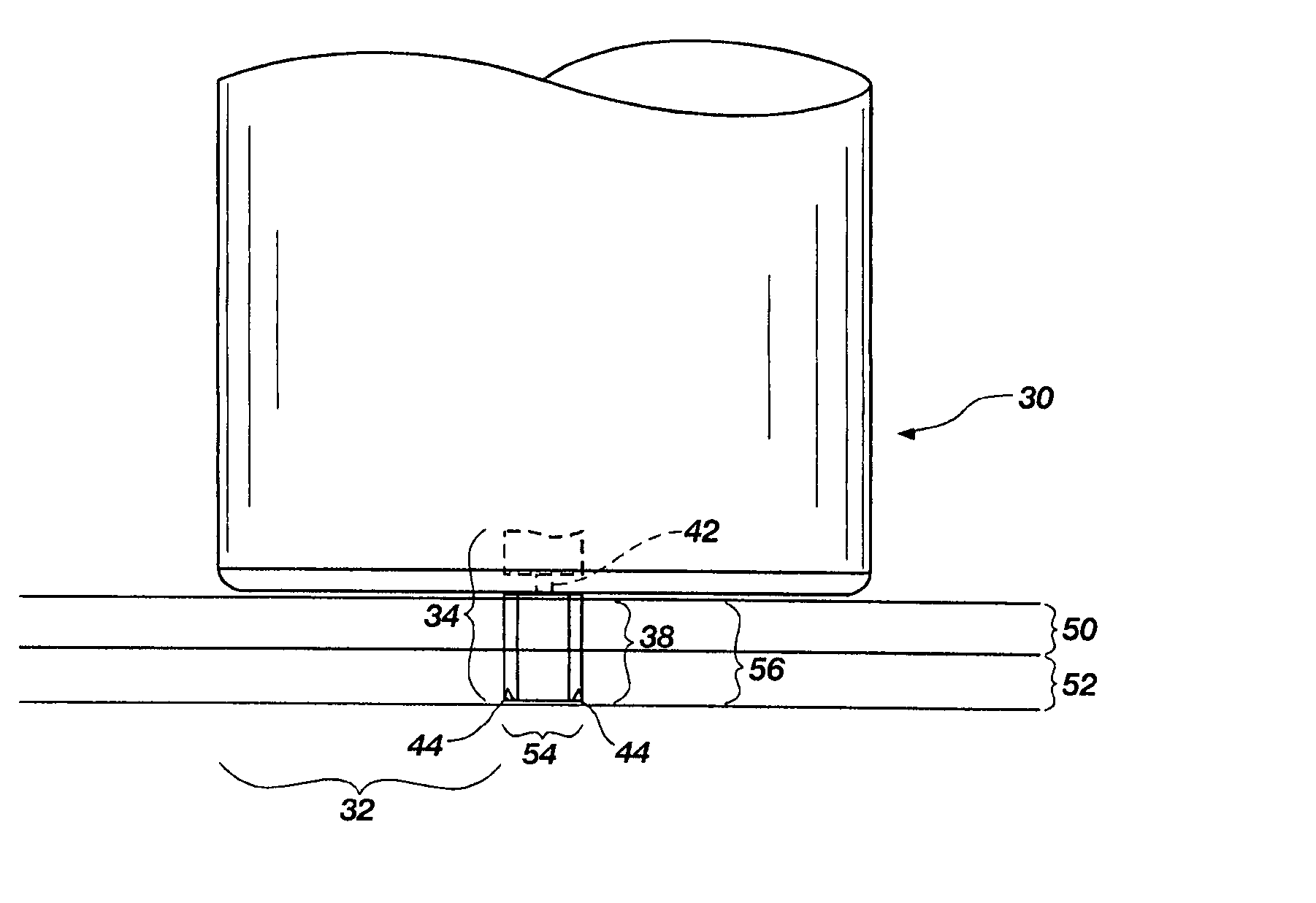

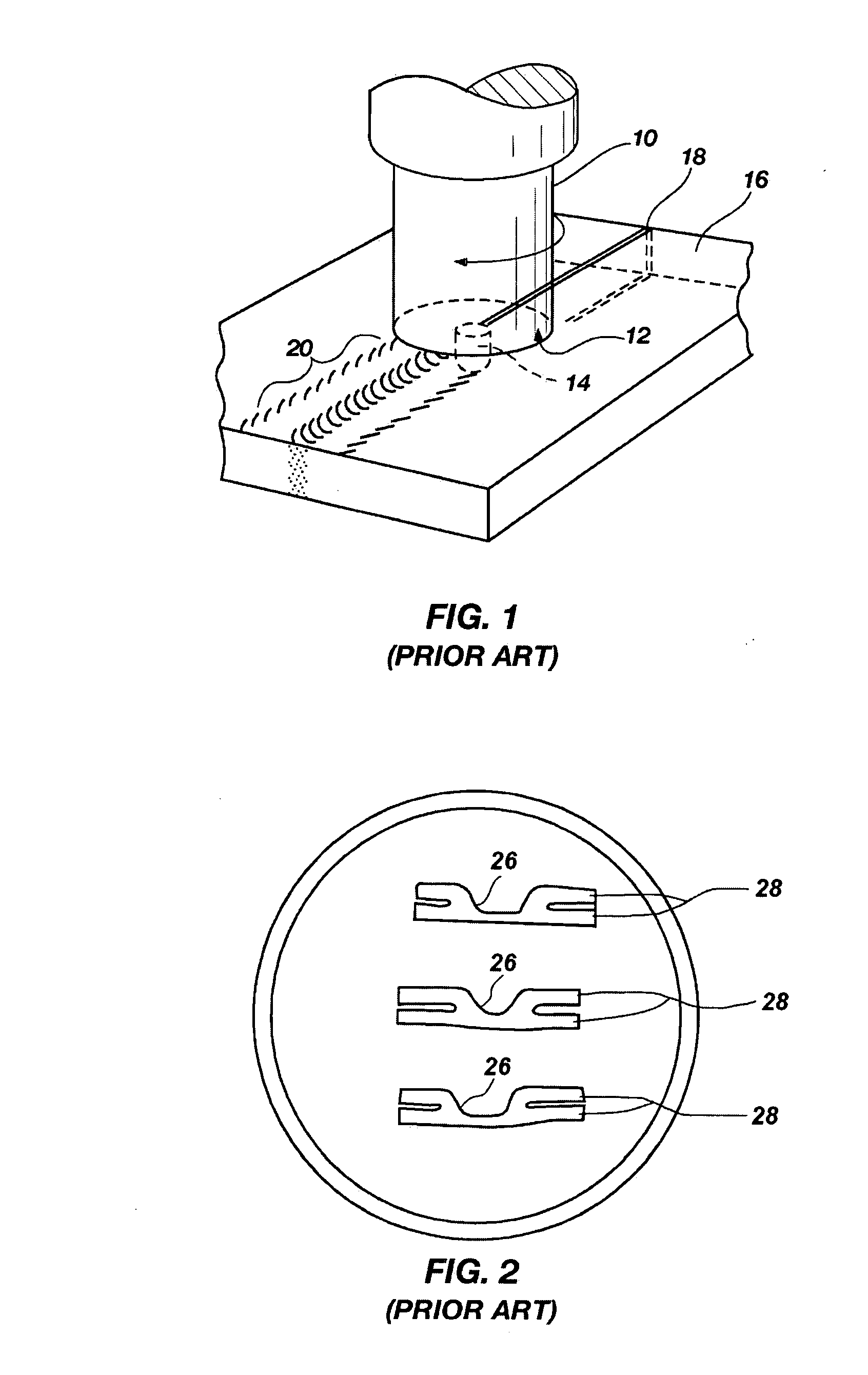

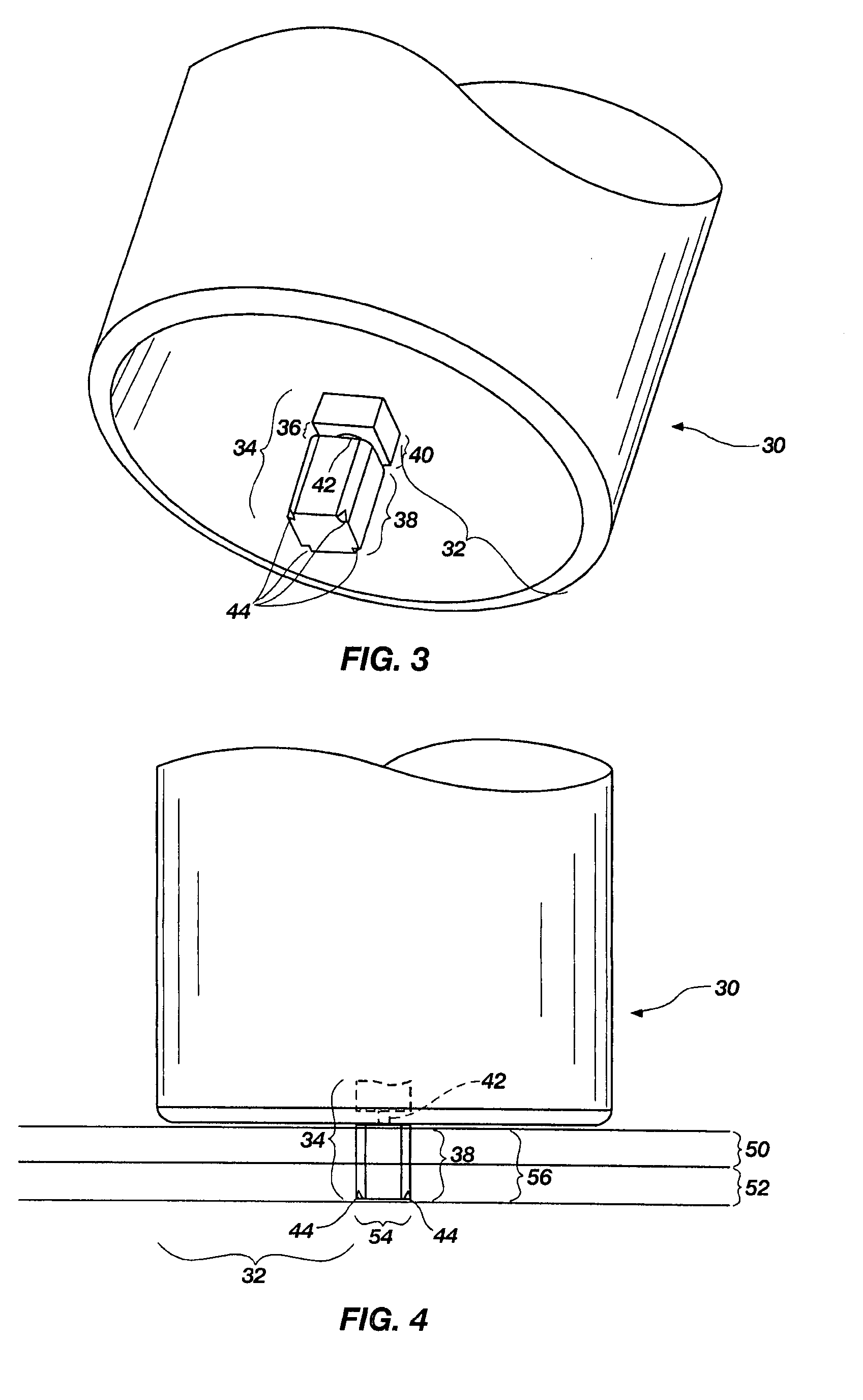

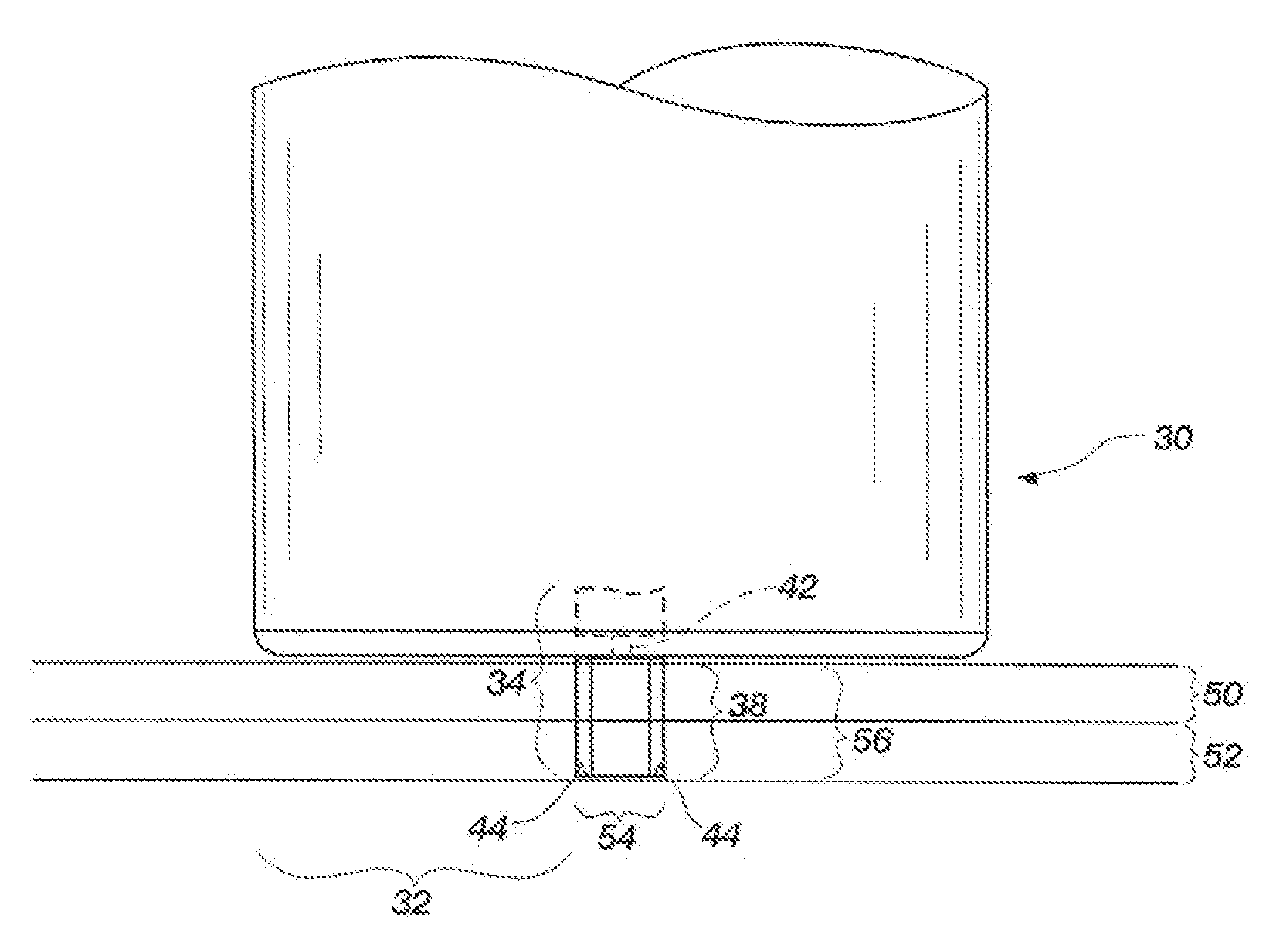

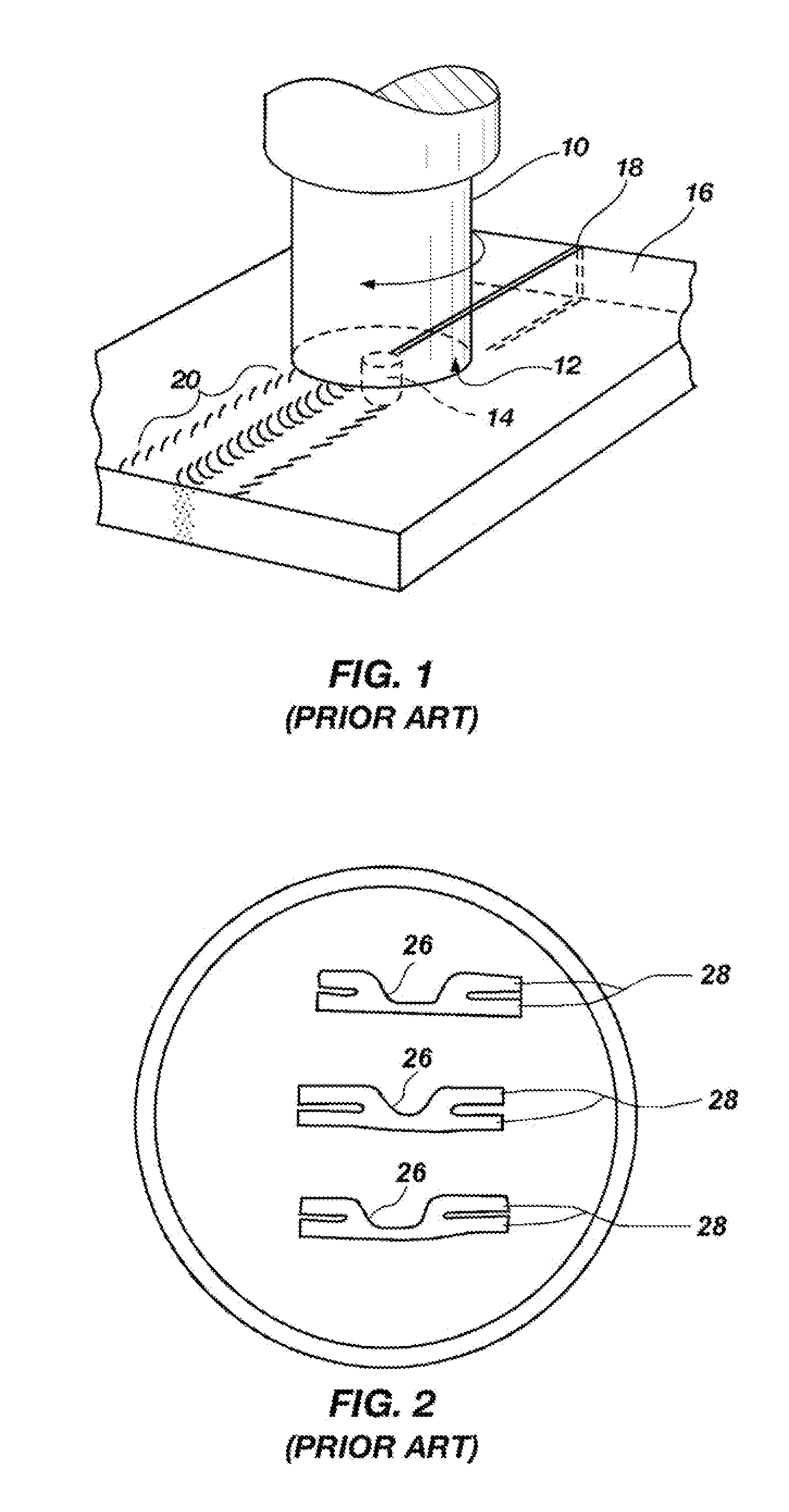

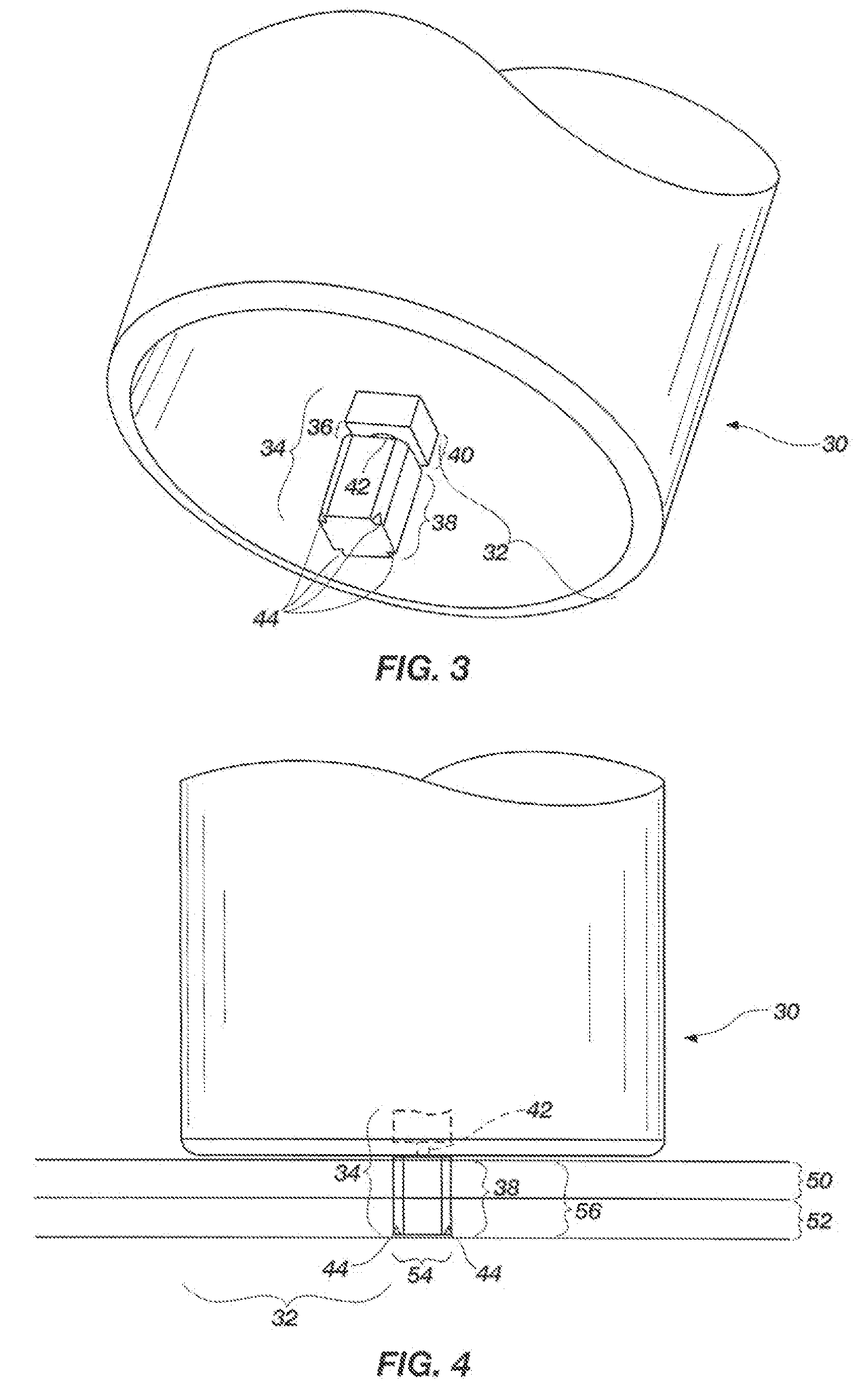

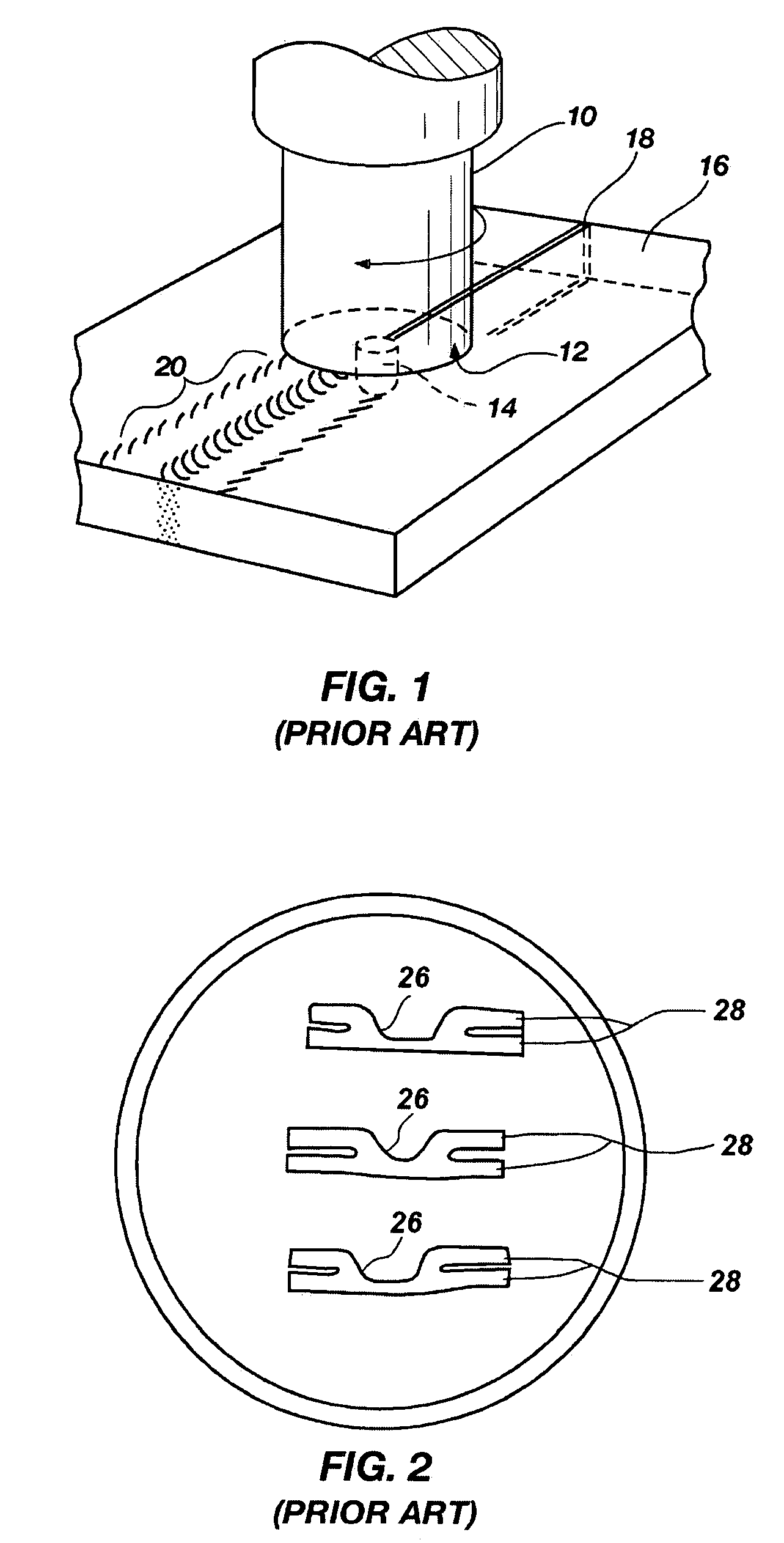

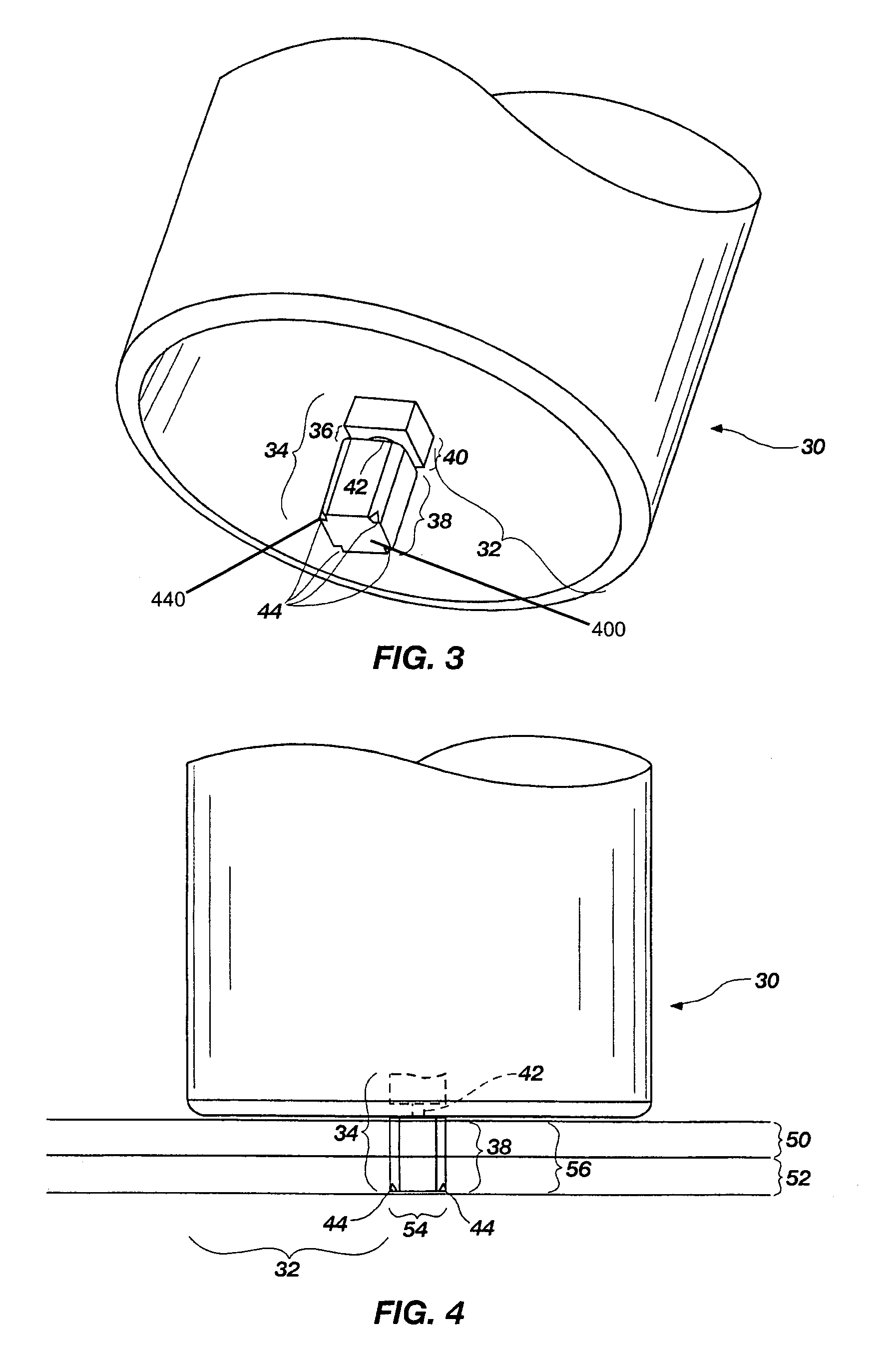

Three-body joining using friction stir processing techniques

ActiveUS20080006678A1Increase rotation speedRotational speedWelding/cutting auxillary devicesAuxillary welding devicesMechanical engineeringFriction stir processing

A friction stir tool is provided to perform friction stir riveting using a partially consumable pin, wherein the pin includes a cutting edge on a bottom surface thereof, wherein the tool is rotated at a first speed to enable cutting by the pin into a first material that is overlapping a second material, wherein after the pin has cut to a sufficient depth, the rotational speed of the tool is increased to thereby enable plasticization of the consumable pin, the first material, and the second material, wherein the tool is then rapidly decelerated until stopped, enabling diffusion bonding between the pin, the first material and the second material.

Owner:MAZAK CORP +1

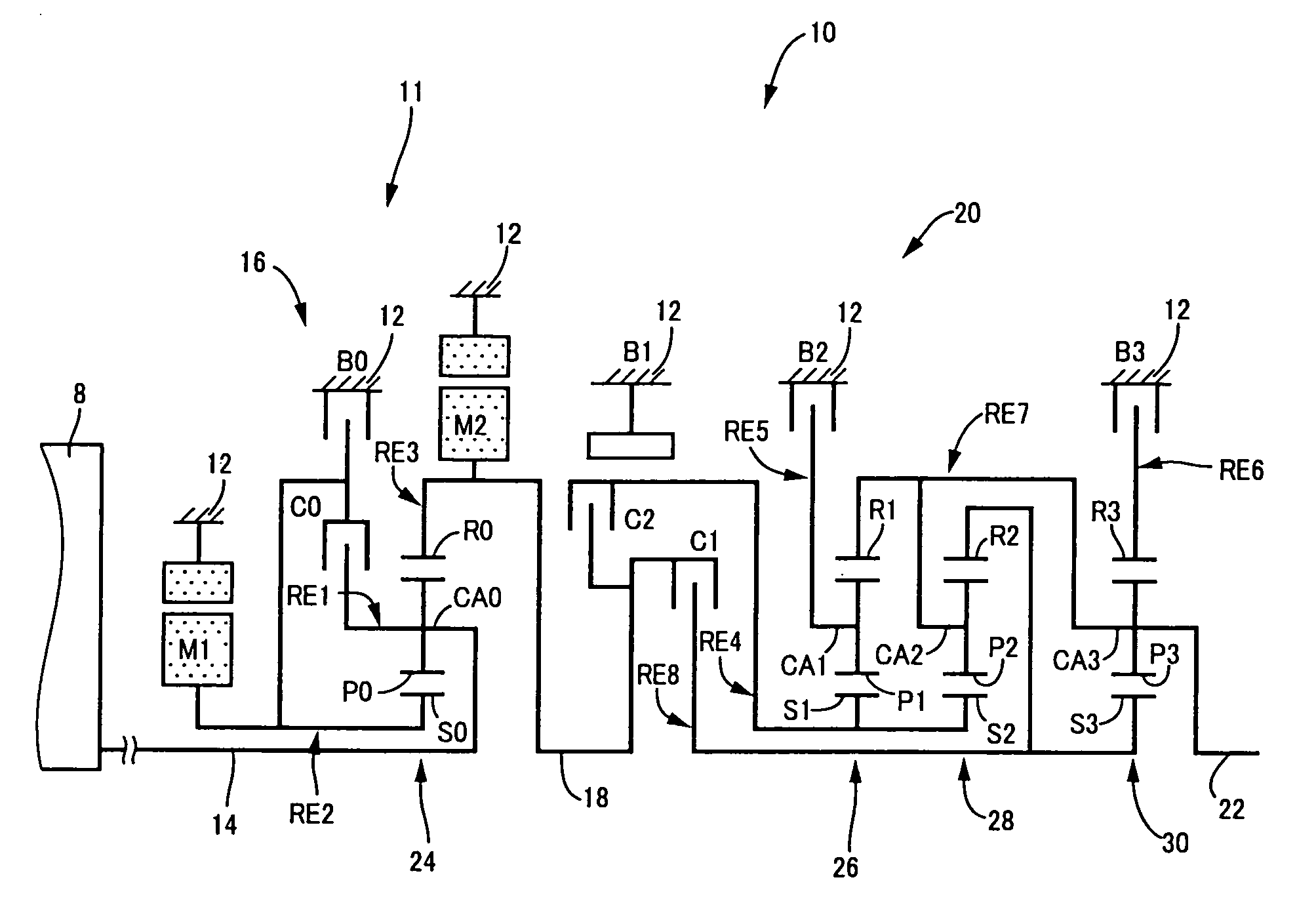

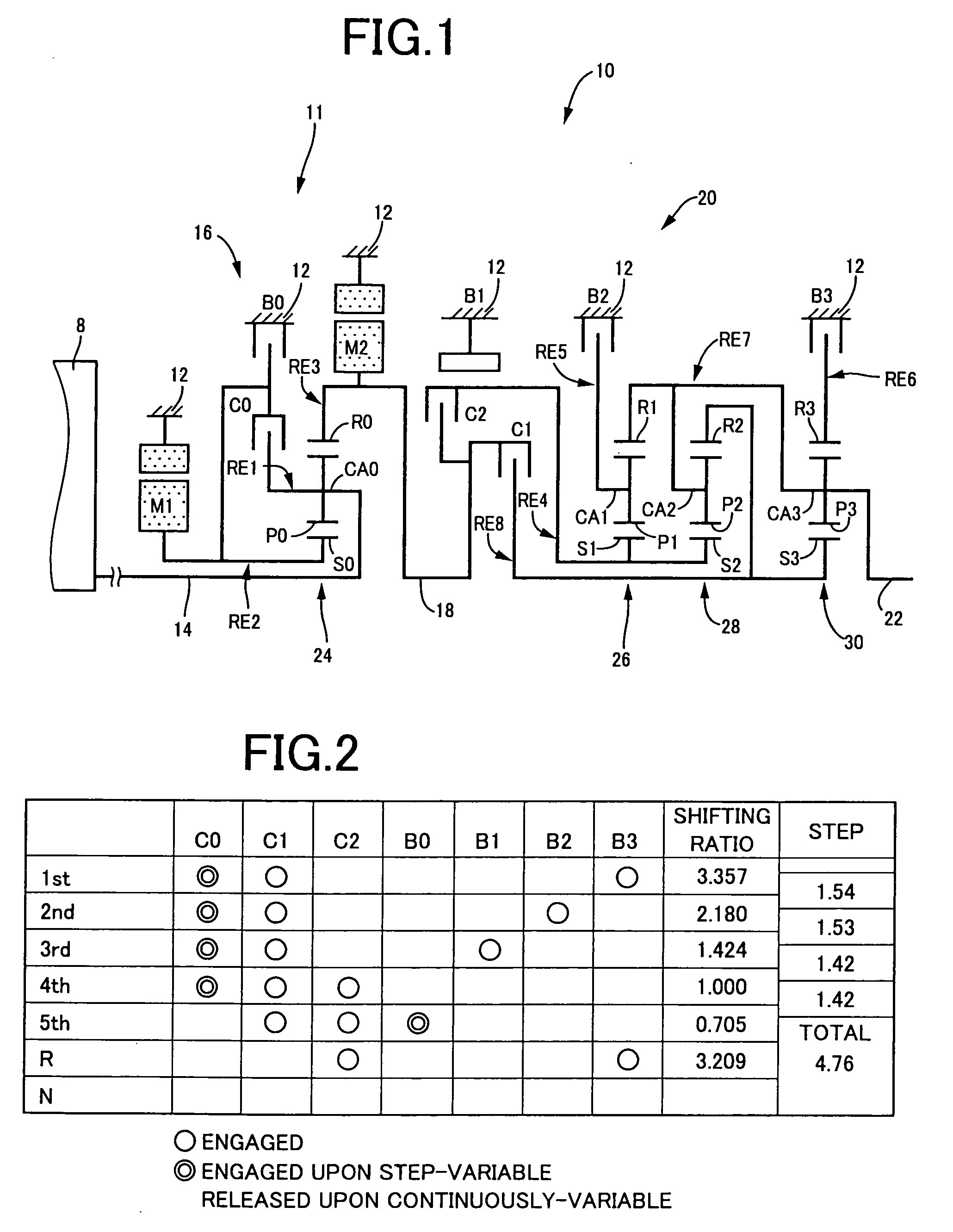

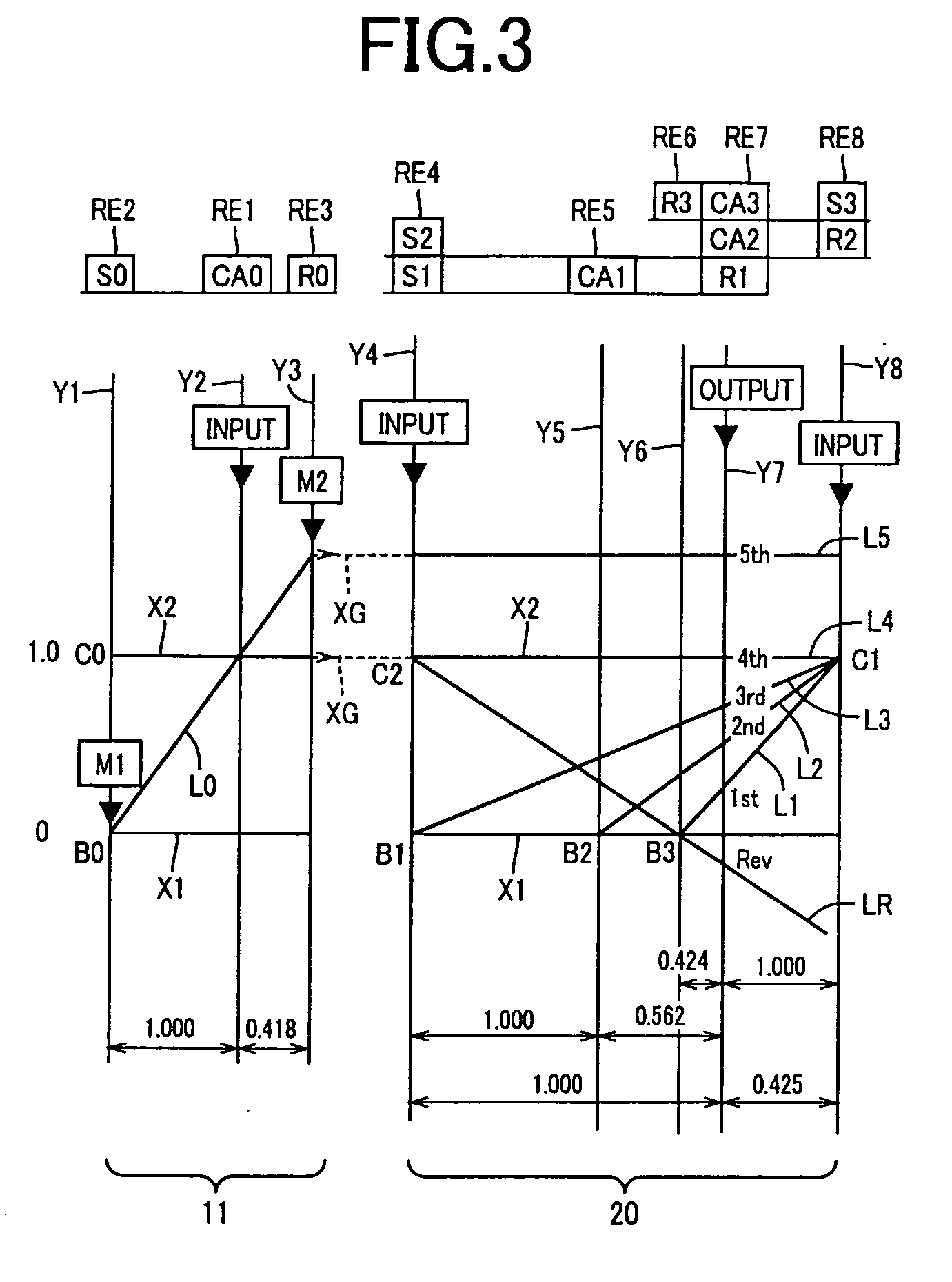

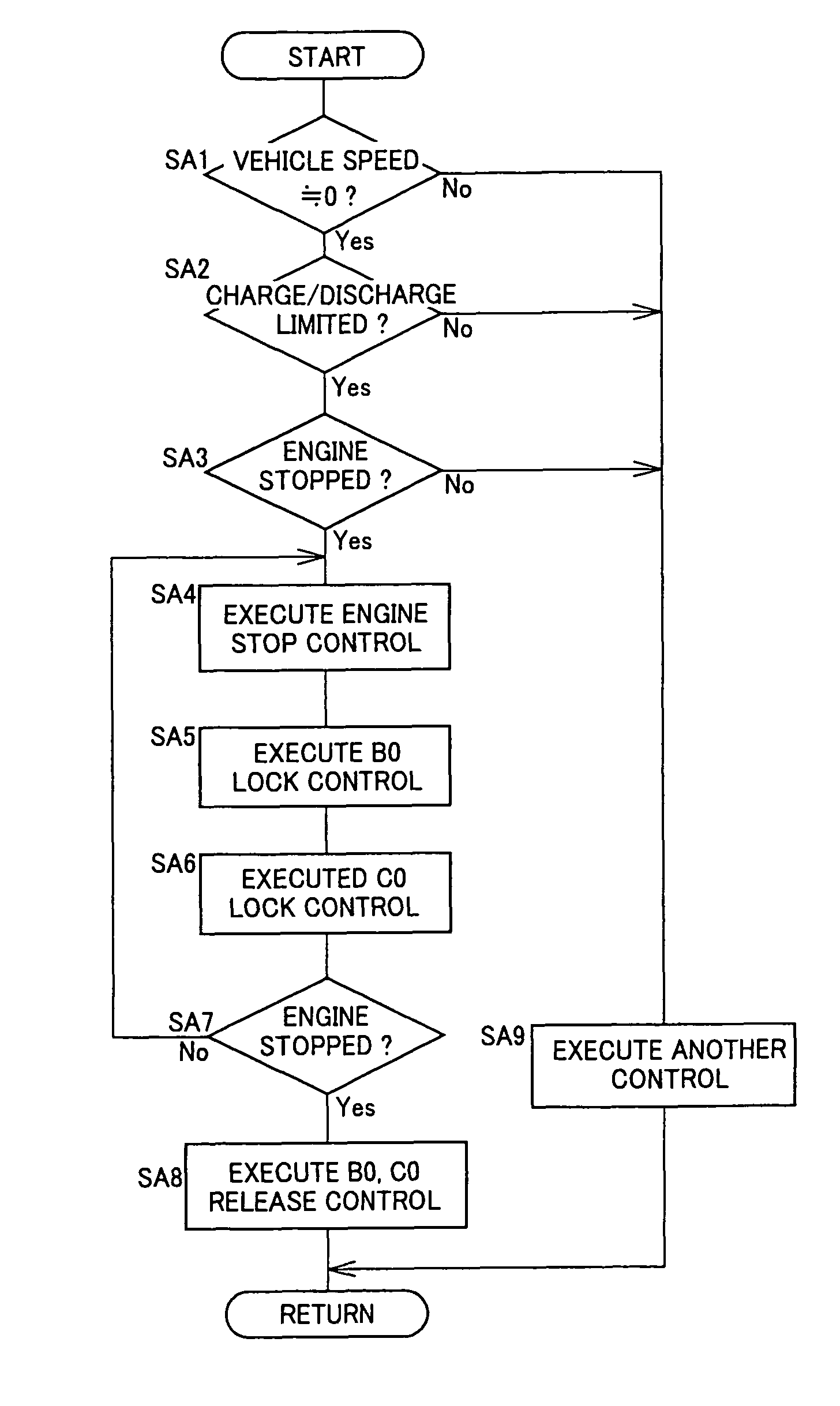

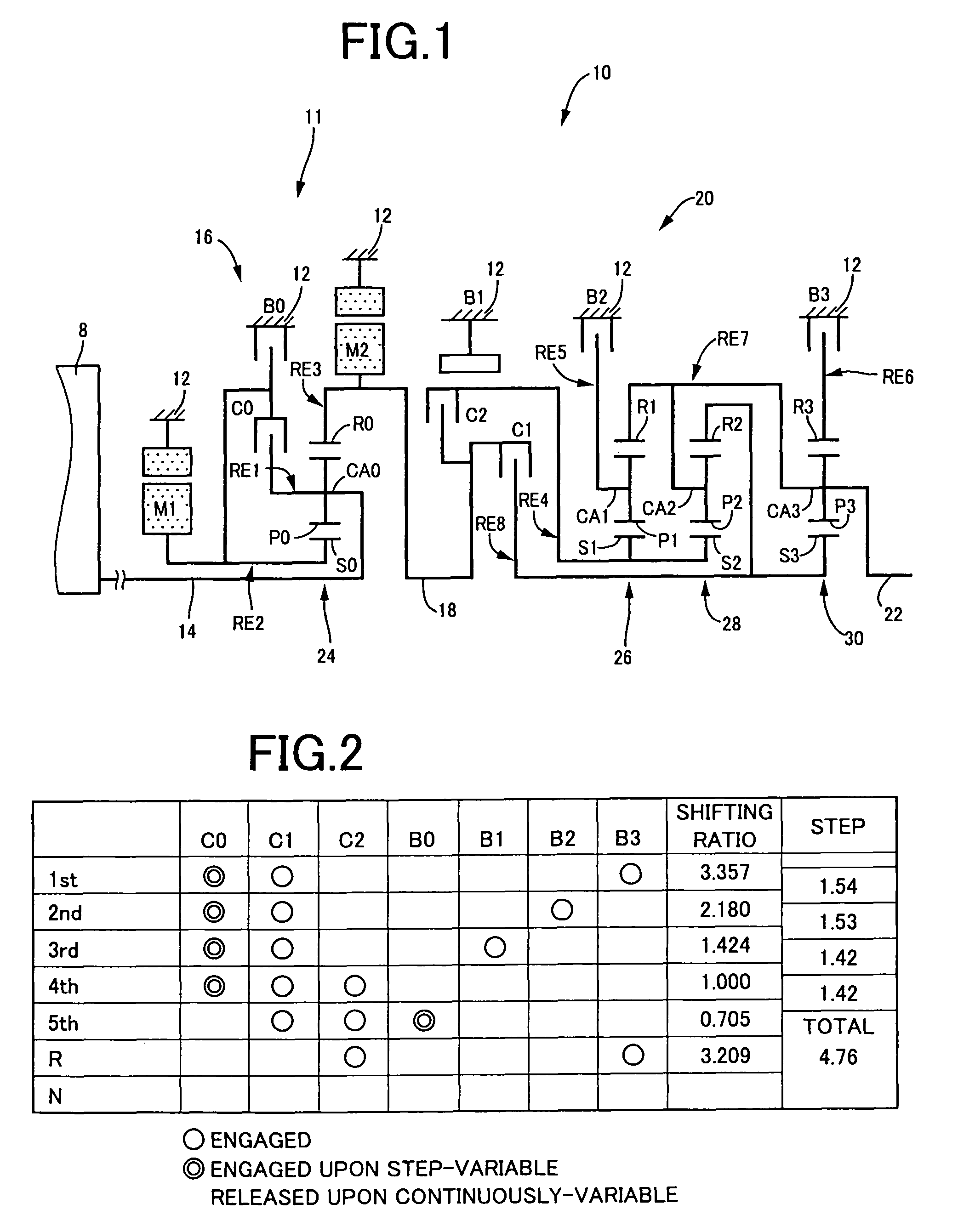

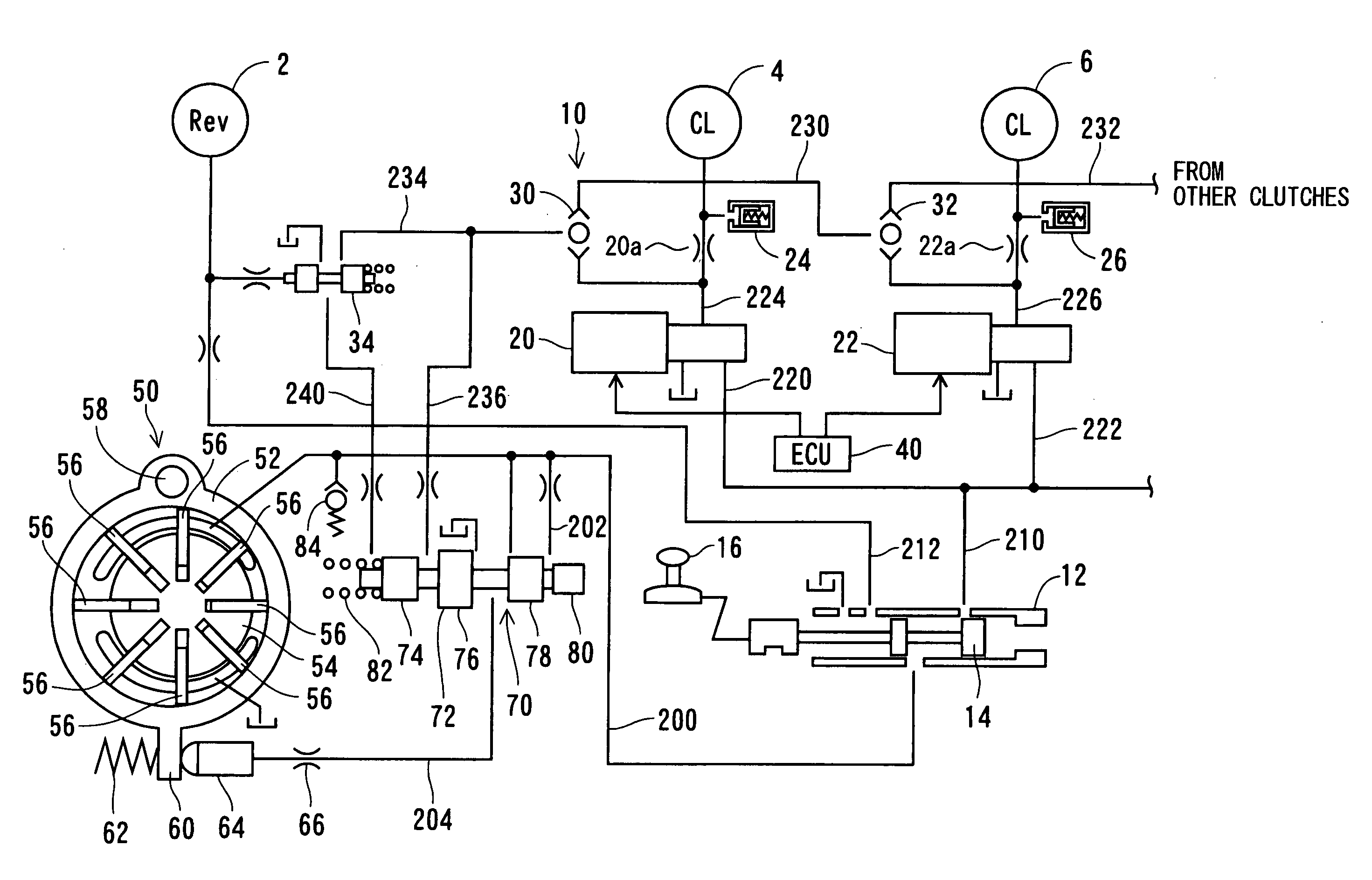

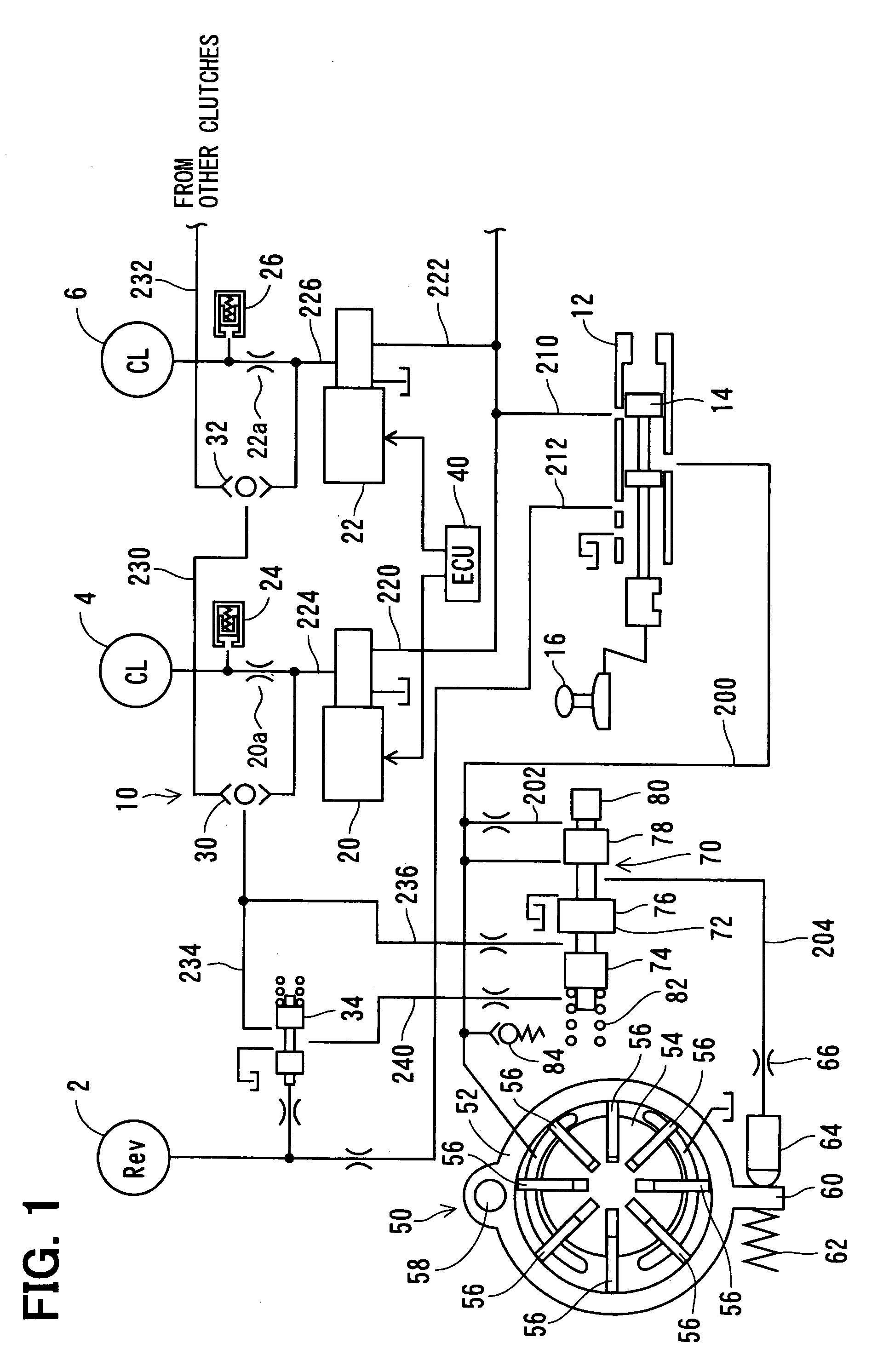

Control device for vehicular power transmitting apparatus

InactiveUS20090075779A1Rotational speedShort timeHybrid vehiclesDigital data processing detailsElectricityControl theory

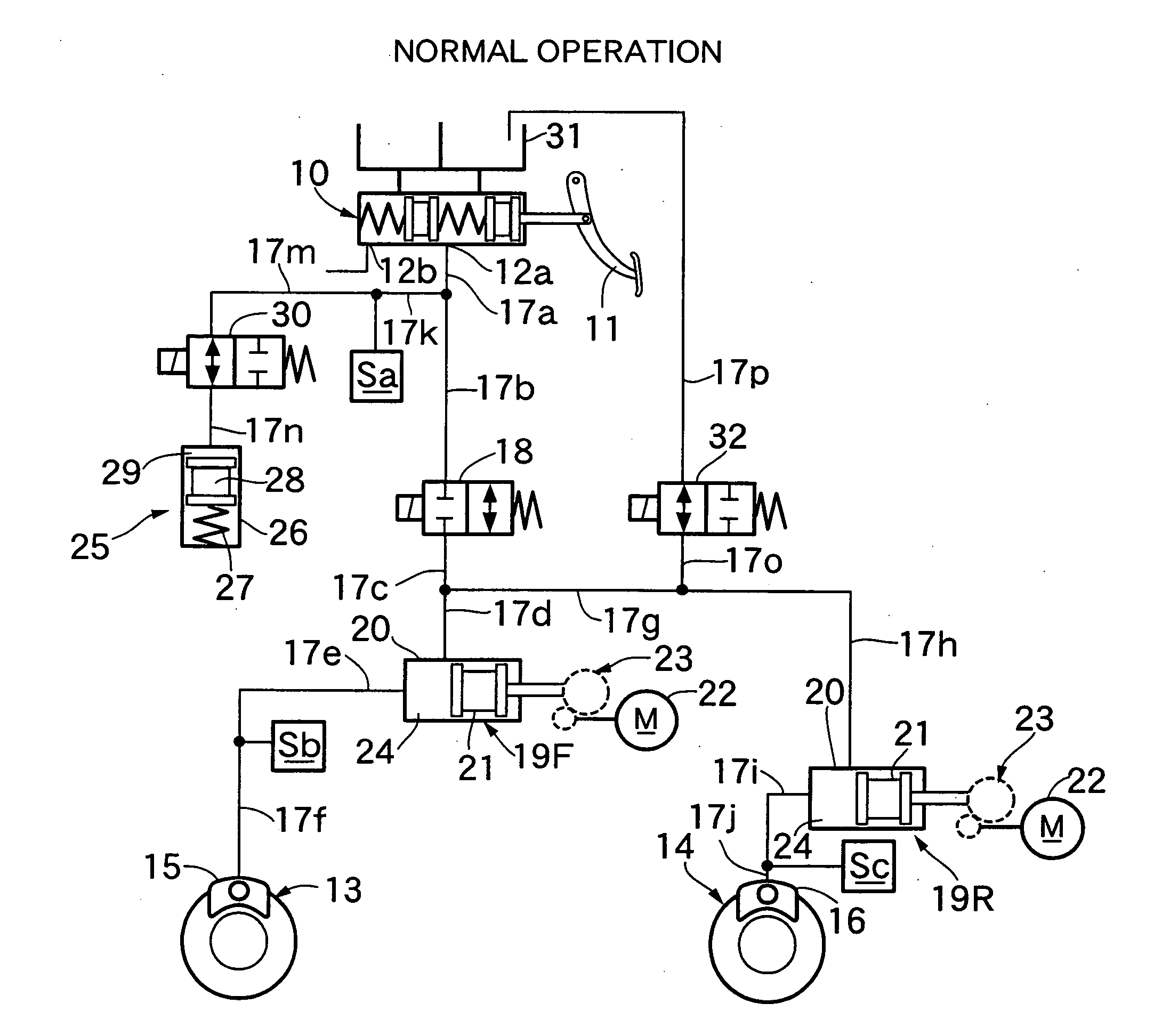

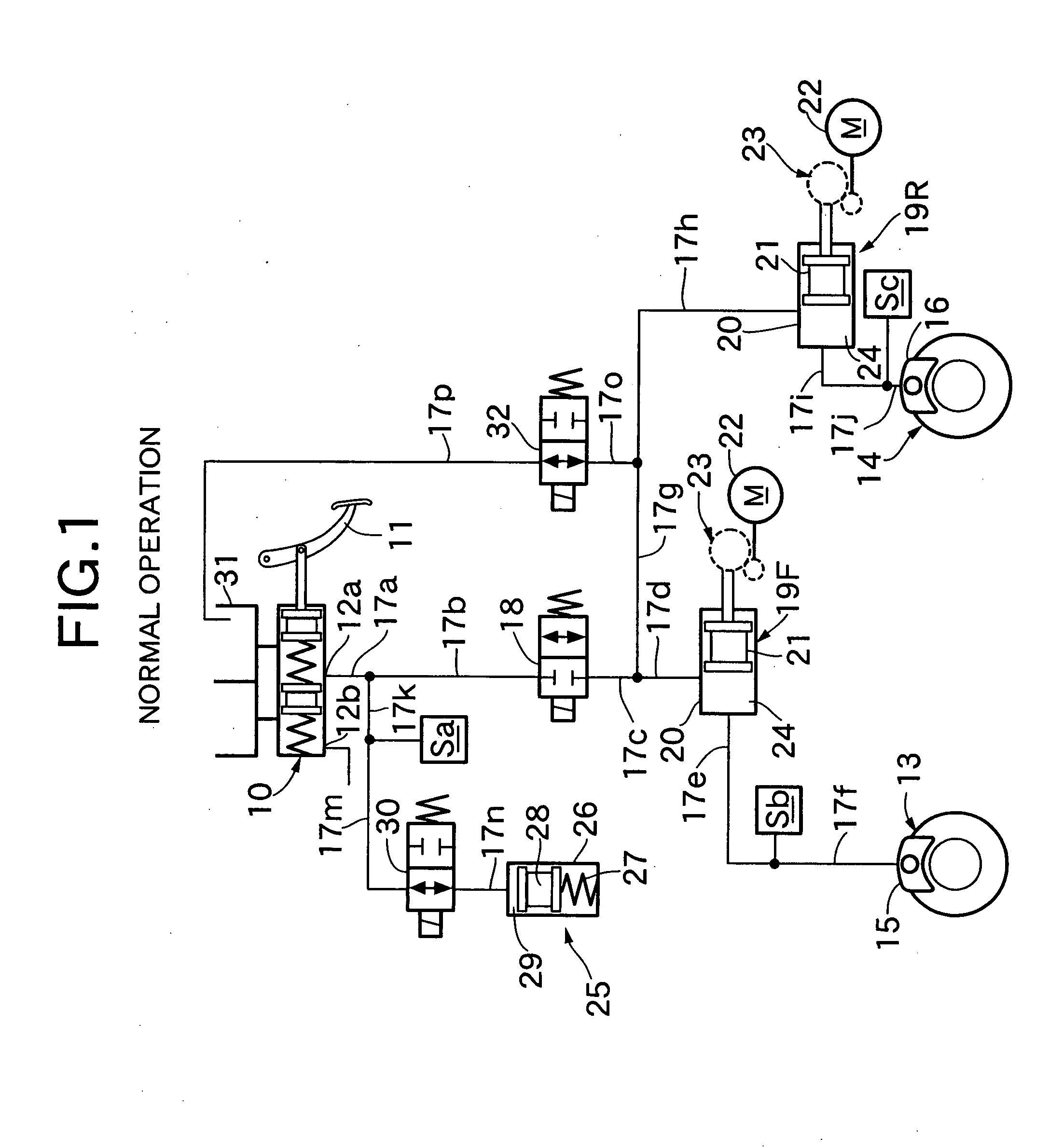

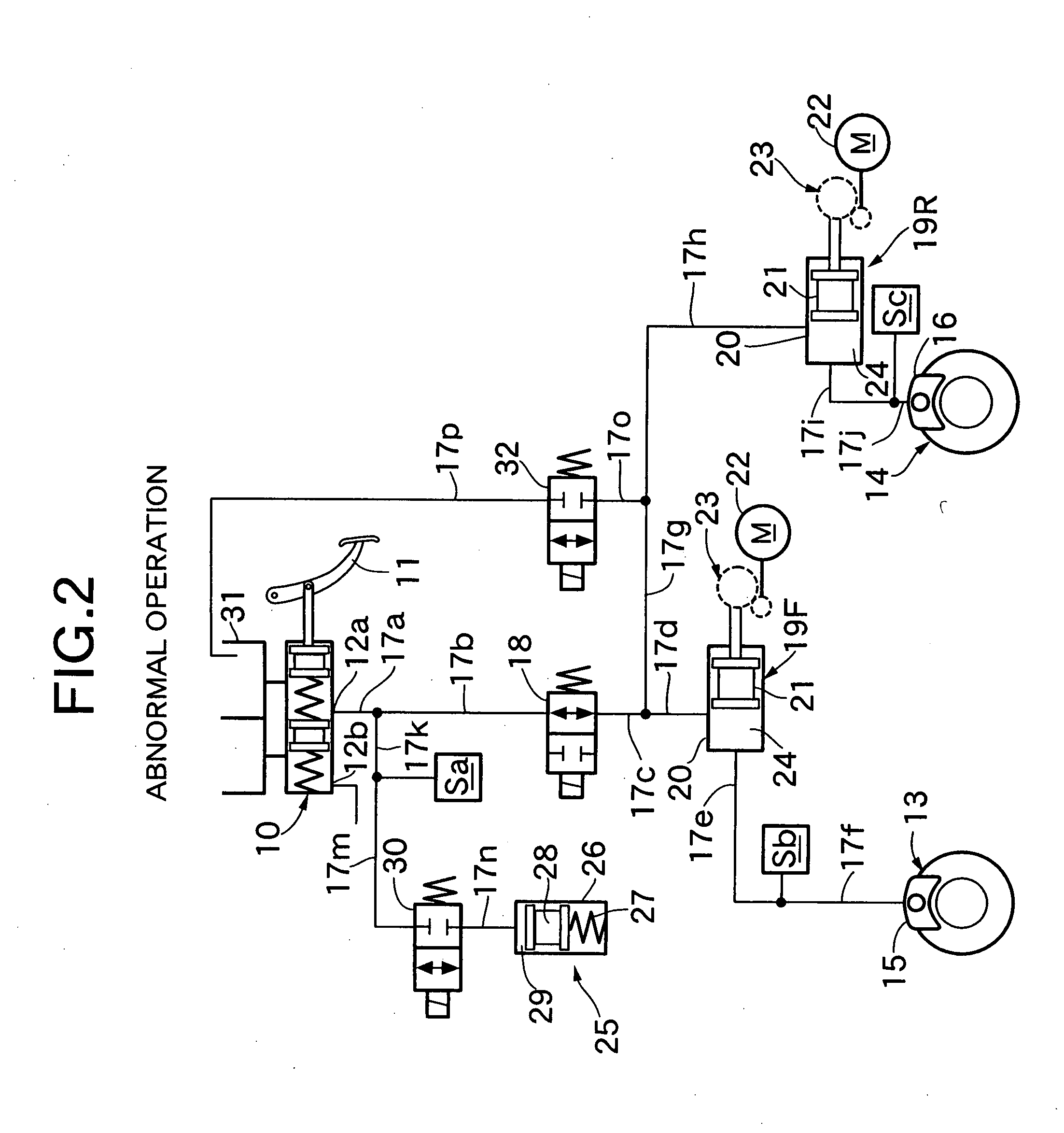

The present invention provides, in a vehicular power transmitting apparatus including a differential portion electrically controlled, a control device which can quickly decrease the engine rotation speed, even if the operational state of an electric motor is limited. An engine-stop controlling means (112) includes limiting means for limiting the differential state of a differential portion (11) by a switching brake (B0) and a switching clutch (C0) when the operational state of a first electric motor (M1) is limited. Therefore, a torque in a direction for decreasing a rotation speed (NE) of an engine (8) is applied by limiting the differential state of the differential portion (11), for example, in a vehicle stopped state. As a result, the rotation speed (NE) of the engine (8) is quickly decreased to pass through a resonance point in a short time, whereby occurrence of resonance phenomena can be prevented.

Owner:TOYOTA JIDOSHA KK

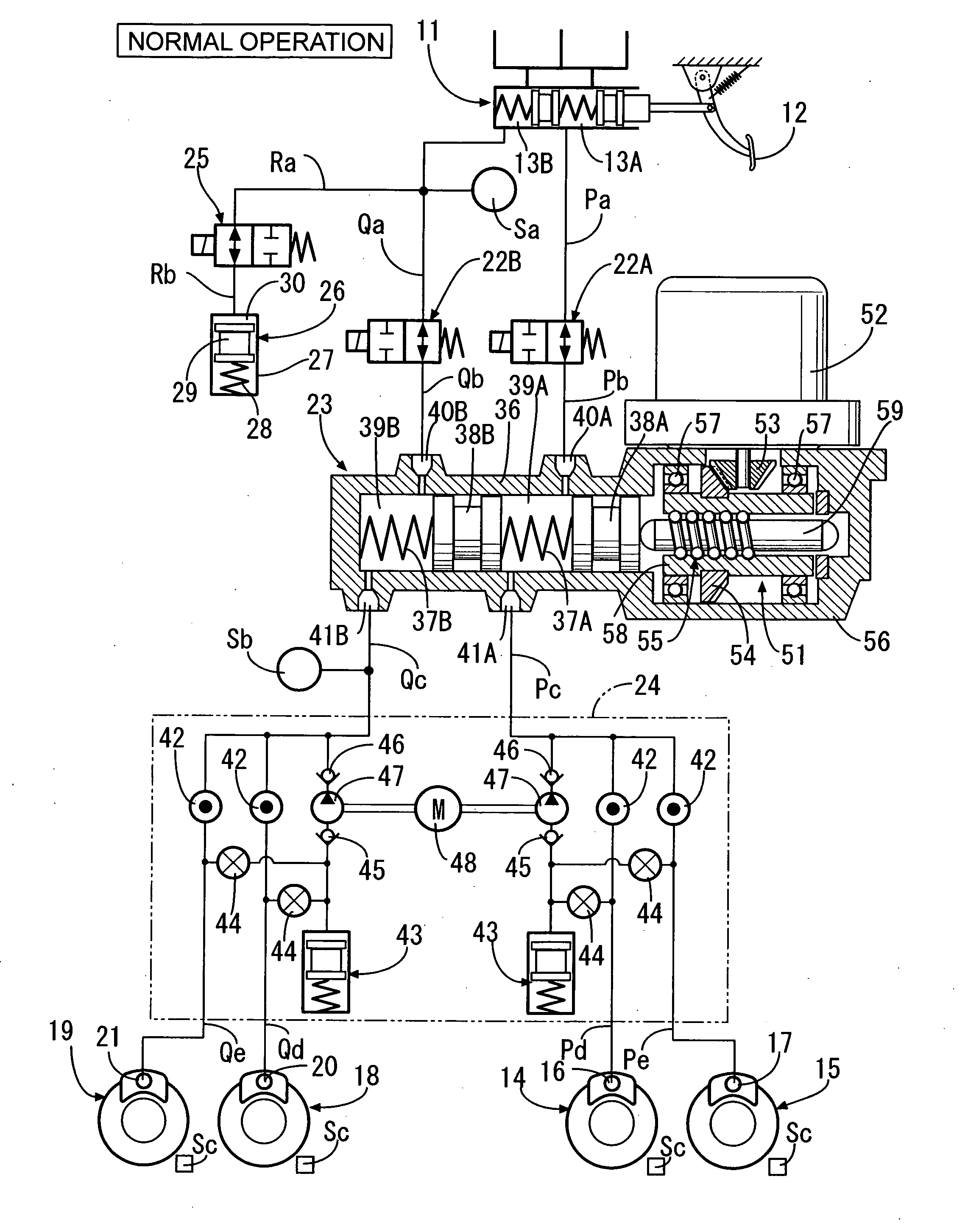

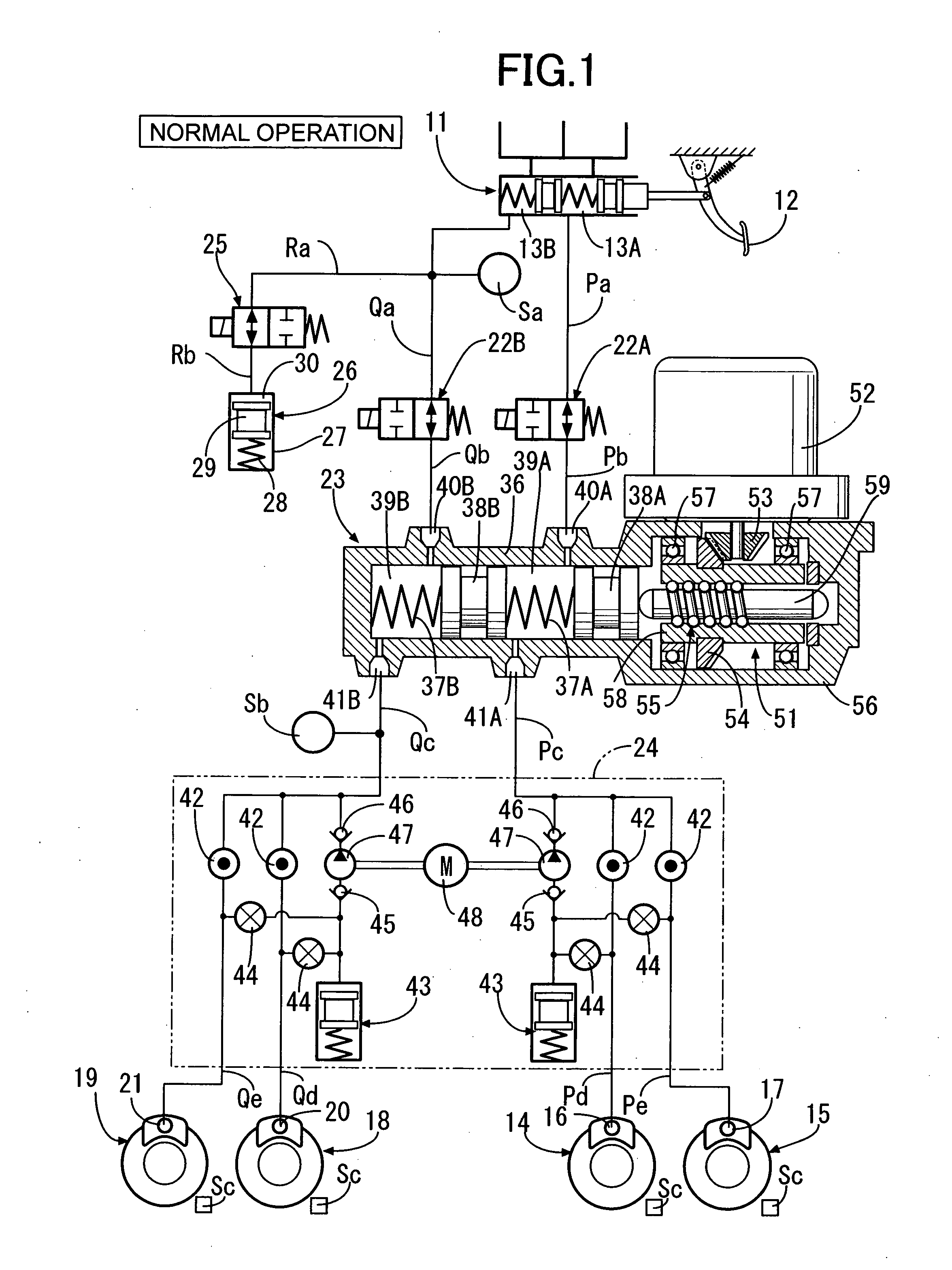

Brake system

InactiveUS20080179941A1Improve responseIncrease in sizeBraking action transmissionApplication and release valvesEngineeringControl theory

A brake system includes an electric brake force generator which brakes a wheel using a driving force of an electric motor and an electric motor controller that performs a field-weakening control of the electric motor. The electric motor controller performs the field-weakening control of the electric motor which then operates the electric brake force generator. Thus, the rotational speed of the electric motor is increased when the field weakening control is performed by the electric motor controller thereby quickly activating the electric braking force generator to enhance response of brake force generation.

Owner:HONDA MOTOR CO LTD

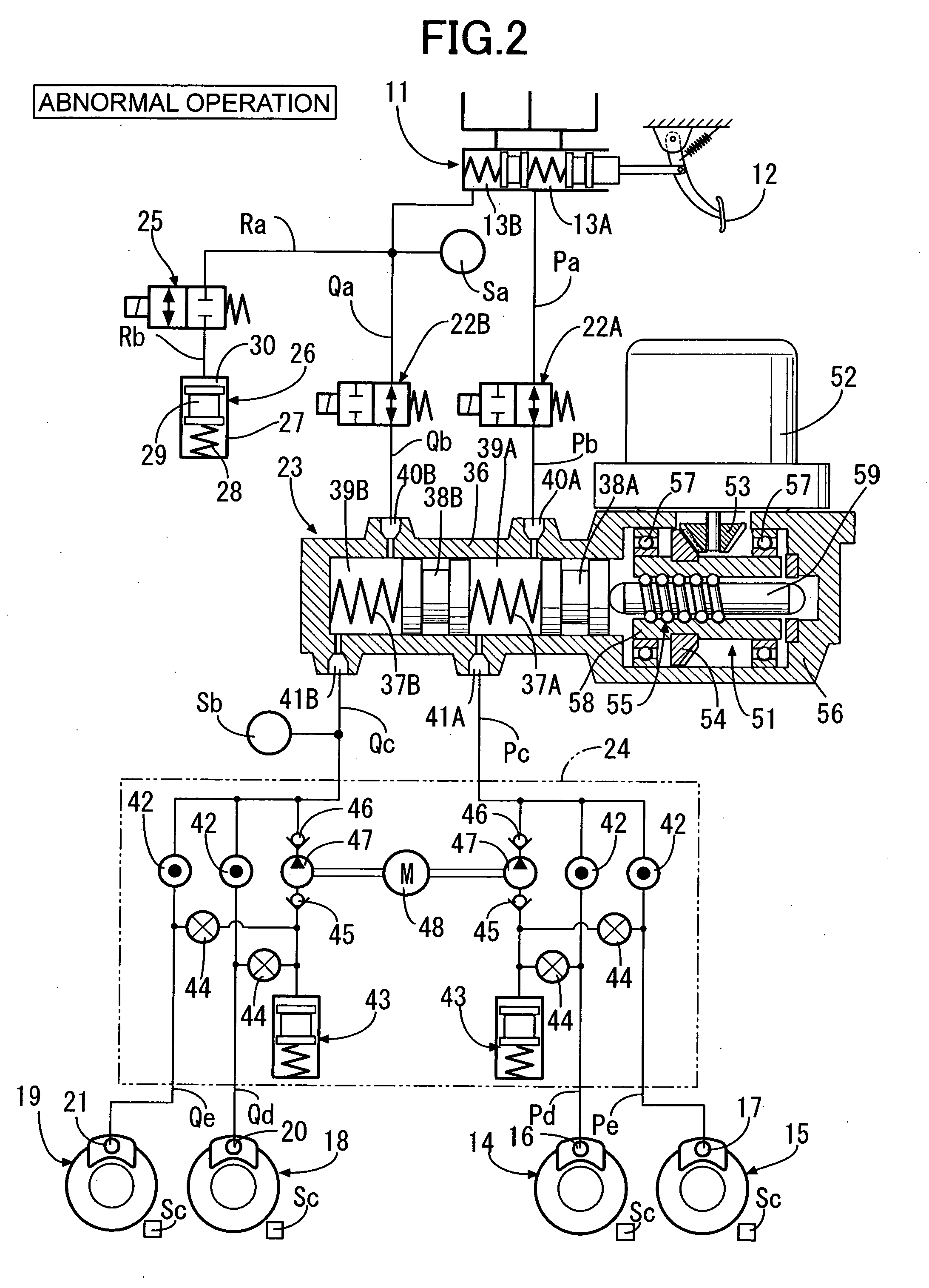

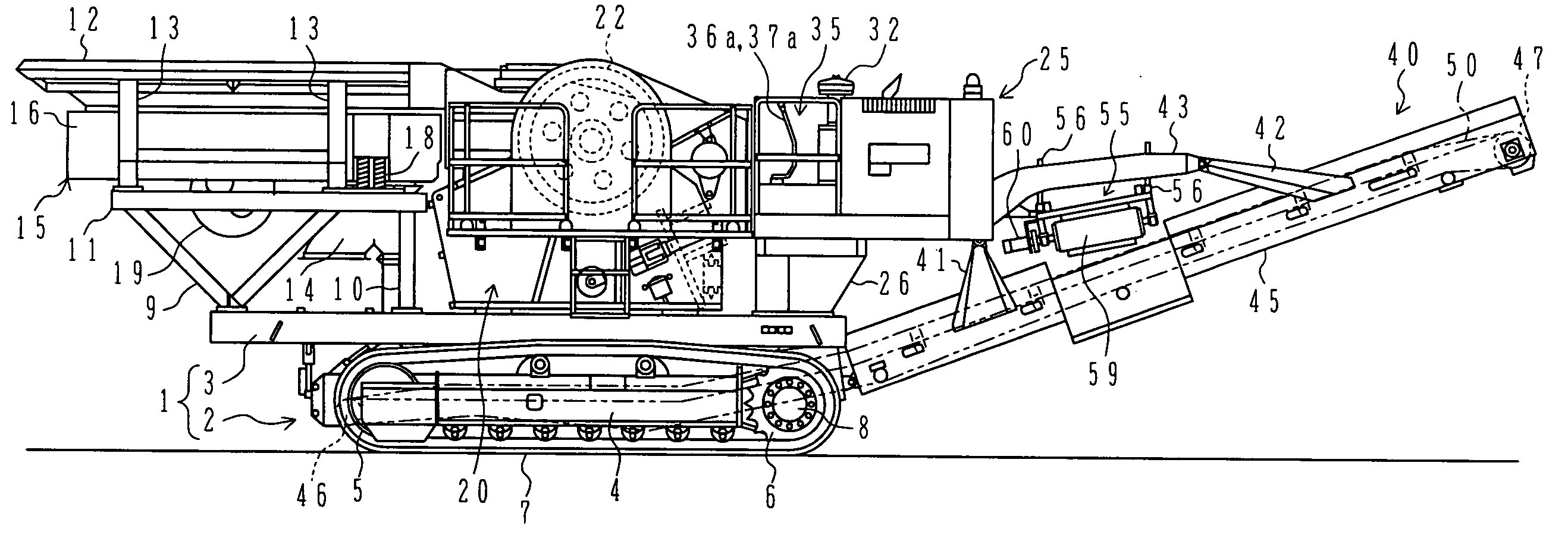

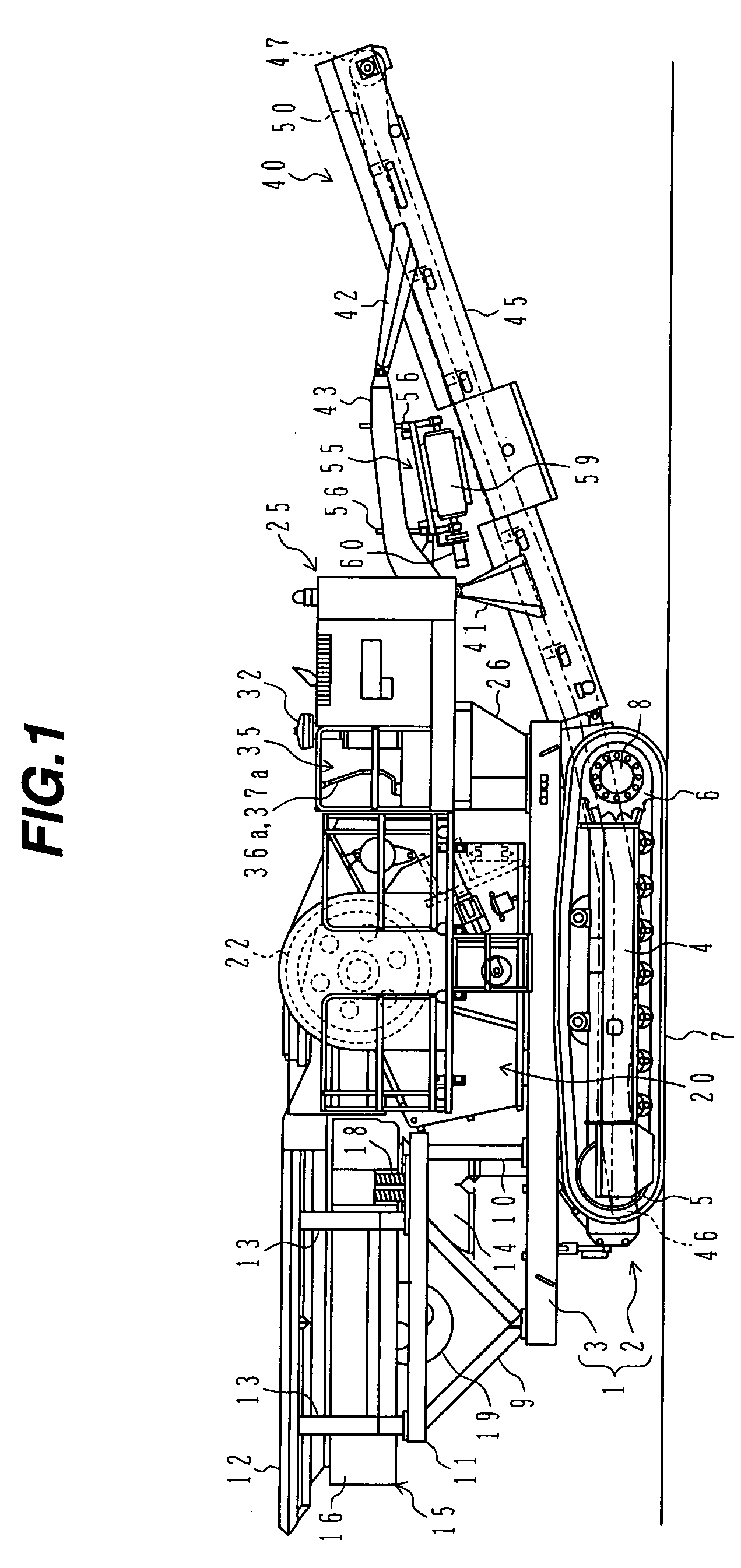

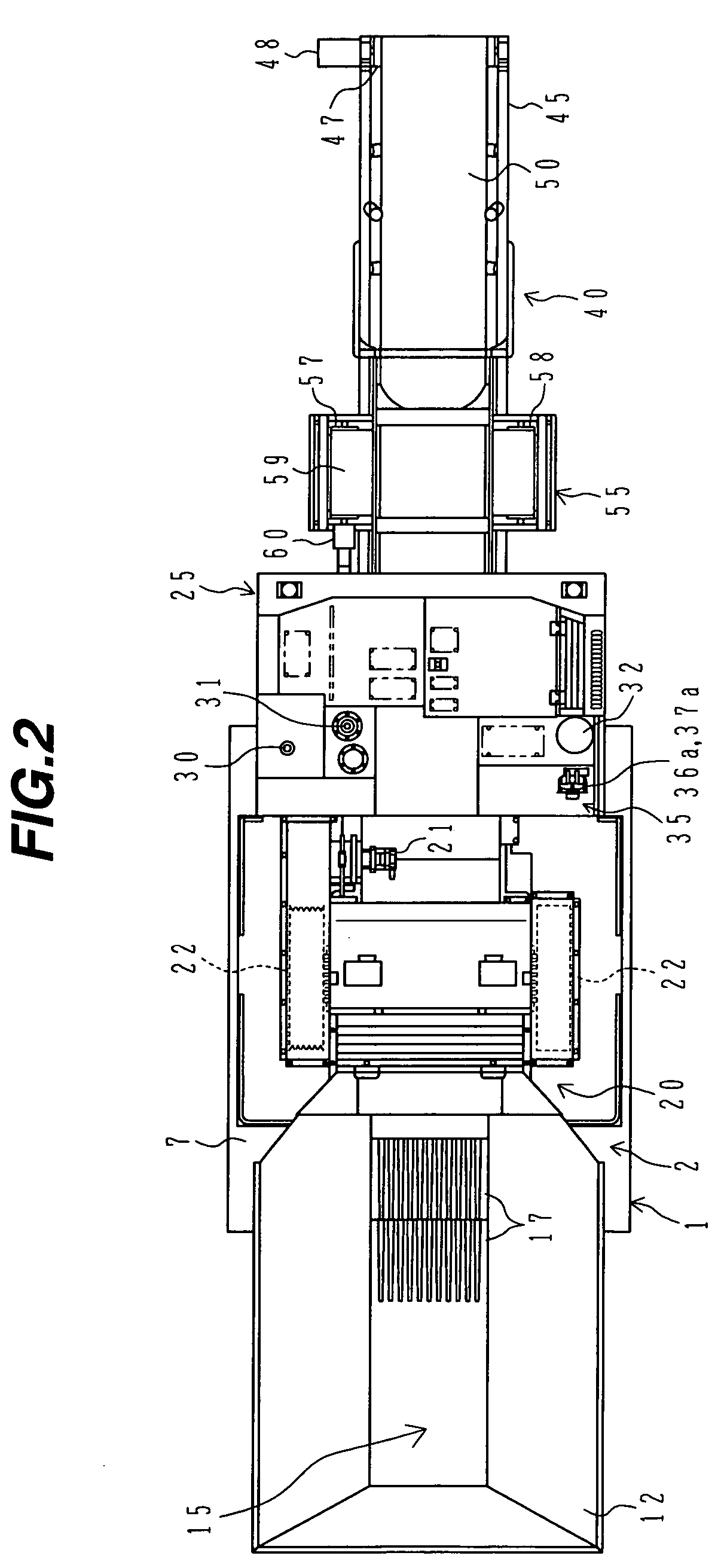

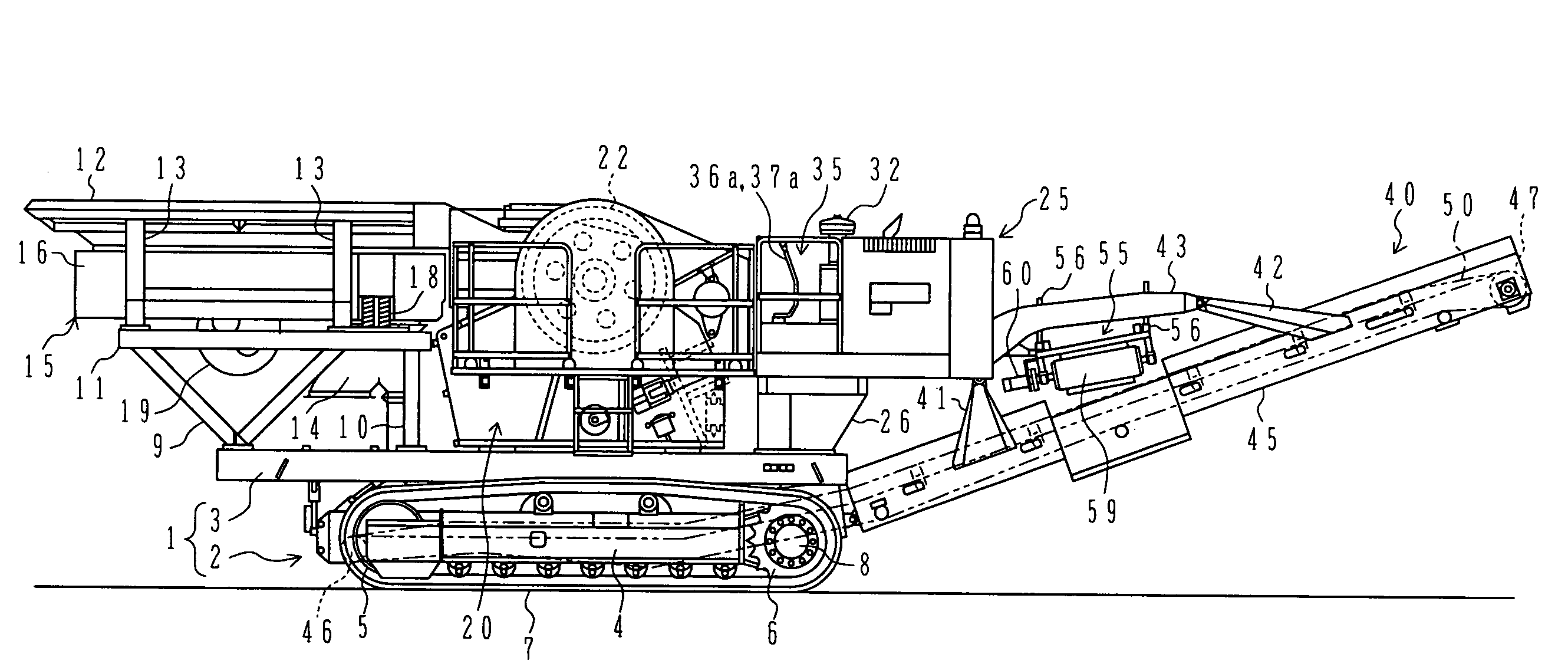

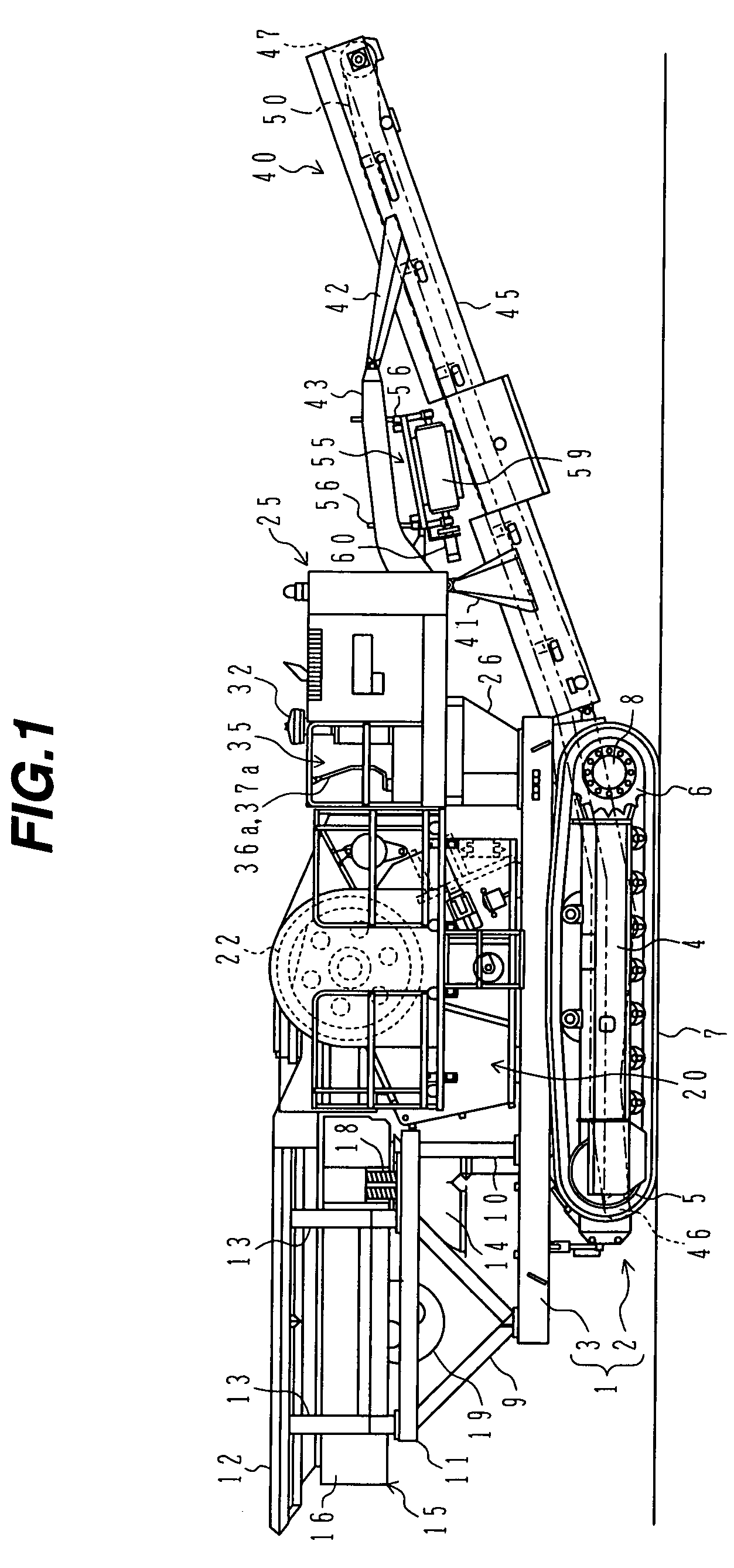

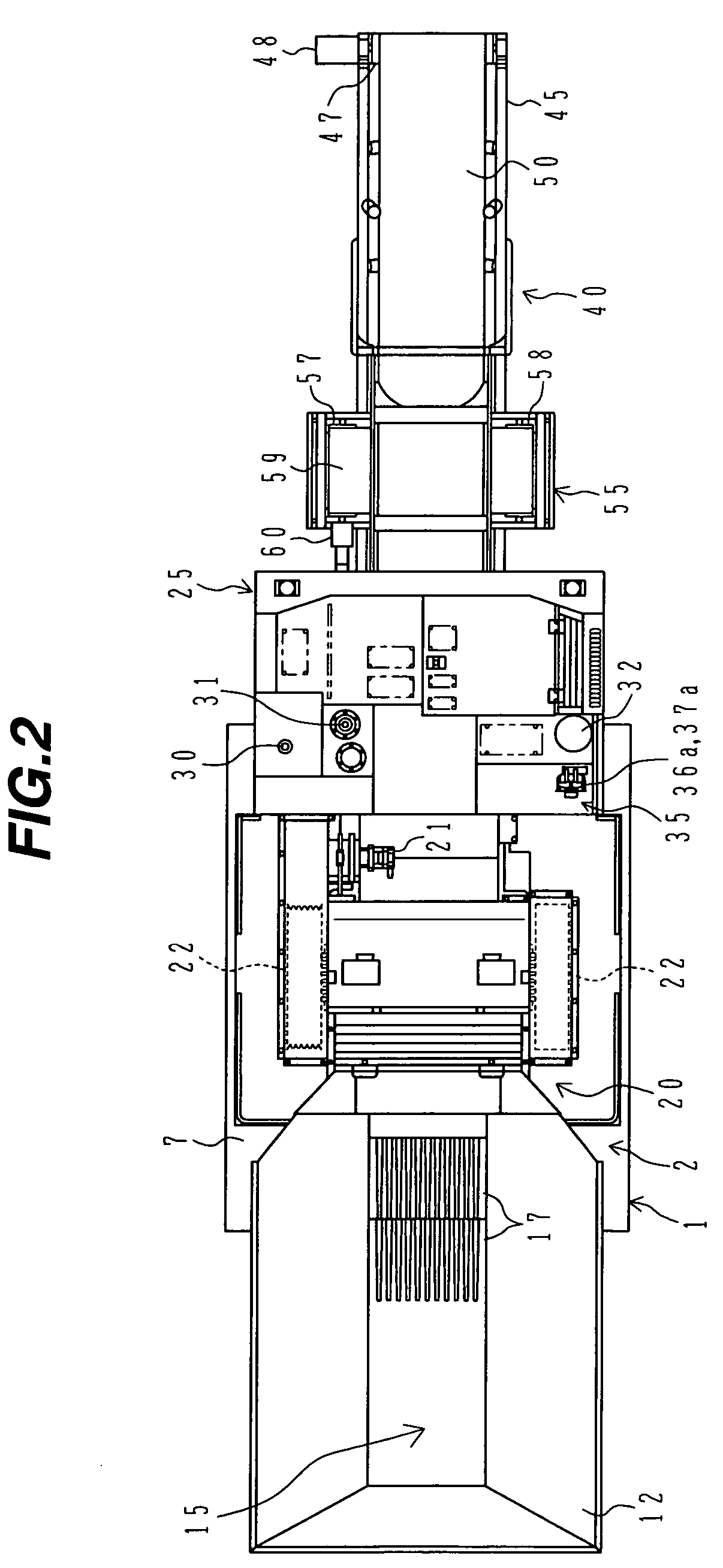

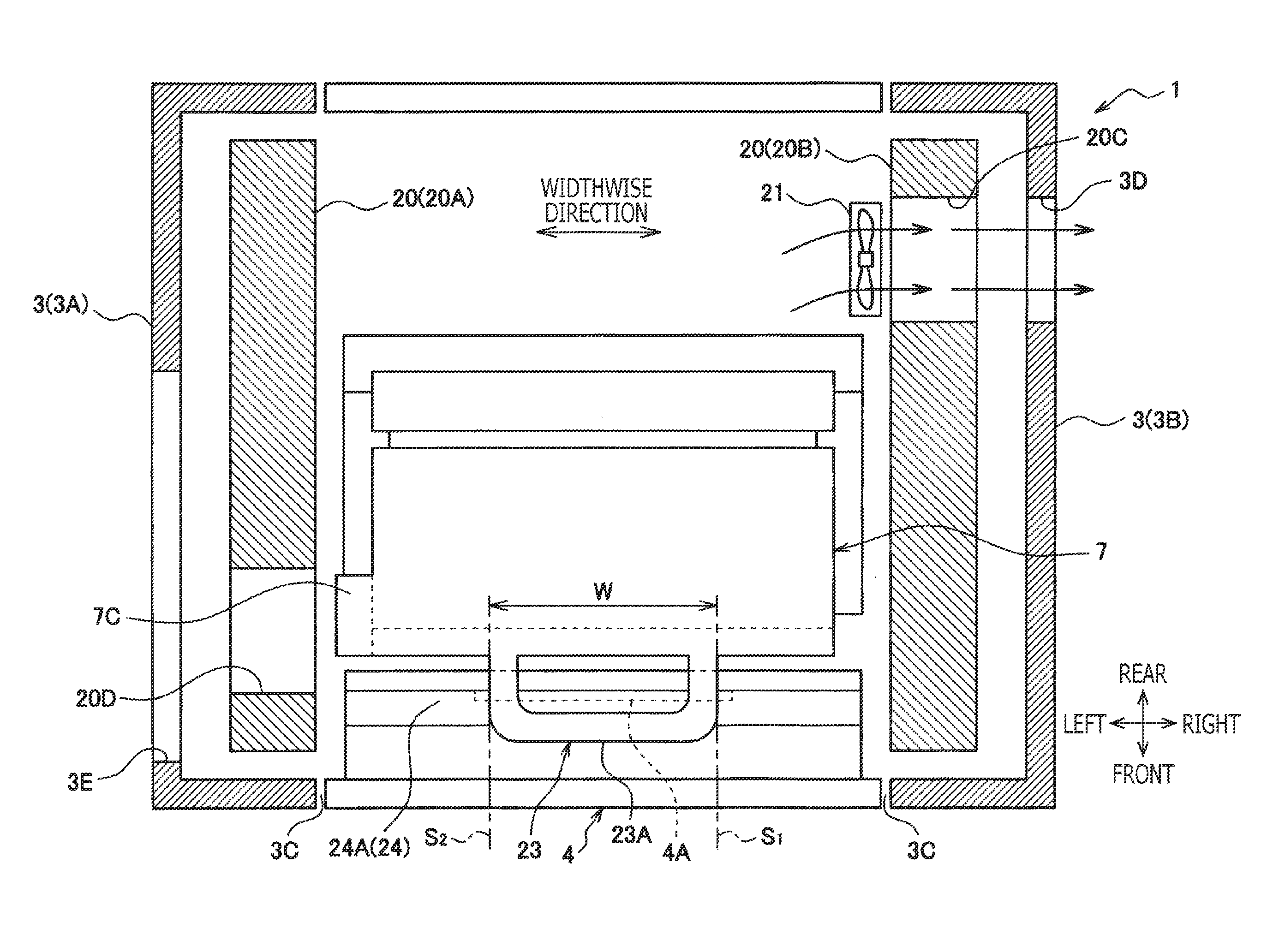

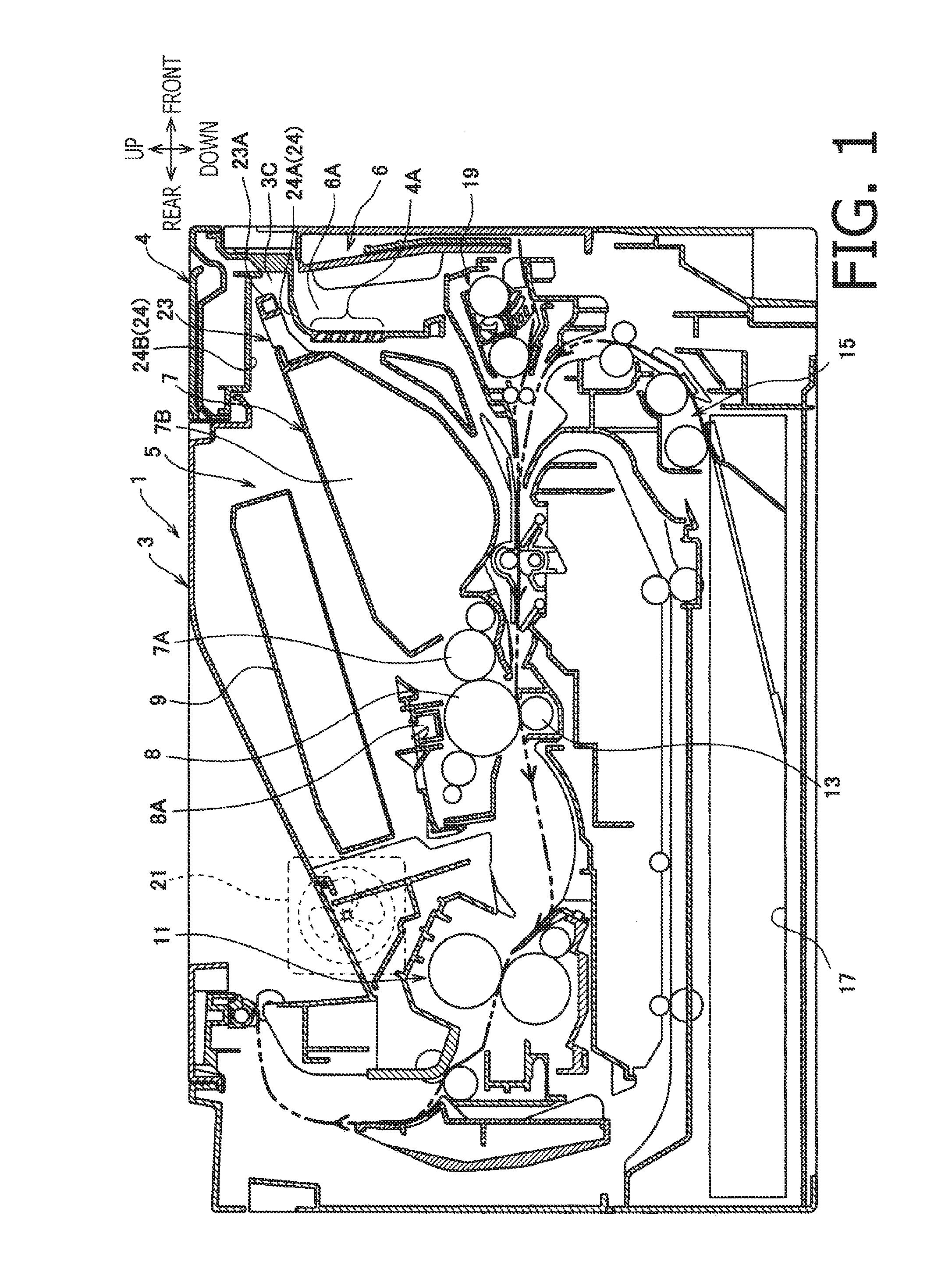

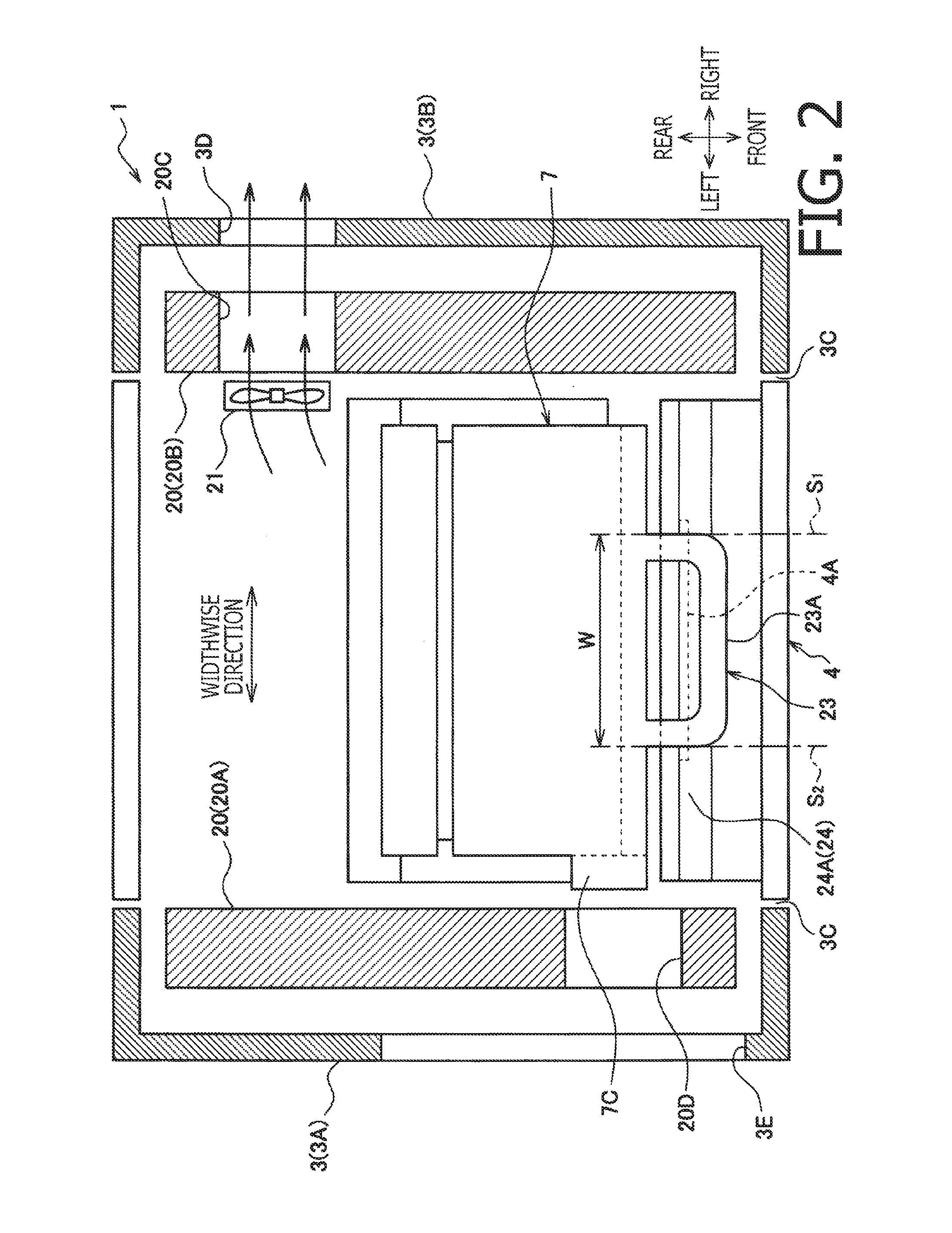

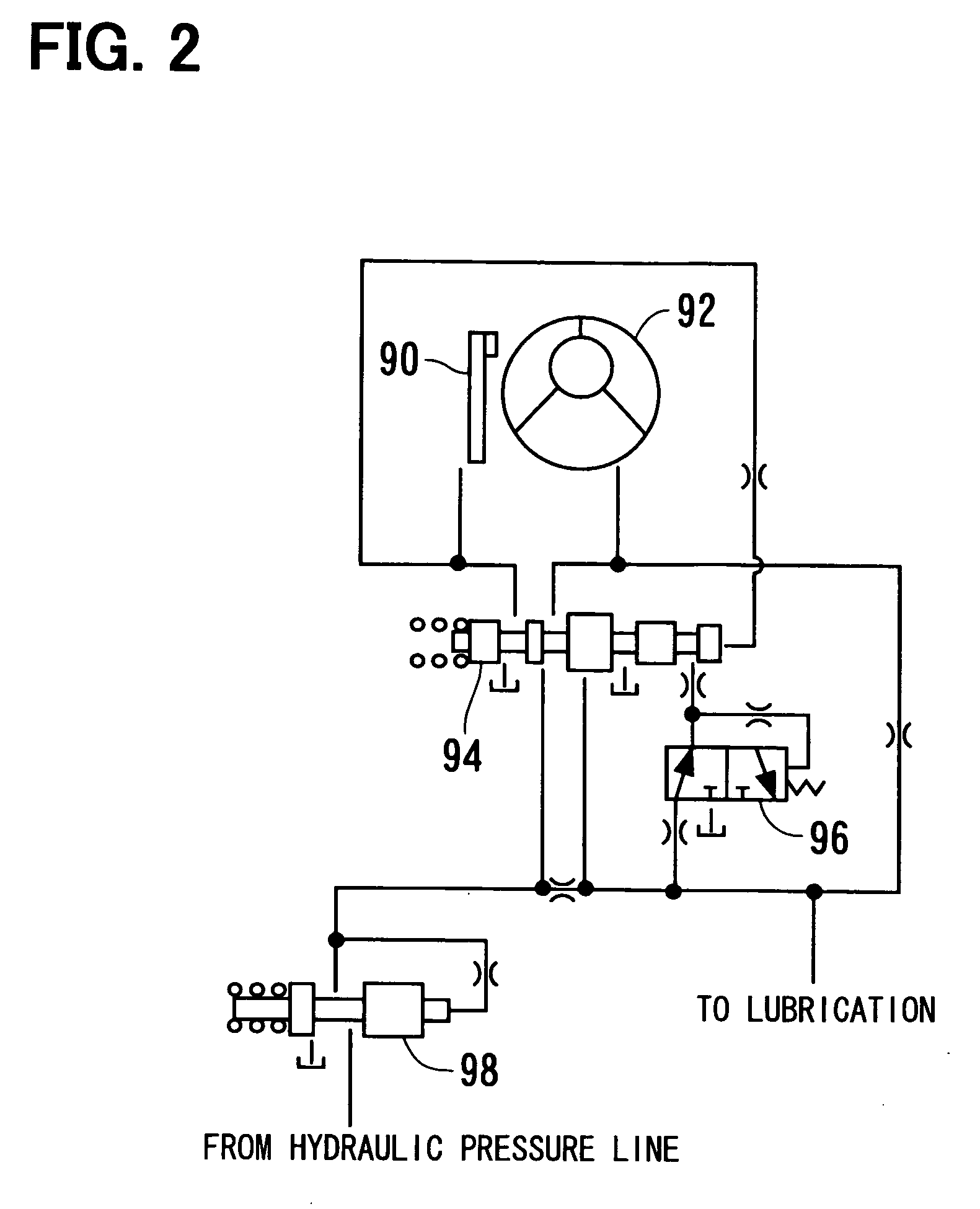

Self-propelling crusher

InactiveUS20050173570A1Reduce crushing efficiencyIncrease speedMowersMulti-purpose machinesEngineeringHydraulic pump

A self-propelled crushing machine comprises a crushing device 20; a hydraulic drive system including a crushing device hydraulic motor 21 for driving the crushing device 20, a first hydraulic pump 62 for driving the crushing device hydraulic motor 21, and an engine 61 for driving the first hydraulic pump 62; a pressure sensor 151 for detecting a load condition of the crushing device 20; and a controller 84″ for executing control to increase a revolution speed of the engine61 in accordance with a detected signal from the pressure sensor 151. Accordingly, even when a heavy load is imposed on the crushing device, a reduction of crushing efficiency can be prevented.

Owner:HITACHI CONSTR MASCH CO LTD

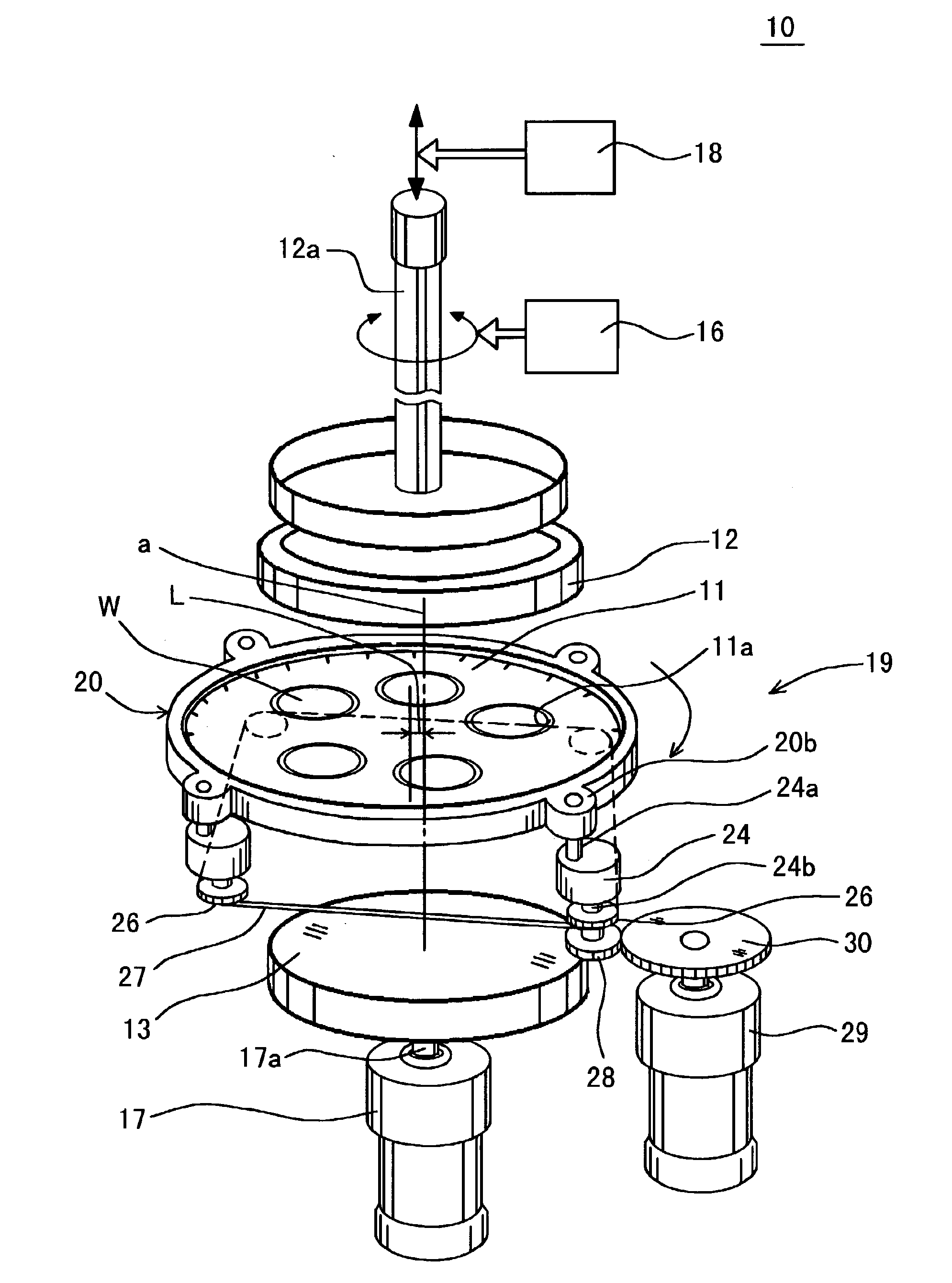

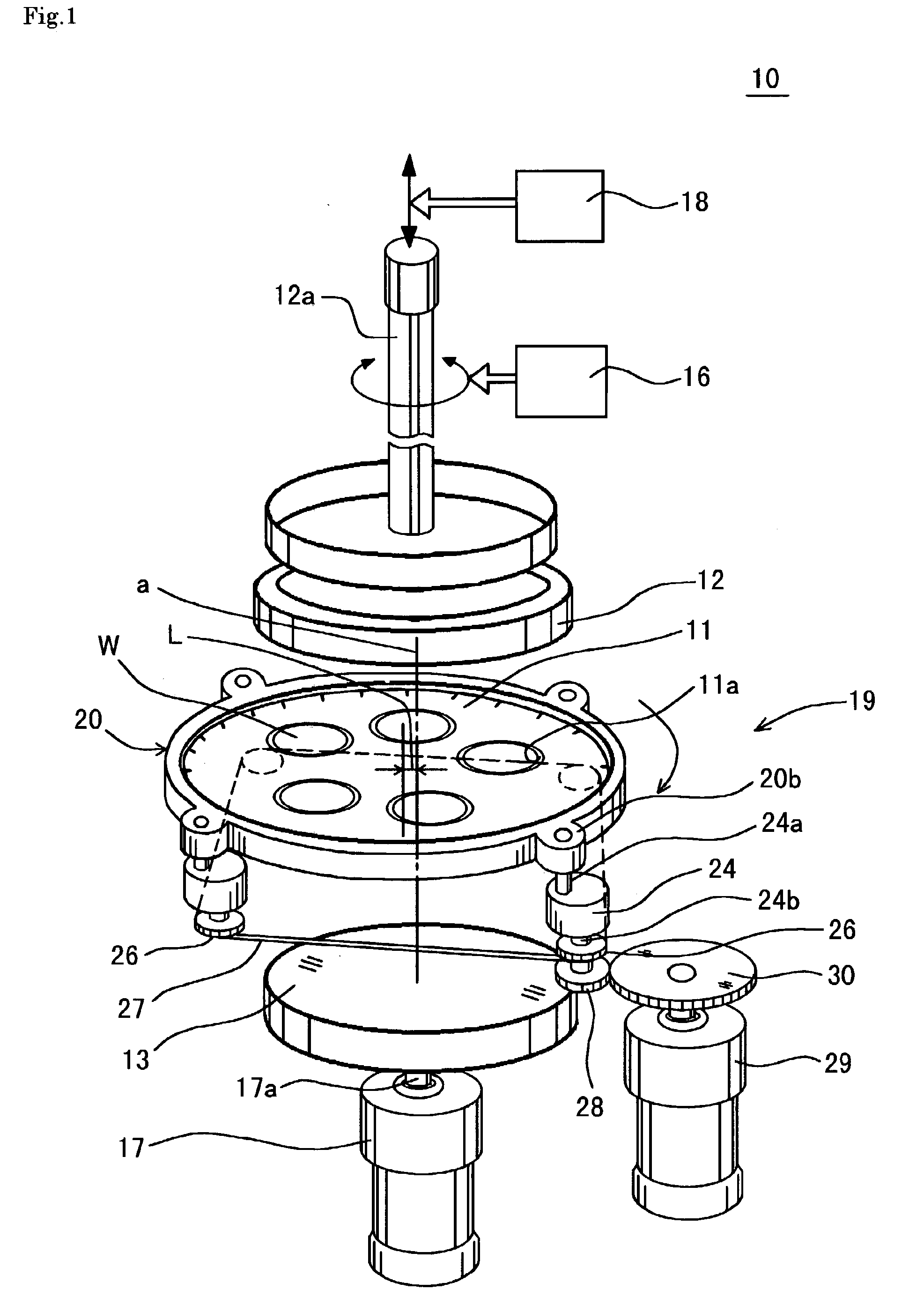

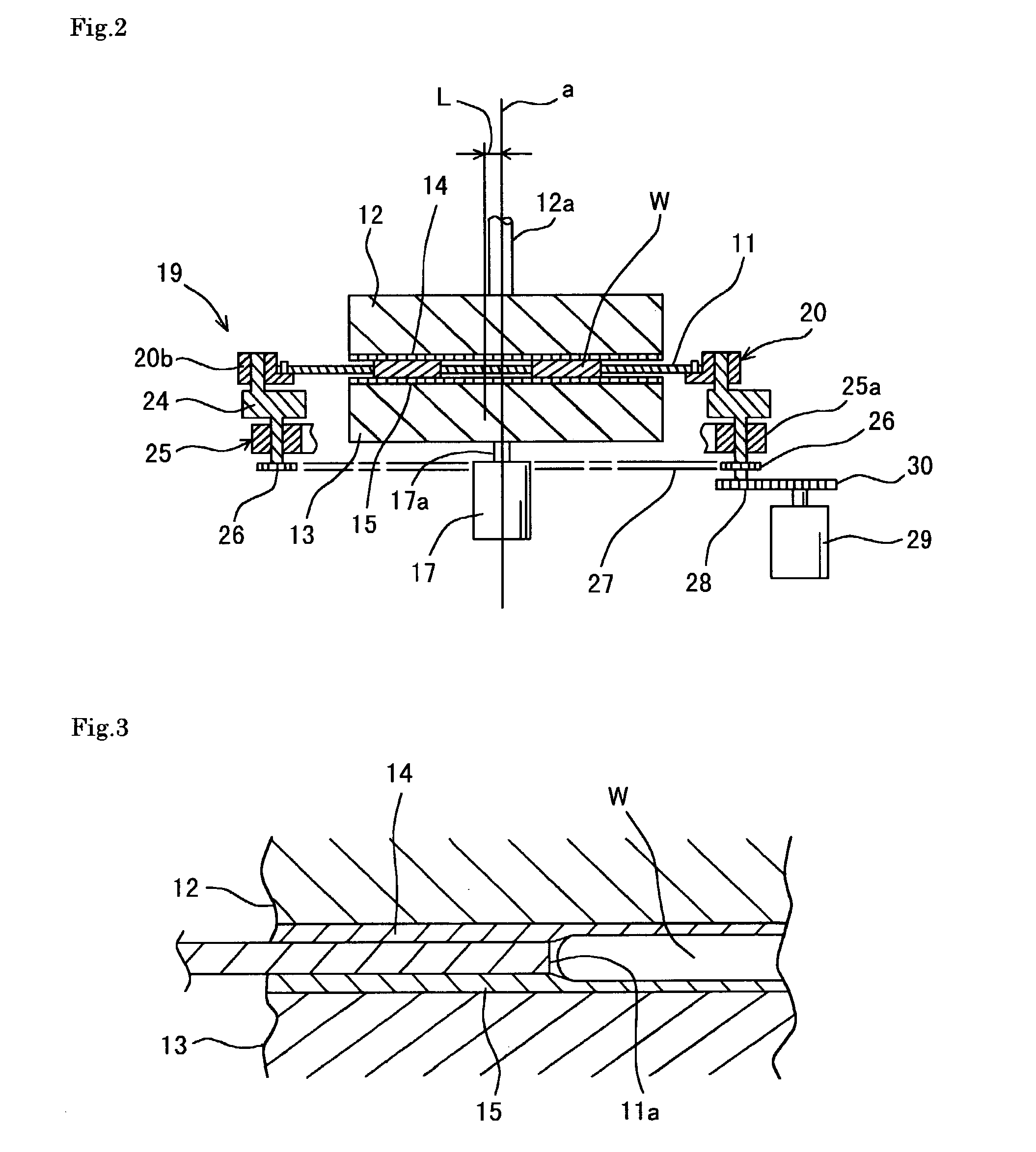

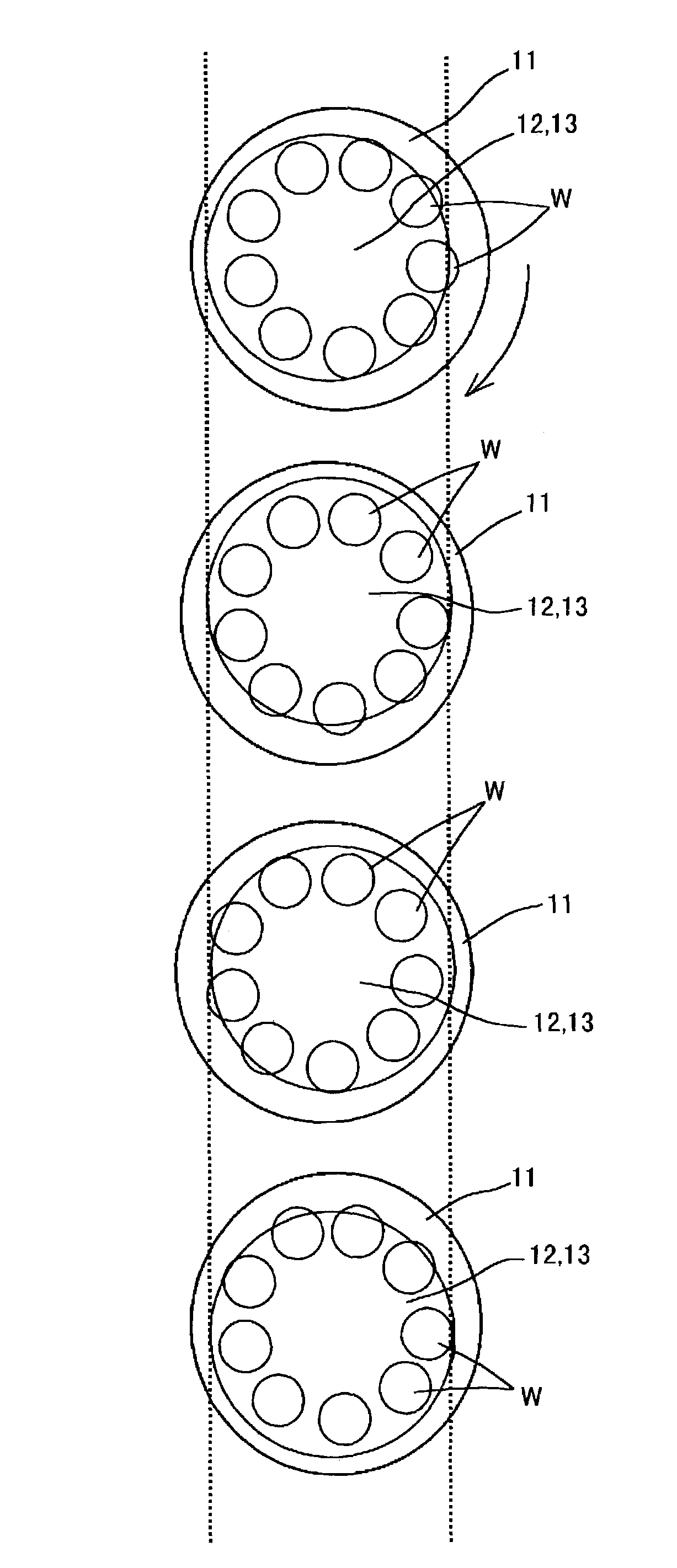

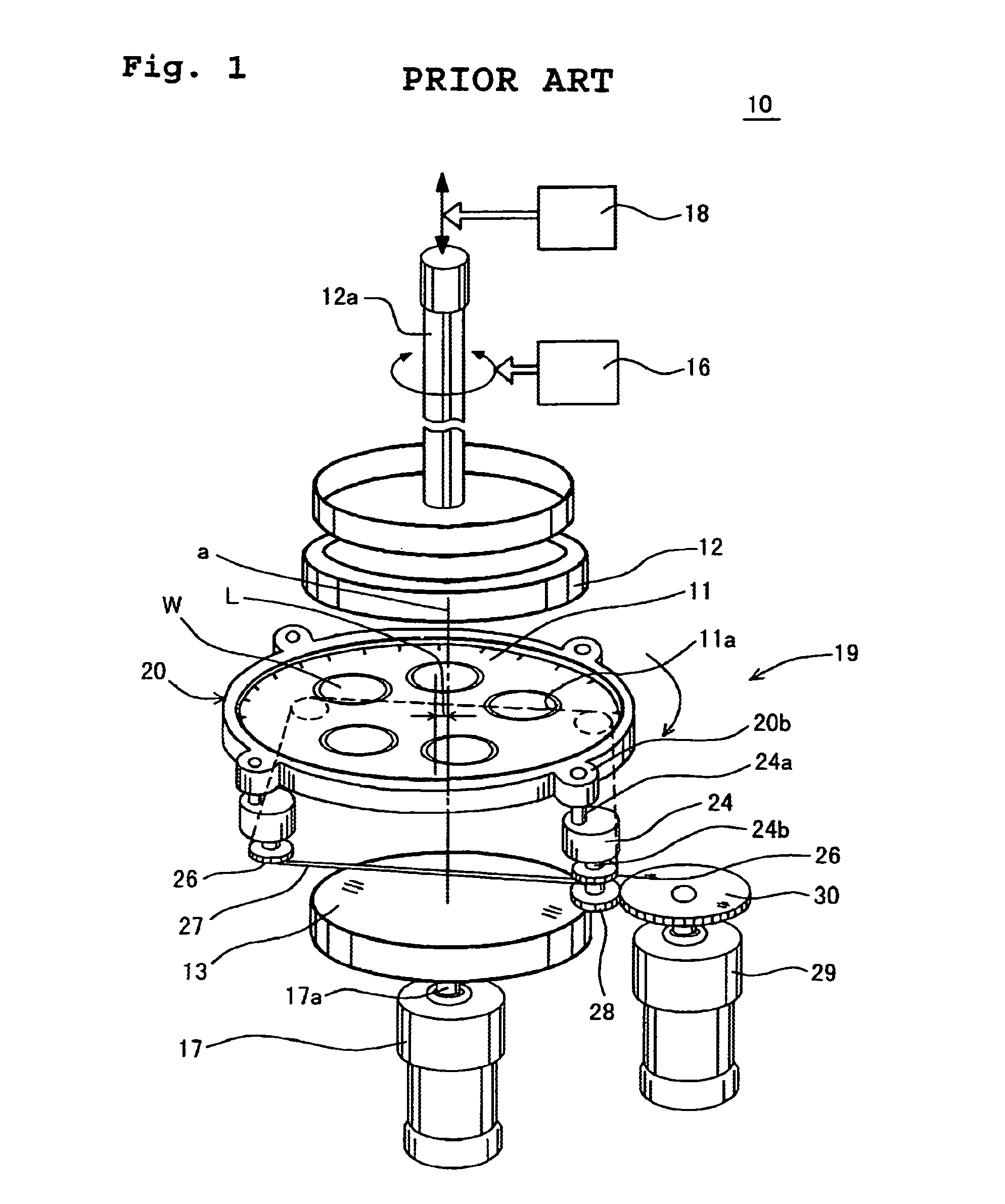

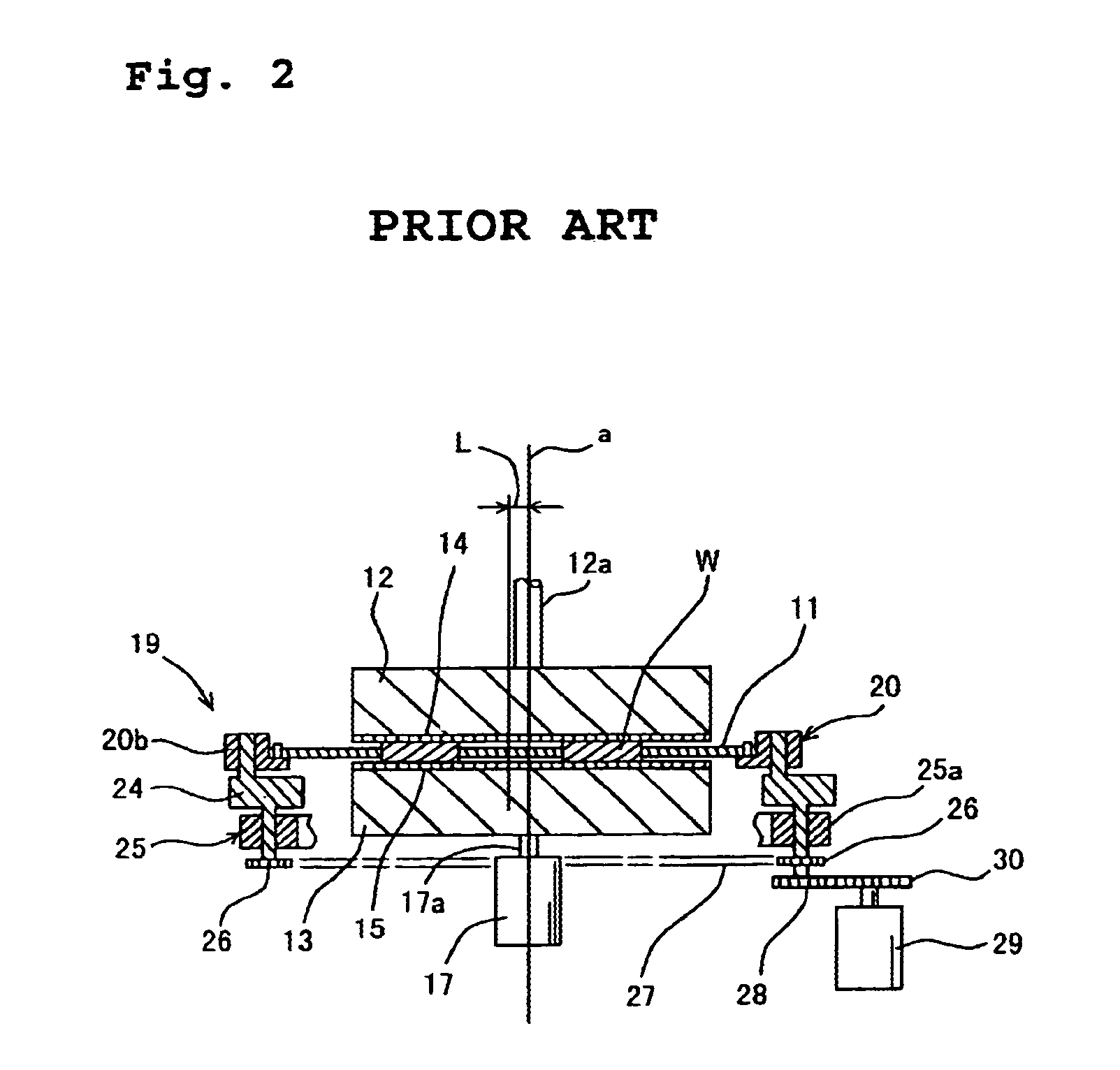

Method of polishing semiconductor wafers by using double-sided polisher

InactiveUS20030181141A1Rotational speedIncrease speedSemiconductor/solid-state device manufacturingLapping machinesWaferingEngineering

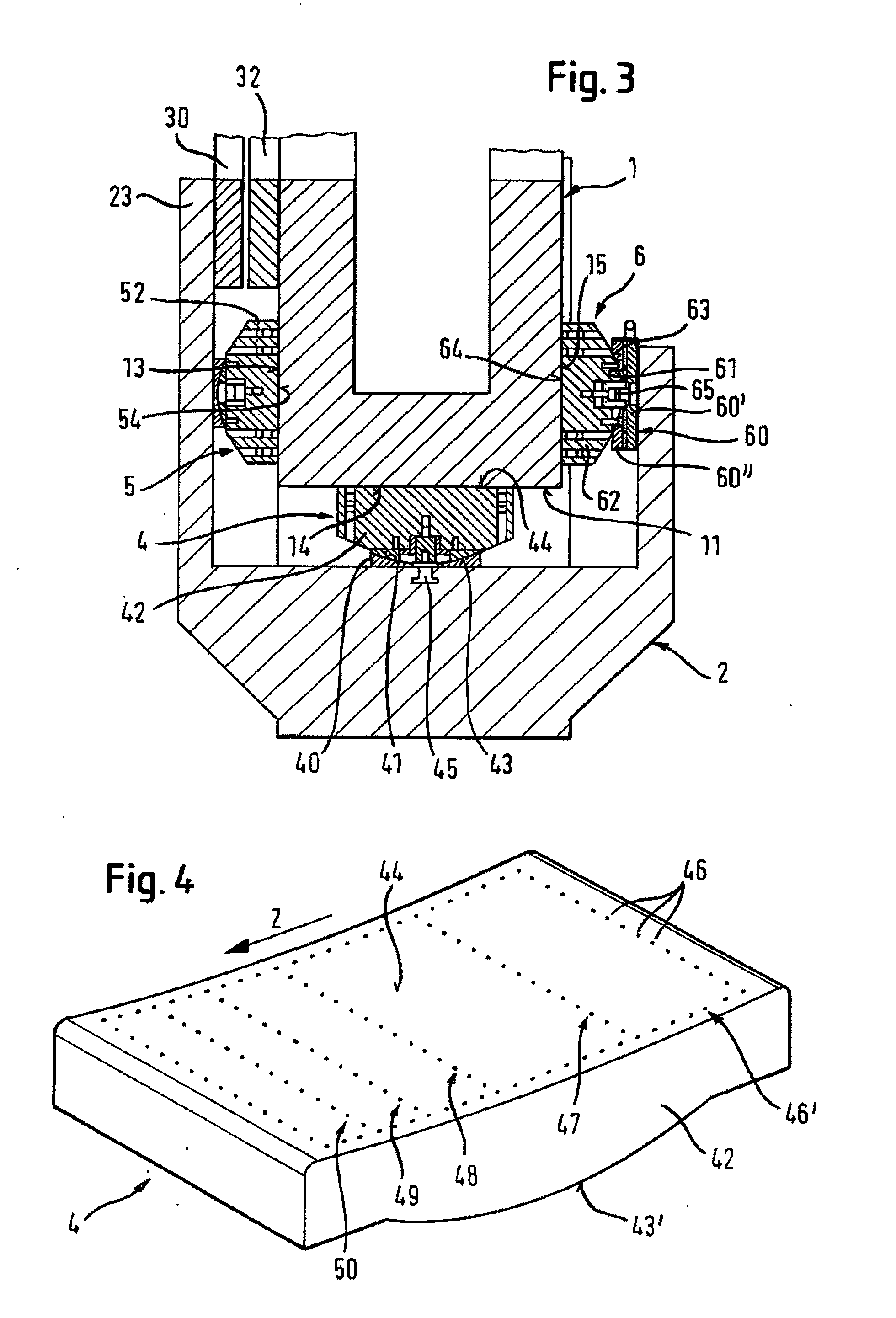

An object of the present invention is to provide a method of polishing semiconductor wafer by using a double-sided polisher which prevents a polish-sagging in an outer periphery of the wafer and thereby improves a degree of flatness of the semiconductor wafer. During polishing of the semiconductor wafer by using a double-sided polisher, a larger difference as compared to the prior art is created between a frictional resistance acting on a front surface of a silicon wafer W from an upper surface plate 12 side and a frictional resistance acting on a back surface of the silicon wafer W from a lower surface plate 13 side. This is because the present invention has employed a hard expanded urethane foam pad 14 and a soft non-woven fabric pad 15, which have different friction coefficients to the silicon wafer W from each other. Thereby, respective wafers W can be rotated at such a high speed as 0.1-1.0 rpm within corresponding wafer holding holes 11a. Accordingly, the rotation of the wafer would not be suspended even if there were any defective condition induced during polishing. Further, partial variation or deviation in polishing volume particular in the outer periphery of the wafer would be hard to occur. Therefore, the polish-sagging is suppressed and thus the improved degree of flatness of the wafer W could be obtained. Further, during this polishing, the semiconductor wafer is polished in a state in which a part of the outer periphery of the semiconductor wafer is protruded by 3-15 mm beyond said respective polishing cloths. During polishing, the outer periphery of the wafer is polished while passing through its non-polishing region at each time when the semiconductor wafer is rotated by a predetermined angle. Therefore, a contact area per unit time of the outer periphery of the wafer with the polishing cloths is reduced as compared to the central region of the wafer. As a result, the polish-sagging in the outer periphery of the wafer is suppressed and the degree of flatness of the wafer is improved.

Owner:SUMITOMO MITSUBISHI SILICON CORP

Method of polishing semiconductor wafers by using double-sided polisher

InactiveUS7470169B2Prevent polish-saggingImprove flatnessSemiconductor/solid-state device manufacturingLapping machinesEngineeringSilicon

Owner:SUMITOMO MITSUBISHI SILICON CORP

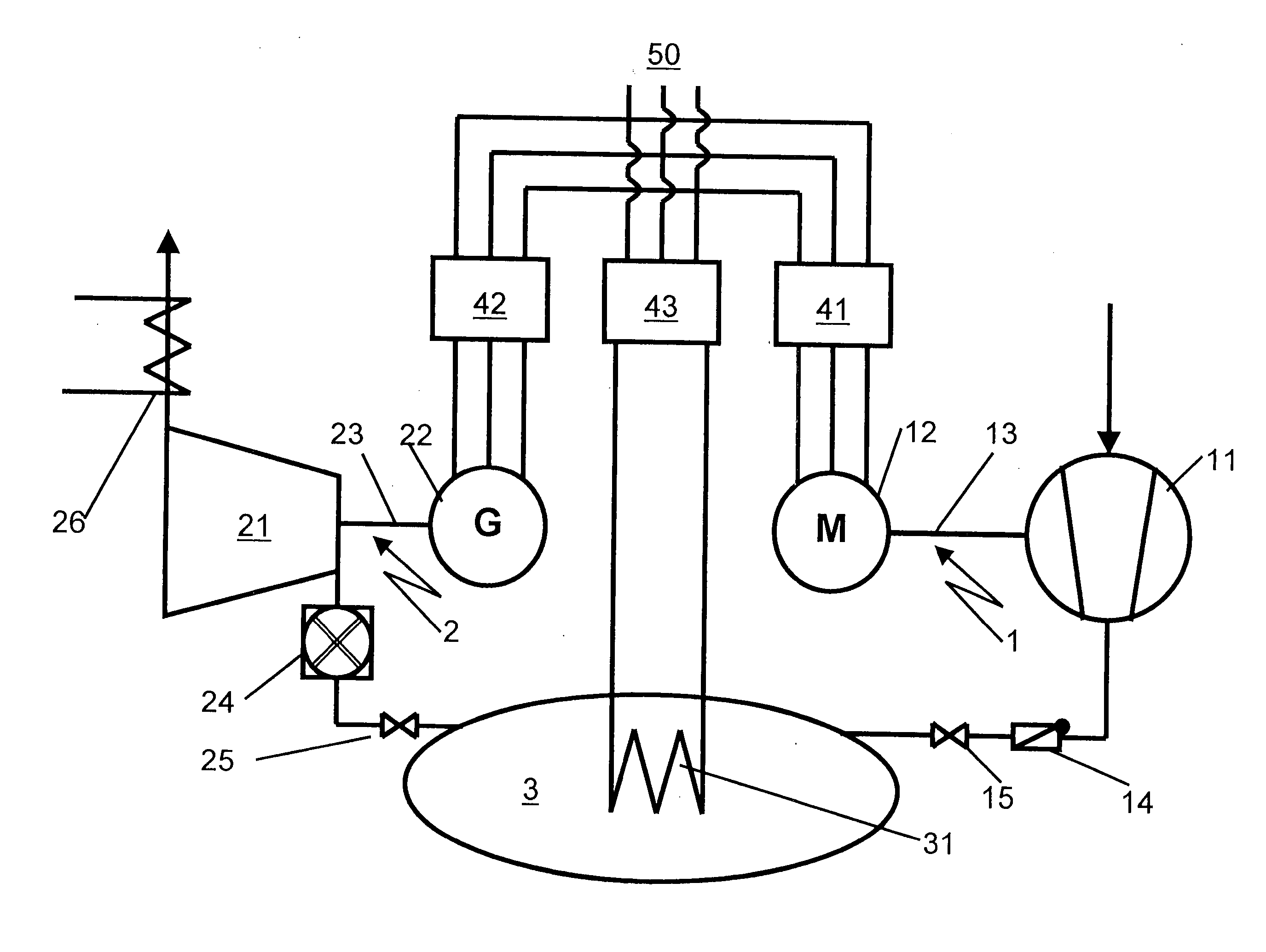

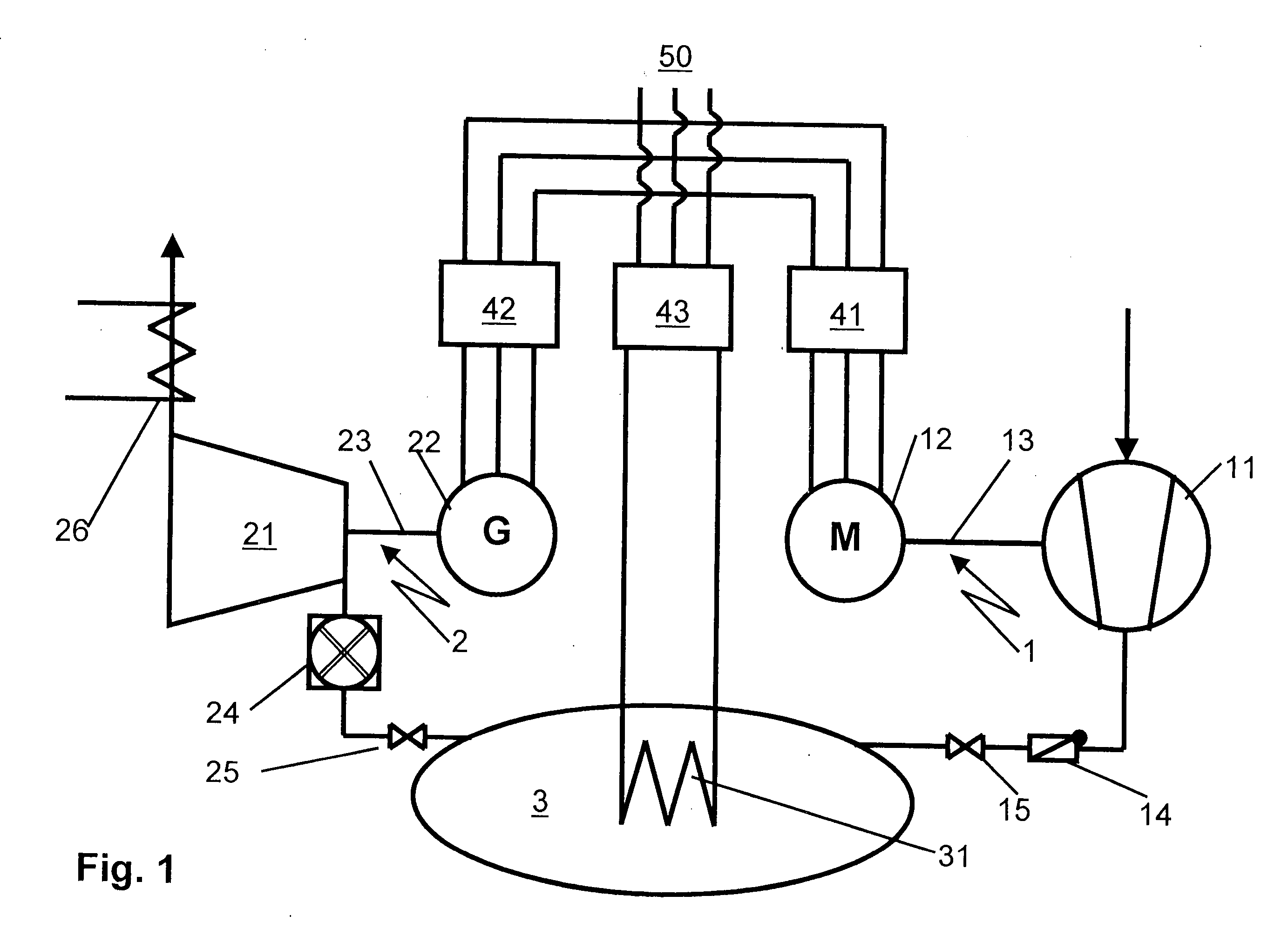

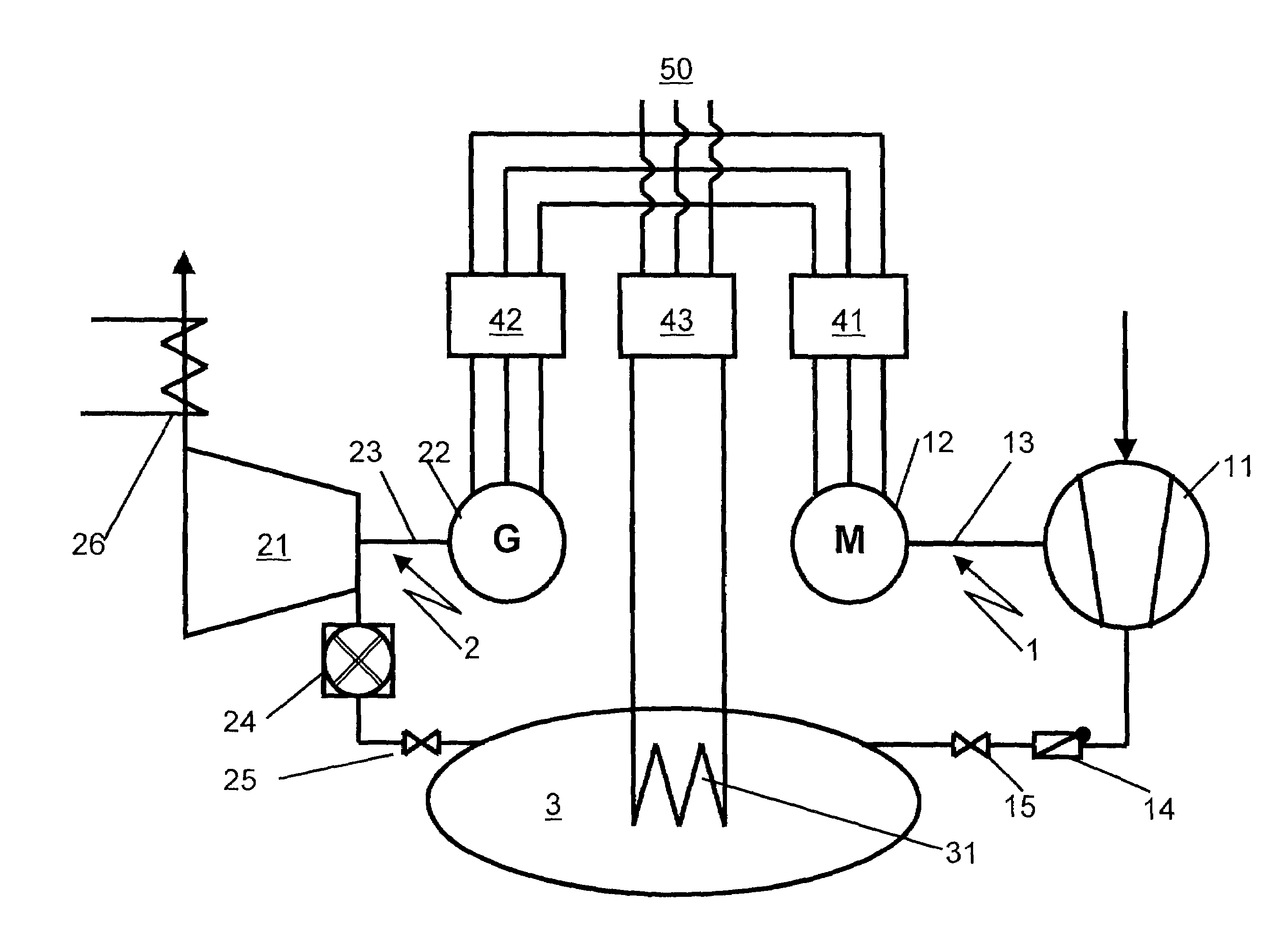

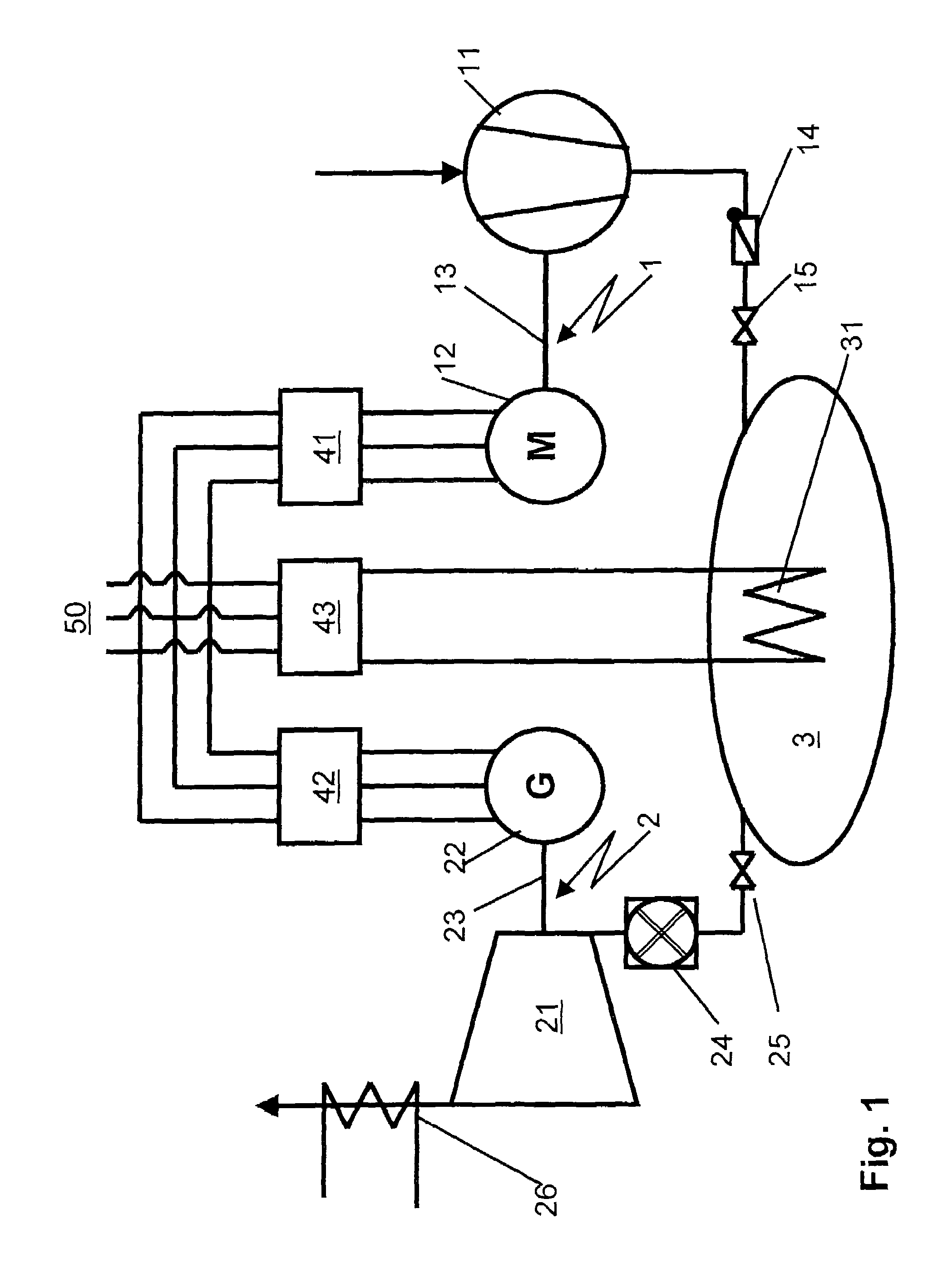

Method and apparatus for operation of a power station

ActiveUS20070255459A1Valid matchEffective supervisionLevel controlSpeed/accelaration controlFrequency changerPower station

A power station comprises a power-consuming shaft run on which a motor and a compressor are arranged, as well as a power-emitting shaft run on which a generator and an expansion machine are arranged. The compressor feeds a compressed fluid into a storage volume. The compressed storage fluid is expanded in the expansion machine, producing work. The generator and the motor are connected to the electrical grid system via frequency converters. This makes it possible to operate the electrical machines at a rotation speed which is asynchronous with respect to the grid system. A method and apparatus is disclosed that allows the net power output of the power station to be matched to the demands of the electrical grid system by varying the rotation speed of at least one of the shaft runs.

Owner:GENERAL ELECTRIC TECH GMBH

Method and apparatus for operation of a power station

ActiveUS7566992B2Valid matchEffective supervisionLevel controlSupport structure mountingFrequency changerPower station

A power station comprises a power-consuming shaft run on which a motor and a compressor are arranged, as well as a power-emitting shaft run on which a generator and an expansion machine are arranged. The compressor feeds a compressed fluid into a storage volume. The compressed storage fluid is expanded in the expansion machine, producing work. The generator and the motor are connected to the electrical grid system via frequency converters. This makes it possible to operate the electrical machines at a rotation speed which is asynchronous with respect to the grid system. A method and apparatus is disclosed that allows the net power output of the power station to be matched to the demands of the electrical grid system by varying the rotation speed of at least one of the shaft runs.

Owner:GENERAL ELECTRIC TECH GMBH

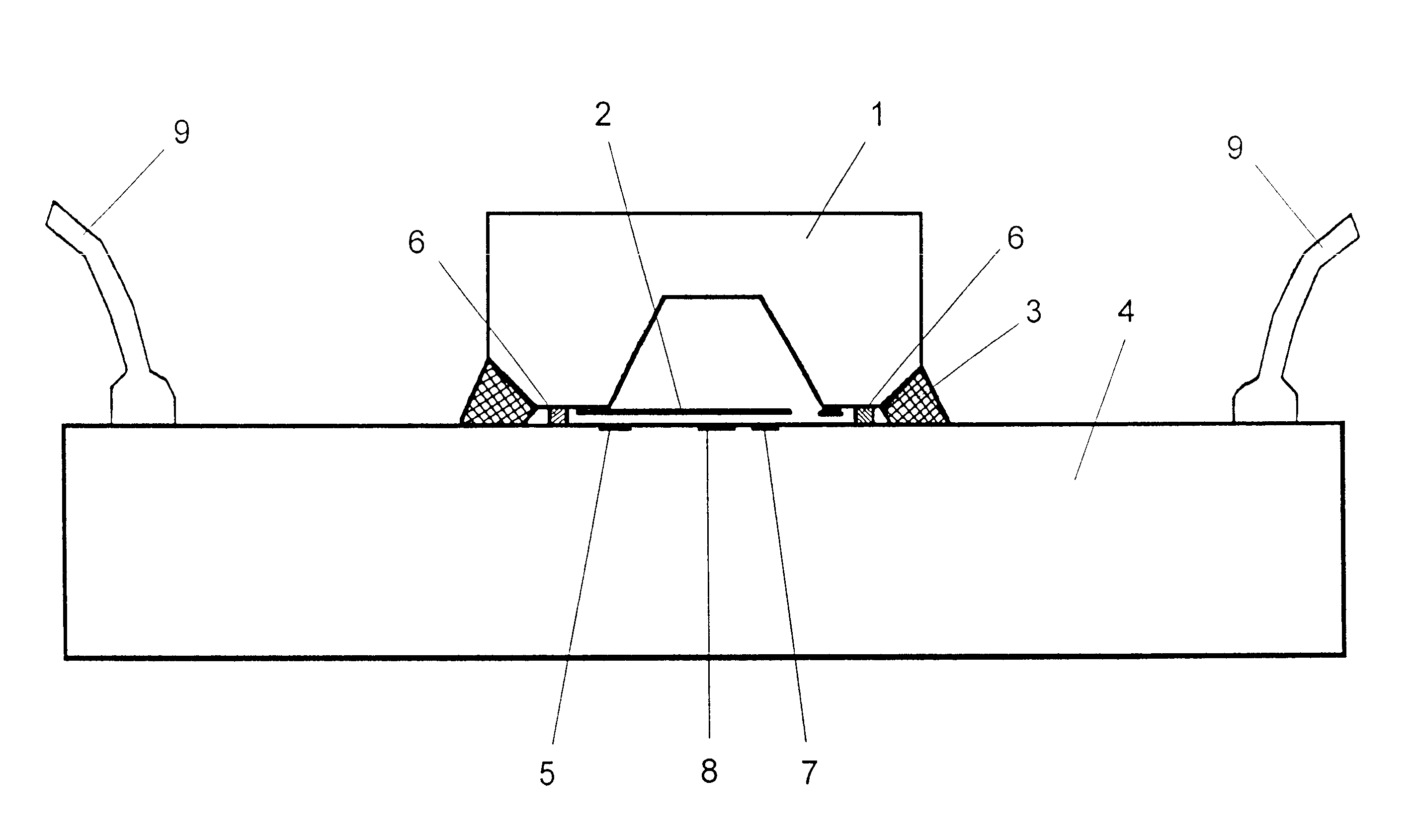

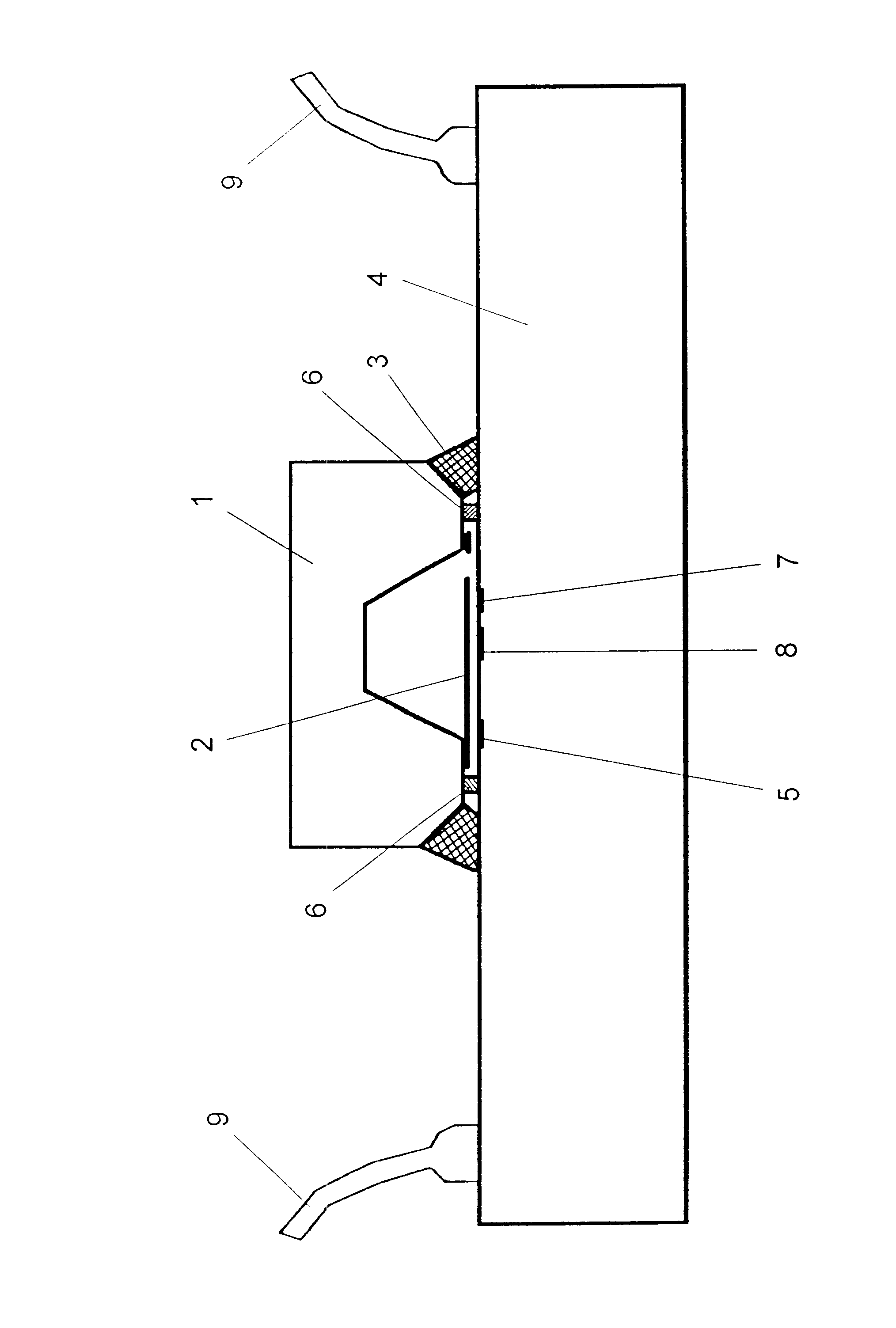

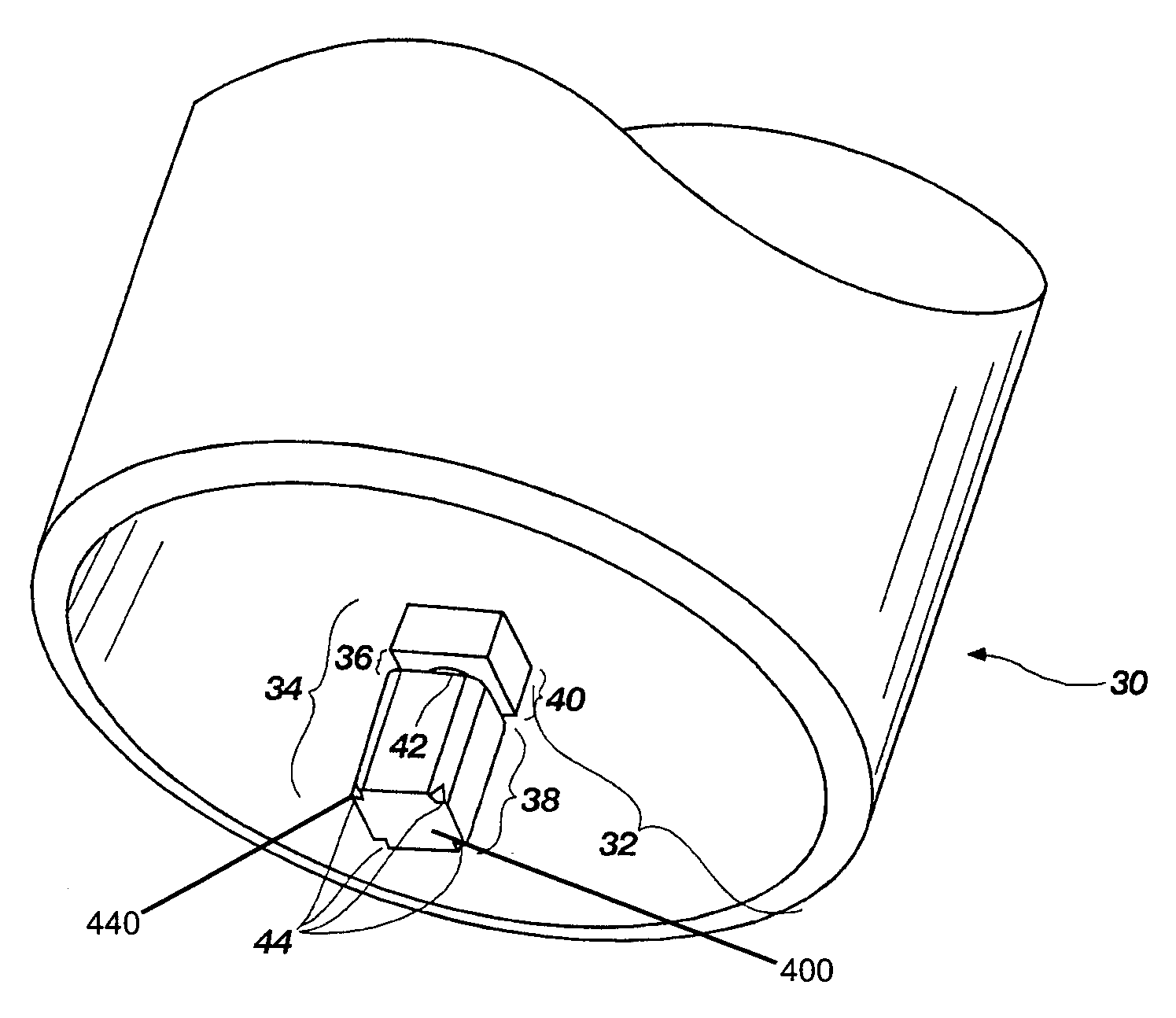

Microsensor having a sensor device connected to an integrated circuit by a solder joint

InactiveUS6520014B1Accurate measurementReduced risk of corrosionAcceleration measurement using interia forcesSemiconductor/solid-state device detailsElectricityIntegrated circuit

In a microsensor with a micro-electromechanical sensor element and an integrated circuit for measuring, calibration and compensation electronics, whereby the sensor is connected electrically to the integrated circuit (IC), the micro-electromechanical sensor element is arranged directly on the integrated circuit with accurate positioning, and is connected with electric conductivity via a circulating soldered joint.

Owner:AUSTRIA MIKRO SYST INT

Three-body joining using friction stir processing techniques

ActiveUS20110073634A1Increase rotation speedRotational speedWelding/cutting auxillary devicesAuxillary welding devicesEngineeringFriction stir processing

A friction stir tool is provided to perform friction stir riveting using a partially consumable pin, wherein the pin includes a cutting edge on a bottom surface thereof, wherein the tool is rotated at a first speed to enable cutting by the pin into a first material that is overlapping a second material, wherein after the pin has cut to a sufficient depth, the rotational speed of the tool is increased to thereby enable plasticization of the consumable pin, the first material, and the second material, wherein the tool is then rapidly decelerated until stopped, enabling diffusion bonding between the pin, the first material and the second material.

Owner:MAZAK CORP

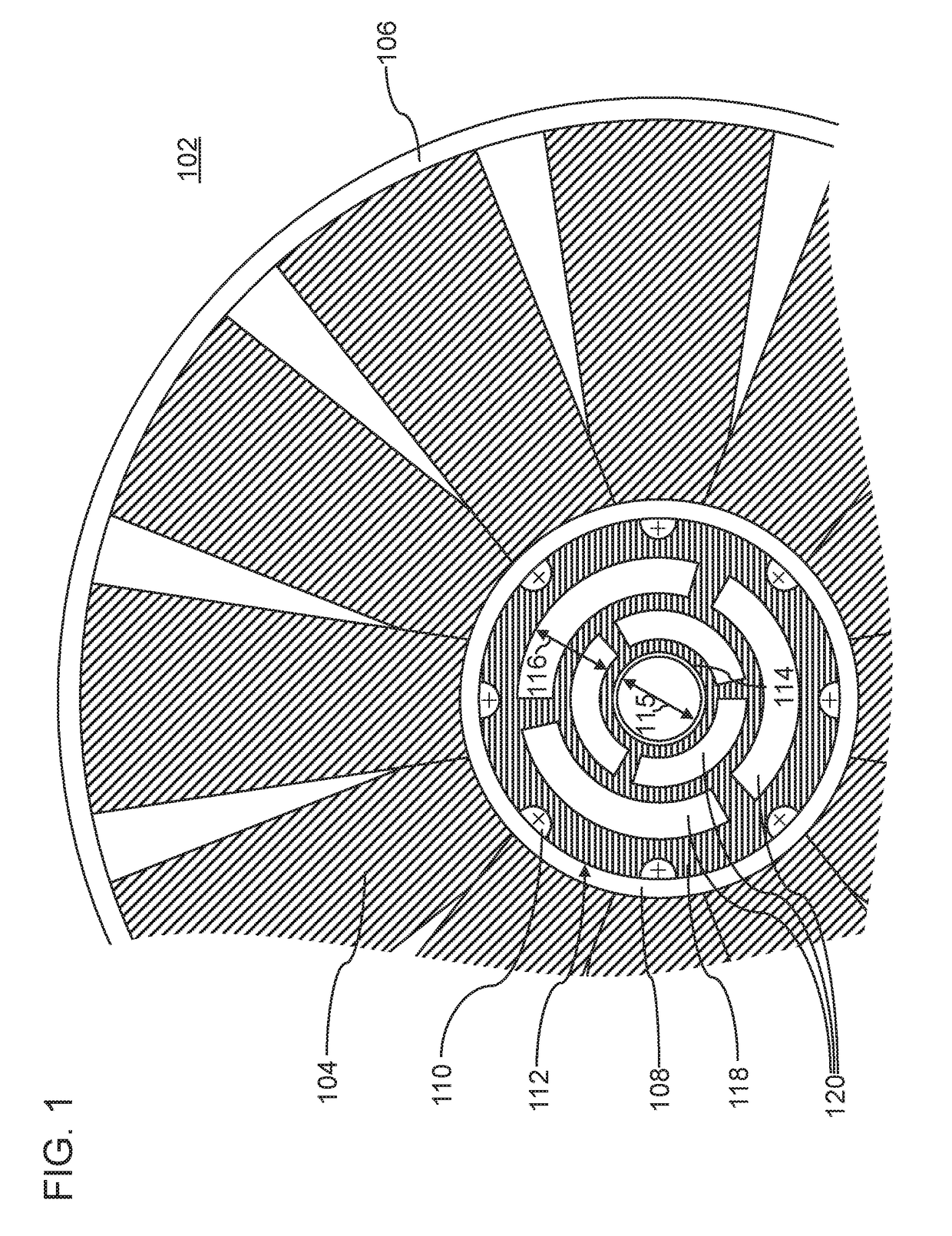

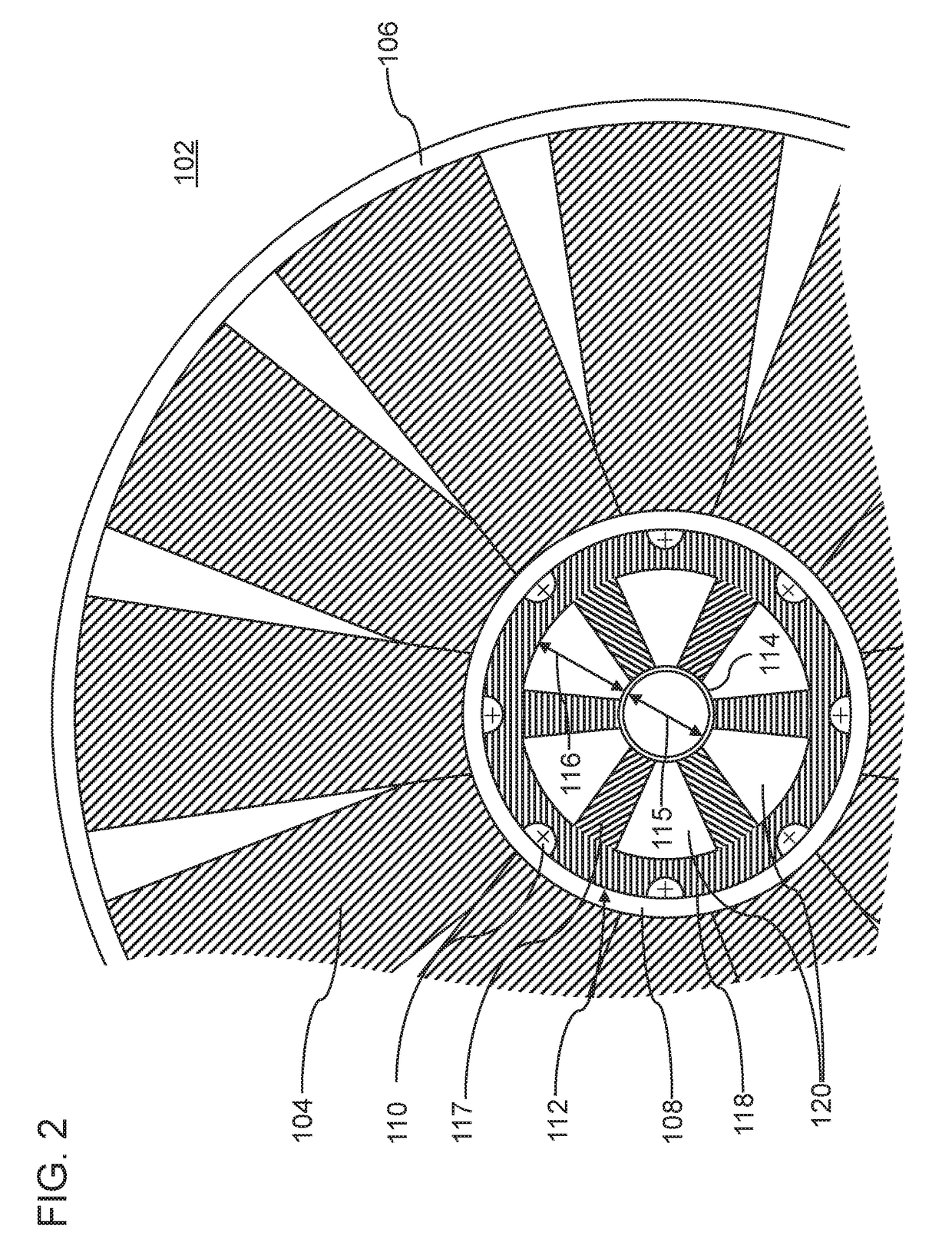

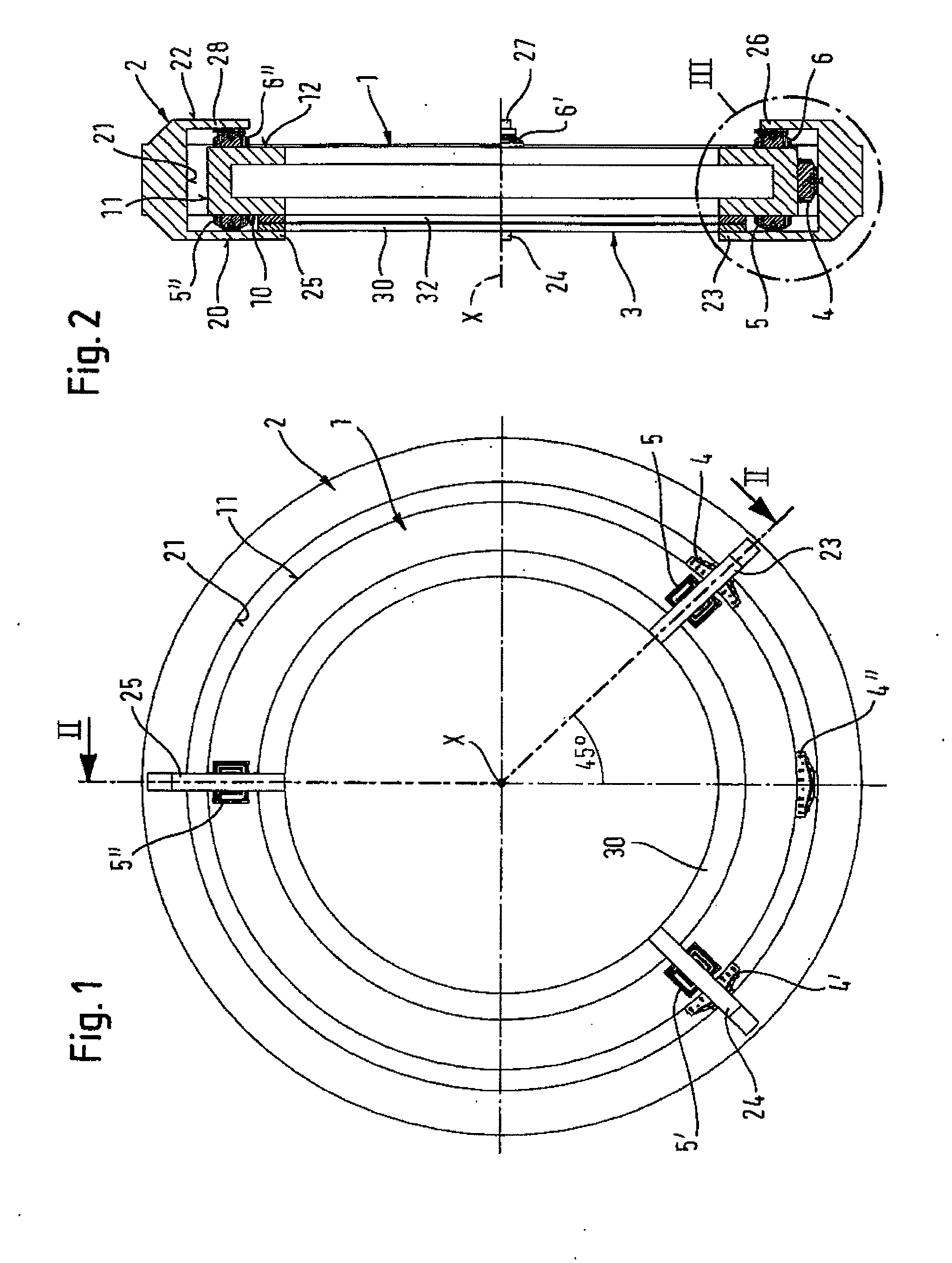

Axial fan wheel

ActiveUS20180112675A1Prevent air recirculationReduce power consumptionAir-treating devicesPump componentsImpellerDrive shaft

An axial fan wheel, in particular for the radiator of a motor vehicle engine, is described. The axial fan wheel includes a crown ring having a multiplicity of rotor blades, a hub having an inner ring which is connected or connectable to a drive shaft, and having, for the purpose of torque transmission, connection surfaces along an outer periphery of the hub which are connected to the inner ring and to the crown ring. The hub has through-passages between the inner ring and the outer periphery. At least one element, arranged rotationally fixedly on the axial fan wheel inside the crown ring, is designed to maintain a pressure difference in the axial direction when the axial fan wheel rotates.

Owner:MAN TRUCK & BUS AG

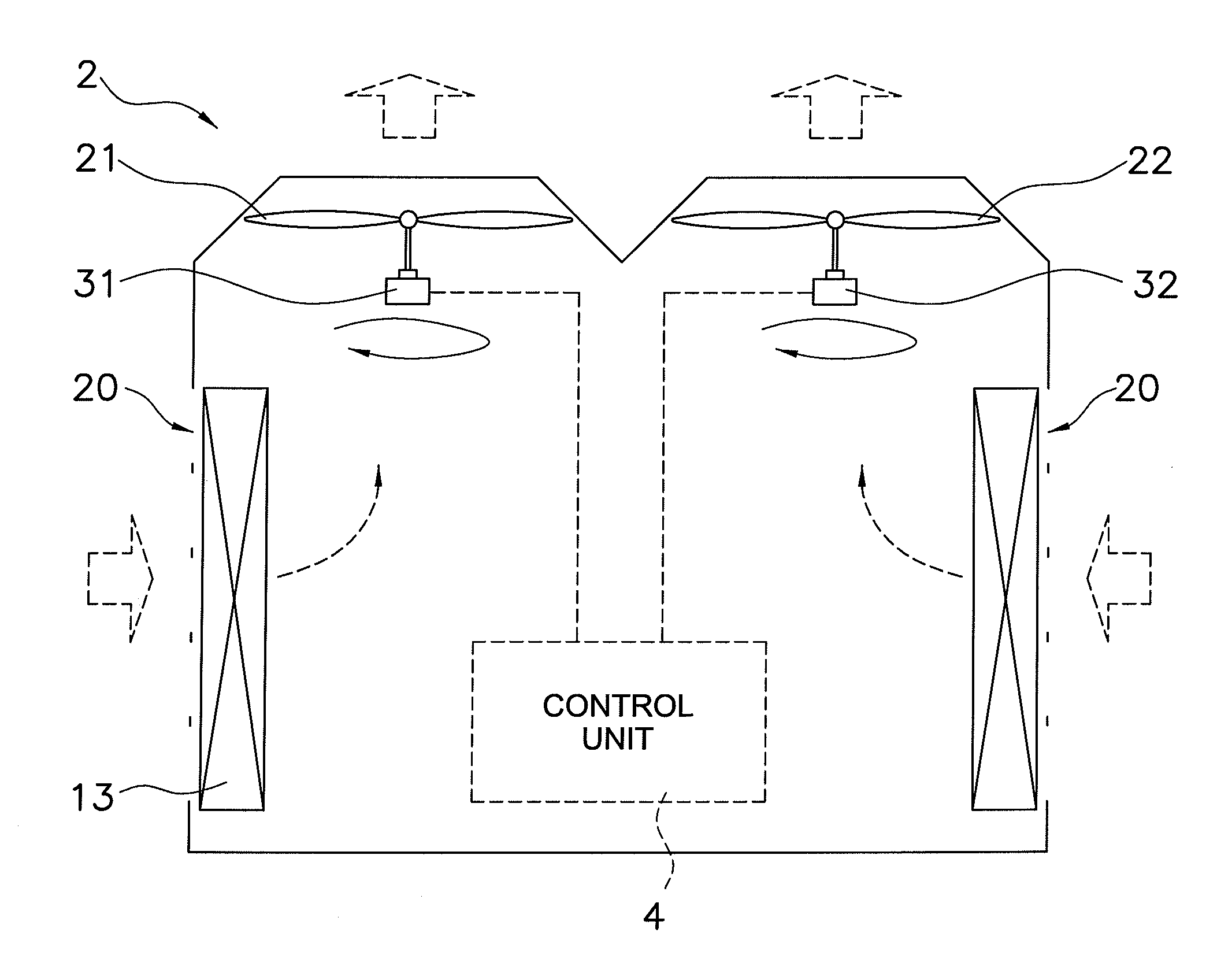

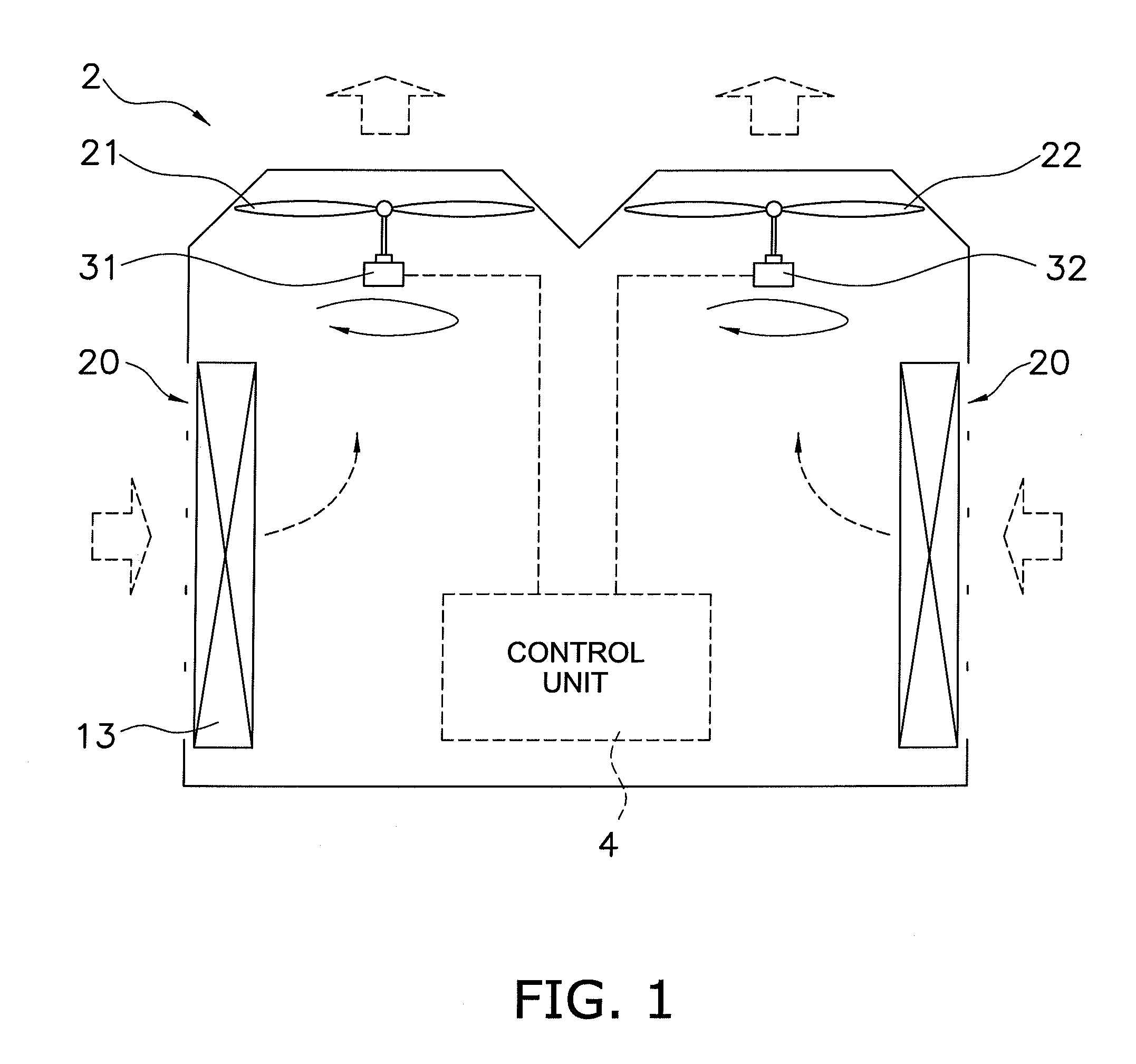

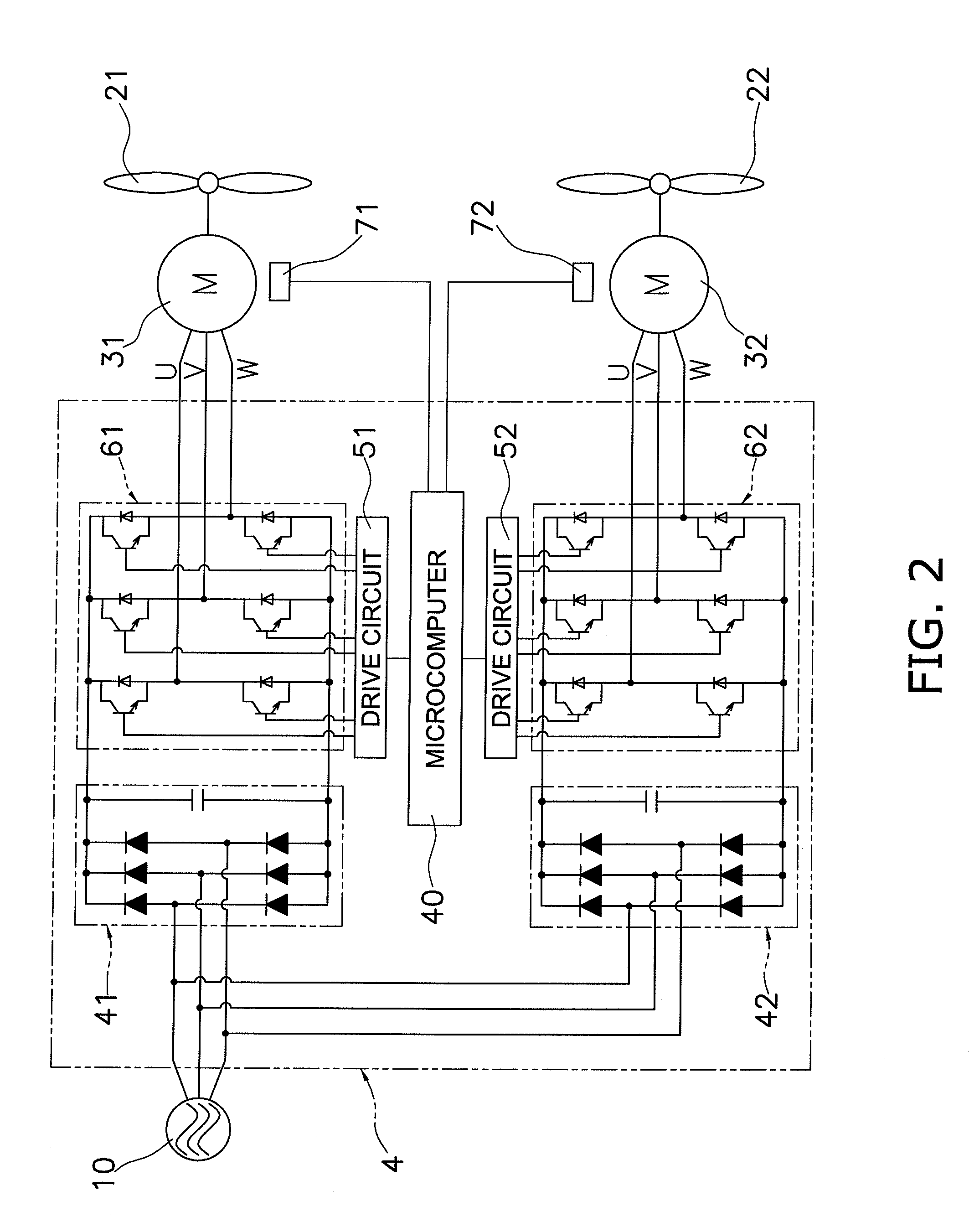

Fan control system

InactiveUS20100114379A1Reduce fan speedReduce dynamic pressureDC motor speed/torque controlSpace heating and ventilationControl systemRotation velocity

A fan control system includes first and second adjacent fans, first and second motors configured to rotate the first and second fans, and a control unit configured to control rotational speeds of the first and second motors in order to control rotational speeds of the first and second fans. The first and second motors are energized such that the rotational speeds of the first and second fans reach target rotational speeds prior to increasing the rotational speeds of the first and second fans to required rotational speeds. The target rotational speeds are lower than the required rotational speeds. The first and second motors are energized such that the rotational speeds of the first and second fans reach the required rotational speeds after the rotational speeds of the first and second fans reach the target rotational speeds.

Owner:DAIKIN IND LTD

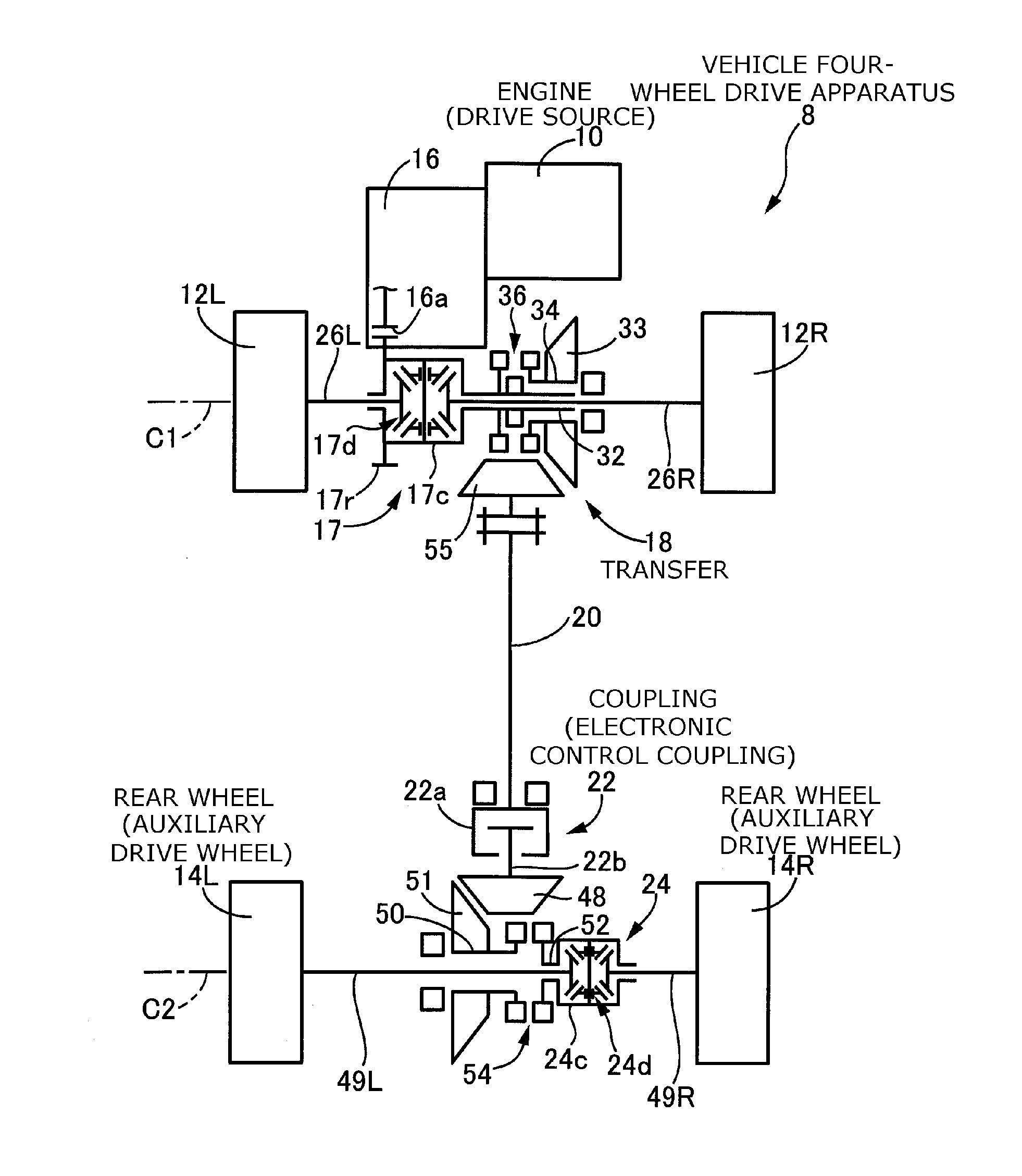

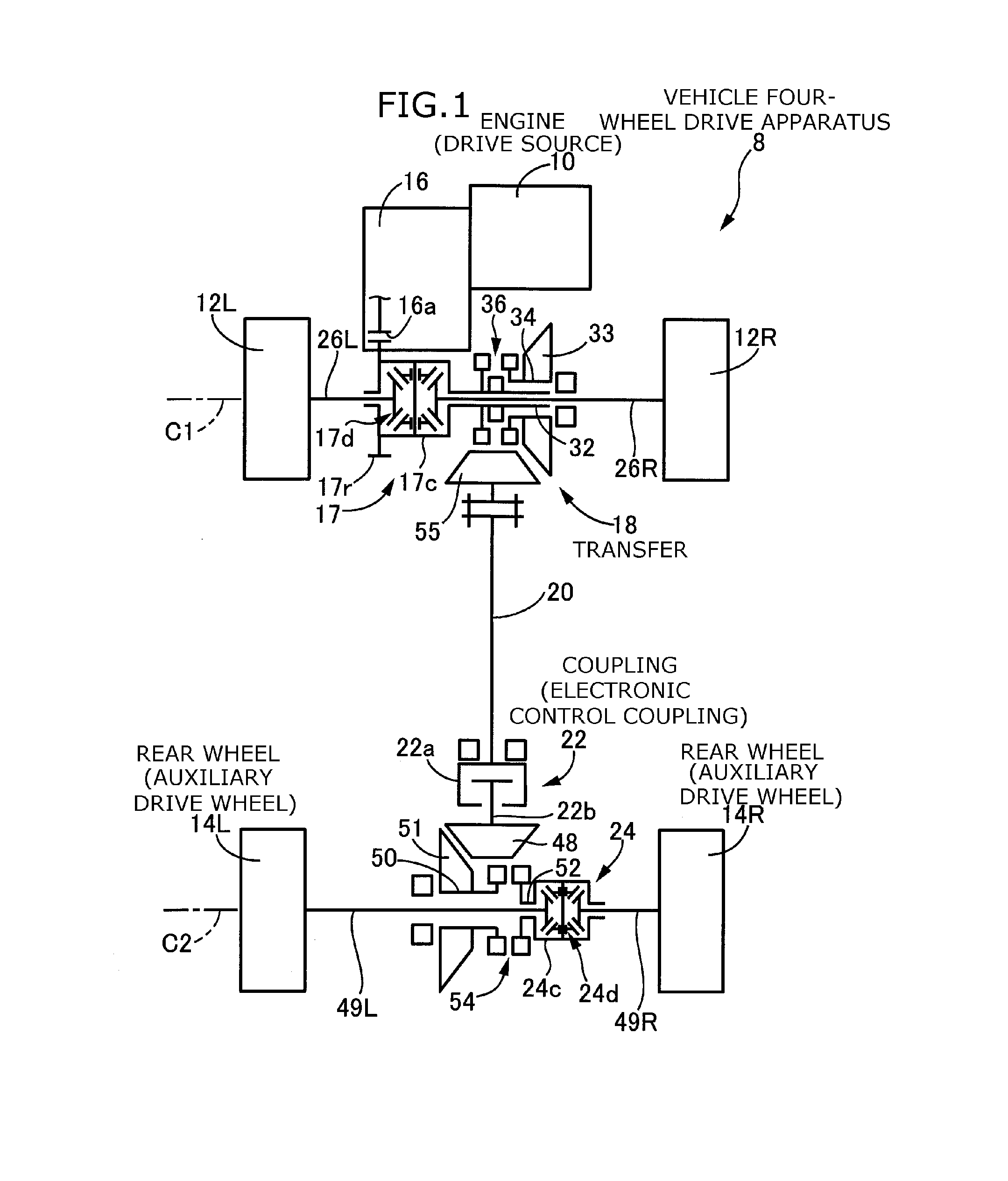

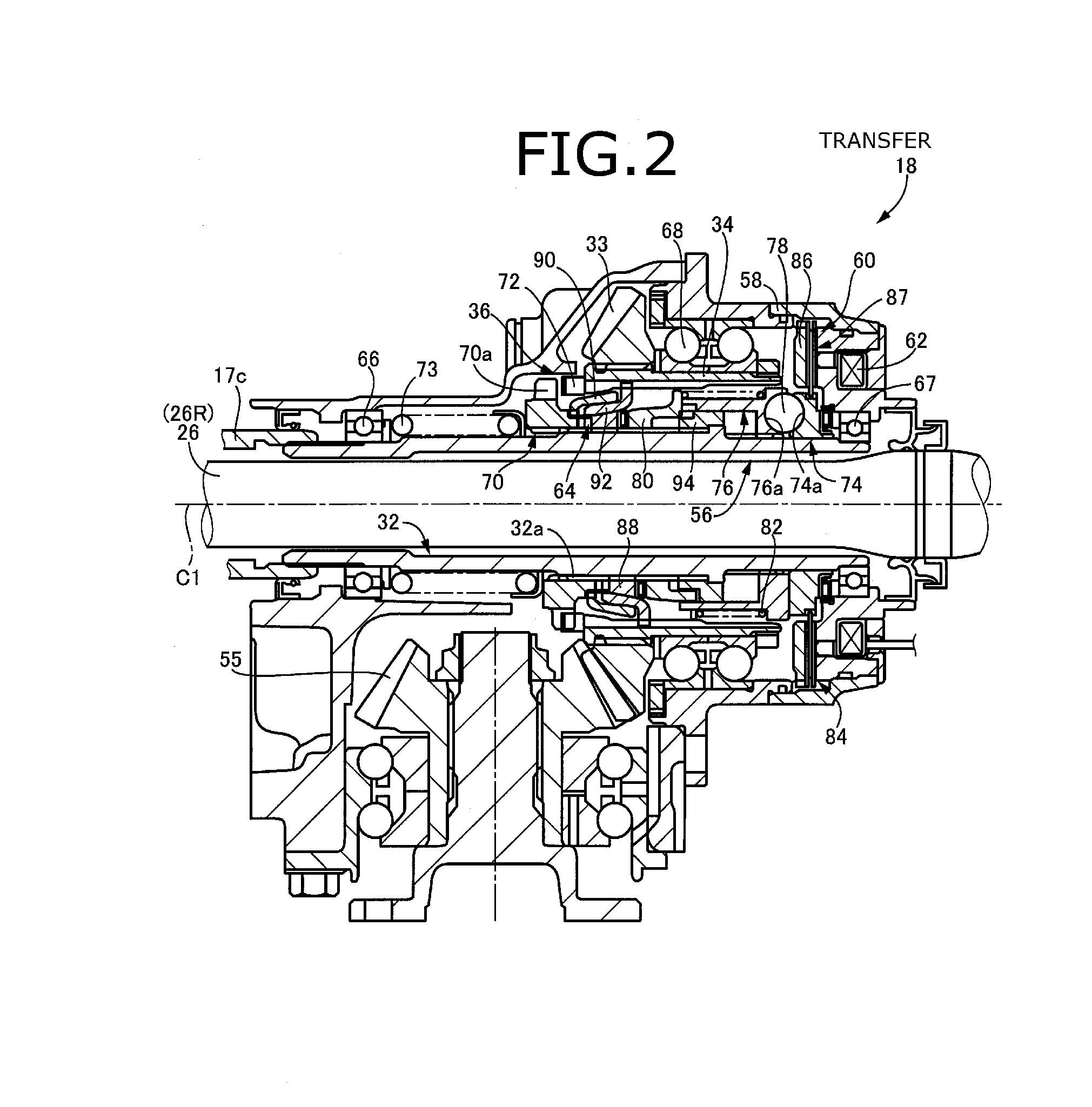

Vehicle four-wheel drive apparatus

ActiveUS20160101689A1Eliminate energyEasy to adjustGearingControl devicesRotation velocityEngineering

By driving a first electromagnetic solenoid and a second electromagnetic solenoid, if first cams of a first thrust force amplification mechanism and a second thrust force amplification mechanism are connected to non-rotary members, since second cams are rotated at rotating speeds that are proportional to a vehicle speed V, the relative rotations between the first cam and the second cam increase. Therefore, the first thrust force amplification mechanism and the second thrust force amplification mechanism can be actuated quickly, to thereby switch connection / disconnection states of the first connection / disconnection mechanism and the second connection / disconnection mechanism quickly.

Owner:JTEKT CORP

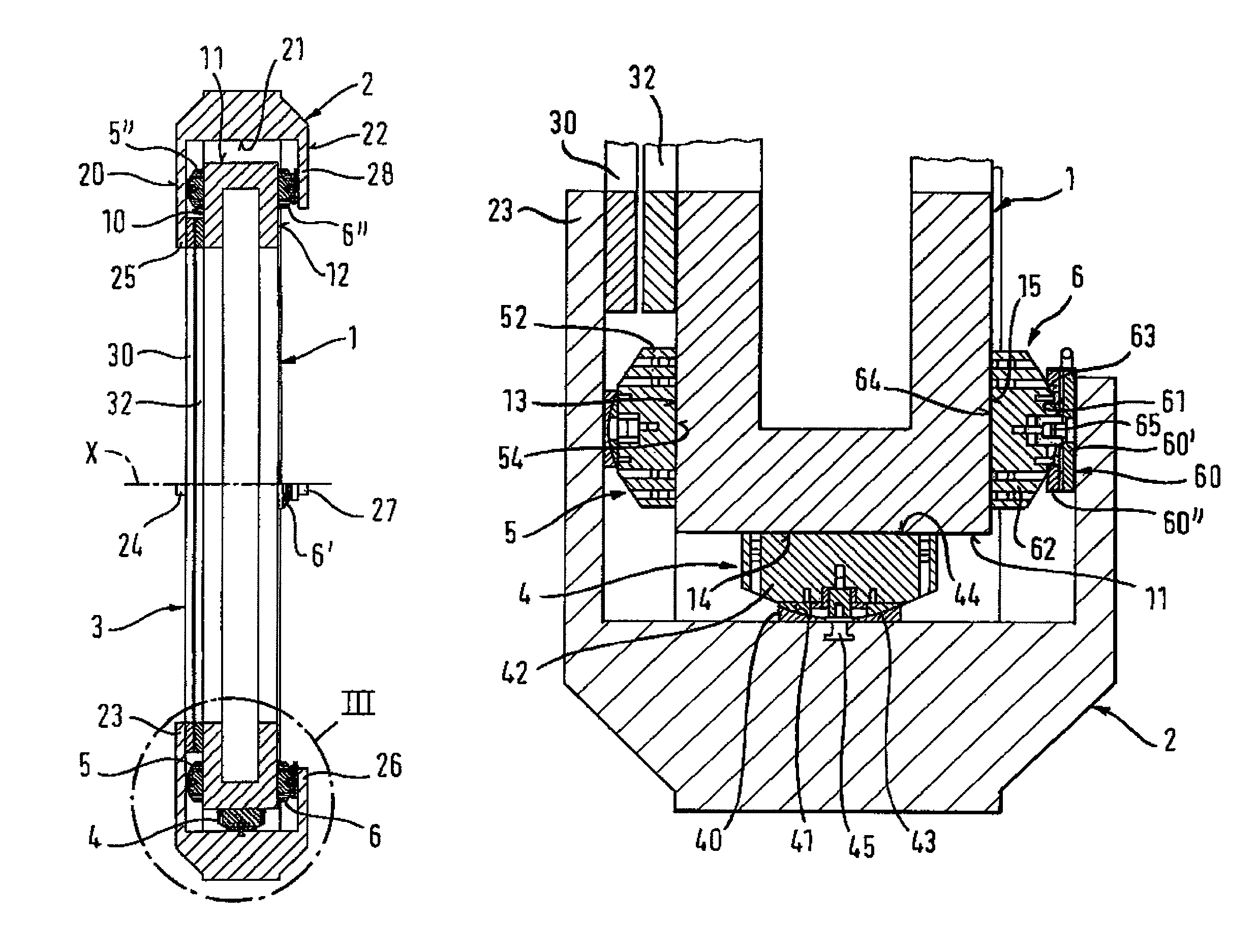

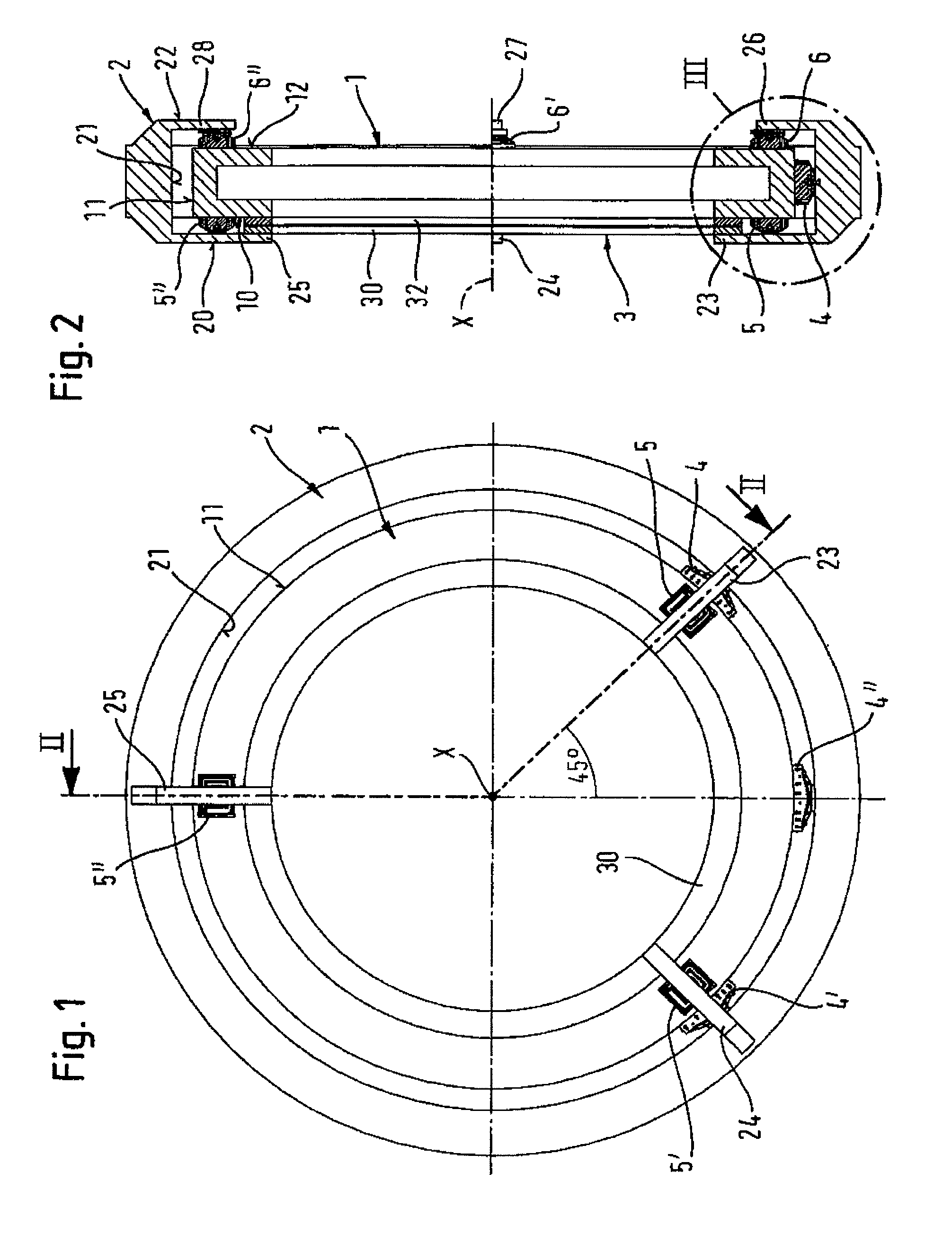

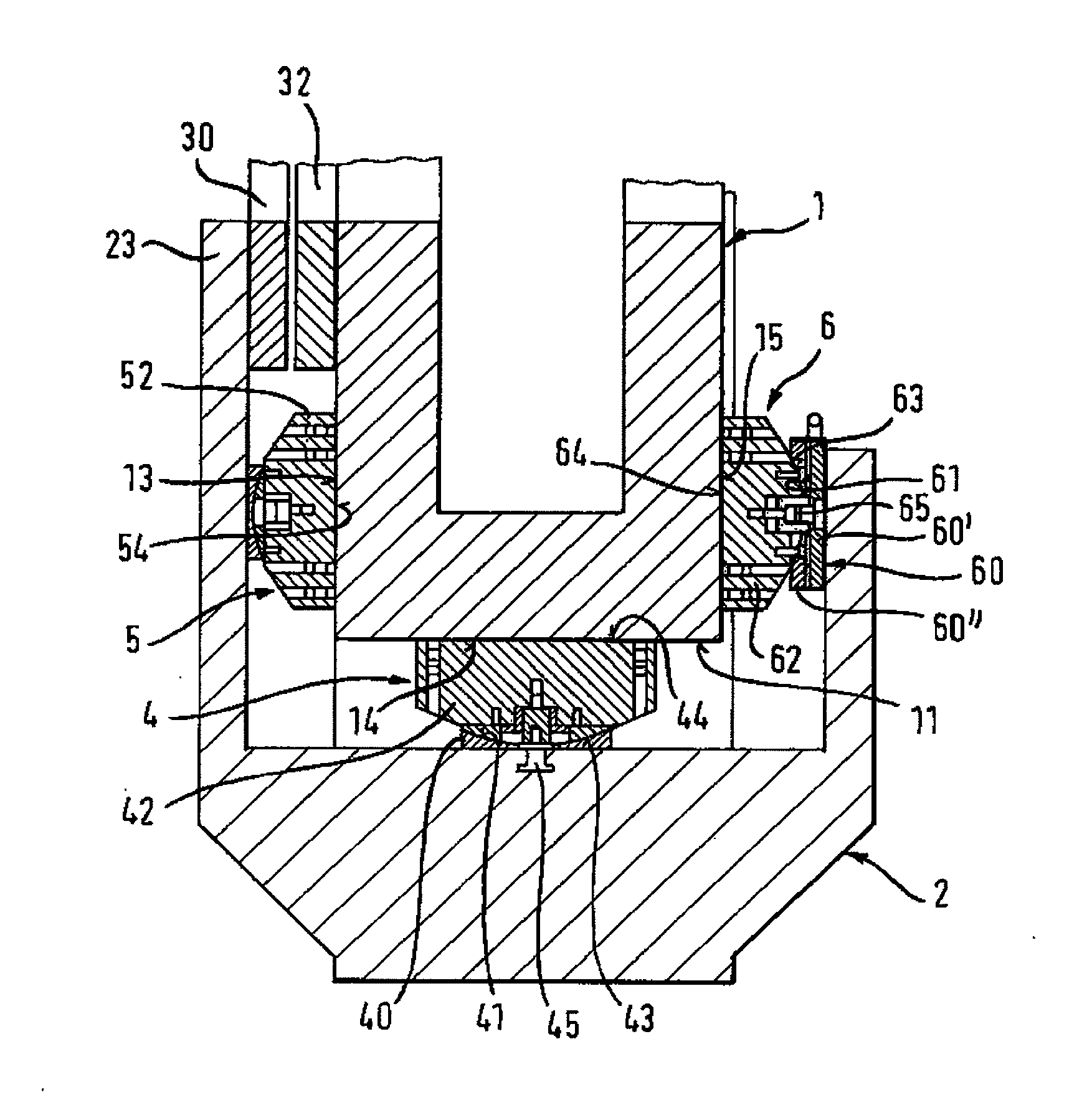

Apparatus with a directly driven rotating body and aerostatic bearings

ActiveUS8796893B2Reduce impactRotational speedRadiation diagnosis data transmissionShaftsRotational axisEngineering

Owner:AEROLAS GMBH AEROSTATISCHE LAGER LASERTECHN

Apparatus With a Directly Driven Rotating Body and Aerostatic Bearings

ActiveUS20100254640A1Reduce the impactReduce impactRadiation diagnosis data transmissionShaftsRotational axisEngineering

A device having a directly driven rotating body (1), its circumference (11) being radially seated on radial bearings (4, 4′) in relation to the stationary body (2), and its at least one first face side (10) being axially seated in relation to the stationary body (2), wherein aerostatic bearings (5, 5′, 5″) are provided for the axial support mounting, characterized in that the first face side (10) has an annular magnet arrangement (32), which is configured coaxially to the axis of rotation (X) of the rotating body (1), and that the stationary body (2) has at least one electric coil arrangement (30), which is located opposite the annular magnet arrangement (32) in the axial direction and which forms together with the annular magnet arrangement (32) the components of an electrical direct drive (3) for the rotating body (1).

Owner:AEROLAS GMBH AEROSTATISCHE LAGER LASERTECHN

Brake by wire type brake system

InactiveUS20070216218A1Improve operational responsivenessIncrease rotation speedBraking action transmissionSingle motor speed/torque controlElectric signalBraking system

A BBW type brake system which operates fluid pressure generators having electric motors as drive sources based on an electrical signal to brake a wheel, field weakening control of the electric motors is performed in the initial stage of operation of the fluid pressure generators to increase the rotational speed of the electric motors. Therefore, it is possible to reduce a time lag before the braking force actually generates after the electrical signal for operating the fluid pressure generators is outputted, thereby improving operational responsiveness. After the braking force actually generates, the field weakening control is cancelled to secure a required braking force with a sufficient torque.

Owner:HONDA MOTOR CO LTD

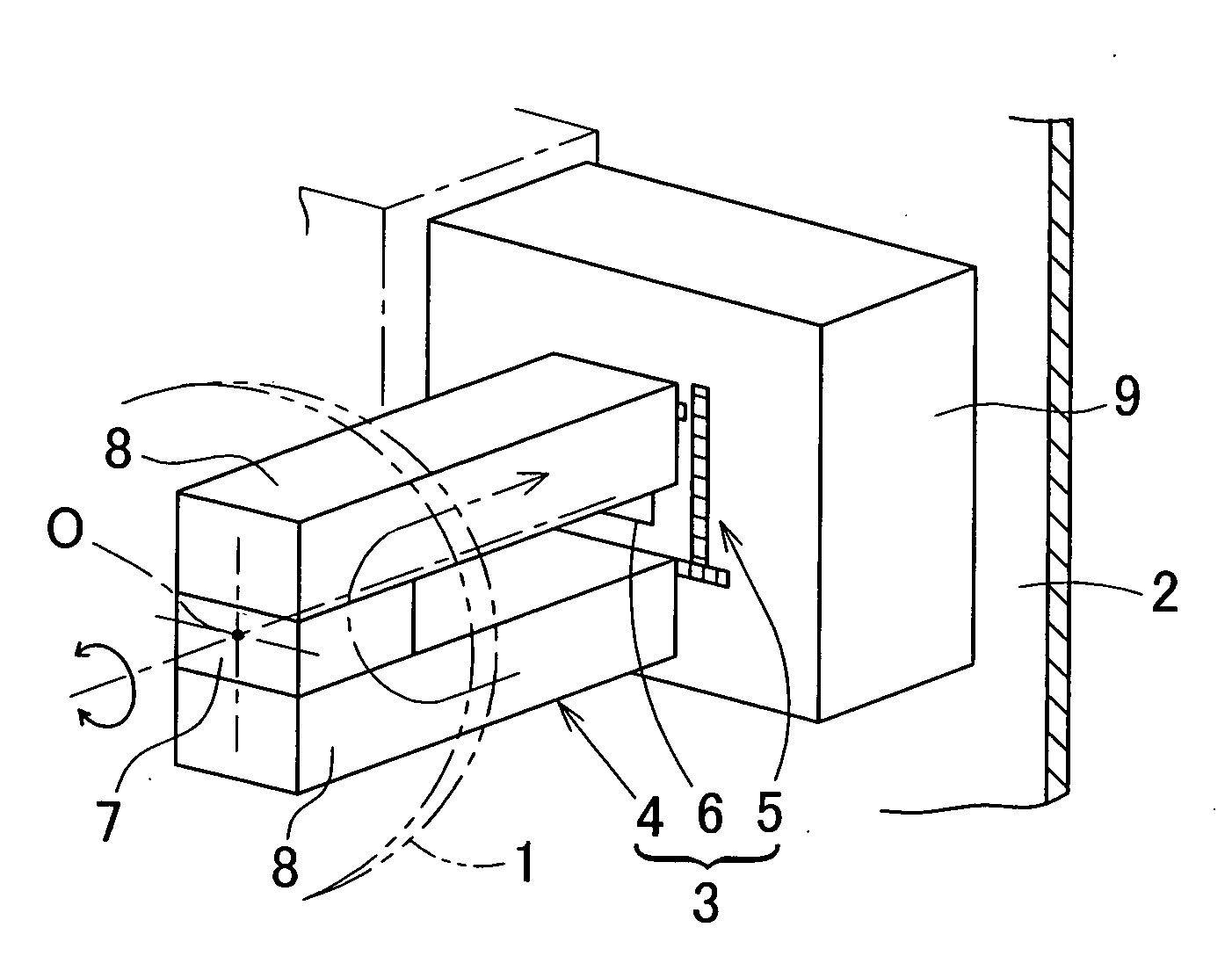

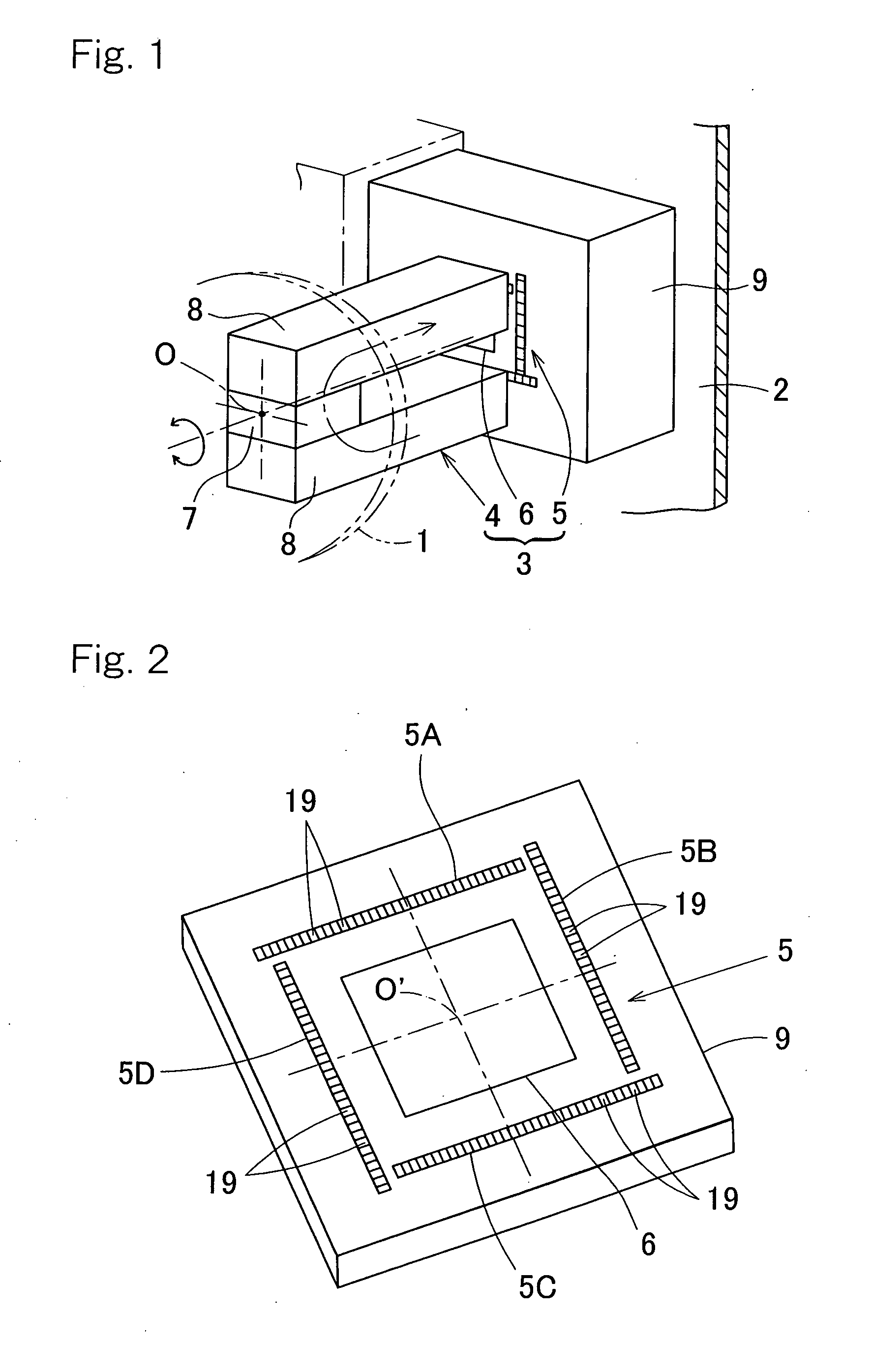

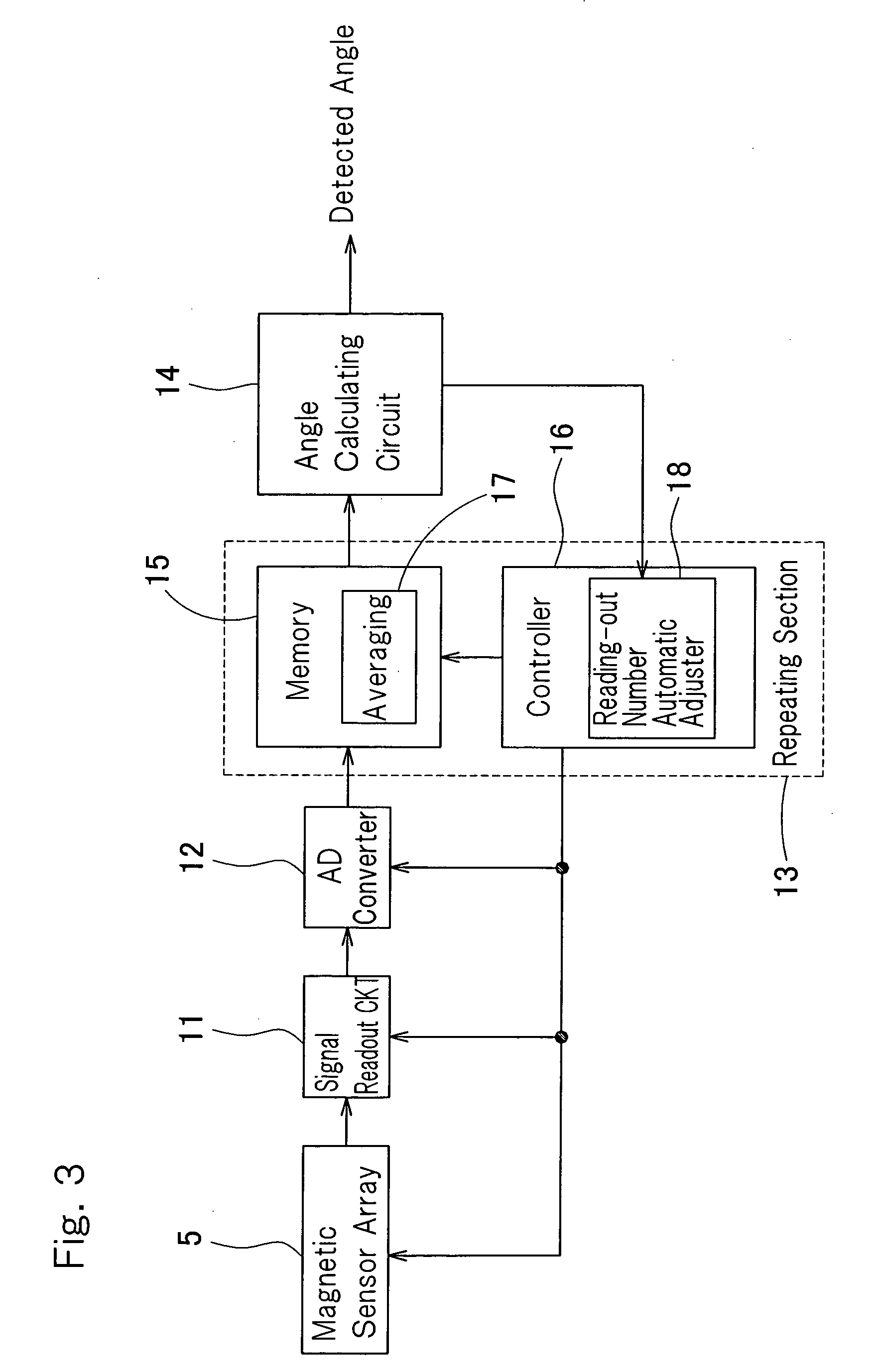

Rotation sensor and bearing assembly using the same

InactiveUS20090102468A1Reduce in quantitySmall sizeMagnetic measurementsUsing electrical meansSensor arrayAngle of rotation

A rotation sensor includes a magnetic sensor array (5) including magnetic sensor elements (19) in line, a rotatable magnet (4) confronting the magnetic sensor array (5), a signal readout circuit (11) for reading out a signal from the magnetic sensor array (5), a repeating section (13) for causing the signal readout circuit (11) to repeat reading out the signal from the magnetic sensor array (5) several number of times, and calculating a summation or an average of several readout signals, and an angle calculating circuit (14) for detecting an angle of rotation of the magnet (4) from the summation or the average of the signals calculated by the repeating section (13).

Owner:NTN CORP

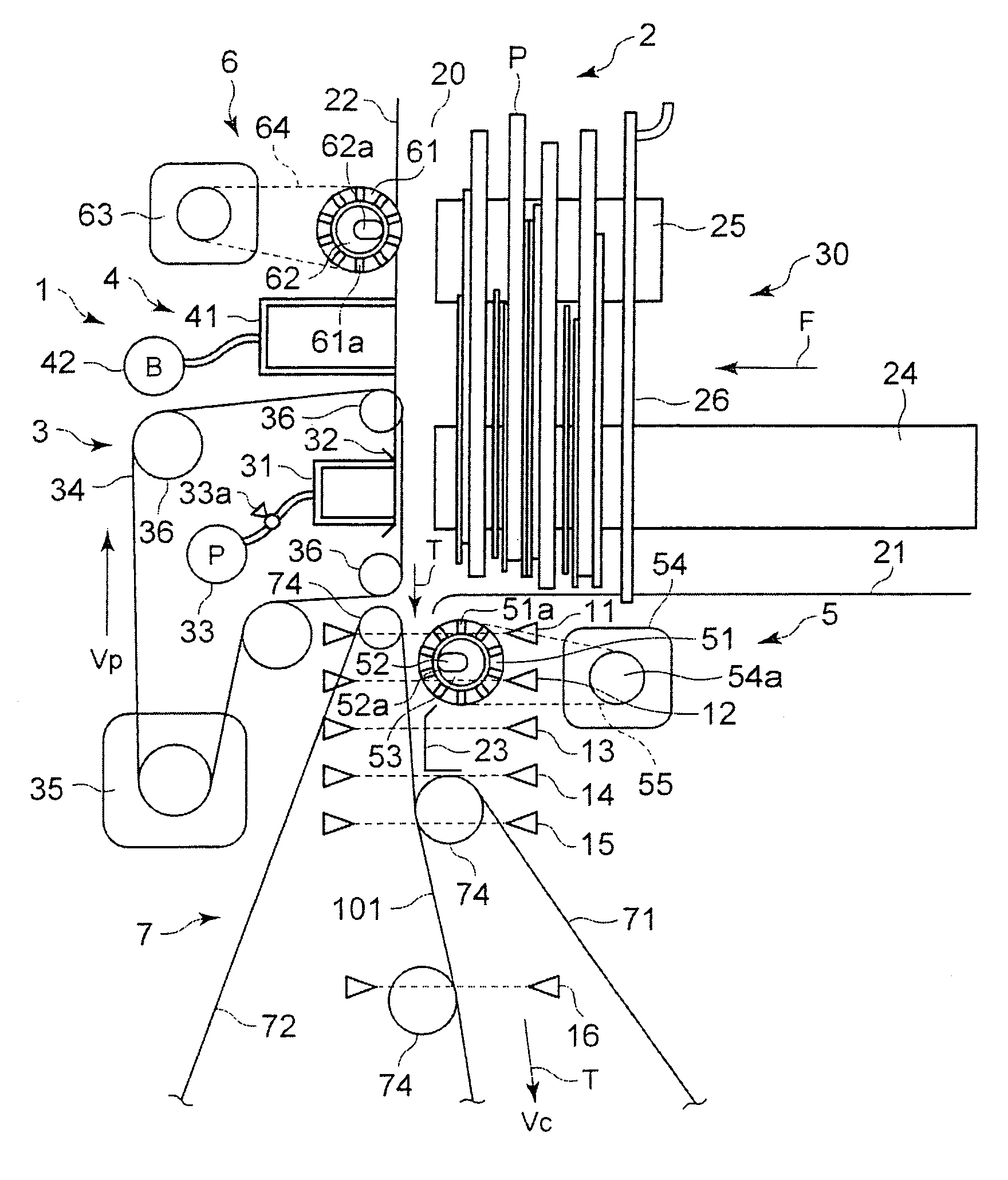

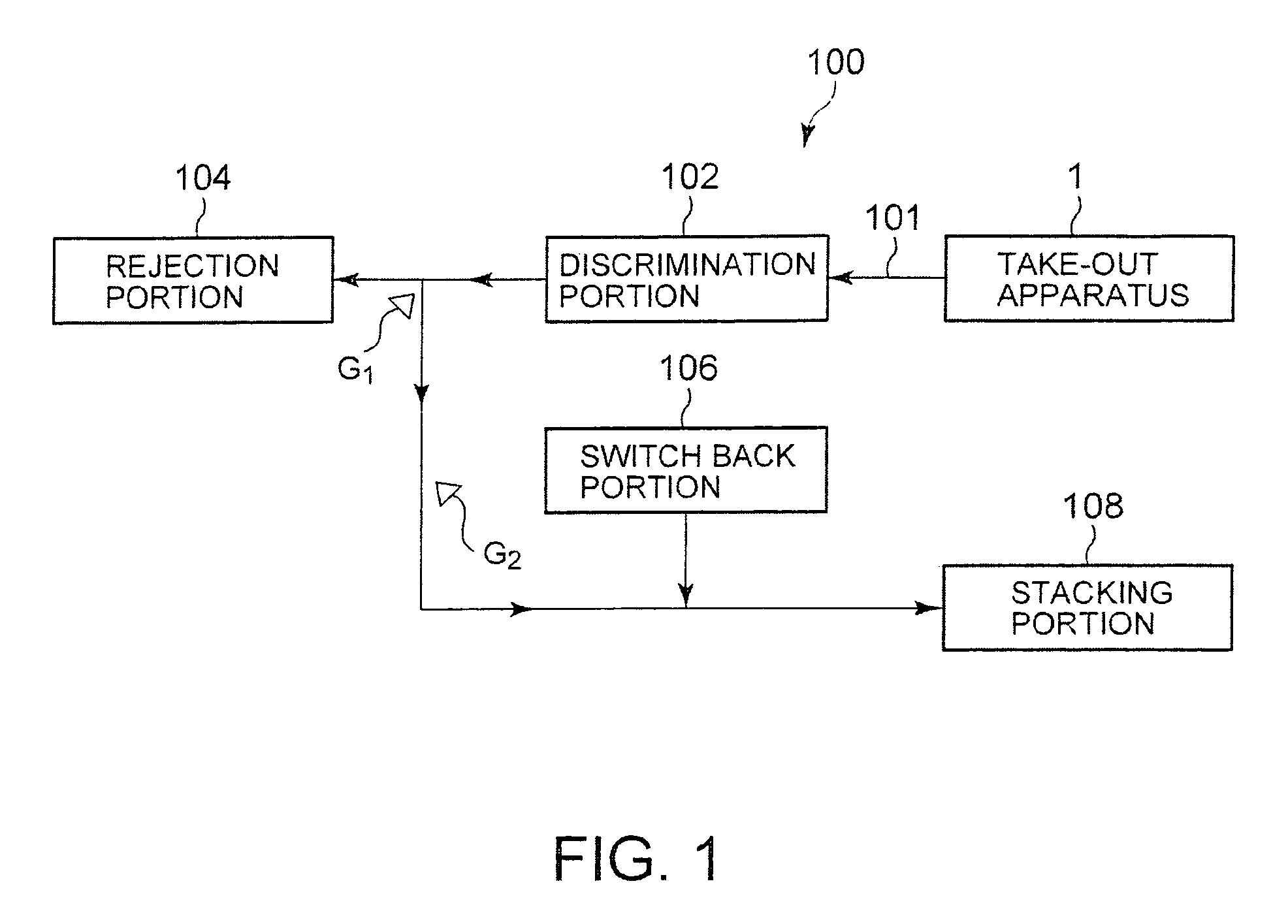

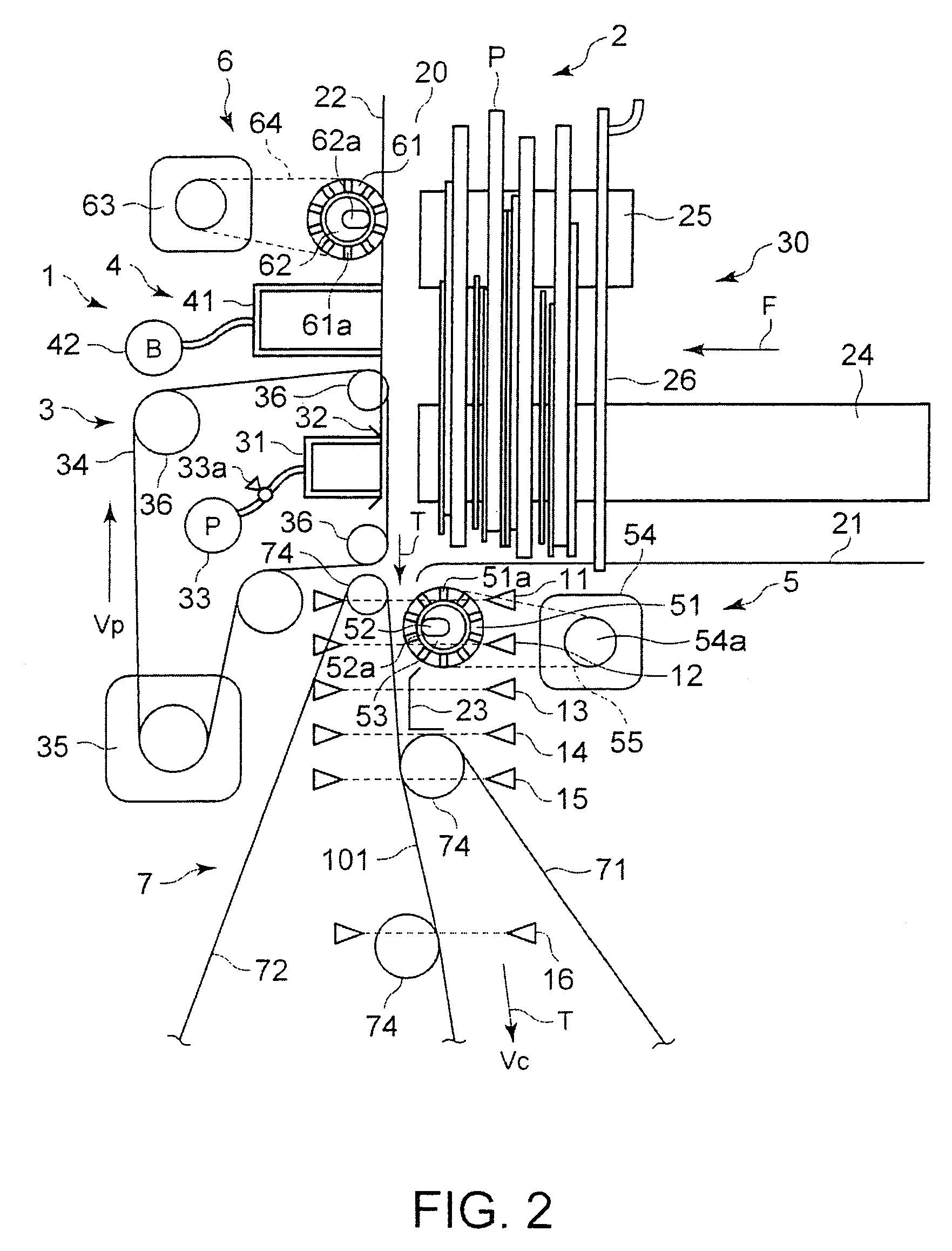

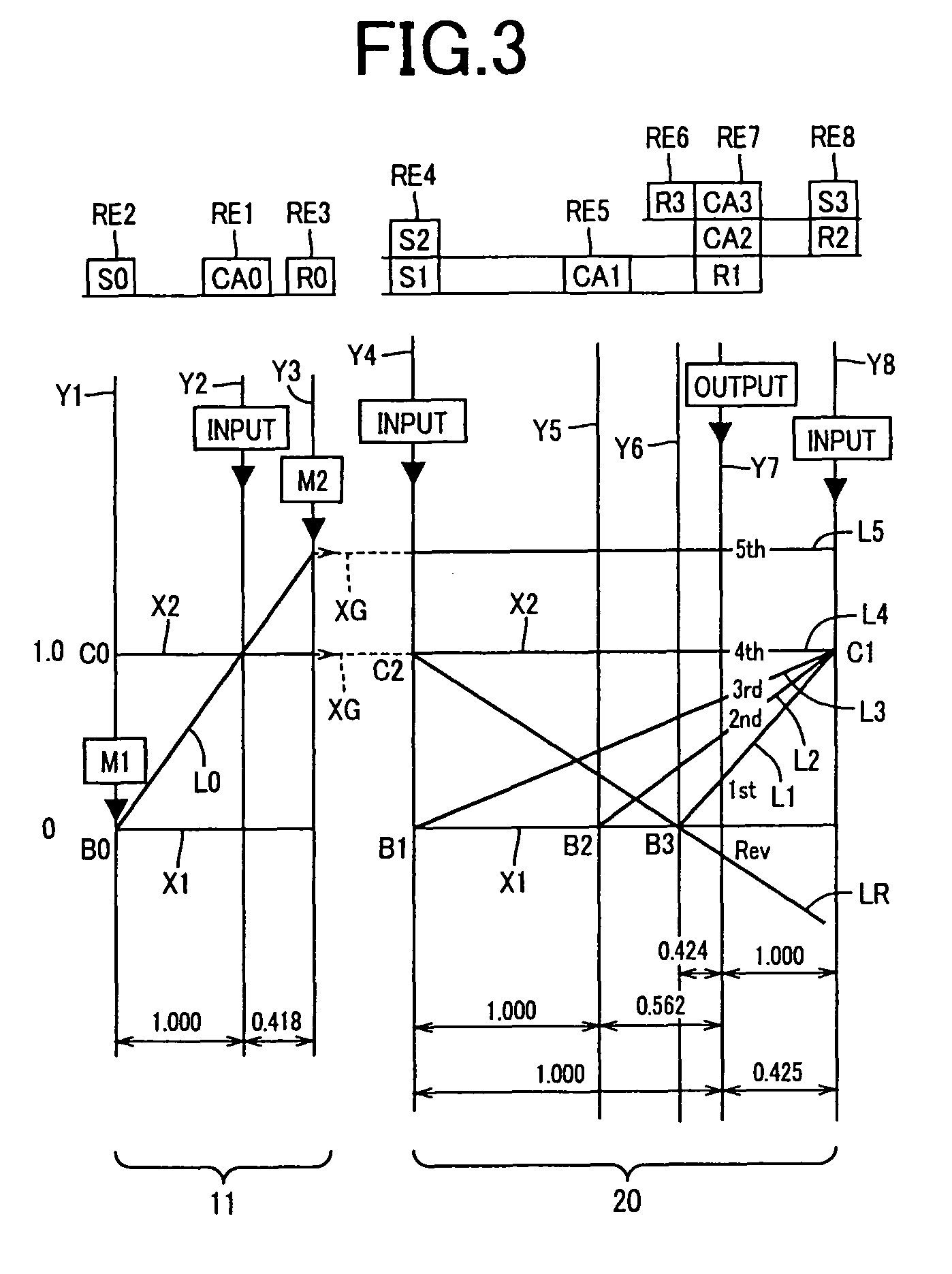

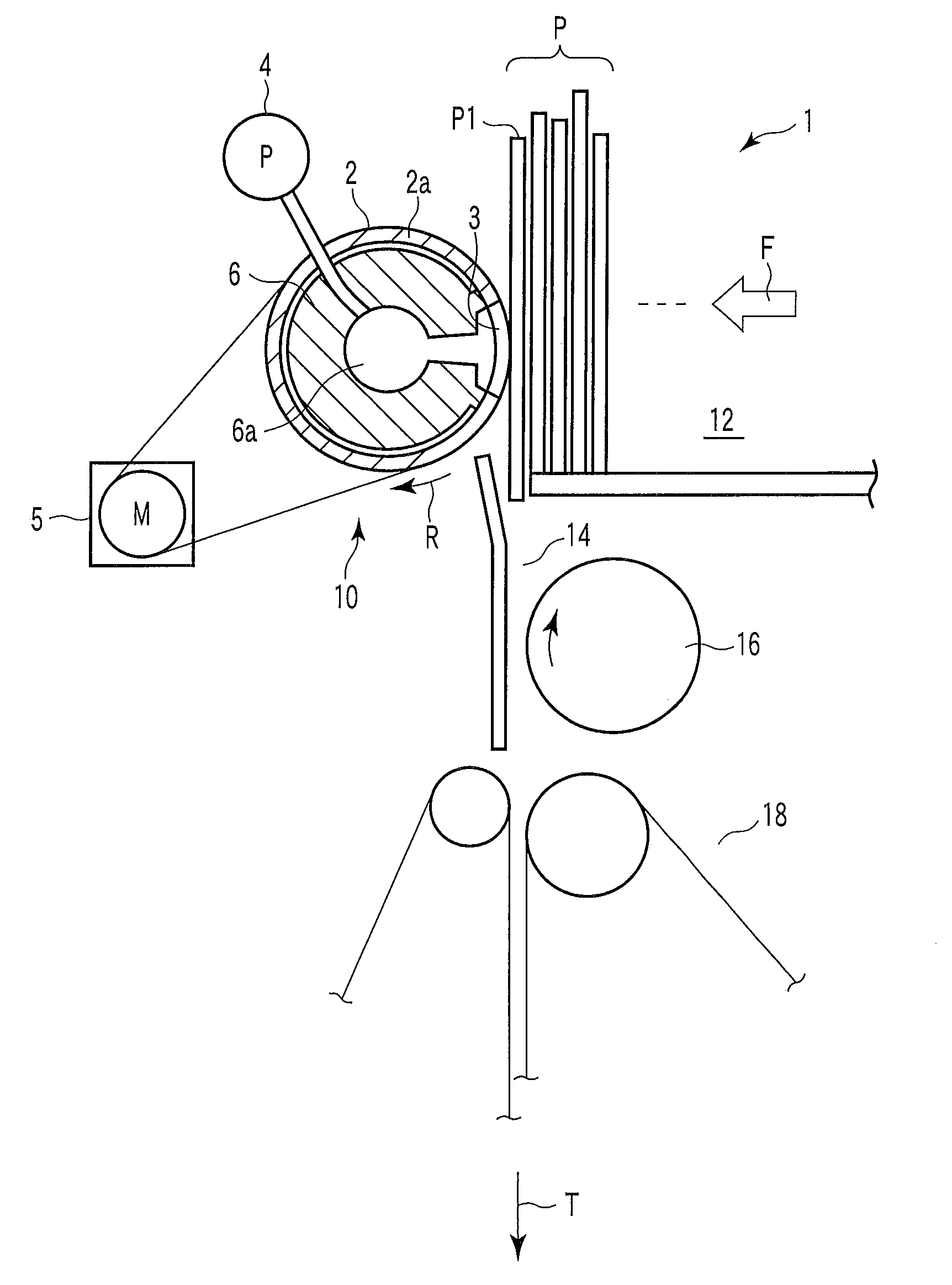

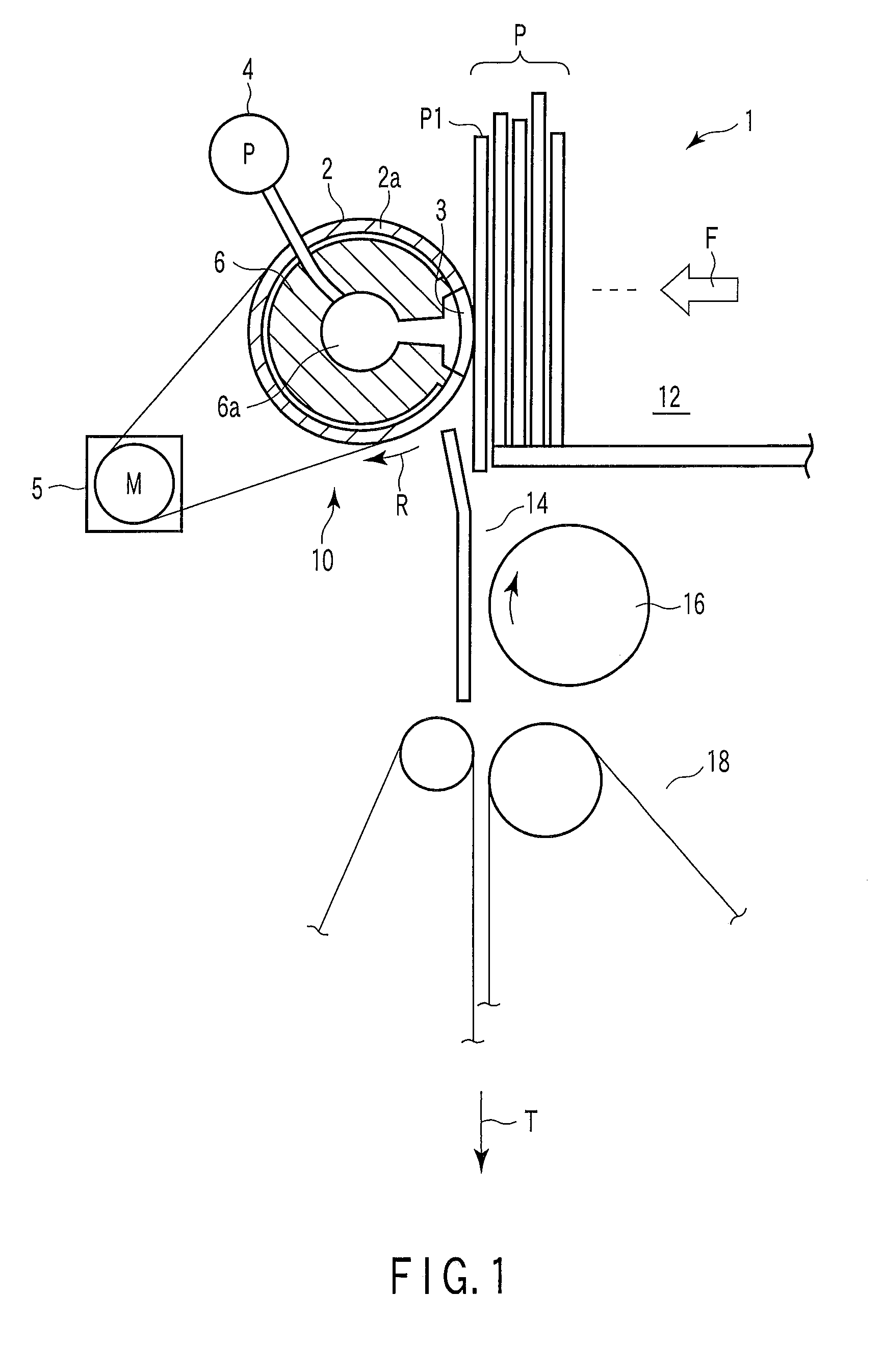

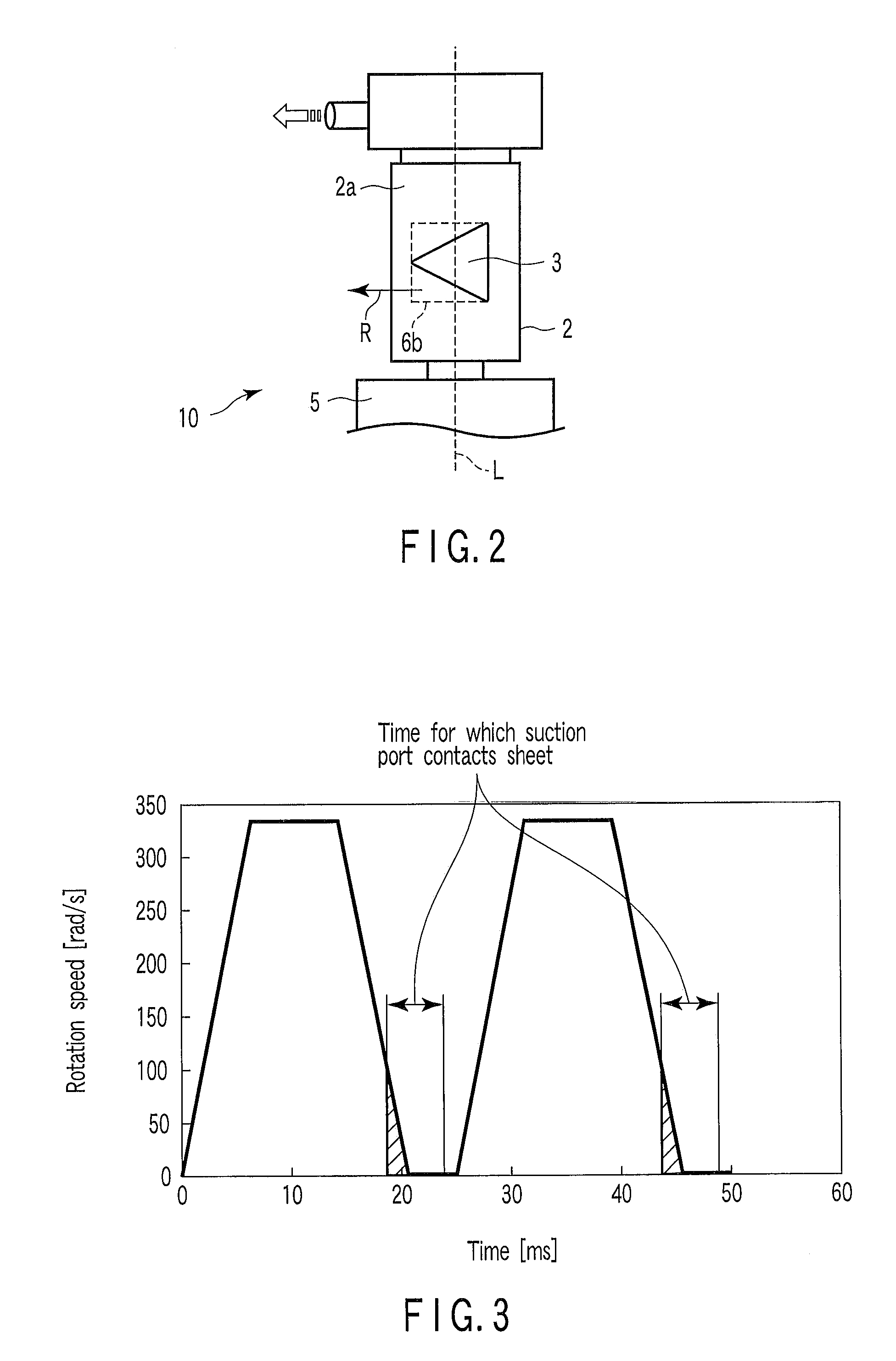

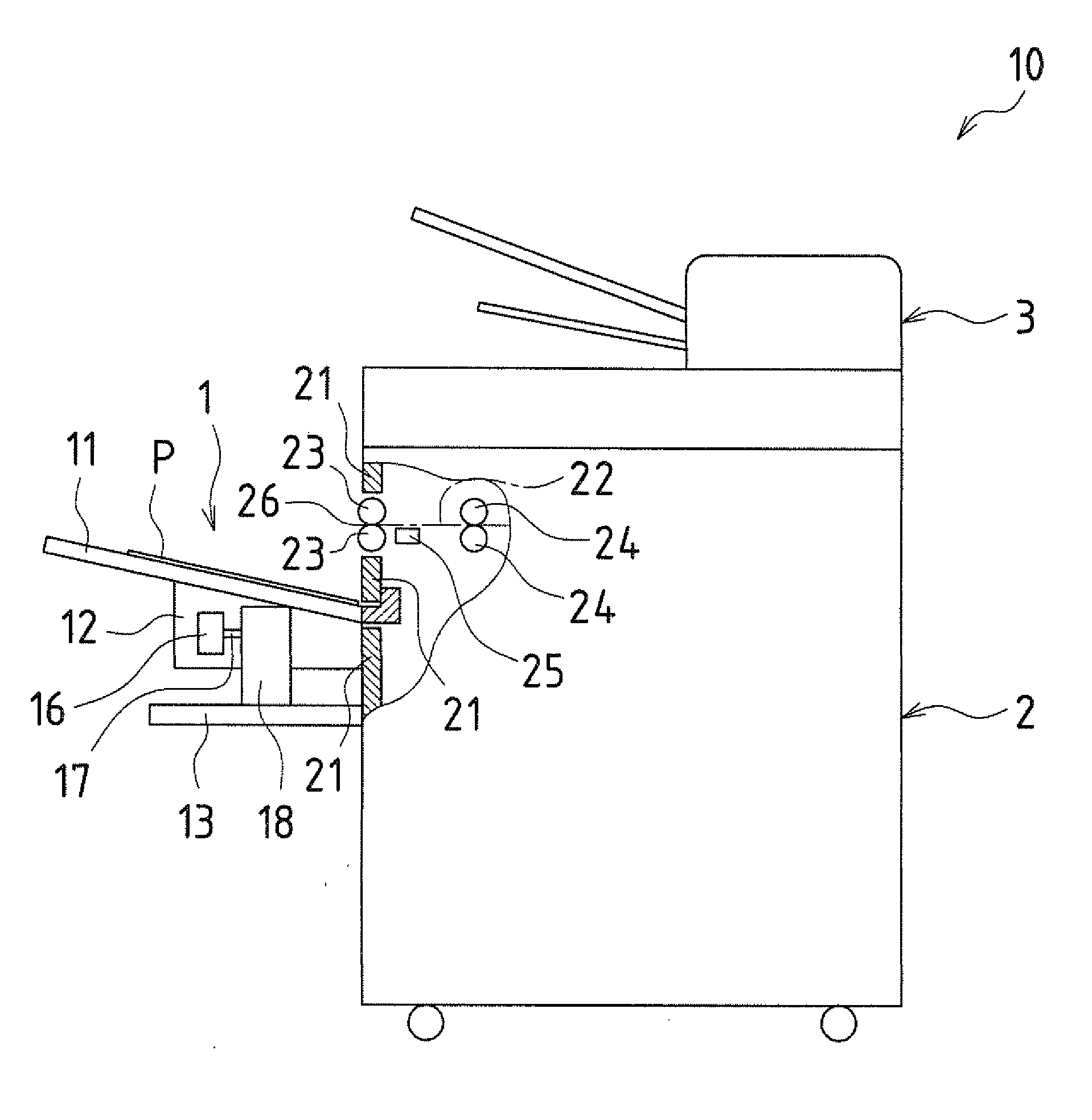

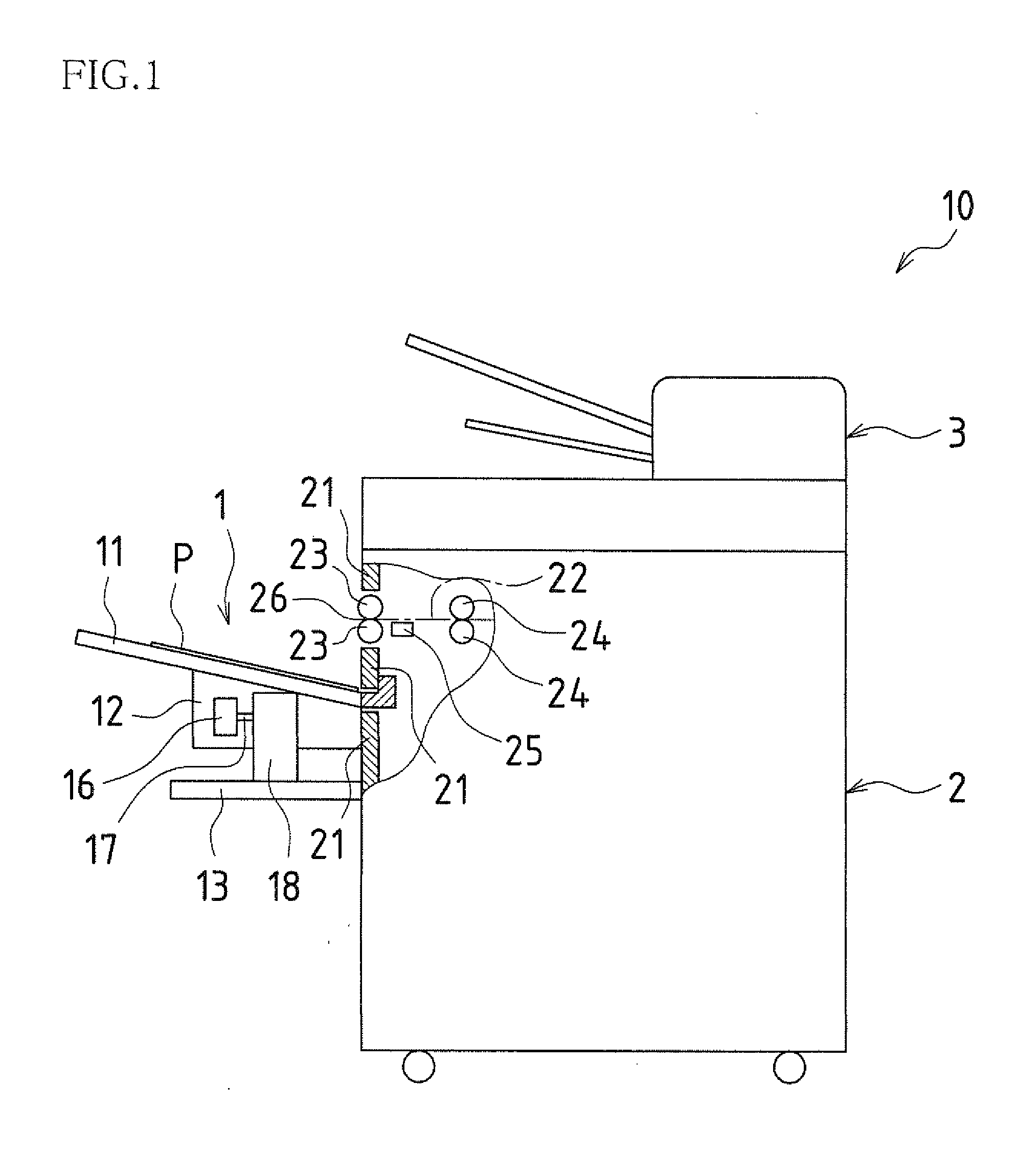

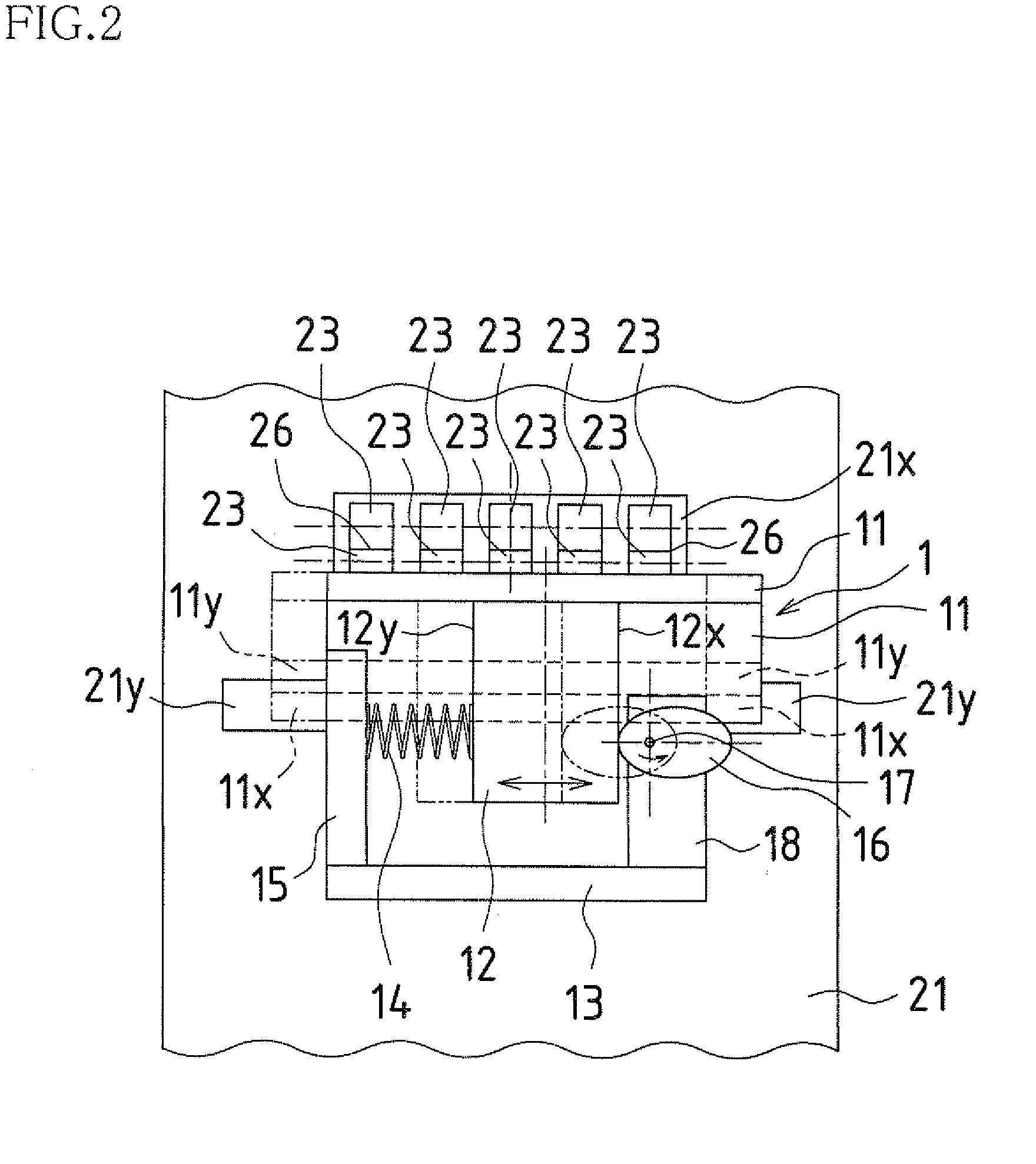

Sheet take-out apparatus, sheet processing apparatus, and sheet take-out method

ActiveUS7845629B2Reduce speedRotational speedFunction indicatorsArticle feedersLeading edgeEngineering

To provide a sheet take-out apparatus for preventing double feed of sheets and controlling gaps to a desired value, a sheet processing apparatus, and a sheet take-out method. A take-out apparatus includes a supply structure for supplying postal matter to a take-out position, a take-out structure for taking out the postal matter from the take-out position, and a conveying structure for receiving and conveying the postal matter taken out on a conveying path. When a leading edge of the postal matter is held by the conveying structure, an absorbing operation of a vacuum pump is stopped and a moving speed of a take-out belt is reduced. Furthermore, when the postal matter is detected by a sensor, the take-out belt is stopped.

Owner:KK TOSHIBA

Control device for vehicular power transmitting apparatus

InactiveUS8052570B2Reduce speedShorten the time periodHybrid vehiclesDigital data processing detailsElectricityEngineering

The present invention provides, in a vehicular power transmitting apparatus including a differential portion electrically controlled, a control device which can quickly decrease the engine rotation speed, even if the operational state of an electric motor is limited. An engine-stop controlling means (112) includes limiting means for limiting the differential state of a differential portion (11) by a switching brake (B0) and a switching clutch (C0) when the operational state of a first electric motor (M1) is limited. Therefore, a torque in a direction for decreasing a rotation speed (NE) of an engine (8) is applied by limiting the differential state of the differential portion (11), for example, in a vehicle stopped state. As a result, the rotation speed (NE) of the engine (8) is quickly decreased to pass through a resonance point in a short time, whereby occurrence of resonance phenomena can be prevented.

Owner:TOYOTA JIDOSHA KK

Sheet takeout device

A sheet takeout mechanism has a takeout roller that rotates in contact with a sheet located at a takeout position, and a motor that intermittently rotates the takeout roller. A triangular suction port is formed on a suction surface of the takeout roller and has a vertex located downstream in a rotation direction of the takeout roller. When a negative pressure is exerted on the sheet via the suction port, the suction force is weak at the beginning of suction and then increases gradually.

Owner:KK TOSHIBA

Self-propelling crusher

InactiveUS7318463B2Reduce crushing efficiencyIncrease speedMowersMulti-purpose machinesHydraulic pumpEngineering

A self-propelled crushing machine comprises a crushing device 20; a hydraulic drive system including a crushing device hydraulic motor 21 for driving the crushing device 20, a first hydraulic pump 62 for driving the crushing device hydraulic motor 21, and an engine 61 for driving the first hydraulic pump 62; a pressure sensor 151 for detecting a load condition of the crushing device 20; and a controller 84″ for executing control to increase a revolution speed of the engine 61 in accordance with a detected signal from the pressure sensor 151. Accordingly, even when a heavy load is imposed on the crushing device, a reduction of crushing efficiency can be prevented.

Owner:NIHON KENKI CO LTD

Three-body joining using friction stir processing techniques

ActiveUS7845545B2Rotational speedIncrease rotation speedWelding/cutting auxillary devicesAuxillary welding devicesEngineeringFriction stir processing

A friction stir tool is provided to perform friction stir riveting using a partially consumable pin, wherein the pin includes a cutting edge on a bottom surface thereof, wherein the tool is rotated at a first speed to enable cutting by the pin into a first material that is overlapping a second material, wherein after the pin has cut to a sufficient depth, the rotational speed of the tool is increased to thereby enable plasticization of the consumable pin, the first material, and the second material, wherein the tool is then rapidly decelerated until stopped, enabling diffusion bonding between the pin, the first material and the second material.

Owner:MAZAK CORP +1

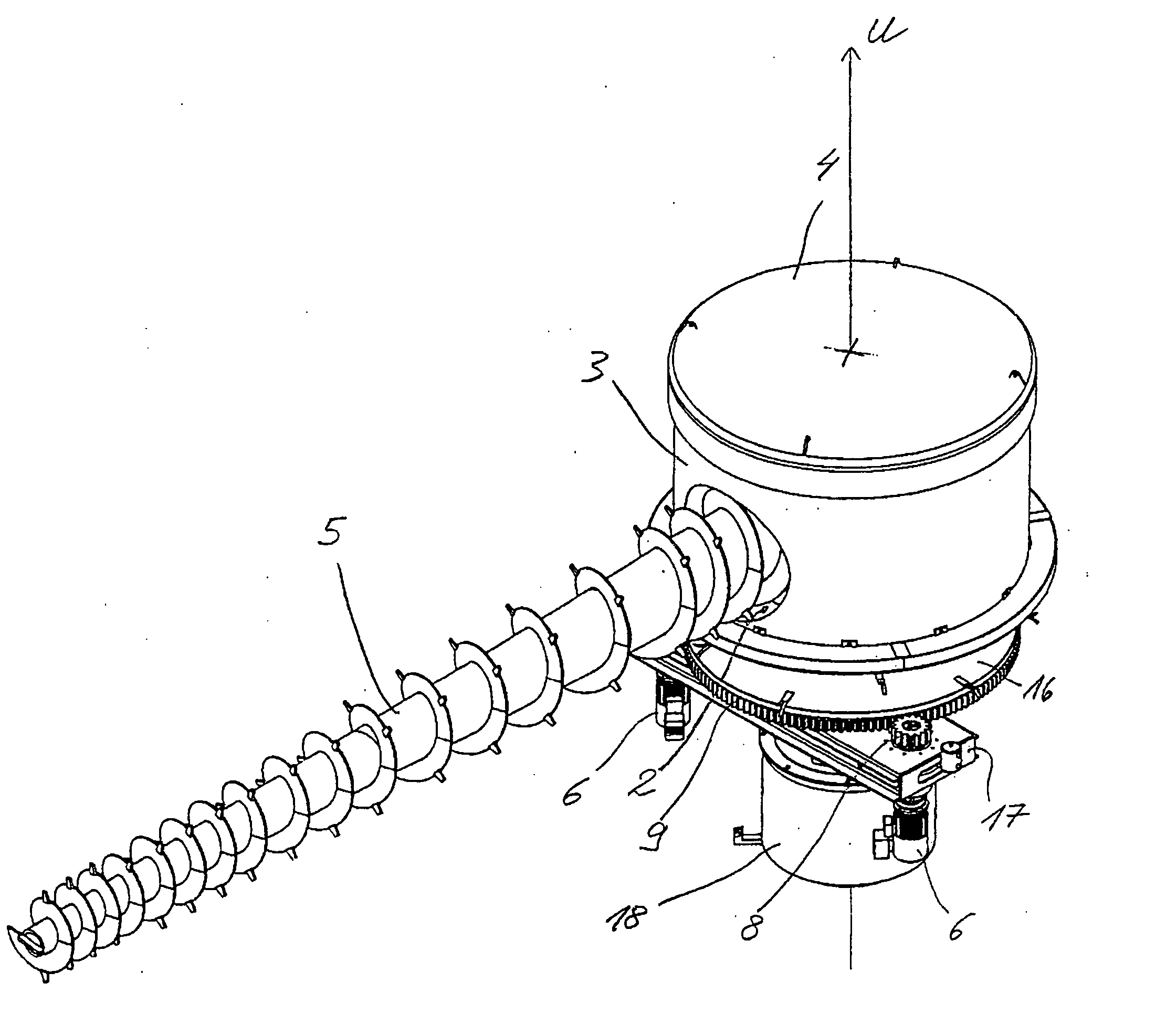

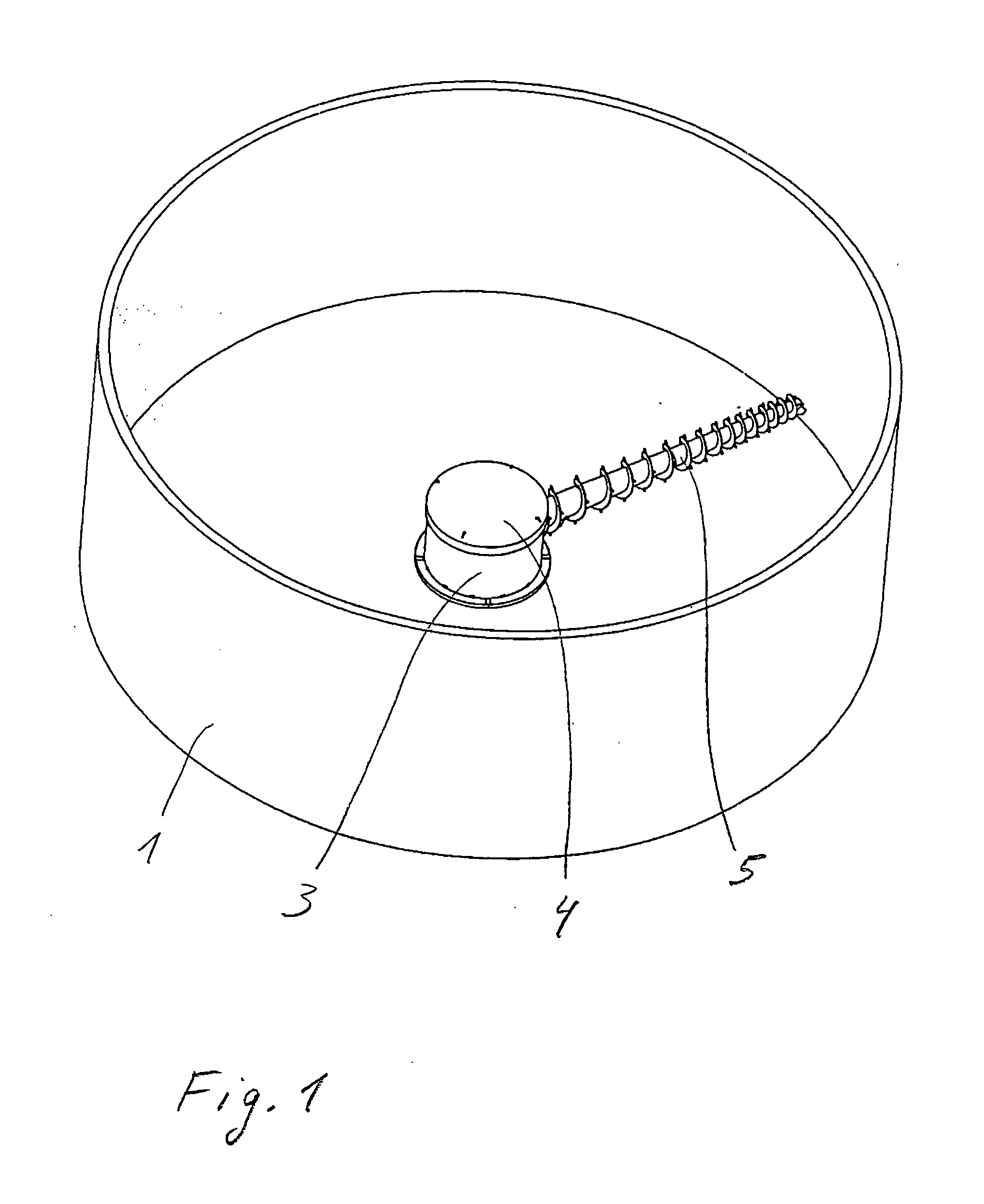

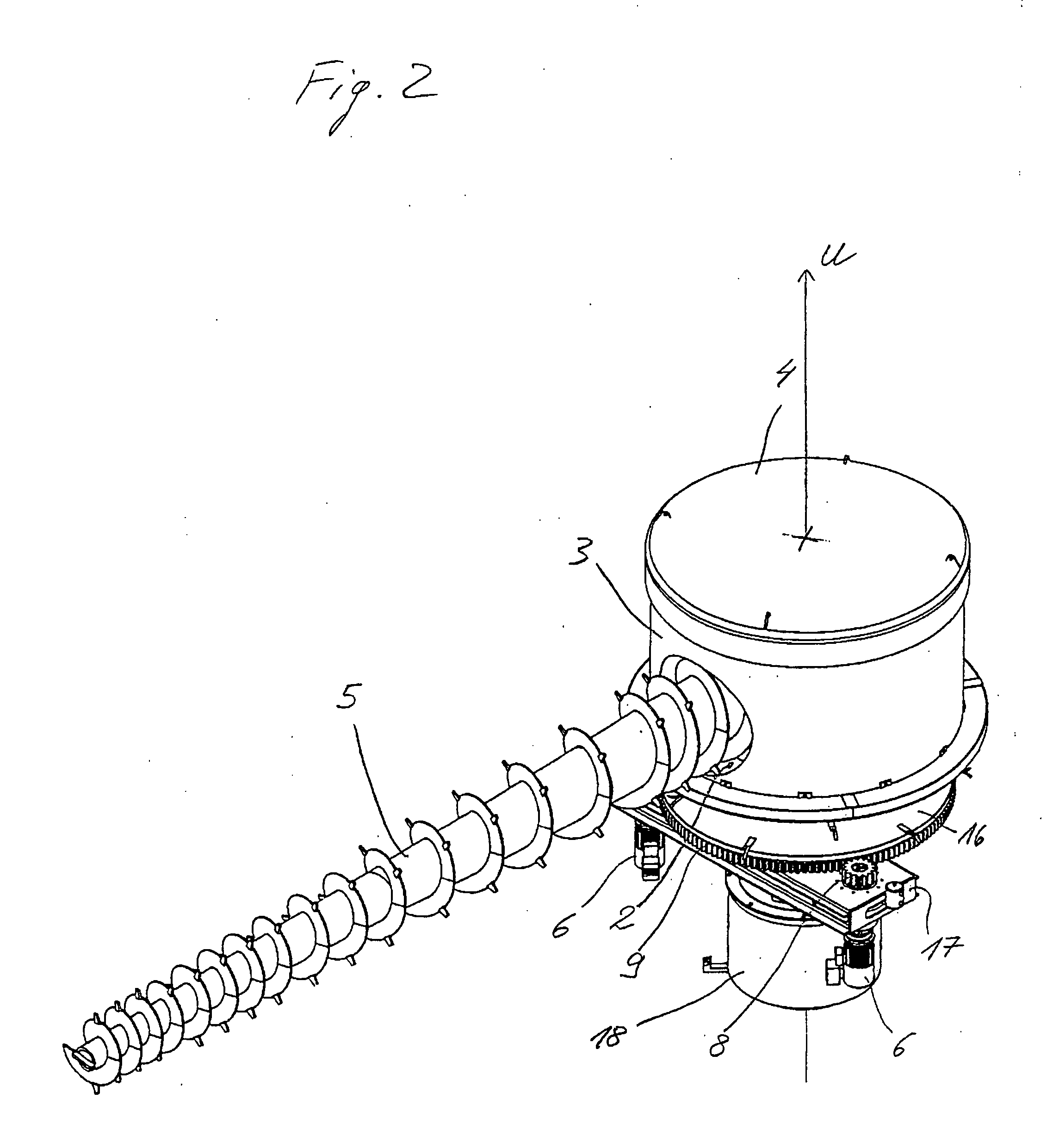

Device for conveying bulk material

InactiveUS20060104757A1Increase torqueEasy to operateLarge containersLoading/unloadingMechanical engineeringEngineering

Owner:SHW STORAGE & HANDLING SOLUTIONS

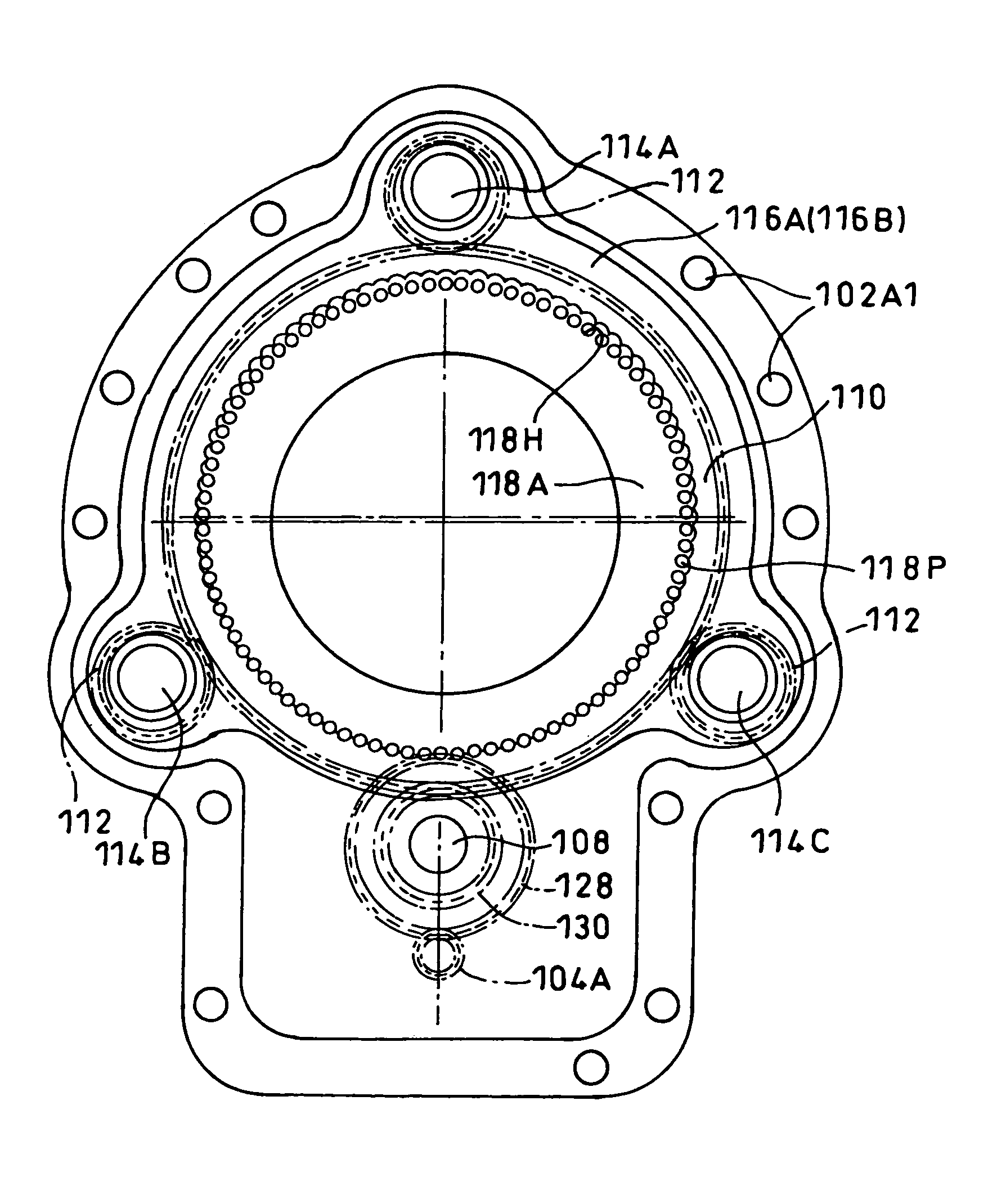

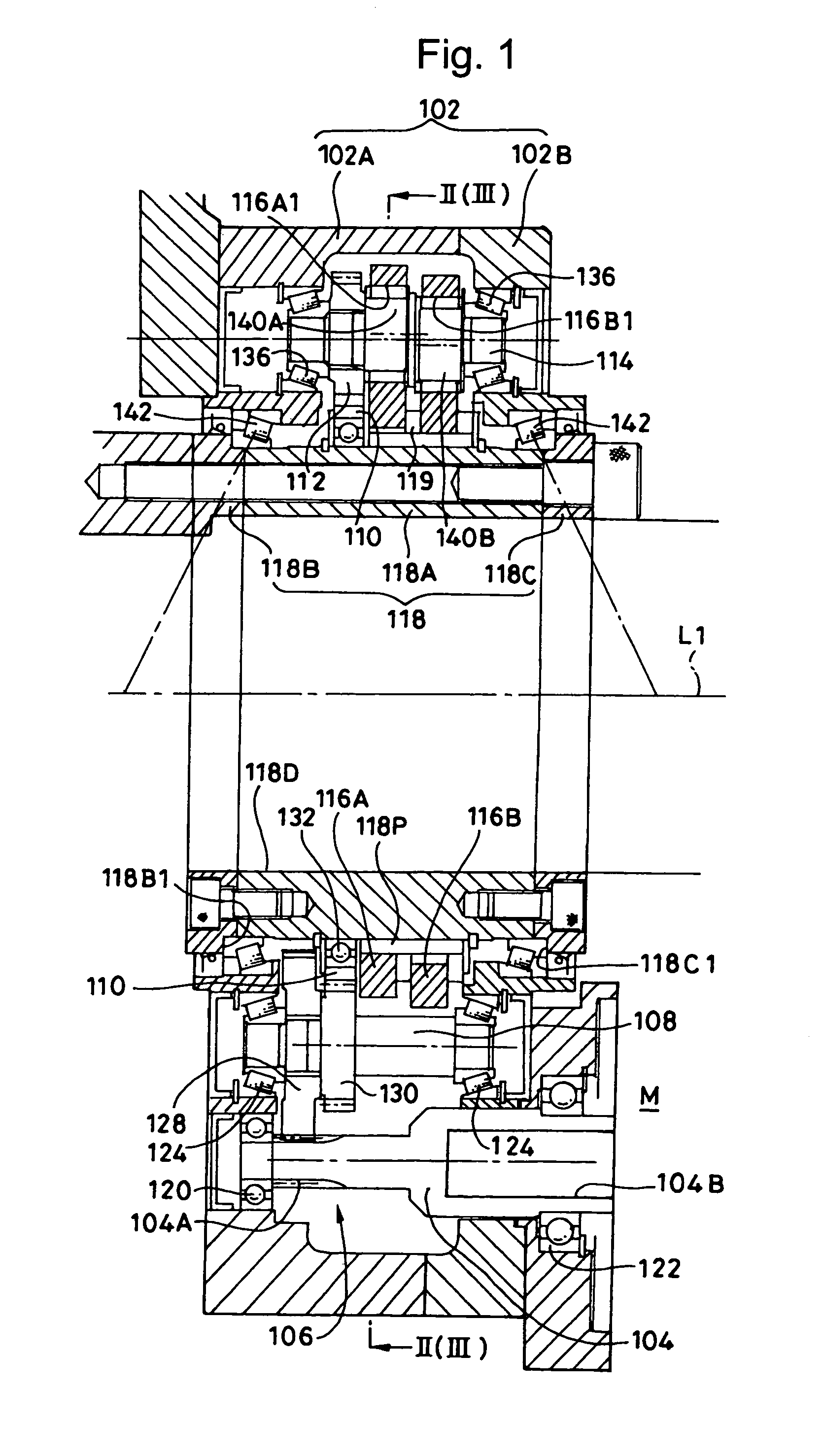

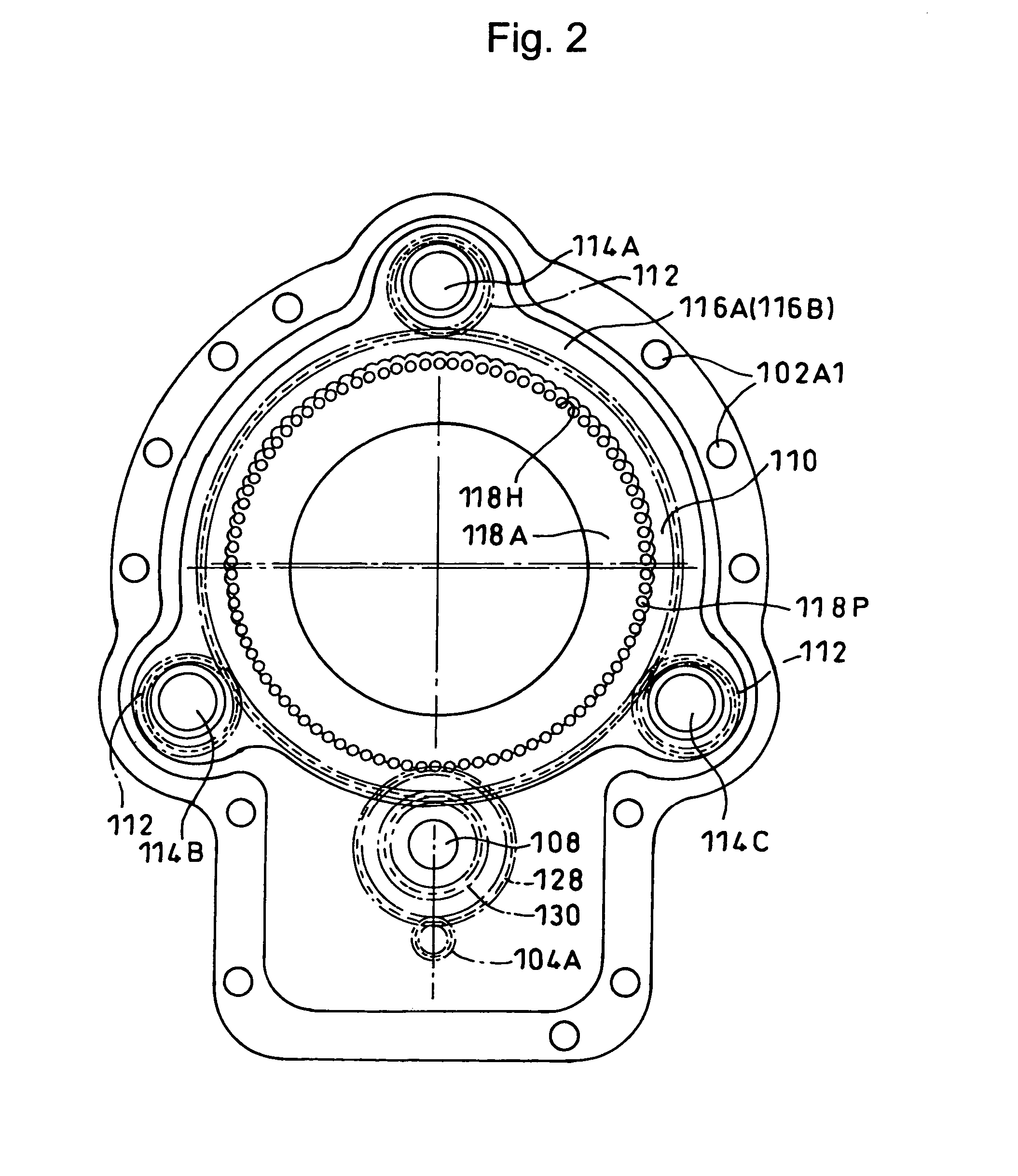

Internal teeth oscillation type inner gearing planetary gear system

InactiveUS7070533B2Smoothness of power transmissionEasy to fixPortable liftingToothed gearingsGear wheelGear system

An internal teeth oscillating inner gearing planetary gear system, wherein installation space for piping, wiring, etc. can be easily secured in the central portion of the system according to a particular application. The gear system is configured such that rotation of an input shaft is reduced by internal teeth oscillating bodies oscillatingly rotating with respect to an external gear. Eccentric shafts are plurally provided. Eccentric shaft gears are provided for the plurality of eccentric shafts, respectively. A transmitting external gear with which the eccentric shaft gears and a driving source-end pinion concurrently mesh is also provided.

Owner:SUMITOMO HEAVY IND LTD

Image forming apparatus

ActiveUS20160246252A1Rotational speedFrictionElectrographic process apparatusImage formationMechanical engineering

An image forming apparatus to form an image electro-photographically is provided. The image forming apparatus includes a housing formed to have an opening; a cover being movable between an open position and an exposing position and having a ventilation port, through which air is allowed to flow; a cartridge having a developer roller and being detachably attached to a body of the image forming apparatus through the opening; a discharging fan arranged on an opposite side from the opening across the cartridge; a handle arranged on the cartridge to extend from the cartridge in a direction toward the opening in an upper position with respect to the ventilation port, when the cartridge is attached to the body and the opening is covered by the cover; and a facing part arranged on the cover to face the handle in a vertically displaced position with respect to the handle.

Owner:BROTHER KOGYO KK

Automatic transmission control device

InactiveUS20080227599A1Increase fluid pressureShorten the time periodDigital data processing detailsGearing controlFluid controlWorking fluid

In an automatic transmission control device, multiple electromagnetic valves control fluid pressure of working fluid to be applied to multiple friction elements of an automatic transmission device, so that a transmission gear is changed by engaging some of the friction gears and / or disengaging the other of the friction elements. The electromagnetic valve controls its output pressure in such a manner that the output pressure is temporally increased when starting the transmission gear change. A maximum fluid pressure is selected from the output pressures of the multiple electromagnetic valves and is applied to a pressure control valve, which controls a fluid control pressure applied to a capacity varying device for changing a discharge amount of a pump. As a result, the fluid pressure applied to the friction elements can be rapidly increased at proper timings.

Owner:DENSO CORP

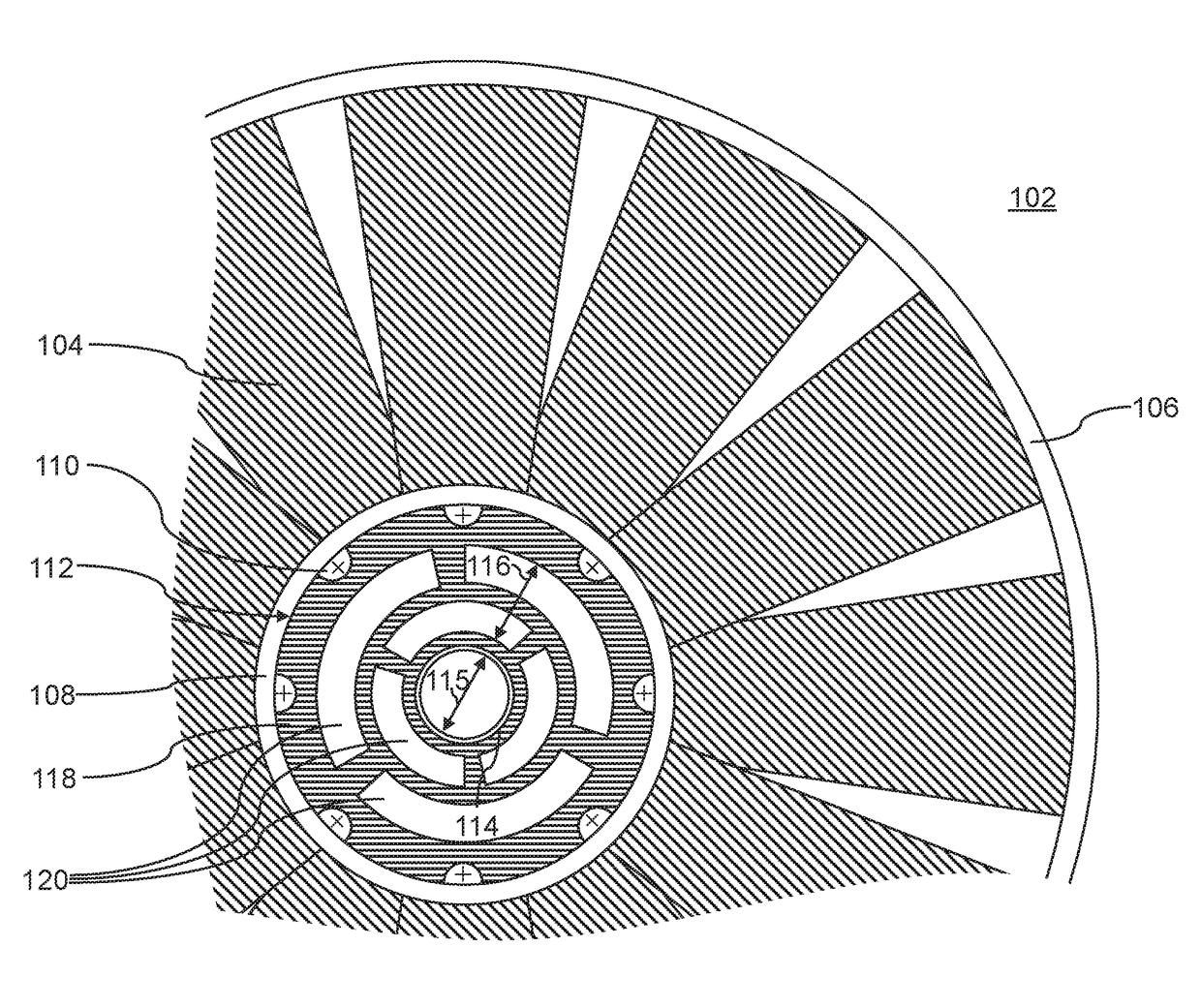

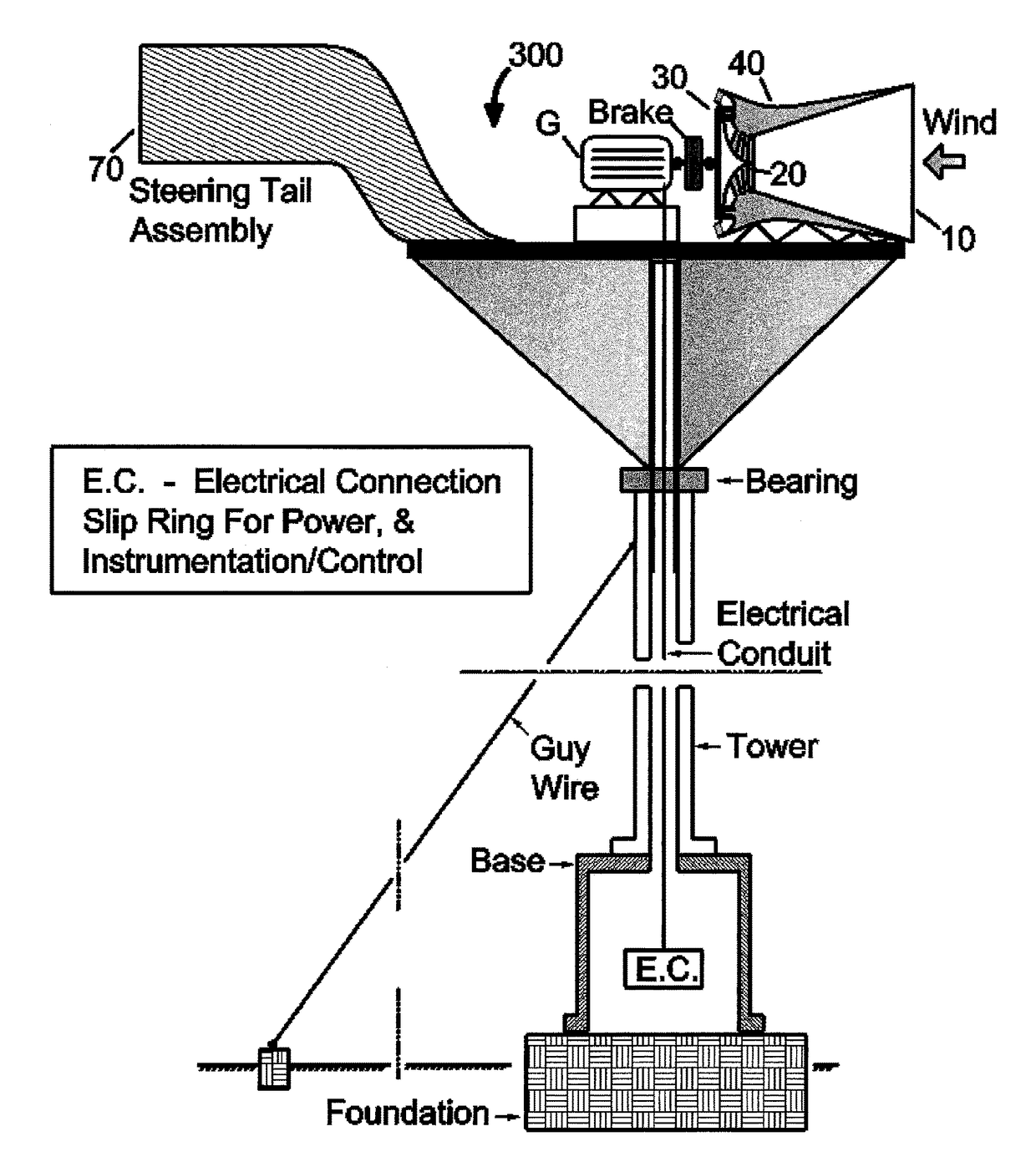

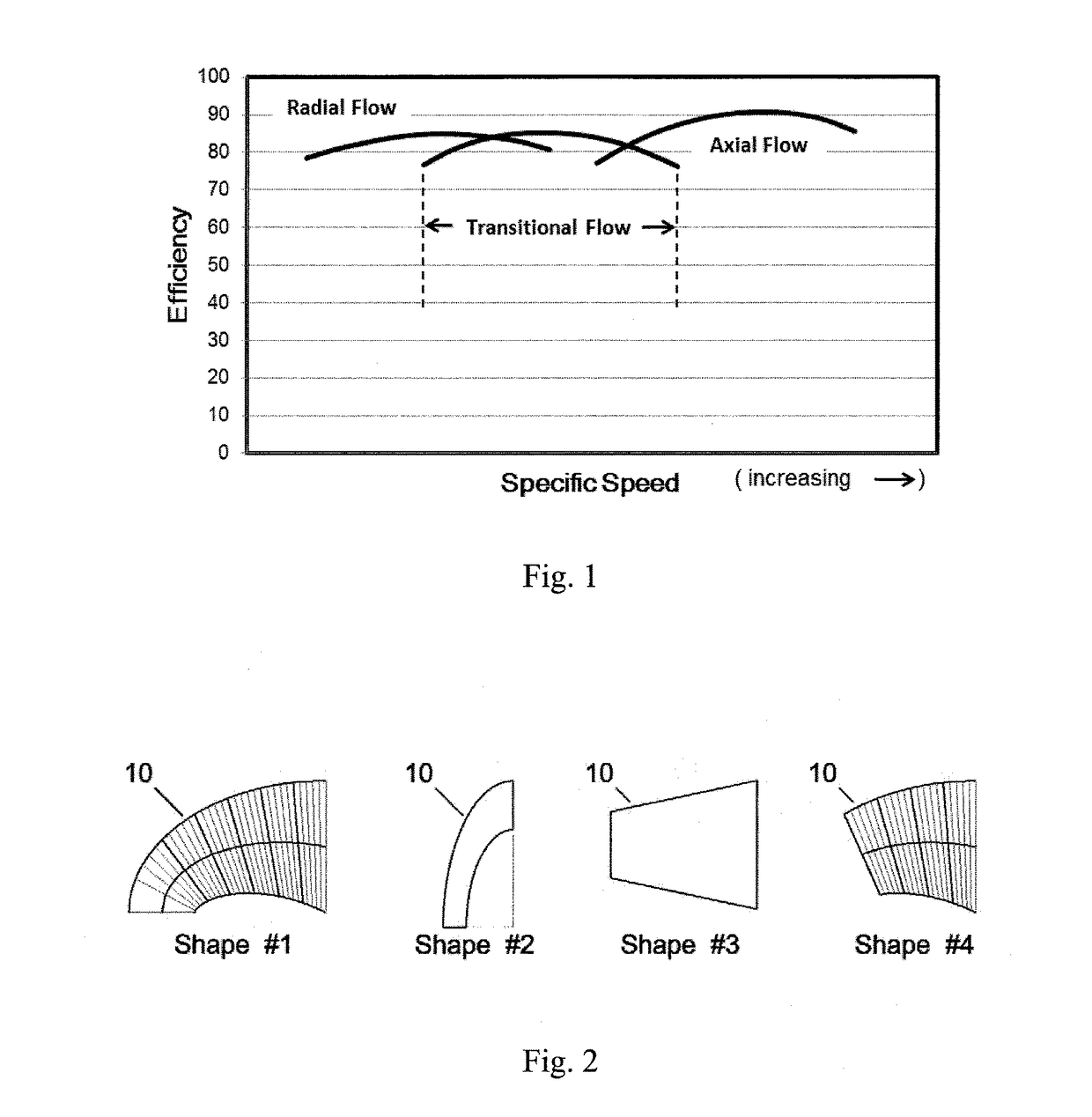

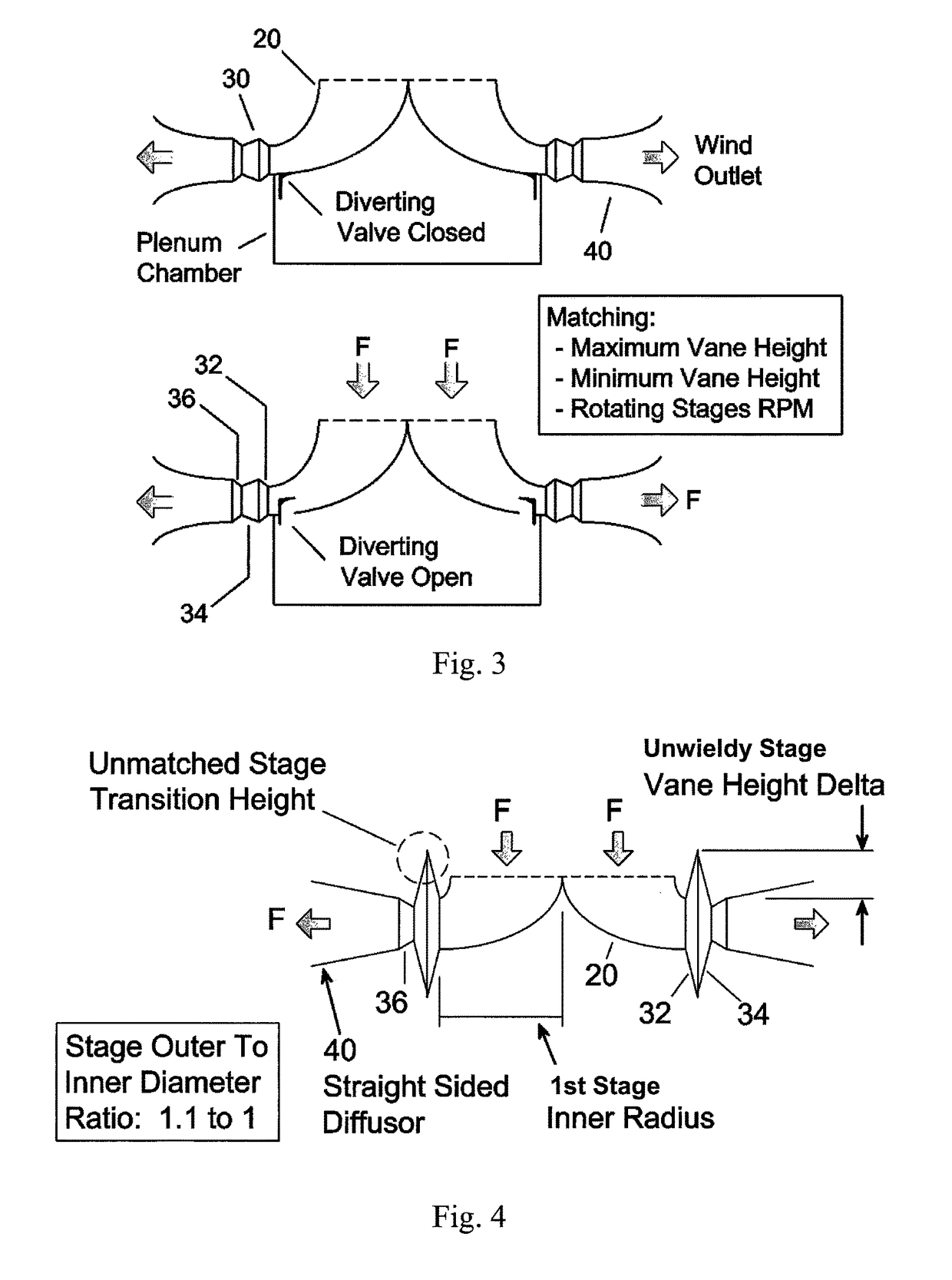

Multi-stage radial flow turbine

ActiveUS9856853B2Less efficientImprove efficiencyWorking fluid for enginesWind motor supports/mountsTurbineRadial turbine

A multi-stage radial turbine for usage in energy capture from fluid streams with low to moderate relative speed.

Owner:FRENCH JOHN

Discharge tray apparatus

ActiveUS20080186522A1Simple configurationRotational speedVisual presentation using printersElectrographic process apparatusWaste managementFixed interval

A discharge tray apparatus according to one embodiment of the present invention is a discharge tray apparatus wherein a plurality of sheets of recording paper that have been successively transported at a fixed speed and a fixed interval, discharged from a discharge opening, and have landed on a discharge tray, are received and placed onto the discharge tray, the discharge tray apparatus being provided with a discharge tray moving means that performs a tray shift operation that moves the discharge tray in a horizontal direction approximately perpendicular to the discharge direction, such that after a preceding paper successively transported earlier has been placed on the discharge tray, a succeeding paper succeedingly transported after the preceding paper is placed at a position different from the placement position of the preceding paper on the discharge tray. This discharge tray moving means performs the tray shift operation with a decelerating movement that reduces the movement speed of the discharge tray just before movement of the discharge tray stops.

Owner:SHARP KK

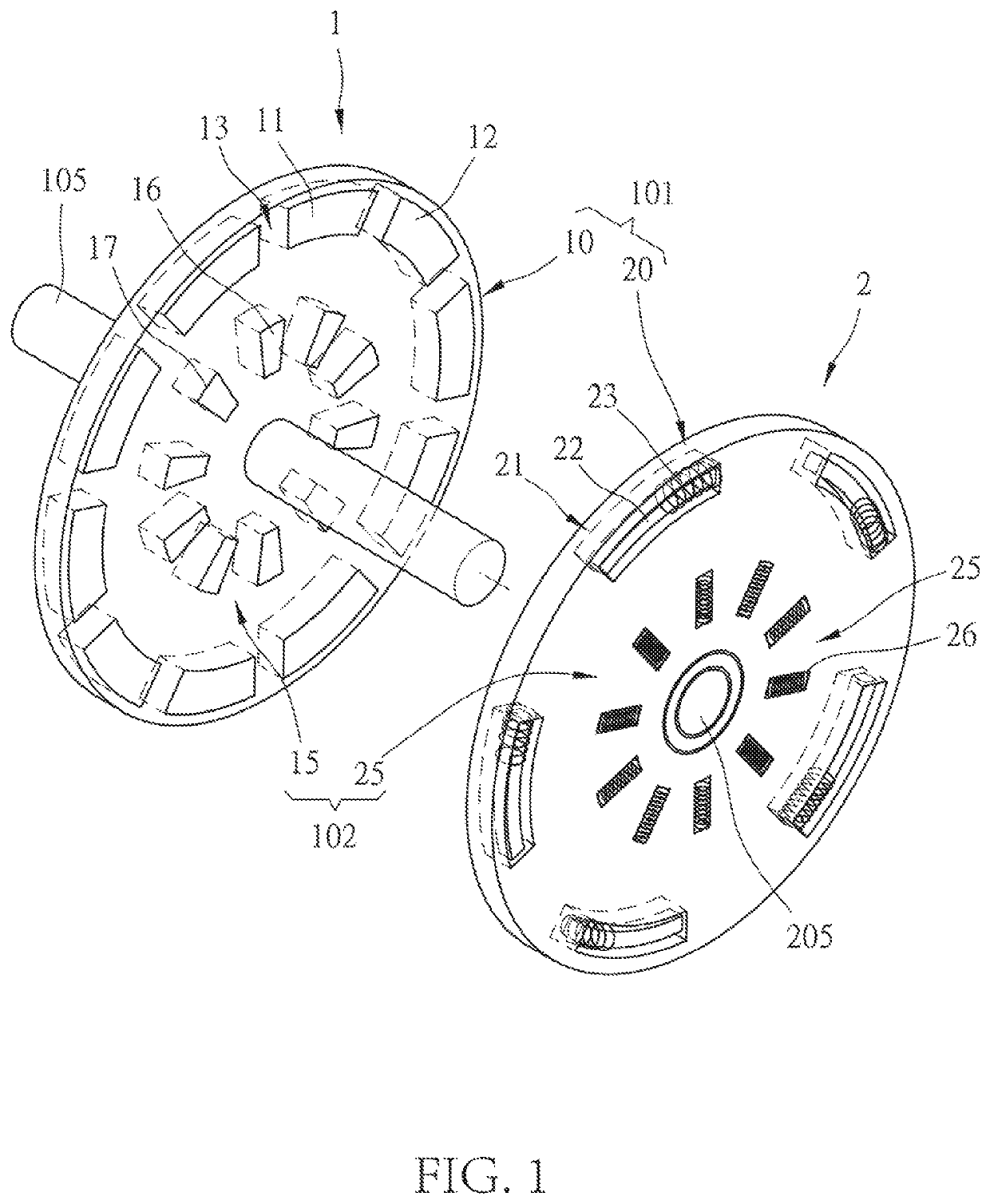

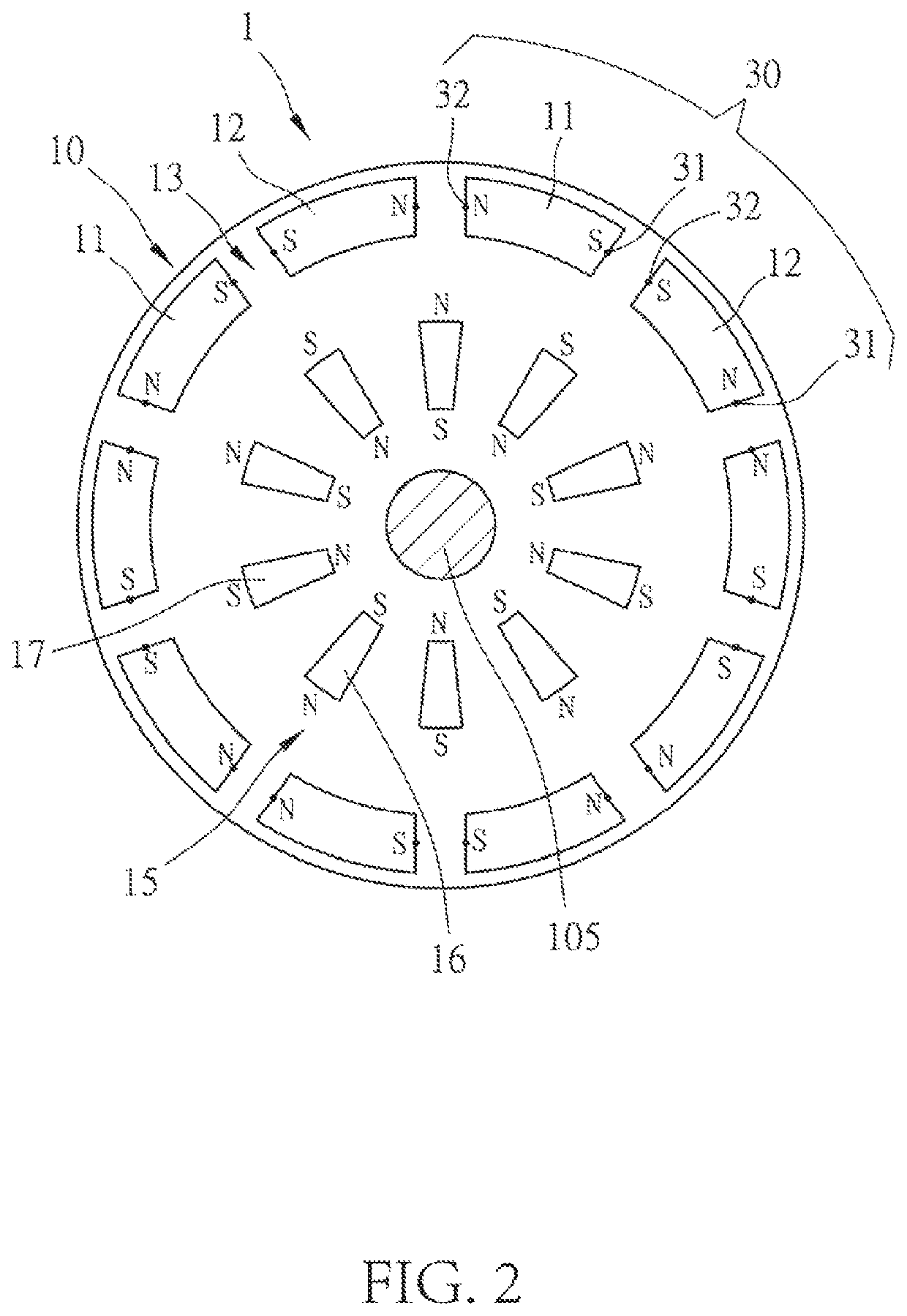

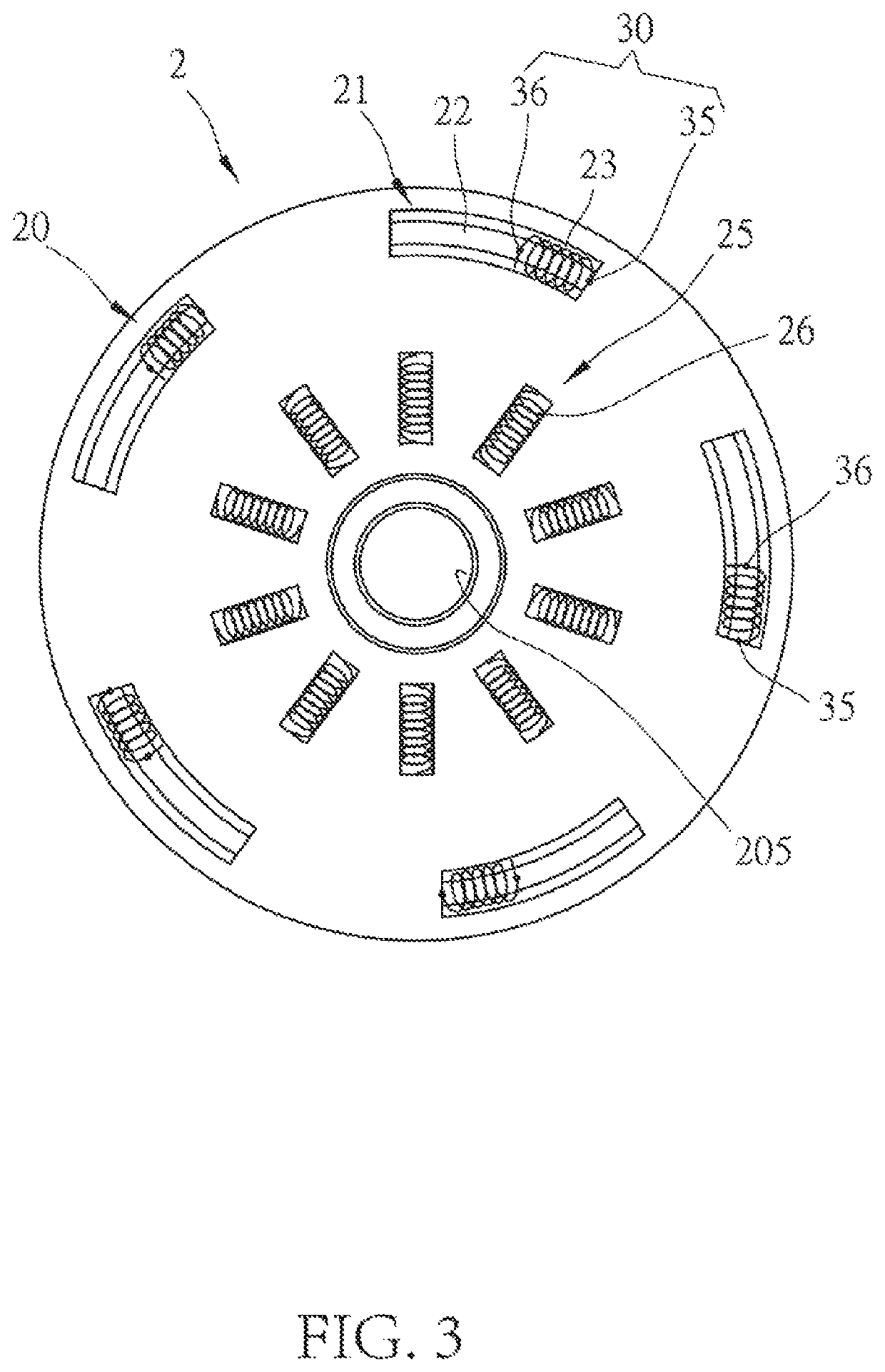

Coaxial electromagnetic apparatus

ActiveUS10804789B2Reduce lossesEliminating magnetic dragDynamo-electric machinesMagnetic currentElectric machine

A coaxial electromagnetic apparatus formed of at least one magnetic disk and at least one coil disk synchronously and relatively movable and staggered at intervals. The magnetic disk and the coil disk are respectively provided with at least one power-driven module and at least one power generation module. The power-driven modules are provided at the outermost diameters of the magnetic disk and the coil disk. The power generation modules are provided at the innermost diameters of the magnetic disk and the coil disk. A rotation speed of the magnetic disk is increased due to torque amplification and good magnetic current management of the power-driven modules, thereby achieving low power consumption and large thrust of the power-driven modules. The power generation modules generate high cutting frequency to increase power generated and meet the requirement for supplying power to the power-driven modules, thereby achieving autonomous power generation and a self-propelled motor.

Owner:YUZEN SUSTAINABLE ENERGY PTE LTD +1

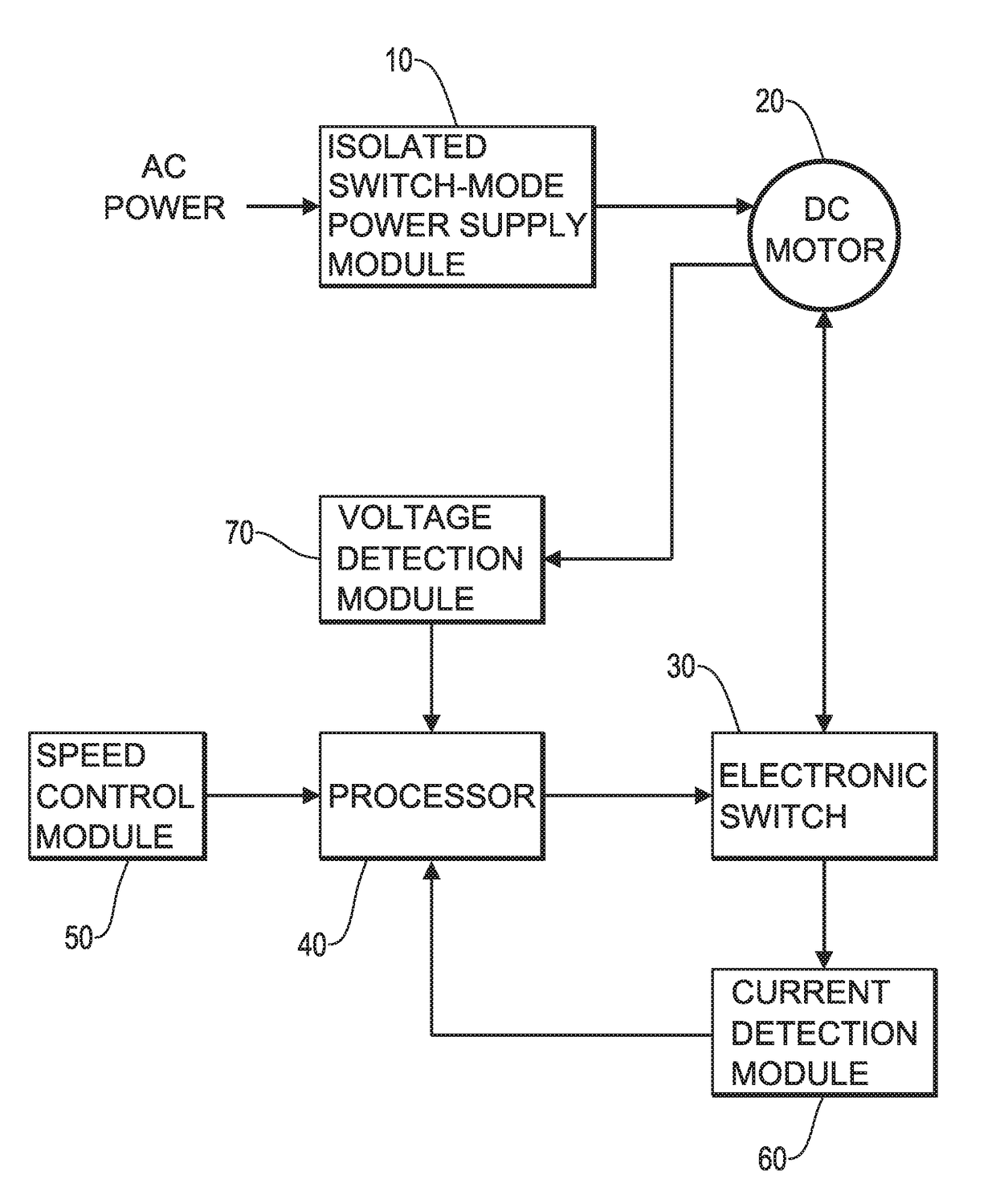

Closed-loop control device of a mechanical sewing machine and method for controlling the same

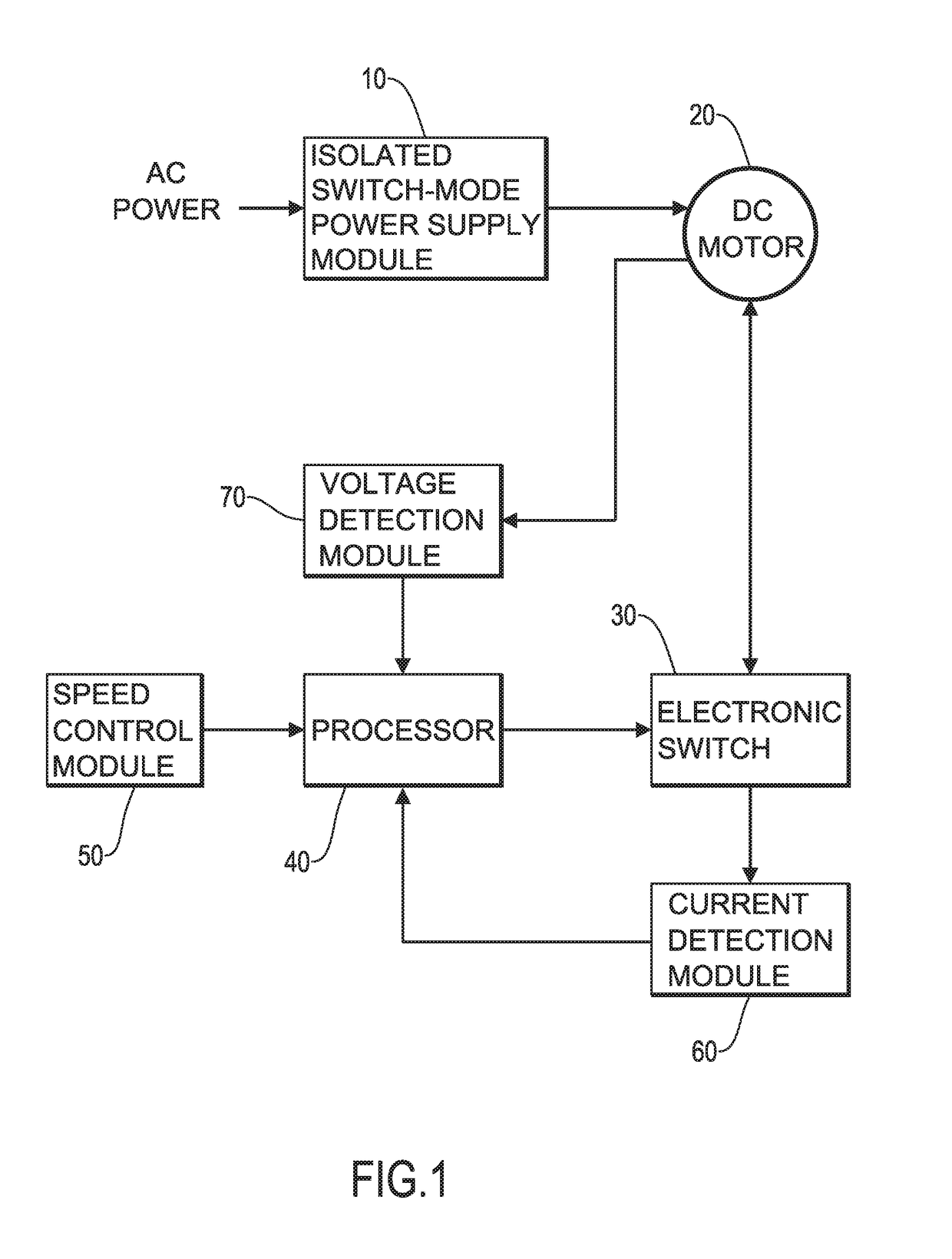

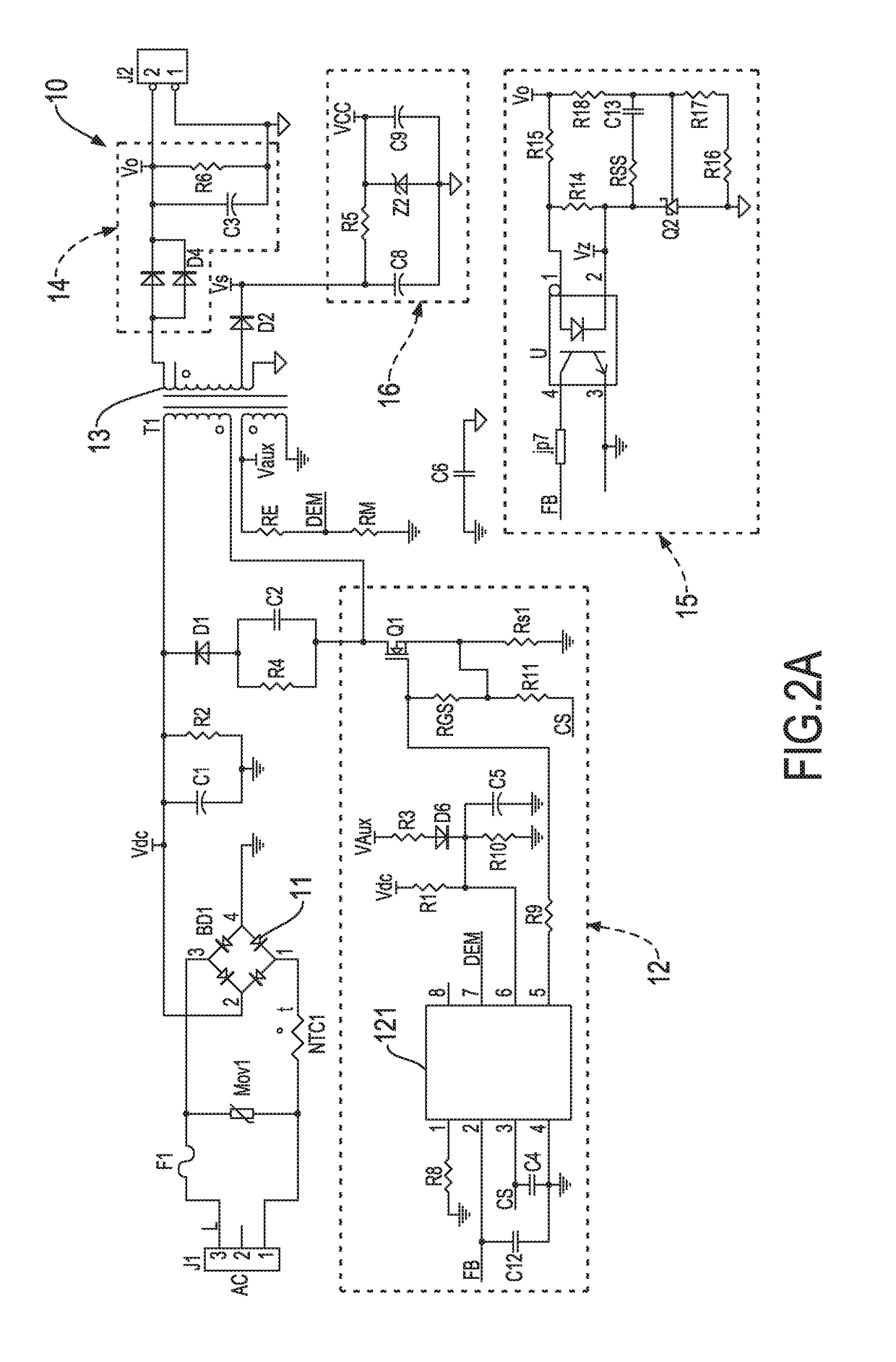

ActiveUS20170275799A1Rise in operating voltageHigh voltageElectric motor controlSewing-machine control devicesControl electronicsAC power

A closed-loop control device of a mechanical sewing machine includes an isolated switch-mode power supply module, a DC motor, a speed control module, a processor, an electronic switch, a current detection module and a voltage detection module. The isolated switch-mode power supply module rectifies an AC power to a DC power and supplies the DC power to the DC motor. The speed control module sends a speed signal to the processor. The processor adjusts an output voltage to the DC motor according to the speed signal. The current detection module and the voltage detection module further detect an operating current signal and an operating voltage signal of the DC motor for the processor to control a turn-on time of the electronic switch to adjust an average operating voltage of the DC motor according to the operating current signal, the operating voltage signal and the speed signal.

Owner:CHEN HSUAN TAI