Patents

Literature

83results about How to "More area" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

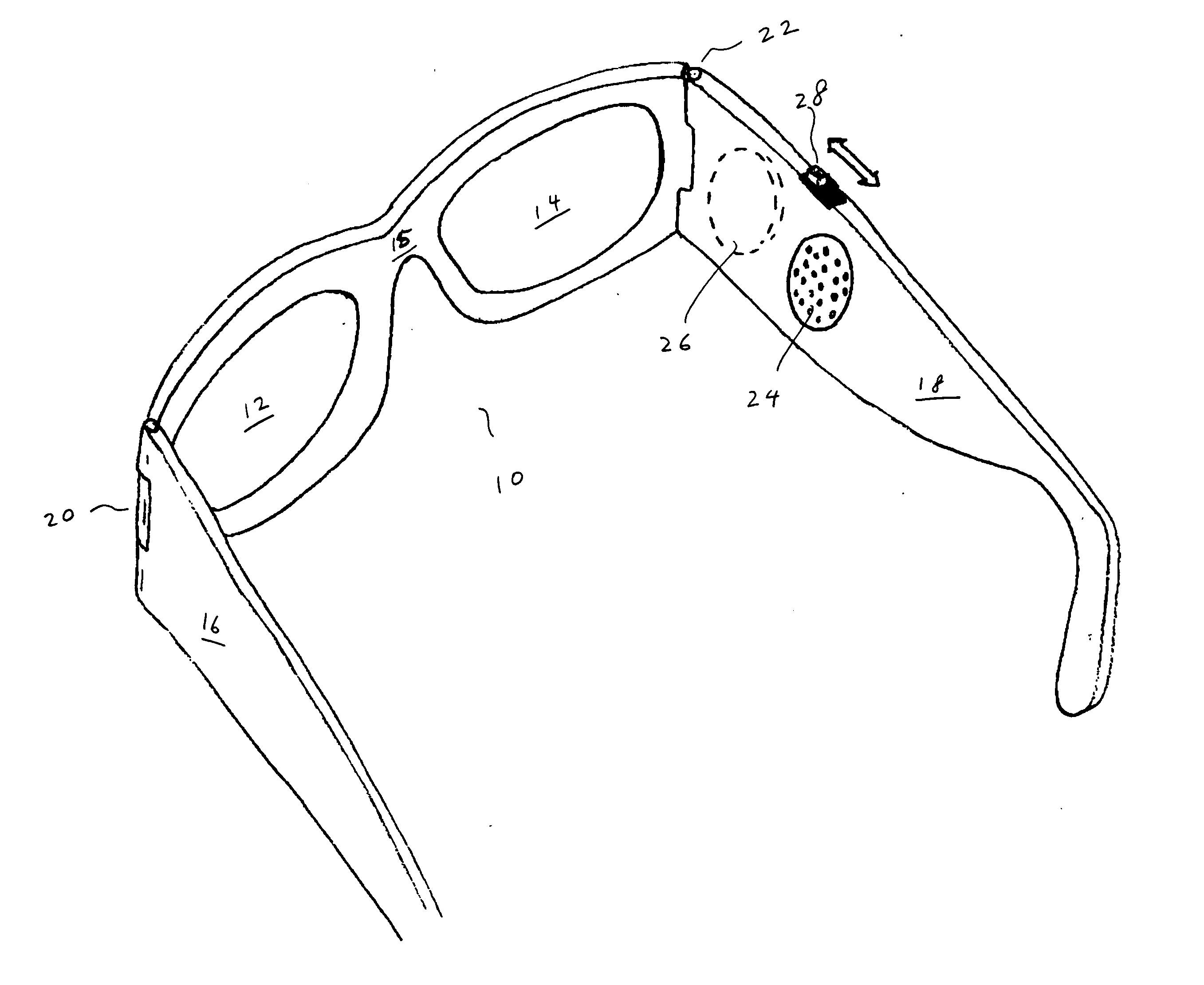

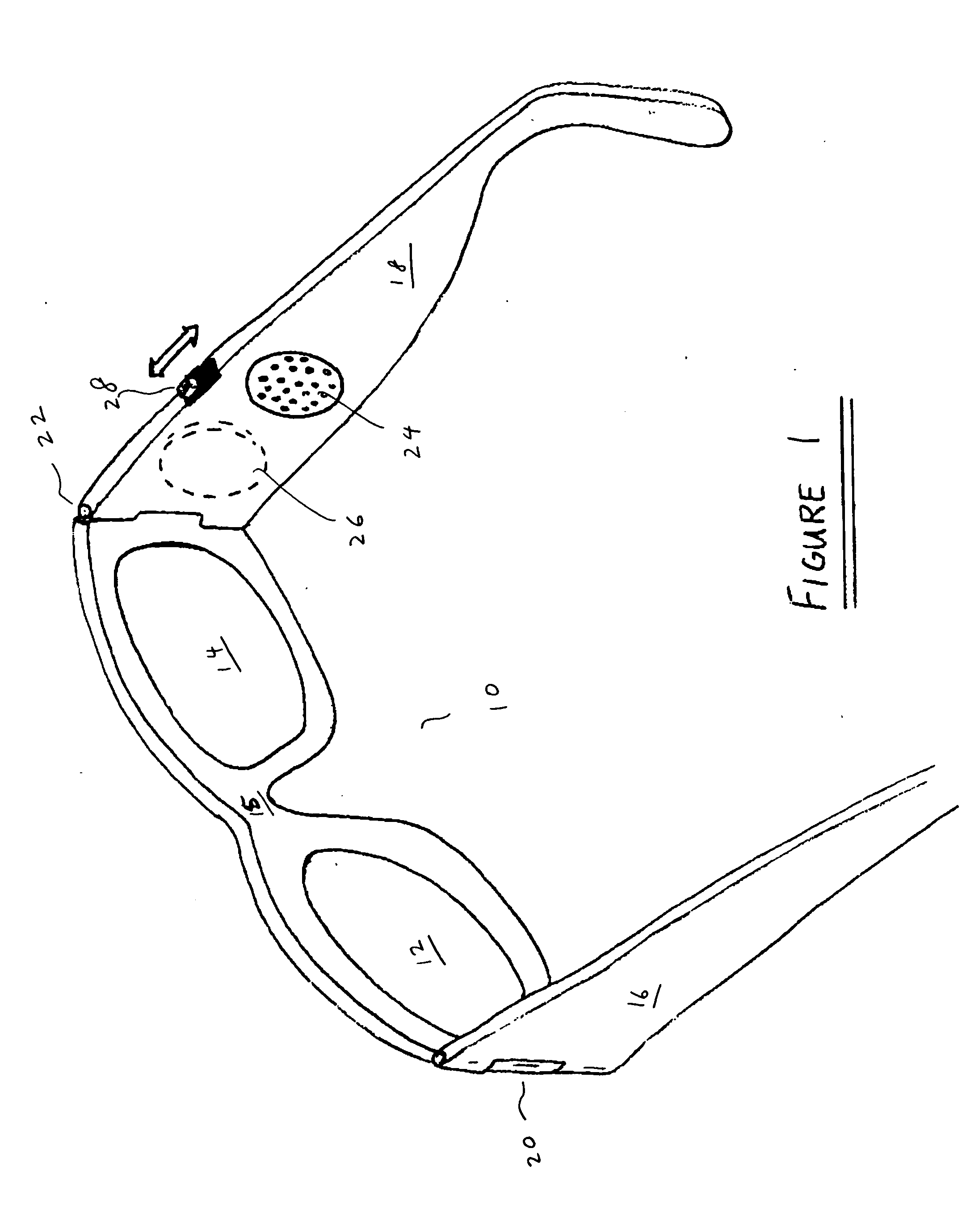

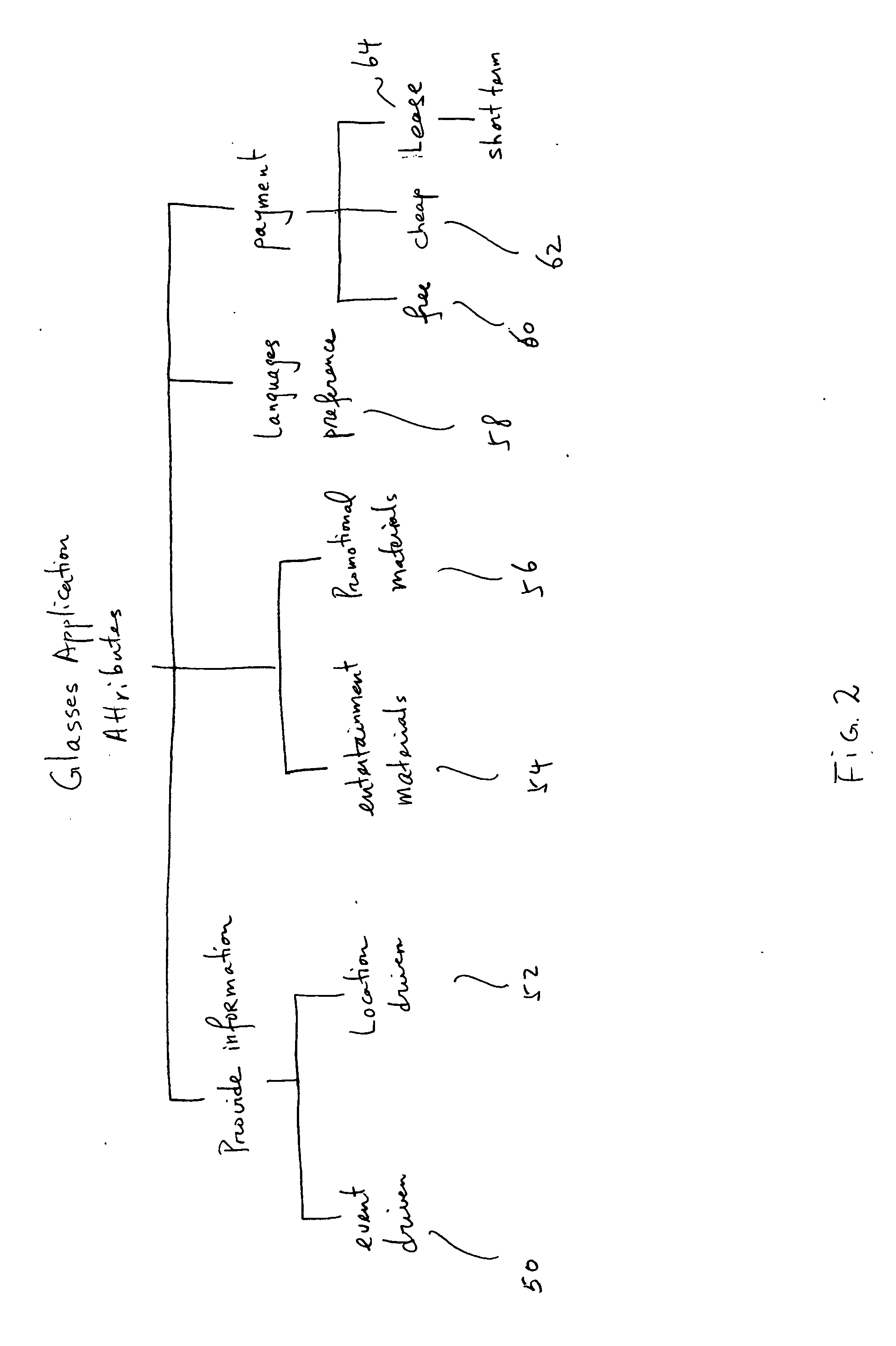

Event eyeglasses

InactiveUS20050248719A1More areaSpectales/gogglesNon-optical adjunctsInformation transmissionEyewear

A pair of glasses with first and second lens holders for receiving lenses, a bridge element that couples the lens holders, and a pair of temples. The temples are pivotally secured to the lens holders. In one embodiment, the glasses further include a speaker being powered by a power source. The pair of glasses can deliver information through the speaker to the person wearing the glasses. The information being delivered can be wirelessly transmitted to the glasses from a remote device. The information can be pre-recorded and available at the glasses, or the information can be wirelessly received by the glasses as it is produced. The information can be relevant to an event, and available for a relatively short duration of time. In another embodiment, a pair of glasses further includes an information input mechanism that allows the person to input information into the glasses. Such input information can be wirelessly transmitted from the glasses to a remote device.

Owner:HOWELL THOMAS A +3

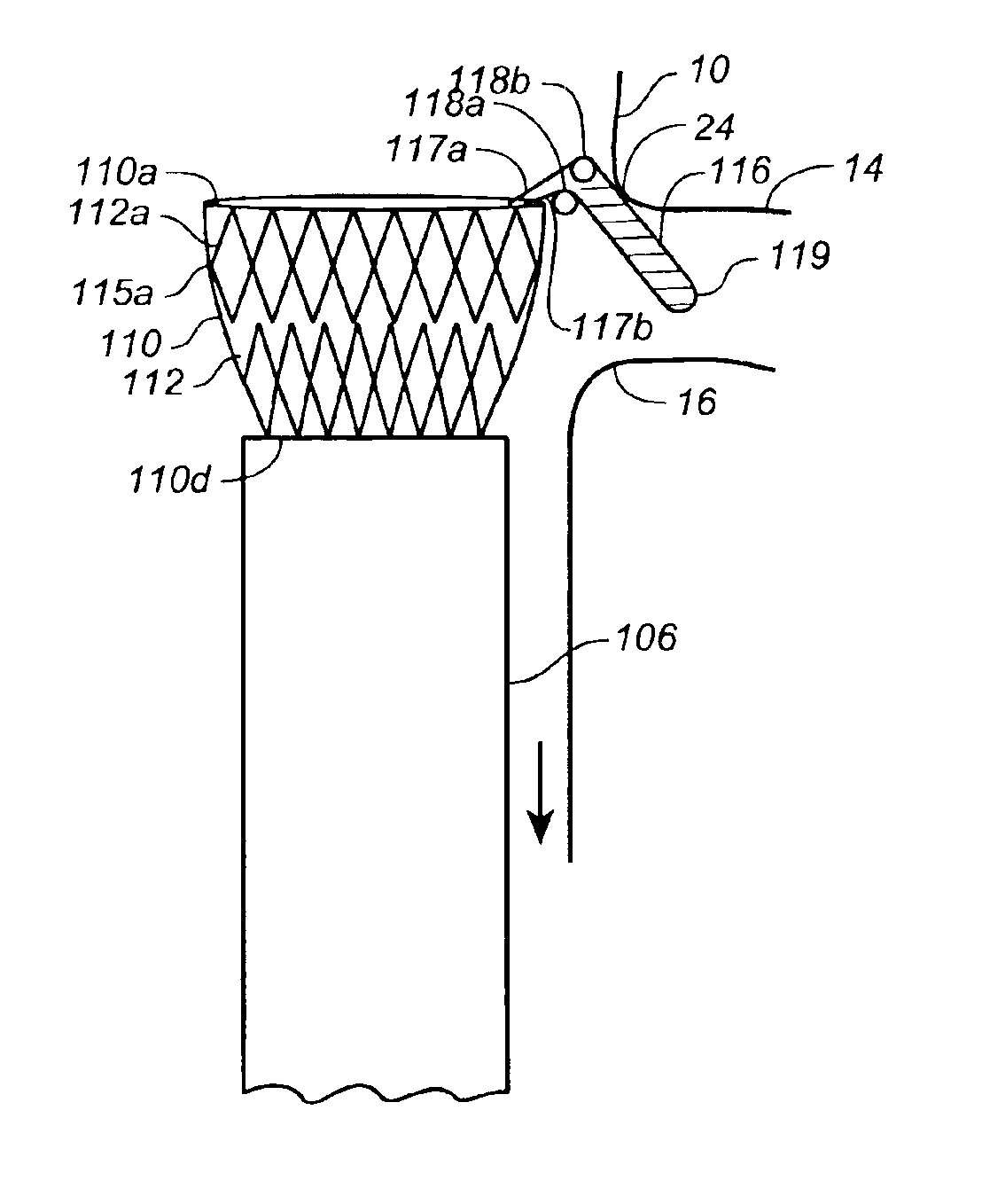

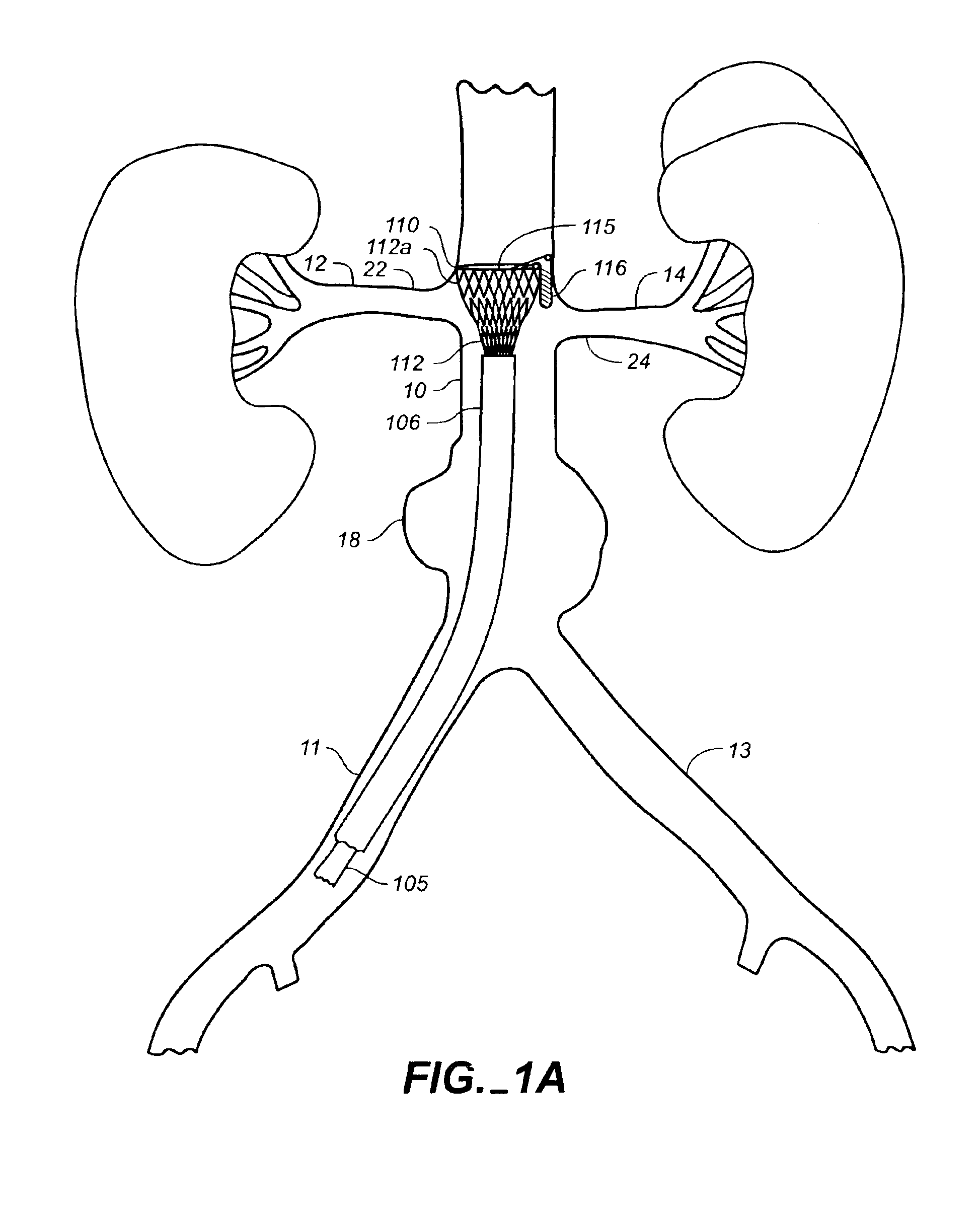

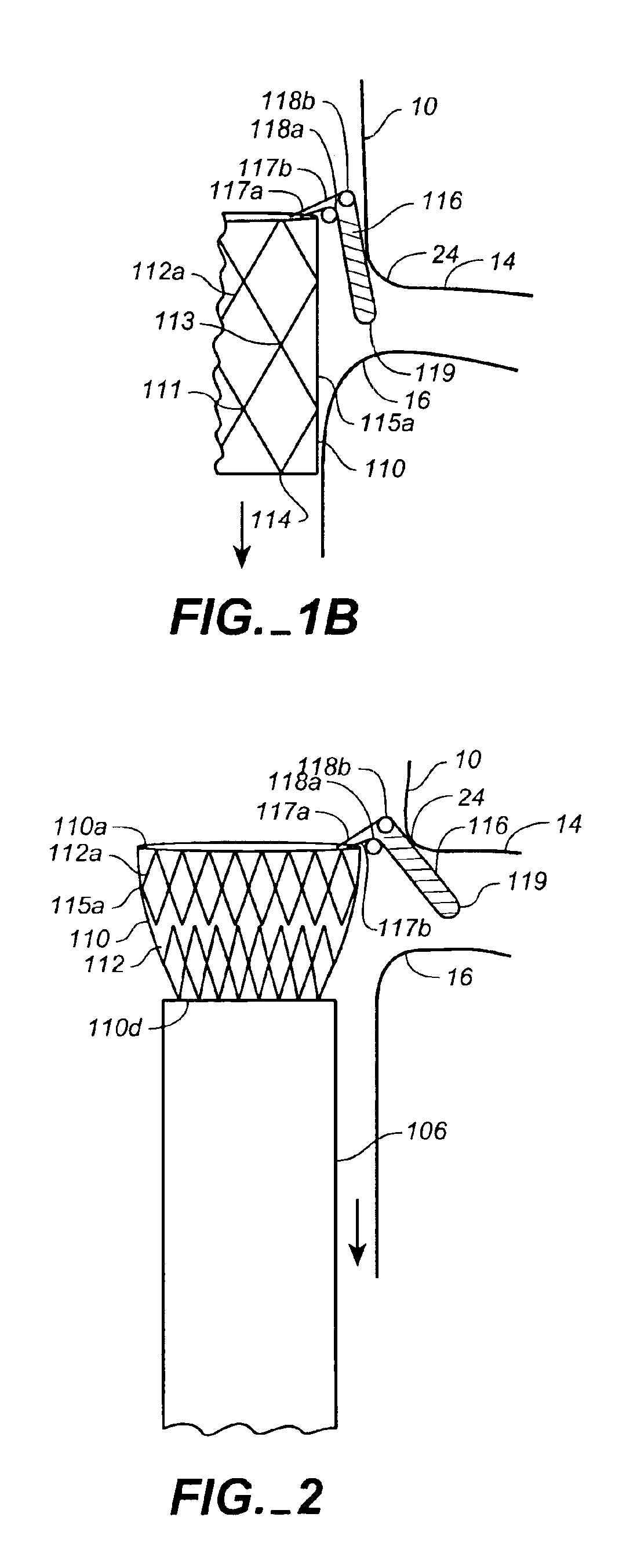

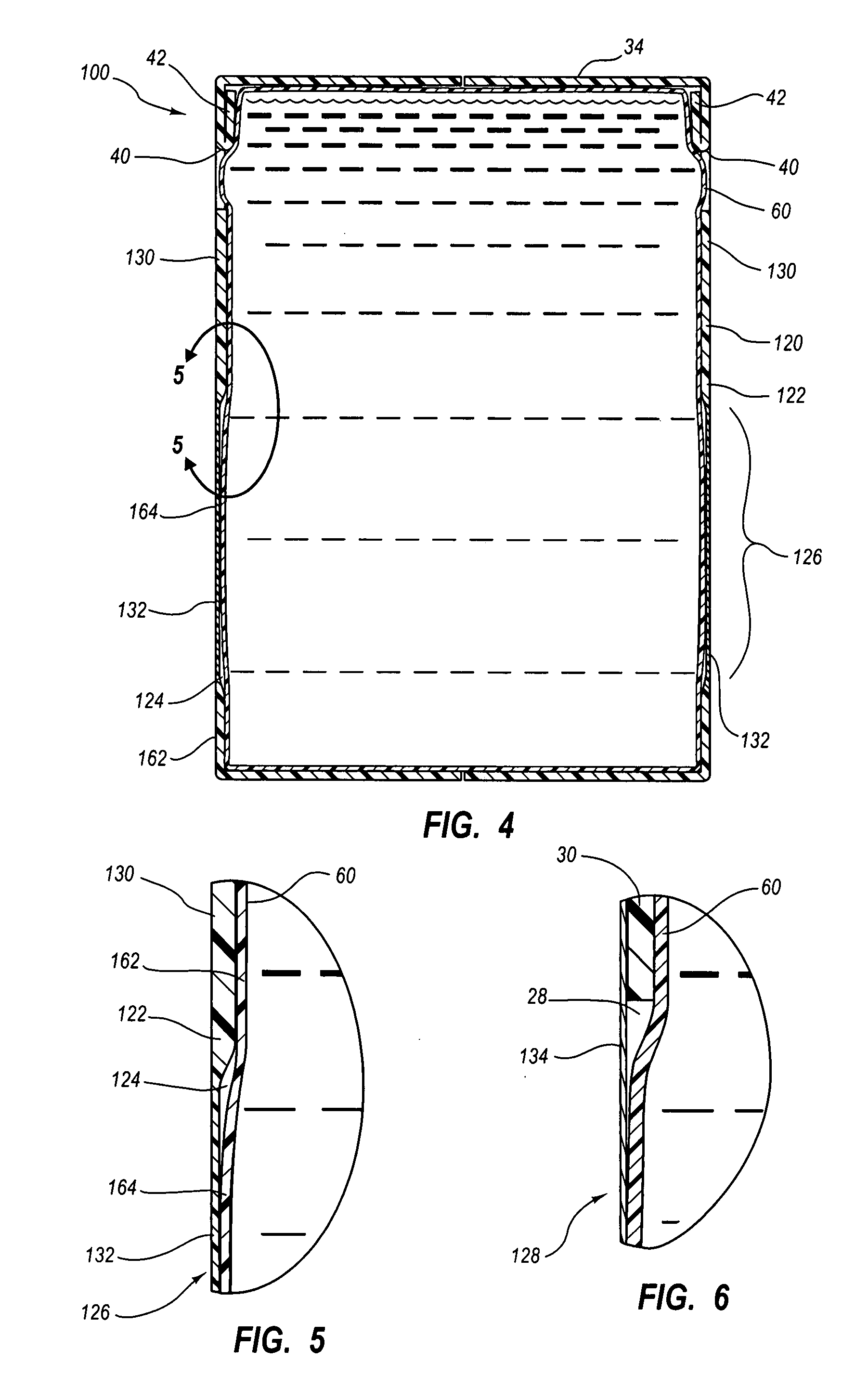

System for transrenal/intraostial fixation of endovascular prosthesis

InactiveUS6918926B2Promote migrationEasy to fixStentsBlood vesselsEndovascular prosthesisBlood vessel

An endoluminal prosthesis is provided with an improved fixation system for coupling the endoluminal prosthesis to an inner wall of a lumen and to reduce distal migration. According to an embodiment of the present invention, a laterally protruding member atraumatically engages the ostium of a side or branch vessel. The protruding member may be fixed to a portion of a prosthesis. In one embodiment the protruding member is provided on a modular fixation device for initial fixation within the body lumen with the finger member within the side or branch vessel. A primary endoluminal prosthesis is then fixed to the modular fixation device to bypass a diseased portion of the anatomy.

Owner:MEDTRONIC VASCULAR INC

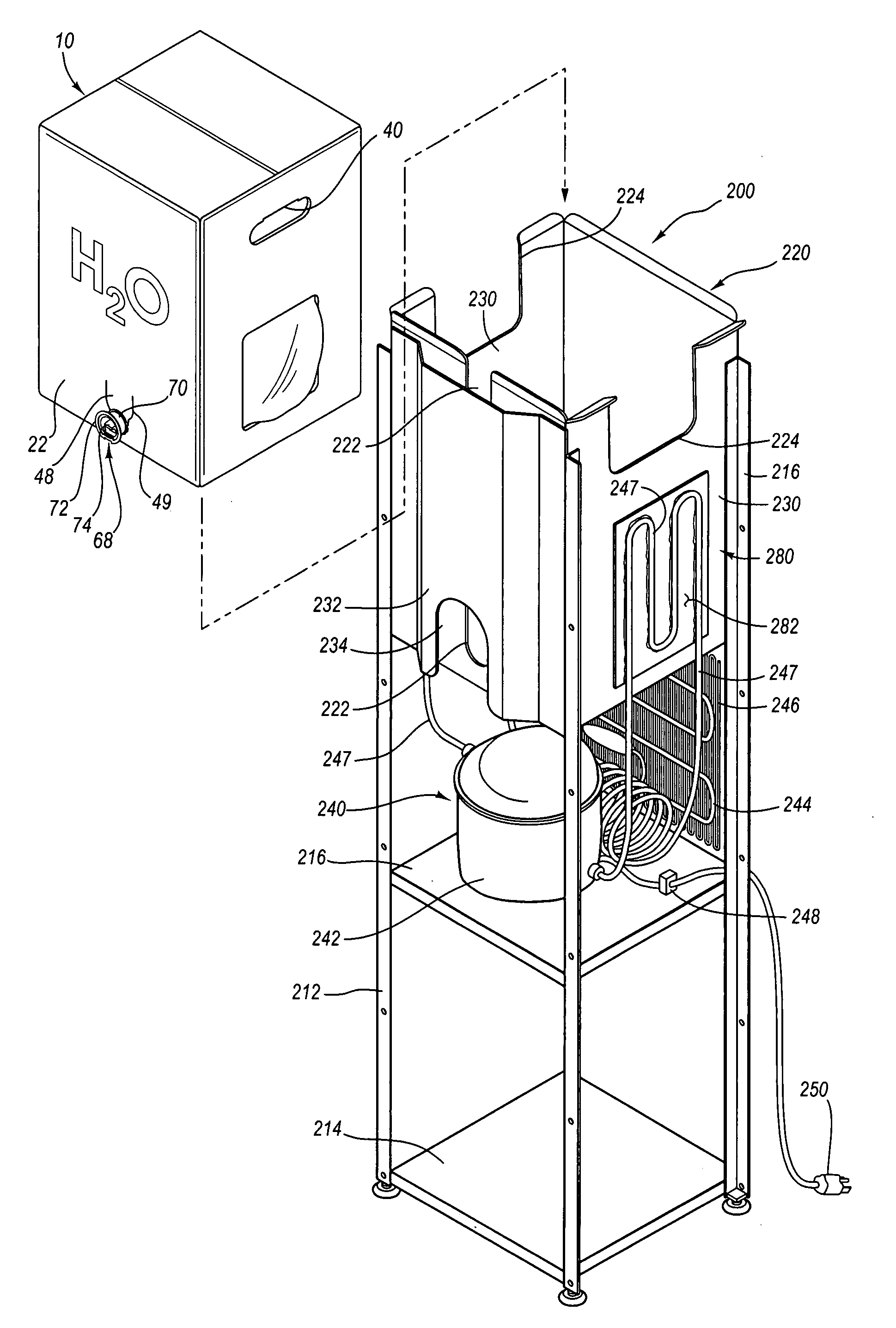

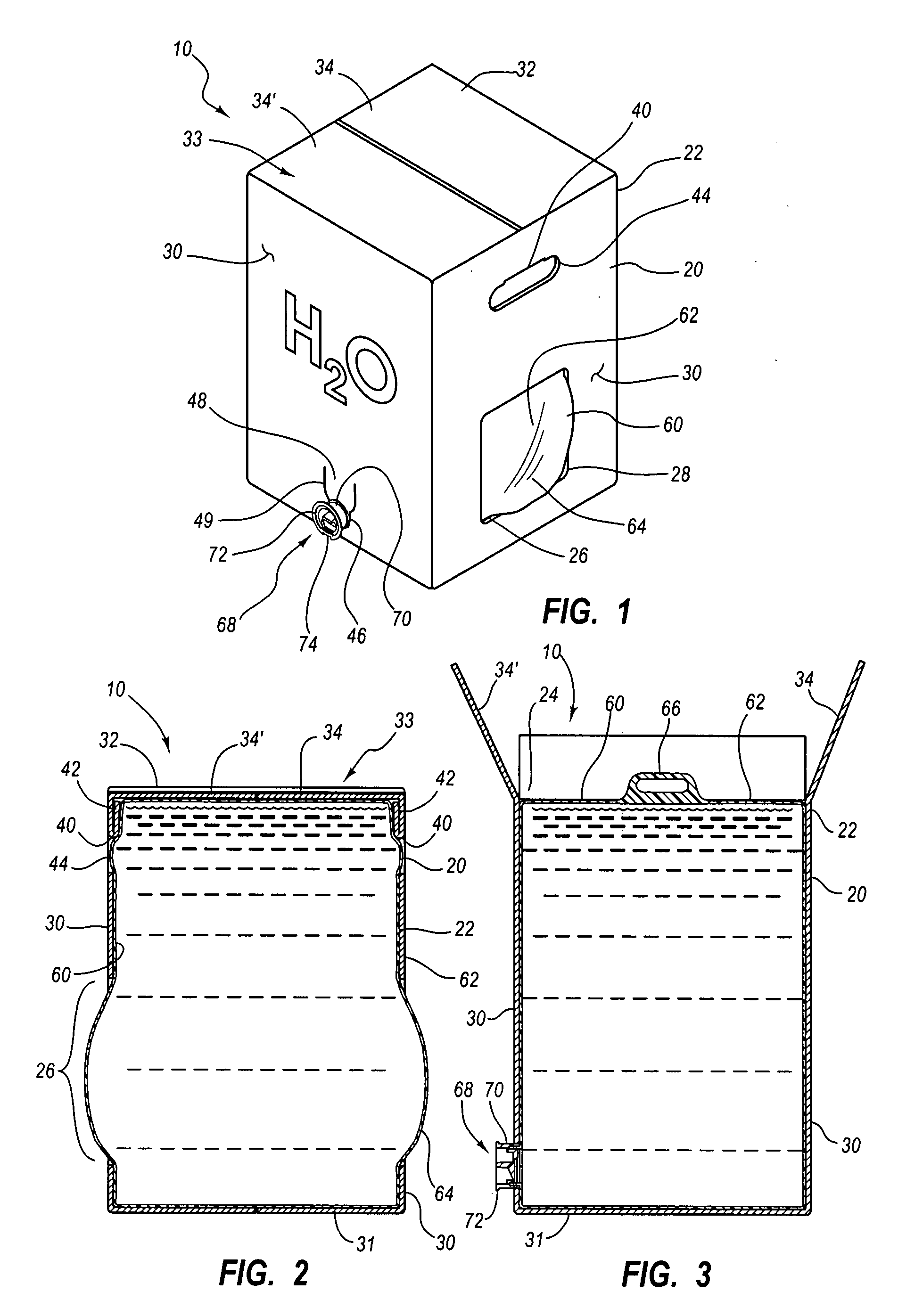

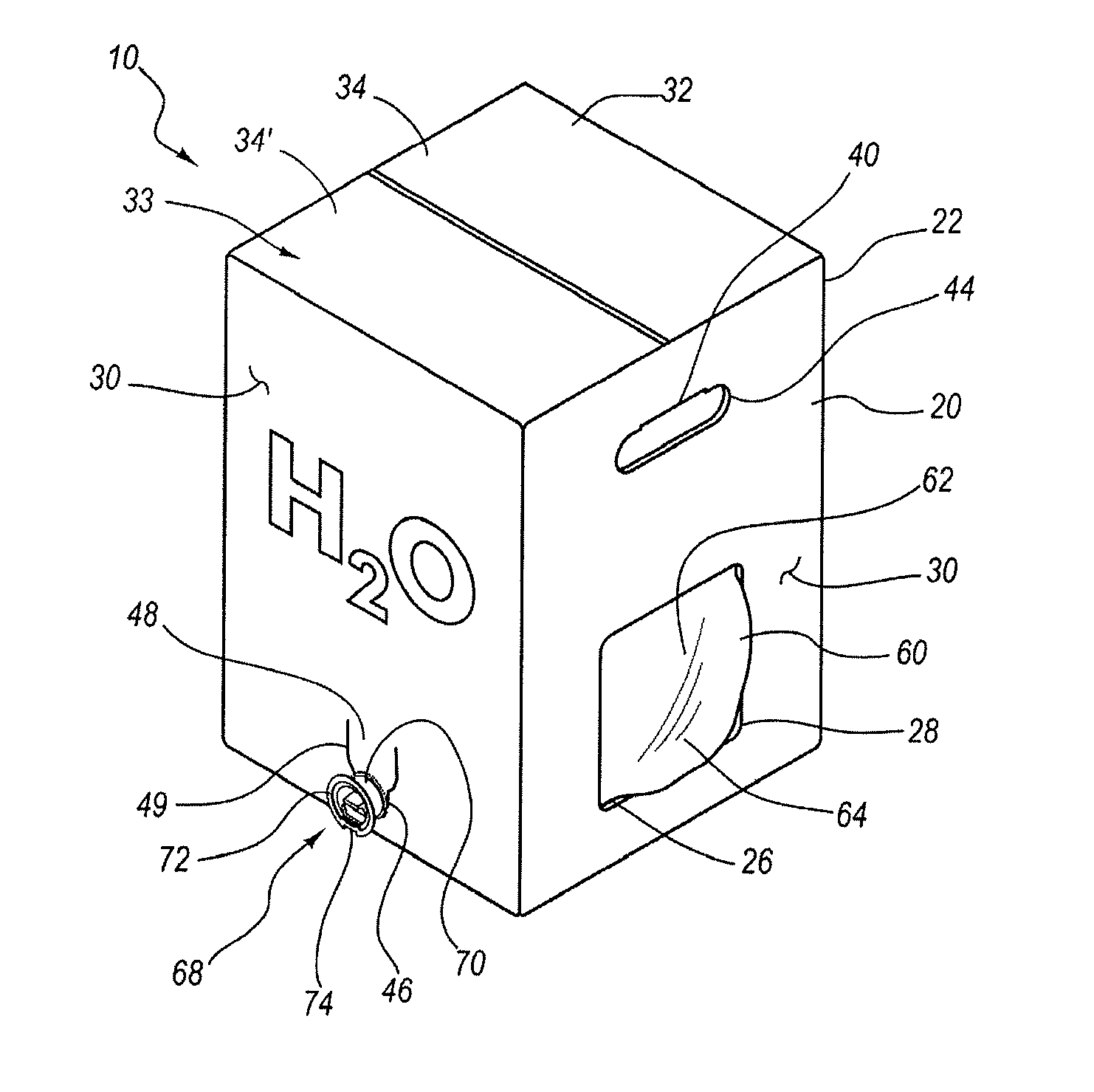

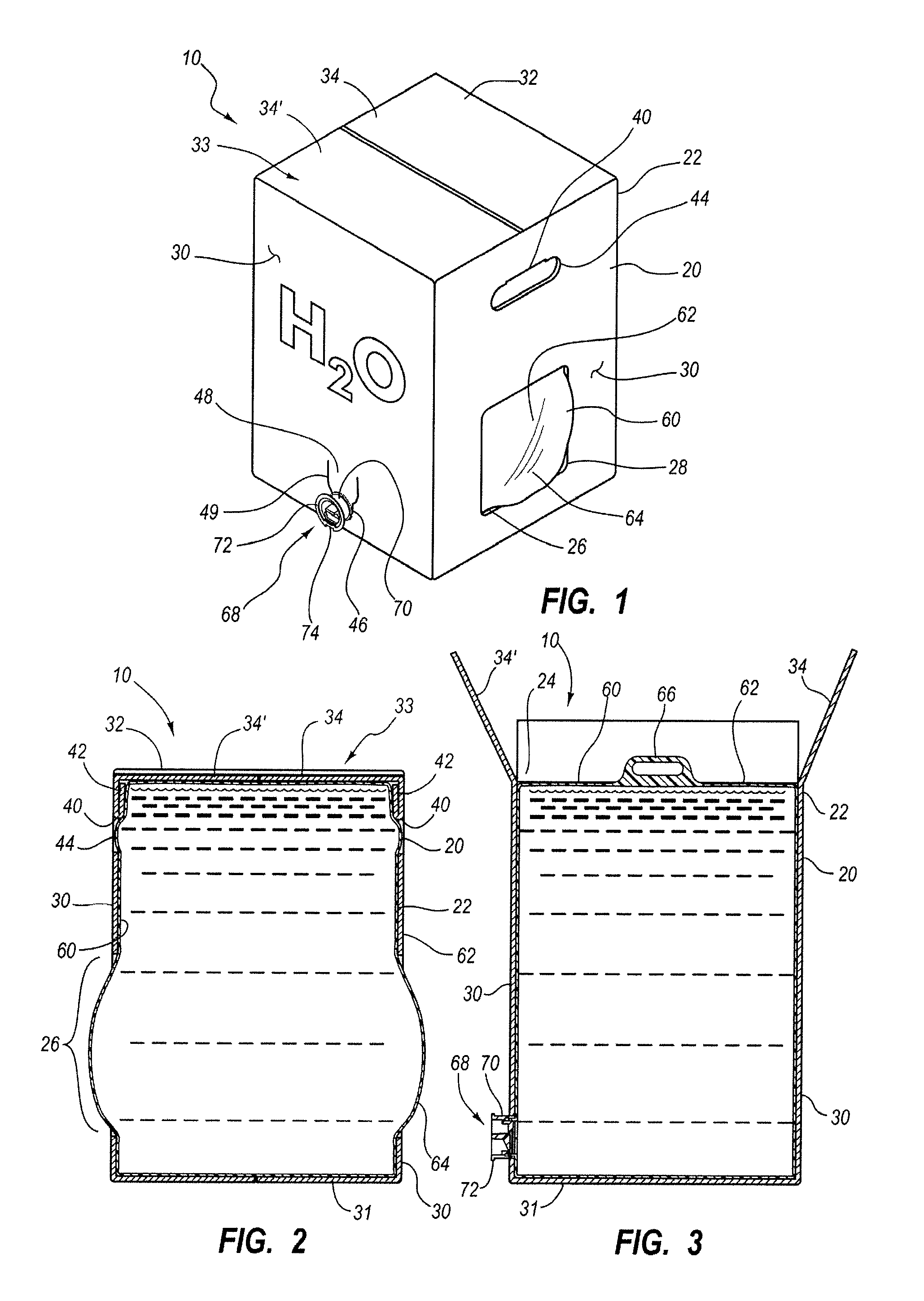

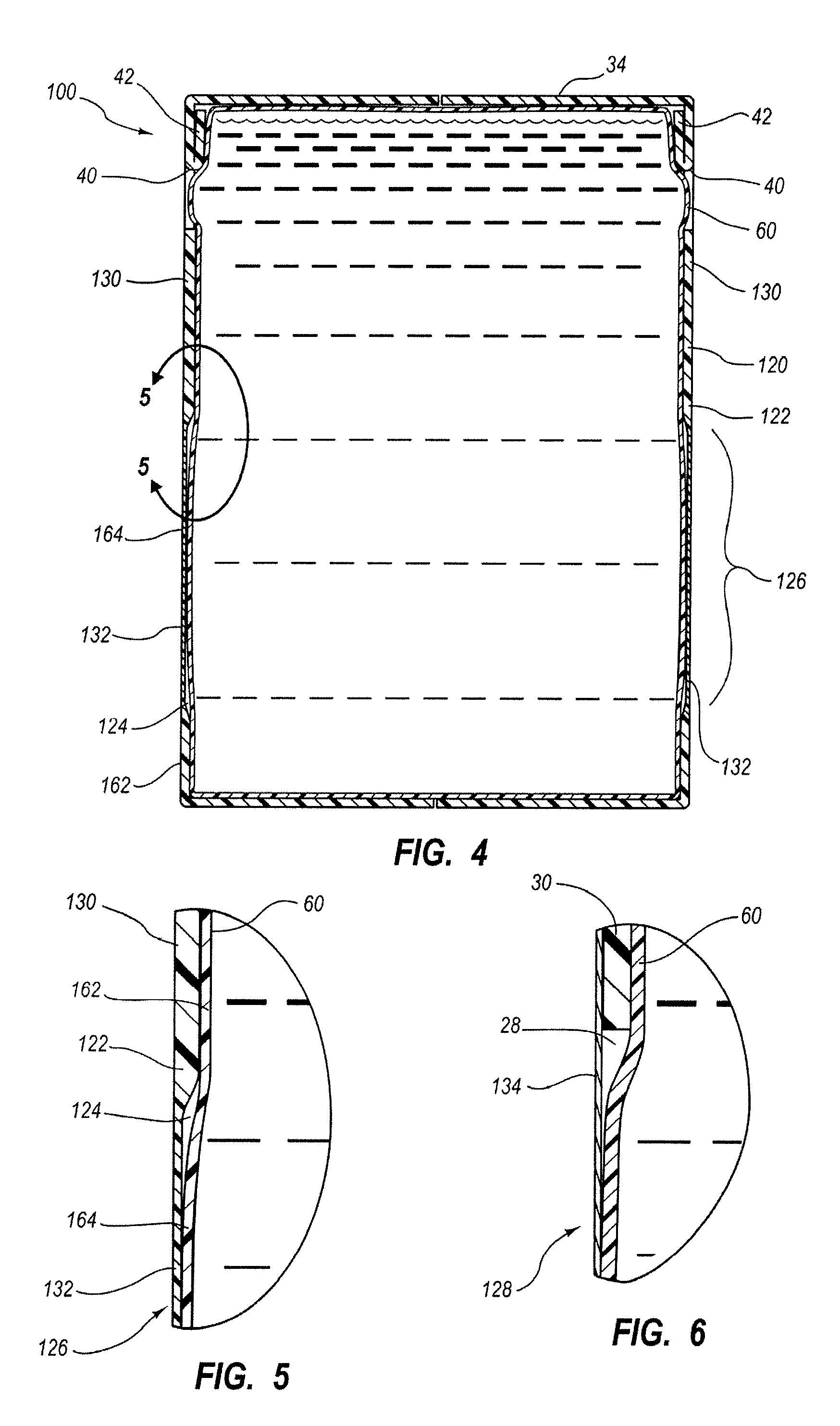

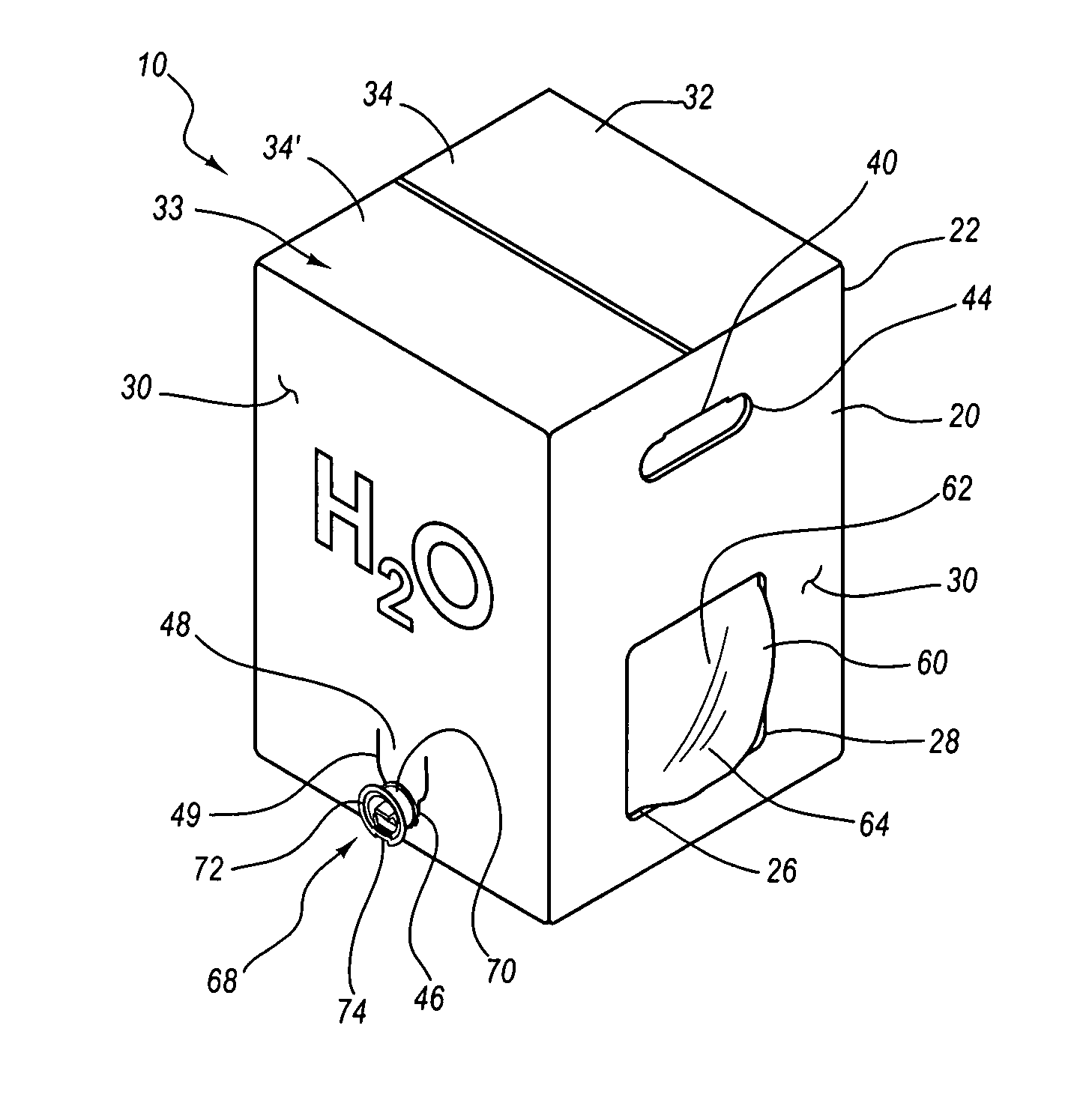

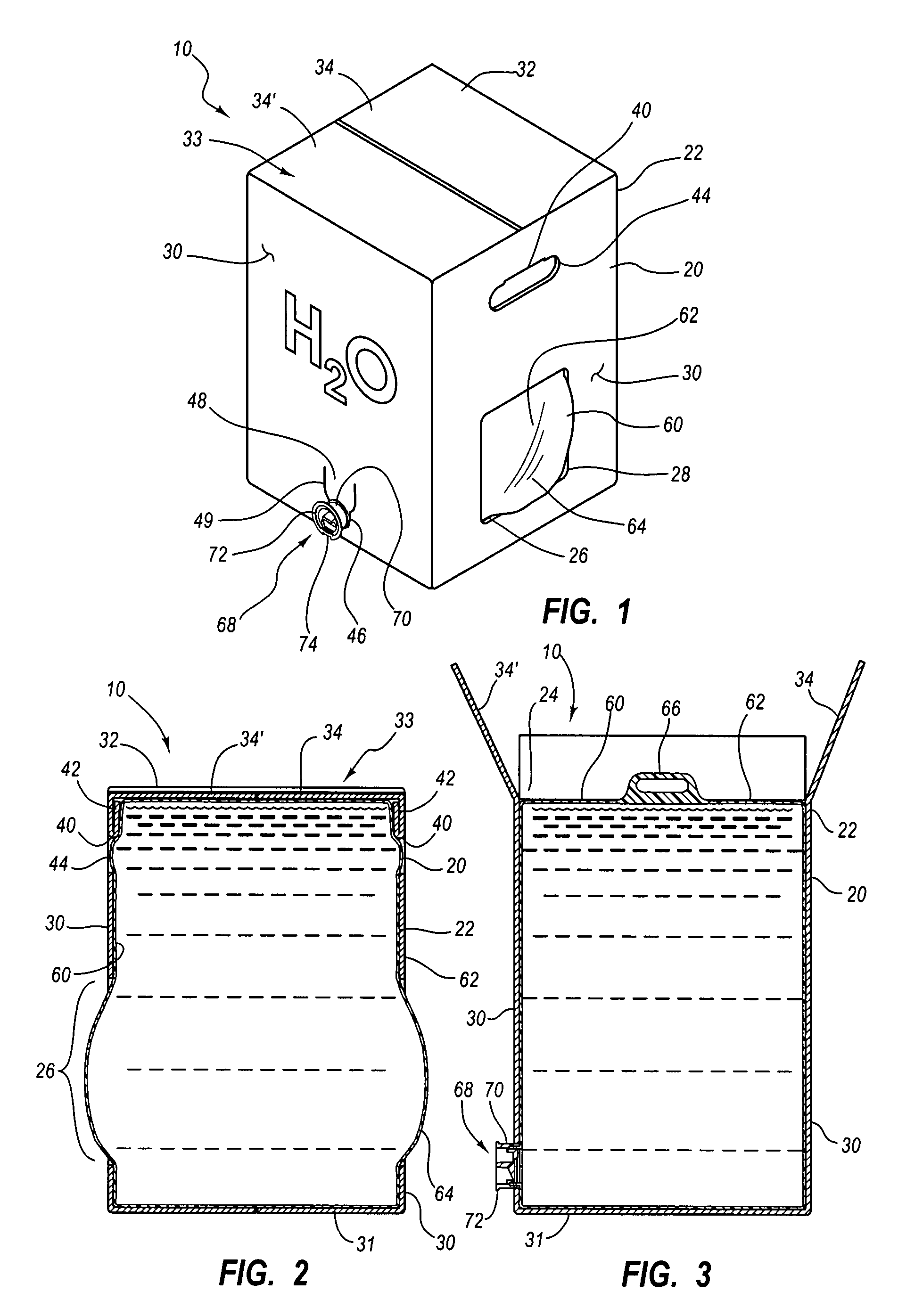

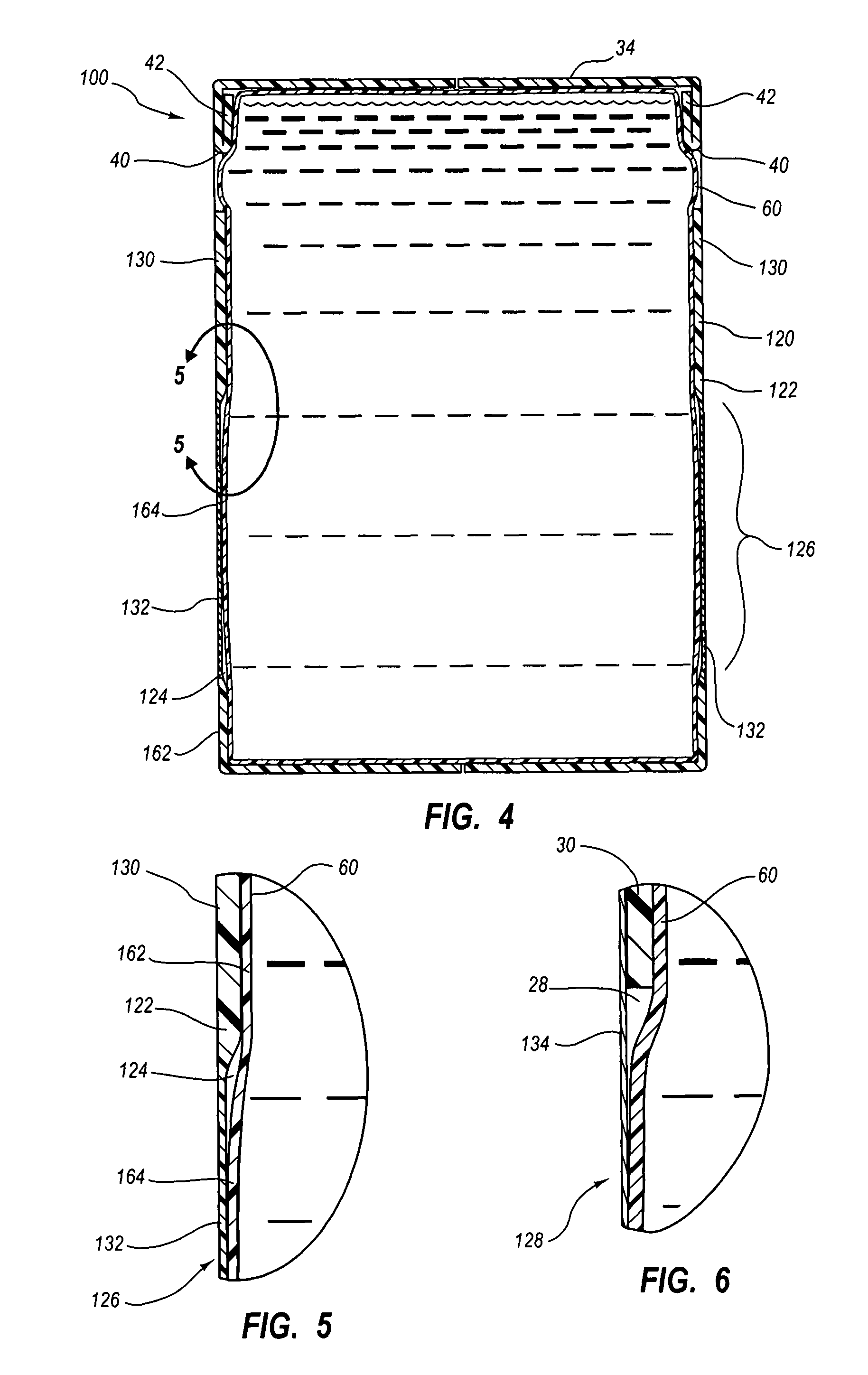

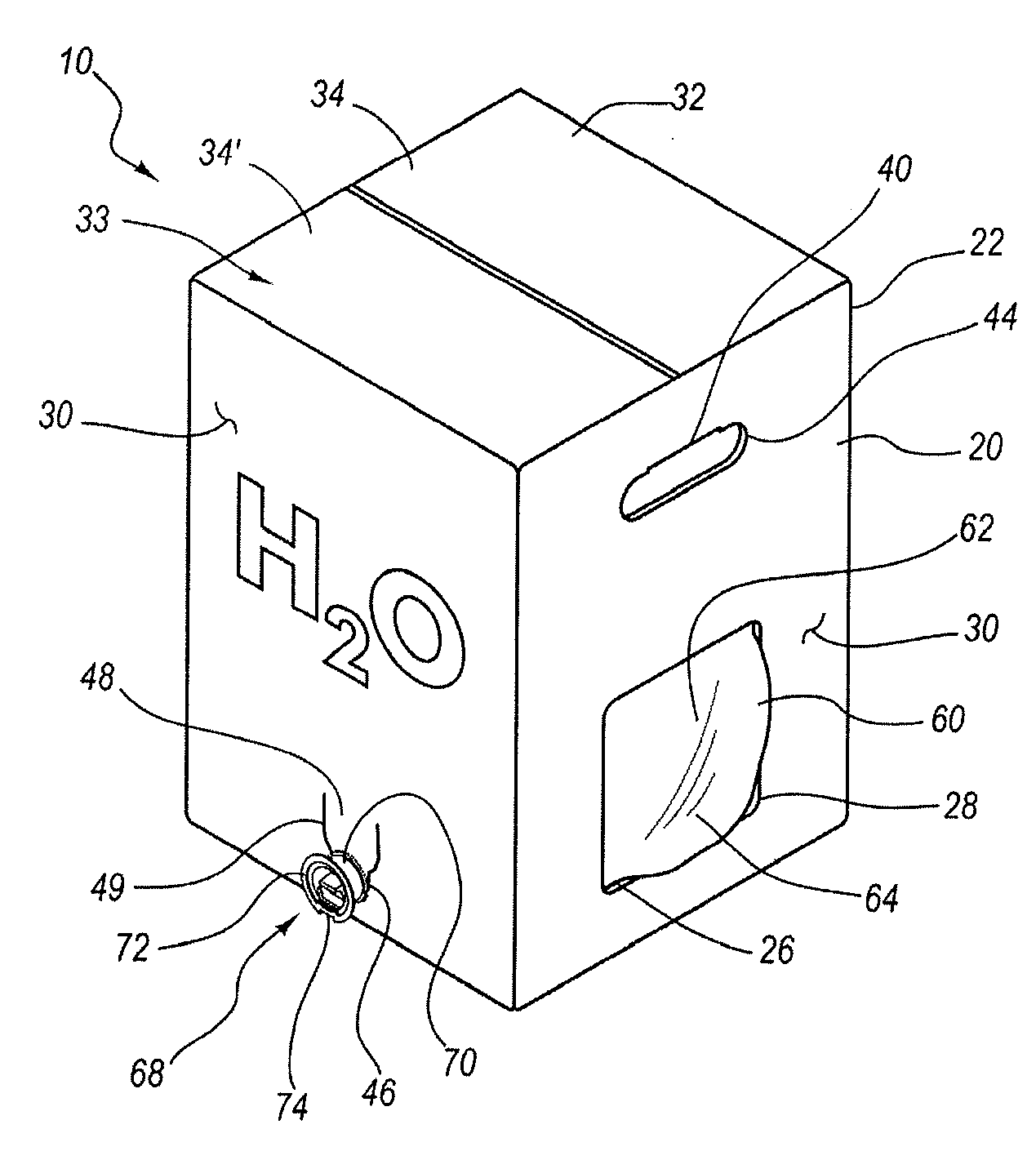

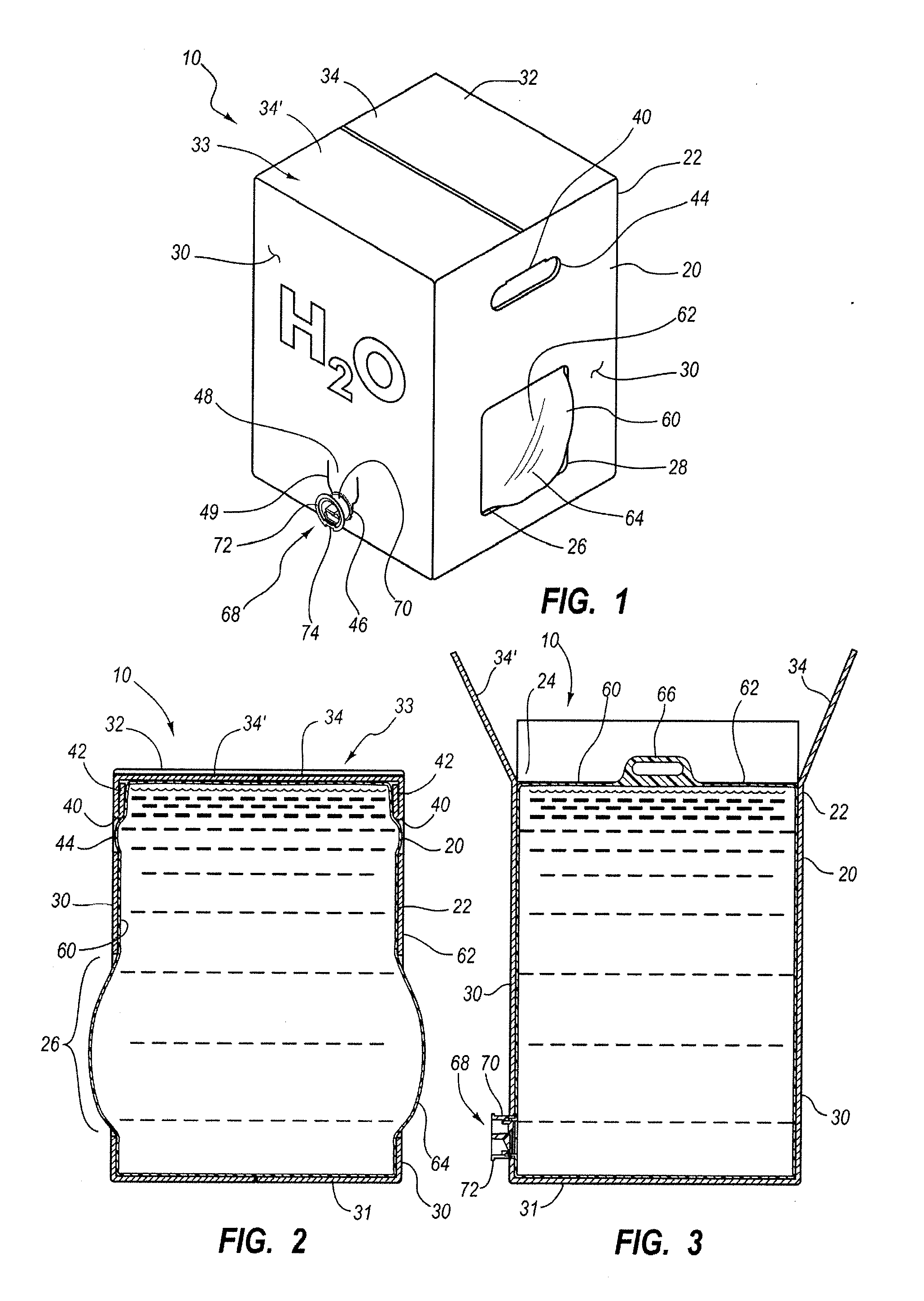

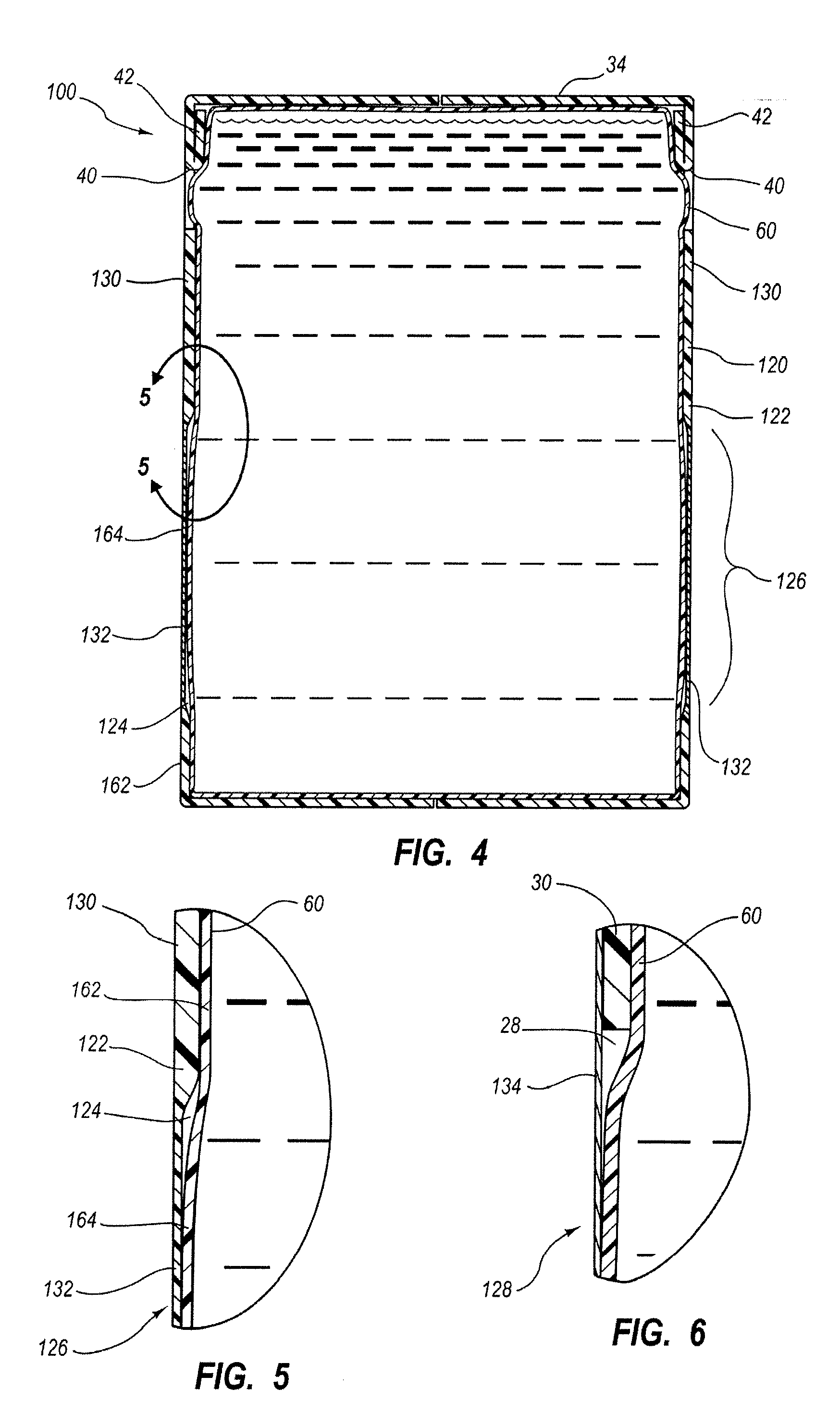

Temperature controlled liquid dispenser, containers therefore, and bag-in-box container construction

InactiveUS20080277417A1Improve thermal conductivityThermal energy is effectively and efficiently transferredDomestic cooling apparatusLiquid flow controllersTemperature controlThermal energy

A dispenser for relative rapid cooling or heating of the contents of a liquid storage container provides a receptacle for receiving the liquid storage container therein and positioning a thermal transfer portion of the liquid storage container in thermal conductive relationship with a thermal conduction pad associated with the receptacle. Thermal energy is effectively and efficiently transferred from the thermal conduction pad to the liquid in the liquid storage container. The thermal conduction pad is controlled to provide and maintain the desired temperature to the liquid. The liquid is dispensed directly from the container. Various types of containers can be used in the dispenser, with a special bag-in-box container having a inner container and outer box with thermal conduction windows in the box to provide good heat transfer between the thermal conduction pads and the inner container constituting an aspect of the invention. A special rigid container can also be used.

Owner:GROESBECK R CLAY

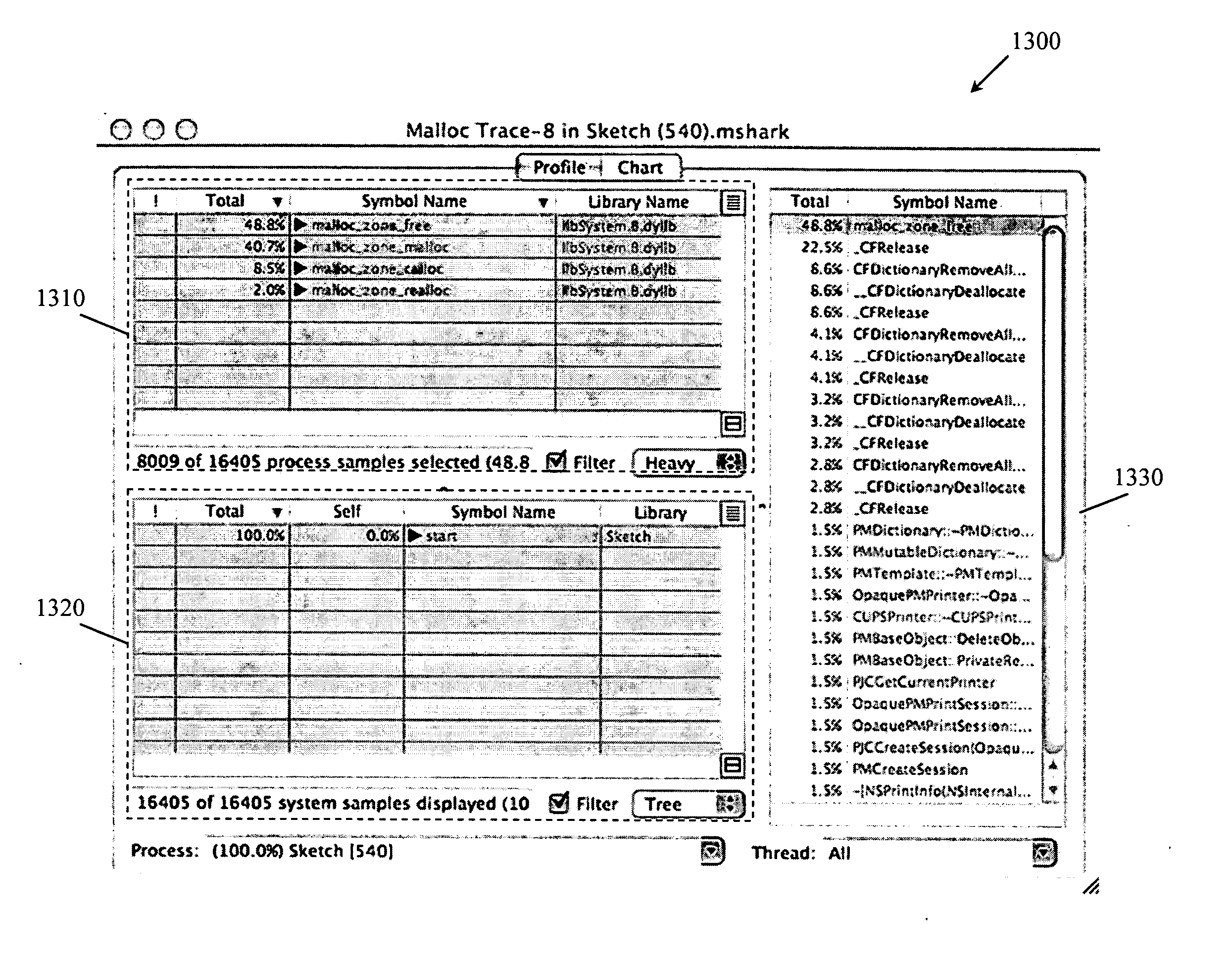

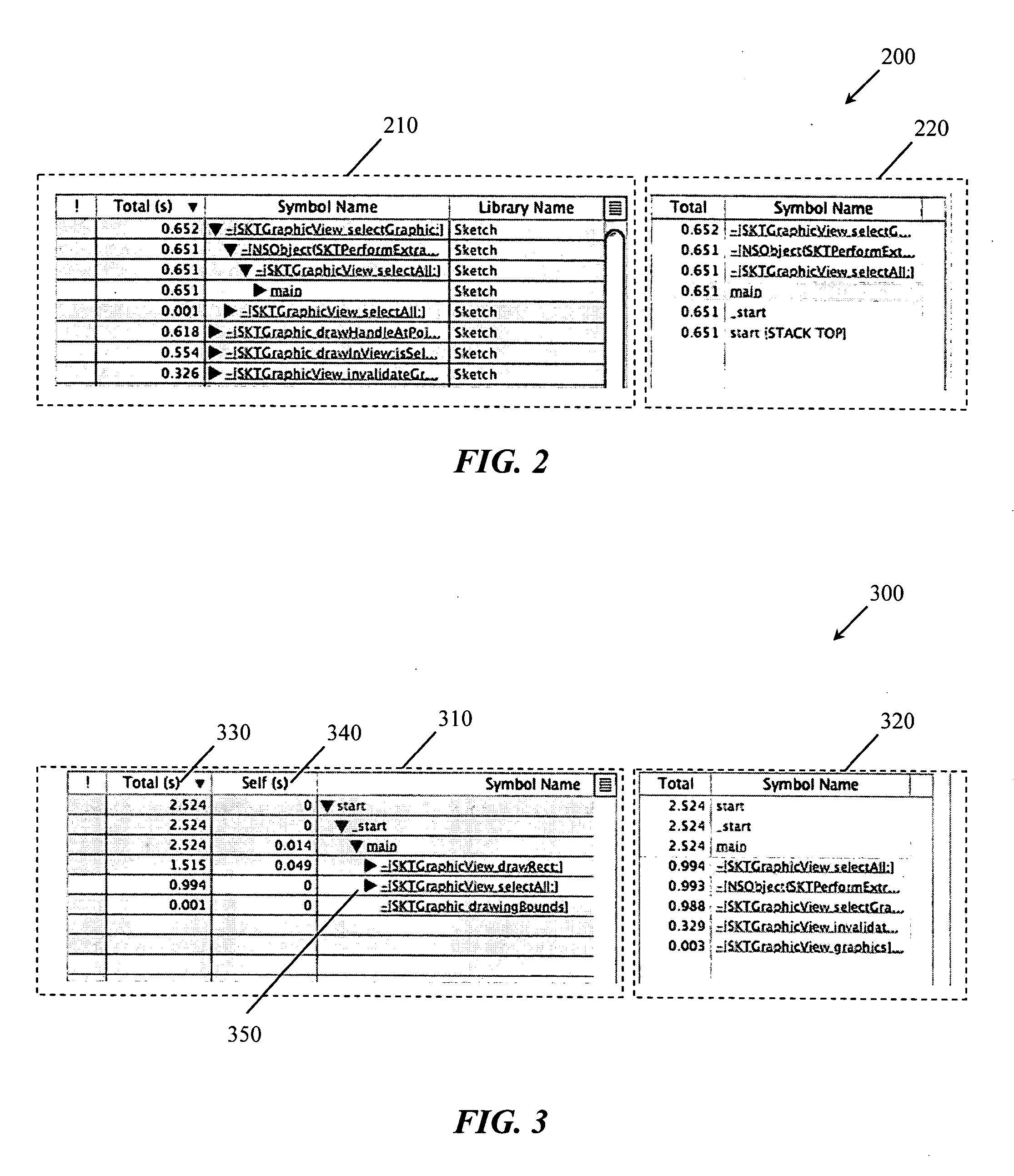

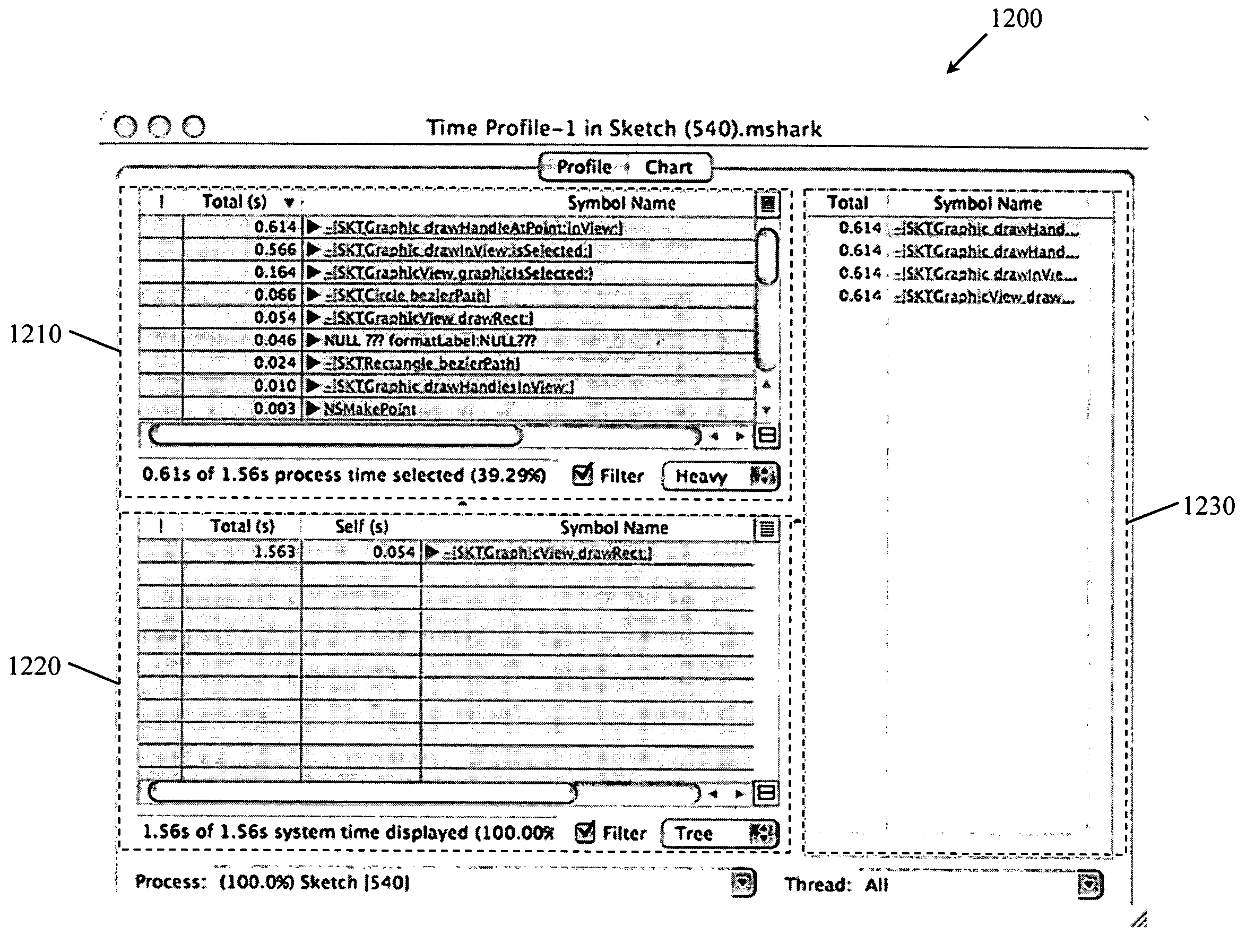

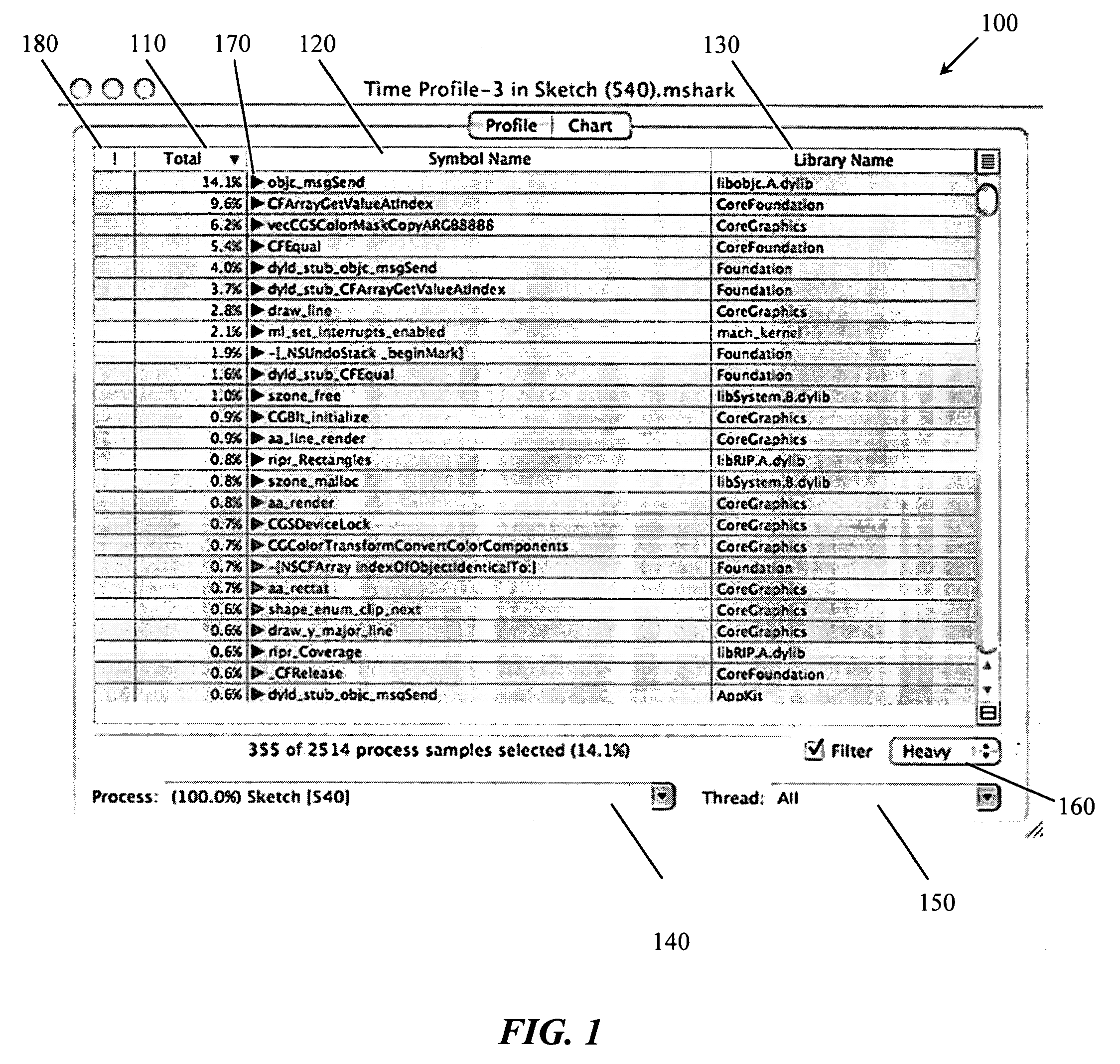

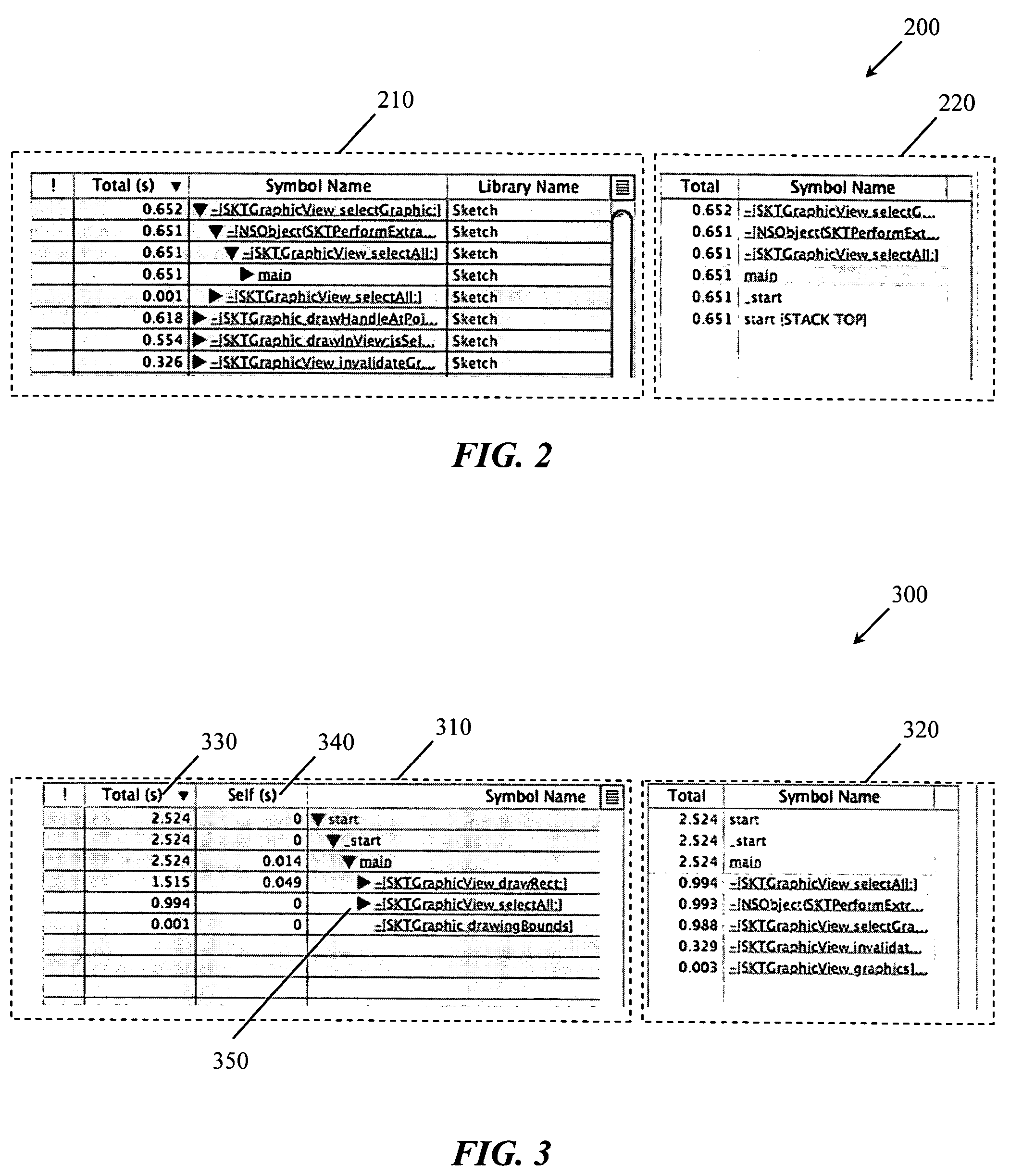

Software performance analysis using data mining

ActiveUS20050283765A1Good sense of costEasy to understandHardware monitoringSpecific program execution arrangementsSoftware performance analysisTheoretical computer science

A system, method, and computer program for analyzing code execution and software performance characteristics are disclosed. Samples of code during run-time can be displayed as both a top-down tree of calls from a particular function and a bottom-up tree of calls to the particular function. Data mining techniques, including filtering and focusing, remove code that is not of interest and display code that is more relevant to performance analysis. In particular, functions contained in libraries such as system libraries can be stripped from view. The cost associated with an excluded function can be propagated to a calling function, in either the top-down or bottom-up tree. The principles of the present invention can find particular usefulness with respect to analyzing crashlogs.

Owner:APPLE INC

Temperature controlled liquid dispenser, containers therefore, and bag-in-box container construction

ActiveUS8459503B2Improve thermal conductivityThermal energy is effectively and efficiently transferredDomestic cooling apparatusLighting and heating apparatusLiquid liquid partitionThermal energy

A dispenser for relative rapid cooling or heating of the contents of a liquid storage container provides a receptacle for receiving the liquid storage container therein and positioning a thermal transfer portion of the liquid storage container in thermal conductive relationship with a thermal conduction pad associated with the receptacle. Thermal energy is effectively and efficiently transferred from the thermal conduction pad to the liquid in the liquid storage container. The thermal conduction pad is controlled to provide and maintain the desired temperature to the liquid. The liquid is dispensed directly from the container. Various types of containers can be used in the dispenser, with a special bag-in-box container having a inner container and outer box with thermal conduction windows in the box to provide good heat transfer between the thermal conduction pads and the inner container constituting an aspect of the invention. A special rigid container can also be used.

Owner:GROESBECK R CLAY

Temperature controlled liquid dispenser, containers therefore, and bag-in-box container construction

InactiveUS7975879B2Improve thermal conductivityThermal energy is effectively and efficiently transferredDomestic cooling apparatusLiquid flow controllersTemperature controlThermal energy

Owner:GROESBECK R CLAY

Software performance analysis using data mining

ActiveUS7644397B2Quick and efficient analysisFind quicklyHardware monitoringSpecific program execution arrangementsSoftware performance analysisTheoretical computer science

A system, method, and computer program for analyzing code execution and software performance characteristics are disclosed. Samples of code during run-time or from crash logs can be displayed as both a top-down tree of calls from a particular function and a bottom-up tree of calls to the particular function. Data mining techniques, including filtering and focusing, remove code that is not of interest and display code that is more relevant to performance analysis. In particular, functions contained in libraries such as system libraries can be stripped from view. The cost associated with an excluded function can be propagated to a calling function, in either the top-down or bottom-up tree.

Owner:APPLE INC

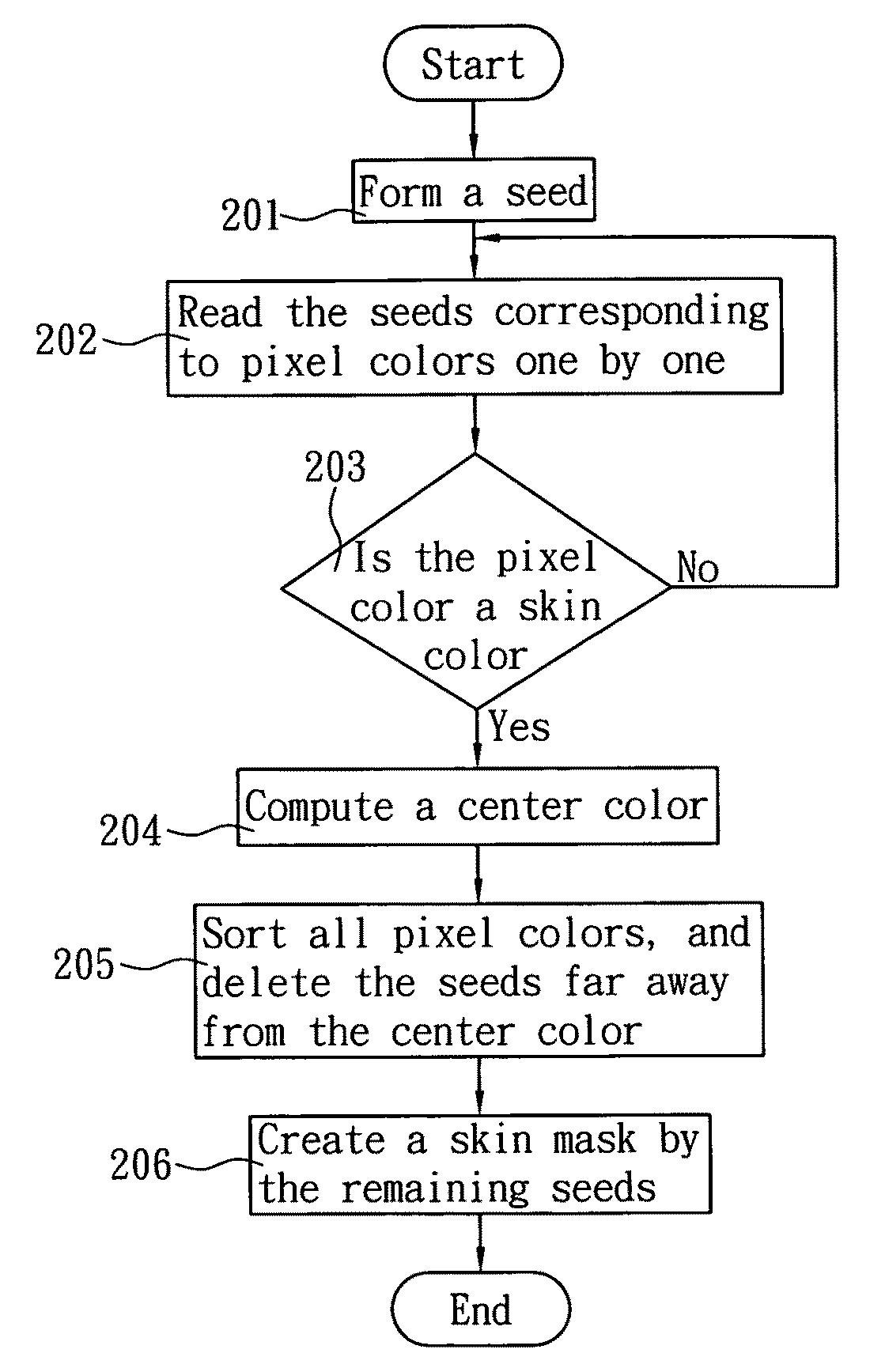

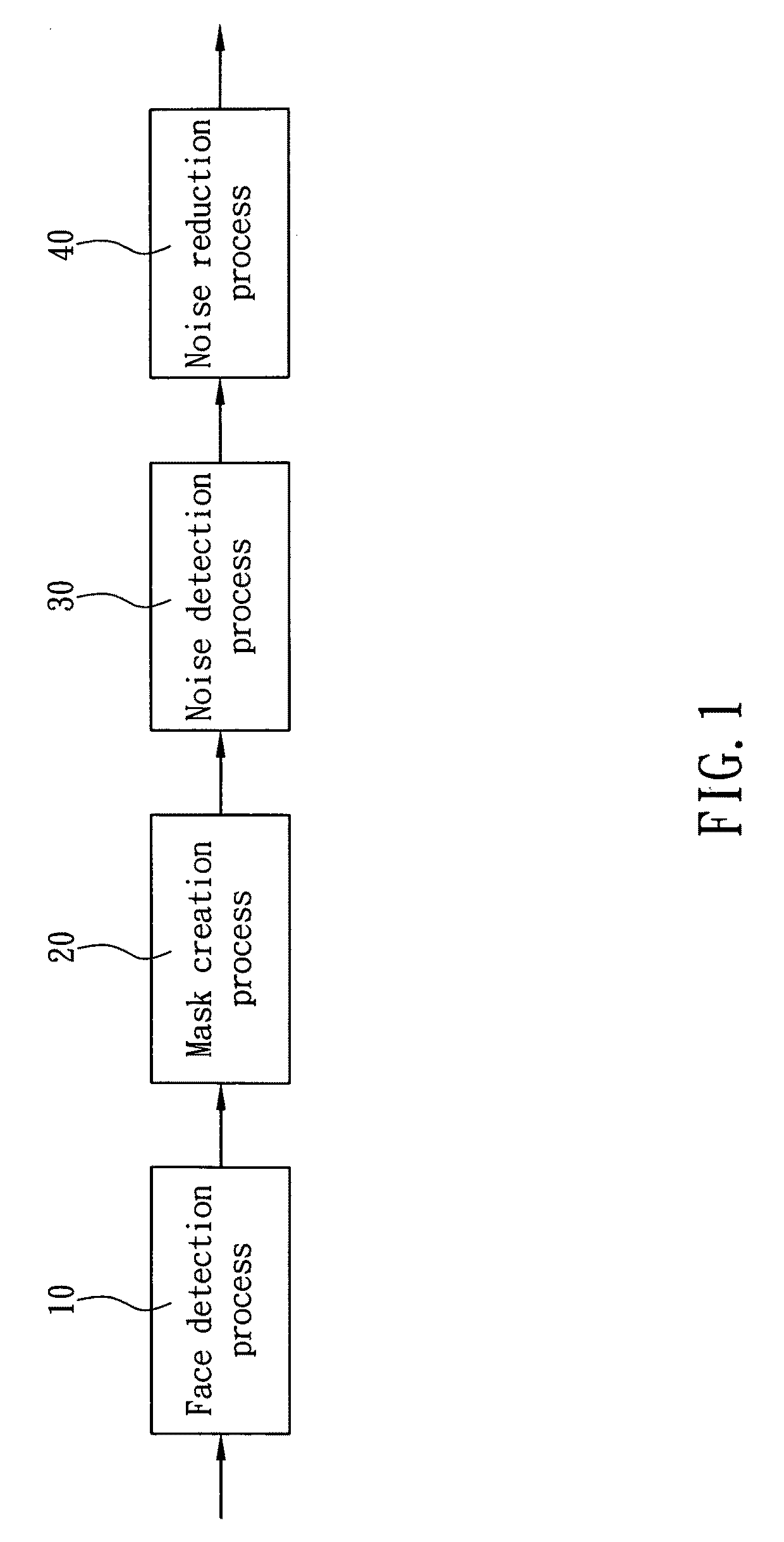

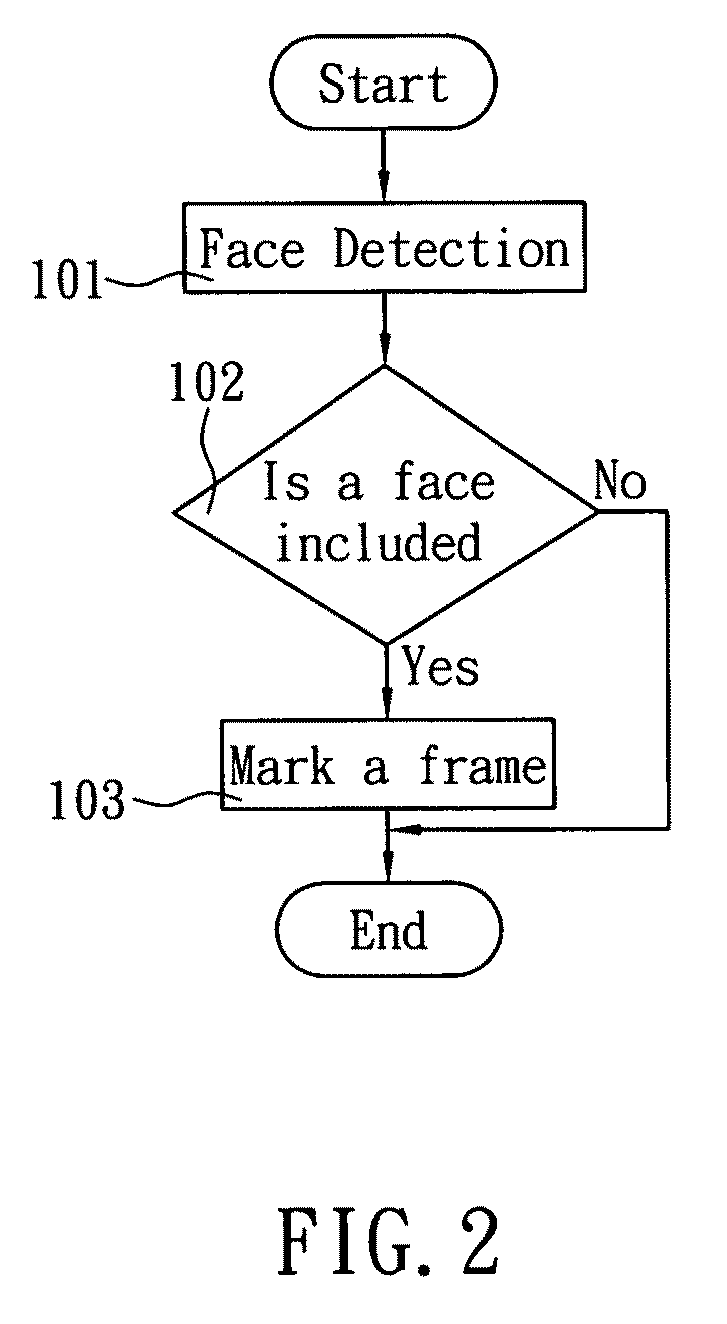

Face image processing method

ActiveUS8295557B2Easy to removeSimple process and operationImage enhancementImage analysisFace detectionImaging processing

A face image processing method is applied to an electronic device, such that the electronic device can perform a face detection to a digital image to obtain a face image in the digital image automatically, and perform a skin color detection to the face image to exclude non-skin features such as eyes, eyeglasses, eyebrows, a moustache, a mouth and nostrils on the face image, and form a skin mask in an area range of the face image belonging to skin color, and finally perform a filtering process to the area range of the face image corresponding to the skin mask to filter high-frequency, mid-frequency and low-frequency noises of an abnormal skin color in the area range of the face image, so as to quickly remove blemishes and dark spots existed in the area range of the face image.

Owner:ARCSOFT CORP LTD

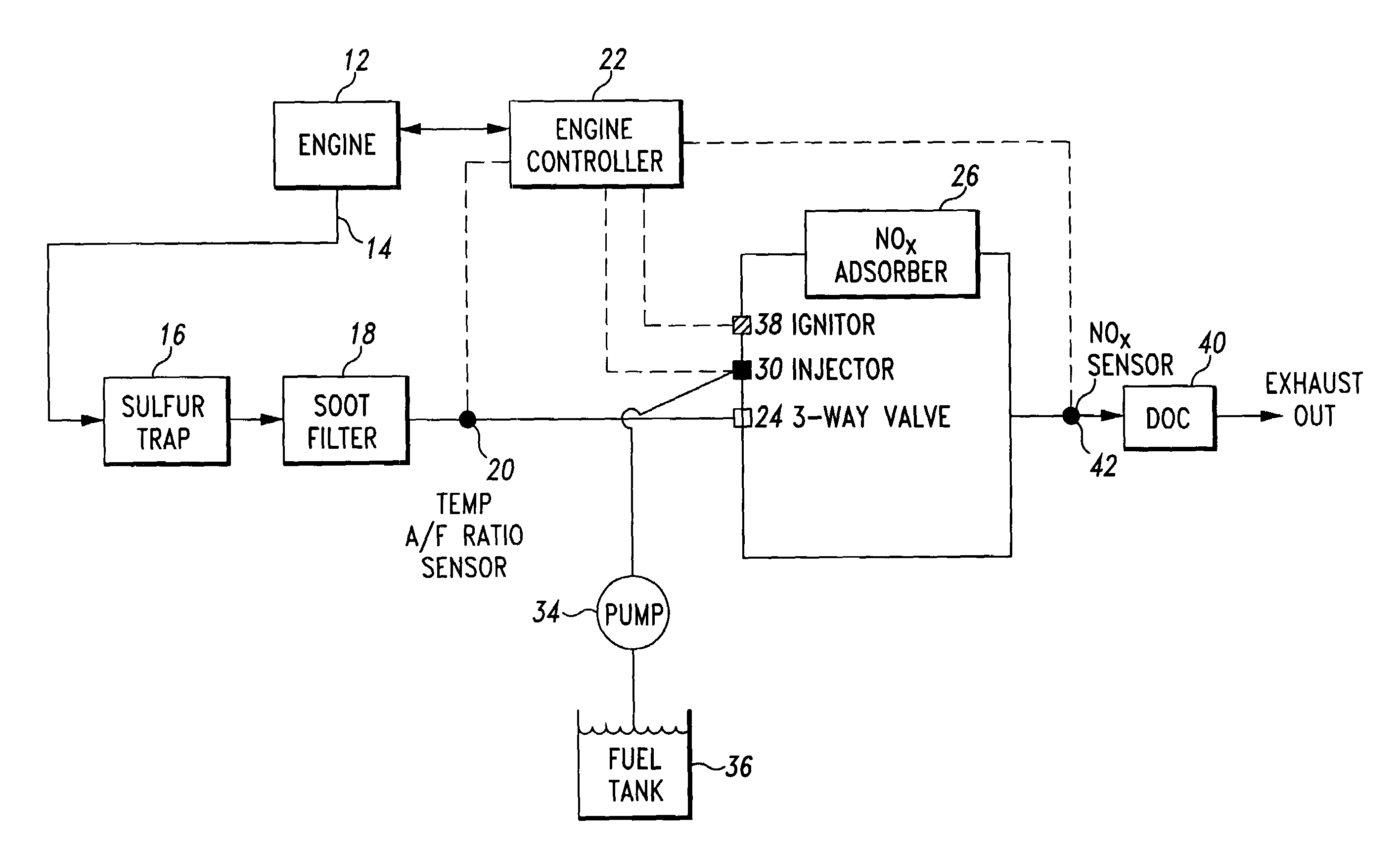

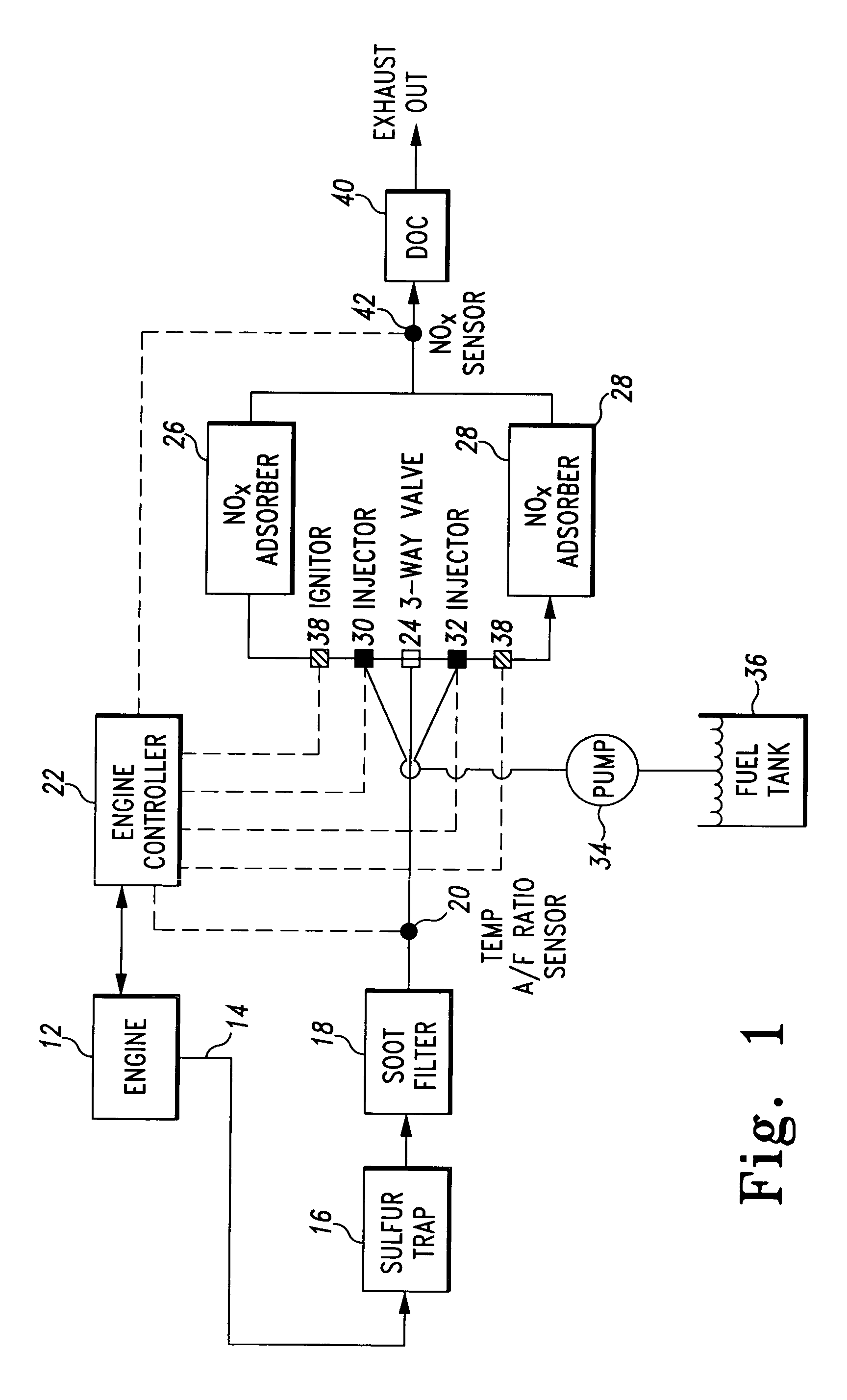

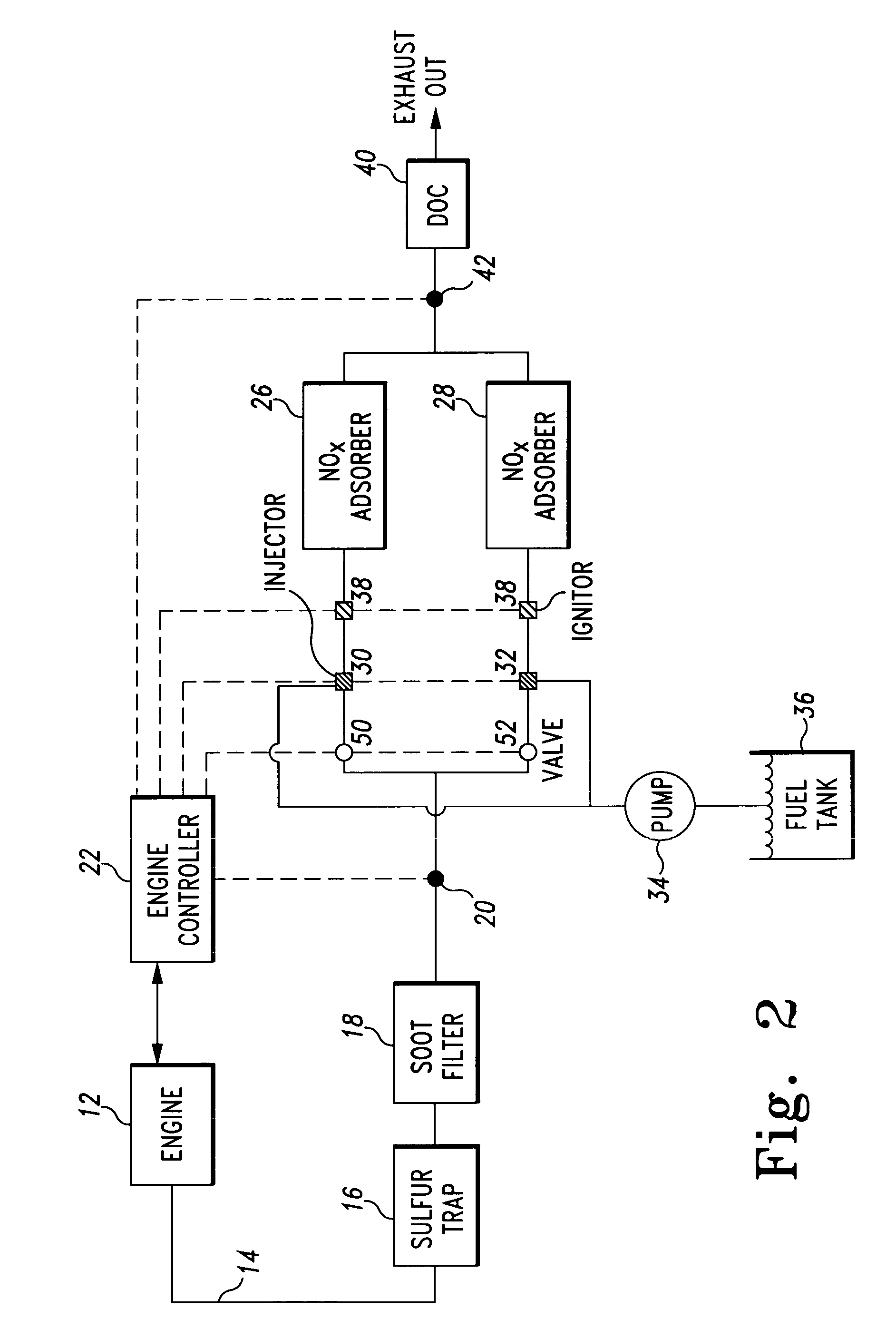

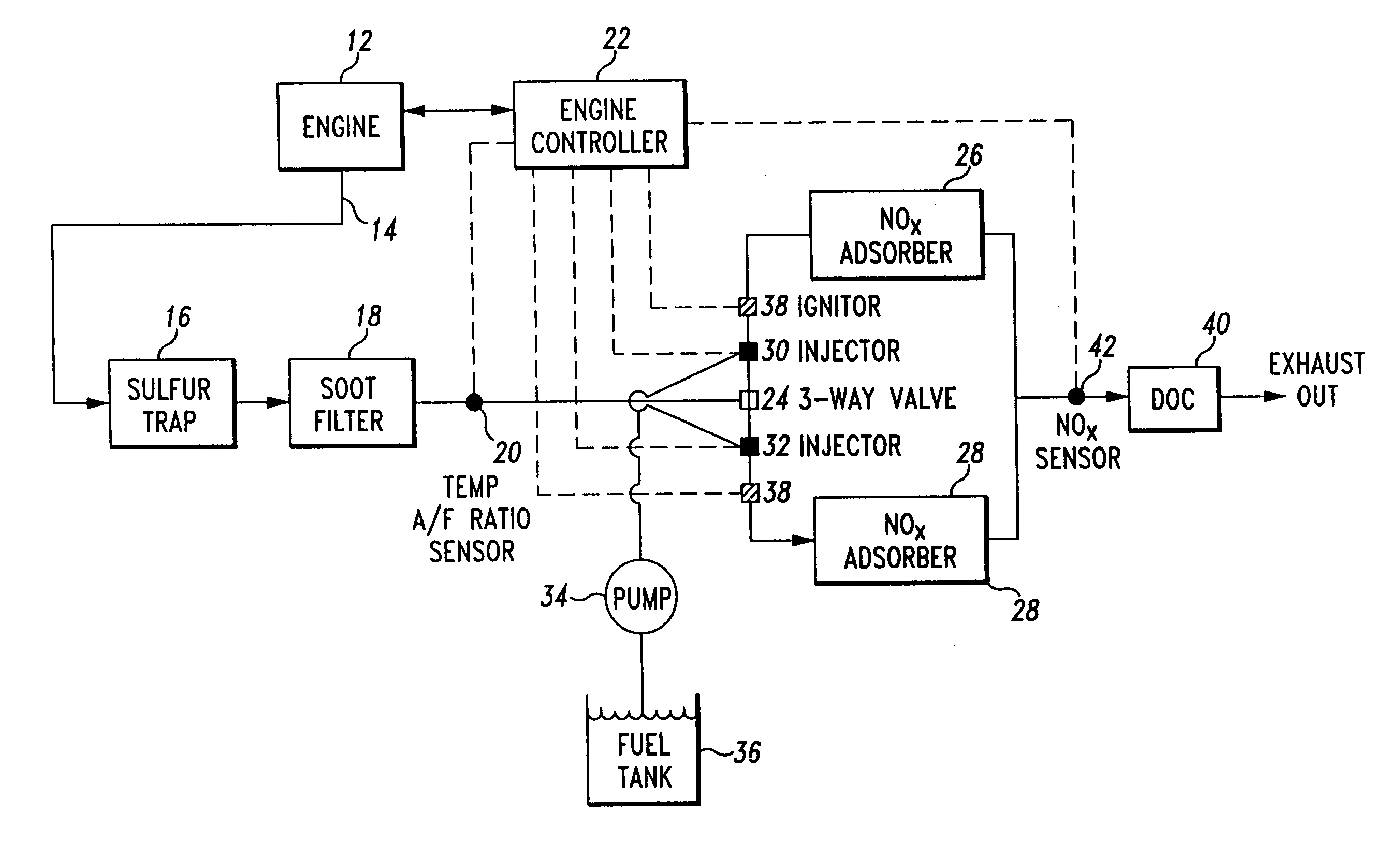

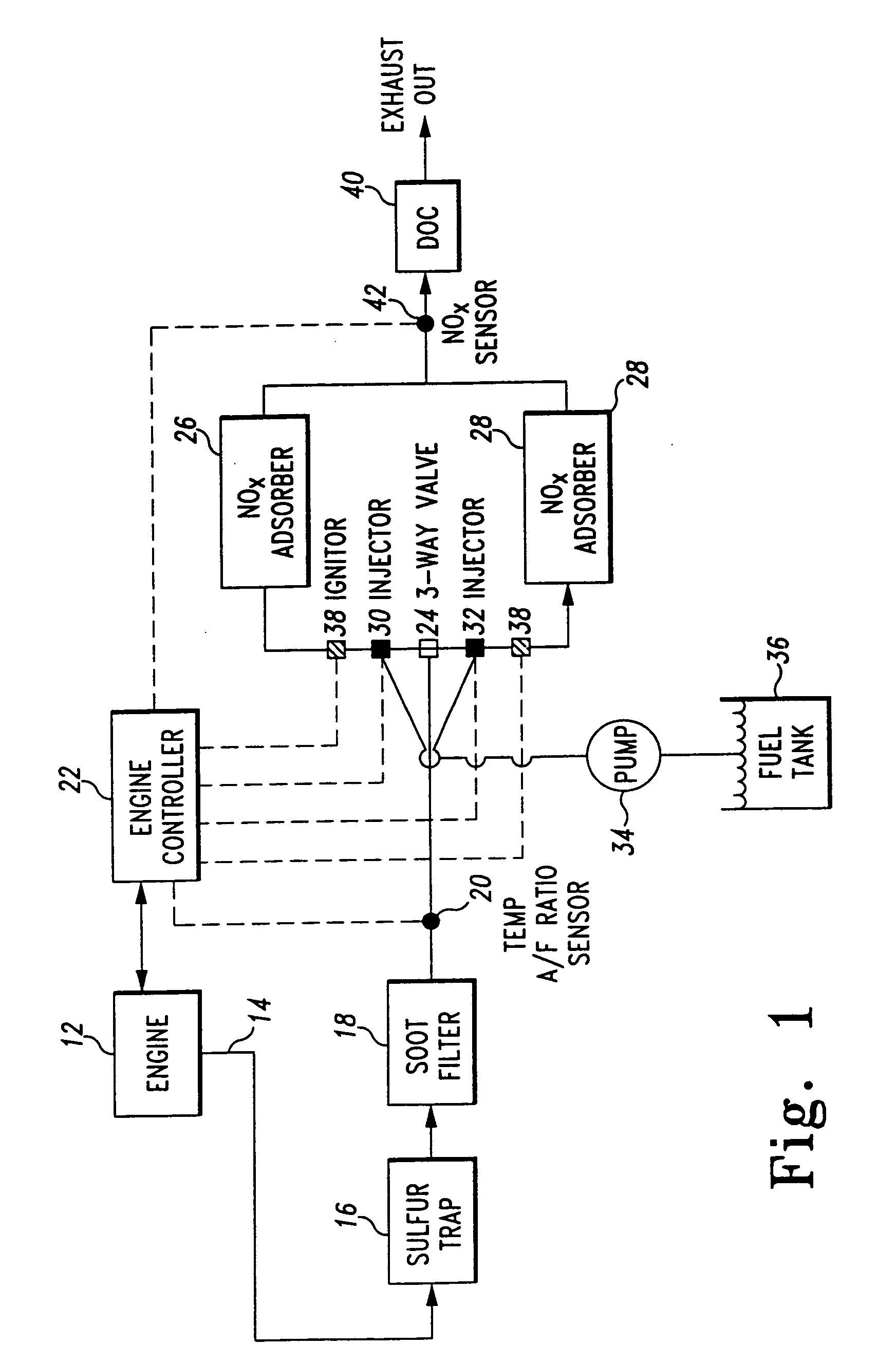

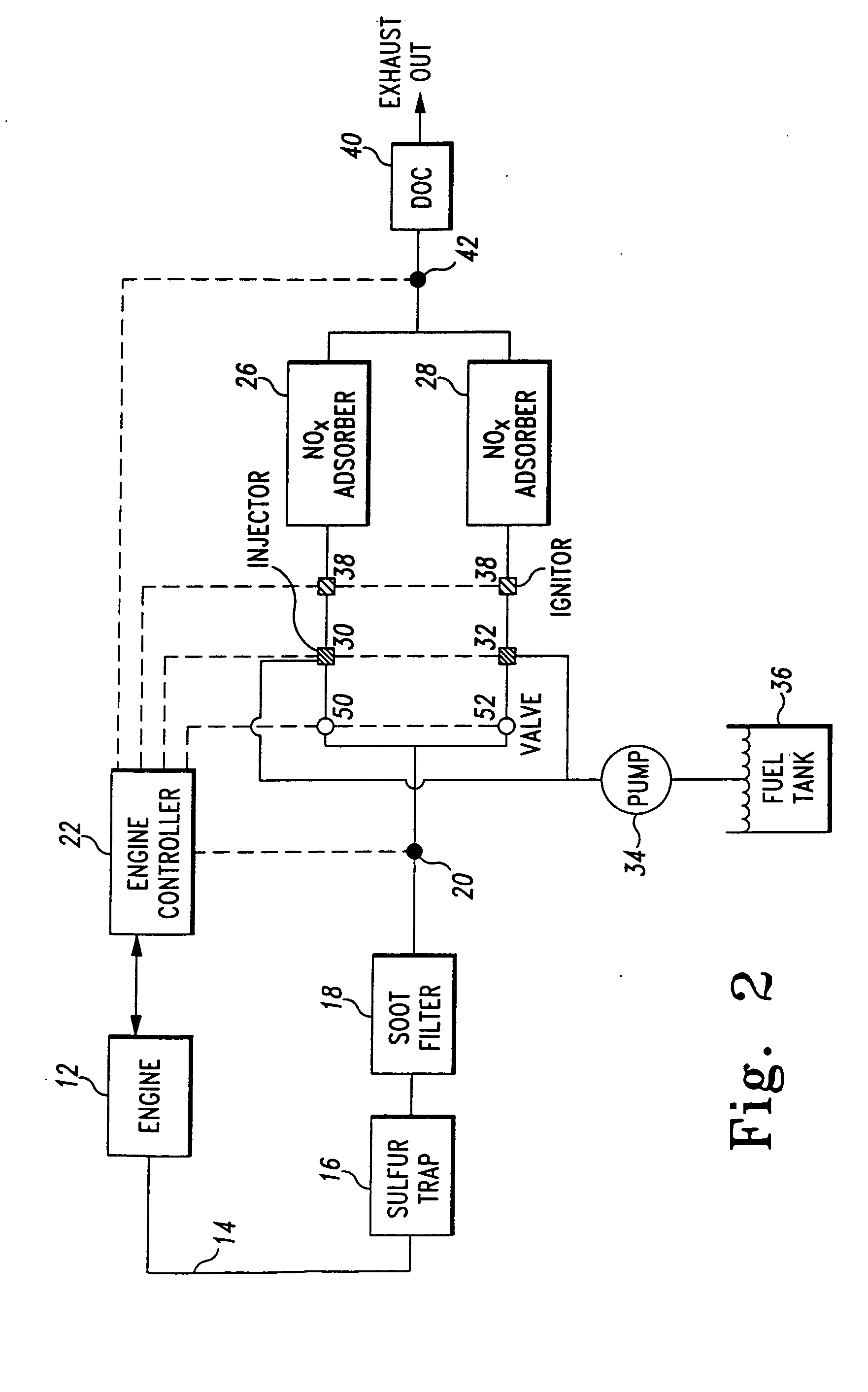

NOx adsorber aftertreatment system for internal combustion engines

InactiveUS7117667B2More surface areaMore time areaCombination devicesInternal combustion piston enginesCombustionExhaust fumes

The present invention provides for an NOx adsorber aftertreatment system for internal combustion engines which utilizes a parallel arrangement of an adsorber catalyst and a bypass. The exhaust flow from the engine is routed through the adsorber during lean operation. At a predetermined regeneration time (for example, when the adsorber catalyst is 20% full), the exhaust gas flow is reduced through the parallel leg that contains the adsorber catalyst to be regenerated (e.g., 20% through the catalyst leg, 80% of the flow to the bypass leg). A quantity of hydrocarbon is injected into the reduced-flow catalyst leg in order to make the mixture rich. Since the flow has been reduced in this leg, only a small fraction of the amount of hydrocarbon that would have been required to make the mixture rich during full flow is required. This will result in a substantial reduction in the fuel penalty incurred for regeneration of the adsorber catalyst. Once the leg has been regenerated, the exhaust flow is switched to flow 100% through the adsorber leg.

Owner:CUMMINS FILTRATION INC

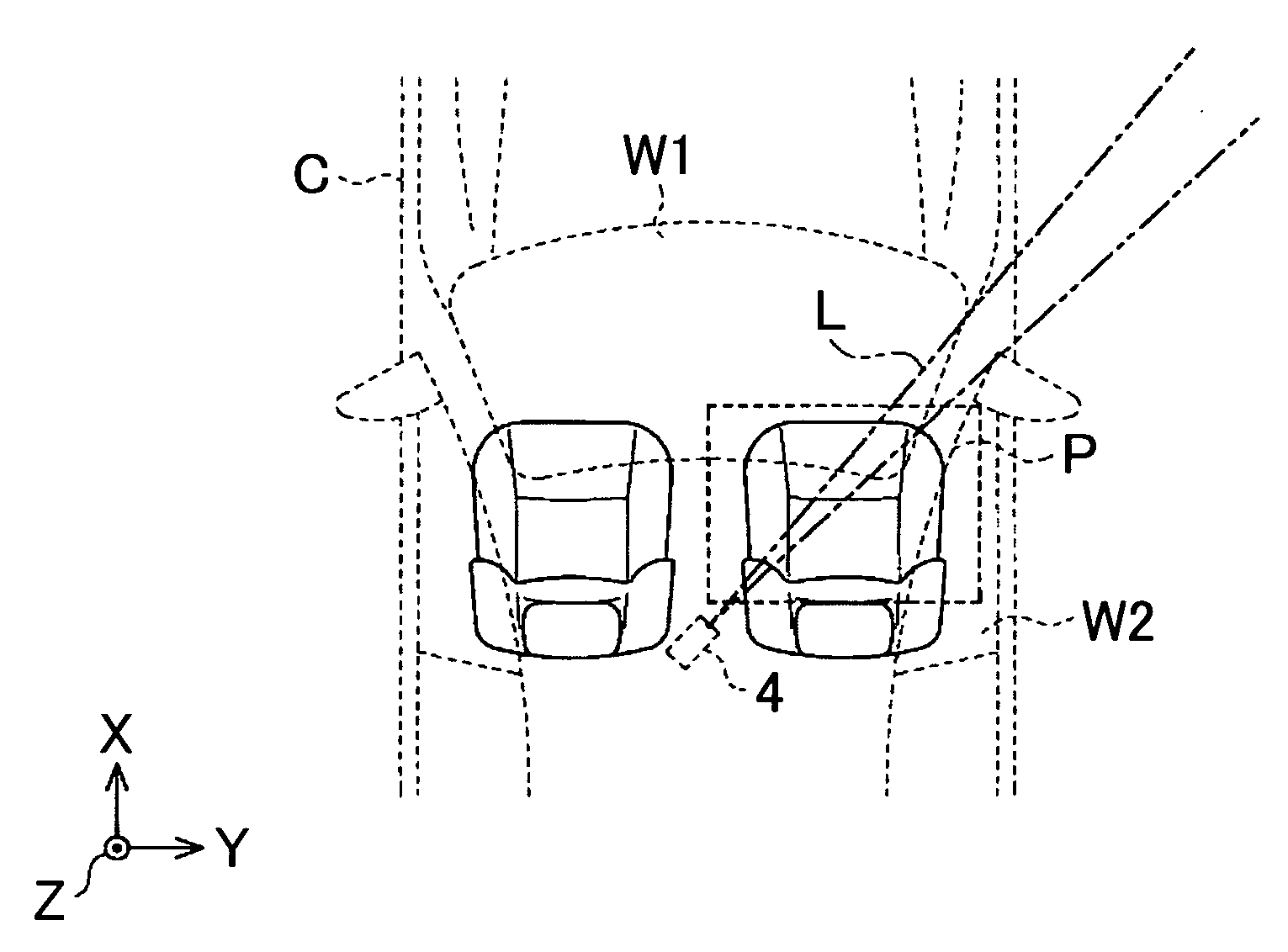

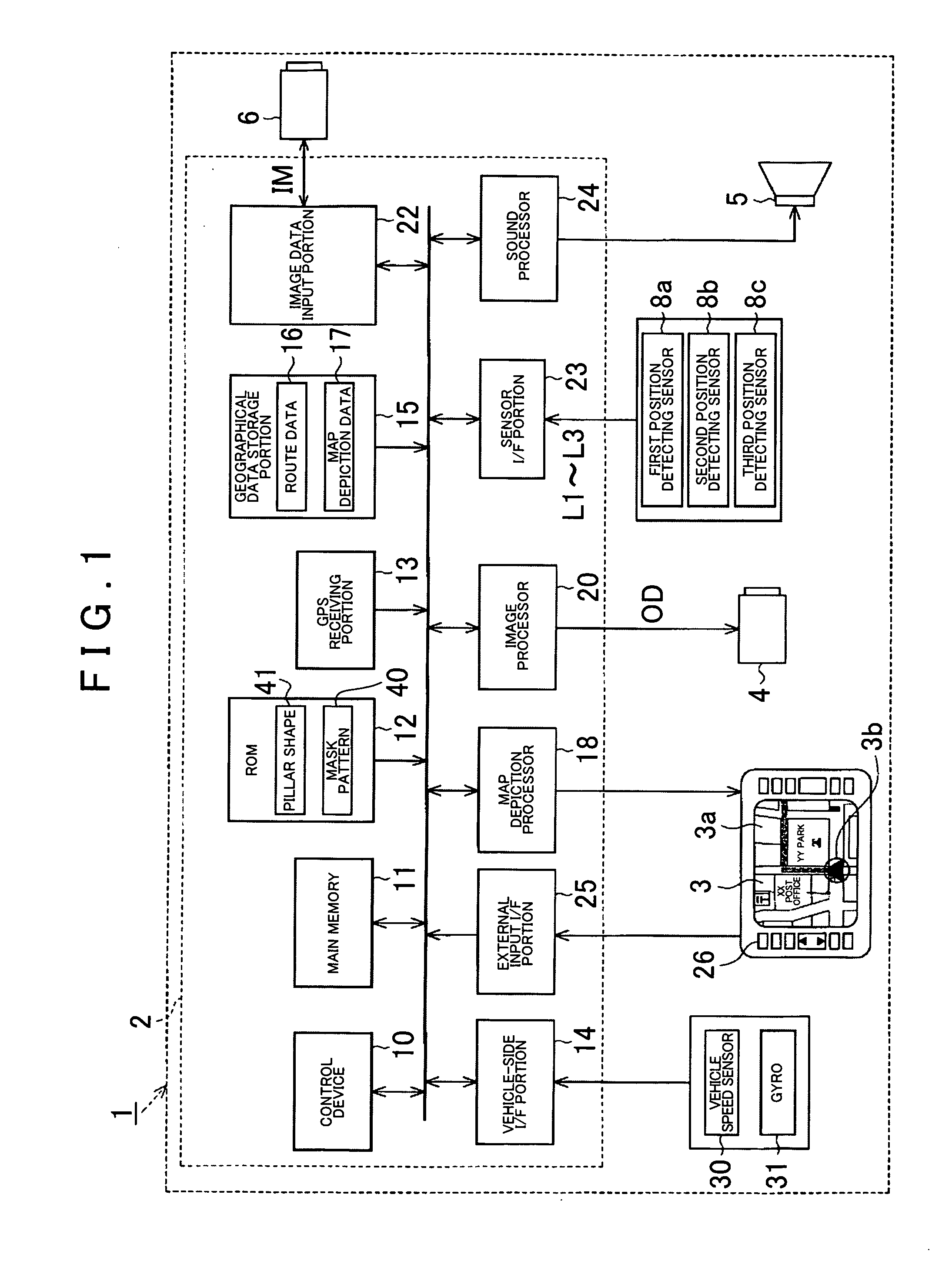

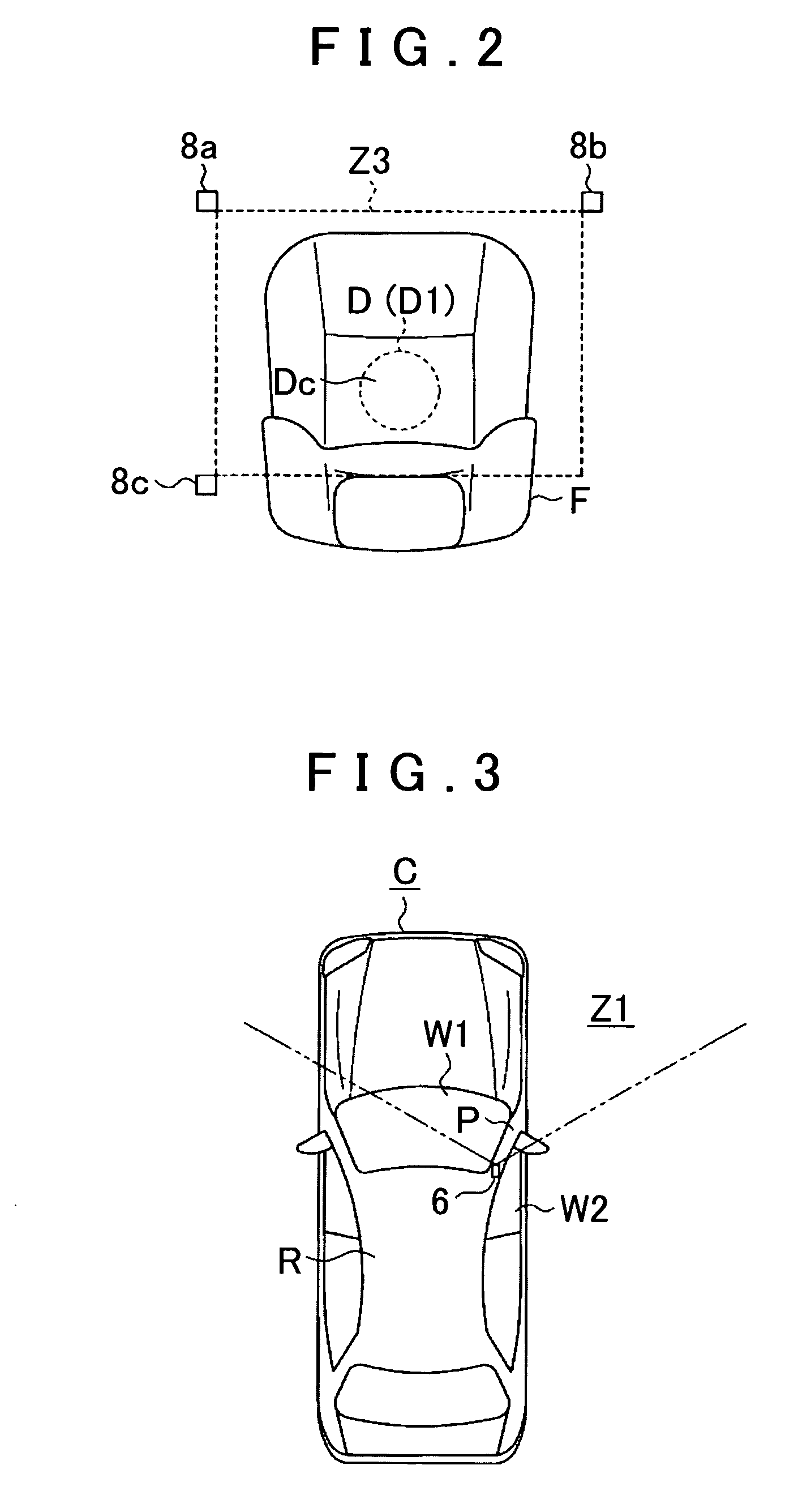

Driving support method and driving support device

ActiveUS20080204557A1Improve continuityReduces area not displayedColor television detailsClosed circuit television systemsComputer graphics (images)Image plane

A driving support device uses a camera mounted on a vehicle for imaging a blind spot area created by a pillar of the vehicle and displays an image taken by the camera on the interior surface of the pillar. A virtual plane passing through boundaries of the blind spot area is set, and an image plane of the camera is set at a predetermined position where a non-displayed area or an excess area, created by deviation between the virtual plane and the image plane of the camera, is reduced. Image data input from the camera is subjected to coordinate transformation on the virtual plane, and an image corresponding to the blind spot area created by the pillar is displayed on the interior surface of the pillar, based on the image data subjected to coordinate transformation on the virtual plane.

Owner:AISIN AW CO LTD

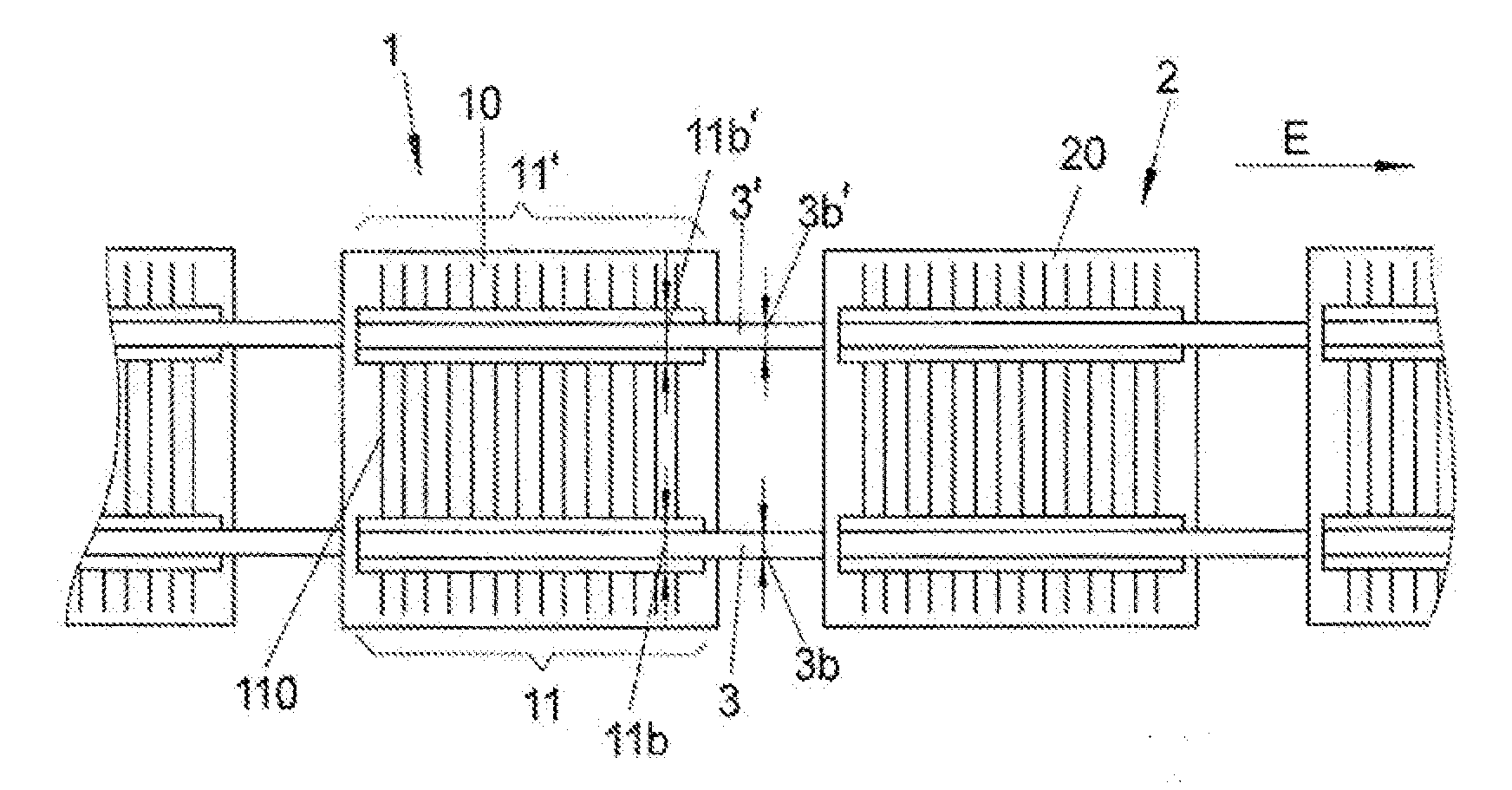

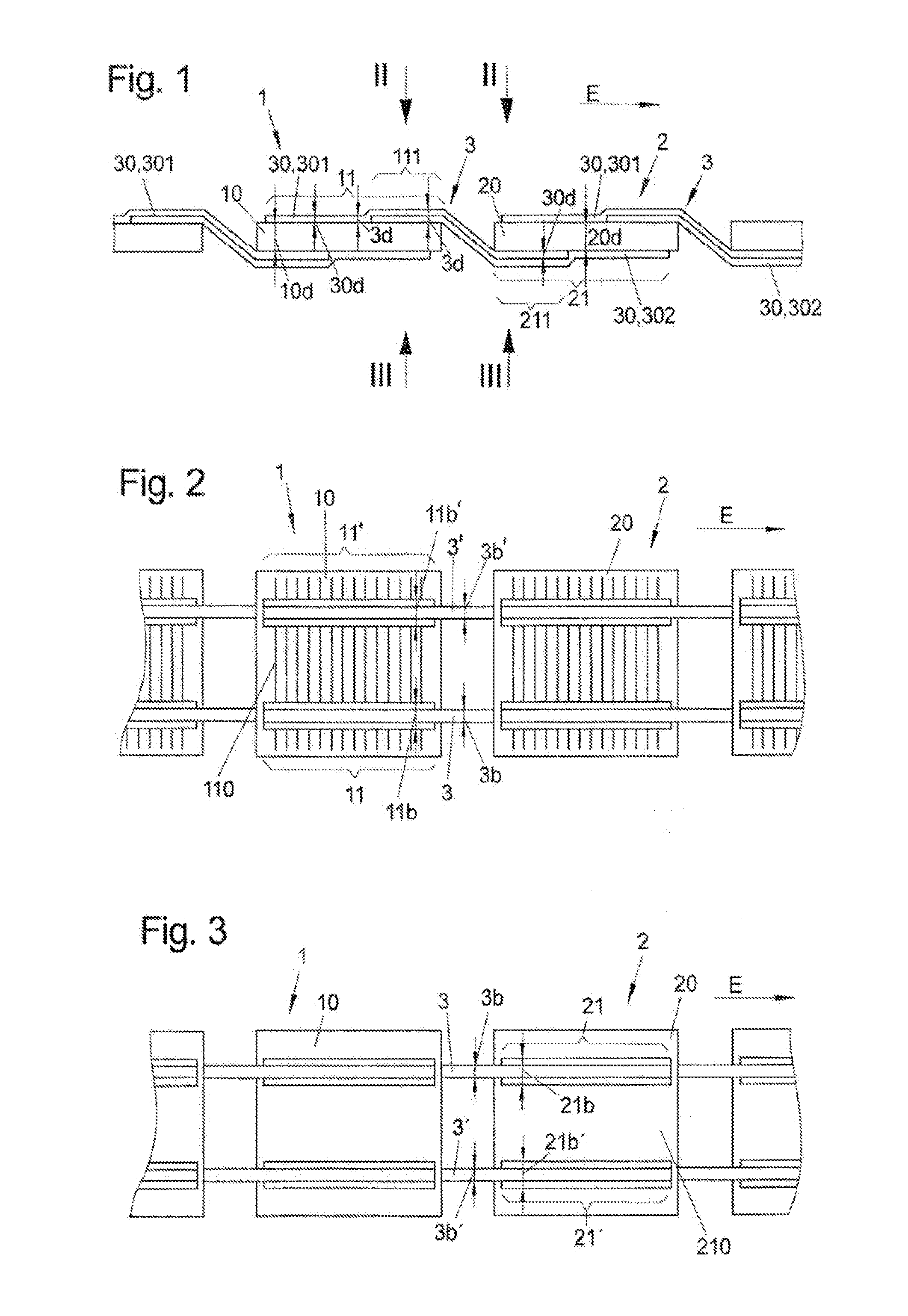

Solar Cell String And Solar Module Equipped With Such Solar Cell String

InactiveUS20120042925A1More areaIncreasing the thicknessPV power plantsPhotovoltaic energy generationEngineeringElectrode Contact

A solar cell string contains a solar cell (1), formed by a wafer substrate (10) having a flat electrode contact segment (11), having a further solar cell (2) disposed adjacent to the solar cell (1), formed by a further wafer substrate (20) having a further flat electrode contact segment (21) and at least one cell connector (3) having a cell connector width and a cell connector thickness (3d) oriented substantially perpendicular to the electrode contact segments (11, 21). The cell connector extends along an extension direction (E) from the electrode contact segment (11) of the solar cell (1) to the further electrode contact segment (21) of the further solar cell (2), wherein the cell connector (3) electrically connects electrodes of the solar cell (1) to further electrodes of the further solar cell (2). The cell connector thickness (3d) of the linear cell connector (3) tapers down at least in segments along the extension direction (E) thereof, starting from the solar cell (1), in the direction of the further solar cell (2).

Owner:Q CELLS SE

Temperature Controlled Liquid Dispenser, Containers Therefore, and Bag-In-Box Container Construction

ActiveUS20110266287A1Improve thermal conductivityThermal energy is effectively and efficiently transferredDomestic cooling apparatusLighting and heating apparatusThermal energyTemperature control

A dispenser for relative rapid cooling or heating of the contents of a liquid storage container provides a receptacle for receiving the liquid storage container therein and positioning a thermal transfer portion of the liquid storage container in thermal conductive relationship with a thermal conduction pad associated with the receptacle. Thermal energy is effectively and efficiently transferred from the thermal conduction pad to the liquid in the liquid storage container. The thermal conduction pad is controlled to provide and maintain the desired temperature to the liquid. The liquid is dispensed directly from the container. Various types of containers can be used in the dispenser, with a special bag-in-box container having a inner container and outer box with thermal conduction windows in the box to provide good heat transfer between the thermal conduction pads and the inner container constituting an aspect of the invention. A special rigid container can also be used.

Owner:GROESBECK R CLAY

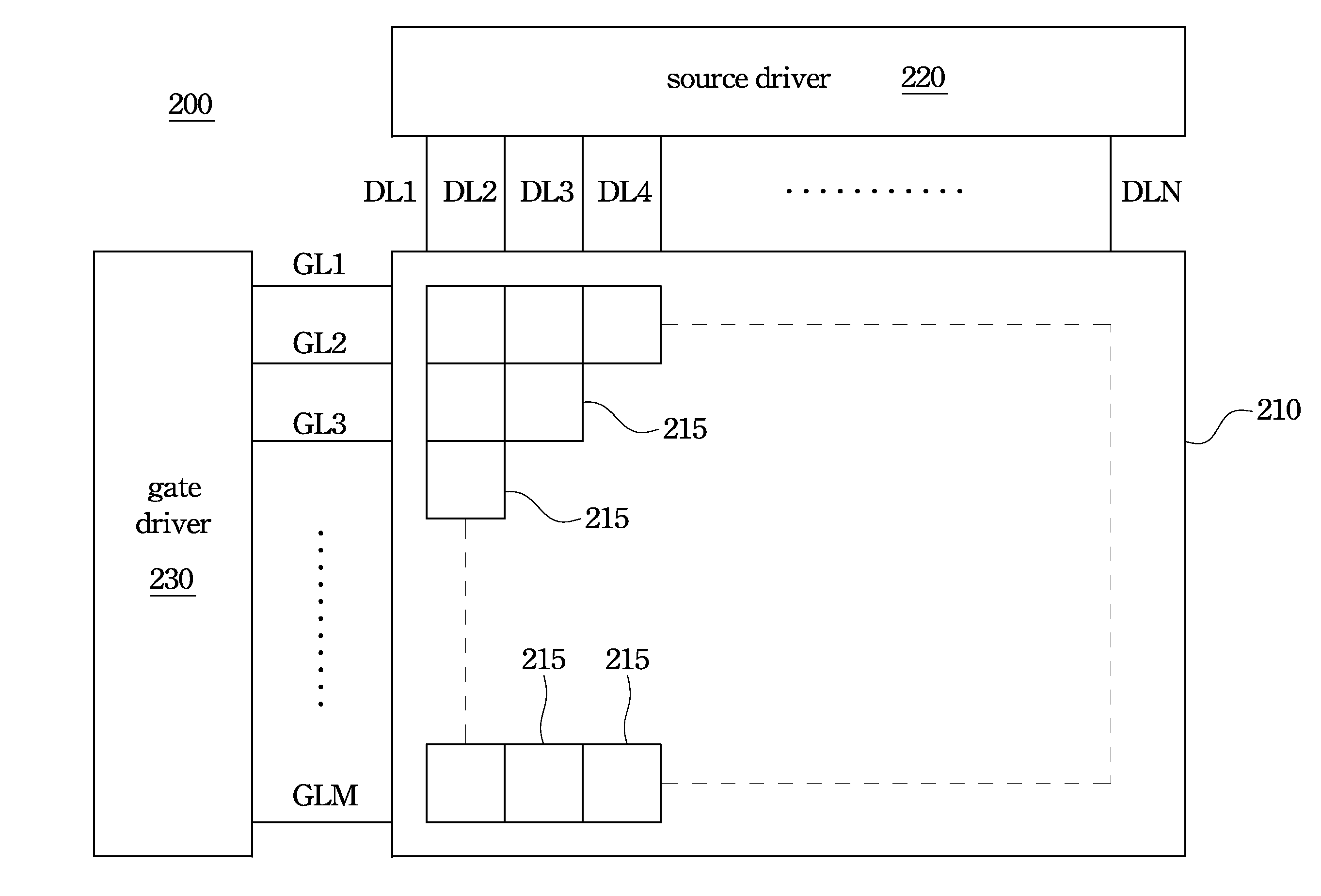

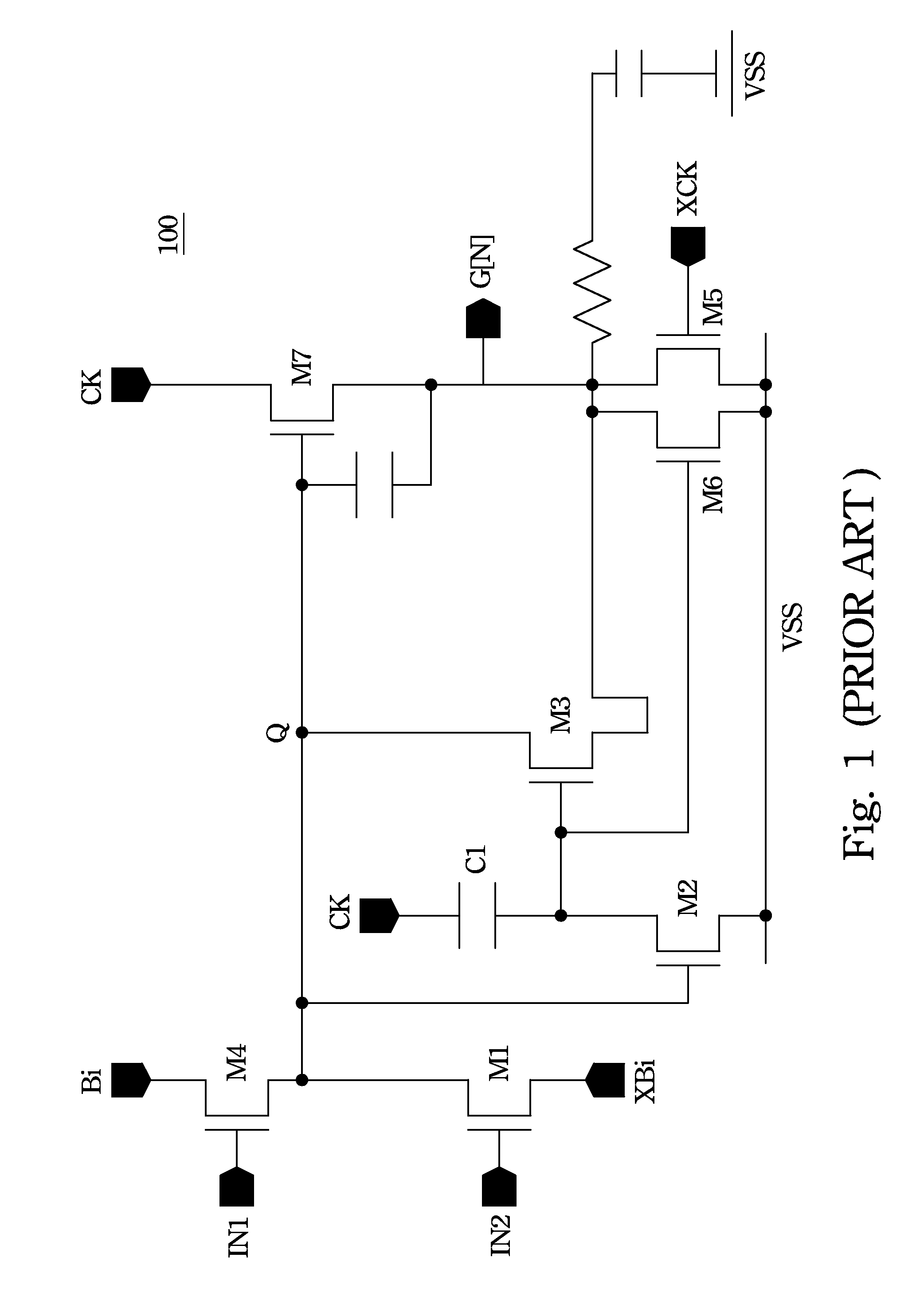

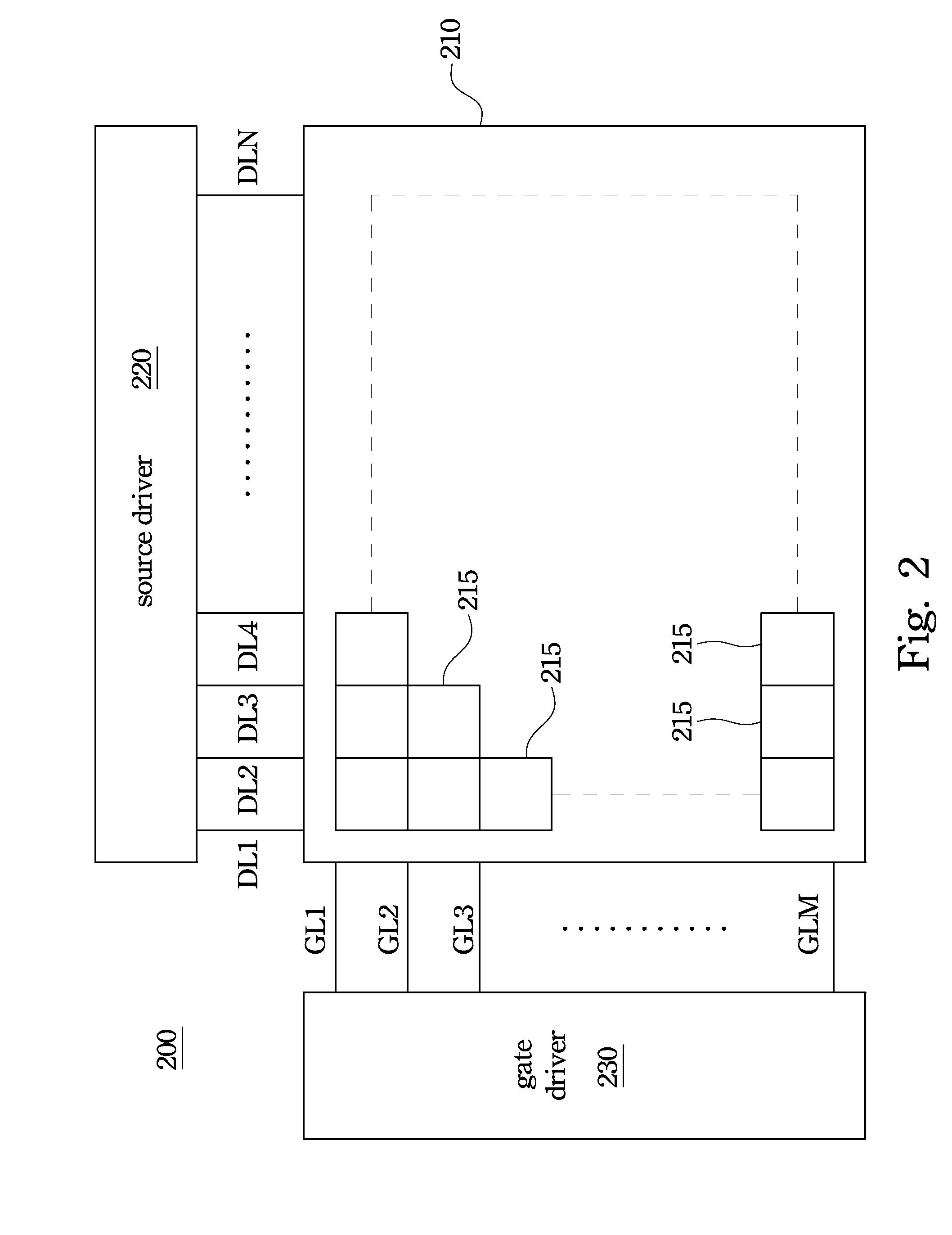

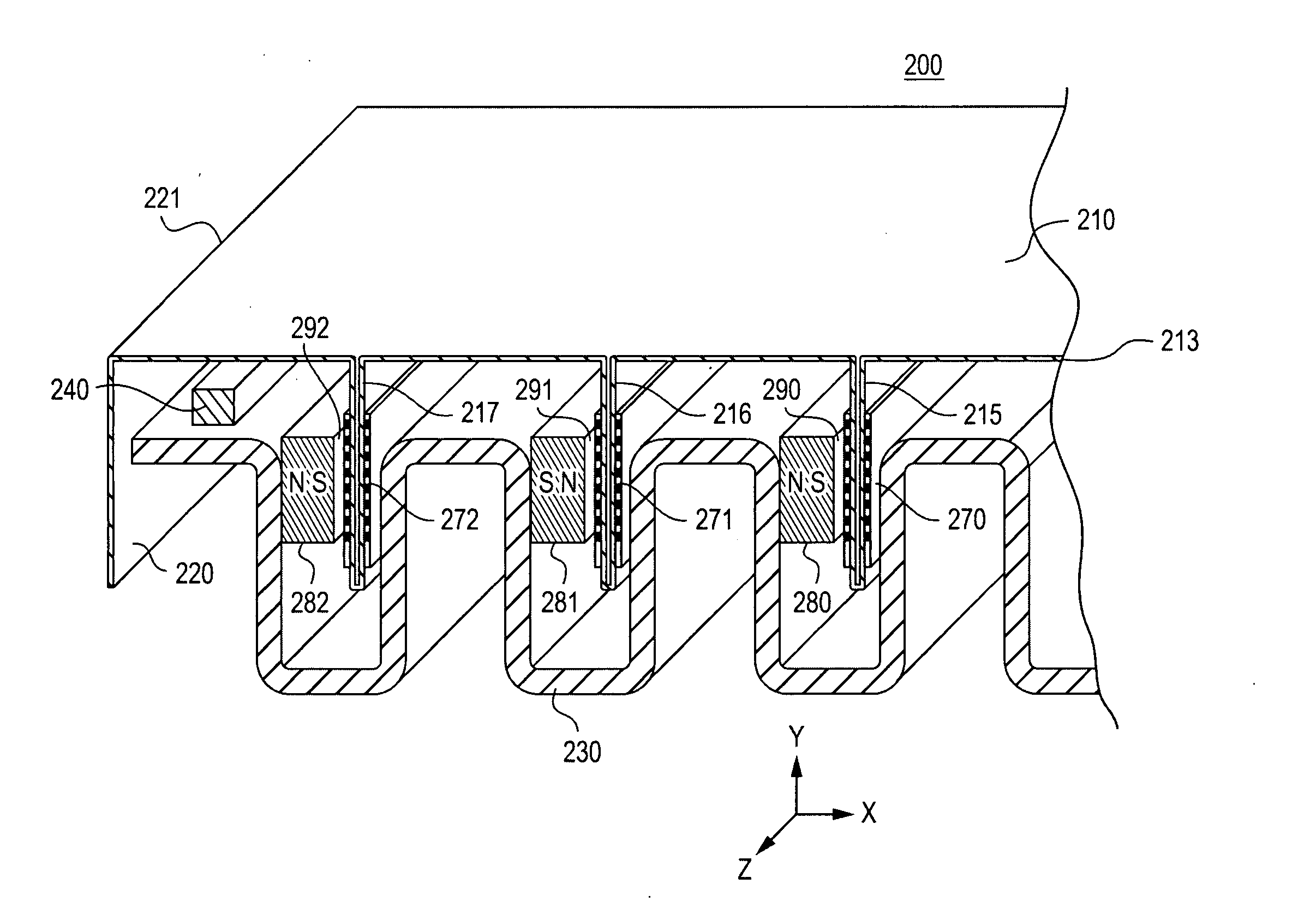

Display panel and gate driver therein

ActiveUS20130135284A1Improve abilitiesIncreased power consumptionCathode-ray tube indicatorsDigital storageShift registerGate driver

A gate driver includes cascade-connected driving stages. Each of the driving stages includes a first shift register circuit and a second shift register circuit. The first shift register circuit is configured for outputting a present stage driving signal and a next stage driving signal. The second shift register circuit is electrically coupled to the first shift register circuit and configured for outputting a present stage gate signal, a first next stage gate signal, and a second next stage gate signal. Furthermore, a display panel is also provided herein.

Owner:AU OPTRONICS CORP

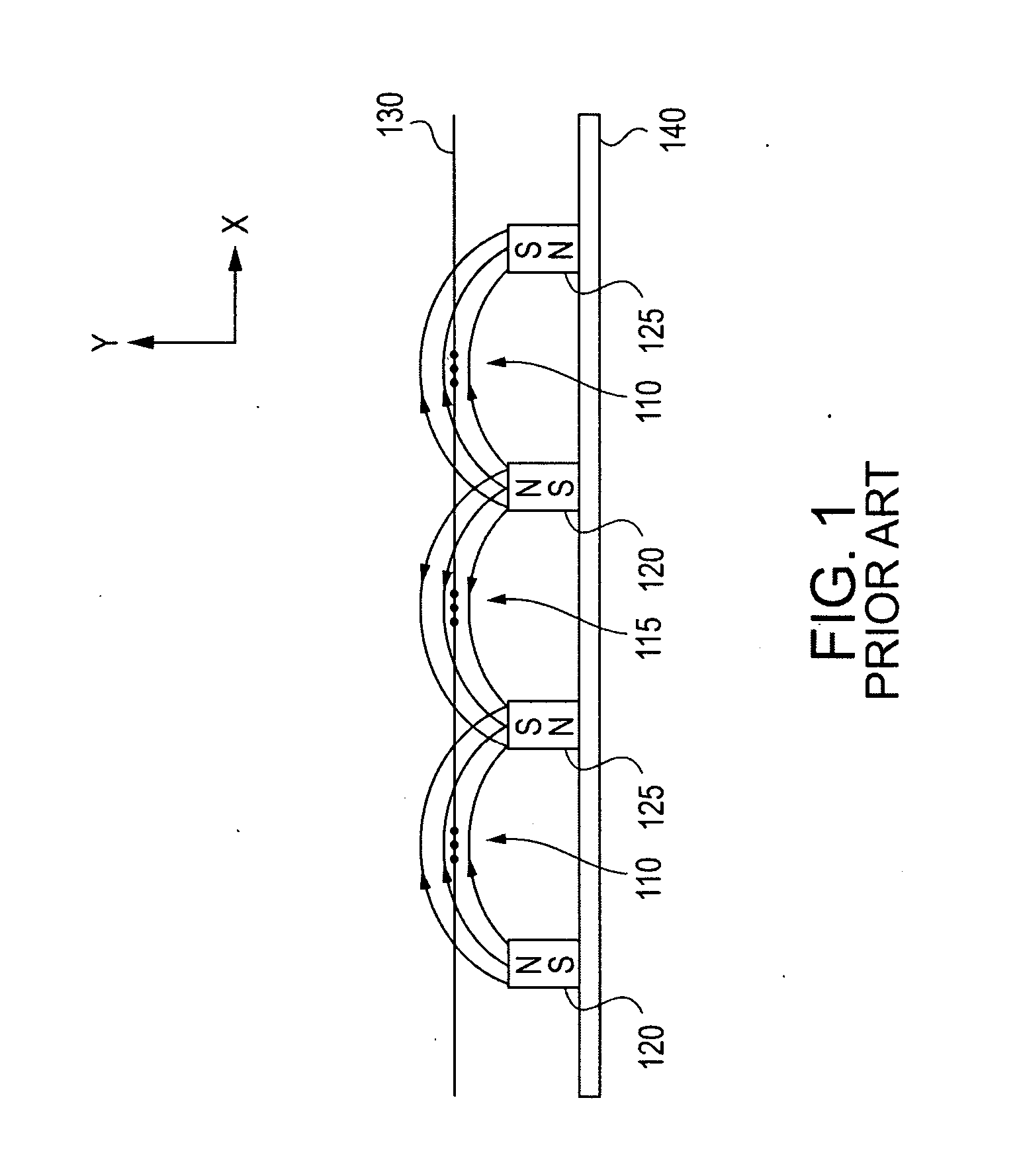

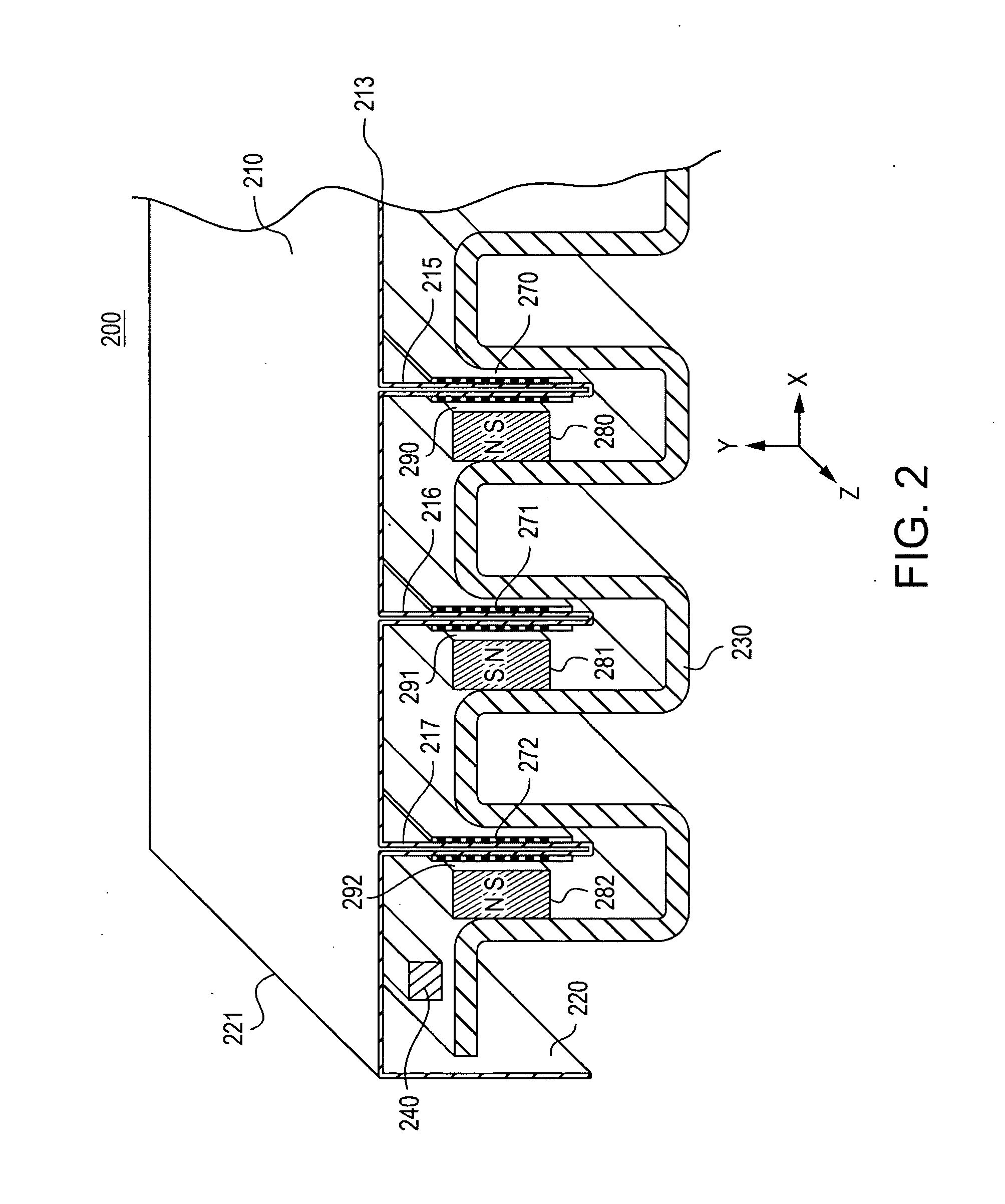

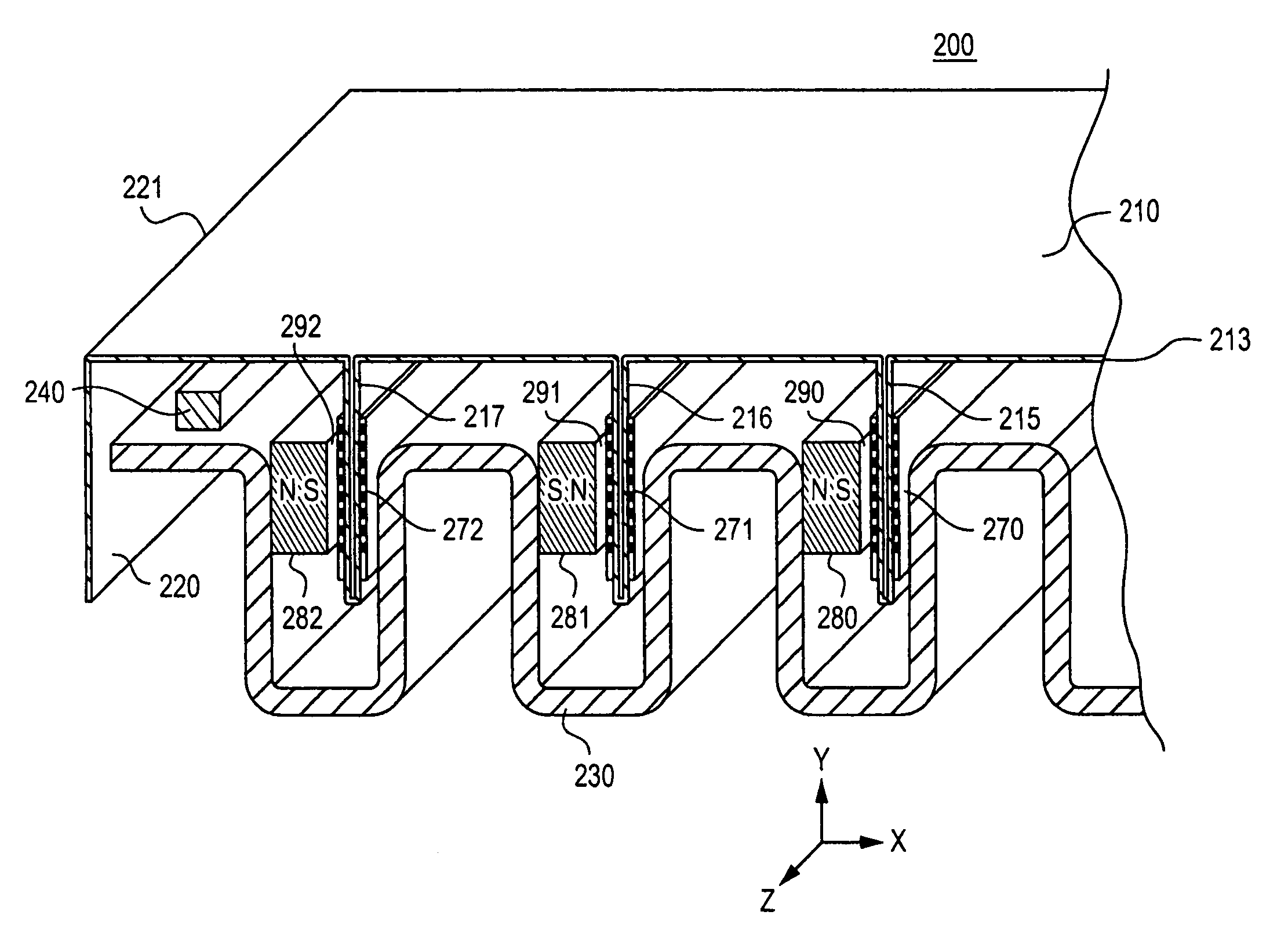

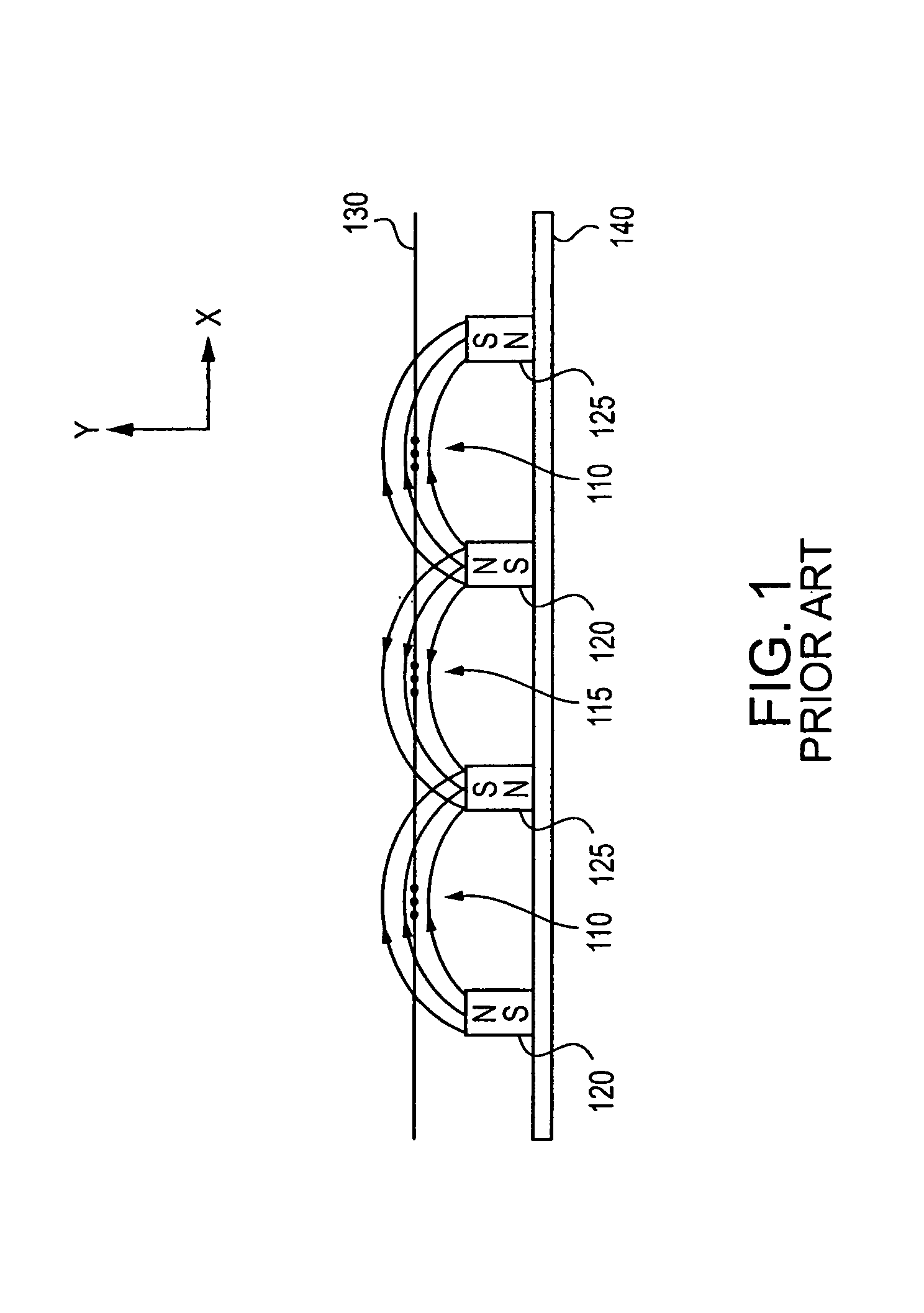

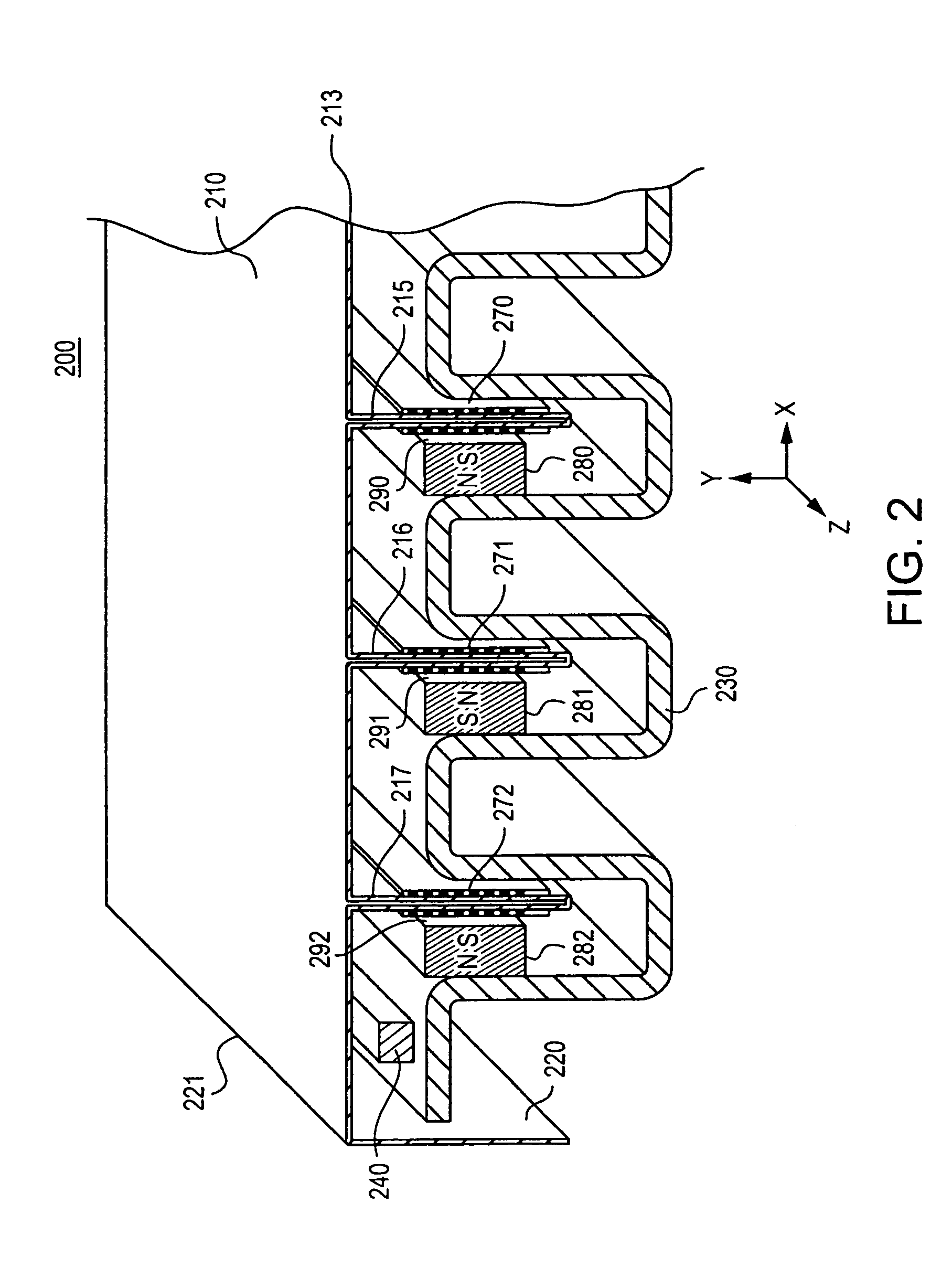

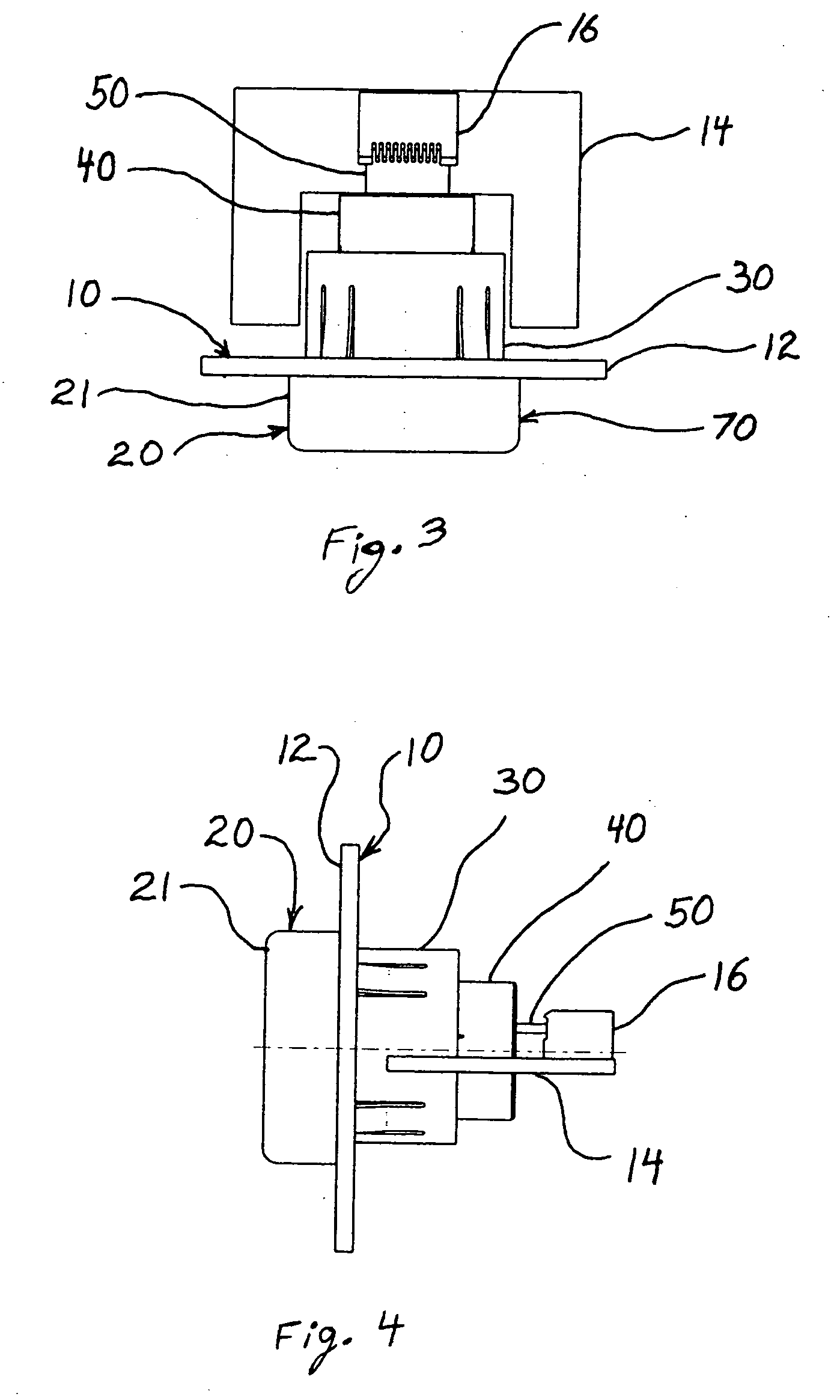

Low-profile transducer

ActiveUS20050031153A1Low-profileReduce depthBroadcast circuit arrangementsPlane diaphragmsTransducerEngineering

One embodiment of a low-profile transducer includes a at least one fin perpendicularly mounted on a planar diaphragm, with a voice coil mounted onto the fin. The voice coil may reside in a strong uniform magnetic field. The locations at which the diaphragm is connected to a frame may be coplanar with a center of mass of the diaphragm. The three-dimensional structure of diaphragm and fins may be formed using origami techniques.

Owner:HARMAN INT IND INC

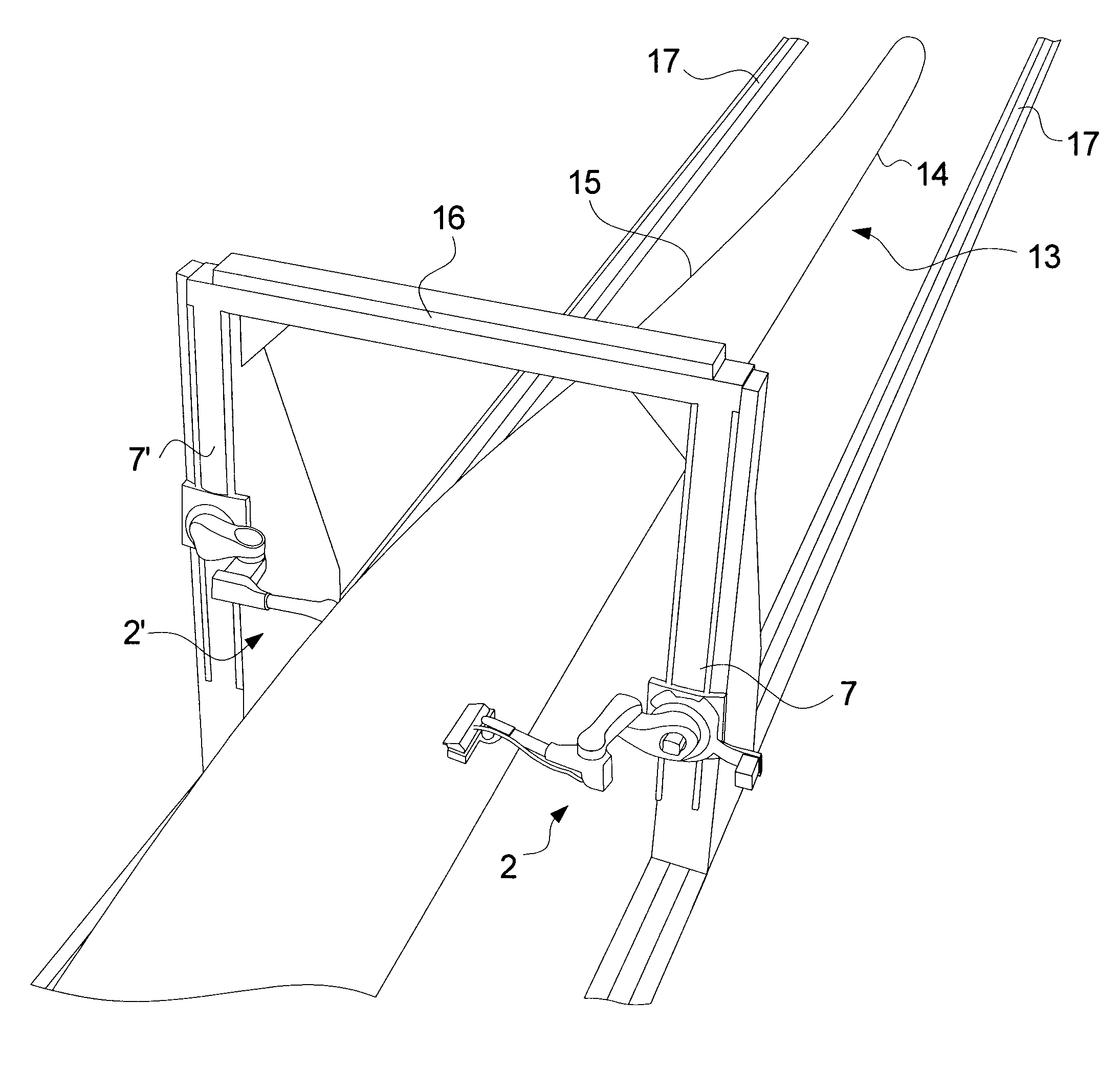

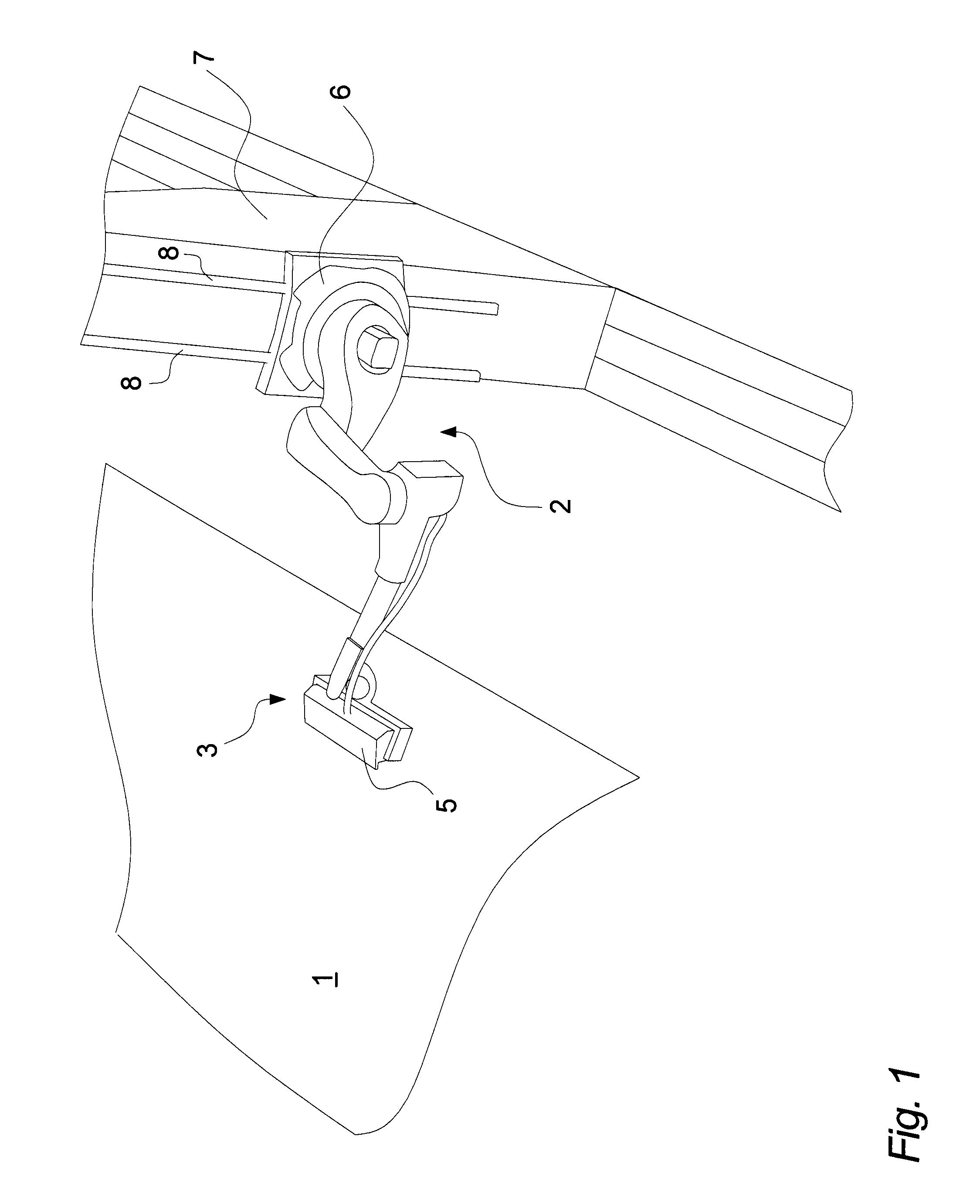

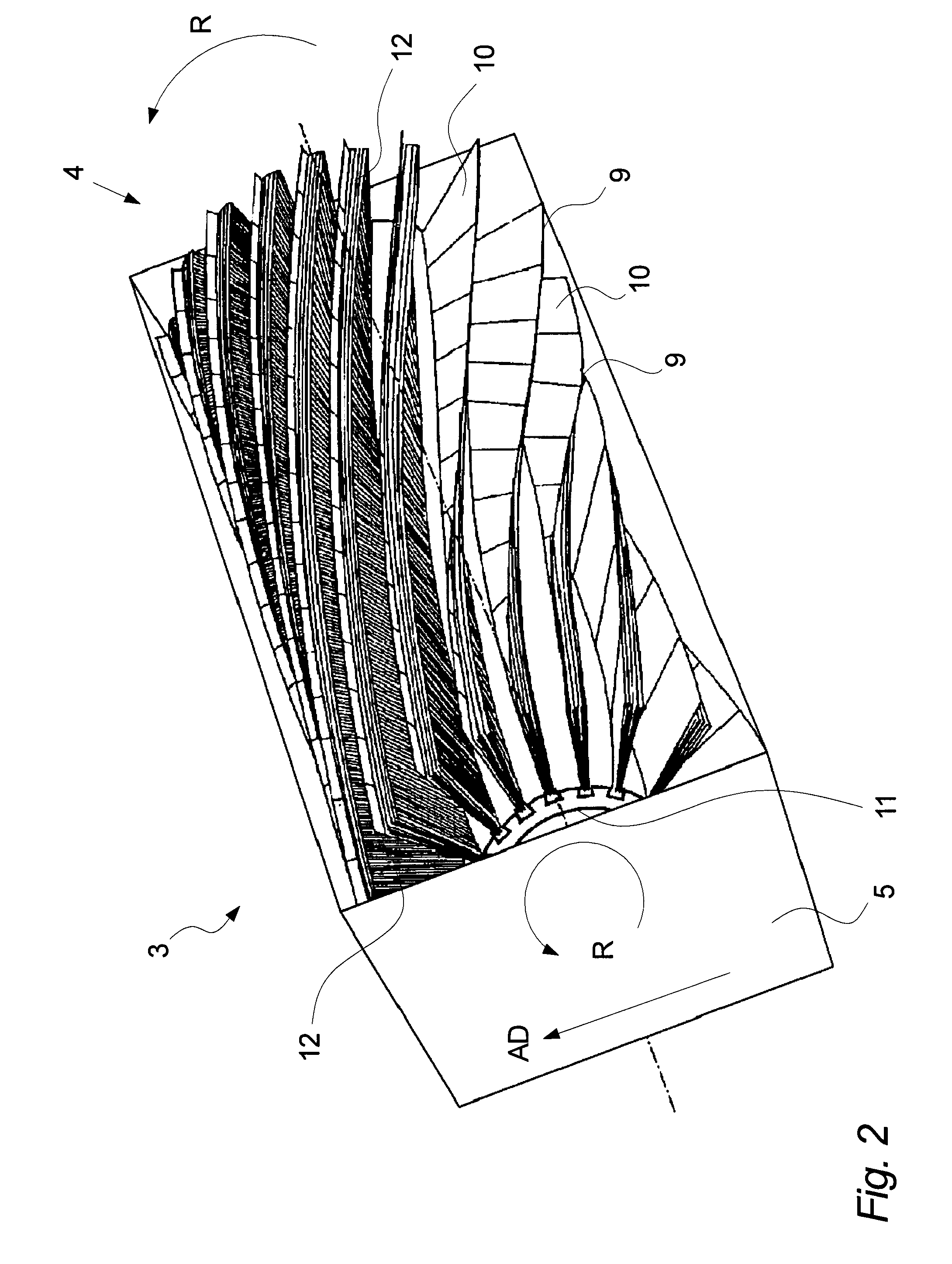

Abrading arrangement to abrade a surface of an item and method of use thereof

InactiveUS20130178134A1Increase freedomMore areaProgramme-controlled manipulatorPolishing machinesRobotic armMechanical engineering

An abrasion arrangement is disclosed to abrade a surface of an item, the arrangement comprising a multiple axis robotic arm having at least five axes, an abrading cylinder mounted on the robotic arm and comprising abrasive means which comprise abrasive lamellae of an abrasive sheet, such as abrasive cloth, of which the front side has abrasive properties and which extend substantially radially from an elongated core and means for driving said core to rotate around a longitudinal axis of the core, and control means for controlling the operation of the robotic arm so to control e.g. the position of the abrading cylinder on said surface, the force with which the abrading cylinder is pressed towards said surface and the velocity with which the abrading cylinder is moved with respect to said surface.

Owner:ELTRONIC

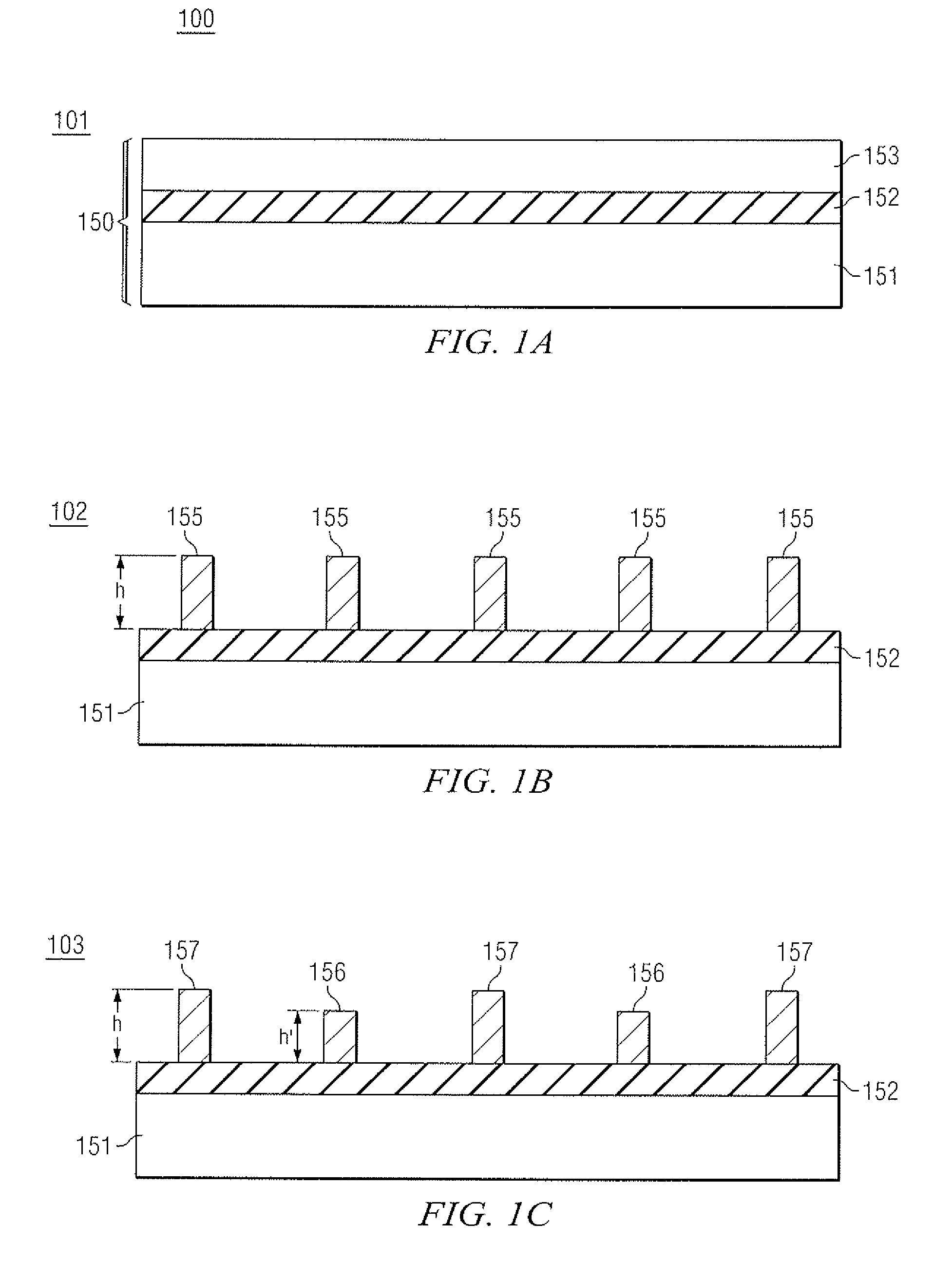

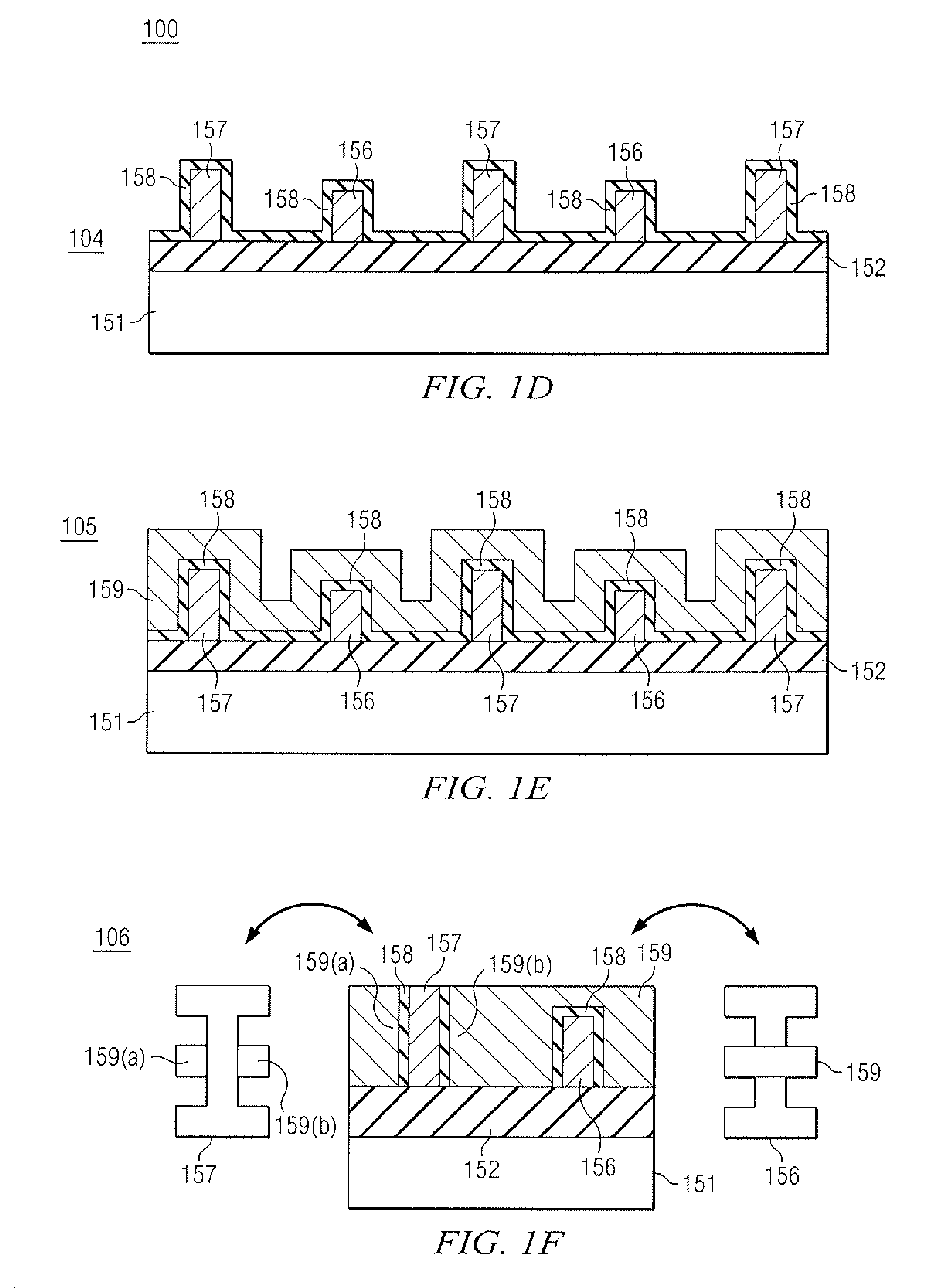

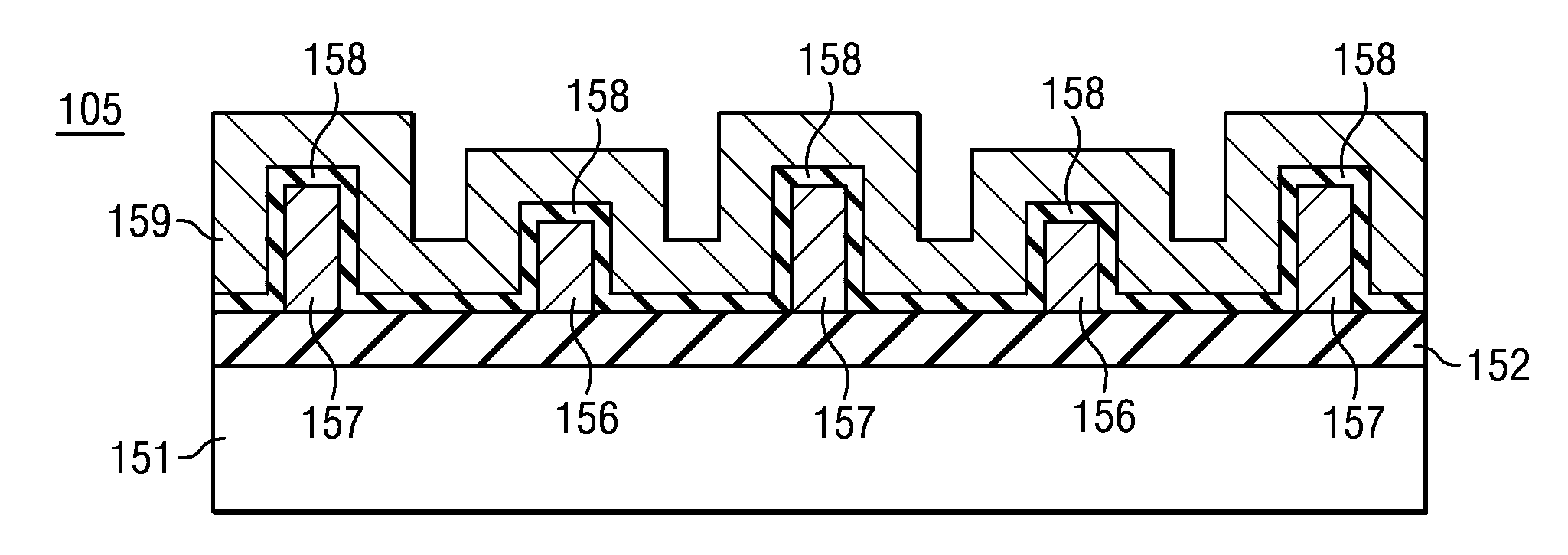

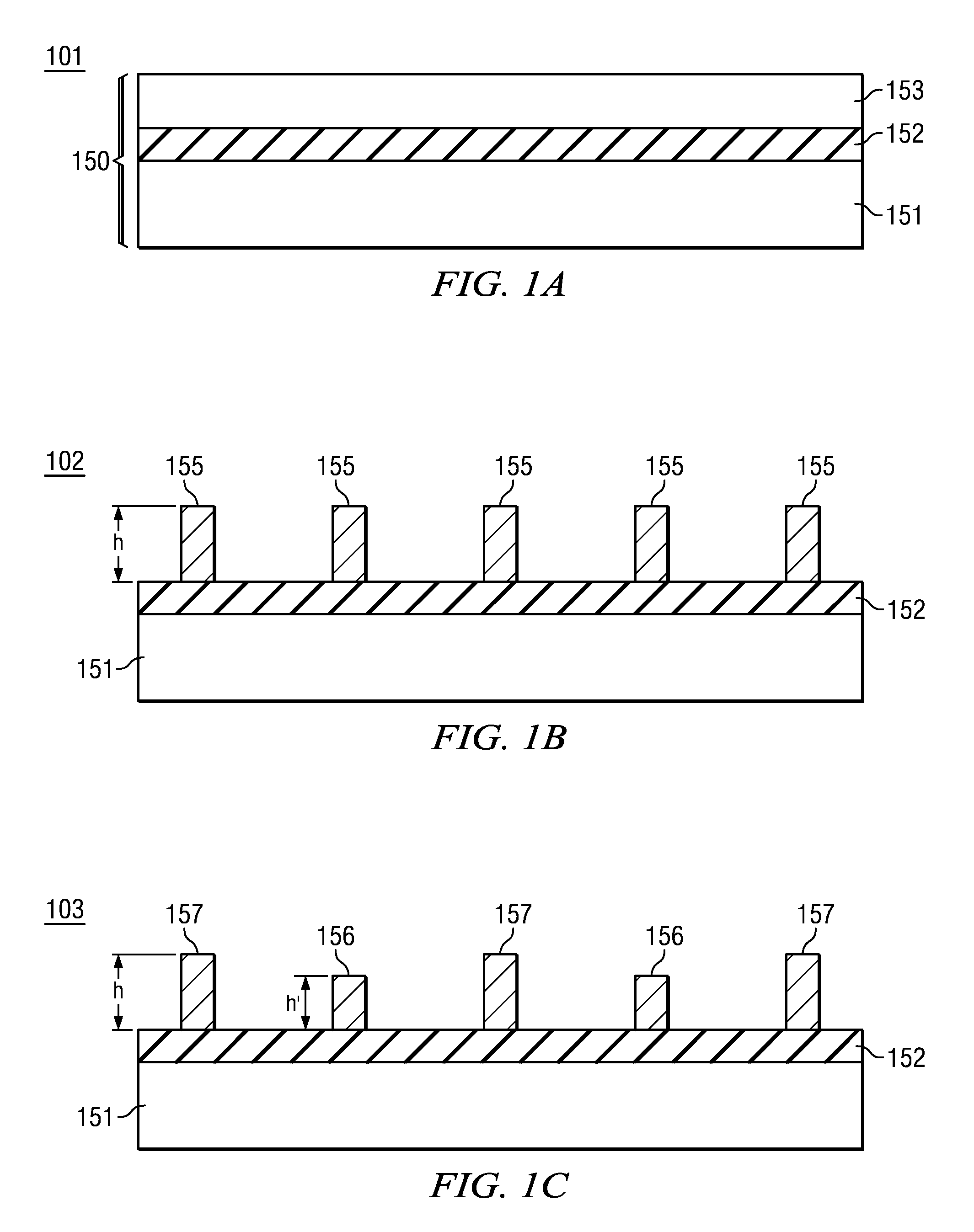

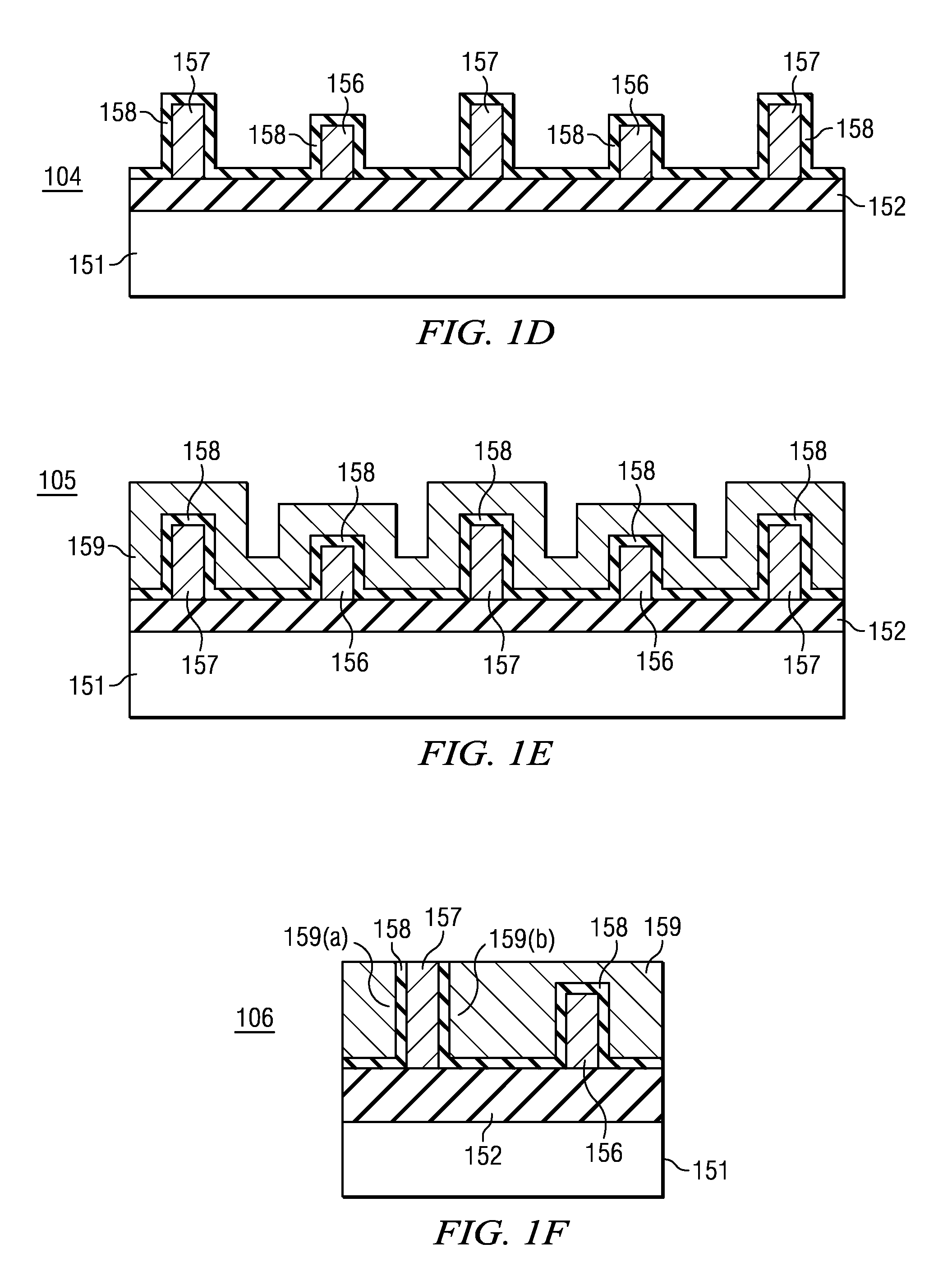

Process for forming both split gate and common gate finfet transistors and integrated circuits therefrom

A method to fabricate an integrated circuit (IC) that includes a plurality of MOSFETs including at least one common gate FinFET device and at least one split gate FinFET device. A substrate having a semiconductor surface is provided. A plurality of fins are formed from the semiconductor surface including at least one taller fin of a first height and at least one shorter fin of a second height, wherein the first height is at least 10% greater than the second height. Gate slacks are formed on the taller and shorter fins such that a gate electrode for the taller fin is a split gate electrode and a gate electrode for the shorter fin is a common gate electrode. Fabrication of the IC is completed, wherein the split gate FinFET includes the split gate electrode and the common gate FinFET device includes the common gate electrode. An IC includes a substrate having a semiconductor surface, a plurality of semiconductor fins including at least one taller fin of a first height and at least one shorter fin of a second height, wherein the first height is at least 10% greater than the second height, and at least one common gate FinFET device formed from the shorter fin and at least one split gate FinFET device providing a parallel gate transistor pair comprising a first and a second transistor formed from the taller fin.

Owner:TEXAS INSTR INC

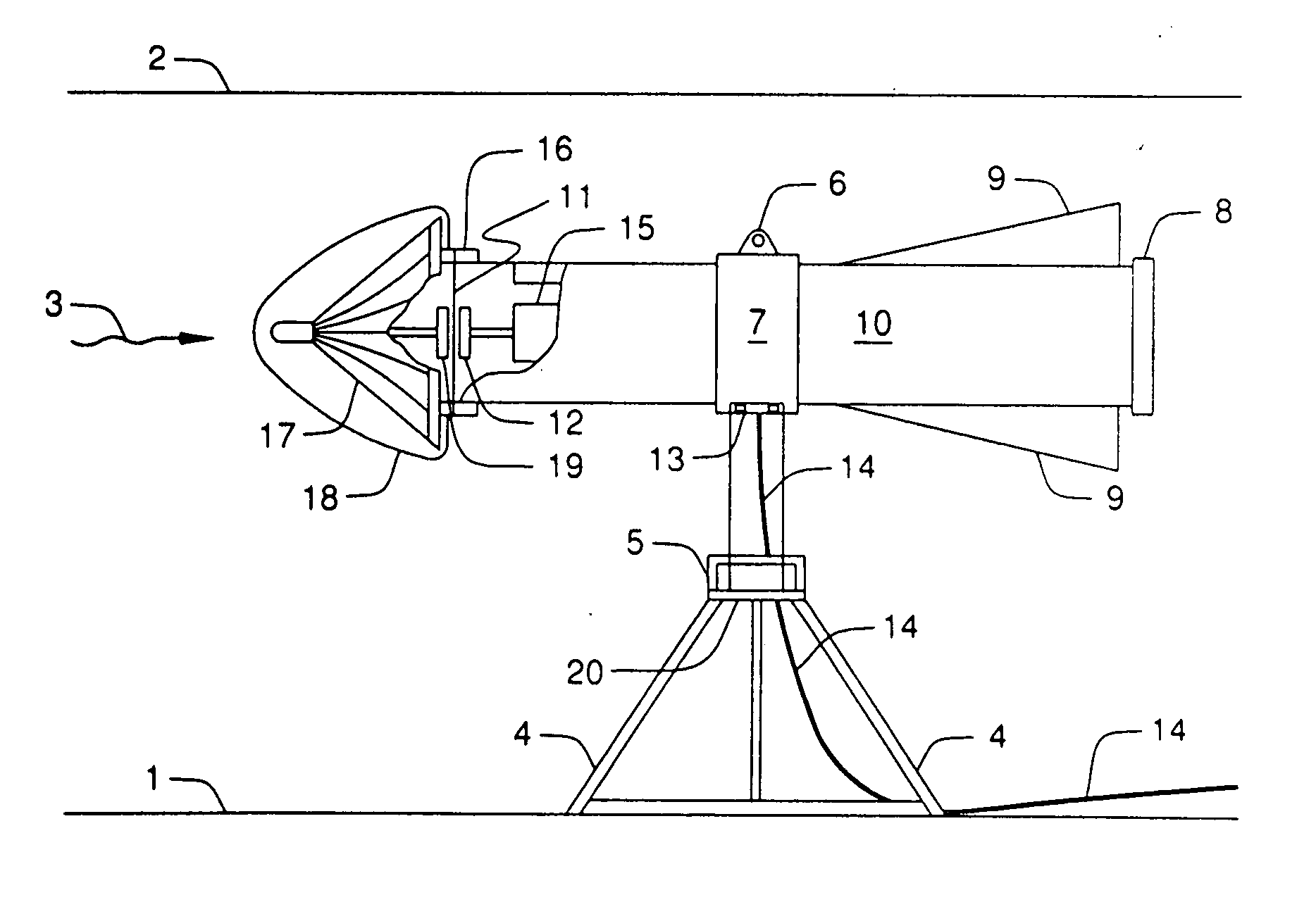

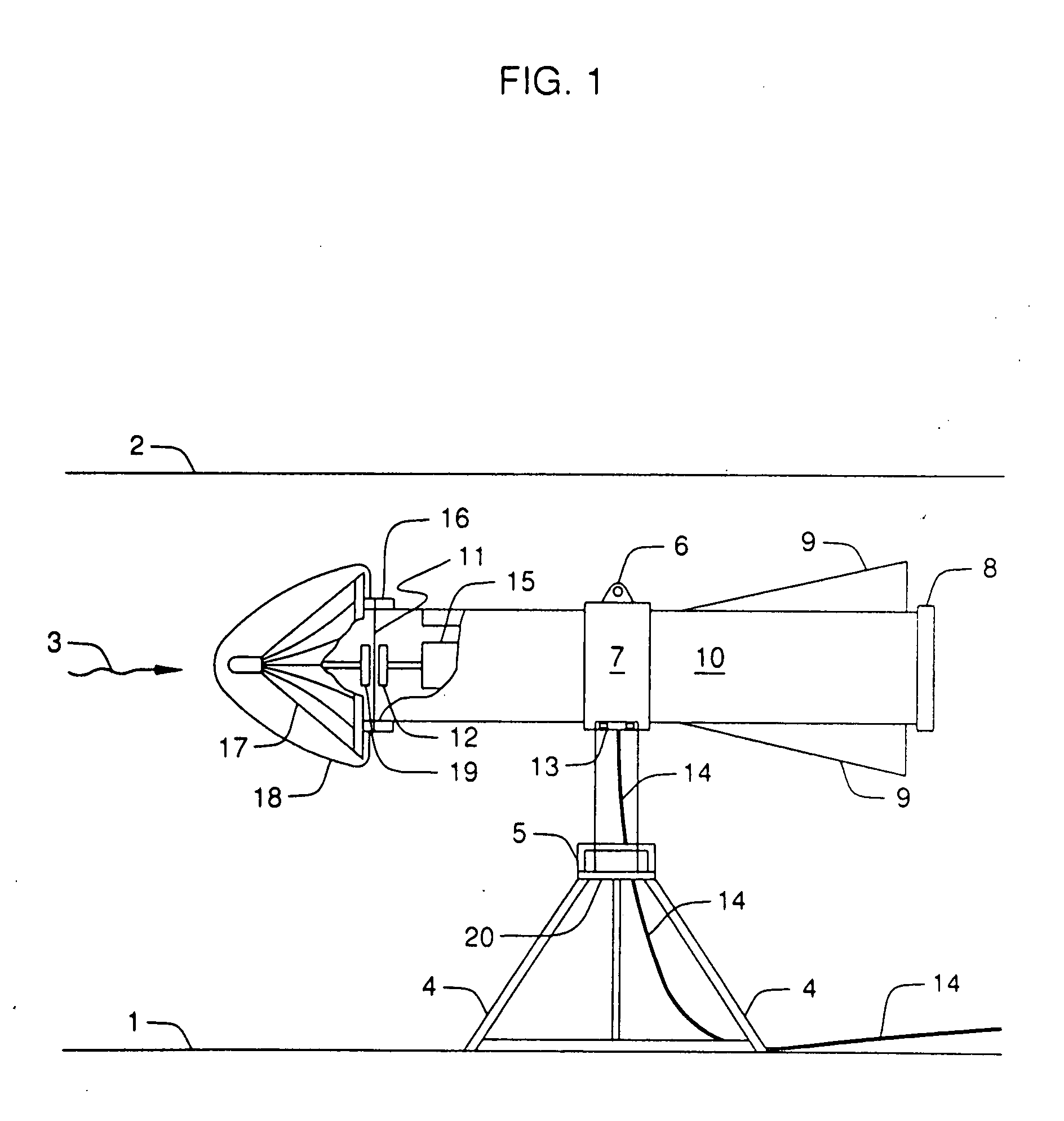

Tidal/water current electrical generating system

InactiveUS20090146430A1Economic and safe and efficientAvoid excessive diameterMachines/enginesEngine componentsImpellerAlternator

An integral system to utilize the flow of water, fresh or ocean, to generate electric power from river flow or tidal currents, consisting of three parts, an especially designed impeller to convert the water flow into rotary mechanical motion, a totally encapsulated alternator / generator, and a pedestal upon which the entire device is mounted which is set into the sea bed or river bed and which is fitted with a swivel bearing which allows a limited rotation of the alternator / impeller assembly, and with fins to keep the impeller pointed into the existing current and which also serve as heatsinks for the alternator / generator.

Owner:SEAR WALTER EDMOND

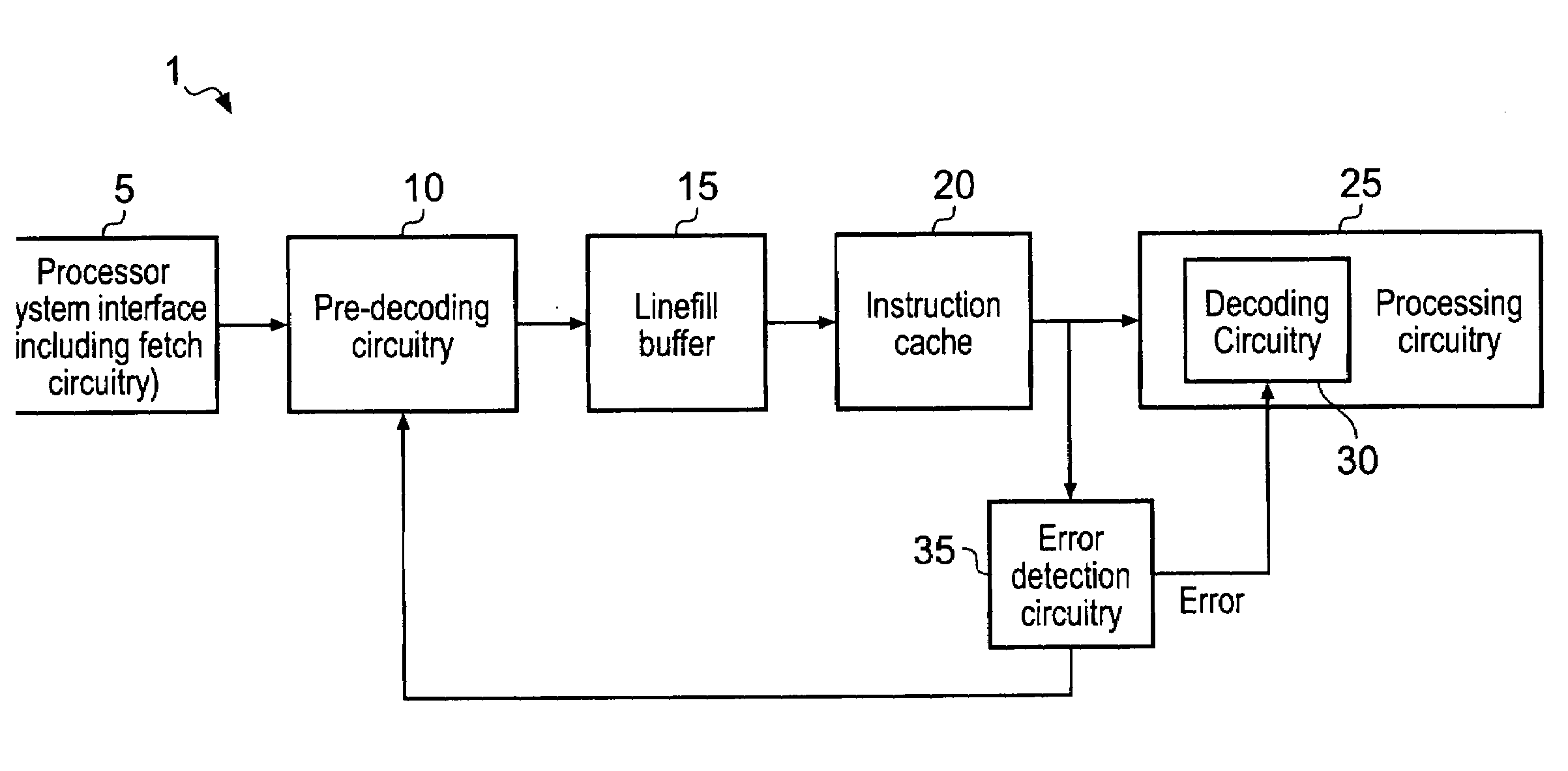

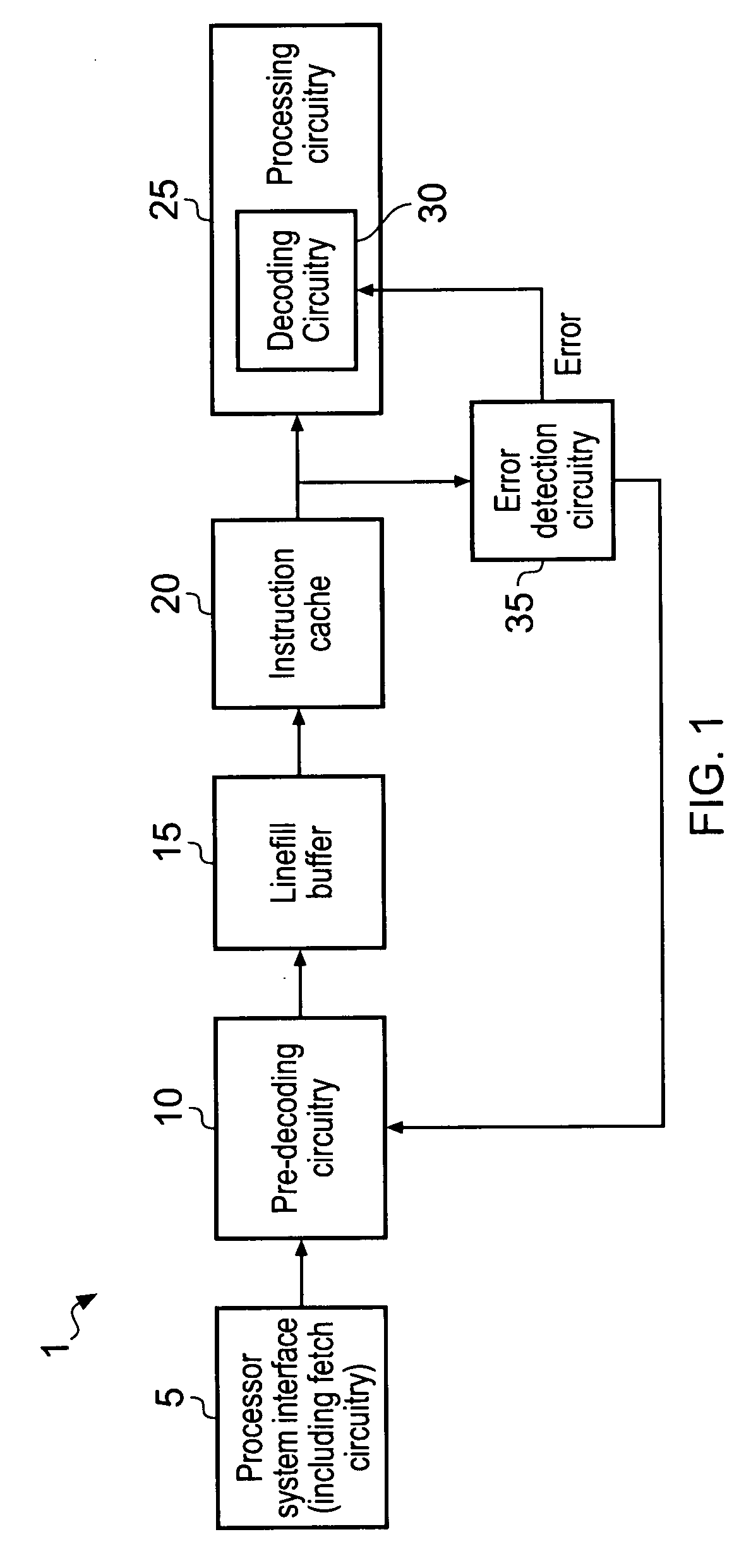

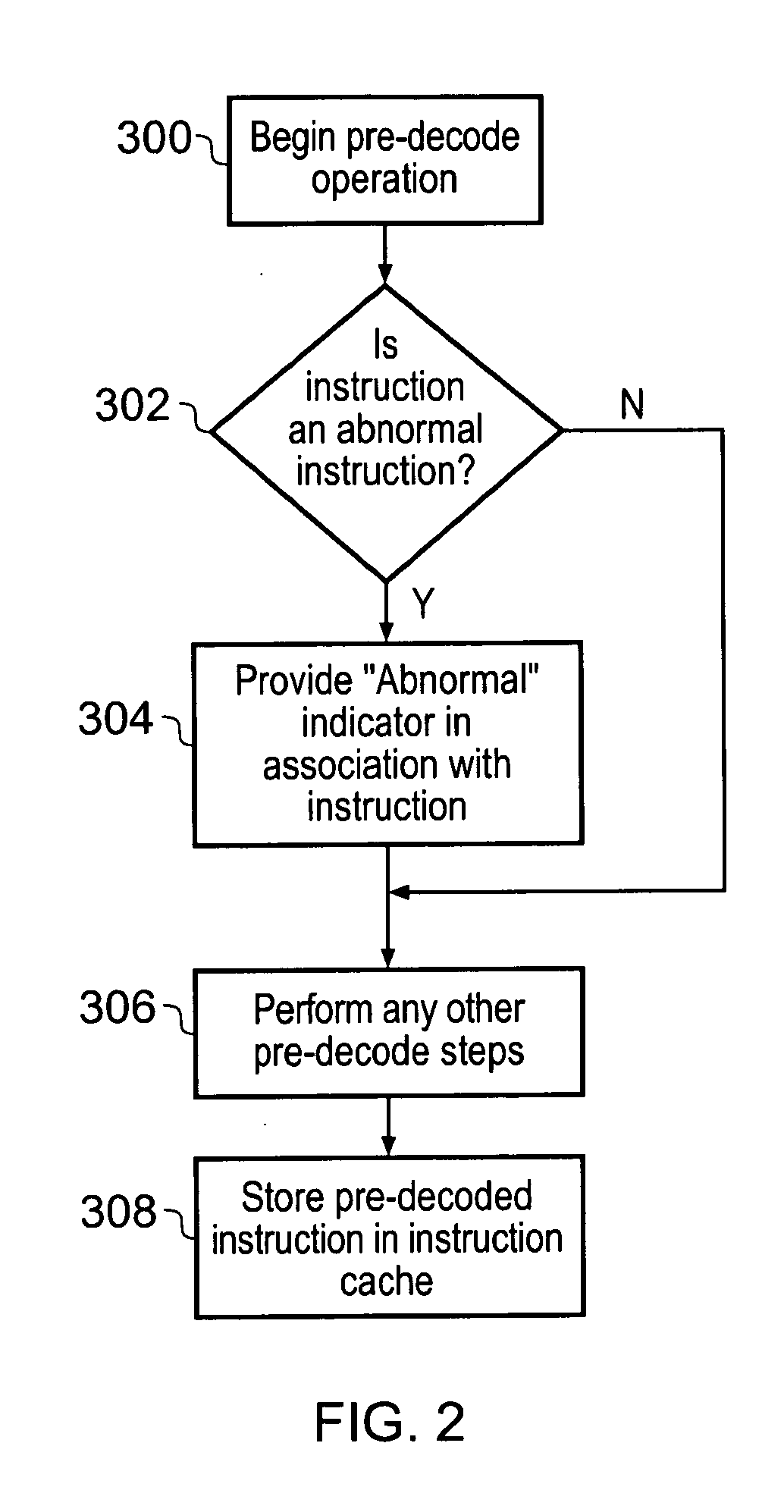

Data processing apparatus and method for handling instructions to be executed by processing circuitry

ActiveUS20090249033A1Reduce in quantityMore areaInstruction analysisMemory adressing/allocation/relocationInstruction setData processing

A data processing apparatus and method are provided for handling instructions to be executed by processing circuitry. The processing circuitry has a plurality of processor states, each processor state having a different instruction set associated therewith. Pre-decoding circuitry receives the instructions fetched from the memory and performs a pre-decoding operation to generate corresponding pre-decoded instructions, with those pre-decoded instructions then being stored in a cache for access by the processing circuitry. The pre-decoding circuitry performs the pre-decoding operation assuming a speculative processor state, and the cache is arranged to store an indication of the speculative processor state in association with the pre-decoded instructions. The processing circuitry is then arranged only to execute an instruction in the sequence using the corresponding pre-decoded instruction from the cache if a current processor state of the processing circuitry matches the indication of the speculative processor state stored in the cache for that instruction. This provides a simple and effective mechanism for detecting instructions that have been corrupted by the pre-decoding operation due to an incorrect assumption of processor state.

Owner:ARM LTD

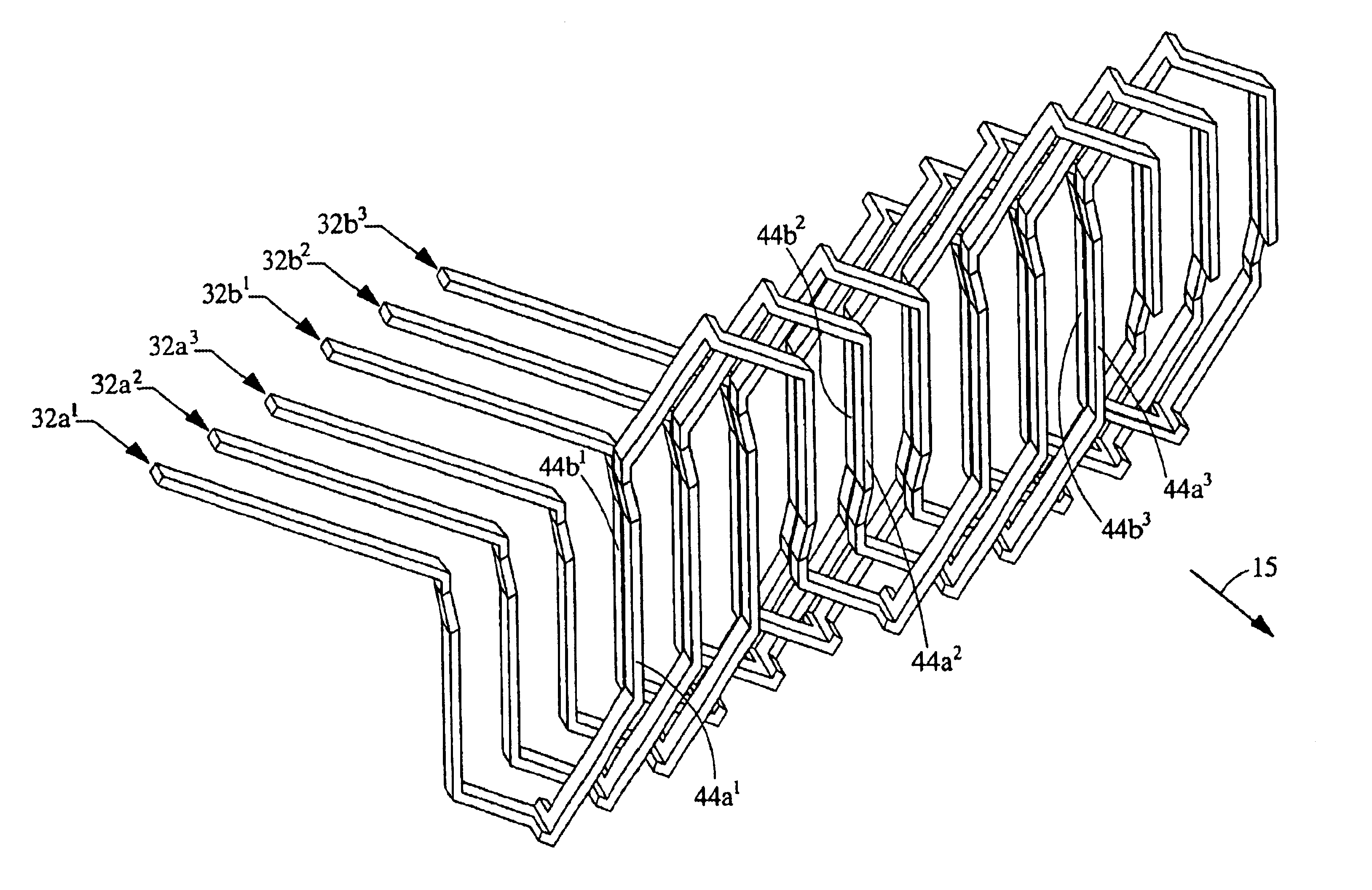

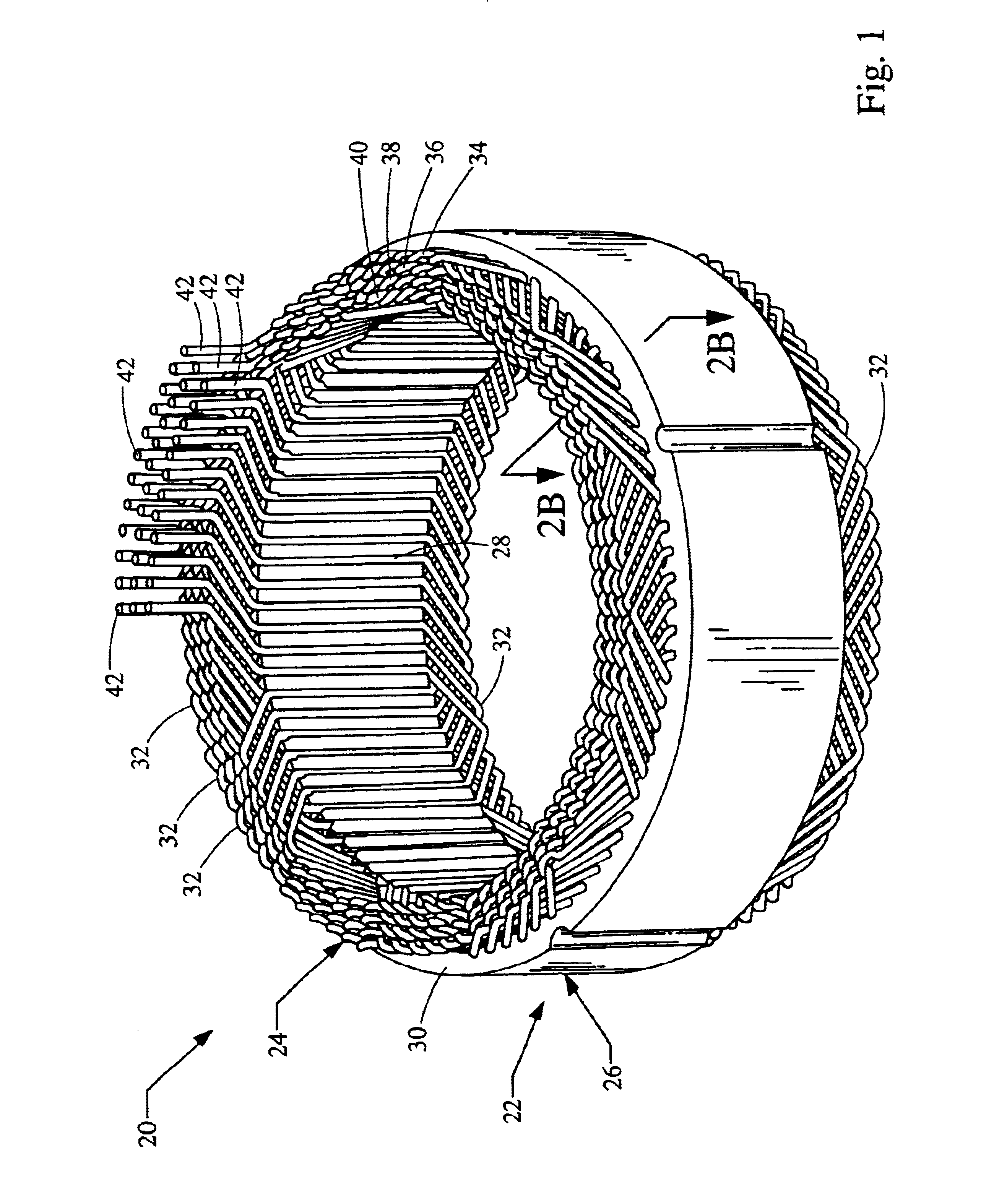

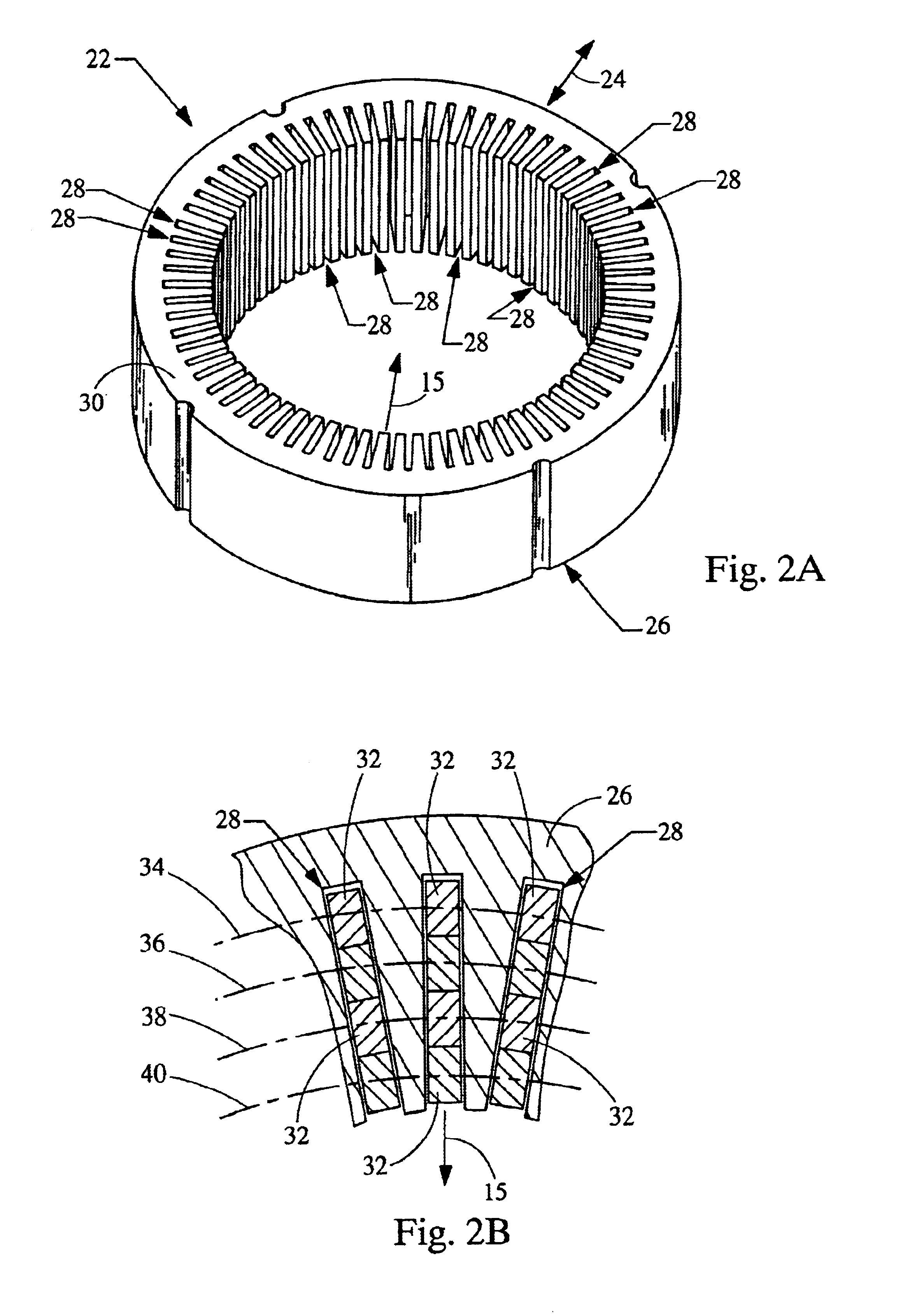

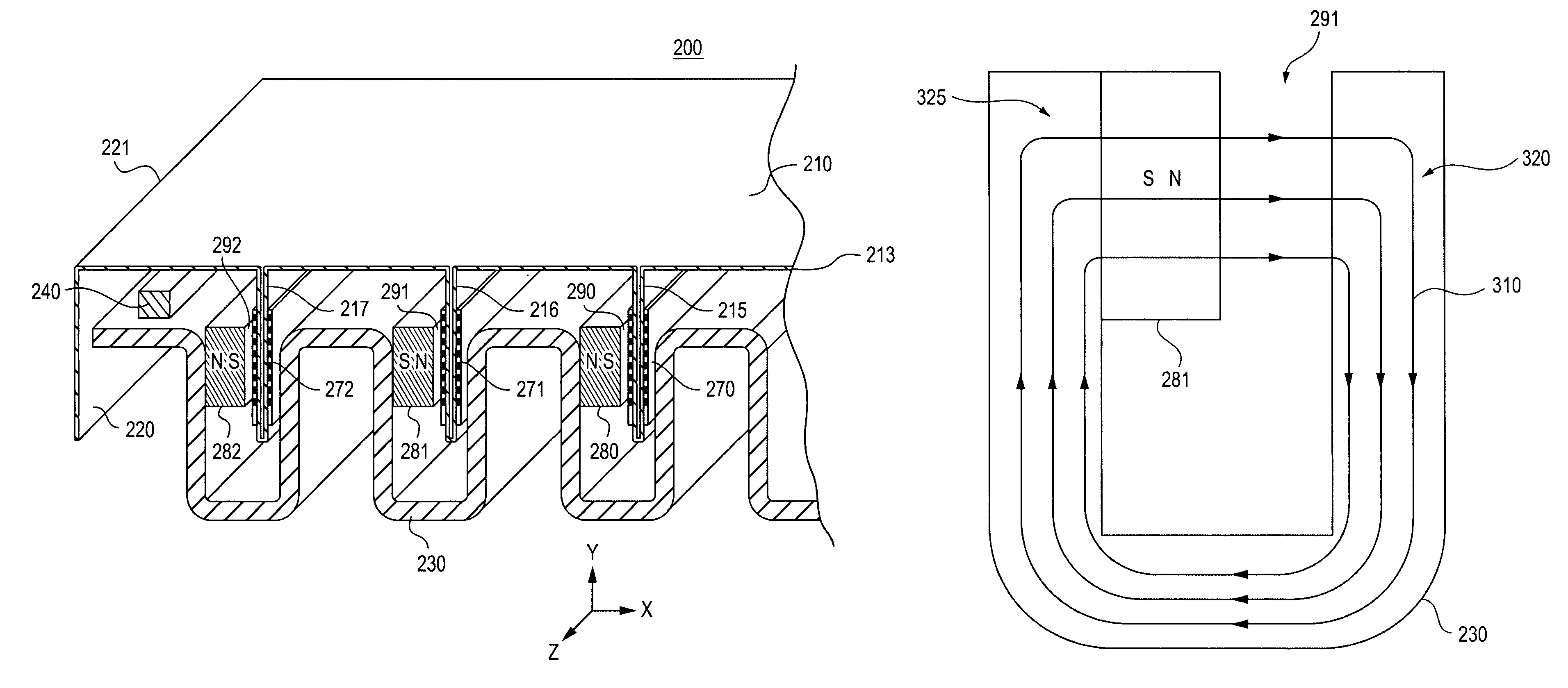

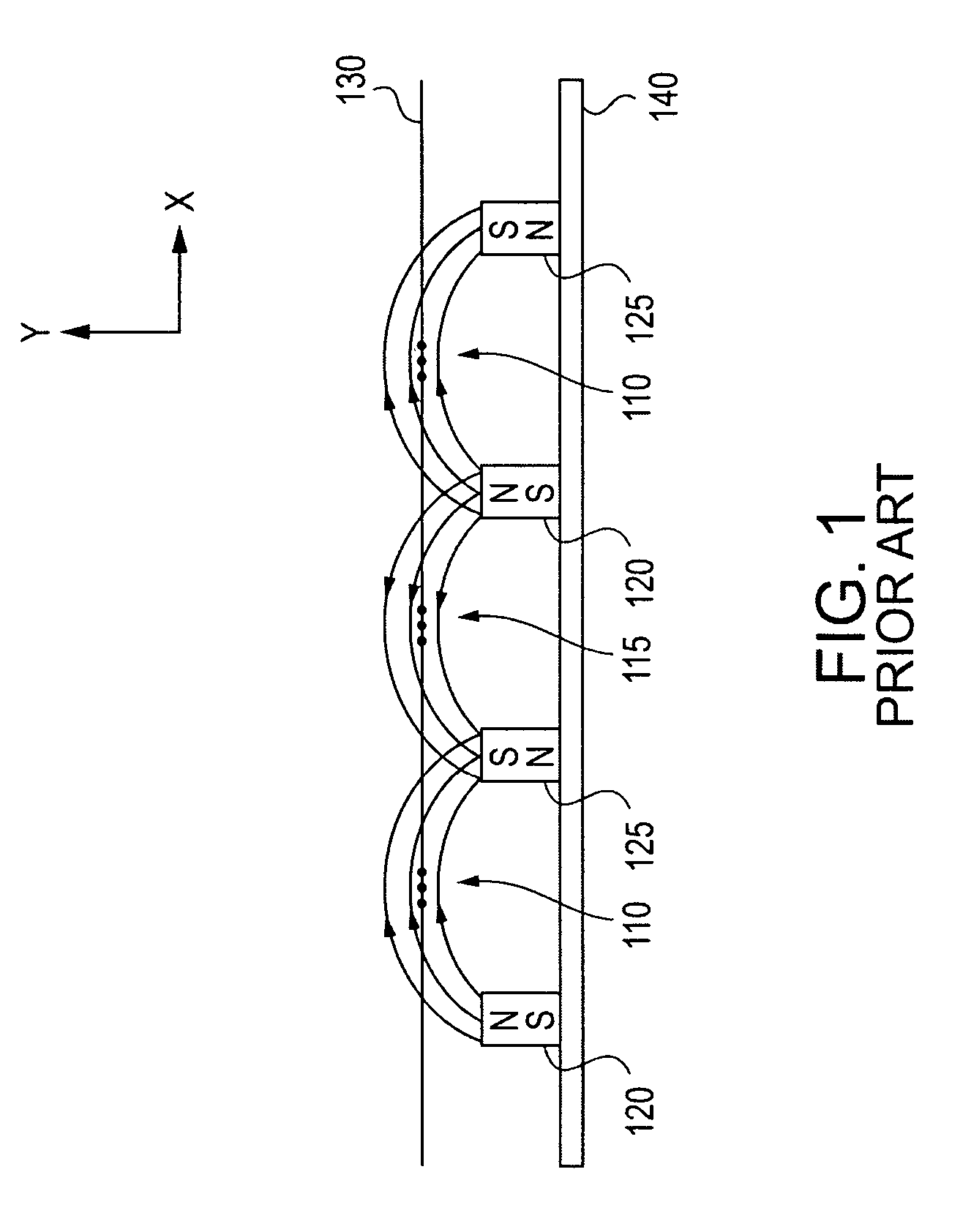

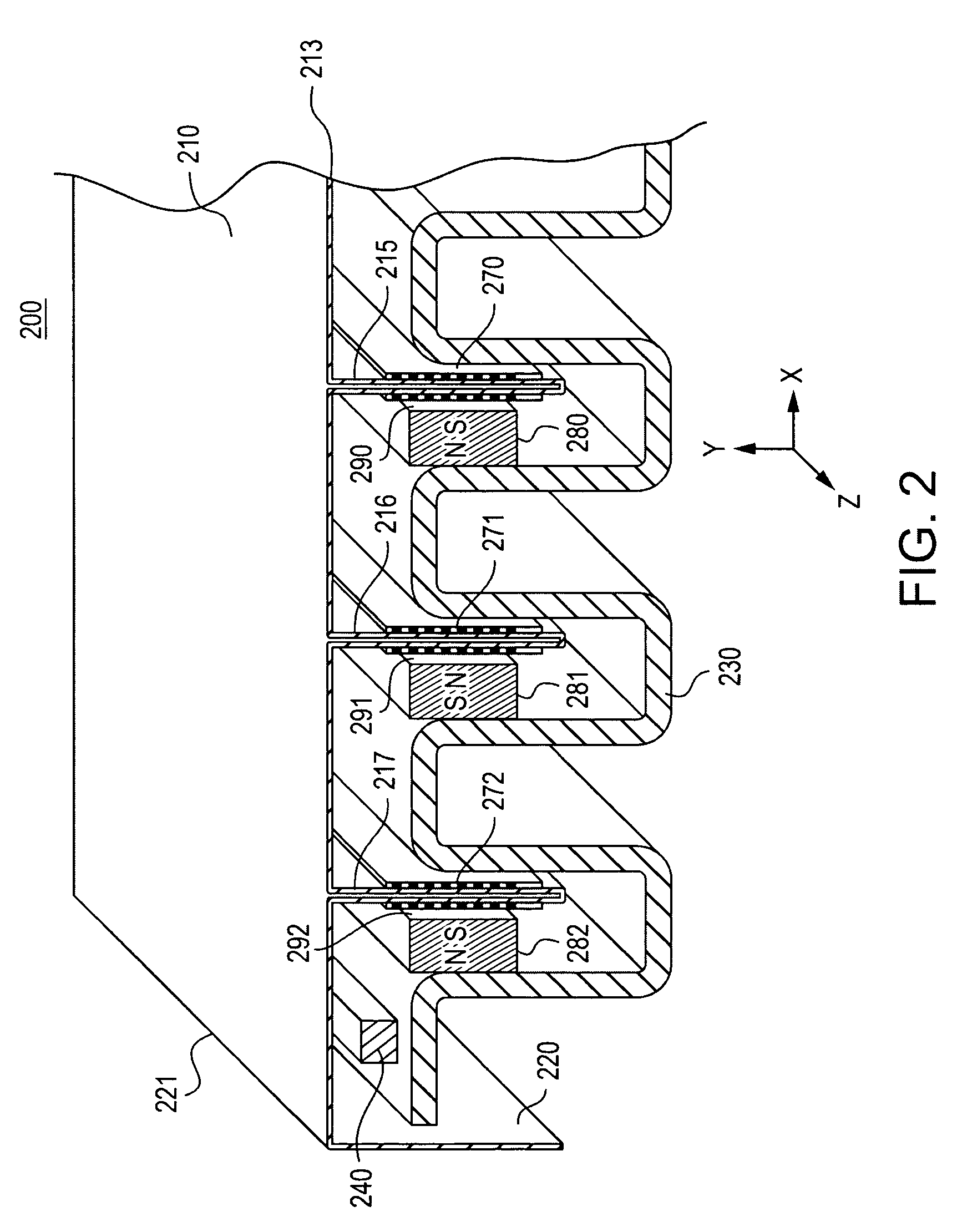

Alternator stator having a multiple filar construction to improve convective cooling

InactiveUS6930426B2Reduce coolingHigh levelSynchronous generatorsMagnetic circuitAlternatorElectrical conductor

Owner:BORGWARNER INC

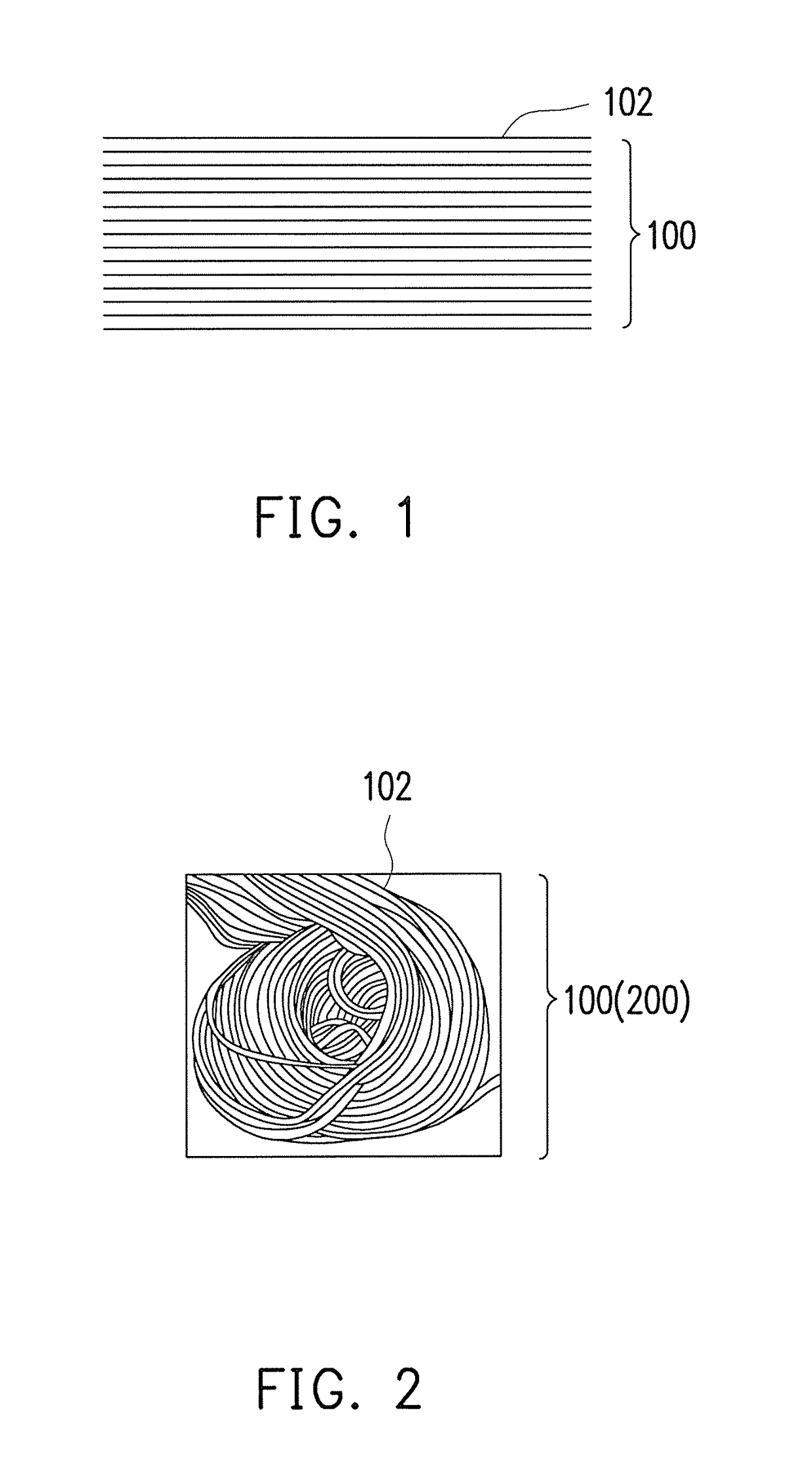

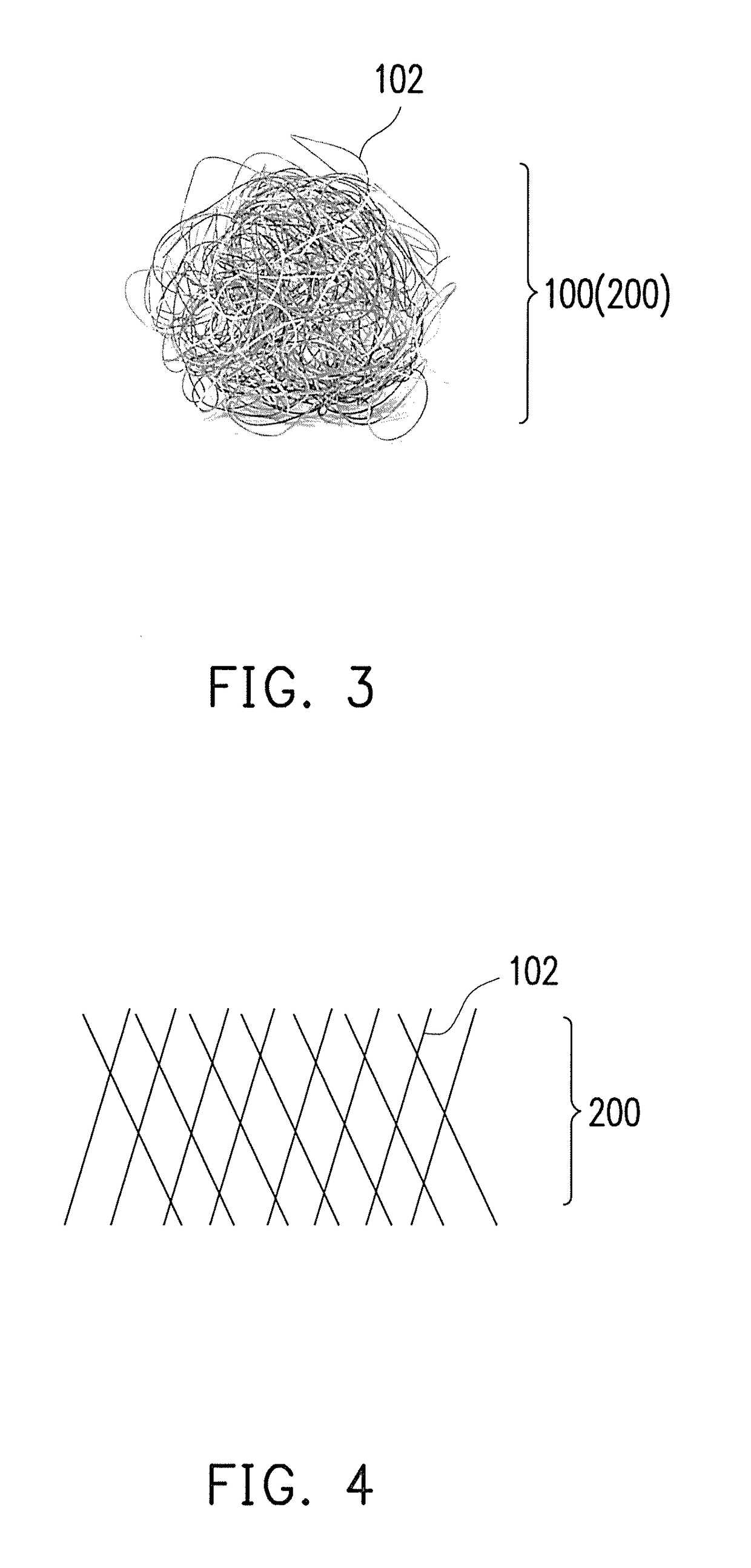

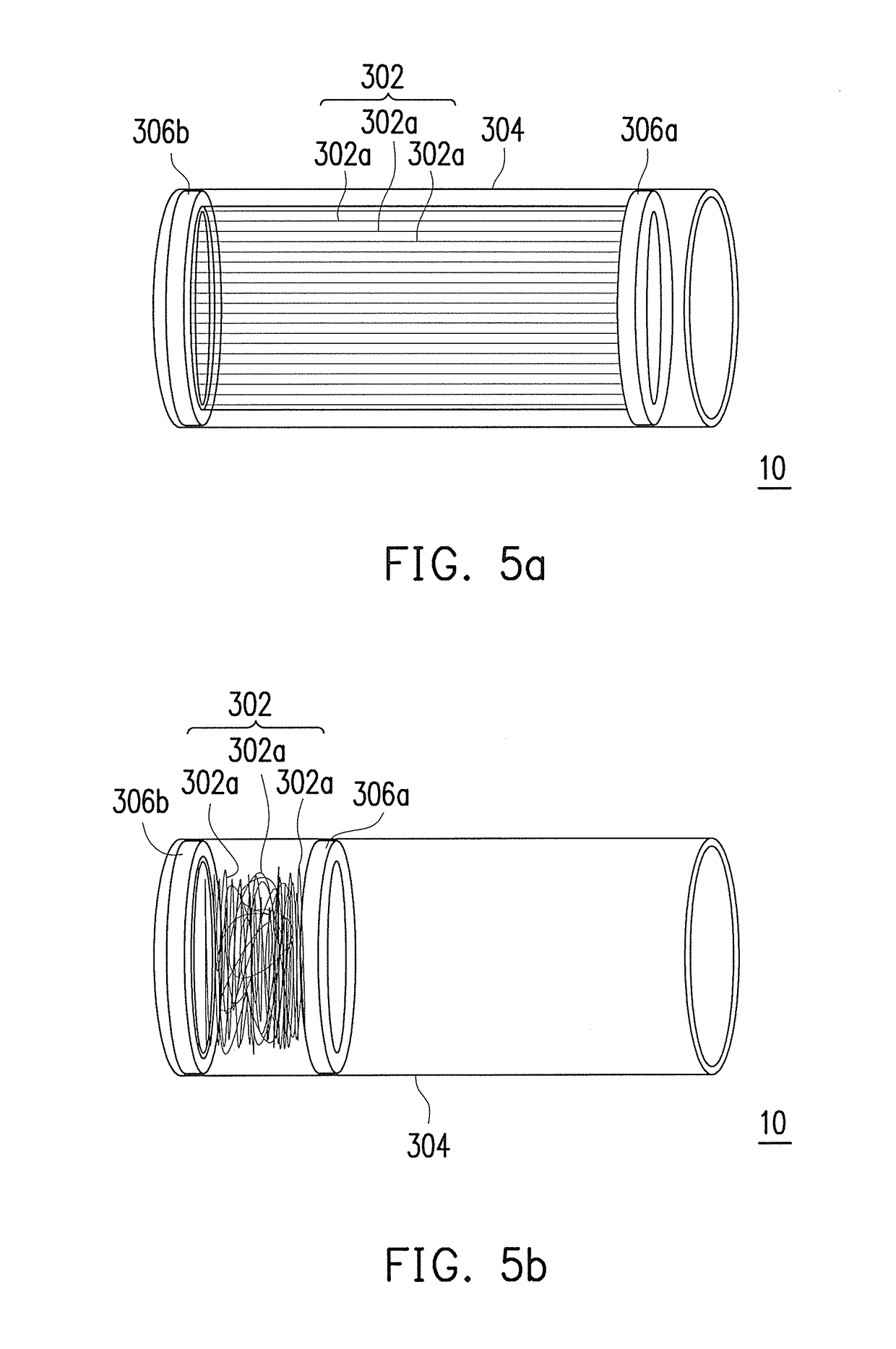

Cell culture carrier module, bioreactor and cell recovery method

InactiveUS20170166859A1High recovery rateMore areaBioreactor/fermenter combinationsBiological substance pretreatmentsRecovery methodBioreactor

A cell culture carrier module, a bioreactor and a cell recovery method are provided. The cell culture carrier module includes at least one cell culture carrier capable of transforming between a two dimensional structure and a three dimensional structure. The cell culture carrier exhibits the two dimensional structure in a loosened state and exhibits the three dimensional structure in a compressed state.

Owner:IND TECH RES INST

NOx adsorber aftertreatment system for internal combustion engines

InactiveUS20070175206A1More areaMany timesInternal combustion piston enginesExhaust apparatusCombustionHydrocotyle bowlesioides

The present invention provides for an NOx adsorber aftertreatment system for internal combustion engines which utilizes a parallel arrangement of an adsorber catalyst and a bypass. The exhaust flow from the engine is routed through the adsorber during lean operation. At a predetermined regeneration time (for example, when the adsorber catalyst is 20% full), the exhaust gas flow is reduced through the parallel leg that contains the adsorber catalyst to be regenerated (e.g., 20% through the catalyst leg, 80% of the flow to the bypass leg). A quantity of hydrocarbon is injected into the reduced-flow catalyst leg in order to make the mixture rich. Since the flow has been reduced in this leg, only a small fraction of the amount of hydrocarbon that would have been required to make the mixture rich during full flow is required. This will result in a substantial reduction in the fuel penalty incurred for regeneration of the adsorber catalyst. Once the leg has been regenerated, the exhaust flow is switched to flow 100% through the adsorber leg.

Owner:MITAL RAHUL +2

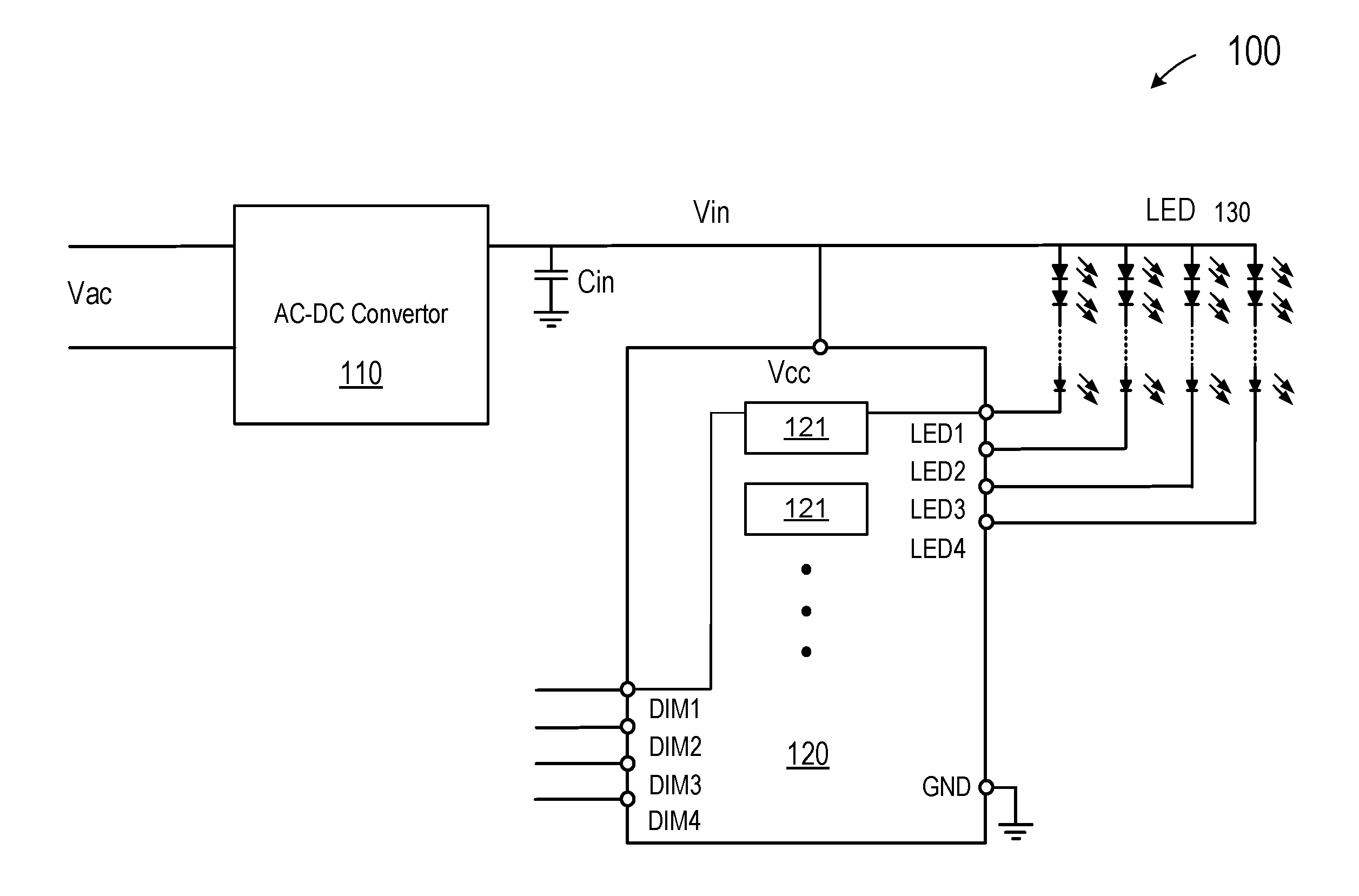

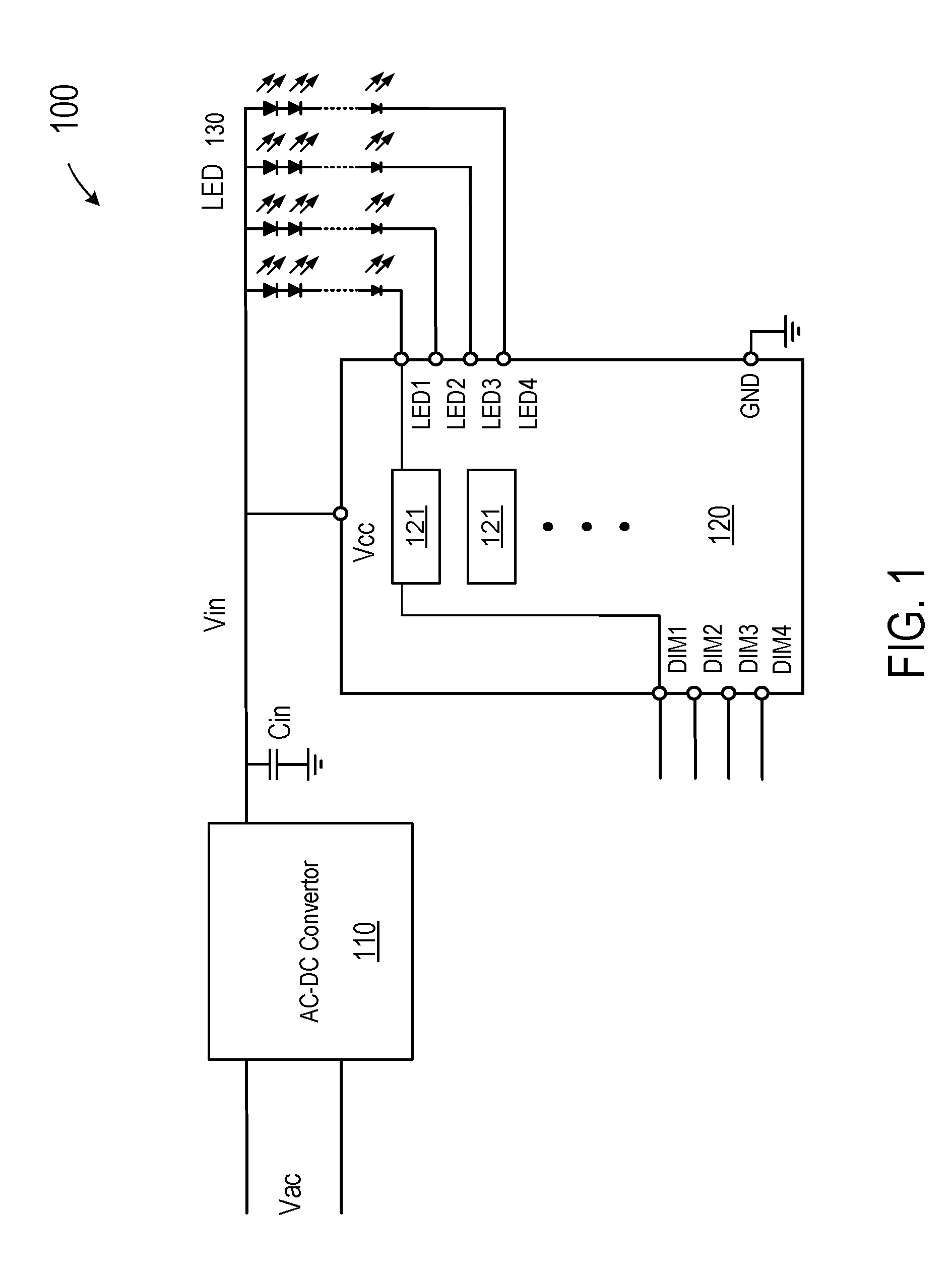

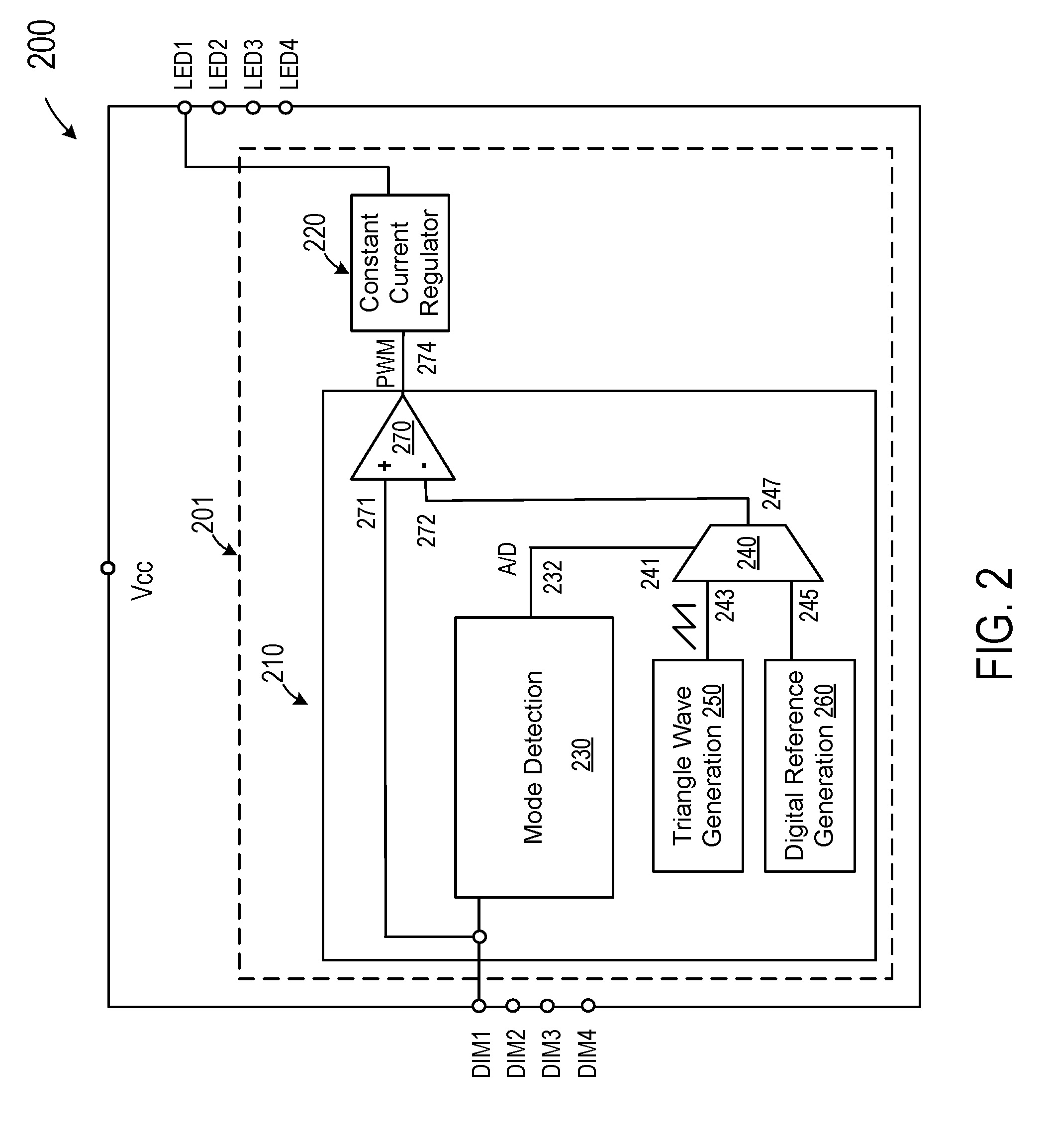

Analog and digital dimming control for LED driver

ActiveUS20160255693A1Increase costIncreased complexityElectrical apparatusElectroluminescent light sourcesControl signalMultiplexer

A control circuit includes an input terminal for receiving an input signal, which maybe either a digital input signal or an analog input signal, and the control circuit is configured to provide a digital control signal in response to the input signal. The control circuit may include a mode detection circuit for determining whether the input signal is a digital signal or an analog signal and providing a mode signal, a multiplexer circuit configured to select either a digital reference signal or an analog reference signal in response to the mode signal, and a comparator configured for comparing the input signal with the reference signal selected by the multiplexer to provide the PWM control signal.

Owner:DIODES INC

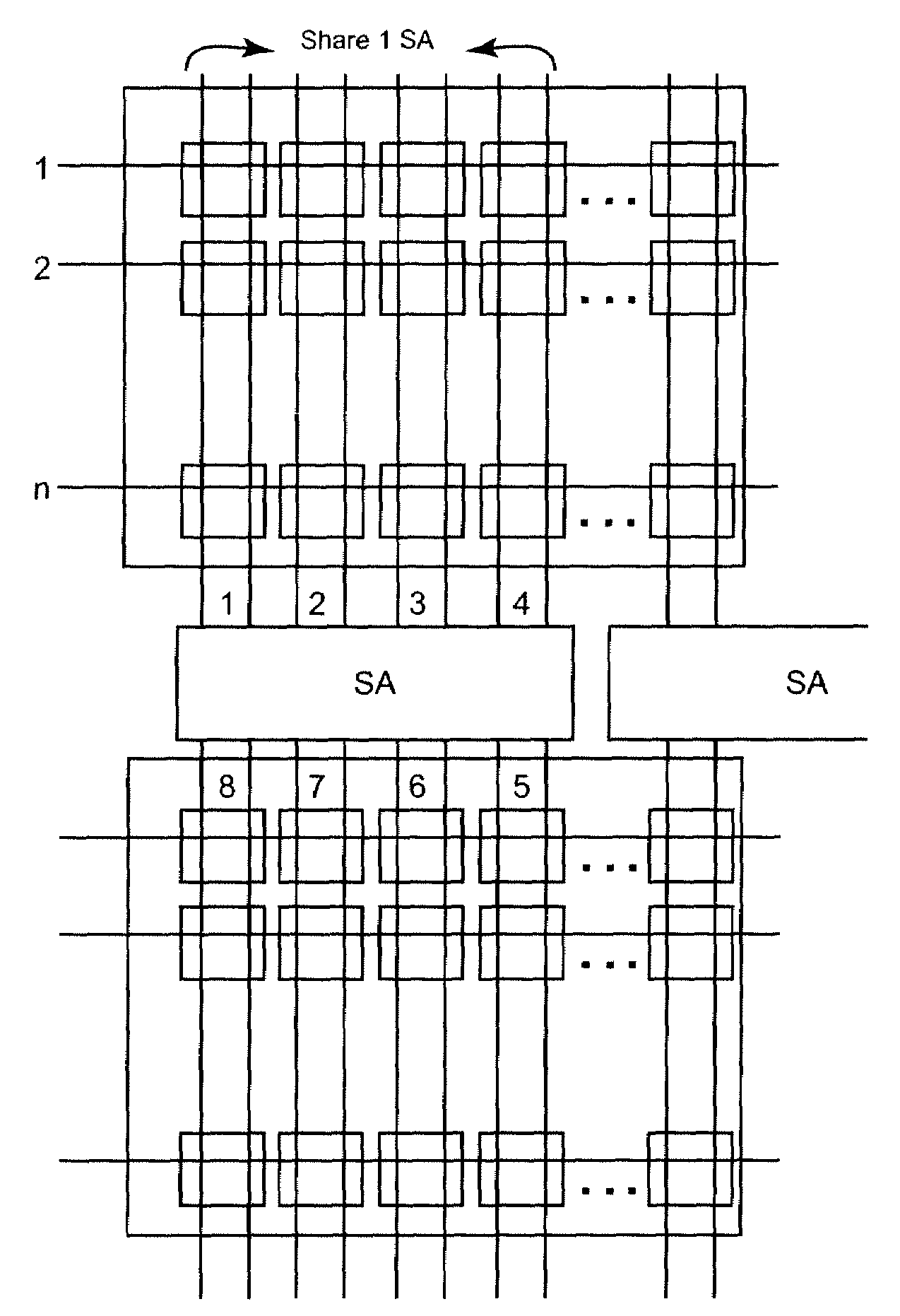

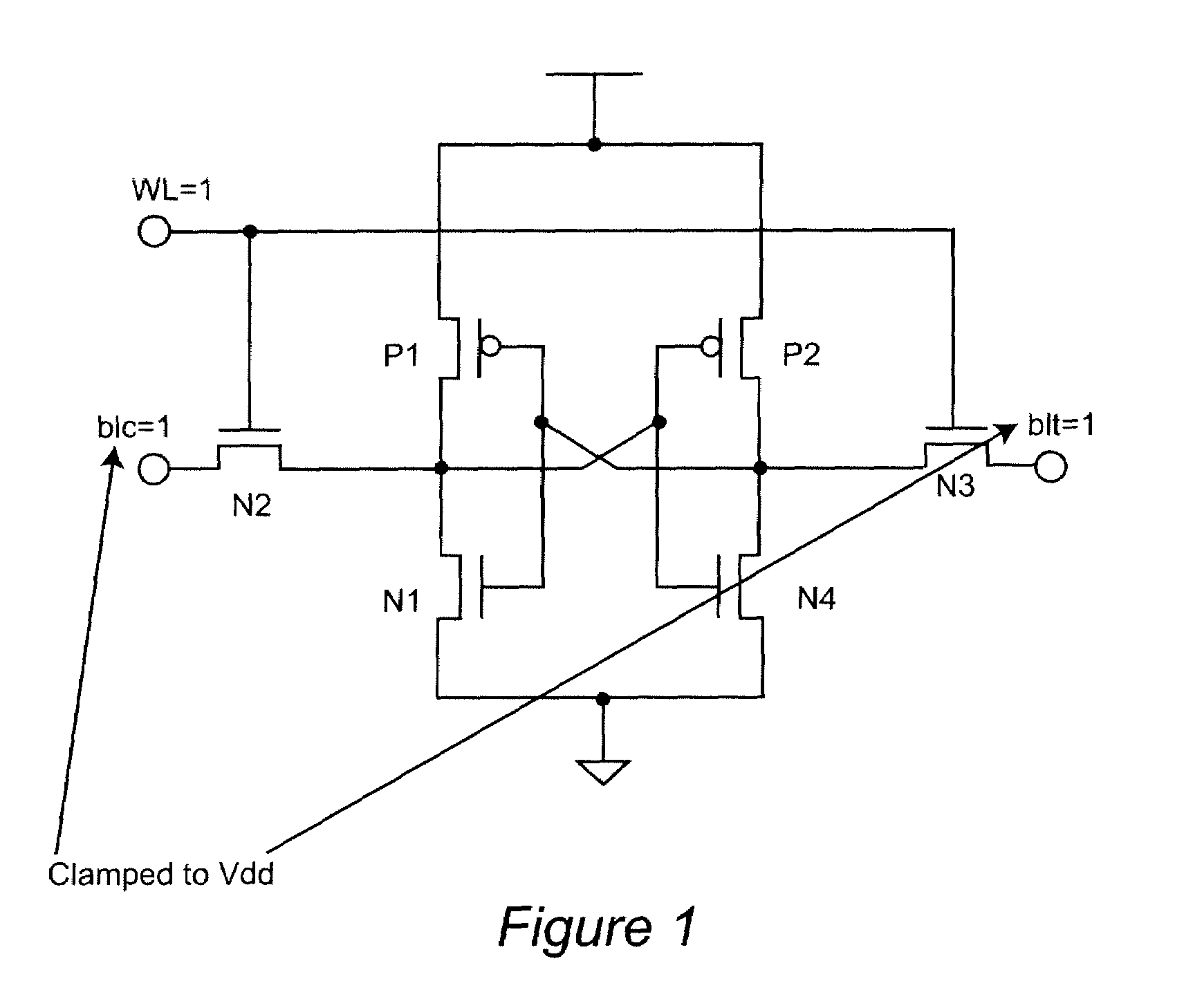

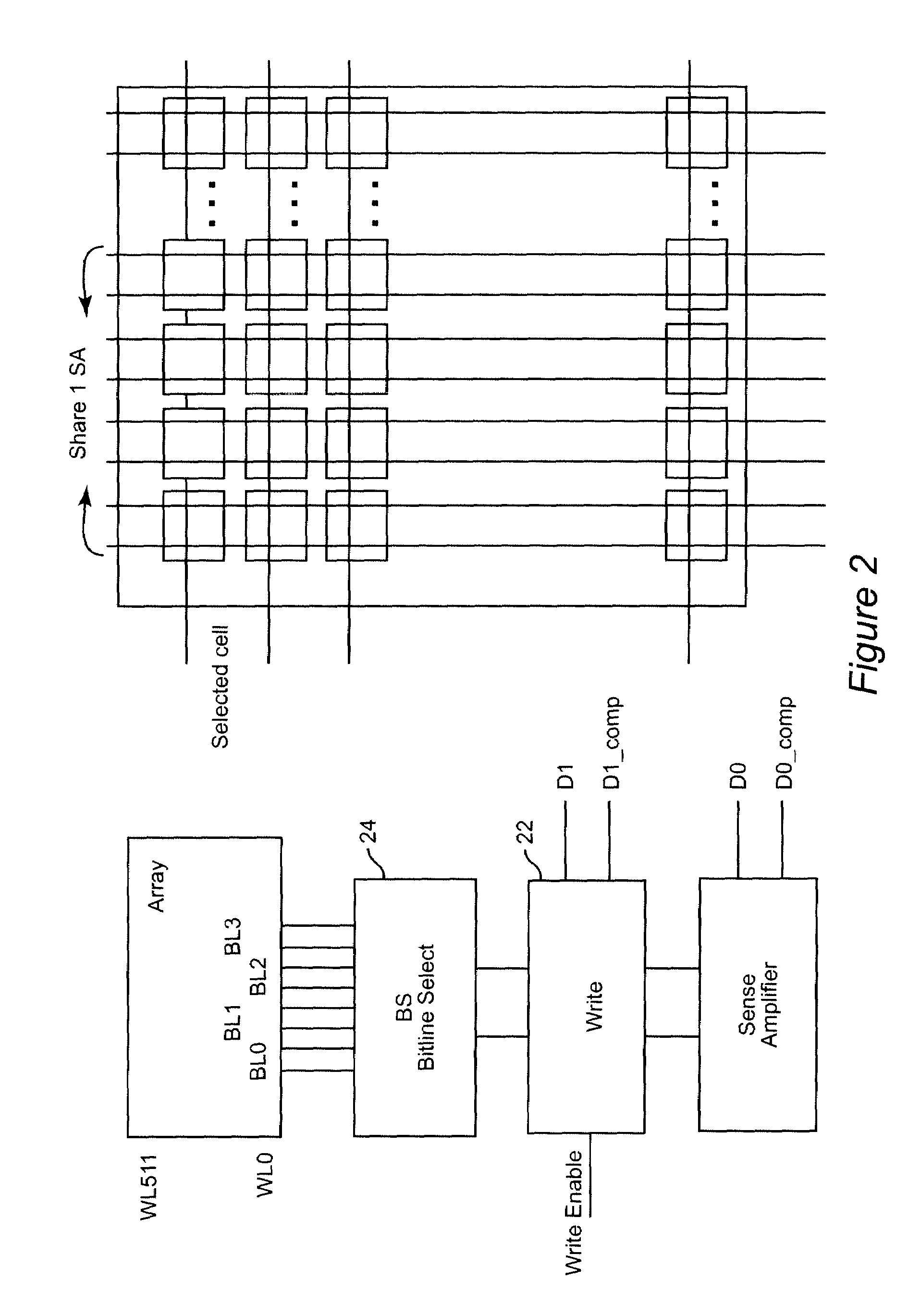

3-d SRAM array to improve stability and performance

ActiveUS20080310207A1Increase of SRAM memory cell capacityAchieve effectDigital storageBit lineAudio power amplifier

A design structure for a three-dimensional memory circuit provides reduction in memory cell instability due to half-select operation by reduction of the number of memory cells sharing a sense amplifier and, potentially, avoidance of half-select operation by placing some or all peripheral circuits including local evaluation circuits functioning as a type of sense amplifier on an additional chips or chips overlying the memory array. Freedom of placement of such peripheral circuits is provided with minimal increase in connection length since word line decoders may be placed is general registration with ant location along the word lines while local evaluation circuits and / or sense amplifiers can be placed at any location generally in registration with the bit line(s) to which they correspond.

Owner:TWITTER INC

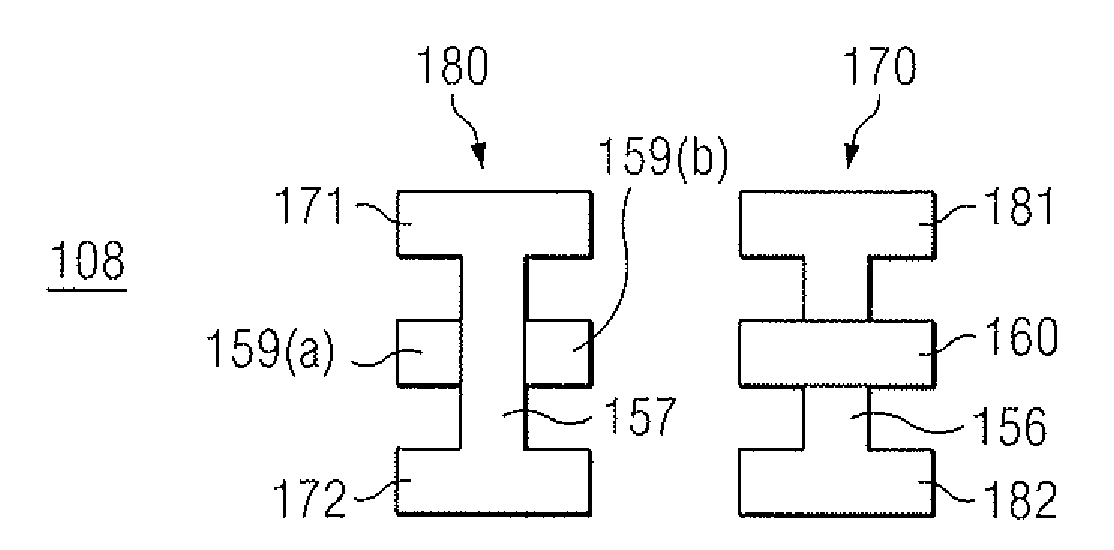

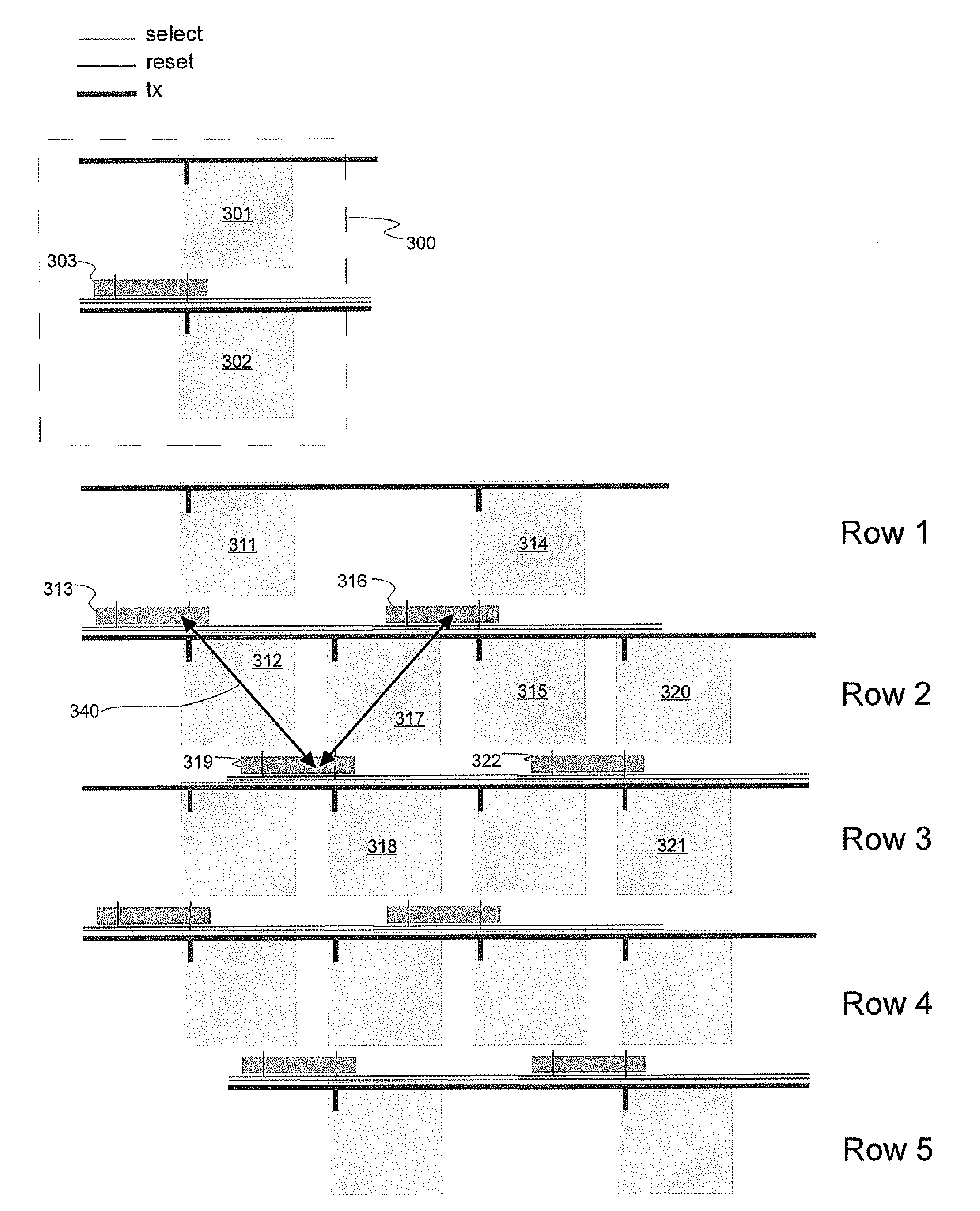

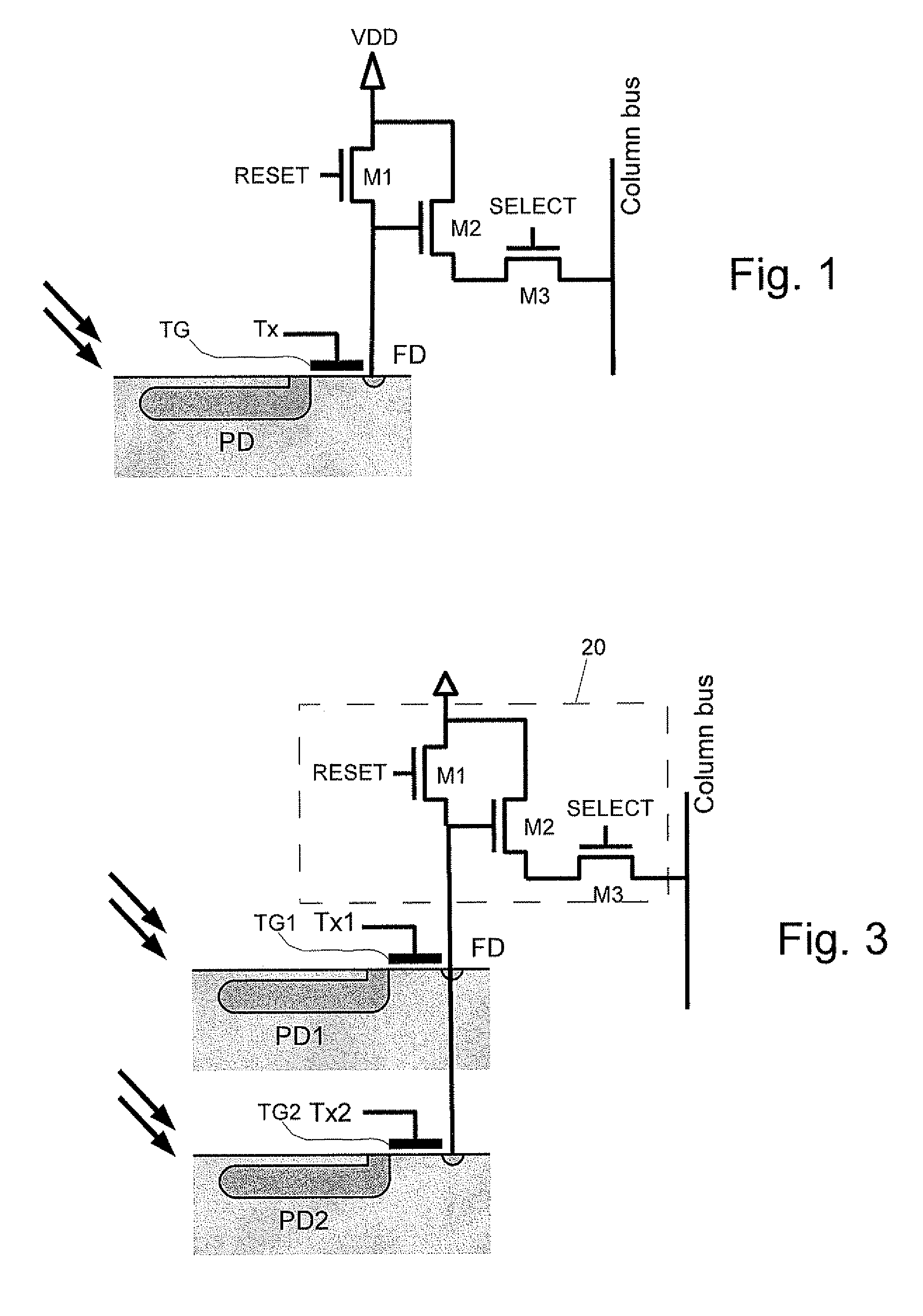

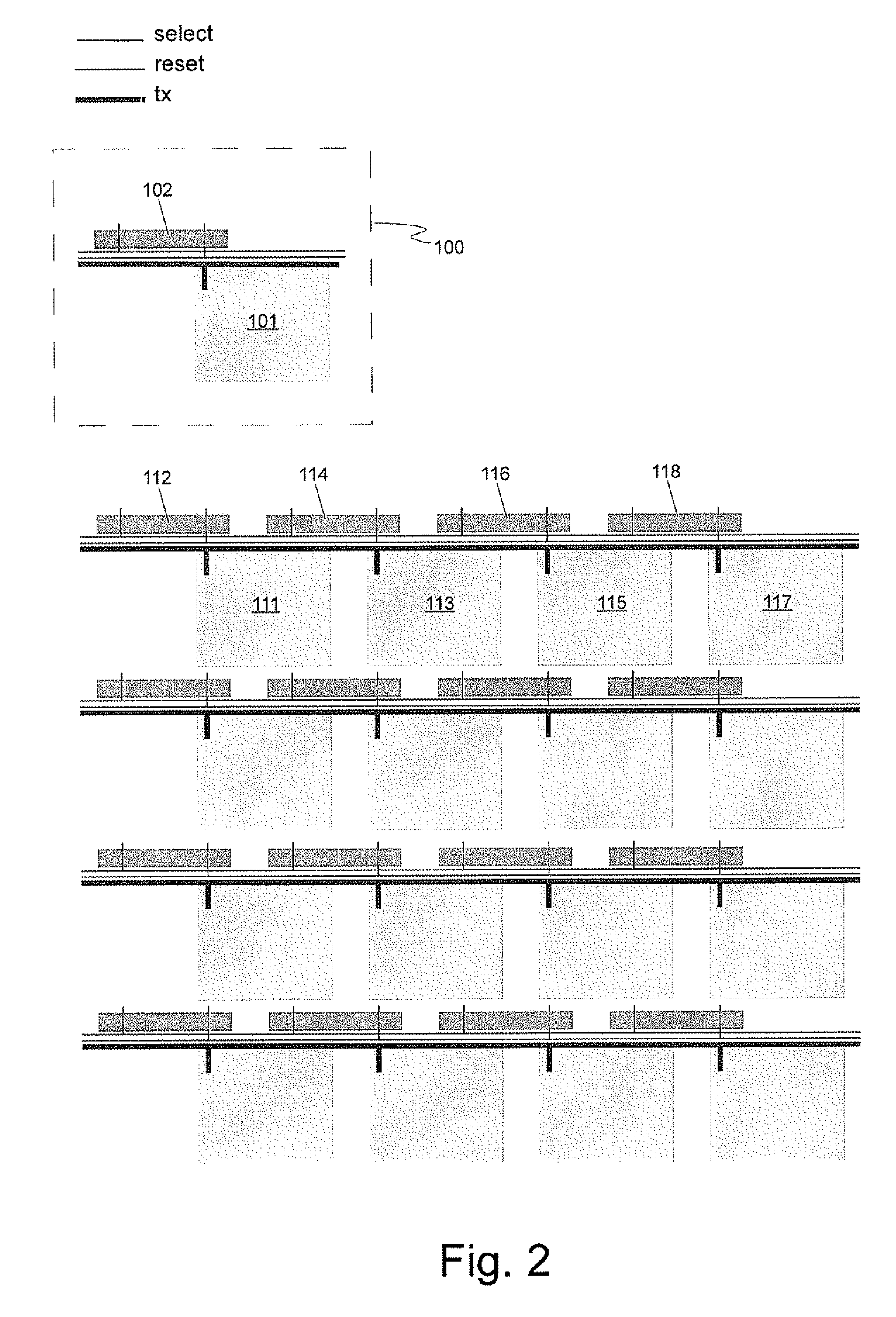

Pixel array with shared readout circuitry

ActiveUS8334491B2Advantages in of performanceAdvantages in of powerTelevision system detailsTelevision system scanning detailsComputer architectureHemt circuits

A pixel array comprises a plurality of photo-sensitive elements arranged in rows and columns and readout circuitry for reading a value of a photo-sensitive element. Shared readout circuitry is provided for a pair of adjacent photo-sensitive elements. Adjacent instances of the shared readout circuitry are staggered with respect to one another. For a layout having shared readout circuitry for a pair of photo-sensitive elements, adjacent instances of the shared readout circuitry are offset by a horizontal distance of one column and a vertical distance of one row of the array. The shared readout circuitry can serve a pair of adjacent photo-sensitive elements in a row or column of the array, or a pair of photo-sensitive elements which are diagonally adjacent in the array. An improved yield and symmetry results from staggering instances of the shared readout circuitry.

Owner:CMOSIS

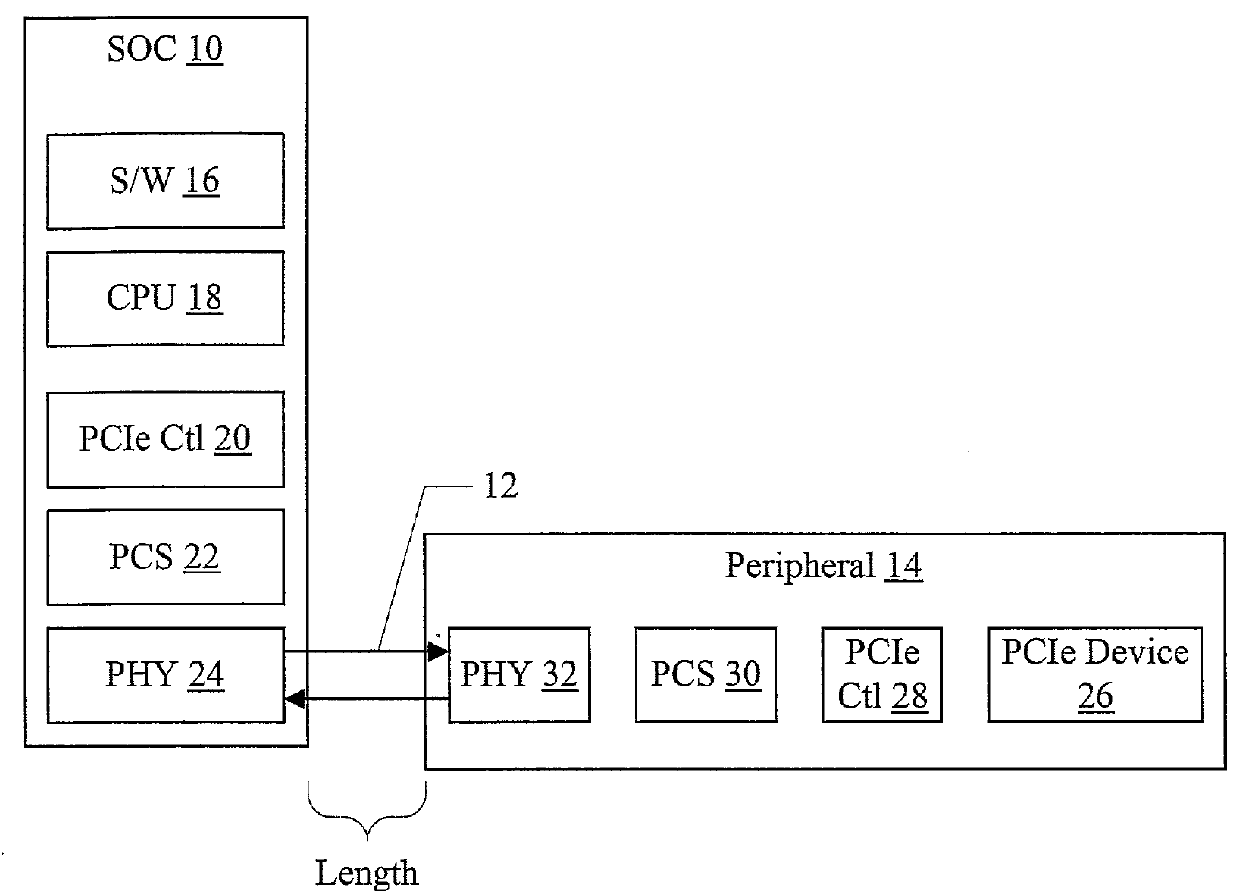

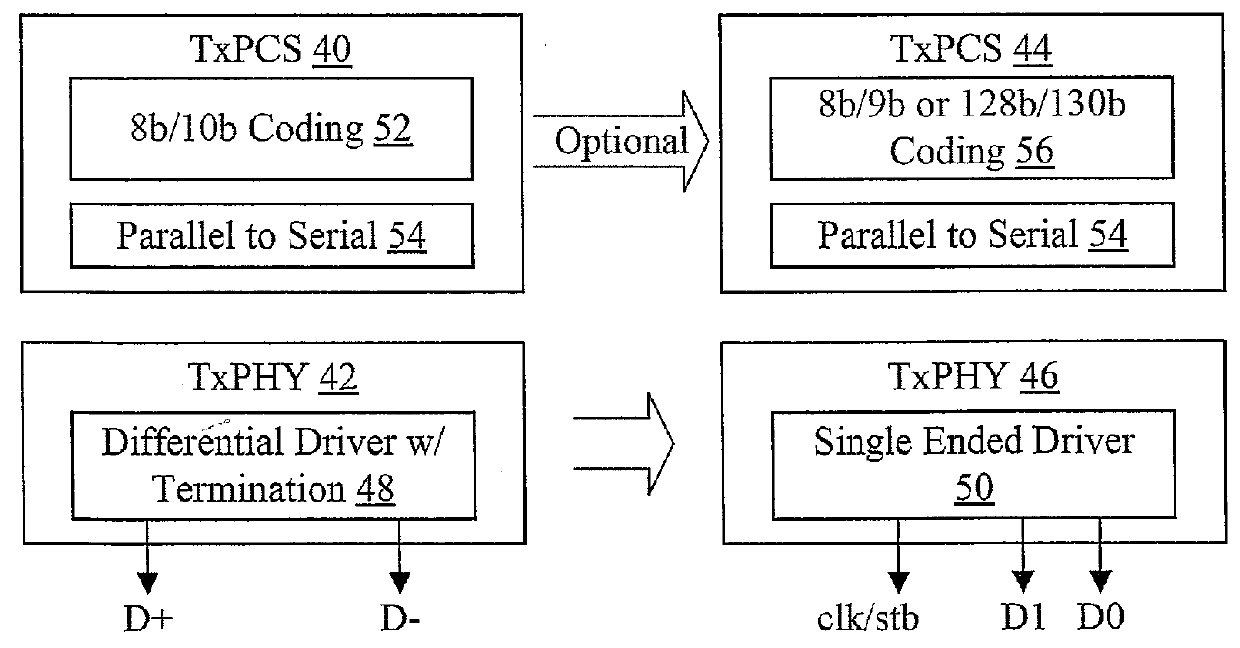

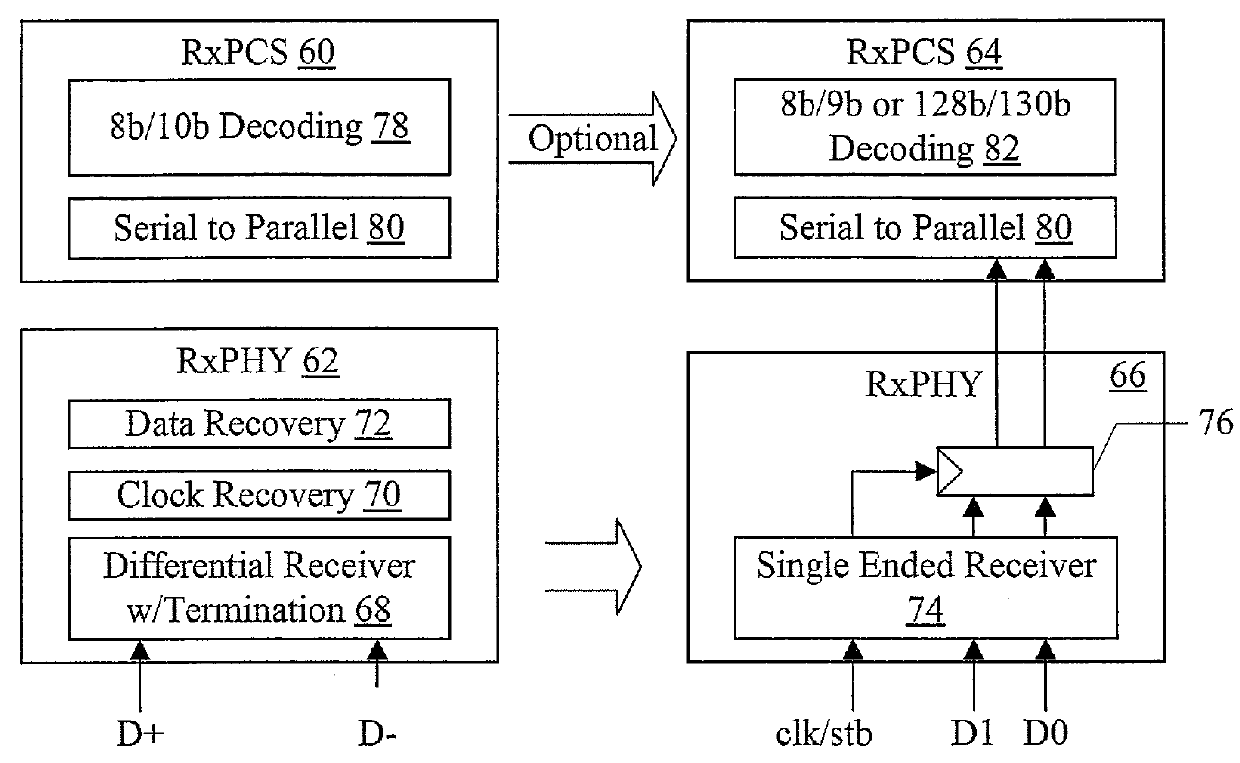

Physical Layer for Peripheral Interconnect with Reduced Power and Area

ActiveUS20160034025A1Simpler and more power-efficientMore areaPower supply for data processingEnergy efficient computingPower efficientTechnical standard

An integrated circuit (IC) implements an industry standard-defined peripheral interconnect to connect to another integrated circuit or component in a system. The industry standard specification includes a software interface that is well-defined and implemented by various software in the system, and thus is desirable to retain. However, the physical interconnect in the systems employing the integrated circuit may be short, and thus the elaborate physical layer definition may consume more integrated circuit area and power than is otherwise desirable in the IC. The IC may implement a simpler and more power-efficient physical layer, reducing both power consumption and semiconductor substrate area consumption, in some embodiments.

Owner:APPLE INC

Acoustic transducer with folded diaphragm

InactiveUS7412065B2Broader array of sound wavesReduce depthTransducer casings/cabinets/supportsDeaf-aid setsTransducerEngineering

Owner:HARMAN INT IND INC

Process for forming integrated circuits with both split gate and common gate FinFET transistors

ActiveUS7888192B2Easy to operateIncrease the areaTransistorSolid-state devicesGate dielectricEngineering

A method is disclosed for forming an integrated circuit including a common gate FinFET device and a split gate FinFET device. Taller fins and shorter fins of different heights are formed in a semiconductor surface. Layers of gate dielectric material and gate electrode material are formed over tops and sides of the fins. The gate electrode material layer is planarized using chemical-mechanical polishing to remove the gate electrode material from the tops of the taller fins, leaving the gate electrode material over the tops of the shorter fins. The planarized material is patterned to form split (dual) gate structures on the sides of the taller fins and common gate structures on the tops and sides of the shorter fins.

Owner:TEXAS INSTR INC

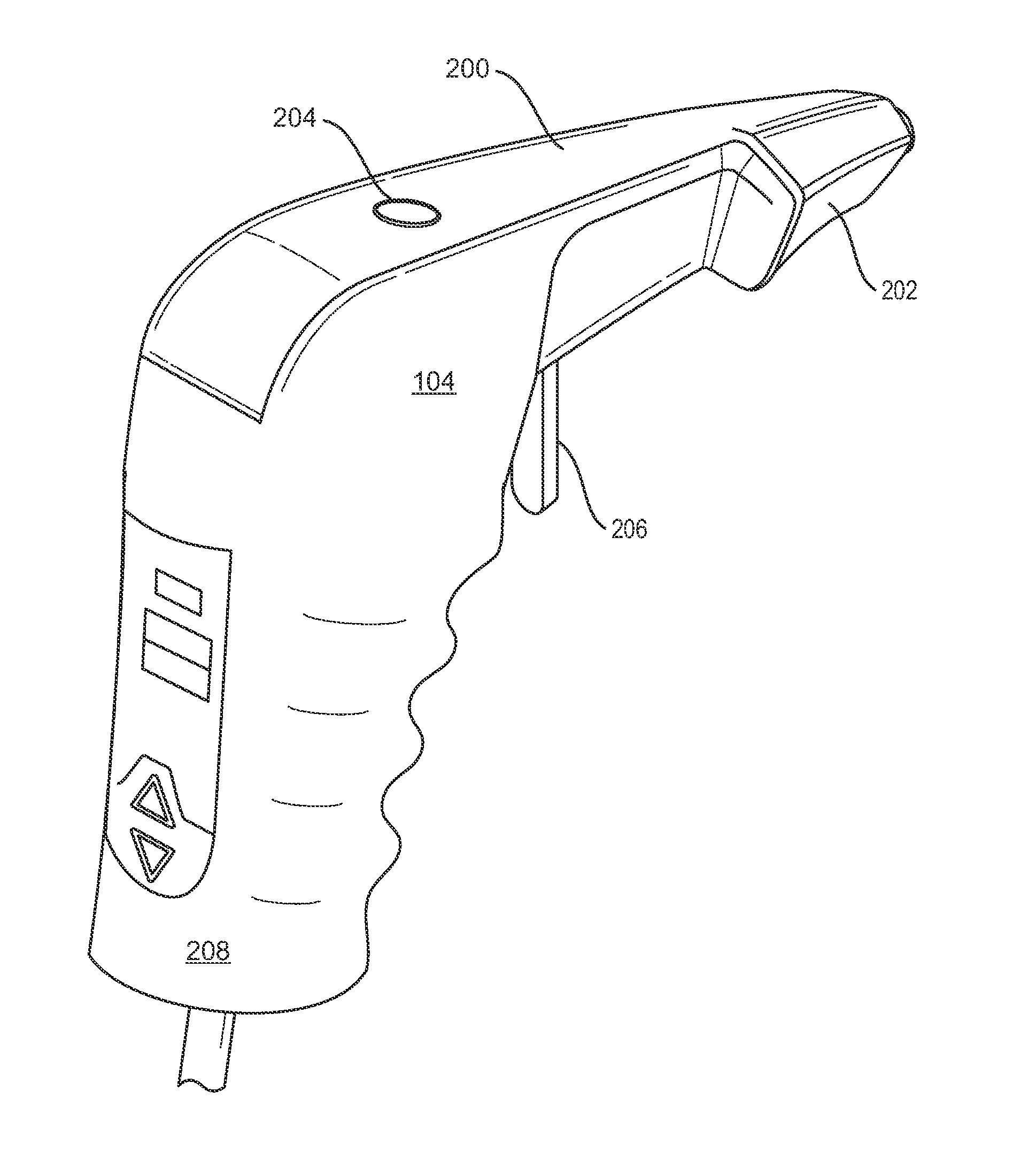

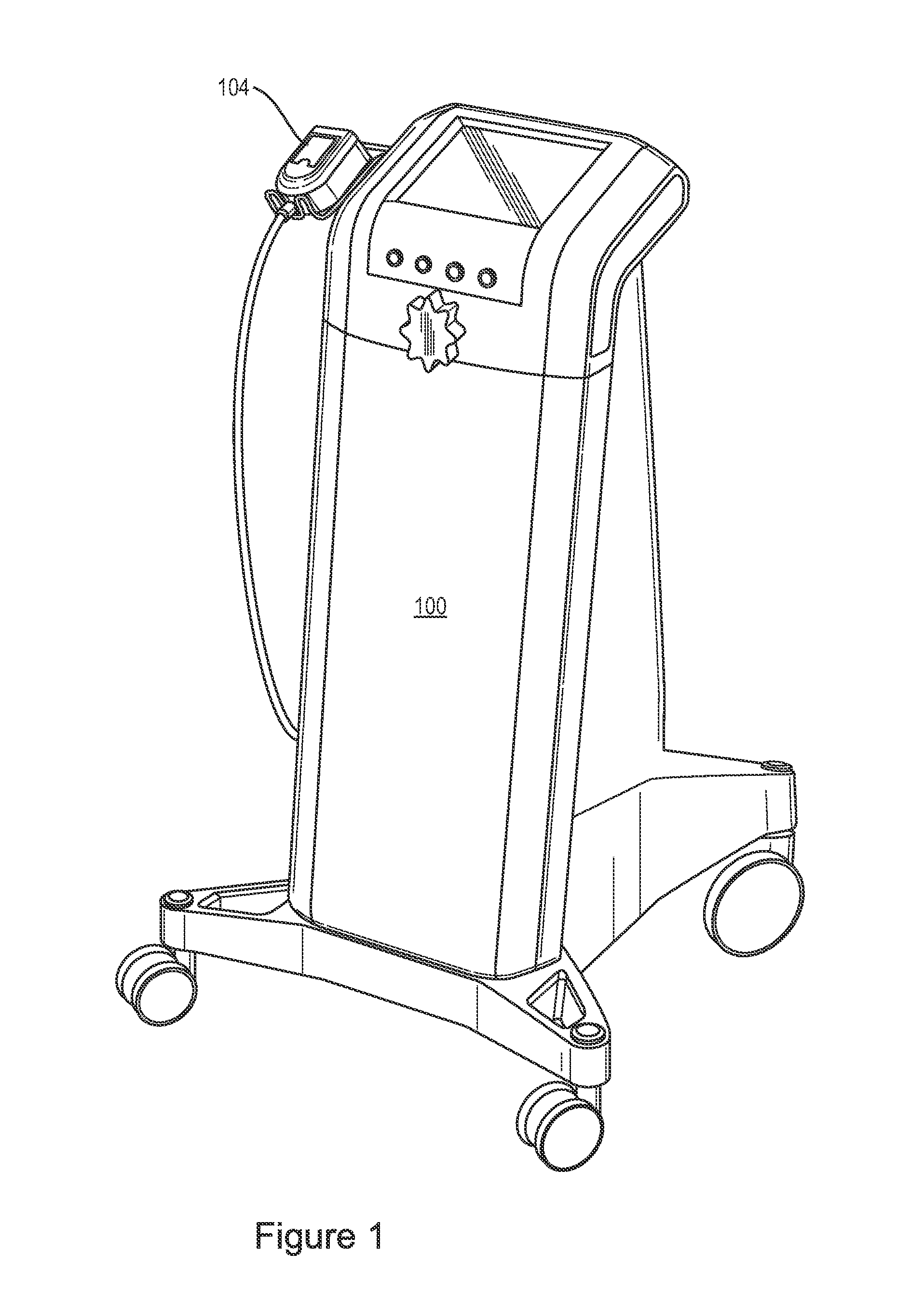

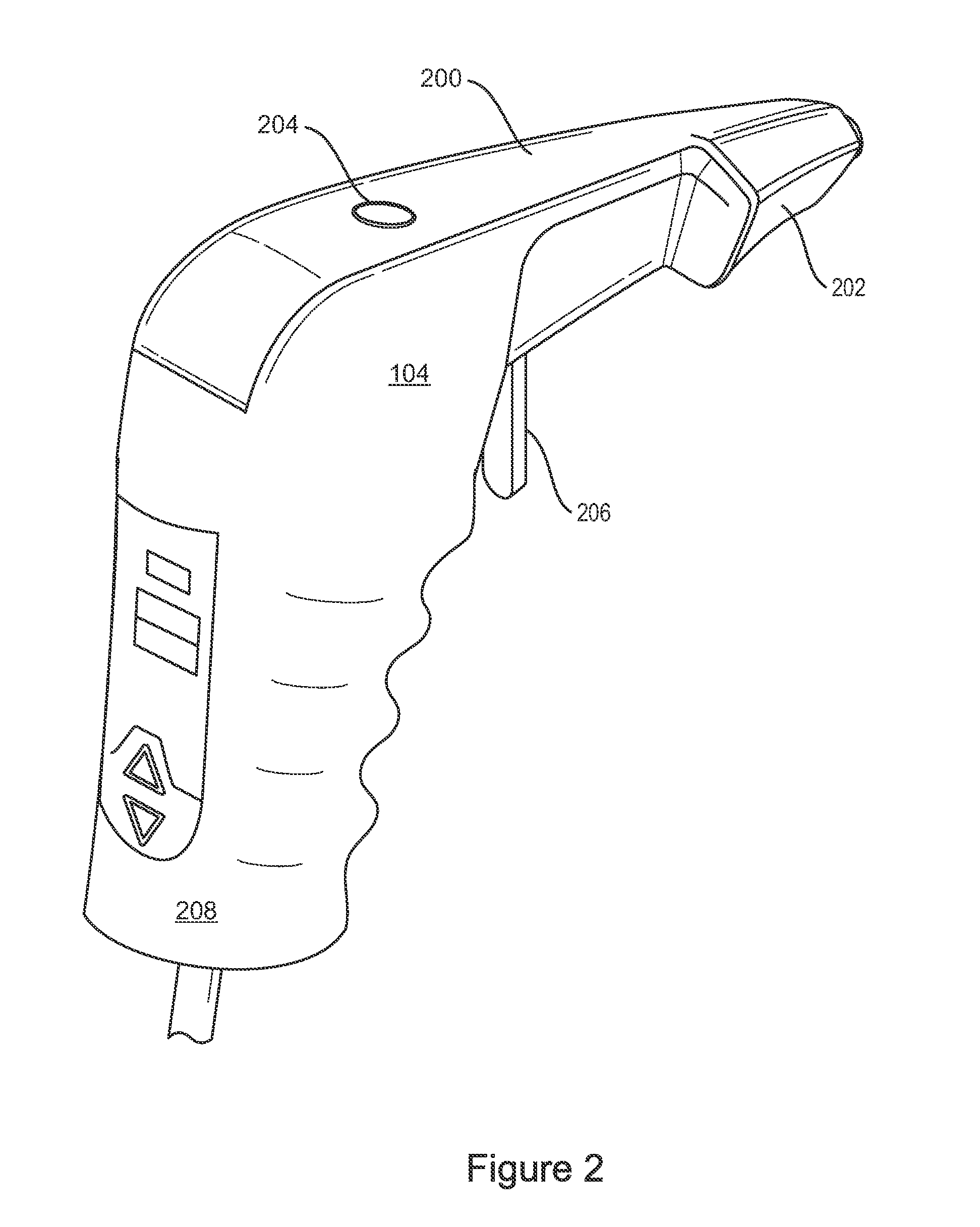

Non-surgical method for tightening both external pubic and internal vaginal tissues in a single procedure

InactiveUS20140148878A1Good lookingImprove tightnessSurgical instrument detailsLight therapyVaginal tissueSkin tightening

A non-surgical method for improving both the external pubic appearance and the internal vaginal tightness of a female patient in a single procedure includes providing a cosmetic skin-tightening device having a wand having a tip that applies heating energy to skin collagen, where the wand is shaped such that the tip can be inserted into the patient's vagina. During the procedure, the wand is alternately passed over the external pubic skin and inserted into the patient's vagina, thereby tightening both the pubic and vaginal regions during a single procedure while preventing overheating of any one area. The heat energy can be conductively transmitted heat or a radiated energy such as infra-red, laser, or radio frequency energy. A disposable sleeve can be applied over the wand to facilitate cleaning and sterilization after use. A vaginal lubricant and / or ultrasound gel can be applied.

Owner:KHATRI KHALILULLAH A

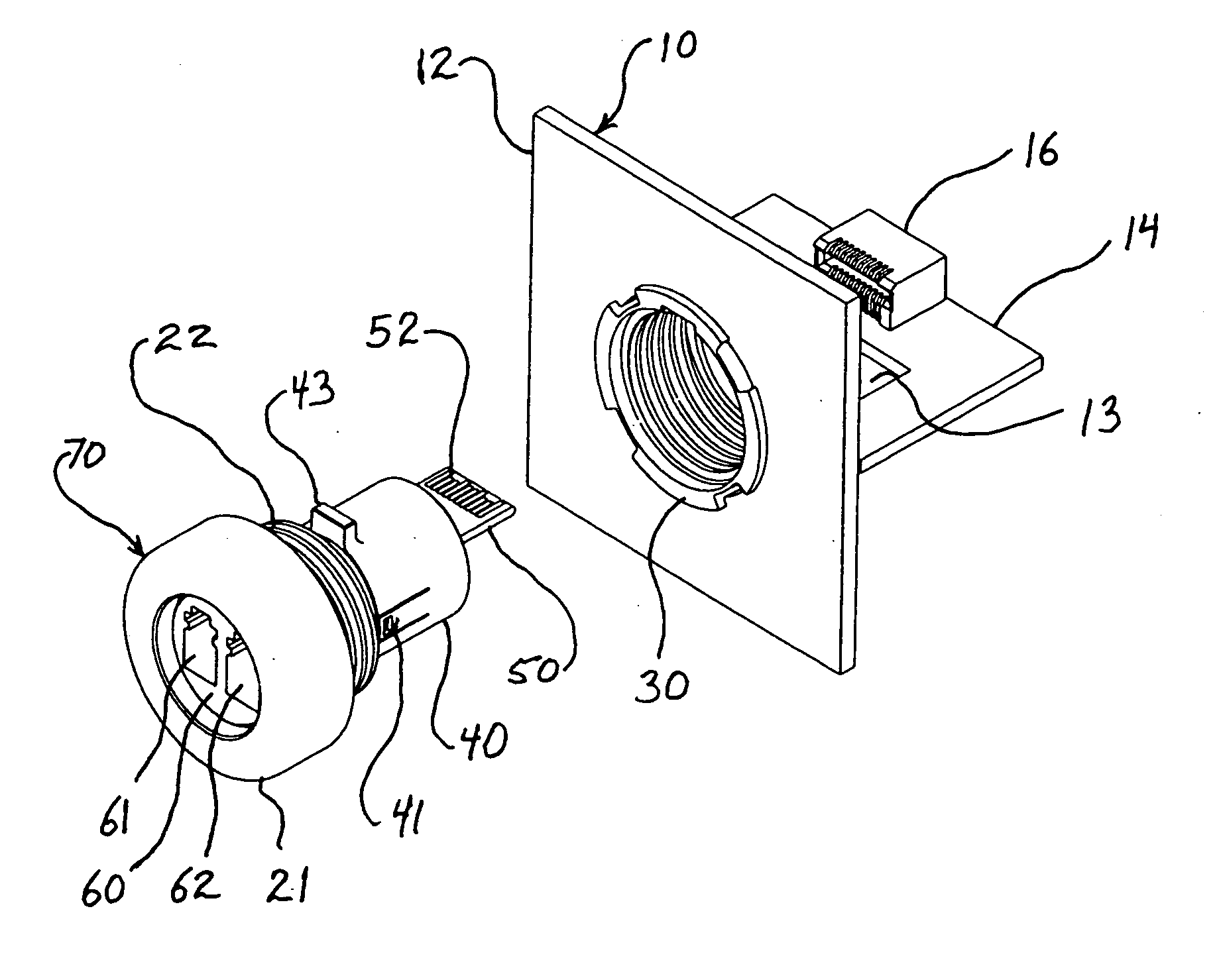

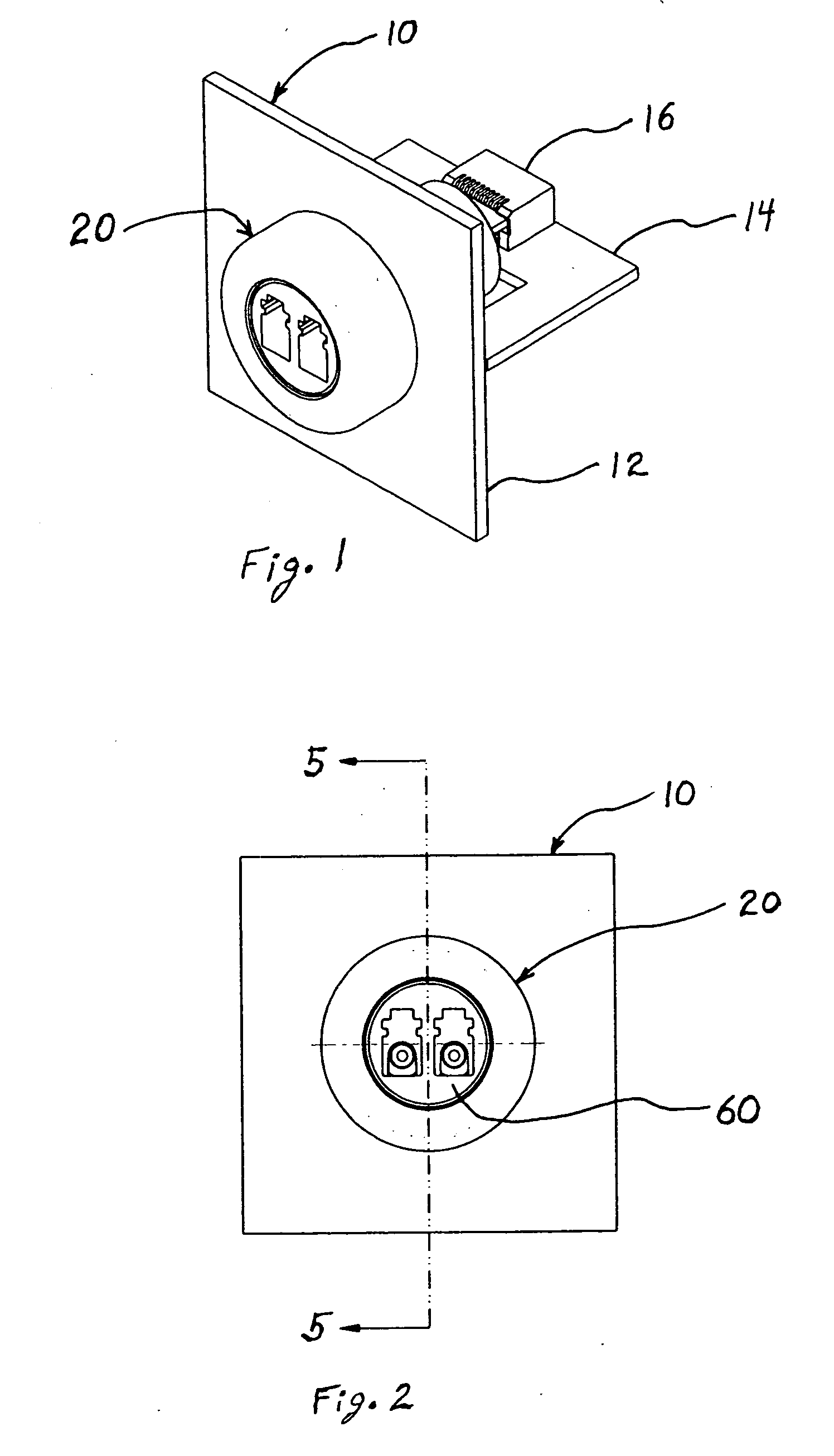

Optoelectronic device in combination with a push-in cage

InactiveUS20080170375A1Easily matedMore areaEngagement/disengagement of coupling partsTwo-part coupling devicesEngineering

Owner:STRATOS INT

Low-profile transducer

ActiveUS7450729B2Broader array of sound wavesReduce depthPlane diaphragmsTransducer casings/cabinets/supportsTransducerEngineering

One embodiment of a low-profile transducer includes a at least one fin perpendicularly mounted on a planar diaphragm, with a voice coil mounted onto the fin. The voice coil may reside in a strong uniform magnetic field. The locations at which the diaphragm is connected to a frame may be coplanar with a center of mass of the diaphragm. The three-dimensional structure of diaphragm and fins may be formed using origami techniques.

Owner:HARMAN INT IND INC