Patents

Literature

210results about How to "Solve narrow bandwidth" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

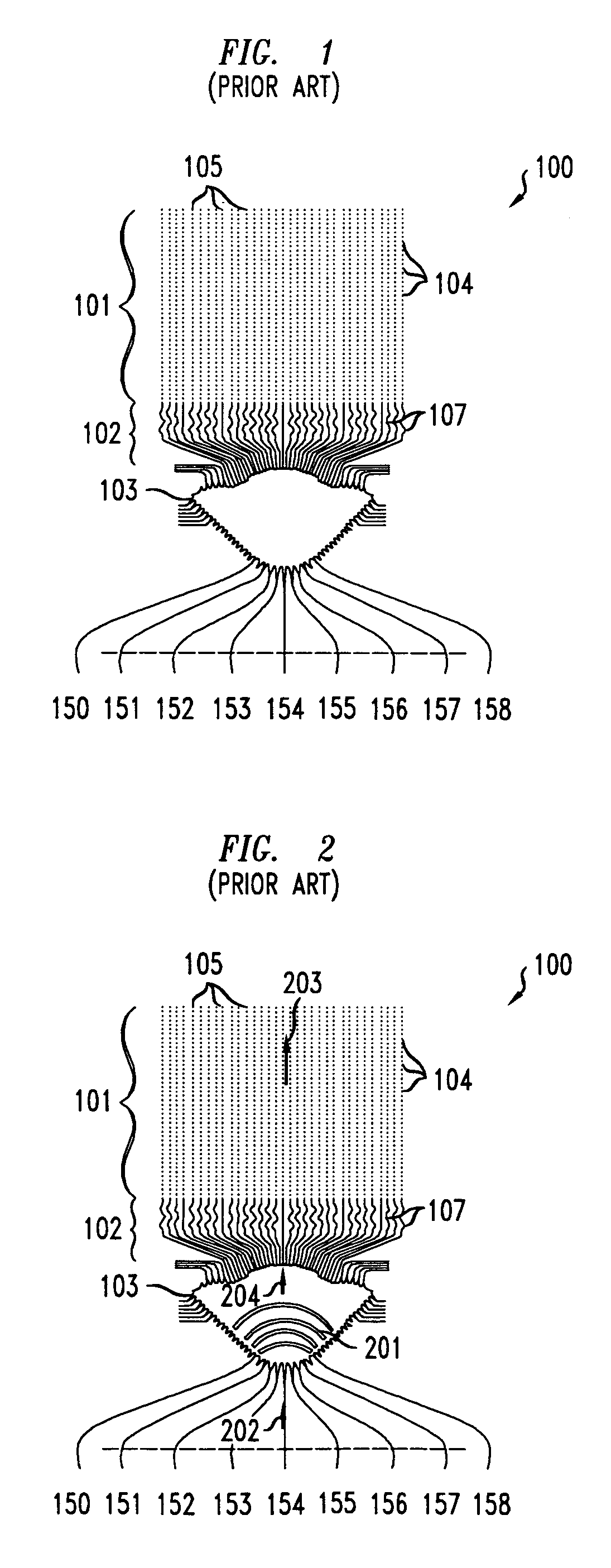

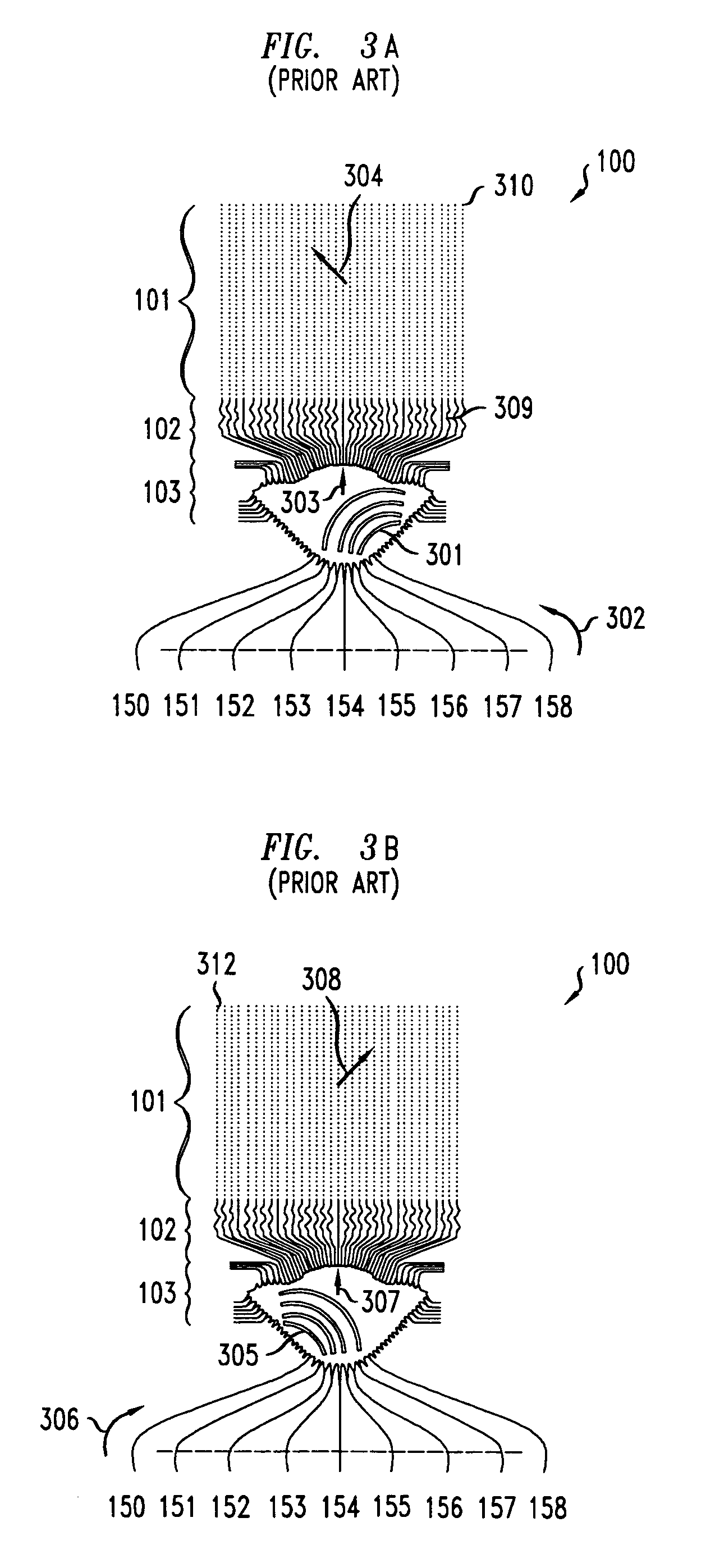

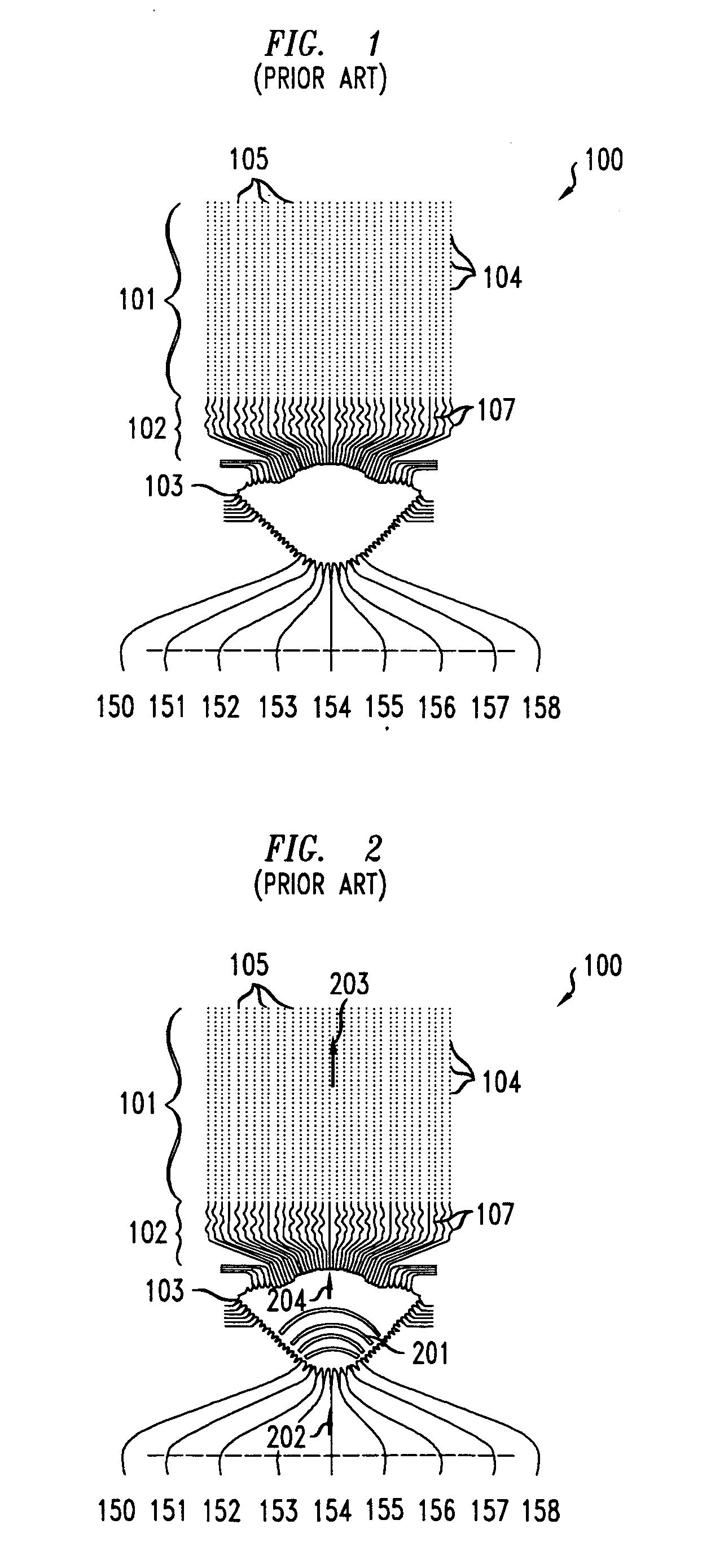

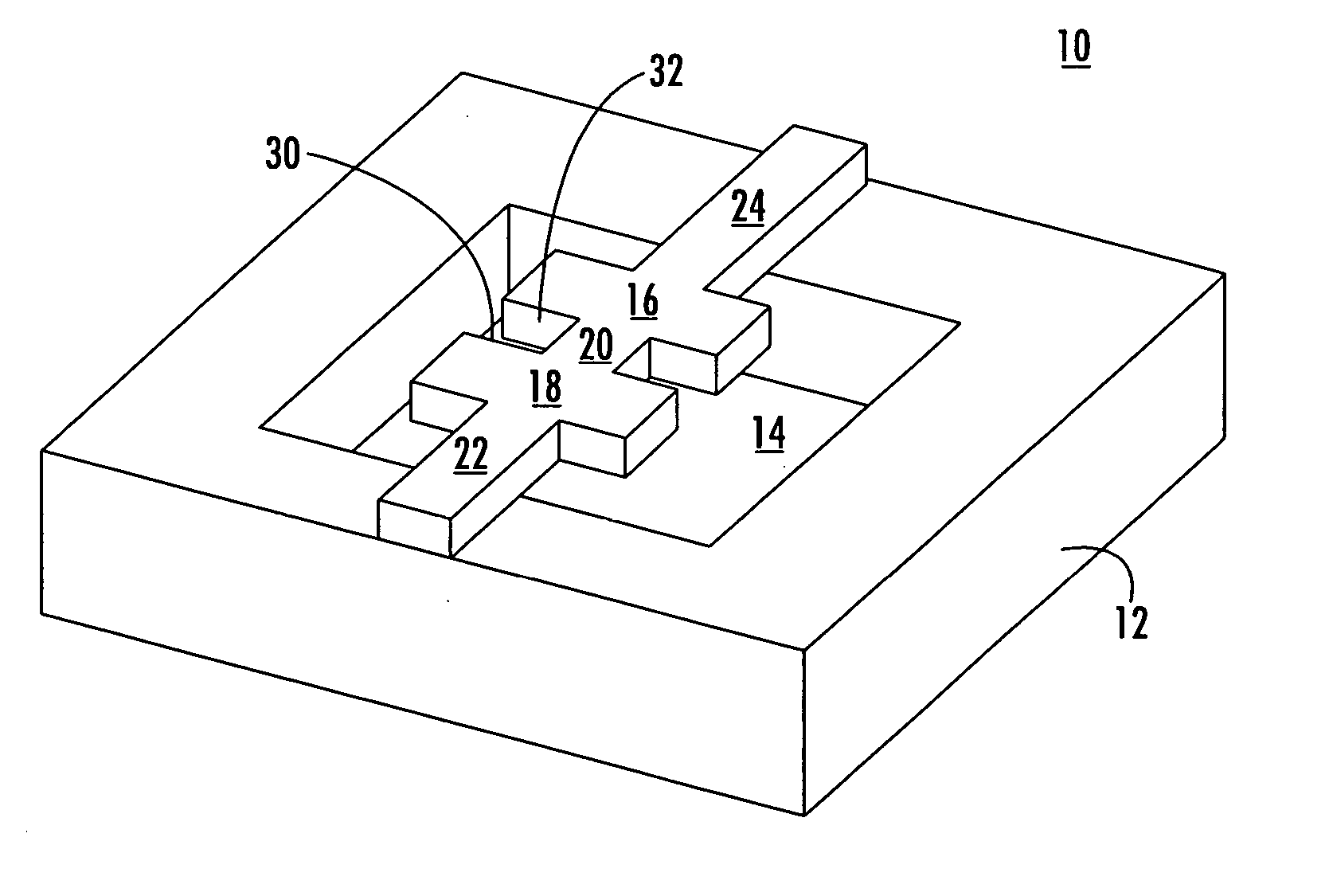

Phased array metamaterial antenna system

ActiveUS6958729B1Reduce sidelobeIncrease amplitude performanceSimultaneous aerial operationsRadiating elements structural formsSolid substratePhased array

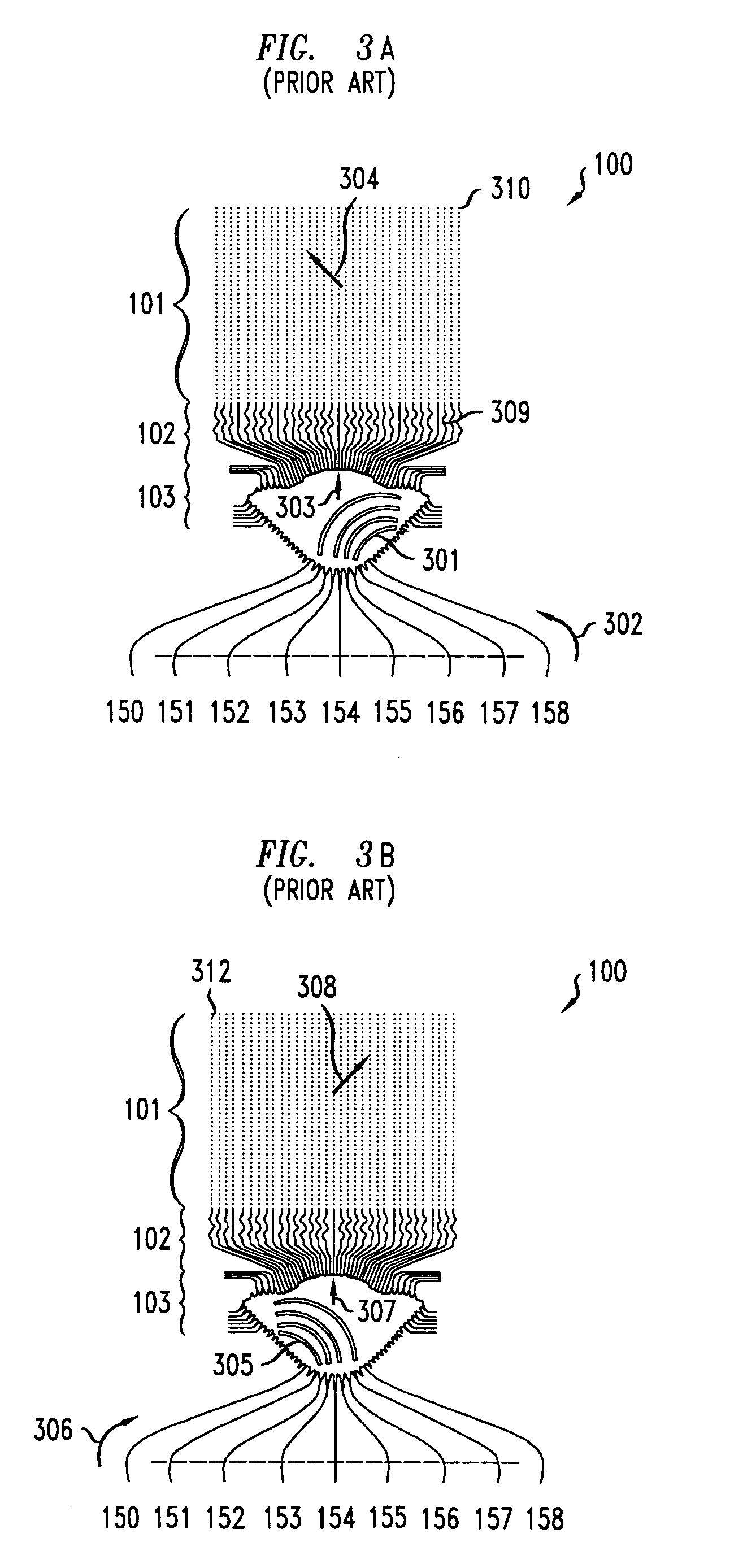

An efficient, low-loss, low sidelobe, high dynamic range phased-array radar antenna system is disclosed that uses metamaterials, which are manmade composite materials having a negative index of refraction, to create a biconcave lens architecture (instead of the aforementioned biconvex lens) for focusing the microwaves transmitted by the antenna. Accordingly, the sidelobes of the antenna are reduced. Attenuation across microstrip transmission lines may be reduced by using low loss transmission lines that are suspended above a ground plane a predetermined distance in a way such they are not in contact with a solid substrate. By suspending the microstrip transmission lines in this manner, dielectric signal loss is reduced significantly, thus resulting in a less-attenuated signal at its destination.

Owner:LUCENT TECH INC

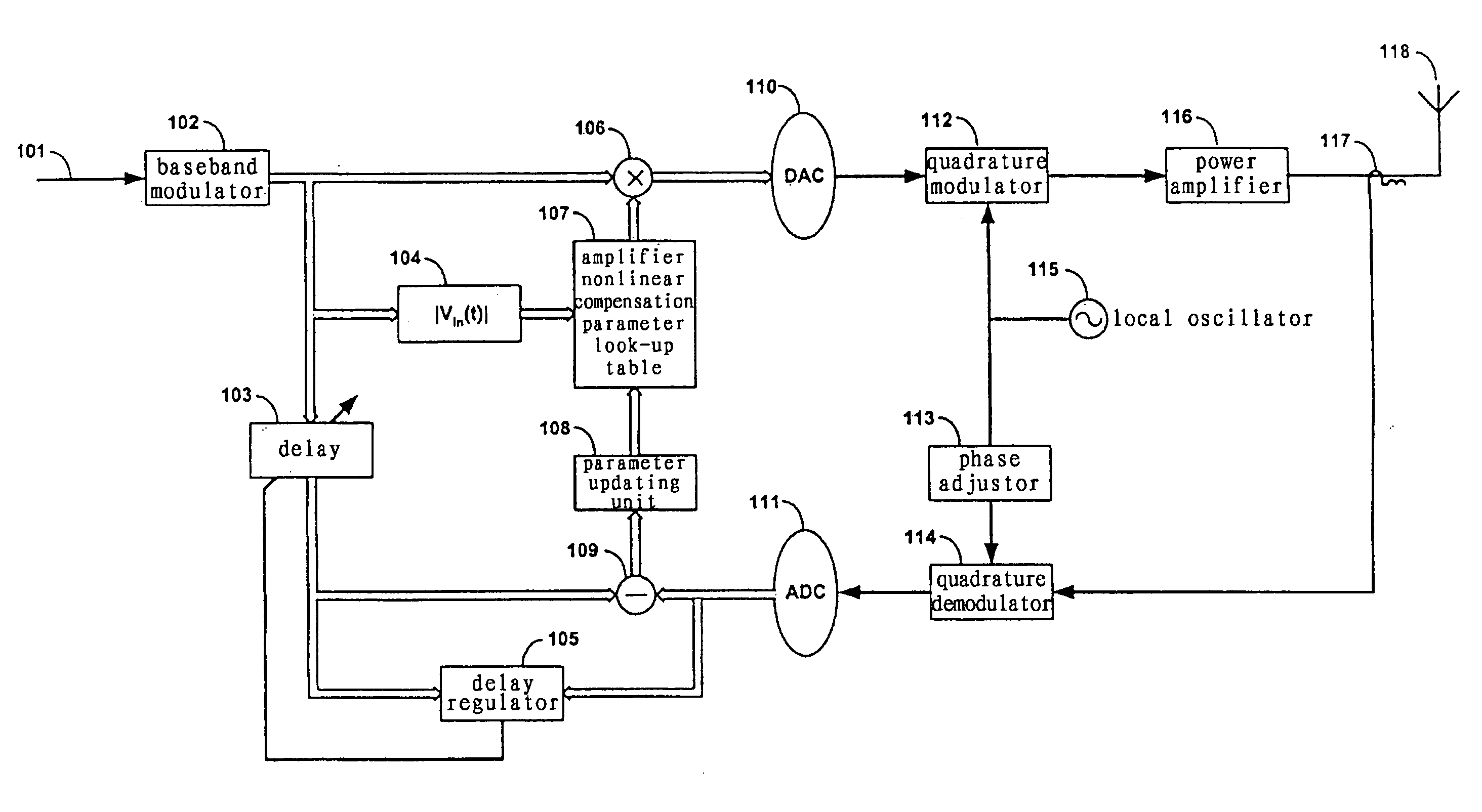

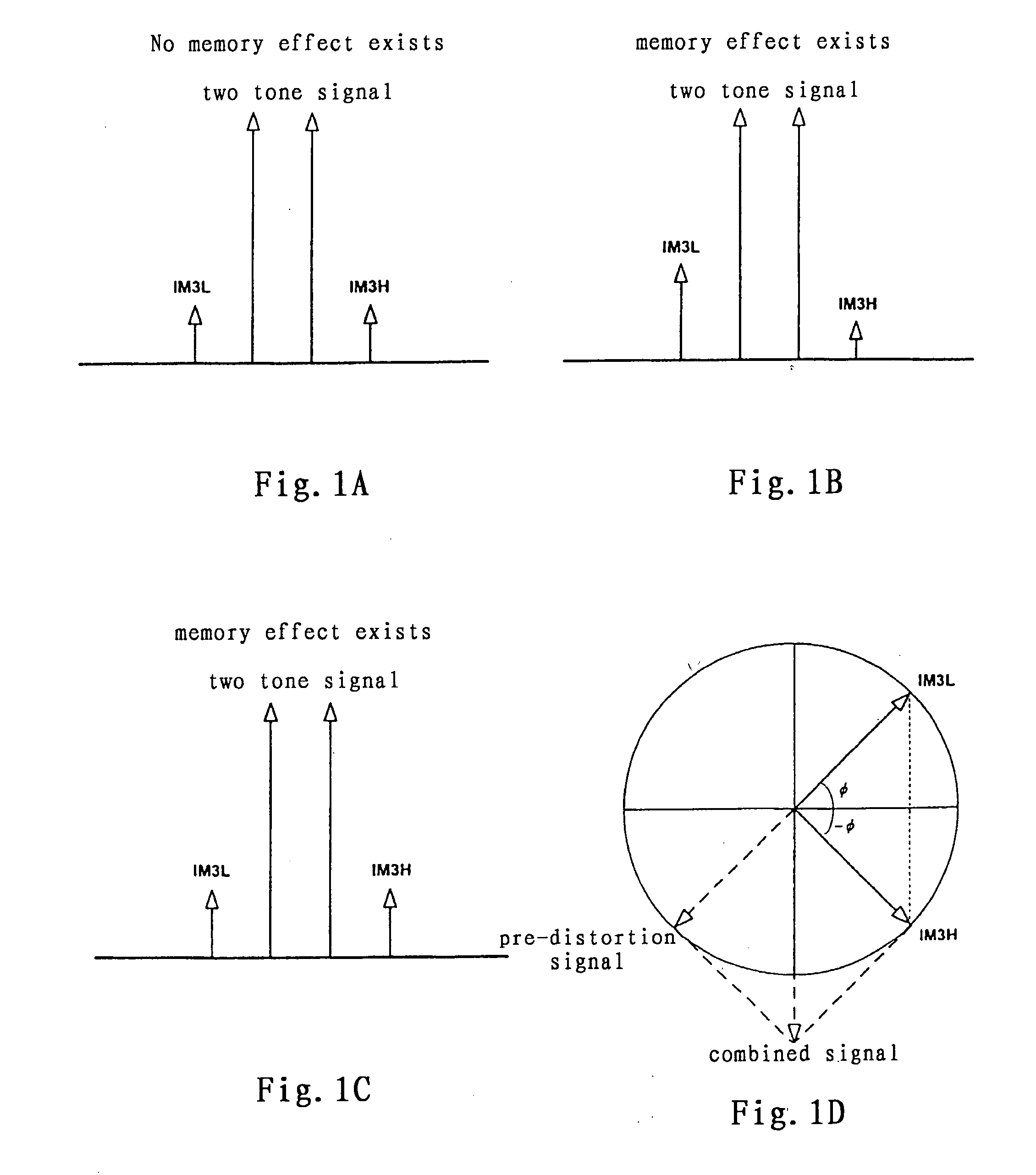

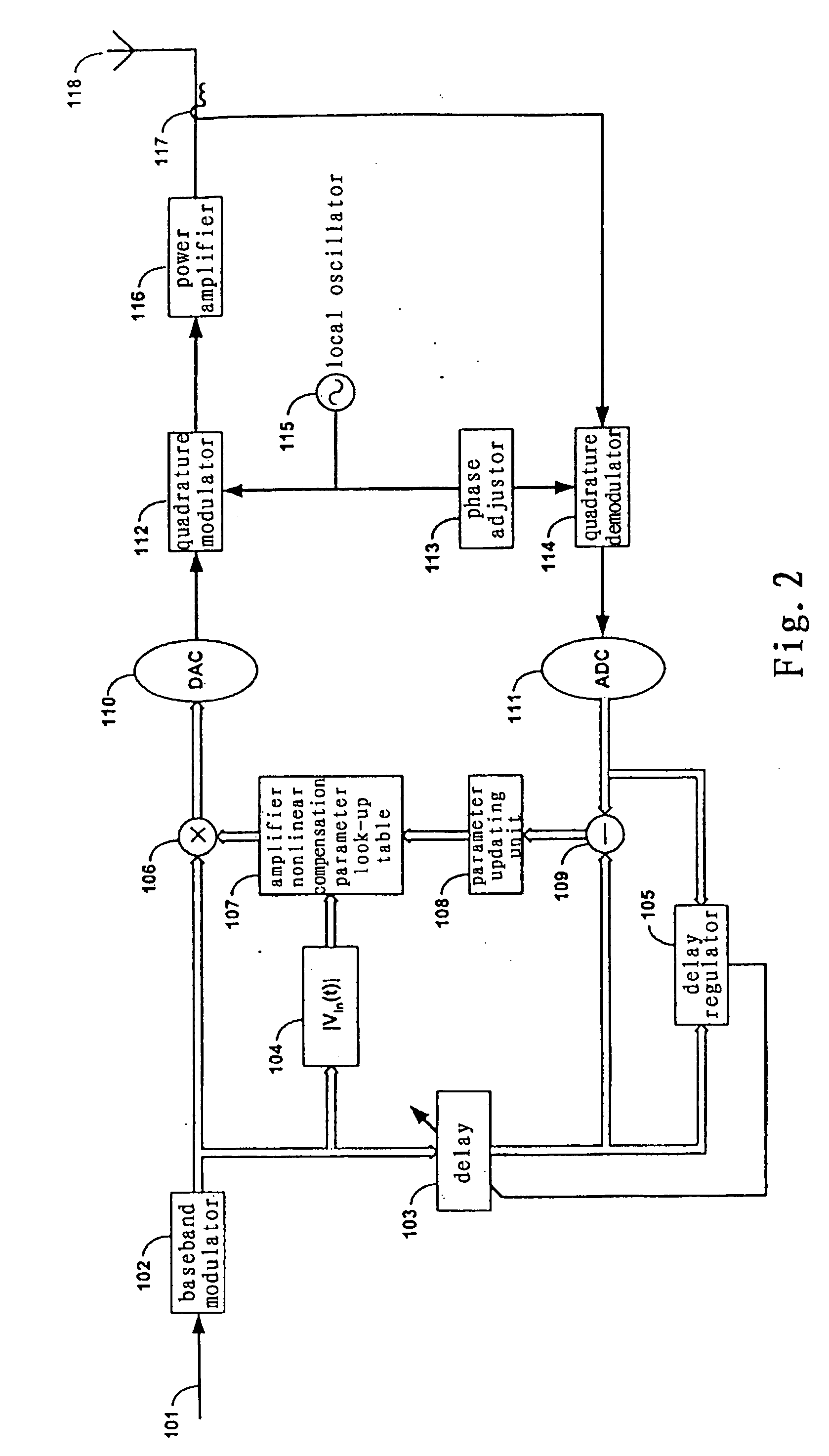

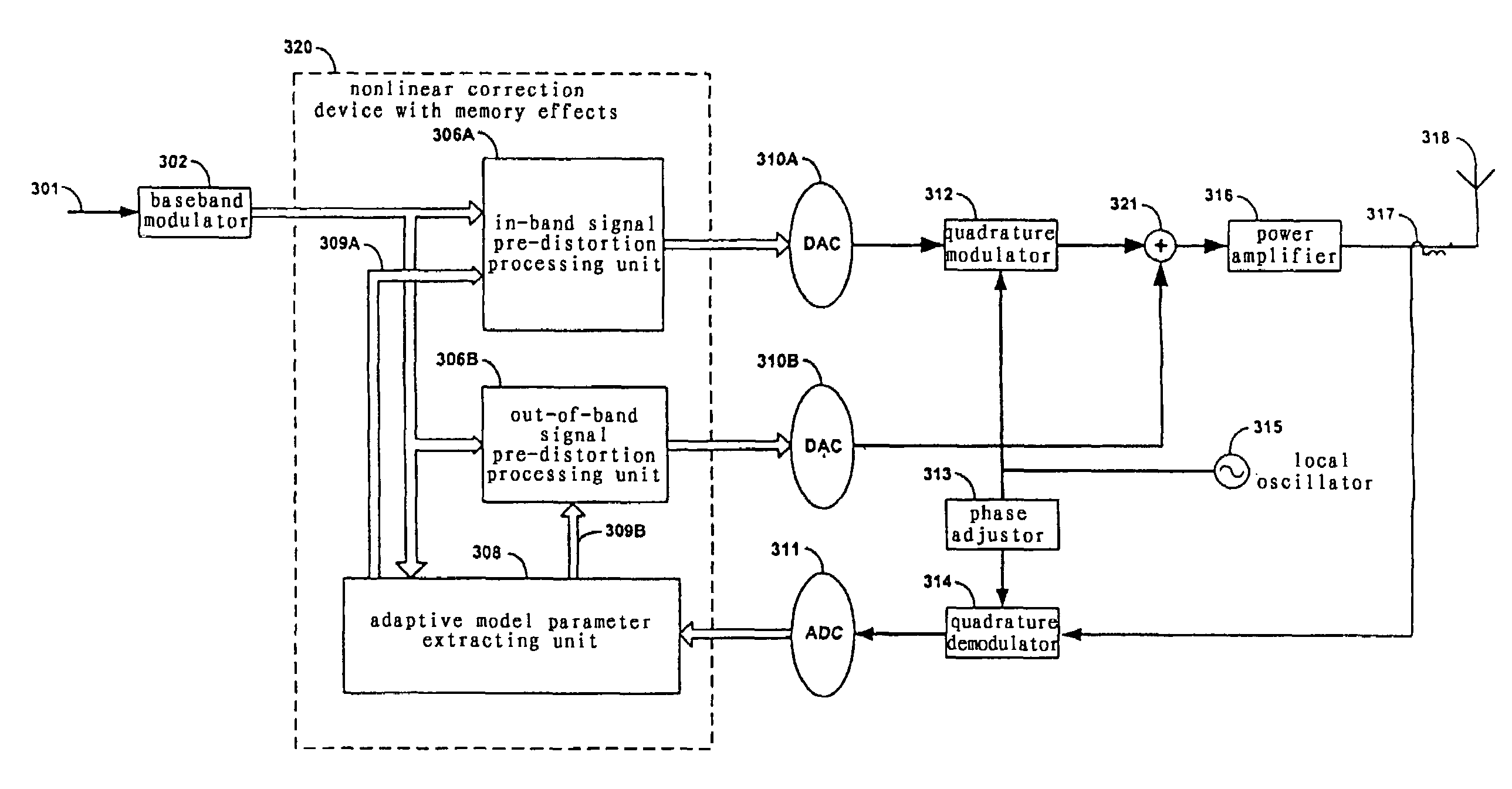

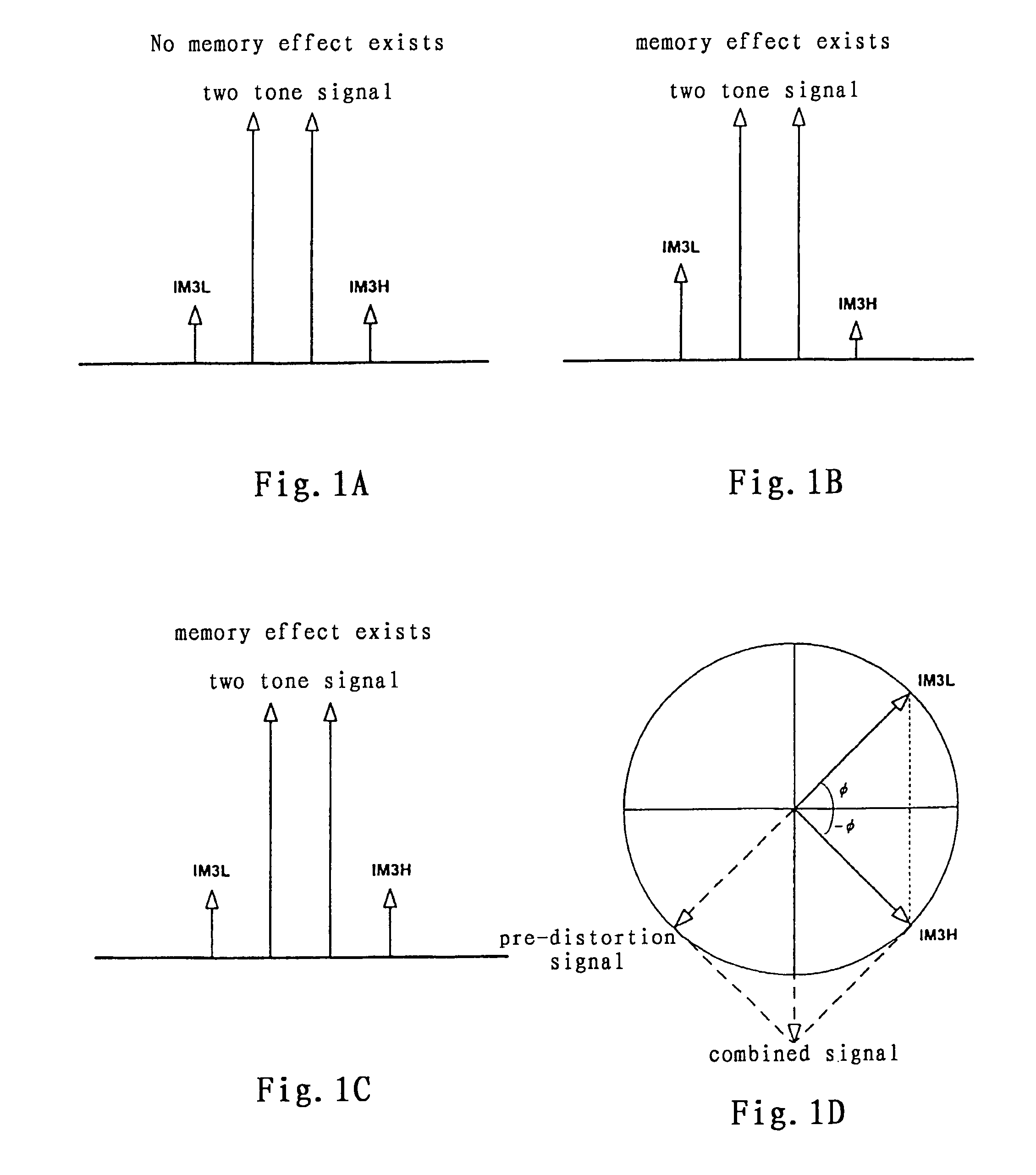

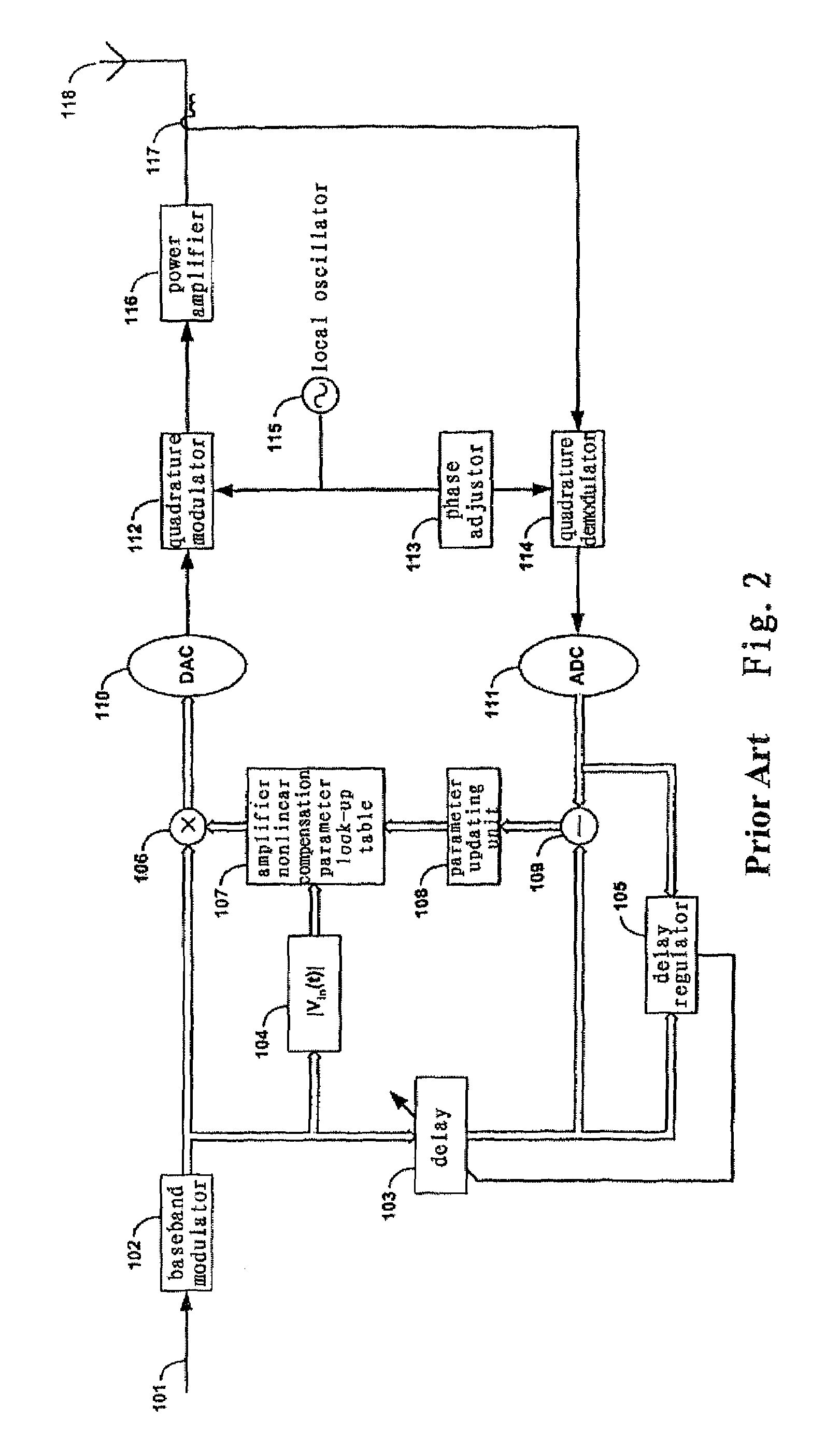

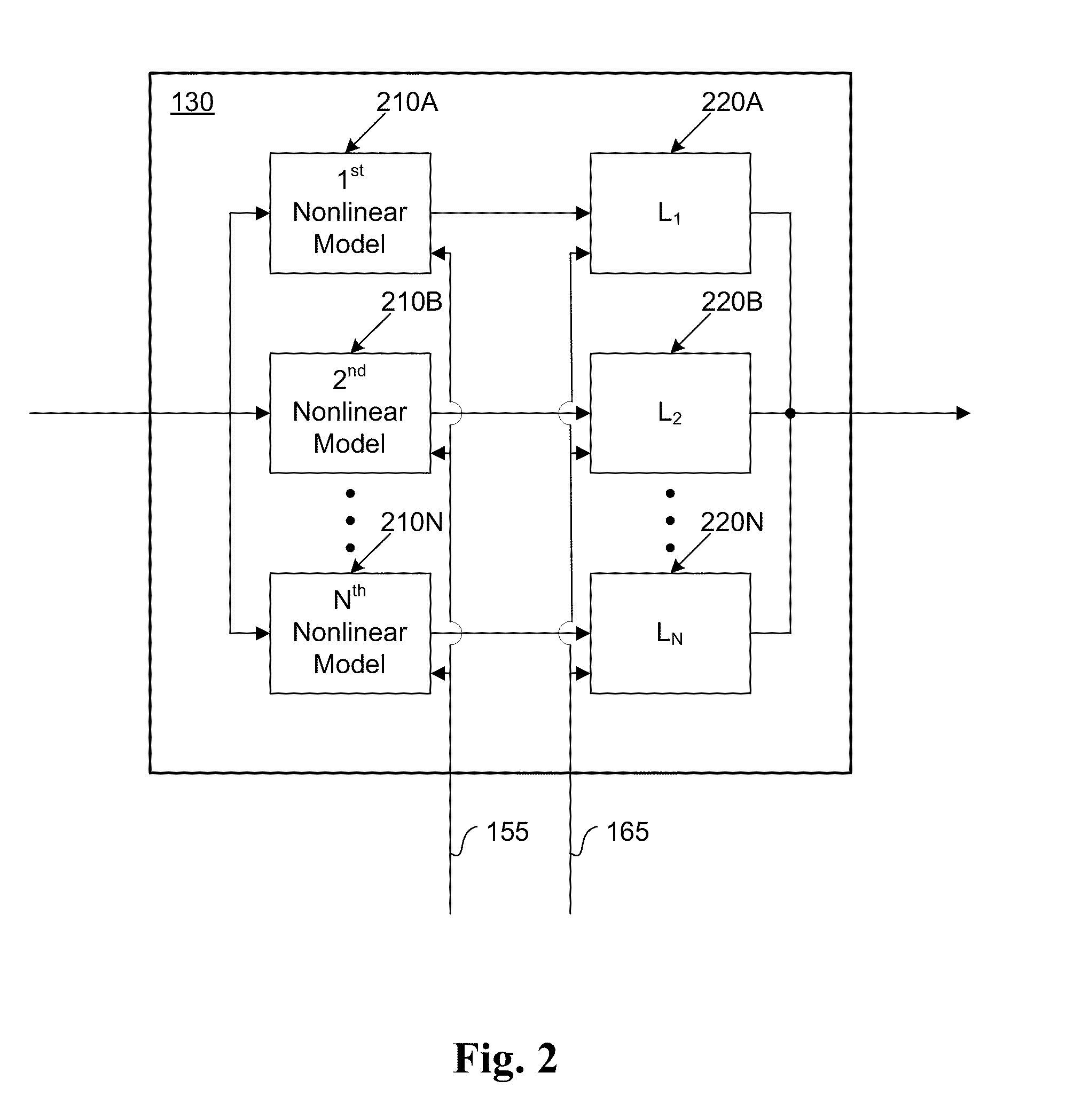

Method and system for broadband predistortion linearization

InactiveUS20060240786A1Improve linearization performanceExtends linearization bandwidthAmplifier modifications to reduce non-linear distortionAmplifiers with memory effect compensationTime domainRadio frequency

The invention relates to a method and system for wideband digital pre-distortion linearization, which is used to overcome the influence of memory effect in radio frequency power amplifier, to expand digital pre-distortion linearization bandwidth, and to improve digital pre-distortion linearization performance. The method and system can get an in-band pre-distortion signal and an out-of-band pre-distortion signal according to the characteristic parameter of the amplifier; the in-band pre-distortion signal is up-converted and the up-converted signal is added to the out-of-band pre-distortion signal, which is not up-converted, then the combined signal is inputted to the power amplifier as an input signal; a part of the output signal from the power amplifier, serving as a feedback signal, can be compared with the original input signal, and the characteristic parameter of the amplifier for generating the in-band pre-distortion signal and the out-of-band pre-distortion signal is adaptively regulated according to the comparison result, so that the waveform of time domain or the frequency domain of the feedback signal can be close to that of the original input signal as much as possible.

Owner:ZTE CORP

Phased array metamaterial antenna system

ActiveUS20050225492A1Low Sidelobe PerformanceReduce sidelobeRadiating elements structural formsWaveguidesSolid substratePhased array

An efficient, low-loss, low sidelobe, high dynamic range phased-array radar antenna system is disclosed that uses metamaterials, which are manmade composite materials having a negative index of refraction, to create a biconcave lens architecture (instead of the aforementioned biconvex lens) for focusing the microwaves transmitted by the antenna. Accordingly, the sidelobes of the antenna are reduced. Attenuation across microstrip transmission lines may be reduced by using low loss transmission lines that are suspended above a ground plane a predetermined distance in a way such they are not in contact with a solid substrate. By suspending the microstrip transmission lines in this manner, dielectric signal loss is reduced significantly, thus resulting in a less-attenuated signal at its destination.

Owner:LUCENT TECH INC

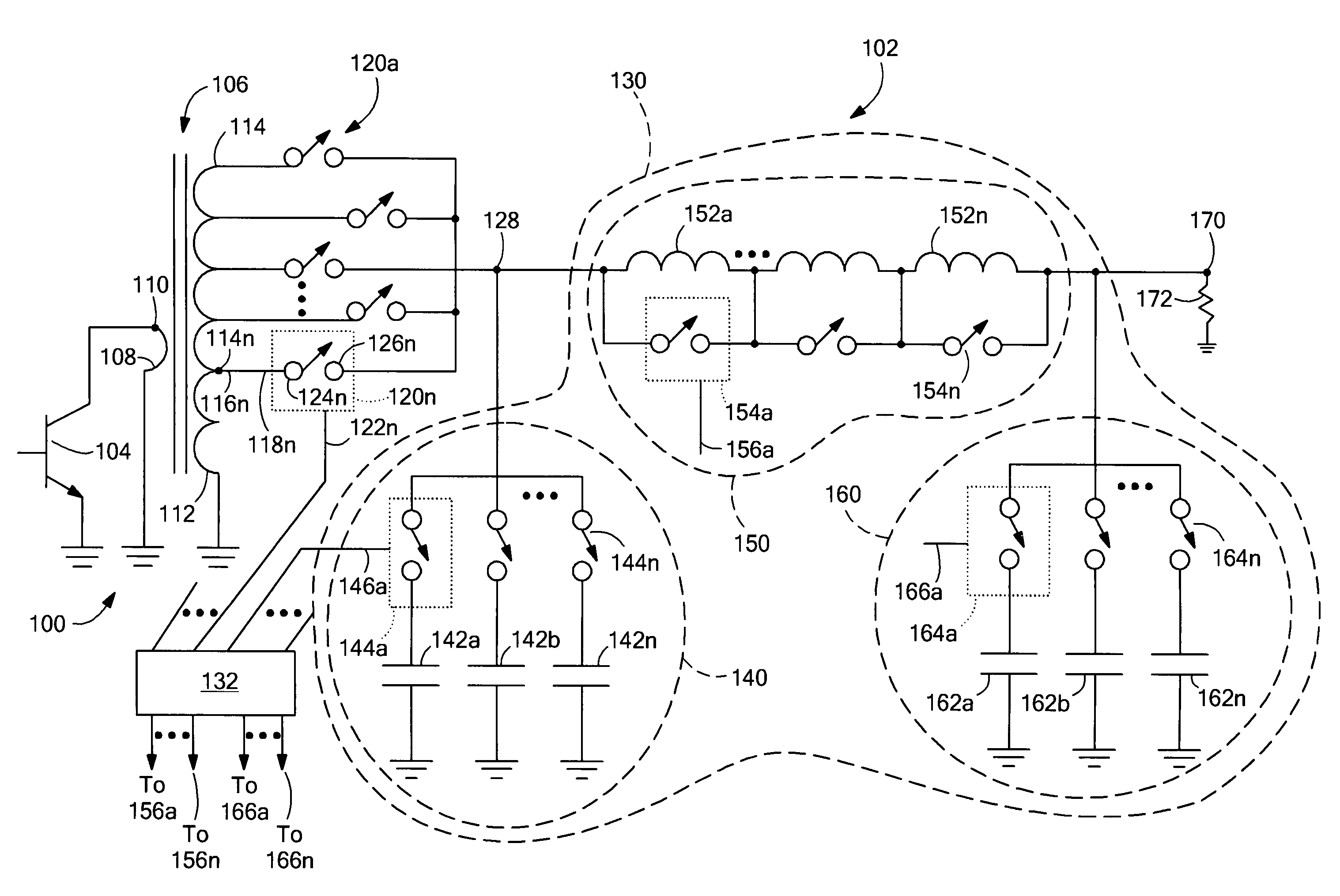

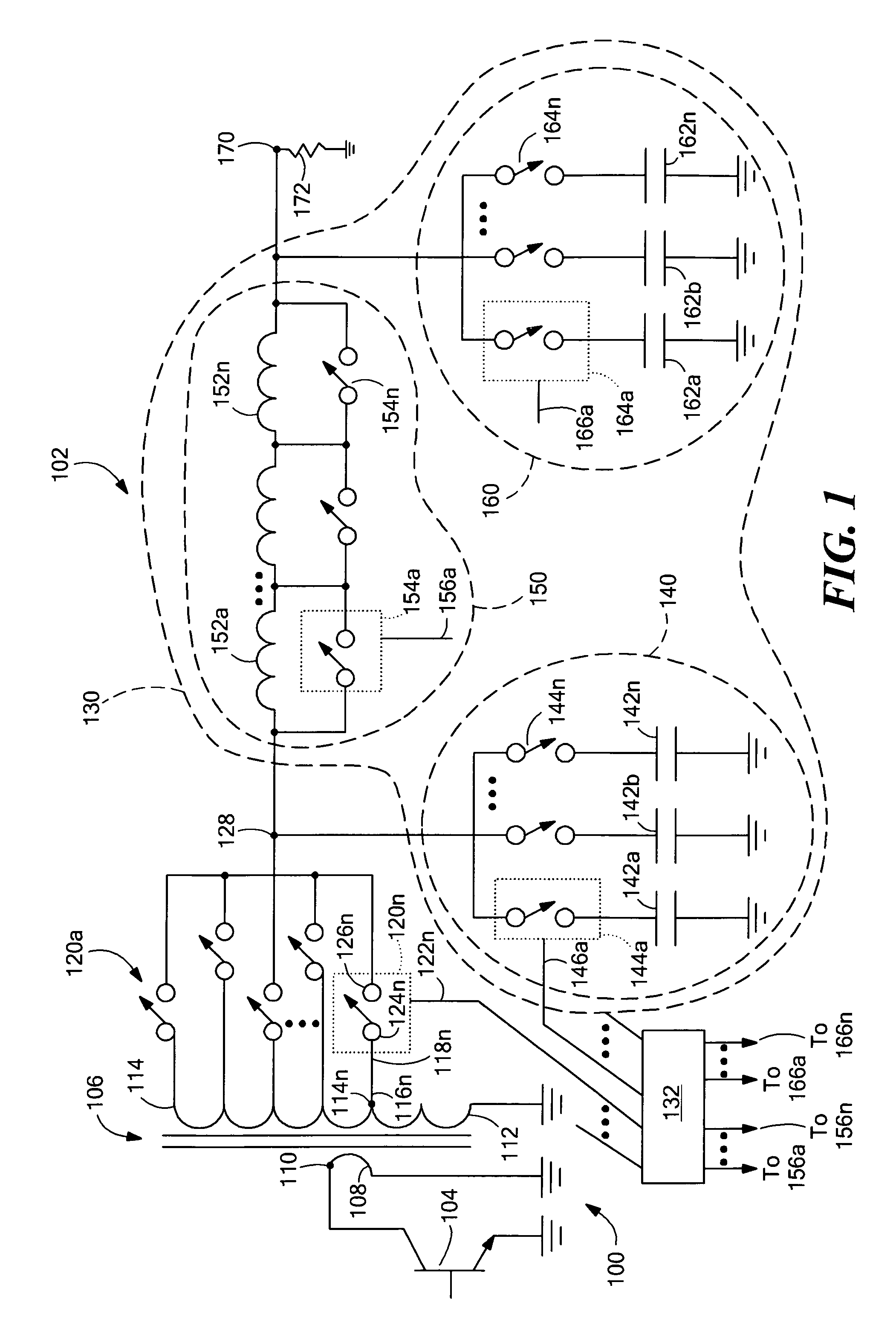

Mems-tuned high power, high efficiency, wide bandwidth power amplifier

InactiveUS6992543B2High output power levelAdvantage in sizeMultiple-port networksAmplifier with semiconductor-devices/discharge-tubesTransformerControl signal

A circuit for matching the impedance of an output load to an active device includes a transformer including a first winding having a terminal for coupling to the output of the active device and a second winding electromagnetically coupled to the first winding, and a plurality of taps, each of the plurality of taps having a first end coupled to a position on the second winding corresponding to a ratio of the second winding to first winding differing from other ones of the plurality of taps, and a second end. The matching circuit further includes a plurality of MEMS switches each having a control input for receiving a corresponding control signal, a first terminal coupled to the second end of a corresponding one of the plurality of taps, and a switched output selectively coupled to a matching junction in response to the corresponding control signal.

Owner:RAYTHEON CO

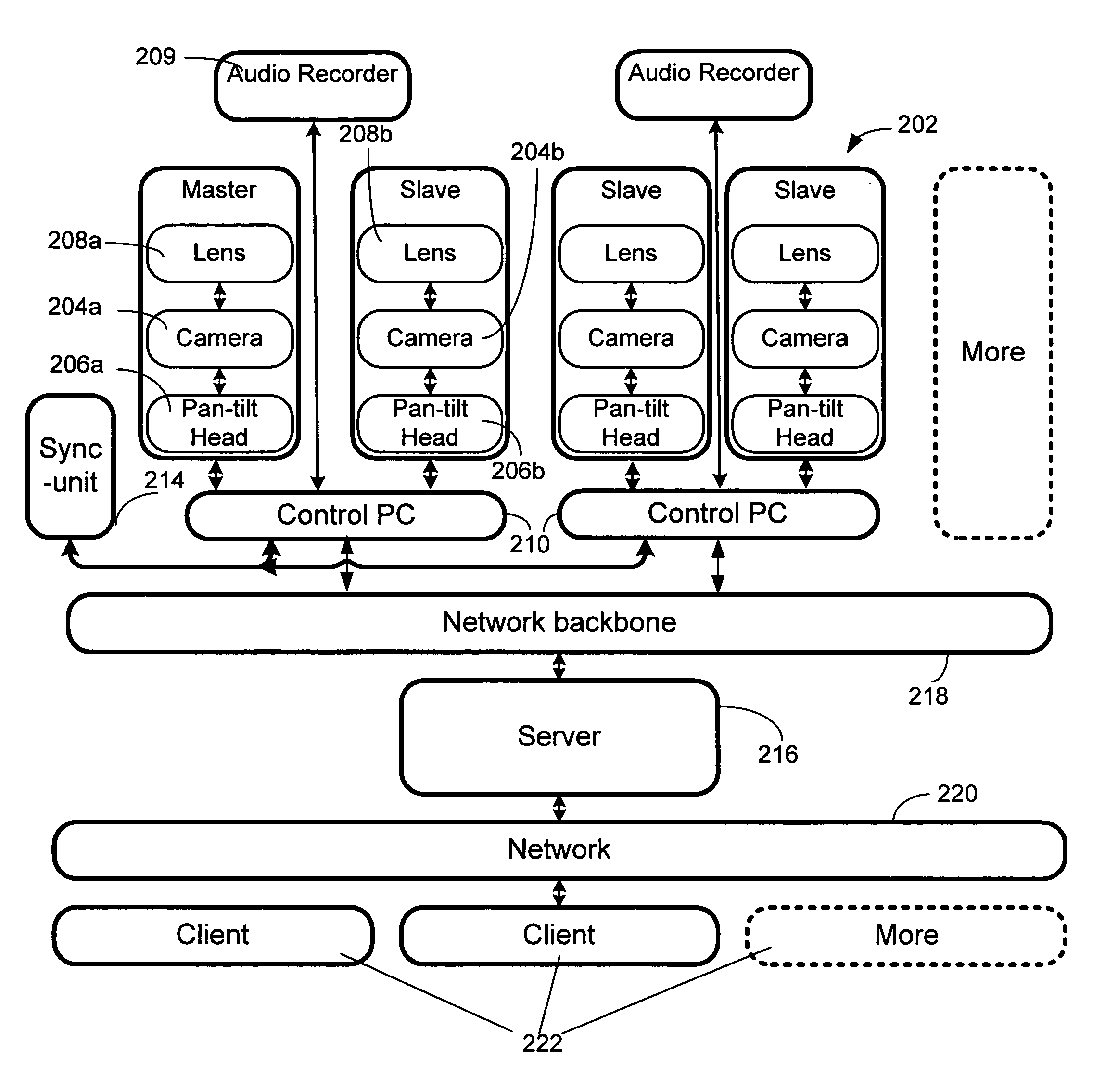

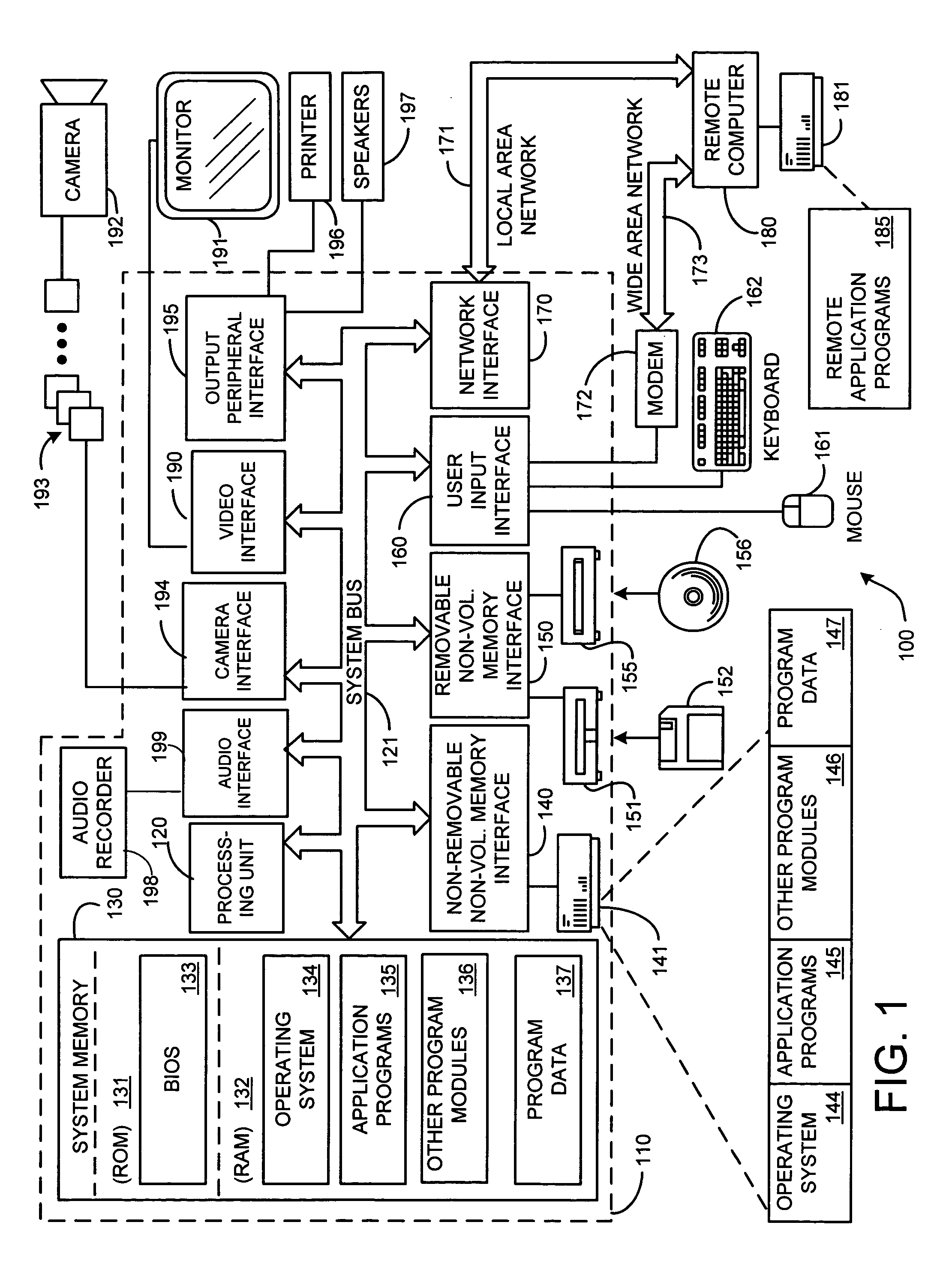

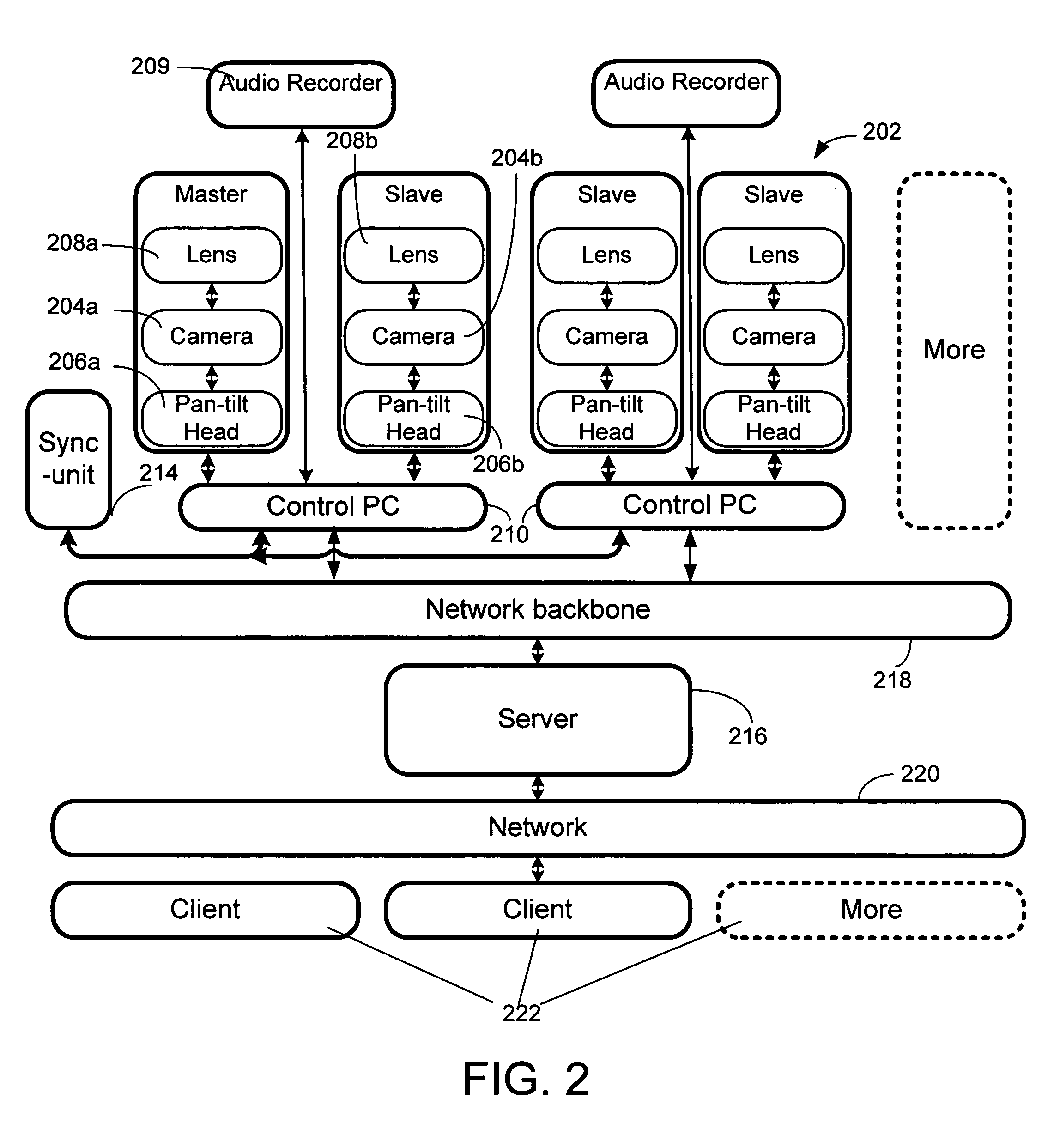

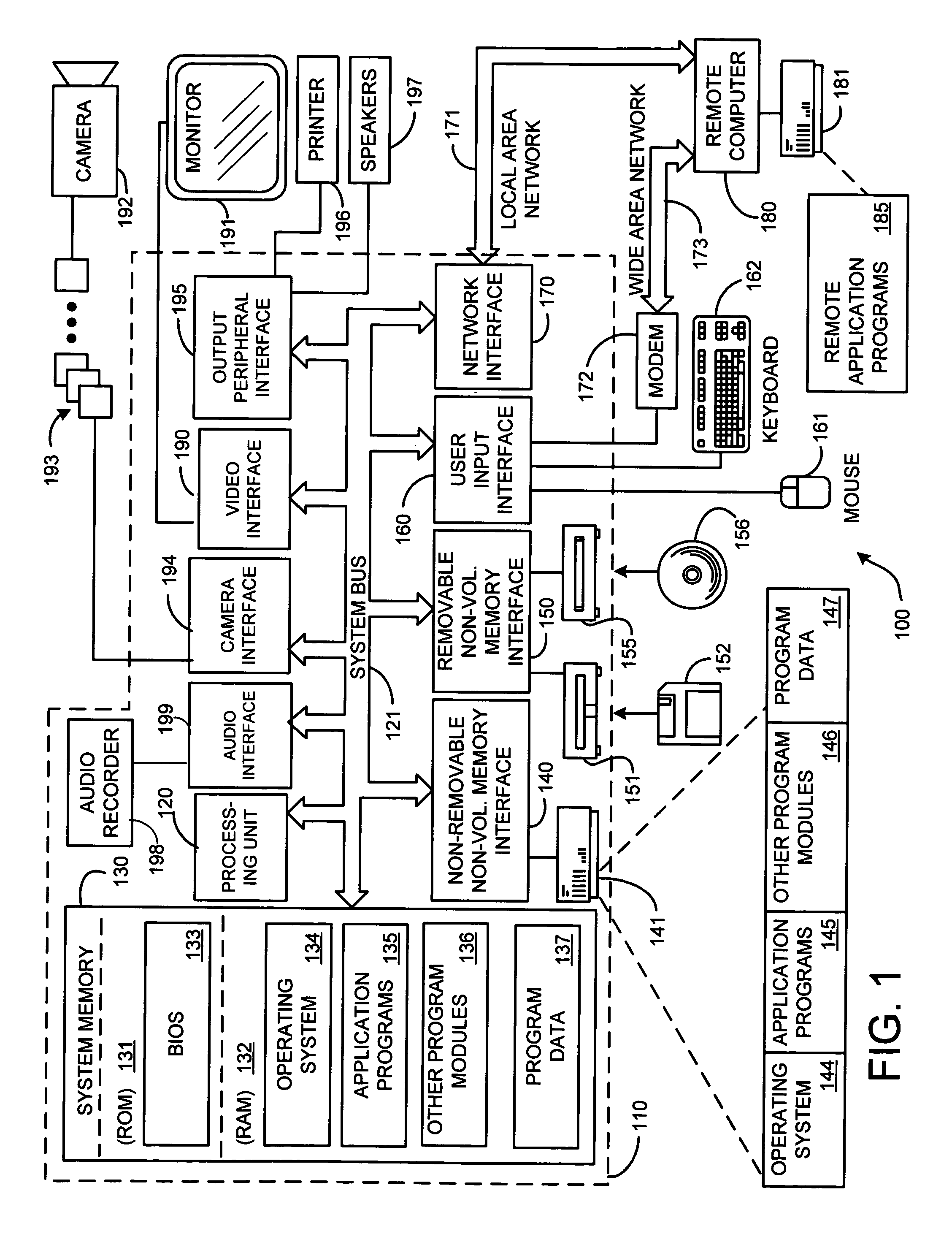

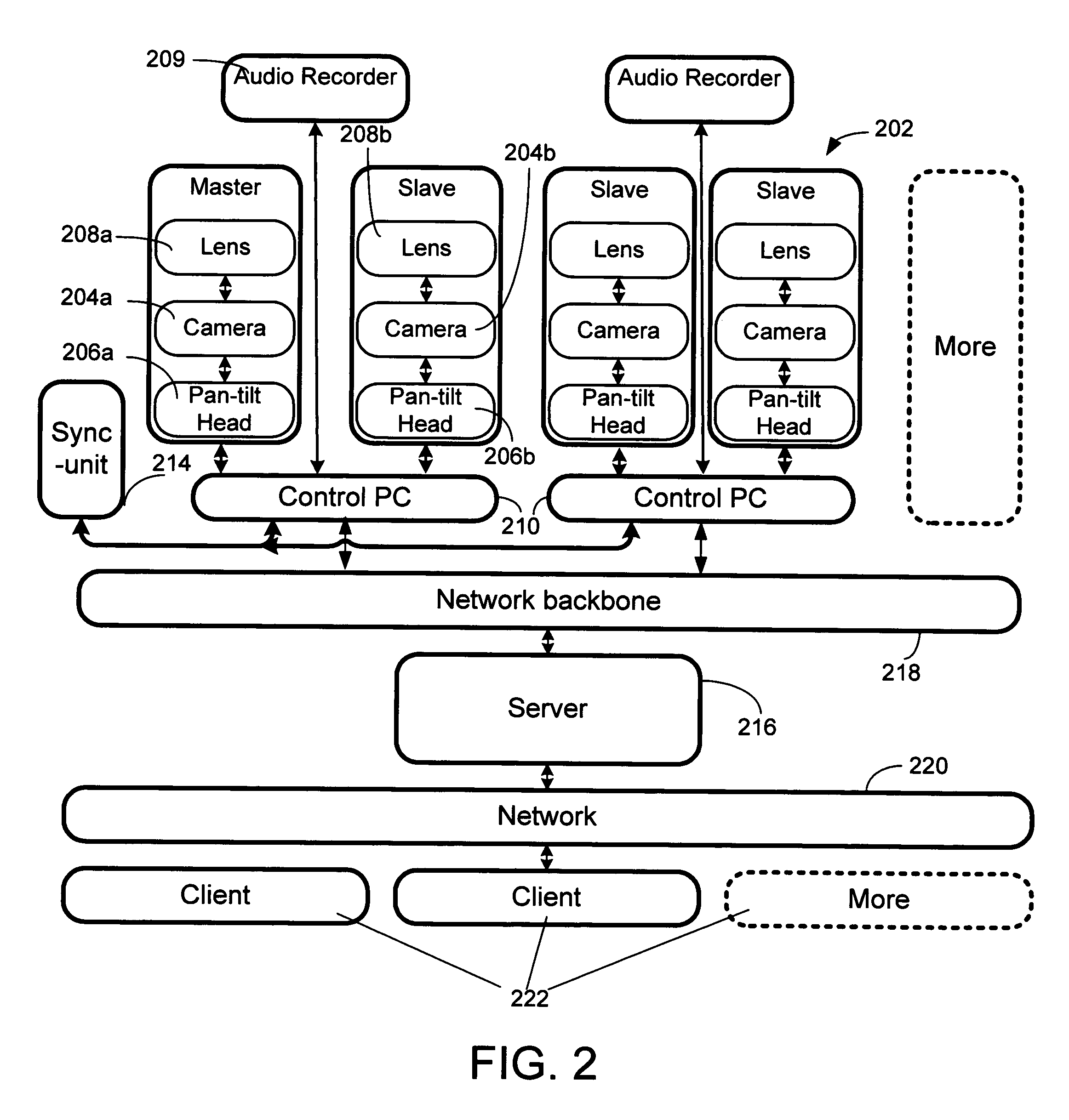

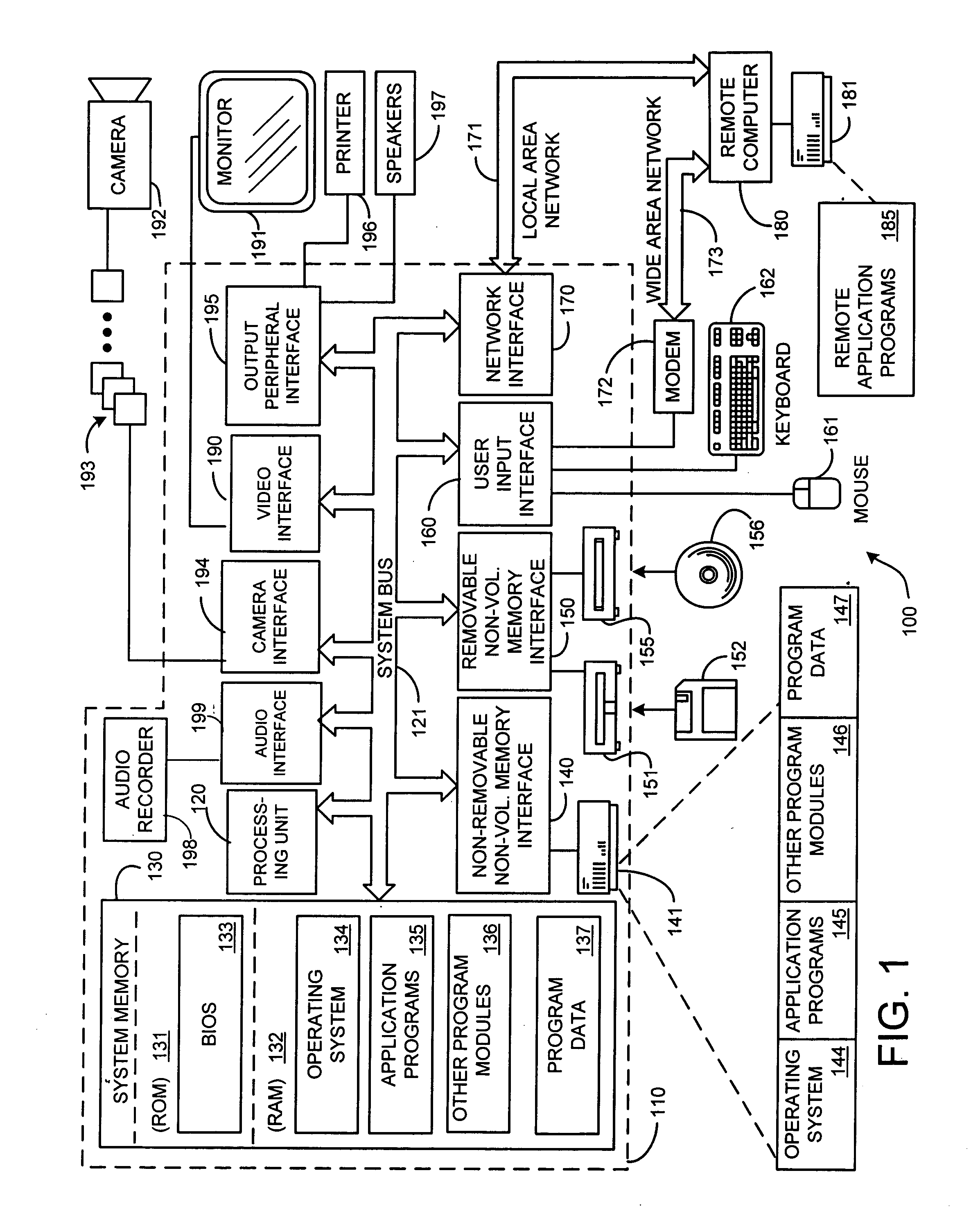

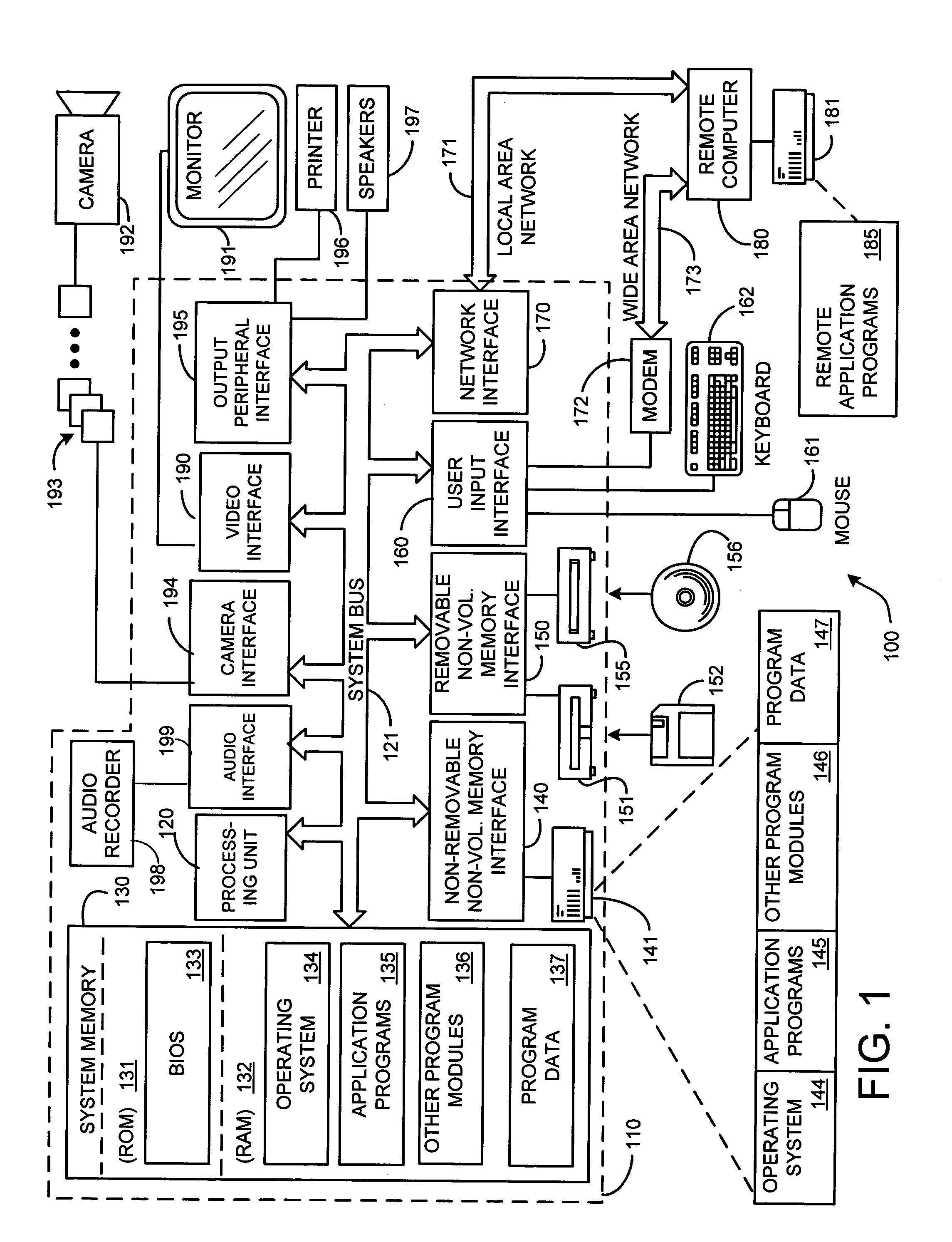

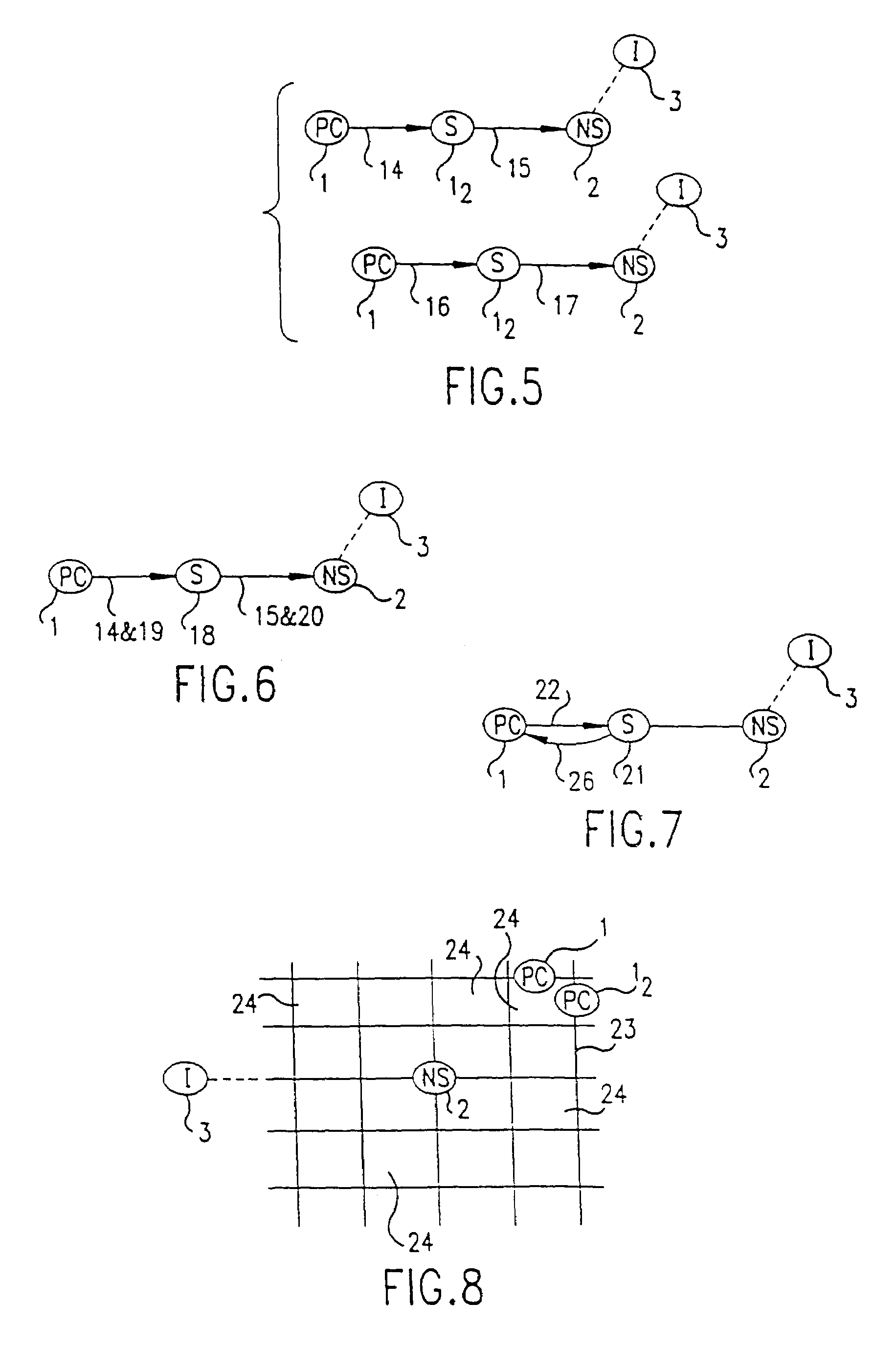

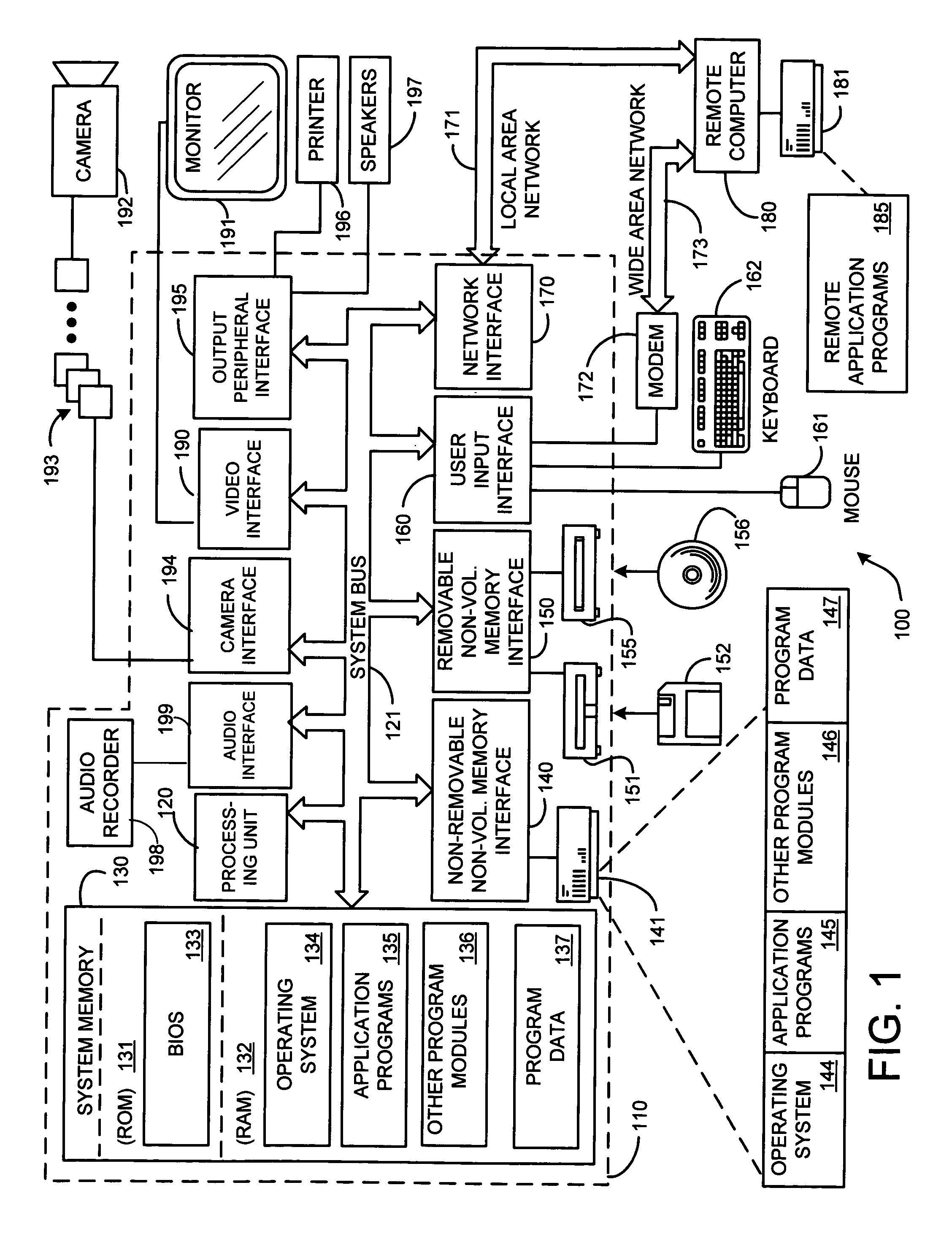

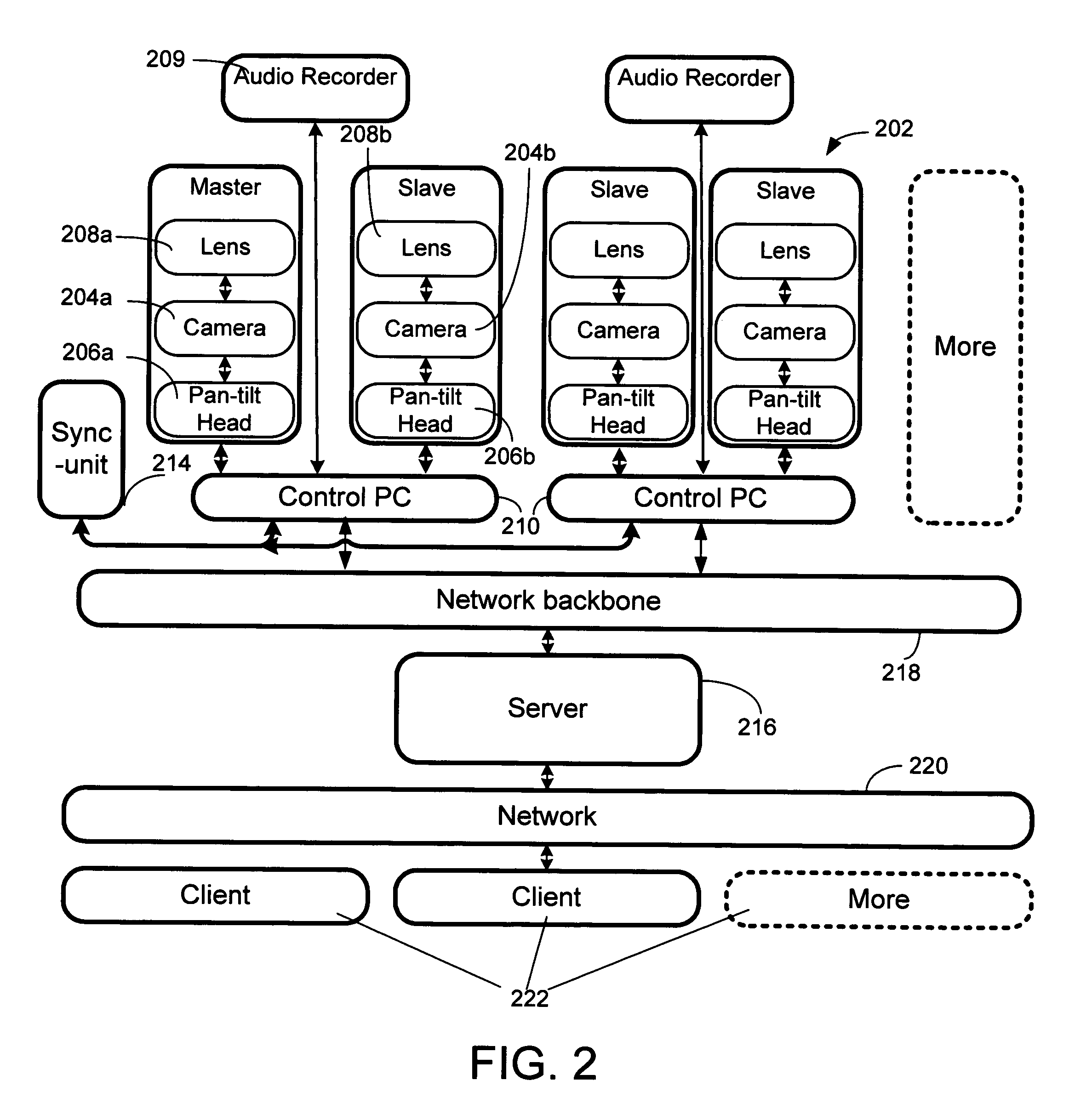

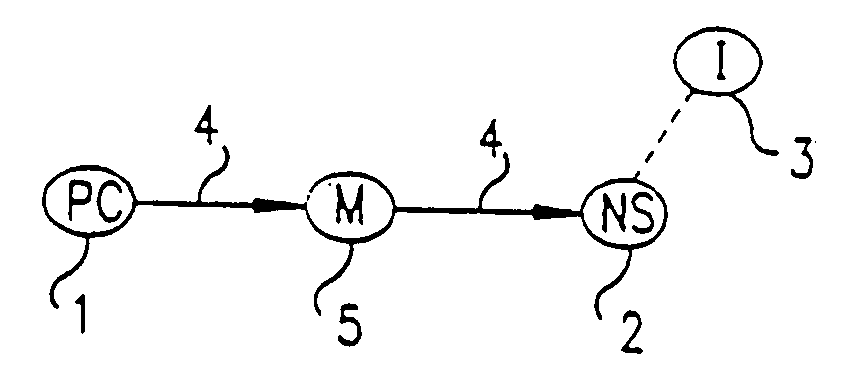

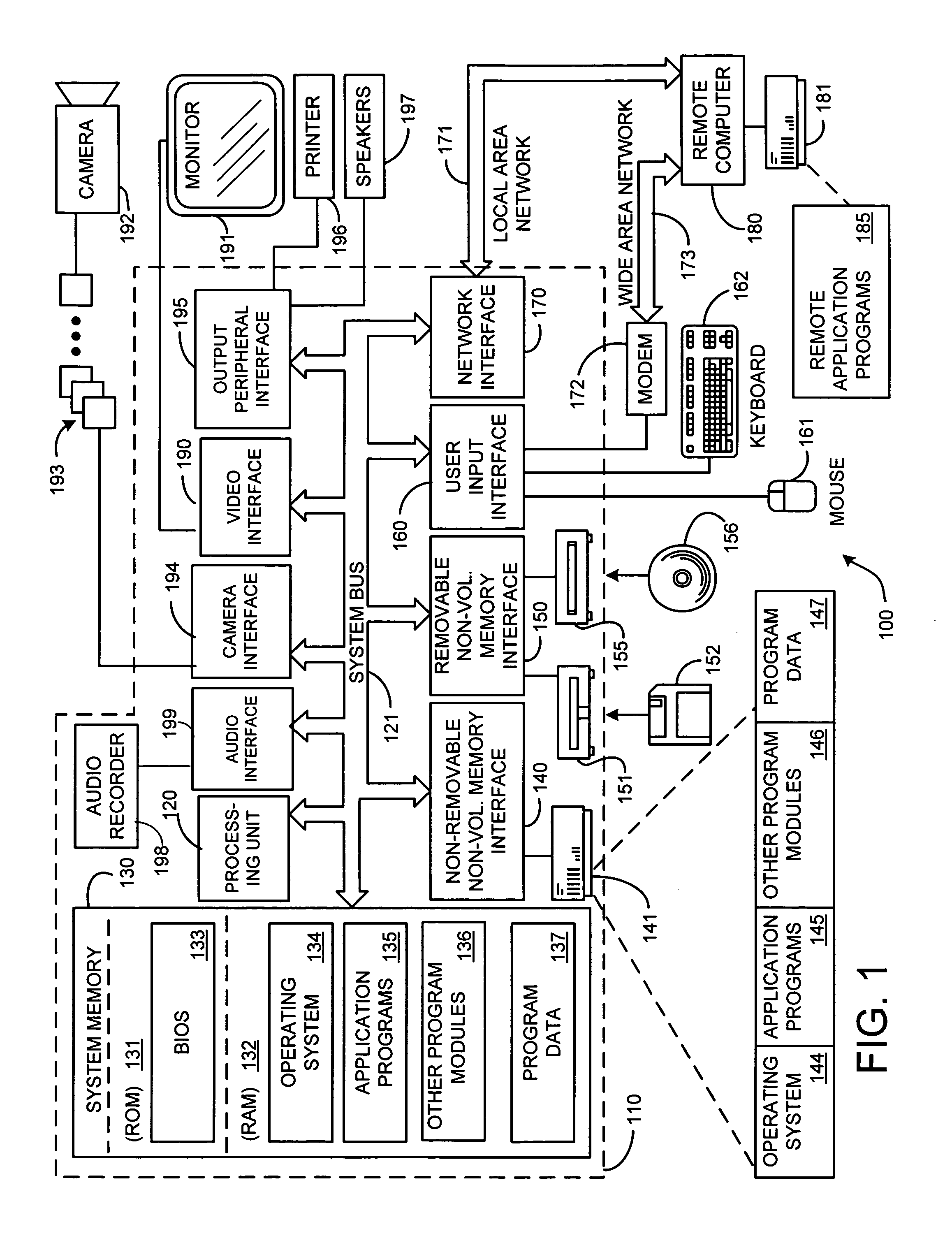

System and Method for Client Services for Interactive Multi-View Video

InactiveUS20060023066A1Computer processing power becomes strongSolve narrow bandwidthTelevision system detailsColor television detailsComputer graphics (images)Control selection

Interactive multi-view video presents new types of video capture systems, video formats, video compression algorithms, and services. Many video cameras are allocated to capture an event from various related locations and directions. The captured videos are compressed and are sent to a server in real-time. Users can subscribe to a new type of service that allows users to connect to the servers and receive multi-view videos interactively. In addition to conventional playing controls, users can manipulate controls to the camera positions and orientations, select viewing directions and enjoy special effects such as a sweeping effect and a freeze-and-rotate effect, and so on. Interactive multi-view video provides a brand-new experience in watching events.

Owner:MICROSOFT TECH LICENSING LLC

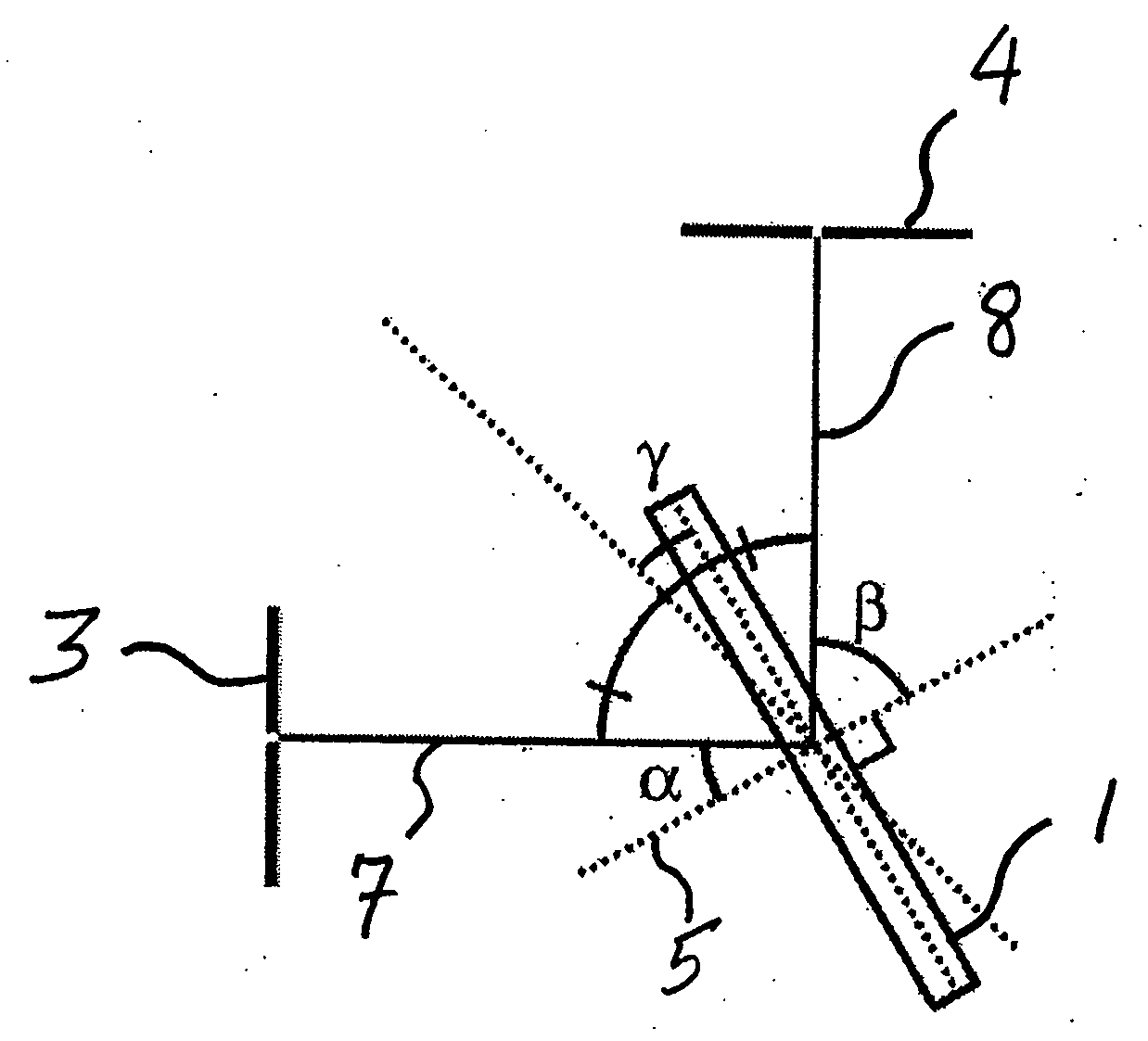

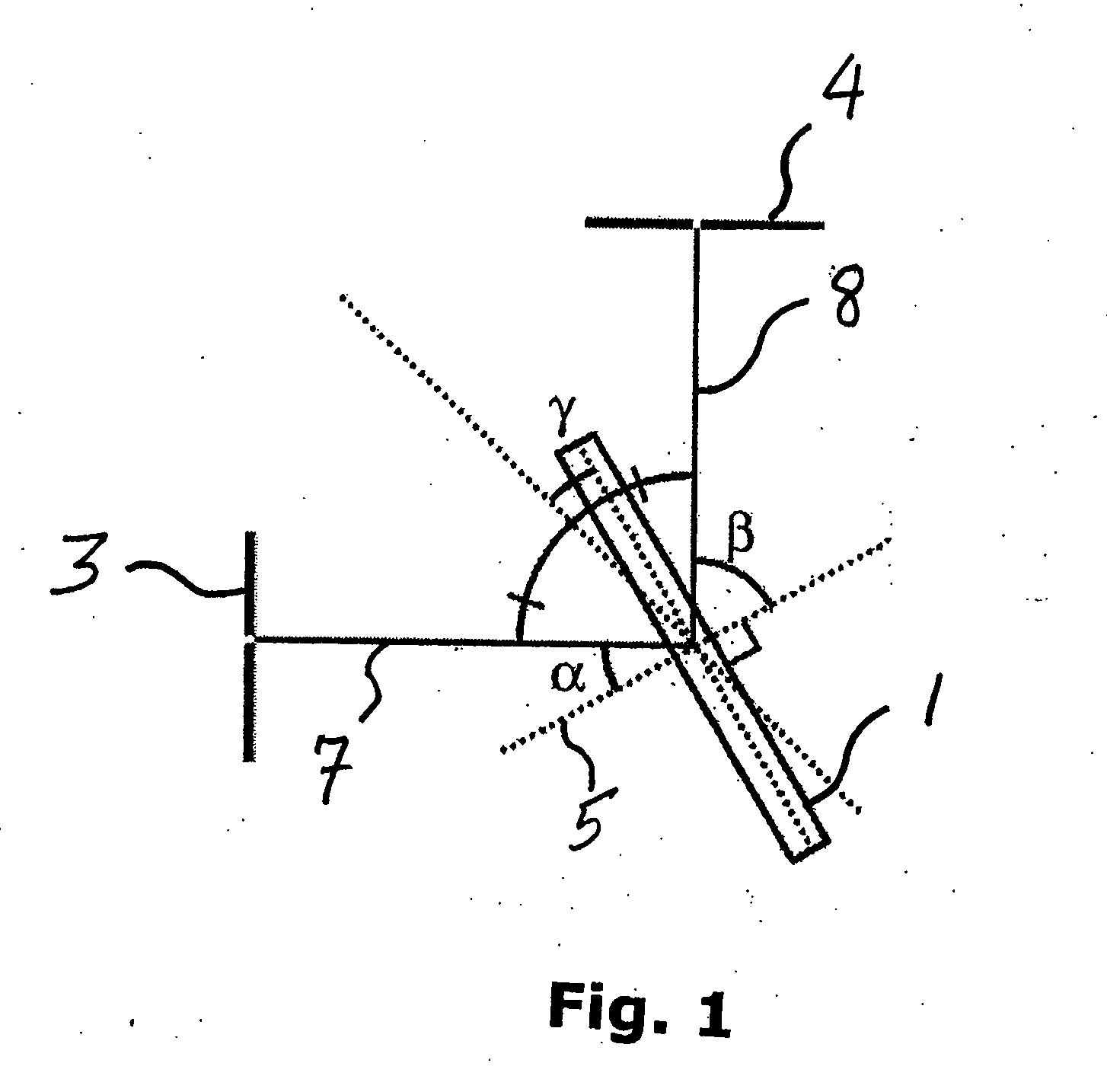

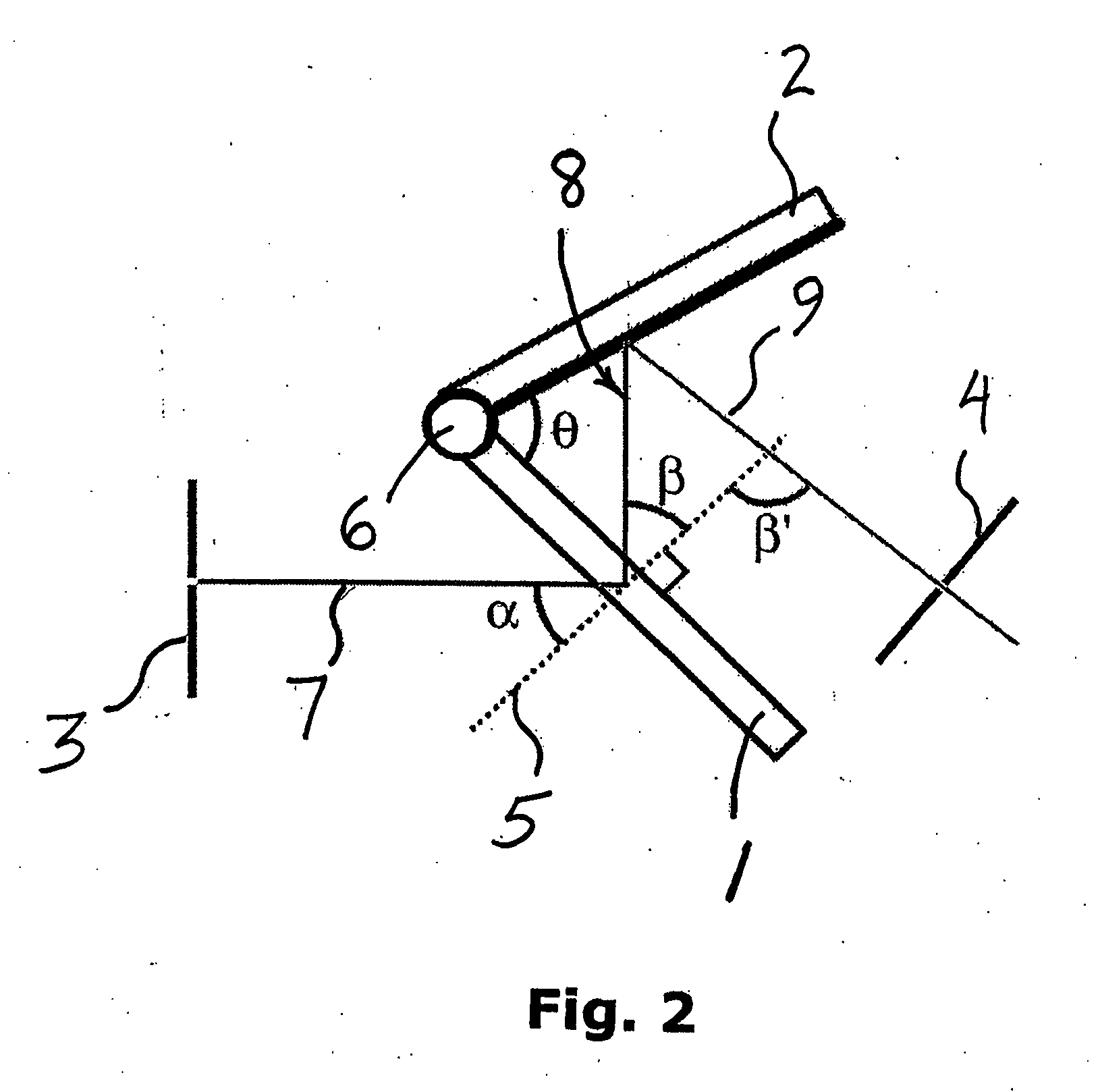

Angle-tunable transmissive grating

InactiveUS20070160325A1High spectral purityHigh Power Handling CapabilitySpectrum generation using diffraction elementsOptical resonator shape and constructionRotational axisGrating

A tunable transmissive grating comprises a transmissive dispersive element, a reflective element, and an angle θ formed between the two elements. A first optical path is formed according to the angle θ, wherein light dispersing from the dispersive element is directed onto the reflective element and reflects therefrom. At least one element is rotatable about a rotational center to cause a second optical path and thereby tune the wavelength of the light reflecting from the reflective element. Both elements can be rotatable together around a common rotational center point according to certain embodiments, and / or each element can be independently rotated around a rotational axis associated only with that element. According to some embodiments, the relative angle θ formed between the elements is held constant; however, in other embodiments θ can vary.

Owner:MASSACHUSETTS INST OF TECH

Compact tunable antenna

InactiveUS7164387B2Broad tuning bandwidthLow efficiencySimultaneous aerial operationsAntenna supports/mountingsLength waveCellular telephone

The present disclosure relates to a method and an antenna for transmitting / receiving a RF signal at a plurality of different frequencies. Transmitting / receiving a RF signal at a plurality of different frequencies is achieved by providing a F antenna comprising a plurality of switches which can be used to adjust the resonant frequency of the antenna. By providing a F antenna, the antenna will be much smaller than the wavelength at which the antenna is operating. This allows the antenna to be used in compact devices such as PDA's and cellular phones.

Owner:HRL LAB

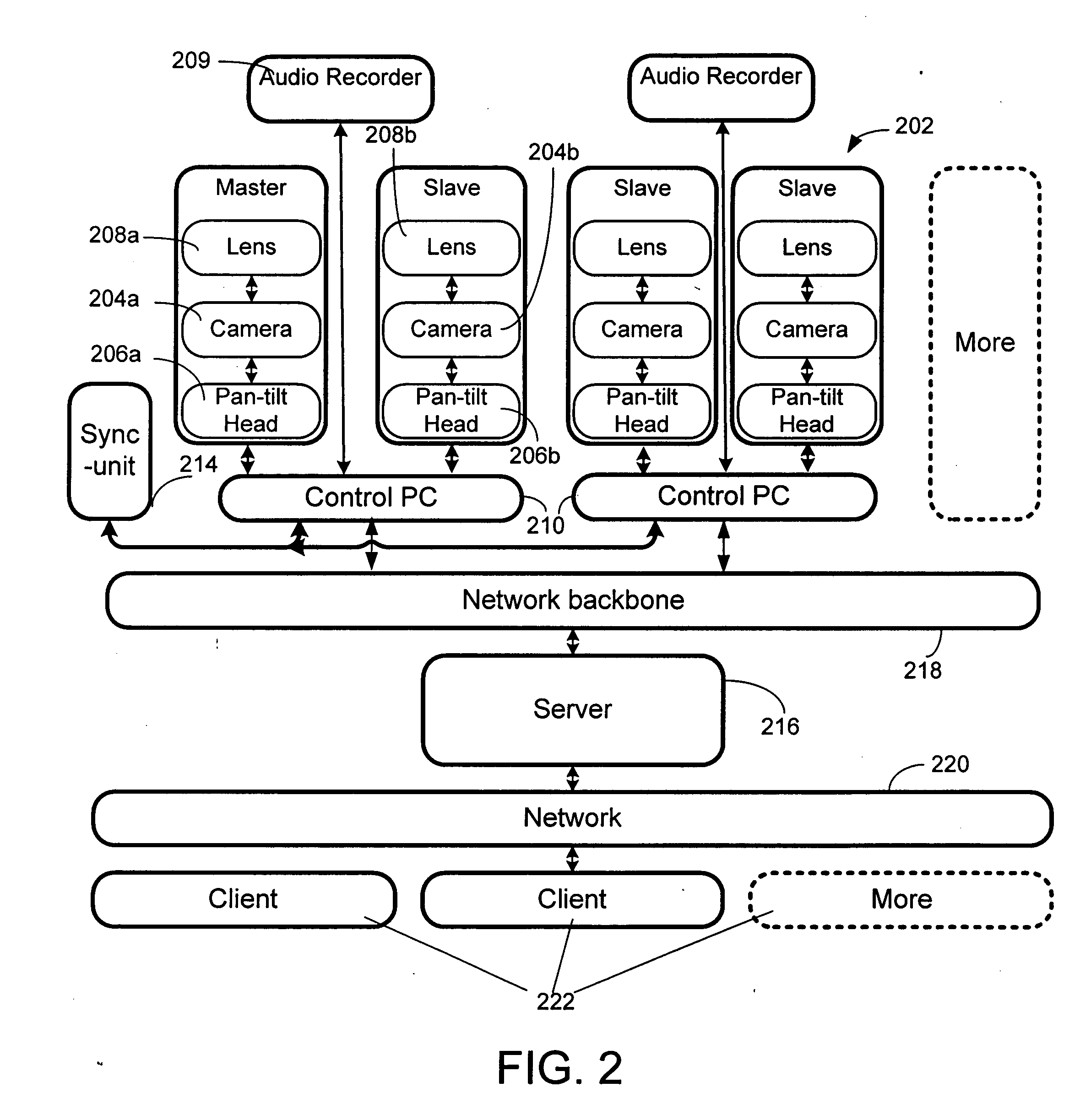

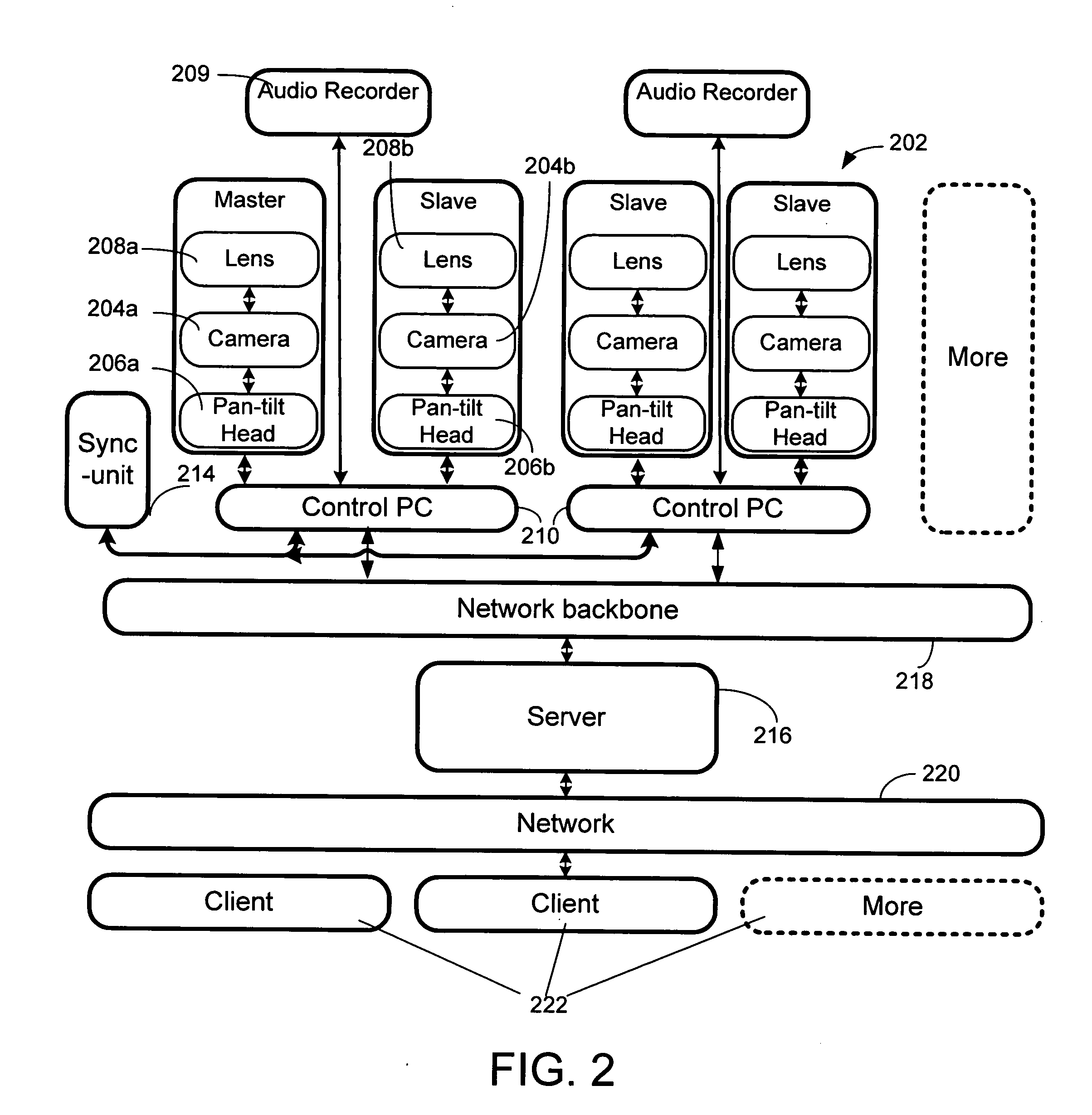

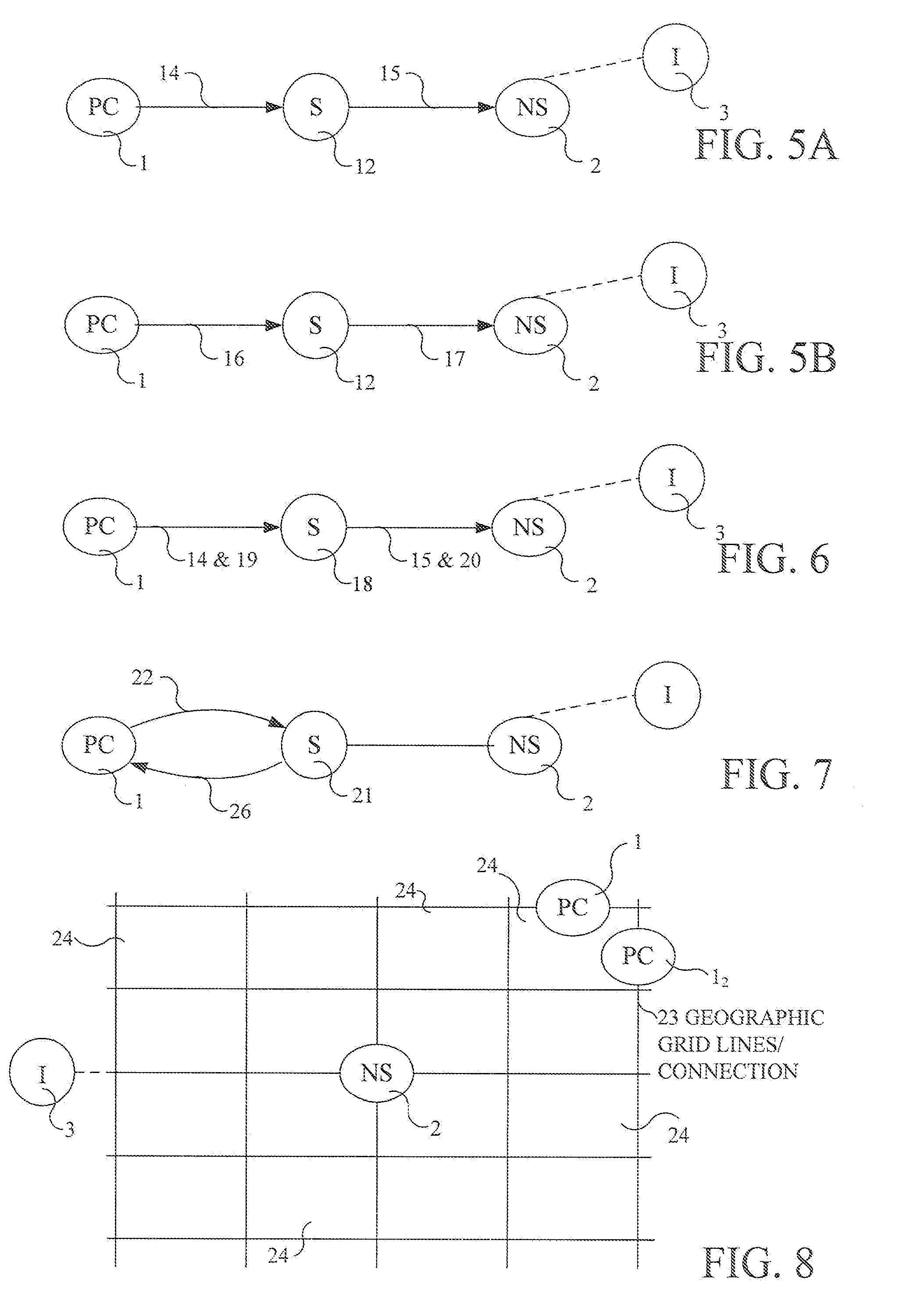

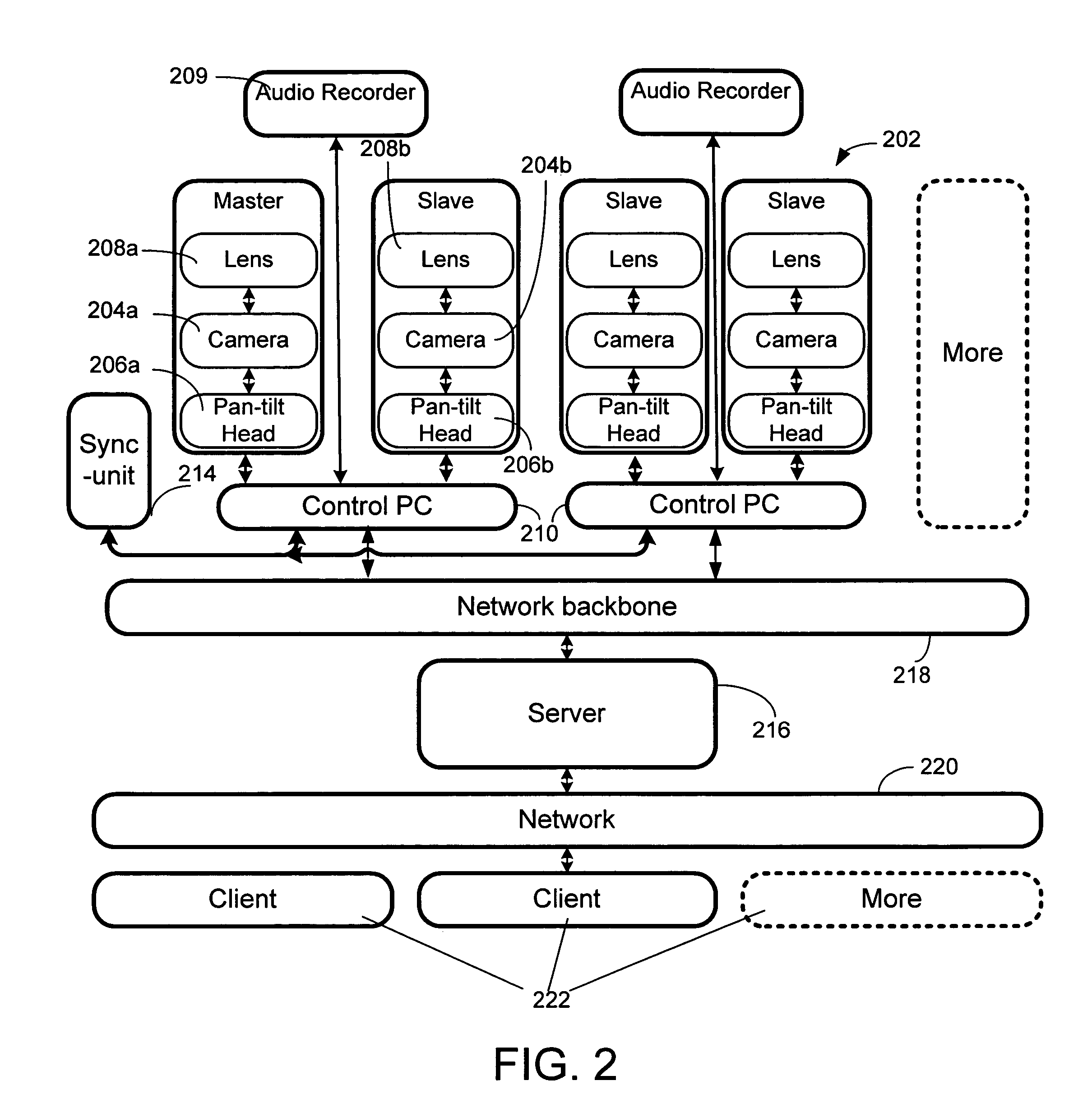

System and method for interactive multi-view video

InactiveUS7671893B2Computer processing power becomes strongSolve narrow bandwidthTelevision system detailsColor television detailsComputer graphics (images)Type of service

Interactive multi-view video presents a new type of video capture system. Many video cameras are allocated to capture an event from various related locations and directions. The captured videos are compressed in control PCs and are sent to a server in real-time. The compressed video can also be transcoded through an off-line compression approach to further reduce the data amount. Users can subscribe to a new type of service that allows users to connect to the servers and receive multi-view videos interactively.

Owner:MICROSOFT TECH LICENSING LLC

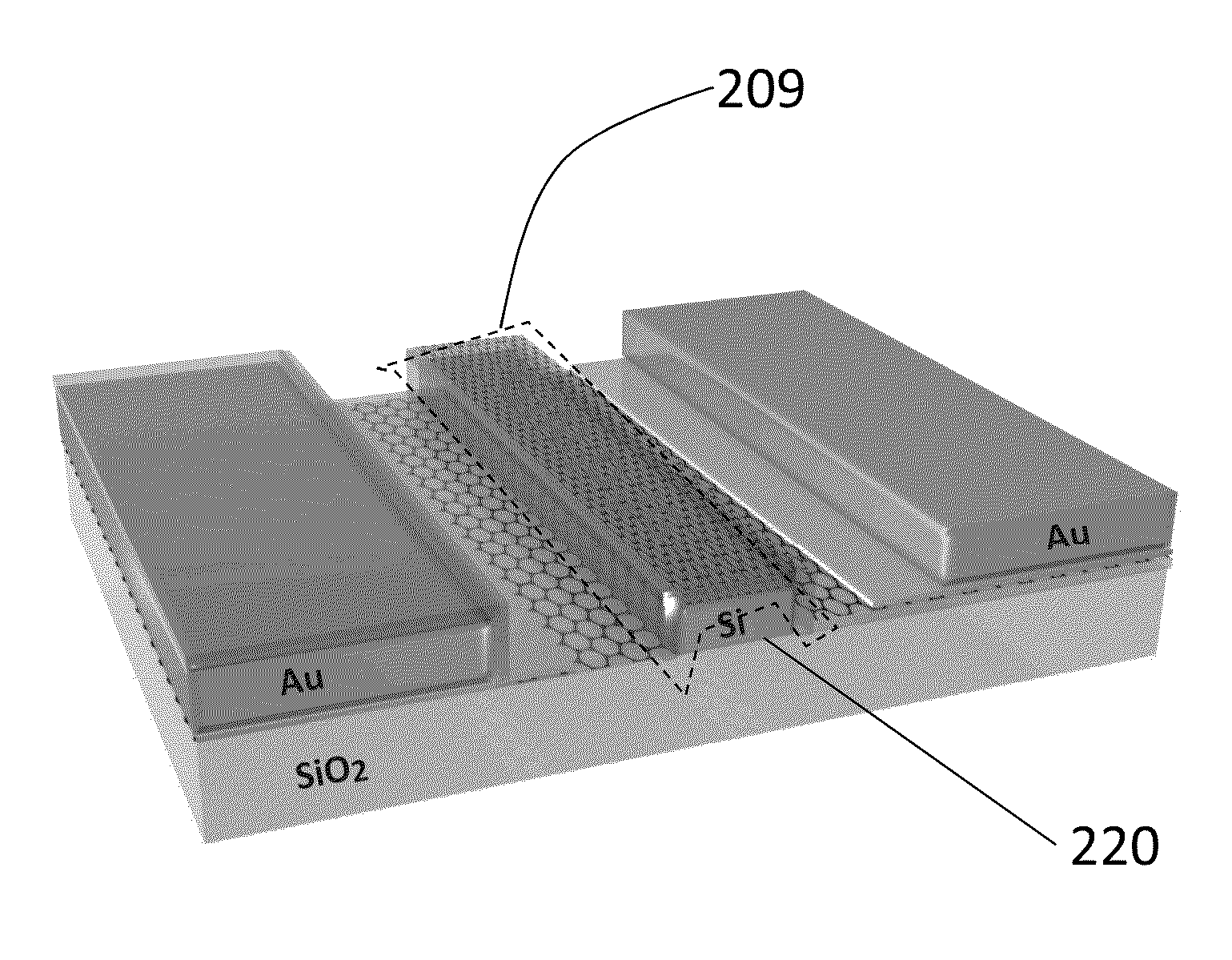

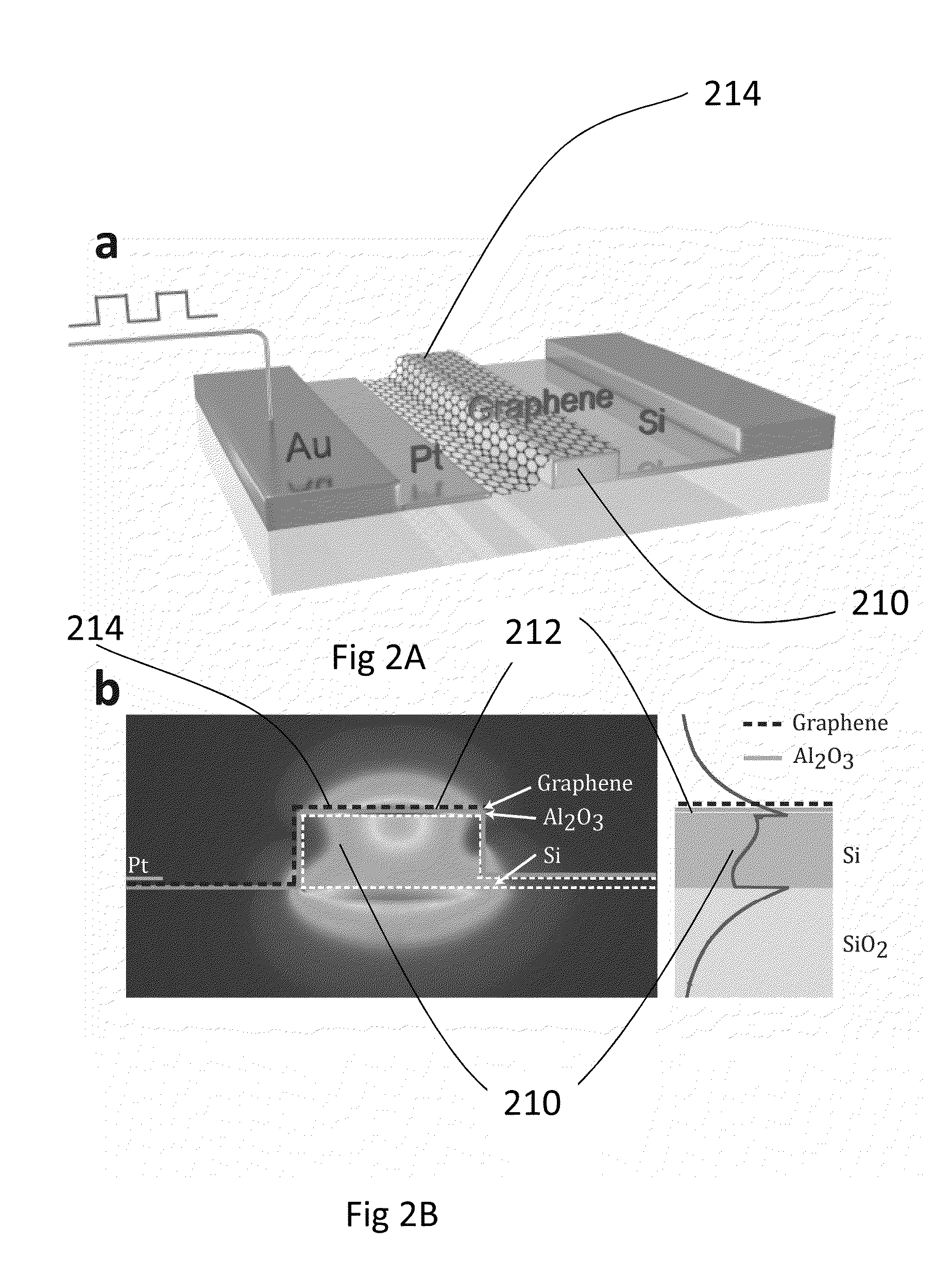

Graphene based optical modulator

ActiveUS20140056551A1Increase speedSmall footprintNanoopticsNon-linear opticsMonolayer grapheneEngineering

The present invention provides for a one or more layer graphene optical modulator. In a first exemplary embodiment the optical modulator includes an optical waveguide, a nanoscale oxide spacer adjacent to a working region of the waveguide, and a monolayer graphene sheet adjacent to the spacer. In a second exemplary embodiment, the optical modulator includes at least one pair of active media, where the pair includes an oxide spacer, a first monolayer graphene sheet adjacent to a first side of the spacer, and a second monolayer graphene sheet adjacent to a second side of the spacer, and at least one optical waveguide adjacent to the pair.

Owner:RGT UNIV OF CALIFORNIA

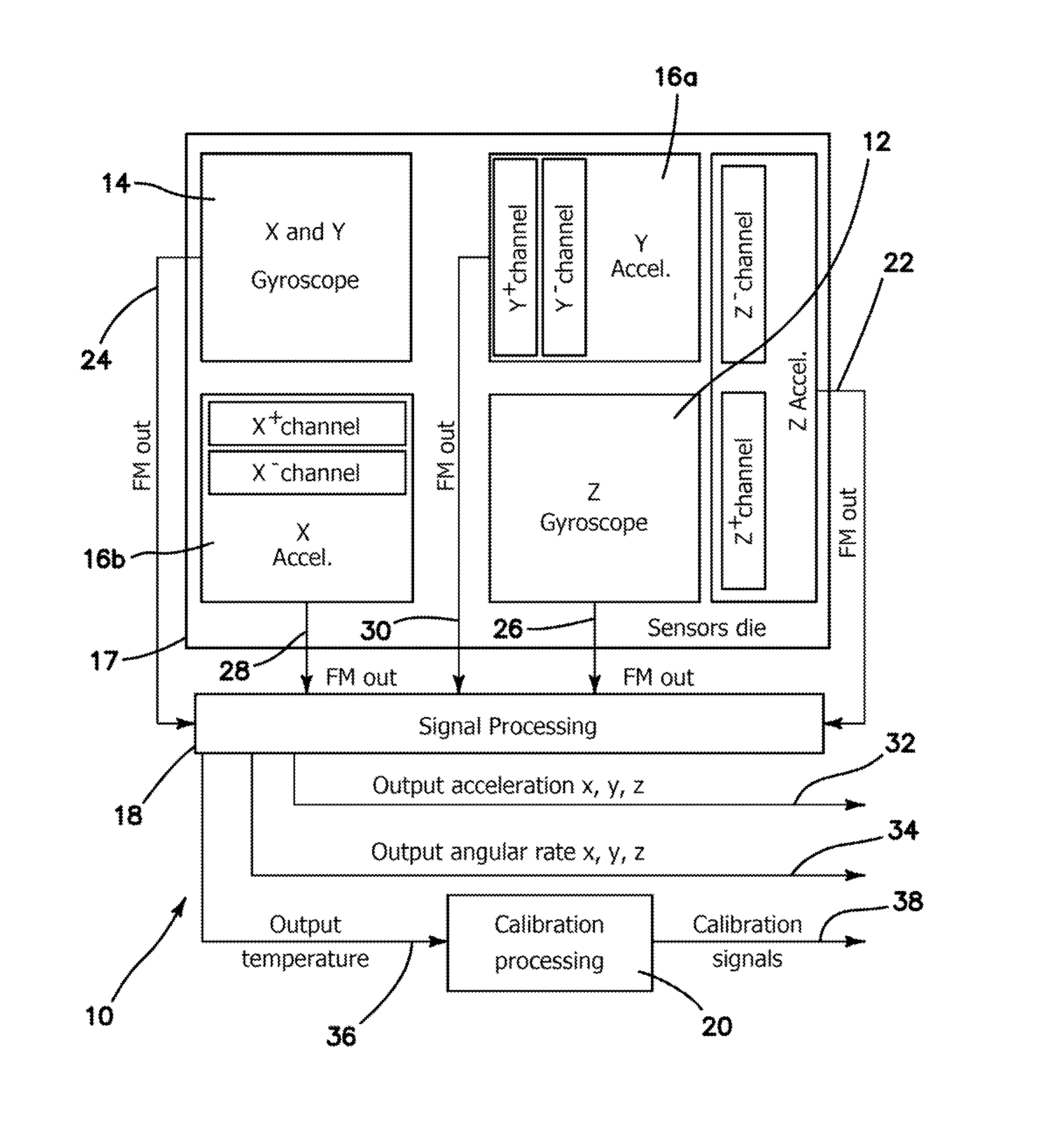

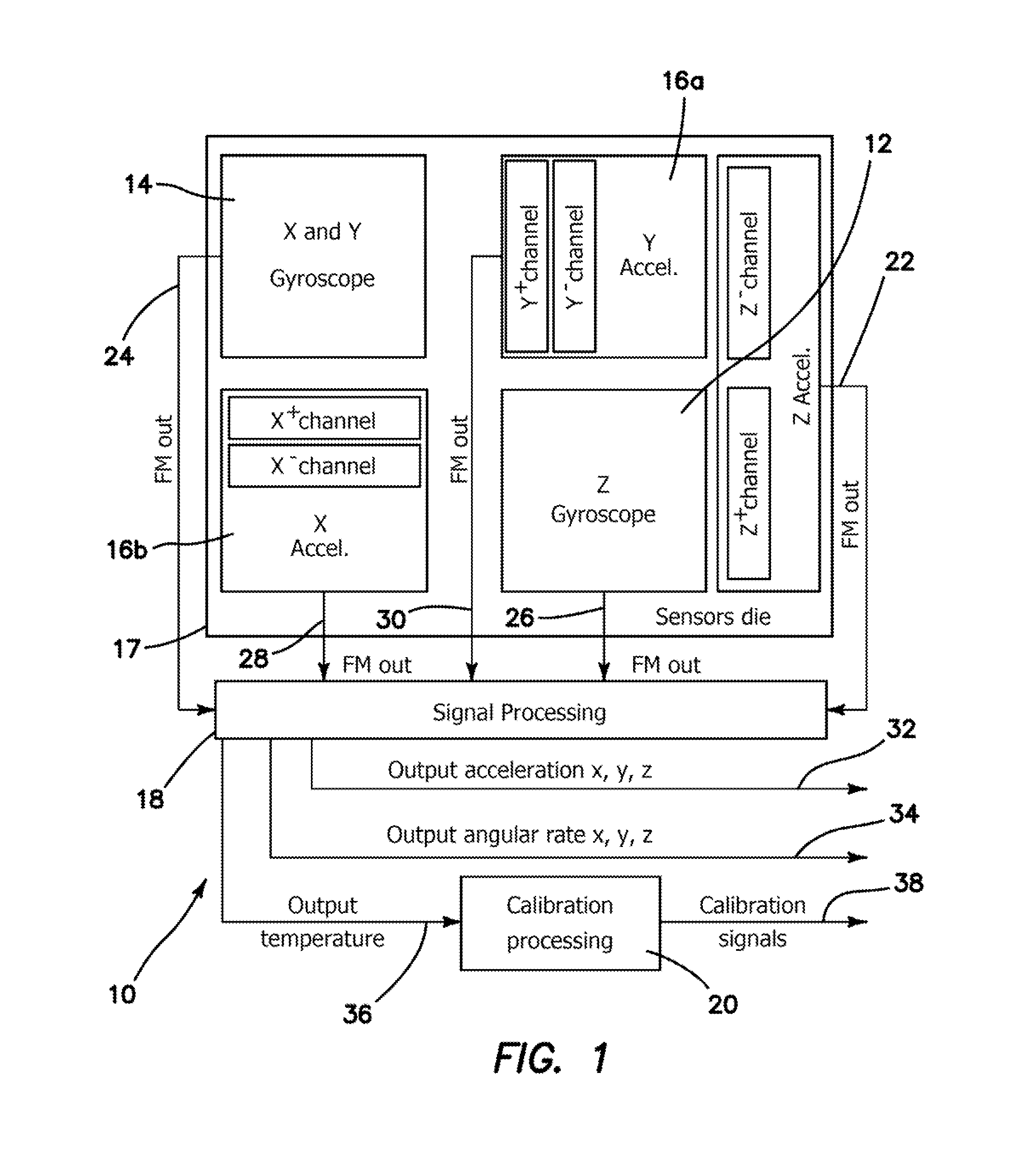

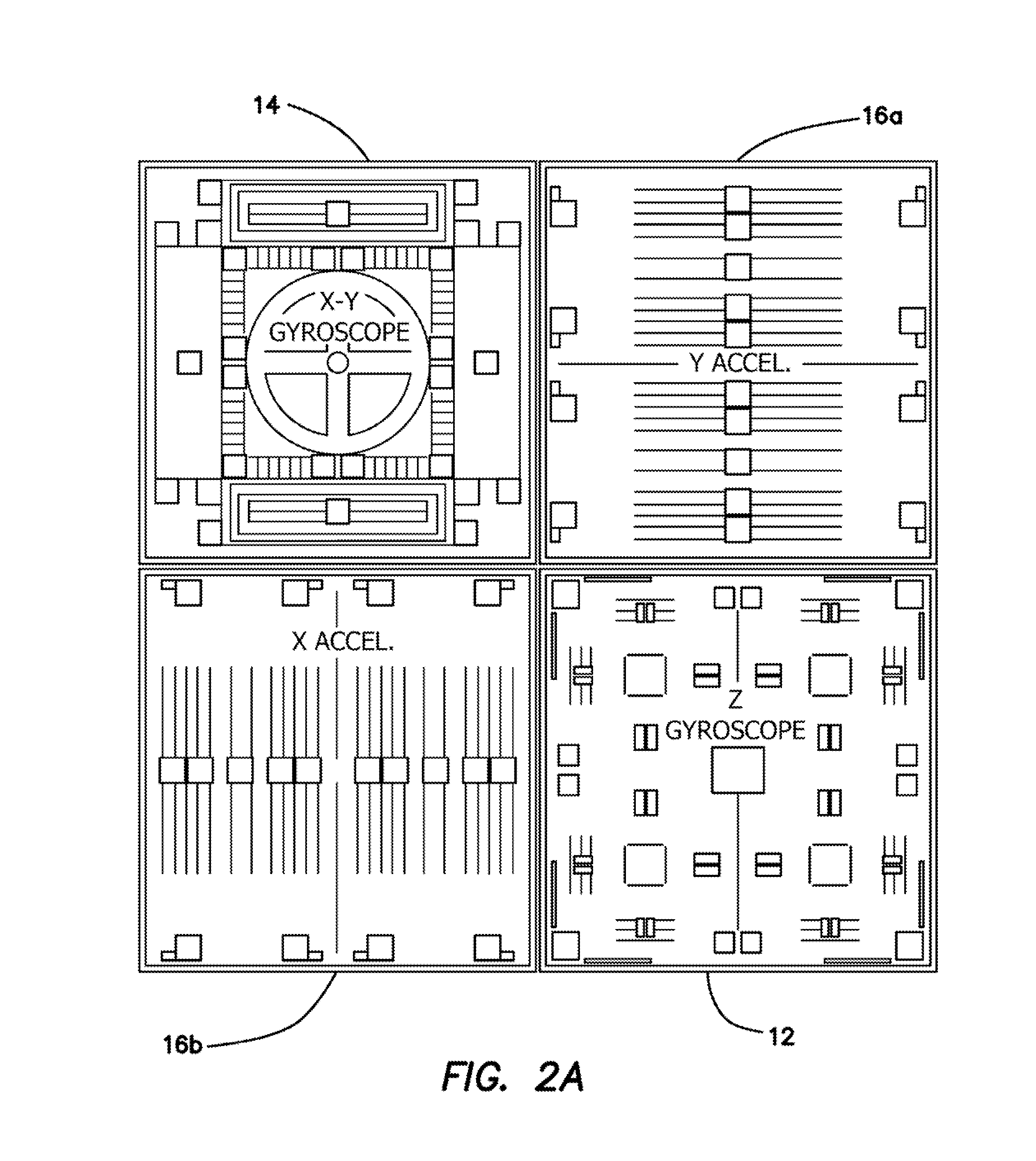

Multi-Axis Chip-Scale MEMS Inertial Measurement Unit (IMU) Based on Frequency Modulation

ActiveUS20140208823A1Ultra-high precisionUltra-high stabilityTesting/calibration of speed/acceleration/shock measurement devicesGyroscopes/turn-sensitive devicesGyroscopeAccelerometer

A multi-axis microelectromechanical-systems (MEMS) inertial measurement unit (IMU) is fabricated in a vacuum sealed single packaged device. An FM vibratory gyroscope and an FM resonant accelerometer both for generating FM output signals is fabricated in the silicon chip using MEMS. A signal processor is coupled to the an FM vibratory gyroscope and to the FM resonant accelerometer for receiving the FM gyroscopic output signals and the FM accelerometer output signals. The signal processor generates simultaneous and decoupled measurement of input acceleration, in put rotation rate, and temperature and / or temperature distribution within the IMU, self-calibration of the biases and scale factors of the IMU and its support electronics against temperature variations and other common mode errors, and reduction of the cross axis sensitivity by reducing acceleration errors in the gyroscope and rotation errors in the accelerometer.

Owner:RGT UNIV OF CALIFORNIA

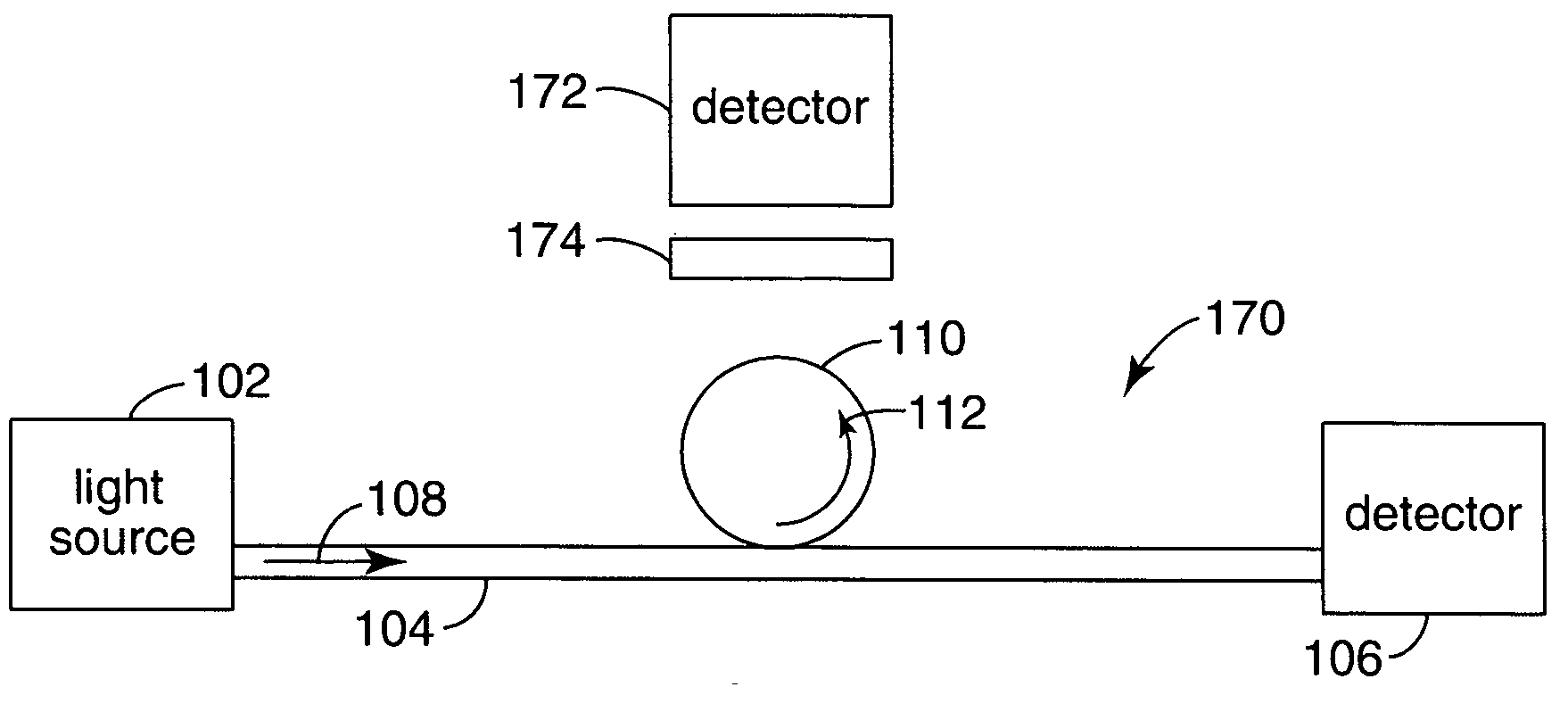

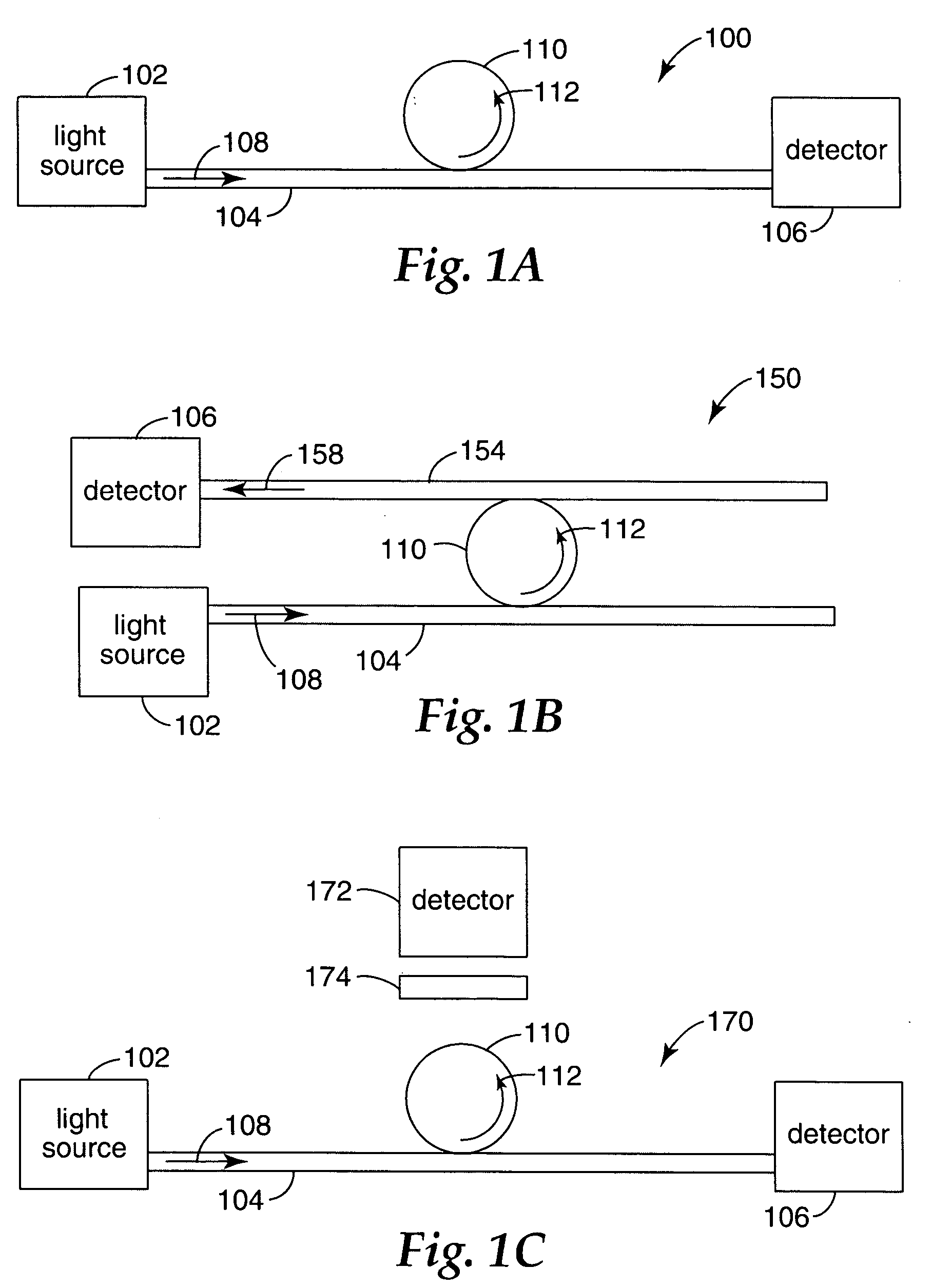

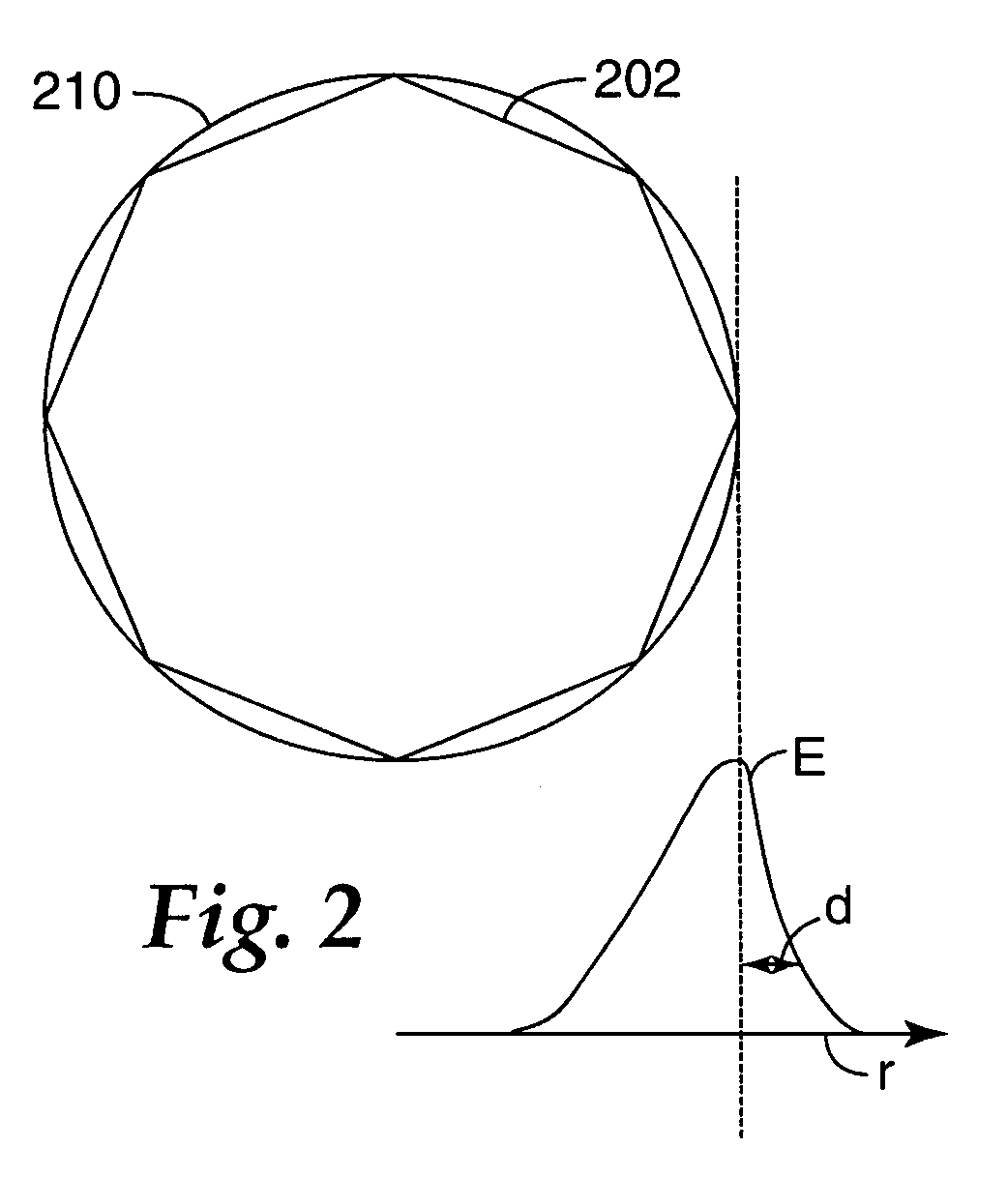

Dielectric microcavity fluorosensors excited with a broadband light source

InactiveUS20050263679A1Solve narrow bandwidthRadiation pyrometryBeam/ray focussing/reflecting arrangementsWhispering galleryBroadband light source

A microresonator sensor apparatus has a microcavity resonator that defines equatorial whispering gallery modes (EWGMs), whose frequencies are separated by the free spectral range (FSR). The EWGMs lie in a plane perpendicular to a microcavity resonator axis. A light source is optically coupled to inject light into the microcavity resonator. The light source produces output light having an output spectrum whose bandwidth is approximately equal to or broader than the FSR of the EGWMs. One or more fluorescent materials are excited using the excitation light coupled into the microcavity resonator. A fluorescent signal arising from fluorescence of the one or more fluorescent materials is then detected.

Owner:3M INNOVATIVE PROPERTIES CO

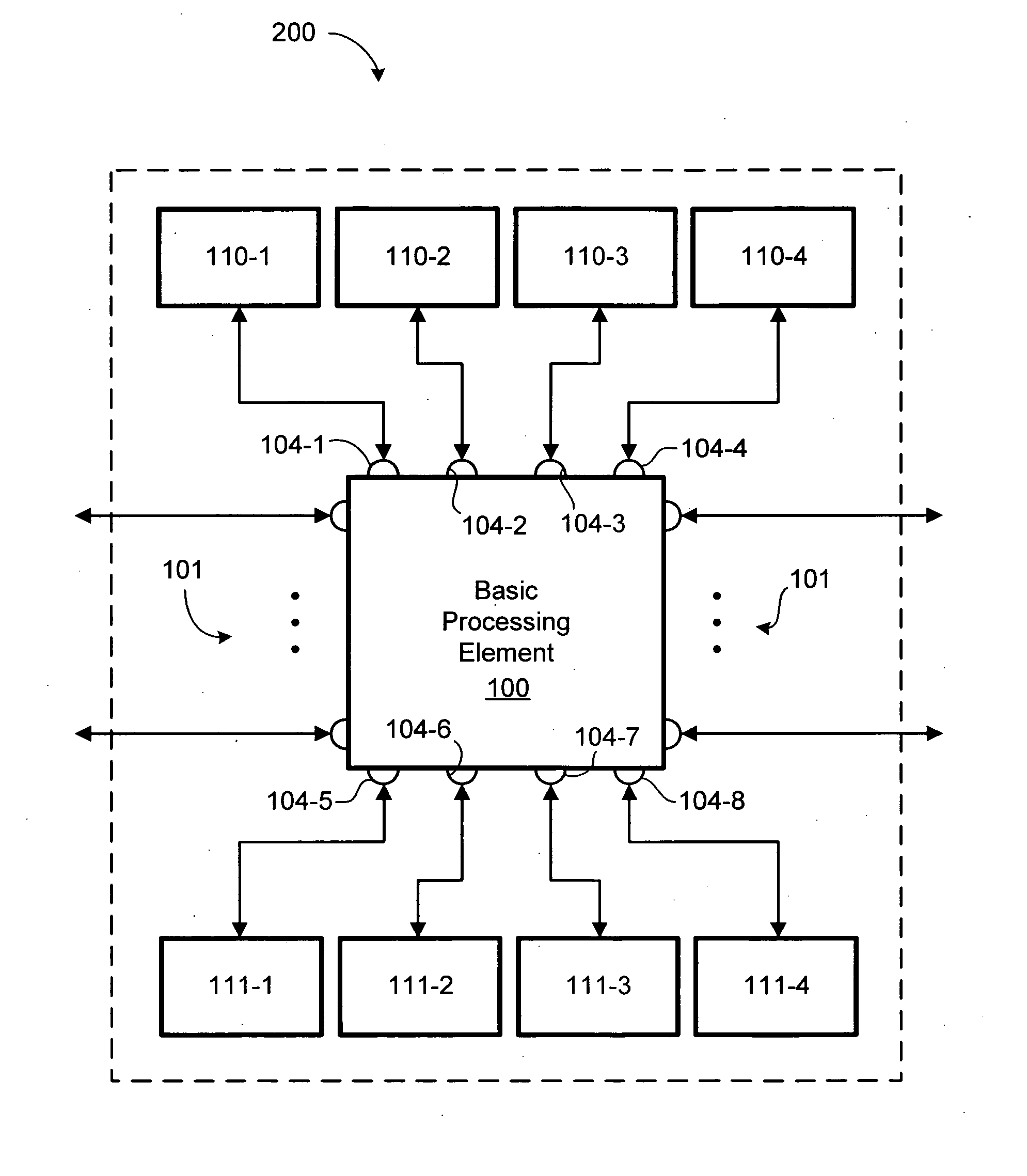

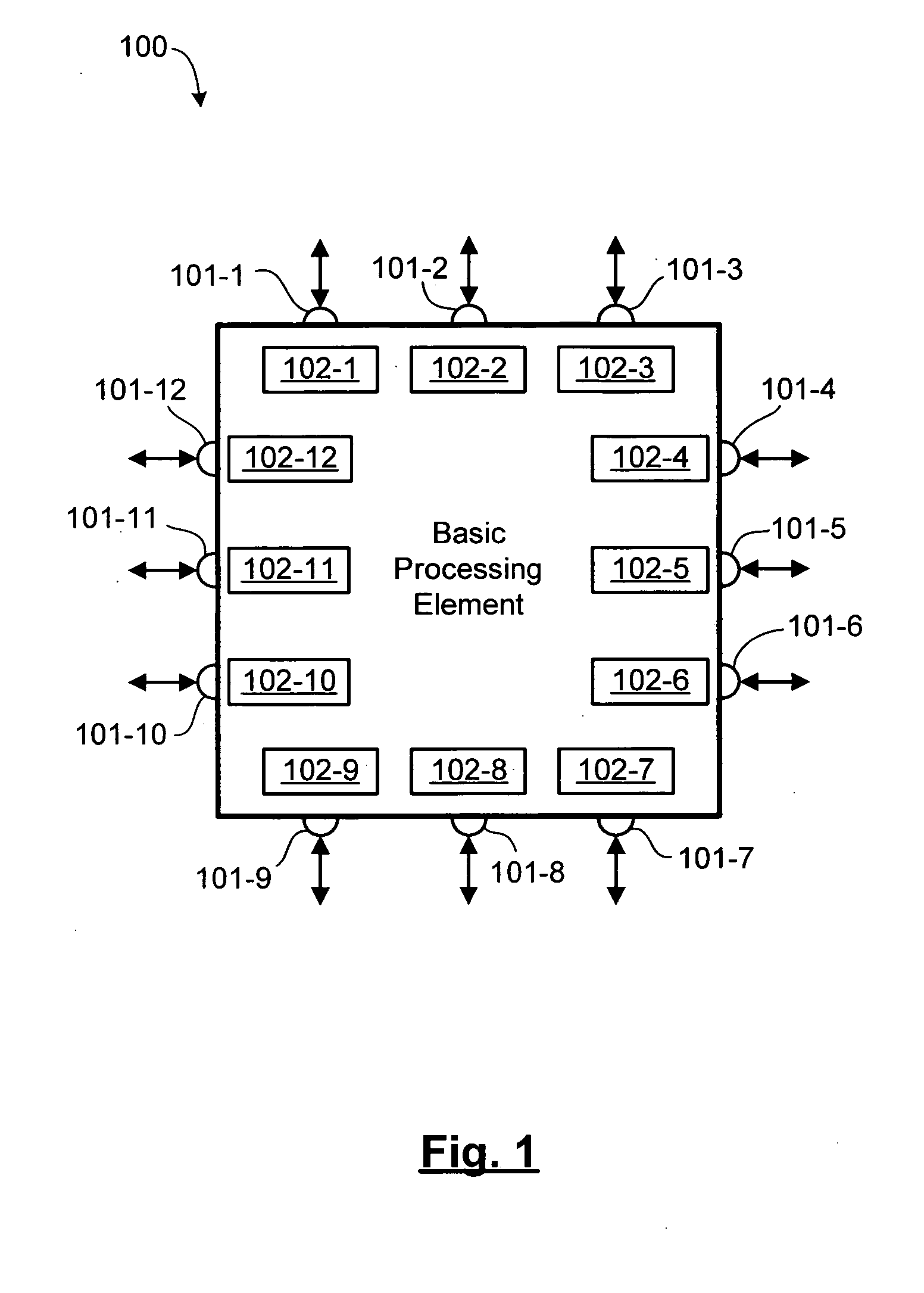

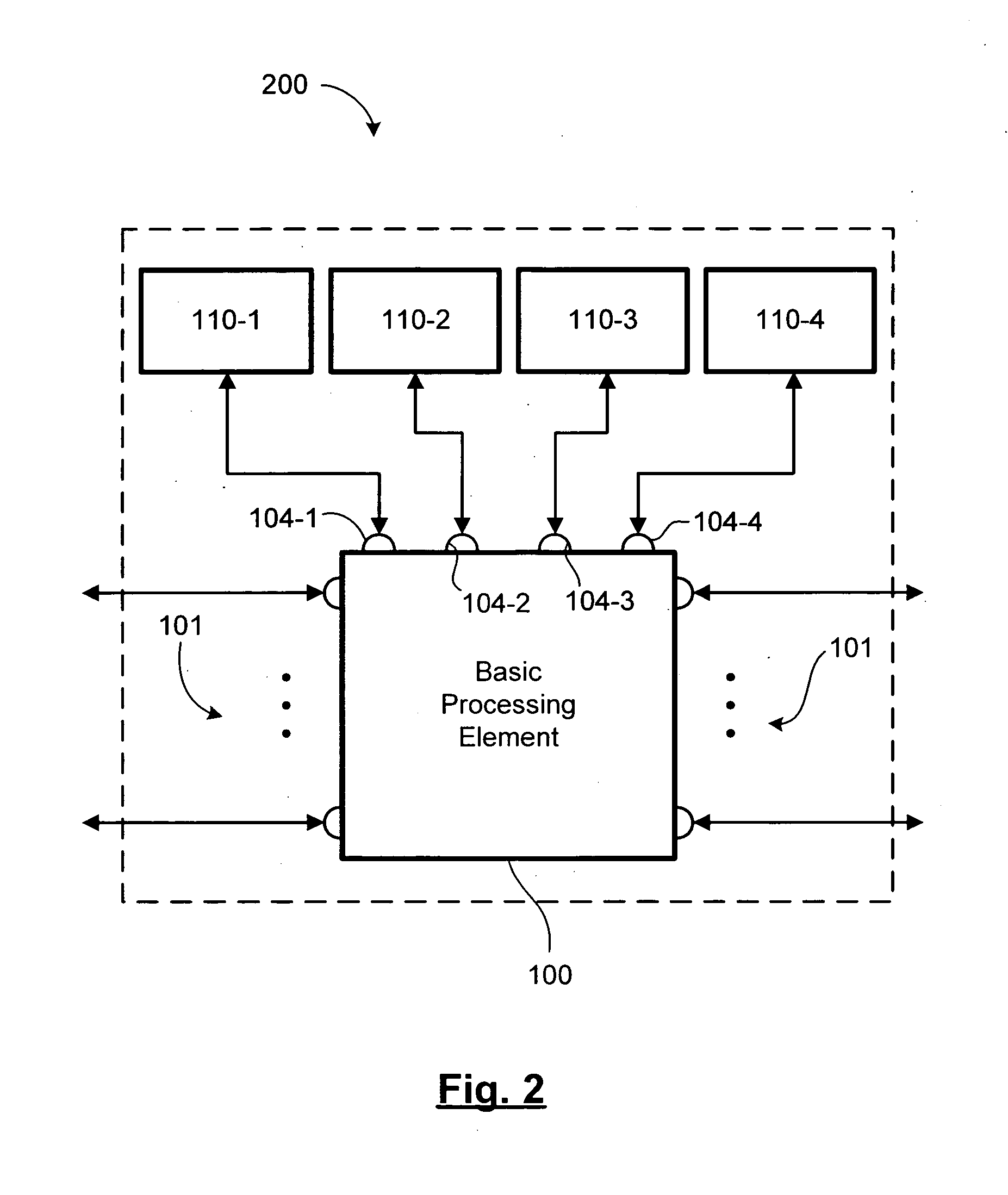

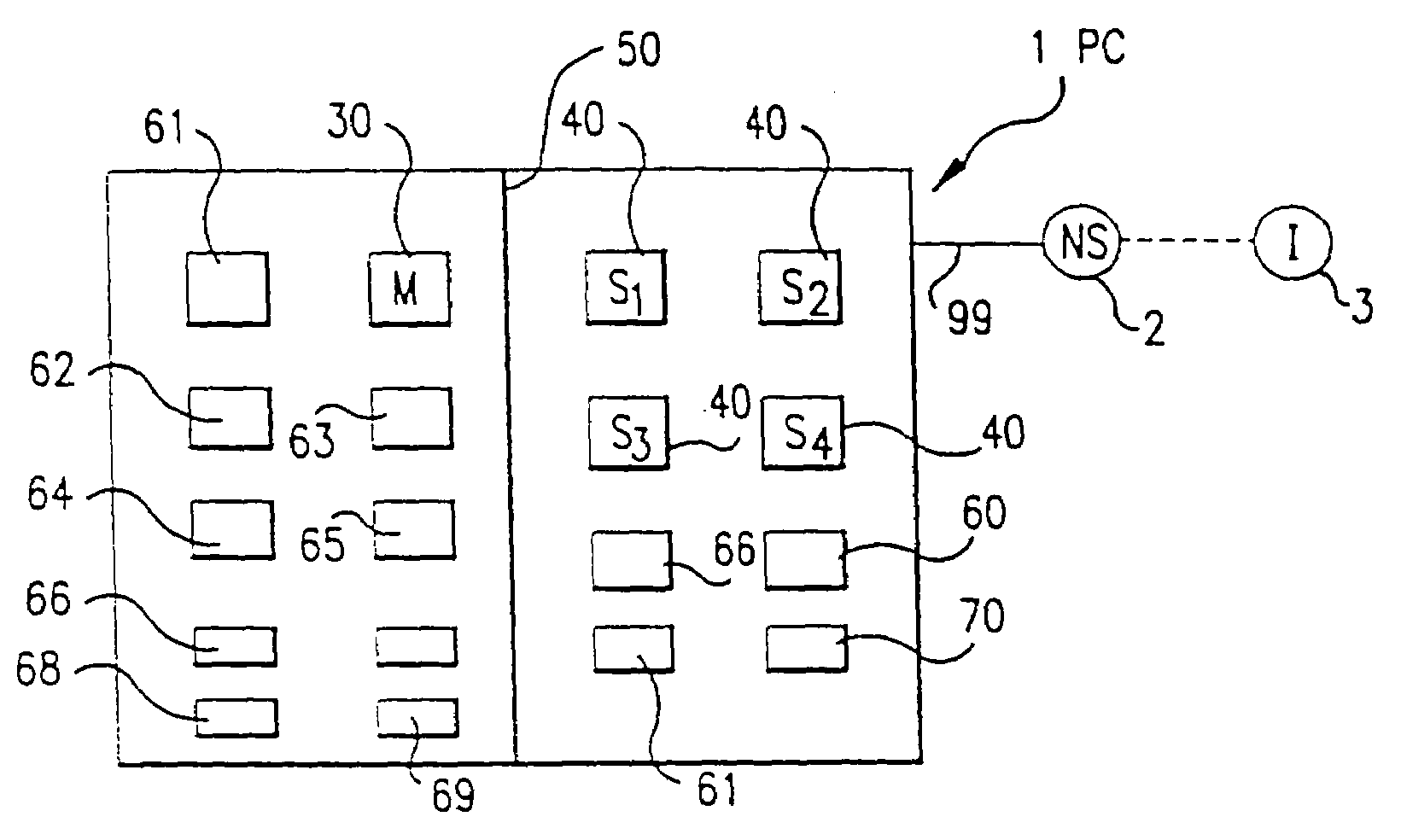

Multi-processor reconfigurable computing system

ActiveUS20060031659A1Reduce communication delayImproved bandwidth throughputGeneral purpose stored program computerInput/output processes for data processingCross connectionMulti processor

A reconfigurable multi-processor computing system including a plurality of configurable processing elements each having a plurality of integrated high-speed serial input / output ports. Interconnects link the plurality of processing elements, wherein at least one of the integrated high-speed serial input / output ports of each processing element is connected by at least one interconnect to at least one of the integrated high-speed serial input / output ports of each other processing element, thereby creating a full mesh network. The full mesh network is located on a processor card, multiples of which may be grouped in a shelf having a backplane card with a shelf controller card for providing cross-connects between processor cards. Multiple shelves may be interconnected to form a large computer system.

Owner:ARCHES COMPUTING SYST

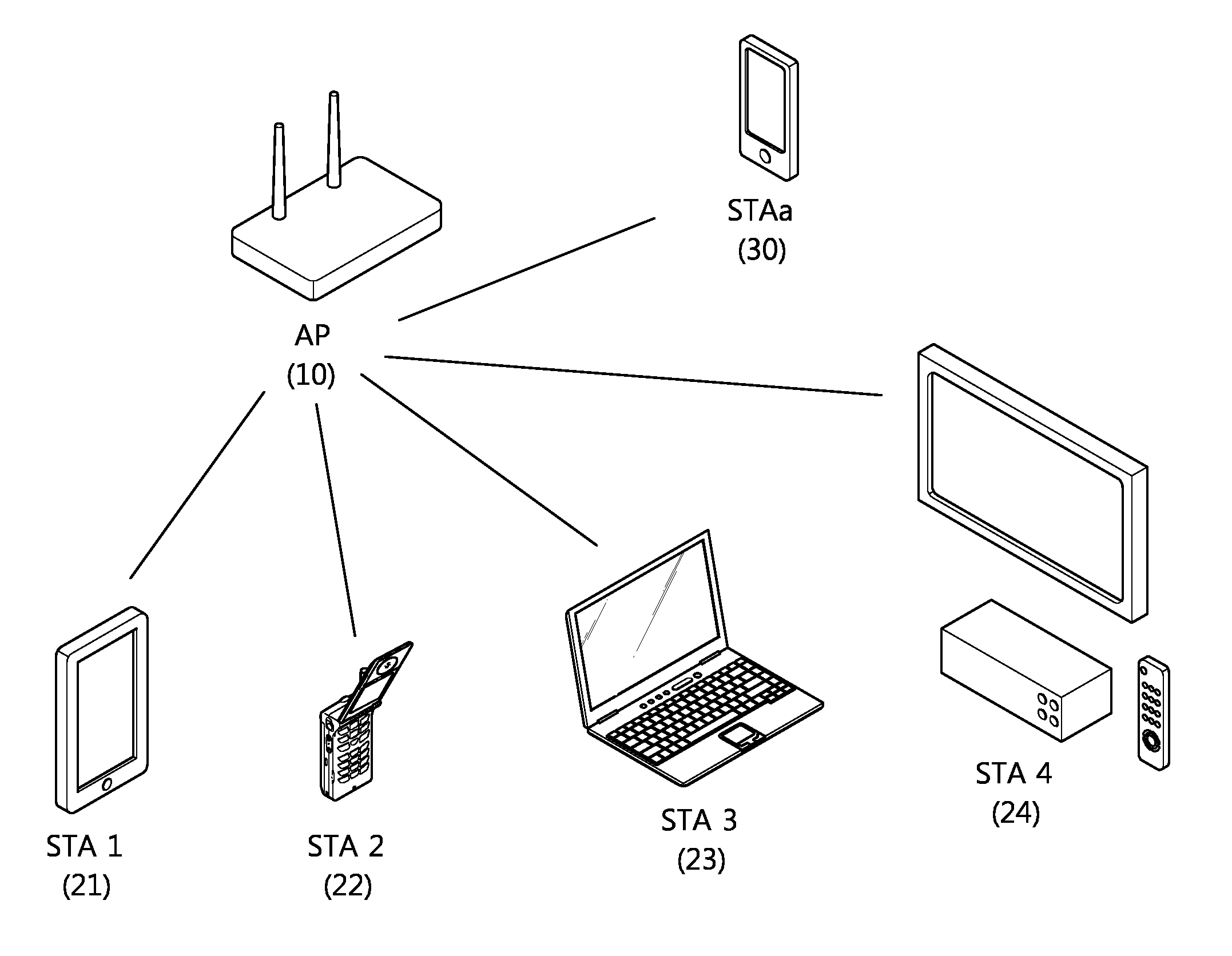

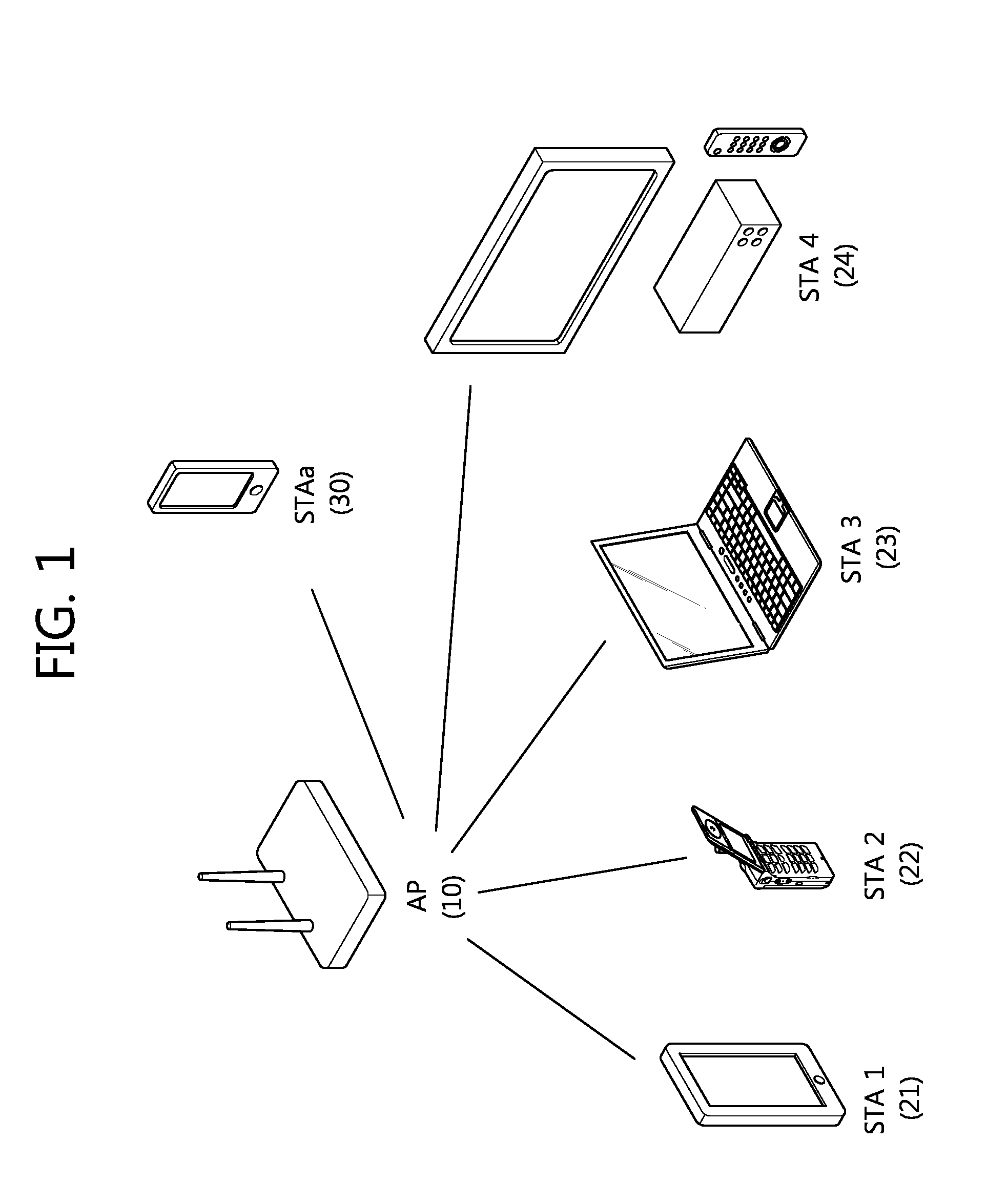

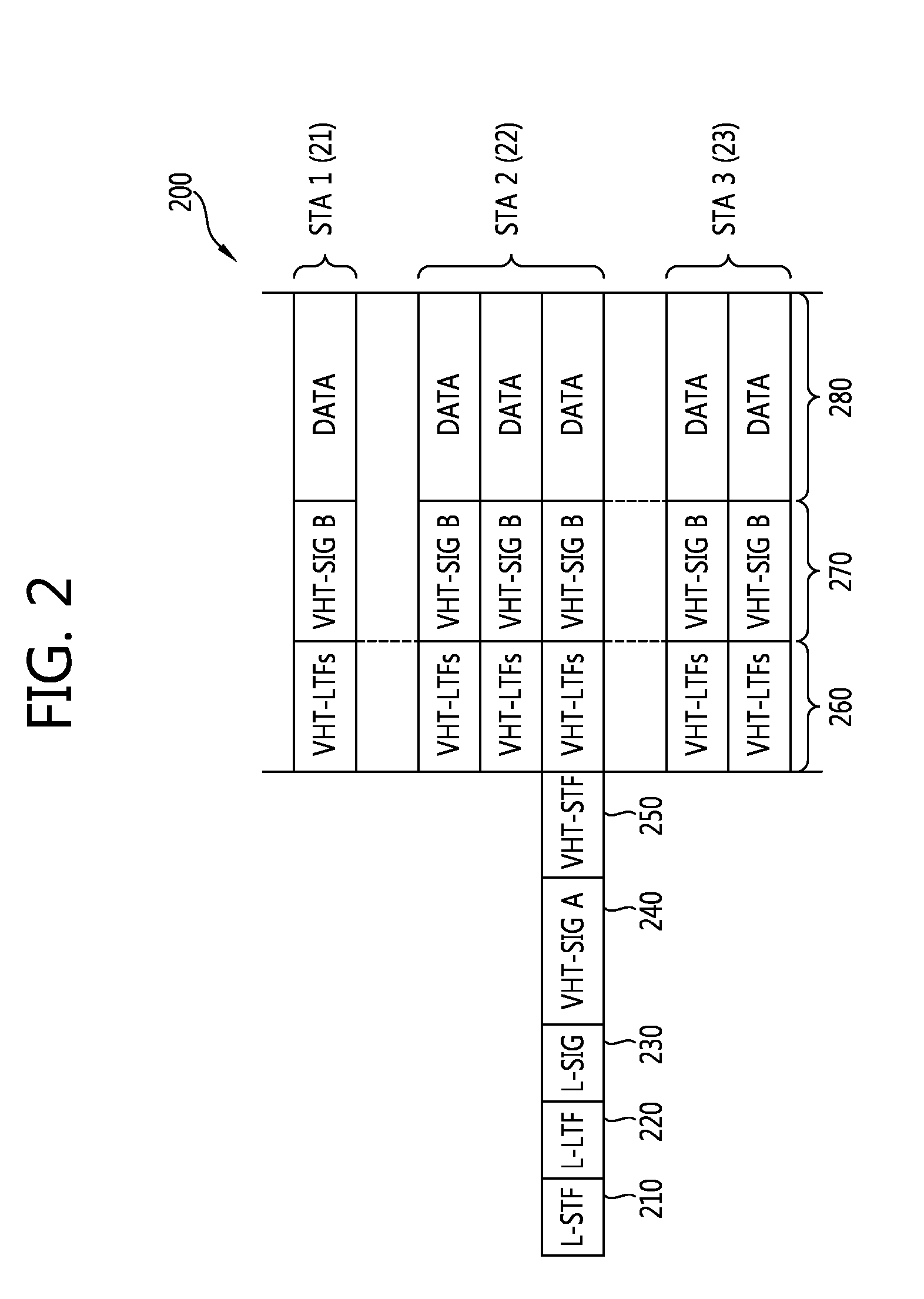

Method for channel sounding in wireless local area network and apparatus for the same

ActiveUS20120140753A1Extended operating distanceImprove reliabilityReceivers monitoringError preventionChannel soundingChannel feedback

A channel sounding method in a wireless local area network (WLAN) system is provided. The method, performed by a transmitter, includes transmitting a null data packet announcement (NDPA) frame to a receiver to initiate a channel sounding procedure; transmitting a null data packet (NDP) to the receiver and receiving a feedback frame. The feedback frame includes a plurality of segment frames and a channel feedback report. The channel feedback report is split into a plurality of feedback segments. Each of the plurality of feedback segments is respectively included in each of the plurality of segment frames. The each of the plurality of segment frames includes a first-segment subfield indicating whether the each of the plurality of feedback segment included is a first segment and a remaining-segment subfield indicating the number of remaining feedback segments.

Owner:LG ELECTRONICS INC

Method and system for broadband predistortion linearization

InactiveUS7583754B2Remove to bandwidthLower performance requirementsAmplifier modifications to reduce non-linear distortionAmplifiers with memory effect compensationTime domainAudio power amplifier

The invention relates to a method and system for wideband digital pre-distortion linearization, which is used to overcome the influence of memory effect in radio frequency power amplifier, to expand digital pre-distortion linearization bandwidth, and to improve digital pre-distortion linearization performance. The method and system can get an in-band pre-distortion signal and an out-of-band pre-distortion signal according to the characteristic parameter of the amplifier; the in-band pre-distortion signal is up-converted and the up-converted signal is added to the out-of-band pre-distortion signal, which is not up-converted, then the combined signal is inputted to the power amplifier as an input signal; a part of the output signal from the power amplifier, serving as a feedback signal, can be compared with the original input signal, and the characteristic parameter of the amplifier for generating the in-band pre-distortion signal and the out-of-band pre-distortion signal is adaptively regulated according to the comparison result, so that the waveform of time domain or the frequency domain of the feedback signal can be close to that of the original input signal as much as possible.

Owner:ZTE CORP

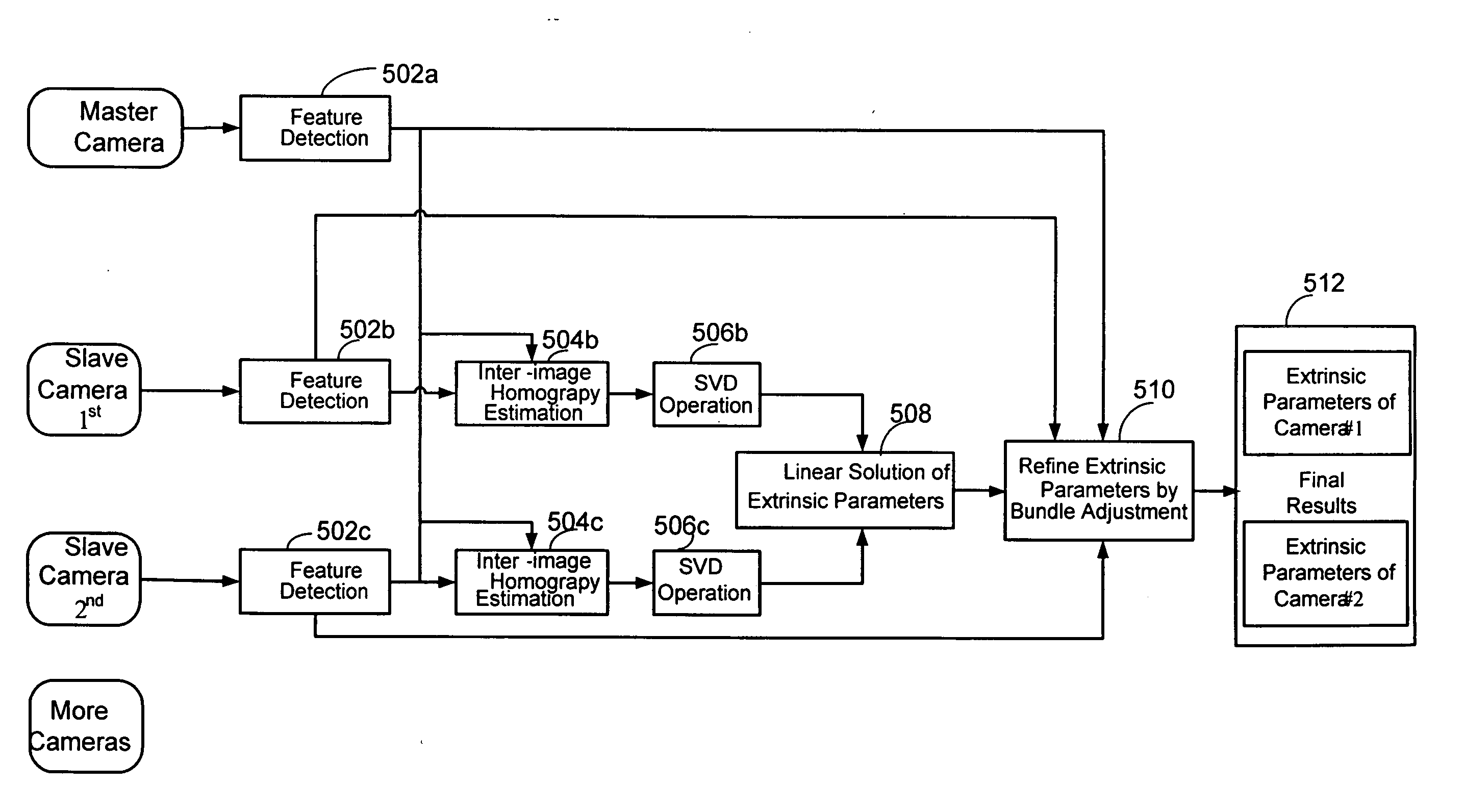

System and method for calibrating multiple cameras without employing a pattern by inter-image homography

InactiveUS20060024041A1Computer processing power becomes strongNetwork bandwidth becomes broadImage analysisCharacter and pattern recognitionHomographyType of service

Interactive multi-view video presents new types of video capture systems, video formats, video compression algorithms, and services. Many video cameras are allocated to capture an event from various related locations and directions. The captured videos are compressed in control PCs and are sent to a server in real-time. Users can subscribe to a new type of service that allows users to connect to the servers and receive multi-view videos interactively. In one embodiment of the invention, an automatic pattern-free calibration tool is employed to calibrate the multiple cameras. In contrast with a pattern-based method which uses the correspondences between image points and pattern points, the pattern-free calibration method is based on the correspondences between image points from different views.

Owner:MICROSOFT TECH LICENSING LLC

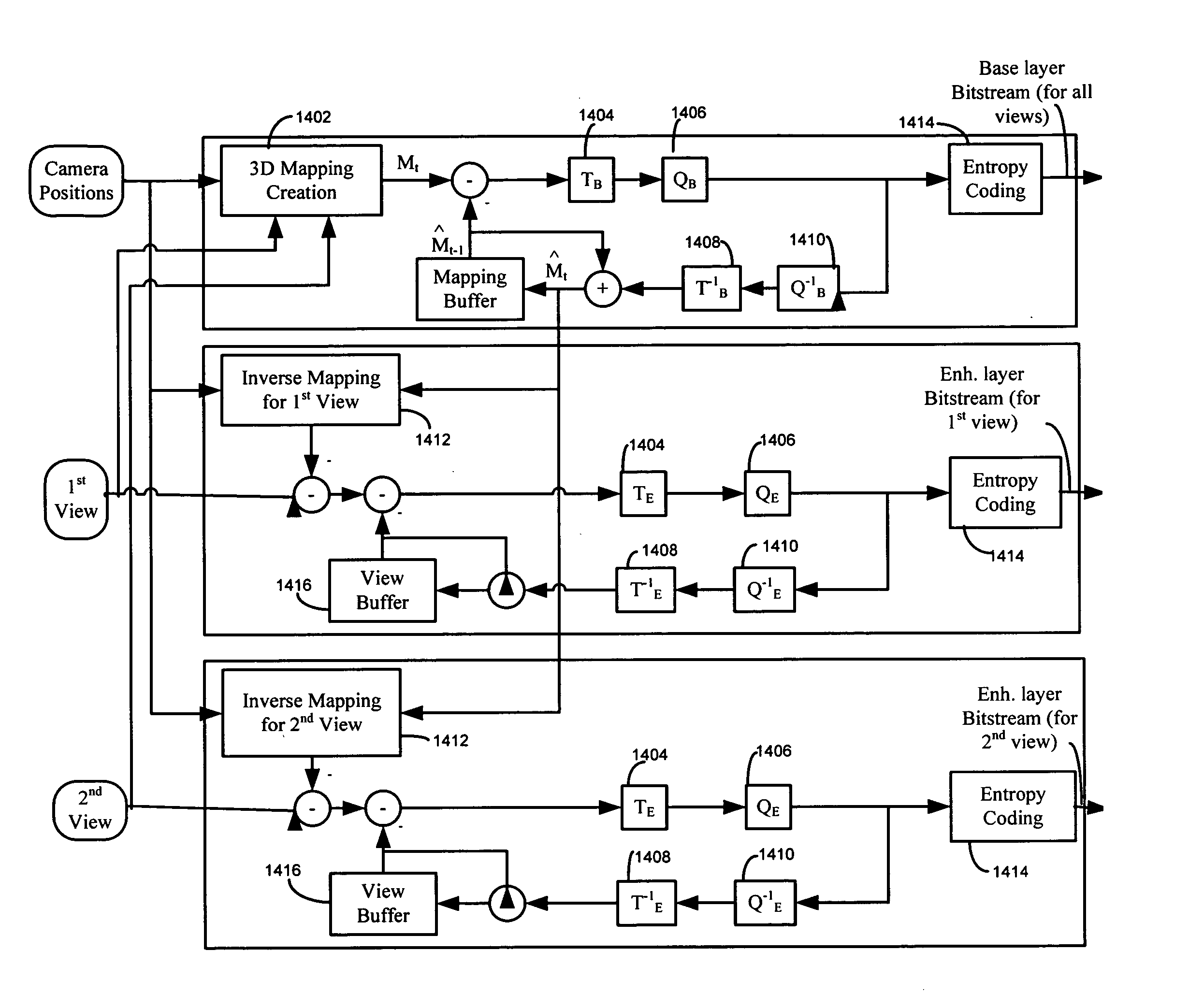

System and method for off-line multi-view video compression

InactiveUS20060023782A1Computer processing power becomes strongSolve narrow bandwidthColor television with pulse code modulationColor television with bandwidth reductionAcquired characteristic3d mapping

Interactive multi-view video presents new types of video capture systems, video formats, video compression algorithms, and services. Many video cameras are allocated to capture an event from various related locations and directions. The captured videos are compressed and are sent to a server in real-time. The compressed video can also be transcoded through an off-line compression approach to further reduce the data amount. A key idea of off-line compression is to decompose all views into a 3D mapping, which consists of a group of feature points in the 3D environment. Each feature point is represented by its 3D coordinates (x, y, z) and the corresponding color components (Y, U, V). The created mapping is the minimum set of feature points that can reconstruct all of the pixels in each view. After the 3D mapping creation, the obtained feature points are predicted and transformed to further decompose the correlations among them. The transformed results are quantized and encoded as a ‘base layer’ bit stream. The dequantized feature points are mapped back onto each view to form a predicted view image. The predicted image is close to the original one; however, there are still some differences between them. The difference is encoded independently as an ‘enhancement layer’ of each view image.

Owner:MICROSOFT TECH LICENSING LLC

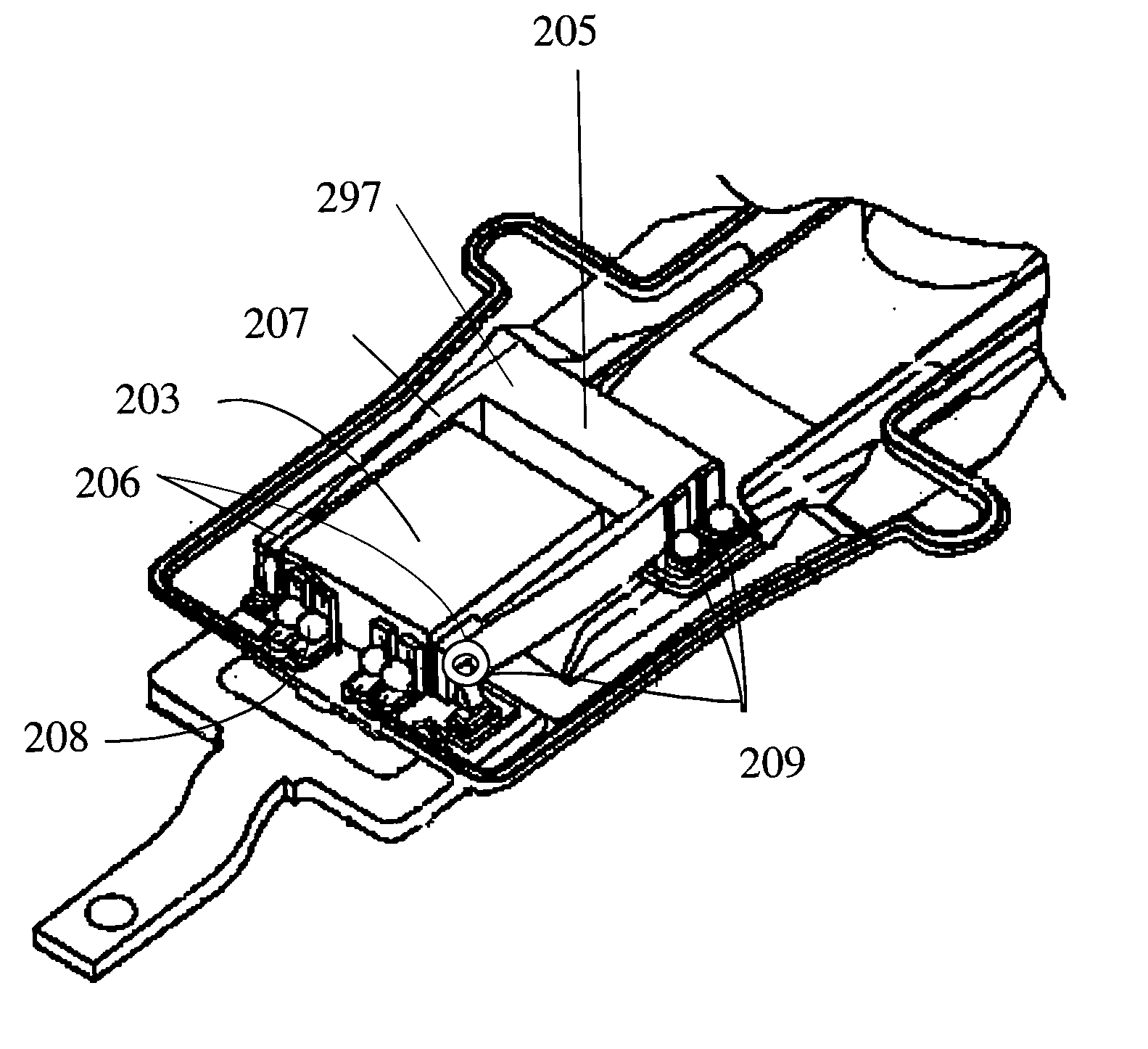

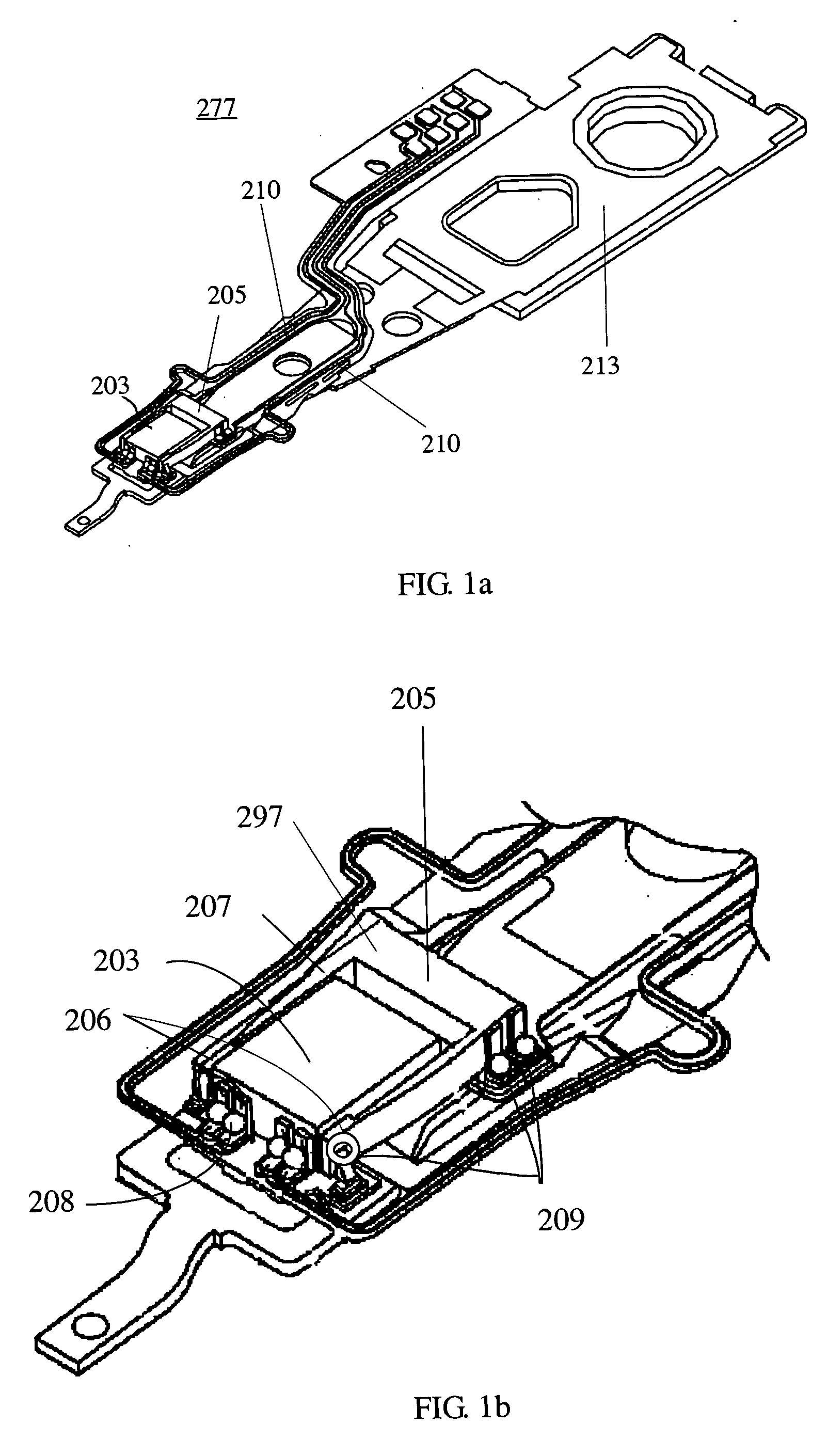

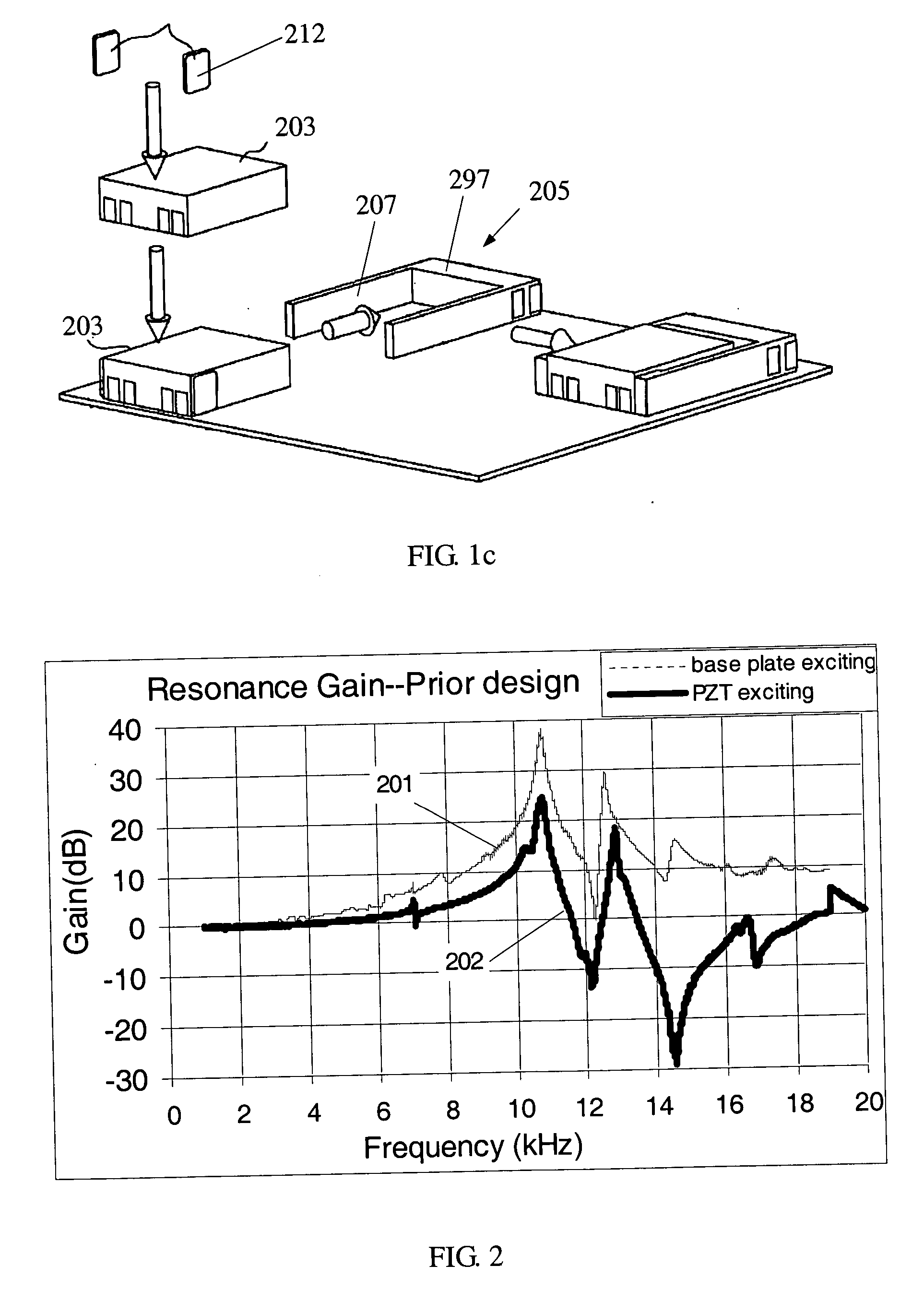

Micro-actuator, head gimbal assembly and disk drive unit with the same

InactiveUS20060193086A1Good resonance performance and position adjusting performanceSimple structureElectrical connection between head and armRecord information storageMicro actuatorEngineering

A HGA of the invention includes a slider; a micro-actuator to adjust the position of the slider; and a suspension to load the slider and the micro-actuator. The micro-actuator includes two side arms; a load plate for supporting the slider, which is connected with at least one of the side arms; a piezoelectric element connected with the side arms; and a base shaft to couple with the suspension, which is connected with the side arms and positioned between the load plate and the piezoelectric element. The invention also discloses a disk drive unit using such a HGA.

Owner:SAE MAGNETICS (HK) LTD

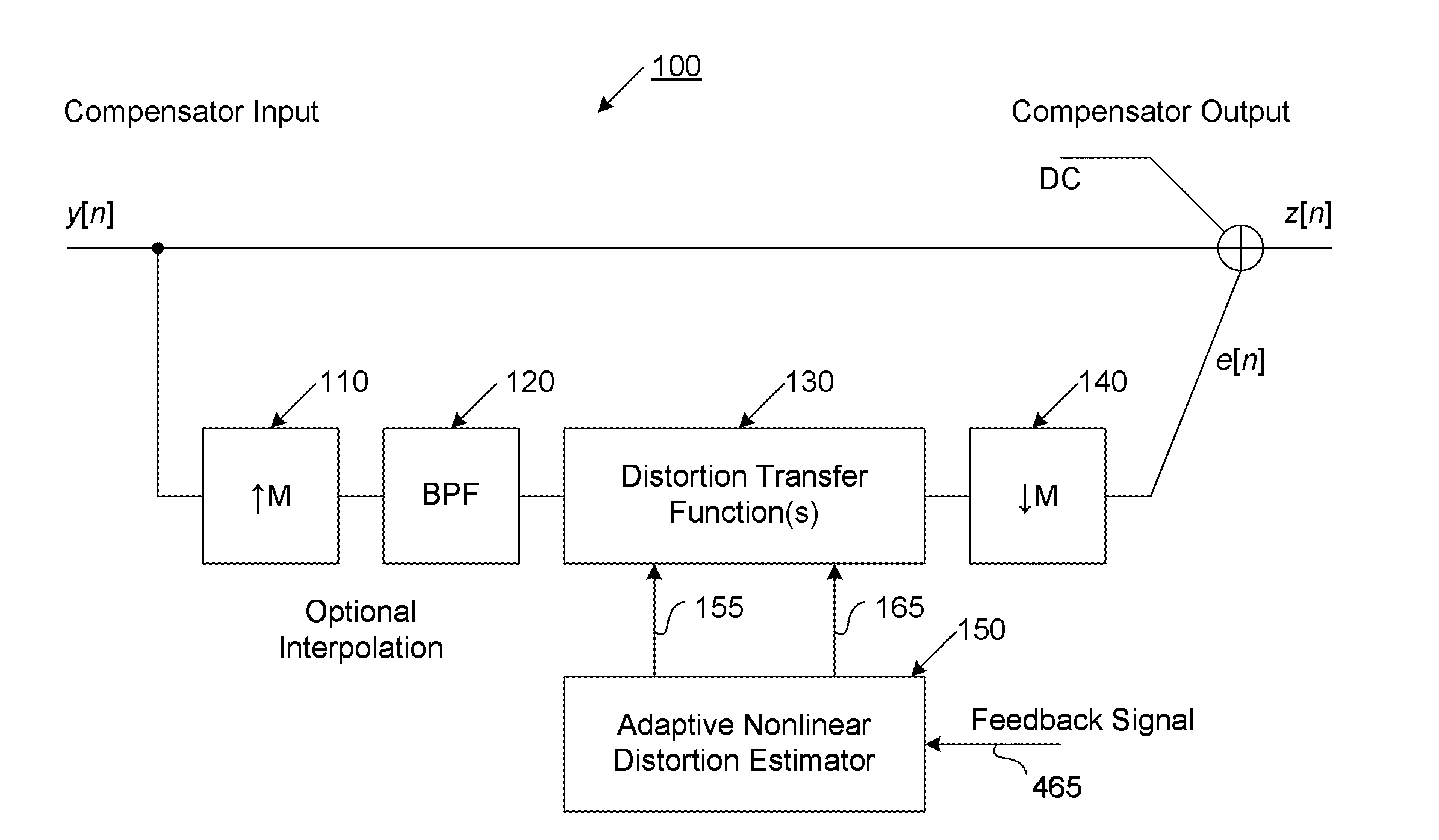

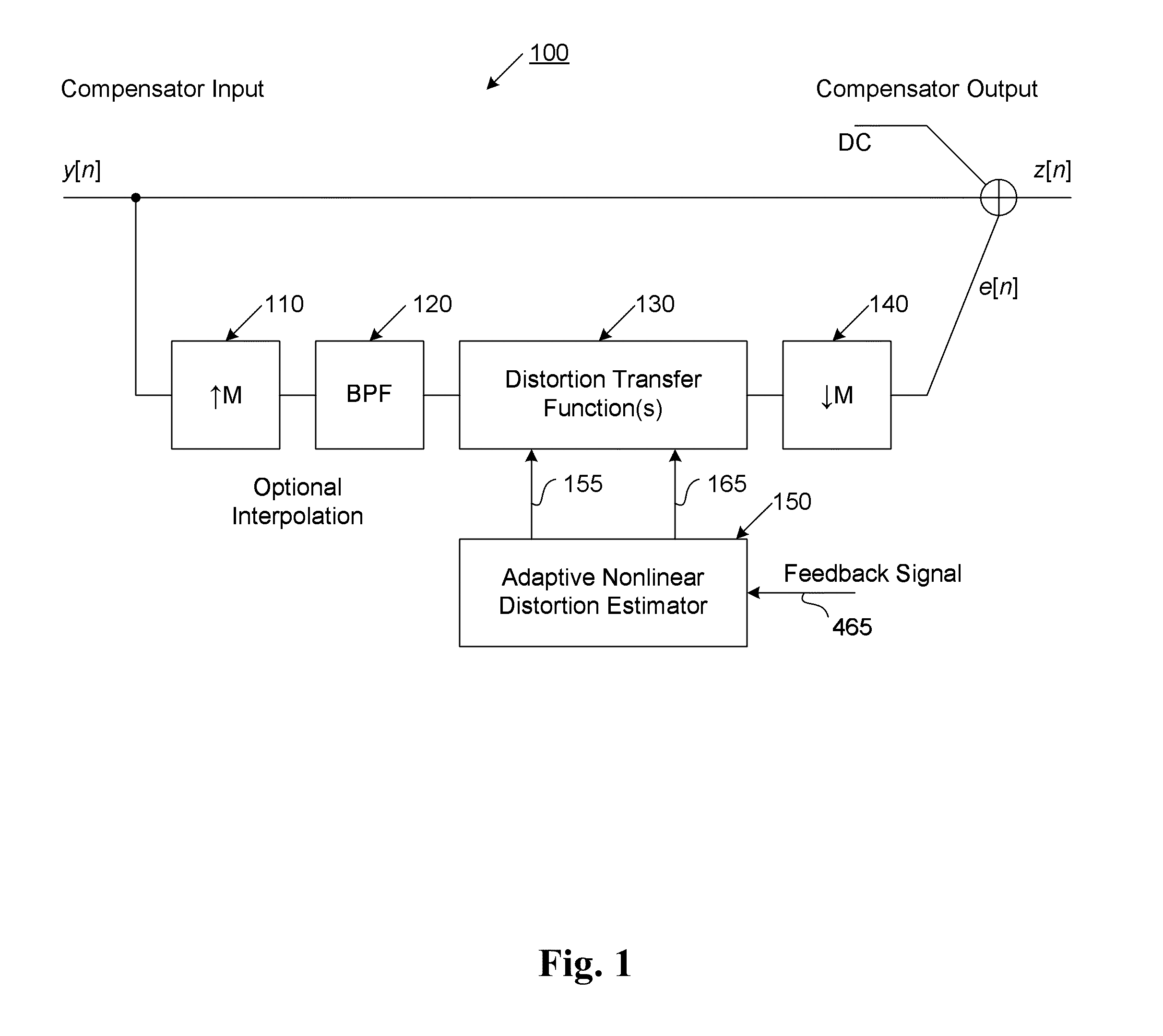

Amplifier linearizer

ActiveUS20110095819A1Reduce nonlinear distortionLow powerResonant long antennasElectric signal transmission systemsNonlinear distortionCurve fitting

The present invention provides an advanced adaptive predistortion linearization technique to dramatically reduce nonlinear distortion in power amplifiers over a very wide instantaneous bandwidth (up to 2 GHz) and over a wide range of amplifier types, input frequencies, signal types, amplitudes, temperature, and other environmental and signal conditions. In an embodiment of the invention, the predistortion linearization circuitry comprises (1) a higher-order polynomial model of an amplifier's gain and phase characteristics—higher than a third-order polynomial model; (2) an adaptive calibration technique; and (3) a heuristic calibration technique. The higher-order polynomial model is generated by introducing, for example, a plurality of multi-tone test signals with varying center frequency and spacing into the power amplifier. From the power amplifier's corresponding output, the nonlinearities are modeled by employing a higher-order curve fit to capture the irregularities in the nonlinear transfer function. Different distortion transfer functions can be implemented for different operating conditions. The adaptive calibration technique is based on a feedback analysis technique, which updates the applicable distortion transfer function by analyzing the error signal between the introduced input signal and the output signal in real-time. The heuristic calibration technique implements different distortion transfer functions based on historical operating conditions and optimal configurations of the power amplifier.

Owner:TM IP HLDG LLC

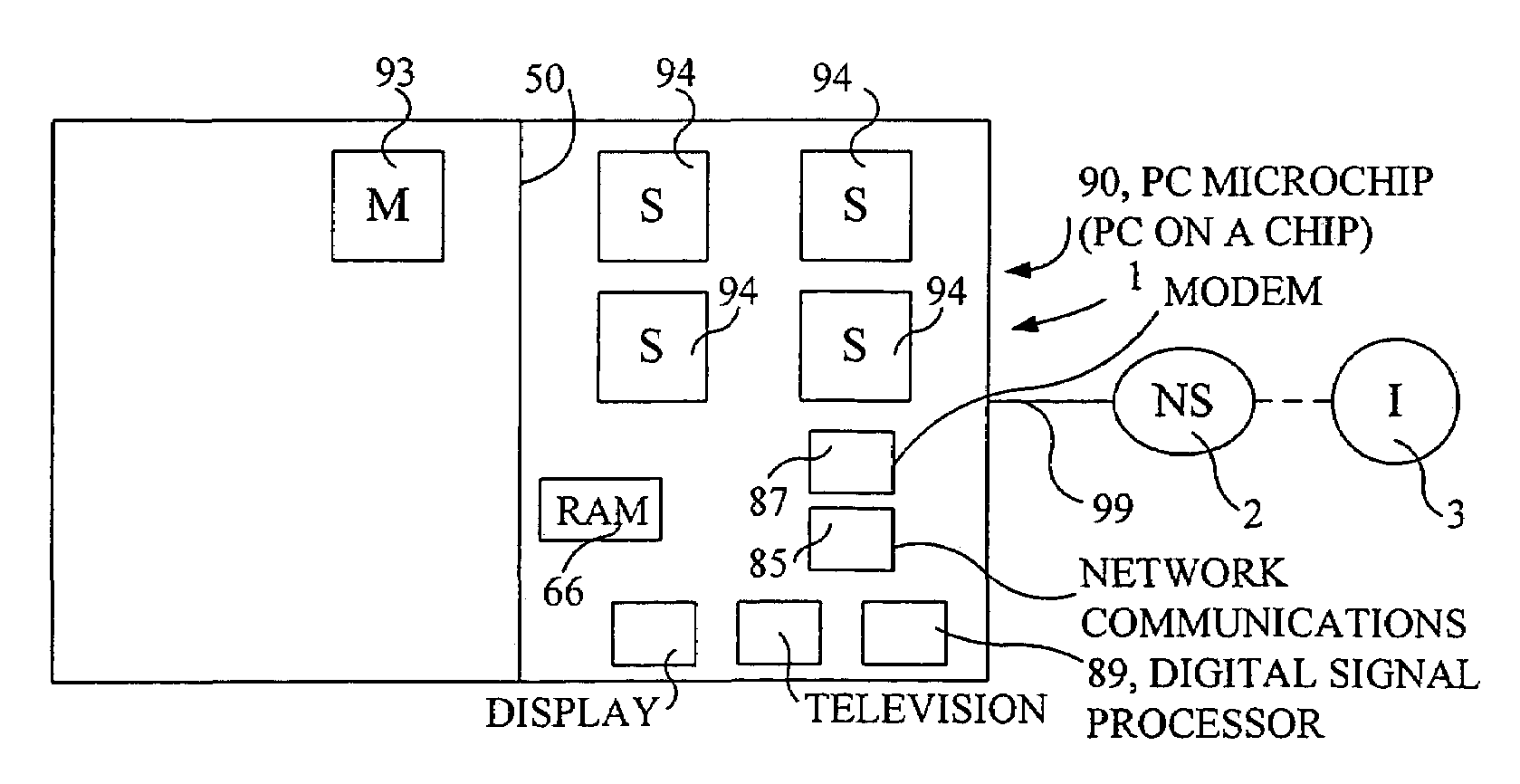

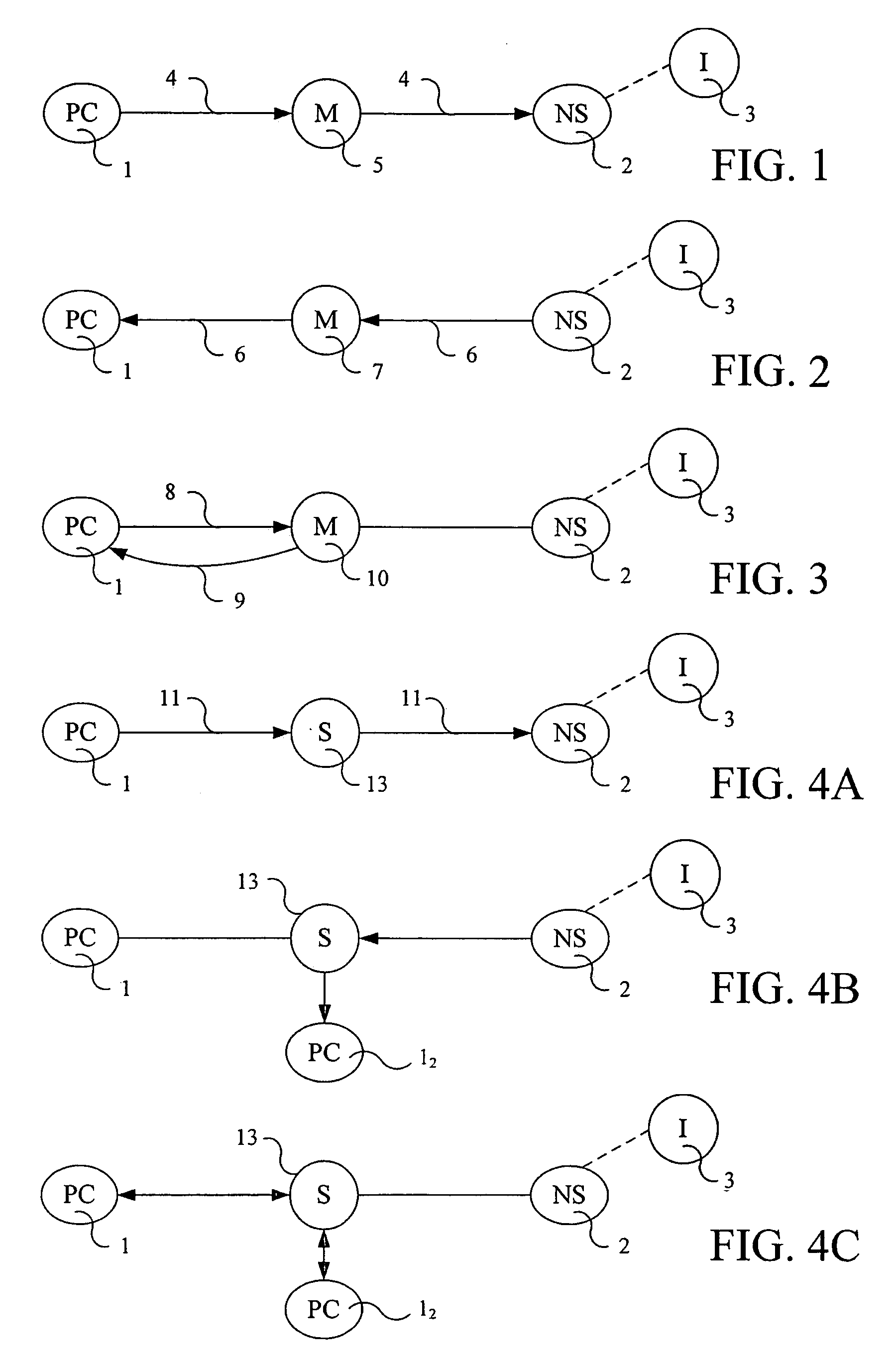

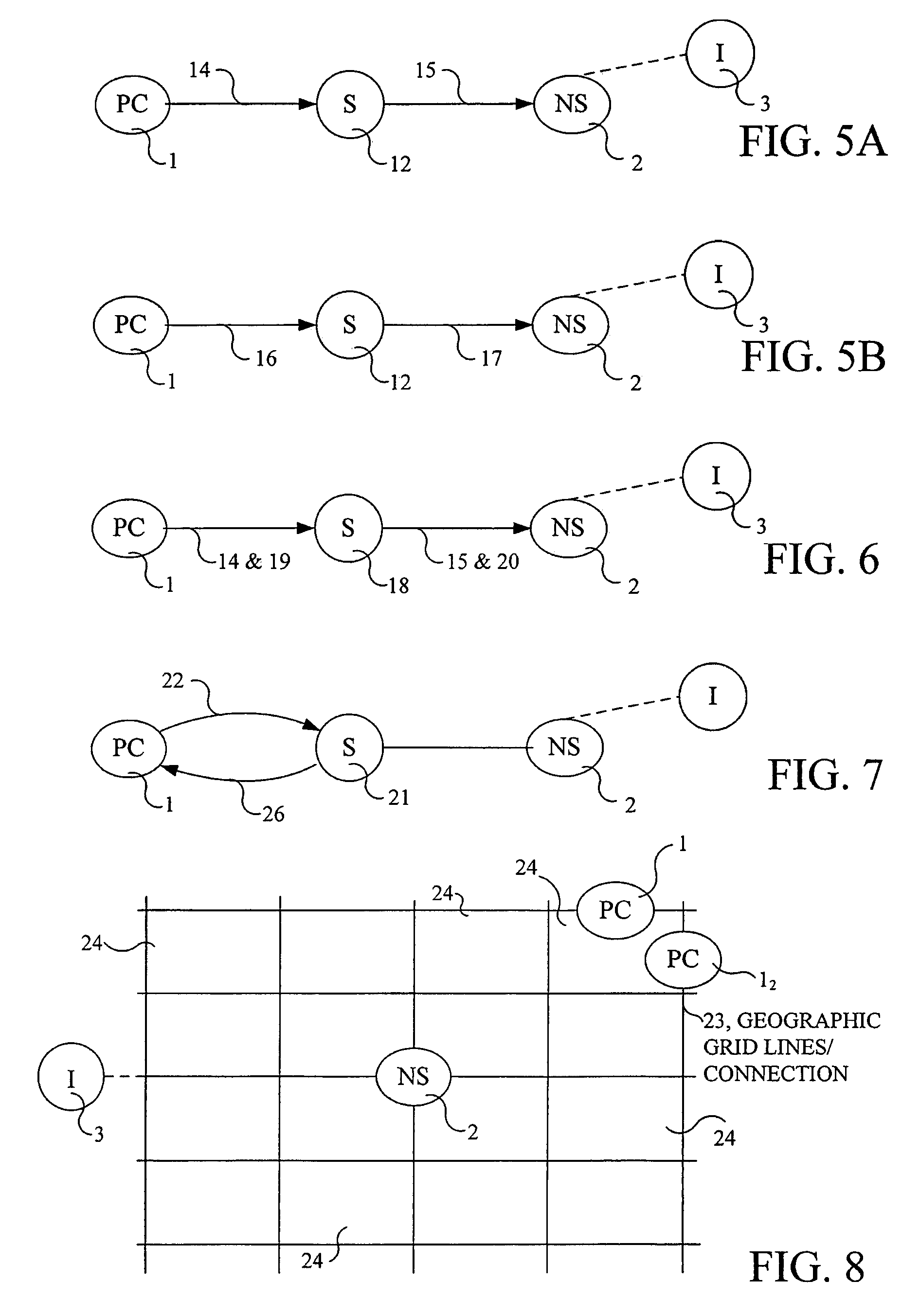

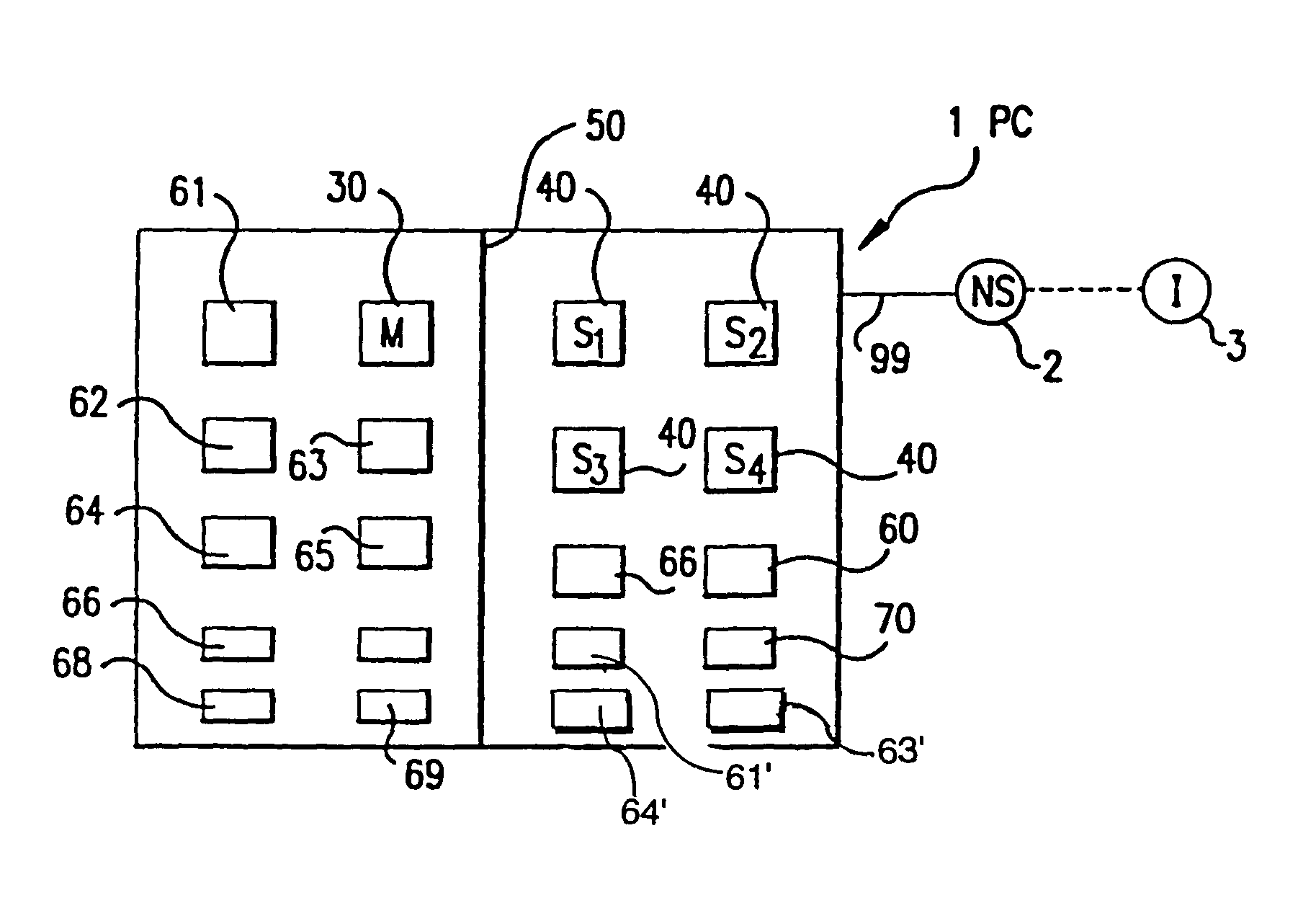

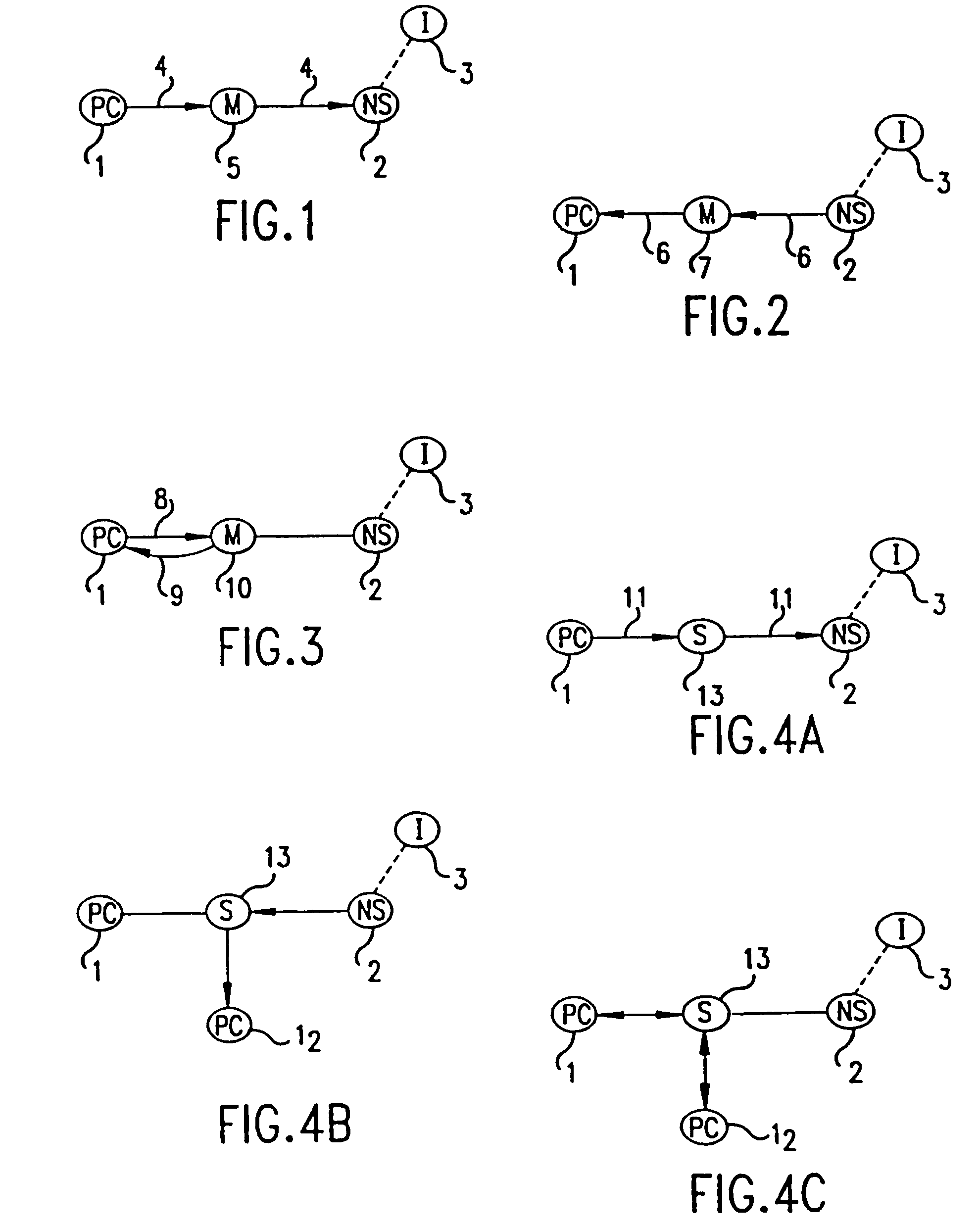

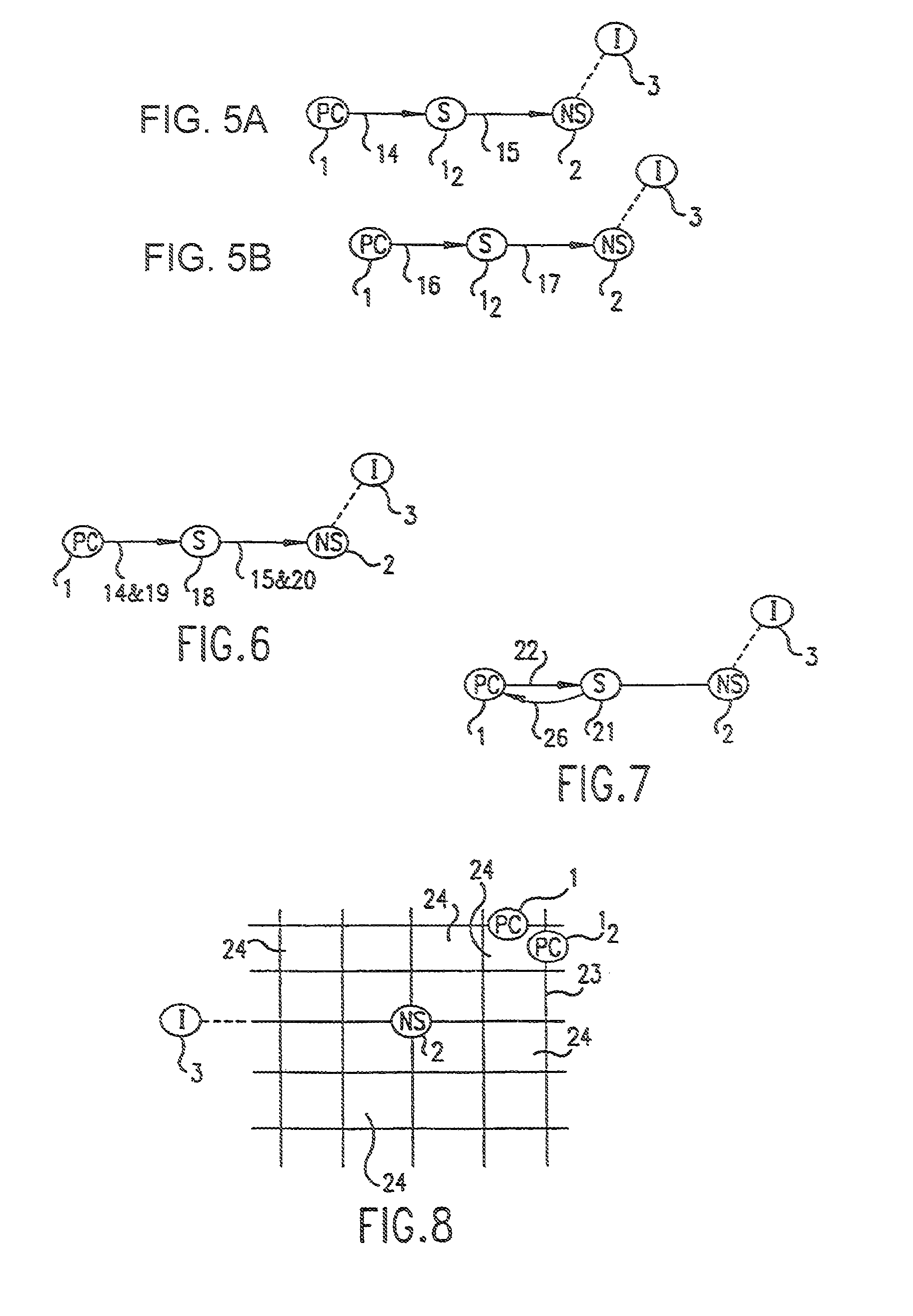

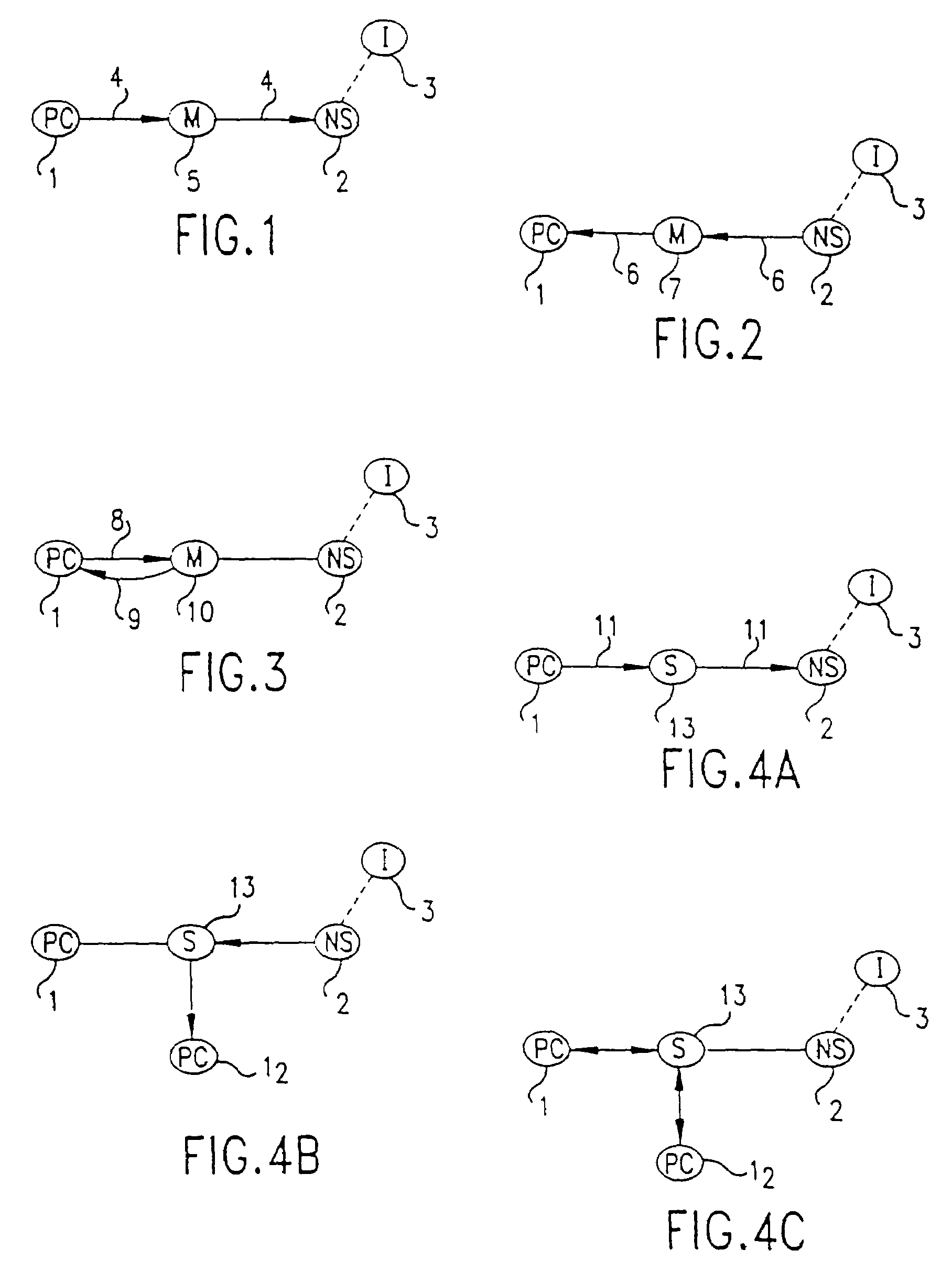

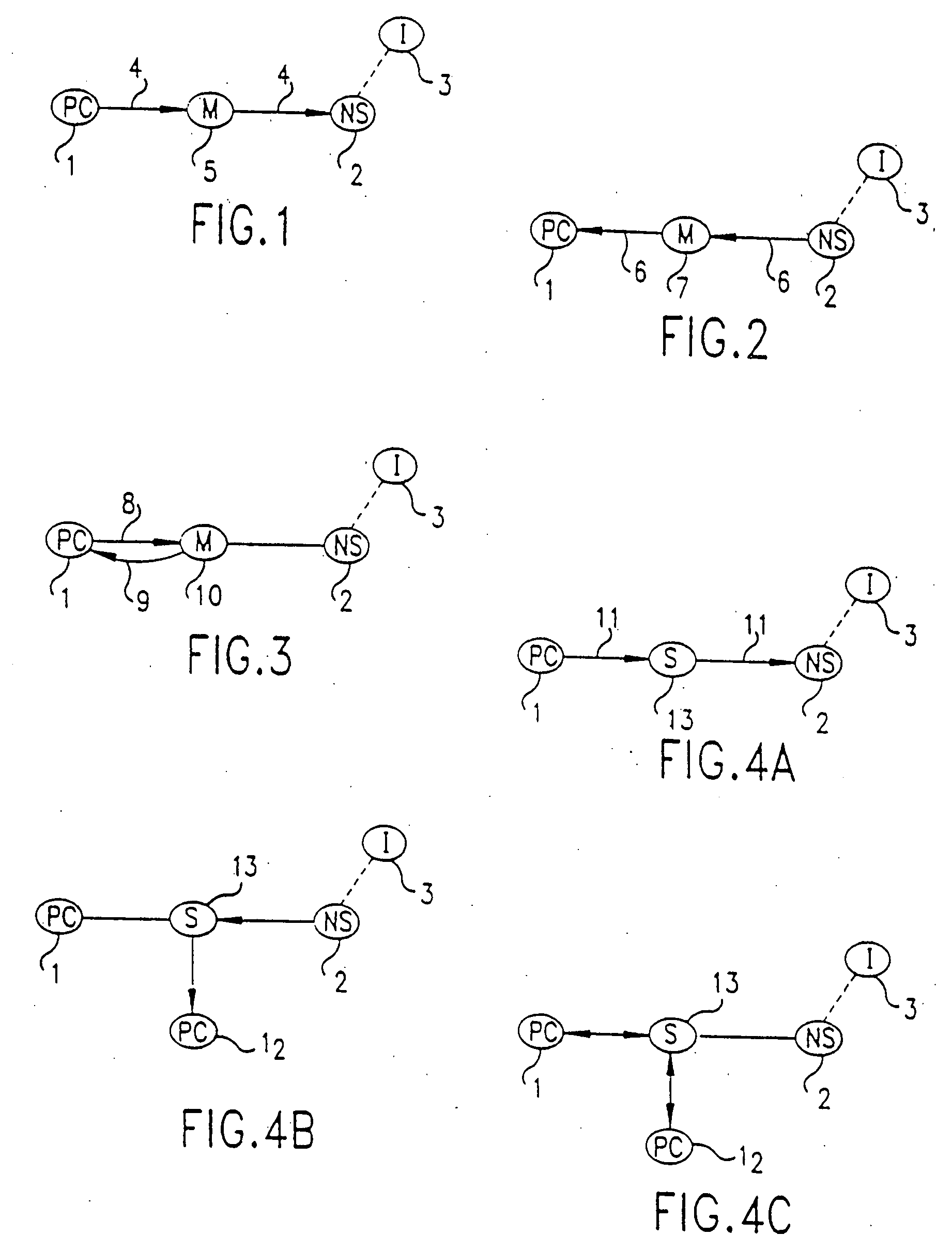

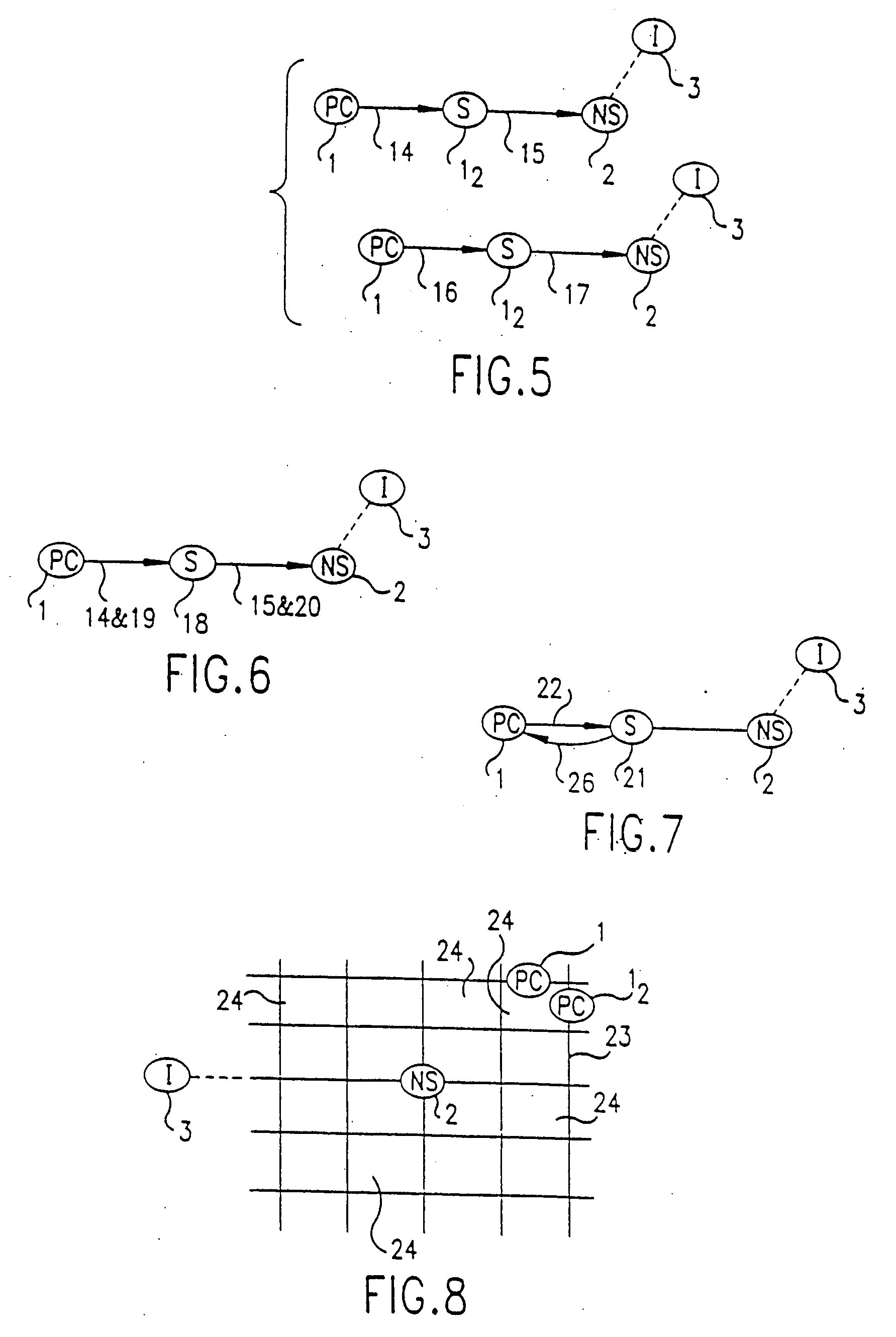

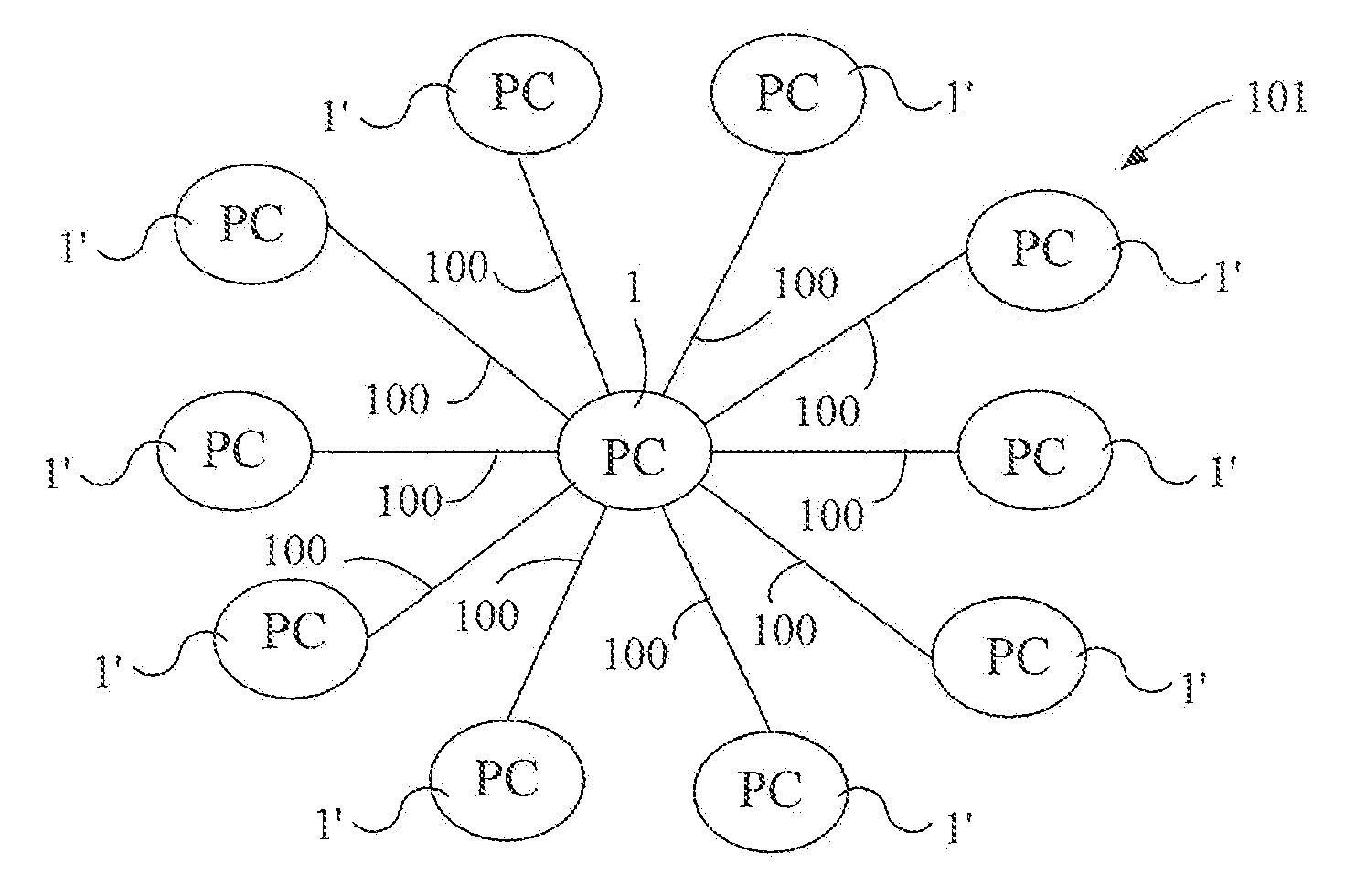

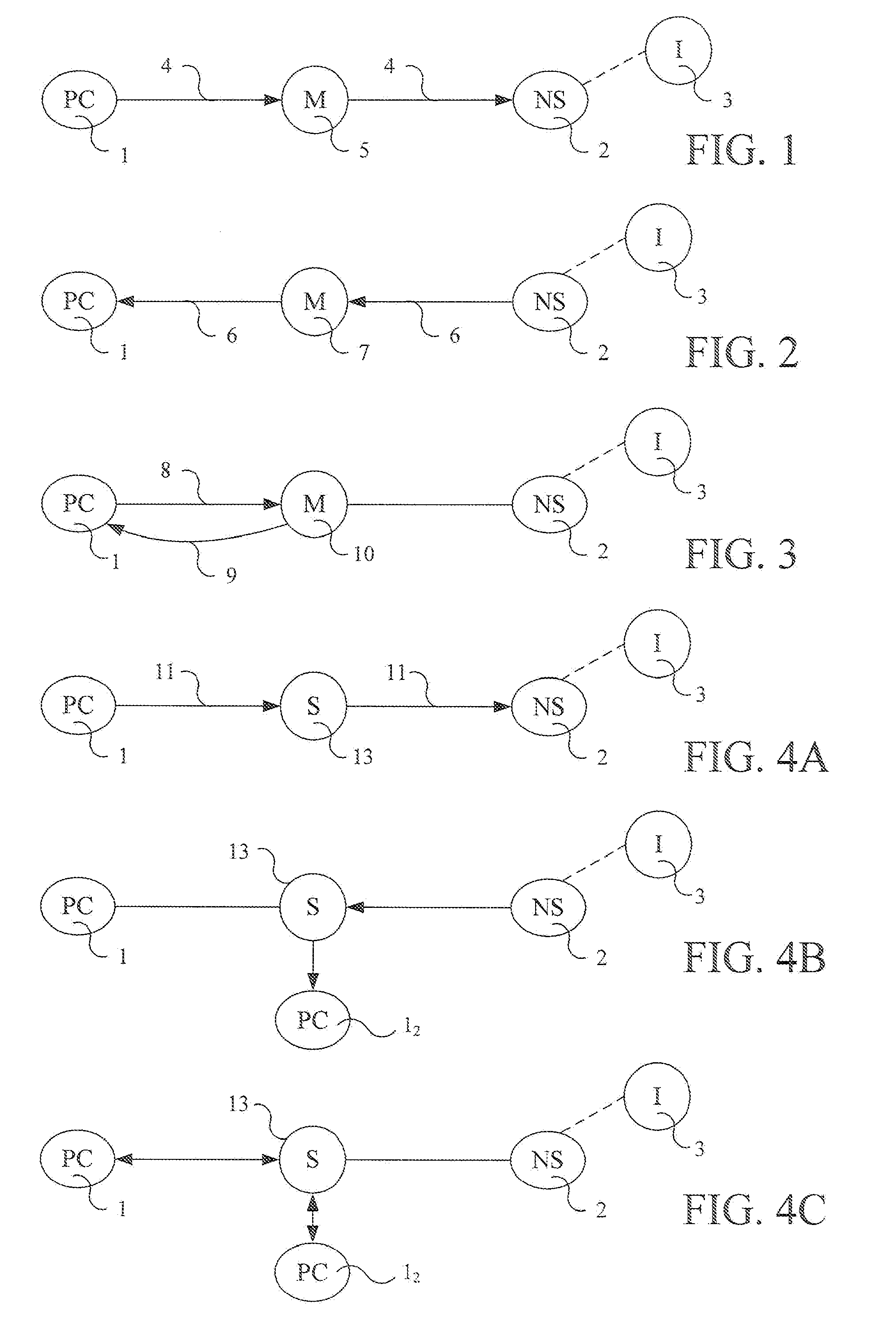

Personal and server computers having microchips with multiple processing units and internal firewalls

InactiveUS7634529B2Limit performanceLimitless flexibilityResource allocationMultiple digital computer combinationsPower managementPersonal computer

A system comprising a personal computer configured to operate with another computer connected to a network of computers. The personal computer includes a microchip having a microprocessor with a control unit and at least two processing units, the control unit being configured to allow a user of the personal computer to control the two processing units, and the microchip including a power management component. The personal computer includes an internal firewall configured to allow and / or deny access to portions of the microchip both to the user of the personal computer and to a user of the microchip from the network of computers during a shared use of the microchip; and the internal firewall is configured to deny access to portions of the microchip from the network of computers.

Owner:ELLIS III FRAMPTON E

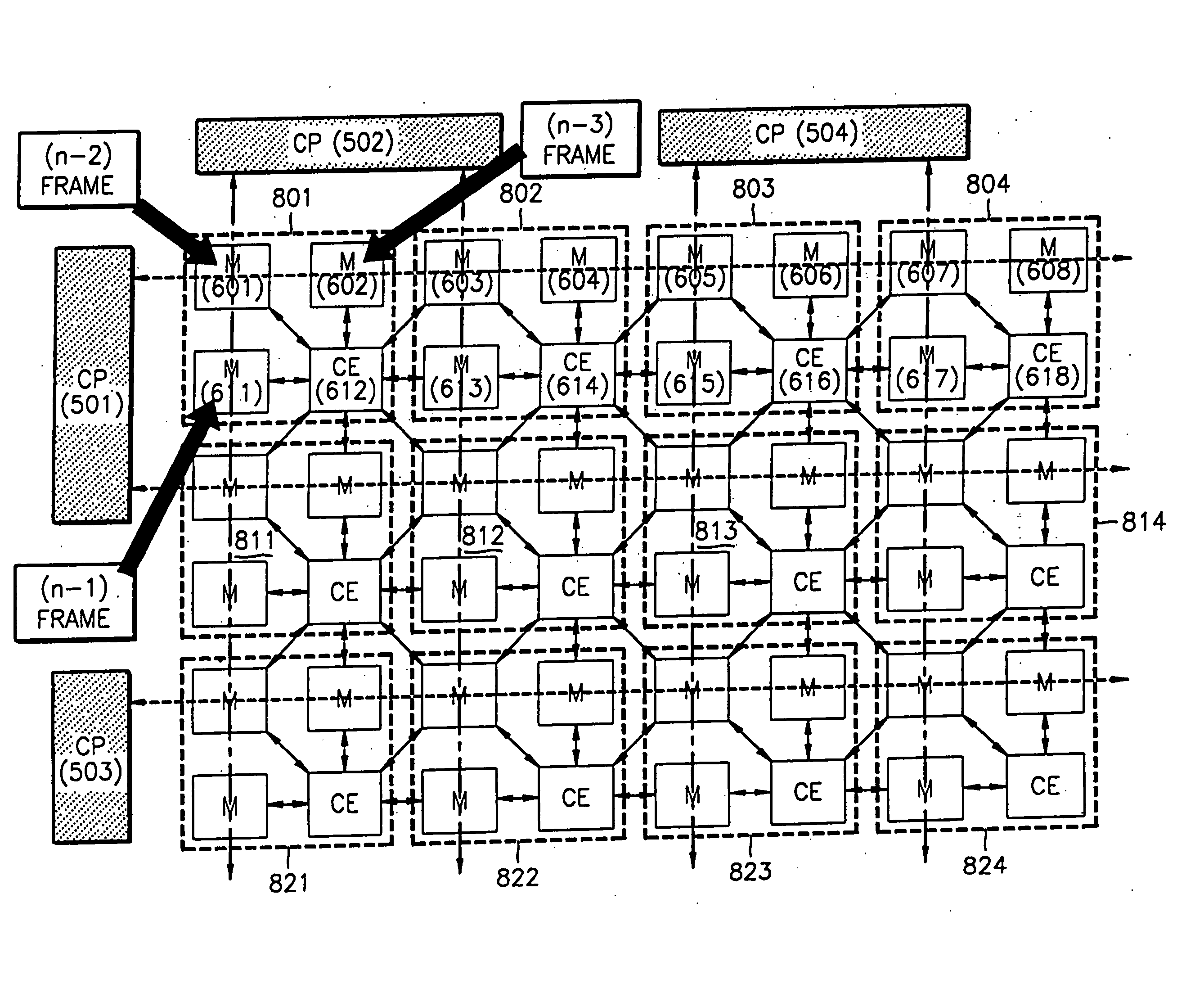

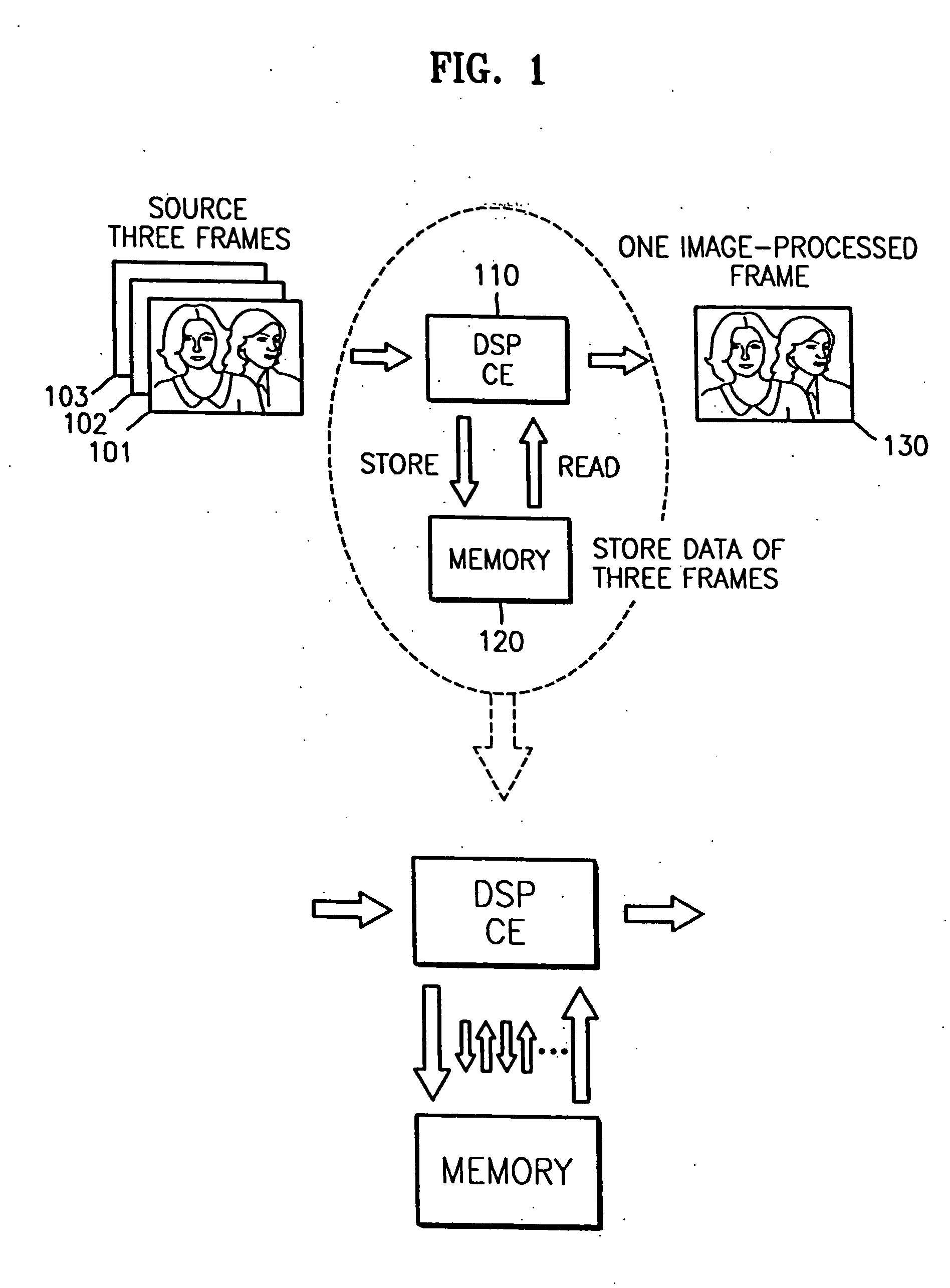

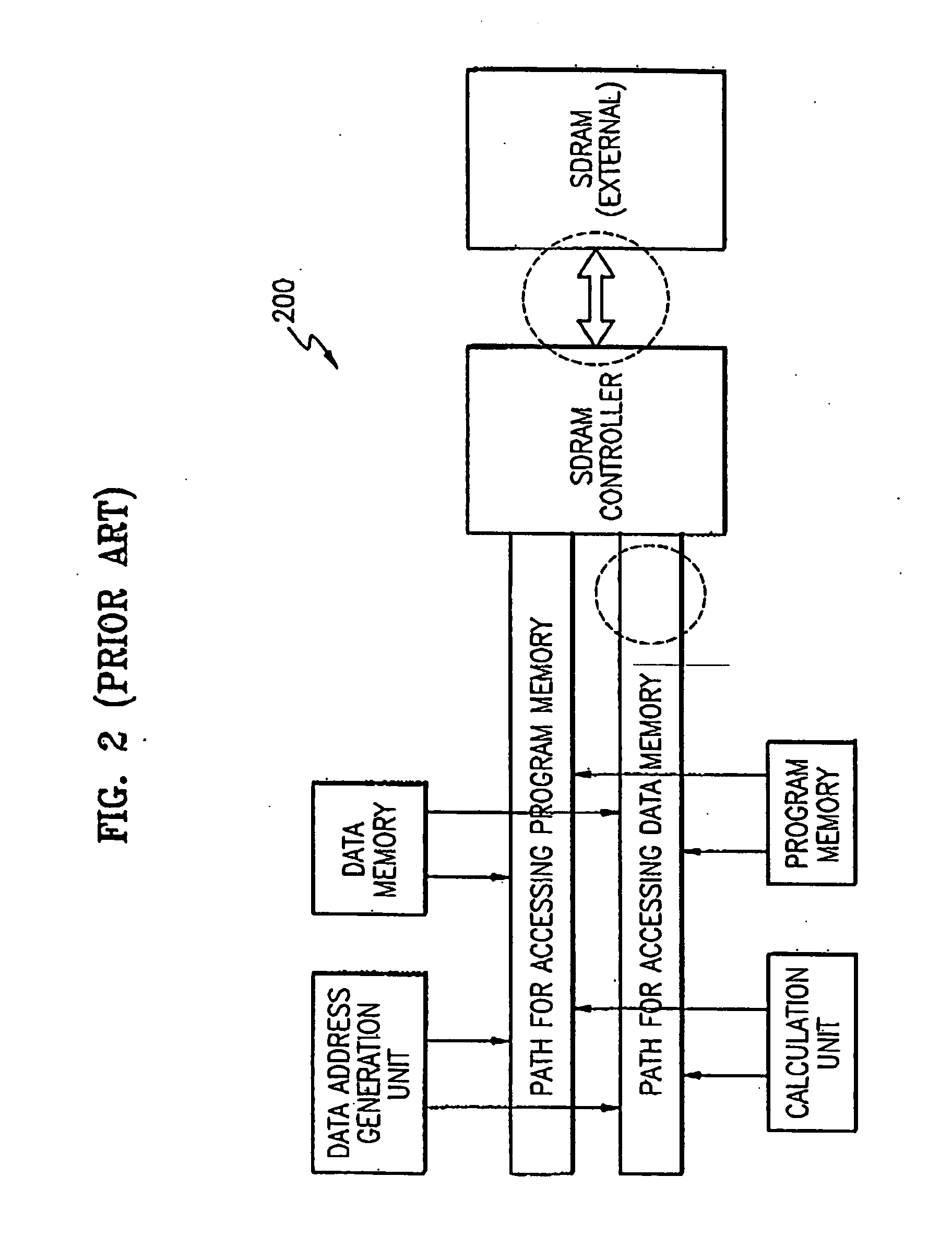

DSP (digital signal processing) architecture with a wide memory bandwidth and a memory mapping method thereof

InactiveUS20050083338A1Reduce memory access timeIncrease data rateSingle instruction multiple data multiprocessorsImage data processing detailsDsp architectureComputer architecture

A DSP (Digital Signal Processing) architecture with a wide memory bandwidth and a memory mapping method thereof. The DSP architecture includes: a first communication port; first, second, and third memory devices, which are connected with the first communication port and are arranged in a first row direction of the DSP architecture; a fourth memory device, a calculation element, and a fifth memory device, which are arranged in a second row direction below a first row direction of the DSP architecture; and sixth, seventh, and eighth memory devices, which are connected with the first communication port and arranged in a third row direction of the DSP architecture, wherein the calculation element is connected with the first through the eight memory devices. In the DSP architecture, the calculation element and the first through the eighth memory devices form one arrangement unit, wherein the calculation element is disposed in the center of the arrangement unit, the first through the eighth memory devices are connected to the calculation element, and a plurality of arrangement units are arranged in row directions and column directions of the DSP architecture. Therefore, since a wide data bandwidth is provided between the calculation element of the DSP architecture and the memory devices, it is possible to reduce memory access times when data is processed, and accordingly, to process data with a high data rate, such as a moving image with a high resolution.

Owner:SAMSUNG ELECTRONICS CO LTD

Computer and microprocessor control units that are inaccessible from the internet

InactiveUS7814233B2Optimize networkHighly economicalBiocideResource allocationMicroprocessor control unitInternet access

A computer configured for a connection to a network of computers including the Internet, comprising: a microchip including a microprocessor including a master control unit configured using hardware and firmware, and two processing units; an internal hardware firewall that is located between a protected portion and an unprotected portion of the microchip; said protected portion including said master control unit and one of the processing units, said unprotected portion including one or more of the processing units that are separate from and located outside of the internal hardware firewall; said hardware firewall denying access to said protected portion by the network; and said hardware firewall permitting access by another computer in the network to one or more of the processing units included in the unprotected portion for an operation with said another computer in the network; and an active configuration of a circuit integrated into the microchip.

Owner:ELLIS

Internal firewall for a personal computer to deny access by a network to a user's secure portion

InactiveUS7047275B1Optimize networkHighly economicalResource allocationMultiple digital computer combinationsComputer accessPersonal computer

A system and method is provided for an internal firewall configured to operate in a personal computer, which is configured to operate with other computers connected to a network. The personal computer includes at least two microprocessors. The firewall is configured to deny access to a first microprocessor of the personal computer by one of the other computers of the network during a shared operation involving the personal computer and the other computers of the network. The firewall is also configured to allow access to a second microprocessor of the personal computer by the other computers during the shared operation.

Owner:ELLIS

System and method for interactive multi-view video

InactiveUS20060023073A1Computer processing power becomes strongSolve narrow bandwidthTelevision system detailsColor television detailsComputer graphics (images)Type of service

Interactive multi-view video presents a new type of video capture system. Many video cameras are allocated to capture an event from various related locations and directions. The captured videos are compressed in control PCs and are sent to a server in real-time. The compressed video can also be transcoded through an off-line compression approach to further reduce the data amount. Users can subscribe to a new type of service that allows users to connect to the servers and receive multi-view videos interactively.

Owner:MICROSOFT TECH LICENSING LLC

Global network computers

InactiveUS20060190565A1Optimize networkHighly economicalResource allocationMultiple digital computer combinationsThe InternetNetwork service

This invention generally relates to one or more computer networks having computers like personal computers or network servers with microprocessors linked by broadband 5 transmission means and having hardware, software, firmware, and other means such that at least one parallel processing operation occurs that involve at least two computers in the network. More particularly, this invention relates to one or more large networks composed of smaller networks and large numbers of computers connected, like the Internet, wherein more than one separate parallel processing operation involving more than one different set of computers occurs simultaneously and wherein ongoing processing linkages can be established between virtually any microprocessors of separate computers connected to the network. Still more particularly, this invention relates to business arrangements enabling the shared used of network microprocessors for parallel and other processing, wherein personal computer owners provide microprocessor processing power to a network, preferably for parallel processing, in exchange for network linkage to other personal and other computers supplied by network providers, including linkage to other microprocessors for parallel or other processing; the basis of the exchange between owners and providers being whatever terms to which the parties agree, subject to governing laws, regulations, or rules, including payment from either party to the other based on periodic measurement of net use or provision of processing power.

Owner:ELLIS III FRAMPTON E

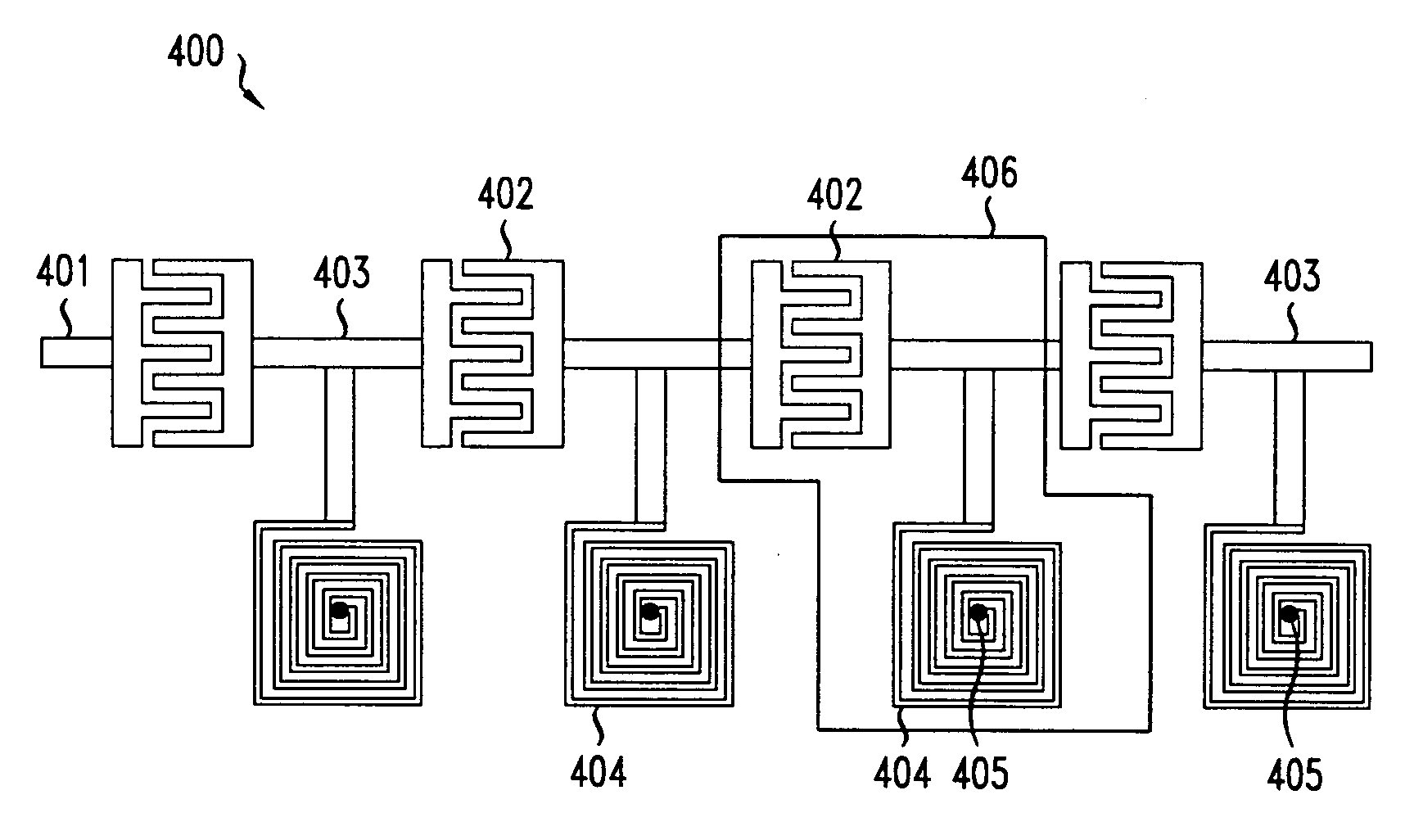

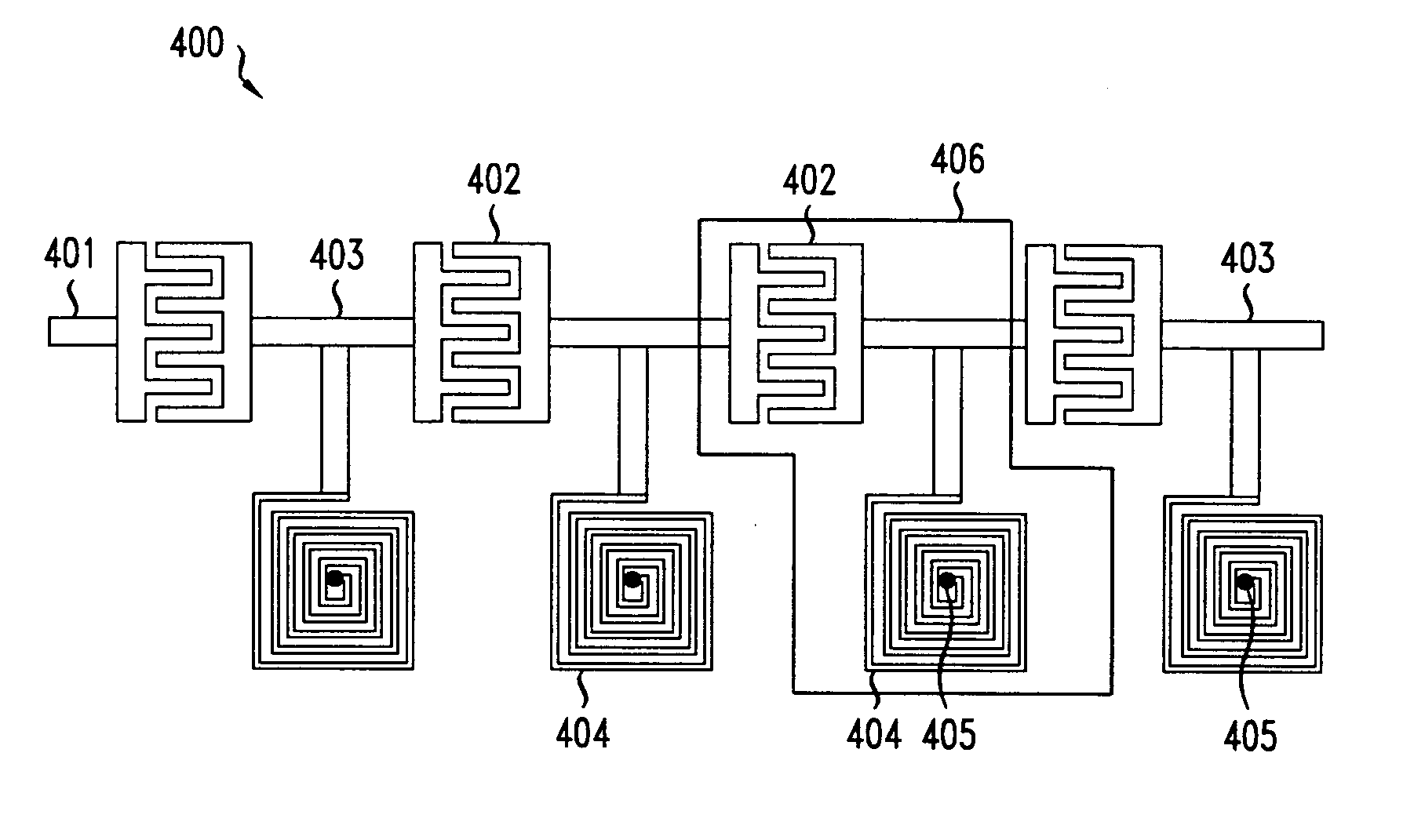

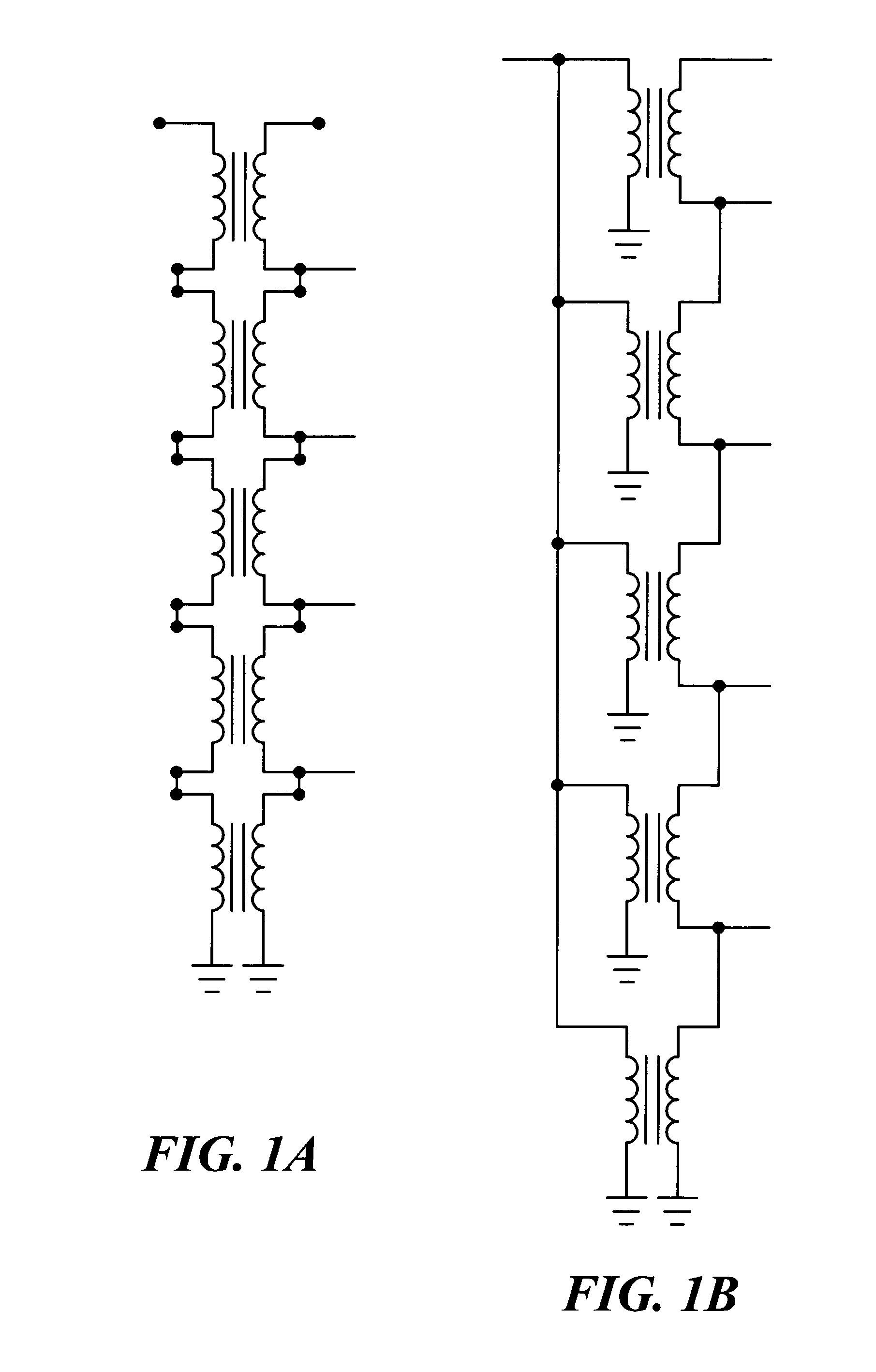

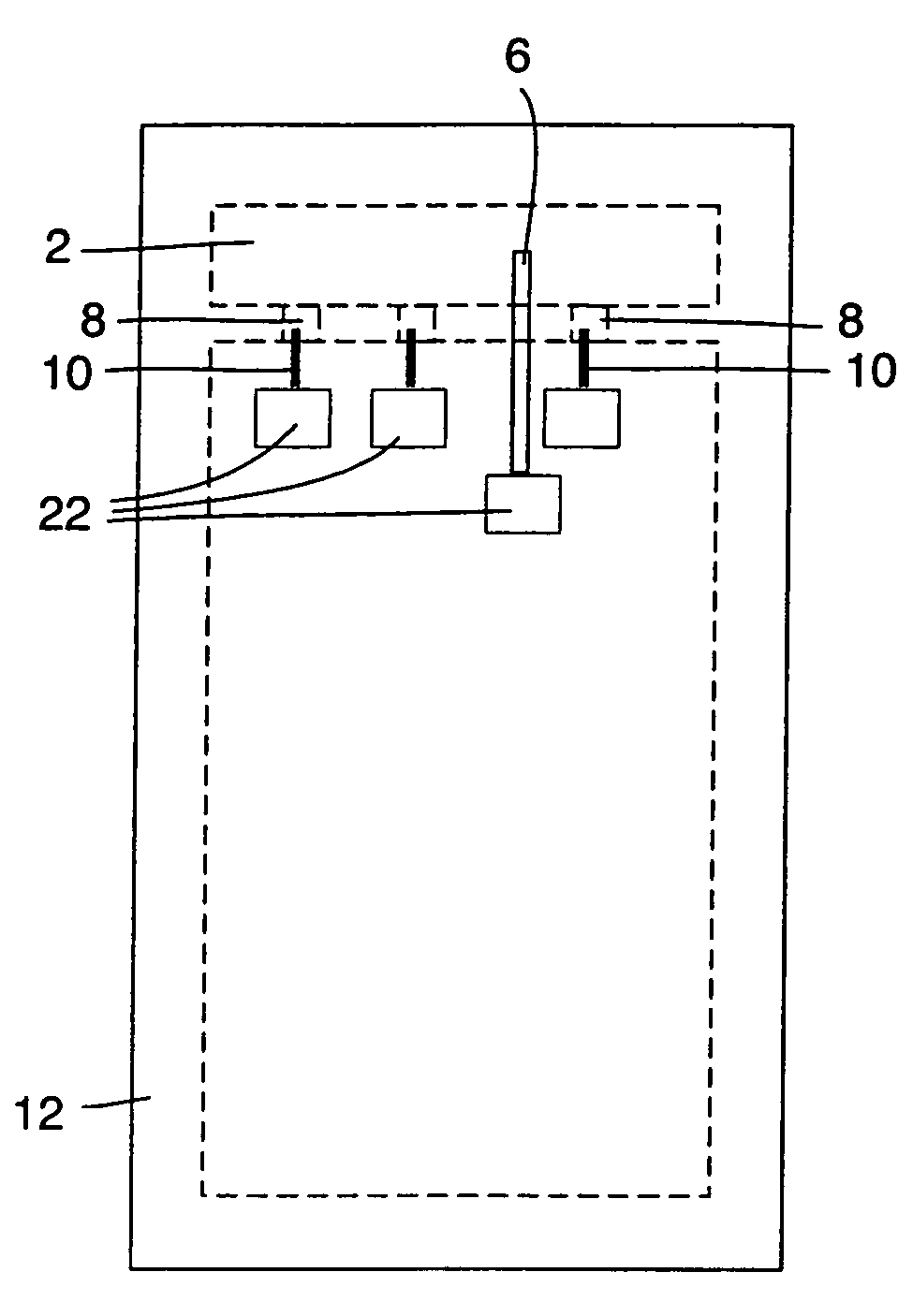

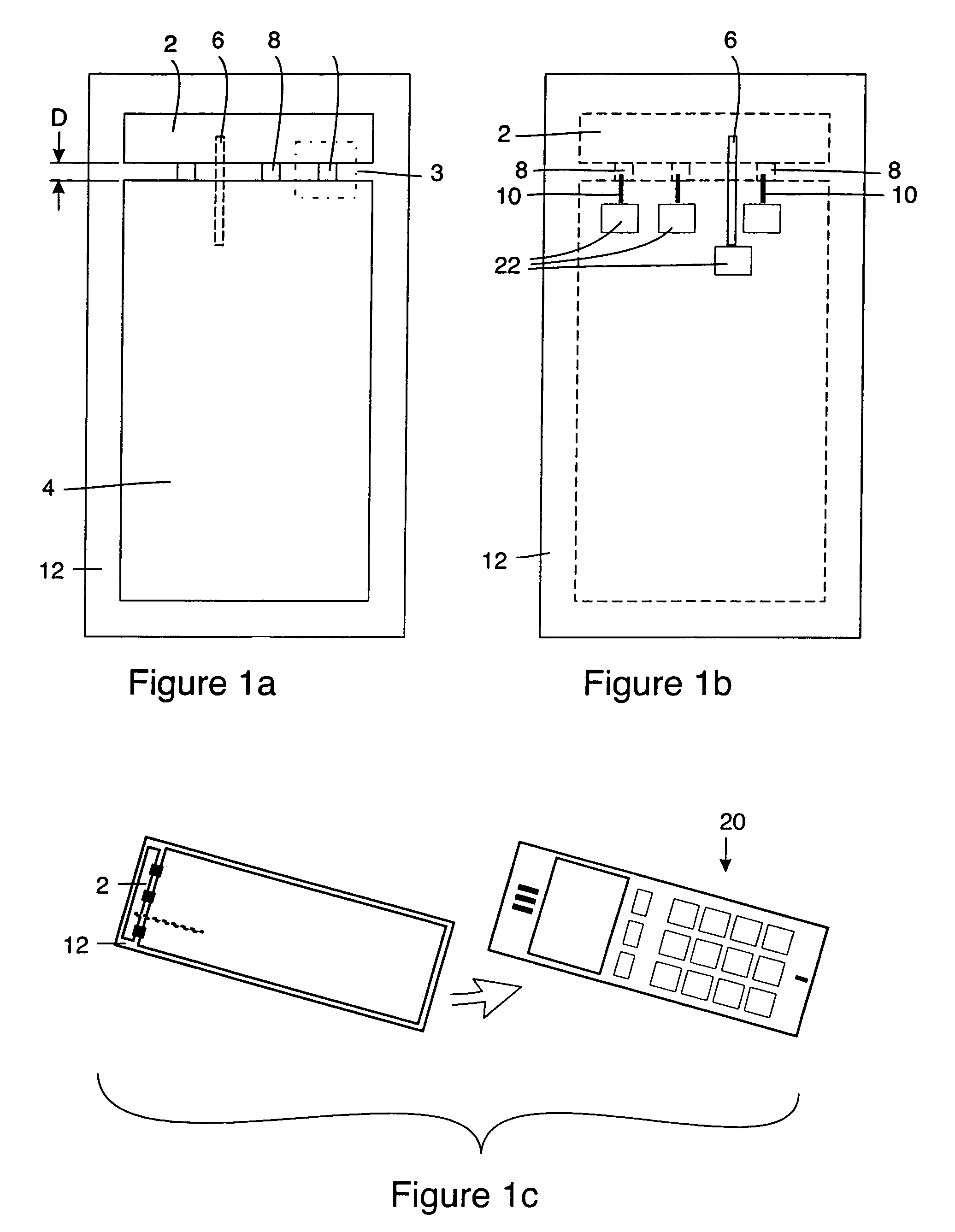

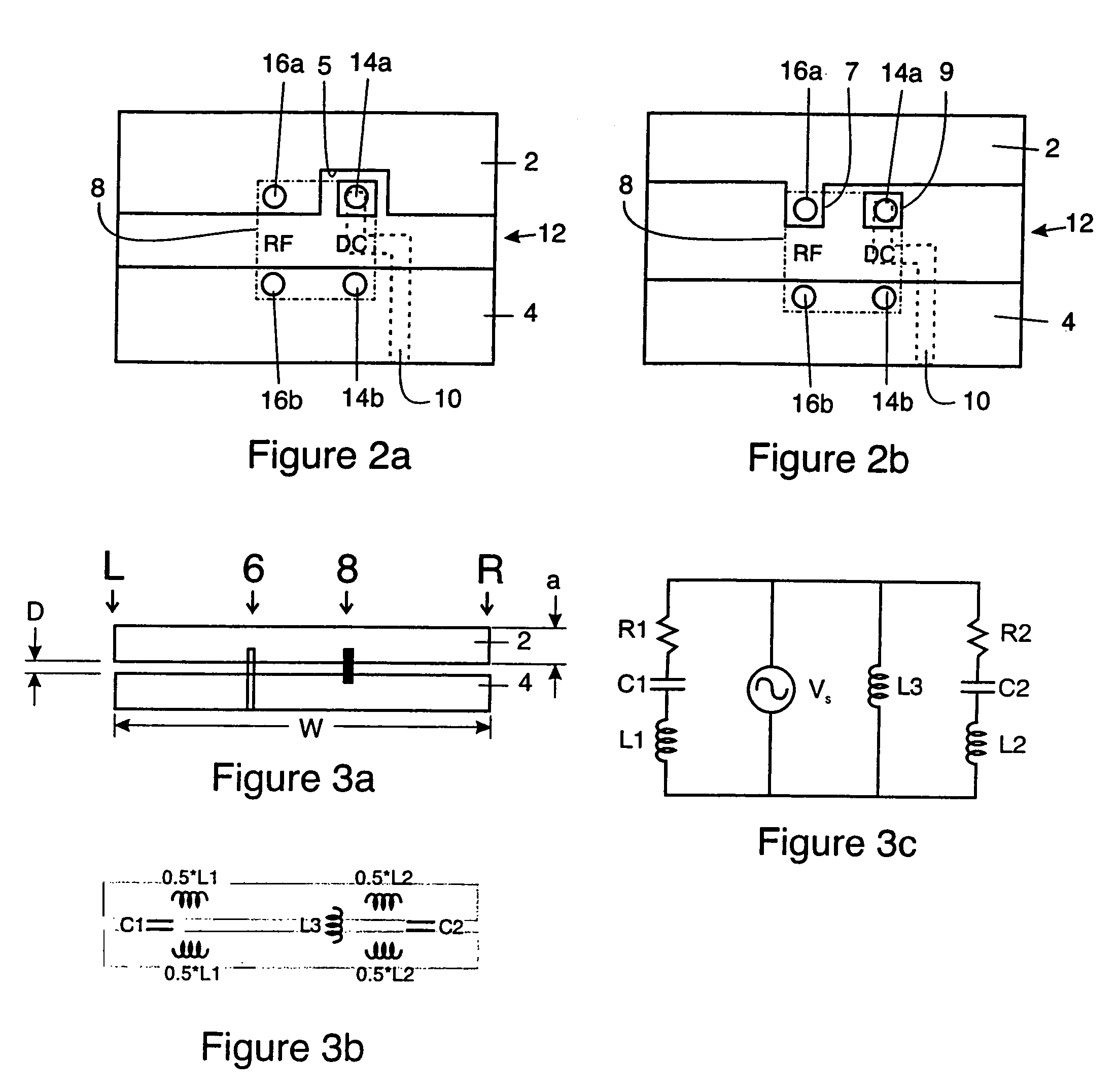

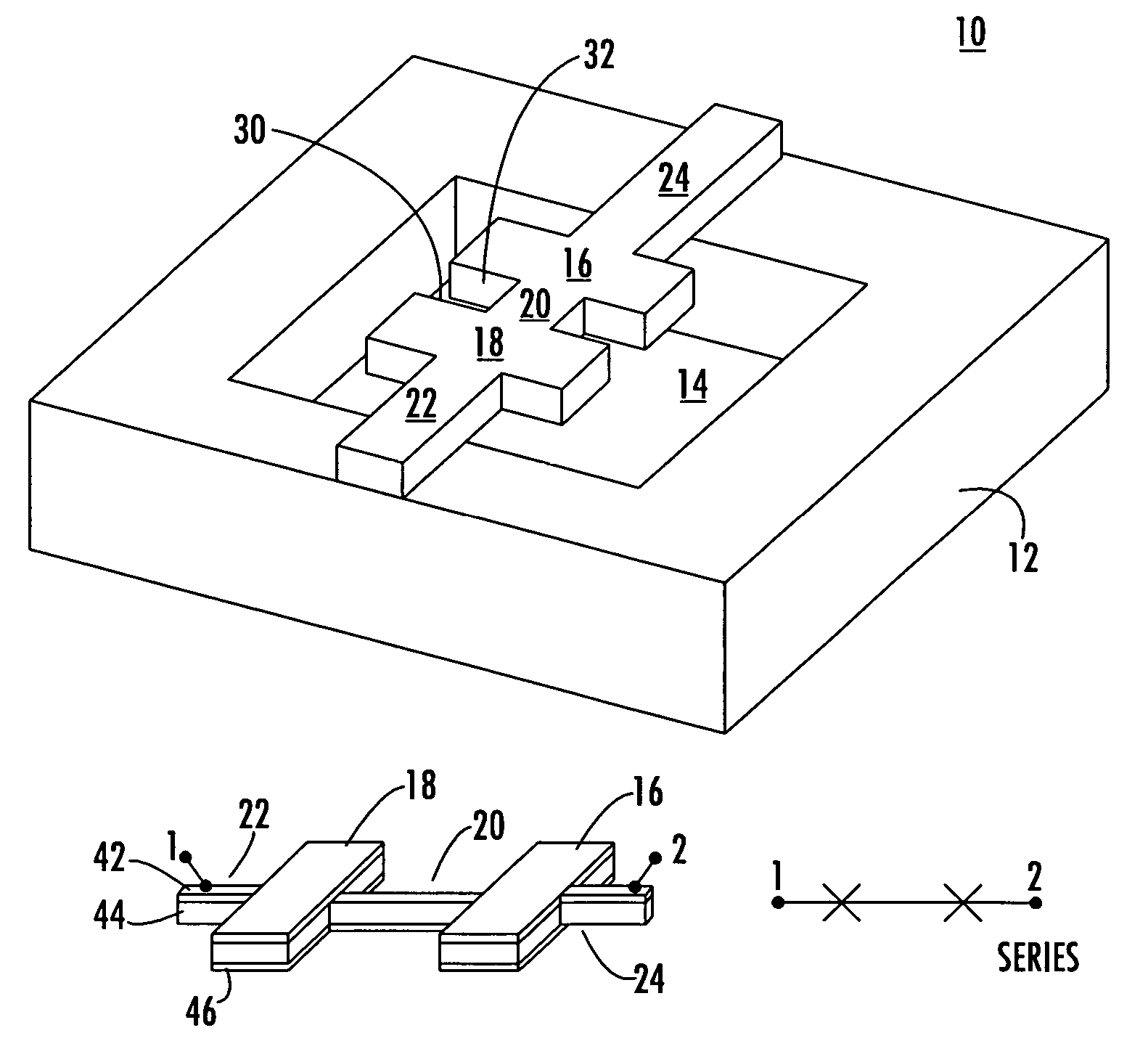

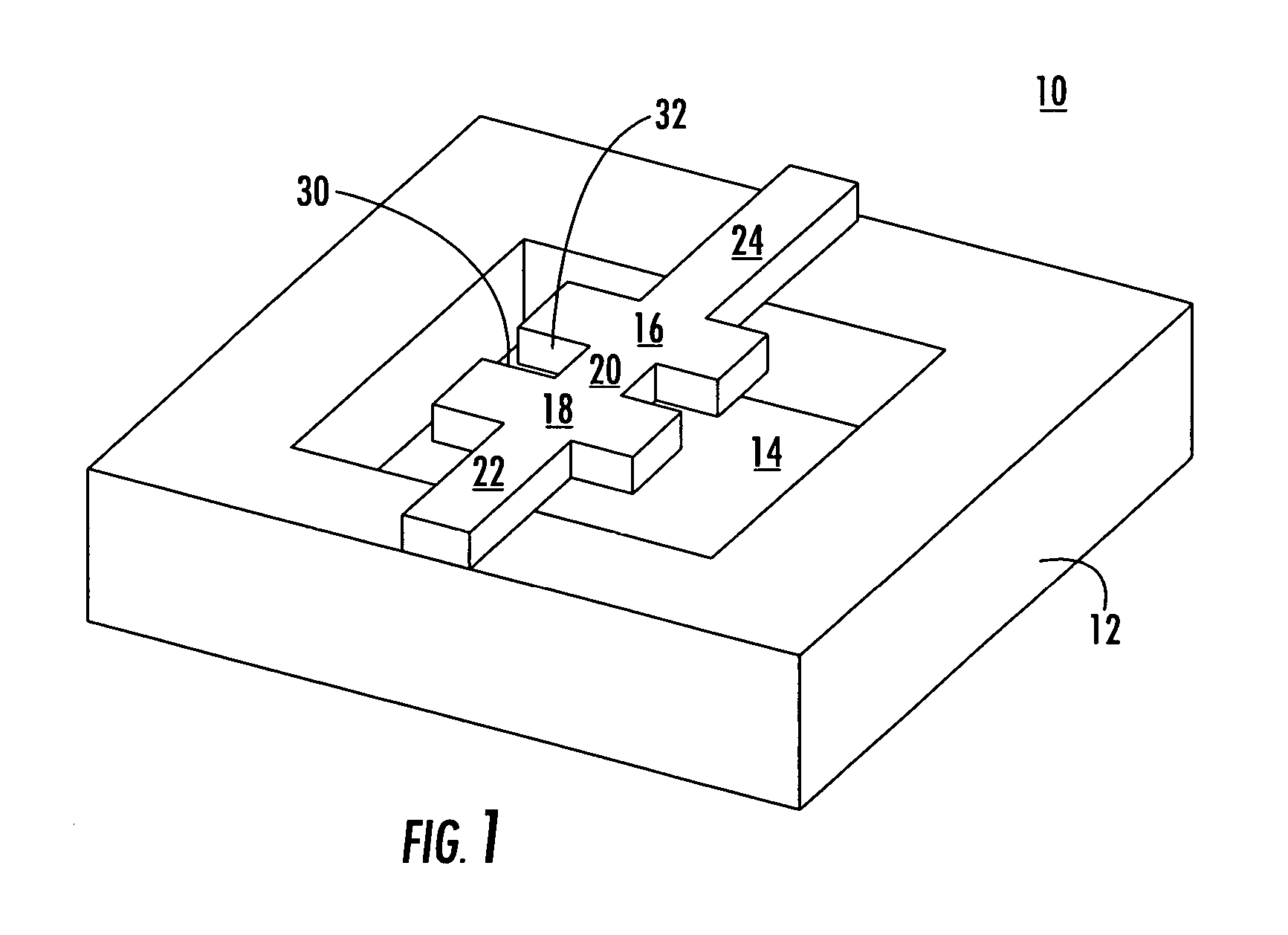

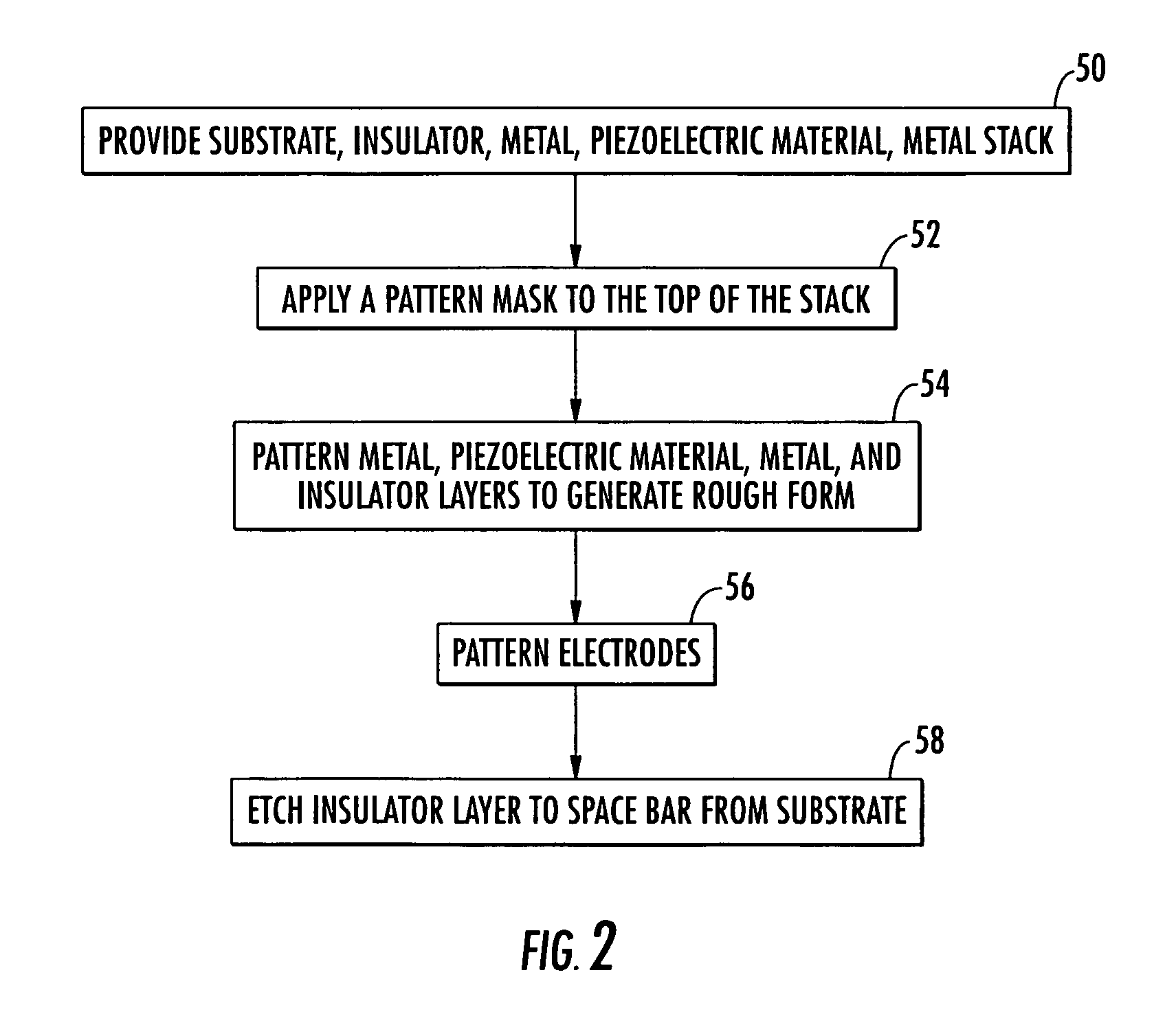

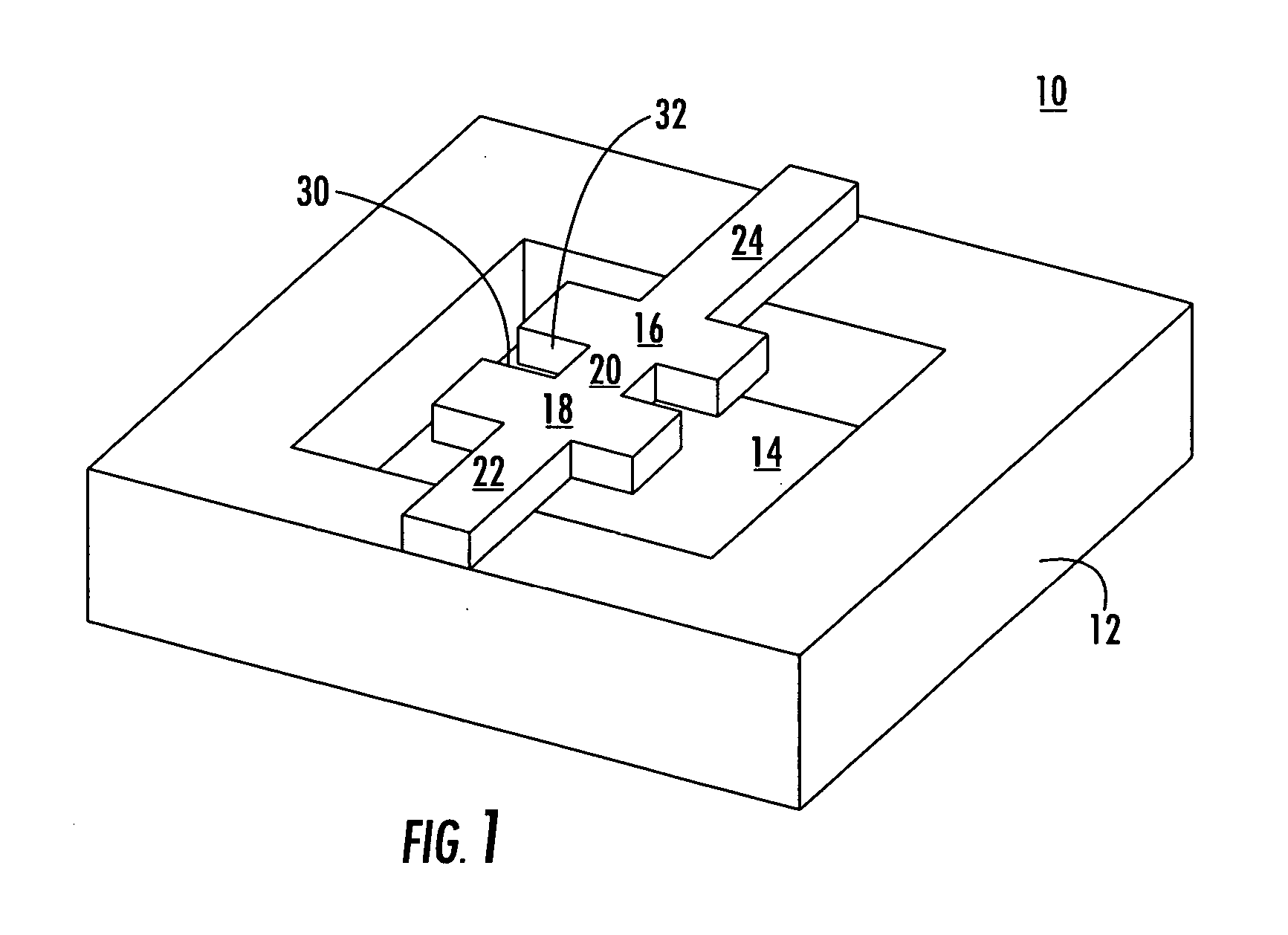

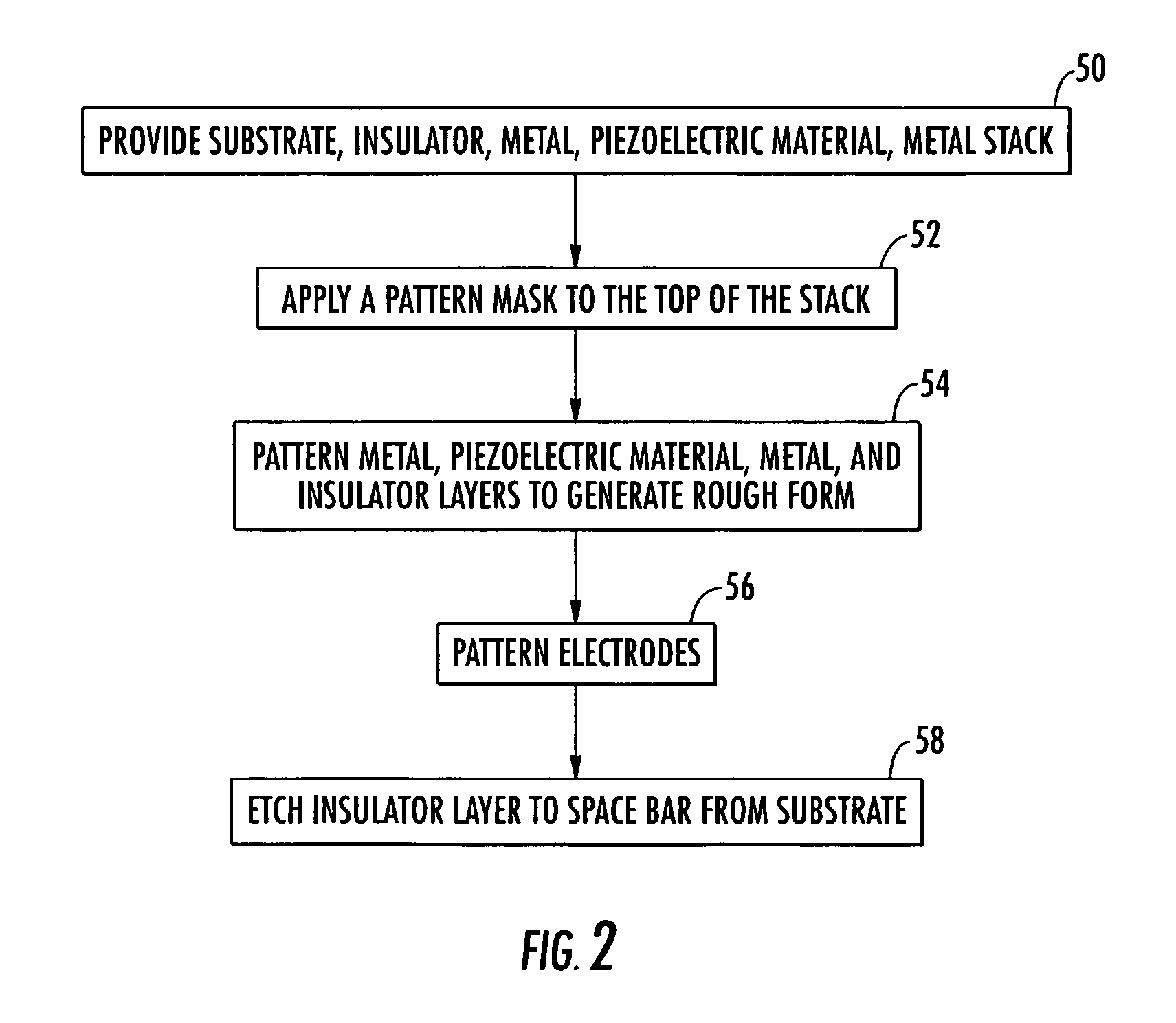

Resonator system with a plurality of individual mechanically coupled resonators and method of making same

InactiveUS7312674B2Solve narrow bandwidthLarge actuation voltagePiezoelectric/electrostriction/magnetostriction machinesImpedence networksResonanceCondensed matter physics

A resonator system wherein a plurality of resonators each including piezoelectric material are suspended relative to a substrate. An edge of each resonator is mechanically coupled to an edge of another resonator and the plurality of resonators expand and contract reaching resonance in response to an applied electric field.

Owner:CHARLES STARK DRAPER LABORATORY

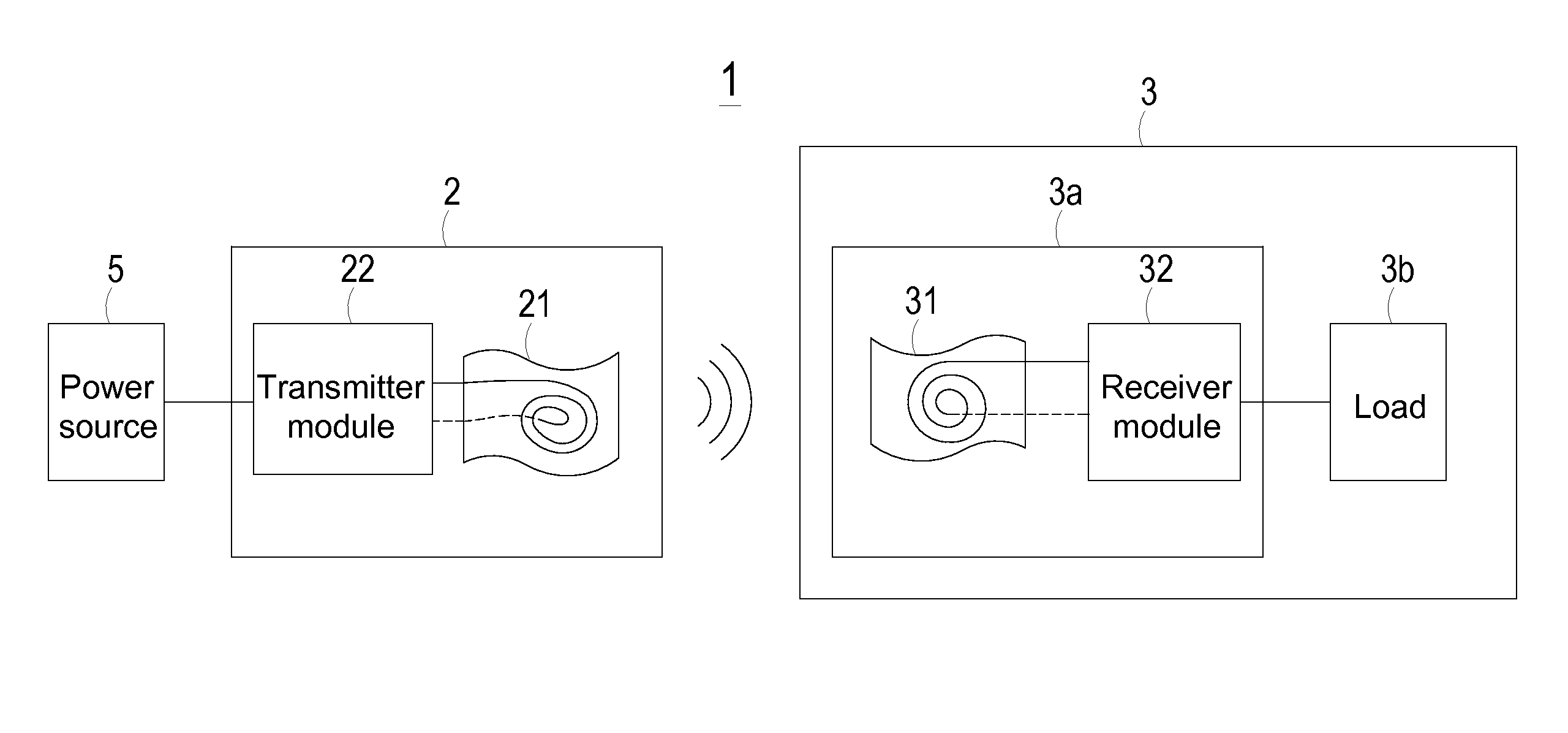

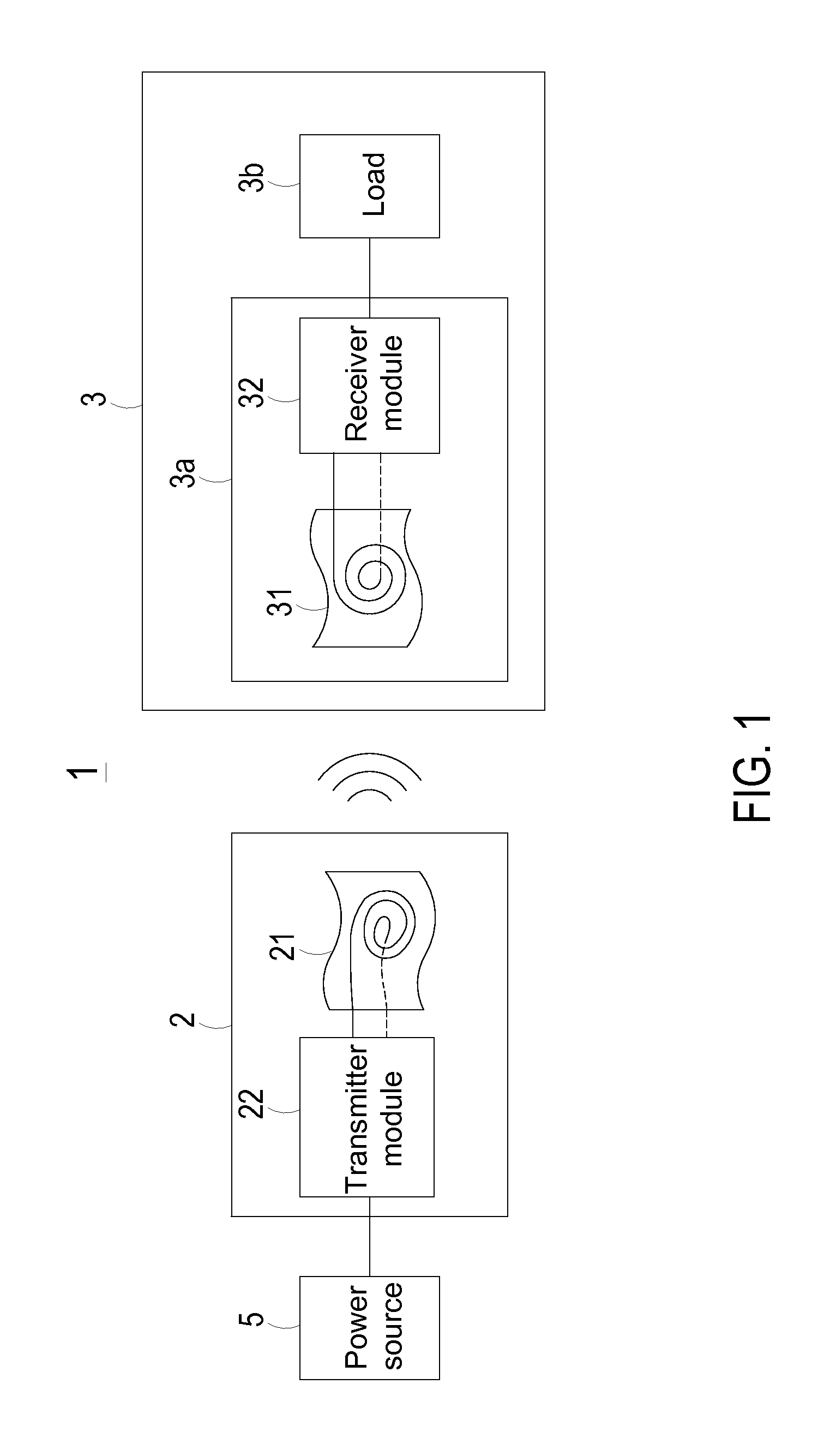

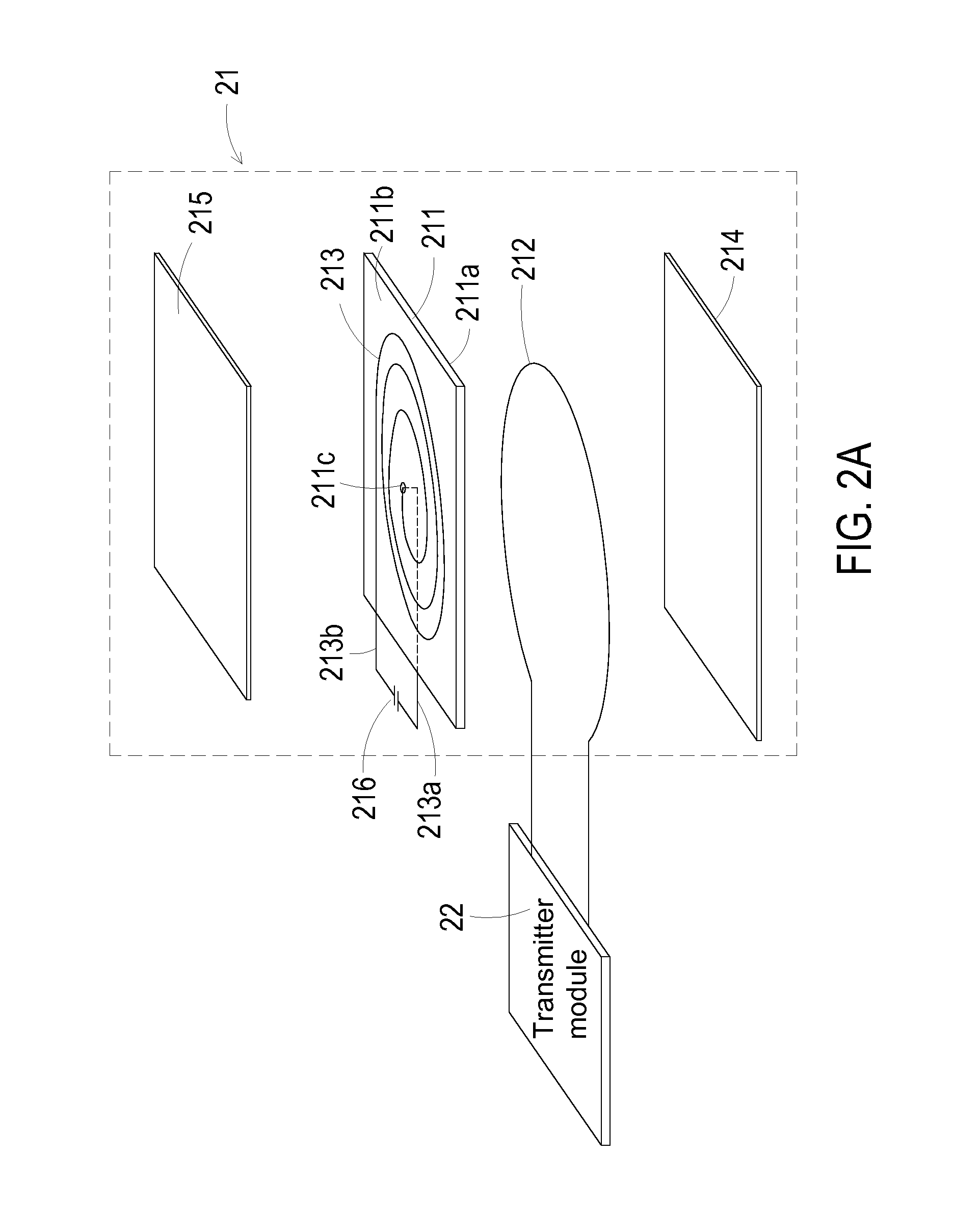

Thin-film coil assembly, flexible wireless charging device and wireless charging system

InactiveUS20160322156A1Increase flexibilityCost-effectiveNear-field transmissionBatteries circuit arrangementsCapacitorCoupling effect

A thin-film coil assembly includes a flexible substrate, an oscillation starting antenna, a resonant antenna, a first protective layer and a second protective layer. The flexible substrate has a first surface and a second surface opposed to the first surface. The oscillation starting antenna is disposed on the first surface of the flexible substrate. The resonant antenna is disposed on the second surface of the flexible substrate. Moreover, at least one capacitor is connected between a first end and a second end of the resonant antenna. An electromagnetic wave with a specified resonant frequency is emitted or received by the thin-film coil assembly in response to a resonant coupling effect of the resonant antenna and the oscillation starting antenna. The first protective layer covers the oscillation starting antenna. The second protective layer covers the resonant antenna.

Owner:J TOUCH CORPORATION

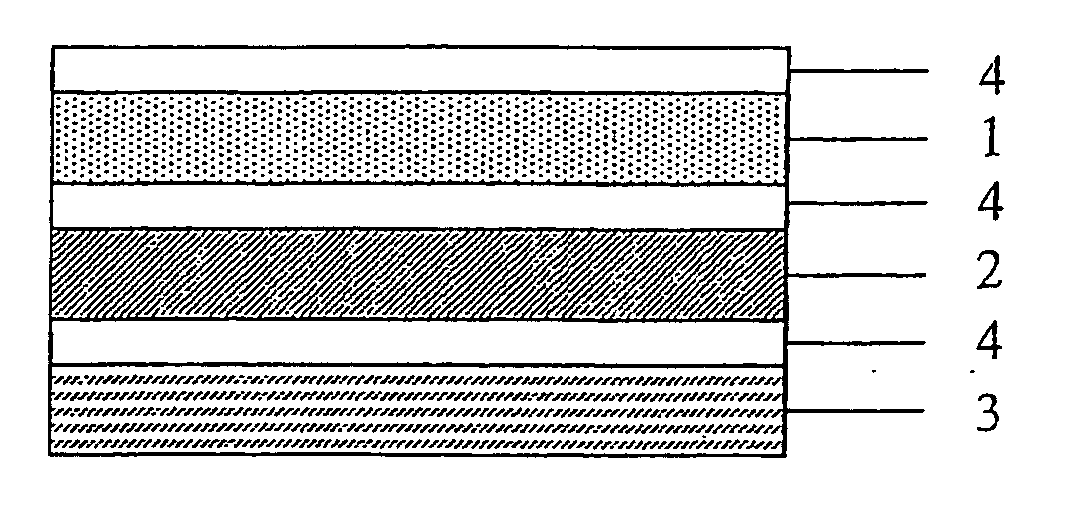

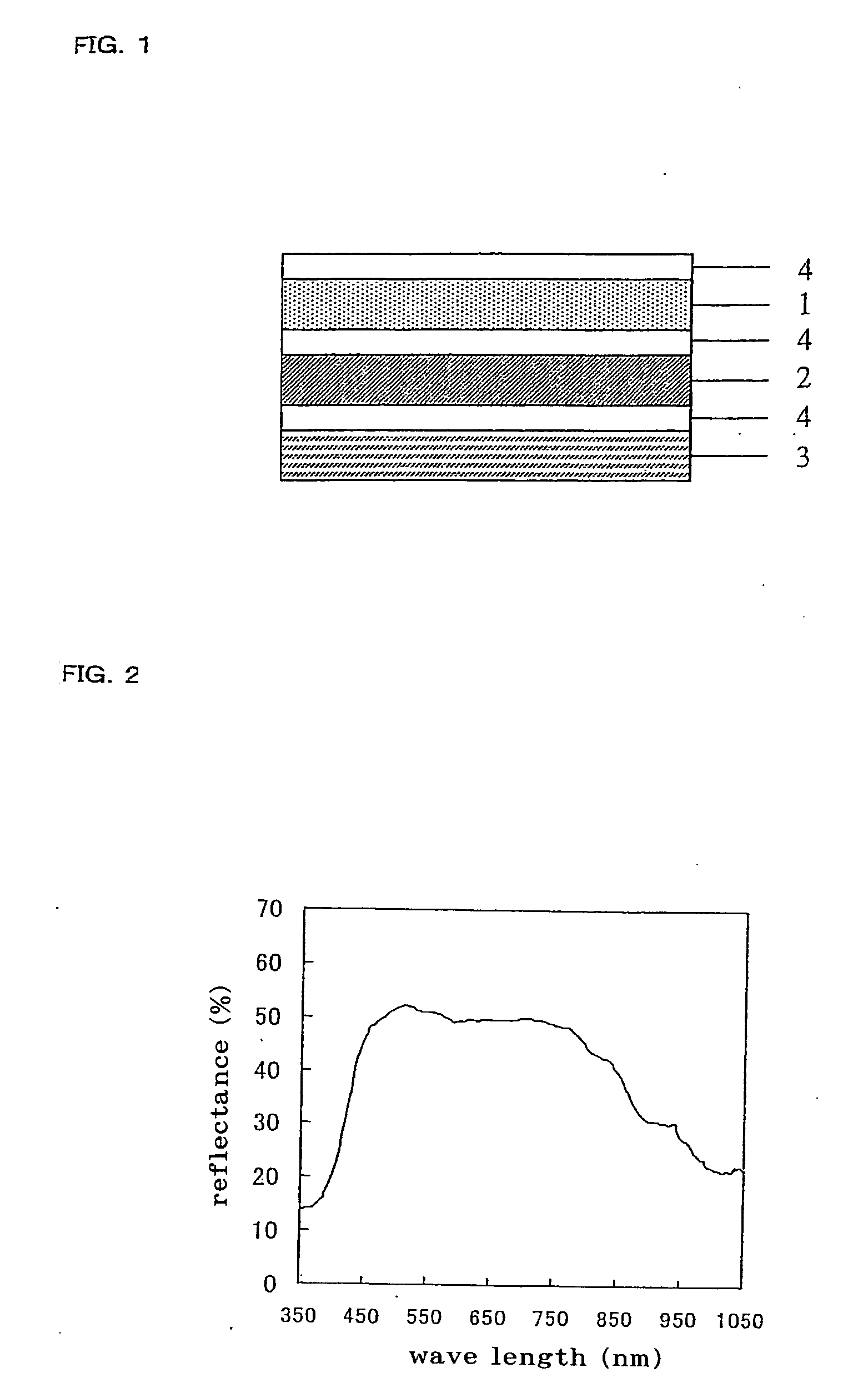

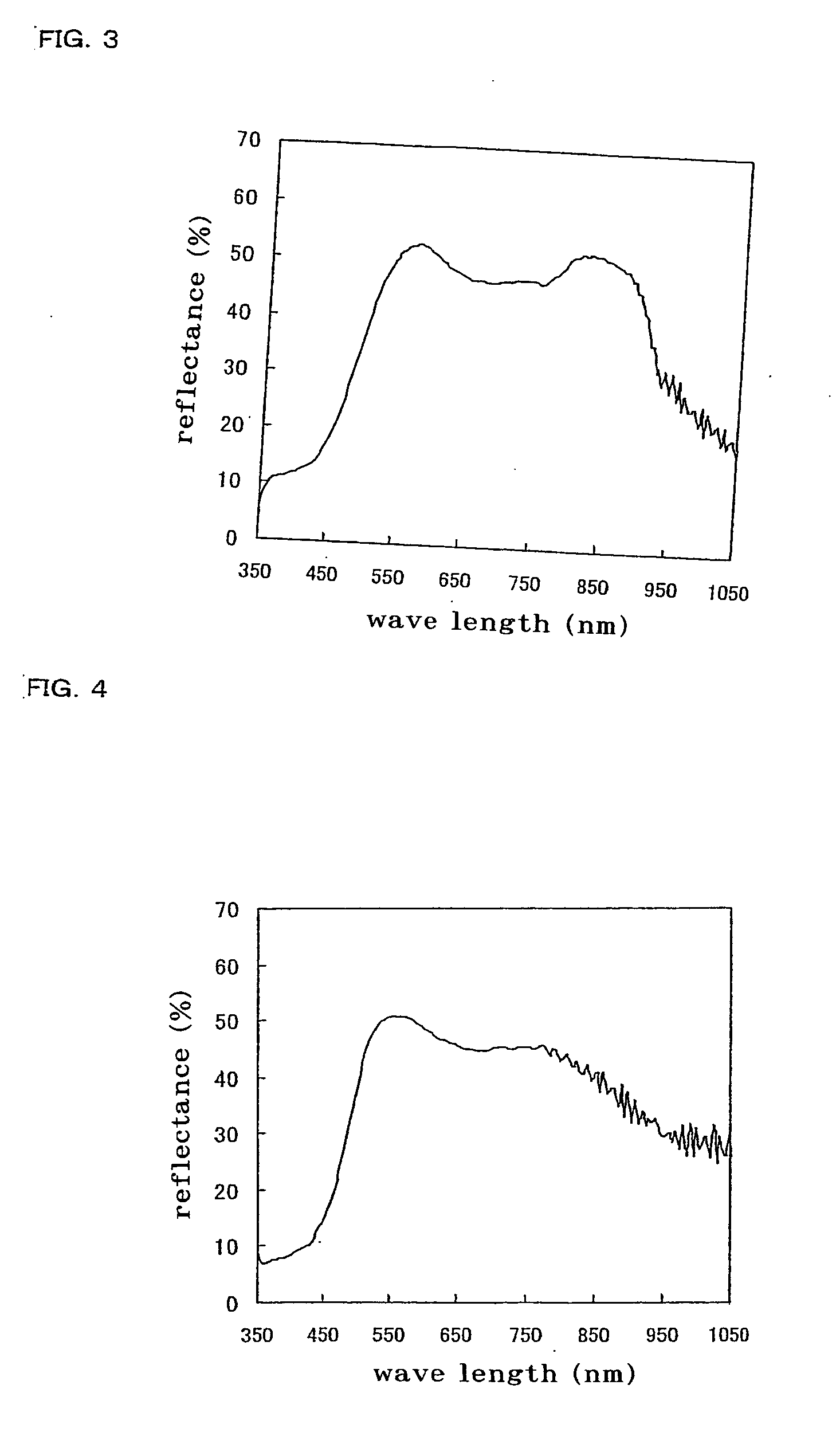

Broad band-cholesteric liquid crystal film and process for producing the same, circularly polarizing plate, linearly polarizing element, illuminator, and liquid-crystal display

InactiveUS20060119783A1Wide reflection bandIncreased durabilityLiquid crystal compositionsPolarising elementsLiquid-crystal displayUltraviolet lights

A broad band cholesteric liquid crystal film of the present invention comprises a cholesteric liquid crystal film obtained by polymerizing a liquid crystal mixture containing a polymerizable mesogen compound (a), a polymerizable chiral agent (b) and a photopolymerization initiator (c) between two substrates with ultraviolet light, and has a reflection bandwidth of 200 nm or more. The broad band cholesteric liquid crystal film of the present invention has a broad reflection band and is excellent in durability.

Owner:NITTO DENKO CORP

Resonator system with a plurality of individual mechanically coupled resonators and method of making same

ActiveUS20050140467A1Large actuation voltageAvoid the needImpedence networksPiezoelectric/electrostriction/magnetostriction machinesResonanceCondensed matter physics

A resonator system wherein a plurality of resonators each including piezoelectric material are suspended relative to a substrate. An edge of each resonator is mechanically coupled to an edge of another resonator and the plurality of resonators expand and contract reaching resonance in response to an applied electric field.

Owner:CHARLES STARK DRAPER LABORATORY

Global network computers for shared processing

InactiveUS20110004931A1Optimize networkHighly economicalBiocideResource allocationThe InternetComputer access

A computer configured for a connection to a network of computers including the Internet, comprising: a microchip including a microprocessor including a master control unit configured using hardware and firmware, and two processing units; an internal hardware firewall that is located between a protected portion and an unprotected portion of the microchip; said protected portion including said master control unit and one of the processing units, said unprotected portion including one or more of the processing units that are separate from and located outside of the internal hardware firewall; said hardware firewall denying access to said protected portion by the network; and said hardware firewall permitting access by another computer in the network to one or more of the processing units included in the unprotected portion for an operation with said another computer in the network; and an active configuration of a circuit integrated into the microchip.

Owner:ELLIS III FRAMPTON E

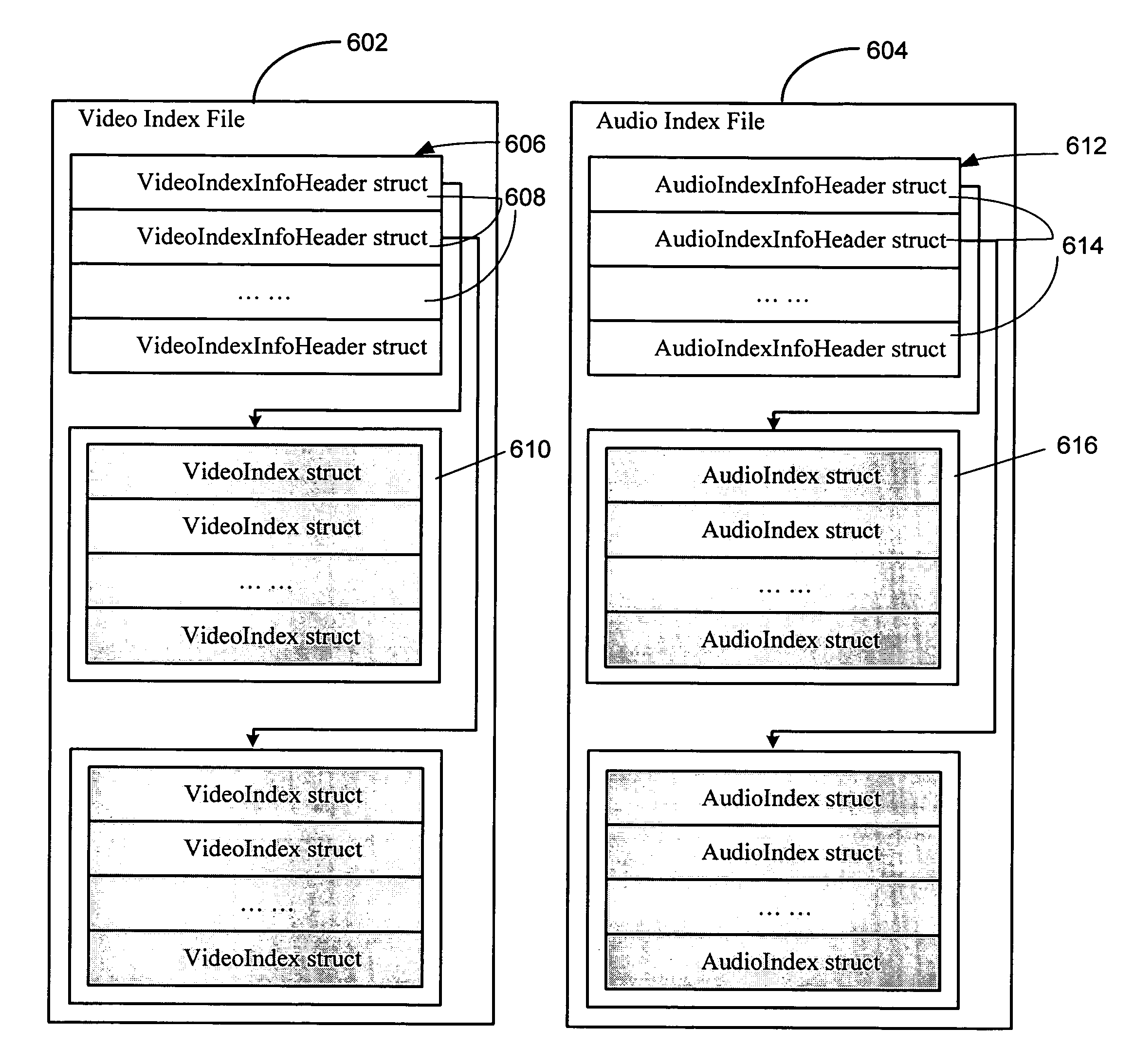

Multi-view video format

InactiveUS7444664B2Computer processing power becomes strongSolve narrow bandwidthTelevision system detailsRecording carrier detailsComputer graphics (images)Video capture

Interactive multi-view video presents new types of video capture systems, video formats, video compression algorithms, and services. Many video cameras are allocated to capture an event from various related locations and directions. The captured videos and any associated audio streams are captured in a video beam format which allows for the efficient and expedient search of the vast amount of data in real-time and allows the data to be stored for off-line access.

Owner:MICROSOFT TECH LICENSING LLC