Patents

Literature

73results about How to "Avoid excessive diffusion" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Low zirconium, hafnium-containing compositions, processes for the preparation thereof and methods of use thereof

InactiveUS20060062910A1Improve propertyDesire morphologyGroup 4/14 organic compounds without C-metal linkagesSemiconductor/solid-state device manufacturingSemiconductorMetal

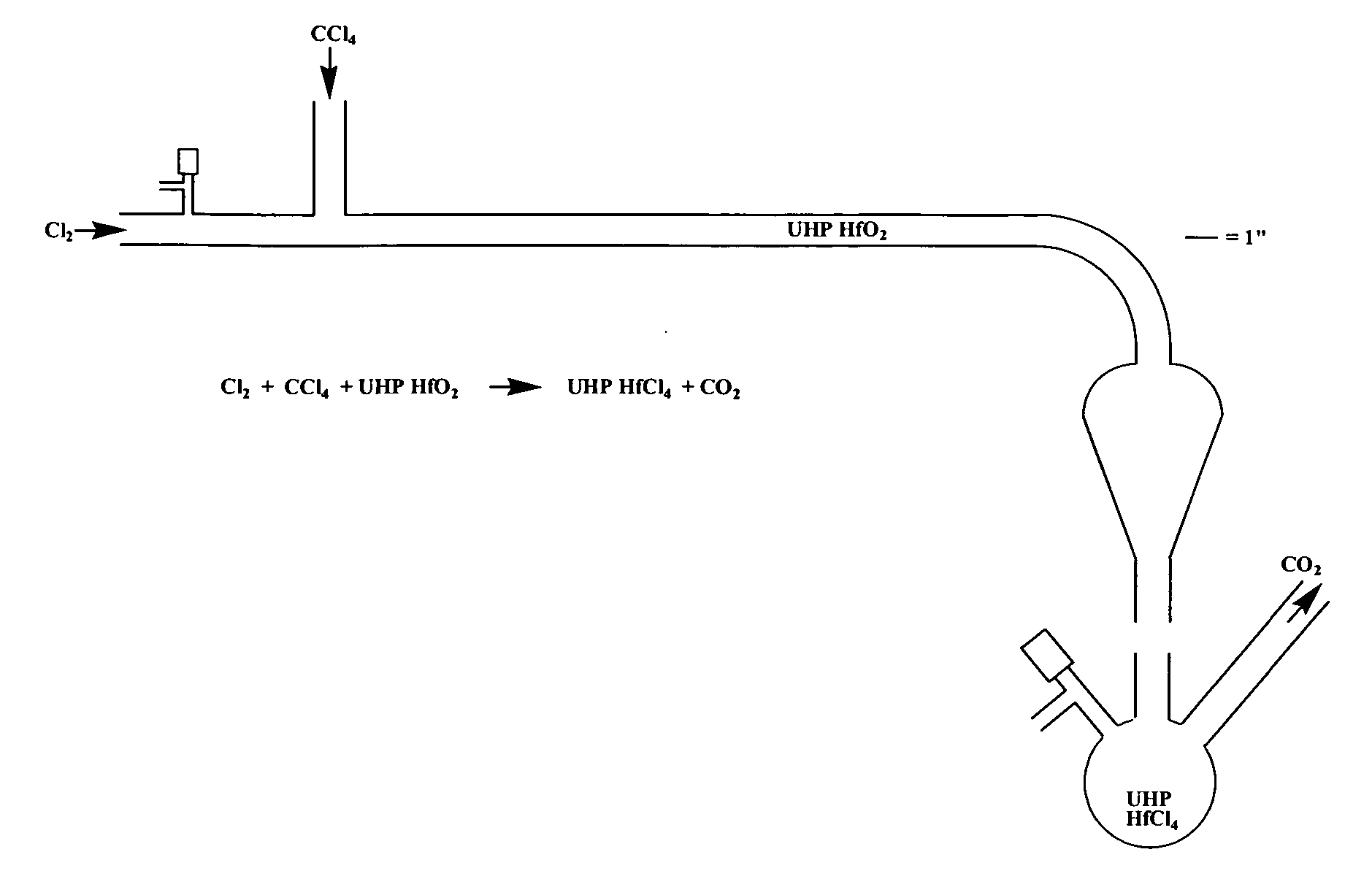

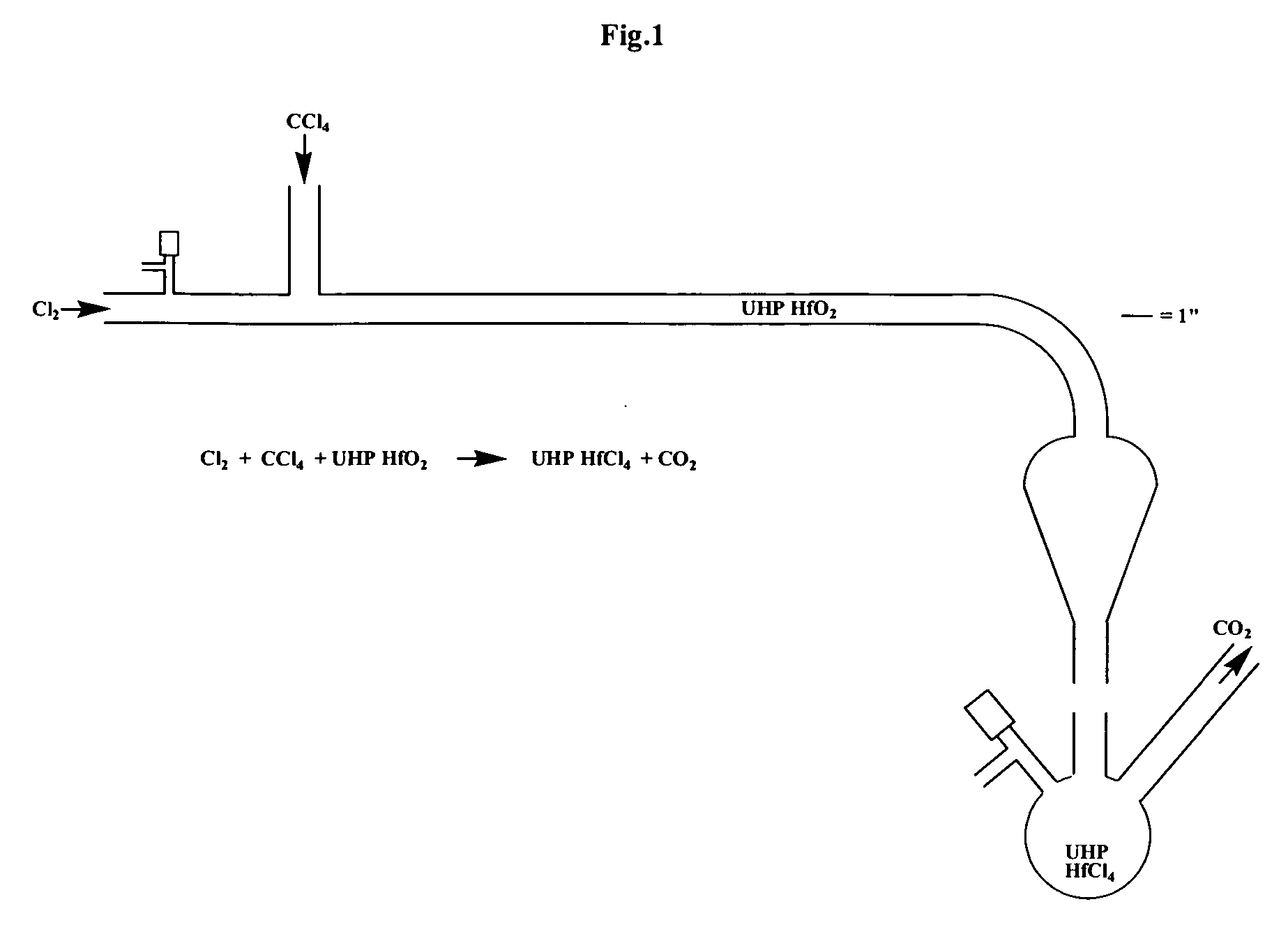

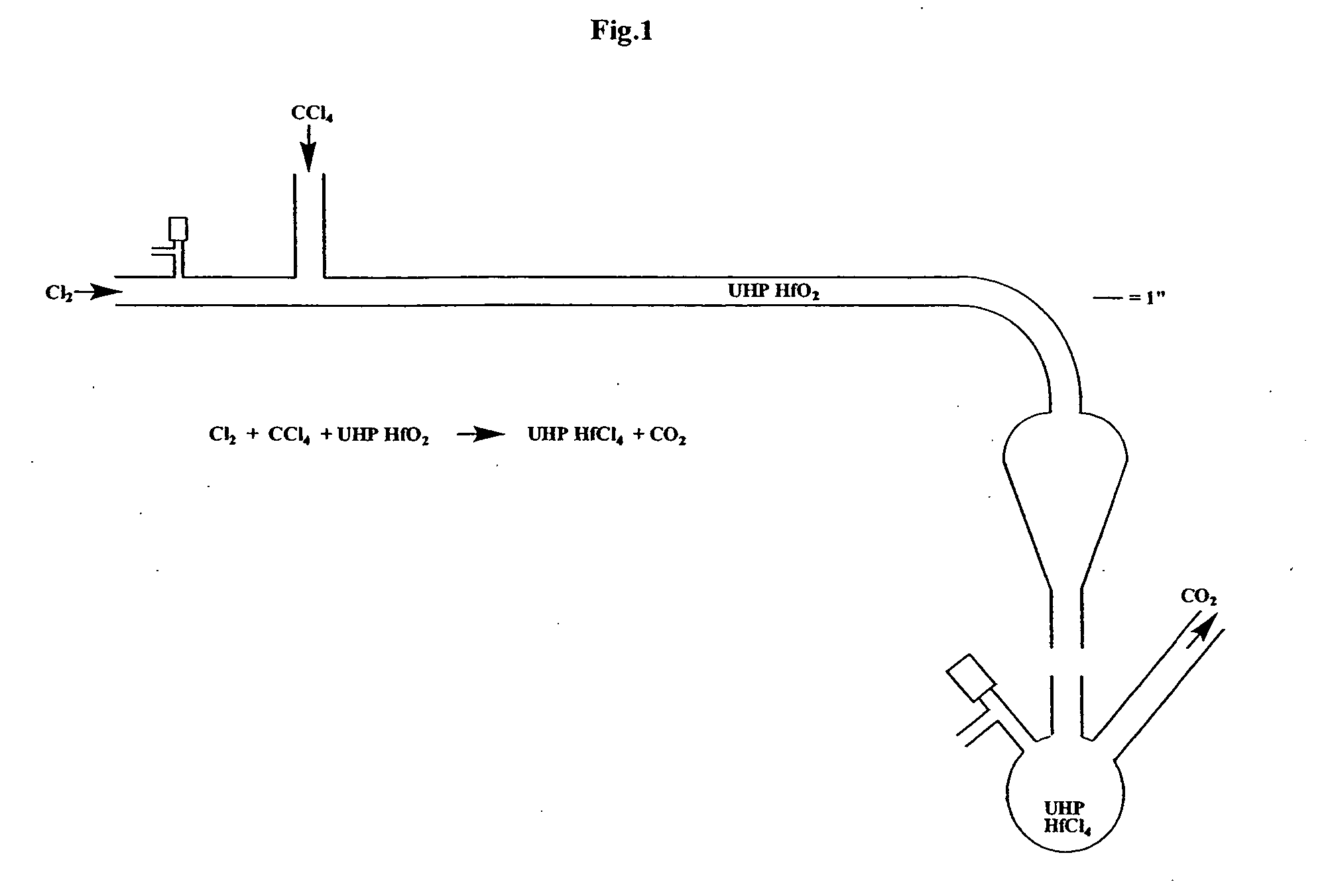

This invention relates to hafnium-containing compositions having a zirconium concentration of less than about 500 parts per million, a process for producing the hafnium-containing compositions, organometallic precursor compositions containing a hafnium-containing compound and having a zirconium concentration of less than about 500 parts per million, a process for producing the organometallic precursor compositions, and a method for producing a film or coating from the organometallic precursor compositions. The organometallic precursor compositions are useful in semiconductor applications as chemical vapor deposition (CVD) or atomic layer deposition (ALD) precursors for film depositions.

Owner:PRAXAIR TECH INC

Low zirconium, hafnium-containing compositions, processes for the preparation thereof and methods of use thereof

InactiveUS20060193979A1Improve propertiesDesired morphologyGroup 4/14 organic compounds without C-metal linkagesPretreated surfacesHafniumChemical vapor deposition

This invention relates to hafnium-containing compositions having a zirconium concentration of less than about 500 parts per million, a process for producing the hafnium-containing compositions, organometallic precursor compositions containing a hafnium-containing compound and having a zirconium concentration of less than about 500 parts per million, a process for producing the organometallic precursor compositions, and a method for producing a film or coating from the organometallic precursor compositions. The organometallic precursor compositions are useful in semiconductor applications as chemical vapor deposition (CVD) or atomic layer deposition (ALD) precursors for film depositions.

Owner:PRAXAIR TECH INC

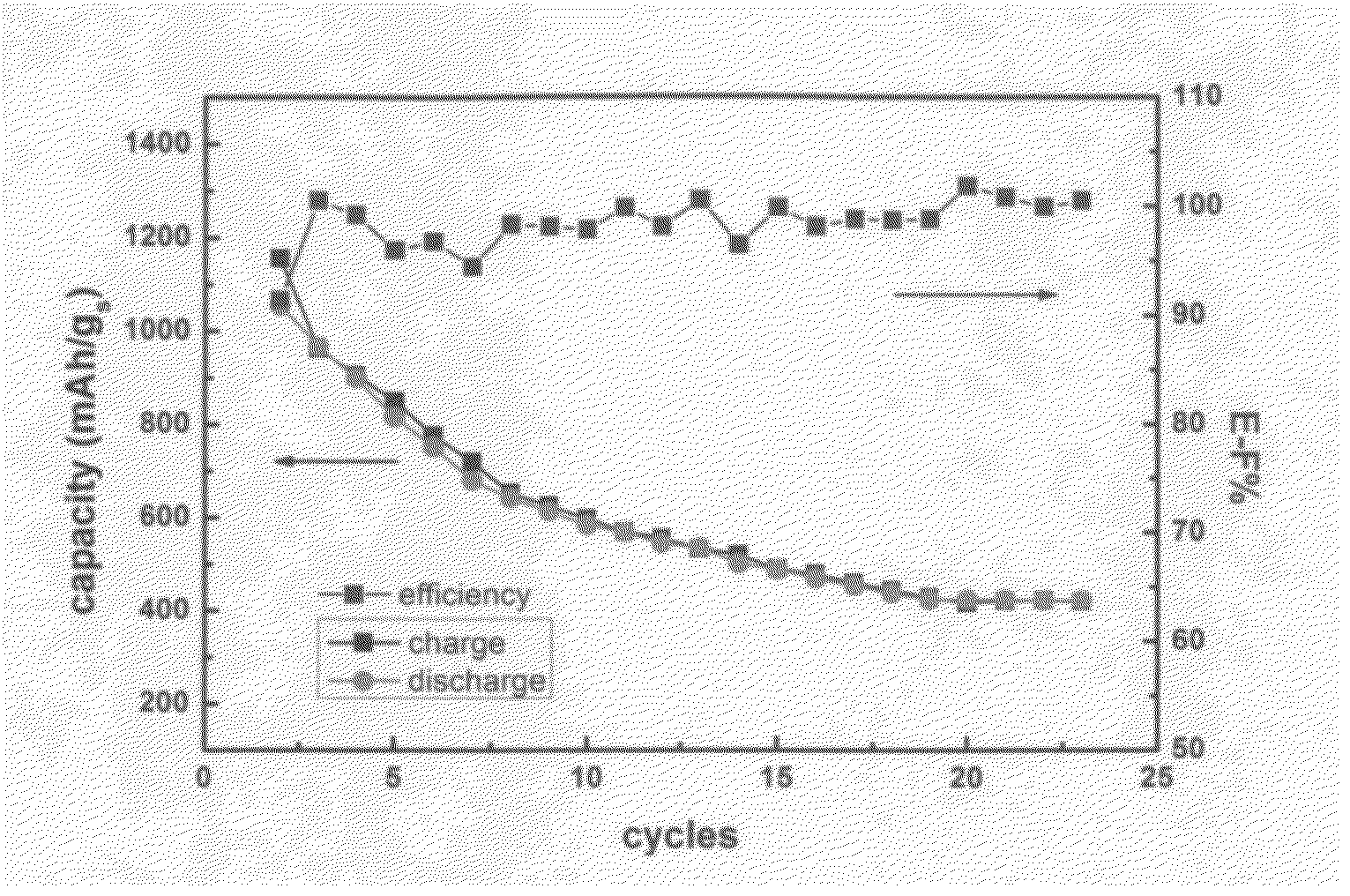

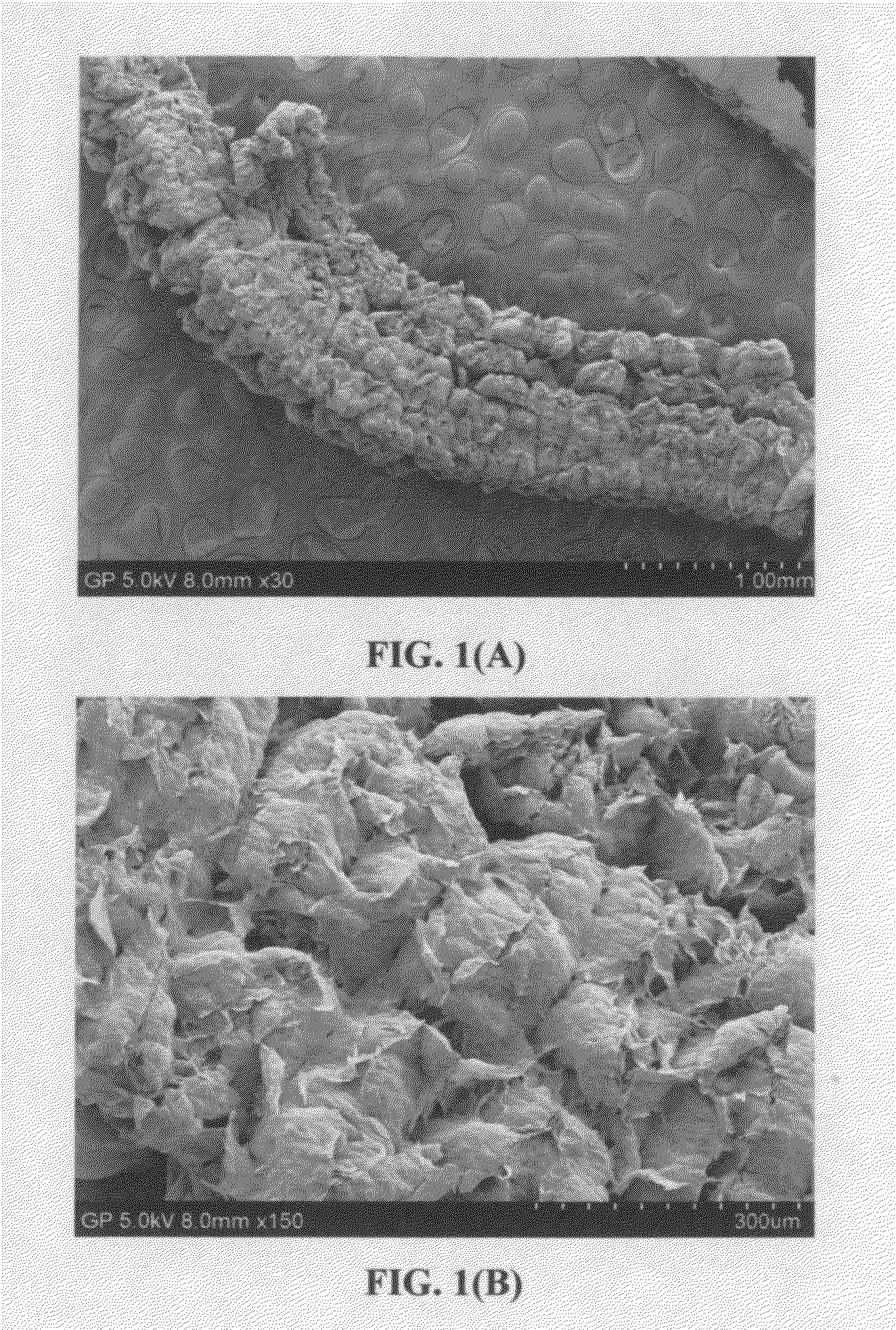

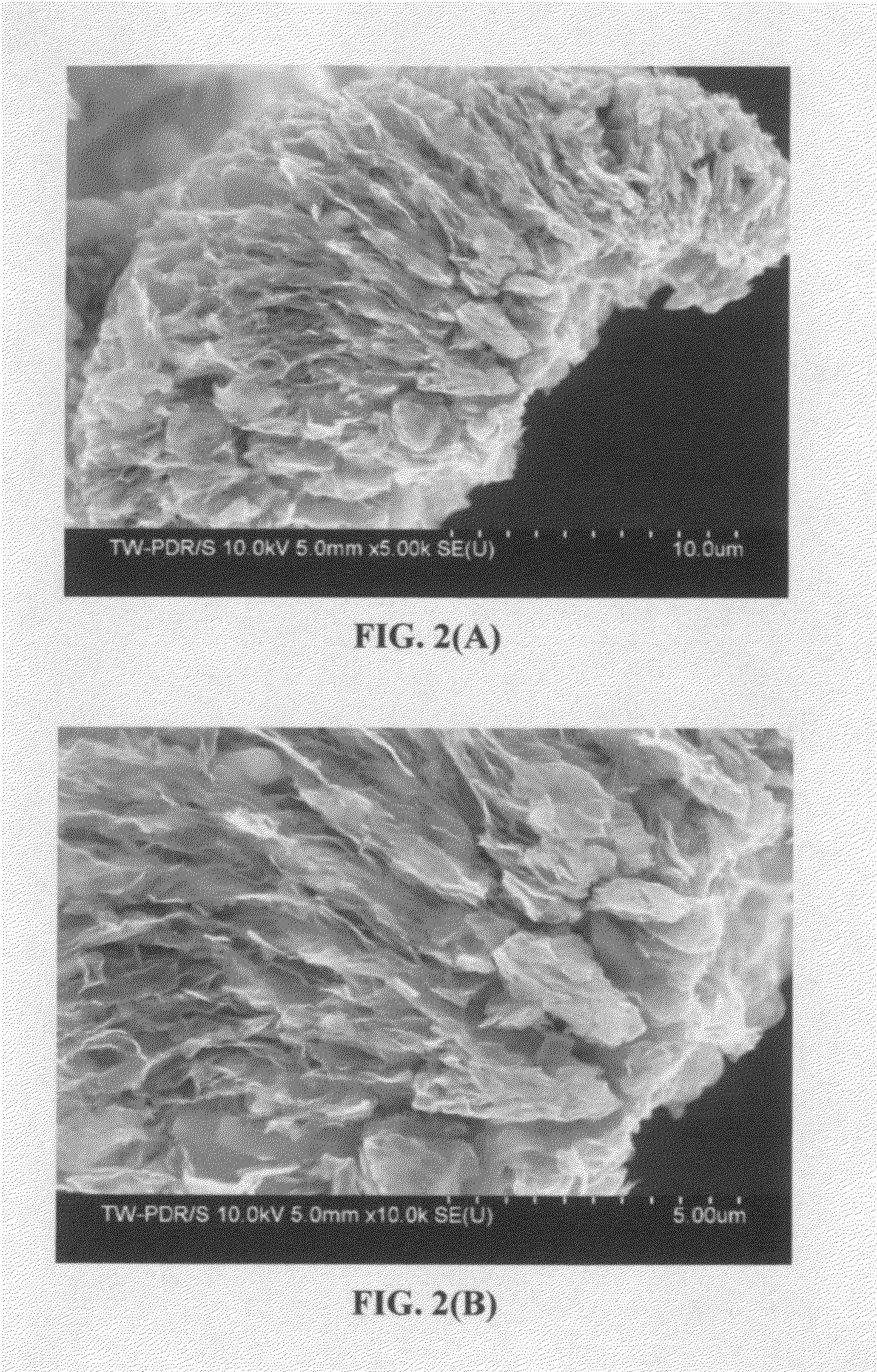

Lithium secondary batteries containing lithium salt-ionic liquid solvent electrolyte

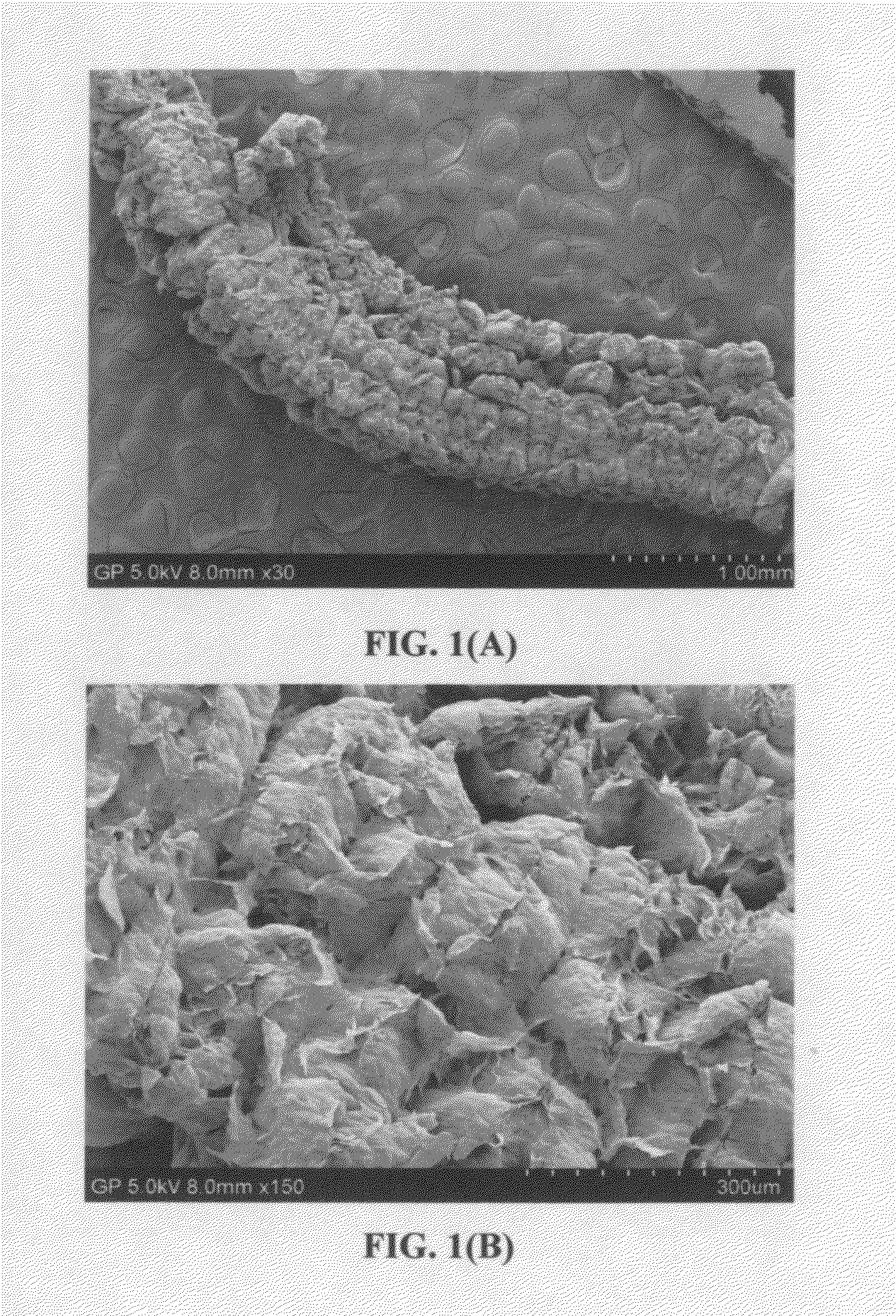

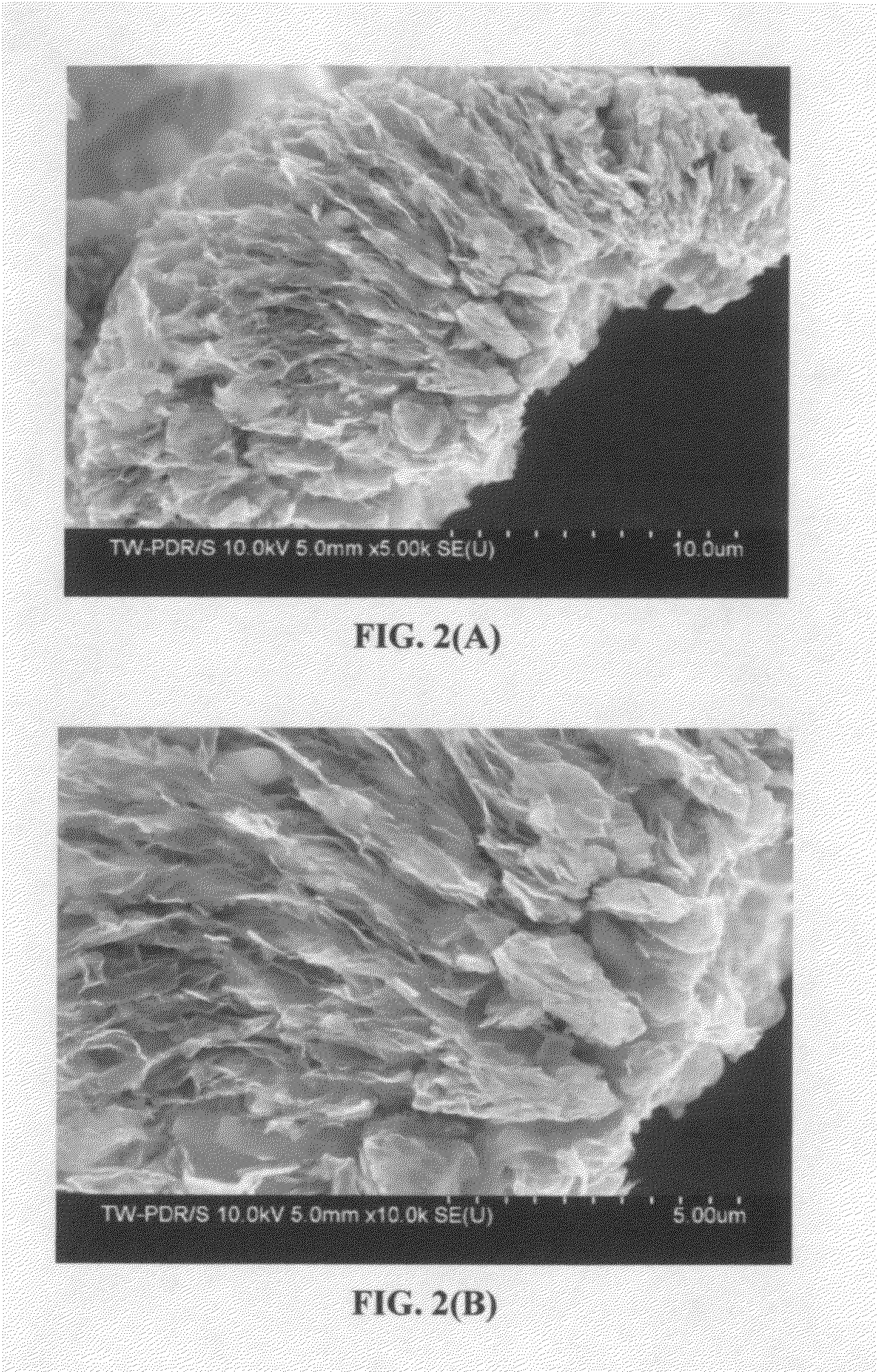

ActiveUS20140342249A1Reduce electrical conductivityLow ionic conductivityFuel and secondary cellsCell electrodesNano structuringLithium metal

A rechargeable lithium metal or lithium-ion cell comprising a cathode having a cathode active material and / or a conductive supporting structure, an anode having an anode active material and / or a conductive supporting nano-structure, a porous separator electronically separating the anode and the cathode, a highly concentrated electrolyte in contact with the cathode active material and the anode active material, wherein the electrolyte contains a lithium salt dissolved in an ionic liquid solvent with a concentration greater than 3 M. The cell exhibits an exceptionally high specific energy, a relatively high power density, a long cycle life, and high safety with no flammability.

Owner:GLOBAL GRAPHENE GRP INC

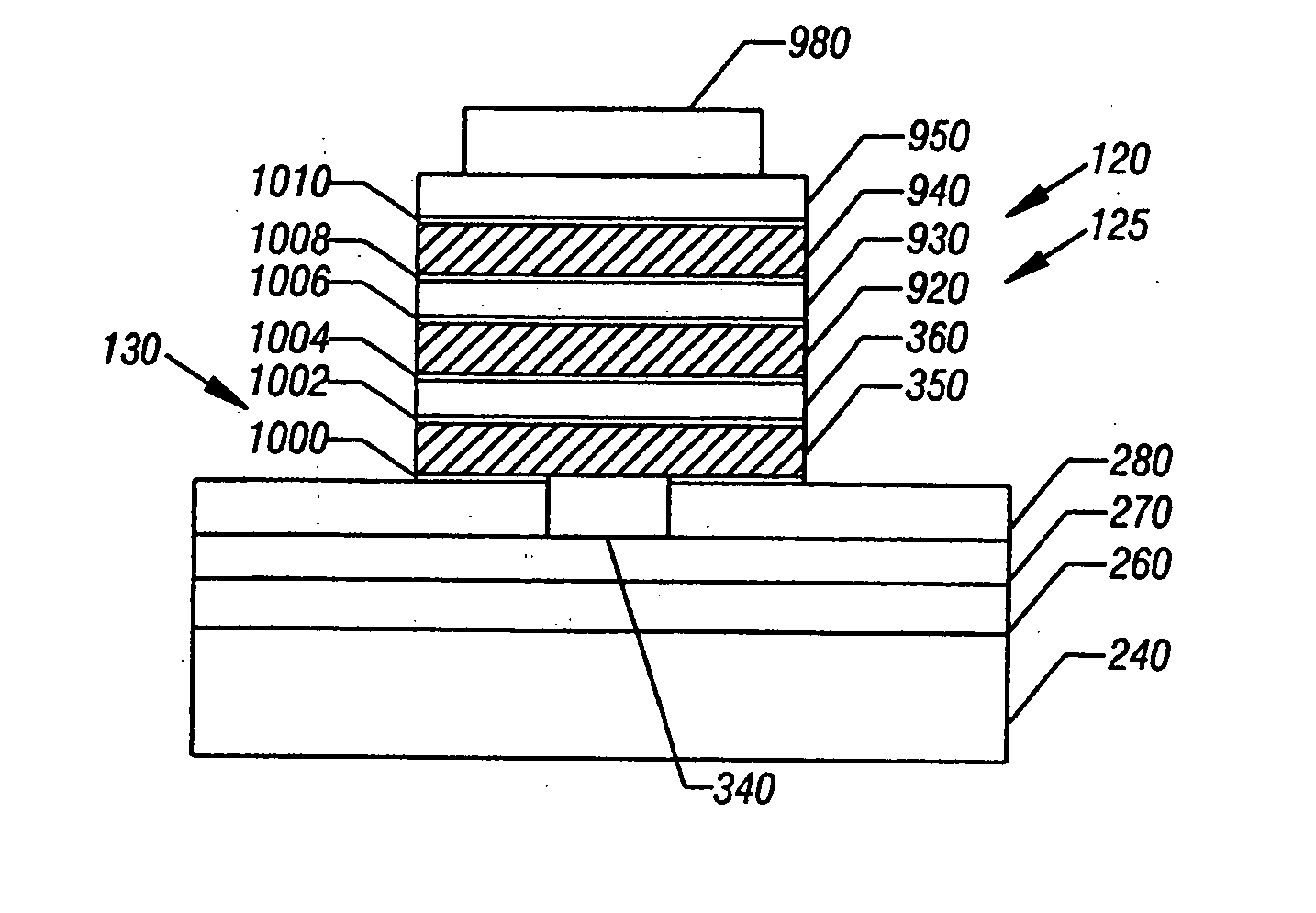

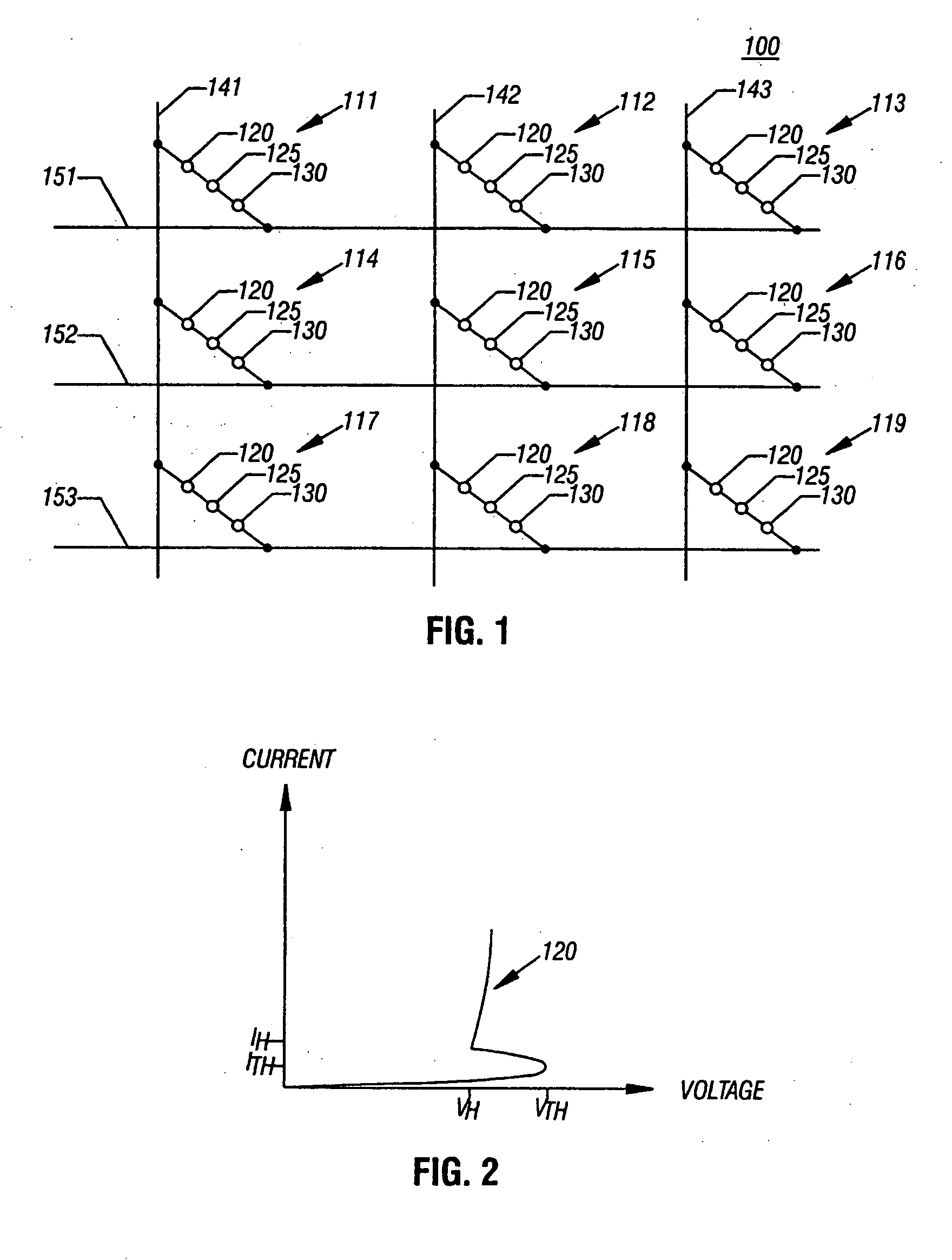

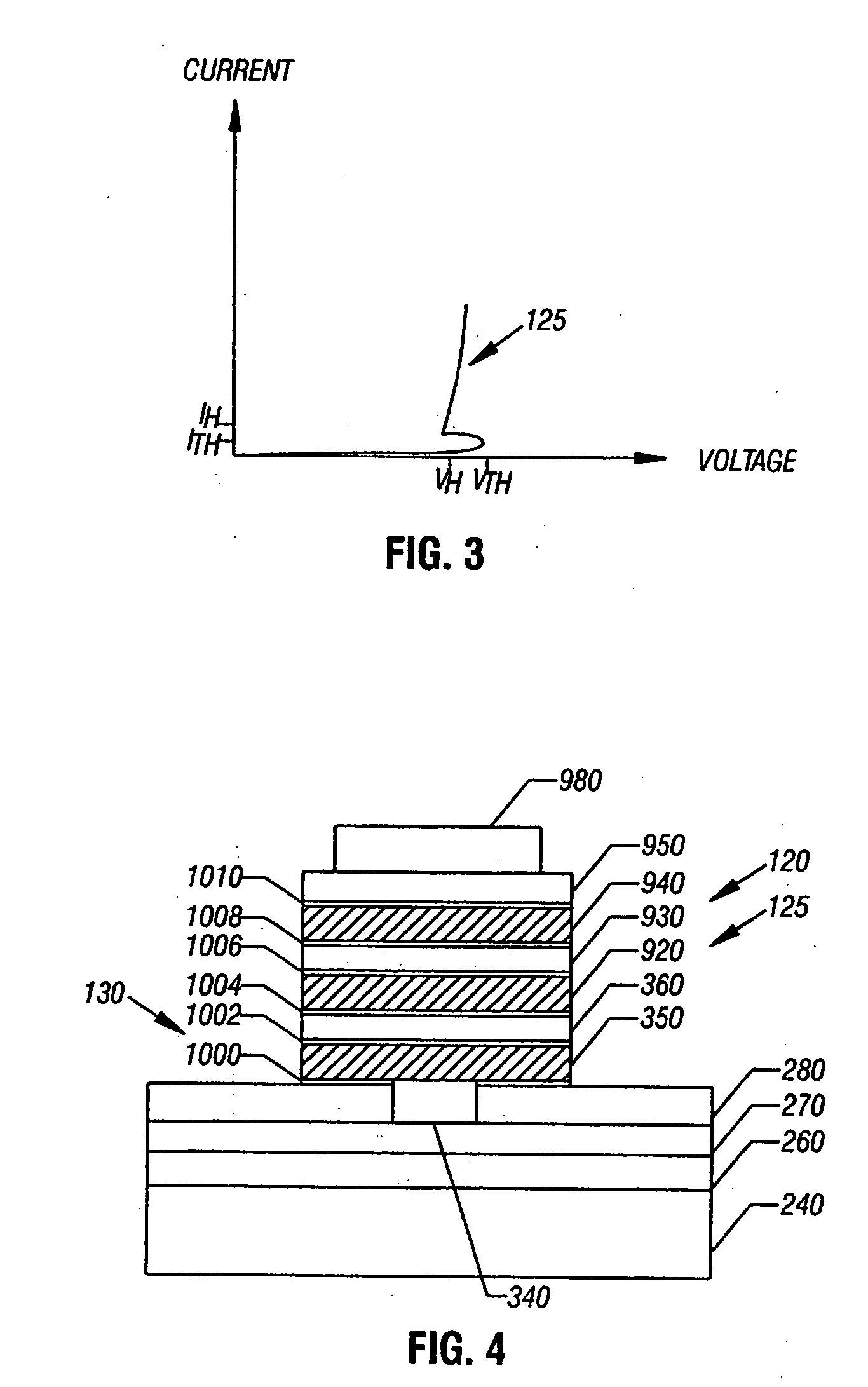

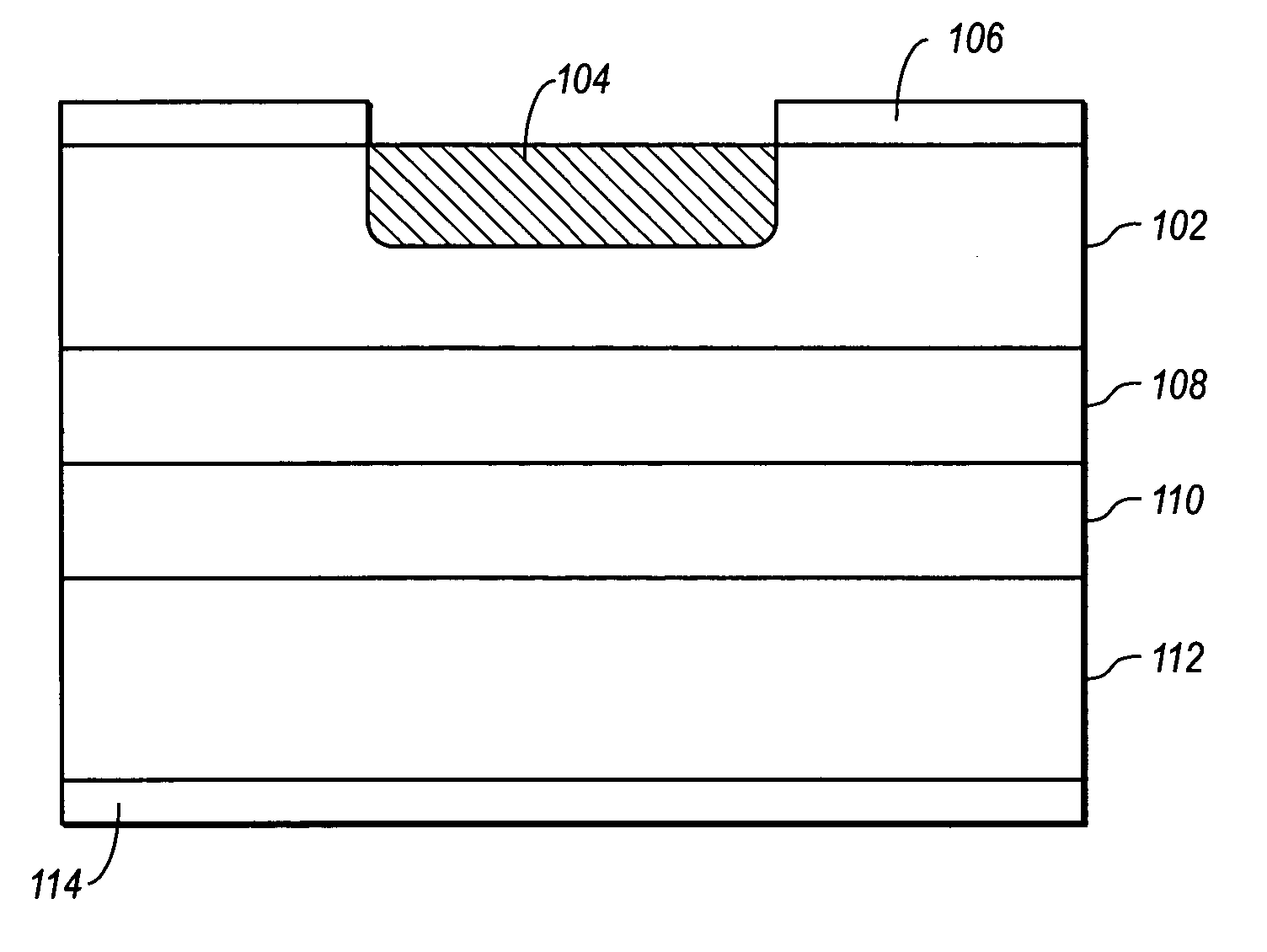

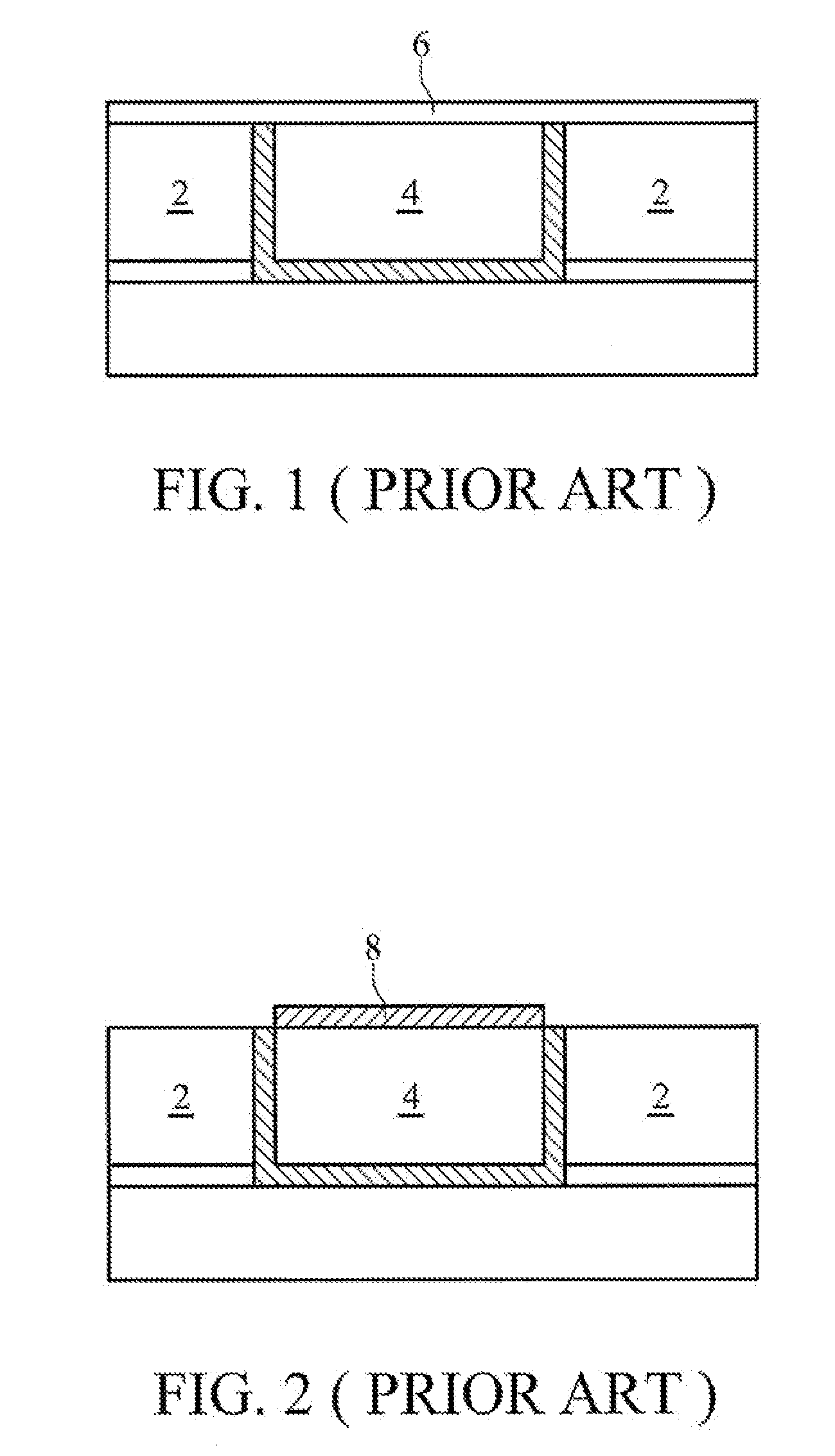

Phase change memory device having an adhesion layer and manufacturing process thereof

InactiveUS20060278900A1Improve adhesionAvoid excessive diffusionSolid-state devicesSemiconductor devicesPhase-change memoryManufacturing technology

A memory includes a phase change memory element having a memory layer of a calcogenide material and a glue layer of an alloy of the form TiaXbNc where X is selected in the group comprising silicon, aluminum, carbon, or boron, and c may be 0. The nitrogen and silicon are adapted to reduce the diffusion of titanium toward the chalcogenide layer.

Owner:STMICROELECTRONICS SRL

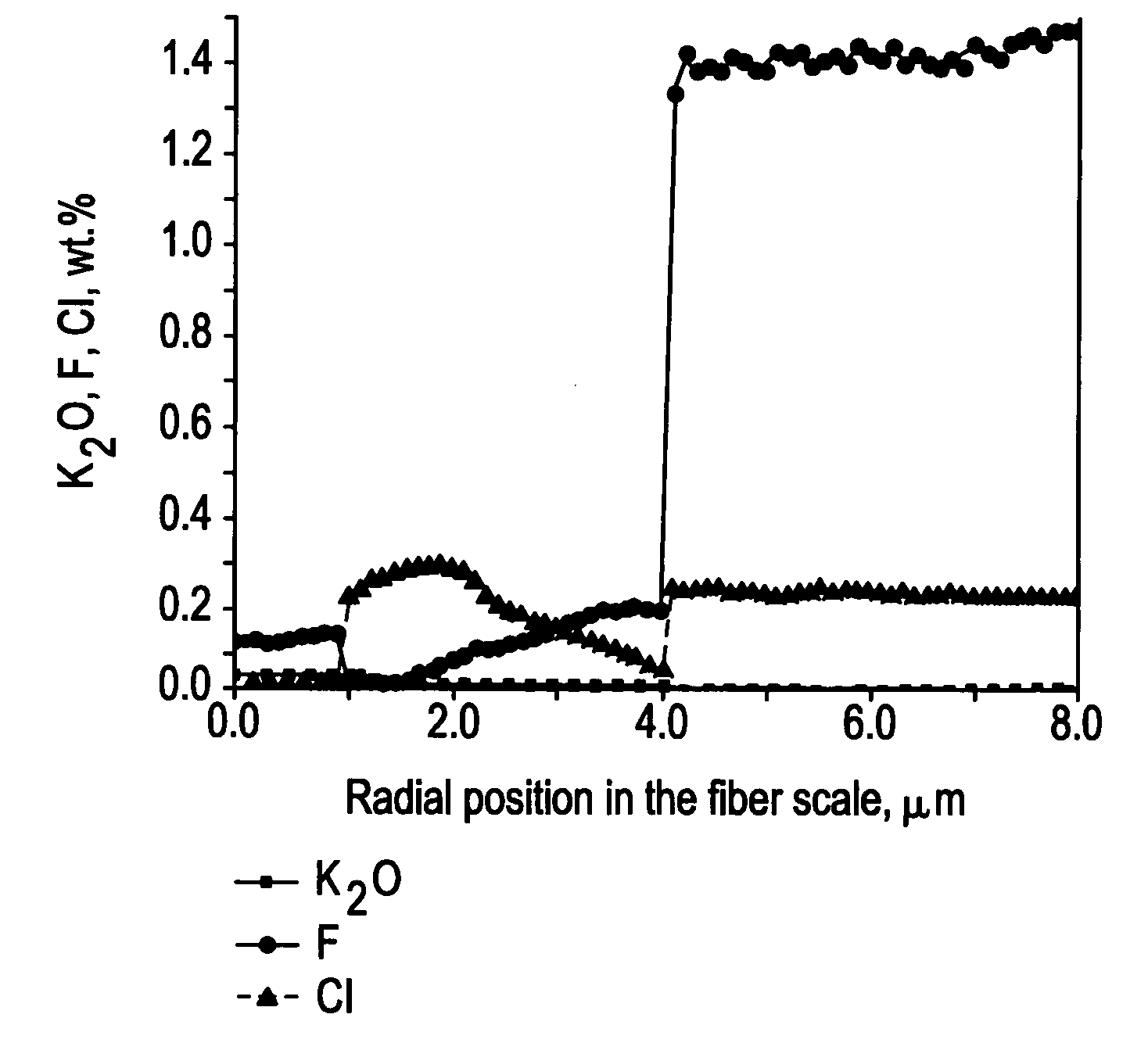

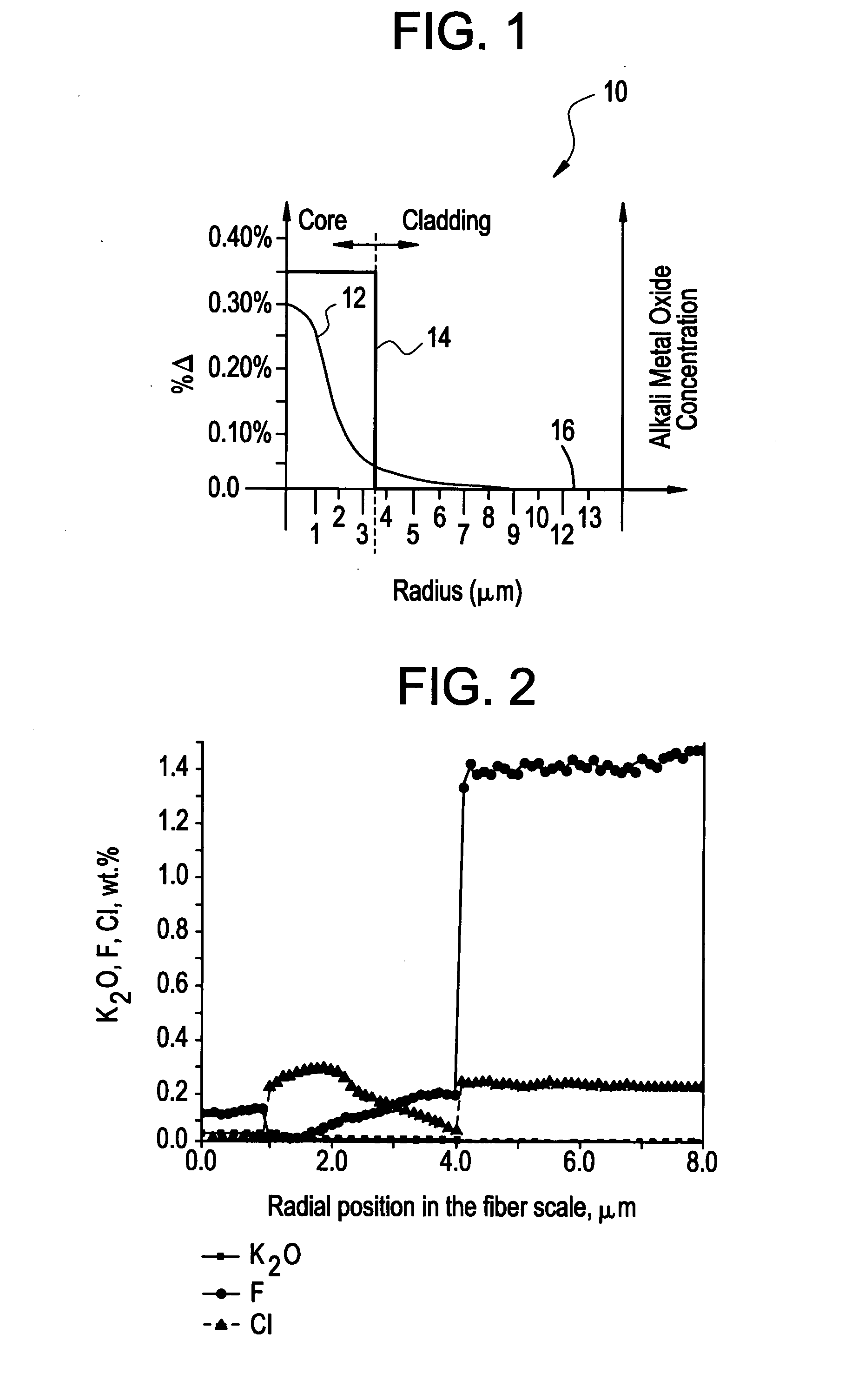

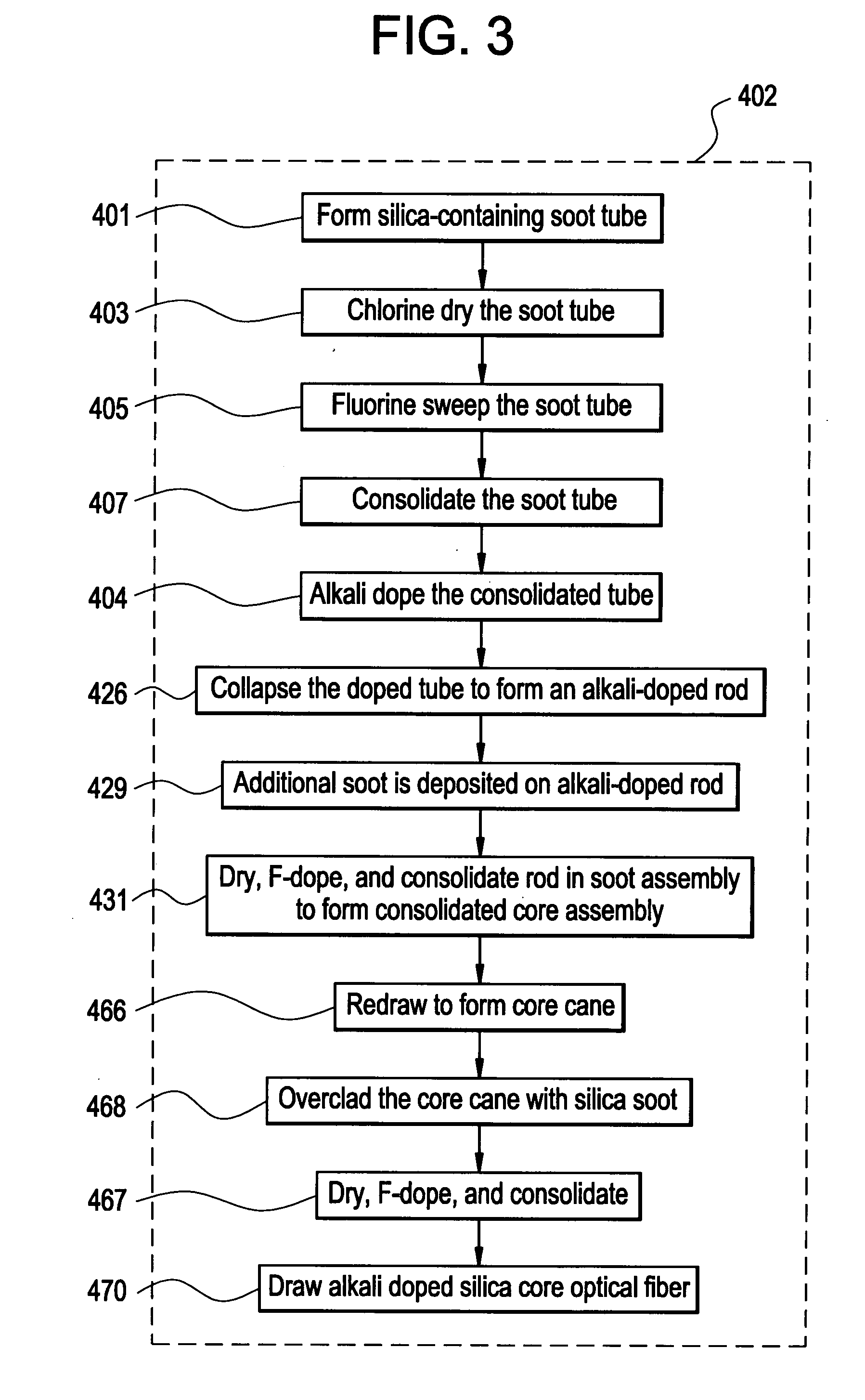

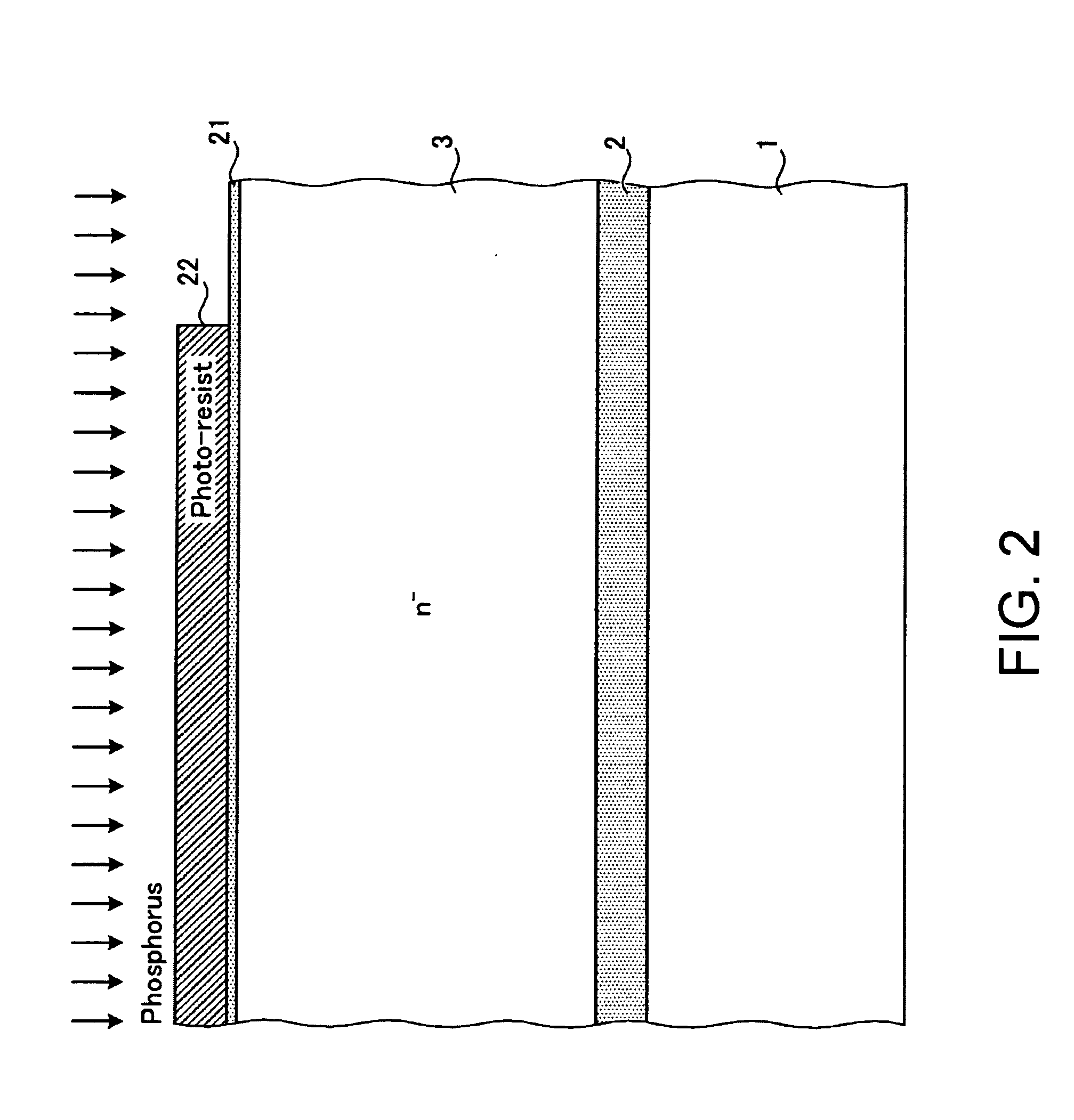

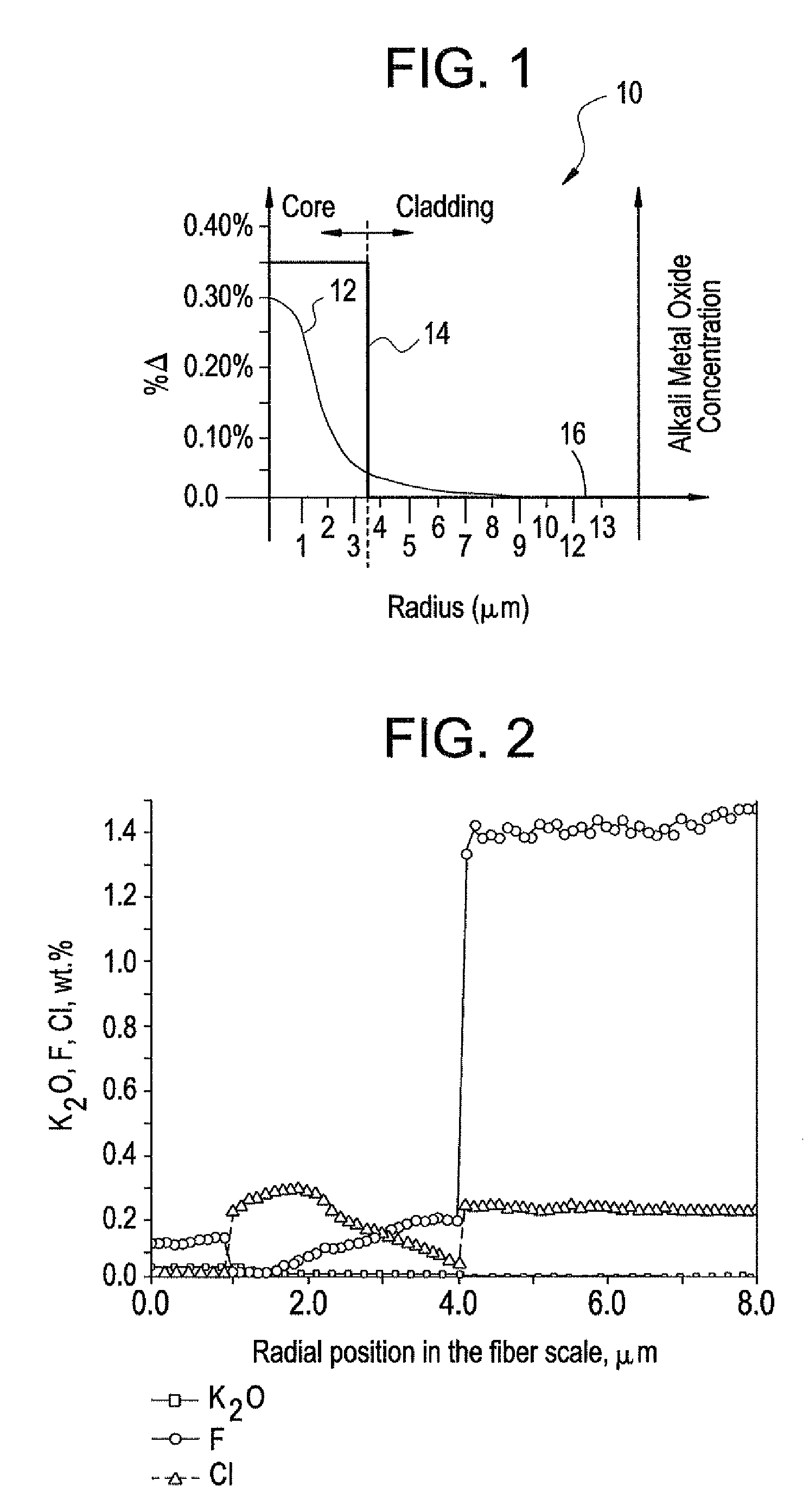

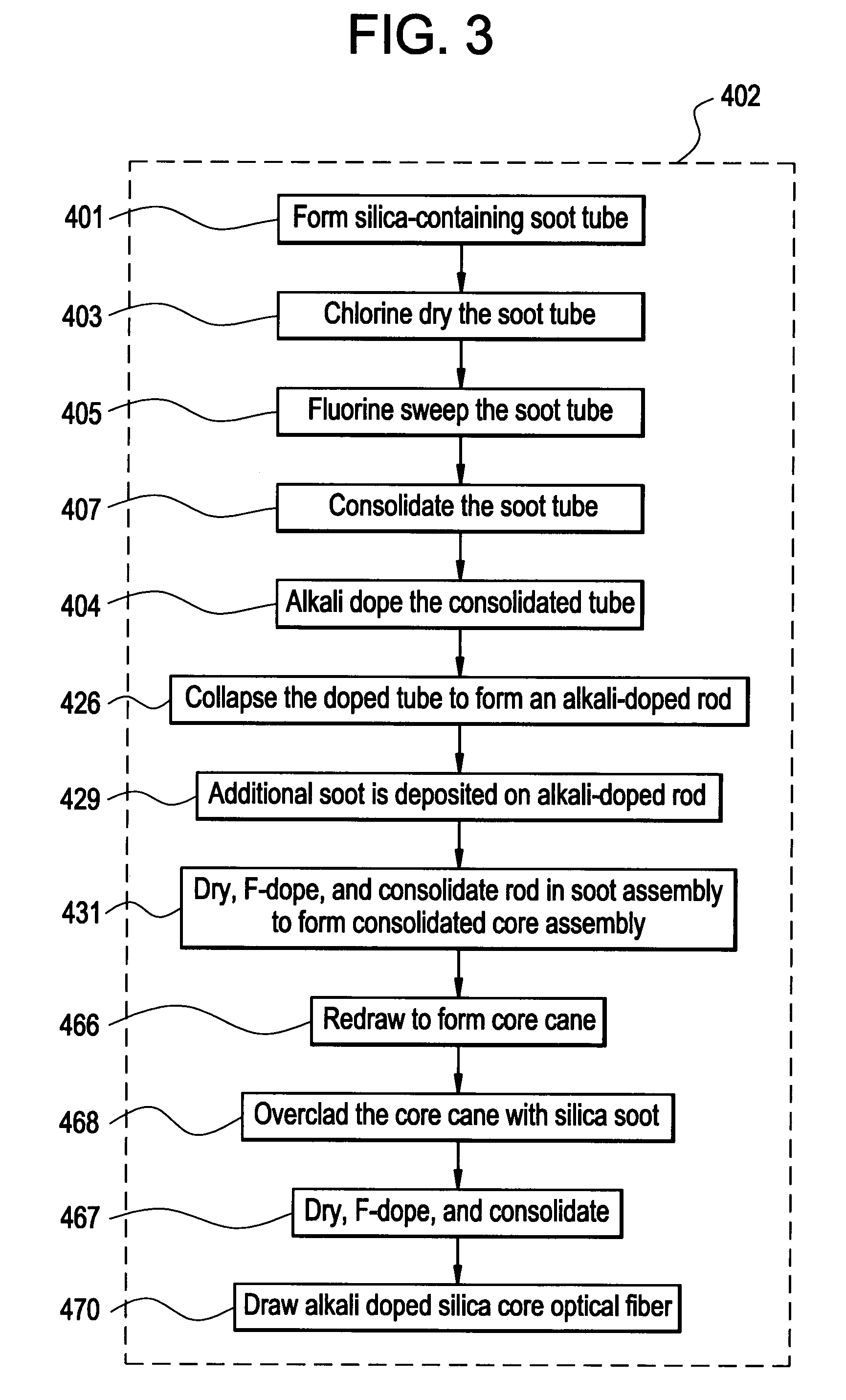

Optical fiber containing alkali metal oxide

ActiveUS20070297735A1Reduce lossReduce concentrationGlass making apparatusOptical fibre with multilayer core/claddingDopantAlkali metal oxide

Disclosed is an optical fiber having a silica-based core comprising an alkali metal oxide selected from the group consisting of K2O, Na2O, LiO2, Rb2O, Cs2O and mixtures thereof in an average concentration in said core between about 50 and 500 ppm by weight, said core further comprising chlorine and fluorine, wherein the average concentration of fluorine in said core is greater than the average concentration of alkali metal oxide in said core and the average concentration of chlorine in said core is greater than the average concentration of alkali metal oxide in said core; and a silica-based cladding surrounding and directly adjacent the core. By appropriately selecting the concentration of alkali metal oxide dopant in the core and the cladding, a low loss optical fiber may be obtained.

Owner:CORNING INC

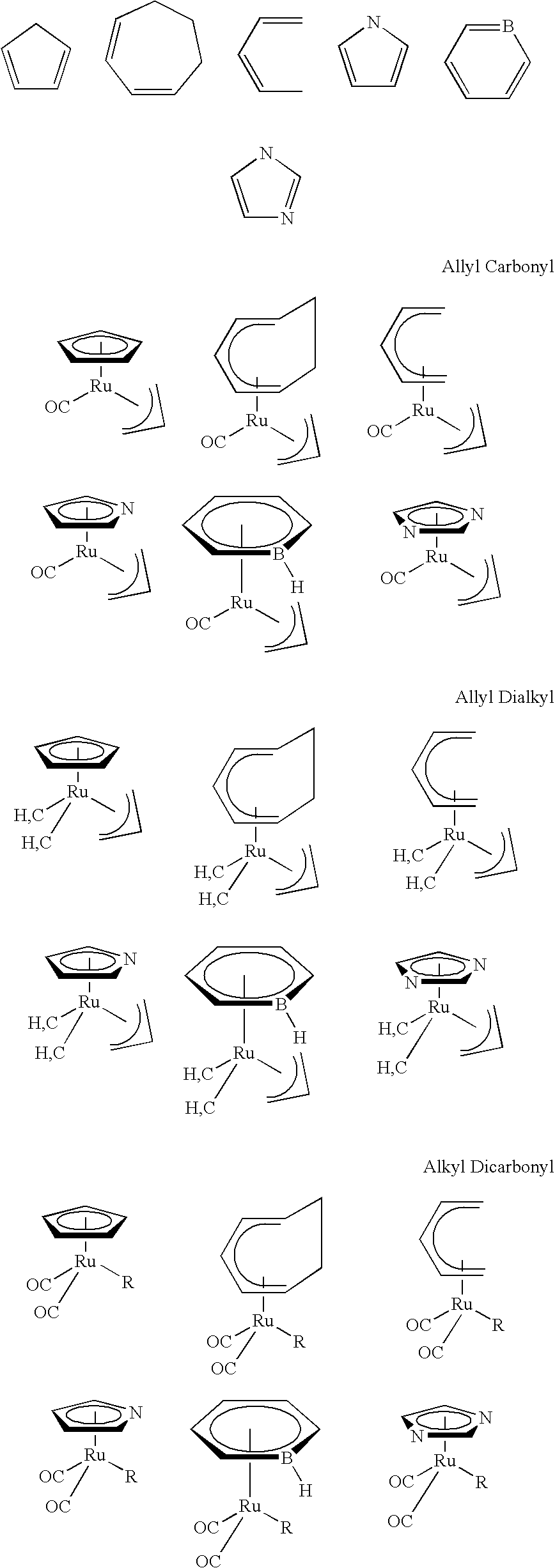

Deposition precursors for semiconductor applications

InactiveUS20080248648A1Improve responseHigh crystallinityCobalt organic compoundsSemiconductor/solid-state device manufacturingElectron donorGas phase

This invention relates to organometallic compounds comprising at least one metal or metalloid and at least one substituted anionic 6 electron donor ligand having sufficient substitution (i) to impart decreased carbon concentration in a film or coating produced by decomposing said compound, (ii) to impart decreased resistivity in a film or coating produced by decomposing said compound, or (iii) to impart increased crystallinity in a film or coating produced by decomposing said compound. The organometallic compounds are useful in semiconductor applications as chemical vapor or atomic layer deposition precursors for film depositions.

Owner:PRAXAIR TECH INC

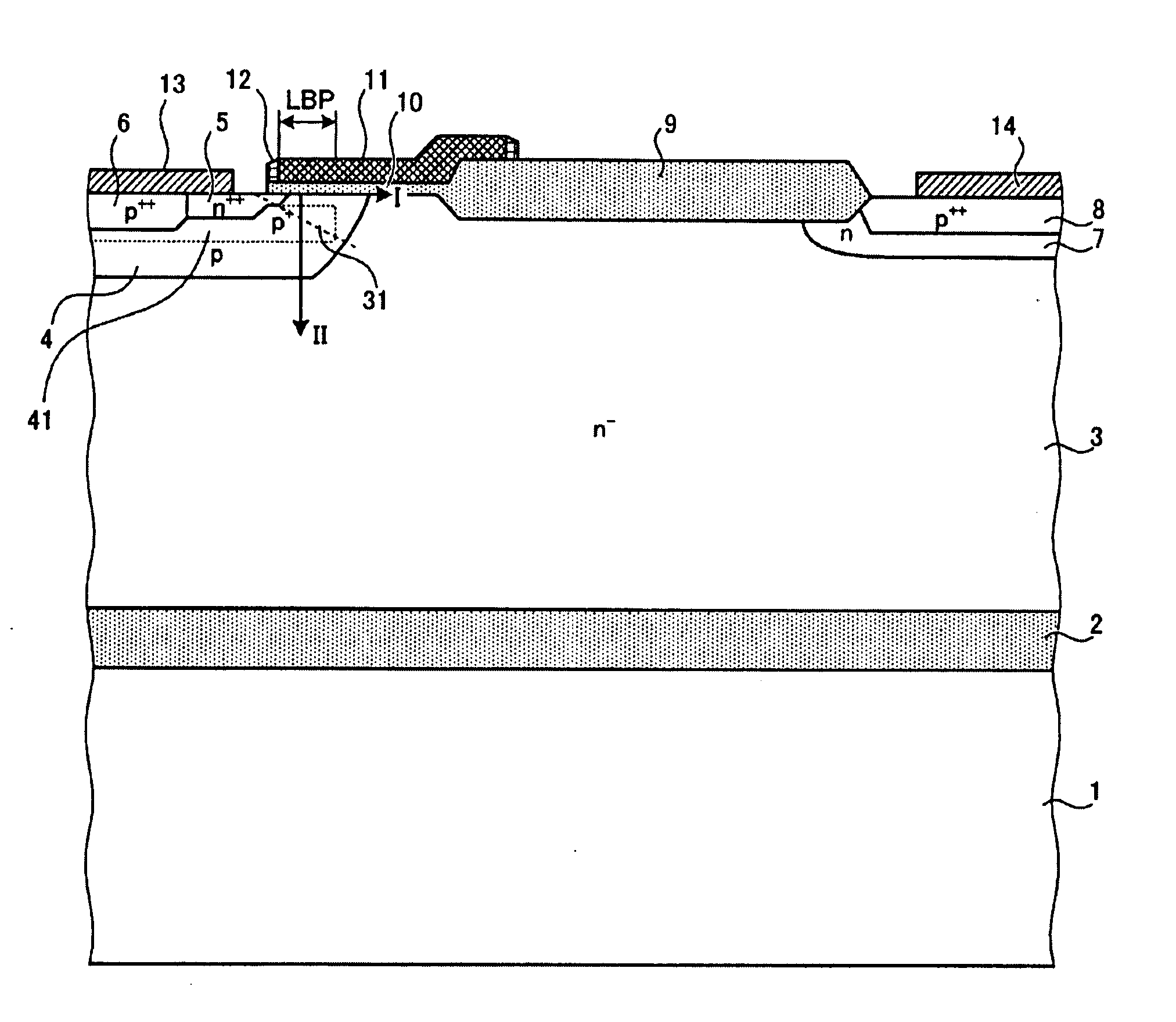

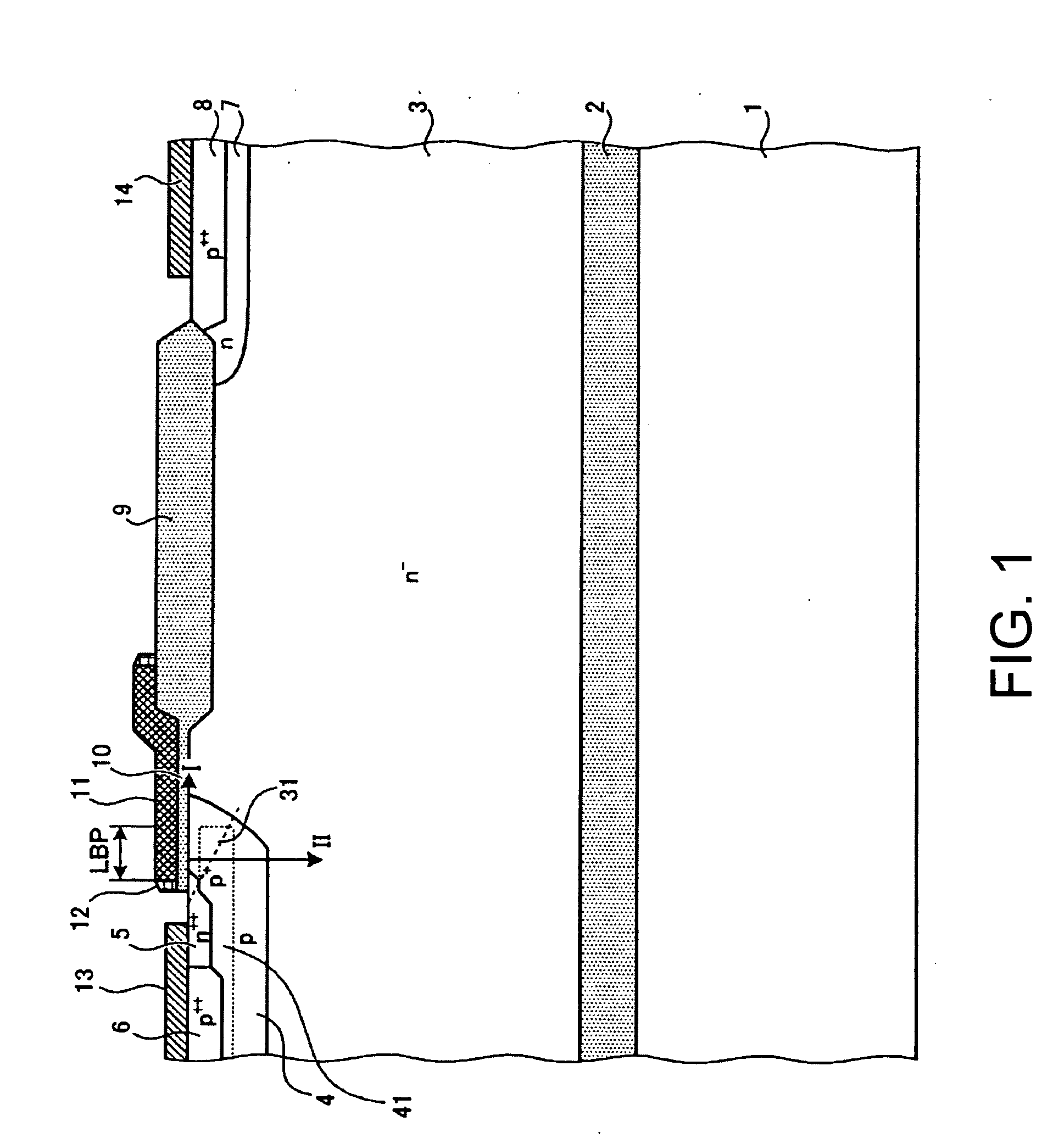

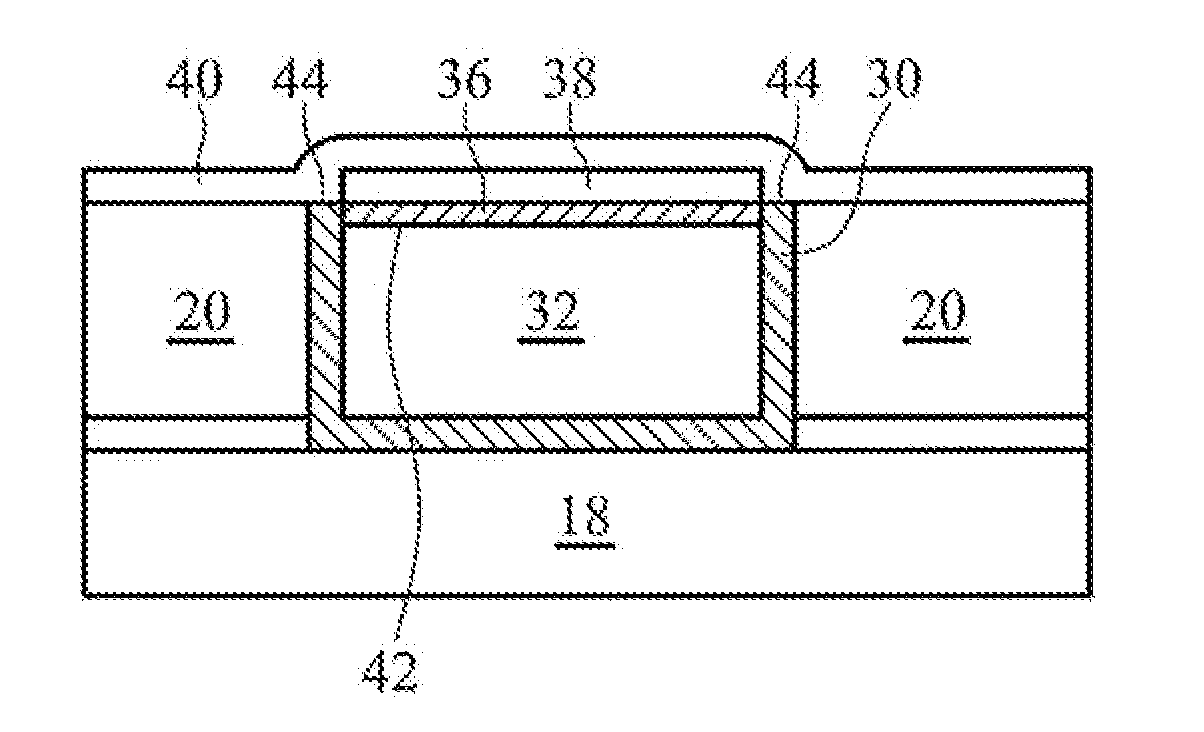

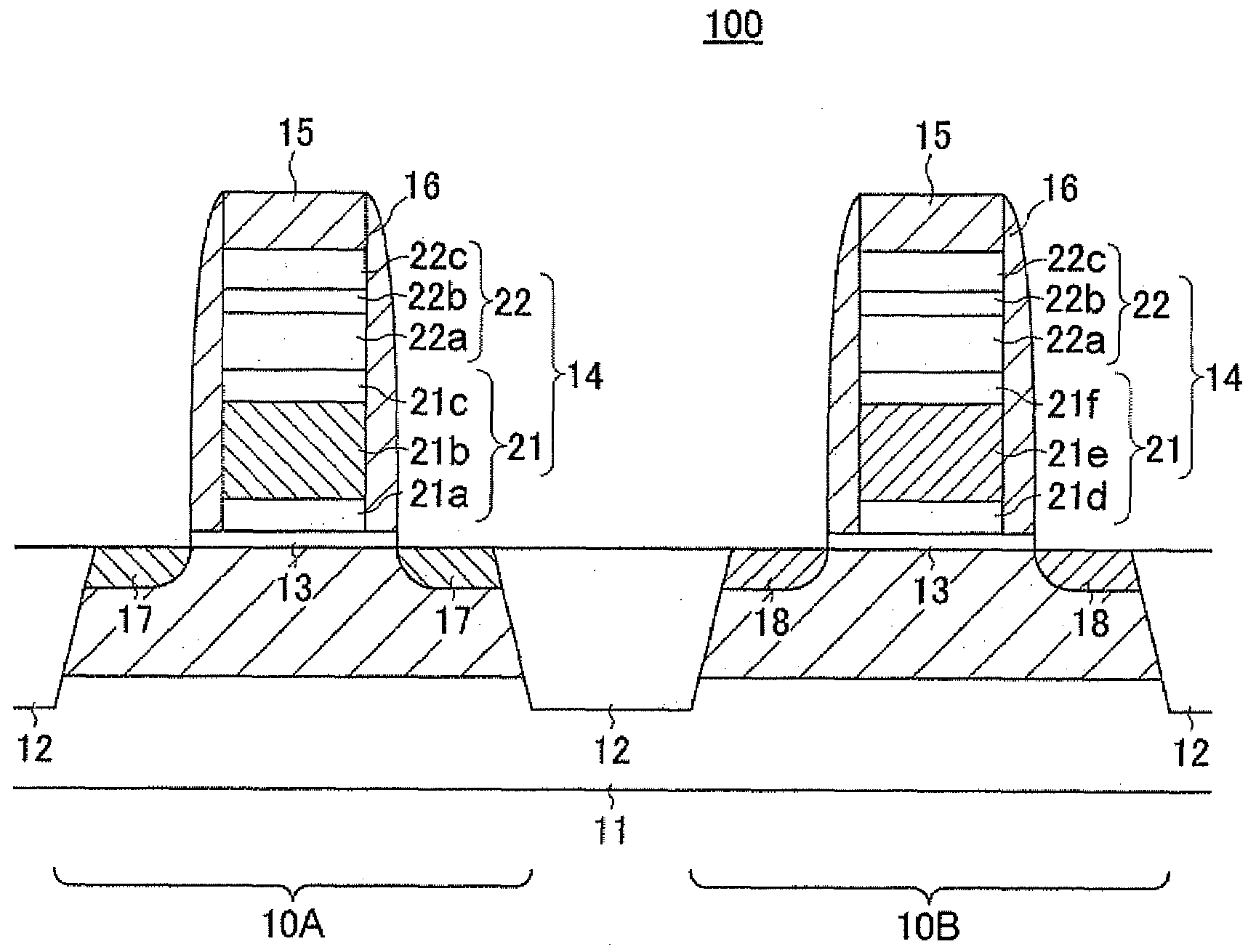

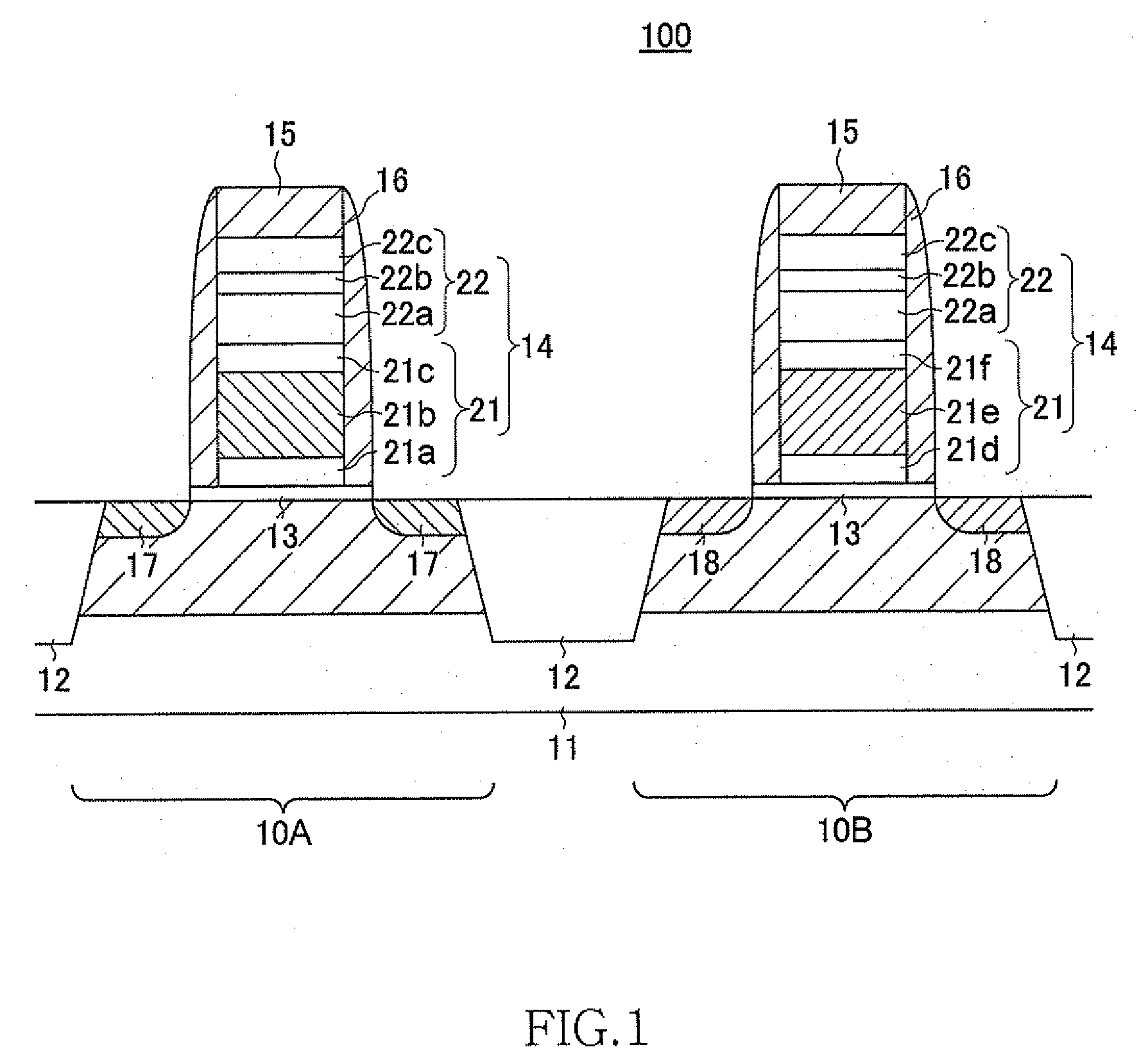

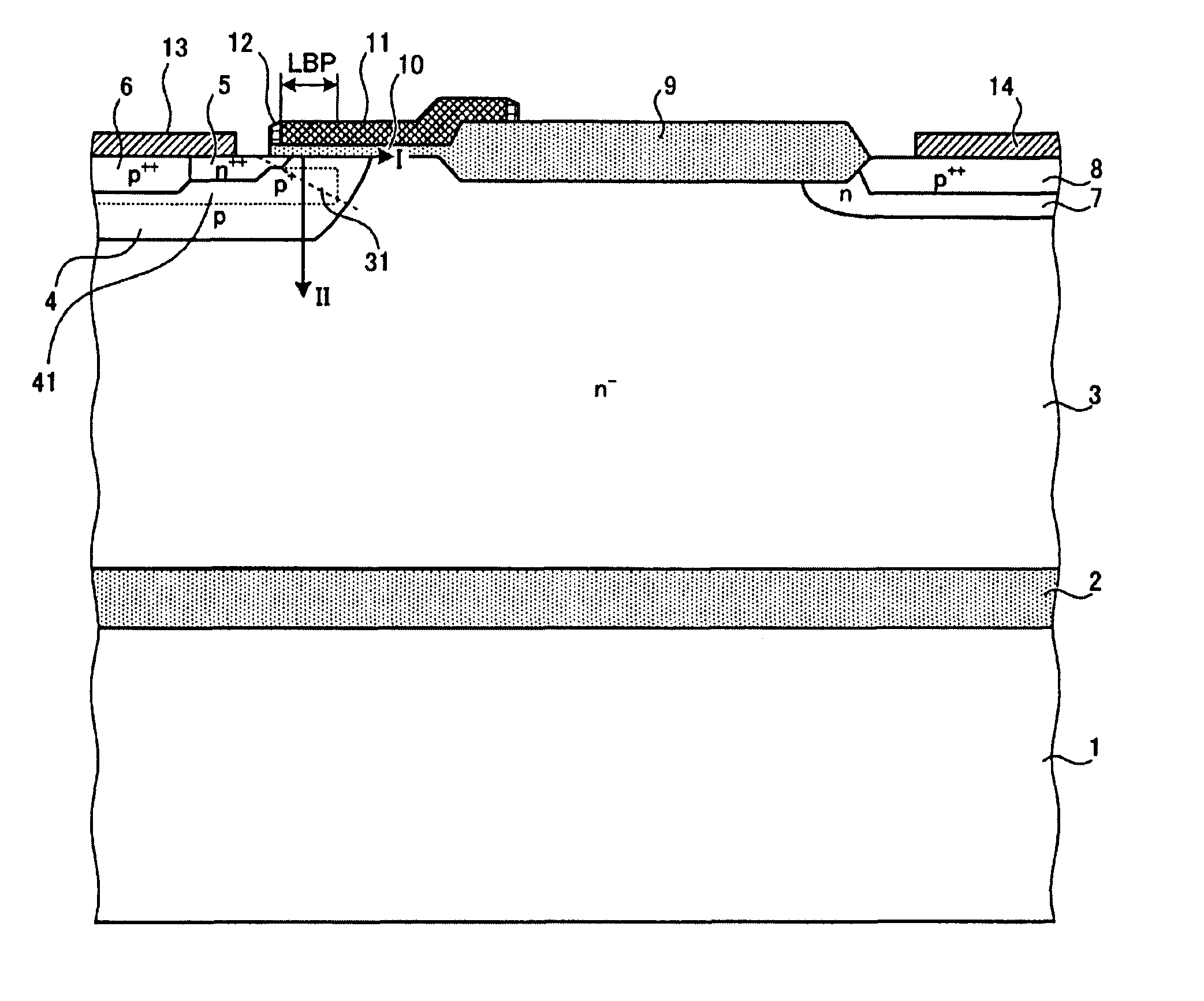

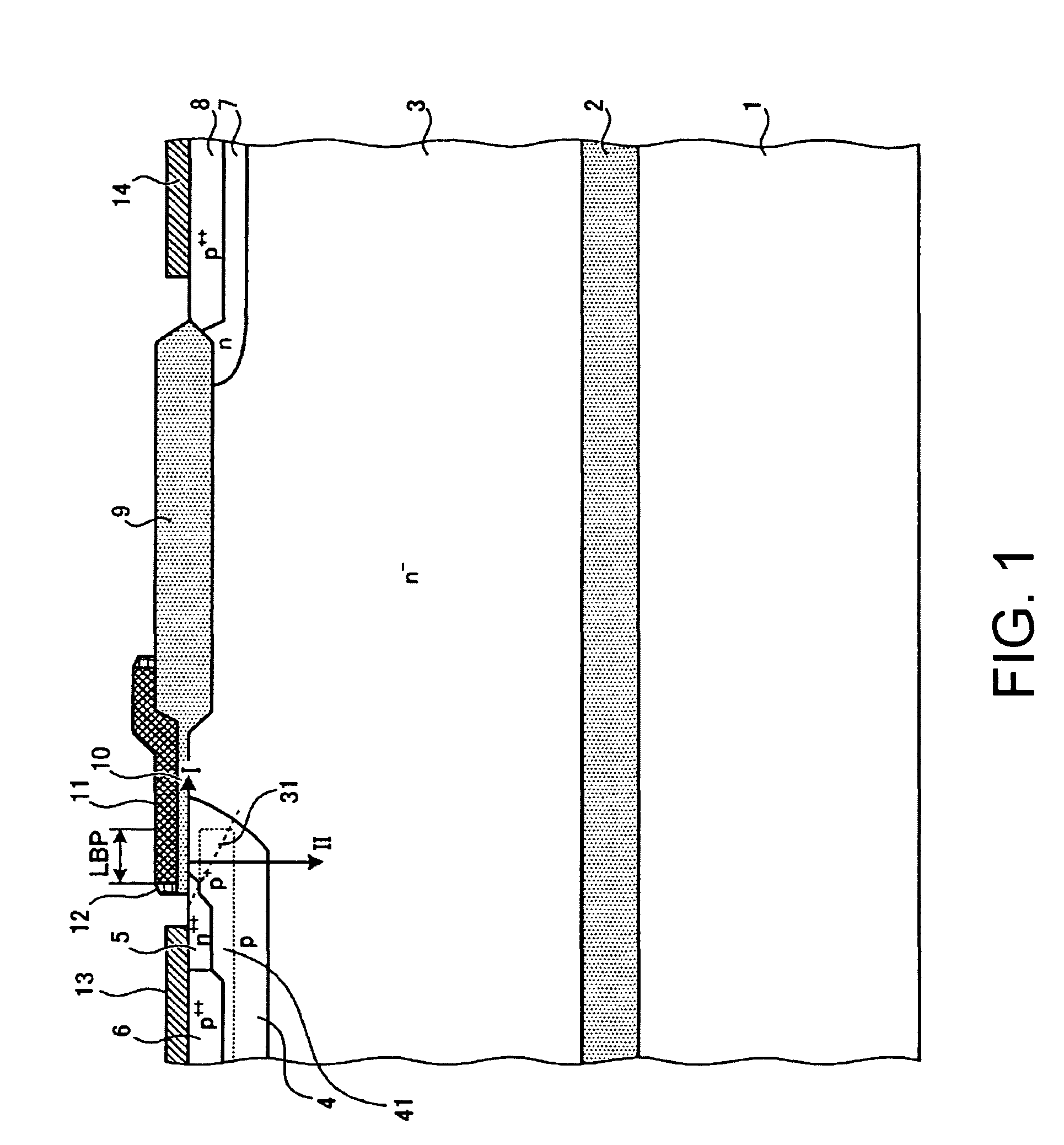

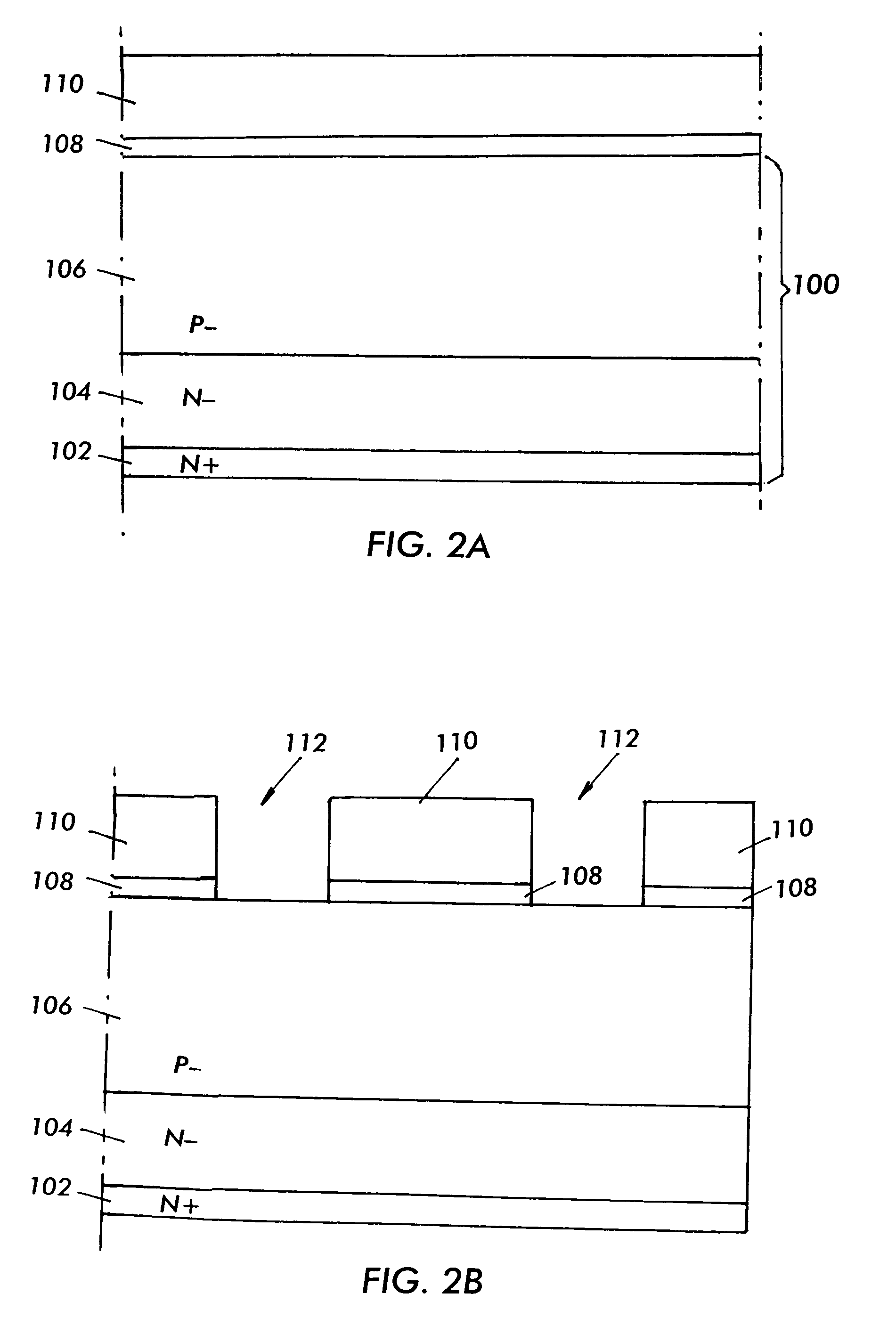

Semiconductor device and manufacturing method thereof

InactiveUS20090194785A1Avoid excessive diffusionSuppress a punchthrough occurring in the channelTransistorSemiconductor/solid-state device manufacturingBody regionSemiconductor

A p-type body region and an n-type buffer region are formed on an n− drift region. An n++ emitter region and a p++ contact region are formed on the p-type body region in contact with each other. A p++ collector region is formed on the n-type buffer region. An insulating film is formed on the n− drift region, and a gate insulating film is formed on the n++ emitter region, the p-type body region, and the n drift region. A gate electrode is formed on the insulating film and the gate insulating film. A p+ low-resistivity region is formed in the p-type body region and surrounding the interface between the n++ emitter region and between the p-type body region and the p++ contact region. The p-type body region has two local maxima of an impurity concentration profile at the interface between the body region and the gate insulating film.

Owner:FUJI ELECTRIC CO LTD

Optical fiber containing alkali metal oxide

ActiveUS7536076B2Reduce lossReduce concentrationGlass making apparatusOptical fibre with multilayer core/claddingDopantAlkali metal oxide

Disclosed is an optical fiber having a silica-based core comprising an alkali metal oxide selected from the group consisting of K2O, Na2O, LiO2, Rb2O, Cs2O and mixtures thereof in an average concentration in said core between about 50 and 500 ppm by weight, said core further comprising chlorine and fluorine, wherein the average concentration of fluorine in said core is greater than the average concentration of alkali metal oxide in said core and the average concentration of chlorine in said core is greater than the average concentration of alkali metal oxide in said core; and a silica-based cladding surrounding and directly adjacent the core. By appropriately selecting the concentration of alkali metal oxide dopant in the core and the cladding, a low loss optical fiber may be obtained.

Owner:CORNING INC

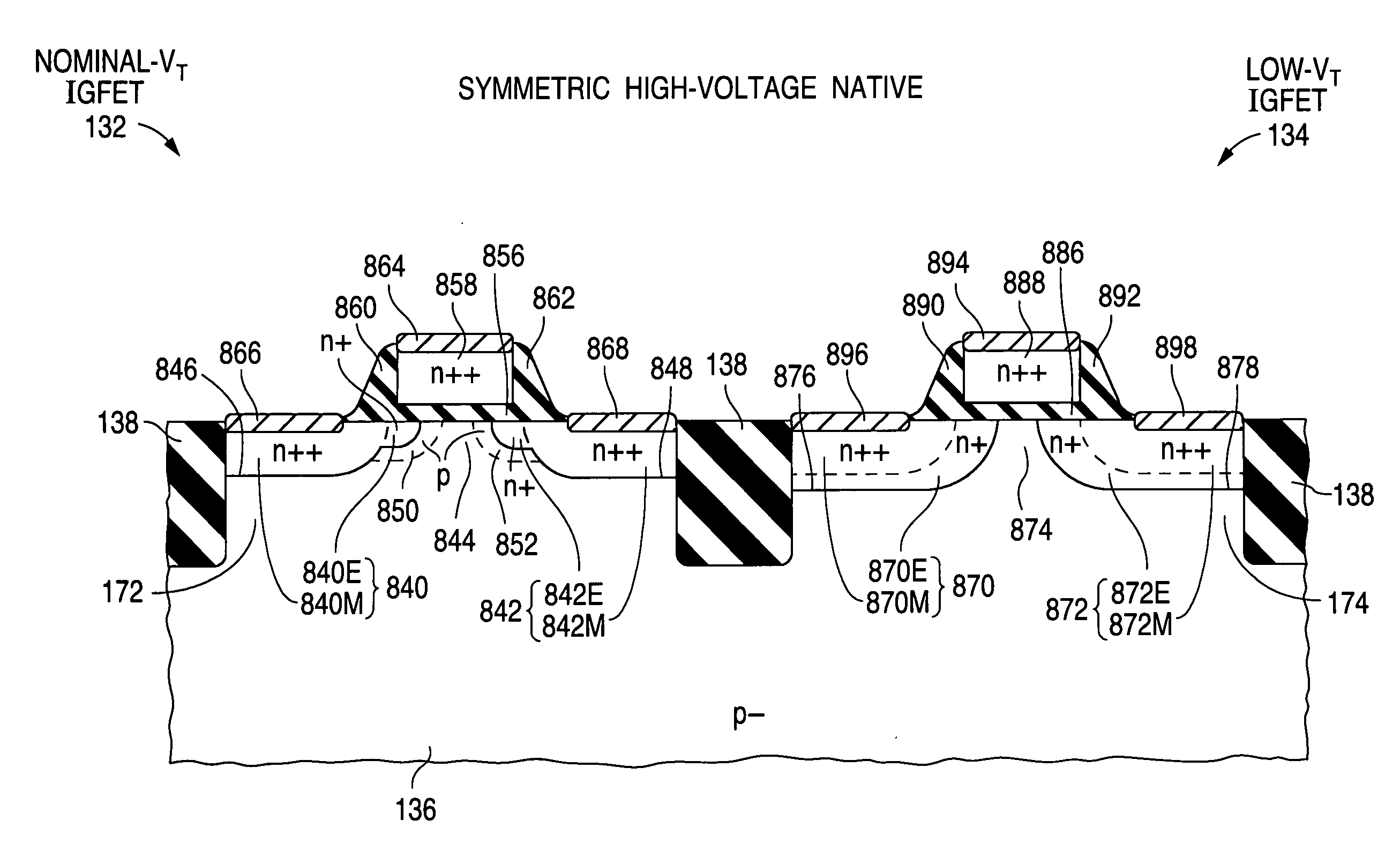

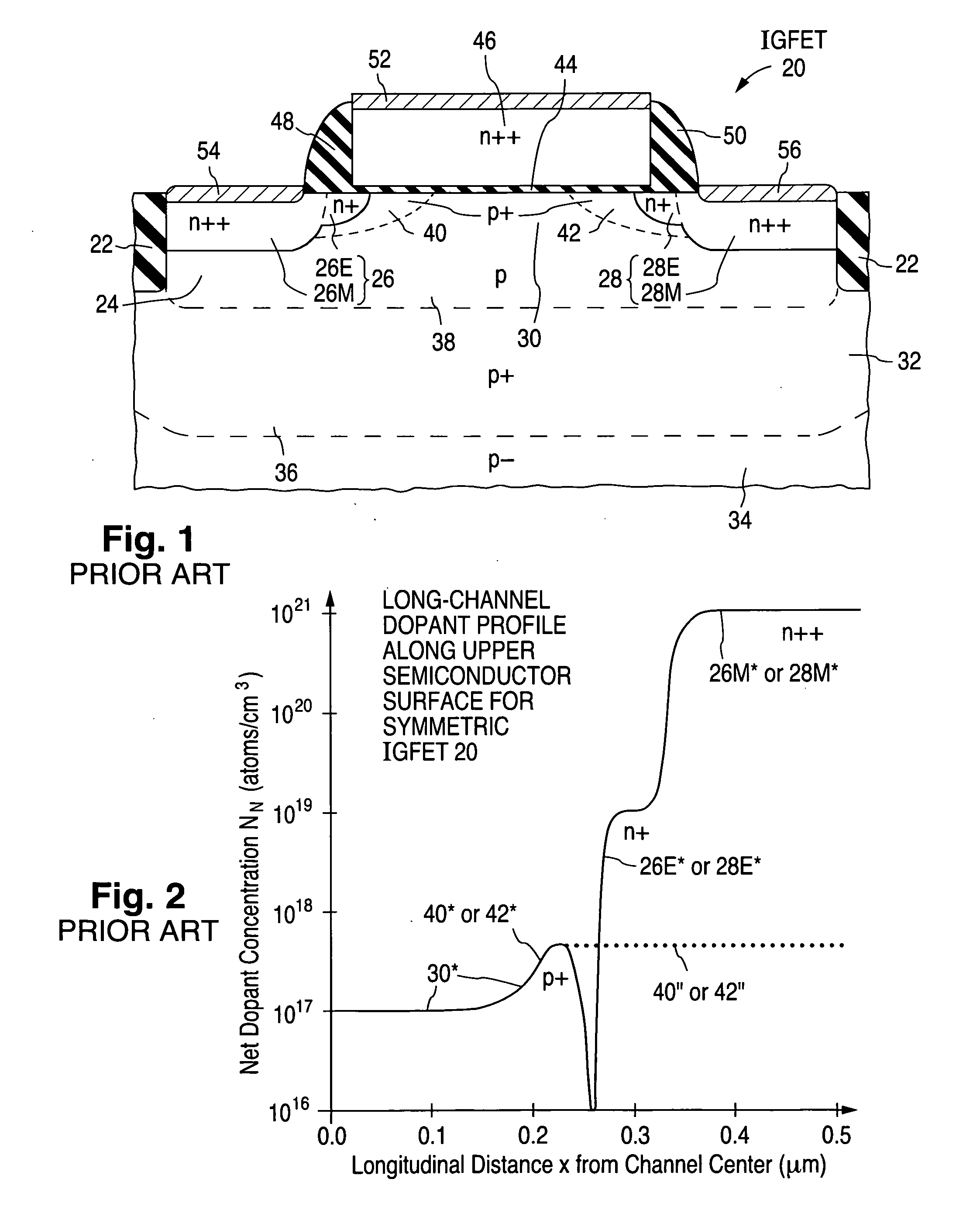

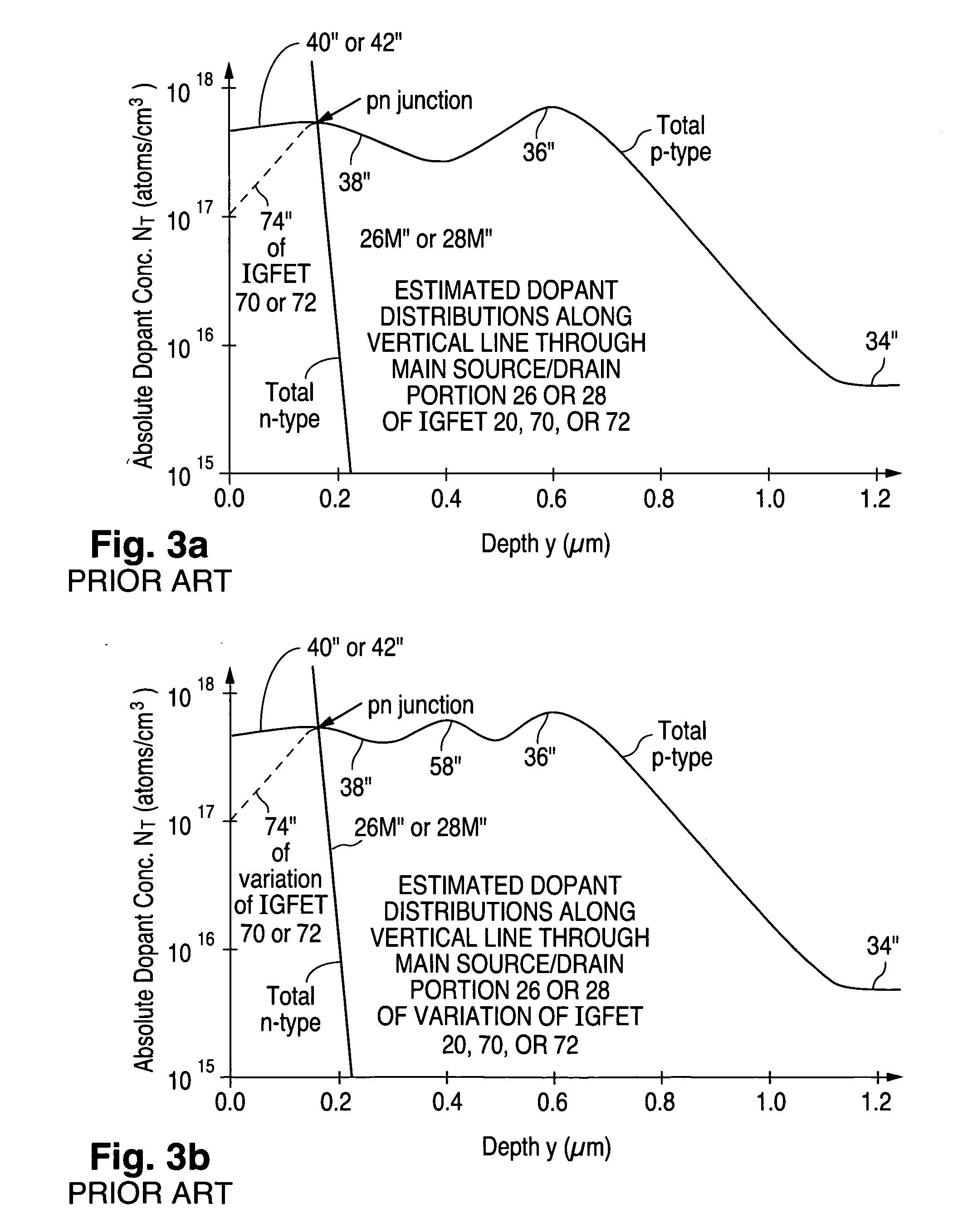

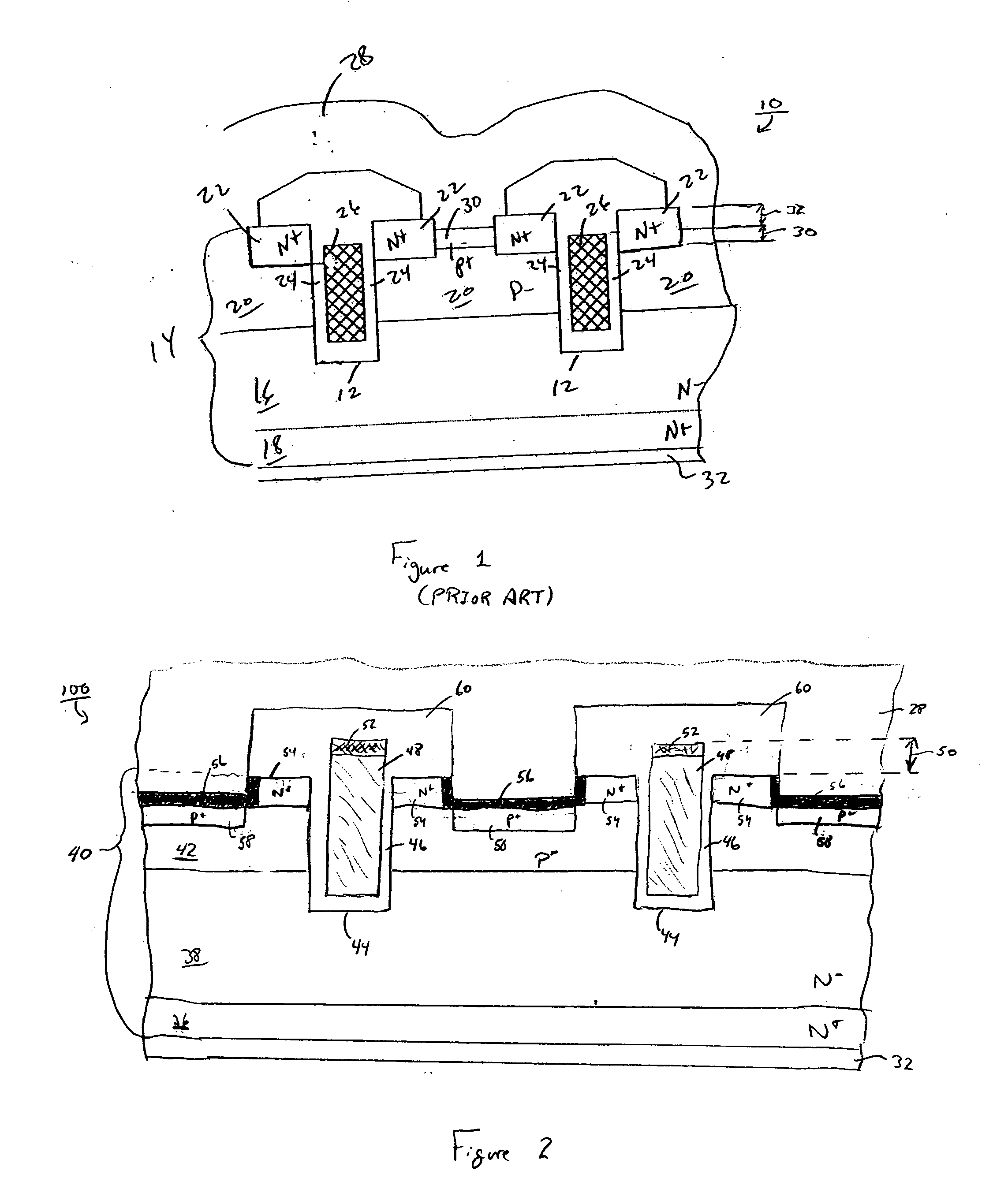

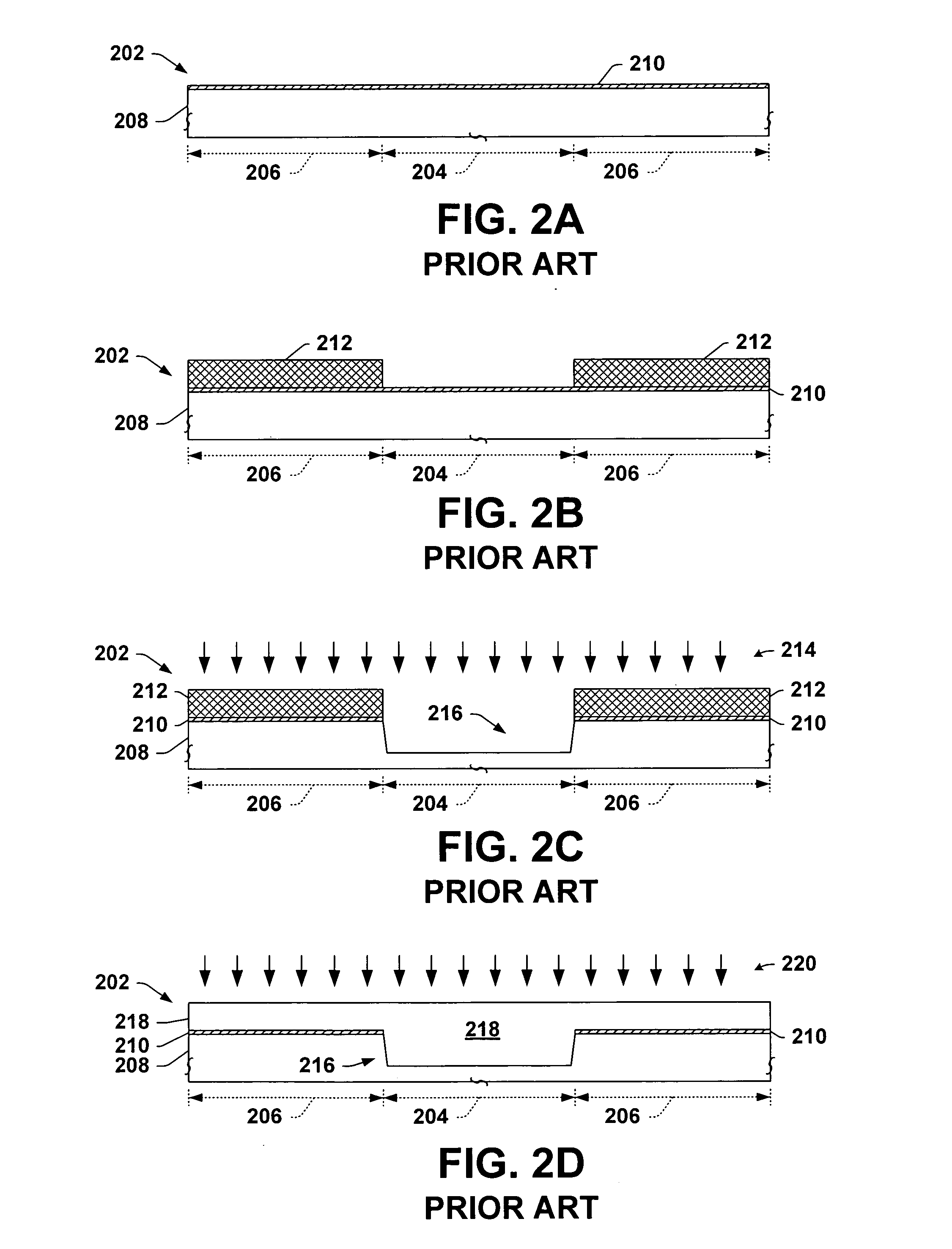

Configuration and fabrication of semiconductor structure in which source and drain extensions of field-effect transistor are defined with different dopants

ActiveUS20100244150A1Enhanced interactionLess variabilityTransistorSolid-state devicesDopantGate dielectric

An insulated-gate field-effect transistor (100) provided along an upper surface of a semiconductor body contains a pair of source / drain zones (240 and 242) laterally separated by a channel zone (244). A gate electrode (262) overlies a gate dielectric layer (260) above the channel zone. Each source / drain zone includes a main portion (240M or 242M) and a more lightly doped lateral extension (240E or 242E) laterally continuous with the main portion and extending laterally under the gate electrode. The lateral extensions, which terminate the channel zone along the upper semiconductor surface, are respectively largely defined by a pair of semiconductor dopants of different atomic weights. With the transistor being an asymmetric device, the source / drain zones constitute a source and a drain. The lateral extension of the source is then more lightly doped than, and defined with dopant of higher atomic weight, than the lateral extension of the drain.

Owner:NAT SEMICON CORP

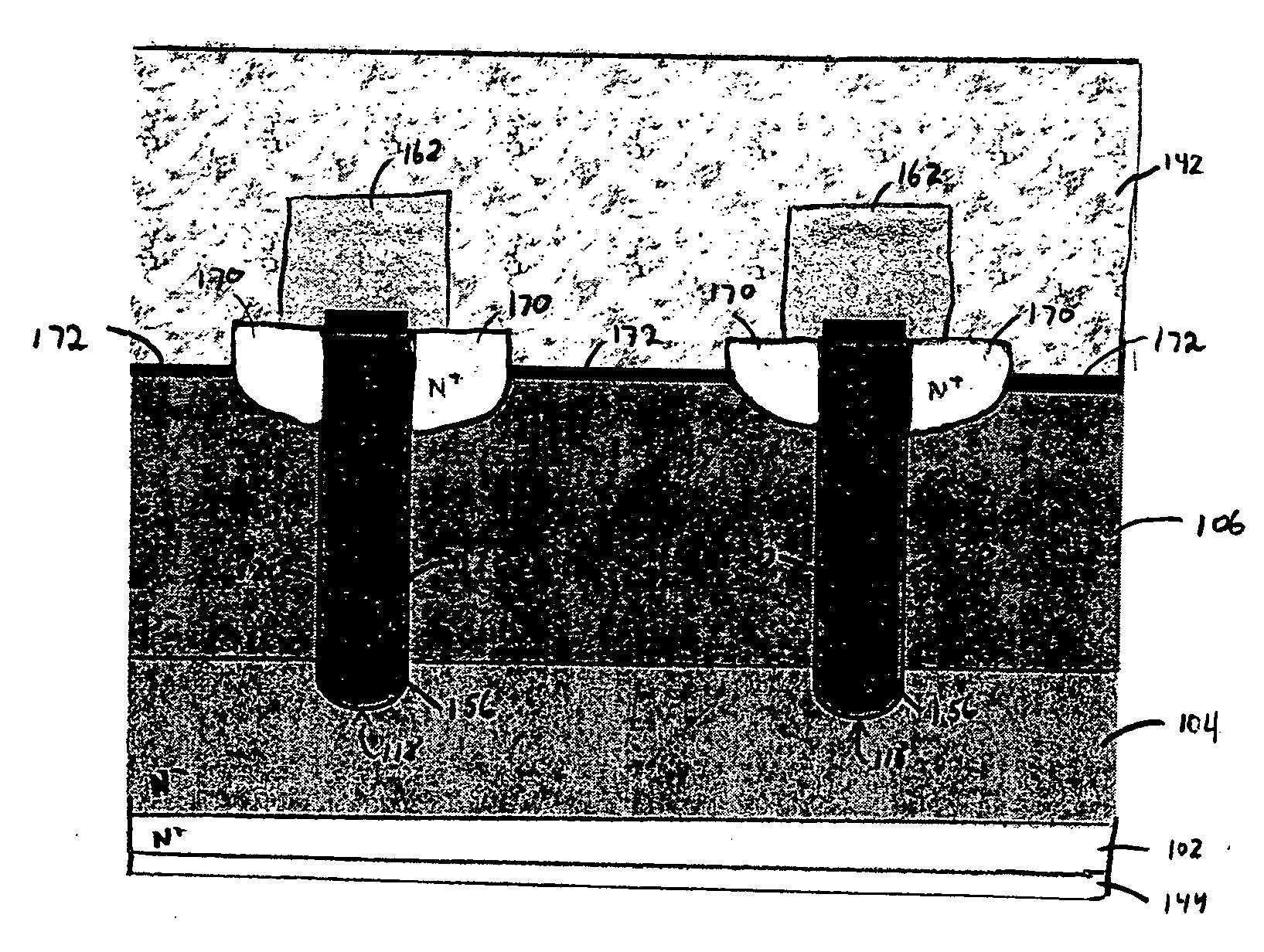

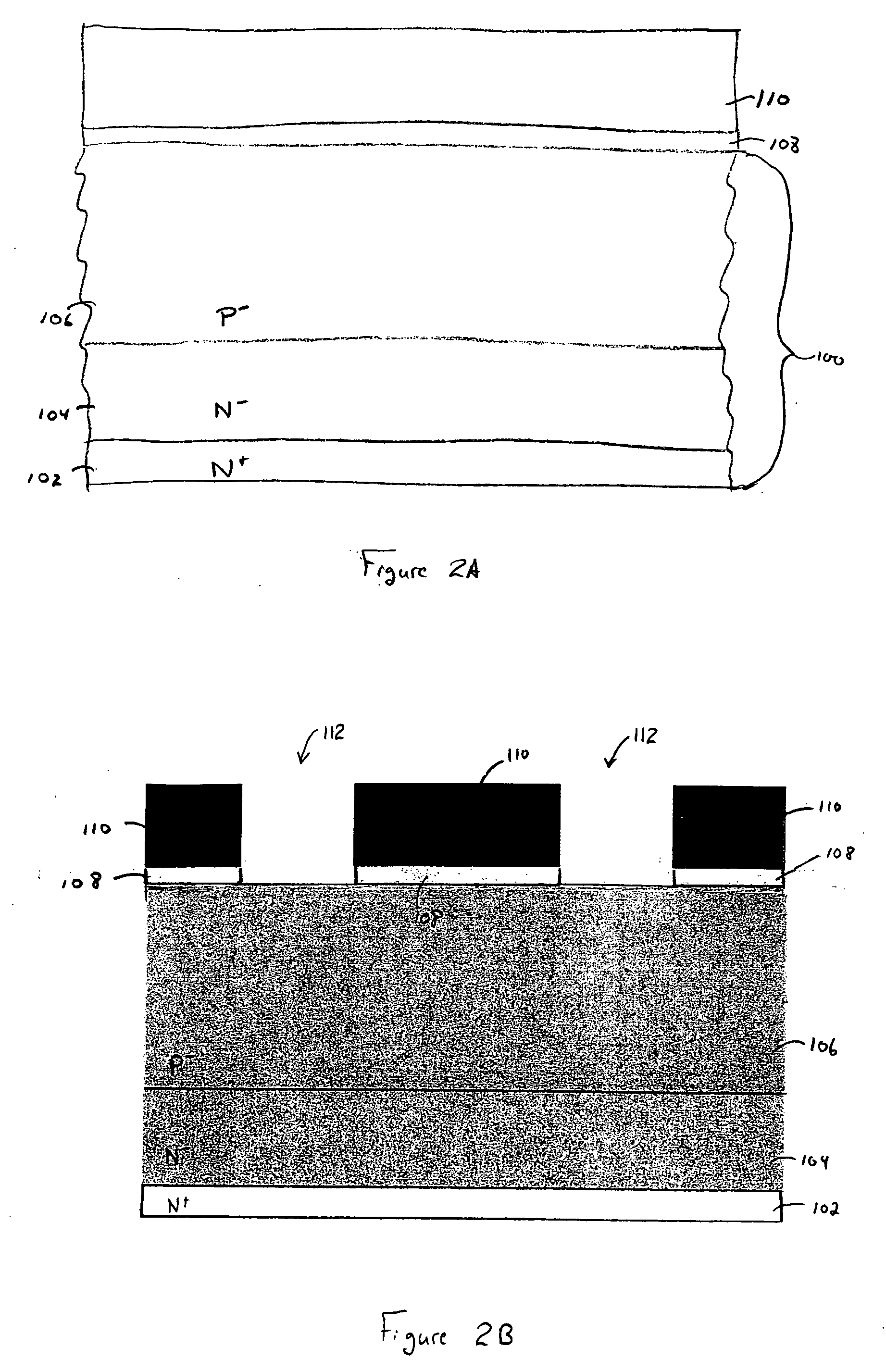

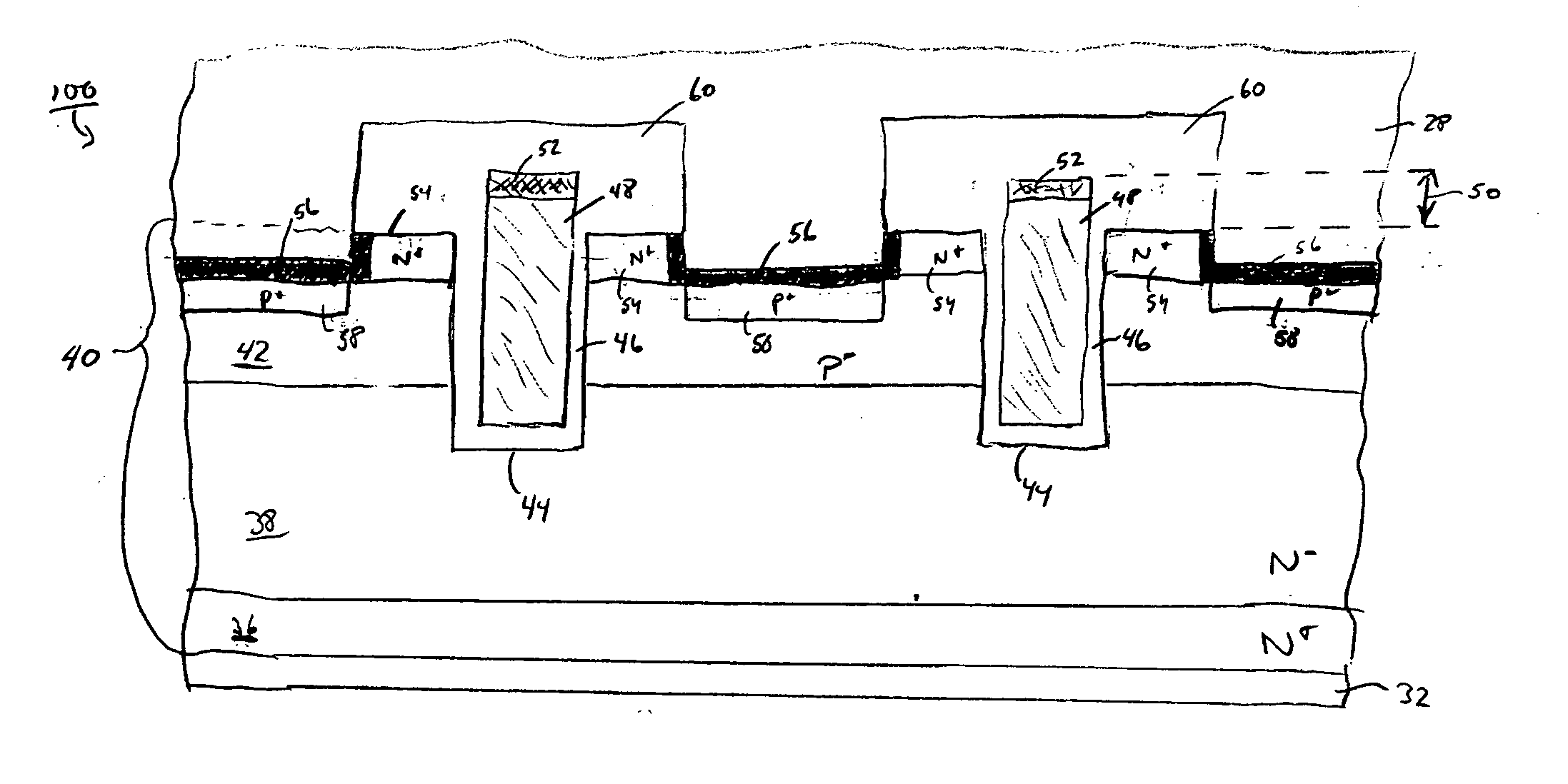

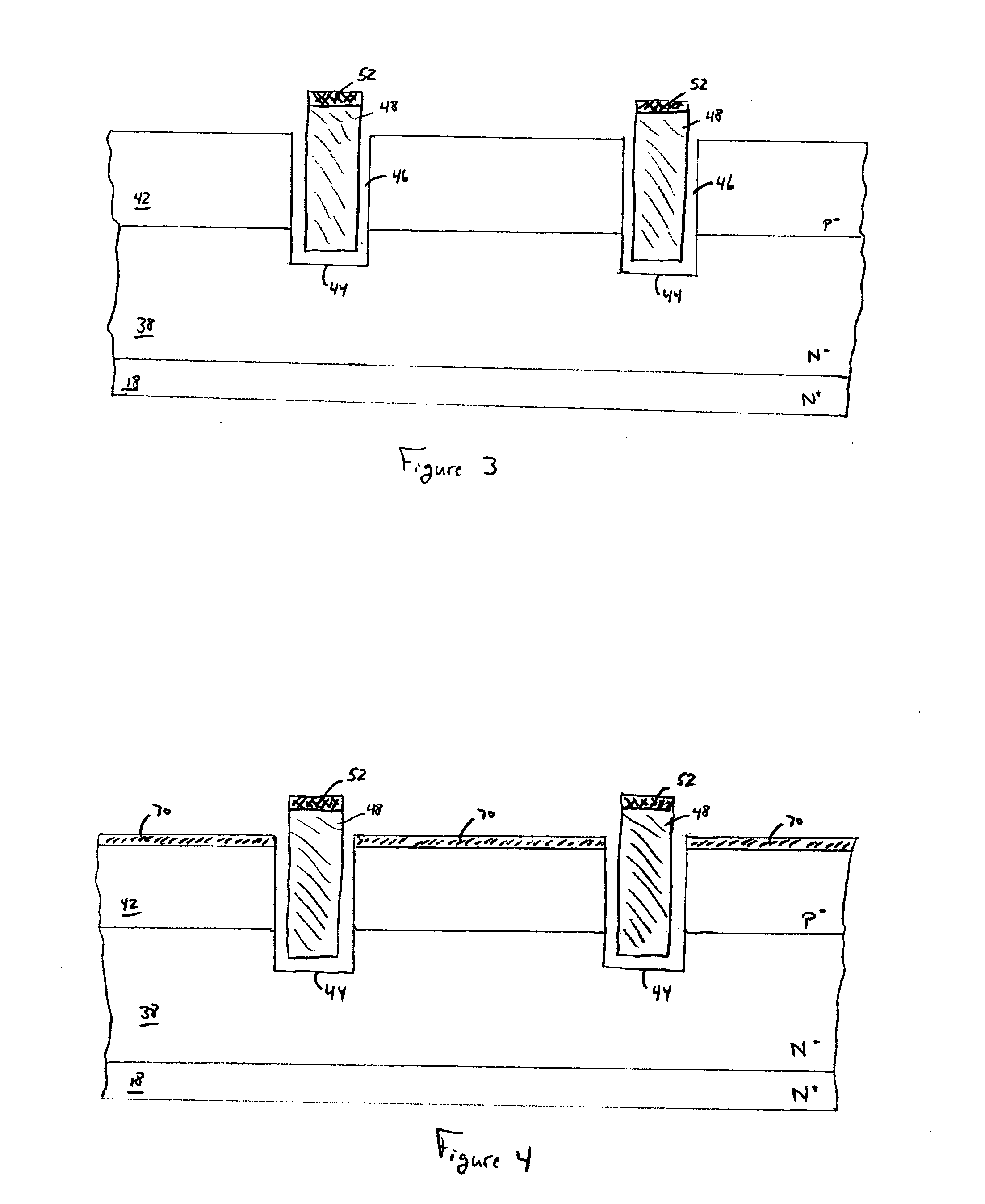

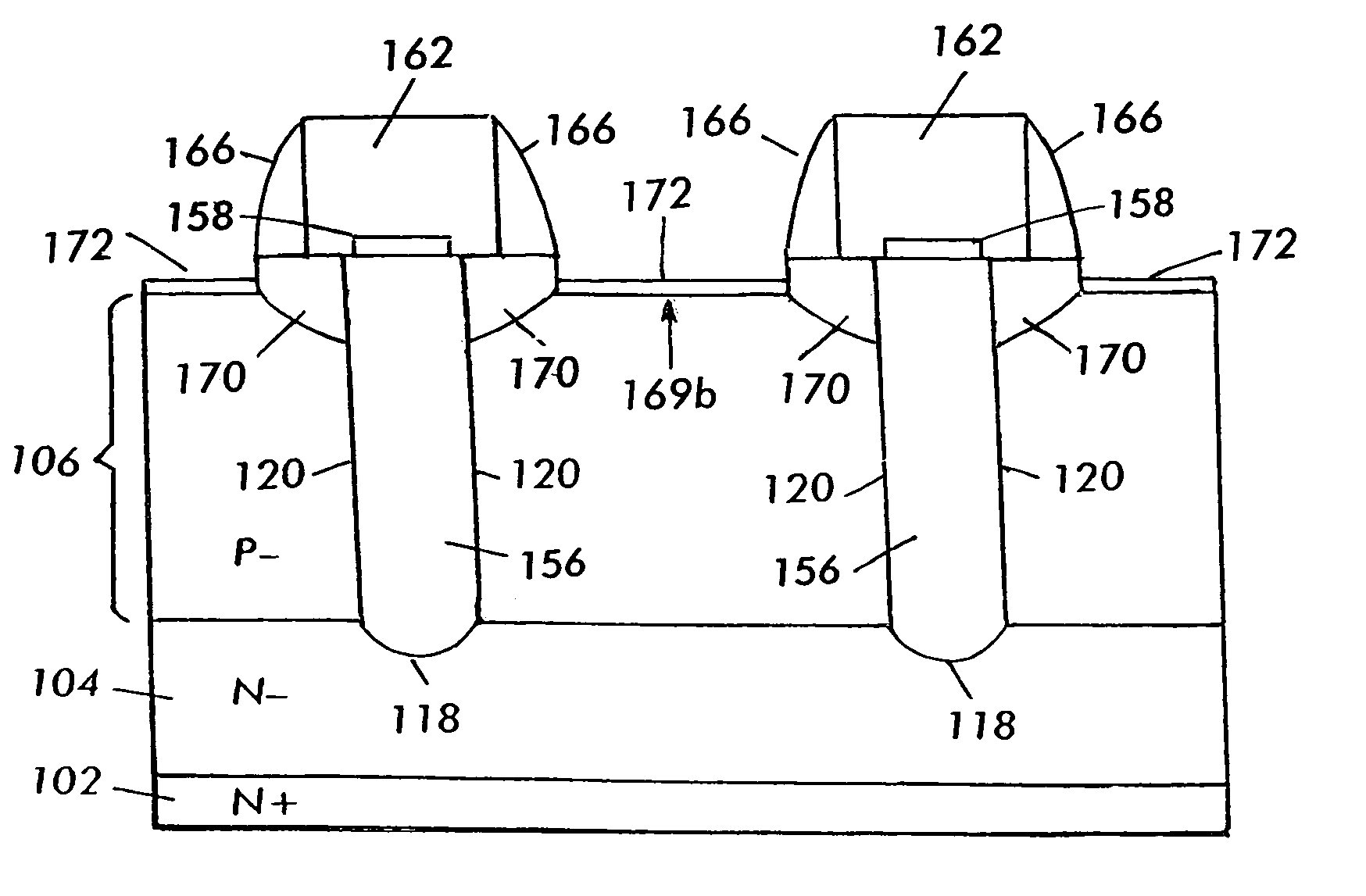

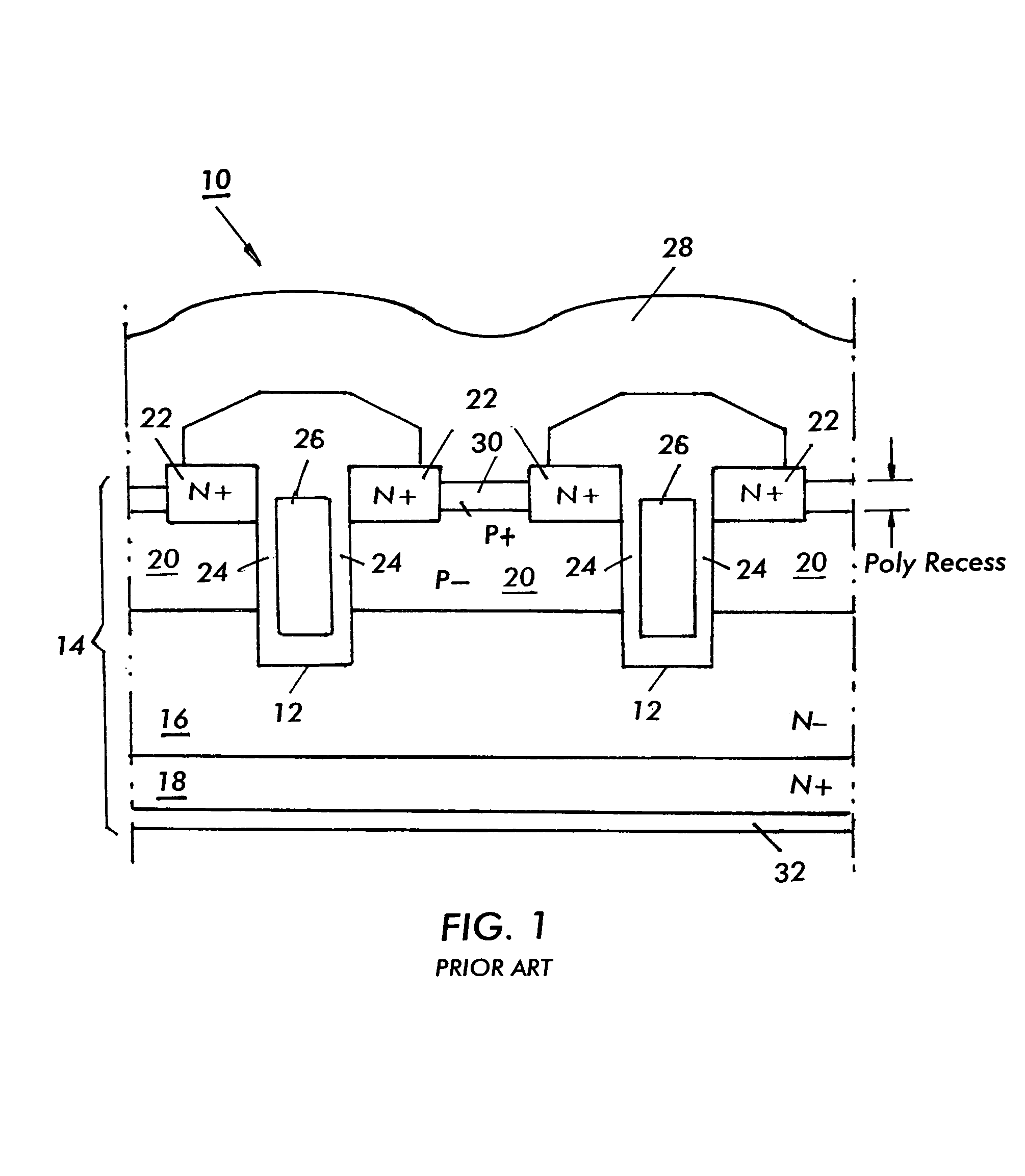

Trench power MOSFET fabrication using inside/outside spacers

ActiveUS20050208724A1Increase cell densityReduce widthSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceManufacturing technology

A fabrication process for a trench type power semiconductor device includes forming inside spacers over a semiconductor surface. Using the spacers as masks, trenches with gates are formed in the semiconductor body. After removing the spacers, source implants are formed in the semiconductor body along the trench edges and are then driven. Insulation caps are then formed over the trenches. Outside spacers are next formed along the sides of the caps. Using these spacers as masks, the semiconductor surface is etched and high conductivity contact regions formed. The outside spacers are then removed and source and drain contacts formed. Alternatively, the source implants are not driven. Rather, prior to outside spacer formation a second source implant is performed. The outside spacers are then formed, portions of the second source implant etched, any remaining source implant driven, and the contact regions formed. The gate electrodes are either recessed below or extend above the semiconductor surface.

Owner:INFINEON TECH AMERICAS CORP

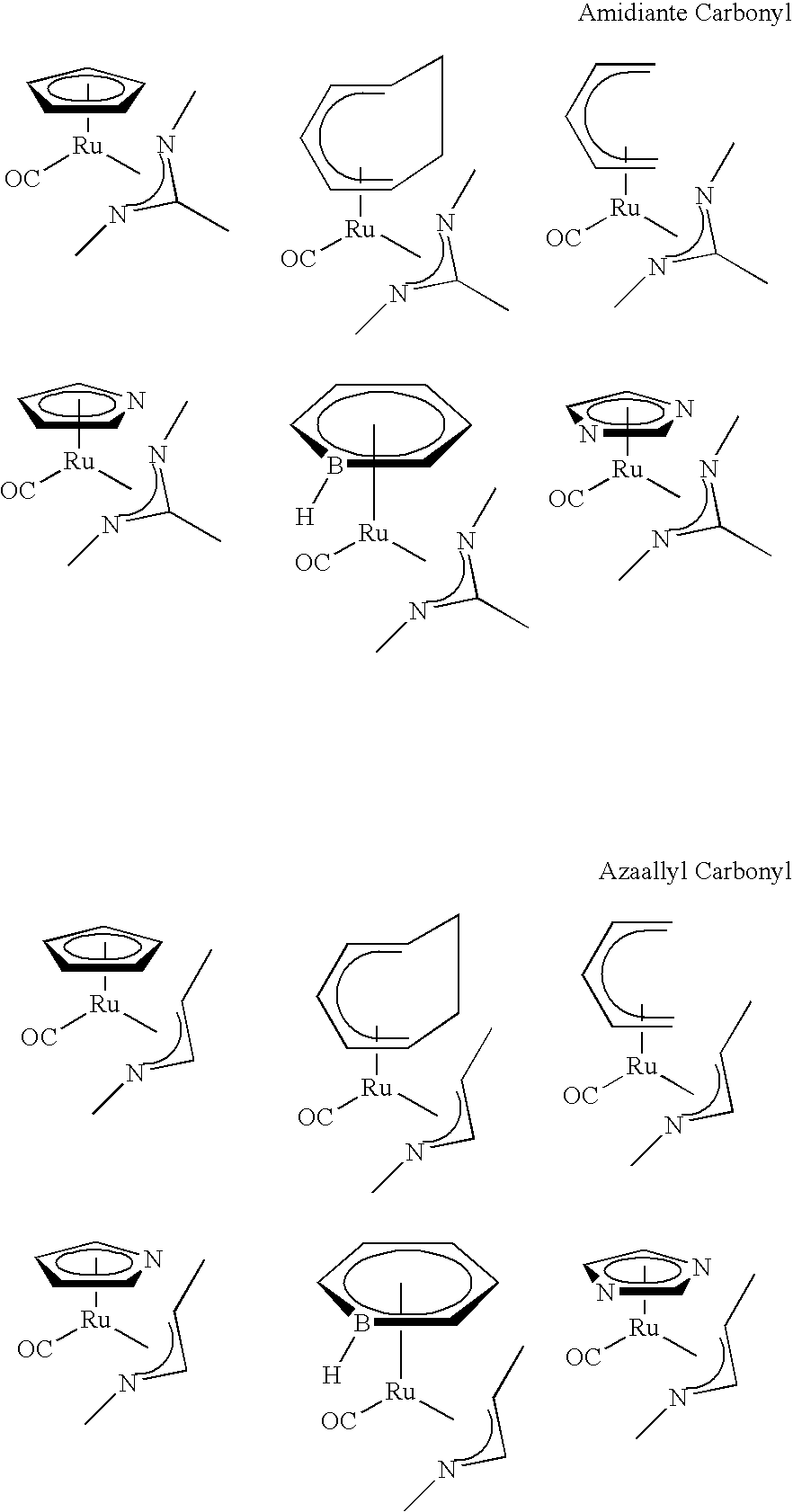

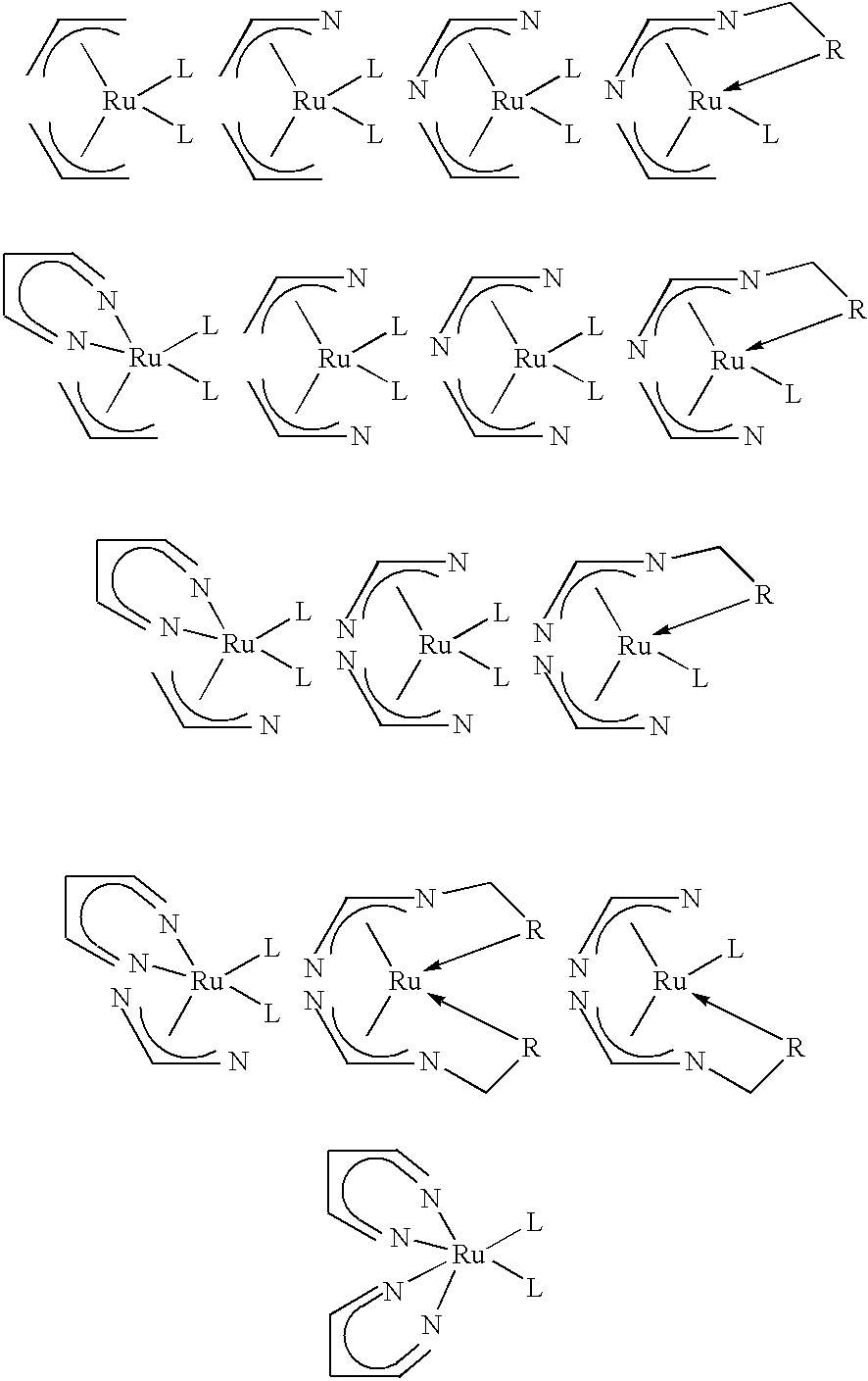

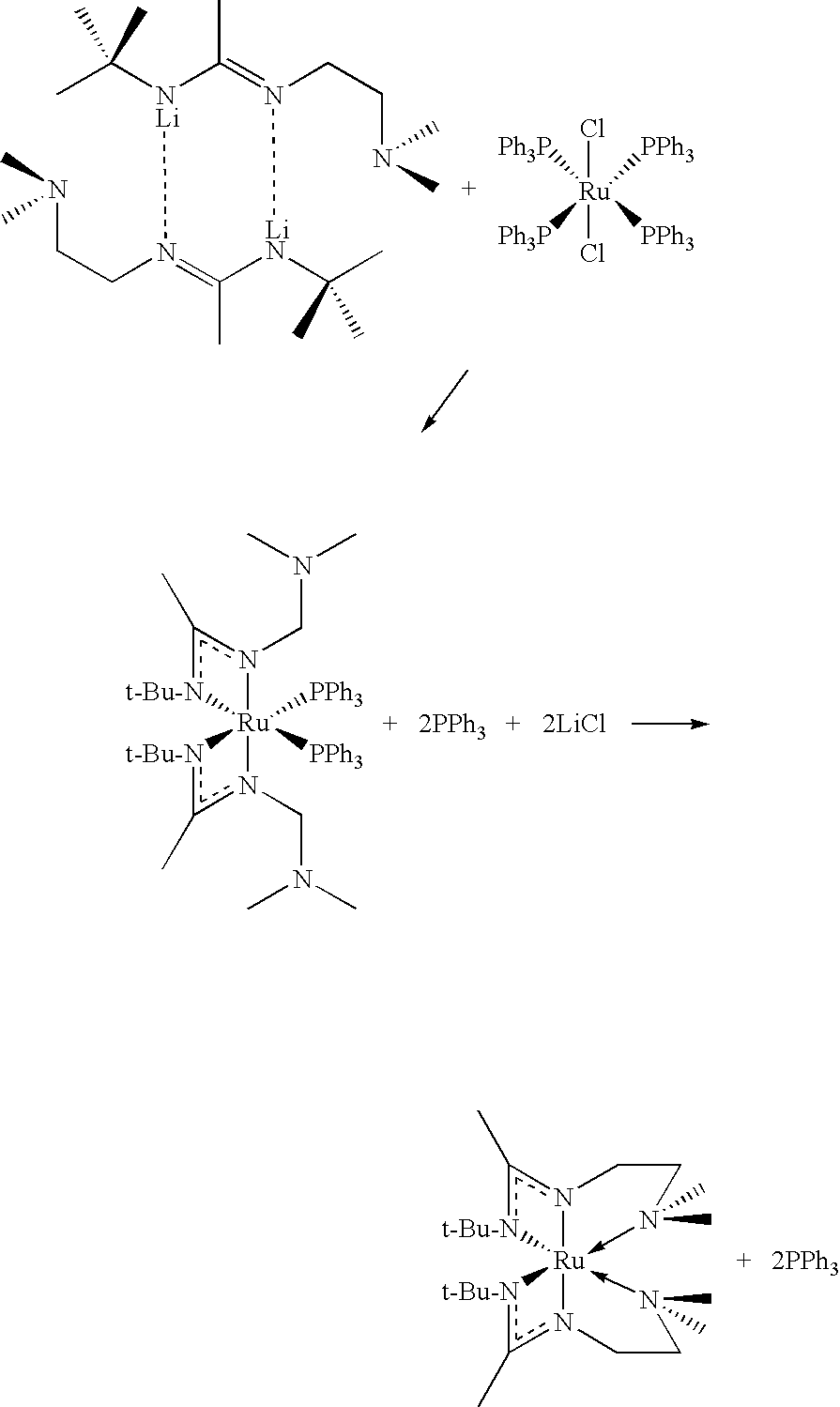

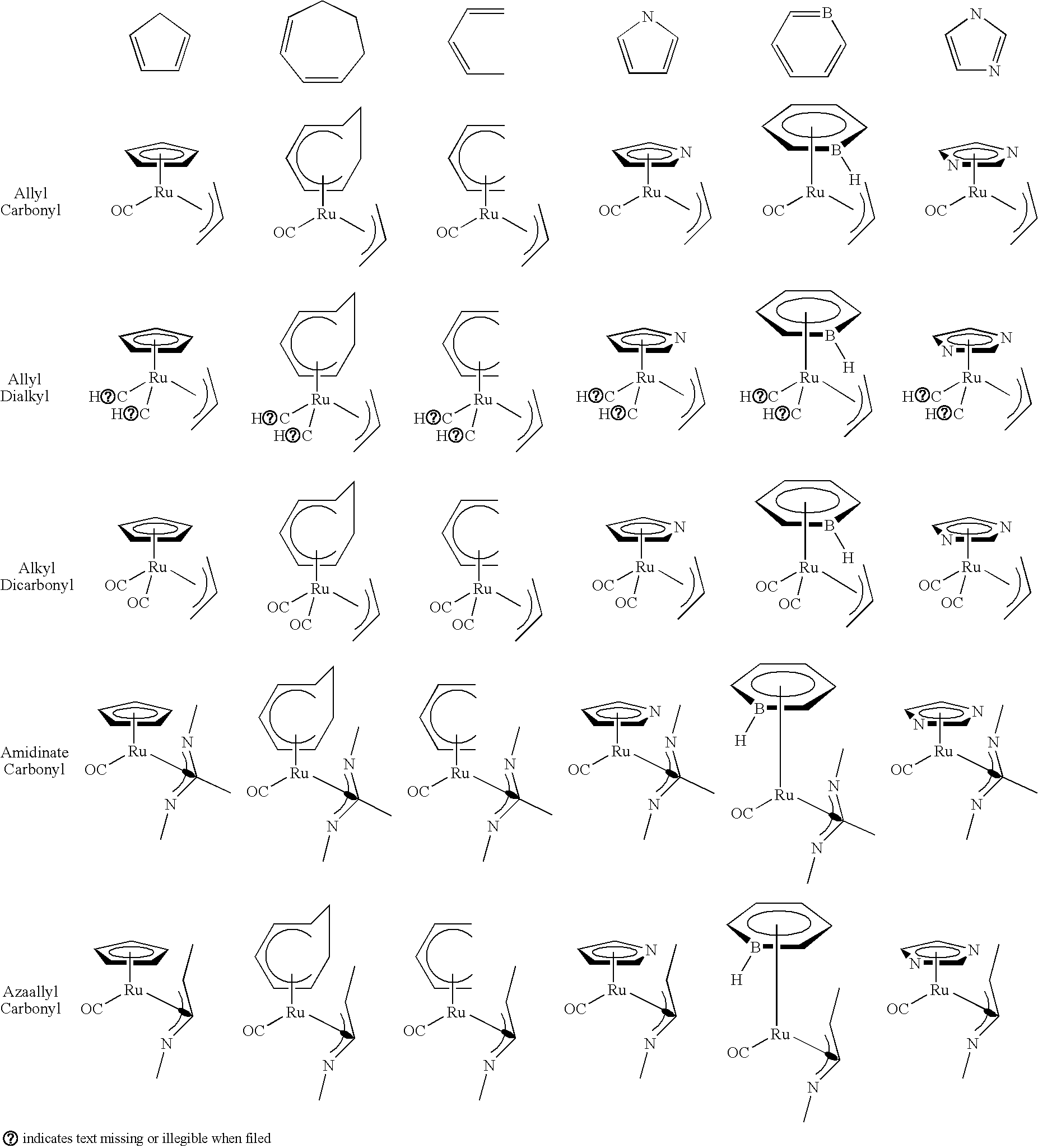

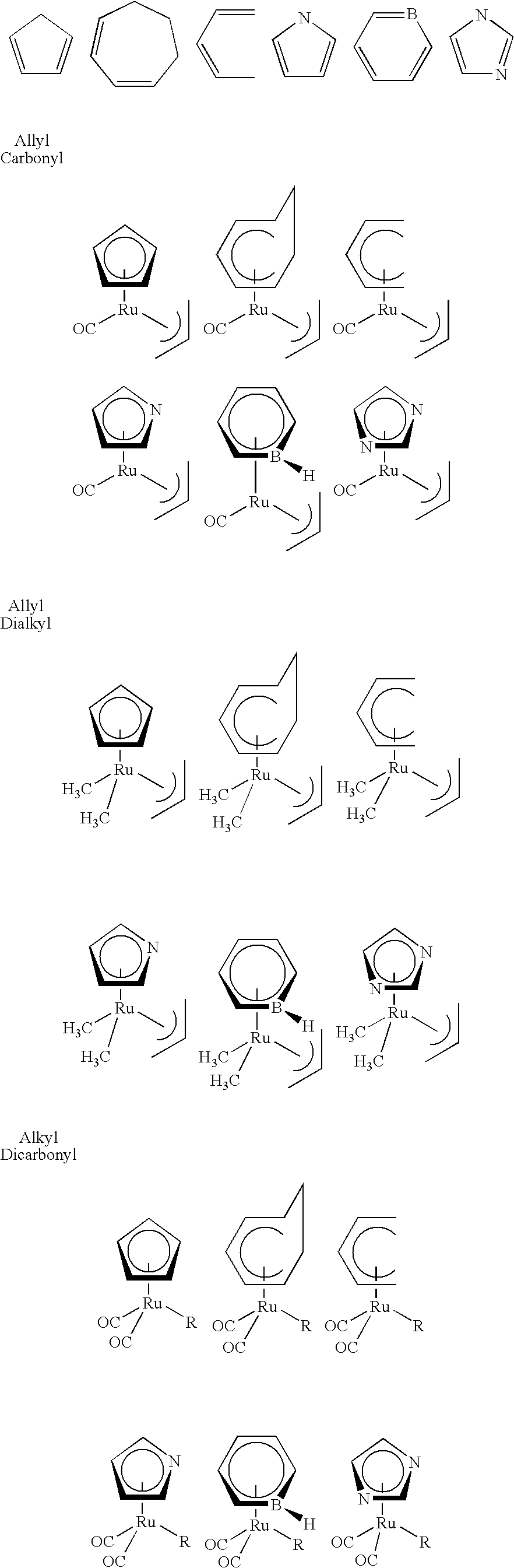

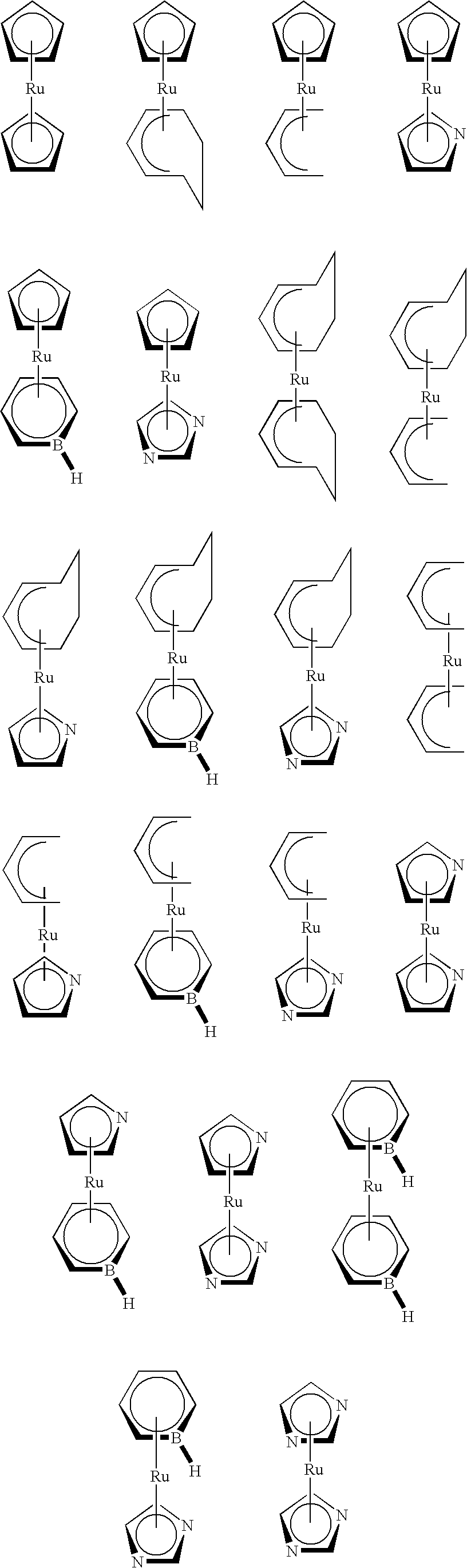

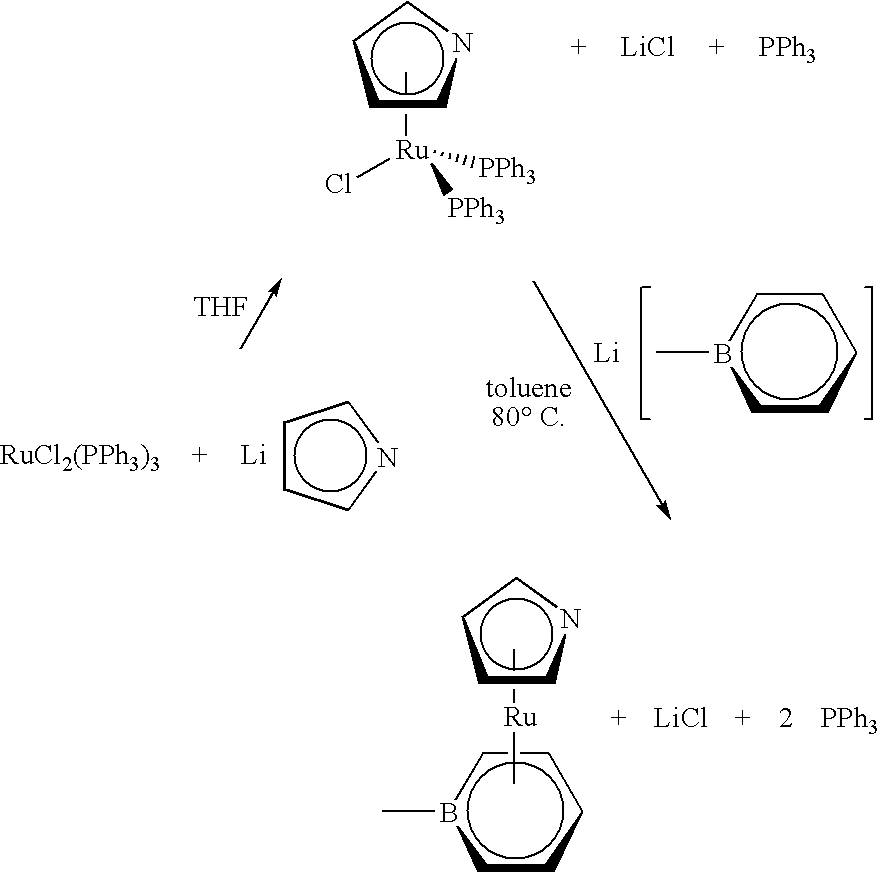

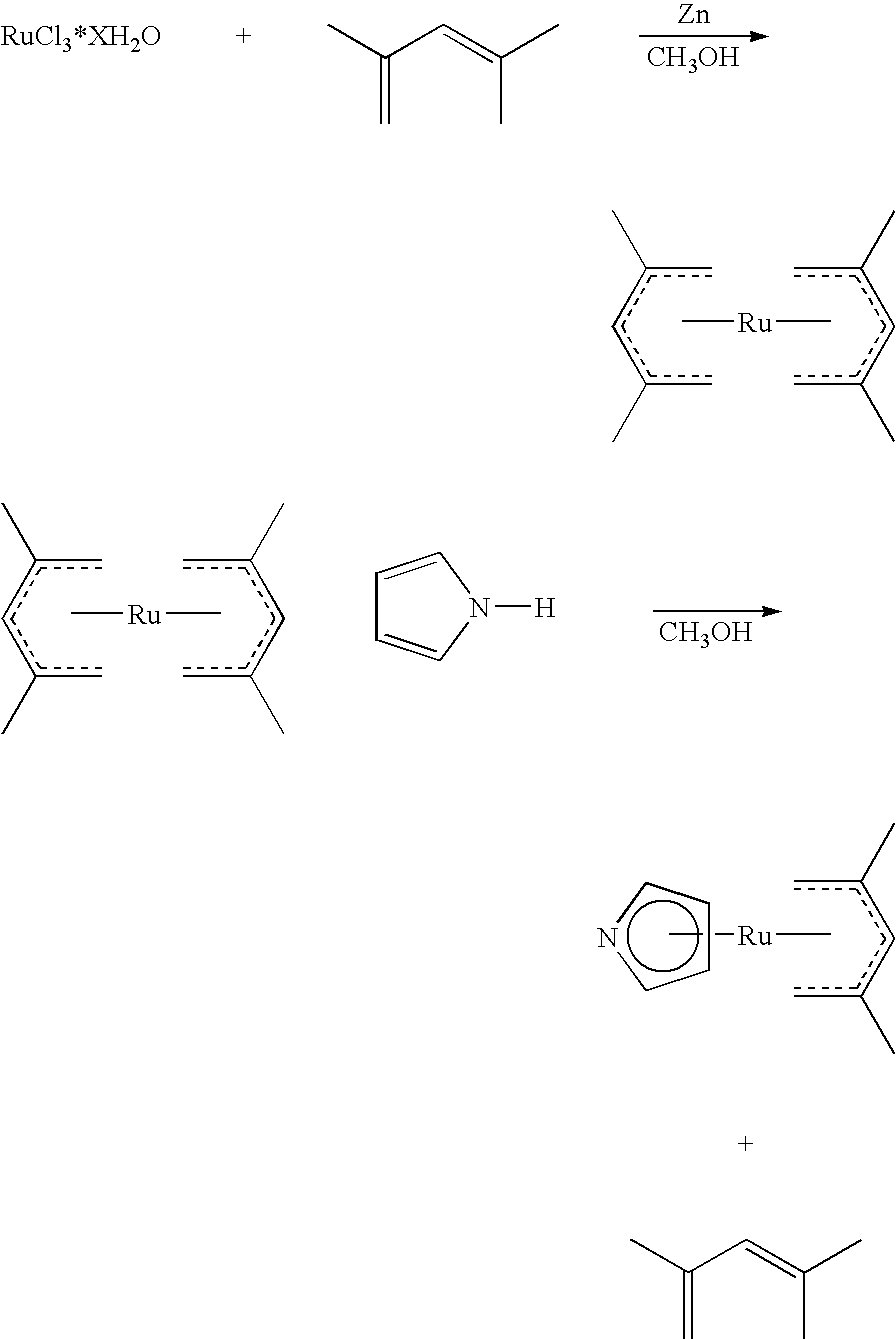

Processes for the production of organometallic compounds

InactiveUS20060229462A1Improve propertiesDesired morphologyRuthenium organic compoundsIron organic compoundsGas phaseRuthenium Compounds

Owner:PRAXAIR TECH INC

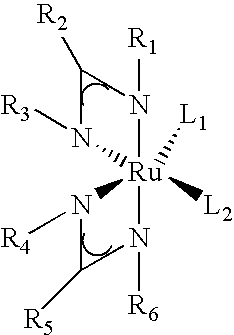

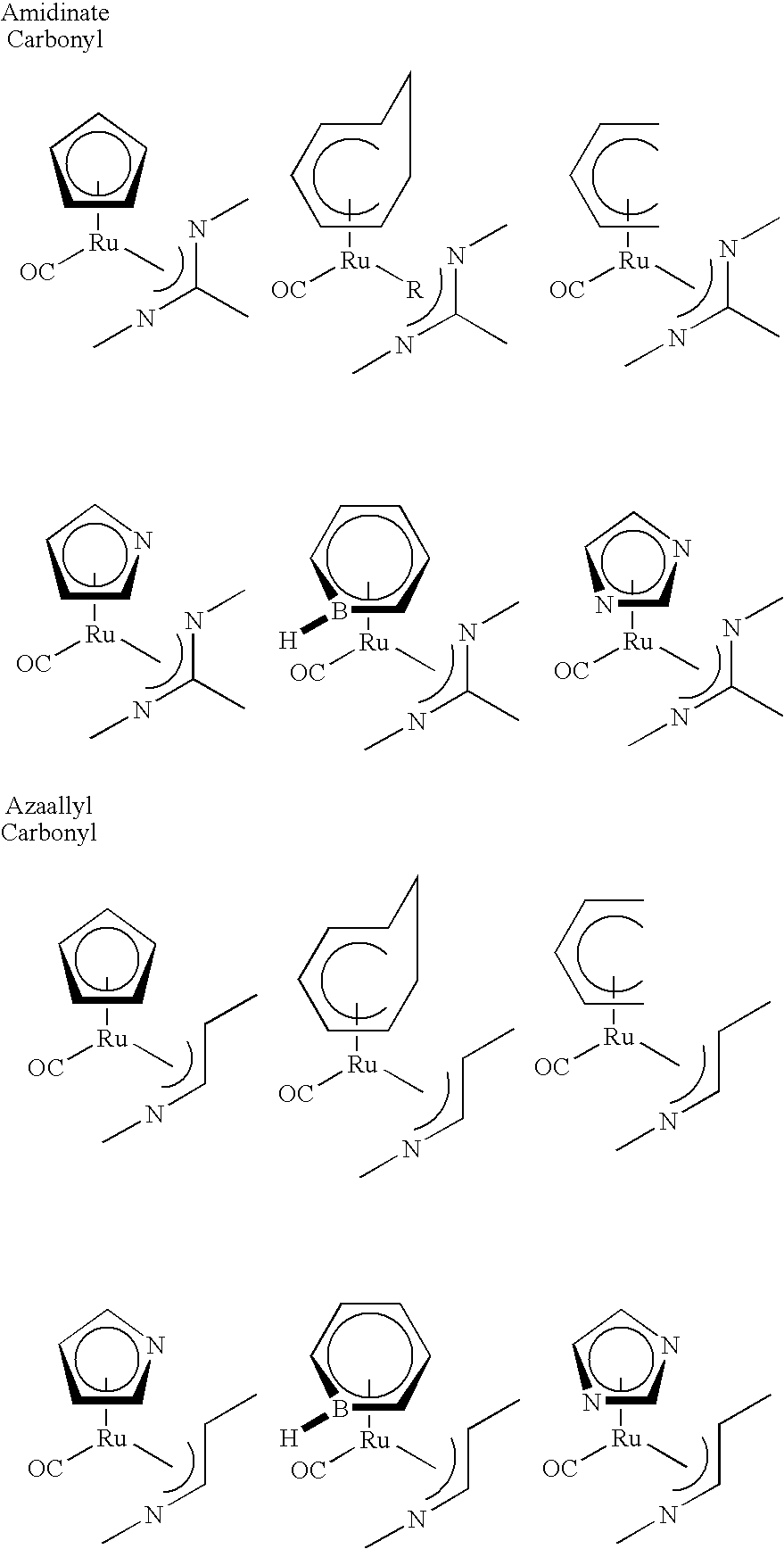

Organometallic compounds, processes for the preparation thereof and methods of use thereof

InactiveUS20090205968A1Improve propertiesDesired morphologyRuthenium organic compoundsSpecial surfacesGas phaseElectron donor

This invention relates to organometallic compounds having the formula (L1)M(L2)y wherein M is a metal or metalloid, L1 is a substituted or unsubstituted anionic 6 electron donor ligand, L2 is the same or different and is (i) a substituted or unsubstituted anionic 2 electron donor ligand, (ii) a substituted or unsubstituted anionic 4 electron donor ligand, (iii) a substituted or unsubstituted neutral 2 electron donor ligand, or (iv) a substituted or unsubstituted anionic 4 electron donor ligand with a pendant neutral 2 electron donor moiety; and y is an integer of from 1 to 3; and wherein the sum of the oxidation number of M and the electric charges of L1 and L2 is equal to 0; a process for producing the organometallic compounds, and a method for producing a film or coating from the organometallic compounds. The organometallic compounds are useful in semiconductor applications as chemical vapor or atomic layer deposition precursors for film depositions.

Owner:INTEL CORP +1

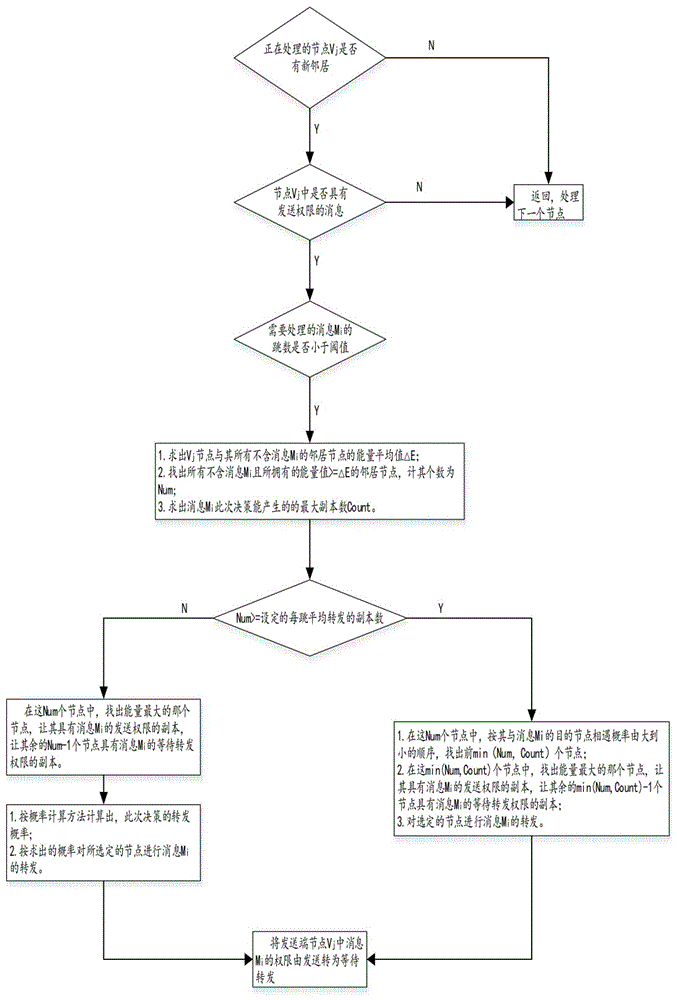

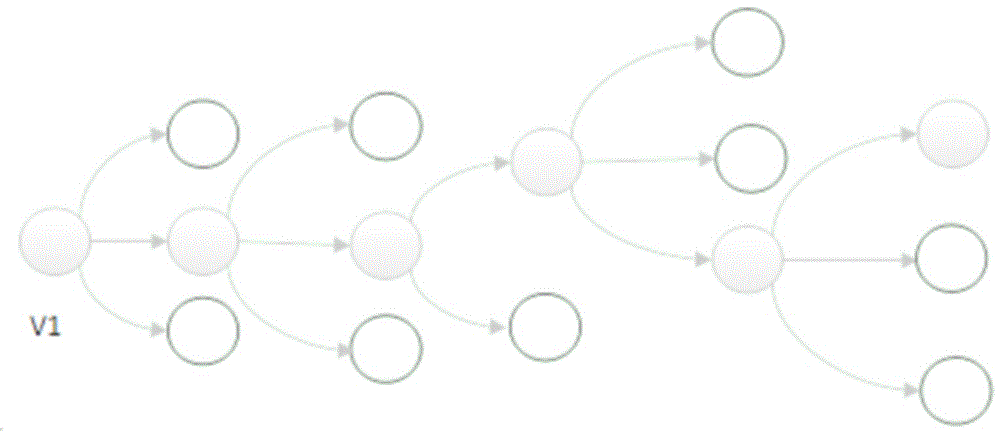

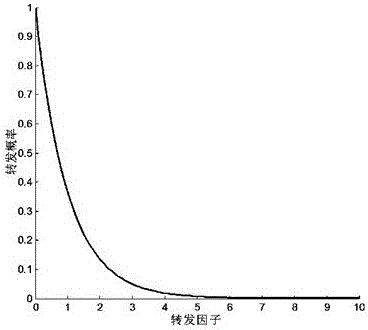

Routing method for opportunity network

ActiveCN105704777AImprove delivery rateLow overhead rateNetwork topologiesHigh level techniquesEnergy balancedLife time

The invention discloses a self-adaptive controllable multicast routing method for an opportunity network and a network node. Aiming at characteristics of node movement and link frequent change in the opportunity network, the invention discloses a new routing measure standard. According to the measure standard, node energy, possibility that a relay node meets an information destination node, information lifetime, information hop count and information expected copy numbers in the network are taken into account comprehensively. Based on the measure standard, the self-adaptive controllable multicast routing method is disclosed. Simulation test results show that problems of node failure caused by overload of nodes and too quick energy consumption is avoided; energy balance between network nodes is ensured; network service lifetime is prolonged; information delivery rate in the network is improved; and the copy number of information in the network is controlled effectively.

Owner:上海前瞻创新研究院有限公司

Lithium secondary batteries containing lithium salt-ionic liquid solvent electrolyte

ActiveUS9190696B2High viscosityMore viscousFuel and secondary cellsActive material electrodesElectrical batteryLithium metal

A rechargeable lithium metal or lithium-ion cell comprising a cathode having a cathode active material and / or a conductive supporting structure, an anode having an anode active material and / or a conductive supporting nano-structure, a porous separator electronically separating the anode and the cathode, a highly concentrated electrolyte in contact with the cathode active material and the anode active material, wherein the electrolyte contains a lithium salt dissolved in an ionic liquid solvent with a concentration greater than 3 M. The cell exhibits an exceptionally high specific energy, a relatively high power density, a long cycle life, and high safety with no flammability.

Owner:GLOBAL GRAPHENE GRP INC

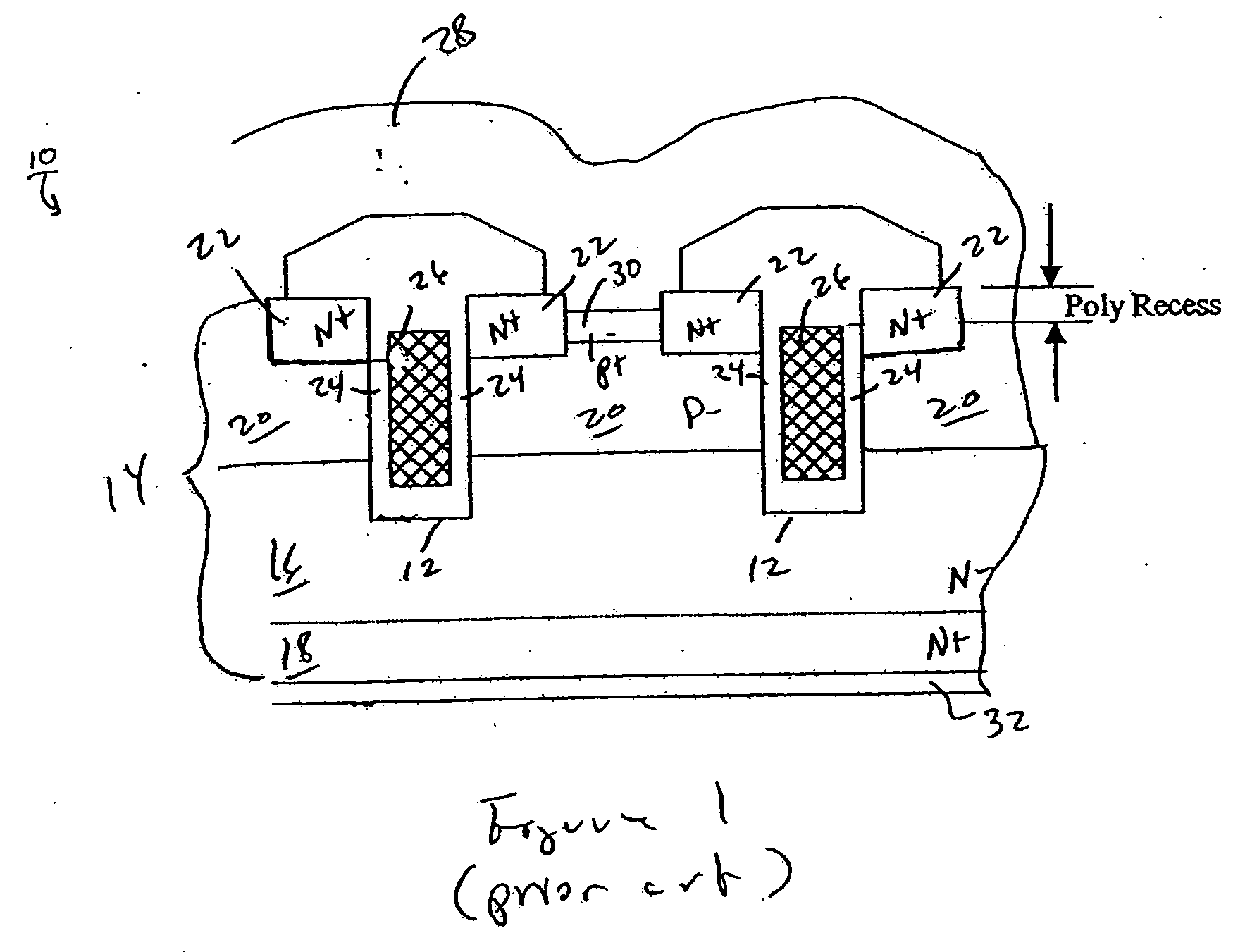

Low temperature process and structures for polycide power MOSFET with ultra-shallow source

ActiveUS20050173760A1Reduced vertical depthReduce depthTransistorSolid-state devicesPower semiconductor deviceEngineering

A trench type power semiconductor device includes proud gate electrodes that extend out of the trenches and above the surface of the semiconductor body. These proud gate electrodes allow for making ultra-shallow source regions within the semiconductor body using, for example, a low temperature source drive. In addition, a method for manufacturing the trench type power semiconductor device includes a low temperature process flow once the gate electrodes are formed.

Owner:INFINEON TECH AMERICAS CORP

Organometallic compounds, processes for the preparation thereof and methods of use thereof

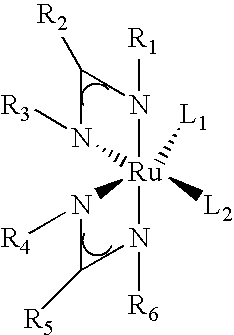

InactiveUS20090199739A1Improve responseImprove propertiesRuthenium organic compoundsSemiconductor/solid-state device manufacturingGas phaseElectron donor

This invention relates to organometallic compounds having the formula (L1)yM(L2)z wherein M is a metal or metalloid, L1 is the same or different and is (i) a substituted or unsubstituted anionic 4 electron donor ligand or (ii) a substituted or unsubstituted anionic 4 electron donor ligand with a pendant neutral 2 electron donor moiety, L2 is the same or different and is (i) a substituted or unsubstituted anionic 2 electron donor ligand or (ii) a substituted or unsubstituted neutral 2 electron donor ligand; y is an integer of 2; and z is an integer of from 0 to 2; and wherein the sum of the oxidation number of M and the electric charges of L1 and L2 is equal to 0; a process for producing the organometallic compounds, and a method for producing a film or coating from the organometallic compounds. The organometallic compounds are useful in semiconductor applications as chemical vapor or atomic layer deposition precursors for film depositions.

Owner:PRAXAIR TECH INC

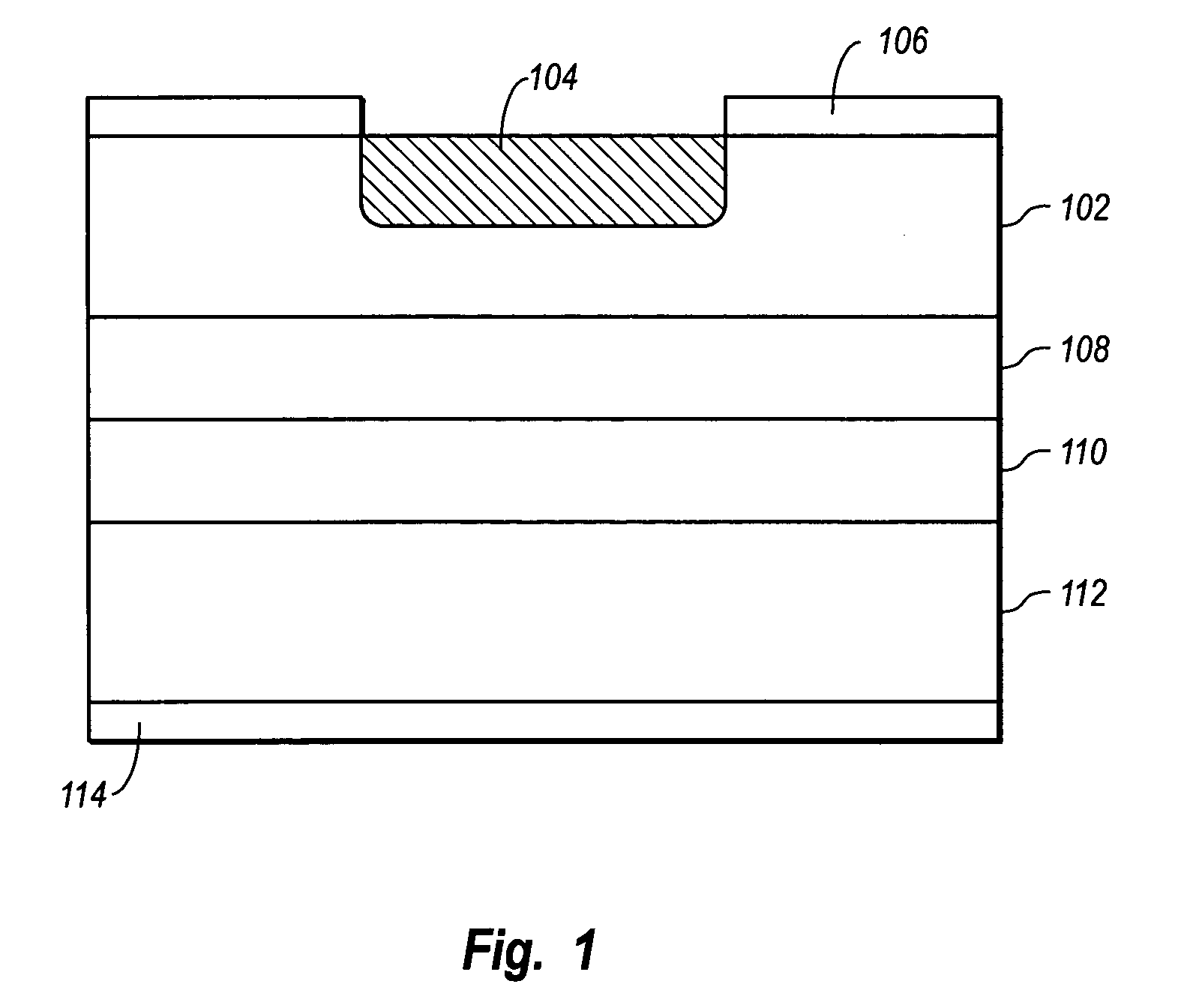

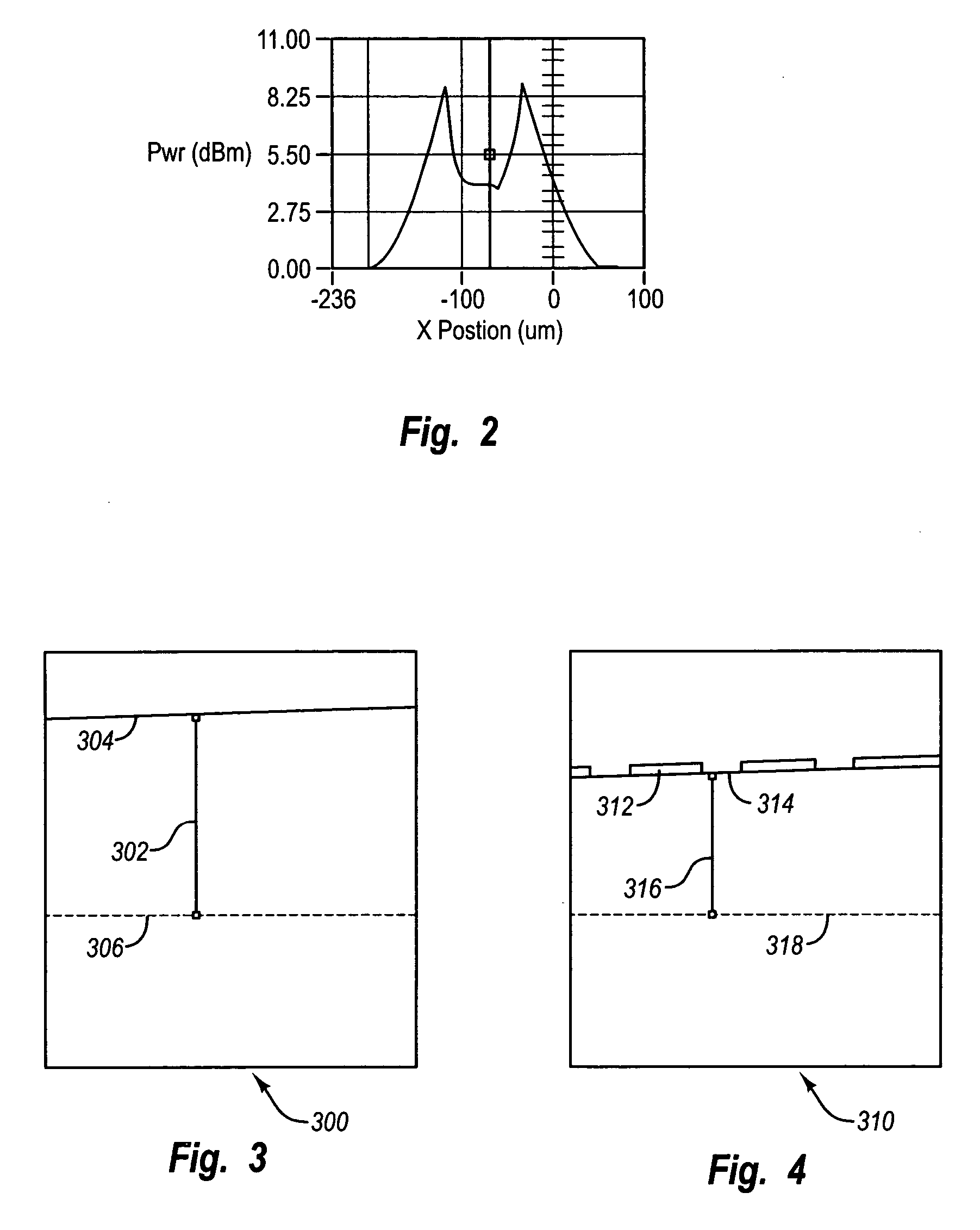

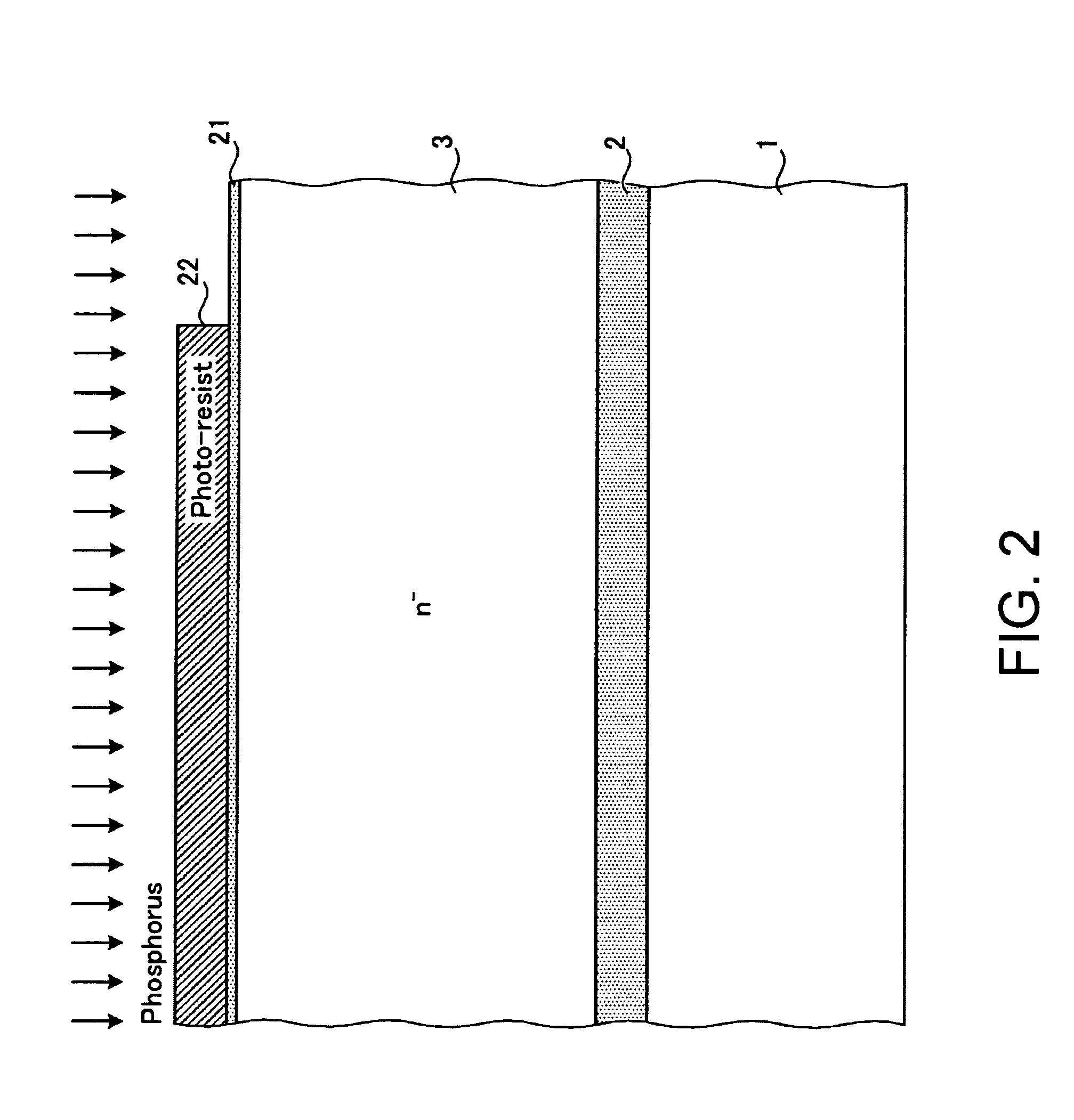

Starved source diffusion for avalanche photodiode

InactiveUS20060081874A1The method is simple and reliableReducing edge gainPhotovoltaic energy generationSemiconductor devicesDopantEdge effects

Starved source diffusion methods for forming avalanche photodiodes (APDs) are provided for controlling the edge effect. The edge effect is controlled by reducing edge gain near the edges of an APD active region. This is accomplished by creating a sloped diffusion front near the edges of the active region. The sloped diffusion front is advantageously formed in a single doping step by using a patterned mask during doping. The patterned mask reduces the depth to which dopants diffuse in areas where it only partly covers the underlying layer. By covering more of the underlying layer nearer the edge and progressively less towards the center, the sloped diffusion front is formed. The shallower diffusion depth near the edge reduces the edge gain, and therefore the edge effect. As a result, an APD to fiber misalignment is less likely, and possibility of edge breakdown is greatly reduced.

Owner:II VI DELAWARE INC

Selective Formation of Boron-Containing Metal Cap Pre-layer

InactiveUS20090014877A1Improve reliabilityImprove the immunitySemiconductor/solid-state device detailsSolid-state devicesBoron containingOptoelectronics

An interconnect structure with improved reliability is provided. The interconnect structure includes a semiconductor substrate; a dielectric layer over the semiconductor substrate; a metallic wiring in the dielectric layer; a pre-layer over the metallic wiring, wherein the pre-layer contains boron; and a metal cap over the pre-layer, wherein the metal cap contains tungsten, and wherein the pre-layer and the metal cap are formed of different materials.

Owner:TAIWAN SEMICON MFG CO LTD

Semiconductor device and manufacturing method thereof

InactiveUS20090065779A1Excessive diffusion of the impurities of the second doped polysilicon film is reducedPrevent VthSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductorImpurity

A semiconductor device includes a silicon substrate; a gate insulation film formed on the silicon substrate; and a gate electrode formed on the gate insulation film; wherein the gate electrode has a first doped polysilicon film formed on the gate insulation film, and a second doped polysilicon film formed on the first doped polysilicon film; wherein the first doped polysilicon film includes first impurities; and wherein the second doped polysilicon film includes second impurities that has the opposite conductivity type from the first impurities.

Owner:ELPIDA MEMORY INC

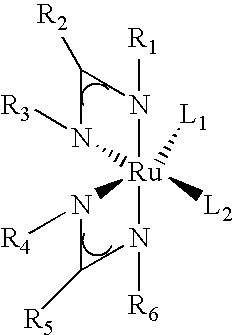

Organometallic compounds, processes for the preparation thereof and methods of use thereof

InactiveUS20090205538A1Improve responseImprove propertiesRuthenium organic compoundsSemiconductor/solid-state device manufacturingElectron donorMoiety

This invention relates to organometallic compounds having the formula (L1)M(L2)y wherein M is a metal or metalloid, L1 is a substituted or unsubstituted anionic 6 electron donor ligand, L2 is the same or different and is (i) a substituted or unsubstituted anionic 2 electron donor ligand, (ii) a substituted or unsubstituted anionic 4 electron donor ligand, (iii) a substituted or unsubstituted neutral 2 electron donor ligand, or (iv) a substituted or unsubstituted anionic 4 electron donor ligand with a pendant neutral 2 electron donor moiety; and y is an integer of from 1 to 3; and wherein the sum of the oxidation number of M and the electric charges of L1 and L2 is equal to 0; a process for producing the organometallic compounds, and a method for producing a film or coating from the organometallic compounds. The organometallic compounds are useful in semiconductor applications as chemical vapor or atomic layer deposition precursors for film depositions.

Owner:PRAXAIR TECH INC

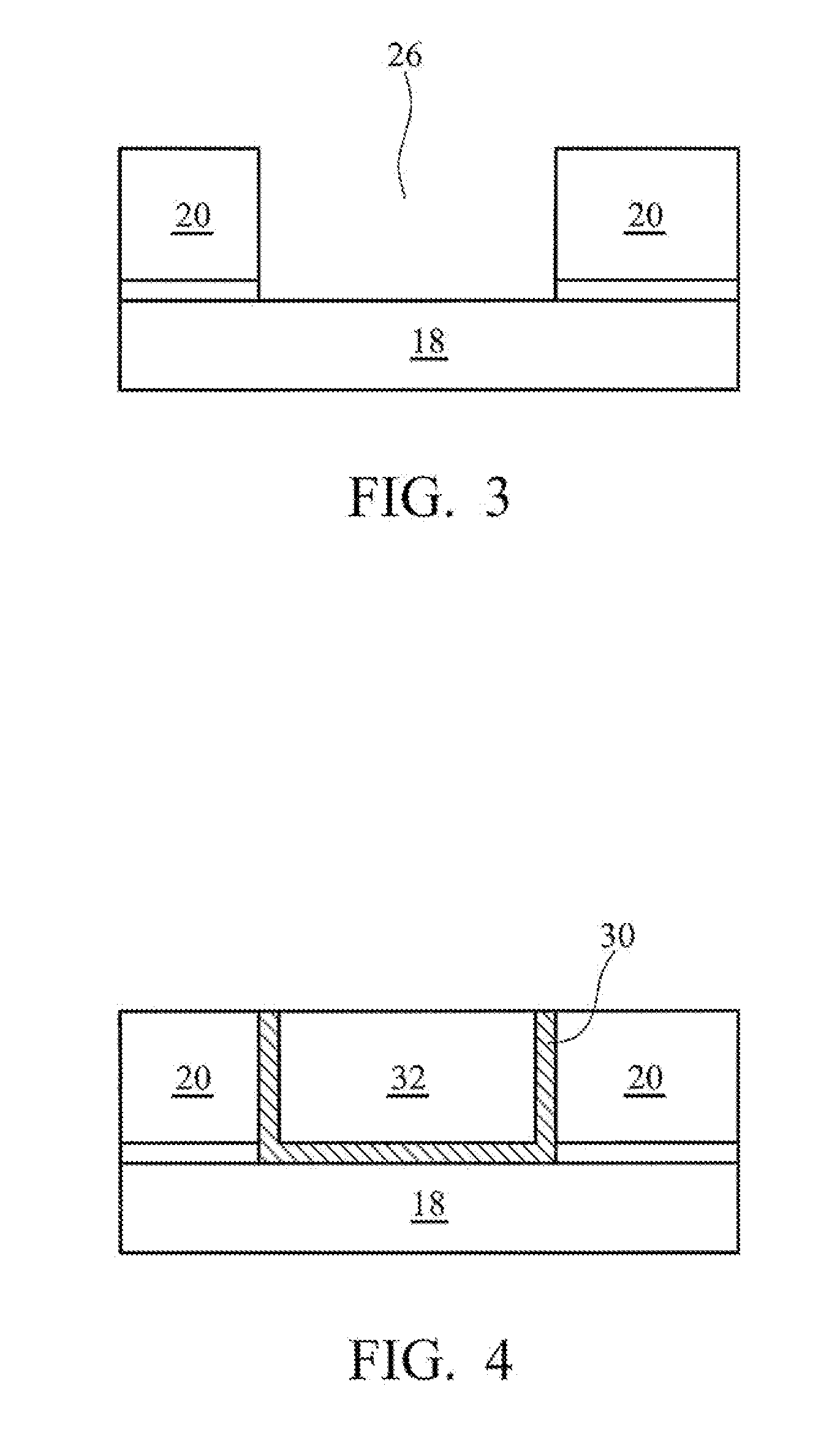

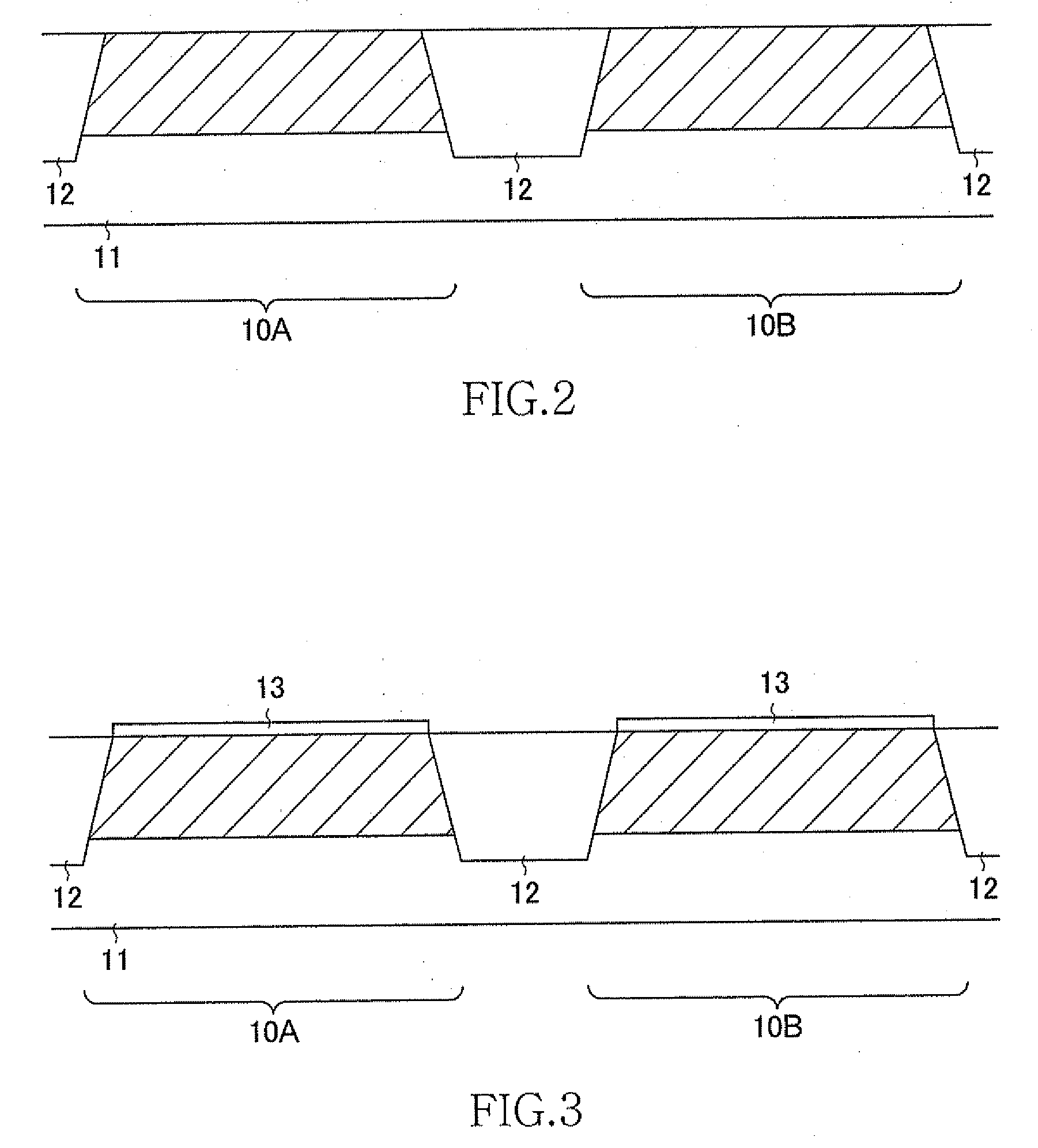

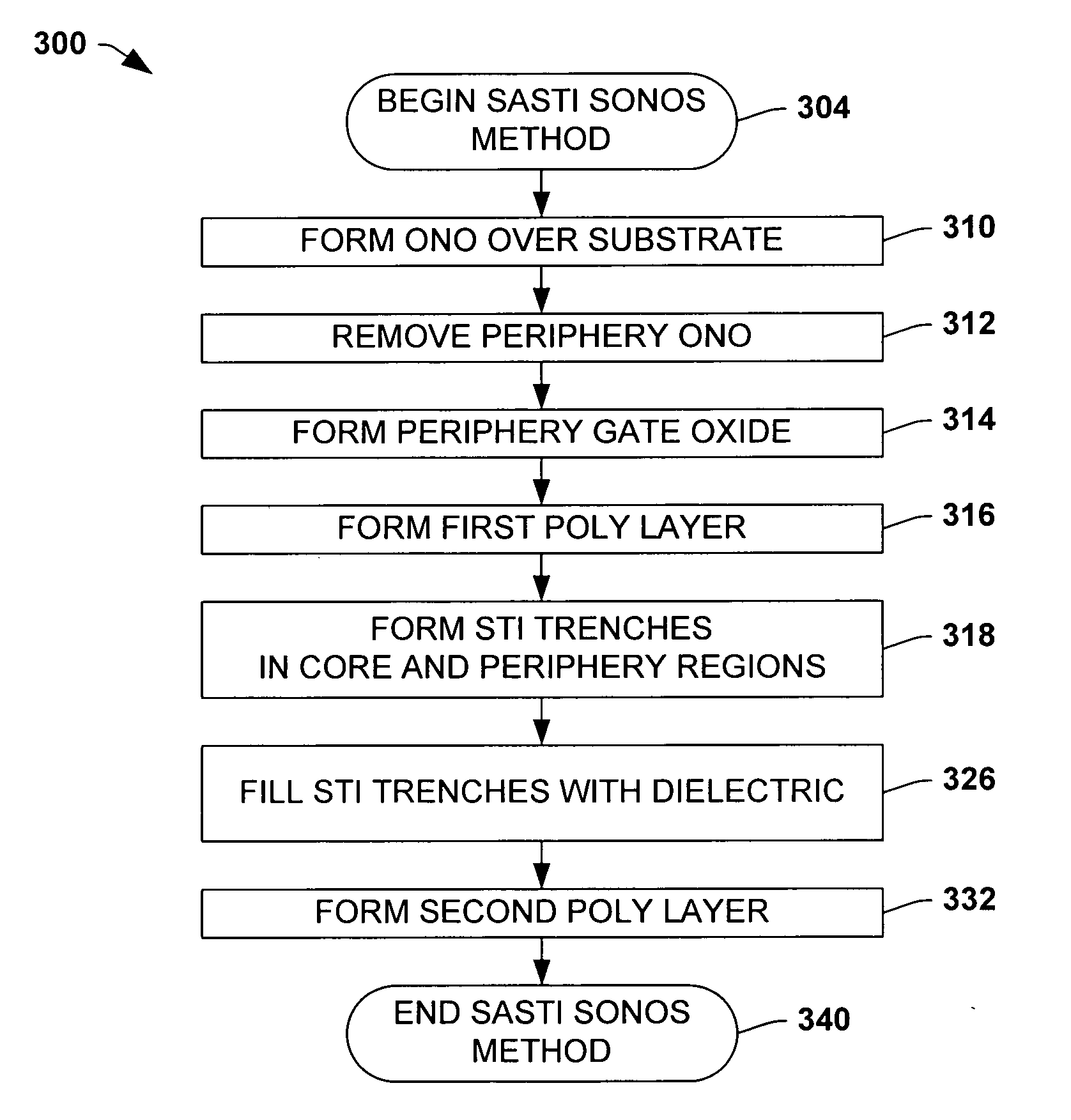

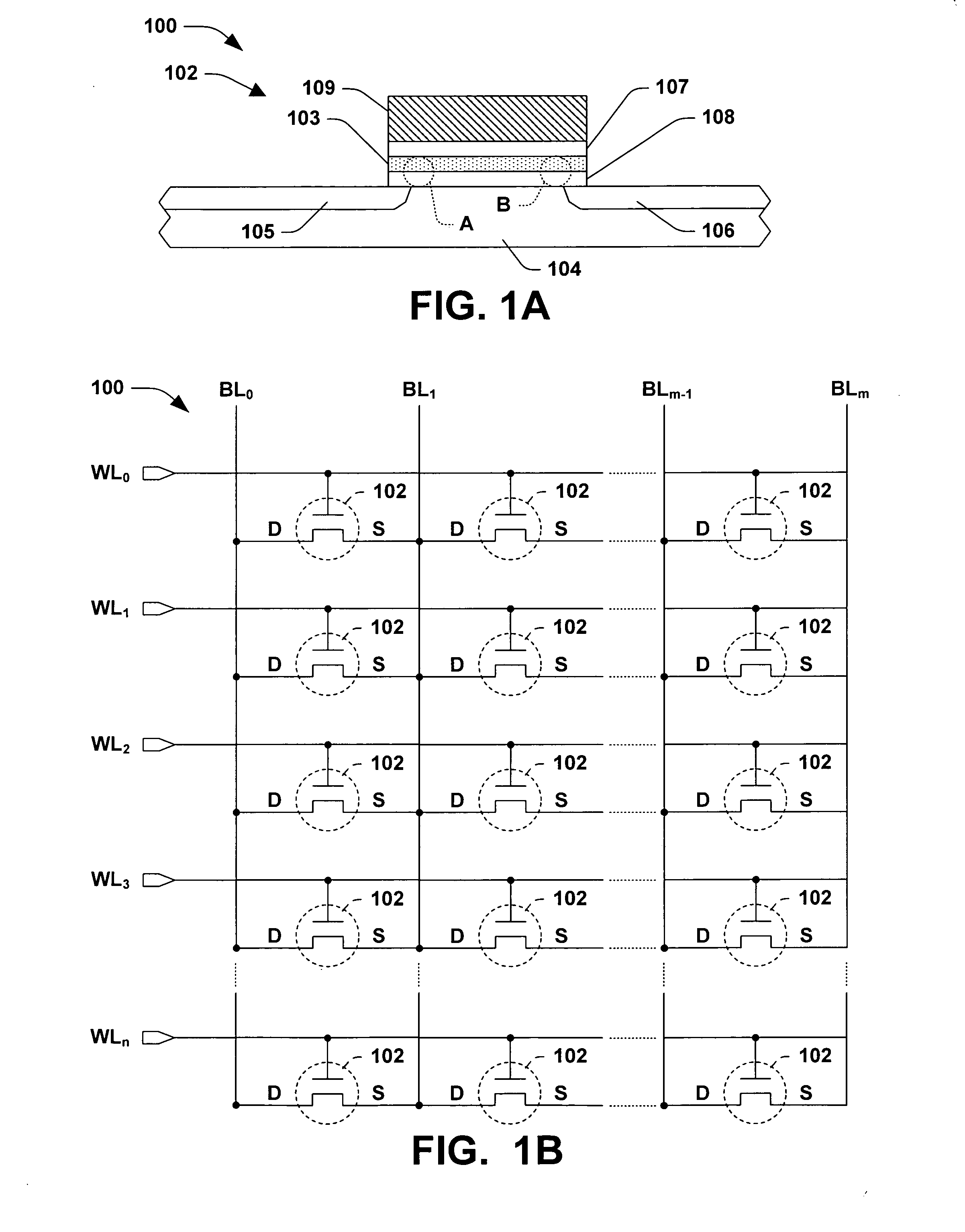

Self-aligned STI SONOS

ActiveUS20060240635A1Easy to manufactureMitigates active region lossSolid-state devicesSemiconductor/solid-state device manufacturingDielectricGate dielectric

Methods 300 and 350 are disclosed for fabricating shallow isolation trenches and structures in multi-bit SONOS flash memory devices. One method aspect 300 comprises forming 310 a multi-layer dielectric-charge trapping-dielectric stack 420 over a substrate 408 of the wafer 402, for example, an ONO stack 420, removing 312 the multi-layer dielectric-charge trapping-dielectric stack 420 in a periphery region 406 of the wafer 402, thereby defining a multi-layer dielectric-charge trapping-dielectric stack 420 in a core region 404 of the wafer 402. The method 300 further comprises forming 314 a gate dielectric layer 426 over the periphery region 406 of the substrate 408, forming 316 a first polysilicon layer 428 over the multi-layer dielectric-charge trapping-dielectric stack 420 in the core region 402 and the gate dielectric 426 in the periphery region 406 , then concurrently forming 318 an isolation trench 438 in the substrate 408 in the core region 404 and in the periphery region 406. Thereafter, the isolation trenches are filled 326 with a dielectric material 446, and a second polysilicon layer 452 that is formed 332 over the first polysilicon layer 428 and the filled trenches 438, forming an self-aligned STI structure 446. The method 300 avoids ONO residual stringers at STI edges in the periphery region, reduces active region losses, reduces thinning of the periphery gate oxide and the ONO at the STI edge, and reduces dopant diffusion during isolation implantations due to reduced thermal process steps.

Owner:MONTEREY RES LLC

Organometallic compounds, processes for the preparation thereof and methods of use thereof

InactiveUS20090209777A1Improve propertiesDesired morphologyRuthenium organic compoundsChemical vapor deposition coatingGas phaseElectron donor

Owner:PRAXAIR TECH INC

Semiconductor device and manufacturing method thereof

InactiveUS7999317B2Avoid excessive diffusionSuppress a punchthrough occurring in the channelTransistorSemiconductor/solid-state device manufacturingBody regionImpurity

A p-type body region and an n-type buffer region are formed on an n− drift region. An n++ emitter region and a p++ contact region are formed on the p-type body region in contact with each other. A p++ collector region is formed on the n-type buffer region. An insulating film is formed on the n− drift region, and a gate insulating film is formed on the n++ emitter region, the p-type body region, and the n drift region. A gate electrode is formed on the insulating film and the gate insulating film. A p+ low-resistivity region is formed in the p-type body region and surrounding the interface between the n++ emitter region and between the p-type body region and the p++ contact region. The p-type body region has two local maxima of an impurity concentration profile at the interface between the body region and the gate insulating film.

Owner:FUJI ELECTRIC CO LTD

Trench power MOSFET fabrication using inside/outside spacers

ActiveUS7390717B2Increase cell densityReduce widthSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceSemiconductor package

Owner:INFINEON TECH AMERICAS CORP

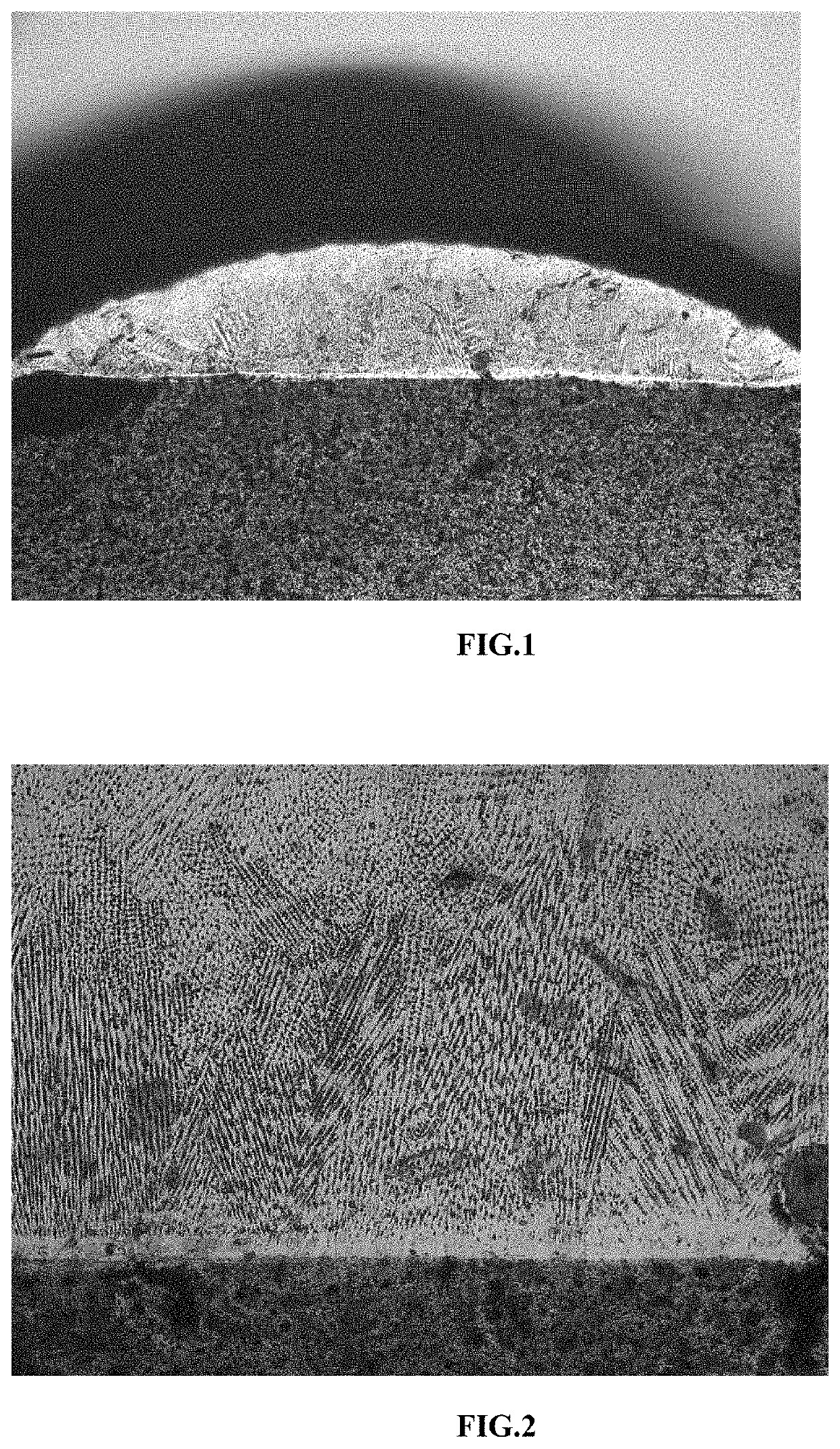

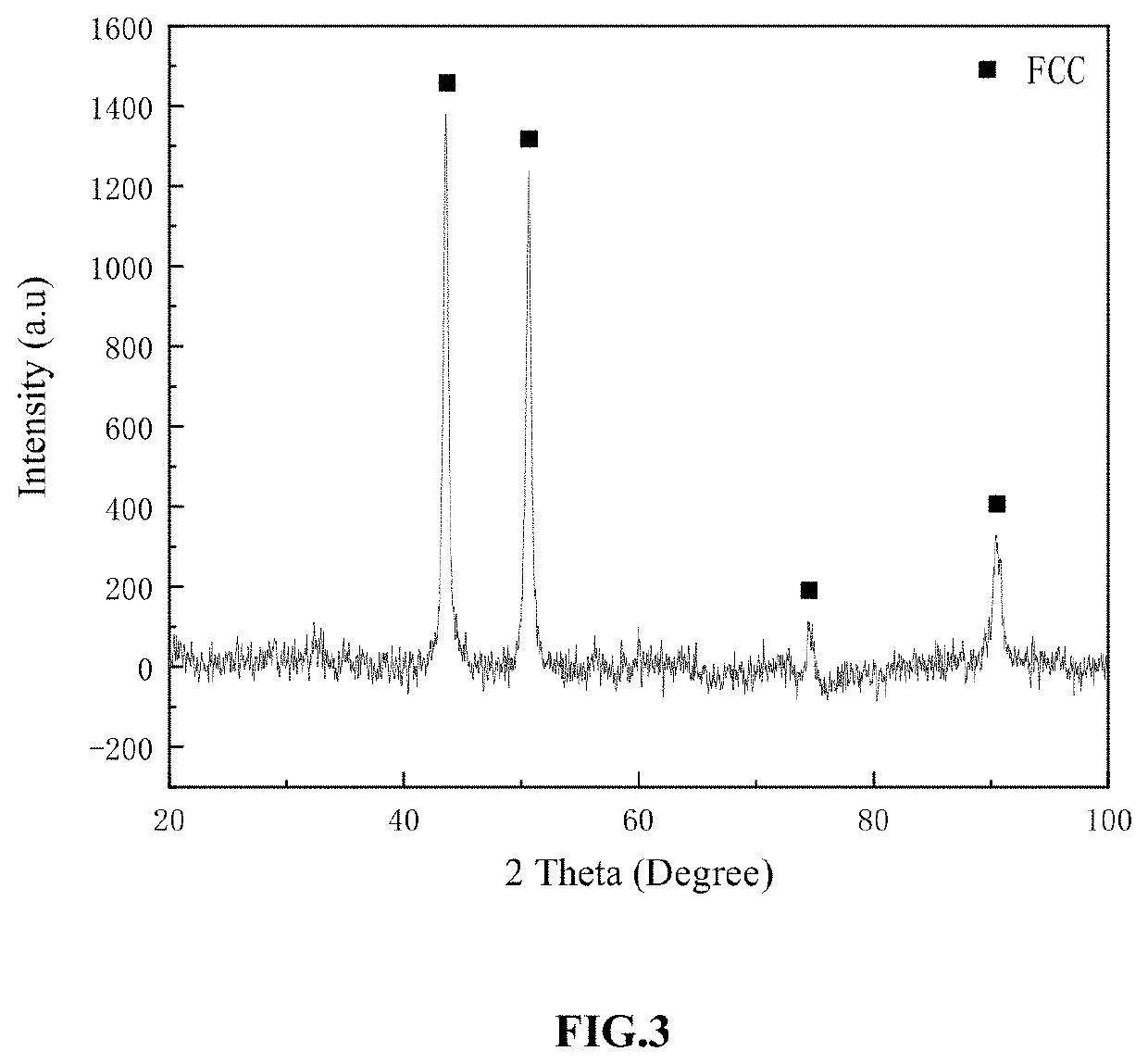

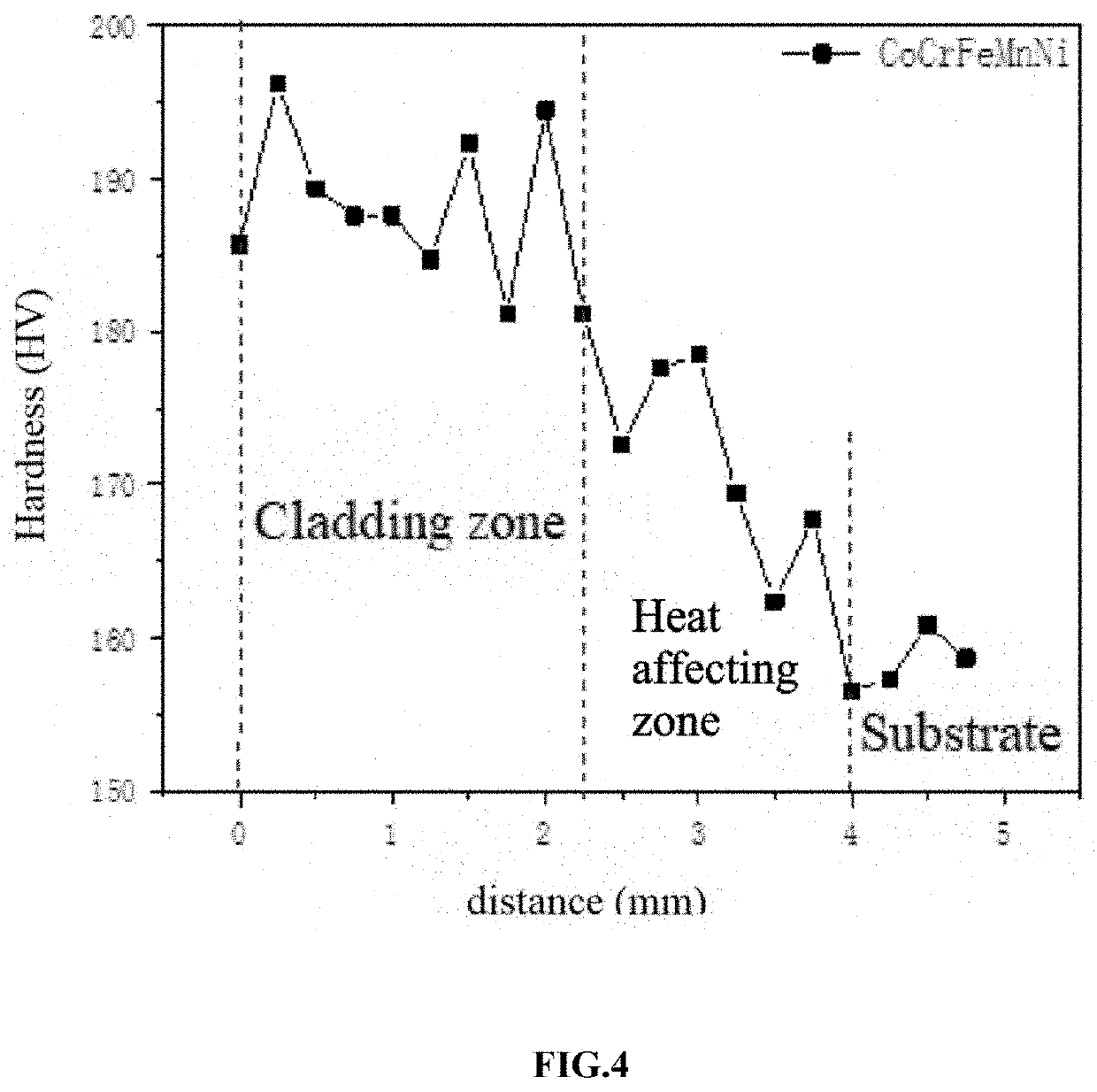

High entropy alloy powder for laser cladding and application method thereof

PendingUS20220097133A1High energy densityHigh cool speedAdditive manufacturing apparatusTransportation and packagingHigh entropy alloysTemperature treatment

The present disclosure discloses a high-entropy alloy powder for laser cladding and a use method thereof. The alloy powder is CoCrFeMnNiCx, and x has a value of 0.1-0.15. The specific method includes: subjecting a 45 steel substrate to surface pretreatment, mixing the weighed CoCrFeMnNi high-entropy alloy powder with different content of a nano-C powder uniformly and pre-placed on the pre-treated substrate surface to form a prefabricated layer, then placing the prefabricated layer at 80-90° C. for constant temperature treatment for 8-12 h, and under a protective atmosphere, subjecting the cladding powder to laser cladding on the surface of the 45 steel. The method of the present disclosure prepares a CoCrFeMnNiCx high-entropy alloy coating with performance superior to the CoCrFeMnNi high-entropy alloy coating.

Owner:KUNMING UNIV OF SCI & TECH

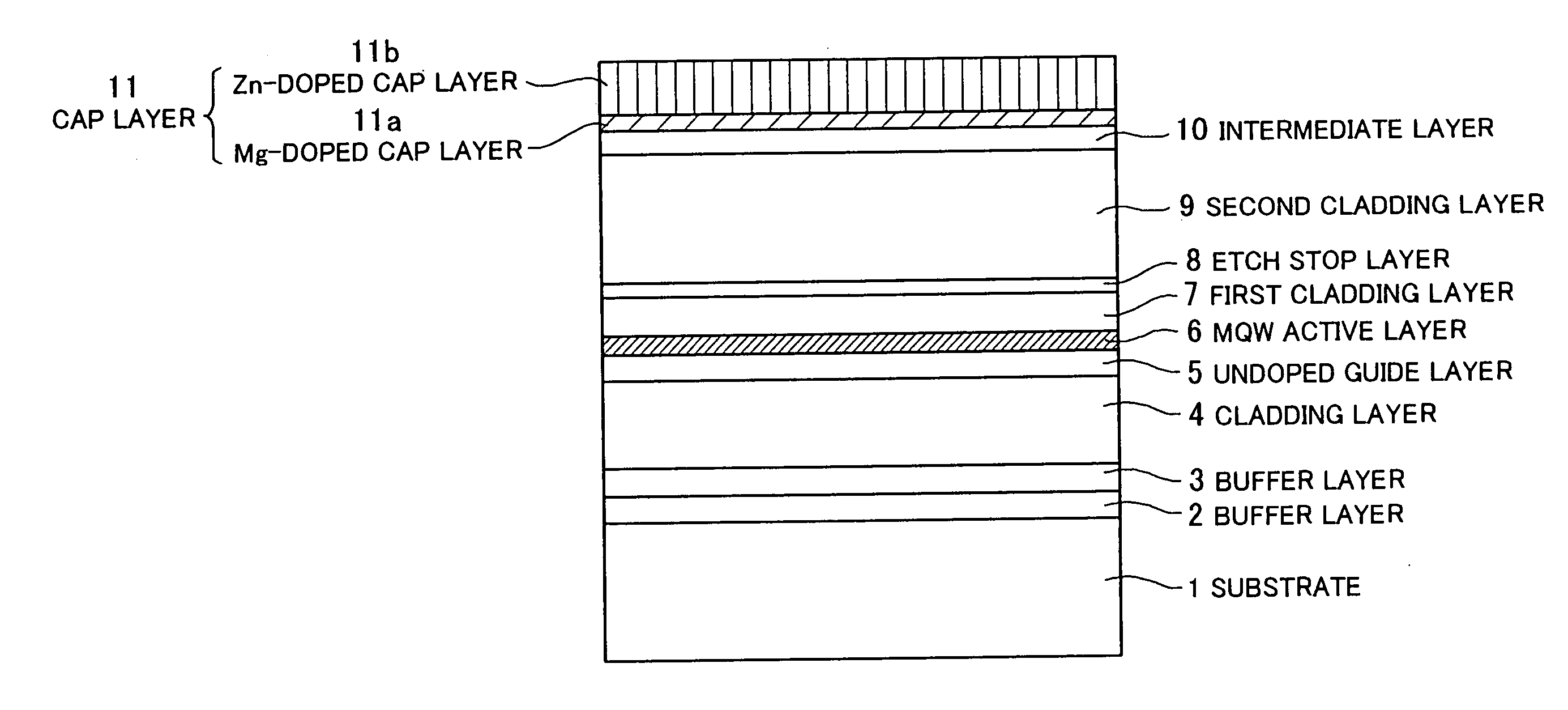

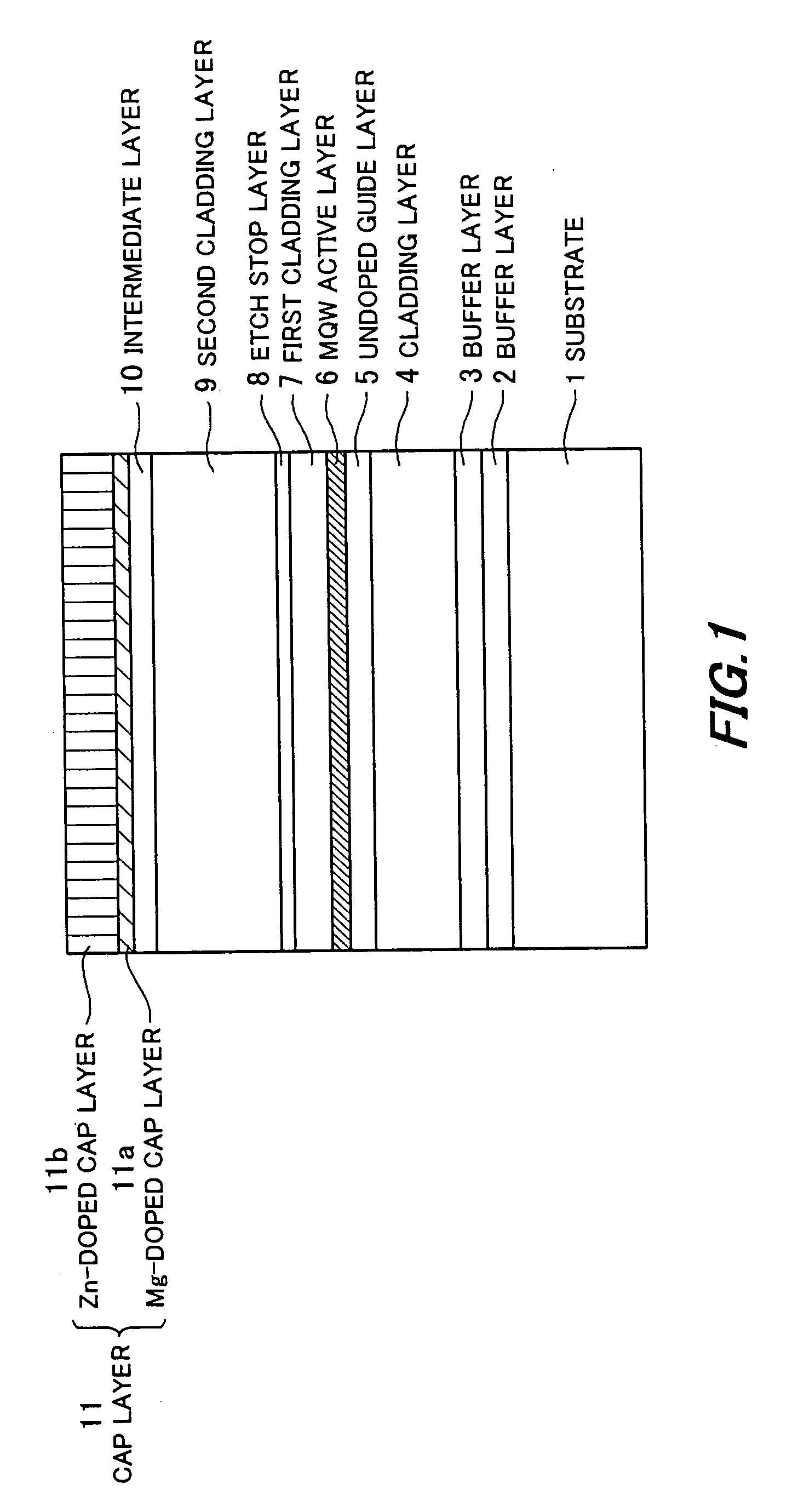

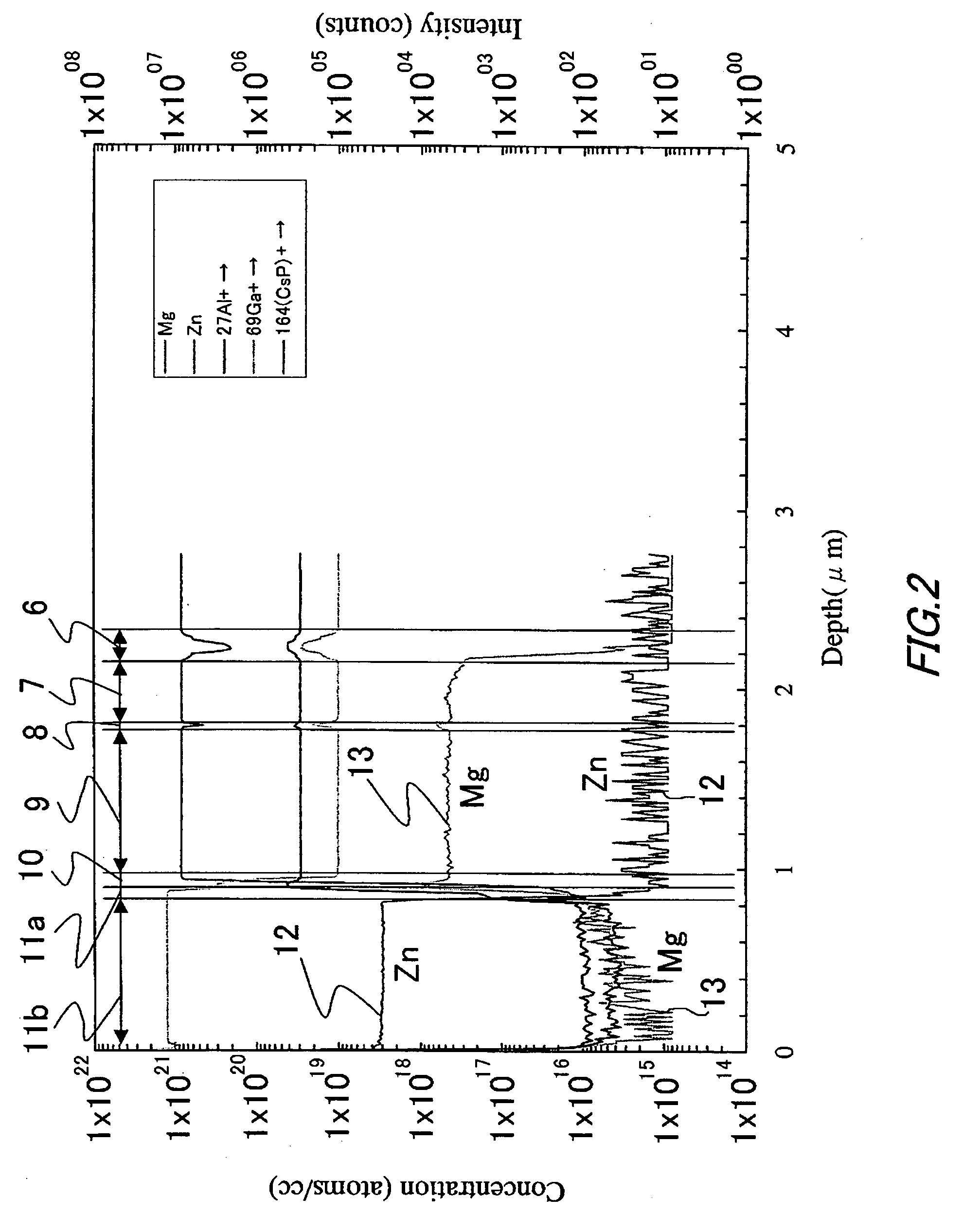

Epitaxial wafer for semiconductor light-emitting devices, and semiconductor light-emitting device

InactiveUS20060001042A1Avoid excessive diffusionExcellent in high-powerSolid-state devicesSemiconductor devicesDopantZn doped

An epitaxial wafer for semiconductor light-emitting devices has an n-type substrate, on which are sequentially formed an n-type cladding layer, an active layer, a p-type cladding layer having Mg as a p-type dopant, and a p-type cap layer. The p-type cap layer has at least two Mg-doped and Zn-doped layers that are formed sequentially from the substrate side.

Owner:HITACHI CABLE

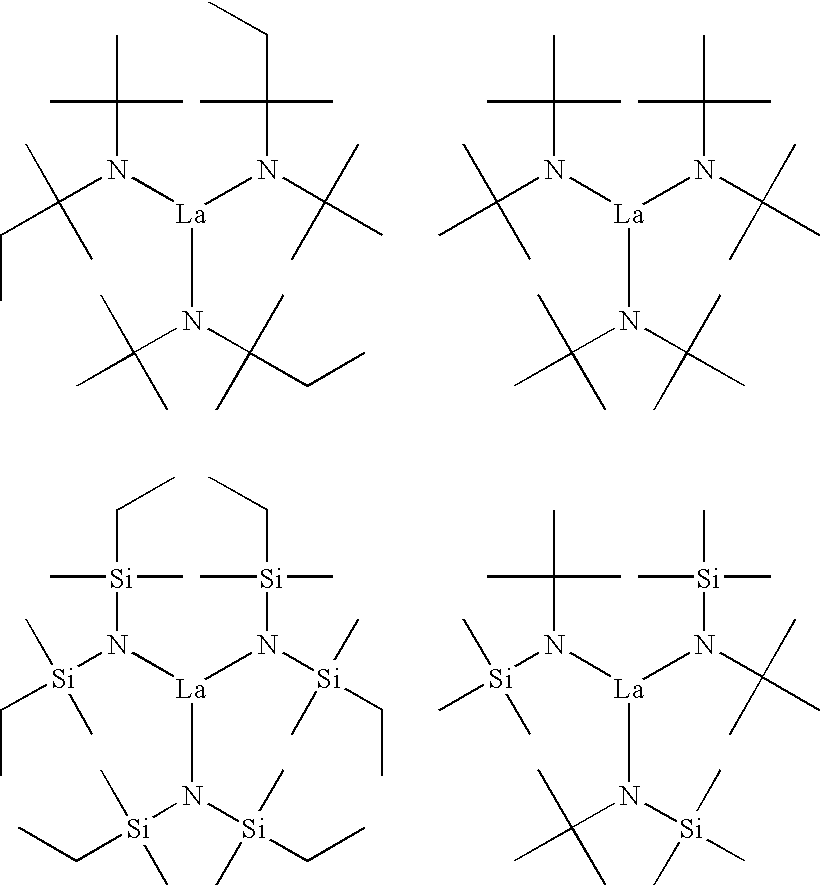

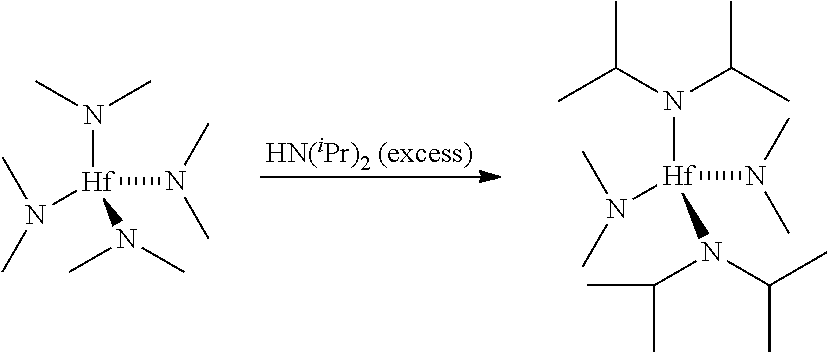

Organometallic compounds having sterically hindered amides

ActiveUS20080032062A1Improve propertiesDesired morphologySilicon organic compoundsGroup 3/13 organic compounds without C-metal linkagesHeteroatomOxidation state

This invention relates to organometallic compounds represented by the formula M(NR1R2)x wherein M is a metal or metalloid, R1 is the same or different and is a hydrocarbon group or a heteroatom-containing group, R2 is the same or different and is a hydrocarbon group or a heteroatom-containing group; R1 and R2 can be combined to form a substituted or unsubstituted, saturated or unsaturated cyclic group; R1 or R2 of one (NR1R2) group can be combined with R1 or R2 of another (NR1R2) group to form a substituted or unsubstituted, saturated or unsaturated cyclic group; x is equal to the oxidation state of M; and wherein said organometallic compound has (i) a steric bulk sufficient to maintain a monomeric structure and a coordination number equal to the oxidation state of M with respect to anionic ligands, and (ii) a molecular weight sufficient to possess a volatility suitable for vapor deposition.; a process for producing the organometallic compounds, and a method for producing a film or coating from organometallic precursor compounds.

Owner:PRAXAIR TECH INC

Organometallic compounds, processes for the preparation thereof and methods of use thereof

InactiveUS20090200524A1Improve responseImprove propertiesRuthenium organic compoundsConductive materialGas phaseElectron donor

This invention relates to organometallic compounds having the formula L1ML2 wherein M is a metal or metalloid, L1 is a substituted or unsubstituted 6 electron donor anionic ligand, and L2 is a substituted or unsubstituted 6 electron donor anionic ligand, wherein L1 and L2 are the same or different, a process for producing the organometallic compounds, and a method for producing a film or coating from the organometallic compounds. The organometallic compounds are useful in semiconductor applications as chemical vapor or atomic layer deposition precursors for film depositions.

Owner:PRAXAIR TECH INC

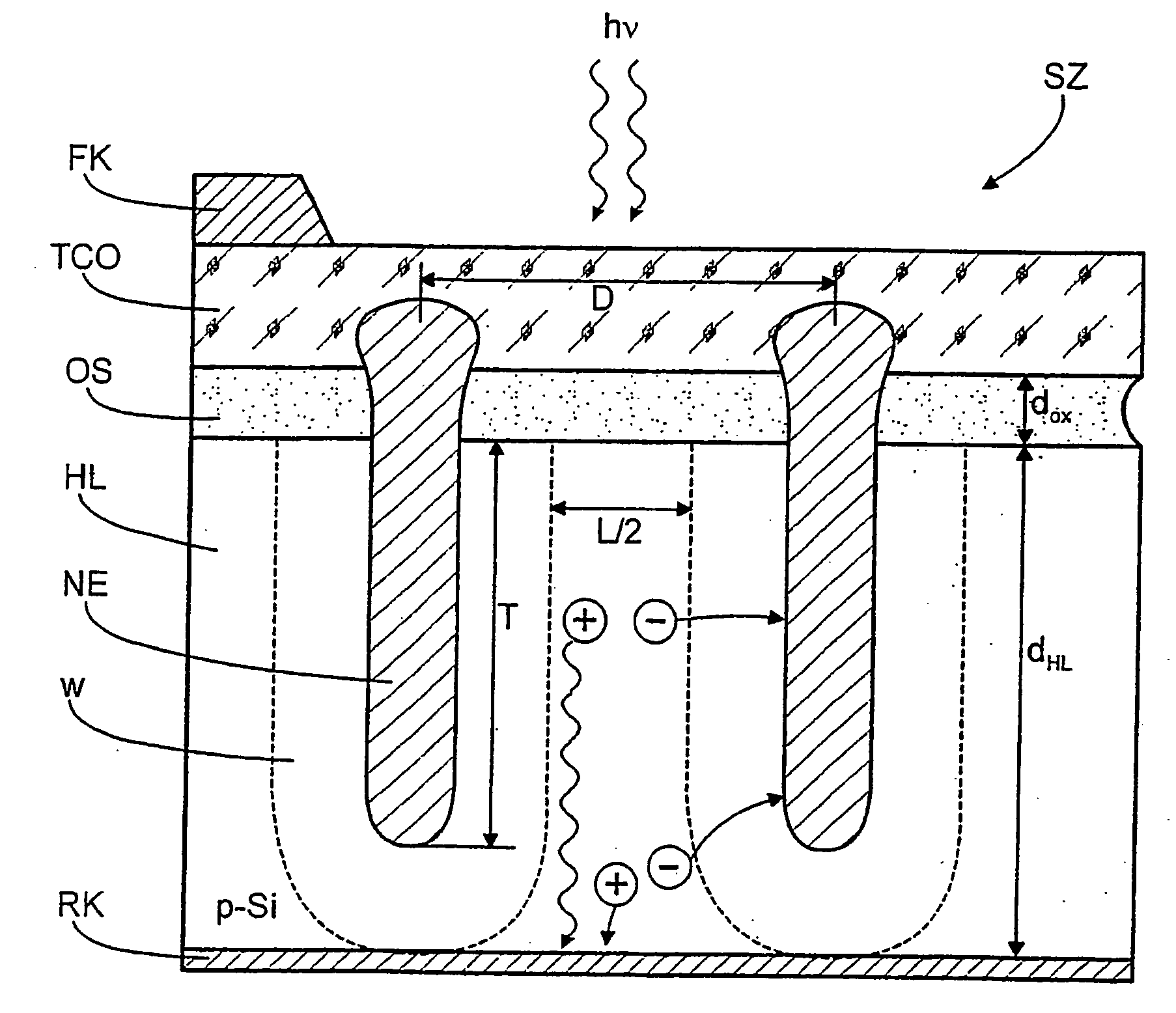

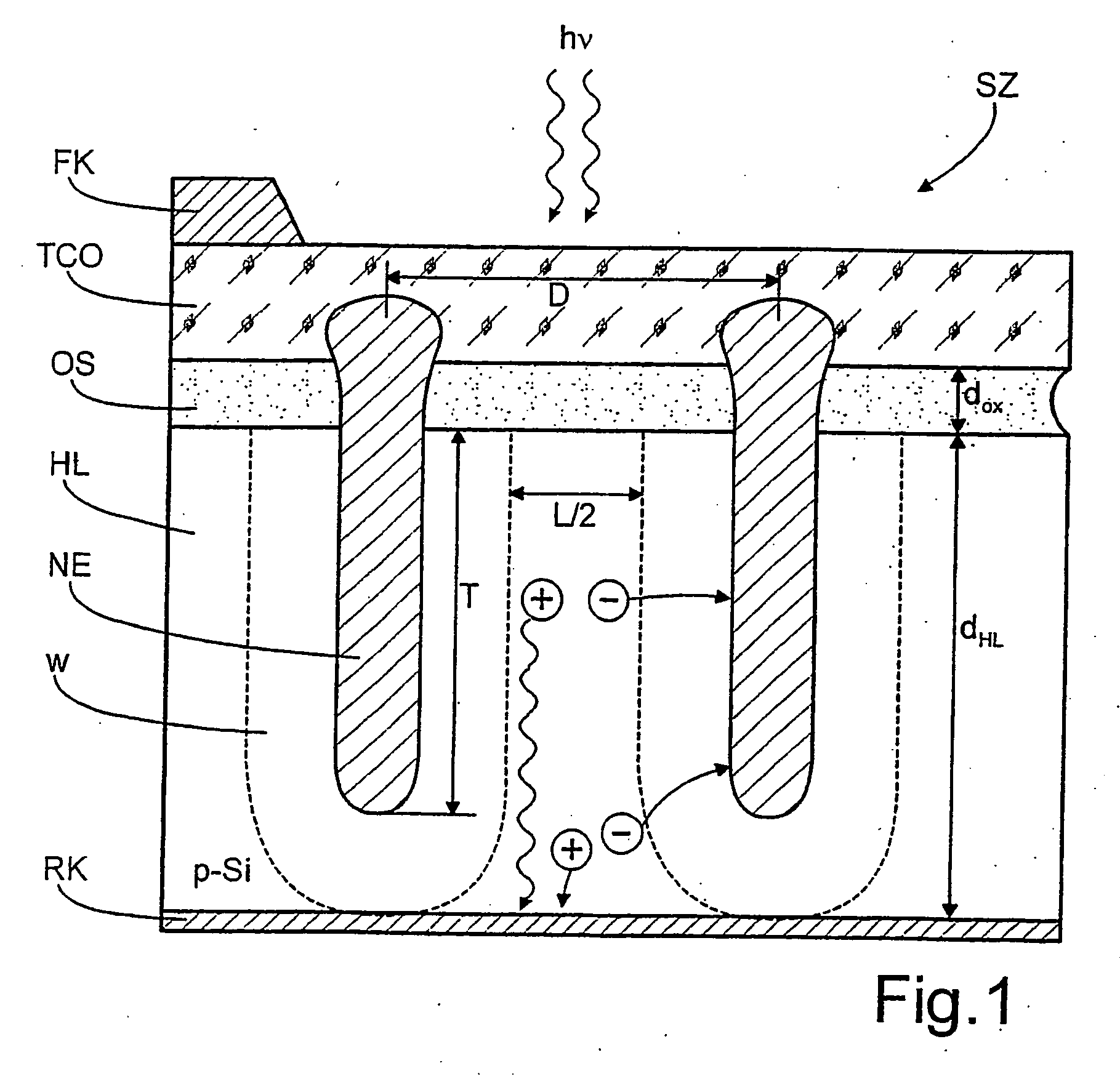

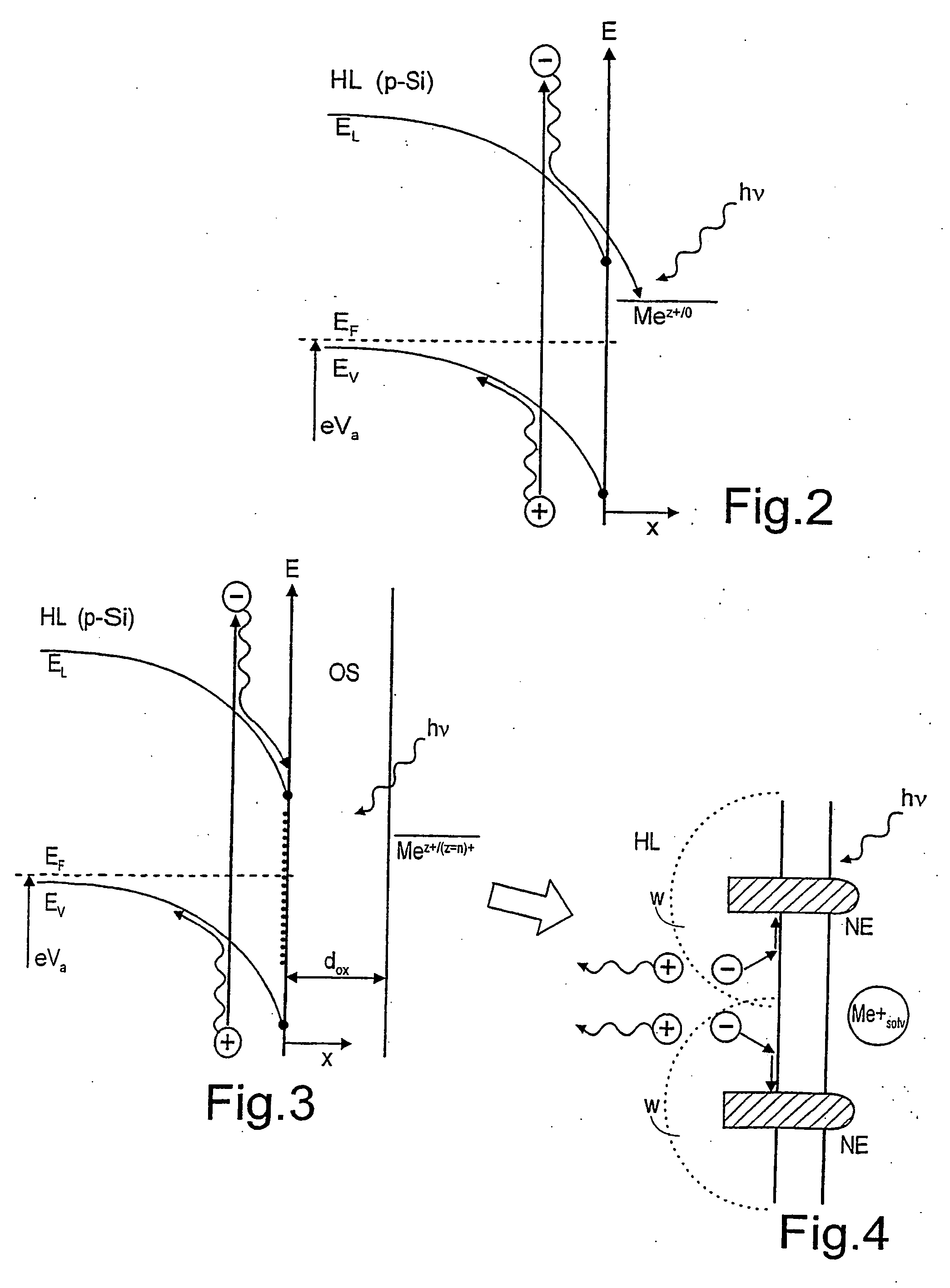

Photovoltaic solar cell...

InactiveUS20070028957A1Reduce complexityLow costPV power plantsFinal product manufactureEngineeringPhotocurrent

A photovoltaic solar cell (SZ) of improved light-to-current conversion properties is provided with nano emitters (NE) of acicular or rib-like form and are separated from each other at a uniform distance D≦√{square root over (2)}L and penetrating to a penetration depth T≥dHL-L2+winto the semiconductor layer (HL).

Owner:HELMHOLTZ ZENT BERLIN FUER MATERIALIEN & ENERGIE GMBH

Heteroleptic organometallic compounds

ActiveUS7956207B2Improve propertiesDesired morphologyTitanium organic compoundsGroup 3/13 element organic compoundsChemical compoundHeteroatom

This invention relates to organometallic compounds represented by the formula (L1)xM(L2)y wherein M is a metal or metalloid, L1 and L2 are different and are each a hydrocarbon group or a heteroatom-containing group; x is a value of at least 1; y is a value of at least 1; x+y is equal to the oxidation state of M; and wherein (i) L1 has a steric bulk sufficiently large such that, due to steric hinderance, x cannot be a value equal to the oxidation state of M, (ii) L2 has a steric bulk sufficiently small such that, due to lack of steric hinderance, y can be a value equal to the oxidation state of M only in the event that x is not a value of at least 1, and (iii) L1 and L2 have a steric bulk sufficient to maintain a heteroleptic structure in which x+y is equal to the oxidation state of M; a process for producing the organometallic compounds, and a method for producing a film or coating from organometallic precursor compounds.

Owner:PRAXAIR TECH INC