Patents

Literature

34results about How to "Reduce delay time" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

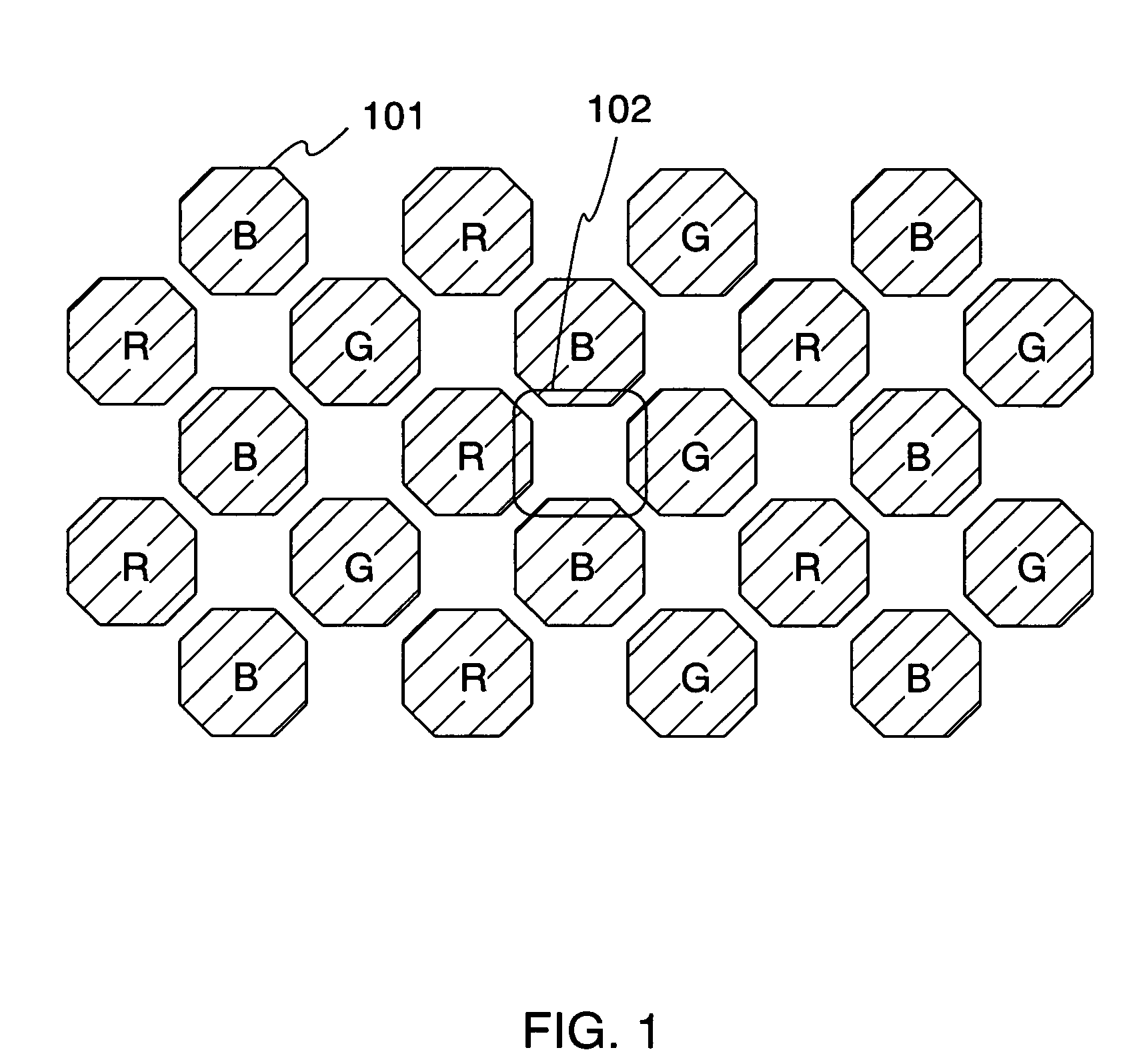

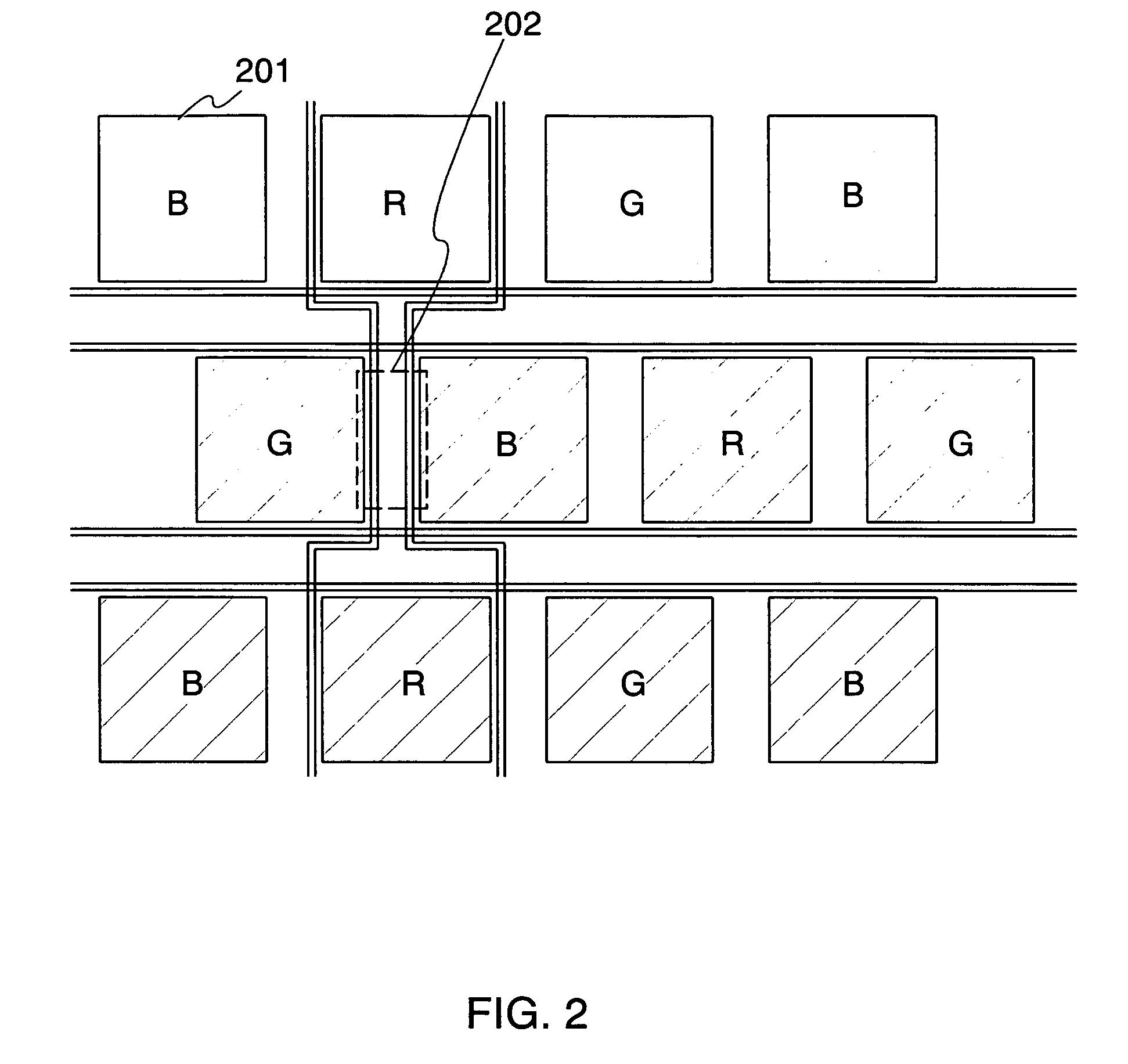

Display device, and computer, camera, portable information terminal device, image reproducing device, clock, mobile phone device and other electronic apparatuses using the display device

InactiveUS20060274090A1Reduce delay timeConvenient ArrangementElectrical apparatusElectroluminescent light sourcesDisplay deviceMobile phone

In a display device using a delta arrangement, in a case where a circuit of a large number of elements such as a static memory is arranged every pixel, a wire becomes complicated to cause wiring delay. A shape of a pixel electrode is formed polygonally to arrange in a case where the number of elements such as a static memory is large or in a case where an area of an element required to be included in a pixel is large in a delta arrangement. The shape of the pixel electrode is arranged in a polygon so that a wire along a pixel shape can be used. Even in a case of a pixel with a large number of elements, parasitic resistance of a wire and parasitic capacitance of a wire can be reduced so that wiring delay can be solved.

Owner:SEMICON ENERGY LAB CO LTD

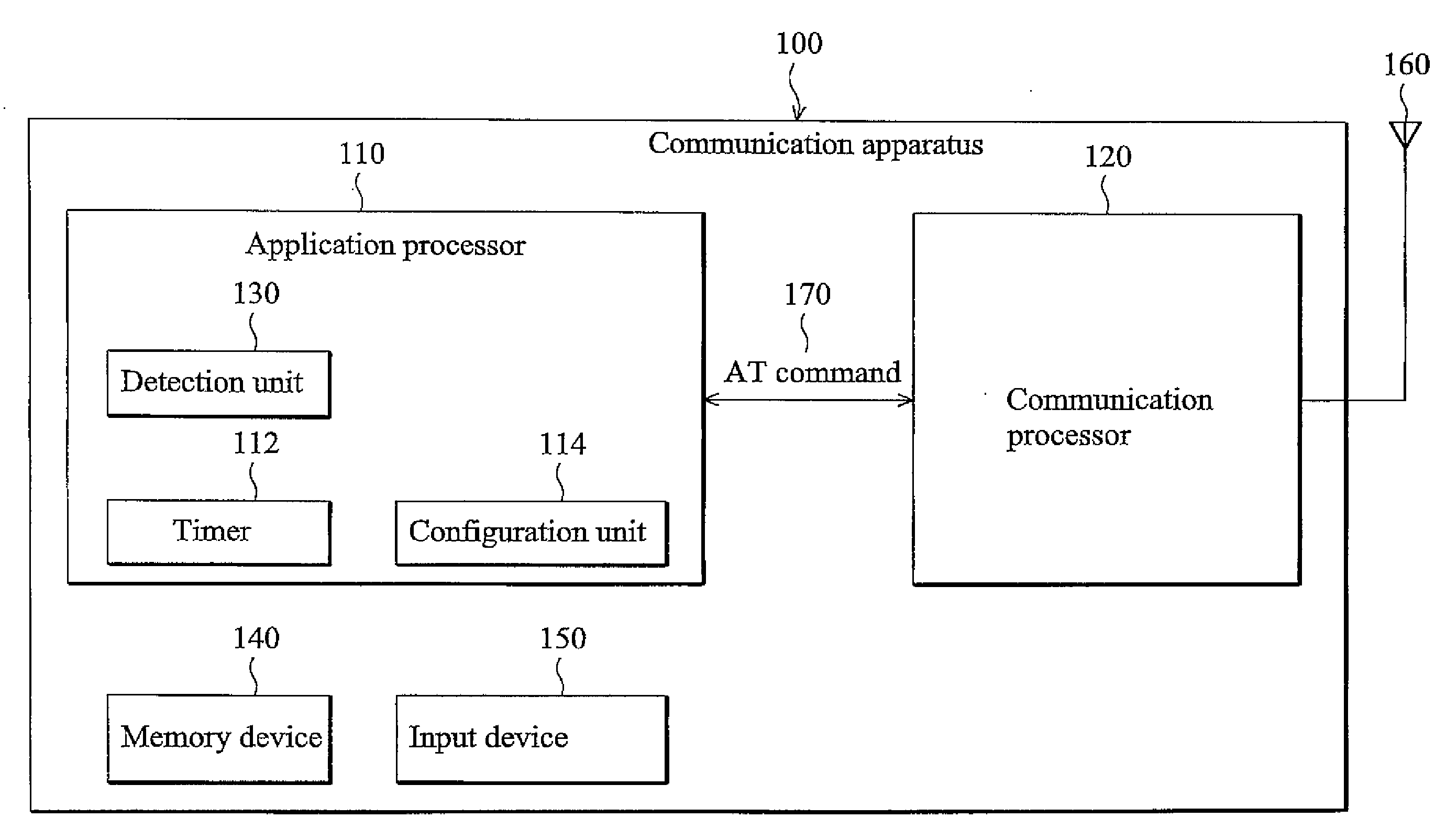

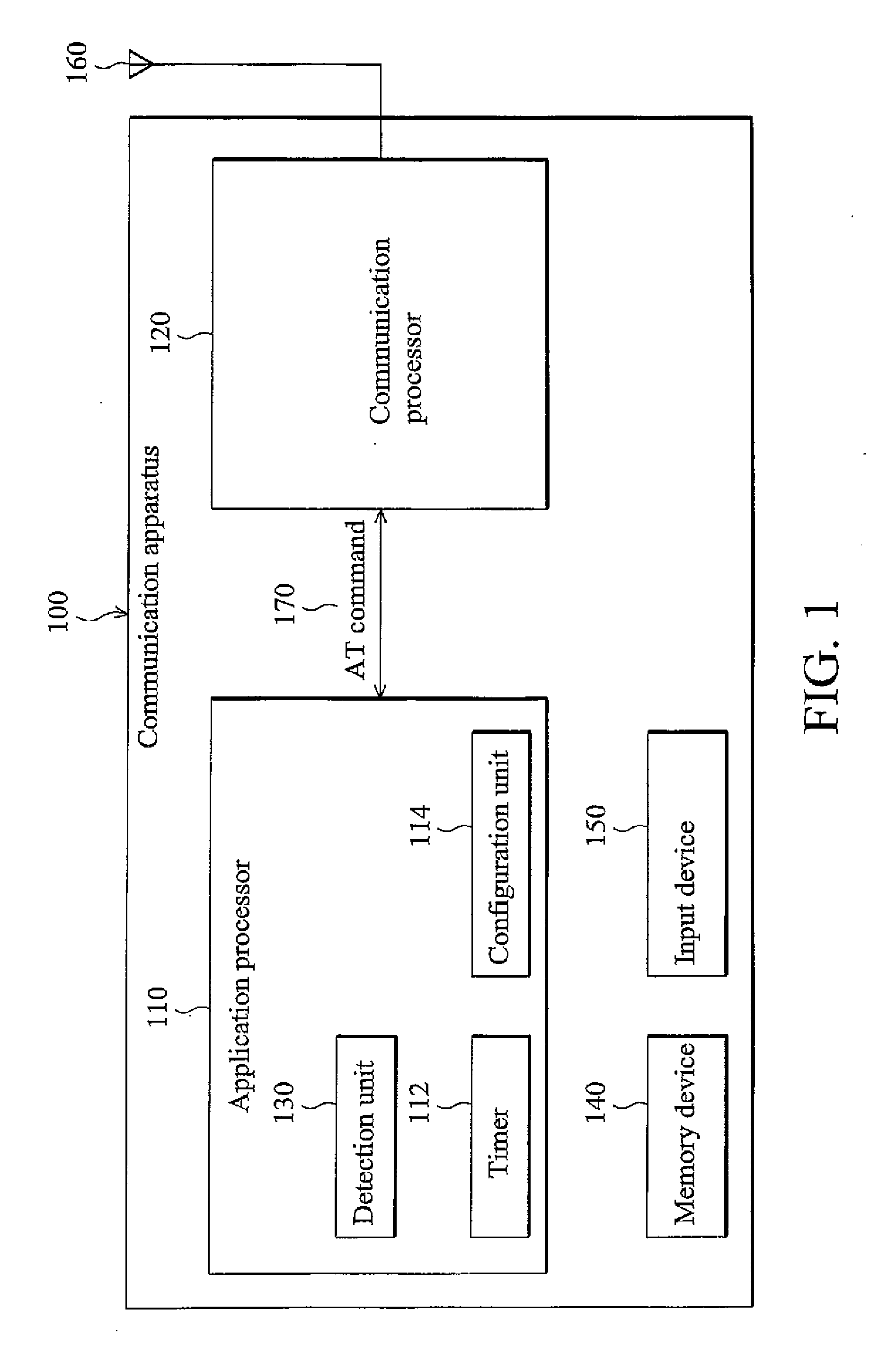

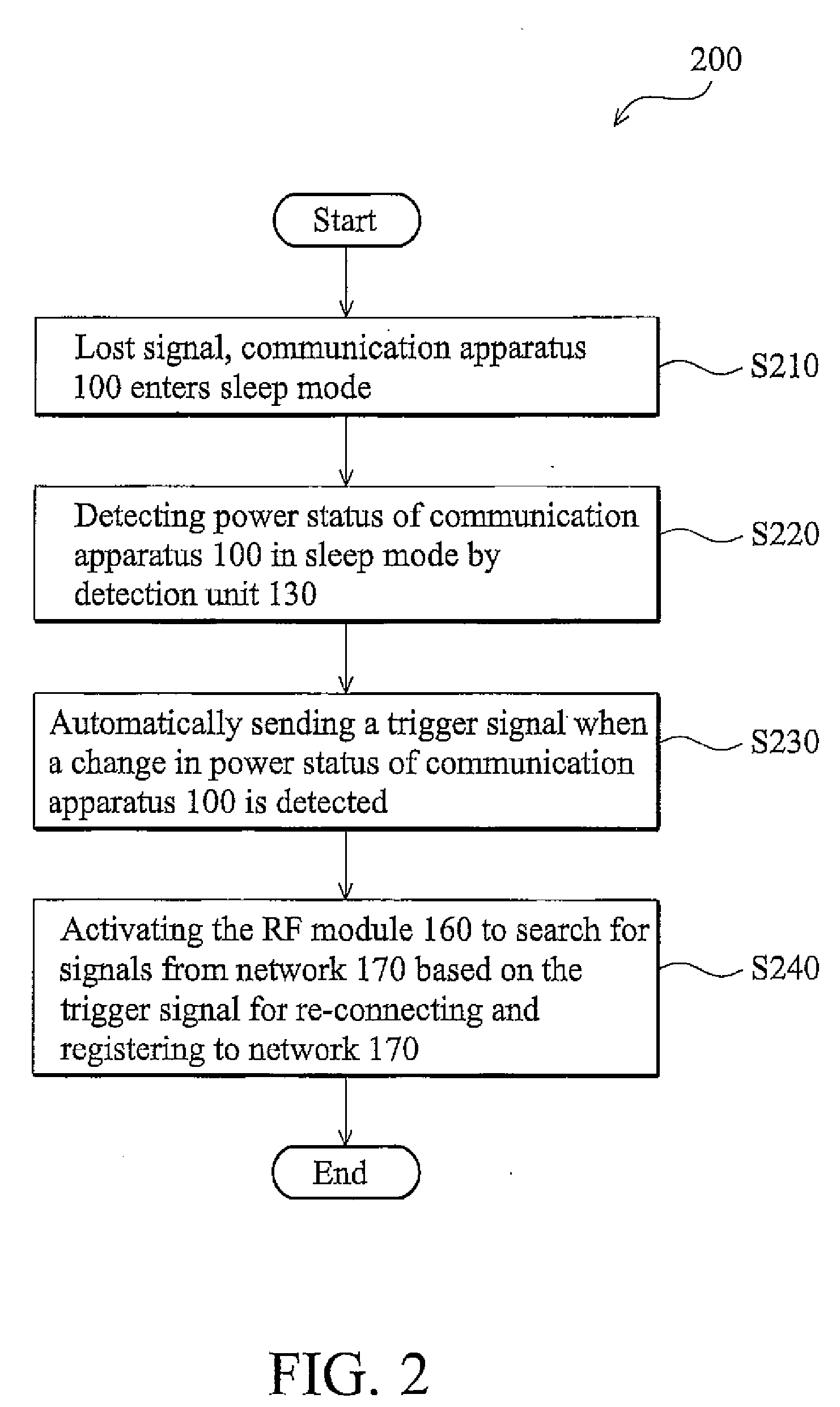

Communication apparatus and network search method thereof

InactiveUS20090073871A1Reduce delay timeImprove conveniencePower managementError preventionRadio frequencyNetwork method

A network search method for a communication apparatus connected to a network is disclosed. The method comprises the following steps. The communication apparatus enters a sleep mode when the communication apparatus loses signals from the network. Then, power status of the communication apparatus is detected. A trigger signal is automatically sent when a change in power status of the communication apparatus is found. Next, a radio frequency module is enabled to search for the signals from the network according to the trigger signal so as to re-connect to the network.

Owner:HTC CORP

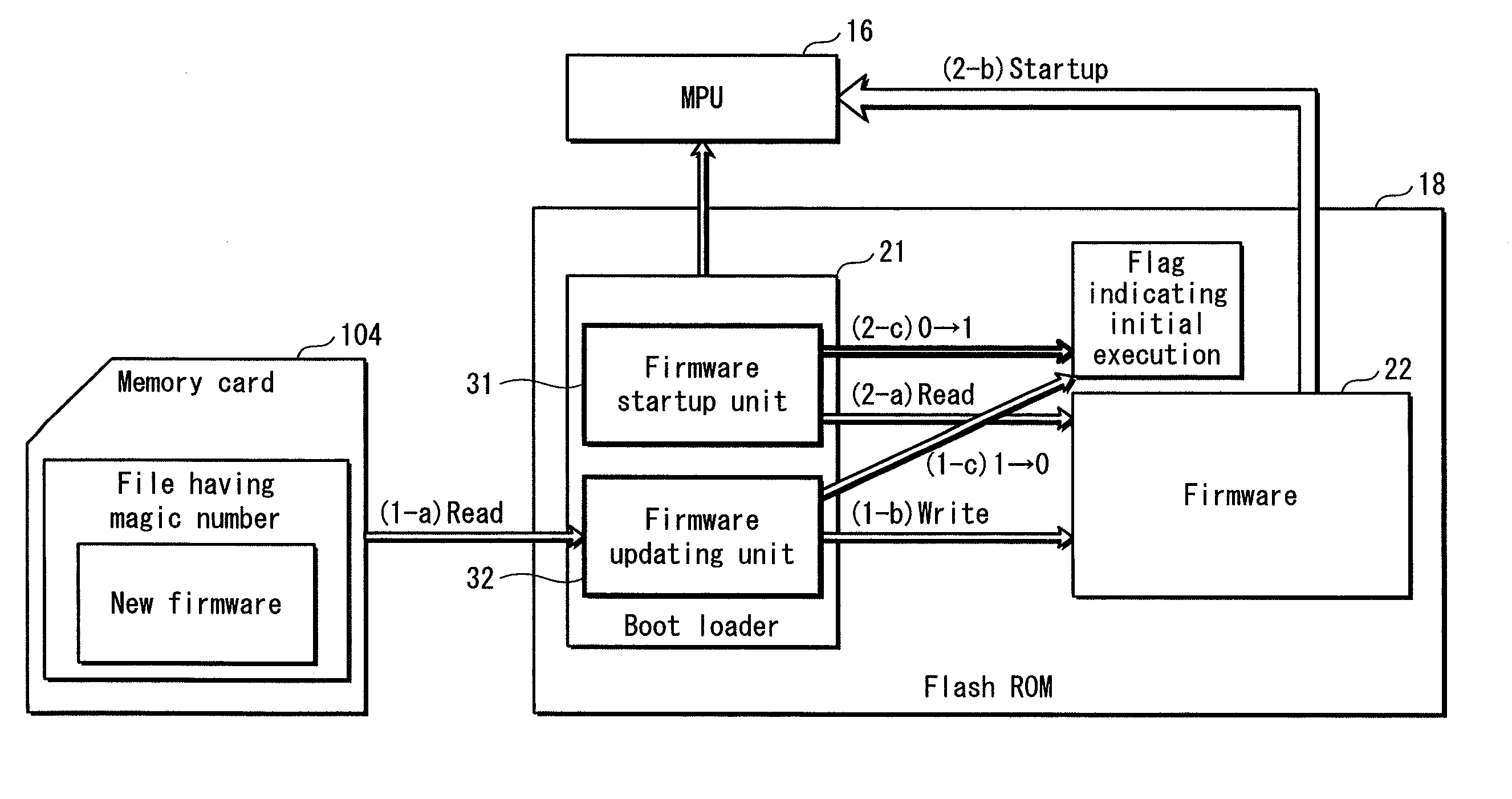

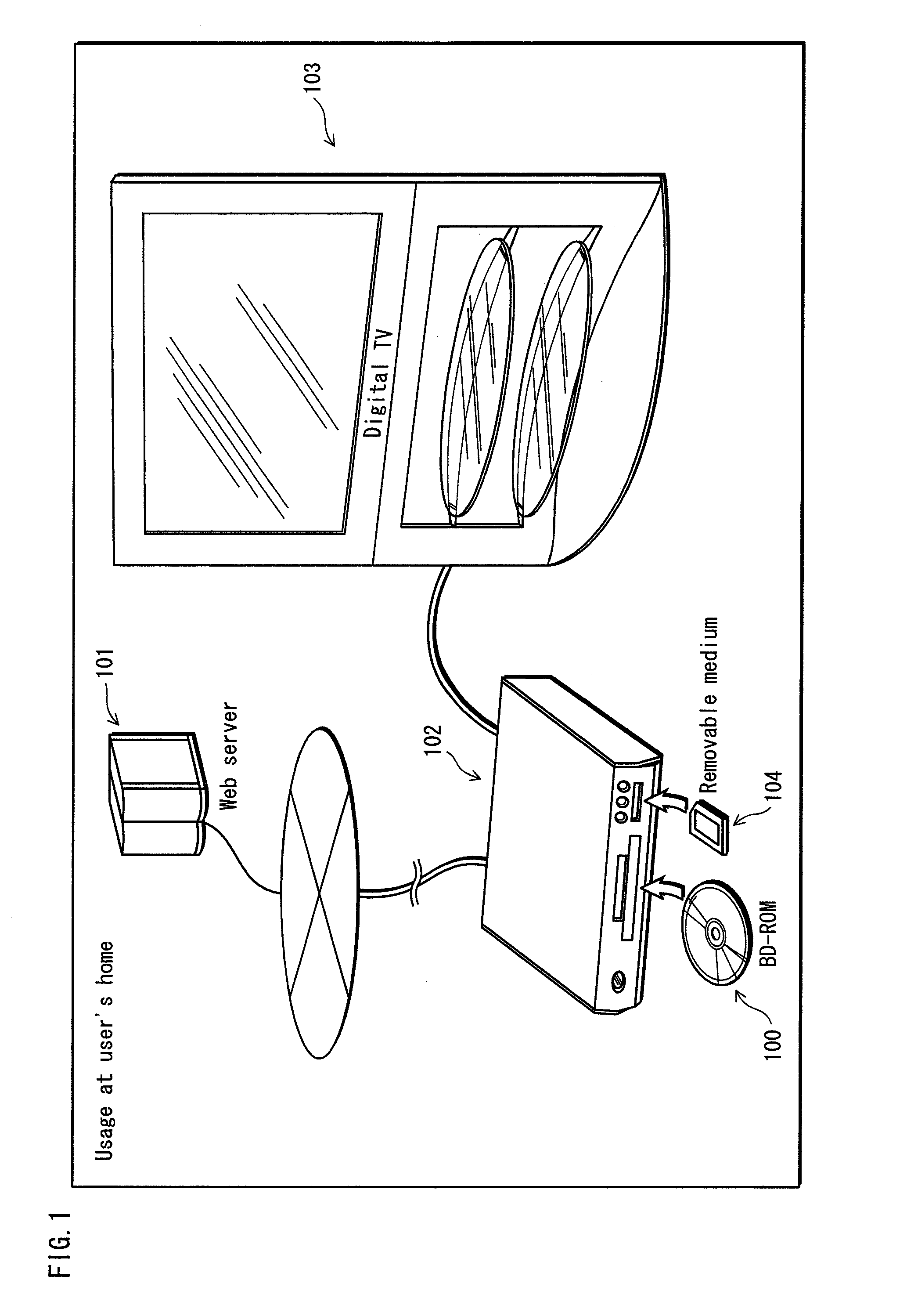

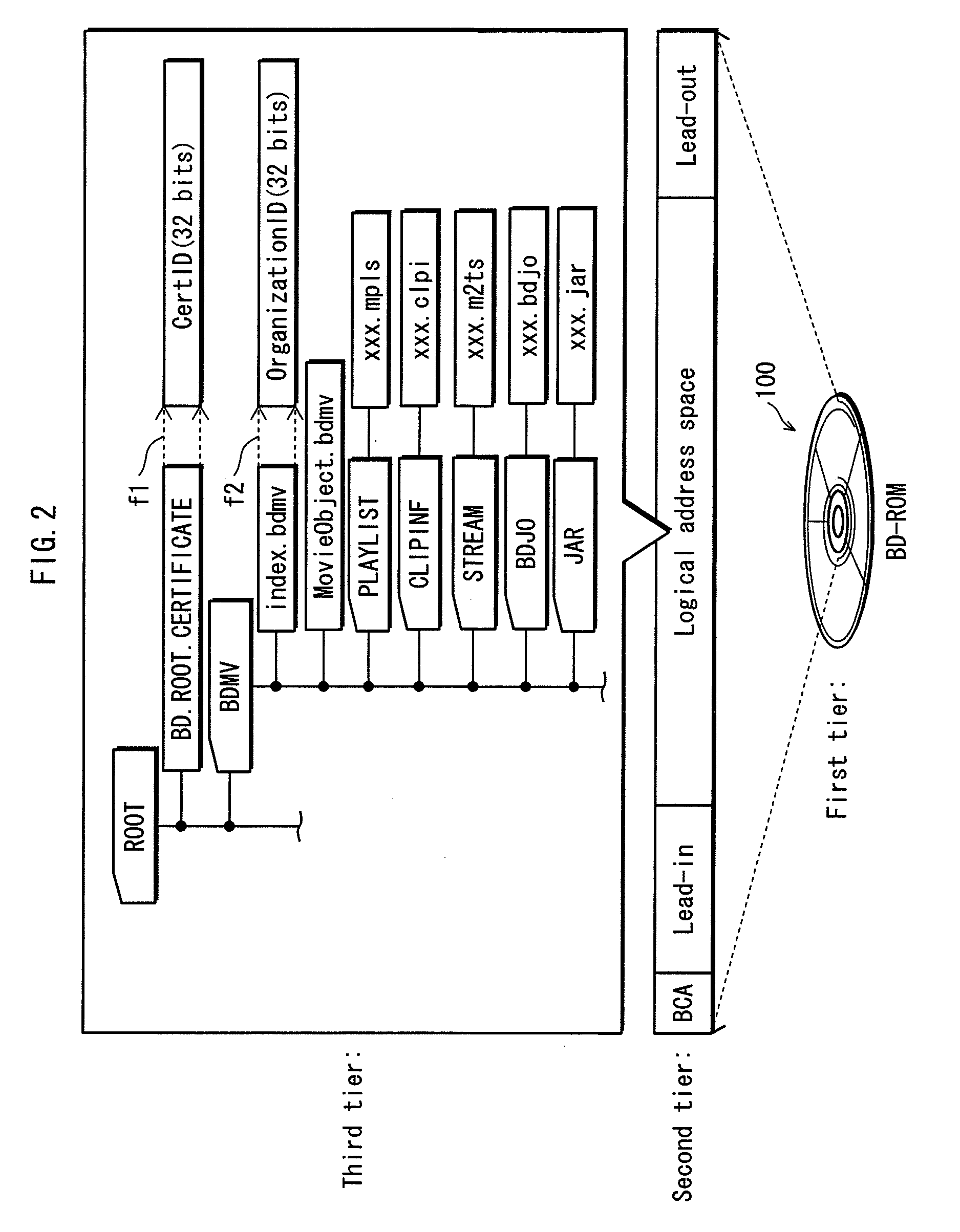

Reproducing apparatus, system lsi, and initialization method

InactiveUS20100031347A1Preventing delay of startRapid responseLink editingDigital data processing detailsFirmwareComputer engineering

Hardware of a playback apparatus 102 includes a drive 1 and a decoder, and firmware 22 of the playback apparatus 102 accesses a BD-ROM loaded on a drive 1, according to a BD-J application, to bring the decoder into AV playback operations. The drive unit constitutes a local storage. A benchmark score is built in the firmware 22 in advance. The benchmark score shows a turn-around time from when a processing request is made to the hardware via the firmware 22 to when a response returns. Such a benchmark score is written into an application data area in the local storage when the firmware 122 is initially executed.

Owner:PANASONIC CORP

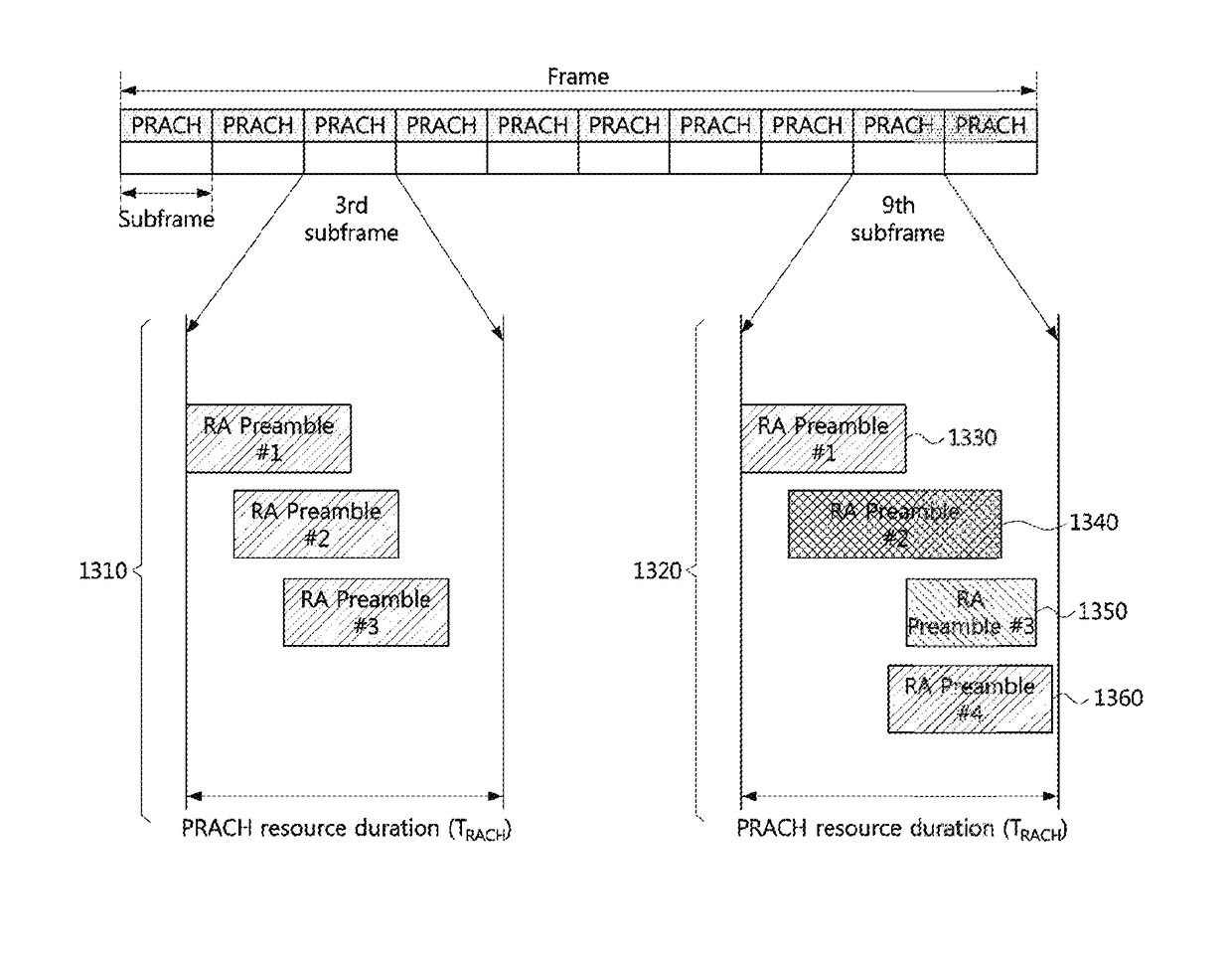

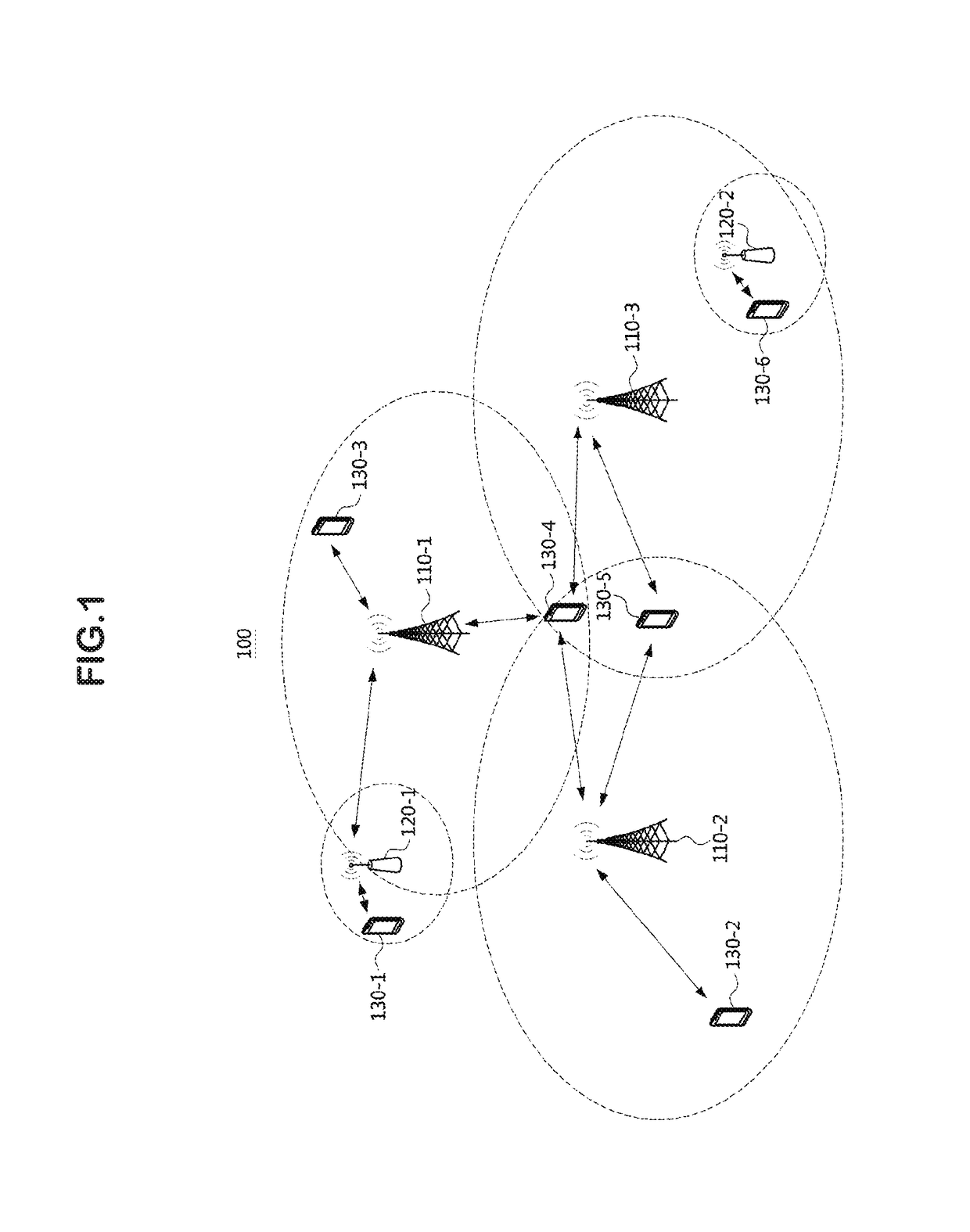

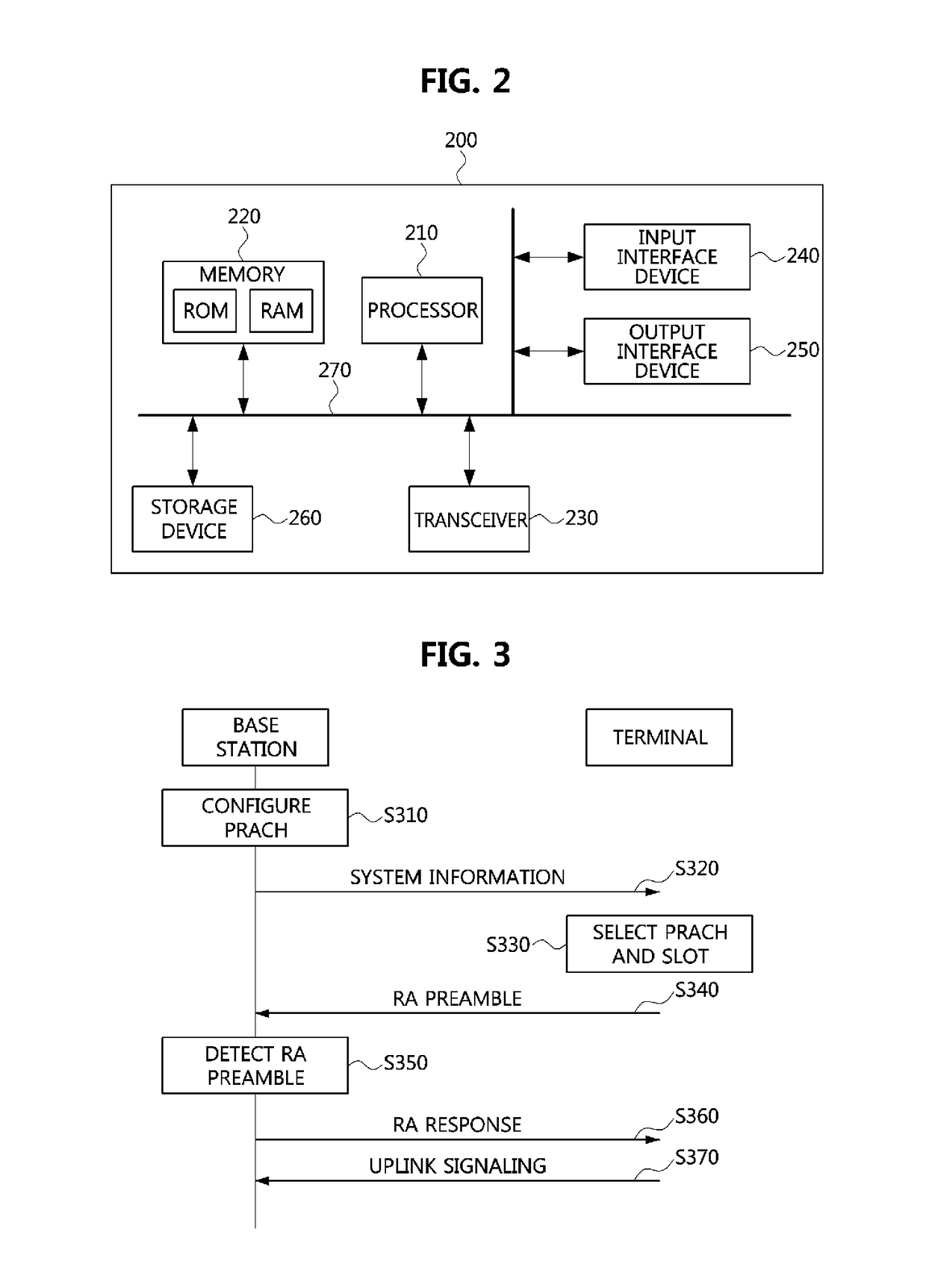

Method for random access in wireless communication system and apparatus for the same

ActiveUS20180220466A1Increase resource consumptionReduce delay timeWireless communicationPreambleSystem information

Disclosed are a random access method and a random access apparatus in a wireless communication system. An operation method of a terminal in a communication system, according to the present invention, comprises receiving system information including configuration information on a physical random access channel (PRACH) composed of a plurality of access slots from a first base station; selecting one access slot among the plurality of access slots based on the configuration information; and transmitting a random access preamble to the first base station through the one access slot. Therefore, the capacity of the random access channel can be increased without further occupation of radio resources.

Owner:ELECTRONICS & TELECOMM RES INST

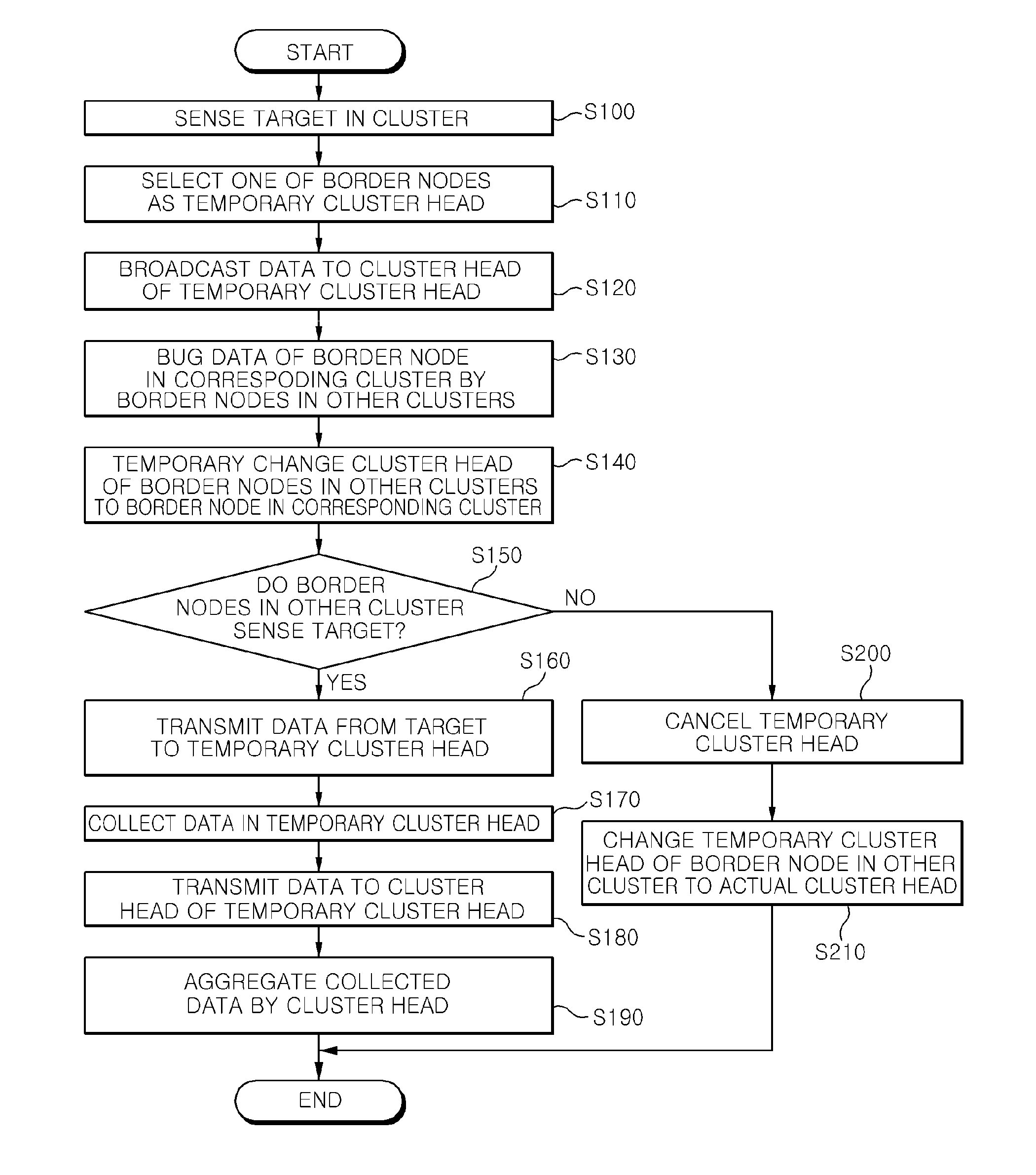

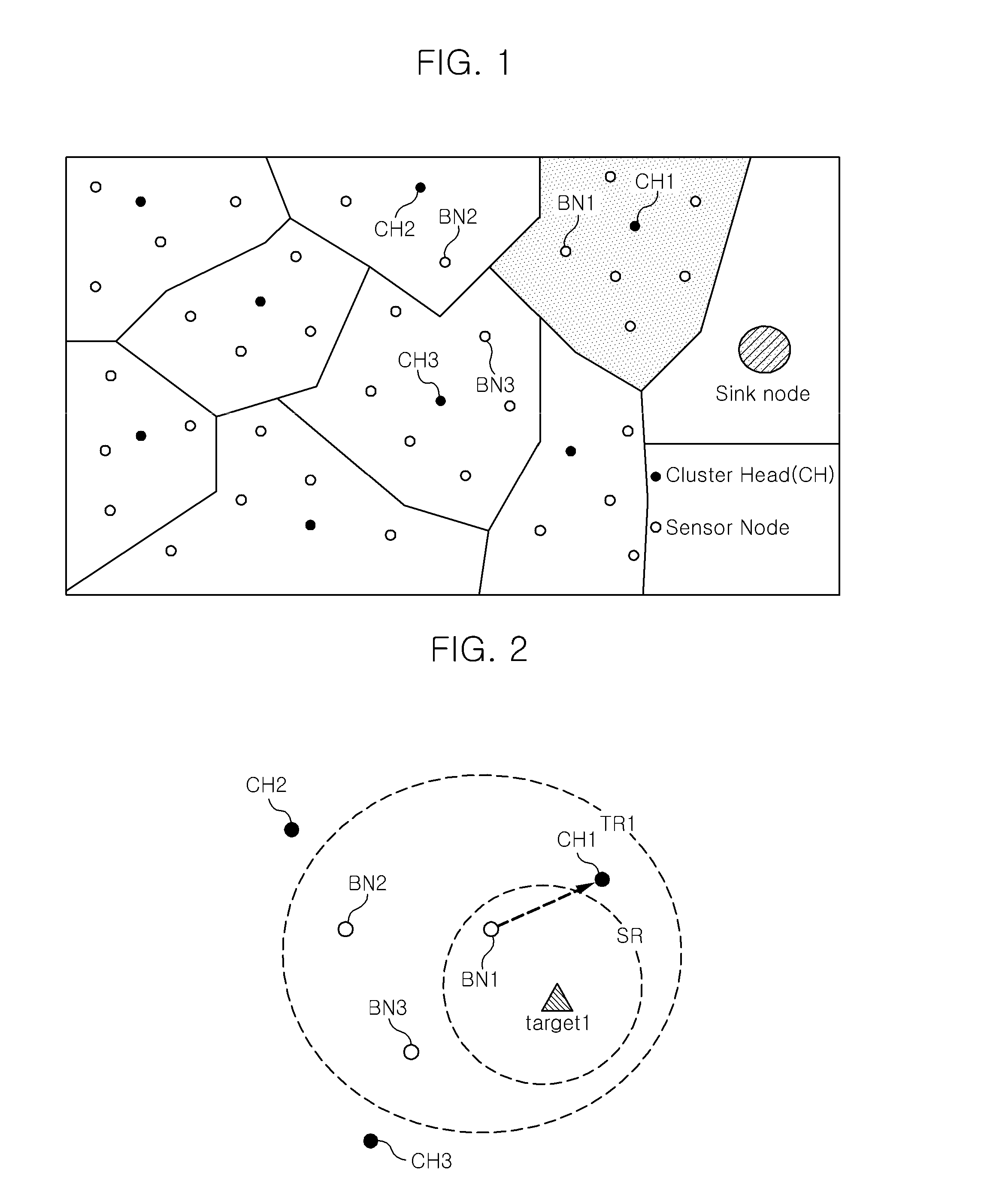

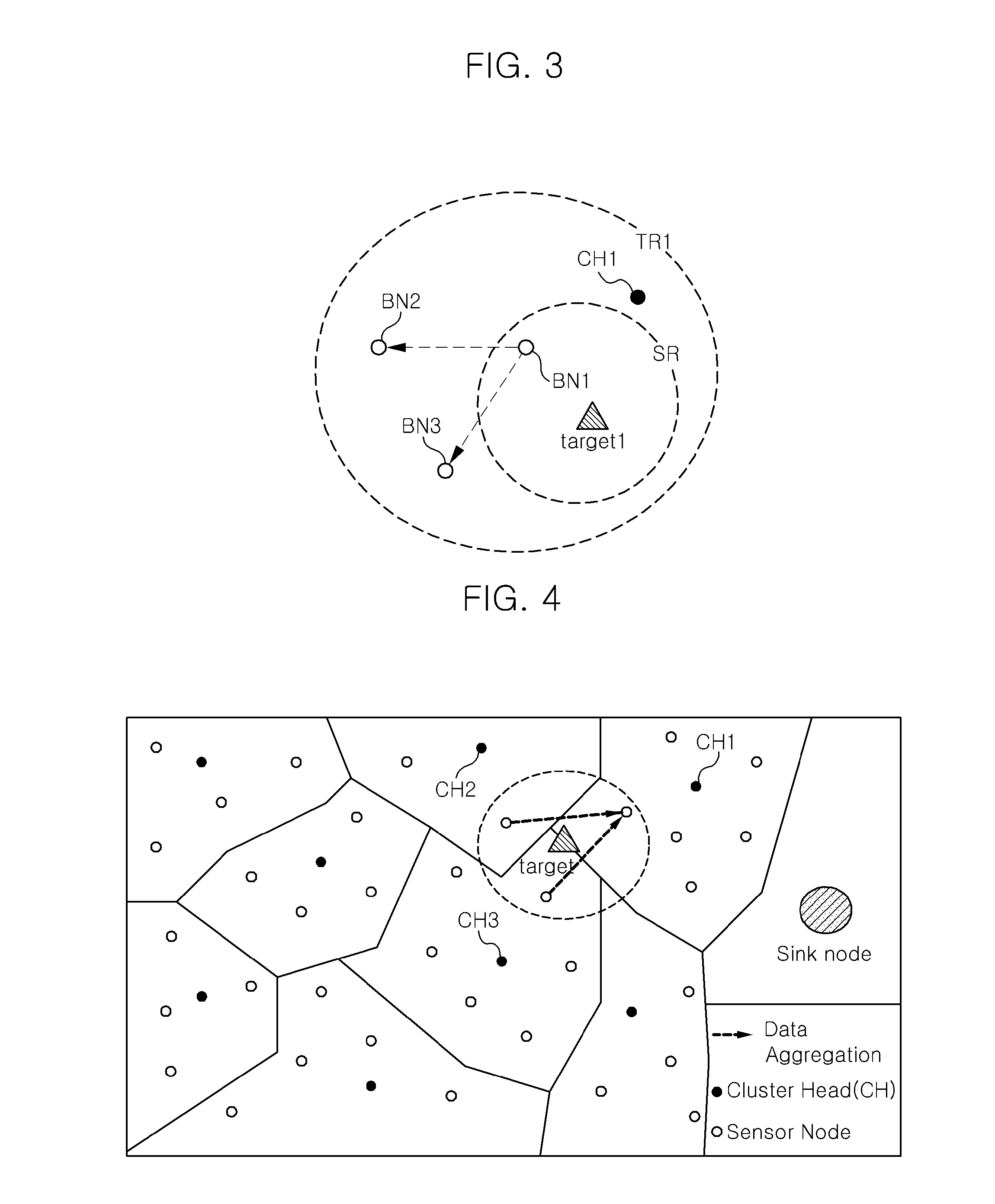

Method for cluster based data transmission in wireless sensor networks

ActiveUS20110130162A1High data efficiencyImprove energy efficiencyNetwork traffic/resource managementAssess restrictionWireless mesh networkWireless sensor networking

The present invention relates to a method for cluster based data in wireless sensor networks. The method includes: selecting any one of border nodes positioned at the edge of a cluster as a temporary cluster head as a temporary cluster head when a target is sensed in the cluster; bugging data of the temporary cluster head by border nodes in other adjacent cluster which do not sense the target to temporarily change the border node selected as the temporary cluster head to a cluster head of each of the border nodes; when the target is sensed by at least one of the border nodes, collecting data from each of the border nodes by the temporary cluster head to transferring the collected data to an actual cluster head of the temporary cluster head; and aggregating the collected data by actual cluster head of the temporary cluster head.

Owner:ELECTRONICS & TELECOMM RES INST

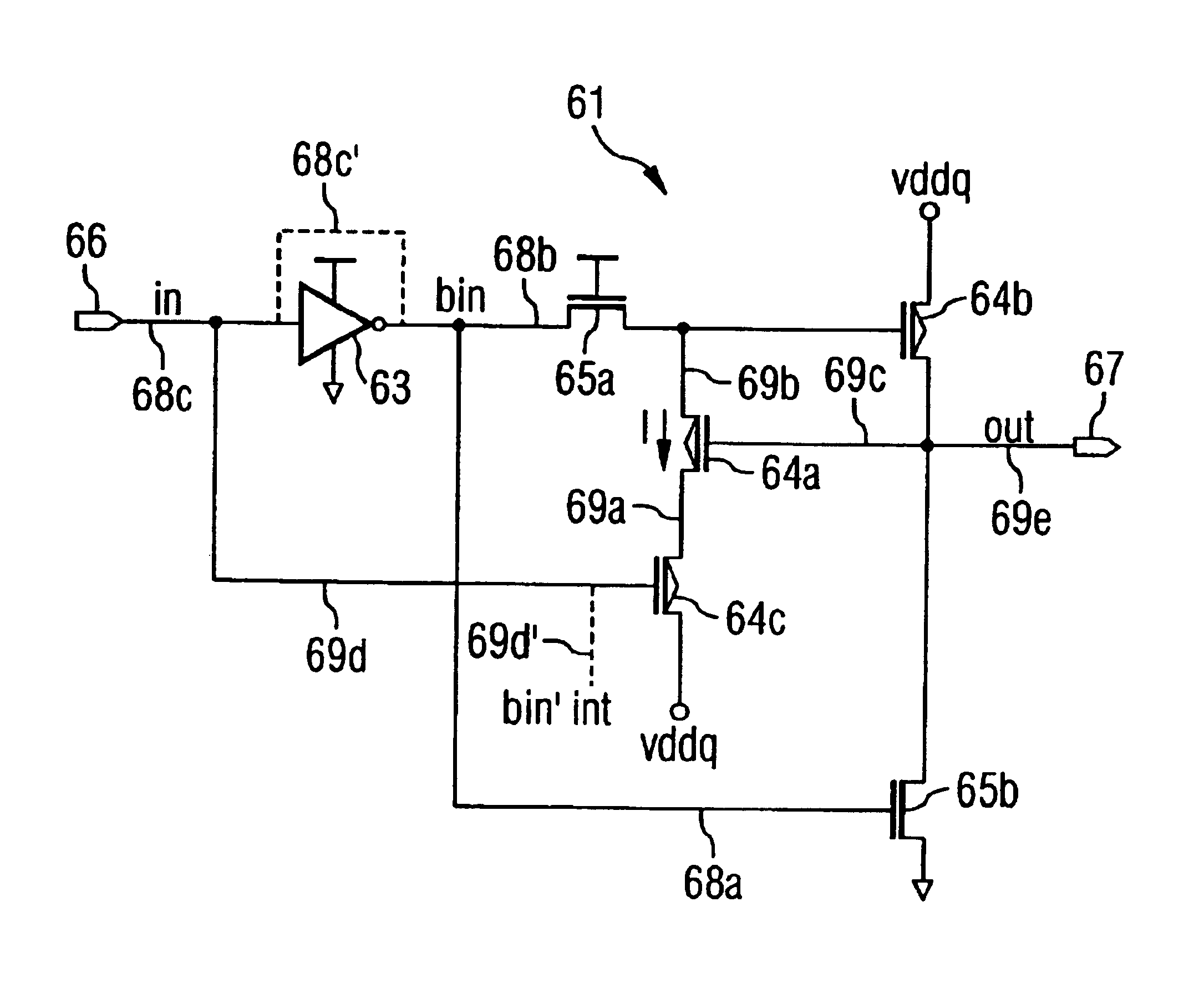

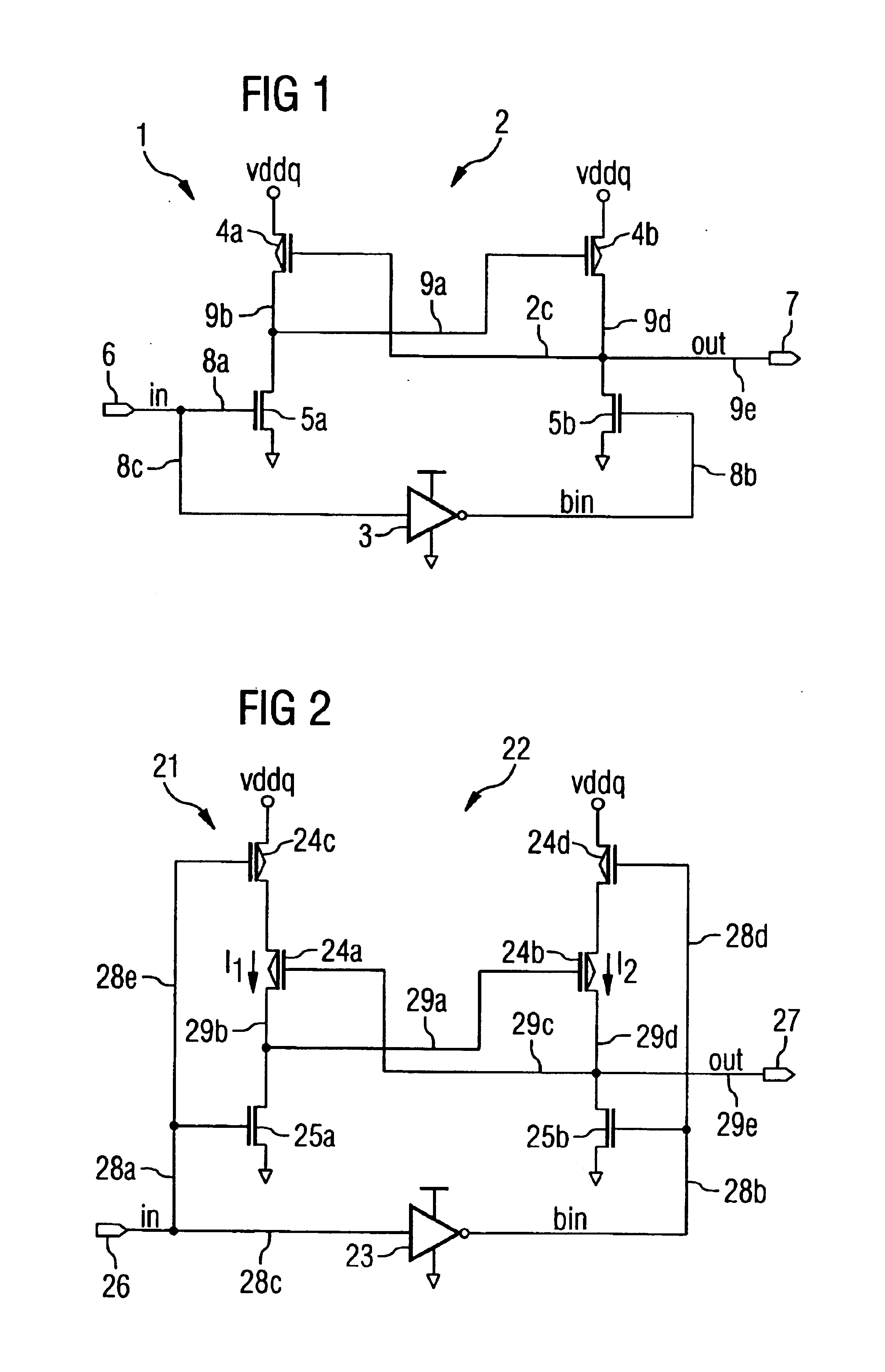

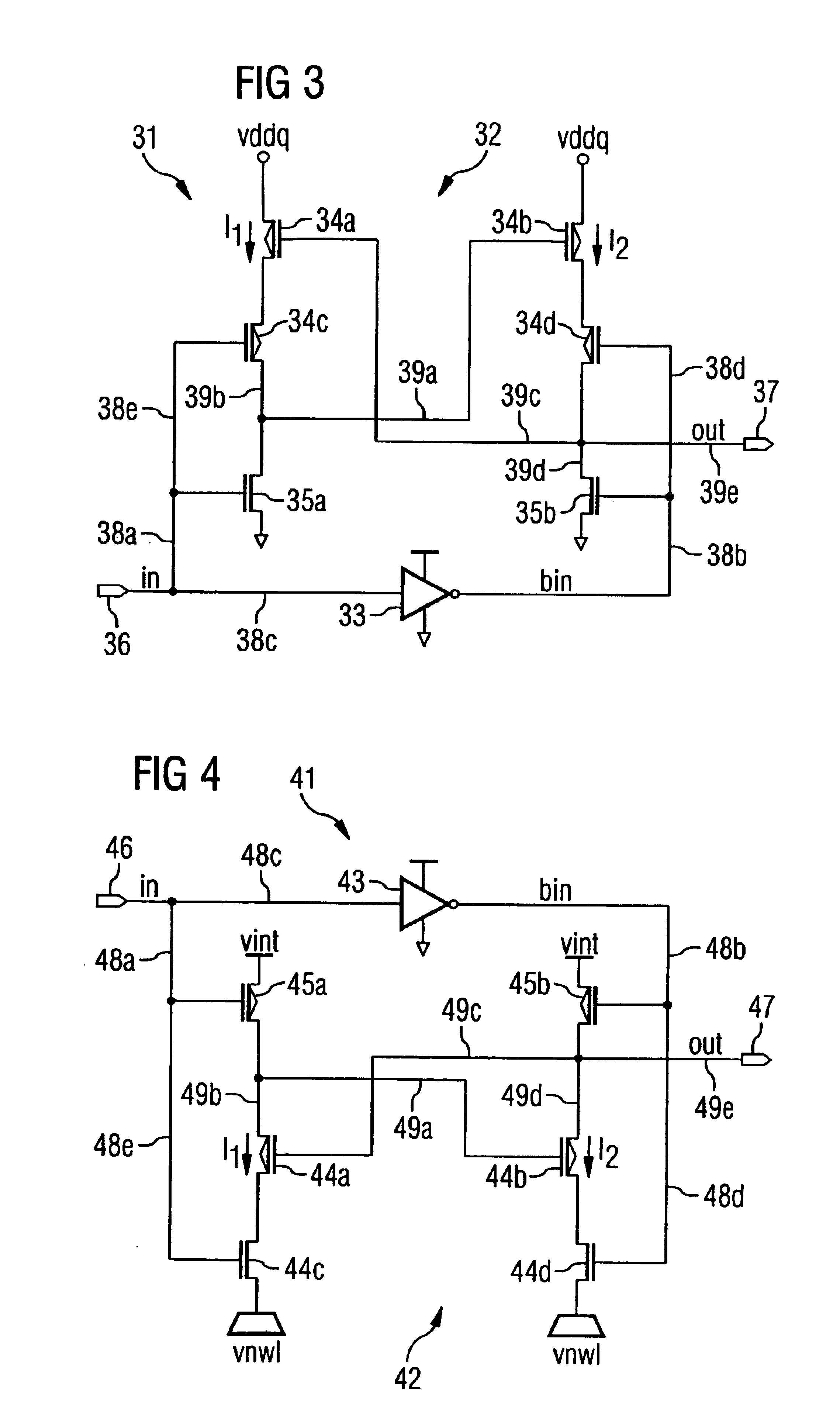

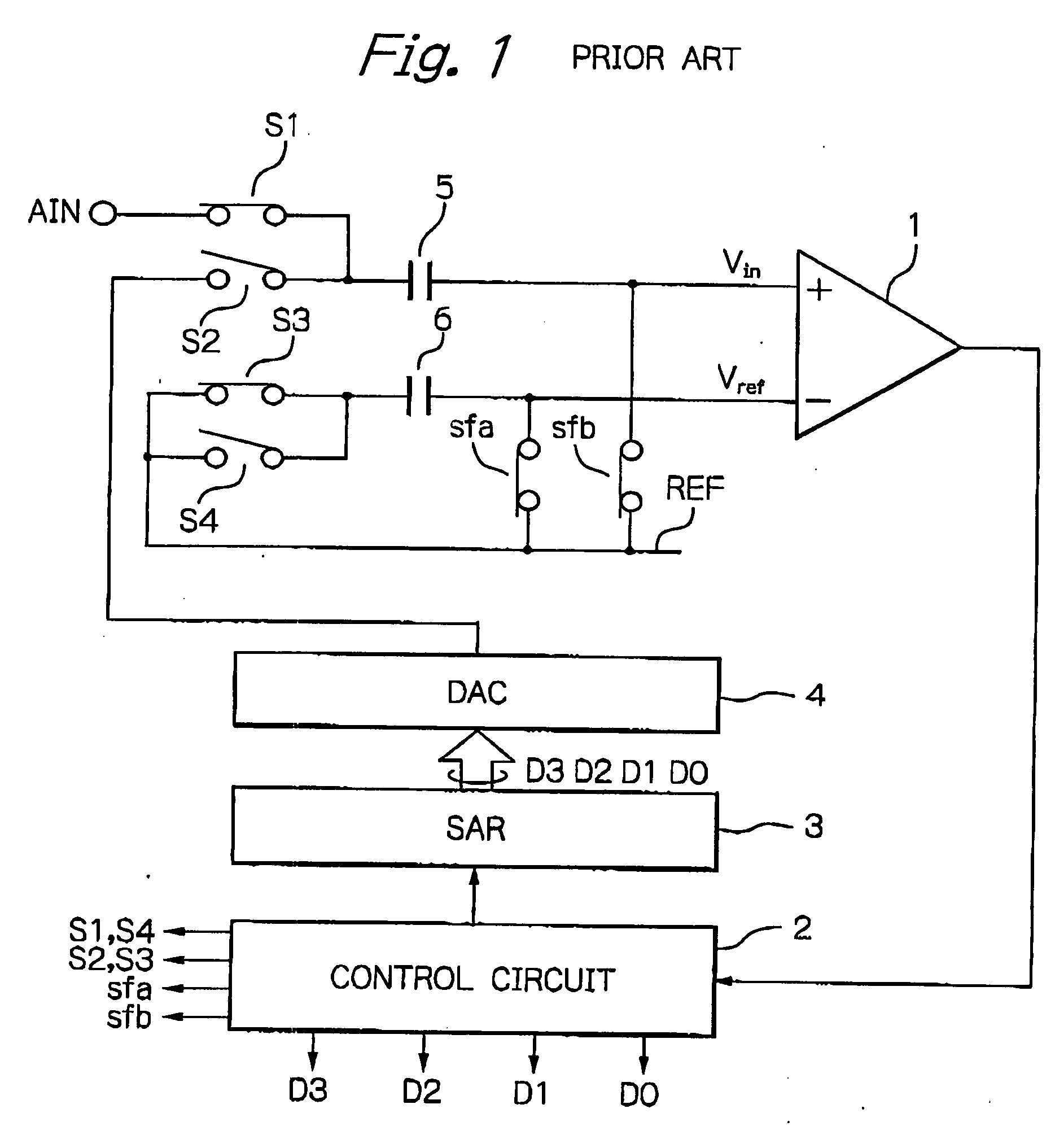

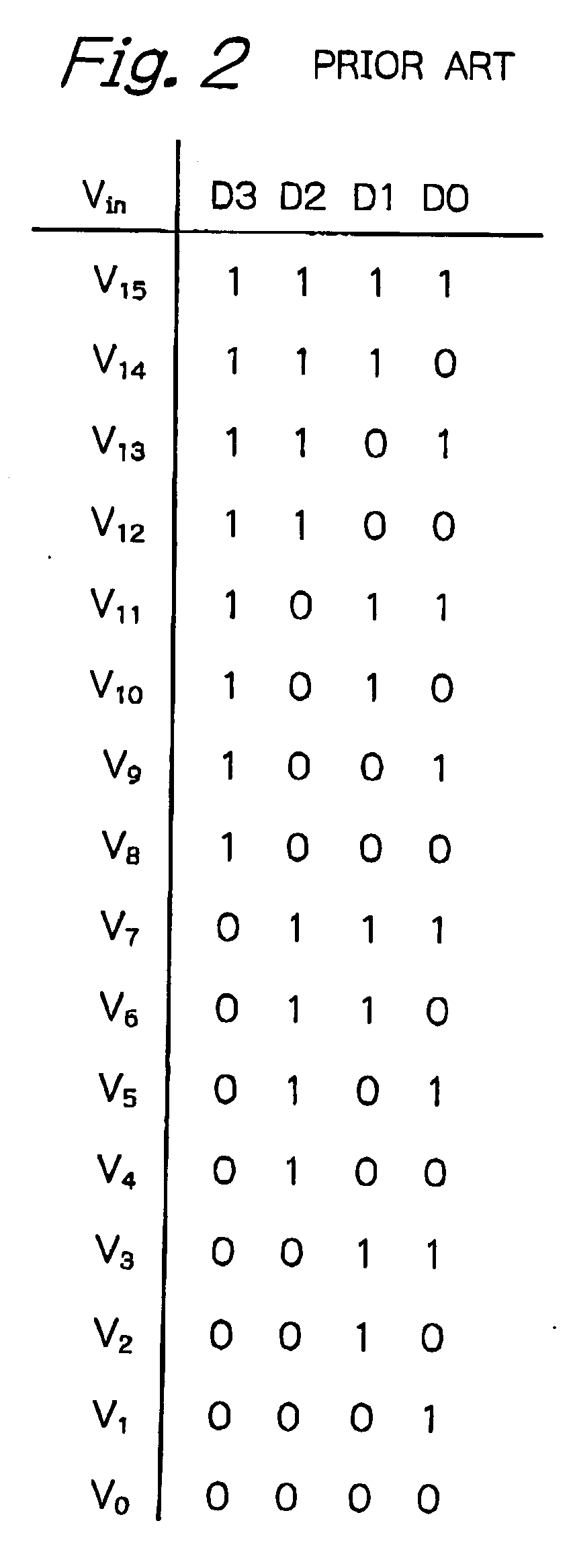

Voltage level converter device

InactiveUS6930622B2Increase switch speedReduce delay timeCode conversionElectric pulse generatorEngineeringLevel converter

A voltage level converter device for the conversion of an input signal, which is at a first voltage level, into an output signal, which is at a second voltage level that differs from the first voltage level, where the voltage level converter device has at least one transistor, and in which an additional transistor, controlled by a control signal at a voltage level corresponding to that of the input signal, is provided in a current path that is to be accordingly switched on or off when the output signal switches over for switching that path on or off.

Owner:POLARIS INNOVATIONS

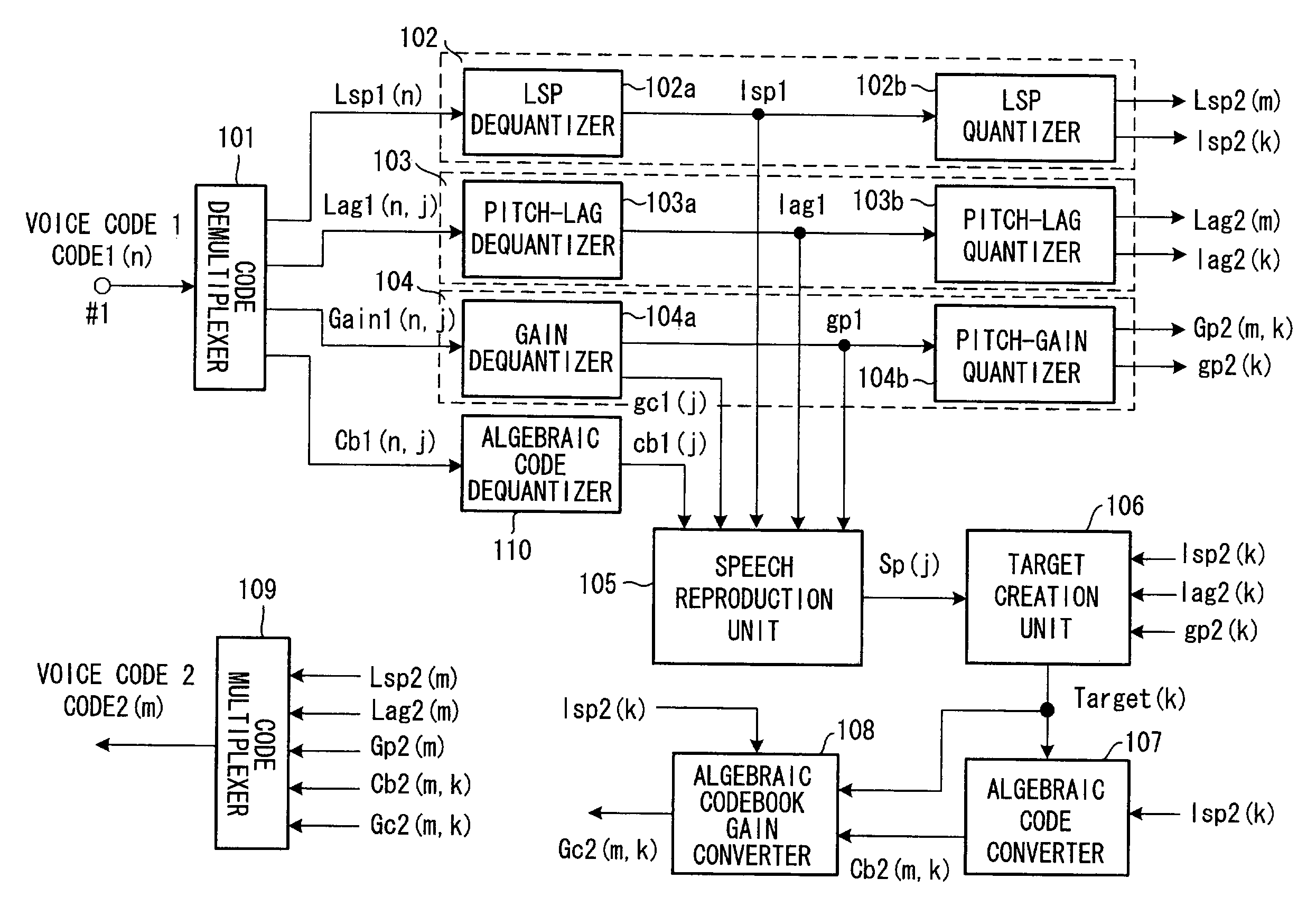

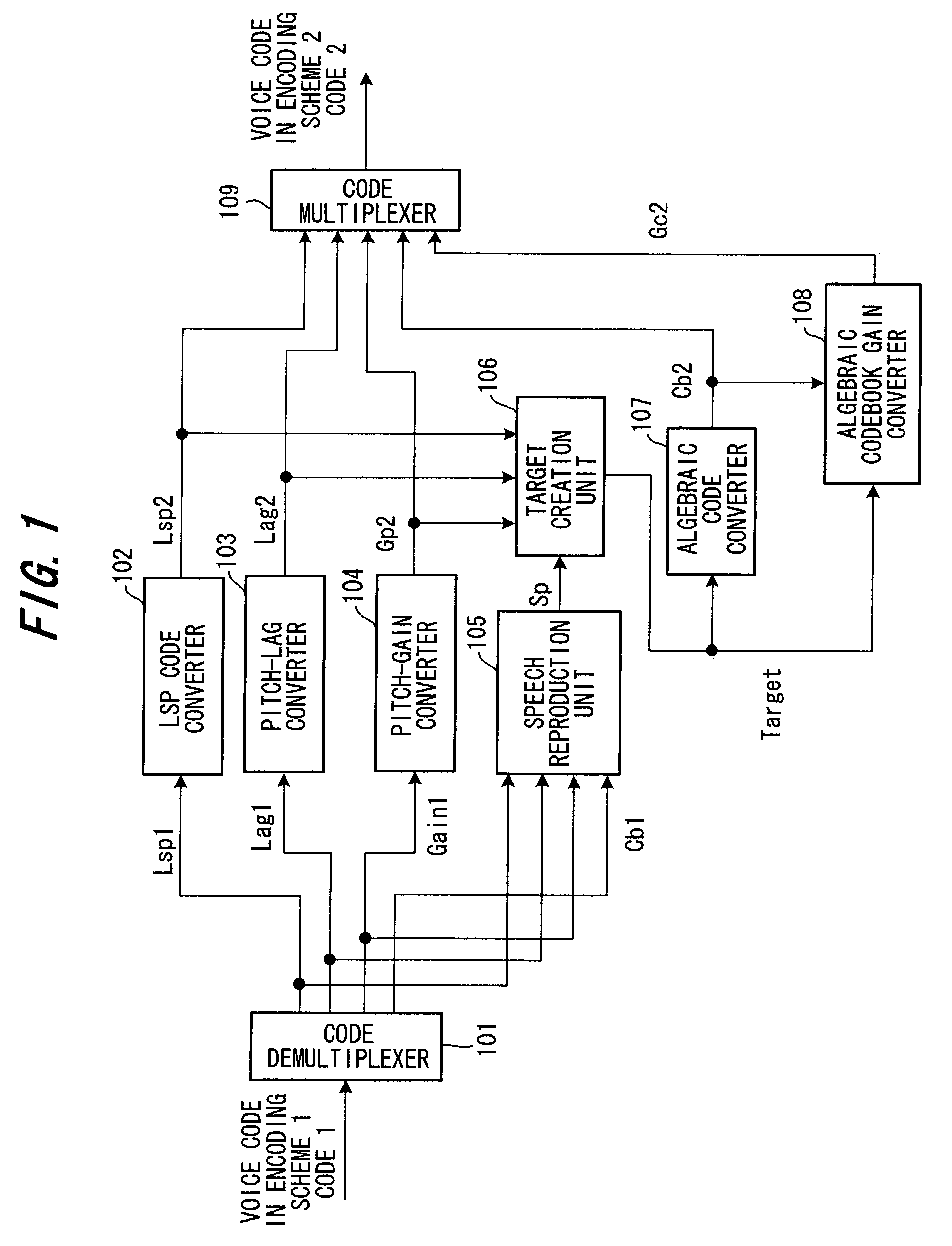

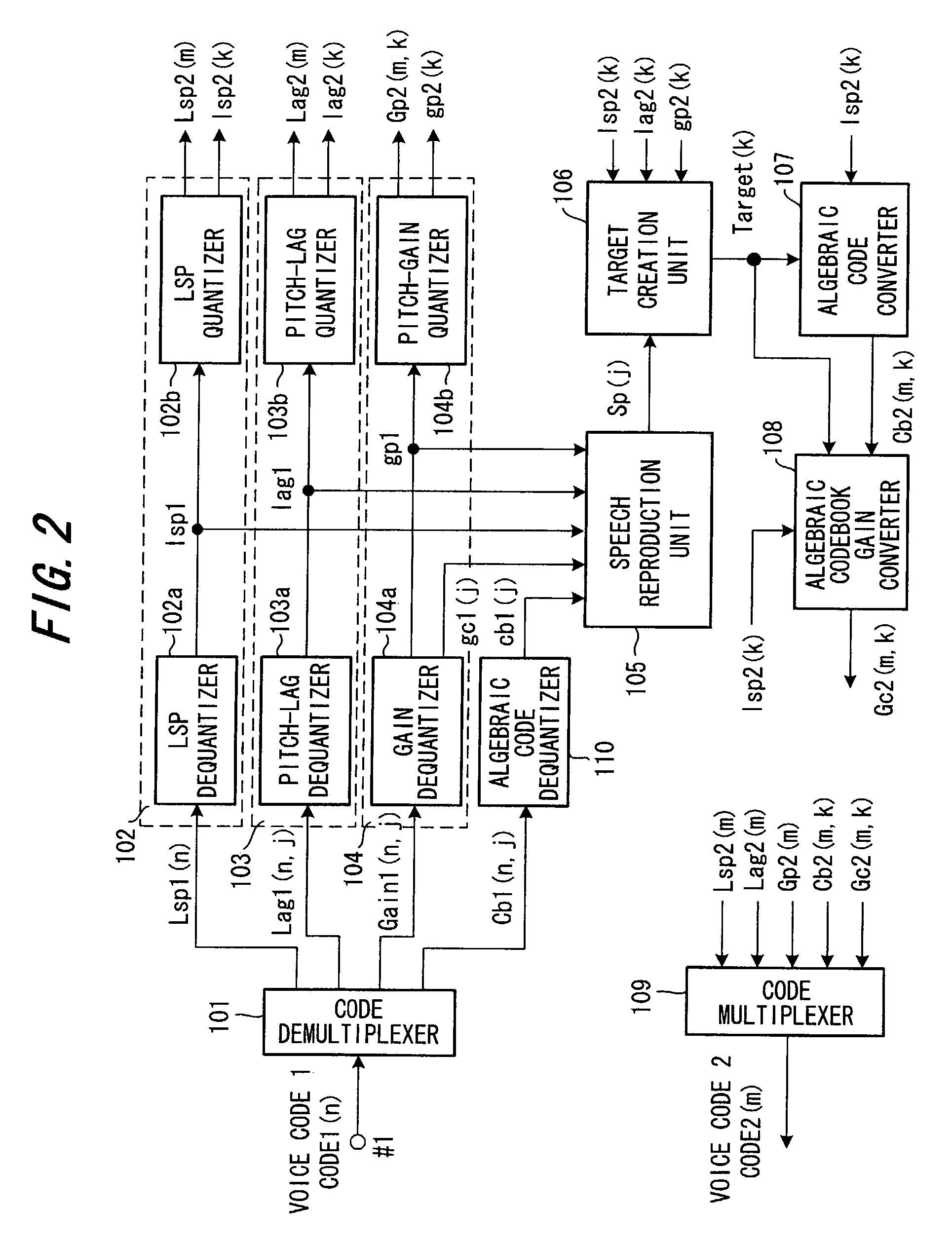

Voice code conversion method and apparatus

InactiveUS7590532B2Possible to performQuality improvementSpeech analysisComputer hardwareTarget signal

It is so arranged that a voice code can be converted even between voice encoding schemes having different subframe lengths. A voice code conversion apparatus demultiplexes a plurality of code components (Lsp1, Lag1, Gain1, Cb1), which are necessary to reconstruct a voice signal, from voice code in a first voice encoding scheme, dequantizes the codes of each of the components and converts the dequantized values of code components other than an algebraic code component to code components (Lsp2, Lag2, Gp2) of a voice code in a second voice encoding scheme. Further, the voice code conversion apparatus reproduces voice from the dequantized values, dequantizes codes that have been converted to codes in the second voice encoding scheme, generates a target signal using the dequantized values and reproduced voice, inputs the target signal to an algebraic code converter and obtains an algebraic code (Cb2) in the second voice encoding scheme.

Owner:FUJITSU LTD

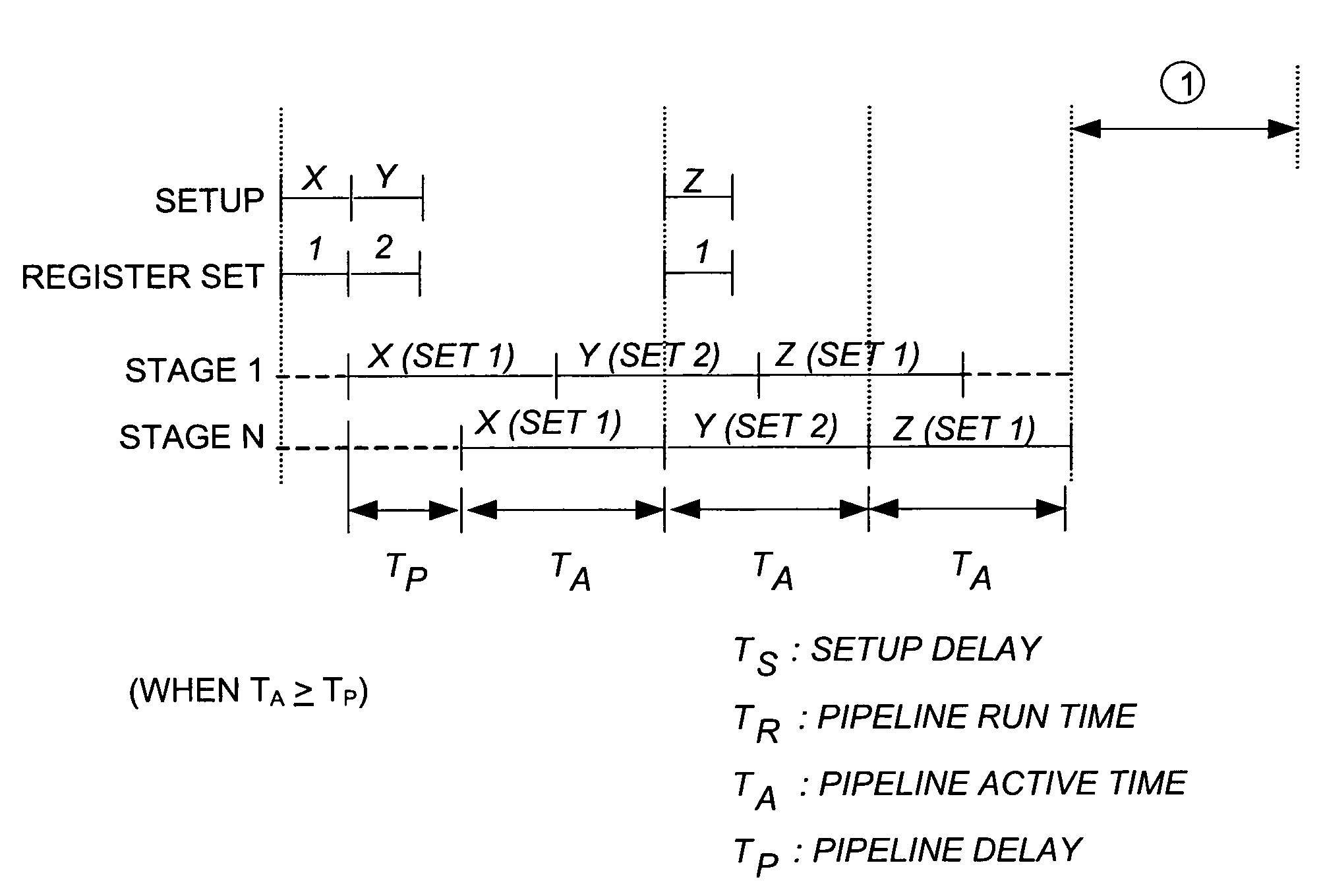

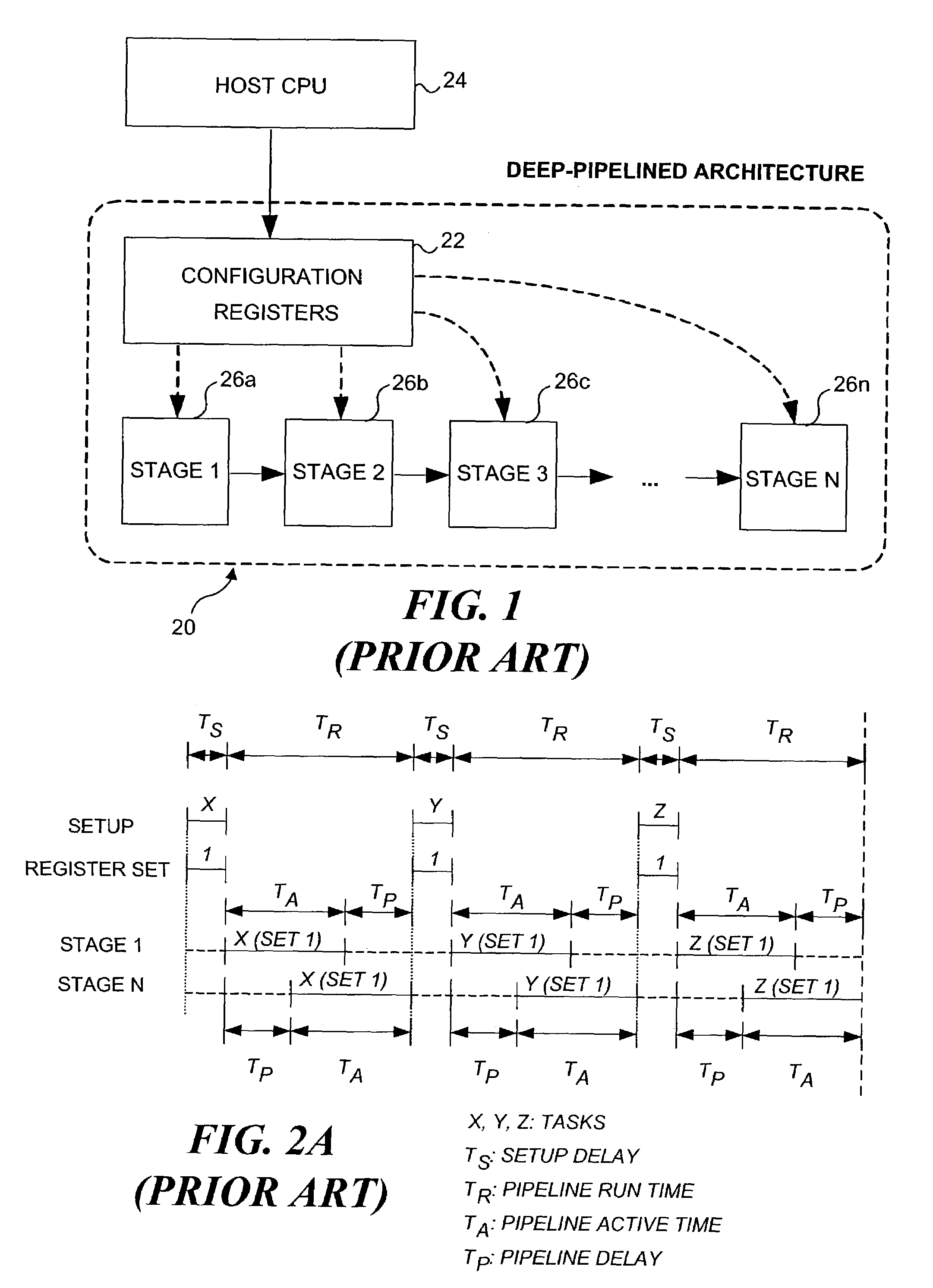

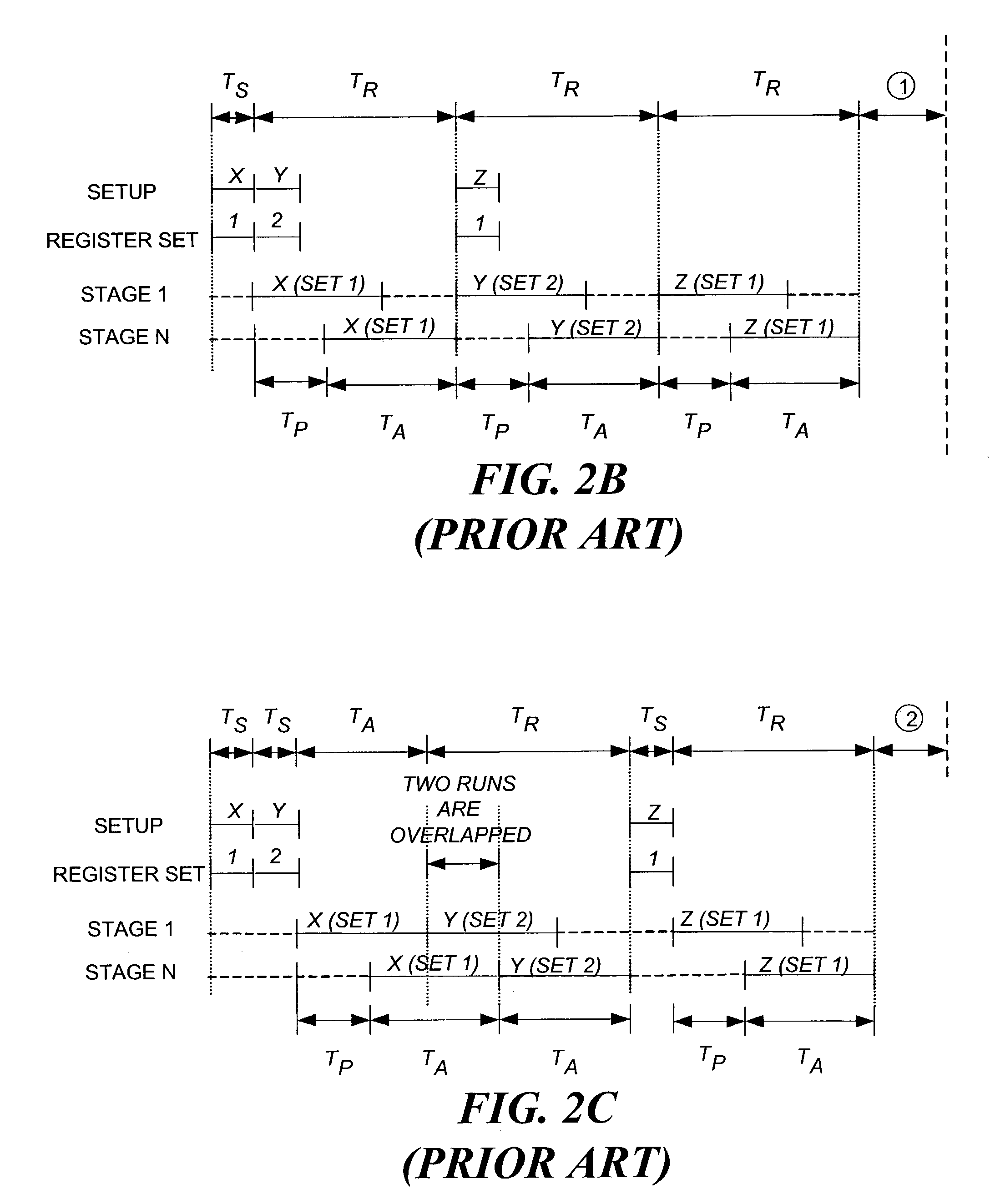

Processor employing loadable configuration parameters to reduce or eliminate setup and pipeline delays in a pipeline system

ActiveUS7383426B2Reduce delay timeReduce degradationConcurrent instruction executionArchitecture with single central processing unitFLOPSDynamic control

A deep-pipeline system substantially reduces the overhead of setup delays and pipeline delays by dynamically controlling access of a plurality of configuration register sets by both a host central processing unit (CPU) and the stages of the pipelines. A master configuration register set is loaded with configuration parameters by the host CPU in response to an index count provided by a setup-index counter. A plurality of other counters are employed to track timing events in the system. In one embodiment, a run-index counter provides a run-index count to the first stage of the pipeline that is propagated along the stages, enabling configuration register sets to transfer configuration parameters to the stages of the pipeline when required to enable processing of a task. In an alternative embodiment, a plurality of D flip-flops sequentially propagates a state for successive registers, so that the setup-index counter is not required.

Owner:UNIV OF WASHINGTON

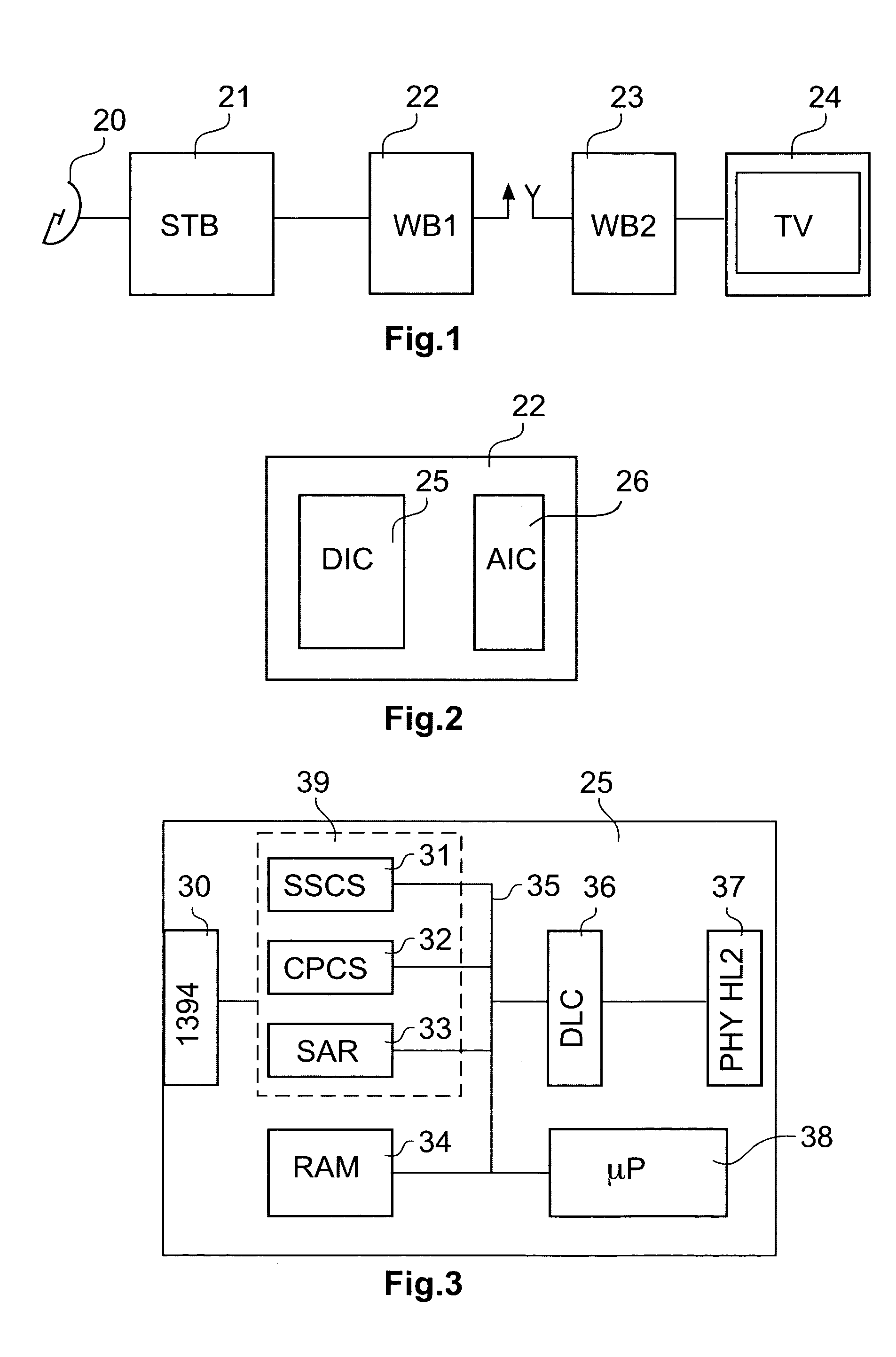

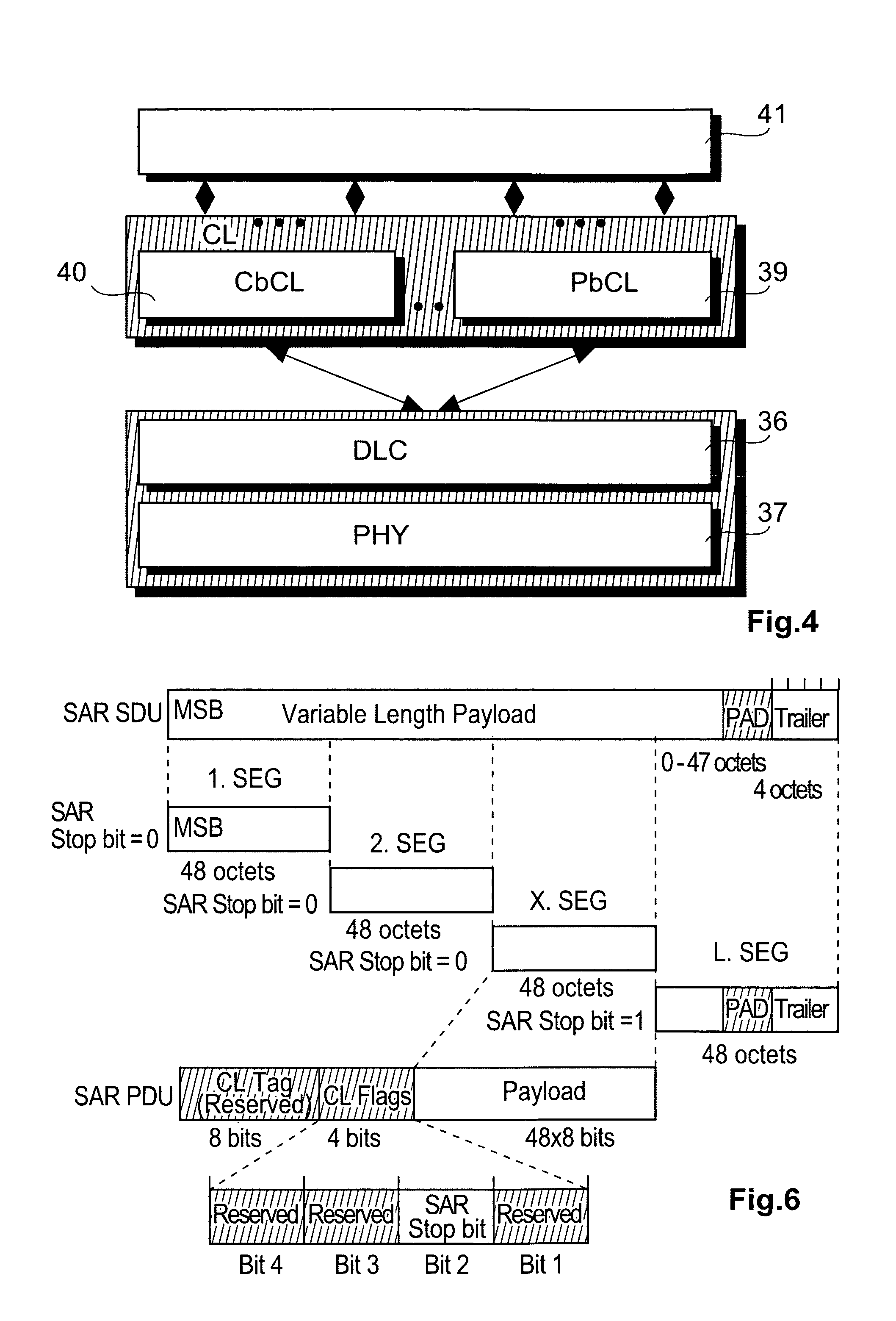

Method for processing data packets received via a first interface and device for carrying out the method

InactiveUS20050063405A1Reduce delay timeReduce latencyNetwork traffic/resource managementNetwork topologiesInterface designIEEE 1394

During the transmission of data packets received on a wired connection via a first interface (e.g. IEEE 1394 interface) via a second interface designed for the wireless transmission of data, e.g. HIPERLAN / 2 interface, the problem exists that between receiving the data and transmitting the data via the second interface a relatively large delay time can arise which must be bridged by means of a suitably dimensioned buffer memory. The invention provides means that enable the maximum delay time to be further reduced. For this purpose, according to the invention, the necessary processing of the received IEEE 1394 bus packets is already performed section by section immediately after a received data packet has arrived. After the complete number of bus packets falling within a transmission frame has been received, there is therefore no longer any lengthy processing time required and the probability of missing the time slots reserved in the next transmission frame is significantly reduced. The buffer memory for bridging the delay time period can therefore be correspondingly smaller.

Owner:INTERDIGITAL CE PATENT HLDG

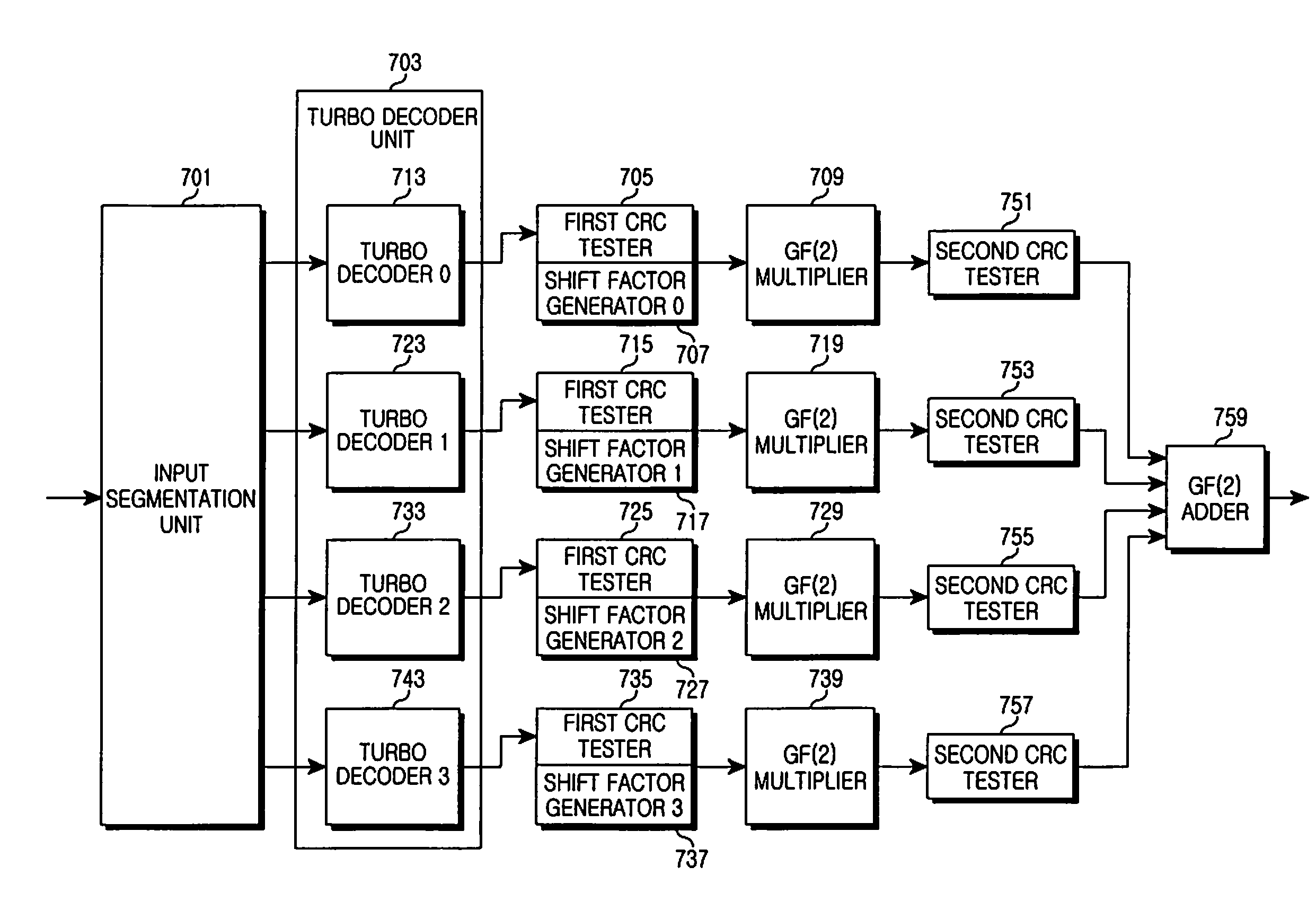

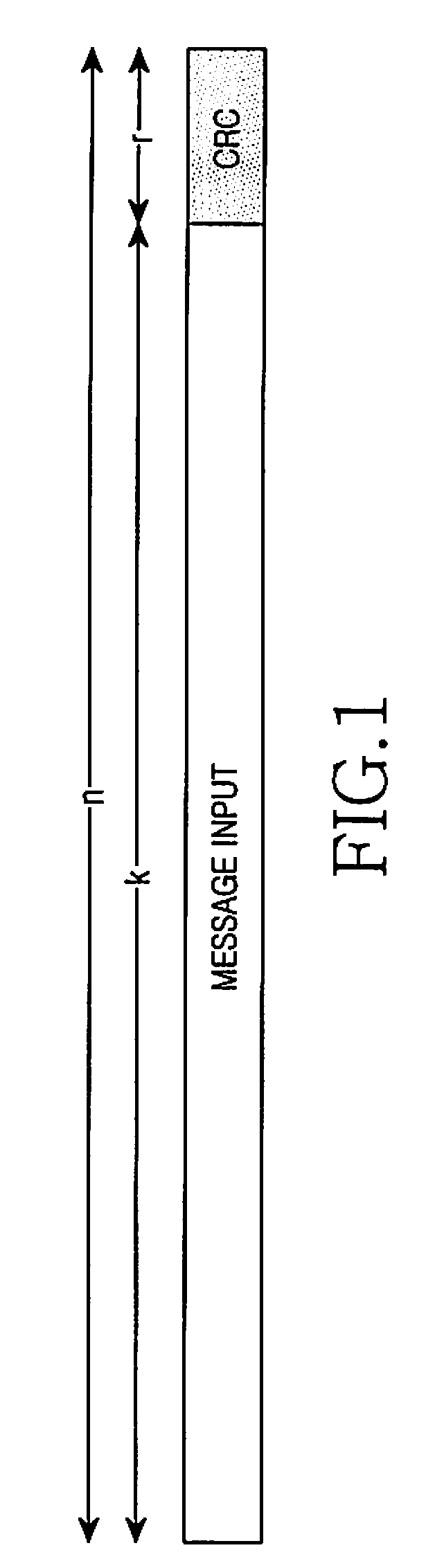

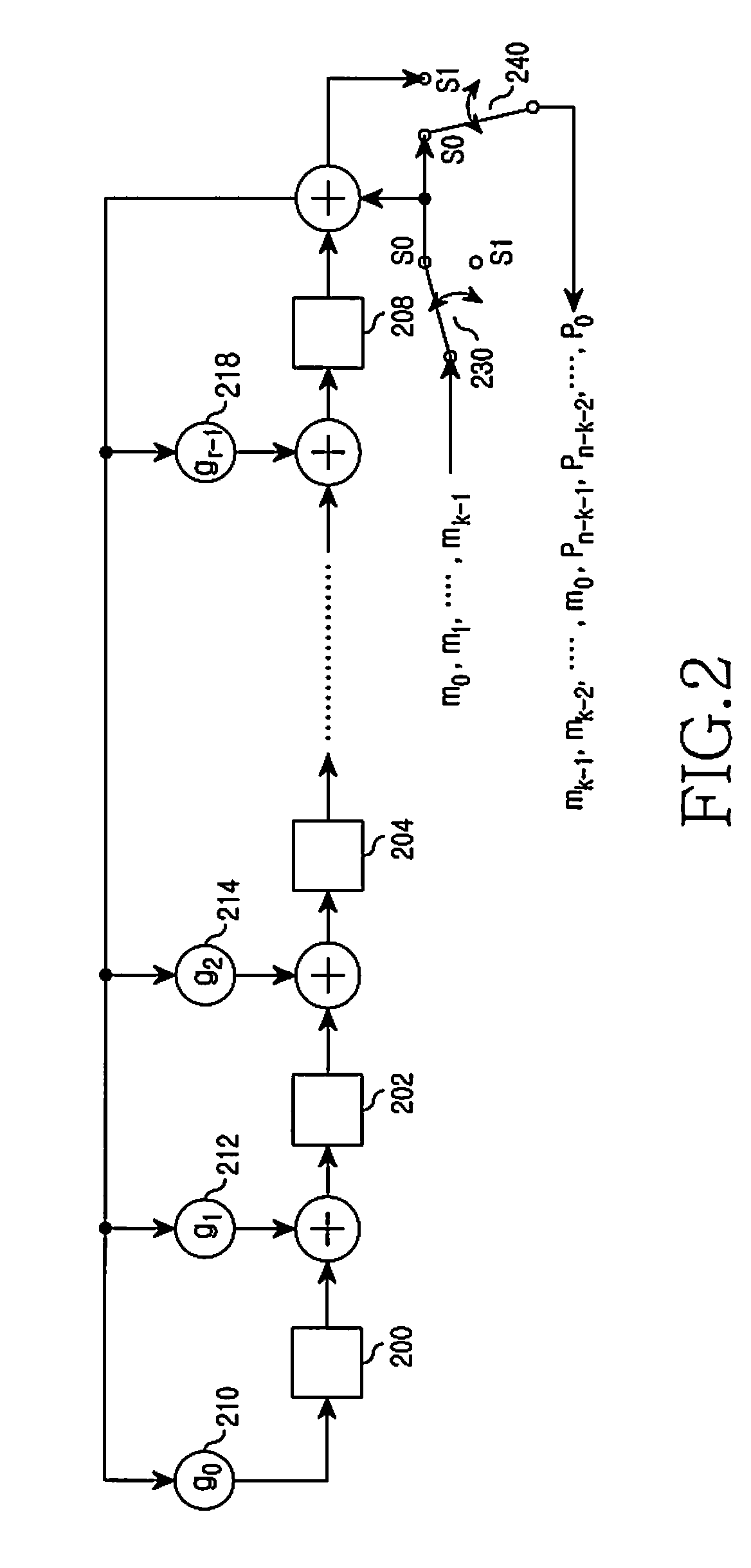

Method and apparatus for cyclic redundancy check in communication system

InactiveUS20100017692A1Improve data processing rateReduce delay timeError preventionCode conversionCyclic redundancy checkCommunications system

A method for performing a Cyclic Redundancy Check (CRC) in a communication system is provided. An input message is divided into a predetermined number of segments. The CRC is performed on each segment to generate a CRC code of each segment. Polynomial addition is performed on CRC codes of respective segments to obtain a CRC code of the input message.

Owner:SAMSUNG ELECTRONICS CO LTD

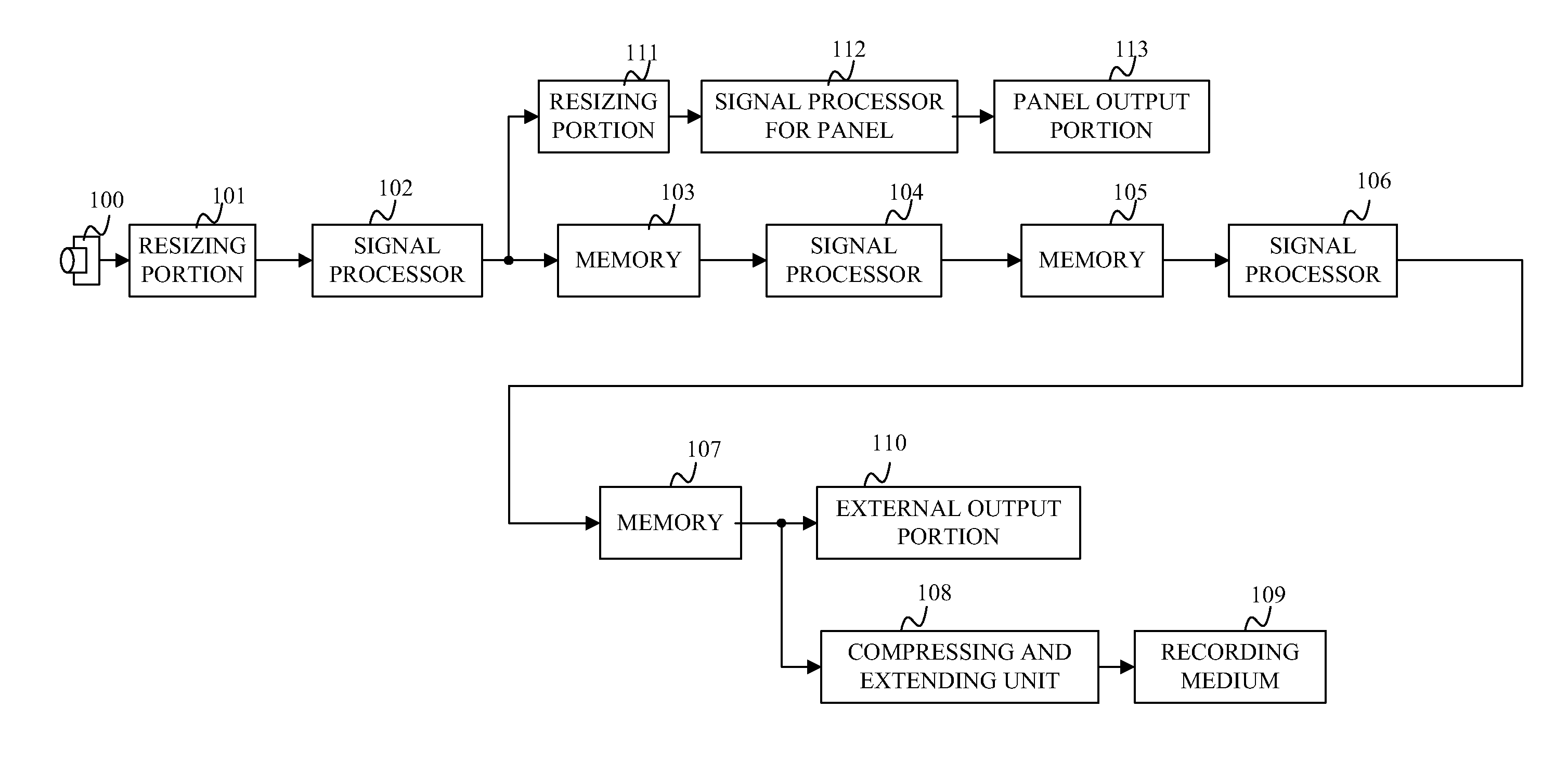

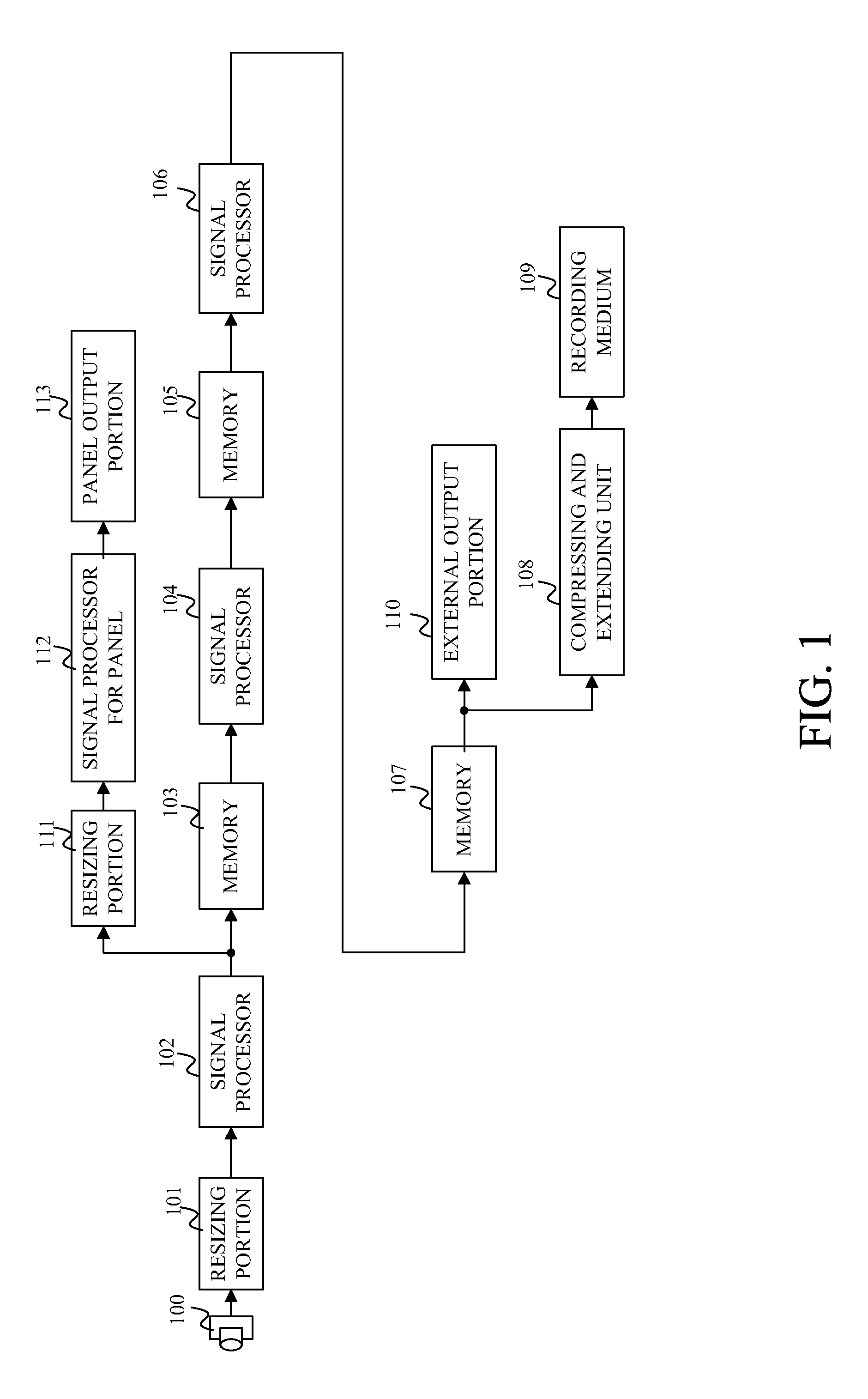

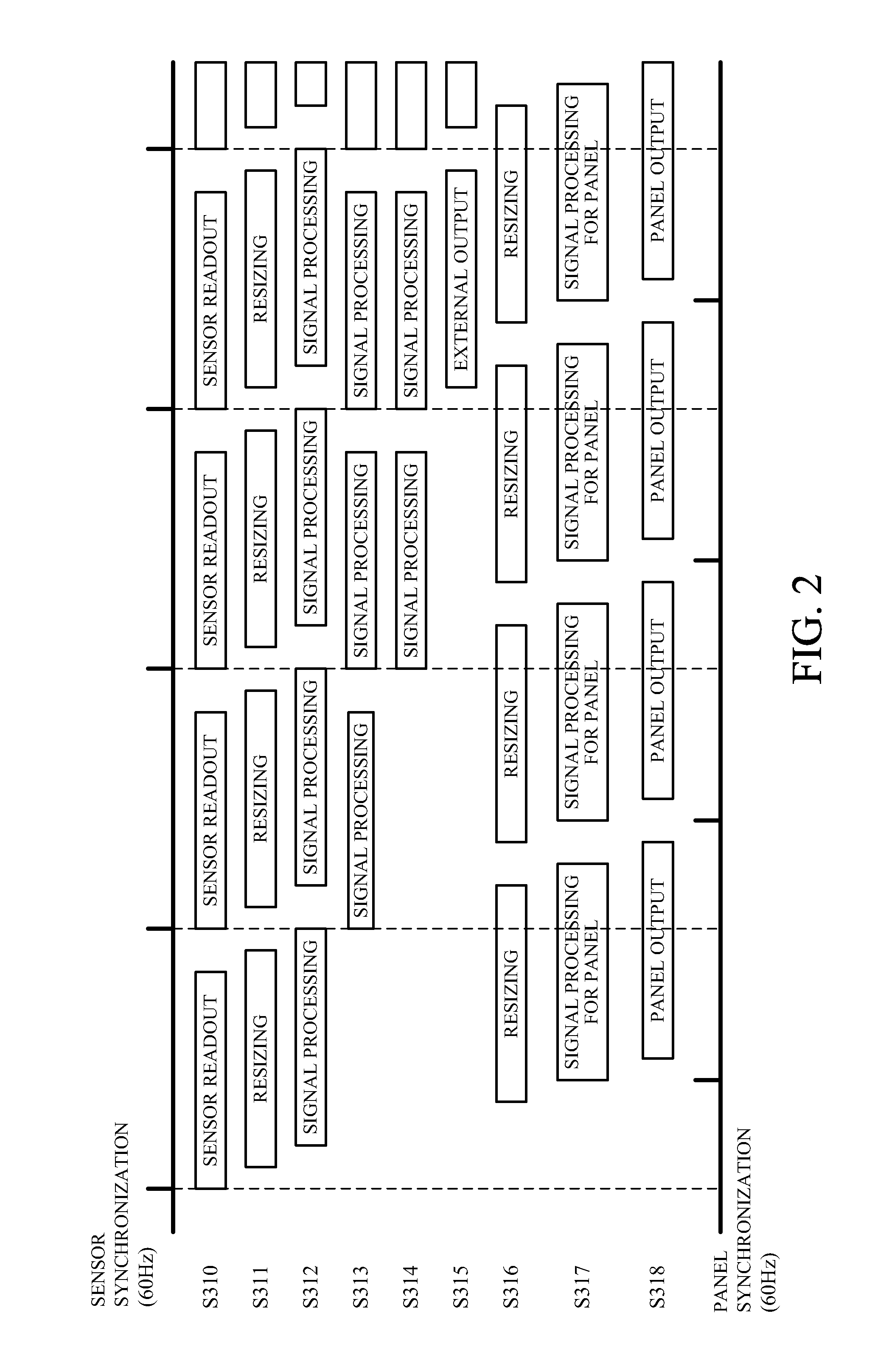

Image signal processing apparatus and a control method thereof, and an image pickup apparatus and a control method thereof

ActiveUS20140192231A1Reduce delay timeEliminating awkward feelingTelevision system detailsBrightness and chrominance signal processing circuitsImage reductionImaging Signal

An image pickup apparatus includes a first image reduction unit configured to reduce the size of an image output by an image pickup element, a memory configured to store the image reduced by the first image reduction unit, an external output unit configured to output the image stored in the memory, a display configured to display an image being shot, a second image reduction unit configured to reduce, to the display size on the display, the image reduced by the first image reduction unit, without causing the reduced image to be stored in the memory and a signal processor for the display configured to perform signal processing of the image reduced to the display size on the display.

Owner:CANON KK

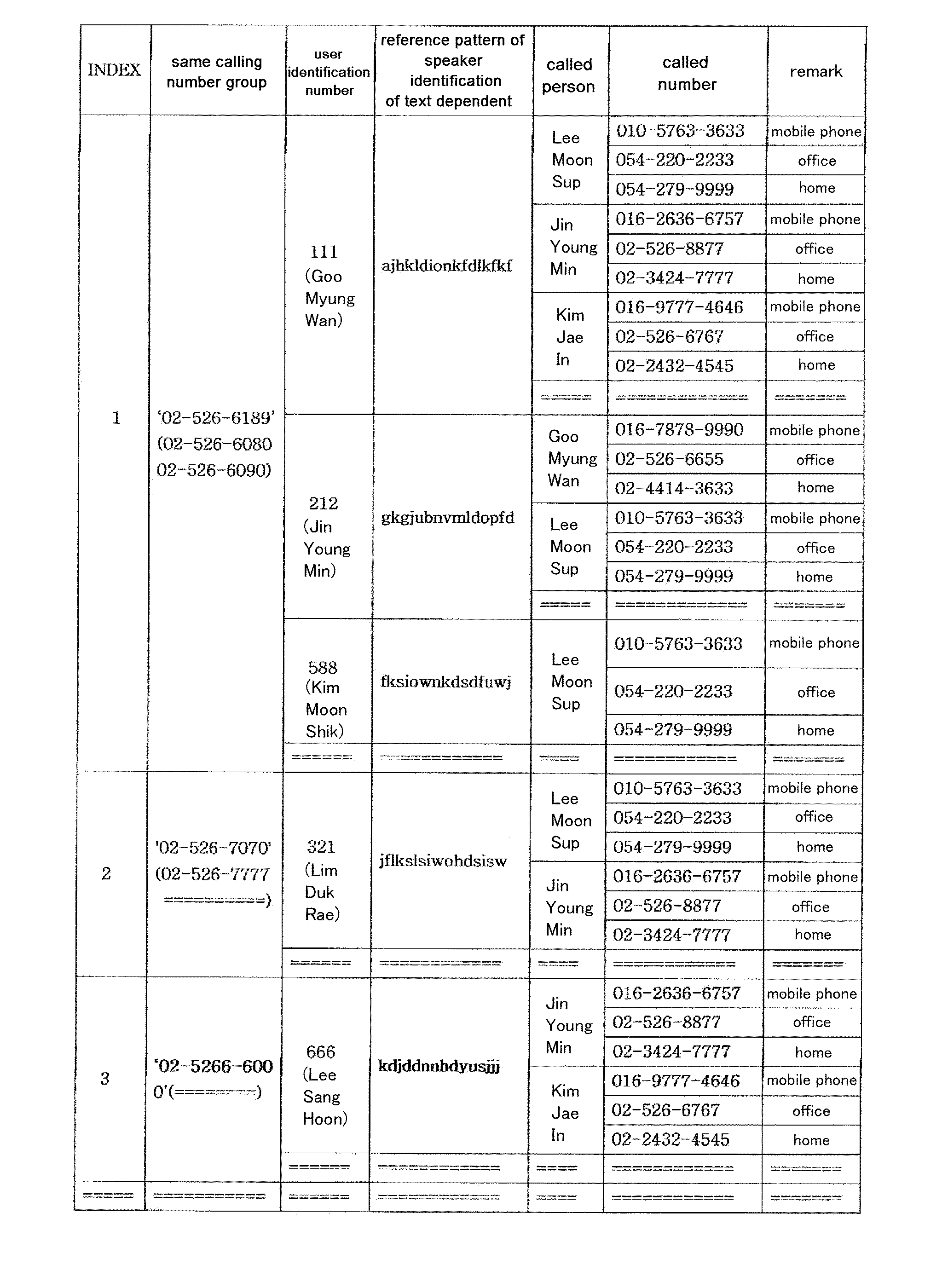

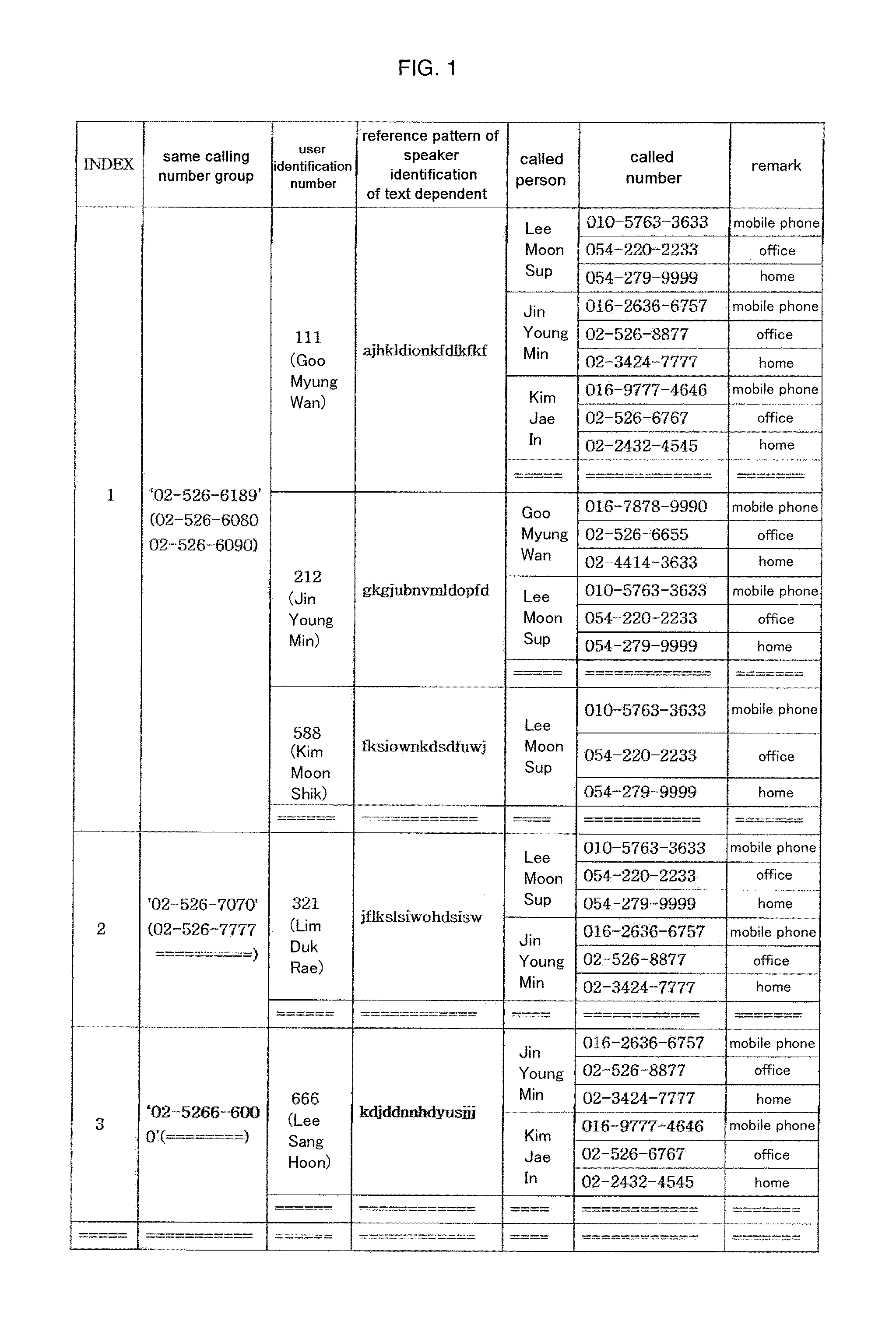

Method of using prefix and suffix for identifying user of a calling terminal

InactiveUS20110268261A1Enhance real-time serviceReduce delay timeSpecial service for subscribersParty-line systemsPersonalizationUser group

The present invention relates to a method that, when users who share one terminal or a plurality of terminals and one calling number or a plurality of calling numbers use individualized database information to utilize communication services, assigns a user identification number that identifies each of the service users in the same user group, attaches the user identification number to the service identification number in the form of a prefix and a suffix, provides the user identification number as a means whereby both an exchange and a server identify a user by the number inputted by the user when a phone is used, and classifies and saves information on each service user, thereby ensuring convenience and security when the user uses communication service. The present invention relates also to a computer-readable recording medium whereon is recorded a program to realize such functions.

Owner:LEE MOONSEUB

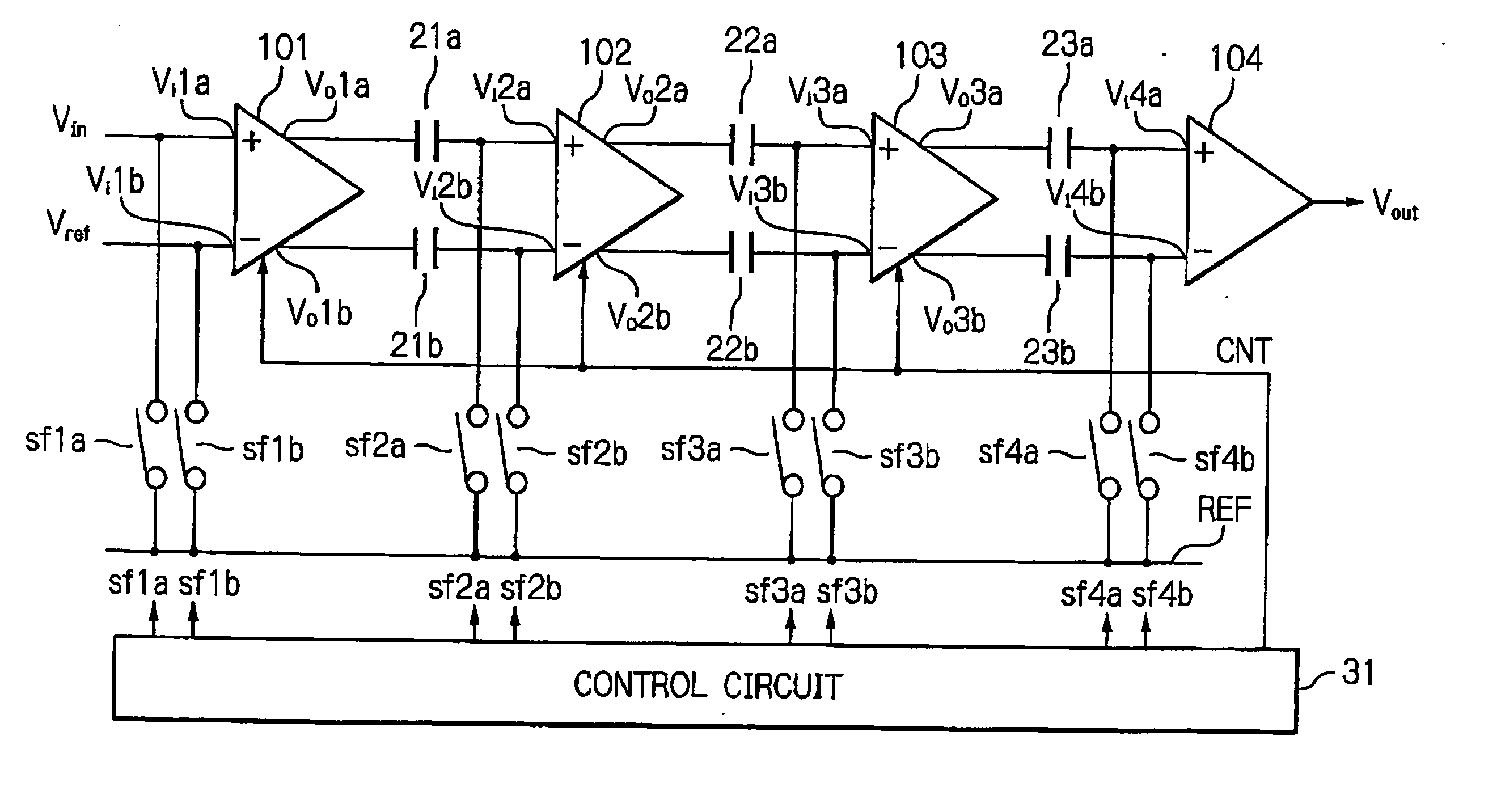

High speed amplifier with controllable amplification and output impedance and comparator using the same

InactiveUS20070279130A1Reduce delay timeHigh speedGain controlAmplifier modifications to reduce temperature/voltage variationConstant current sourceVoltage reference

In an amplifier including first and second power supply terminals, first and second output terminals, a first load connected between the first power supply terminal and the first output terminal, a second load connected between the first power supply terminal and the second output terminal, a constant current source connected to the second power supply terminal, a first transistor connected between the first output terminal and the constant current source, a control terminal of the first transistor being adapted to receive an input voltage, and a second transistor connected between the second output terminal and the constant current source, a control terminal of the second transistor being adapted to receive a reference voltage, an amplification and output impedance switching circuit is connected between the first and second output terminals, so that the amplifier and output impedance switching circuit controls an amplification and output impedance of the amplifier in accordance with a control signal.

Owner:RENESAS ELECTRONICS CORP

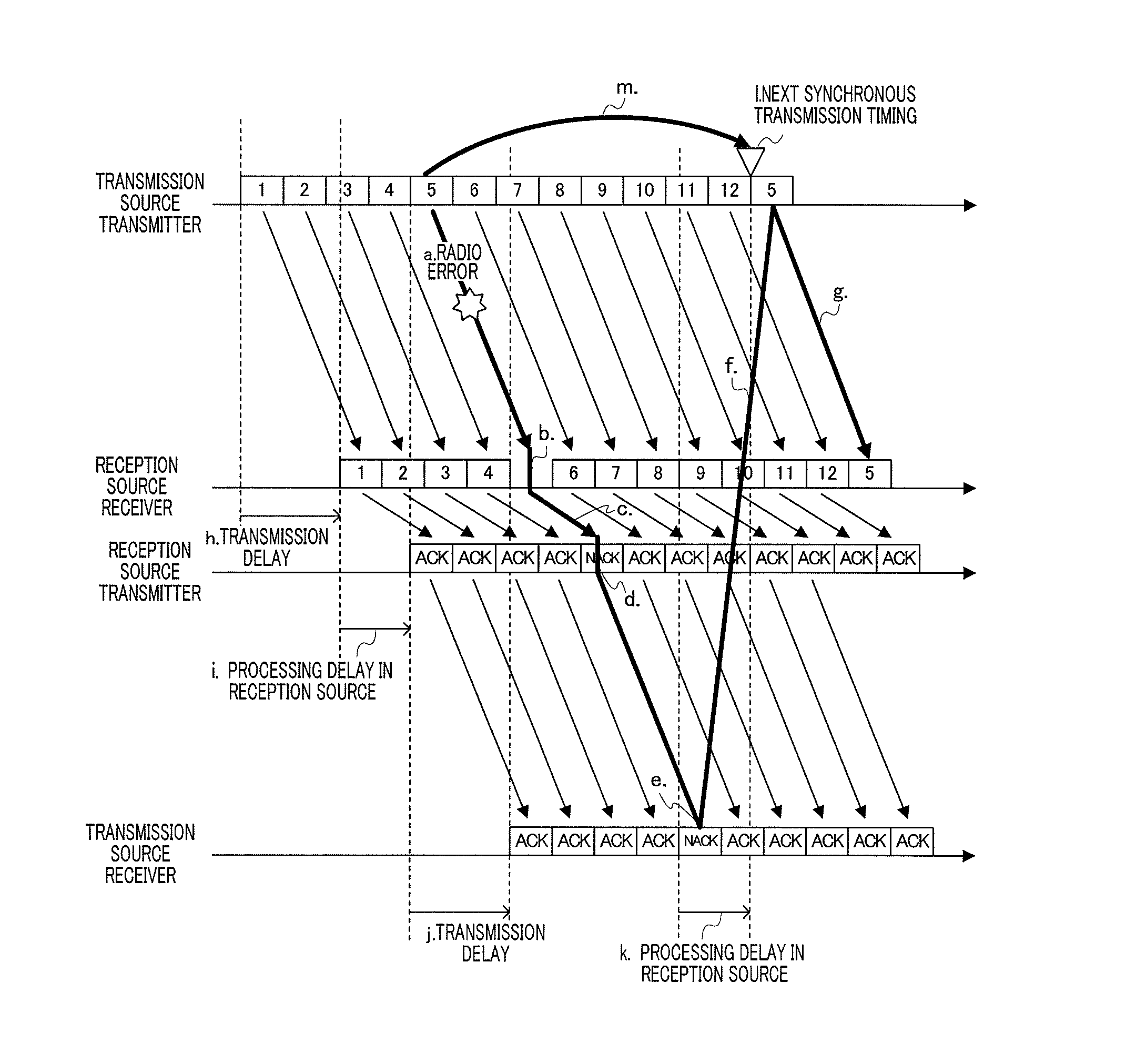

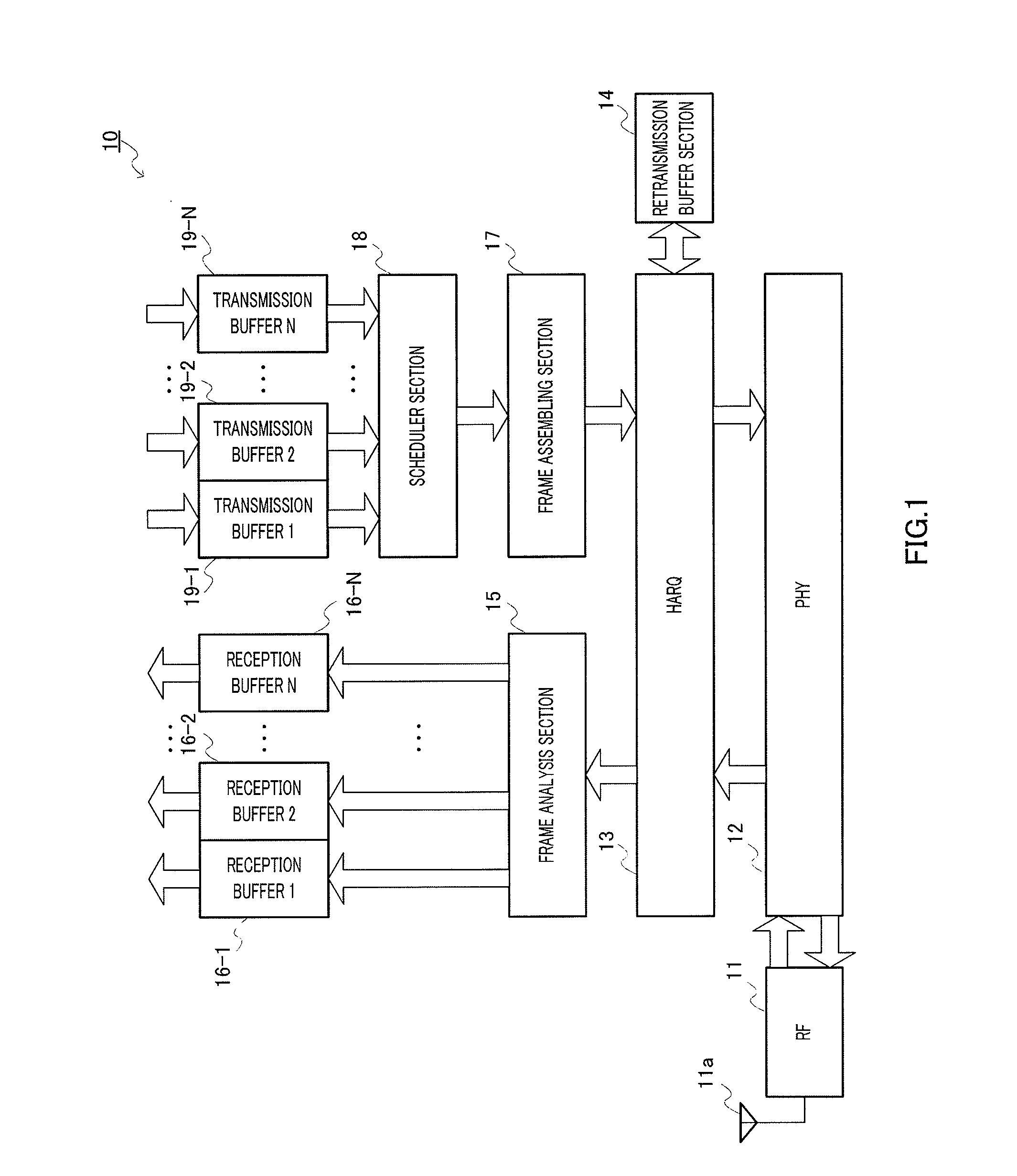

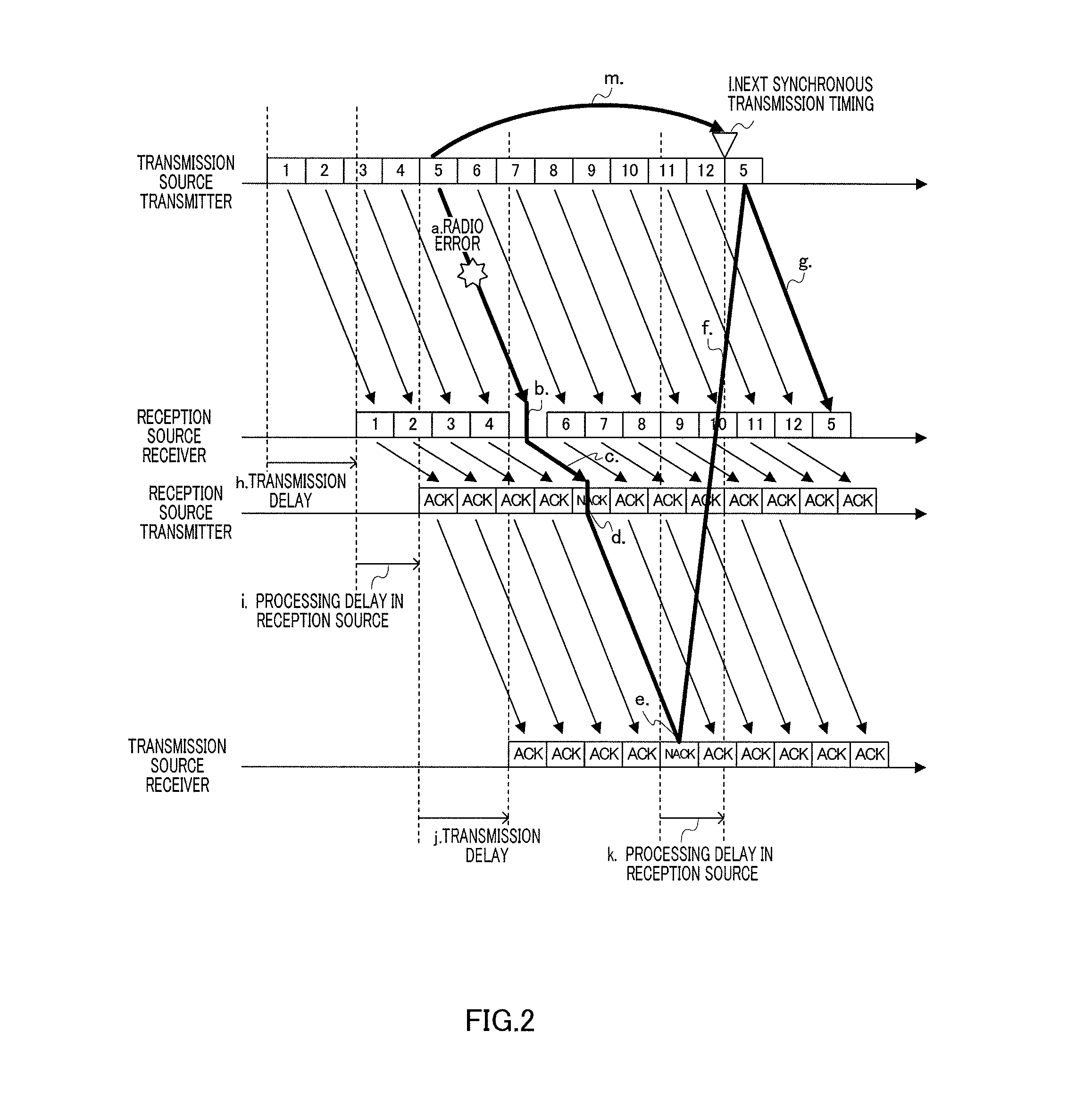

Packet transmission device and packet transmission method

InactiveUS20110075679A1Reduce delay timeImprove communication qualityError preventionNetwork traffic/resource managementRadio channelSelf adaptive

Provided are a packet transmission device and a packet transmission method which can effectively use a radio band while suppressing a processing overhead. A packet transmission device (100) includes: a transmission path judgment unit (110) which judges a transmission path state according to a radio channel quality estimation result; and an adaptive scheduler unit (108) which includes a low QoS packet into a transmission frame constituent element with a higher priority if the transmission path state is judged to be bad and a high QoS packet into the transmission frame constituent element with a higher priority if the transmission path state is judged to be good. That is, the adaptive scheduler unit (108) allocates a low QoS packet with a higher priority when it is judged that the possibility of generation of a radio error is high and the transmission path state is bad.

Owner:PANASONIC CORP

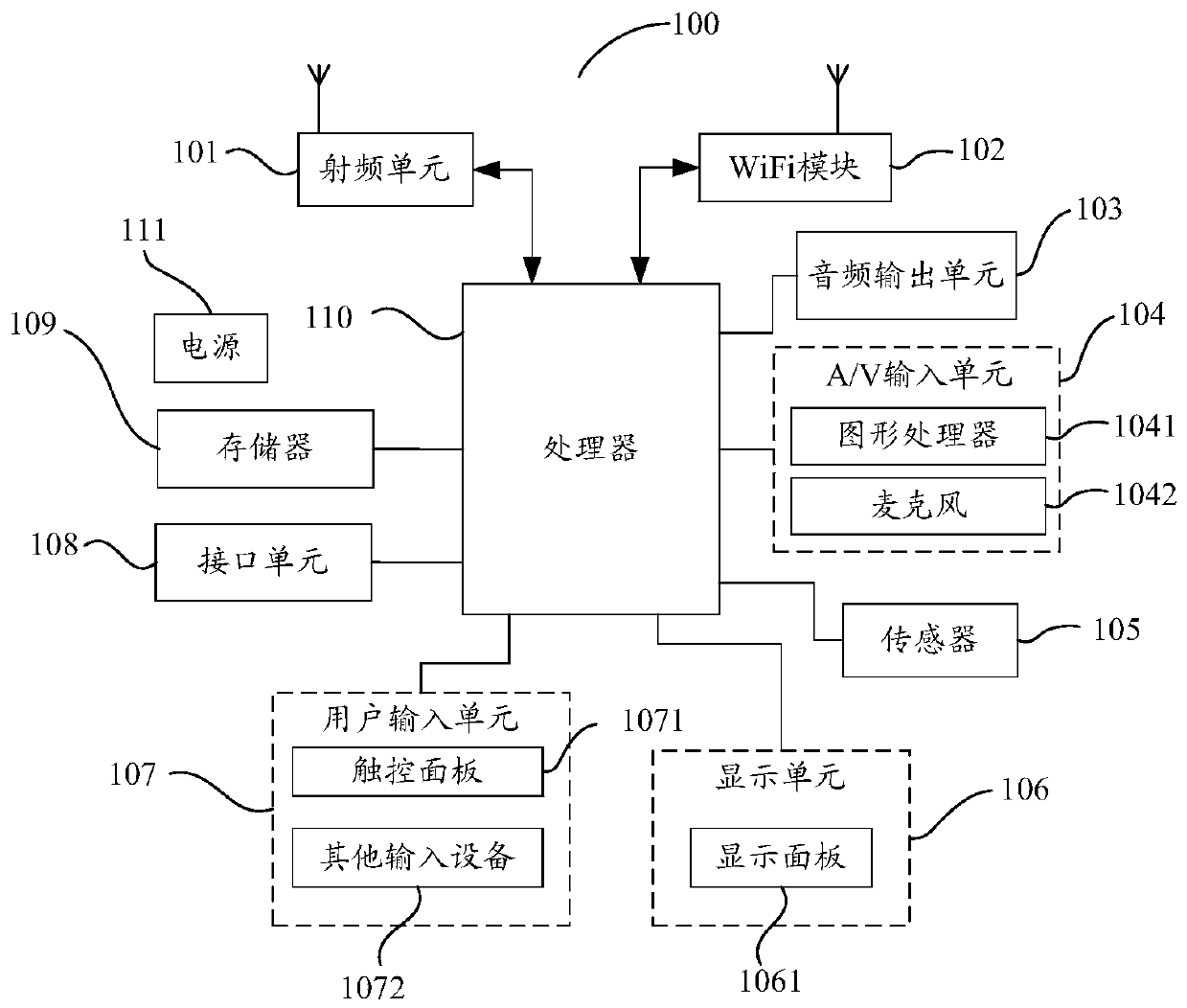

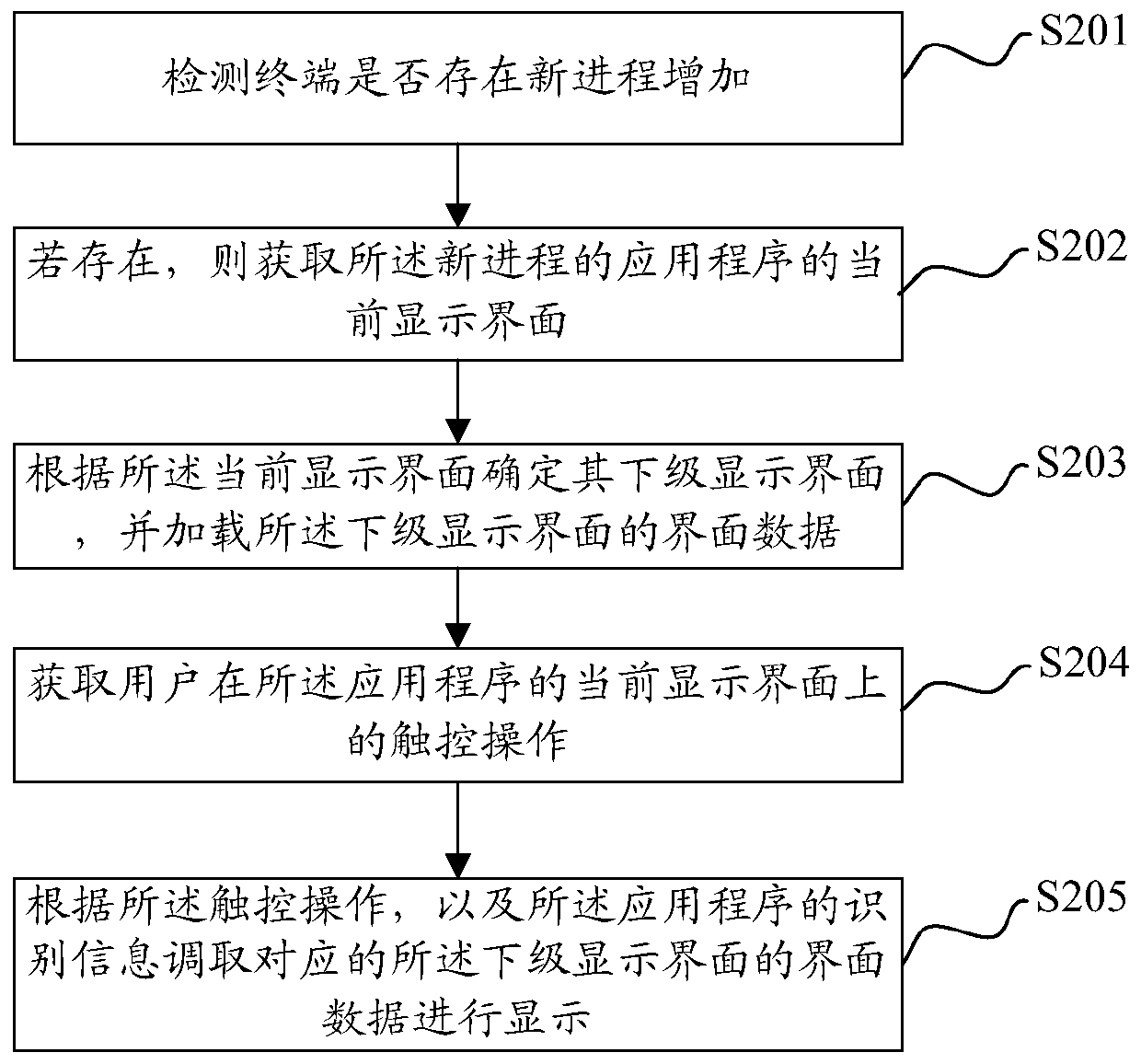

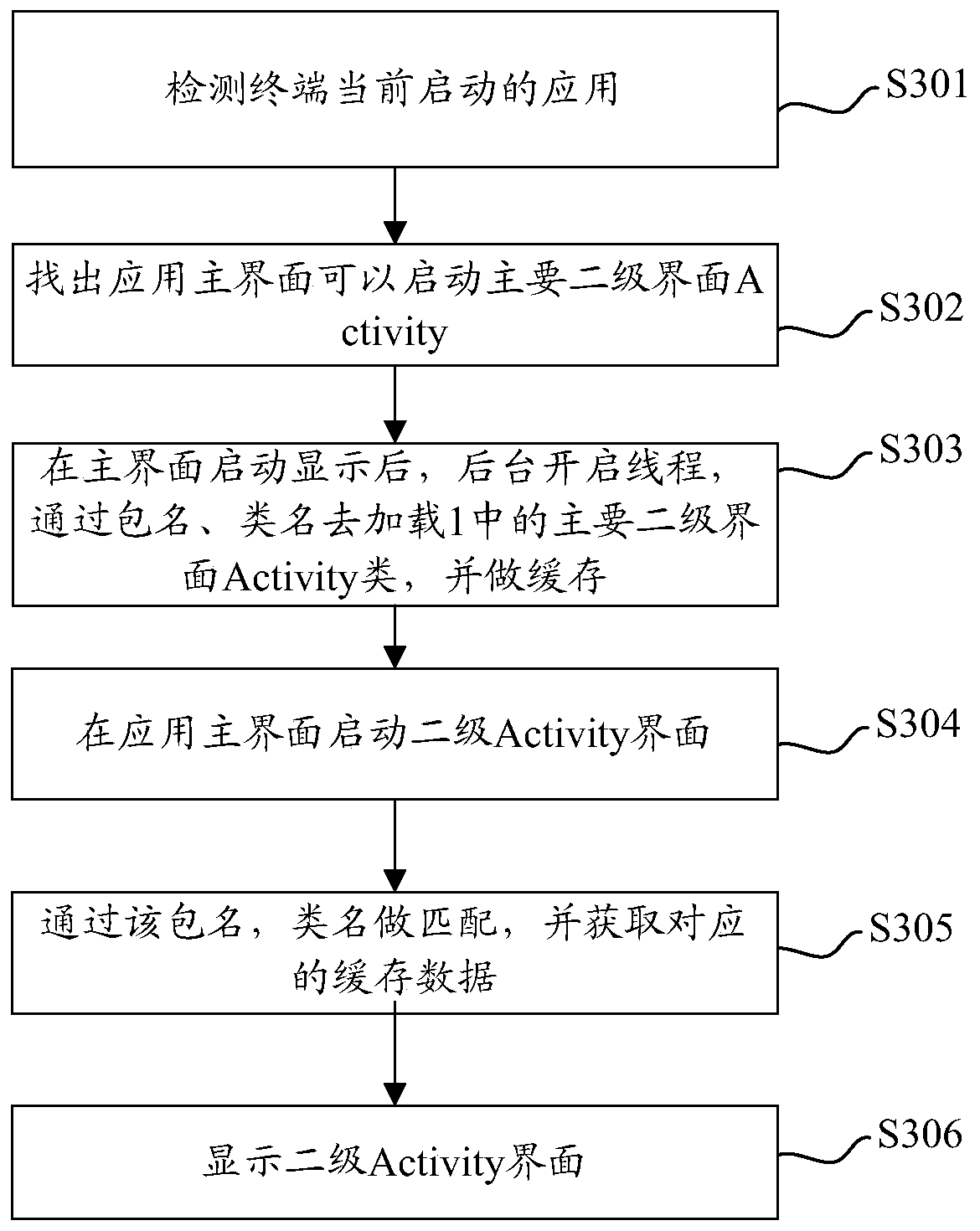

Application interface loading method, mobile terminal and computer readable storage medium

InactiveCN109697088AFast startupImprove user experienceProgram loading/initiatingInput/output processes for data processingTime delaysApplication software

The invention discloses an application interface loading method. The invention discloses a mobile terminal and a computer readable storage medium. The method comprises the following steps: after a terminal detects that a new process is started; a current display interface of the application program is determined, according to the content of the current display interface, interface data of a next-level display interface is loaded, after the touch operation is obtained, the touch operation is executed; according to the embodiment of the invention, the interface data of the subordinate display interface loaded in advance is called for display according to the touch operation and the identification information of the application program, and the existing time delay duration of triggering one time and loading one time is greatly shortened in a pre-loading and calling manner, so that the starting speed of a next interface is increased, and the use experience of a user is also improved.

Owner:NUBIA TECHNOLOGY CO LTD

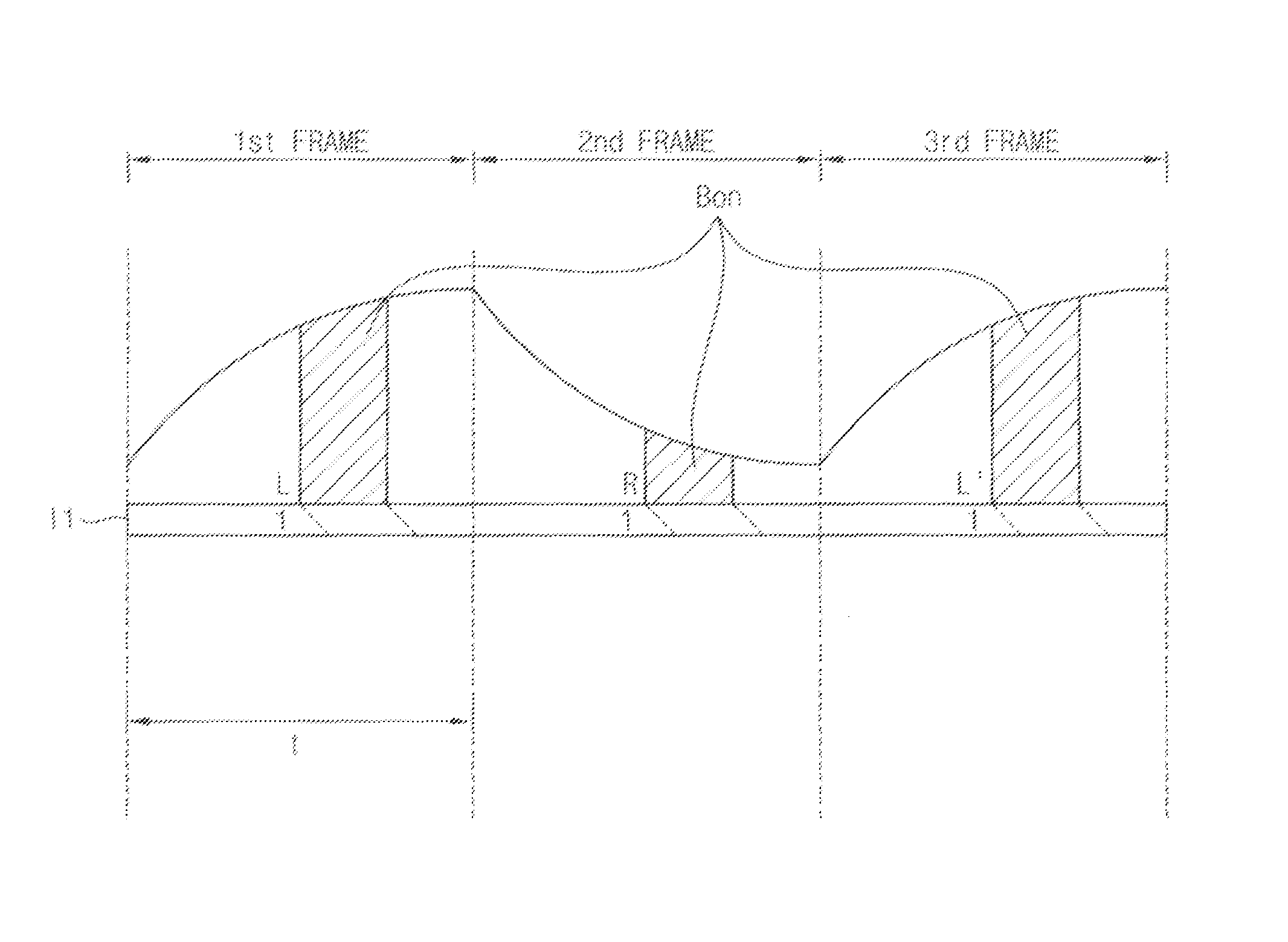

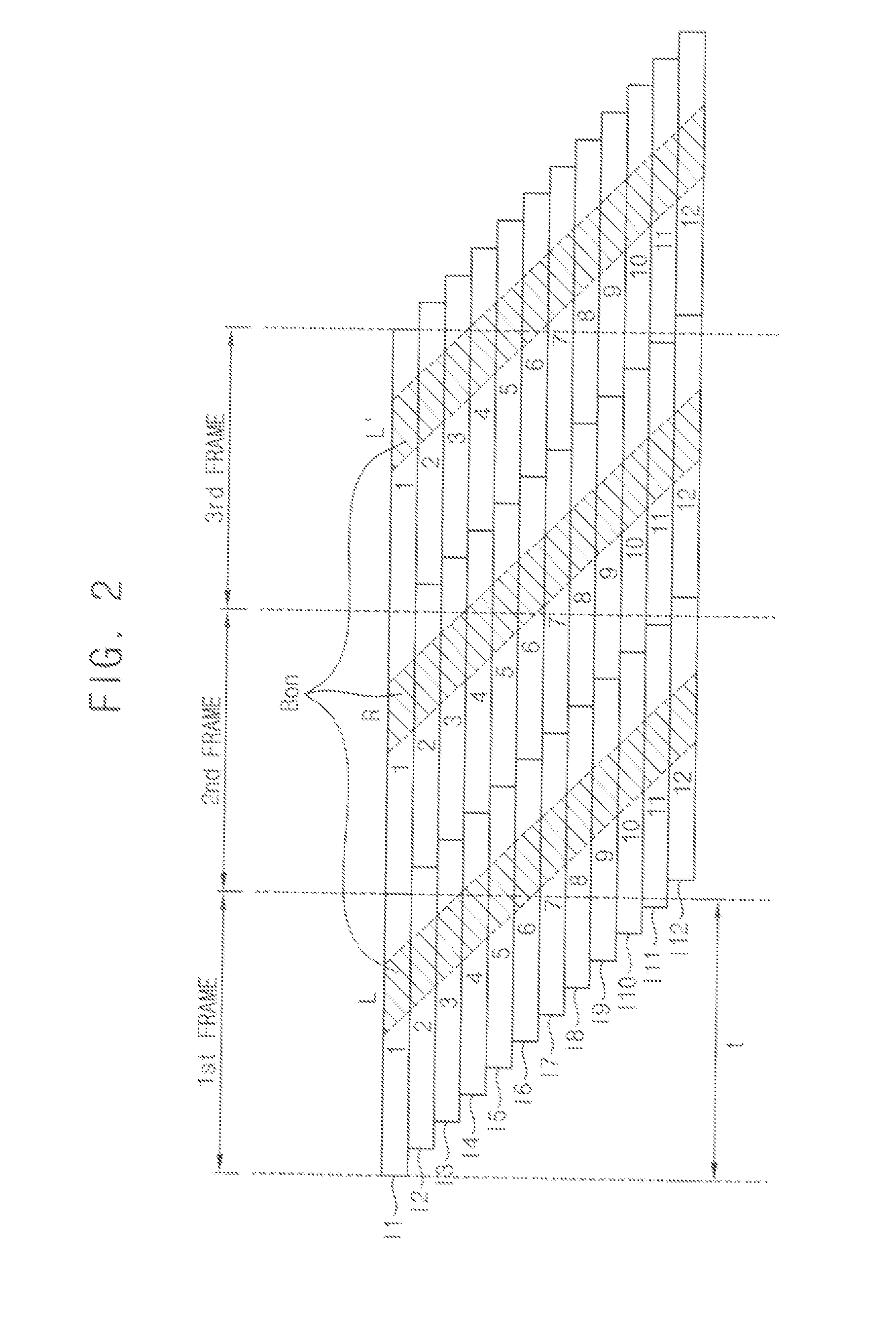

Method of driving a display device

InactiveUS20130271441A1Reduce latencyIncrease brightnessCathode-ray tube indicatorsNon-linear opticsDisplay deviceComputer science

A method of driving a display device includes a preliminary frame charging step and a main frame charging step. The method comprises a preliminary frame charging step of simultaneously charging liquid crystal cells in a pixel line group having a selected pixel row and a unselected pixel row with pixel data of the selected pixel row of the pixel line group and a main frame charging step of charging liquid crystal cells in the unselected pixel line group with pixel data of the unselected pixel line group.

Owner:SAMSUNG DISPLAY CO LTD

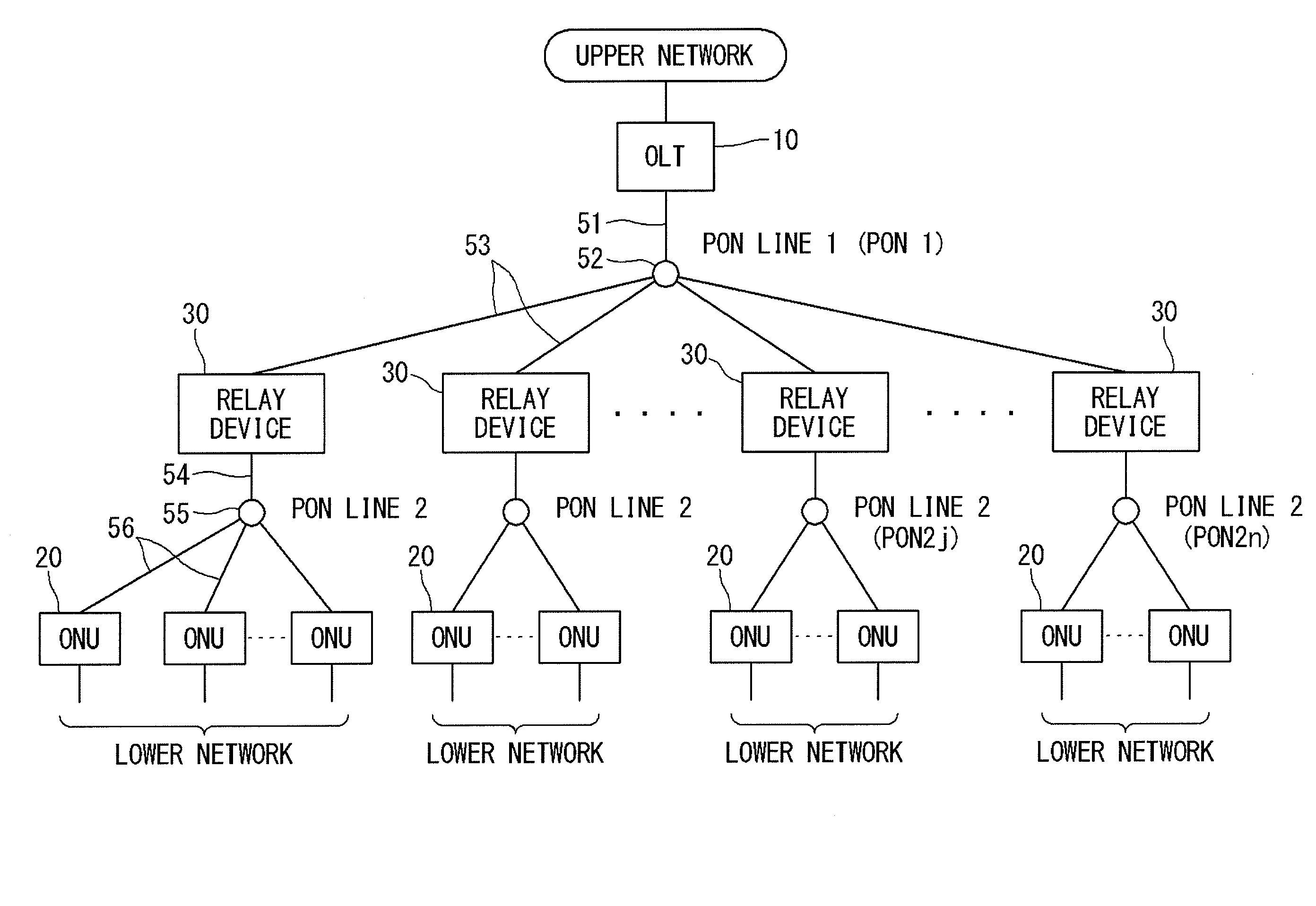

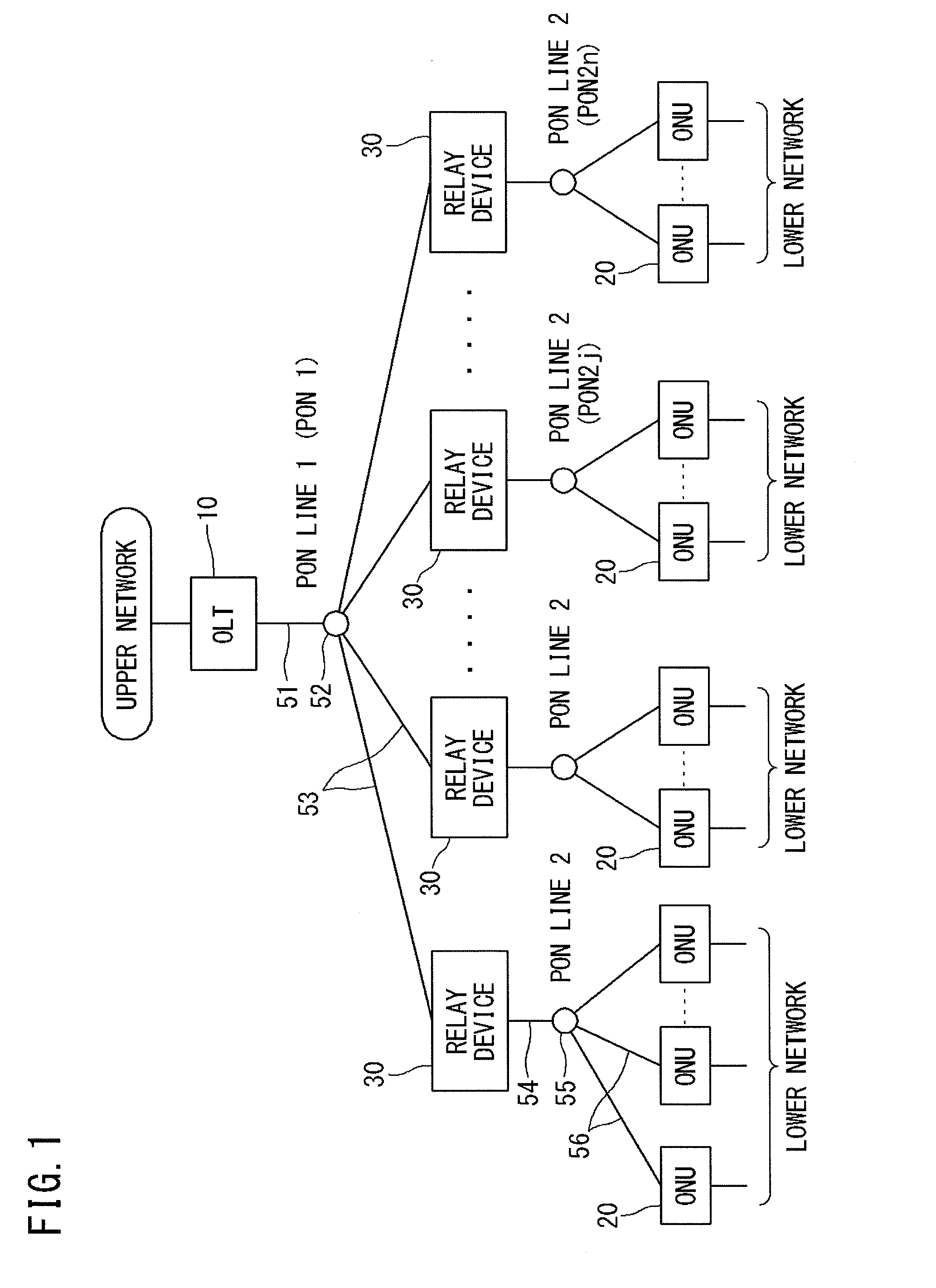

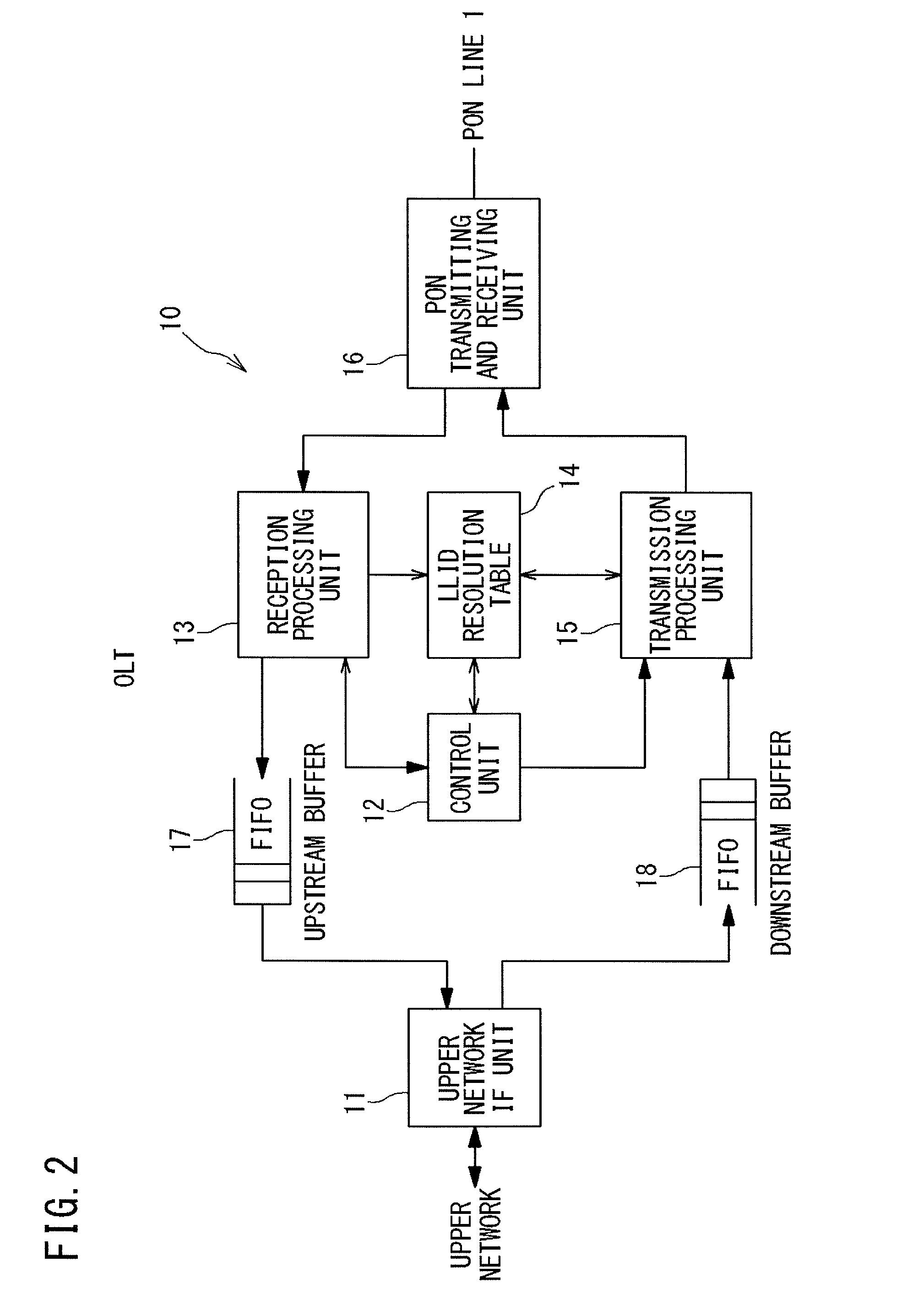

Relay device, station side device, and communication system and communication method using relay device

InactiveUS20150326318A1Reduce delay timeReduce latencyMultiplex system selection arrangementsOptical multiplexMulti accessControl unit

A relay device of the present invention includes a relay processing unit that relays a downstream frame received by a first transmitting and receiving unit to a second transmitting and receiving unit, and relays an upstream frame received by the second transmitting and receiving unit to the first transmitting and receiving unit; and a control unit that follows upstream multiple access control performed by a station side device in a first line, for transmission of the upstream frame to be transmitted by the first transmitting and receiving unit to the station side device, and independently performs upstream multiple access control for reception of the upstream frame received by the second transmitting and receiving unit from a home side device in a second line. The control unit reports an amount of data that the home side device in the second line will be allowed to transmit, to the station side device in the first line before the data arrives at the second transmitting and receiving unit.

Owner:SUMITOMO ELECTRIC IND LTD

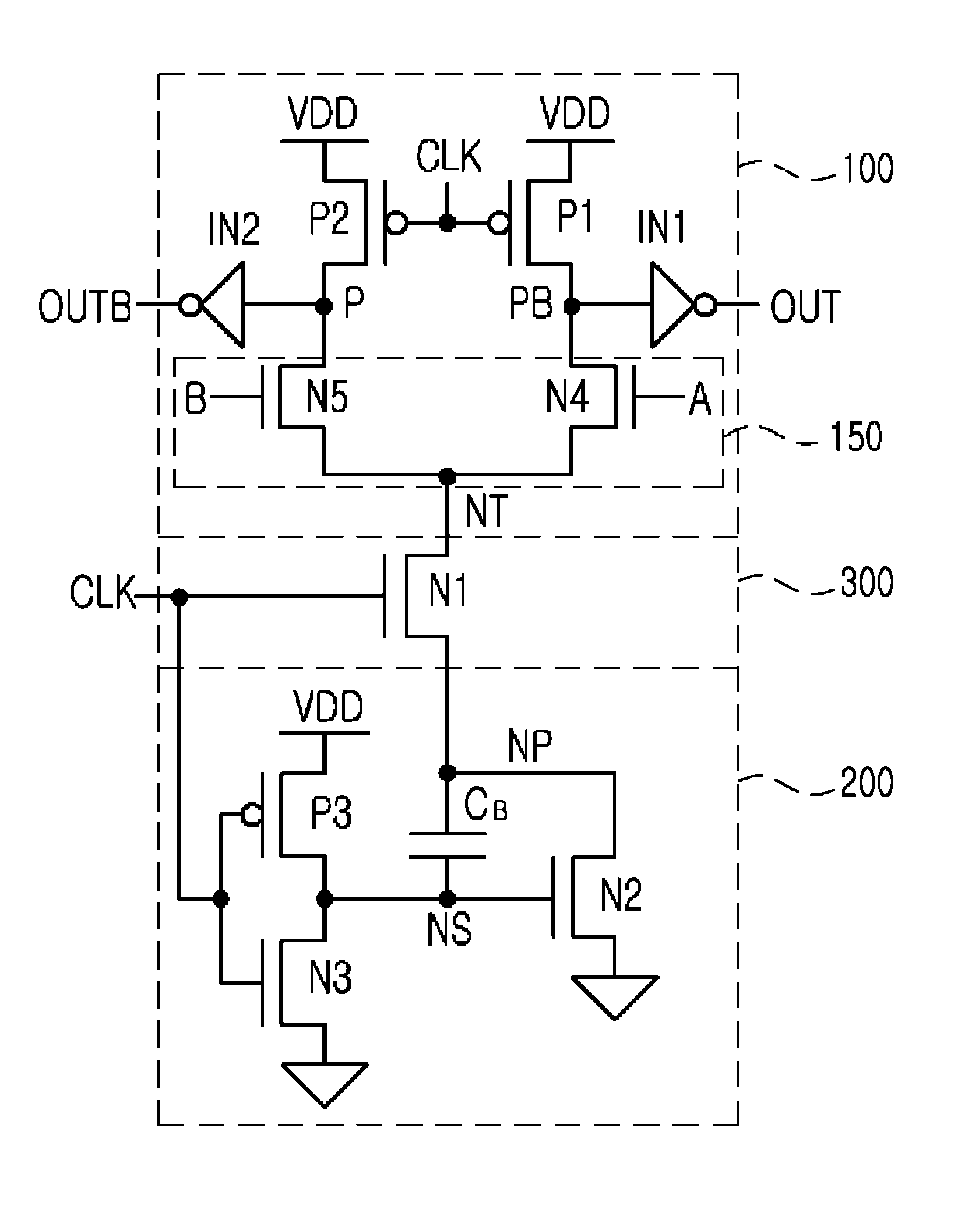

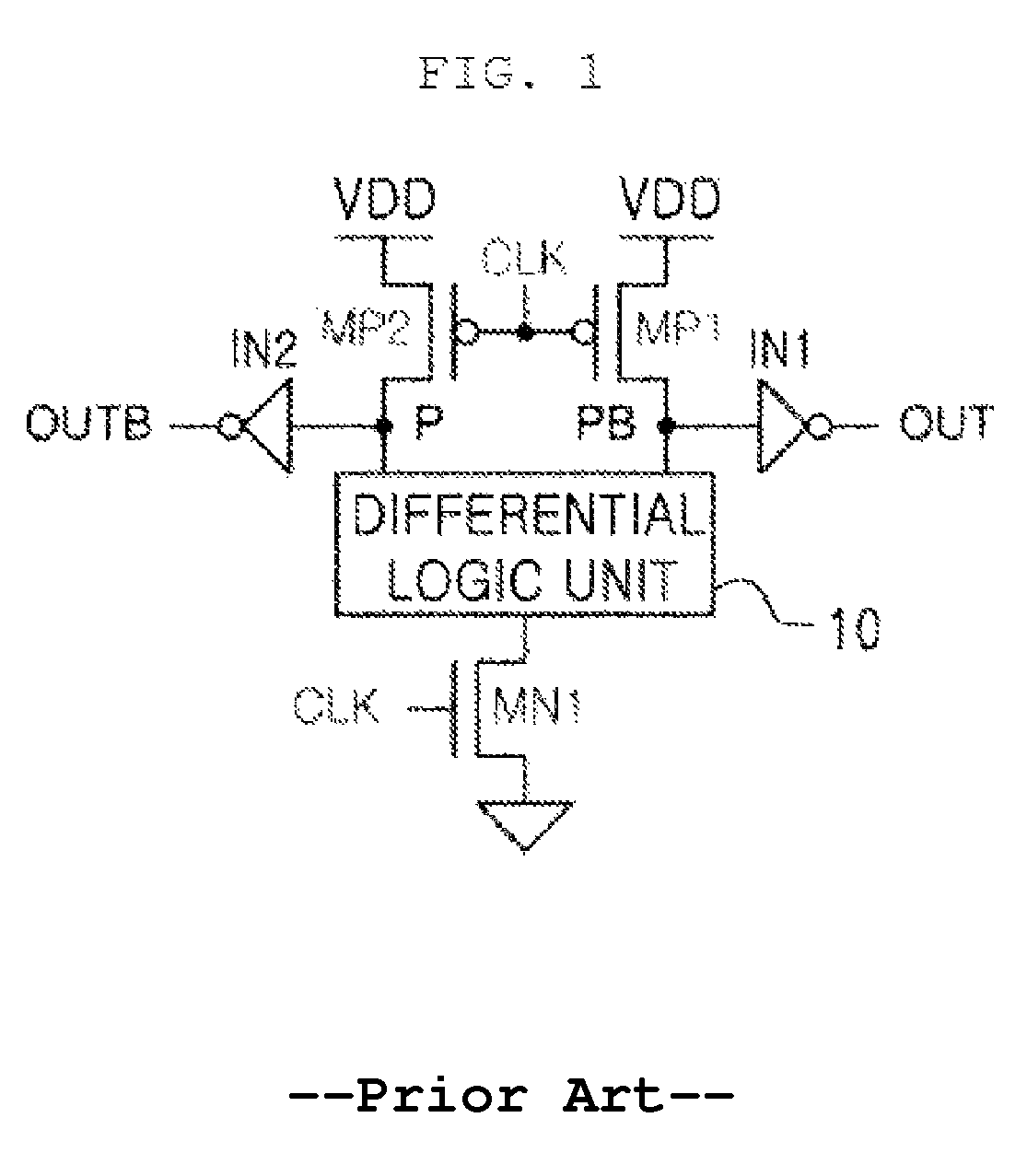

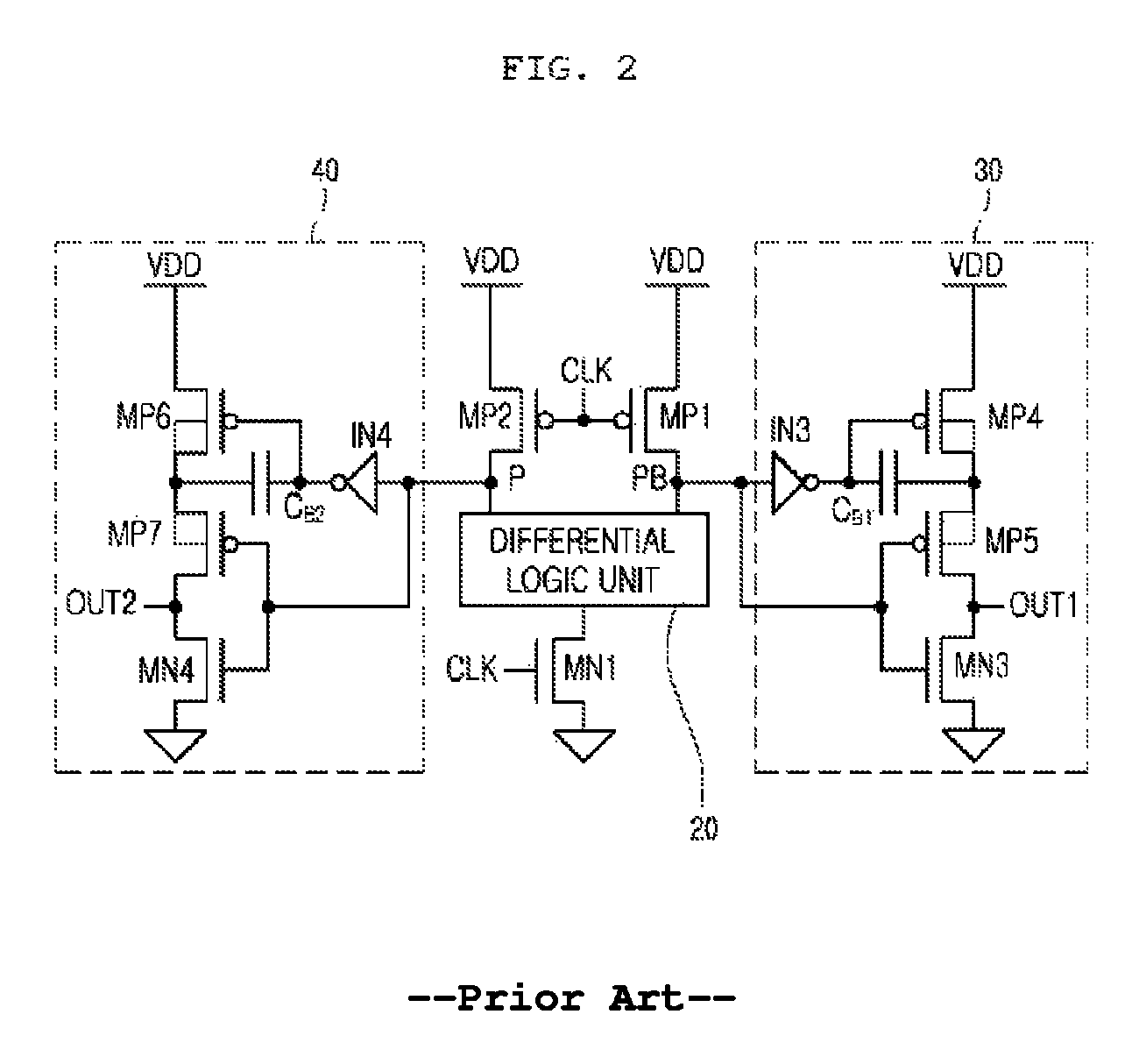

CMOS differential logic circuit using voltage boosting technique

ActiveUS8907701B2Prevent slowdownImprove energy efficiencyReliability increasing modificationsLogic circuits coupling/interface using field-effect transistorsCapacitancePropagation delay

The present invention discloses a CMOS differential logic circuit. The CMOS differential logic circuit includes a precharge differential logic unit, which is precharged to a source voltage in response to a clock signal and is configured to output voltage having an increased load-driving ability using a boosting voltage; a voltage-boosting unit, which is pulled down by a ground voltage in response to the clock signal and is configured to boost the pulled-down voltage using capacitive coupling and output the boosting voltage; and a switching unit, which is configured to couple the precharge differential logic unit and the voltage-boosting unit in response to the clock signal. The propagation delay of a signal from the input terminal to the output terminal of a circuit in a low-source-voltage environment can be reduced, and the operating speed of the circuit and energy efficiency of the operation thereof can be improved.

Owner:RES & BUSINESS FOUND SUNGKYUNKWAN UNIV

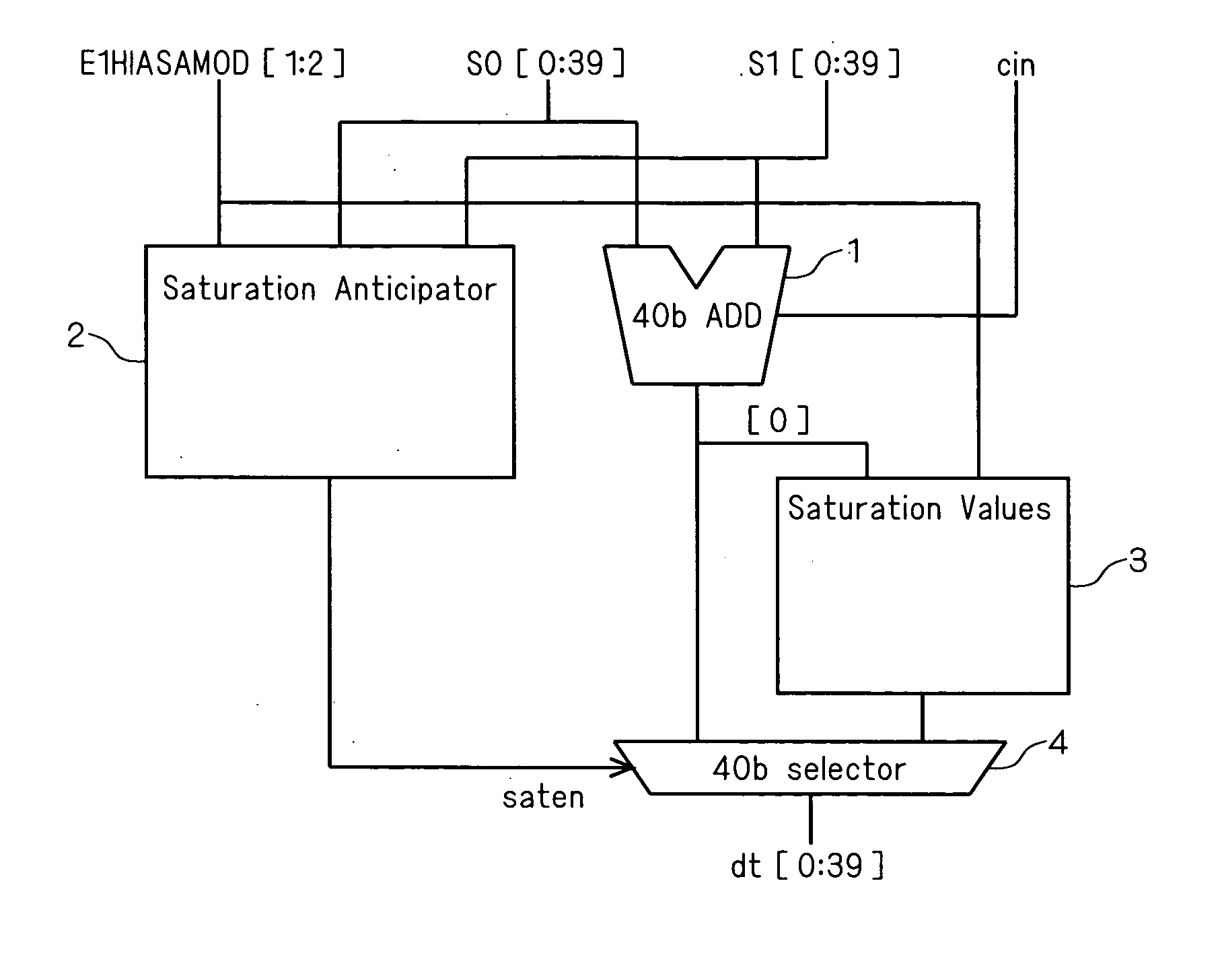

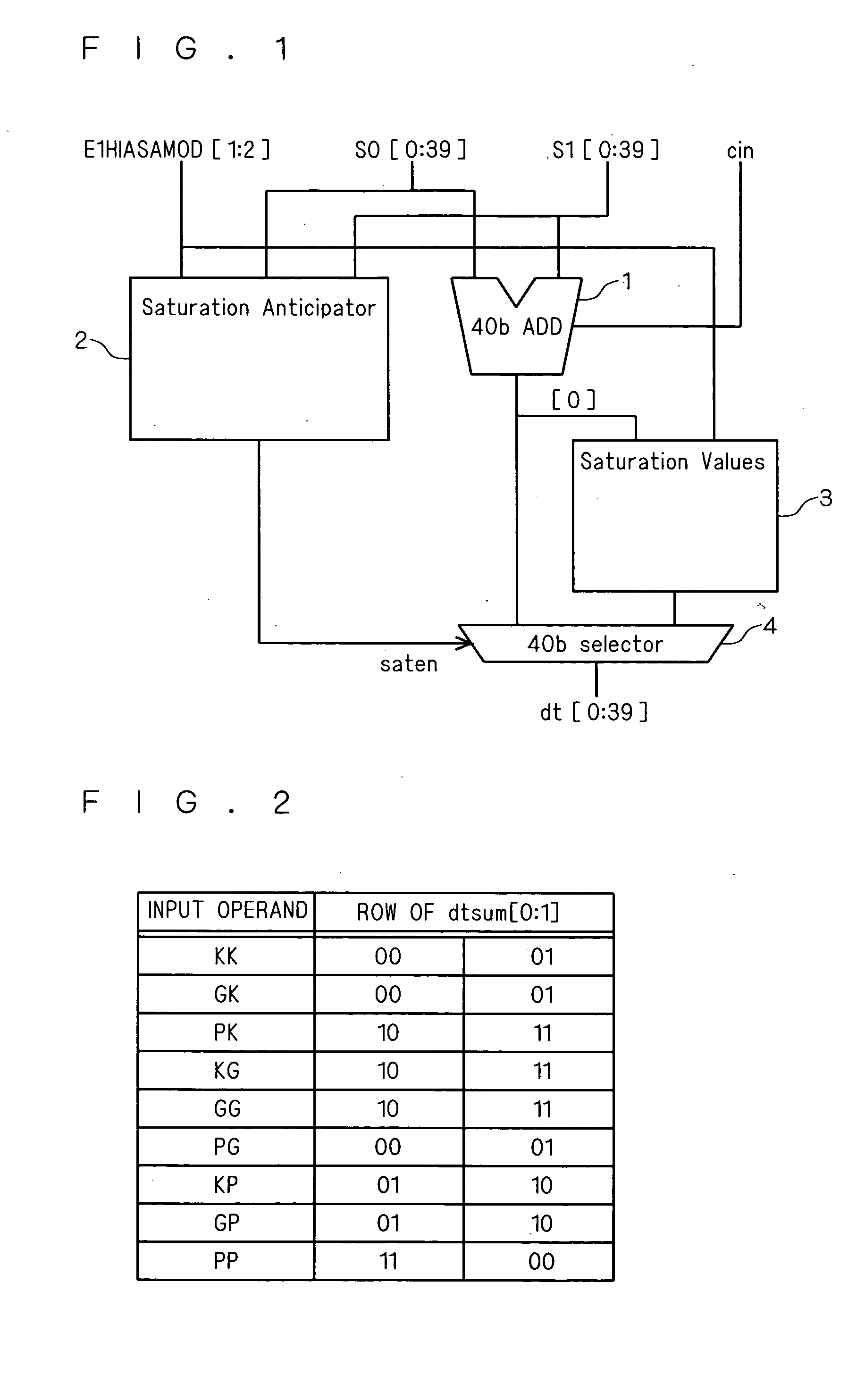

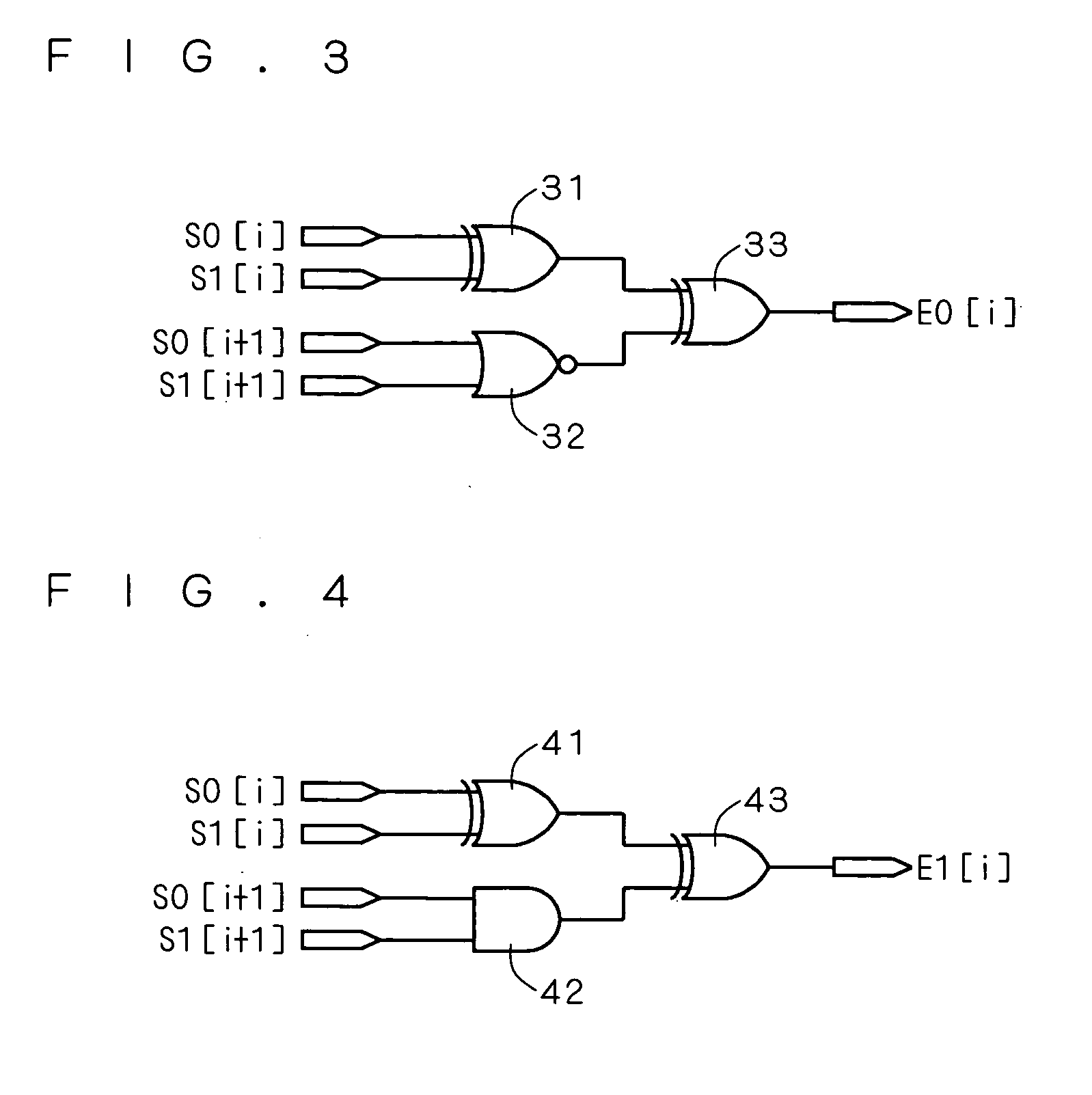

Arithmetic unit

InactiveUS20060066460A1Increase speedReduce delay timeCode conversionProgram controlBit-lengthProcess rate

The present invention provides an arithmetic unit performing a saturation process that can reduce a delay time relating to an arithmetic process and a saturation process, thereby being capable of increasing a processing speed. An arithmetic unit according to the present invention includes an arithmetic processing section that performs an adding or subtracting operation of a first input operand and a second input operand and outputs the arithmetic result, a saturation anticipating section that anticipates whether the arithmetic result is within a representation range of a predetermined bit length based upon the first input operand and the second input operand, and outputs a saturation anticipating signal, and a selecting section selecting that the maximum value or minimum value within the representation range of the predetermined bit length is made to be the output result in case where the arithmetic result is anticipated not to be within the representation range of the predetermined bit length in the saturation anticipating signal from the saturation anticipating section, while selecting that the arithmetic result is made to be the output result in case where the arithmetic result is anticipated to be within the representation range of the predetermined bit length in the saturation anticipating signal. Herein, the saturation anticipating section is operated in parallel with respect to the arithmetic processing section.

Owner:RENESAS TECH CORP

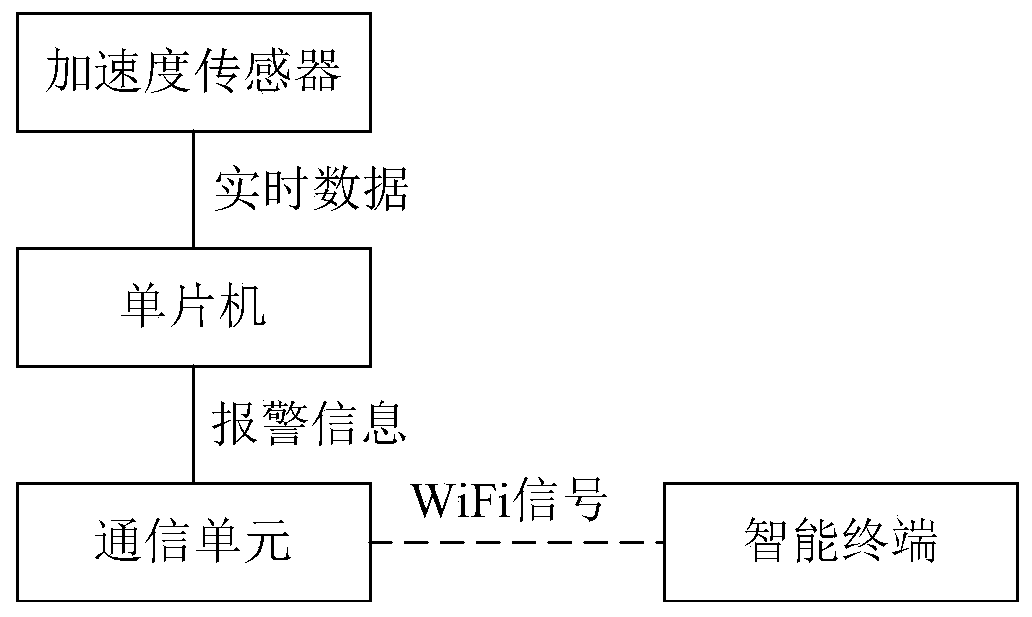

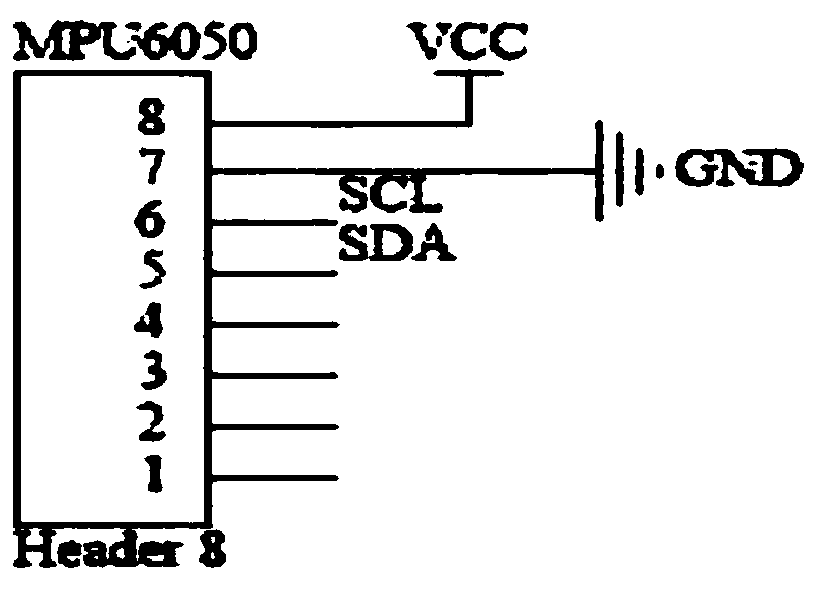

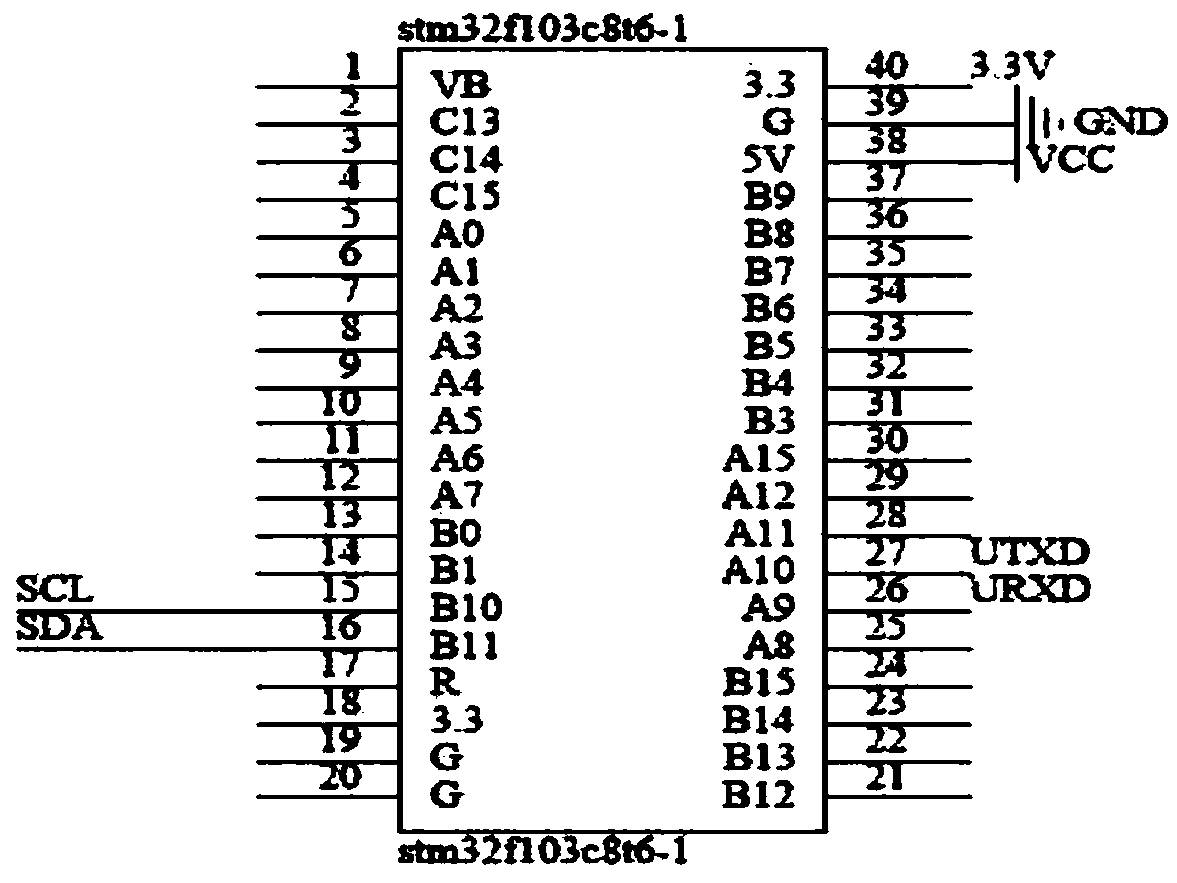

Automobile major accident alarm system and method

InactiveCN110021153AReduce delay timeQuick helpTelephonic communicationAlarmsAlarm triggerCommunication unit

The invention relates to an automobile major accident alarm system and method. The automobile major accident alarm system comprises an acceleration sensor, a single chip microcomputer, a communicationunit, and an intelligent terminal, wherein the acceleration sensor is used for collecting acceleration data of travelling of an automobile; the single chip microcomputer is used for judging whether the acceleration of the automobile is greater than a threshold value of the acceleration or not and whether the angle of inclination of the automobile is greater than a threshold value of the angle ofinclination or not according to the acceleration data, and determining whether the automobile has a traffic accident or not according to judgment results; and the single chip microcomputer is furtherused for transmitting an alarm trigger signal to the communication unit in the case of determining occurring of the traffic accident; the communication unit is used for sending the alarm trigger signal to the intelligent terminal; and the intelligent terminal is used for obtaining current position information and performing alarm operation when receiving the alarm trigger signal; and as for alarmoperation, the current position information and prestored owner information are sent to a preset emergency contact person and / or an alarm number is dialed. According to the automobile major accident alarm system and method, the functions of real-time accurate positioning, intelligent and diverse alarm for help and the like are realized through the intelligent terminal.

Owner:CHENGDU UNIV OF INFORMATION TECH

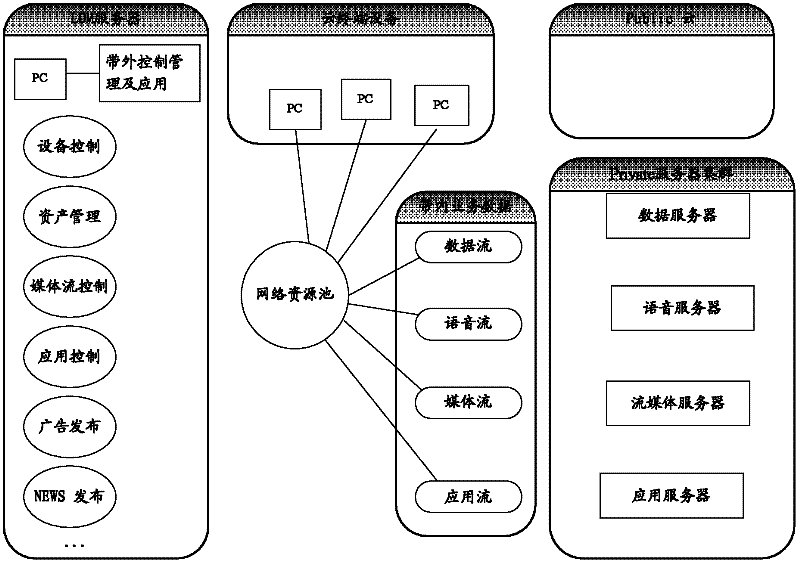

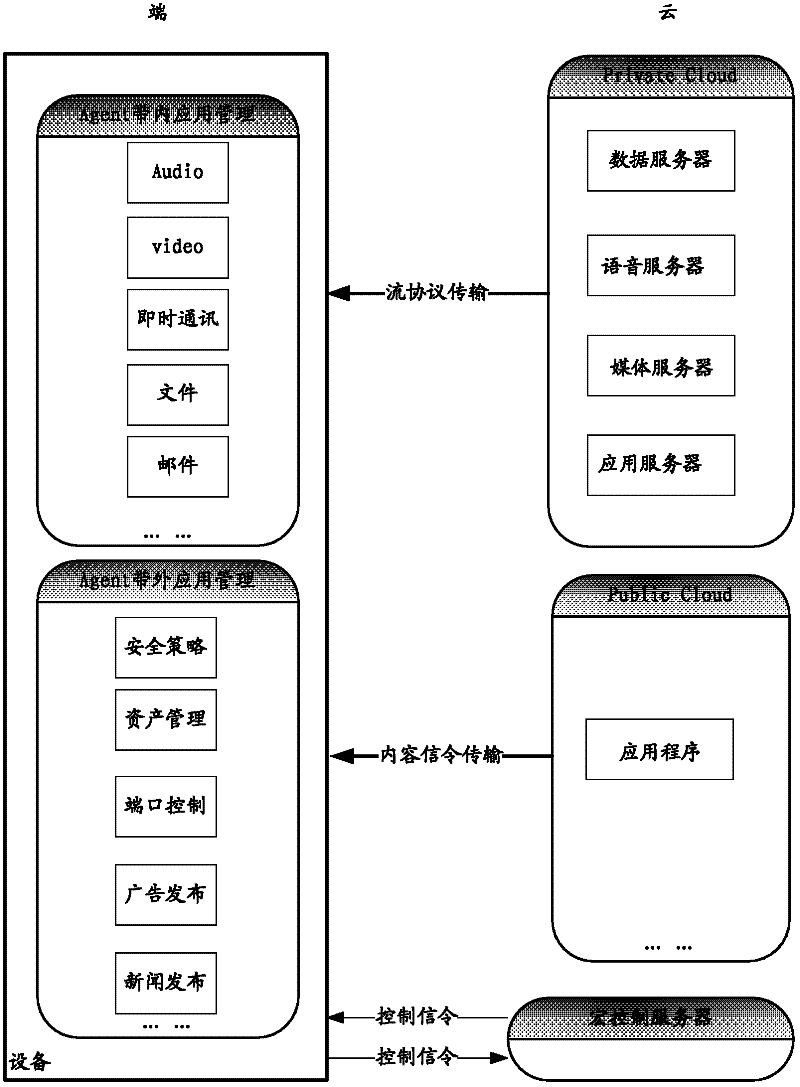

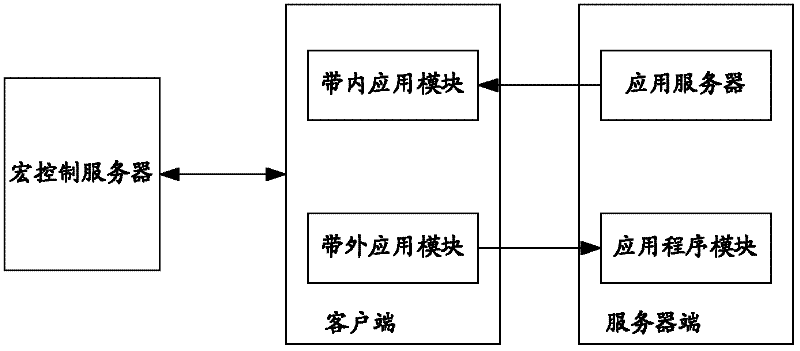

Cloud equipment macro control method and system thereof

ActiveCN102368783AReduce operating costsReduce delay timeTransmissionResource poolQuality of service

The invention provides a cloud equipment macro control method and a system thereof. The method is characterized in that: through using network data shunting technology, network data is divided into in-band business data and outband network management data which are connected with a corresponding server respectively through a network resource pool to carry out data transmission and interaction. In the invention, through using the network data shunting technology, the network data is divided into the in-band business data and the outband network management data which are connected with the corresponding server respectively through the network resource pool to carry out data transmission and interaction, and control and management of an application program are realized. Operation cost is reduced, operation efficiency is raised, machine delay time is reduced, service quality is raised, functions are complete, customizability is strong, and different management programs can be customized according to different user requirements.

Owner:广州烽云信息科技有限公司

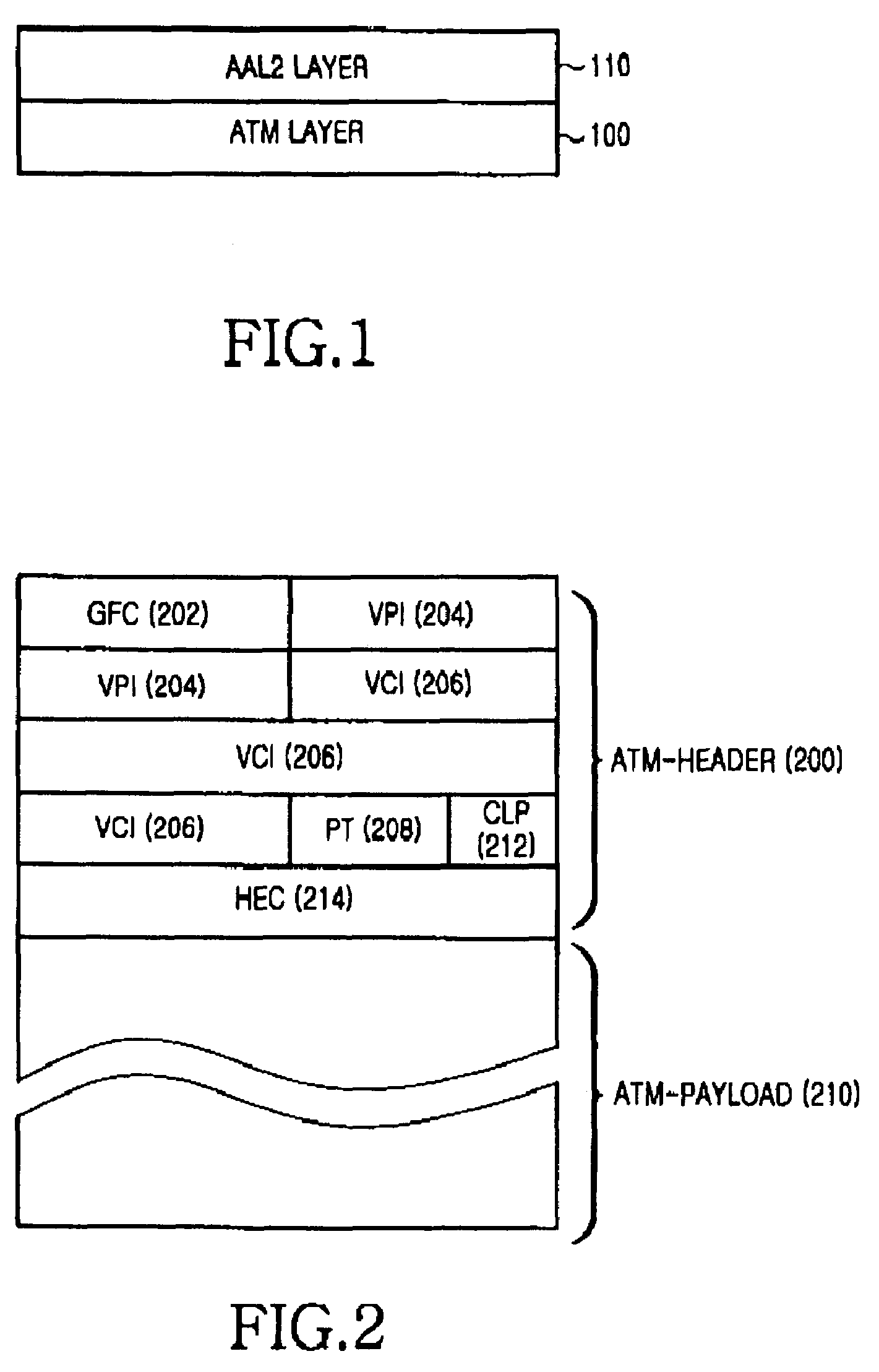

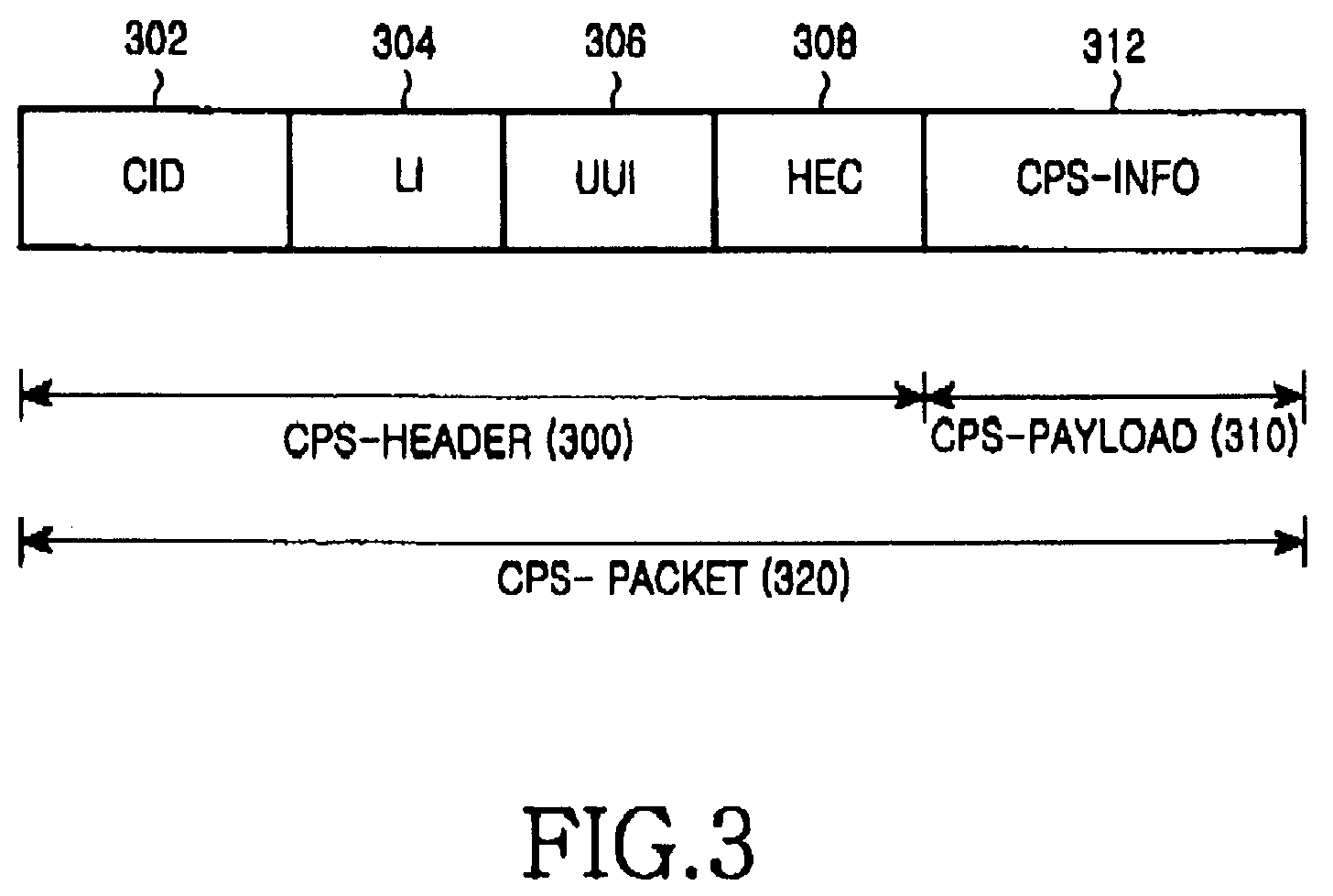

AAL2 switching apparatus and method

InactiveUS7403533B2Reduce delay timeReduce latencyTime-division multiplexData switching by path configurationAsynchronous Transfer ModeComputer network

Disclosed is an AAL2 (ATM (Asynchronous Transfer Mode) Adaptation Layer 2) switching apparatus. A cell deassembler for deassembling a payload of a received ATM cell into a CPS (Common Part Sublayer) packet, and generating a first VPC (Virtual Path Connection) by using the header of the ATM cell. A header converter for receiving the CPS packet from the cell deassembler and converting the first VPC into a second VPC by using a lookup table which have a number of VPCs and CIDs (Channel Identifiers) for changing the VPC. A cell assembler for receiving the CPS packet from the header converter, assembling an ATM cell which have the CPS packet and an ATM header generated from the second VPC.

Owner:SAMSUNG ELECTRONICS CO LTD

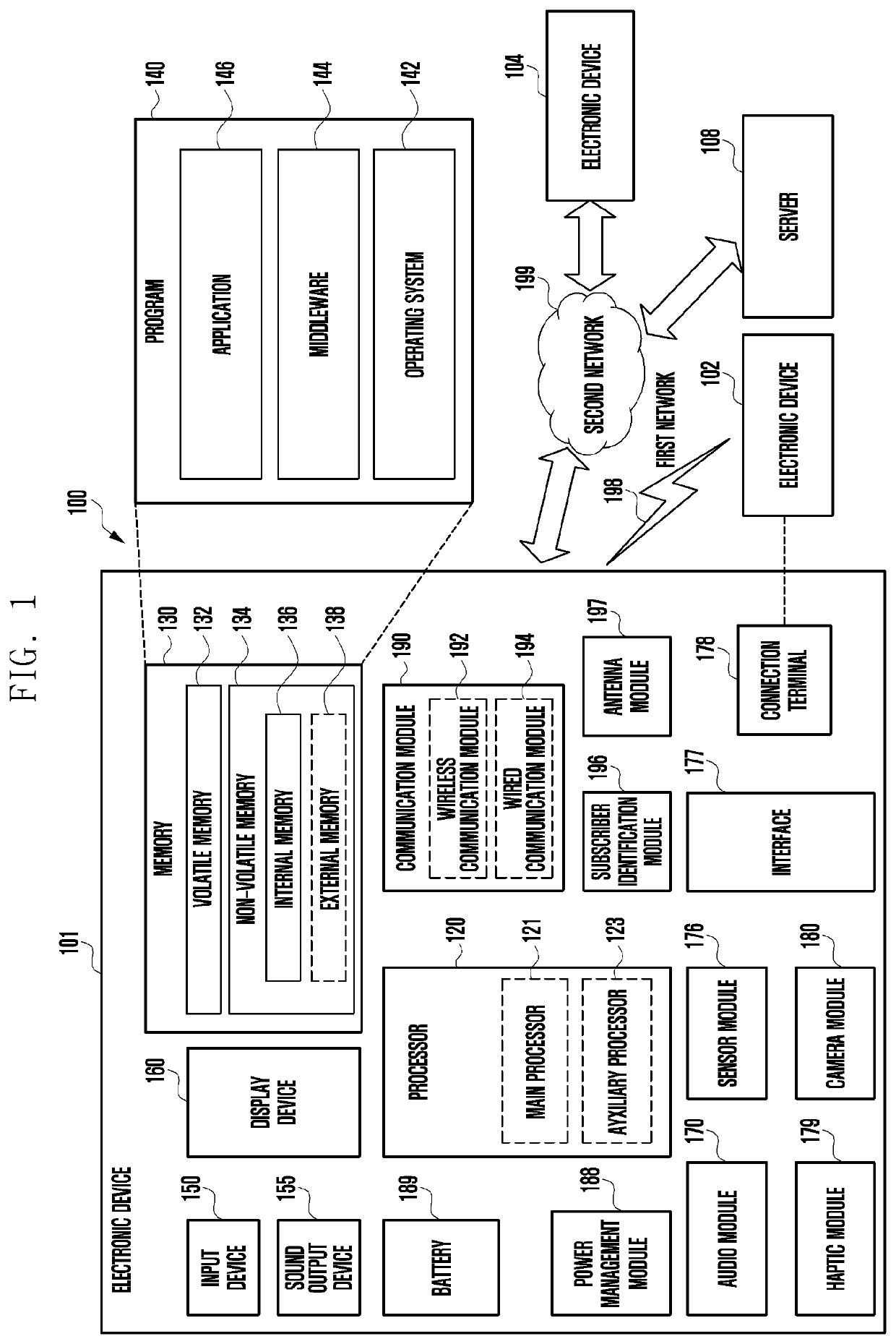

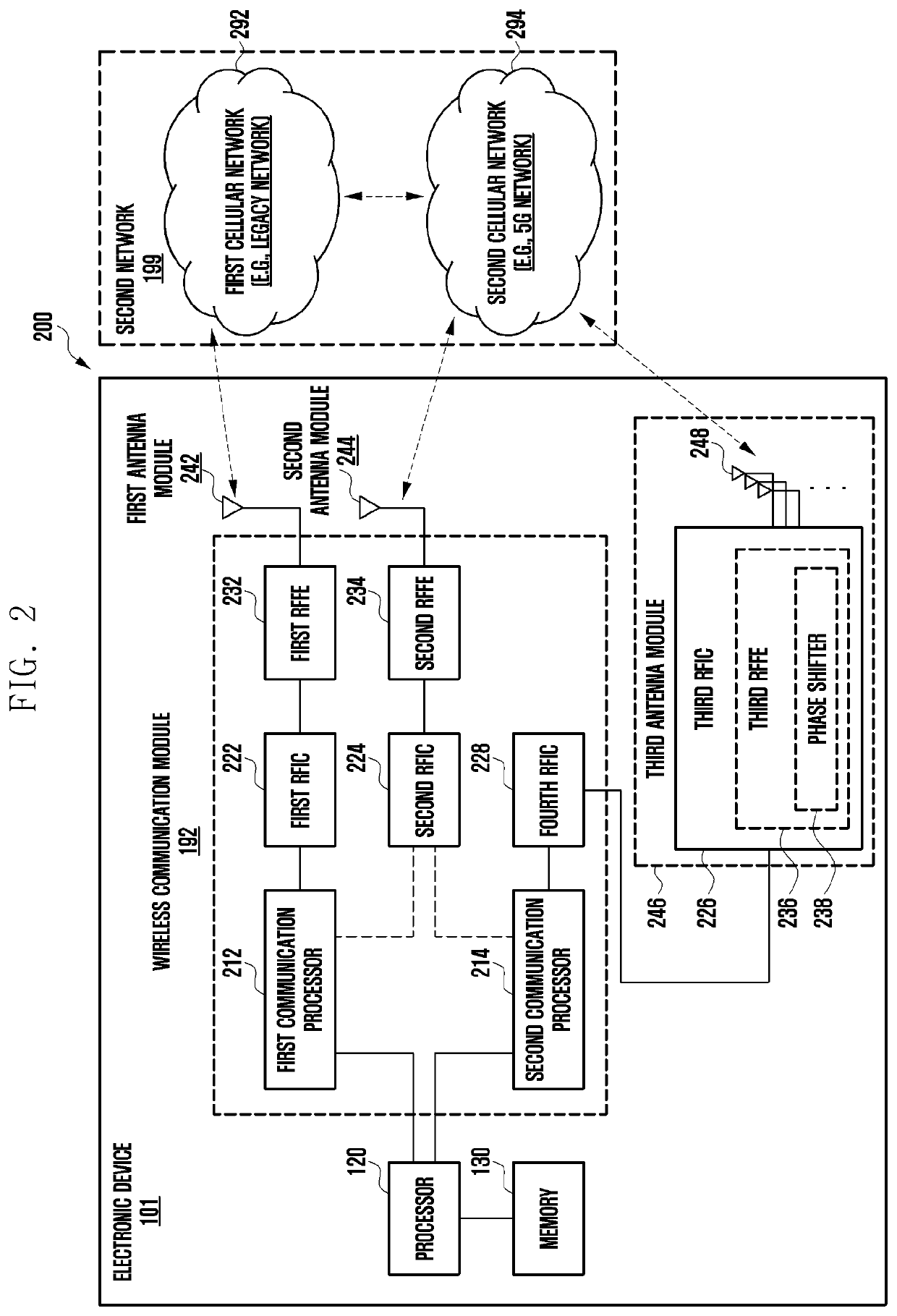

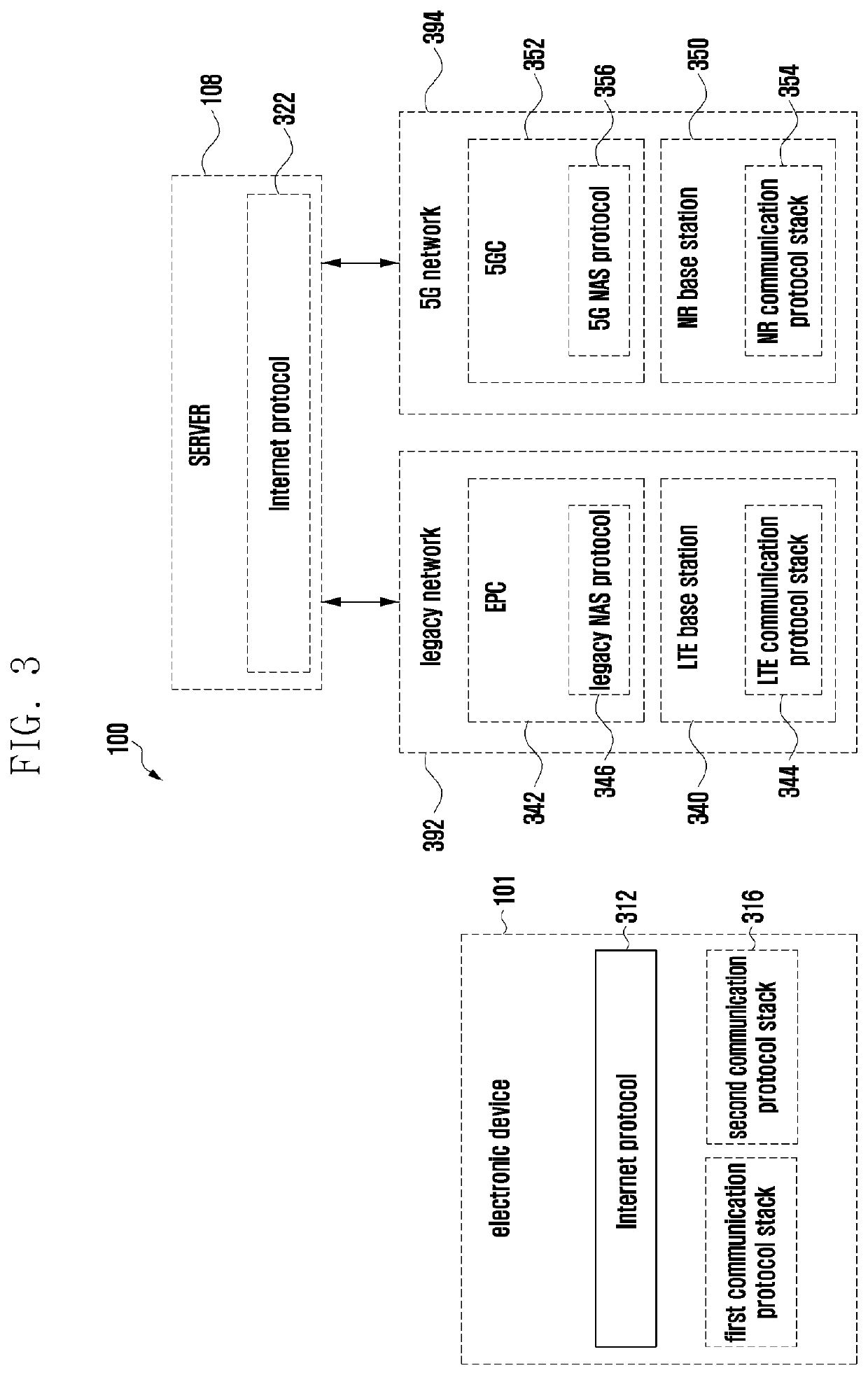

Electronic device for performing node selection based on system information block and operation method thereof

ActiveUS20210168700A1Quick searchReduce delay timeAssess restrictionNetwork topologiesSystem informationCellular communication

An electronic device may include at least one communication processor and an application processor. The at least one communication processor is configured to: receive first system information including information on whether at least one node supporting first cellular communication supports DC or second system information including information on a node which is adjacent to the at least one node and supports second cellular communication, from the at least one node via the first cellular communication; update, based on the first or second system information, a database which includes information indicating whether the at least one node supports the DC and information indicating whether the node adjacent to the at least one node supports the second cellular communication; determine, based on the updated database, a searching order of at least one node included in the updated database; and search for a node to be registered, based on the determined searching order.

Owner:SAMSUNG ELECTRONICS CO LTD

Method for remedying square billet uniflow casting halt

The invention relates to a method for remedying square billet uniflow casting halt. The method comprises the following steps of 1 closing an accidental flow sliding plate, stopping casting and outputting a tail billet to avoid steel throwing of the tail billet; 2 stopping argon supply for an accidental flow, enabling the upper casting portion of the accidental flow to be in an idle state and preventing moving steel flows from scouring the sliding plate; 3 dismounting a submersed nozzle of the accidental flow so as to facilitate plugging and ingot guiding; 4 enabling the accidental flow to penetrate a bottom-installed ingot guiding rod, performing plugging again and then installing the baked submersed nozzle again to prevent steel from being casted at the cold nozzle; and 5 performing normal continuous casting of other non-accidental flows in a continuous casting mode and starting to perform casting of the accidental flow in a re-starting mode after plugging. Compared with the prior art, the method for remedying the square billet uniflow casting halt has the advantages of being capable of achieving continuous casting, greatly improving the production efficiency, effectively shortening the production delay time, improving the product quality and the yield and being considerable in production effectiveness.

Owner:ANGANG STEEL CO LTD

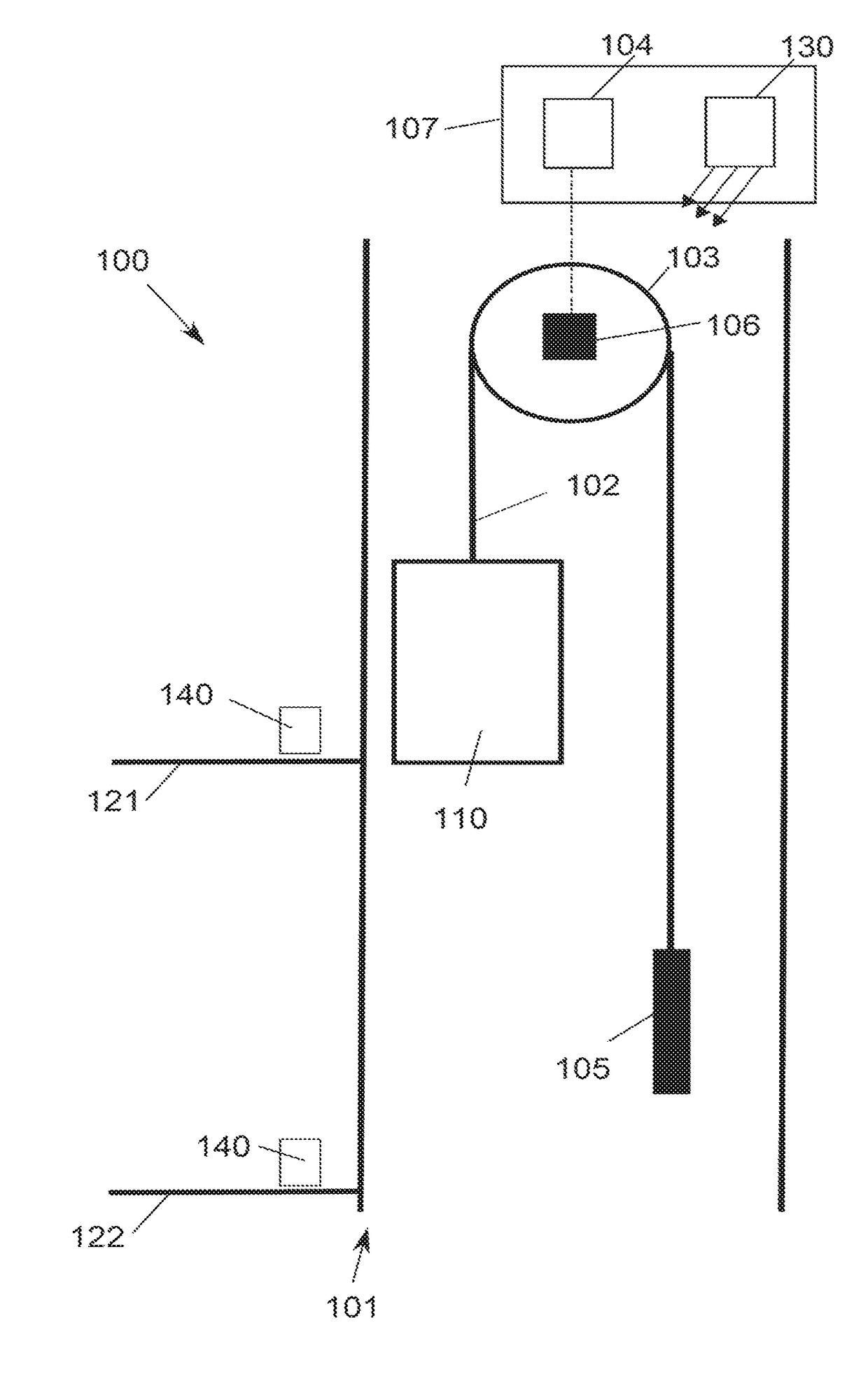

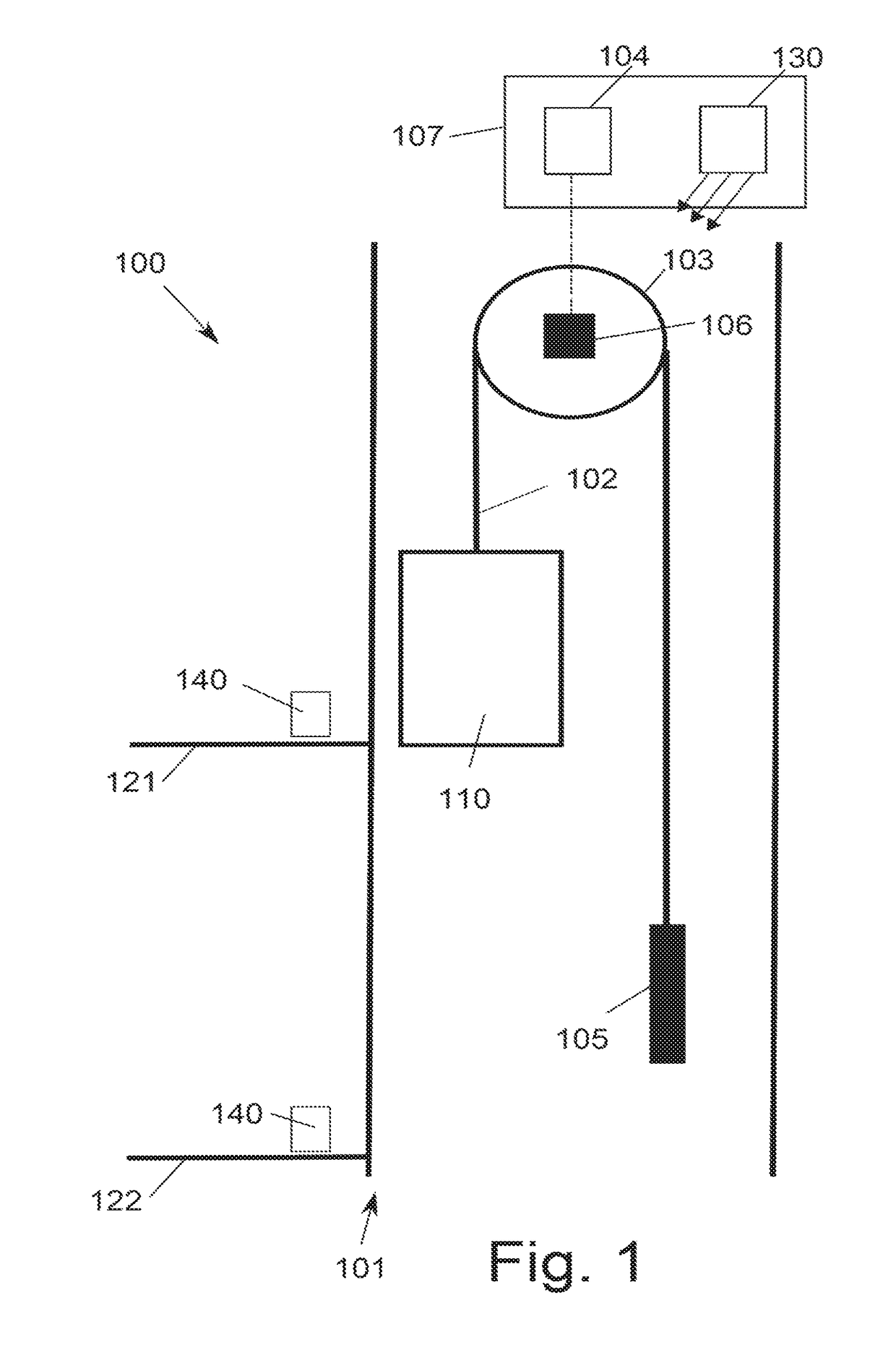

Method for operating a lift system

ActiveUS20180029827A1Time delayReduce delay timeElevatorsBuilding liftsFloor levelAutomotive engineering

Owner:TK ELEVATOR INNOVATION & OPERATIONS GMBH

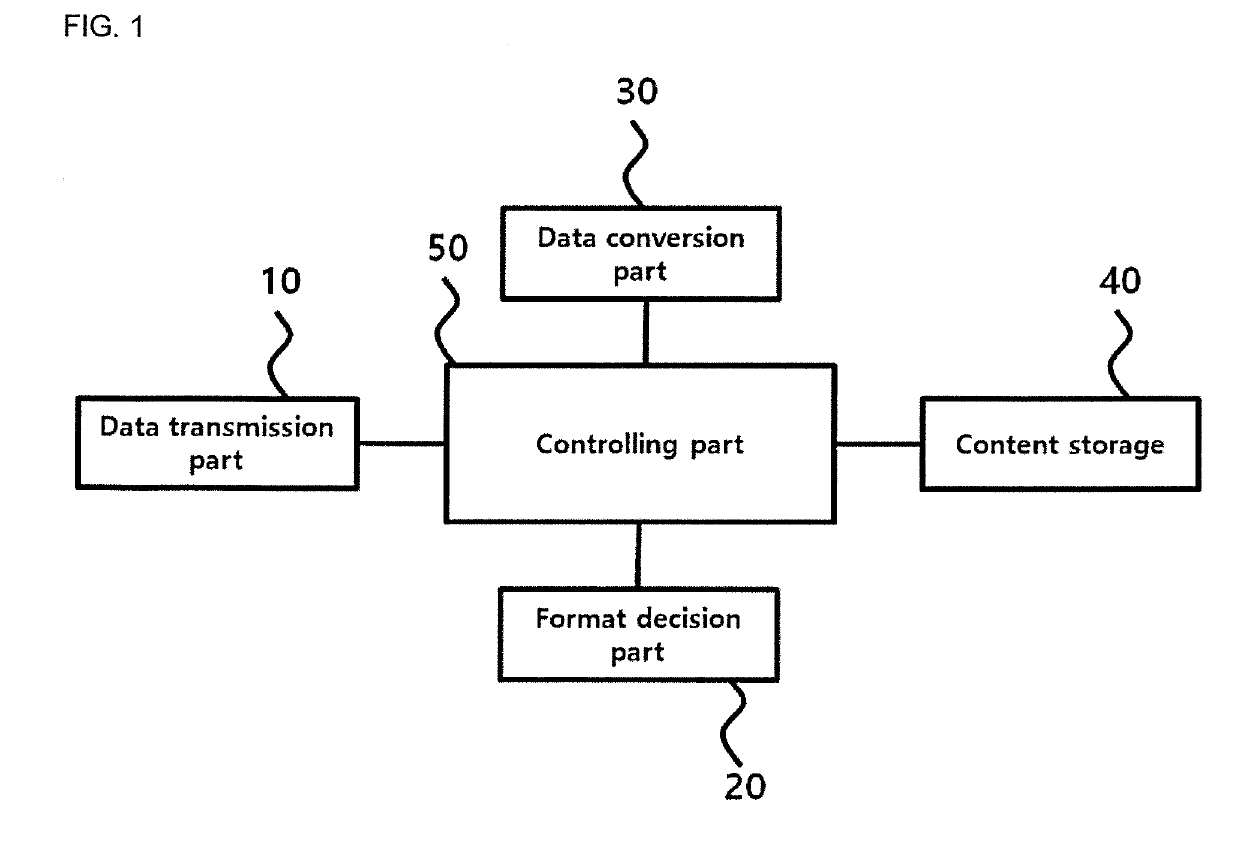

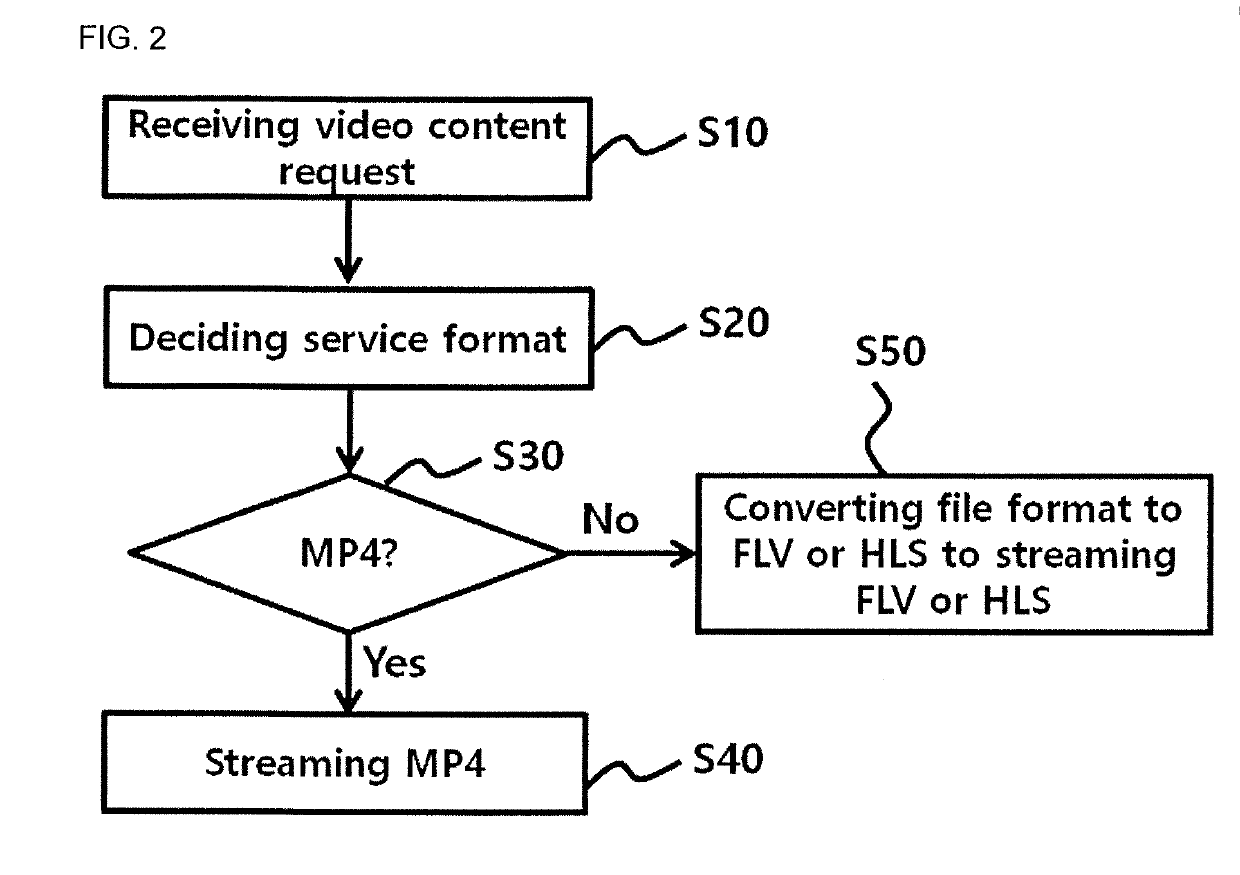

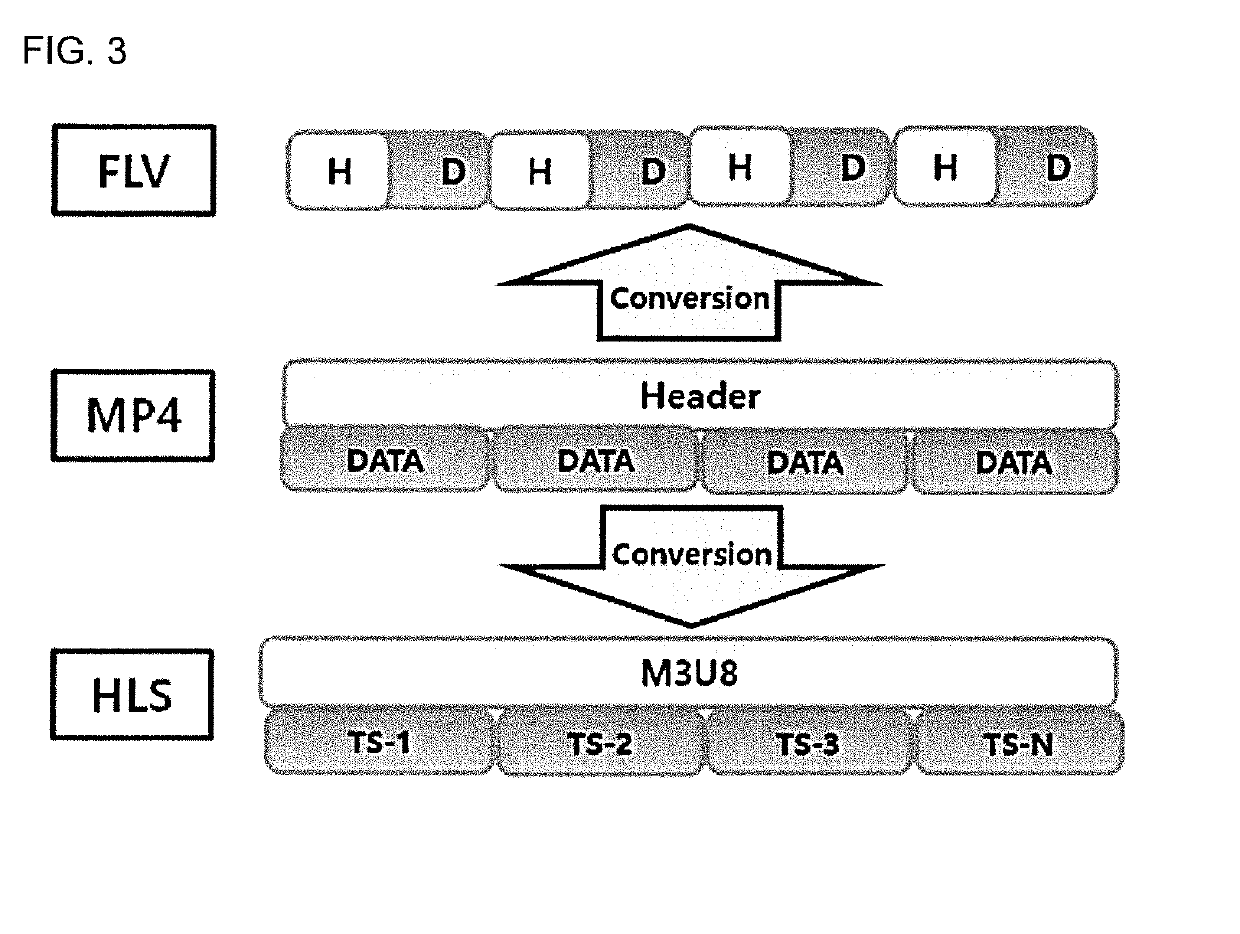

Method of real-time file format conversion streaming service

InactiveUS20190335218A1Reduce latencyUtilize storage spaceSelective content distributionComputer terminalWorld Wide Web

Method of real-time file format conversion streaming disclosed. The method includes receiving a request for video content from a user terminal, selecting a service format based on a device check on the user terminal, if a file format of requested video content is MP4, based on the service format, maintaining the file format of service content to be provided, or converting the file format to FLV or HLS file format by analyzing a header data, and streaming the service content to the user terminal.

Owner:PANDORA TV

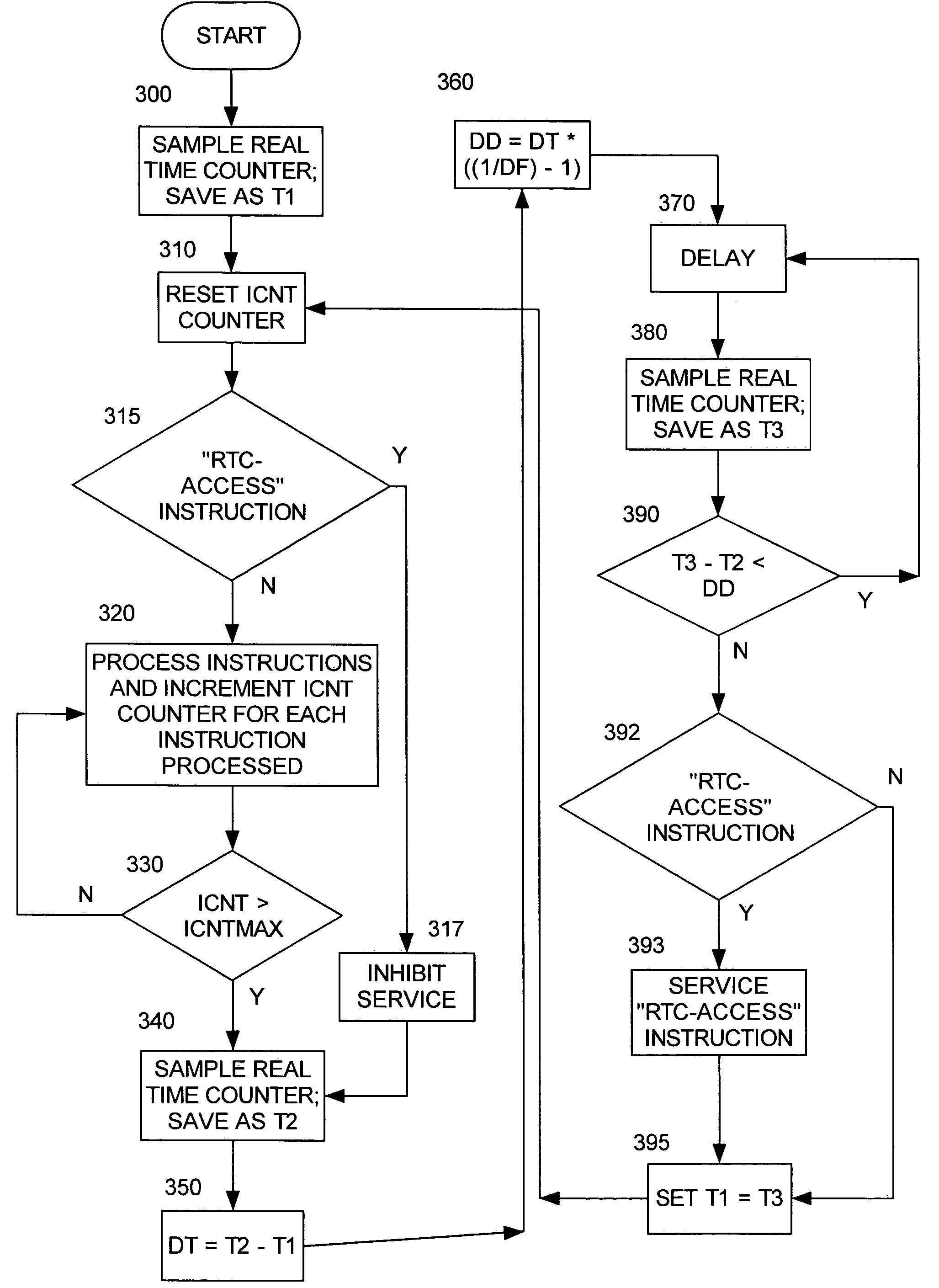

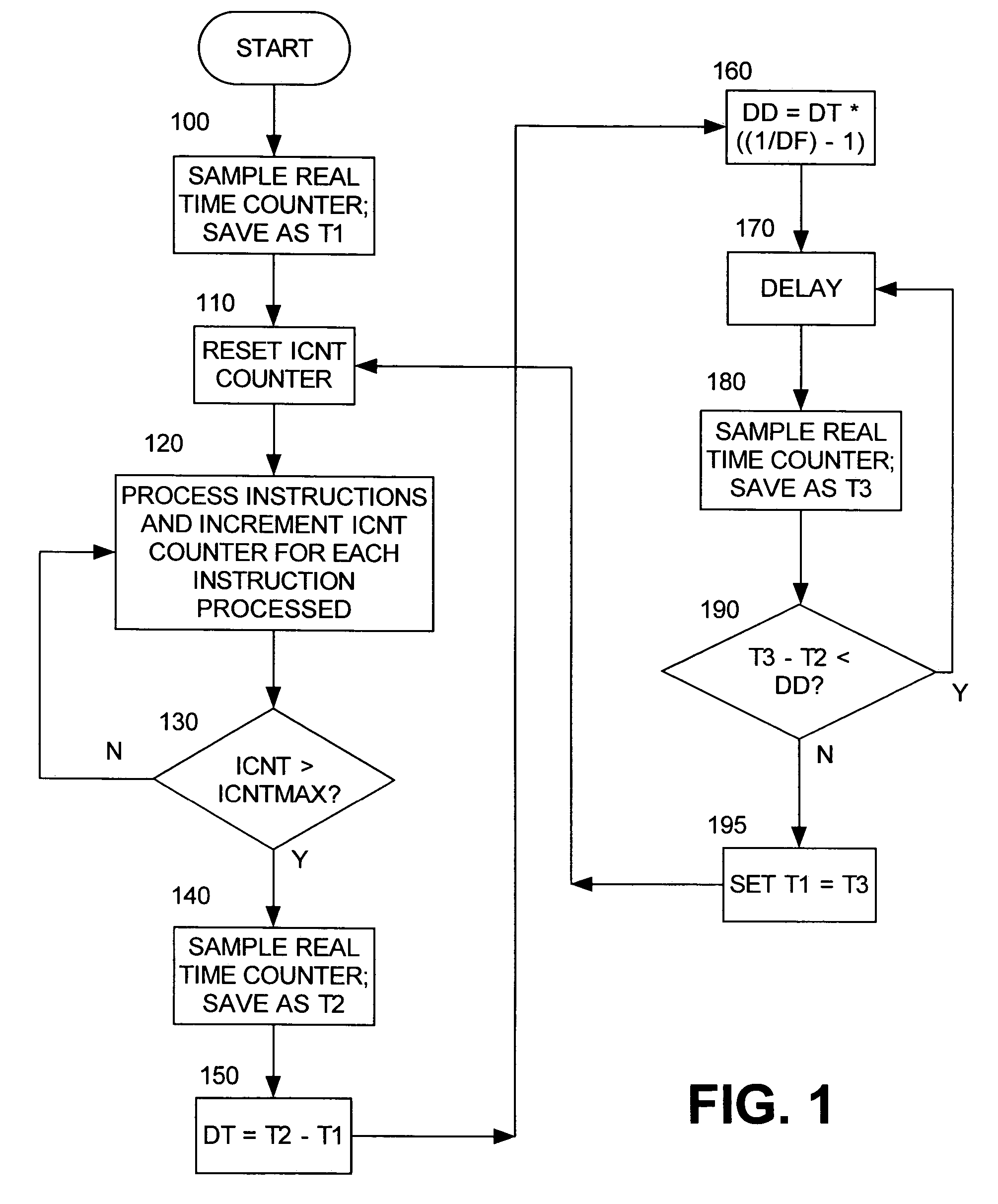

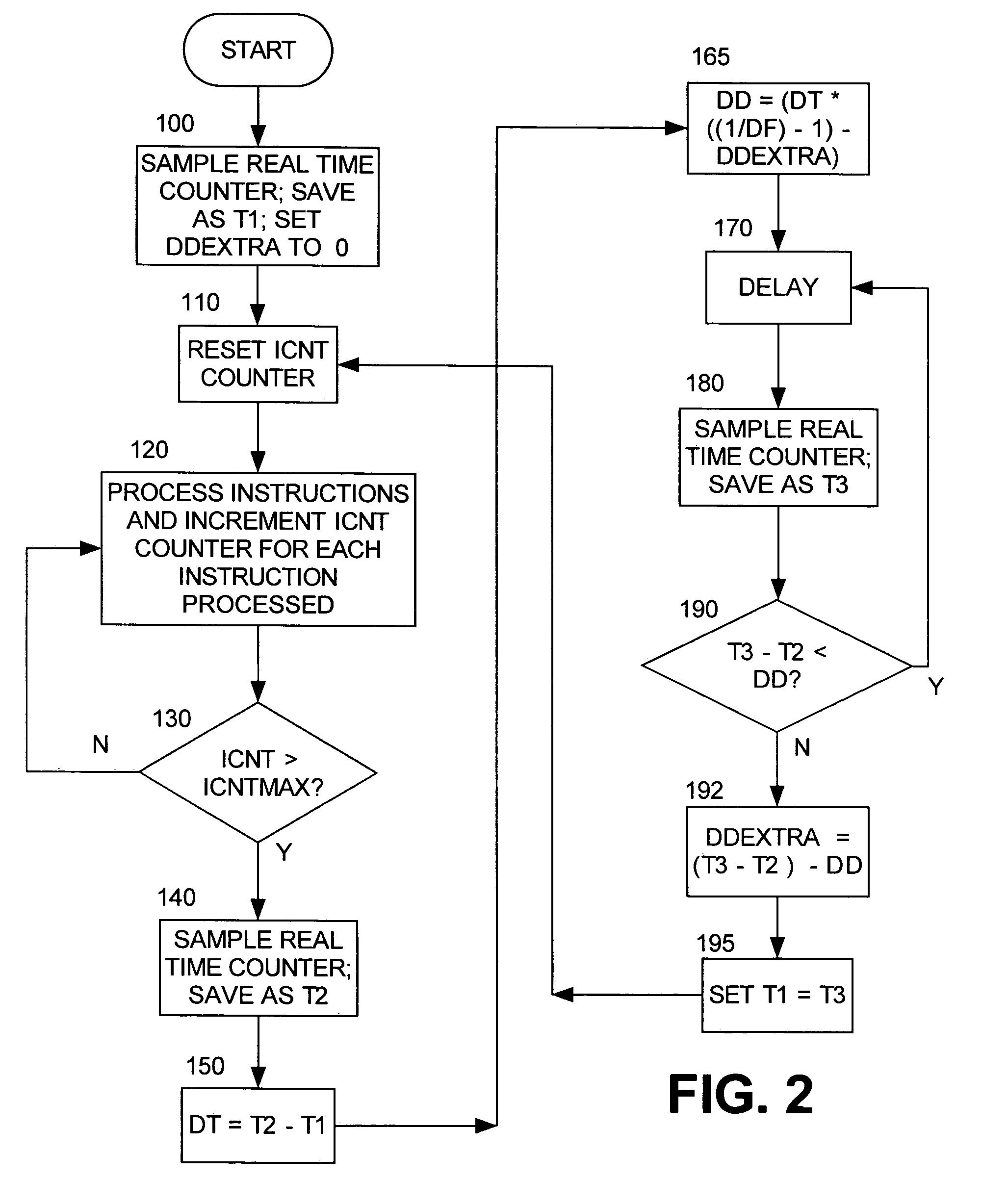

Process for providing submodel performance in a computer processing unit

ActiveUS7219253B2Accurately establishedNegligible loadFactor VIIPeptide/protein ingredientsTime differenceDerating

A simple and accurate processor derating method includes: sampling a real-time counter / clock too obtain an initial time value T1; resetting an Icnt Counter; incrementing the Icnt Counter to reflect the processing of each instruction; comparing the count in the Icnt Counter to a predetermined count IcntMax and if the count in the Icnt Counter is at least IcntMax, then sampling the RTC to obtain a second time T2. T1 is then subtracted from T2 to obtain a time difference DT which is multiplied by ((1−1 / DF)−1) to obtain a Degradation Delay DD period, DF being a constant having a value which is the desired submodel performance with respect to full performance. The Degradation Delay is instituted, the RTC is sampled from time to time to obtain a test third time T3. When a test T3 minus T2 is not less than DD, then T1 is set to T3. Then, the procedure is repeated for a next group of instructions. Optionally, further accuracy can be achieved by treating “wait-type” and / or “RTC-access-type” instructions specially and also by calculating a DDExtra period value which is used to adjust the next DD.

Owner:BULL HN INFORMATION SYST INC

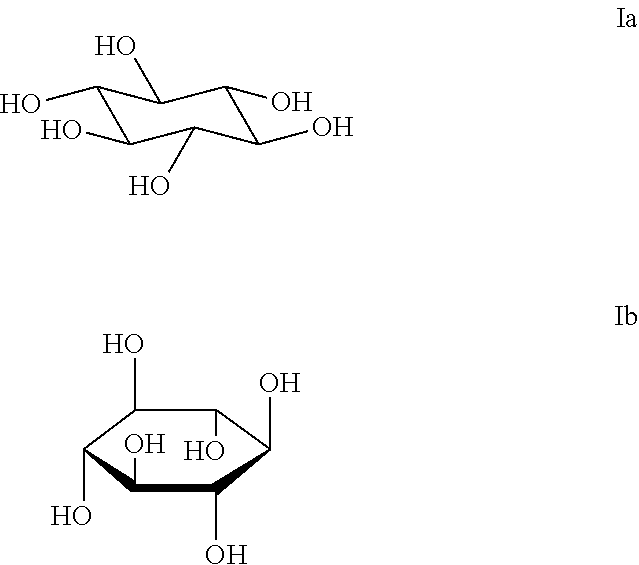

Combination treatments for bipolar disorders

UndeterminedUS20140194428A1Reduce delay timeReduce recurrenceBiocideHydroxy compound active ingredientsBipolar mood disorderValproic Acid

The invention relates generally to novel compositions and methods comprising a scyllo-inositol compound and one or both of valproic acid compound and lamotrigine. The compositions and methods provide beneficial effects in the treatment of bipolar disorders.

Owner:ELAN PHARM INC

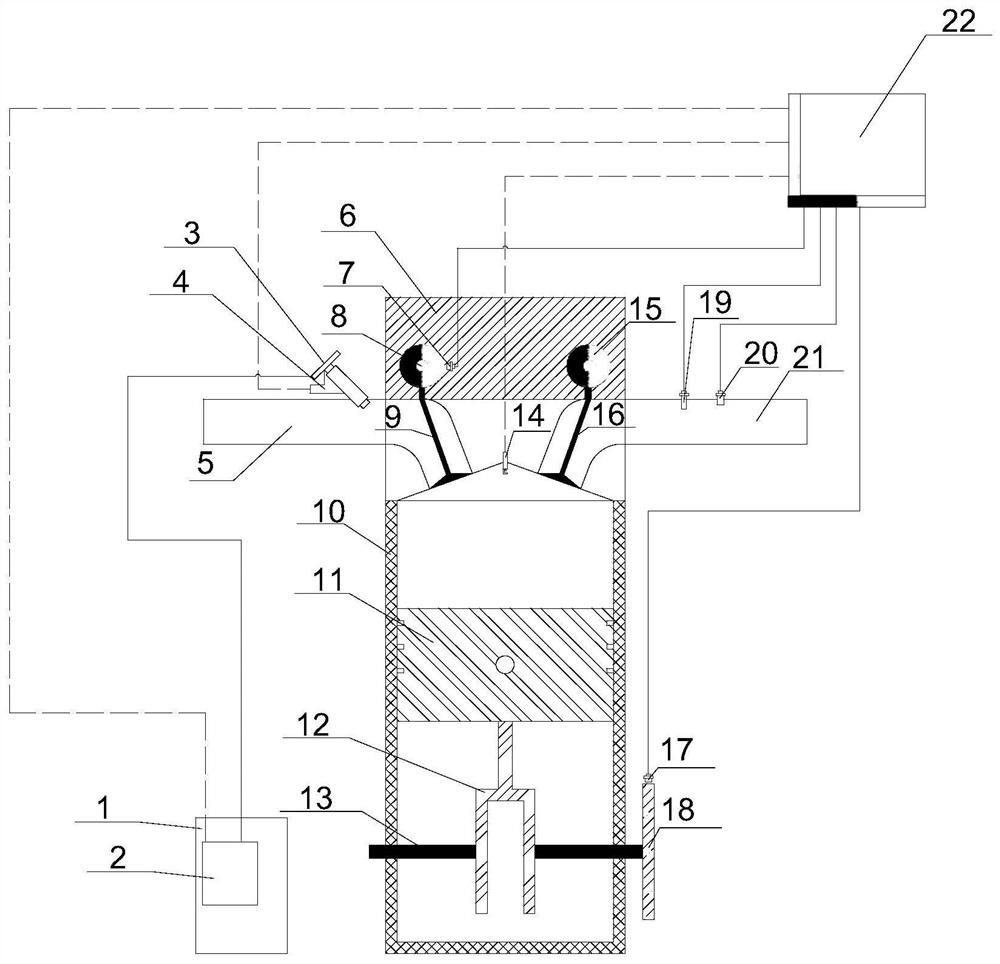

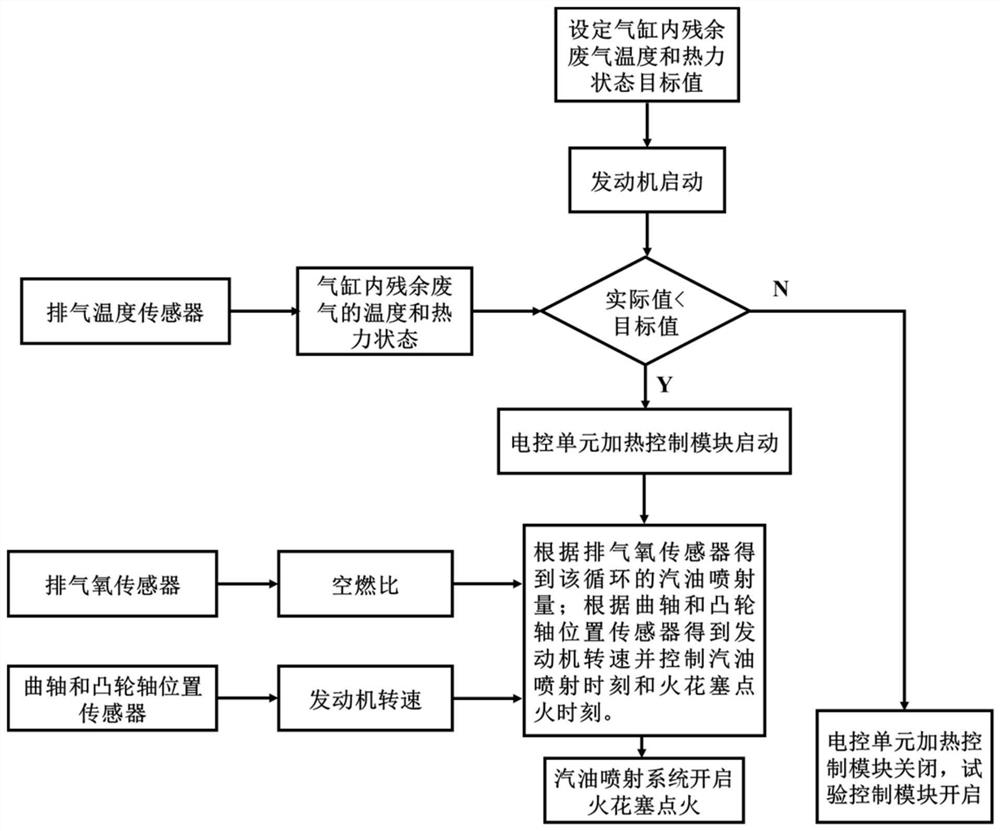

Method for controlling initial temperature of gas in first firing cycle cylinder of engine

ActiveCN112377320AReduce delay timeFast heatingElectrical controlMachines/enginesCombustion chamberGasoline

The invention discloses a method for controlling the initial temperature of gas in a first firing cycle air cylinder of an engine. According to the method, a heating process is controlled by using anengine electronic control unit, mixed gas in the air cylinder is ignited by using sparks to heat a combustion chamber by adjusting the mass of gasoline injected into an air inlet pipe and the amount of air on the condition that the opening degree of a throttle valve meets test requirements, the temperature of residual waste gas in the air cylinder and thethermodynamic state in the combustion chamber are calculated according to a temperature sensor installed in an exhaust passage, and after the set temperature of the residual waste gas in the air cylinder and the set thermodynamic state are achieved, the electronic control unit is automatically switched to an engine combustion process test control mode with the set temperature of the gas in the air cylinder.

Owner:TIANJIN UNIV

Method for Controlling the Initial Temperature of Gas in the Cylinder of the Engine's First Ignition Cycle

ActiveCN112377320BReduce delay timeFast heatingElectrical controlMachines/enginesCombustion chamberAir volume

The invention discloses a method for controlling the initial temperature of the gas in the cylinder of the engine's first ignition cycle. The heating process is controlled by the engine electronic control unit. Gasoline quality and air volume, use the spark to ignite the mixed gas in the cylinder to heat the combustion chamber, and calculate the residual exhaust gas temperature in the cylinder and the thermal state in the combustion chamber according to the temperature sensor installed in the exhaust passage. After the residual exhaust gas temperature and thermal state, the electronic control unit is automatically switched to the engine combustion process test control mode at the set cylinder gas temperature.

Owner:TIANJIN UNIV