Patents

Literature

31results about How to "Solve the slow calculation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

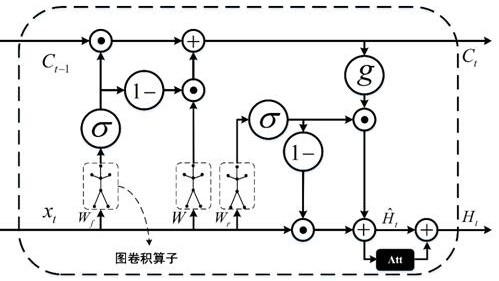

A motion classification method based on simple loop network and attention mechanism of joint space-time is proposed

ActiveCN109376720ACalculation speedSolve the slow calculationCharacter and pattern recognitionNeural learning methodsHuman behaviorClassification methods

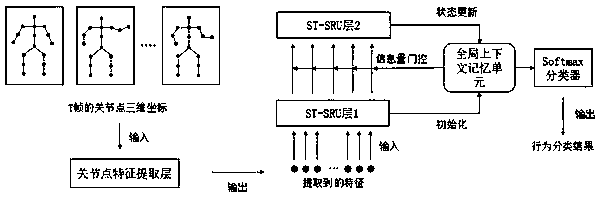

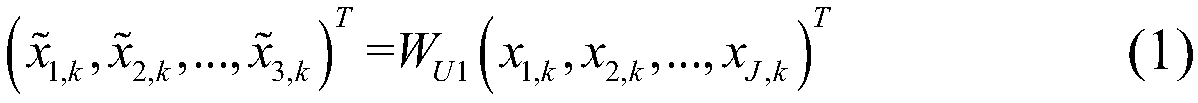

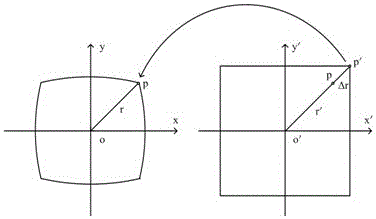

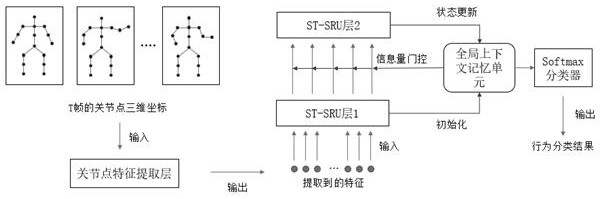

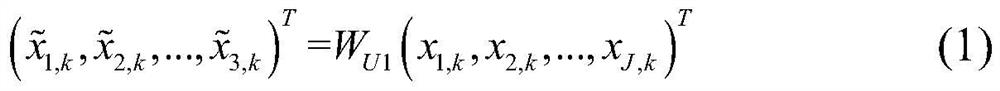

The invention relates to an action classification method based on a connection node spatio-temporal simple circulating network and an attention mechanism. Firstly, the space dimension of SRU model isextended, and an iterative computation method of ST-SRU model. Then, in the proposed ST-SRU model and global contextual attention mechanism, GCA-ST-SRU method. Finally, the proposed method is appliedto human behavior recognition. Firstly, the features of human joints are extracted by depth network, and then the human joints are extracted by GCA-ST-SRU method recognizes the extracted features. Themethod of the invention can reduce training time consumption and improve classification accuracy, and has obvious efficiency advantages. The method of the invention can quickly deduce the speed, which is favorable for the design of the real-time motion recognition system, and is suitable for running on the platform with limited computing power, and has wide application prospect in the fields of computer vision, intelligent monitoring, human-computer interaction and the like.

Owner:HANGZHOU DIANZI UNIV

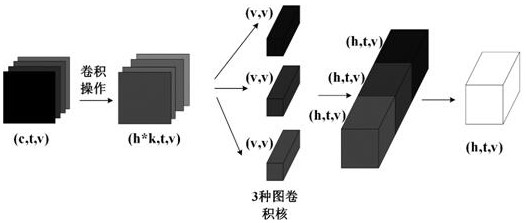

Skeleton action recognition method based on multi-stream spatial attention graph convolution SRU network

PendingCN112733656AImprove the efficiency of action recognitionSolve the slow calculationCharacter and pattern recognitionNeural architecturesSpace time domainTheoretical computer science

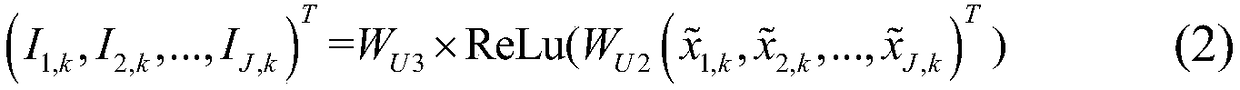

The invention provides a skeleton action recognition method based on a multi-stream spatial attention graph convolution SRU network. The method comprises the following steps: firstly, embedding a graph convolution operator into a simple cycle unit to construct a graph convolution model to capture time-space domain information of skeleton data; meanwhile, in order to enhance the discrimination between the joint points, a spatial attention network and a multi-stream data fusion mode are designed, and a graph convolution simple cycle network model is further expanded into a multi-stream spatial attention graph convolution SRU. According to the method, the high classification precision is maintained, the complexity of the method is remarkably reduced, the reasoning speed of the model is increased, the balance between the calculation efficiency and the classification precision is achieved, and the method has a very wide application prospect.

Owner:HANGZHOU DIANZI UNIV

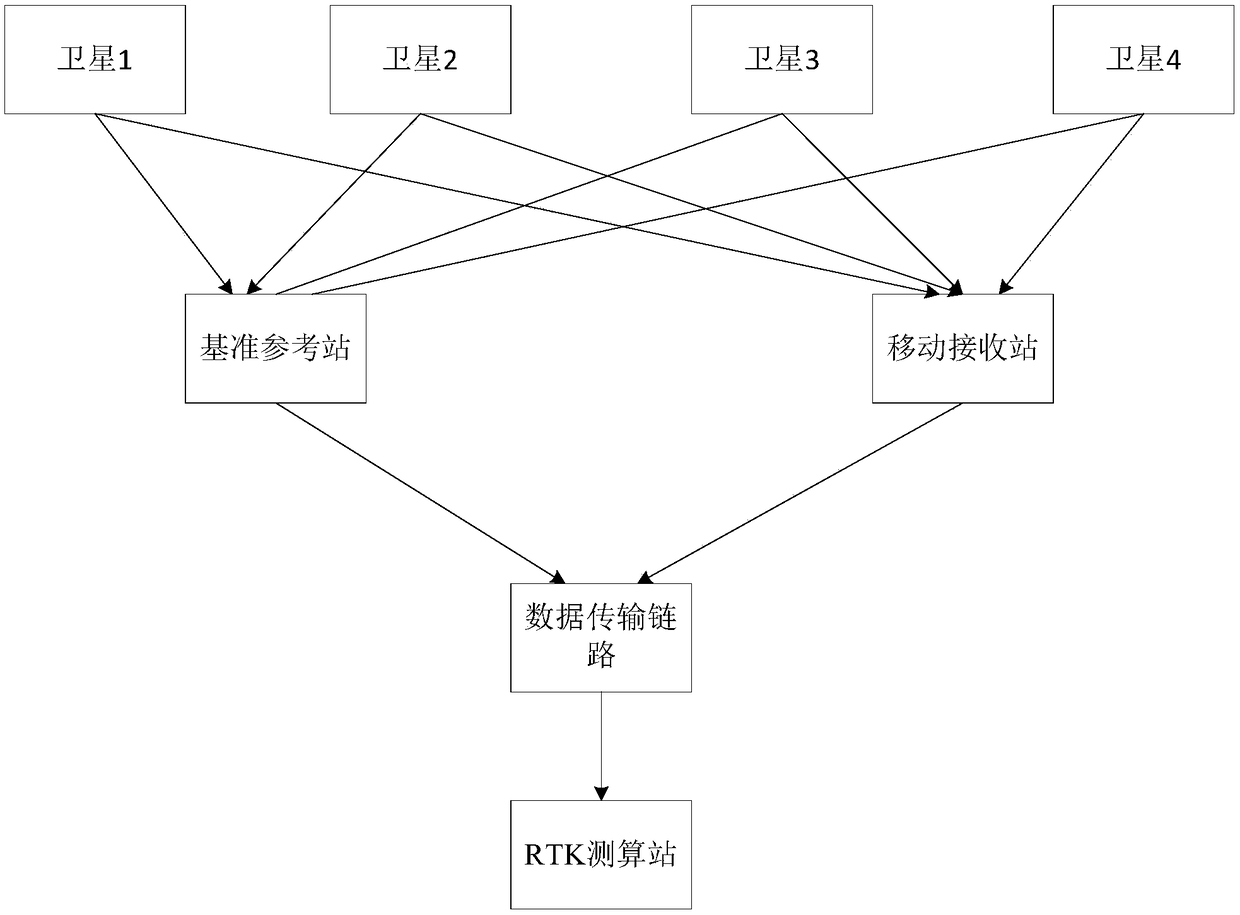

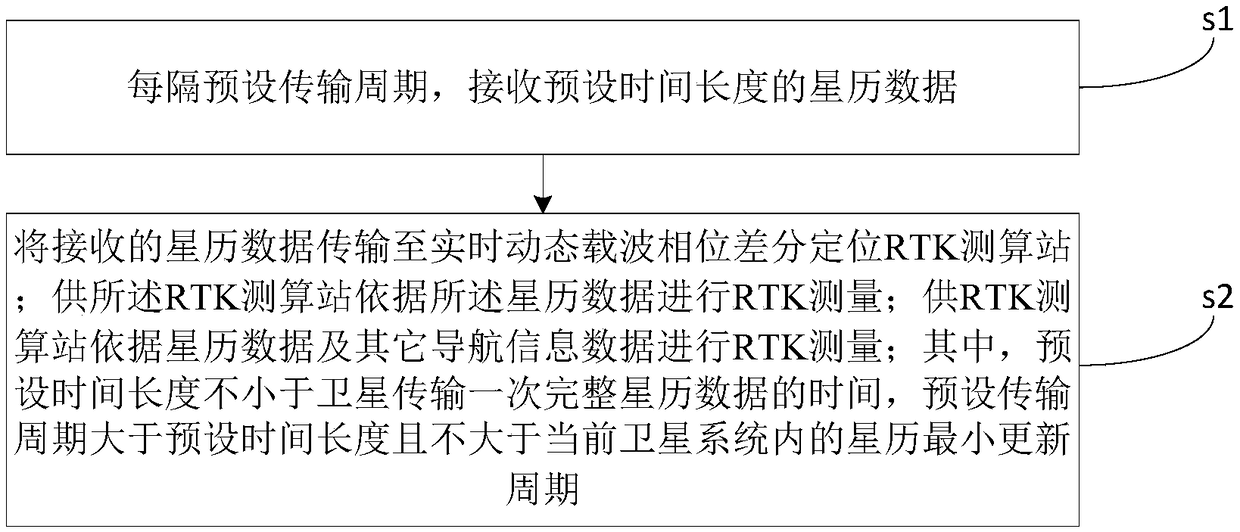

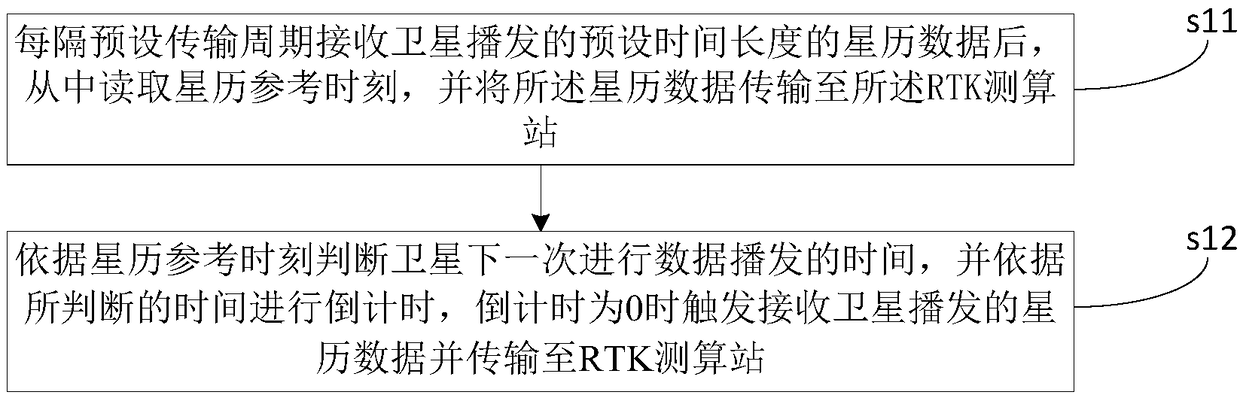

Method for transmitting ephemeris data during RTK measurement and RTK measurement system

PendingCN109471139AReduce data volumeSmall amount of calculationSatellite radio beaconingHigh level techniquesEphemerisBand width

The invention discloses a method for transmitting ephemeris data during RTK measurement, which is applied to a mobile receiving station and comprises the following steps: receiving ephemeris data withpreset time length every preset transmission period and transmitting the ephemeris data to a real-time dynamic carrier phase difference partial positioning RTK measuring and calculating station; theRTK measuring station carries out RTK measurement according to ephemeris data and other navigation information data; wherein the preset time length is not less than the time for the satellite to transmit the complete ephemeris data once, and the preset transmission period is greater than the preset time length and is not greater than the ephemeris minimum updating period in the current satellite system. The method for transmitting ephemeris data during RTK measurement reduces the repeated data transmitted to the RTK measuring and calculating station by the mobile receiving station, thereby reducing the data volume transmitted by the mobile receiving station, improving the RTK measuring and calculating speed and enabling the same transmission bandwidth to accommodate more data transmitted by the mobile receiving station, thereby increasing the number of mobile receiving stations that the data link can accommodate to transmit data. The invention further discloses a mobile receiving station and an RTK measuring system based on the method.

Owner:河南准位信息技术有限公司

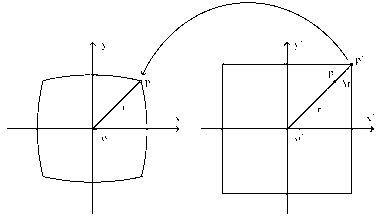

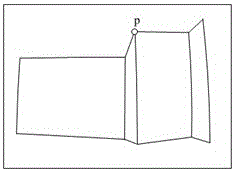

Image distortion correction method

InactiveCN103268597ASimple methodSolve the slow calculationImage enhancementComputer visionCorrection method

The invention discloses an image distortion correction method, comprising the following steps of: (10) obtaining the data of an original image; (20) establishing an corrected image; (40) measuring the red value, green value and blue value of a pixel on the corrected image; and (50) establishing an corrected image: returning to step (30) until the red value, the green value and the blue value of each pixel on the corrected image are measured, thereby establishing the corrected image. Under the condition that the image distortion coefficient is known, each pixel on the distortion corrected image is inversely measured to obtain the position of the pixel in the original image, and then the red, green and blue color values of the pixel are measured by bilinear interpolation. The correction process is simple and efficient.

Owner:SOUTHEAST UNIV

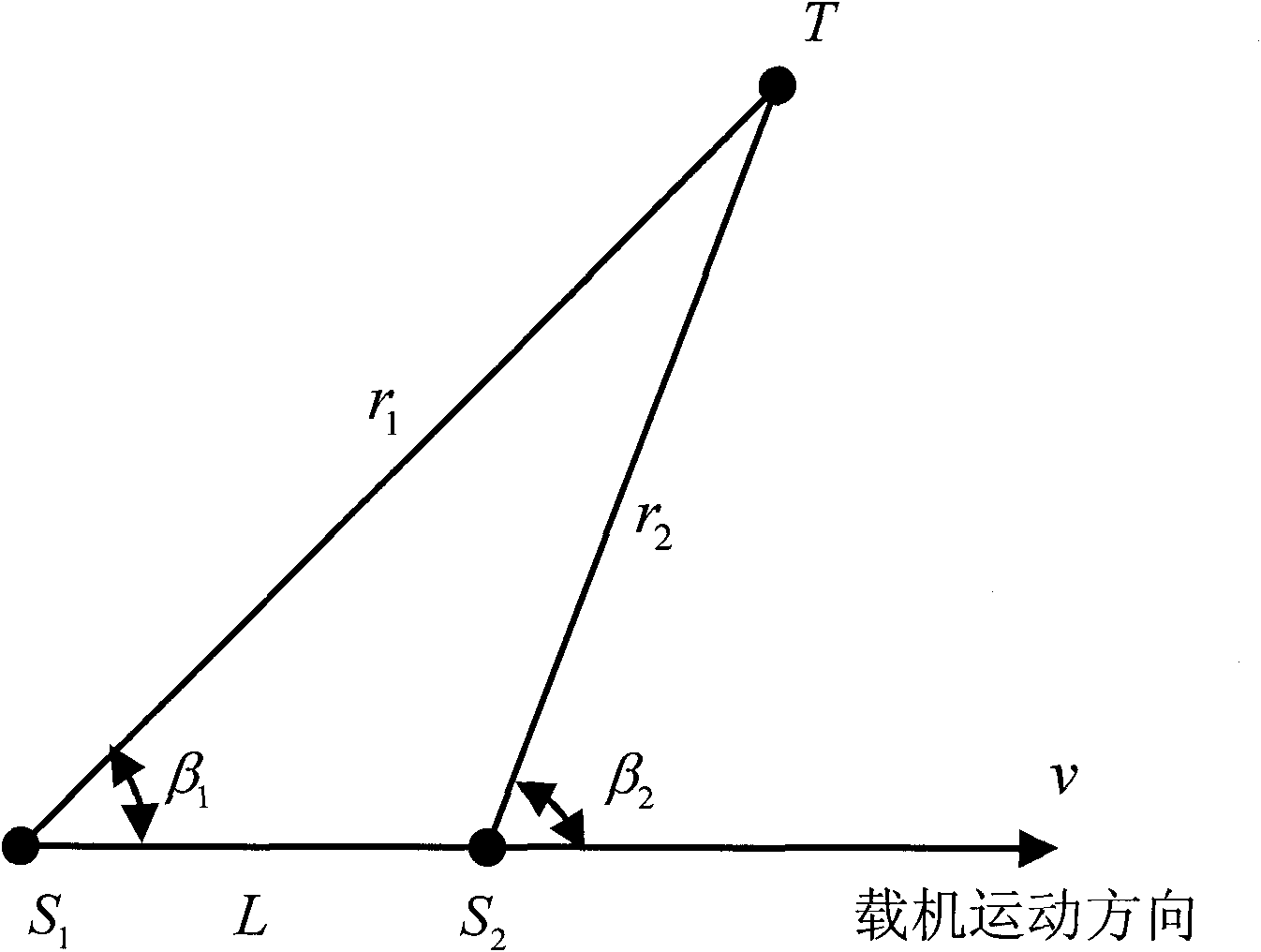

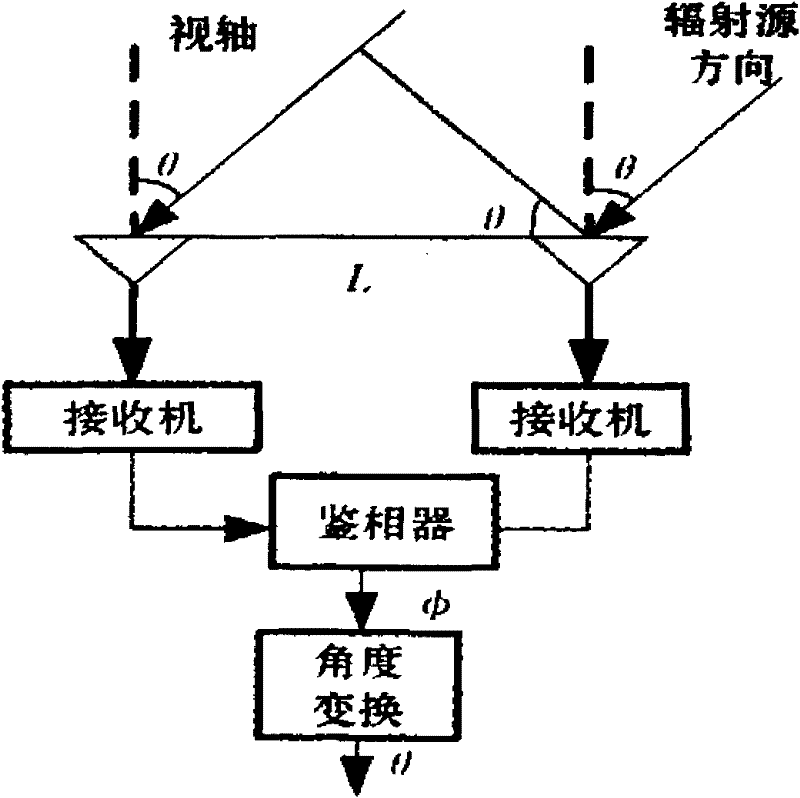

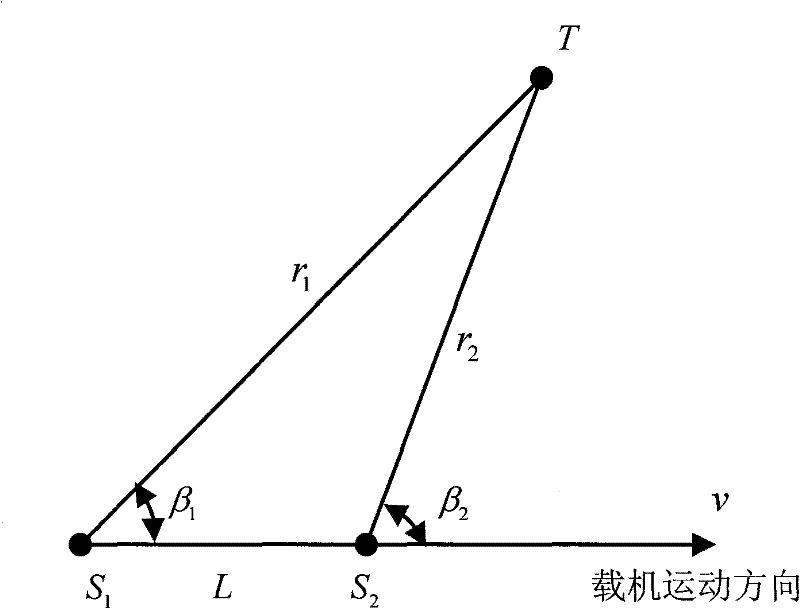

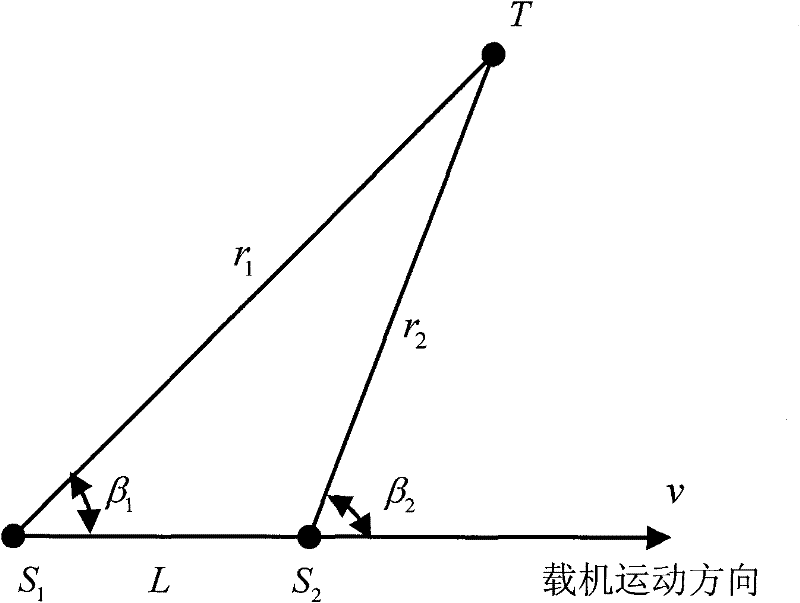

Airborne single baseline Doppler-phase difference direction finding method

ActiveCN101813762ASolve the slow calculationIncrease the lengthDirection finders using radio wavesPhase differenceArray element

The invention discloses an airborne single baseline Doppler-phase difference direction finding method by which an entire cycle solution of a radial distance can be directly obtained through comprehensively utilizing the relation among a speed vector equation, a Doppler frequency shift and a change rate, therefore, an entire cycle value of a path difference between radial distances of two adjacent array elements of single baseline can be obtained. The path difference is entirely determined after the value of a non-entire cycle part of the path difference is determined by further utilizing a phase difference. Hence, under the condition that the length of the baseline is determined, the direction of an object can be directly obtained according to a trigonometric function relationship. The invention has a series of advantages of low installation requirement, short measuring time, suitability for bandwidth detection, and the like.

Owner:CHINESE AERONAUTICAL RADIO ELECTRONICS RES INST

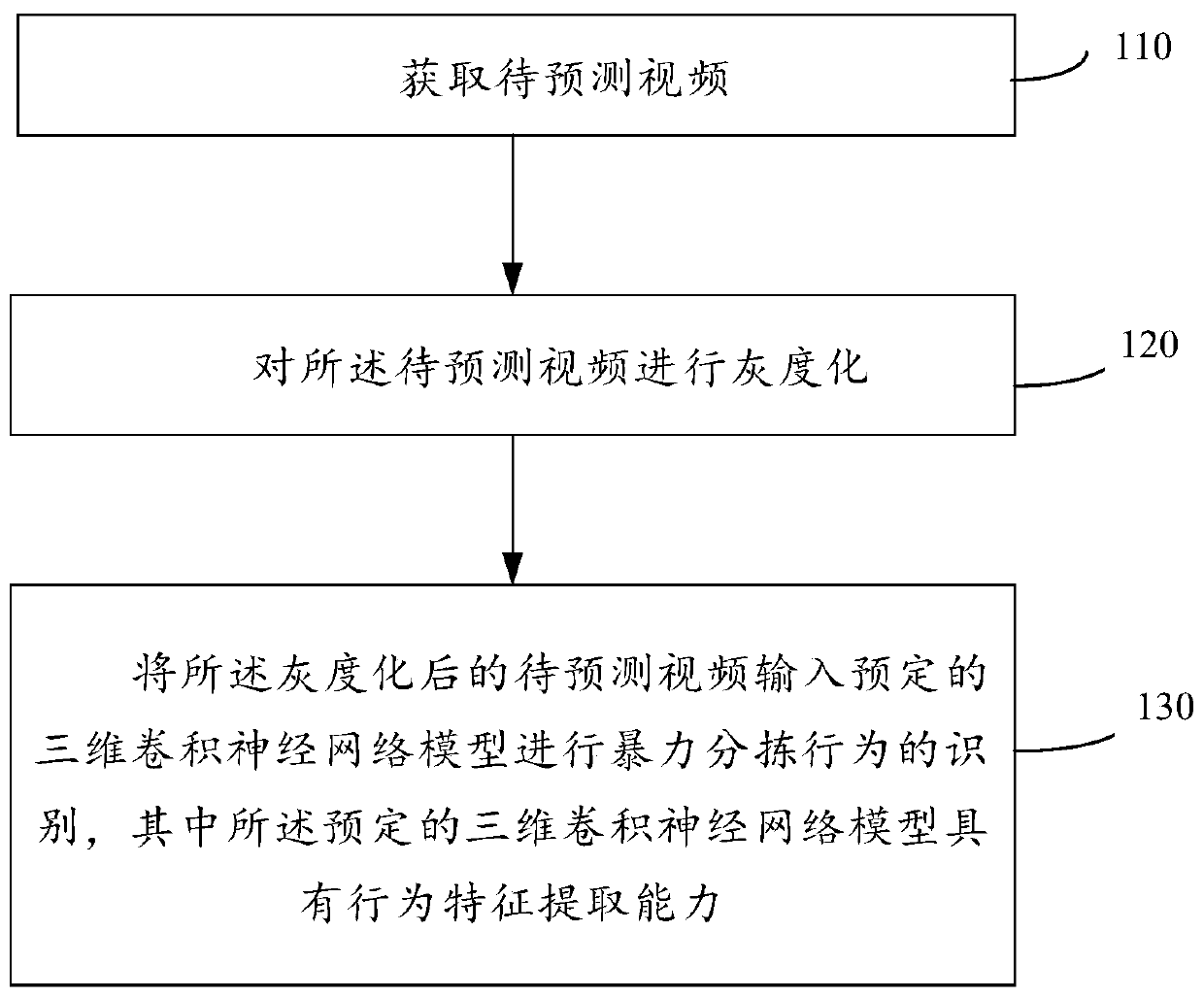

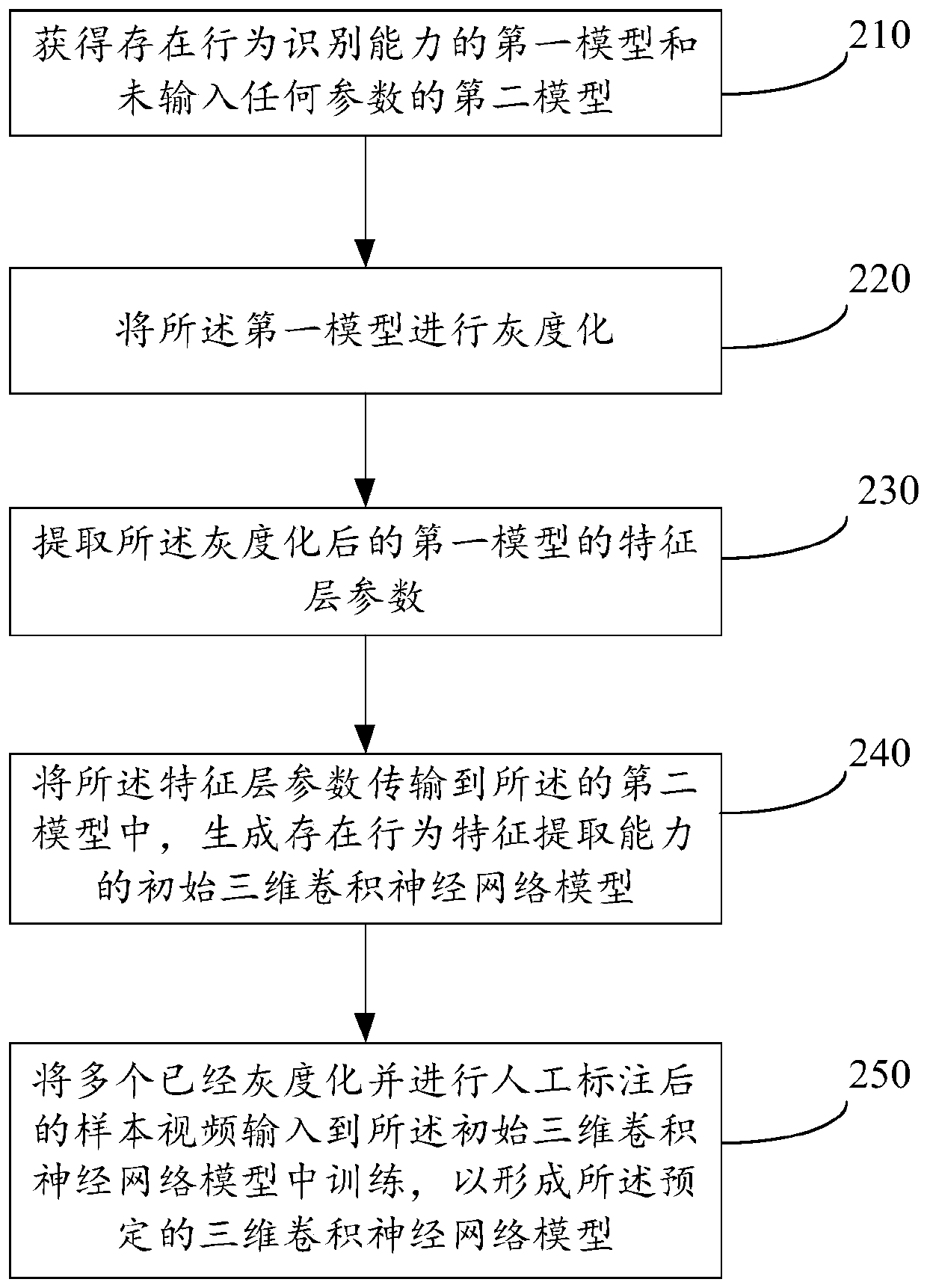

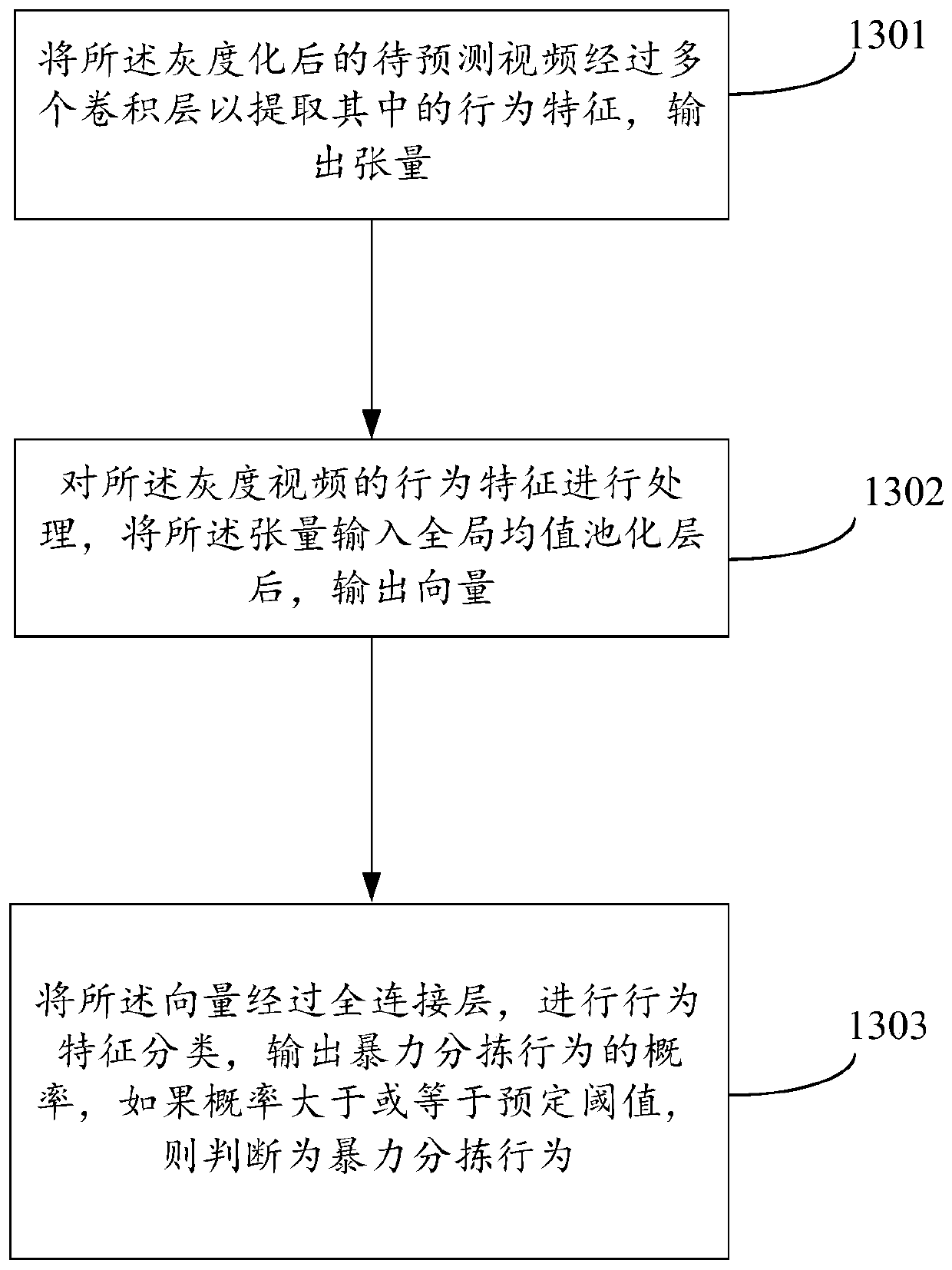

Violent sorting behavior recognition method and device

PendingCN111126115ALow resolution accuracyImprove accuracyCharacter and pattern recognitionNeural architecturesFeature extractionEngineering

The invention discloses a violent sorting behavior recognition method and device. The method comprises the steps of obtaining a to-be-predicted video; graying the video to be predicted; and inputtingthe grayed to-be-predicted video into a predetermined three-dimensional convolutional neural network model to perform violent sorting behavior identification, wherein the predetermined three-dimensional convolutional neural network model has a behavior feature extraction capability. According to the method, a three-dimensional convolutional neural network model is constructed by utilizing a modelwith behavior feature extraction capability, and learning and violent sorting behavior recognition are carried out by utilizing a grayscale video. Therefore, the violent sorting behavior recognition period is shortened, and the judgment accuracy is improved.

Owner:SF TECH

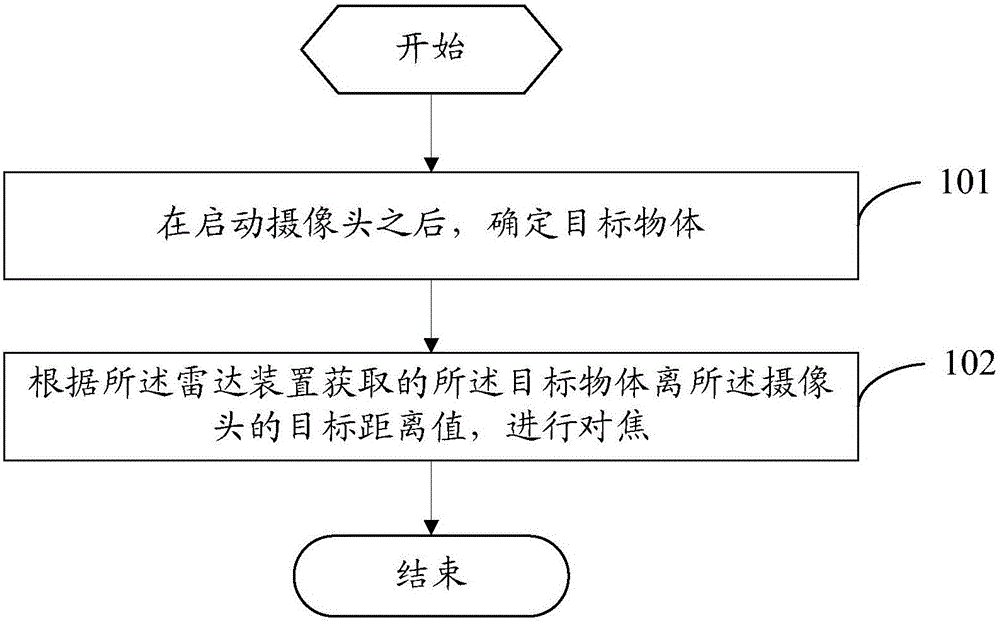

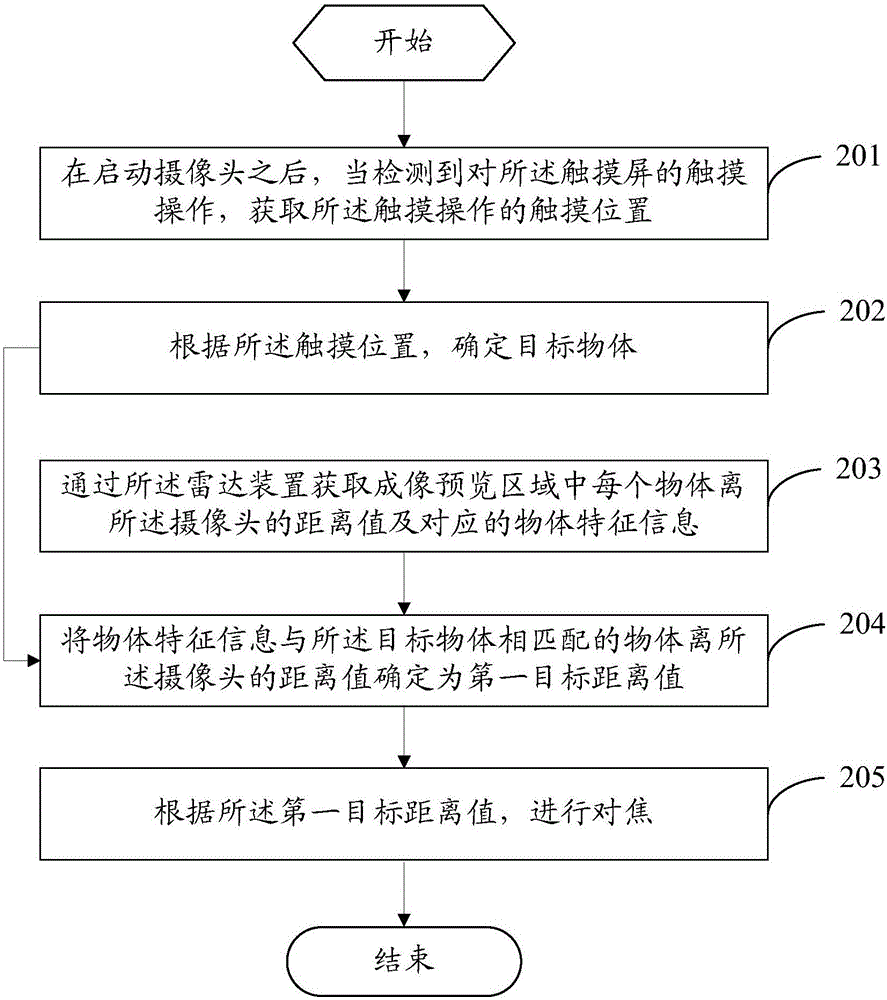

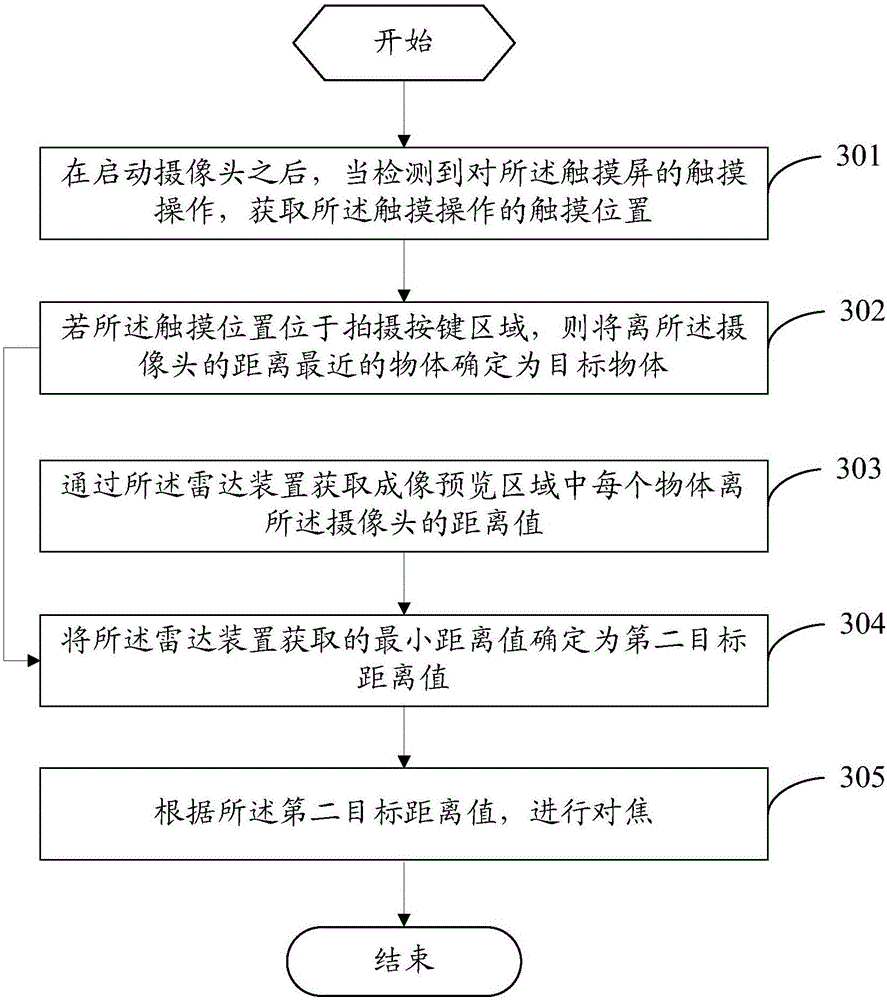

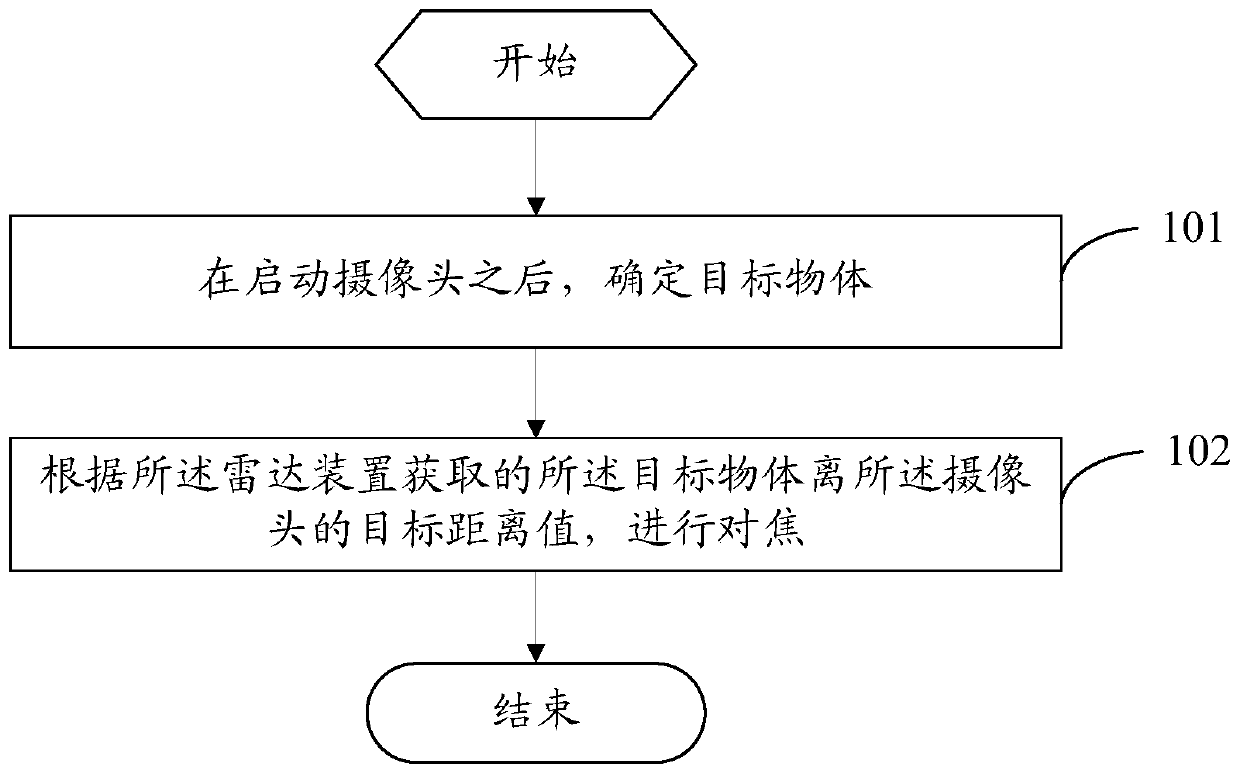

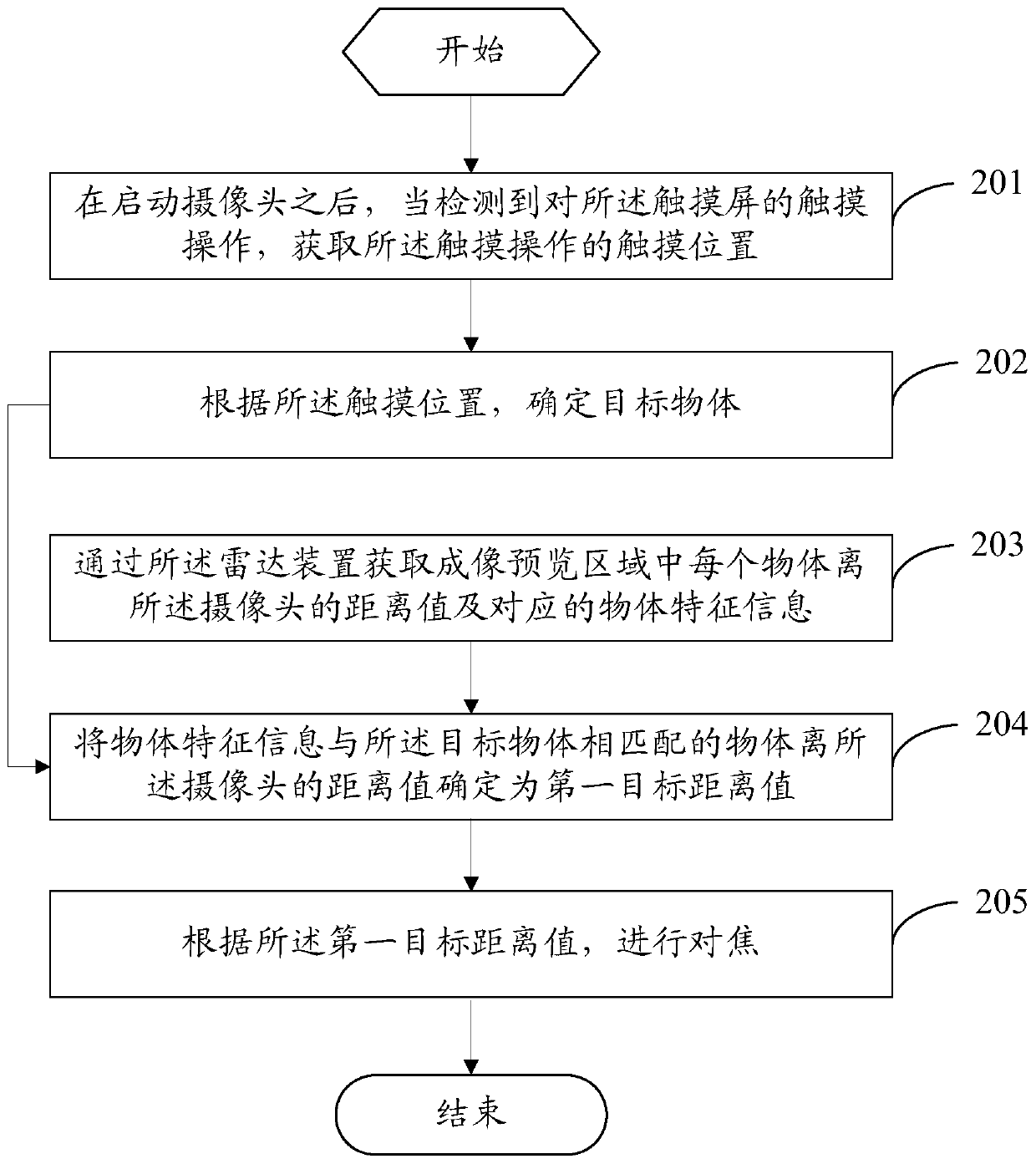

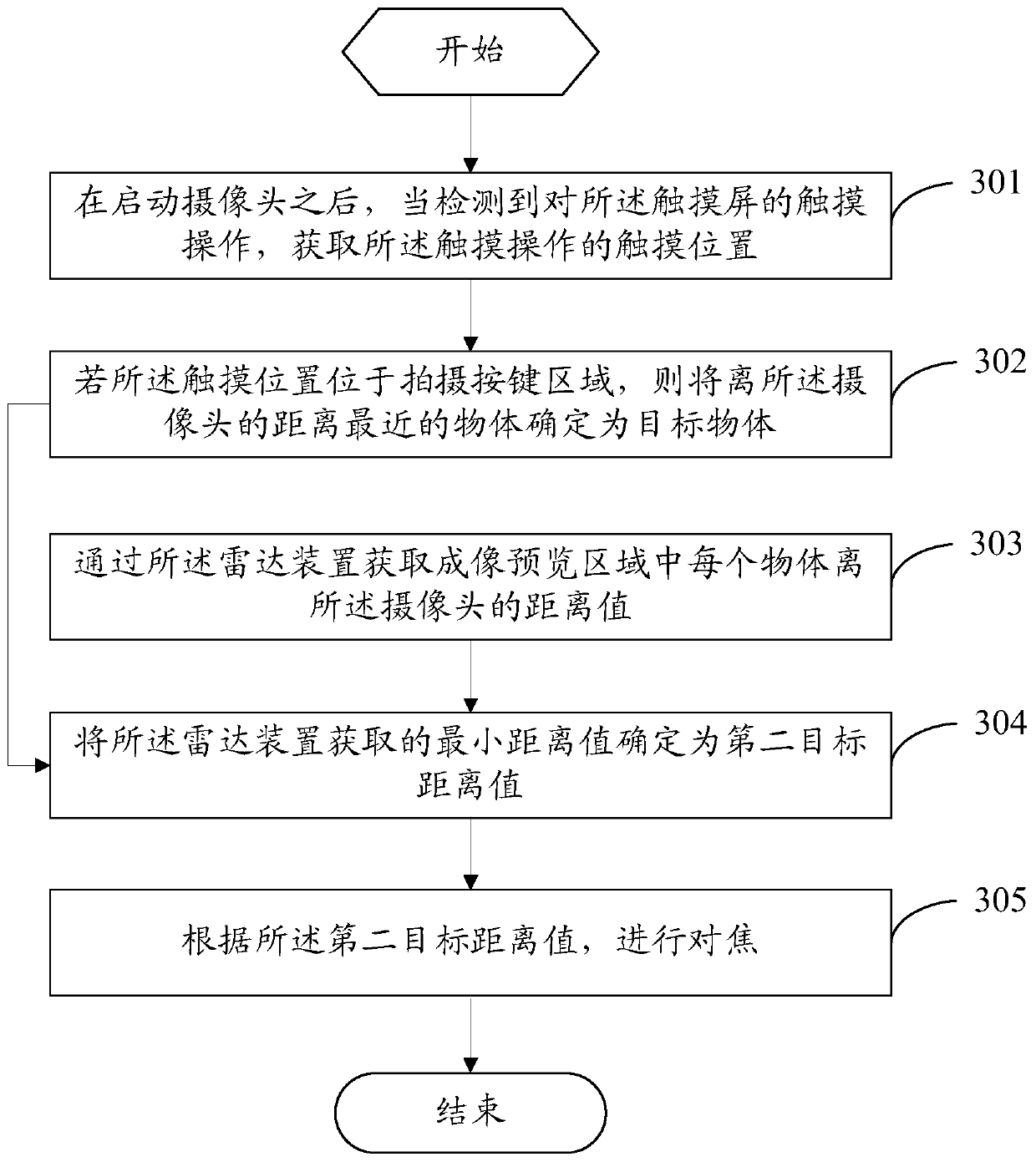

Photographing focus method and mobile terminal

ActiveCN106791375ASolve the slow calculationNot limited by ambient light brightnessTelevision system detailsColor television detailsRadarComputer vision

The embodiment of the invention provides a photographing focus method and a mobile terminal. The method is applied to the mobile terminal with a radar device. The method comprises the steps of determining a target object after a camera is started; and carrying out focus according to a target distance value obtained by the radar device from the target object to the camera. In this way, according to the embodiment of the invention, the distance value from the target object to the camera is obtained through the radar device, and the focus is carried out on the target object according to the distance value. Information such as the distance to the target and an object feature is calculated by the radar device through utilization of an electromagnetic wave, so the influence of environment illumination brightness is eliminated. Visibly, according to the photographing focus method provided by the embodiment of the invention, the focus is carried out accurately under a weak light condition.

Owner:VIVO MOBILE COMM CO LTD

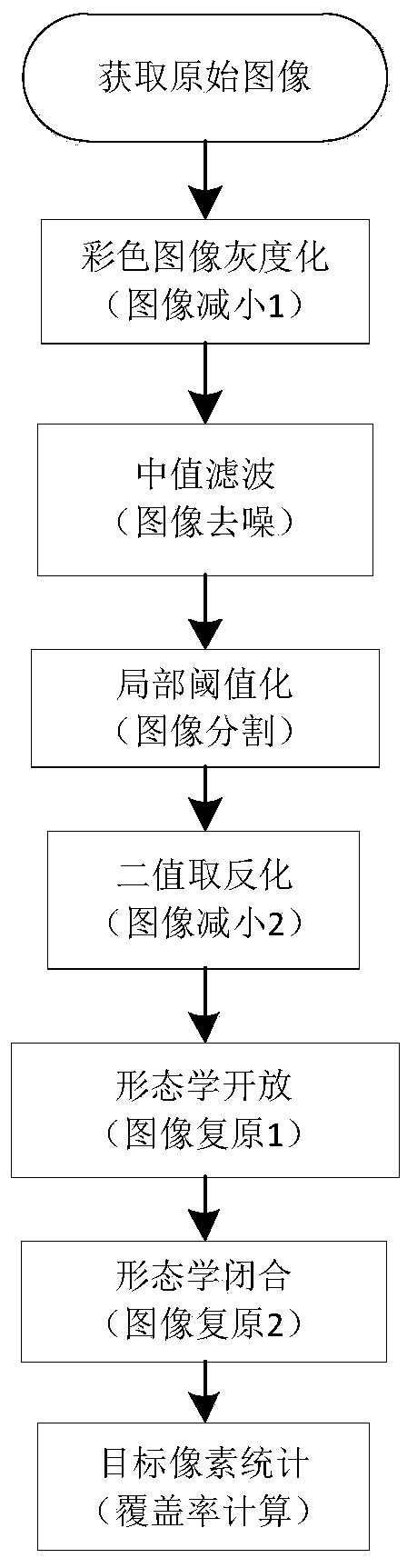

Digital shot blasting coverage rate measurement method based on computer vision technology

InactiveCN111192273AReduce laborShort timeImage enhancementImage analysisVisual technologyImaging processing

The invention discloses a digital shot blasting coverage rate measurement method based on a computer vision technology, and belongs to the technical field of digital image processing. The method comprises the steps of image acquisition, gray scale conversion, noise elimination, region segmentation, binarization processing, filling, pseudo connection elimination and statistics, and image processingfor surface dents after shot blasting of a plate. A computer program is adopted for shot blasting image processing, the consistency of multiple times of measurement is guaranteed, the measurement error is controlled within 5%, the measurement and calculation speed is high, the method does not depend on personal experience, the compatibility with other computer-aided manufacturing equipment is good, the portability is good, and possibility is brought to detection feedback link work in automatic shot blasting control circulation.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

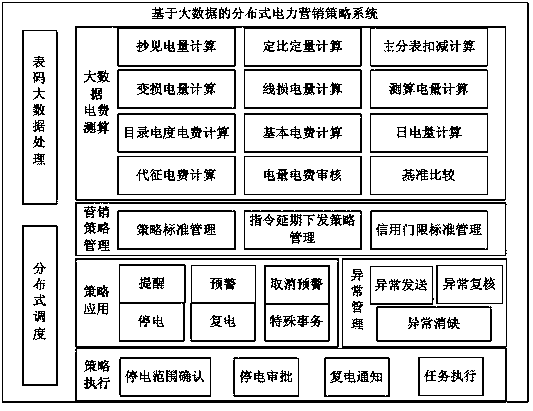

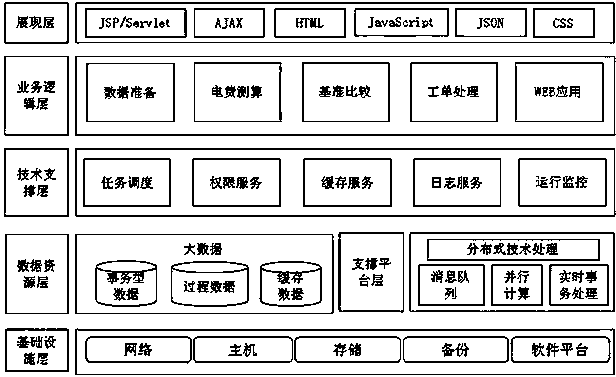

Distributed power marketing strategy method and system based on big data

InactiveCN107742192ASolve the slow calculationReduce workloadOffice automationResourcesElectricity priceBroadband

Provided are a distributed power marketing strategy method and system based on big data. According to the method, by using the broadband carrier of an electricity information collection system to achieve automatic meter reading, meter number data is transmitted back in real time. By conducting distributed processing on user profiles, electricity price number, distribution data, meter number and other big data information, electric charge measurement is completed. By conducting distributed processing on marketing strategy management and an electric charge measurement result, strategy application is generated. Finally, strategy execution on a marketing strategy application result is completed, and an execution result is fed back. The method includes the steps of using the broadband carrier to conduct meter number data collection, distributed-electric charge measurement of the big data and distributed processing, and thus generating the marketing strategy application result, an executionstrategy application and a returned strategy execution result. According to the technical scheme, the problems that traditional power marketing strategy is not high in automation degree and poor in performance are solved, and the distributed processing mode base on the big data is used in power marketing strategy processing, so that the power marketing industry personnel' working efficiency is greatly improved.

Owner:STATE GRID JIANGXI ELECTRIC POWER CO LTD RES INST +1

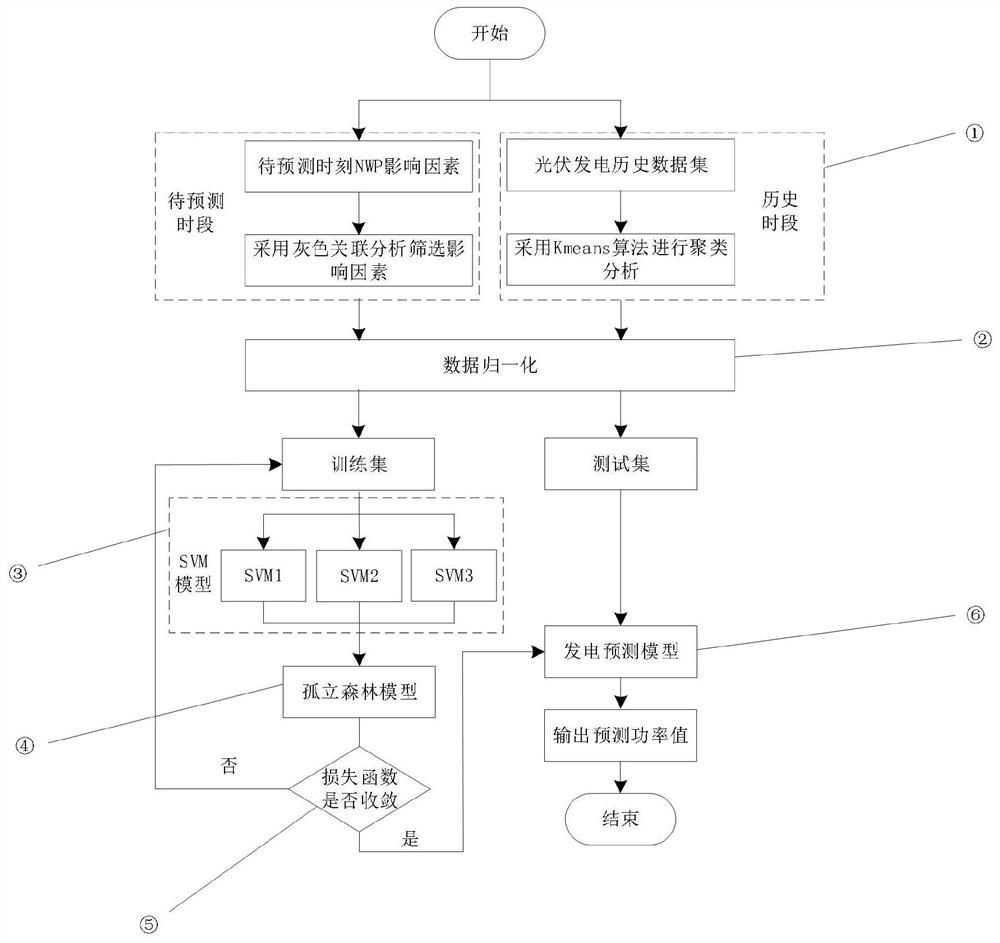

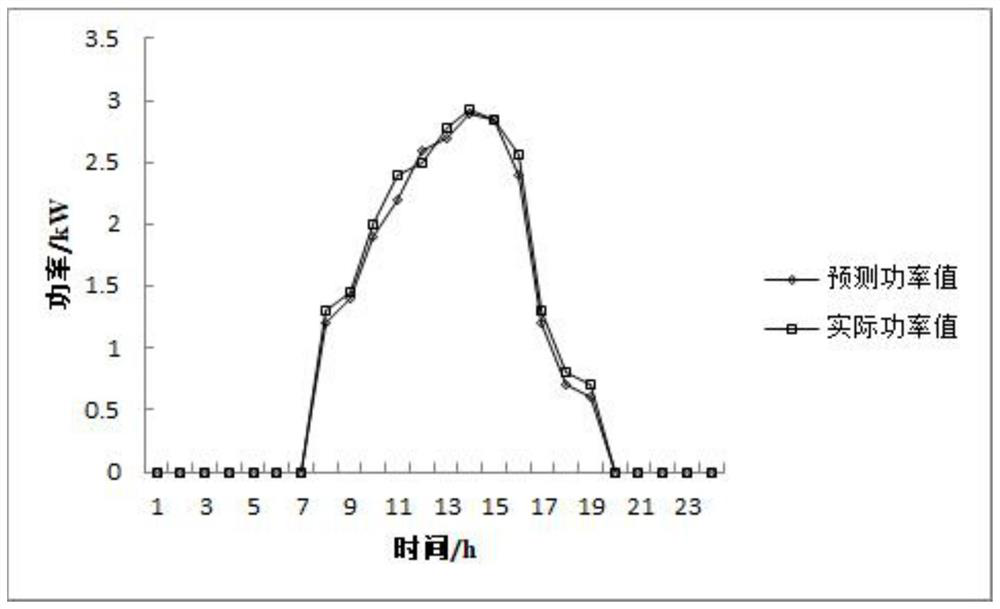

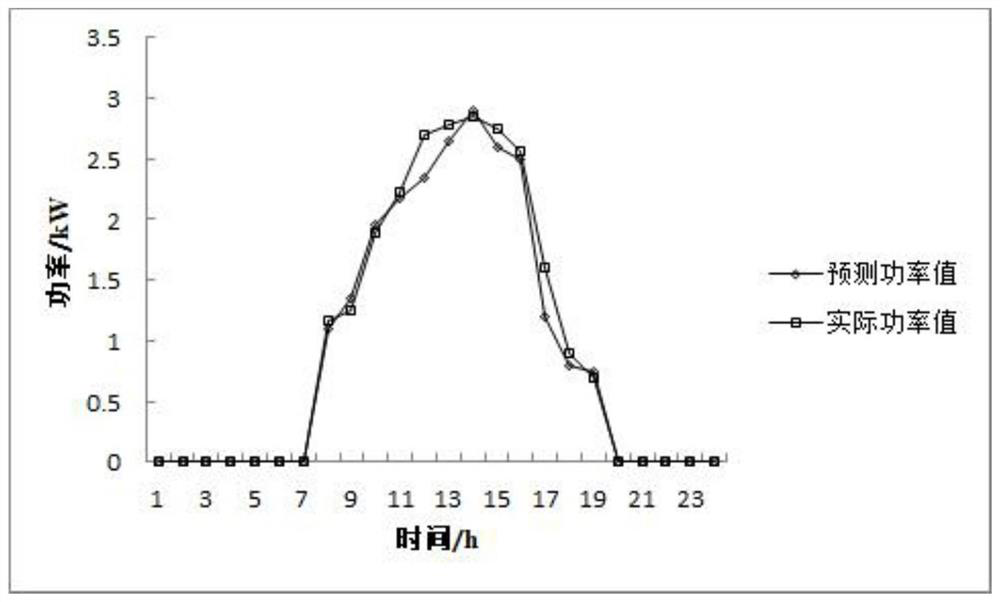

Photovoltaic power generation power prediction method

PendingCN114004139AEffective fitHigh precisionLoad forecast in ac networkKernel methodsMissing dataPhotovoltaic power station

The invention discloses a photovoltaic power generation power prediction method which comprises the following steps: acquiring meteorological data and historical power generation power data of a photovoltaic power station in a certain region at the same moment, supplementing missing data and removing abnormal data; and analyzing and quantifying meteorological factors and historical power generation power on a prediction day, and unifying the dimension of the corrected data by adopting data normalization. Constructing a combined SVM model; constructing an isolated forest model; and comparing predicted power output by the model with theoretical power, outputting a prediction result when an error is within an allowable range, and performing iterative correction until the error meets the requirement when the error does not meet the requirement; and inputting a training set and a test set of the historical power into a power generation prediction model to obtain predicted power. The method can reduce the prediction error, improves the prediction precision, effectively improves the utilization rate of photovoltaic power generation, and is higher in generalization capability.

Owner:SHENYANG INST OF ENG

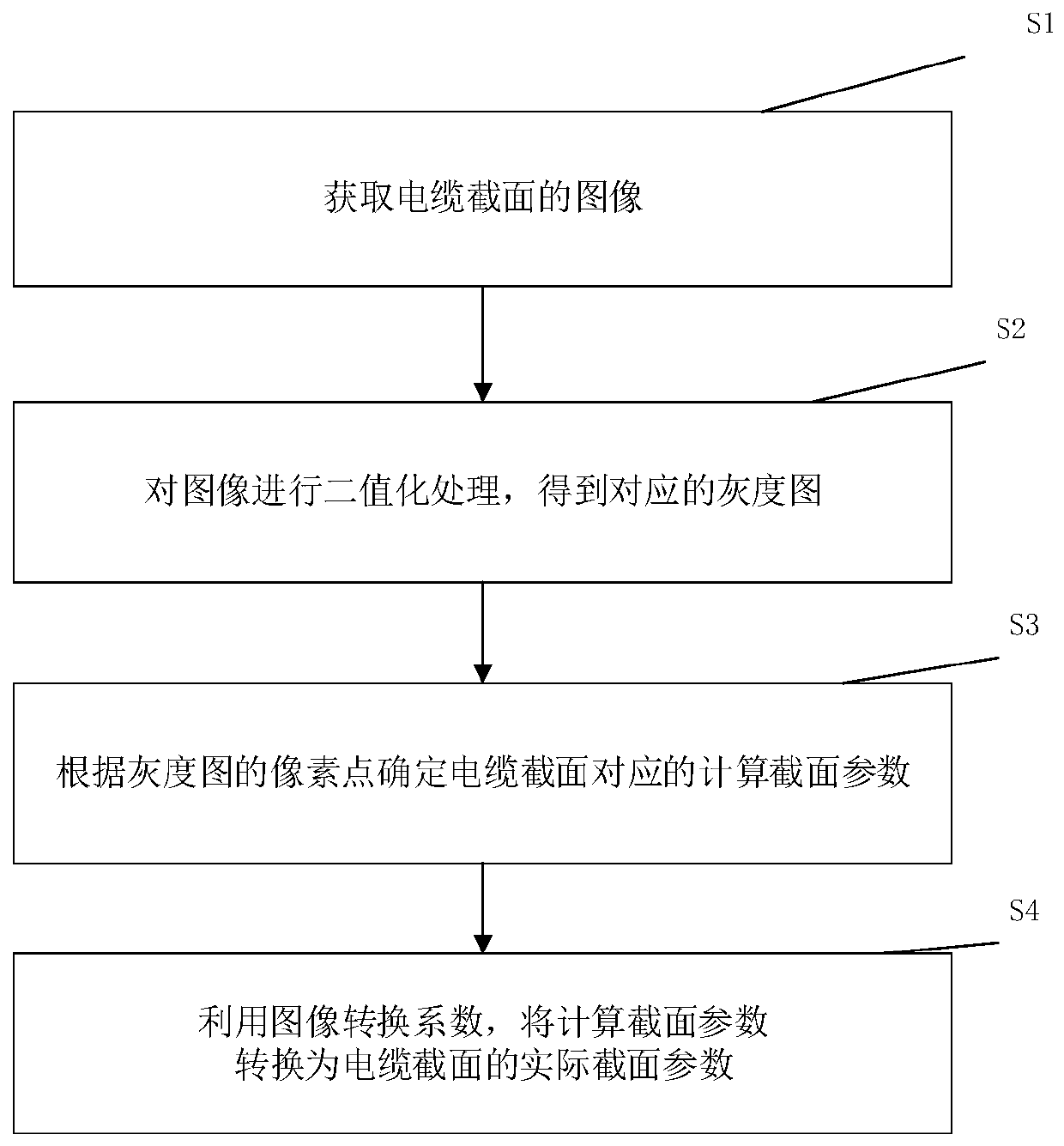

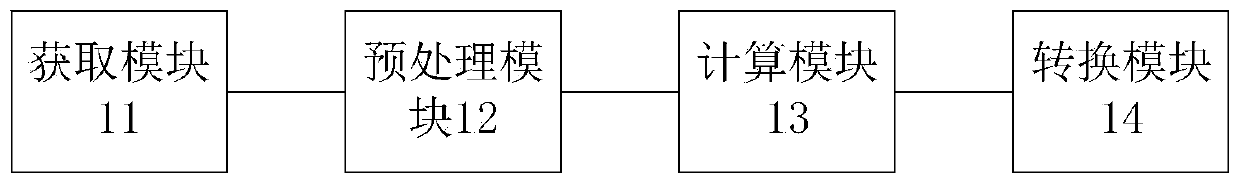

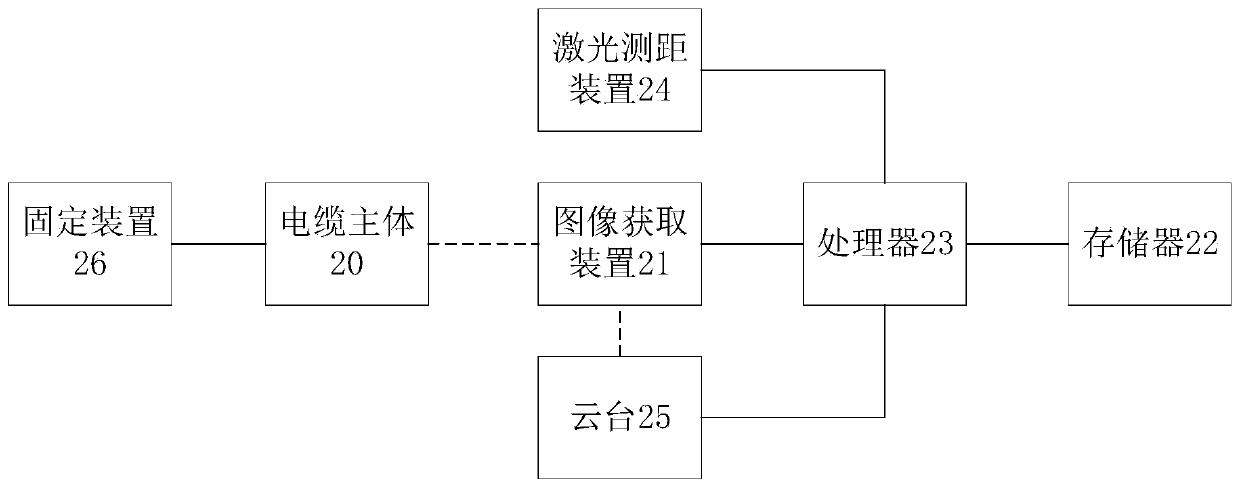

Cable section structure measuring and calculating method, system, and device and readable storage medium

InactiveCN110108219AImprove reliabilityConvenient Calculation ActionImage analysisUsing optical meansImaging processingInsulation layer

The invention discloses a cable section structure measuring and calculating method. The cable section structure measuring and calculating method comprises the steps that an image of the cable sectionis obtained; the image is binarization-processed, and a corresponding grayscale image is obtained; according to pixel points of the grayscale image, a calculation section parameter corresponding to the cable section is determined, and the calculation section parameter comprises the insulation layer thickness, the shielding layer thickness and / or the insulation layer eccentricity degree; and the calculation section parameter is converted to an actual section parameter of the cable section by using image conversion coefficient. According to the cable section structure measuring and calculating method, the actual section parameter of cable section can be obtained directly through image processing, cables do not need to be sliced up, therefore, it is not necessary to consider influence of theslicing technology on the measuring and calculating accuracy, the measuring and calculating speed is much higher than the speed of a laboratory measuring and calculating method, the time required forinspection is greatly shortened, all cables can be inspected, and reliability of the whole batch of the cables is improved. The invention further correspondingly discloses a cable section structure measuring and calculating system and device, and a readable storage medium.

Owner:STATE GRID CHONGQING ELECTRIC POWER CO ELECTRIC POWER RES INST +2

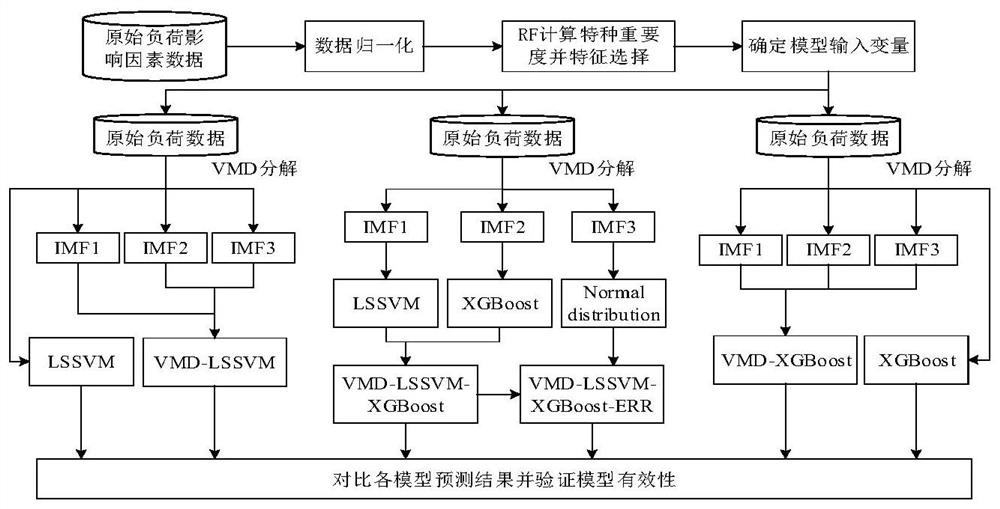

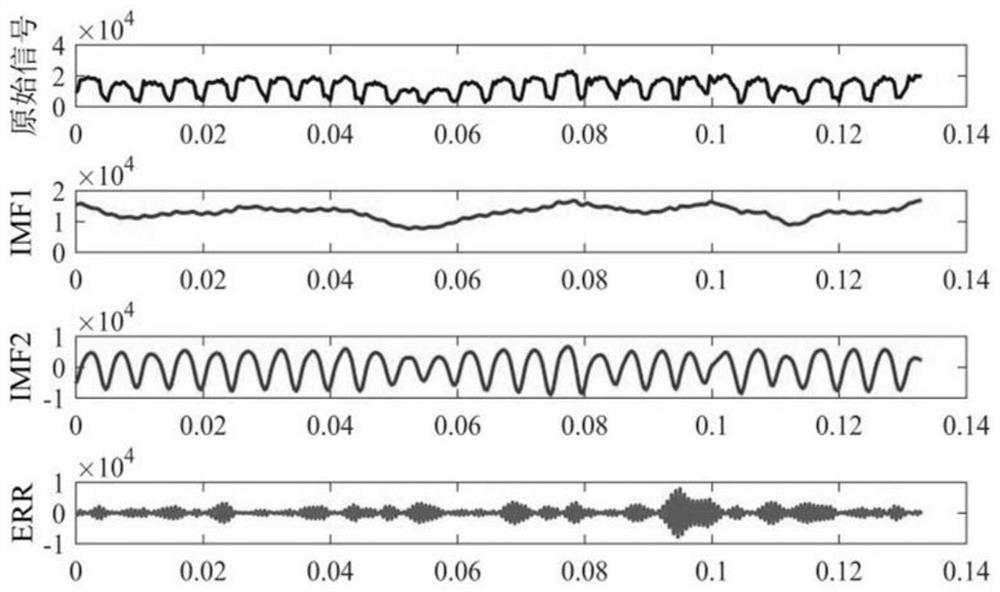

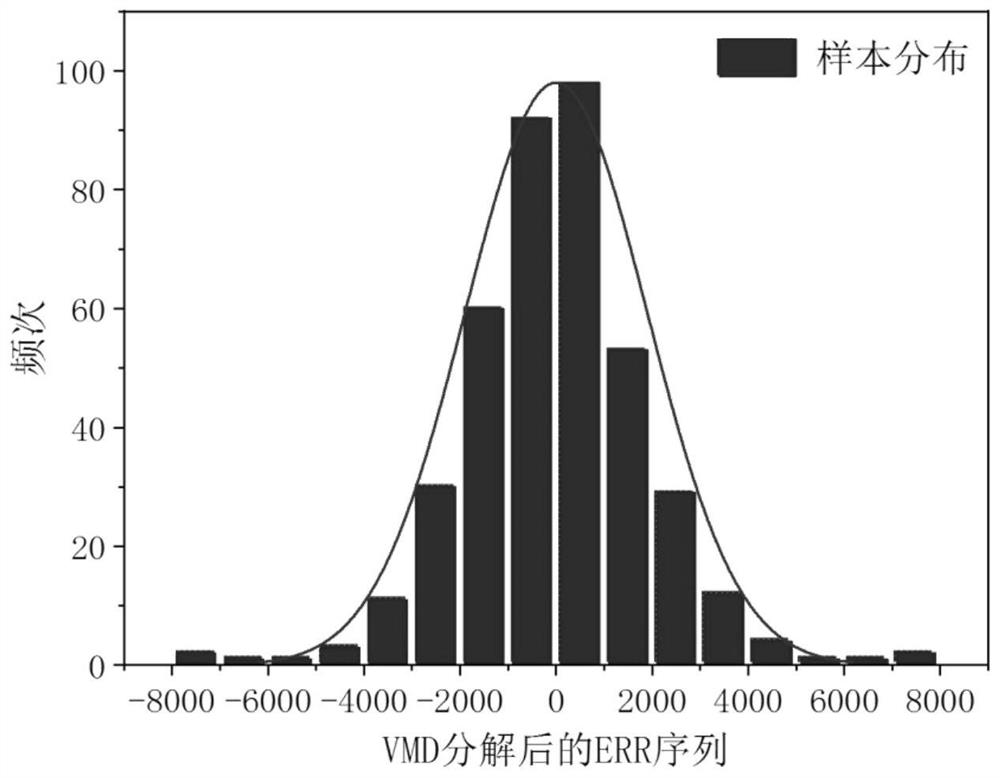

Air conditioner cooling load prediction method and system considering data characteristics after frequency domain decomposition

ActiveCN112990603AReduce dimensionalityRemove redundant informationForecastingResourcesLoad forecastingLeast squares support vector machine

The invention discloses an air conditioner cooling load prediction method and system considering data characteristics after frequency domain decomposition. The method comprises the following steps: taking factors of which the load sequence importance is greater than a set threshold value as input variables; decomposing an original load sequence into two intrinsic mode functions IMF1 and IMF2 and an error sequence ERR by using a variational mode decomposition technology; establishing a least square support vector machine prediction model for the intrinsic mode function IMF1 to obtain a prediction component of an IMF1 subsequence; establishing an extreme gradient boosting decision tree prediction model for the intrinsic mode function IMF2 to obtain a prediction component of an IMF2 sub-sequence; performing normal fitting on the probability distribution of the error sequence ERR showing the Gaussian noise part to obtain a prediction component of a sub-sequence of the error sequence ERR; and superposing the prediction component of the IMF1 sub-sequence, the prediction component of the IMF2 sub-sequence and the prediction component of the error sequence ERR sub-sequence, and outputting to obtain a final cold load prediction value. According to the method, the prediction precision under the environment noise condition is improved, and the method has the practical engineering application background and important practical significance.

Owner:XI'AN UNIVERSITY OF ARCHITECTURE AND TECHNOLOGY

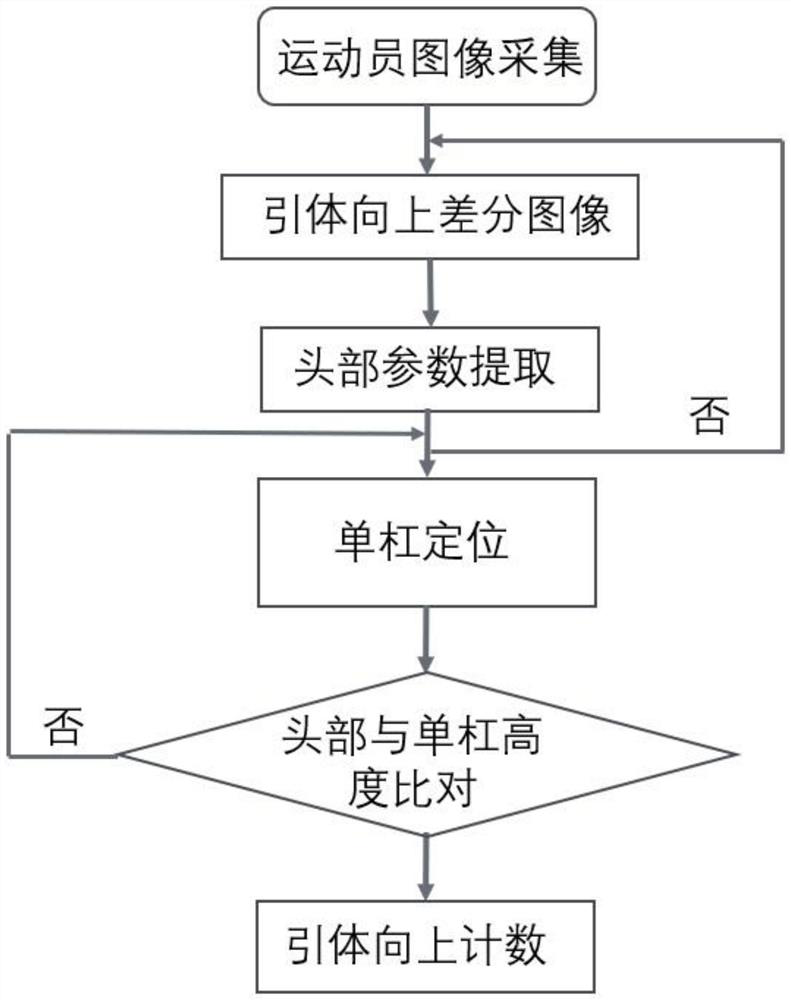

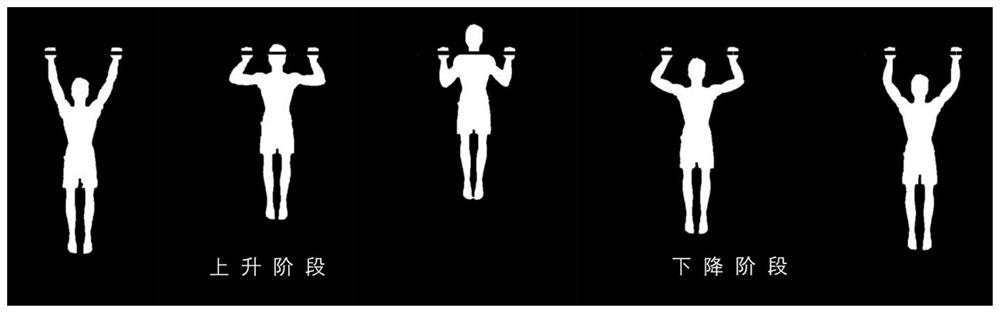

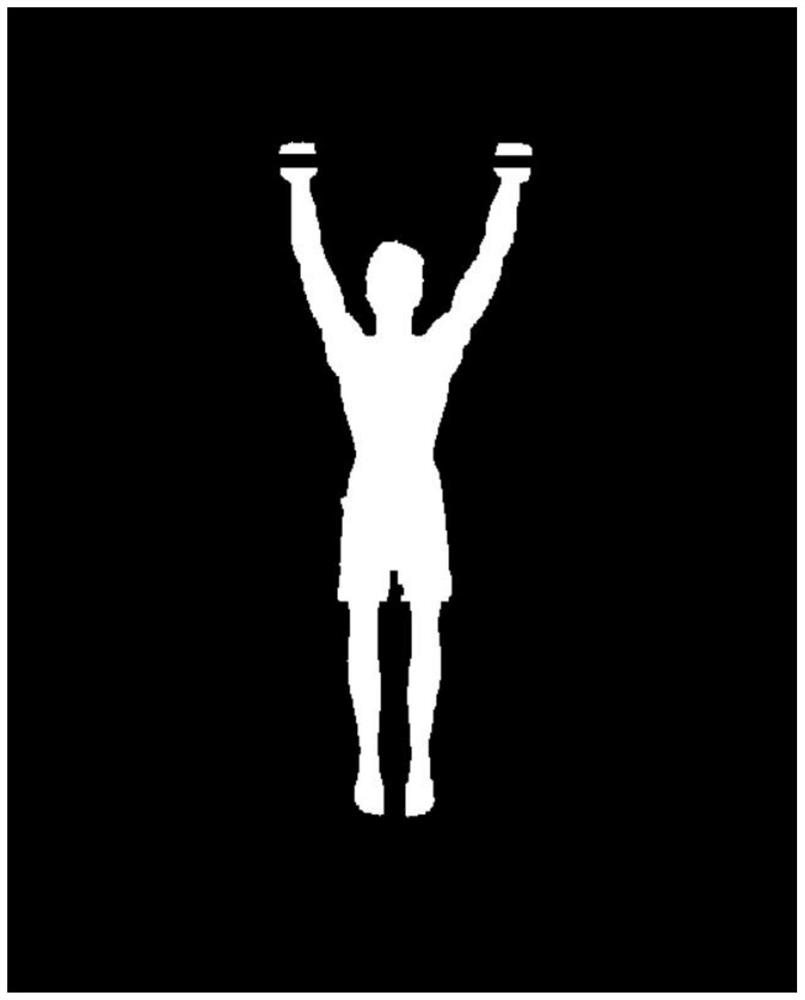

Pull-up counting method based on image difference

PendingCN114519684ASimple positioningTrack target bigImage enhancementImage analysisImage extractionHuman body

The invention relates to the technical field of pull-up counting, in particular to a pull-up counting method based on image difference, which comprises the following steps: an athlete image acquisition step: acquiring a human body image of an athlete by adopting a camera, and preprocessing the acquired human body image to obtain a grey-scale map; and a background image extraction and real-time updating step: taking the smooth image of the grey-scale image in the athlete image acquisition step as a reference background image, comparing the contour of the current frame with the background contour, calculating the difference between the current frame and the reference background image, obtaining a difference image, and performing real-time updating. According to the method, the inter-frame difference image processing technology is adopted, the head area of the human body and the real-time position of the horizontal bar during pull-up are detected, positioning is simple, the problem that the calculation speed is low due to the fact that the calculation amount of pull-up is large is solved, and the effect that the number of pull-up completed by an athlete is calculated in real time is achieved.

Owner:SHENZHEN MAXVISION TECH

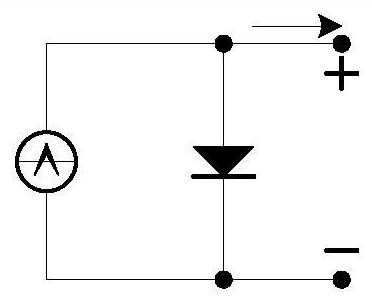

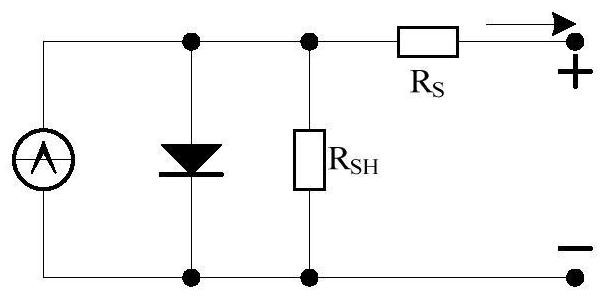

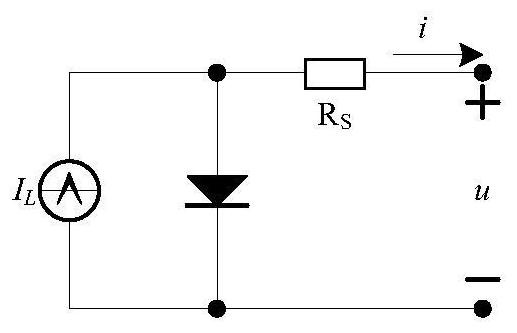

Photovoltaic power generation physical reference control method

PendingCN113064463ASolve the slow calculationHigh precisionPhotovoltaic energy generationAdaptive controlControl theoryBattery cell

The invention relates to a photovoltaic power generation physical reference control method, in particular to a control method adopting physical reference, and belongs to the field of photovoltaic power generation or optimal control methods. The photovoltaic power generation real object reference control method realizes the maximum output power of the photovoltaic cell. According to the first method, the open-circuit voltage and the short-circuit current of the reference photovoltaic cell are measured, the optimal reference resistance is calculated, and the working photovoltaic cell is controlled to reach the maximum output power. The second method comprises the following steps: measuring the open-circuit voltage and the short-circuit current of the reference photovoltaic cell, measuring the current at 80% of the open-circuit voltage and the voltage at 80% of the short-circuit current, calculating the optimal reference resistance, and controlling the working photovoltaic cell to reach the maximum output power. The third method comprises the following steps: measuring the open-circuit voltage or short-circuit current of the reference photovoltaic cell, scanning in a range of 50%-100% of the open-circuit voltage or short-circuit current, measuring the current or voltage at the same time, calculating the voltage and current or optimal reference resistance when the maximum output power is recorded, and controlling the working photovoltaic cell to reach the maximum output power.

Owner:朱仁庆

A shooting focusing method and mobile terminal

ActiveCN106791375BSolve the slow calculationNot limited by ambient light brightnessTelevision system detailsColor television detailsRadarComputer terminal

Examples of the present invention provide a shooting focus method and mobile terminal, where the method is applied to a mobile terminal with radar device, including: determine the target object after starting the camera;The target distance value of the camera is focused.In this way, the embodiments of the present invention obtain the distance value of the target object to the camera through the radar device, and then focus on the target object according to the distance value.Because the radar device uses electromagnetic waves to calculate the distance of the target and object characteristics, it is not limited to the brightness of environmental light.It can be seen that the shooting focusing method of the embodiment of the present invention achieves the purpose of accurate focusing on weak light conditions.

Owner:VIVO MOBILE COMM CO LTD

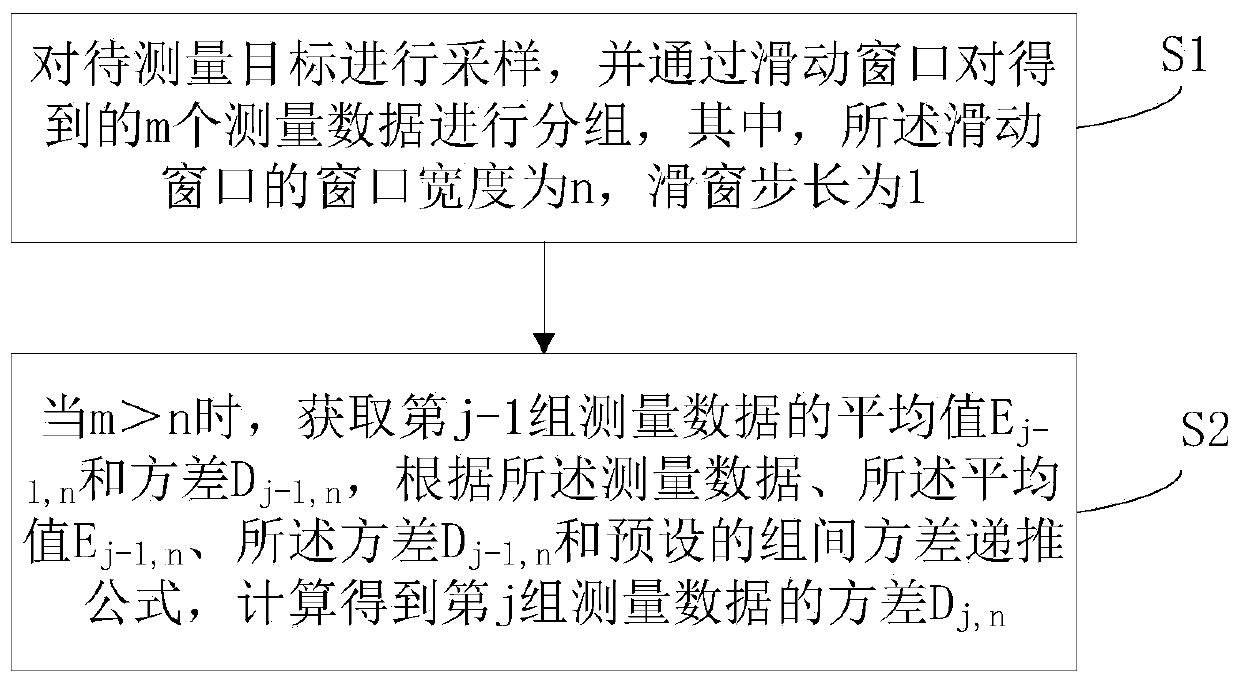

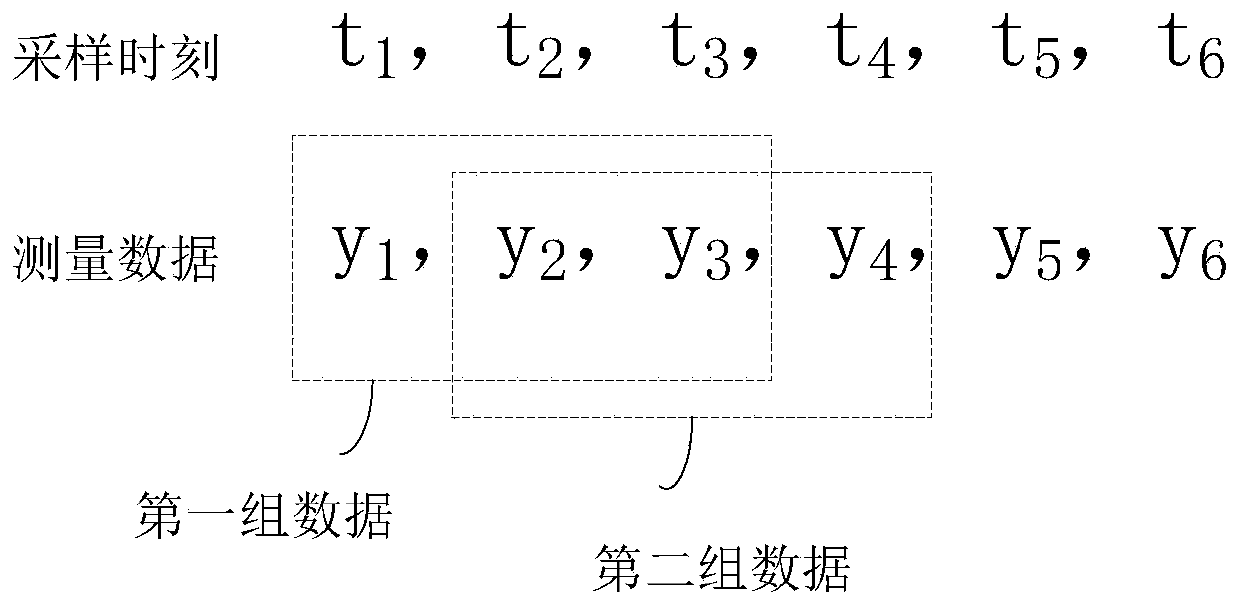

Method and device for determining data variance in real time

PendingCN110069748AFast recursionSolve the slow calculationComplex mathematical operationsSlide windowControl system

The invention discloses a method and a device for determining data variance in real time, and relates to the field of real-time measurement and control. The method comprises the steps that a to-be-measured target is sampled, m pieces of obtained measurement data are grouped through a sliding window, the window width of the sliding window is n, and the step length of the sliding window is 1;averageEj-1, n and variance Dj-1 of a j-1th group of measurement data are obtained, according to the measurement data, an average value Ej-1, n, variance Dj-1,n and preset inter-class variance recursion formula, the variance Dj and n of the jth group of measurement data are calcualted. The method and the device for determining the data variance in real time provided by the invention are suitable for a real-time measurement and control system, the variance of the current group of measurement data can be quickly derived, and even if the data volume of each group of measurement data is very large, thecalculated amount cannot be increased, so that the measurement and calculation speed of the variance is increased, and the real-time requirement of the real-time measurement and control system is ensured.

Owner:BEIJING INST OF RADIO MEASUREMENT

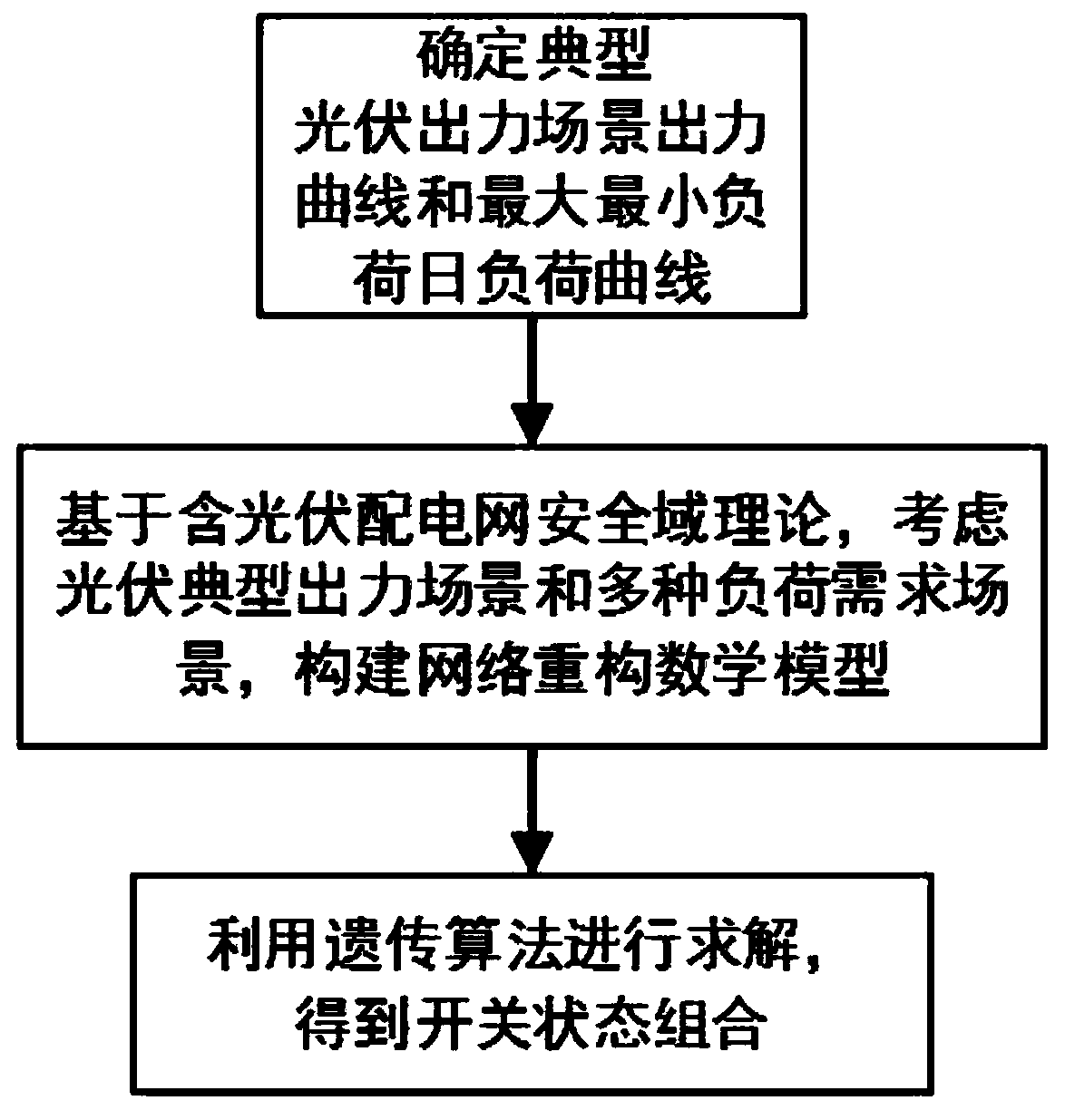

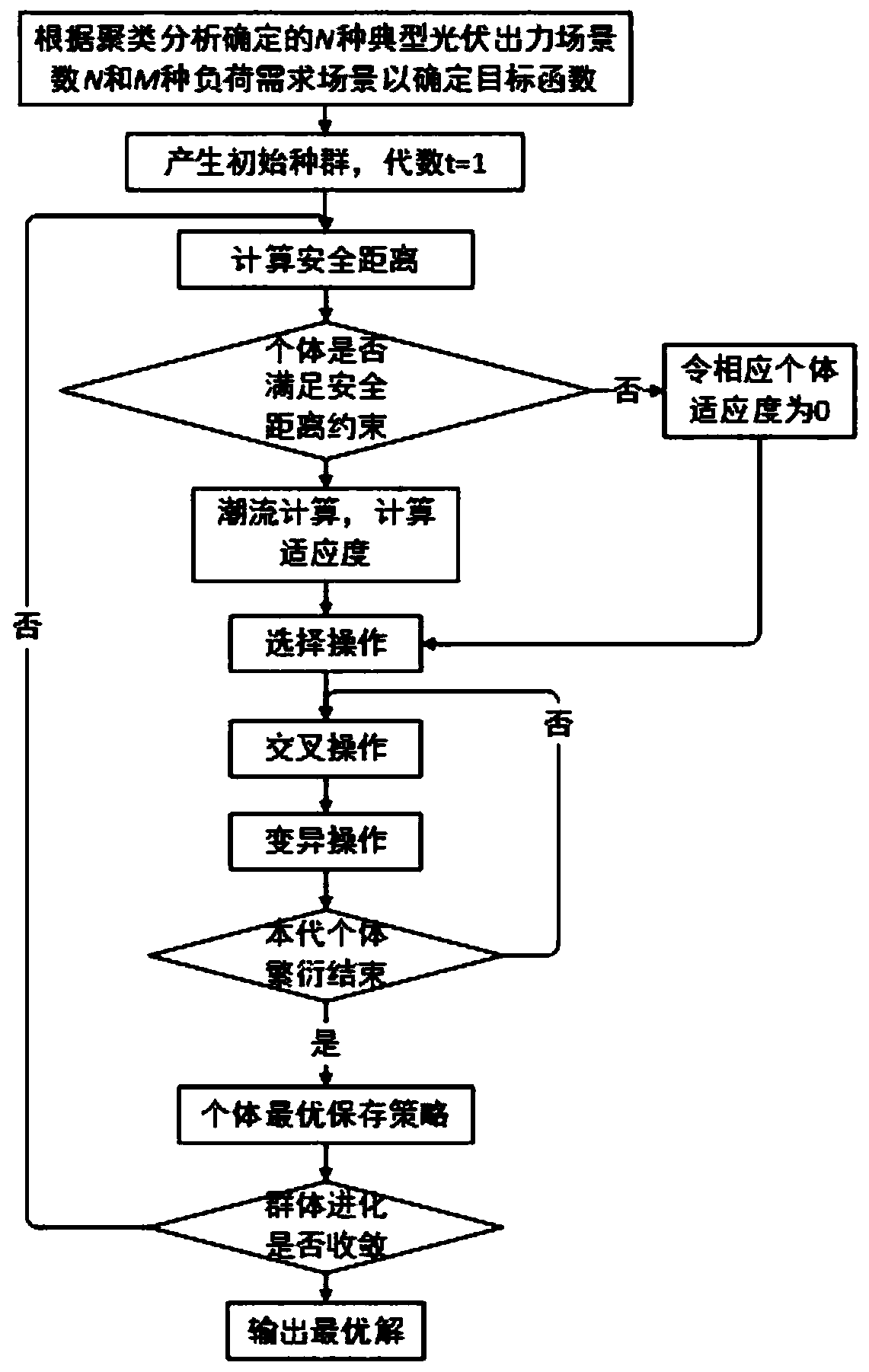

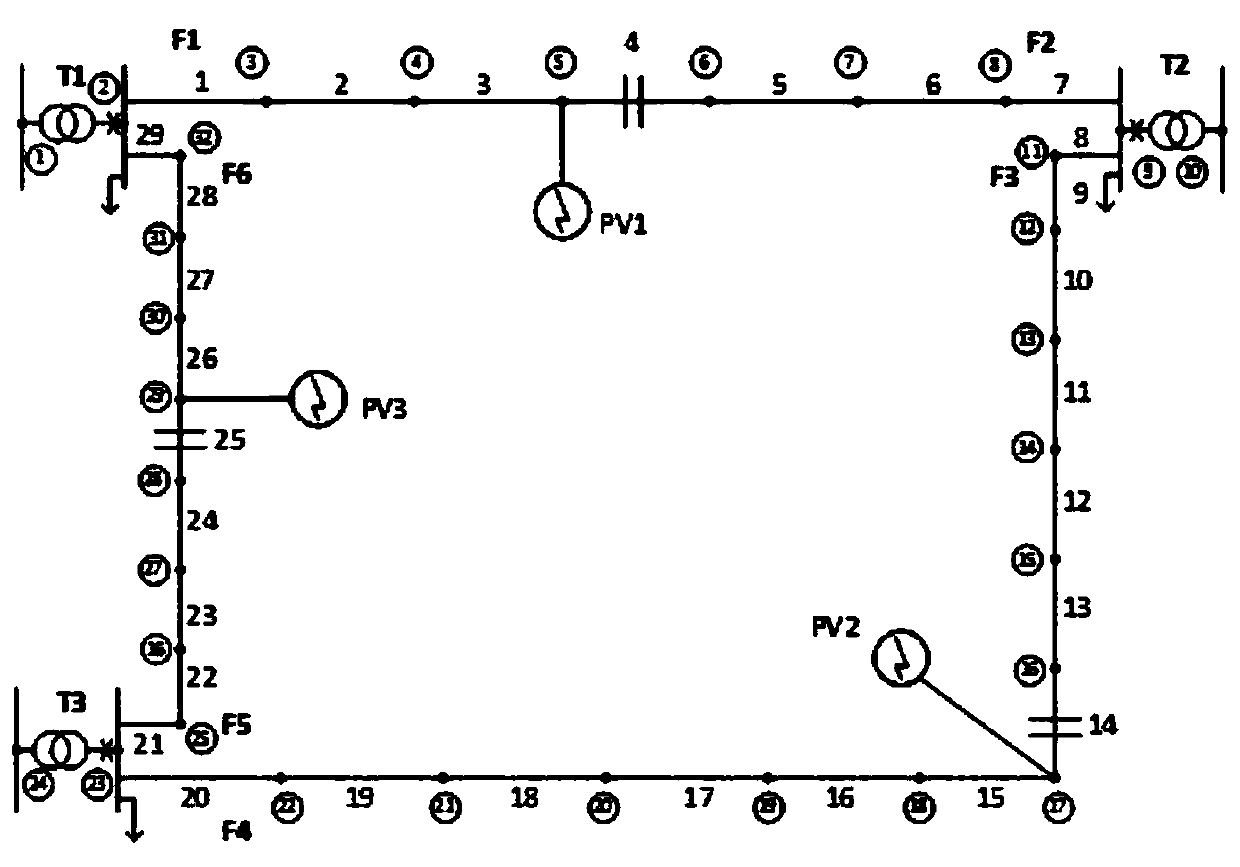

A Reconfiguration Method for Photovoltaic Distribution Network Considering Multidimensional Security Constraints

ActiveCN108242807BSolve the slow calculationGuaranteed uptimeSingle network parallel feeding arrangementsPhotovoltaic energy generationMathematical modelSecurity domain

The invention relates to a photovoltaic power supply included distribution network reconfiguration method considering multidimensional safety constraints. The method comprises the steps of 1, collecting modeling parameters of a target distribution network; 2, collecting preset time T-day historical data of the output of a photovoltaic power plant in a target area, conducting a cluster analysis ona photovoltaic output curve to determine an optimal cluster number N, and obtaining a cluster center Z0 of the N typical photovoltaic output scenarios as an output curve of the corresponding output scenario; 3, determining a load demand scenario and a typical photovoltaic output scenario curve, and based on distribution network security domain indicators, constructing a photovoltaic distribution network reconstruction mathematical model considering multi-scenario N-1 safety constraints; and 4, using a genetic algorithm to solve the photovoltaic distribution network reconstruction mathematicalmodel considering the multi-scenario N-1 safety constraints, and obtaining an optimal reconstruction scheme for the photovoltaic distribution network. The method of the invention improves the safety domain theory of the distribution network, makes the N-1 safety constraints of the photovoltaic distribution network a part of the network optimization reconstruction model, and avoids the problem of slow calculation speed caused by a point-by-point simulation method.

Owner:HEYUAN POWER SUPPLY BUREAU GUANGDONG POWER GRID CO LTD

A Correction Method for Image Distortion

InactiveCN103268597BSimple methodSolve the slow calculationImage enhancementComputer visionCorrection method

The invention discloses an image distortion correction method, comprising the following steps of: (10) obtaining the data of an original image; (20) establishing an corrected image; (40) measuring the red value, green value and blue value of a pixel on the corrected image; and (50) establishing an corrected image: returning to step (30) until the red value, the green value and the blue value of each pixel on the corrected image are measured, thereby establishing the corrected image. Under the condition that the image distortion coefficient is known, each pixel on the distortion corrected image is inversely measured to obtain the position of the pixel in the original image, and then the red, green and blue color values of the pixel are measured by bilinear interpolation. The correction process is simple and efficient.

Owner:SOUTHEAST UNIV

Action Classification Method Based on Joint Spatiotemporal Simple Recurrent Network and Attention Mechanism

ActiveCN109376720BCalculation speedSolve the slow calculationCharacter and pattern recognitionNeural learning methodsClassification methodsEngineering

The invention relates to an action classification method based on joint point space-time simple loop network and attention mechanism. First, the ordinary SRU model is extended to the space dimension, and a ST-SRU model that performs iterative calculations in both time and space dimensions is designed. Then, based on the proposed ST‑SRU model, the global context attention mechanism is introduced, and the GCA‑ST‑SRU method is proposed. Finally, the proposed method is used for human behavior recognition. First, the features of human joints are extracted by deep network, and then the extracted features are recognized by GCA‑ST‑SRU method. The method of the invention can reduce training time consumption and improve classification accuracy, and has obvious efficiency advantages. The rapid inference speed of the method of the invention is beneficial to the design of a real-time action recognition system, is suitable for running on a platform with limited computing power, and has broad application prospects in the fields of computer vision, intelligent monitoring, human-computer interaction and the like.

Owner:HANGZHOU DIANZI UNIV

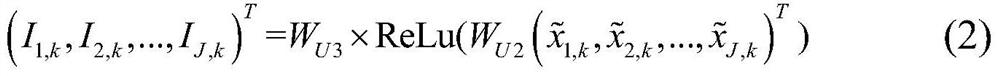

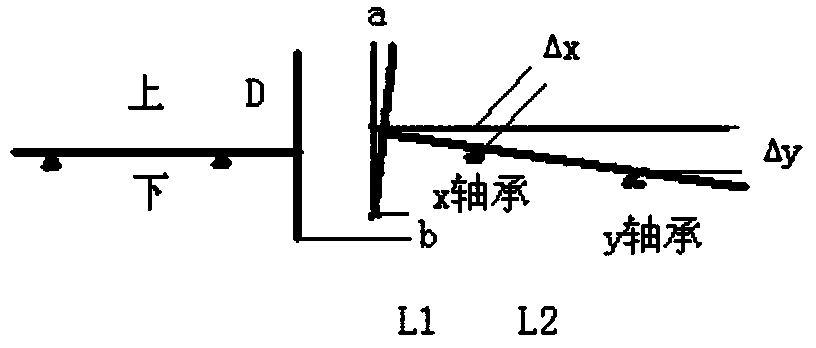

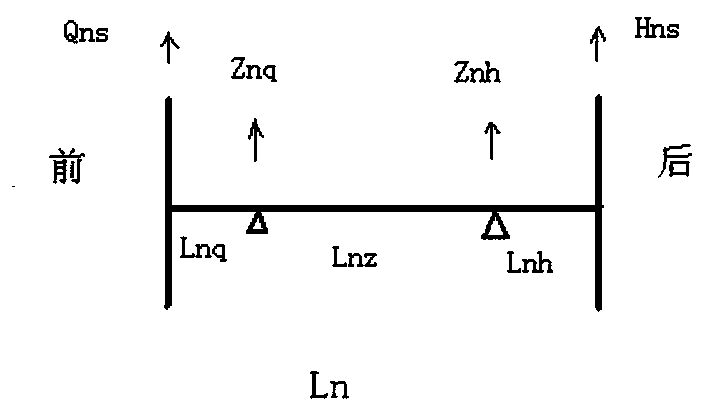

A Calculation Method of Shafting Center of Steam Turbine

ActiveCN105912873BCalculations are clearSolve the slow calculationSpecial data processing applicationsInformaticsEngineeringTurbine

The invention discloses a measurement and calculation method of a turbine shaft system center. The measurement and calculation method comprises the following steps: firstly, carrying out modeling on a turbine shaft system before repair, and measuring the center number value of the turbine shaft system before repair, the length of each rotor and the diameter of the rear clutch of each rotor to obtain the modeling data of the turbine shaft system before repair; then, according to the modeling data of the turbine shaft system before repair, calculating the adjustment amount of each rotor clutch; and taking the adjustment amount of each rotor clutch as an intermediate value to calculate to obtain the adjustment amount of a corresponding rotor bearing so as to calculate the adjustment amount of a corresponding bearing regulation spacer according to the adjustment amount of each bearing and the position of each adjustment spacer. Firstly, the center number value of the turbine shaft system before repair is measured, the adjustment amount of each rotor clutch is calculated, the adjustment amount of each rotor clutch is taken as the intermediate value to calculate the adjustment amount of the corresponding bearing, an influence value on a rear clutch opening value after the rotor bearing is regulated does not need to be measured and calculated, measurement and calculation can be well organized, and a measurement and calculation amount and measurement fault possibility are effectively reduced.

Owner:DATANG SHANDONG ELECTRIC POWER OVERHAUL & OPERATION

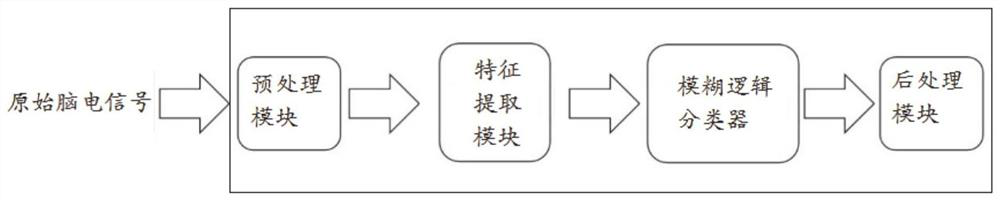

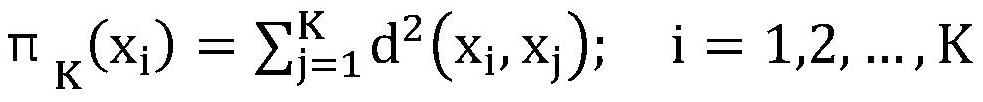

Automatic epileptic seizure detection system based on 1D-LBP and fuzzy logic classification

PendingCN114129131ASimple calculationImprove efficiencyDiagnostic recording/measuringSensorsMedicineMachine learning

The invention provides an epileptic seizure automatic detection system based on 1D-LBP and fuzzy logic classification, and the system comprises an electroencephalogram signal preprocessing module which is configured to segment an obtained electroencephalogram signal by taking a set time length as a unit, and carries out the filtering processing; the feature extraction module is configured to extract one-dimensional signal uniform local binary pattern texture features on the electroencephalogram signals represented by time-frequency; the classification module is configured to use a pre-trained fuzzy logic classifier to classify the extracted information and determine whether epileptic seizure occurs or not, and the classification distance of the fuzzy logic classifier is selected according to specific conditions; according to the method, the defect of low efficiency of epilepsy detection in the prior art is overcome, redundant information can be effectively eliminated, key information can be effectively extracted, the false detection rate in epilepsy detection is reduced, the speed is high, and the detection accuracy is high.

Owner:SHANDONG NORMAL UNIV

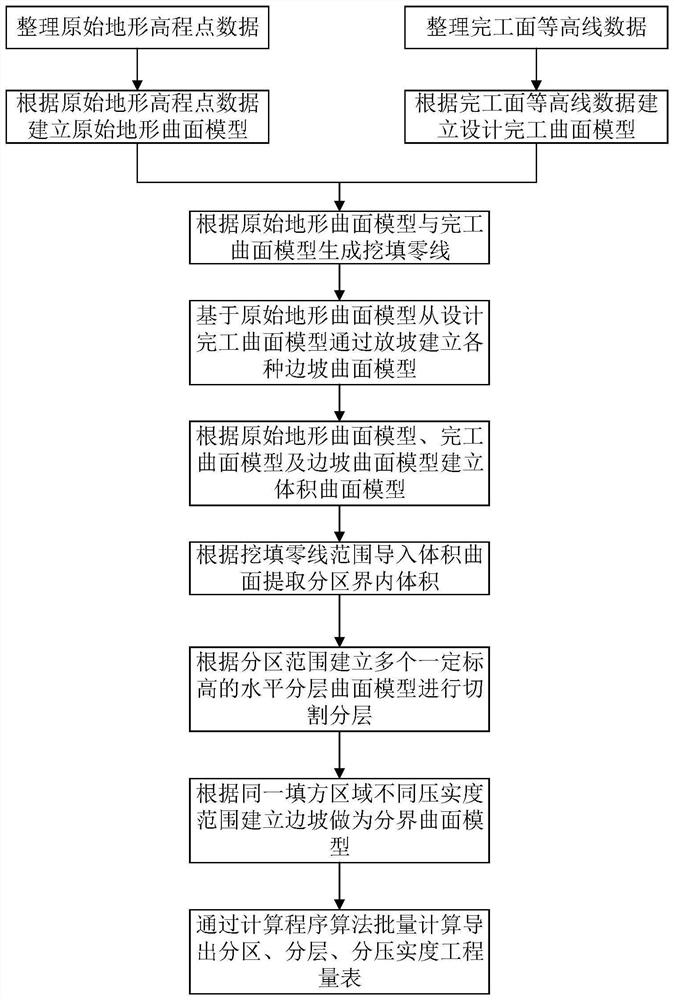

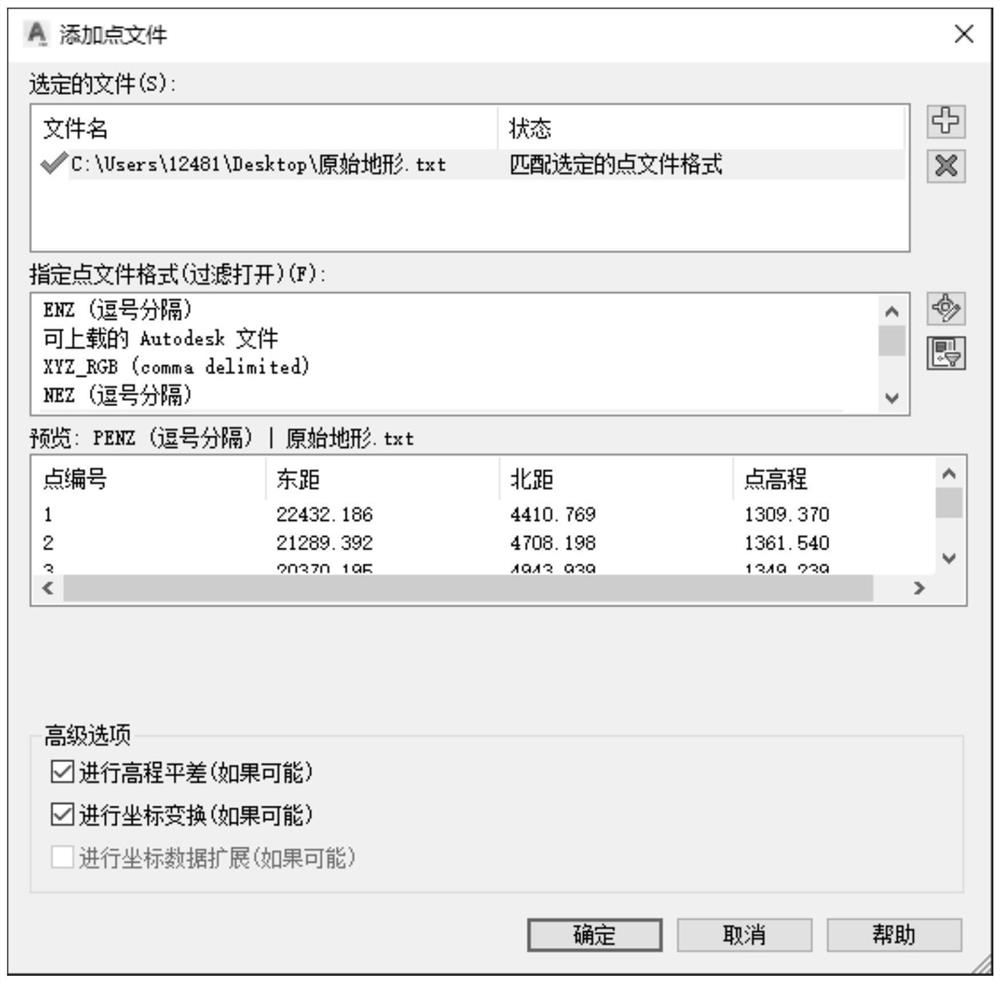

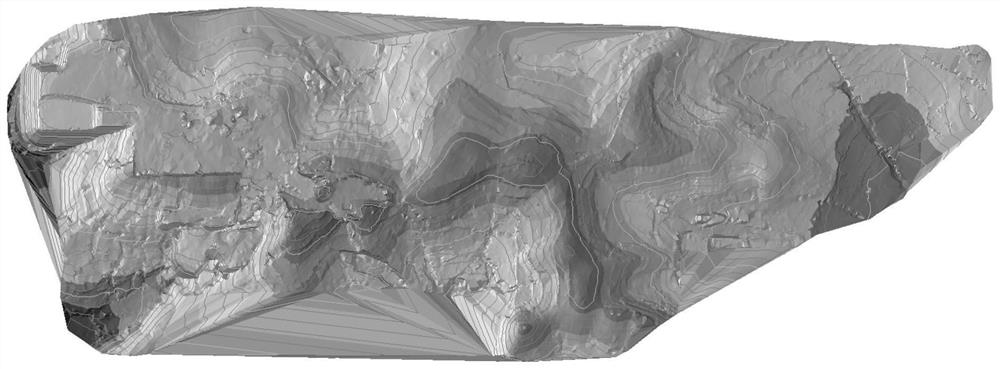

BIM (Building Information Modeling)-based special-shaped earthwork engineering quantity measuring and calculating method and device

PendingCN114201794AImprove work efficiencyImprove measurement accuracyGeometric CADDesign optimisation/simulationTerrainClassical mechanics

The invention discloses a BIM (Building Information Modeling)-based special-shaped earthwork engineering quantity measuring and calculating method and device, and the method comprises the steps: S01, building an original terrain curved surface model, and designing a finished curved surface model; s02, establishing a volume curved surface model according to the original terrain curved surface model and the designed curved surface model, and calculating the total volume of earthwork of each excavation and filling partition; s03, determining a partition range according to the original terrain curved surface model and the designed curved surface model, and establishing a plurality of horizontal layered curved surface models; and S04, establishing boundary curved surface models among the areas with different compaction degrees, performing layering according to each currently obtained curved surface model, generating a volume curved surface of each layer, and performing calculation according to a volume curved surface iterative subtraction method to obtain the filling earth-rock work amount of each layer with different compaction degrees. The method can achieve the measurement and calculation of the engineering quantity of the ultra-large special-shaped earthwork, and has the advantages of being simple in implementation method, high in flexibility, high in measurement and calculation efficiency, high in measurement and calculation precision and the like.

Owner:SINOHYDRO BUREAU 8 CO LTD

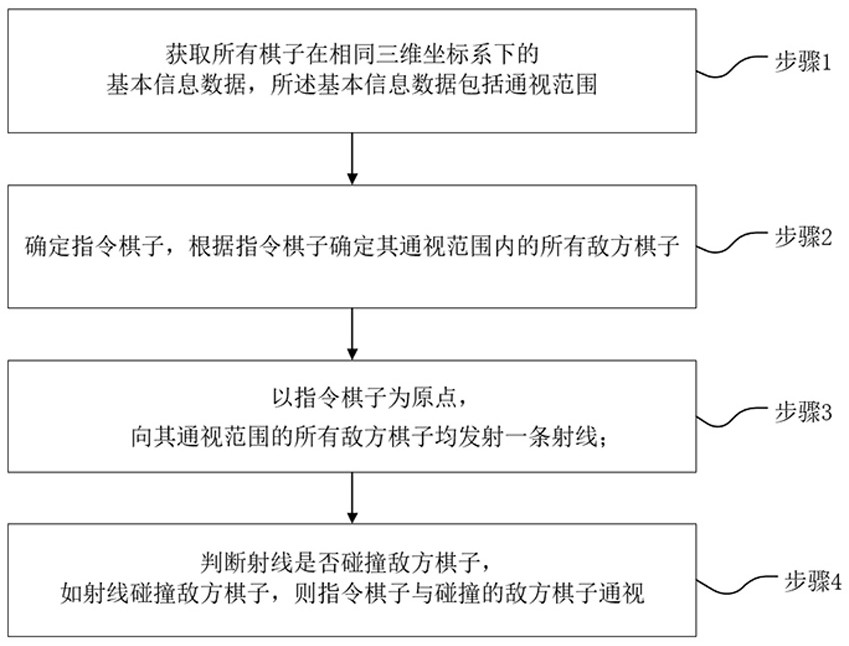

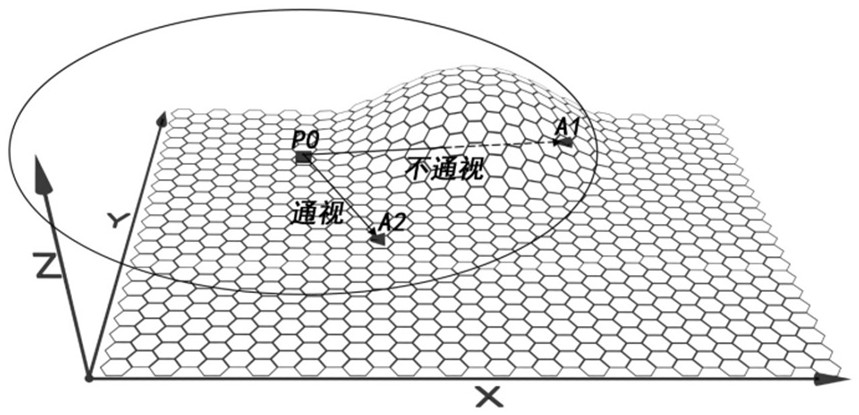

Wargame intervisibility analysis method, terminal equipment and computer readable storage medium

ActiveCN112507571ASolve the slow calculationReduce the number of calculationsDesign optimisation/simulationSpecial data processing applicationsAlgorithmTheoretical computer science

The invention discloses a weapon go-through analysis method, terminal equipment and a computer readable storage medium, and the method comprises the steps: obtaining the basic information data of allchess pieces under the same three-dimensional coordinate system, and the basic information data comprises a go-through range; determining instruction chess pieces, and determining all enemy chess pieces in the intervisibility range of the instruction chess pieces according to the instruction chess pieces; taking the instruction chess piece as an original point, and emitting a ray to all enemy chess pieces in the intervisibility range of the instruction chess piece; judging whether the rays collide with the enemy chess pieces or not, and if yes, instructing the chess pieces to be seen through with the collided enemy chess pieces. According to the method, the problems of slow intervisibility calculation and low efficiency in traditional weapon chess deduction are solved, the calculation frequency is reduced, the time is saved, the intervisibility result of the chess pieces can be obtained in a shorter time, and the calculation efficiency and accuracy are improved; meanwhile, the method is simple in overall operation, and CPU resource consumption and memory occupation of the intelligent equipment are reduced.

Owner:JIANGSU BOZHI SOFTWARE TECH CO LTD

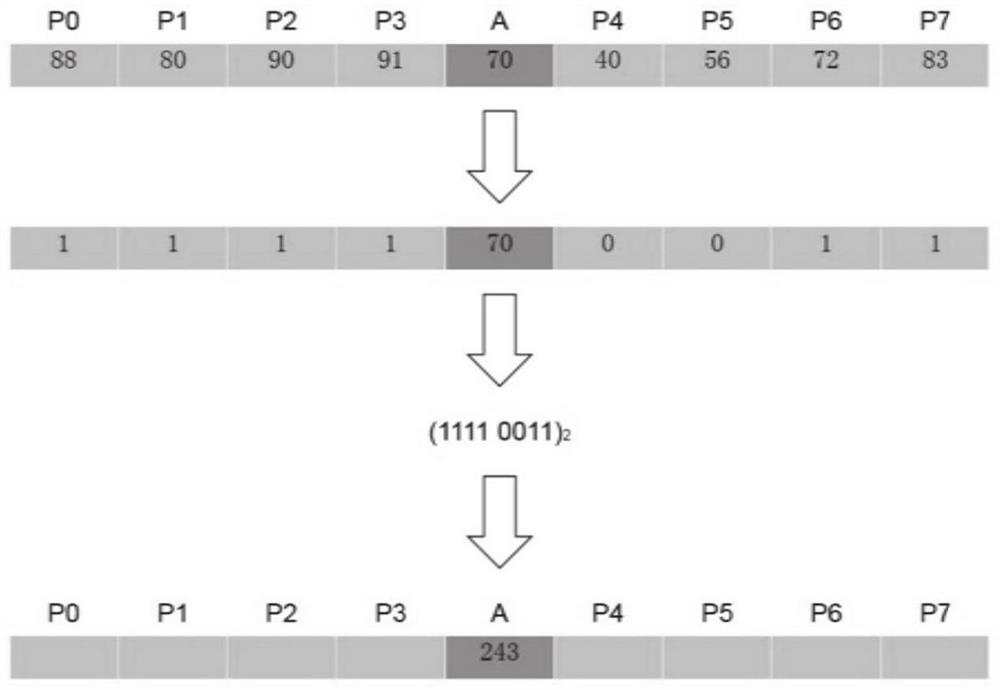

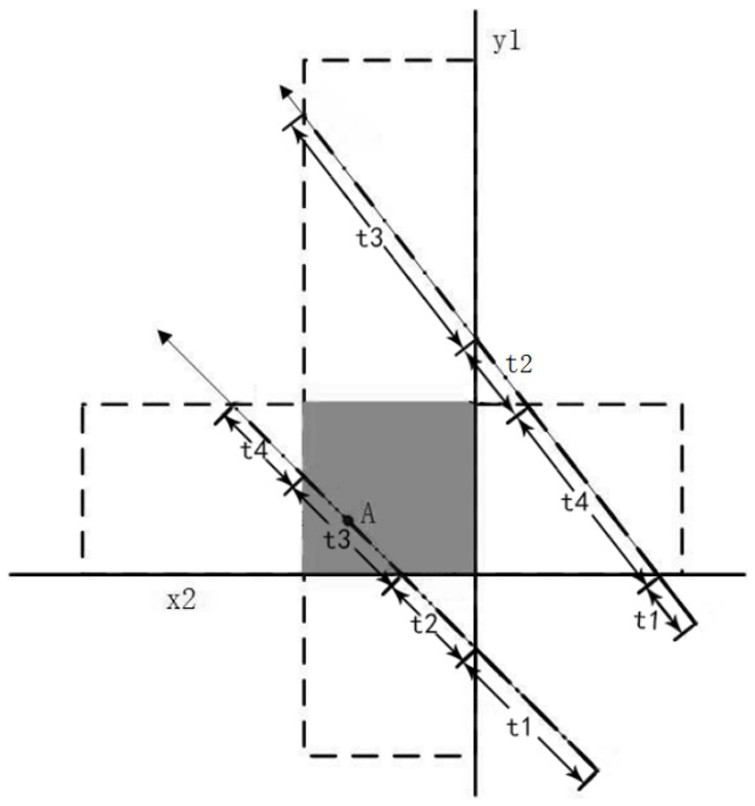

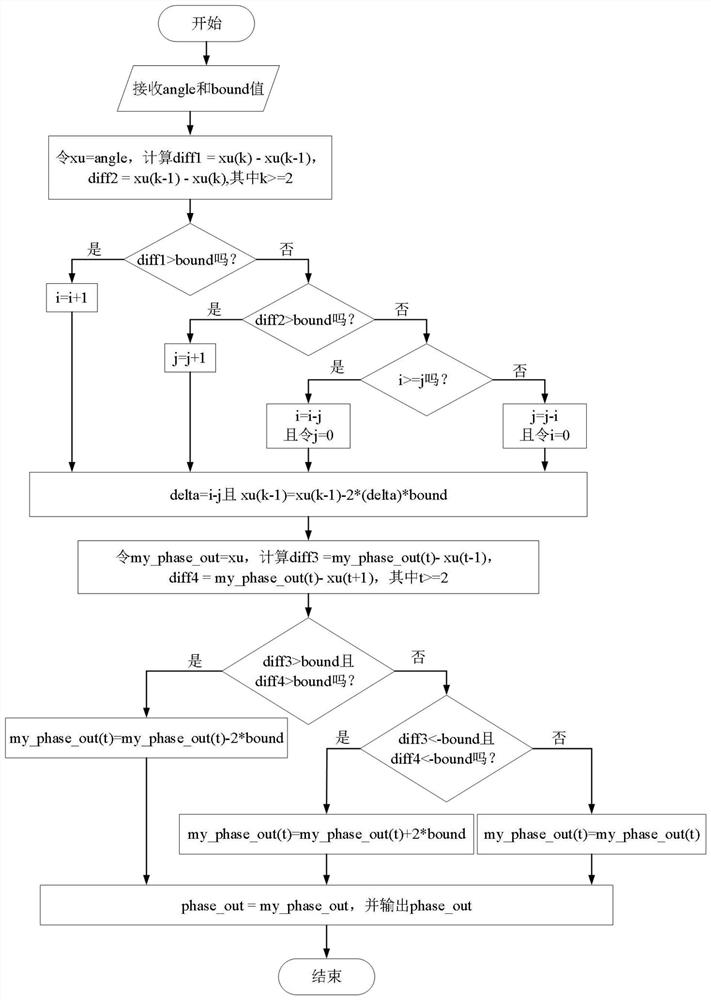

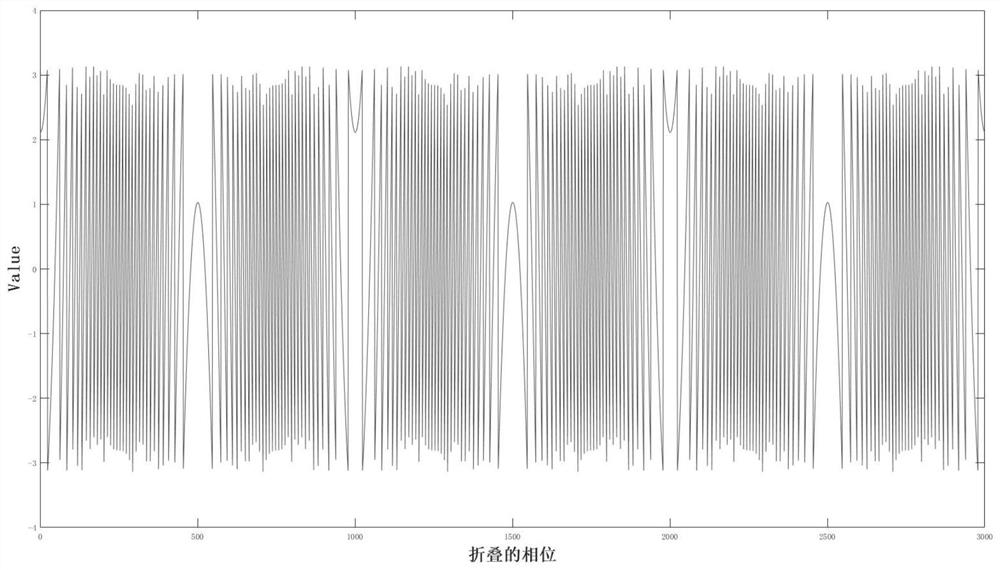

Phase unwrapping algorithm based on double counters

PendingCN114489565ASolve the slow calculationImprove real-time performanceDigital data processing detailsPhysicsRound complexity

The invention relates to the technical field of signal processing, in particular to a phase unwrapping algorithm based on double counters, which comprises the following steps of: calculating a difference value between a front phase and a rear phase, judging whether the difference value is greater than a threshold value of phase truncation, adding 1 to a corresponding counter if the difference value is greater than the threshold value, and judging the relative size of the counter if not; subtracting the counter with the small numerical value from the counter with the large numerical value, assigning a result to the counter with the large numerical value, setting the numerical value of the counter with the small numerical value to be 0, calculating a difference value of the two counters, and performing first-step compensation on the phase. Calculating the difference between the current phase value and the rear phase value as well as the difference between the current phase value and the front phase value, comparing the difference results of the phase values with a threshold value, and if the difference results of the phase values are greater than the threshold value, subtracting two times of the threshold value from the current phase value; if the numerical difference results are all smaller than the threshold value, the current phase value is added with two times of the threshold value, otherwise, the current phase value is kept unchanged, the problems that a phase unwrapping algorithm is low in speed and high in complexity are solved, and the phase unwrapping algorithm is suitable for an FPGA platform at the same time.

Owner:NAT INST OF METROLOGY CHINA +1

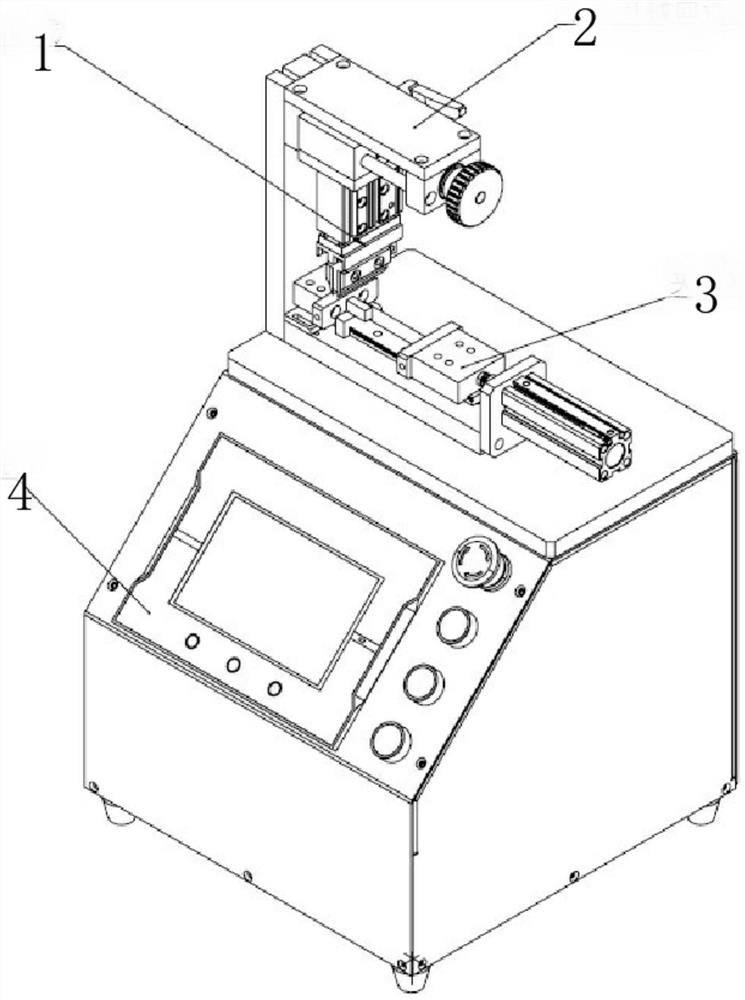

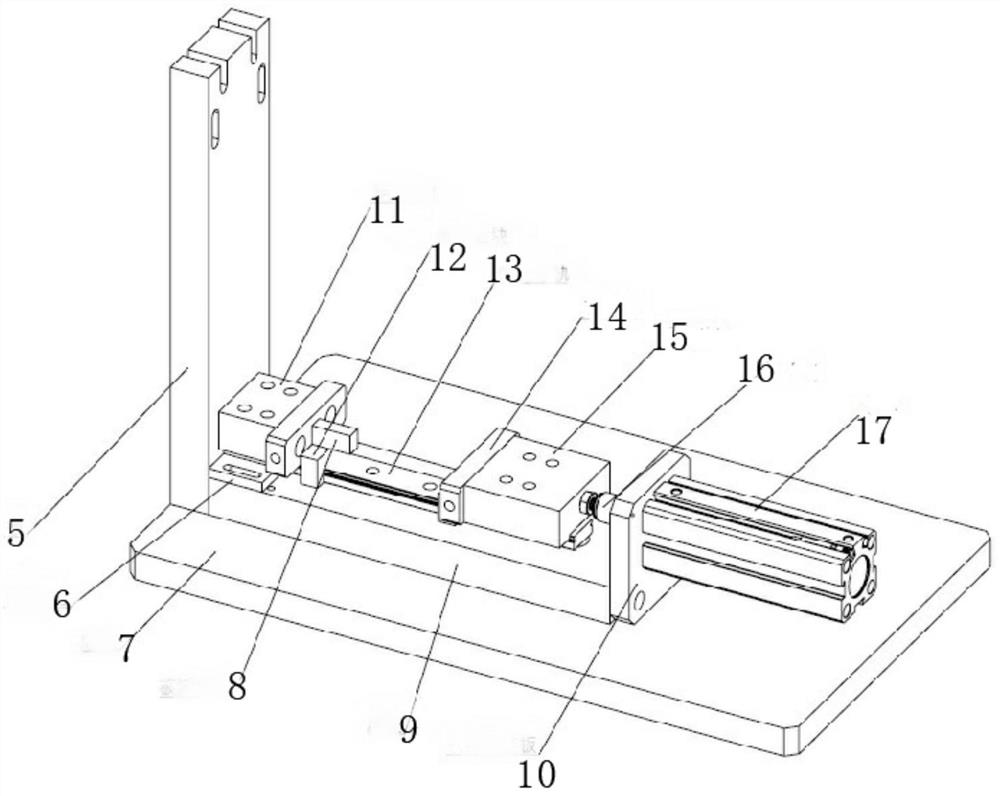

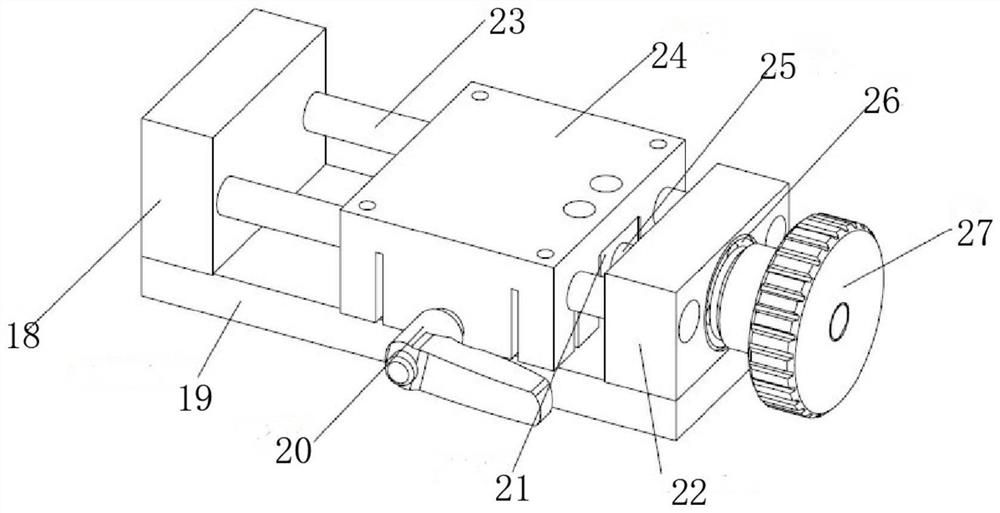

Carbon brush connection resistor test platform

PendingCN113552420AQuick and automatic measurementQuick calculationResistance/reactance/impedenceElectrical testingControl systemClassical mechanics

The invention discloses a carbon brush connection resistance test platform. The test platform comprises a tested carbon brush and a control system which are used for operating and controlling the test platform and outputting a measurement result and are integrated at a front end of the test platform; a clamp assembly which is located at a top end of the control system and used for testing the tested carbon brush; a pressing cylinder transverse adjusting assembly which is positioned above the clamp assembly and is used for fixing the tested carbon brush according to the specification of the tested carbon brush; a downward pressing cutter assembly which is located below the downward pressing cylinder transverse adjusting assembly and used for measuring and calculating the resistance of the measured carbon brush and further calculating resistivity of the measured carbon brush. The test platform is advantaged in that the carbon brush can be directly measured, operation steps are few, the measuring speed is high, the accuracy rate is high, external human intervention is avoided, the external measurement condition is stable, the measurement result can be directly output on the touch screen, and practicability is high.

Owner:威海新光电碳制品有限公司

Airborne single baseline Doppler-phase difference direction finding method

ActiveCN101813762BSolve the slow calculationIncrease the lengthDirection finders using radio wavesPhase differenceFrequency shift

The invention discloses an airborne single baseline Doppler-phase difference direction finding method by which an entire cycle solution of a radial distance can be directly obtained through comprehensively utilizing the relation among a speed vector equation, a Doppler frequency shift and a change rate, therefore, an entire cycle value of a path difference between radial distances of two adjacentarray elements of single baseline can be obtained. The path difference is entirely determined after the value of a non-entire cycle part of the path difference is determined by further utilizing a phase difference. Hence, under the condition that the length of the baseline is determined, the direction of an object can be directly obtained according to a trigonometric function relationship. The invention has a series of advantages of low installation requirement, short measuring time, suitability for bandwidth detection, and the like.

Owner:CHINESE AERONAUTICAL RADIO ELECTRONICS RES INST

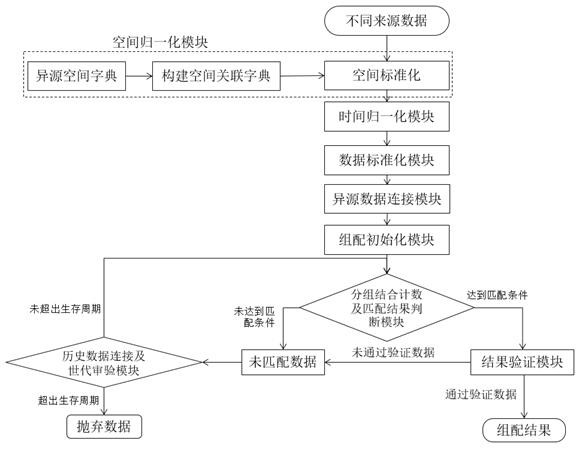

A method and system for target recognition based on multi-source spatio-temporal data assembly

ActiveCN108573039BSolve the slow calculationLow costOther databases retrievalSpecial data processing applicationsData connectionOriginal data

The invention belongs to the field of data processing, and in particular relates to a target recognition method and system based on multi-source spatio-temporal data assembly. The present invention includes a space normalization module, a time normalization module, a data standardization module for standardizing raw data, a heterogeneous data connection module, an assembly initialization module, a group combination counting and matching result judging module, and a result The verification module and historical data connection and generation verification module use the above modules to normalize the spatial characteristics of information sources, standardize the space and time dimensions of data from different sources, and set its data identification code driven by a selected data source As a keyword, the data identification codes from other data sources that appear at the same time and at the same place will be integrated and counted. The present invention adopts the method of splitting calculation first and then merging results to calculate step by step, processes massive data, has high adaptability to equipment performance, flexible calculation, high real-time performance and accurate results.

Owner:YANTAI HAIYI SOFTWARE

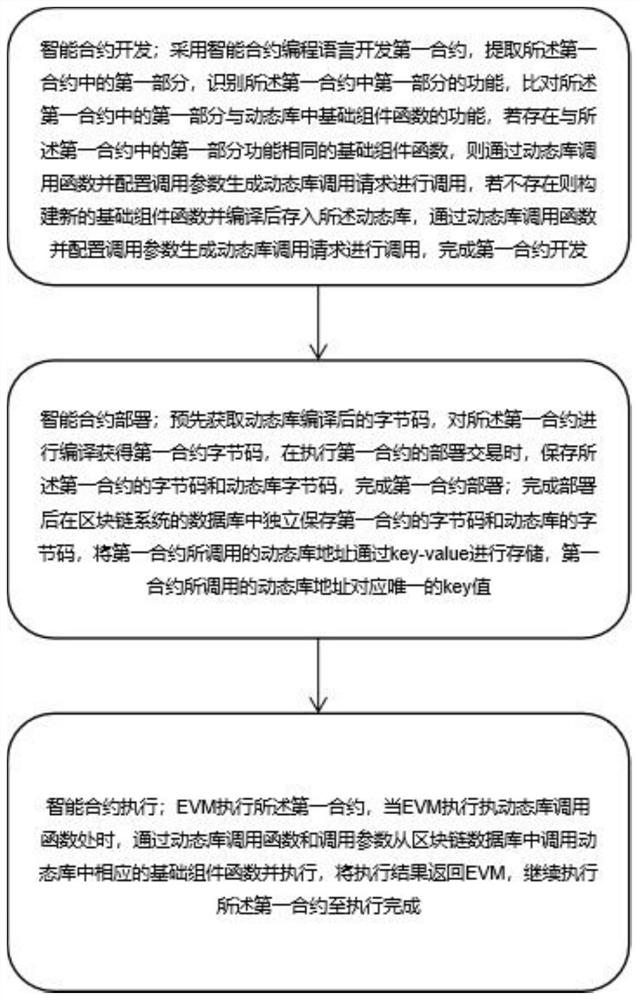

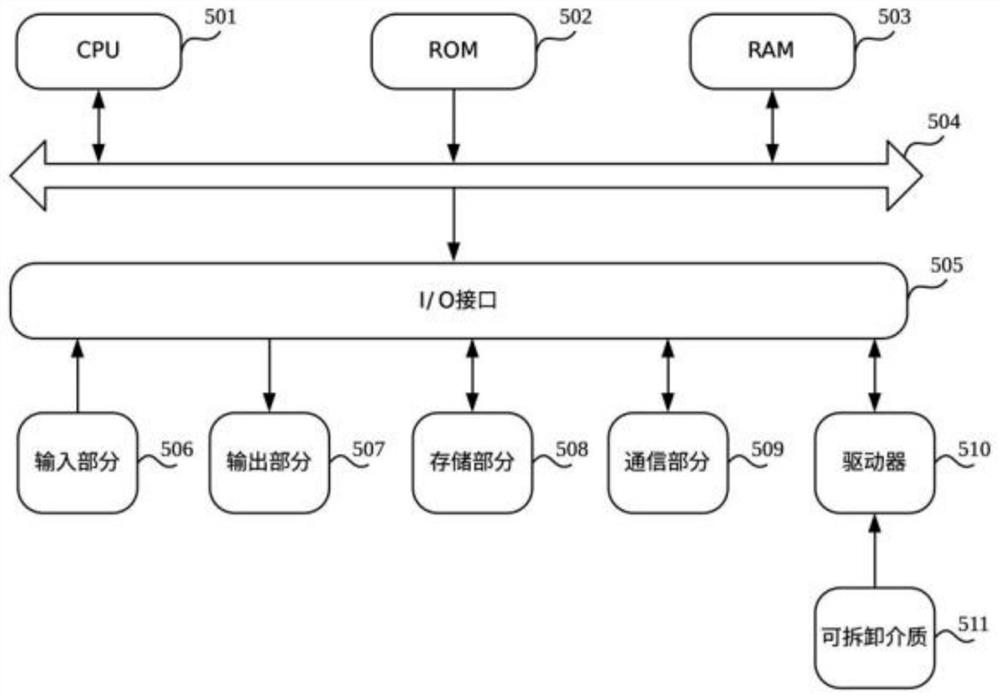

Method and equipment for efficiently executing EVM smart contract and storage medium

ActiveCN113778564ASolve the slow calculationImprove execution efficiencyDatabase distribution/replicationProgramming languages/paradigmsOperational systemSmart contract

The invention belongs to the technical field of computers, and particularly relates to a method and equipment for efficiently executing an EVM smart contract and a storage medium. According to the method provided by the invention, for a part needing to be calculated in a large amount in the EVM smart contract, the part needing to be calculated in a large amount is realized in a form of issuing basic component functions which are written by native codes and have the same function, and in the process of executing the smart contract by the EVM, the part needing to be calculated in a large amount directly obtains a result by calling the basic component functions and configuration parameters in a dynamic library; the dynamic library is written and compiled by adopting a native code and then directly depends on an operating system to run, then a result is fed back to the EVM, the EVM continues to execute the intelligent contract, and the EVM does not execute a part needing a large amount of calculation, so that the problems that the calculation speed of the EVM is low, and the contract of the part which is written and calculated by adopting an intelligent contract programming language is too large in size and has repeated deployment are solved; and the execution efficiency of the contract can be greatly improved for the EVM smart contract needing a large amount of calculation.

Owner:HANGZHOU FUZAMEI TECH CO LTD

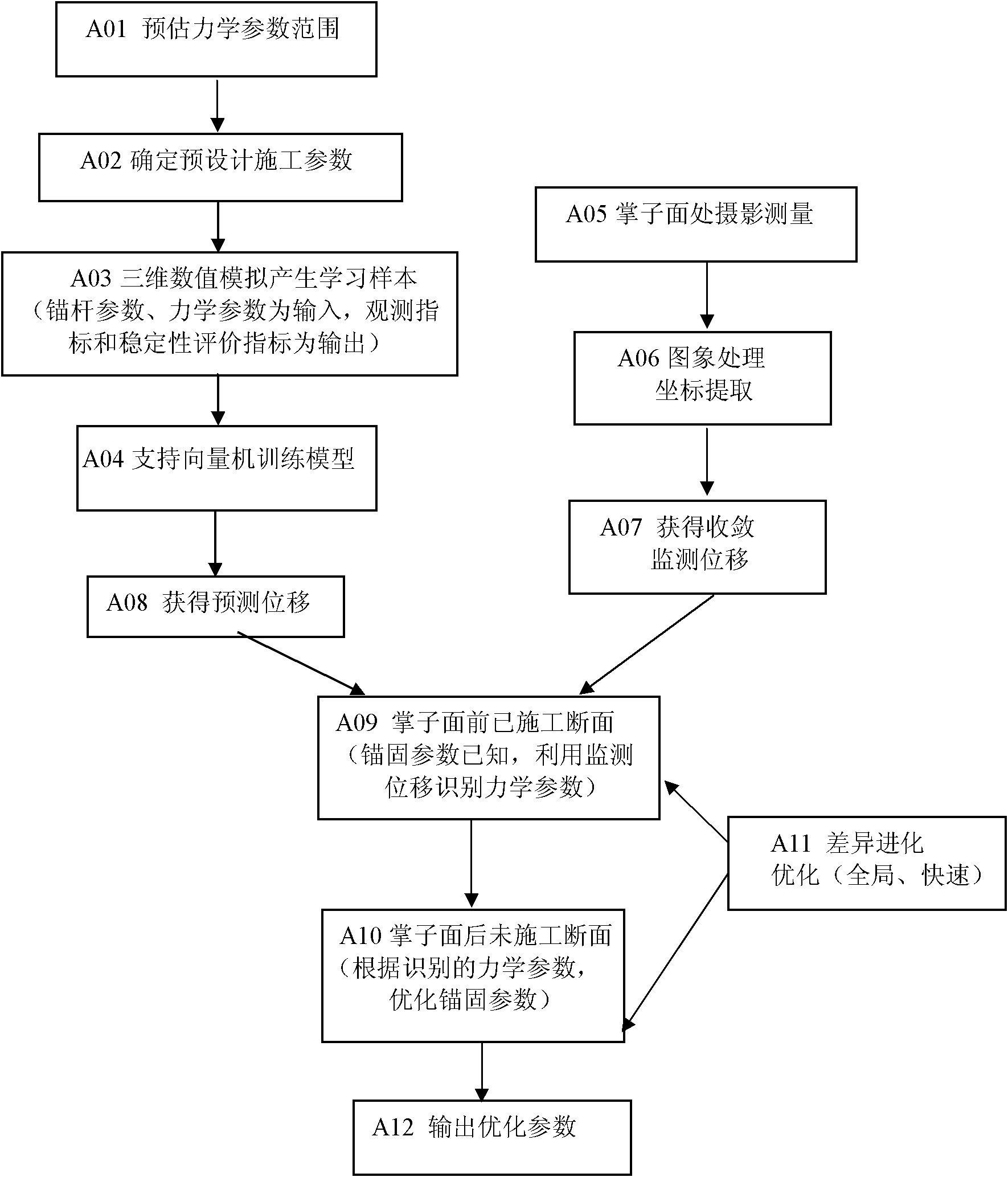

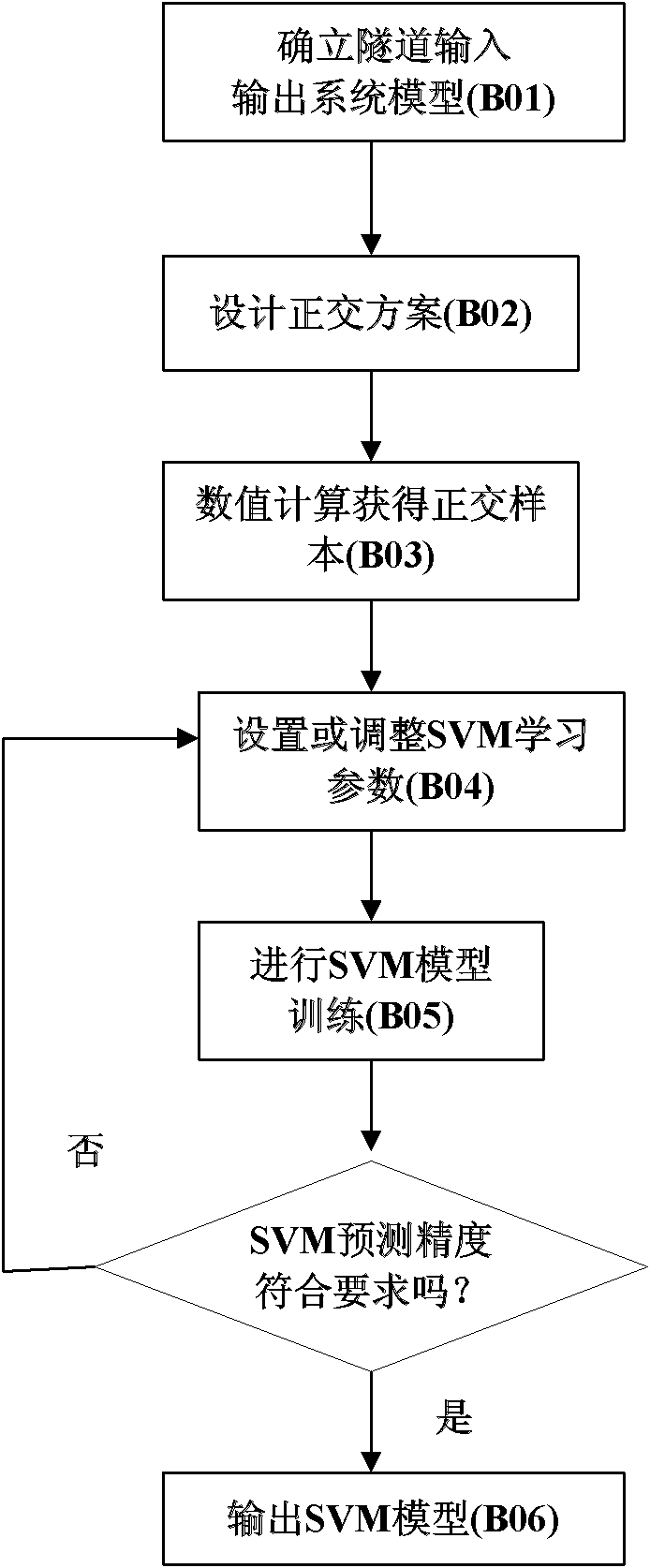

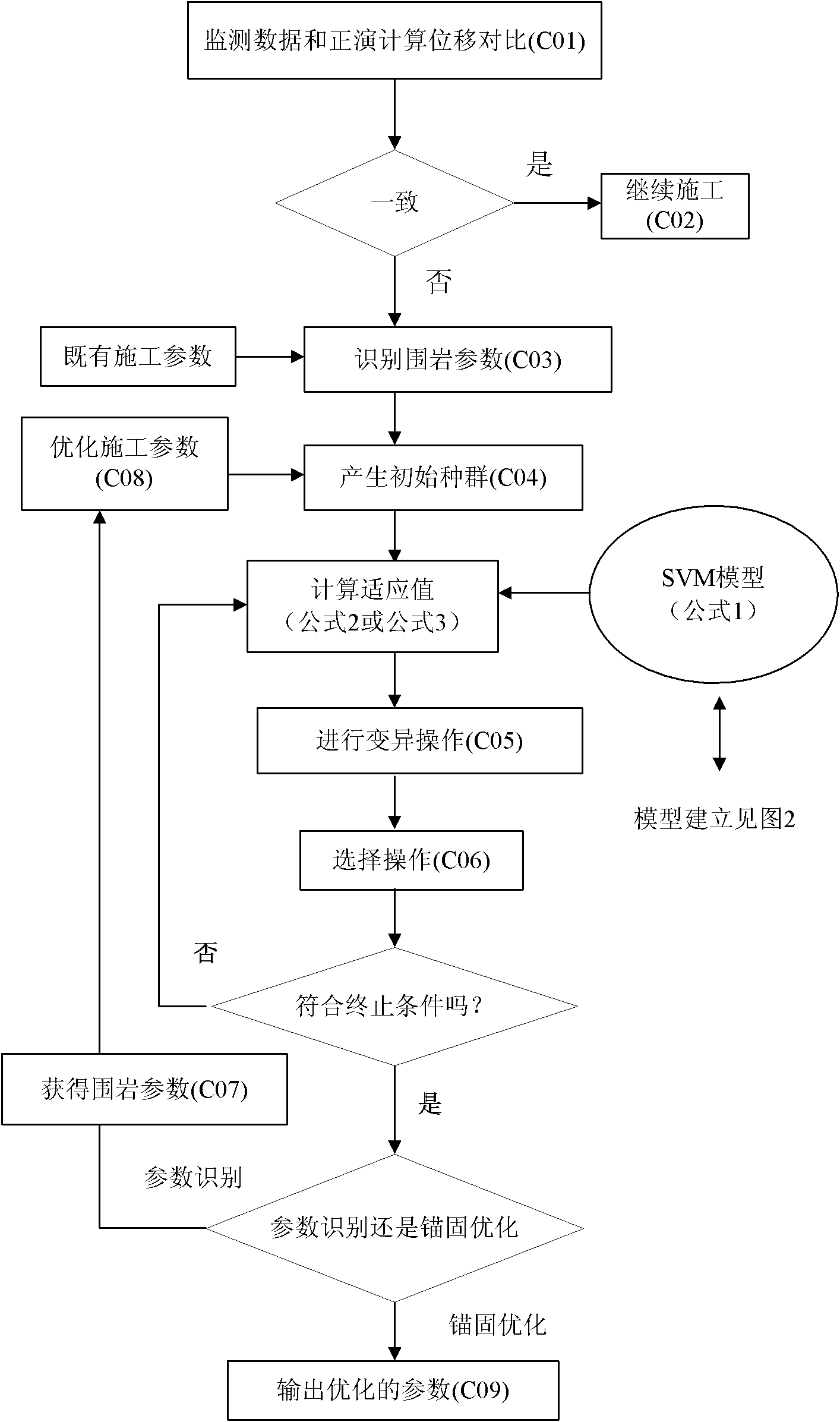

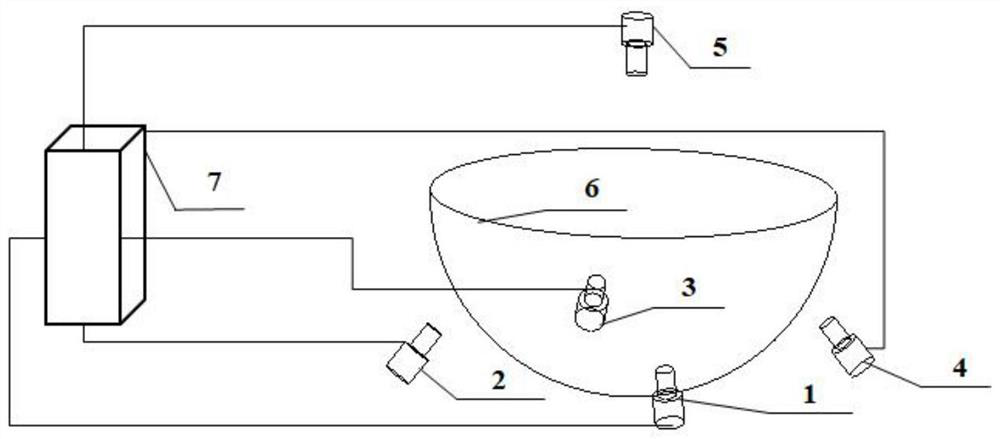

Quick feedback analyzing system in tunnel constructing process

InactiveCN102155231BOvercoming the blindness of pre-designDynamic information construction improvementMining devicesTunnelsEngineeringFeedback analysis

The invention discloses a quick feedback analyzing system in a tunnel constructing process. The system adopts a scheme: understanding currently adopted designing construction parameters; establishing a tunnel excavation three-dimensional finite element numerical grid calculation model; acquiring surrounding rock layering and convergent displacement monitoring information after a tunnel is excavated; establishing a non-linear support vector machine model; fixing an anchoring parameter according to the actual construction parameter, and optimally identifying rock mechanic parameters by adoptinga differential optimization algorithm; optimizing the construction parameter of an anchoring scheme by adopting a differential evolution algorithm; and optimizing the rock mechanic parameters by calling the differential evolution and optimization algorithms to further solve the construction parameter of the anchoring scheme, and outputting the construction parameter of the optimized anchoring scheme as a construction scheme through a computer display screen to guide the constructors to construct. The quick feedback analyzing system ensures that the monitoring information is used for optimizing the anchoring parameter while being used for identifying the surrounding rock parameters, so that the dynamic information construction is improved to a level of quantitative analysis.

Owner:DALIAN MARITIME UNIVERSITY

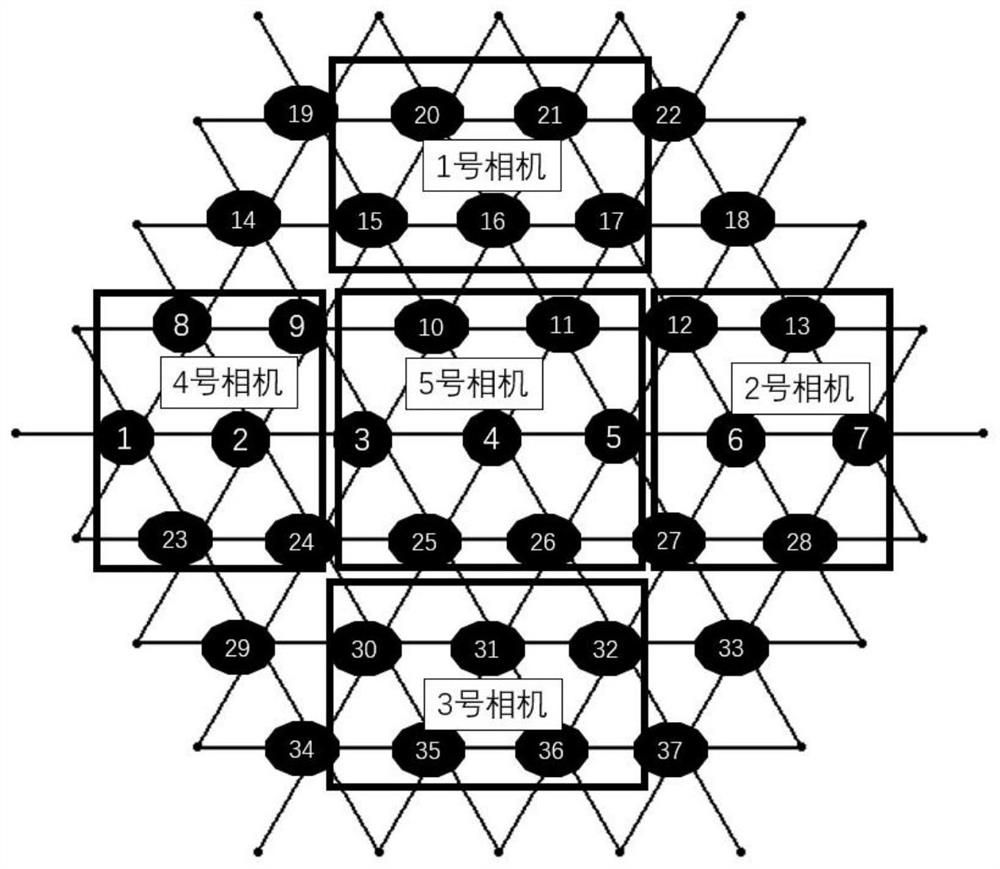

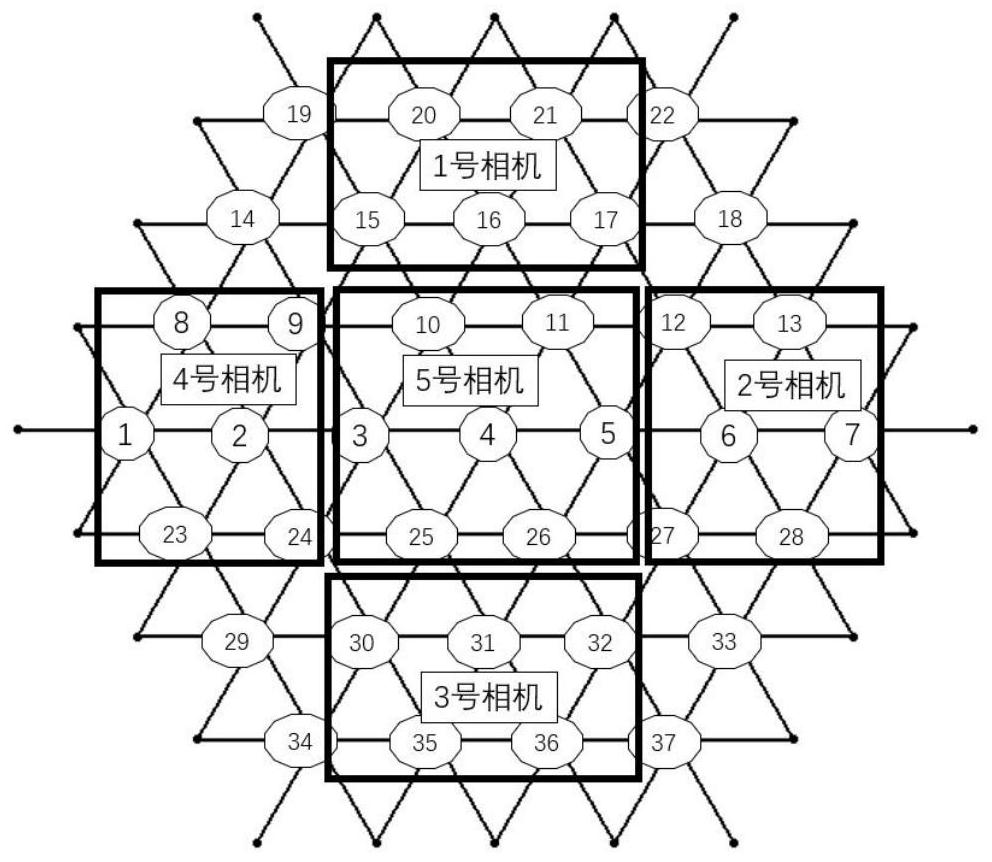

Visual positioning feedback method for cable net type chain nodes

PendingCN113920157AImprove the speed of 3D recognition and positioningSolve the slow calculationImage enhancementImage analysisImaging processingCable net

The invention discloses a visual positioning feedback method for cable net type chain nodes, which is applied to a system consisting of n industrial cameras and lenses, a visual industrial personal computer, a general personal computer and a motion servo actuating mechanism, and the method comprises the following steps: determining spatial three-dimensional coordinates of each chain node through paraboloid simulation; enabling the general control computer to send a signal to the motion servo execution system to control each motor to move to a target initial position; enabling the general control computer to send a signal to the image processing industrial control computer, controlling the n cameras to carry out image synchronous acquisition and processing on each chain node in the cable net surface, feeding back the calculated spatial three-dimensional coordinates of each node to the general control computer, enabling the general control machine to compare the coordinate spatial position of each node fed back visually with a theoretical value, and further sending an error compensation amount to the motion servo execution mechanism for adjustment, and after multiple times of repetition, enabling each node in the cable net surface to reach a specified theoretical position, so a cable net paraboloid meeting requirements is formed.

Owner:HEFEI INSTITUTES OF PHYSICAL SCIENCE - CHINESE ACAD OF SCI