Patents

Literature

50results about How to "Expensive to operate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

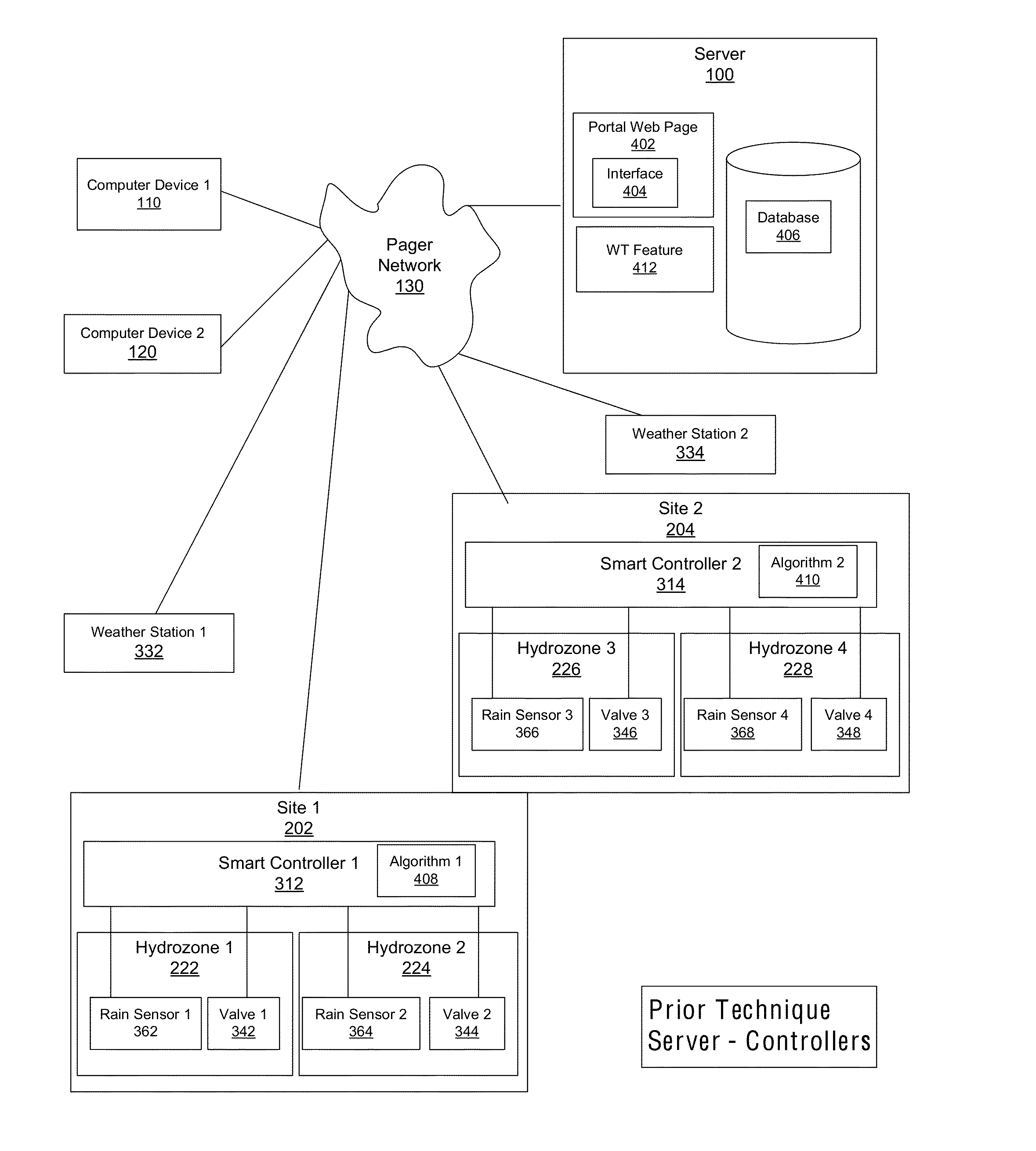

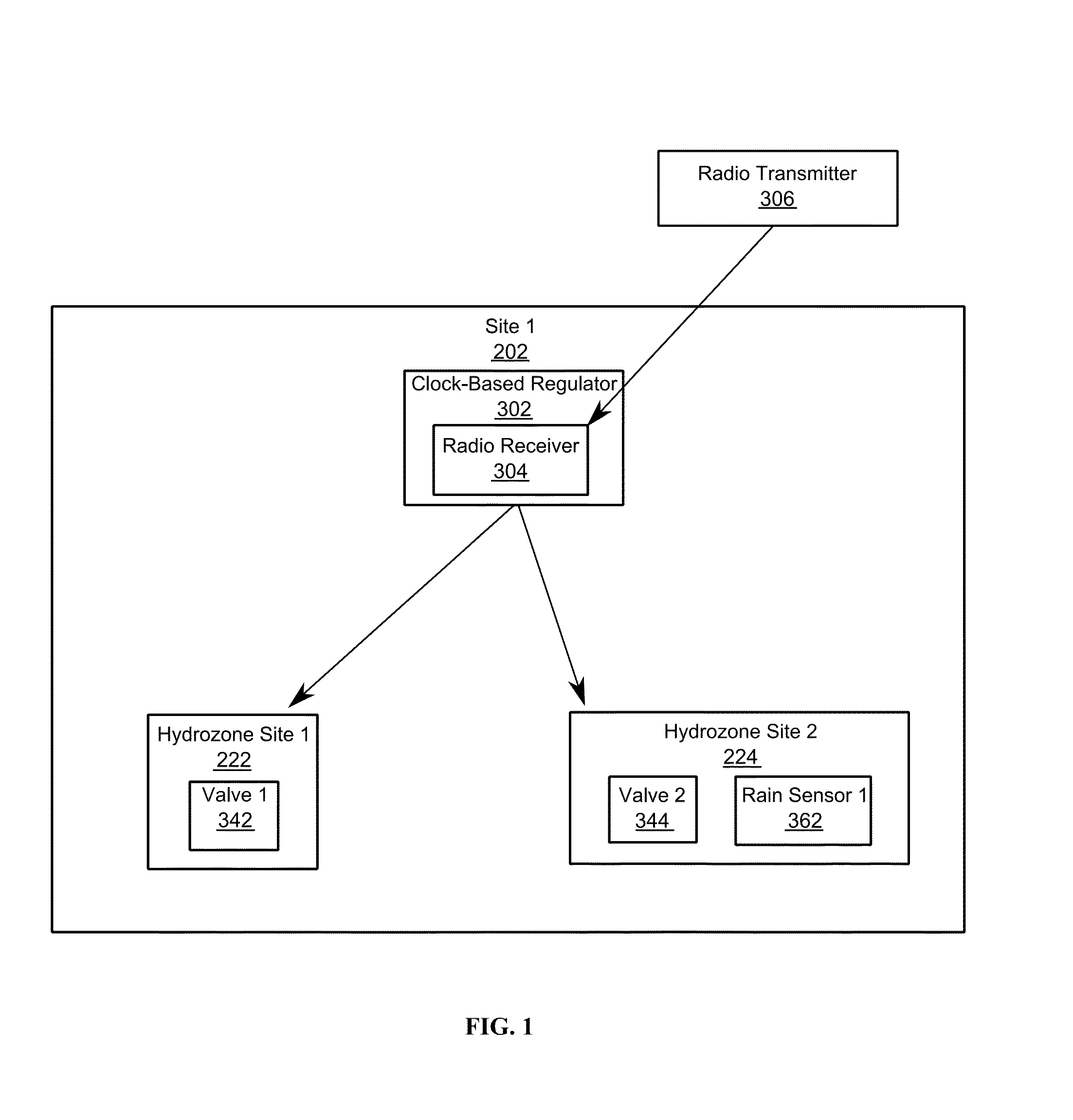

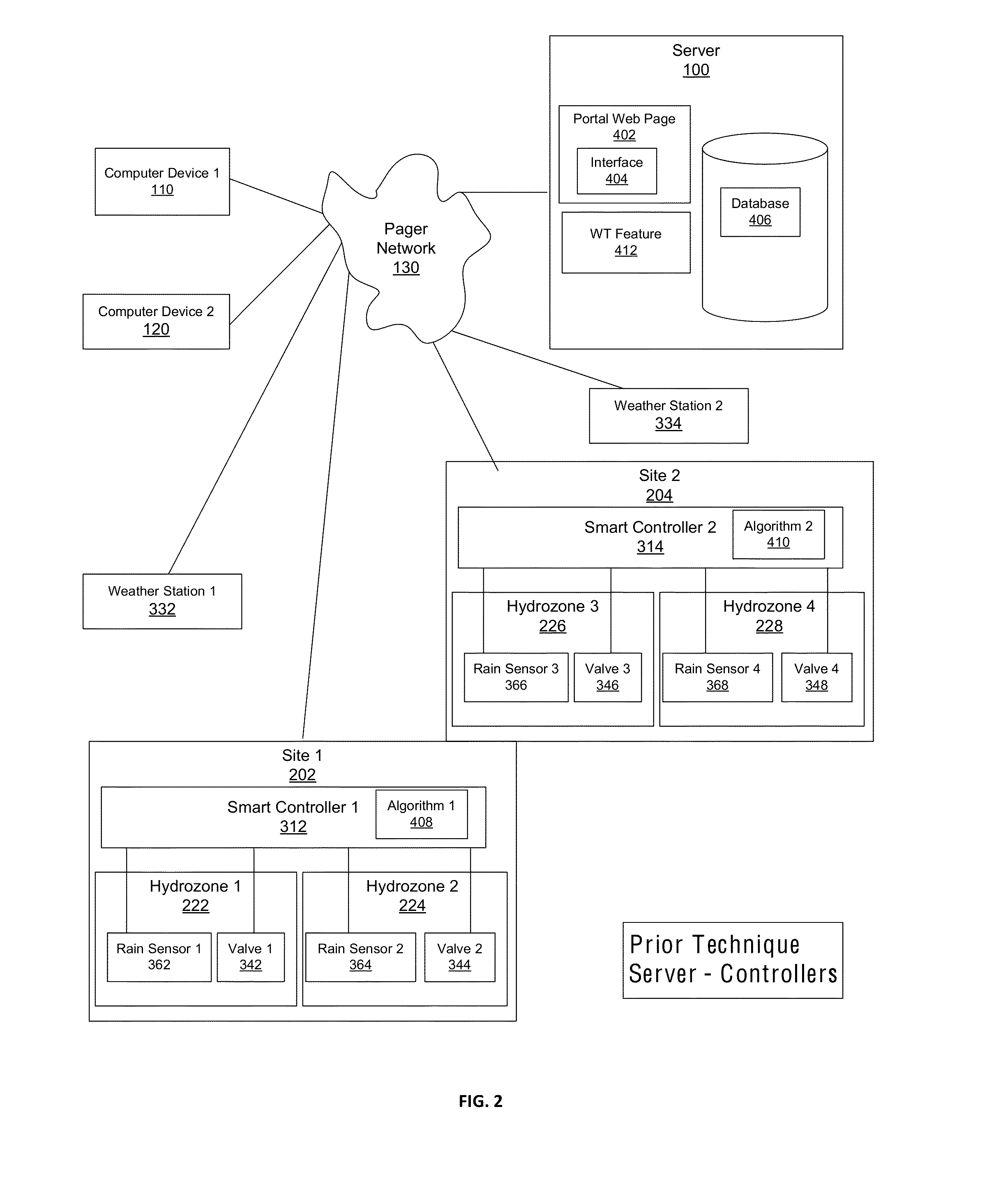

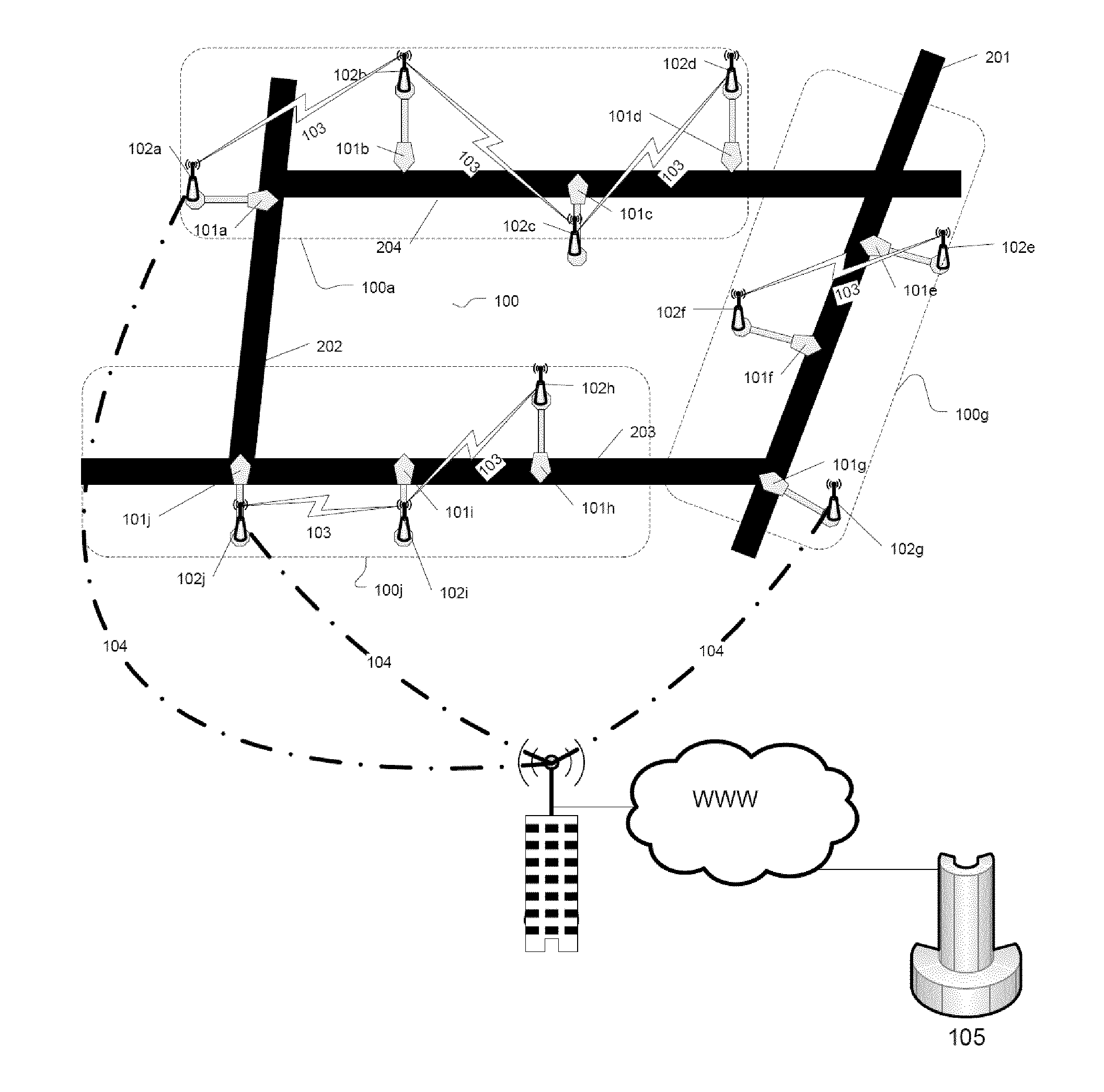

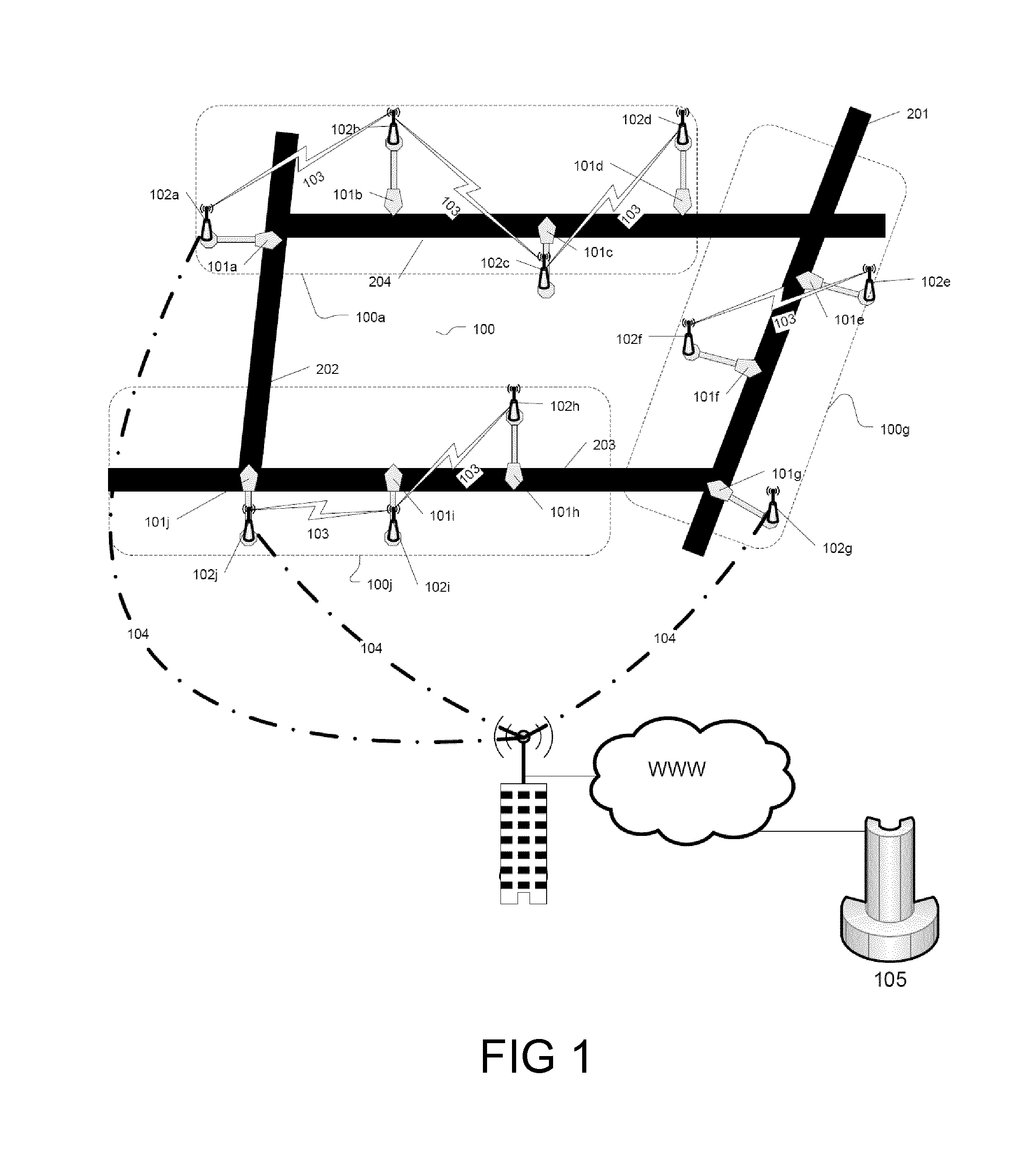

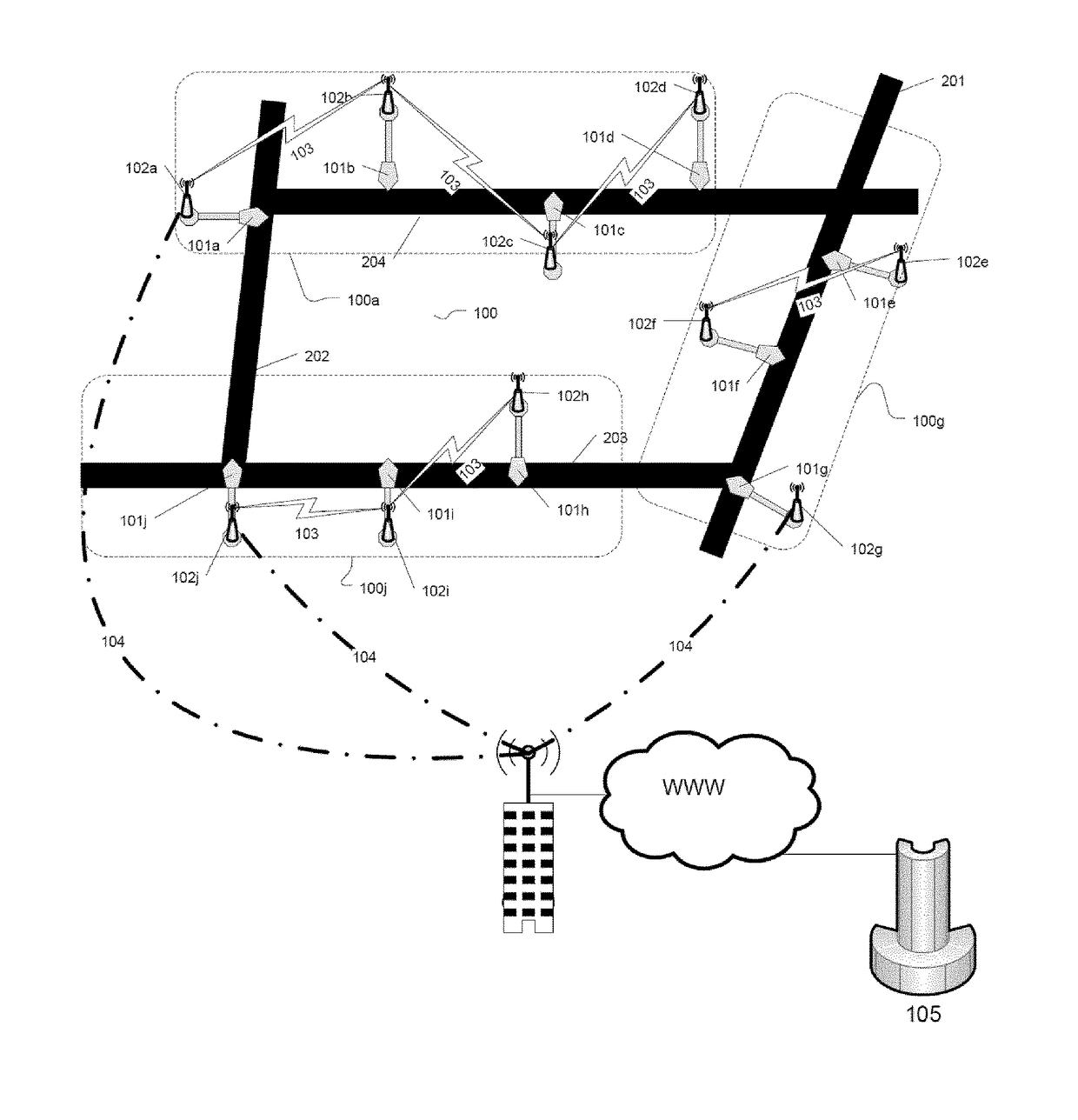

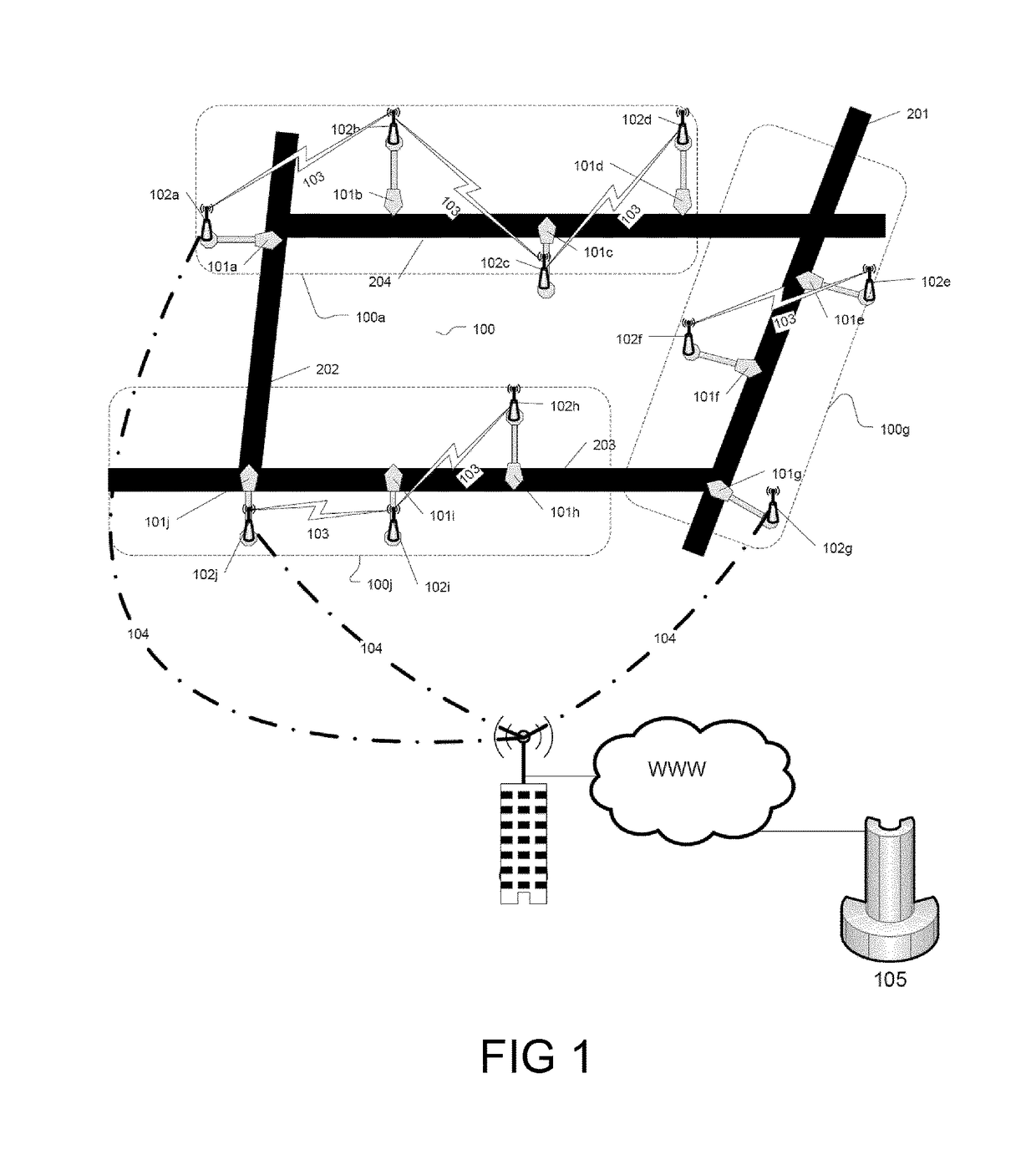

System and method for automated, range-based irrigation

InactiveUS20140236868A1Efficient modificationEfficient irrigationData processing applicationsElectric devicesDecision controlMonitoring and control

A centralized irrigation system provides decision-making or non-decision-making controllers in combination with a client server architecture that employs range-based irrigation algorithms for monitoring and control. Range-based control strategies determine a total volumetric water holding capacity for a volume of soil and a range of desirable soil moisture in a root zone, and compare a calculated root zone soil moisture to that range in order to determine the volume of water to be applied during an irrigation event. The system permits a shared-savings business model where the vendor provides a system and the customer only pays the vendor a portion of the savings obtained by using the system.

Owner:BANYAN WATER

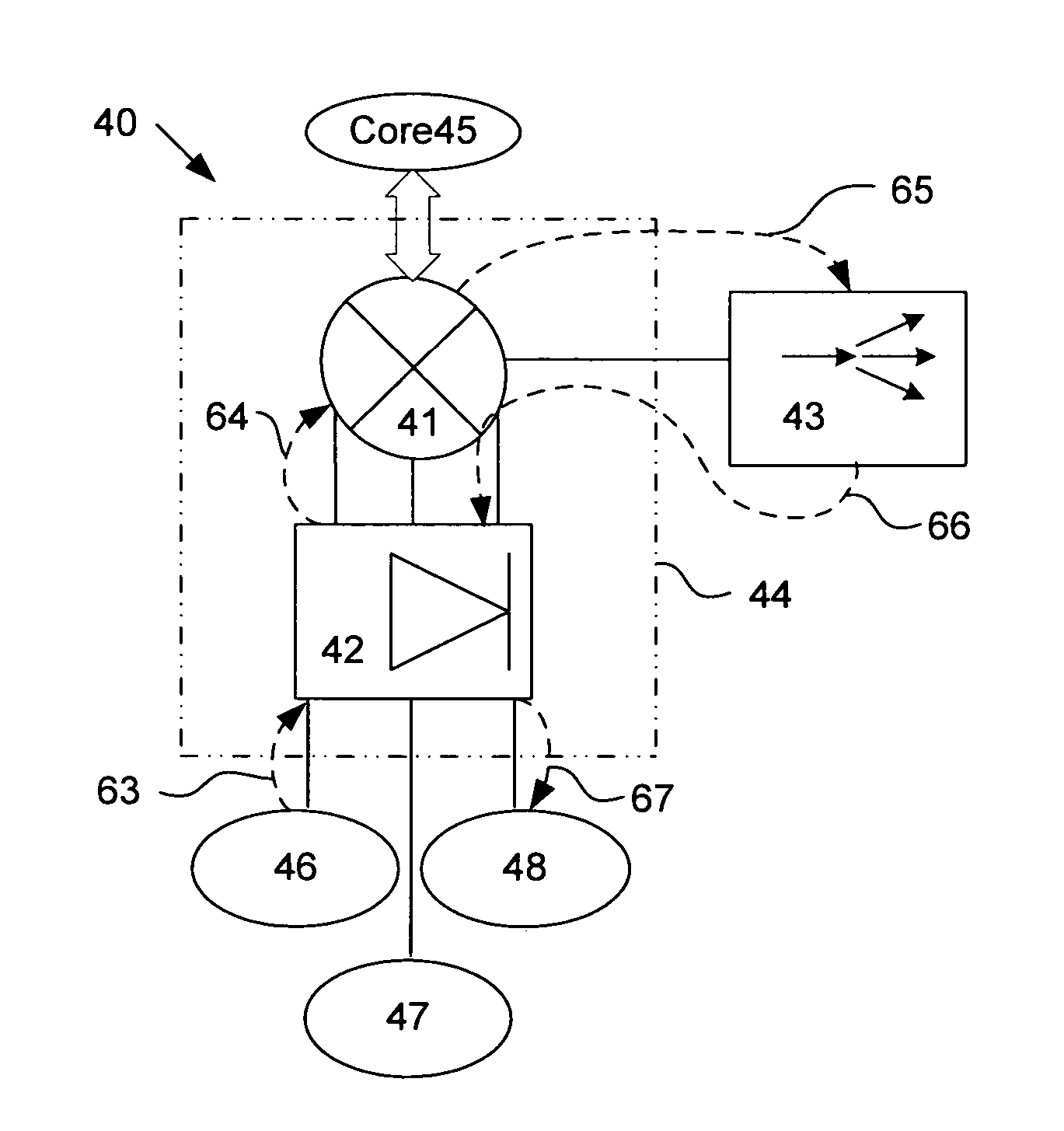

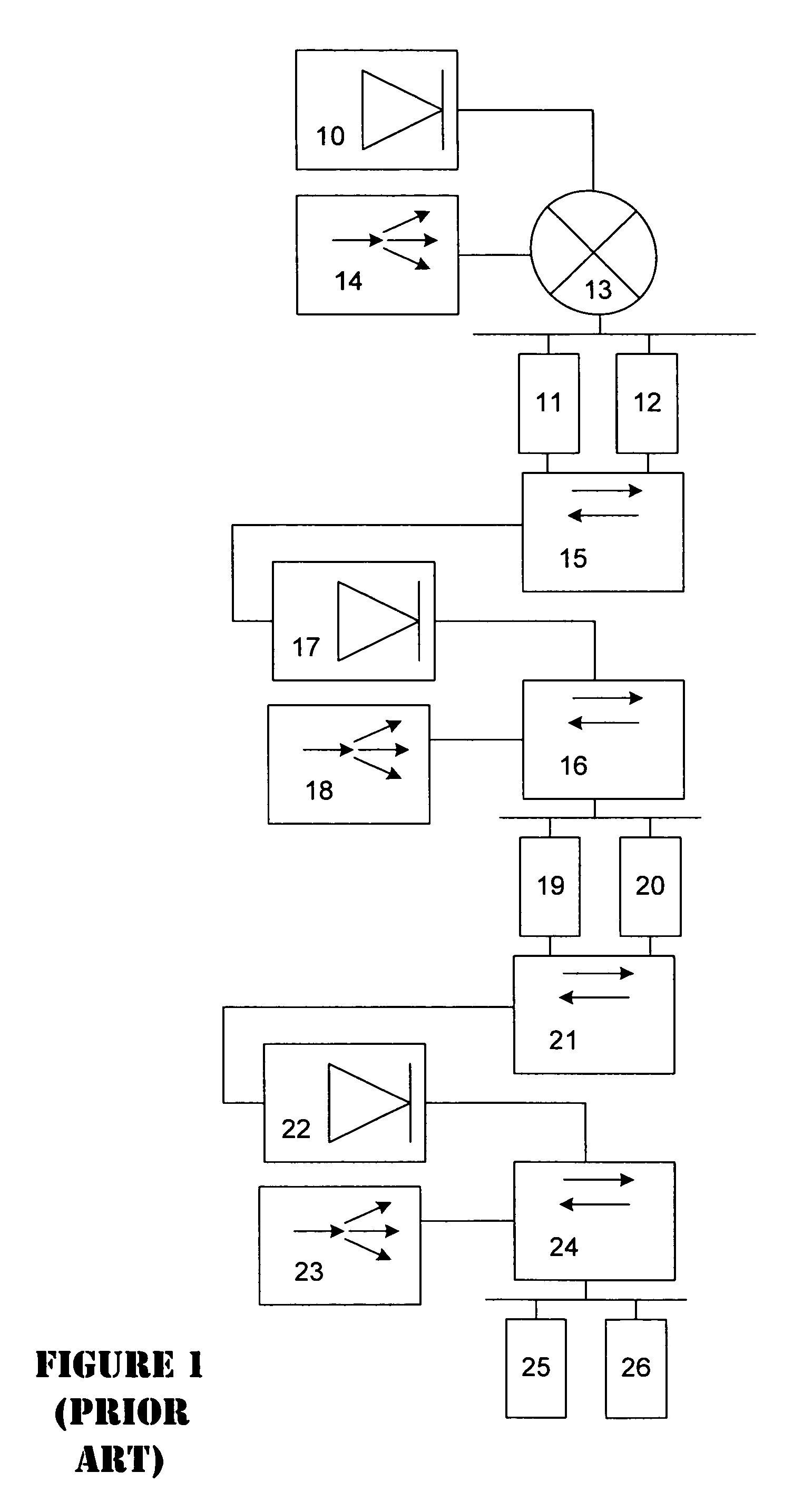

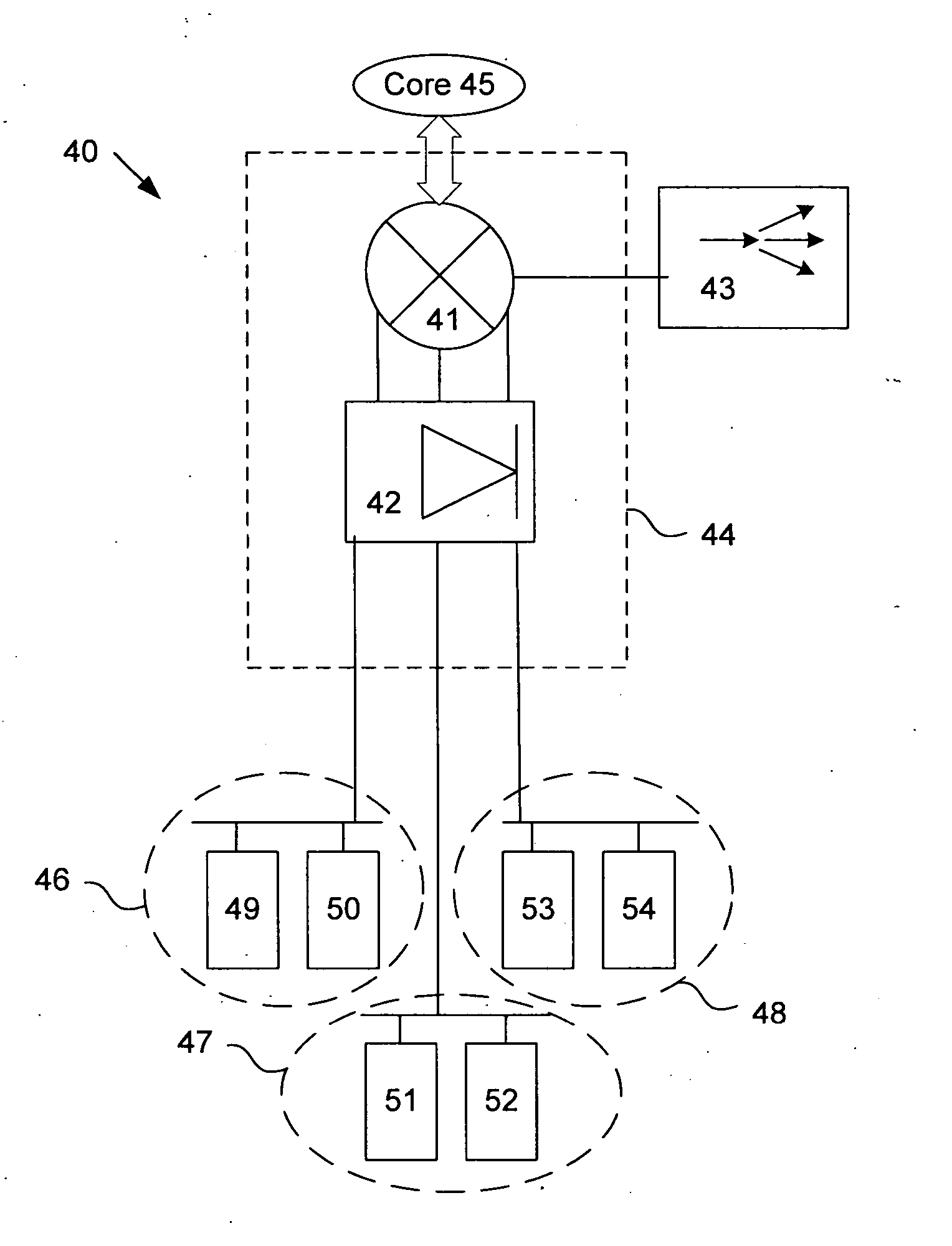

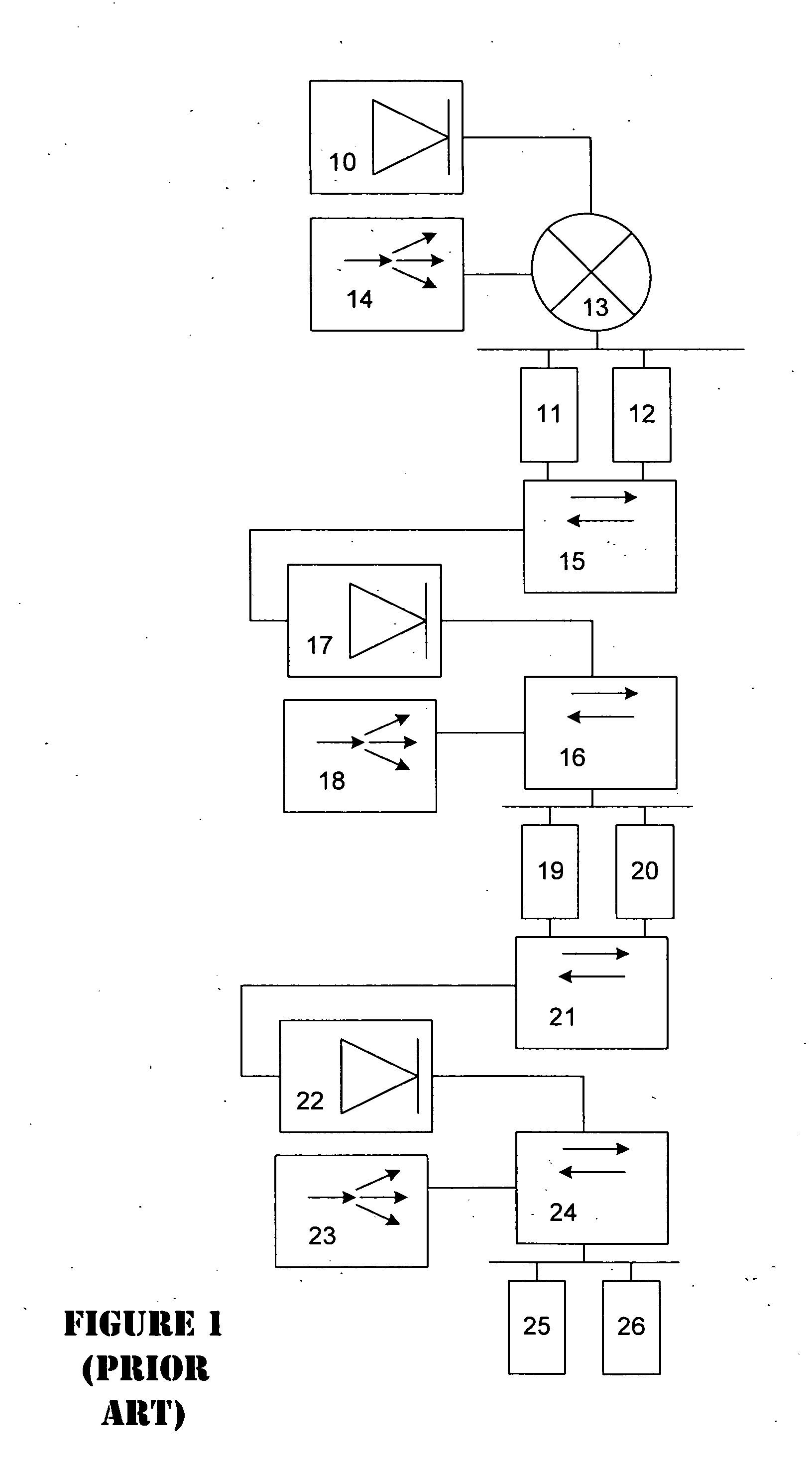

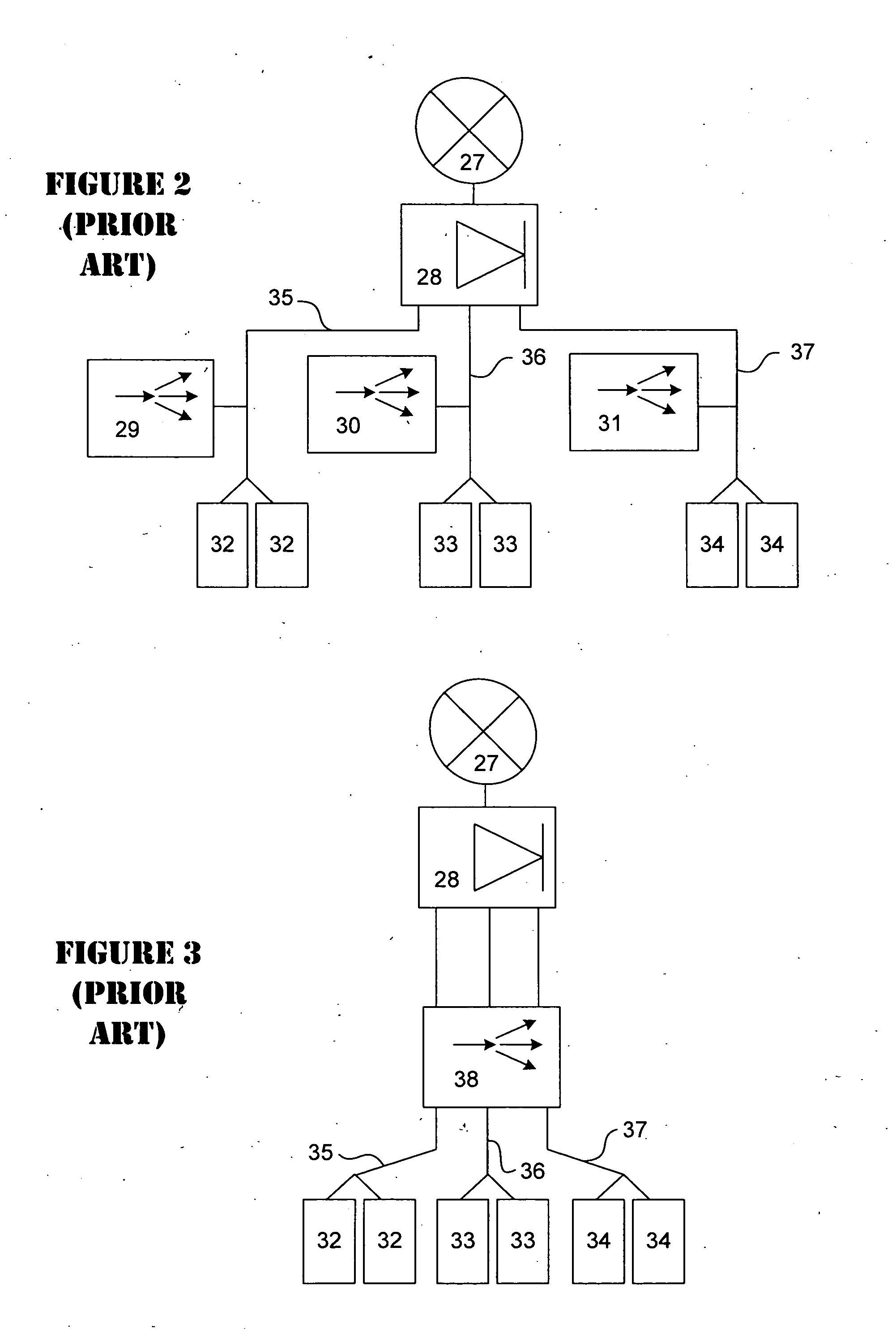

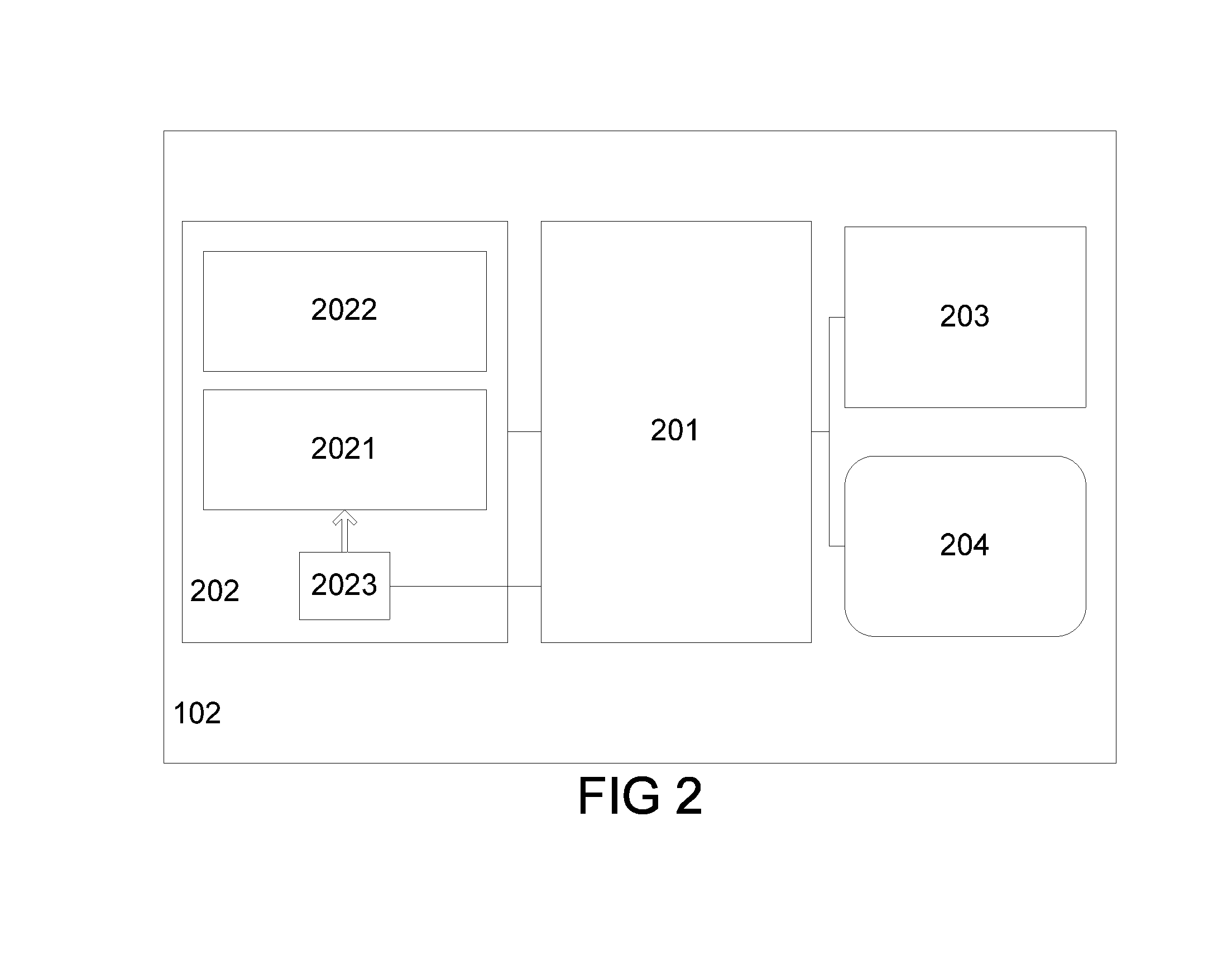

One arm data center topology with layer 4 and layer 7 services

ActiveUS7571470B2Expensive to operateExpensive to setComputer security arrangementsMultiple digital computer combinationsTraffic capacityData center

A one-arm data center topology routes traffic between internal sub-nets and between a sub-net and an outside network through a common chain of services. The data center topology employs layer 4 services on a common chassis or platform to provide routing and firewall services while reducing the number of devices necessary to implement the data center and simplifying configuration. Load balancing is provided by a load balancing device. In the one-arm topology, policy based routing or client network address translations or NAT pushes traffic to the CSM.

Owner:CISCO TECH INC

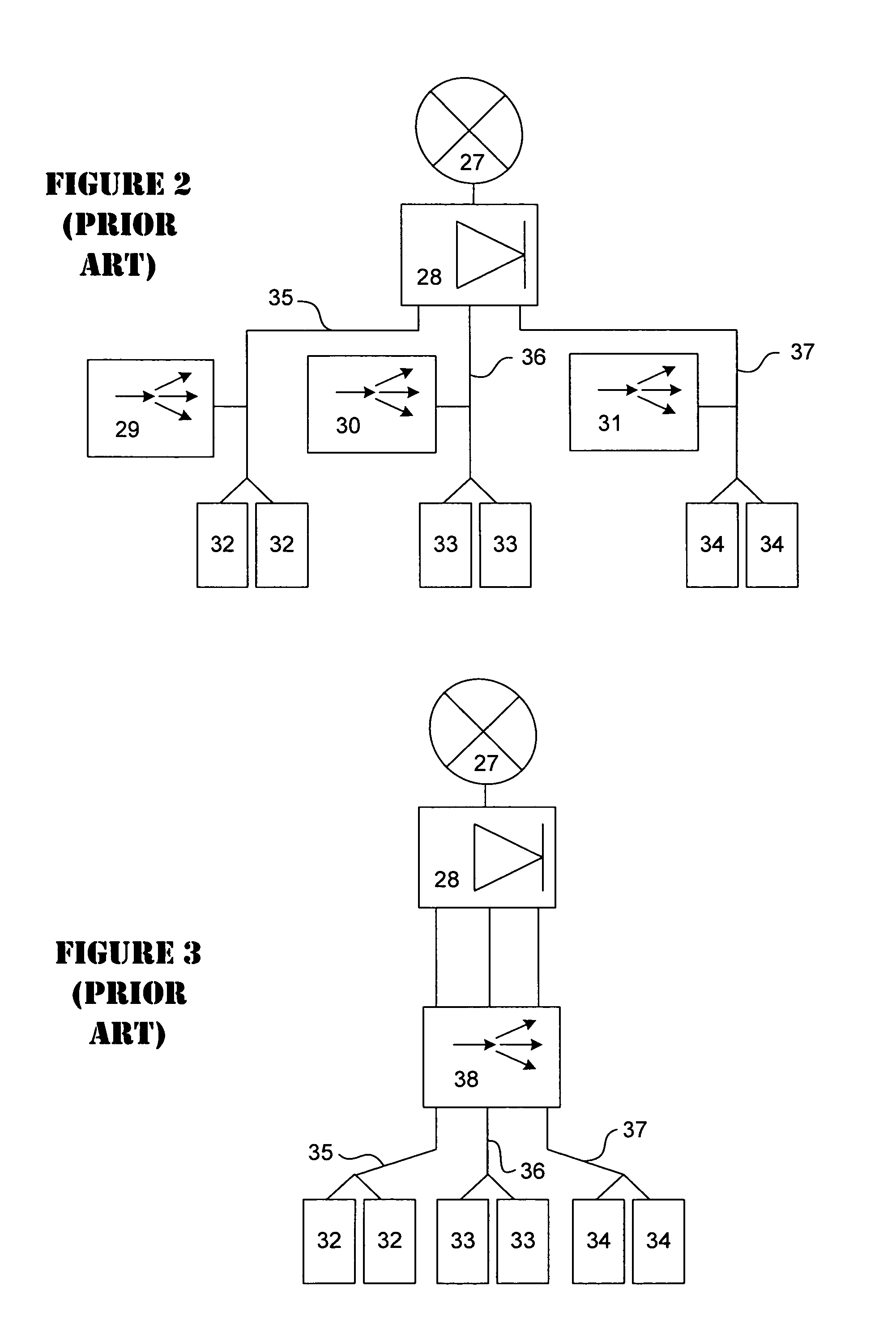

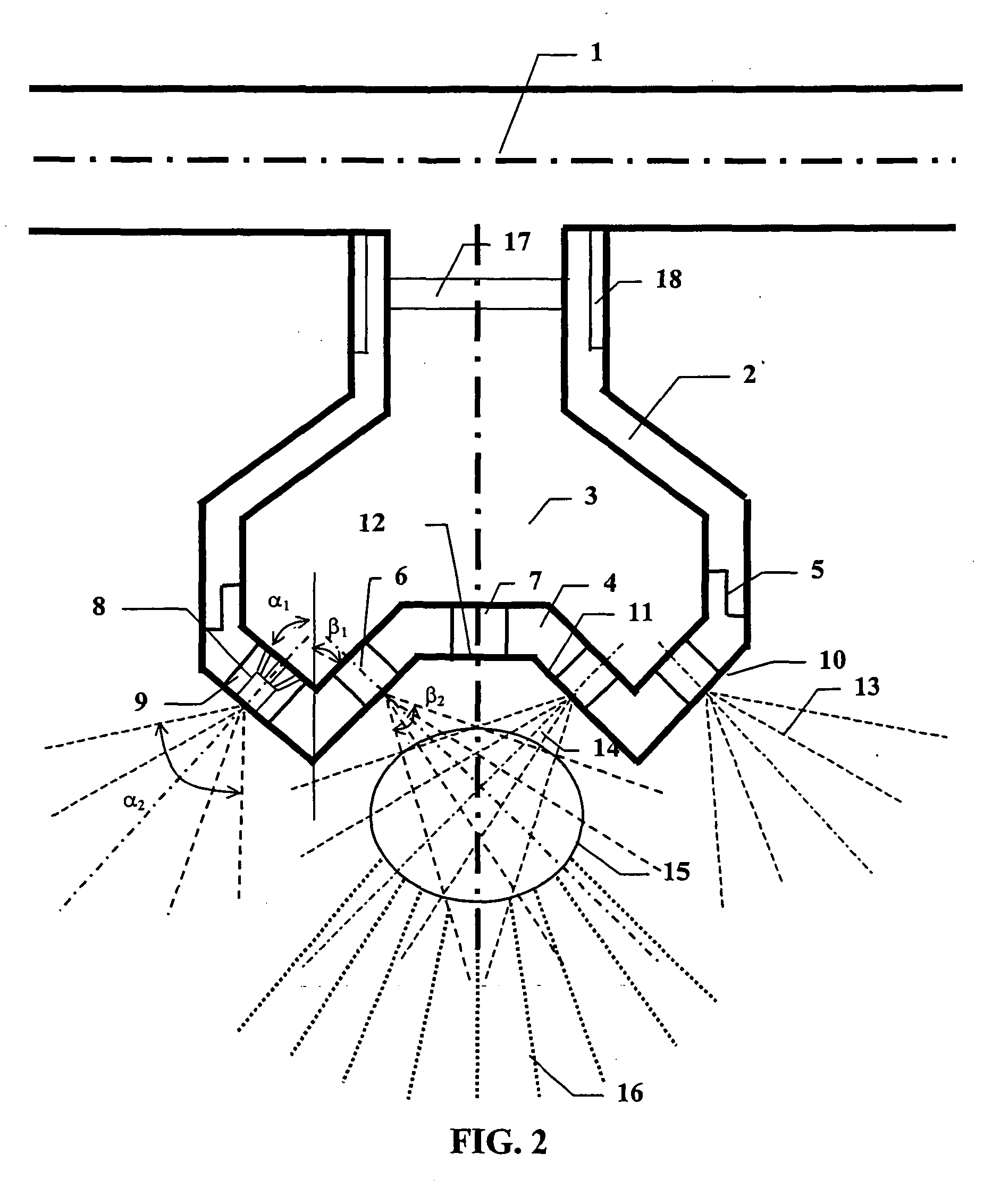

Spray head and nozzle arrangement for fire suppression

InactiveUS20050011652A1Increase heat transfer rateEnhanced inhibitory effectBurnersSpray nozzlesSpray nozzleEngineering

A water spray head for spraying water spray mist in a fire prevention system, includes a water supply duct; a spray head upper body; a fluid chamber; and a “w” shaped bottom, on which at least two rings of nozzles are installed. The water spray head has a body with a “w” shaped bottom, a chamber and two rings of liquid mist nozzles on the slant walls of the “w” shaped bottom. The liquid mist sprays from the nozzles at the inner ring may collide with each other directly or tangentially to form finer liquid droplets and a more uniformly distributed “solid cone” water spray. The water mist formation of the individual nozzle is also designed to be based on the collision of liquid streams from multiple small flow channels in a large flow channel, thereby forming even finer droplets.

Owner:AGENCY FOR SCI TECH & RES

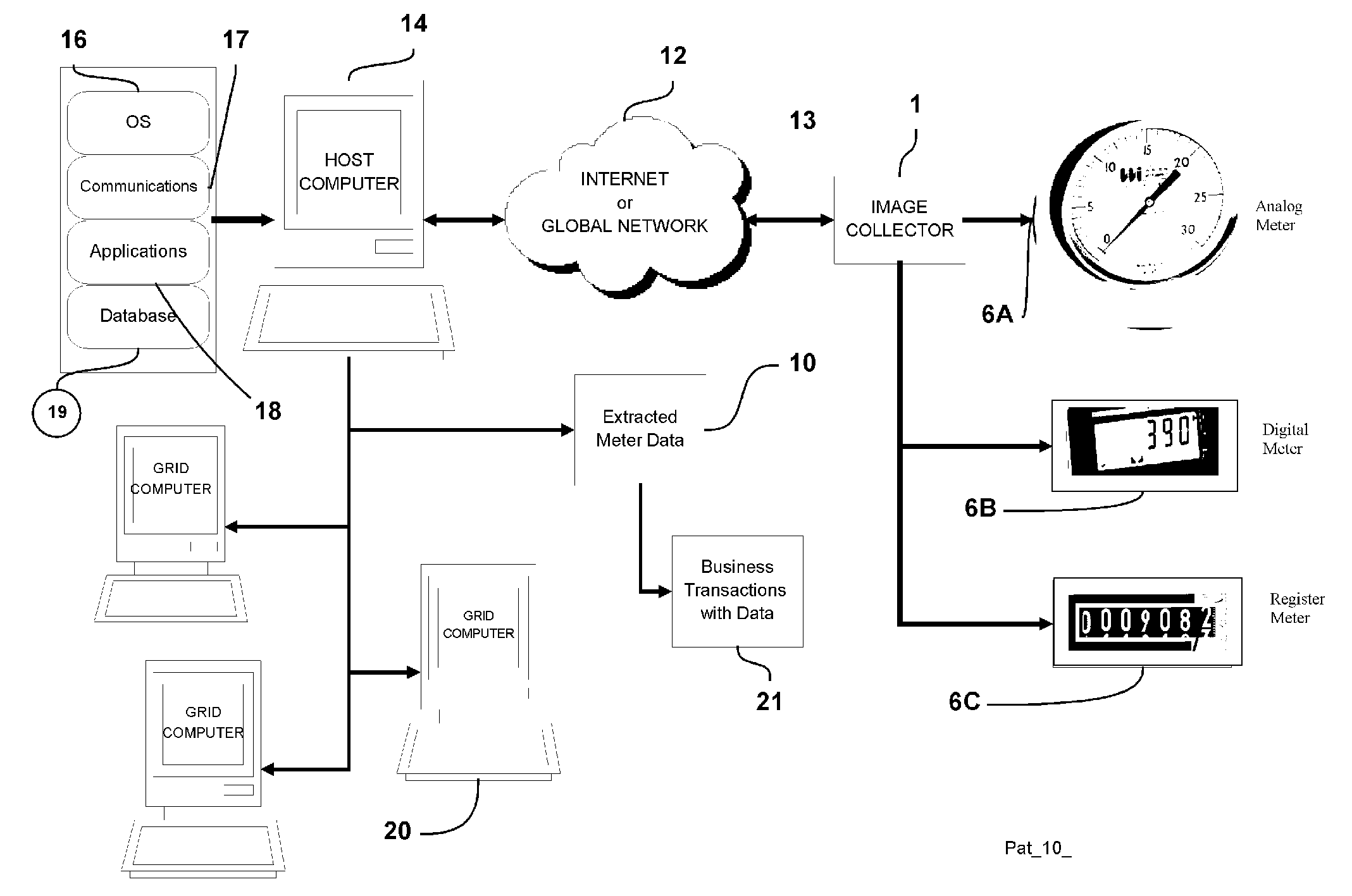

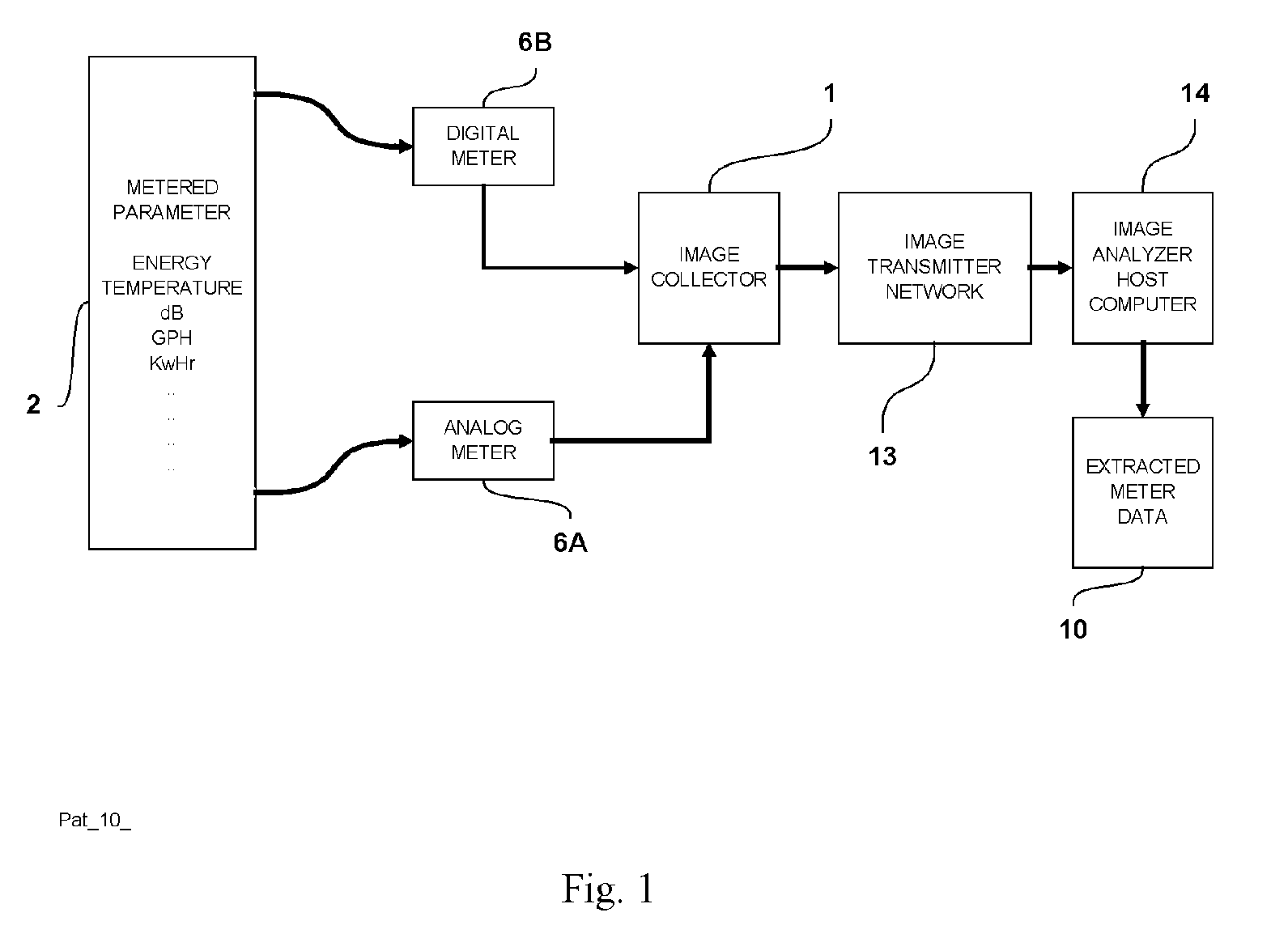

Remote meter reading using transmitted visual graphics.

InactiveUS20060036967A1Reduce operating costsImprove abilitiesTariff metering apparatusFluid pressure measurementGraphicsDisplay device

A technique for remote meter reading (RMR) of a plurality of meters uses visual image devices coupled to pattern recognition technologies to allow unattended meters, gages, registers, screens, and other similar display equipment to communicate their output data without human intervention to a central source and to provide this data on a global network. Historically, meters, gages and similar devices were either read by the human eye or by data-loggers and controllers which transmitted these data to a host system. With this invention the display devices can be read autonomously by the method described herein and a visual graphic of the meter face is transmitted to a host which then recognizes the data value embedded in the visual. Substantial increases in efficiency; performance and economics can be achieved with this invention which introduces the concept of “visualmetering”.

Owner:CRICHLOW HENRY B

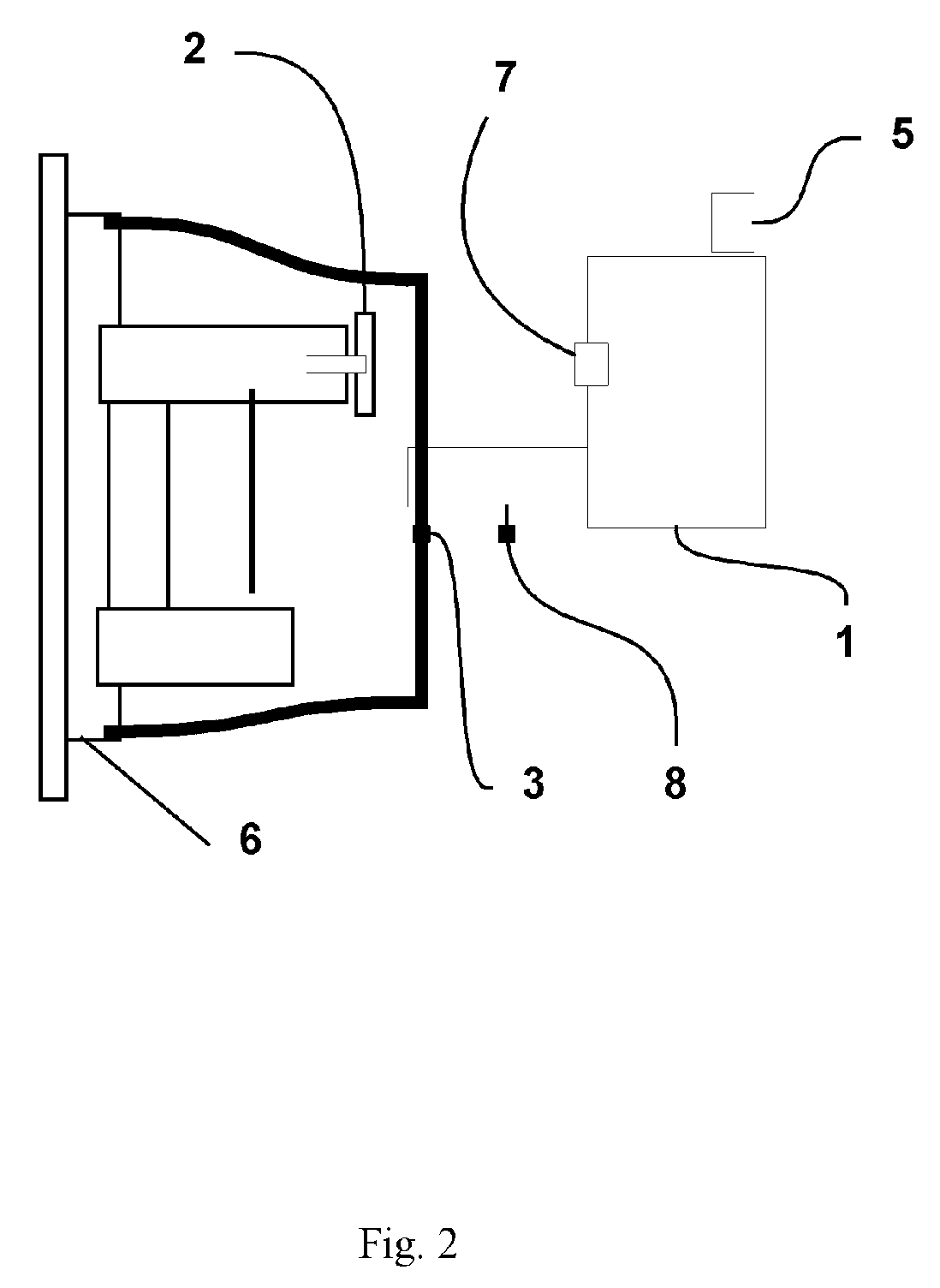

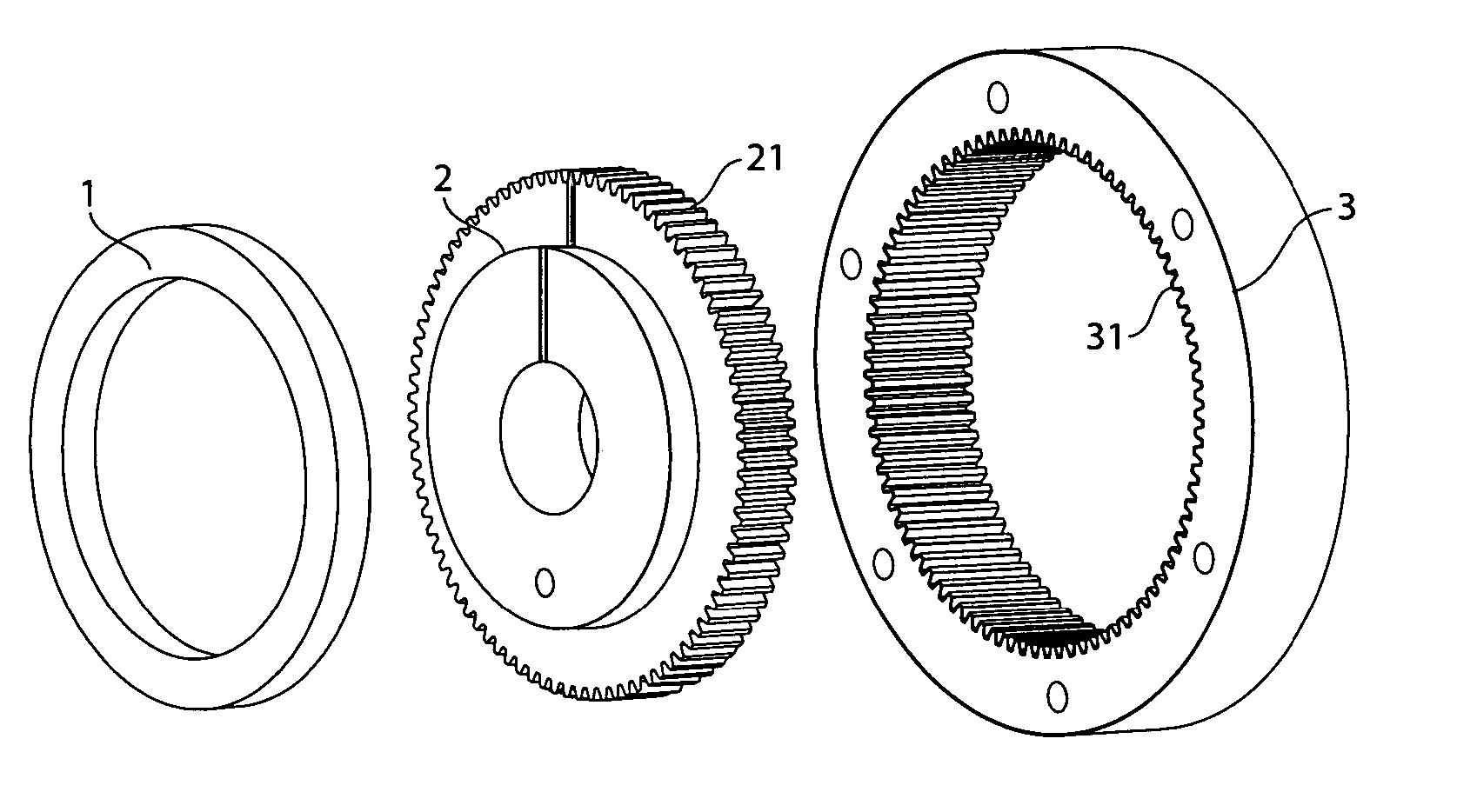

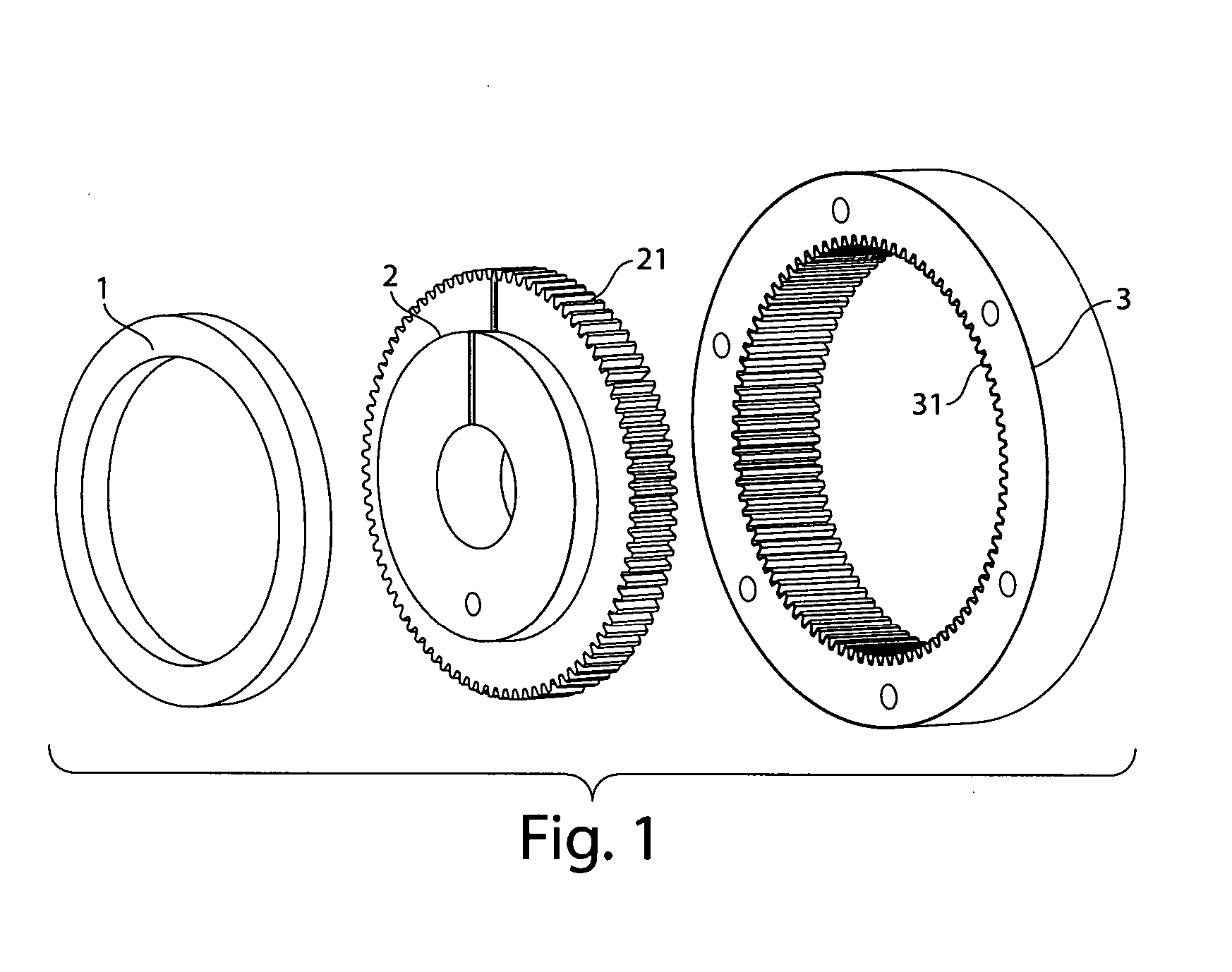

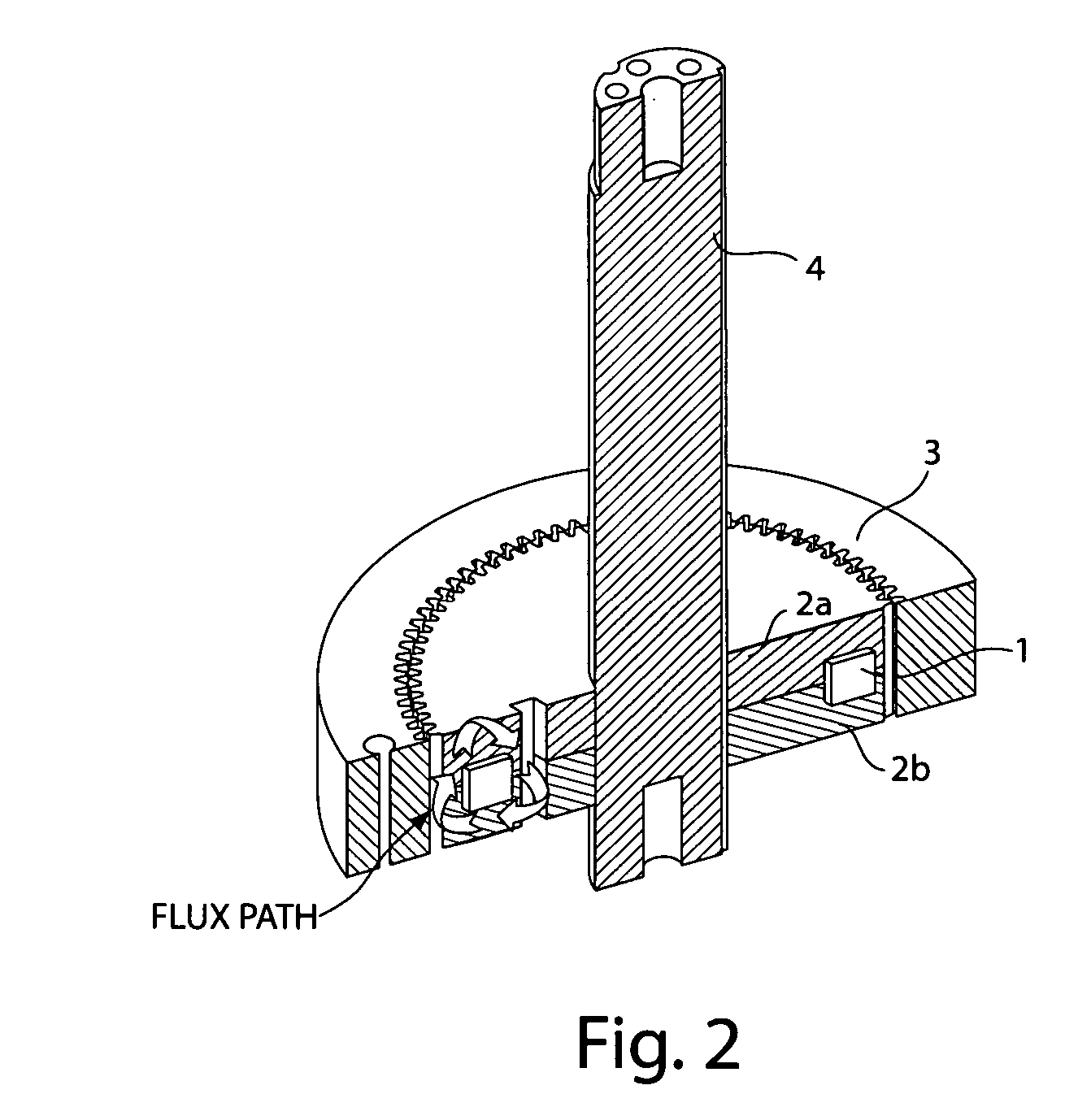

Transverse flux switched reluctance motor and control methods

InactiveUS20060091755A1Eliminate end turn lossHigh densitySynchronous generatorsElectronic commutation motor controlTransverse fluxElectric machine

A variable reluctance motor and methods for control. The motor may include N motor phases, where N equals three or more. Each motor phase may include a coil to generate a magnetic flux, a stator and a rotor. A flux-carrying element for the rotor and / or stator may be made entirely of SMC. The stators and rotors of the N motor phases may be arranged relative to each other so that when the stator and rotor teeth of a selected phase are aligned, the stator and rotor teeth in each of the other motor phases are offset from each other, e.g., by an integer multiple of 1 / N of a pitch of the stator or rotor teeth. A fill factor of the coil relative to the space in which it is housed may be at least 60%, and up to 90% or more. The stator and rotor flux-carrying elements together may include at most three separable parts.

Owner:PRECISE AUTOMATION

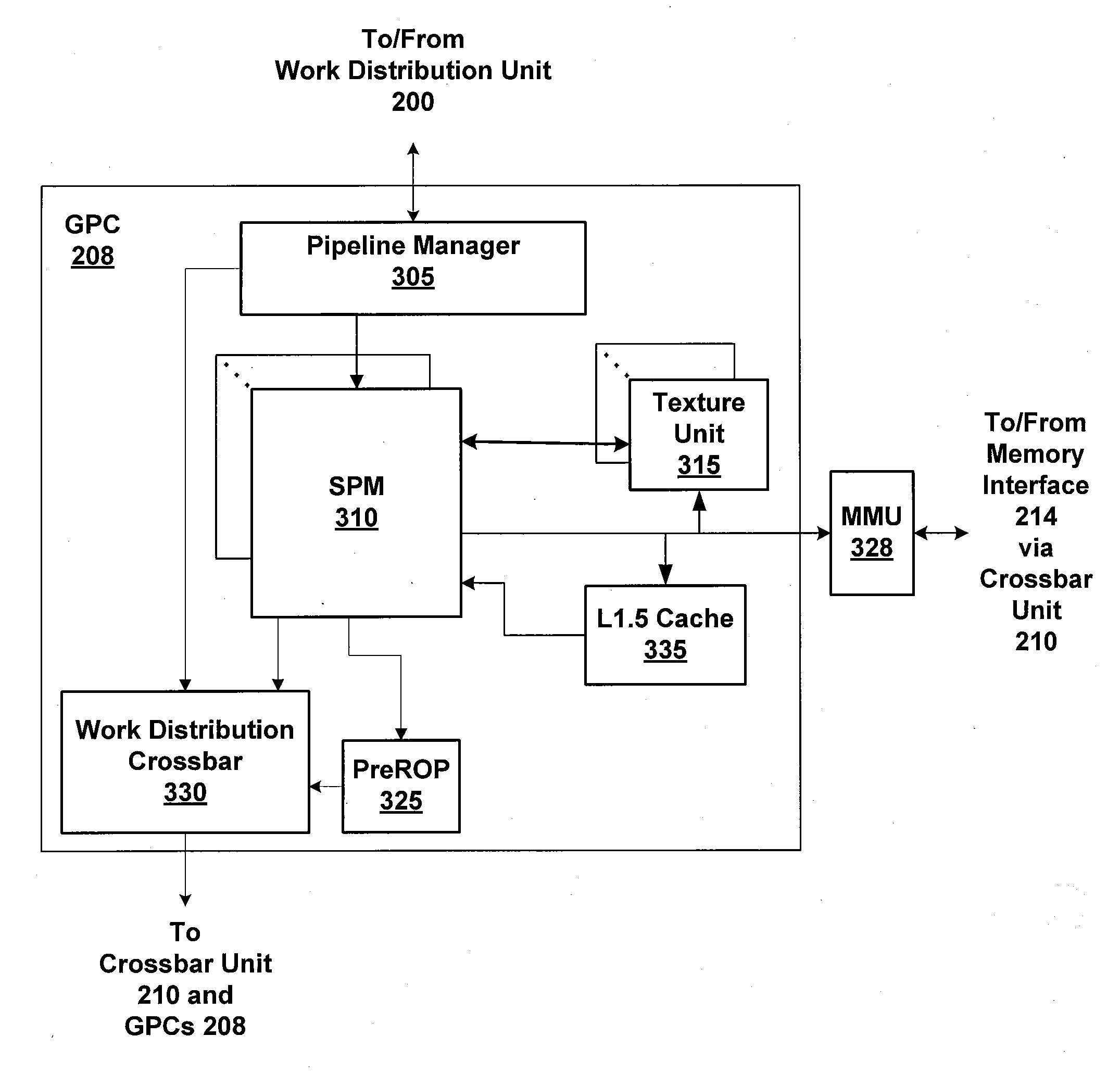

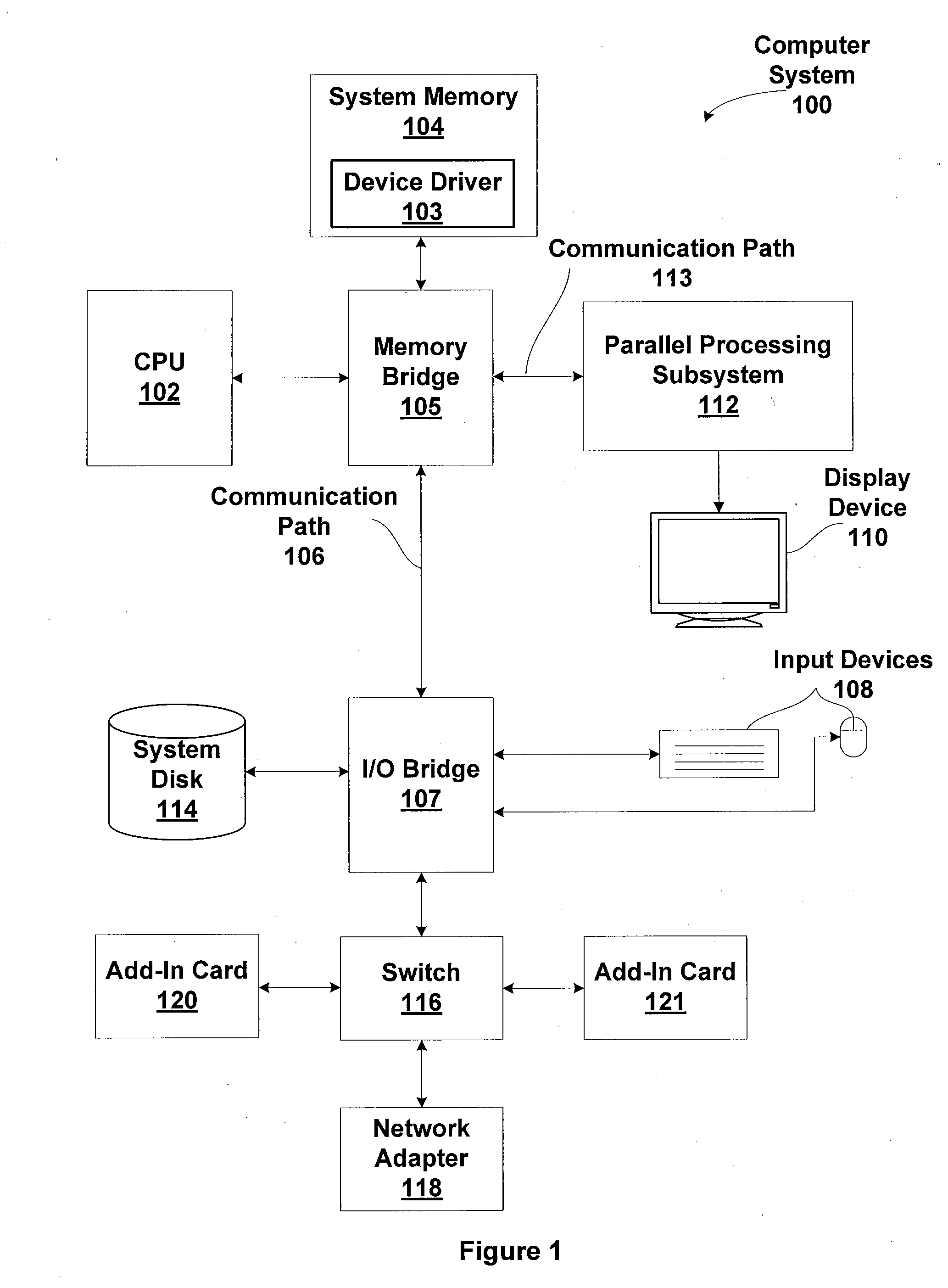

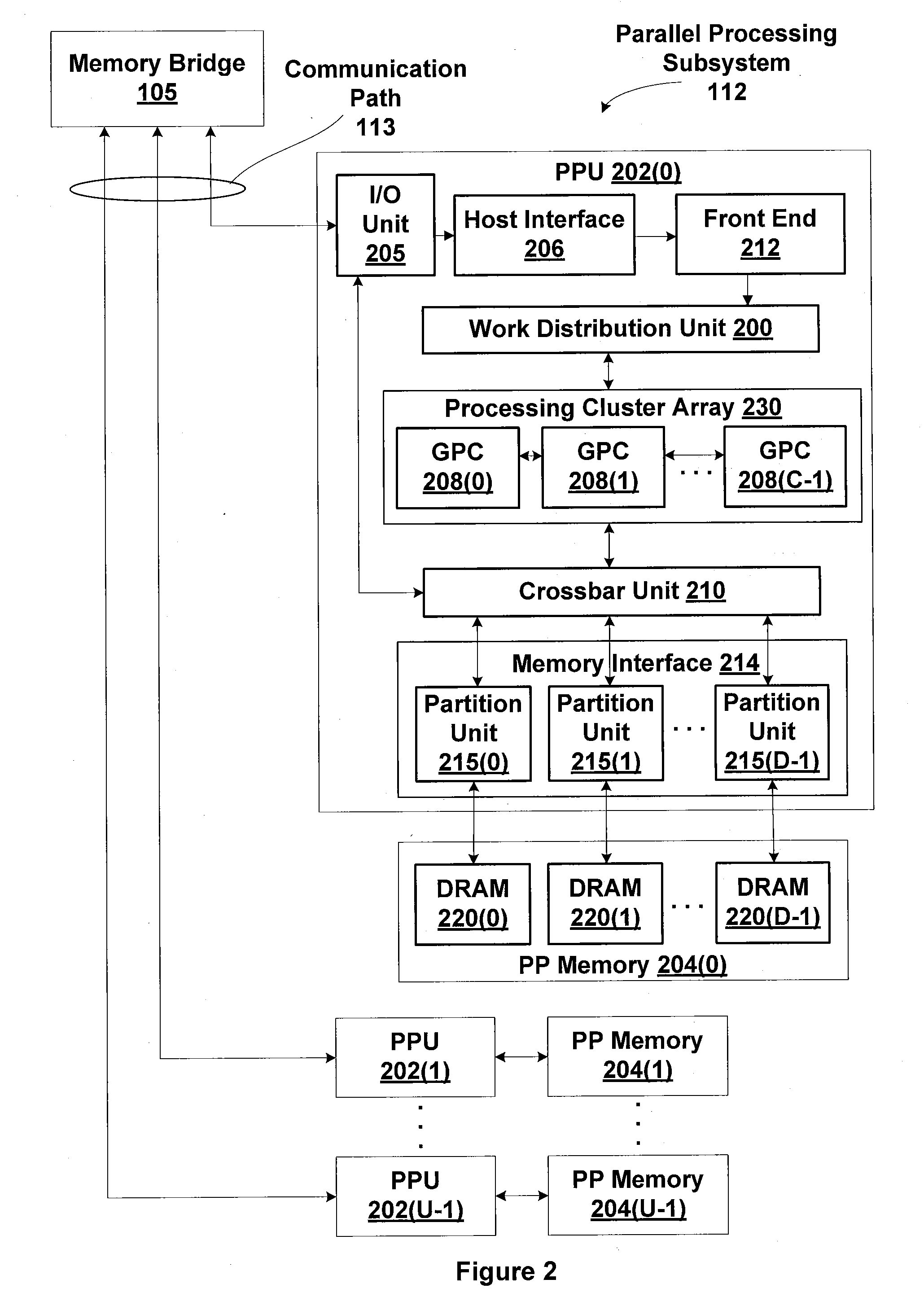

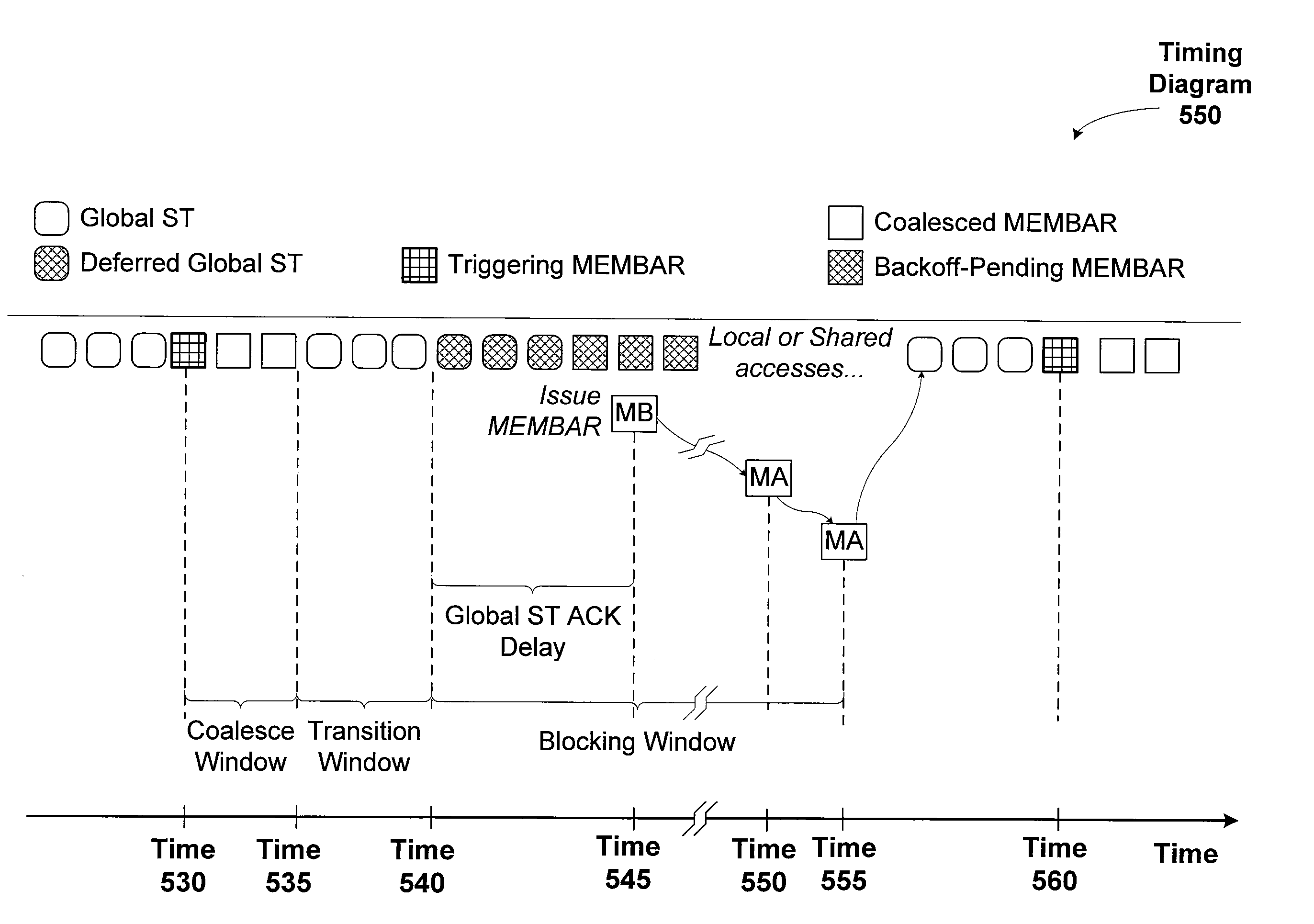

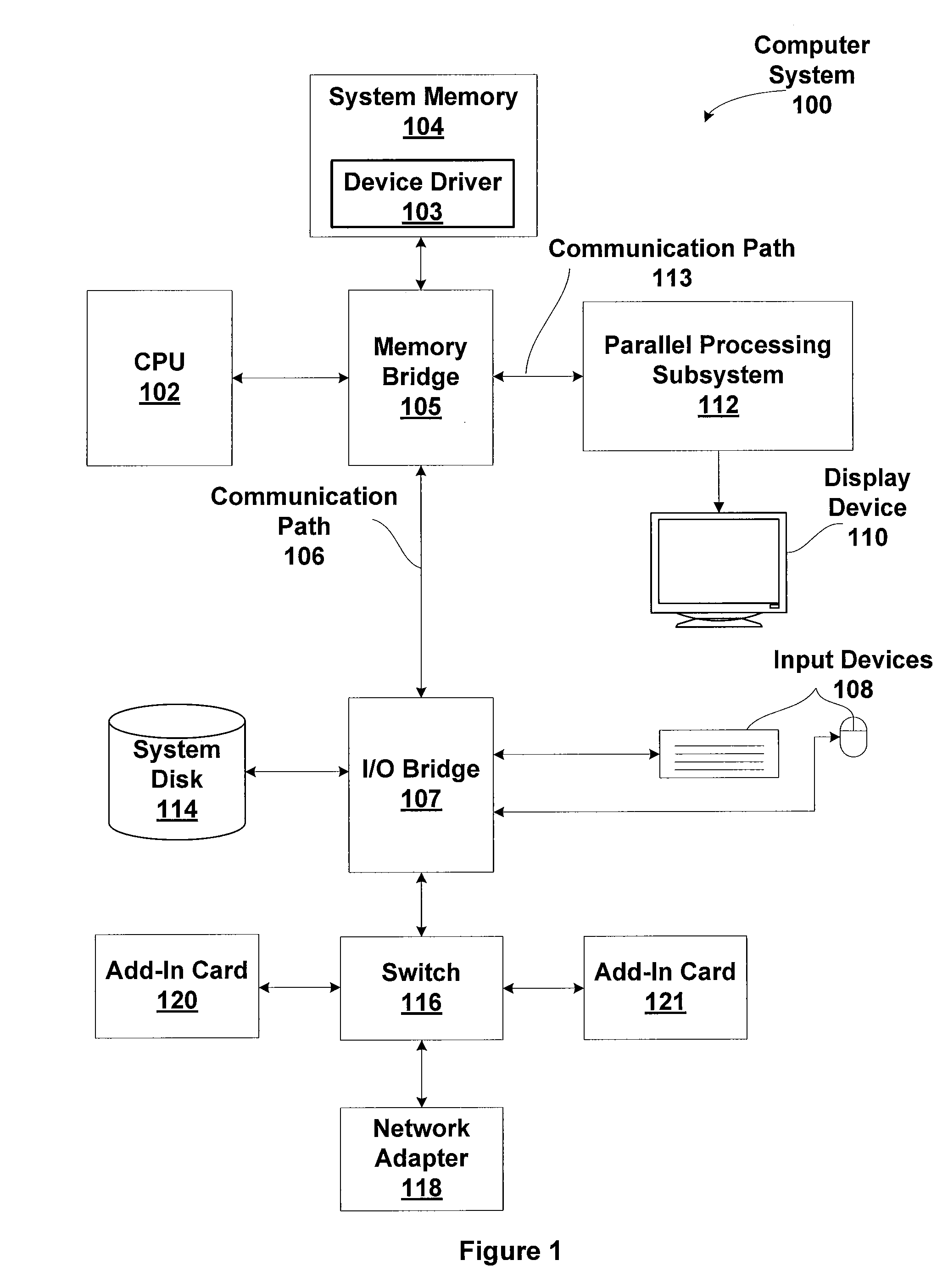

Coalescing memory barrier operations across multiple parallel threads

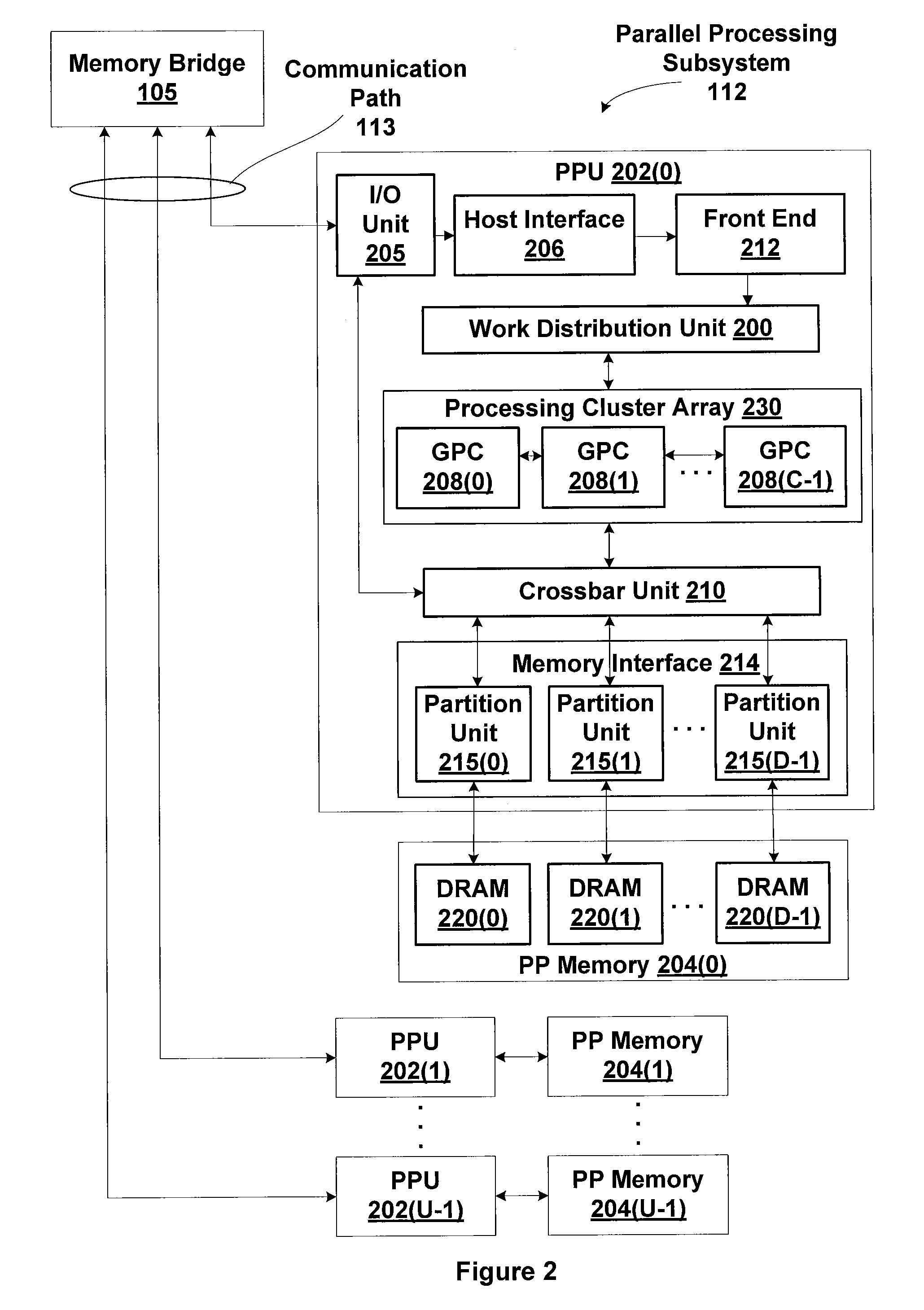

ActiveUS20110078692A1Expensive to operateReduce the impactMultiprogramming arrangementsMemory systemsParallel computingSystem level

One embodiment of the present invention sets forth a technique for coalescing memory barrier operations across multiple parallel threads. Memory barrier requests from a given parallel thread processing unit are coalesced to reduce the impact to the rest of the system. Additionally, memory barrier requests may specify a level of a set of threads with respect to which the memory transactions are committed. For example, a first type of memory barrier instruction may commit the memory transactions to a level of a set of cooperating threads that share an L1 (level one) cache. A second type of memory barrier instruction may commit the memory transactions to a level of a set of threads sharing a global memory. Finally, a third type of memory barrier instruction may commit the memory transactions to a system level of all threads sharing all system memories. The latency required to execute the memory barrier instruction varies based on the type of memory barrier instruction.

Owner:NVIDIA CORP

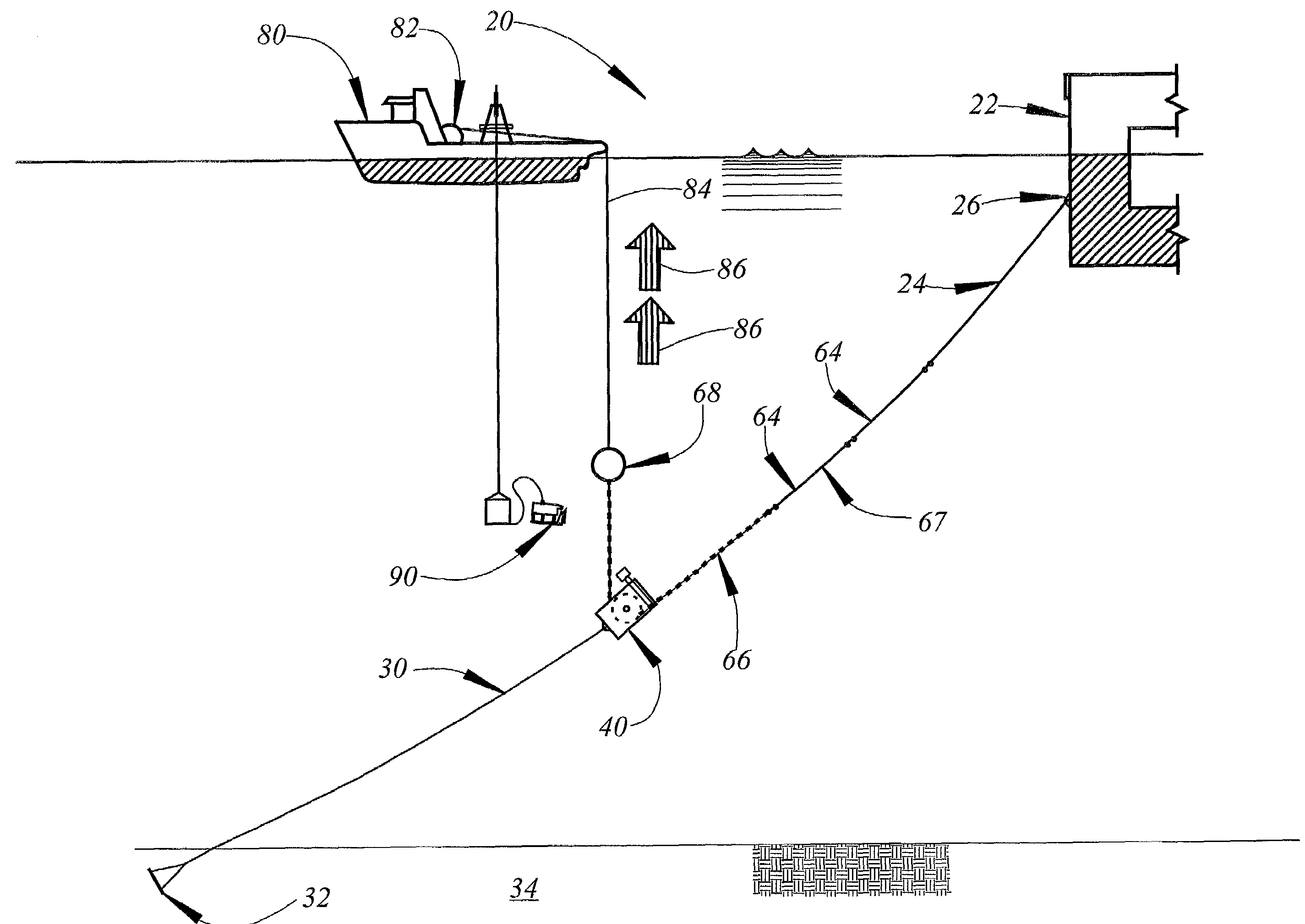

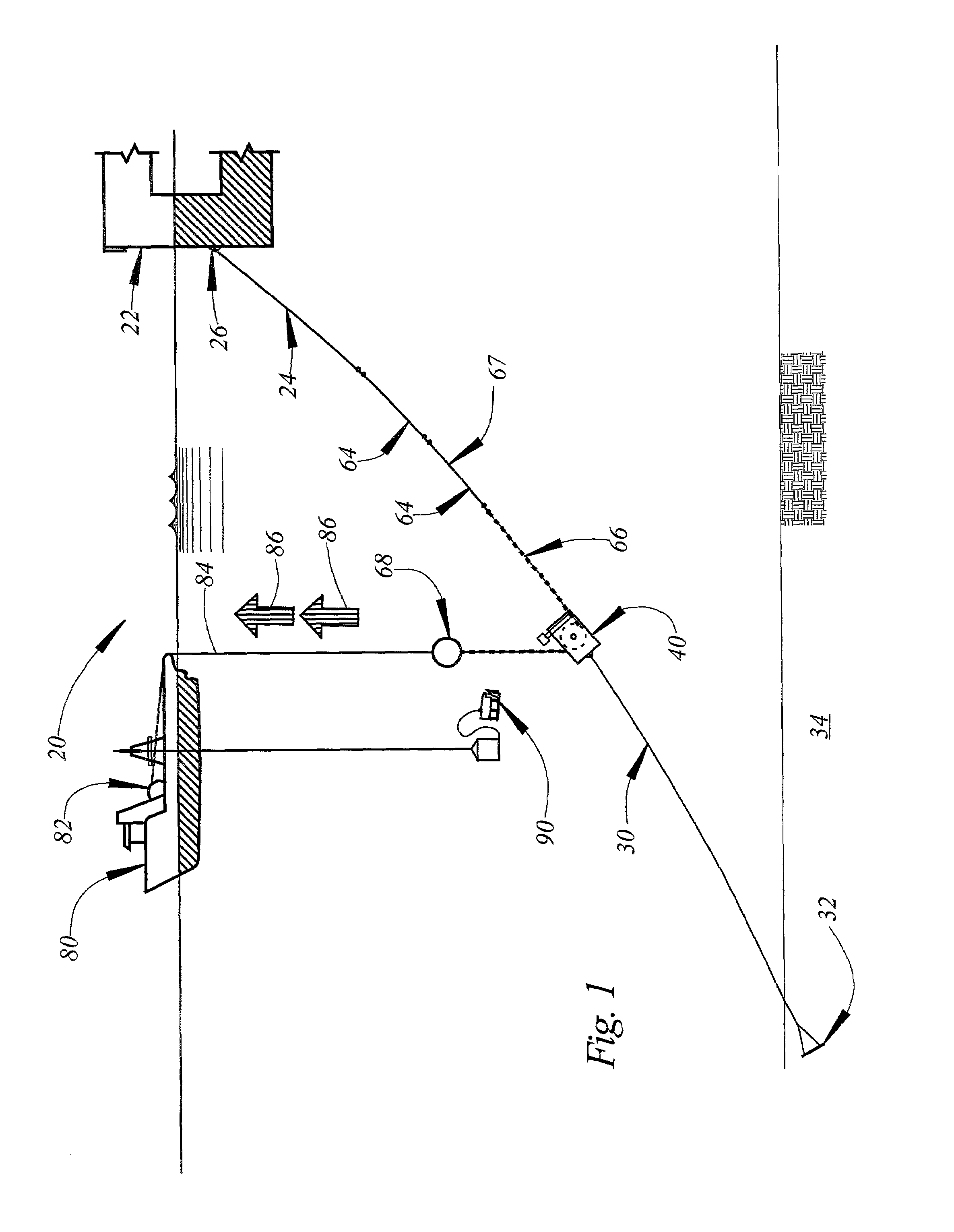

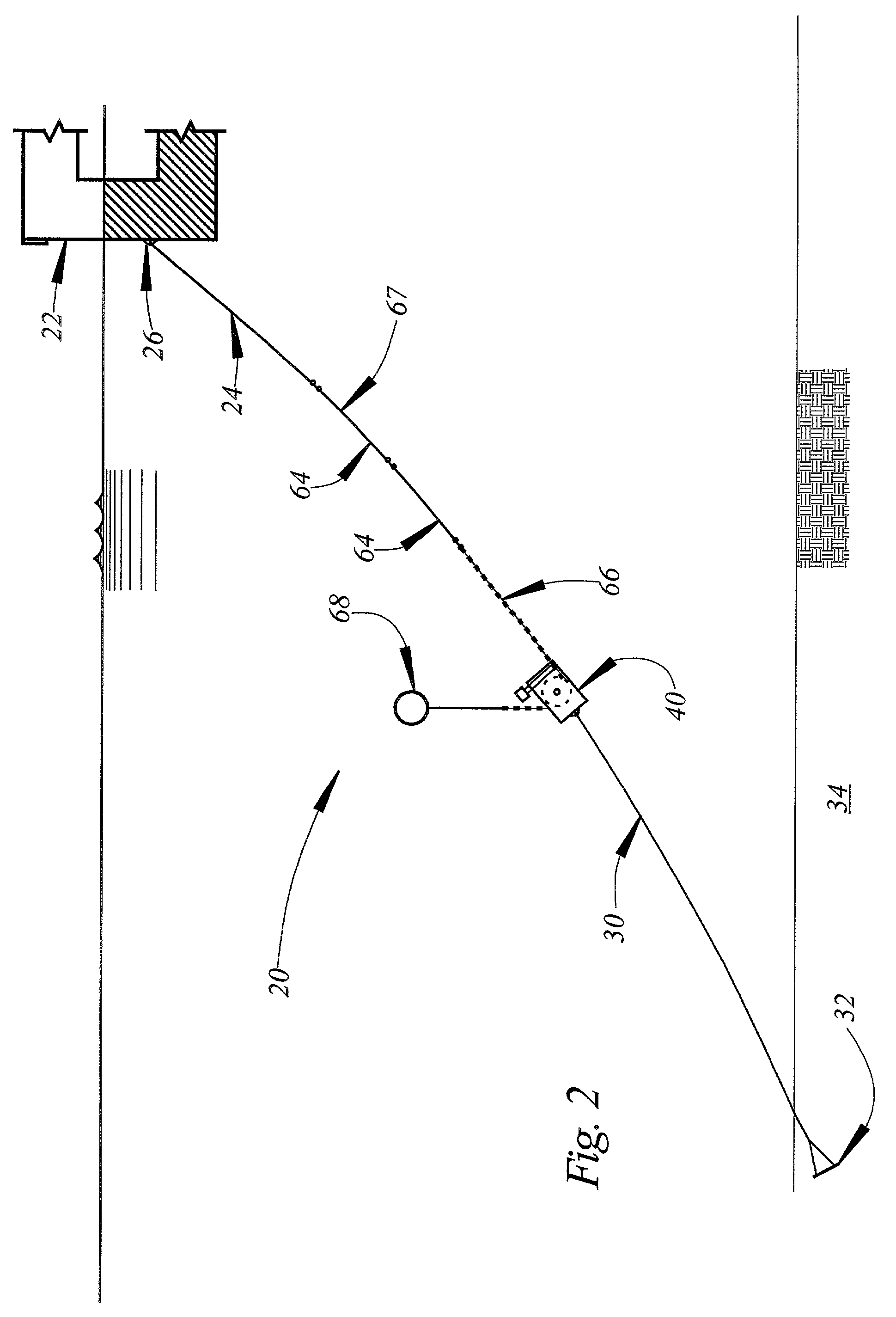

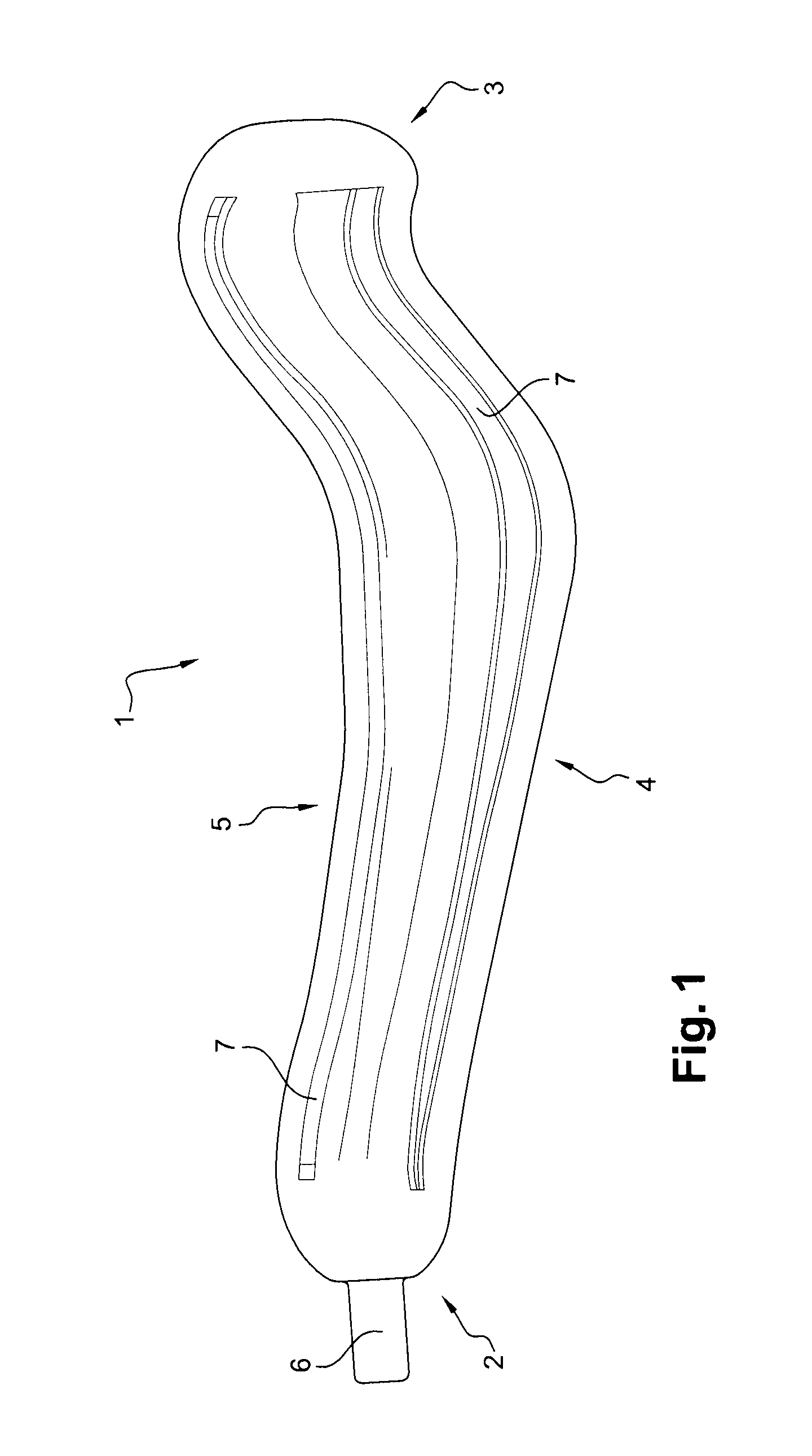

Method of and apparatus for offshore mooring

ActiveUS6983714B2Expensive to operateClamp firmlyAnchorsAnchoring arrangementsMarine engineeringPulley

In a method of and apparatus for offshore mooring, a clamping apparatus includes a clamping mechanism and a pulley. A mooring line connected to an anchor or a pendant line connected to a vessel to be moored extends through the clamping mechanism and around the pulley of the clamping apparatus. The distal end of the line extending through the clamping apparatus is connected to an anchor handling vessel. The anchor handling vessel is employed to apply a predetermined tension to the pendant line and the preset mooring line. A remote operated vehicle is then employed to actuate the clamping apparatus and to disengage the anchor handling vessel.

Owner:TECH FRANCE SA

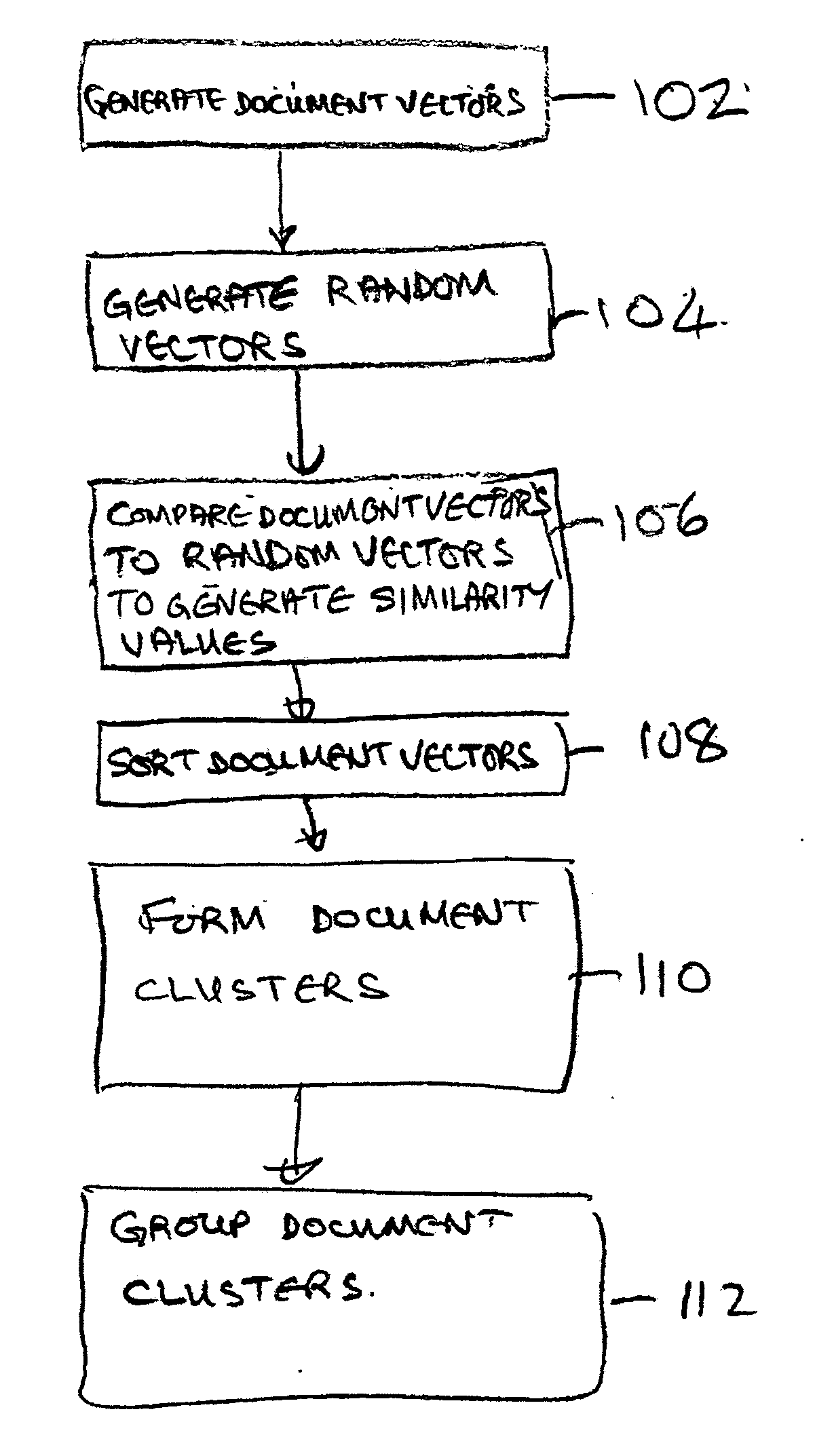

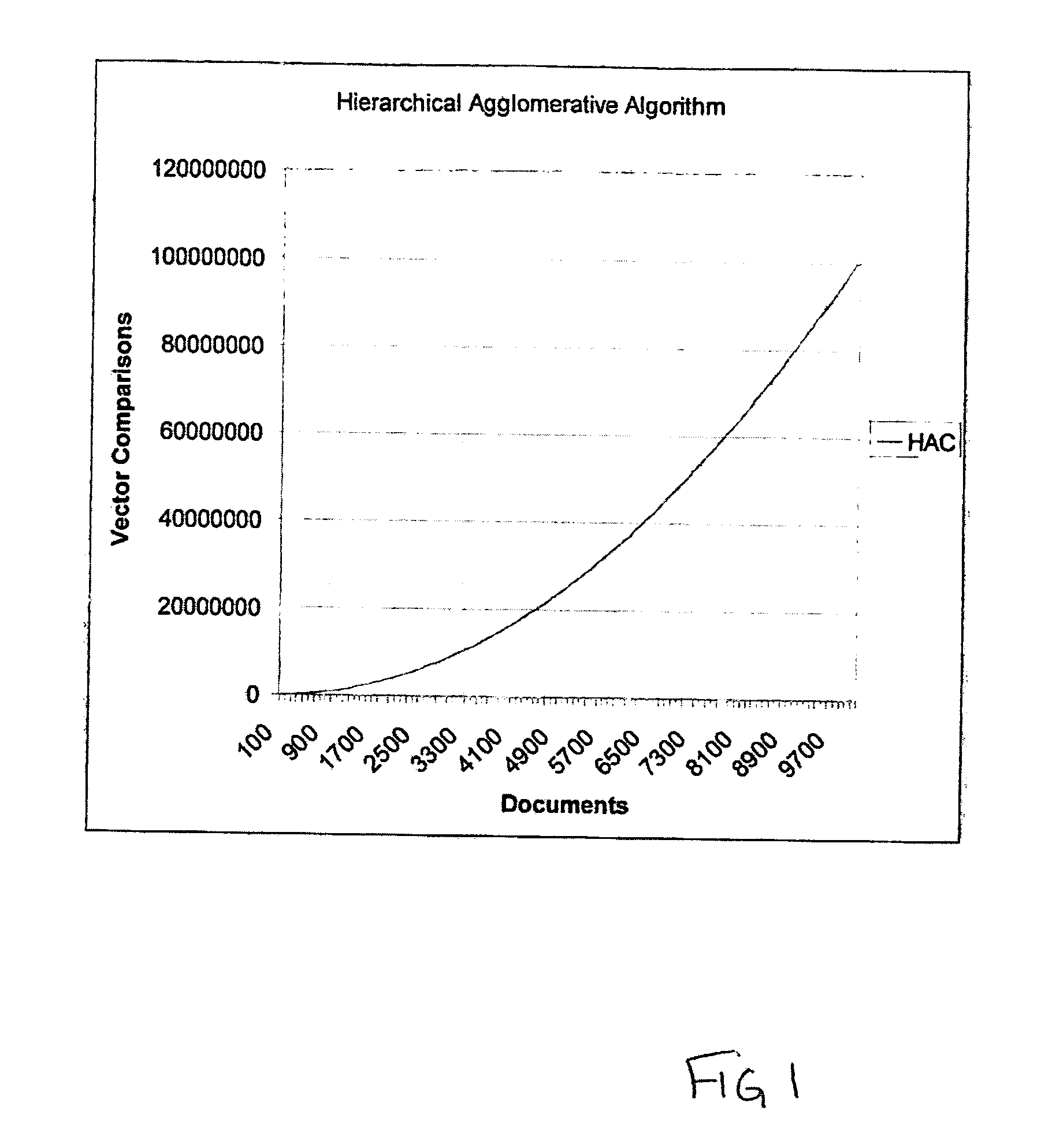

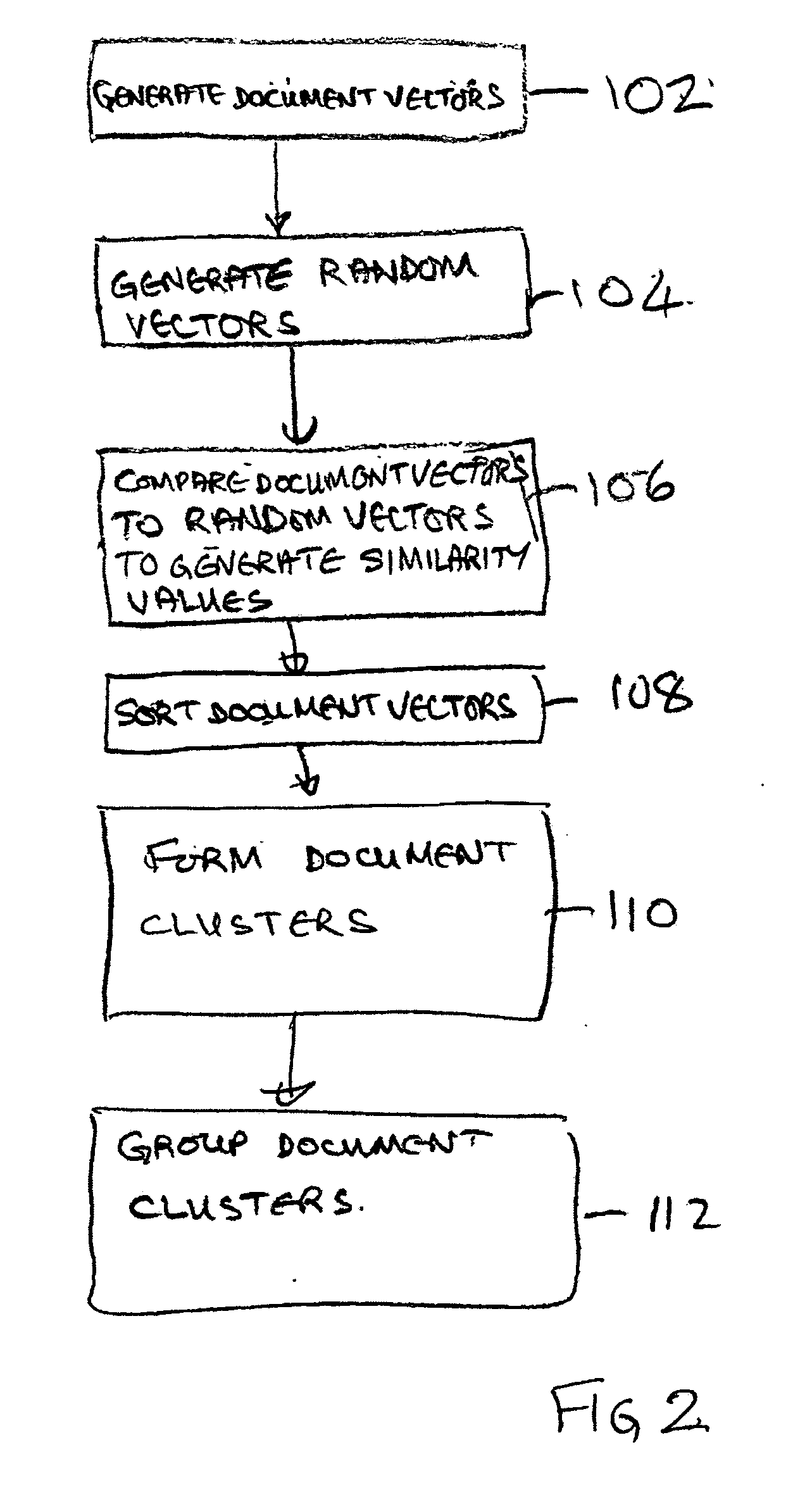

Clustering system and method

InactiveUS20080082531A1Promote formationExpensive to operateDigital data information retrievalSpecial data processing applicationsReference vectorDocument preparation

In order to clustering documents, document vectors are formed for each of a plurality of documents of a corpus and plurality of reference vectors is generated. The document vectors are then compared to the reference vectors to generate similarity values for each of the document vectors. The document vectors are then sorted based on the similarity values for the document vectors to form a sorted list. Clusters are then formed based on the similarity between adjacent document vectors in the sorted list.

Owner:CA TECH INC

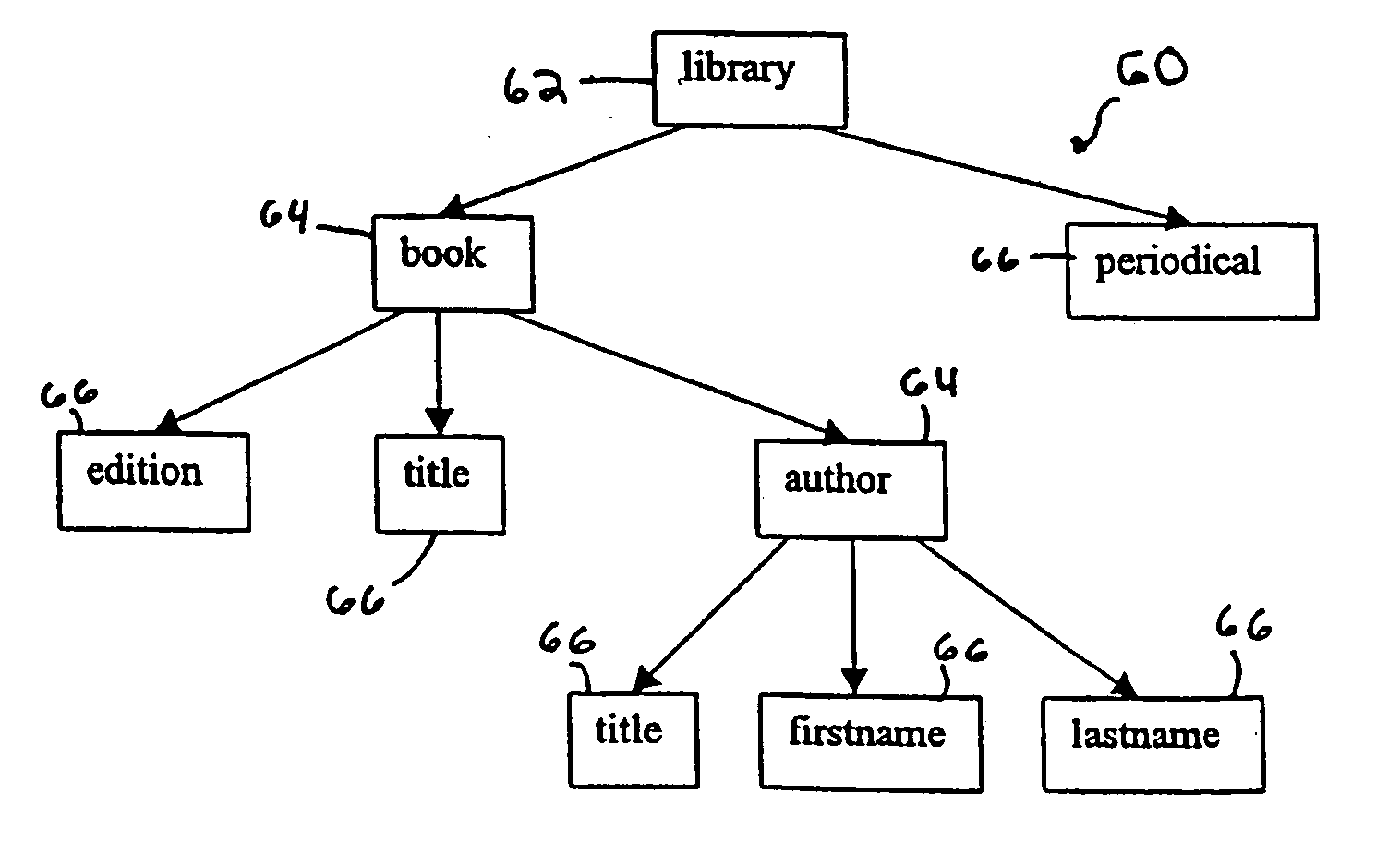

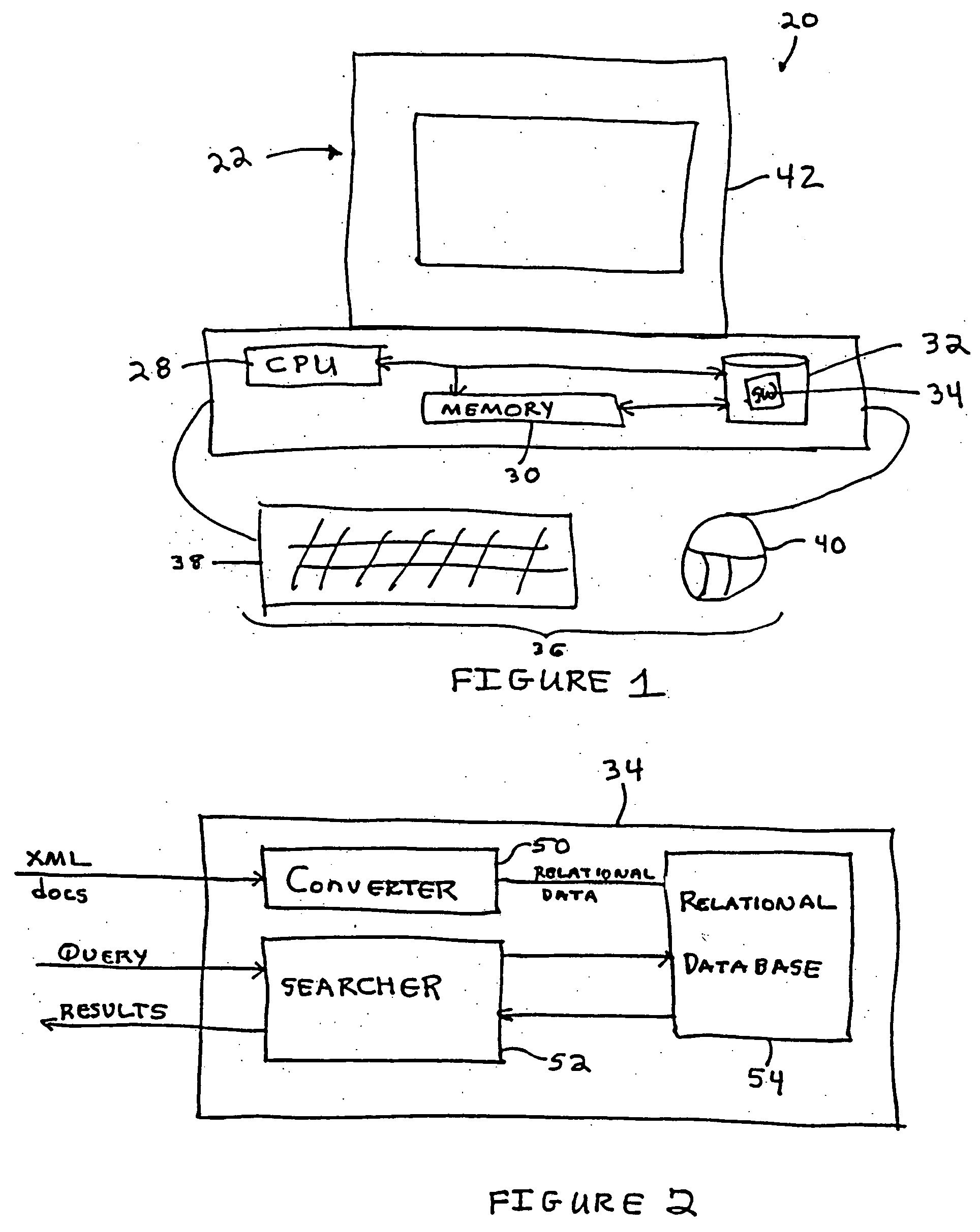

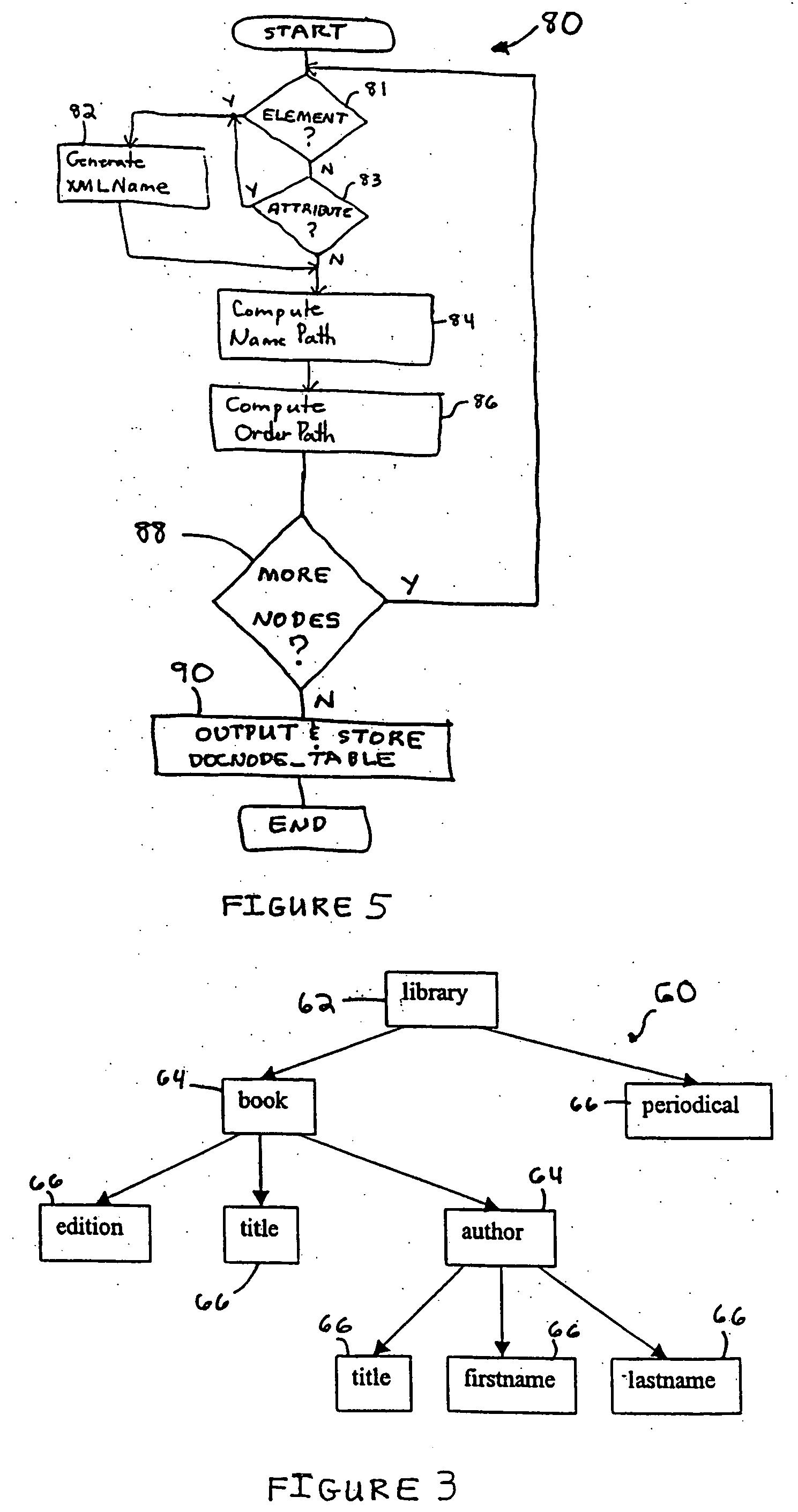

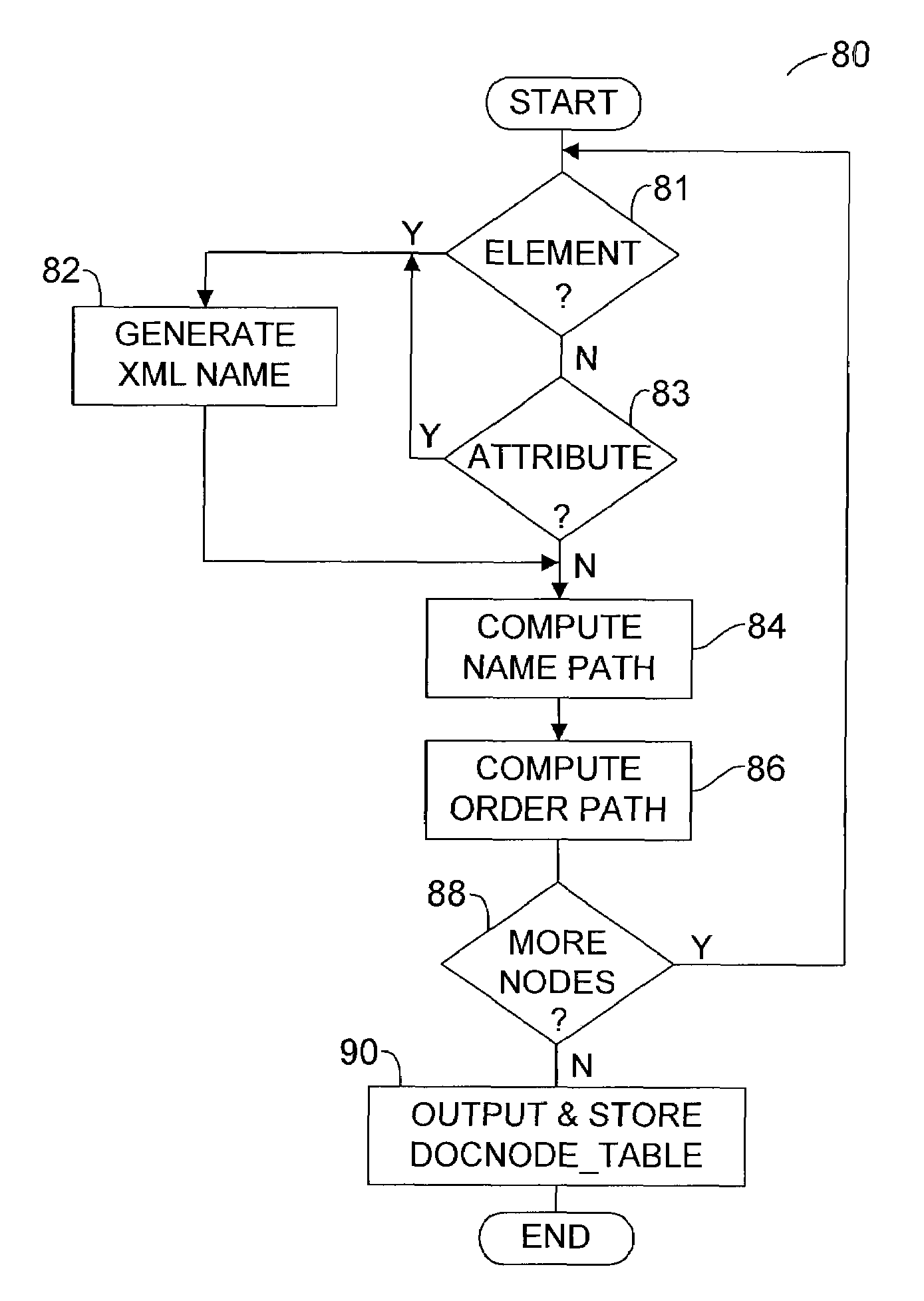

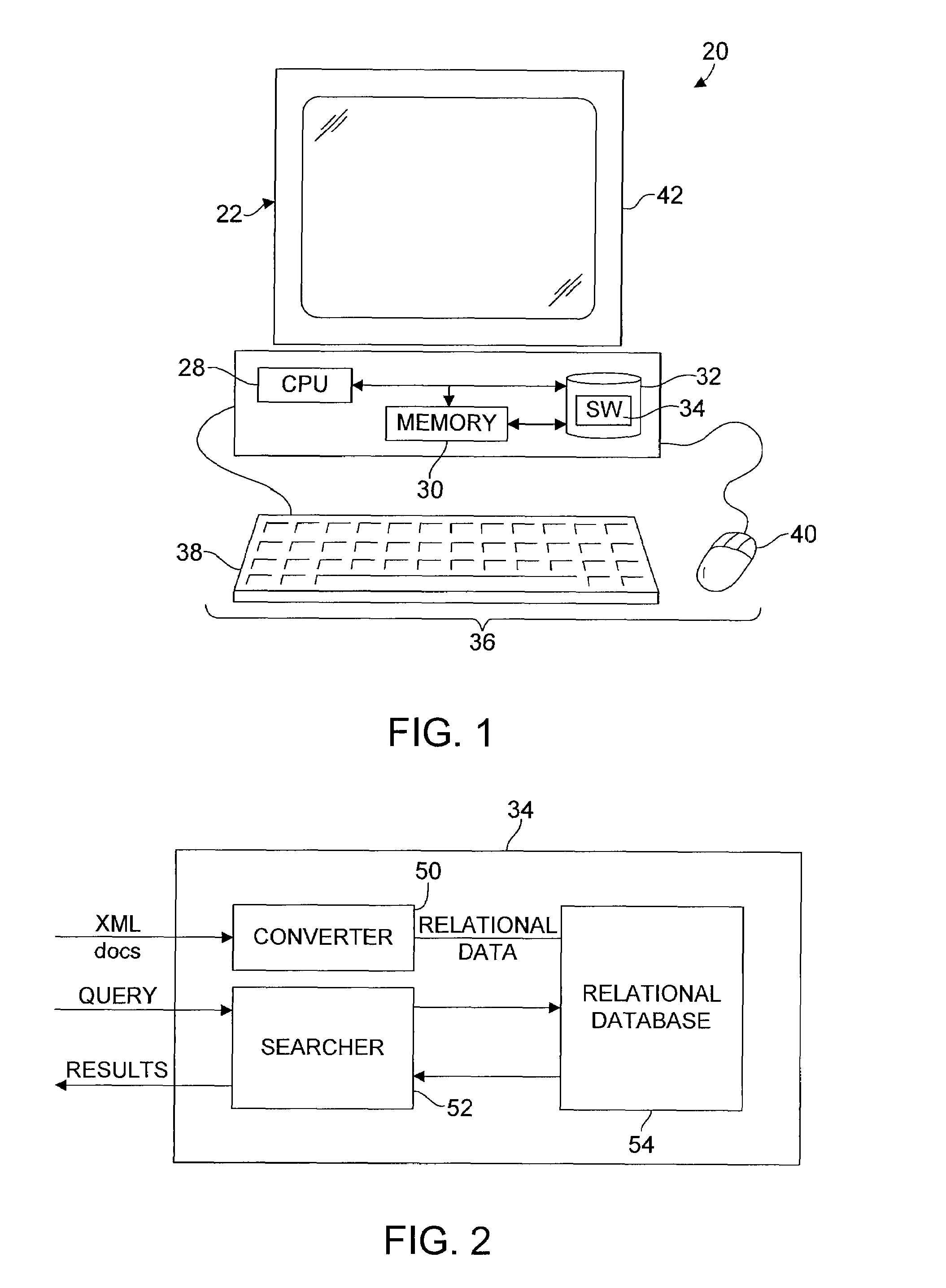

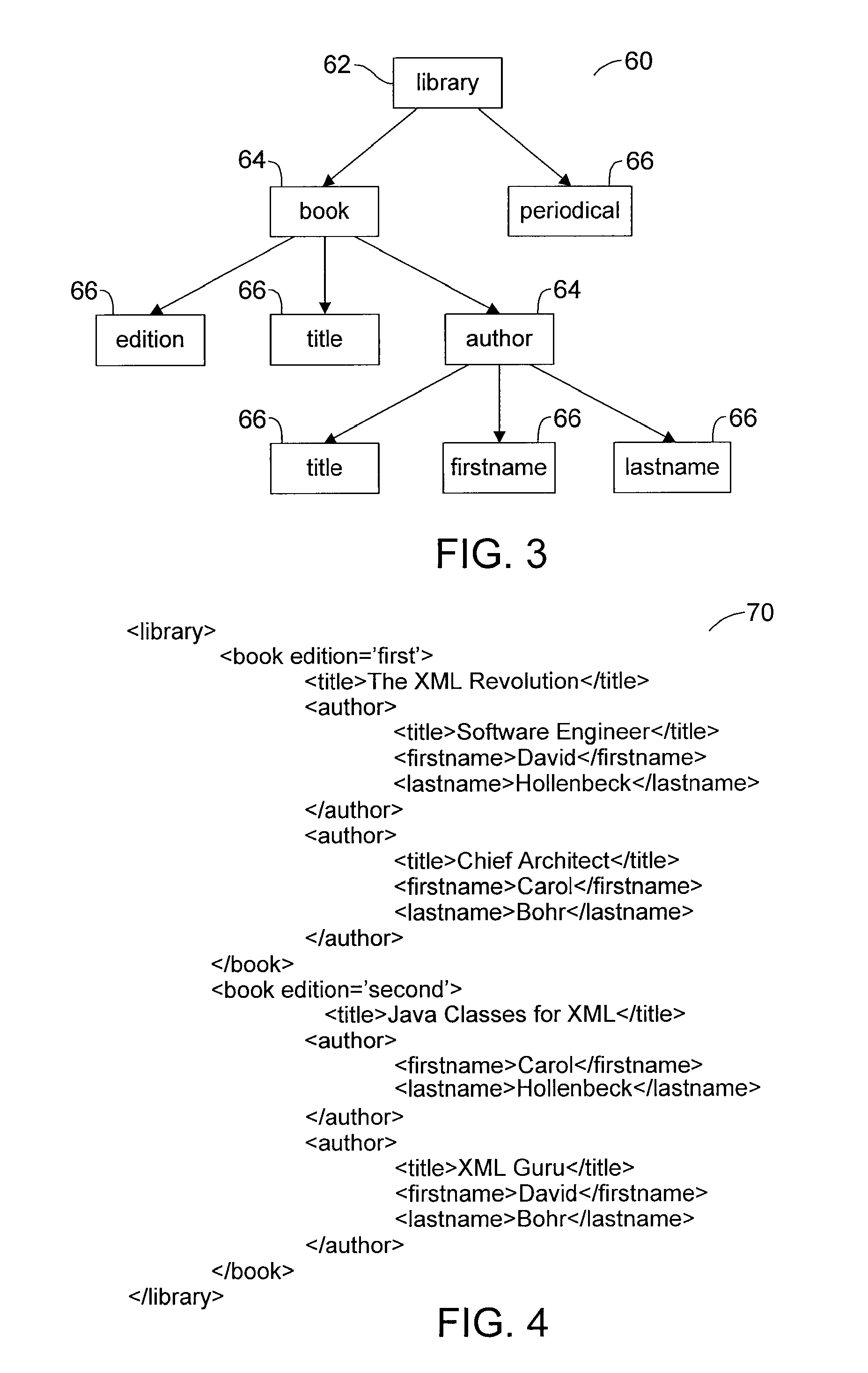

System and method for the storage, indexing and retrieval of XML documents using relational databases

ActiveUS20060101320A1Efficient storageEfficient indexingData processing applicationsRelational databasesRelational databasePaper document

A system and method for assigning attributes to XML document nodes to facilitate their storage in relational databases and the subsequent retrieval and re-construction of pertinent nodes and fragments in original document order is provided. Since these queries are performed using relational database query engines, the speed of their execution is significantly faster than that using more exotic systems such as object-oriented databases. Furthermore, this method is portable across all vendor platforms, and so can be deployed at client sites without additional investments in database software.

Owner:PROGRESS SOFTWARE

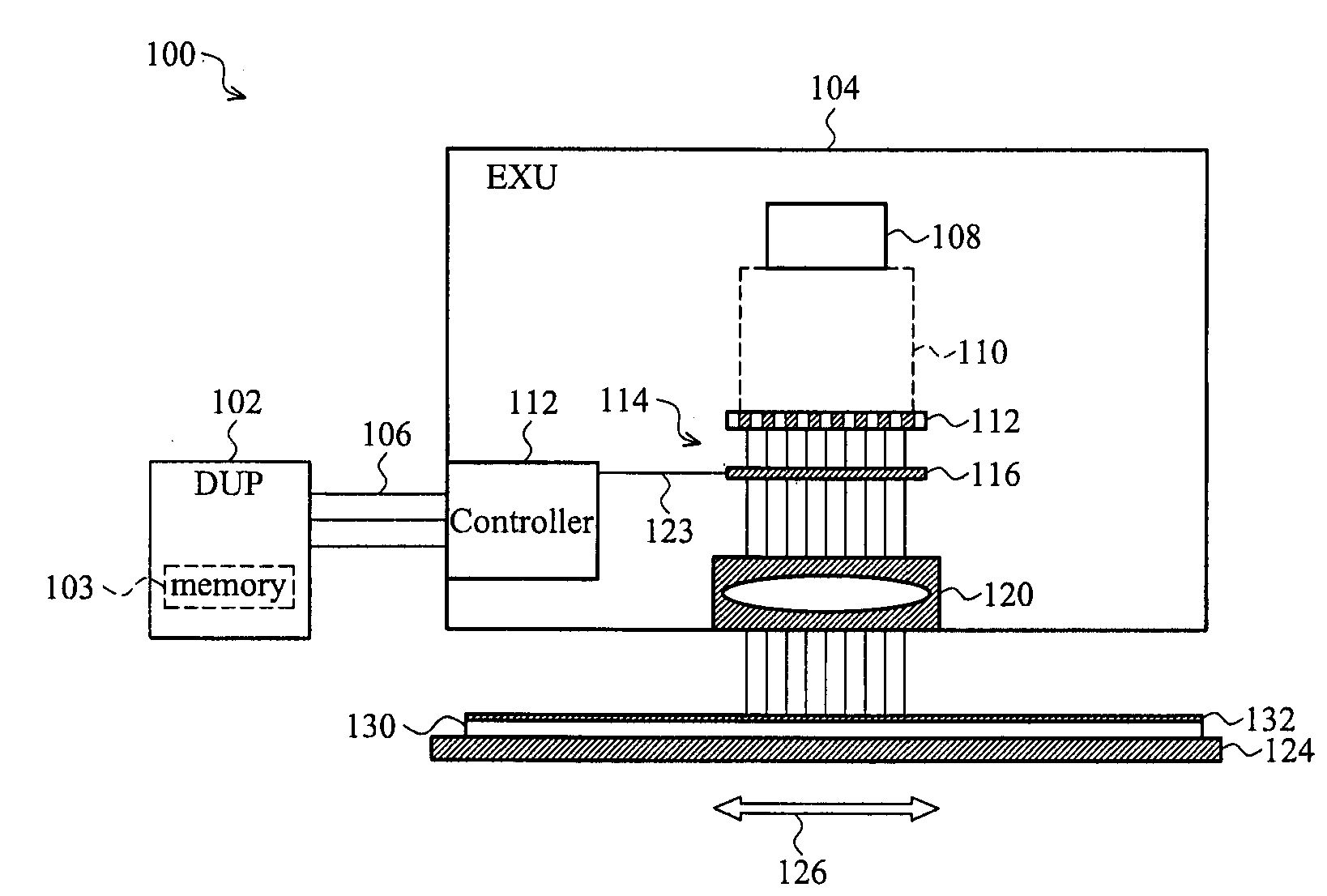

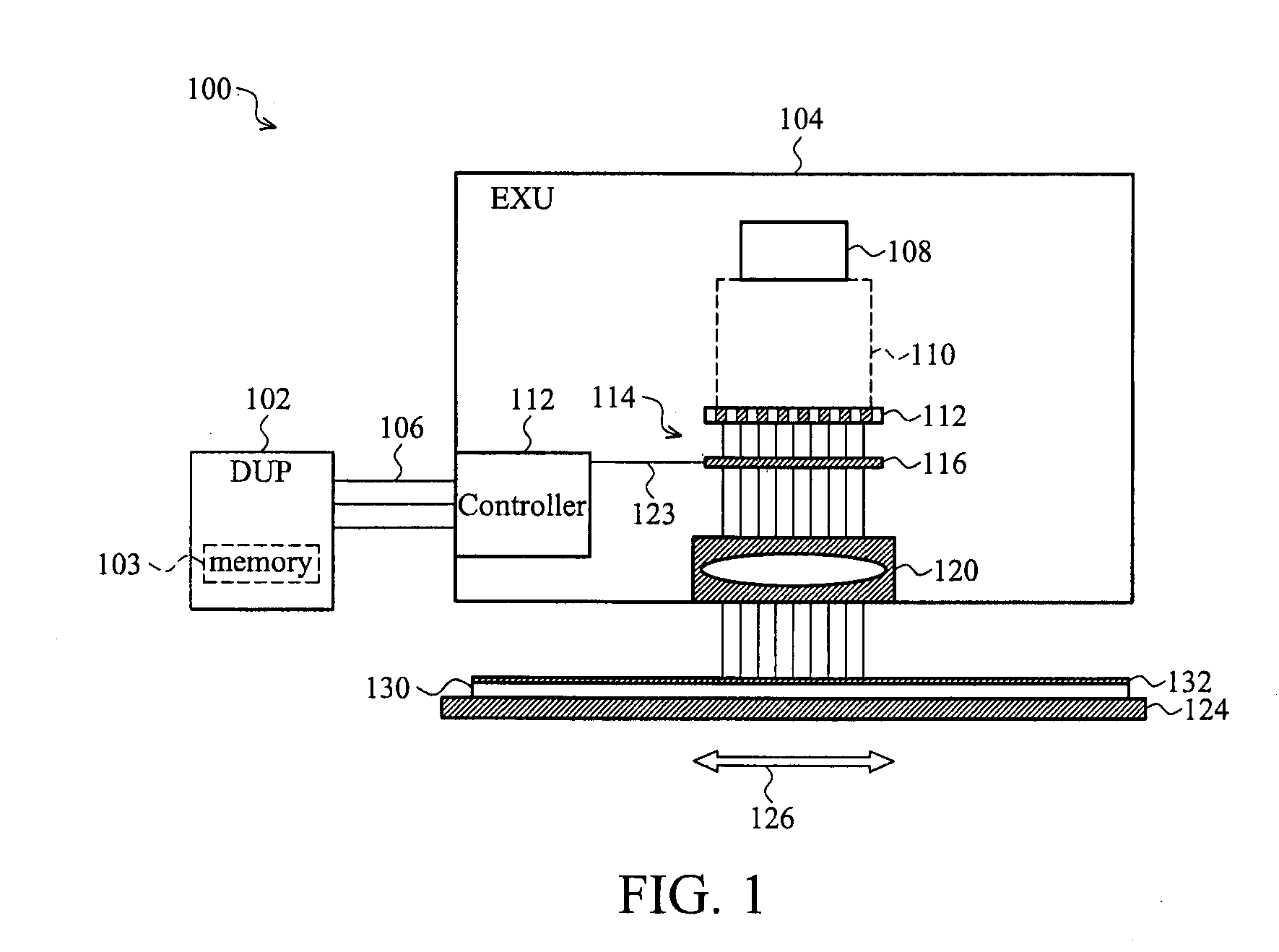

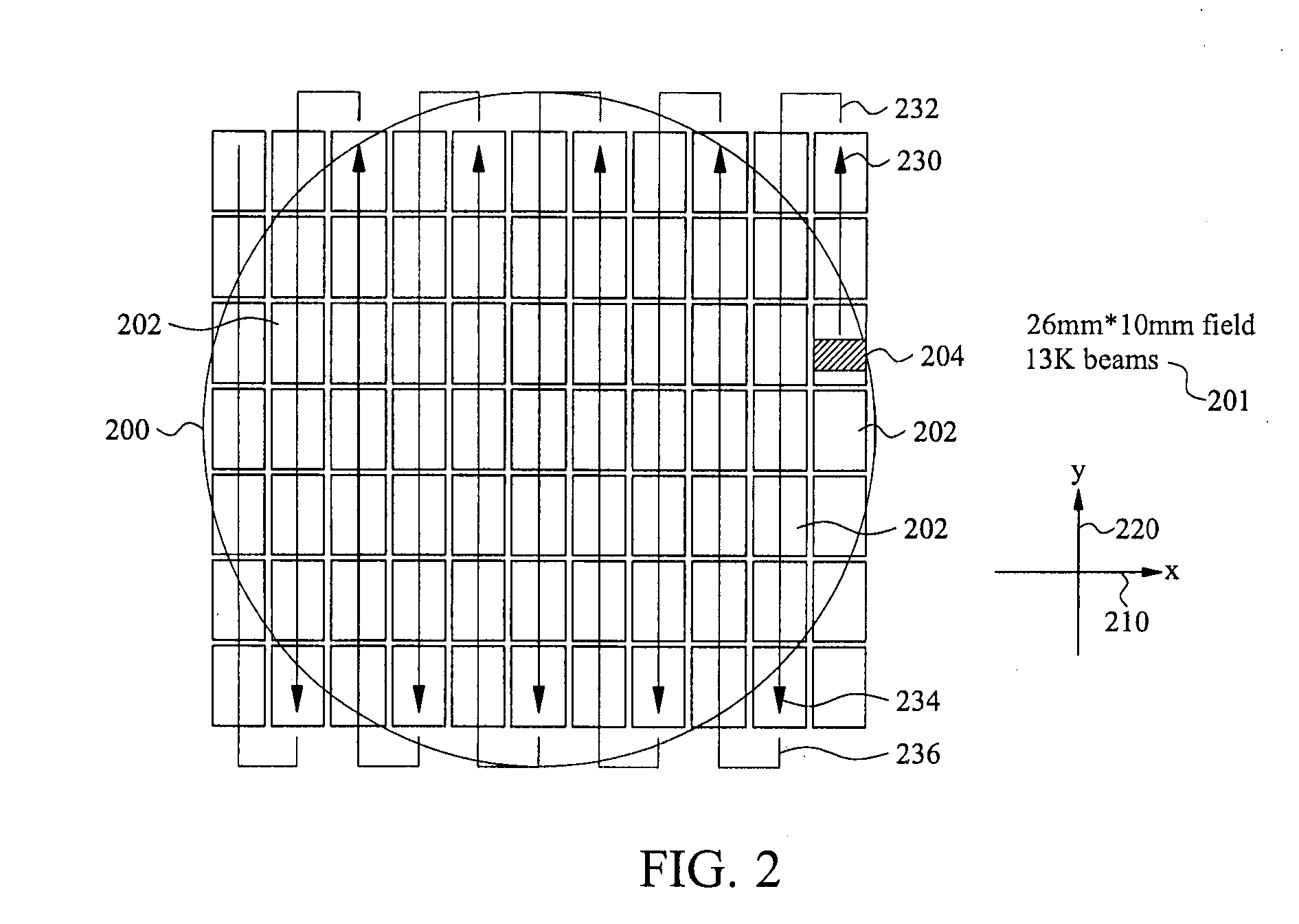

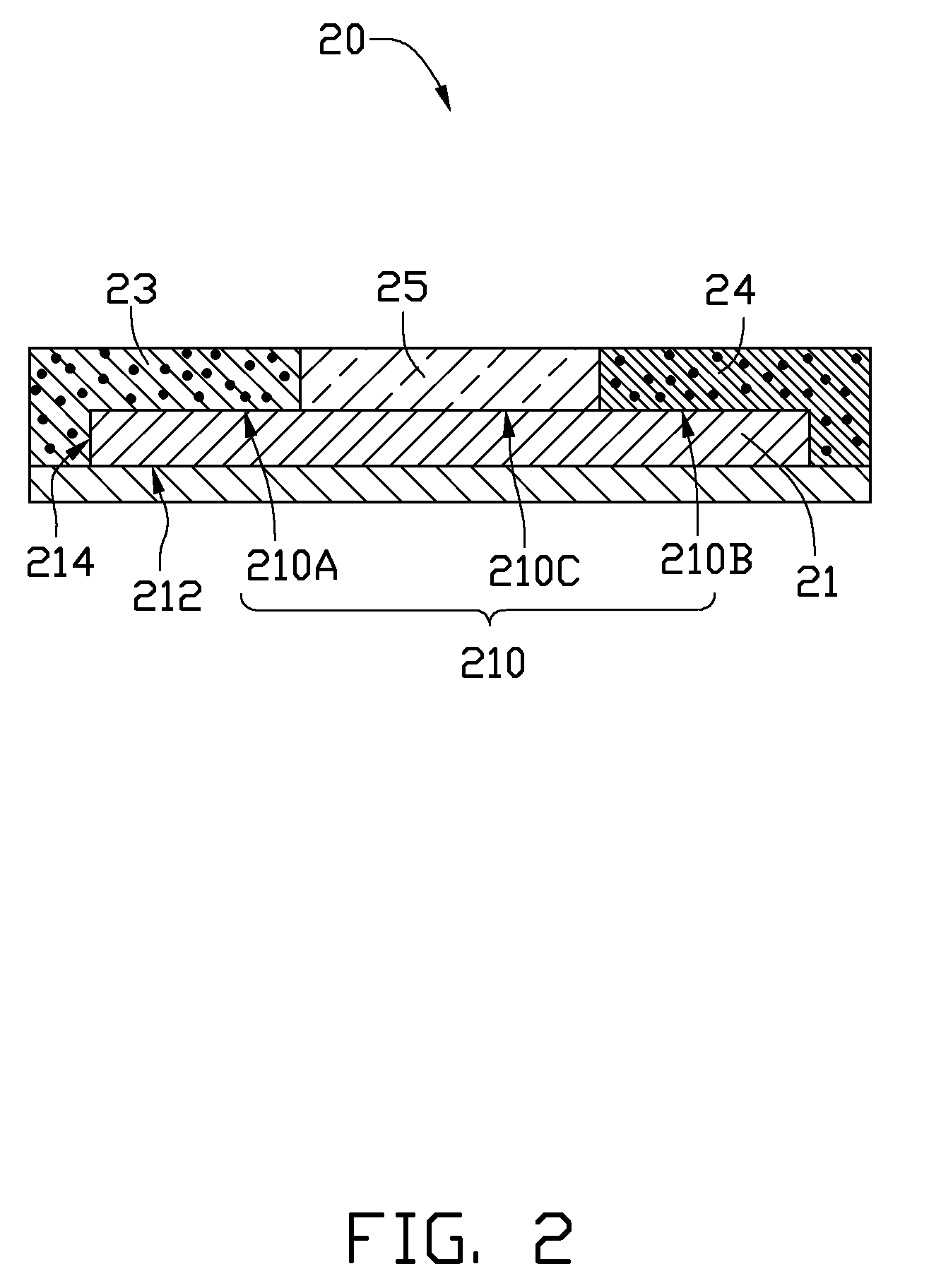

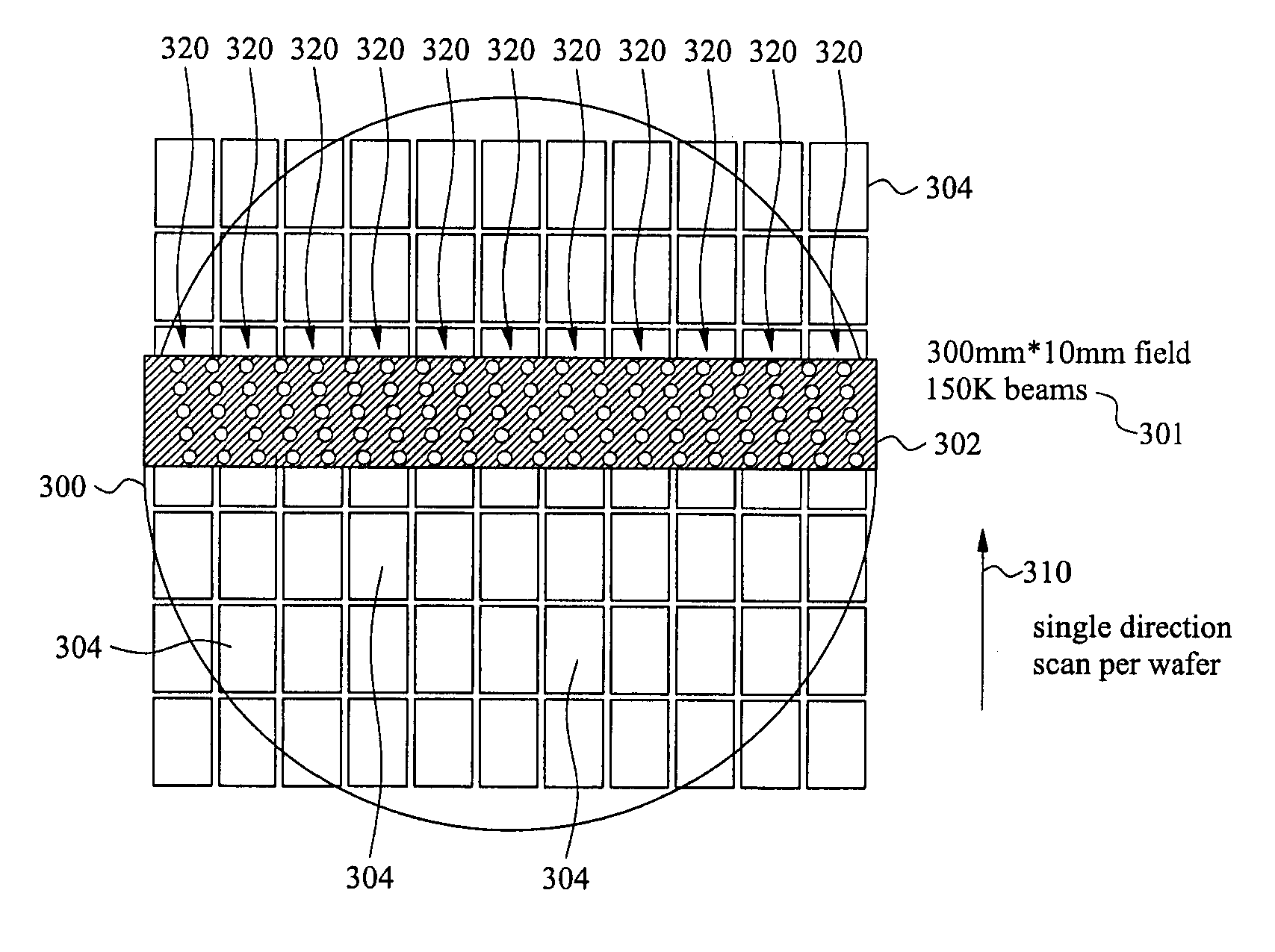

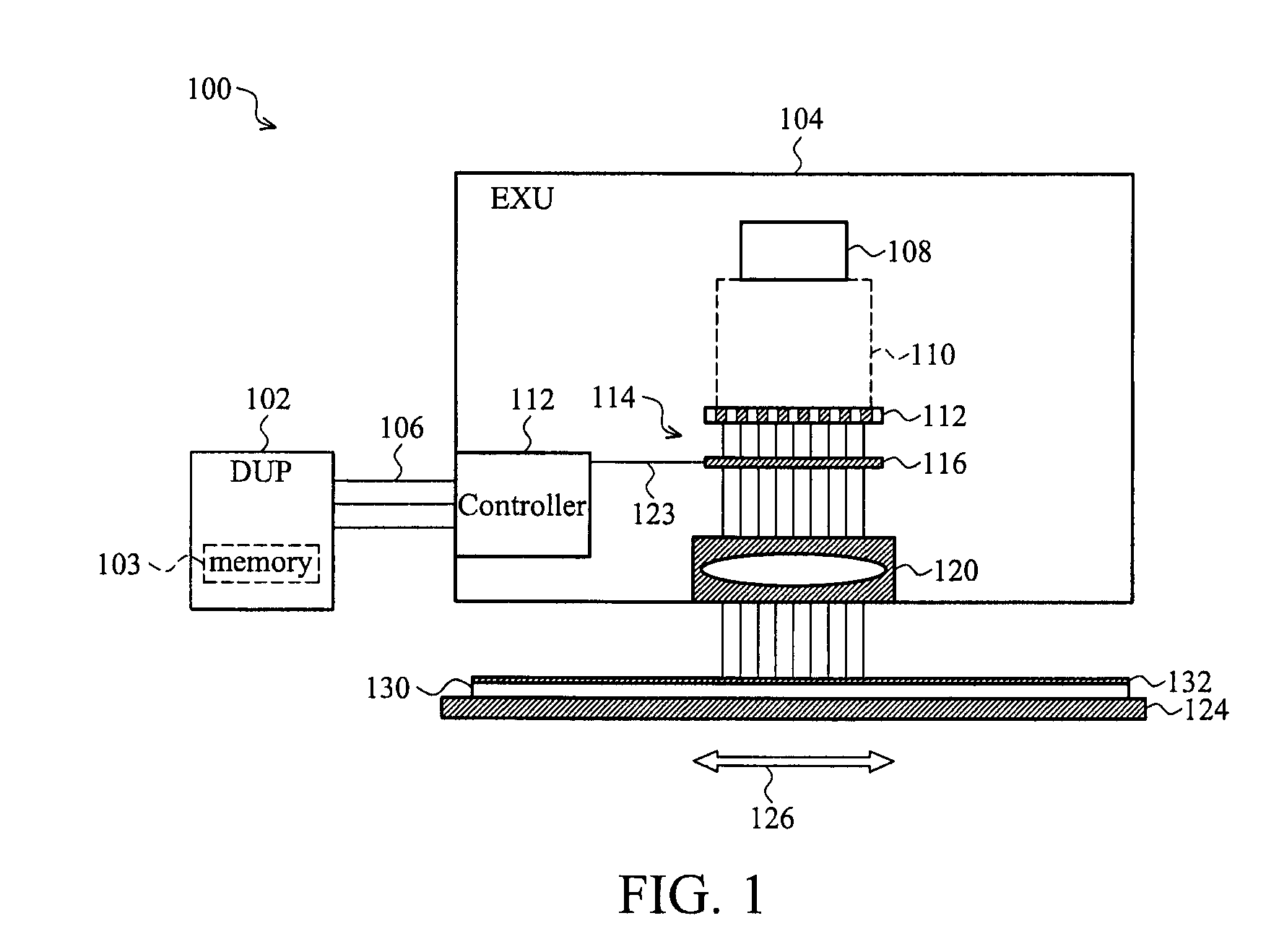

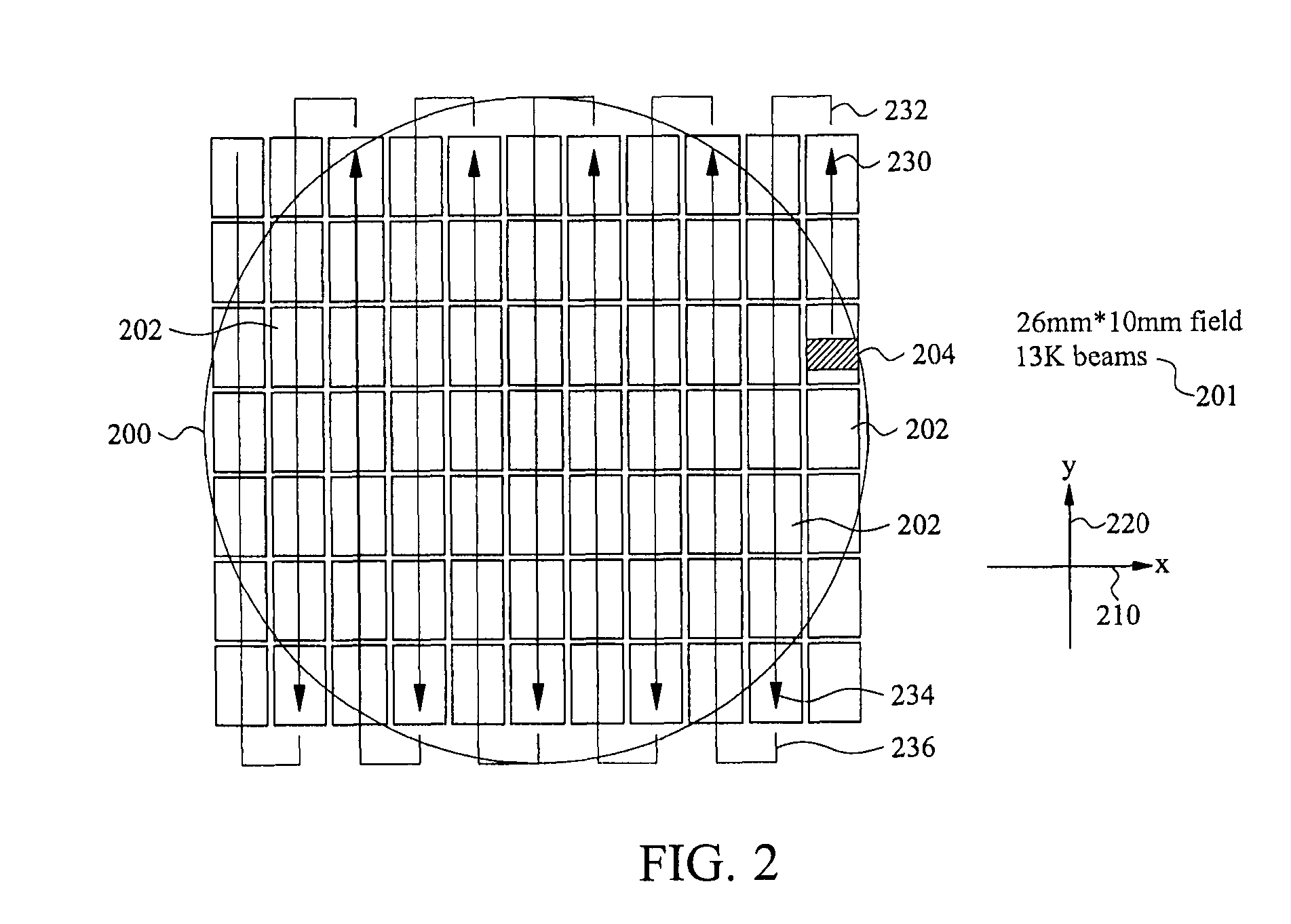

System and Method for Direct Writing to a Wafer

ActiveUS20090268184A1Expensive to ownExpensive to operateElectric discharge tubesNanoinformaticsField sizeComputer module

A direct-write (DW) exposure system is provided which includes a stage for holding a substrate and configured to scan the substrate along an axis during exposure, a data processing module for processing pattering data and generating instructions associated with the patterning data, and an exposure module that includes a plurality of beams that are focused onto the substrate such that the beams cover a width that is larger than a width of a field size and a beam controller that controls the plurality of beams in accordance with the instructions as the substrate is scanned along the axis. The widths are in a direction different from the axis.

Owner:TAIWAN SEMICON MFG CO LTD

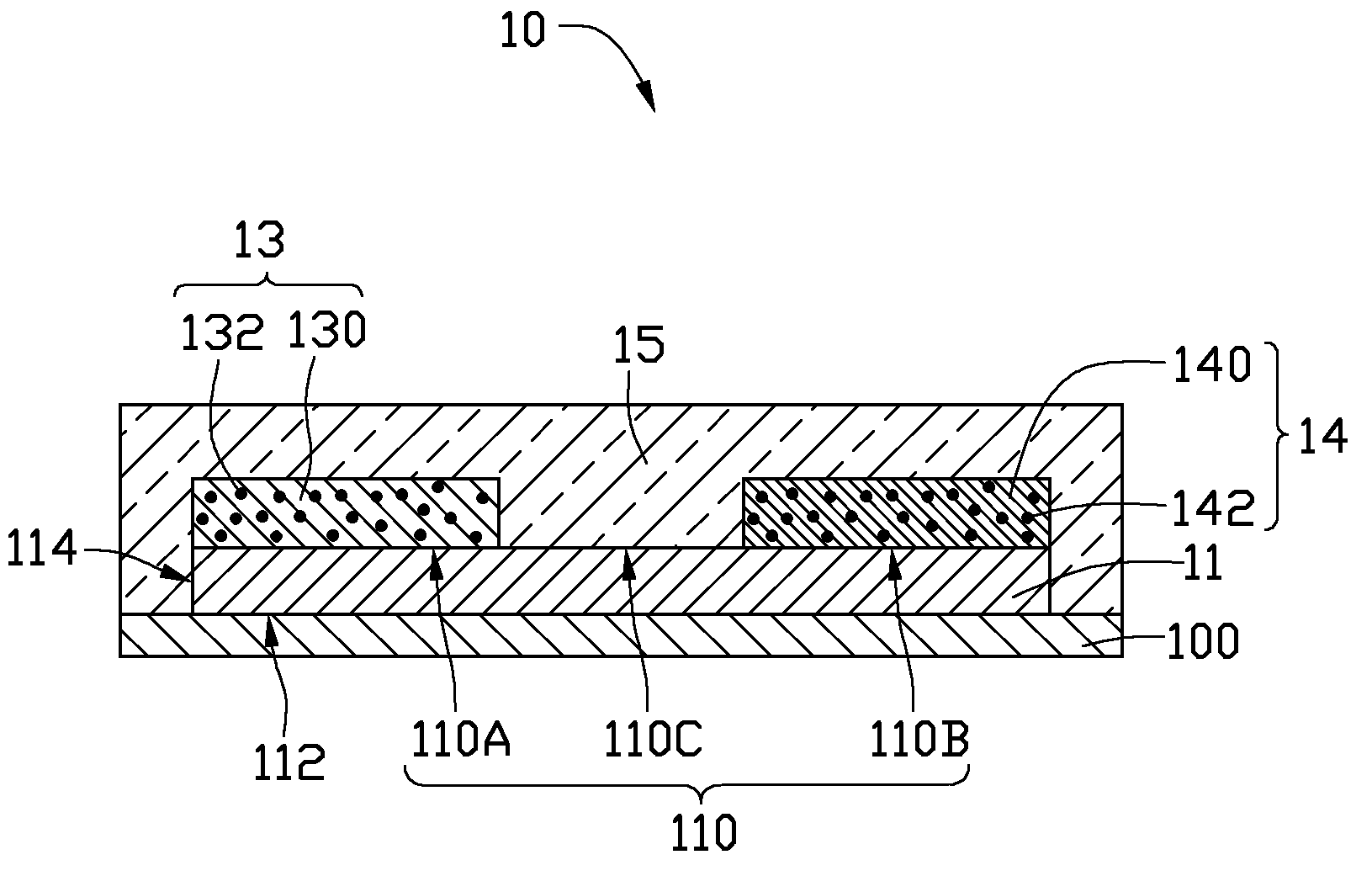

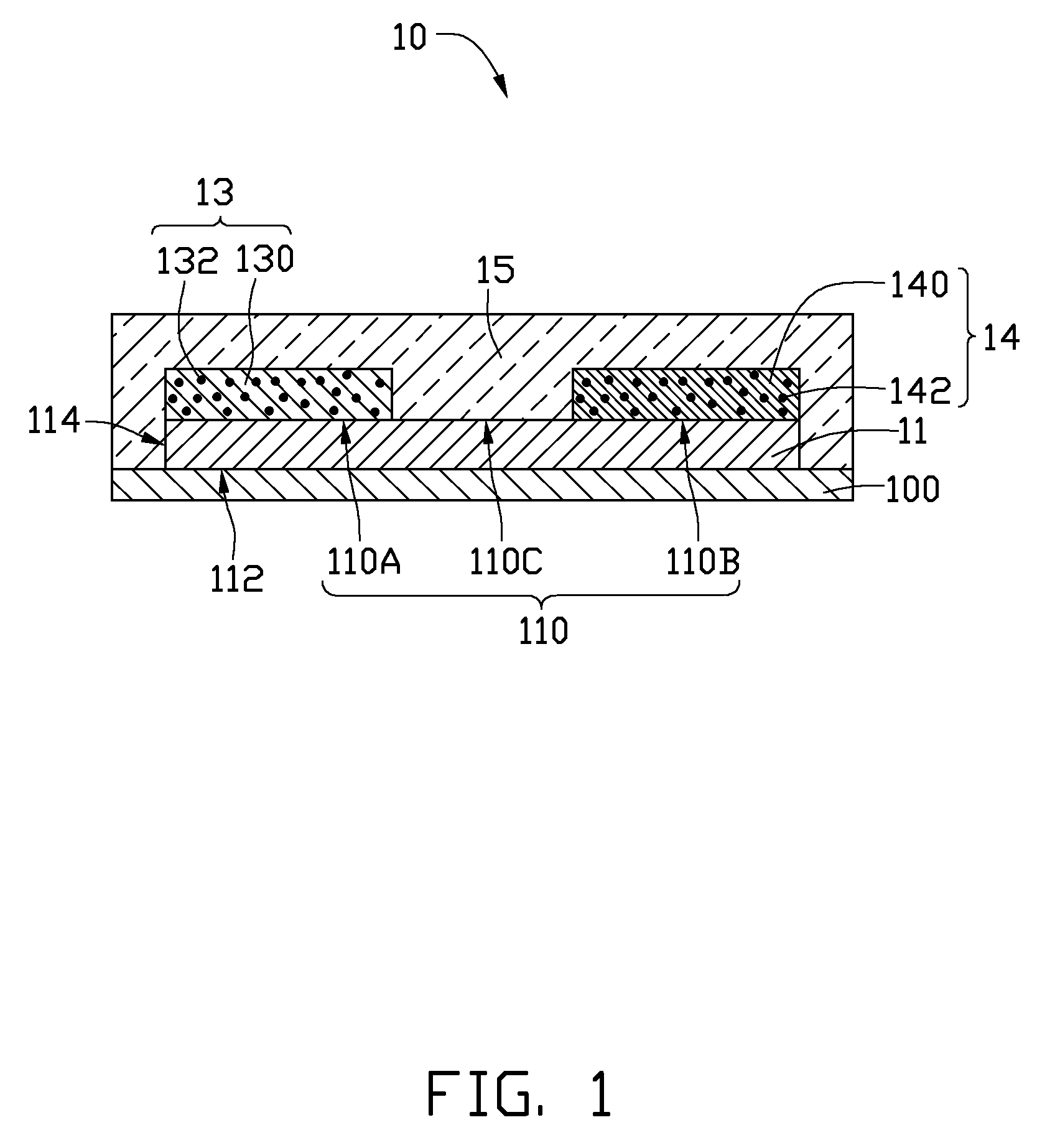

Light emitting diode with light conversion

InactiveUS20100148200A1High luminous efficiencyReduce power consumptionSolid-state devicesSemiconductor devicesOptical wavelengthDiode

An exemplary light emitting diode includes a light emitting diode chip, two optical wavelength converting layers, and an encapsulant layer. The light emitting diode chip has an light emitting surface. The light emitting diode chip is used to emit a monochromatic light from the light emitting surface. The light emitting surface includes a first region, a second region, and a third region. The two optical wavelength converting layers covers the first and the third regions of the light emitting surface. The two optical wavelength converting layers are configured for converting the monochromatic light received from the light emitting diode chip and emitting light with a converted wavelength from the light emitting diode. The encapsulant layer covers the second region of the light emitting surface for directing light therefrom.

Owner:FOXSEMICON INTEGRATED TECH INC

System and method for the storage, indexing and retrieval of XML documents using relational databases

ActiveUS7353222B2Efficient indexingImprove performanceData processing applicationsRelational databasesRelational databaseClient-side

A system and method for assigning attributes to XML document nodes to facilitate their storage in relational databases and the subsequent retrieval and re-construction of pertinent nodes and fragments in original document order is provided. Since these queries are performed using relational database query engines, the speed of their execution is significantly faster than that using more exotic systems such as object-oriented databases. Furthermore, this method is portable across all vendor platforms, and so can be deployed at client sites without additional investments in database software.

Owner:PROGRESS SOFTWARE

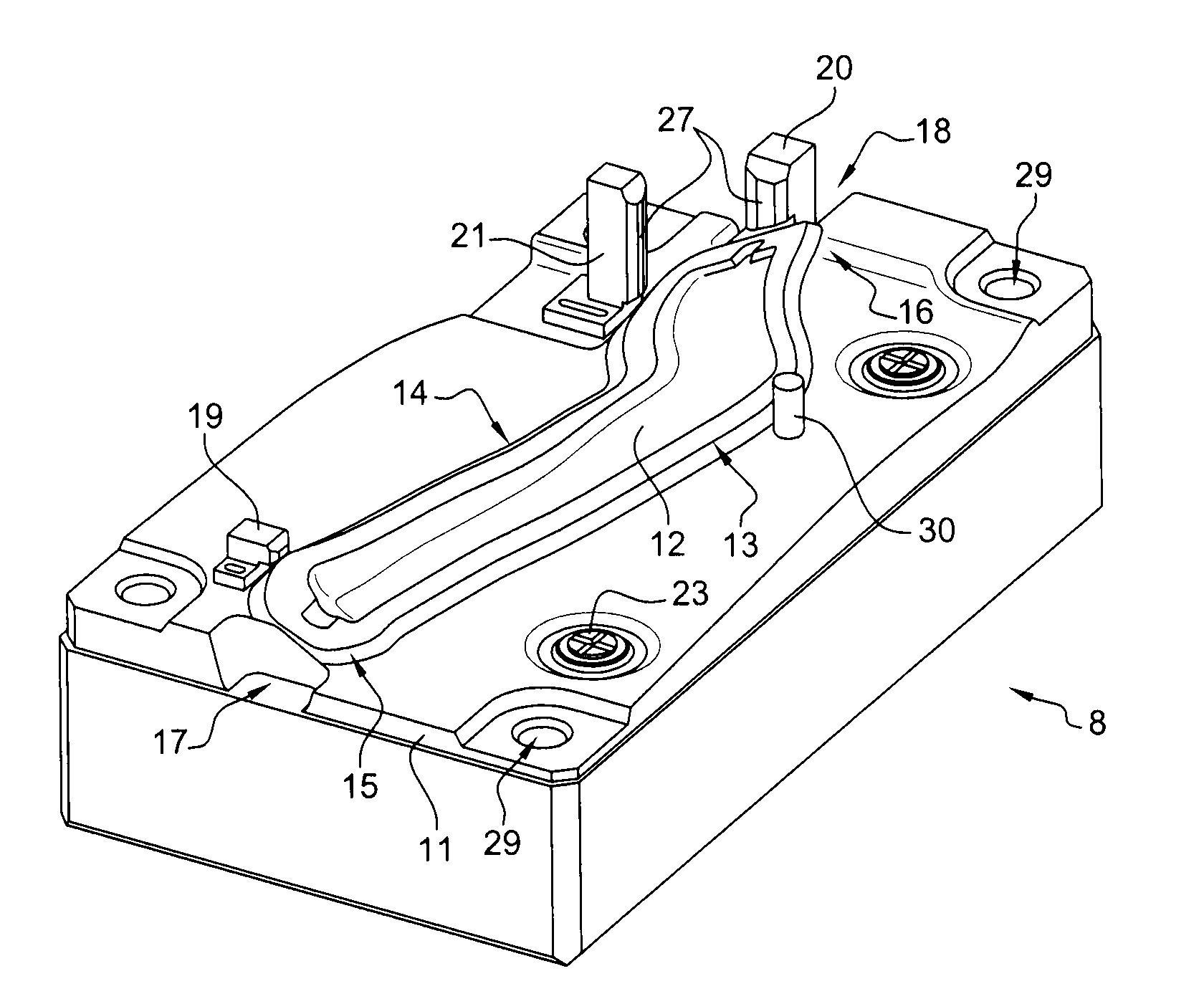

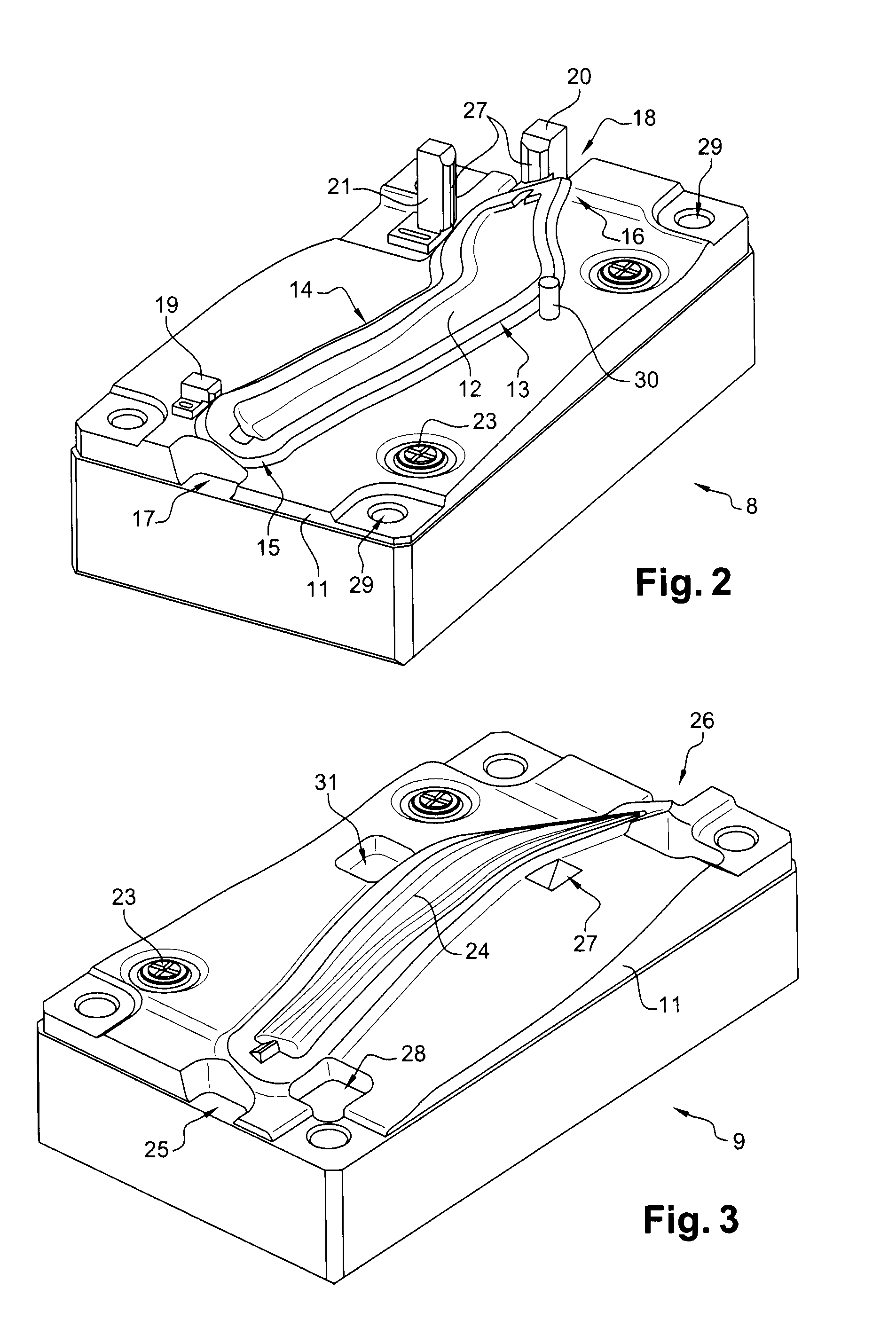

Tooling and a method for hot forging pieces of sheet metal

ActiveUS20120174384A1Simple and effective and inexpensiveEasy to controlShaping toolsTool carrier control devicesLeading edgeEngineering

The invention provides tooling and a method for hot forging pieces of sheet metal that are to form metal reinforcement mounted on the leading or trailing edge of a turbine engine blade, by means of bottom and top matrices each presenting a twisted elongate surface for use in shaping an initially plane piece of sheet metal, the shaping surface of the bottom matrix presenting a high portion, a low portion, and two end zones. The bottom matrix includes studs for positioning and guiding the piece, the studs being situated at the periphery of the corresponding shaping surface.

Owner:SN DETUDE & DE CONSTR DE MOTEURS DAVIATION S N E C M A

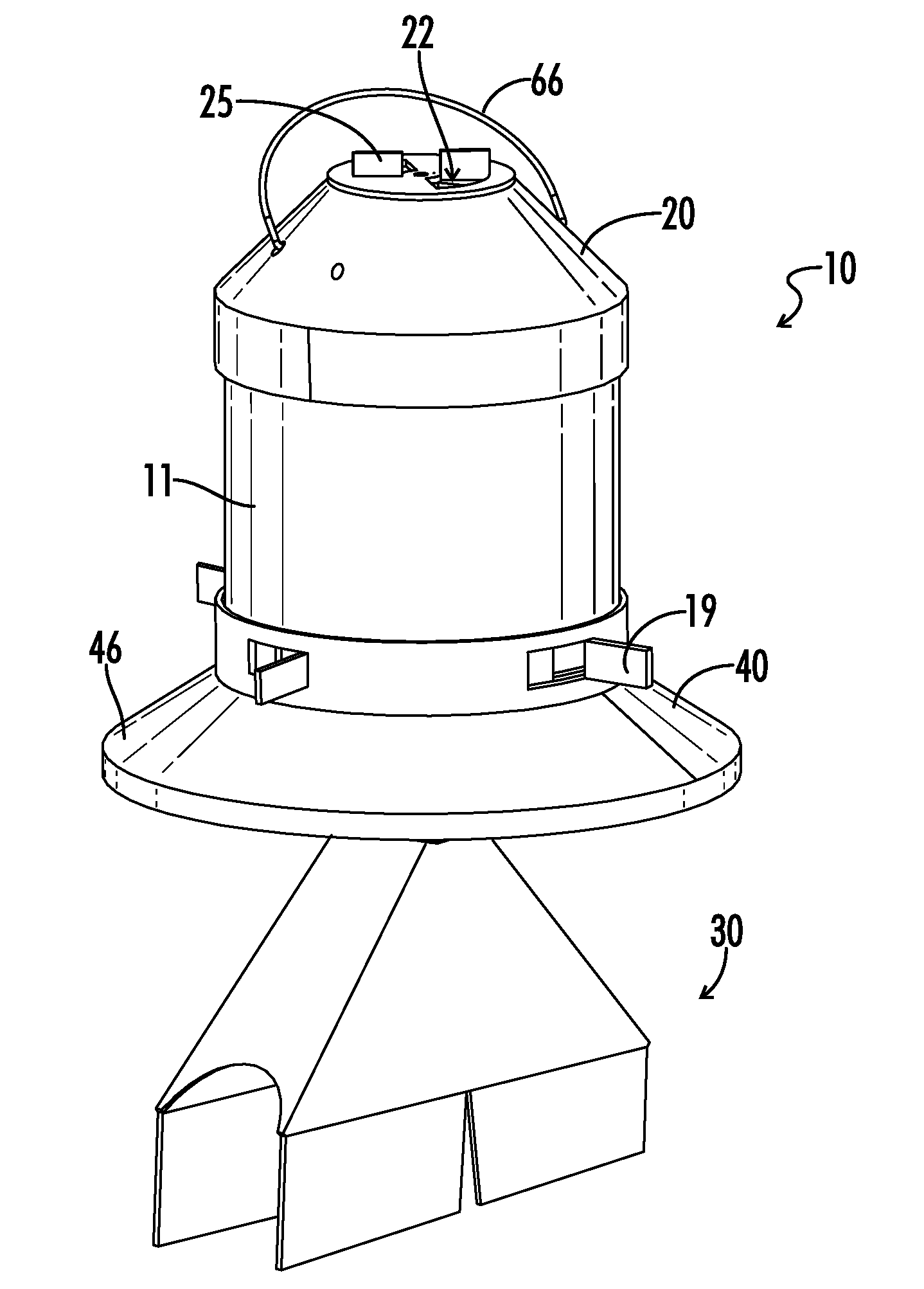

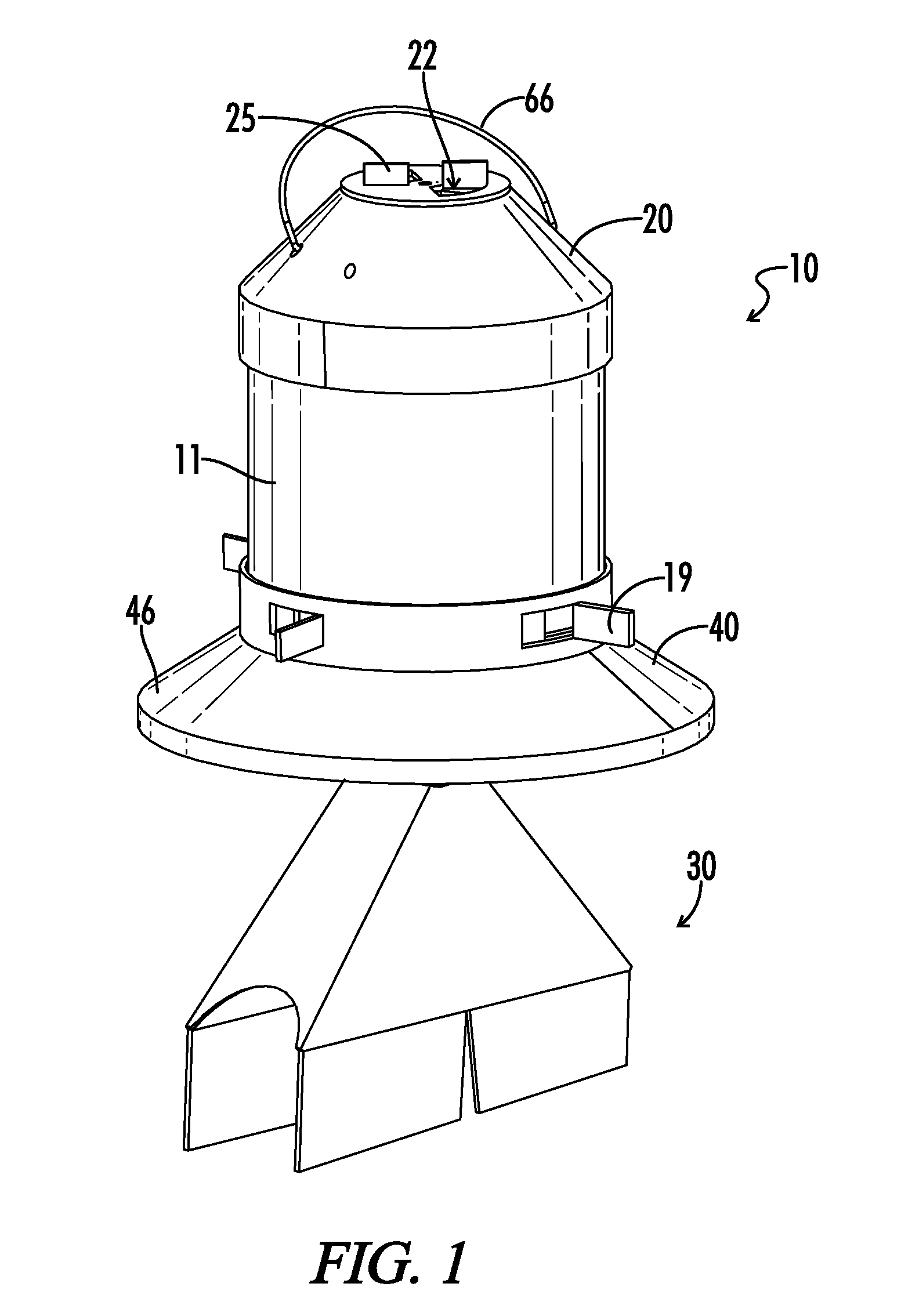

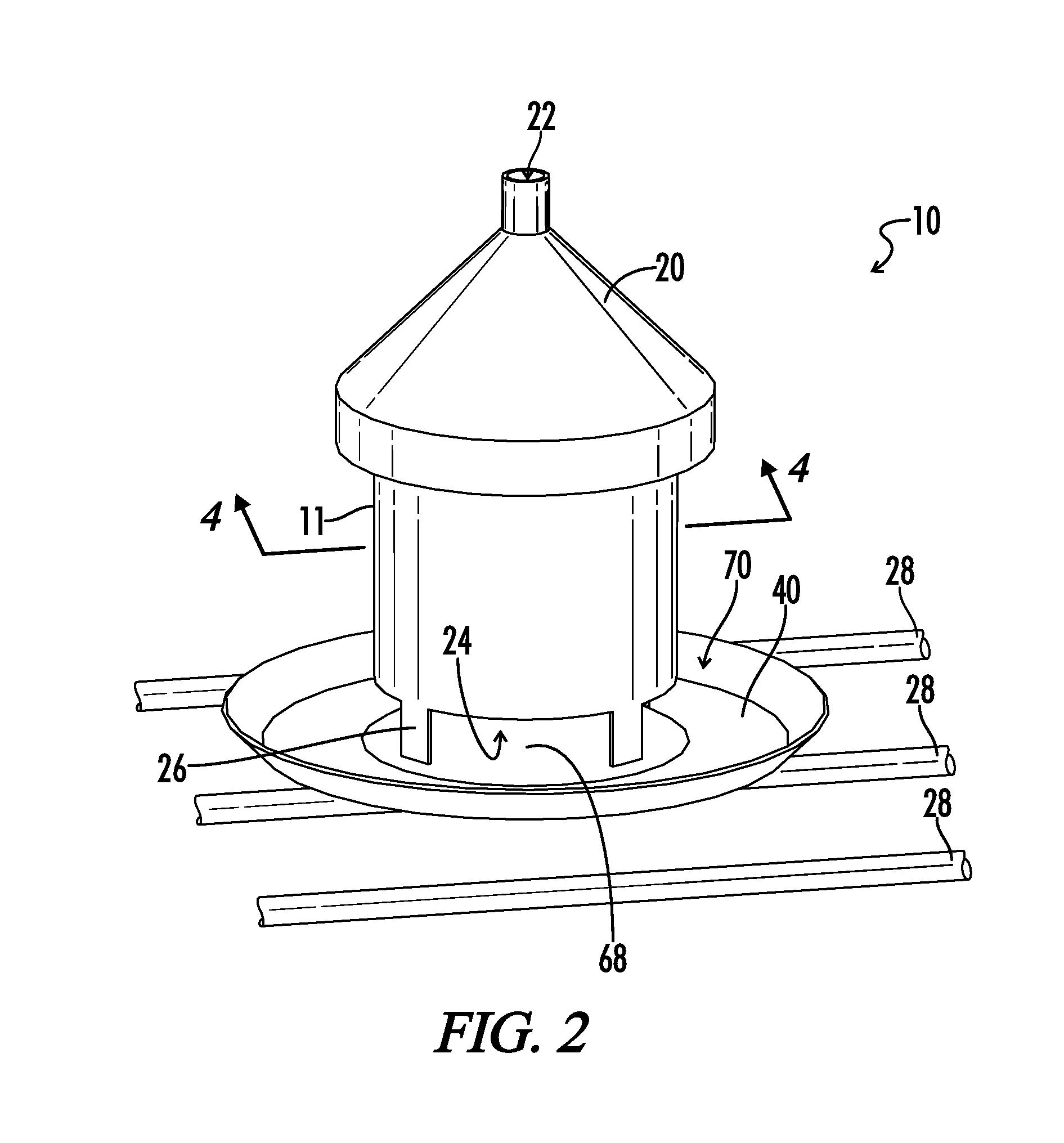

Grill smoker apparatus

ActiveUS20140299005A1Faster the smoke flavor is imparted to the foodSmoke flavorAir-treating devicesClimate change adaptationEngineeringConcentrator

A grill smoker apparatus provides a container and a cover. A carrier is disposed in the container. The carrier is configured to store smoke producing material such as wood chips. The carrier may be removable from the container for filling the container, for emptying the container, for replacing the container or for cleaning the smoker apparatus. The carrier includes an outer dimension smaller than the inner dimension of the container. As such, a carrier gap is defined between the inner container wall and the outer region of the carrier. The carrier gap may form a uniform, annular gap in some embodiments. Alternatively, the carrier gap has a non-uniform radial dimension around the perimeter of the container. The carrier gap provides enhanced airflow to the smoke producing material in the carrier for improving smoker performance. A heat concentrator also focuses heat to the smoker apparatus for igniting the smoke producing material.

Owner:VINETT KEVIN

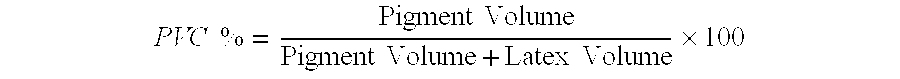

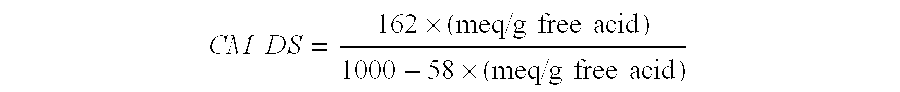

Ether derivatives of raw cotton linters for water-borne coatings

ActiveUS20070105985A1Better TEExpensive to operateLignocellulosic adhesivesLignin material coatingsChemistryEther

A water-borne coating composition containing an ether derivative of raw cotton linters (RCL), a latex polymer, and water in which the ether derivative RCL provides improved rheological properties when compared to analogous cellulose ether compounds produced from more refined cellulose sources while not substantially degrading the coating composition's aesthetic qualities.

Owner:HERCULES LLC

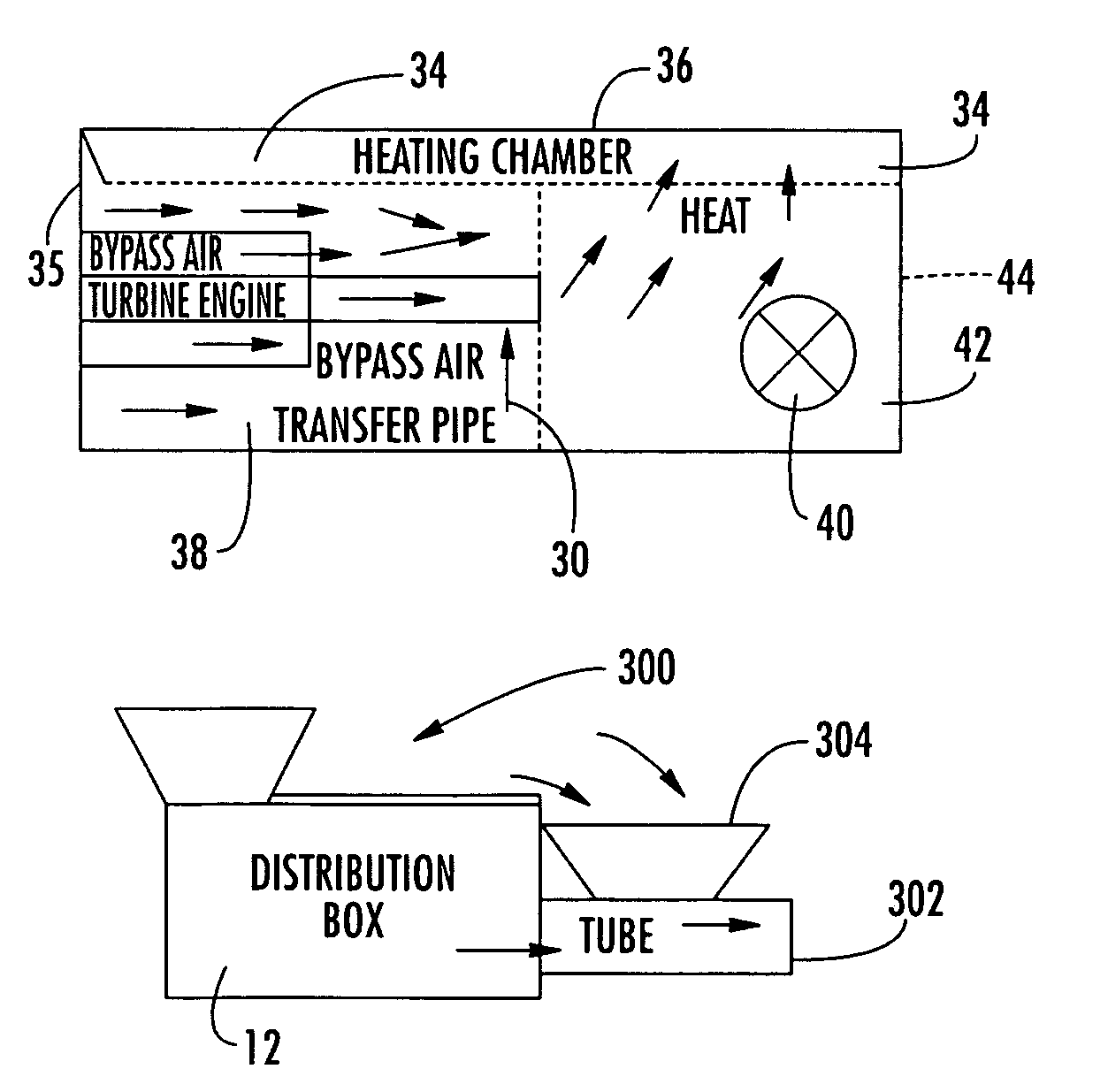

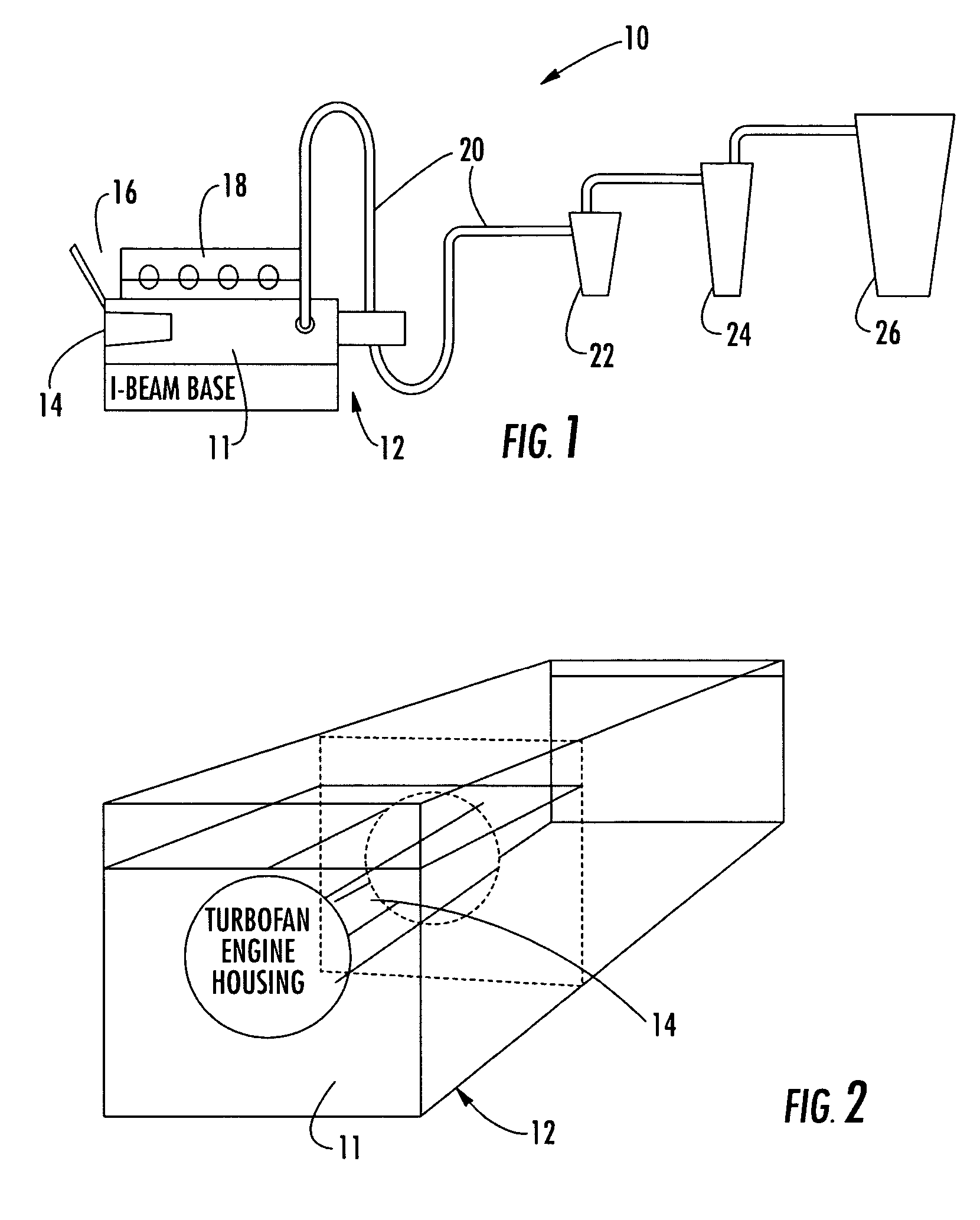

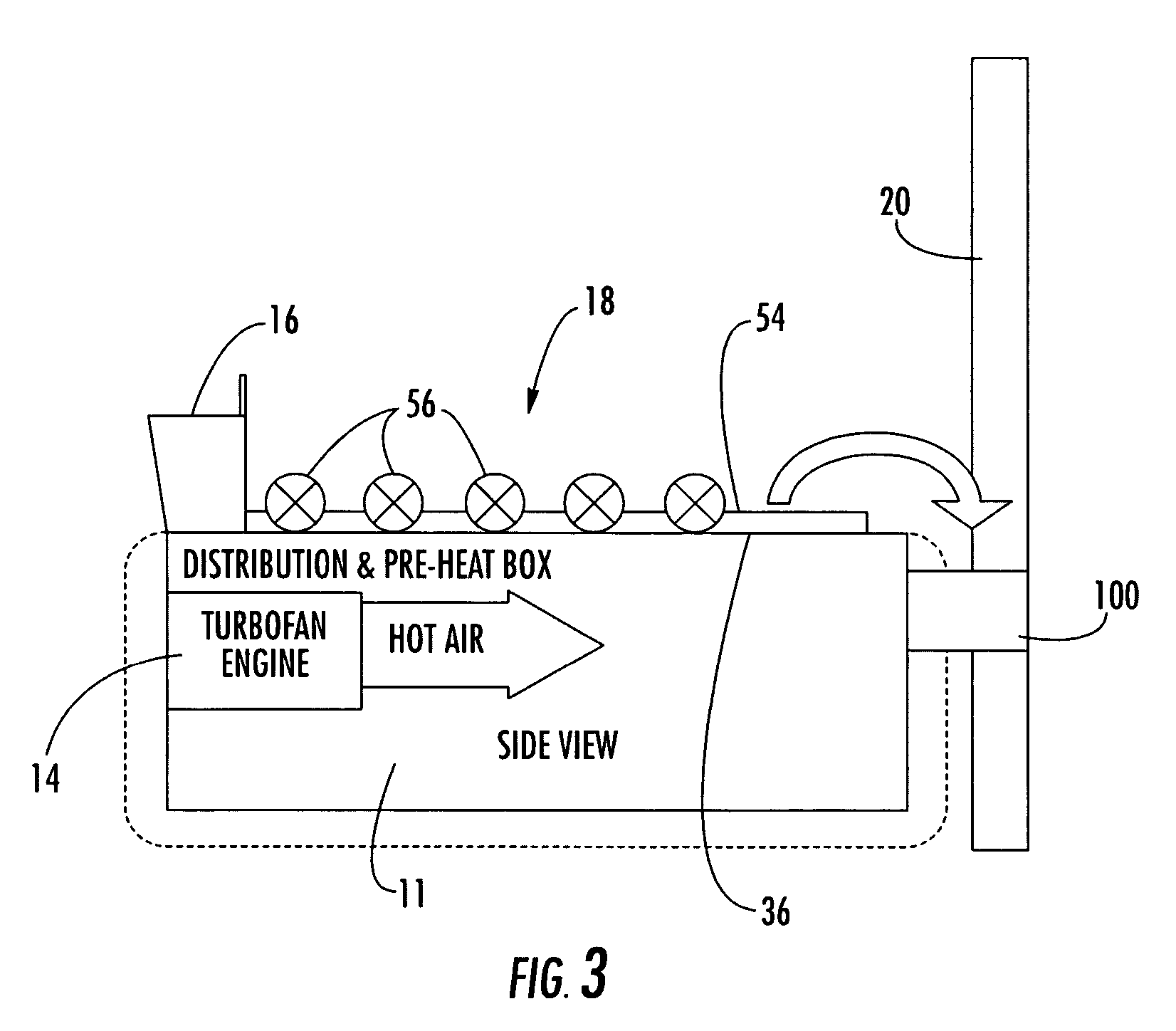

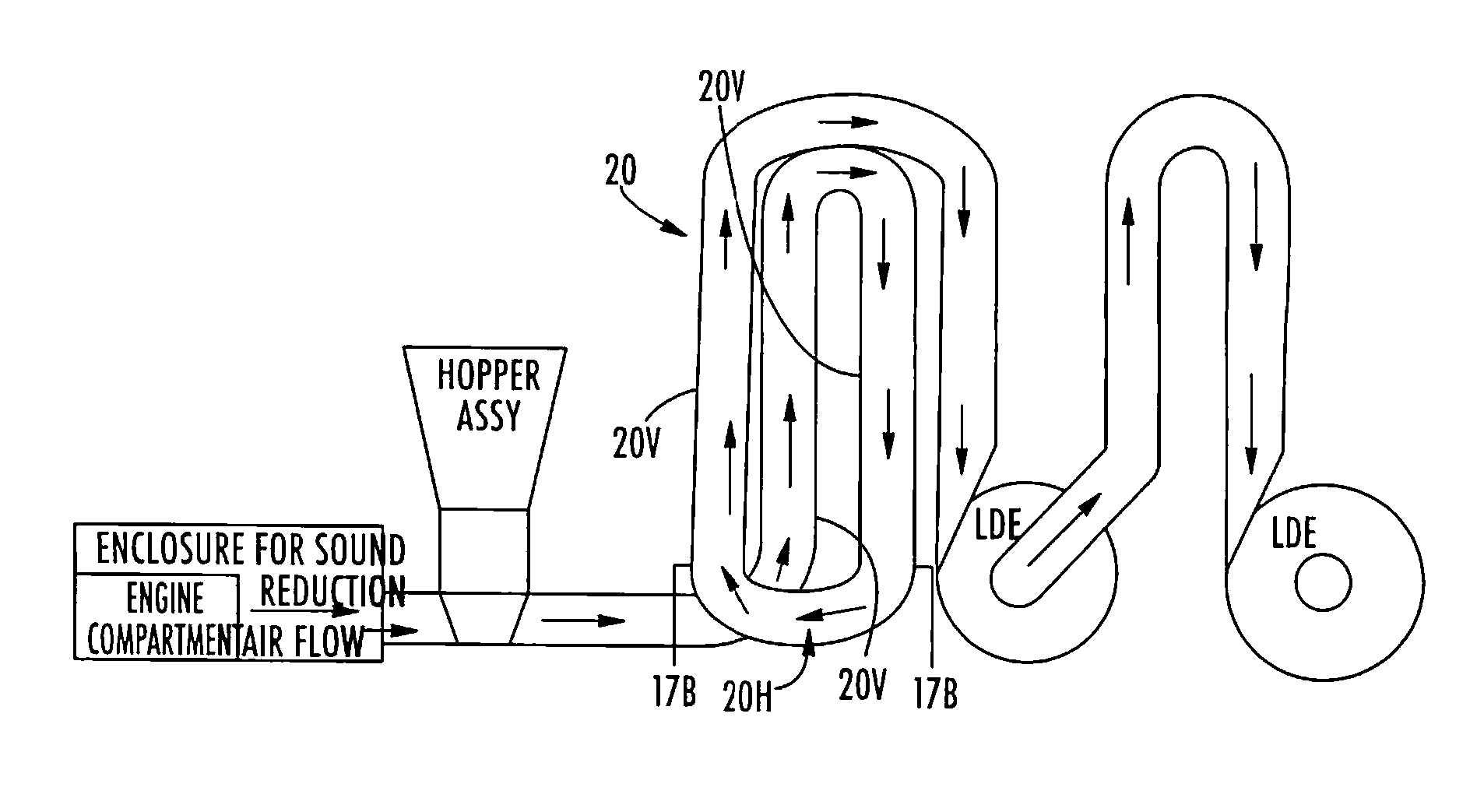

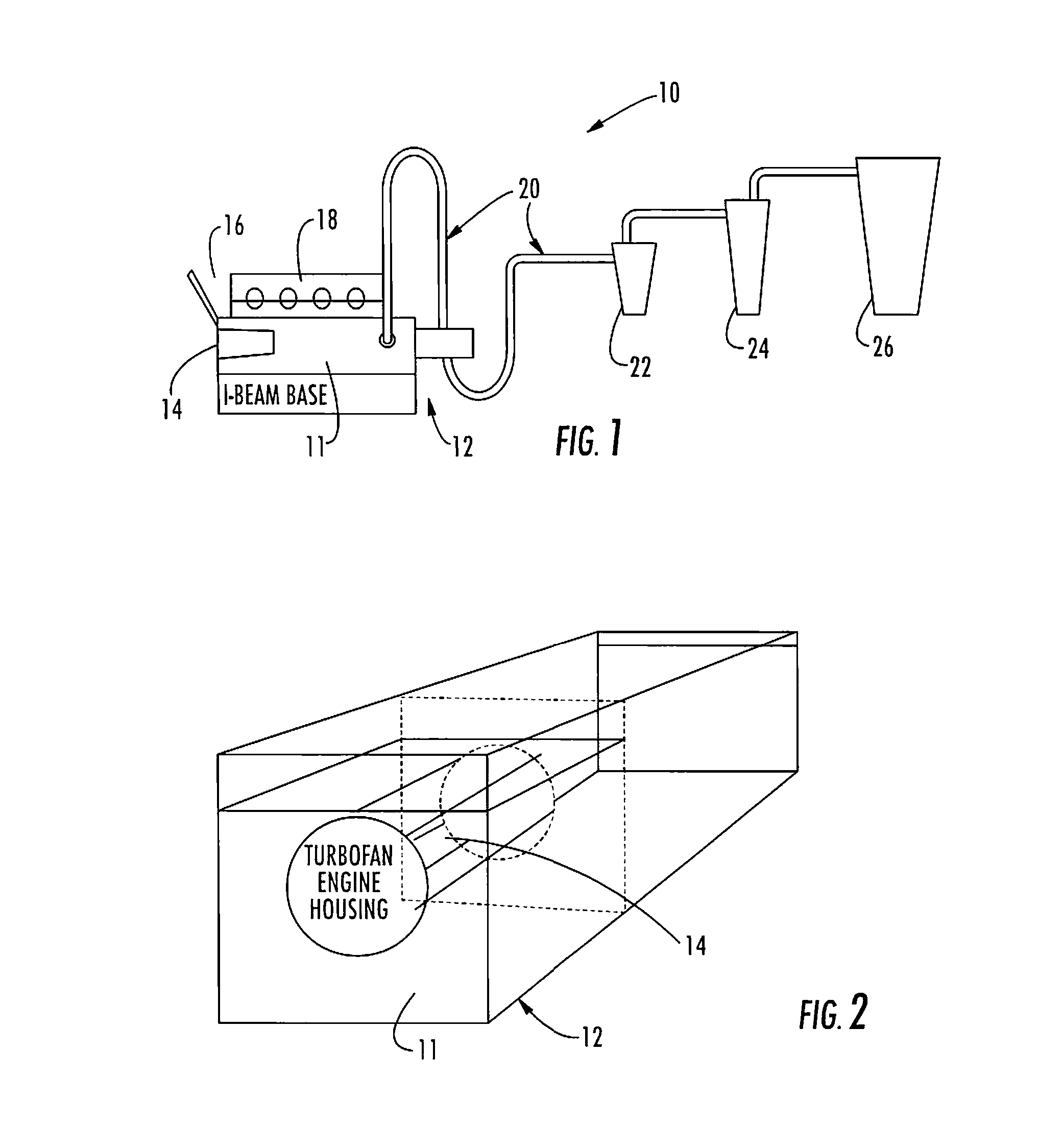

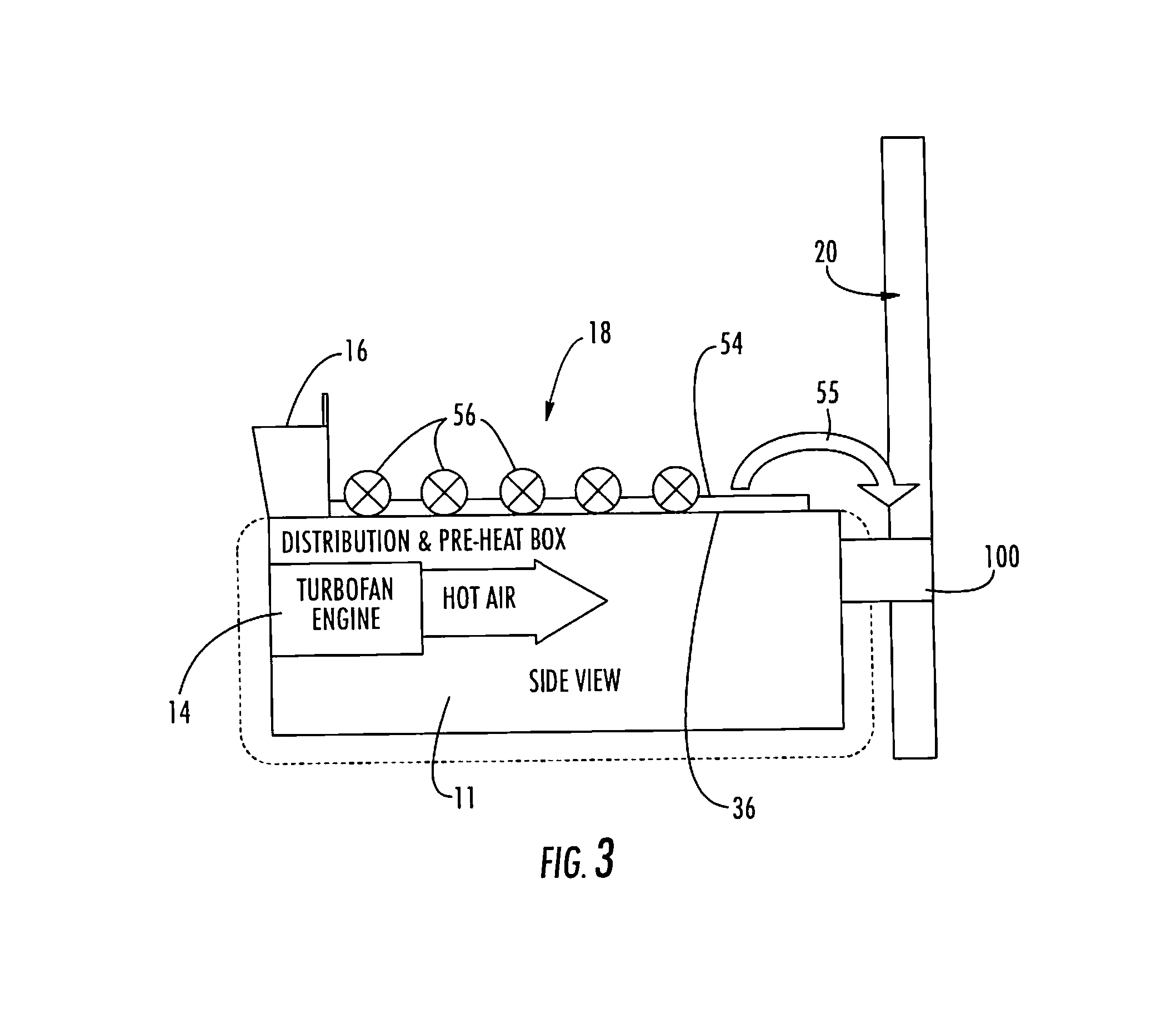

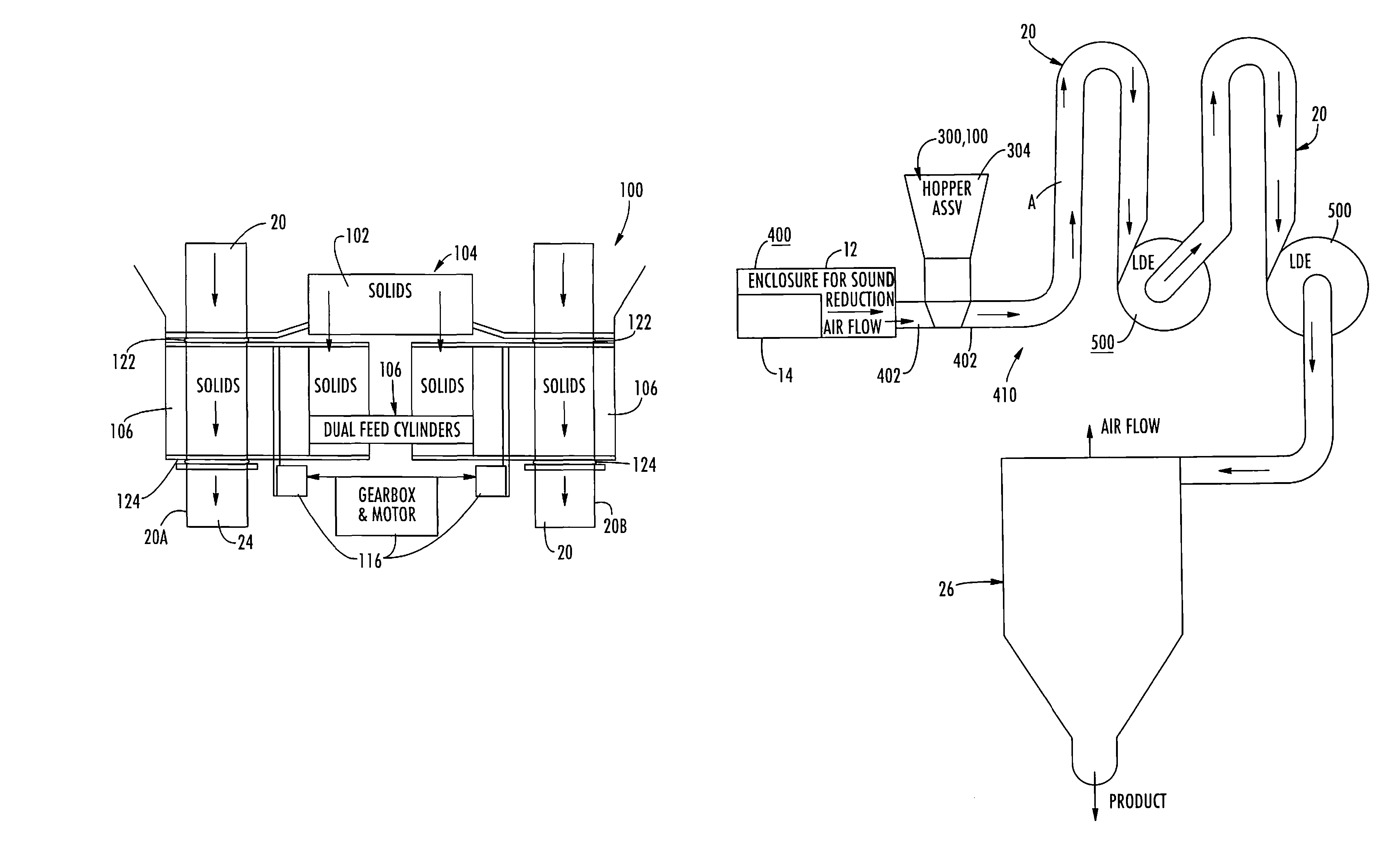

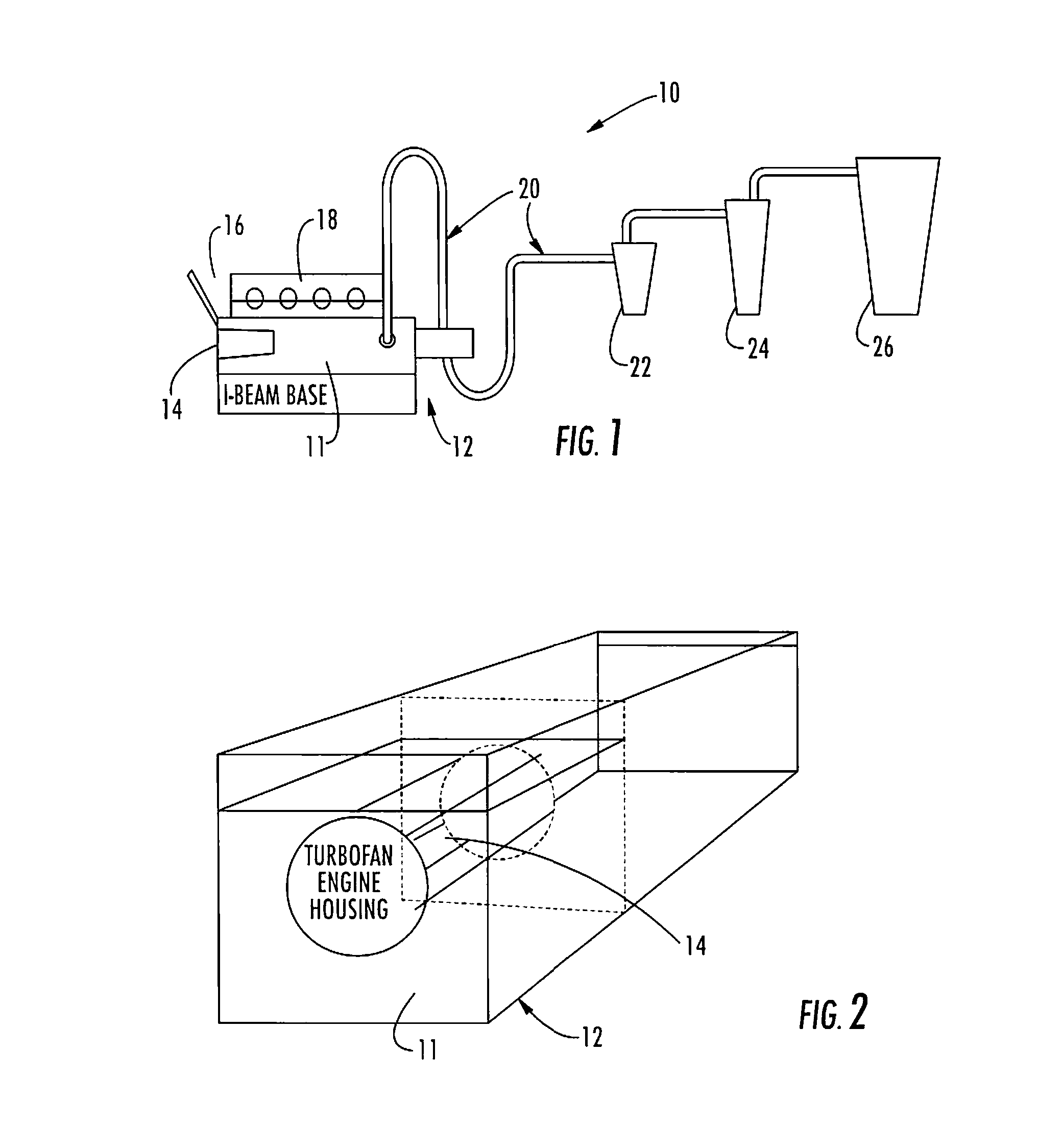

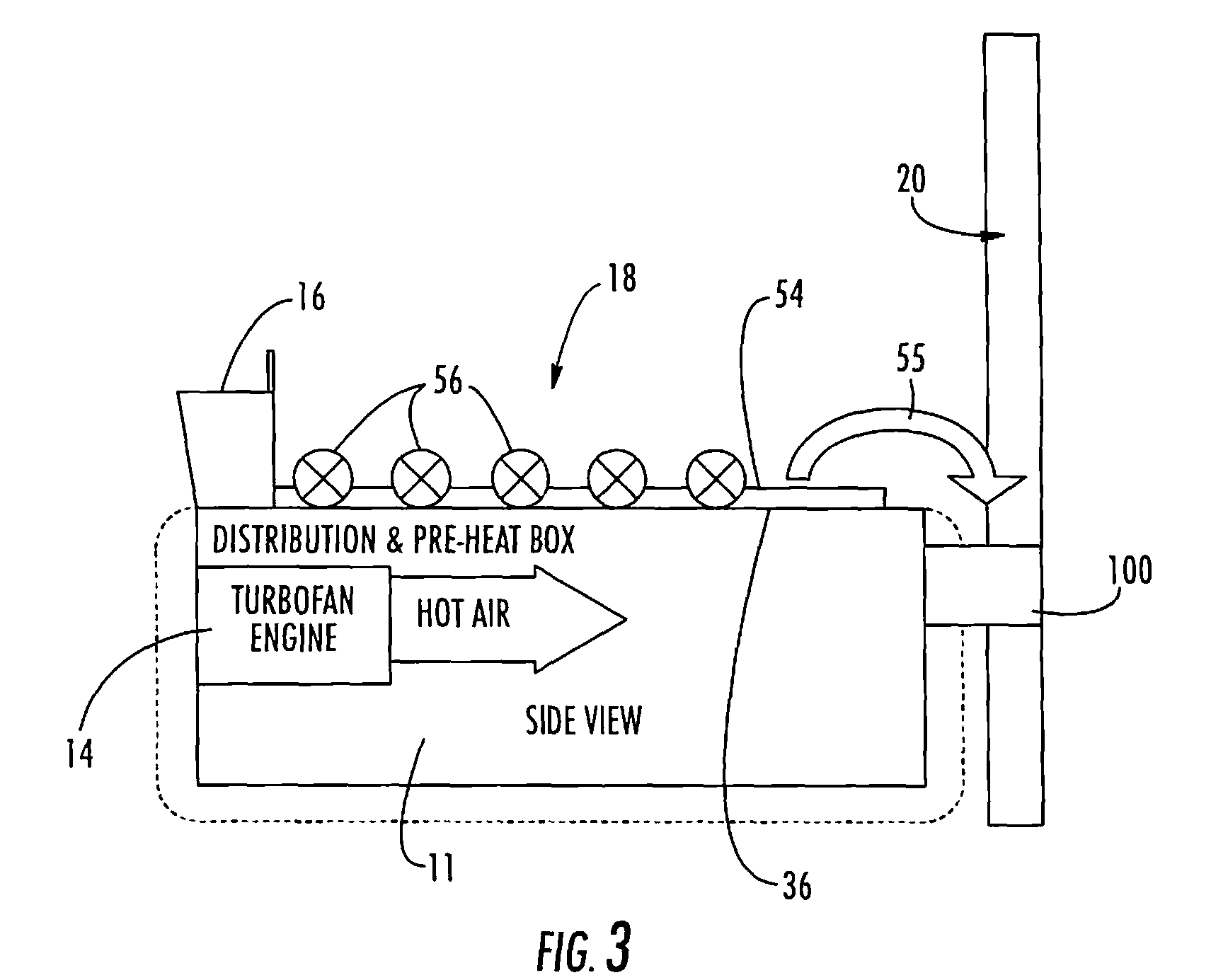

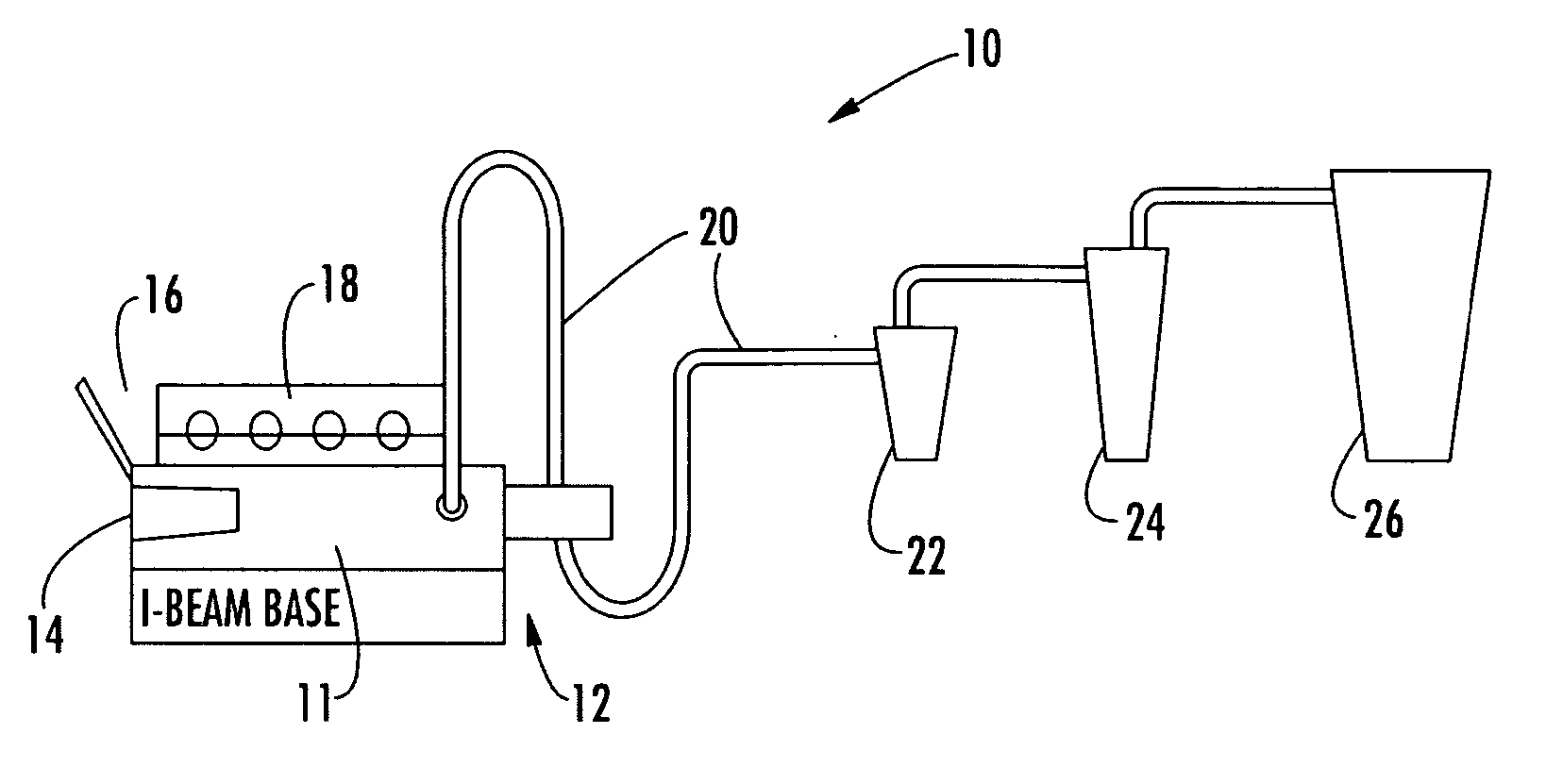

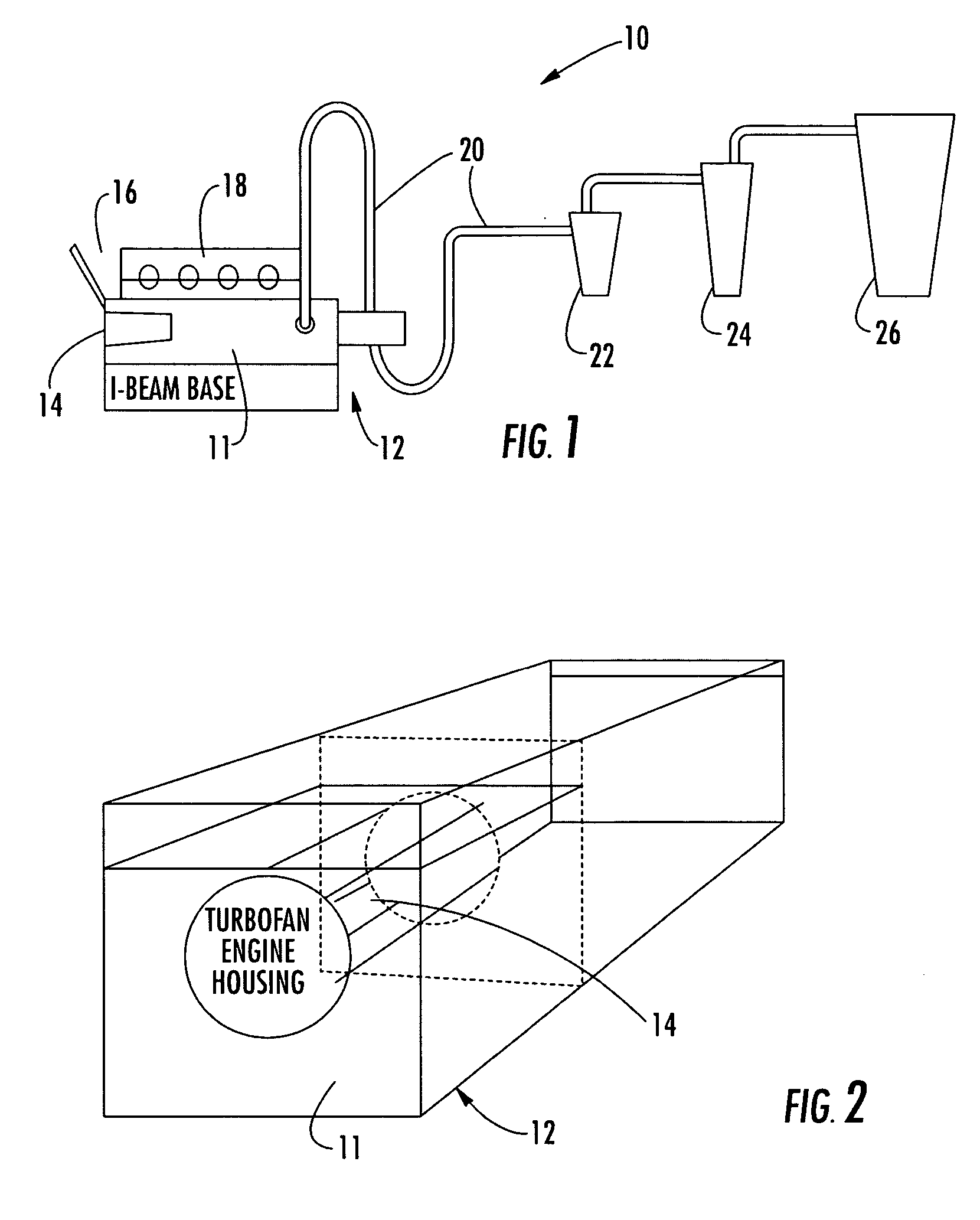

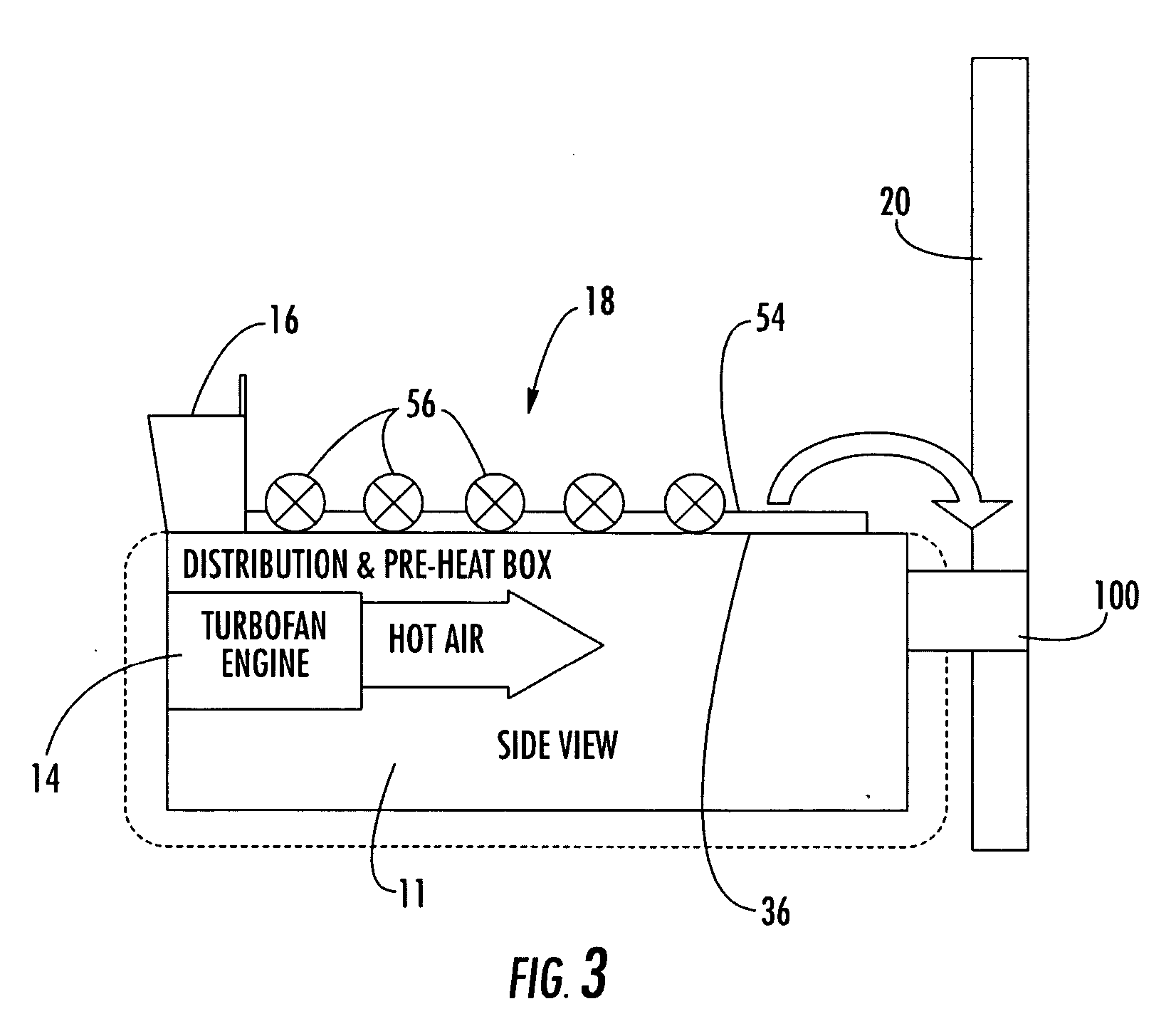

Air dryer system and method employing a jet engine

InactiveUS7178262B2Quality improvementExpensive to operateDrying solid materials with heatBoiling apparatusJet engineAir dryer

An air dryer and process employs a jet engine for producing high quality dried products. A turbofan jet engine in an air-drying system uses both thermal and non-thermal air-drying. The turbofan jet engine is housed within an air distribution chamber for directing exhaust air and bypass air from the jet engine into a product drying tube, where it is dried through a combination of thermal drying from heat content in an engine exhaust, and by the kinetic energy of air flowing past the product traveling through the drying tube, that may include a physical impediment for retarding retard the speed of the product solids flowing in the air stream through the tube.

Owner:STAPLES WESLEY A

System and Method Employing Turbofan Jet Engine for Drying Bulk Materials

InactiveUS20080000100A1Operate operating costQuality improvementDrying solid materials with heatDrying gas arrangementsJet engineTurbofan

An air drying system and process employs a turbofan jet engine for producing high quality dried products. The air drying system uses both thermal and non-thermal air drying. The turbofan jet engine is housed within an air distribution chamber for directing exhaust air and bypass air from the jet engine into a product drying tube, where it is dried through a combination of thermal drying from heat content in an engine exhaust, and by the kinetic energy of air flowing past the product traveling through the drying tube, that may include a physical impediment for retarding retard the speed of the product solids flowing in the air stream through the tube.

Owner:STAPLES WESLEY A

One arm data center topology with layer 4 and layer 7 services

ActiveUS20060095579A1Expensive to operateExpensive to setMultiple digital computer combinationsProgram controlTraffic capacityData center

A one-arm data center topology routes traffic between internal sub-nets and between a sub-net and an outside network through a common chain of services. The data center topology employs layer 4 services on a common chassis or platform to provide routing and firewall services while reducing the number of devices necessary to implement the data center and simplifying configuration. Load balancing is provided by a load balancing device. In the one-arm topology, policy based routing or client network address translations or NAT pushes traffic to the CSM.

Owner:CISCO TECH INC

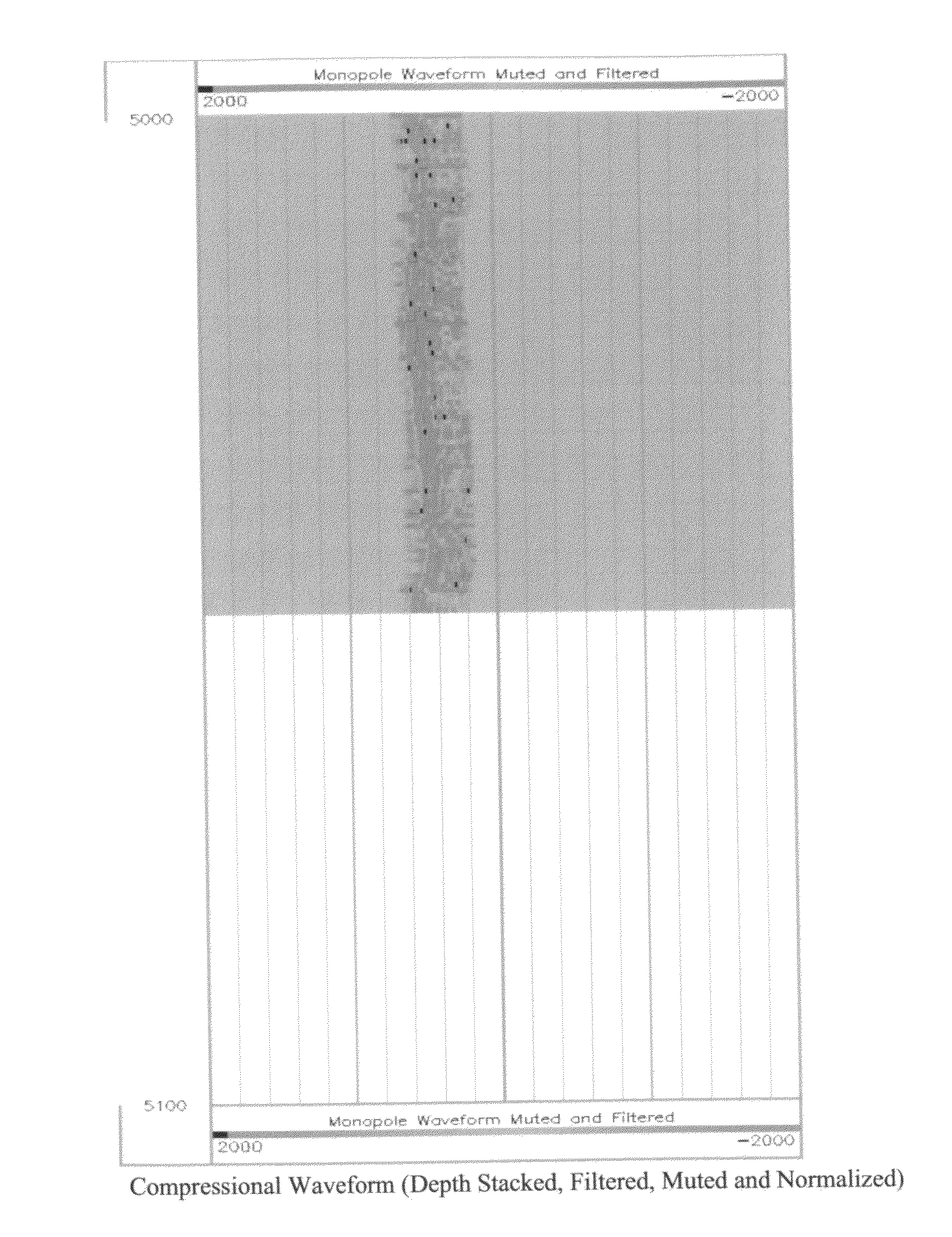

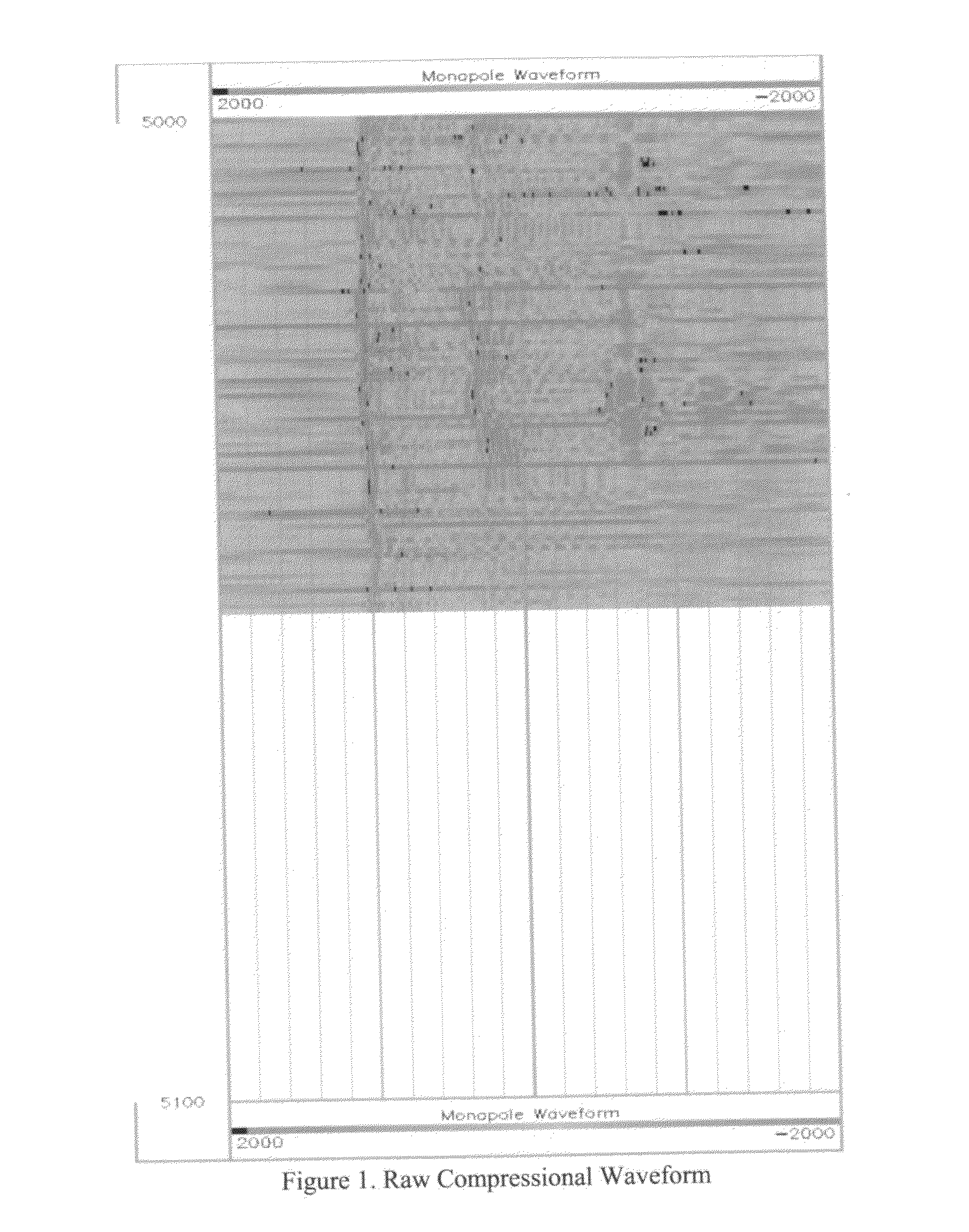

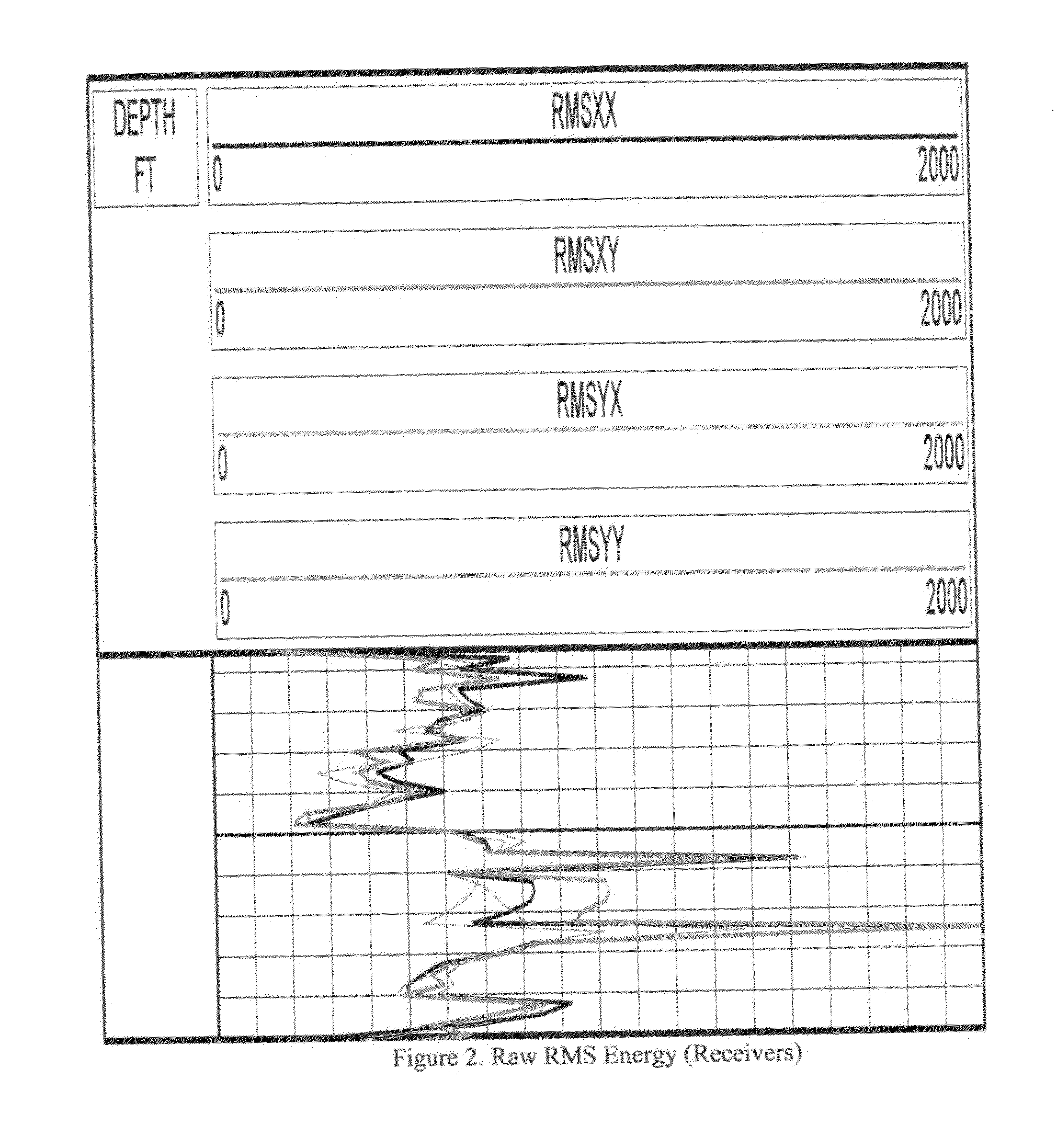

Estimation of anisotropy from compressional waves from array sonic waveforms in well logging

InactiveUS20120092958A1Accurate and complete resultExpensive to operateSeismic signal processingSeismology for water-loggingPresent dayRotation method

The present invention provides an improved method for estimating anisotropic formation from wave data using present-day logging tools that allow for the detection of compressional wave splitting to identify fracture direction. This methodology for analyzing compressional waveforms uses the Alford rotation method.

Owner:GEOBIZ

System and method for direct writing to a wafer

ActiveUS7851774B2Expensive to ownExpensive to operateStability-of-path spectrometersBeam/ray focussing/reflecting arrangementsField sizeLight beam

A direct-write (DW) exposure system is provided which includes a stage for holding a substrate and configured to scan the substrate along an axis during exposure, a data processing module for processing pattering data and generating instructions associated with the patterning data, and an exposure module that includes a plurality of beams that are focused onto the substrate such that the beams cover a width that is larger than a width of a field size and a beam controller that controls the plurality of beams in accordance with the instructions as the substrate is scanned along the axis. The widths are in a direction different from the axis.

Owner:TAIWAN SEMICON MFG CO LTD

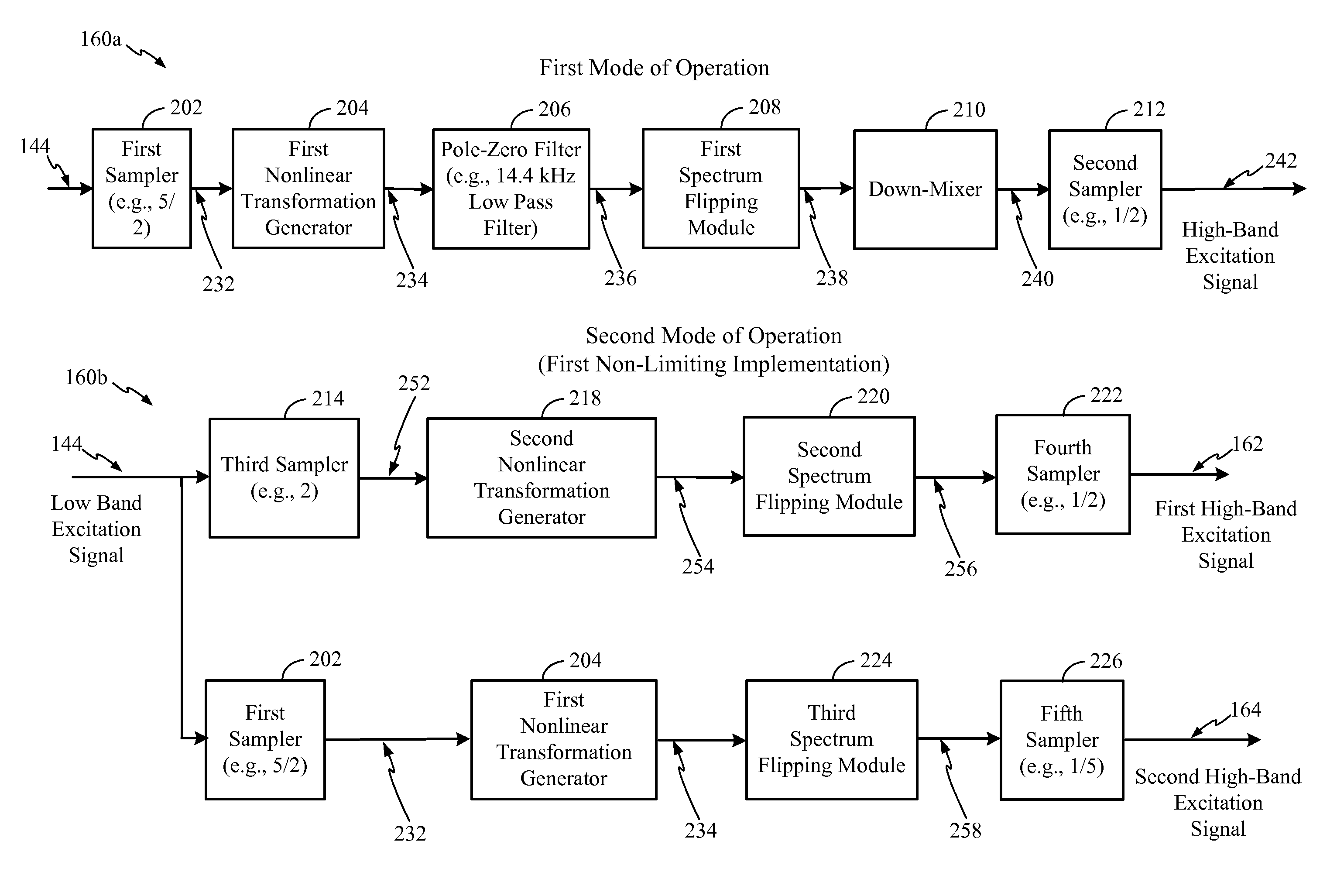

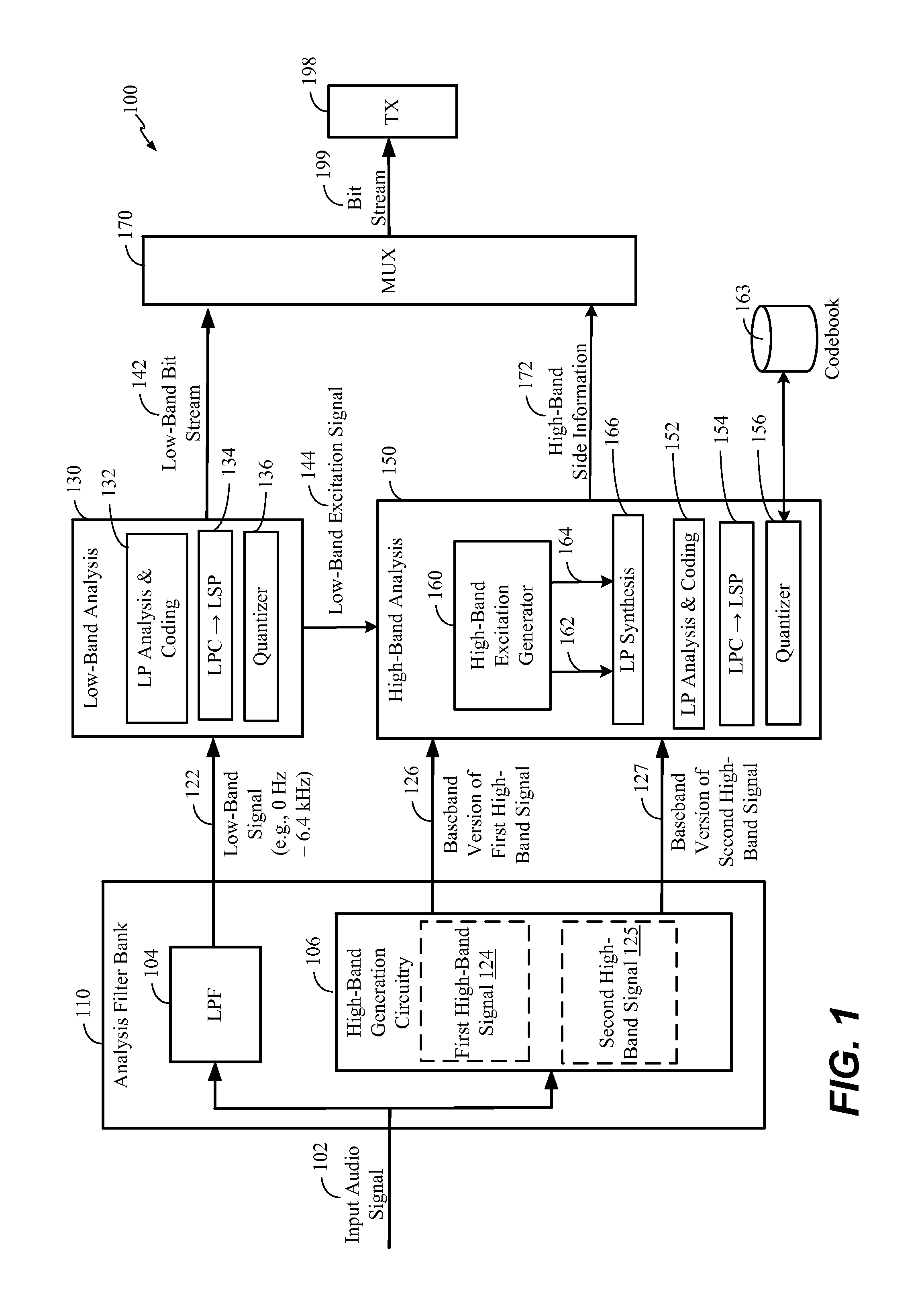

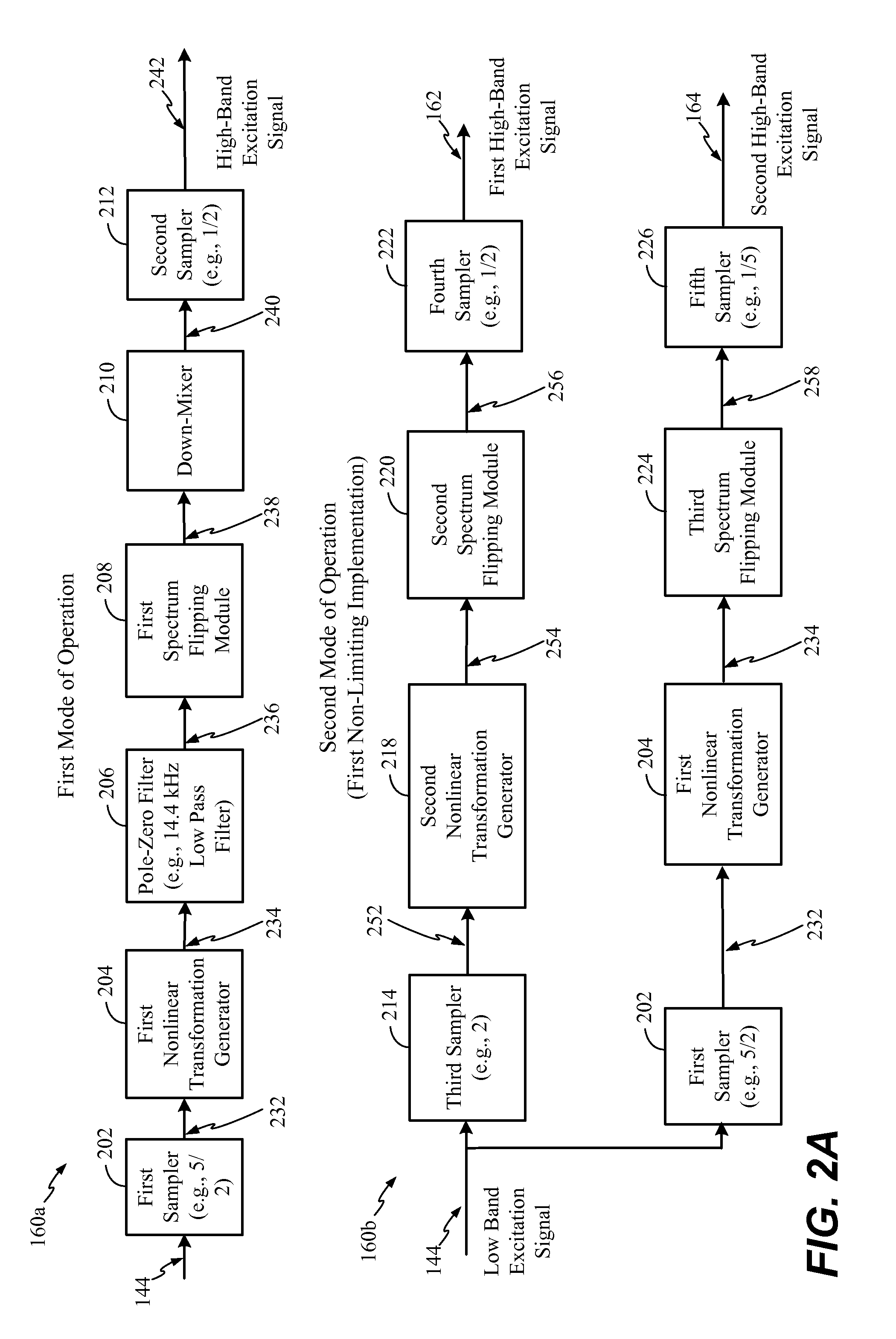

High-band signal coding using multiple sub-bands

A method includes receiving, at a vocoder, an audio signal sampled at a first sample rate. The method also includes generating, at a low-band encoder of the vocoder, a low-band excitation signal based on a low-band portion of the audio signal. The method further includes generating a first baseband signal at a high-band encoder of the vocoder. Generating the first baseband signal includes performing a spectral flip operation on a nonlinearly transformed version of the low-band excitation signal. The first baseband signal corresponds to a first sub-band of a high-band portion of the audio signal. The method also includes generating a second baseband signal corresponding to a second sub-band of the high-band portion of the audio signal. The first sub-band is distinct from the second sub-band.

Owner:QUALCOMM INC

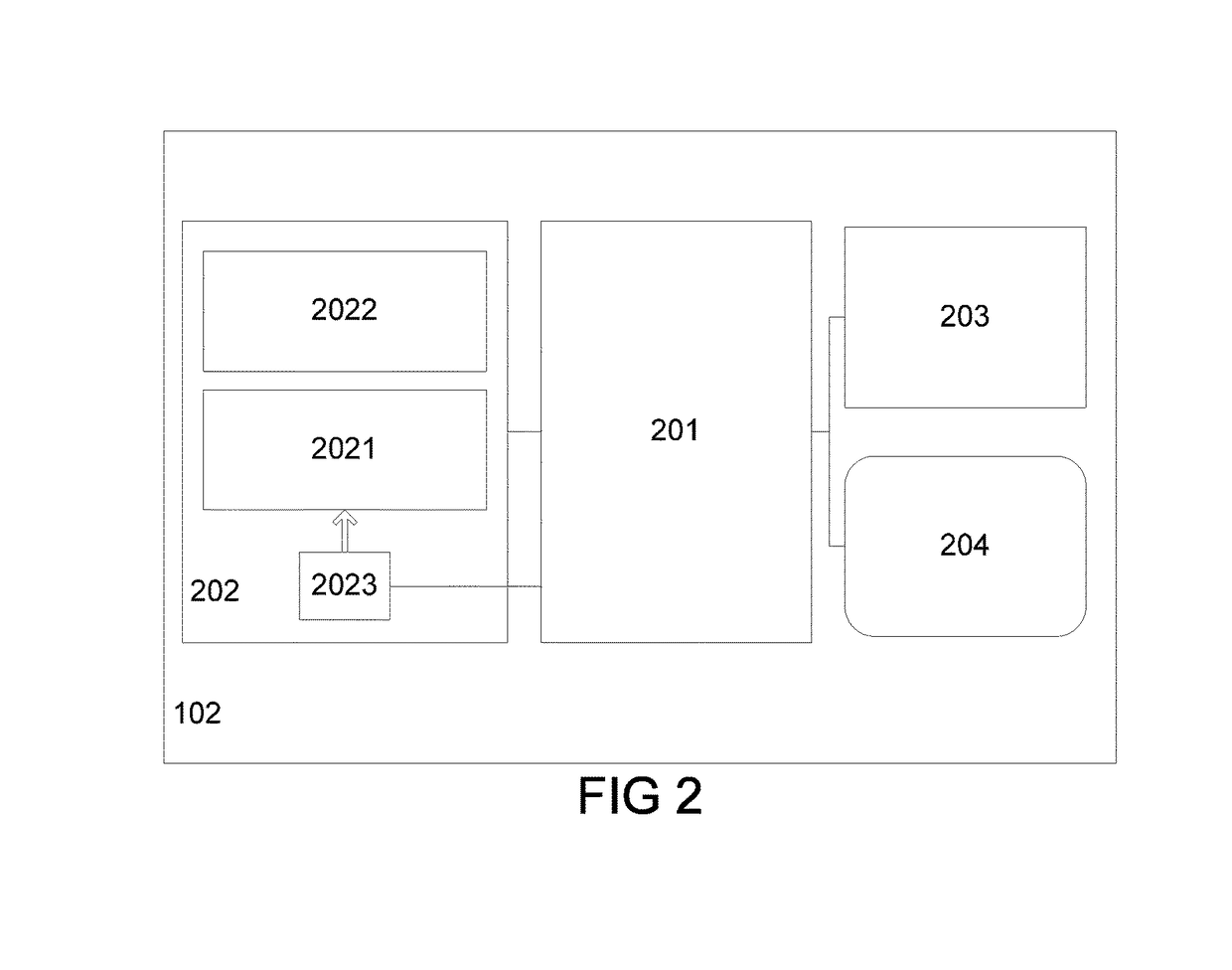

A method for operating a communication device in a communication network, a communication device, a luminaire equipped with such communication device

ActiveUS20160156765A1Easy to debugSimplify configuration phaseNetwork topologiesConnection managementTransceiverCommunication device

This invention related to a communication device and a method for operating a communication device comprising a transceiver being adapted to communicate in a communication network, comprising a configuration phase including the step of (a1) the communication device obtaining by means of a first telecommunication mode a selected role profile selected out of a set of role profiles, said selected role profile defining the role of the communication device in the communication network in an operation phase, and an operation phase including the steps of (b1) the communication device disabling or maintaining its transceiver to communicate by means of the first telecommunication mode depending on the selected role profile; (b2) the communication device communicating in the network using a second telecommunication mode.

Owner:SIGNIFY HLDG BV

System and method employing turbofan jet engine for drying bulk materials

InactiveUS7984566B2Quality improvementExpensive to operateDrying solid materials with heatDrying gas arrangementsJet engineHot blast

Owner:STAPLES WESLEY A

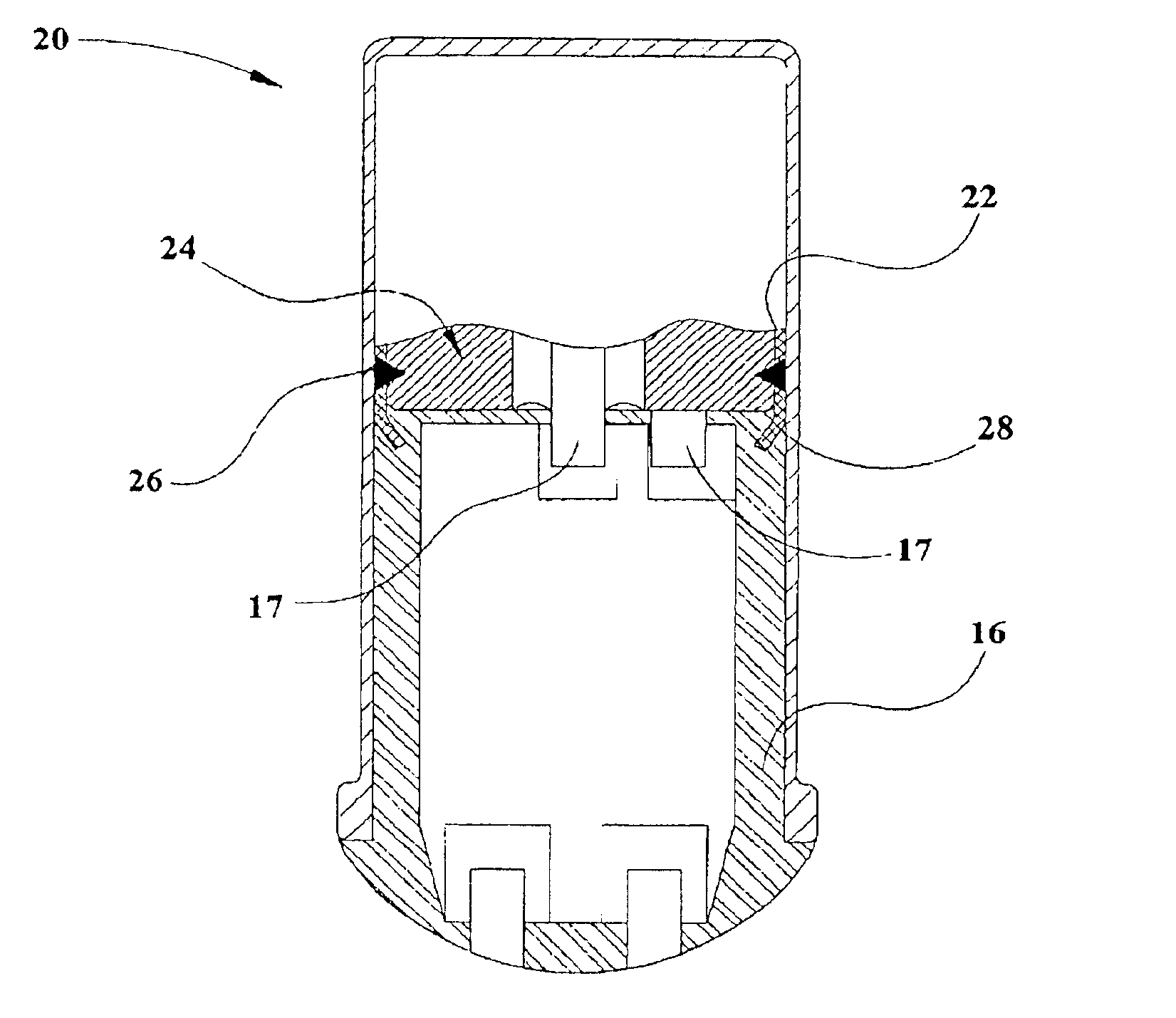

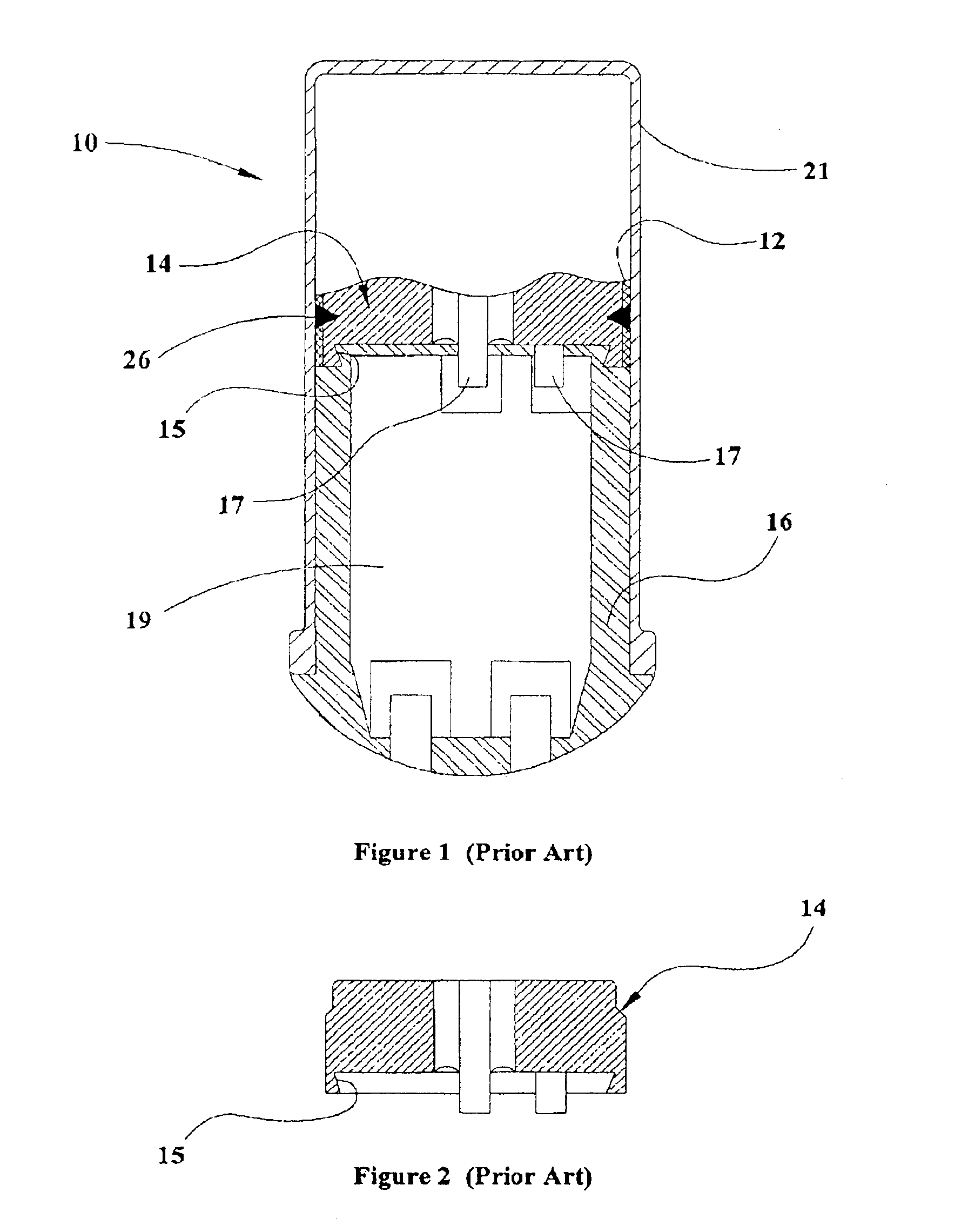

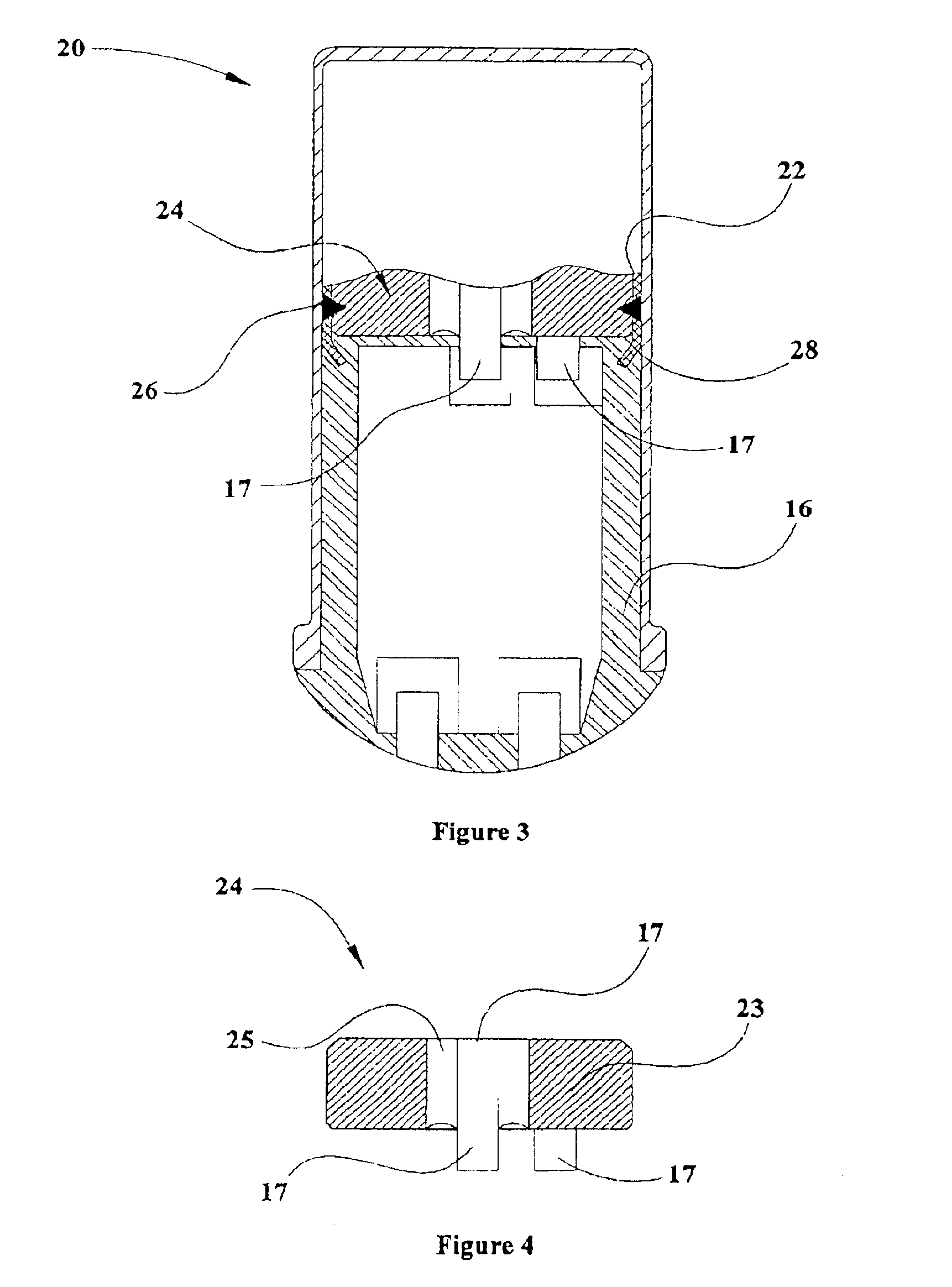

Pyrotechnic initiator having output can with encapsulation material retention feature

InactiveUS6907827B2Expensive to operateEffective and economical encapsulation material retention featureBlasting cartridgesElectric fuzesPyrotechnic initiatorEngineering

A pyrotechnic initiator is provided with an encapsulation material retention feature on the output can, such as a swaged end or anchors.

Owner:DAICEL CHEM IND LTD

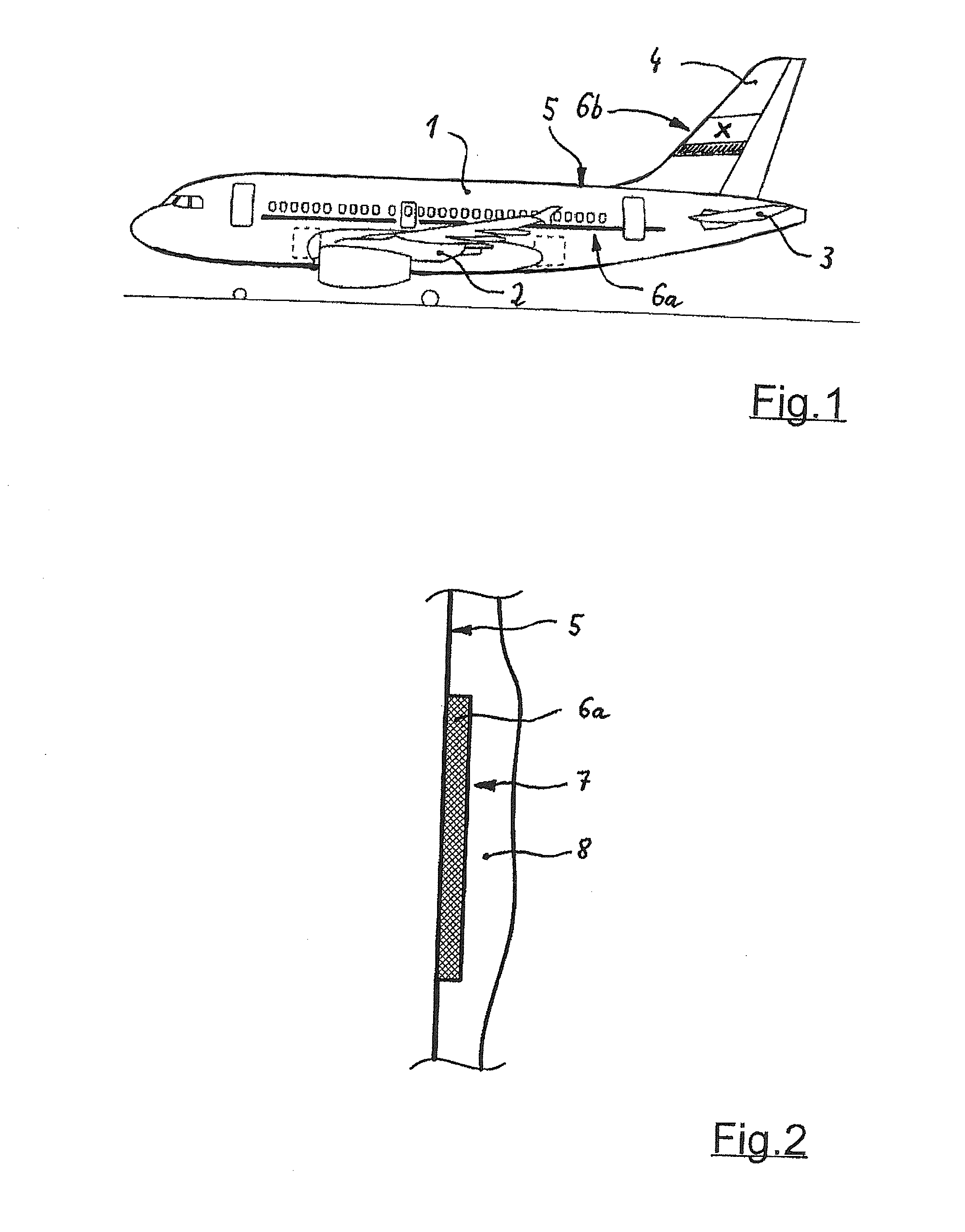

Aircraft with painted exterior surface and decorative film

InactiveUS20100316853A1Keep for a long timeQuality improvementAdhesive articlesSynthetic resin layered productsPolypropyleneAirplane

An aircraft includes a fuselage having a painted exterior surface having a first color; a decorative film including plastic and having a second color different from the first color and adhesively bonded to the fuselage, wherein the decorative film includes at least one of a polyvinyl fluoride film, a polyester film, a polyvinyl chloride film, a polyethylene film, and a polypropylene film, wherein the decorative film is formable via one of polymerization, polyaddition and polycondensation; and a layer of clear paint containing a UV filter for erosion protection and covering the decorative film.

Owner:AIRBUS OPERATIONS GMBH

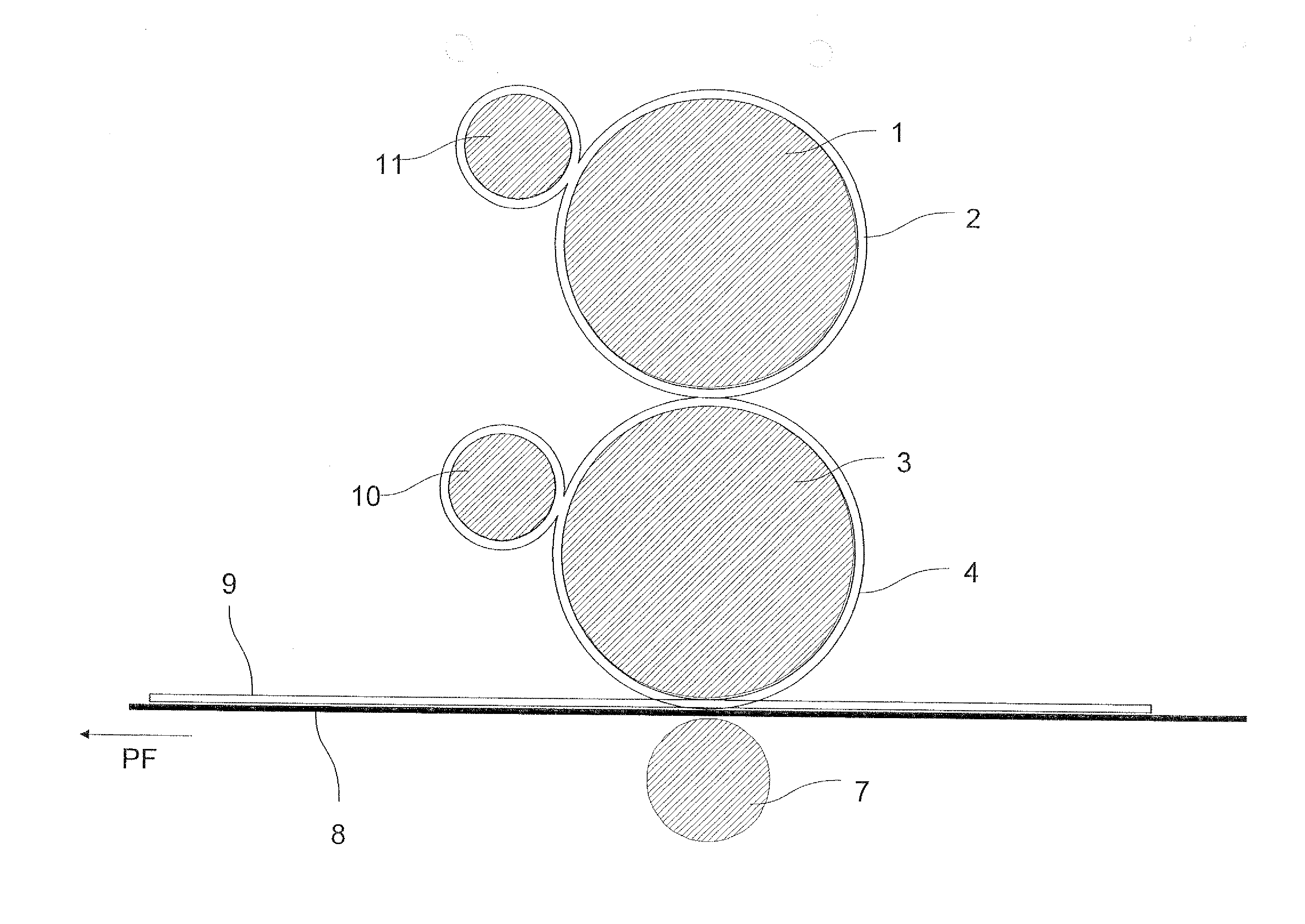

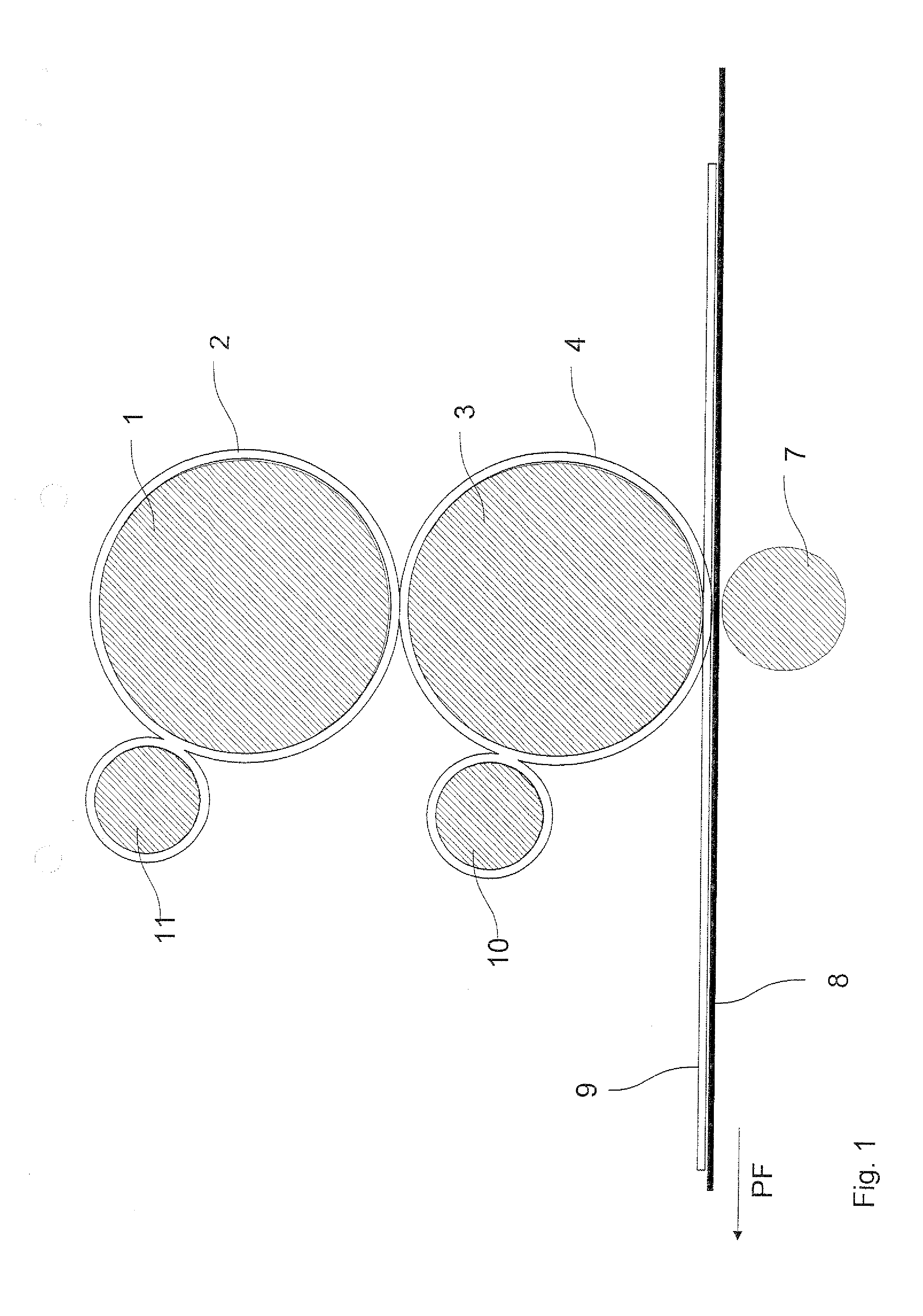

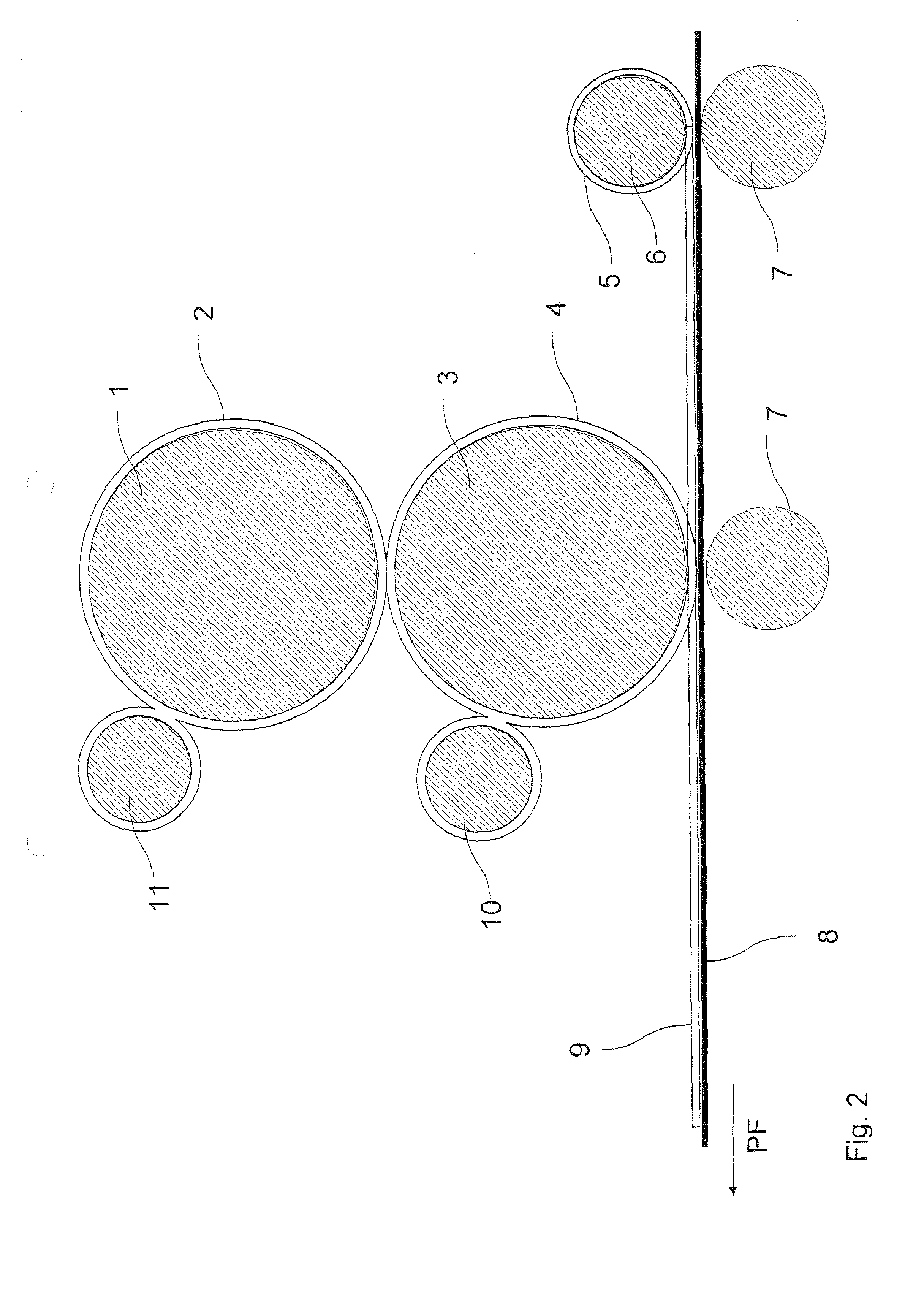

Toner for printing method and method for electrophoretic printing process

InactiveUS20110003245A1Keep dryAvoid contactElectrographic processes using photoelectrophoresisElectrographic process apparatusChemistryElectrophoresis

Owner:OCE PRINTING SYST

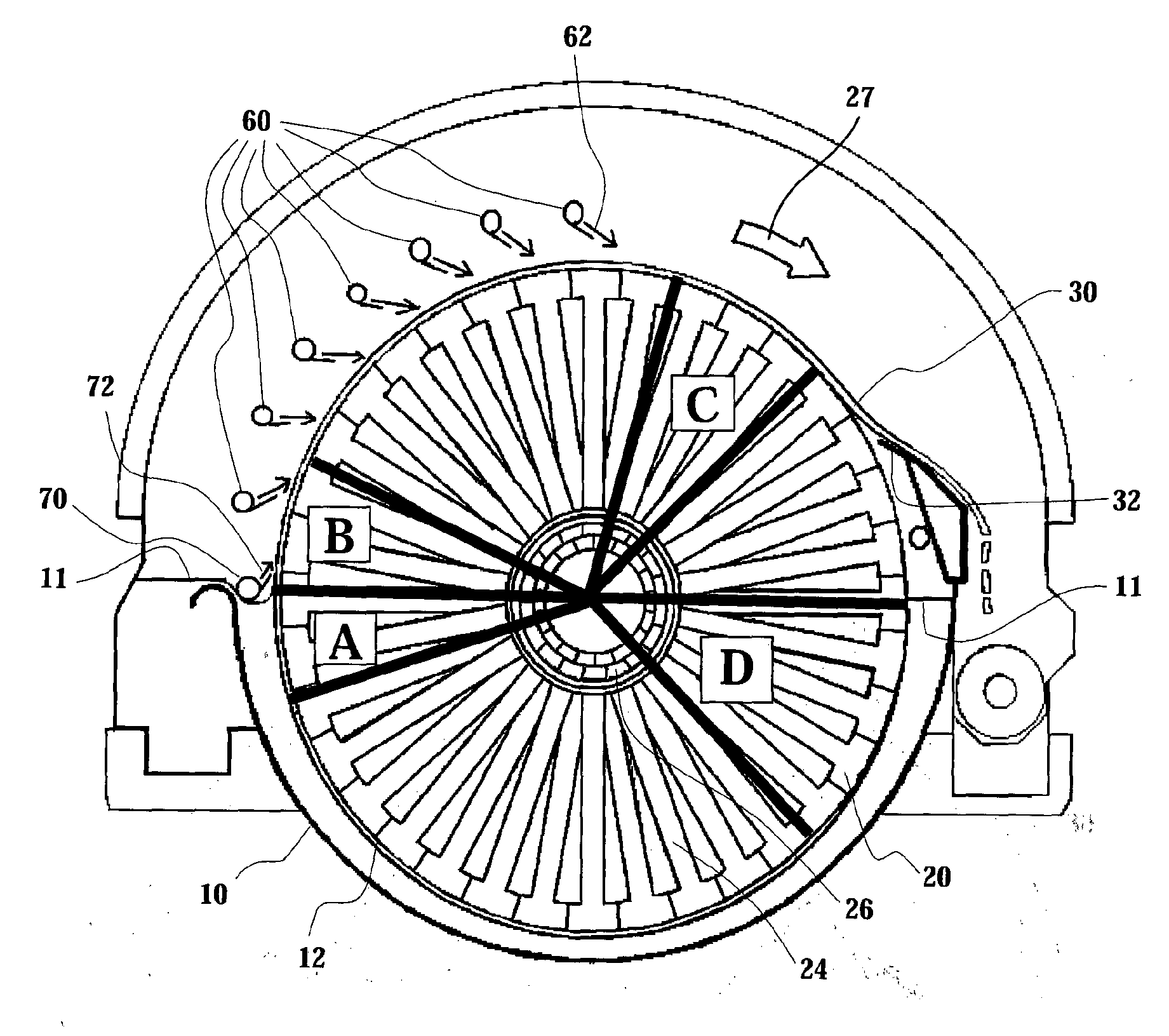

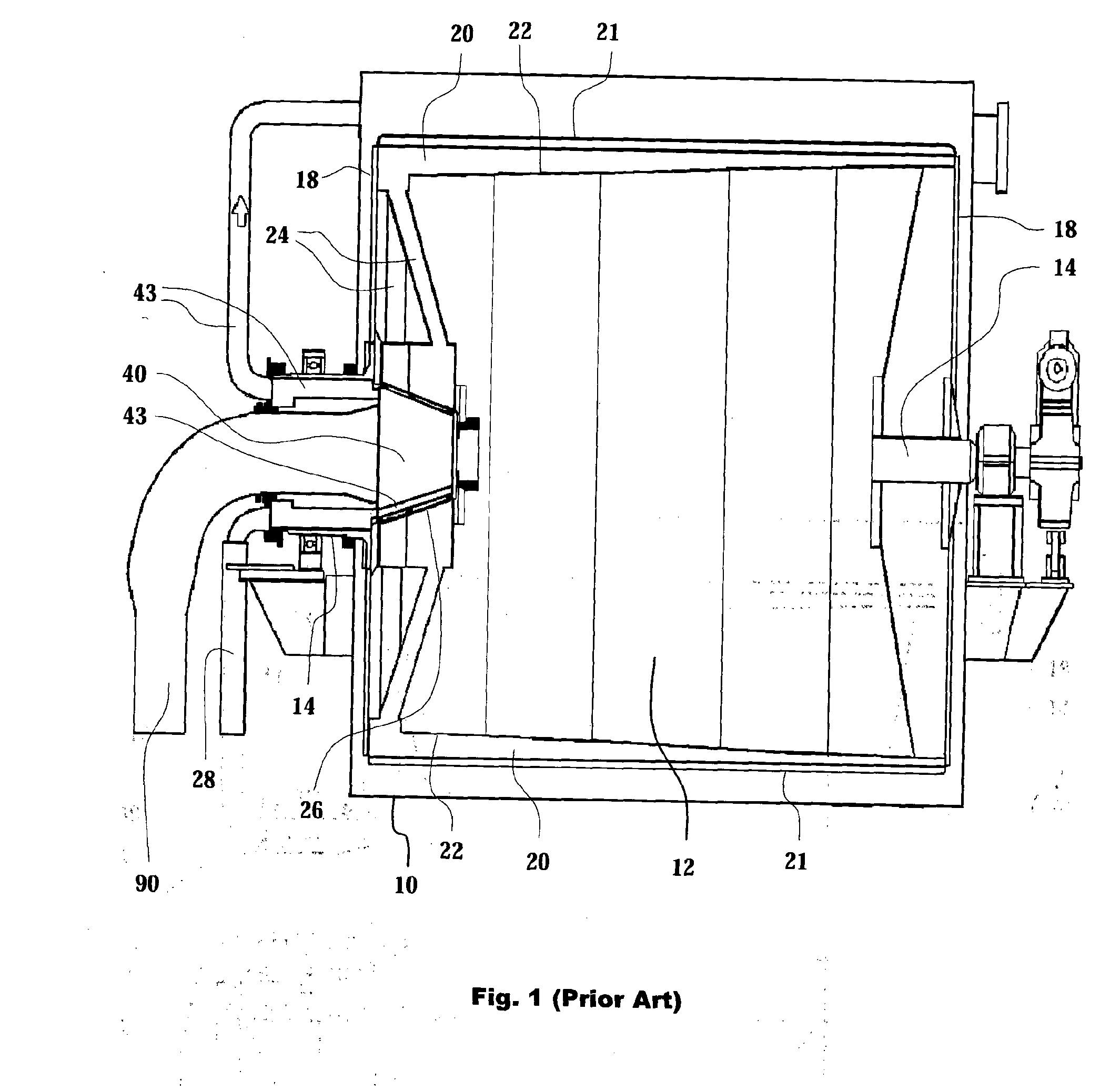

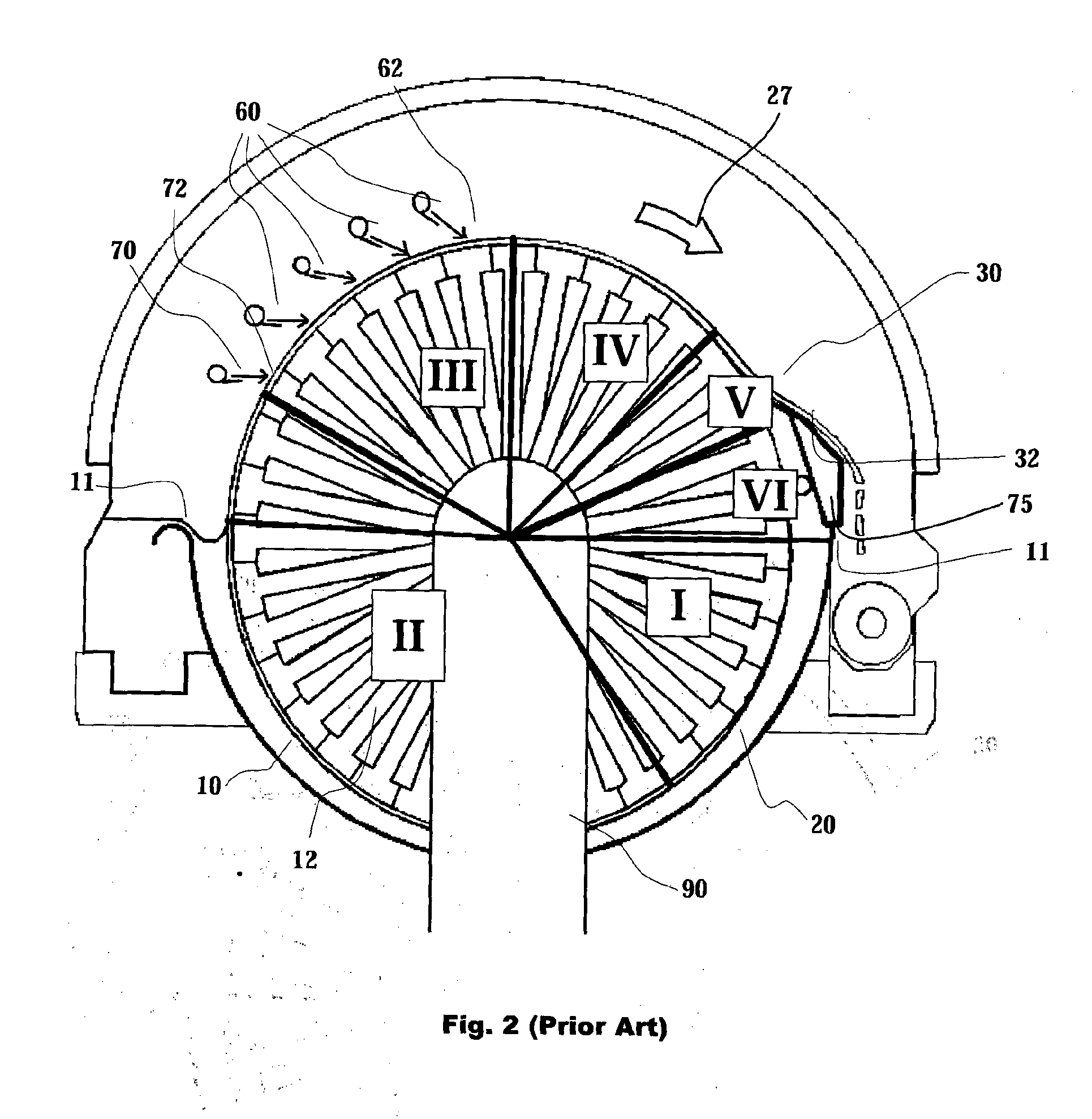

Method and apparatus for washing pulp by means of intensified suction

ActiveUS20140353260A1Improve Emissions ConsistencyReduce impurityWashing/displacing pulp-treating liquorsWater/sewage treatmentFiltrationPulp and paper industry

A method and an apparatus for washing a solids-containing suspension by means of a suction drum washer comprising a drum provided with a filtration surface, a main vacuum source such as a drop leg and washing tubes connected to the frame of the suction drum washer. A washing liquid stream is introduced by a first washing tube is directed to contact the pulp layer on the surface of the drum in a point below 10 degrees after the surface of the suspension and a vacuum of at least 0.1 bar greater than the main vacuum source, i.e. intensified suction is applied by means of a separate vacuum source to filtering surface at the contacting point of the first liquid stream and the pulp layer or maximum of 10 degrees before the contacting point. The intensified suction may be utilized also for boosting end of filtration stage (II) and drying stage (IV). Filtrate from the drying stage (IV) can be used at the same washer as a washing liquid at the first or the second washing tube.

Owner:ANDRIZ OY

Method for operating a communication device in a communication network, a communication device, a luminaire equipped with such communication device

ActiveUS9930166B2Simplify configuration phaseReduce maintenanceNetwork topologiesConnection managementTransceiverCommunication device

This invention related to a communication device and a method for operating a communication device comprising a transceiver being adapted to communicate in a communication network, comprising a configuration phase including the step of (a1) the communication device obtaining by means of a first telecommunication mode a selected role profile selected out of a set of role profiles, said selected role profile defining the role of the communication device in the communication network in an operation phase, and an operation phase including the steps of (b1) the communication device disabling or maintaining its transceiver to communicate by means of the first telecommunication mode depending on the selected role profile; (b2) the communication device communicating in the network using a second telecommunication mode.

Owner:SIGNIFY HLDG BV

Coalescing memory barrier operations across multiple parallel threads

ActiveUS9223578B2Reduce impactExpensive to operateMultiprogramming arrangementsConcurrent instruction executionParallel computingSystem level

One embodiment of the present invention sets forth a technique for coalescing memory barrier operations across multiple parallel threads. Memory barrier requests from a given parallel thread processing unit are coalesced to reduce the impact to the rest of the system. Additionally, memory barrier requests may specify a level of a set of threads with respect to which the memory transactions are committed. For example, a first type of memory barrier instruction may commit the memory transactions to a level of a set of cooperating threads that share an L1 (level one) cache. A second type of memory barrier instruction may commit the memory transactions to a level of a set of threads sharing a global memory. Finally, a third type of memory barrier instruction may commit the memory transactions to a system level of all threads sharing all system memories. The latency required to execute the memory barrier instruction varies based on the type of memory barrier instruction.

Owner:NVIDIA CORP

Air dryer system and method employing a jet engine

InactiveUS20060053653A1Quality improvementExpensive to operateDrying solid materials with heatDrying machines with non-progressive movementsJet engineAir dryer

An air dryer and process employs a jet engine for producing high quality dried products. A turbofan jet engine in an air-drying system uses both thermal and non-thermal air-drying. The turbofan jet engine is housed within an air distribution chamber for directing exhaust air and bypass air from the jet engine into a product drying tube, where it is dried through a combination of thermal drying from heat content in an engine exhaust, and by the kinetic energy of air flowing past the product traveling through the drying tube, that may include a physical impediment for retarding retard the speed of the product solids flowing in the air stream through the tube.

Owner:STAPLES WESLEY A