Patents

Literature

44results about How to "Reduce crystal defect density" patented technology

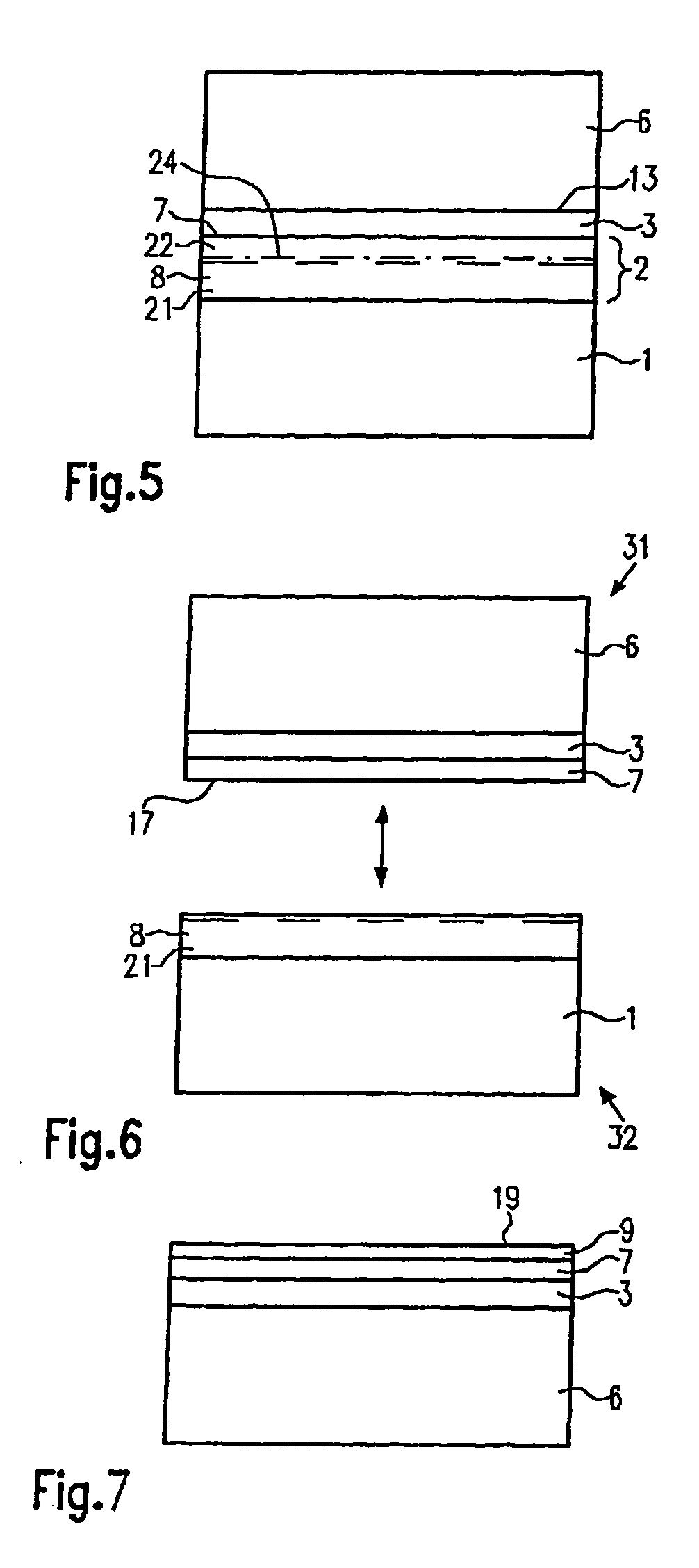

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

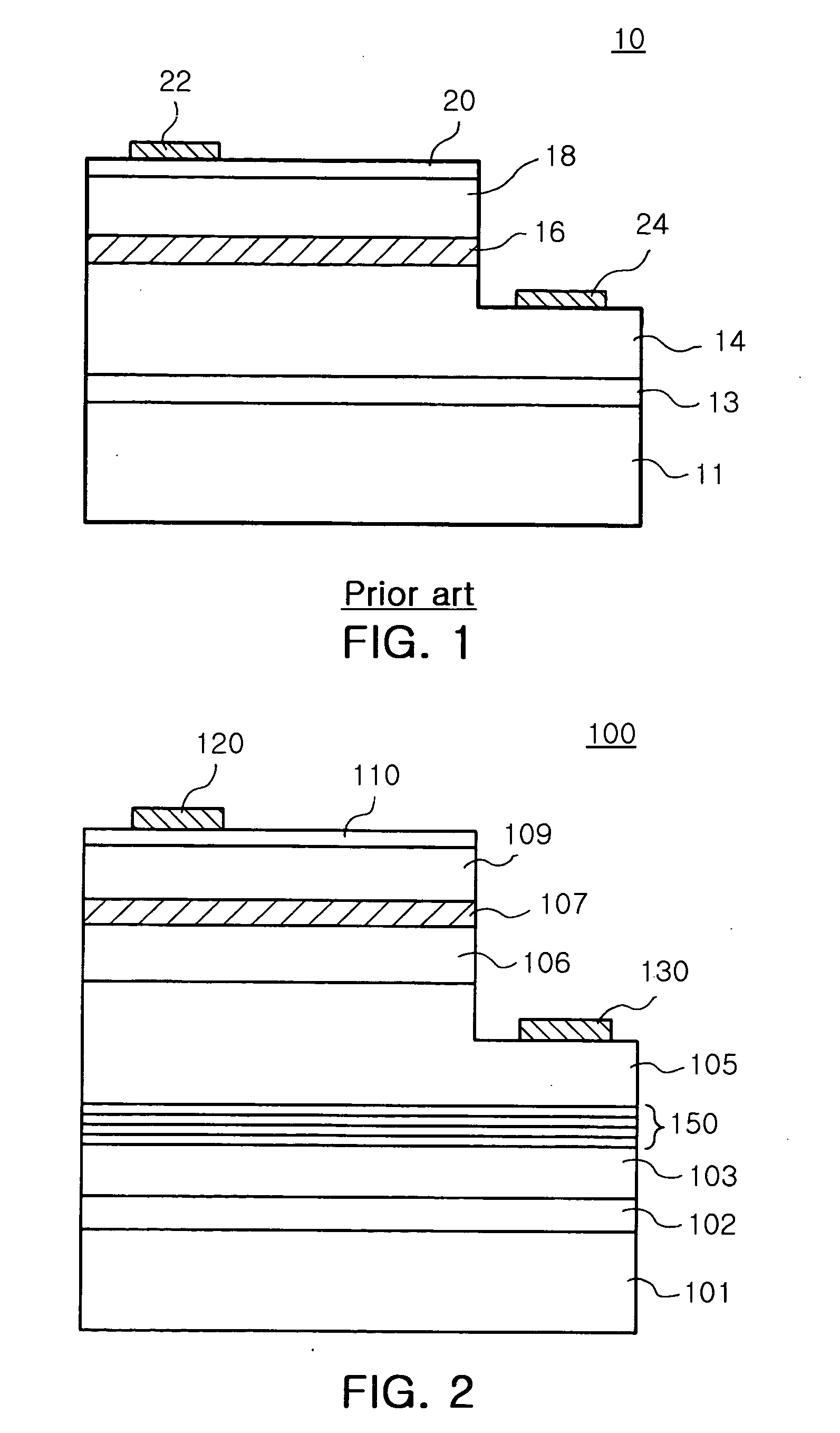

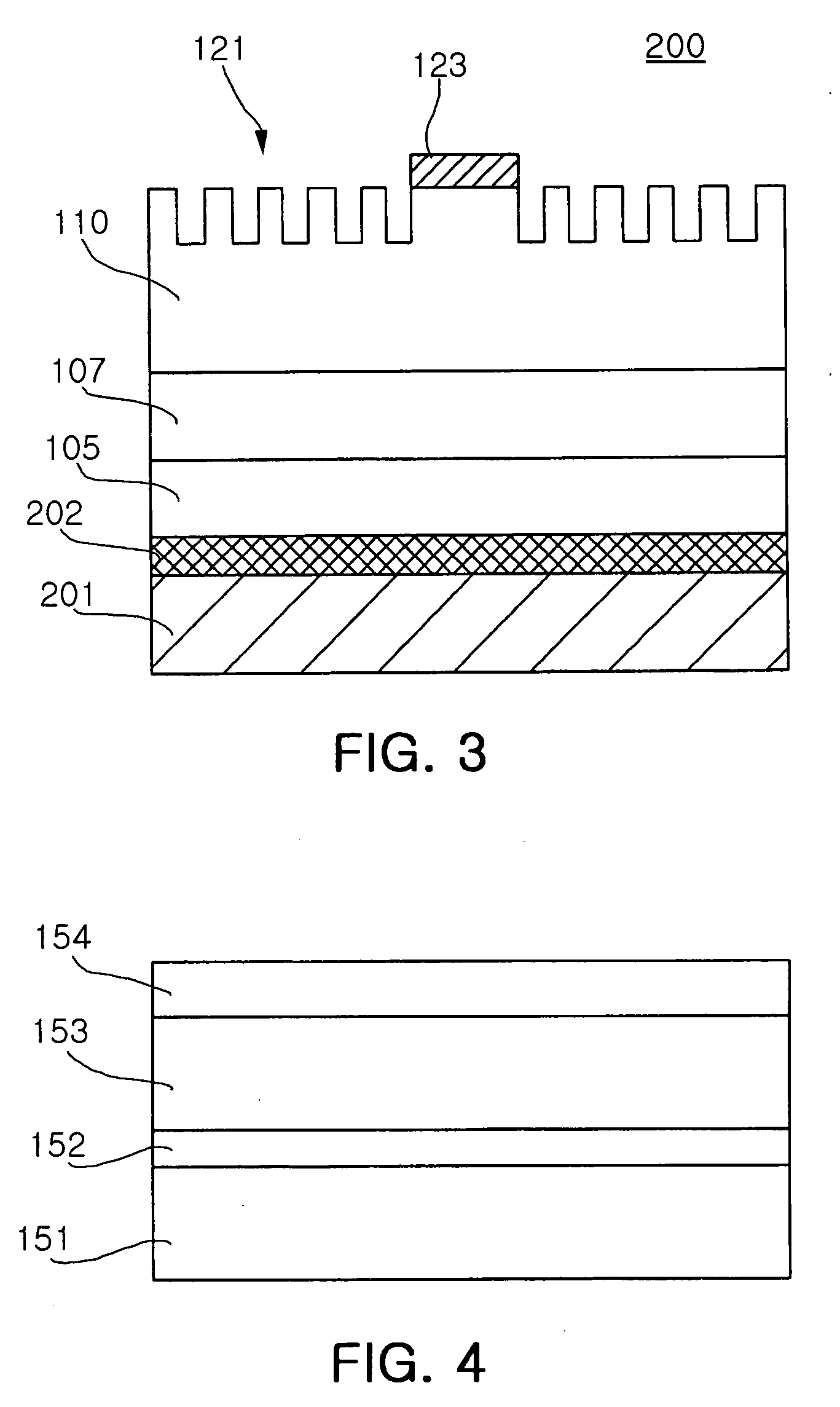

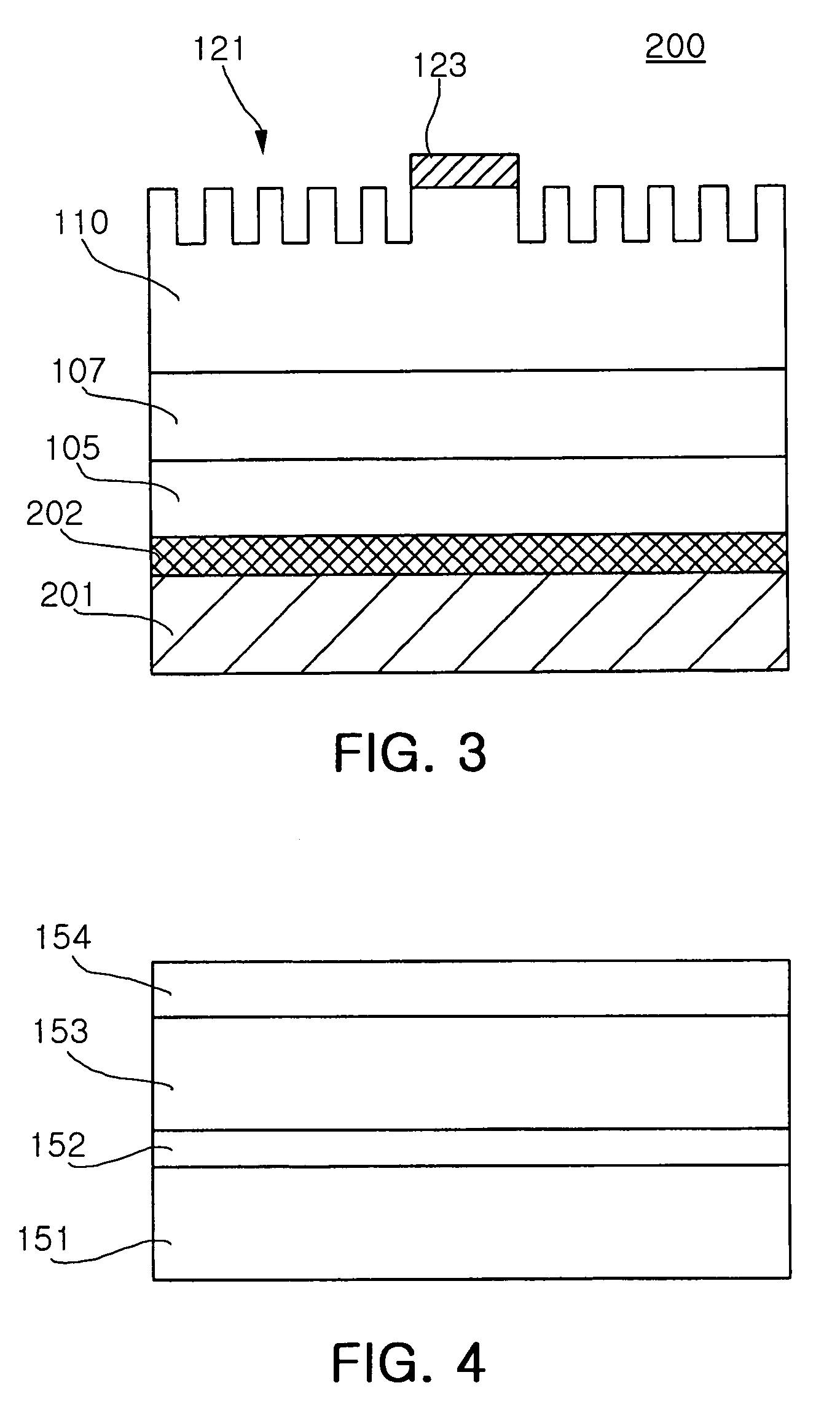

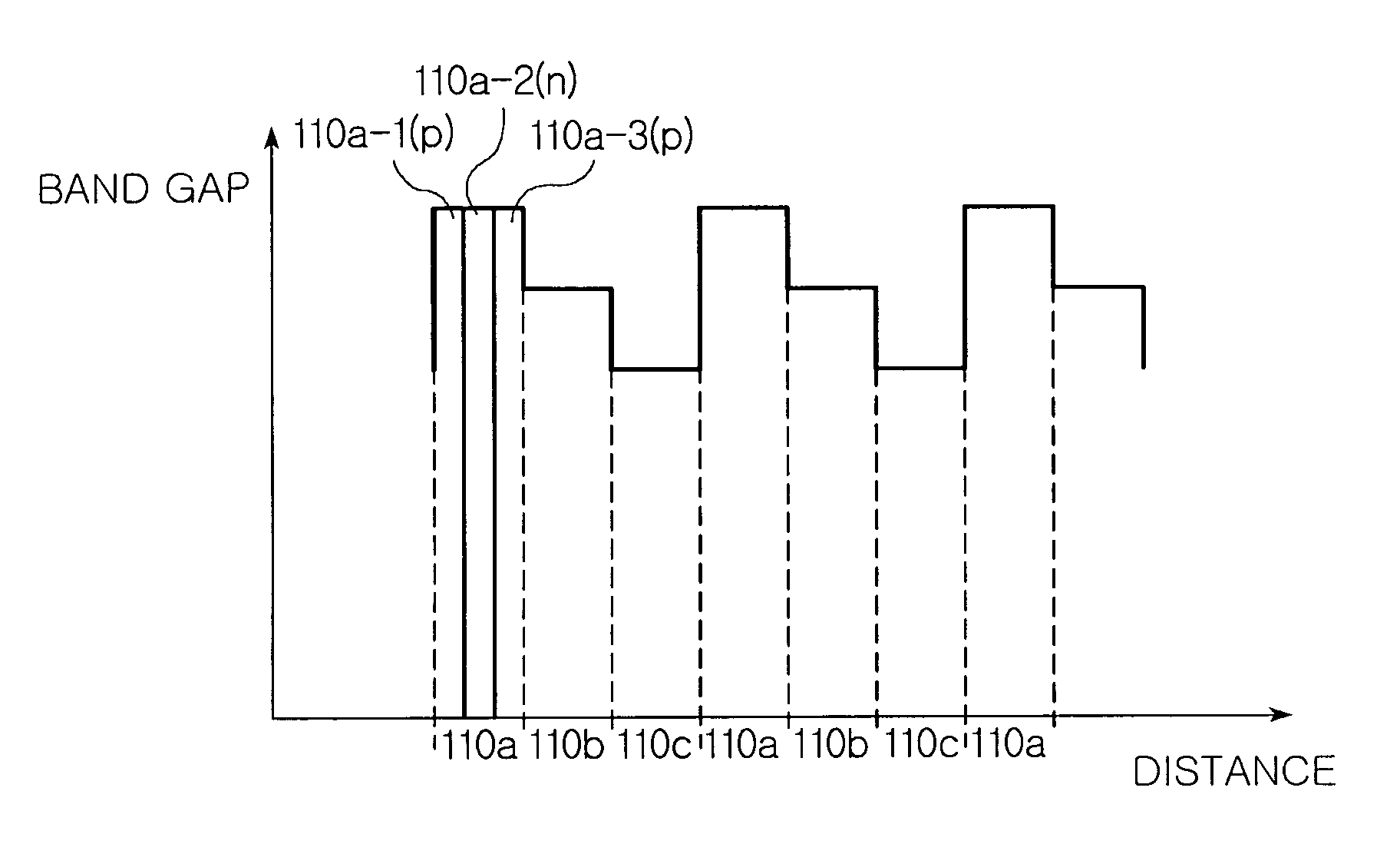

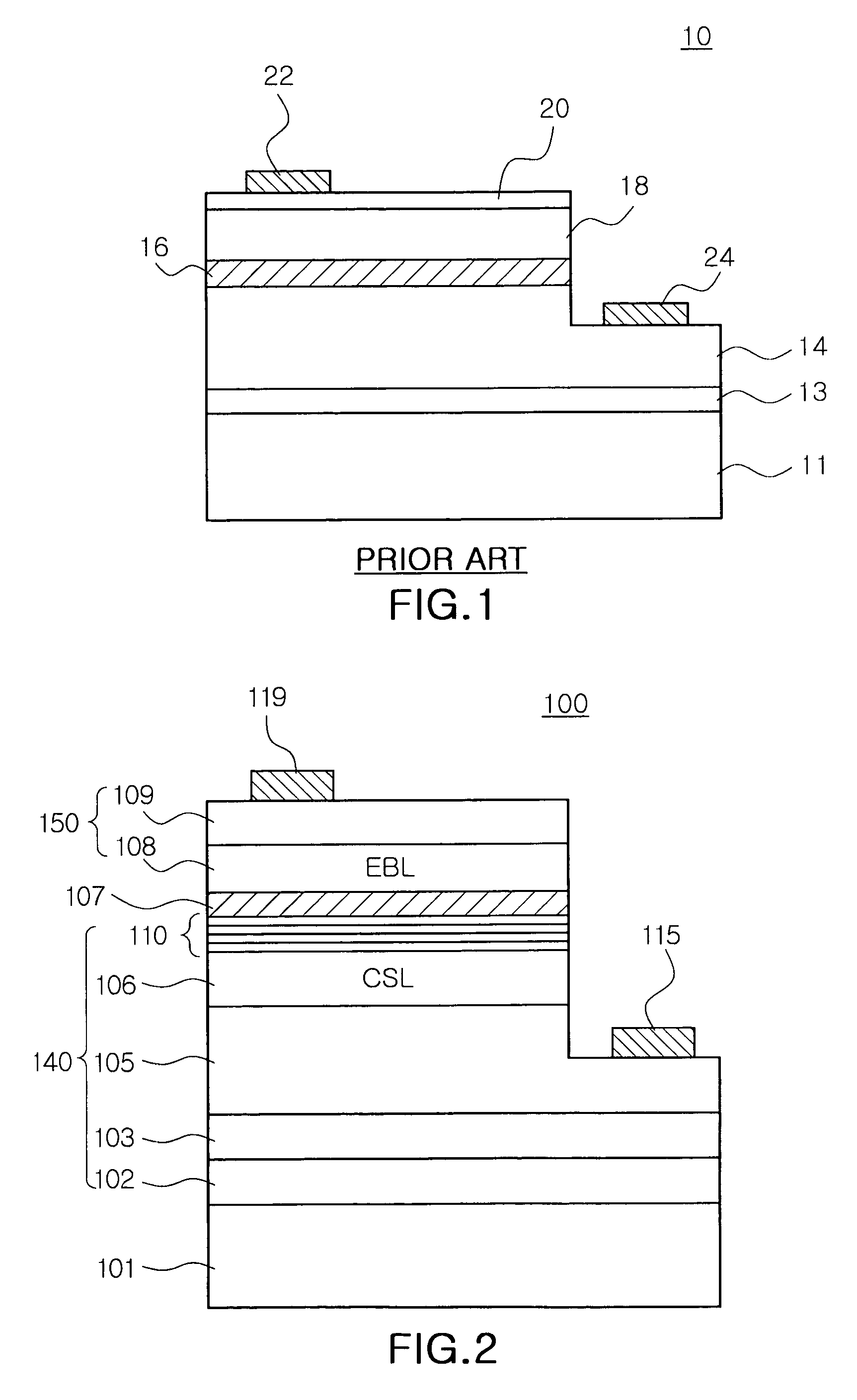

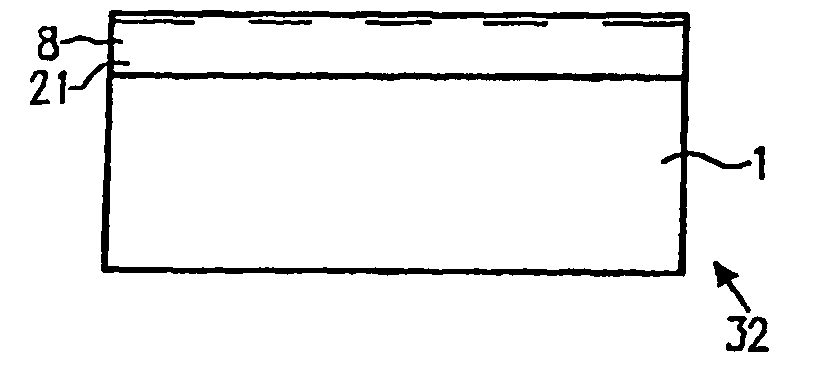

Nitride semiconductor light emitting device

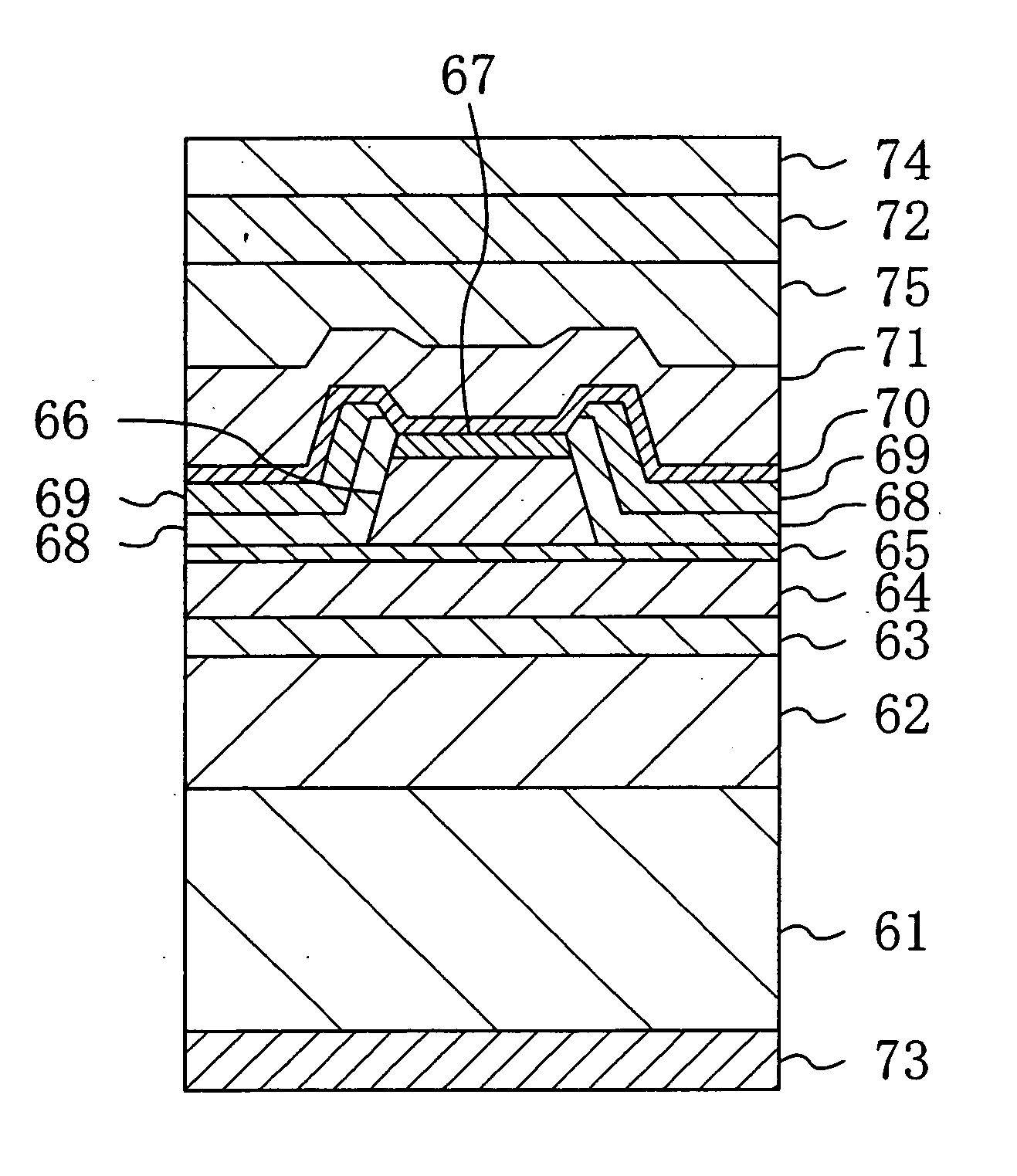

ActiveUS20080251781A1Reduce crystal defect densityIncrease brightnessSemiconductor devicesContact formationInter layer

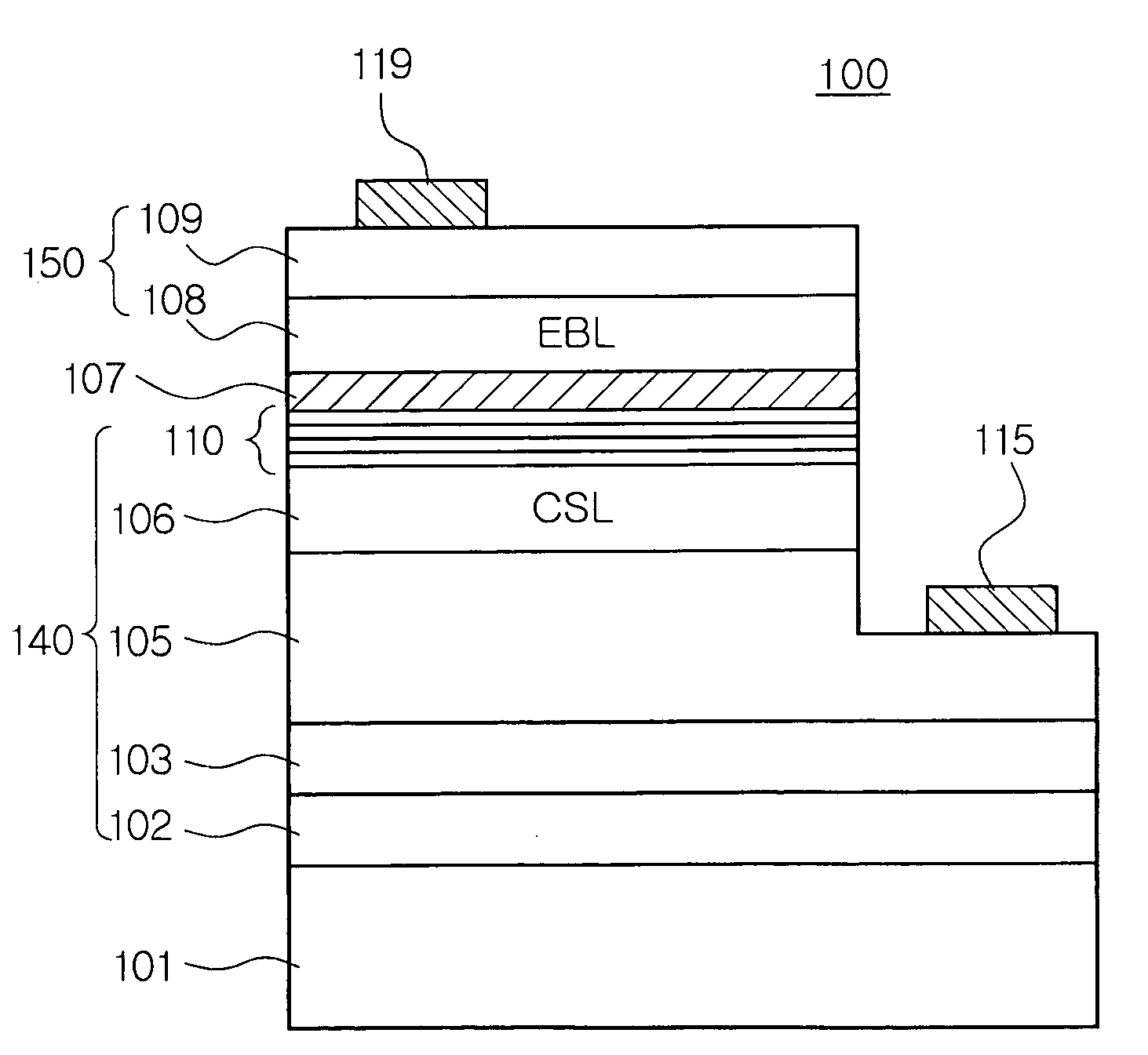

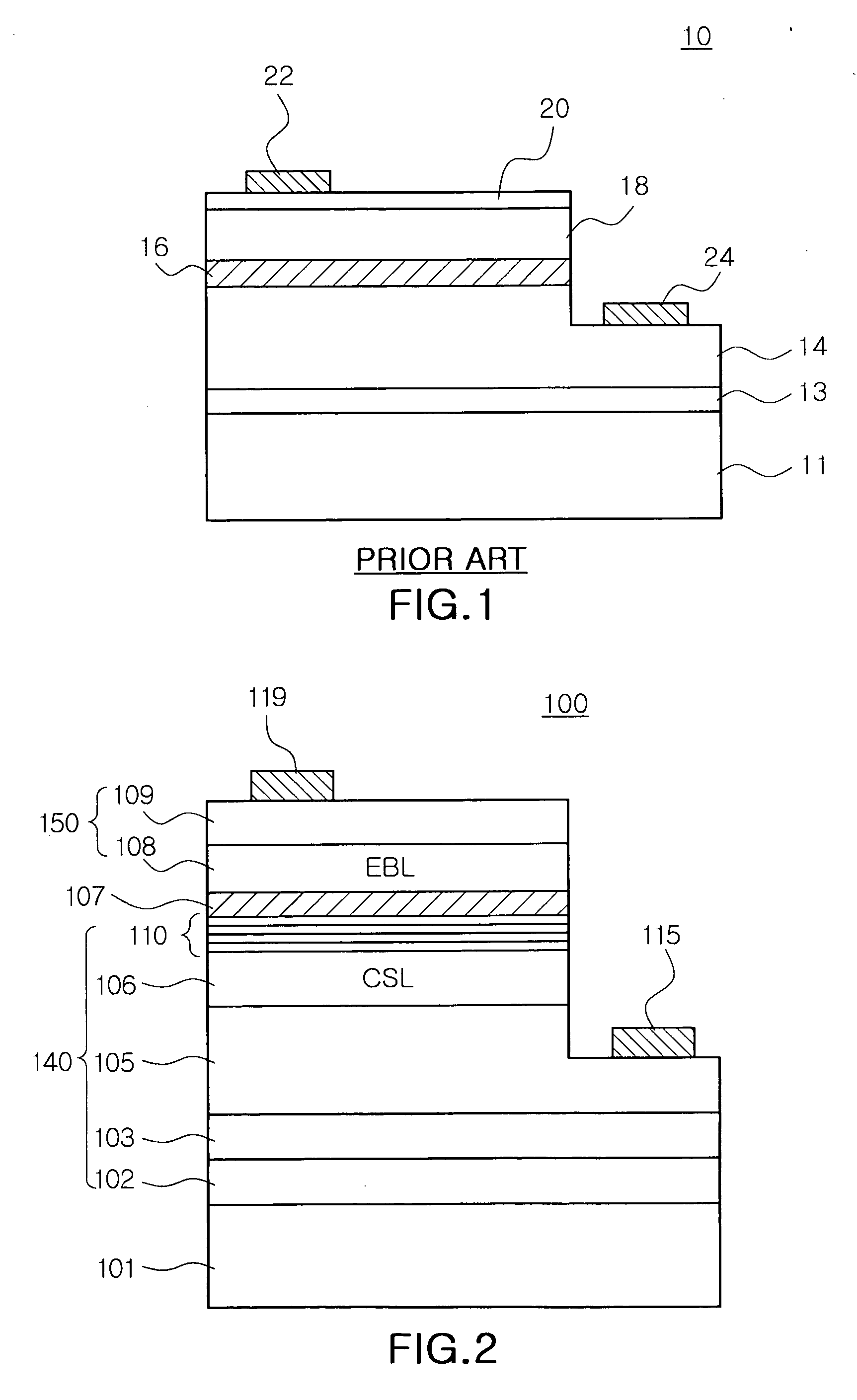

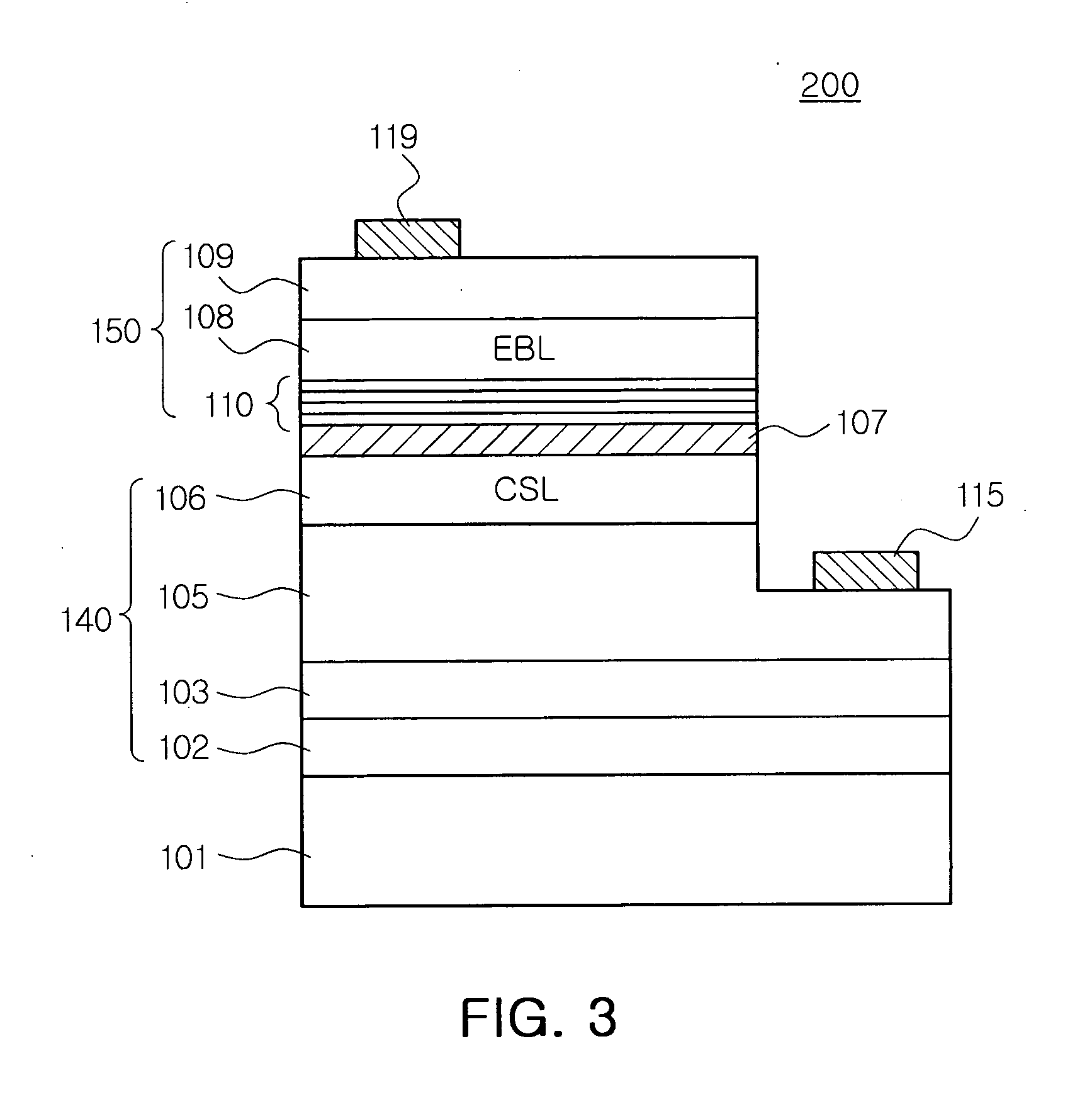

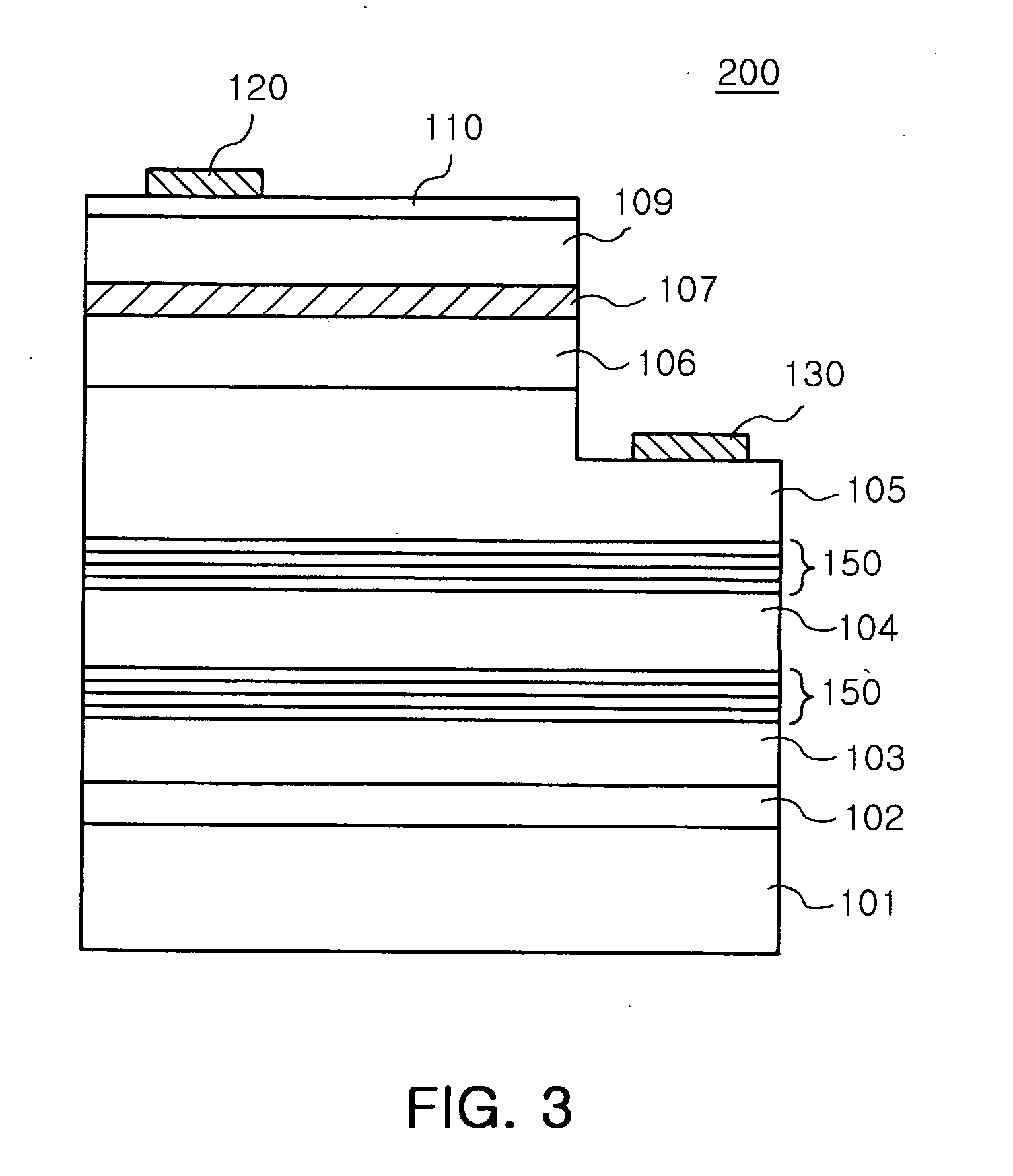

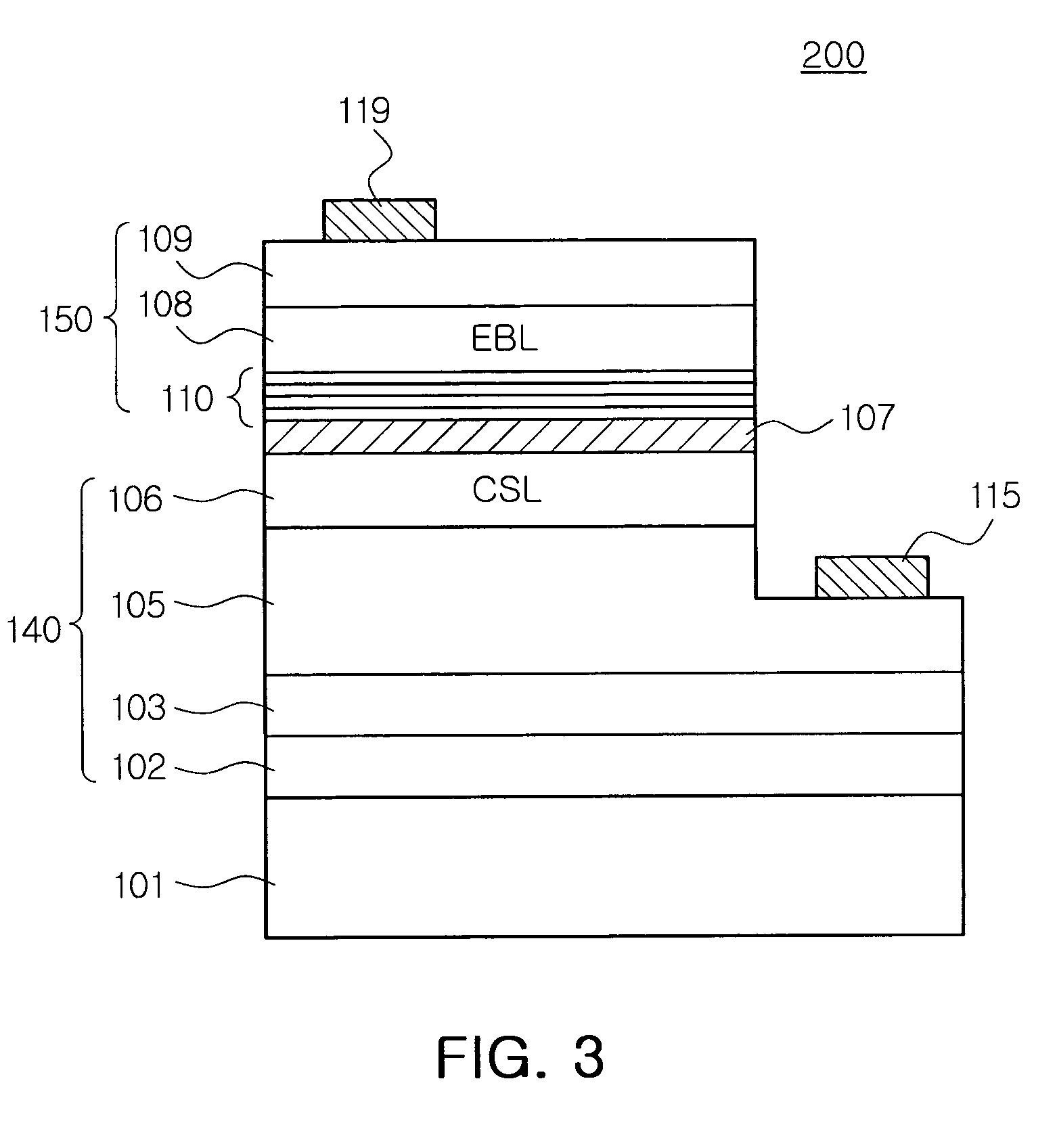

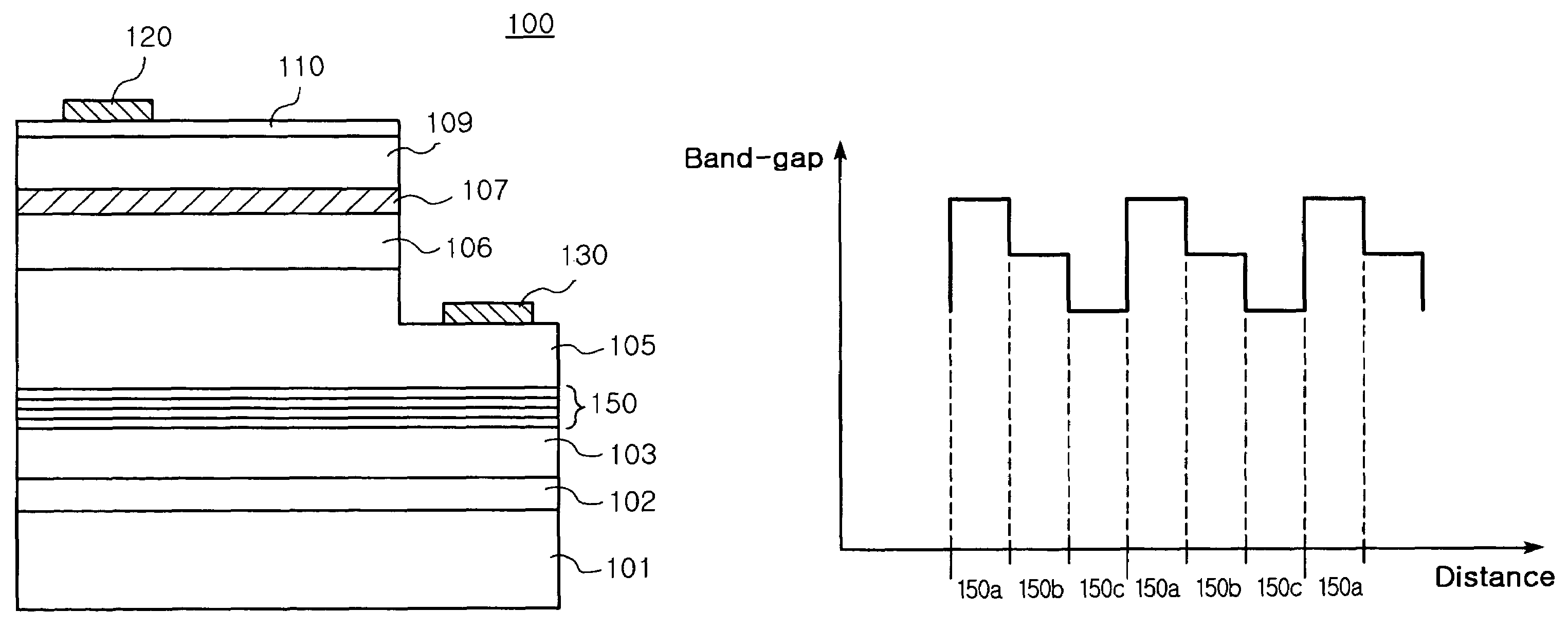

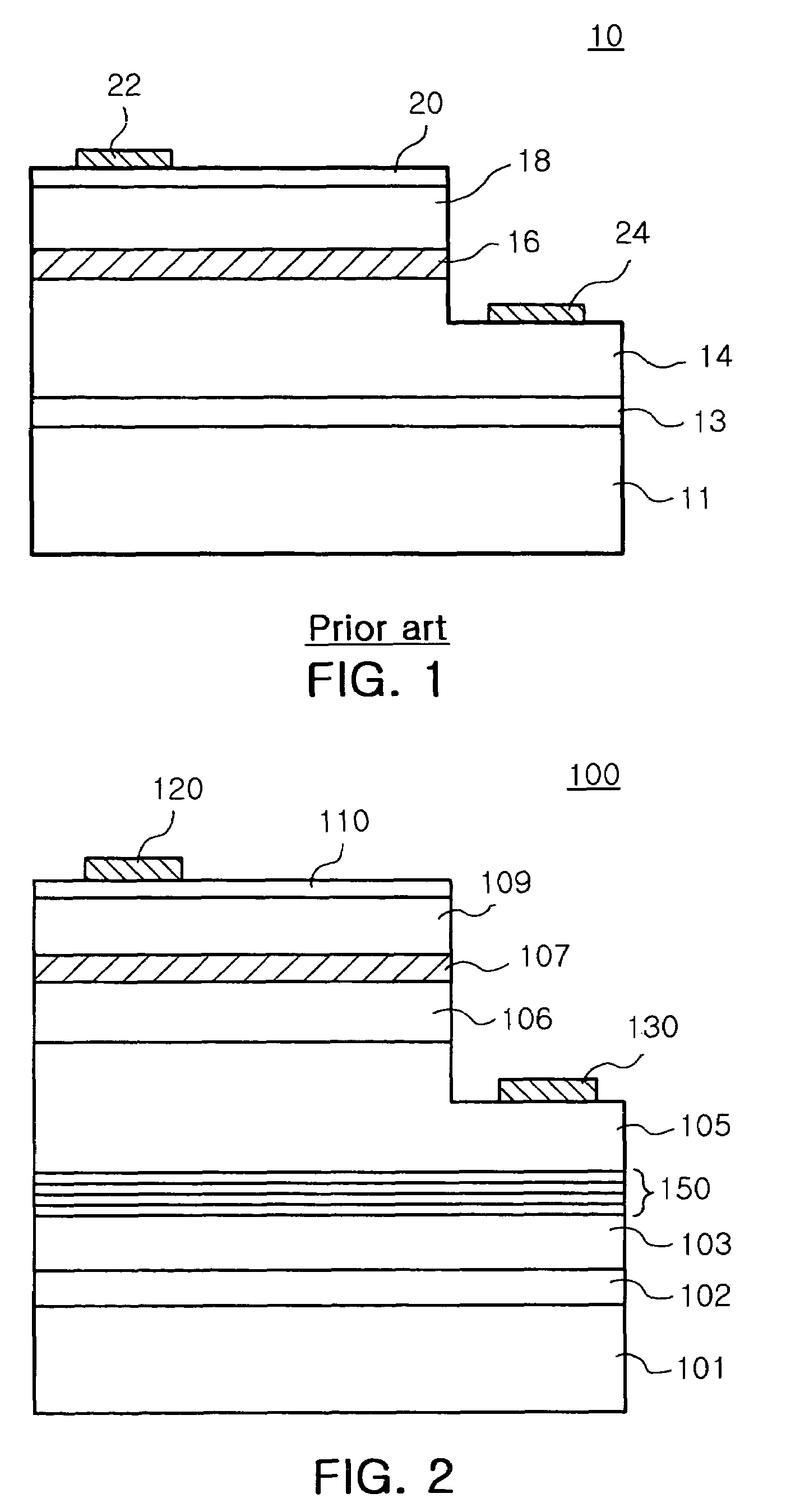

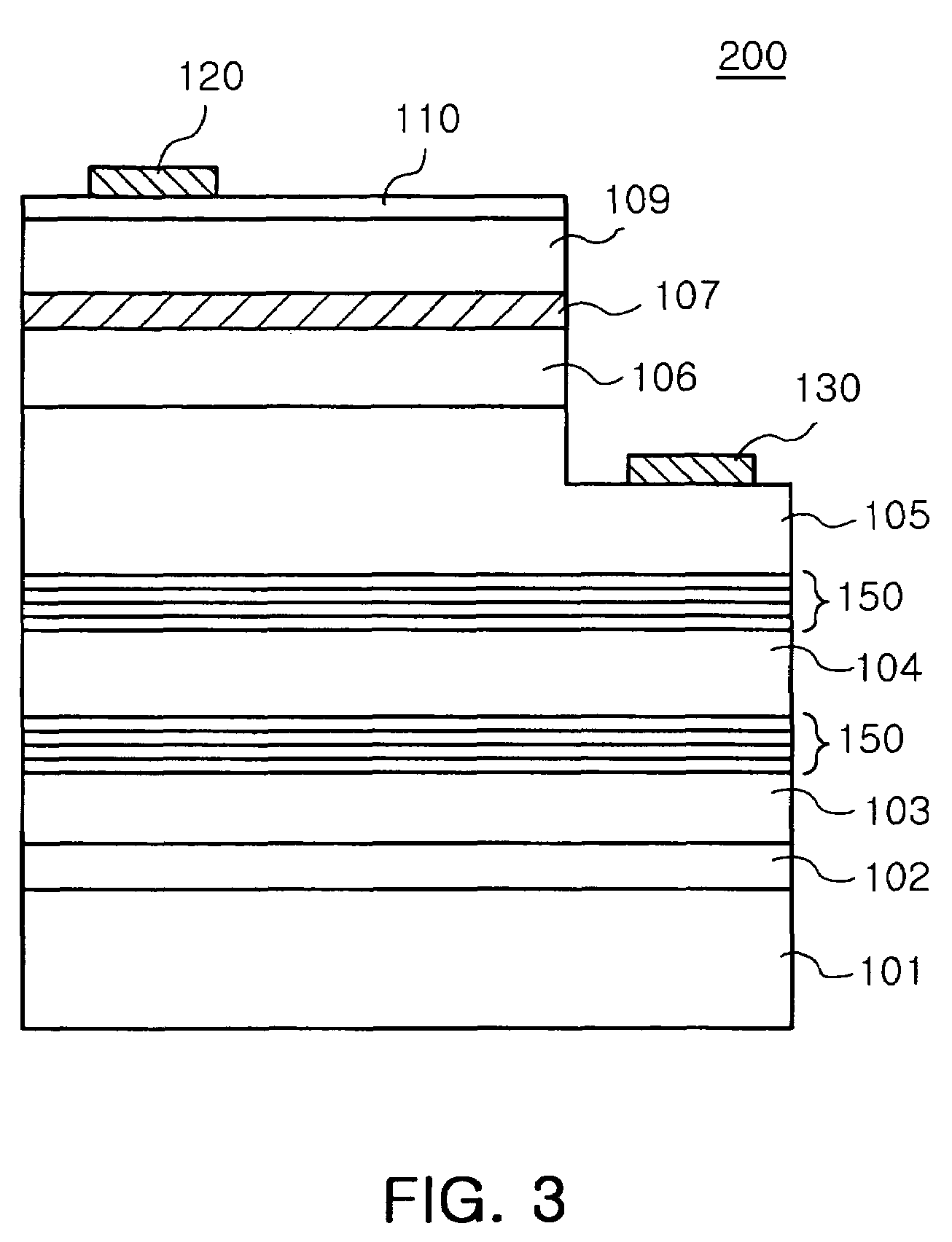

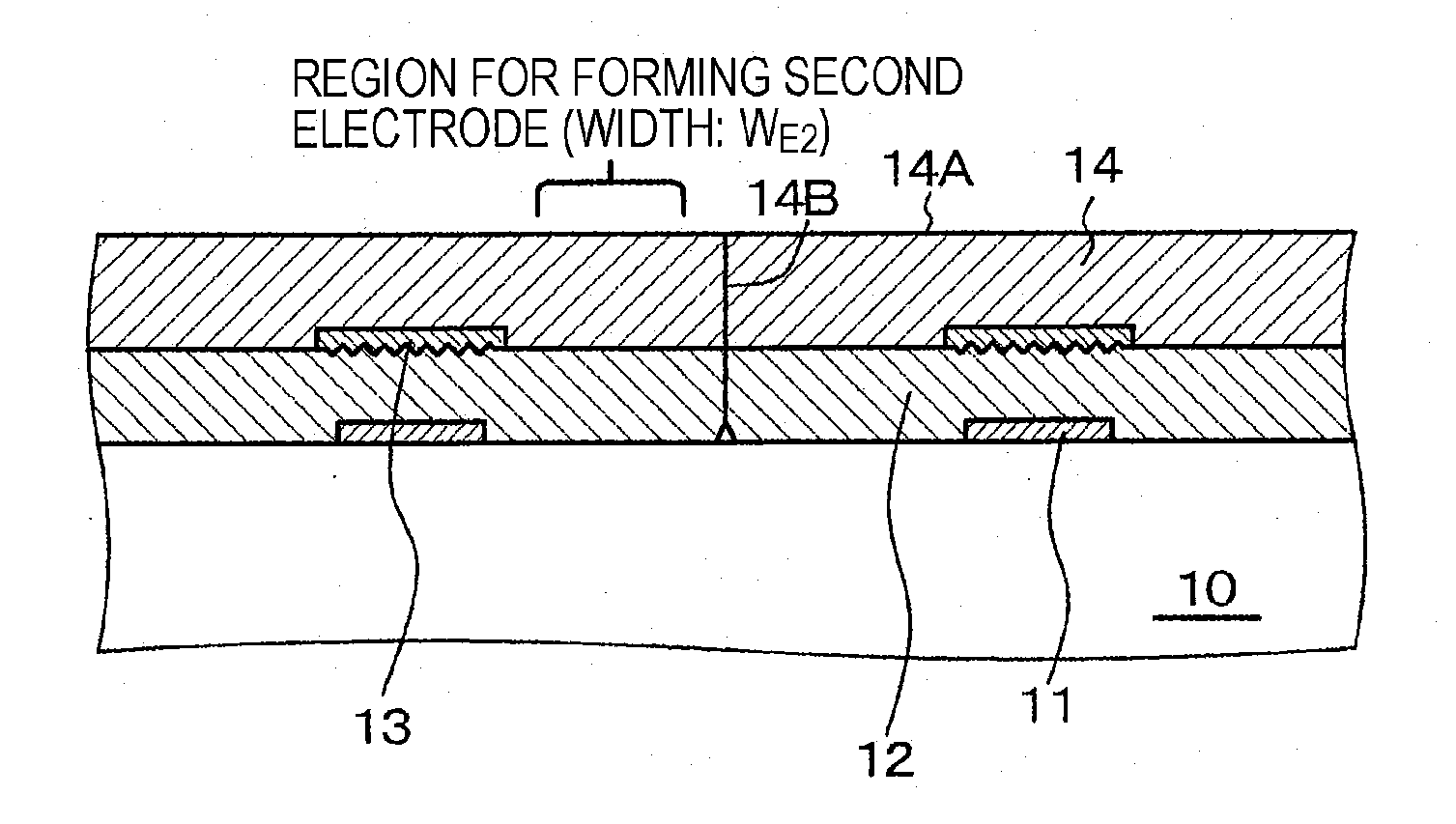

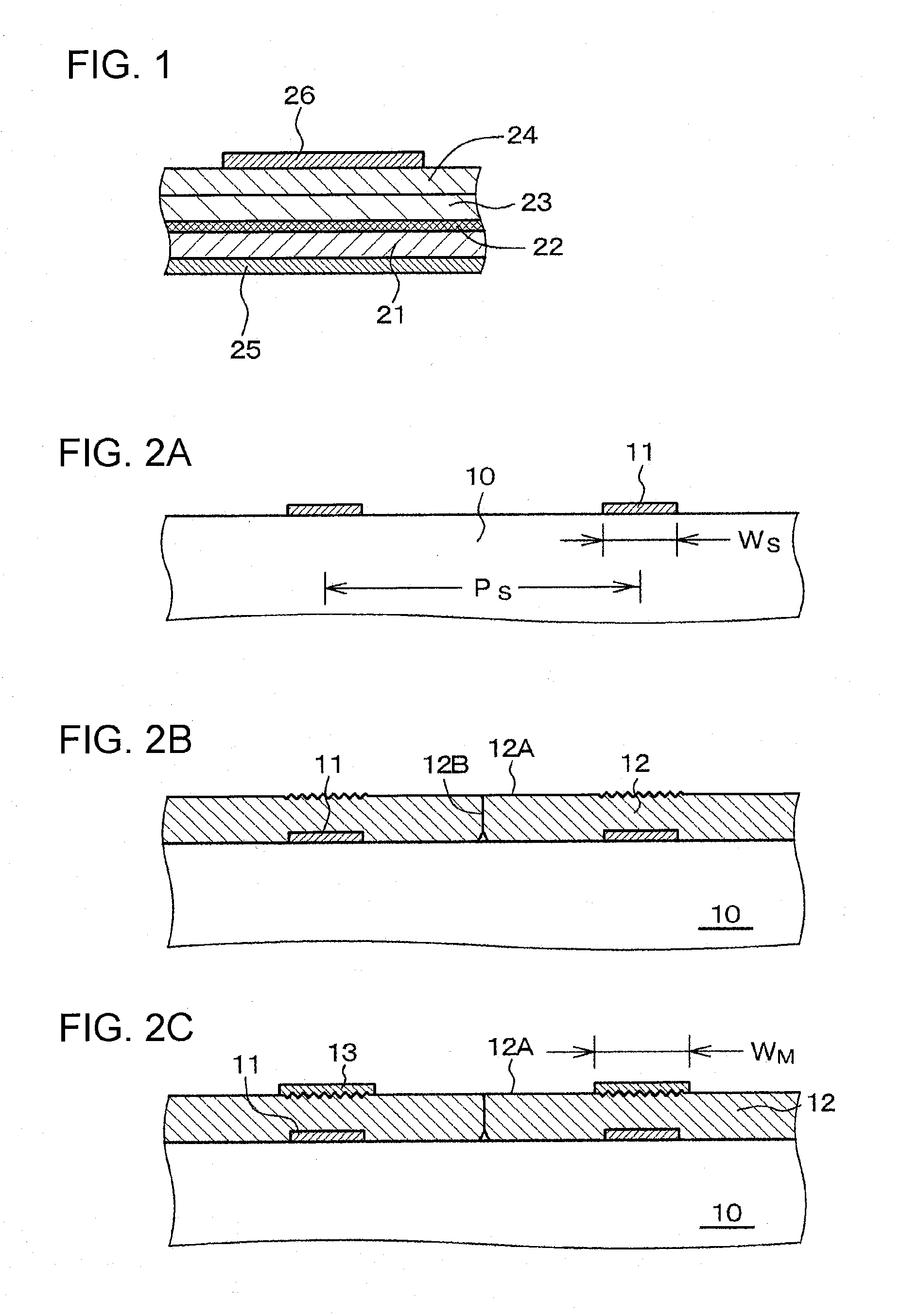

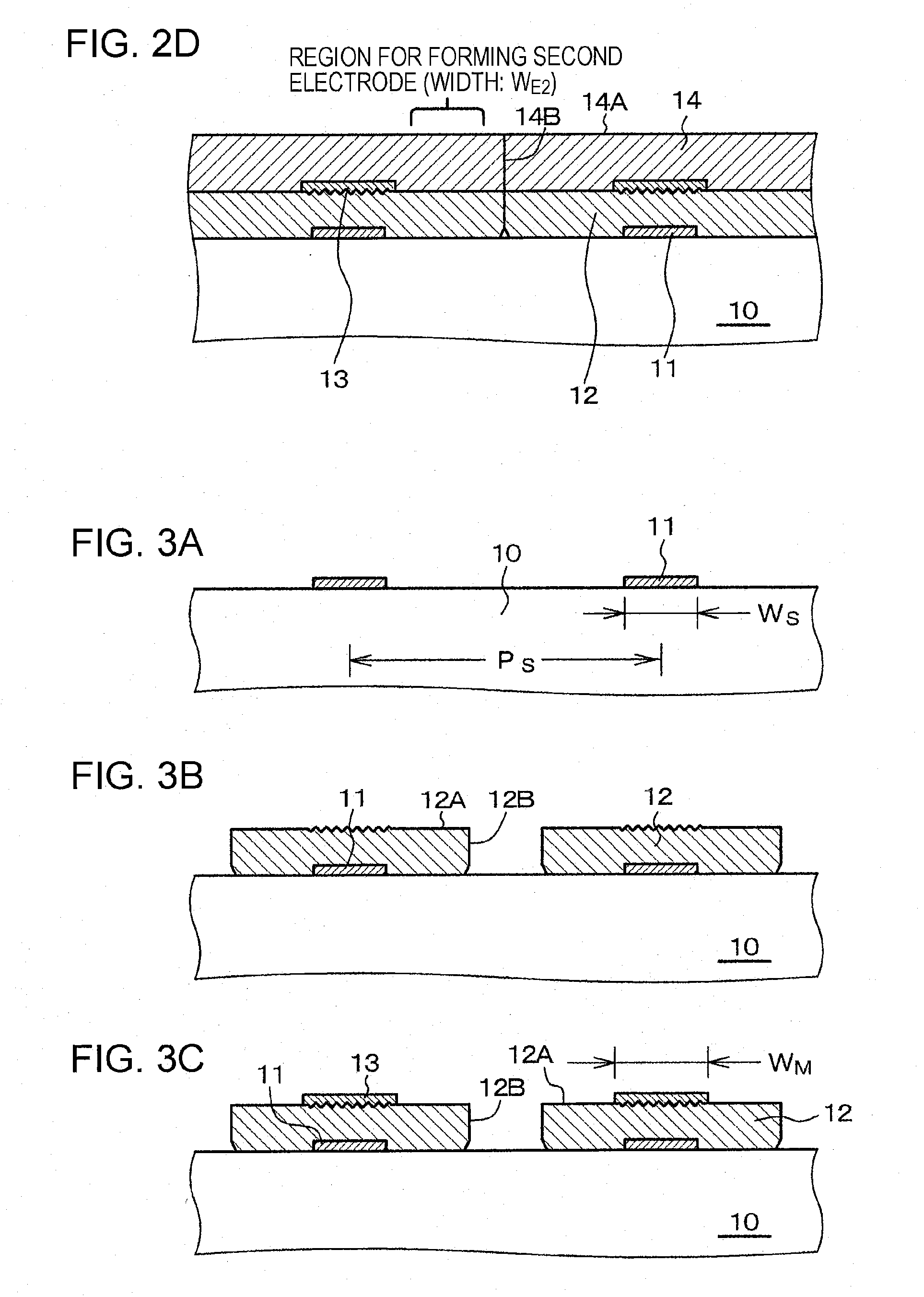

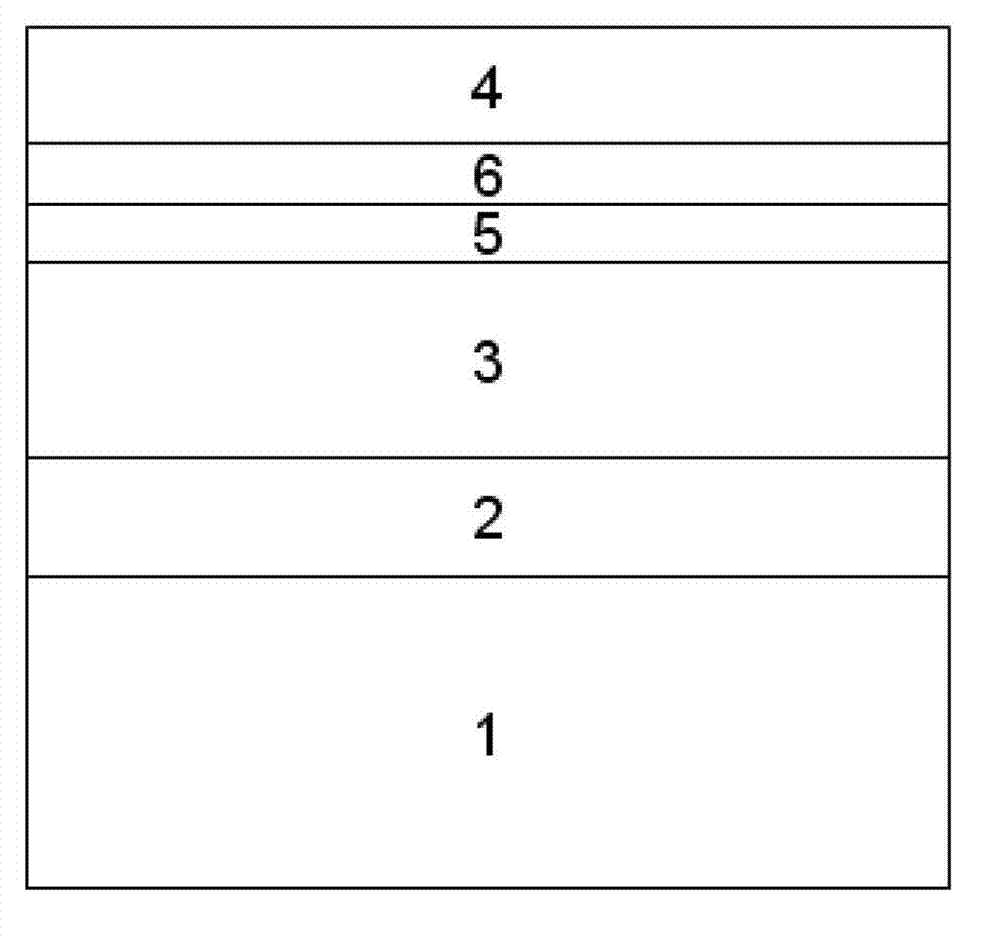

There is provided a nitride semiconductor light emitting device including: an n-type semiconductor region; an active layer formed on the n-type semiconductor region; a p-type semiconductor region formed on the active layer; an n-electrode disposed in contact with the n-type semiconductor region; a p-electrode formed on the p-type semiconductor region; and at least one intermediate layer formed in at least one of the n-type semiconductor region and the p-type semiconductor region, the intermediate layer disposed above the n-electrode, wherein the intermediate layer is formed of a multi-layer structure where at least three layers with different band gaps from one another are deposited, wherein the multi-layer structure includes one of an AlGaN layer / GaN layer / InGaN layer stack and an InGaN layer / GaN layer / AlGaN layer stack.

Owner:SAMSUNG ELECTRONICS CO LTD

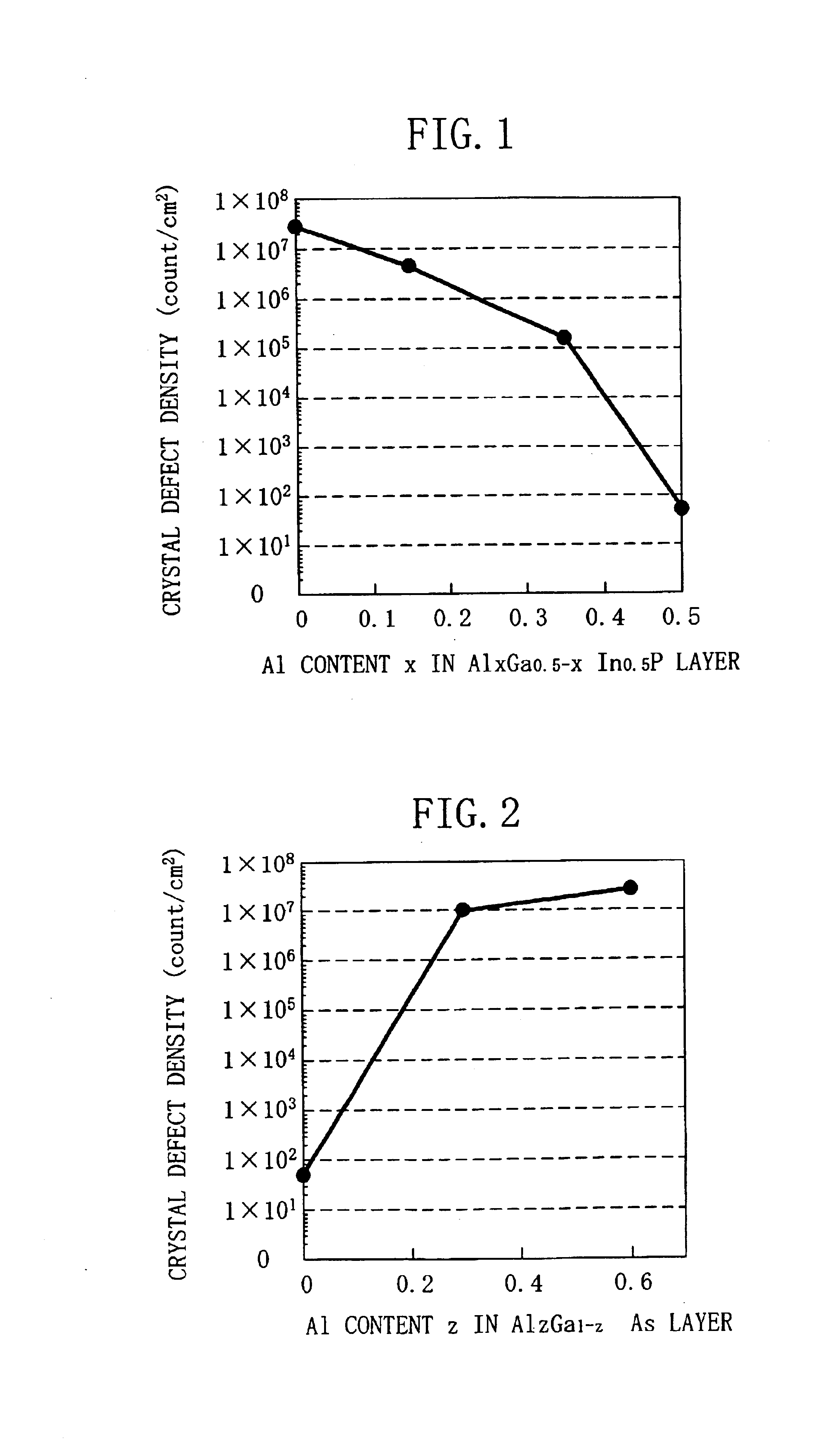

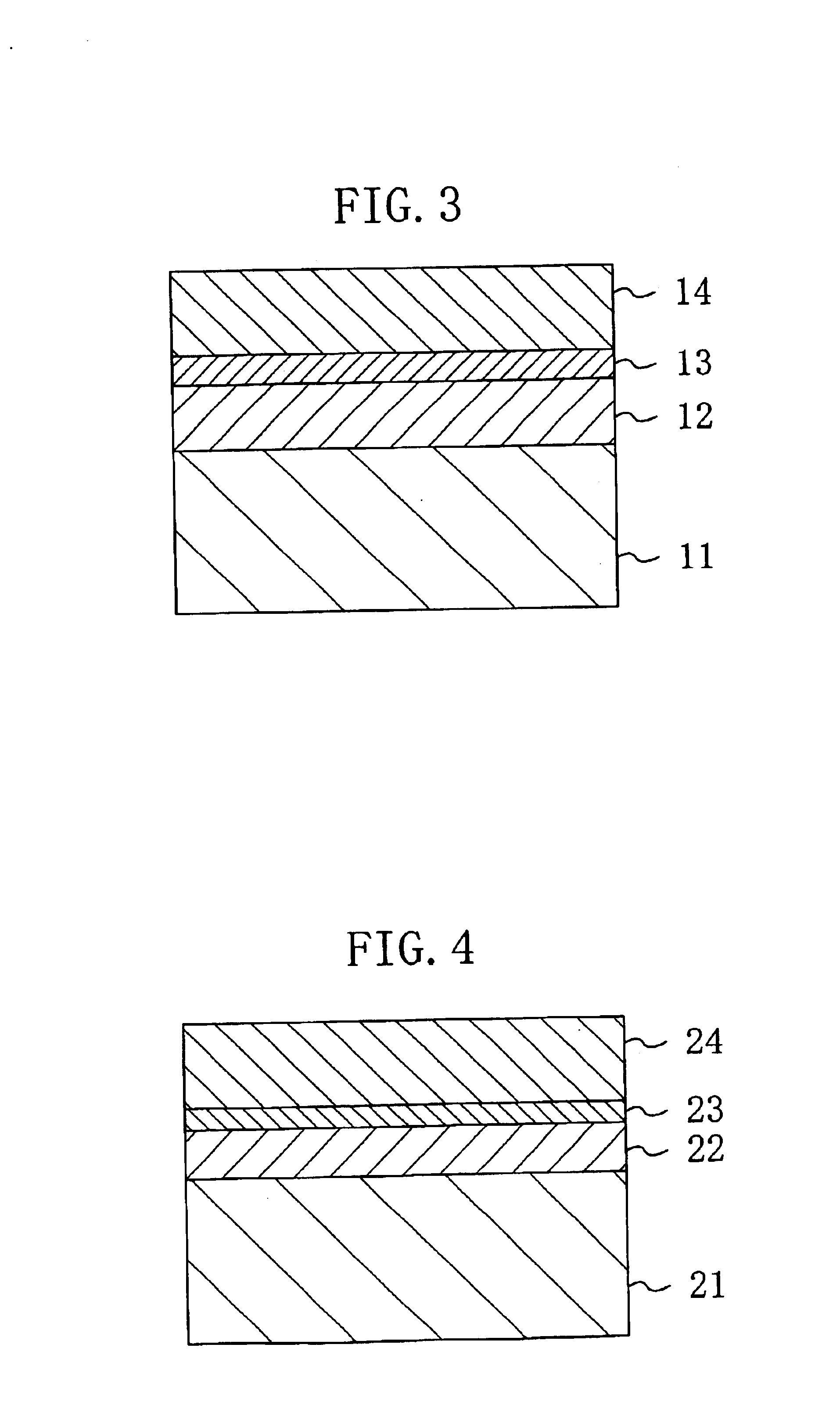

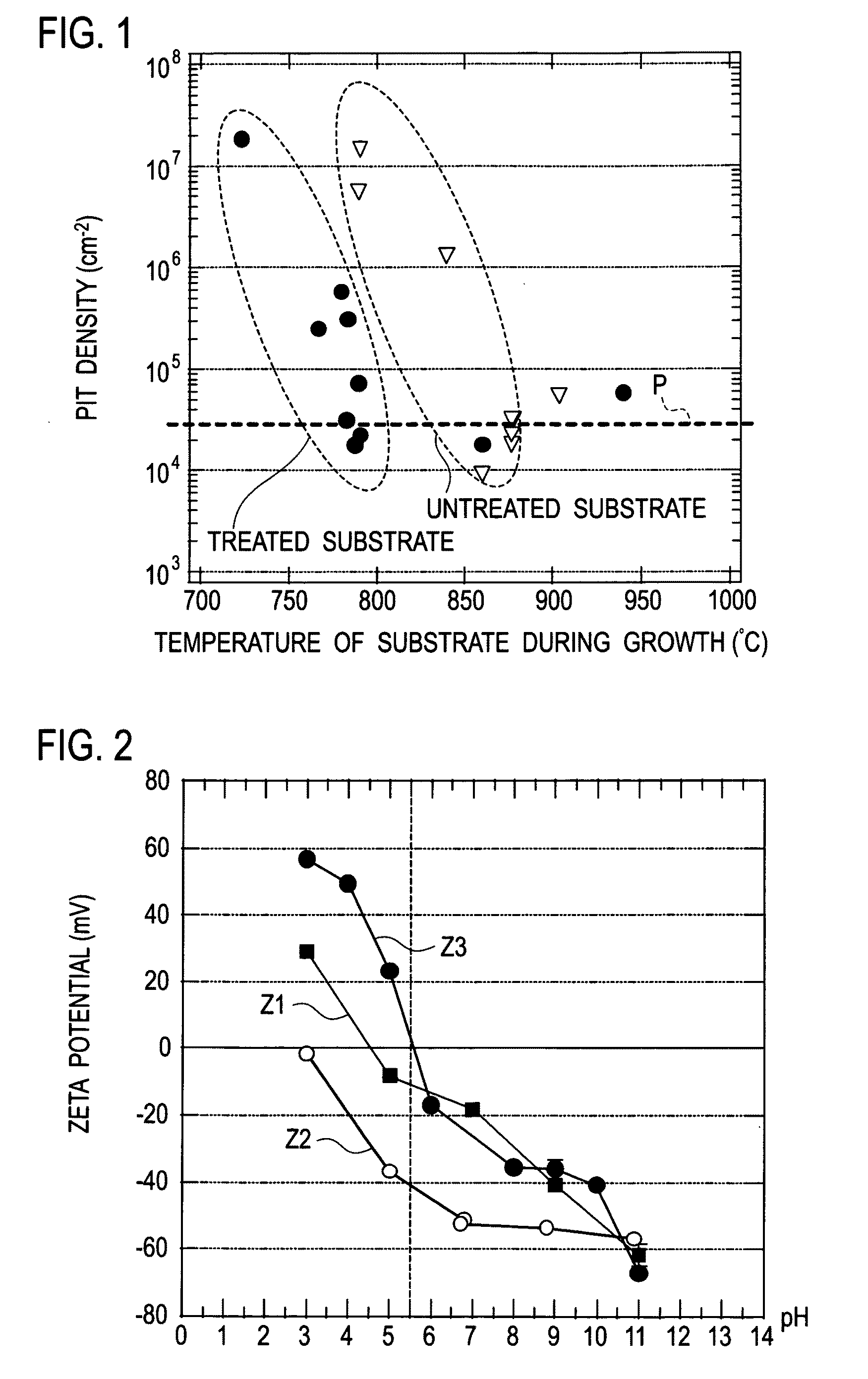

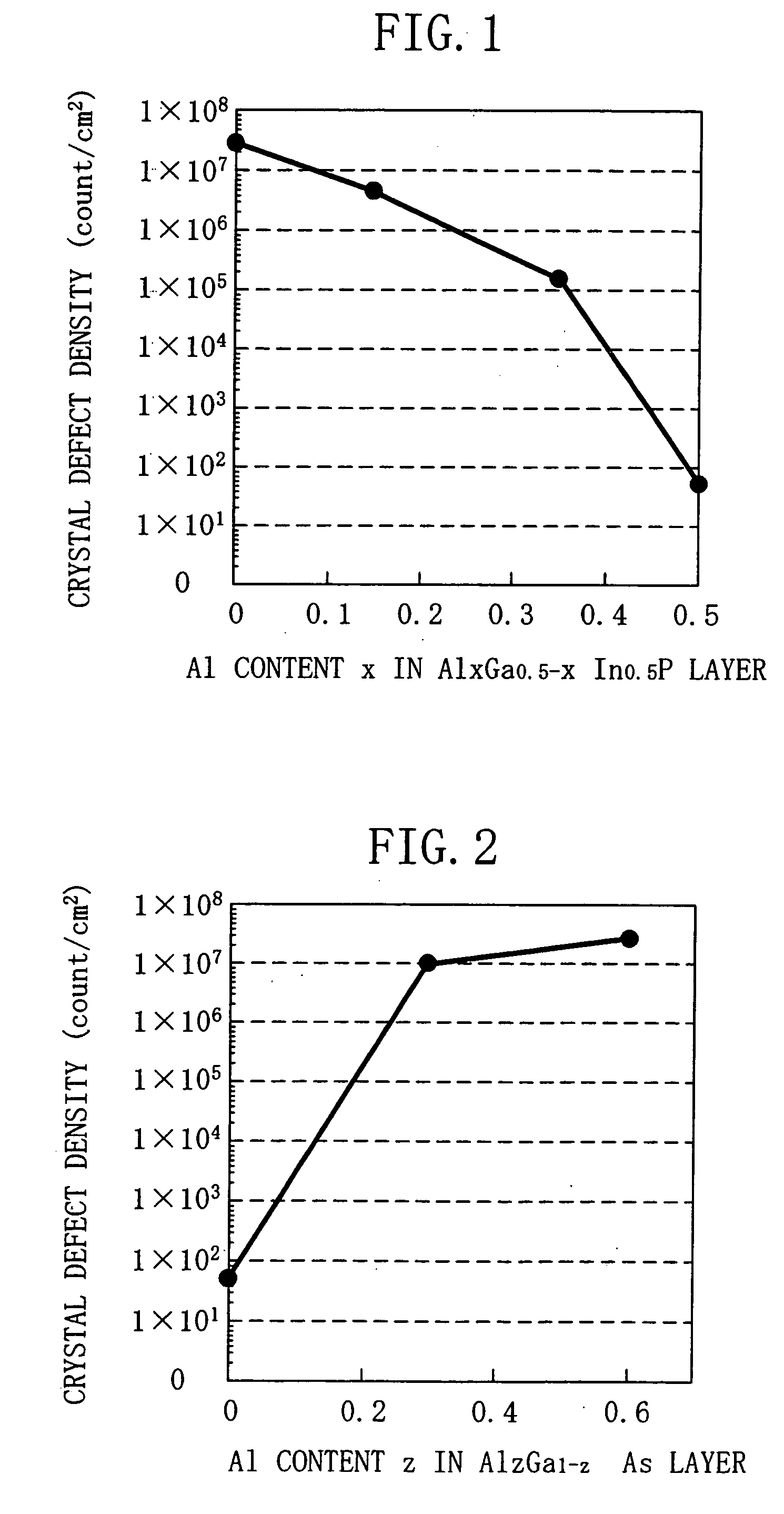

Group III-V compound semiconductor and group III-V compound semiconductor device using the same

InactiveUS6841409B2Reduce crystal defect densityPromote migrationSemiconductor/solid-state device detailsSolid-state devicesComputer scienceAl content

An AlGaInP layer is formed on a substrate made of GaAs, and an AlGaAs layer is formed on the AlGaInP layer via a buffer layer therebetween. The buffer layer has a thickness of about 1.1 nm and is made of AlGaInP whose Ga content is smaller than that of the AlGaInP layer. The buffer layer may alternatively be made of AlGaAs whose Al content is smaller than that of the AlGaAs layer.

Owner:PANASONIC CORP

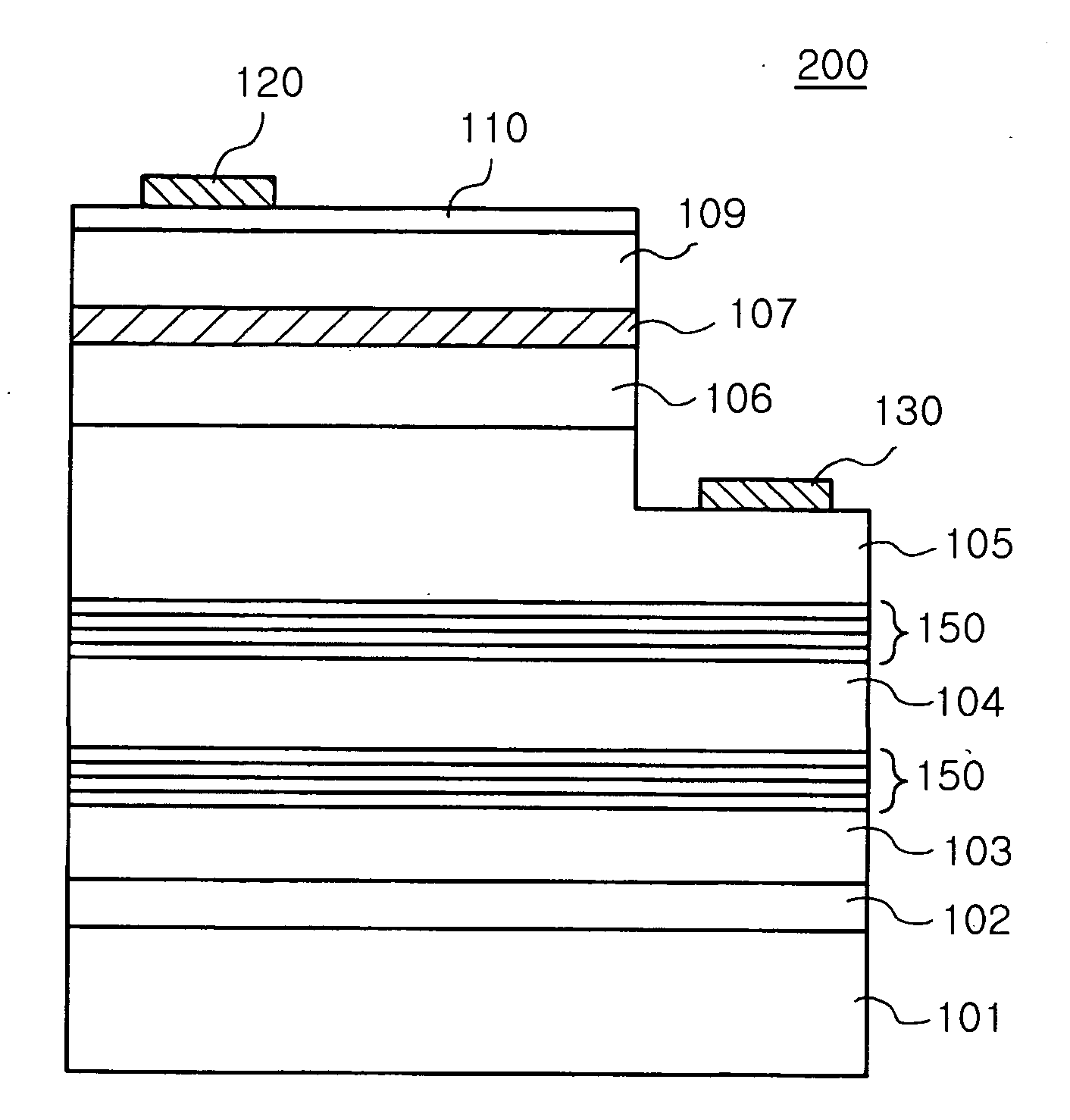

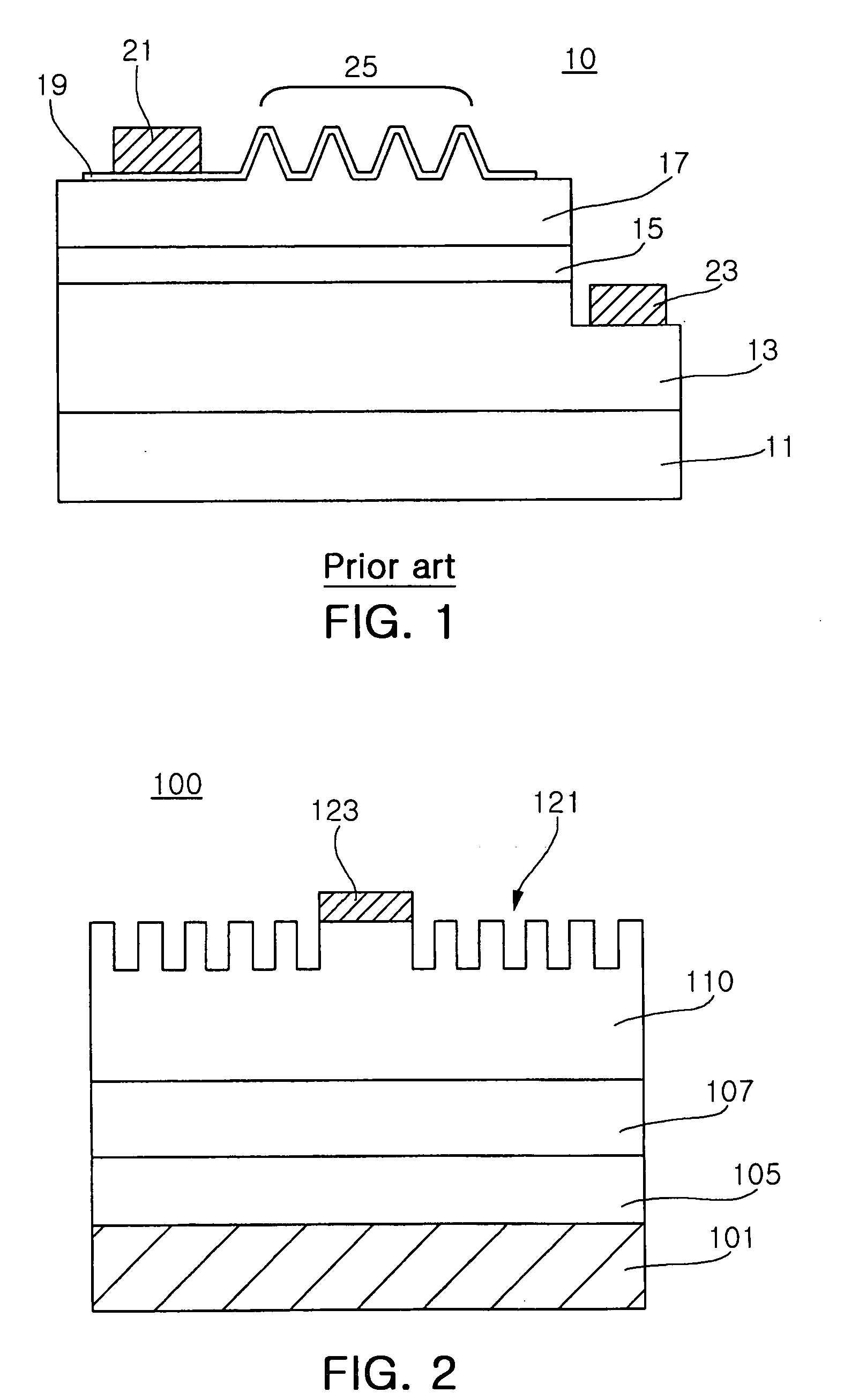

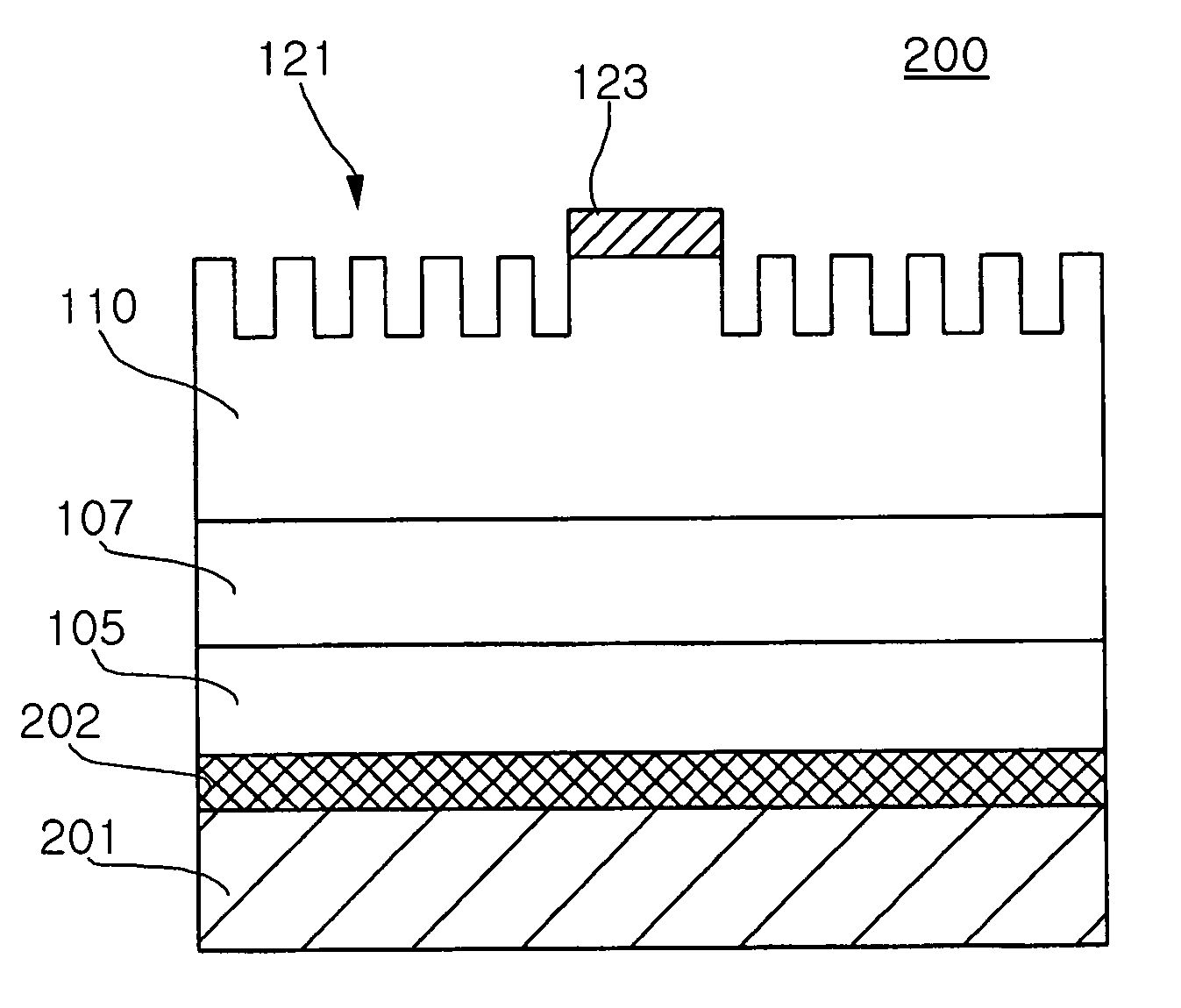

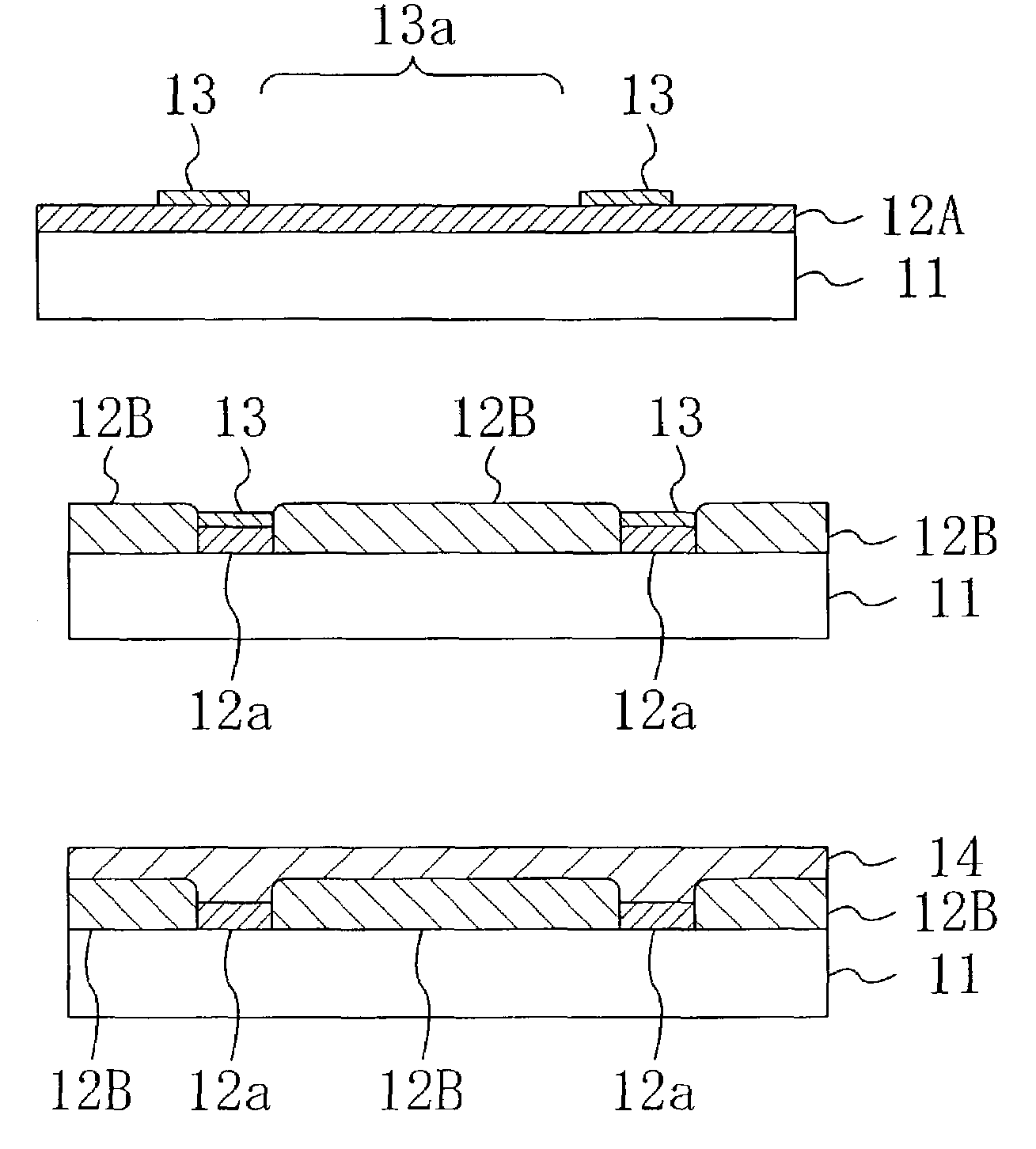

Nitride semiconductor light emitting device

Disclosed herein is a nitride semiconductor light emitting device, which is improved in luminance and reliability. The light emitting device, comprises an n-type nitride semiconductor layer, an active layer and a p-type nitride semiconductor layer sequentially formed on a substrate, an n-side electrode formed on a portion of an upper surface of the n-type nitride semiconductor layer, and at least one intermediate layer formed between the substrate and the n-type nitride semiconductor layer. The intermediate layer has a multilayer structure of three or more layers having different band-gaps, and is positioned below the n-side electrode.

Owner:SAMSUNG ELECTRONICS CO LTD

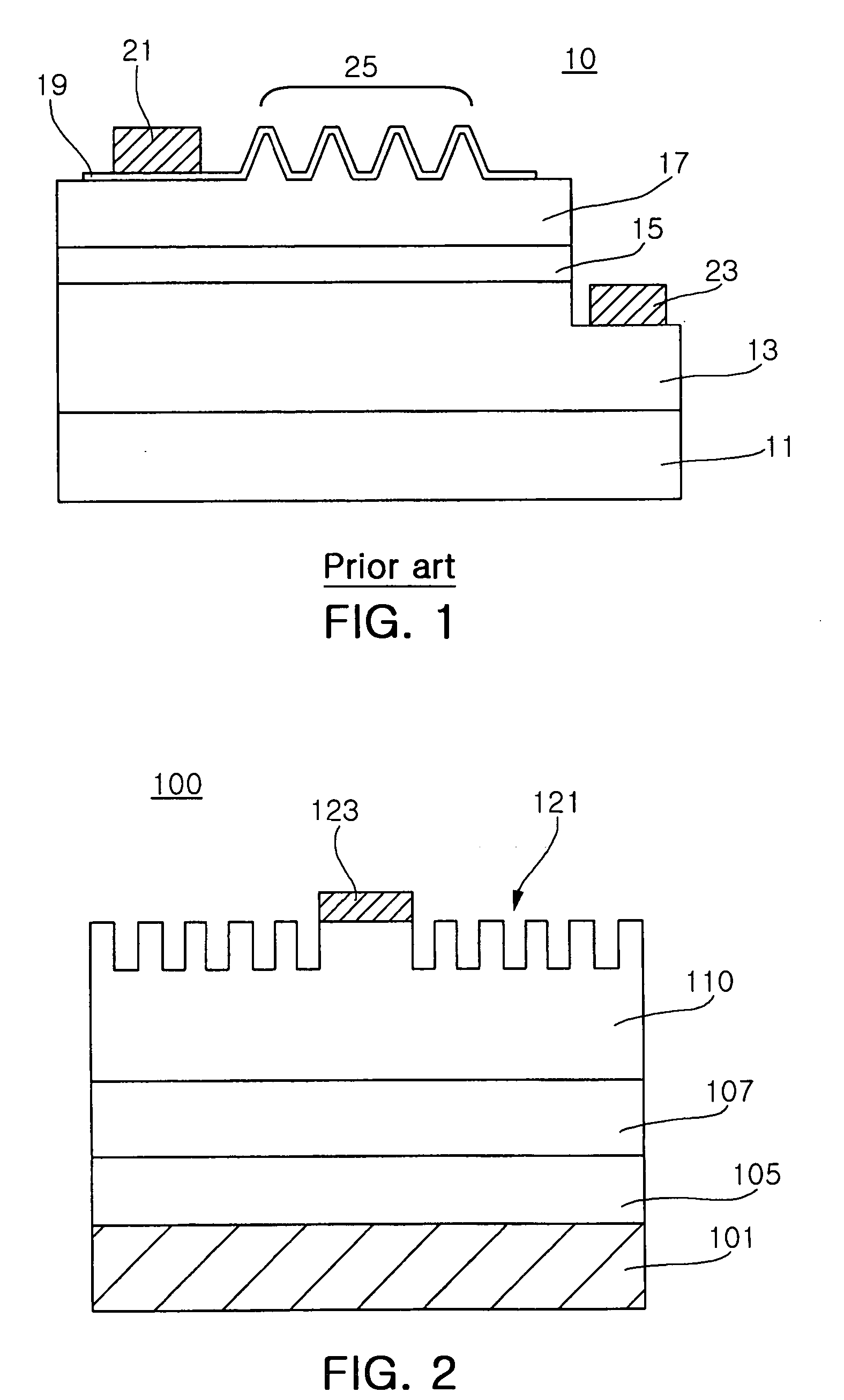

Group-III nitride semiconductor light-emitting diode, light-emitting diode lamp, light source, electrode for group-III nitride semiconductor light-emitting diode, and method for producing the electrode

InactiveUS20020000563A1Easy to displayHigh luminous intensitySemiconductor/solid-state device manufacturingSemiconductor devicesDriving currentLight emission

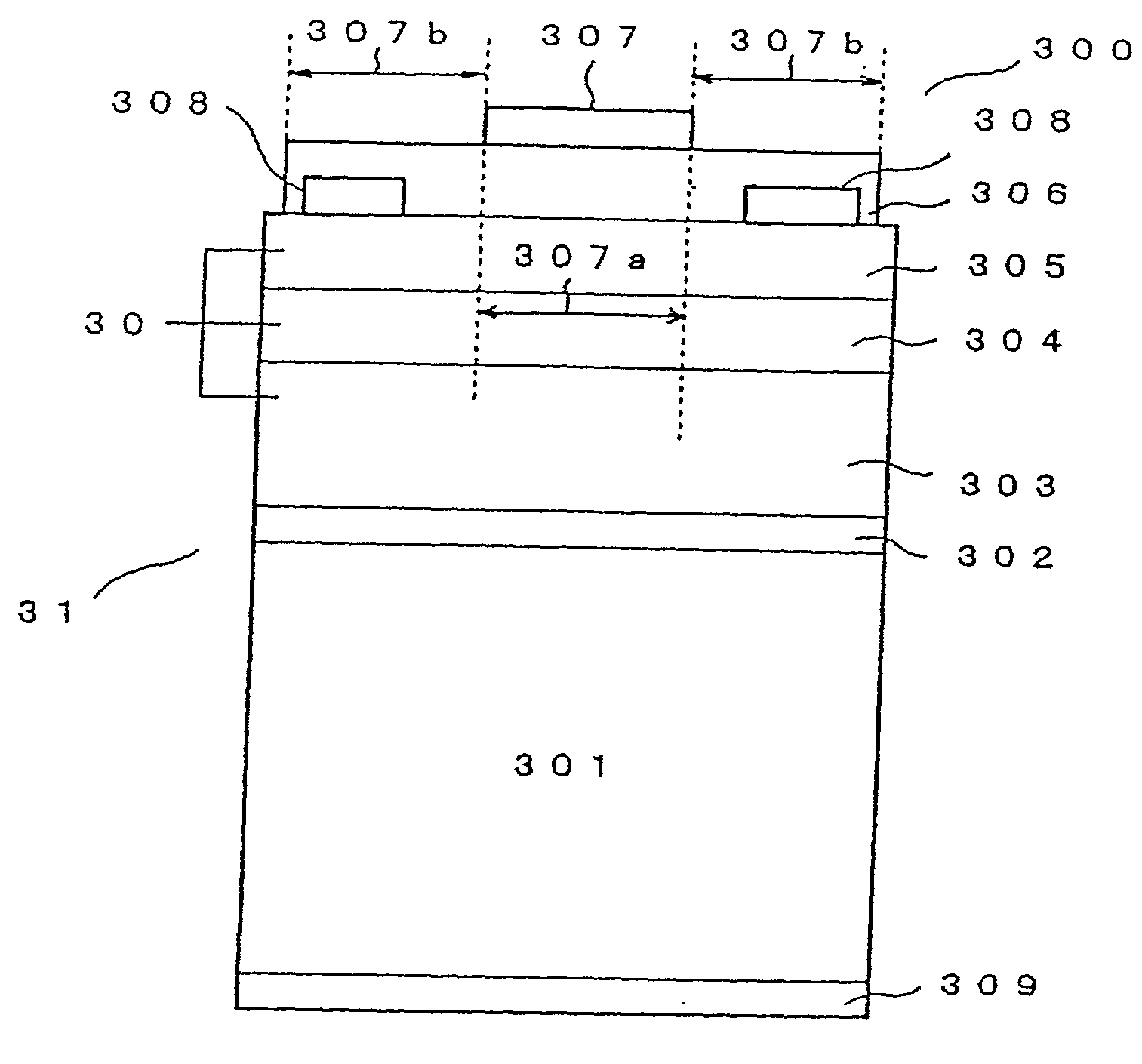

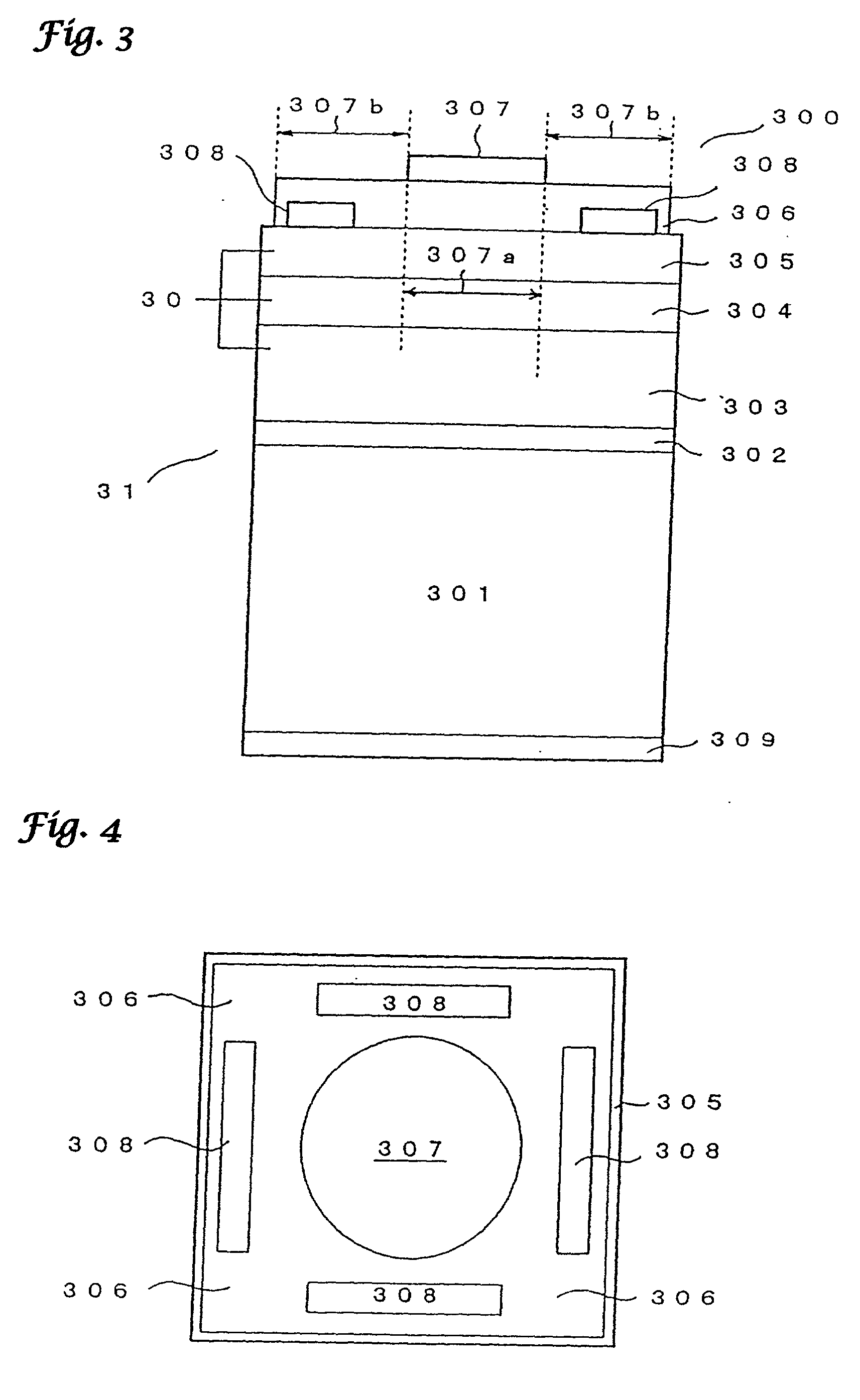

The present invention solves the problem of conventional group-III nitride semiconductor LED in that, since the LED driving current is supplied only from a pad electrode serving also as an ohmic electrode, the driving current cannot diffuse over a wide range of the light-emitting region and a group-III nitride semiconductor LED having high light emission intensity cannot be successfully provided. A group-III nitride semiconductor LED having high light emission intensity, which is fabricated using a stacked layer structure obtained by providing a surface ohmic electrode, a window layer including an electrically conducting transparent oxide crystal layer and a pad electrode on an electrically conducting substrate through a boron phosphide (BP)-based buffer layer to allow the driving current to diffuse over a wide range of the light-emitting region is provided.

Owner:SHOWA DENKO KK

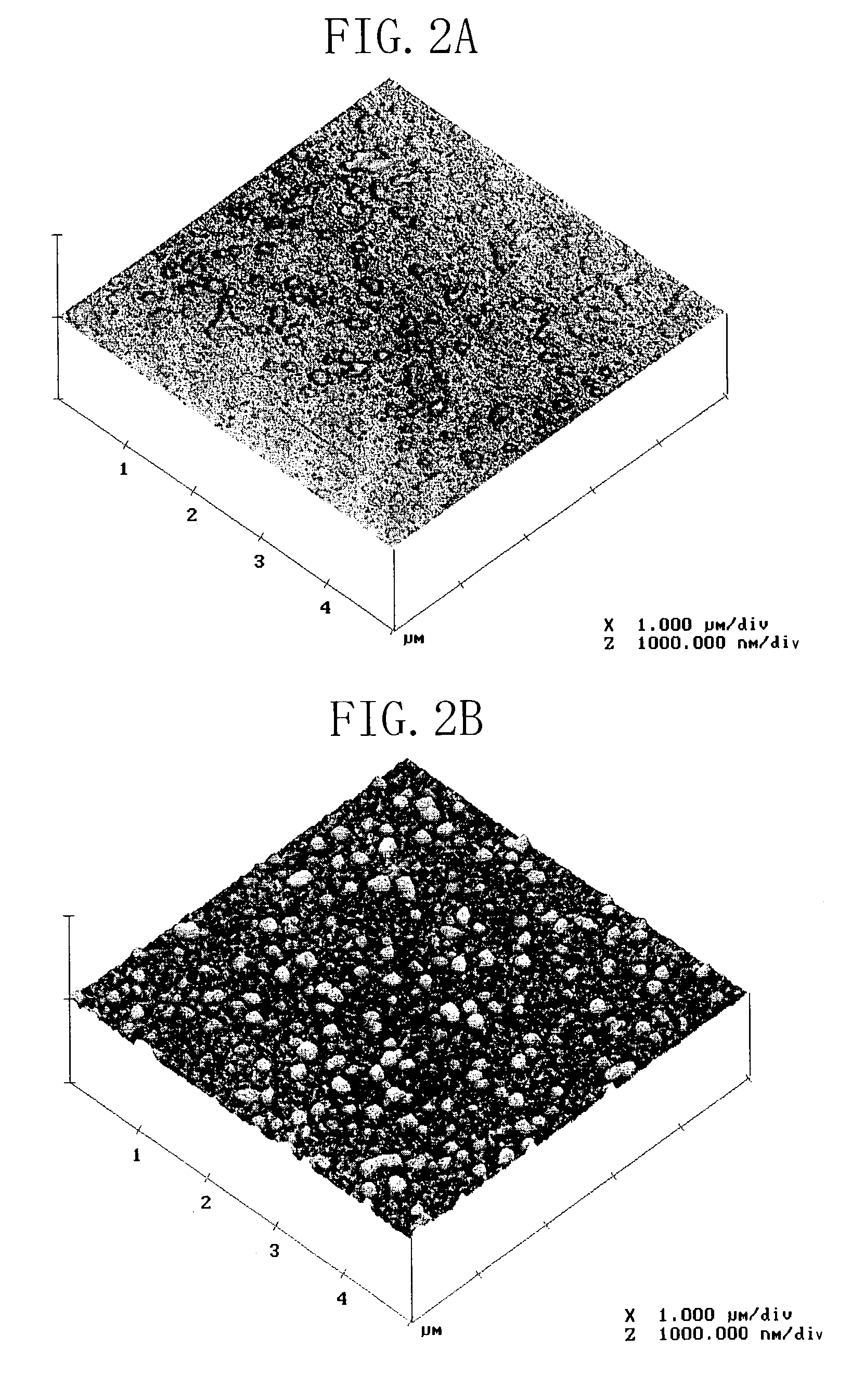

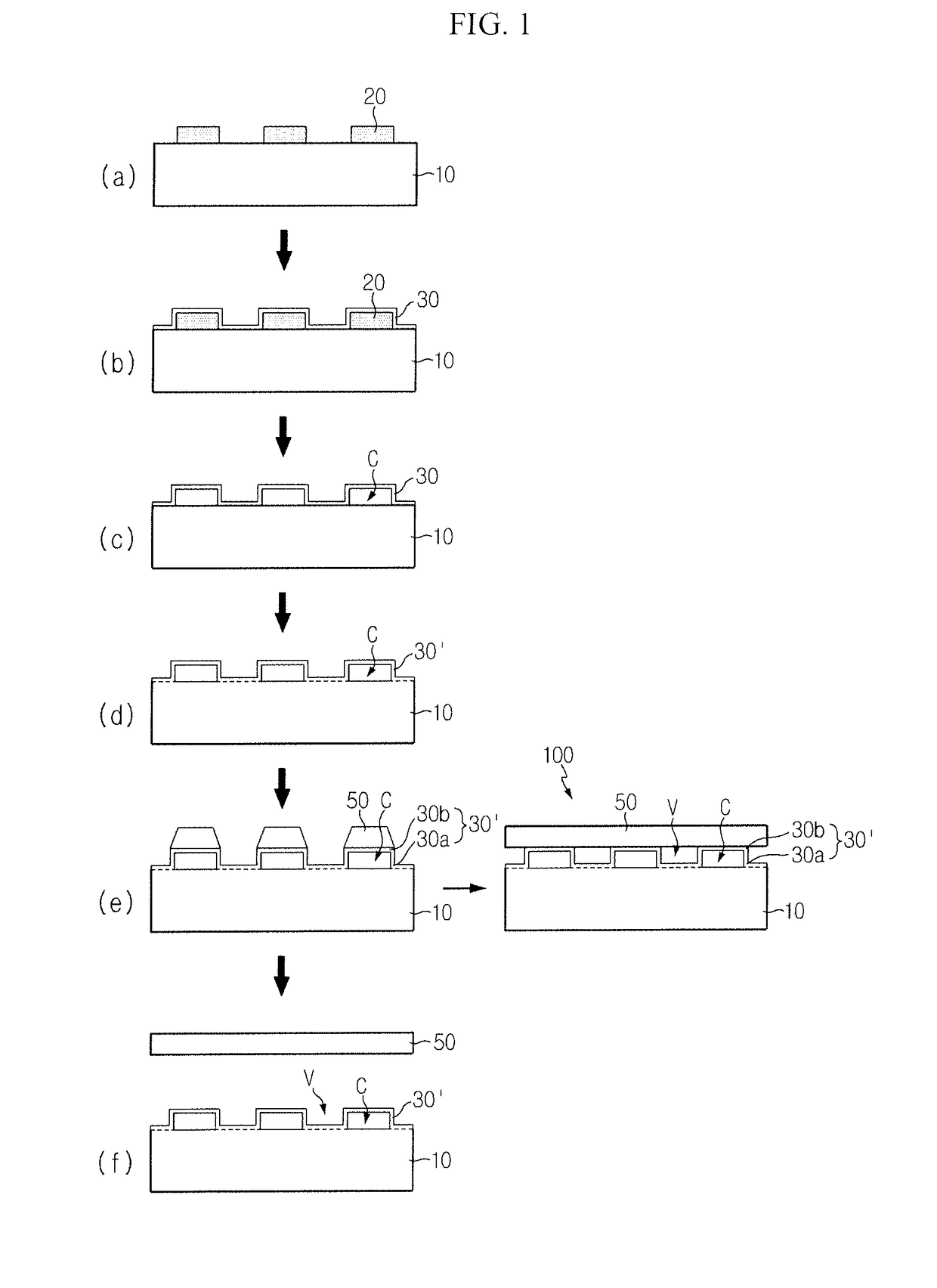

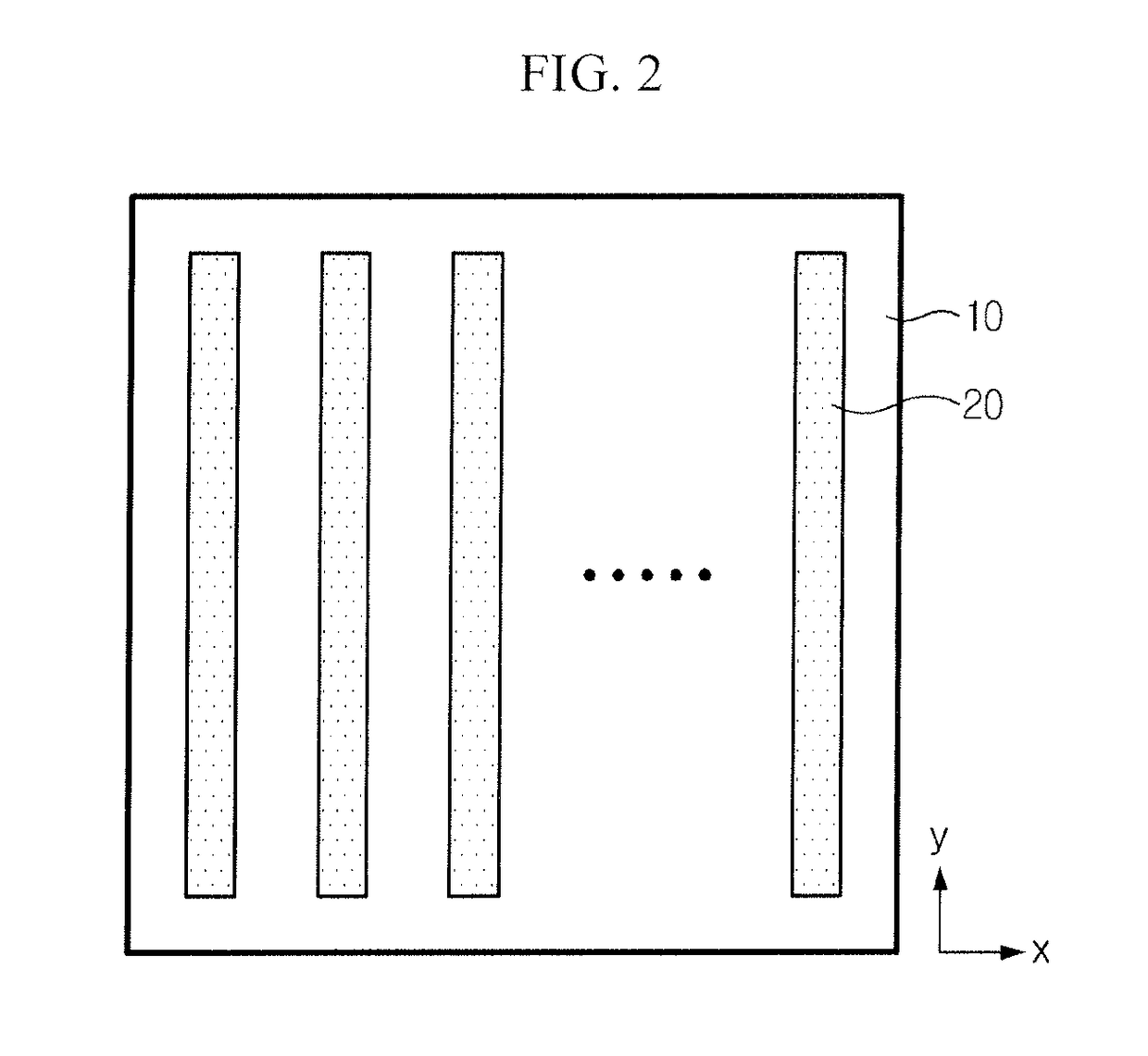

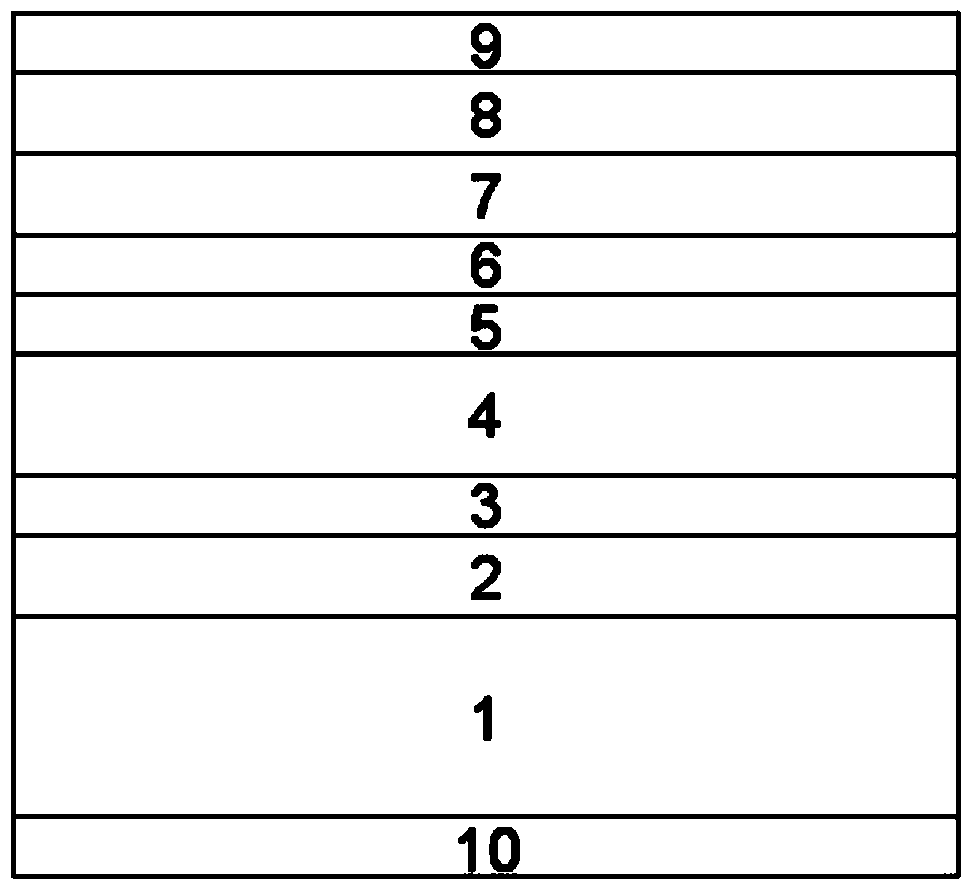

Method for manufacturing vertical group III-nitride light emitting device

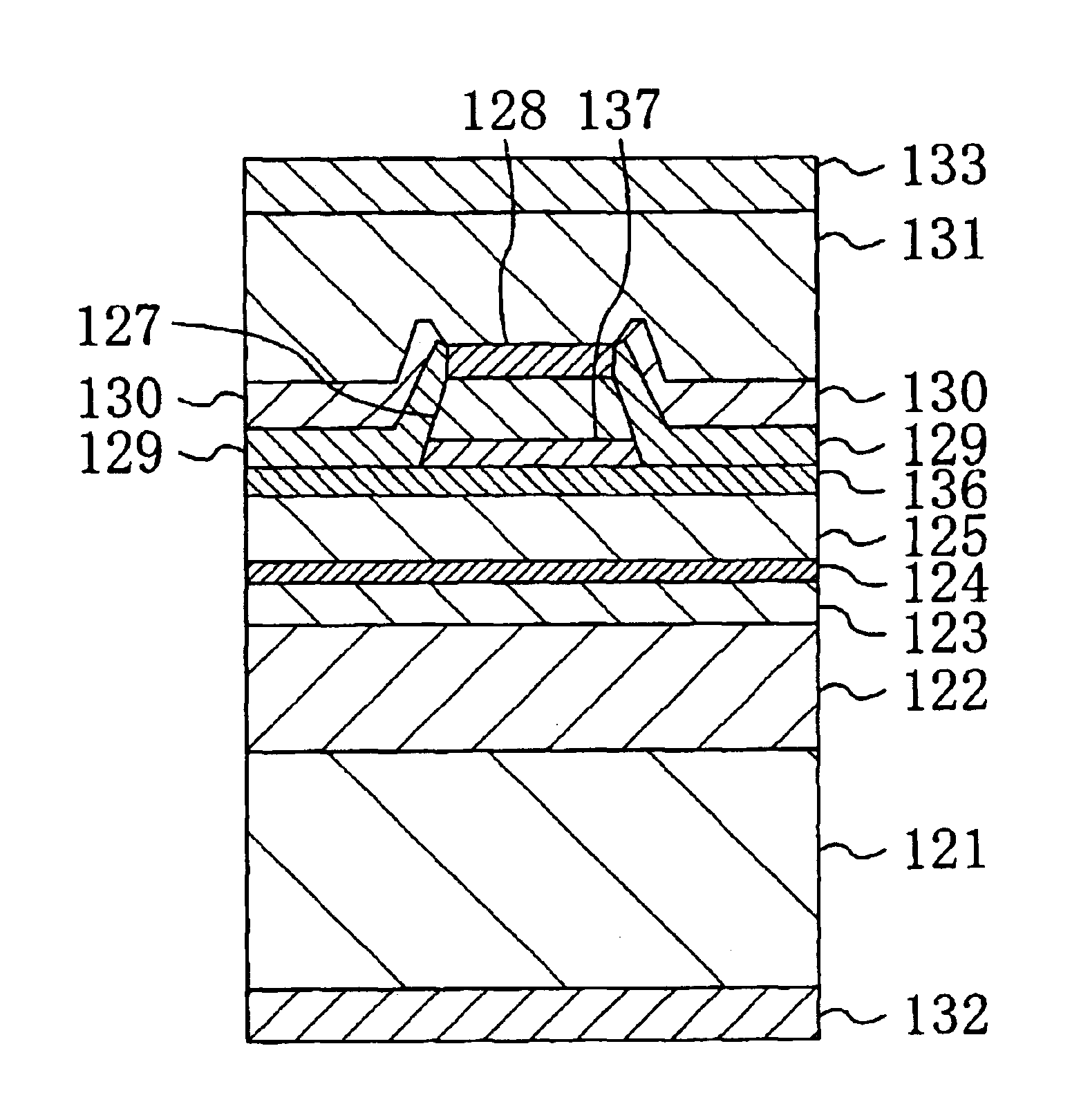

ActiveUS20060234408A1Light extraction efficiencyEasy to makeSemiconductor/solid-state device manufacturingSemiconductor devicesGalliumActive layer

The invention provides a vertical group III-nitride light emitting device improved in external extraction efficiency and a method for manufacturing the same. The method includes forming an undoped GaN layer and an insulating layer on a basic substrate. Then, the insulating layer is selectively etched to form an insulating pattern, and an n-doped AlxGayIn(1-x-y)N layer, an active layer and a p-doped AlmGanIn(1-m-n)N layer are sequentially formed on the insulating pattern. A conductive substrate is formed on the p-doped AlmGanIn(1-m-n)N layer. The basic substrate, the undoped gaN layer and the insulating pattern are removed, and an n-electrode is formed on a part of the exposed surface of the n-doped AlxGayIn(1-x-y)N layer.

Owner:SAMSUNG ELECTRONICS CO LTD

Method for manufacturing vertical group III-nitride light emitting device

ActiveUS7485482B2Light extraction efficiencyEasy to makeSemiconductor/solid-state device manufacturingSemiconductor devicesActive layerLight emitting device

The invention provides a vertical group III-nitride light emitting device improved in external extraction efficiency and a method for manufacturing the same. The method includes forming an undoped GaN layer and an insulating layer on a basic substrate. Then, the insulating layer is selectively etched to form an insulating pattern, and an n-doped AlxGayIn(1-x-y)N layer, an active layer and a p-doped AlmGanIn(1-m-n)N layer are sequentially formed on the insulating pattern. A conductive substrate is formed on the p-doped AlmGanIn(1-m-n)N layer. The basic substrate, the undoped gaN layer and the insulating pattern are removed, and an n-electrode is formed on a part of the exposed surface of the n-doped AlxGayIn(1-x-y)N layer.

Owner:SAMSUNG ELECTRONICS CO LTD

Nitride semiconductor light emitting device

ActiveUS7888670B2Reduce crystal defect densityIncrease brightnessSemiconductor devicesContact formationInter layer

Owner:SAMSUNG ELECTRONICS CO LTD

Nitride semiconductor light emitting device

ActiveUS7462876B2Reduce crystal defect densityQuality improvementSemiconductor devicesActive layerLight emitting device

Disclosed herein is a nitride semiconductor light emitting device, which is improved in luminance and reliability. The light emitting device, comprises an n-type nitride semiconductor layer, an active layer and a p-type nitride semiconductor layer sequentially formed on a substrate, an n-side electrode formed on a portion of an upper surface of the n-type nitride semiconductor layer, and at least one intermediate layer formed between the substrate and the n-type nitride semiconductor layer. The intermediate layer has a multilayer structure of three or more layers having different band-gaps, and is positioned below the n-side electrode.

Owner:SAMSUNG ELECTRONICS CO LTD

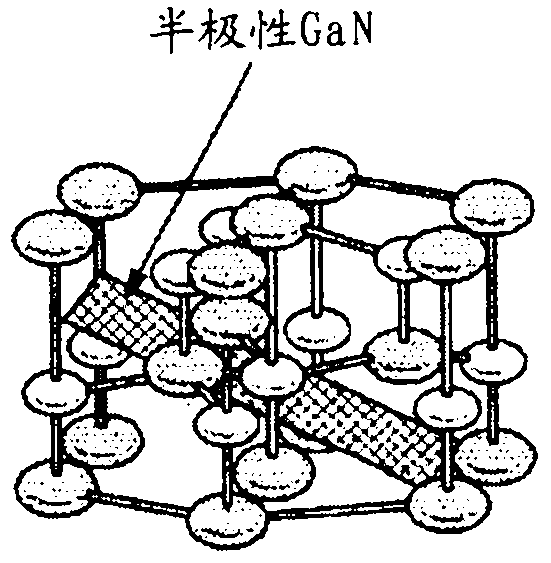

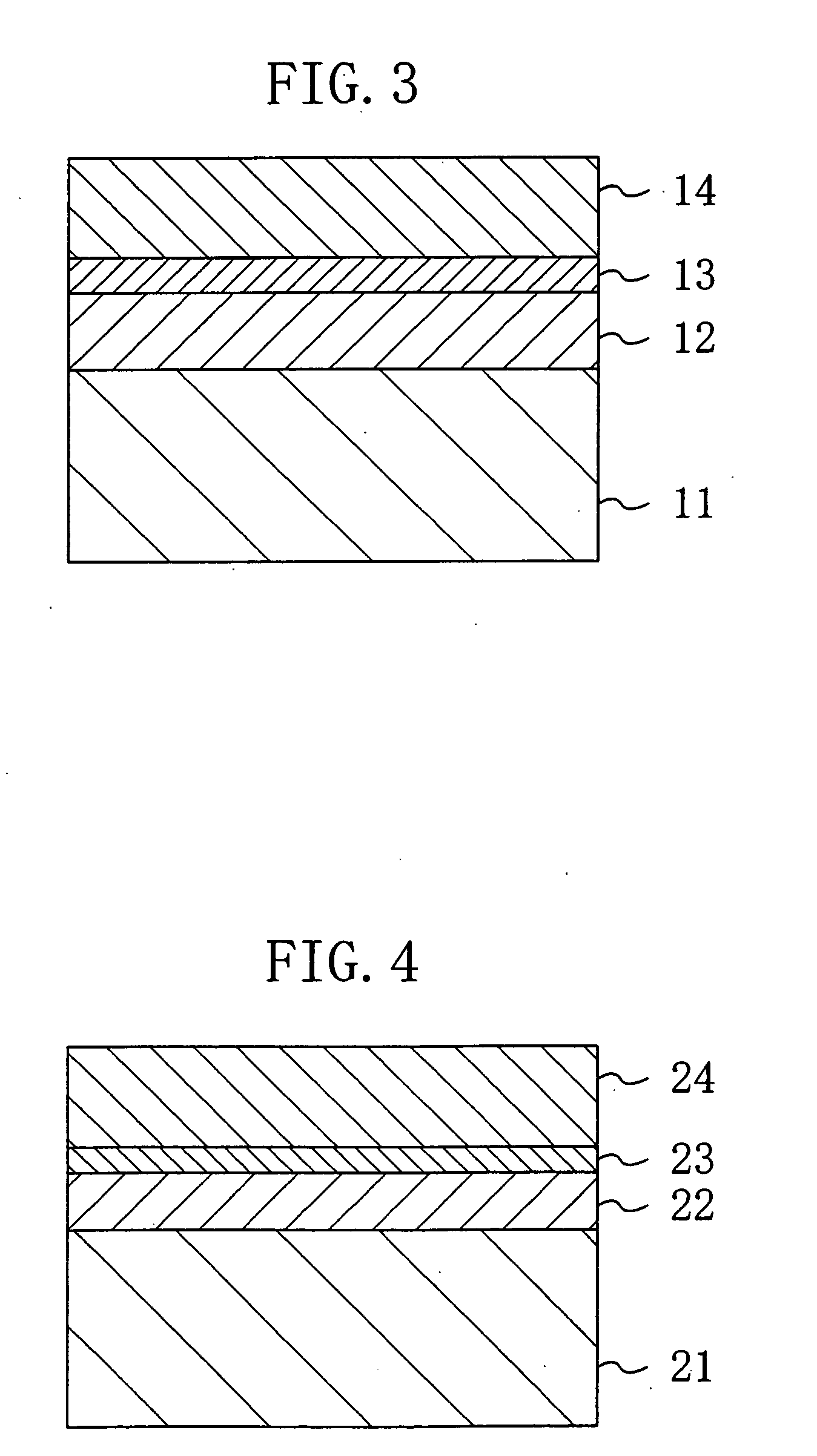

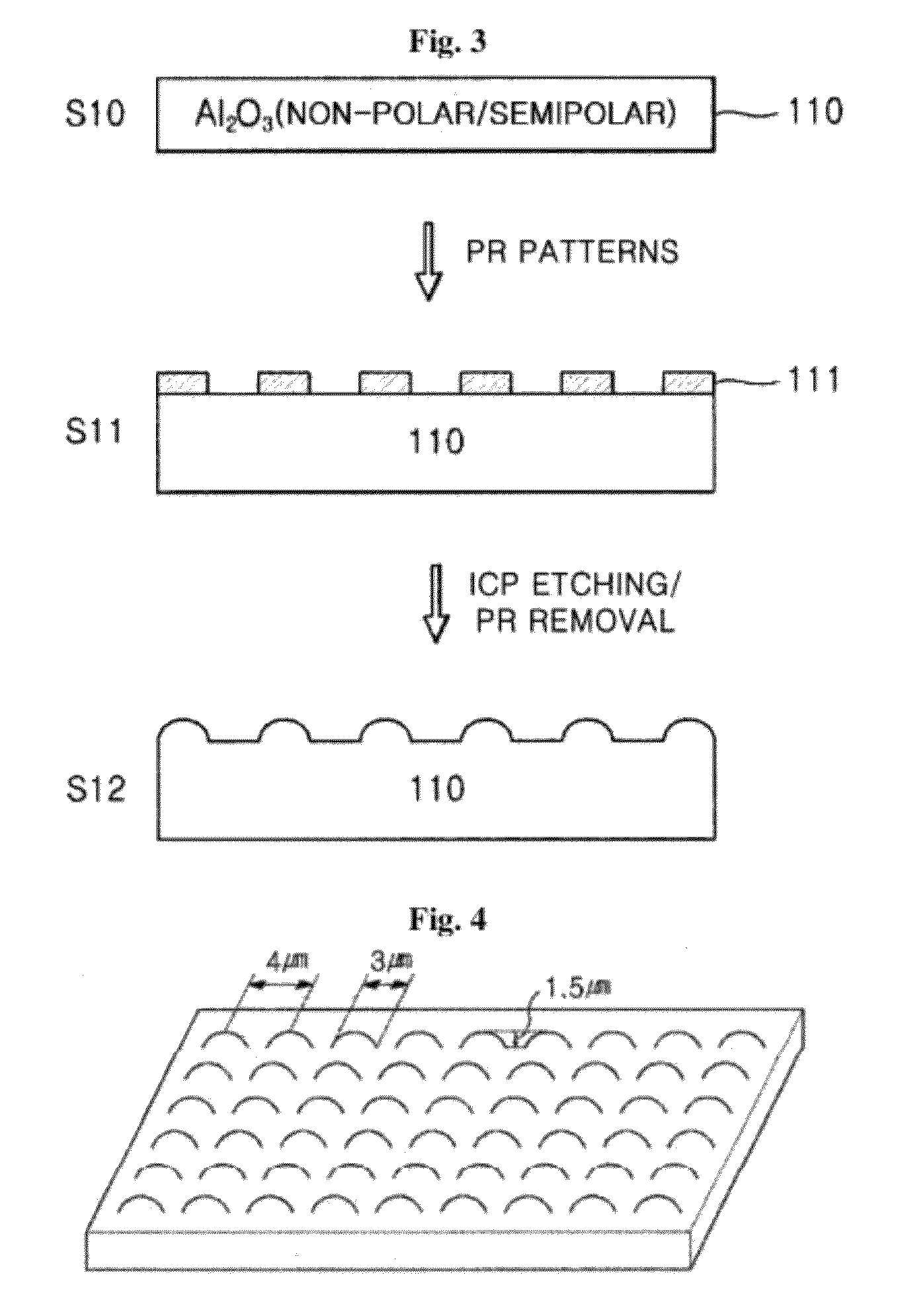

Gan-Based Light-Emitting Element and Method for Producing Same

InactiveUS20080048195A1Reduce crystal defect densityAvoid it happening againSemiconductor/solid-state device manufacturingSemiconductor devicesGalliumContact layer

A GaN-based semiconductor light-emitting element capable of suppressing the occurrence of piezoelectric spontaneous polarization in the thickness direction of an active layer and reducing the driving voltage of a light-emitting diode is provided. The GaN-based semiconductor light-emitting element has a structure with a first GaN-based compound semiconductor layer 21 having the top face parallel to the a-plane and having a first conductivity type, an active layer 22 having the top face parallel to the a-plane, a second GaN-based compound semiconductor layer 23 having the top face parallel to the a-plane and having a second conductivity type, and a contact layer 24 composed of a GaN-based compound semiconductor and having the top face parallel to the a-plane, stacked in that order. The GaN-based semiconductor light-emitting element further includes a first electrode 25 disposed on the first GaN-based compound semiconductor layer 21 and a second electrode 26 disposed on the contact layer 24.

Owner:SONY CORP

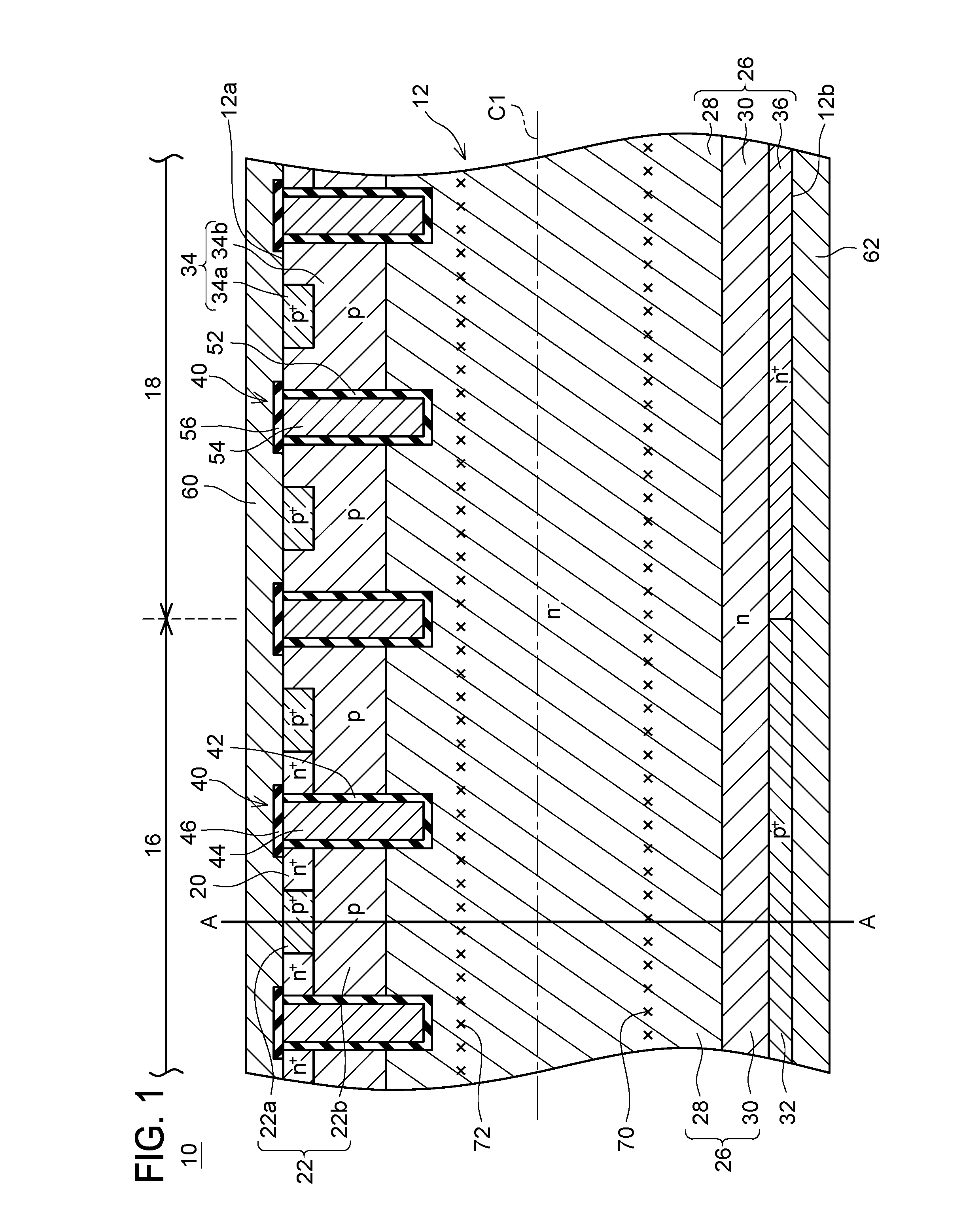

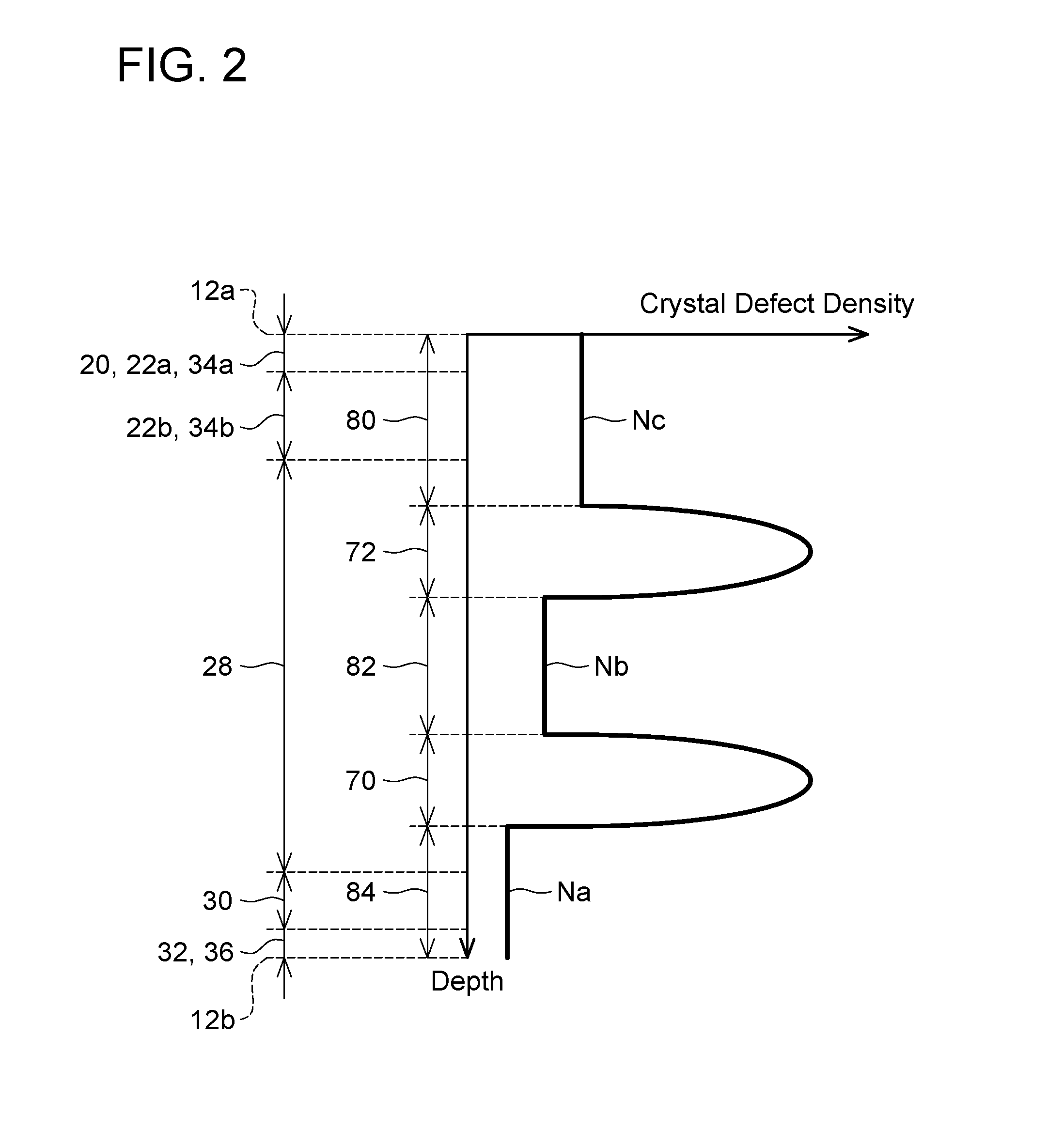

Semiconductor device and method for manufacturing the same

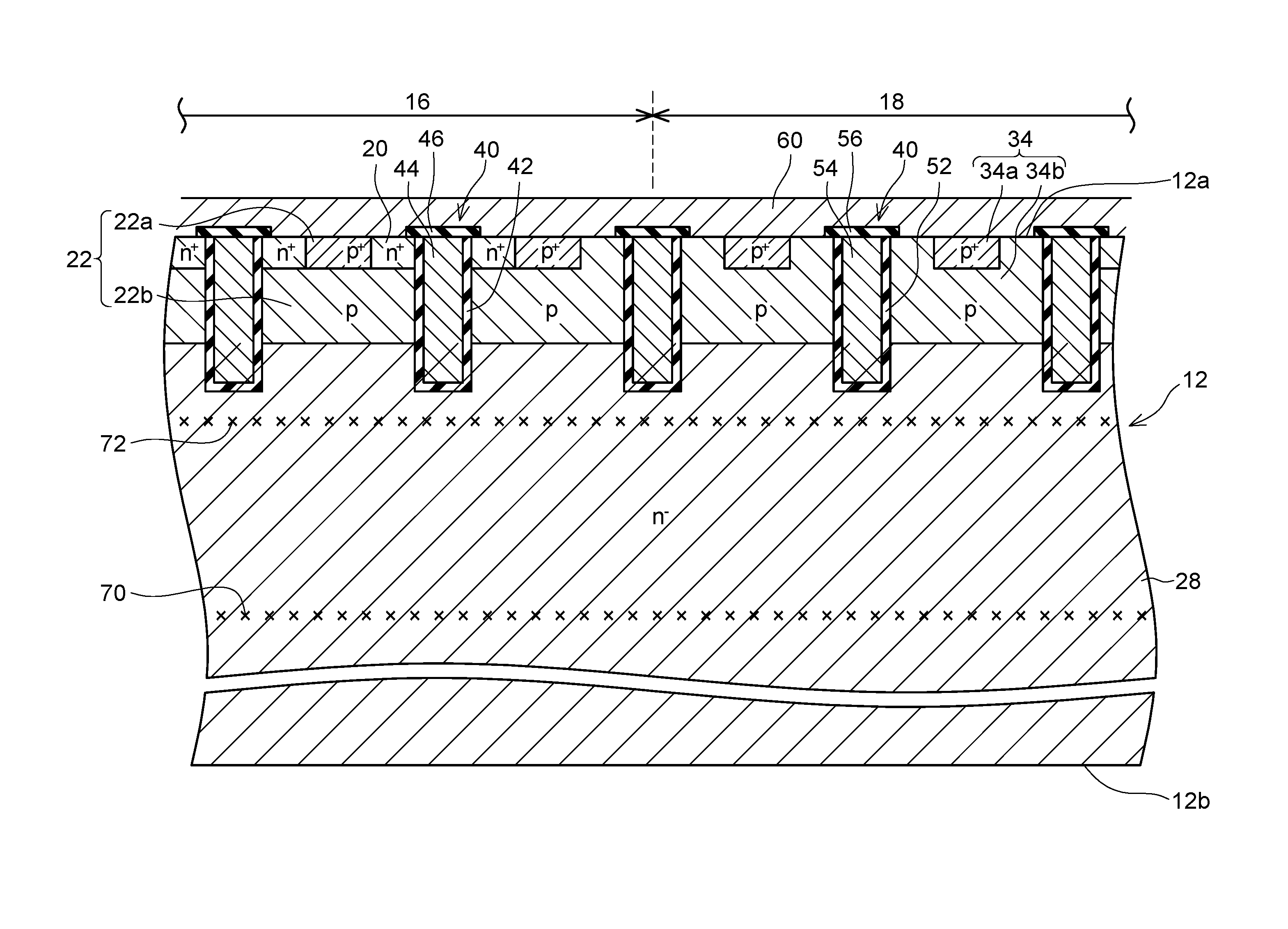

InactiveUS20160254374A1Suppress mutationReduce crystal defect densityTransistorSolid-state devicesControl layerCrystallographic defect

A semiconductor device includes a semiconductor substrate that includes an IGBT region. A first lifetime control layer extending along a planar direction of the semiconductor substrate is provided in a range in a drift region that is closer to the rear surface than an intermediate portion of the semiconductor substrate in a thickness direction. A crystal defect density in the first lifetime control layer is higher than any of a crystal defect density in a region adjacent to the first lifetime control layer on the rear surface side and a crystal defect density in a region adjacent to the first lifetime control layer on a front surface side. A crystal defect density in a region between the first lifetime control layer and the rear surface is lower than a crystal defect density in a region between the first lifetime control layer and the front surface.

Owner:TOYOTA JIDOSHA KK

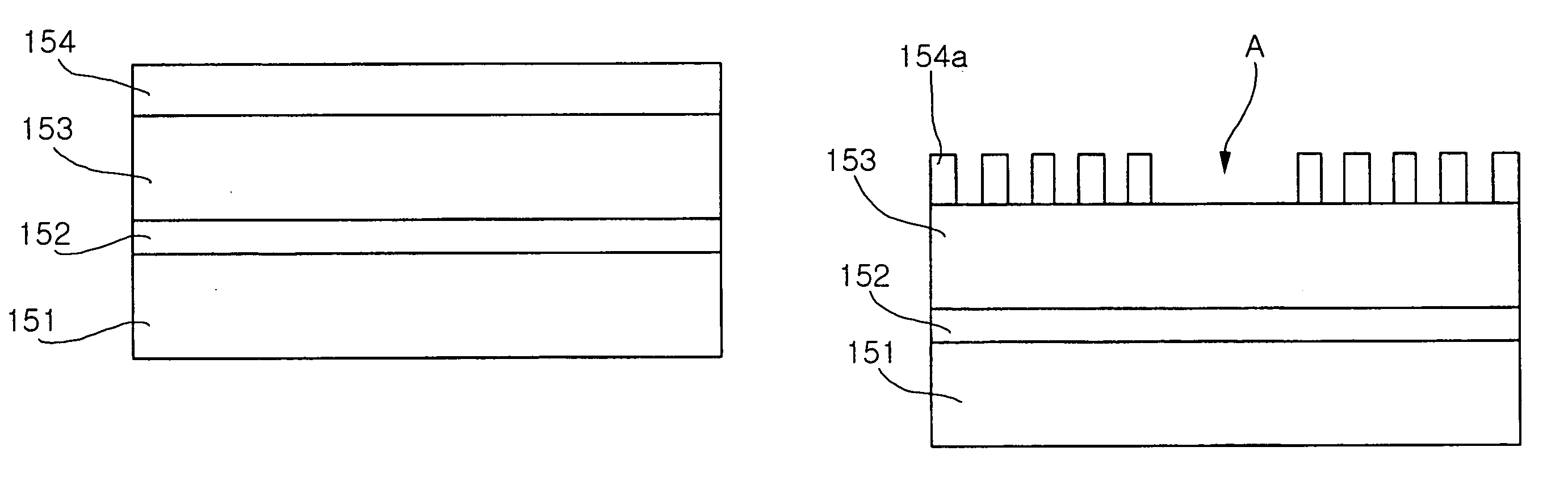

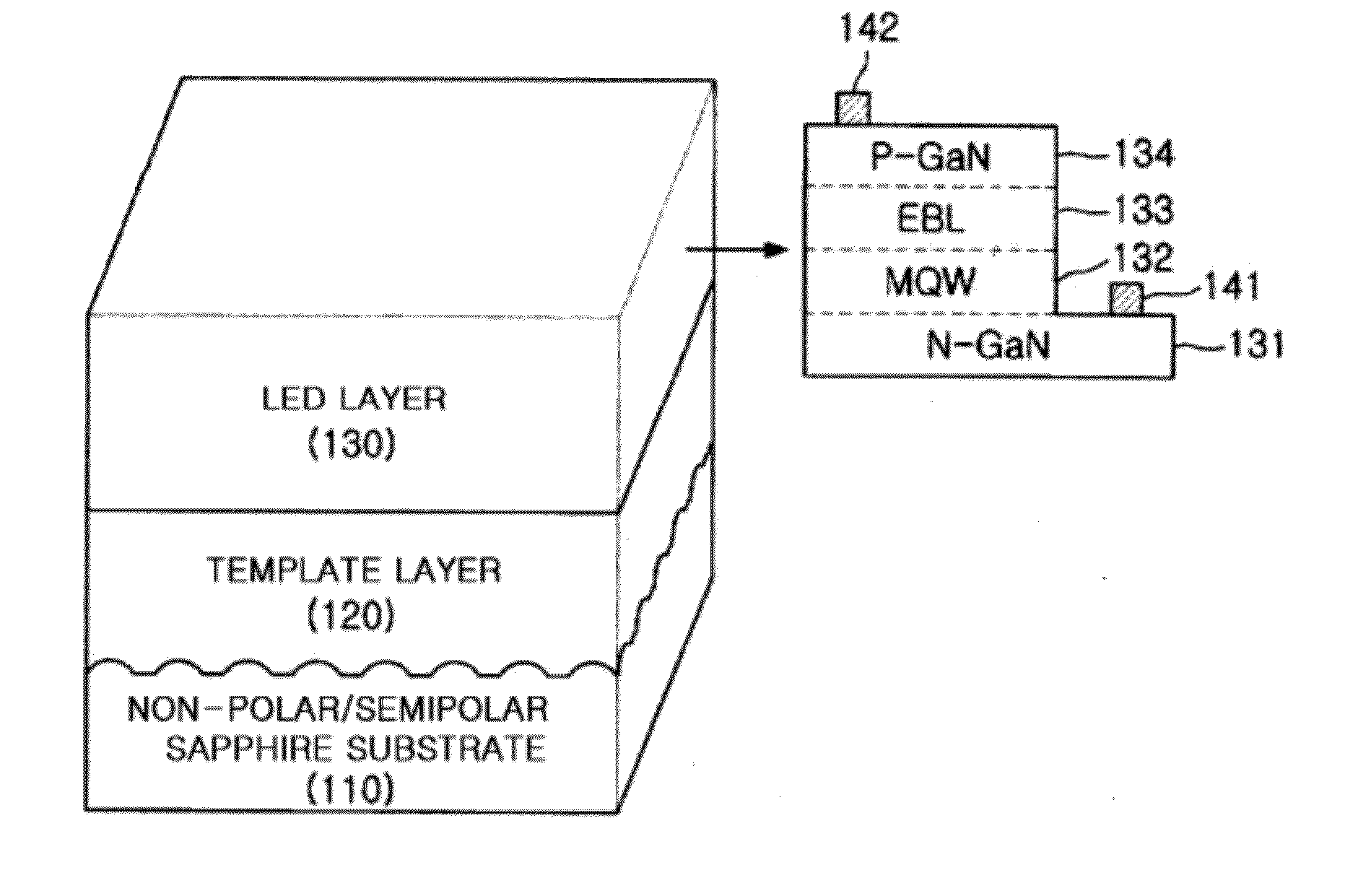

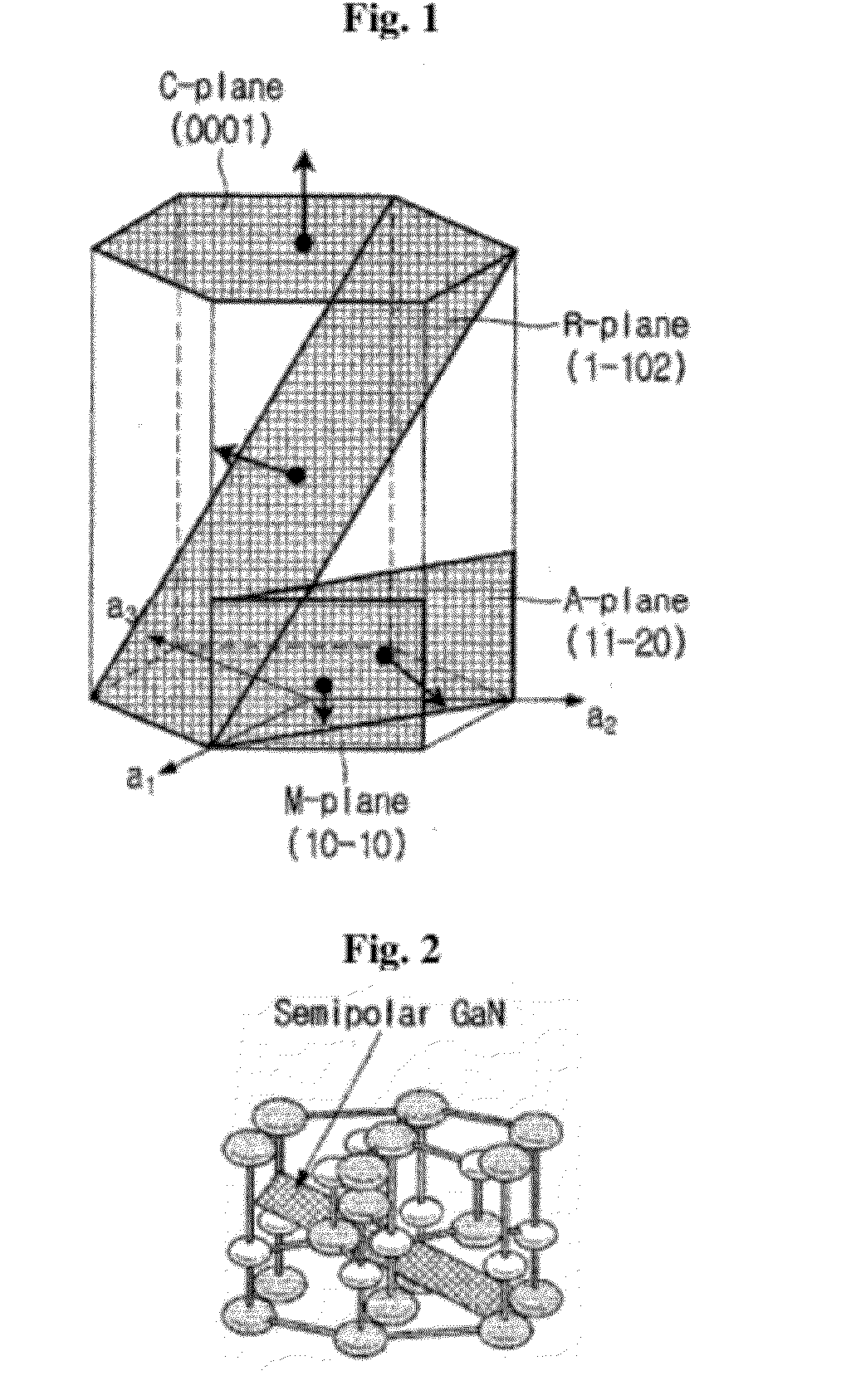

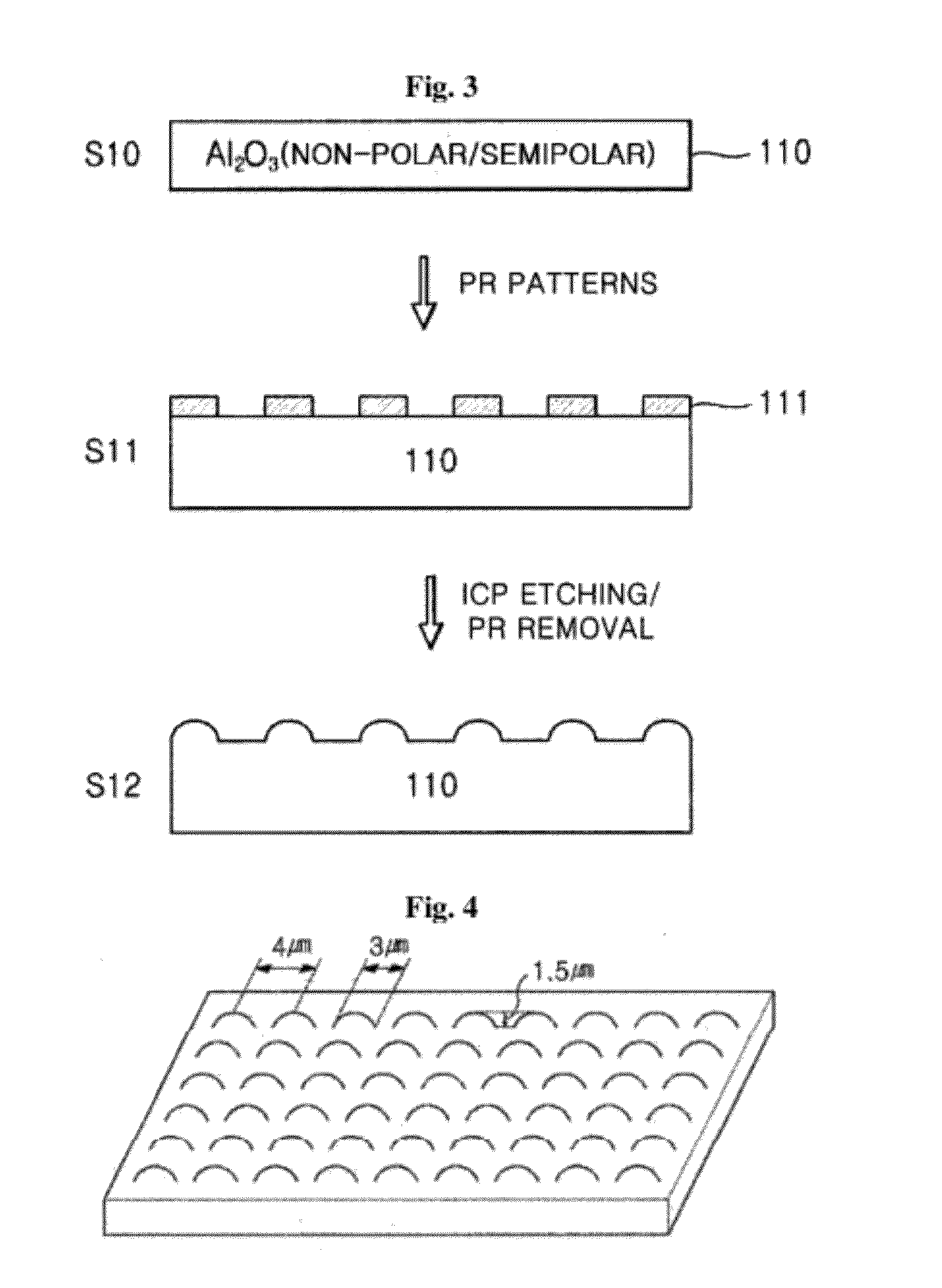

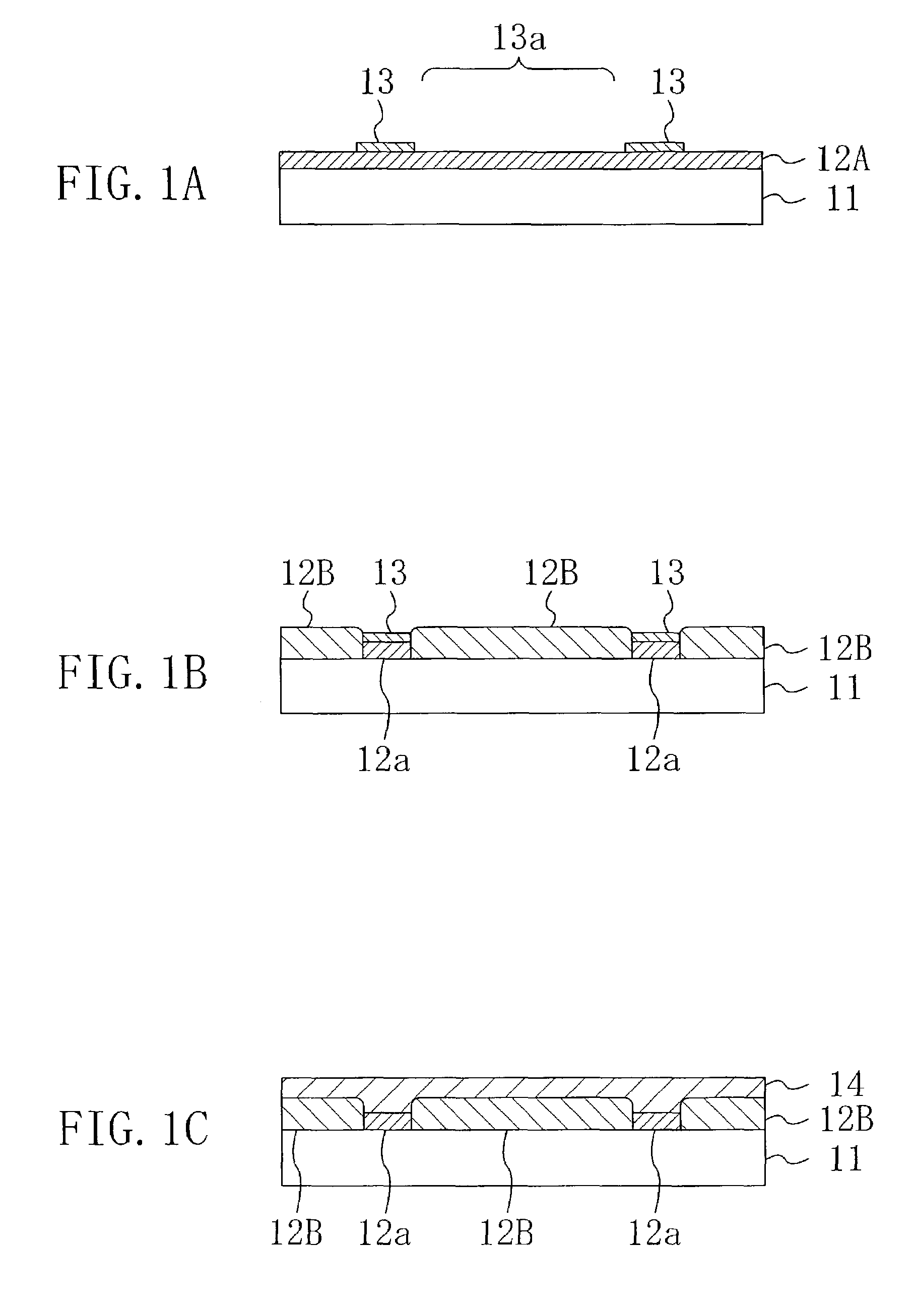

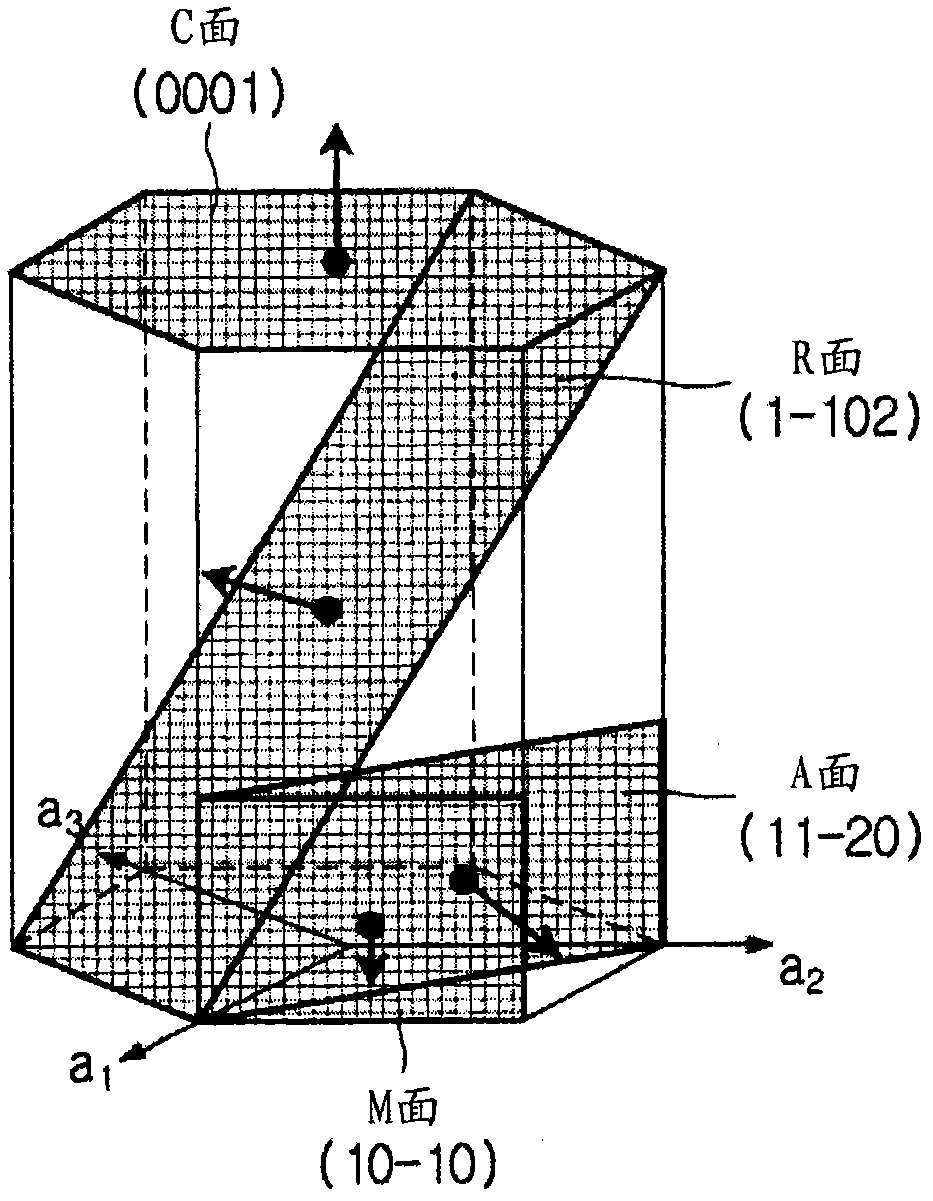

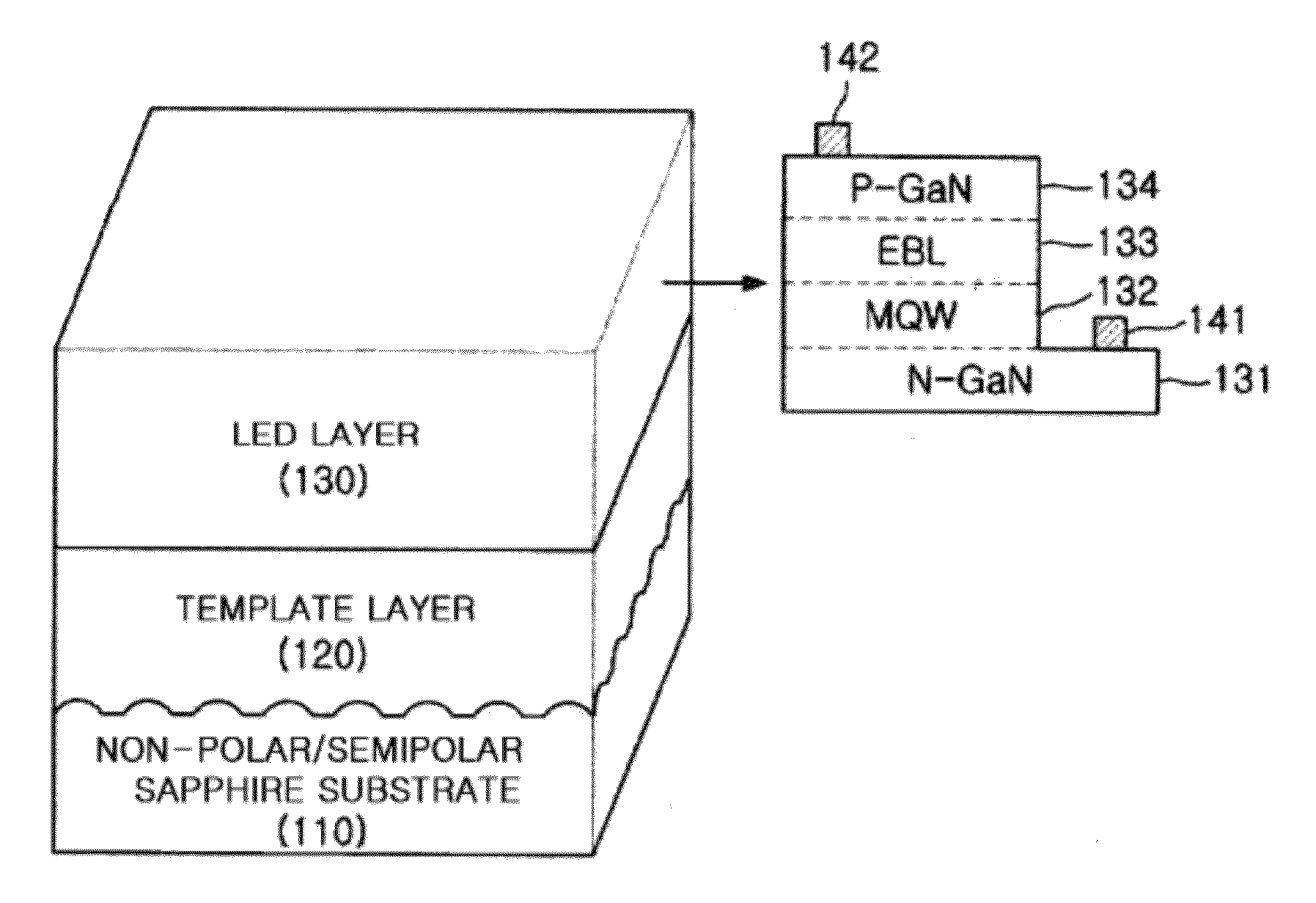

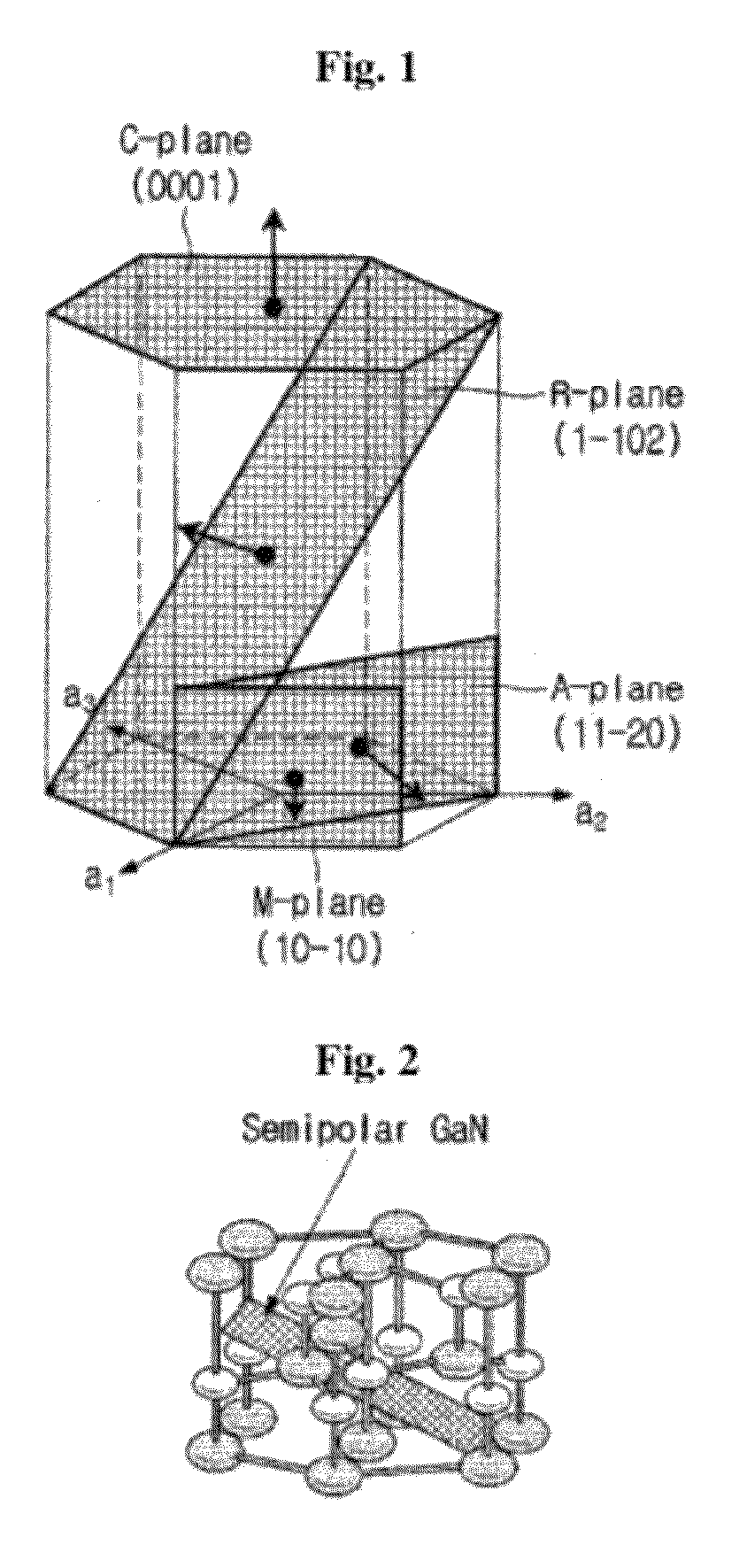

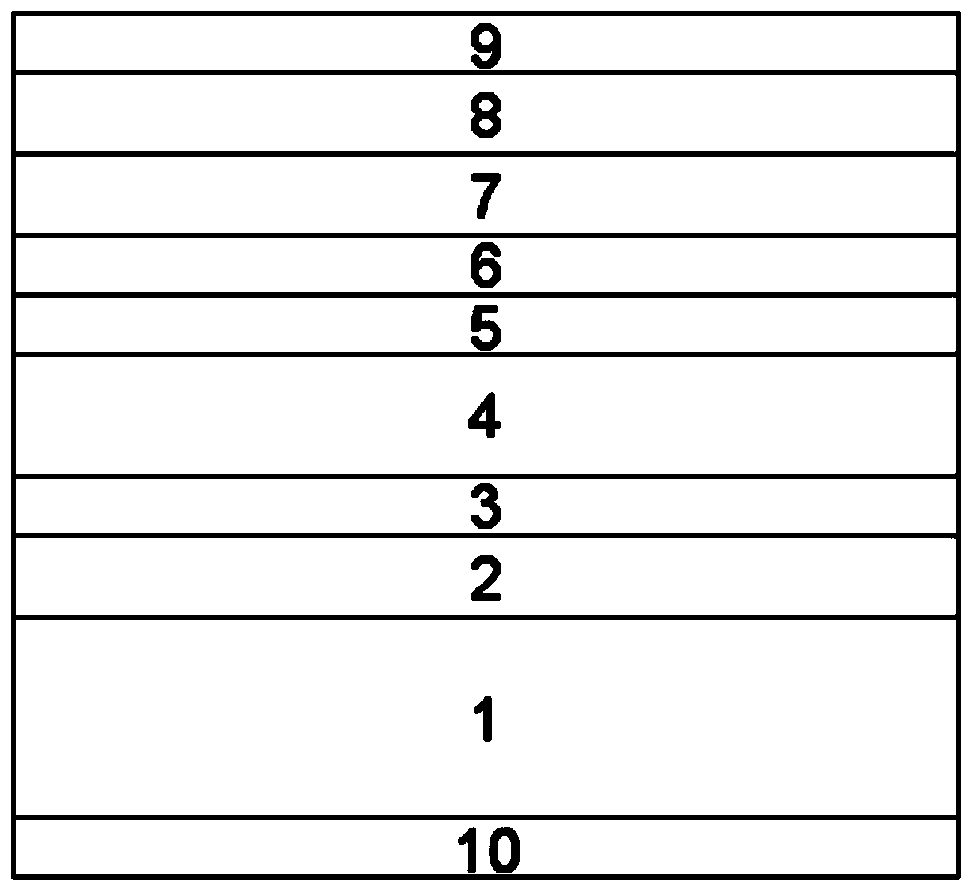

High-quality non-polar/semi-polar semiconductor element on an unevenly patterned substrate and a production method therefor

ActiveUS20120153257A1Low crystal defect densityEliminate the effects ofSemiconductor/solid-state device manufacturingSemiconductor devicesCrystal planePatterned substrate

Provided are a high-quality non-polar / semi-polar semiconductor device with reduced defect density and improved internal quantum efficiency and light extraction efficiency, and a manufacturing method thereof. The manufacturing method is a method for manufacturing a semiconductor device, in which a template layer and a semiconductor device structure are formed on a sapphire substrate having a crystal plane for growing a non-polar or semi-polar nitride semiconductor layer. The sapphire substrate is etched to form uneven patterns, and the template layer including a nitride semiconductor layer and a GaN layer is formed on the sapphire substrate in which the uneven patterns are formed.

Owner:SEOUL VIOSYS CO LTD +1

GaN-based semiconductor light-emitting diode and manufacture method thereof

InactiveCN102856449AImprove performanceExtend your lifeSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringContact layer

The invention provides a manufacture method of a GaN-based semiconductor light-emitting diode. The manufacture method includes the steps of forming of a GaN substrate and deposition of a p-type contact layer, an active layer, an n-type electronic barrier layer, an n-type transition layer and an n-type contact layer on the GaN substrate, wherein forming of the GaN substrate includes the steps: placing a GaN wafer into a high-temperature and high-pressure device at the normal temperature and under the normal pressure; heating and pressurizing the GaN wafer simultaneously for 10-15 minutes, wherein the heating temperature is 820-880 DEG C, and the pressurizing pressure is 4.1-4.6GPa; stopping heating to enable the GaN wafer to be cooled to the normal temperature; slowly releasing pressure to enable the GaN wafer to be recovered to the normal pressure; and taking the GaN wafer out after annealing in the high-temperature and high-pressure device for 20-30minutes. By the manufacture method, crystal defect density in a light-emitting diode substrate can be obviously reduced, the performance of the light-emitting diode is improved, and the service life of the light-emitting diode is prolonged.

Owner:JIANGSU WINAD LIGHTING TECH

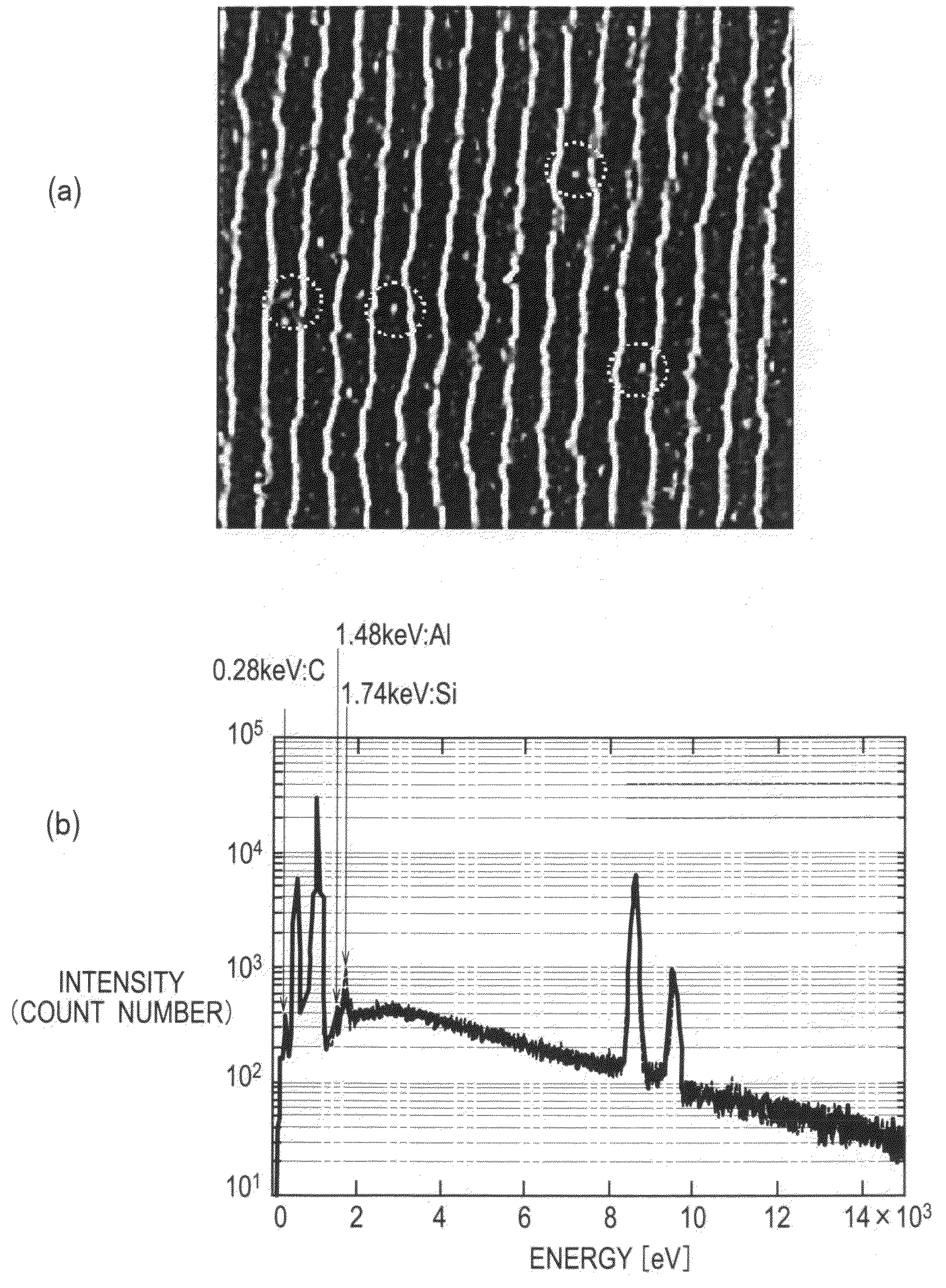

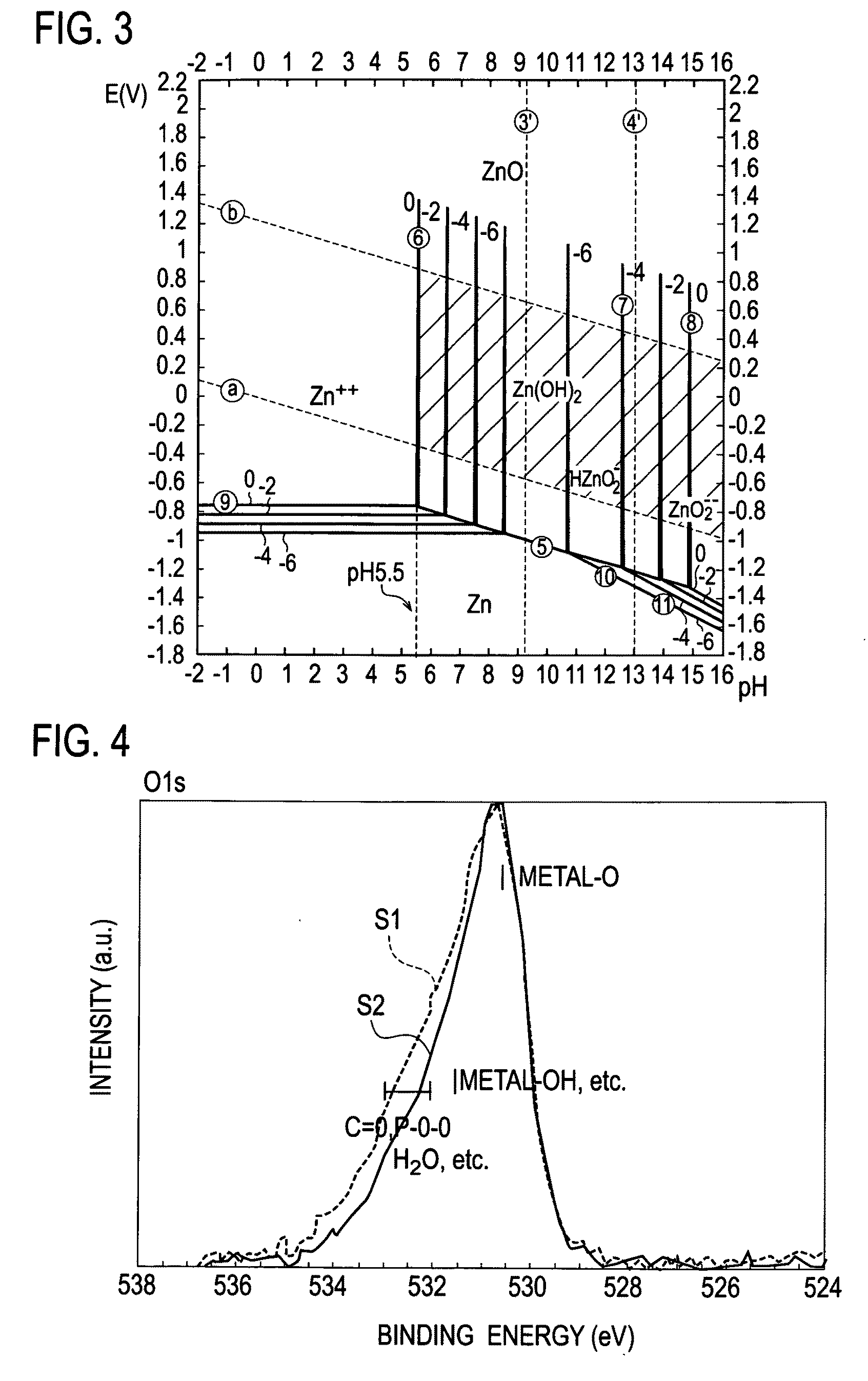

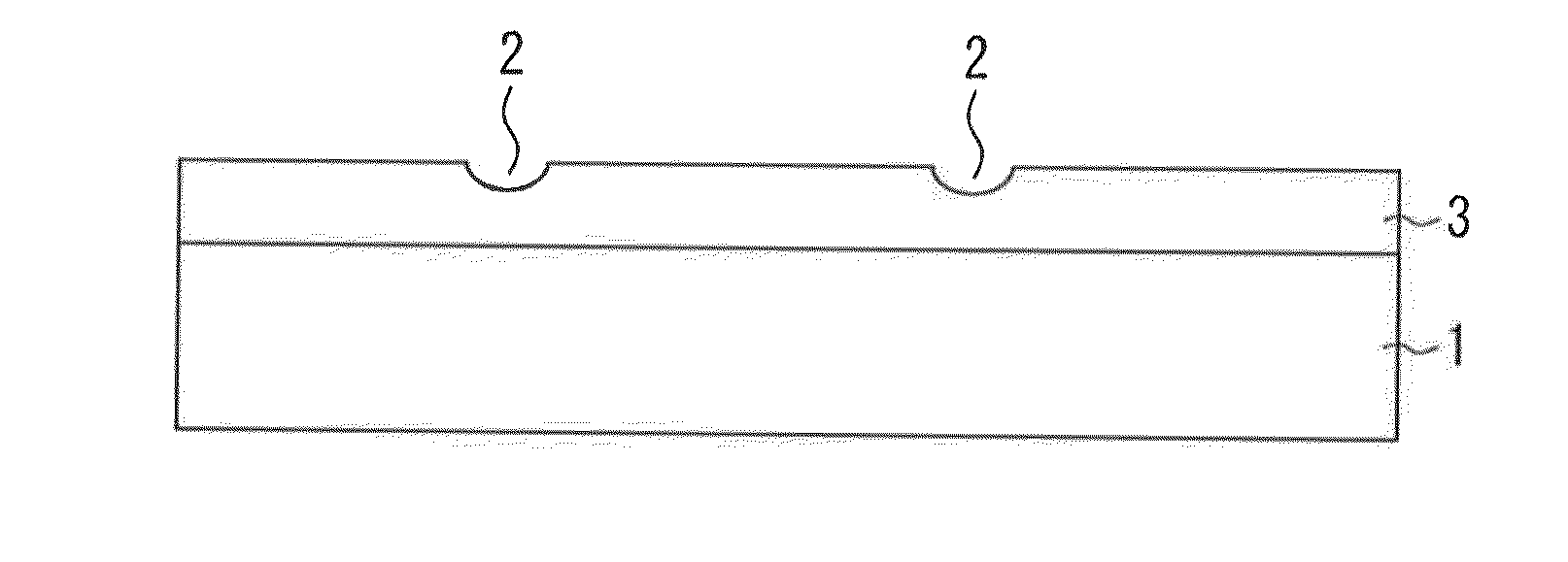

ZnO-BASED SUBSTRATE AND METHOD OF TREATING ZnO-BASED SUBSTRATE

InactiveUS20100133470A1Inhibit productionReduce crystal defect densityAfter-treatment apparatusPolycrystalline material growthEtchingCrystallographic defect

Provided are a ZnO-based substrate having a surface suitable for crystal growth, and a method of manufacturing the ZnO-based substrate. The ZnO-based substrate is made in a way that almost no hydroxide groups exist on a crystal growth-side surface of a MgxZn1-xO substrate (0≦x<1). To this end, as a method of treating the substrate, a final treatment to be applied on the crystal growth-side surface of the MgxZn1-xO substrate (0≦x<1) is acidic wet etching at pH 3 or lower. Thereby, it is possible to prevent production of a hydroxide of Zn, and to reduce the density of crystal defects in a thin film formed on the ZnO-based substrate.

Owner:ROHM CO LTD

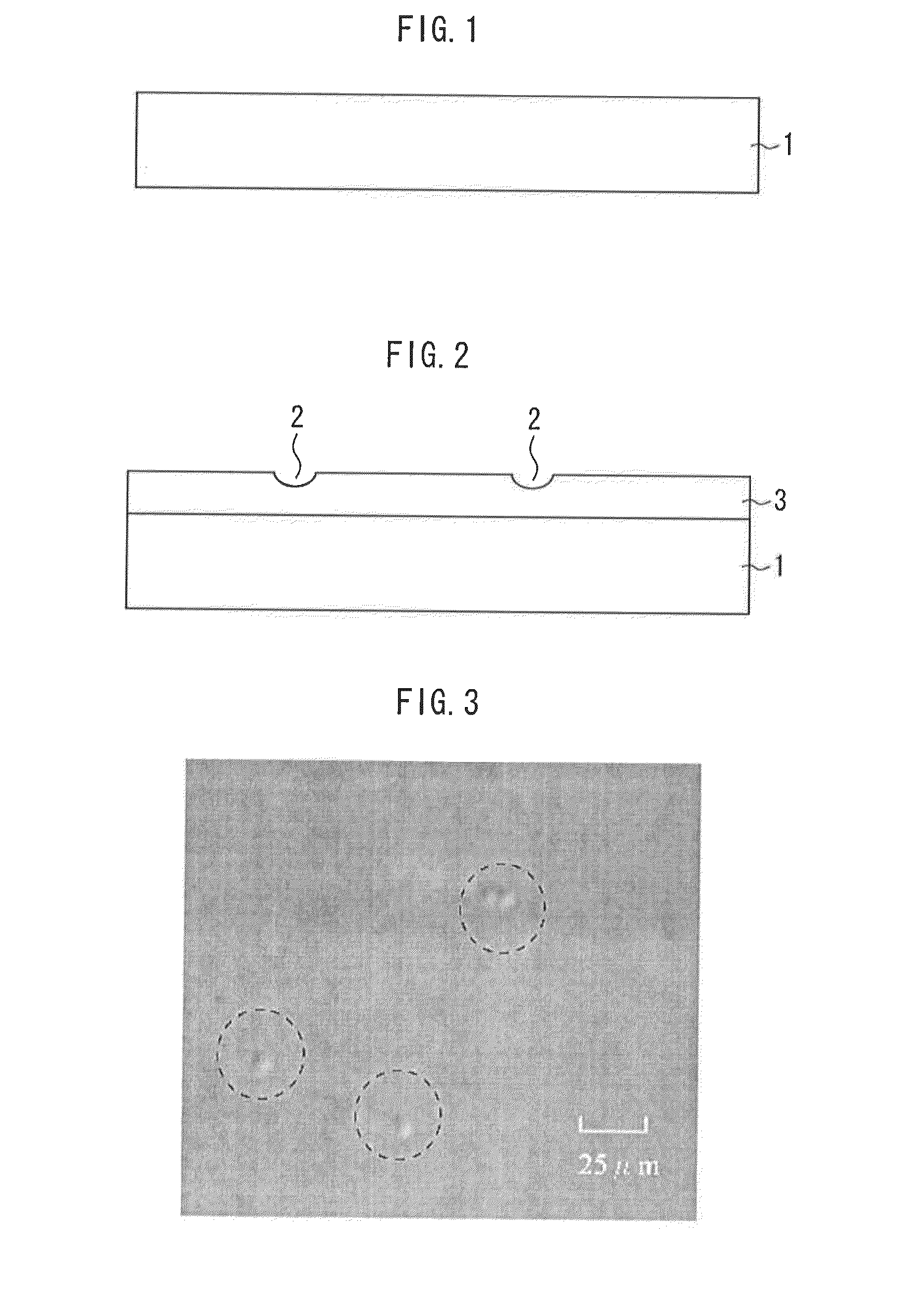

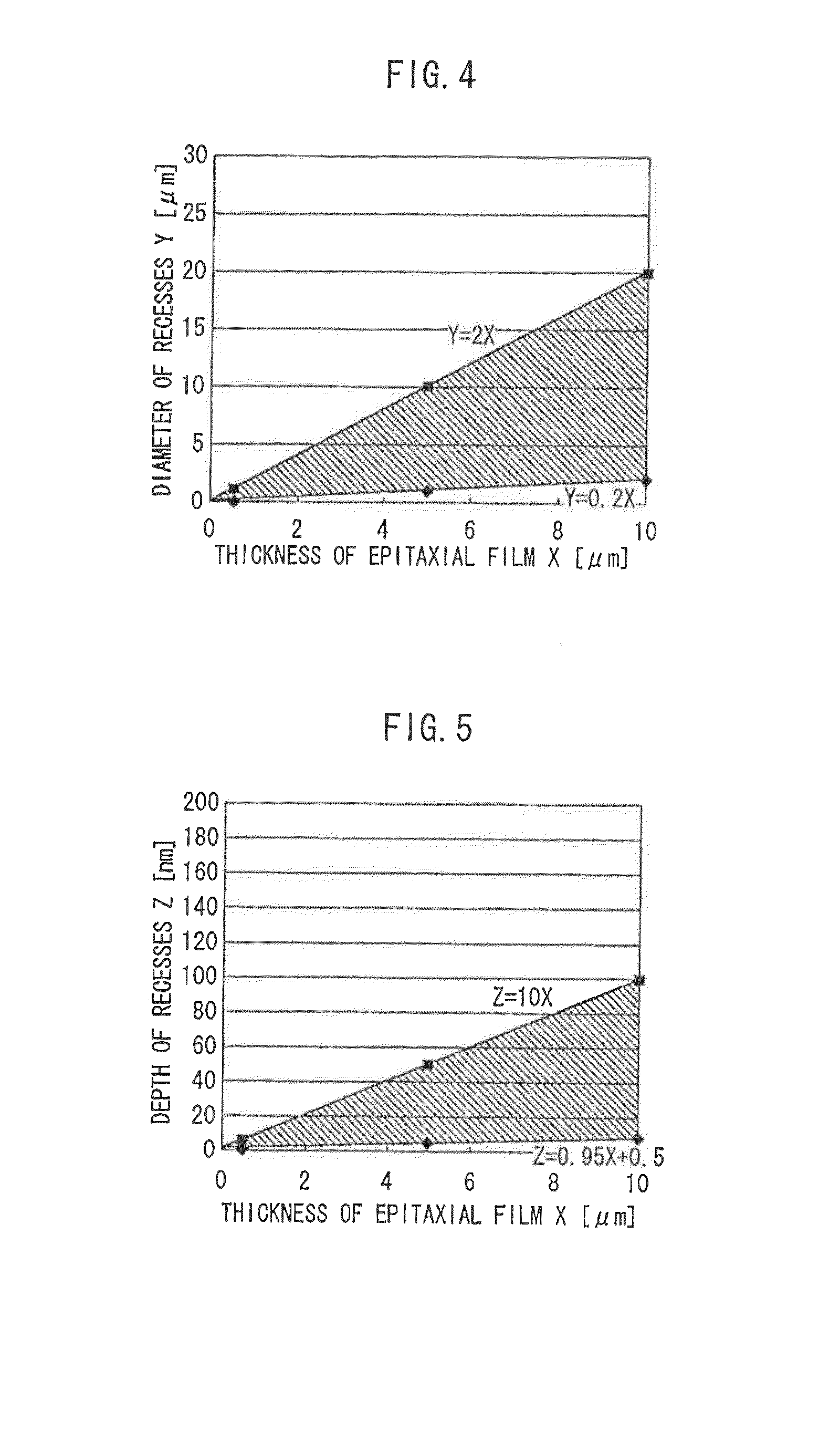

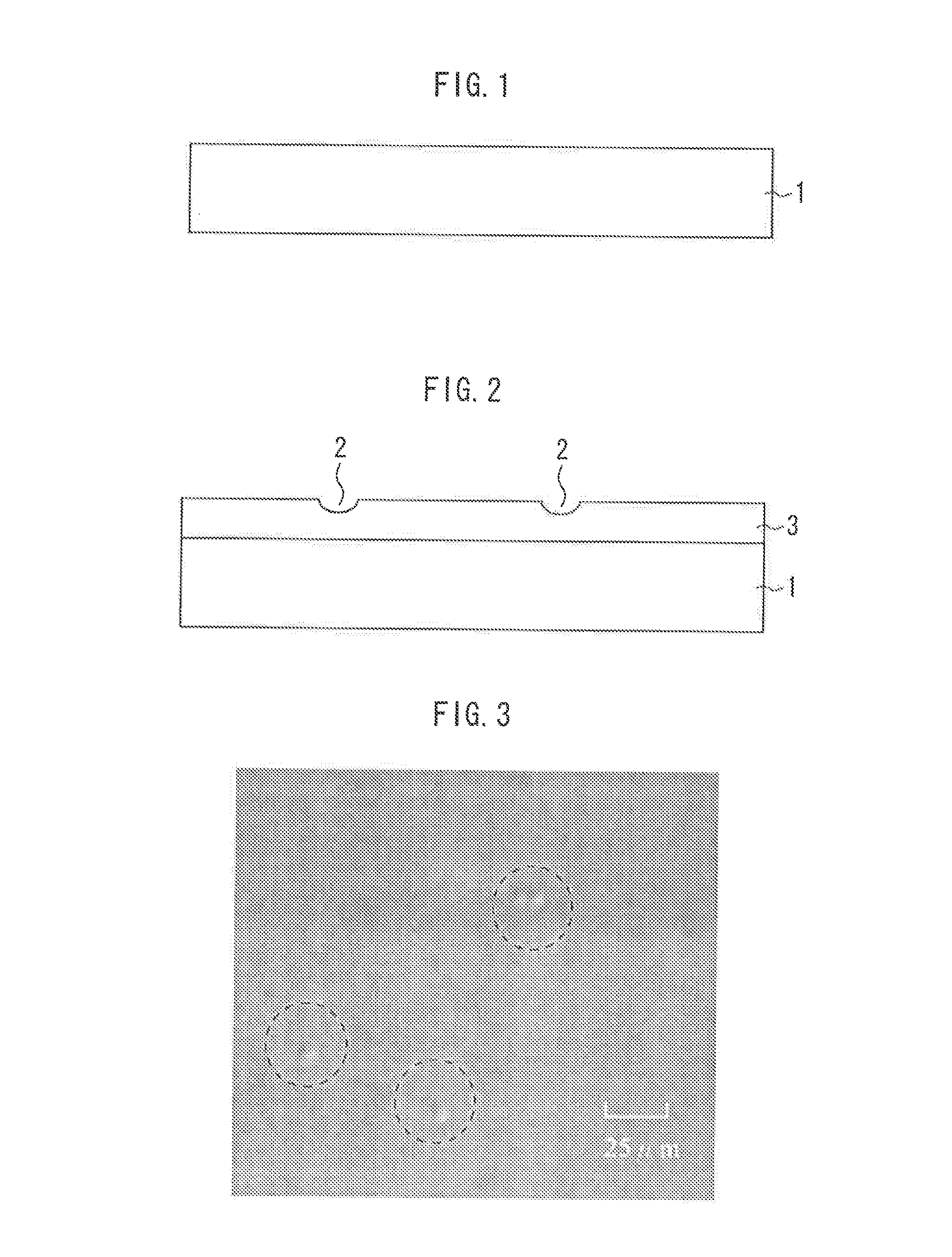

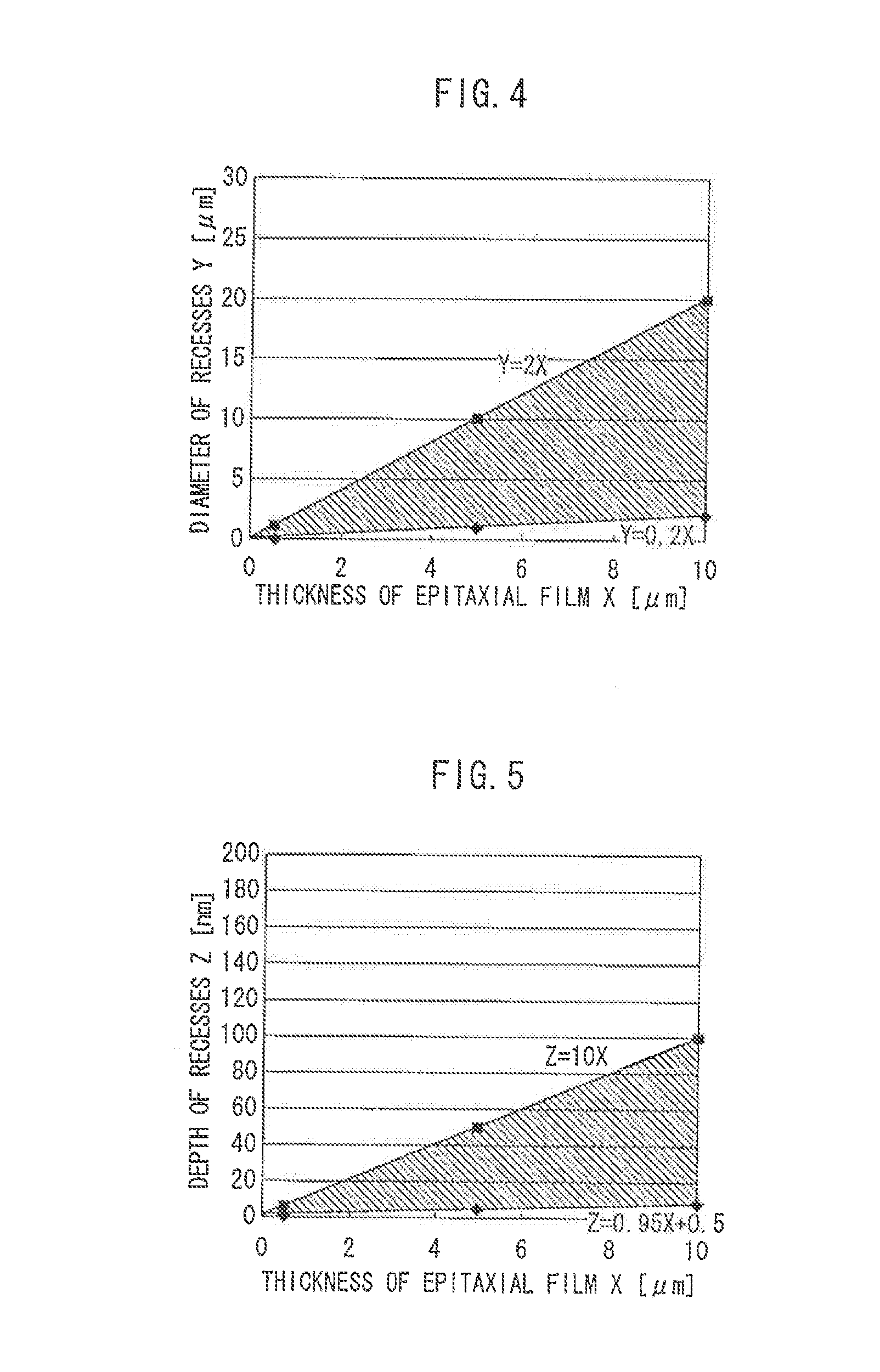

SINGLE-CRYSTAL 4H-SiC SUBSTRATE AND METHOD FOR MANUFACTURING THE SAME

ActiveUS20140295136A1Reduce crystal defect densityPolycrystalline material growthLayered productsSingle crystal substrateSingle crystal

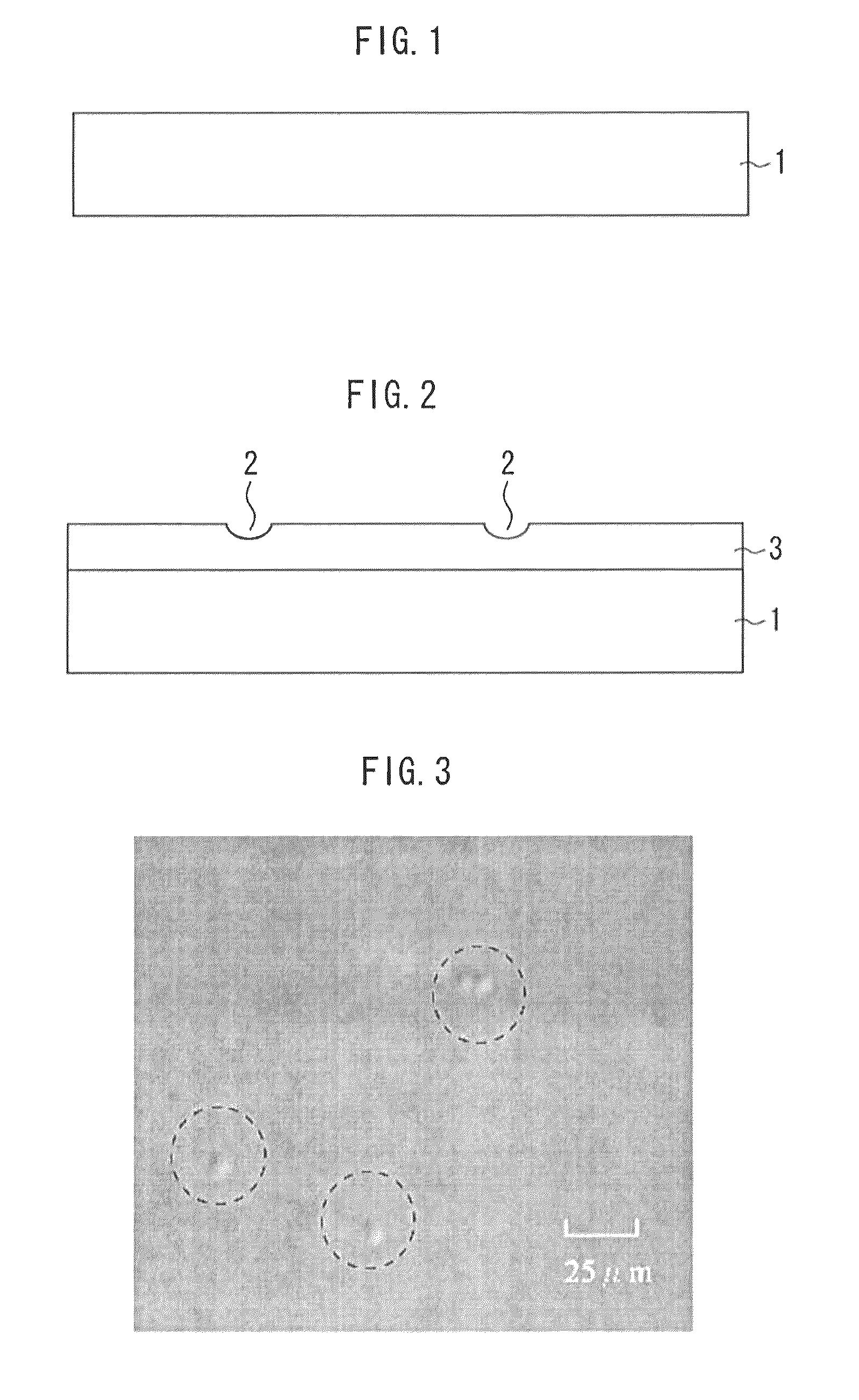

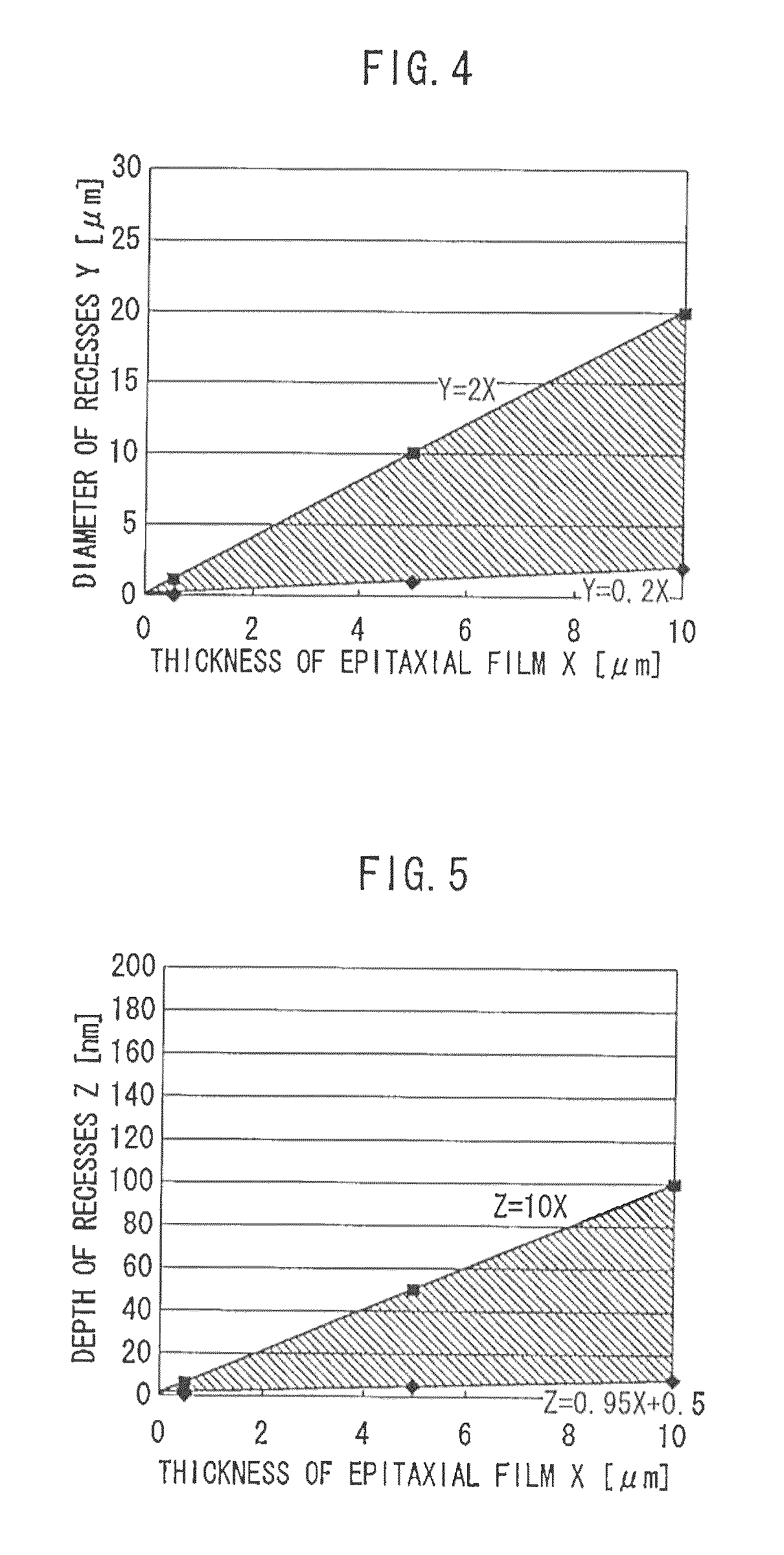

A method for manufacturing a single-crystal 4H-SiC substrate includes: preparing a flat 4H-SiC bulk single-crystal substrate; and epitaxially growing a first single-crystal 4H-SiC layer having recesses on the 4H-SiC bulk single-crystal substrate, wherein the first single-crystal 4H-SiC layer has a thickness of X (μm), the recesses have a diameter Y (μm) no smaller than 0.2*X (μm) and no larger than 2*X (μm), and a depth of Z (nm) no smaller than (0.95*X (μm) +0.5 (nm)) and no larger than 10*X (μm).

Owner:MITSUBISHI ELECTRIC CORP

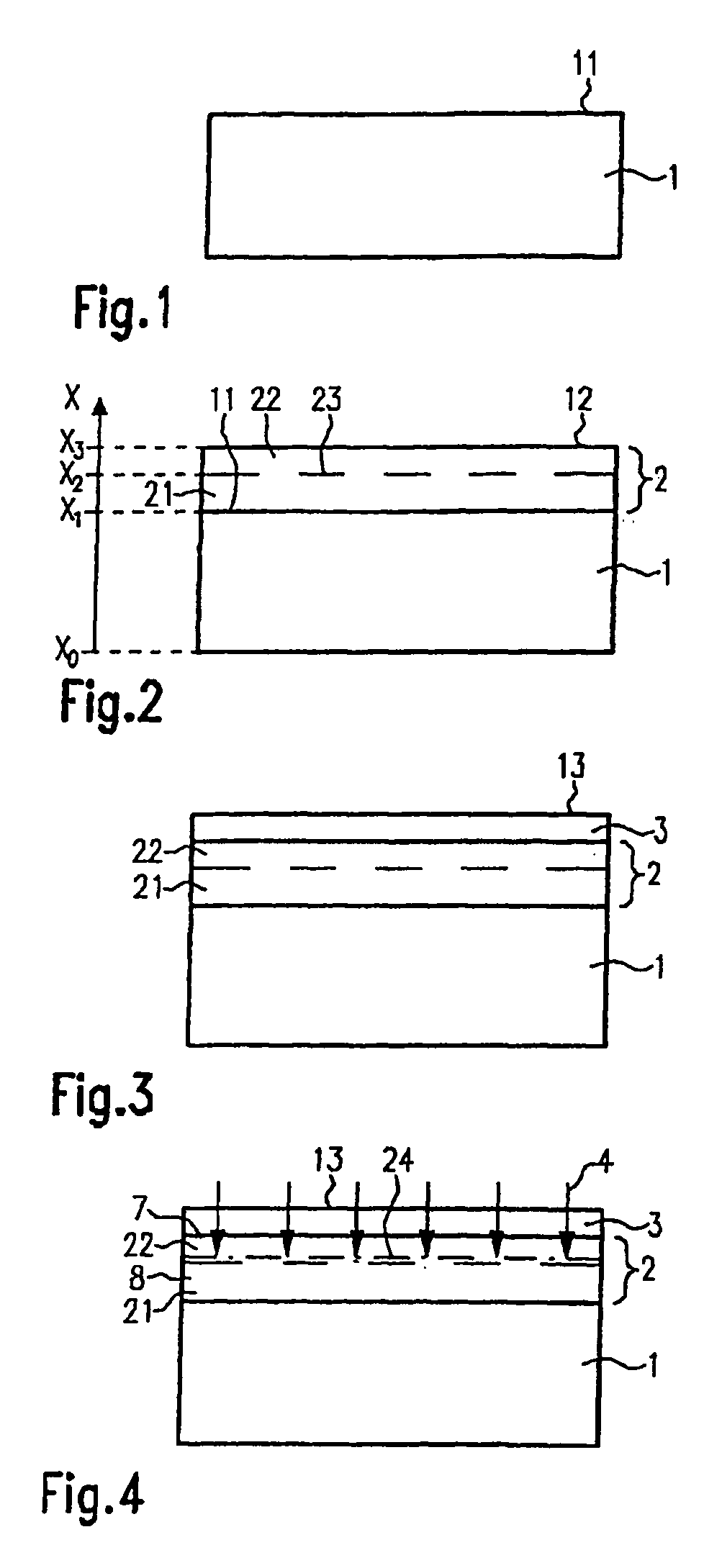

Method for manufacturing semiconductor thin film

ActiveUS7008839B2Reduce crystal defect densityReduce defect densitySemiconductor/solid-state device manufacturingPhysicsElectrical conductor

A substrate with a second semiconductor layer and a second mask film formed thereon is subjected to a heat treatment in an oxidizing atmosphere. Thus, second oxidized regions are formed through oxidization of the second semiconductor layer in regions of the second semiconductor layer that are not covered by the second mask film. At the same time, a second base layer is formed in each region that is interposed by the second oxidized regions. Then, the second mask film is removed, and a third semiconductor layer is selectively grown on the surface of the second base layer that is exposed between the second oxidized regions so as to cover the second oxidized regions, after which the first oxidized regions and the second oxidized regions covering the entire upper surface of the substrate are removed.

Owner:PANASONIC CORP

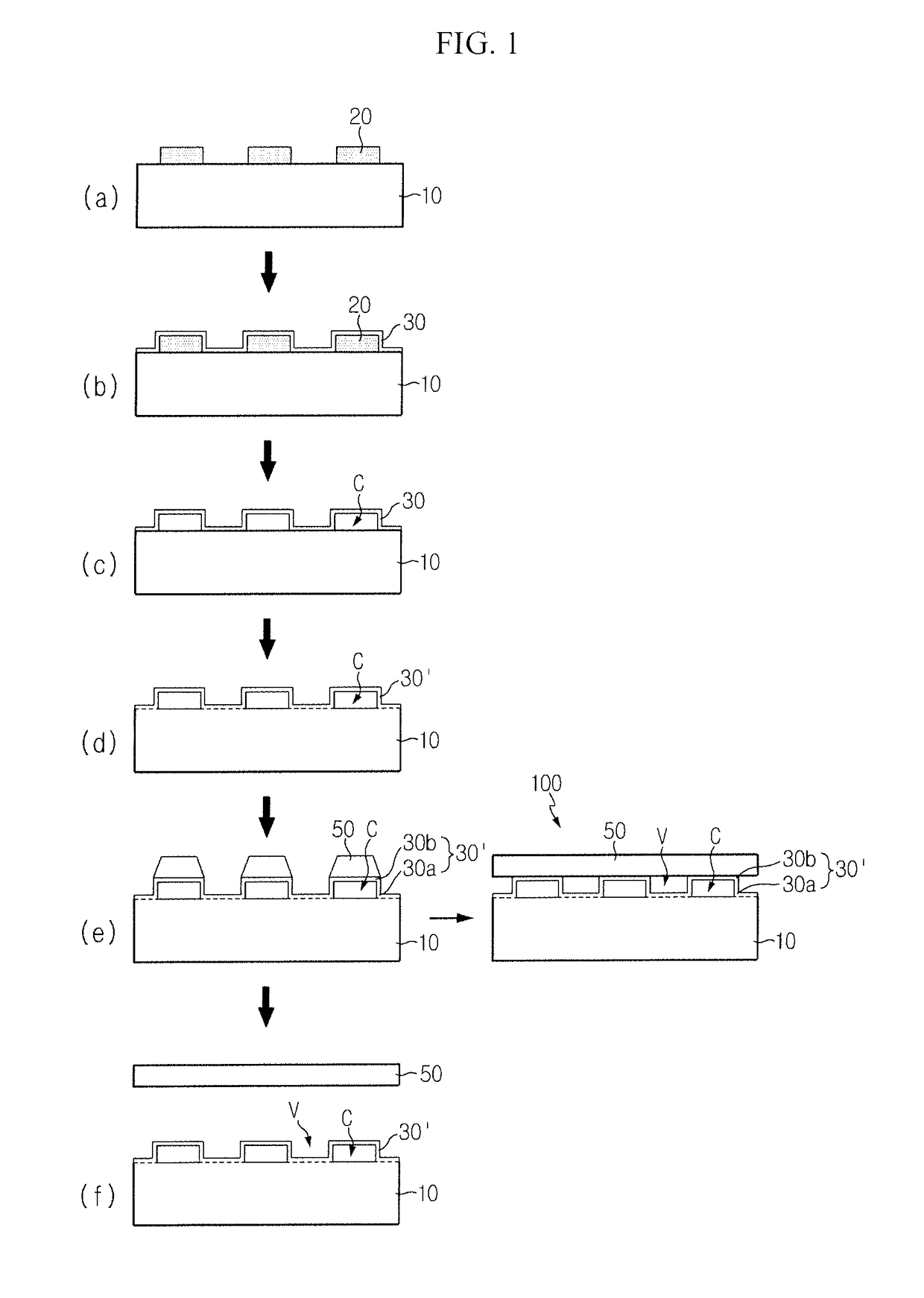

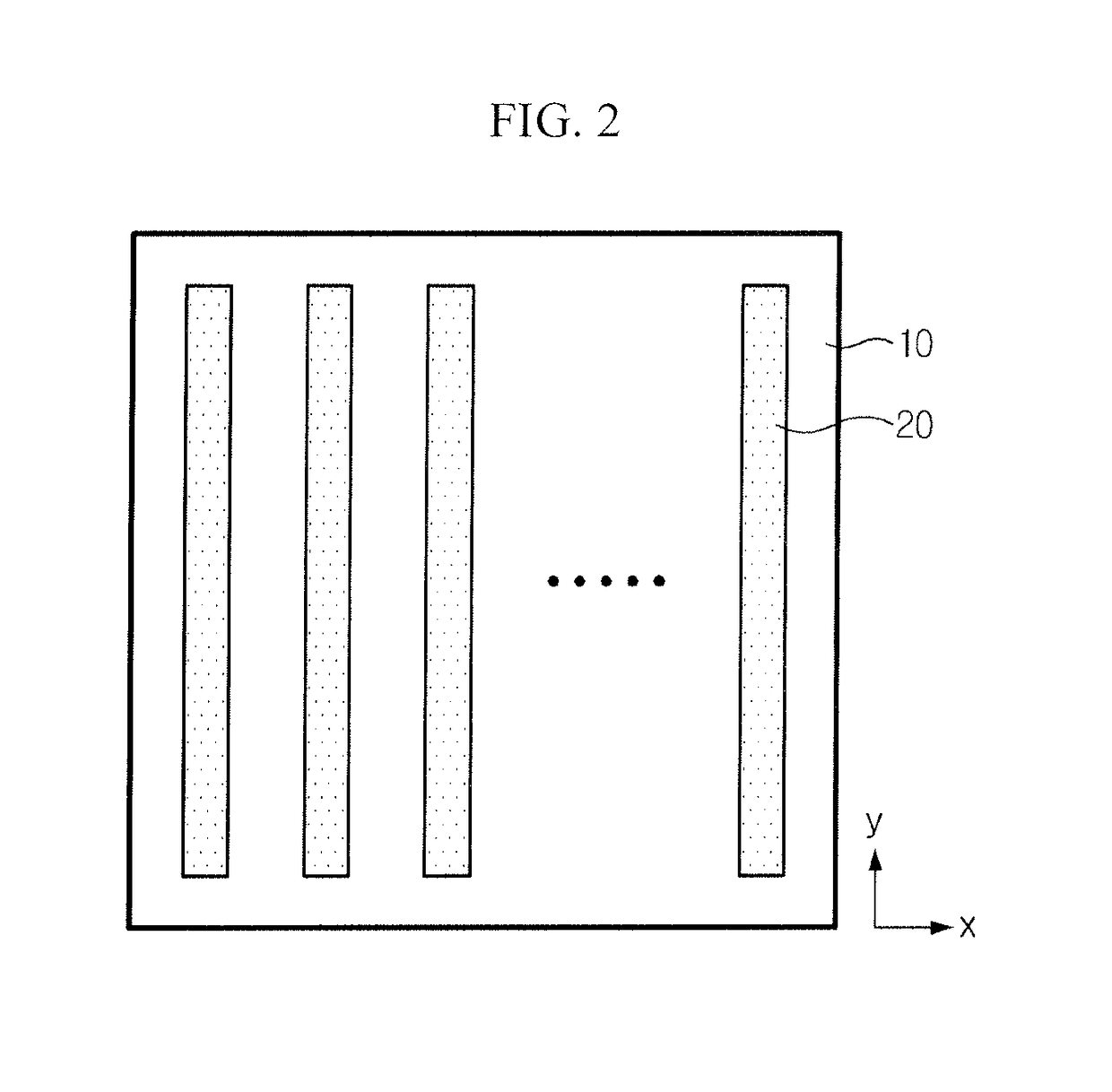

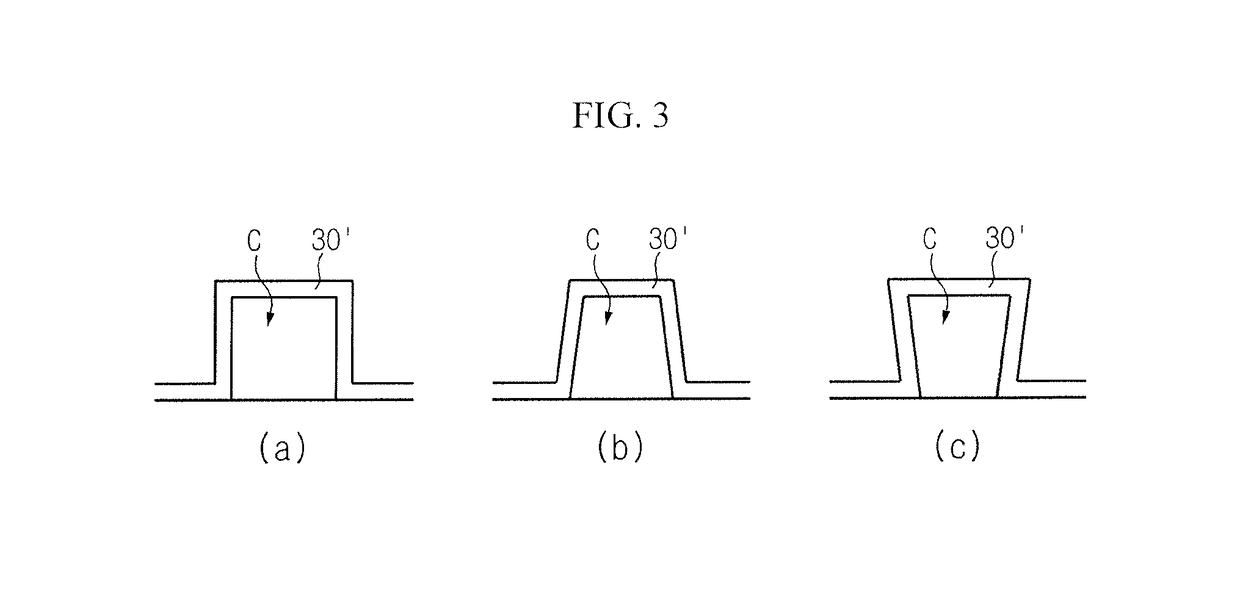

Semiconductor stacking structure, and method and apparatus for separating nitride semiconductor layer using same

ActiveUS20170271556A1Low defect densityHigh qualitySemiconductor/solid-state device manufacturingSemiconductor devicesSingle crystalSeparation method

A semiconductor stacking structure according to the present invention comprises: a monocrystalline substrate which is disparate from a nitride semiconductor; an inorganic thin film which is formed on a substrate to define a cavity between the inorganic thin film and the substrate, wherein at least a portion of the inorganic thin film is crystallized with a crystal structure that is the same as the substrate; and a nitride semiconductor layer which is grown from a crystallized inorganic thin film above the cavity. The method and apparatus for separating a nitride semiconductor layer according the present invention mechanically separate between the substrate and the nitride semiconductor layer. The mechanical separation can be performed by a method of separation of applying a vertical force to the substrate and the nitride semiconductor layer, a method of separation of applying a horizontal force, a method of separation of applying a force of a relative circular motion, and a combination thereof.

Owner:SAMSUNG ELECTRONICS CO LTD

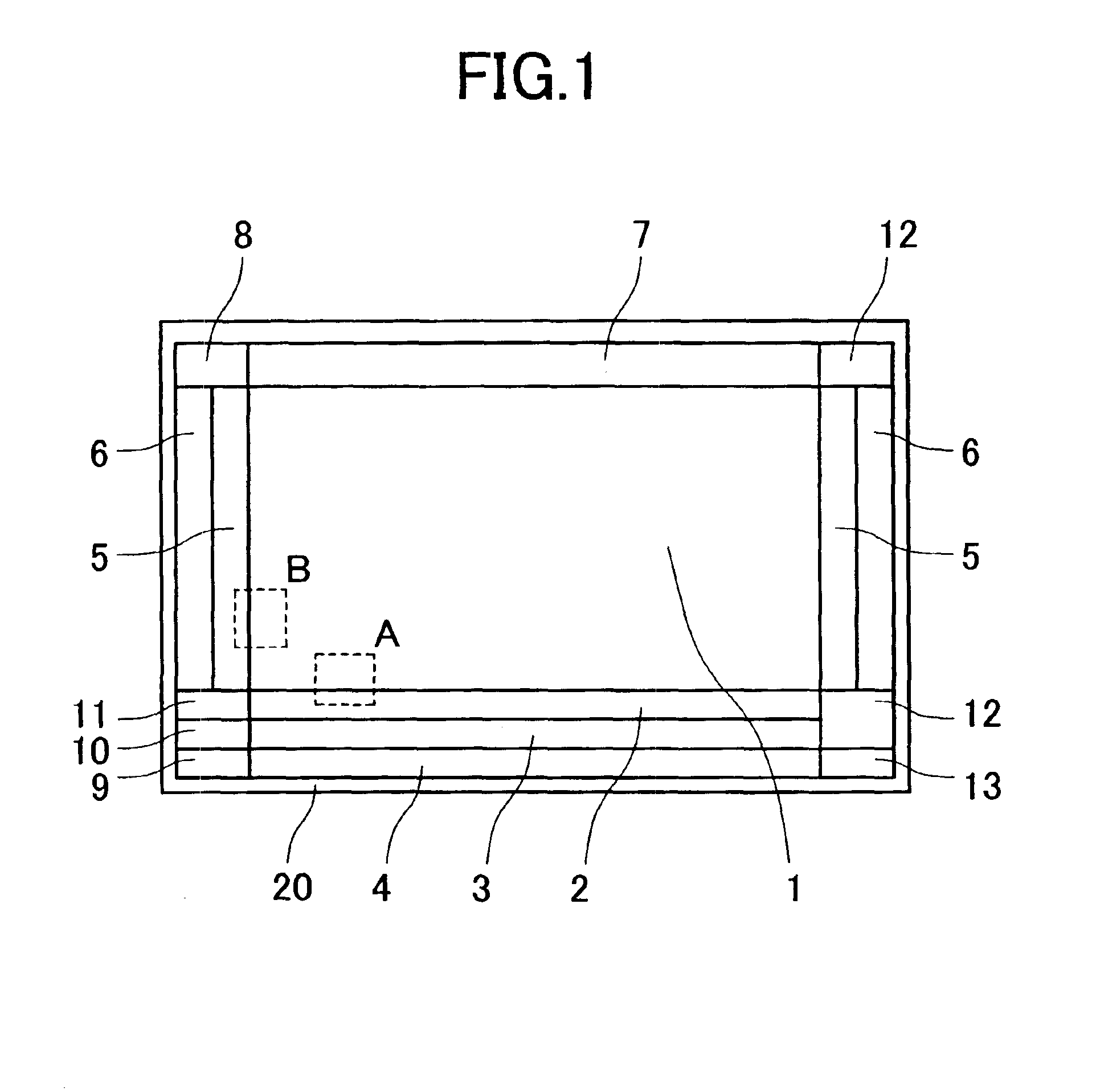

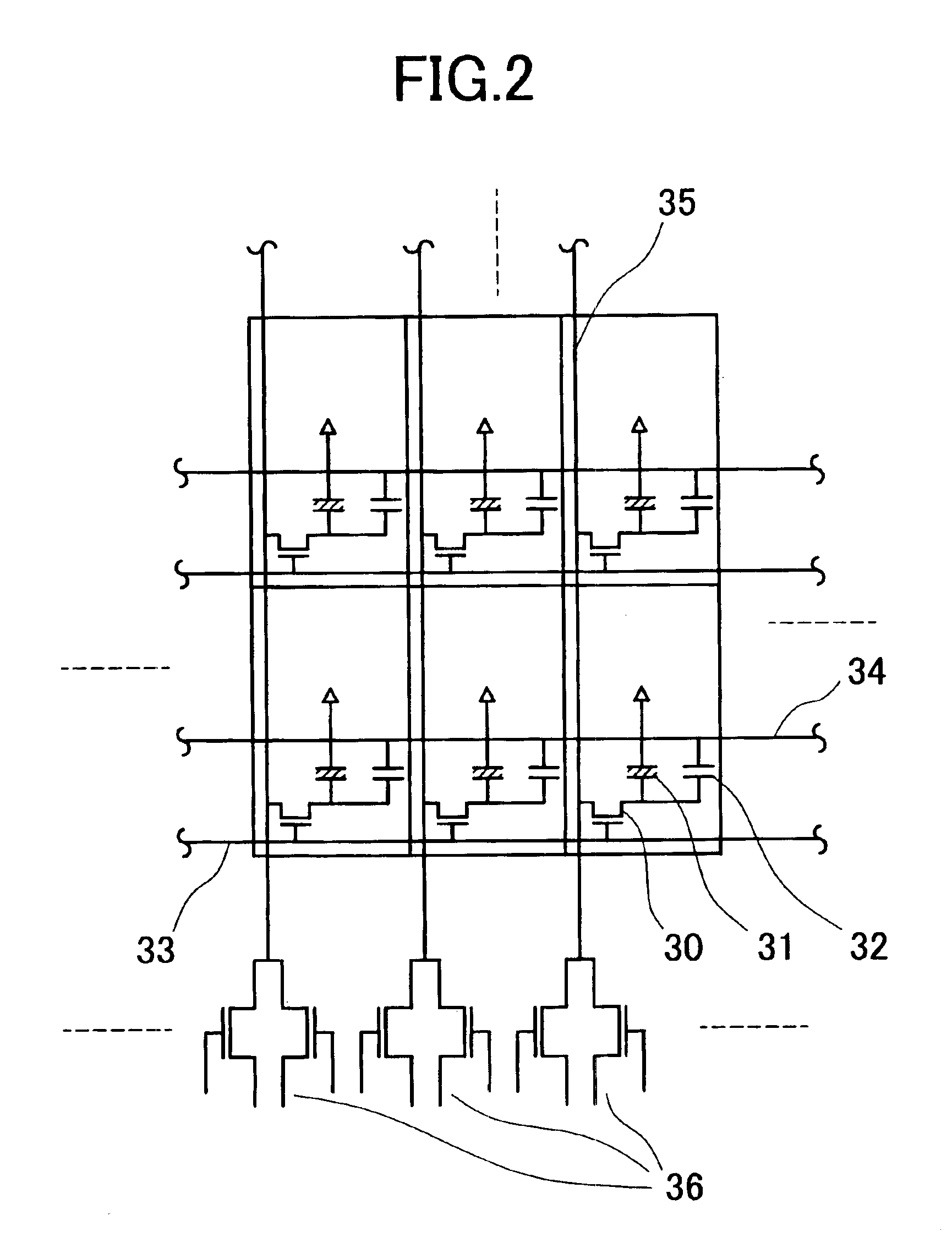

Display device and a method for manufacturing the same

InactiveUS6949419B2Easy to manufactureImprove performanceTransistorStatic indicating devicesComputer moduleDisplay device

An image display device which includes a display pixel block and circuit blocks peripheral thereto. Each block has a circuit made of high-performance thin film transistors. The display pixel block and the peripheral circuit blocks including the four corners of the display device are formed on an image display device substrate of circuit-built-in type thin film transistors having a small circuit occupation surface area. A circuit including thin film transistors of a polycrystalline silicon film anisotropically crystal-grown and having crystal grains aligned in its longitudinal direction with a current direction is provided in the whole or partial surface of the display pixel block and circuit blocks. The longitudinal direction is aligned with a horizontal or vertical direction within the block, and blocks aligned in the horizontal and vertical directions can be arranged as mixed when viewed from an identical straight line.

Owner:PANASONIC LIQUID CRYSTAL DISPLAY CO LTD +1

Manufacturing method of GaN substrate laser diode

InactiveCN102832539AImprove performanceExtend your lifeLaser detailsSemiconductor lasersLight guideCrystallographic defect

The invention discloses a manufacturing method of a GaN substrate laser diode. The manufacturing method comprises the following steps of: forming a GaN substrate and successively depositing a p-type coating layer, a p-type light guide layer, an active layer, an n-type blocking layer, an n-type light guide layer and an n-type coating layer, wherein the method for forming the GaN substrate comprises the following steps of: putting a GaN wafer into a high-temperature and high-pressure device, heating and pressurizing the GaN wafer with the heating temperature being 820-880 DEG C and the applied pressure being 4.1-4.6GPa, and maintaining for 10-15 minutes; stopping heating and pressurizing so that the GaN wafer is restored to normal temperature and normal pressure; and annealing for 20-30 minutes in the high-temperature and high-pressure device, and taking out the GaN wafer. The manufacturing method disclosed by the invention has the advantages that the crystal defect density of the laser diode substrate can be obviously reduced, and the performance and the service life of the laser diode are improved.

Owner:JIANGSU WINAD LIGHTING TECH

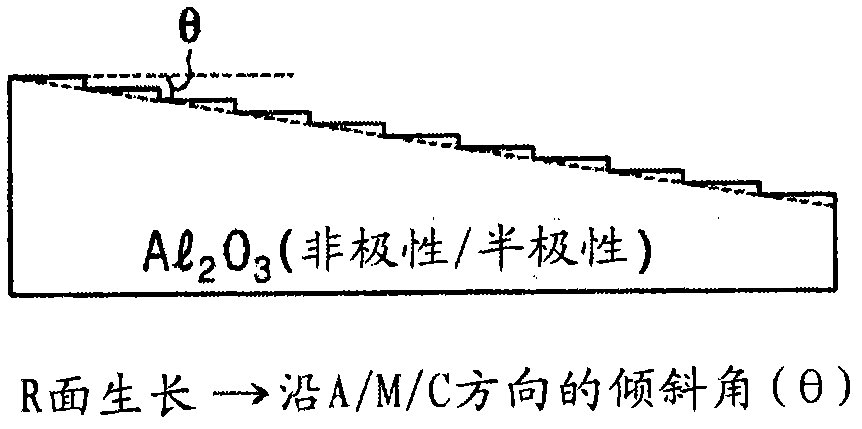

High quality non-polar/semi-polar semiconductor element on tilt substrate and fabrication method thereof

InactiveCN102549778AImprove reliabilityImprove performanceSemiconductor devicesQuantum efficiencyCrystal plane

The present invention relates to a high quality non-polar / semi-polar semiconductor element and a fabrication method thereof, wherein a nitride semiconductor crystal is formed on a sapphire crystal plane that enables the growth of a non-polar / semi-polar nitride semiconductor layer to eliminate an piezoelectric effect; and a template layer is formed on a corresponding off-axis of the sapphire crystal plane tilted in a predetermined direction to reduce the defect density of the semiconductor element and improves the internal quantum efficiency and extraction efficiency. In the fabrication method of a semiconductor element by forming a template layer and a semiconductor element structure on the sapphire substrate having a crystal plane for the growth of a non-polar or semi-polar nitride semiconductor layer, the sapphire substrate is a substrate having the crystal plane tilted in a predetermined direction, and a nitride semiconductor layer and the template layer comprising a GaN layer are formed on the tilt substrate.

Owner:SEOUL VIOSYS CO LTD

Group III-V compound semiconductor and group III-V compound semiconductor device using the same

InactiveUS20050106771A1Crystal defect densityReduce crystal defect densitySolid-state devicesSemiconductor/solid-state device manufacturingComputer scienceAl content

An AlGaInP layer is formed on a substrate made of GaAs, and an AlGaAs layer is formed on the AlGaInP layer via a buffer layer therebetween. The buffer layer has a thickness of about 1.1 nm and is made of AlGaInP whose Ga content is smaller than that of the AlGaInP layer. The buffer layer may alternatively be made of AlGaAs whose Al content is smaller than that of the AlGaAs layer.

Owner:GK BRIDGE 1

Method for casting high efficiency polycrystalline silicon ingots

InactiveCN104195632AReduce defect densityReduce defectsPolycrystalline material growthSingle crystal growth detailsOrganic solventIngot casting

The invention discloses a method for casting high efficiency polycrystalline silicon ingots. The method comprises the following steps: (1) preparing a nucleating agent, namely mixing germanium powder with silicon nitride powder, adding pure water and an organic solvent, uniformly stirring to obtain a nucleating agent suspension liquid and spraying the nucleating agent onto the bottom of a quartz crucible, wherein the mass percentage of the germanium powder is 20%-80% and the mass percentage of the silicon nitride powder is 80%-20%; (2) preserving heat of the quartz crucible at 20-100 DEG C till the nucleating agent in the step (1) is completely dried; and (3) increasing the temperature difference between the top and the bottom of the quartz crucible to ensure that the whole furnace of silicon materials are molten starting from the upper part till totally molten, and carrying out crystal growth and cooling on the molten silicon materials to complete the ingot casting. The ingot casting method disclosed by the invention has the advantages that the crystal grain structure is optimized, so that the crystal defect density in polycrystalline silicon is reduced, the silicon wafer crystal defect is less and the minority carrier lifetime is longer; and compared with conventional polycrystalline silicon wafers, the polycrystalline silicon ingots have the advantage that the efficiency of polycrystalline silicon batteries adopting the polycrystalline silicon ingots is increased by 0.3-0.5%.

Owner:ALTUSVIA ENERGY TAICANG

Method of forming a non-polar/semi-polar semiconductor template layer on unevenly patterned substrate

ActiveUS9099609B2Eliminate the effects ofReduce layeringSemiconductor/solid-state device manufacturingSemiconductor devicesQuantum efficiencyCrystal plane

Provided are a high-quality non-polar / semi-polar semiconductor device with reduced defect density and improved internal quantum efficiency and light extraction efficiency, and a manufacturing method thereof. The manufacturing method is a method for manufacturing a semiconductor device, in which a template layer and a semiconductor device structure are formed on a sapphire substrate having a crystal plane for growing a non-polar or semi-polar nitride semiconductor layer. The sapphire substrate is etched to form uneven patterns, and the template layer including a nitride semiconductor layer and a GaN layer is formed on the sapphire substrate in which the uneven patterns are formed.

Owner:SEOUL VIOSYS CO LTD +1

Method for manufacturing p-type GaAs-based laser diode

InactiveCN103746050AImprove performanceExtend your lifeSemiconductor devicesRoom temperatureCrystallographic defect

The invention discloses a method for manufacturing a p-type GaAs-based laser diode. The method comprises the following steps: forming a GaAs substrate, and depositing a p-type coating layer, a p-type photoconductive layer, an active layer, an n-type barrier layer, an n-type photoconductive layer and an n-type coating layer in sequence. A method for forming the GaAs substrate comprises the following steps: putting a GaAs wafer in a high-temperature and high-pressure device; pressurizing while heating the GaAs wafer for 10-15 minutes at the heating temperature of 860-890 DEG C and the pressurizing pressure of 5.0-5.5GPa; ending heating and pressurizing so as to recover the GaAs wafer to the normal temperature and normal pressure; annealing for 20-30 minutes in the high-temperature and high-pressure device, and then, taking out the GaAs wafer. According to the method, the crystal defect density in the substrate of the light emitting diode can be obviously reduced, the performance of the laser diode is improved, and the service life of the laser diode is prolonged.

Owner:JIANGSU YOURUN MICROELECTRONICS CO LTD

Semiconductor structure for providing strained crystalline layer on insulator and method for fabricating same

ActiveUS20060088979A1Reduce crystal defect densitySimple methodSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureAlloy

A method for fabricating a semiconductor structure having a high-strained crystalline layer with a low crystal defect density is disclosed. The structure includes a substrate having a first material comprising germanium or a Group(III)-Group(V)-semiconductor or alloy thereof. In addition, a crystalline epitaxial first layer, comprising a graded buffer layer and a substantially relaxed layer, is provided. The buffer layer is sufficiently relaxed to provide relaxation of the substantially relaxed layer deposited thereon. A further layer may be provided on the first layer, and the transfer of at least the further layer is facilitated by providing a weakened zone in the first layer.

Owner:SOITEC SA

Manufacturing method for N-shaped GaAs substrate laser diode

InactiveCN103762501AImprove performanceExtend your lifeLaser detailsSemiconductor lasersLight guideCrystallographic defect

The invention discloses a manufacturing method for an N-shaped GaAs substrate laser diode. The manufacturing method comprises the steps that a GaAs substrate is formed, and an n-shaped coating layer, an n-shaped light guide layer, an active layer, a p-shaped barrier layer, a p-shaped light guide layer and a p-shaped coating layer are sequentially deposited. The forming method of the GaAs substrate comprises the steps that a GaAs wafer is placed in a high-temperature high-pressure device, the GaAs wafer is heated and pressurized, the heating temperature ranges from 860 DEG C to 890 DEG C, pressure ranging from 5.0 GPa to 5.5 GPa is exerted, and the GaAs wafer is heated and pressurized for 10 minutes to 15 minutes; heating and pressing are stopped, and the GaAs wafer returns to a normal temperature and pressure state; annealing is conducted for 20 minutes-30 minutes in the high-temperature high-pressure device, and the GaAs wafer is taken out. According to the method, crystal defect density of the substrate of the laser diode can be obviously reduced, performance of the laser diode is enhanced, and service life of the laser diode is prolonged.

Owner:NANTONG MINICHIP MICRO ELECTRONICS

Semiconductor stacking structure, and method and apparatus for separating nitride semiconductor layer using same

ActiveUS10205052B2Relieve pressureReduce defect densitySemiconductor/solid-state device manufacturingSemiconductor devicesHorizontal forceSingle crystal substrate

A semiconductor stacking structure according to the present invention comprises: a monocrystalline substrate which is disparate from a nitride semiconductor; an inorganic thin film which is formed on a substrate to define a cavity between the inorganic thin film and the substrate, wherein at least a portion of the inorganic thin film is crystallized with a crystal structure that is the same as the substrate; and a nitride semiconductor layer which is grown from a crystallized inorganic thin film above the cavity. The method and apparatus for separating a nitride semiconductor layer according the present invention mechanically separate between the substrate and the nitride semiconductor layer. The mechanical separation can be performed by a method of separation of applying a vertical force to the substrate and the nitride semiconductor layer, a method of separation of applying a horizontal force, a method of separation of applying a force of a relative circular motion, and a combination thereof.

Owner:SAMSUNG ELECTRONICS CO LTD

Organic photoelectric transistor and preparation method thereof

ActiveCN108807684AExcellent near-infrared absorption characteristicsStrong absorption propertiesFinal product manufactureSolid-state devicesSemiconductor materialsCharge carrier mobility

The invention provides an organic photoelectric transistor, which belongs to the technical field of a semiconductor material. The organic photoelectric transistor successively comprises a silicon substrate layer, gold electrodes and a metal zinc phthalocyanine nano crystal active layer; wherein the metal zinc phthalocyanine nano crystal active layer covers the gold electrodes and an area between the gold electrodes. The metal zinc phthalocyanine nano crystal active layer in the transistor provided by the invention has excellent near-infrared spectral absorption characteristics, so that the response performance of the photosensitive transistor for near-infrared spectrum can be improved; the metal zinc phthalocyanine nano crystal is prepared by adopting an ultrasonic technology, and the crystal defect density is low, so that the adsorption of molecules such as O2, H2O and CO2 in the air in the photosensitive transistor active layer can be effectively reduced, and the stability of a device in an atmosphere environment can be improved; and meanwhile, the field effect carrier migration rate is excellent, so that the optical response of the photosensitive transistor can be effectively improved.

Owner:SOUTH UNIVERSITY OF SCIENCE AND TECHNOLOGY OF CHINA

Manufacturing method of GaN substrate laser diode

InactiveCN102856787AImprove performanceExtend your lifeSemiconductor laser structural detailsLight guideHigh pressure

The invention discloses a manufacturing method of a GaN substrate laser diode. The manufacturing method comprises the following steps of: forming a GaN substrate, and sequentially depositing an n type coating layer, an n type light guide layer, an active layer, a p type barrier layer, a p type light guide layer and a p type coating layer, wherein the method for forming the GaN substrate comprises the steps of putting a GaN wafer into a high-temperature and high-pressure device, and pressurizing the GaN wafer when heating the GaN wafer, wherein the heating temperature is 820-880 DEG C, the pressurizing pressure is 4.1-4.6 GPa, and the pressurizing is kept for 10-15min; stopping heating and pressurizing to enable the GaN wafer to restore to constant temperature and constant pressure; and after annealing in the high-temperature and high-pressure device for 20-30min, taking out the GaN wafer. With the adoption of the method, the crystal defect density in the laser diode substrate can be obviously reduced, the performance of the laser diode is improved, and the service life of the laser diode is prolonged.

Owner:JIANGSU WINAD LIGHTING TECH

Single-crystal 4H-SiC substrate

ActiveUS9422640B2Reduce crystal defect densityPolycrystalline material growthFrom chemically reactive gasesSingle crystal substrateOptoelectronics

Owner:MITSUBISHI ELECTRIC CORP

SINGLE-CRYSTAL 4H-SiC SUBSTRATE

ActiveUS20160298264A1Reduce crystal defect densityPolycrystalline material growthSemiconductor/solid-state device manufacturingSingle crystal substrateOptoelectronics

A single-crystal 4H-SiC substrate includes a 4H-SiC bulk single-crystal substrate; and an epitaxial first single-crystal 4H-SiC layer on the 4H-SiC bulk single-crystal substrate and having recesses. The recesses have a diameter no smaller than 2 μm and no larger than 20 μm. The recesses have a depth no smaller than 0.01 μm and no larger than 0.1 μm. A single-crystal 4H-SiC substrate also includes a 4H-SiC bulk single-crystal substrate; and an epitaxial first single-crystal 4H-SiC layer on the 4H-SiC bulk single-crystal substrate and having recesses. The density of the recesses in the epitaxial first single-crystal 4H-SiC layer is at least 10 / cm2, and the epitaxial first single-crystal 4H-SiC layer has a defect density no larger than 2 / cm2.

Owner:MITSUBISHI ELECTRIC CORP