Patents

Literature

68 results about "Line balancing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Line Balancing. Line balancing is the act of balancing the cycle times of the workers on a production line to the takt time. When everyone has a cycle time that matches the takt time, work flows efficiently. If a line is not balanced, it either has waiting waste where team members are standing around at the end of each cycle,...

Optimal design method for production line layout

ActiveCN103049801AReduce the impact of volatilityIncrease production capacityForecastingProduction lineTotal investment

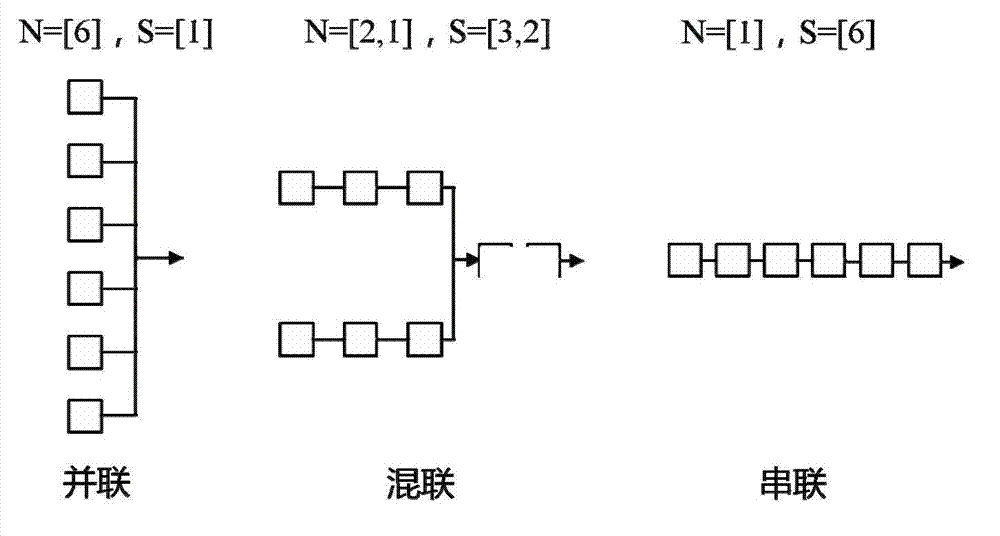

The invention relates to the field of engineering manufacture, in particular to an optimal design method for production line layout. The technical problem that the influence of production fluctuation on production efficiency cannot be reduced by the conventional method so as to reduce enterprise benefits is solved. According to the scheme, the optimal design method for new production line layout mainly comprises the following steps of: acquiring the labor house data of original sub-procedures; generating functional segments and a station number by adopting a line balancing planning method, so that the cycle time of a single line in each functional segment is shortest; when total investment C is determined, finding all N and S combinations consistent with a constraint condition by using an enumeration method; calculating the cycle time of each functional segment; calculating the overall cycle time of each [N, S] scheme; and performing calculation according to the steps, and when the total investment C is determined, determining a scheme with the shortest cycle time in all the [N, S] schemes as a target scheme. The method can be used for the design of the new production line layout and the modification of the conventional production line layout.

Owner:四川长虹智能制造技术有限公司

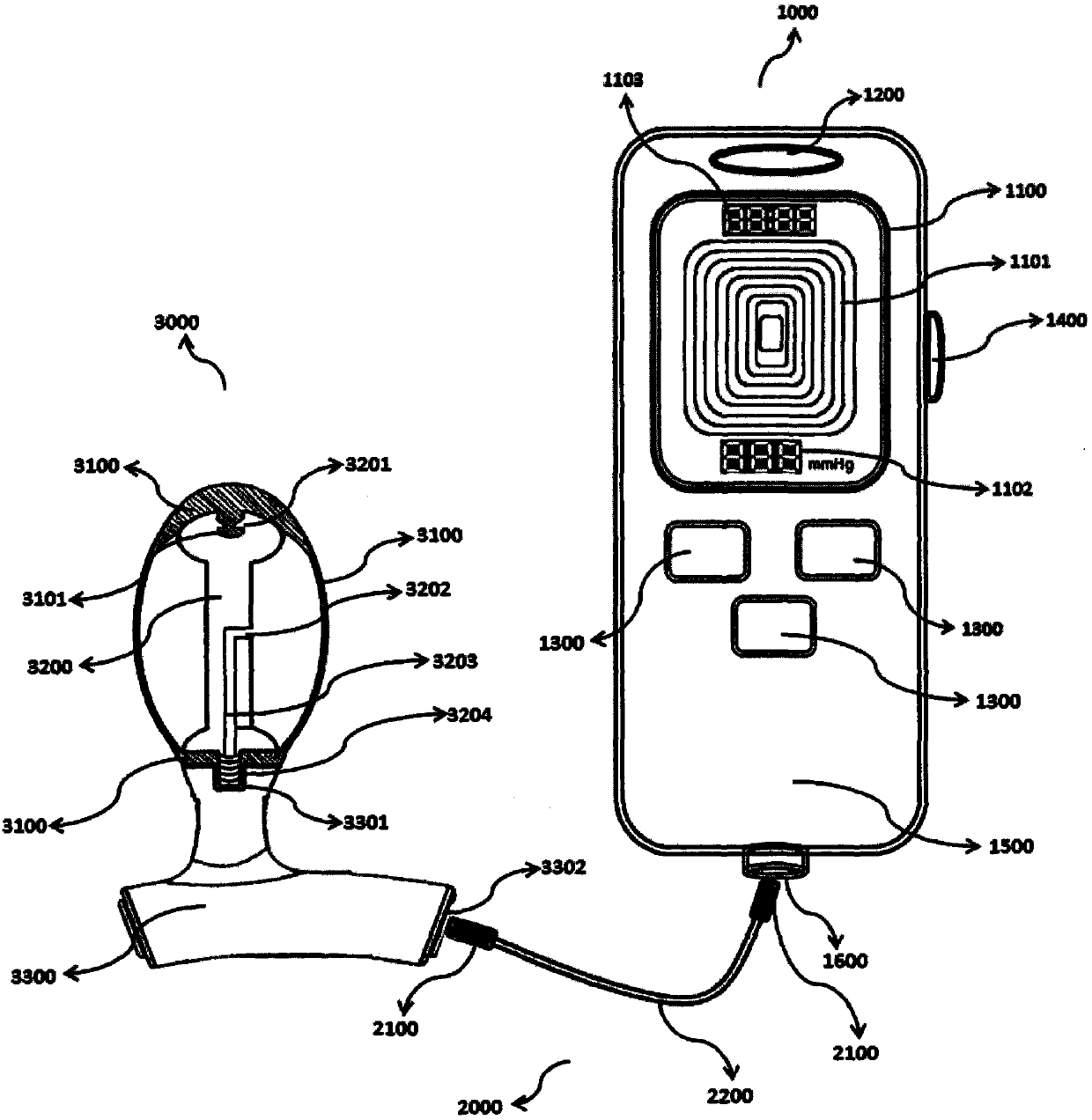

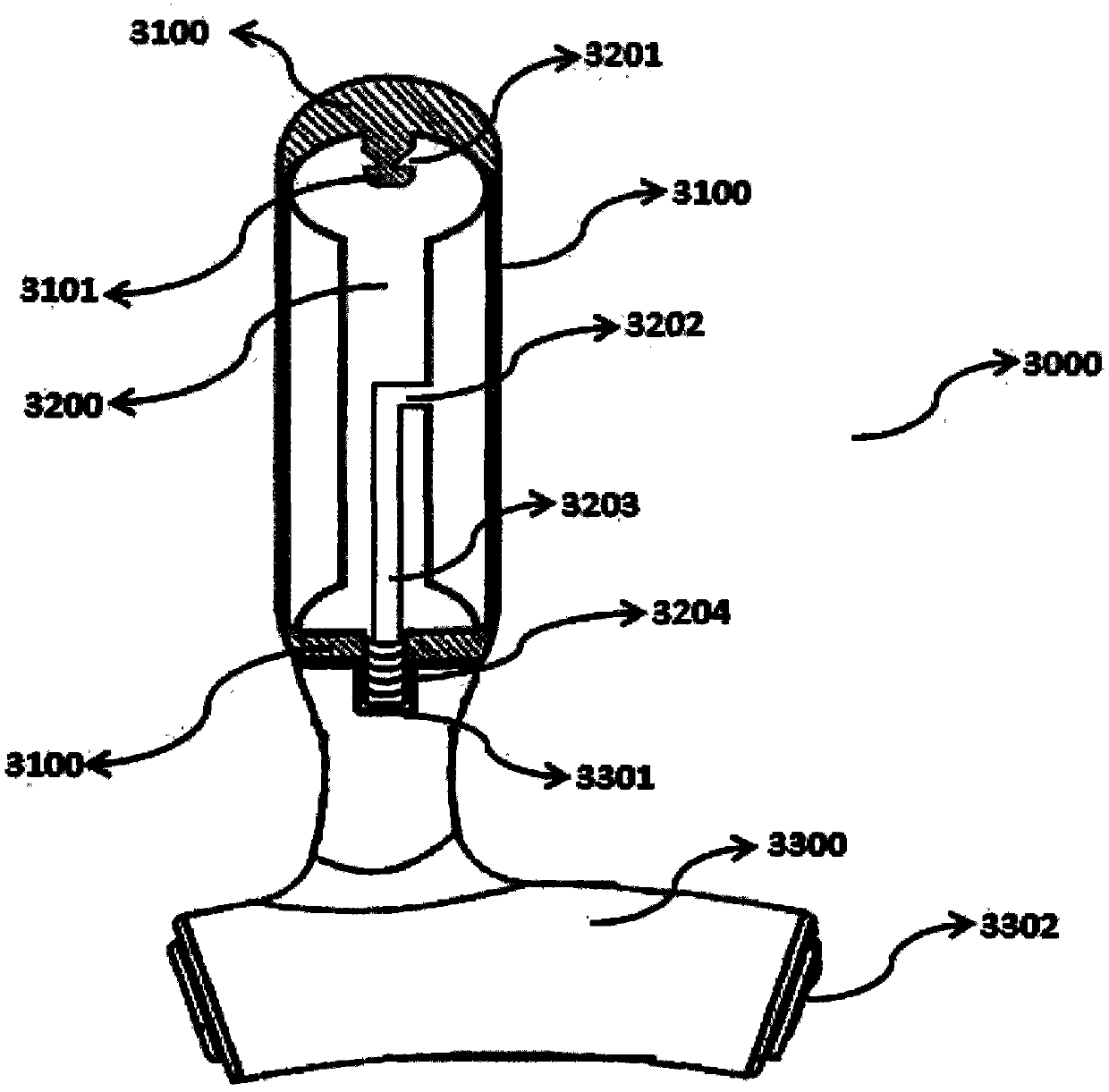

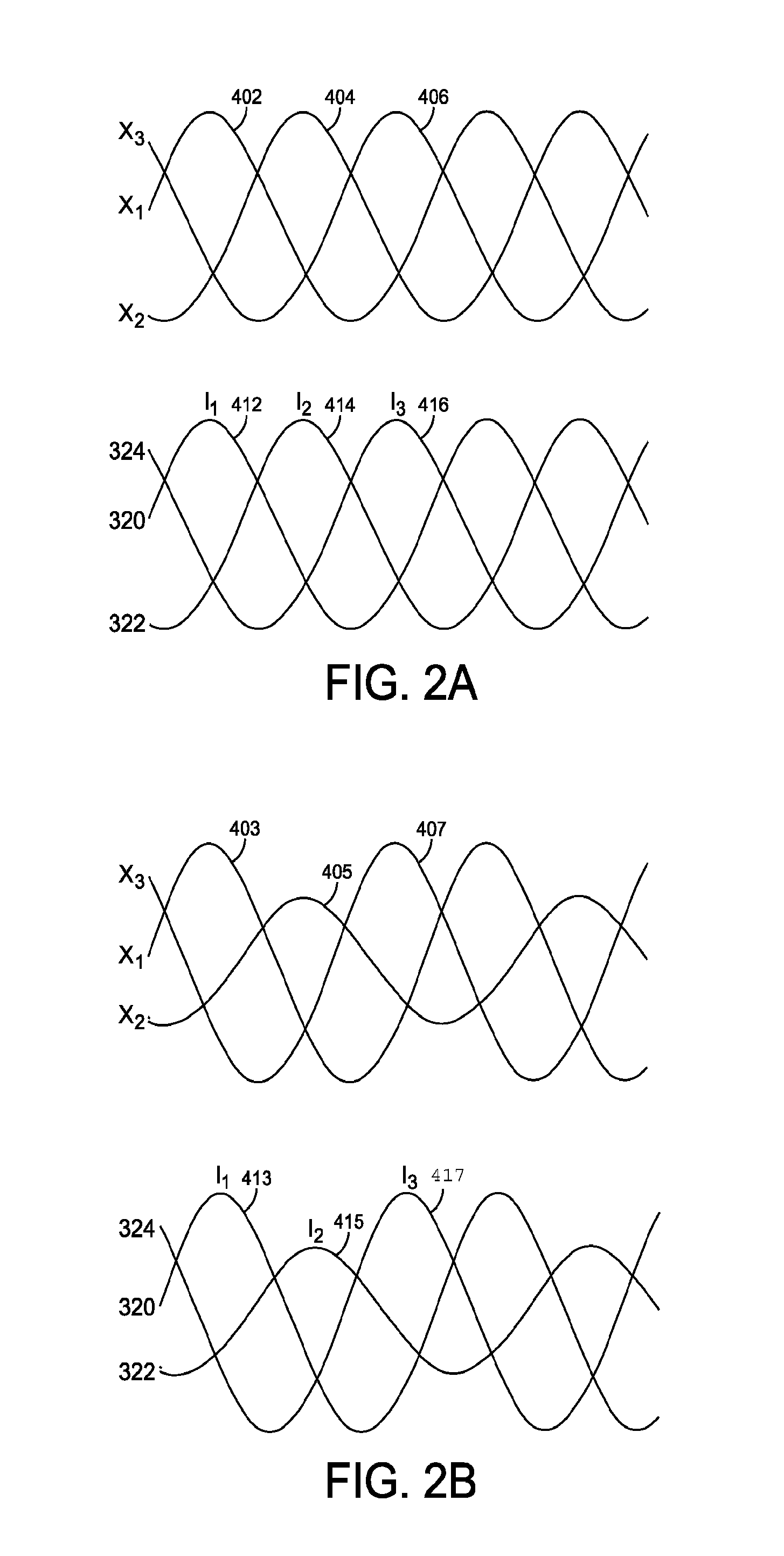

Vaginal contraction rehabilitation treatment equipment

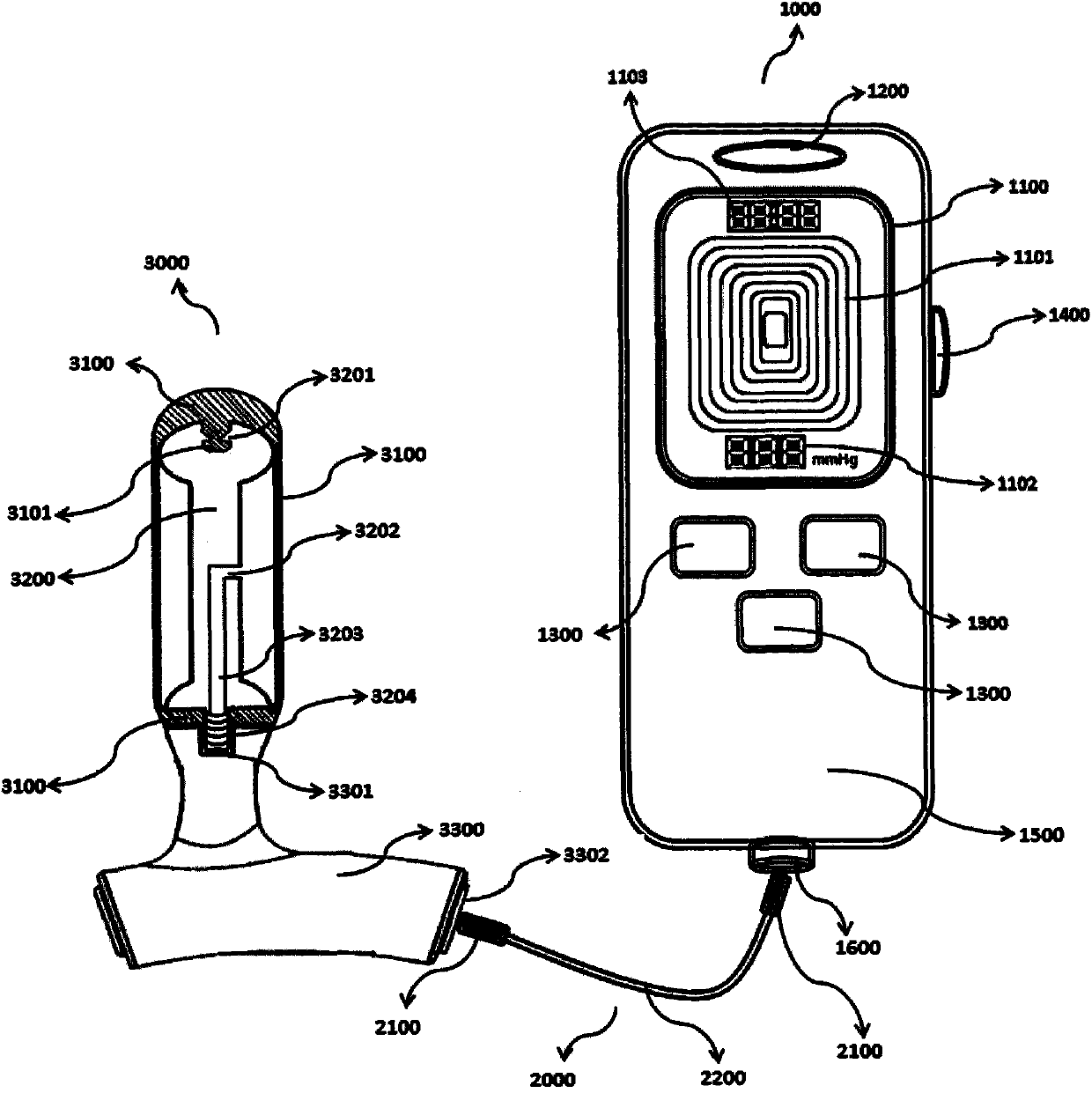

The invention relates to medical equipment, and particularly provides vaginal contraction rehabilitation treatment equipment. The vaginal contraction rehabilitation treatment equipment comprises a detector, a flexible air catheter and a handheld host. The detector and the handheld host are connected through the flexible air catheter. According to the vaginal contraction rehabilitation treatment equipment, a waveband line balance graph can be used for monitoring the strength of contractility of muscles around a vagina, meanwhile, a contraction pressure value and contraction time can also be measured, pelvic floor muscle Kegel exercise can be conducted according to a voice prompt sent by the equipment, and therefore the purpose of treating a urinary incontinence disease and a vaginal relaxation disease of a woman is achieved at last. The vaginal contraction rehabilitation treatment equipment is suitable for hospitals or families and can be used for the treatment of a sexual dysfunction in addition to diagnosis and treatment of the urinary incontinence disease and the vaginal relaxation disease of the woman.

Owner:BEIJING JUNIC MEDICAL TECH +1

Method for determining fittings for constant tables of automatic placement machines

The invention relates to a method for determining fittings for constant tables of automatic placement machines in placement lines at predetermined table locations by means of mixed integer linear optimization based on input data describing the placement infrastructure and input parameters that can be specified by the operator or user. The method can be used regardless of the mounting technique used (for example, plug in mounting technique, surface mounting technique, or a hybrid technique). The method can be advantageously used with other methods, for example, cluster methods for forming fitting groups or line balancing for cycle time optimization.

Owner:SIEMENS AG

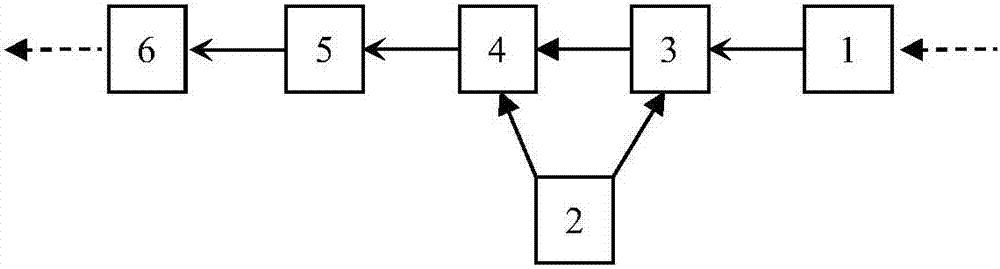

Line Balance Control Method, Line Balance Control Apparatus, and Component Mounting Machine

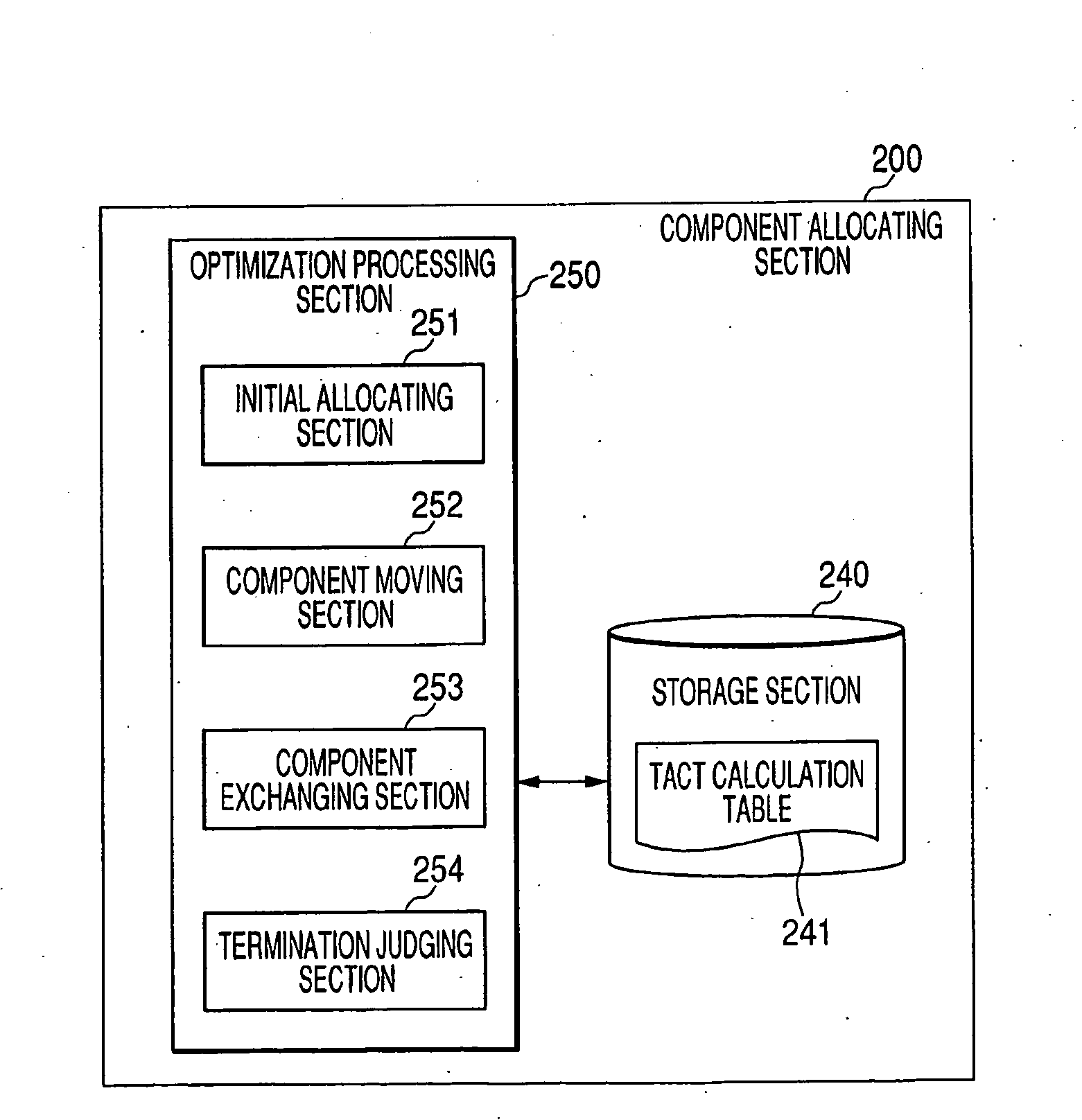

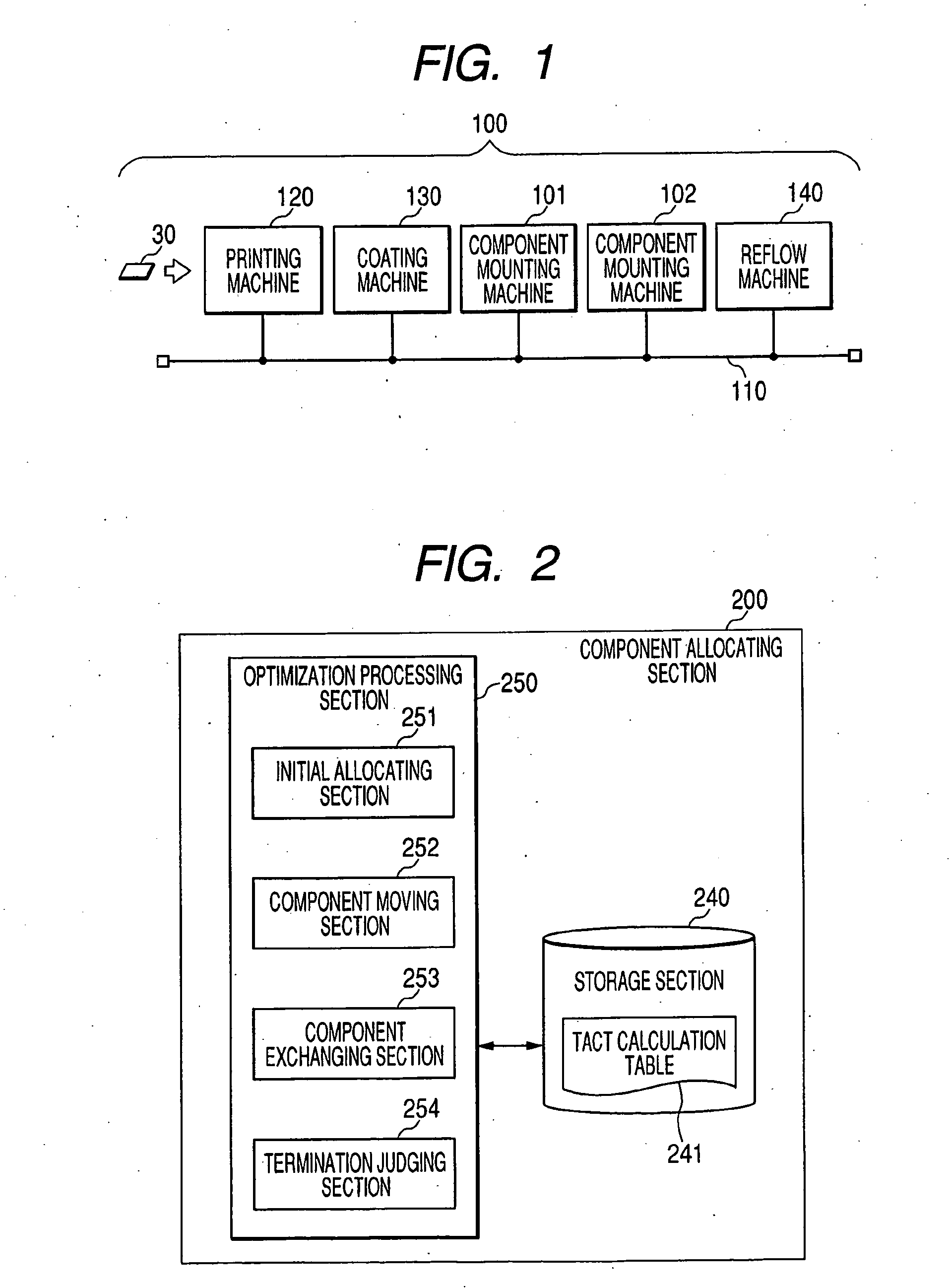

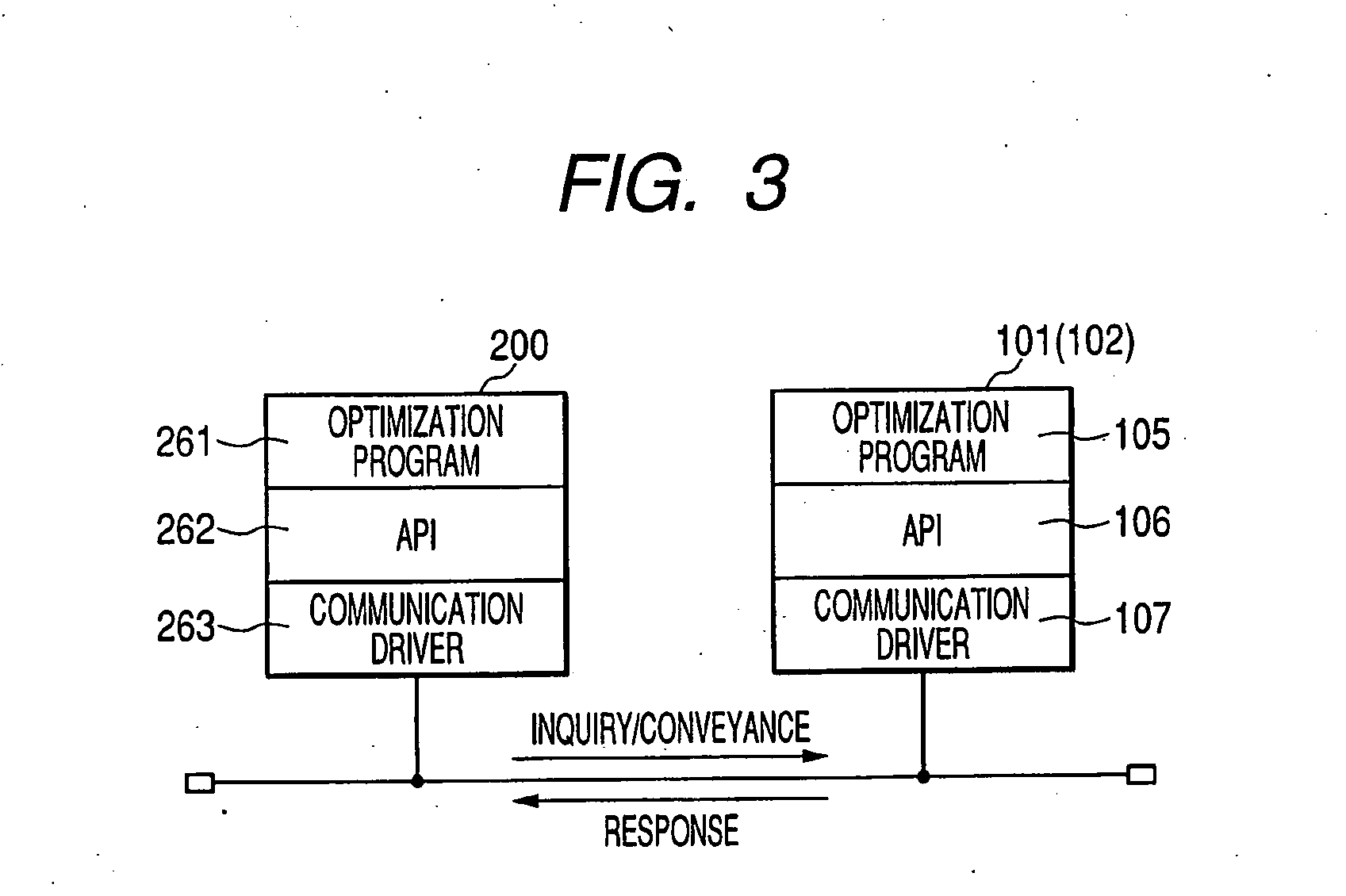

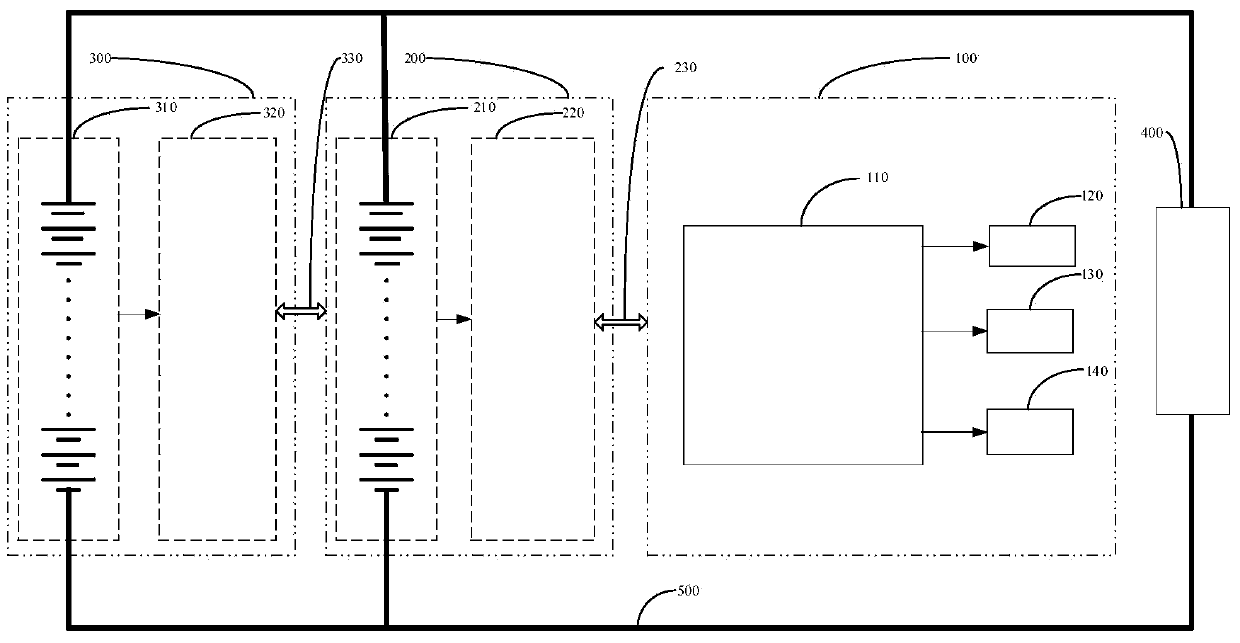

To provide a line balance control method, a line balance control apparatus, and a component mounting machine, which do not require a higher-level device. A production line 100 is equipped with a printing machine 120, a coating machine 130, a component mounting machine 101, a component mounting machine 102, and a reflow machine 140, and they are connected through a communication line 110, respectively. In addition, a line balance control device, which is equipped with possibility inquiring means which makes an inquiry of whether or not it is possible to mount components to be allocated, among the components to be mounted, to the component mounting machines 101, 102, possibility obtaining means which obtains a response to the inquiry in the possibility inquiring means, and allocating means which allocates components to be mounted, to each component mounting machine 101, 102, in such a manner that mounting time at each component mounting machine is equalized, on the basis of the response obtained in the possibility obtaining means, is disposed in a device which configure the production line 100.

Owner:PANASONIC CORP

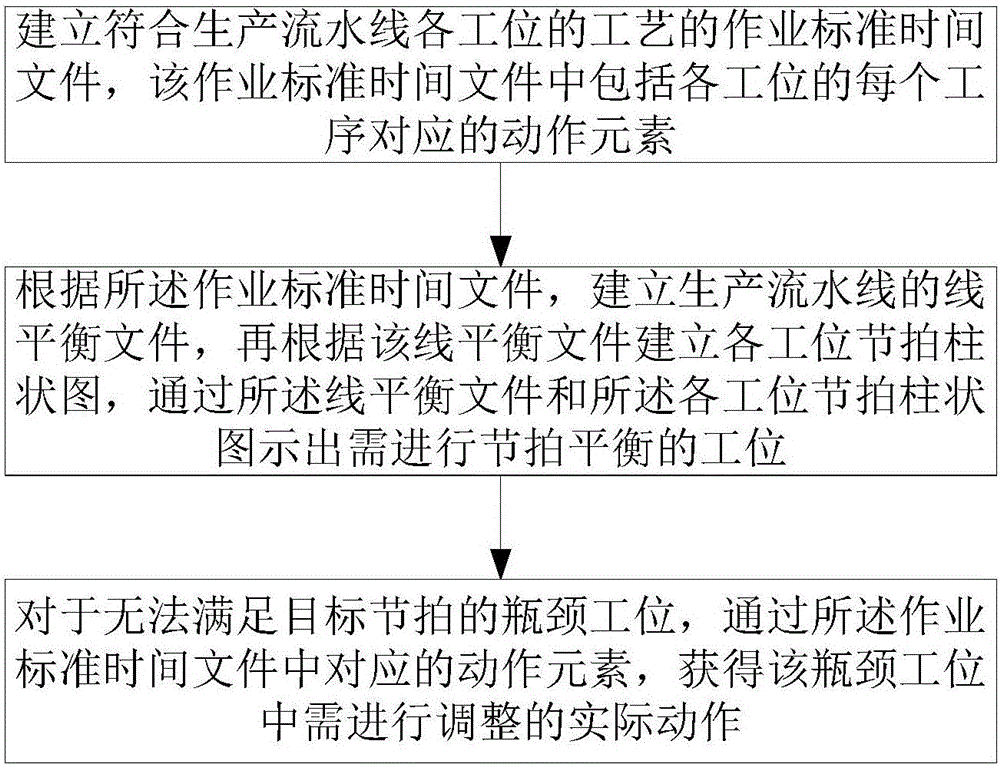

Method and device of optimizing production assembly line work and production assembly line

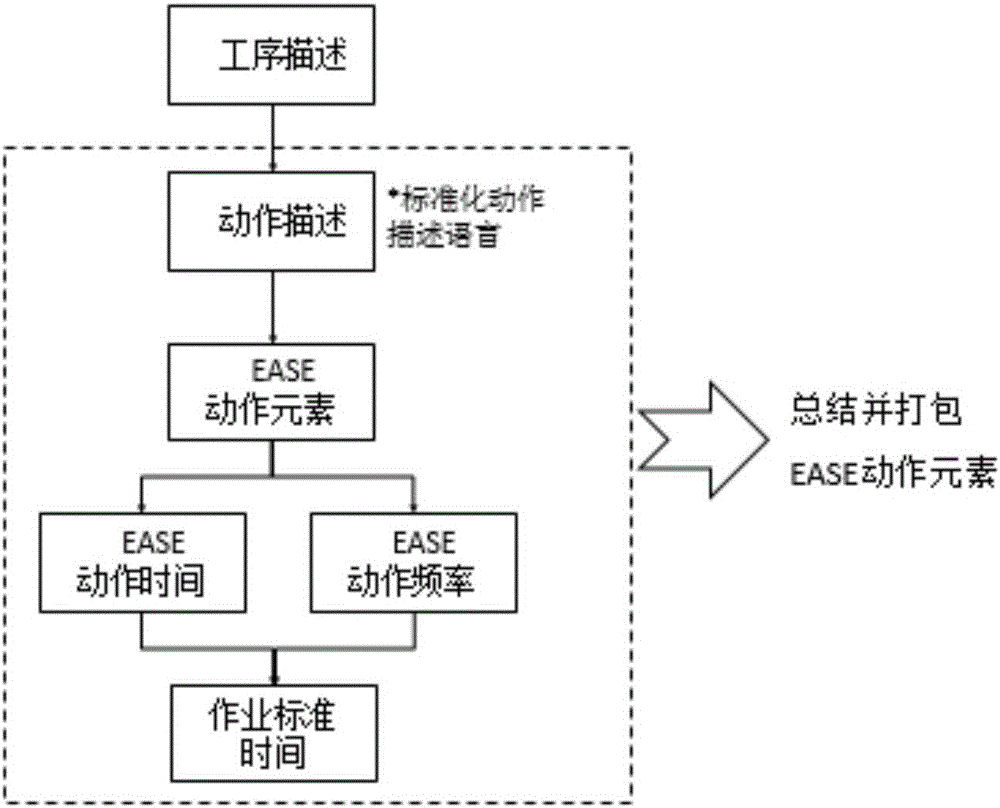

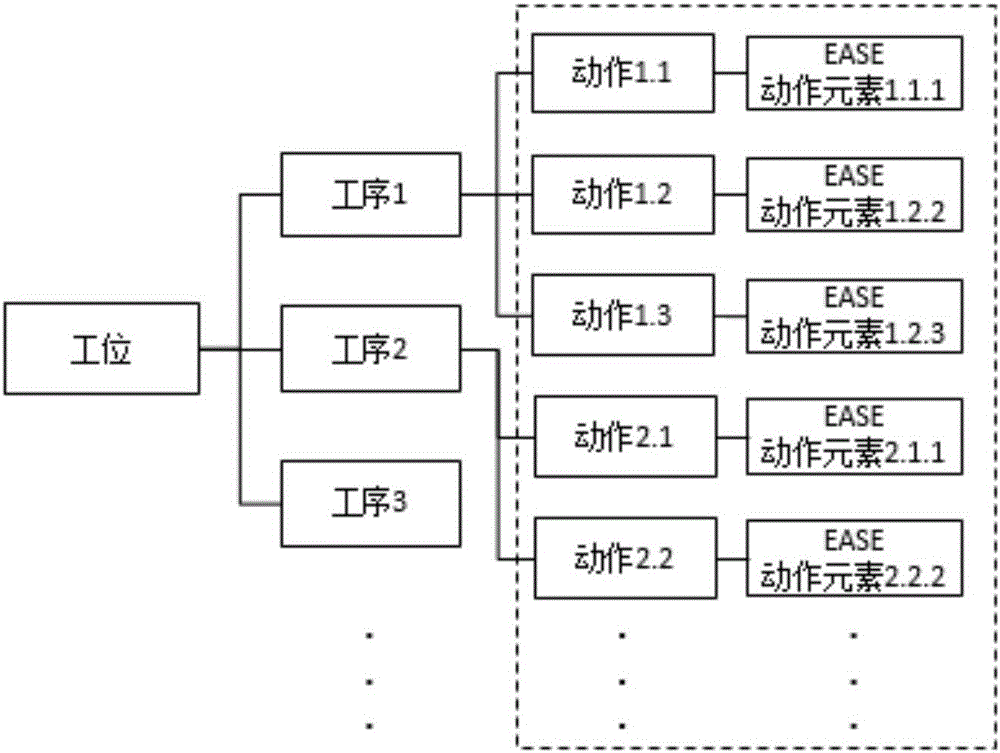

InactiveCN106295840AAchieve standardizationEasy to findForecastingResourcesEngineeringLine balancing

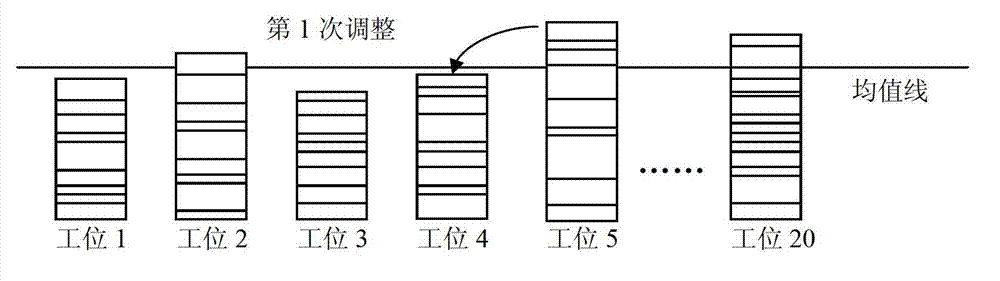

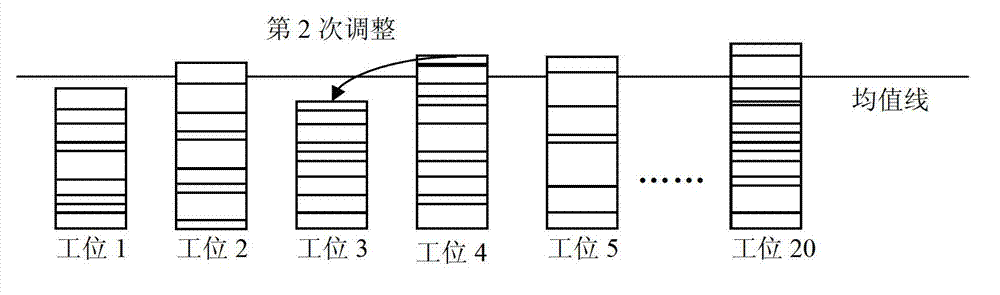

The invention relates to the manufacturing enterprise assembly line technology field, and discloses a method and a device of optimizing production assembly line work and a production assembly line. The method comprises steps that work standard time files in accordance with the various stations of the production assembly line are established, and comprise motion elements corresponding to the operation of the stations; according to the work standard time files, the line balance file of the production assembly is established, and then according to the line balance file, the beat histograms of the various stations are established, and the stations requiring beat balance are shown by the line balance file and the beat histograms of the various stations; according to bottleneck stations, actual motions required to be adjusted in the bottleneck stations are acquired by the corresponding motion elements in the work standard time files. The work standard time files in accordance with the various stations of the production assembly line are established, and the production capability of the assembly line is improved, and the bottleneck stations are optimized.

Owner:BEIJING FOTON CUMMINS ENGINE

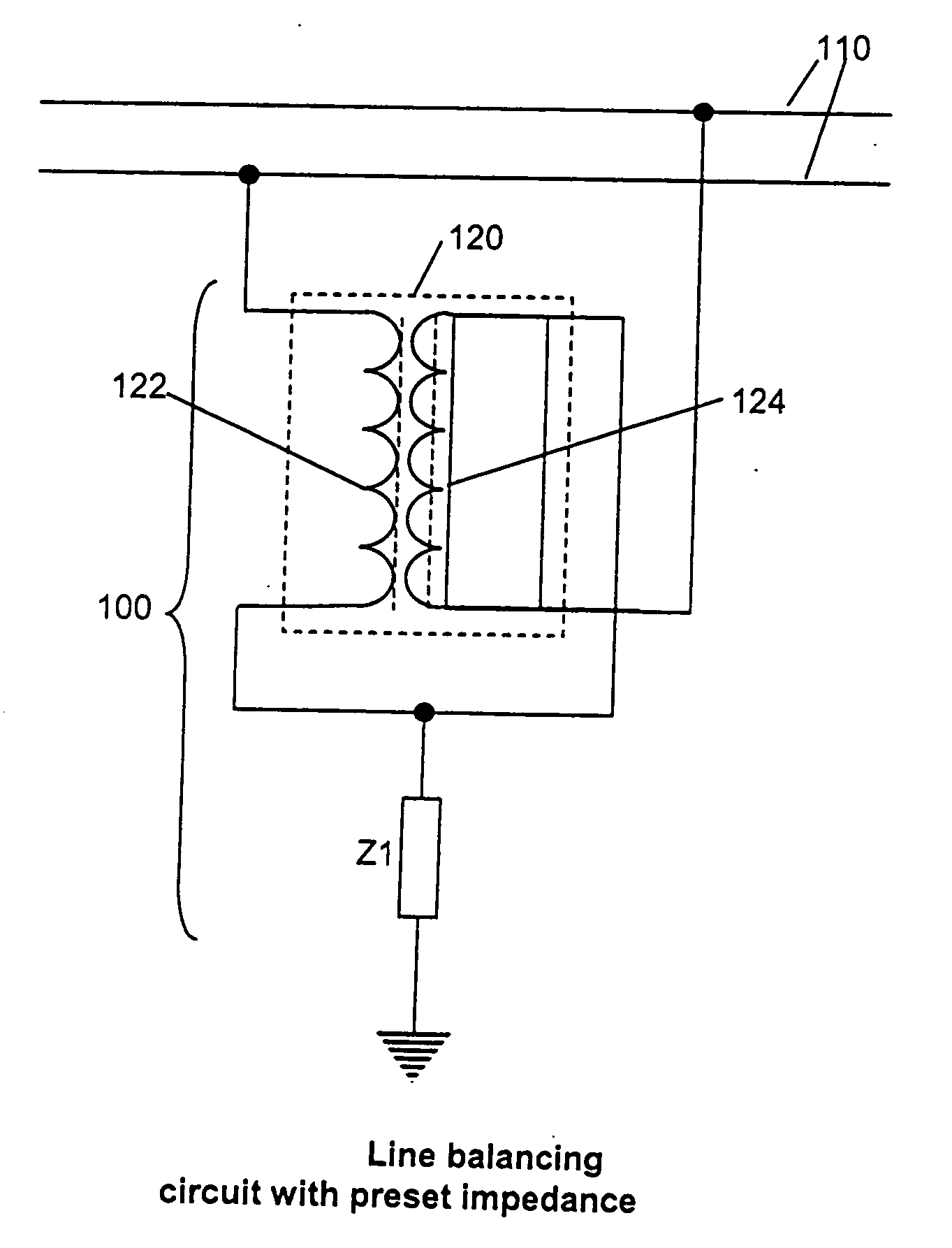

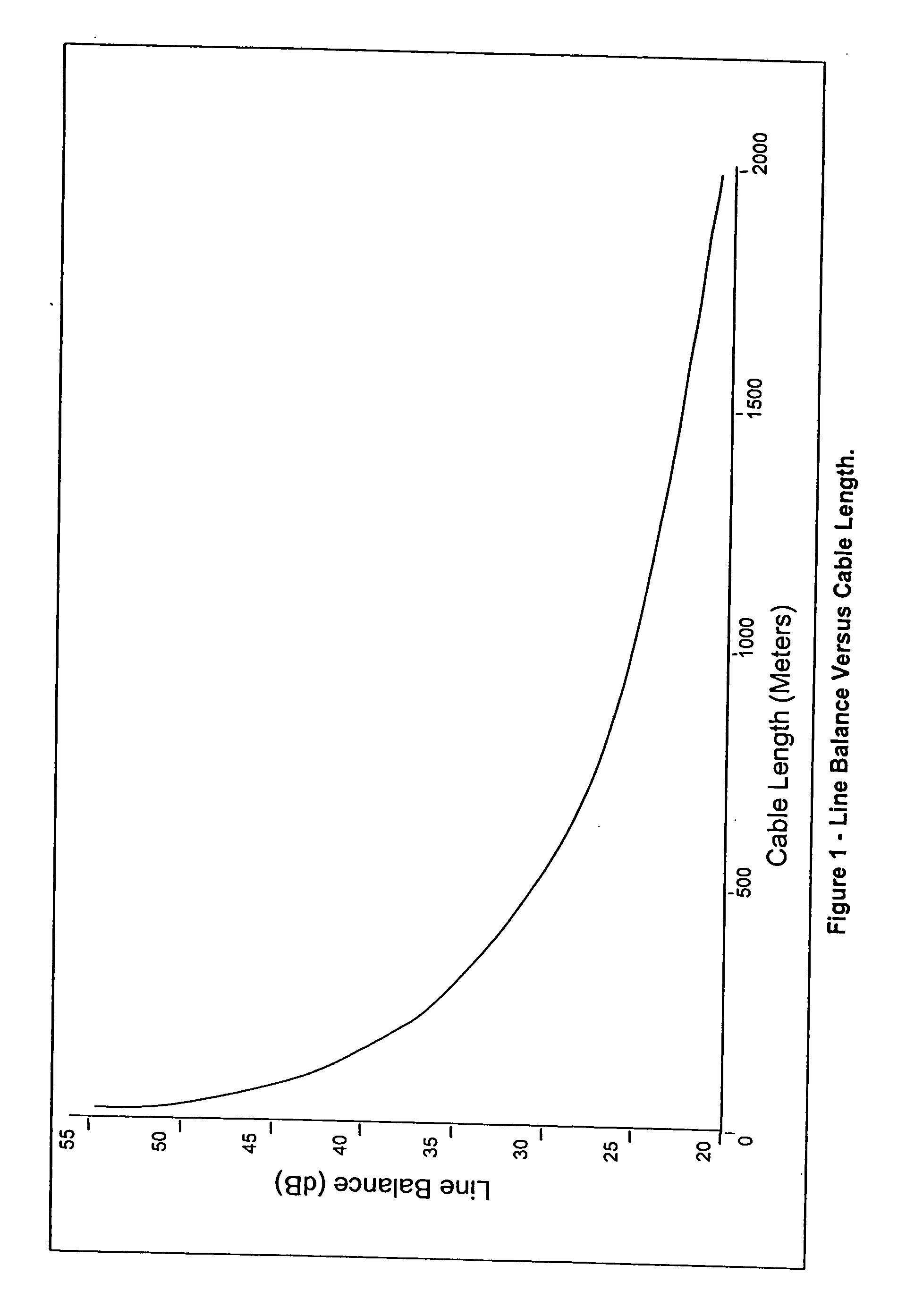

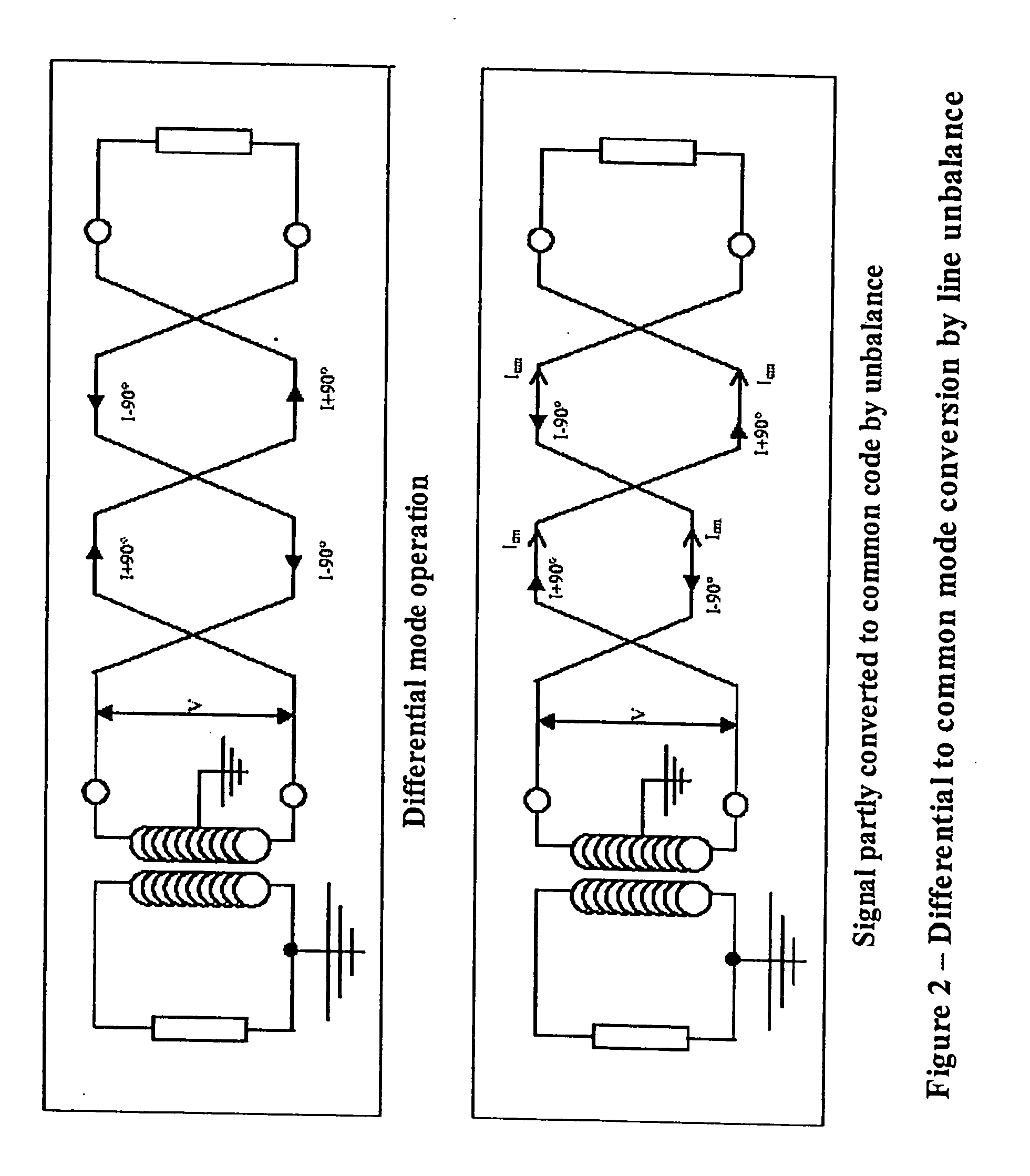

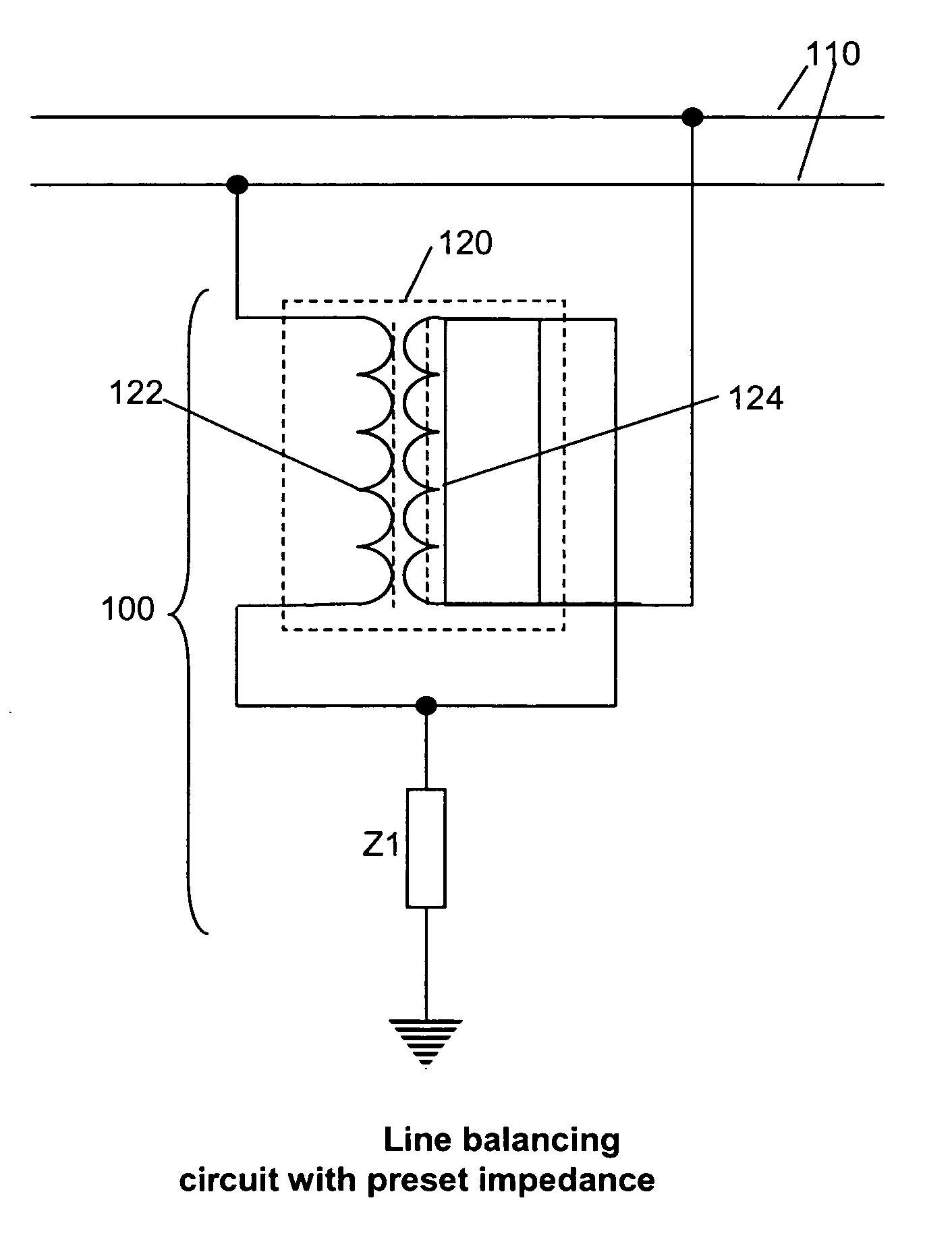

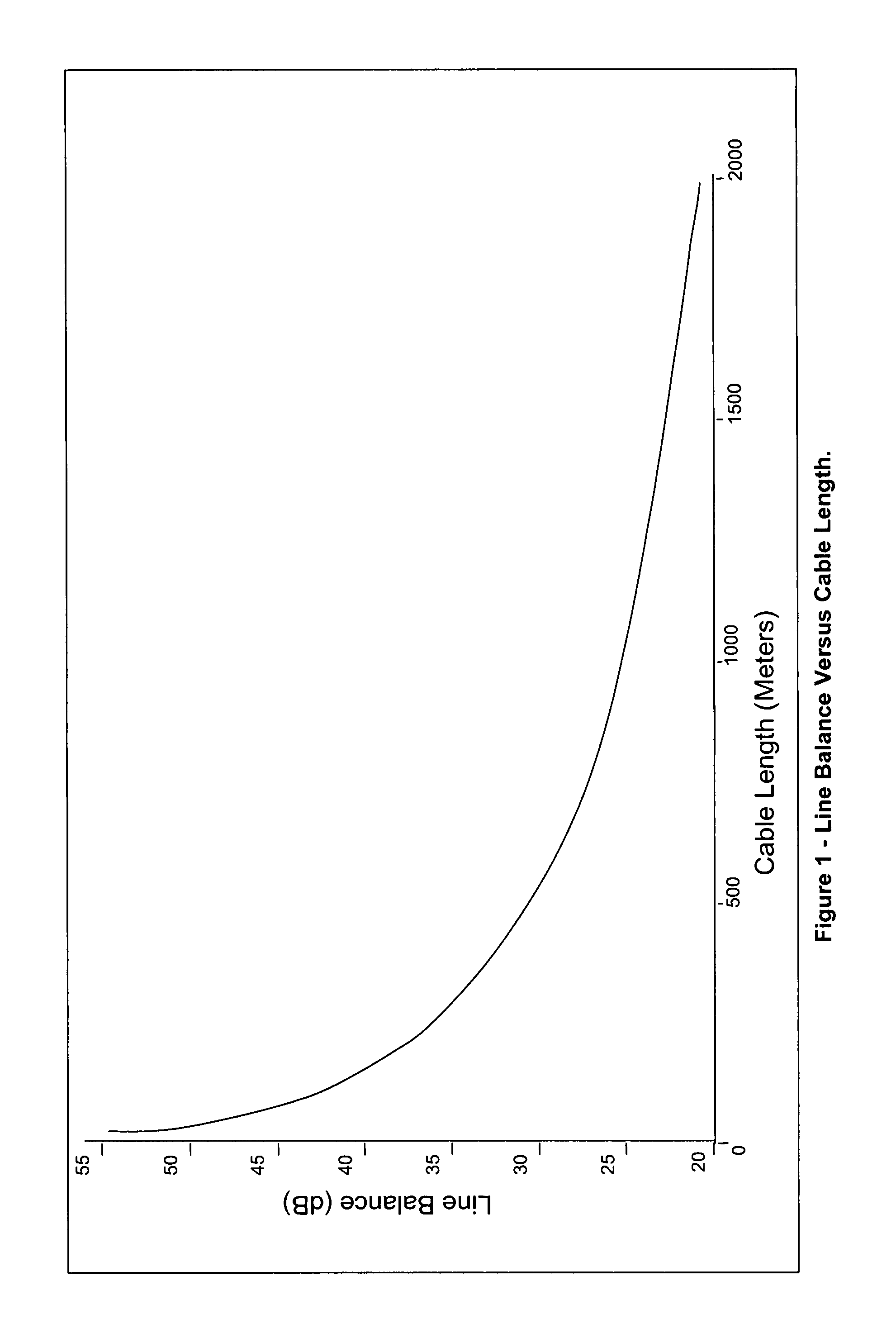

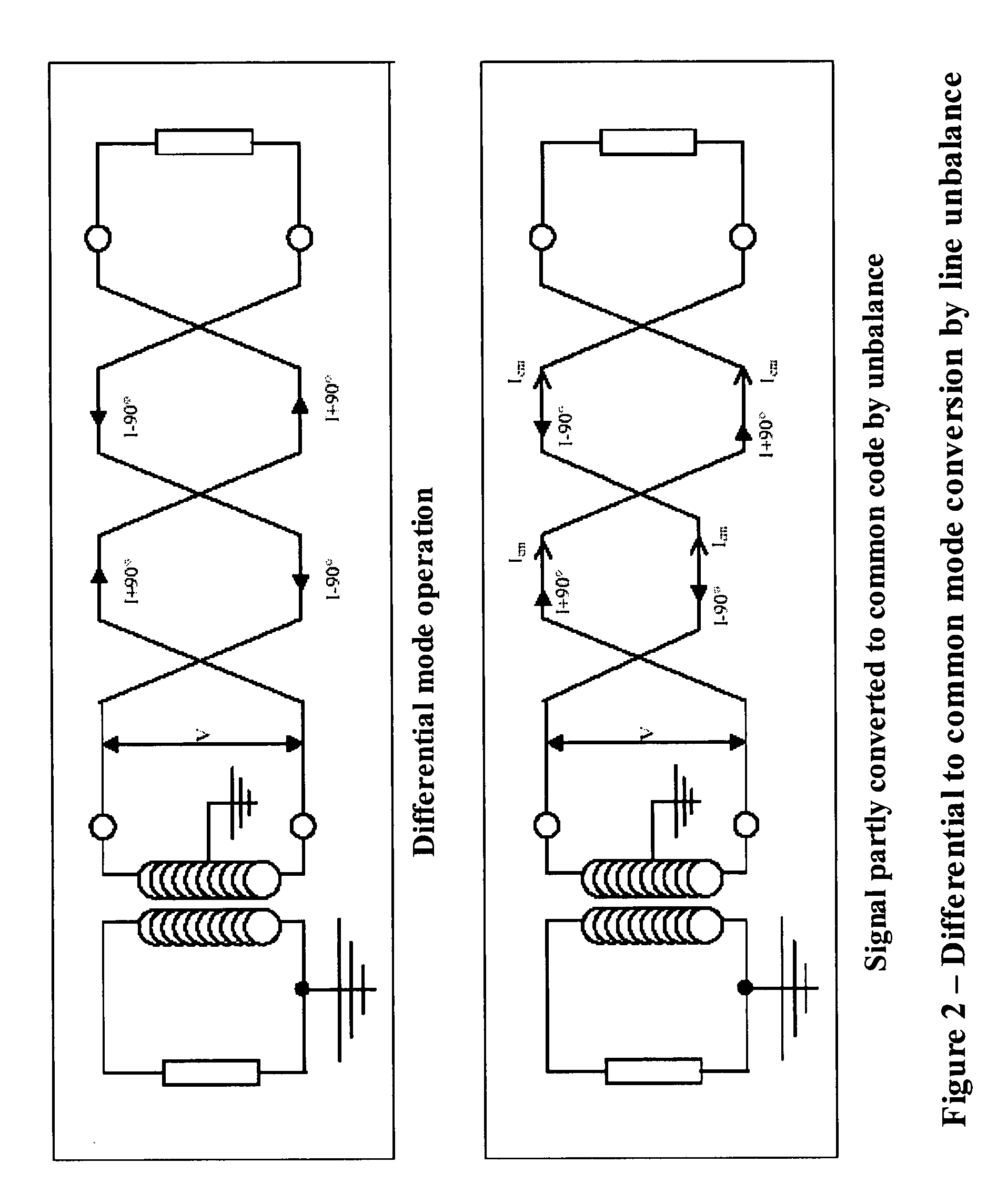

Reduction of noise in a metallic conductor signal pair using controlled line balancing and common mode impedance reduction

InactiveUS20080012658A1Multiple-port networksCurrent interference reductionElectrical conductorElectromagnetic interference

In order to reduce noise on twisted metallic pair signal conductors, circuits are disclosed in which the signal balance between the wires of the pair is significantly improved, thereby reducing the line's susceptibility to external electromagnetic interference and equally reducing its ability to radiate signals into the surrounding medium. Further, the common mode impedance of the wire pair as seen at or close to the junction with the terminating equipment is controlled in order to reduce the ability of signals external to the wire pair to couple into the wire. This reduces noise in the line, as perceived by connected equipment, leading to an increase in the data carrying capacity of the line and the usable length of the line carrying such data.

Owner:ACCELL SYST

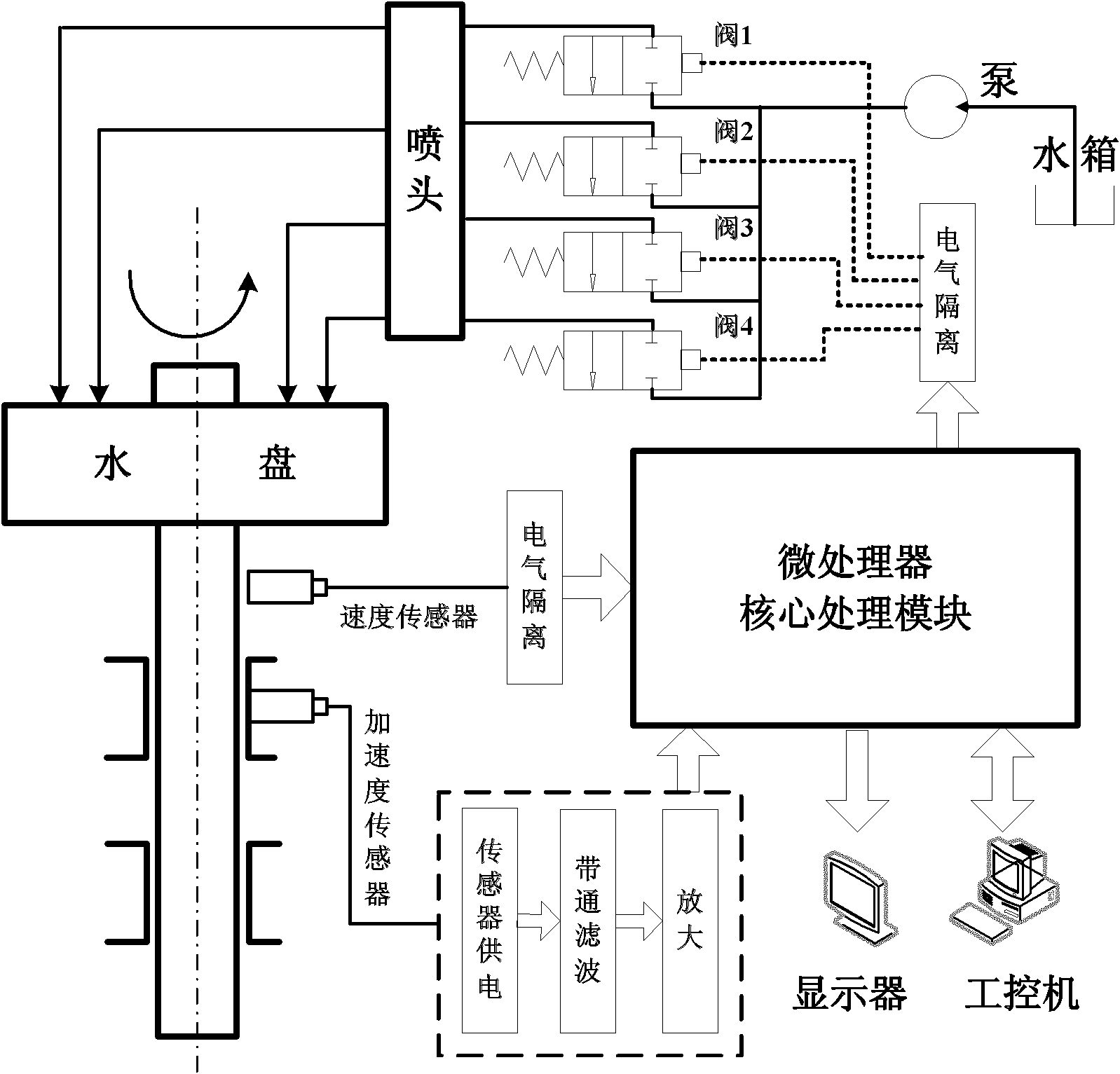

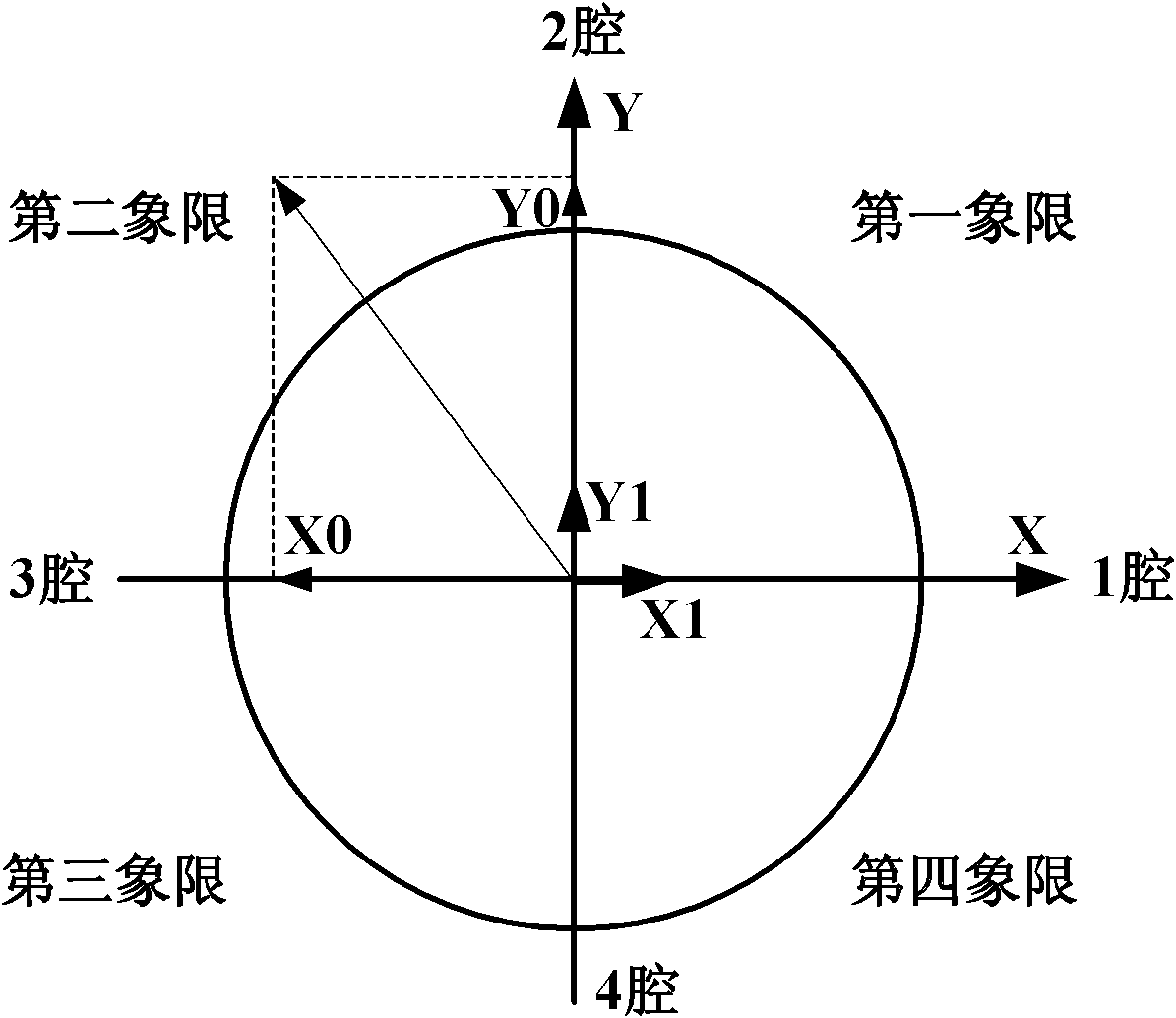

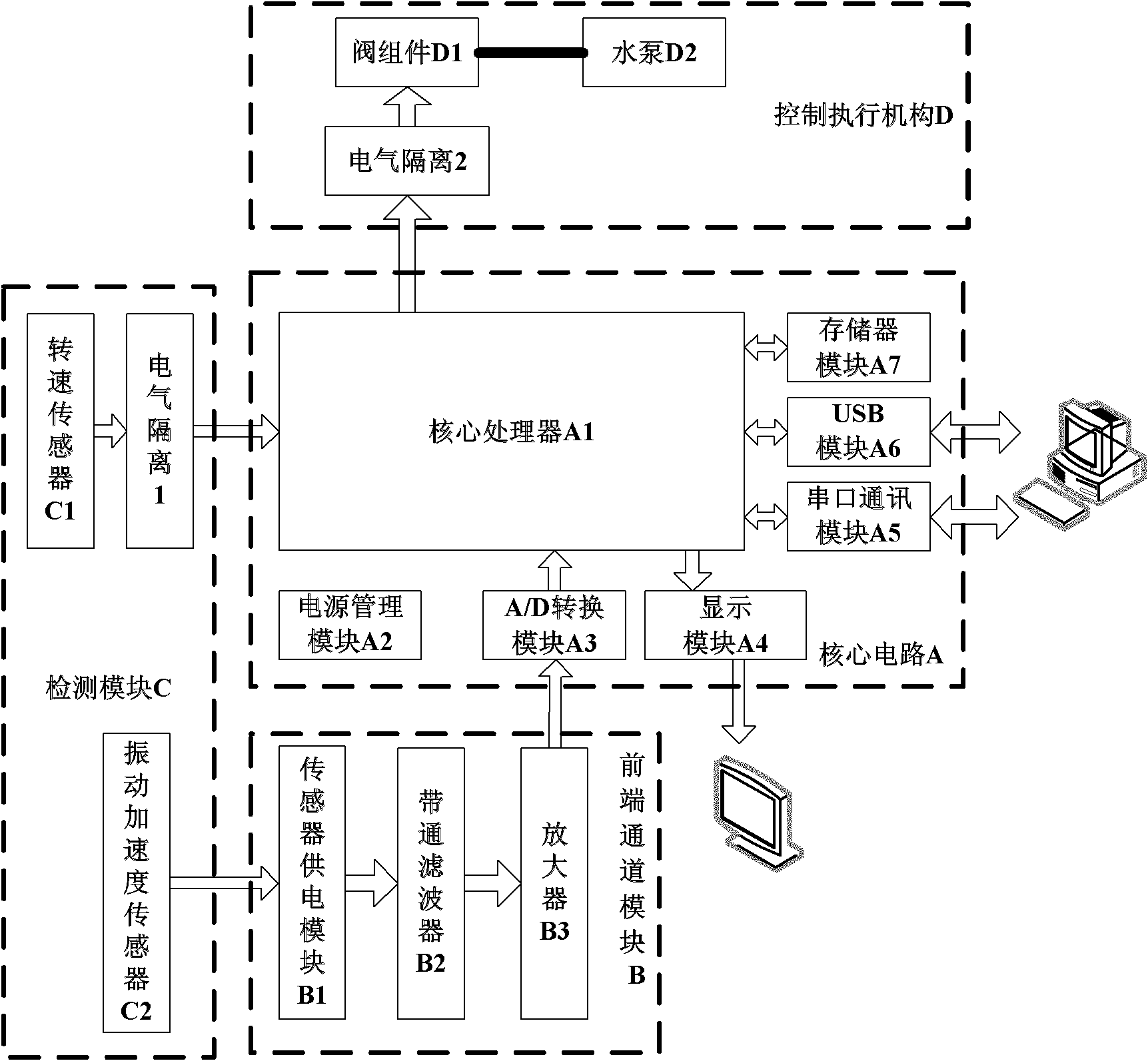

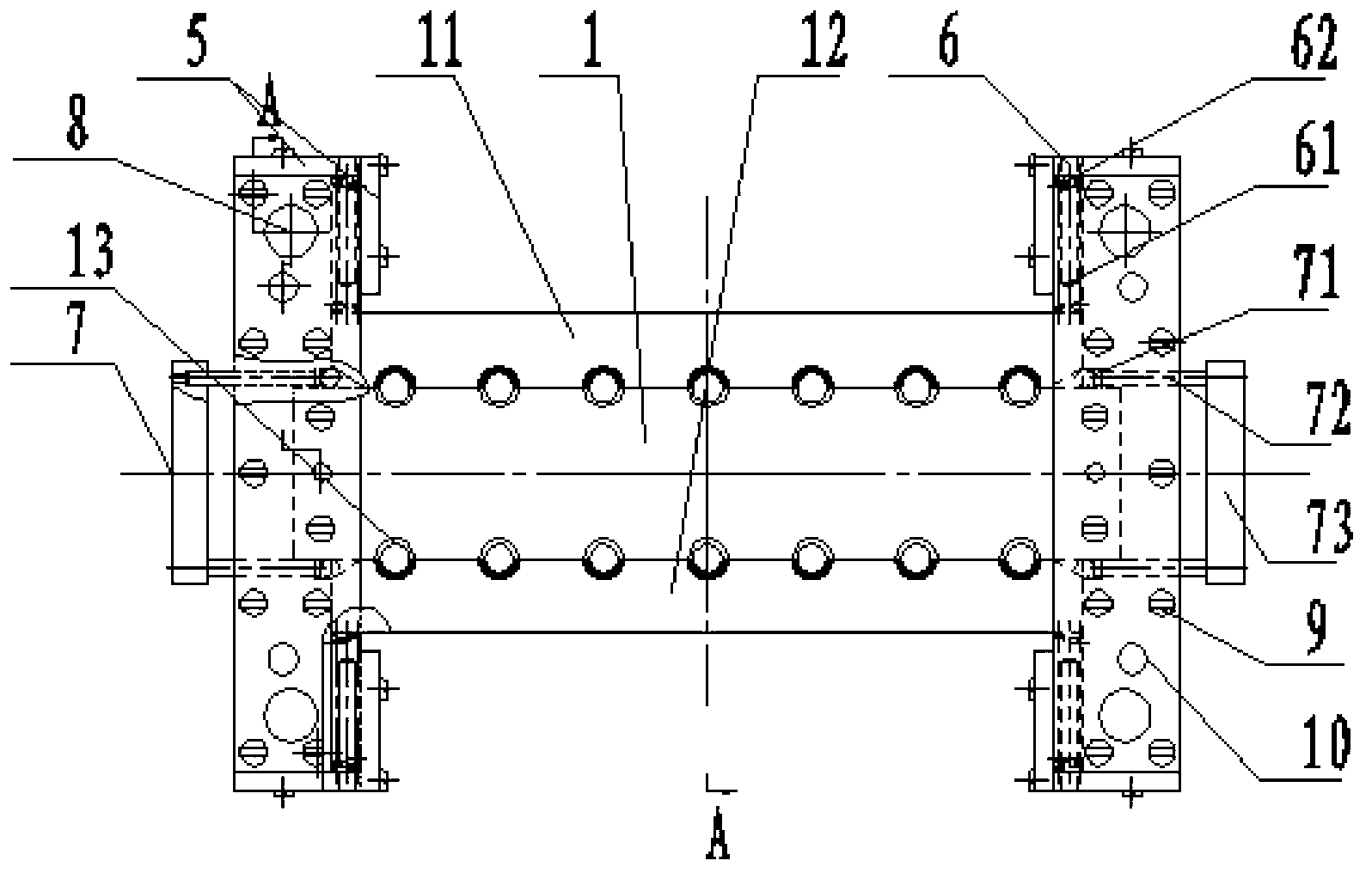

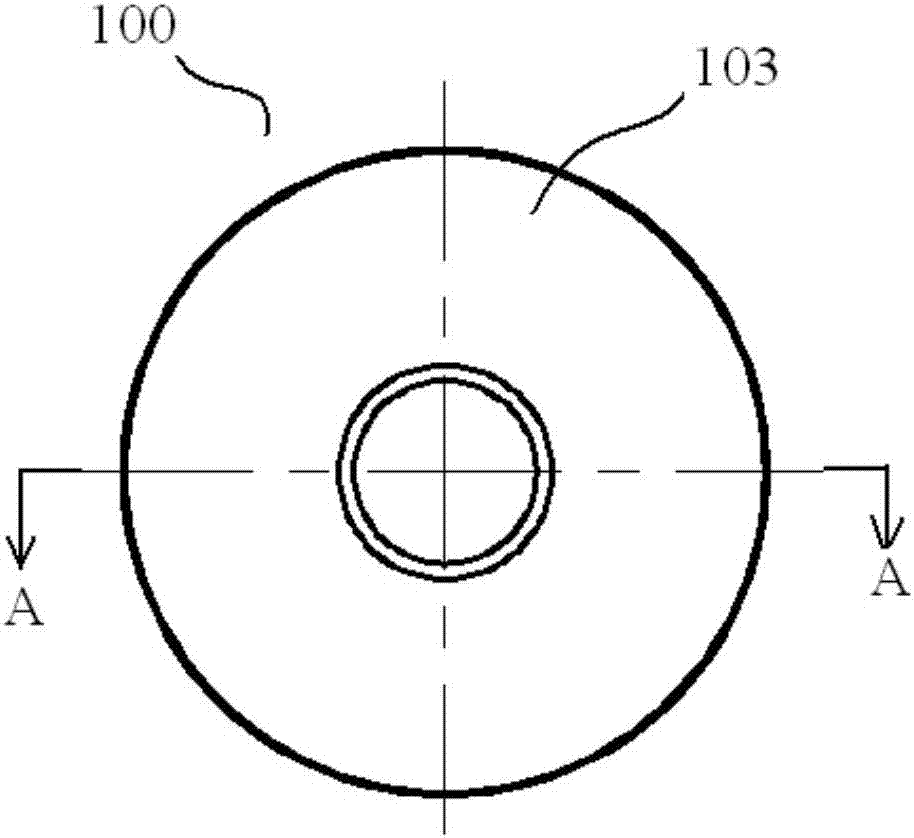

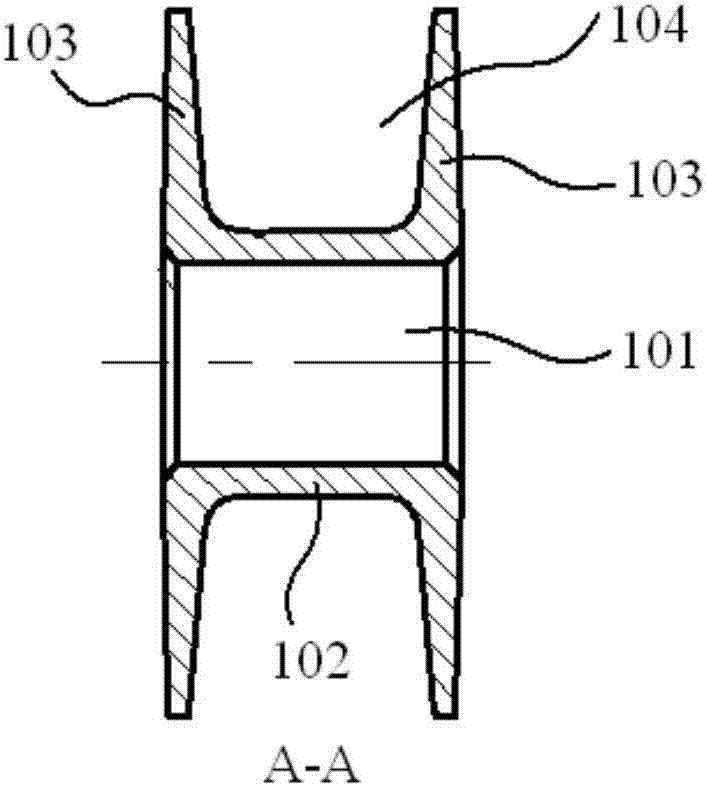

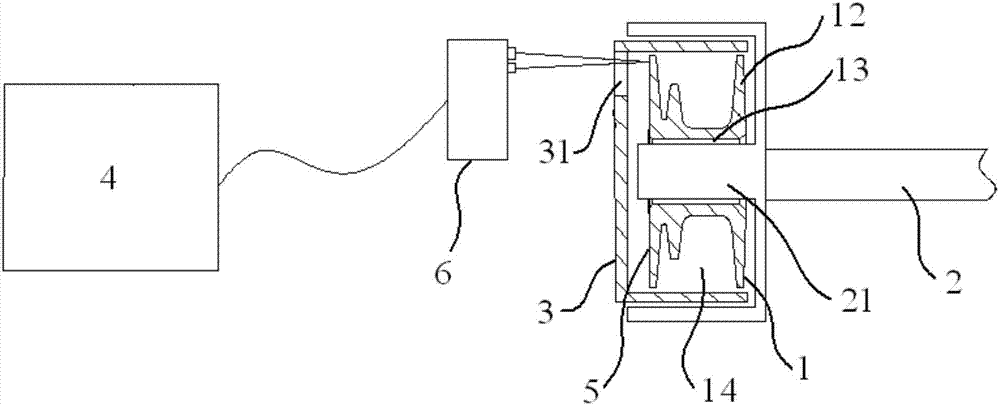

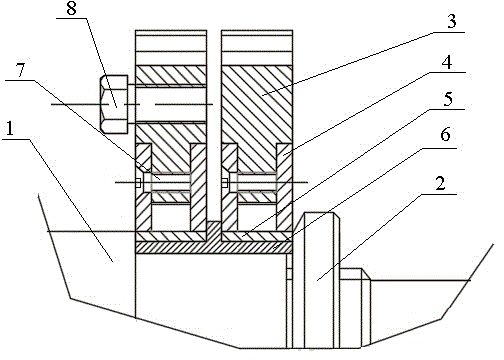

Automatic on-line balancing system of liquid-injection high-speed main shaft

ActiveCN102095554AEase of field applicationImprove balance efficiencyStatic/dynamic balance measurementWater channelSpray nozzle

The invention discloses an automatic on-line balancing system of a liquid-injection high-speed main shaft, which is mainly composed of a mechanical structure part and an electric control part, wherein the mechanical structure part comprises a water pan structure and a spray nozzle part; the water pan is directly installed on one end of the main shaft; a water channel in the water pan can ensure that liquid can be stably and accurately distributed in an appointed water cavity after the liquid is injected into the water pan via a spray nozzle; the spray nozzle is connected with a workbench, and the position and the angle of the spray nozzle can be adjusted; the electric control part obtains the vibration signal of the main shaft in real time; according to the vibration change situation of the main shaft, a valve assembly is controlled to precisely inject water; and vibration information collected before and after water is injected each time is used as a judgement basis for system control. The automatic on-line balancing system of a liquid-injection high-speed main shaft is characterized in that centrifugal force generated by the liquid offsets with the initial amount of the unbalance of the main shaft after repeated liquid injection, and the main shaft system is balanced.

Owner:XI AN JIAOTONG UNIV

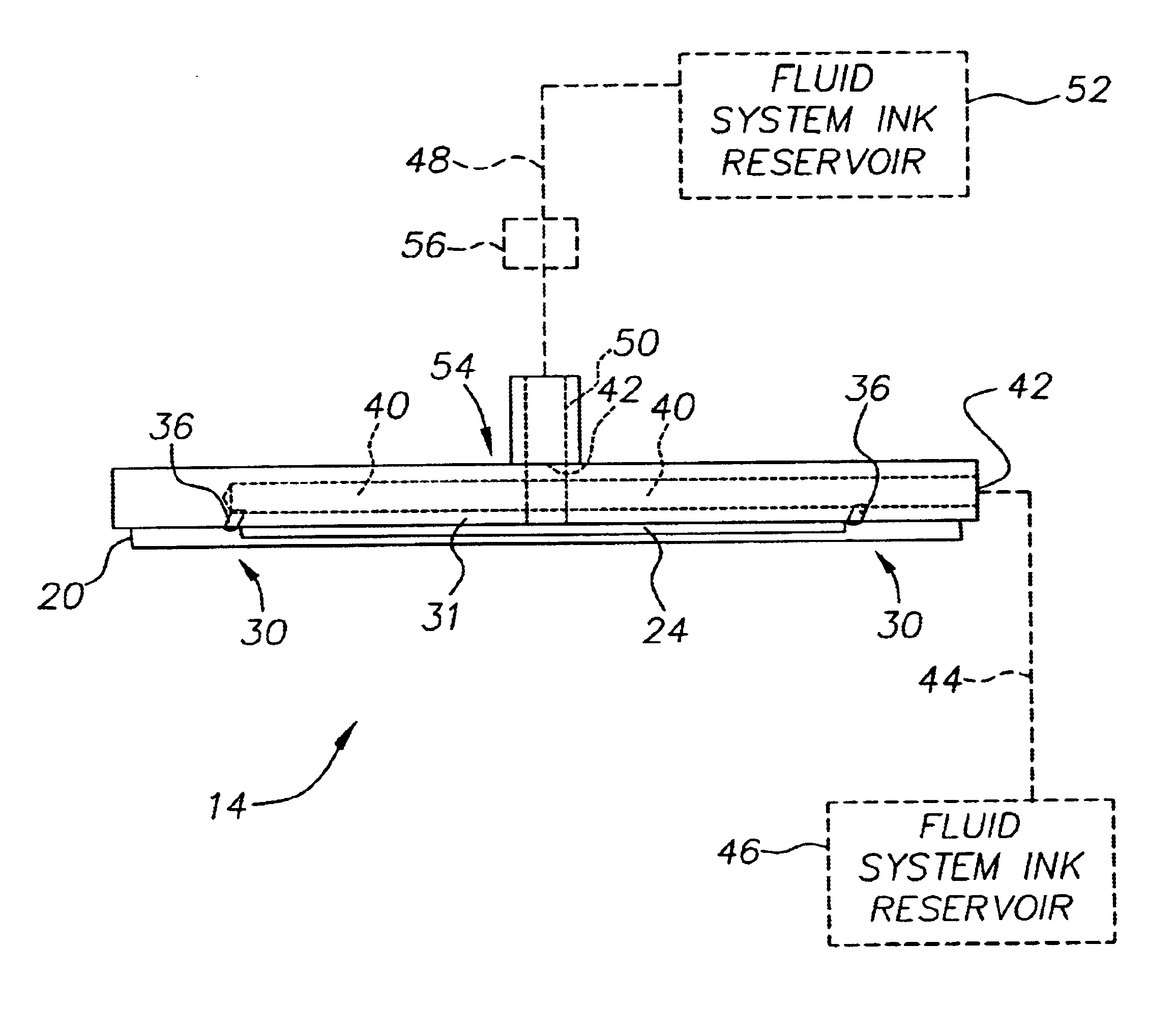

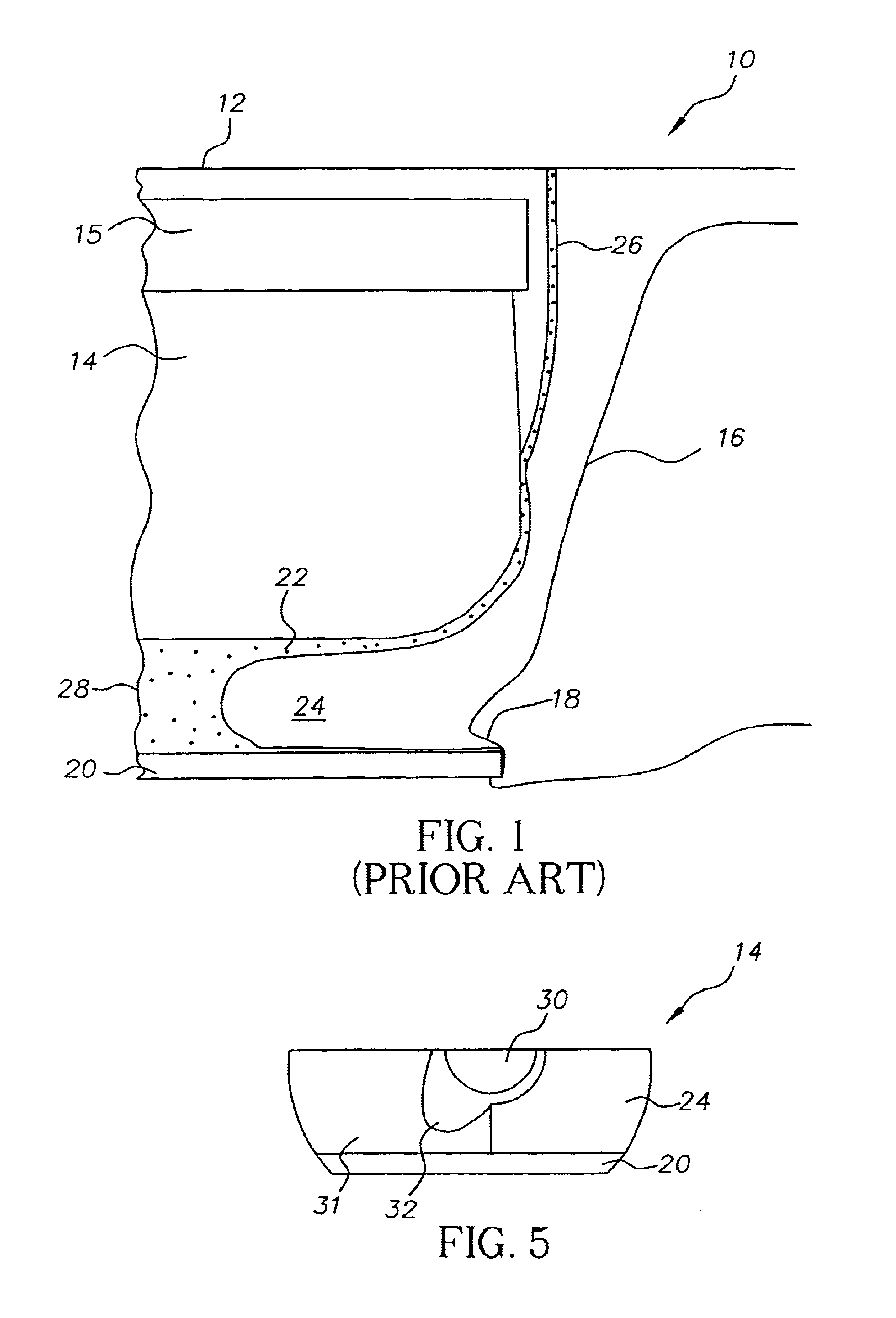

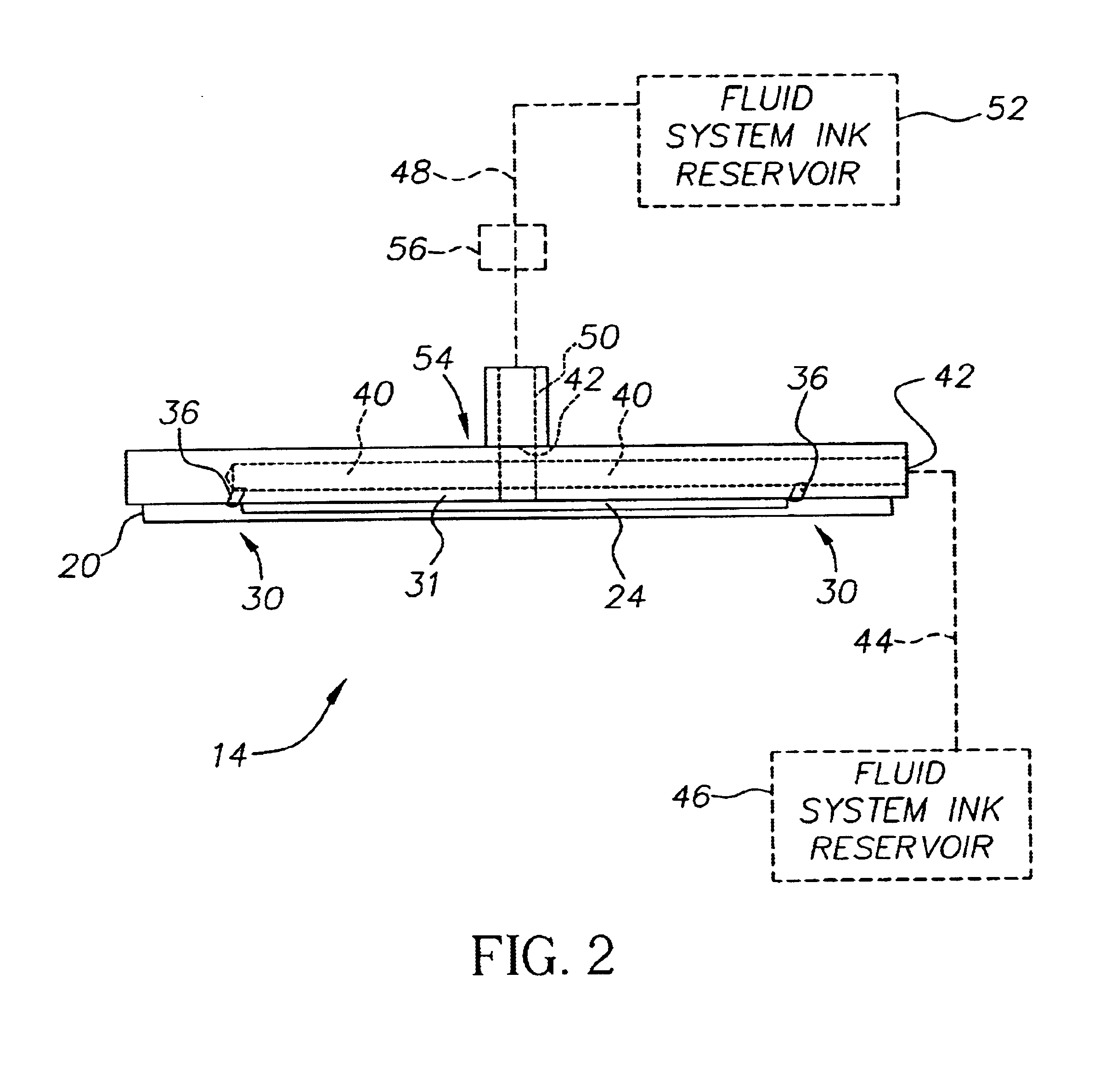

Anti-wicking catcher arrangement for a solvent ink printhead

A catcher design is provided wherein vacuum channels are added to both sides of the catcher to remove ink from the face of the catcher and from the eyelid seal. An additional fluid port on the catcher allows the additional vacuum channels to maintain an increased level of vacuum. A restriction on the catcher line balances the fluid flow between the catcher and the additional vacuum channels. A scoop can be machined into the catch pan to remove fluid from below the catcher face. A manifold can be used to maintain a vacuum source for the catcher throat and the additional channels, while pulling the unprinted ink back to the fluid system. Finally, a wider eyelid seal can allow purge fluid used during shutdown to clear the channels.

Owner:EASTMAN KODAK CO

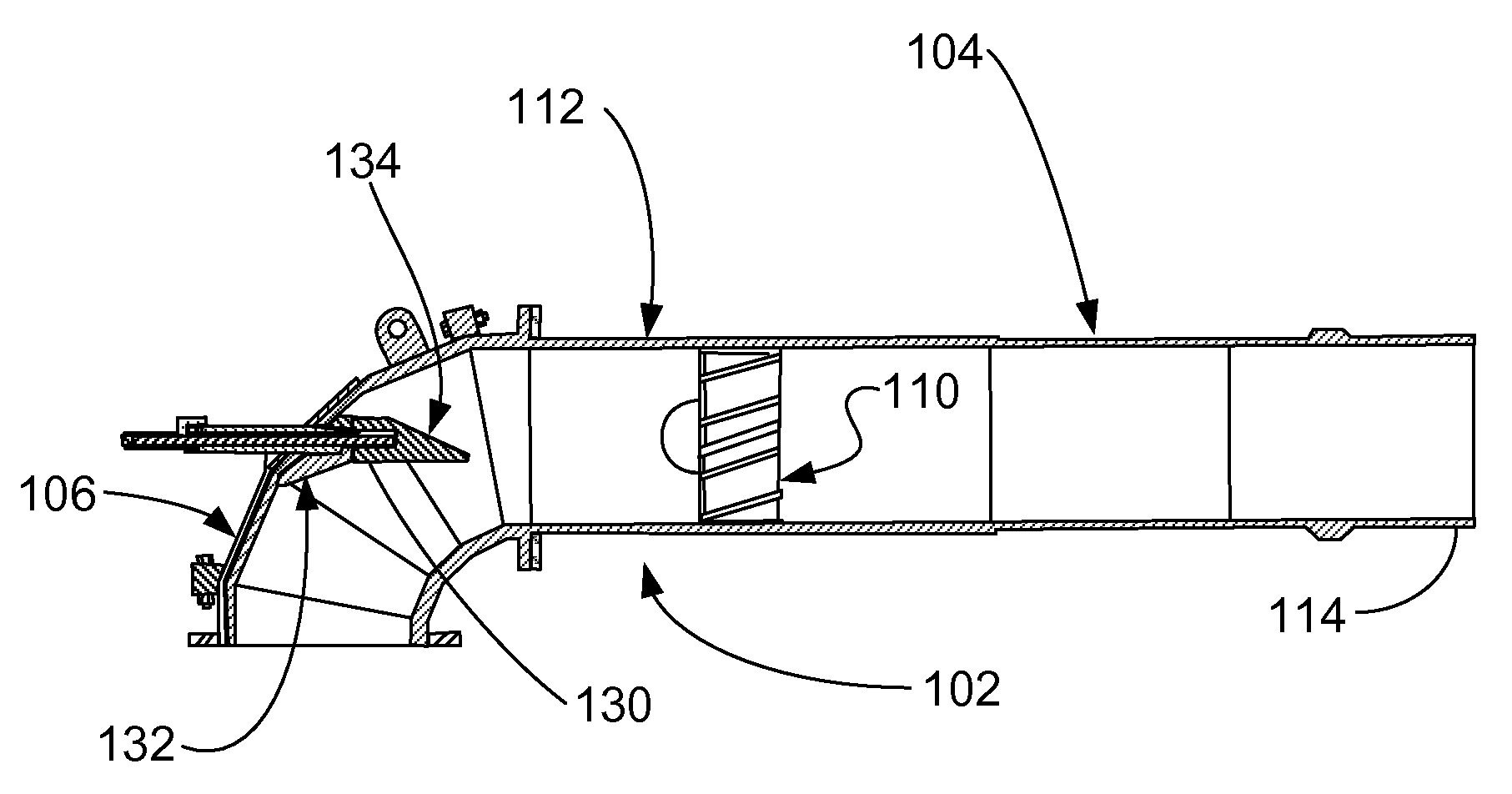

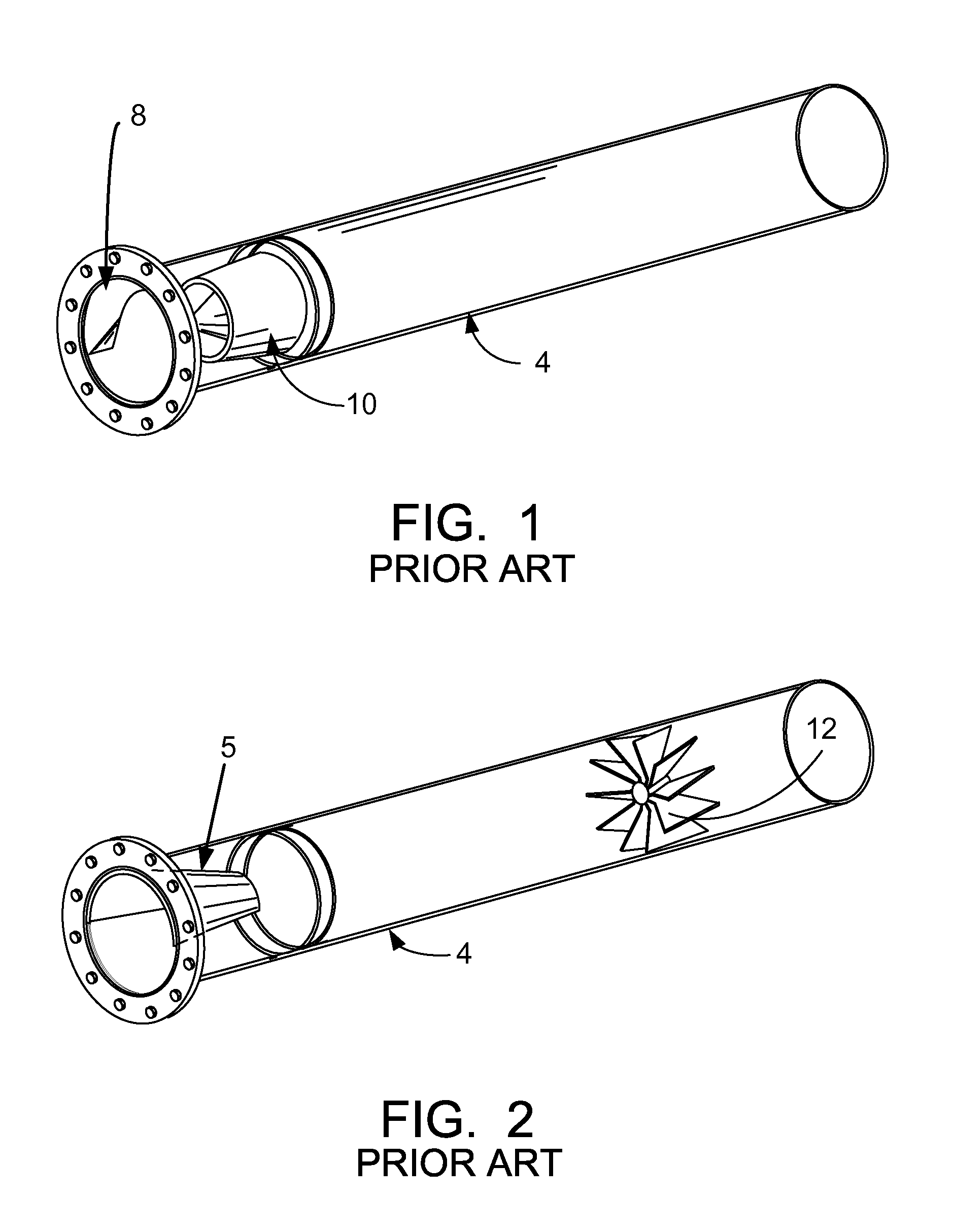

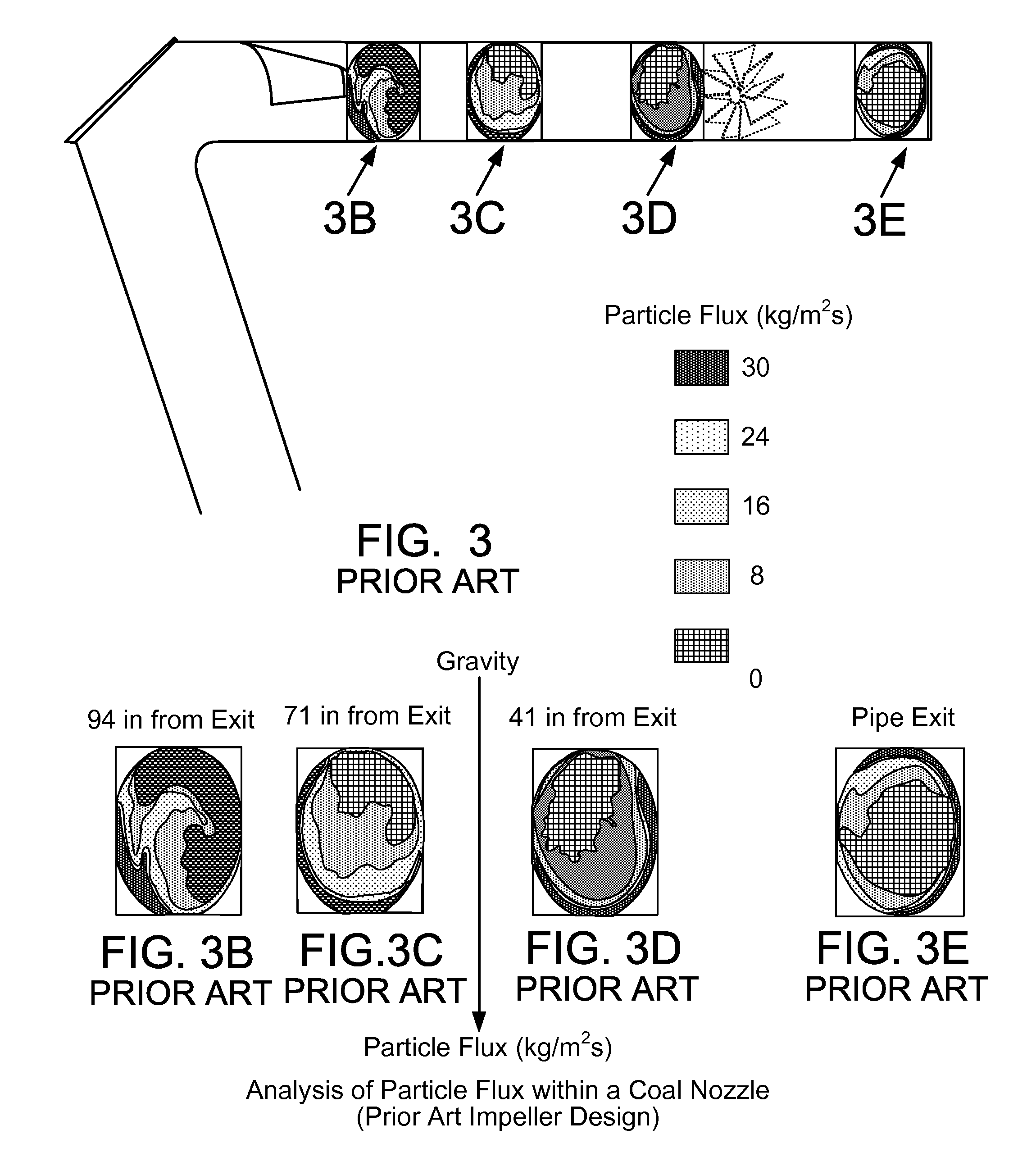

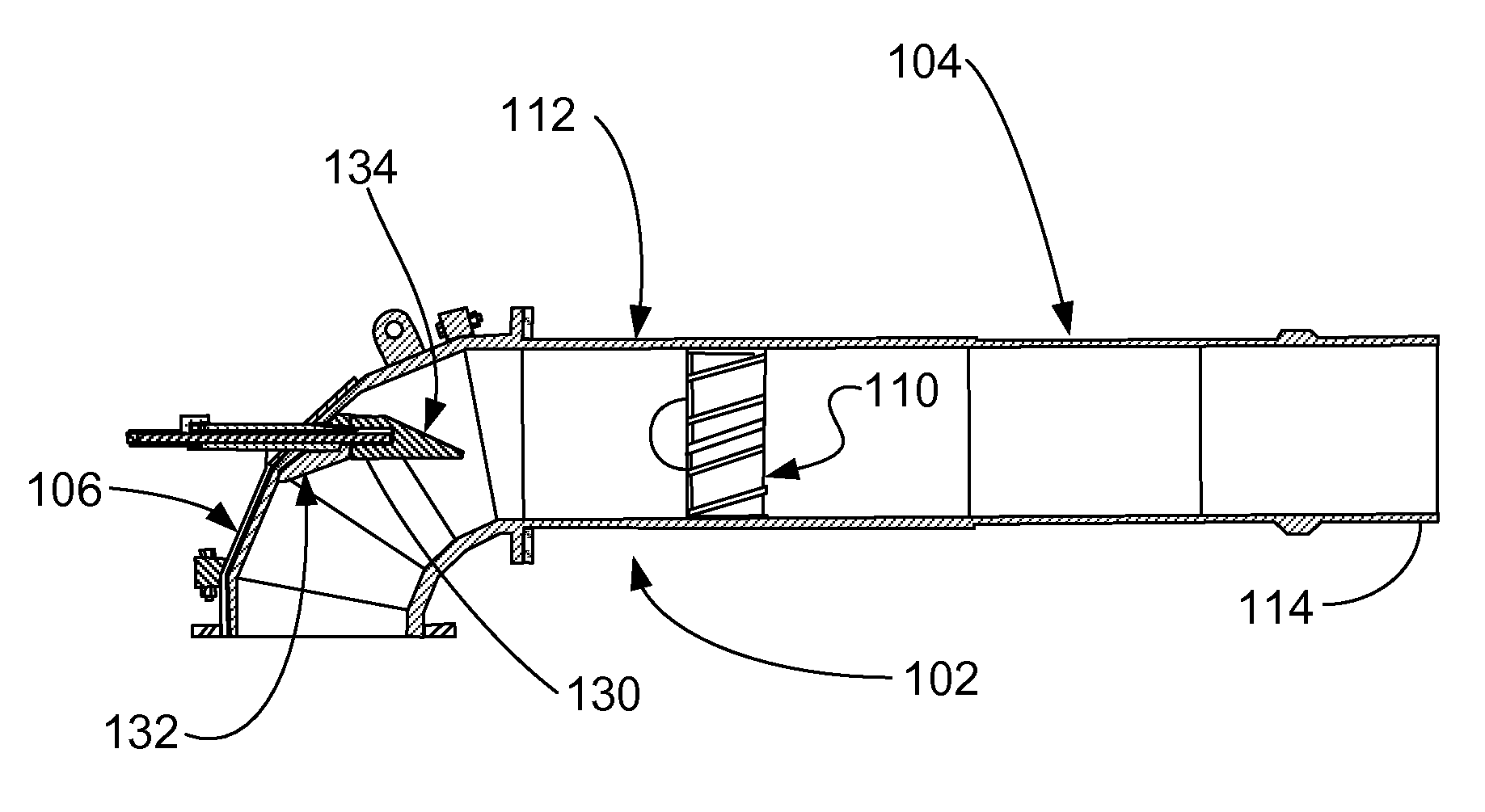

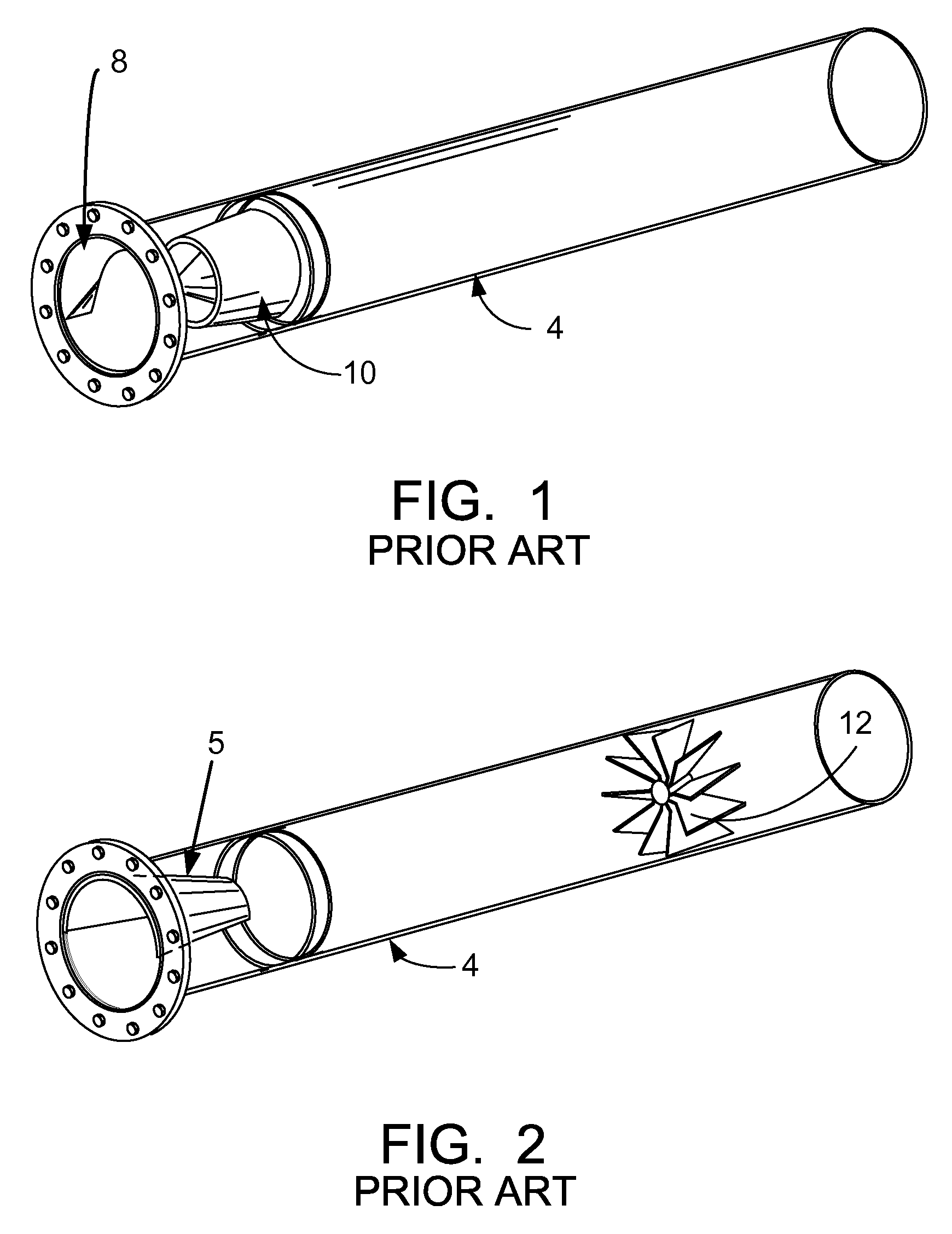

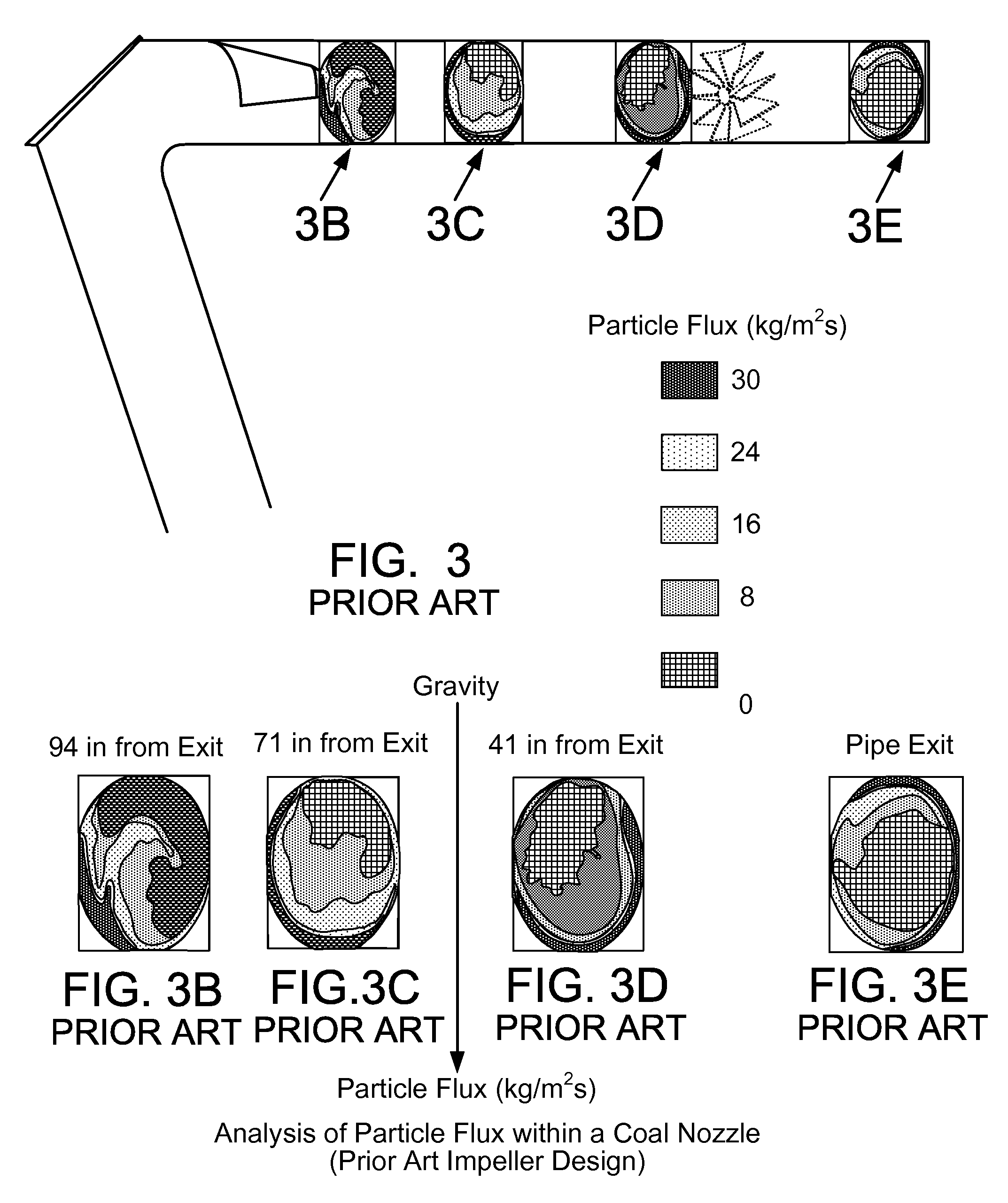

Bladed coal diffuser and coal line balancing device

ActiveUS20100123027A1Combustion using gaseous and pulverulent fuelCombustion using liquid and pulverulent fuelLine balancingStreamflow

A coal nozzle assembly for a pulverized coal burner includes a diffuser. A flow conditioner also may be used with the assembly. The assembly conditions the coal / air flow before the coal / air flow is introduced to the furnace. The flow conditioner directs the coal into the diffuser where it is swirled to form a fuel rich outer ring disposed about an air rich inner portion before the fuel is delivered to the coal nozzle.

Owner:THE BABCOCK & WILCOX CO

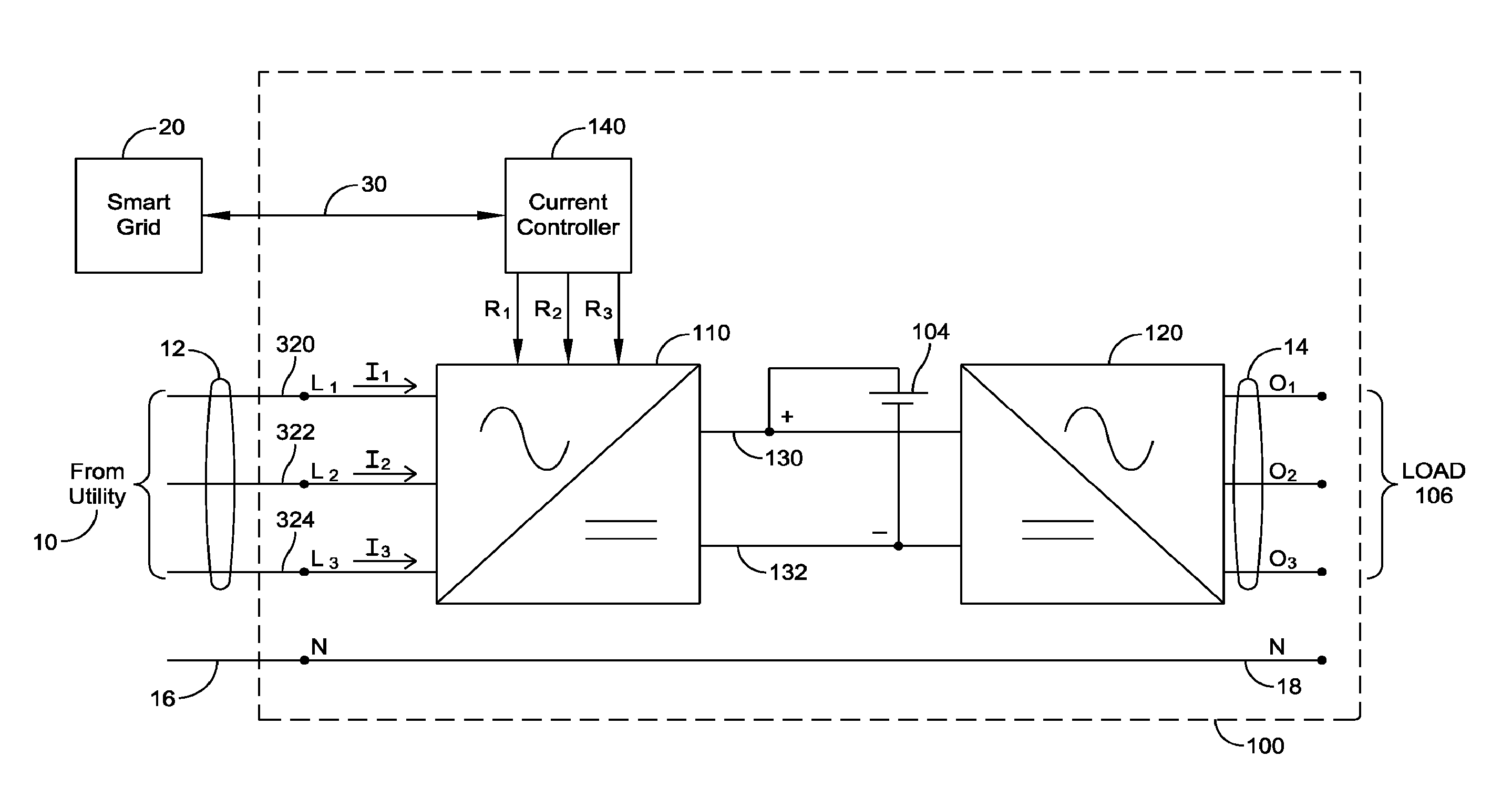

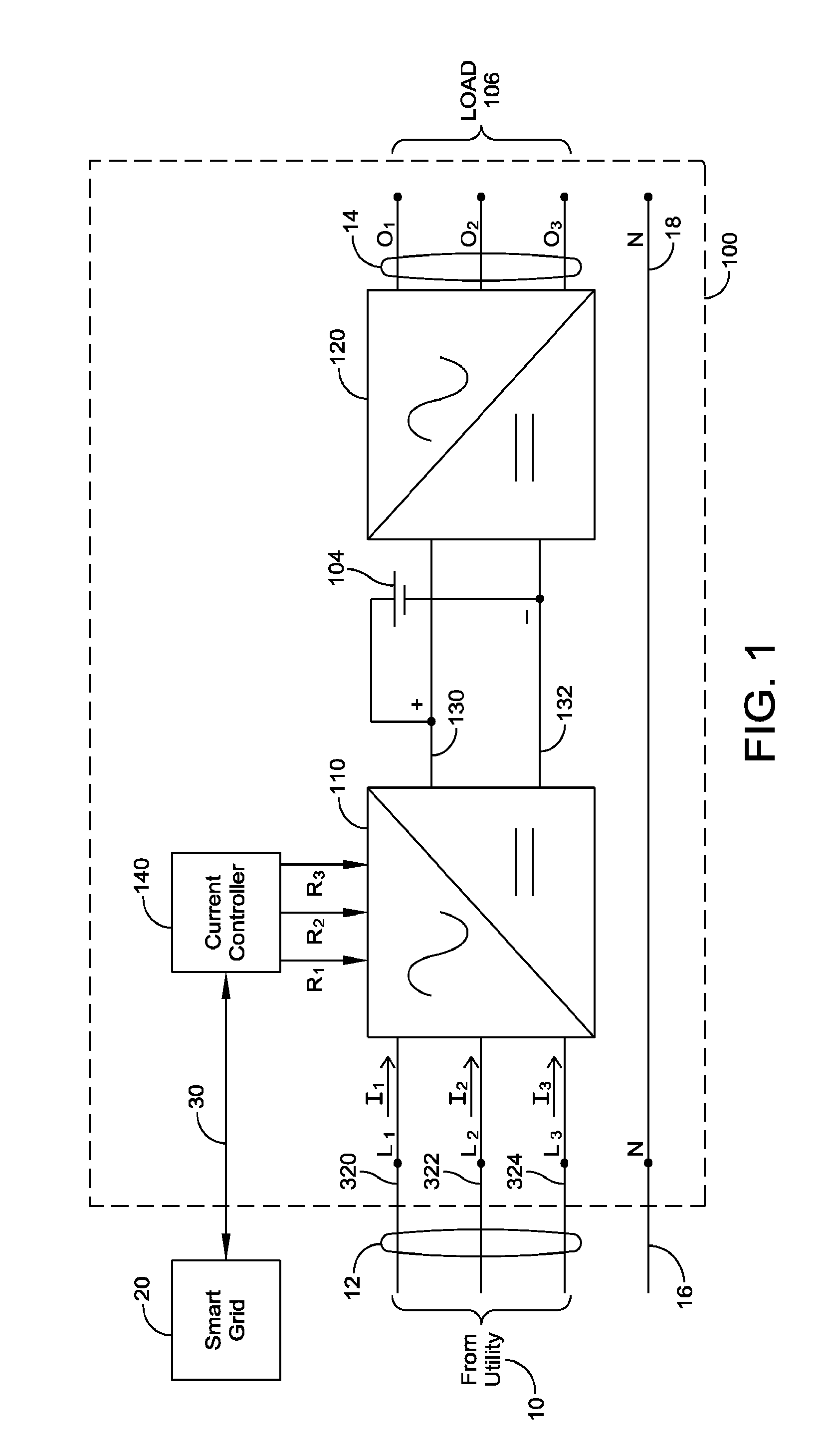

Line balancing ups

ActiveUS20150084423A1Batteries circuit arrangementsPolyphase network asymmetry elimination/reductionPower flowSmart grid

A method for controlling an uninterruptible power supply (UPS) having a polyphase power input and an input power circuit coupled to the polyphase power input includes determining to reduce a load on a first phase of the polyphase power input, and in response thereto, controlling the input power circuit to reduce a first input current drawn from the first phase by a first amount and increase a second input current drawn from a second phase of the polyphase power input by a second amount. The UPS may determine to reduce the load on the first phase in response to a request from a smart grid to reduce the load on the first phase or in response to a local determination to reduce the load on the first phase.

Owner:SCHNEIDER ELECTRIC IT CORP

Multi-insert quick installing and placing clamp for push type injection molding plastic part

The invention is suitable for multi-insert quick installation and placement for a multi-cavity structure injection mould with multiple cavities arranged in an in-line balance manner. The multi-insert quick installing and placing clamp is located by using a guide pillar of a plastic injection mould, and inserts are placed in insert clamping holes outside the mould. Upper clamping plates and lower clamping plates of the inserts are guided to slide in a sliding way, and the inserts are loosened or clamped by using a manual loosening mechanism and an automatic spring resetting mechanism. When the multi-insert quick installing and placing clamp works, the inserts are placed in the insert clamping holes outside the mould by an operator, the clamp is located on the guide pillar of the mould; after the inserts arrive at preset positions in the mould, the upper clamping plates and the lower clamping plates of the inserts loosen the inserts under the action of the manual loosening mechanism to complete that the inserts are automatically placed. After the inserts are installed and placed, the upper clamping plates and the lower clamping plates of the inserts reset under the action of elastic force. The multi-insert quick installing and placing clamp is simple in structure and low in cost due to no limit to types of injectors; the defects of low installing efficiency, poor safety and high production cost in an insert manual mould are overcome, the work efficiency is increased, and the processing cost is lowered.

Owner:JIANGSU VOCATIONAL INST OF ARCHITECTURAL TECH

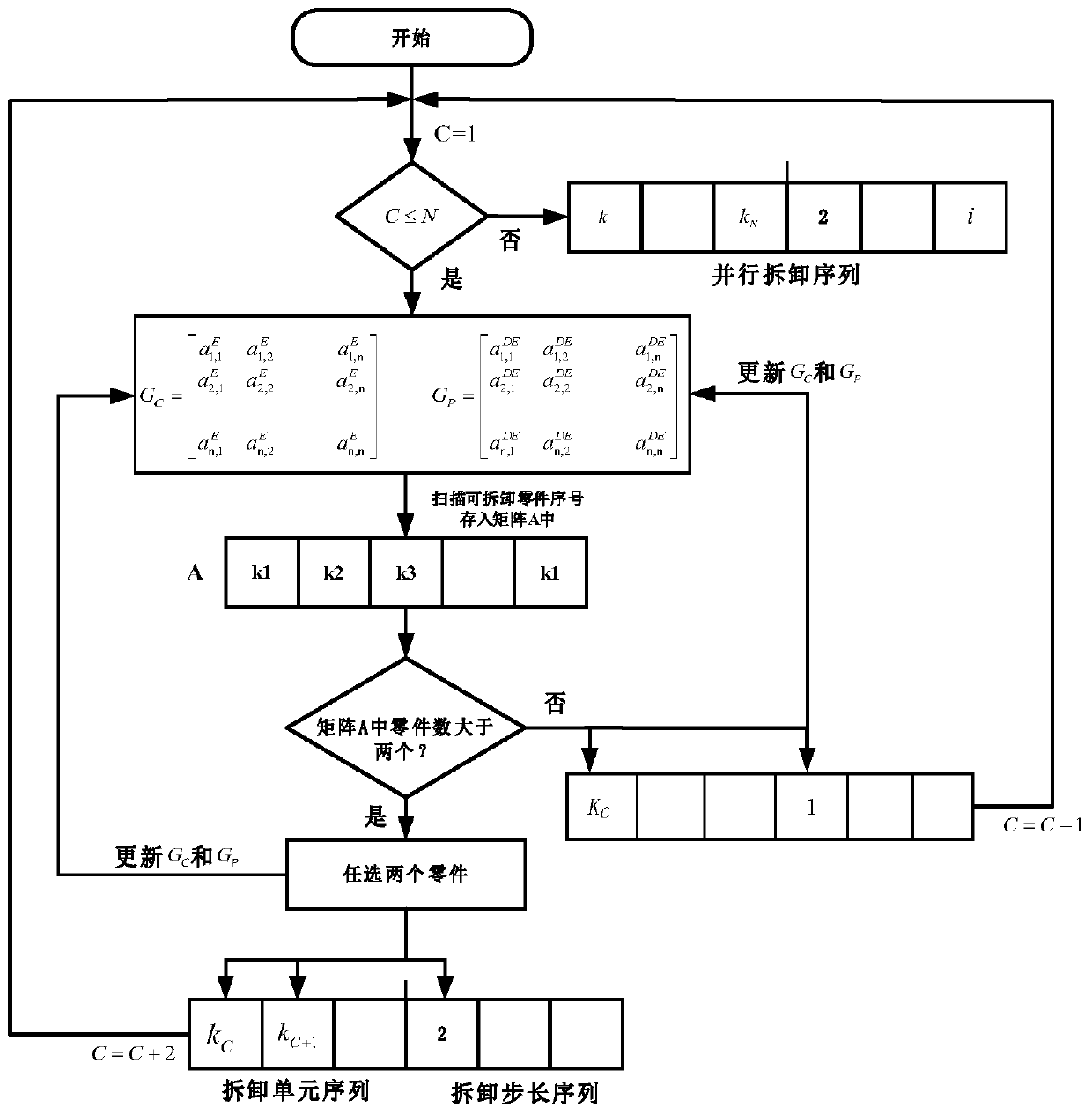

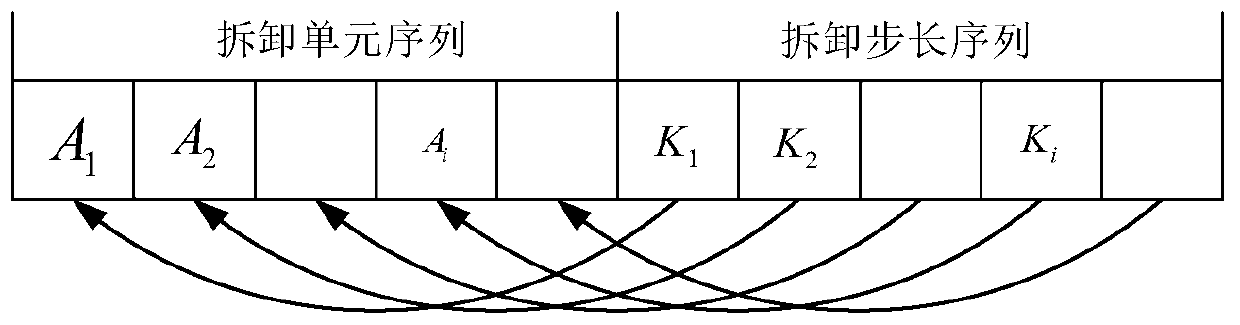

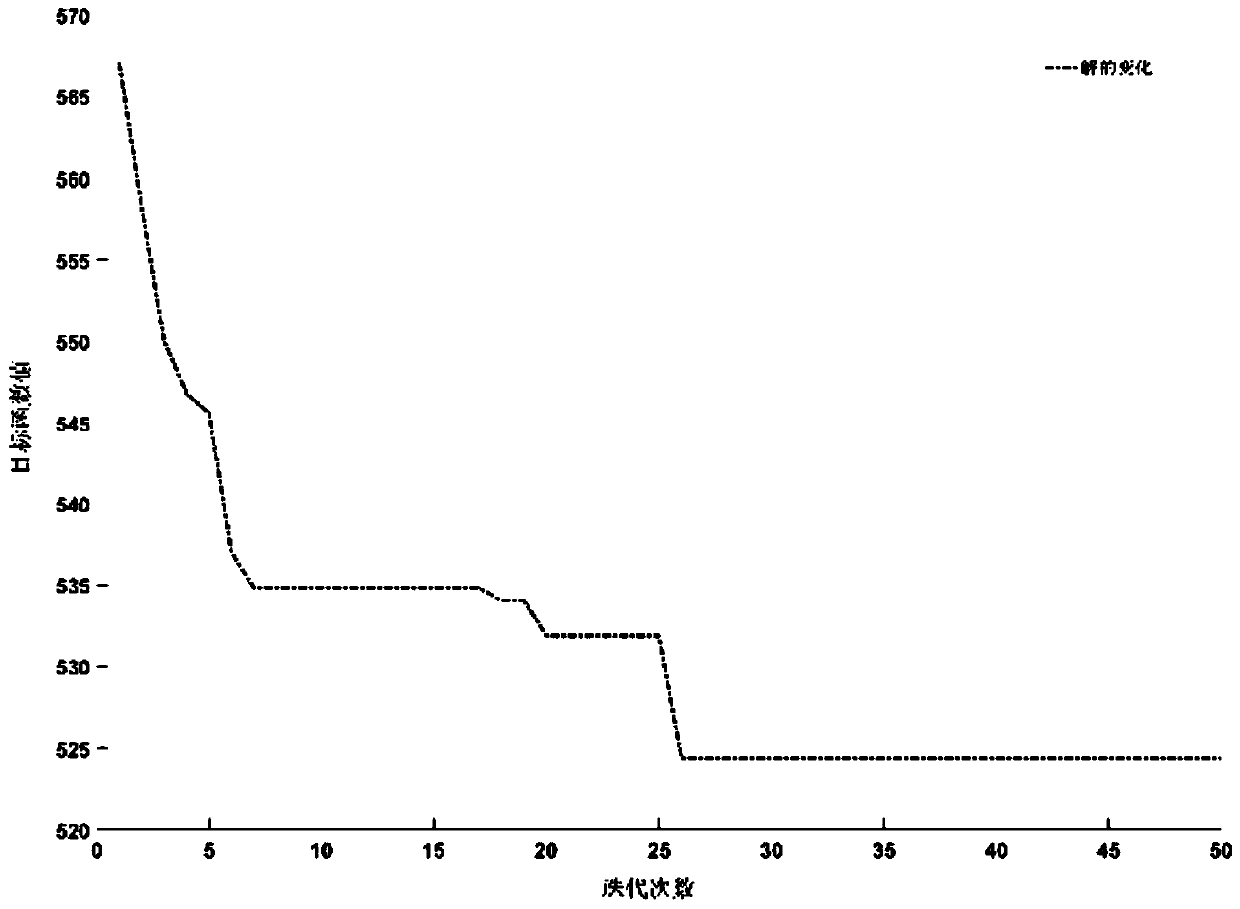

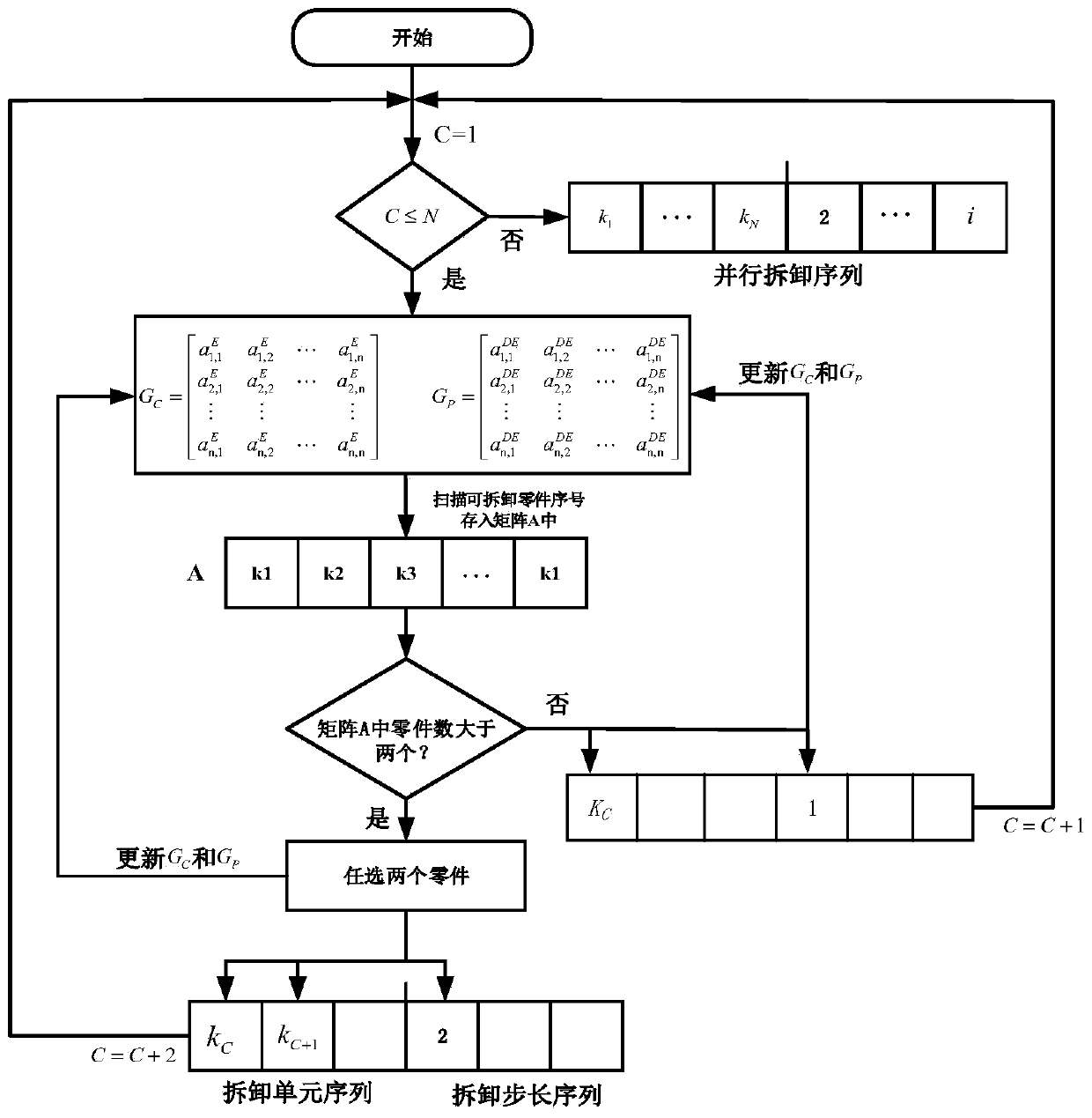

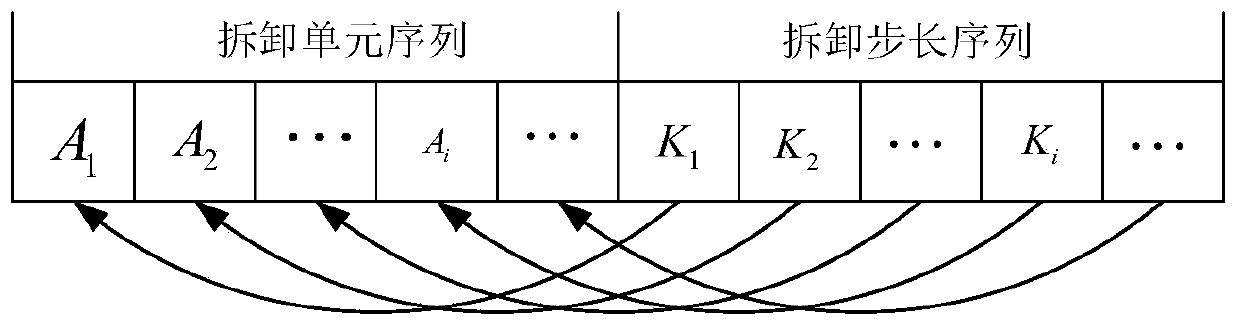

Low-carbon and high-efficiency parallel disassembly line balance optimization method

ActiveCN109814509AEmission reductionStrong convergence speedTotal factory controlProgramme total factory controlGenetic algorithmLine balancing

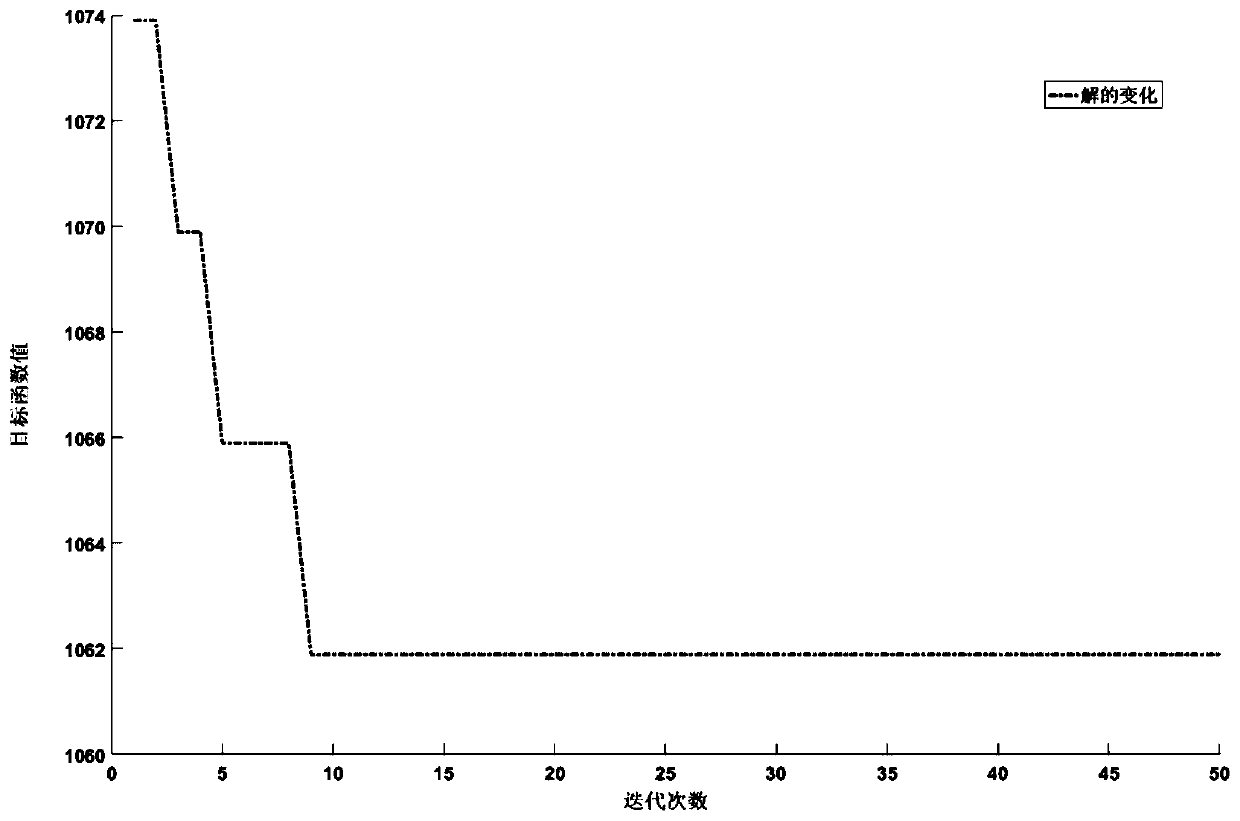

The invention discloses a low-carbon and high-efficiency parallel disassembly line balance optimization method. The method comprises the steps that a parallel disassembly model is established, and anoptimization model of parallel disassembly line balance is established. The optimization goal is to reduce carbon emission and reduce disassembly time, and belongs to multi-objective optimization; onthis basis, the parallel disassembly model is established, then practical constraints of a disassembly balance problem are comprehensively considered, the high-efficiency and low-carbon optimization method of a disassembly sequence is established, when the optimization problem is solved, a weight method is used for converting a multi-target problem into a single-target problem, finally a genetic algorithm is used for solving the disassembly line balance problem, it can be seen from a convergence graph that the genetic algorithm has a high convergence speed, and the model has a certain optimization effect on the disassembly time.

Owner:HEFEI UNIV OF TECH

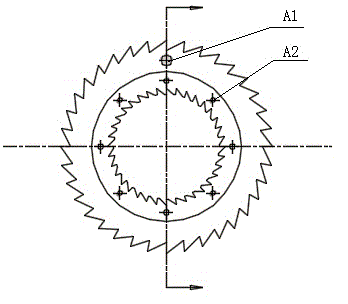

Shuttle peg, rotary shuttle, sewing machine, and shuttle line balance detection device and method

ActiveCN107044009AAvoid excessImprove detection reliabilityBobbin-winding devicesLoop takersBobbinAngular velocity

The invention provides a shuttle peg, a rotary shuttle having same, a sewing machine, and a shuttle line balance detection device and method; the shuttle peg comprises a wrapping post, flanges, a shuttle peg hole axially penetrating the wrapping post and the flanges, and a line winding duct formed between the wrapping post and the flanges; the outer periphery of the wrapping post is provided with a radially protruding isolation board; the isolation board is adjacent to one of the two flanges, and splits the line winding duct into a start winding portion and a main winding portion respectively arranged on two sides of the isolation board; the width of the start winding portion is smaller than that of the main winding portion in the axial direction of the shuttle peg; the shuttle line balance detection device comprises the rotary shuttle having said shuttle peg, a shuttle peg detection unit used for detecting the shuttle peg angular velocity [omega] or the rotation turns M, and a sewing machine electric control module; the shuttle peg detection unit output end is connected with the electric control module. The method and device can improve the sewing machine shuttle line balance detection reliability and sensitivity, and can prevent too many shuttle lines from being left.

Owner:JACK SEWING MASCH CO LTD

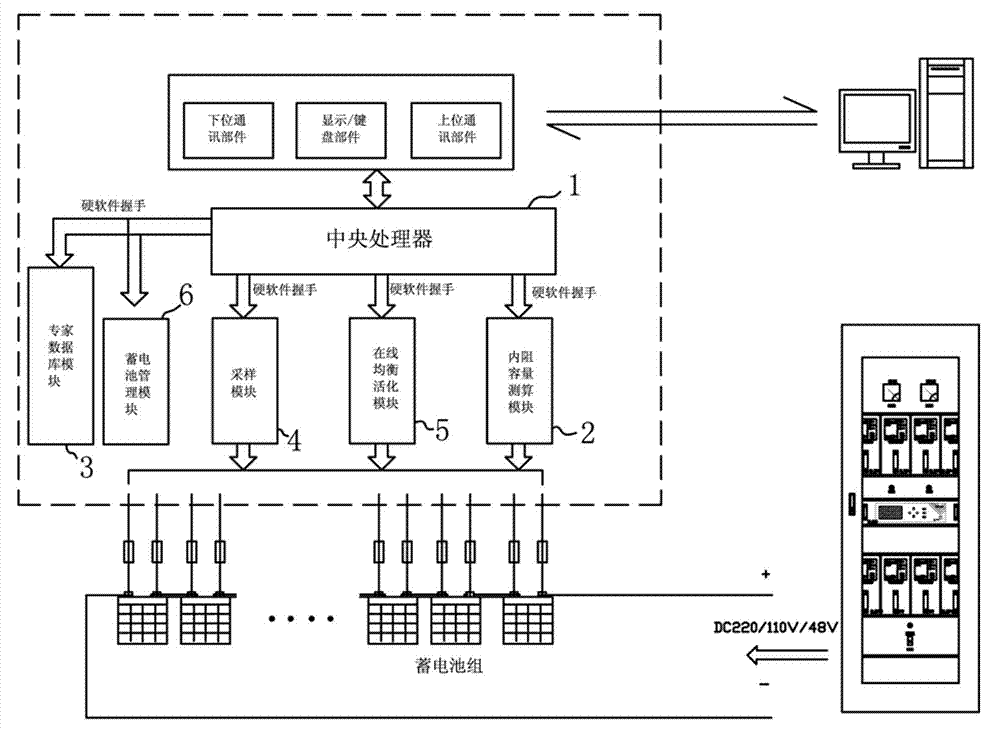

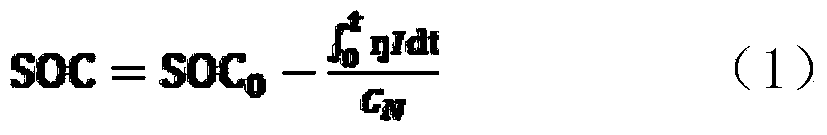

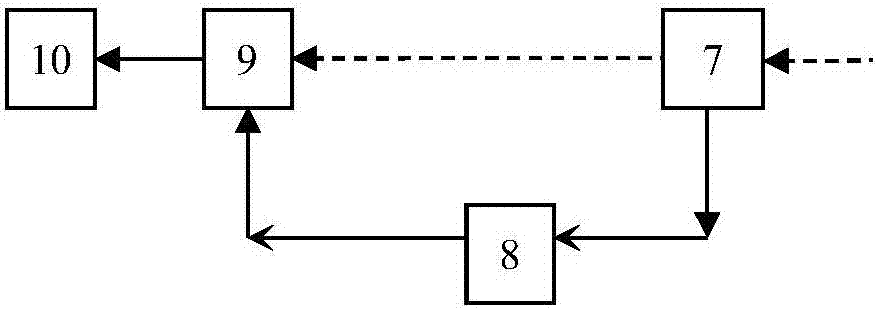

Storage battery set on-line balancing and activating device based on handshaking technology communication

ActiveCN103208657ANo confusionReduce instabilitySecondary cells servicing/maintenanceTechnology communicationSynchronous control

The invention discloses a storage battery on-line balanced and activating device based on handshaking technology communication. The storage battery on-line balanced and activating device comprises a central processing unit, an internal resistance measuring and calculating module, an expert database module, a sampling module, an on-line balanced and activating module and a storage battery management module. The central processing unit sends communication orders through software handshake and controls simultaneously through hardware handshake; the modules send responses to the central processing unit after receiving orders, and perform relative functional process; and the modules send the hardware handshake to the central processing unit after functional process is finished, and the central processing unit decides whether to communicate with the modules or not according to data busy degrees and utilizes the software handshake to send relative responsive orders to the modules. With the storage battery on-line balanced and activating device, each function can be integrated effectively and can be combined and point-to-point managed simultaneously, unstable operating conditions of intelligent storage battery set maintenance devices are eliminated, and overall back-up source system break down caused by instability in maintaining of storage batteries by the intelligent storage battery maintenance devices can be avoided.

Owner:王国平

A parallel disassembly model construction method based on a genetic algorithm

InactiveCN109886458AStrong convergence speedReasonable layoutGenetic modelsForecastingIdle timeAlgorithm

The invention discloses a parallel disassembly model construction method based on a genetic algorithm. The parallel disassembly model construction method comprises the following steps of constructinga parallel disassembly model; establishing a total dismounting time length model, namely an optimization target; and performing procedure optimization based on a genetic algorithm. On the basis of thetraditional disassembly line balance problem, the disassembly time in the disassembly process is taken as an optimization target, a parallel disassembly model is established on the basis, finally, the disassembly line balance problem is solved by using a genetic algorithm, the genetic algorithm has a very high convergence speed, and the model has a certain optimization effect on the disassembly time. According to the method, the high efficiency is taken as an optimization function of a main target, the disassembly time in the disassembly process can be well reduced while the optimization target requirements of the minimum workstation number, the minimum idle time and the like are met, and the method has certain guiding significance in the aspects of reasonable layout of large-batch disassembly lines, improvement of the disassembly efficiency and the like.

Owner:HEFEI UNIV OF TECH

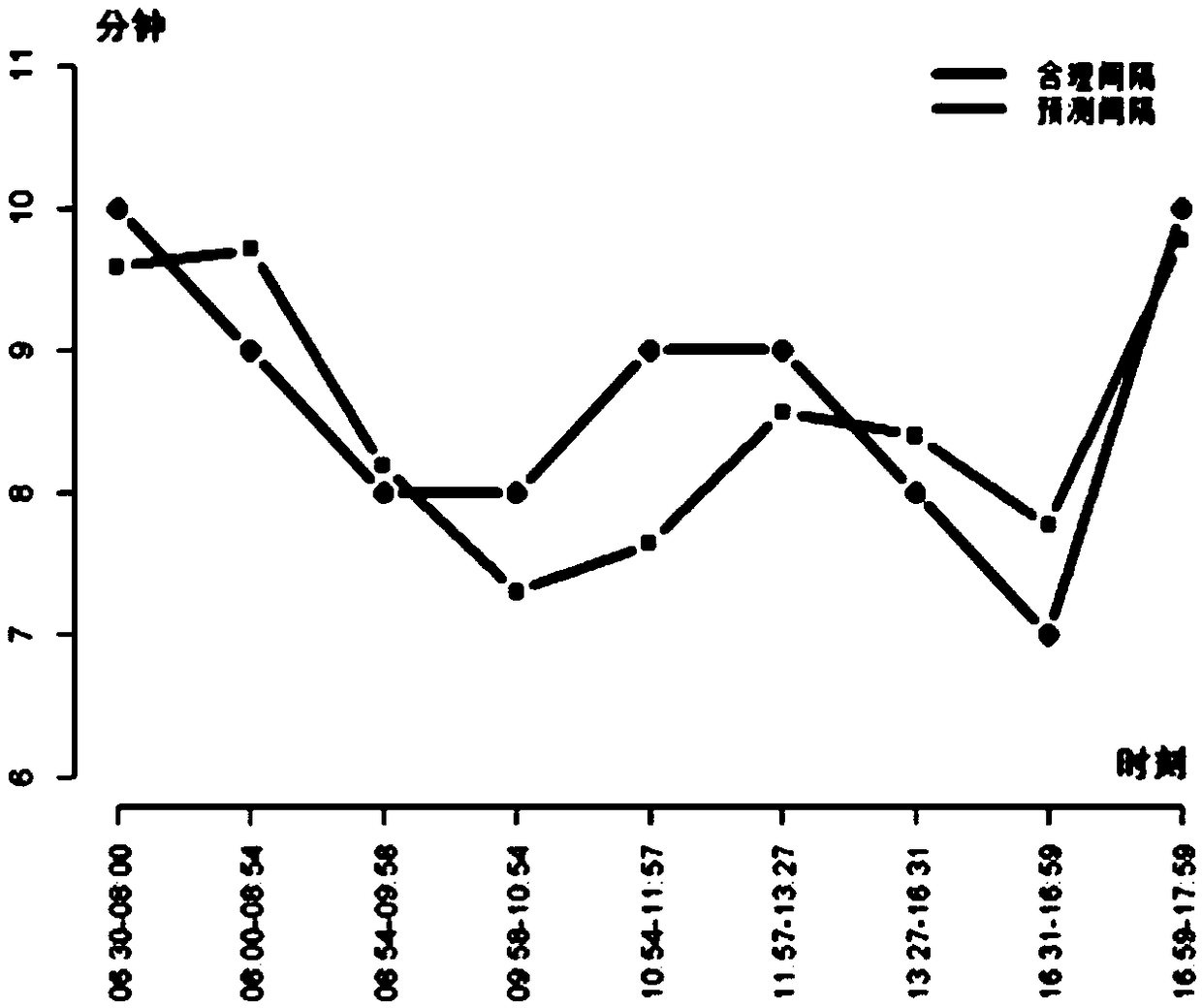

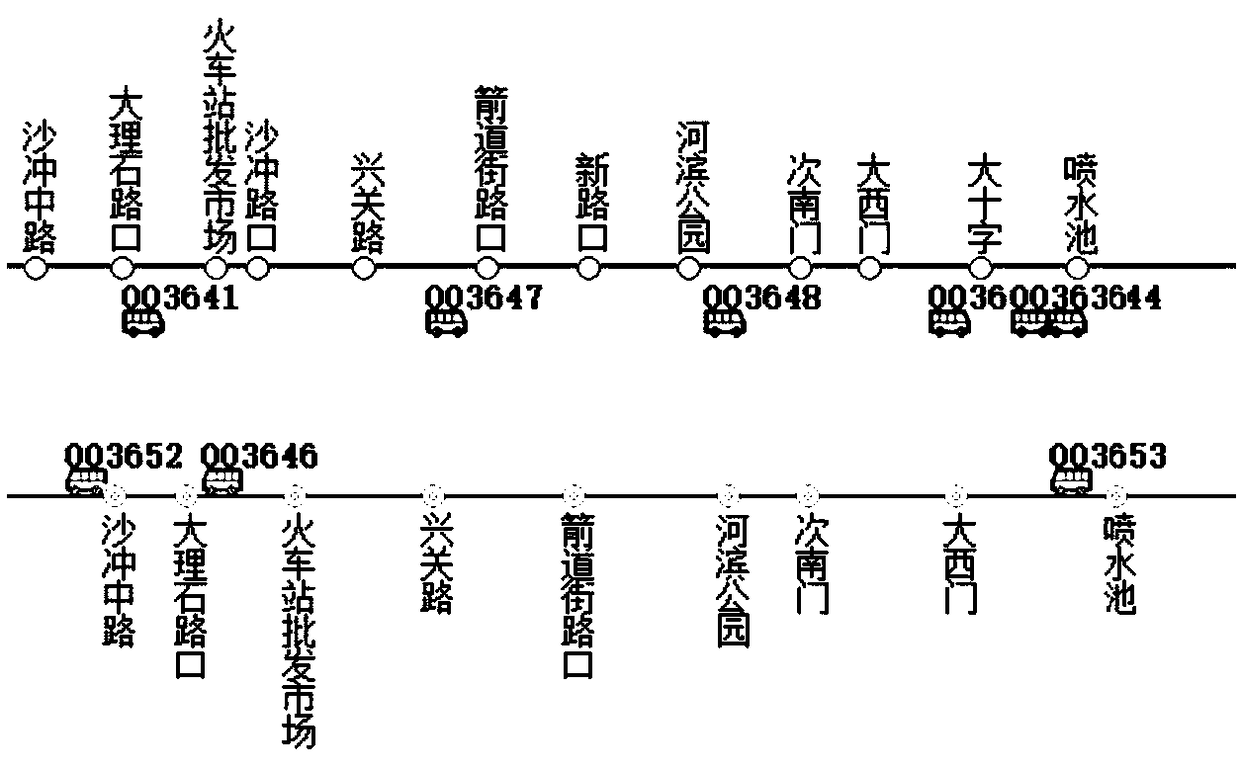

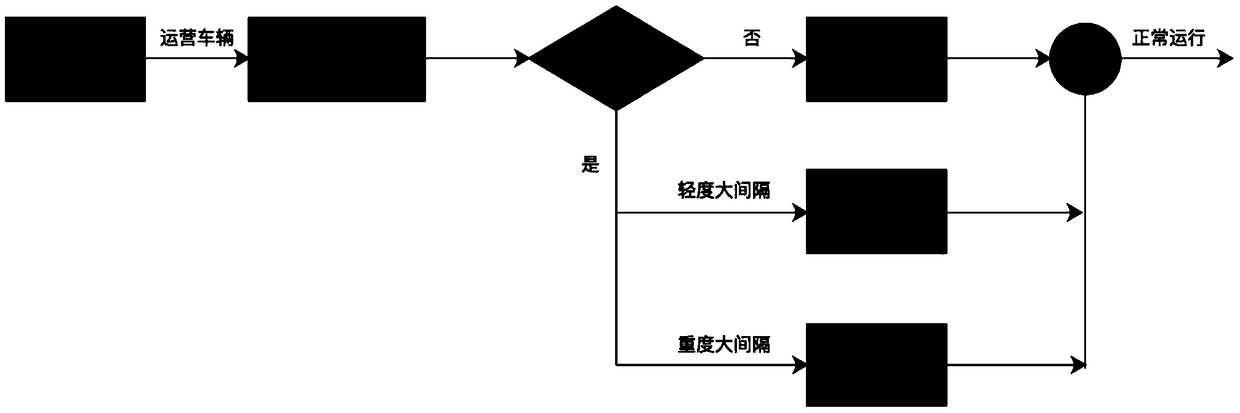

Real-time GPS-based bus short-time dynamic scheduling method

ActiveCN109300326AMake up for the lack of static schedulingReduce distractionsRoad vehicles traffic controlPrimary stationLine balancing

The invention discloses a real-time GPS-based bus short-time dynamic scheduling method. The method comprises the following steps that a maximum line distance maxdis between two adjacent buses on a current line is determined according to real-time GPS data, and in combination with the total length linedis of the current line, a line balance coefficient lambda is determined, wherein a main station and an auxiliary station are regarded as virtual buses to participate in determination of the maximum line distance between the two adjacent buses; the current line balance coefficient lambda is compared with two preset threshold values alpha 1 and alpha 2, and when lambda is smaller than or equal to alpha 1, no adjustment is made; when lambda is greater than alpha 1 and less than or equal to alpha2, a subsequent departure interval is readjusted; when lambda is greater than alpha 2, buses are added from the main station; and the value of the threshold value alpha 1 is a line balance coefficient when the bus of the current line runs according to an ideal state based on a scheduling plan, and it is satisfied that alpha 1 is greater than 0 and less than alpha 2, and alpha 2 is less than 1.

Owner:BEIJING INST OF AEROSPACE CONTROL DEVICES

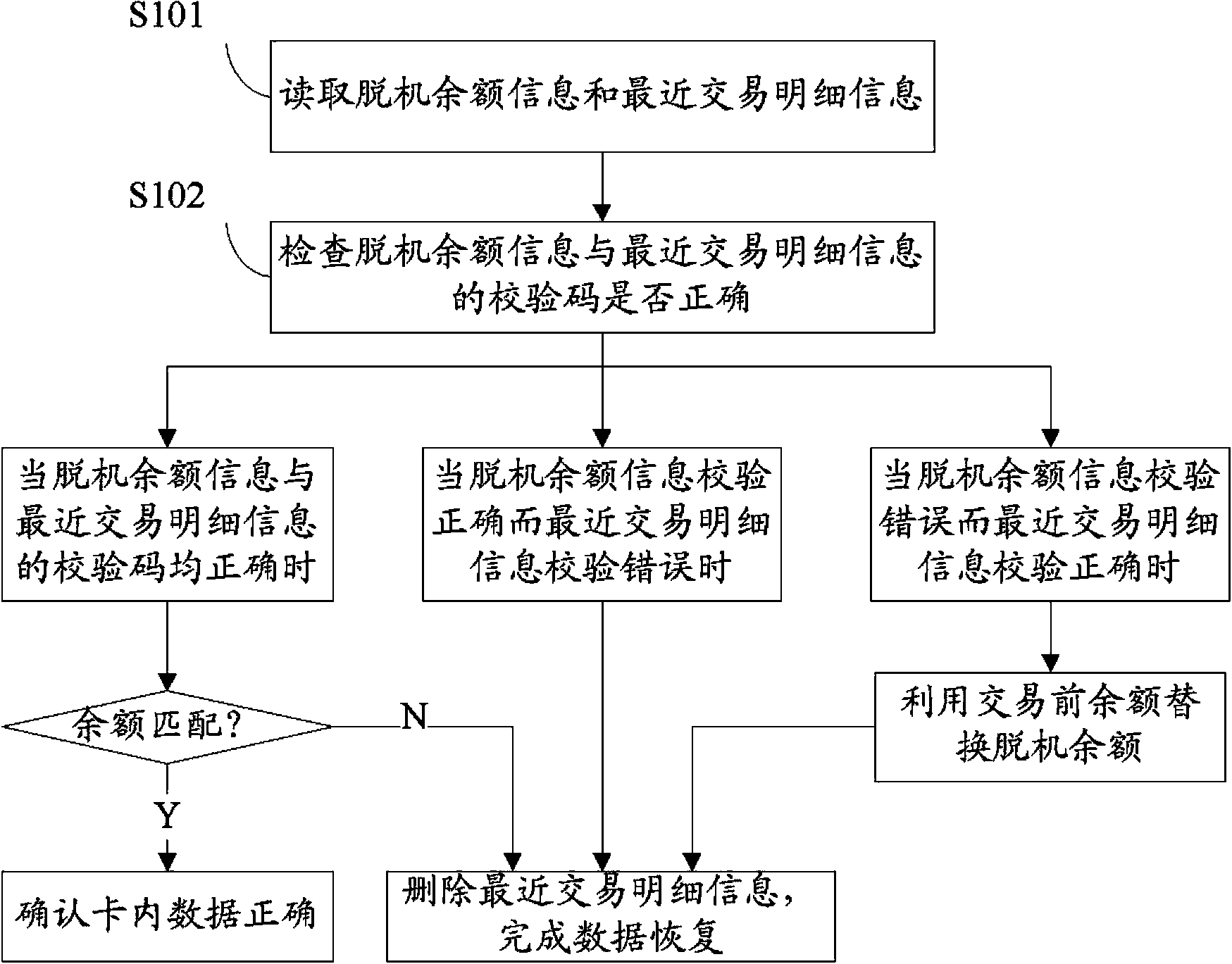

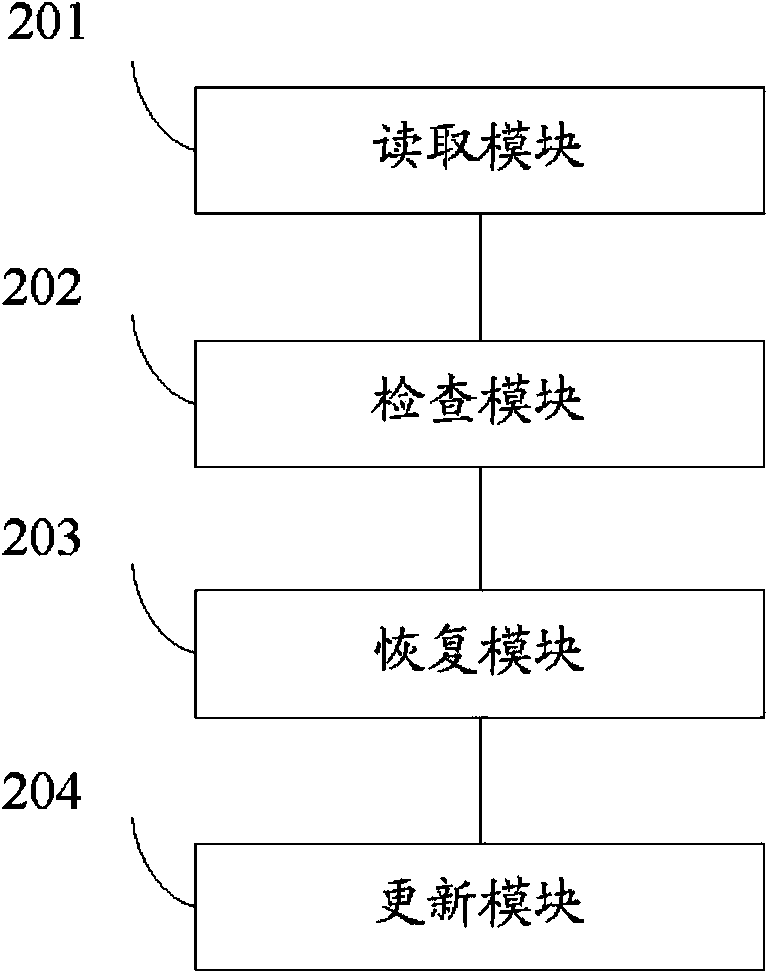

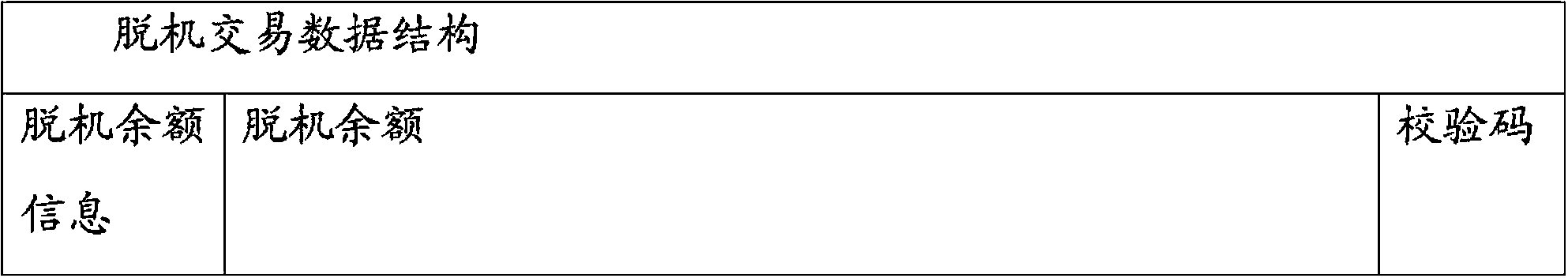

Off-line transaction data processing method and device of logic encryption card

ActiveCN103646467AAvoid breakingCoded identity card or credit card actuationTransaction dataLine balancing

Owner:LAKALA PAYMENT CO LTD

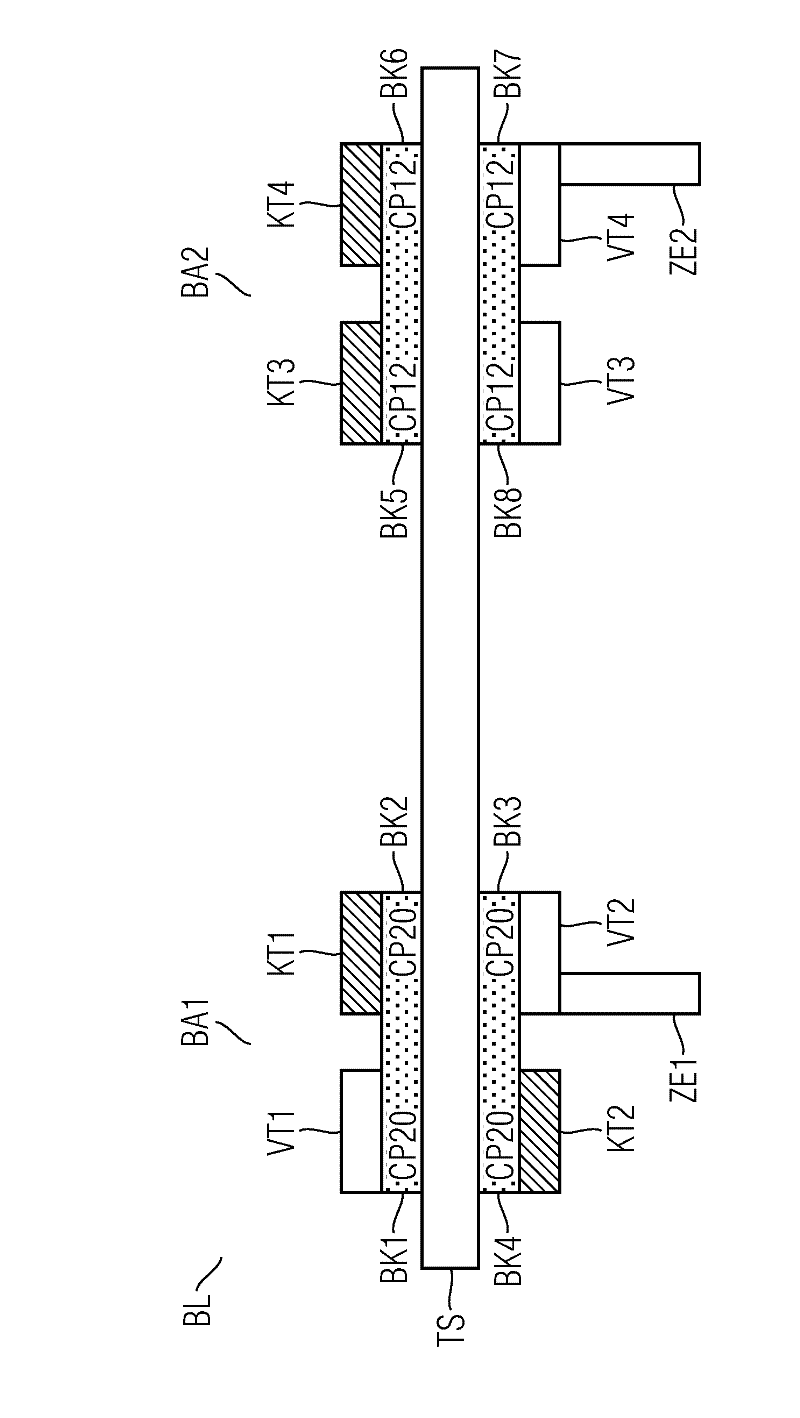

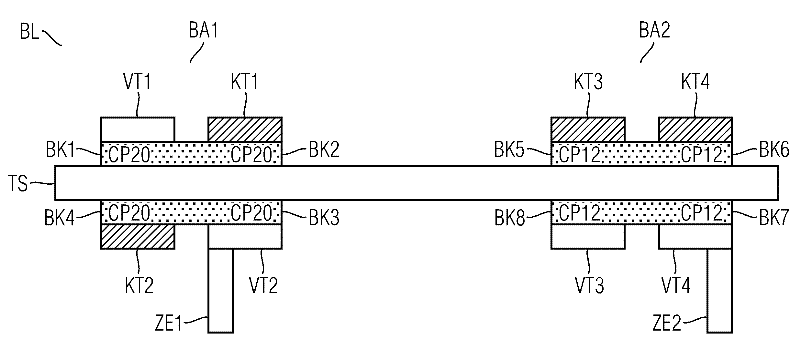

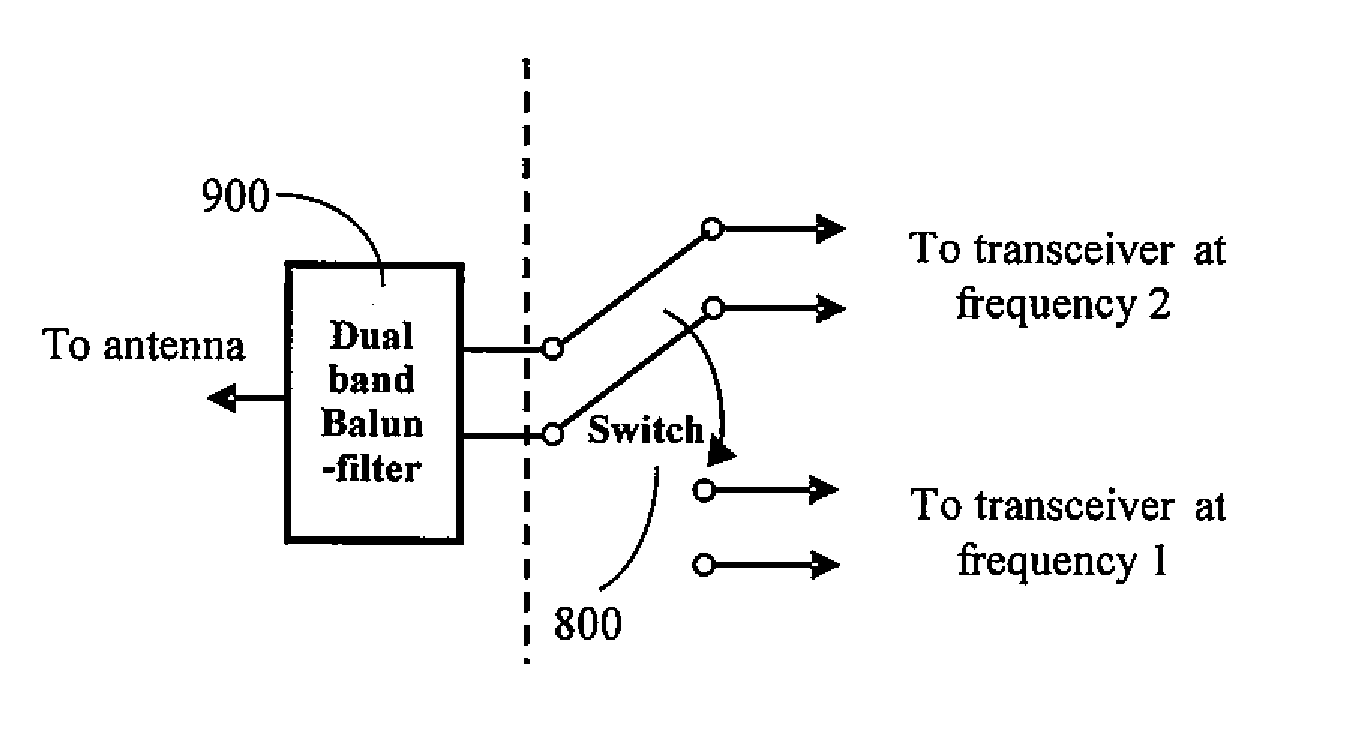

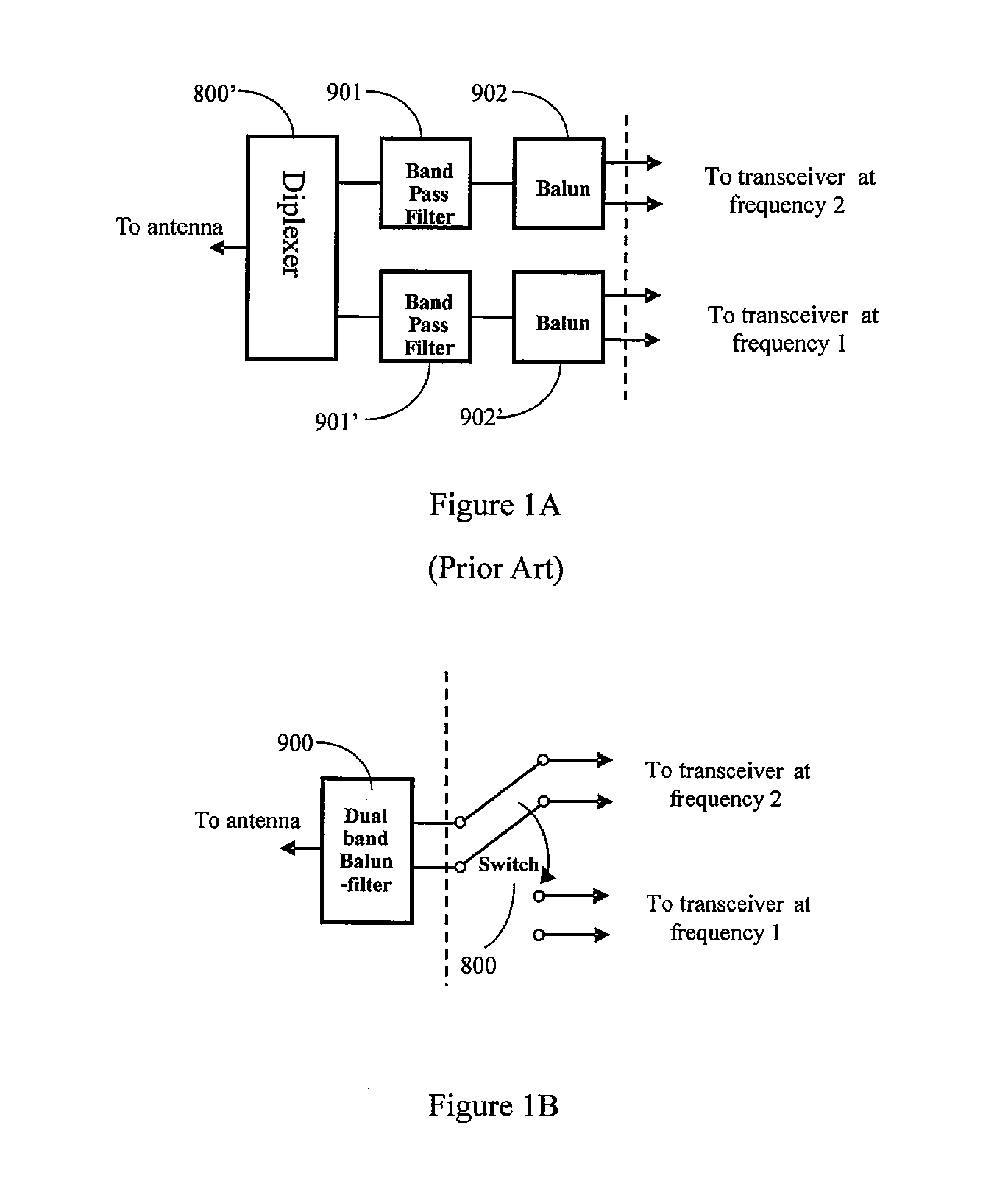

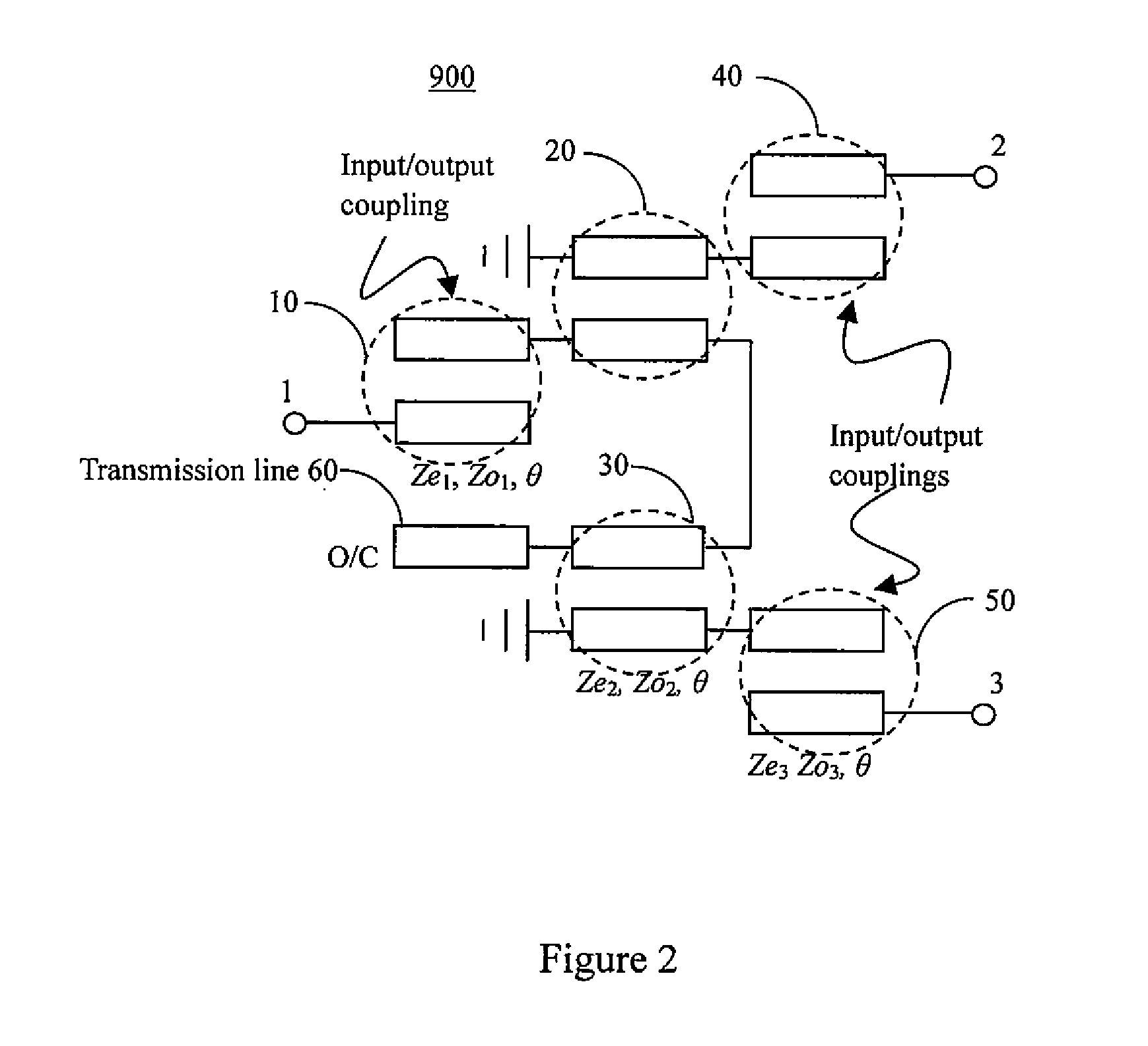

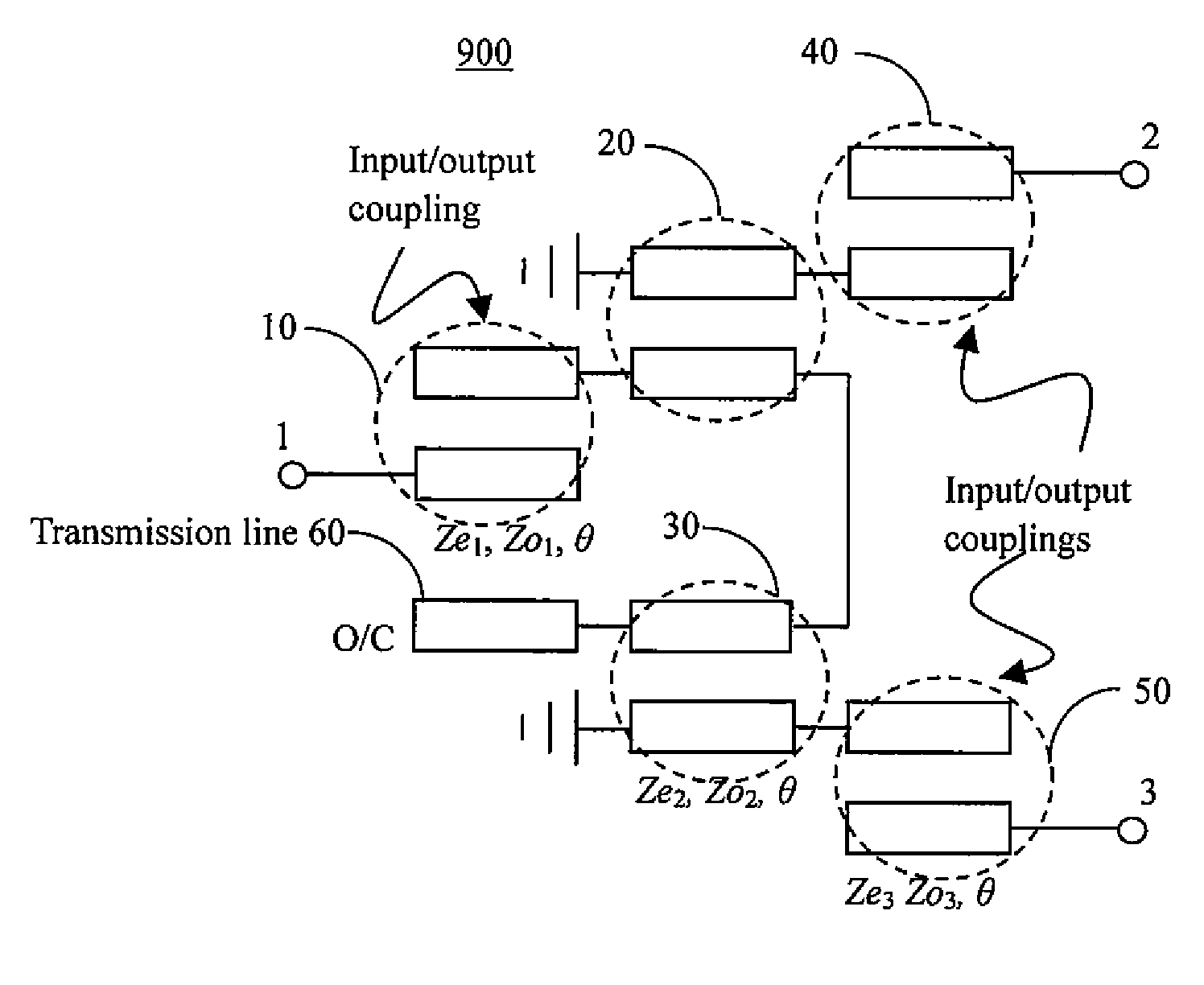

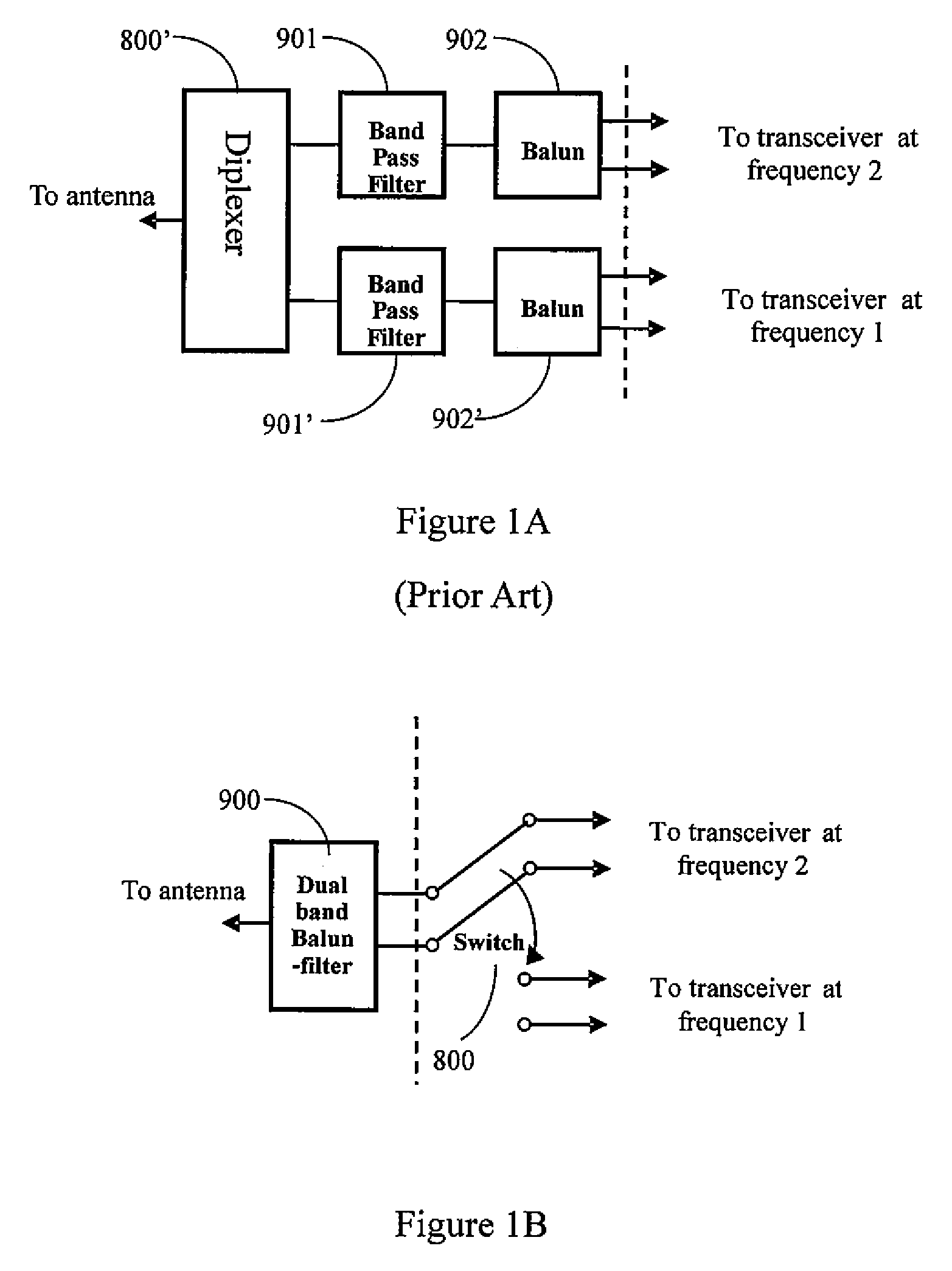

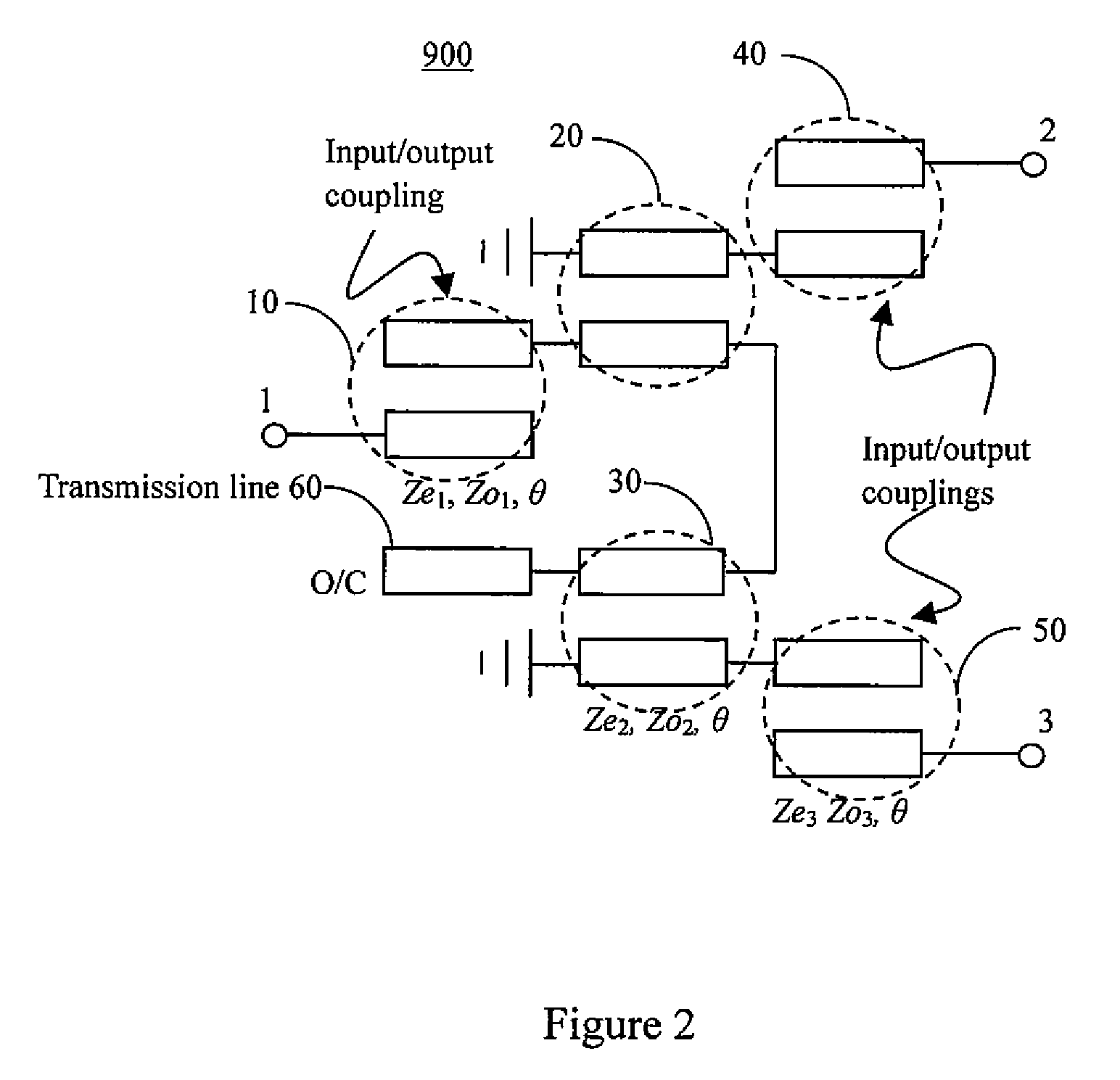

Dual band coupled-line balanced-to-unbalanced bandpass filter

InactiveUS20080231389A1Small sizeLow costMultiple-port networksOne-port networksBandpass filteringEngineering

A dual band balun filter, that includes a first coupled-line section pair provided with a first terminal; a second coupled-line section pair configured to be connected to the first coupled-line section pair, a third coupled-line section pair, and a fourth coupled-line section pair, respectively, and the fourth coupled-line section pair is provided with a second terminal; the third coupled-line section pair is provided with a transmission line and is connected to a fifth coupled-line section pair that is provided with a third terminal; and each of the first to fifth coupled-line section pairs is formed with partial coupled stepped impedance resonators (SIRs).

Owner:THE CHINESE UNIVERSITY OF HONG KONG

Reduction of noise in a metallic conductor signal pair using controlled line balancing and common mode impedance reduction

InactiveUS7728692B2Multiple-port networksCurrent interference reductionCarrying capacityElectrical conductor

In order to reduce noise on twisted metallic pair signal conductors, circuits are disclosed in which the signal balance between the wires of the pair is significantly improved, thereby reducing the line's susceptibility to external electromagnetic interference and equally reducing its ability to radiate signals into the surrounding medium. Further, the common mode impedance of the wire pair as seen at or close to the junction with the terminating equipment is controlled in order to reduce the ability of signals external to the wire pair to couple into the wire. This reduces noise in the line, as perceived by connected equipment, leading to an increase in the data carrying capacity of the line and the usable length of the line carrying such data.

Owner:ACCELL SYST

Dual band coupled-line balanced-to-unbalanced bandpass filter

InactiveUS7541888B2Small sizeLow costMultiple-port networksOne-port networksBandpass filteringLine balancing

Owner:THE CHINESE UNIVERSITY OF HONG KONG

Power battery pack monitoring and balancing device of small power-driven vehicle

InactiveCN104201735AExtend the life cycleEasy to replaceBatteries circuit arrangementsElectric powerPower batteryLiquid-crystal display

The invention discloses a power battery pack monitoring and balancing device of a small power-driven vehicle. The power battery pack monitoring and balancing device comprises intelligent battery modules and a control system, each intelligent battery module comprises a battery string and a battery monitoring and balancing system, and the control system comprises a micro-programmed control unit (MCU) module, a liquid crystal display (LCD) unit, a storage unit and a protecting alarm unit. The intelligent battery modules can be sequentially overlaid on the control system so as to increase or reduce capacity of a power system, damaged intelligent battery modules can be replaced, the control system figures out battery state information for displaying and storage according to information sent by the intelligent battery modules, and protecting alarm actions can be produced in necessity. According to non-balance degrees of the intelligent battery modules, one intelligent battery module is switched in or out so that on-line or off-line balancing modes of the intelligent battery modules can be determined.

Owner:SOUTHWEST JIAOTONG UNIV

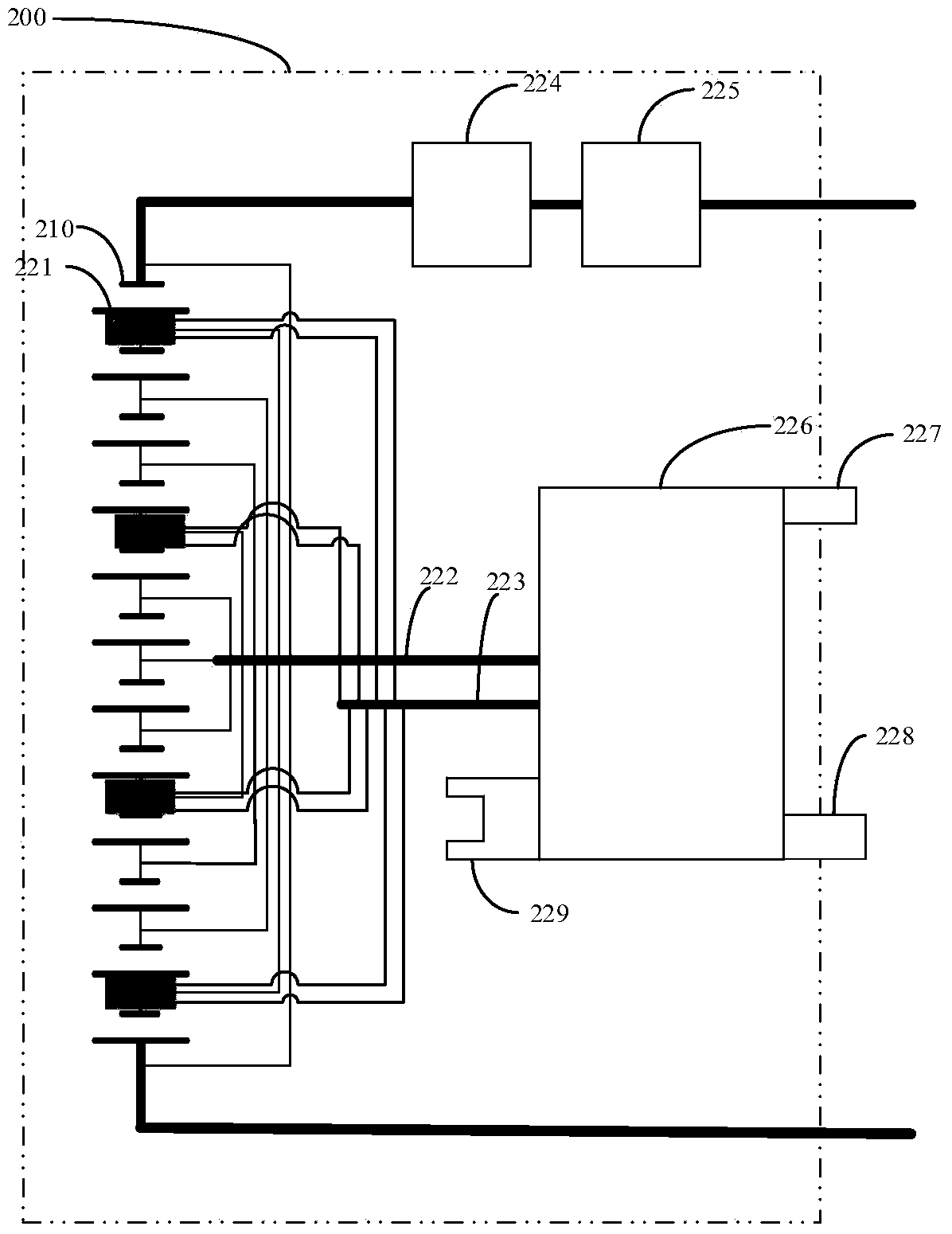

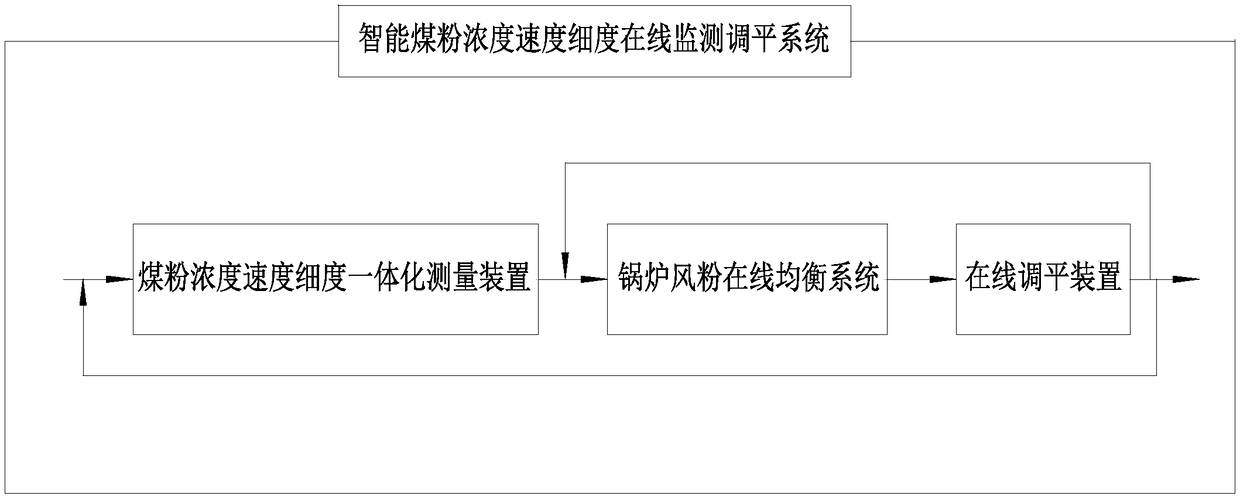

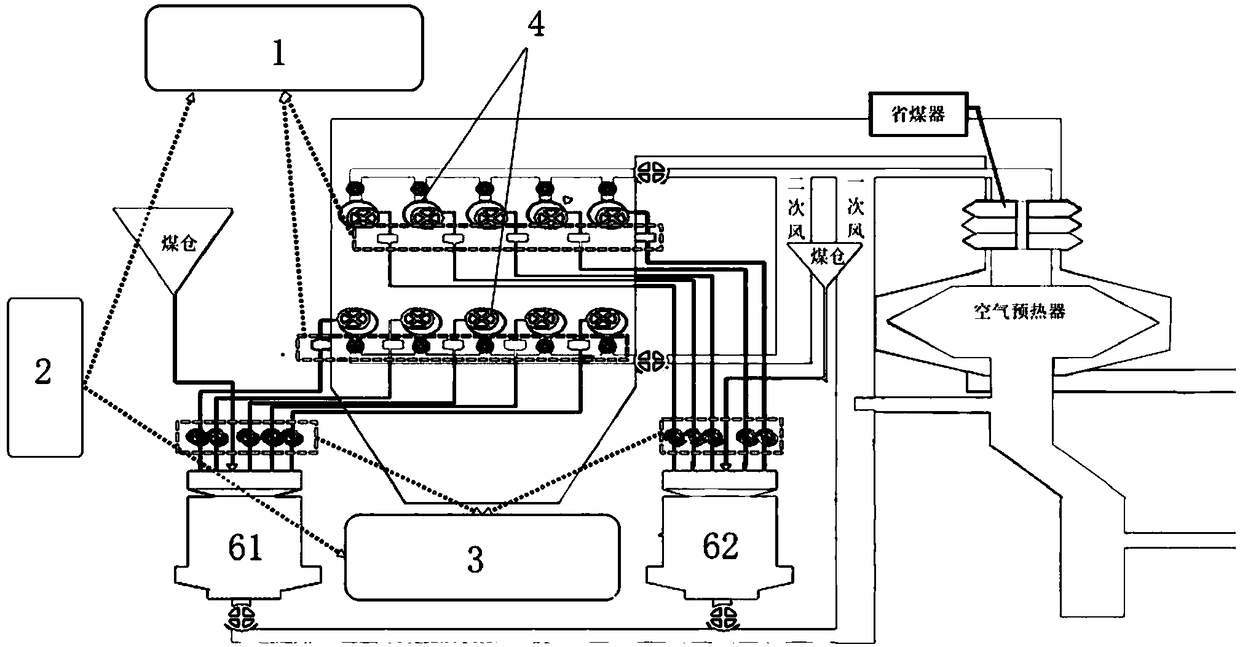

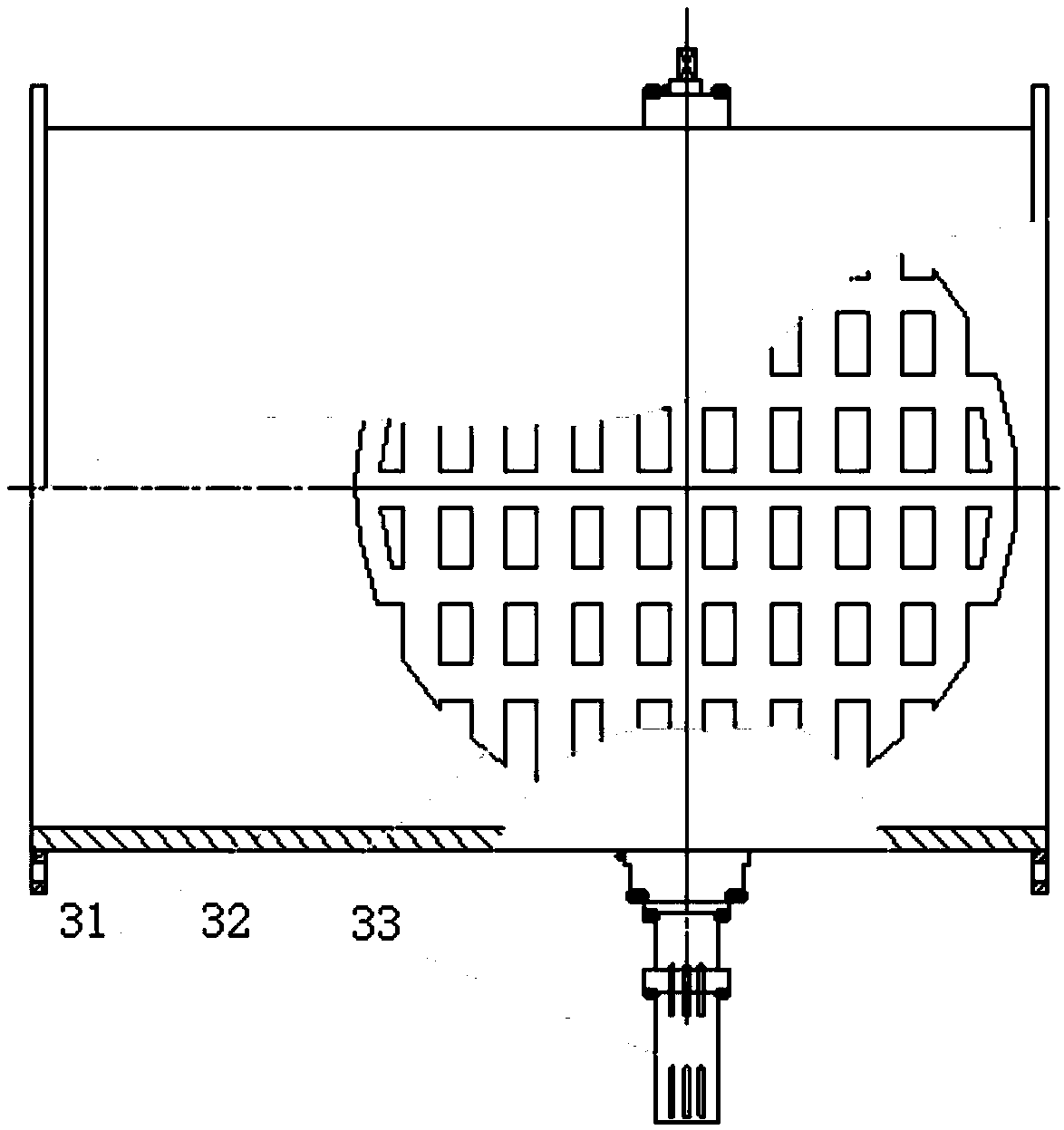

Intelligent pulverized coal concentration, speed and fineness on-line monitoring leveling system and method thereof

InactiveCN108826352ADensity automatic adjustmentConcentration speed automatic adjustmentFuel supply regulationMeasurement deviceClosed loop

The invention discloses an intelligent pulverized coal concentration, speed and fineness on-line monitoring leveling system. The system comprises a pulverized coal concentration, speed and fineness integrated measuring device and an on-line leveling device which are installed in a primary air pipe between a coal mill outlet and a boiler inlet, and the pulverized coal concentration, speed and fineness integrated measuring device and the on-line leveling device are in communication connection with a boiler air and pulverized coal on-line balance system; and the pulverized coal concentration, speed and fineness integrated measuring device is used for collecting concentration, speed and fineness signals of pulverized coal in the primary air pipe, the boiler air and pulverized coal on-line balance system is used for controlling the on-line leveling device to adjust the flow and flowing speed of the pulverized coal inside a coal mill outlet pulverized coal pipe according to a pulverized coalsignal and a current opening signal of the on-line leveling device. According to the intelligent pulverized coal concentration, speed and fineness on-line monitoring leveling system, the integrated on-line measuring and leveling closed loop technology is adopted, primary air and pulverized coal thermal state leveling is achieved, and assistance is provided for achieving optimized burning, improving the boiler efficiency and reducing the net coal consumption rate.

Owner:南京新瓦特智控科技有限公司

Bladed coal diffuser and coal line balancing device

ActiveUS8991323B2Combustion using gaseous and pulverulent fuelCombustion using liquid and pulverulent fuelLine balancingStreamflow

Owner:THE BABCOCK & WILCOX CO

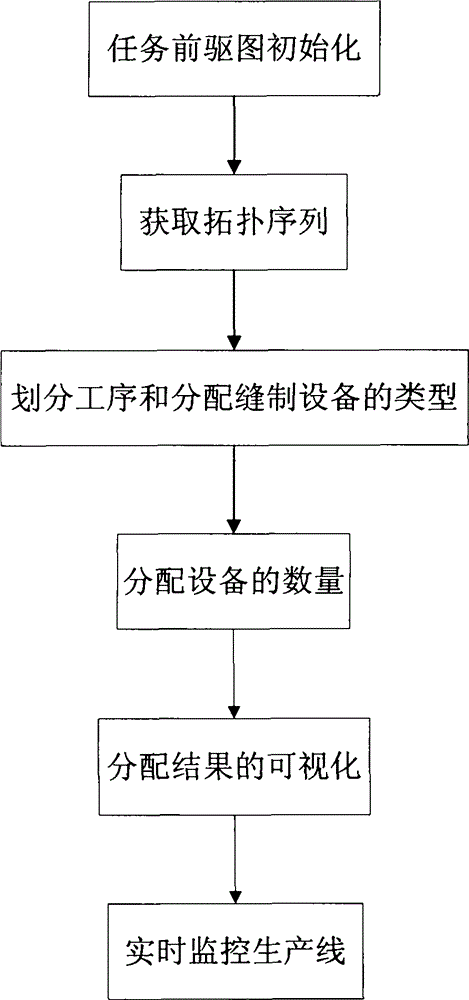

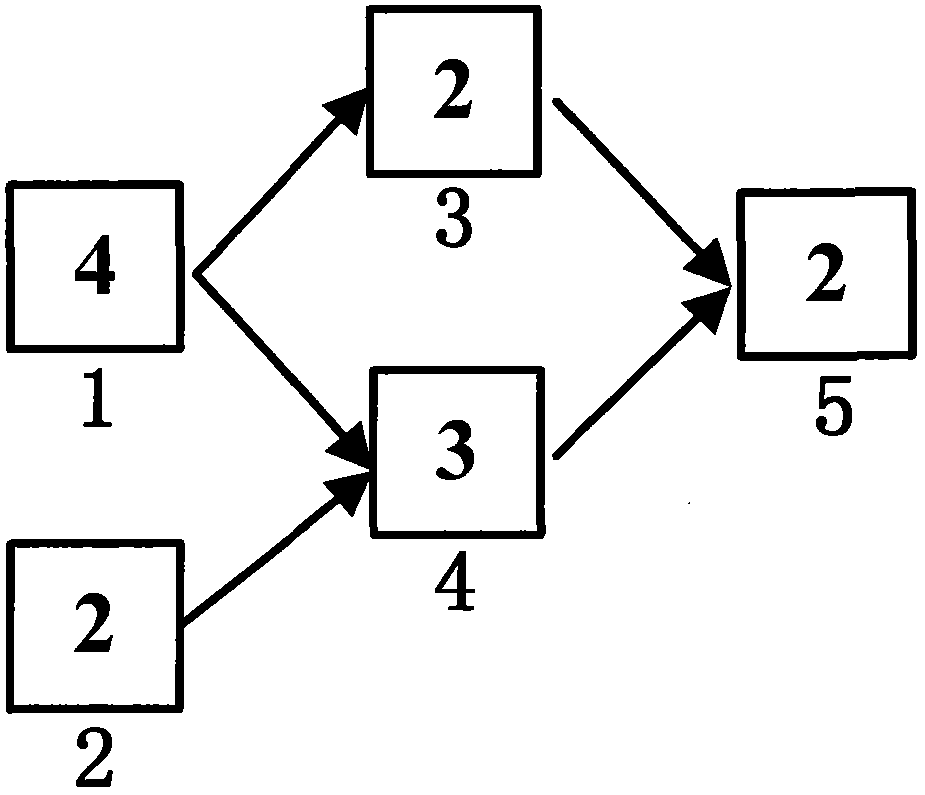

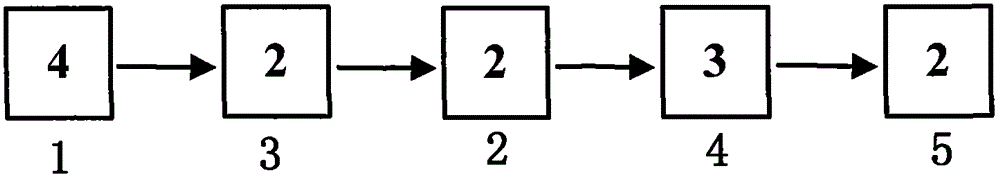

Methods of balancing production lines in the industrial sewing industry

InactiveCN102831492BAdjust in timeAvoid wastingResourcesSpecial data processing applicationsProduction lineDevice type

The invention discloses a method for balancing a production line in an industrial sewing industry. The method comprises the following concrete steps: (1) connecting task nodes in a production line according to a sequence dependency relation of tasks so as to generate a task precursor diagram; (2) according to the sequence of the task nodes in the task precursor diagram, carrying out topological sorting on the task nodes in the task precursor diagram so as to generate a topological sequence; (3) according to the topological sequence, sequentially allocating sewing devices matched with the types of the task nodes to the task nodes, and if adjacent task nodes use the sewing devices of the same type, merging the adjacent task nodes into a same process according to the original sequence; (4) according to the process of division and the type allocating results of the sewing devices and in combination with a production line balancing rate formula, allocating a reasonable number of sewing devices for each process; (5) according to the allocating result, virtualizing a logical production line corresponding to an actual production line in a visual interface by a user; and (6) checking the production line information of the logical production line, so that the user can balance the production line in time.

Owner:XIDIAN UNIV

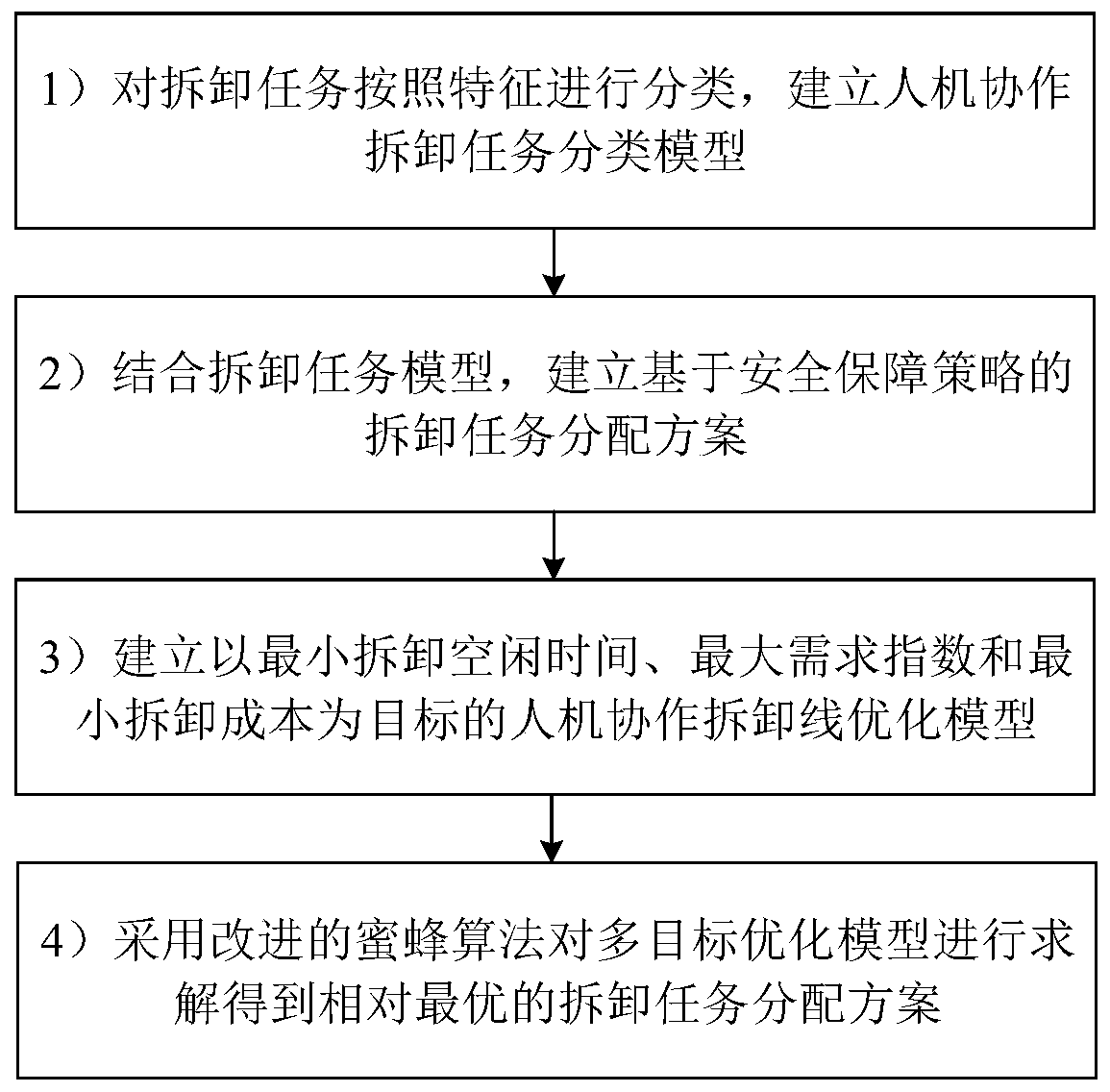

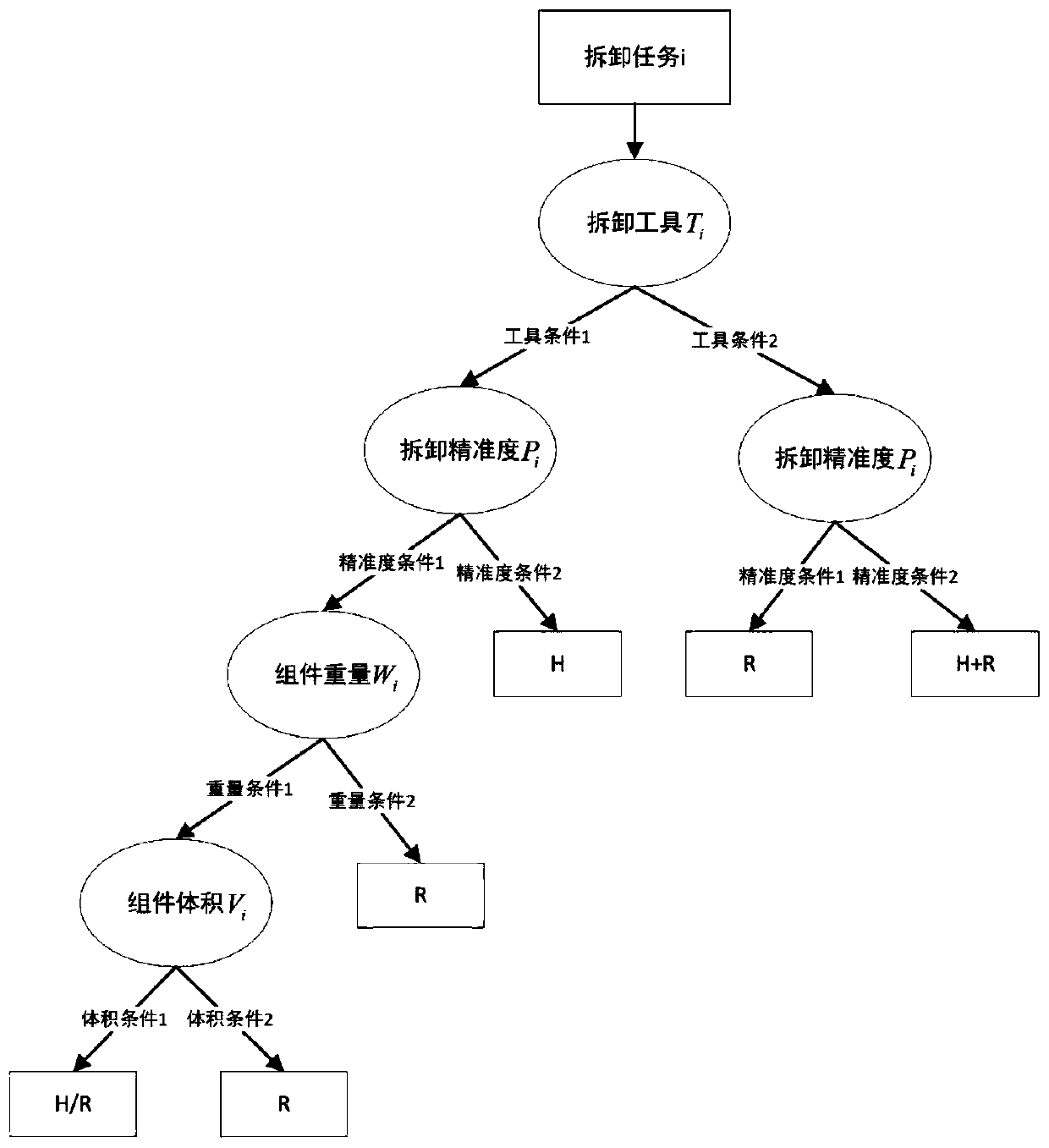

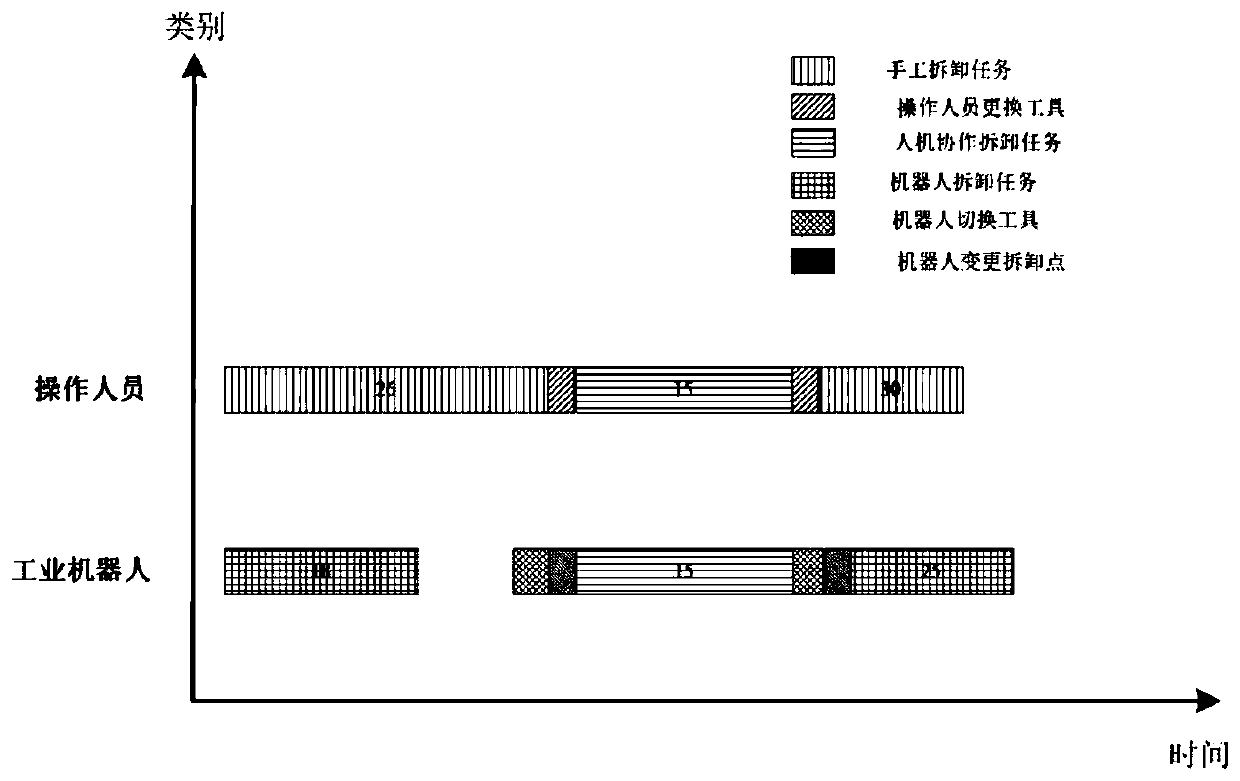

Man-machine cooperation disassembly line balance optimization method based on safety guarantee strategy

ActiveCN110900138AEnsure safetyDismantling costs are shortAssembly machinesMetal working apparatusMan machineMachine

The invention discloses a man-machine cooperation disassembly line balance optimization method based on a safety guarantee strategy. The method comprises the following steps of: 1) establishing a disassembly task classification model for disassembly tasks on a disassembly line according to attribute characteristics of the disassembly tasks, 2) establishing a disassembly task allocation scheme based on a safety guarantee strategy according to a classification result of the disassembly task classification model and a distance between a person and a robot disassembly operation point, 3) establishing a man-machine cooperation disassembly line optimization model taking the minimum disassembly idle time, the maximum demand index and the minimum disassembly cost as targets, and 4) solving a multi-objective optimization model to obtain a relatively optimal disassembly task allocation scheme and a relatively optimal disassembly task sequence. In combination with the disassembly task classification model, the safety of operators is ensured to the greatest extent, and the disassembly cost is minimized while the shortest disassembly time is ensured.

Owner:WUHAN UNIV OF TECH

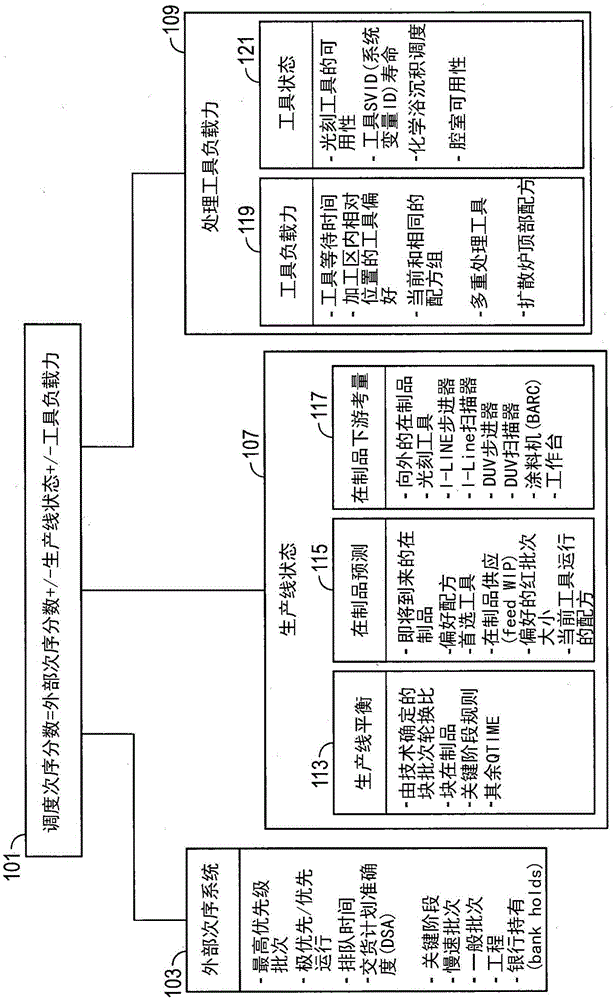

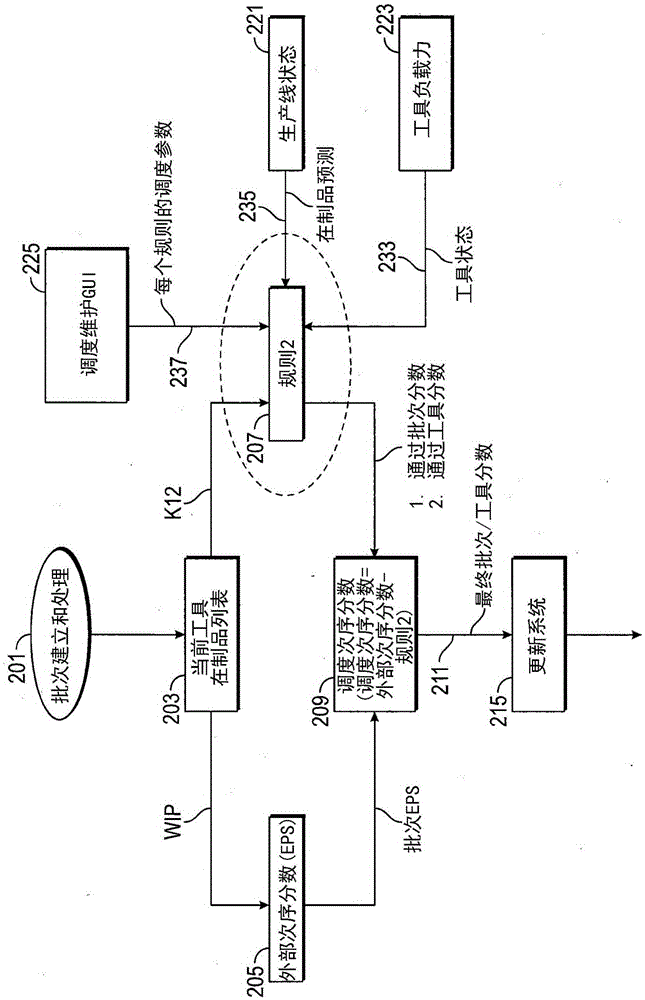

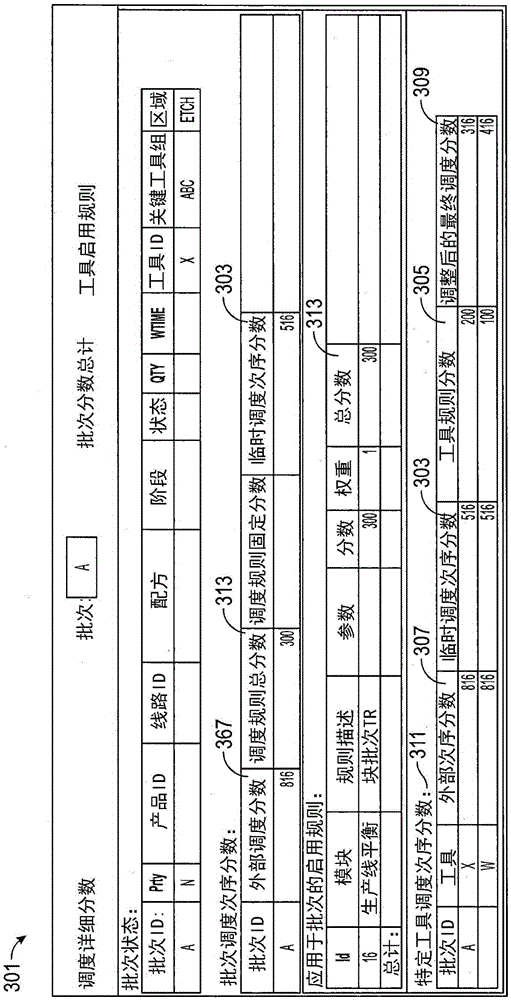

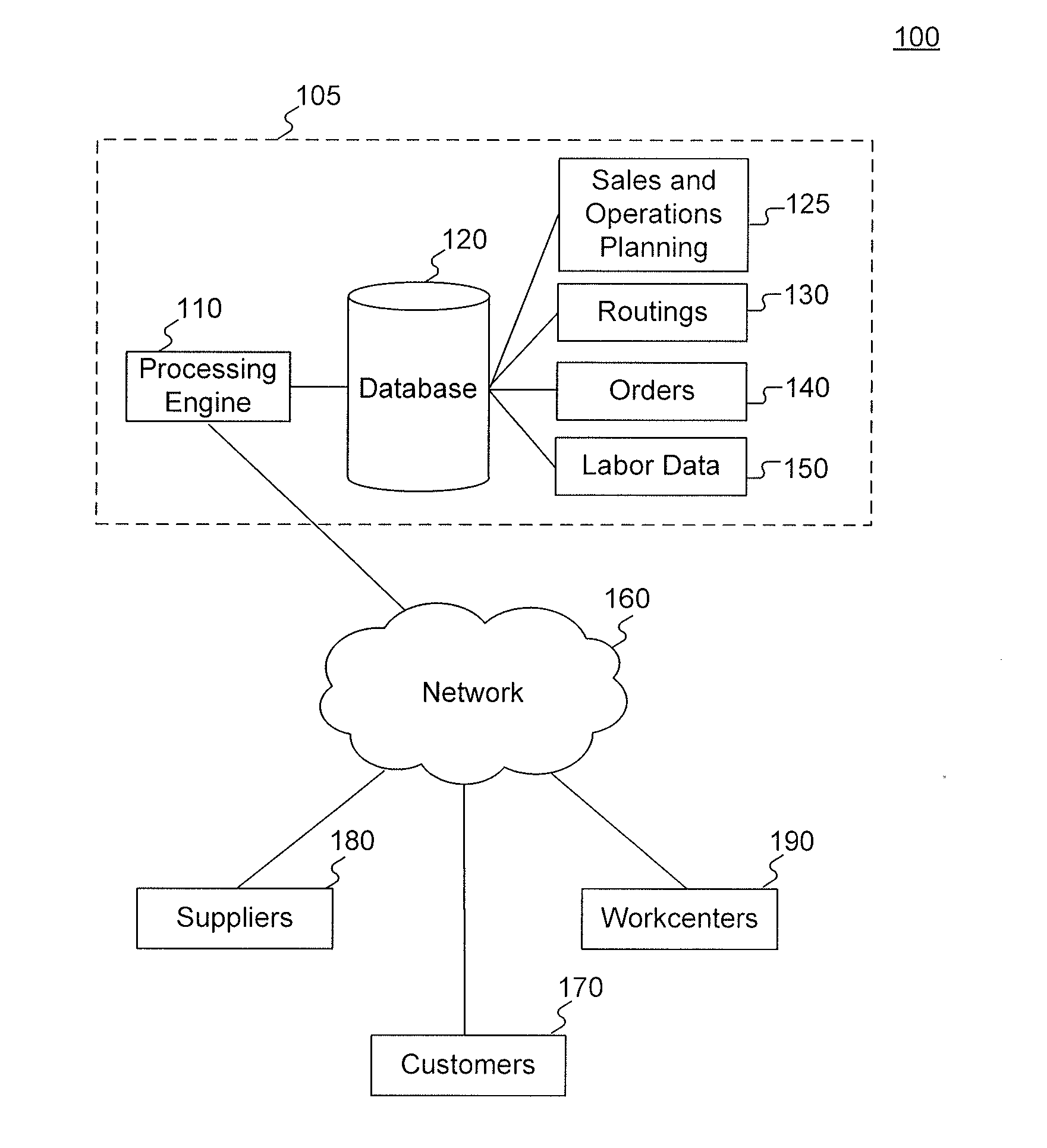

Method and priority system for inventory management in semiconductor manufacturing

InactiveCN105631624AProgramme controlSemiconductor/solid-state device manufacturingComputer moduleInventory management

An inventory tracking system and method for use in semiconductor manufacturing provide for generating a priority score that determines the order in which lots of substrates should be run. The priority score is generated using an algorithm that takes into account external lot priority considerations, inventory factors in the manufacturing facility, and processing tool capability factors. The processing tool capability factors include factors related to tool status and tool restrictions and the inventory factors include factors related to line balance, WIP (work-in-progress) forecasts and various downstream considerations. The priority score is generated dynamically and displayed at each processing operation for each lot that is queued for processing at the indicated operation. Various algorithms are used and different weights are assigned to many factors in calculating numerical values for several factors that combine to produce the priority score. The generated priority score can be tool-specific or module-specific.

Owner:WAFERTECH

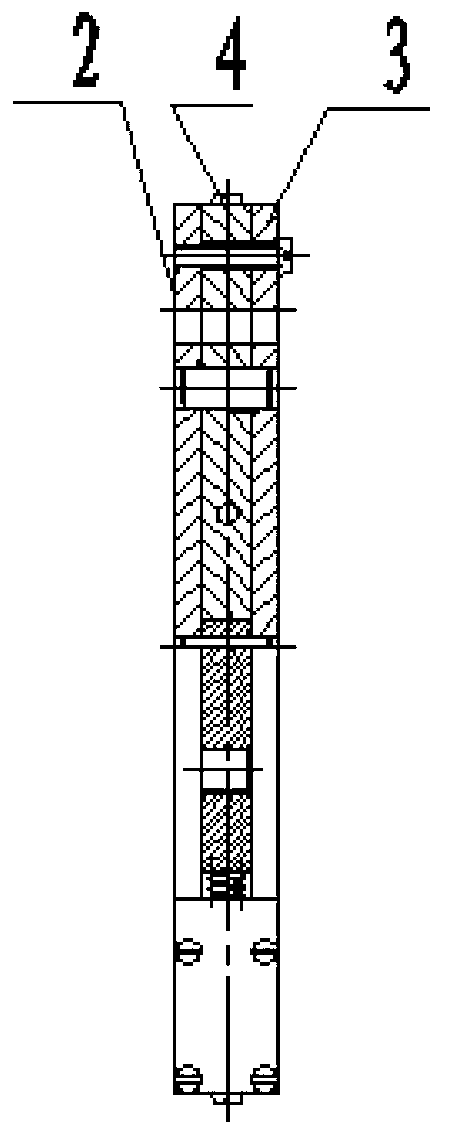

Active high-speed spindle on-line dynamic balancing head and control system thereof

ActiveCN105865715AReduce axial sizeEfficient use ofStatic/dynamic balance measurementDynamic balanceControl signal

The invention relates to an active high-speed spindle on-line dynamic balancing head and a control system thereof and belongs to the precise and ultra-precise machining and automation field. The on-line balancing head is of a purely mechanical structure; the core part of the on-line balancing head includes two balancing disc assemblies for correction and a driving mechanism thereof, wherein the two balancing disc assemblies for correction are in bilateral symmetry. The balancing head is simple and reliable in mechanical structure and small in axial size. The control system of the balancing head includes two parts, namely, a pneumatic system and an electrical system; the pneumatic system can realize electric-to-gas signal conversion, drive the position adjustment of the balancing disc assemblies, and obtain an air source conveniently and causes no pollution to the atmosphere; and the electrical system realizes signal acquisition and analysis and controls signal output. The active high-speed spindle on-line dynamic balancing head and the control system thereof of the invention are of great significance for high-speed precise and ultra-precise machining tools.

Owner:TIANJIN UNIV OF TECH & EDUCATION TEACHER DEV CENT OF CHINA VOCATIONAL TRAINING & GUIDANCE

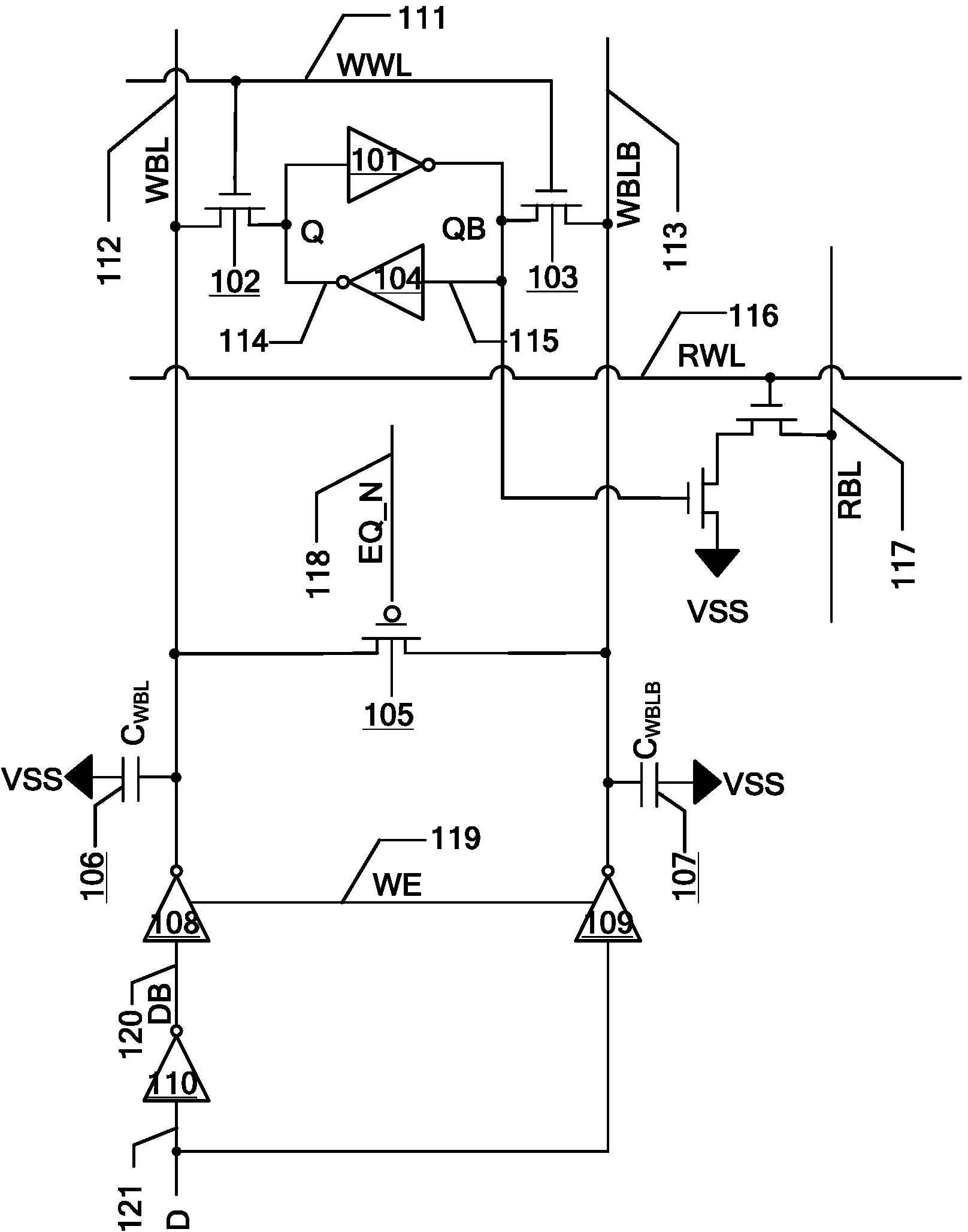

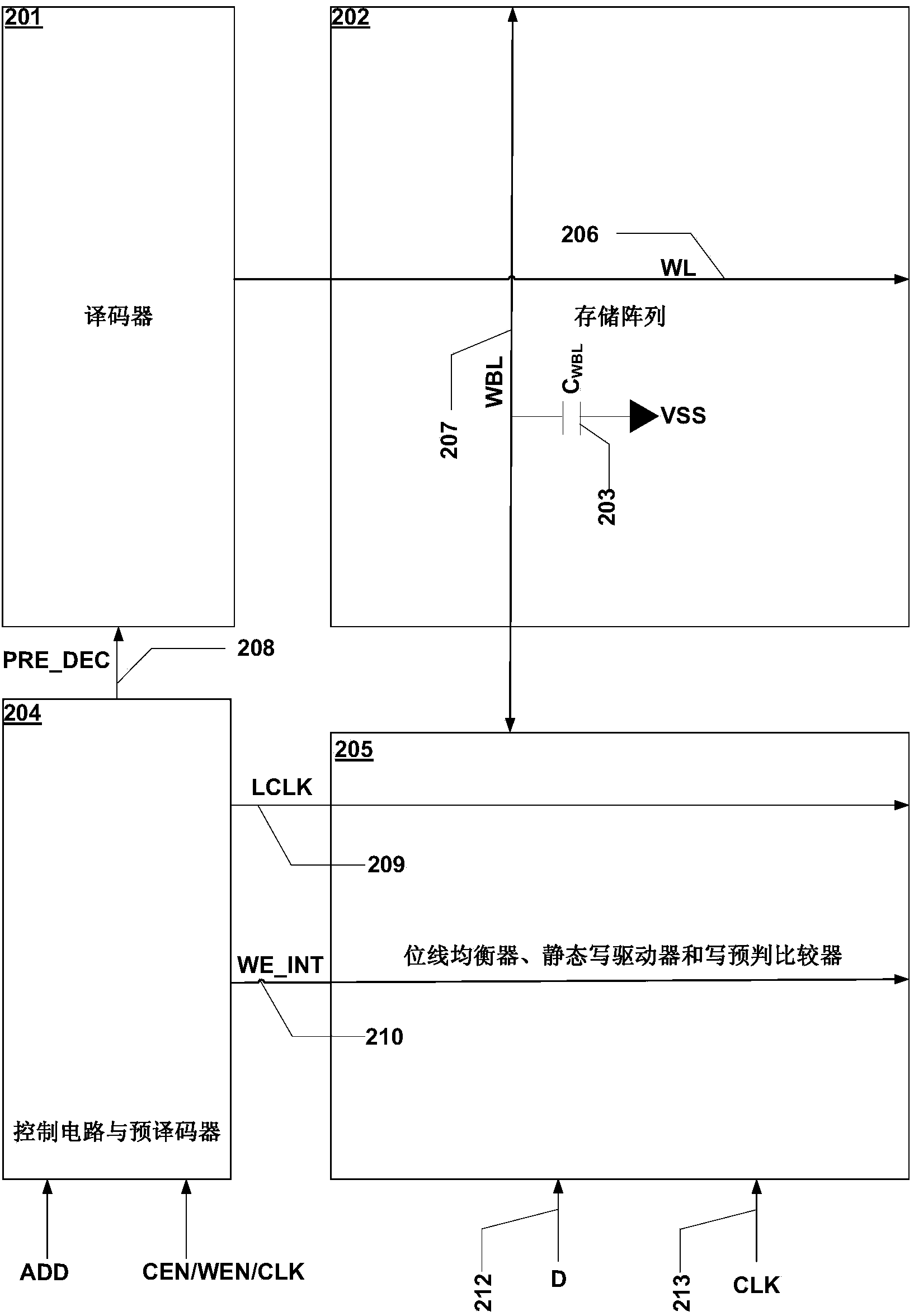

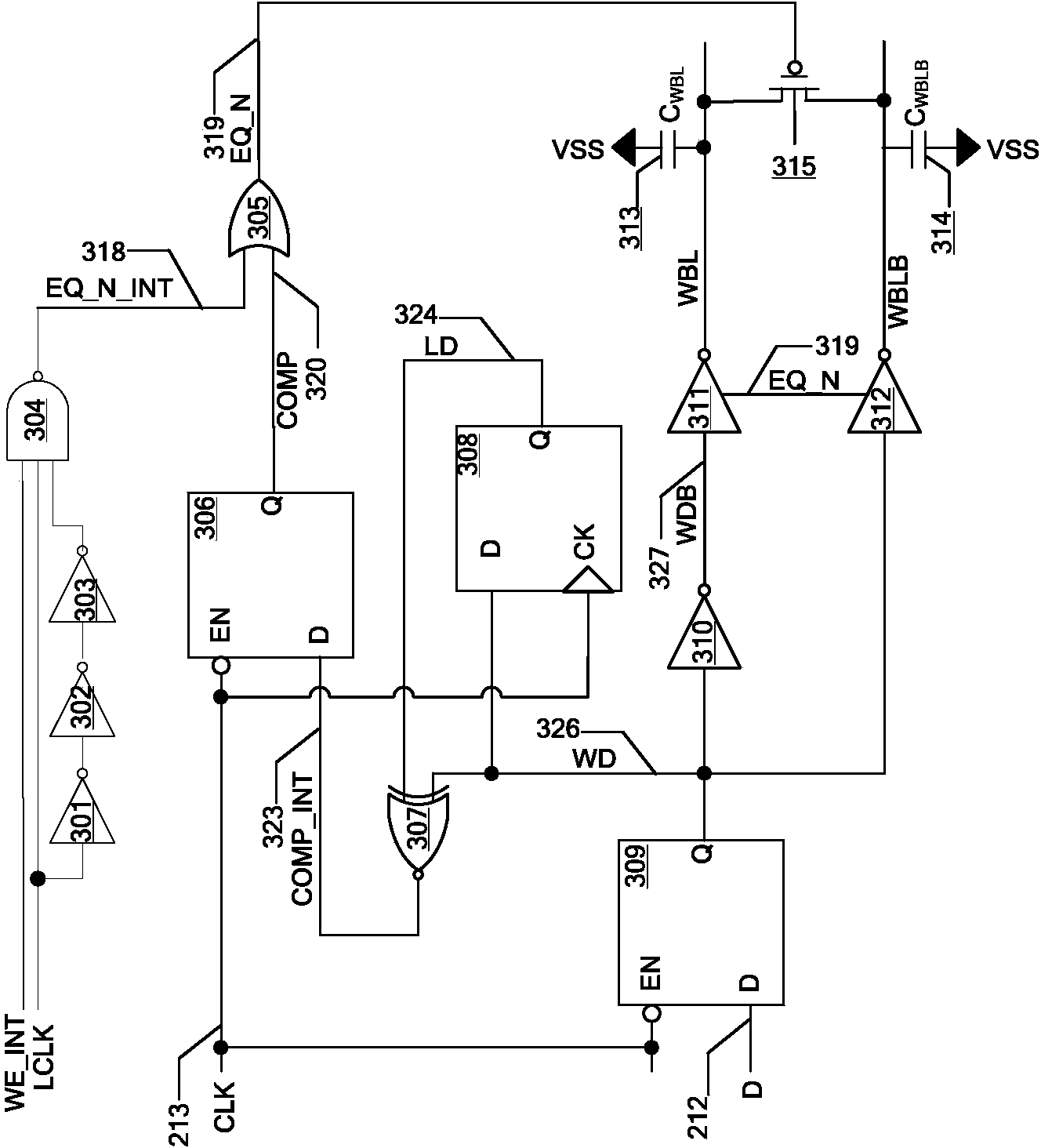

Two-port static random access memory with low writing power consumption

ActiveCN103903646AToggle Power ReductionReduce power consumptionDigital storageStatic random-access memoryComputer architecture

The invention provides a two-port static random access memory with low writing power consumption. A writing prediction comparator compares previous-cycle writing data with current writing data; if the data are different, a writing bit line balance signal is set as a valid signal, and otherwise, the signal is set as an invalid signal; when continuous 0-writing operation or 1-writing operation occurs, because data retained on a bit line are the same as data needing to be written, the writing prediction comparator sets the writing bit line balance signal as the invalid signal, so that the bit line is not turned over; when the data written for successive two times are different, the writing prediction comparator sets the writing bit line balance signal as the valid signal, charges on the writing bit line and a writing bit line back are reallocated, and the writing bit line and the writing bit line back are balanced to an intermediate level; then the writing bit line balance signal is invalid, a writing enable signal is valid, and a writing driver drives the writing bit line and the writing bit line back to a new level. Compared with a conventional two-port static random access memory based on a writing bit line balancing technology, the two-port static random access memory with the low writing power consumption has the advantages that when the turnover rate of the writing data is 50 percent, the turnover power consumption of the writing bit line is reduced by 50 percent.

Owner:XI AN UNIIC SEMICON CO LTD

Steady-state data-based SCADA telemetry wrong data on-line detection system

The present invention relates to a steady-state data-based SCADA telemetry wrong data on-line detection system. The system is technically characterized by comprising a data processing module, a topology data module, a node balance checking module, a line balance checking module, an evaluated value calculation module and an online alarm module. According to the technical scheme of the invention, an effective and feasible method is provided for the online accurate detection of telemetry wrong data. The system can be applied to a scheduling master station. The system serves as one part of a D5000 system and realizes the online and real-time detection function for telemetry data through the node balance and the line balance check based on steady-state telemetry data. Based on the system, the wrong data of telemetry data and a bad measuring point can be timely and accurately detected in the online manner, and then an alarm prompt is sent out. Therefore, reliable telemetry data are provided for the calculation of power grid tidal current, short circuit and stability. Meanwhile, the calculation accuracy for subsequent advanced applications is improved.

Owner:STATE GRID TIANJIN ELECTRIC POWER +2

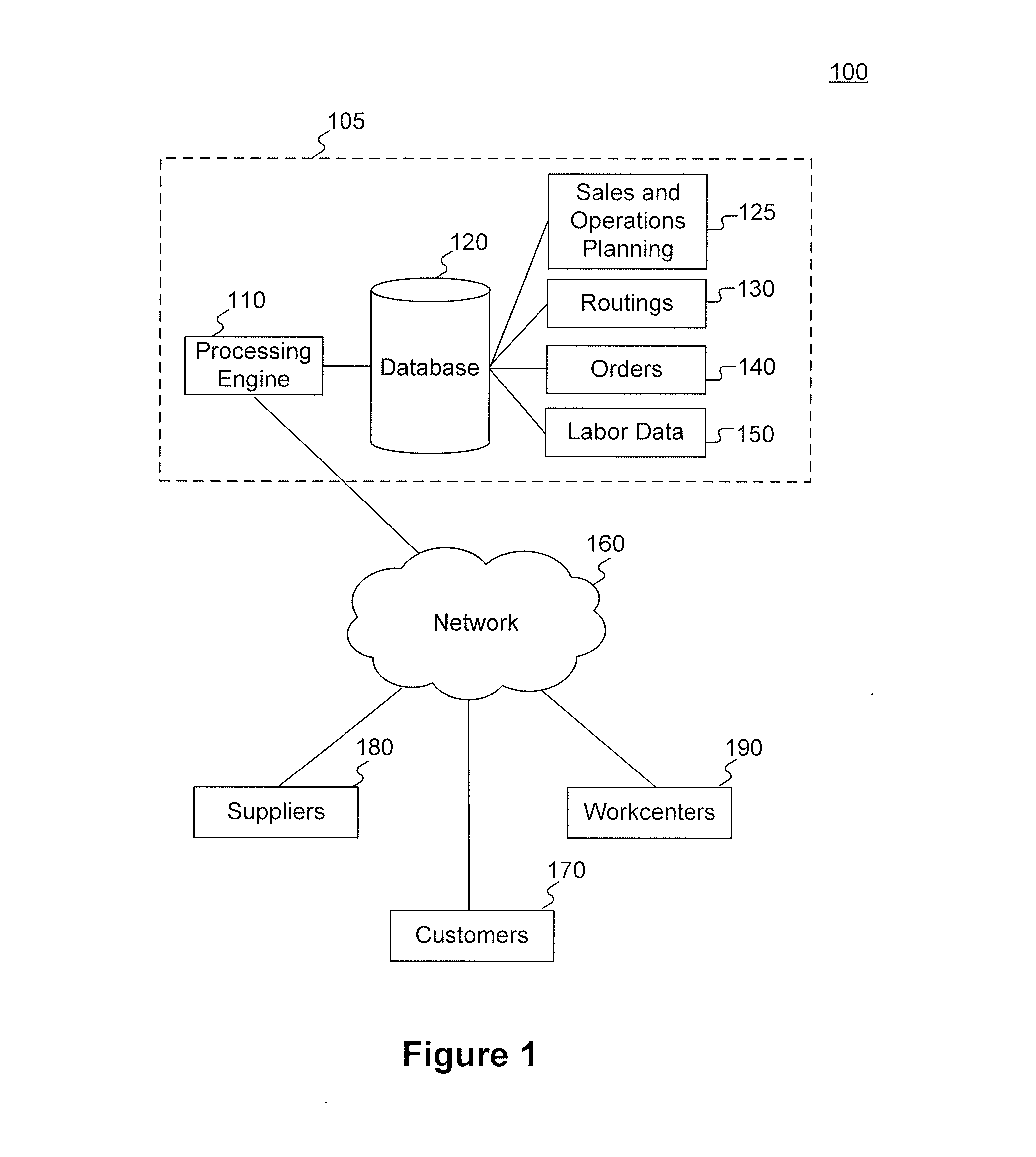

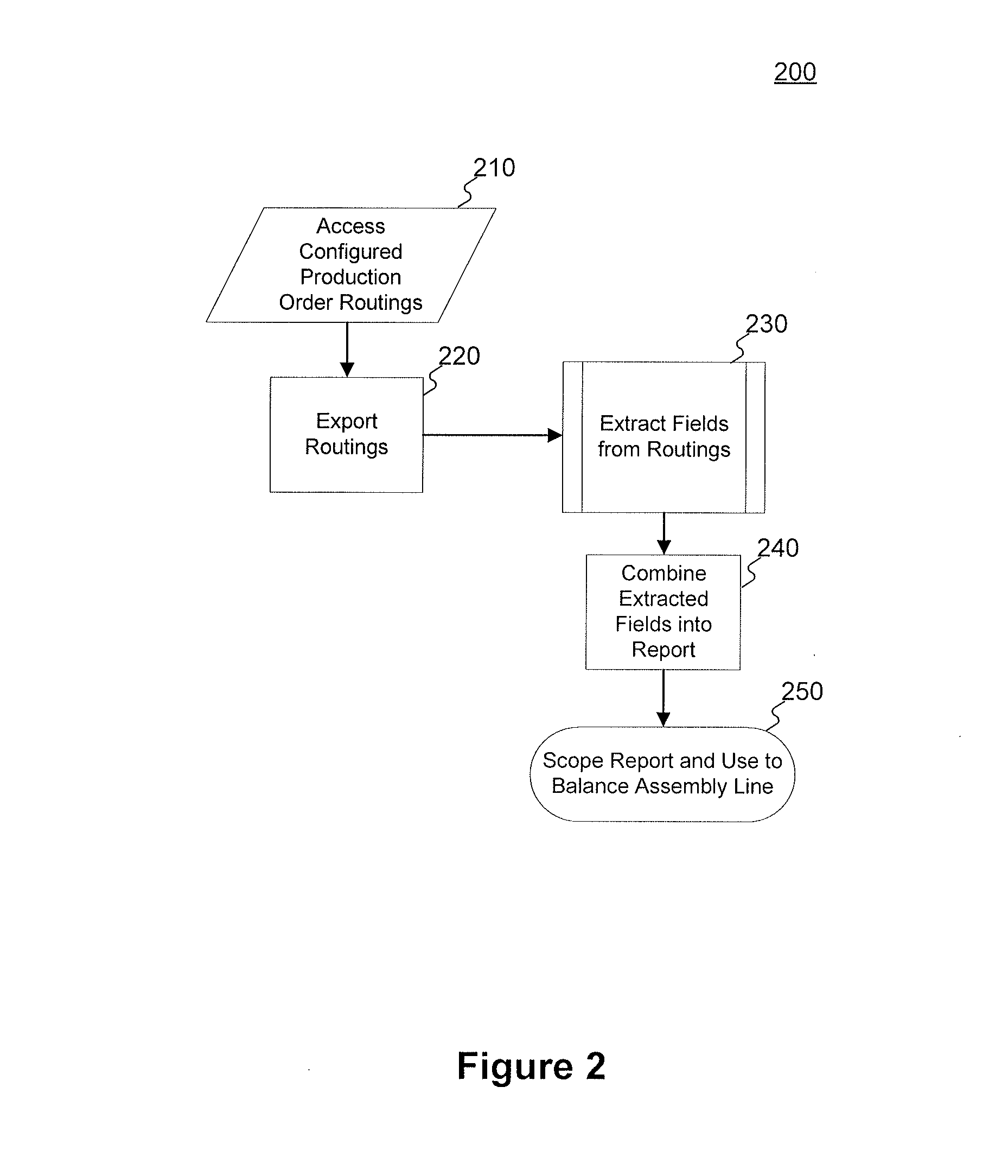

Systems and methods for balancing an assembly line

Systems and methods are disclosed for balancing an assembly line. According to certain embodiments, a plurality of routings is received. A plurality of fields is extracted from each of the plurality of routings. A line balancing report may be generated based on the extracted fields.

Owner:CATERPILLAR INC