Patents

Literature

60 results about "Partial logic" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

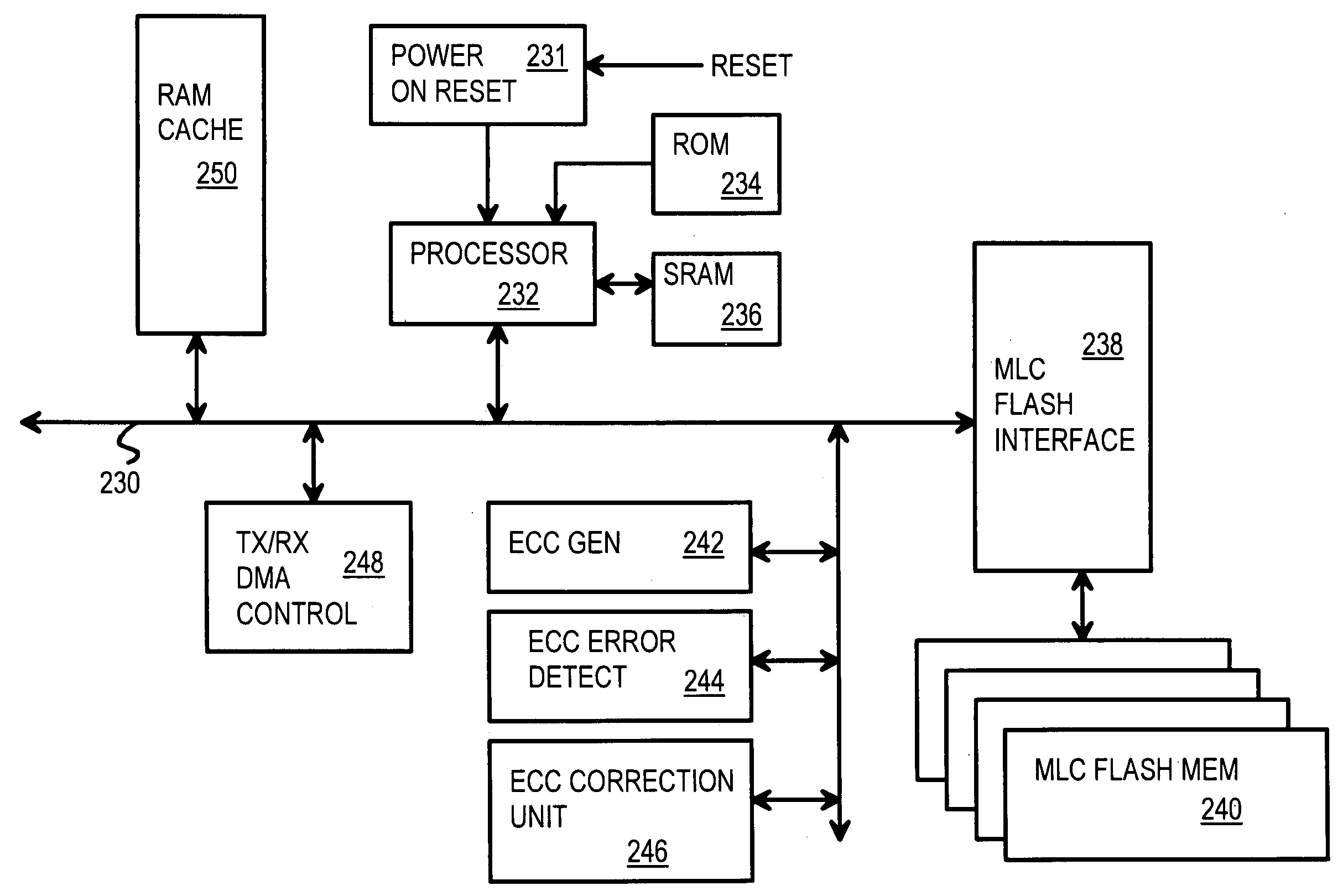

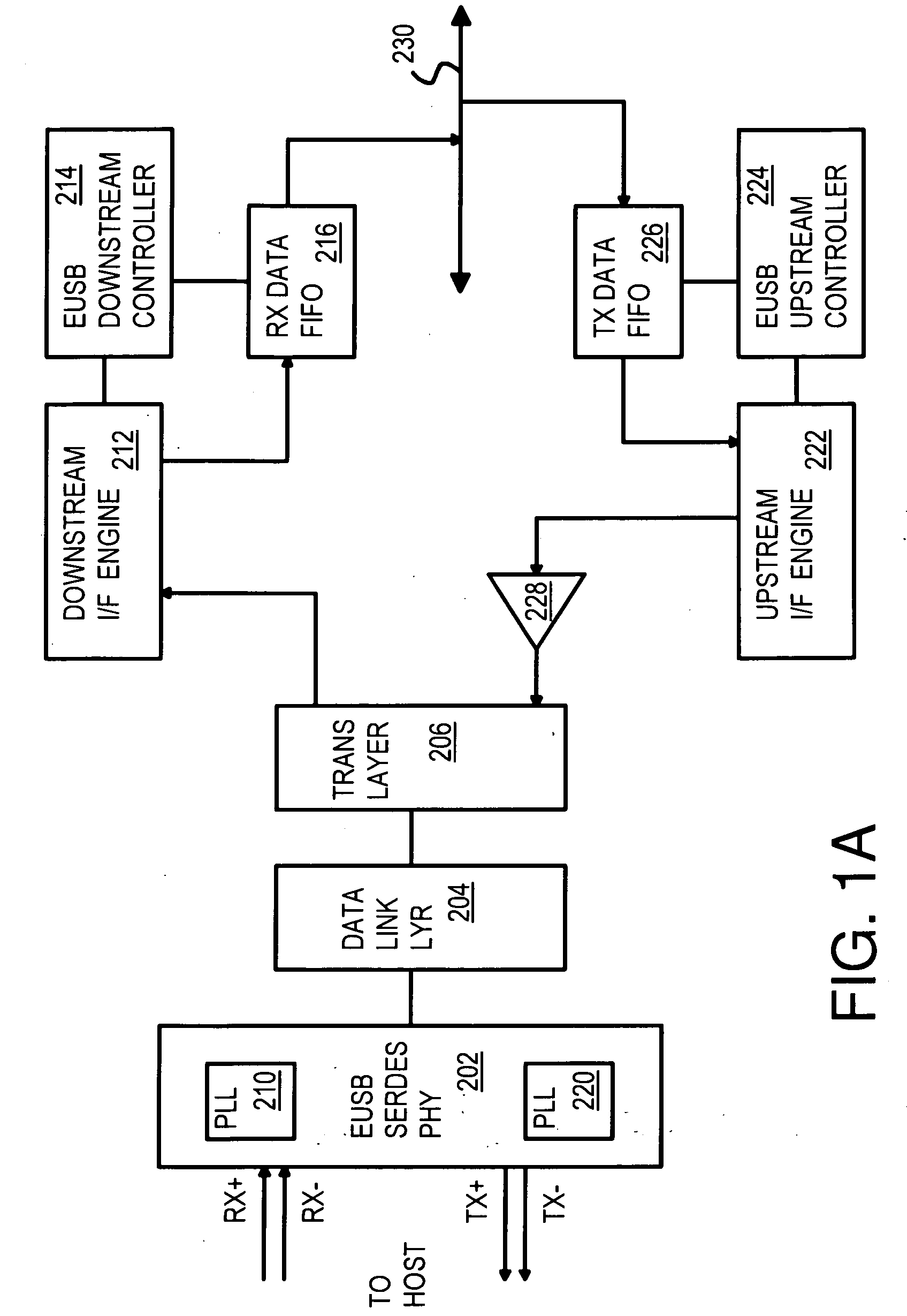

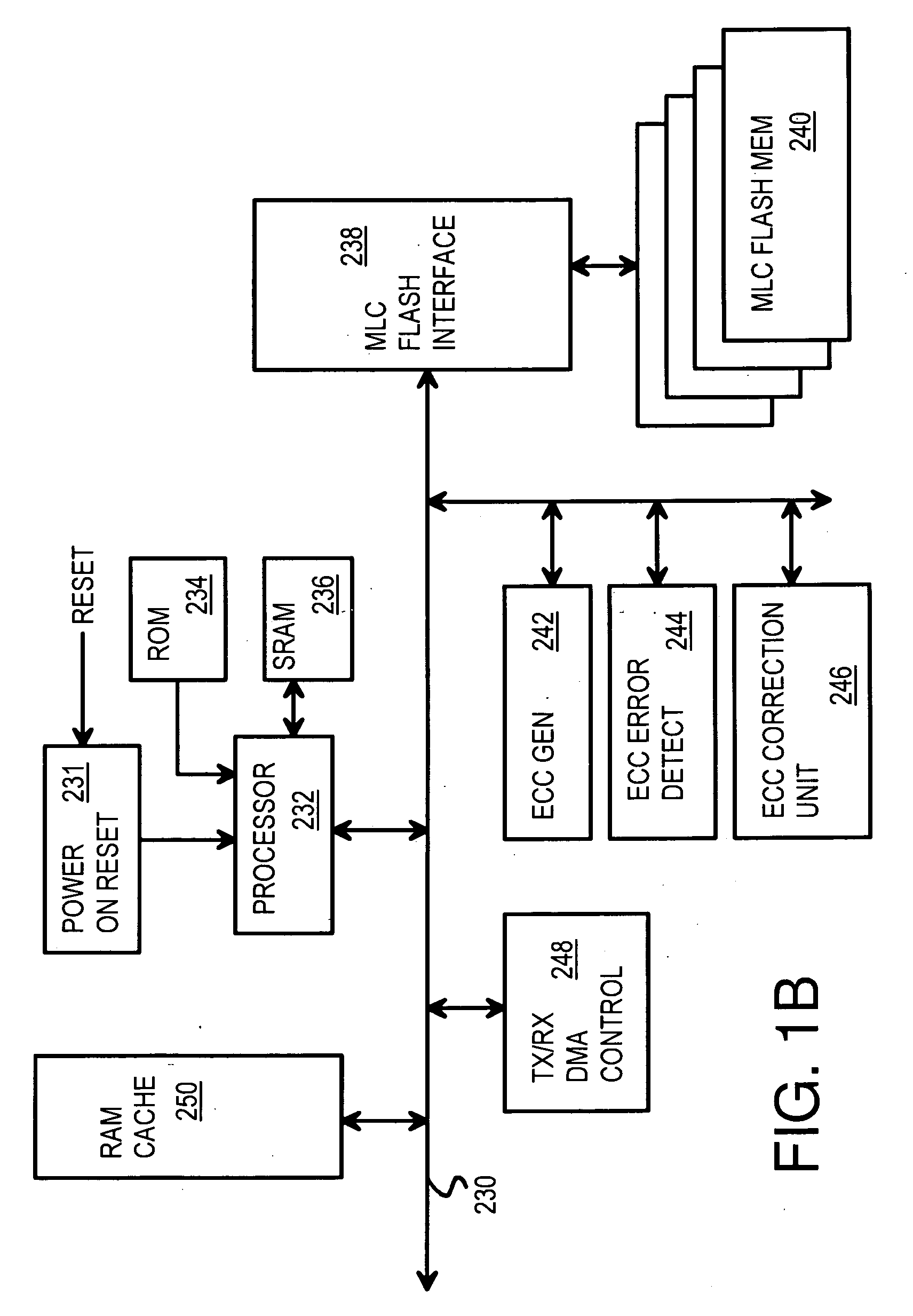

Swappable Sets of Partial-Mapping Tables in a Flash-Memory System With A Command Queue for Combining Flash Writes

InactiveUS20090113121A1Memory architecture accessing/allocationDistillation regulation/controlFlash memory controllerMulti-level cell

A flash controller has a flash interface accessing physical blocks of multi-level-cell (MLC) flash memory. An Extended Universal-Serial-Bus (EUSB) interface loads host commands into a command queue where writes are re-ordered and combined to reduce flash writes. A partial logical-to-physical L2P mapping table in a RAM has entries for only 1 of N sets of L2P mapping tables. The other N−1 sets are stored in flash memory and fetched into the RAM when a L2P table miss occurs. The RAM required for mapping is greatly reduced. A data buffer stores one page of host write data. Sector writes are merged using the data buffer. The data buffer is flushed to flash when a different page is written, while the partial logical-to-physical mapping table is flushed to flash when a L2P table miss occurs, when the host address is to a different one of the N sets of L2P mapping tables.

Owner:SUPER TALENT TECH CORP

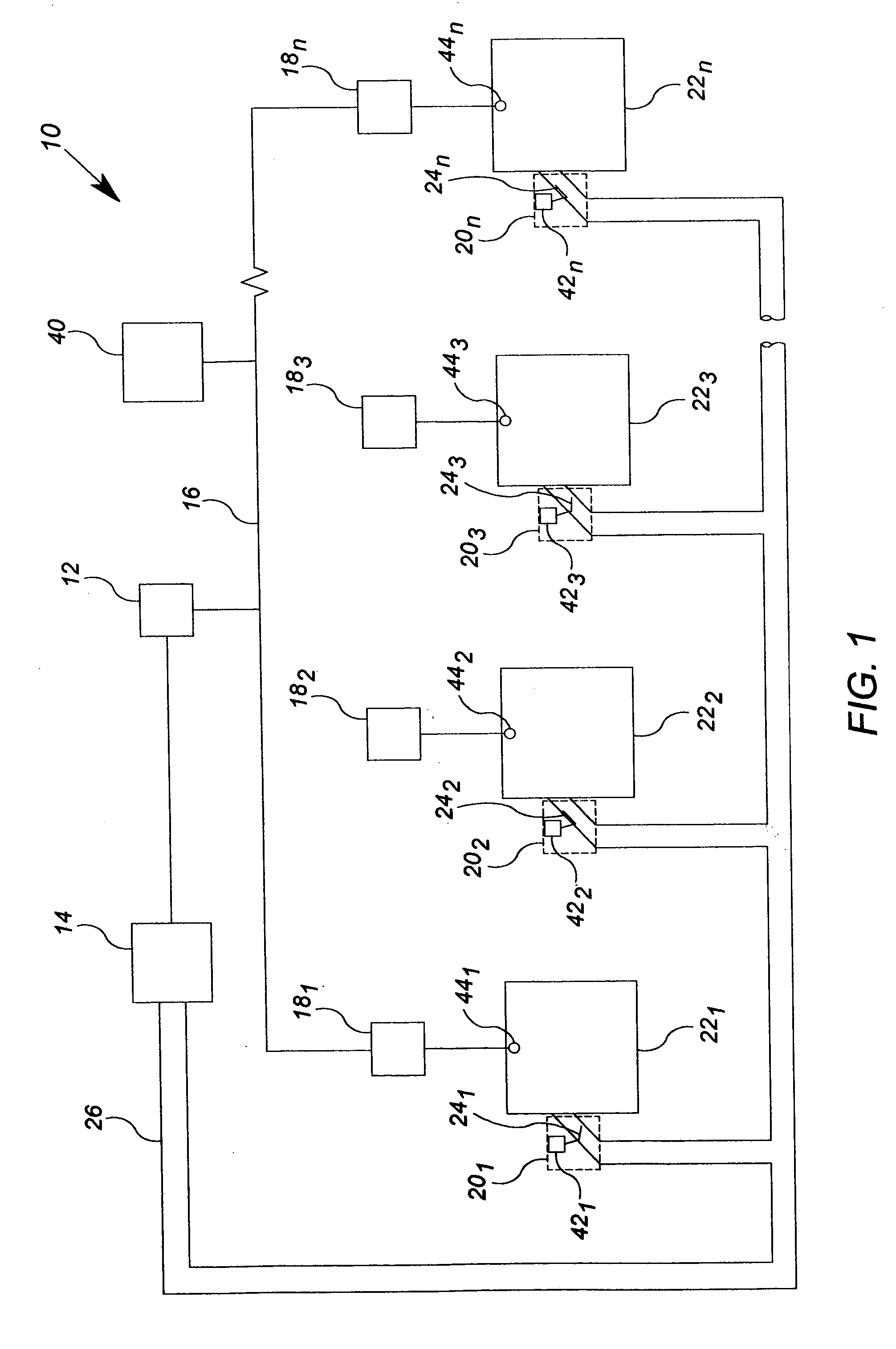

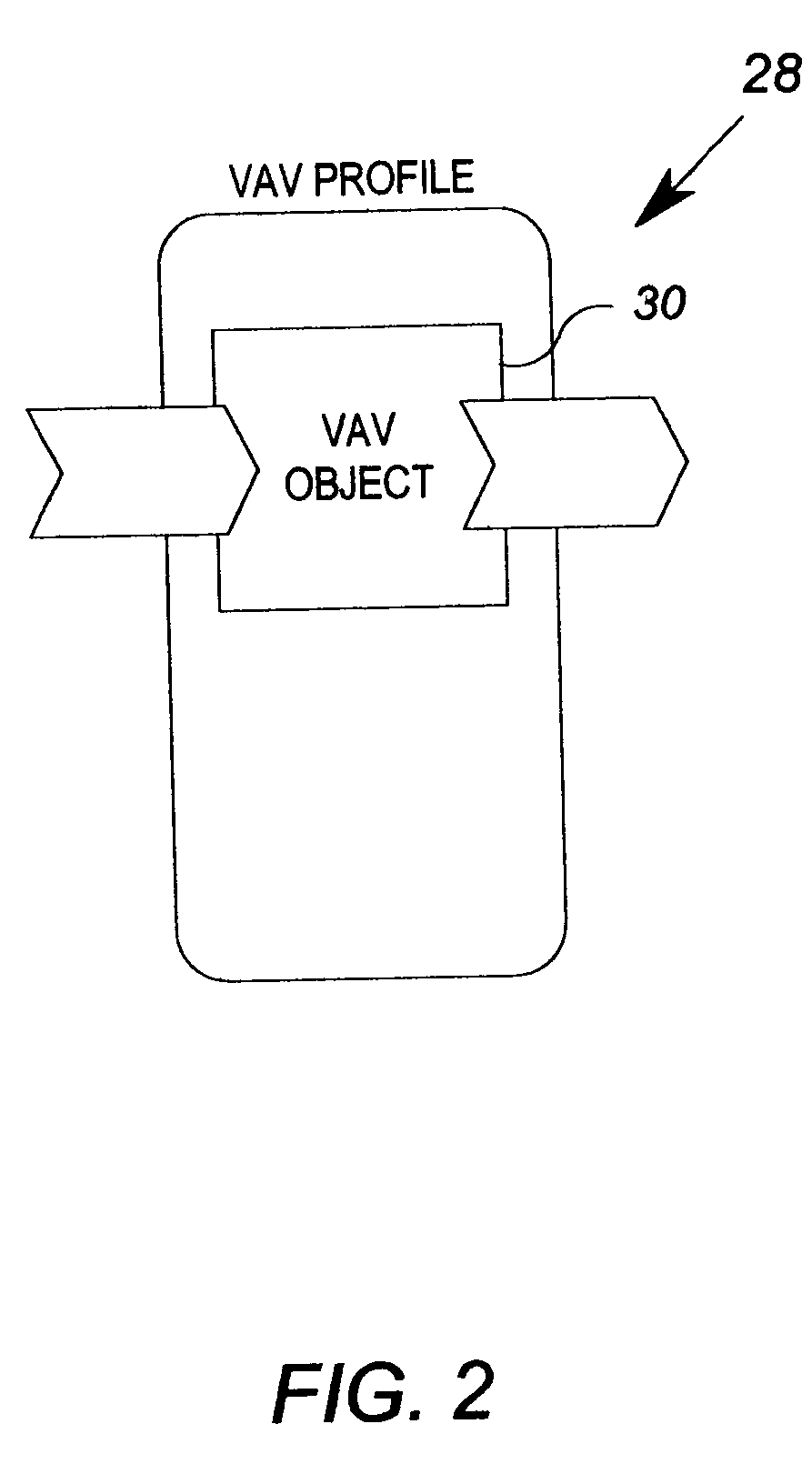

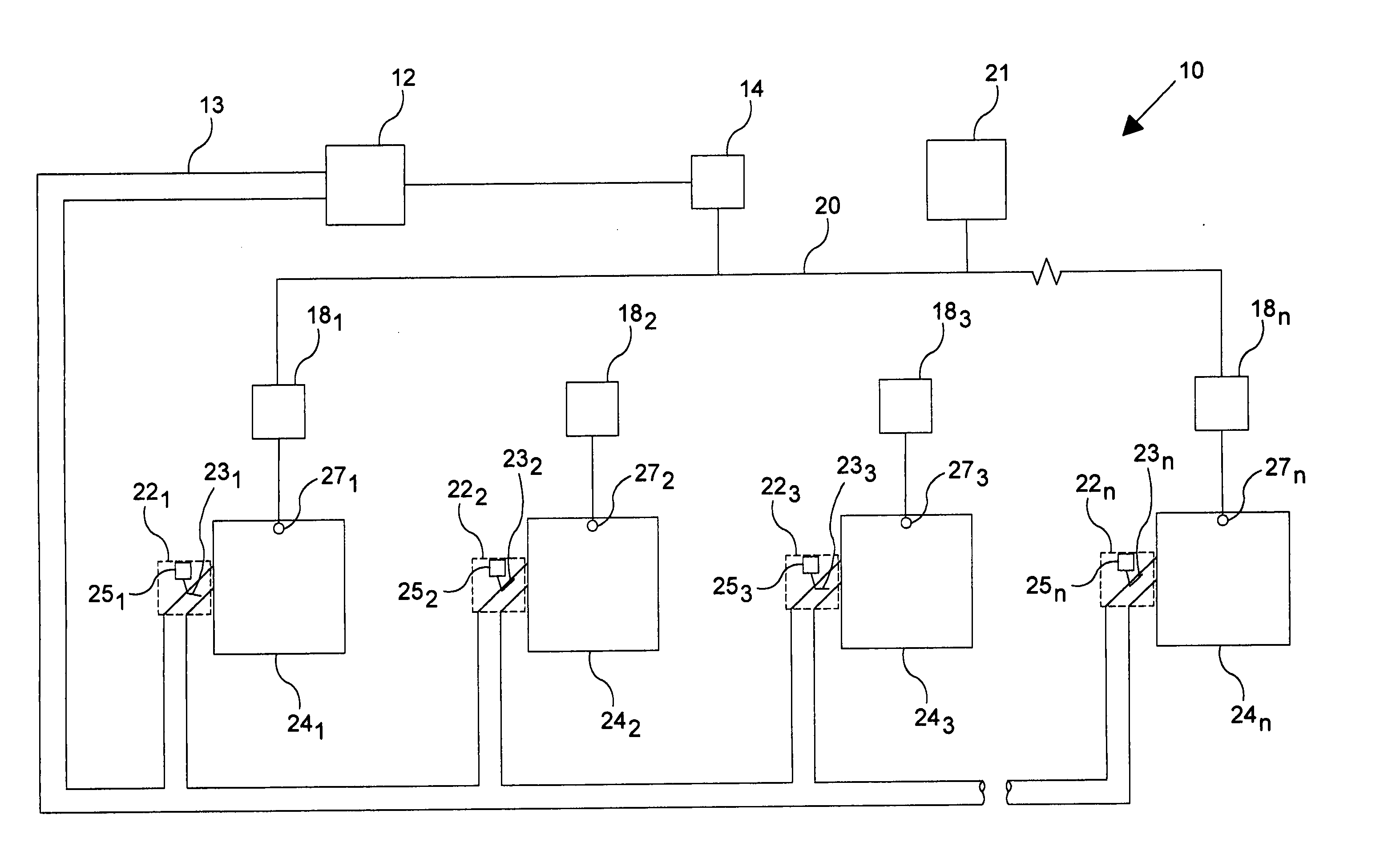

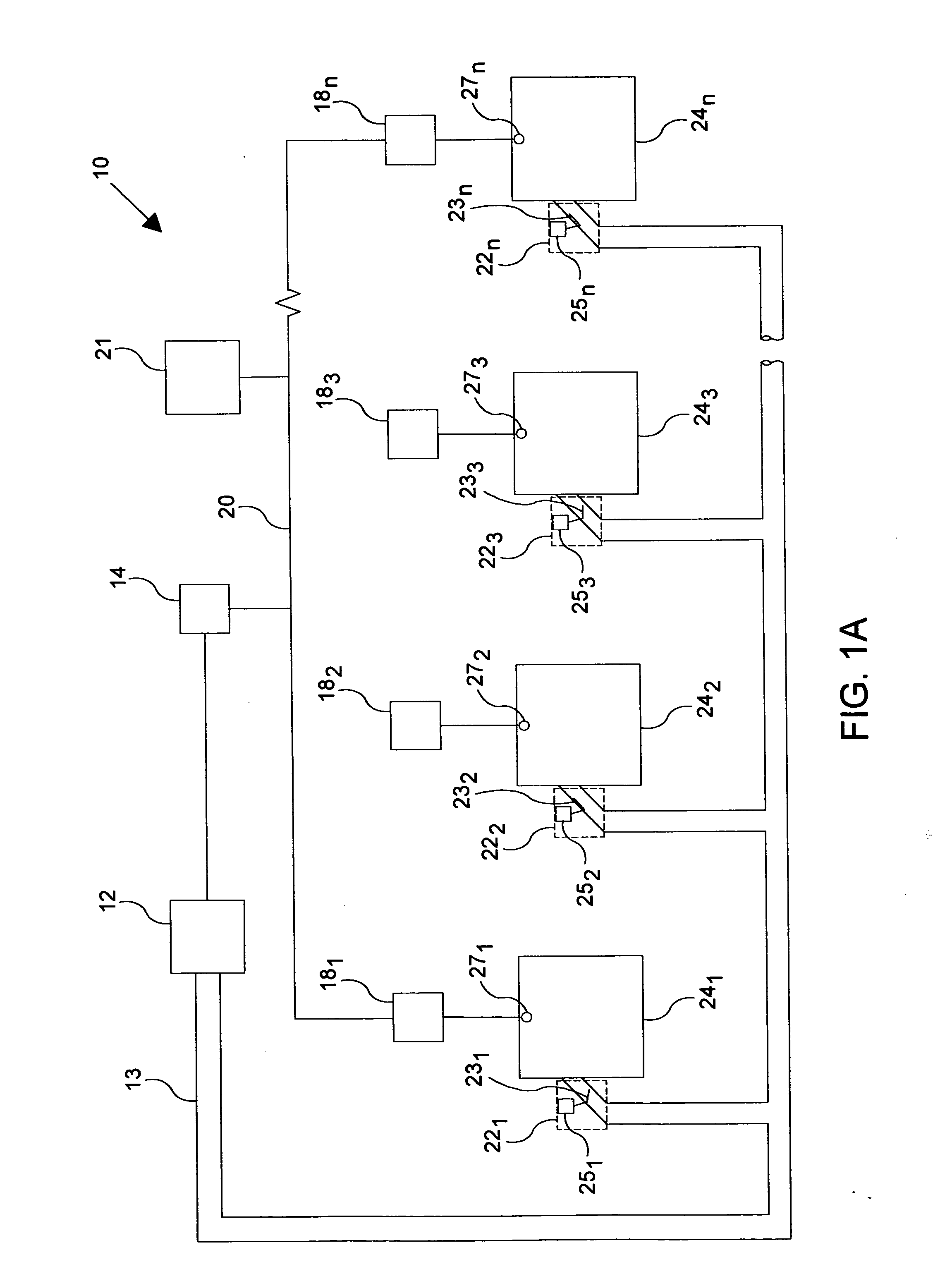

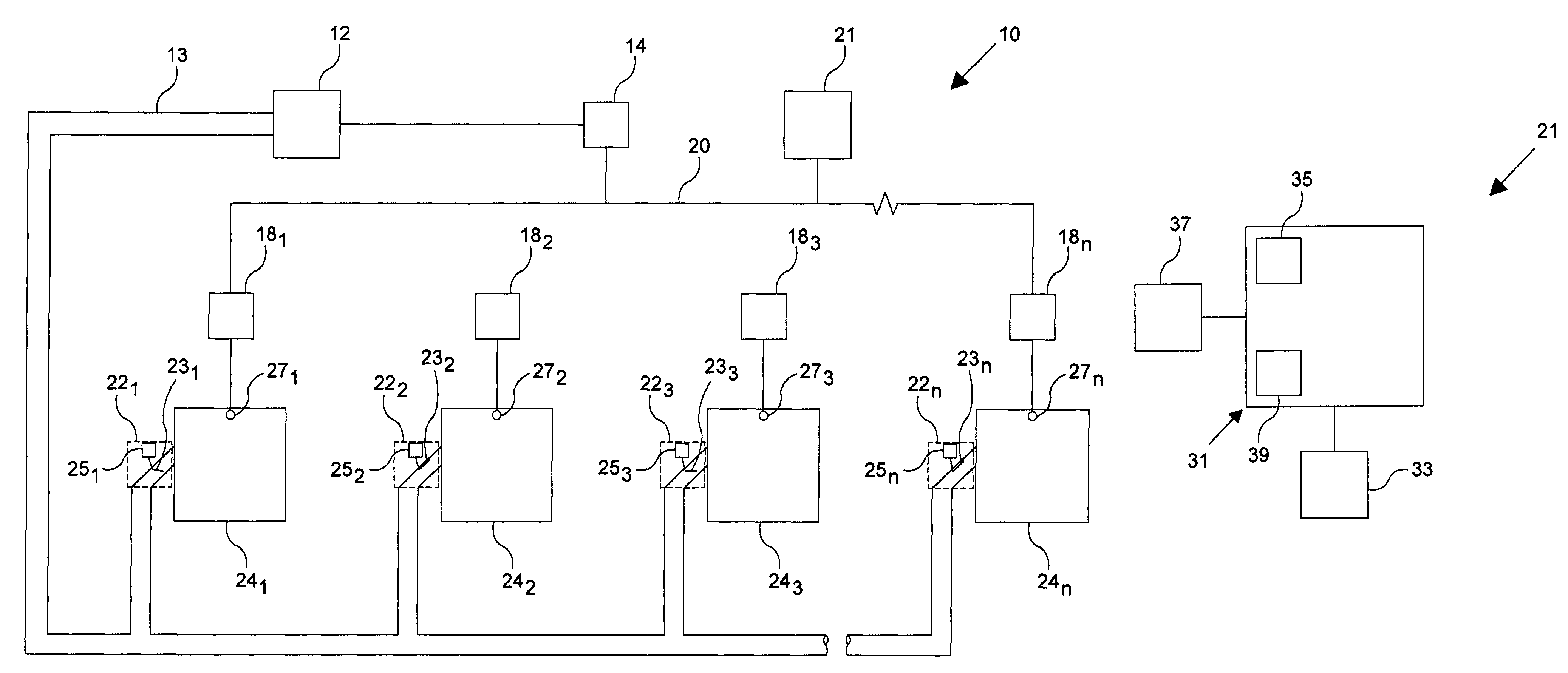

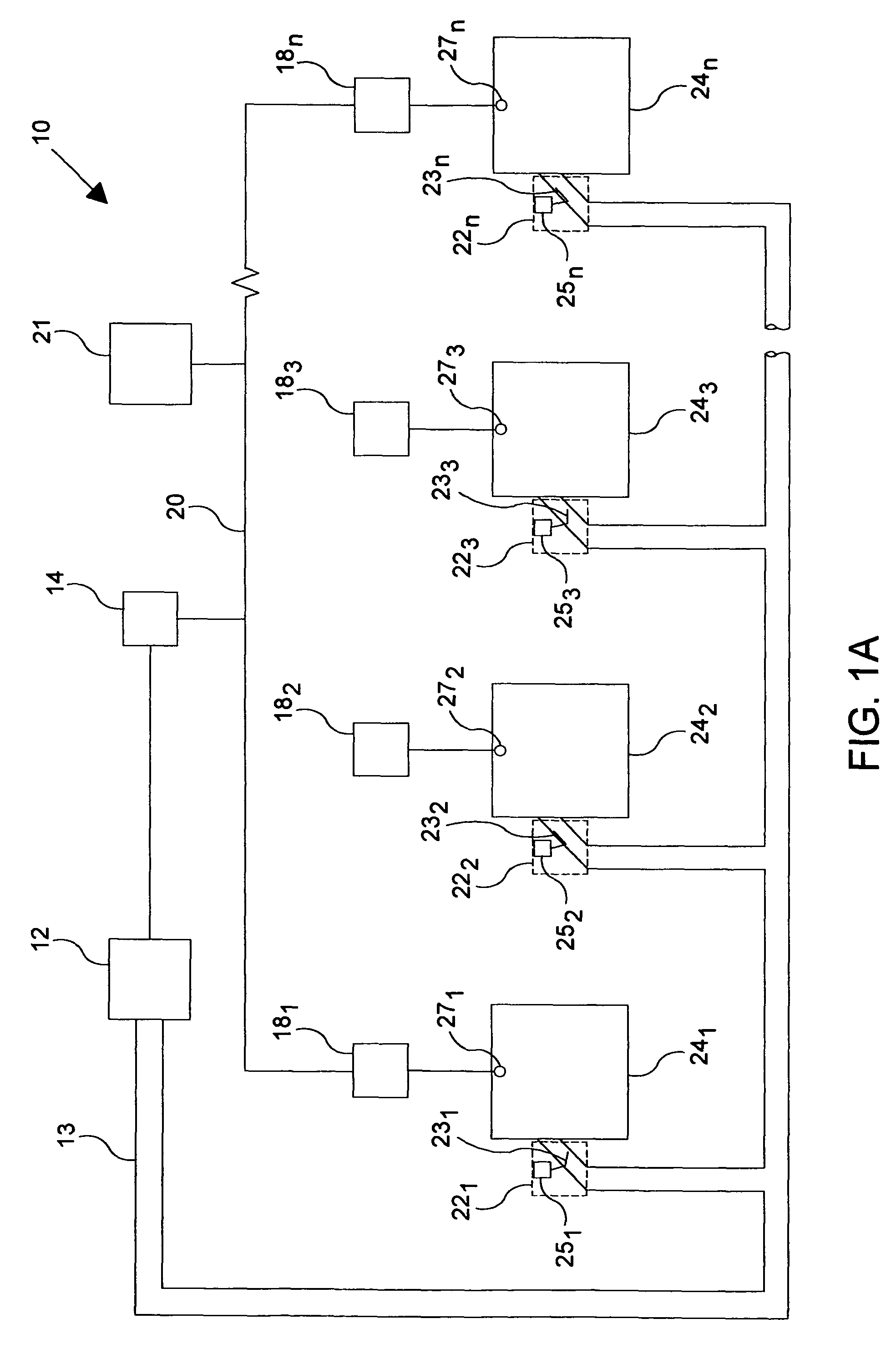

System and method for automatically replacing nodes in a network

ActiveUS20060159007A1Error preventionFrequency-division multiplex detailsNetwork variableAutomatic control

A tool is provided for use when replacing devices in an automatically controlled distributed processing system. In one embodiment a network management tool reestablishes all or a portion of the logical connections formerly provided to a bound node where a replacement device is or will be located. The network management tool compares data associated with the logical connections of the bound node and data associated with the logical connections for the replacement device to determine proper logical connection. The network management tool identifies network variables associated with the bound node that are not associated with the replacement device and deletes those network variables from other devices on the network if the network variable is not useful in the network after the replacement device is bound.

Owner:SIEMENS IND INC

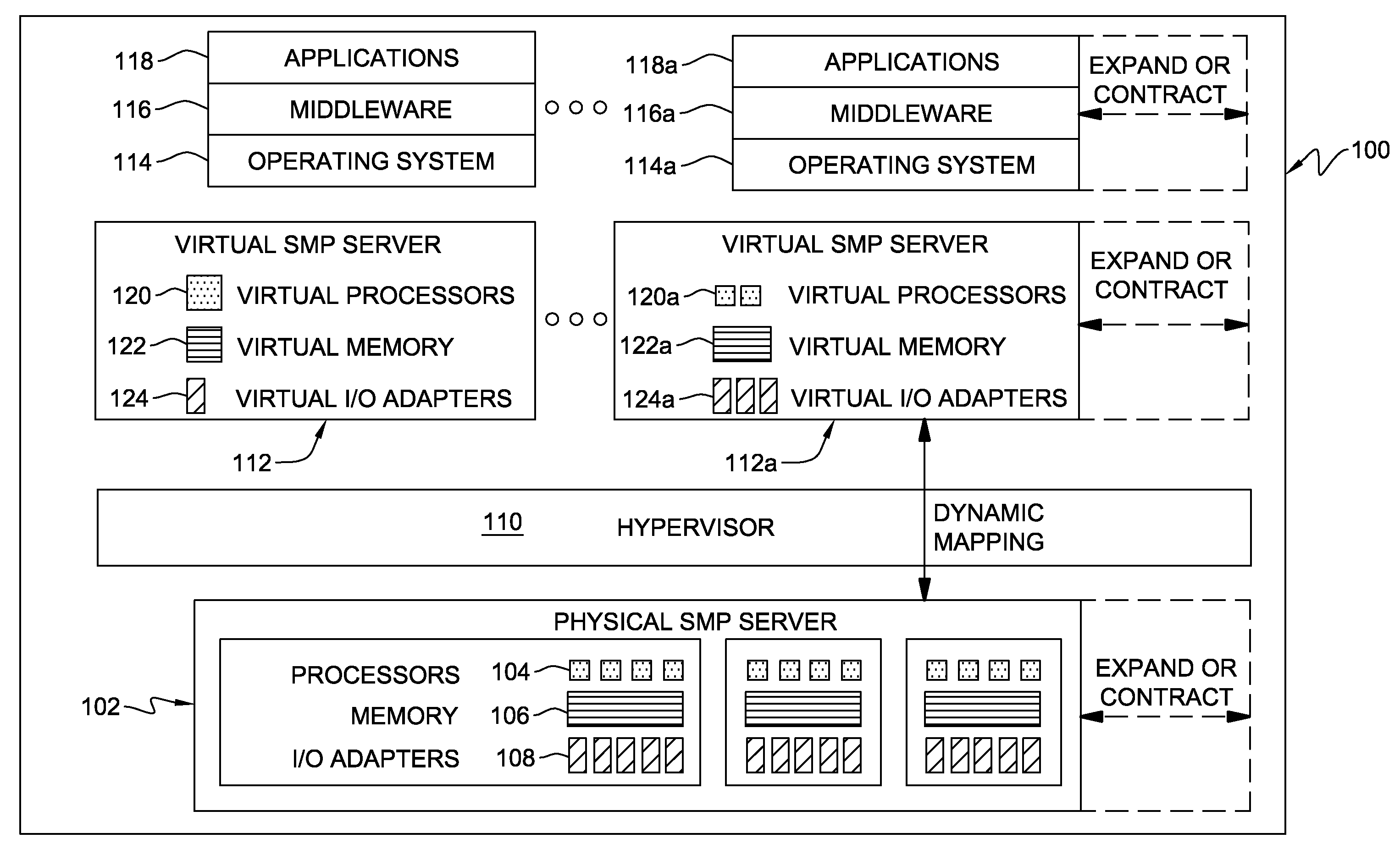

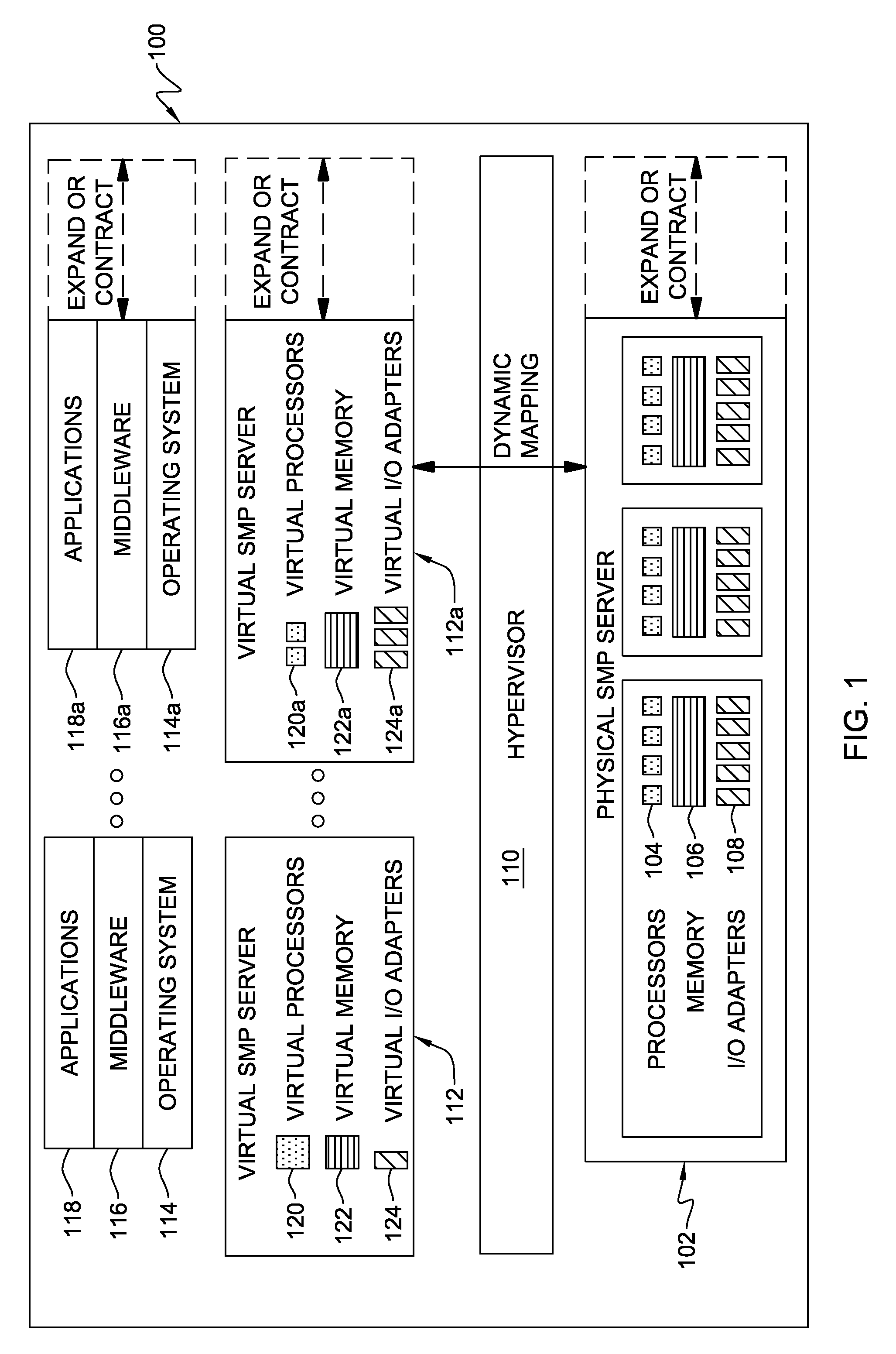

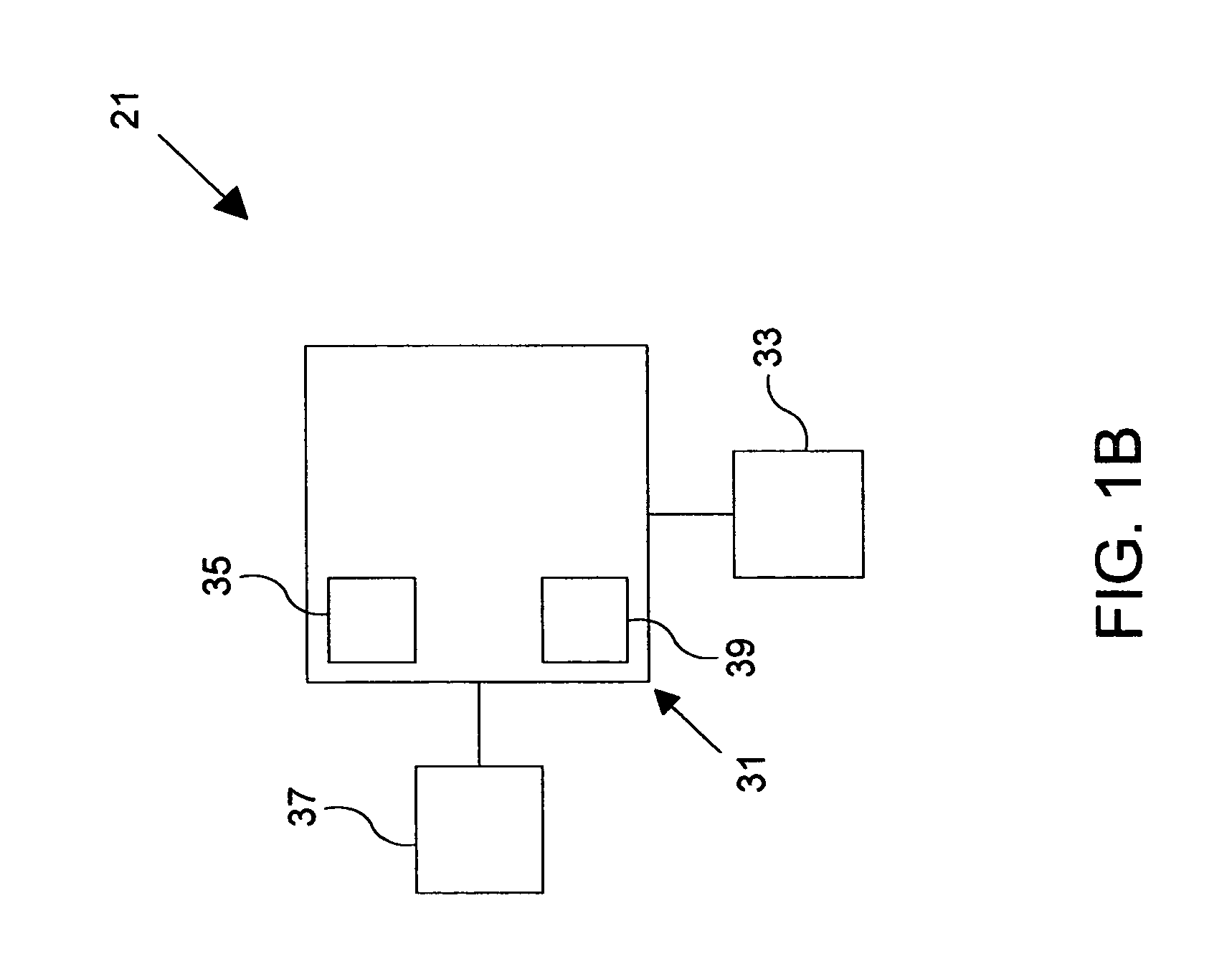

Managing Migration of a Shared Memory Logical Partition from a Source System to a Target System

ActiveUS20090307447A1Small amountMemory loss protectionMemory adressing/allocation/relocationGoal systemPaging

Migration management is provided for a shared memory logical partition migrating from a source system to a target system. The management approach includes managing migration of the logical partition from the source system to the target system by: transferring a portion of logical partition state information for the migrating logical partition from the source system to the target system by copying at the source system contents of a logical page of the migrating logical partition into a state record buffer for forwarding to the target system; forwarding the state record buffer to the target system; and determining whether the migrating logical partition is suspended at the source system, and if not, copying at the target system contents of the state record buffer to paging storage of the target system, the paging storage being external to physical memory managed by a hypervisor of the target system.

Owner:IBM CORP

System and method for automatically replacing nodes in a network

ActiveUS20050055427A1Digital computer detailsData switching networksNetwork variableAutomatic control

A network tool is provided for use when replacing devices in an automatically controlled distributed processing system. The network tool reestablishes all or a portion of the logical connections formerly provided to the node where the replacement device is or will be located. The tool compares data associated with the logical connections of the node and data associated with the logical connections for the replacement device to determine proper logical connection. In one embodiment, the compared data comprises network variables and configuration properties.

Owner:SIEMENS IND INC

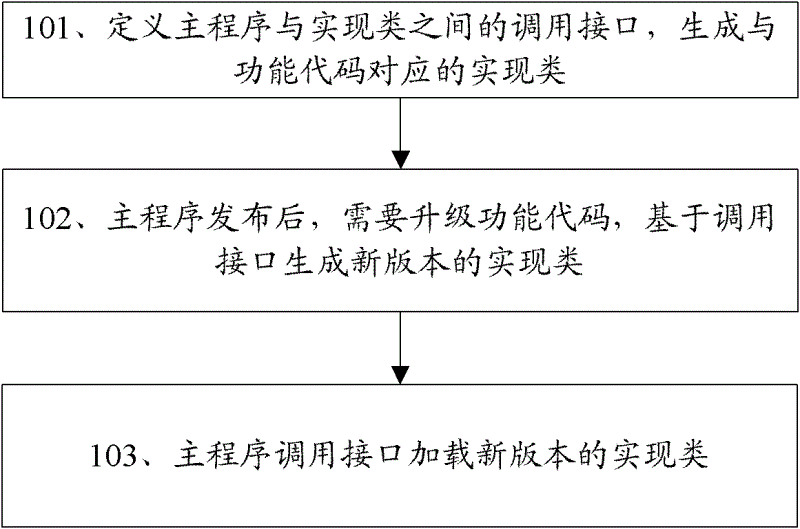

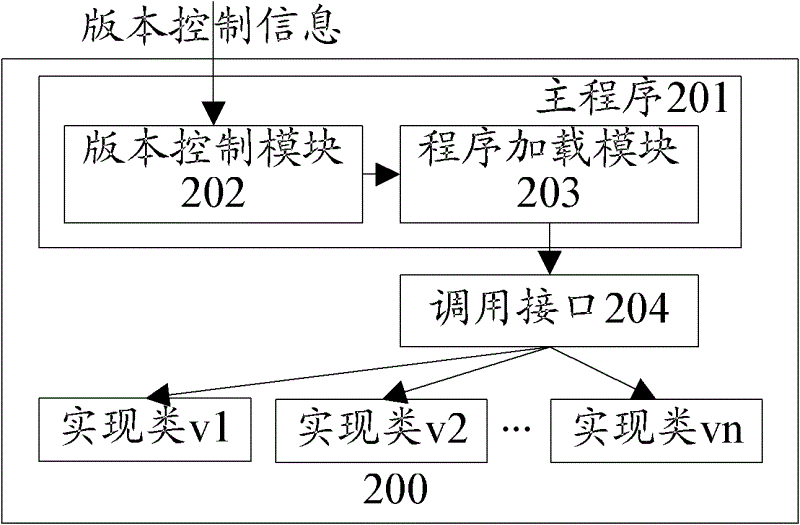

Software upgrading method and software upgrading device

ActiveCN102622241AReduce occupancyAchieve the purpose of silent updateProgram loading/initiatingTraffic capacitySoftware update

The invention discloses a software upgrading method and a software upgrading device which are used for solving the problems that update of application software of a mobile terminal occupies large network flow and is complex and inconvenient. Function codes finishing concrete program functions in a main program are extracted and packaged to form an implementation class, a call interface is abstracted, and the main program calls the implementation class through the call interface so as to finish the concrete program functions. When the function codes need updating, the main program acquires an implementation class of a new version, and the implementation class of an old version is replaced with the implementation class of the new version. When the software is updated, users only need to download code files of part of logic from a server so as to replace original code logic, and because updated content is only a subset of overall program codes, the occupied network flow is small. Under a silent update mode, the software automatically finishes an upgrading process during the software using process of the users, and accordingly the aim of silent update is achieved.

Owner:TENCENT TECH (SHENZHEN) CO LTD

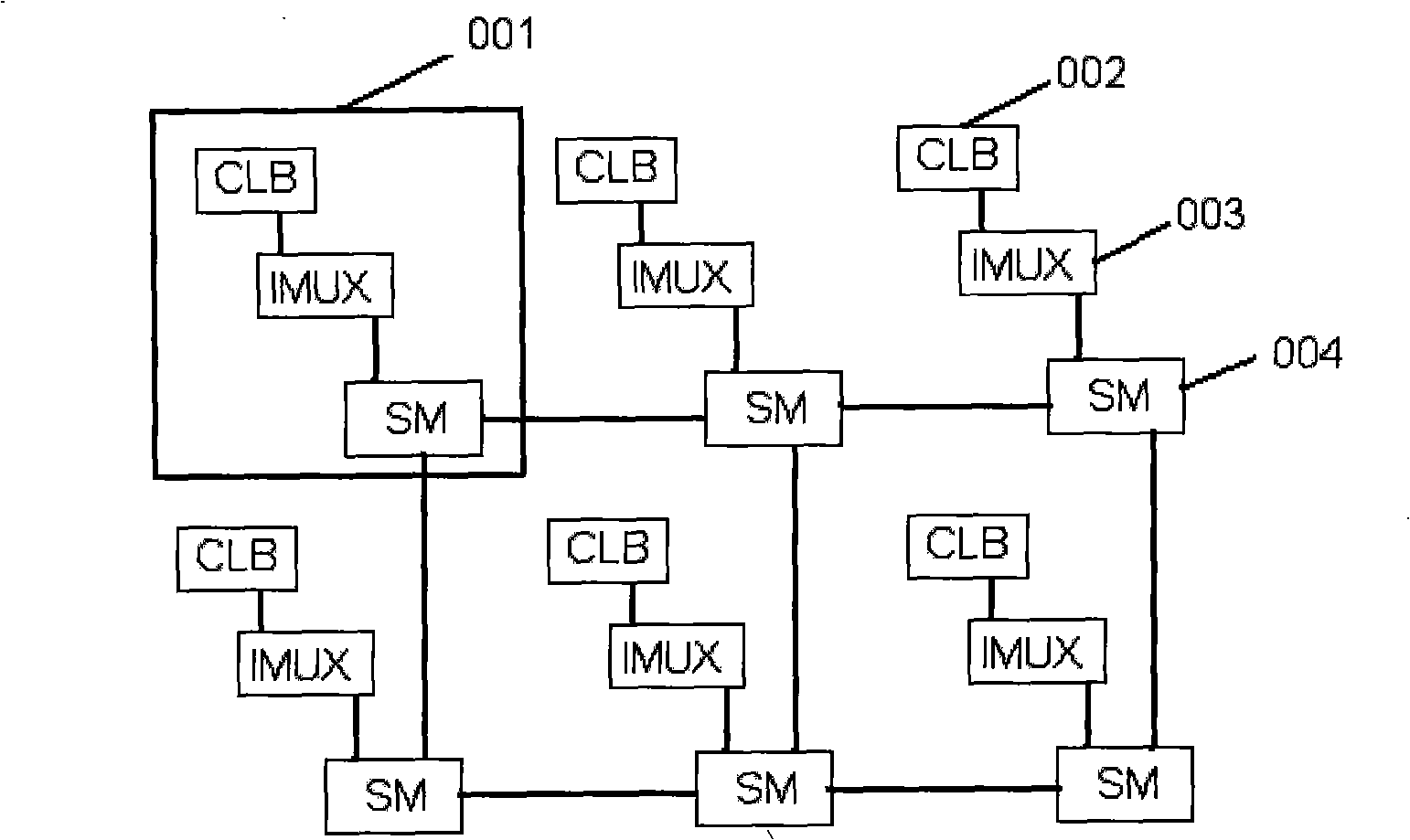

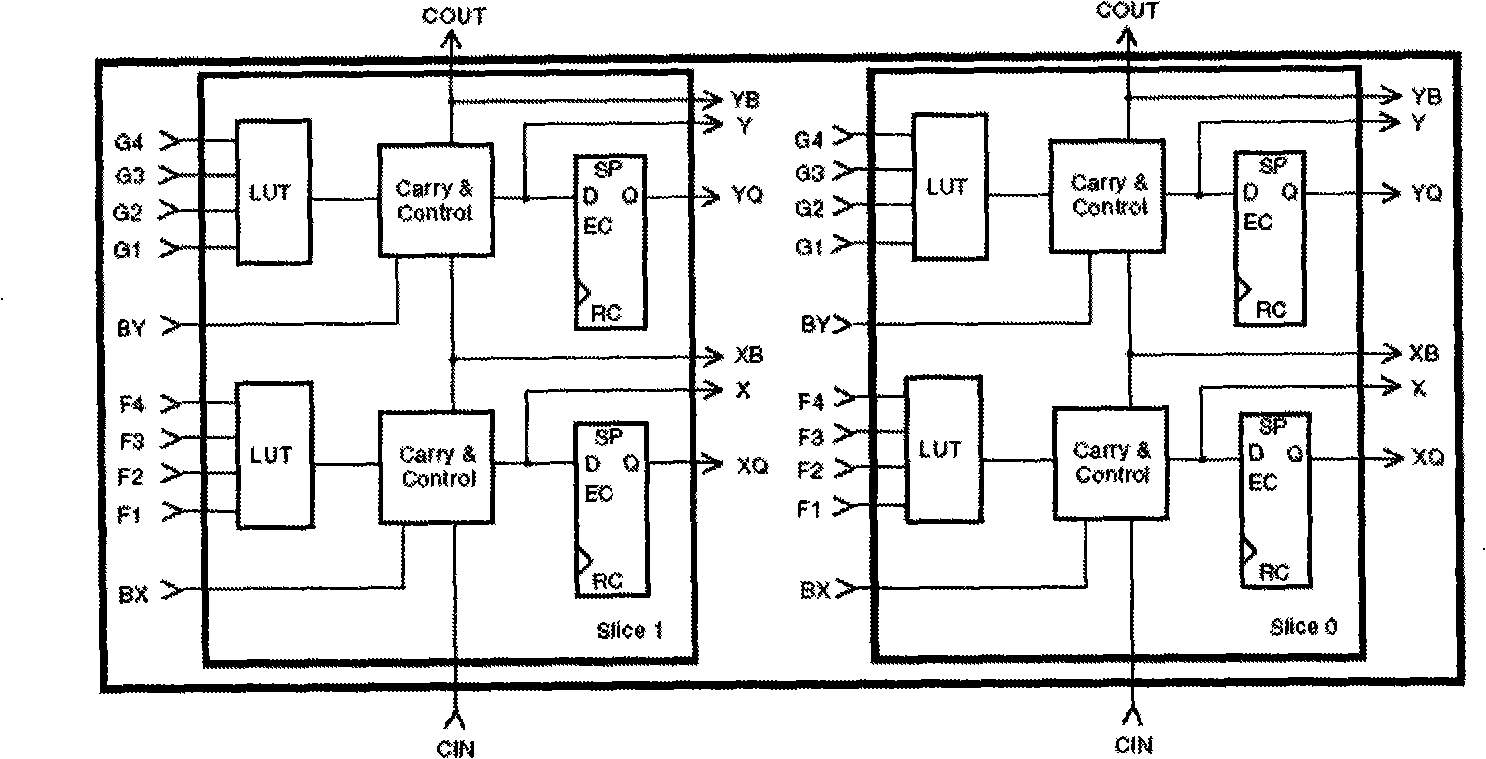

Built-in self-test method of FPGA logical resource

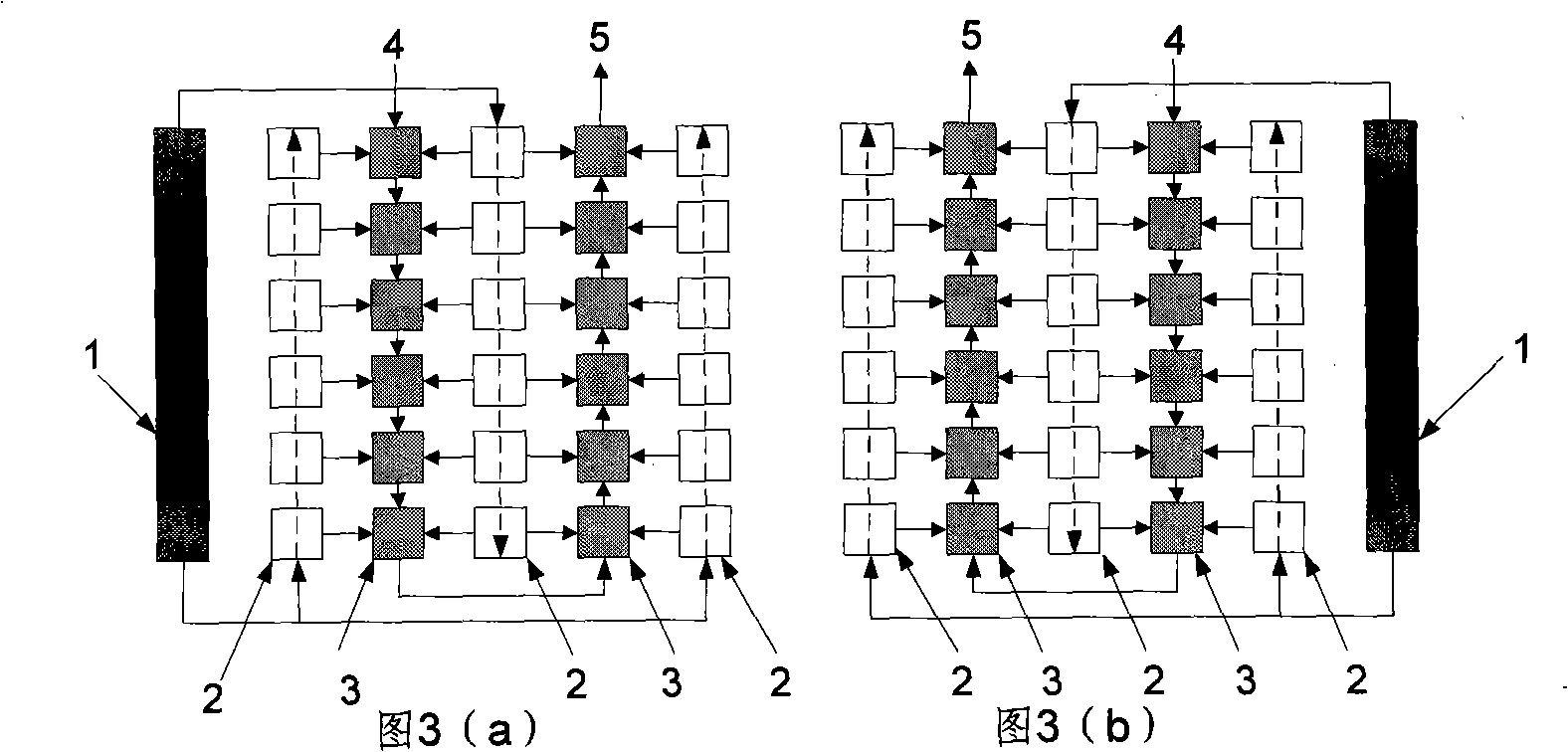

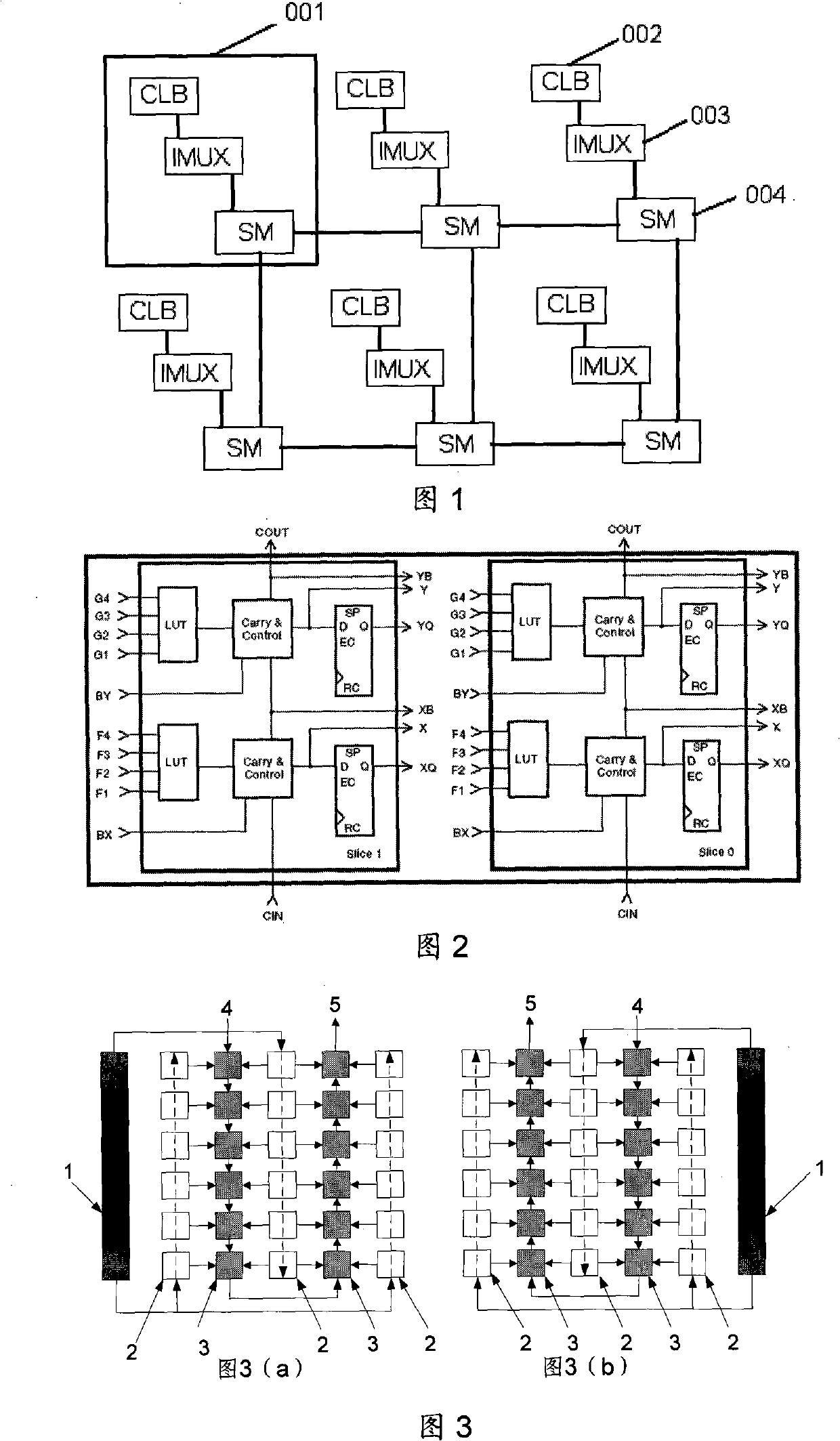

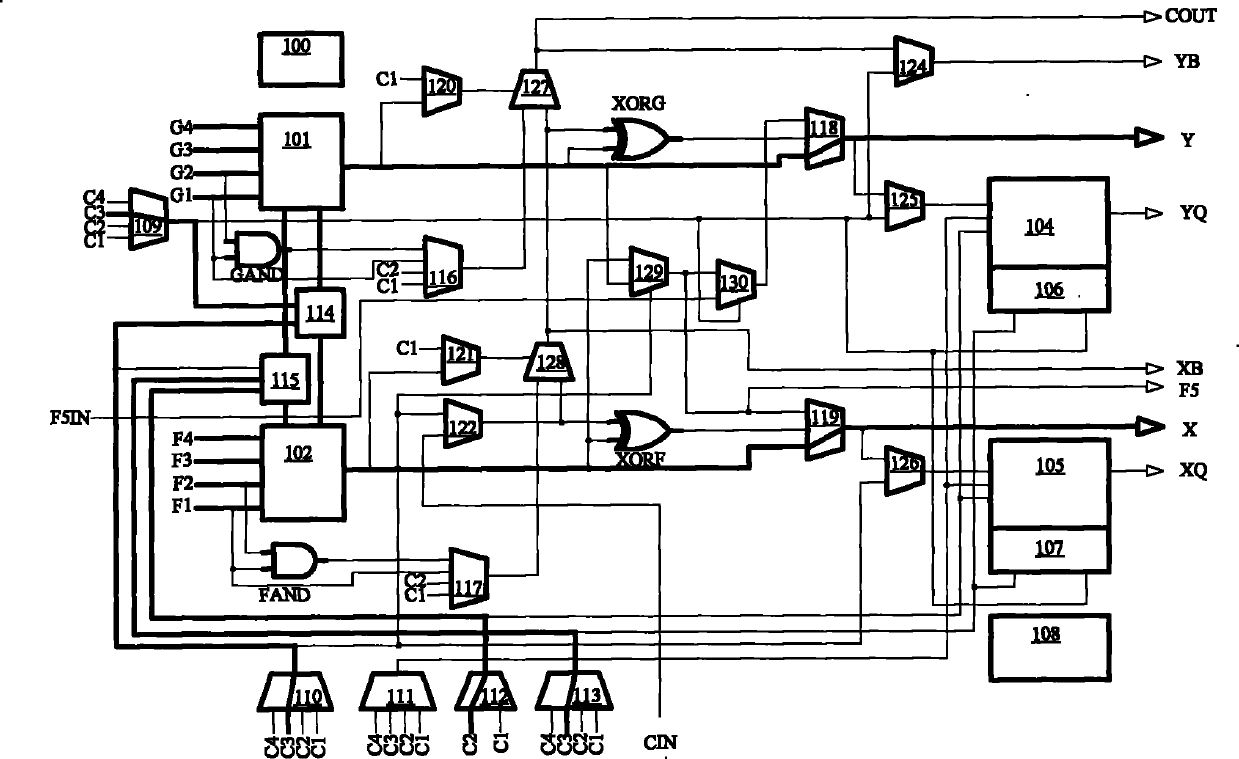

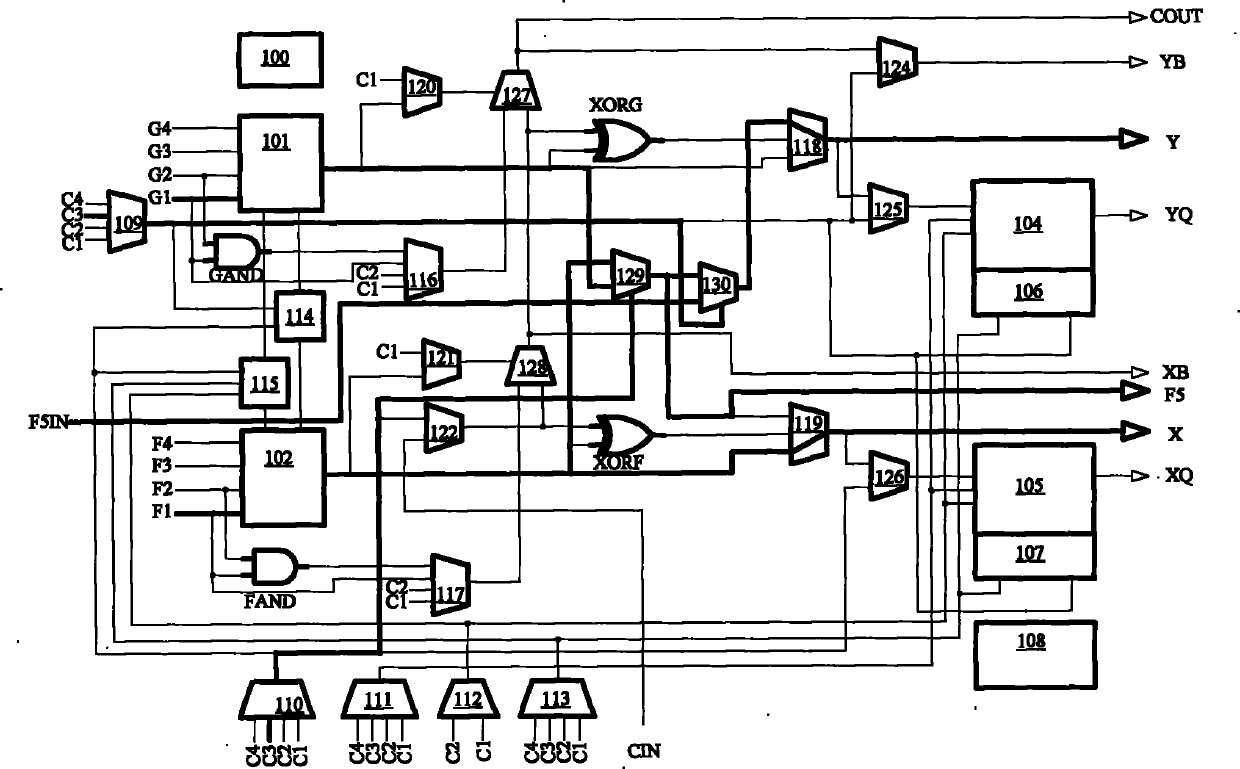

ActiveCN101515020ASimple configuration structureDifficult to designElectrical testingTest efficiencyLeft half

The invention provides a built-in self-test method of FPGA logical resource. The internal logical module of FPGA is alternately divided into a left half part and a right half part according to row. In the test process, the logical module array of the right half part is firstly configured as a to-be-tested circuit, and the rest logical module arrays are configured as a test vector generating circuit and an output response analyzing circuit, and then the logical module array of the left half part is configured as the to-be-tested circuit, and the rest logical module arrays are configured as the test vector generating circuit and the output response analyzing circuit. The circuit structure is not changed in each process. The logical resource is covered by multiple configurations and the test result is output by a built-in scan register chain. All configurations in the invention are as follows: all logical modules configured as the response analyzing circuits are in cascade connection end to end according to one-dimensional array, so as to simplify the self-test result retrieval manner. Provided that the test coverage is 100%, the built-in self-test method reduces times of the configurations of FPGA logical resource, reduces test cost and increases test flexibility, so as to improve test efficiency.

Owner:BEIJING MXTRONICS CORP +1

System and method for configuring nodes in a network

Owner:SIEMENS IND INC

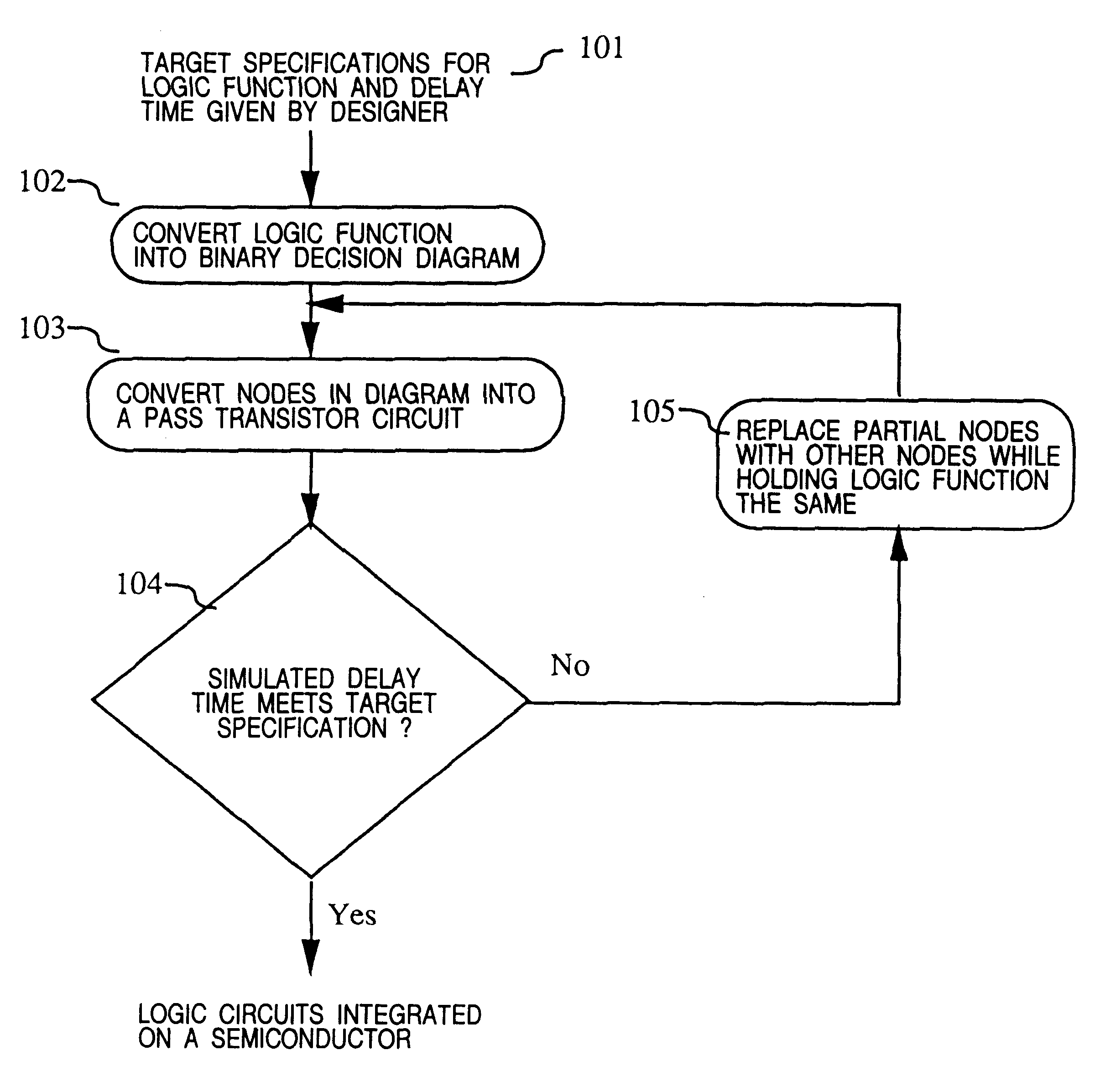

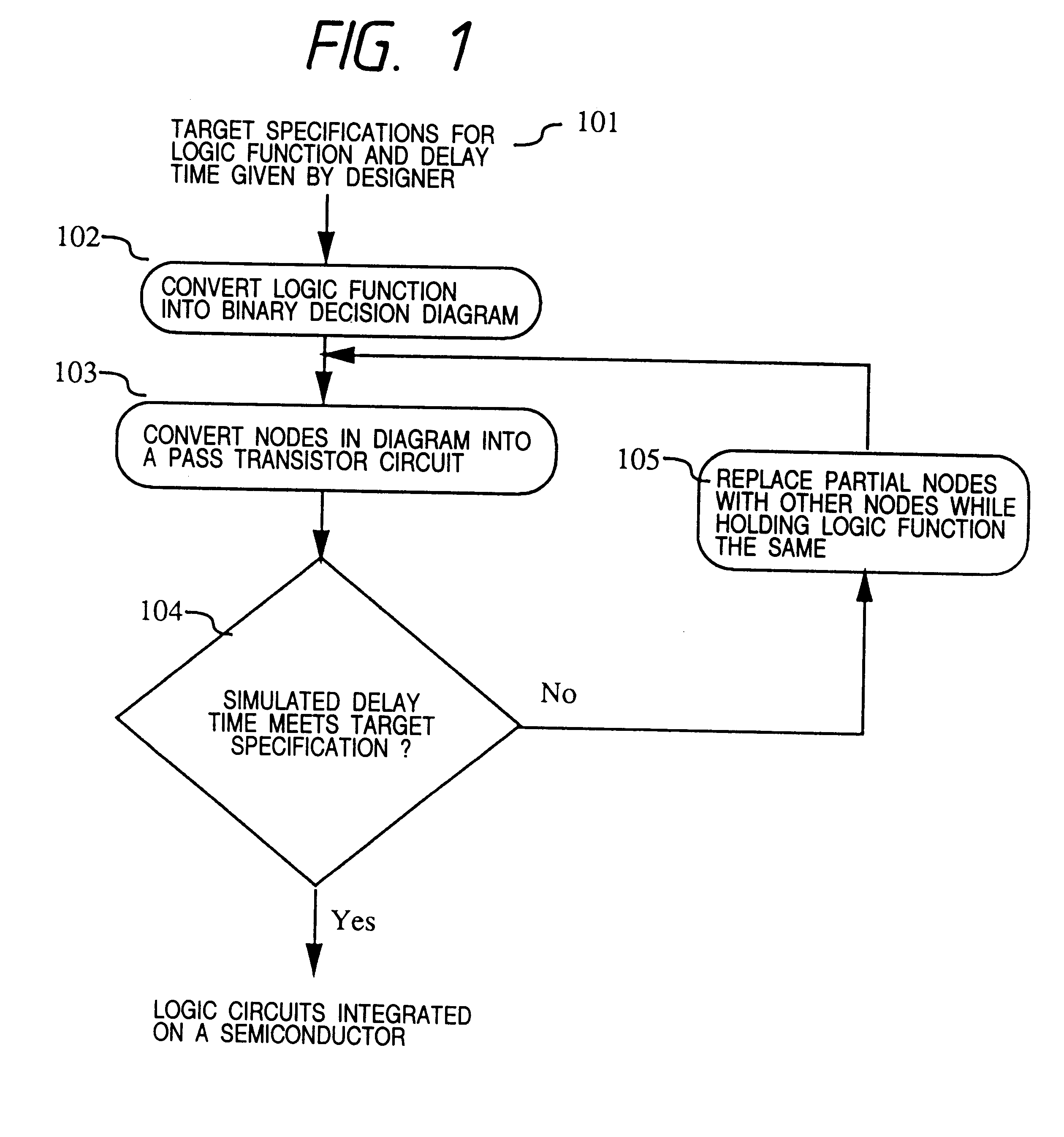

Method for designing semiconductor integrated circuit and automatic designing device

InactiveUS6260185B1Increase the areaIncrease consumptionAnalogue computers for heat flowComputer aided designIntegrated circuitLogic circuitry

A program for automatically designing a logic circuit used for a method of designing a pass transistor circuit, by which the number of required transistors, delay time, power consumption and chip area of the pass transistor circuit is reduced. The program executes the following steps: a) receiving inputted logic functions which define the logical relationship between the inputs and the outputs, and an inputted target specification, b) generating a binary decision diagram from part of the logic functions received at (a), c) replacing the diagram nodes formed at (b) with pass transistor circuit, d) judging whether or not the simulation characteristics of the pass transistor circuit described in (c) meets the target specification described in (a), and executing the following steps when the judgment is "no", e) replacing part of the diagram generated by the procedure described in (b) with another diagram, f) allocating a new binary decision diagram to the control inputs of the nodes of the replaced diagram prepared at (e), and g) repeating the steps (c) and (d) for the diagram prepared at (f).

Owner:HITACHI LTD

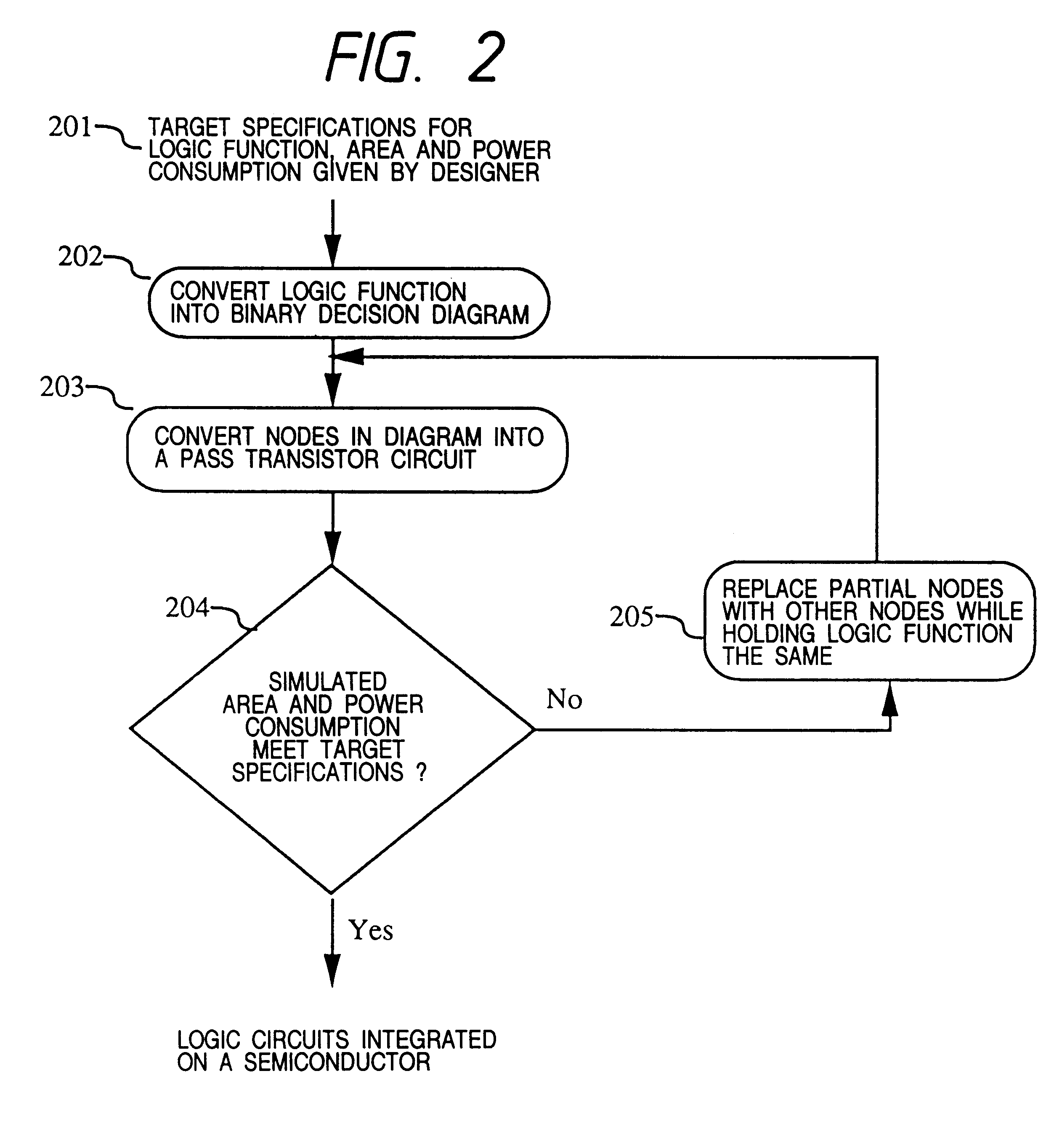

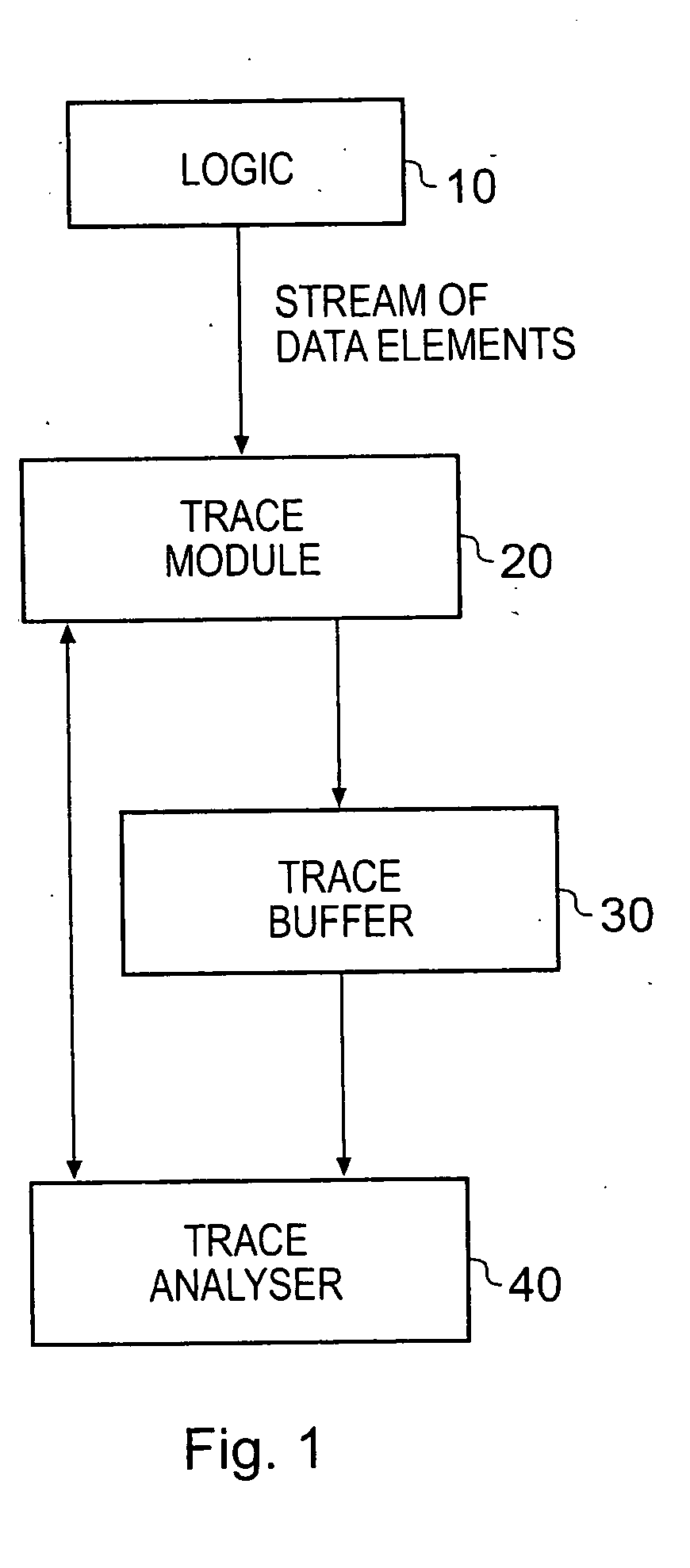

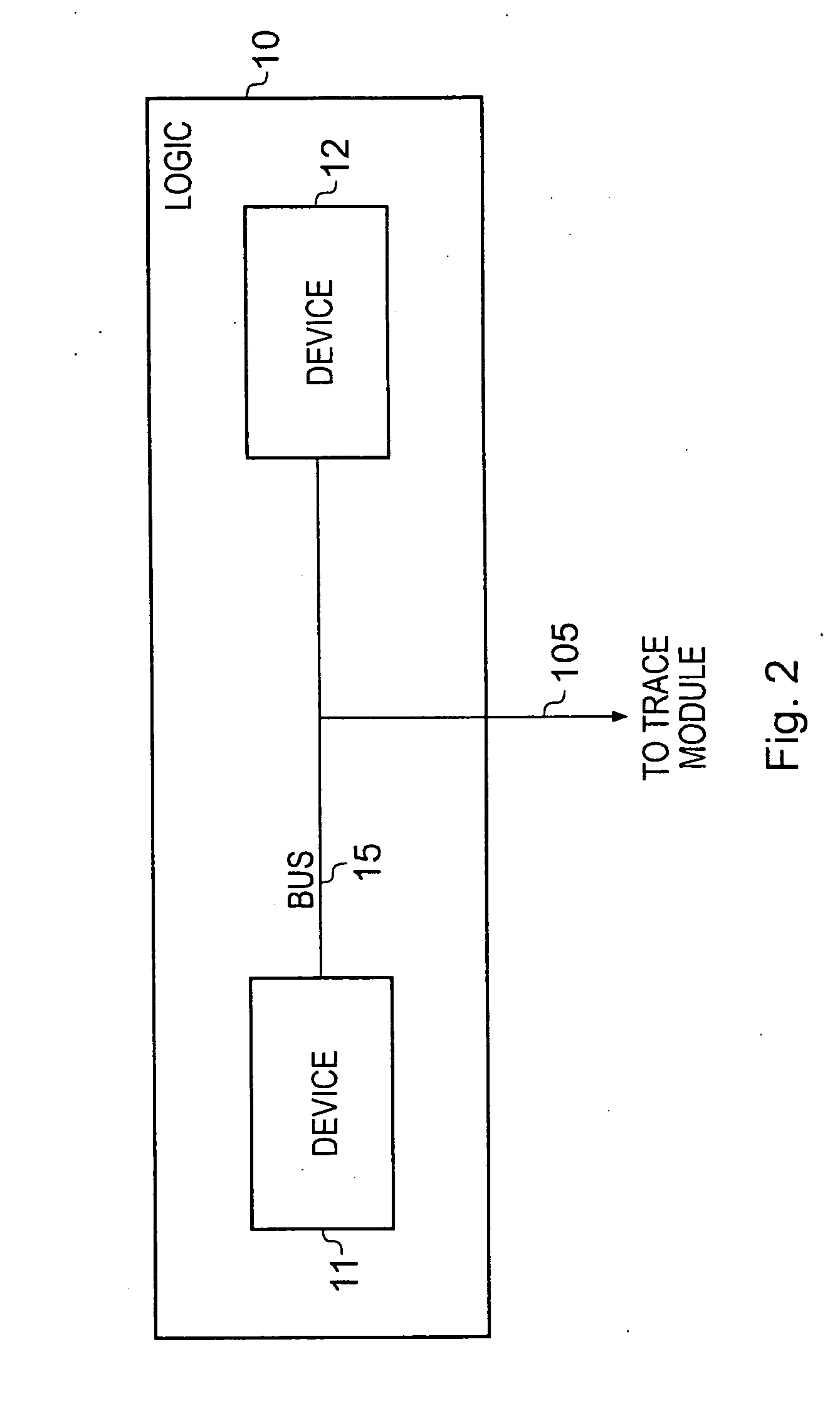

Generation of trace elements within a data processing apparatus

ActiveUS20070226544A1Save bandwidthSave storage spaceError detection/correctionTrace elementParallel computing

A data processing apparatus and method for generating trace elements is provided. The data processing apparatus comprises logic producing a series of data elements, indicative of the operation or state of all or part of the logic. Trace logic is provided for receiving indications of these data elements, and for generating from the indications a stream of trace elements. When for a given data element, at least part of the data element is derivable from a reference to a control value stored in a storage element, the trace logic is operable, dependent on that data element, to omit that part of the associated data element indication from the corresponding trace element generated in respect of the data element, instead including a reference to the corresponding storage element. A trace analysing apparatus can then be used to reconstruct such omitted information based on a copy of the relevant storage element.

Owner:ARM LTD

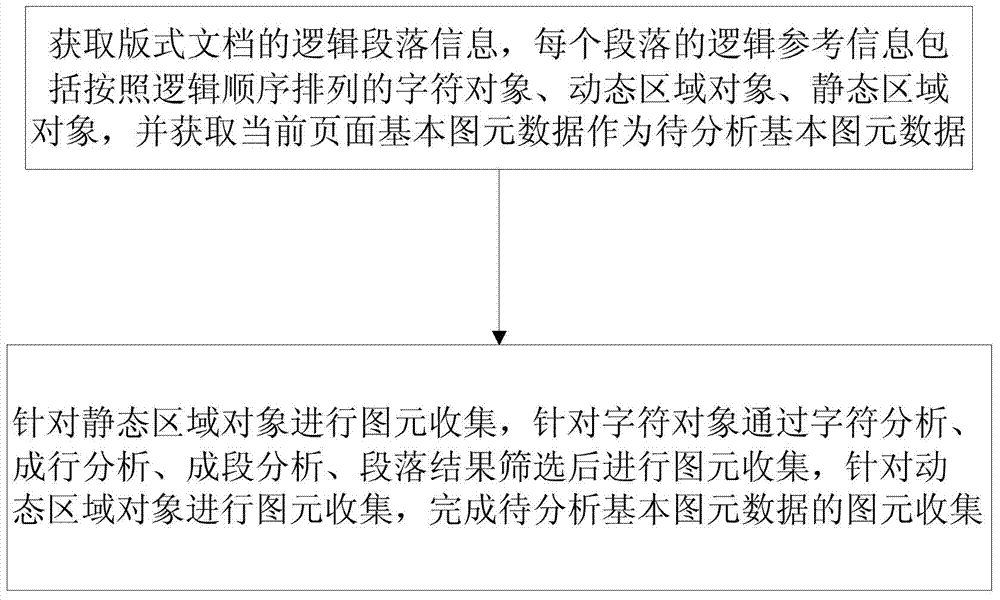

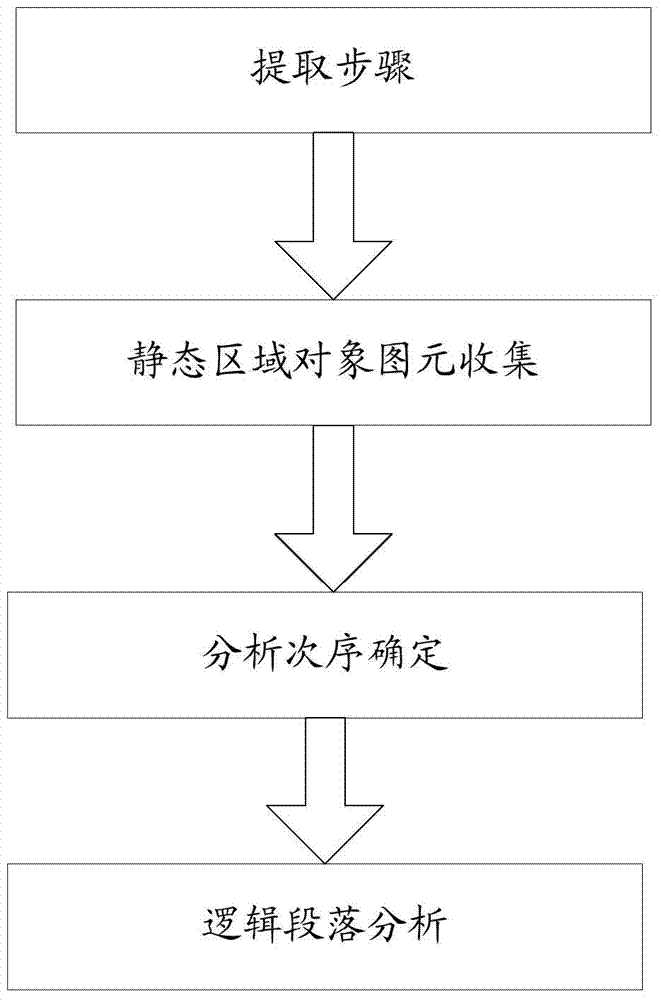

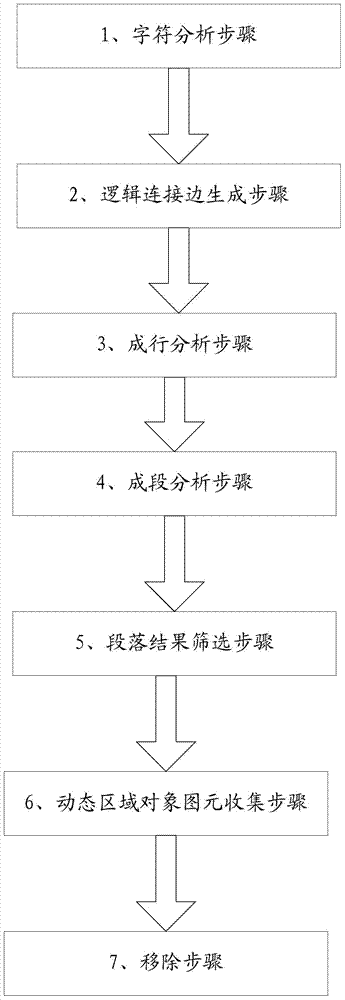

Layout analyzing method and system

ActiveCN104516891AAccurate Layout Analysis ResultsImproved layout analysis resultsCharacter and pattern recognitionSpecial data processing applicationsData informationTheoretical computer science

Embodiments of the present invention provide a layout analysis method, comprising: extraction, collection of basic elements with respect to static area objects, analysis sequence determination and logical paragraph analysis, wherein the logical paragraph analysis comprises character analyzing, logical connection edge generating, line forming analyzing, paragraph forming analyzing, paragraph result filtering, basic elements collecting with respect to the dynamic area objects and basic element removing. According to the embodiments of the present invention, logical reference information and basic element data information are combined, and the logical reference information is fully used during layout analysis, such that a more accurate layout analysis result with respect to a fixed-layout document is acquired, and the layout analysis result is effectively improved.

Owner:NEW FOUNDER HLDG DEV LLC +1

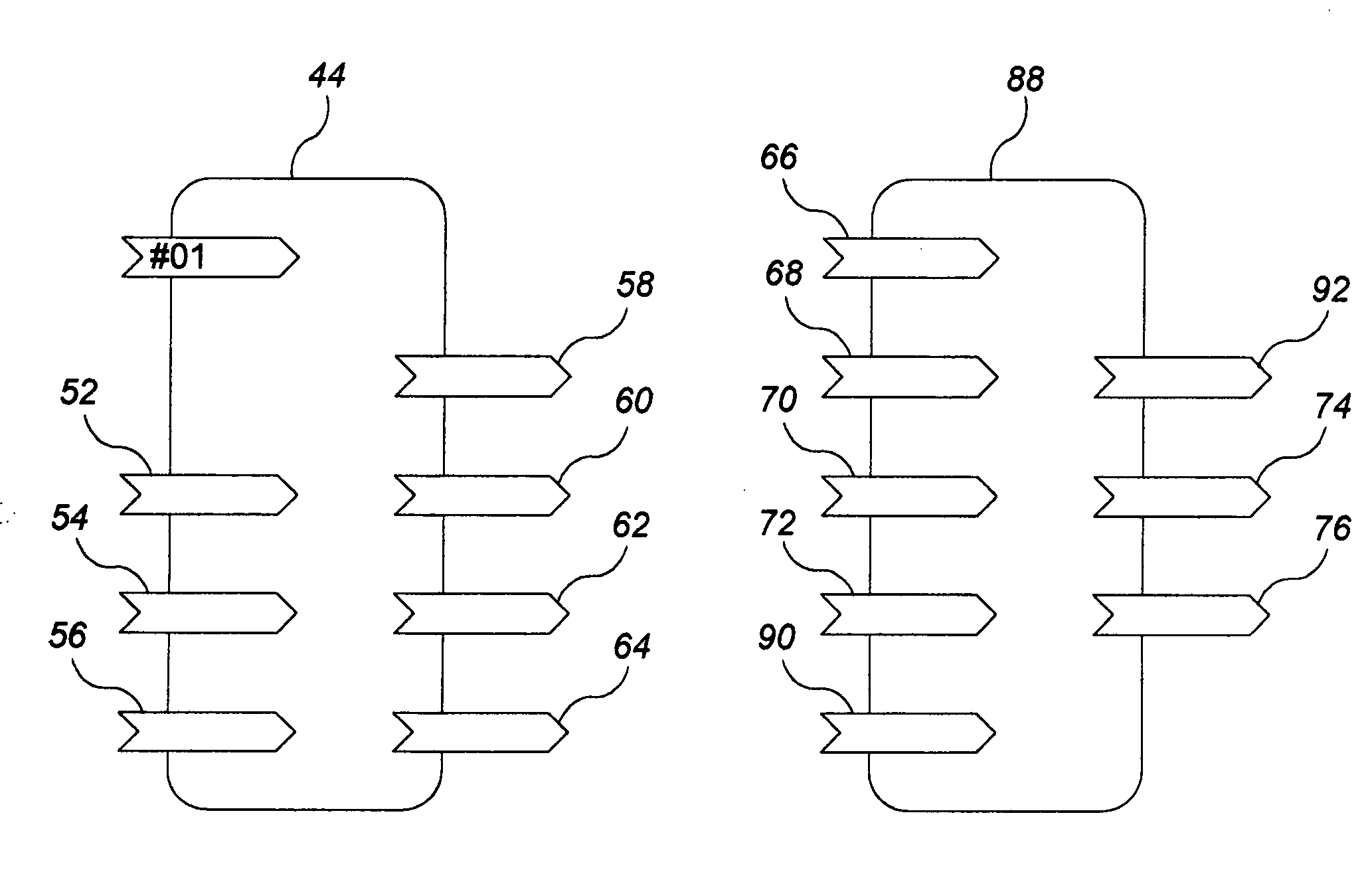

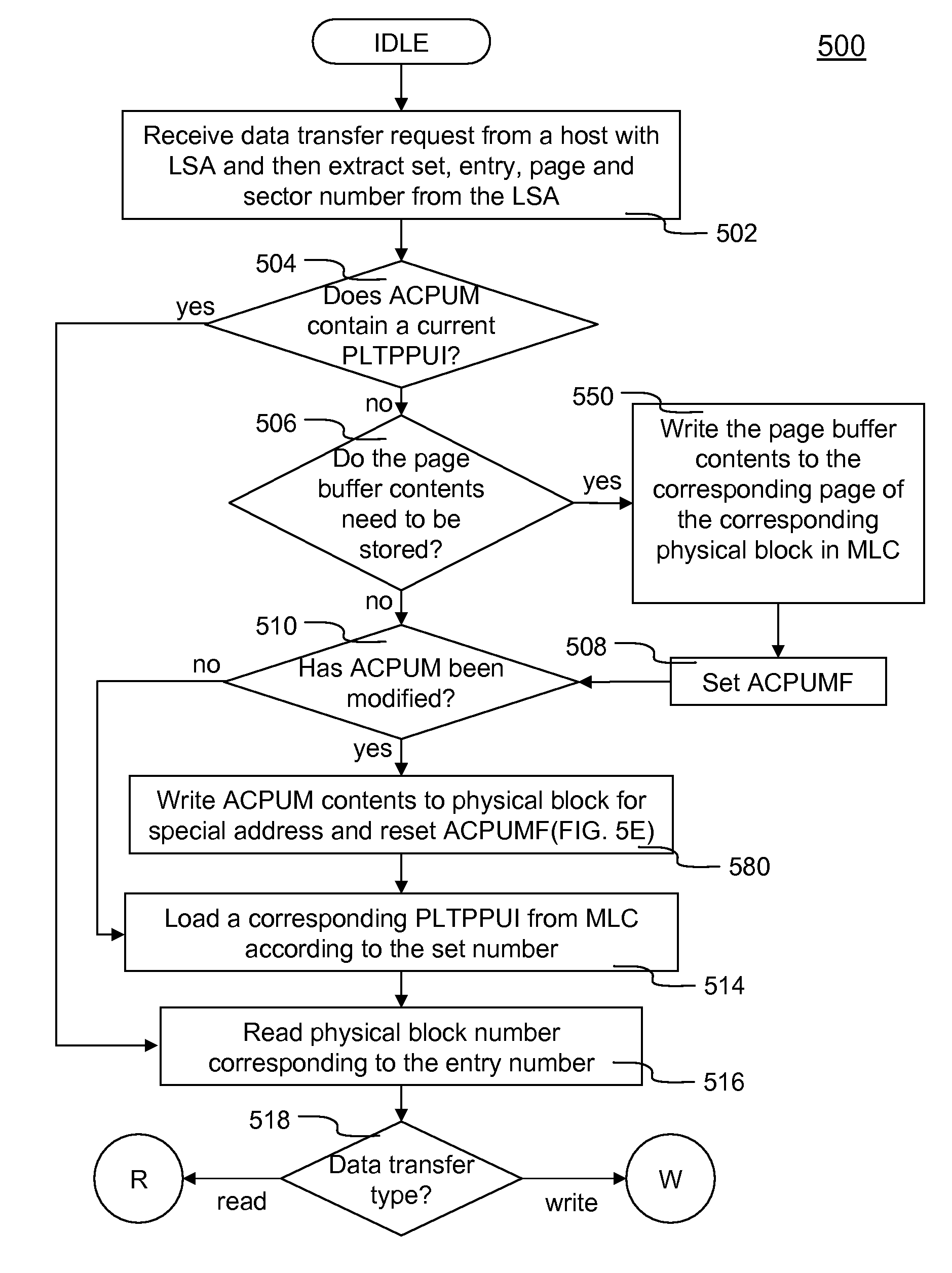

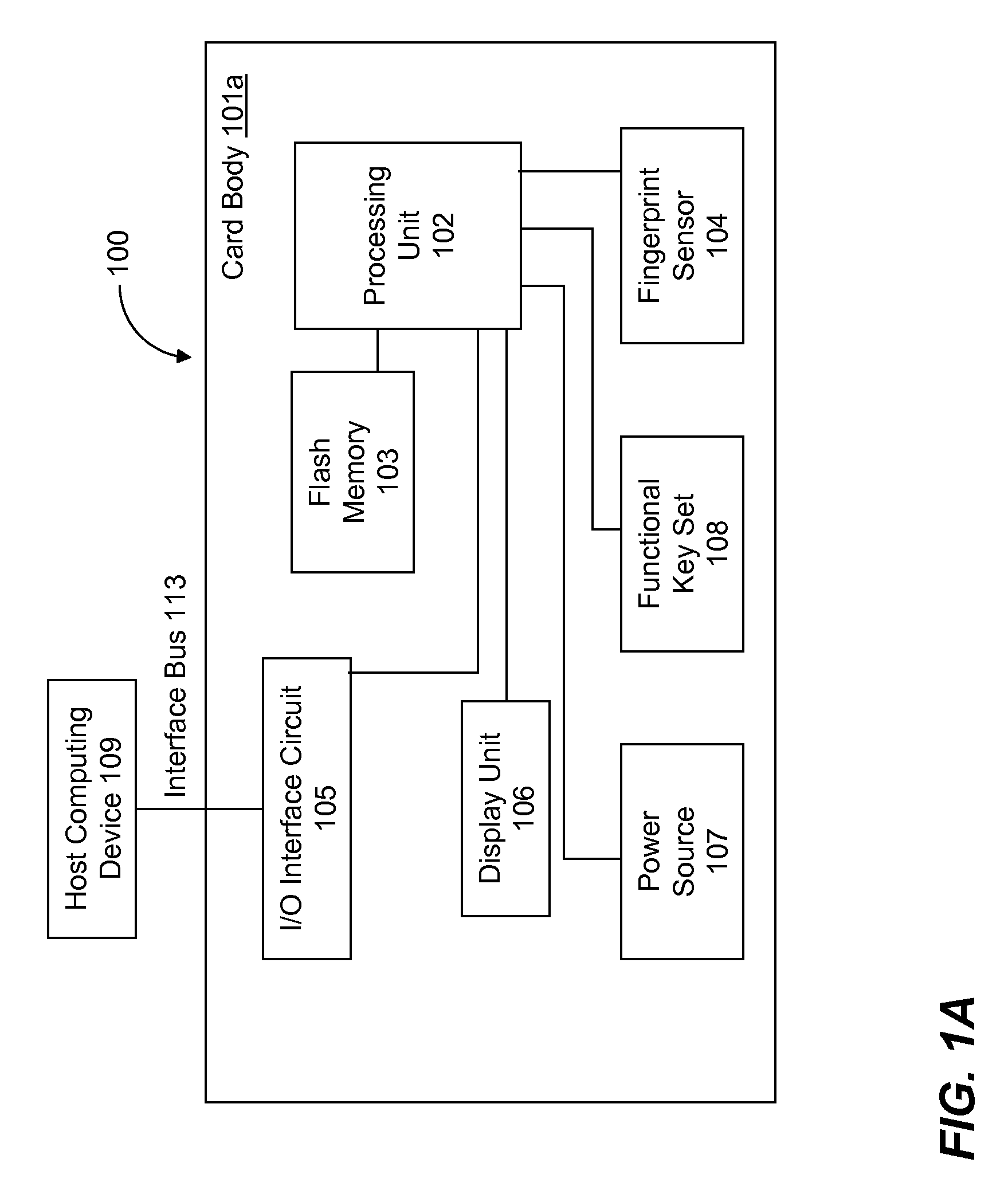

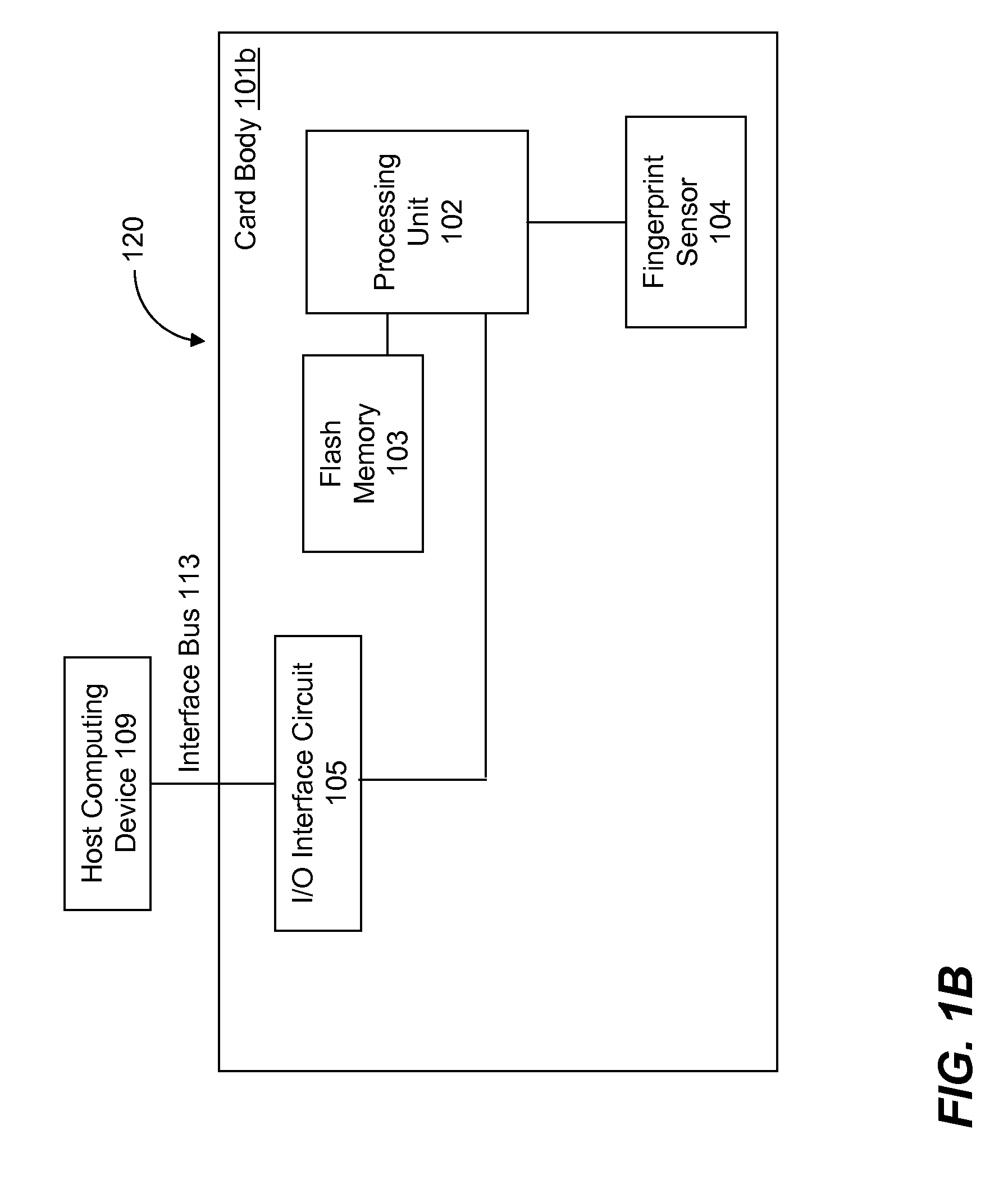

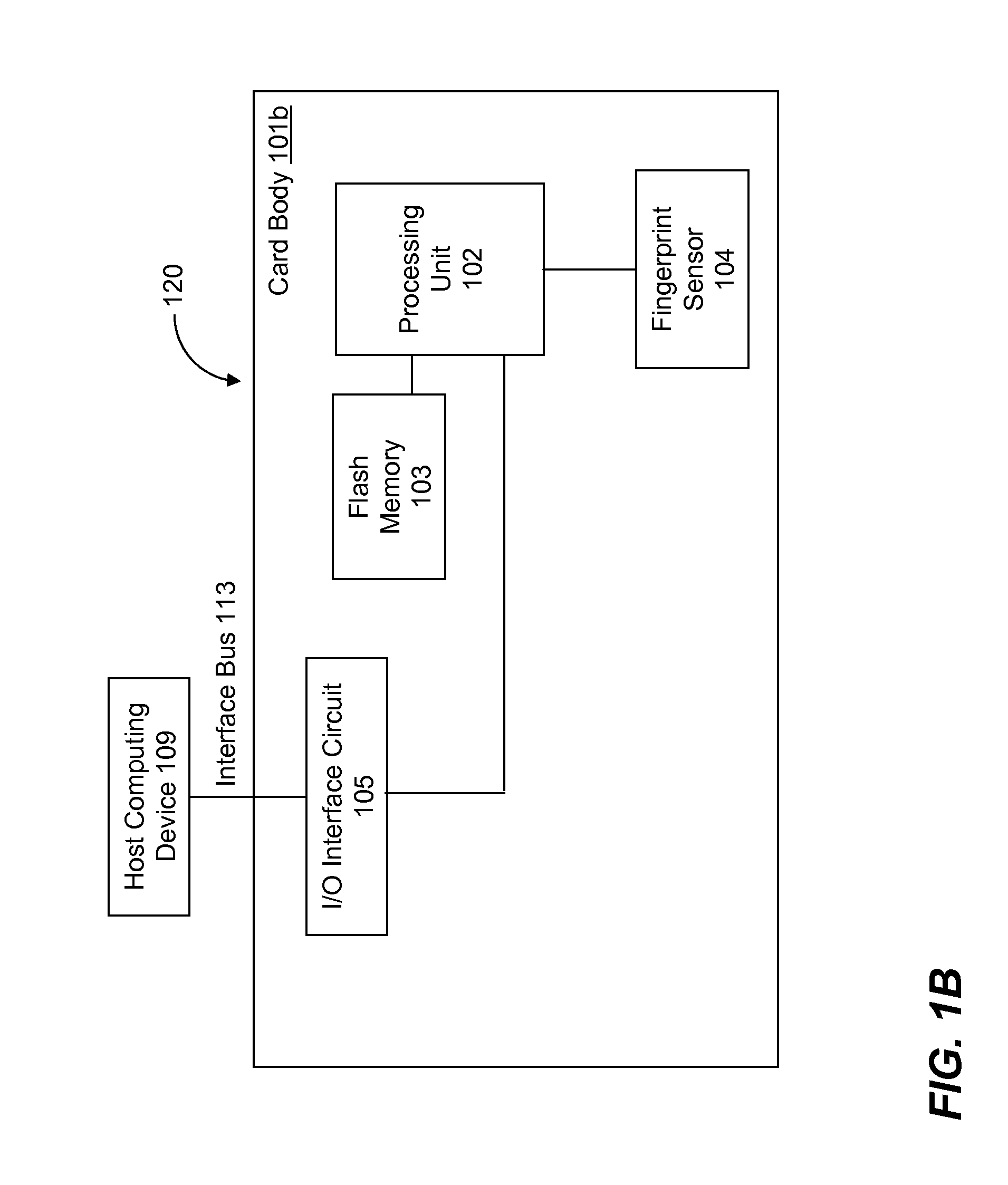

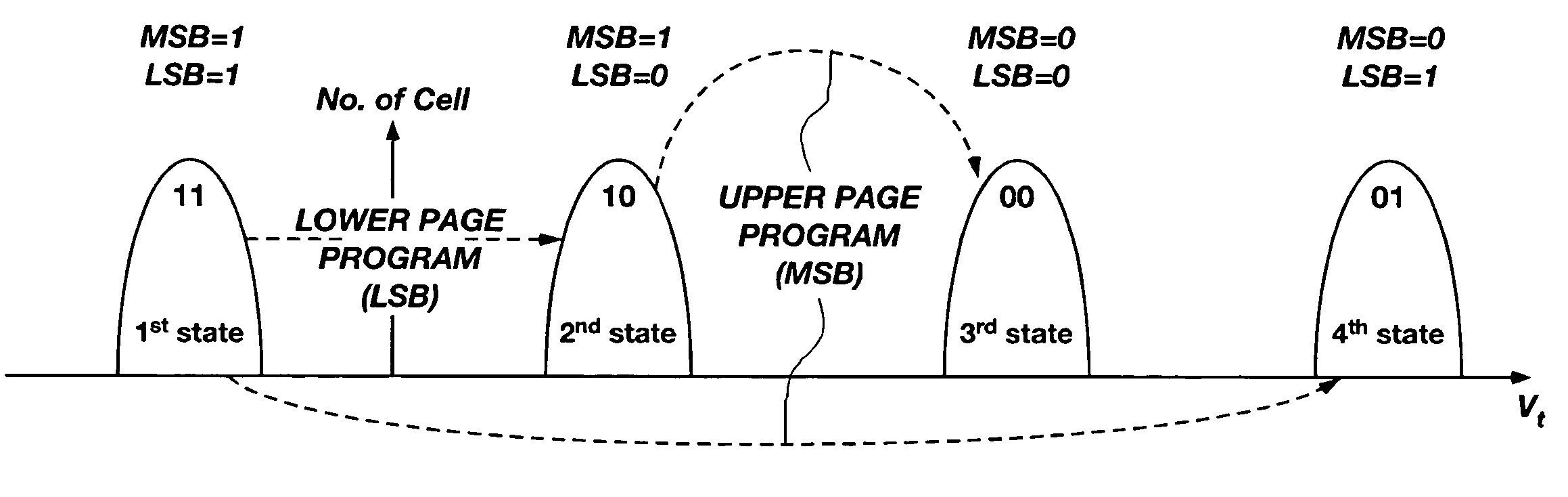

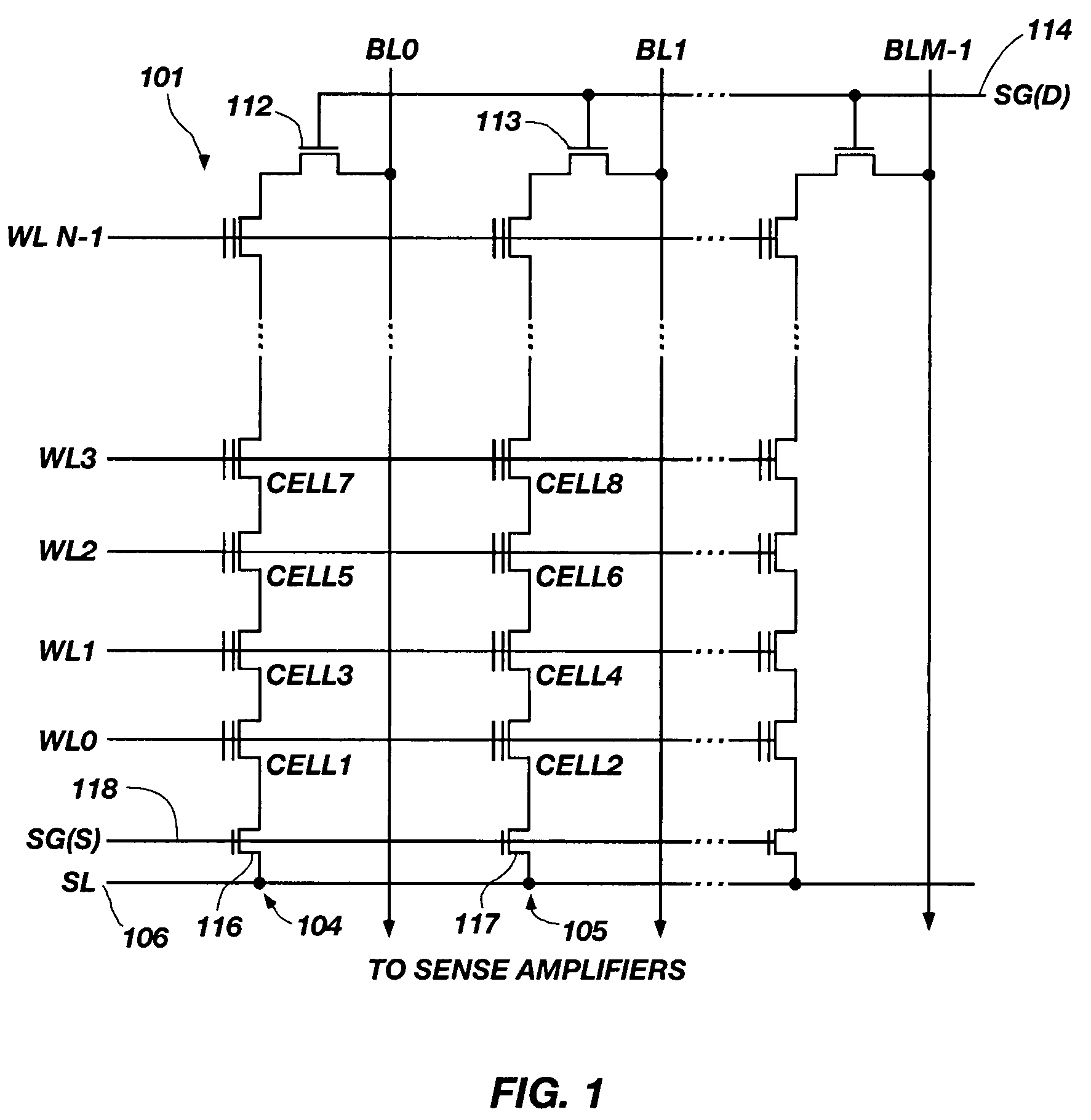

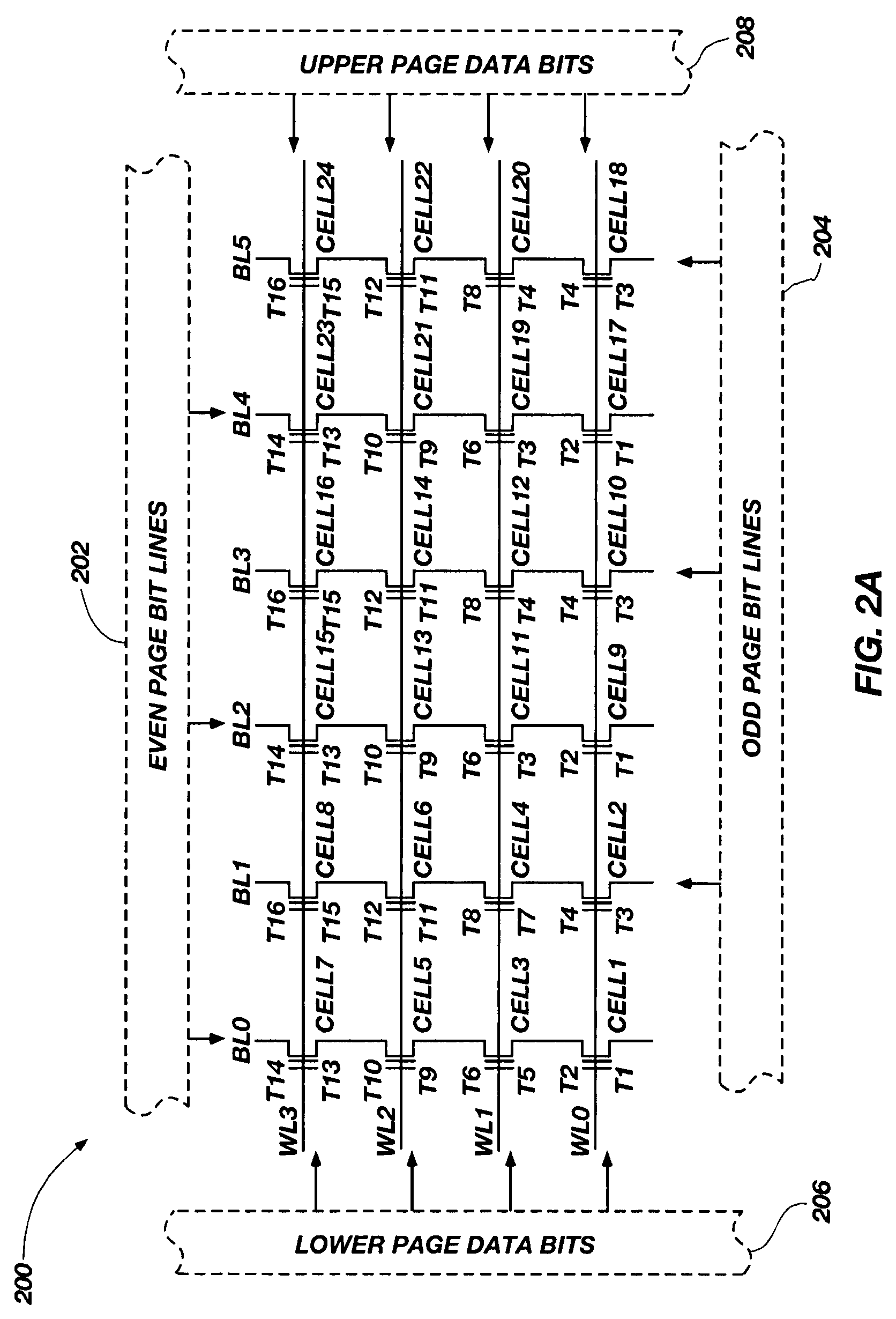

Methods and systems of managing memory addresses in a large capacity multi-level cell (MLC) based flash memory device

Methods and systems of managing memory addresses in a large capacity multi-level cell based flash memory device are described. According to one aspect, a flash memory device comprises a processing unit to manage logical-to-physical address correlation using an indexing scheme. The flash memory is partitioned into N sets. Each set includes a plurality of entries (i.e., blocks). N sets of partial logical entry number to physical block number and associated page usage information (hereinafter ‘PLTPPUI’) are stored in the reserved area of the MLC based flash memory. Only one the N sets is loaded to address correlation and page usage memory (ACPUM), which is a limited size random access memory (RAM). In one embodiment, static RAM (SRAM) is implemented for fast access time for the address correlation. LSA received together with the data transfer request dictates which one of the N sets of PLTPPUI is loaded into ACPUM.

Owner:SUPER TALENT TECH CORP

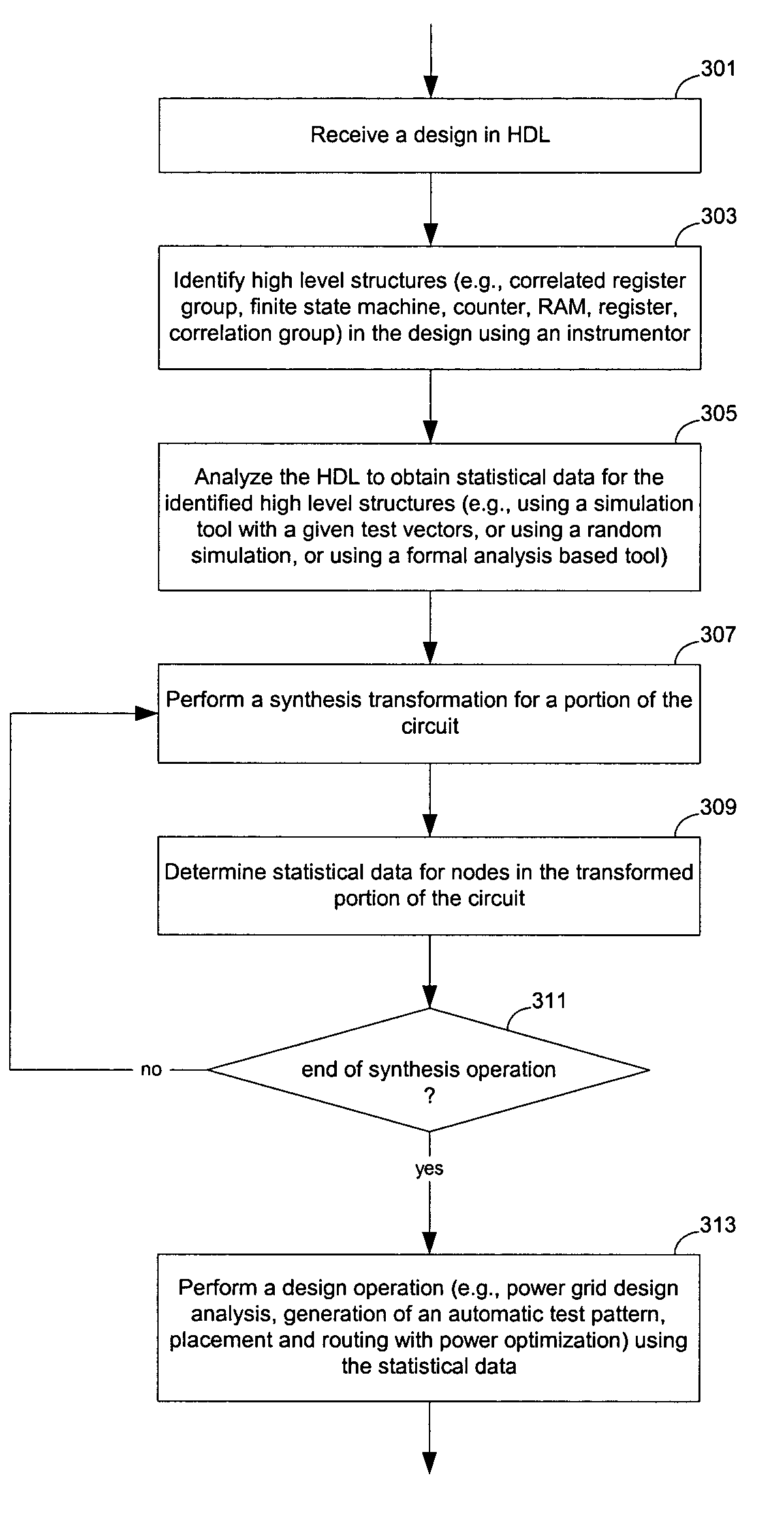

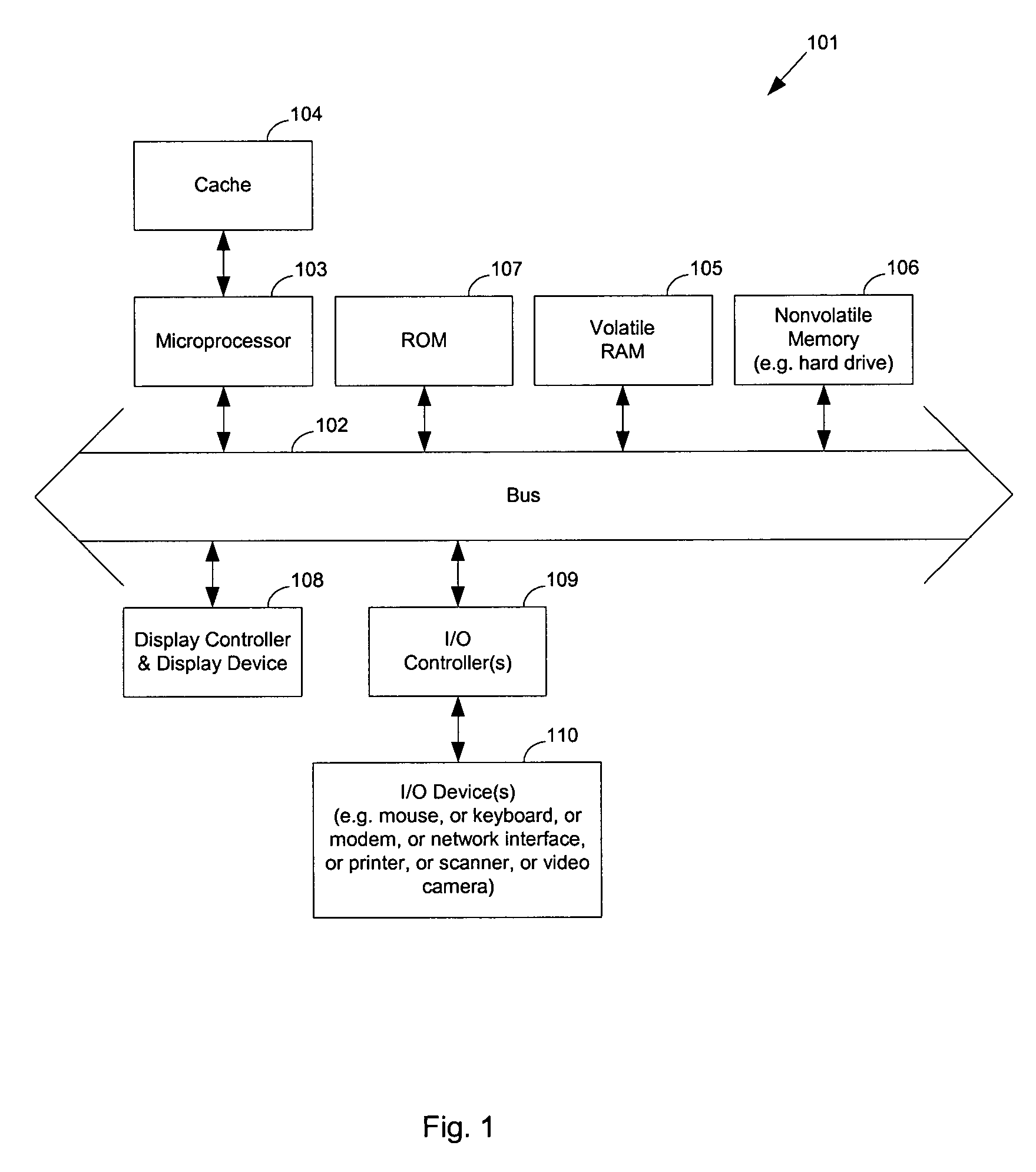

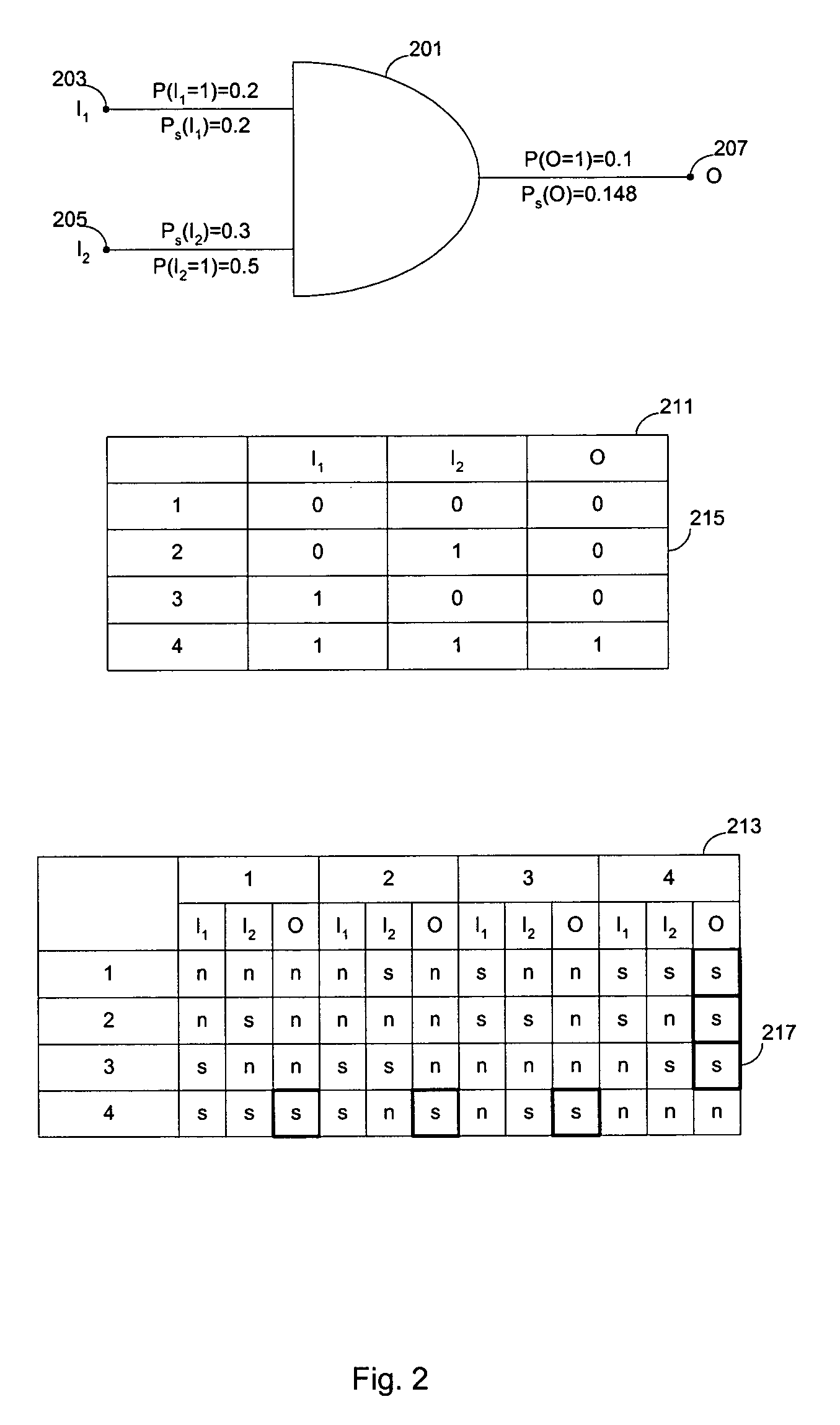

Method and apparatus for circuit design and synthesis

InactiveUS7131078B1Avoid analysisCAD circuit designSoftware simulation/interpretation/emulationSynthesis methodsStatistical analysis

Methods and apparatuses to maintain and propagate statistical data during circuit synthesis. At least one embodiment of the present invention maintains and propagates statistical data during and after circuit synthesis transformation operations. In one example, the signal switching activity is calculated once at the RTL level and then propagated and / or maintained at various nodes of the circuit through the process of logic synthesis. Thus, the statistical analysis of entire circuit during or after the logic synthesis is avoided. In one example, power optimization is performed during logic synthesis. A portion of the logic synthesis transformation is driven by the power consumption optimization; and, the statistical data about circuit activity maintained at the nodes of the circuit during the synthesis process is used to calculate the power consumption at various points in the process of synthesis transformation.

Owner:SYNOPSYS INC

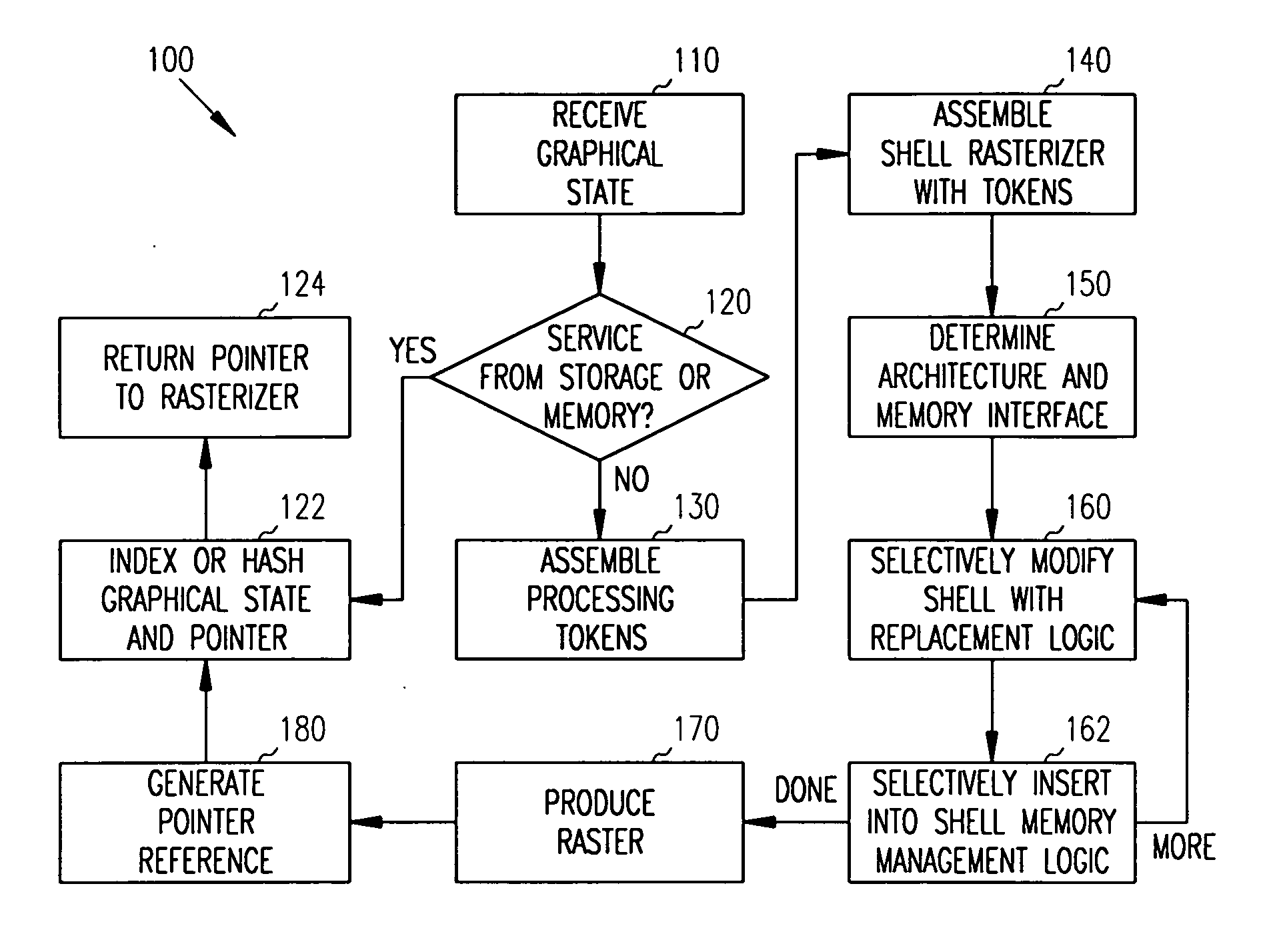

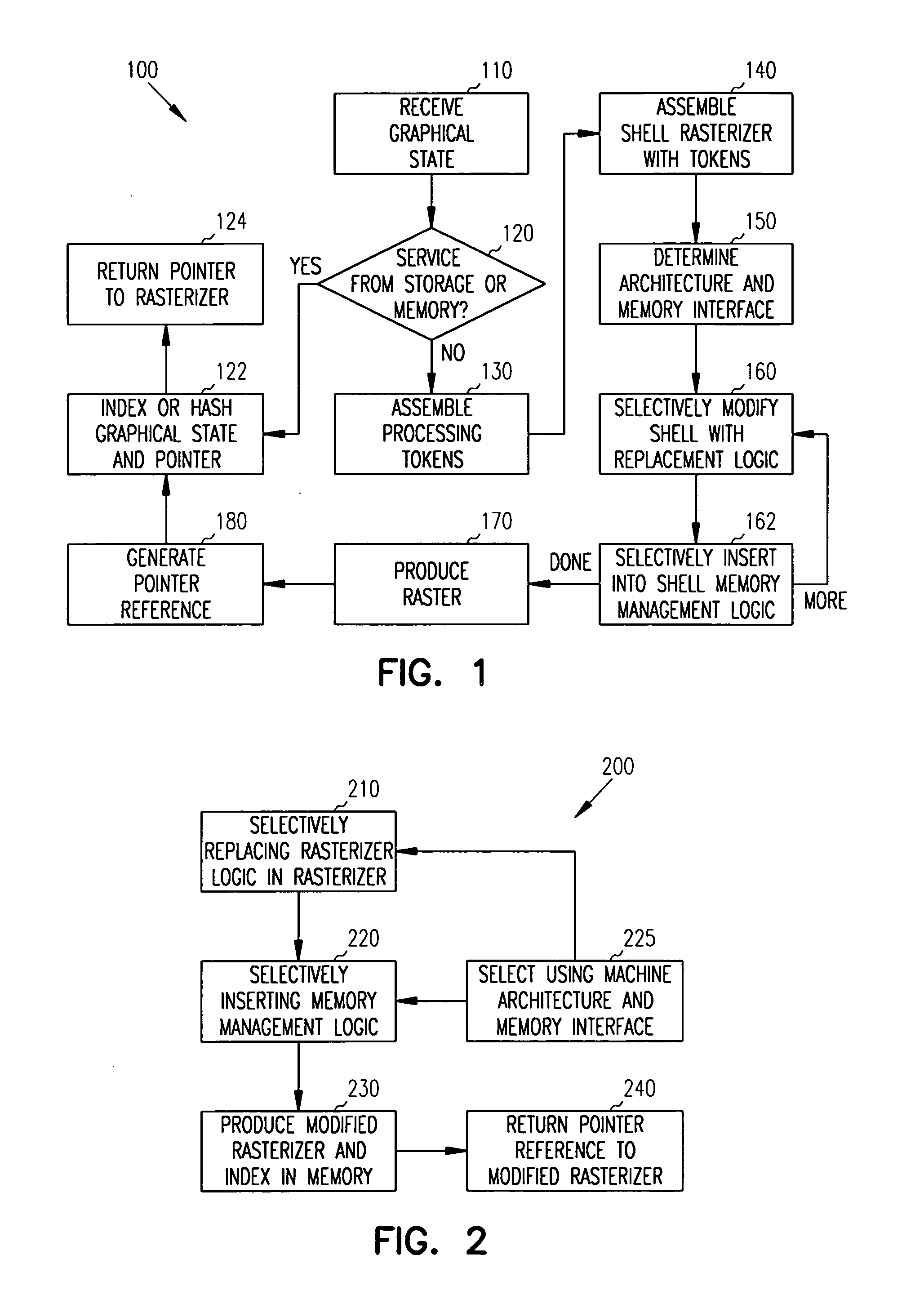

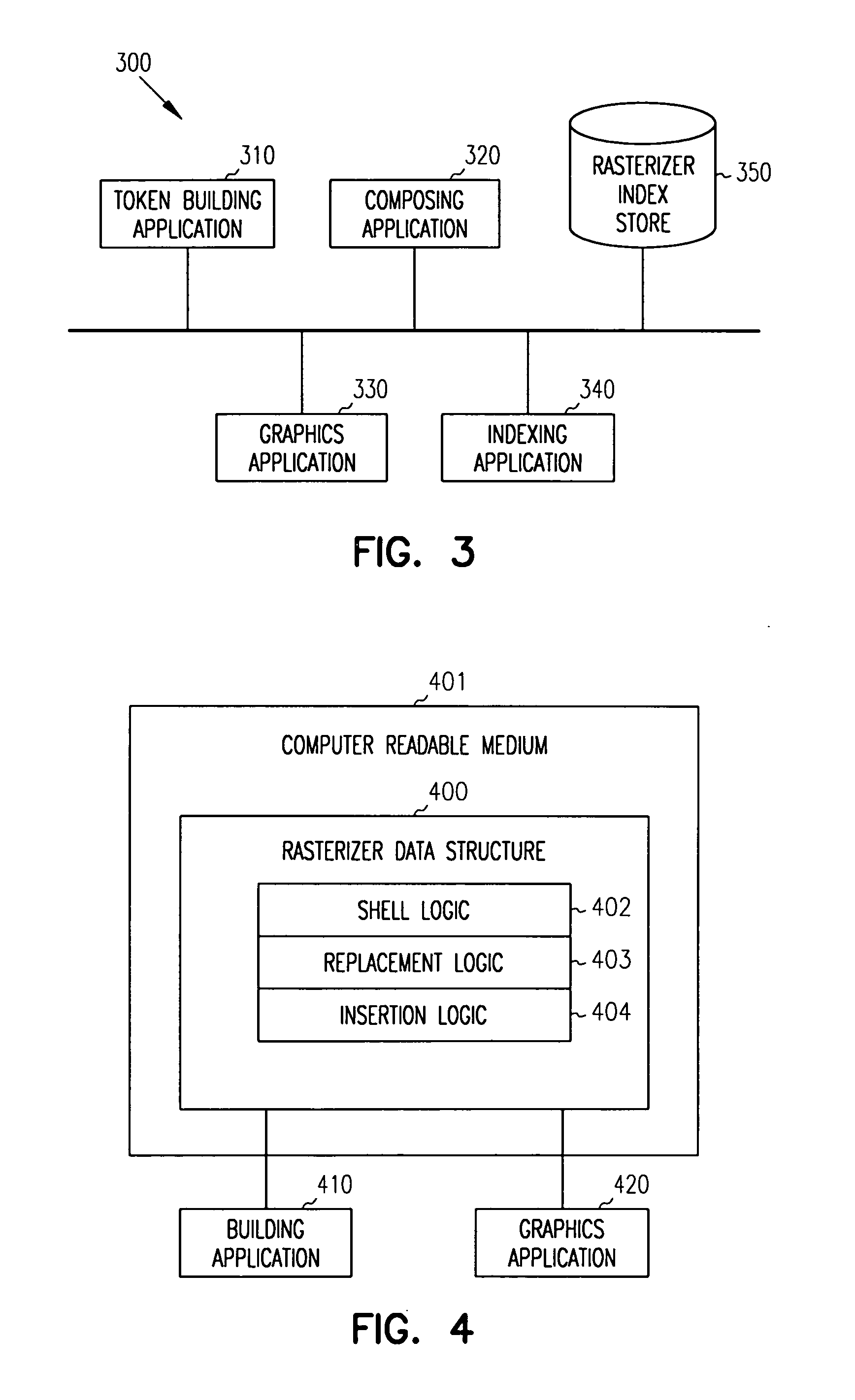

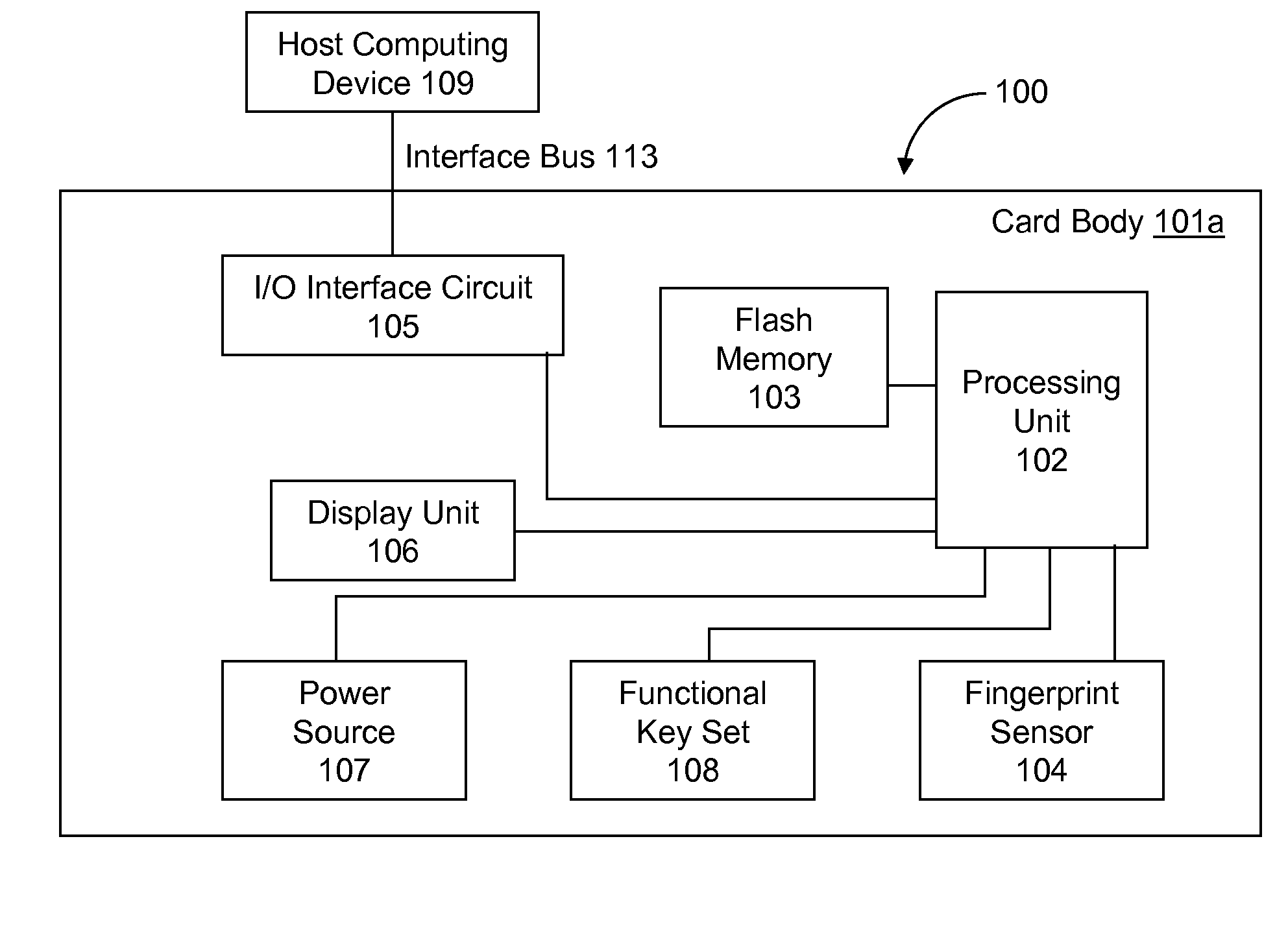

Methods, systems, and data structures for generating a rasterizer

Methods, systems and data structures produce a rasterizer. A graphical state is detected on a machine architecture. The graphical state is used for assembling a shell rasterizer. The machine architecture is used for selecting replacement logic that replaces portions of shell logic in the shell rasterizer. The machine architecture is used for selectively inserting memory management logic into portions of the shell logic to produce.

Owner:INTEL CORP

Memory address management systems in a large capacity multi-level cell (MLC) based flash memory device

ActiveUS20110093653A1Memory architecture accessing/allocationCoupling device detailsMemory addressAccess time

Methods and systems of managing memory addresses in a large capacity multi-level cell based flash memory device are described. According to one aspect, a flash memory device comprises a processing unit to manage logical-to-physical address correlation using an indexing scheme. The flash memory is partitioned into N sets. Each set includes a plurality of entries (i.e., blocks). N sets of partial logical entry number to physical block number and associated page usage information (hereinafter ‘PLTPPUI’) are stored in the reserved area of the MLC based flash memory. Only one the N sets is loaded to address correlation and page usage memory (ACPUM), which is a limited size random access memory (RAM). In one embodiment, static RAM (SRAM) is implemented for fast access time for the address correlation. LSA received together with the data transfer request dictates which one of the N sets of PLTPPUI is loaded into ACPUM.

Owner:SUPER TALENT TECH CORP

Memory page boosting method, device and system

A memory page boosting method, device and system for boosting unselected memory cells in a multi-level cell memory cell is described. The memory device includes a memory array of multi-level cell memory cells configured to store a first portion of logic states and a second portion of logic states. When programming the first portion of logic states, a first boosting process is applied to unselected memory cells and when programming the second portion of logic states, a second boosting process is applied to unselected memory cells.

Owner:MICRON TECH INC

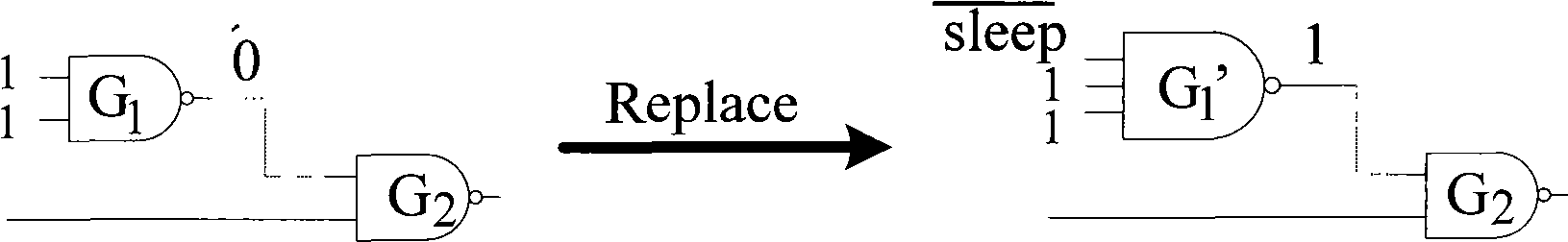

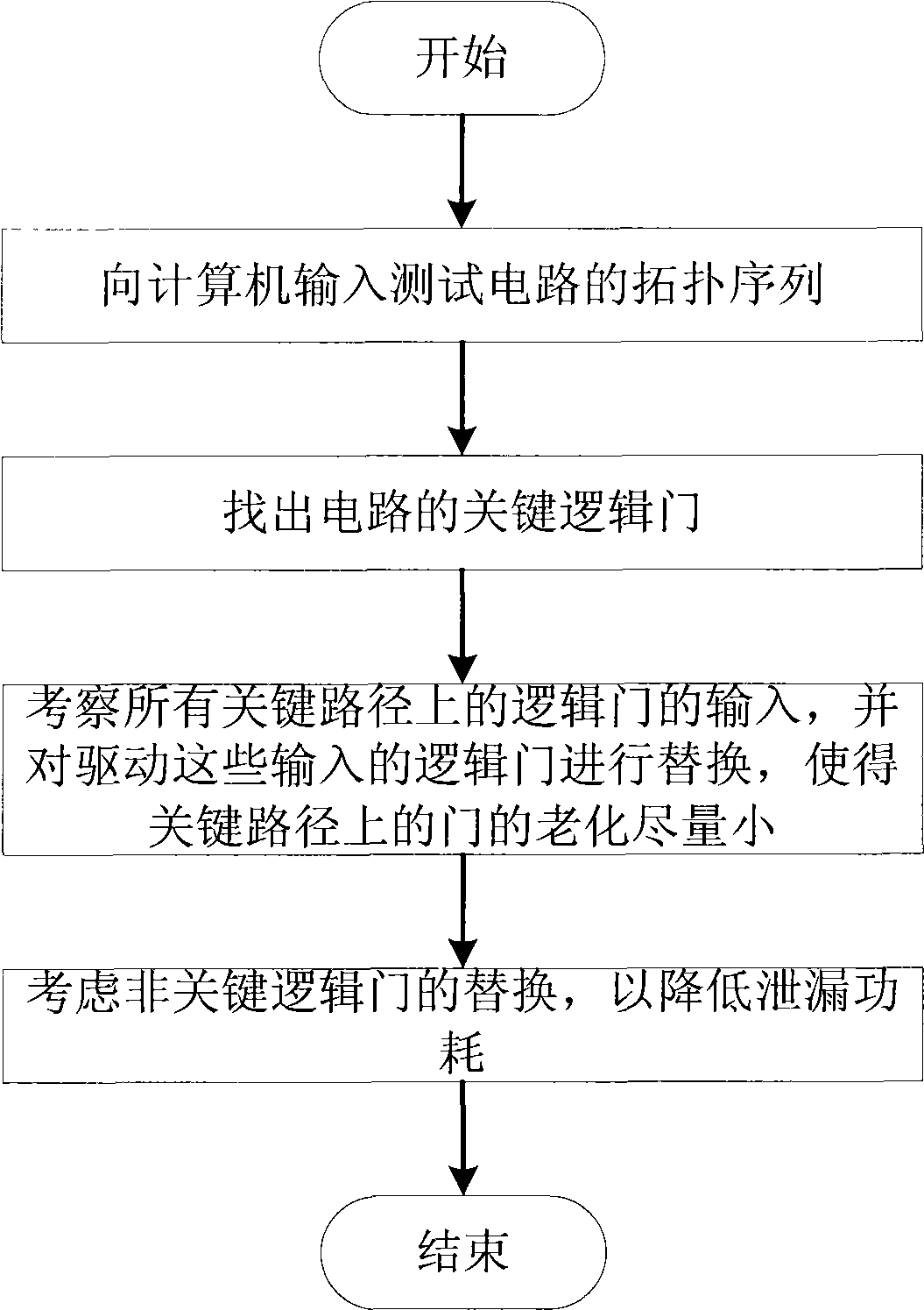

Gate replacing method for easing aging of integrated circuit and reducing leakage power consumption

ActiveCN101533424ADelay agingReduce leakage powerElectronic circuit testingSpecial data processing applicationsSleep stateEngineering

Owner:TSINGHUA UNIV

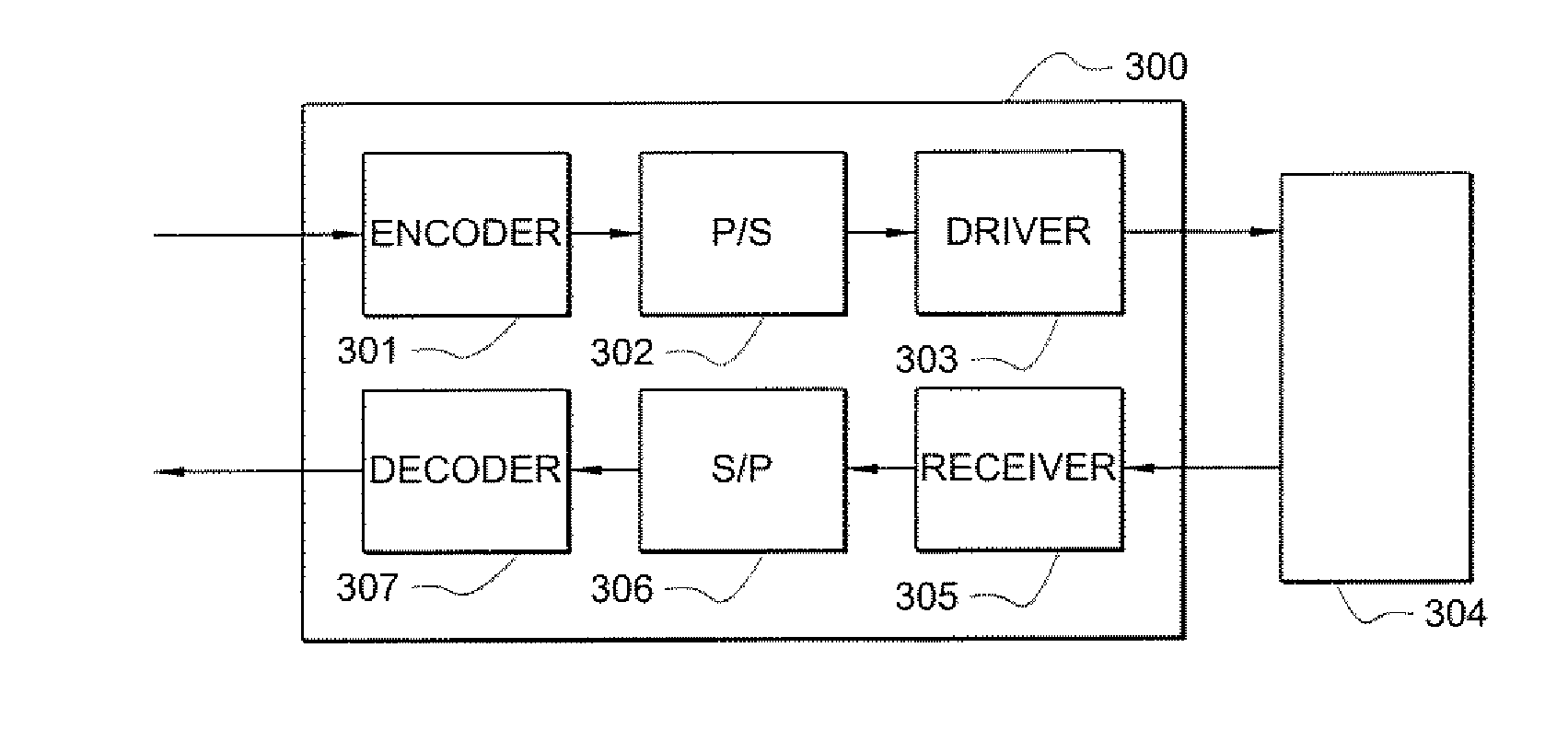

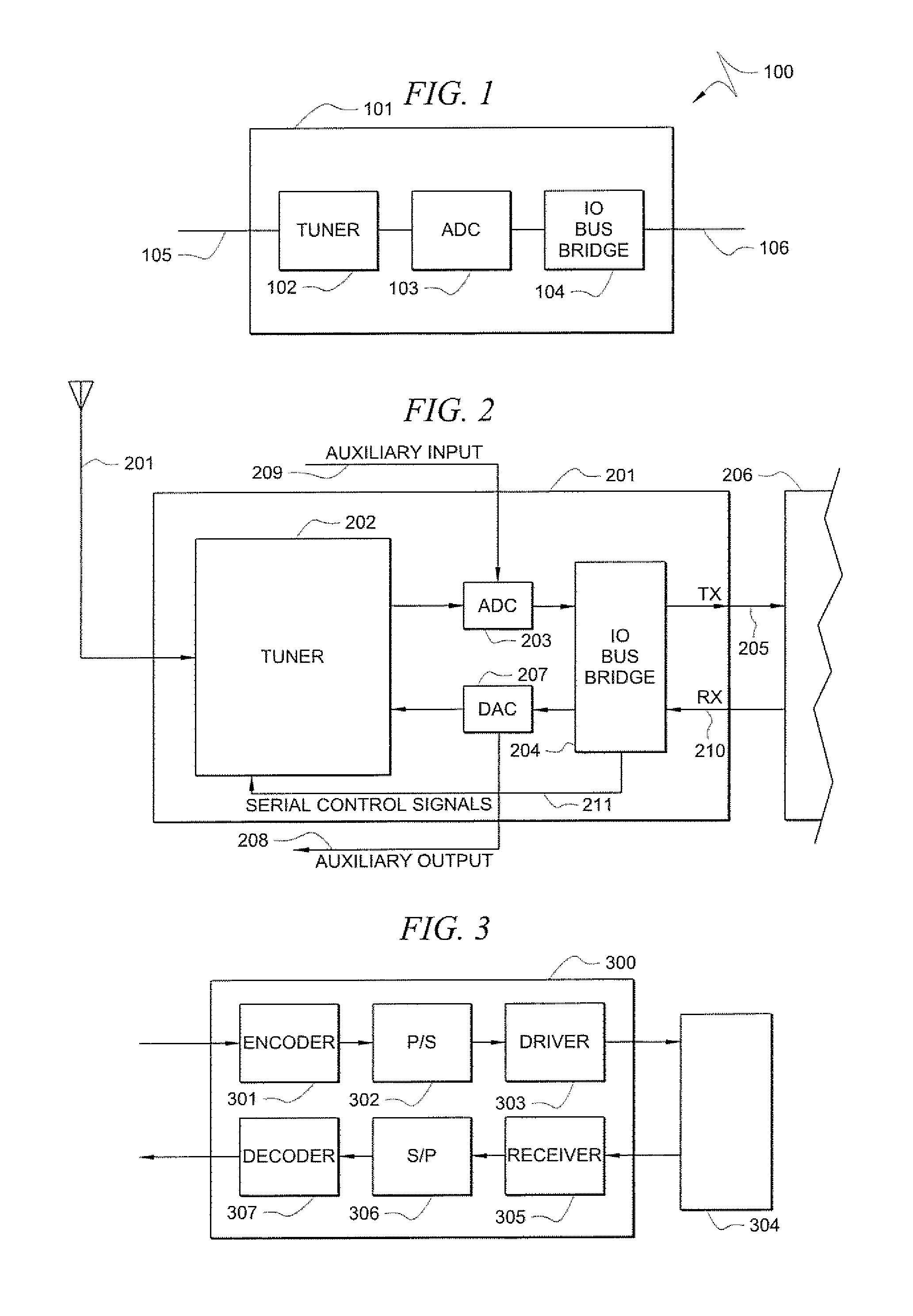

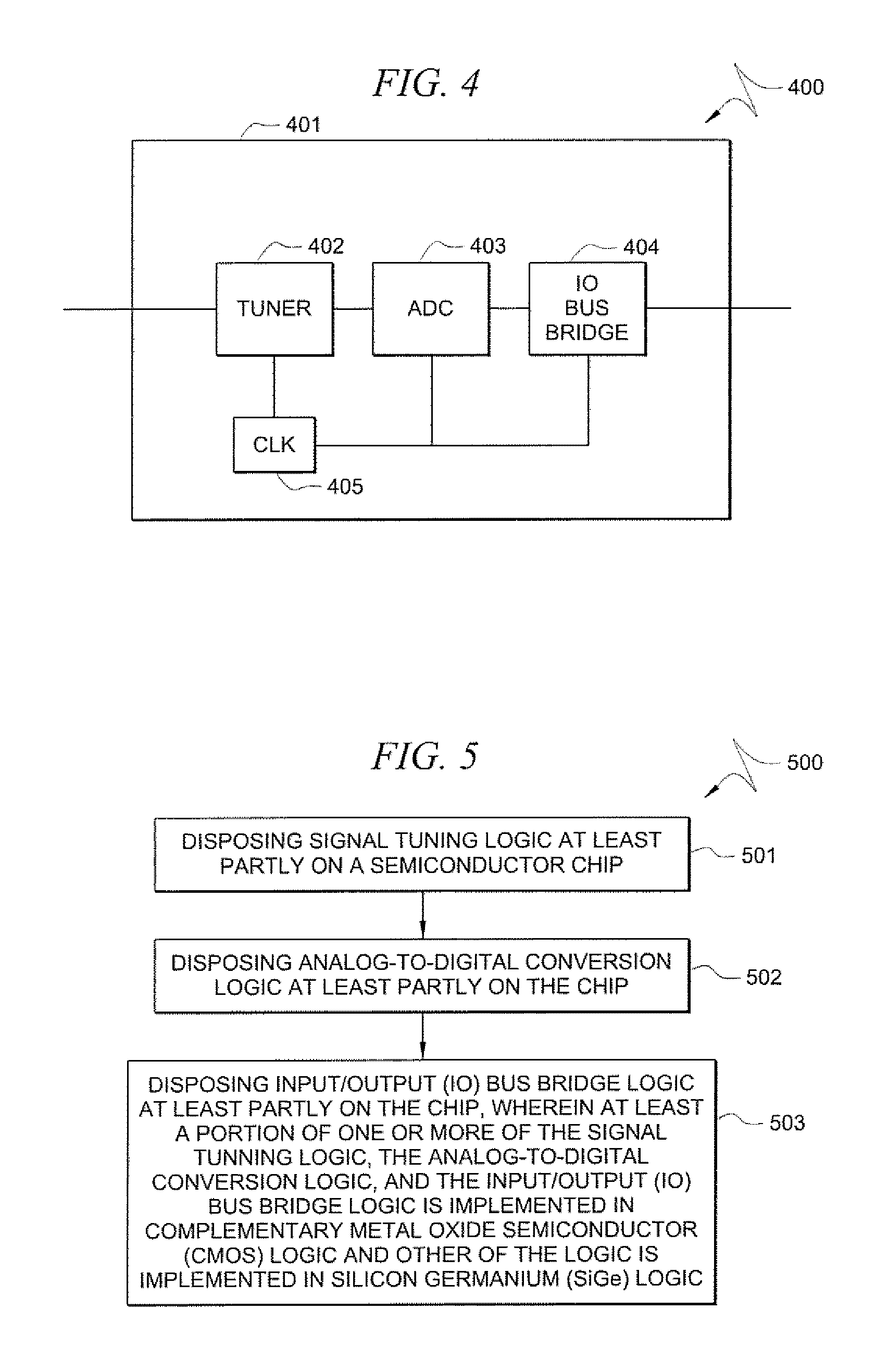

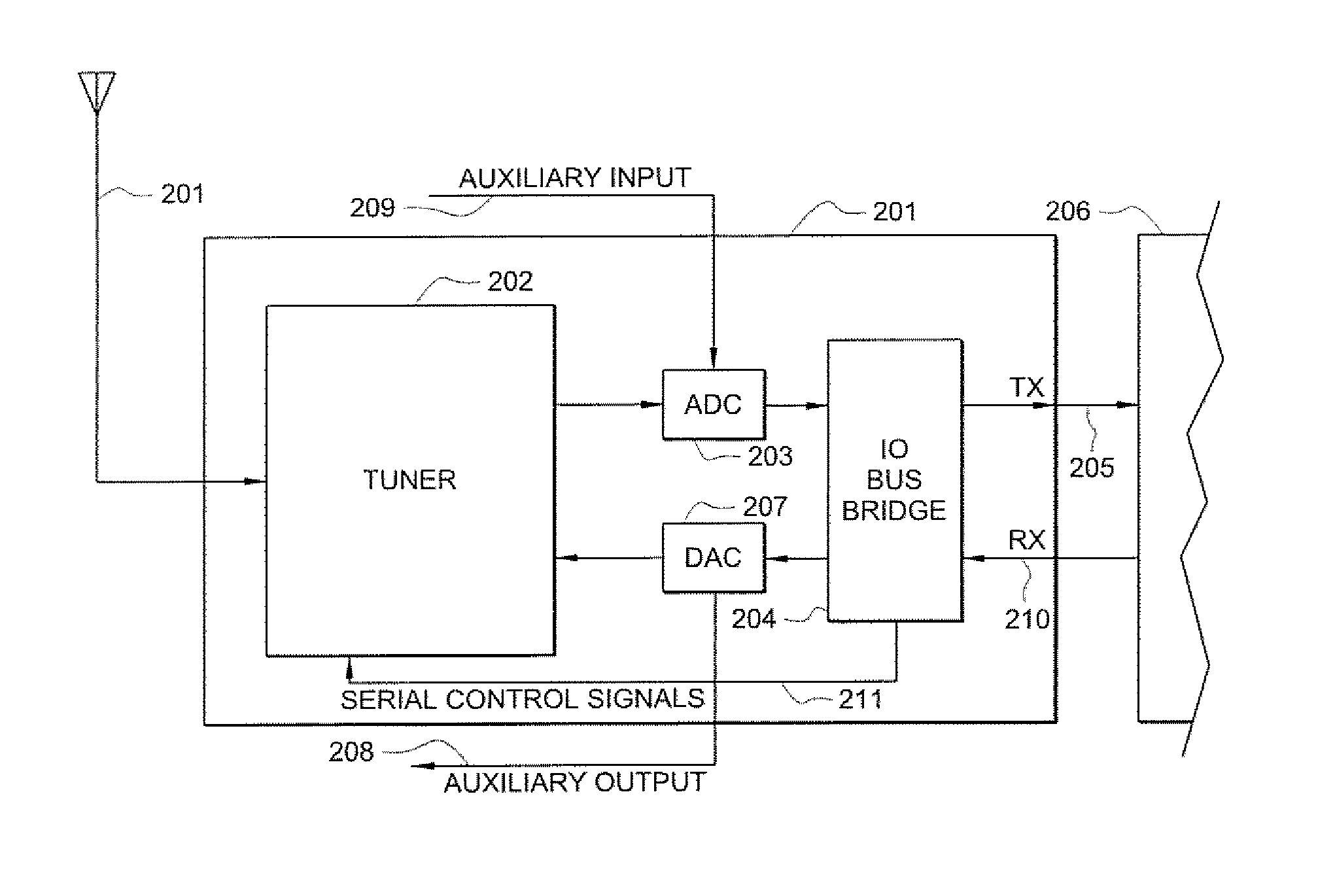

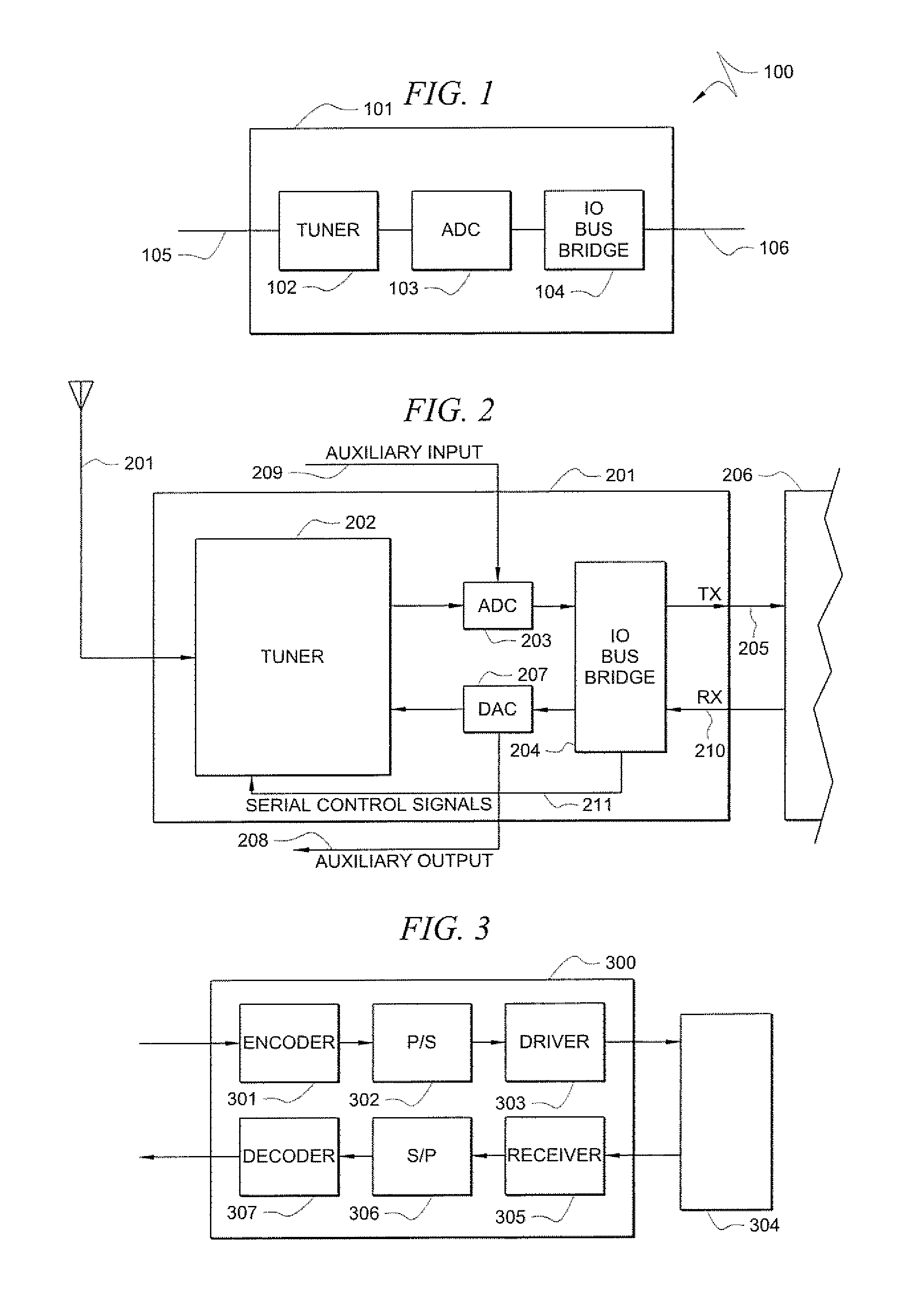

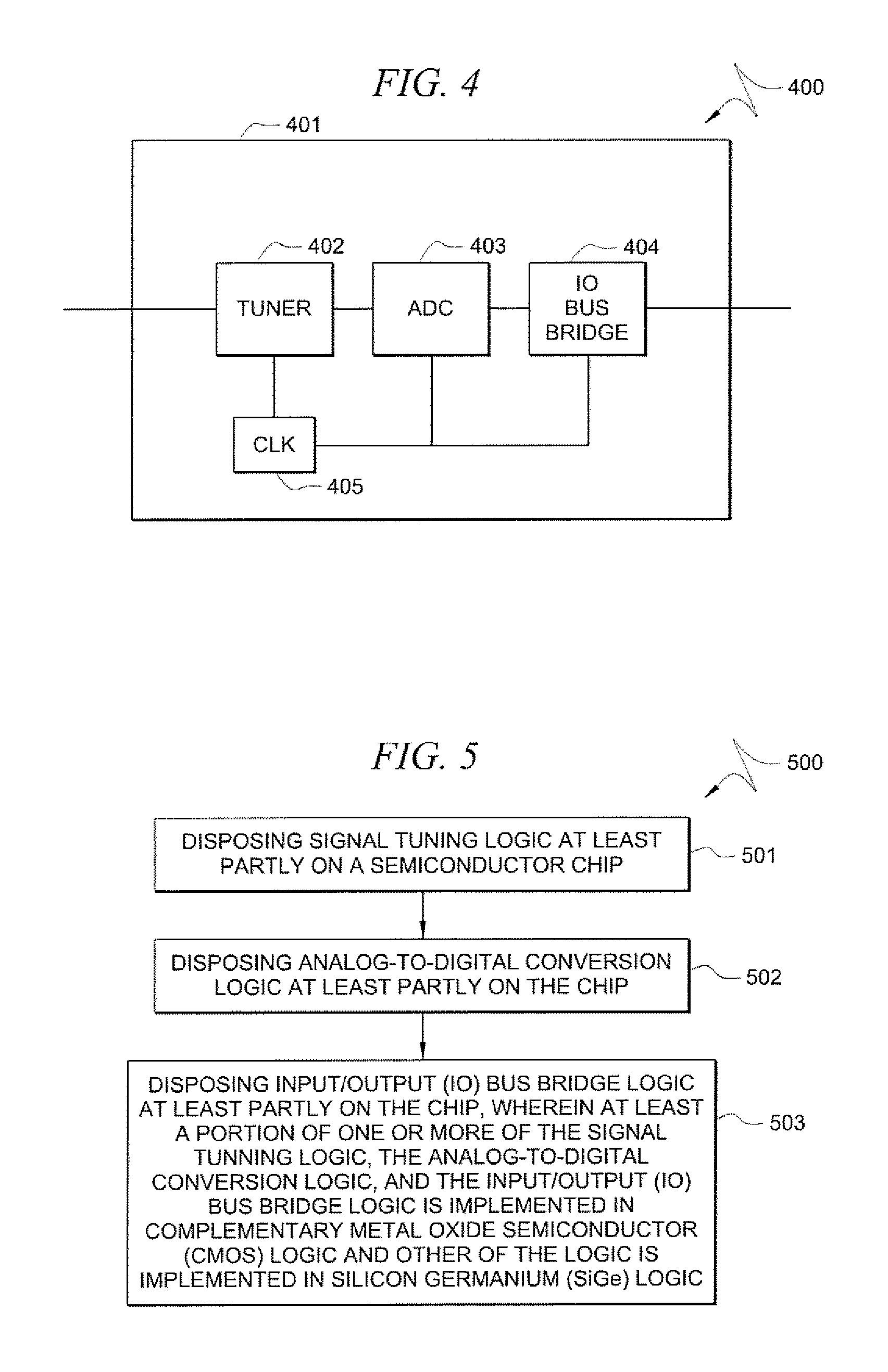

High-performance bipolar tuner solution systems and methods

ActiveUS20080106652A1MiniaturizationLess power usageTelevision system detailsColor television detailsCMOSSemiconductor chip

A system for processing signals comprises a tuner and an input / output (IO) bus bridge, wherein the tuner and the IO bus bridge are formed at least in part on same semiconductor chip, and wherein at least a portion of logic on the chip is implemented in Complementary Metal Oxide Semiconductor (CMOS) logic, and wherein at least another portion of the logic is implemented with silicon germanium (SiGe) logic.

Owner:CSR TECH INC

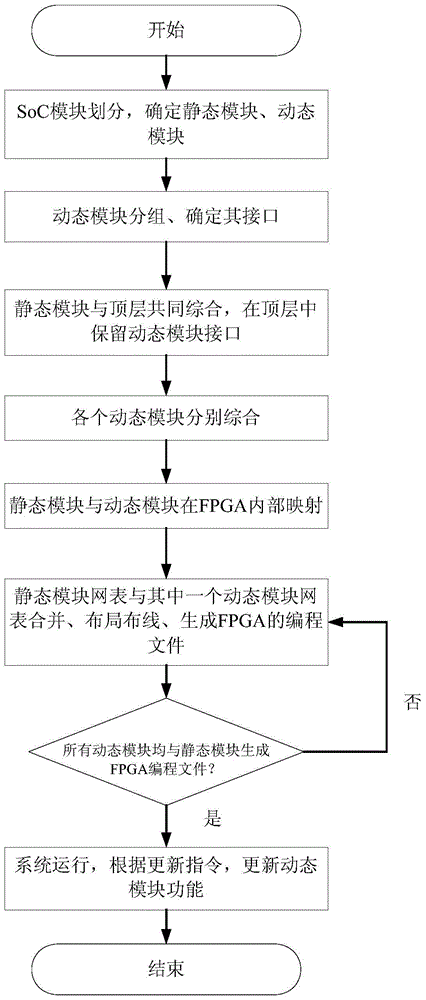

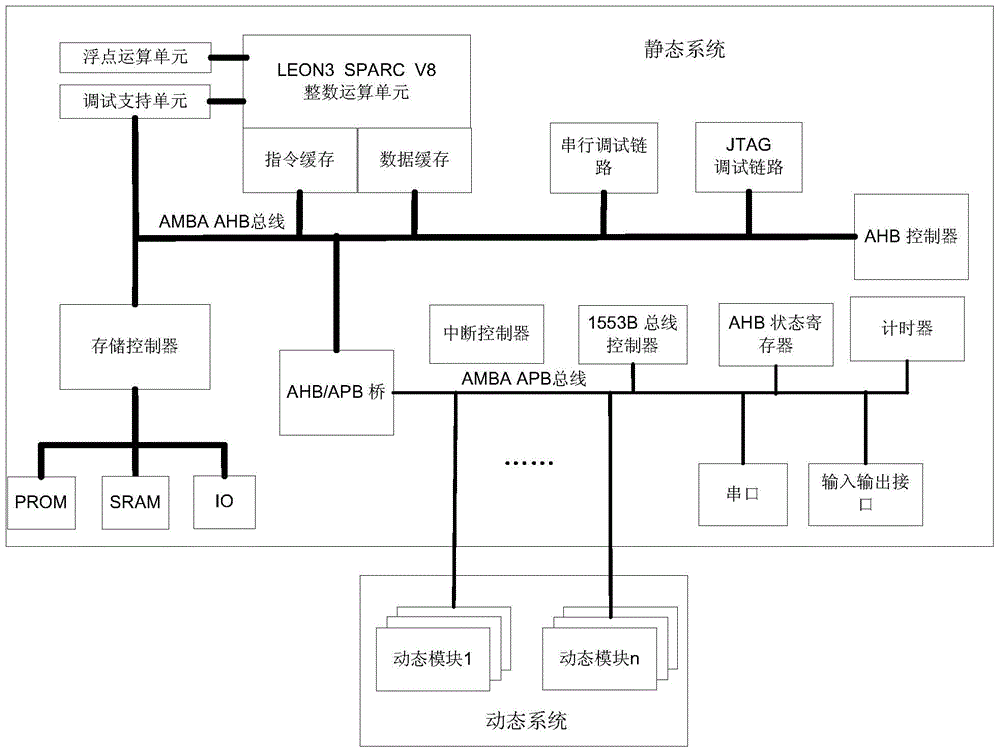

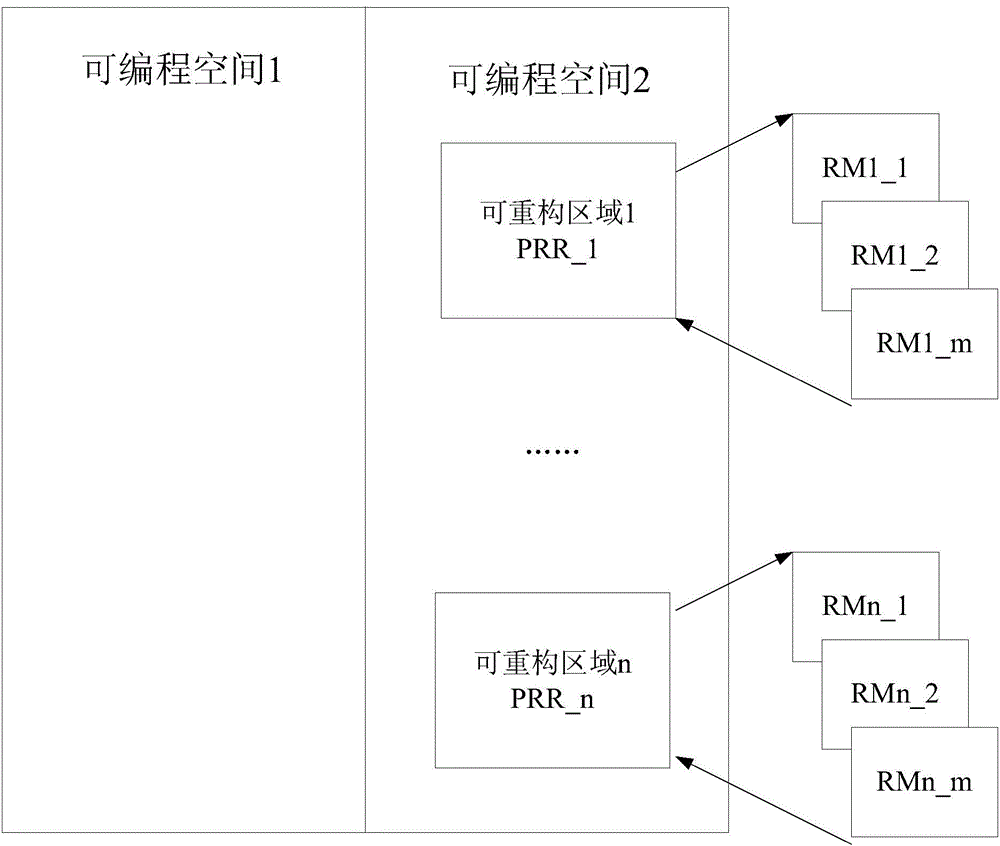

Realizing method for spaceflight SoC (System on a Chip) supporting partial reconstruction

ActiveCN104484309AFlexibleImprove reliabilityArchitecture with single central processing unitComputer architectureDependability

The invention relates to a realizing method for spaceflight SoC (System on a Chip) supporting partial reconstruction. A dynamic system and a static system are defined in an SoC, the two systems are differently designed, a logic of part of an FPGA (Field Programmable Gate Array) can be reconstructed during a running process of the systems. and the logic function of the part, which is not configured, of the FPGA. is not changed, so that the dynamic part can be reconstructed and has the flexibility of software and the high efficiency of hardware, the present state of unchangeable SOC interior function and structure at present is effectively settled, and meanwhile, through a partial reconstructing technique, a configuration bit flow can be periodically refreshed, the configuration bit flow is prevented from generating single event upset, the reliability and fault-tolerant ability of the SOC are increased, and the function of the SOC becomes more flexible.

Owner:BEIJING INST OF CONTROL ENG

High-performance bipolar tuner solution systems and methods

ActiveUS7813707B2MiniaturizationAvoid prolonged useTelevision system detailsColor television detailsCMOSSemiconductor chip

A system for processing signals comprises a tuner and an input / output (IO) bus bridge, wherein the tuner and the IO bus bridge are formed at least in part on same semiconductor chip, and wherein at least a portion of logic on the chip is implemented in Complementary Metal Oxide Semiconductor (CMOS) logic, and wherein at least another portion of the logic is implemented with silicon germanium (SiGe) logic.

Owner:CSR TECH INC

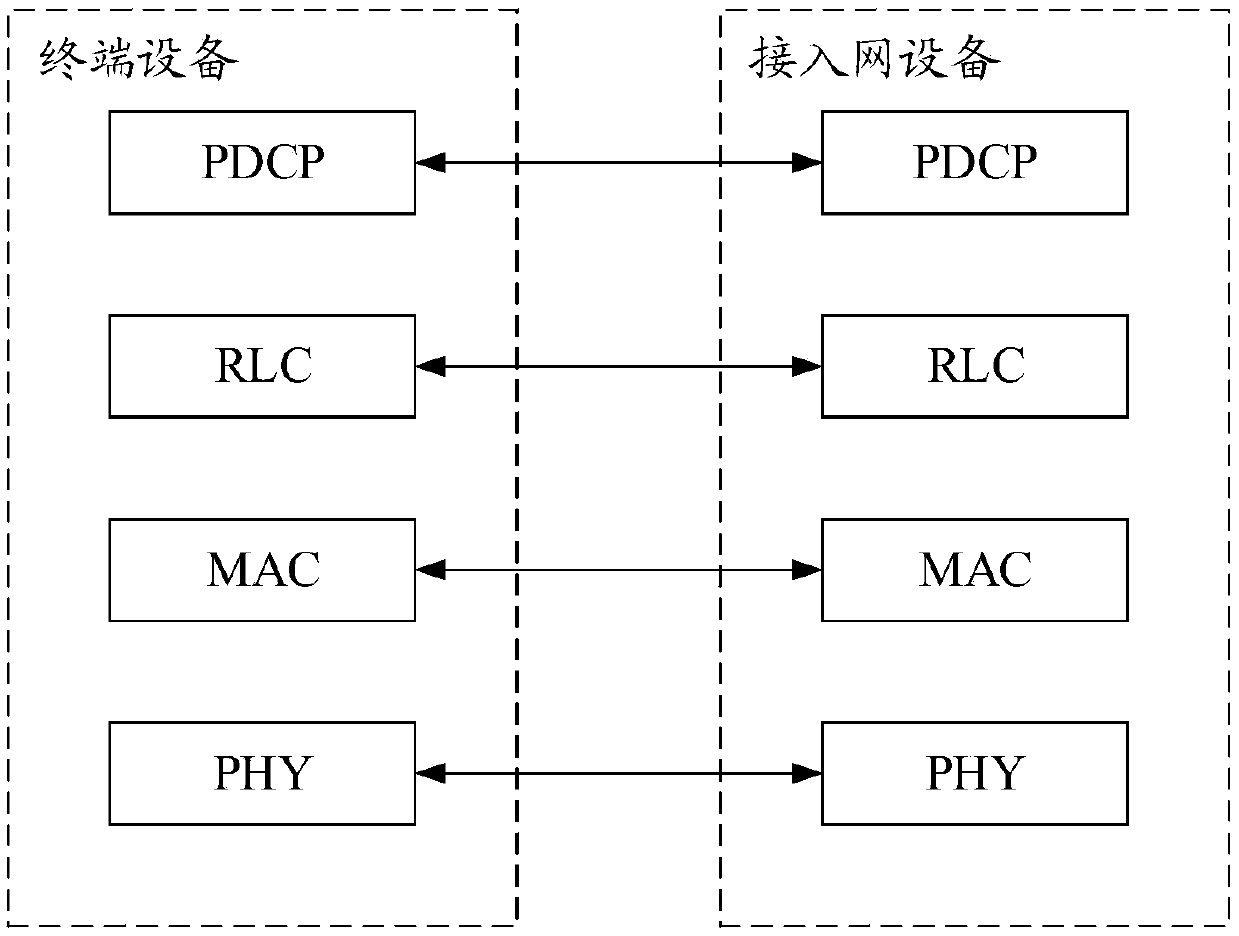

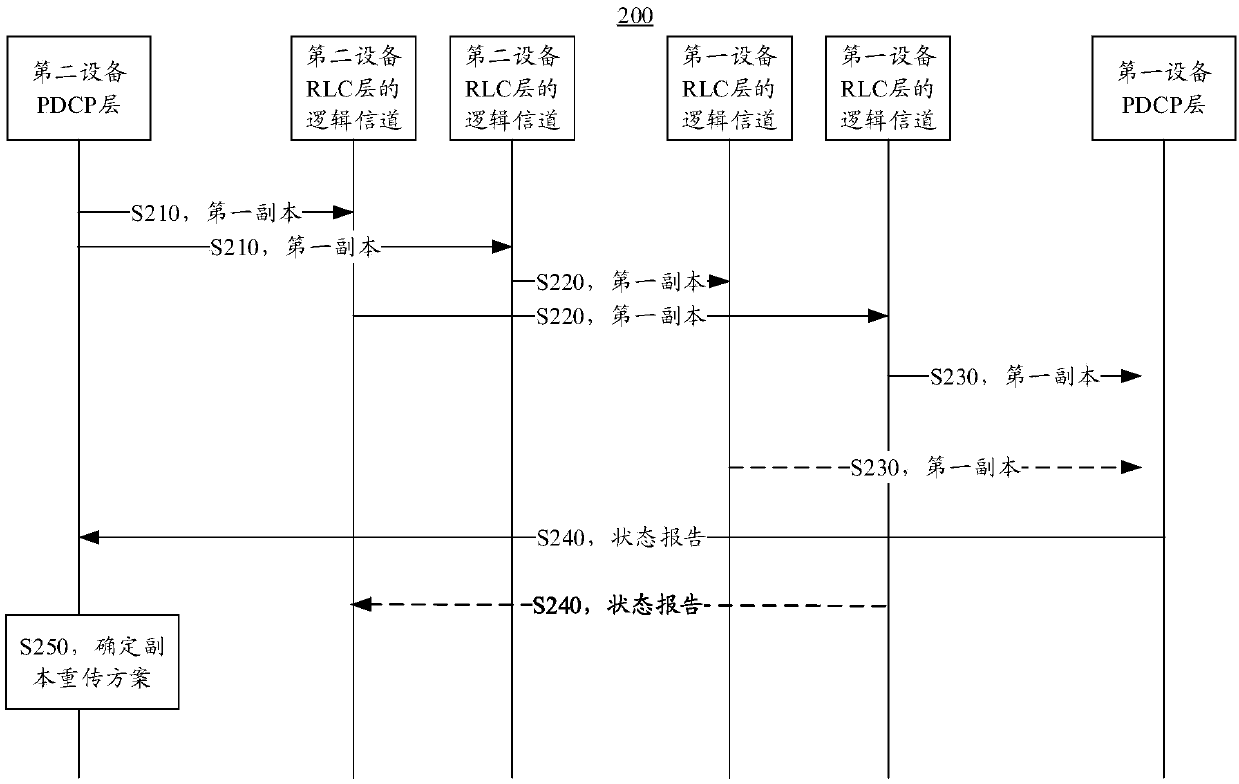

Data transmission method and device

InactiveCN109842907AError prevention/detection by using return channelNetwork traffic/resource managementComputer hardwareNetwork packet

The invention provides a data transmission method and a data transmission device, which can reduce the resource overhead. The method comprises the steps that a first device receives a plurality of first copies of the same data packet sent by a second device on a plurality of logic channels of a radio link control RLC layer; The first device transmits at least a part of a first copy of the plurality of first copies to a packet data convergence protocol (PDCP) layer of the first device on at least a part of the logical channels of the plurality of logical channels; And the first device sends a state report to the second device, wherein the state report is used for indicating at least one of the end of a first time period and the receiving condition of at least one copy of the first device, the first time period is the receiving time of the first device for receiving the at least one copy, and the at least one copy comprises the first copy.

Owner:HUAWEI TECH CO LTD

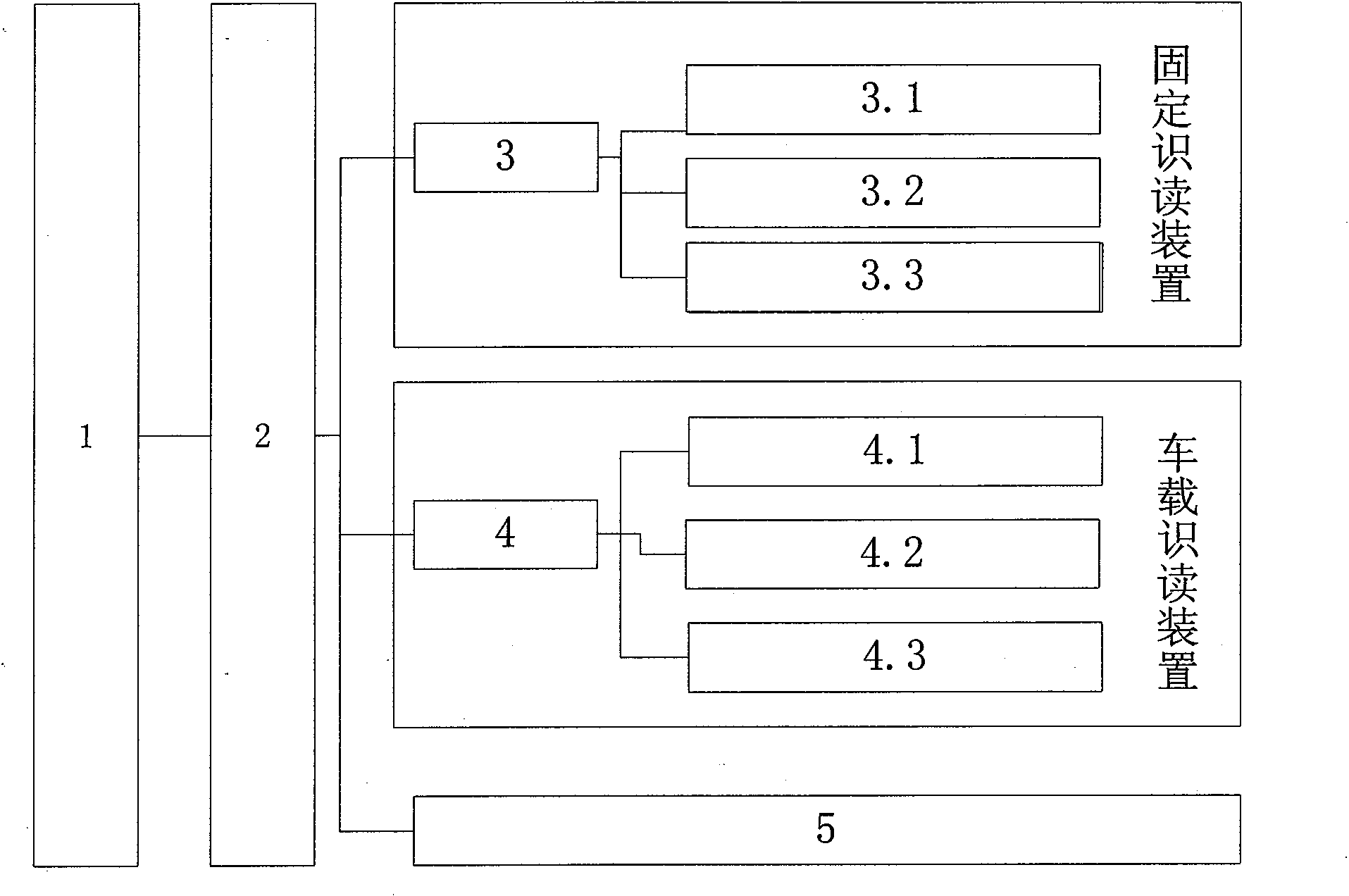

Vehicle monitoring system based on automatic identification technology

InactiveCN102054352AEnabling RFID monitoringImprove recognition accuracyStampsDetection of traffic movementSoftware systemStructure of Management Information

The invention discloses a vehicle monitoring system based on automatic identification technology, and relates to the technical field of electronic information. The vehicle monitoring system consists of an application software system, a middleware server, an identifying and reading device and a vehicle to be detected which are communicated with one another in turn. The application software system provides supervision department-oriented application service; and the middleware server completes data filtering and forwarding and partial logic processing operation. The vehicle monitoring system has the structural characteristic that: the identifying and reading device comprises a fixed identifying and reading device, a vehicle-mounted identifying and reading device and a handheld identifying and reading device and completes vehicle information acquisition and data comparison operation. The vehicle to be detected is stuck with a passive ultrahigh frequency electronic tag to communicate with the identifying and reading device so as to complete the monitoring. Compared with the prior art, the vehicle monitoring system integrates radio frequency, video, radar velocity measurement and other automatic identification technology, effectively improves the accuracy rate of identifying and reading vehicles and has high environmental adaptation.

Owner:TSINGHUA TONGFANG CO LTD

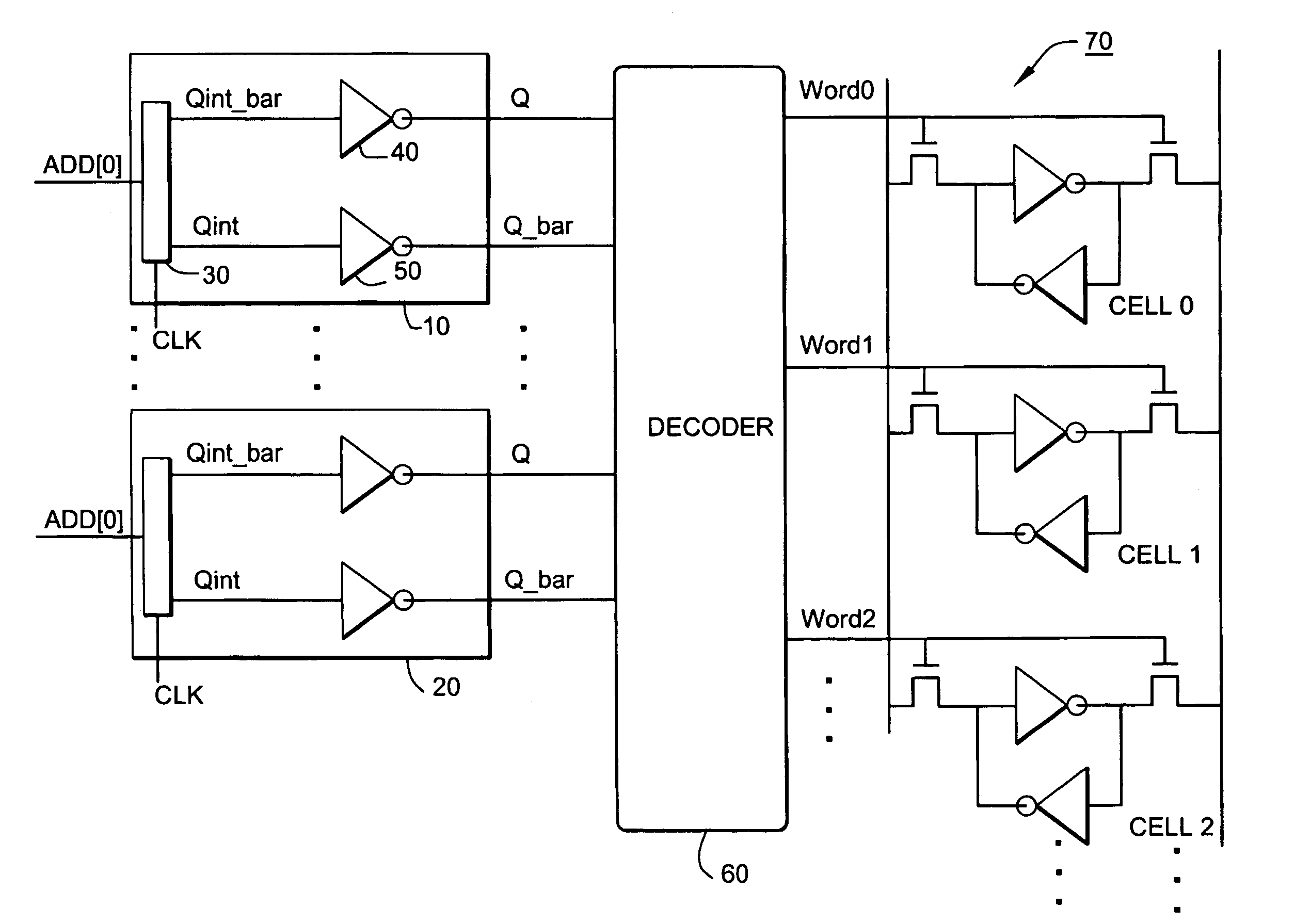

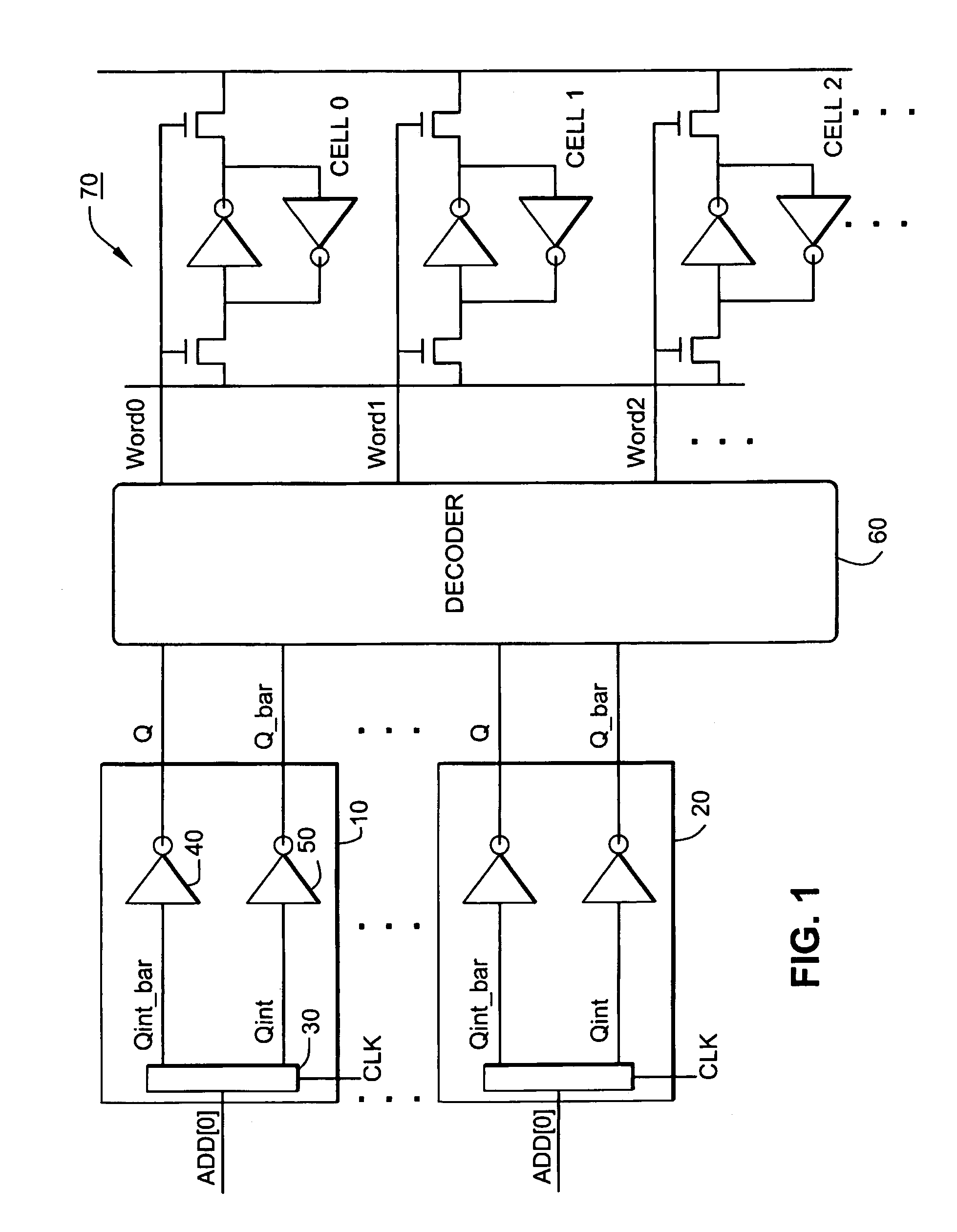

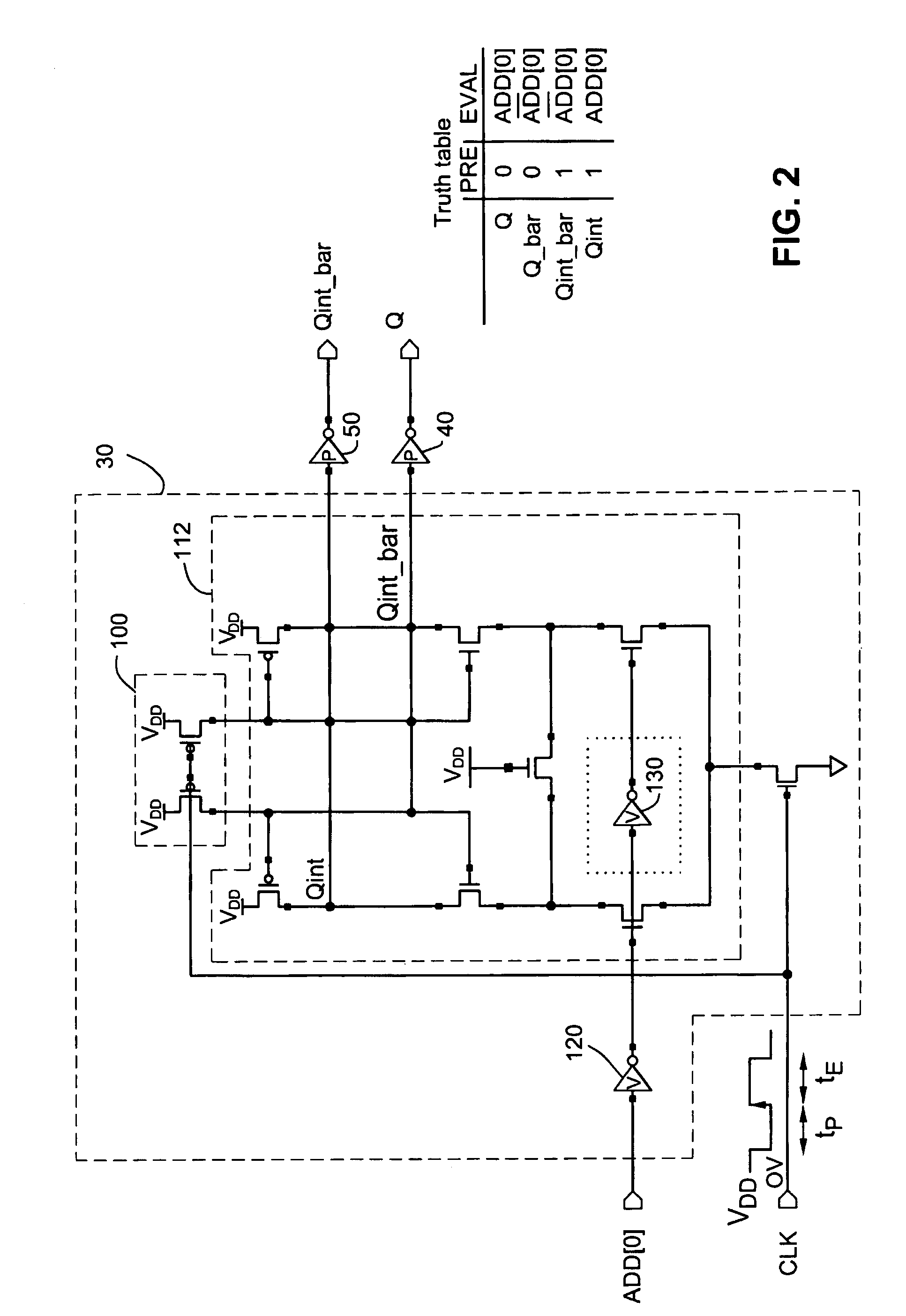

Address decoding

A signal capture element for providing a first pre-charged logic level as first and second interim address portion signals during a pre-charged period and outputting during an evaluate period an address portion logic level as the first interim address portion signal and an inverted address portion logic level as the second interim address portion signal. First and second address portion signals are derivable respectively from first and second interim address portion signals. An inverter circuit for outputting to an address decoder during a pre-charged period a second pre-charged logic level as the first and second address portion signals. The inverter circuit having transfer characteristics that maintain voltage levels such that the first and second address portion signals are interpreted to be at the second pre-charged logic level despite the first or second interim address portion signal failing to transition to a valid logic level during the evaluate period.

Owner:RGT UNIV OF MICHIGAN +1

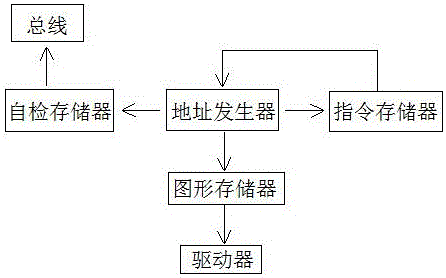

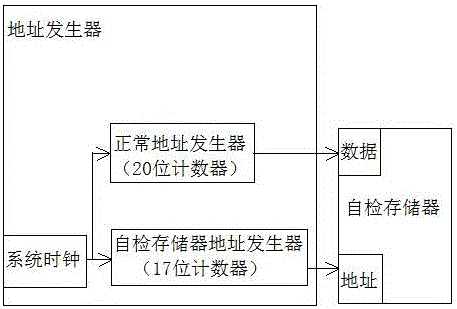

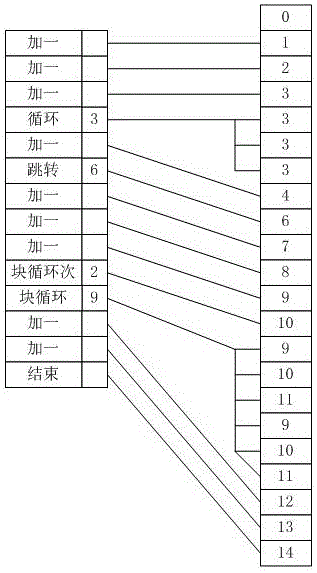

ATE (Automatic Test Equipment) digital testing system and self inspection method thereof

ActiveCN106356102ALow failure rateStatic storageEnergy efficient computingGraphicsInstruction memory

The invention discloses an ATE (Automatic Test Equipment) digital testing system and a self inspection method thereof. The ATE digital testing system comprises an address generator, a picture memory, an instruction memory, a self-inspection memory and a driver, wherein the address generator is connected with the picture memory, the instruction memory and the self-inspection memory; the self-inspection memory is connected with a bus, and the picture memory is connected with the driver. The self-inspection method disclosed by the invention is capable of effectively solving the part which is not verified by a traditional self-inspection method; pictures for self inspection comprise special instructions such as circulation, skip and block circulation except for plus one, then the moving locus of the pictures is monitored, so as to observe whether addresses change correspondingly according to micro-instructions under high-speed operation or not, so that whether the system performance and partial logic of the micro-instructions are normal or not can be verified; multiple potential problems which can not be discovered by traditional self inspection can be embodied to a greater extent, the factory equipment is relatively stable, the fault rate is relatively small, interference can be excluded more easily with pertinence during field failure, and problems are found.

Owner:ACETEC SEMICON

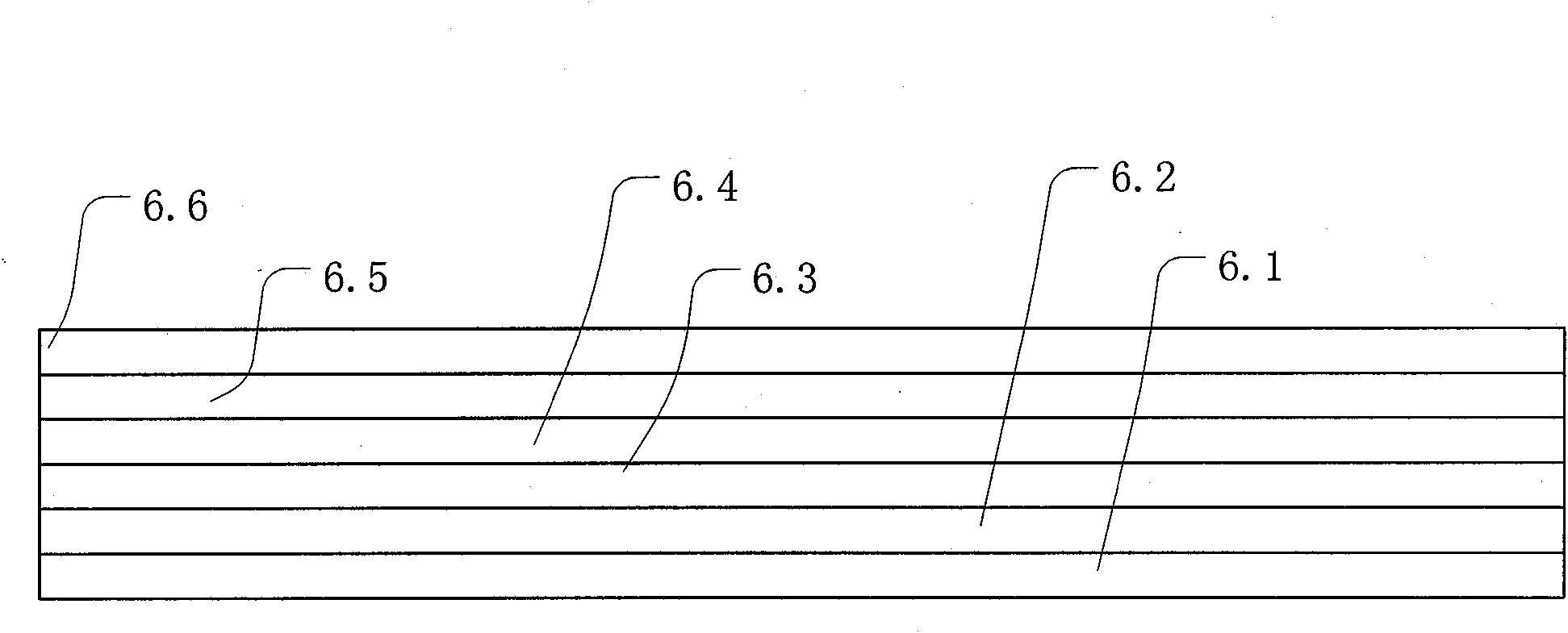

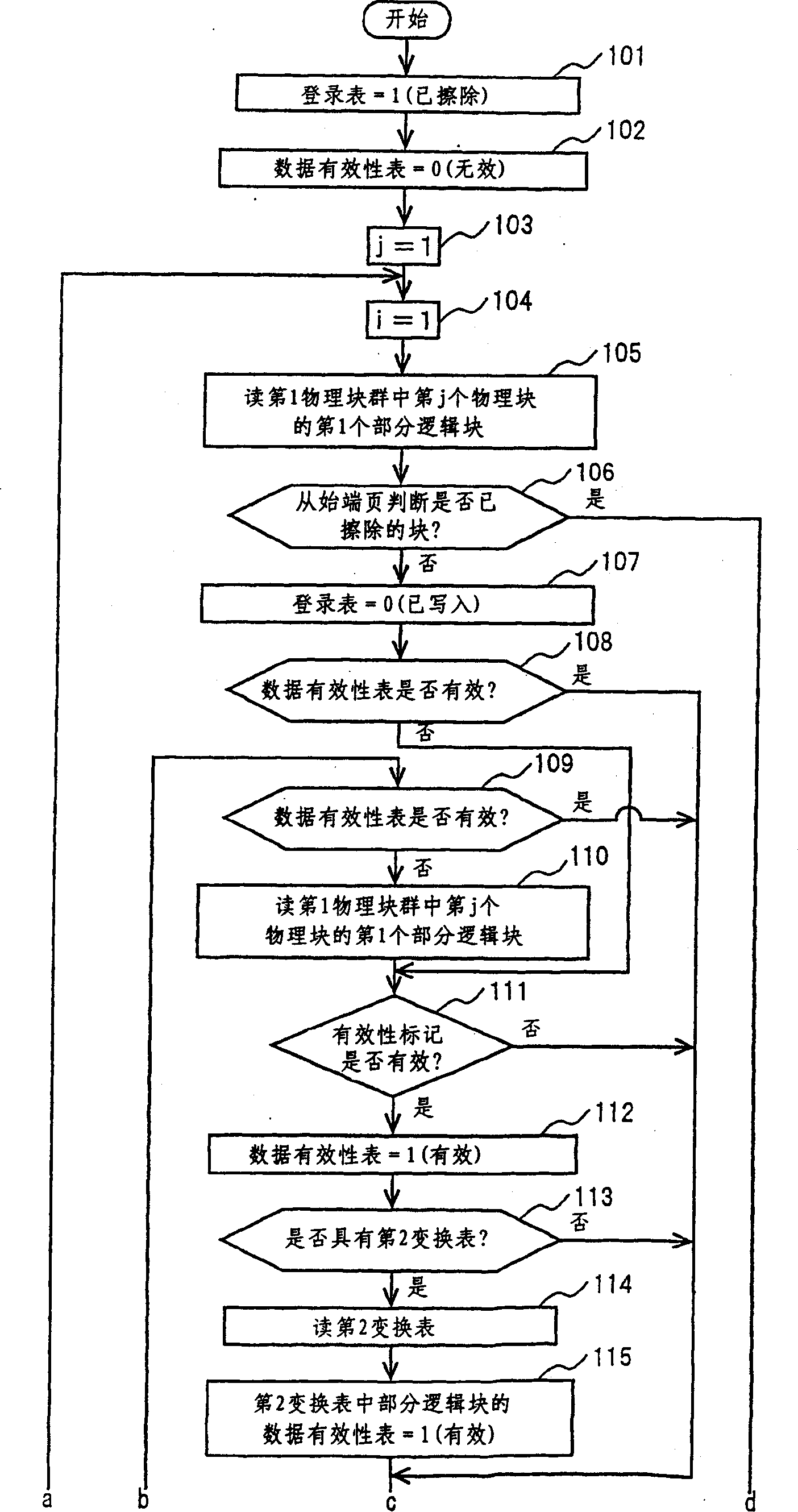

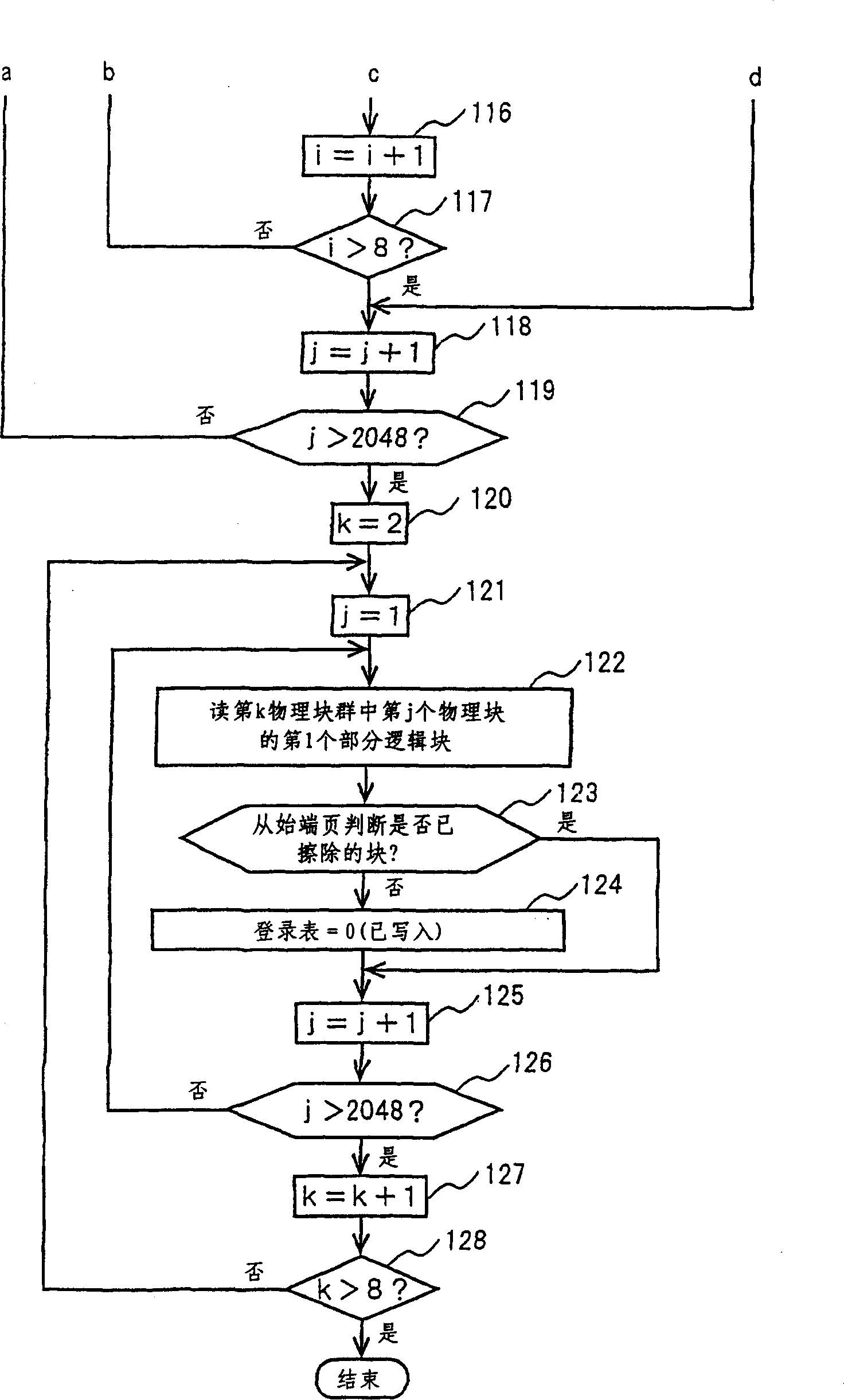

Non-volatile storage device and control method thereof

InactiveCN1473296AMemory adressing/allocation/relocationRead-only memoriesPartial logicNon-volatile memory

The invention provides a non-volatile memory device capable of improving the convenience of portable apparatus by reducing initialization time and the control method thereof. In generating the table of data validity at the time of initialization, the control section reads the validity flag and the second conversion table. When the validity flag is valid, the logical block of the second conversion table is also valid. Consequently, the fourth table generating means can set all the logical blocks on the second conversion table valid for the table of data validity. Therefore, the fourth table generating means can conduct setting of a plurality of logical blocks by reading only once as mentioned above. Furthermore, in regard to the partial logical block set valid for the table of data validity, reading of the validity flag can be omitted and be forwarded to process the next partial logical block.

Owner:PANASONIC CORP

File automatic reviewing tool

InactiveCN107886309AEliminate manual modificationNatural language data processingOffice automationAmbiguityStructural error

The invention relates to a file automatic reviewing tool used for automatically reviewing files; the file automatic reviewing tool comprises the following structures: a file importing module used forimporting reviewed files; a file model defining module used for defining demands of the reviewed file, wherein the file ambiguity, completeness and functionality are included; a natural language identification module used for identifying wrong words in the file, and automatically analyzing the file structural errors and partial logic conflicts; a file reviewing list forming module used for screening reviewing items and automatically forming a file reviewing list of a new project; an automatic reviewing module used for automatically reviewing the file ambiguity, completeness and functionality;an automatic analysis module used for automatically forming a reviewing report according to the reviewing results. The file automatic reviewing tool can use an intelligent file reviewing tool to replace a conventional pure manual reviewing mode.

Owner:四川汉科计算机信息技术有限公司

Built-in self-test method of FPGA logical resource

ActiveCN101515020BSimple configuration structureDifficult to designElectrical testingTest efficiencyLeft half

The invention provides a built-in self-test method of FPGA logical resource. The internal logical module of FPGA is alternately divided into a left half part and a right half part according to row. In the test process, the logical module array of the right half part is firstly configured as a to-be-tested circuit, and the rest logical module arrays are configured as a test vector generating circuit and an output response analyzing circuit, and then the logical module array of the left half part is configured as the to-be-tested circuit, and the rest logical module arrays are configured as thetest vector generating circuit and the output response analyzing circuit. The circuit structure is not changed in each process. The logical resource is covered by multiple configurations and the testresult is output by a built-in scan register chain. All configurations in the invention are as follows: all logical modules configured as the response analyzing circuits are in cascade connection endto end according to one-dimensional array, so as to simplify the self-test result retrieval manner. Provided that the test coverage is 100%, the built-in self-test method reduces times of the configurations of FPGA logical resource, reduces test cost and increases test flexibility, so as to improve test efficiency.

Owner:BEIJING MXTRONICS CORP +1

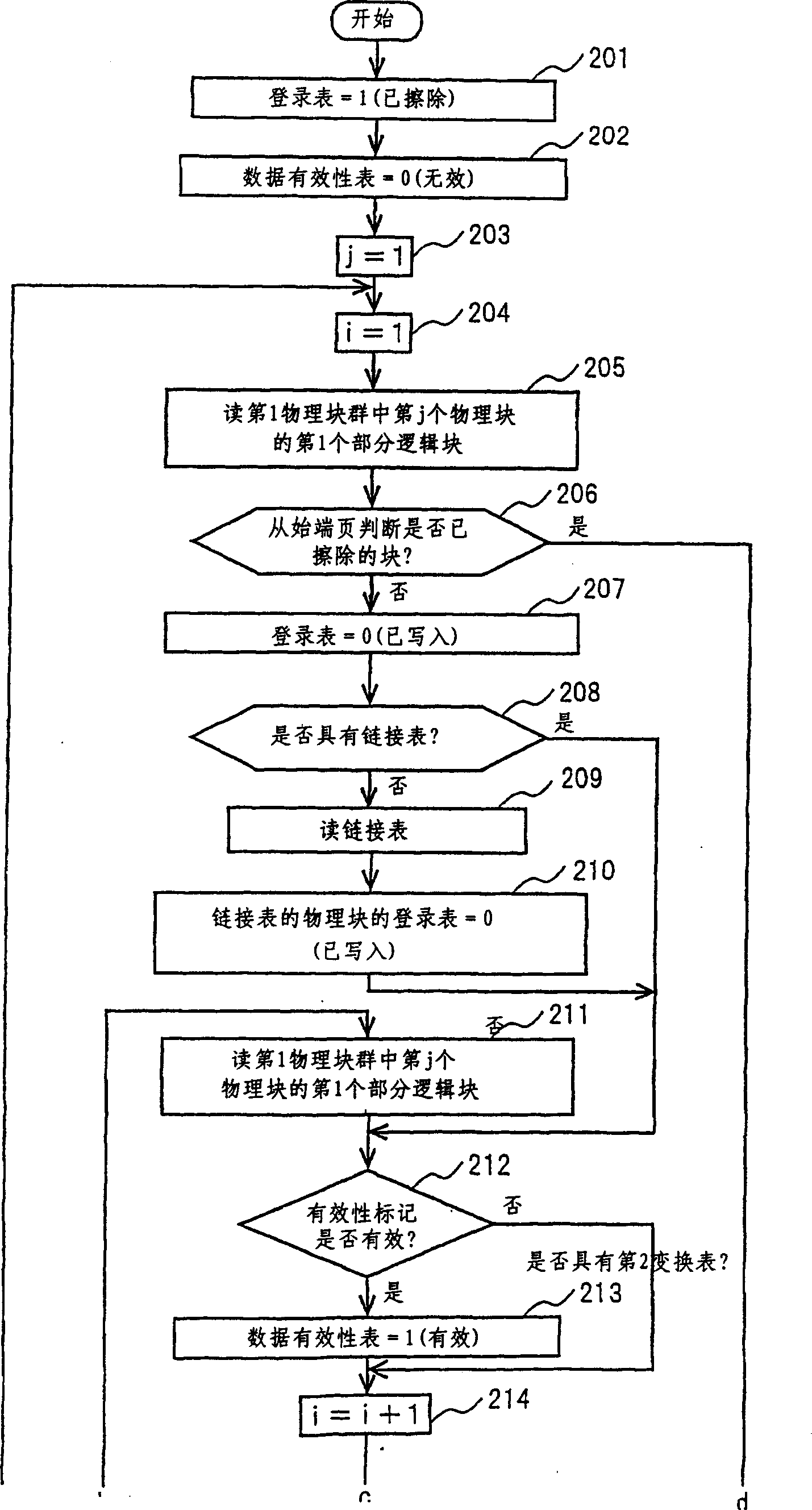

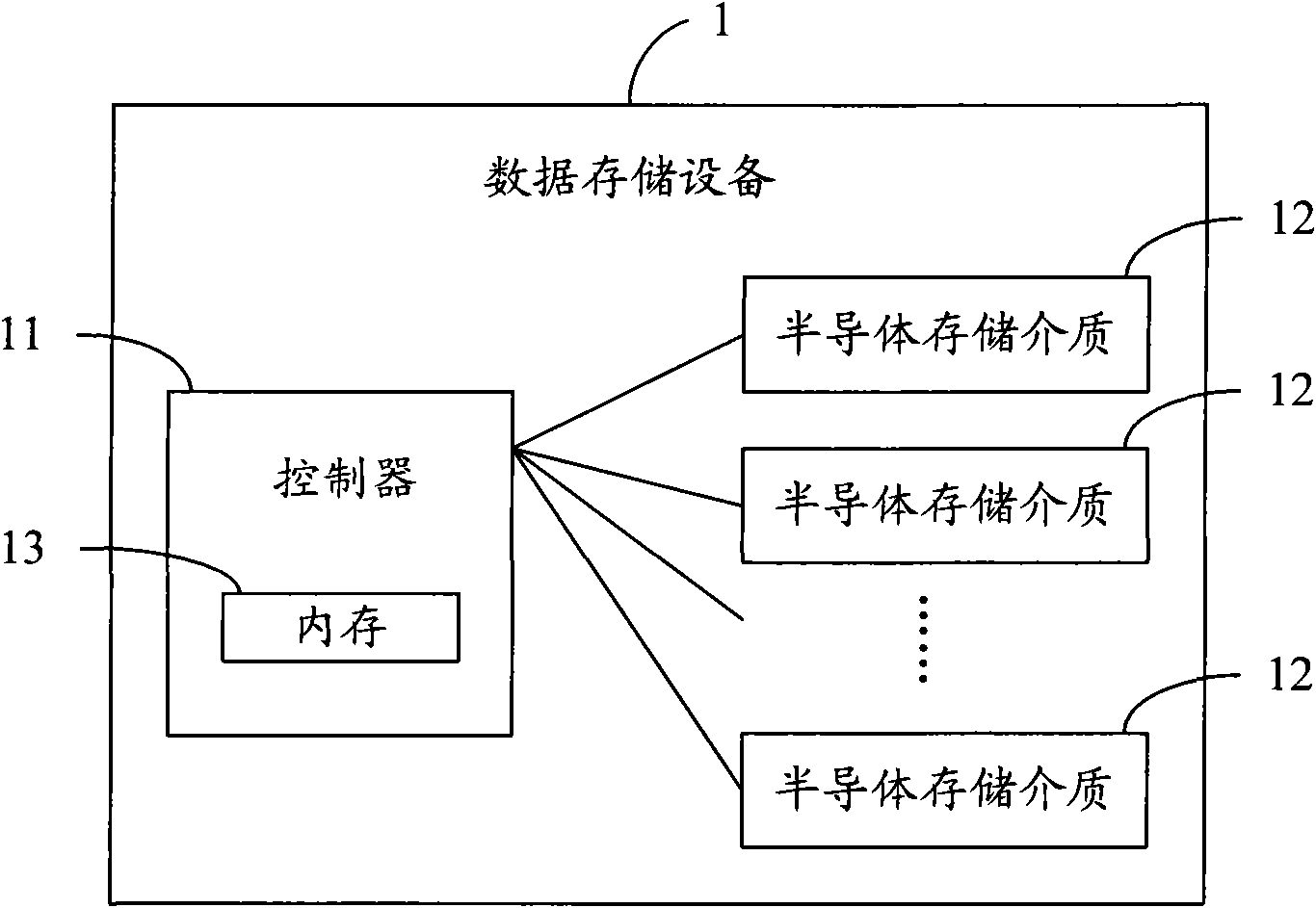

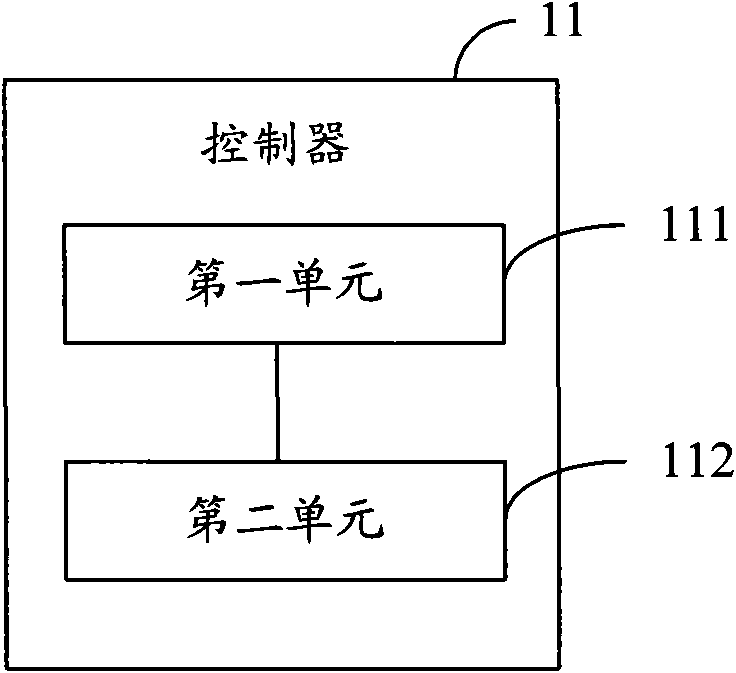

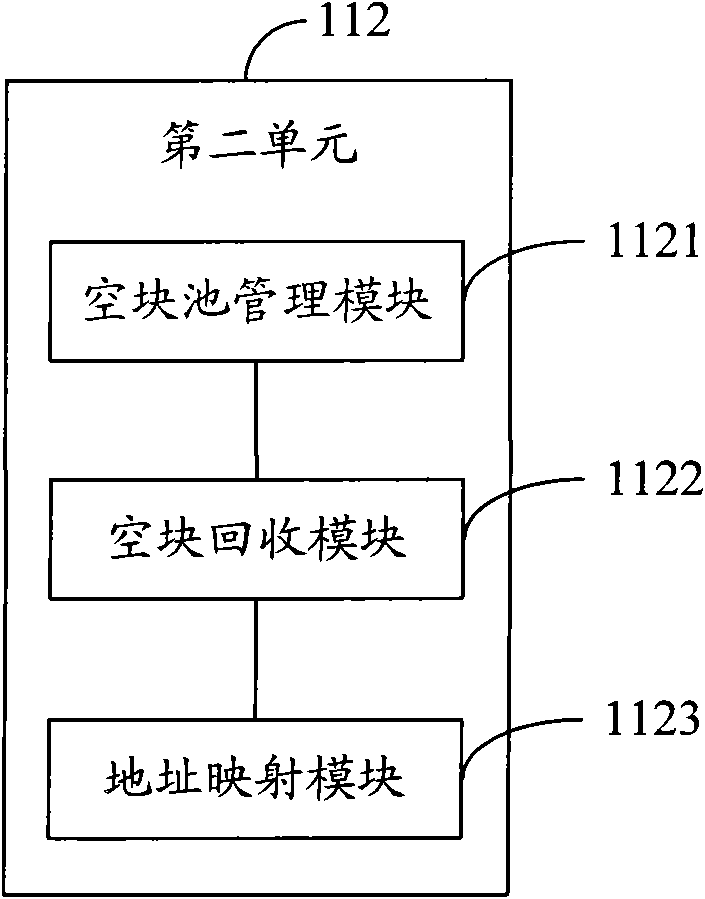

Storage equipment and control method thereof

InactiveCN101770425AReduce the number of empty block recyclingIncrease write speedMemory adressing/allocation/relocationPhysical addressComputer science

The invention provides storage equipment and a control method thereof. The storage equipment comprises a semiconductor storage medium. The method comprises the following steps of: establishing a mapping relationship of a partial logic address and a physical address of a semiconductor storage address hollow block; recording information of a hollow block without the mapping relationship; and operating the hollow block without the mapping relationship. The storage equipment and the control method thereof can effectively reduce the recovery times of the hollow block in the data write-in process, thereby improving the speed of writing in the data.

Owner:NETAK TECH KO LTD

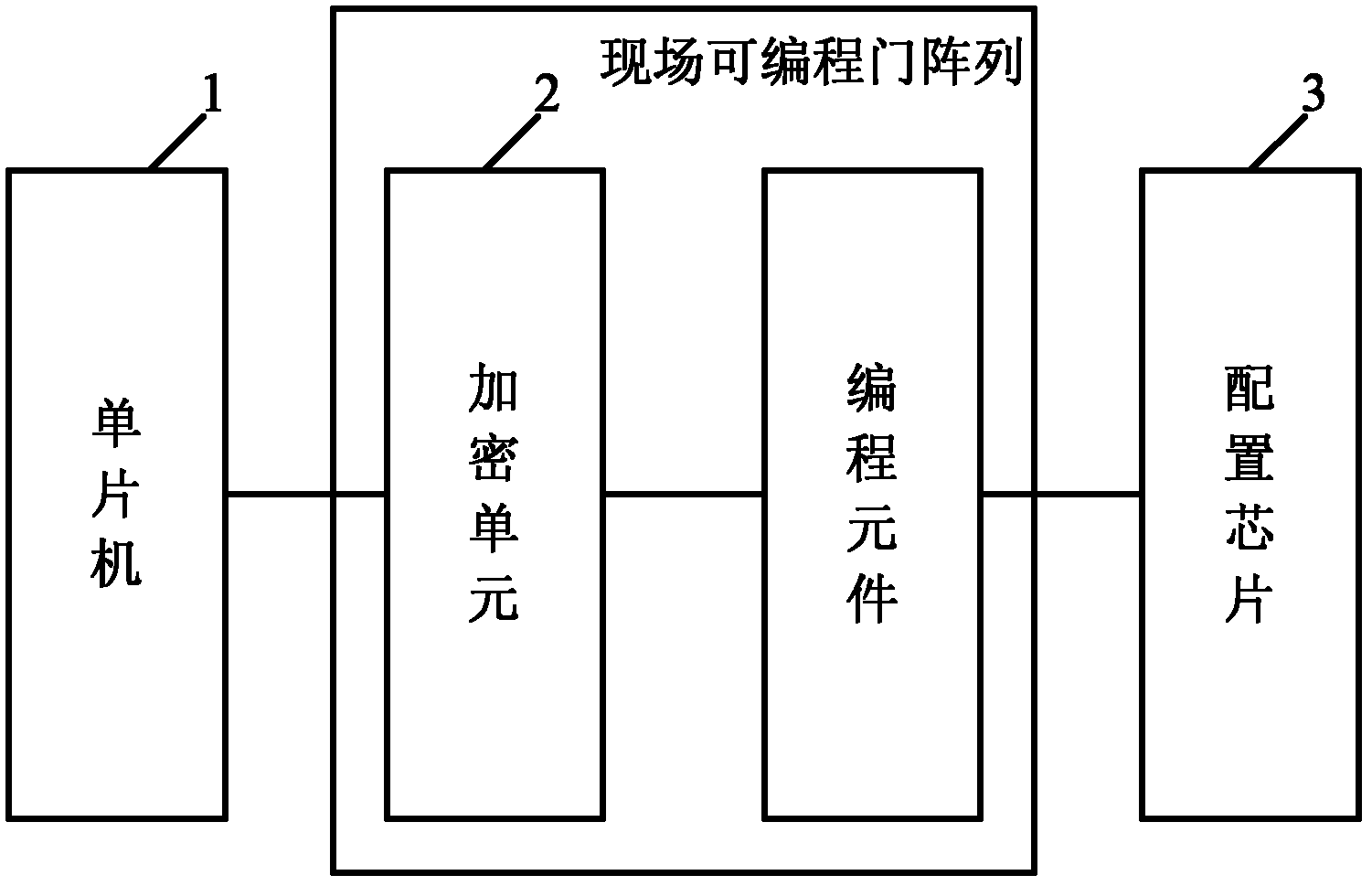

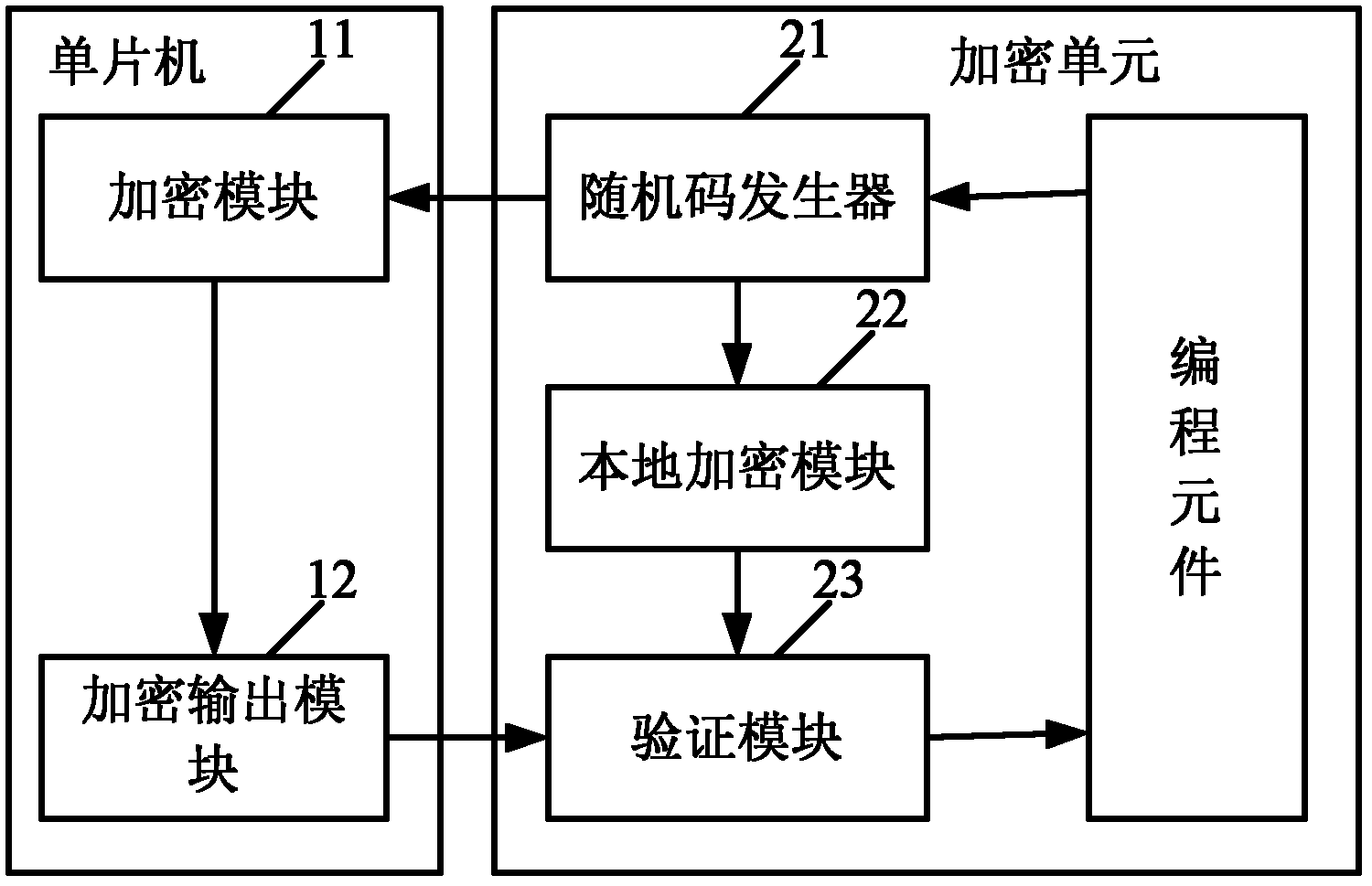

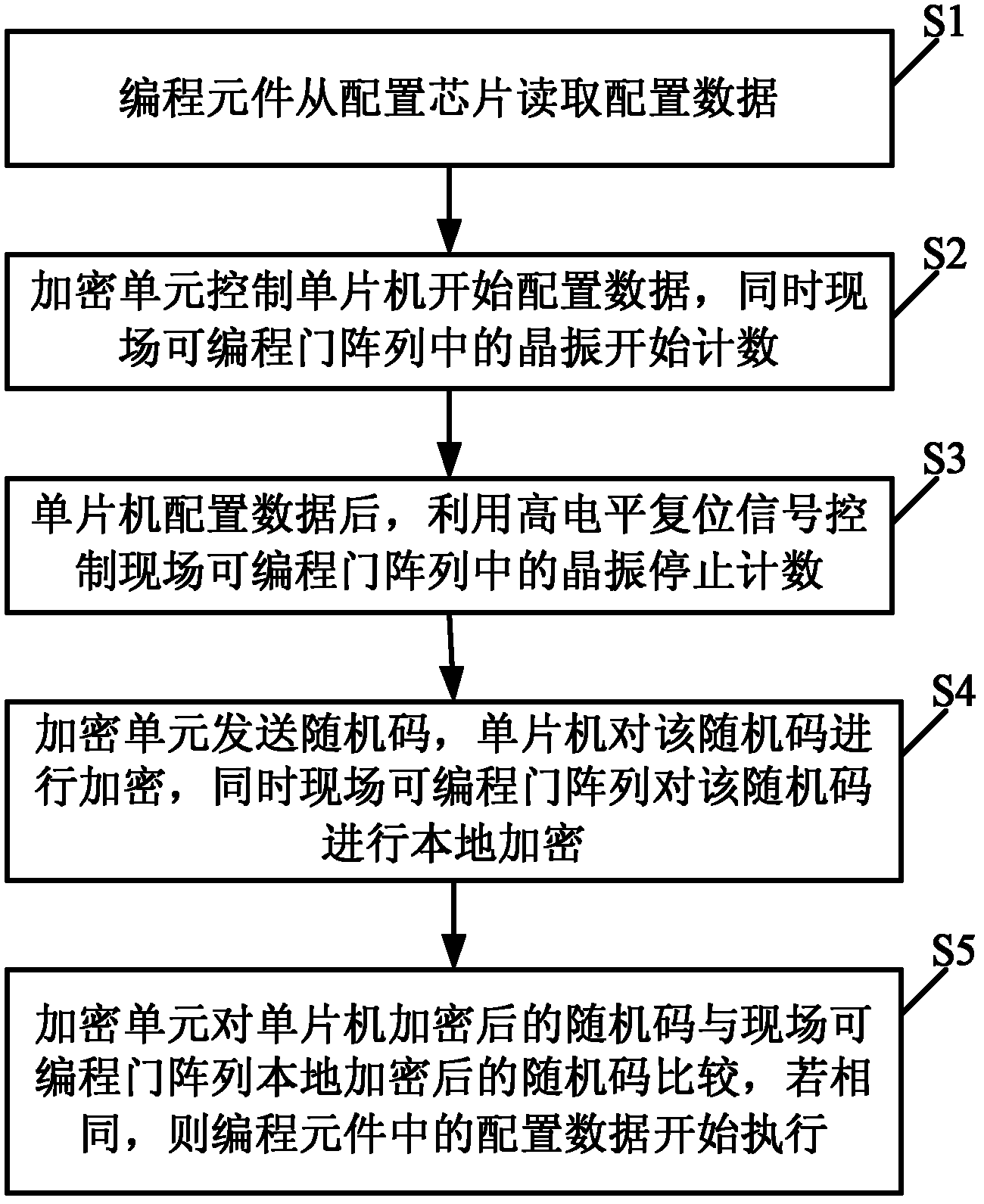

Encryption system and encryption method for field-programmable gate array (FPGA) configuration data

ActiveCN102567671BImprove confidentialityEasy to upgradeDigital data protectionMicrocontrollerConfidentiality

The invention discloses an encryption system and an encryption method for field-programmable gate array (FPGA) configuration data. The system comprises a singlechip, an encryption unit and a configuration chip, wherein the configuration chip is used for sending the configuration data to a programming component; the encryption unit is used for controlling the singlechip to start executing the configuration data after the programming component receives the configuration data and then sending a random code to the singlechip; the singlechip is used for encrypting the random code and then sending the encrypted random code to the encryption unit; and the encryption unit is also used for encrypting the random code at the same time, comparing the encrypted random code with the random code encrypted by the singlechip and controlling the configuration data in the programming component to be executed if the random codes are the same. Compared with the prior art, the invention has the advantages that: the encryption system for the FPGA configuration data is simple, feasible, good in confidentiality and easy to upgrade, and is suitable for encryption of the FPGA configuration data with low cost; and because the external singlechip and a part of logic unit in an FPGA are used in an encryption circuit, excessive hardware cost is not increased.

Owner:DALIAN JIECHENG TECH CO LTD

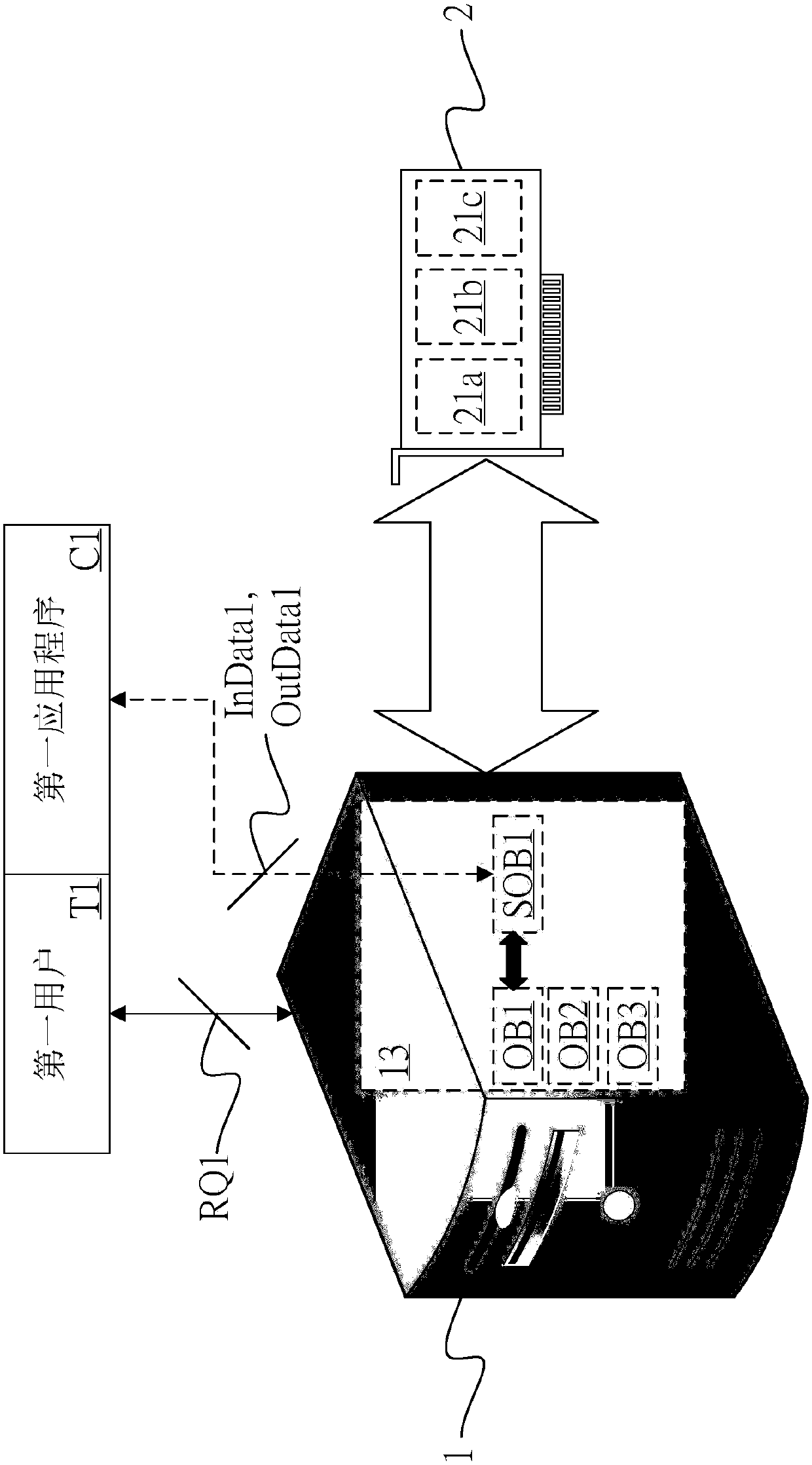

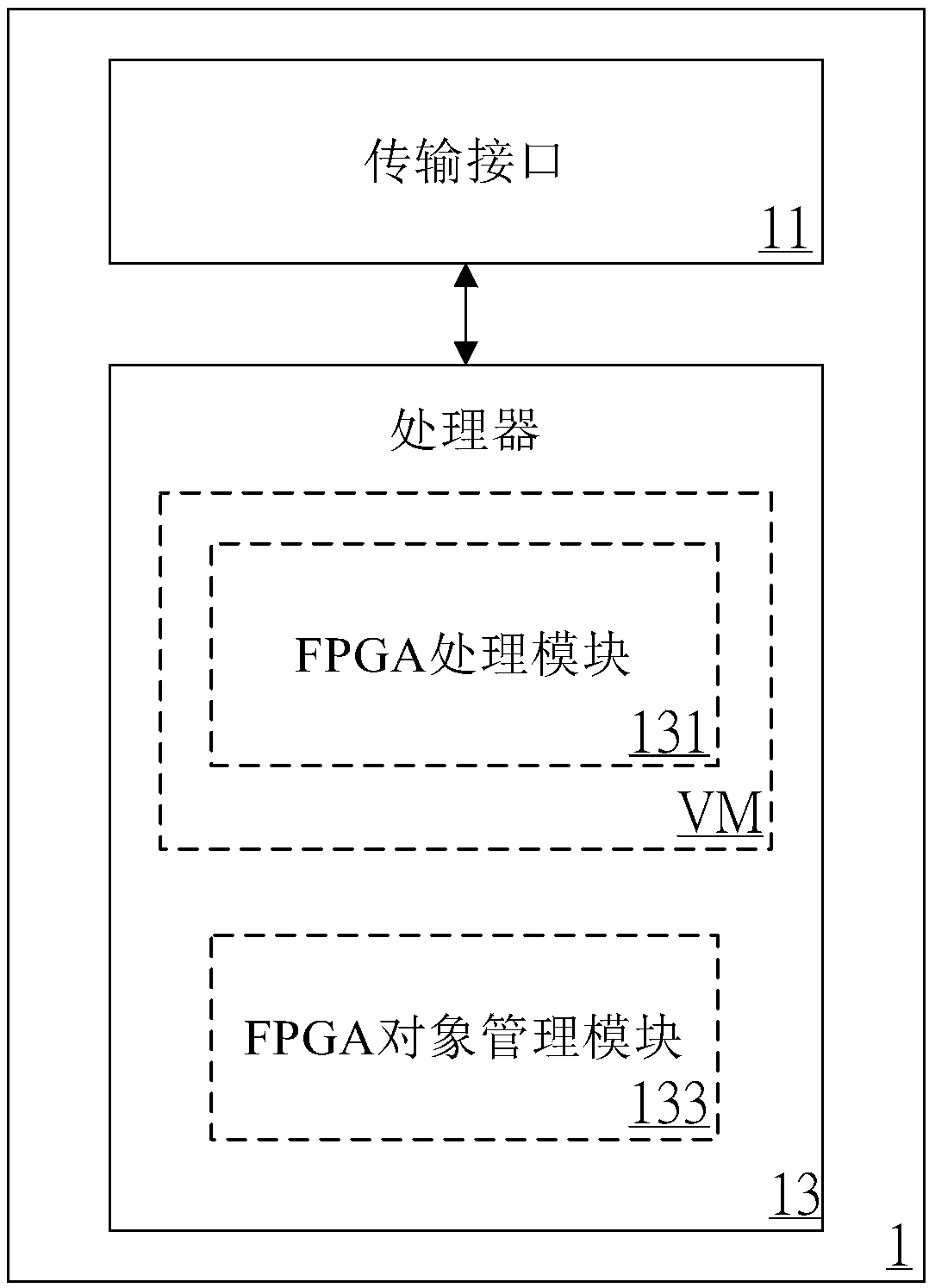

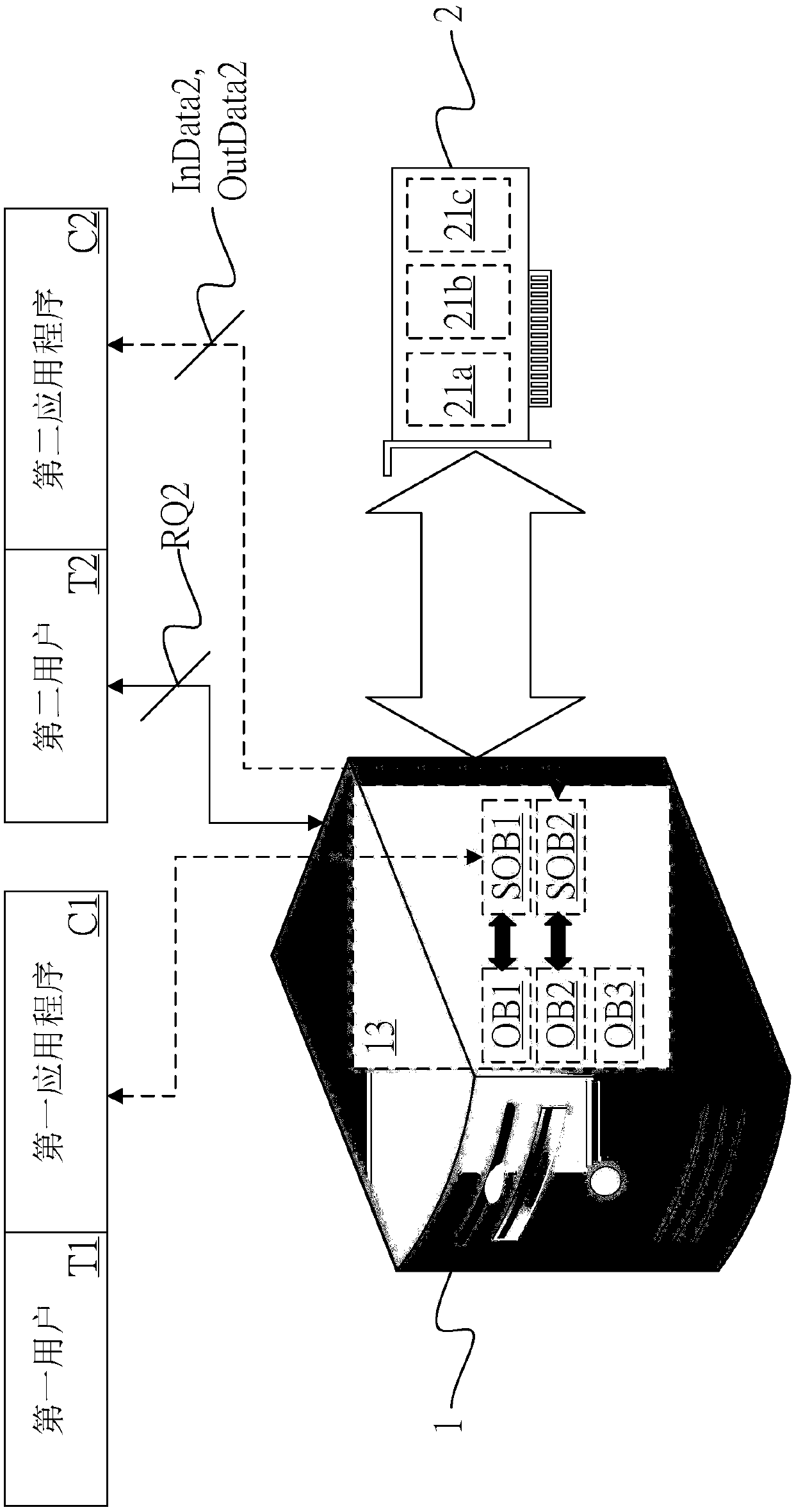

Platform as a service cloud server and multi-tenant operating method thereof

A PaaS cloud server and a multi-tenant operating method thereof are provided. The PaaS cloud server receives an application resource request and determines an available logic circuit object accordingto the application resource request. The PaaS cloud server creates an FPGA service object and pairs the FPGA service object and the logic circuit object. The PaaS cloud server binds the FPGA service object with an application of the tenant and receives an application data from the application. The PaaS cloud server inputs the application data into a part logic circuit of an FGPA circuit corresponding to the logic circuit object according to the pairing of the FPGA service object and the logic circuit object so that the part logic circuit computes a result data of the application data. The PaaScloud server returns the result data to the application.

Owner:INSTITUTE FOR INFORMATION INDUSTRY