Patents

Literature

50 results about "Co-design" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Co-design or codesign is a product, service, or organization development process where design professionals empower, encourage, and guide users to develop solutions for themselves. Co-design encourages the blurring of the role between user and designer, focusing on the process by which the design objective is created. This process believes that by encouraging the trained designer and the user to create solutions together, the final result will be more appropriate and acceptable to the user. It is generally recognized that the quality of design increases if the stakeholders' interests are considered in the design process. Co-design is a development of systems thinking, which according to C. West Churchman "begins when first you view the world through the eyes of another." As it is, co-design in the different research fields is tightly connected to the conception or creation of artifacts in communities context through a shared vision, social learning and mutual understanding among all key stakeholders, taking in consideration different perspectives and expectations that should be hold in consideration during the co-design process.

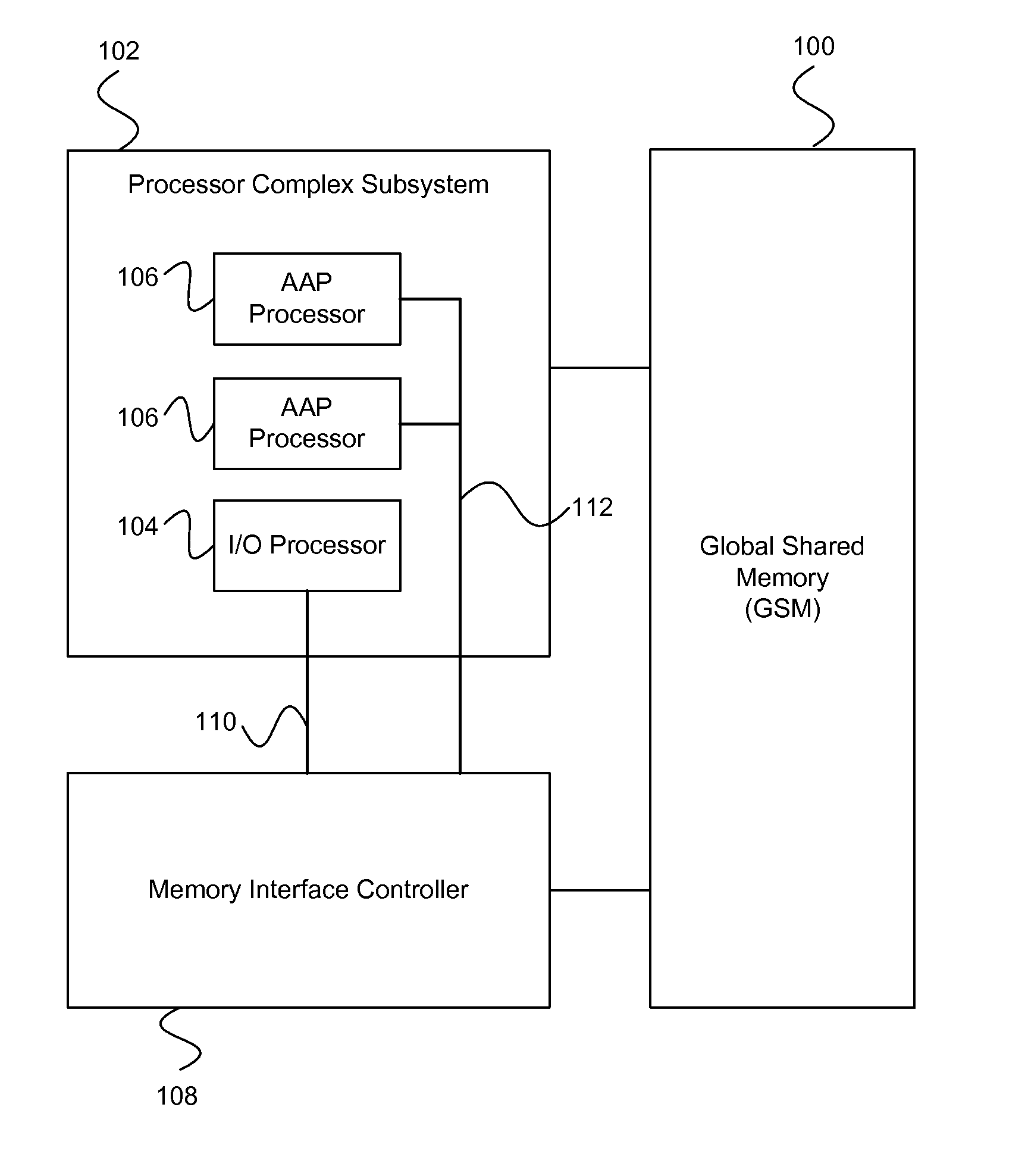

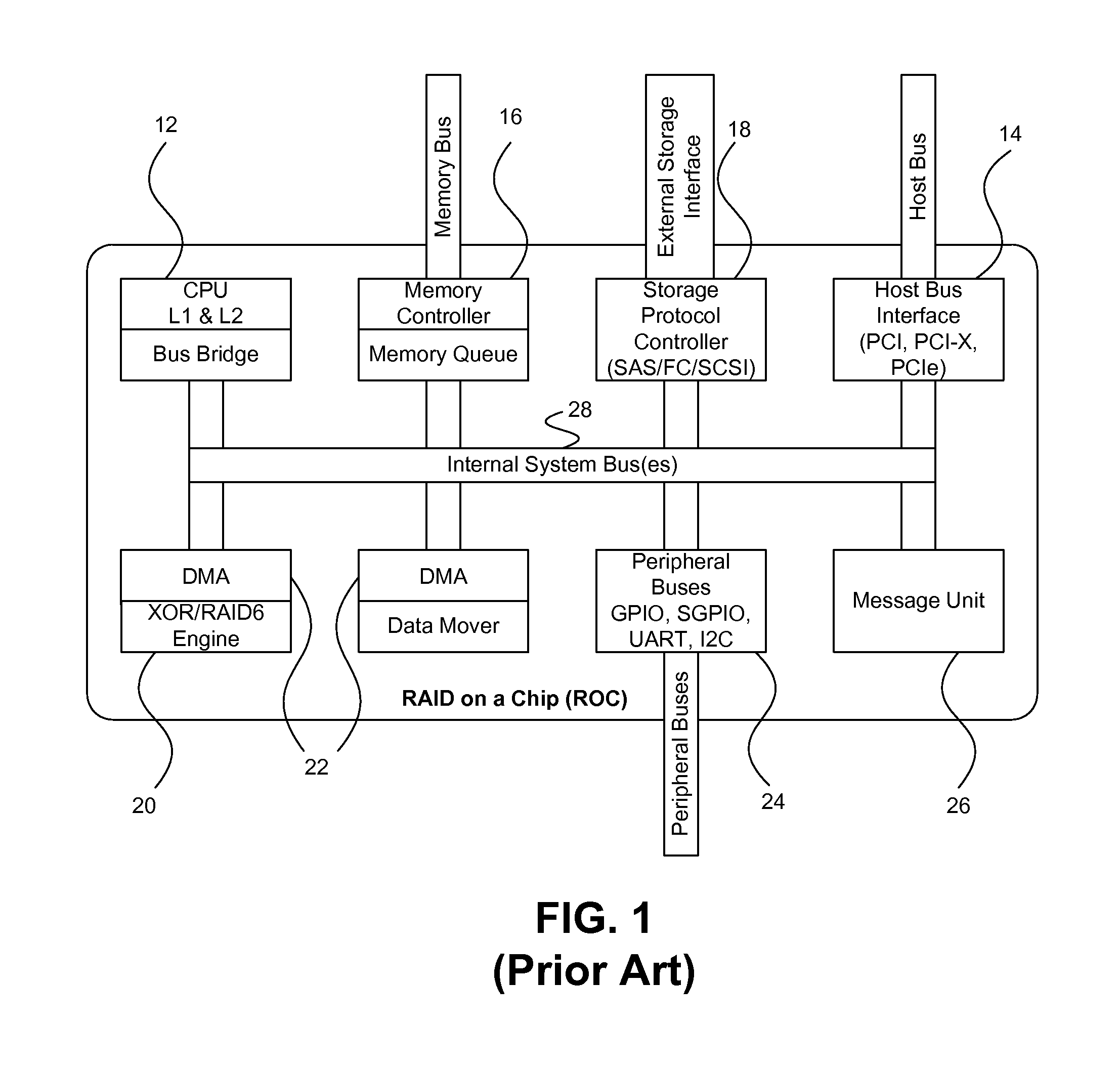

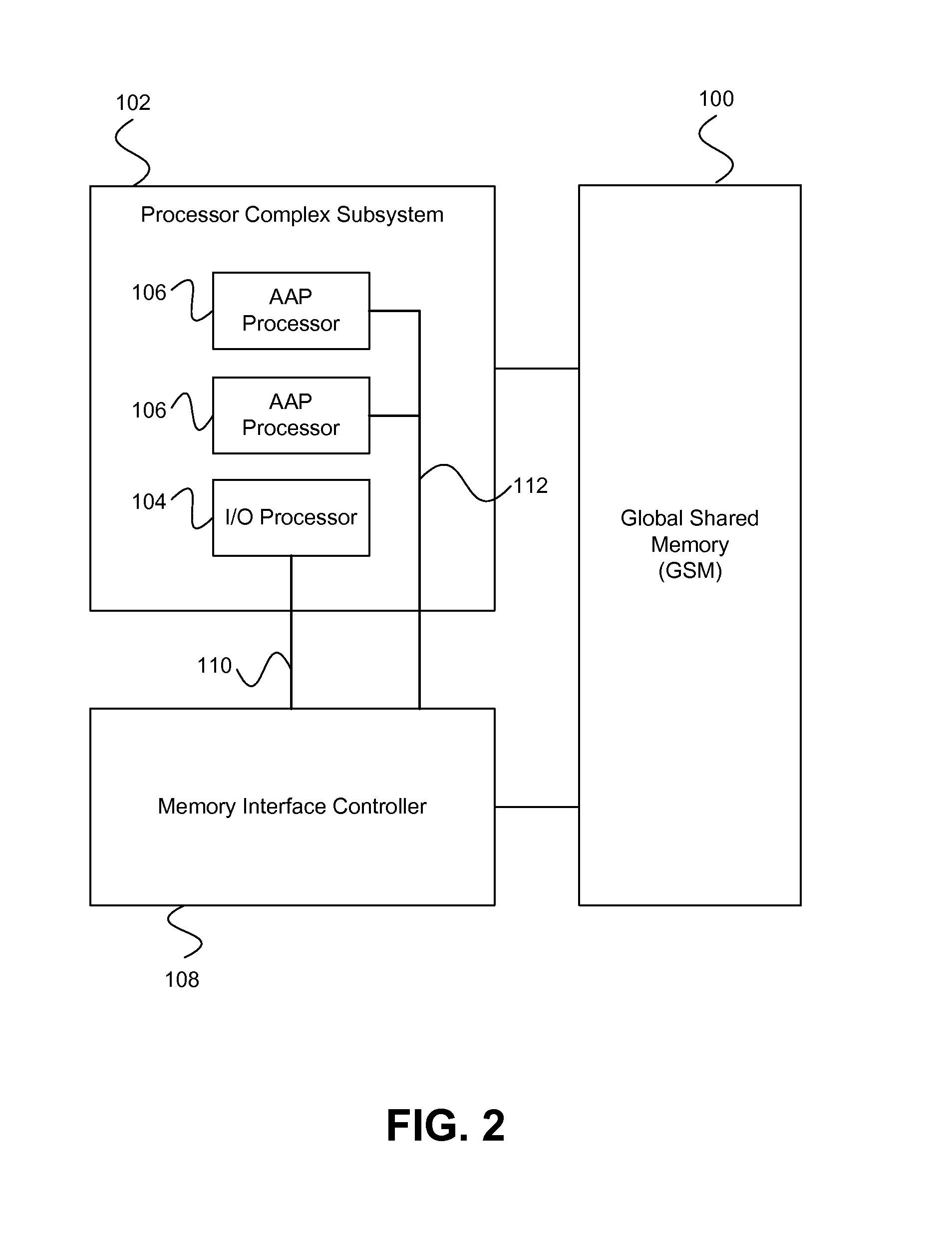

On-chip shared memory based device architecture

ActiveUS7743191B1Reduce disadvantagesLow costRedundant array of inexpensive disk systemsRecord information storageExtensibilityRAID

A method and architecture are provided for SOC (System on a Chip) devices for RAID processing, which is commonly referred as RAID-on-a-Chip (ROC). The architecture utilizes a shared memory structure as interconnect mechanism among hardware components, CPUs and software entities. The shared memory structure provides a common scratchpad buffer space for holding data that is processed by the various entities, provides interconnection for process / engine communications, and provides a queue for message passing using a common communication method that is agnostic to whether the engines are implemented in hardware or software. A plurality of hardware engines are supported as masters of the shared memory. The architectures provide superior throughput performance, flexibility in software / hardware co-design, scalability of both functionality and performance, and support a very simple abstracted parallel programming model for parallel processing.

Owner:MICROSEMI STORAGE SOLUTIONS

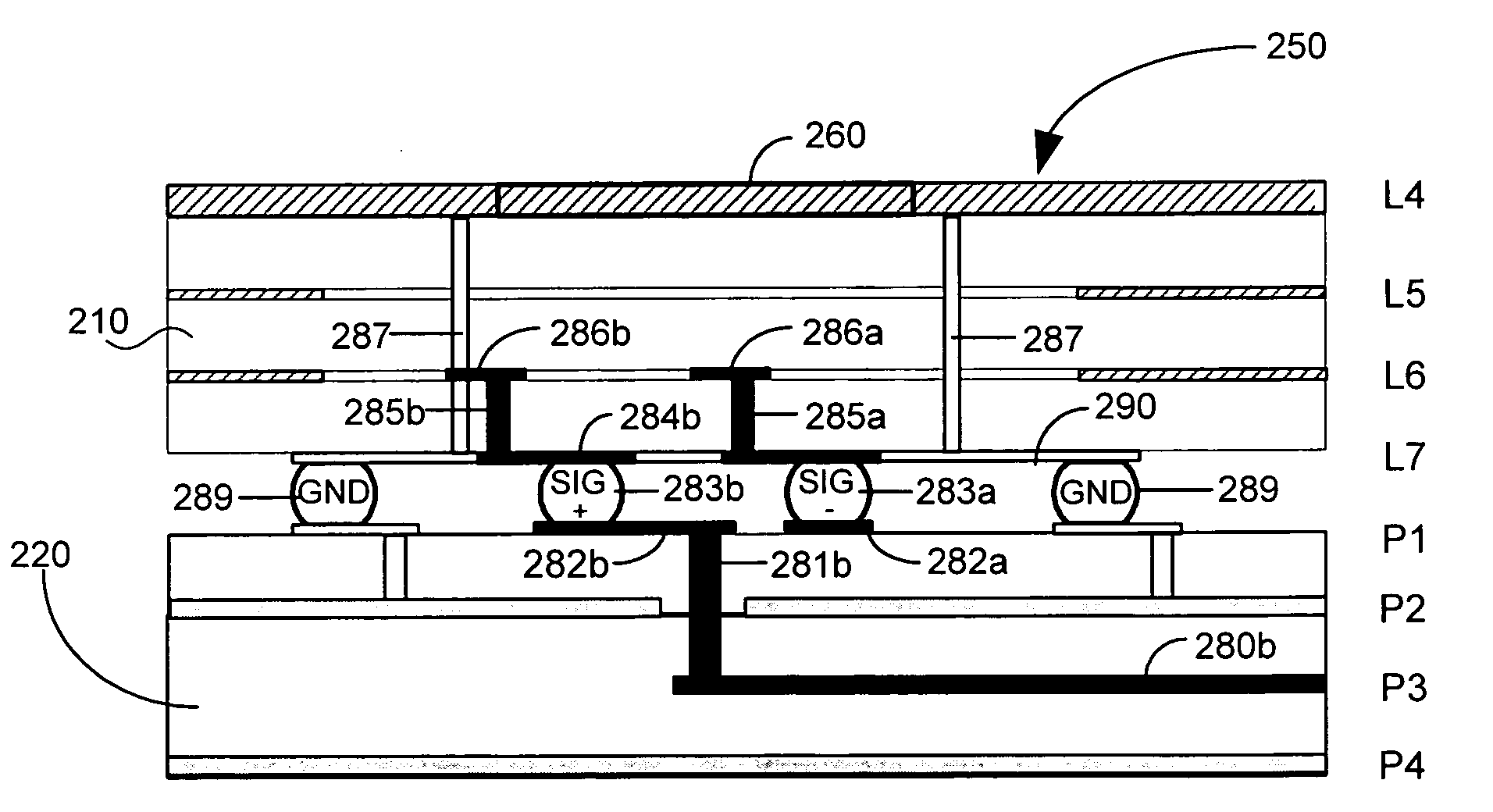

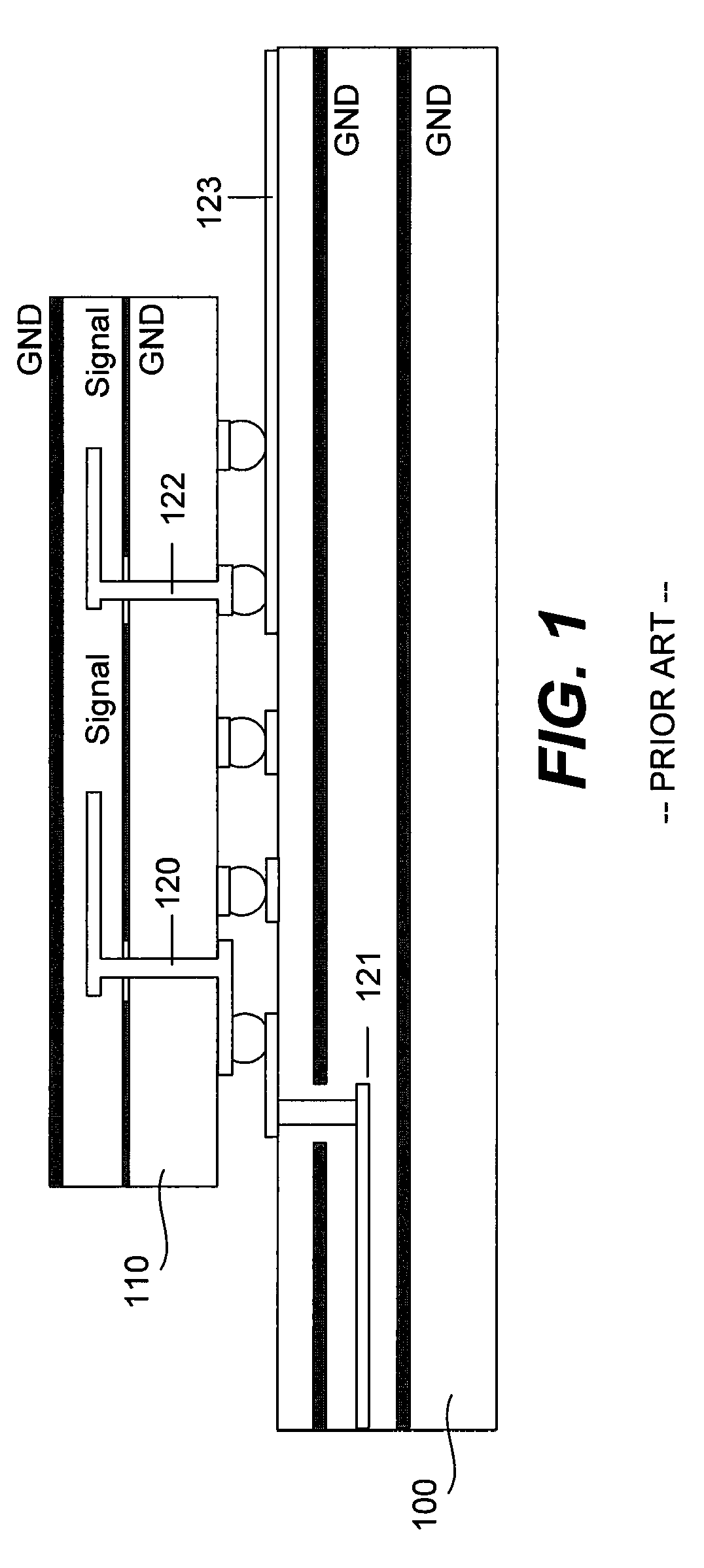

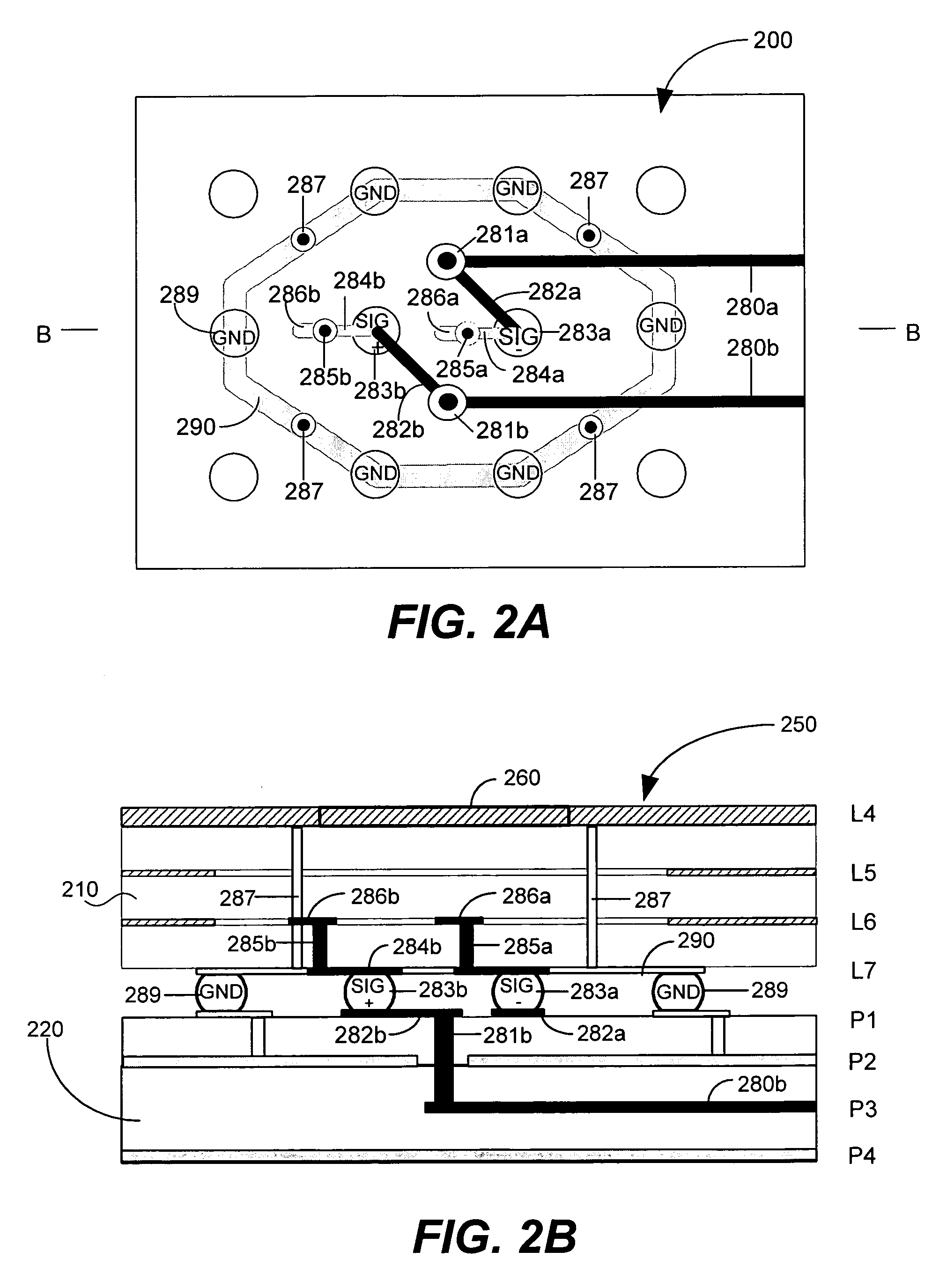

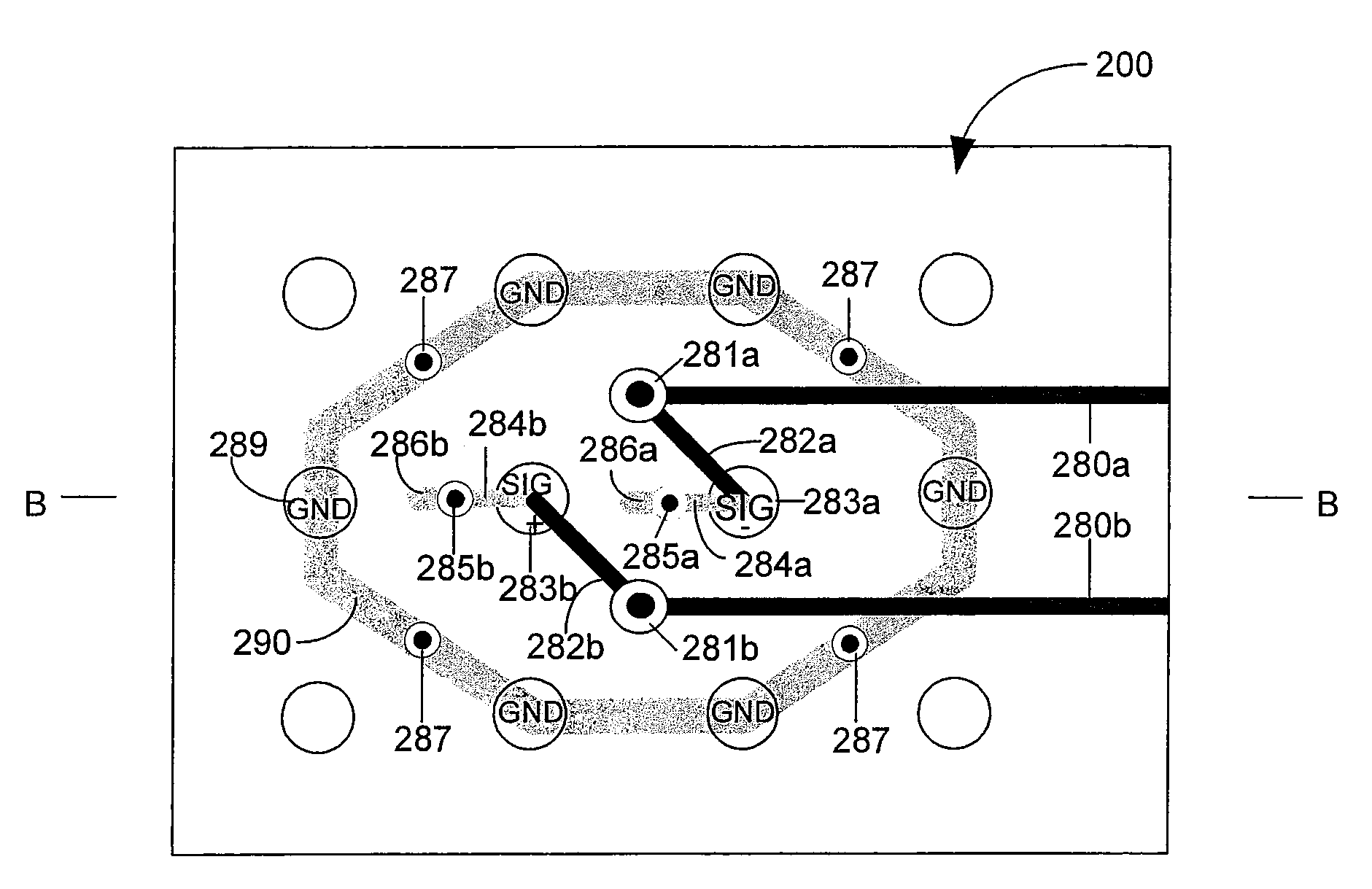

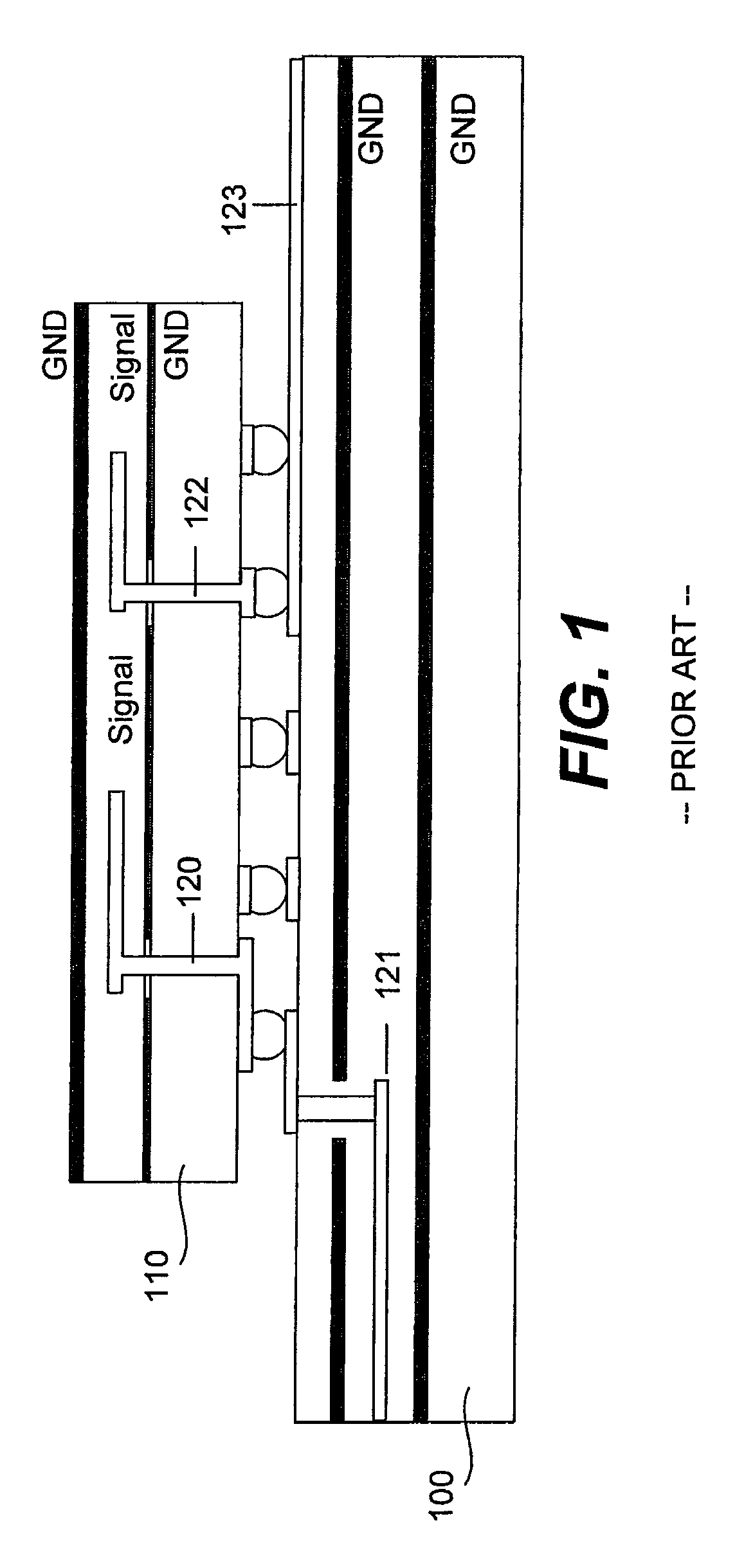

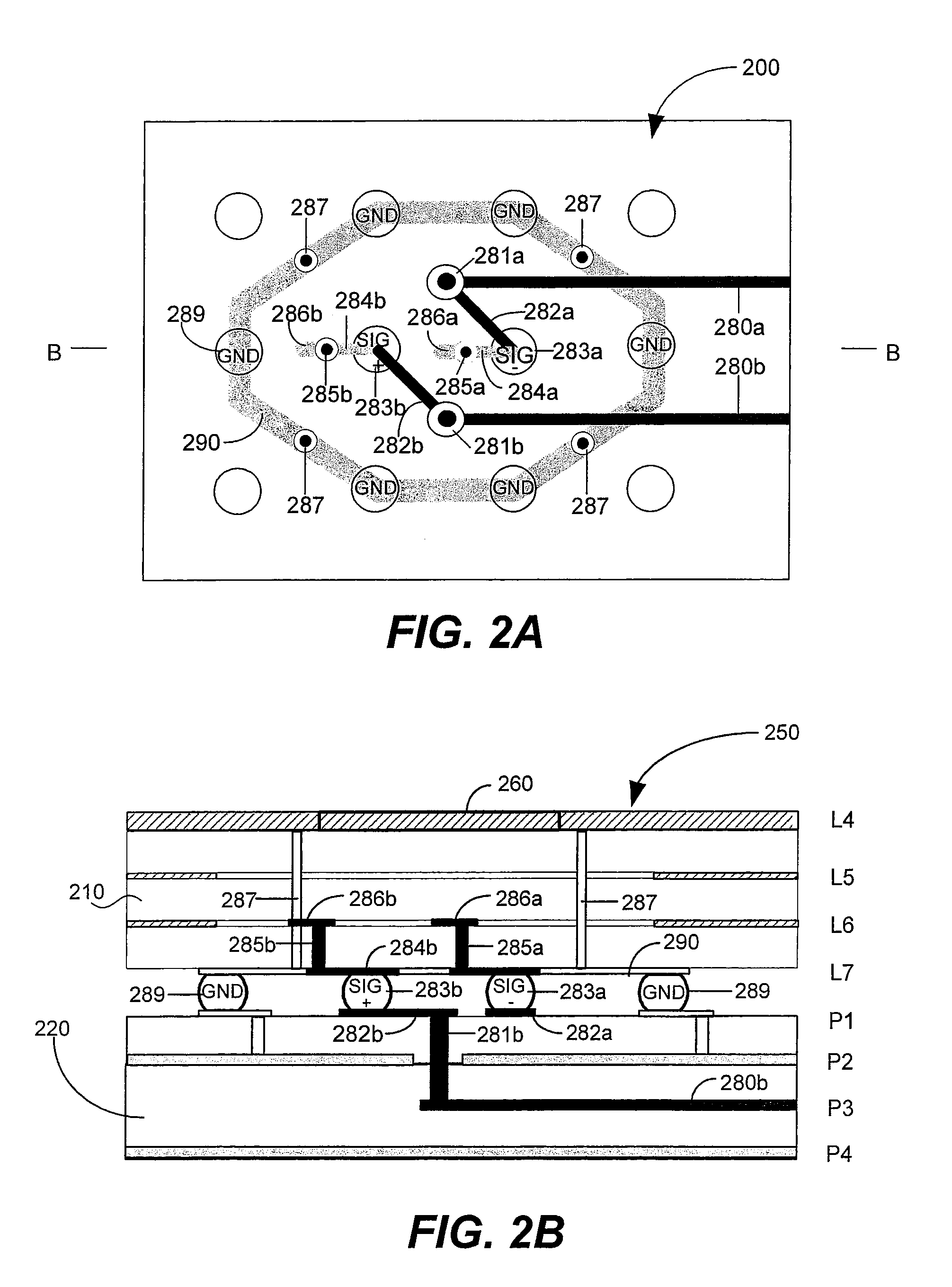

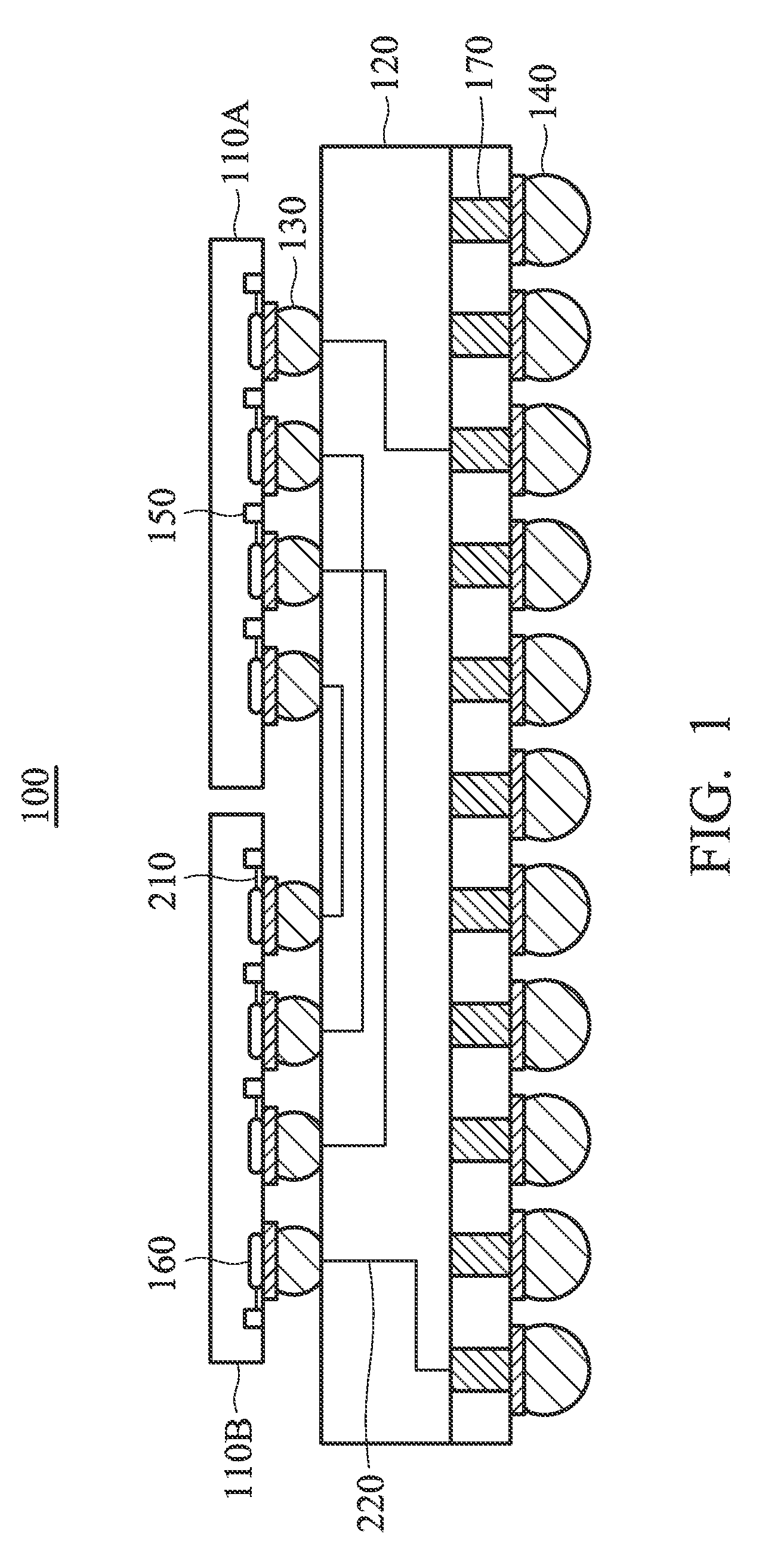

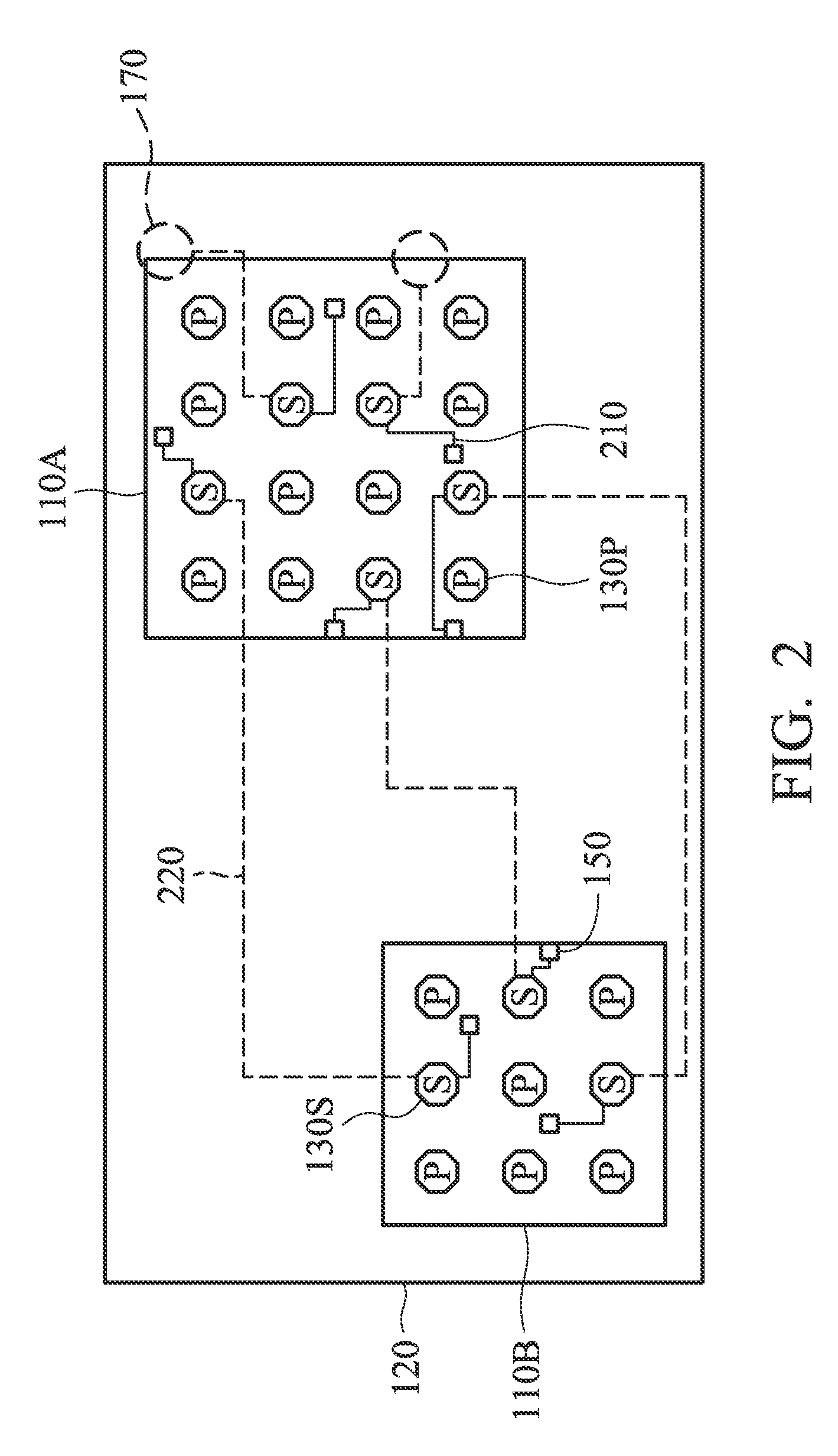

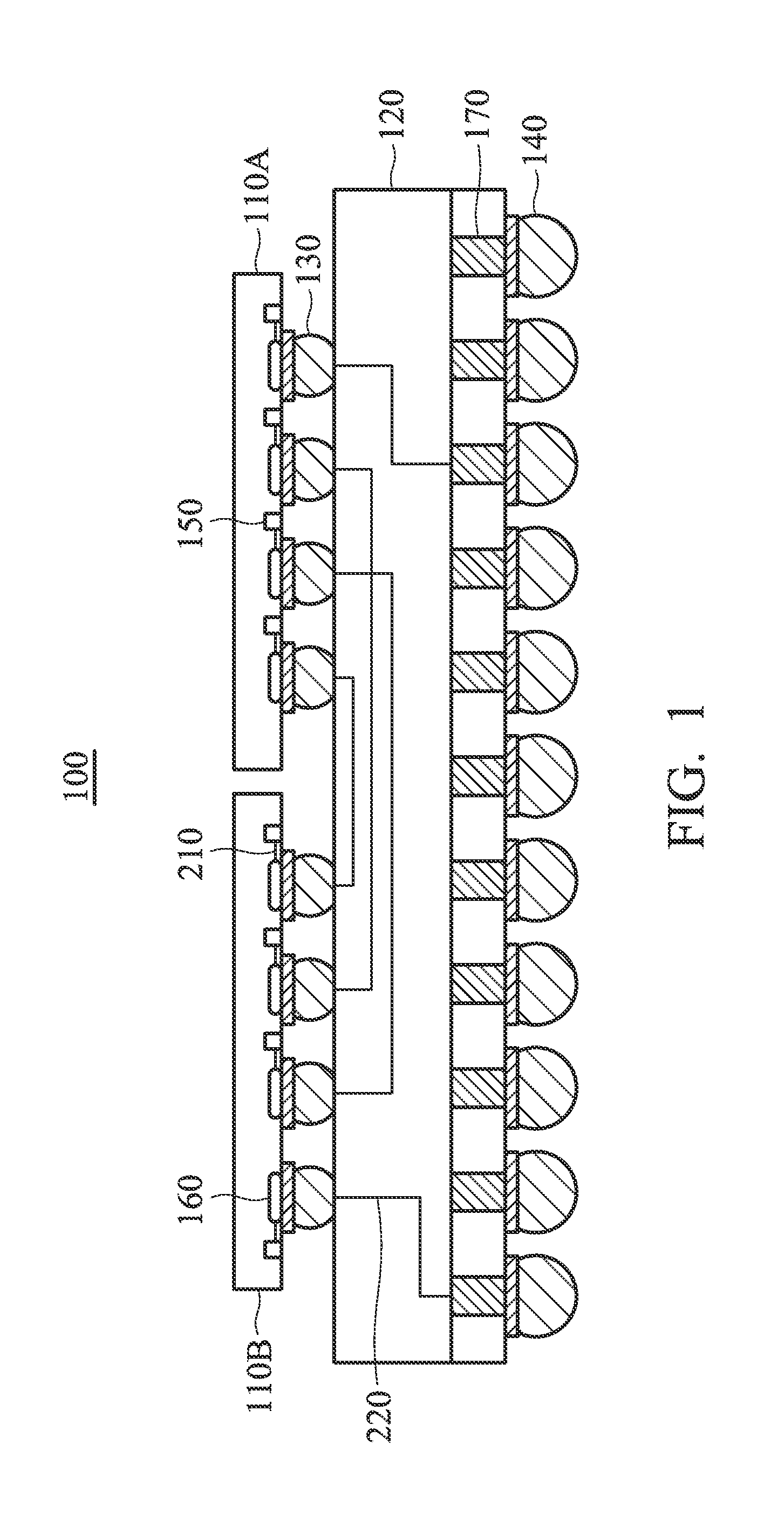

Ball grid array package-to-board interconnect co-design apparatus

InactiveUS7405477B1Signal transmission is convenientAvoid reflectionsSemiconductor/solid-state device detailsPrinted circuit aspectsCopper interconnectData stream

A package-board co-design methodology preserves the signal integrity of high-speed signals passing from semiconductor packages to application PCBs. An optimal architecture of interconnects between package and PCB enhances the signal propagation, minimizes parasitic levels, and decreases electromagnetic interference from adjacent high frequency signals. The invention results in devices with superior signal quality and EMI shielding properties with enhanced capability for carrying data stream at multiple-gigabit per second bit-rates.

Owner:TAHOE RES LTD

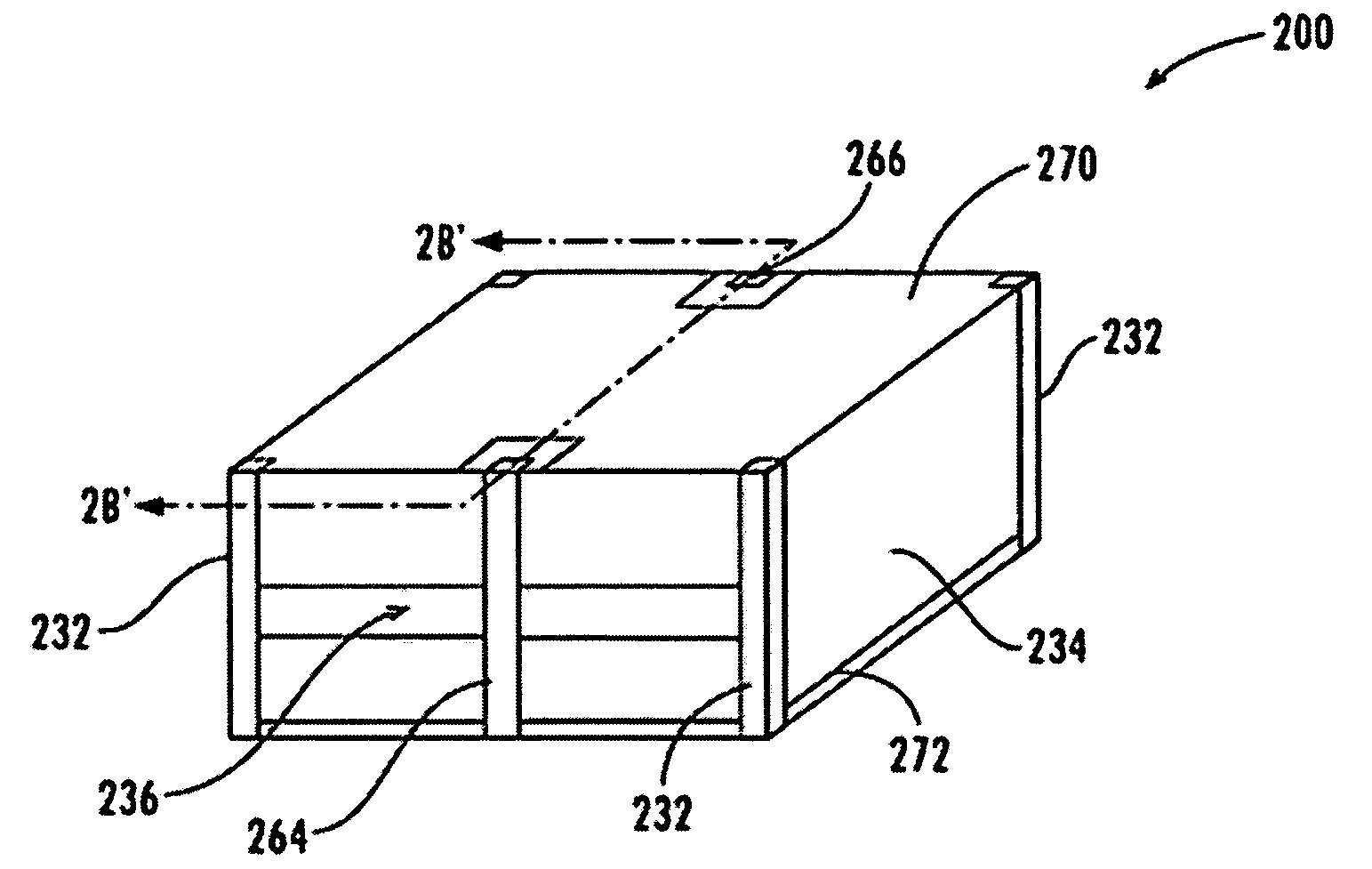

Multi-band RF transceiver with passive reuse in organic substrates

ActiveUS20050248418A1Reduce in quantityReduce phase noiseMultiple-port networksSemiconductor/solid-state device detailsMulti bandLow noise

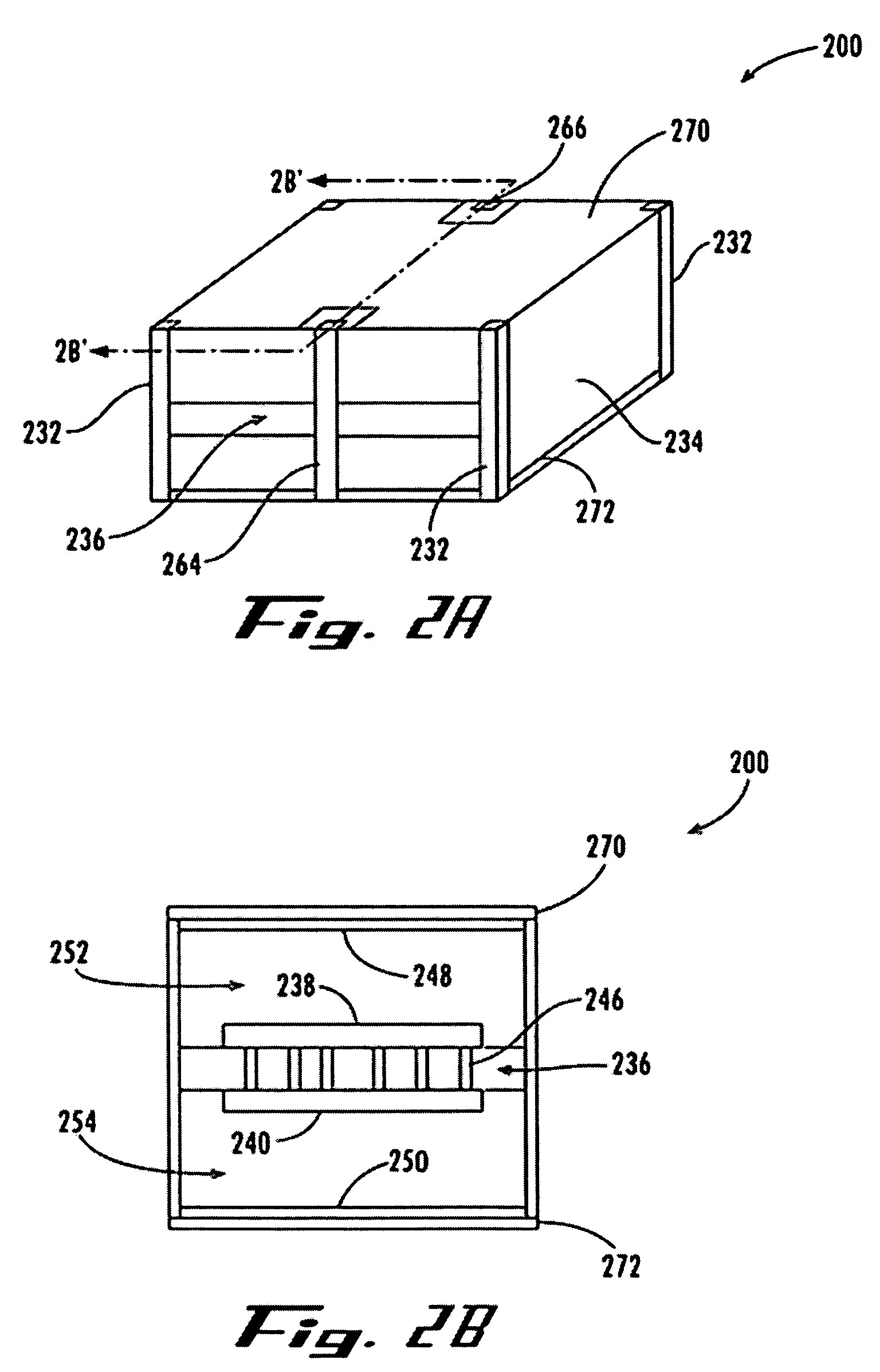

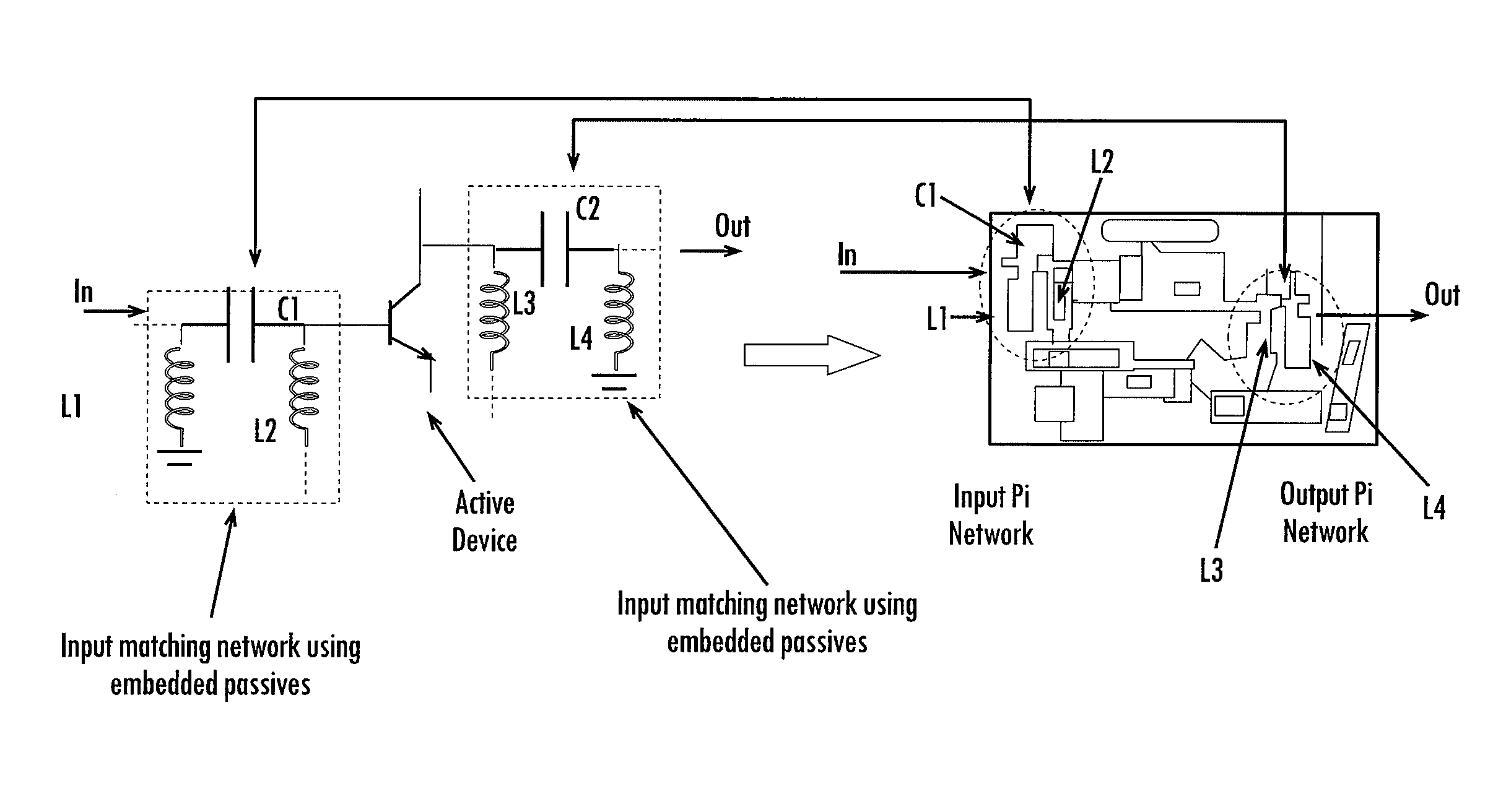

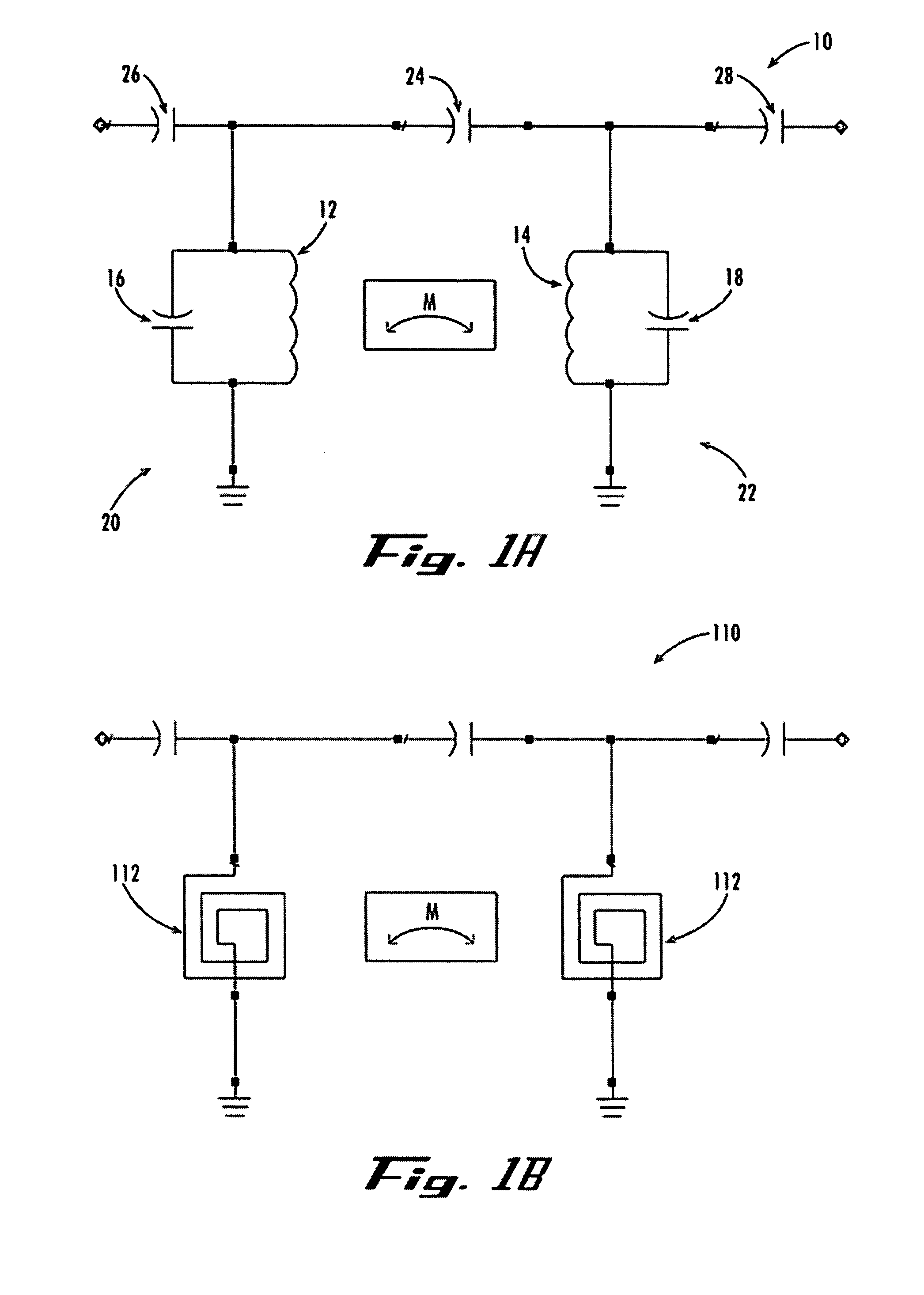

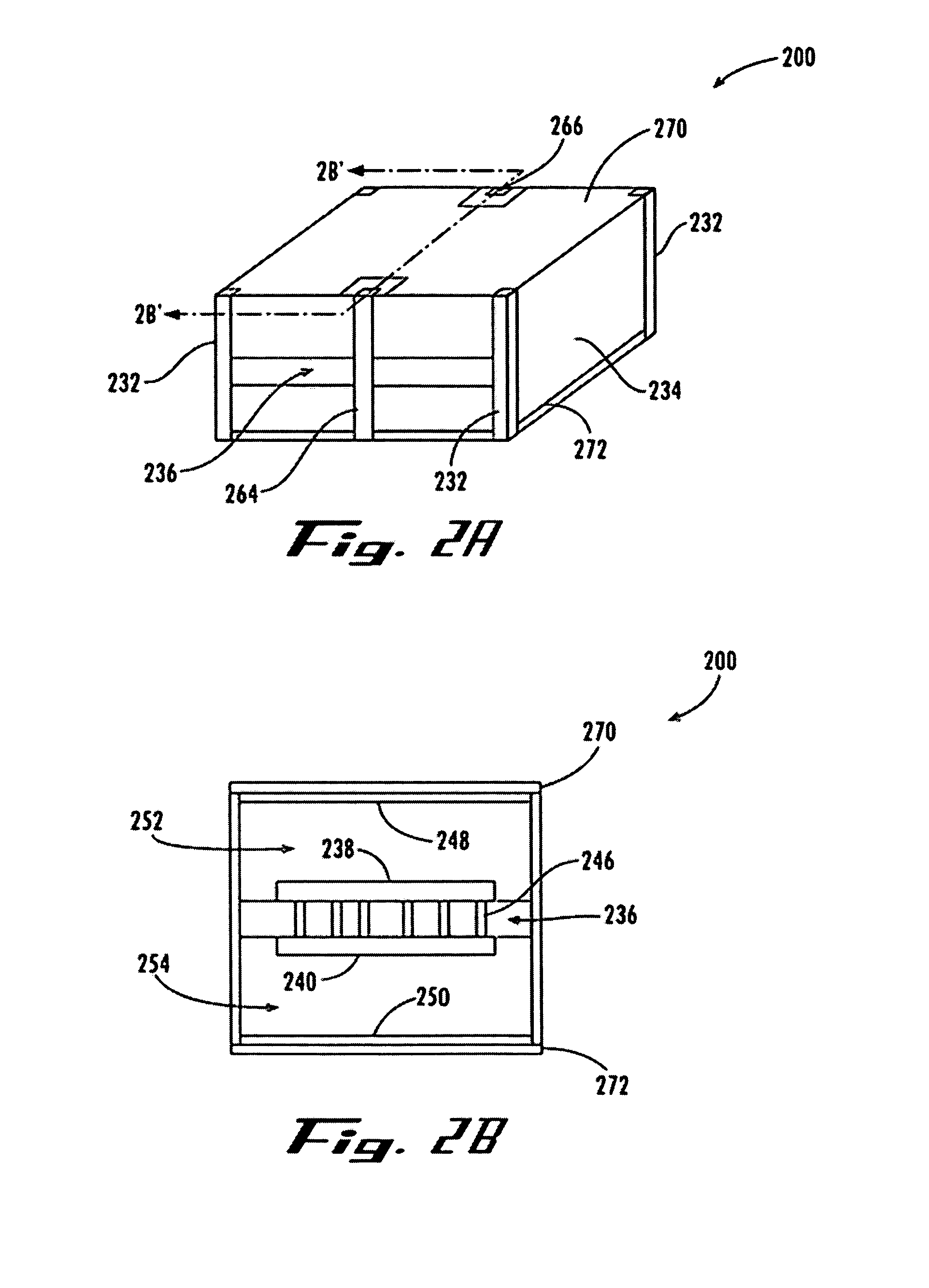

The present invention allows for the use of chip-package co-design of RF transceivers and their components by using discrete active devices in conjunction with passive components. Two particular components are described, including voltage controlled oscillators (VCOs) and low noise amplifiers (LNAs). The high quality passive components for use in the VCOs and LNAs may be obtained by the use of embedded passives in organic substrates. Further, the embedded passives may have multi-band characteristics, thereby allowing multi-band VCOs and LNAs to be implemented with fewer components. In situations where size is a concern, the active devices and passive components utilized in an RF transceiver may be implemented in a low form factor module of less than 1.1 mm thick according to an embodiment of the invention.

Owner:GEORGIA TECH RES CORP

Multi-band RF transceiver with passive reuse in organic substrates

ActiveUS7489914B2Reduce in quantityReduce phase noiseMultiple-port networksSemiconductor/solid-state device detailsMulti bandLow noise

The present invention allows for the use of chip-package co-design of RF transceivers and their components by using discrete active devices in conjunction with passive components. Two particular components are described, including voltage controlled oscillators (VCOs) and low noise amplifiers (LNAs). The high quality passive components for use in the VCOs and LNAs may be obtained by the use of embedded passives in organic substrates. Further, the embedded passives may have multi-band characteristics, thereby allowing multi-band VCOs and LNAs to be implemented with fewer components. In situations where size is a concern, the active devices and passive components utilized in an RF transceiver may be implemented in a low form factor module of less than 1.1 mm thick according to an embodiment of the invention.

Owner:GEORGIA TECH RES CORP

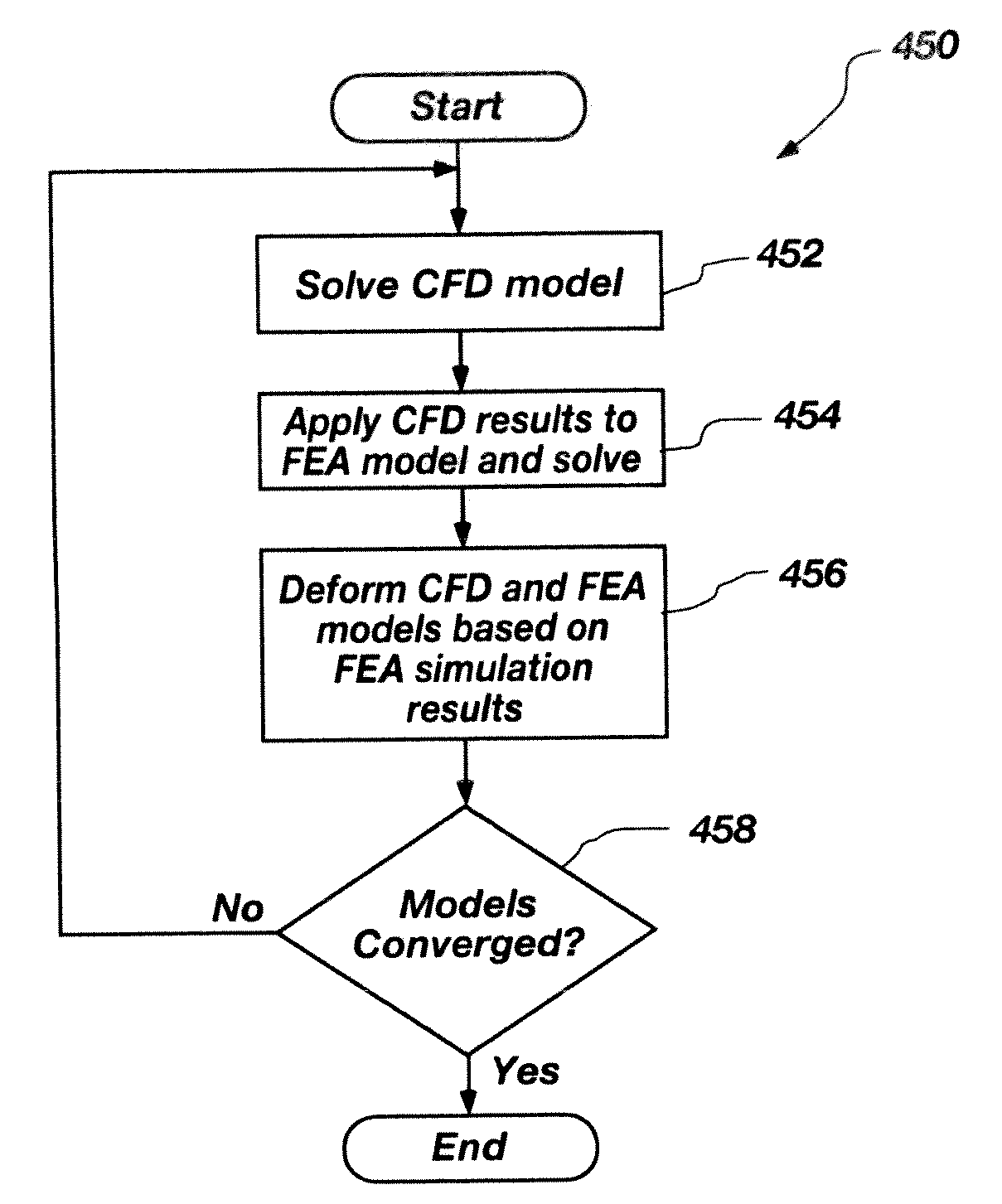

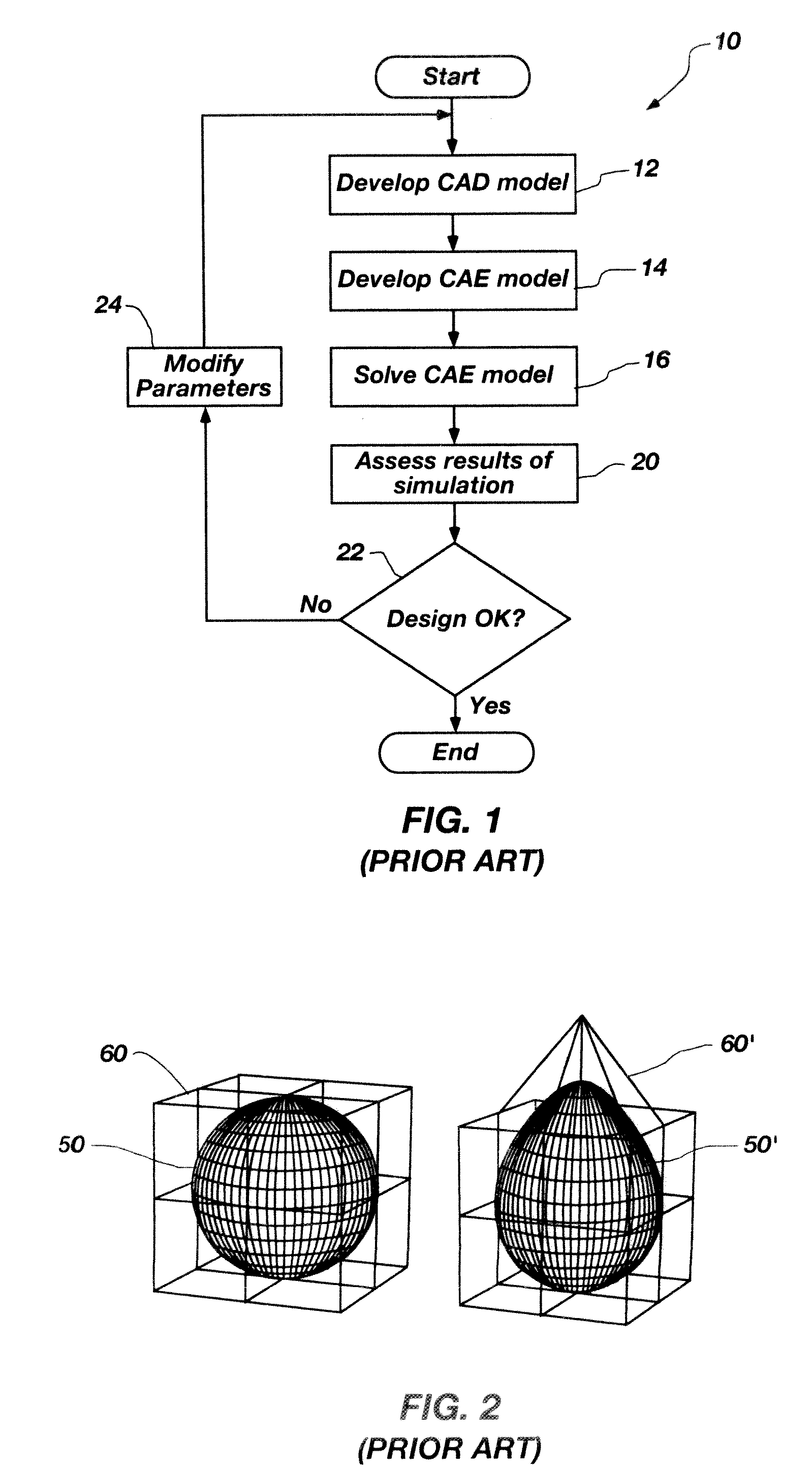

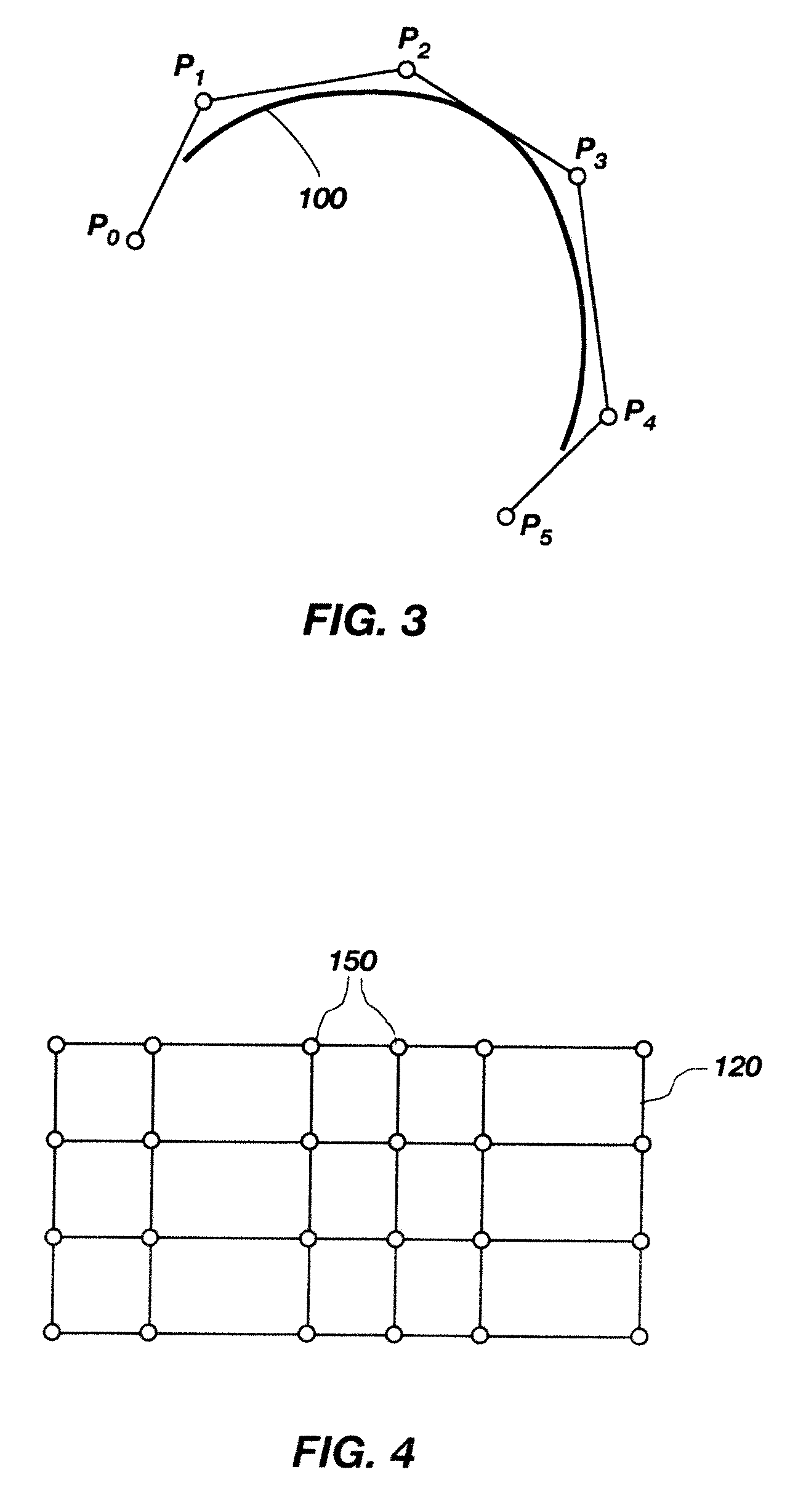

System, methods, and computer readable media, for product design using coupled computer aided engineering models

InactiveUS20080275677A1Reduce database requirementImprove design flexibilityComputation using non-denominational number representationDesign optimisation/simulationComputational scienceModel method

Methods, systems, and computer readable media are used for analyzing a design. A finite element analysis (FEA) model and a correlated computational flow dynamics (CFD) model are defined. A parametric volume is defined with control points forming a mesh bounding a common design object of the models. Control points on the parametric volume are adjusted to develop a design deformation of the FEA model and the CFD model. An analysis loop is performed until a convergence is achieved. The analysis loop includes simulating the CFD model to develop resultant forces and simulating the FEA model with the resultant forces applied to develop resultant displacements. The analysis loop also includes deforming the CFD model and the FEA model to match the resultant displacements by adjusting control points on the parametric volume to generate a corresponding analysis deformation of the FEA model and the CFD model.

Owner:OPTIMAL SOLUTIONS SOFTWARE

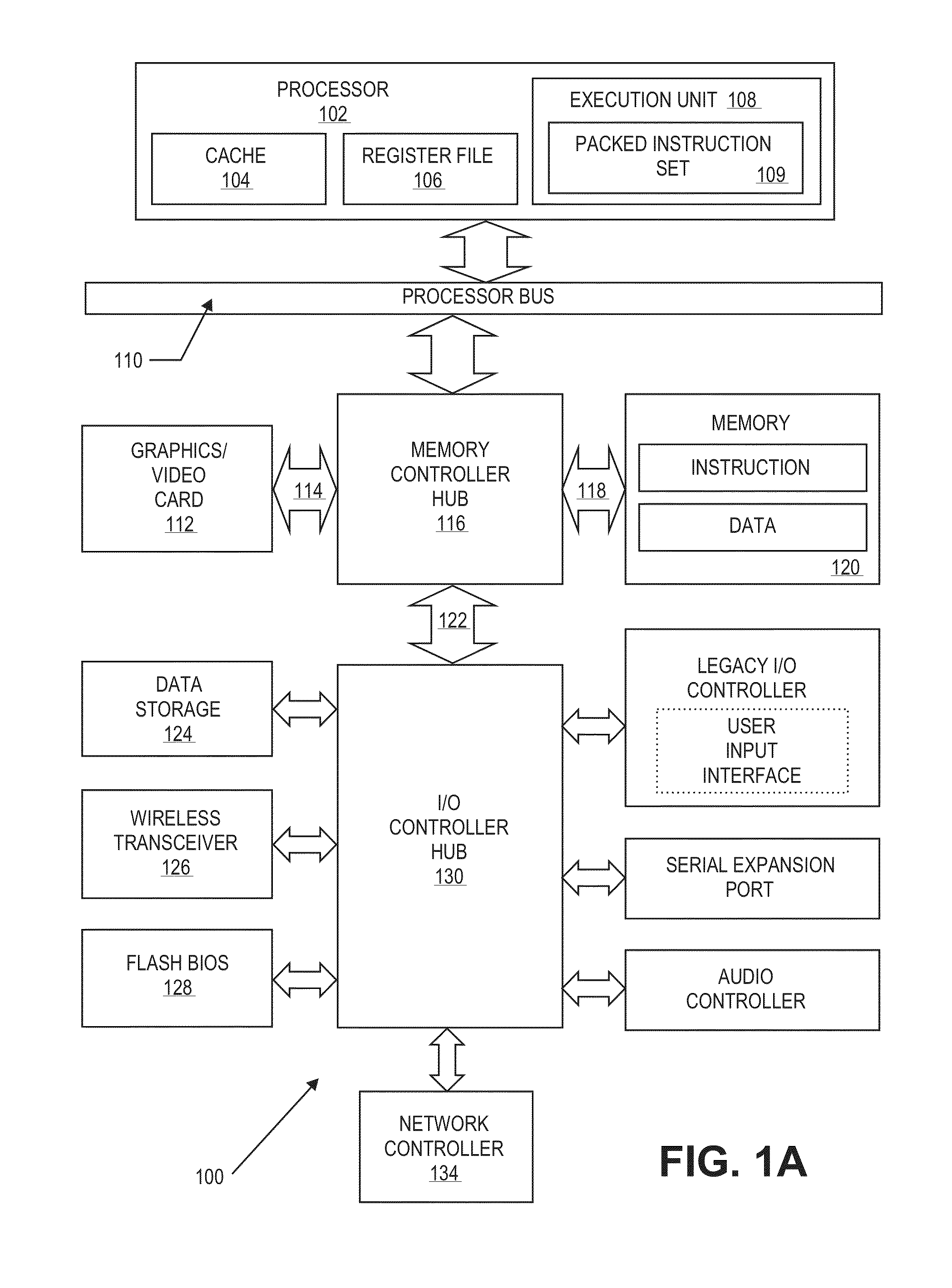

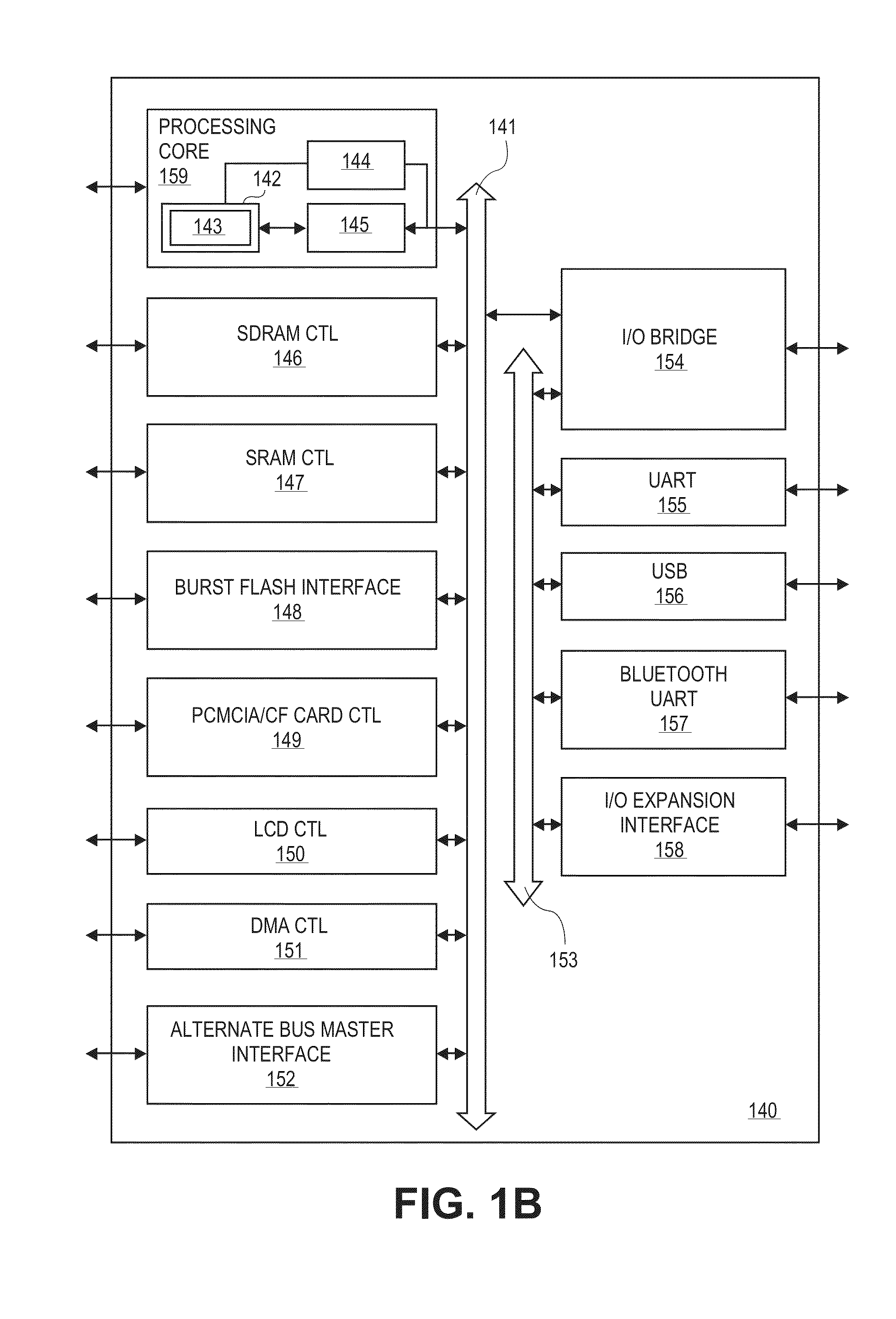

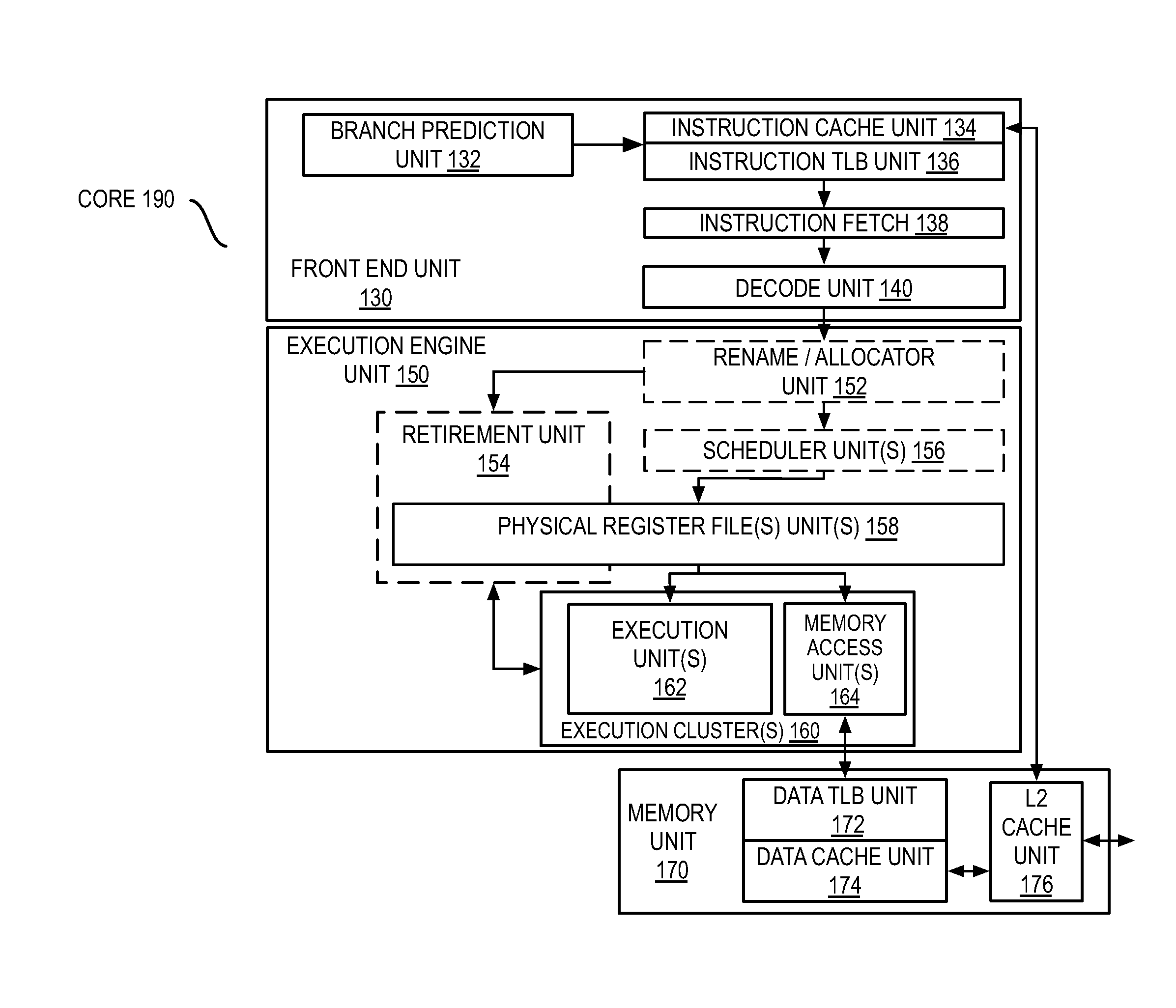

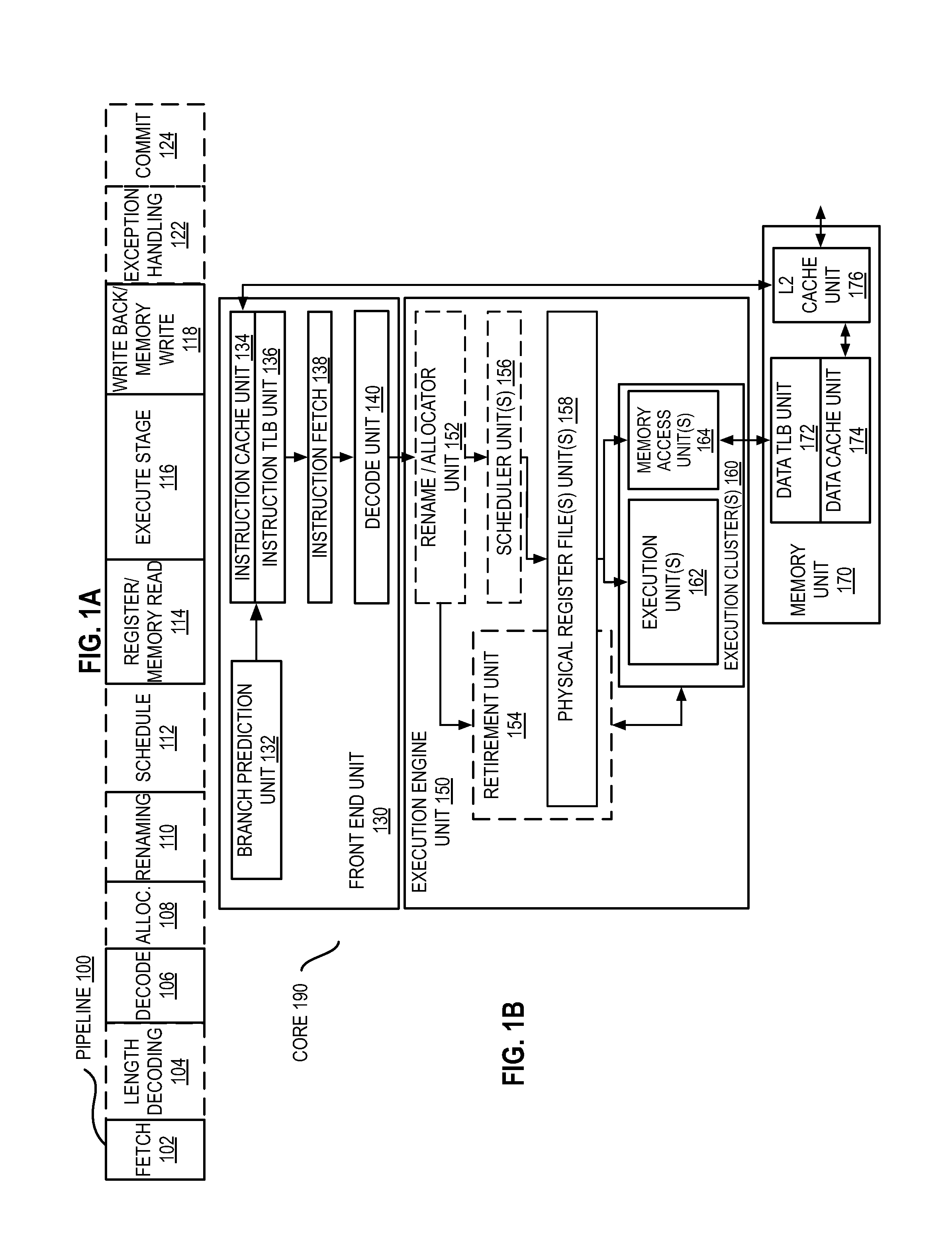

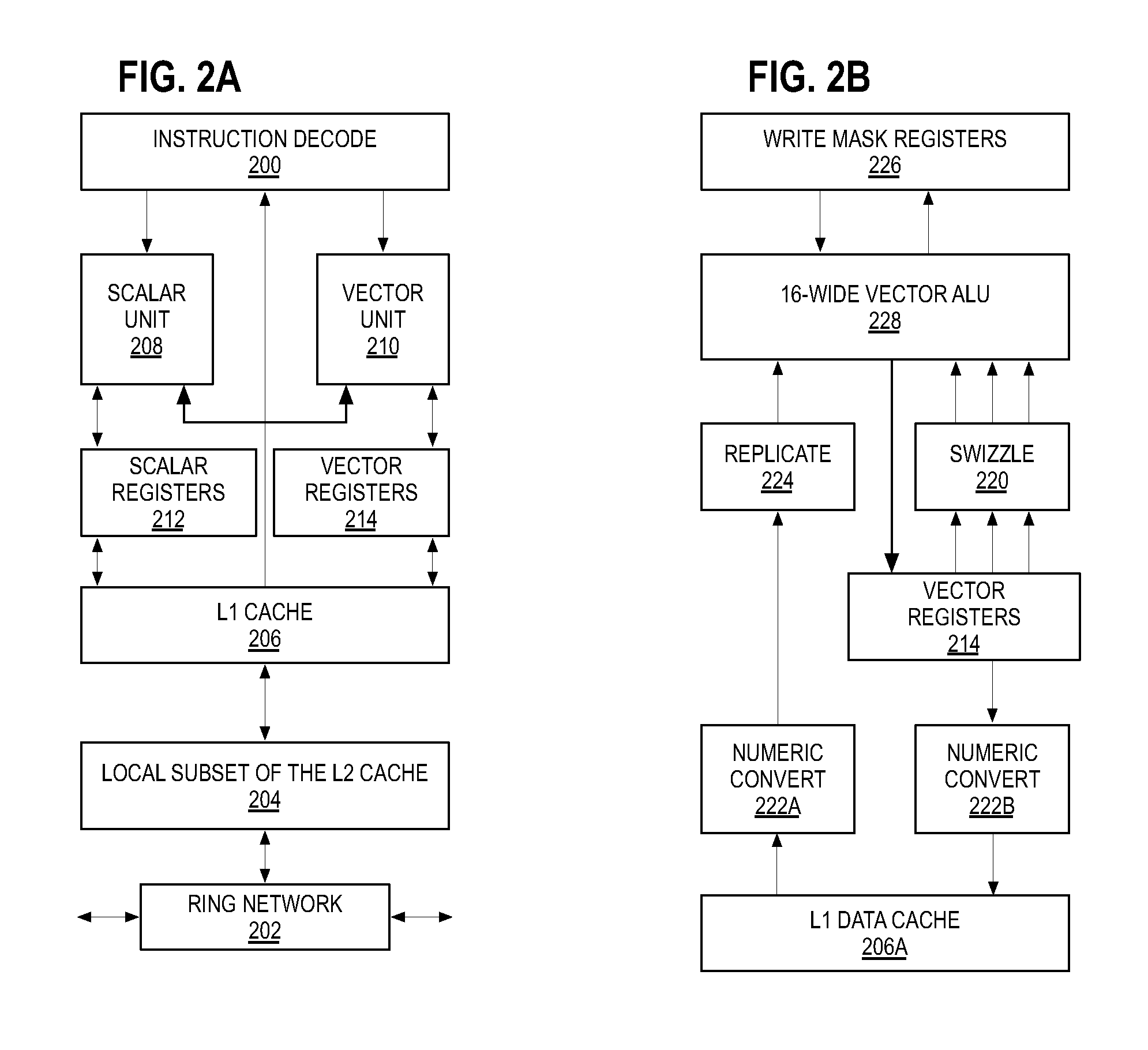

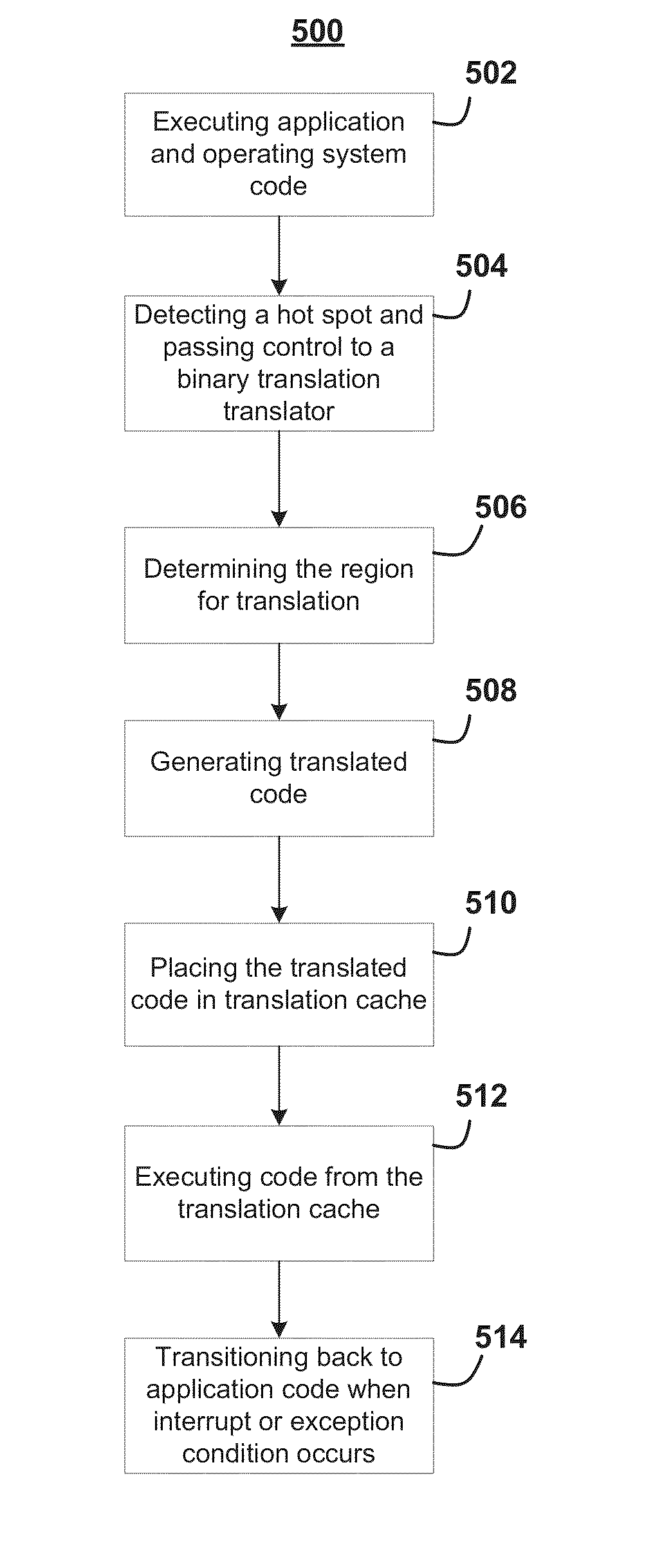

Instruction and logic to perform dynamic binary translation

A micro-architecture may provide a hardware and software co-designed dynamic binary translation. The micro-architecture may invoke a method to perform a dynamic binary translation. The method may comprise executing original software code compiled targeting a first instruction set, using processor hardware to detect a hot spot in the software code and passing control to a binary translation translator, determining a hot spot region for translation, generating the translated code using a second instruction set, placing the translated code in a translation cache, executing the translated code from the translated cache, and transitioning back to the original software code after the translated code finishes execution.

Owner:INTEL CORP

Ball grid array package-to-board interconnect co-design apparatus

ActiveUS7514789B1Reduce electromagnetic interferenceSuperior signal quality and EMI shielding propertySemiconductor/solid-state device detailsPrinted circuit aspectsData streamCopper interconnect

A package-board co-design methodology preserves the signal integrity of high-speed signals passing from semiconductor packages to application PCBs. An optimal architecture of interconnects between package and PCB enhances the signal propagation, minimizes parasitic levels, and decreases electromagnetic interference from adjacent high frequency signals. The invention results in devices with superior signal quality and EMI shielding properties with enhanced capability for carrying data stream at multiple-gigabit per second bit-rates.

Owner:TAHOE RES LTD

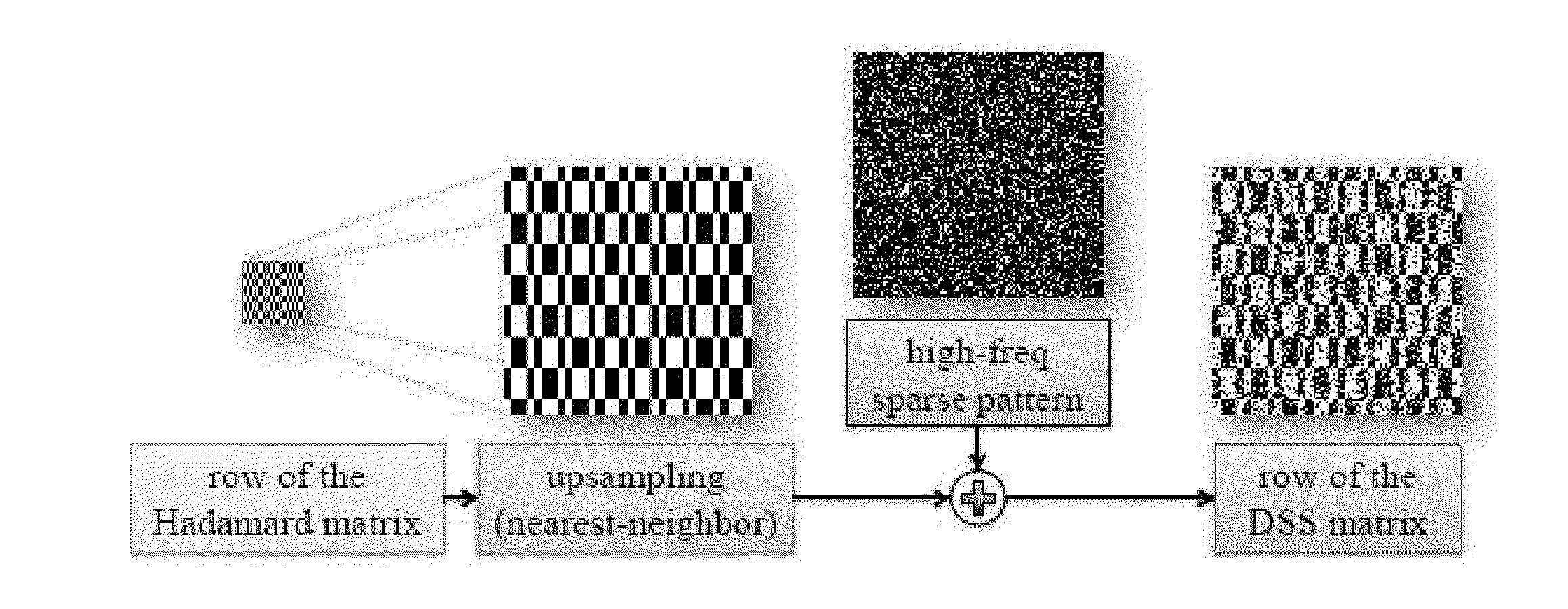

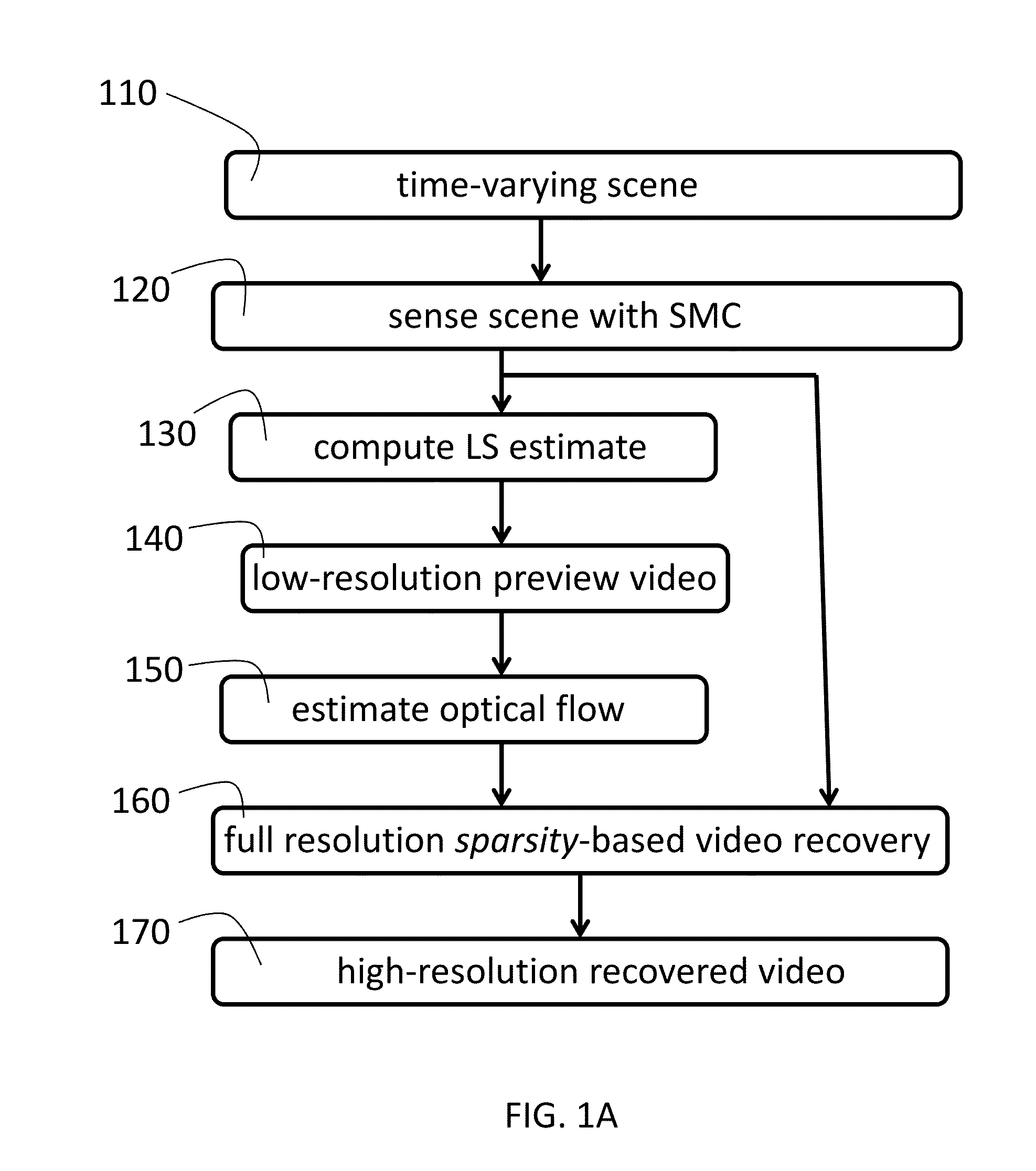

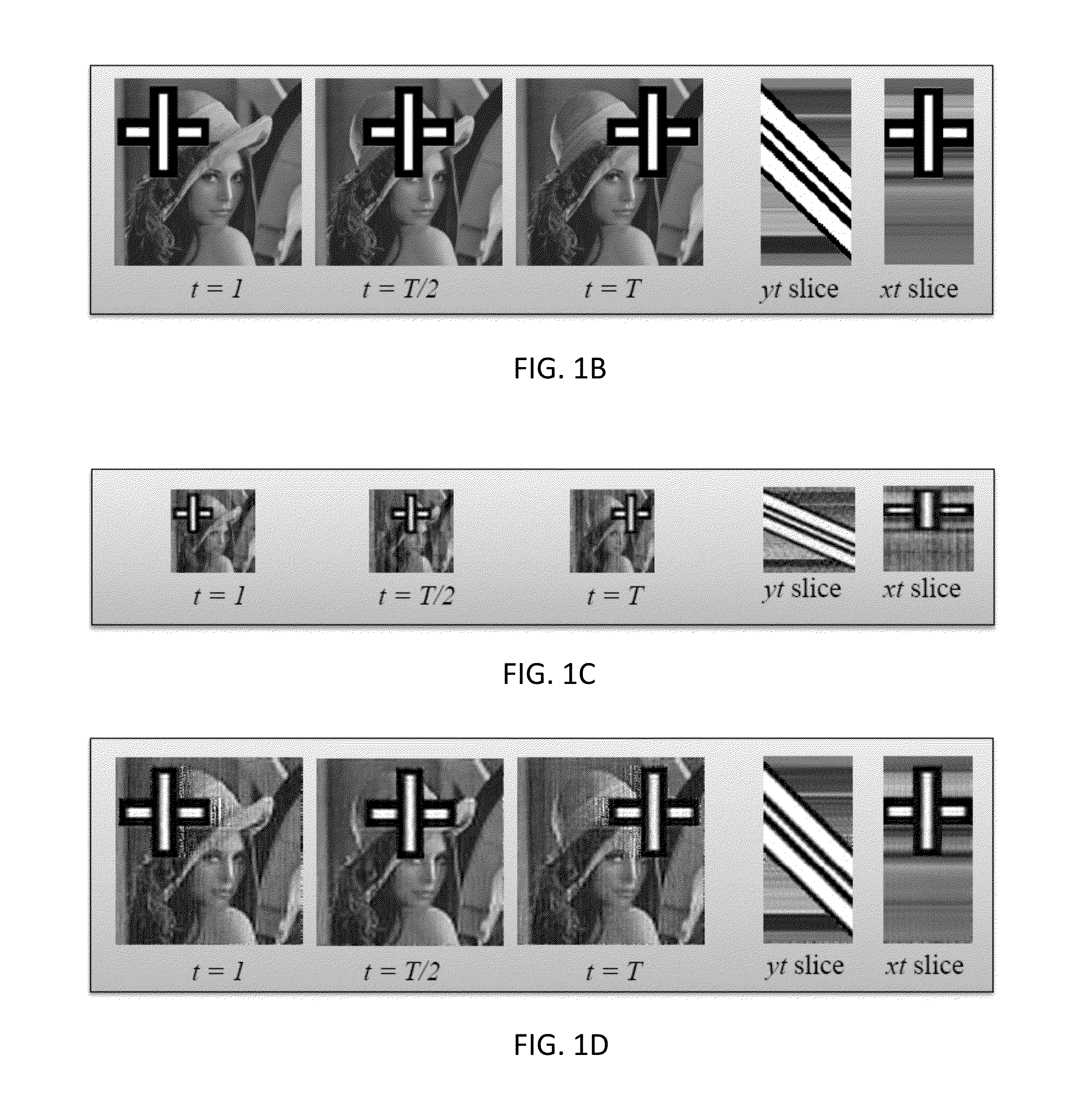

System And Method Of Video Compressive Sensing For Spatial-Multiplexing Cameras

InactiveUS20140063314A1RecoveryFaster transformsTelevision system detailsColor television detailsSpatial light modulatorImage resolution

Compressive sensing (CS)-based spatial-multiplexing cameras (SMCs) sample a scene through a series of coded projections using a spatial light modulator and a few optical sensor elements. A co-designed video CS sensing matrix and recovery algorithm provides an efficiently computable low-resolution video preview. The scene's optical flow is estimated from the preview and fed into a convex-optimization algorithm to recover the high-resolution video.

Owner:RICE UNIV

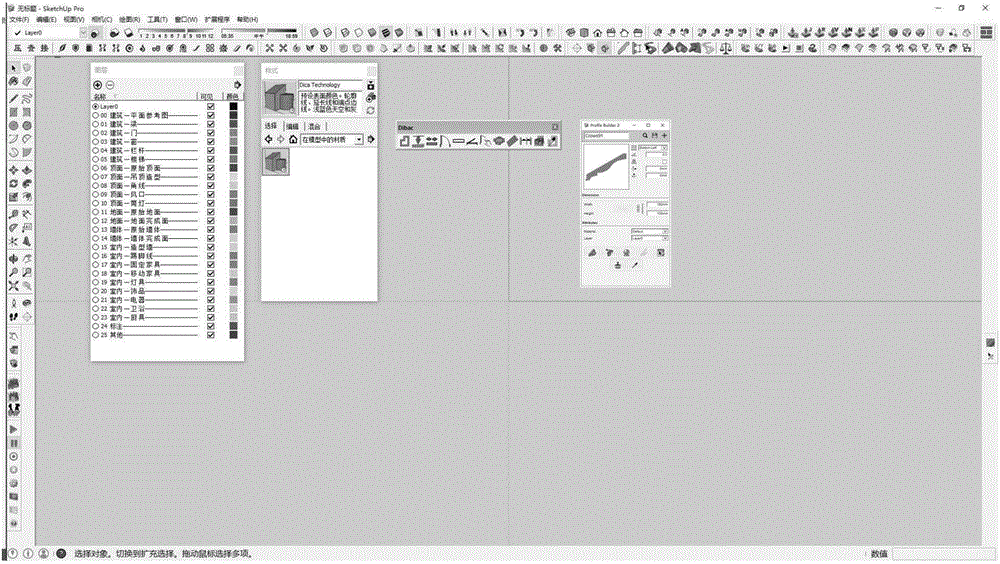

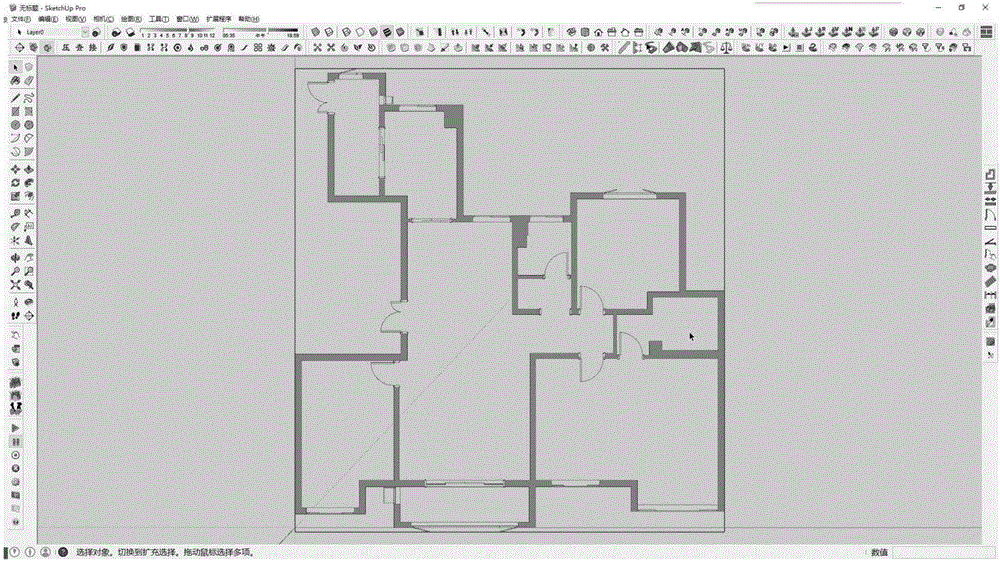

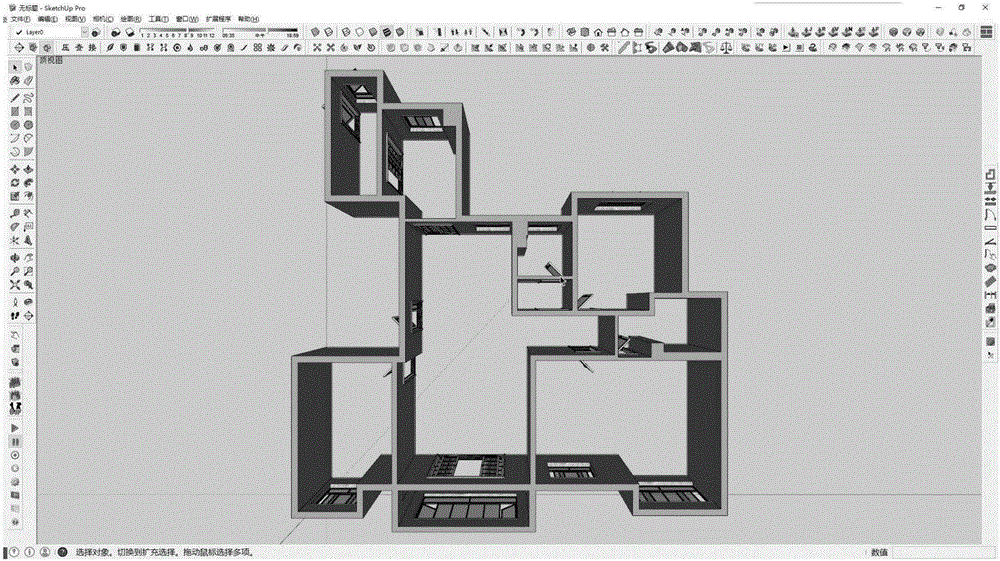

BIM-based fine decoration co-design method

InactiveCN106649938AAccurate quotationSolve the problem that the viewing angle is incomplete and the overall decoration effect cannot be presentedGeometric CADSpecial data processing applicationsSoftware engineeringCollaborative design

The invention relates to a BIM-based fine decoration co-design method. The method comprises the following steps of presetting SketchUp software; converting two-dimensional plane design into three-dimensional design; separating a single space; carrying out single space soft and hard decoration design by utilizing a BIM; and reloading the single space. Through the method, a home owner can immediately change decoration styles, colors and materials under the guidance of a designer according to own hobbies, and virtual decoration is carried out; the home owner no longer passively receives a design scheme provided by the designer, and the home owner participates in and experiences a relaxed and happy design process entirely; and a decoration budget is automatically generated according to decoration contents and selected materials, so that offered price is more accurate and added items are radically avoided.

Owner:杭州迪咖科技有限公司

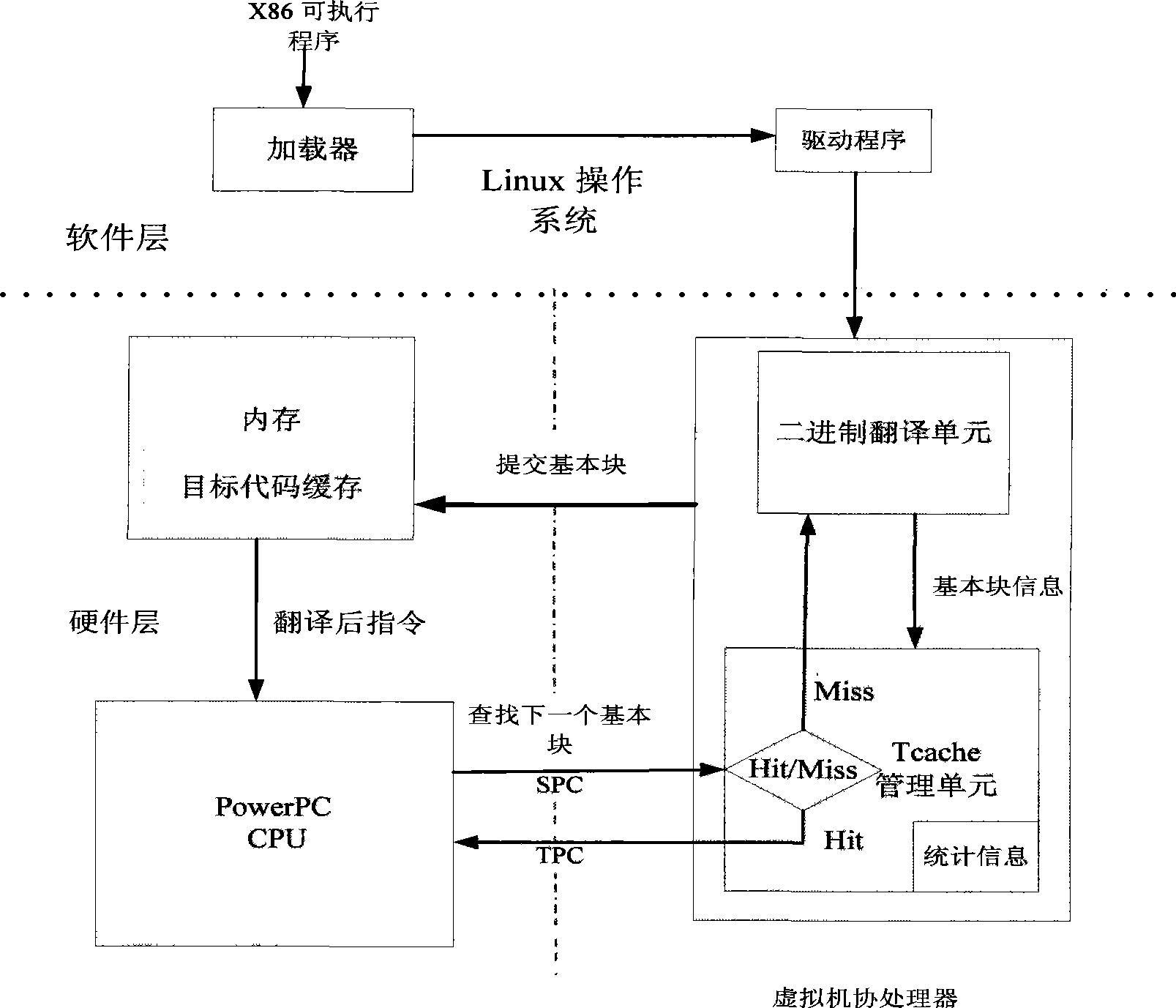

Dynamic binary translation method for cooperation design of software and hardware

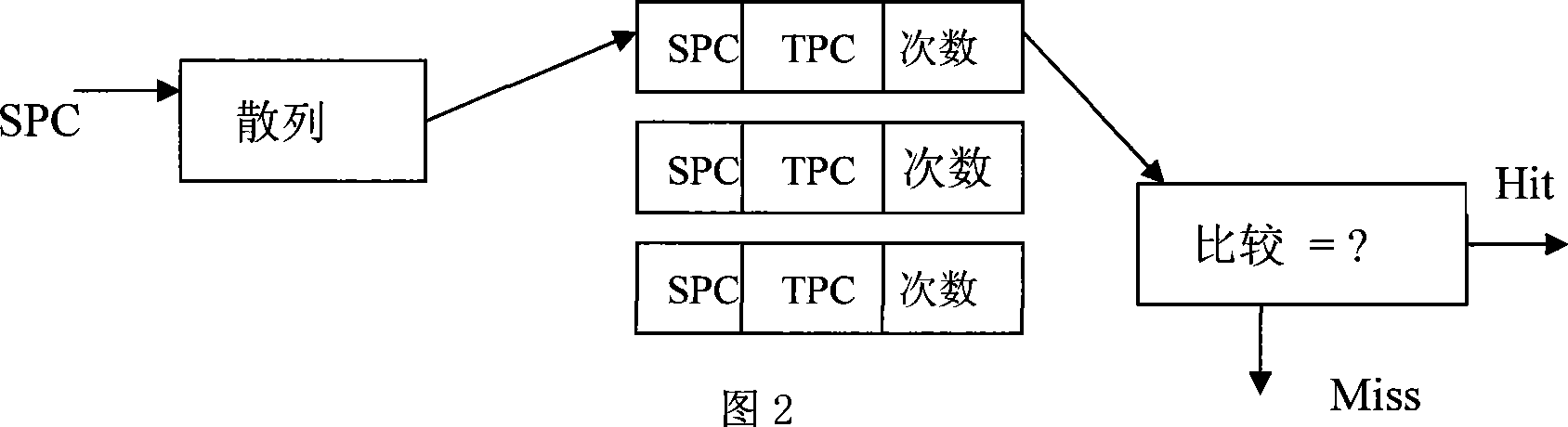

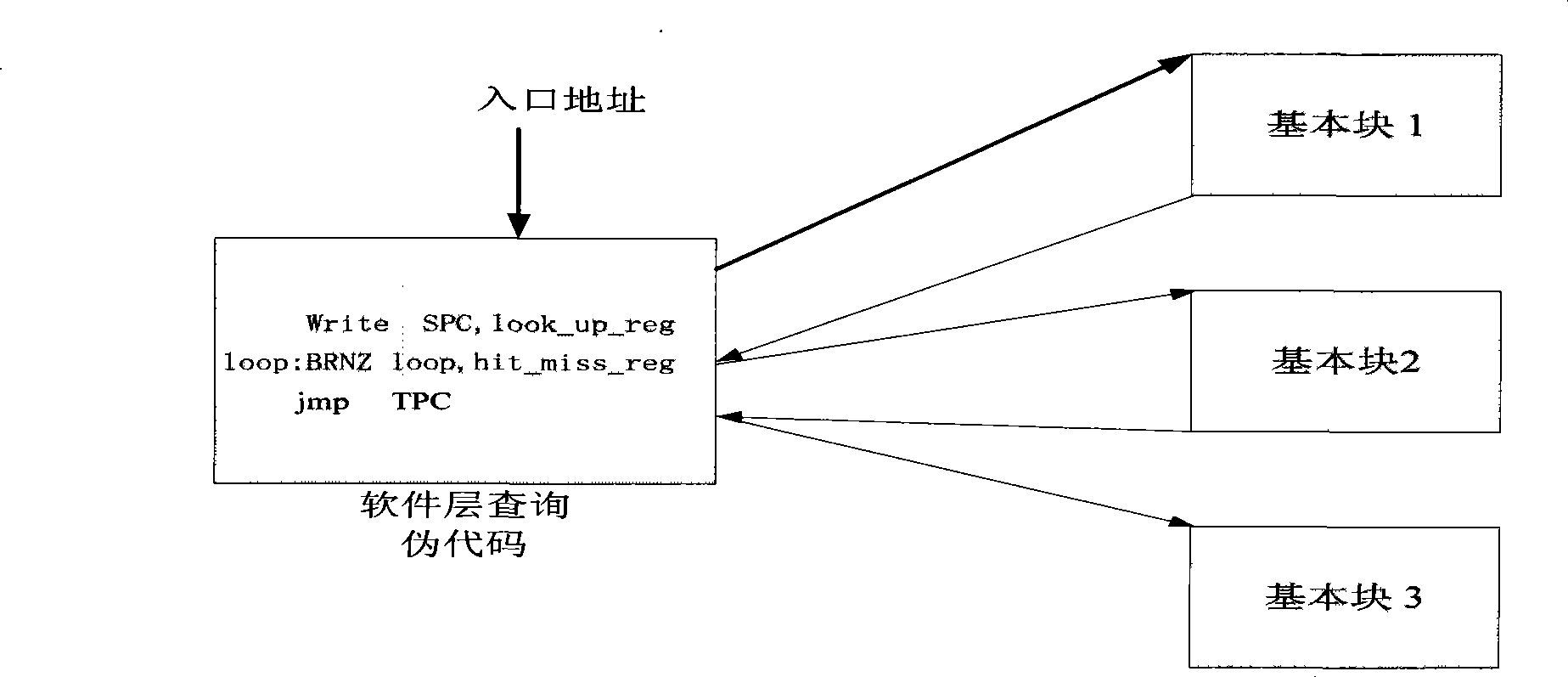

InactiveCN101387969ATcache miss rate reductionAchieve parallelismSoftware simulation/interpretation/emulationMemory systemsStart timeCoprocessor

The invention relates to a dynamic binary translating method of software-hardware co-design for realizing a virtual machine coprocessor of a processor chip on a hardware level, which comprises a binary translator unit, a TCache manager unit and the like, wherein management and check of the TCache is realized via the hardware, and fast check of the Tcache is realized in from of instructions, further, as the binary translator unit is realized via the hardware, a master processor executing the object instruction avoids necessary switching to translate, and the start time and the Miss time can be relieved well. The software portion comprises load of heterogeneous executable program, execution of the object instruction, optimization of hot codes and the like. Through tightly coupling of hardware and software, coexistence between the overall virtual machine and the original system can be effectively controlled, thereby achieving internal parallelism. Because single processor supports a plurality of instruction sets, instruction compatibility problem of heterogeneous processors is solved, further, compared with the conventional virtual machine with pure software, properties and transparency are increased, and the speed of the virtual machine can be close to the local execution speed.

Owner:SHANGHAI JIAO TONG UNIV

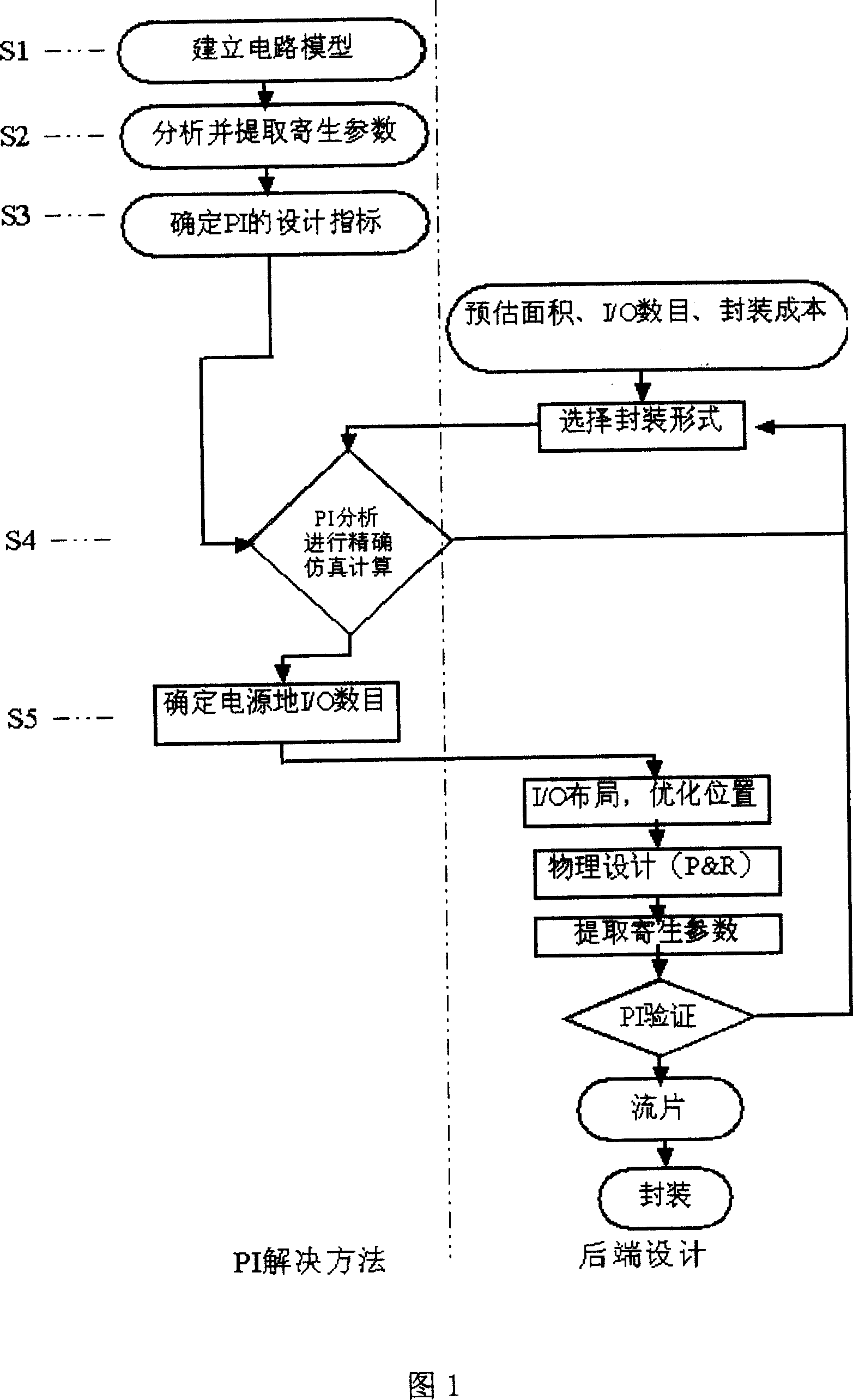

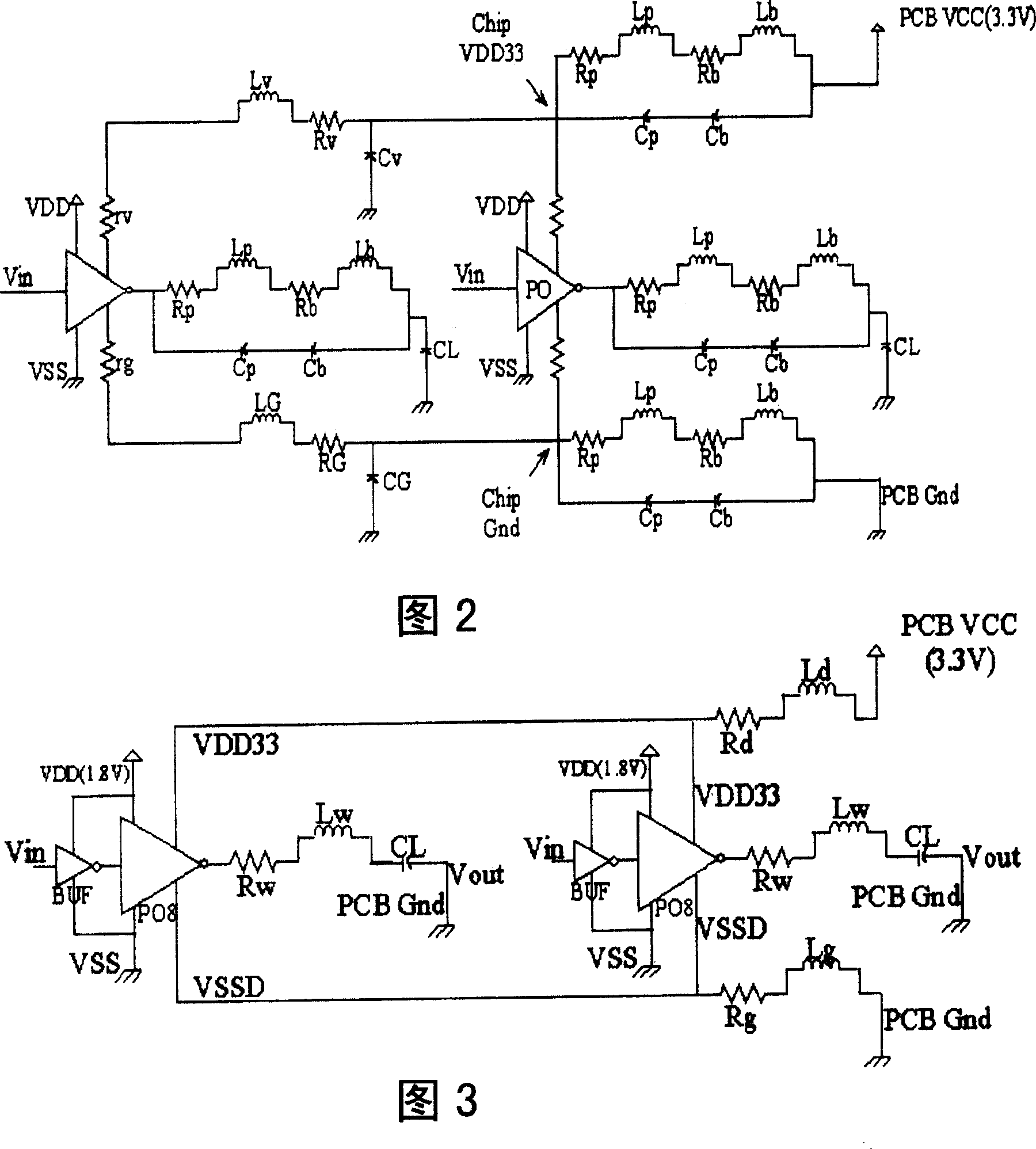

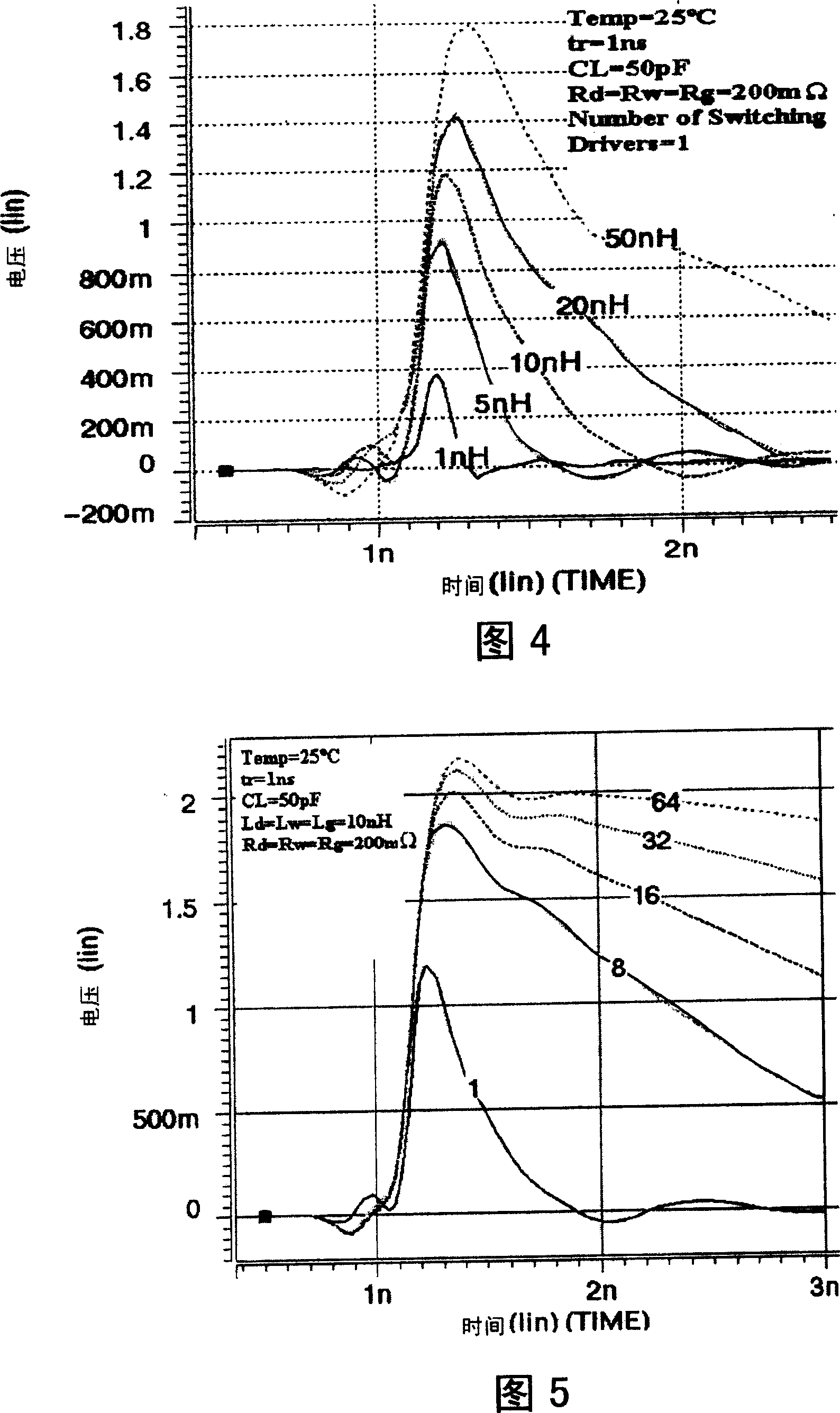

PI solution method based on IC package PCB co-design

ActiveCN101071449AFit for integrity issuesResolve integritySpecial data processing applicationsPower integrityCircuit models

The invention relates to the field of very large scale integrated (VLSI) circuit technique, especially a PI solving method for IC-package-PCB cooperative design for solving power supply integrity problem in back-end design, comprising: 1) building a circuit model suitable for VLSI PI analysis; 2) analyzing and extracting parasitical parameters corresponding to the circuit mode; 3) determining design indexes in the PI design; 4) utilizing EDA tool and owned algorithm model to make accurate simulation and calculation; 5) on the premise of considering power supply integrity, according to the PI design indexes and simulated results, quickly determining a proper number of I / Os of power supply.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

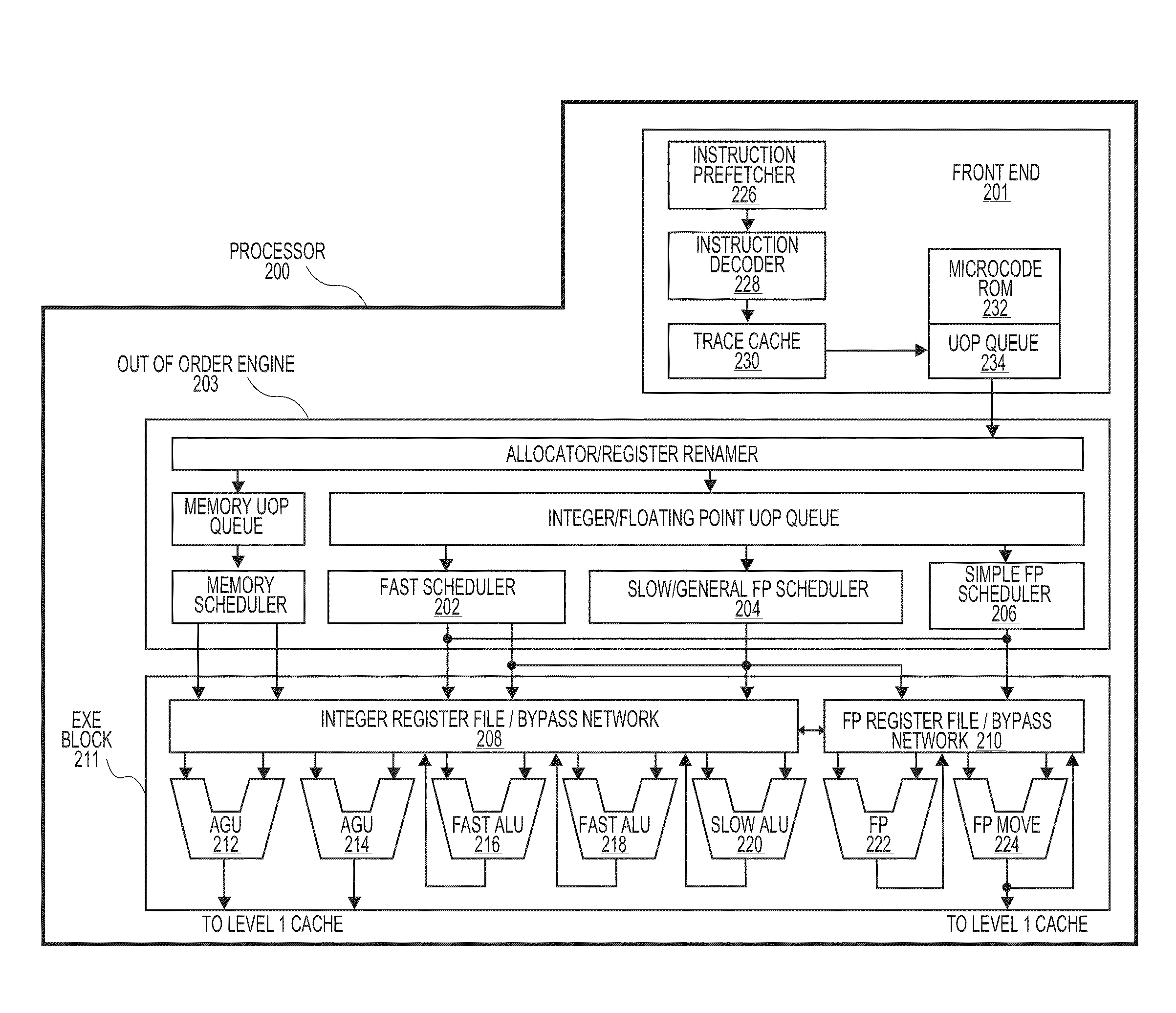

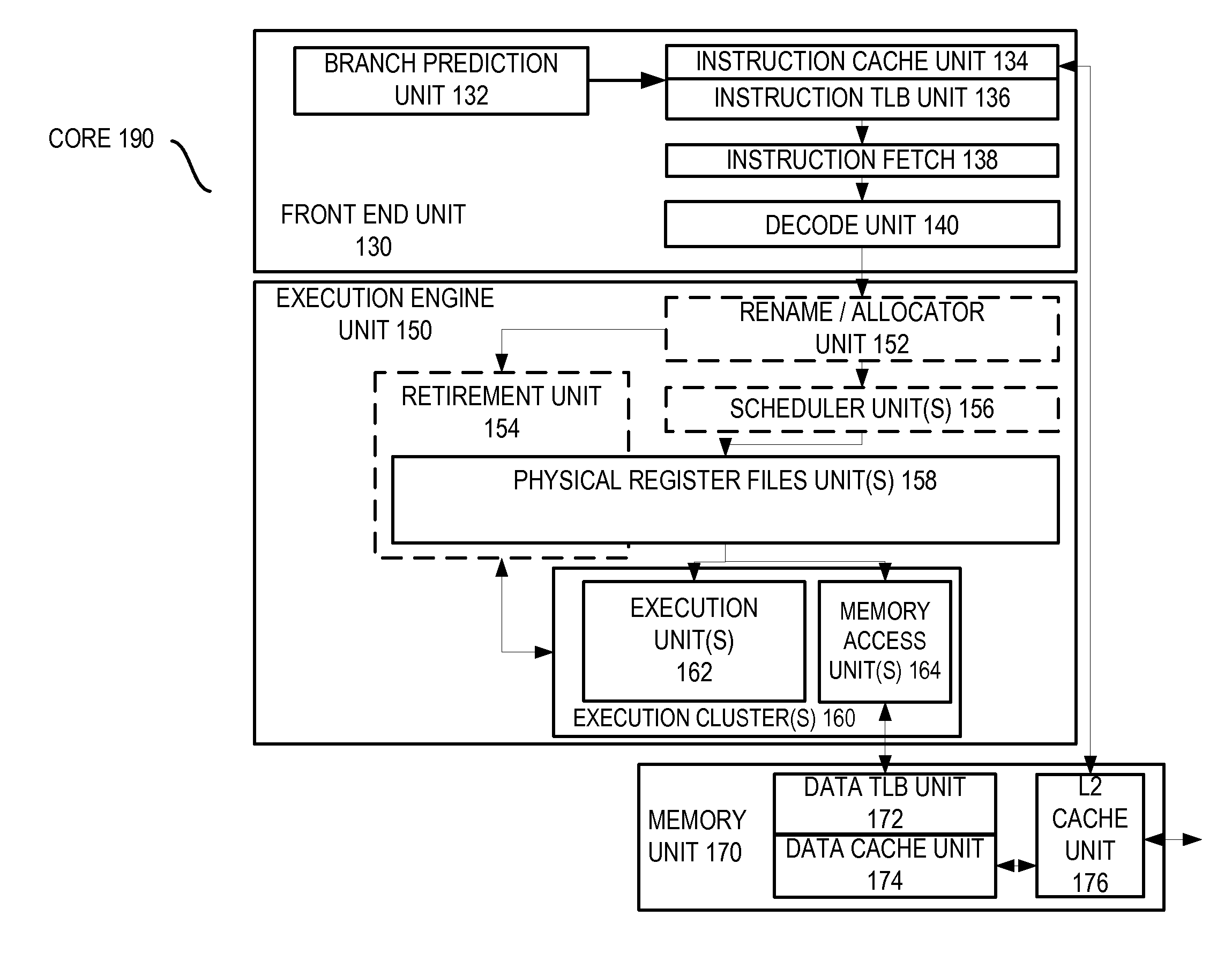

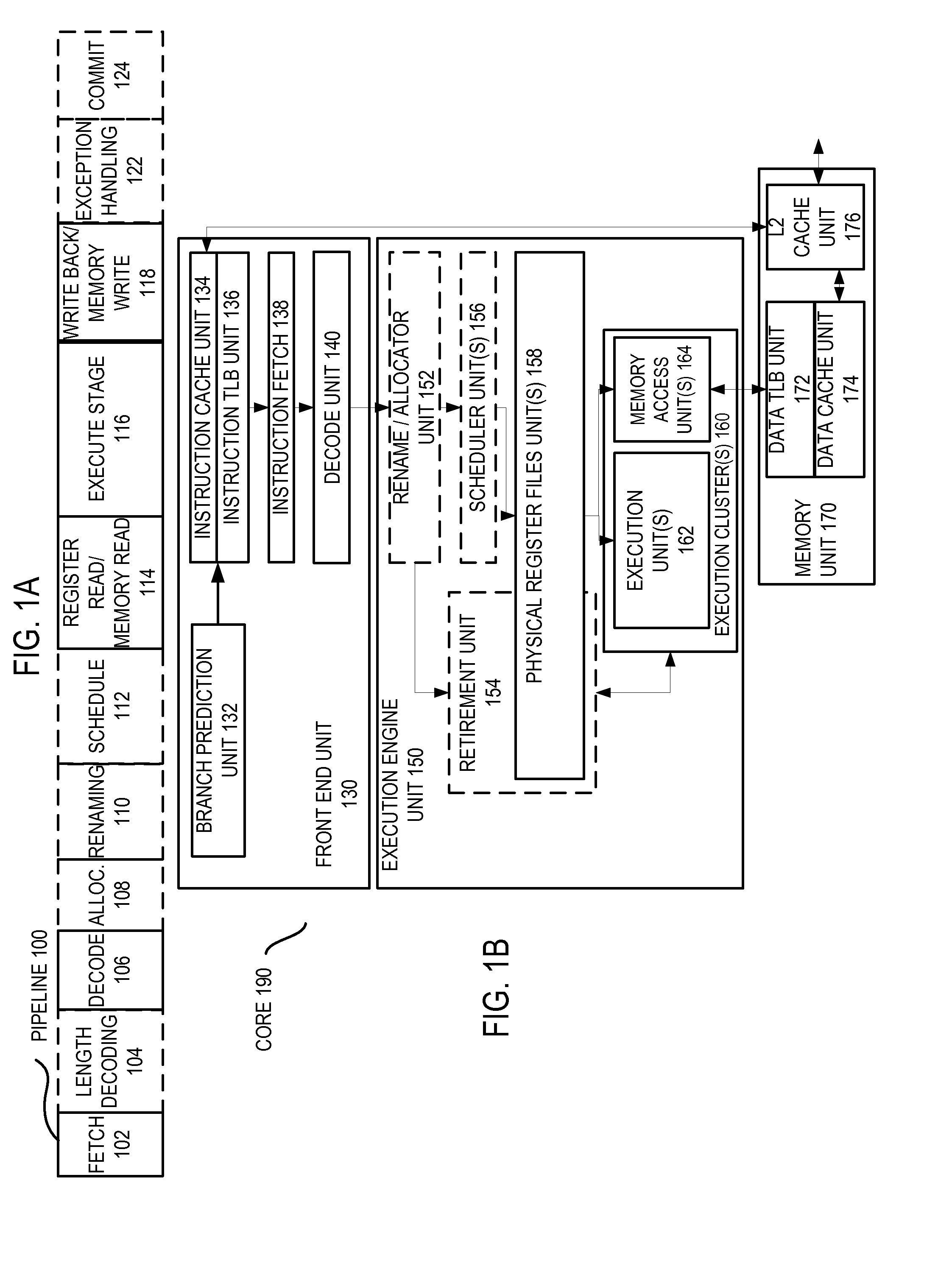

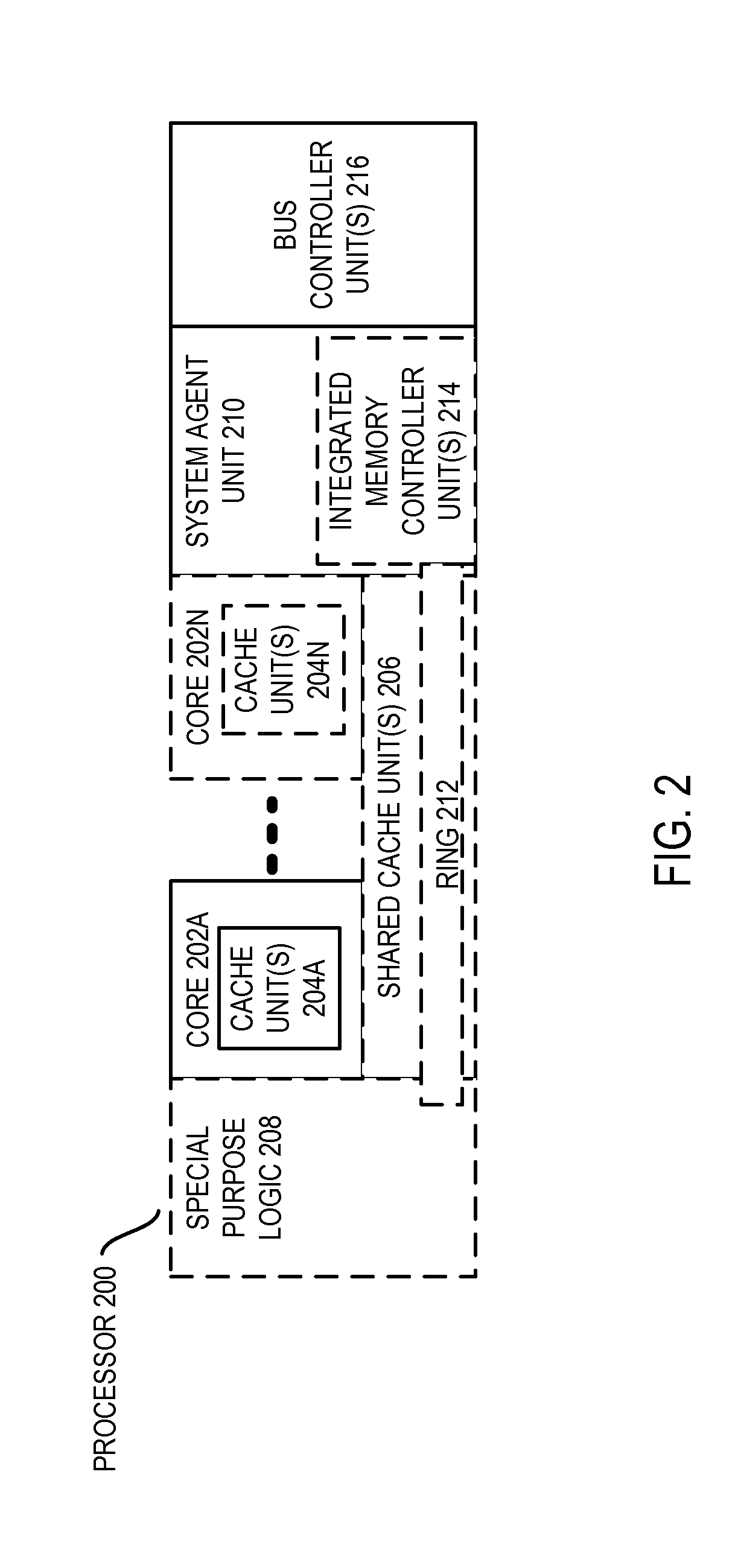

Method and apparatus for implementing a dynamic out-of-order processor pipeline

A hardware / software co-design for an optimized dynamic out-of-order Very Long Instruction Word (VLIW) pipeline. For example, one embodiment of an apparatus comprises: an instruction fetch unit to fetch Very Long Instruction Words (VLIWs) in their program order from memory, each of the VLIWs comprising a plurality of reduced instruction set computing (RISC) instruction syllables grouped into the VLIWs in an order which removes data-flow dependencies and false output dependencies between the syllables; a decode unit to decode the VLIWs in their program order and output the syllables of each decoded VLIW in parallel; and an out-of-order execution engine to execute the syllables preferably in parallel with other syllables, wherein at least some of the syllables are to be executed in a different order than the order in which they are received from the decode unit, the out-of-order execution engine having one or more processing stages which do not check for data-flow dependencies and false output dependencies between the syllables when performing operations.

Owner:INTEL CORP

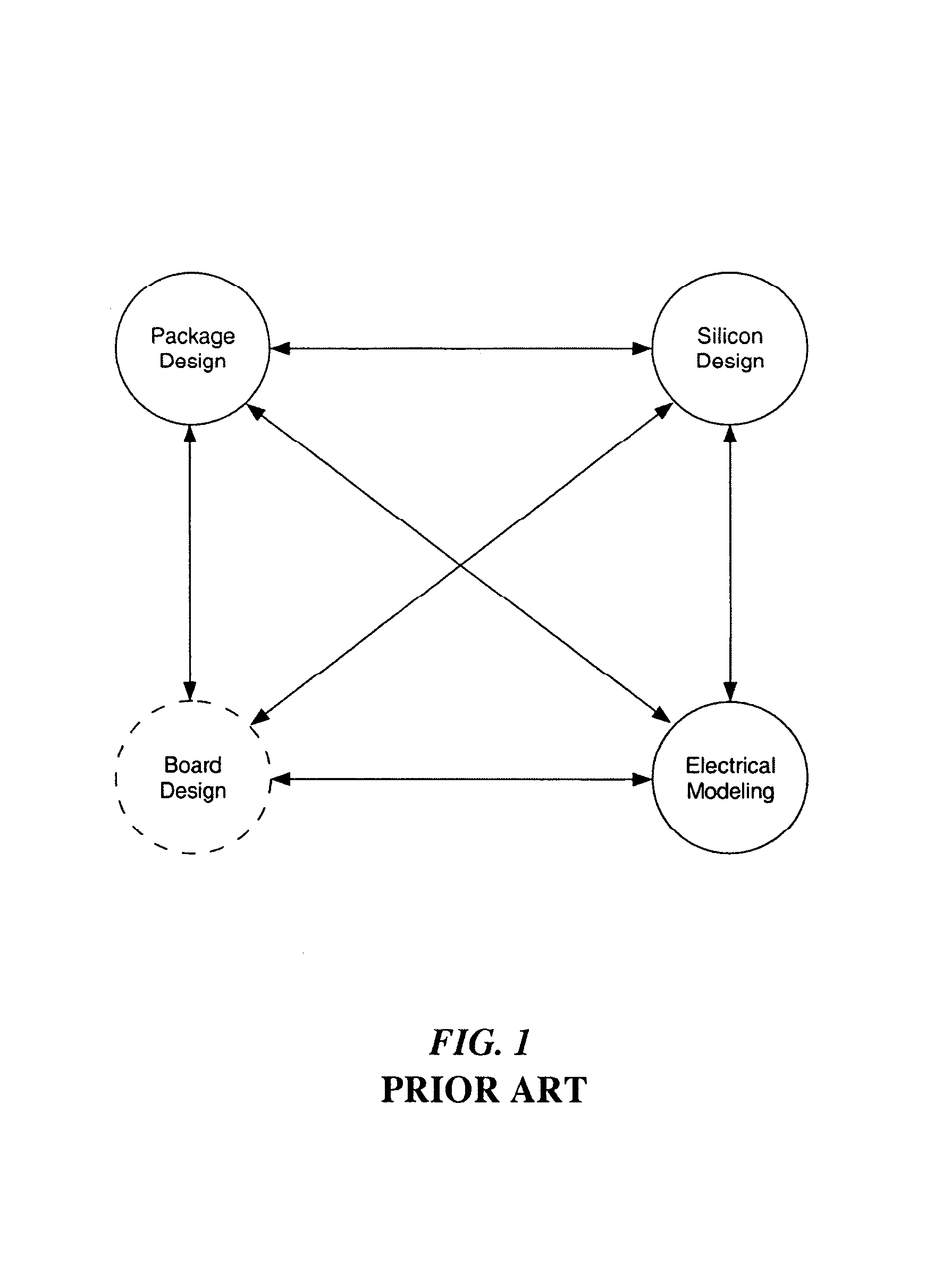

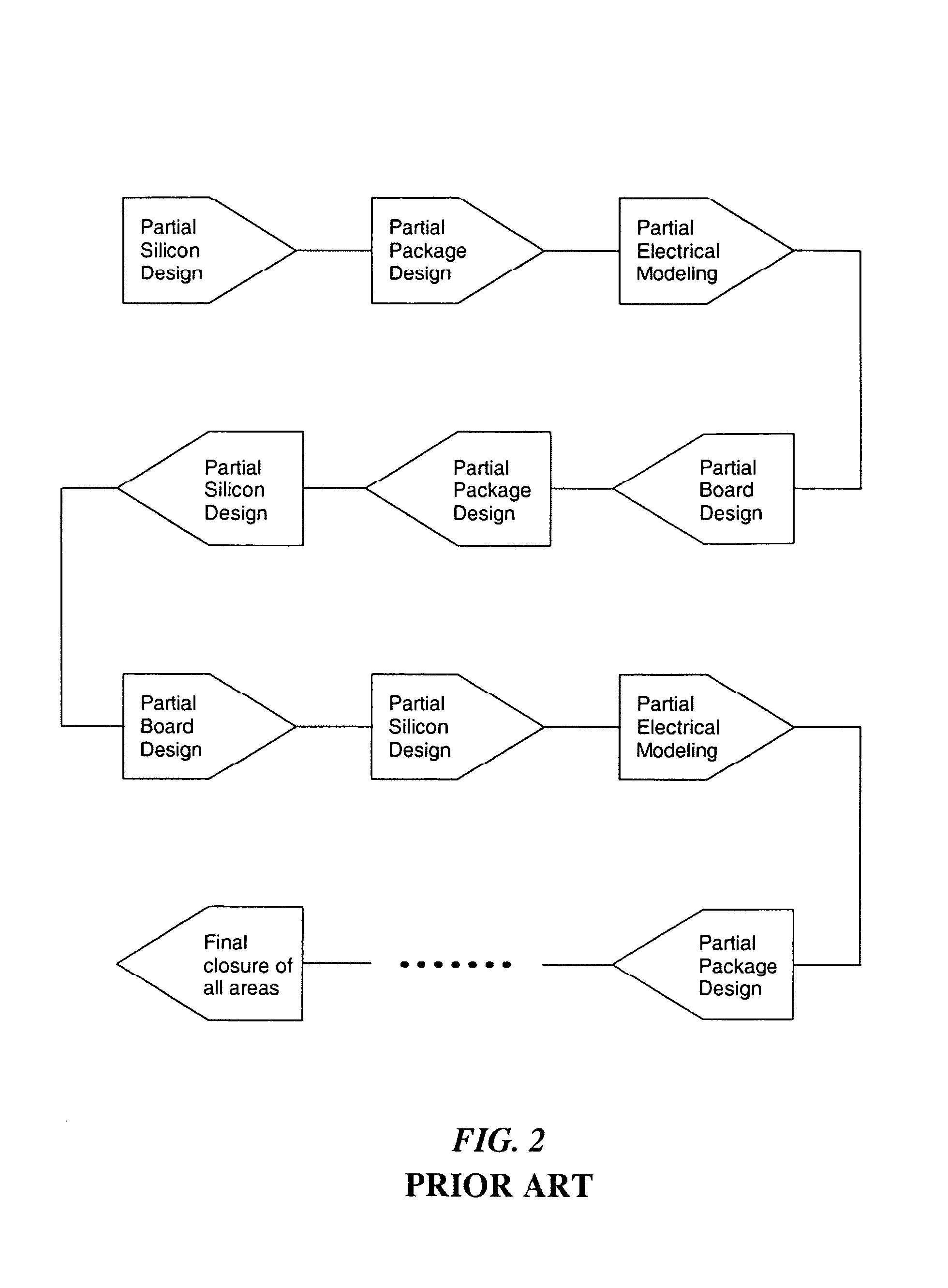

Methods for optimizing package and silicon co-design of integrated circuit

ActiveUS7117467B2Efficient developmentAvoid iterative processSemiconductor/solid-state device detailsSolid-state devicesPackage designSilicon

The present invention is directed to methods for optimizing package and silicon co-design of an integrated circuit. A composite bump pattern for an integrated circuit is created based on a first library including at least one bump pattern template. PCB and Die constraints of the integrated circuit are then reviewed. A partial package design for the integrated circuit is generated based on a second library including at least one partial package template. A partial silicon design for said integrated circuit is started. A full package design for the integrated circuit is then completed. A full silicon design for the integrated circuit is completed.

Owner:BELL SEMICON LLC

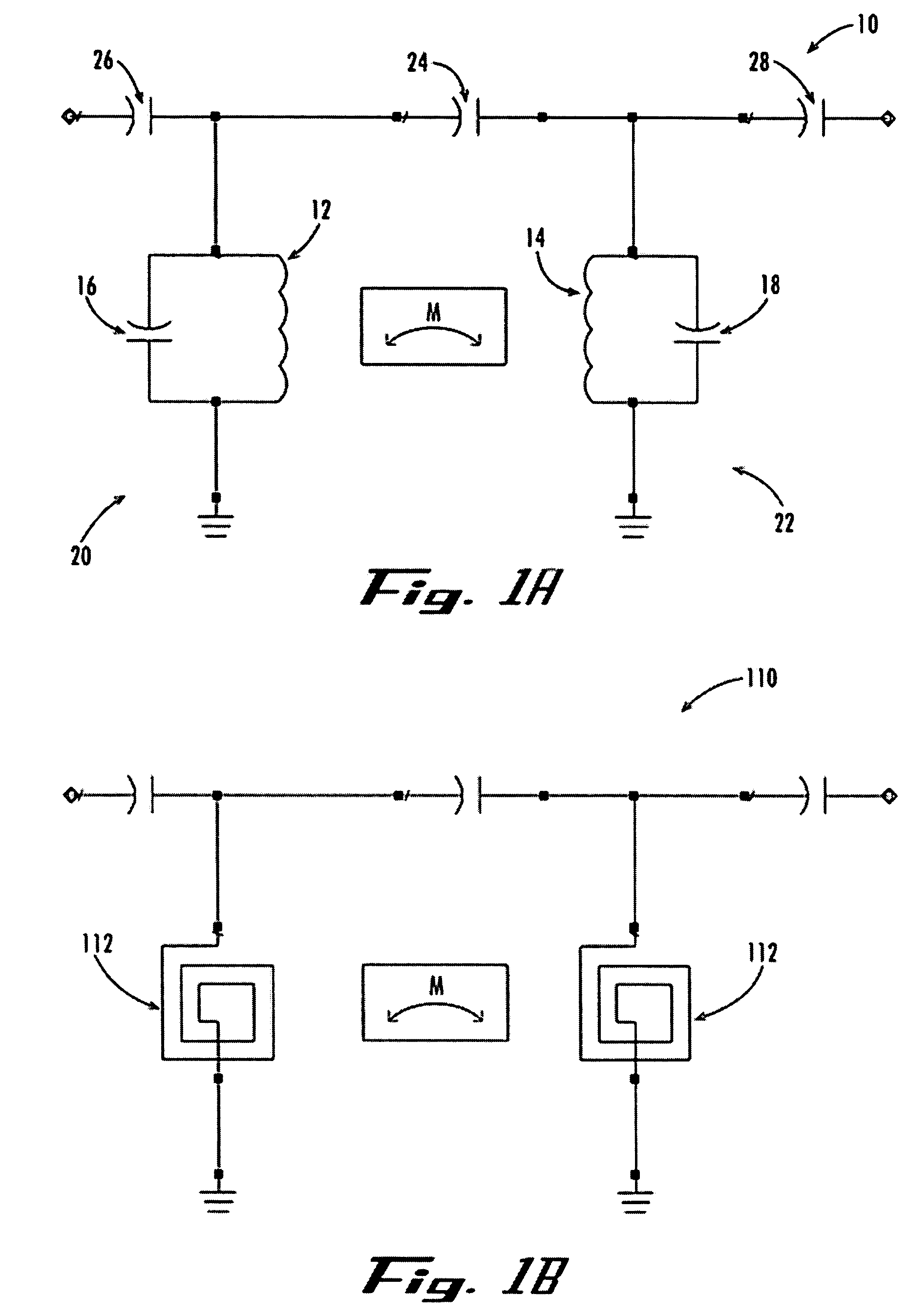

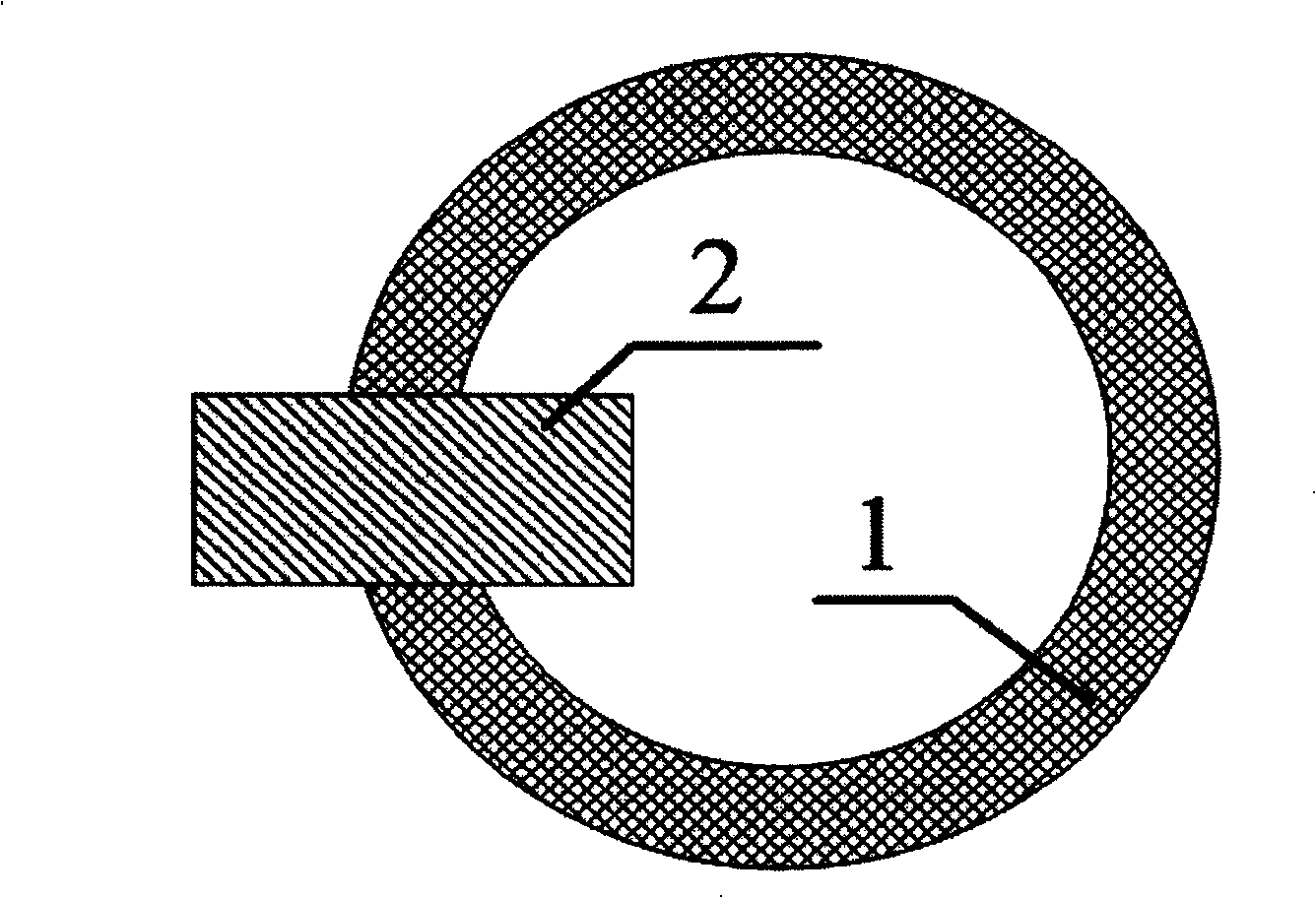

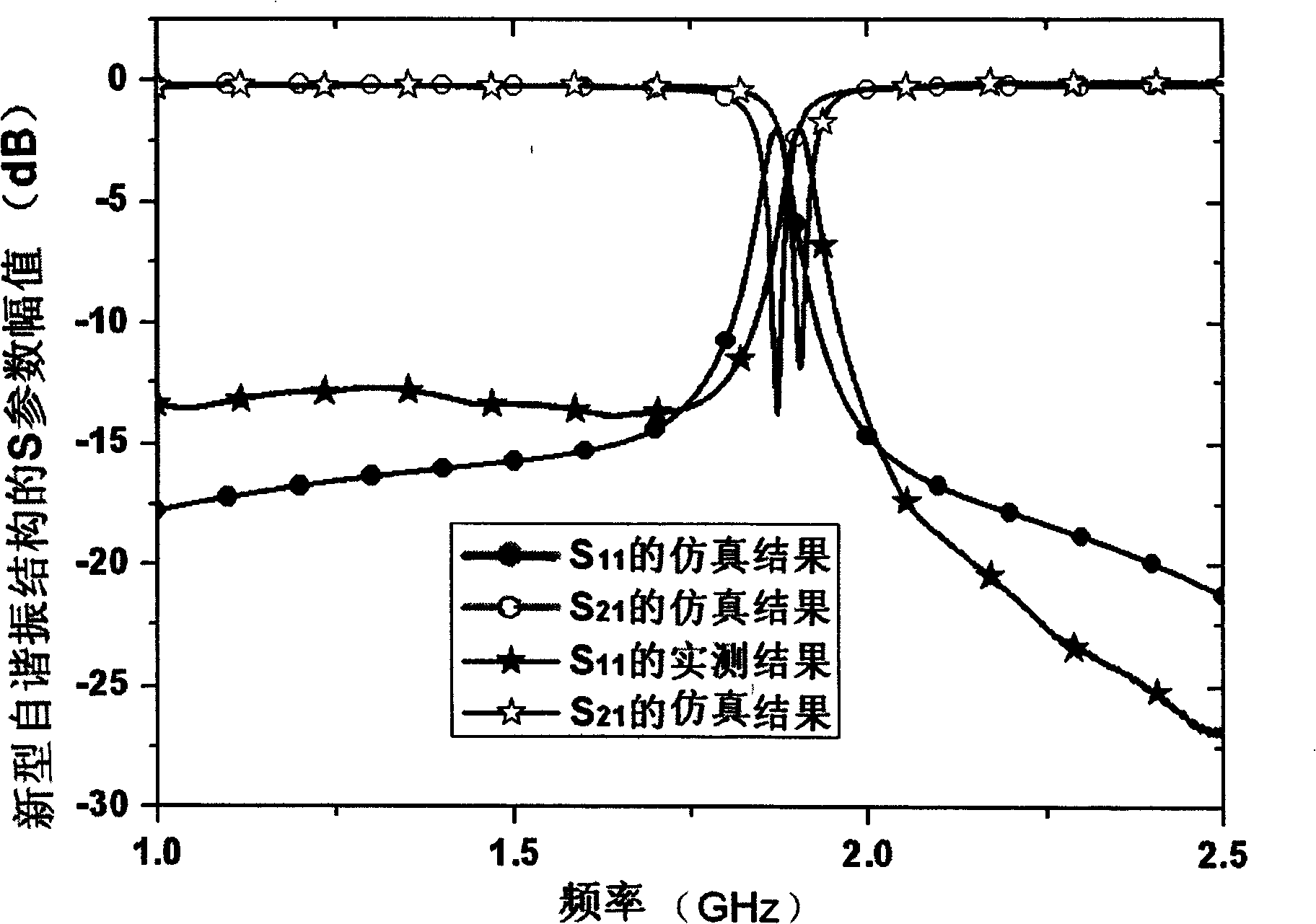

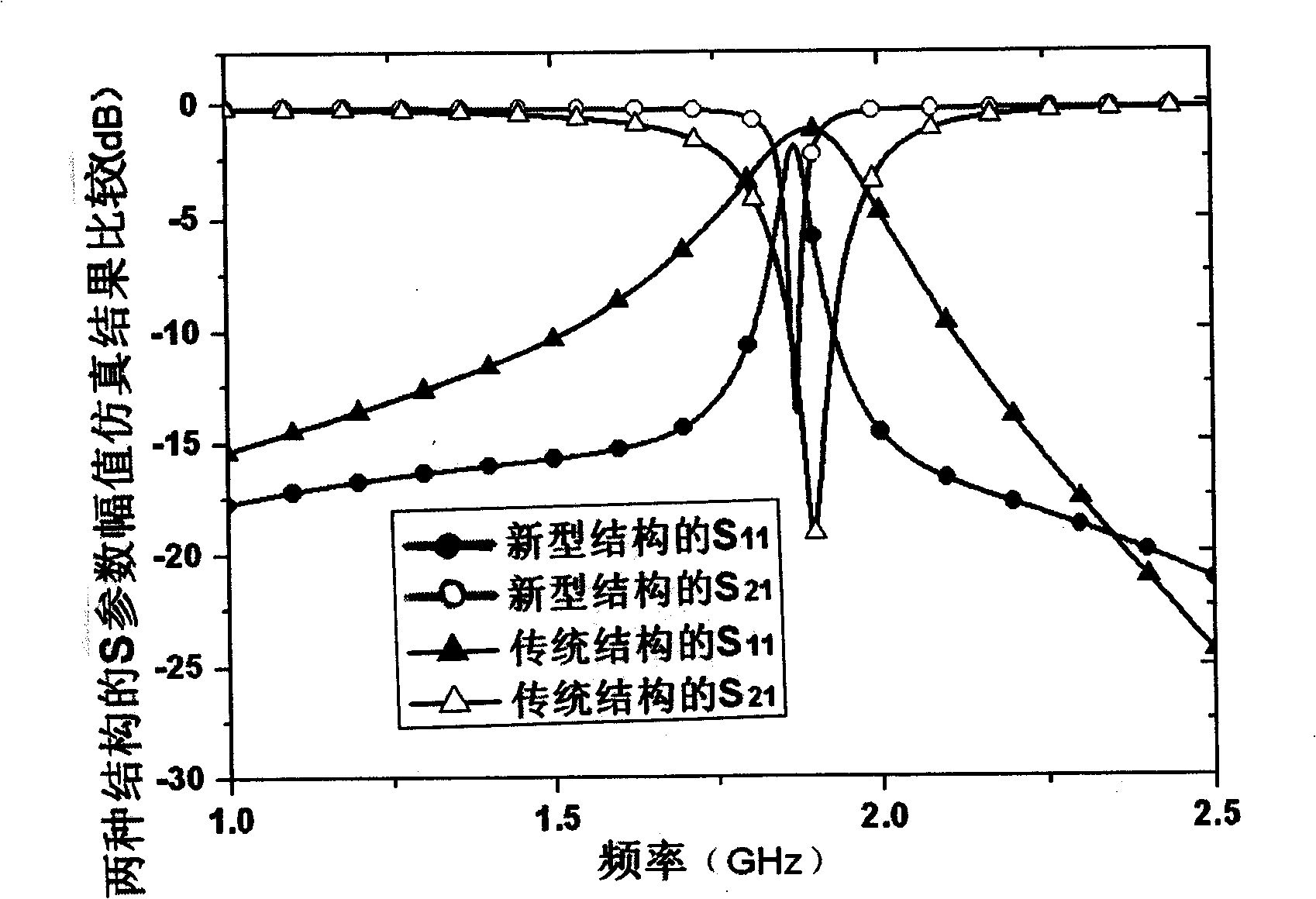

Self-resonance structure based on open hole resonance loop

InactiveCN101262211AHalf Power Relative Bandwidth ReductionHigh Frequency-Phase ResponseImpedence networksResonatorsCapacitancePhase response

The invention relates to a self-resonant structure based on a split resonance ring. The self-resonant structure comprises split ring structure 1 and adjunct circuit structure 2, wherein, the adjunct circuit structure 2 is positioned in an opening of the split ring structure 1 which can be formed by being surrounded by suspended metal strips and can also be a split rectangular ring or a circular ring formed by micro-strip structure printed on a media basic plate; the adjunct circuit structure 2, in whole, can be equivalent to the parallel connection of an inductor and a capacitor and can be realized by welded and lumped inductance and capacitance, also by a metal strip or distributed micro-strip structure printed on a media plate and still by a semi-lumped and semi-distributed circuit. The self-resonant structure based on a split resonance ring provided by the invention has narrow-band bandstop function, high-sensitivity frequency-phase responding and excellent stop-band or reflective characteristics and has the advantages of simple design structure, convenient processing and manufacture and excellent re-design and co-design capability and can be applied to the designs of filters (or a reflector required with high-sensitivity phase induction) in a planar circuit and spatial structure at the same time.

Owner:SOUTHEAST UNIV

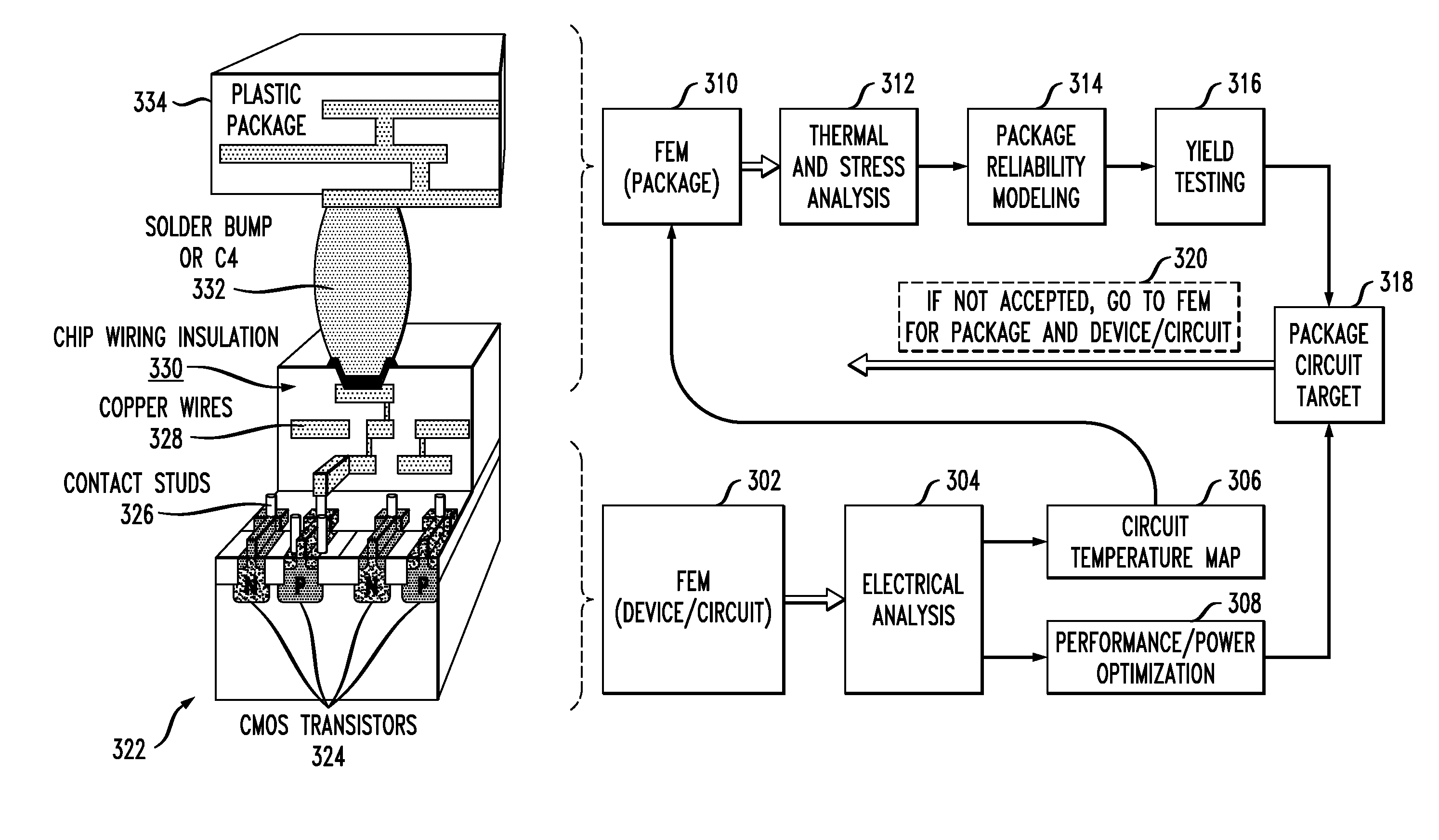

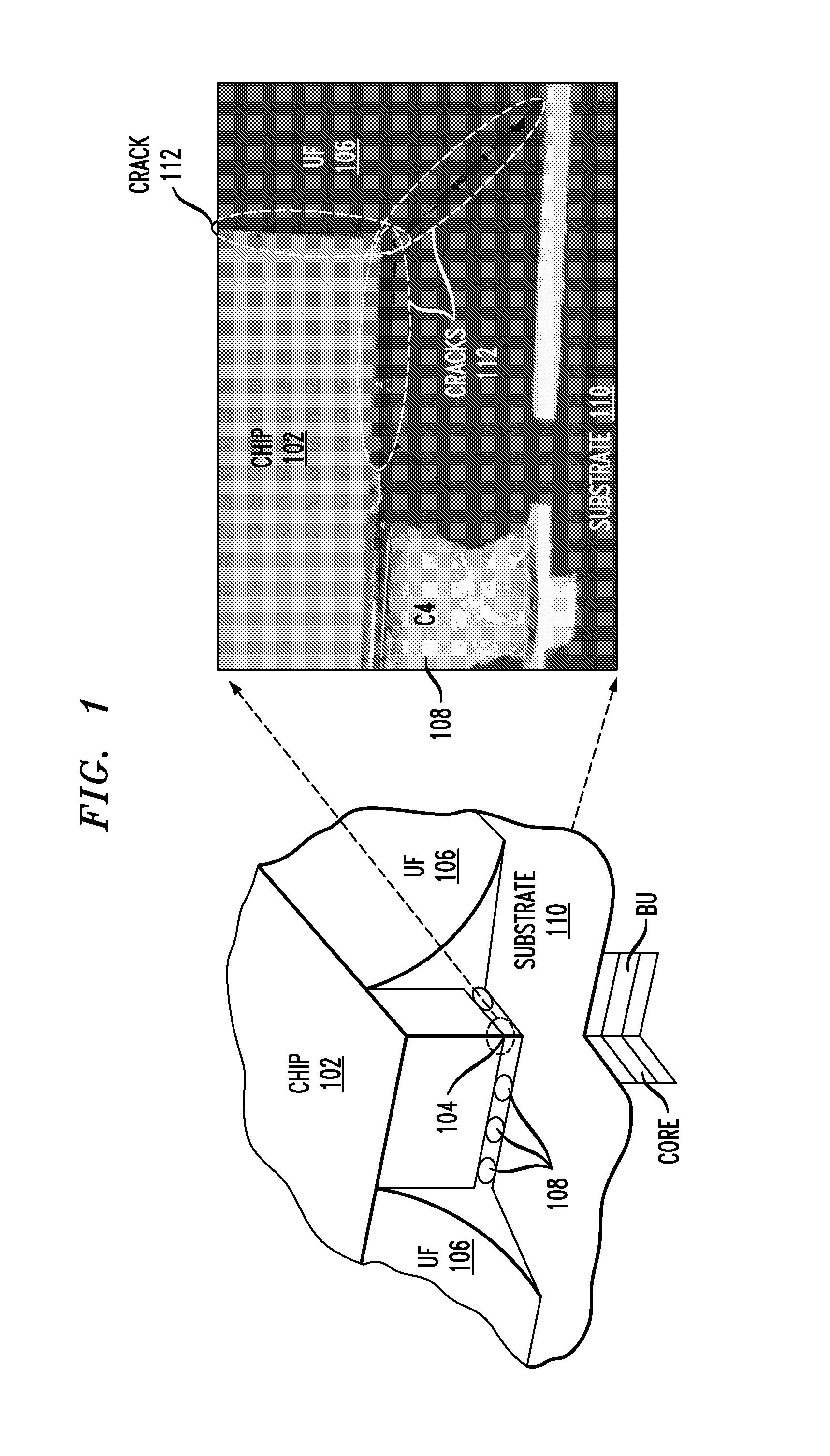

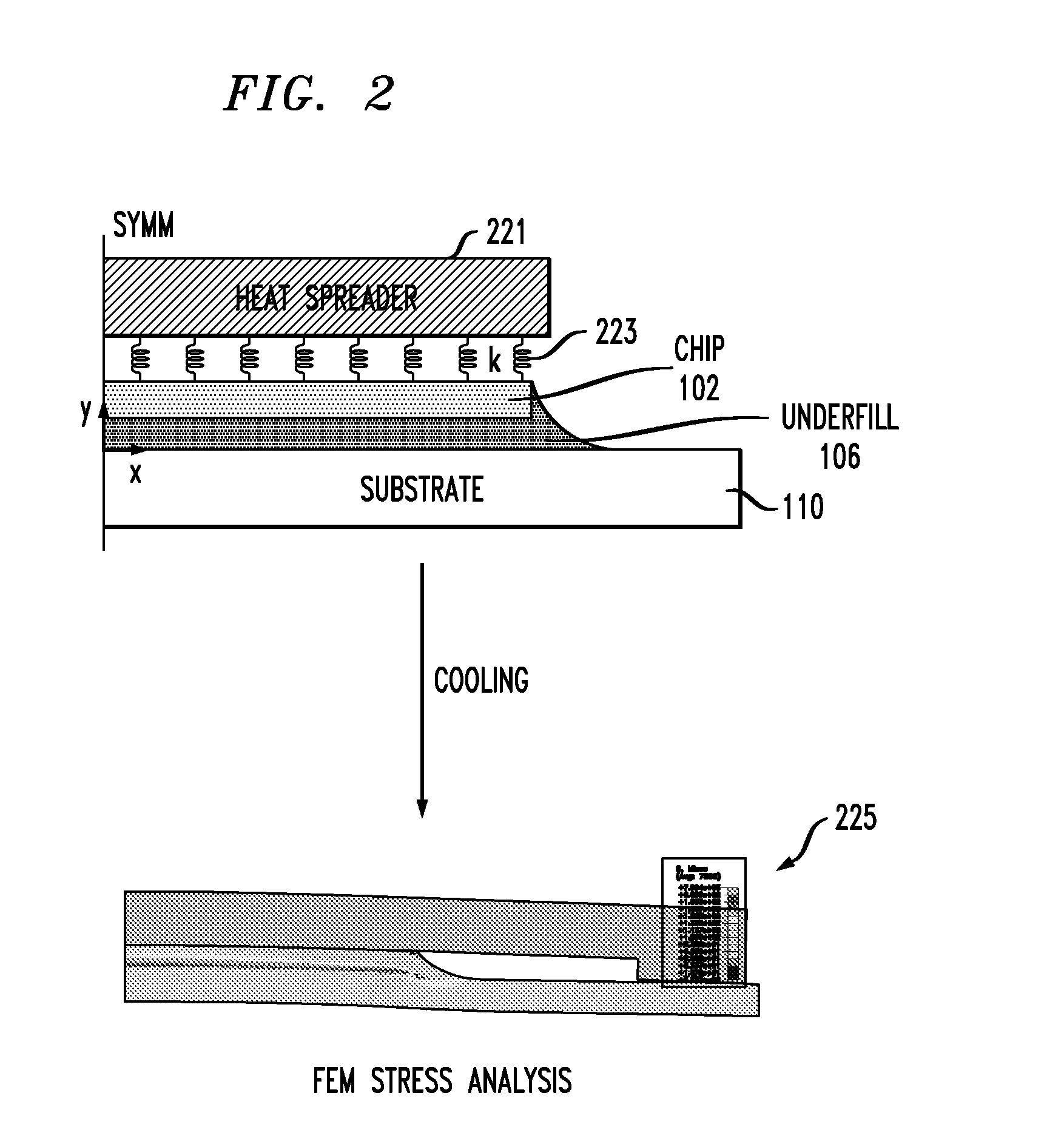

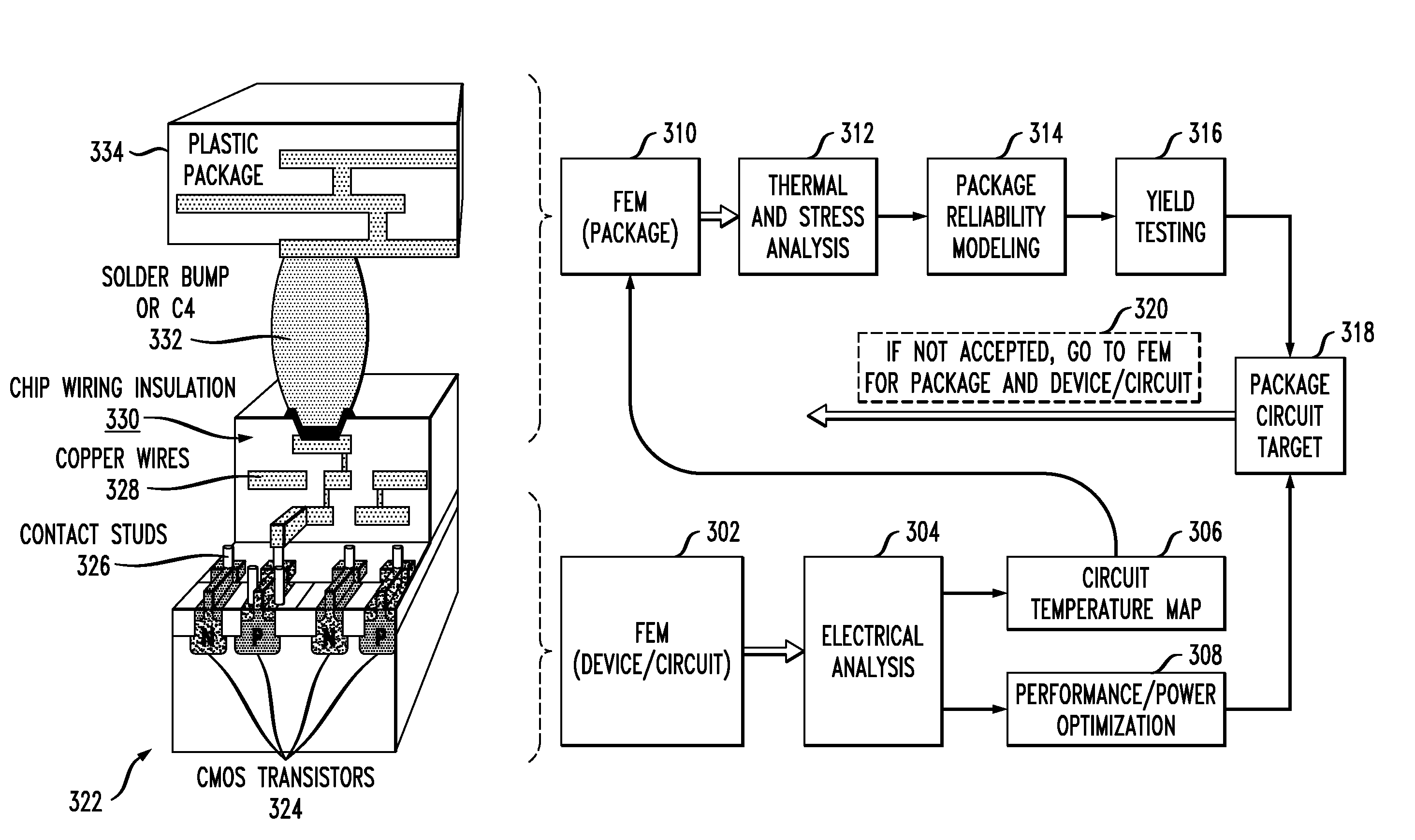

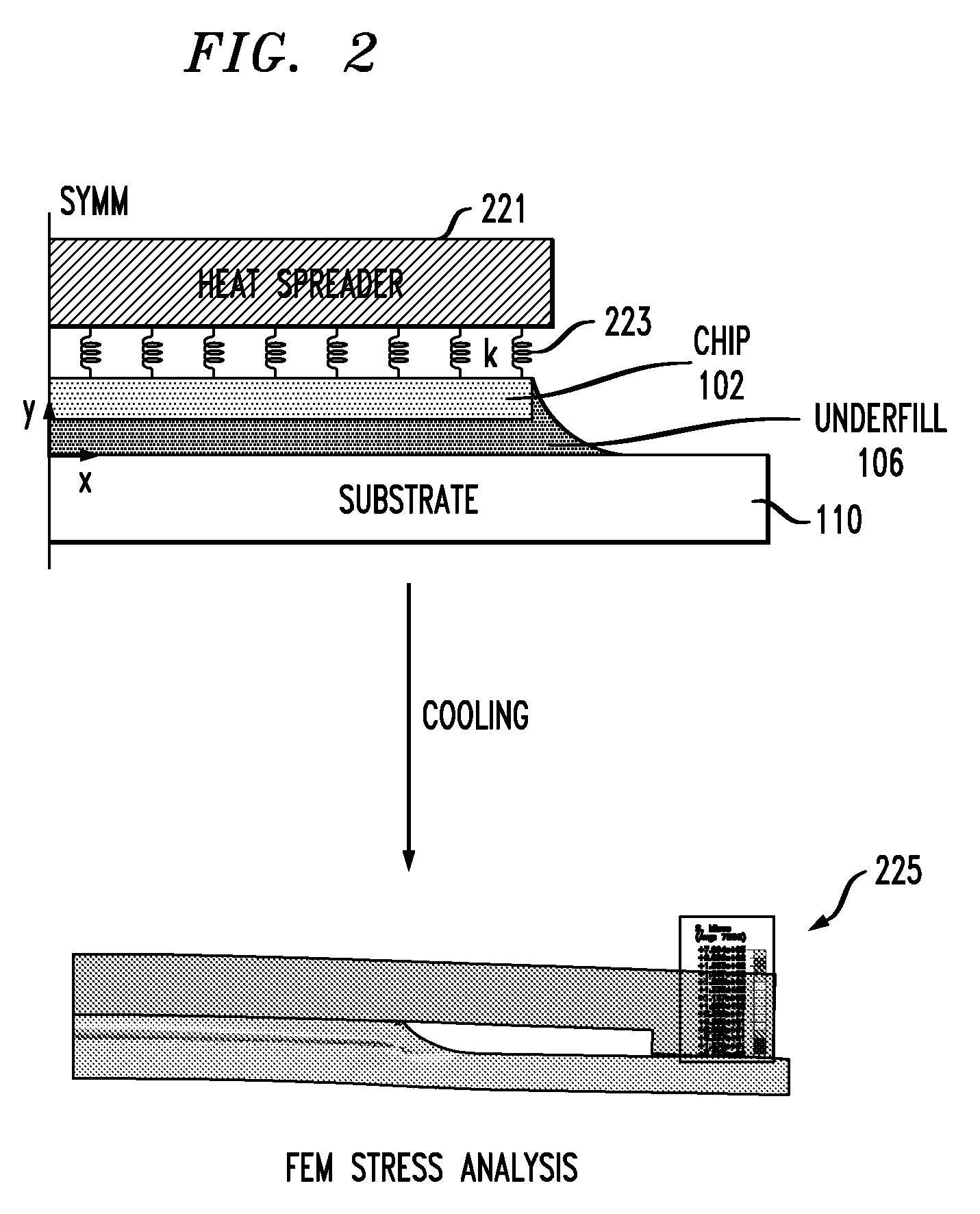

Integrated Framework for Finite-Element Methods for Package, Device and Circuit Co-Design

InactiveUS20110224951A1Improve accuracyReduce in quantityDesign optimisation/simulationCAD circuit designElectricityElement analysis

Electrical finite element analysis is carried out on a circuit design, which includes devices, to determine an acceptable power-performance envelope and to obtain data for circuit temperature mapping. A circuit temperature map is developed for the circuit design, based on the data for circuit temperature mapping. Thermo-mechanical finite element analysis is carried out on a package design for the circuit design, based on the circuit temperature map, to determine a package reliability limit based on thermal stress considerations. It is determined whether the package design and the circuit design jointly satisfy: (i) power-performance conditions specified in the acceptable power-performance envelope; and (ii) the package reliability limit based on the thermal stress considerations.

Owner:GLOBALFOUNDRIES INC

Method and apparatus for implementing and maintaining a stack of predicate values with stack synchronization instructions in an out of order hardware software co-designed processor

Embodiments of a method and apparatus for implementing and maintaining a stack of predicate values with stack synchronization instructions. In one embodiment the apparatus is an out of order hardware / software co-designed processor including instructions to explicitly manage the predicate register stack to maintain stack consistency across branches of executing that push a variable number of predicate values onto the predicate stack. In one embodiment the stack-based predicate register implementation enables early branch calculation and early branch misprediction recovery via early renaming of predicate registers.

Owner:INTEL CORP

Instruction and logic to perform dynamic binary translation

ActiveUS9417855B2Concurrent instruction executionSoftware simulation/interpretation/emulationInstruction setBinary translation

A micro-architecture may provide a hardware and software co-designed dynamic binary translation. The micro-architecture may invoke a method to perform a dynamic binary translation. The method may comprise executing original software code compiled targeting a first instruction set, using processor hardware to detect a hot spot in the software code and passing control to a binary translation translator, determining a hot spot region for translation, generating the translated code using a second instruction set, placing the translated code in a translation cache, executing the translated code from the translated cache, and transitioning back to the original software code after the translated code finishes execution.

Owner:INTEL CORP

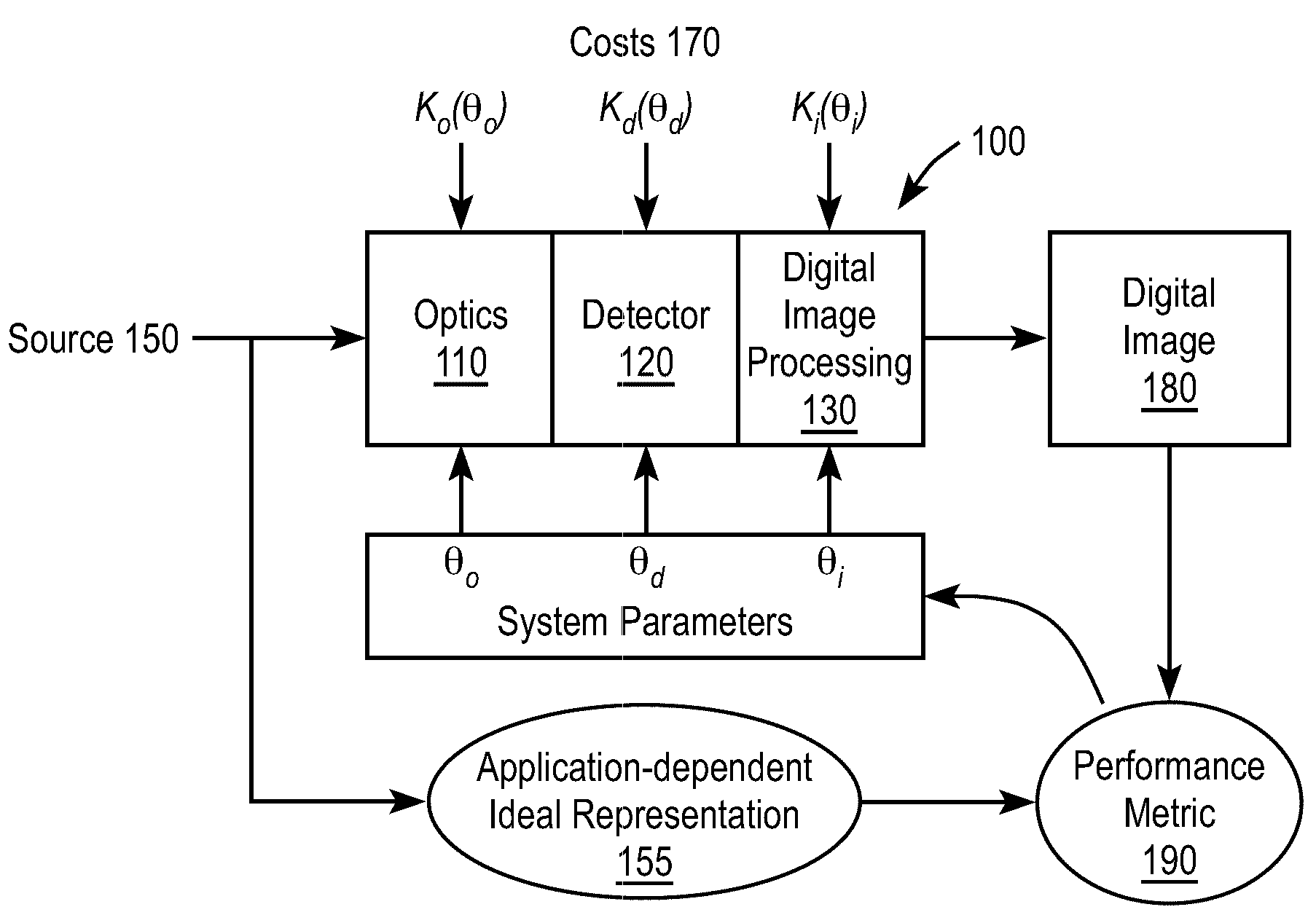

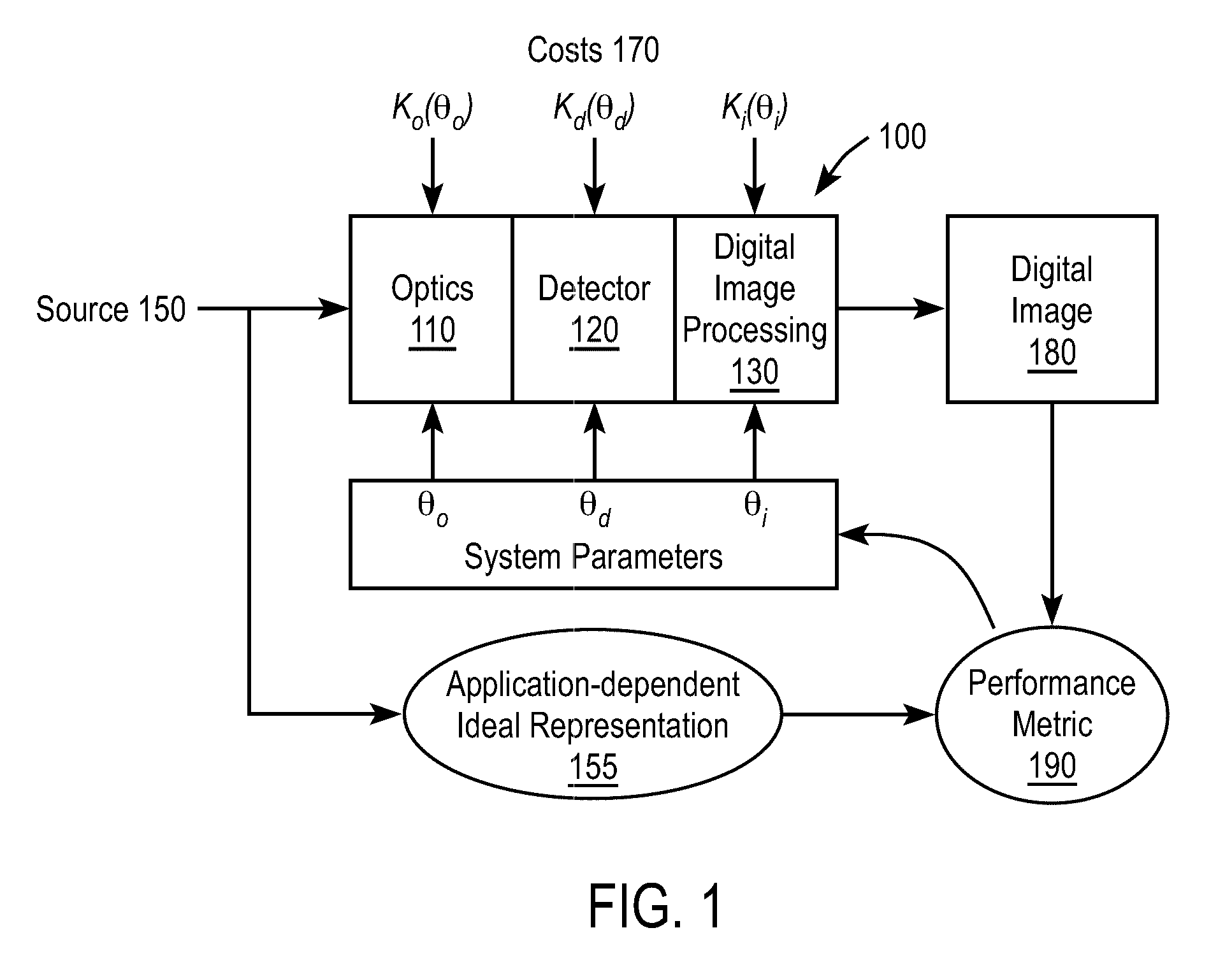

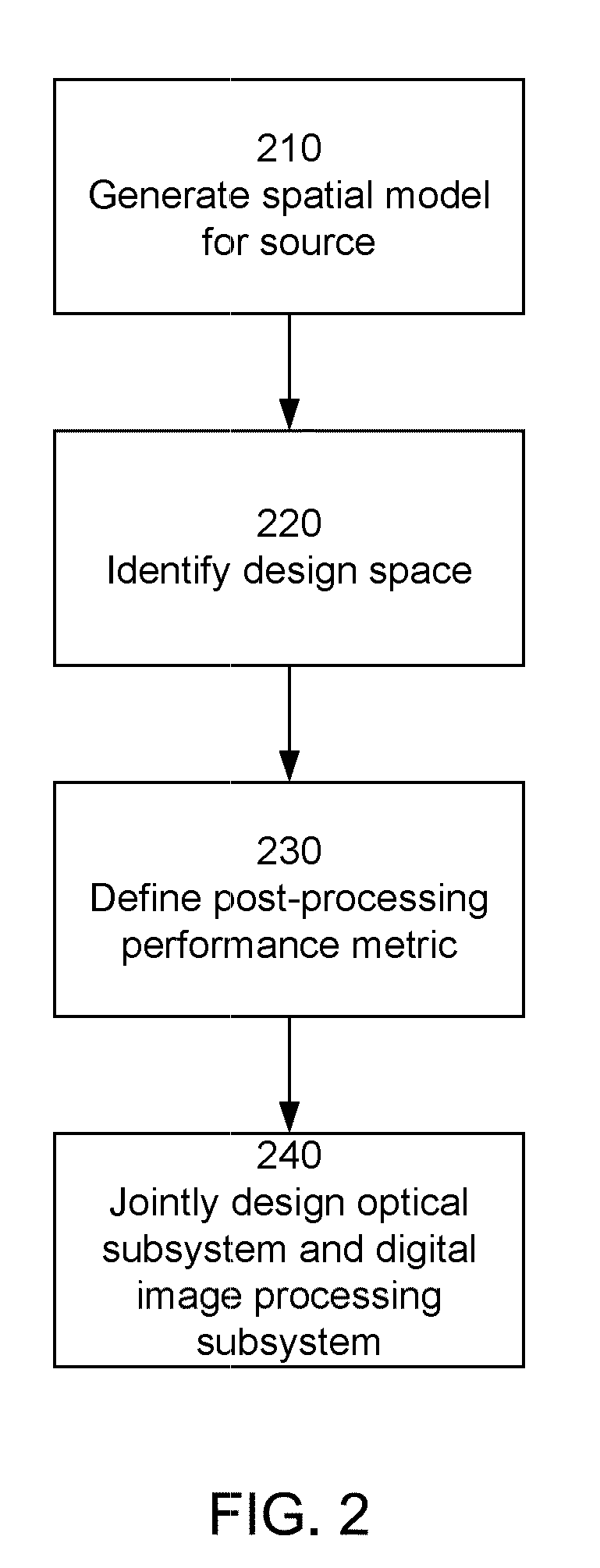

End-to-End Design of Electro-Optic Imaging Systems Using the Nonequidistant Discrete Fourier Transform

InactiveUS20100299113A1Avoid less flexibilitySimple designTelevision system detailsAnalogue computers for electric apparatusFourier transform on finite groupsSpatial model

A unified design strategy takes into account different subsystems within an overall electro-optic imaging system. In one implementation, the design methodology predicts end-to-end imaging performance using a spatial model for the source and models for the optical subsystem, the detector subsystem and the digital image processing subsystem. The optical subsystem and digital image processing subsystems are jointly designed taking into account the entire system. Unconventional techniques such as the nonequidistant DFT (nDFT) are used to accelerate the design process.

Owner:RICOH KK

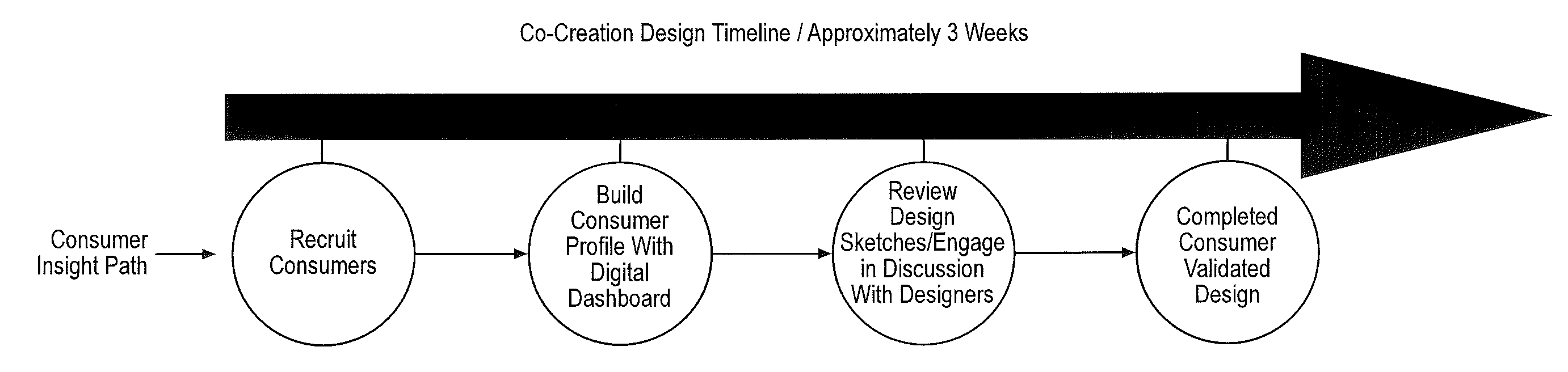

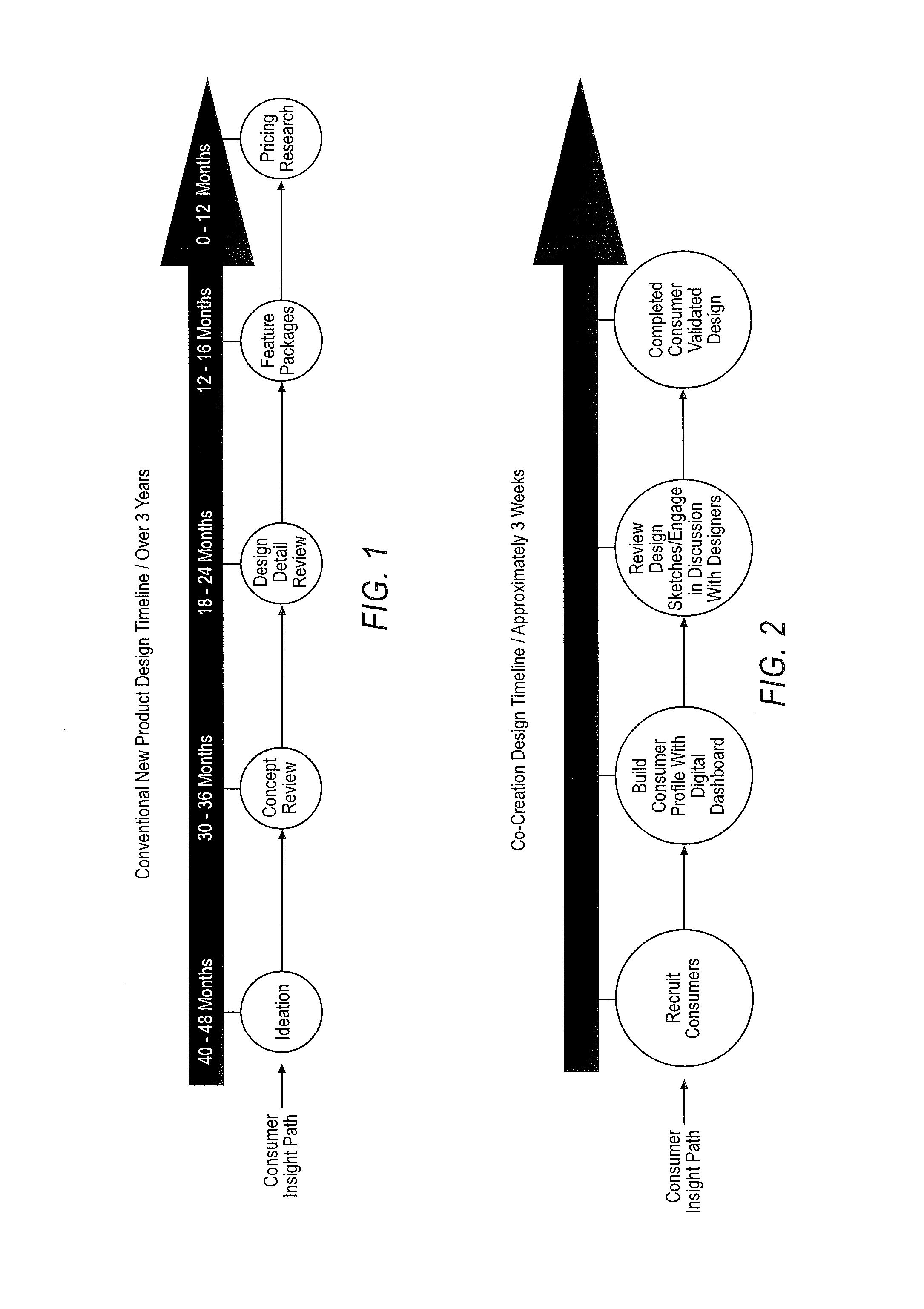

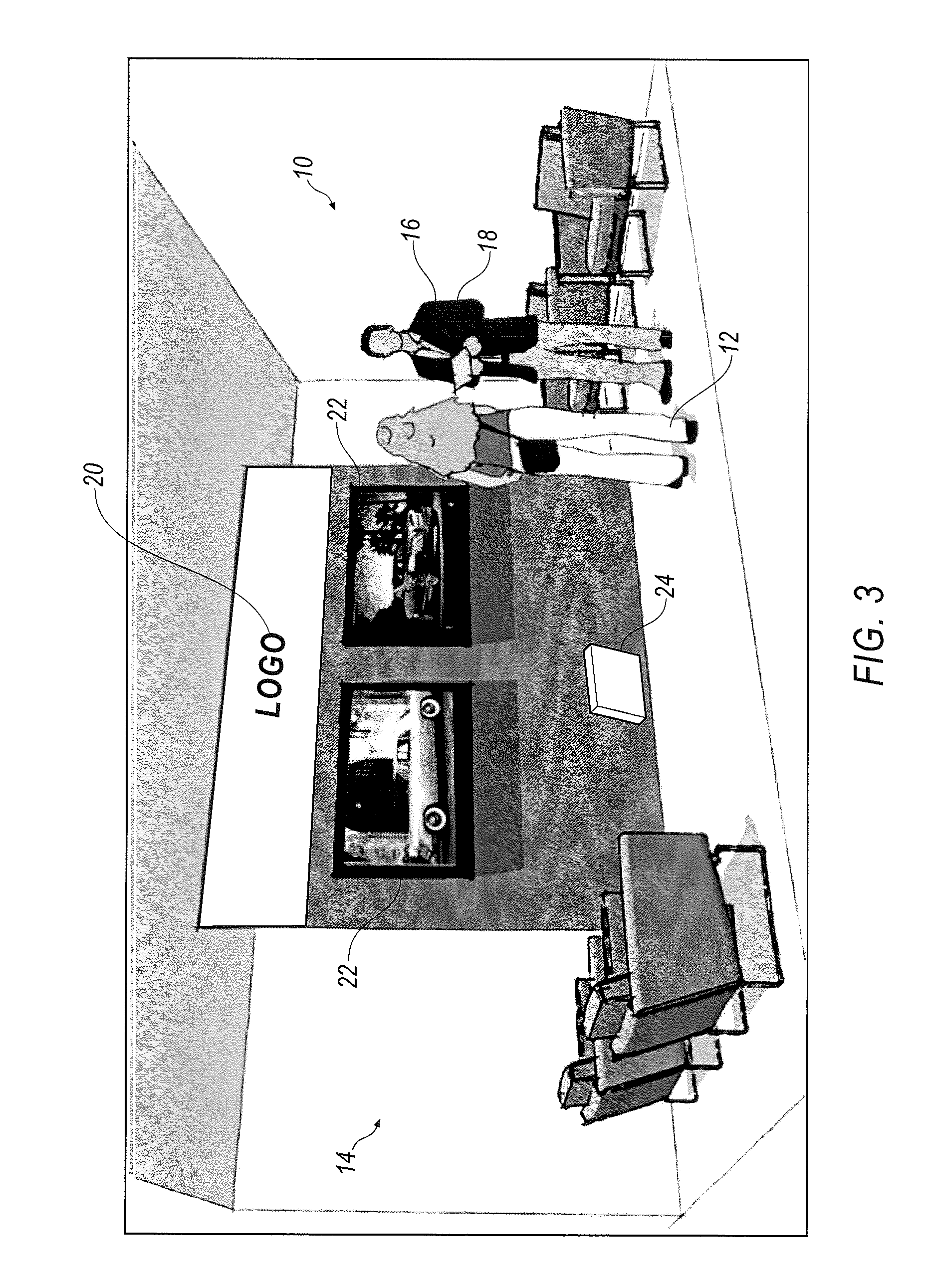

Co-creation design process for creating consumer goods

A method and tool for enhancing customer related research with product manufacturers has been provided. Consumers are invited into a design experience by inputting personal data and product design preferences in order to create a profile. A consumer is then invited to provide specific product design preferences and they can interact with a design tool in order to co-design new products in collaboration with designers. The consumer's data is then aggregated and provided to designers and marketers who will use the information for the next stage of product development.

Owner:SMITH KEVIN

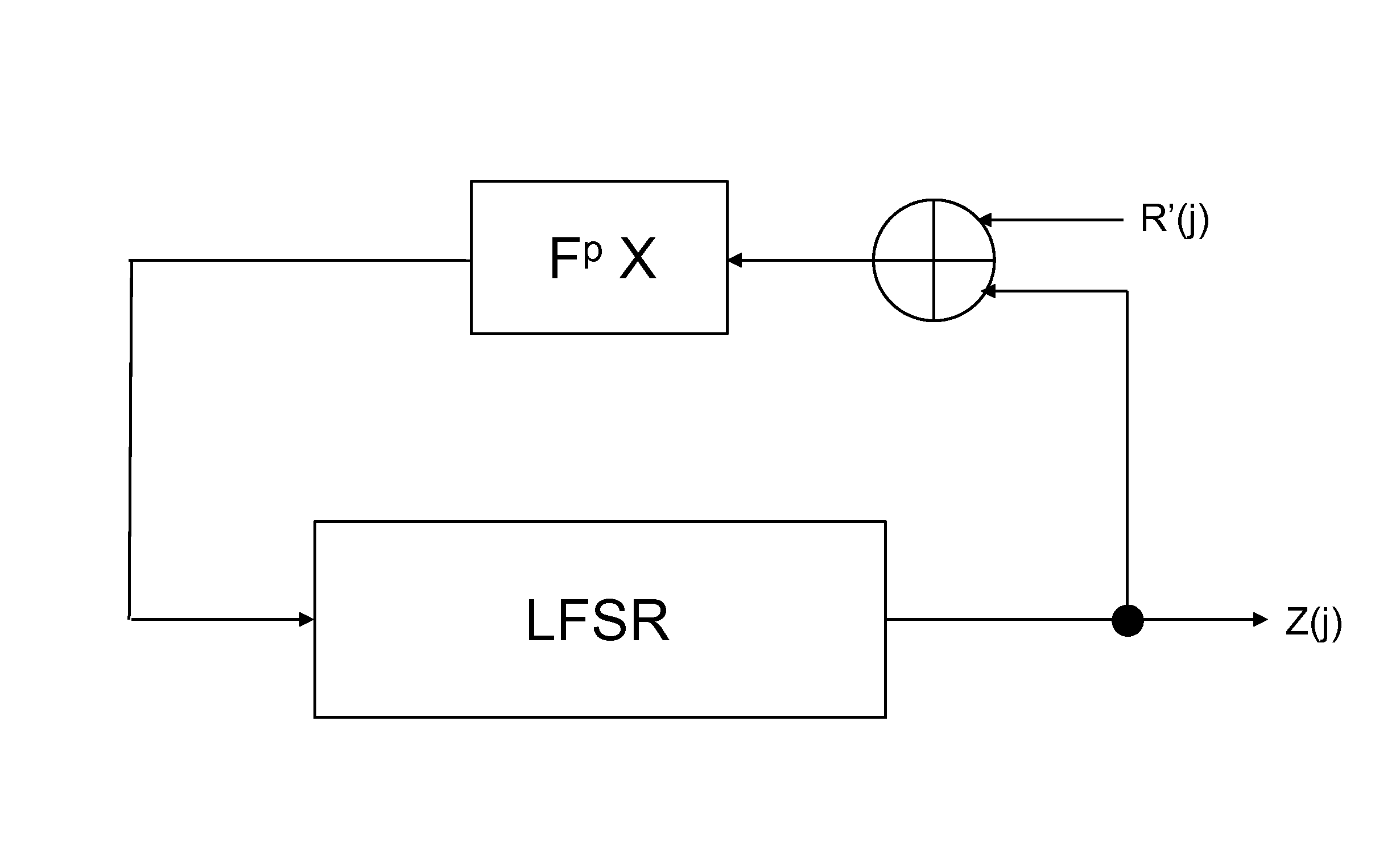

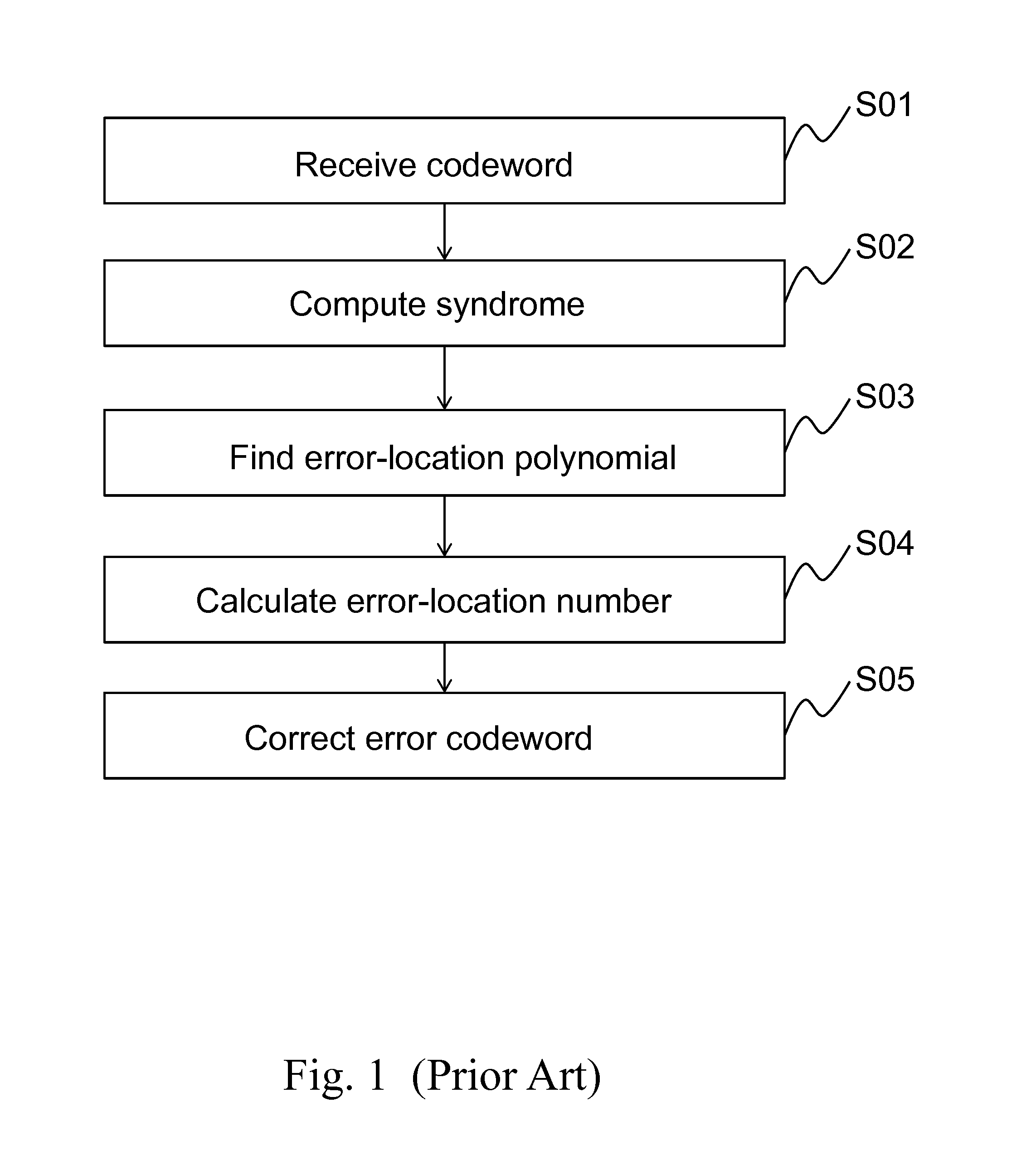

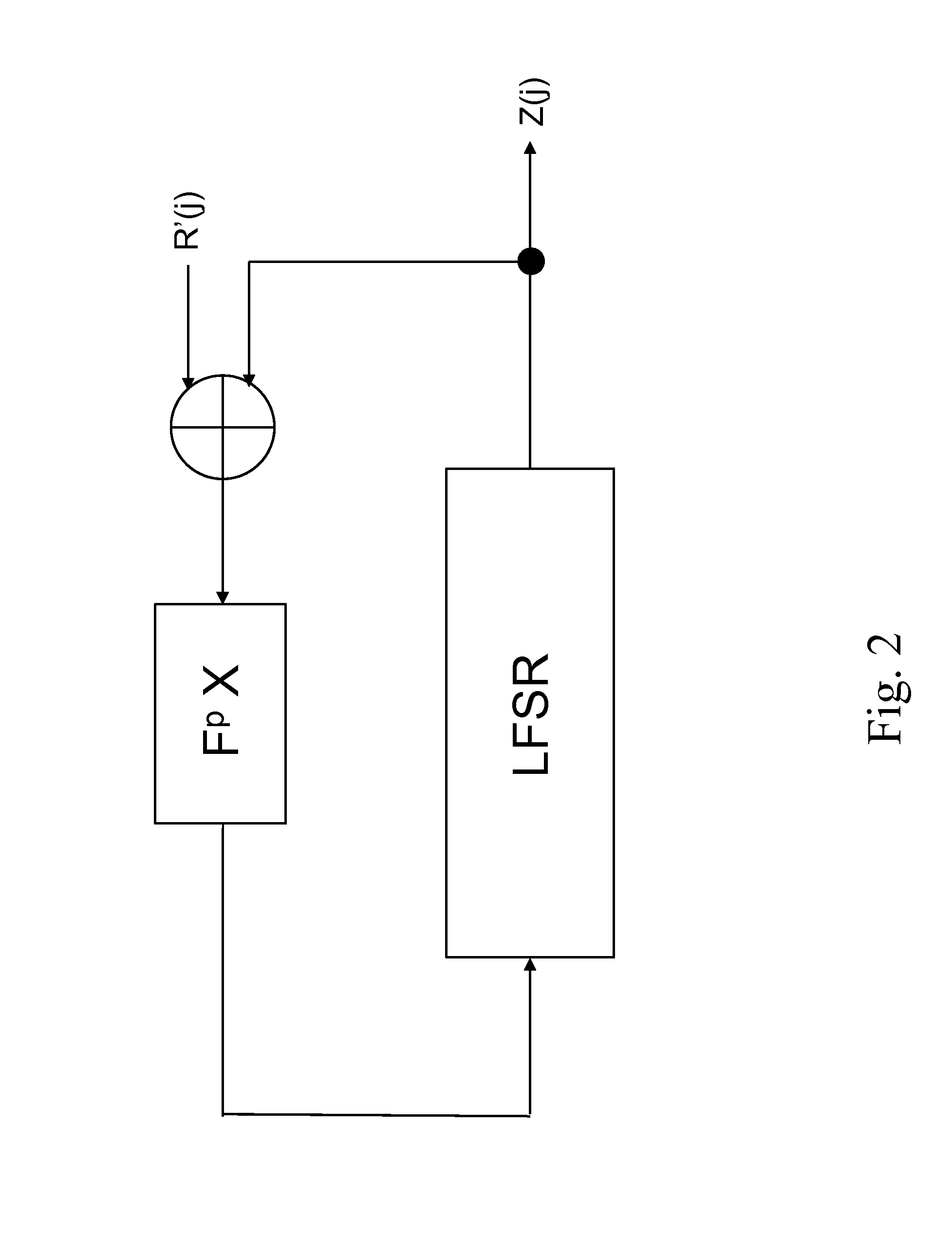

Encoding and syndrome computing co-design circuit for bch code and method for deciding the same

ActiveUS20150318869A1Efficiently reduce common sub-expressionsHigh complexityCode conversionCyclic codesComputer scienceBch coding

An encoding and syndrome computing co-design circuit for BCH code and a method for deciding the circuit are disclosed. The method includes the steps of: building up matrices of XR, XG and XS according to p parallel computations and 2t syndromes; building up FP; building up F′; building up F″; building up matrix of [XSRG F″]; and designing a circuit which fulfills the operation of [XSRG F″].

Owner:STORART TECHSHENZHEN CO LTD

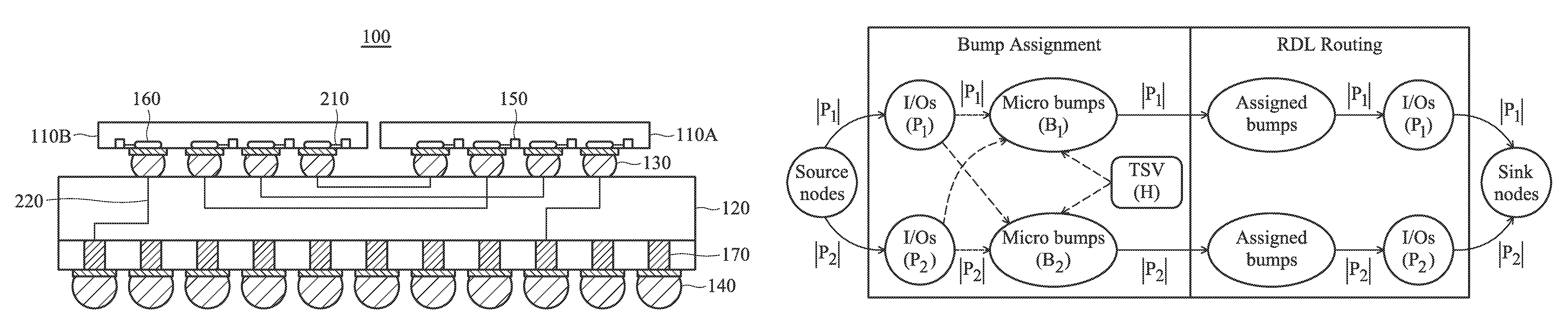

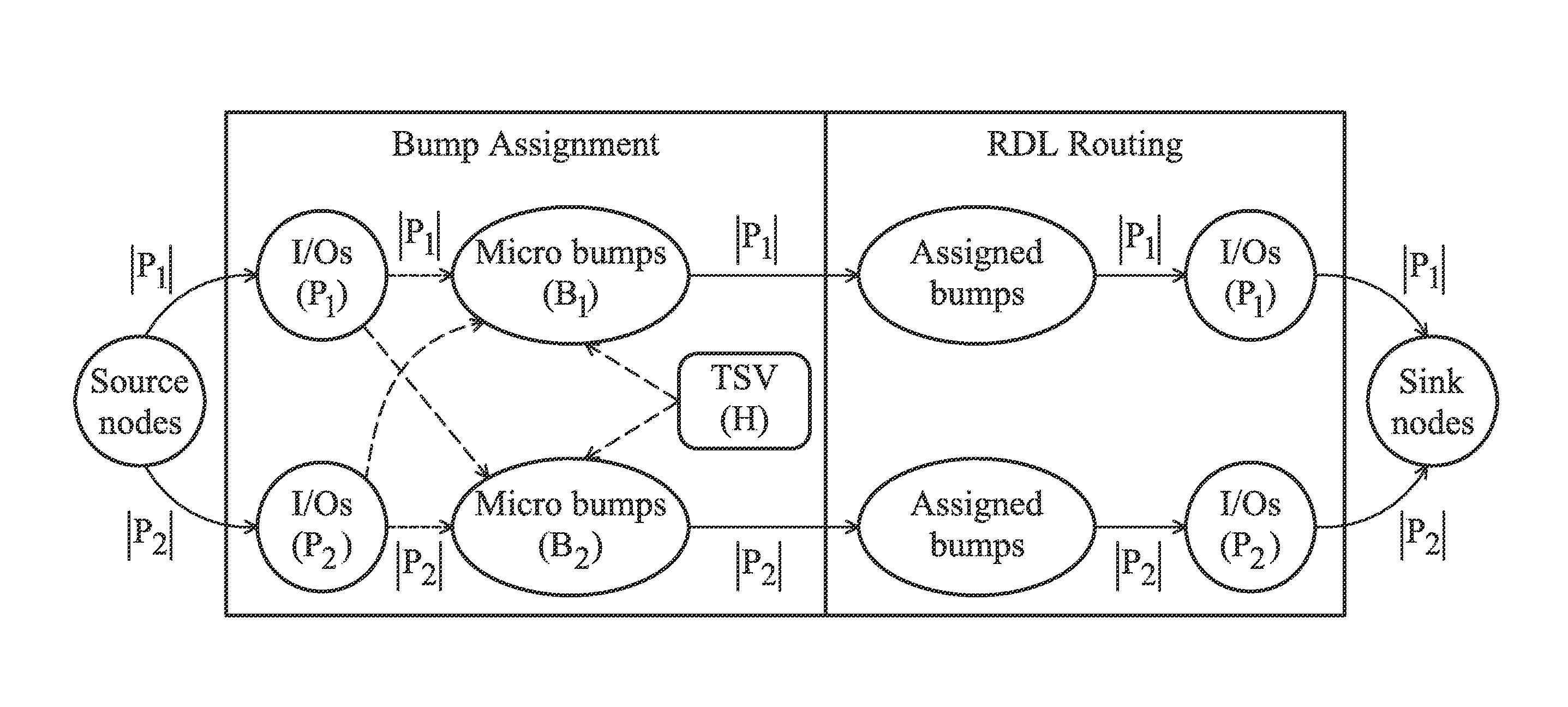

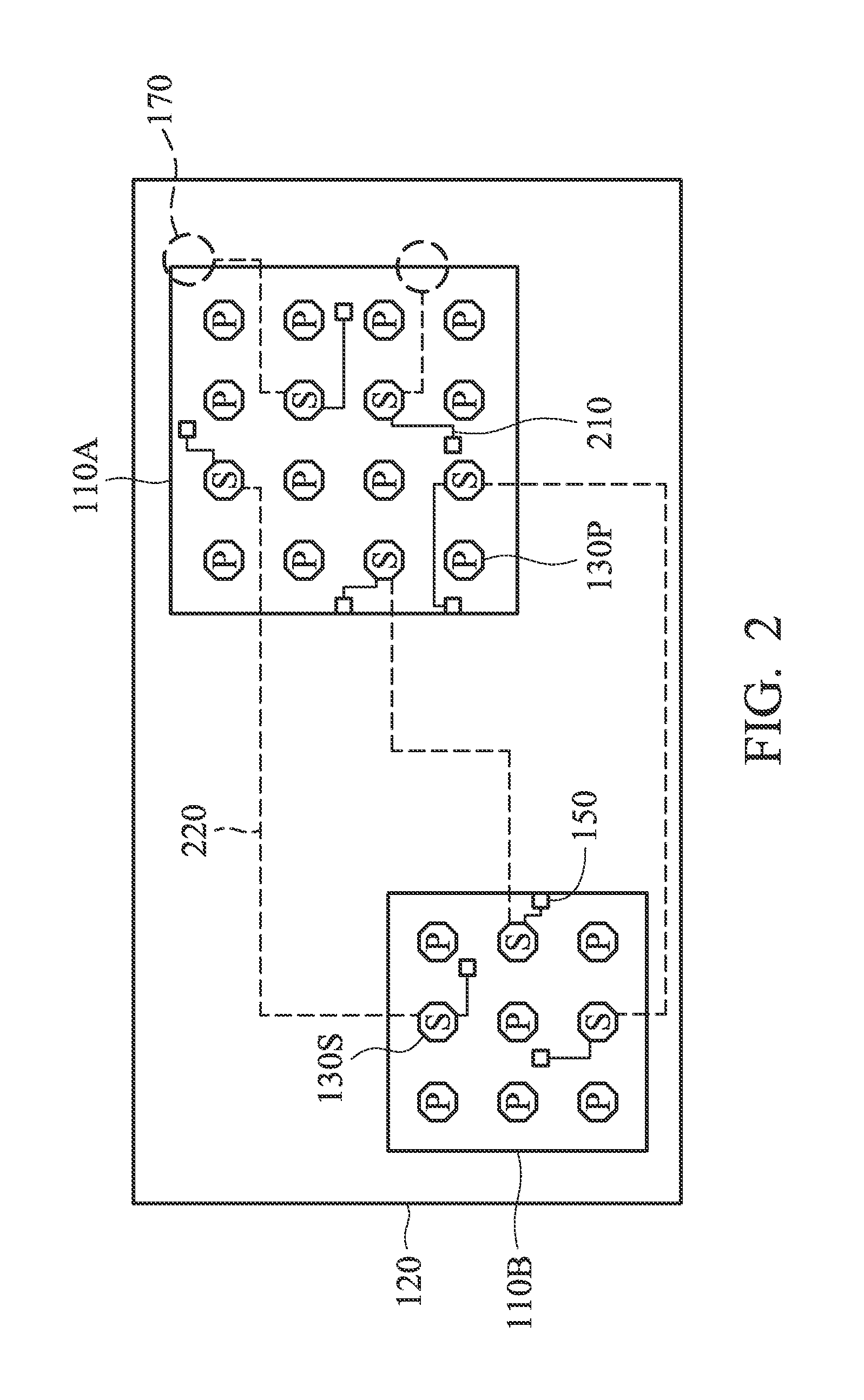

Method for co-designing flip-chip and interposer

ActiveUS9589092B2Minimized wiring lengthAvoid violationsSemiconductor/solid-state device detailsSolid-state devicesInterposerCo-design

A method for co-designing a flip-chip and an interposer is provided. Information regarding I / O pads, power pins and IR constraints of the flip-chip is obtained. A bump planning procedure is performed to obtain a total number of micro bumps of the flip-chip according to the information, and obtain a minimum conductance of each of the power pins of the flip-chip according to a bump placement of the micro bumps of the flip-chip. A chip-interposer routing procedure is performed to obtain a Re-Distribution Layer (RDL) routing of the flip-chip and an interposer routing of the interposer according to the minimum conductance of the power pins of the flip-chip.

Owner:MEDIATEK INC

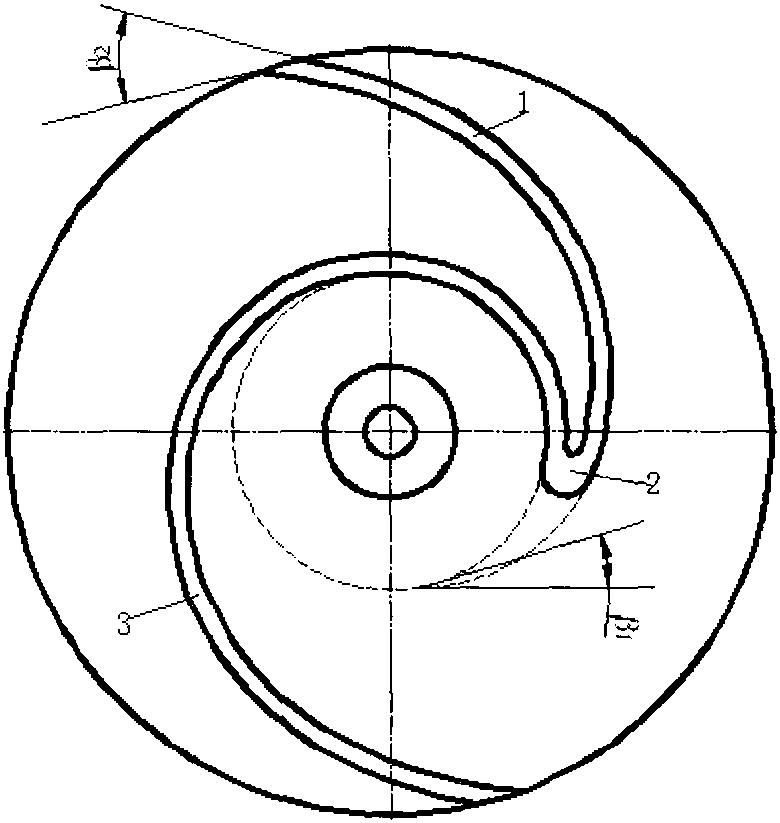

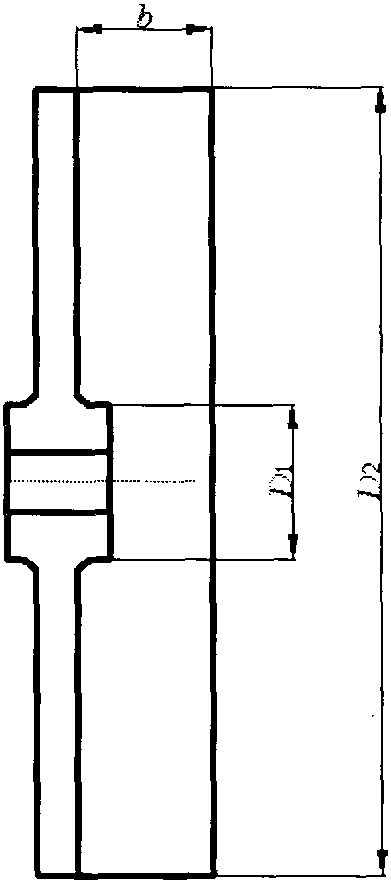

Hydraulic design method for asymmetric solid-liquid two-phase flow centrifugal impeller

ActiveCN105221477AImprove streamline distributionWithout destroying the integrityPump componentsPumpsImpellerFiber

The invention provides a hydraulic design method for an asymmetric solid-liquid two-phase flow centrifugal impeller. The method aims at solving the problems generated in the application process of a solid-liquid two-phase flow pump. An impeller is a semi-open type single flow channel and is suitable for conveying various particles and substances containing fibers. A vane is formed by combining a long vane body and a short vane body. Part of the short vane body and part of the long vane body are symmetric. The flow guide effect is achieved through the long vane body so that the conveyed substances can smoothly reach an impeller outlet and the integrity of the conveyed substances cannot be damaged. The conveyed substances are discharged out of the impeller under the effect of the short vane body. A working face streamline equation of the vane is designed through an arc method and a variable angle spiral line method jointly. In order to rotationally cut various objects, the vane is designed in the manner that the working face is higher than the back face, and the cross section of the vane is designed in a pentagonal shape with three right angles. Inlet and outlet installation angle design formulas of the vane are given. The asymmetric solid-liquid two-phase flow centrifugal impeller designed through the method is good in blockage resistance and high in twining cutting resistance.

Owner:JIANGSU UNIV

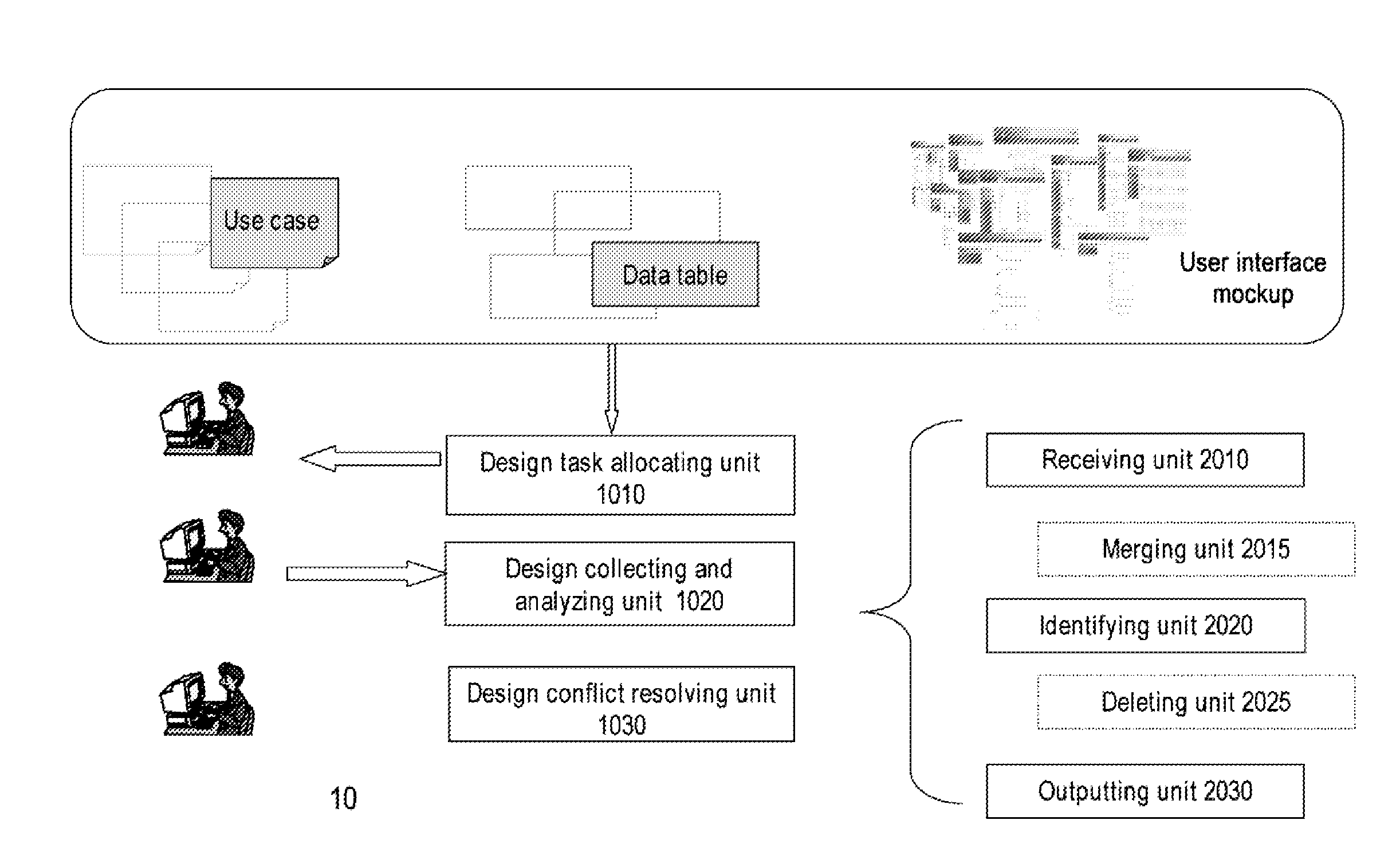

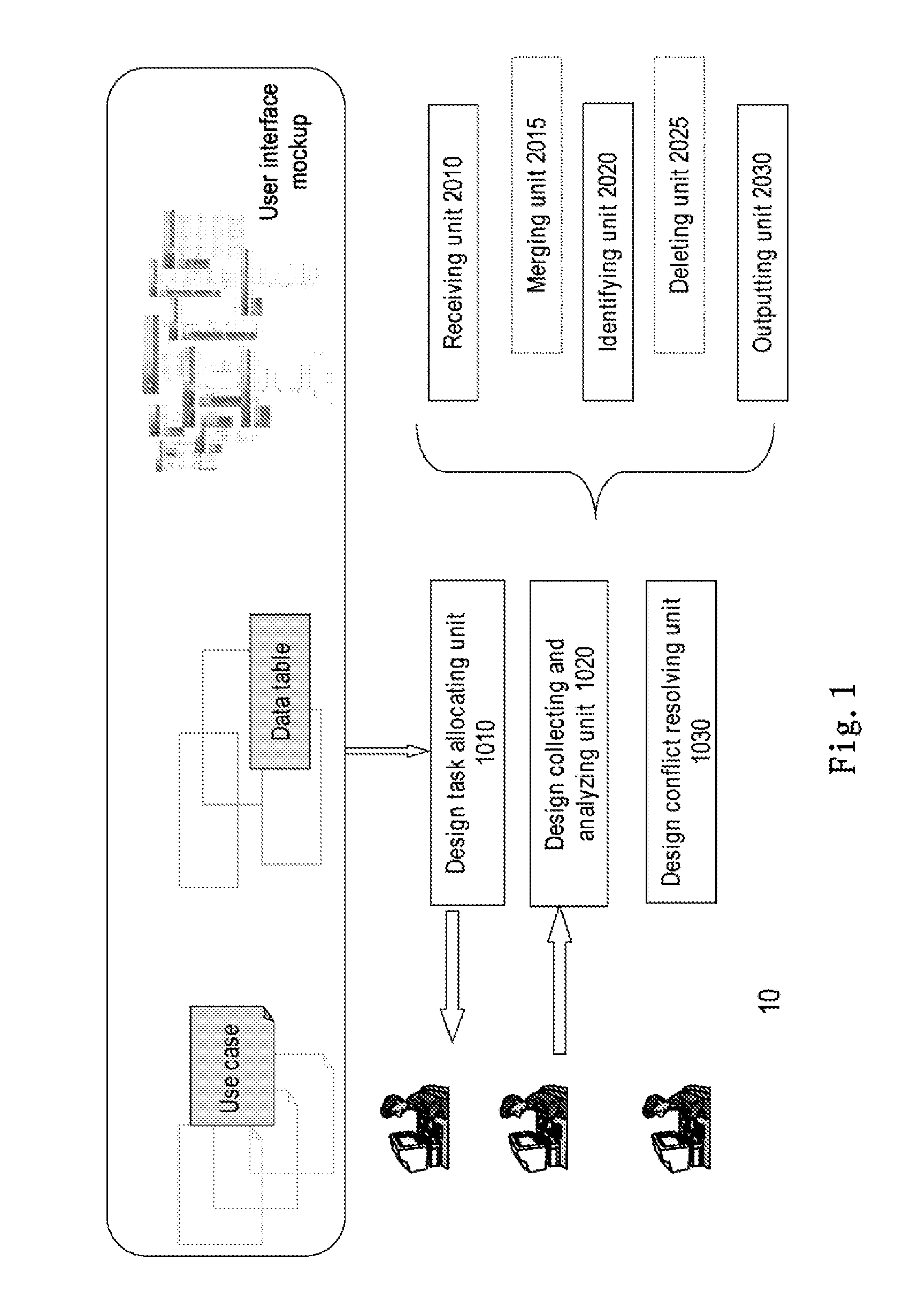

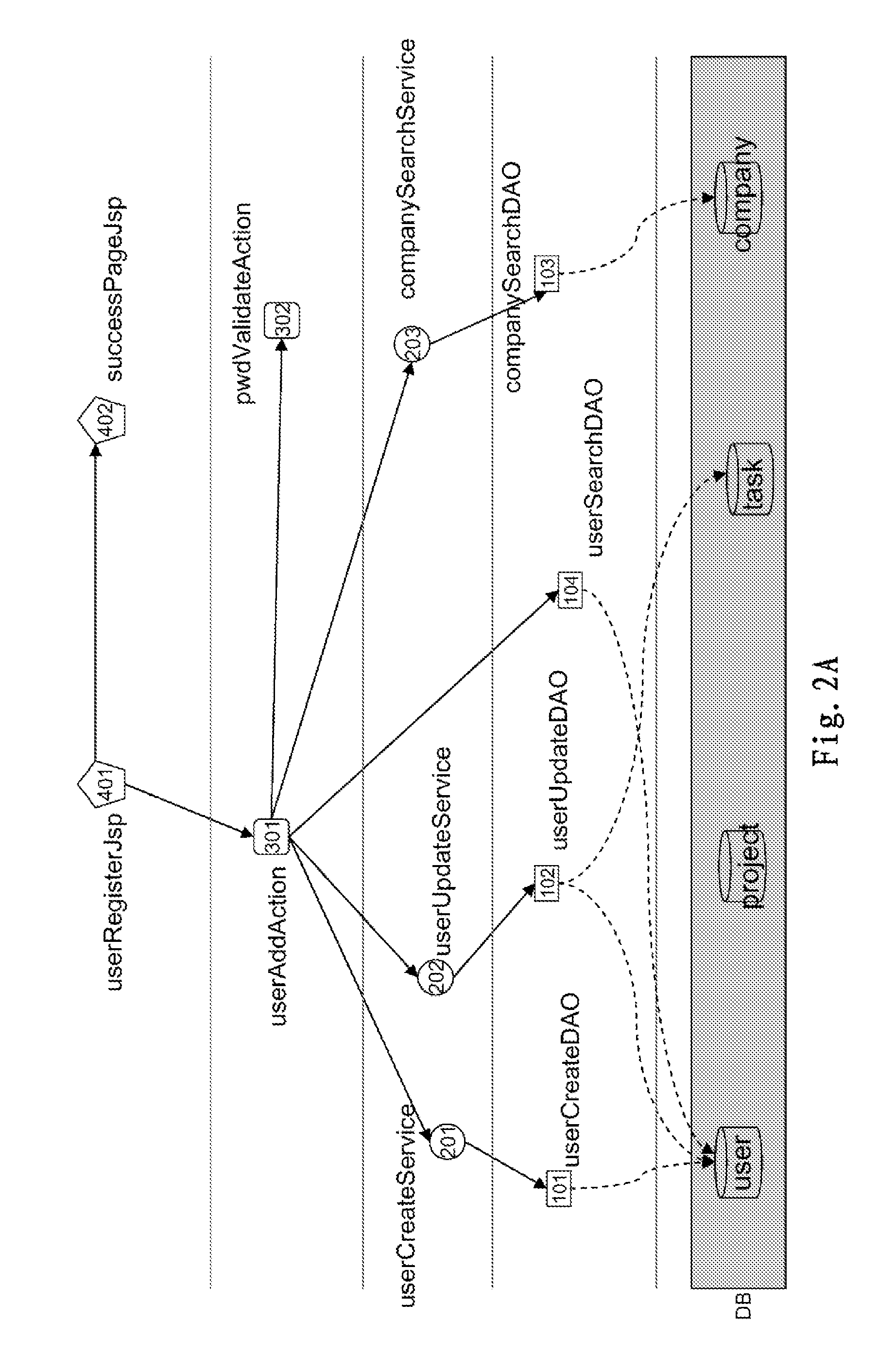

Method and system for handling software design conflicts

InactiveUS20110107303A1Version controlSpecific program execution arrangementsComputer architectureSoftware design

A method and a system for identifying and resolving conflicts between design results from a parallel software design. The method includes: receiving a design diagram, wherein the design diagram includes a plurality of nodes and arrows connecting different nodes, with each node indicating a design artifact, and an arrow directed from one node to another node indicating that a design artifact corresponds to the one node depends on a design artifact corresponding to the other node; determining a level of a design artifact in the design diagram, identifying different design artifacts at a given level of the design diagram that depend on a common design artifact, and marking them as isomorphic design artifacts; and outputting a design diagram with the isomorphic design artifacts marked. A conflict between relevant designs are automatically identified in a bottom-up approach according to a software design hierarchy to facilitate conflict resolution.

Owner:IBM CORP

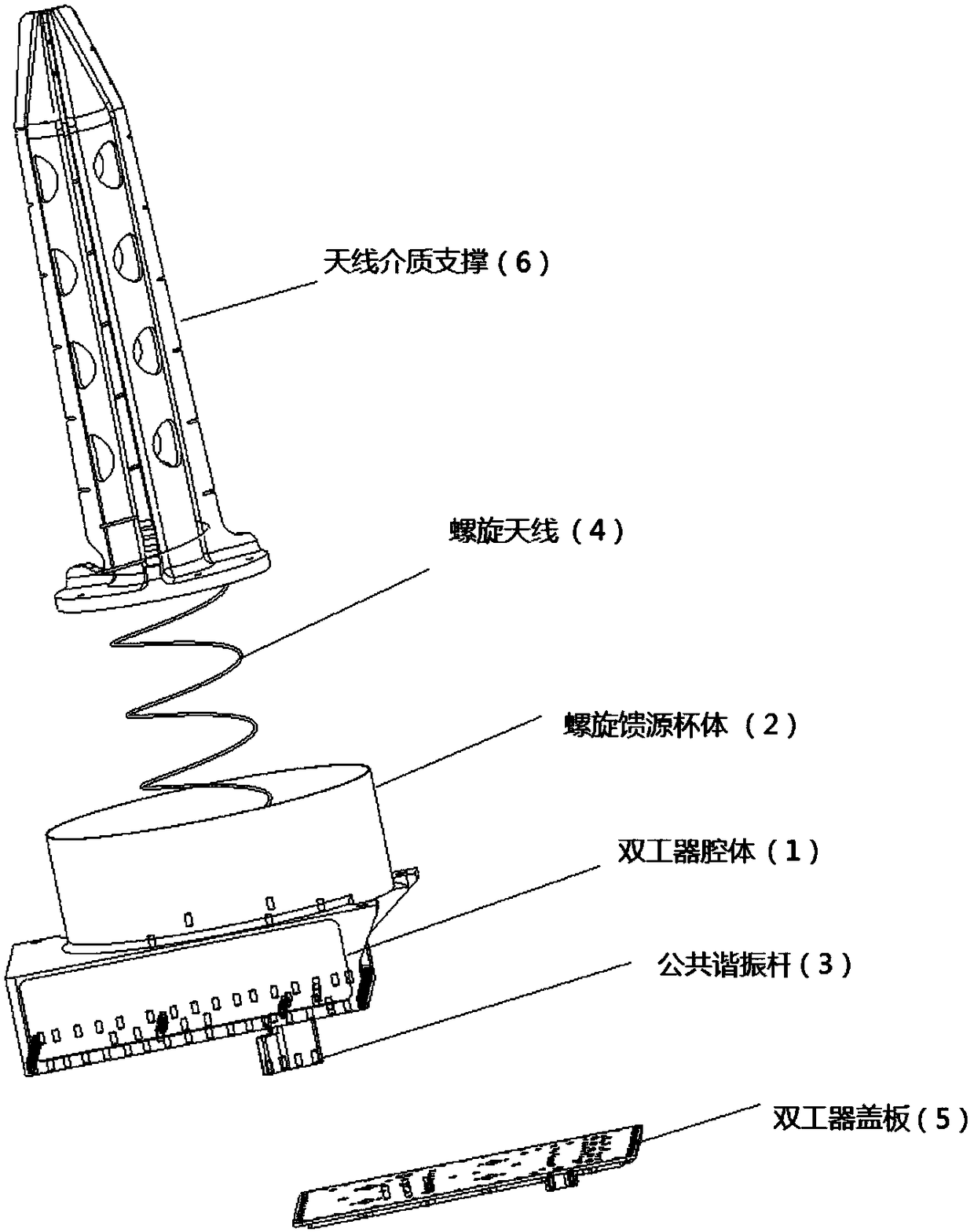

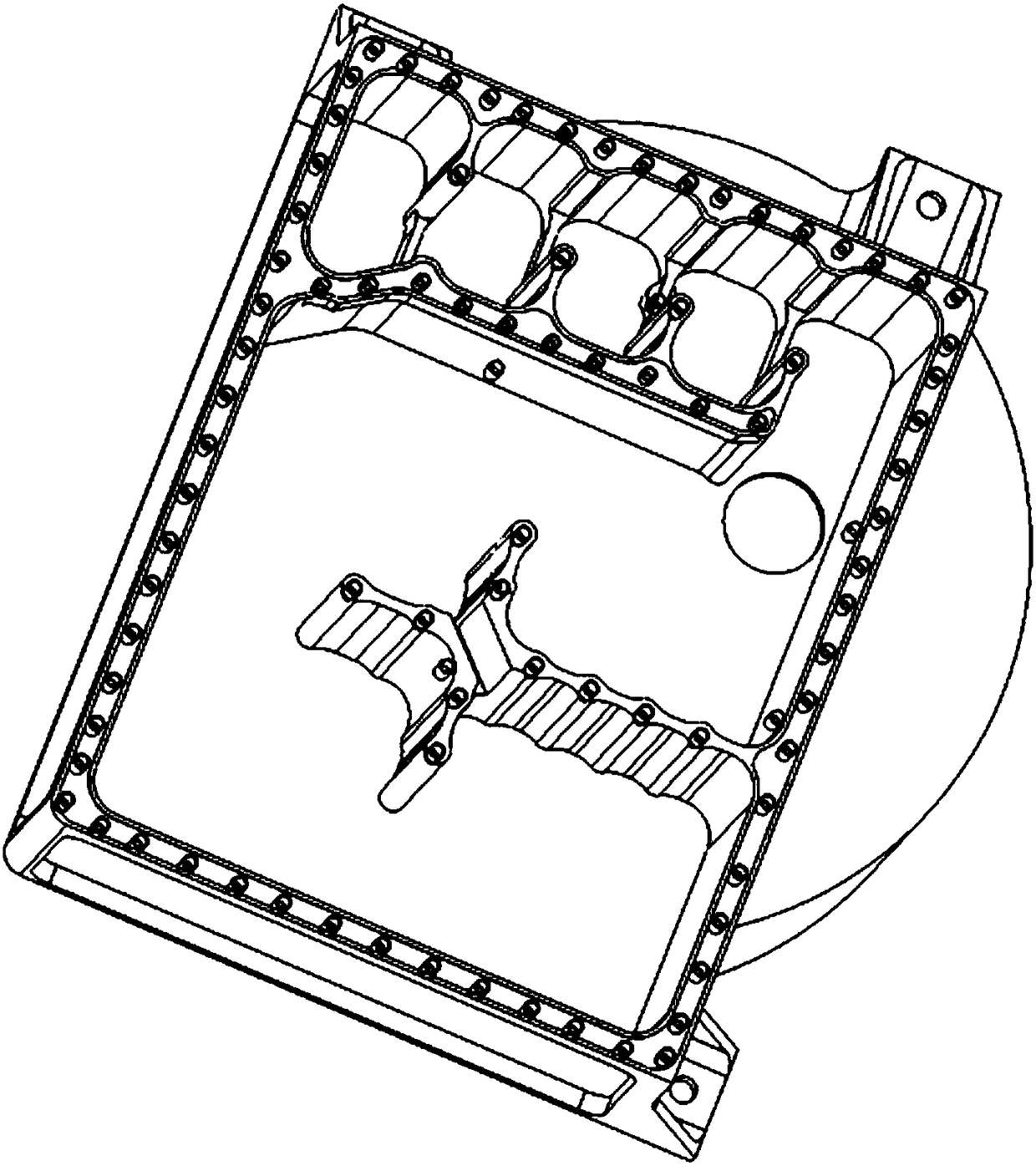

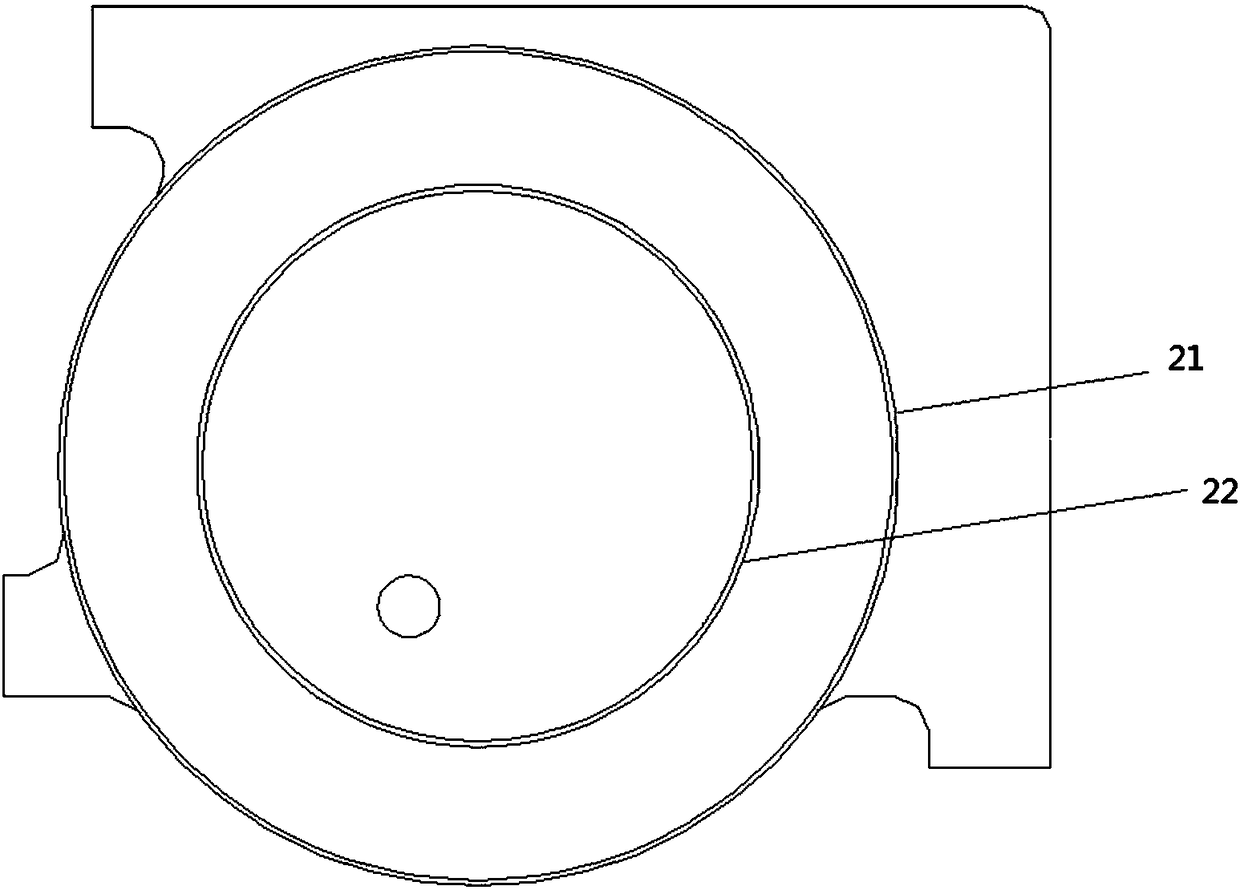

Low passive intermodulation feed source duplexer, and receiving and emitting method thereof

ActiveCN108321475AImproved axle ratio performanceIncrease distanceRadiating elements structural formsAntennas earthing switches associationElectricityElectrical conductor

The invention provides a low passive intermodulation feed source duplexer, and a receiving and emitting method thereof. A duplexer cavity body and an antenna feed source base are designed and processed in an integral manner in terms of structures, the sizes of the duplexer and the antenna feed source can be accurately calculated. A shared resonance rod of the duplexer and inner and outer conductors at a feed source input interface can be co-designed in that a matching port impedance can be designed, the shape, size and distance of the shared resonance rod can be adjusted, and the phase position between two devices can be optimized. Accordingly, an integral design can be realized. The invention is advantageous in that the situation of the conventional design that the duplexer is connected to the antenna feed source through cables can be prevented, and the usage of electric connectors can be reduced, and the part depending on elastic connection can be removed; the contact nonlinearity ofsensitive parts can be prevented, and the PIM feature of the product can be greatly improved, and the aim of reducing the PIM of the system can be achieved; the problem of passive intermodulation inhibition of the microwave duplexer and the antenna feed source system can be resolved.

Owner:XIAN INSTITUE OF SPACE RADIO TECH

Method for co-designing flip-chip and interposer

ActiveUS20150154337A1Minimized wiring lengthAvoid violationsSolid-state devicesComputer aided designInterposerEngineering

A method for co-designing a flip-chip and an interposer is provided. Information regarding I / O pads, power pins and IR constraints of the flip-chip is obtained. A bump planning procedure is performed to obtain a total number of micro bumps of the flip-chip according to the information, and obtain a minimum conductance of each of the power pins of the flip-chip according to a bump placement of the micro bumps of the flip-chip. A chip-interposer routing procedure is performed to obtain a Re-Distribution Layer (RDL) routing of the flip-chip and an interposer routing of the interposer according to the minimum conductance of the power pins of the flip-chip.

Owner:MEDIATEK INC

Integrated framework for finite-element methods for package, device and circuit co-design

InactiveUS8352230B2Improve accuracyReduce in quantityAnalogue computers for electric apparatusDetecting faulty computer hardwareElectricityPackage design

Electrical finite element analysis is carried out on a circuit design, which includes devices, to determine an acceptable power-performance envelope and to obtain data for circuit temperature mapping. A circuit temperature map is developed for the circuit design, based on the data for circuit temperature mapping. Thermo-mechanical finite element analysis is carried out on a package design for the circuit design, based on the circuit temperature map, to determine a package reliability limit based on thermal stress considerations. It is determined whether the package design and the circuit design jointly satisfy: (i) power-performance conditions specified in the acceptable power-performance envelope; and (ii) the package reliability limit based on the thermal stress considerations.

Owner:GLOBALFOUNDRIES INC

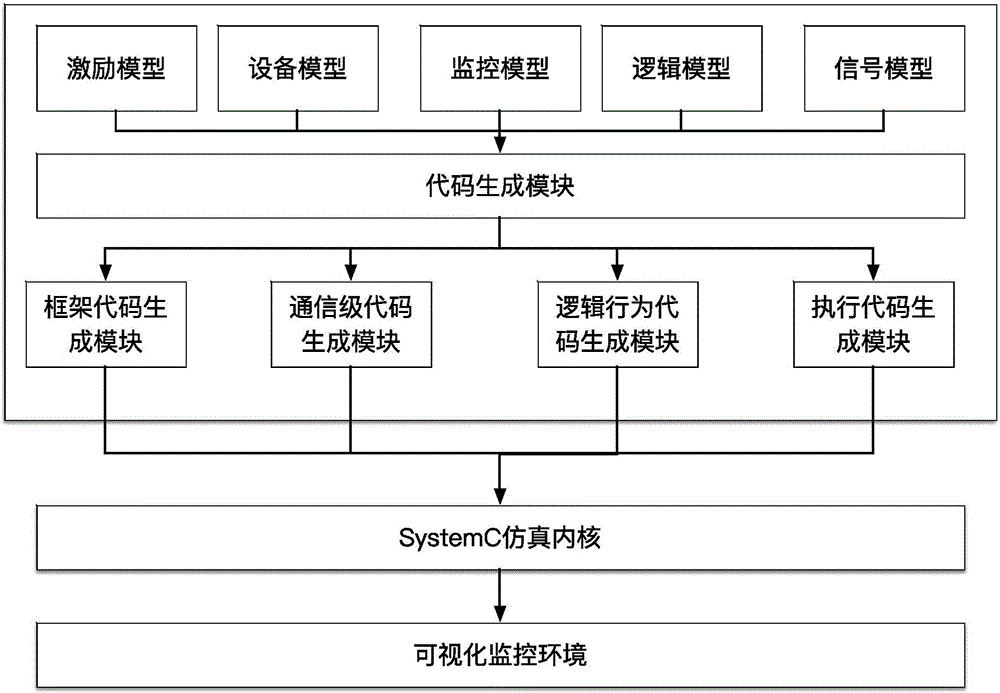

SystemC code generation system based on model

ActiveCN106354515ARealize automatic generationRealize Integrated Simulation VerificationSimulator controlProgramming languages/paradigmsSystemCElectronic systems

The invention discloses a SystemC code generation system based on a model and relates to the technical field of industrial electronic tools. With the adoption of the SystemC code generation system based on the model in the embodiment, automatic generation of model data SystemC codes can be realized through inheriting of behavior logic model data in Modelook, the logic model data is subjected to digital simulation verification directly, so that the economic cost is greatly reduced, and time is saved; besides, the logic model data is verified through hardware / software co-design language, and integrated simulation verification of hardware functions and software functions of an industrial electronic system is realized.

Owner:杭州杉石科技有限公司

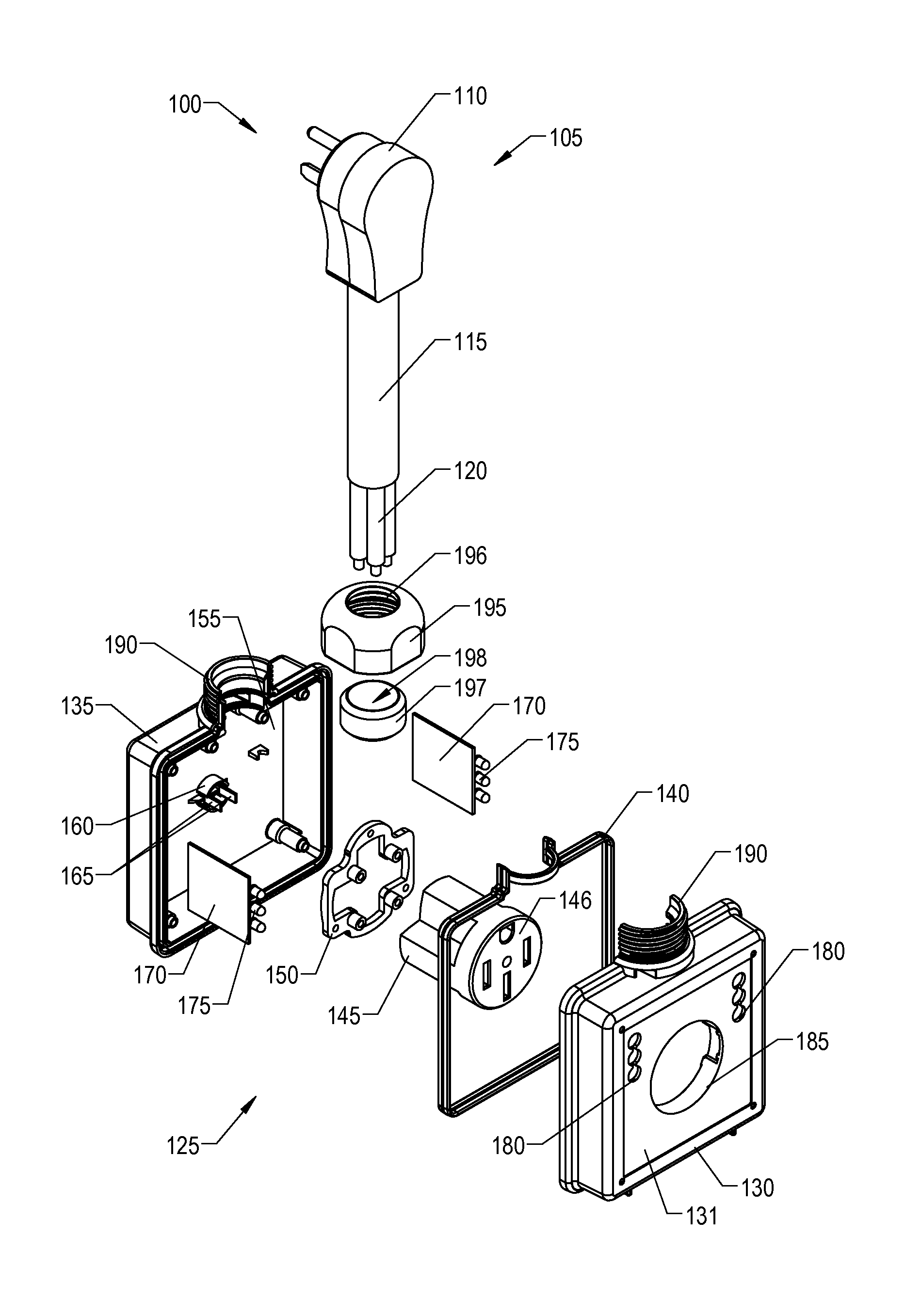

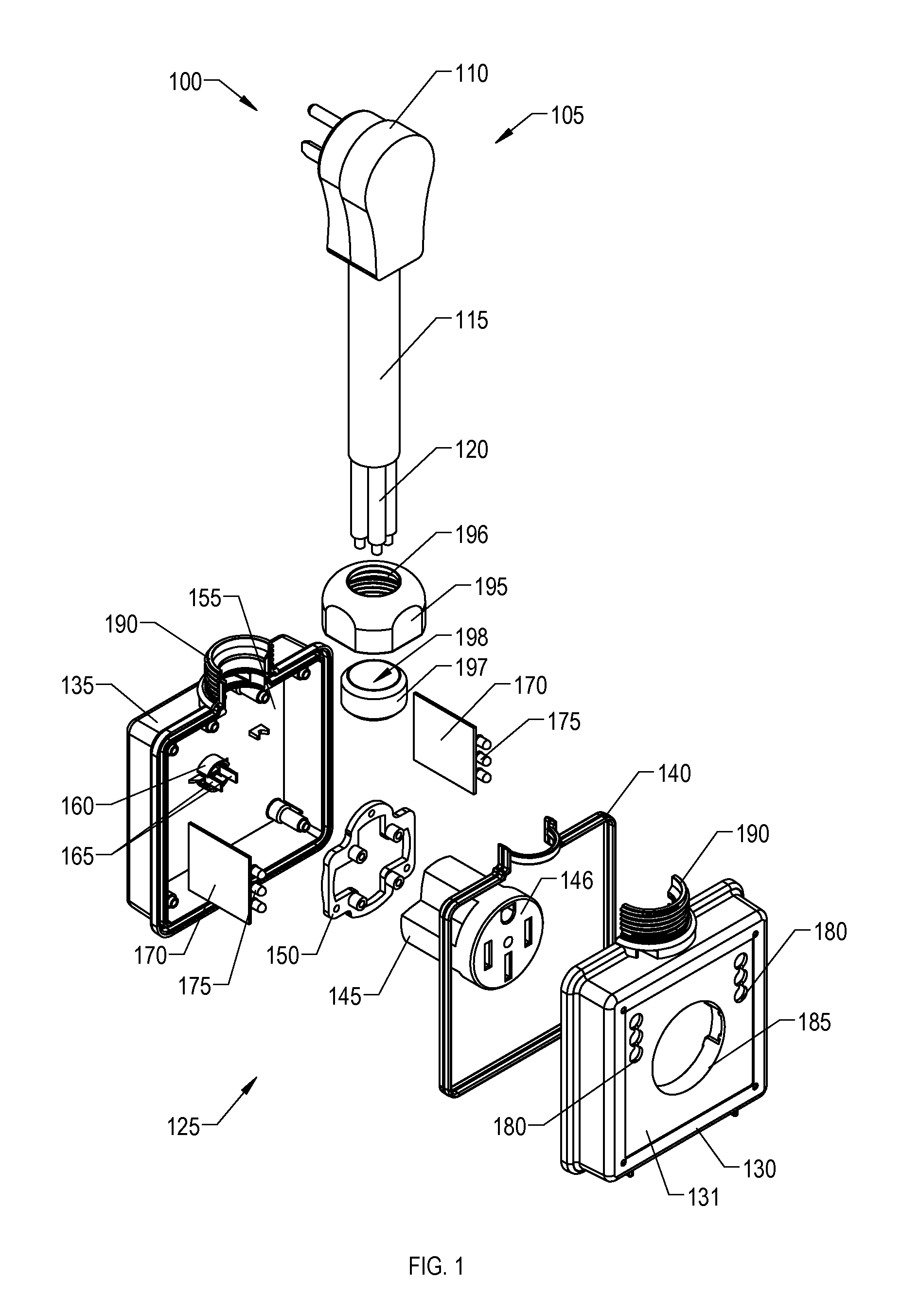

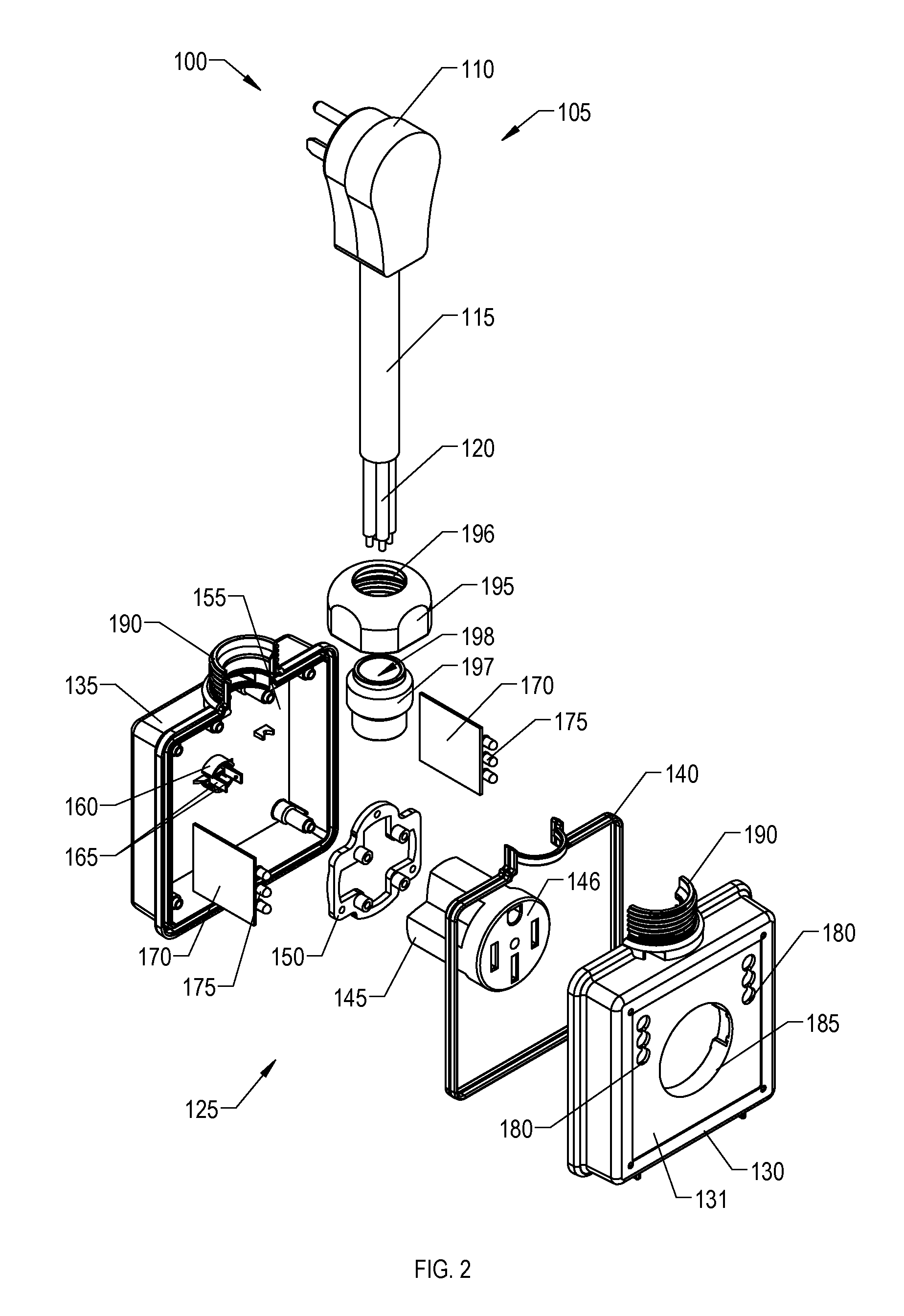

Electrical connection box

Electrical connection boxes for use in recreational vehicle and marine applications must be adapted for a variety of electrical services and electrical connection styles. In order to standardize electrical connection boxes for these uses, a plurality of positioning tabs may be mounted within the connection box to accommodate electrical connection receptacles of various sizes. Unused positioning tabs may be removed during assembly. Further standardization can be achieved through the use of gaskets adapted for use with power cords of different sizes but having common design features to mate with a common seating surface design.

Owner:BRUNSWICK CORPORATION

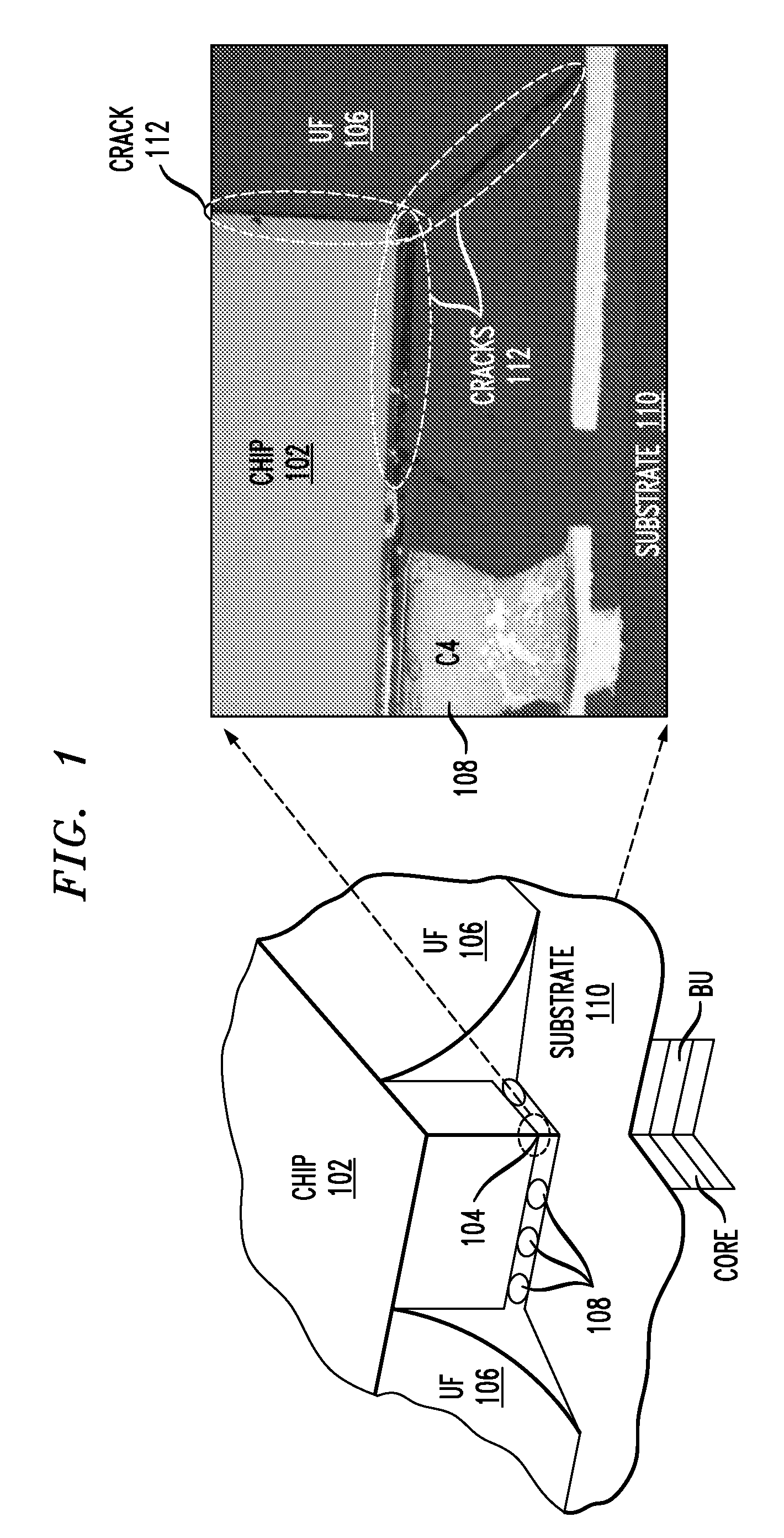

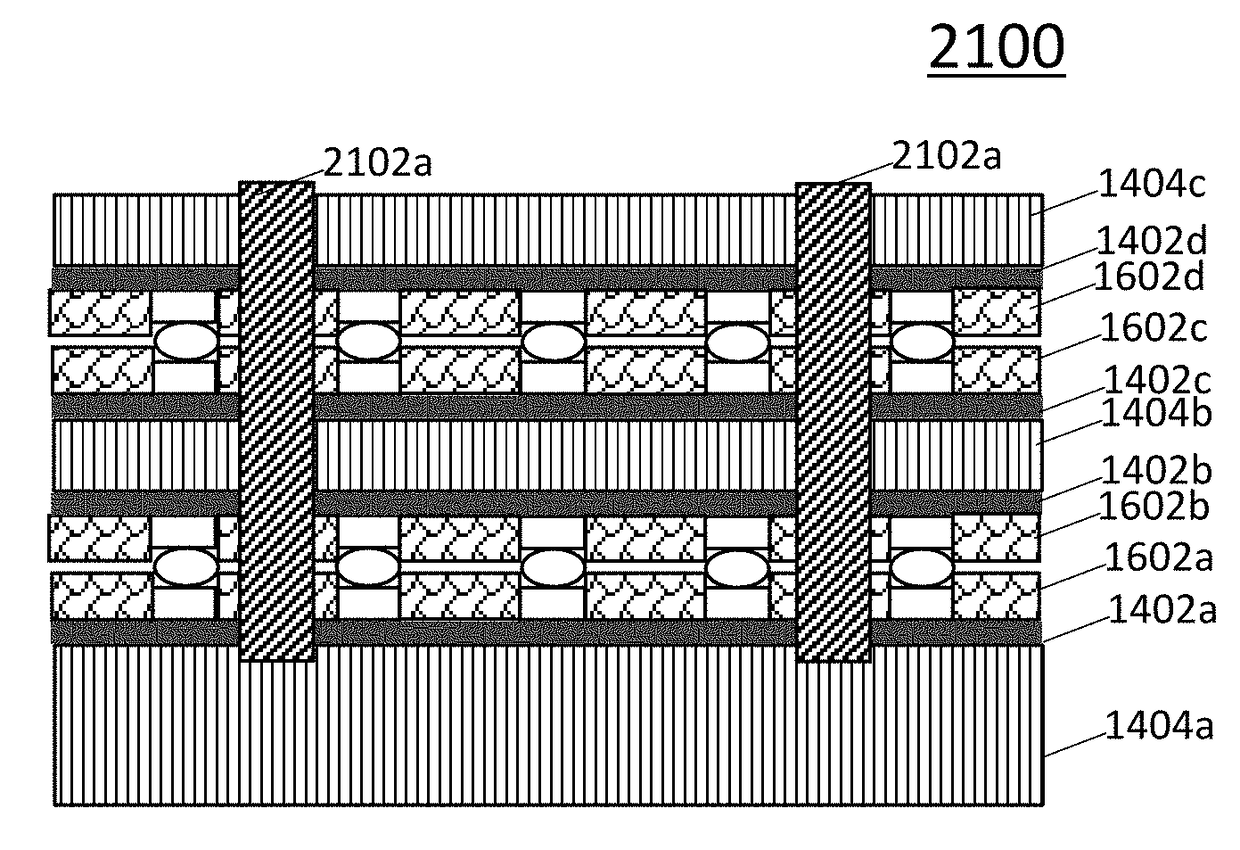

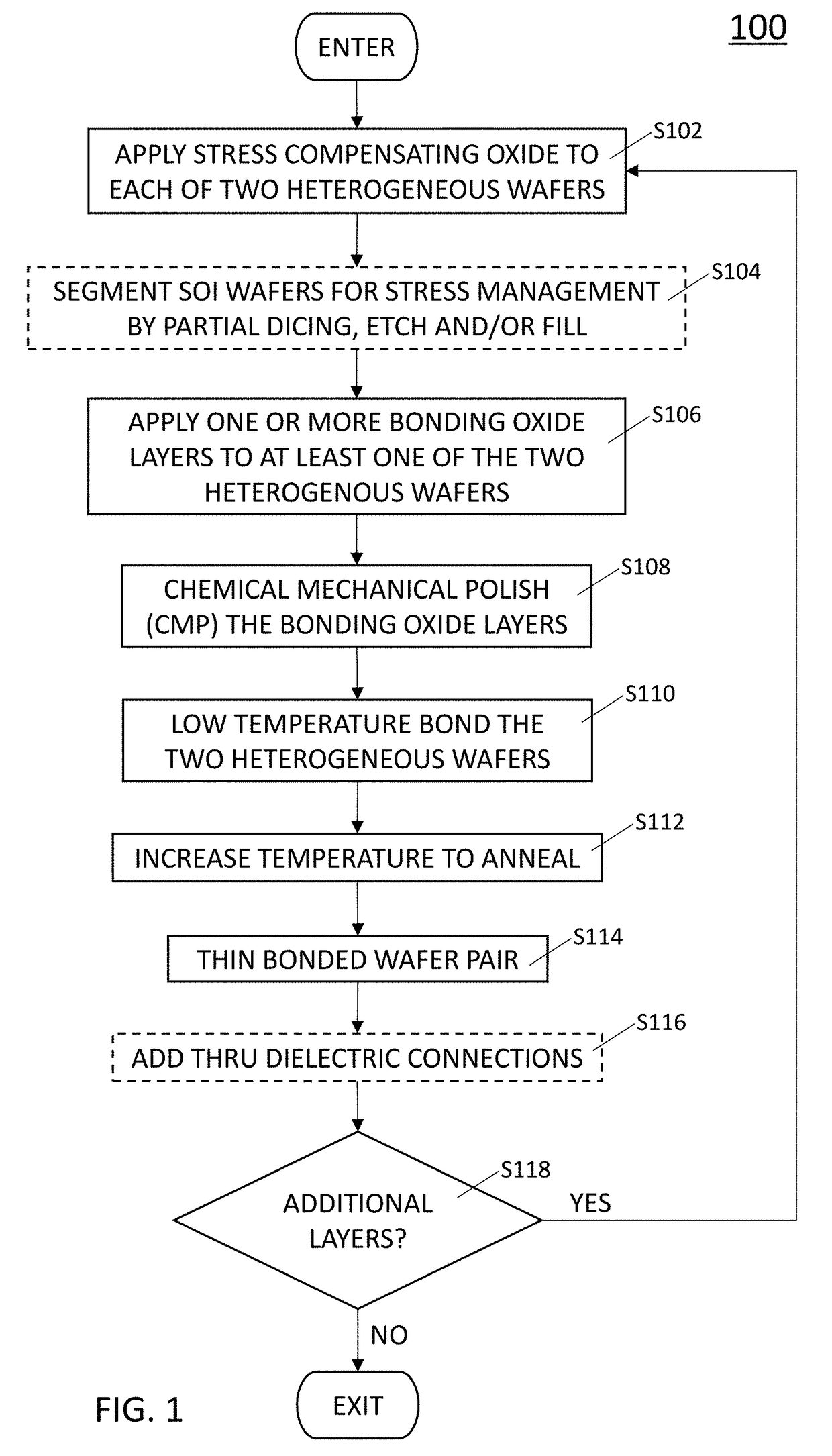

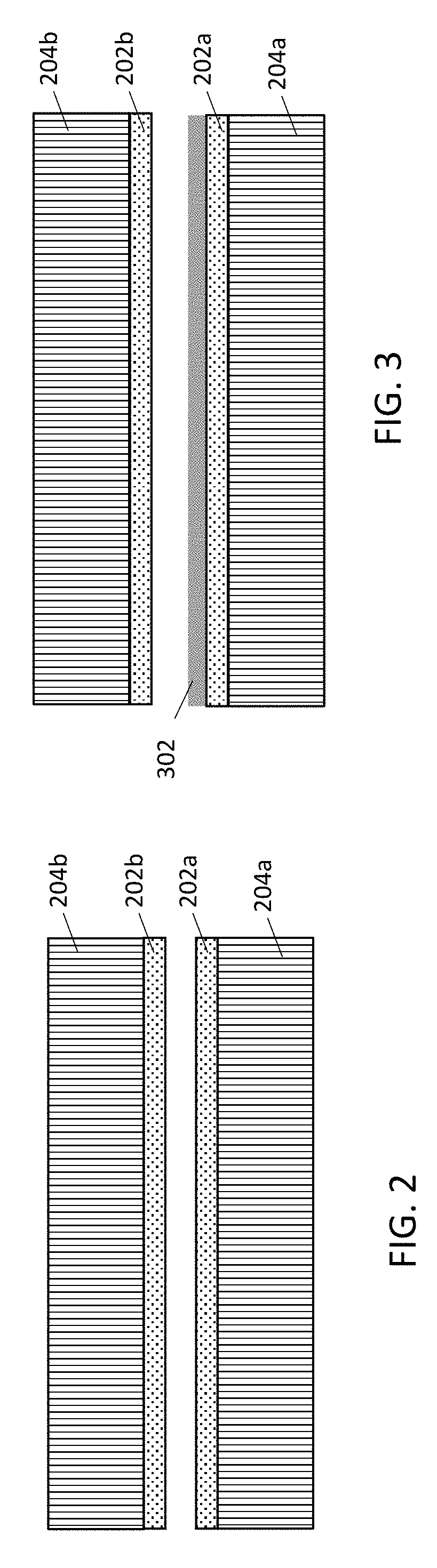

Wafer level integration including design/co-design, structure process, equipment stress management, and thermal management

ActiveUS20180082888A1TransistorSemiconductor/solid-state device detailsEngineeringWafer-scale integration

A multi-layer wafer and method of manufacturing such wafer are provided. The method comprises applying a stress compensating oxide layer to each of two heterogeneous wafers, applying at least one bonding oxide layer to at least one of the two heterogeneous wafers, chemical-mechanical polishing the at least one bonding oxide layer, and low temperature bonding the two heterogeneous wafers to form a multi-layer wafer pair. The multi-layer wafer comprises two heterogeneous wafers, each of the heterogeneous wafers having a stress compensating oxide layer and at least one bonding oxide layer applied to at least one of the two heterogeneous wafers. The two heterogeneous wafers are low temperature bonded together to form the multi-layer wafer.

Owner:IBM CORP

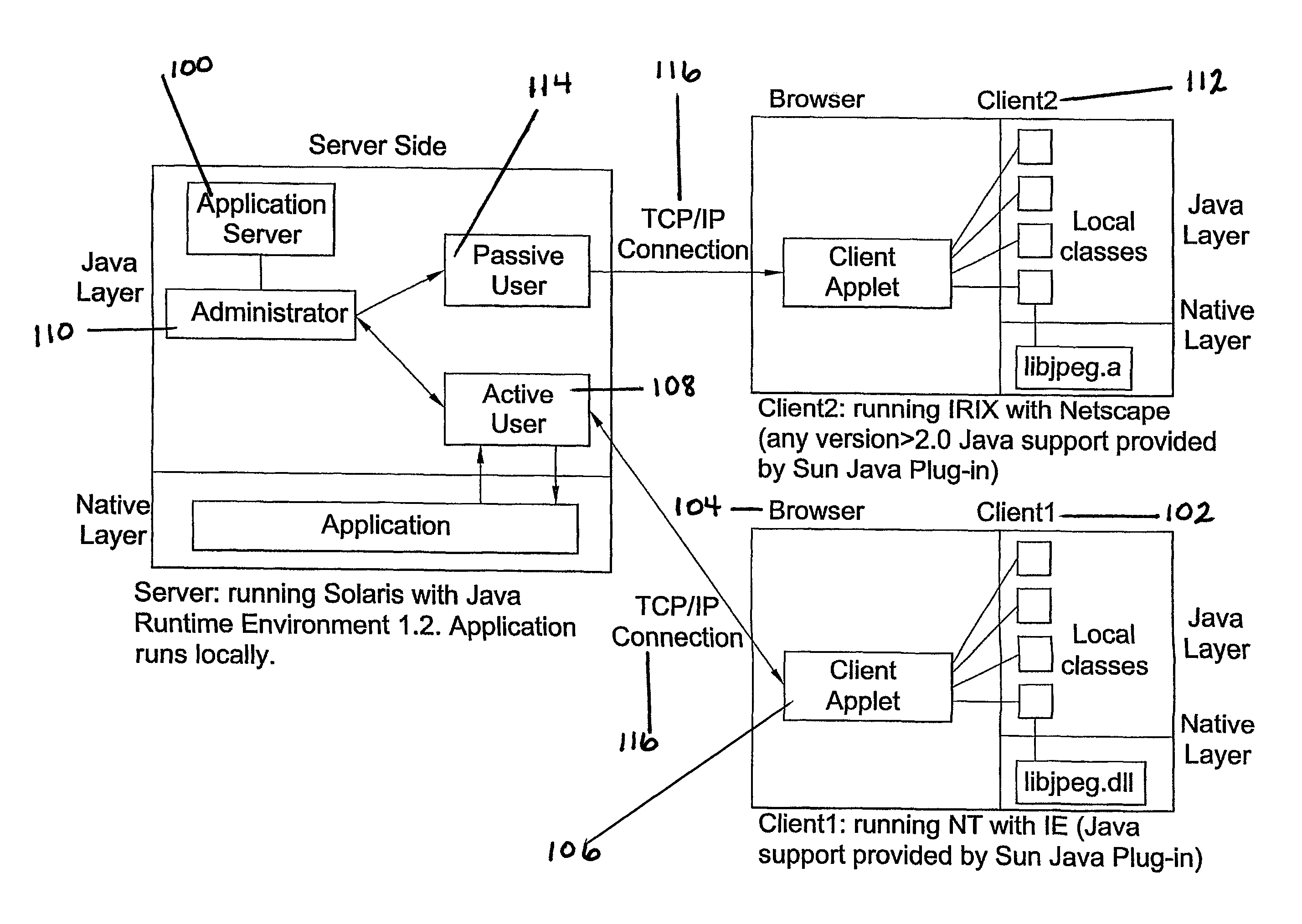

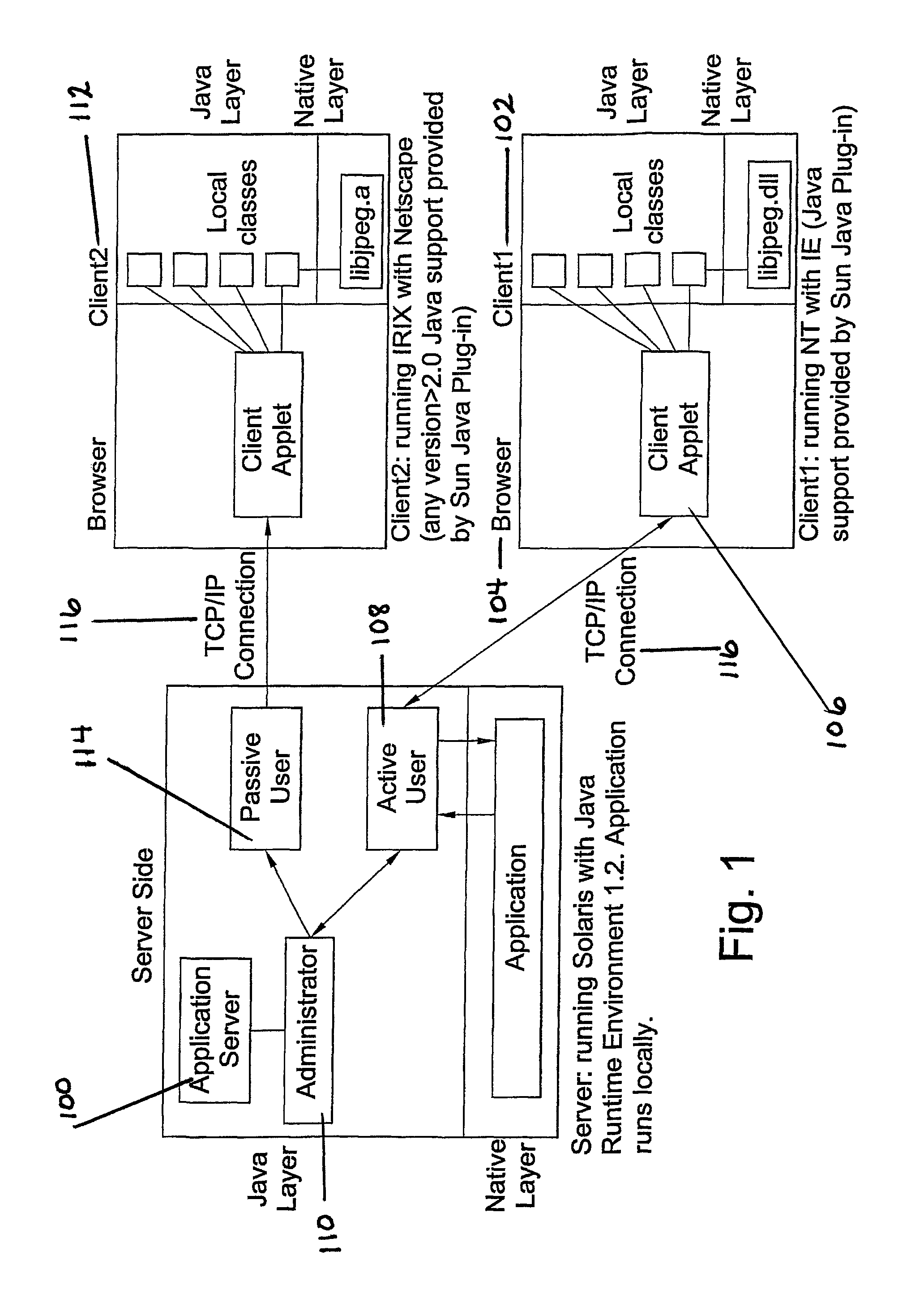

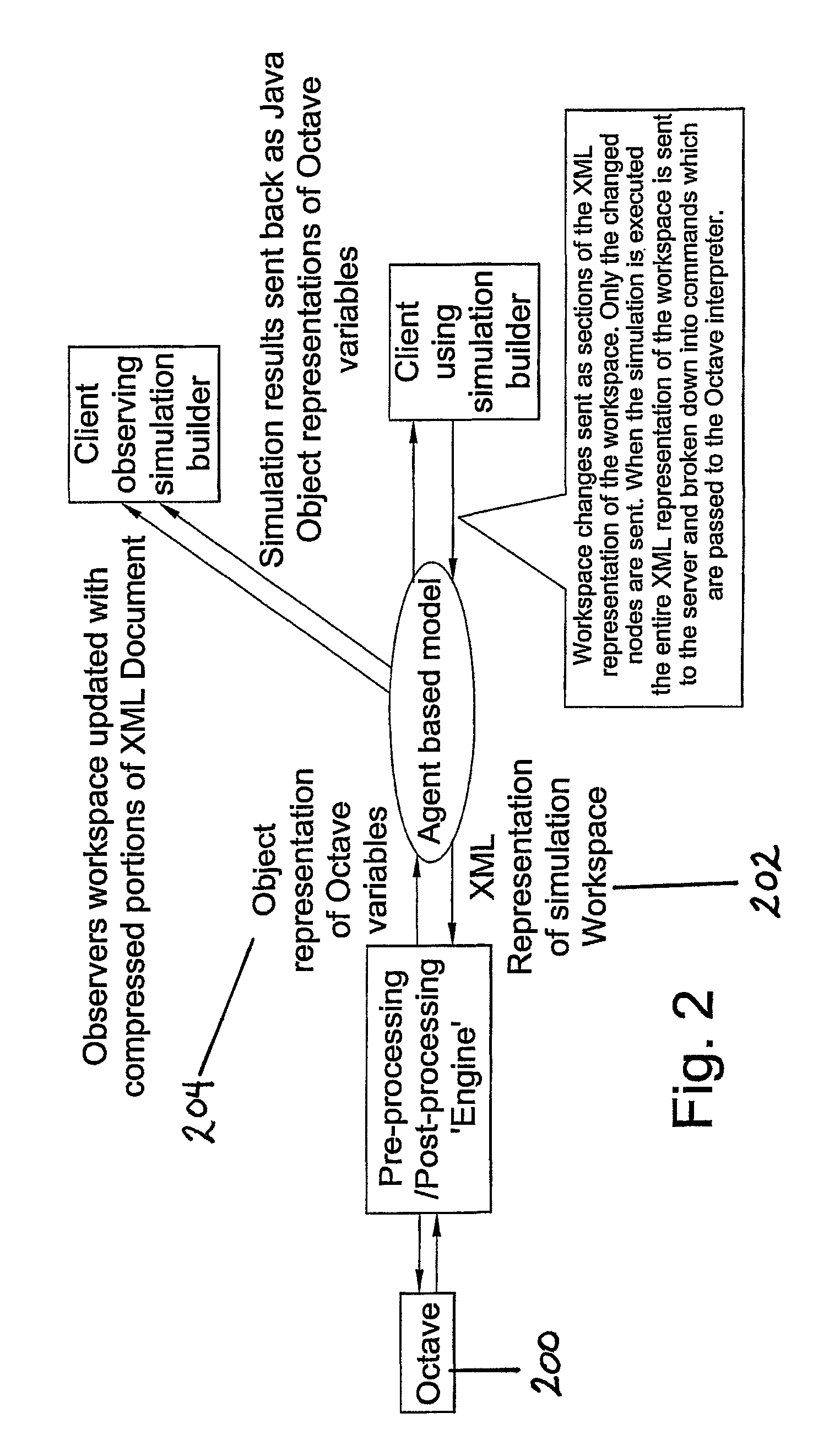

Generic object-based resource-sharing interface for distance co-operation

InactiveUS7761506B2Reduce disadvantagesInterprogram communicationMultiple digital computer combinationsSERCOS interfaceGraphics

A computer program interface for permitting multiple users to share a single copy of a computer program is described. The program interface is written in Java 1.2 or a later version and C++ and permits users who have browser programs enabled in Java to interact with the user interface. The system can be used in a variety of modes which includes a shared mode to allow multiple users to use the system, although other modes include use by a single user. In the shared mode two or more users share the same copy of software interactively over the Internet or an Intranet connection. In one embodiment during the sharing activity only one user, designated the active user, interacts directly with the computer program and the other users, designated passive user, observe what the active user does and what results are produced in response to the active user's activities. The user interface allows intercommunication between users and allows passive users to assume the role of an active user and vice versa but there is only one active use at any time. In another embodiment more than one active user can share a program which permits real-time interaction for example in game playing or co-design. Various aspects of the invention including graphical and command-time user new interface programs are described.

Owner:STRATHCLYDE UNIV OF