Patents

Literature

80results about How to "Reduce diffraction effects" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

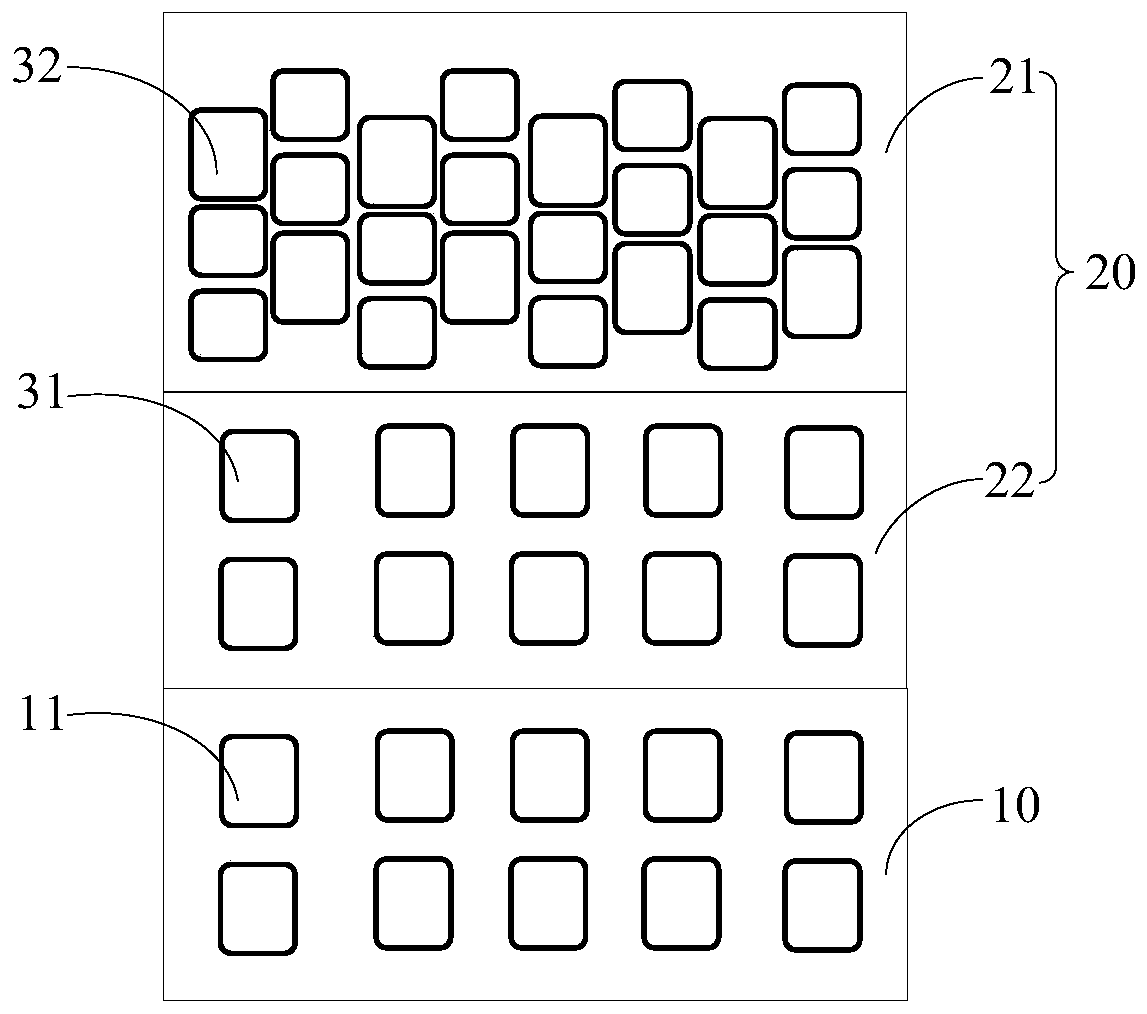

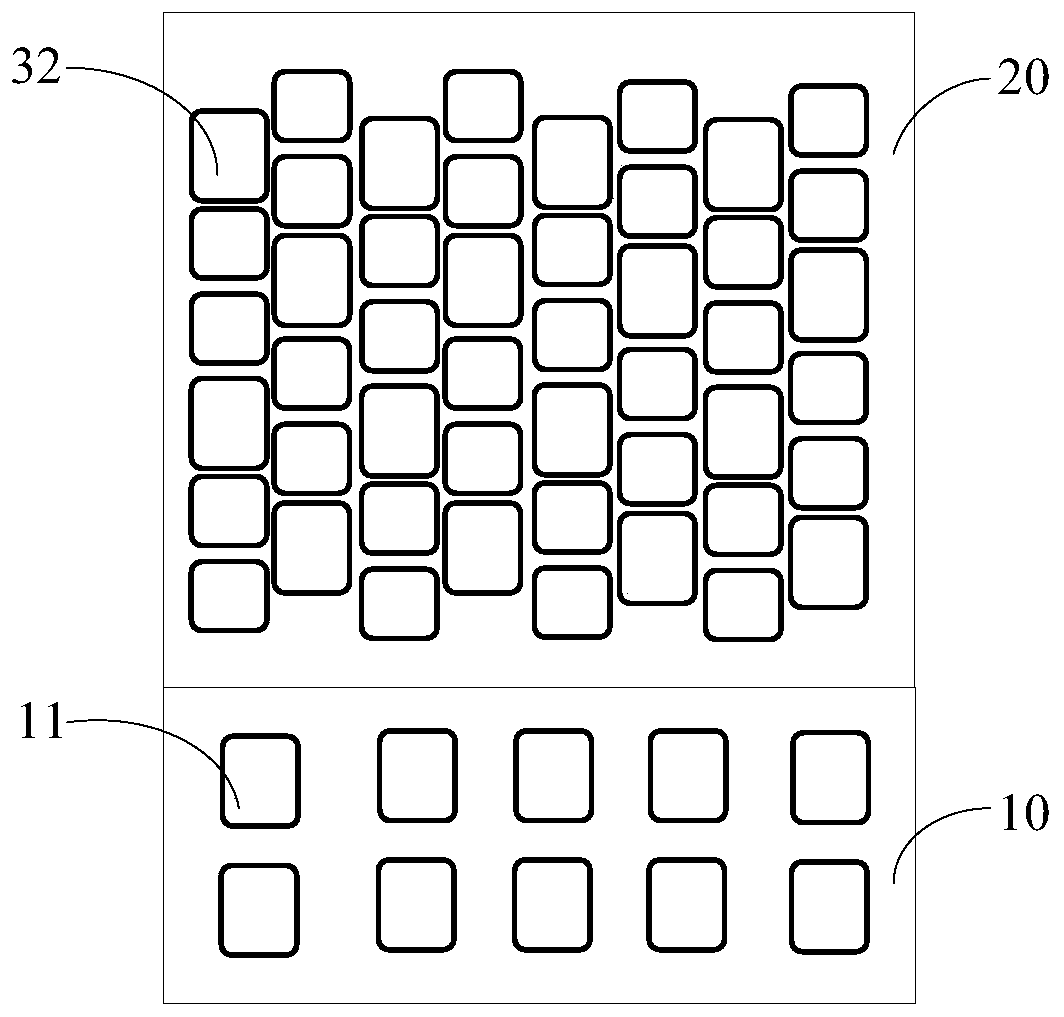

Display base plate, display panel and display device

ActiveCN110189639AGuaranteed to workWork lessTelevision system detailsStatic indicating devicesDisplay deviceTransmittance

The invention provides a display base plate, a display panel and a display device. The display base plate comprises a first display area and a second display area; the light transmittance of the firstdisplay area is larger than the light transmittance of the second display area; a plurality of first sub-pixels are arranged in the first display area, the first sub-pixels comprise first electrodes,light emitting structures arranged on the first electrodes and second electrodes arranged on the light emitting structures, pixel circuits used for driving the first sub-pixels are arranged in the second display area, the first electrodes of the first sub-pixels are electrically connected with the corresponding pixel circuits through wirings, the wirings comprise first segments and second segments which are connected with each other, the first segments are located in the first display area, and the second segments are located in the second display area; and a conducting layer is further arranged in the first display area, the first electrodes are electrically connected with the first segments through the conducting layer, and the electrical resistivity of the conducting layer is smaller than the electrical resistivity of the first electrodes and the electrical resistivity of the first segments of the wirings.

Owner:KUNSHAN GO VISIONOX OPTO ELECTRONICS CO LTD

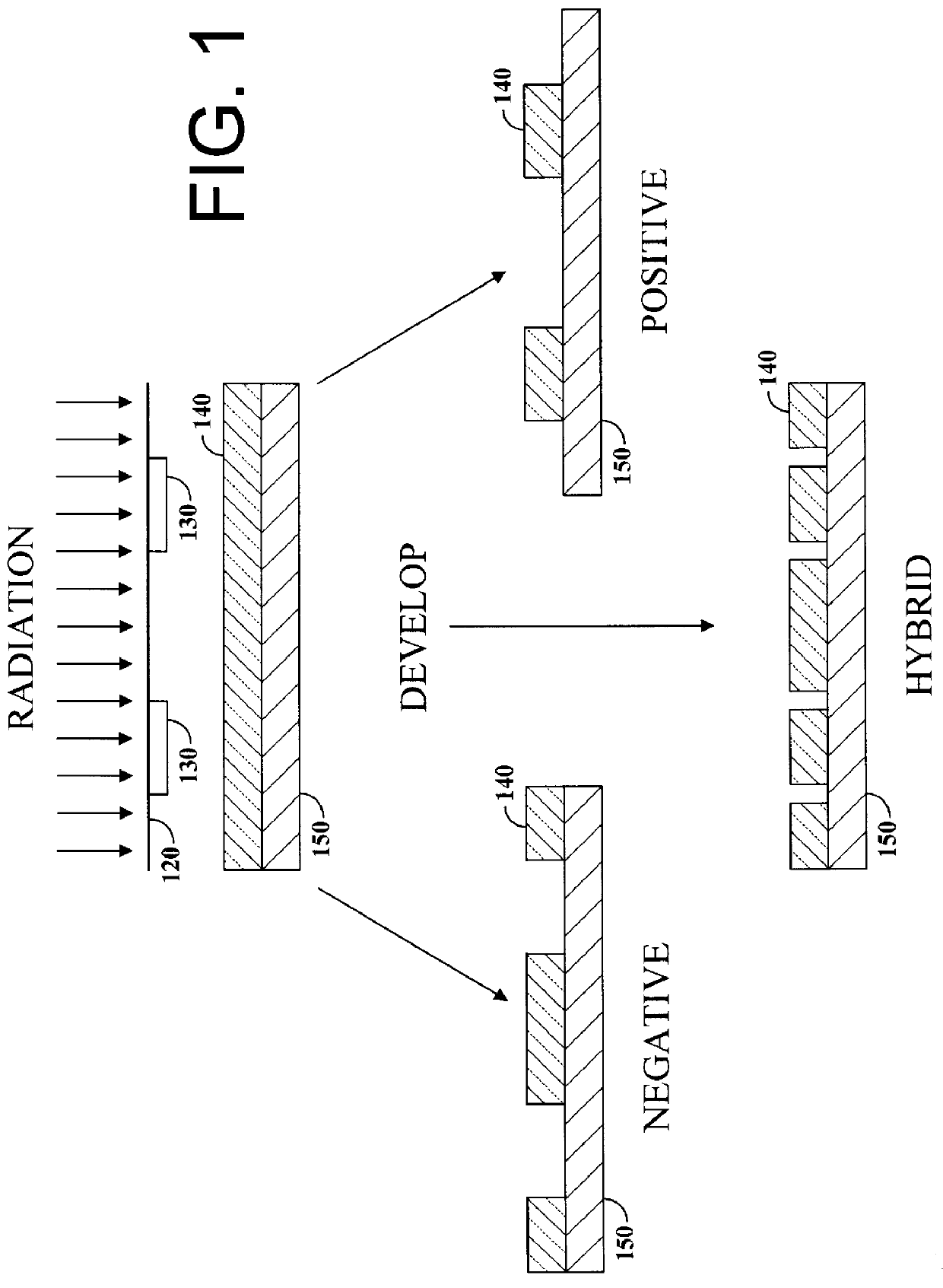

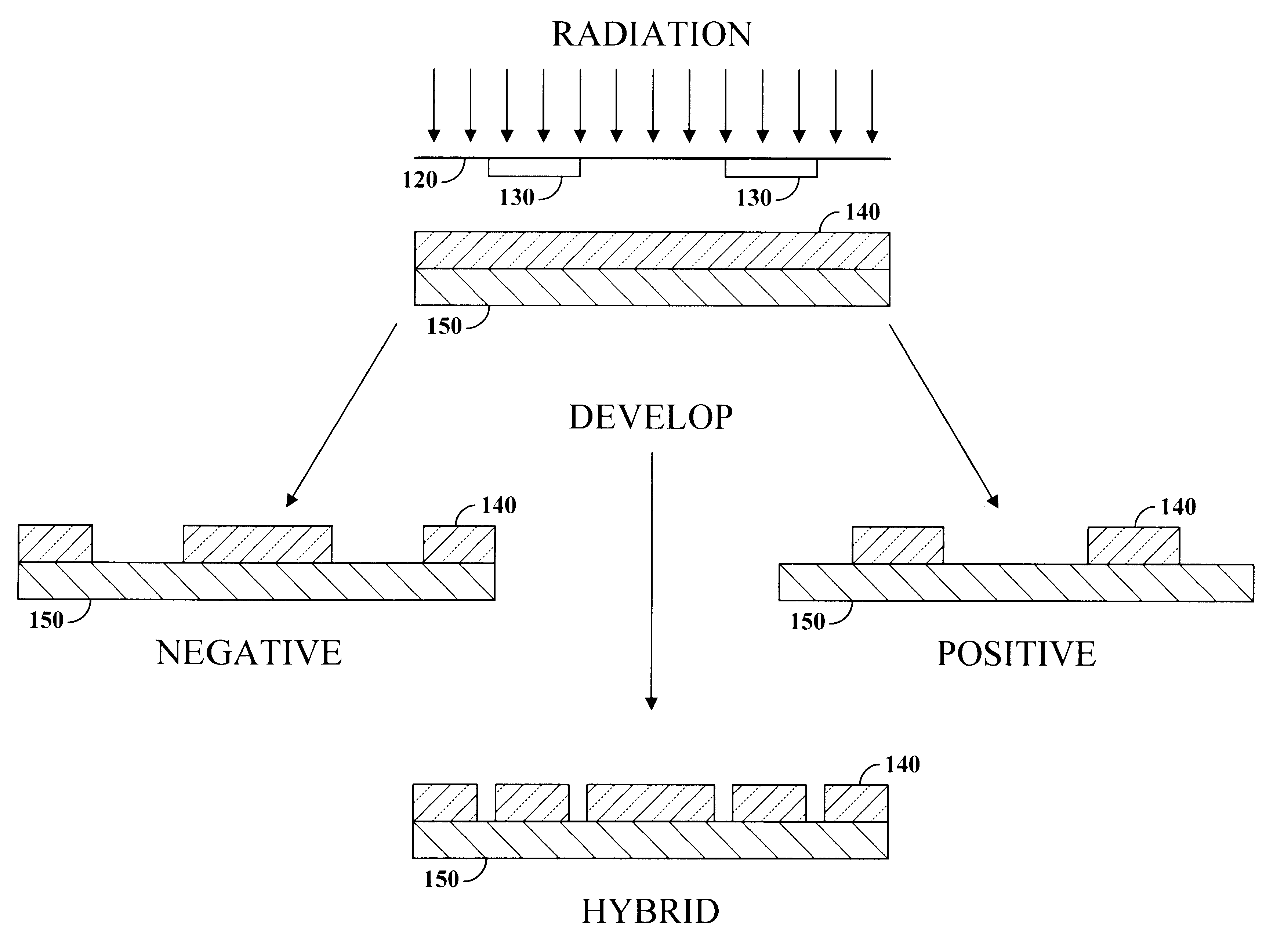

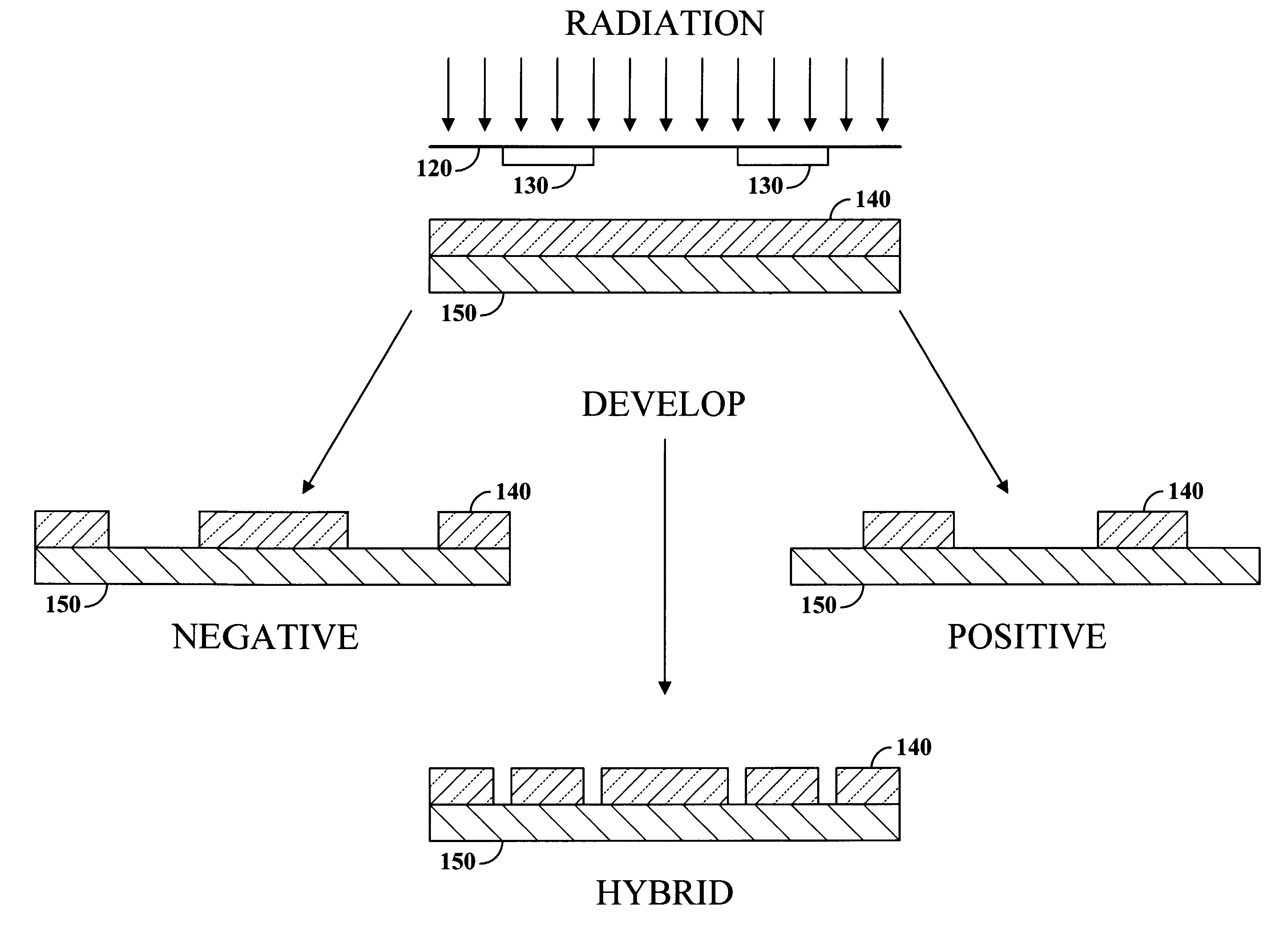

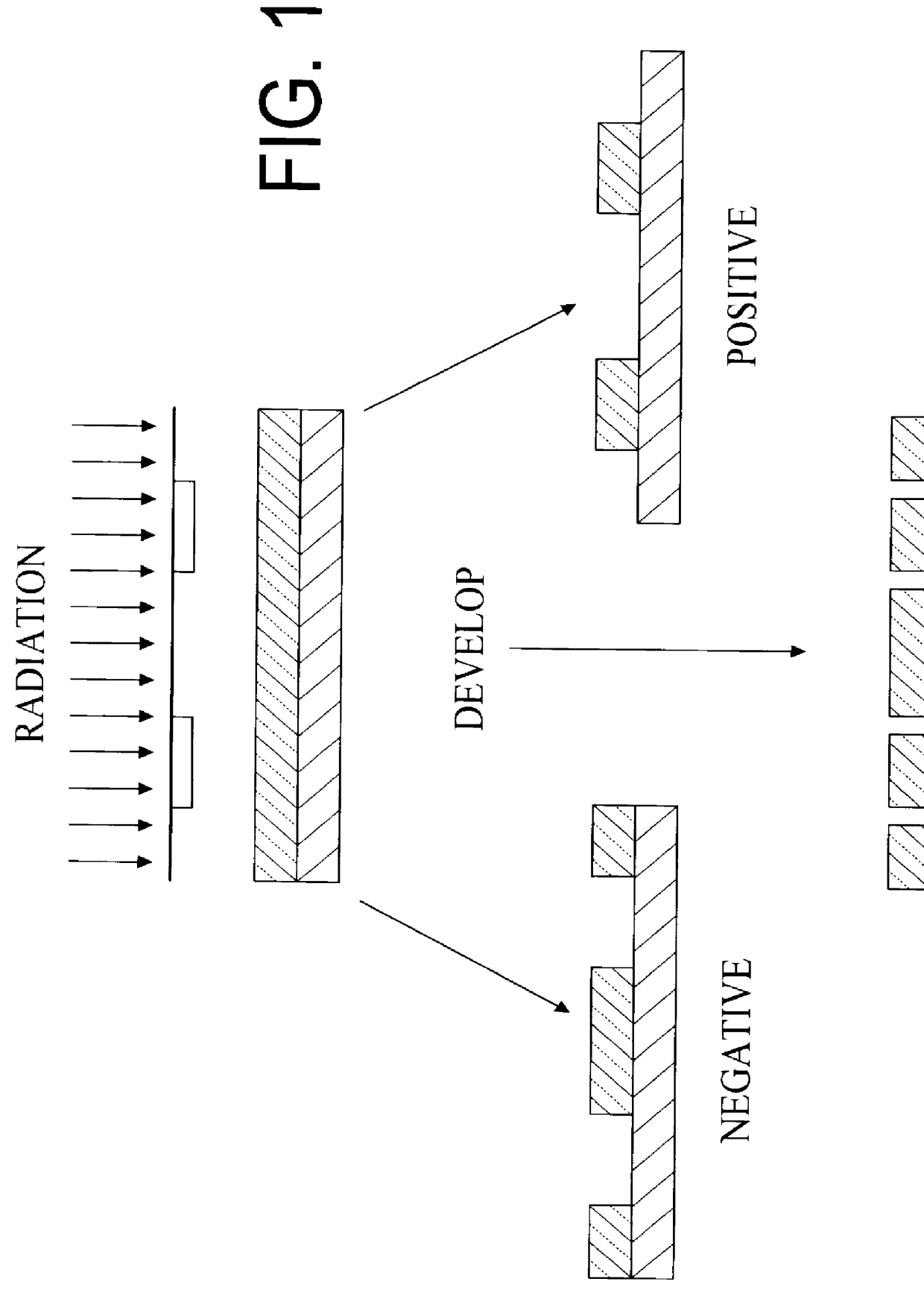

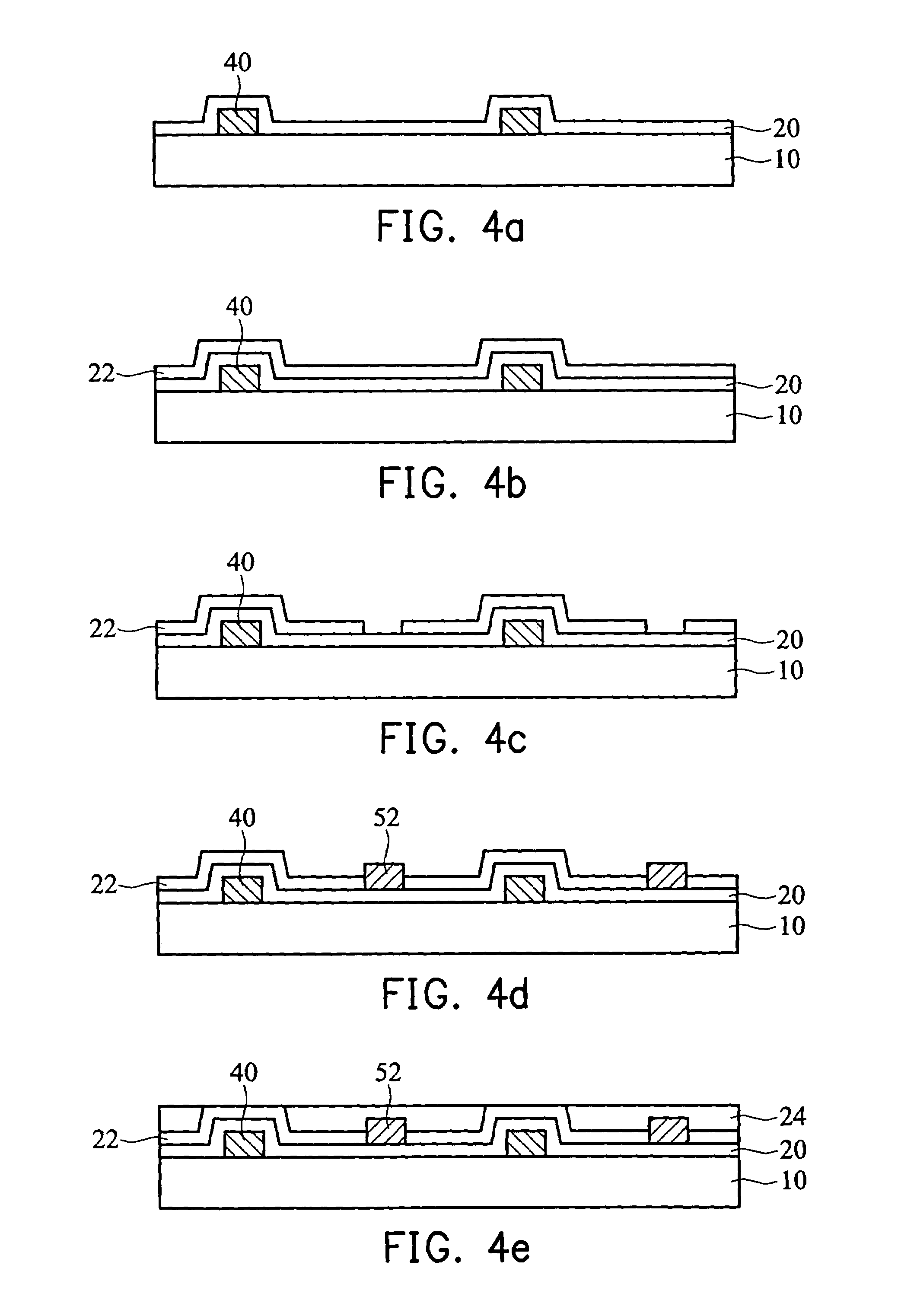

Method of photolithographically defining three regions with one mask step and self aligned isolation structure formed thereby

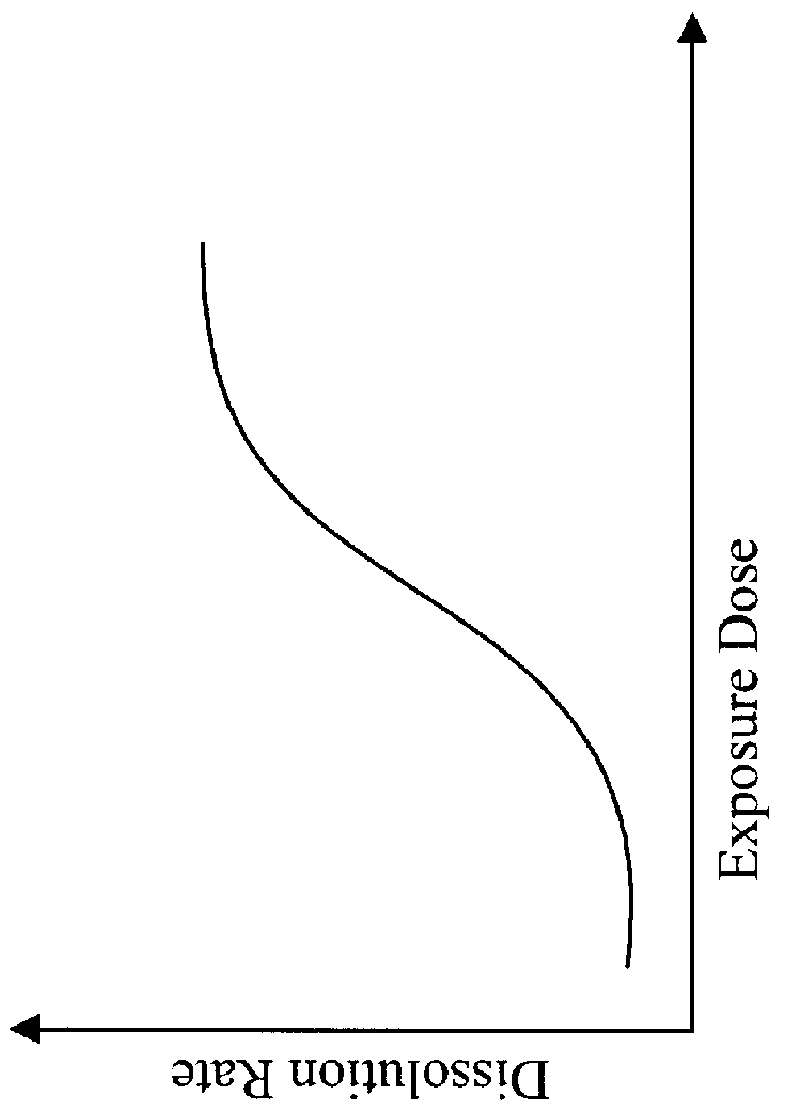

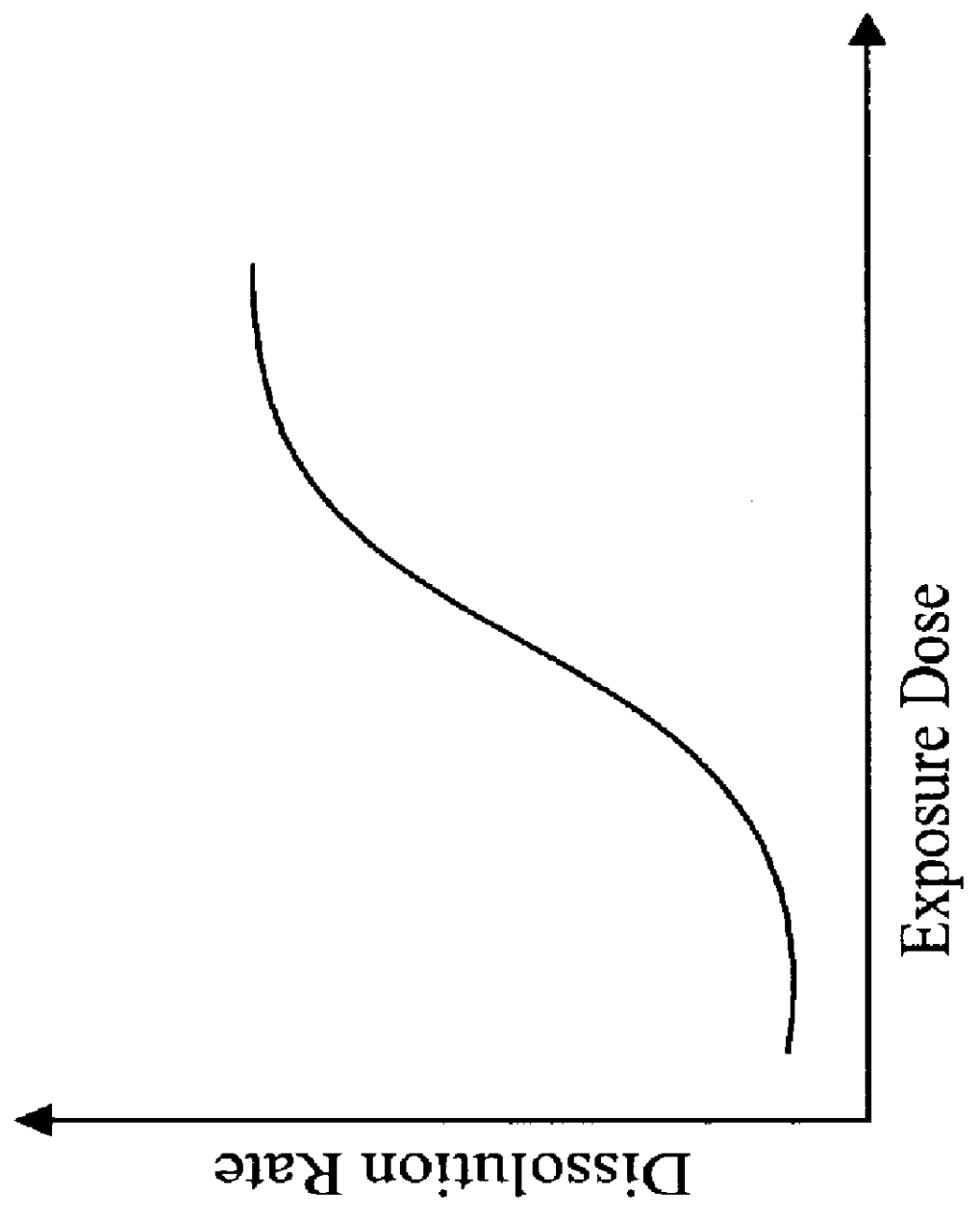

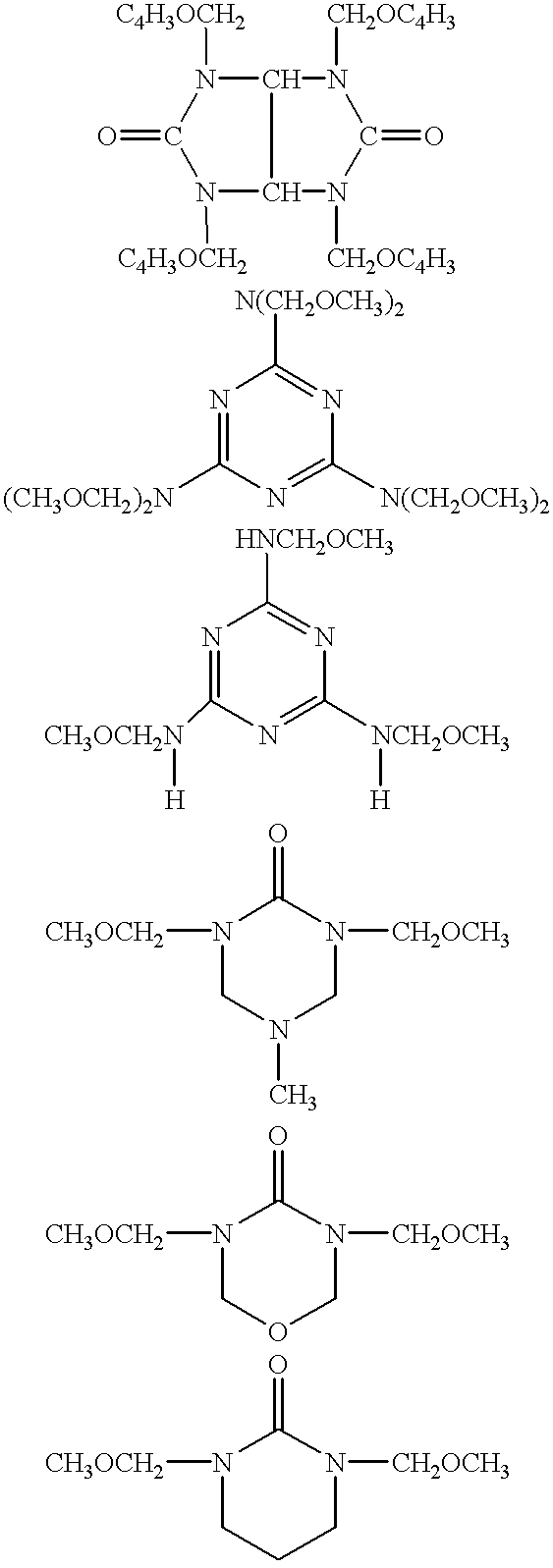

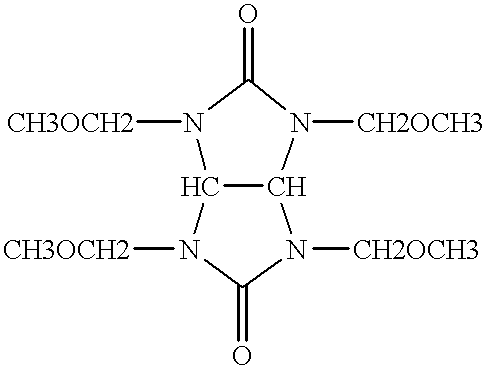

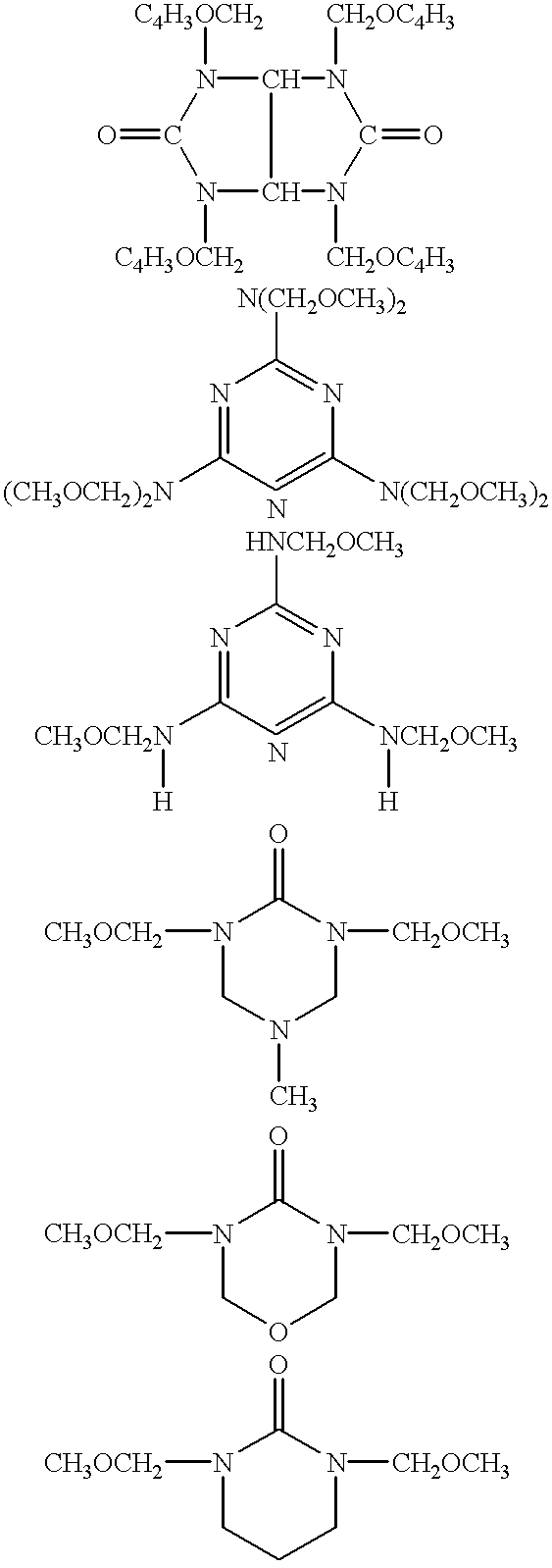

InactiveUS6147394APositive toneMaintaining focusSemiconductor/solid-state device detailsSolid-state devicesResistCross-link

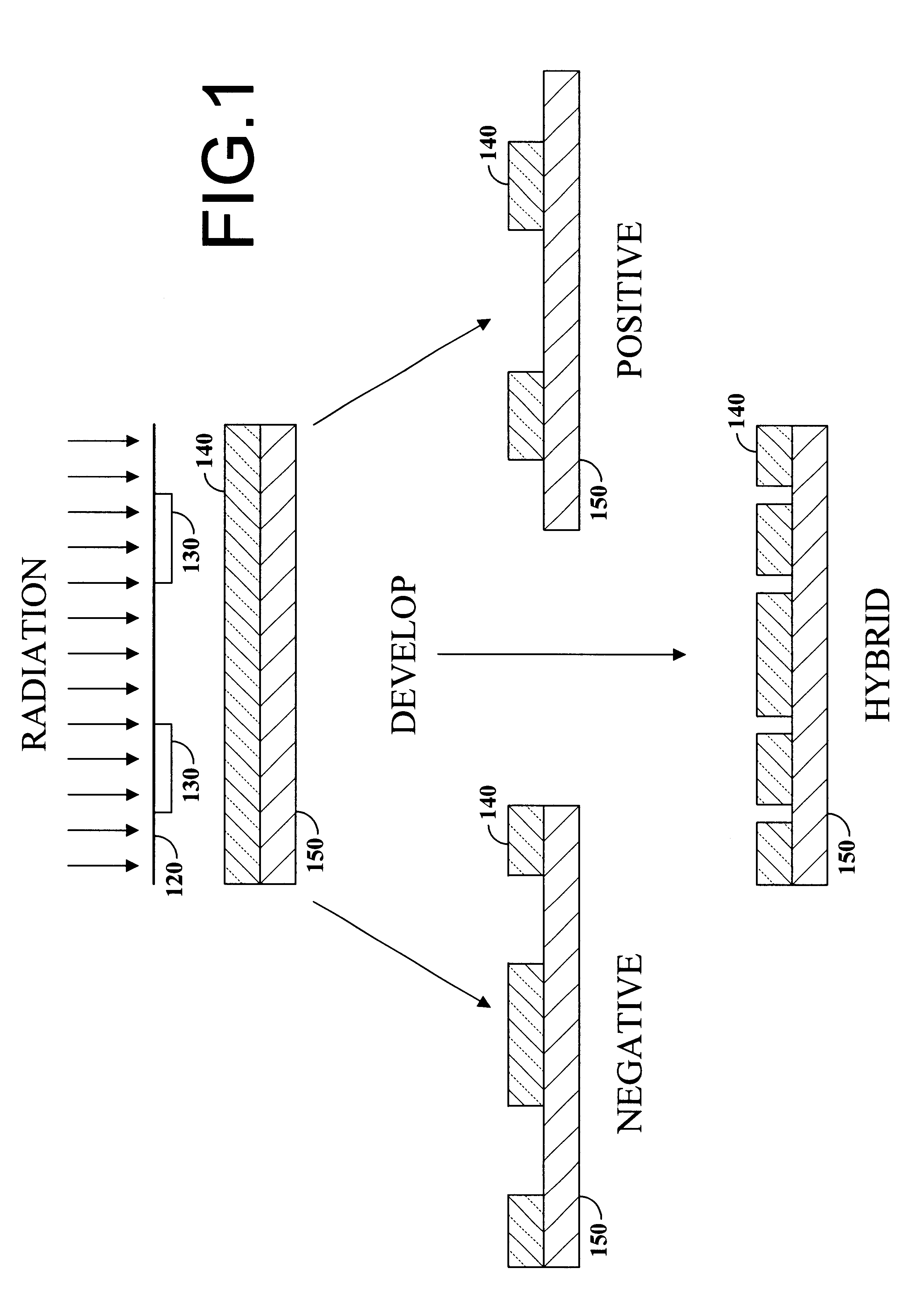

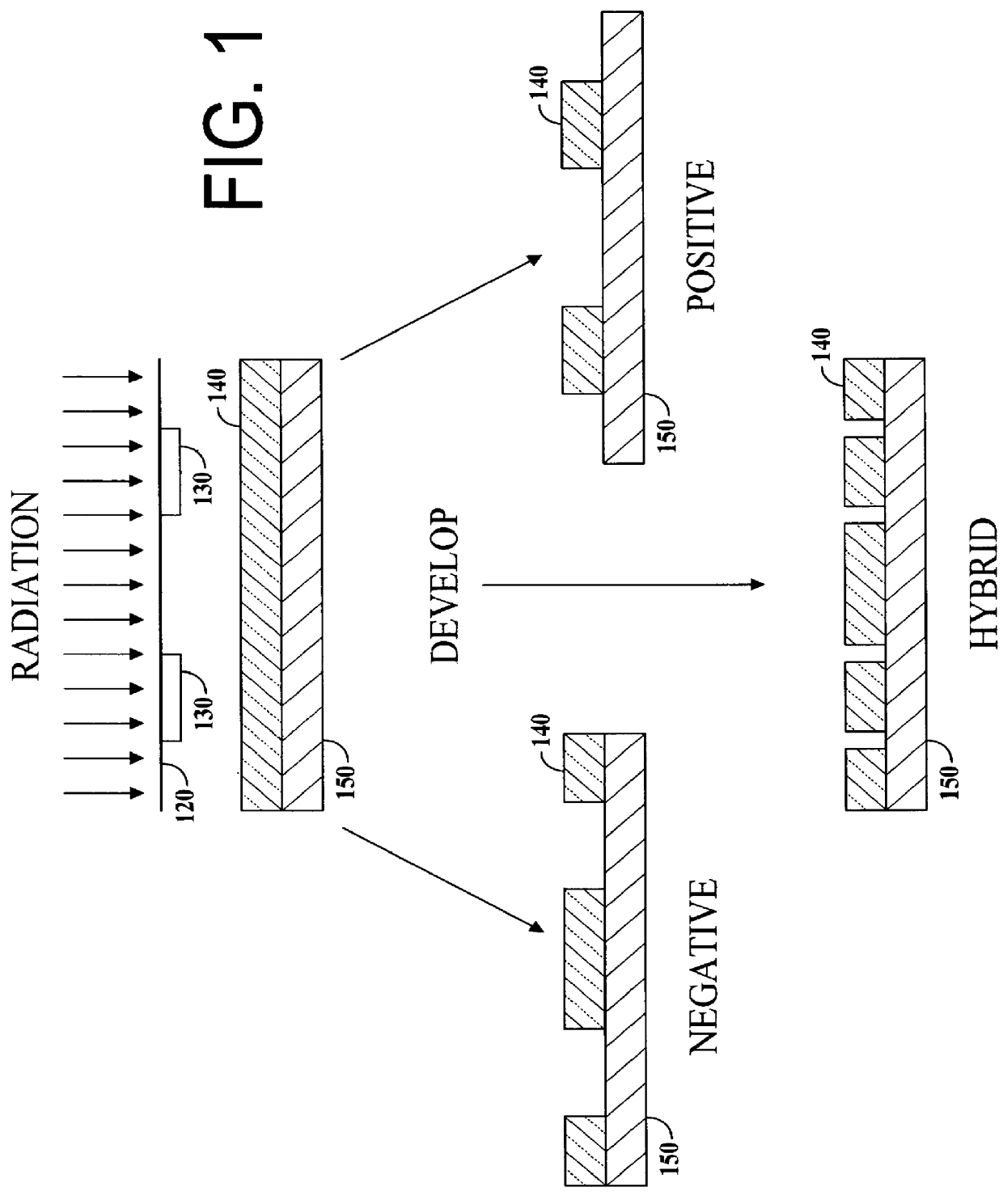

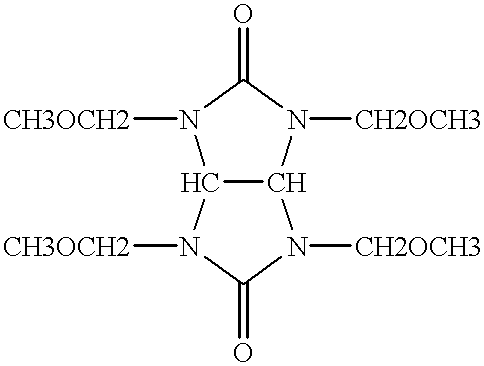

The preferred embodiment of the present invention provides a method for defining three regions on a semiconductor substrate using a single masking step. The preferred embodiment uses a photoresist material having, simultaneously, both a positive tone and a negative tone response to exposure. This combination of materials can provide a new type of resist, which we call a hybrid resist. The hybrid resist comprises a positive tone component which acts at a first actinic energy level and a negative tone component which acts at a second actinic energy level, with the first and second actinic energy levels being separated by an intermediate range of actinic energy. When hybrid resist is exposed to actinic energy, areas of the resist which are subject to a full exposure cross link to form a negative tone line pattern, areas which are unexposed form remain photoactive and form a positive tone pattern, and areas which are exposed to intermediate amounts of radiation become soluble and wash away during development. This exposes a first region on the mask. By then blanket exposing the hybrid resist, the positive tone patterns become soluble and will wash away during development. This exposes a second region on the mask, with the third region still be covered by the hybrid resist. Thus, the preferred embodiment is able to define three regions using a single masking step, with no chance for overlay errors.

Owner:IBM CORP

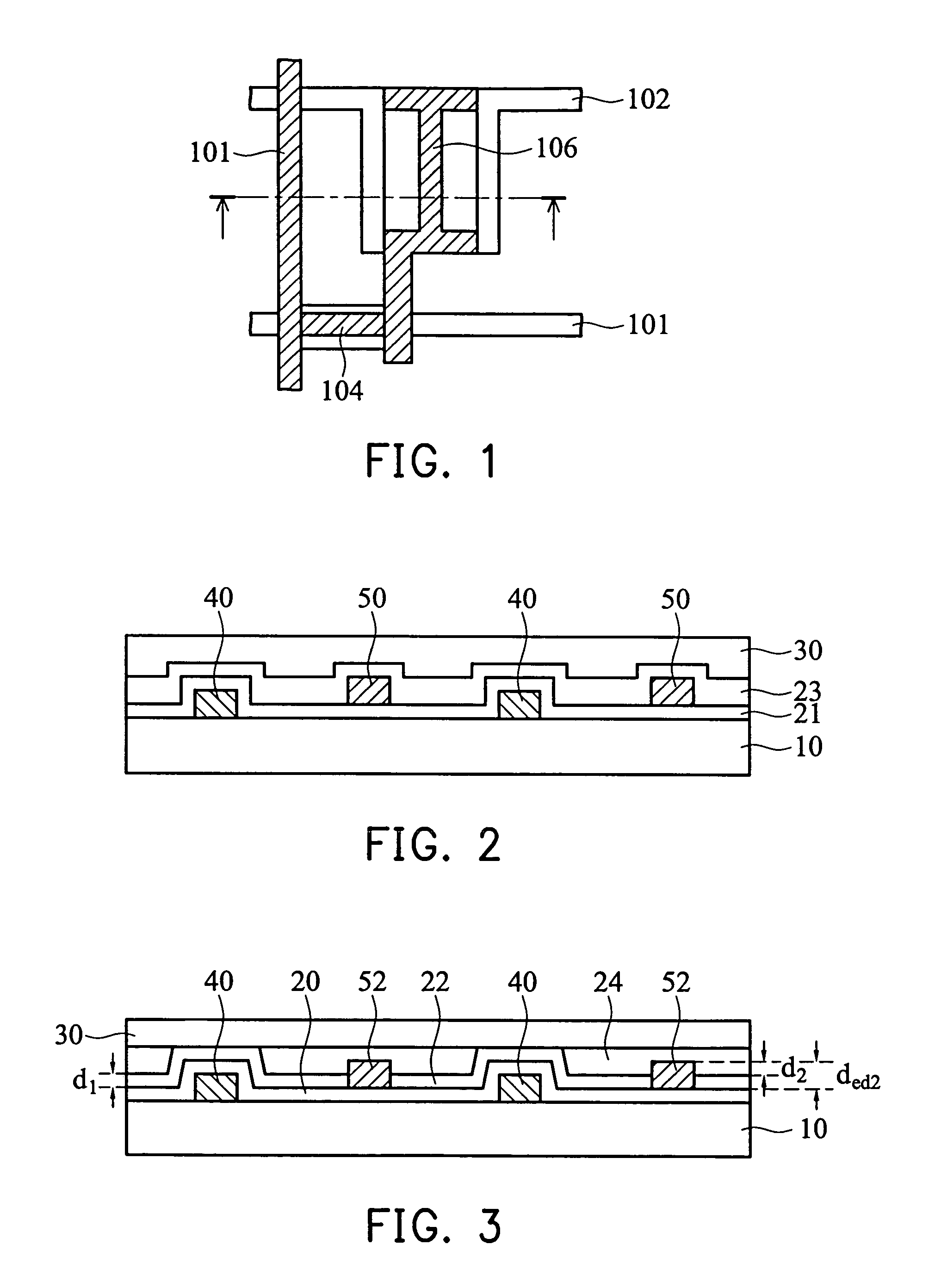

ESD protection structure with implants under trench isolation structures

InactiveUS6218704B1Improve robustnessReduce gradientTransistorThyristorResistElectrostatic discharge

The preferred embodiment of the present invention overcomes the limitations of the prior art and provides a device and method to increase the robustness of electrostatic discharge (ESD) protection devices by reducing the temperature gradient caused by ESD pulses and reducing the likelihood of thermal runaway caused by large ESD pulses. The preferred embodiment forms implants under the trench isolation structures in the ESD devices. The implants reduce the current-caused heating that can lead to thermal runaway, and thus improve the robustness of the ESD protection device. In the preferred embodiment, the implants are formed using hybrid resist. The hybrid resist provides a method to form that implants that does not require additional masking steps or other excessive processing. Additionally, the hybrid resist provides implants that are self aligned with the well regions.

Owner:IBM CORP

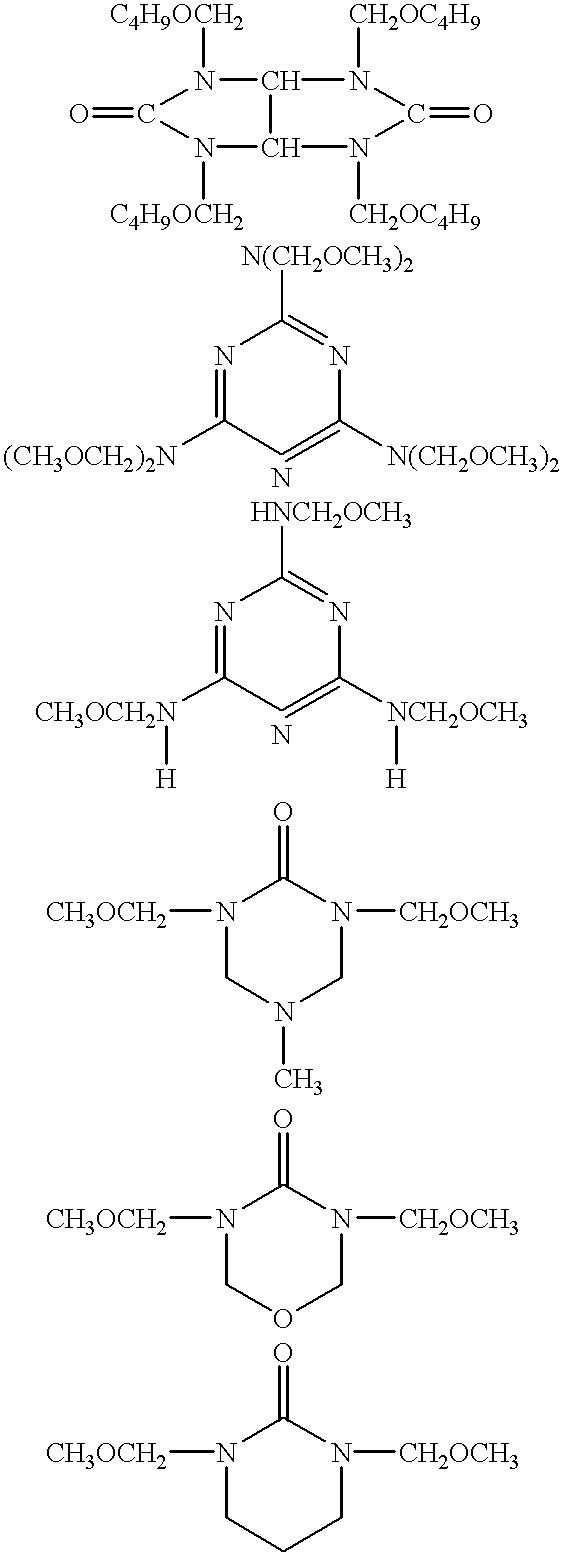

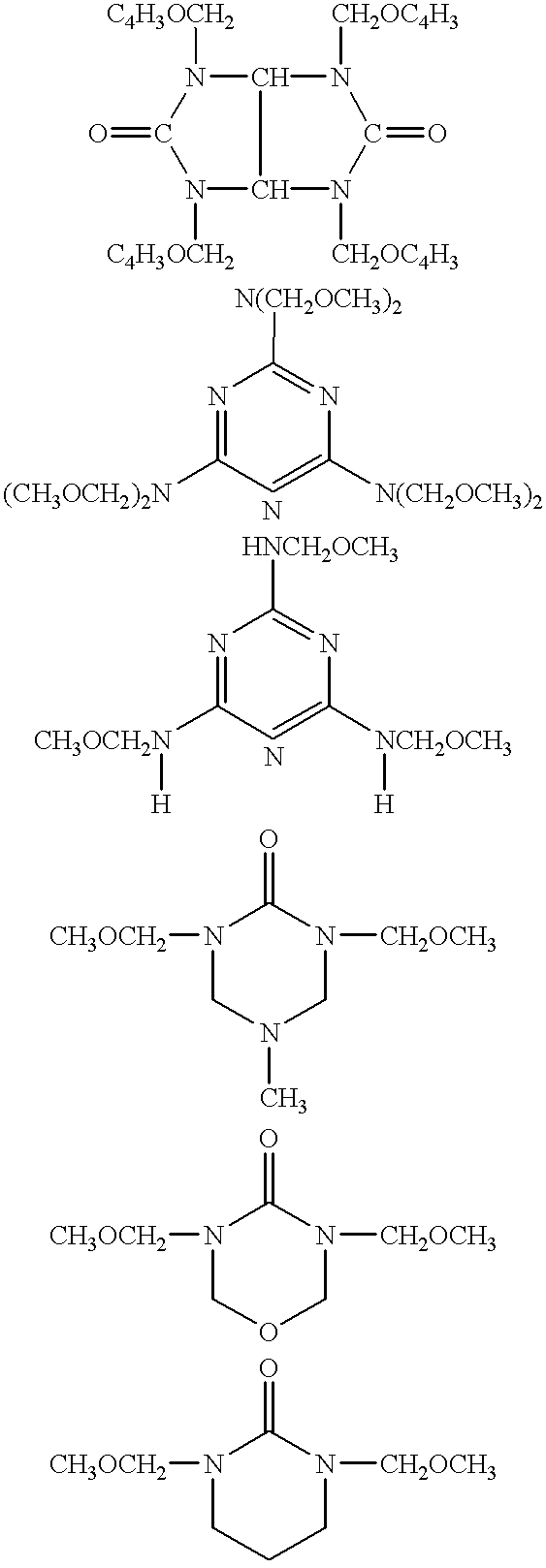

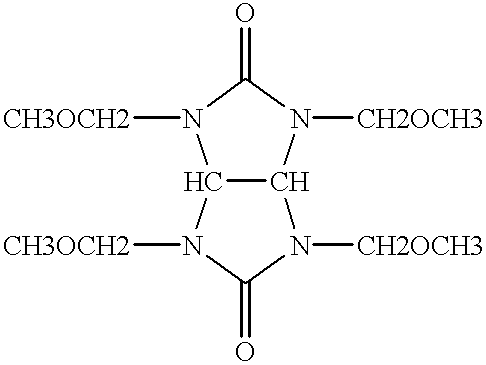

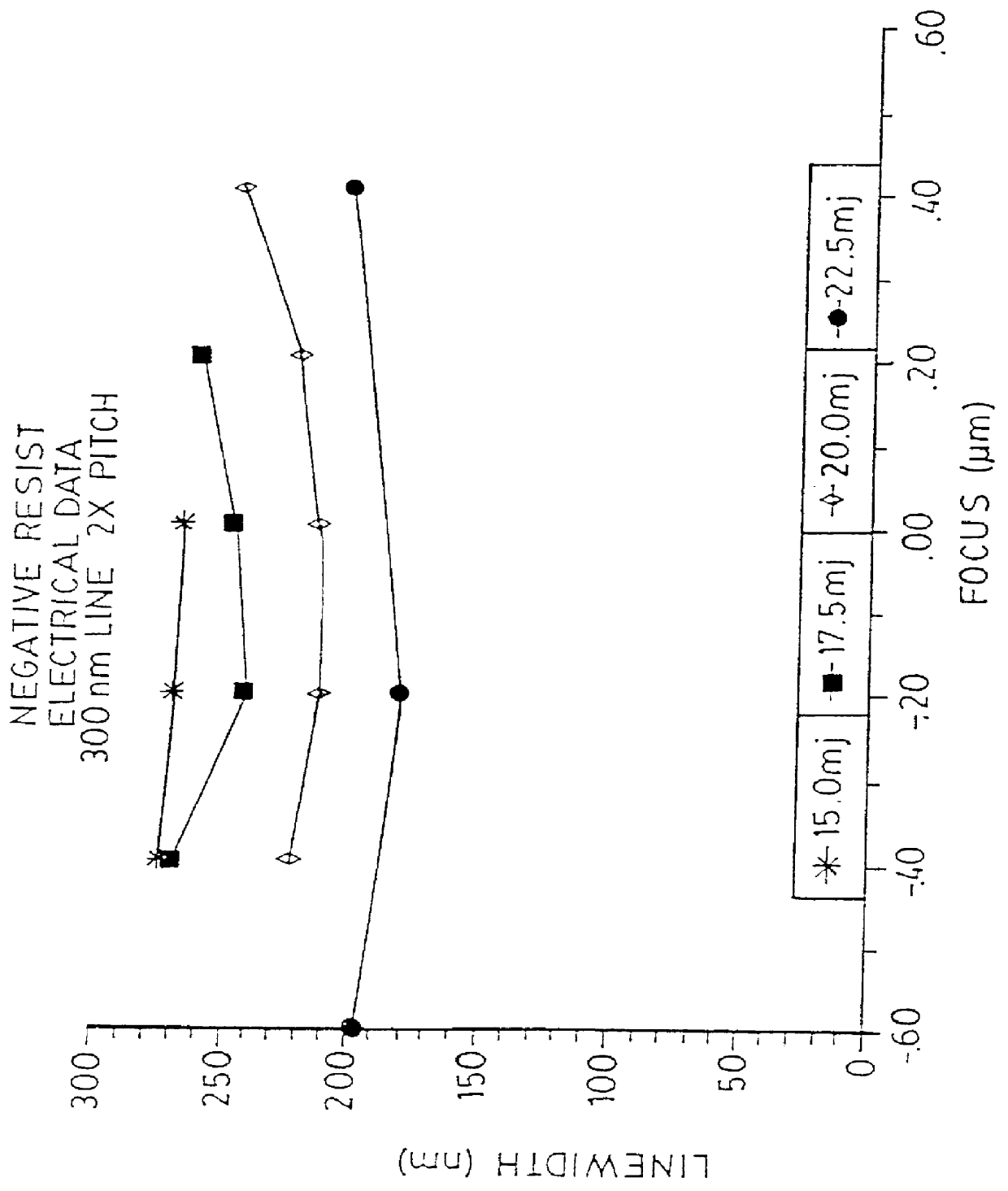

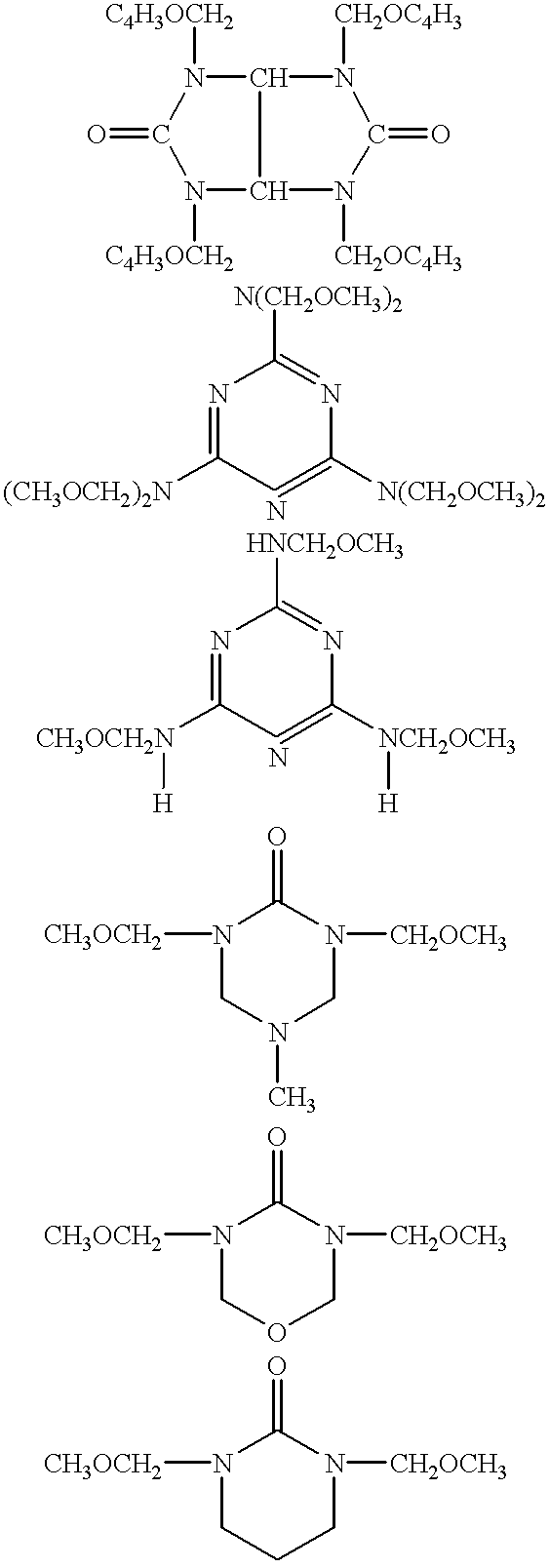

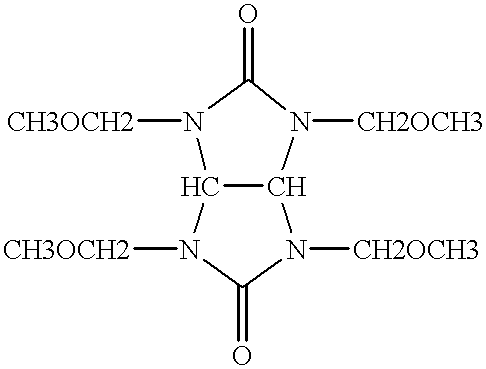

Optimization of space width for hybrid photoresist

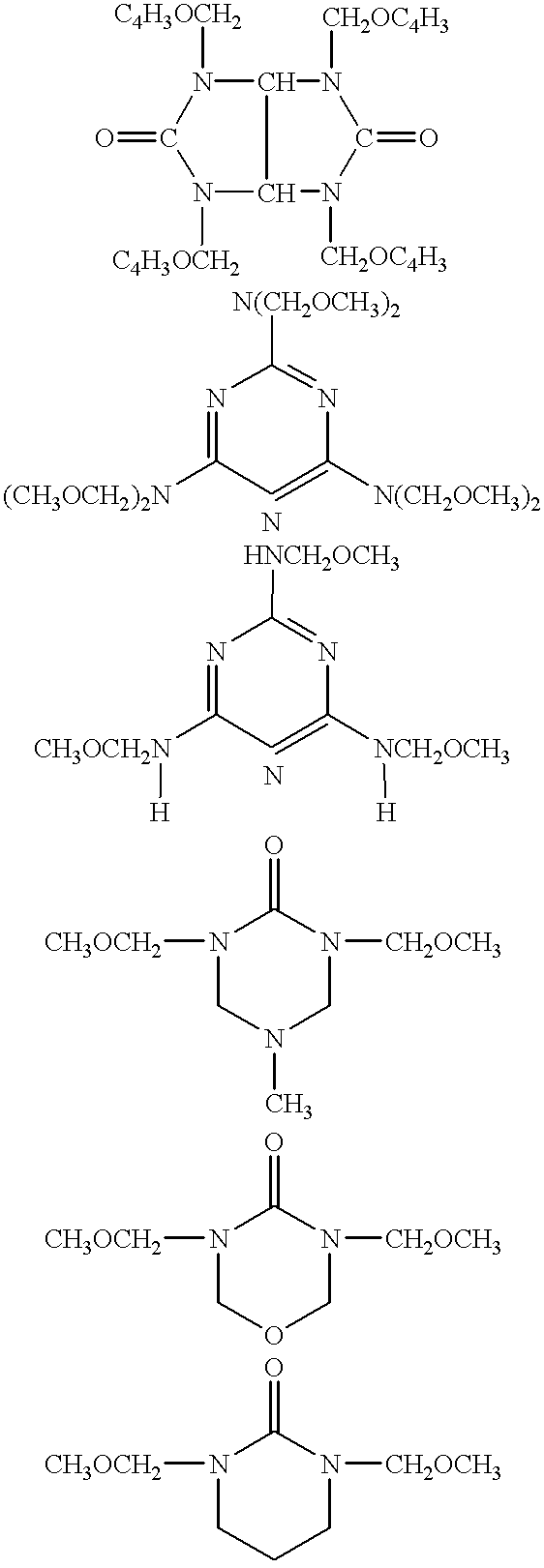

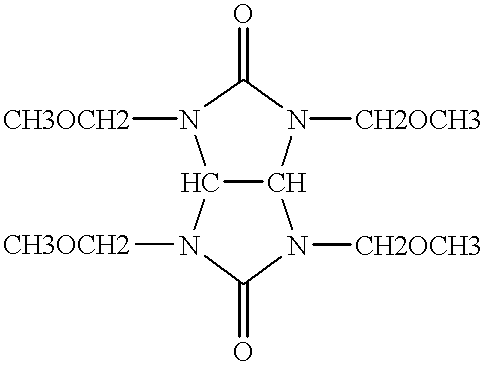

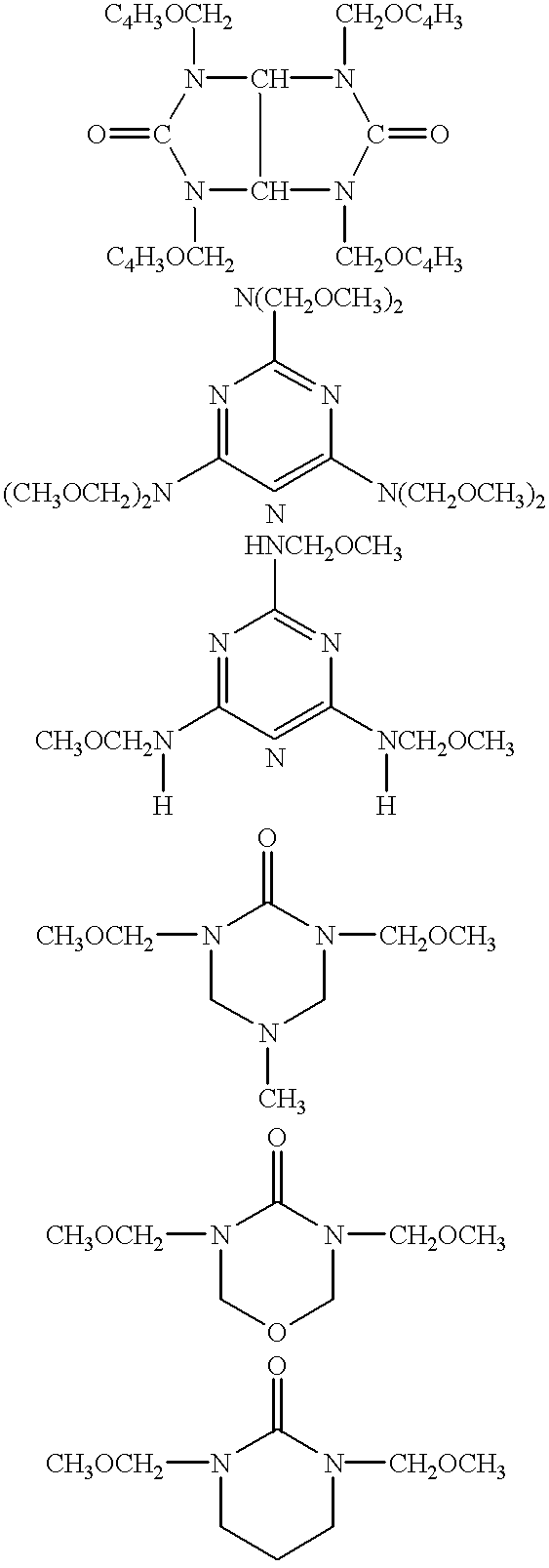

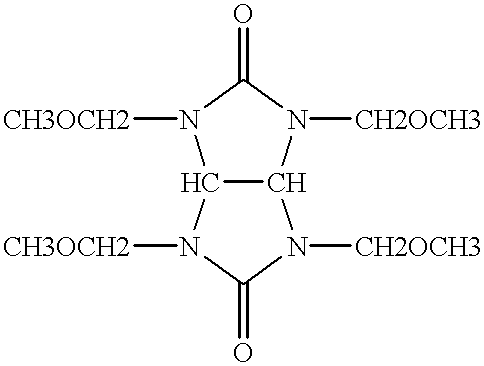

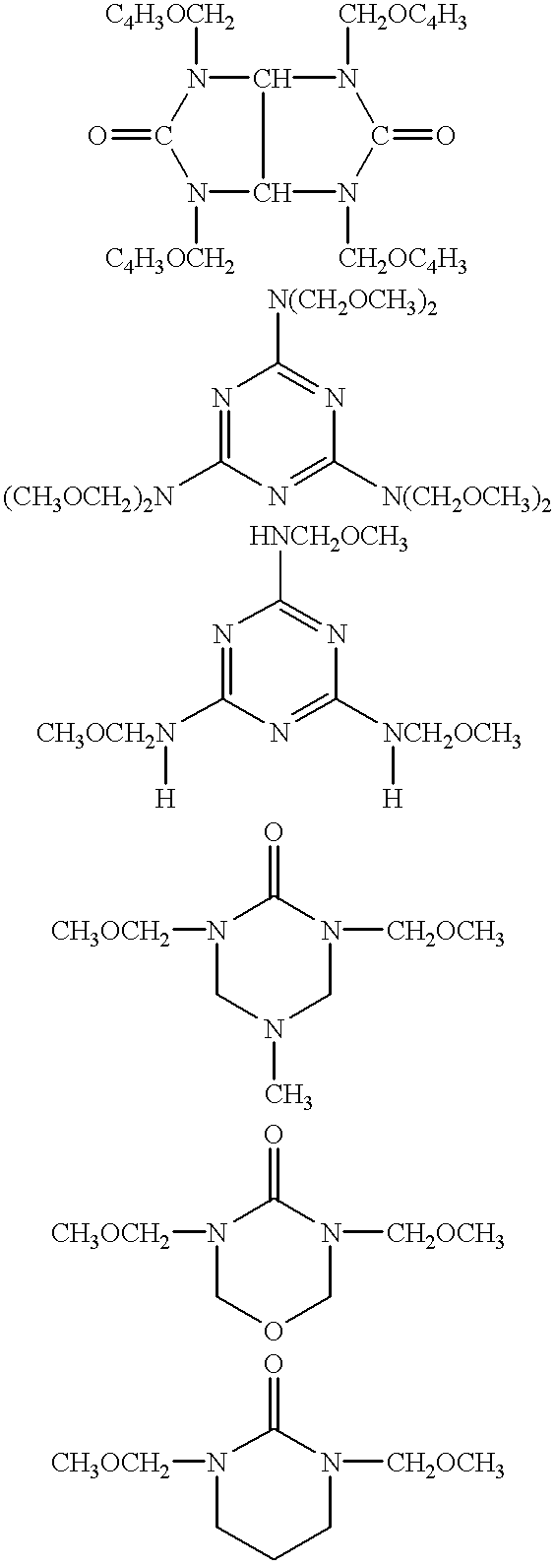

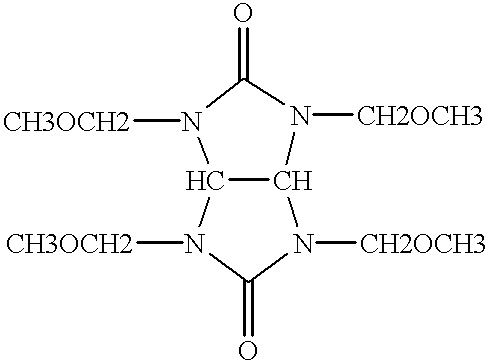

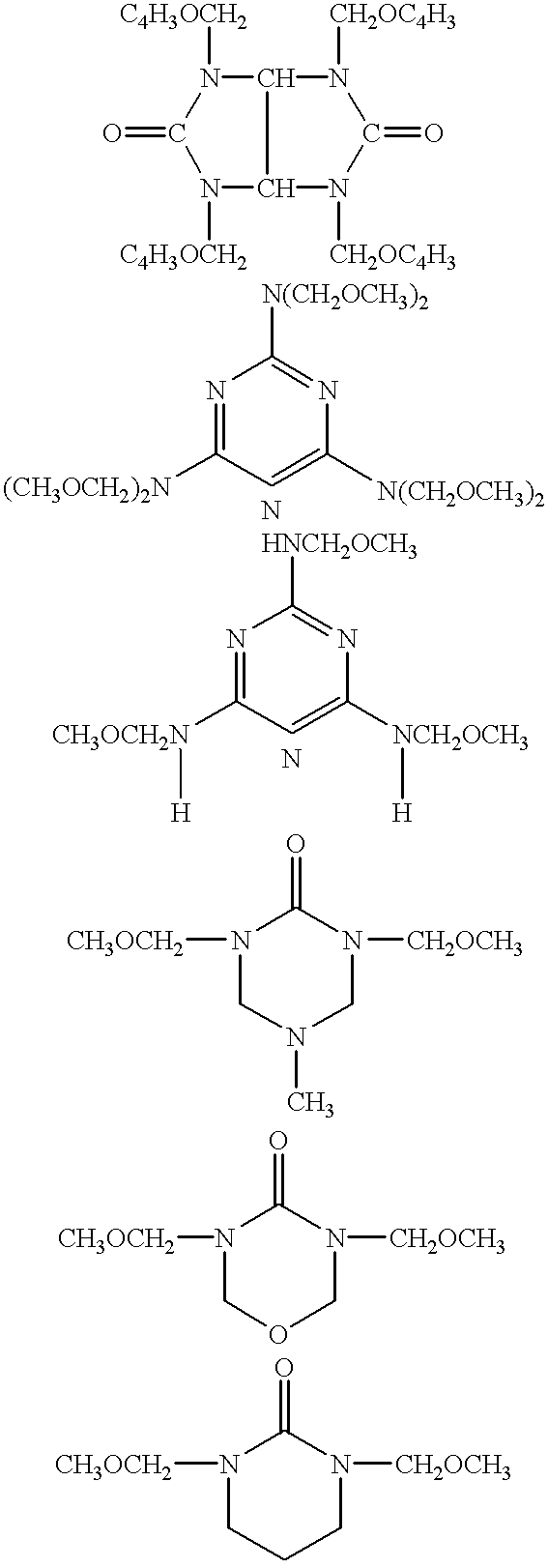

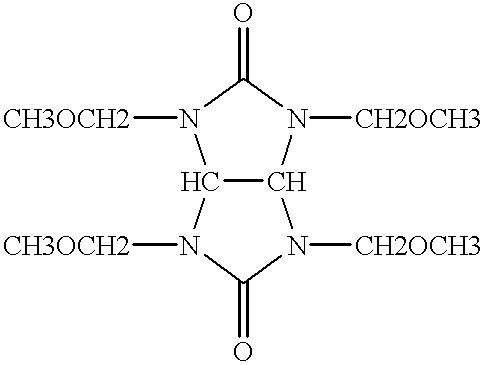

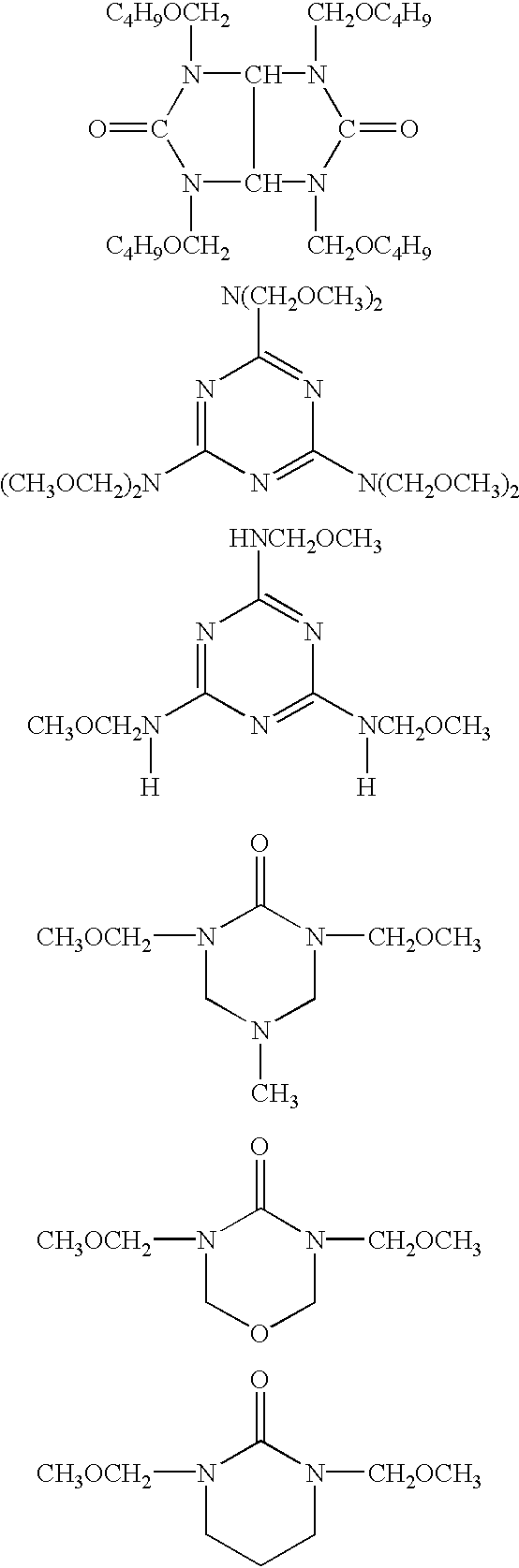

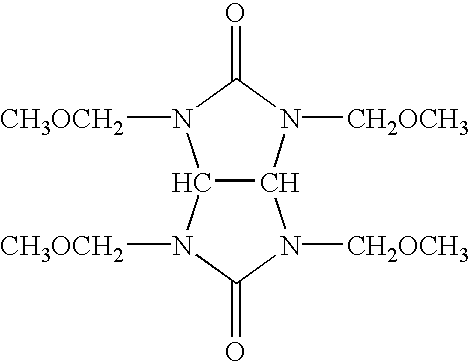

InactiveUS6200726B1Optimizing space widthHigh densityPhotosensitive materialsRadiation applicationsResistStrong acids

A photo resist composition contains at least one photoacid generator (PAG), wherein at least two photoacids are produced upon exposure of the photo resist to actinic energy and wherein the photo resist is capable of producing a hybrid response. The function of providing generation of two photoacids in a hybrid resist is to optimize the use of hybrid resist by varying the hybrid space width. The at least two photoacids may differ in their effectiveness at catalyzing at least one mechanism of the hybrid response. In particular, one photoacid may be a weaker acid and another may be a stronger acid, wherein there exists a difference of at least four orders of magnitude between the acid dissociation constant (Ka) of the weaker acid and the stronger acid. A method for optimizing space width in a hybrid photo resist includes the steps of: 1) selecting a desired space width; 2) selecting at least one photoacid generator (PAG), wherein at least two photoacids will be produced upon exposure to actinic energy in relative proportions sufficient to produce the desired space width in the hybrid photo resist; and 3) forming a hybrid photo resist composition comprising the at least one PAG. The step of selecting at least one PAG may include first determining the space width produced alone by each photoacid in a group of candidate photoacids and then selecting the photoacids and corresponding at least one PAG that will produce the desired space width.

Owner:IBM CORP

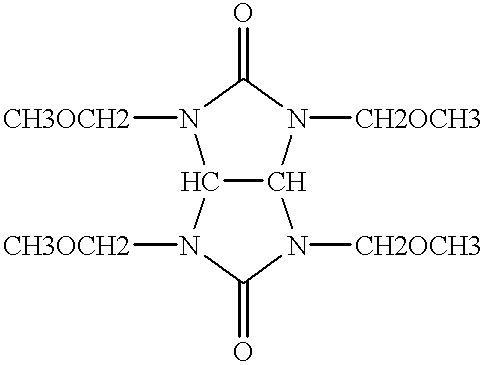

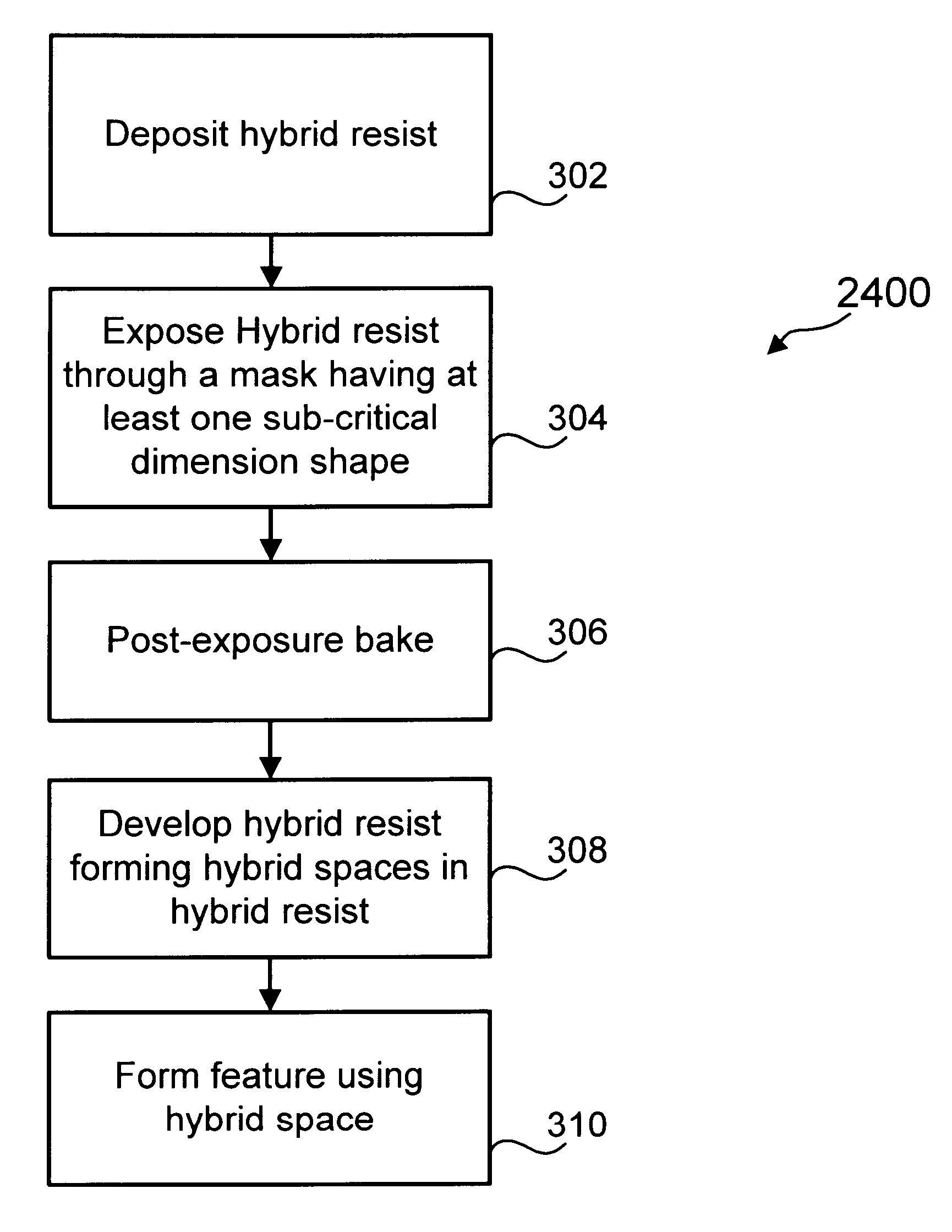

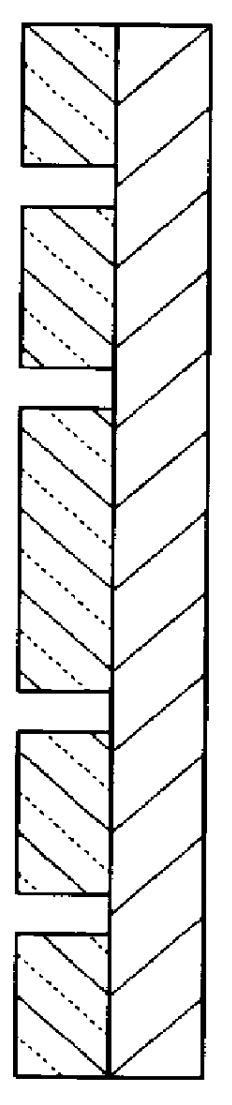

Fused hybrid resist shapes as a means of modulating hybrid resist space width

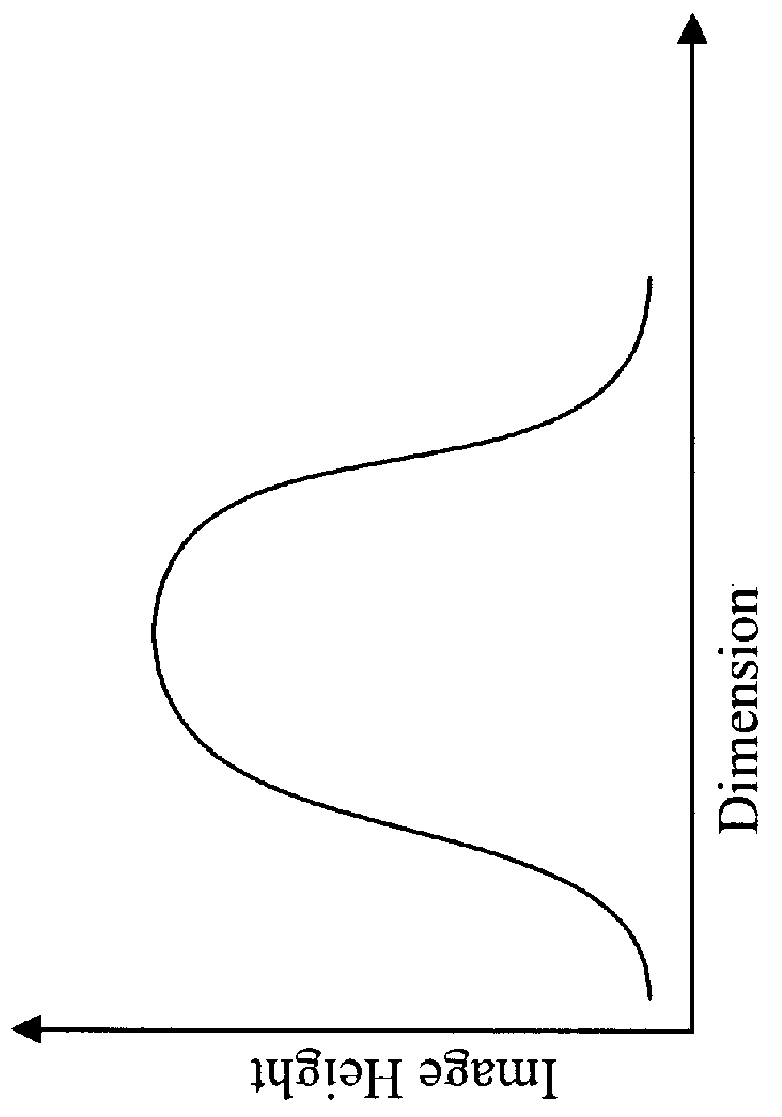

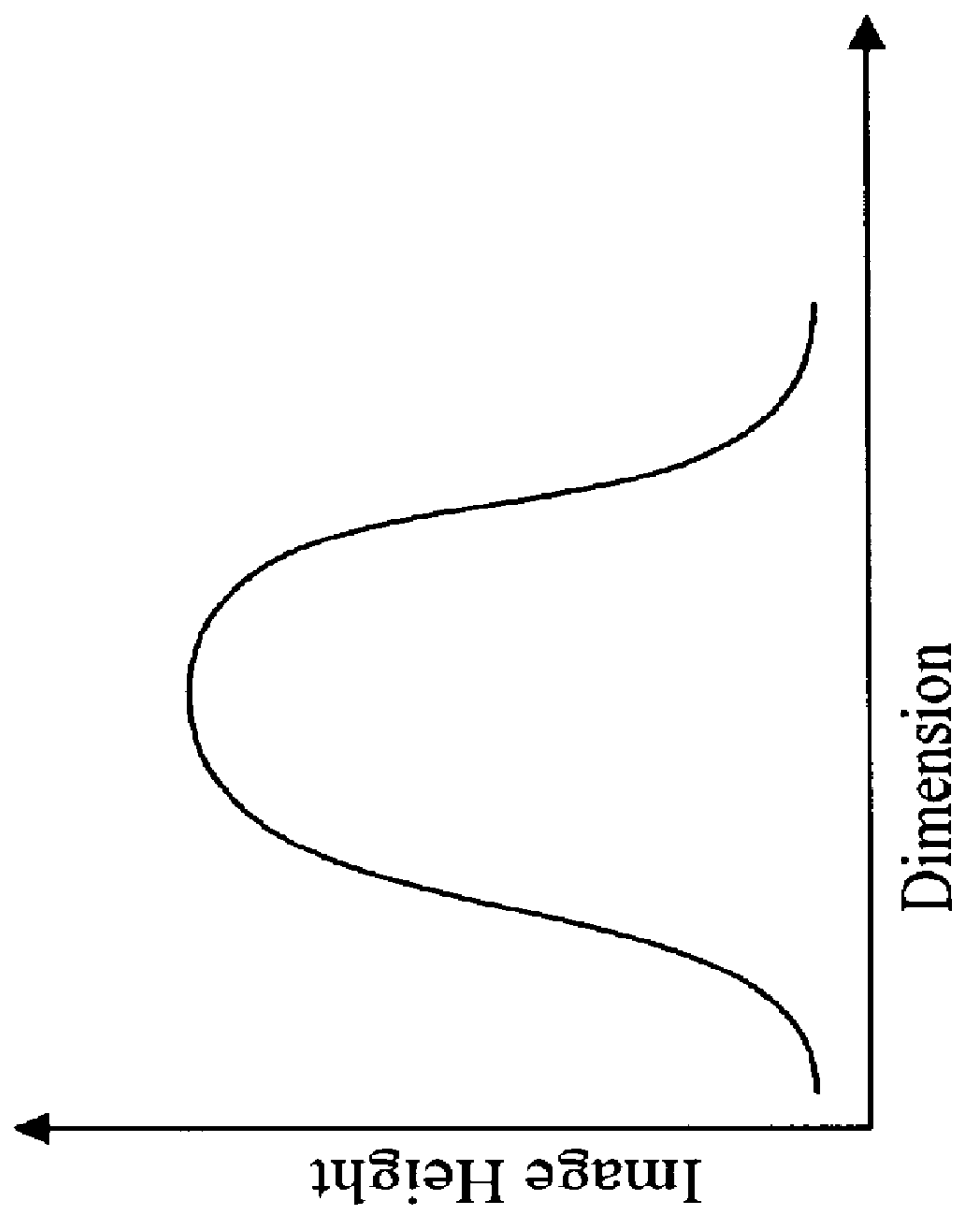

InactiveUS6184041B1Positive toneNegative responsePhoto-taking processesSemiconductor/solid-state device manufacturingDiffraction effectResist

The preferred embodiment of the present invention overcomes the limitations of the prior art and provides a method to form spaces in hybrid resist with varying widths. In particular, the preferred method facilitates the formation of spaces with different widths by using mask shapes (either openings or lines) that are smaller than the diffraction limit of the photolithography tool. Diffraction effects at these dimensions reduce the light intensity reaching the resist surface such that the hybrid resist receives an intermediate exposure. These portions of hybrid resist that receive an intermediate exposure are soluble in developer and thus develop away to form spaces in the hybrid resist. Thus, spaces in the hybrid resist of varying widths can be formed.

Owner:IBM CORP

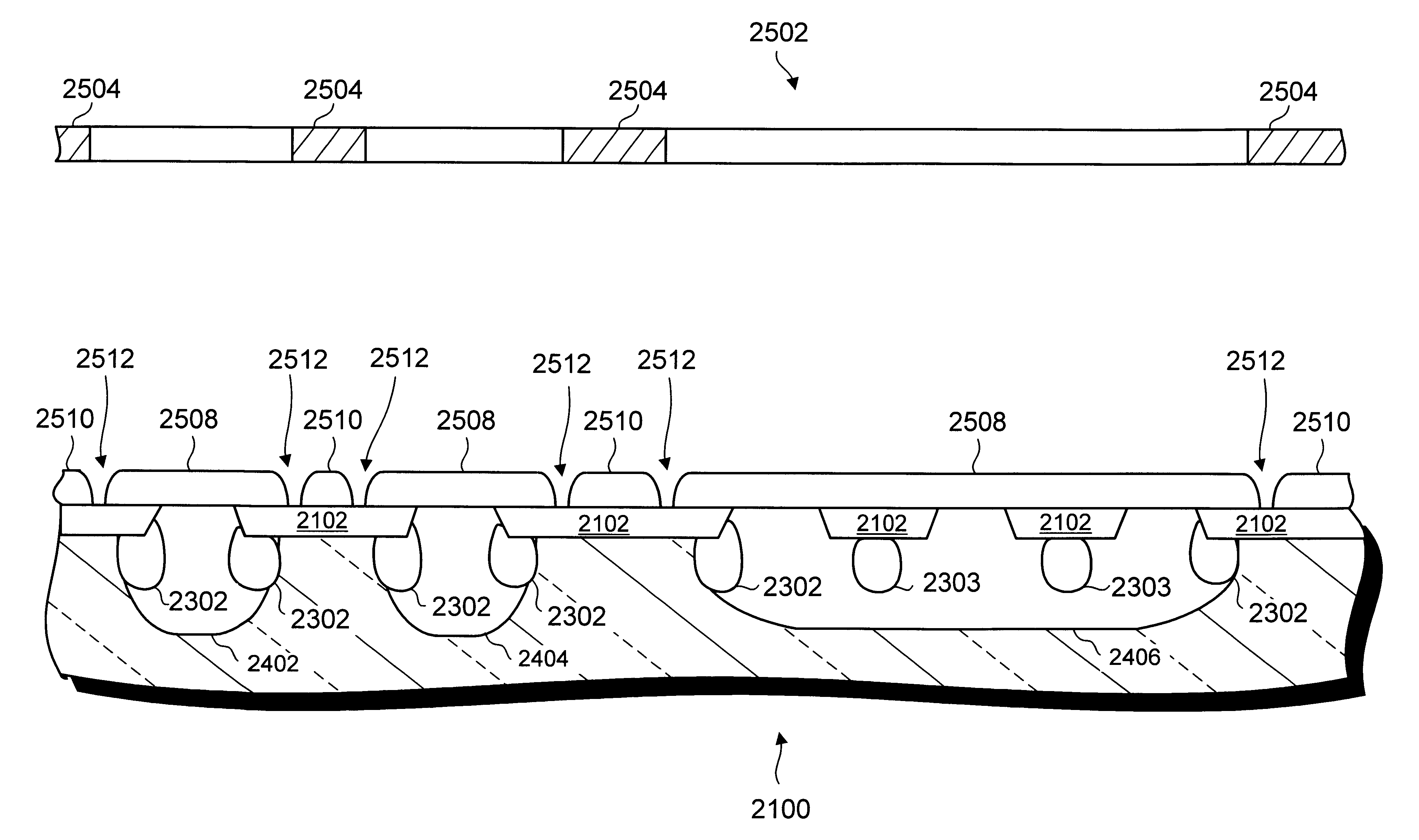

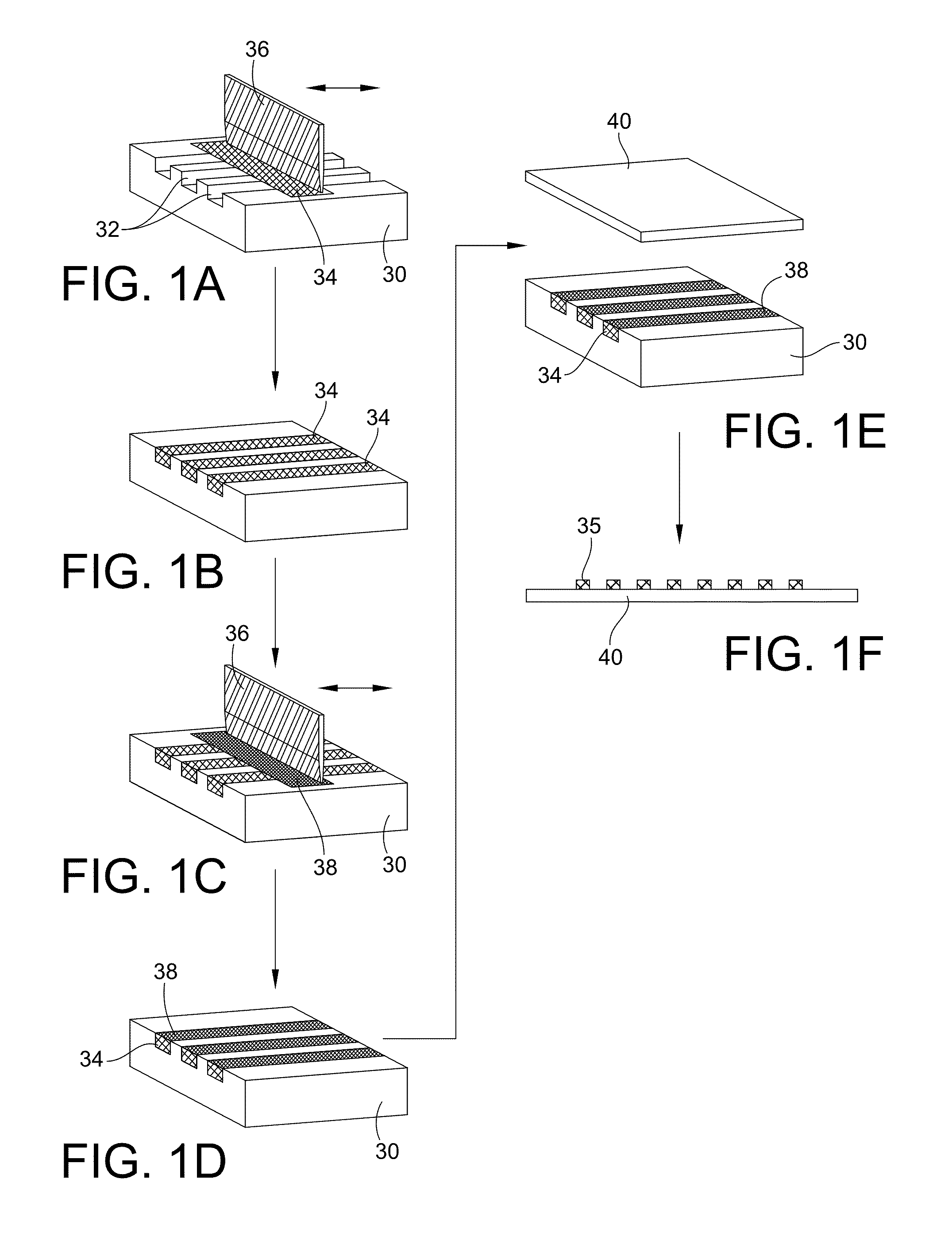

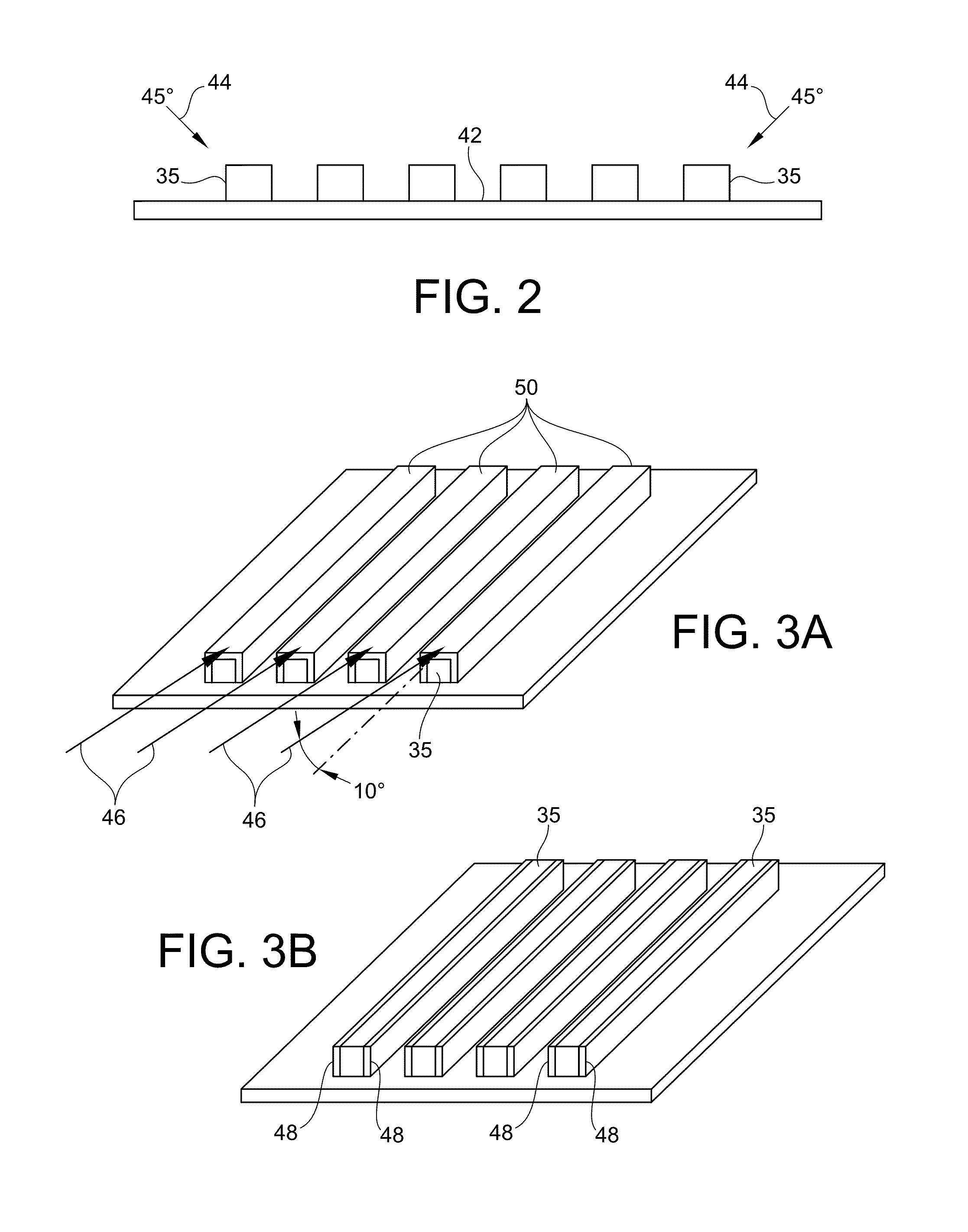

Nanoscale High-Aspect-Ratio Metallic Structure and Method of Manufacturing Same

InactiveUS20120031487A1Improve performanceOvercome problemsMaterial nanotechnologySolid-state devicesMetal formingNanowire

Nanoscale high-aspect-ratio metallic structures and methods are presented. Such structures may form transparent electrode to enhance the performance of solar cells and light-emitting diodes. These structures can be used as infrared control filters because they reflect high amounts of infrared radiation. A grating structure of polymeric bars affixed to a transparent substrate is used. The sides of the bars are coated with metal forming nanowires. Electrodes may be configured to couple to a subset of the rails forming interdigitated electrodes. Encapsulation is used to improve transparency and transparency at high angles. The structure may be inverted to facilitate fabrication of a solar cell or other device on the back-side of the structure. Multiple layered electrodes having an active layer sandwiched between two conductive layers may be used. Layered electro-active layers may be used to form a smart window where the structure is encapsulated between glass to modify the incoming light.

Owner:IOWA STATE UNIV RES FOUND

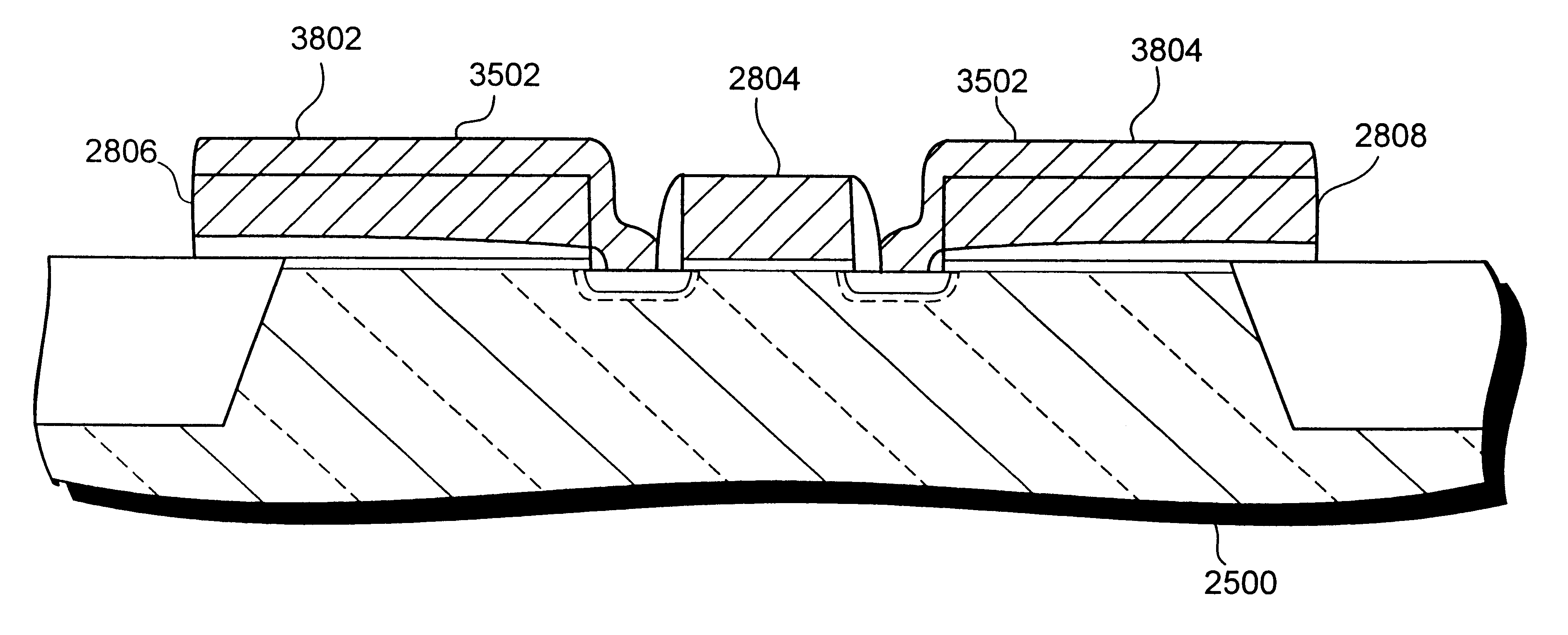

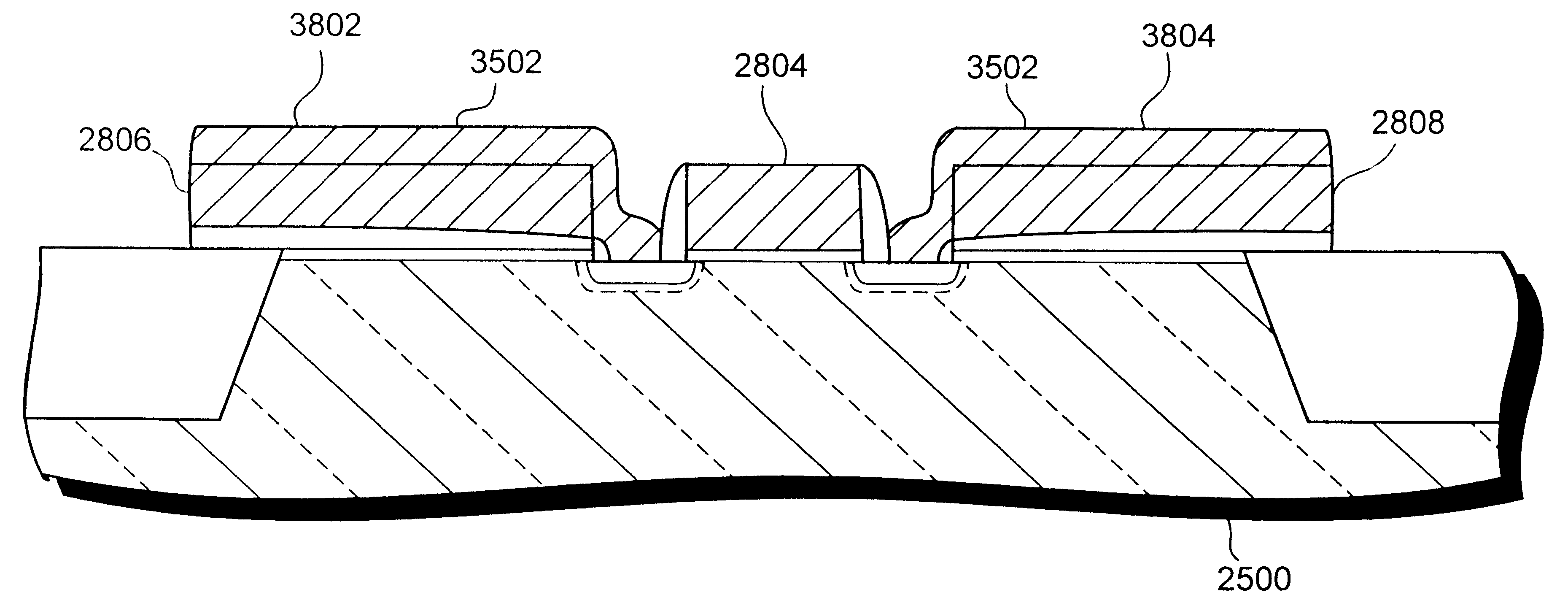

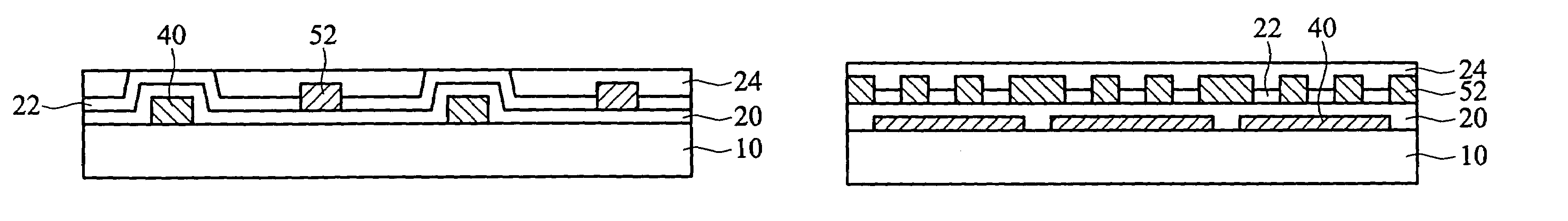

Transistor having raised source and drain

The preferred embodiment of the present invention provides a transistor structure and method for fabricating the same that overcomes the disadvantages of the prior art. In particular, the preferred structure and method results in lower leakage and junction capacitance by using raised source and drains which are partially isolated from the substrate by a dielectric layer. The raised source and drains are preferably fabricated from the same material layer used to form the transistor gate. The preferred method for fabricating the transistor uses hybrid resist to accurately pattern the gate material layer into regions for the gate, the source and the drain. The source and drain regions are then connected to the substrate by growing silicon. The preferred method thus results in an improved transistor structure while not requiring excessive fabrication steps.

Owner:IBM CORP

Method for forming features using self-trimming by selective etch and device formed thereby

InactiveUS6210866B1Reduce solubilityMaintaining focusSolid-state devicesSemiconductor/solid-state device manufacturingResistPattern recognition

The preferred embodiment provides a method for forming unlinked features when using image enhancement techniques. The preferred method is particularly applicable for use in hybrid resist lithographic processes. The method uses a trimming feature embedded in a substrate. The trimming feature acts as a block during a selective etch. This results in unlinked trenches being formed in the substrate. Thus, the preferred method creates unlinked, separate trenches from the "loops" formed by the hybrid resist or other image enhancement techniques. This allows the preferred method to form a plurality of unlinked features rather than the loops or linked features without requiring additional processing steps.

Owner:IBM CORP

Nanoscale High-Aspect-Ratio Metallic Structure and Method of Manufacturing Same

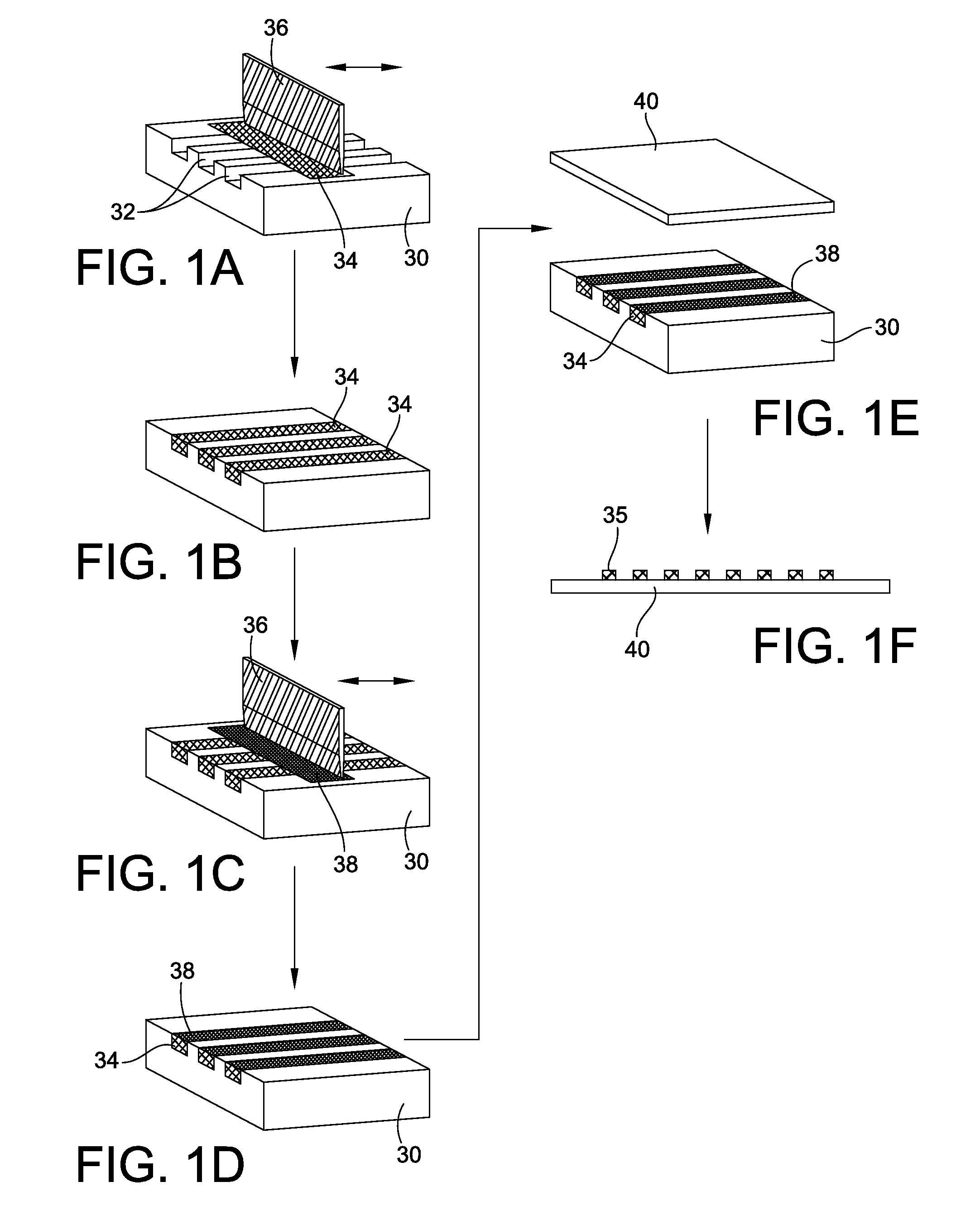

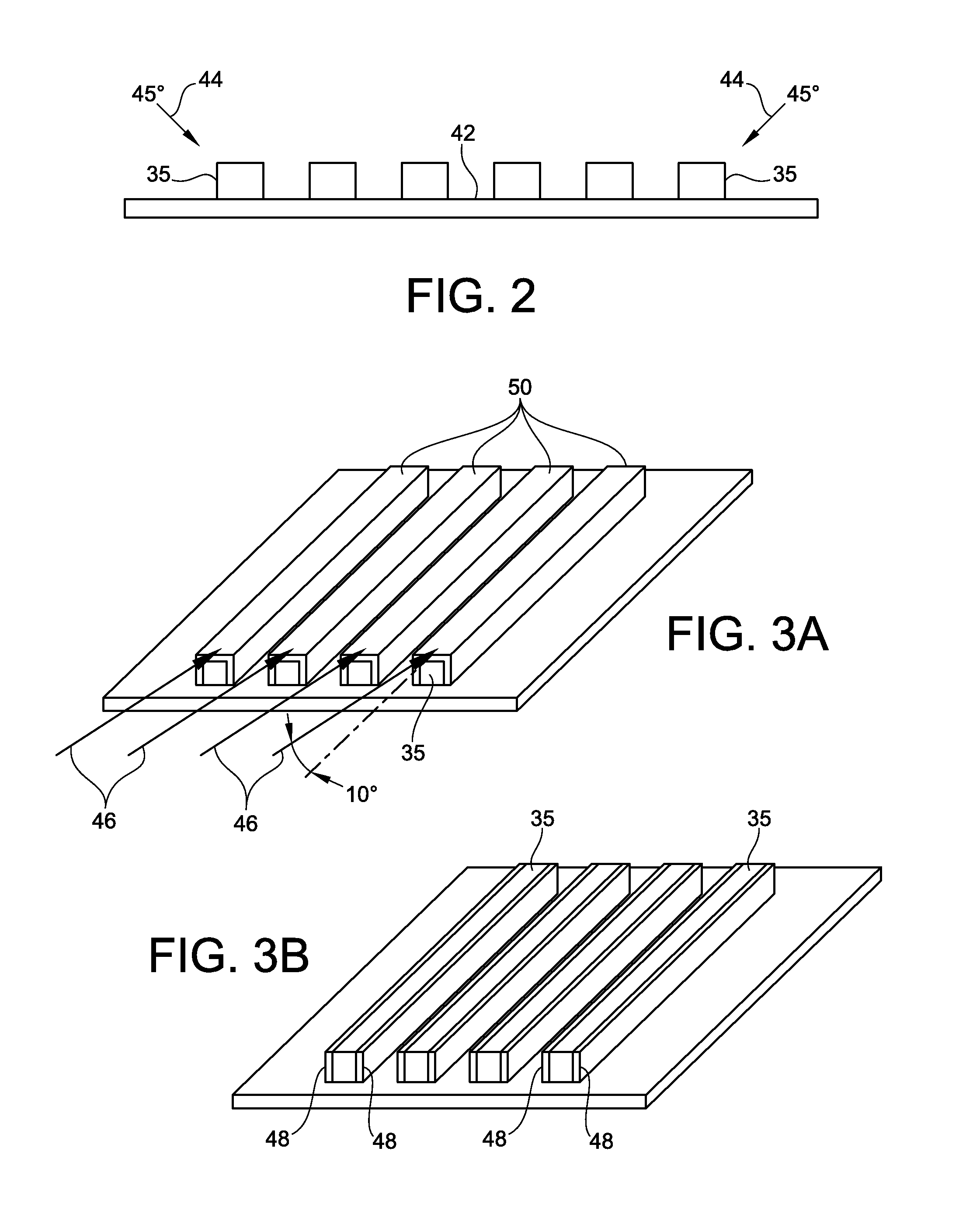

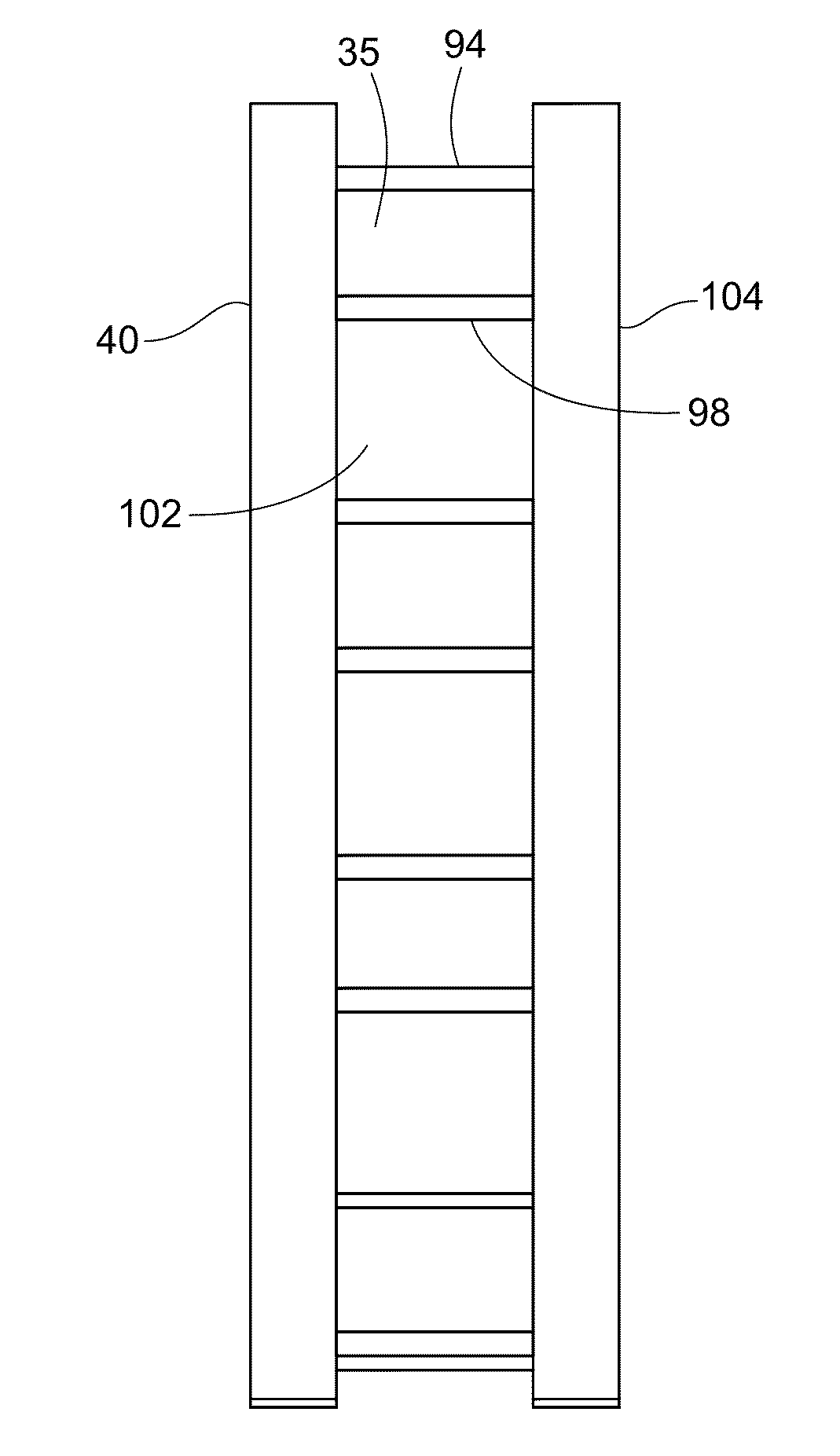

InactiveUS20110203656A1Improve performanceOvercome problemsSemiconductor/solid-state device detailsSolid-state devicesNanowireGrating

Nanoscale high-aspect-ratio metallic structures and methods are presented. Such structures may form transparent electrode to enhance the performance of solar cells and light-emitting diodes. These structures can be used as infrared control filters because they reflect high amounts of infrared radiation. A grating structure of polymeric bars affixed to a transparent substrate is used. The sides of the bars are coated with metal forming nanowires. Electrodes may be configured to couple to a subset of the rails forming interdigitated electrodes. Encapsulation is used to improve transparency and transparency at high angles. The structure may be inverted to facilitate fabrication of a solar cell or other device on the back-side of the structure. Multiple layered electrodes having an active layer sandwiched between two conductive layers may be used. Layered electro-active layers may be used to form a smart window where the structure is encapsulated between glass to modify the incoming light.

Owner:IOWA STATE UNIV RES FOUND

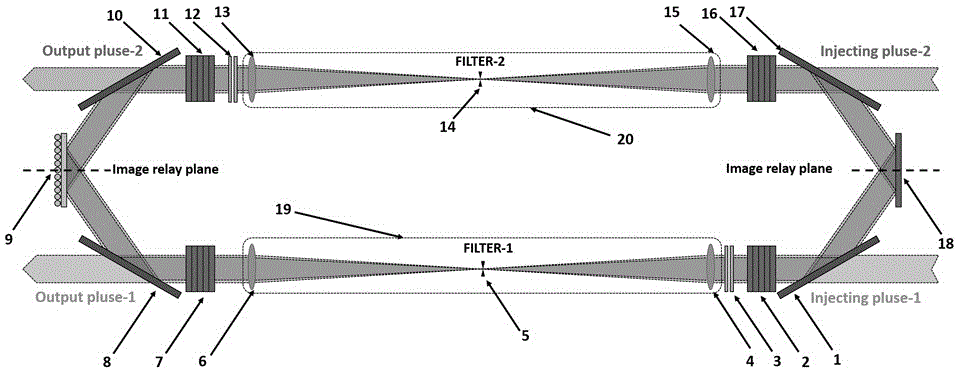

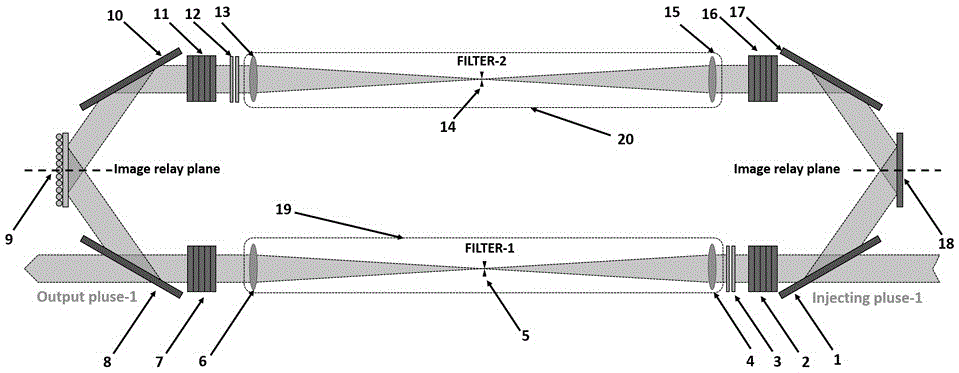

Novel highly-efficient high-power annular laser amplifier

ActiveCN106486882AImprove extraction efficiencyRelax restrictionsActive medium shape and constructionICT adaptationDiffraction effectHigh power lasers

Owner:SUZHOU UNIV

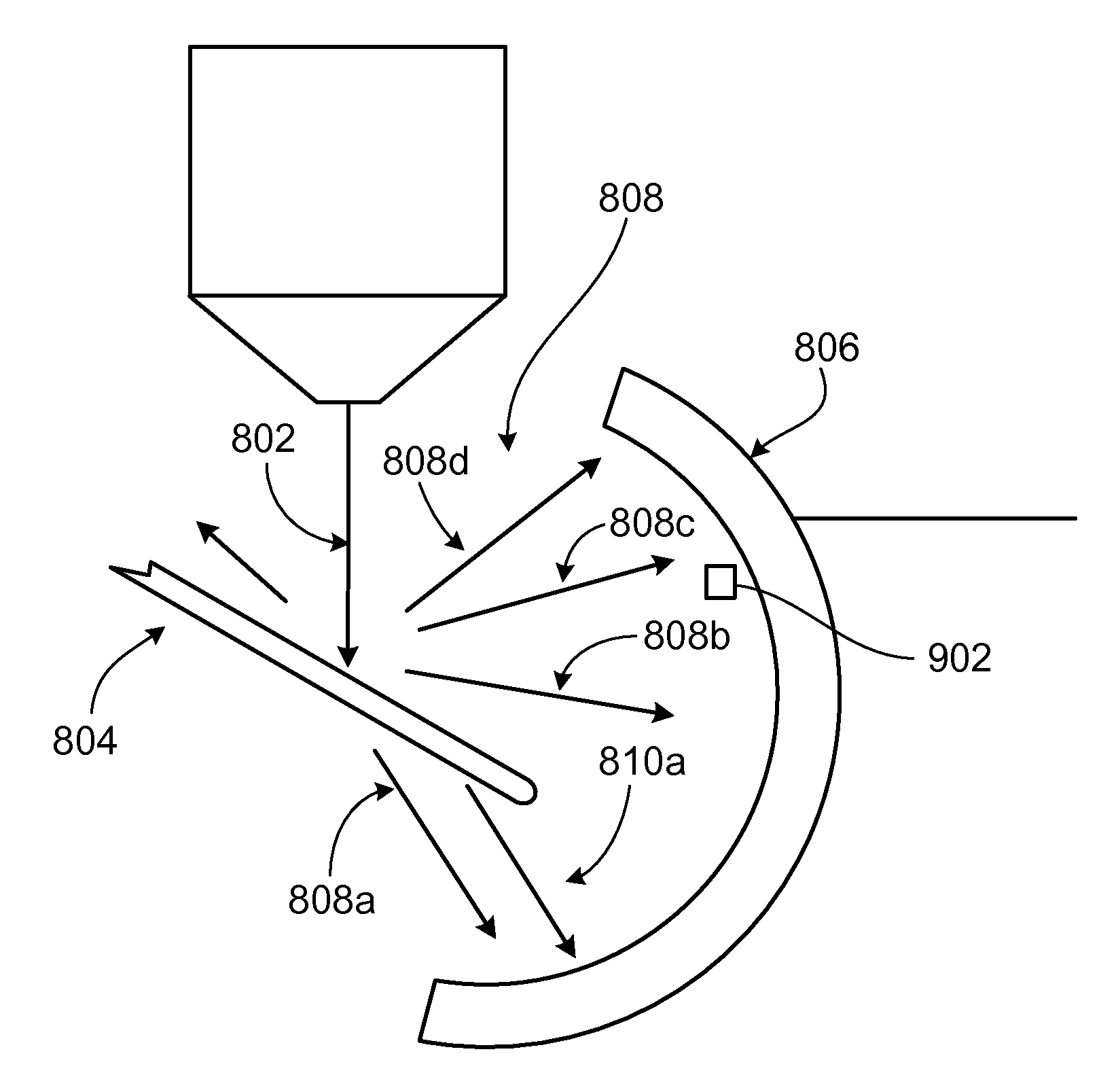

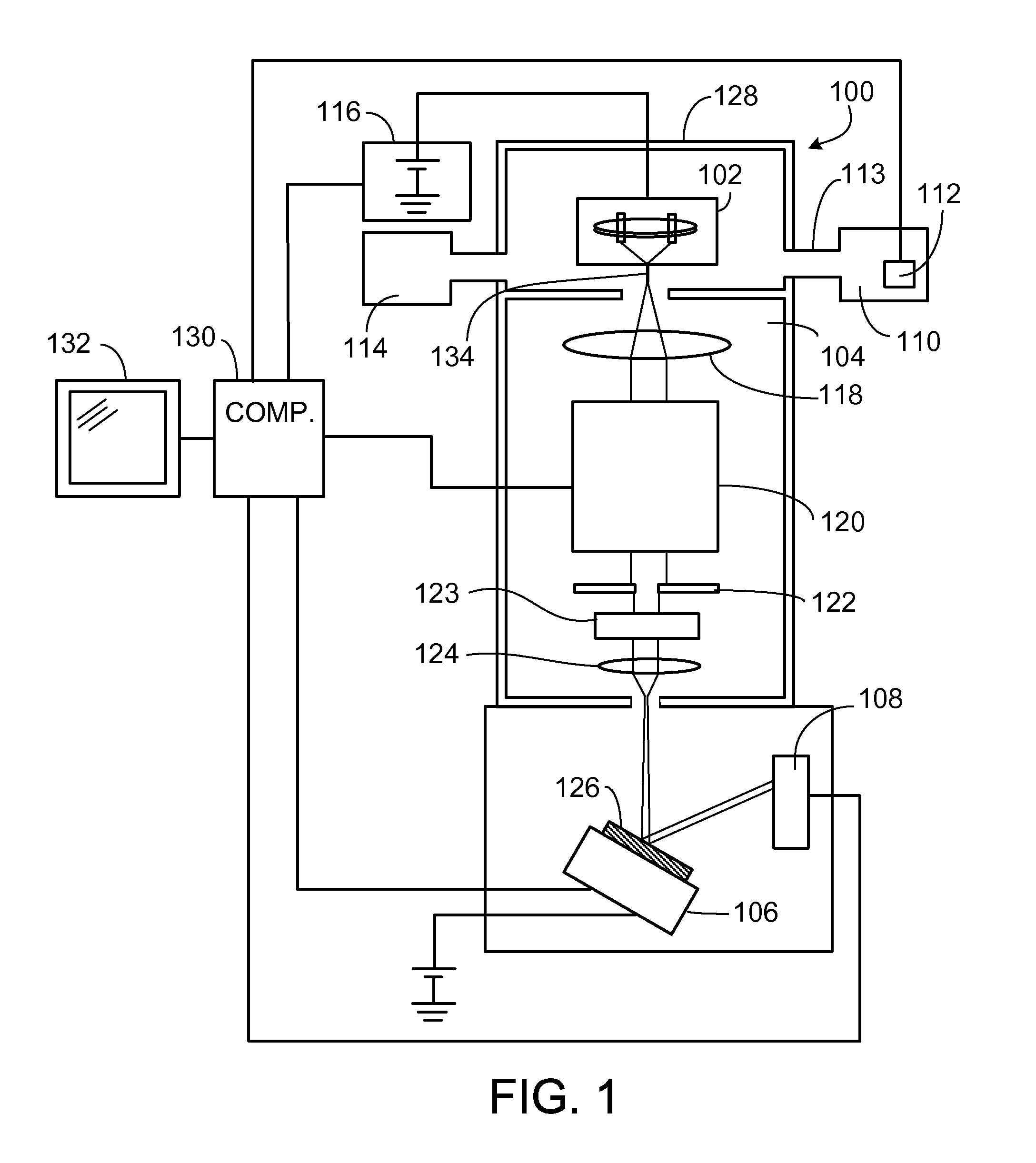

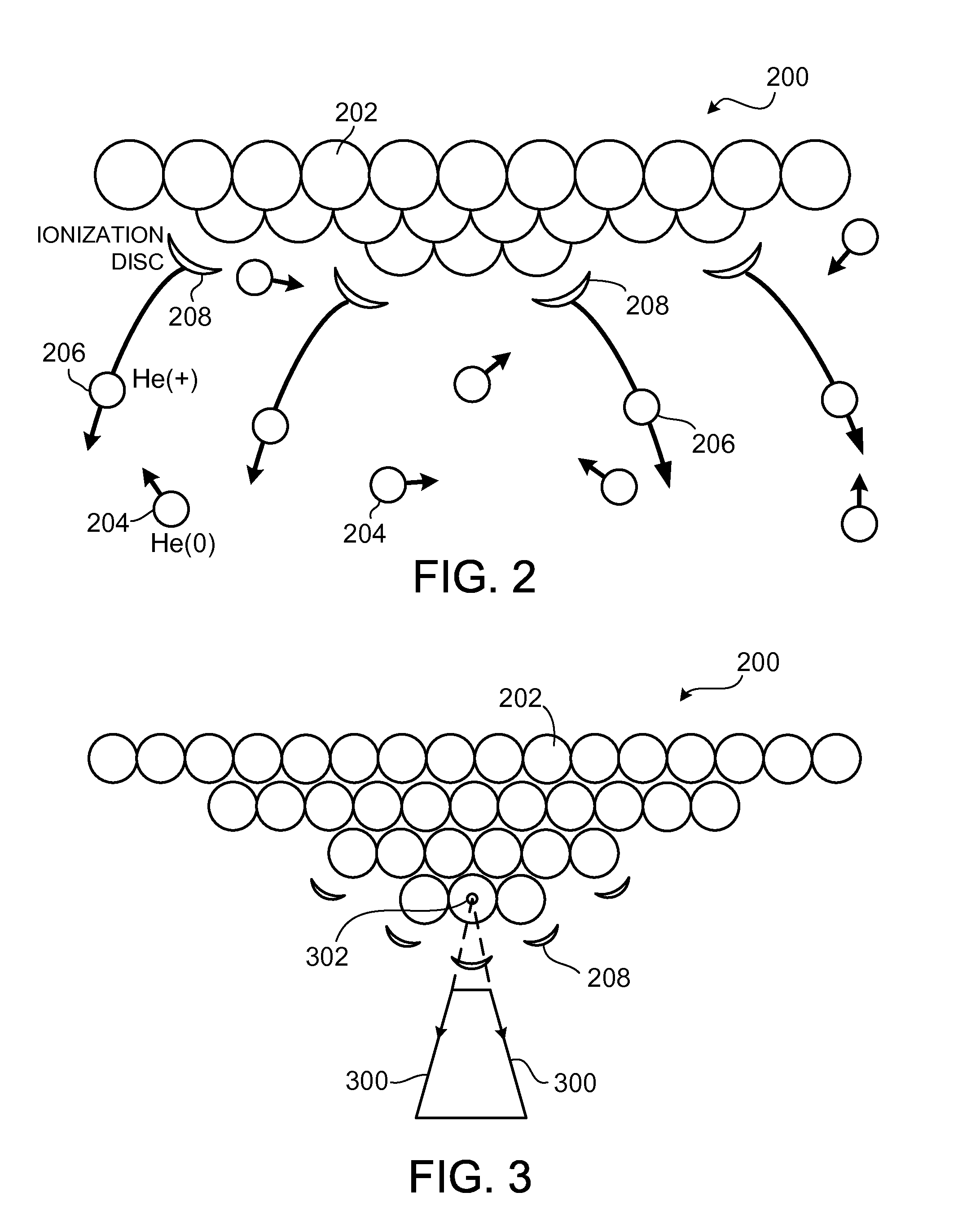

Systems and methods for a gas field ion microscope

ActiveUS7601953B2Increase contrastReduce diffraction effectsMaterial analysis using wave/particle radiationElectric discharge tubesIon beamIon microscopy

In one aspect the invention provides a gas field ion microscope that includes an ion source in connection with an optical column, such that an ion beam generated at the ion source travels through the optical column and impinges on a sample. The ion source includes an emitter having a width that tapers to a tip comprising a few atoms. In other aspects, the invention provides methods for using the ion microscope to analyze samples and enhancing the performance of a gas field ion source.

Owner:ALIS CORP

Method for forming features using frequency doubling hybrid resist and device formed thereby

InactiveUS6245488B1Positive toneNegative responseSemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusResistDevice form

The preferred embodiment of the present invention overcomes the limitations of the prior art by providing a method to form unlinked features using hybrid resist. The method uses a trim process in order to trim the linking features from the "loops" formed by the hybrid resist. This allows the method to form a plurality of unlinked features rather than the loops. In order to trim the ends, a relatively larger trim area is formed adjacent the narrow feature line, either by a second exposure step or by utilizing a grey scale reticle. The broader or wider open area allows features to be formed in the narrow feature lines and being trimmed from the relatively large areas, thereby resulting in district features rather than loops.

Owner:IBM CORP

Method for forming transistors with raised source and drains and device formed thereby

InactiveUS6100013AEnhanced transistor performanceOvercome limitationsTransistorDecorative surface effectsCapacitanceResist

The preferred embodiment of the present invention provides a transistor structure and method for fabricating the same that overcomes the disadvantages of the prior art. In particular, the preferred structure and method results in lower leakage and junction capacitance by using raised source and drains which are partially isolated from the substrate by a dielectric layer. The raised source and drains are preferably fabricated from the same material layer used to form the transistor gate. The preferred method for fabricating the transistor uses hybrid resist to accurately pattern the gate material layer into regions for the gate, the source and the drain. The source and drain regions are then connected to the substrate by growing silicon. The preferred method thus results in an improved transistor structure while not requiring excessive fabrication steps.

Owner:IBM CORP

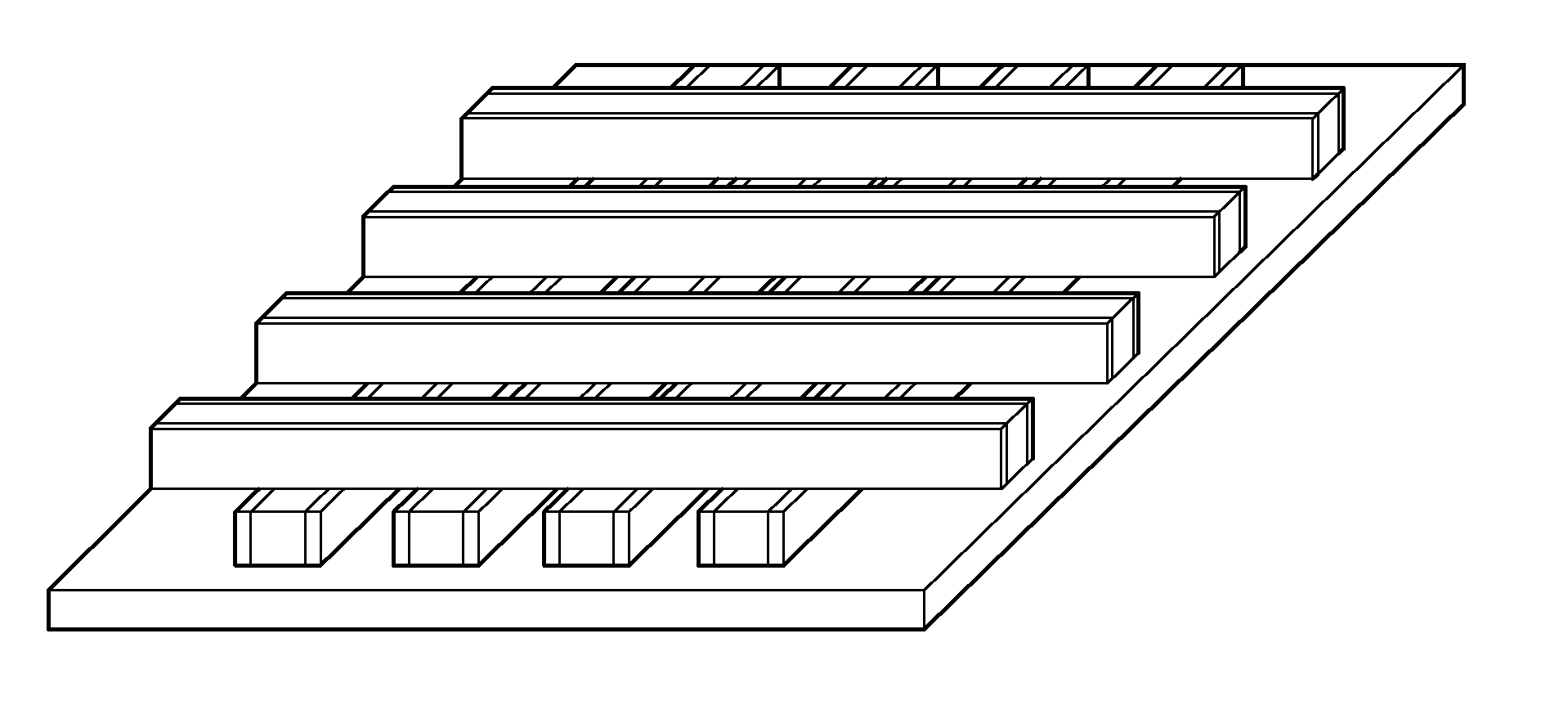

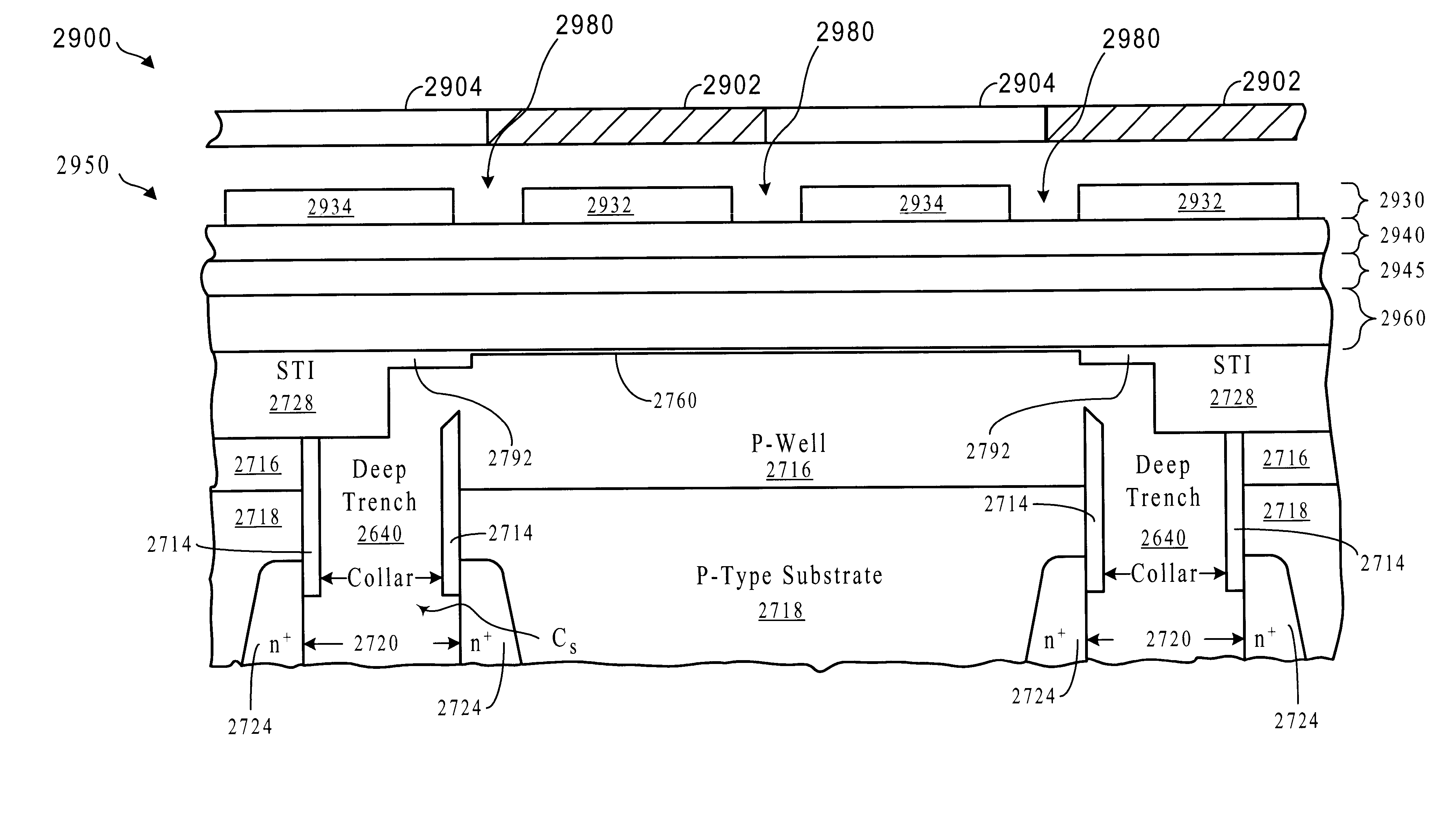

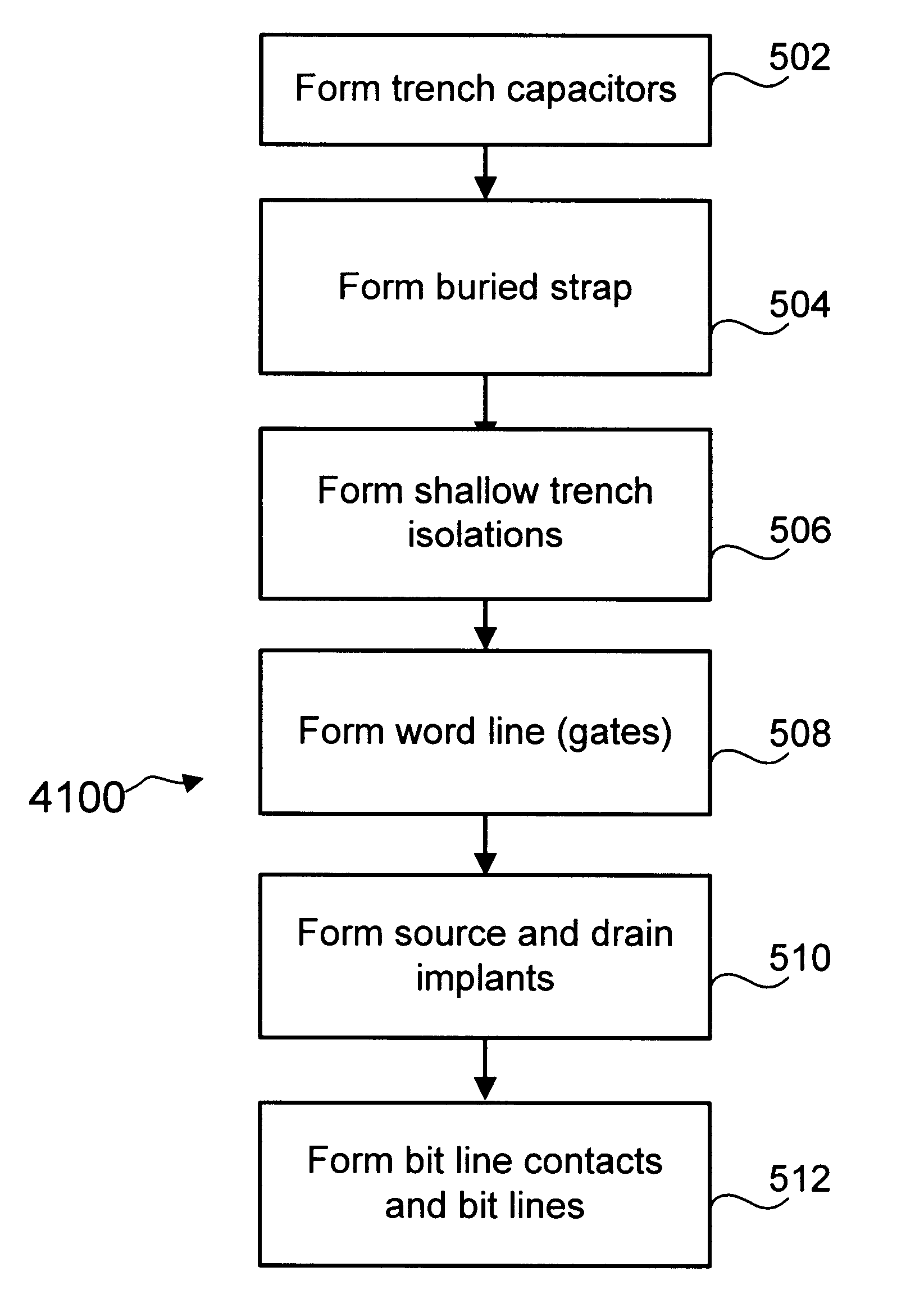

Fabrication of a high density long channel DRAM gate with or without a grooved gate

InactiveUS6426175B2Limit leakage currentIncrease channel lengthTransistorSolid-state devicesMemory chipHigh density

The present invention lengthens gate conductors used in memory chips to limit leakage current, while still allowing the overall size of cells to remain the same. The channel length for each gate is increased by decreasing the size of spaces between gates. Decreases in space size occurs by using photolithographic image enhancement techniques. These techniques allow the space between gate conductors to be smaller while the gate size increases. In addition, a groove may be added that additionally lengthens the effective channel length and provides an additional electrical shield to limit leakage current. These techniques lead to the same density memory cells for a given process with less leakage. Finally, if grooved gate structures are used, having a longer gate conductor allows a three sigma process to be used, which increases yields.

Owner:INT BUSINESS MASCH CORP

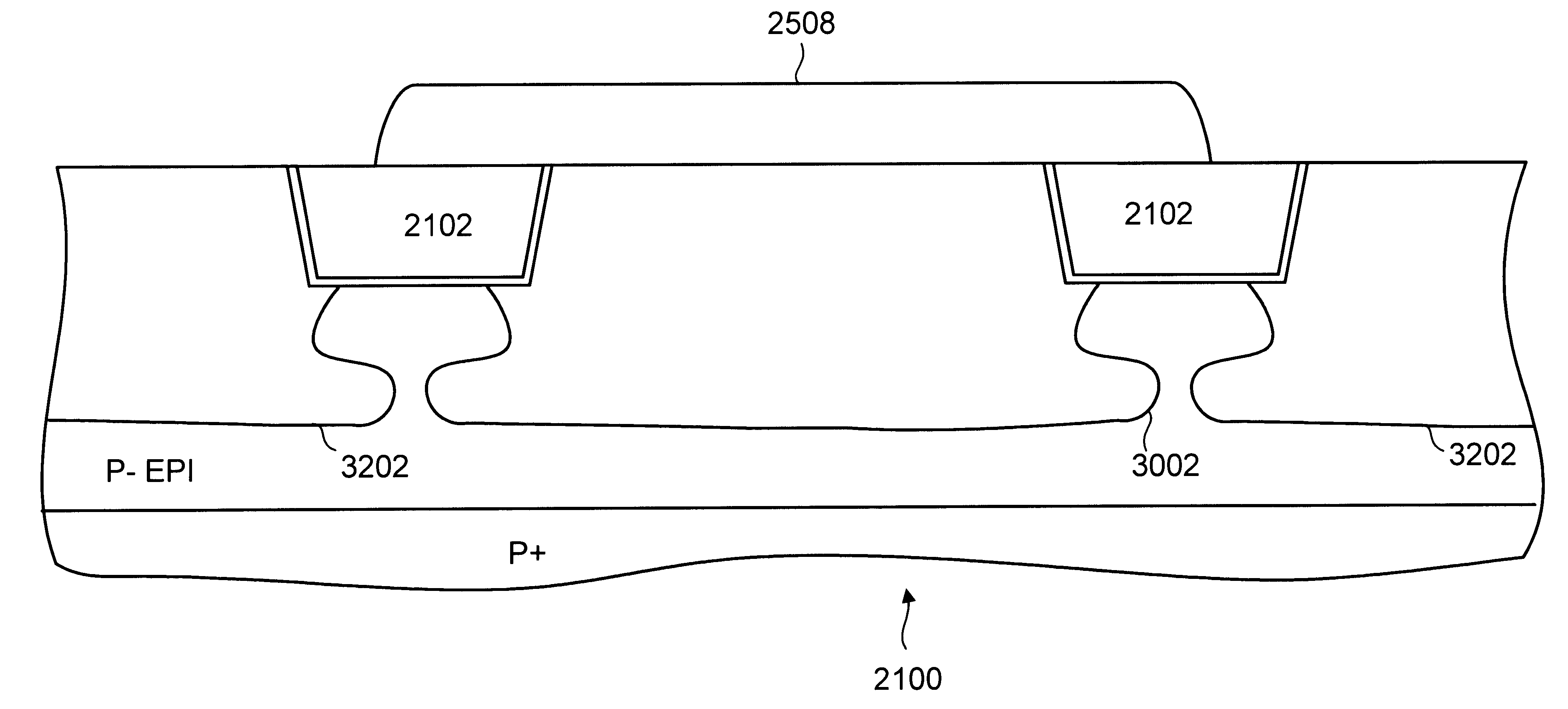

Method and structure to reduce latch-up using edge implants

InactiveUS6033949AIncrease latch-up immunityWafer may have decreased minority carrier lifetimeTransistorSolid-state devicesResistCMOS

The preferred embodiment of the present invention overcomes the limitations of the prior art and provides a device and method to increase the latch-up immunity of CMOS devices by forming implants at the well edges. The preferred method uses hybrid resist to form these implants at the edges of the N-wells and / or P-wells. The implants reduce the lifetime of minority carriers in the parasitic transistor, and hence reduce the gain of the parasitic transistor. This reduces the propensity of the CMOS device to latch-up. The preferred embodiment method allows these implants to be formed without requiring additional masking steps over prior art methods. Furthermore, the preferred method for forming the implants results in implants that are self aligned to the edges of the wells.

Owner:META PLATFORMS INC

Method for manufacturing chromium sidewall attenuation type phase-shifting mask used in extreme ultra-violet lithography

InactiveCN103163726AReduce diffraction effectsIncrease contrastOriginals for photomechanical treatmentMicro nanoDiffraction effect

The invention discloses a method for manufacturing a chromium sidewall attenuation type phase-shifting mask used in extreme ultra-violet lithography. Firstly, a plurality of multilayer reflectors are manufactured according to a manufacturing method for a conventional extreme ultra-violet lithography mask; then a phase-shifting layer structure is manufactured on an electron beam resist by using a micro-nano machining technology, and an absorber material chromium is deposited on a large area; and finally, the absorber material chromium is anisotropically etched, only leaving the attenuation type phase-shifting layer chromium sidewalls, so that the chromium sidewall attenuation type phase-shifting mask used in the extreme ultra-violet lithography can be obtained. The chromium sidewall attenuation type phase-shifting mask is obtained by one time of electron beam exposure, two times of magnetron sputtering deposition of multilayer reflecting layers and the phase-shifting layer, one time of atomic layer deposition of the chromium material on a large area, and one time of anisotropic etching of the chromium material. The chromium sidewall is added in two sides of the attenuation type phase-shifting mask, and the exposure shadow and the diffraction effect in the extreme ultra-violet lithography are depressed by the chromium sidewalls, so that a more efficient function of resolution enhancement than that of a conventional attenuation type phase-shifting mask is obtained.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

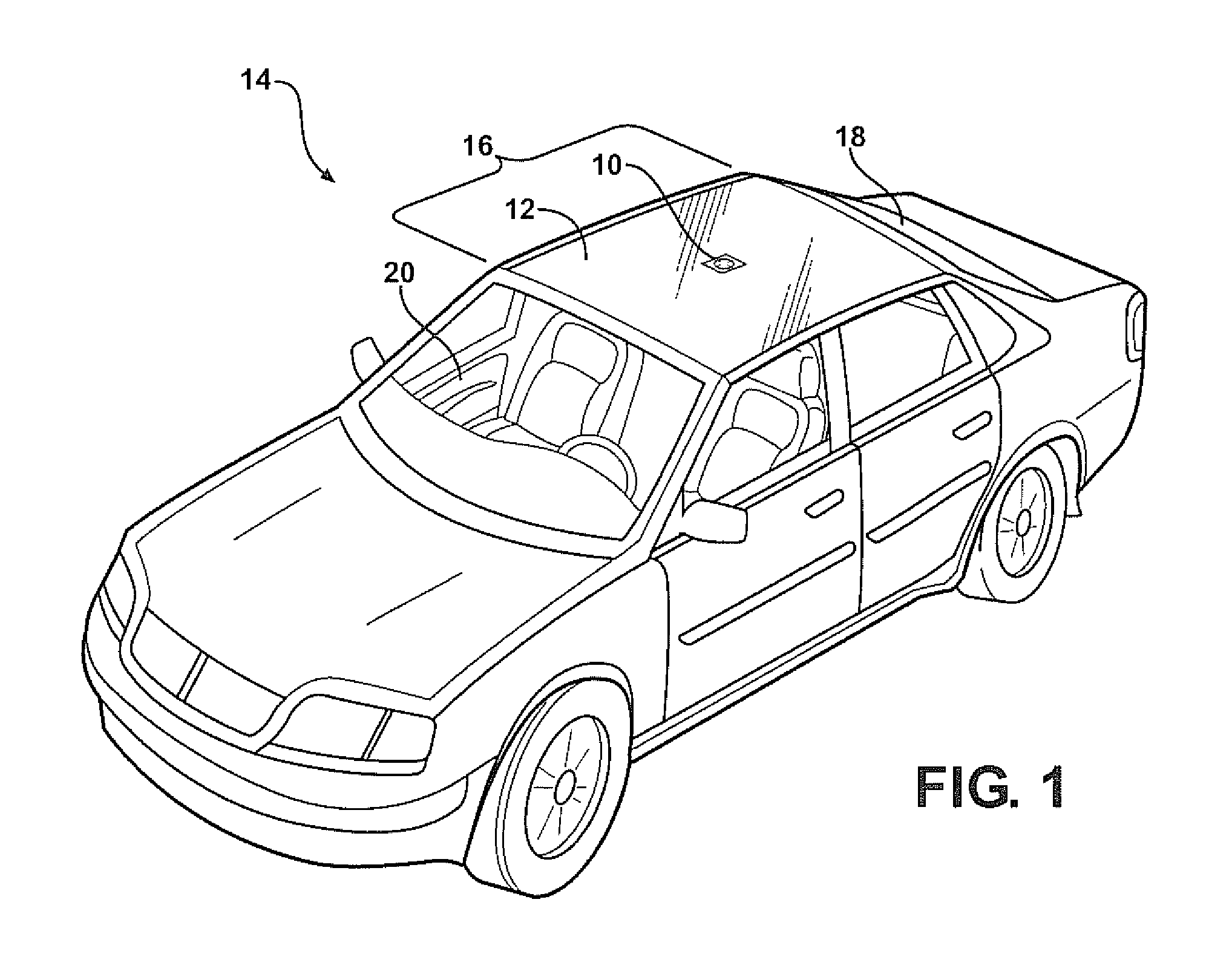

Antenna For Increasing Beamwidth Of An Antenna Radiation Pattern

InactiveUS20120019425A1Avoid sudden interruptionReducing undesired diffraction effectSimultaneous aerial operationsRadiating elements structural formsDielectricAntenna radiation patterns

An antenna includes a ground plane, a dielectric, and an active radiating element. The dielectric is disposed on the ground plane, and the active radiating element is embedded in the dielectric for transmitting and / or receiving an RF signal. The antenna also includes a feeding element and a passive radiating element. The feeding element extends into the dielectric and is electrically coupled to the active radiating element. The passive radiating element is disposed on the ground plane and surrounds a periphery of the dielectric for perturbating the RF signal. The ground plane has a plurality of edges. At least one of the edges extends as a curvilinear lip. The curvilinear lip extends in a direction opposite the passive radiating element for directing the RF signal and for preventing abrupt discontinuity of the RF signal.

Owner:AGC AUTOMOTIVE AMERICAS

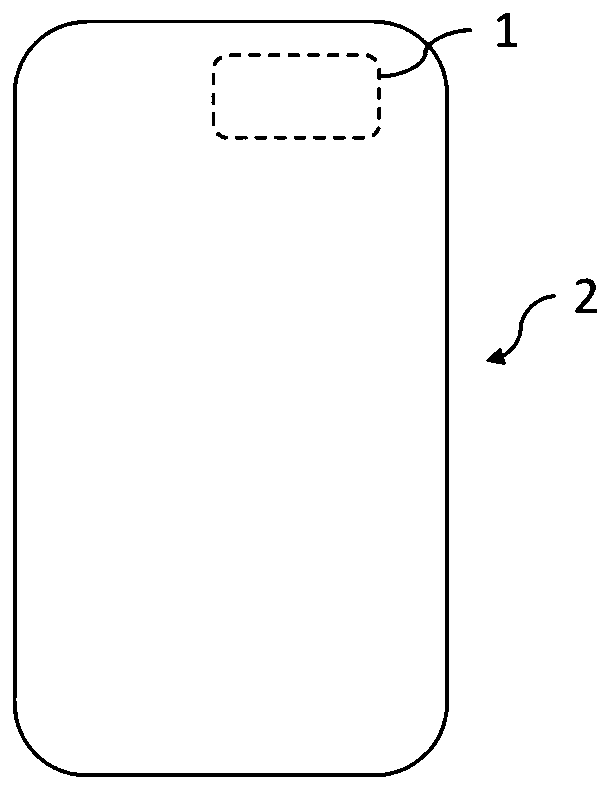

Diffraction suppressing optical member, diffraction suppressing display screen, and under-screen imaging device

ActiveCN111208648AImprove starburst effectImprove image qualityOptical elementsImaging qualityMaterials science

The invention discloses a diffraction suppression optical member. The member is formed into a sheet-shaped piece, the sheet member comprises a first region arranged in a two-dimensional periodic manner and a second region which is arranged around the first region and is approximately in a strip shape, wherein the first region is a light-transmitting region, the second region has a shape generatedby randomly staggering a plurality of unit patterns arranged along the extending direction of the strip shape in a transverse direction perpendicular to the extending direction, and the second regionis light-proof at least on two side edge parts thereof. The invention further discloses a diffraction inhibition display screen with the diffraction inhibition optical member or a corresponding structure and an under-screen camera device. The member is advantaged in that diffraction generated by the periodic structure of the pixel unit in the under-screen camera device can be suppressed, and the imaging quality is improved.

Owner:JIAXING UPHOTON OPTOELECTRONICS TECH CO LTD

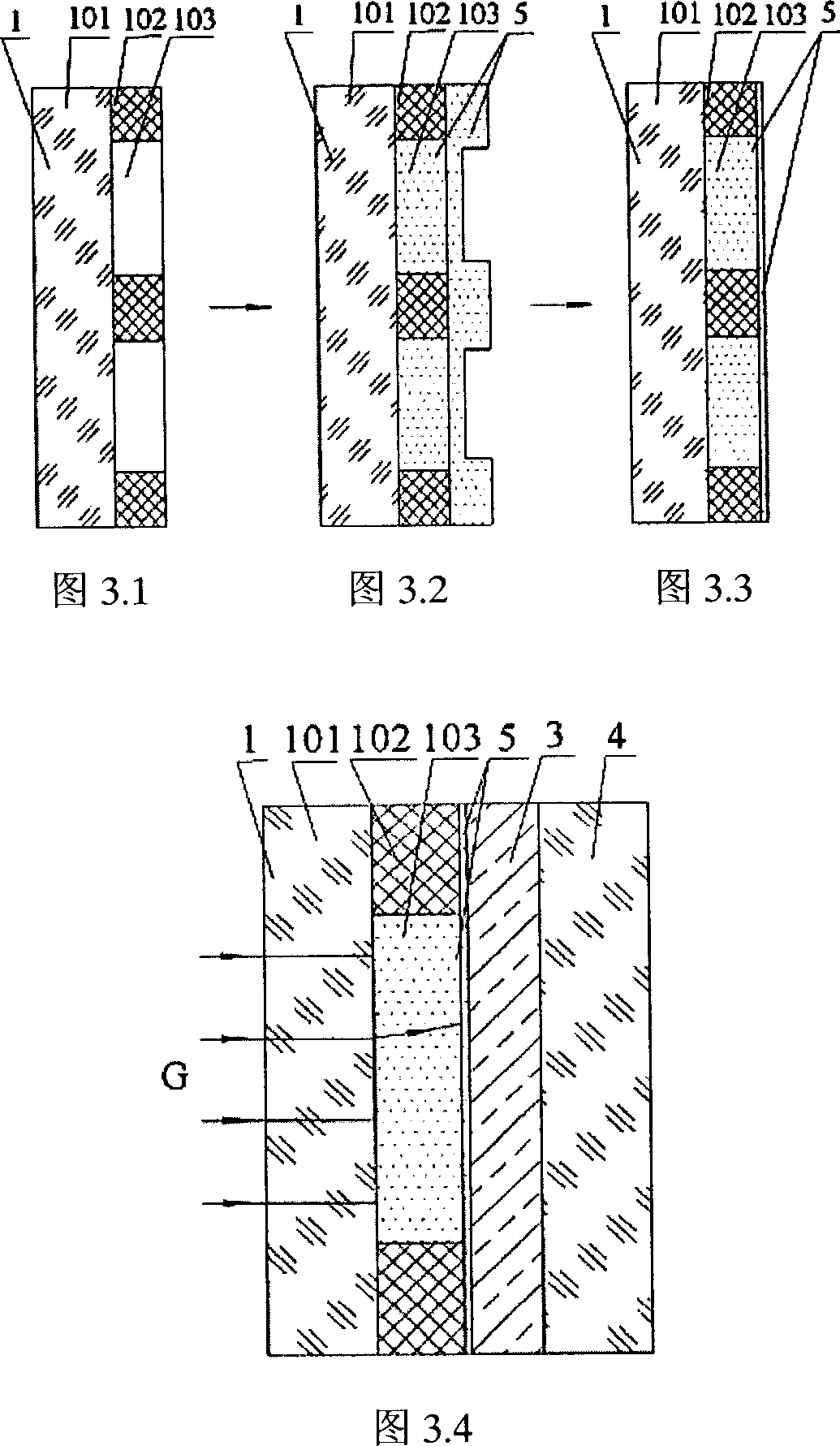

Method of raising photoetching resolution

InactiveCN1375745AWidth improvements and enhancementsWide exposure threshold rangePhotomechanical exposure apparatusMicrolithography exposure apparatusDiffraction effectImage resolution

The method for raising photoetching resolution is characterized by that in the air gap being in chrome film pattern on the masket plate photoetched by adopting closing or contact mode and in the air layer space between masked plate chrome film and photoresist layer on the silicon chip a transparent material whose refractivity is greater than that of masked plate is filled, and the surface of saidtransparent material layer which is positioned in air layer space and contacted with photoresist layer is polished, so that when it is photoetched, the transparent material is filled, therefore the refracted angle of light beam is reduced, diffraction distance is reduced, diffraction effect can be effectively weakened to raise the photoetching resolution.

Owner:SHANGHAI INST OF OPTICS & FINE MECHANICS CHINESE ACAD OF SCI

Method for forming transistors with raised source and drains and device formed thereby

InactiveUS6255178B1Reduce junctionReduce leakageTransistorSemiconductor/solid-state device manufacturingCapacitanceResist

The preferred embodiment of the present invention provides a transistor structure and method for fabricating the same that overcomes the disadvantages of the prior art. In particular, the preferred structure and method results in lower leakage and junction capacitance by using raised source and drains which are partially isolated from the substrate by a dielectric layer. The raised source and drains are preferably fabricated from the same material layer used to form the transistor gate. The preferred method for fabricating the transistor uses hybrid resist to accurately pattern the gate material layer into regions for the gate, the source and the drain. The source and drain regions are then connected to the substrate by growing silicon. The preferred method thus results in an improved transistor structure while not requiring excessive fabrication steps.

Owner:INT BUSINESS MASCH CORP

Method for forming features using frequency doubling hybrid resist and device formed thereby

InactiveUS6277543B1Positive toneNegative responseSemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusResistDevice form

The preferred embodiment of the present invention overcomes the limitations of the prior art by providing a method to form unlinked features using hybrid resist. The method uses a trim process in order to trim the linking features from the "loops" formed by the hybrid resist. This allows the method to form a plurality of unlinked features rather than the loops. In order to trim the ends, a relatively larger trim area is formed adjacent the narrow feature line, either by a second exposure step or by utilizing a grey scale reticle. The broader or wider open area allows features to be formed in the narrow feature lines and being trimmed from the relatively large areas, thereby resulting in district features rather than loops.

Owner:IBM CORP

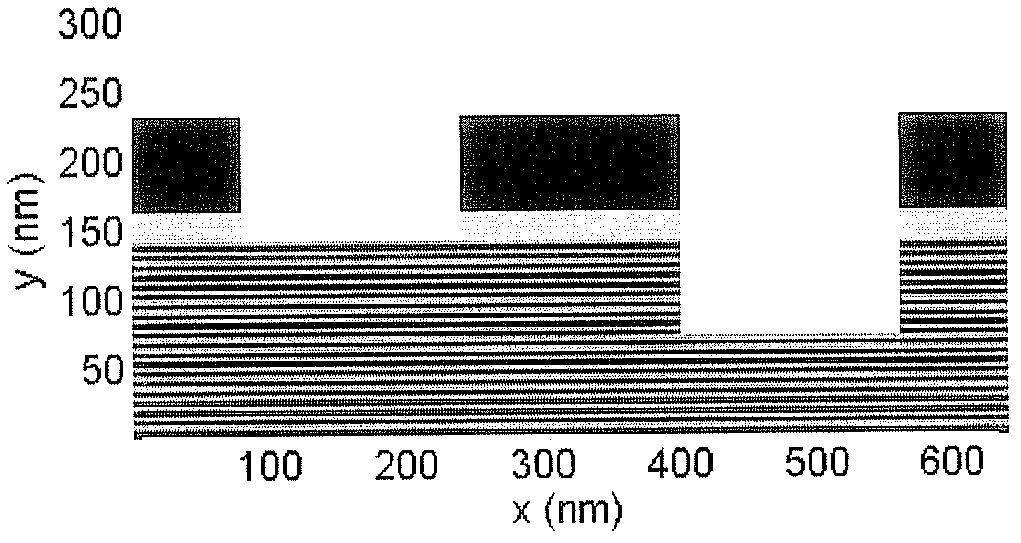

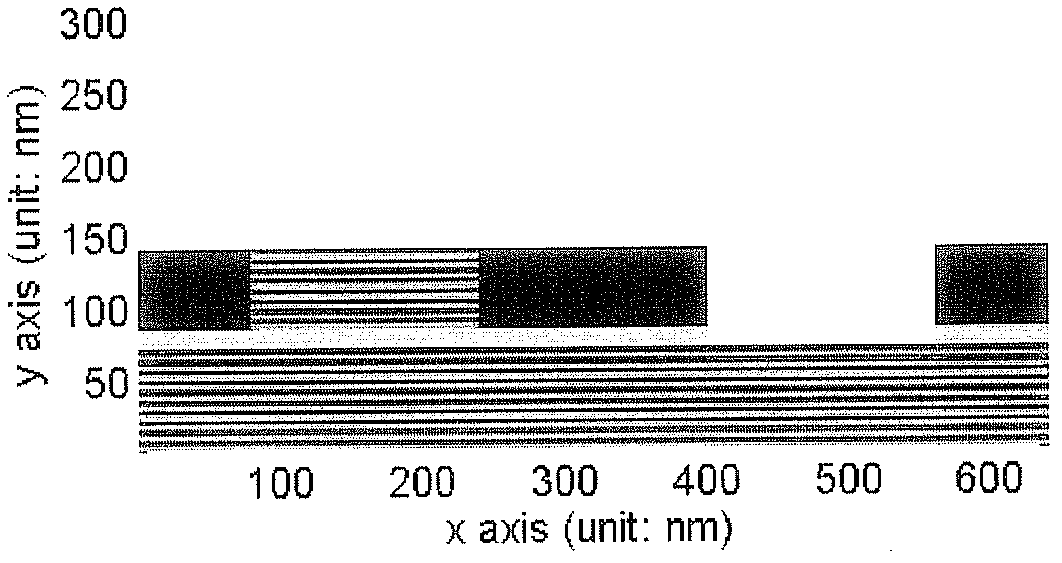

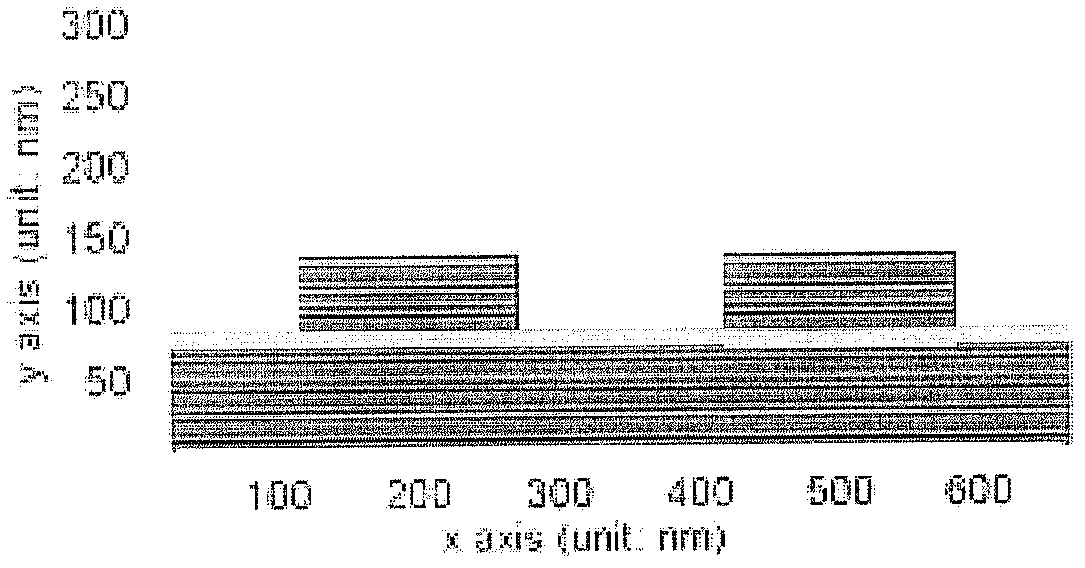

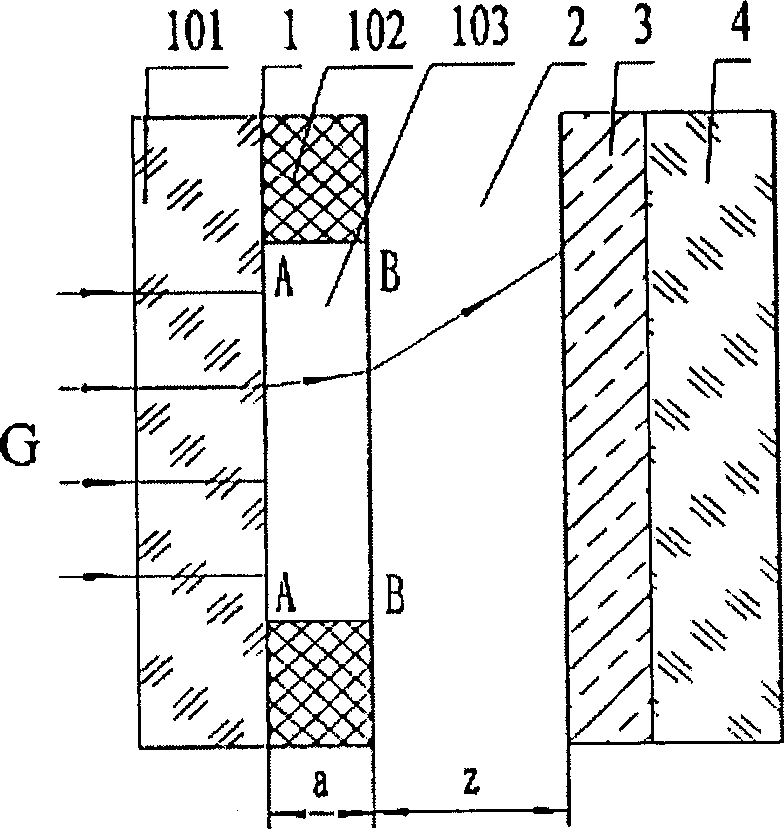

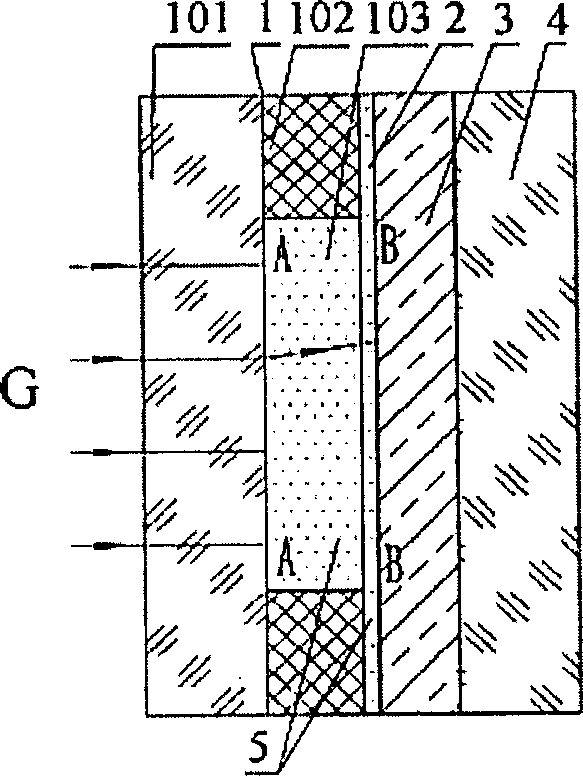

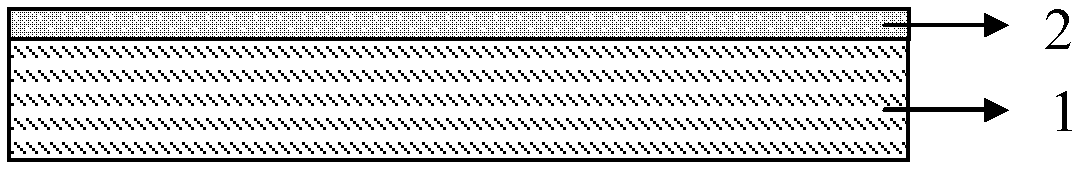

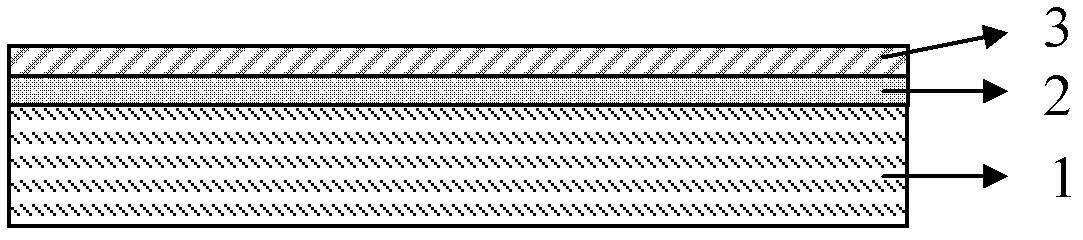

Structure for reducing the diffraction effect in periodic electrode arrangements and liquid crystal device including the same

ActiveUS6977705B1Reduce diffraction effectsPrevent reduced illumination efficiencySemiconductor/solid-state device detailsSolid-state devicesDiffraction effectLiquid-crystal display

Structure for reducing the diffraction effect in periodic electrode arrangements and liquid crystal device including the same. The invention relates to a structure for reducing the diffraction effect in periodic electrode arrangements. The structure is used in a reflective or semi-transparent liquid crystal display with lateral electric fields. The light collecting efficiency is improved by using multiple (two or more) dielectric layers with different refractive index as passivation layers of transparent electrodes, and by adjusting thickness of each dielectric layer to obtain the same optical path between the passivation layers and the transparent electrodes when incident light is transmitted.

Owner:IND TECH RES INST

Method and structure to reduce latch-up using edge implants

InactiveUS6232639B1Improve immunityWafer may have decreased minority carrier lifetimeTransistorSolid-state devicesResistCMOS

The preferred embodiment of the present invention overcomes the limitations of the prior art and provides a device and method to increase the latch-up immunity of CMOS devices by forming implants at the well edges. The preferred method uses hybrid resist to form these implants at the edges of the N-wells and / or P-wells. The implants reduce the lifetime of minority carriers in the parasitic transistor, and hence reduce the gain of the parasitic transistor. This reduces the propensity of the CMOS device to latch-up. The preferred embodiment method allows these implants to be formed without requiring additional masking steps over prior art methods. Furthermore, the preferred method for forming the implants results in implants that are self aligned to the edges of the wells.

Owner:IBM CORP

Incident light angle detector for light sensitive integrated circuit

ActiveUS7466002B2Maintain efficiencyImprove accuracySemiconductor/solid-state device testing/measurementVacuum evaporation coatingPhotovoltaic detectorsPhotodetector

A detector configuration determines the direction of illumination incident on a photosensitive device. Multiple mask layers include holes which form an interlayer optical path through which radiation reaches a photodetector. The interlayer optical path provides a selected nominal maximum signal angle and the detector senses when radiation is received at or near that angle. In one embodiment, three holes in three metallization layers provide an arbitrarily narrow interlayer optical path with improved angular detection relative to that provided by two holes. An illumination direction-sensing array may use multiple instances of the detector configuration. The detector configuration may provide enhanced utility and economy by being adapted to use only those fabrication steps used for fabricating other primary circuits on an IC.

Owner:MITUTOYO CORP

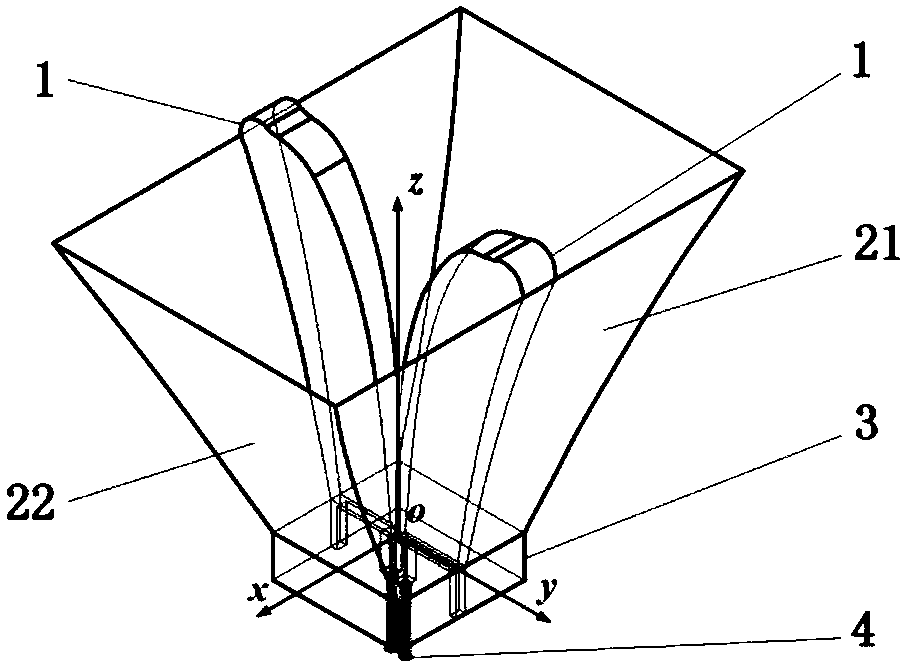

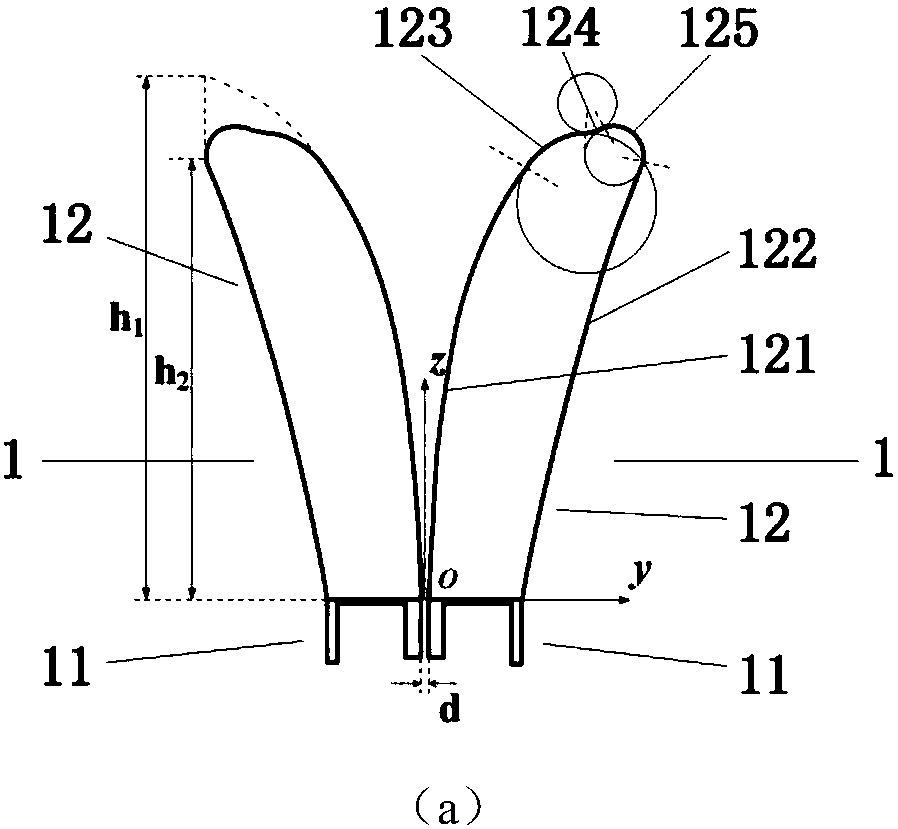

Double-ridged horn antenna based on specially-shaped ridge loading

ActiveCN108063315ASuppression of diffraction effectsReduce back radiationWaveguide hornsAntennas earthing switches associationCoaxial lineHorn antenna

The invention provides a double-ridged horn antenna based on specially-shaped ridge loading. While the matching characteristics in the working frequency band of the double-ridged horn antenna are ensured, the gain radiation characteristics of the antenna are enhanced. The antenna comprises two oppositely-arranged specially-shaped ridge plates, a horn shell, a back cavity and two feed coaxial lines, wherein each specially-shaped ridge plate comprises a back cavity matching section and a specially-shaped transition section, and the ridge line of the specially-shaped transition section is formedby two exponential curve sections and three arc sections in smooth connection; the horn shell adopts a rectangular horn structure formed by a pair of curved surface metal walls and a pair of plane metal walls in a mutual splicing mode; the two specially-shaped ridge plates are loaded to different curved surface metal walls; the back cavity adopts a cuboid thin wall structure; and the shielding layer of the feed coaxial line is connected with the back cavity, and the inner core passes through the sealing end of the back cavity to be connected with the back cavity matching section. The double-ridged horn antenna based on specially-shaped ridge loading has an ultra wide working frequency band, and can be applied to fields such as communication, remote sensing and antenna measurement.

Owner:XIDIAN UNIV +1

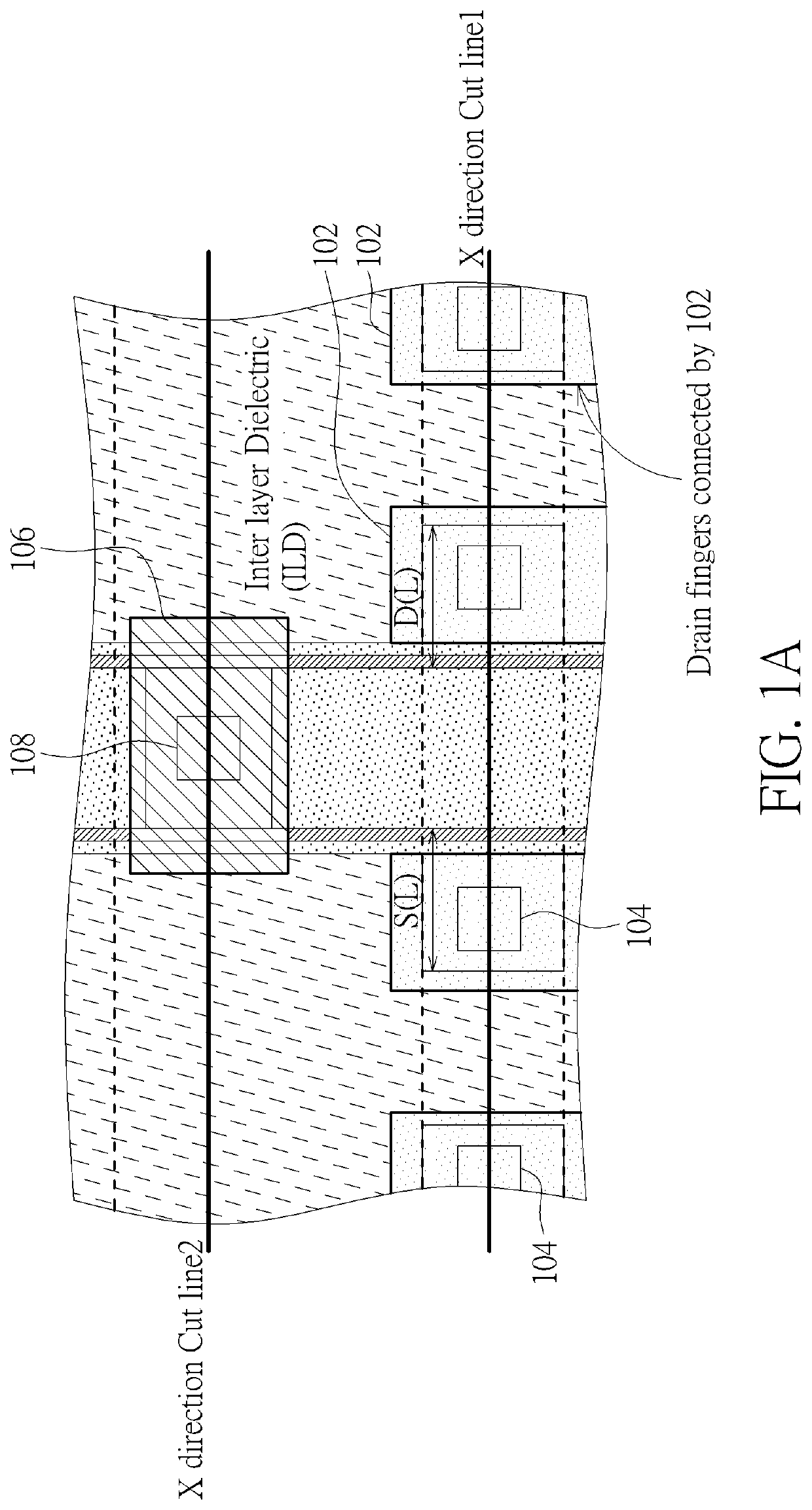

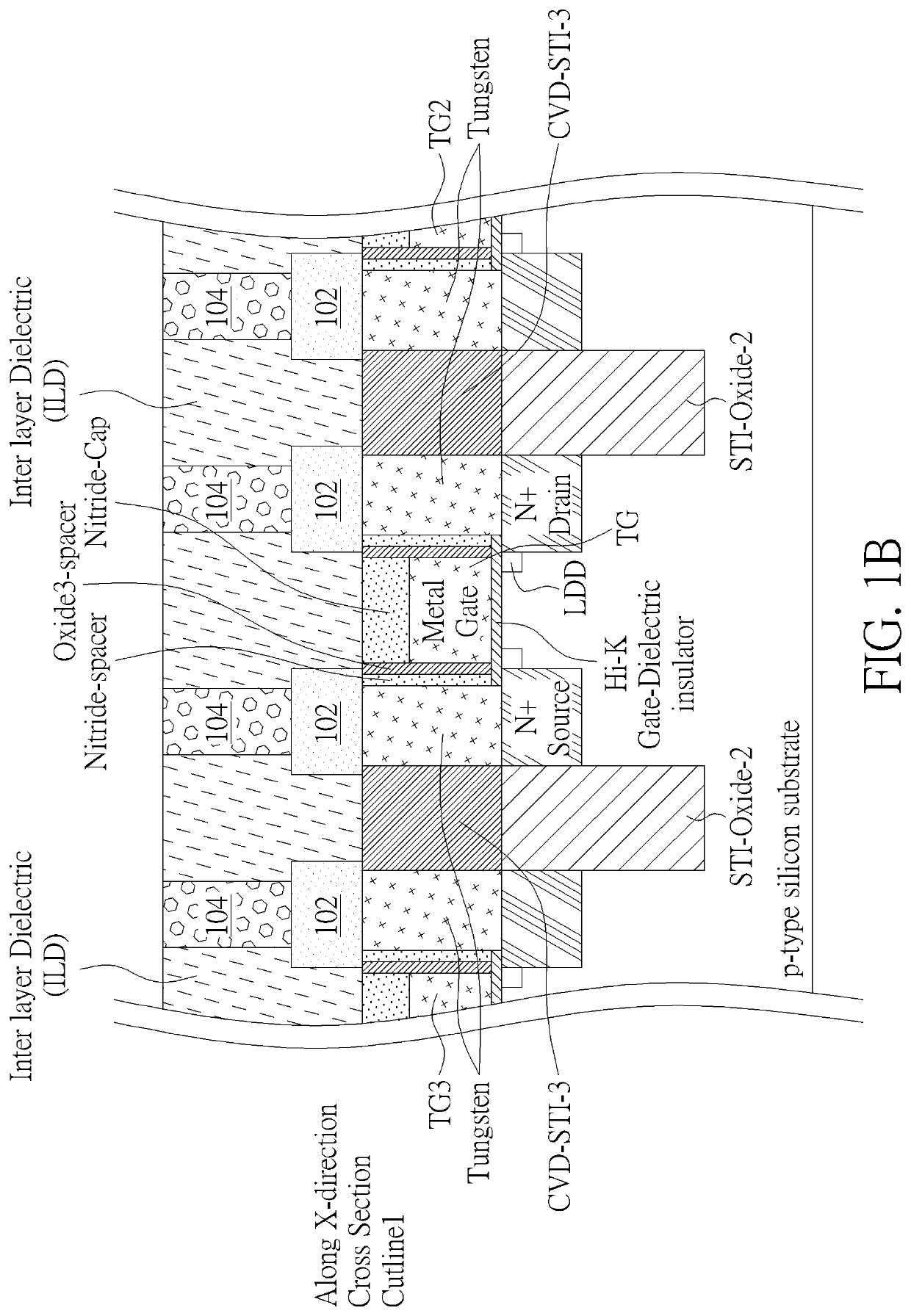

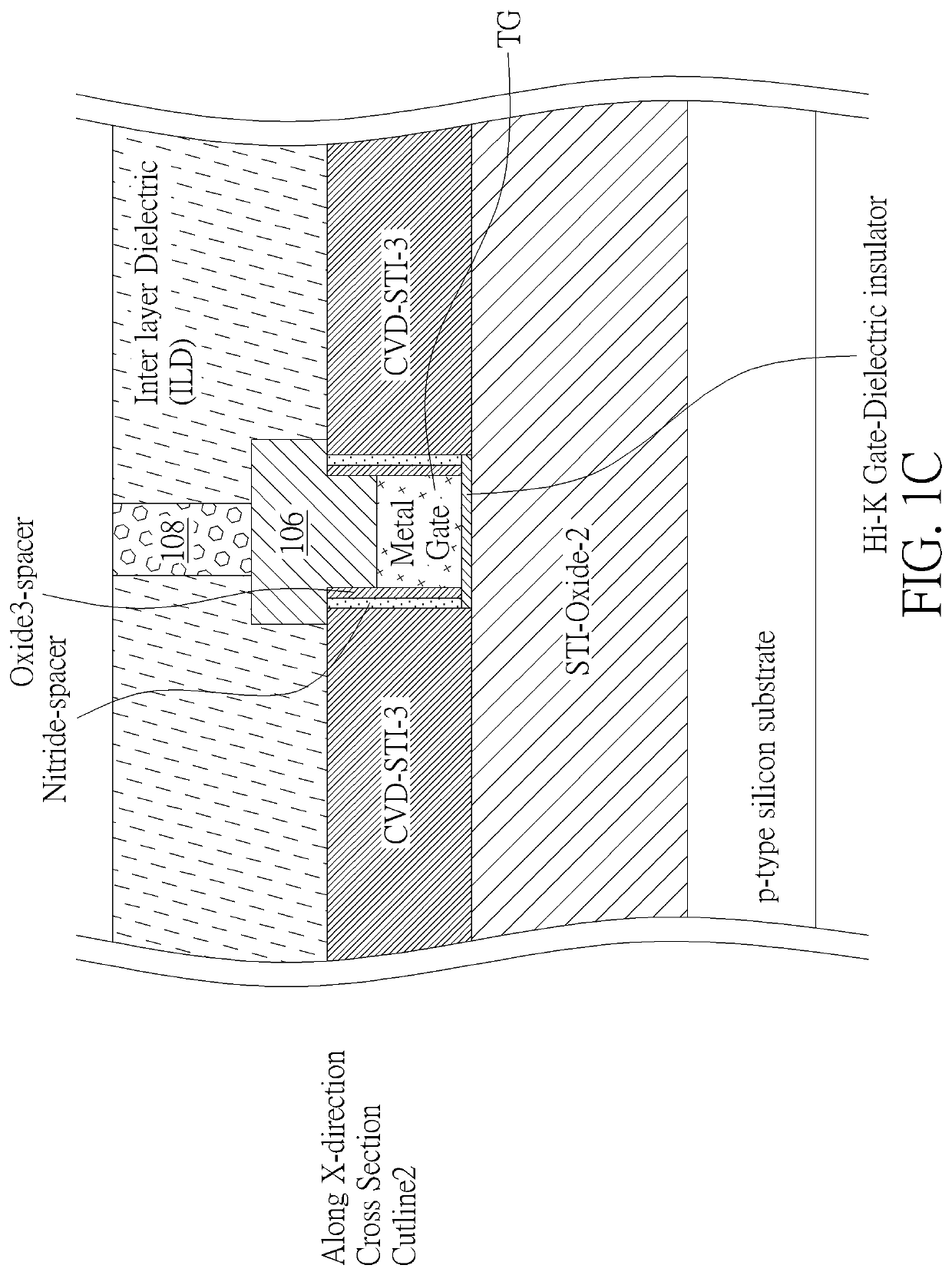

Transistor structure with metal interconnection directly connecting gate and drain/source regions

PendingUS20220077315A1Reduce photolithography process sensitivityReduce diffraction effectsTransistorSemiconductor/solid-state device detailsLithography processMetal interconnect

A transistor structure includes a semiconductor substrate, a gate structure, a channel region, and a first conductive region. The semiconductor substrate has a semiconductor surface. The gate structure is above the semiconductor surface, and a first concave is formed to reveal the gate structure. The channel region is under the semiconductor surface. The first conductive region is electrically coupled to the channel region, and a second concave is formed to reveal the first conductive region. A mask pattern in a photolithography process is used to define the first concave, and the mask pattern only defines one dimension length of the first concave.

Owner:ETRON TECH INC +1

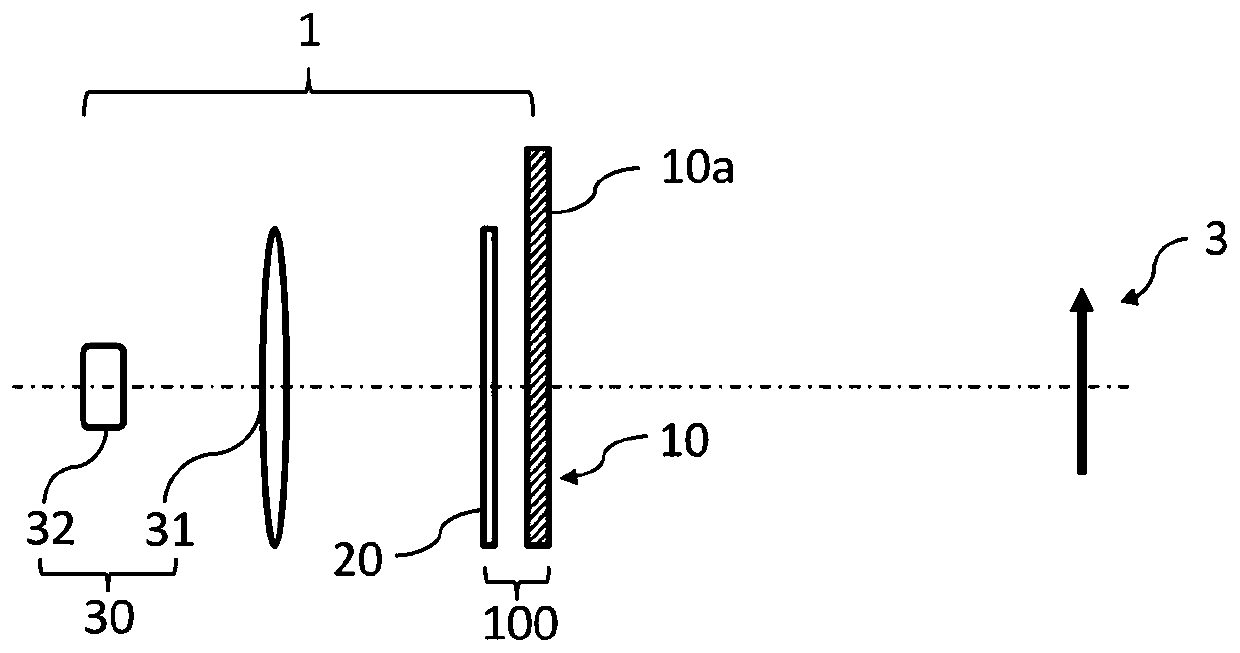

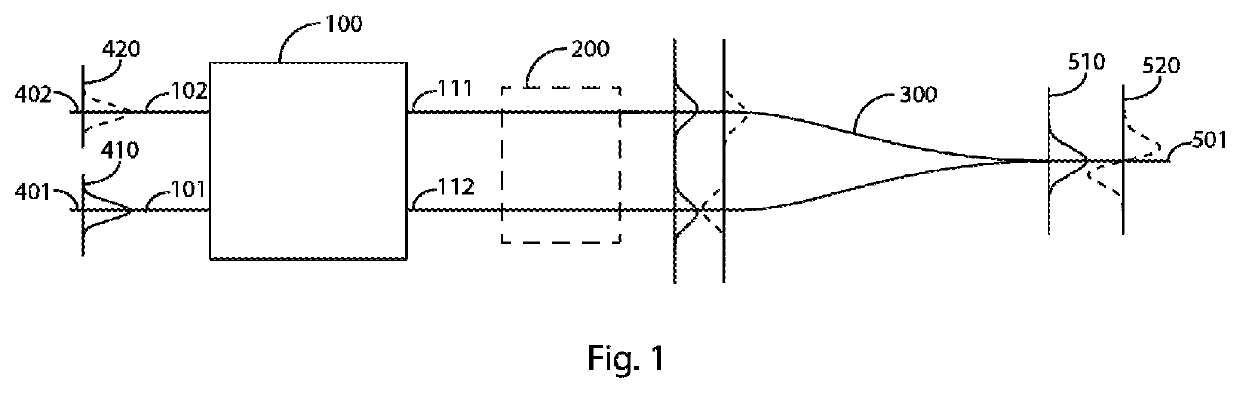

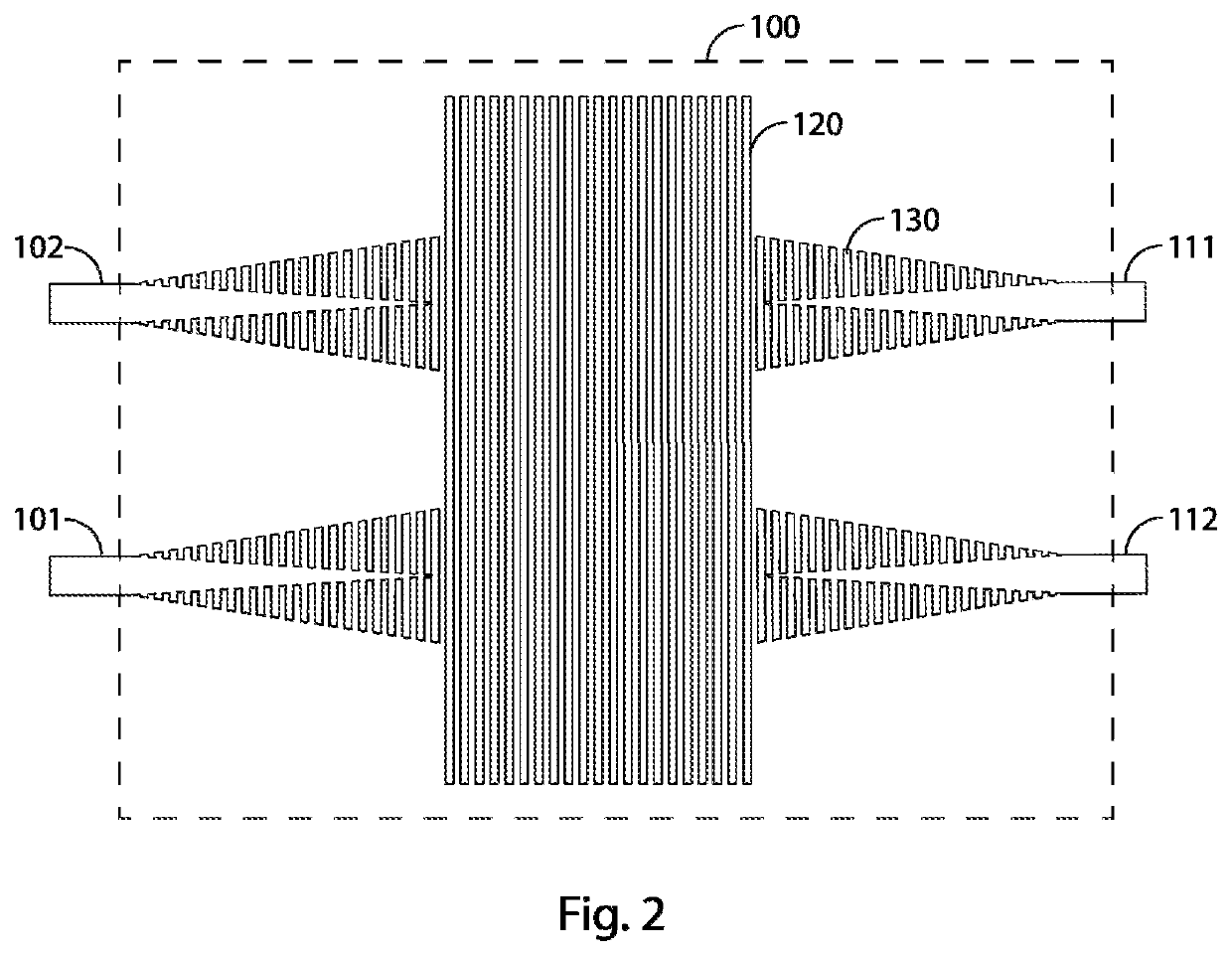

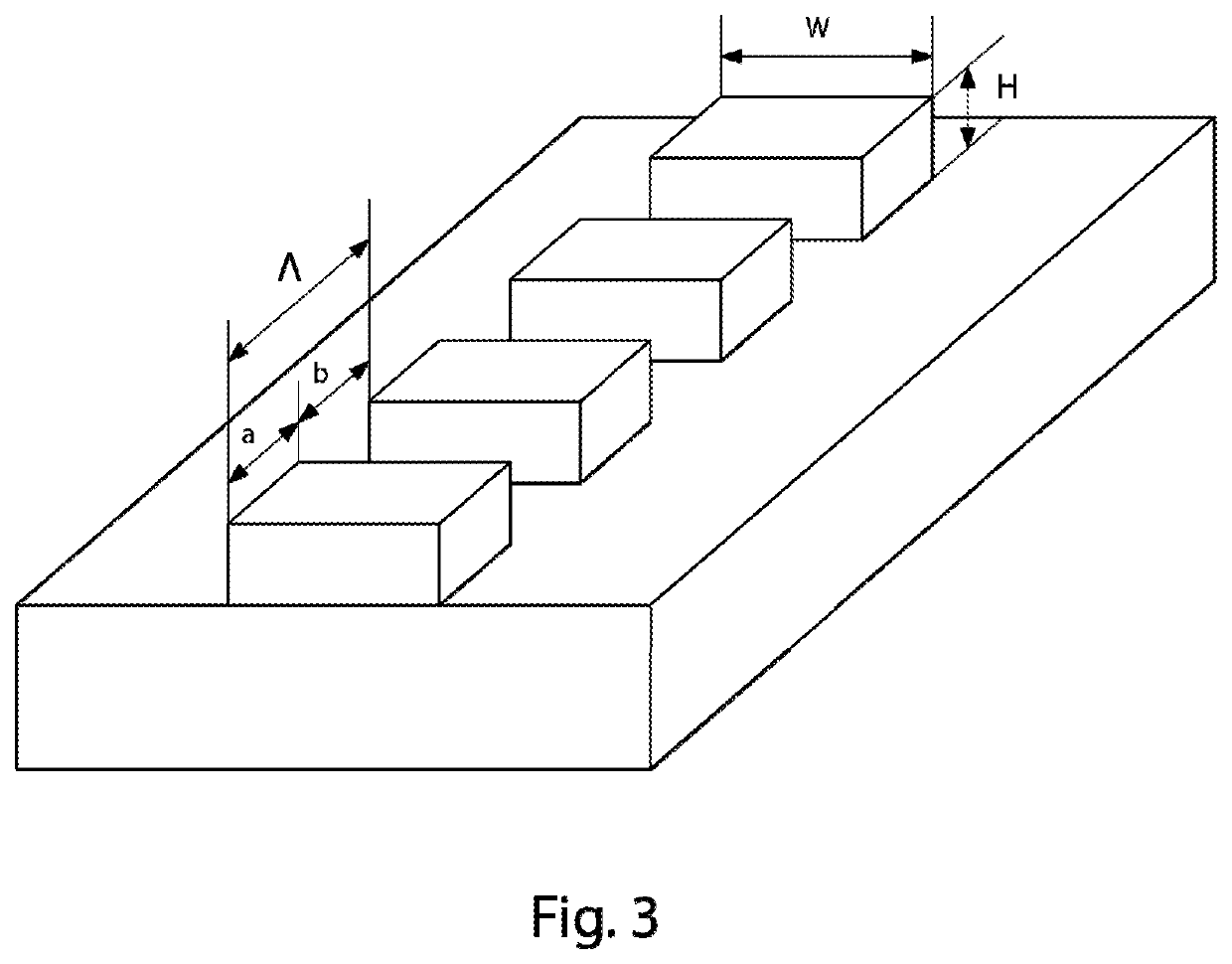

Integrated mode converter and multiplexer

ActiveUS20200225412A1Increased operating bandwidthReduce diffraction effectsCoupling light guidesOptical waveguide light guideConvertersHigh bandwidth

An integrated mode converter and multiplexer ( / demultiplexer) is disclosed, which combines a multimode interference coupler (100), at least one phase-shifter (200) and a symmetrical Y-junction (300). The dispersion of the multimode interference coupler (100) is engineered through subwavelength structures in order to achieve a very wide bandwidth. Several phase-shifter (200) topologies for further bandwidth enhancement are disclosed, as well as architectures for multiplexing a greater number of optical modes.

Owner:CONSEJO SUPERIOR DE INVESTIGACIONES CIENTIFICAS (CSIC) +1

Diffraction suppression optical component design method, display screen and under-screen camera device

ActiveCN111402712AReduce diffraction effectsImprove image qualityTelevision system detailsColor television detailsDiffraction effectImaging quality

The invention discloses a design method of a phase type diffraction suppression optical component for a transparent display screen. The method comprises the following steps: acquiring light field complex amplitude distribution of a plane wave on a plane which is separated from the screen by a distance d after the plane wave penetrates through the transparent display screen, and designing a diffraction suppression optical component to make the diffraction suppression optical component have a transmittance function and meet the condition that C is a constant. The invention also discloses the diffraction suppression optical component and an under-screen camera device having the same. According to the invention, the phase type diffraction suppression optical component suppresses the diffraction effect in the under-screen device by providing phase modulation, and improves the under-screen imaging quality.

Owner:JIAXING UPHOTON OPTOELECTRONICS TECH CO LTD

Super-resolution dry-method surface plasma photo-etching method

ActiveCN102636965ASmall molecular weightStrong absorption capacityPhotomechanical exposure apparatusPhotosensitive material processingCooking & bakingEtching

The invention discloses a super-resolution dry-method surface plasma photo-etching method, comprising the following steps of: 1) washing a substrate; 2) plating a layer of inorganic photoresist TeOx on the substrate; 3) plating a layer of metal thin film on a TeOx film layer; 3) repeatedly plating for a plurality of periods and finally plating one layer of inorganic photoresist; 5) placing a multi-layer film below a mask plate with a certain pattern and exposing; 6) carrying out dry-method developing on the exposed multi-layer film; and 7) finally removing the residual Ag layer. The super-resolution dry-method surface plasma photo-etching method disclosed by the invention has the advantages that a dry method is used to develop the inorganic photoresist so as to obtain the pattern with a regular and steep edge, the problems of the traditional inorganic photoresist that the edge of the pattern is irregular due to the solvent expansion effect and pattern lines are easy to collapse due to post-baking can be solved; and furthermore, a metal layer can amplify the transmission of development vector waves and reduce the light diffraction effect in the exposing process. Therefore, the quality of an SP photo-etched pattern is improved.

Owner:INST OF OPTICS & ELECTRONICS - CHINESE ACAD OF SCI

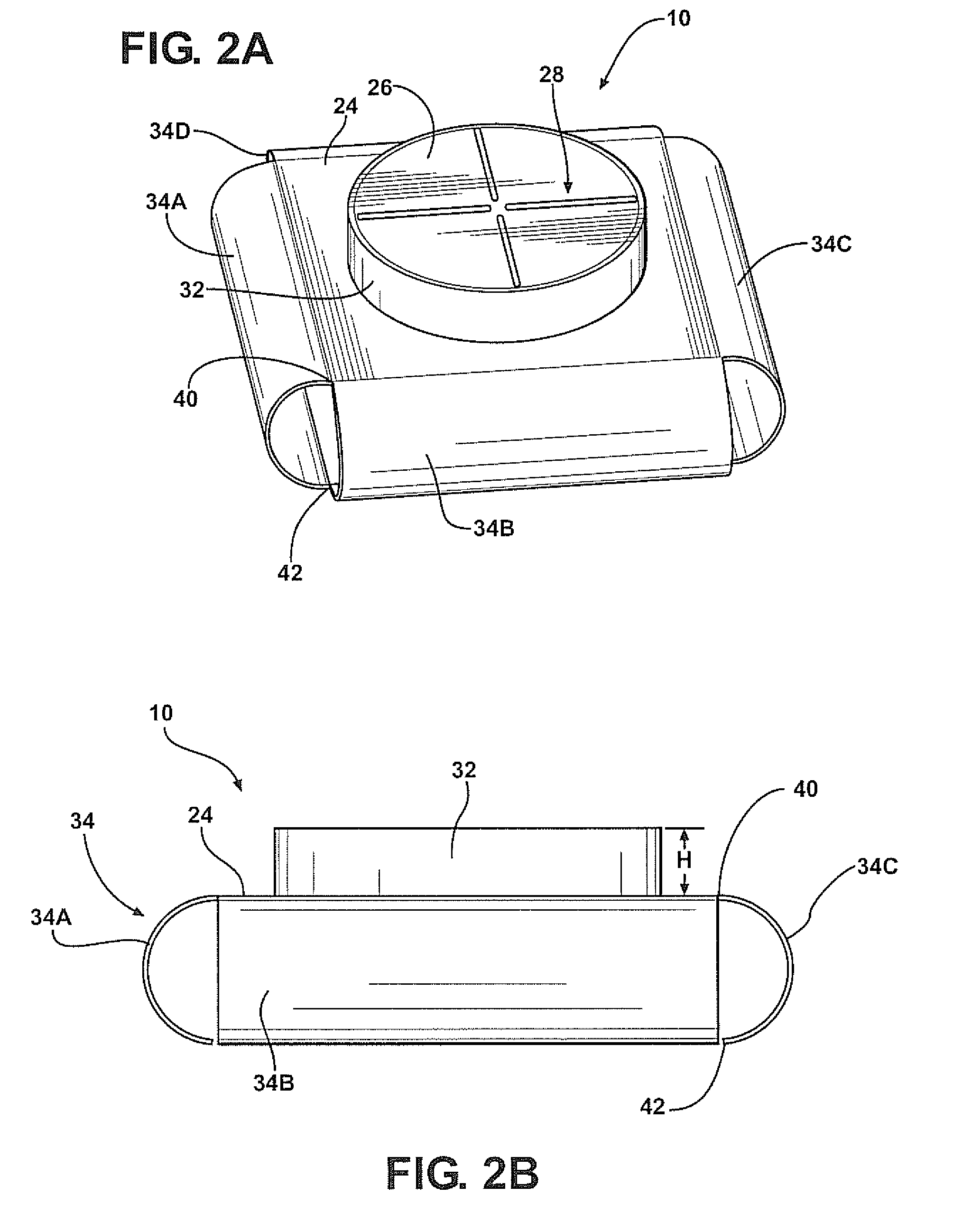

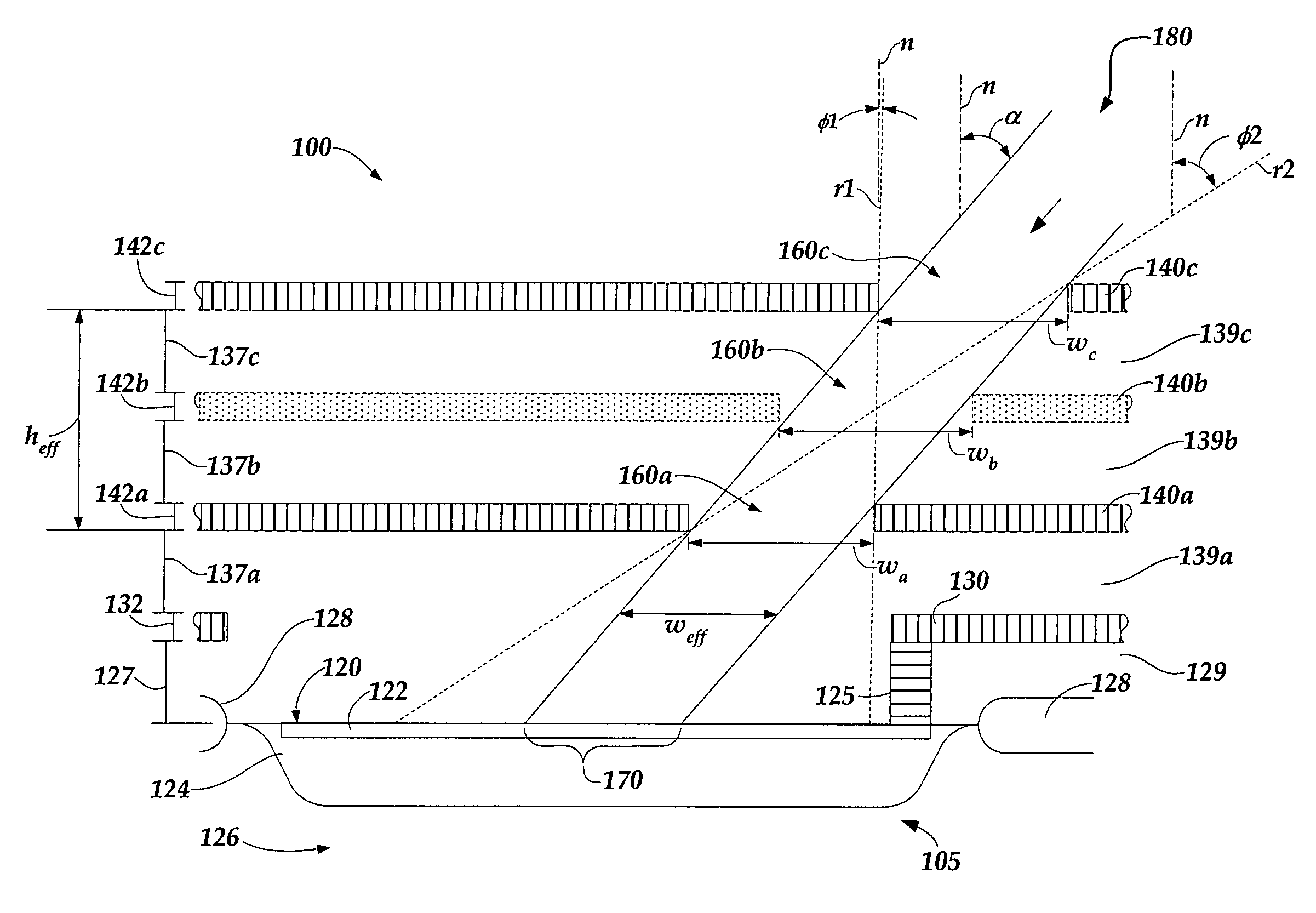

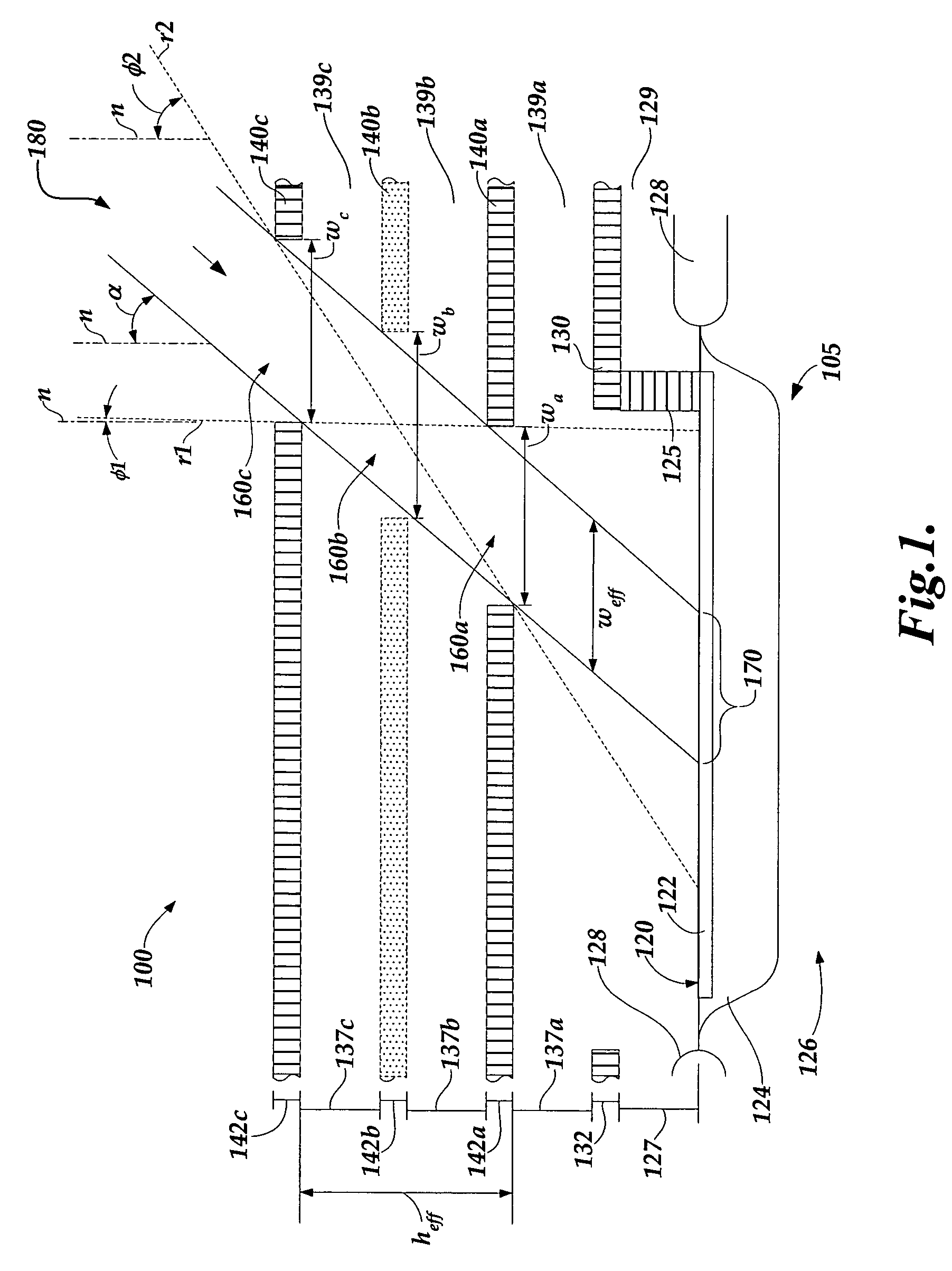

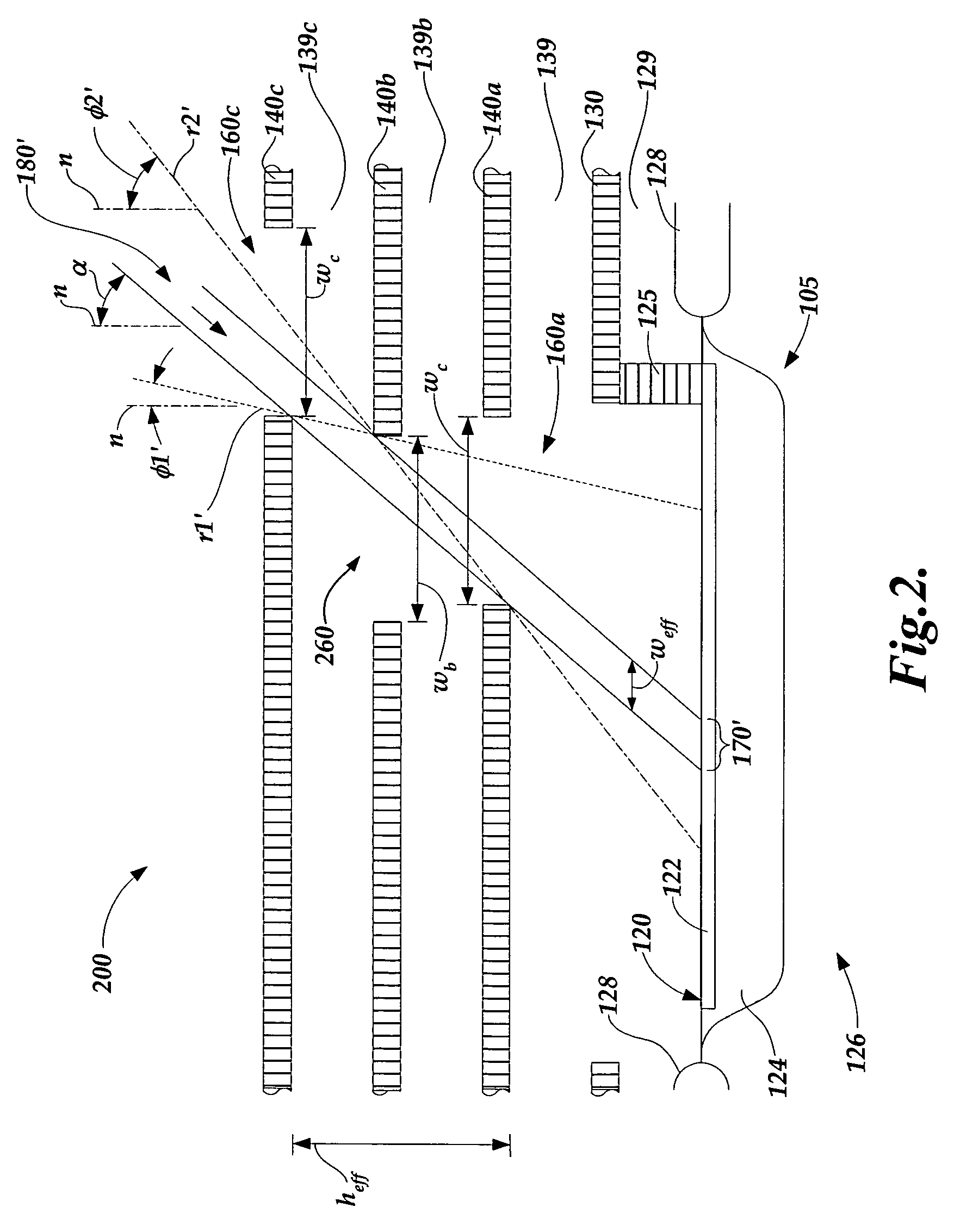

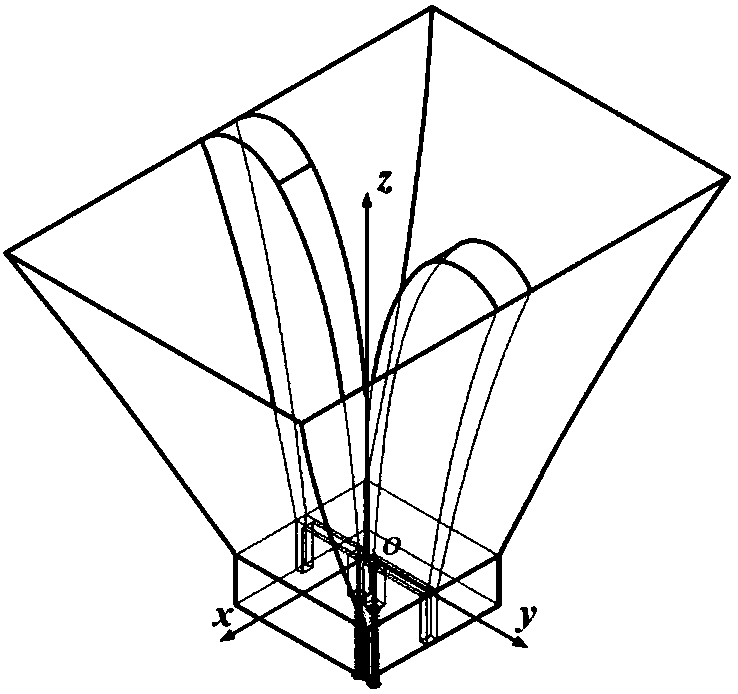

Wide frequency range horn with modular method for reducing diffraction effects

InactiveUS7845462B2Diffraction reductionImprove versatilitySound producing devicesFrequency/directions obtaining arrangementsDiffraction effectEngineering

A middle to high frequency straight pathway horn with wide horizontal dispersion characteristics having extended terminus side walls which approach a perpendicular angle compared to the horn axis which are further extended by a rearwardly divergent angled or curved surface from the terminus frontal plane to reduce the deleterious effects of horn mouth, edge, and baffle diffraction, allowing for traditional front baffle mounting or free-standing use. Modular baffle elements allow the invention to be configured for the further reduction of diffraction effects in a variety of applications.

Owner:MOORE DANA A