Patents

Literature

31results about How to "Increase unit density" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

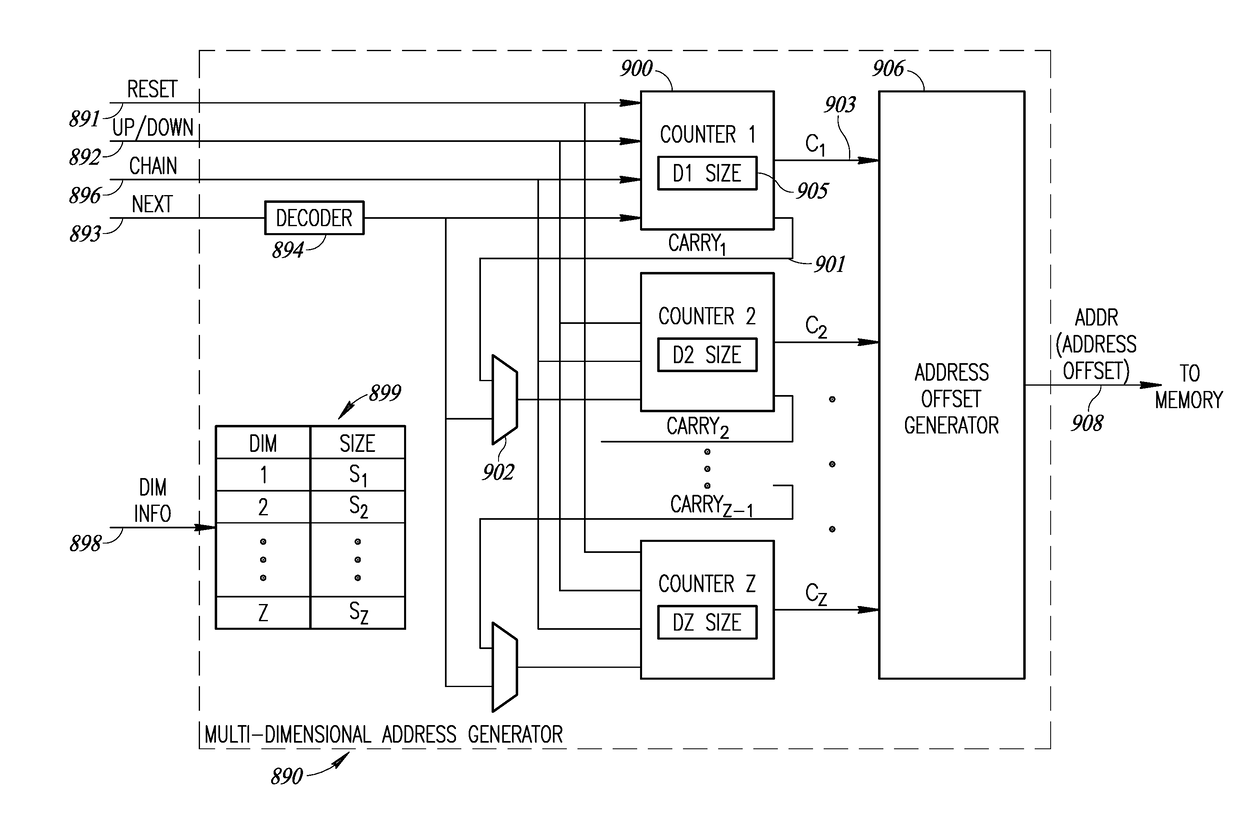

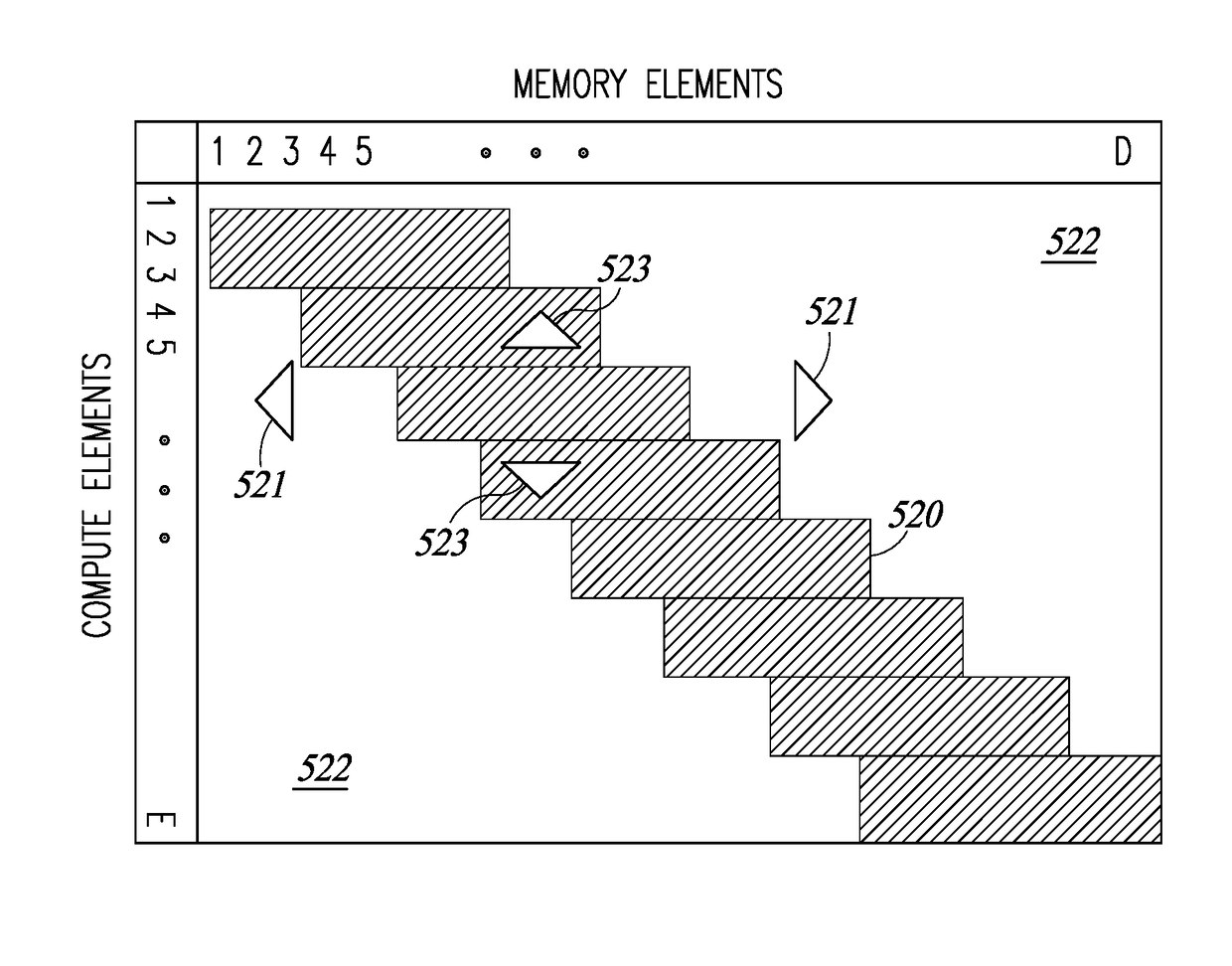

System And Method Of Memory Access Of Multi-Dimensional Data

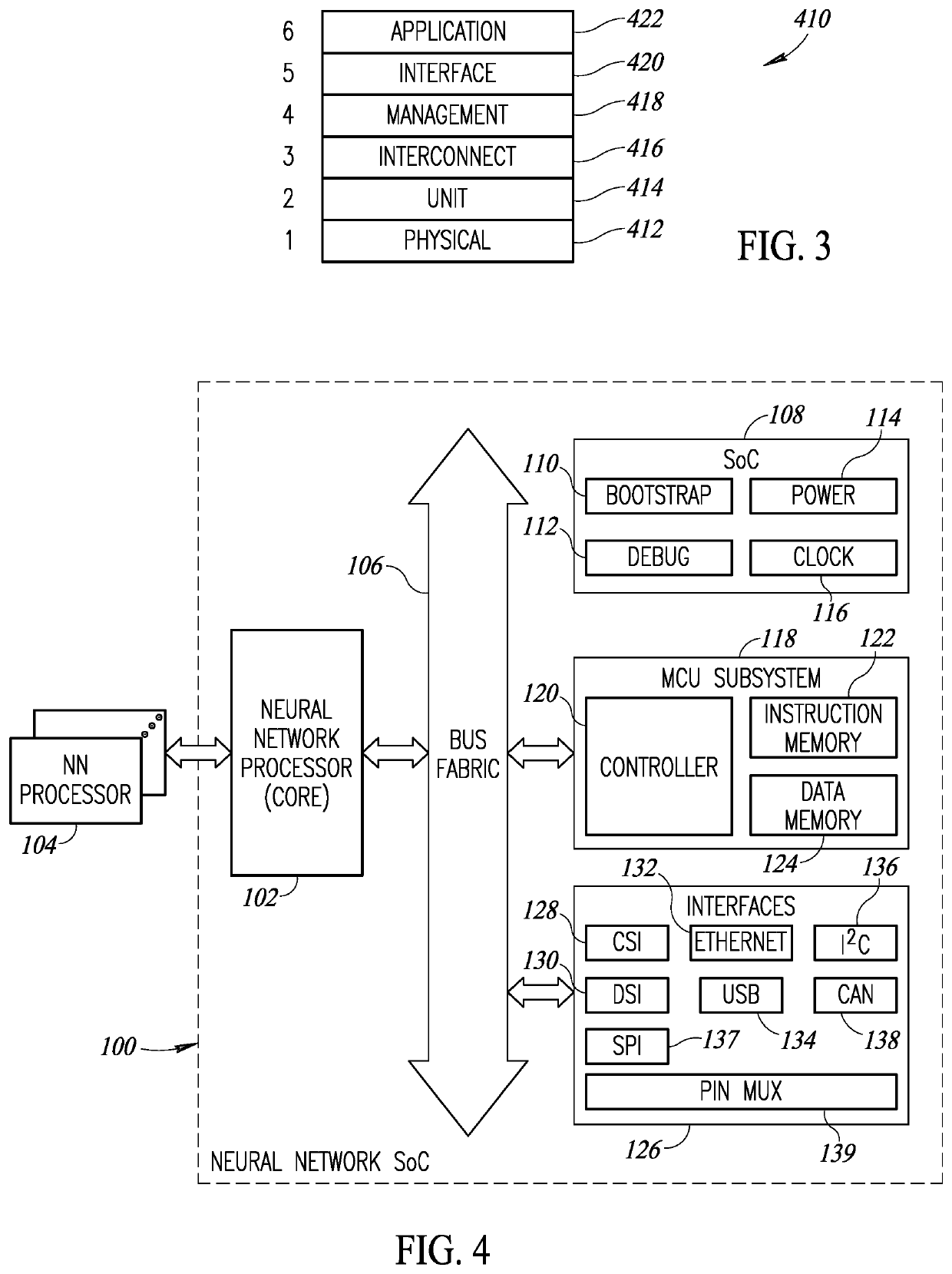

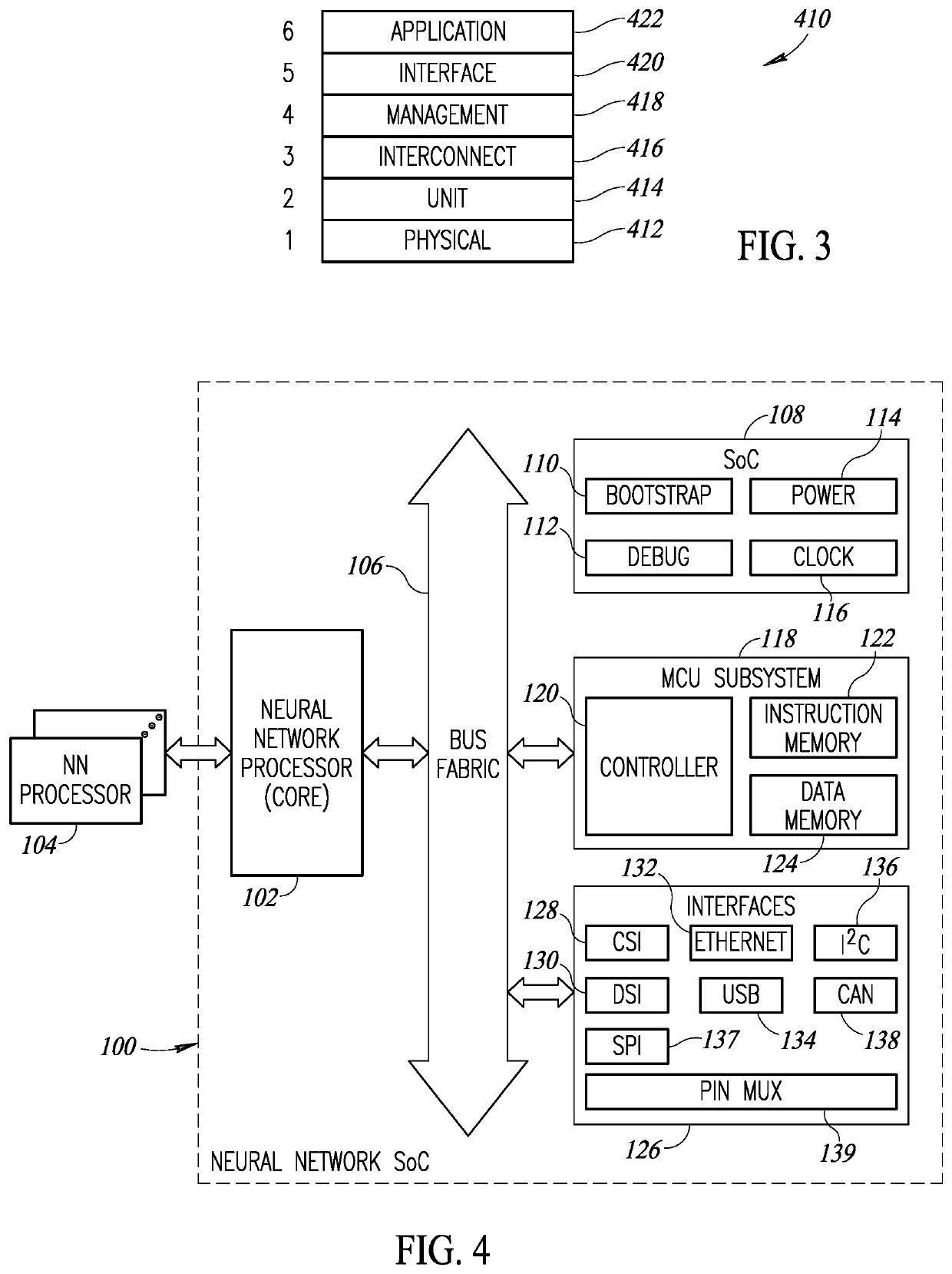

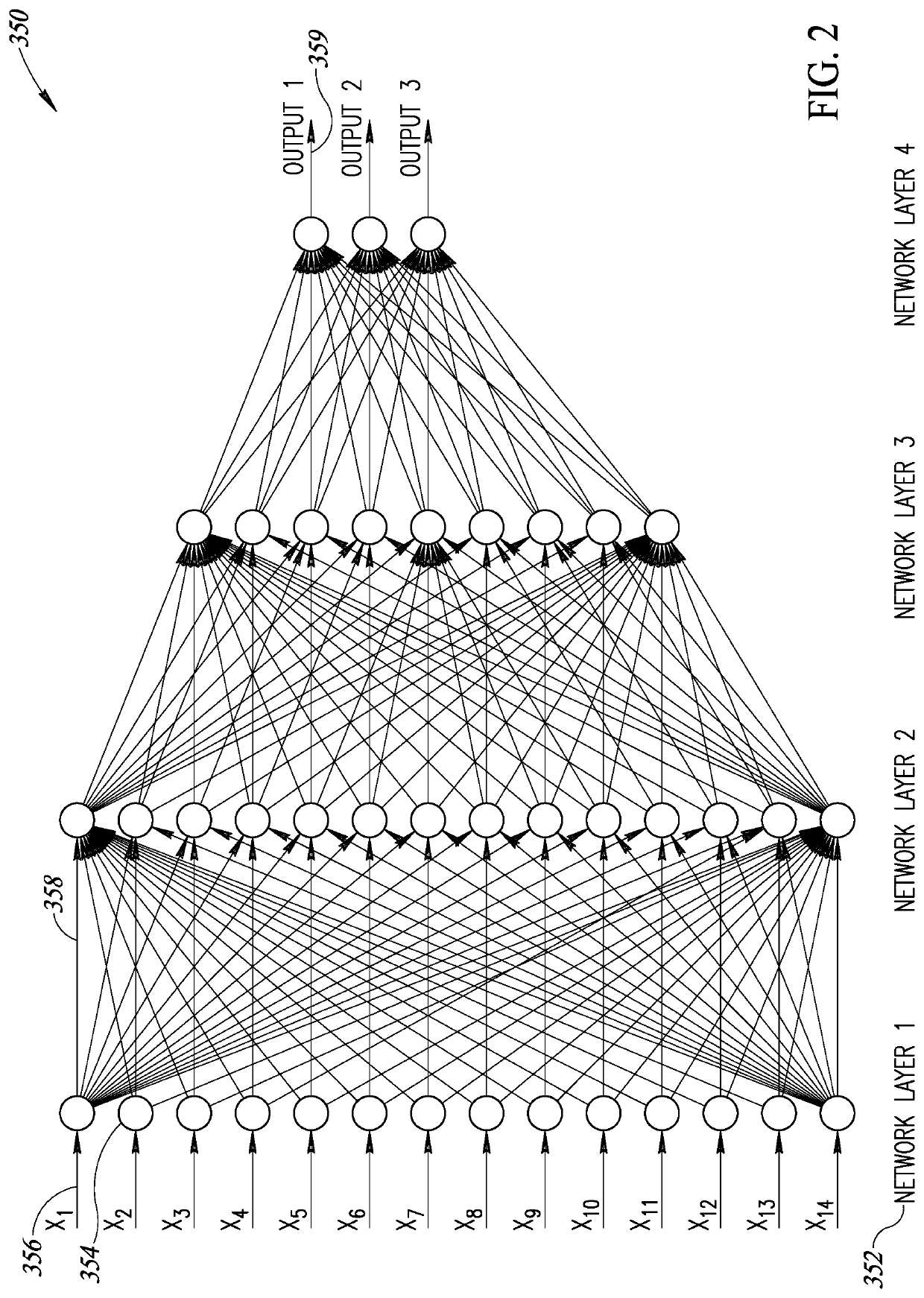

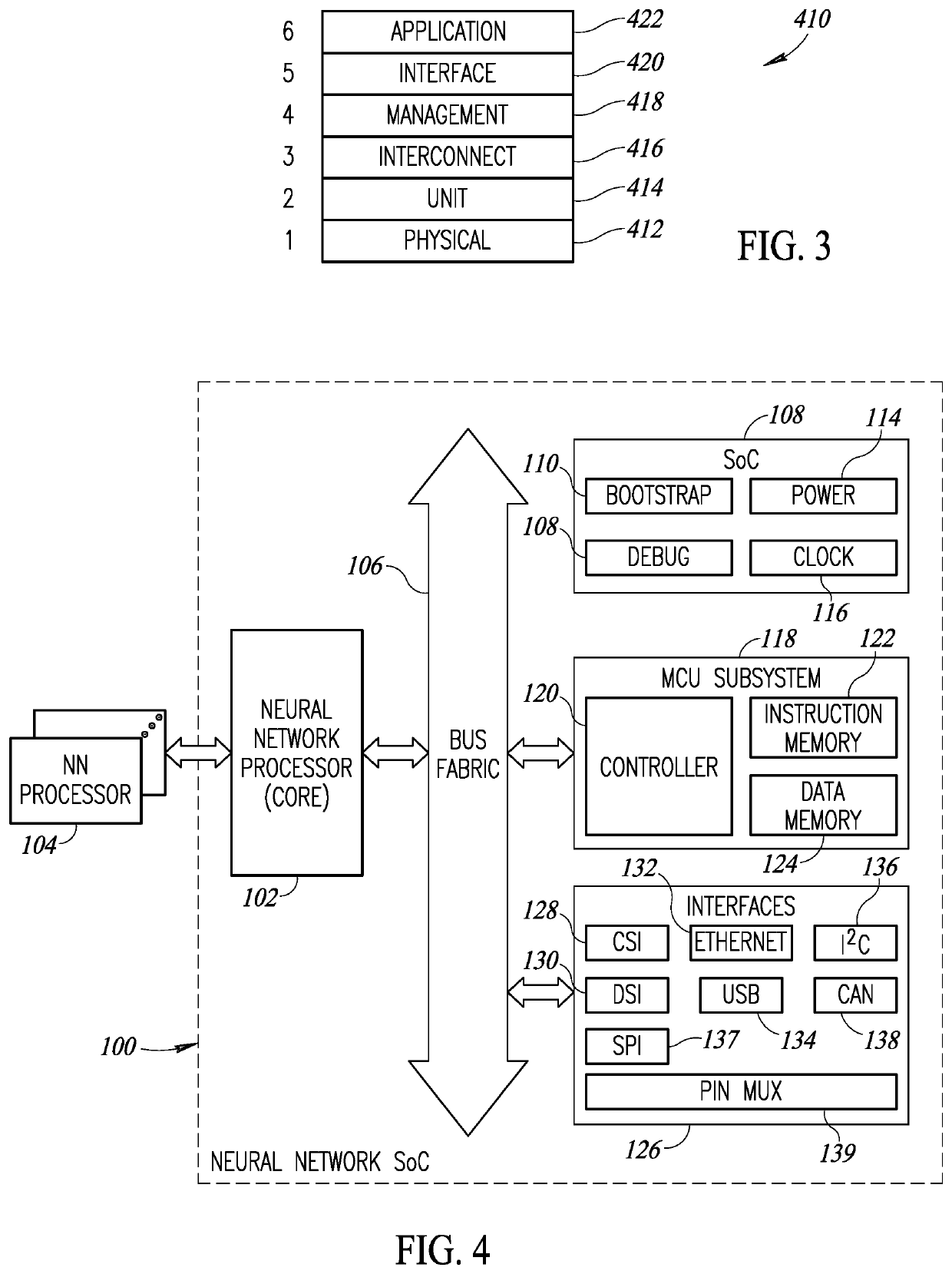

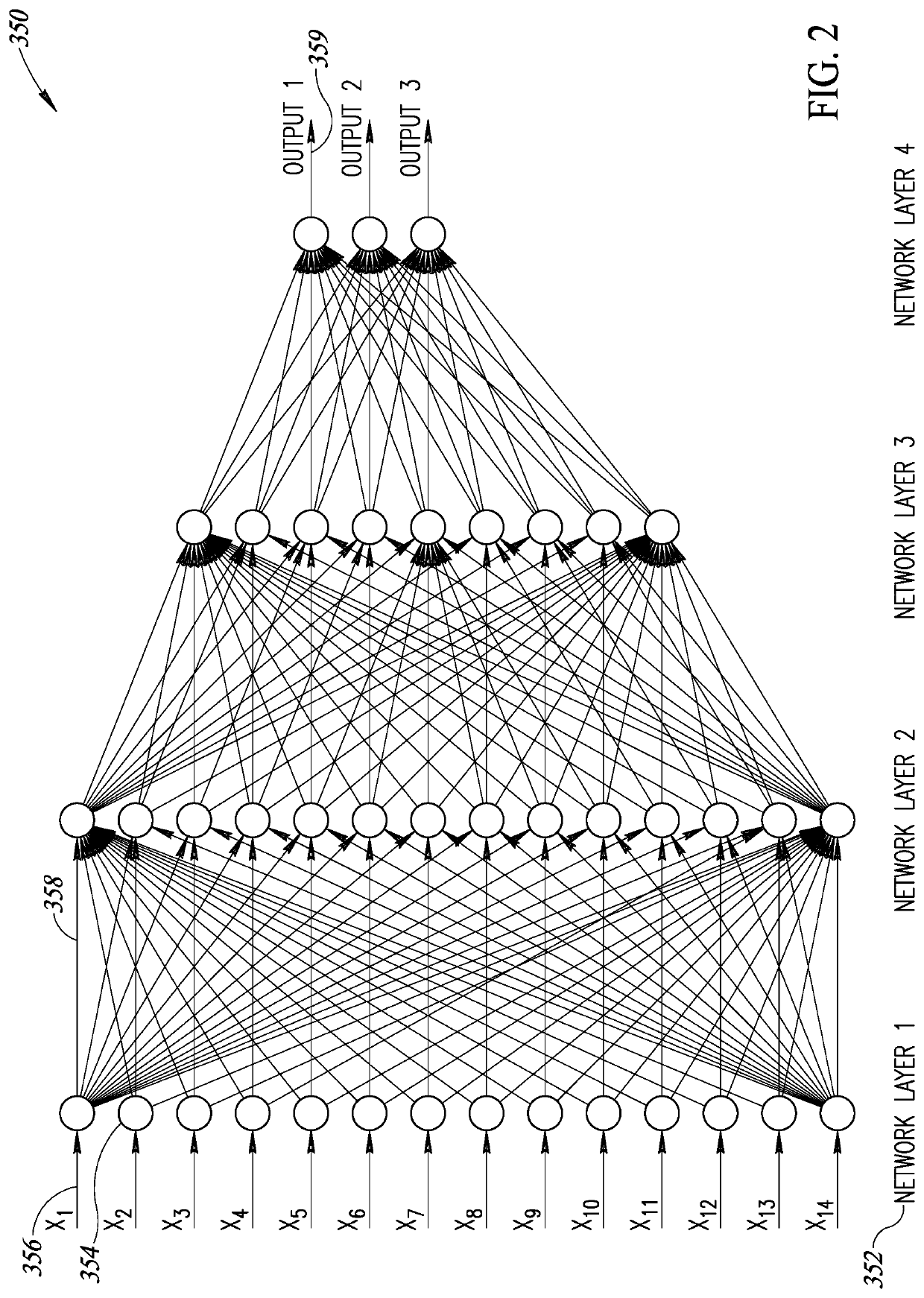

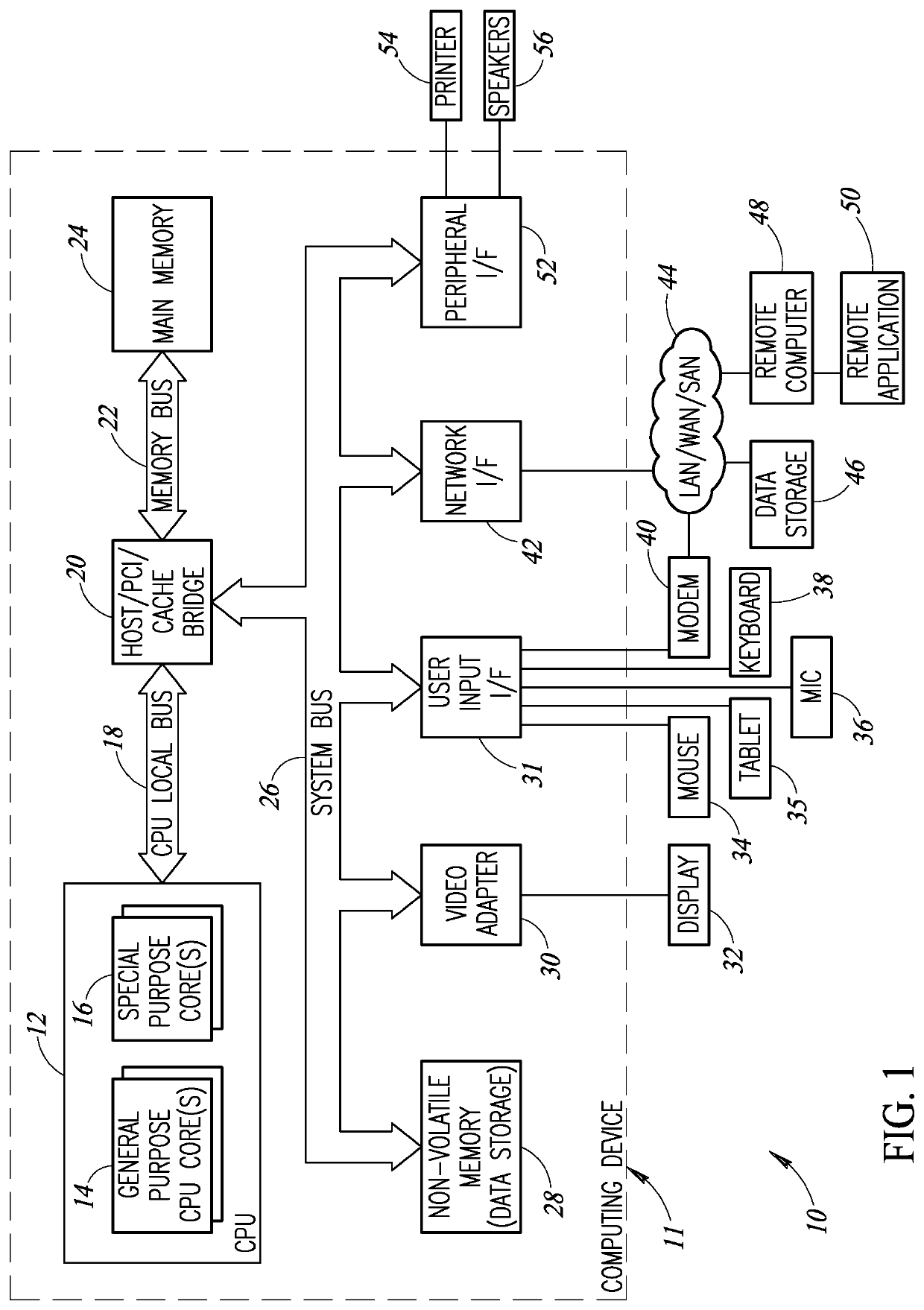

ActiveUS20180285254A1More efficientIncrease unit densityDigital data processing detailsMemory adressing/allocation/relocationLean controlNerve network

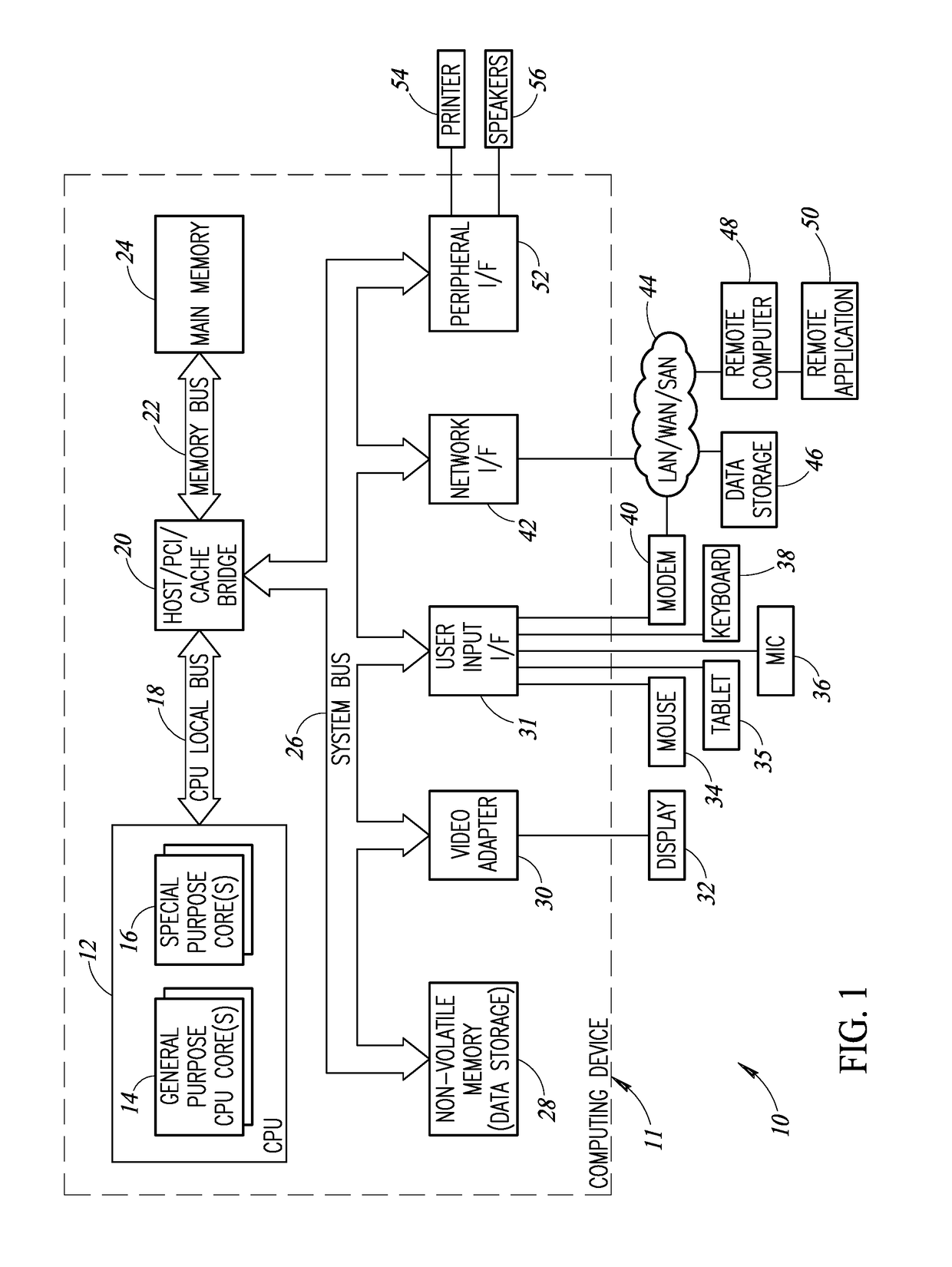

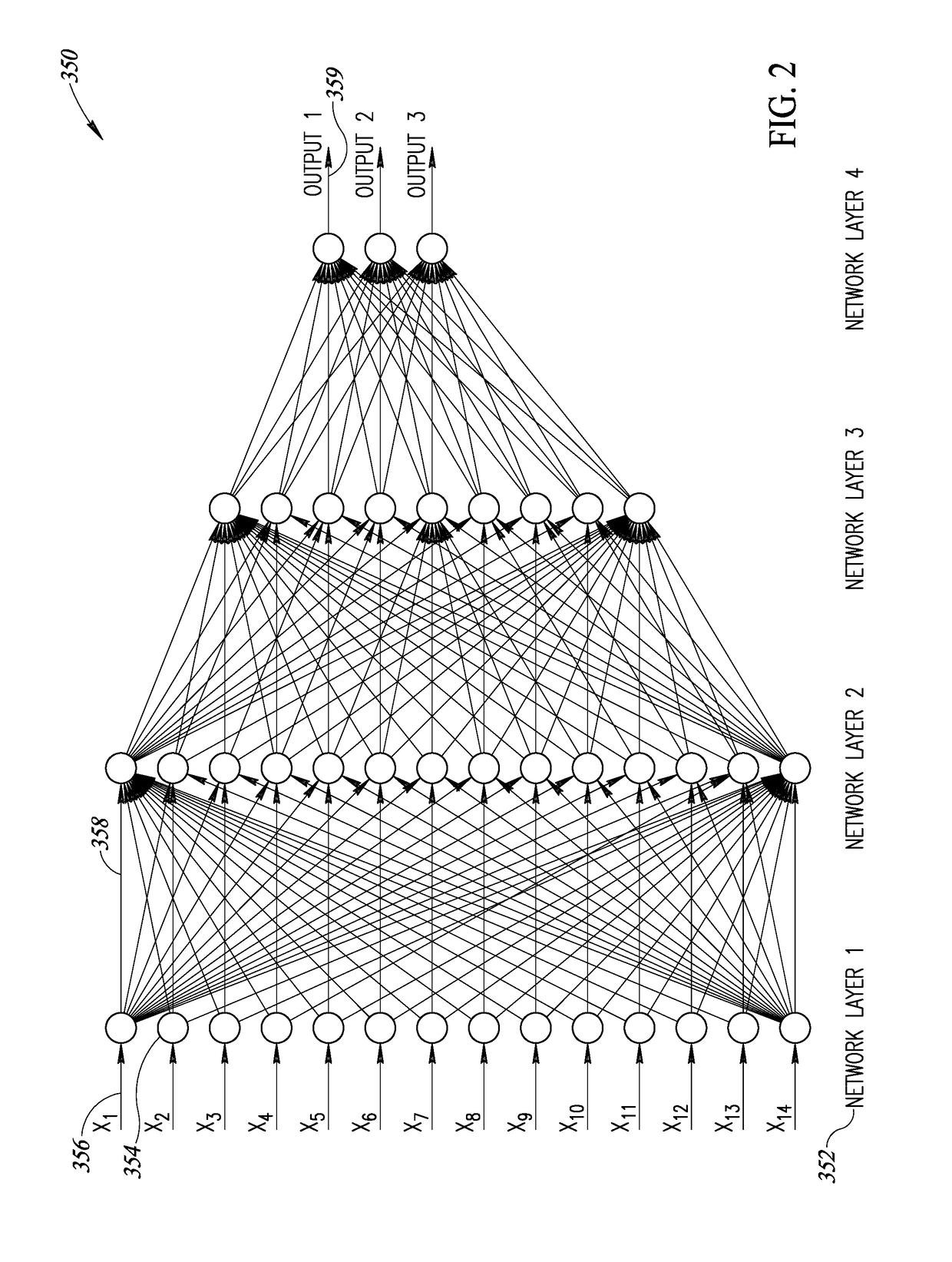

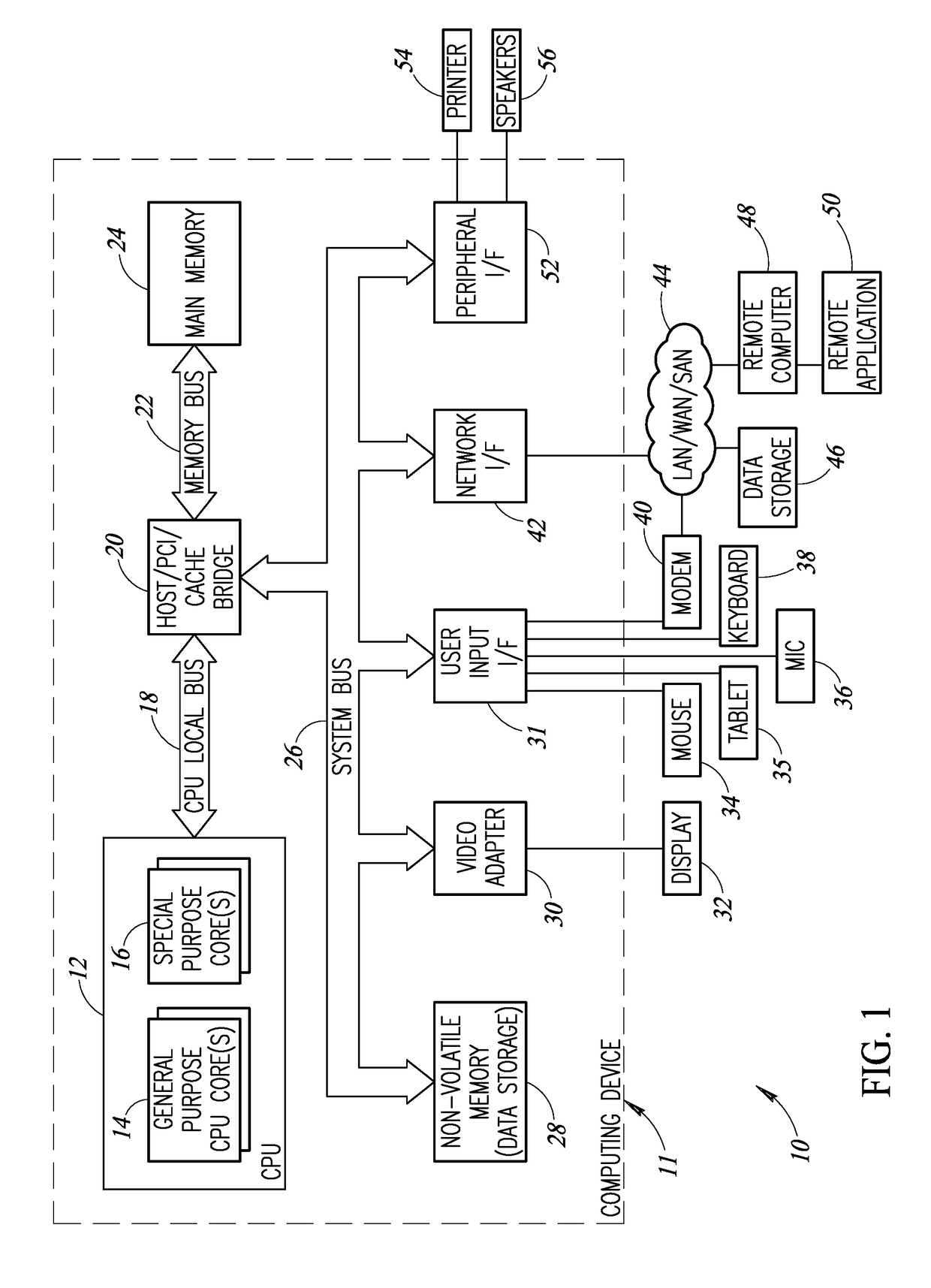

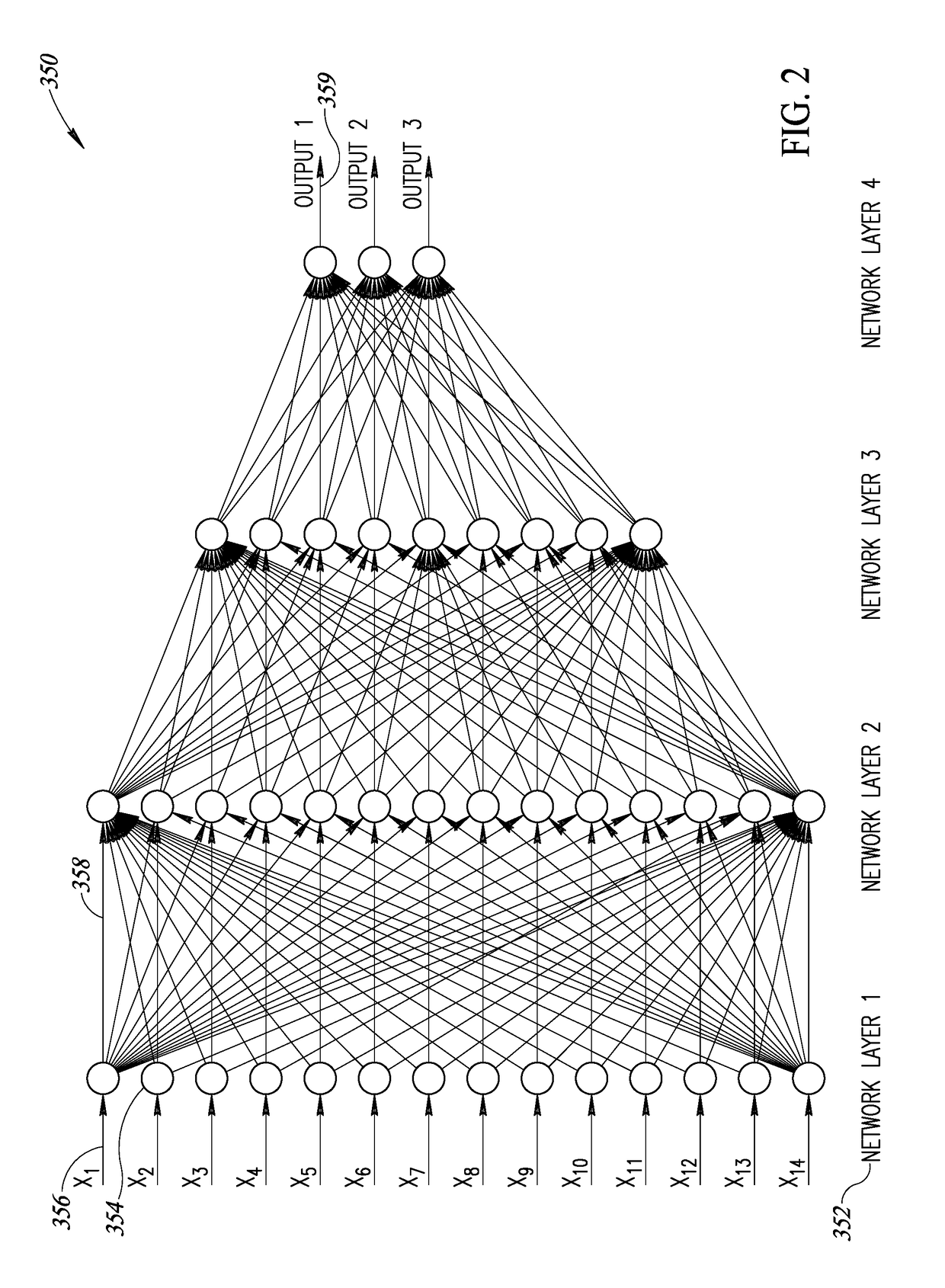

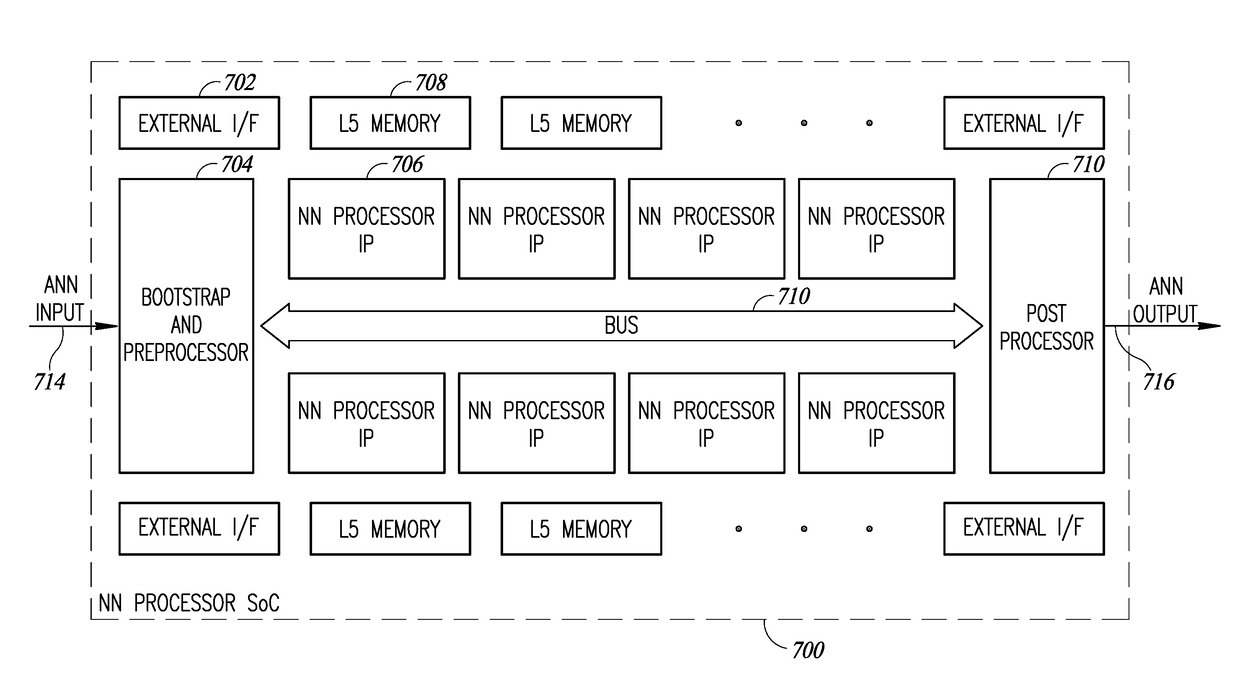

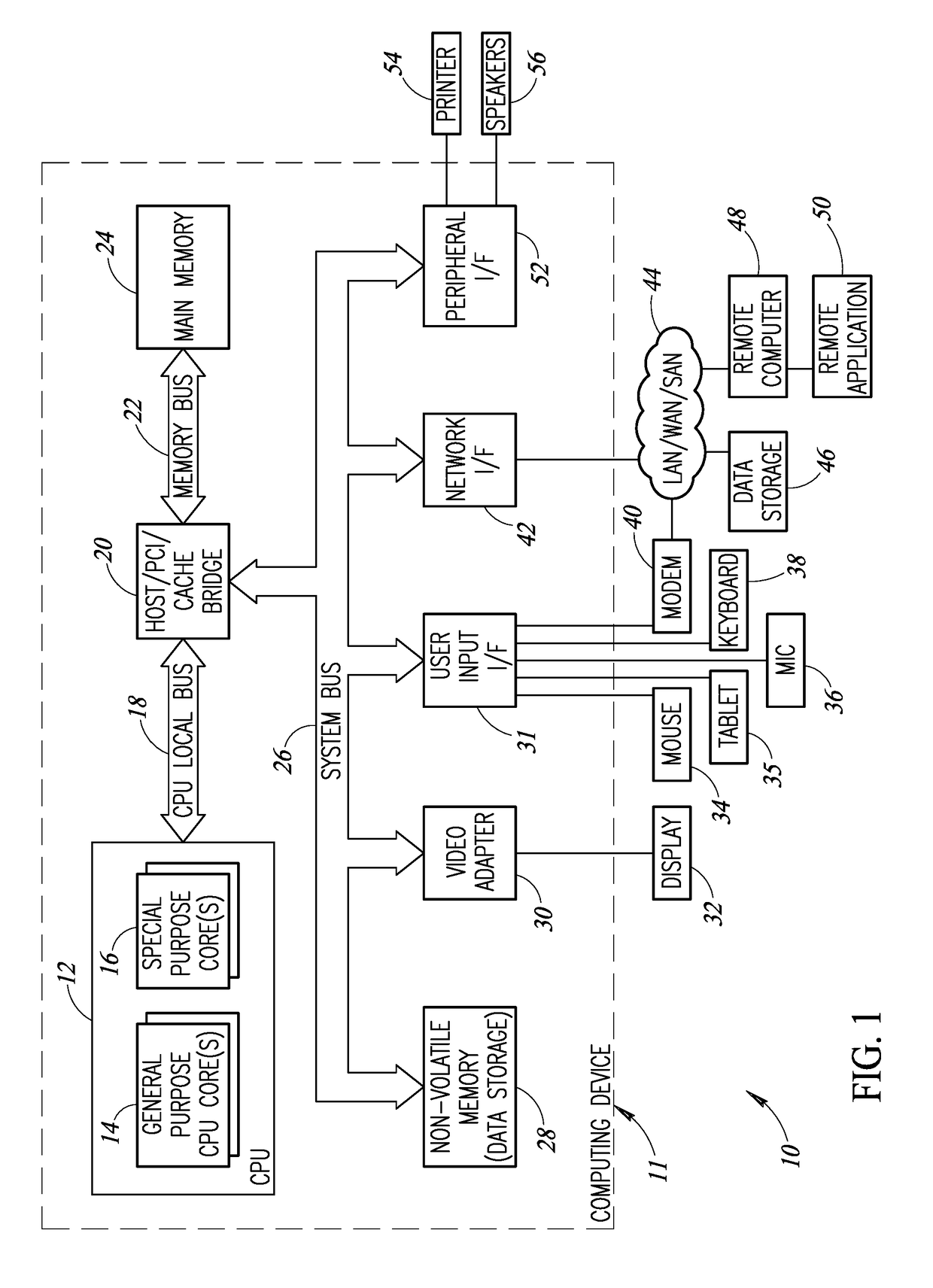

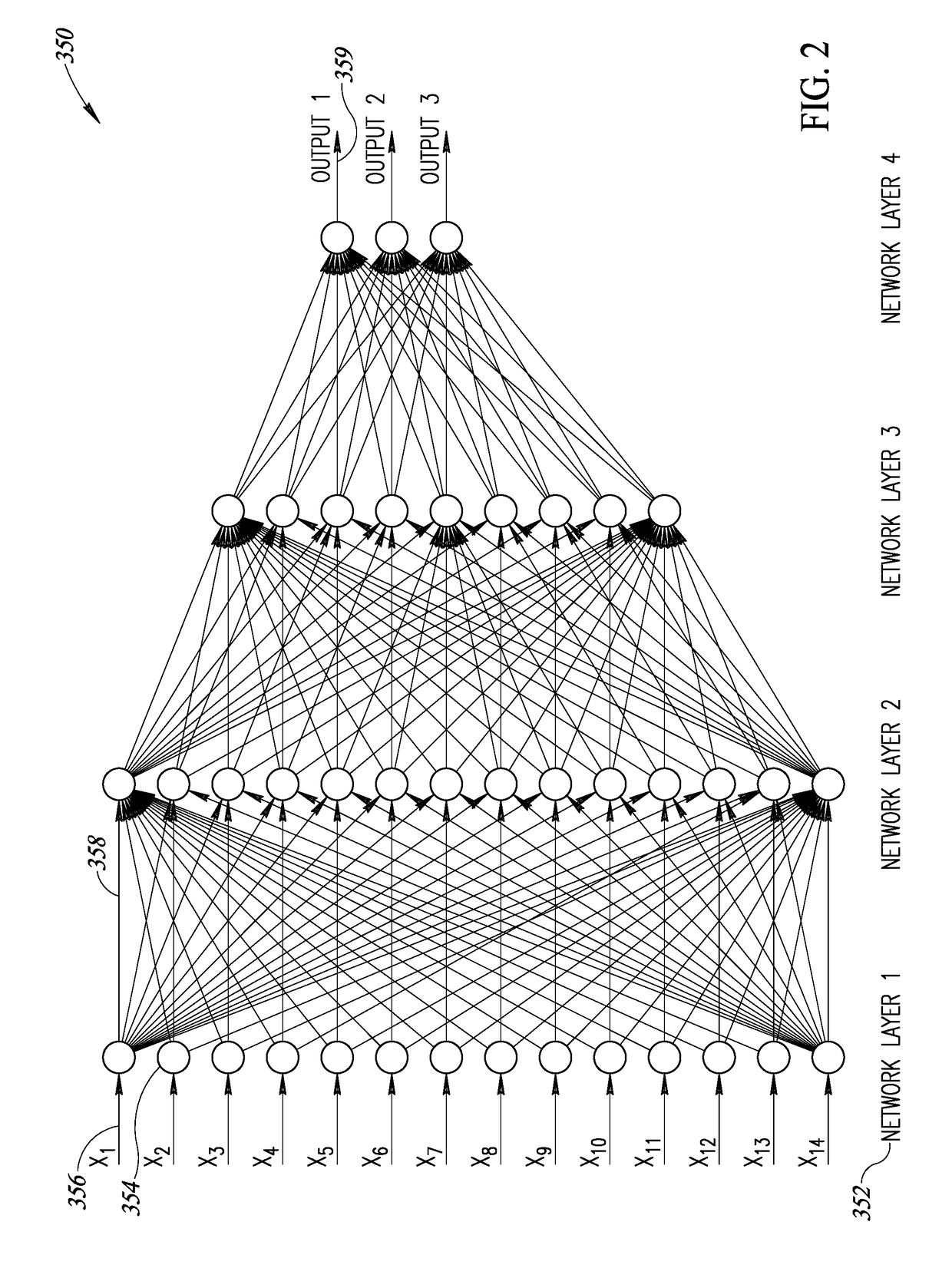

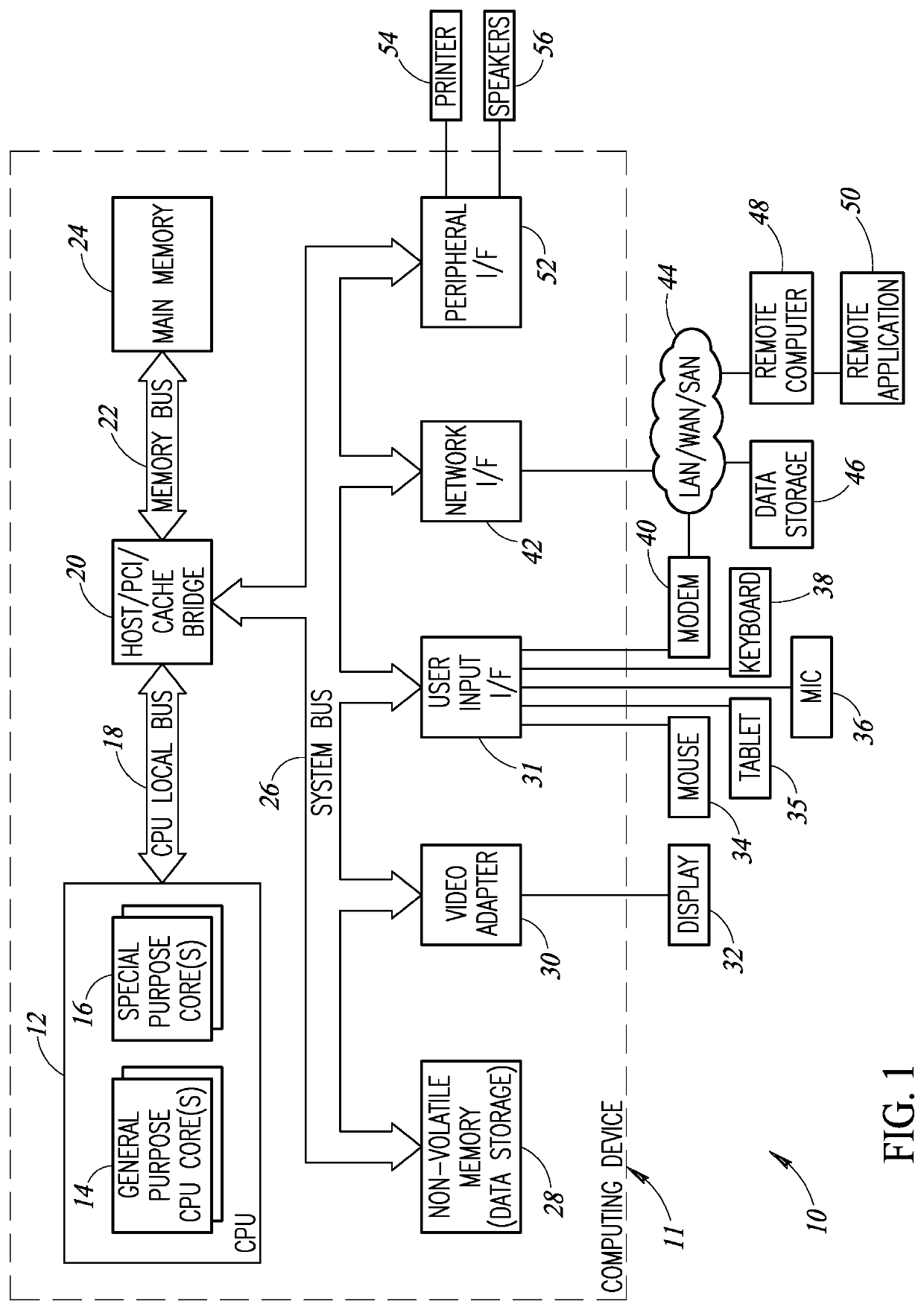

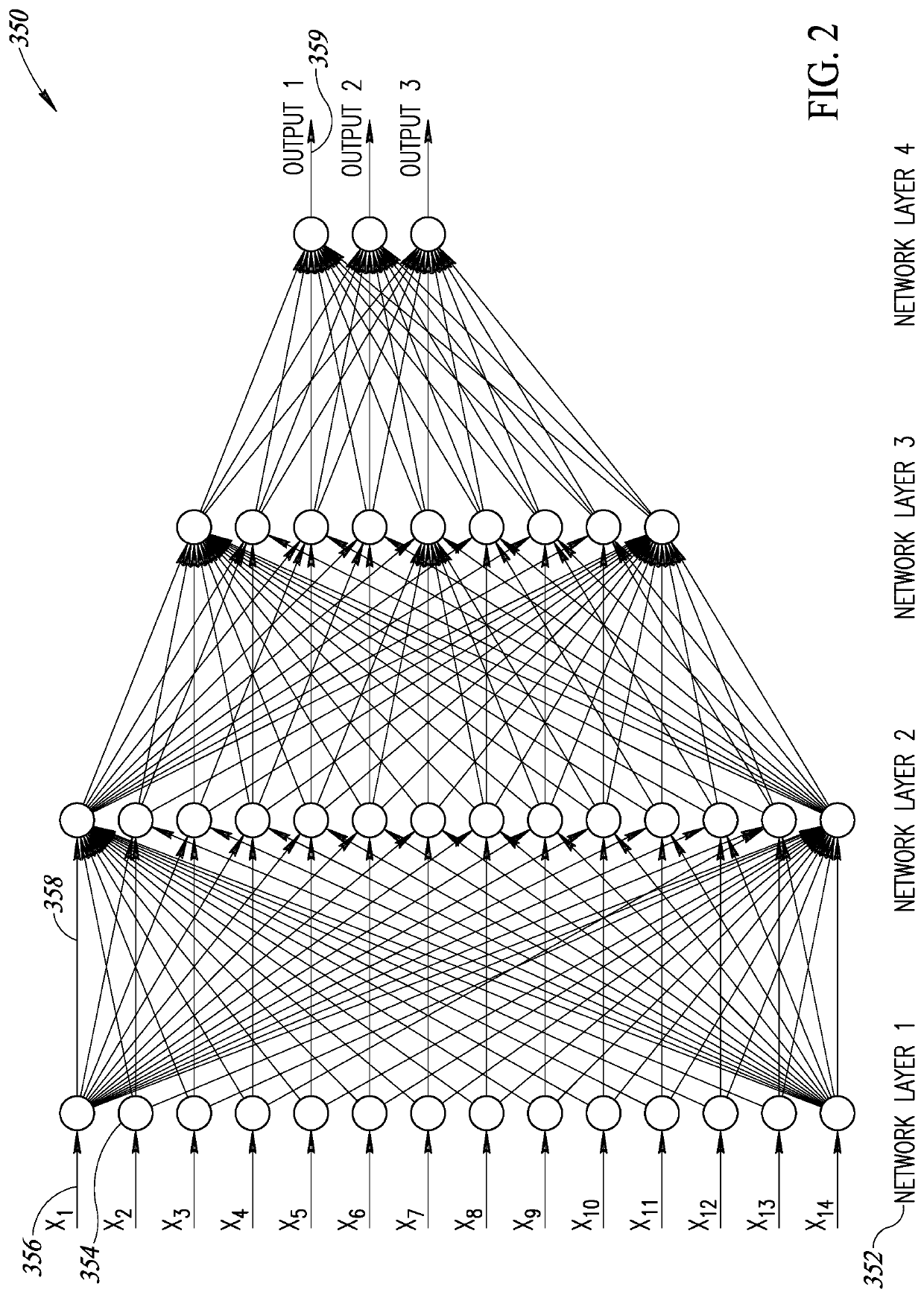

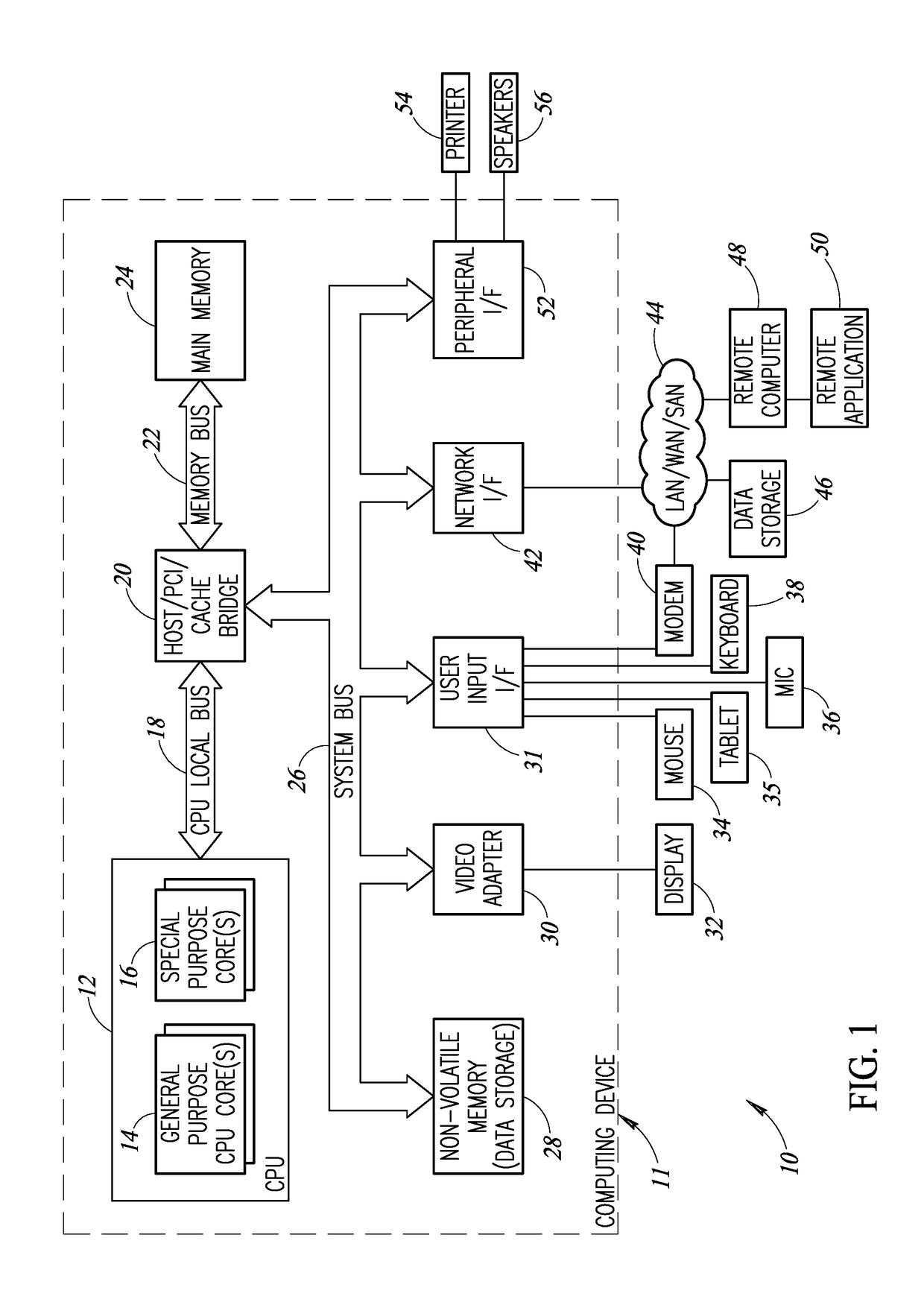

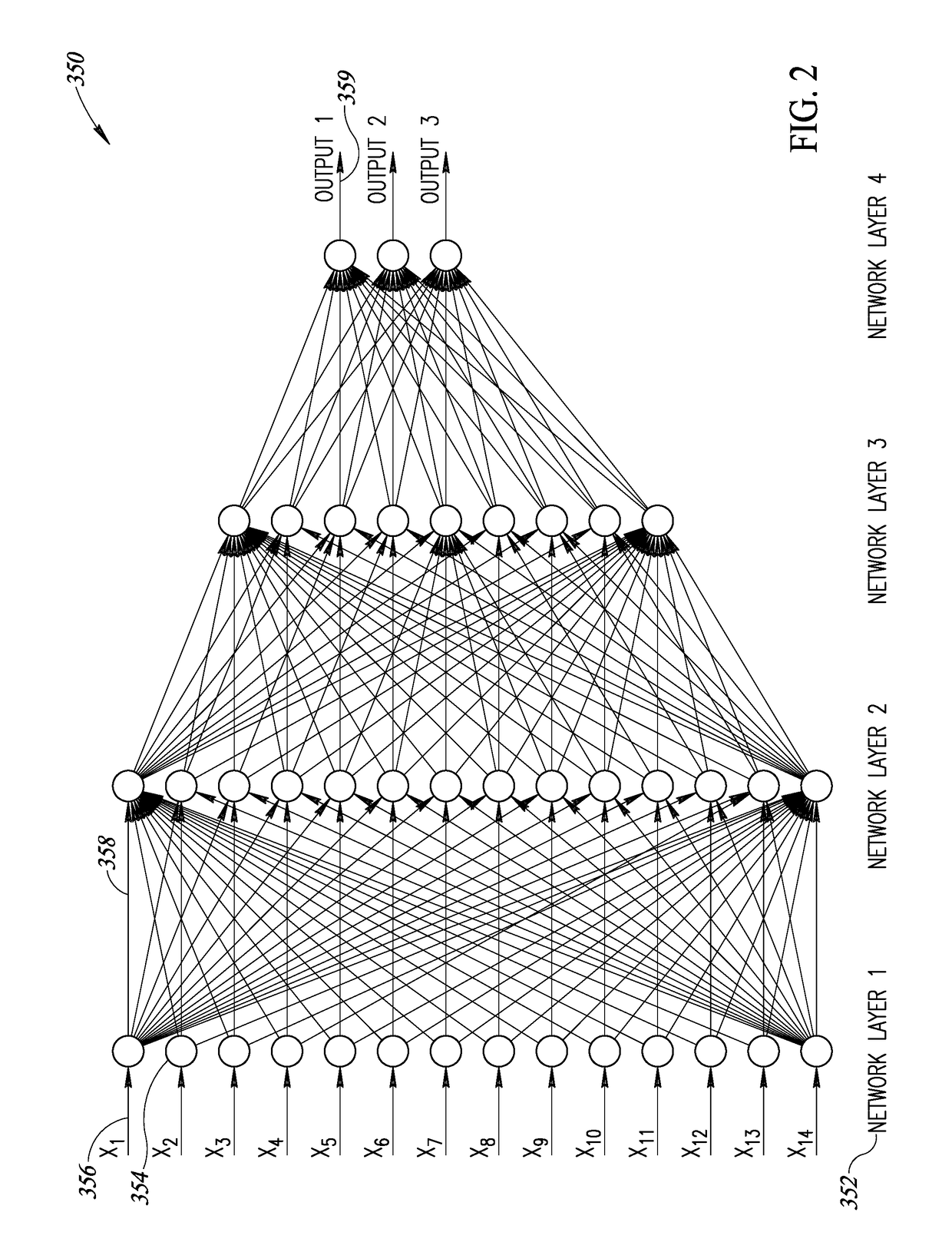

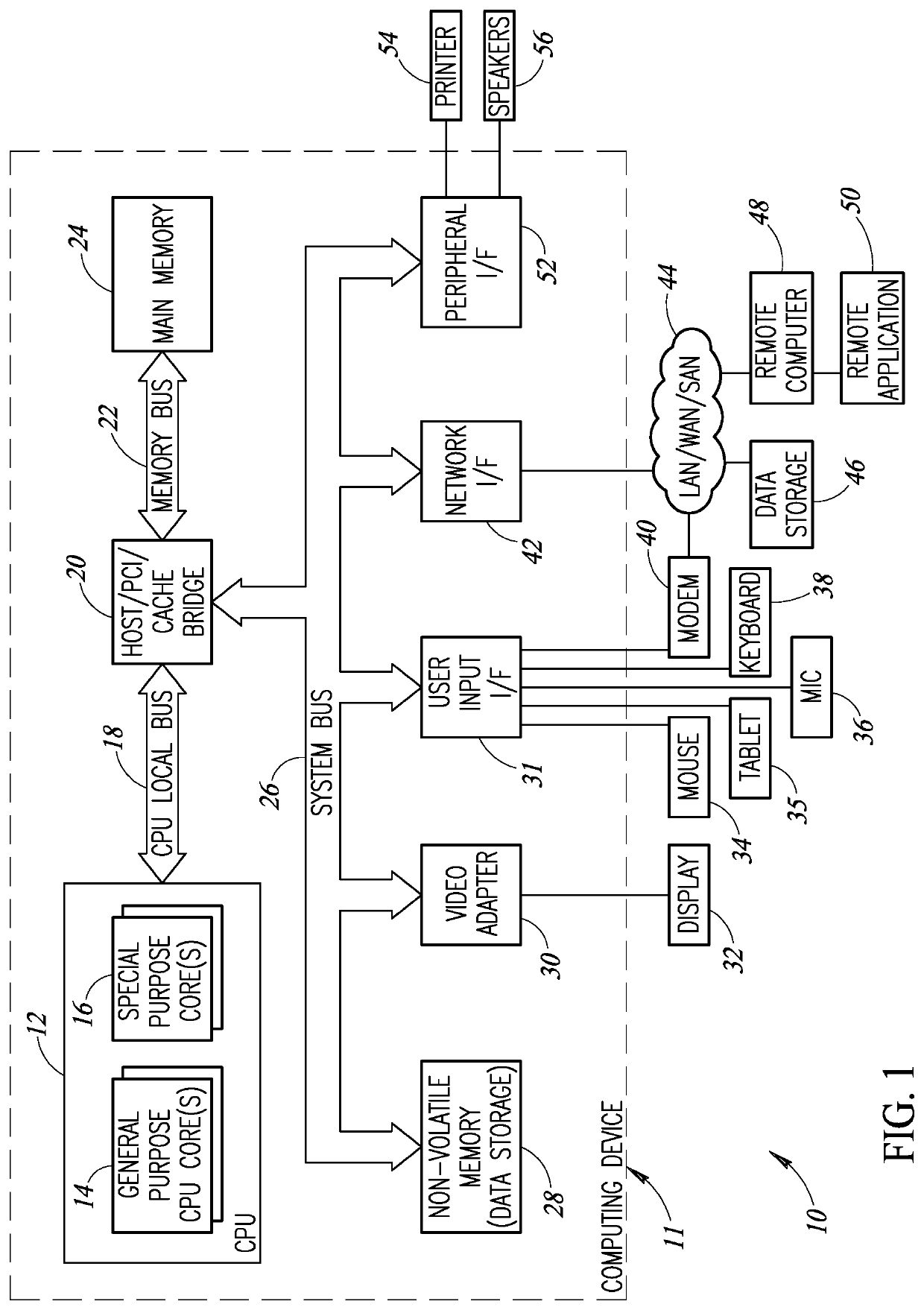

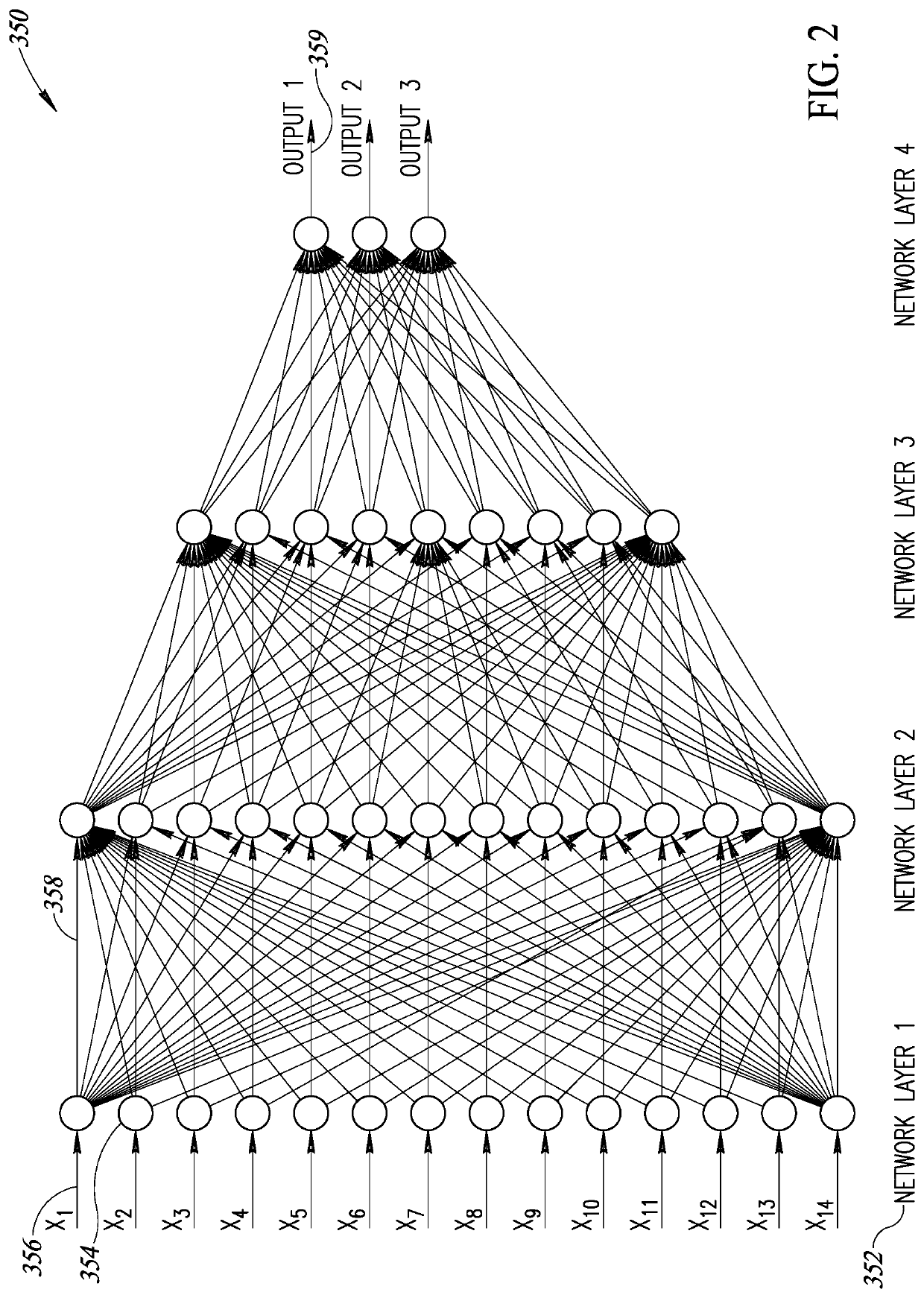

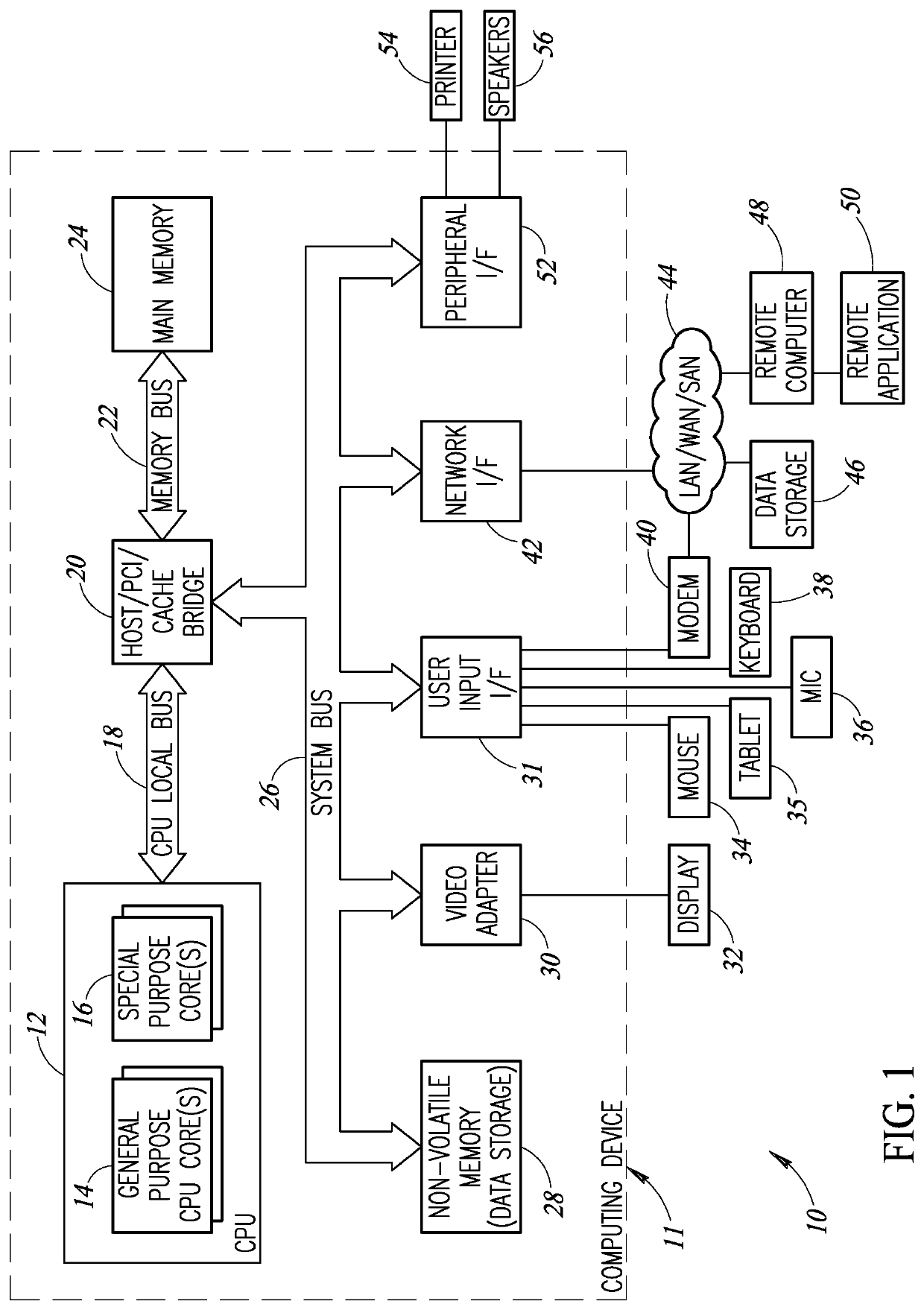

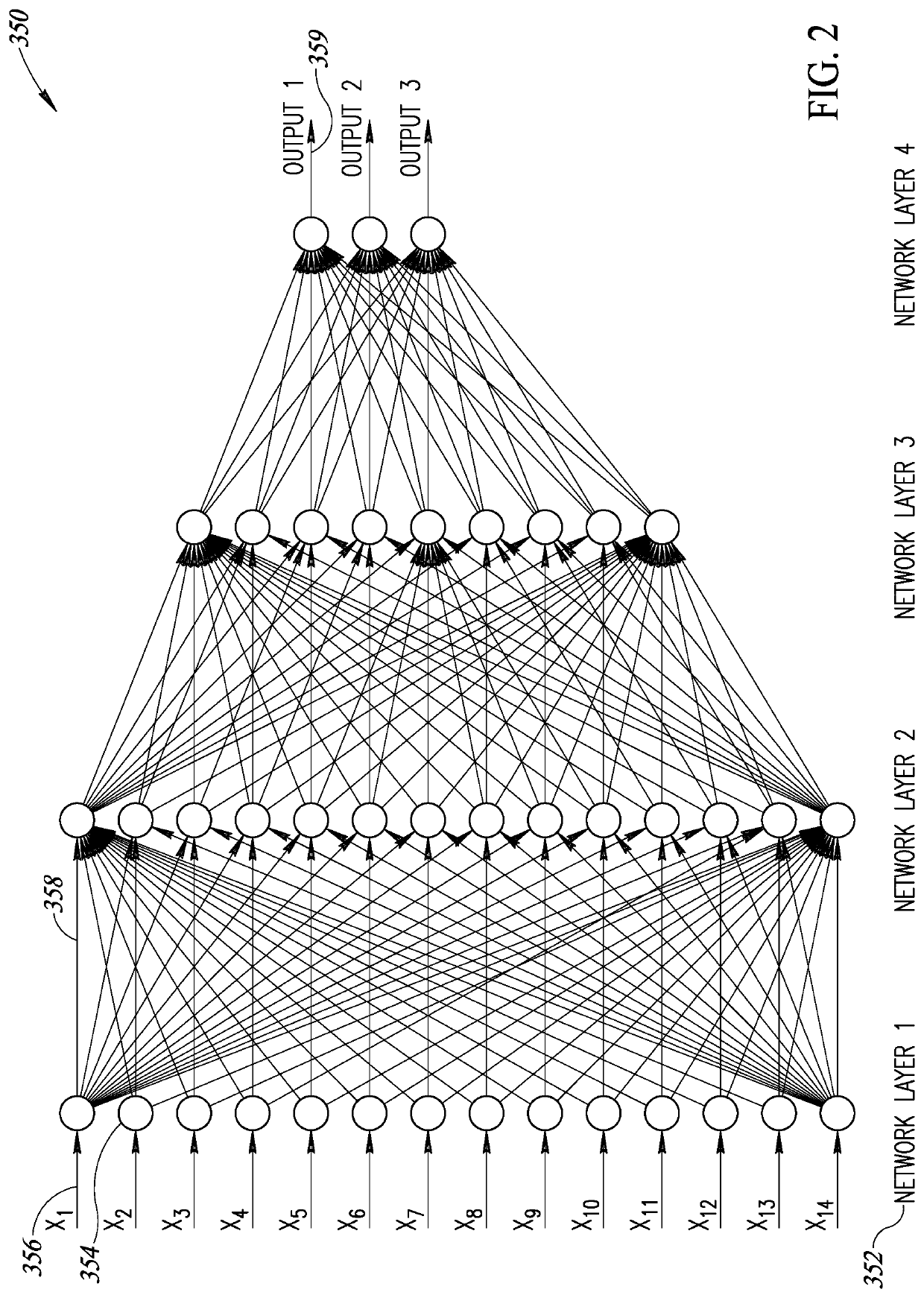

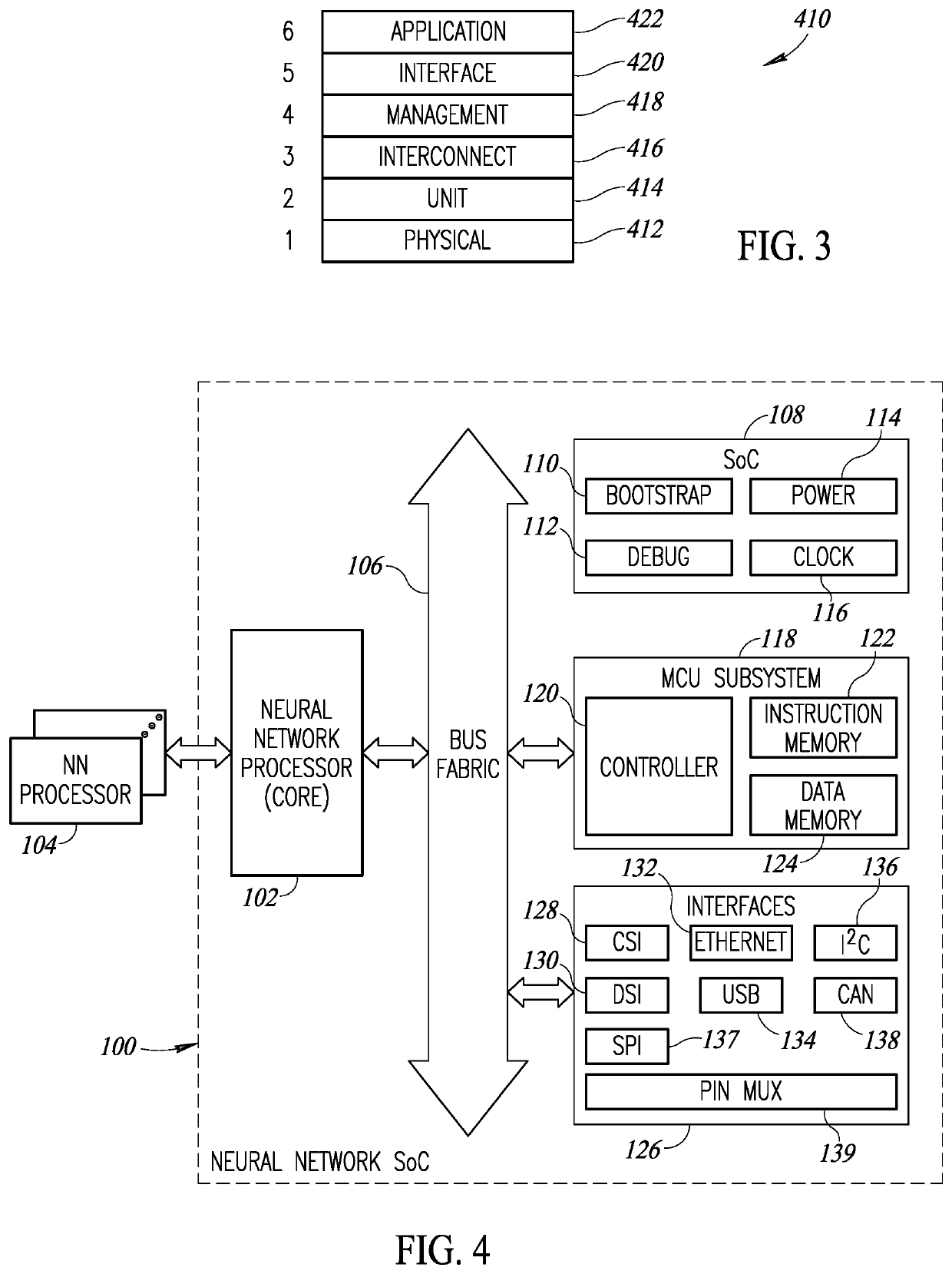

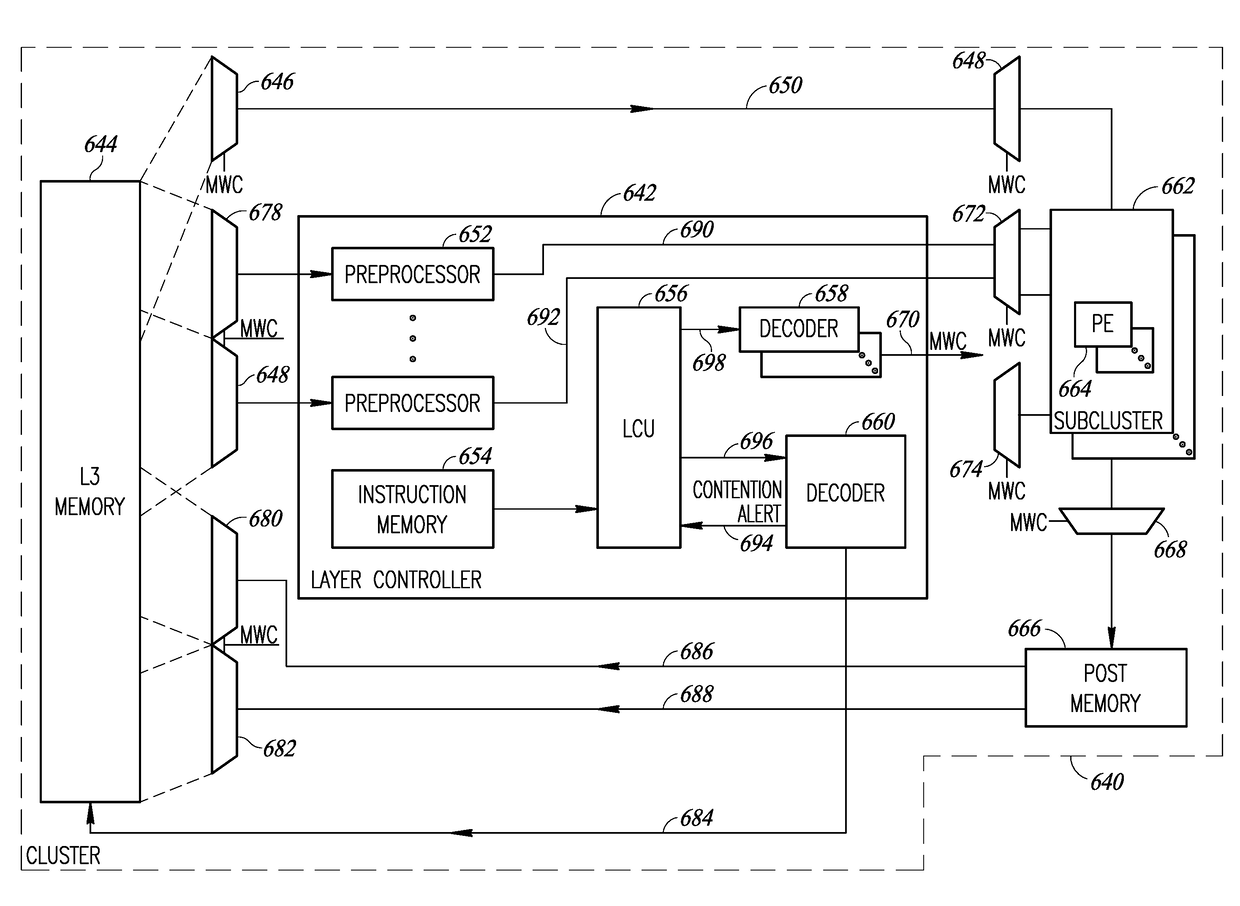

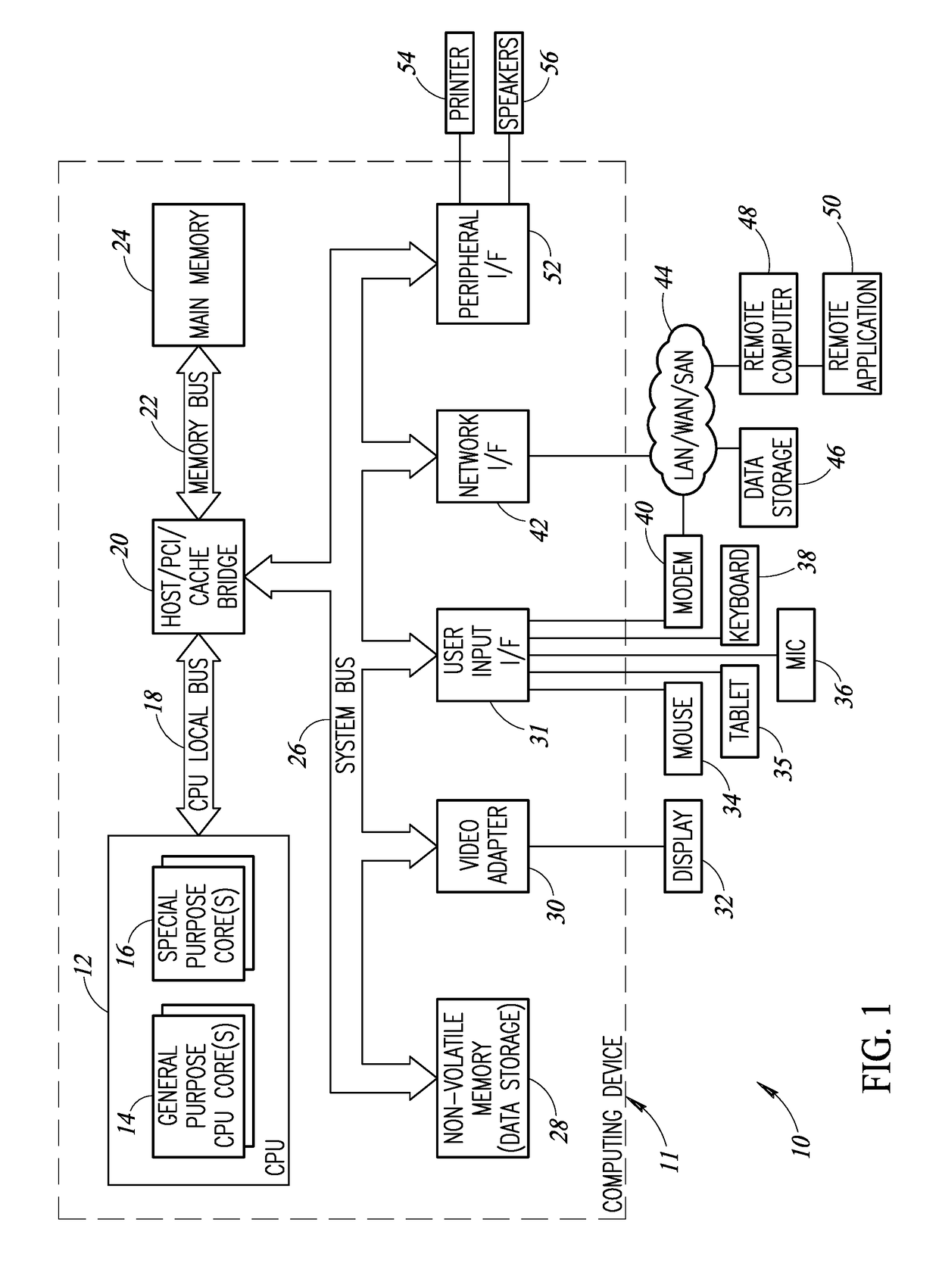

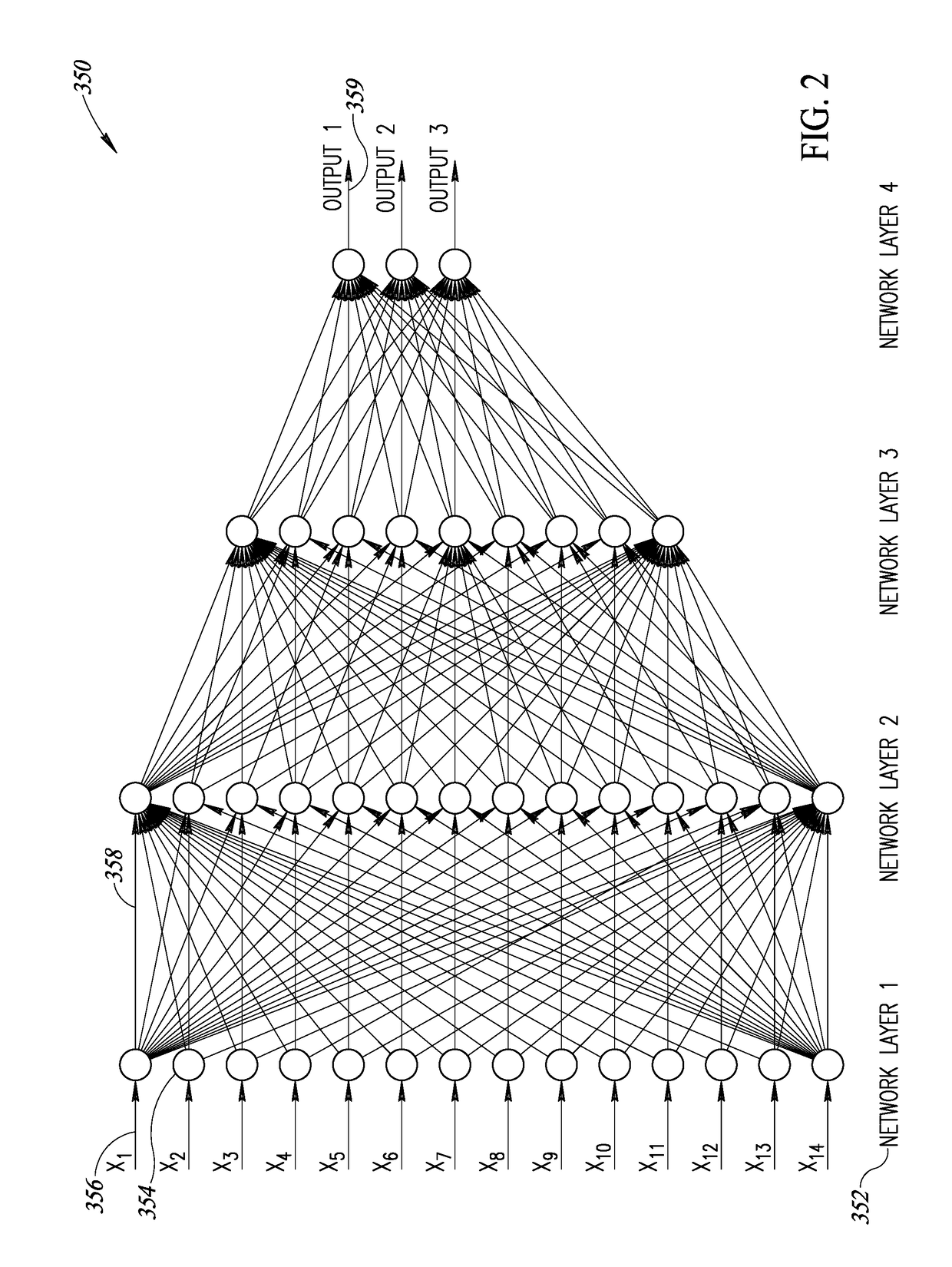

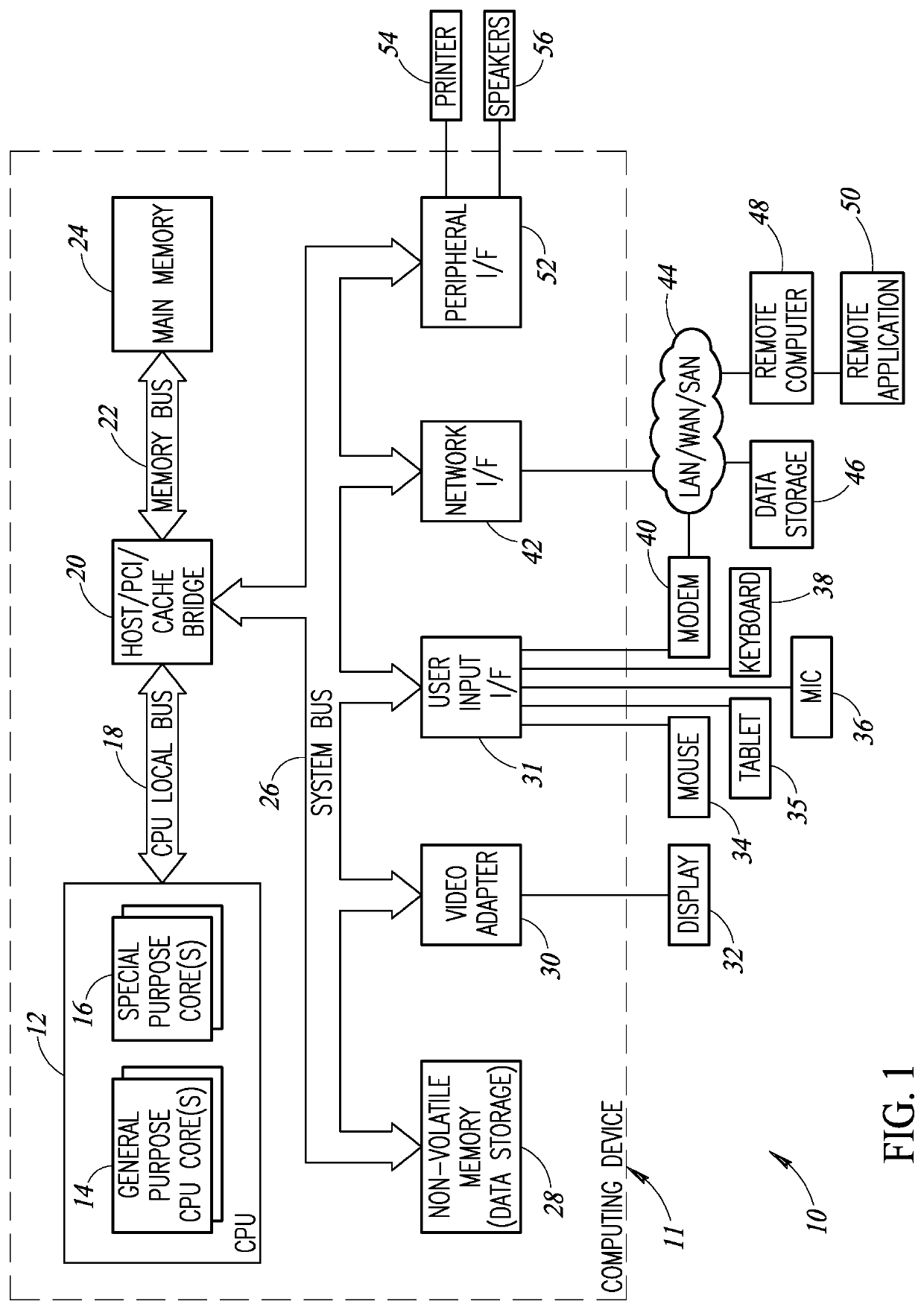

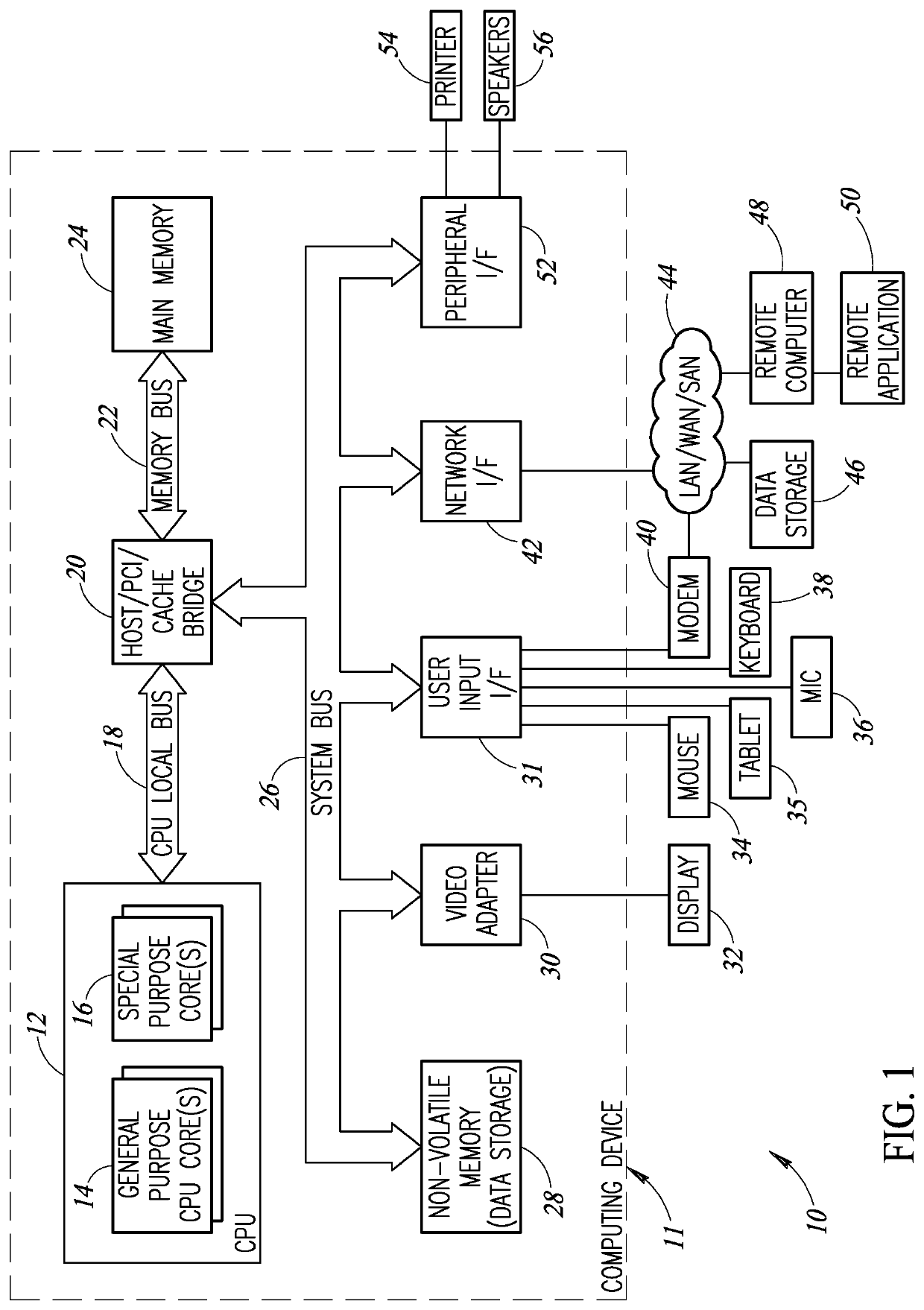

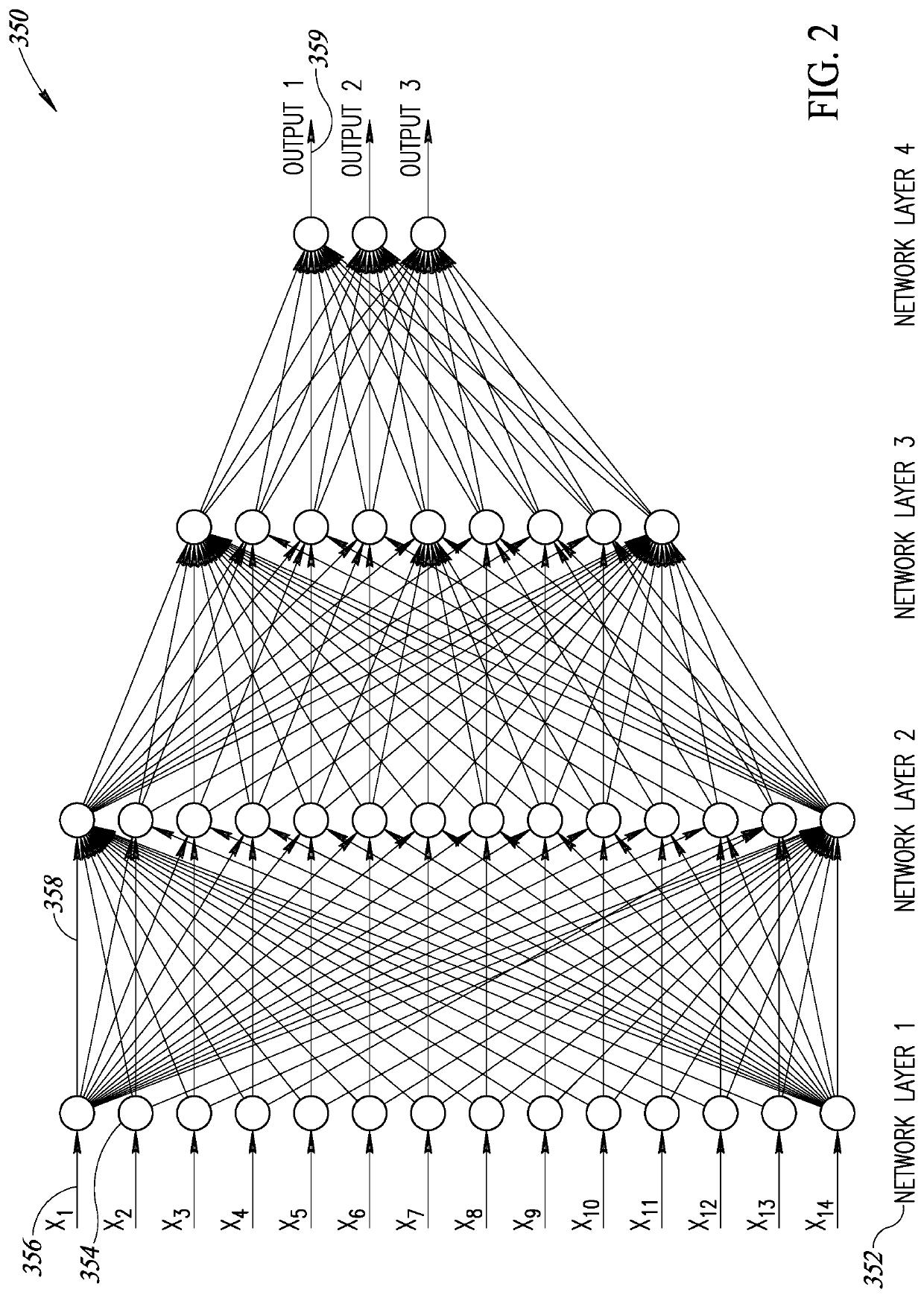

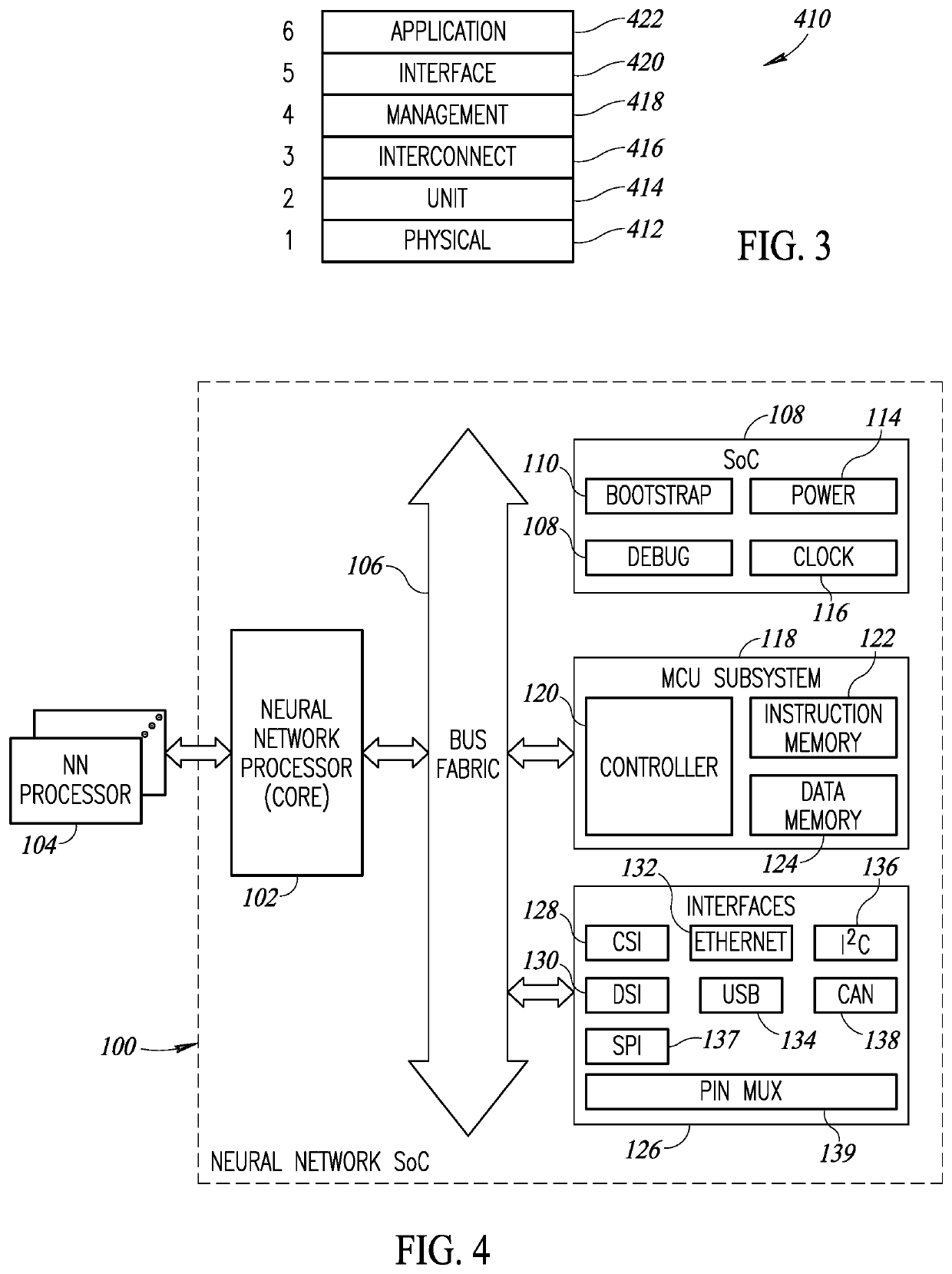

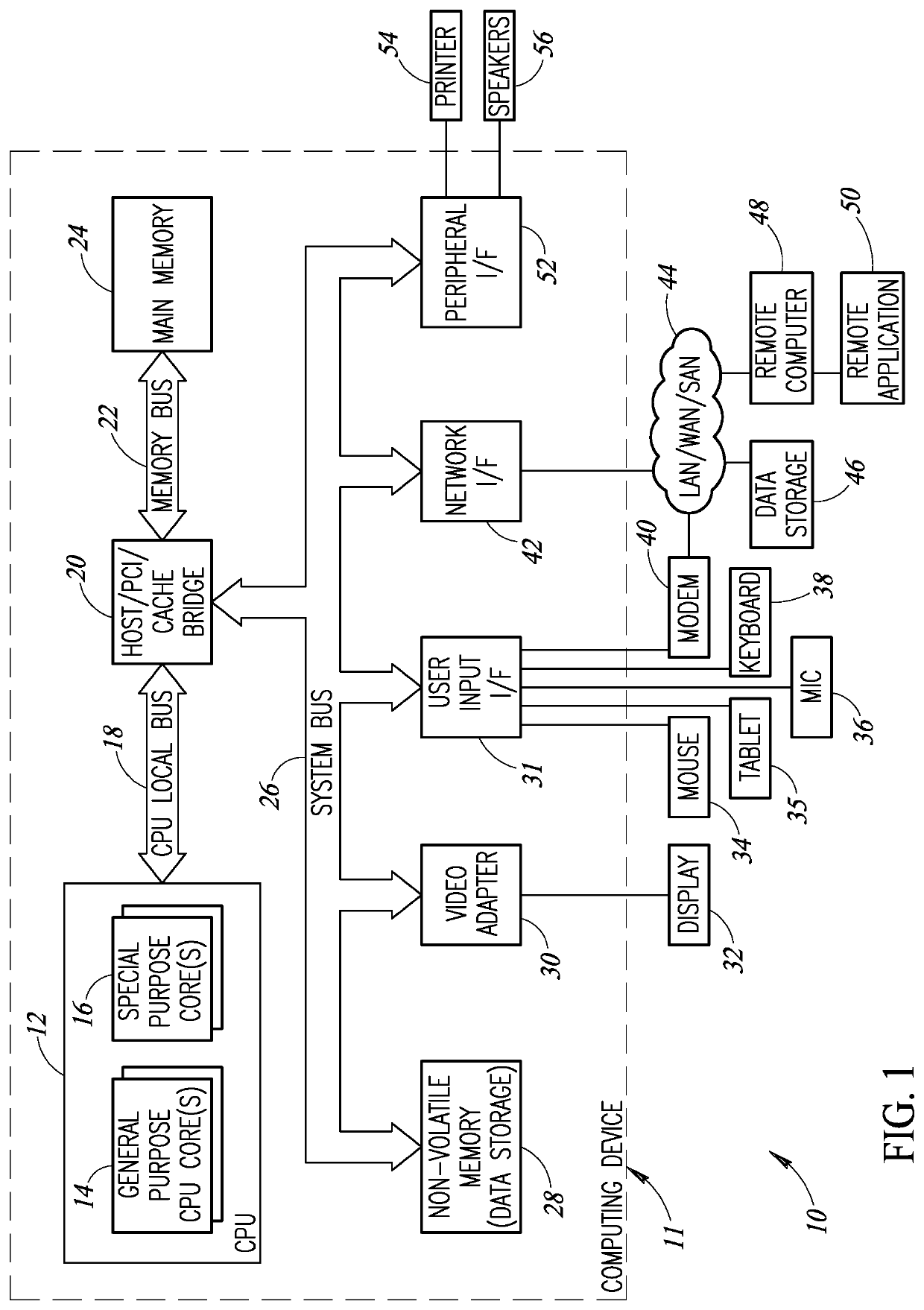

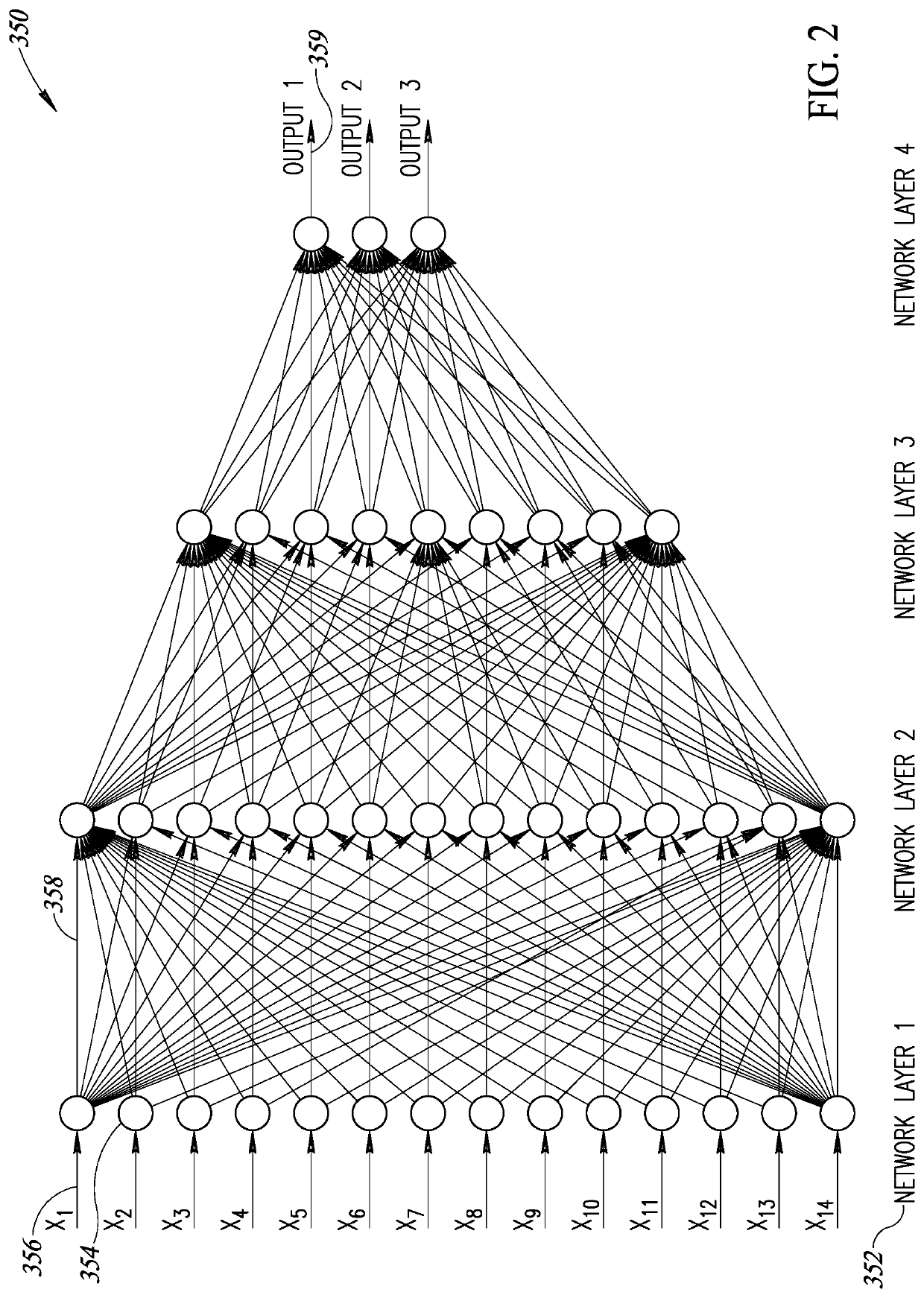

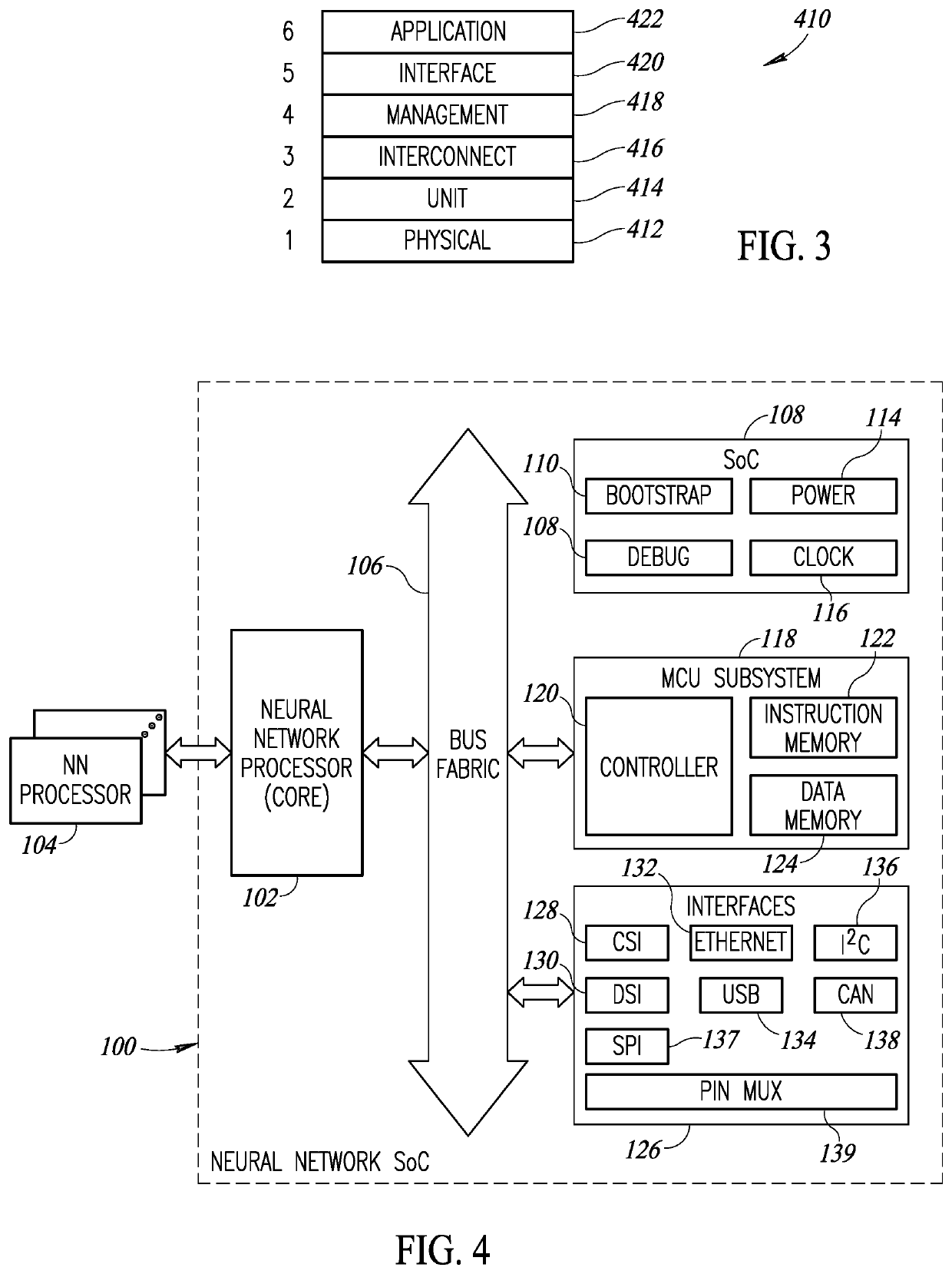

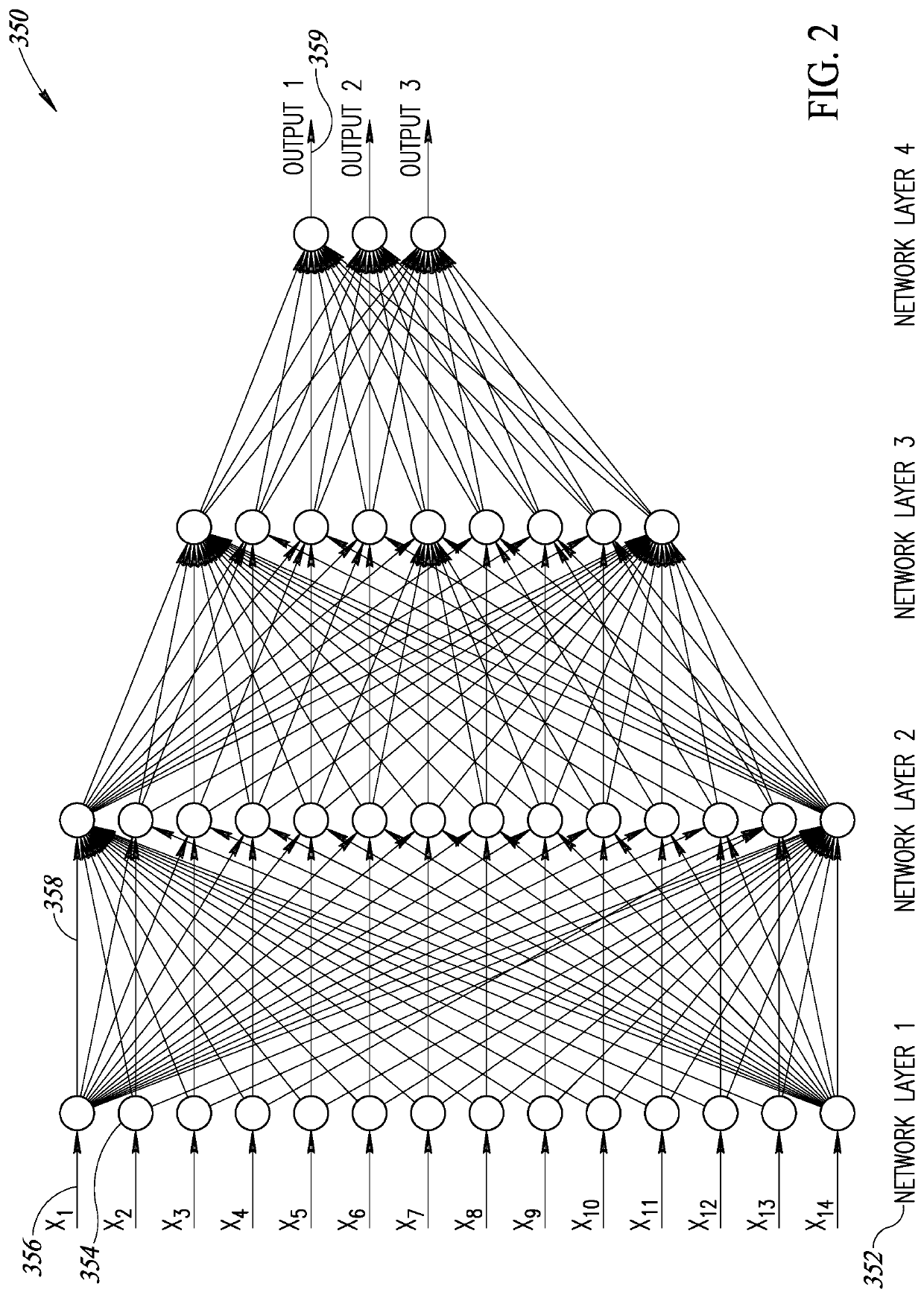

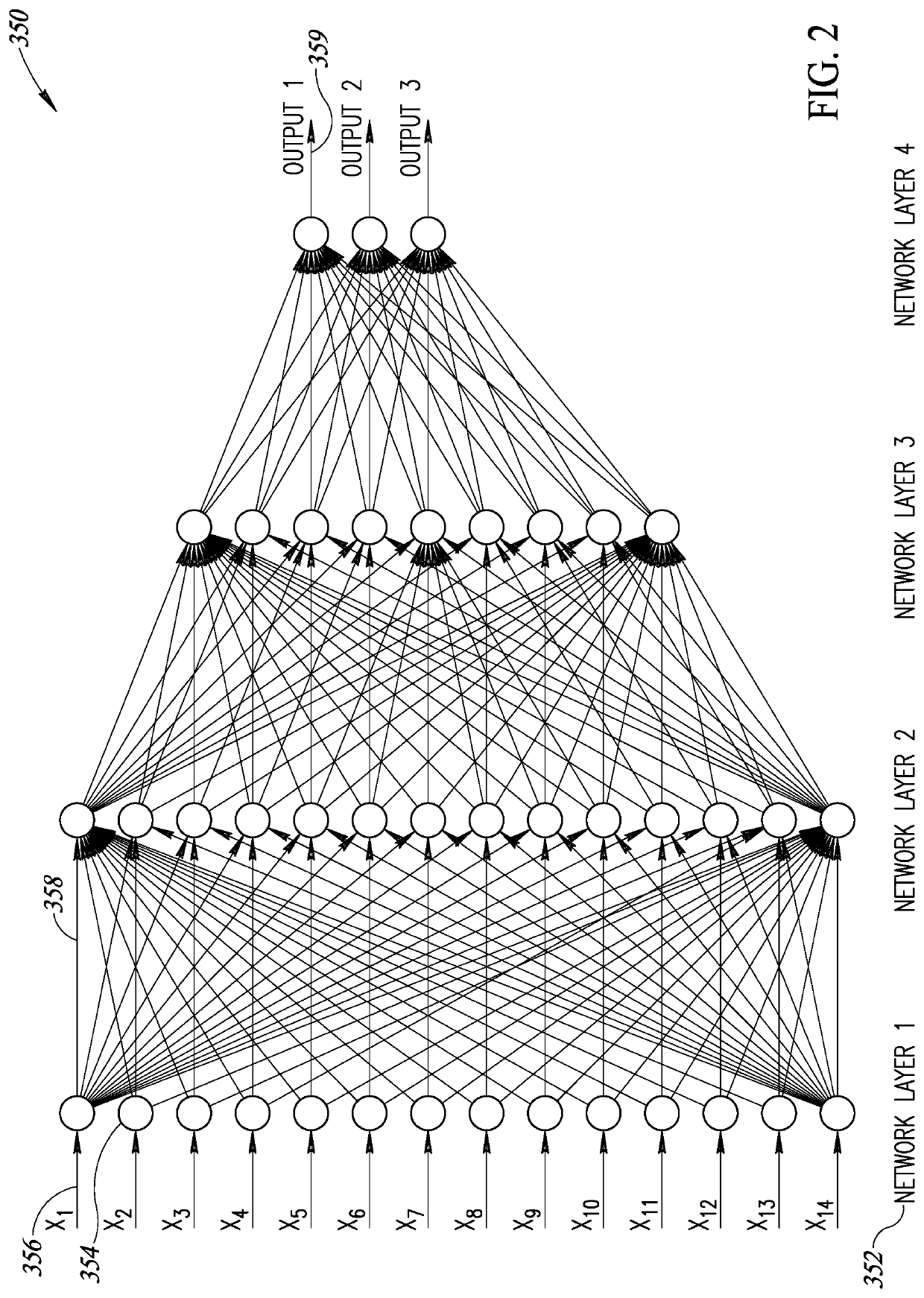

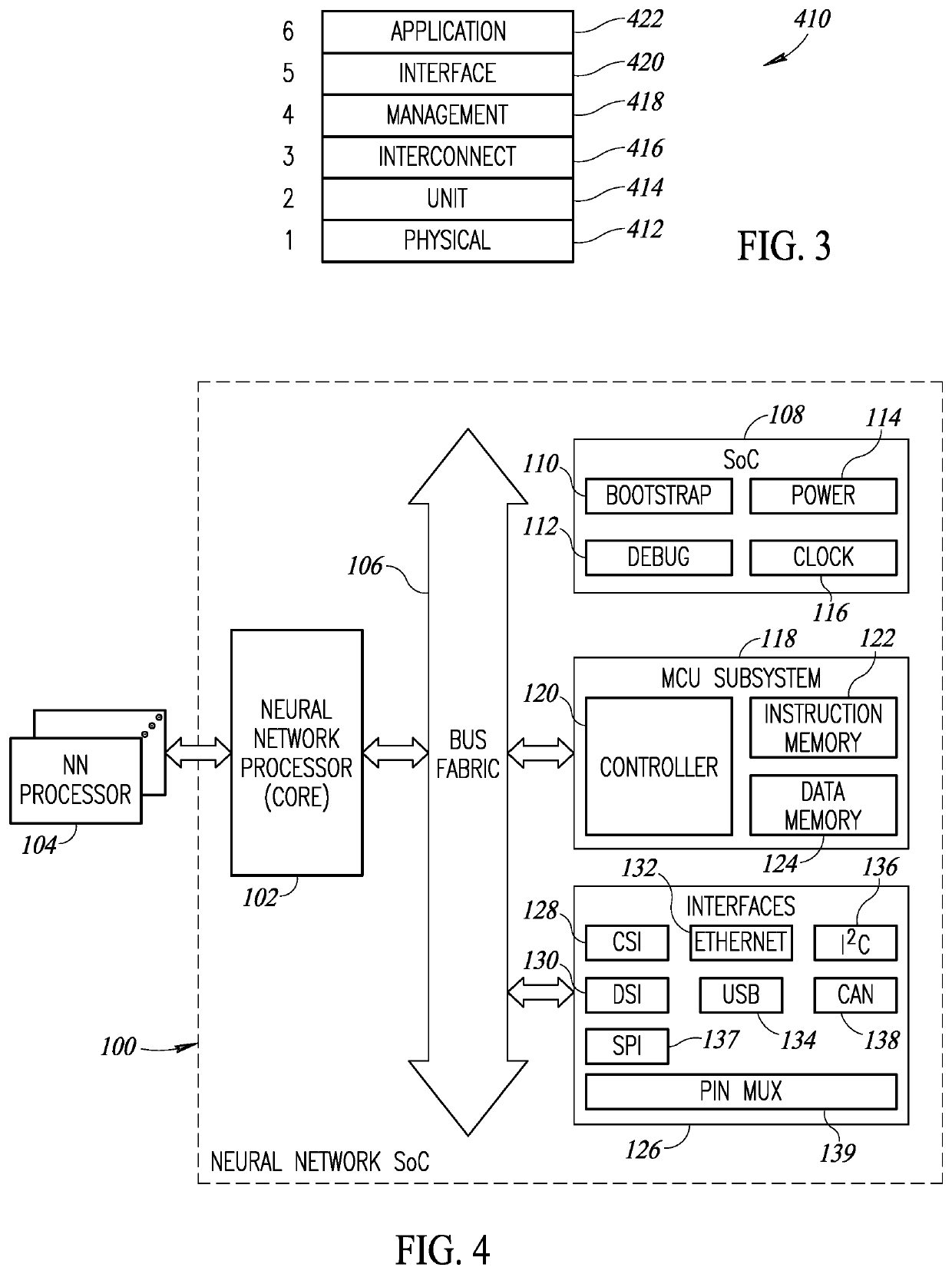

A novel and useful system and method of accessing multi-dimensional data in memory. The invention is applicable to neural network (NN) processing engines adapted to implement artificial neural networks (ANNs). The NN processor is constructed from self-contained computational units organized in a hierarchical architecture. The homogeneity enables simpler management and control of similar computational units, aggregated in multiple levels of hierarchy. Computational units are designed with minimal overhead as possible, where additional features and capabilities are aggregated at higher levels in the hierarchy. On-chip memory provides storage for content inherently required for basic operation at a particular hierarchy and is coupled with the computational resources in an optimal ratio. Lean control provides just enough signaling to manage only the operations required at a particular hierarchical level. Dynamic resource assignment agility is provided which can be adjusted as required depending on resource availability and capacity of the device.

Owner:HAILO TECH LTD

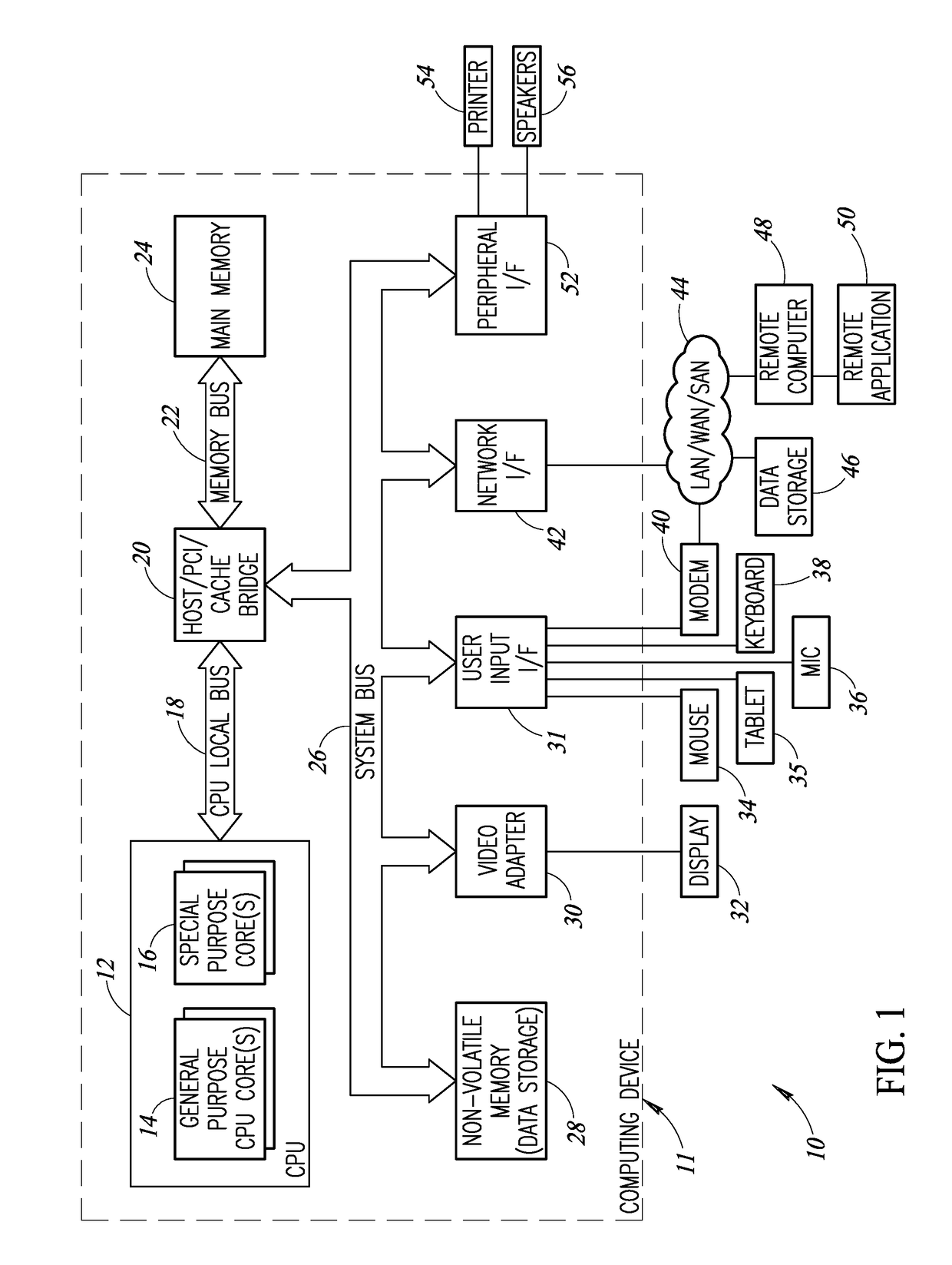

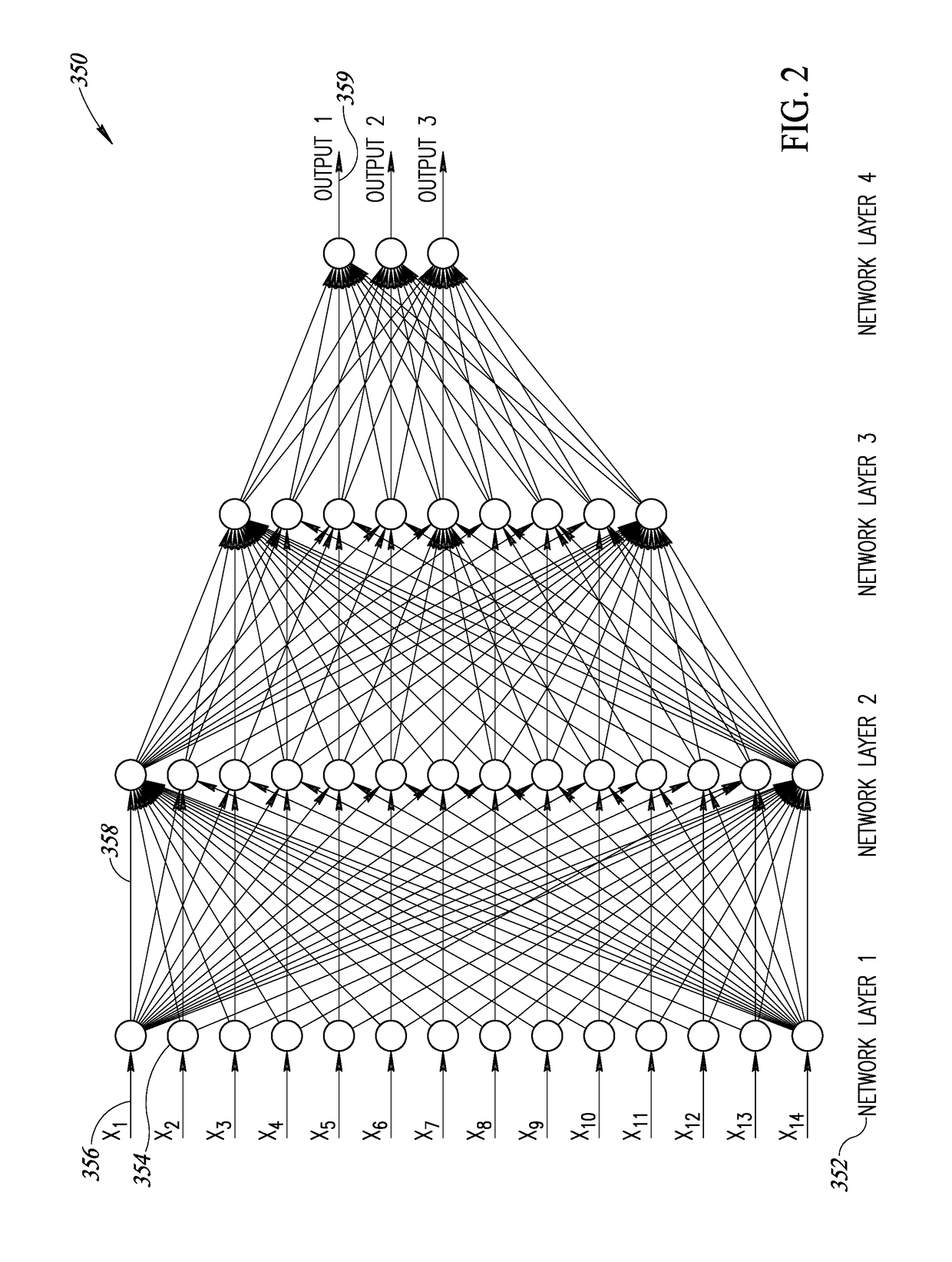

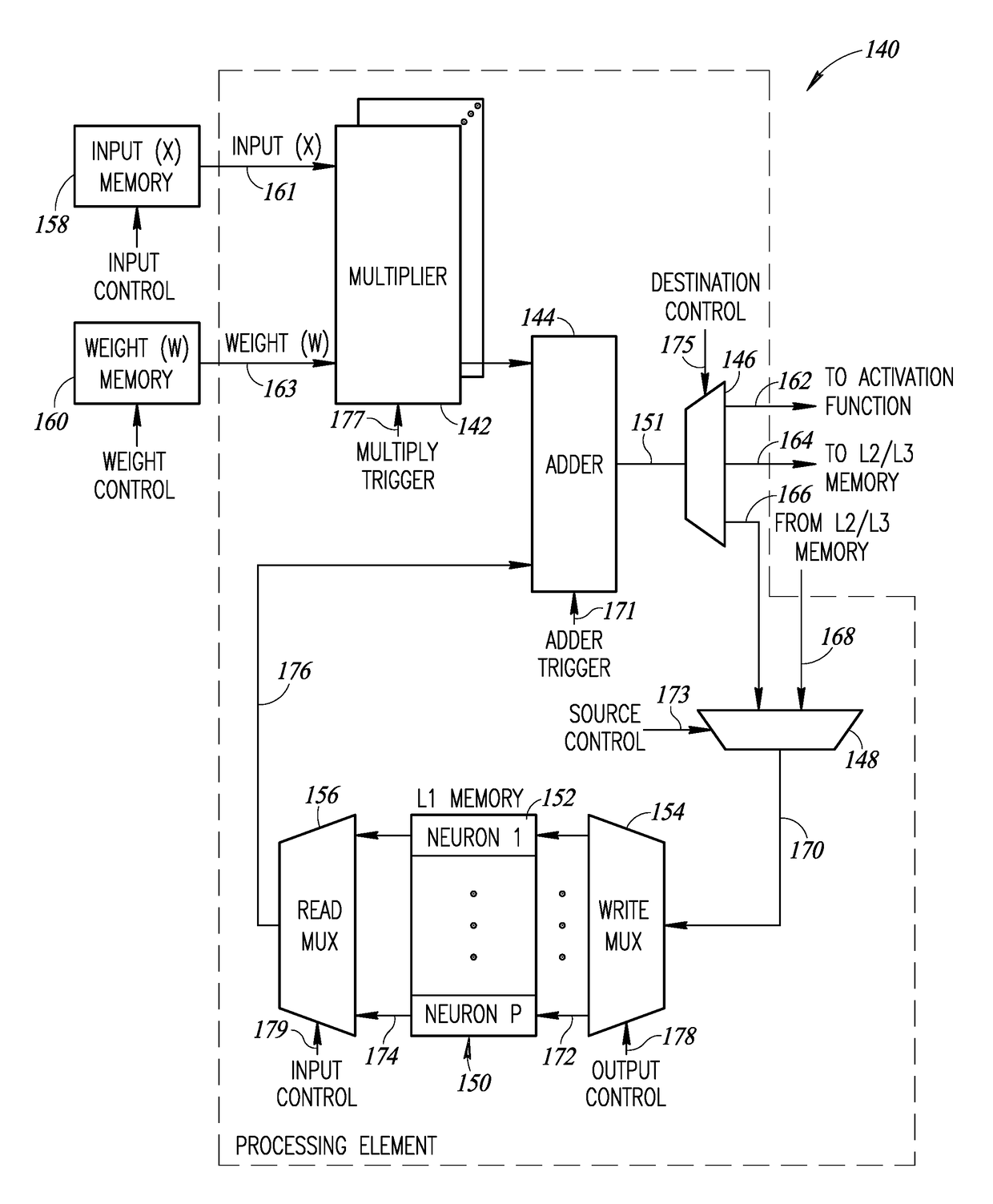

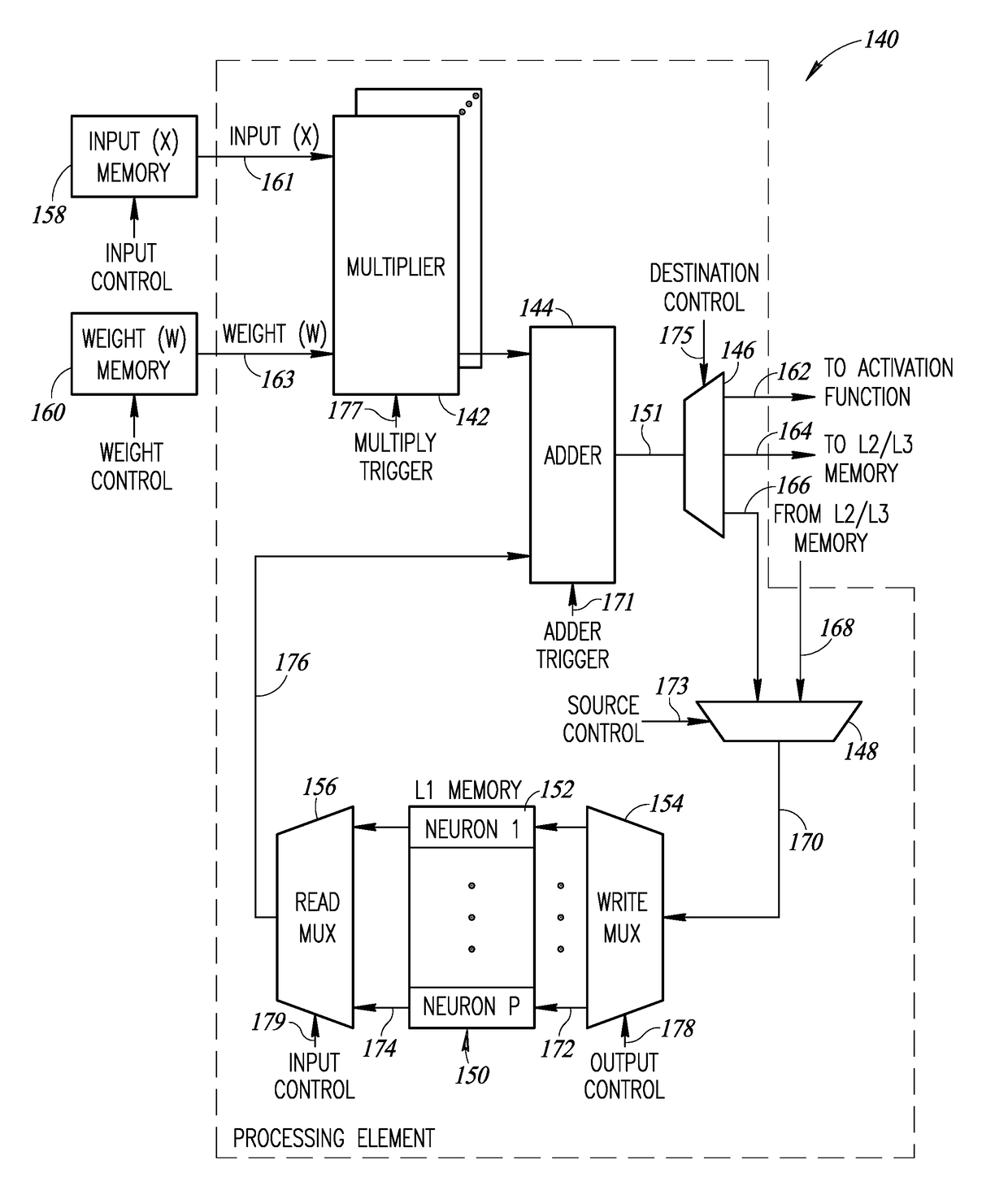

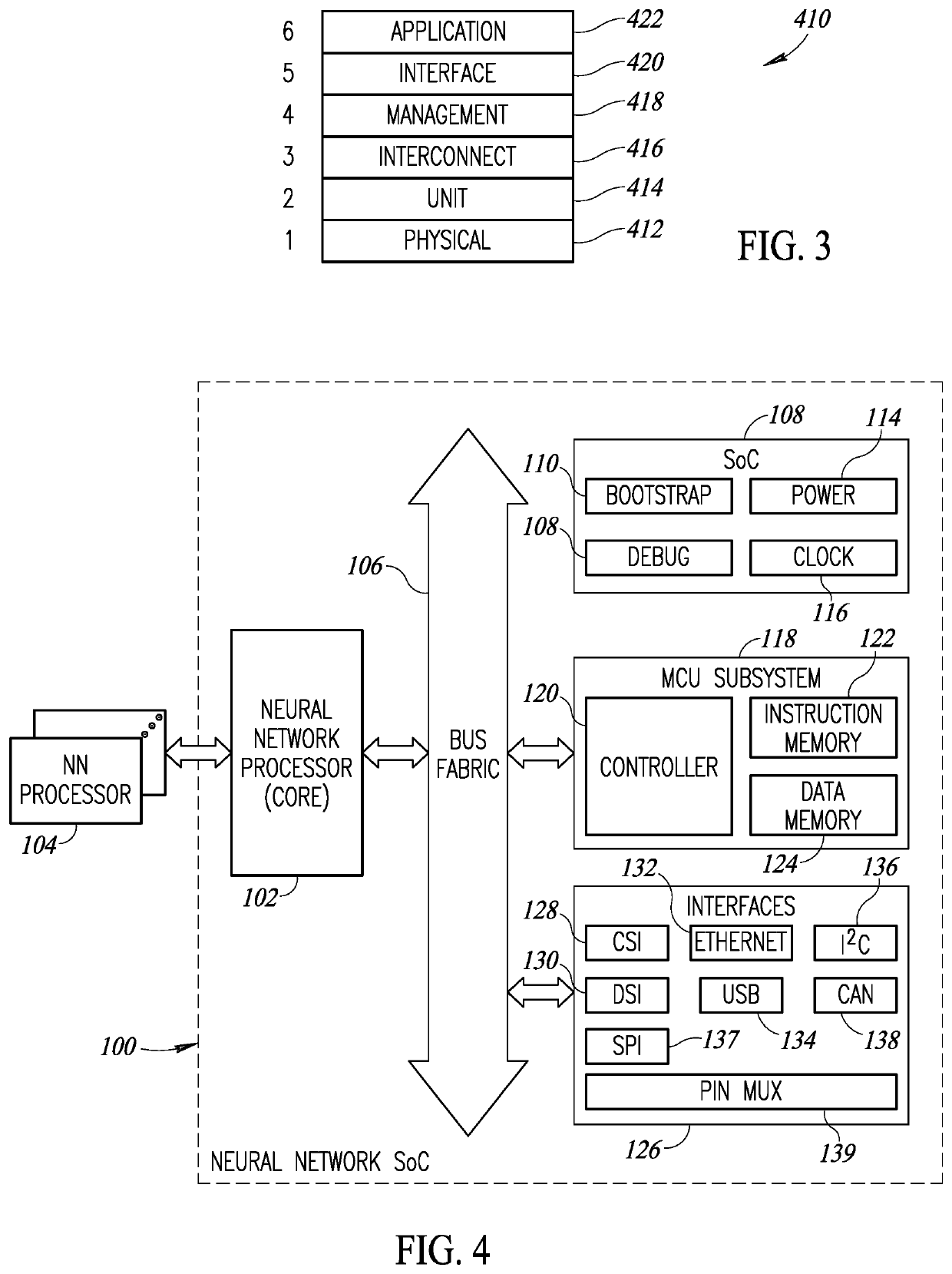

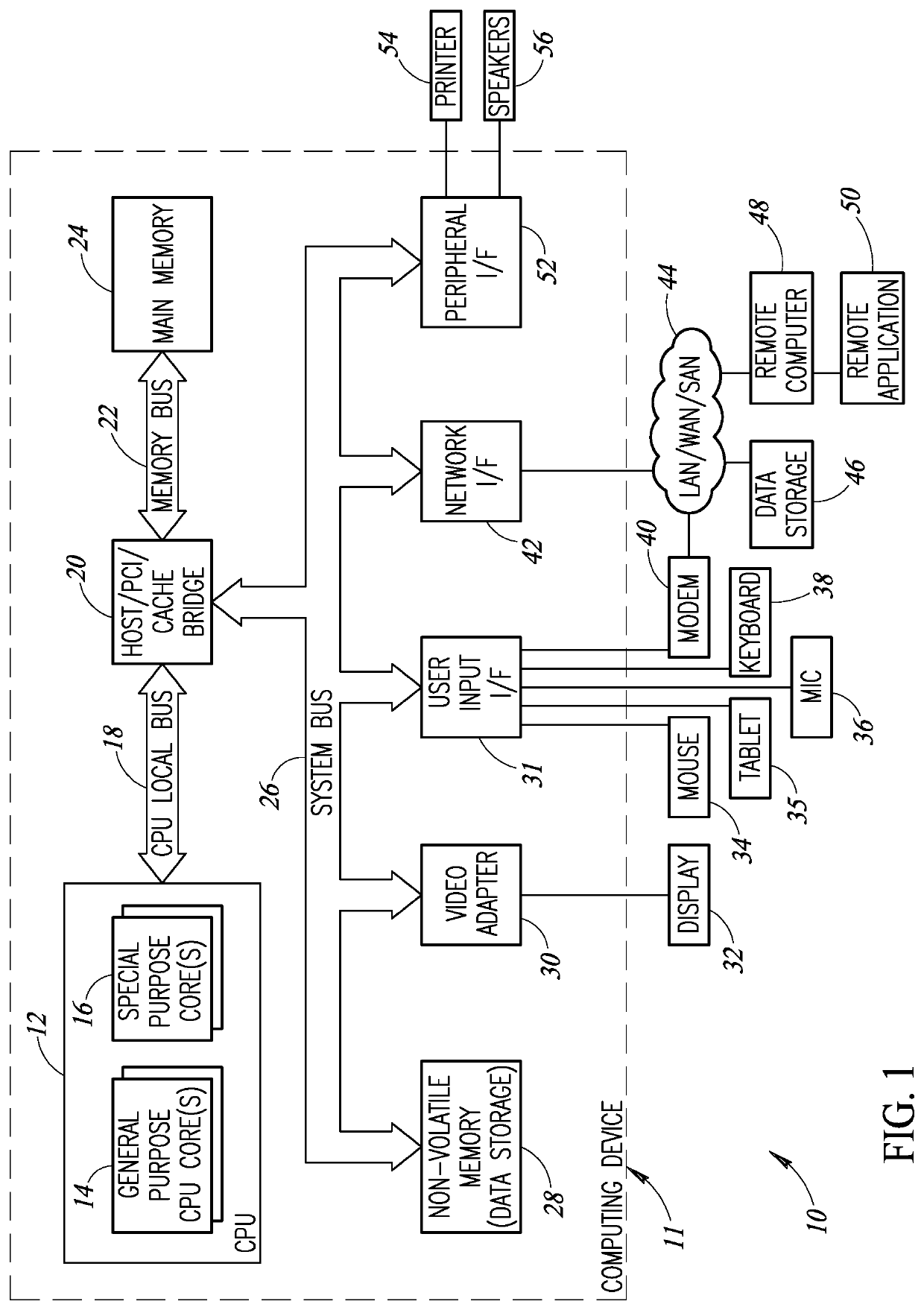

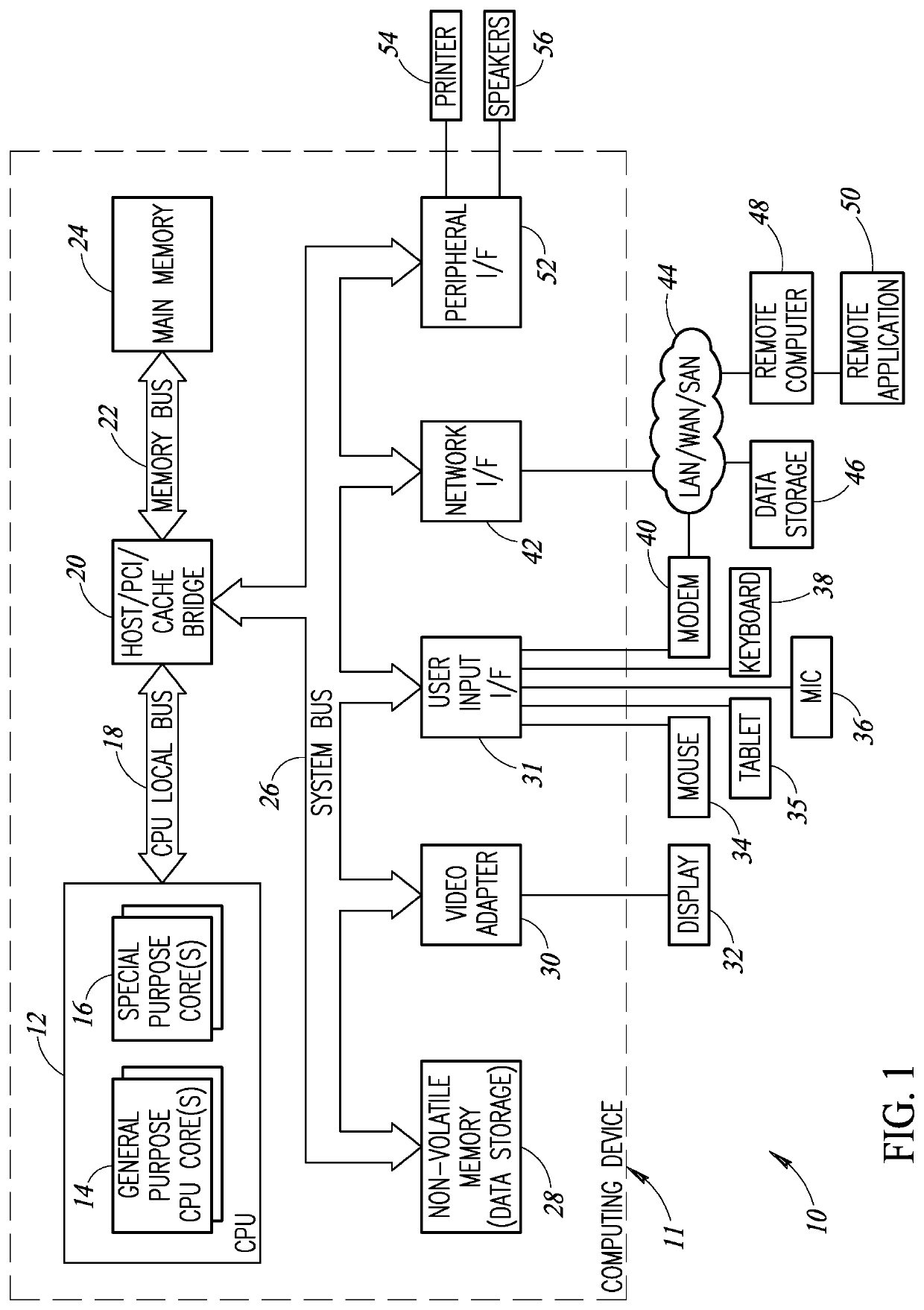

Neural Network Processing Element Incorporating Compute And Local Memory Elements

ActiveUS20180285727A1High computational unit densityReduce power consumptionResource allocationDigital data processing detailsLean controlNerve network

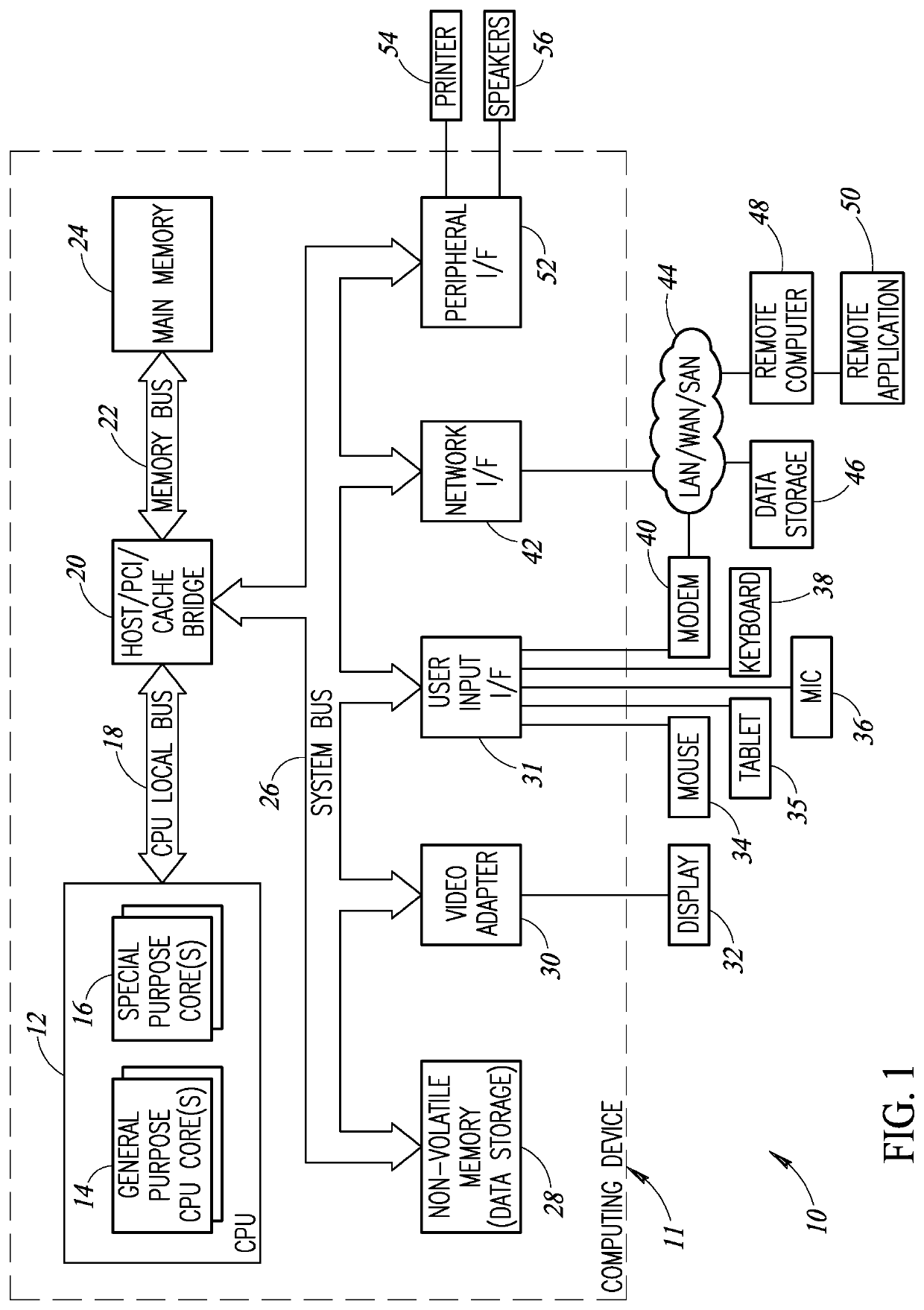

A novel and useful neural network (NN) processing core adapted to implement artificial neural networks (ANNs) and incorporating processing circuits having compute and local memory elements. The NN processor is constructed from self-contained computational units organized in a hierarchical architecture. The homogeneity enables simpler management and control of similar computational units, aggregated in multiple levels of hierarchy. Computational units are designed with minimal overhead as possible, where additional features and capabilities are aggregated at higher levels in the hierarchy. On-chip memory provides storage for content inherently required for basic operation at a particular hierarchy and is coupled with the computational resources in an optimal ratio. Lean control provides just enough signaling to manage only the operations required at a particular hierarchical level. Dynamic resource assignment agility is provided which can be adjusted as required depending on resource availability and capacity of the device.

Owner:HAILO TECH LTD

Neural Network Processor Incorporating Multi-Level Hierarchical Aggregated Computing And Memory Elements

ActiveUS20180285718A1High computational unit densityReduce power consumptionDigital data processing detailsMemory adressing/allocation/relocationLean controlProcessing core

A novel and useful neural network (NN) processing core adapted to implement artificial neural networks (ANNs). The NN processor is constructed from self-contained computational units organized in a hierarchical architecture. The homogeneity enables simpler management and control of similar computational units, aggregated in multiple levels of hierarchy. Computational units are designed with minimal overhead as possible, where additional features and capabilities are aggregated at higher levels in the hierarchy. On-chip memory provides storage for content inherently required for basic operation at a particular hierarchy and is coupled with the computational resources in an optimal ratio. Lean control provides just enough signaling to manage only the operations required at a particular hierarchical level. Dynamic resource assignment agility is provided which can be adjusted as required depending on resource availability and capacity of the device.

Owner:HAILO TECH LTD

Neural Network Processor Incorporating Inter-Device Connectivity

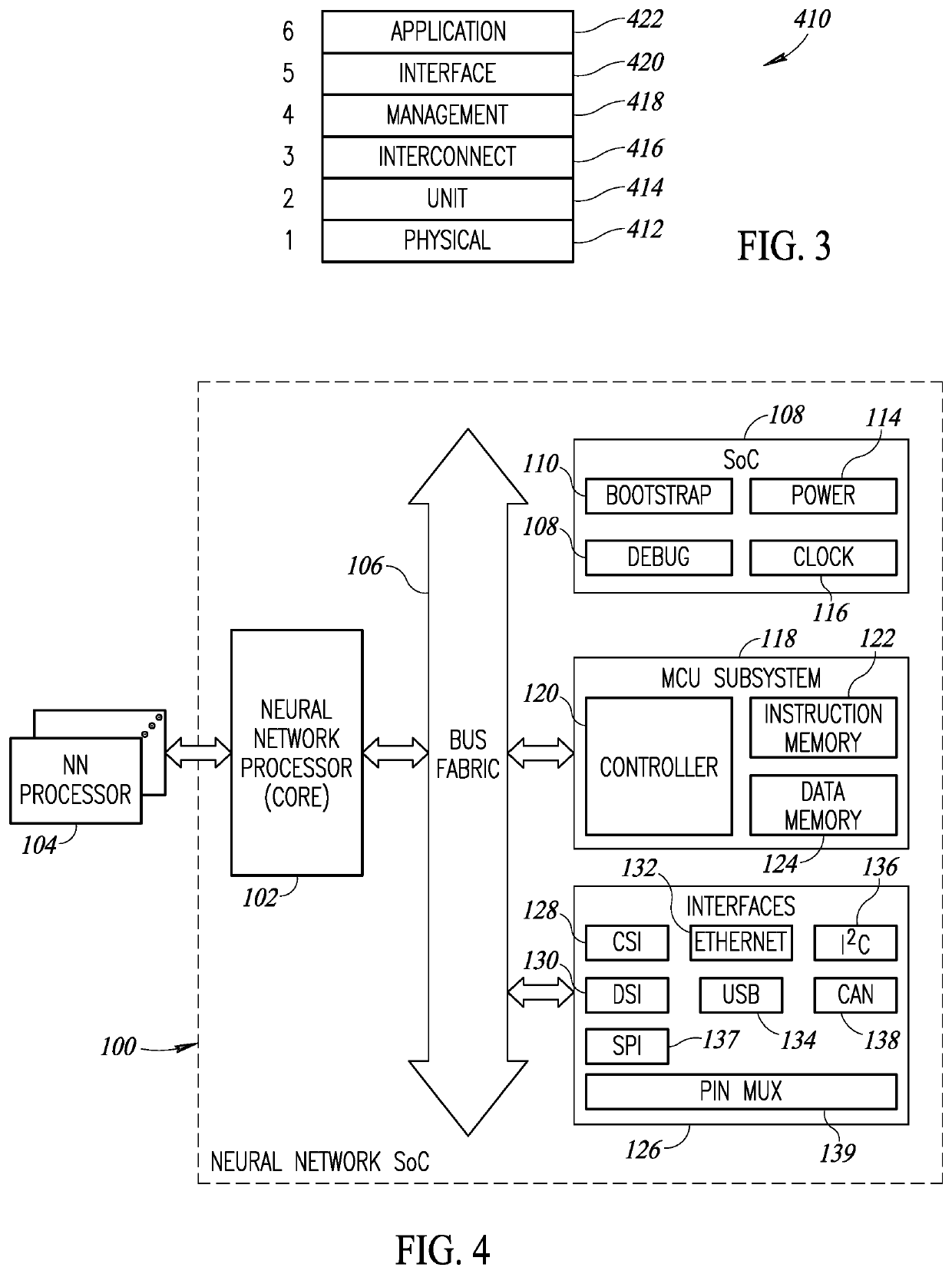

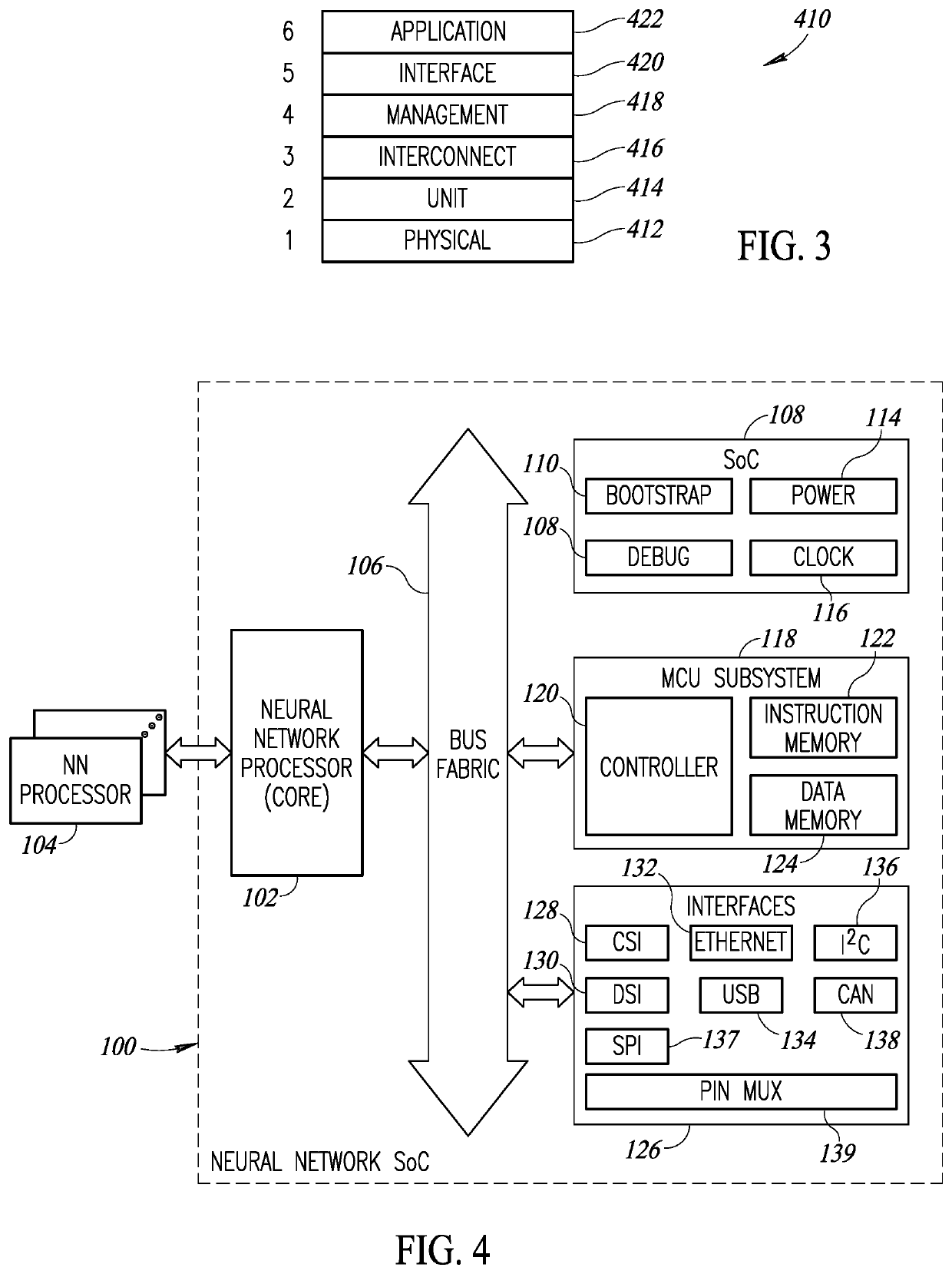

ActiveUS20180285726A1More efficientIncrease unit densityResource allocationDigital data processing detailsNerve networkMultiple single-level

A novel and useful neural network (NN) processing core incorporating inter-device connectivity and adapted to implement artificial neural networks (ANNs). A chip-to-chip interface spreads a given ANN model across multiple devices in a seamless manner. The NN processor is constructed from self-contained computational units organized in a hierarchical architecture. The homogeneity enables simpler management and control of similar computational units, aggregated in multiple levels of hierarchy. Computational units are designed with minimal overhead as possible, where additional features and capabilities are aggregated at higher levels in the hierarchy. On-chip memory provides storage for content inherently required for basic operation at a particular hierarchy and is coupled with the computational resources in an optimal ratio. Lean control provides just enough signaling to manage only the operations required at a particular hierarchical level. Dynamic resource assignment agility is provided which can be adjusted as required depending on resource availability and capacity of the device.

Owner:HAILO TECH LTD

Structured Weight Based Sparsity In An Artificial Neural Network

ActiveUS20200285892A1NN memory requirementReduce the amount requiredKernel methodsCharacter and pattern recognitionTheoretical computer scienceTerm memory

A novel and useful system and method of improved power performance and lowered memory requirements for an artificial neural network based on packing memory utilizing several structured sparsity mechanisms. The invention applies to neural network (NN) processing engines adapted to implement mechanisms to search for structured sparsity in weights and activations, resulting in a considerably reduced memory usage. The sparsity guided training mechanism synthesizes and generates structured sparsity weights A compiler mechanism within a software development kit (SDK), manipulates structured weight domain sparsity to generate a sparse set of static weights for the NN. The structured sparsity static weights are loaded into the NN after compilation and utilized by both the structured weight domain sparsity mechanism and the structured activation domain sparsity mechanism. The application of structured sparsity lowers the span of search options and creates a relatively loose coupling between the data and control planes.

Owner:HAILO TECH LTD

Configurable And Programmable Sliding Window Based Memory Access In A Neural Network Processor

ActiveUS20180285725A1More efficientIncrease unit densityResource allocationDigital data processing detailsDynamic resourcePrimitive operation

A novel and useful neural network (NN) processing core adapted to implement artificial neural networks (ANNs) and incorporating configurable and programmable sliding window based memory access. The memory mapping and allocation scheme trades off random and full access in favor of high parallelism and static mapping to a subset of the overall address space. The NN processor is constructed from self-contained computational units organized in a hierarchical architecture. The homogeneity enables simpler management and control of similar computational units, aggregated in multiple levels of hierarchy. Computational units are designed with minimal overhead as possible, where additional features and capabilities are aggregated at higher levels in the hierarchy. On-chip memory provides storage for content inherently required for basic operation at a particular hierarchy and is coupled with the computational resources in an optimal ratio. Lean control provides just enough signaling to manage only the operations required at a particular hierarchical level. Dynamic resource assignment agility is provided which can be adjusted as required depending on resource availability and capacity of the device.

Owner:HAILO TECH LTD

Neural network intermediate results safety mechanism in an artificial neural network processor

ActiveUS11263077B1High computational unit densityReduce power consumptionInput/output to record carriersNeural architecturesData streamSpatial mapping

Novel and useful system and methods of several functional safety mechanisms for use in an artificial neural network (ANN) processor. The mechanisms can be deployed individually or in combination to provide a desired level of safety in neural networks. Multiple strategies are applied involving redundancy by design, redundancy through spatial mapping as well as self-tuning procedures that modify static (weights) and monitor dynamic (activations) behavior. The various mechanisms of the present invention address ANN system level safety in situ, as a system level strategy that is tightly coupled with the processor architecture. The NN processor incorporates several functional safety concepts which reduce its risk of failure that occurs during operation from going unnoticed. The mechanisms function to detect and promptly flag and report the occurrence of an error with some mechanisms capable of correction as well. The safety mechanisms cover data stream fault detection, software defined redundant allocation, cluster interlayer safety, cluster intralayer safety, layer control unit (LCU) instruction addressing, weights storage safety, and neural network intermediate results storage safety.

Owner:HAILO TECH LTD

Data stream fault detection mechanism in an artificial neural network processor

ActiveUS11221929B1Reduce riskMore efficientDetecting faulty hardware using neural networksNeural architecturesData streamSpatial mapping

Novel and useful system and methods of several functional safety mechanisms for use in an artificial neural network (ANN) processor. The mechanisms can be deployed individually or in combination to provide a desired level of safety in neural networks. Multiple strategies are applied involving redundancy by design, redundancy through spatial mapping as well as self-tuning procedures that modify static (weights) and monitor dynamic (activations) behavior. The various mechanisms of the present invention address ANN system level safety in situ, as a system level strategy that is tightly coupled with the processor architecture. The NN processor incorporates several functional safety concepts which reduce its risk of failure that occurs during operation from going unnoticed. The mechanisms function to detect and promptly flag and report the occurrence of an error with some mechanisms capable of correction as well. The safety mechanisms cover data stream fault detection, software defined redundant allocation, cluster interlayer safety, cluster intralayer safety, layer control unit (LCU) instruction addressing, weights storage safety, and neural network intermediate results storage safety.

Owner:HAILO TECH LTD

Neural Network Processor Incorporating Separate Control And Data Fabric

ActiveUS20180285719A1High computational unit densityReduce power consumptionDigital data processing detailsMemory adressing/allocation/relocationLean controlNerve network

A novel and useful neural network (NN) processing core adapted to implement artificial neural networks (ANNs) and incorporating strictly separate control and data planes. The NN processor is constructed from self-contained computational units organized in a hierarchical architecture. The homogeneity enables simpler management and control of similar computational units, aggregated in multiple levels of hierarchy. Computational units are designed with minimal overhead as possible, where additional features and capabilities are aggregated at higher levels in the hierarchy. On-chip memory provides storage for content inherently required for basic operation at a particular hierarchy and is coupled with the computational resources in an optimal ratio. Lean control provides just enough signaling to manage only the operations required at a particular hierarchical level. Dynamic resource assignment agility is provided which can be adjusted as required depending on resource availability and capacity of the device.

Owner:HAILO TECH LTD

Layer control unit instruction addressing safety mechanism in an artificial neural network processor

ActiveUS11237894B1High computational unit densityReduce power consumptionNon-redundant fault processingRedundant data error correctionData streamSpatial mapping

Novel and useful system and methods of several functional safety mechanisms for use in an artificial neural network (ANN) processor. The mechanisms can be deployed individually or in combination to provide a desired level of safety in neural networks. Multiple strategies are applied involving redundancy by design, redundancy through spatial mapping as well as self-tuning procedures that modify static (weights) and monitor dynamic (activations) behavior. The various mechanisms of the present invention address ANN system level safety in situ, as a system level strategy that is tightly coupled with the processor architecture. The NN processor incorporates several functional safety concepts which reduce its risk of failure that occurs during operation from going unnoticed. The mechanisms function to detect and promptly flag and report the occurrence of an error with some mechanisms capable of correction as well. The safety mechanisms cover data stream fault detection, software defined redundant allocation, cluster interlayer safety, cluster intralayer safety, layer control unit (LCU) instruction addressing, weights storage safety, and neural network intermediate results storage safety.

Owner:HAILO TECH LTD

Software Defined Redundant Allocation Safety Mechanism In An Artificial Neural Network Processor

PendingUS20220100601A1Lower power consumptionSimpler management and controlFunctional testingRedundant data error correctionMachine learningSpatial mapping

Novel and useful system and methods of several functional safety mechanisms for use in an artificial neural network (ANN) processor. The mechanisms can be deployed individually or in combination to provide a desired level of safety in neural networks. Multiple strategies are applied involving redundancy by design, redundancy through spatial mapping as well as self-tuning procedures that modify static (weights) and monitor dynamic (activations) behavior. The various mechanisms of the present invention address ANN system level safety in situ, as a system level strategy that is tightly coupled with the processor architecture. The NN processor incorporates several functional safety concepts which reduce its risk of failure that occurs during operation from going unnoticed. The mechanisms function to detect and promptly flag and report the occurrence of an error with some mechanisms capable of correction as well. The safety mechanisms cover data stream fault detection, software defined redundant allocation, cluster interlayer safety, cluster intralayer safety, layer control unit (LCU) instruction addressing, weights storage safety, and neural network intermediate results storage safety.

Owner:HAILO TECH LTD

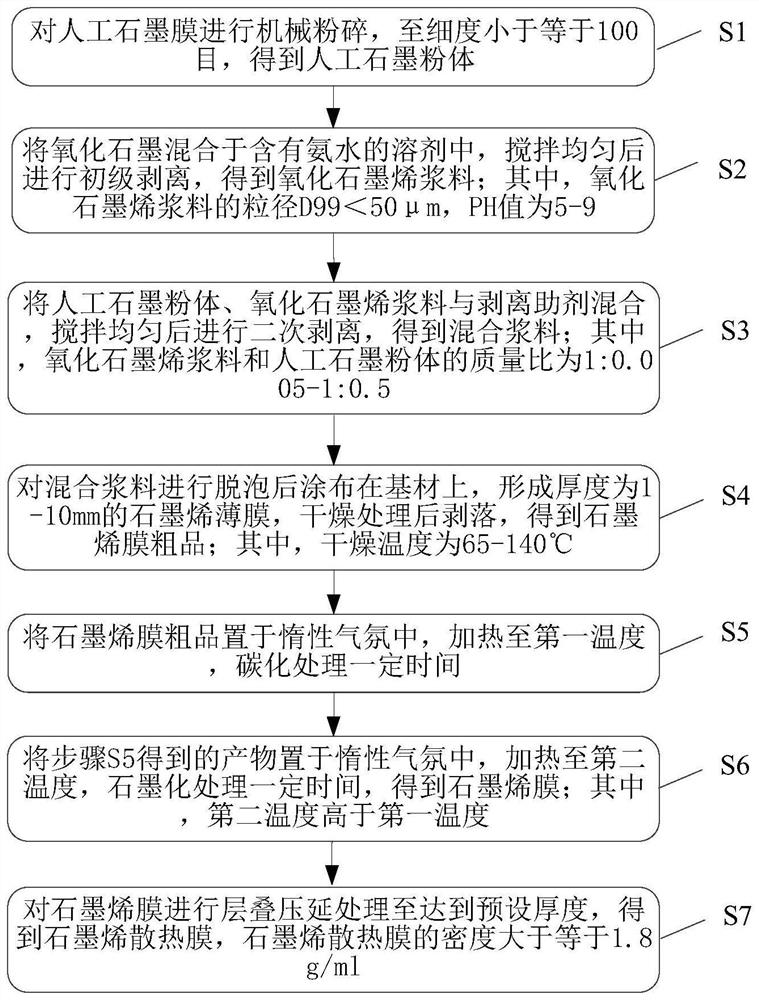

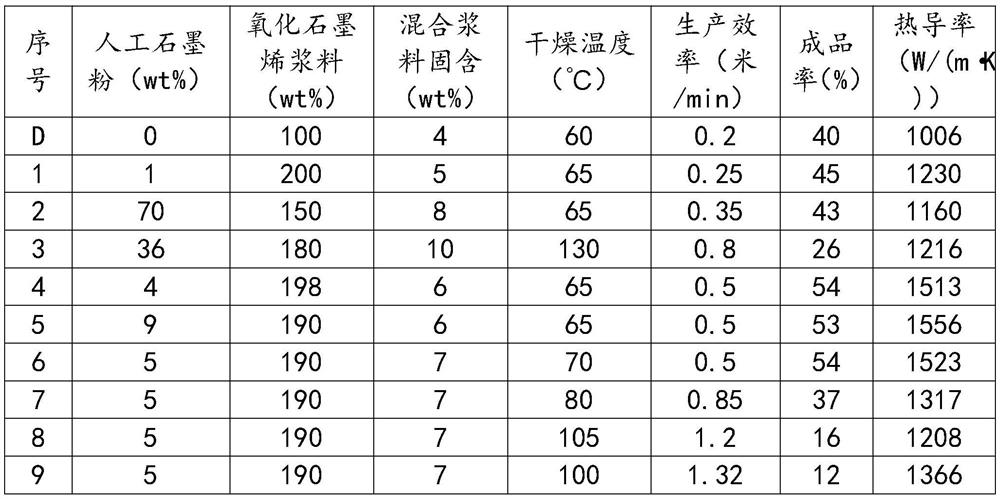

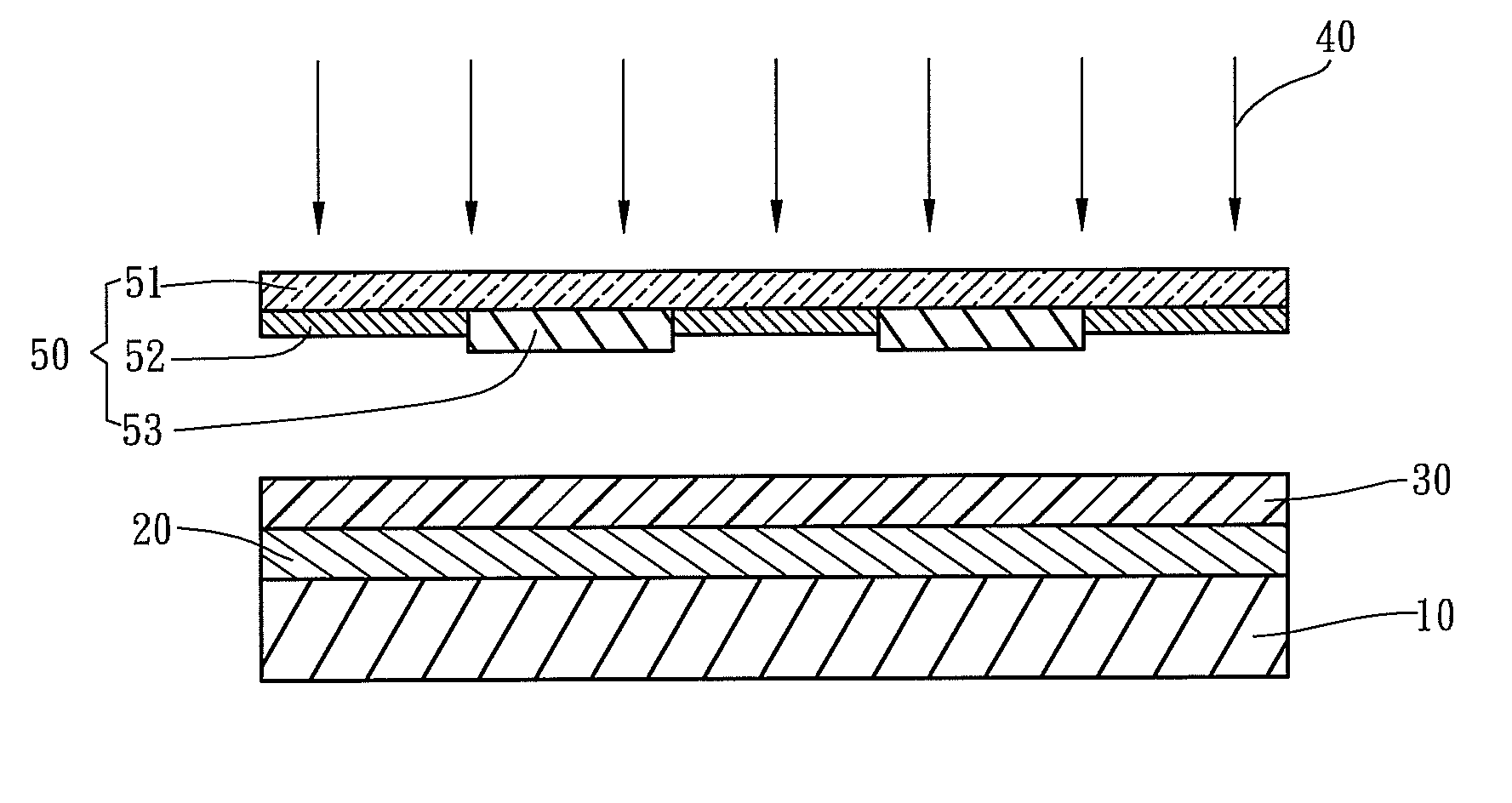

High-thermal-conductivity graphene heat dissipation film and preparation method thereof

ActiveCN114314573AWide range of choicesReduce raw material range restrictionsGrapheneGraphene membraneGraphite oxide

The invention relates to the technical field of heat dissipation materials, in particular to a graphene heat dissipation film and a preparation method thereof. The method comprises the following steps: S1, mechanically crushing an artificial graphite film to obtain artificial graphite powder; s2, mixing graphite oxide in a solvent containing ammonia water, uniformly stirring, and carrying out primary stripping to obtain graphene oxide slurry; s3, mixing the artificial graphite powder, the graphene oxide slurry and a stripping aid, uniformly stirring, and performing secondary stripping to obtain mixed slurry; s4, defoaming the mixed slurry, coating the mixed slurry on a base material, drying, and stripping to obtain a graphene film crude product; s5, placing the graphene film crude product in an inert atmosphere, heating to a first temperature, and carrying out carbonization treatment for a certain time; s6, placing a product obtained in the step S5 in an inert atmosphere, heating to a second temperature, and graphitizing to obtain a graphene film; and S7, carrying out lamination calendaring treatment on the graphene film to obtain the graphene heat dissipation film. The heat dissipation performance of the material can be effectively improved, and the cost is reduced.

Owner:XIAMEN KNANO GRAPHENE TECH CORP

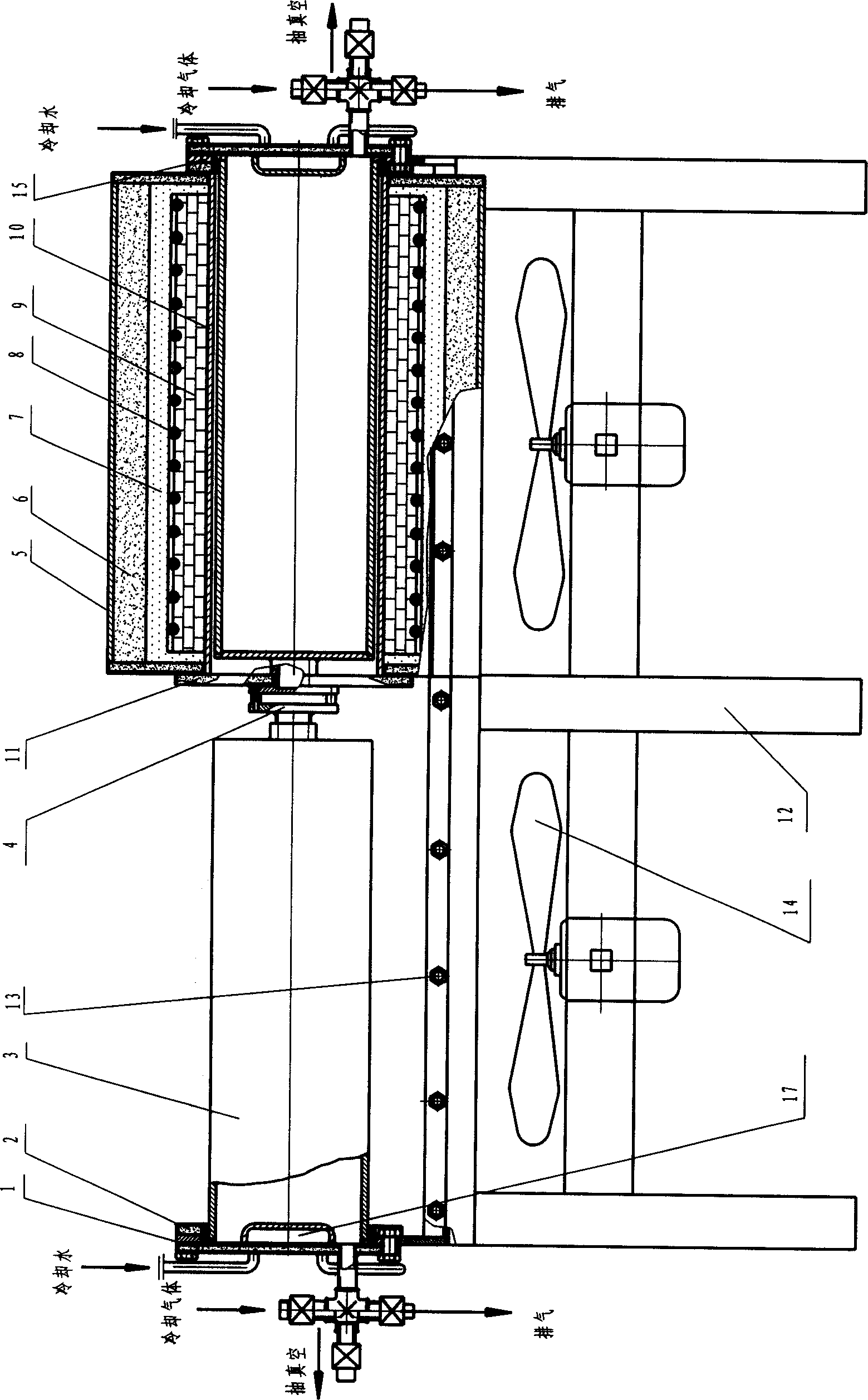

Vacuum sintering method of negative plate of nickel-hydrogen battery

InactiveCN1599105AIncrease unit densityIncrease specific energyElectrode manufacturing processesAlkaline accumulator electrodesElectric capacityEngineering

The invention relates to a manufacturing method of the cathode of the nickel hydrogen battery and specially relates to the manufacturing method of burning and cooling the cathode of the nickel hydrogen battery in specific vacuum furnace. Put the shaped cathodes into the two furnace chambers, A and B, pump the air out till the pressure is 2 multiplied by 10 to the power -2, input the cooling air to protect it, heat it to the temperature of 900deg.C and keep the temperature. Start cooling water till the temperature is less than 700deg.C, open the fan till the temperature is below 200deg.C, input the cooling air till the temperature drops to 45deg.C and take it out. The specific vacuum furnace designed by the invention has double furnace chambers, double heat preservation structures, can increase and reduce the temperature pretty quickly (A and B heat or cool it alternatively.) and is featured by low cost, simple operation and easy application. The cathode burn in vacuum has high electric capacity; the battery is featured by long useful life and strong overcharge and over-discharge endurance and the cathode plate has strong intensity, good flexibility and high yield and is promising to have wide market.

Owner:马志刚

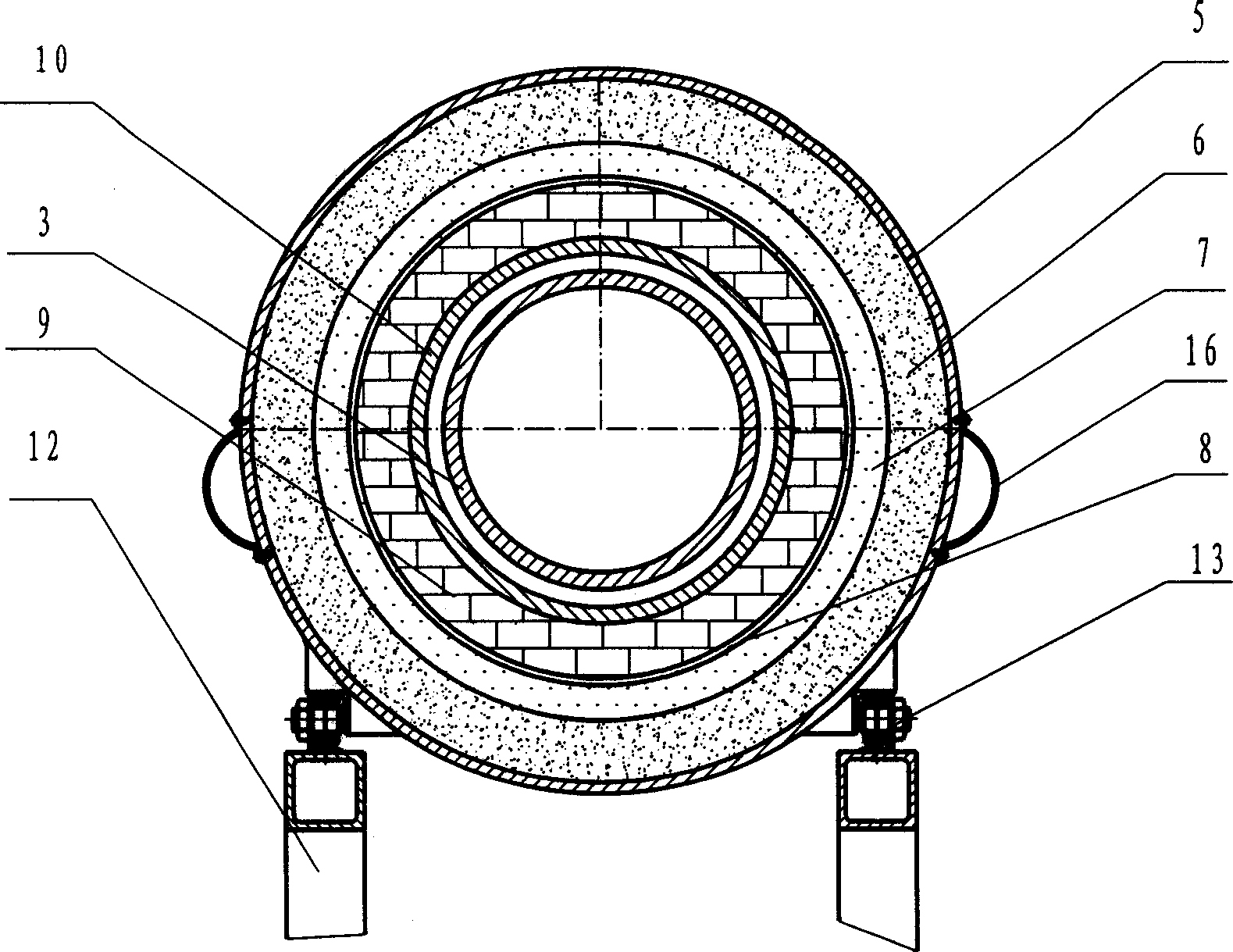

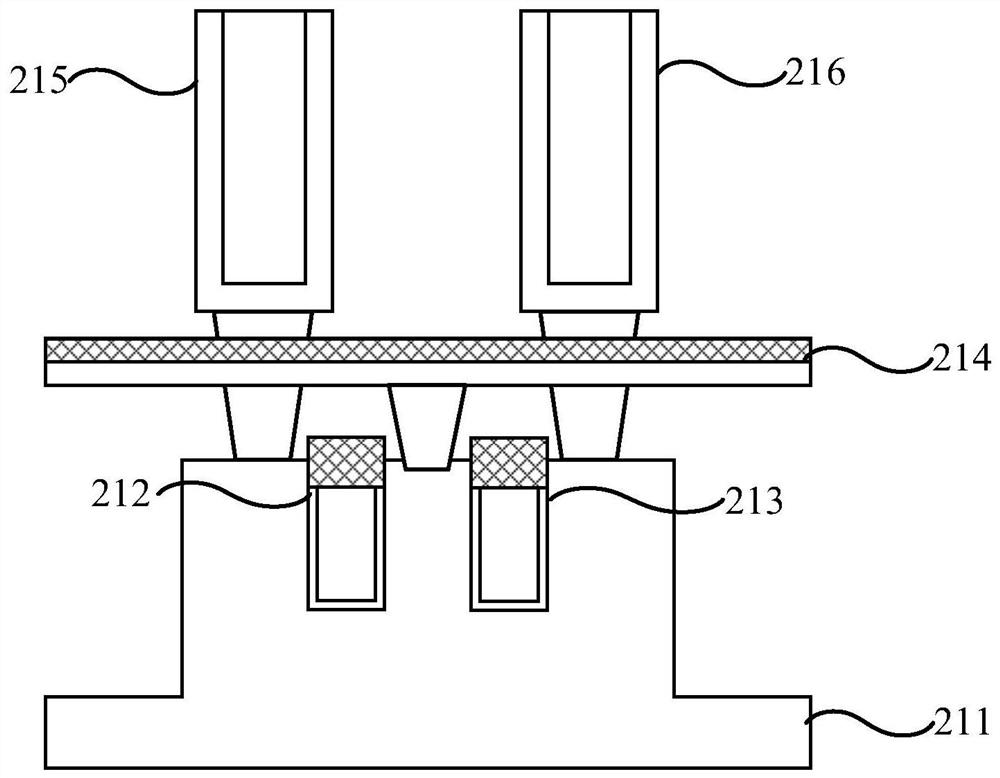

Semiconductor device with groove gate structure and manufacturing method of semiconductor device

ActiveCN106328697AReduce spacingIncrease unit densitySemiconductor devicesMetal electrodesDielectric layer

The invention relates to a semiconductor device with a groove gate structure. The semiconductor device comprises a drift region, a metal electrode on the drift region, a groove, a gate oxide layer on the inner surface of the groove, a polysilicon gate in the groove, a dielectric layer arranged in the groove and at the upper part of the polysilicon gate and doped regions at two sides of the top of the groove, wherein the groove penetrates to the drift region from the lower part of the metal electrode. The invention further relates to a manufacturing method of the semiconductor device with the groove gate structure. According to the semiconductor device, use of a pore plate can be avoided by changing the design of the doped regions and the groove and depositing the dielectric layer in front of a pore and etching back the dielectric layer; and the unit intensity of the groove is improved to achieve the effect of improving the current density of a product. Meanwhile, the pore plate is not used, so that the production cost of the product can be reduced and the competitiveness of the product is strengthened.

Owner:CSMC TECH FAB2 CO LTD

Cluster Interlayer Safety Mechanism In An Artificial Neural Network Processor

PendingUS20220101042A1Reduce riskMore efficientCode conversionCharacter and pattern recognitionData streamSpatial mapping

Novel and useful system and methods of several functional safety mechanisms for use in an artificial neural network (ANN) processor. The mechanisms can be deployed individually or in combination to provide a desired level of safety in neural networks. Multiple strategies are applied involving redundancy by design, redundancy through spatial mapping as well as self-tuning procedures that modify static (weights) and monitor dynamic (activations) behavior. The various mechanisms of the present invention address ANN system level safety in situ, as a system level strategy that is tightly coupled with the processor architecture. The NN processor incorporates several functional safety concepts which reduce its risk of failure that occurs during operation from going unnoticed. The mechanisms function to detect and promptly flag and report the occurrence of an error with some mechanisms capable of correction as well. The safety mechanisms cover data stream fault detection, software defined redundant allocation, cluster interlayer safety, cluster intralayer safety, layer control unit (LCU) instruction addressing, weights storage safety, and neural network intermediate results storage safety.

Owner:HAILO TECH LTD

System And Method Of Input Alignment For Efficient Vector Operations In An Artificial Neural Network

ActiveUS20200005127A1Avoid readingReduce memory bandwidthHandling data according to predetermined rulesProgram controlAlgorithmTerm memory

A novel and useful system and method of input alignment for streamlining vector operations that reduce the required memory read bandwidth. The input aligner as deployed in the NN processor, functions to facilitate the reuse of data read from memory and to avoid having to re-read that data in the context of neural network calculations. The input aligner functions to distribute input data (or weights) to the appropriate compute elements while consuming input data in a single cycle. Thus, the input aligner is operative to lower the required read bandwidth of layer input in an ANN. This reflects the fact that normally in practice, a vector multiplication is performed every time instance. This considers the fact that in many native calculations that take place in an ANN, the same data point is involved in multiple calculations.

Owner:HAILO TECH LTD

Cluster Intralayer Safety Mechanism In An Artificial Neural Network Processor

PendingUS20220101043A1Lower power consumptionSimpler management and controlCode conversionCharacter and pattern recognitionMachine learningSpatial mapping

Novel and useful system and methods of several functional safety mechanisms for use in an artificial neural network (ANN) processor. The mechanisms can be deployed individually or in combination to provide a desired level of safety in neural networks. Multiple strategies are applied involving redundancy by design, redundancy through spatial mapping as well as self-tuning procedures that modify static (weights) and monitor dynamic (activations) behavior. The various mechanisms of the present invention address ANN system level safety in situ, as a system level strategy that is tightly coupled with the processor architecture. The NN processor incorporates several functional safety concepts which reduce its risk of failure that occurs during operation from going unnoticed. The mechanisms function to detect and promptly flag and report the occurrence of an error with some mechanisms capable of correction as well. The safety mechanisms cover data stream fault detection, software defined redundant allocation, cluster interlayer safety, cluster intralayer safety, layer control unit (LCU) instruction addressing, weights storage safety, and neural network intermediate results storage safety.

Owner:HAILO TECH LTD

Weights Safety Mechanism In An Artificial Neural Network Processor

PendingUS20220103186A1High computational unit densityReduce power consumptionError detection/correctionCode conversionData streamSpatial mapping

Novel and useful system and methods of several functional safety mechanisms for use in an artificial neural network (ANN) processor. The mechanisms can be deployed individually or in combination to provide a desired level of safety in neural networks. Multiple strategies are applied involving redundancy by design, redundancy through spatial mapping as well as self-tuning procedures that modify static (weights) and monitor dynamic (activations) behavior. The various mechanisms of the present invention address ANN system level safety in situ, as a system level strategy that is tightly coupled with the processor architecture. The NN processor incorporates several functional safety concepts which reduce its risk of failure that occurs during operation from going unnoticed. The mechanisms function to detect and promptly flag and report the occurrence of an error with some mechanisms capable of correction as well. The safety mechanisms cover data stream fault detection, software defined redundant allocation, cluster interlayer safety, cluster intralayer safety, layer control unit (LCU) instruction addressing, weights storage safety, and neural network intermediate results storage safety.

Owner:HAILO TECH LTD

System and method of input alignment for efficient vector operations in an artificial neural network

ActiveUS11238334B2More efficientIncrease unit densityHandling data according to predetermined rulesNeural architecturesAlgorithmTerm memory

A novel and useful system and method of input alignment for streamlining vector operations that reduce the required memory read bandwidth. The input aligner as deployed in the NN processor, functions to facilitate the reuse of data read from memory and to avoid having to re-read that data in the context of neural network calculations. The input aligner functions to distribute input data (or weights) to the appropriate compute elements while consuming input data in a single cycle. Thus, the input aligner is operative to lower the required read bandwidth of layer input in an ANN. This reflects the fact that normally in practice, a vector multiplication is performed every time instance. This considers the fact that in many native calculations that take place in an ANN, the same data point is involved in multiple calculations.

Owner:HAILO TECH LTD

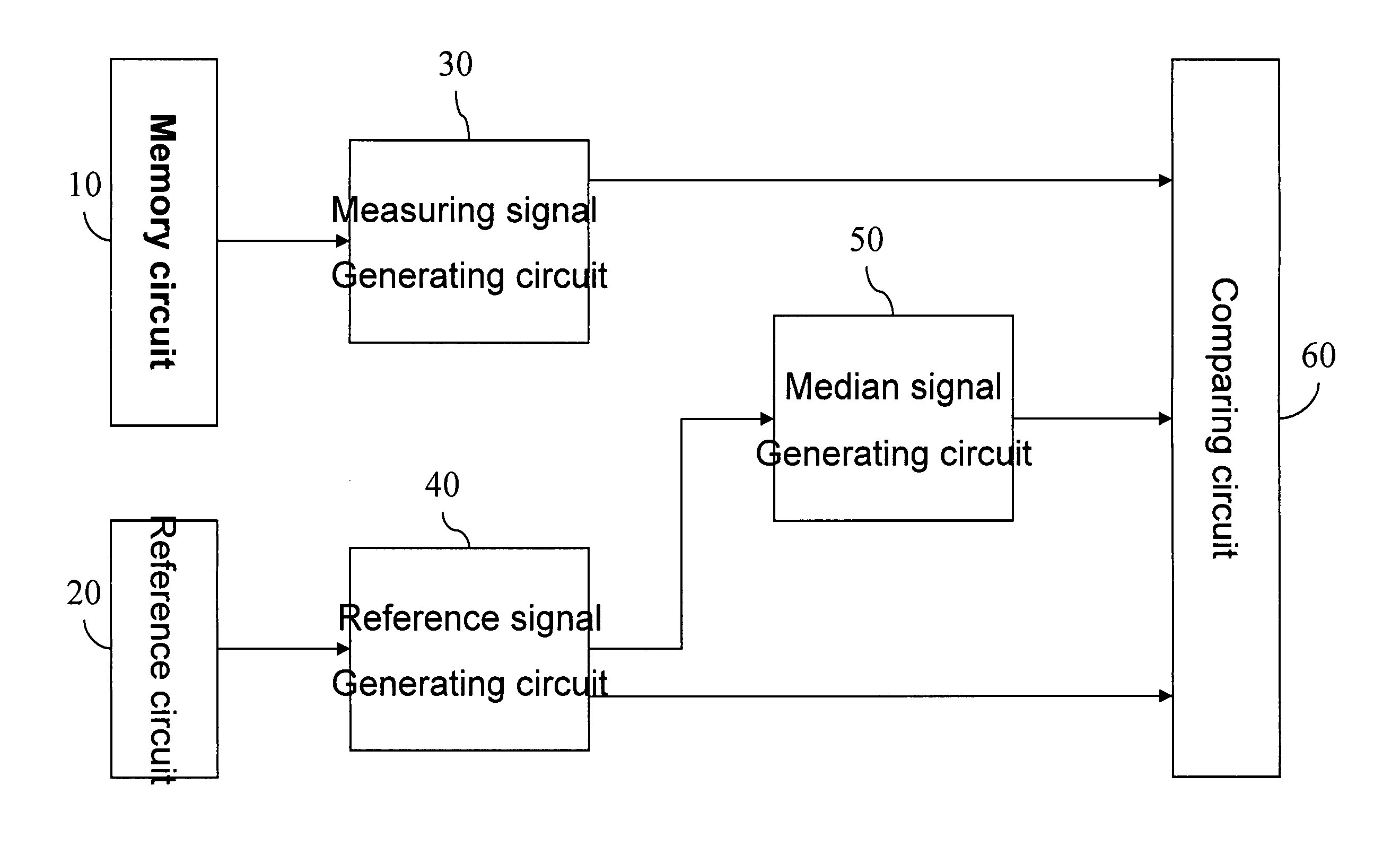

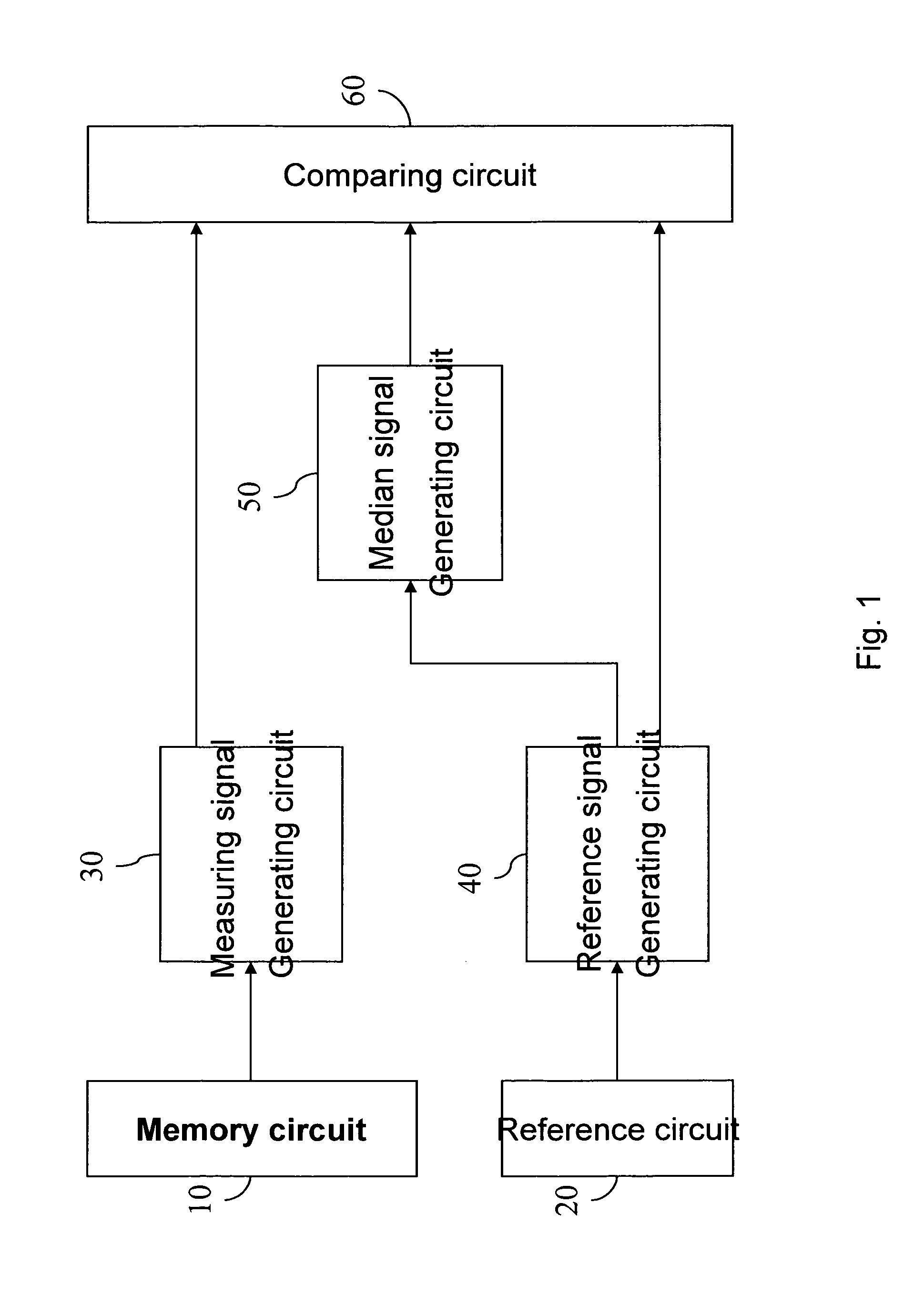

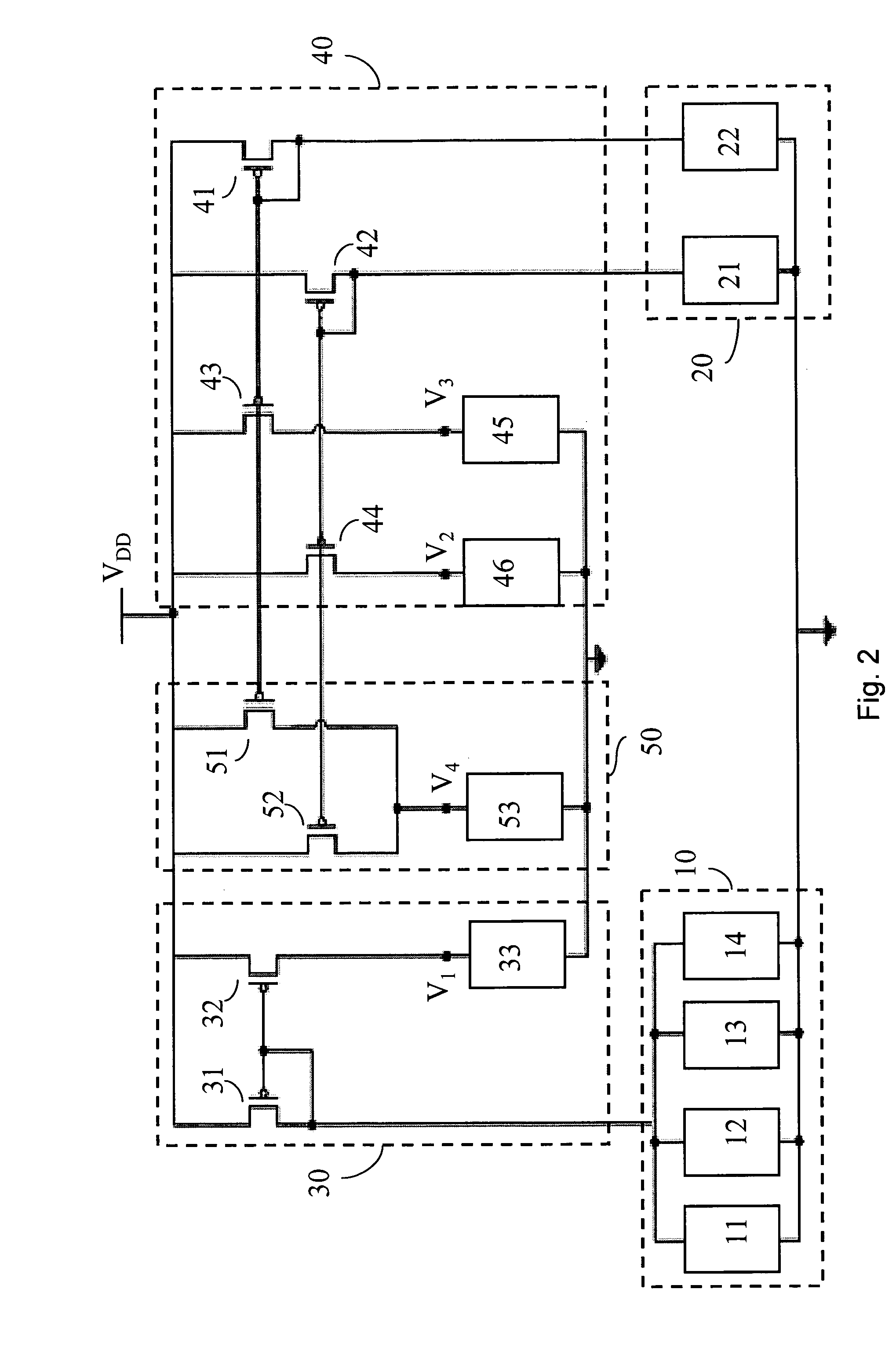

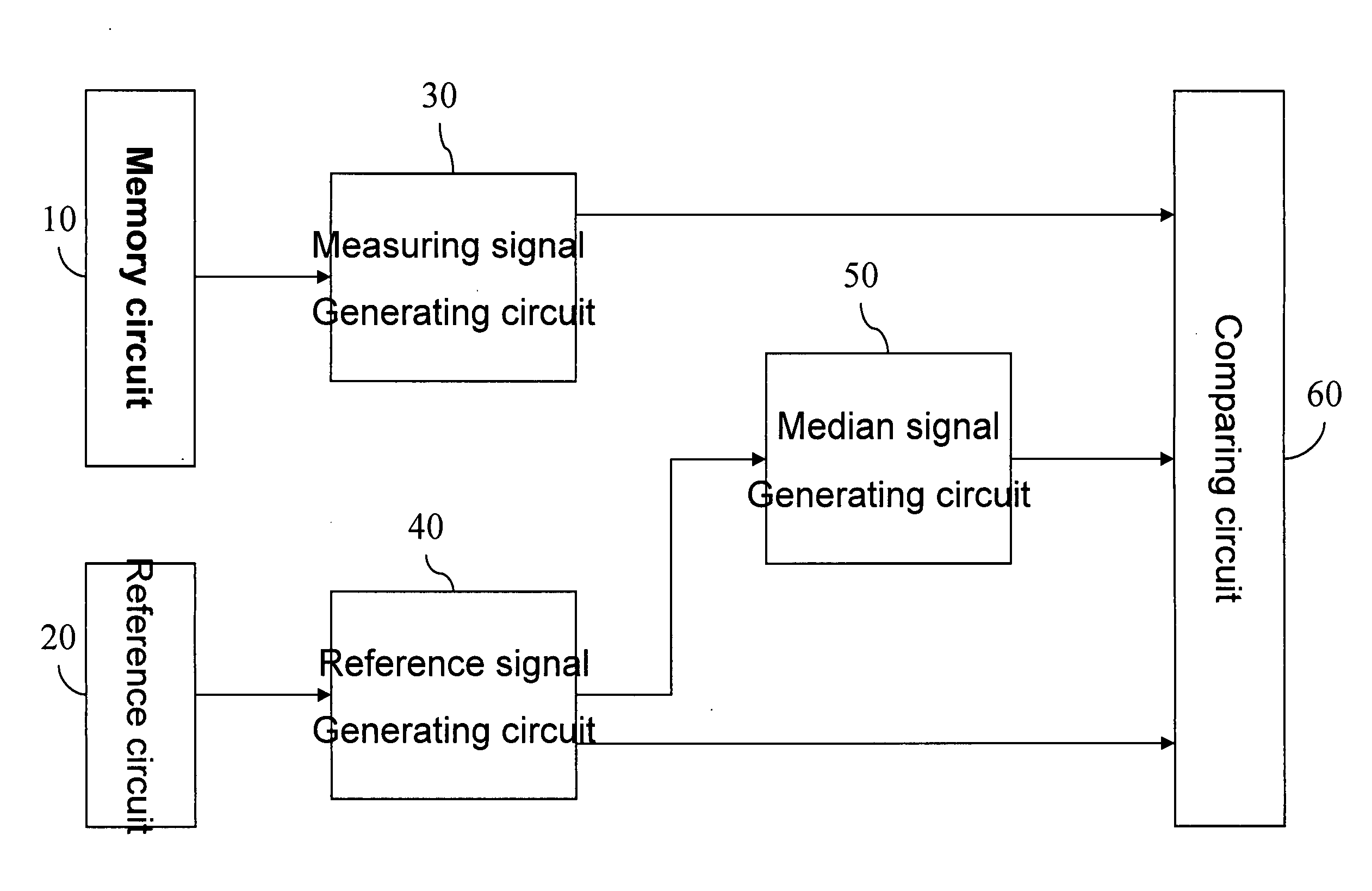

Memory accessing circuit and method

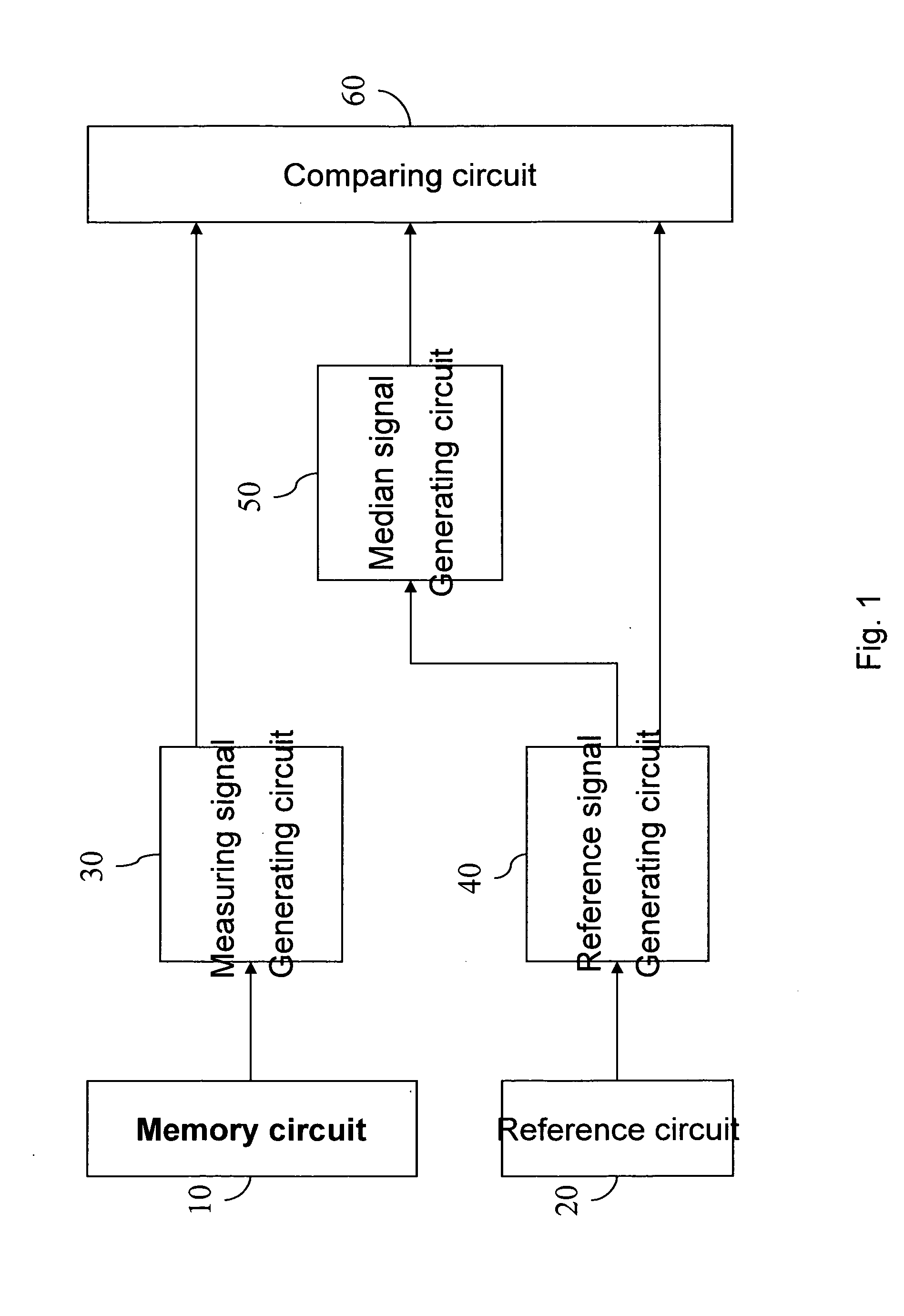

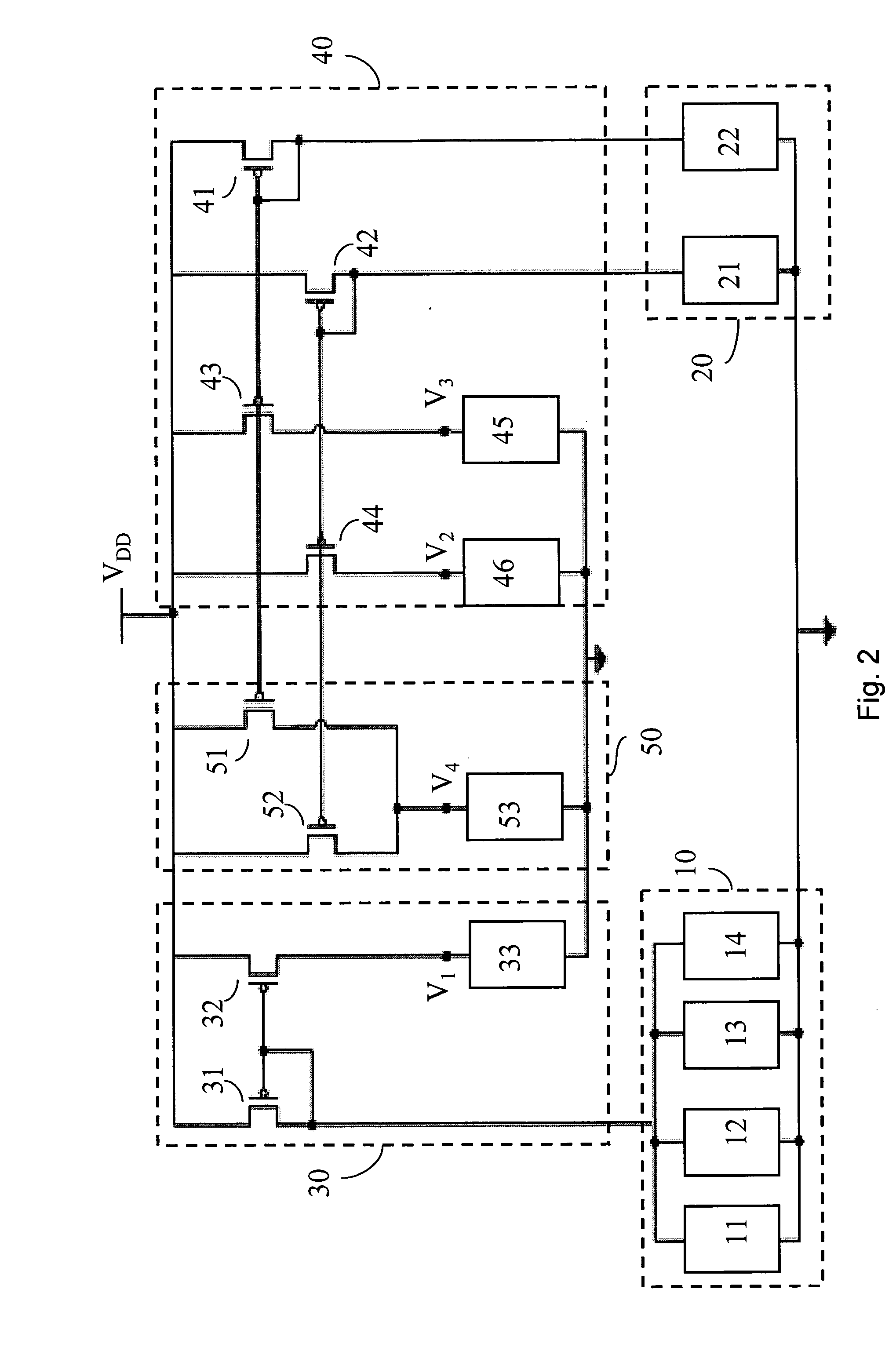

The present invention relates to a memory accessing circuit, which is for accessing a memory circuit with 2N impedance states. The memory accessing circuit includes a testing signal generating circuit, for generating a testing signal by detecting the impedance state of the memory circuit; a reference signal generating circuit, for generating 2N−1 reference signals by detecting the impedance states of a reference circuit having 2N−1 impedance paths; a median signal generating circuit, for generating (2N−1)−1, median signals by receiving the 2N−1 reference signals; and a comparing circuit, for comparing the testing signal and the (2N−1) median signals. The present invention further provides a memory accessing method thereof.

Owner:IND TECH RES INST

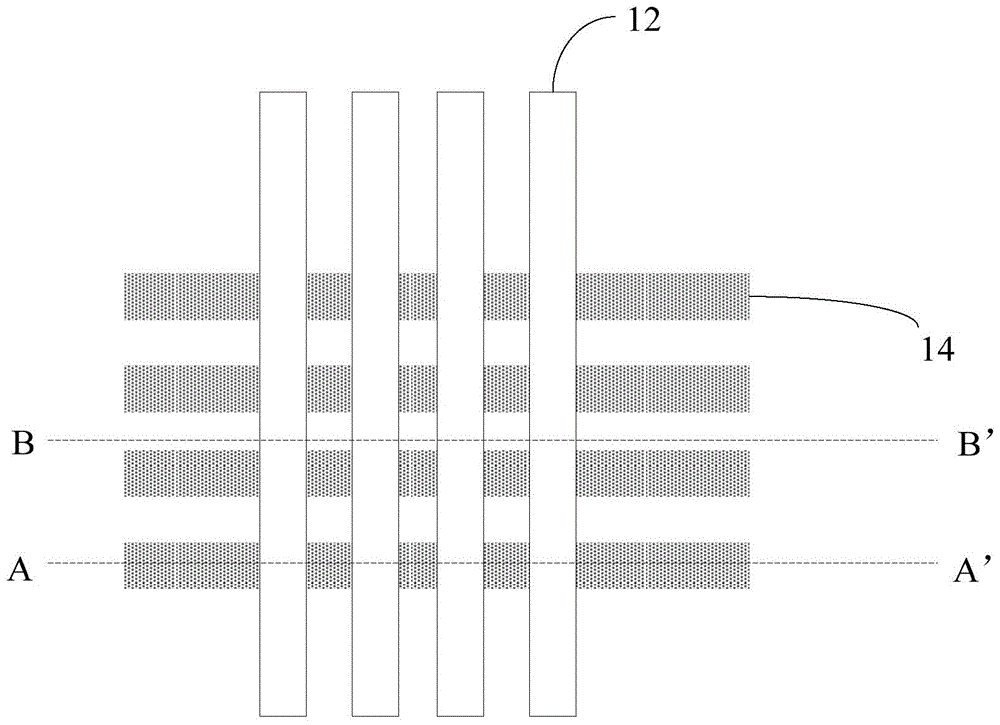

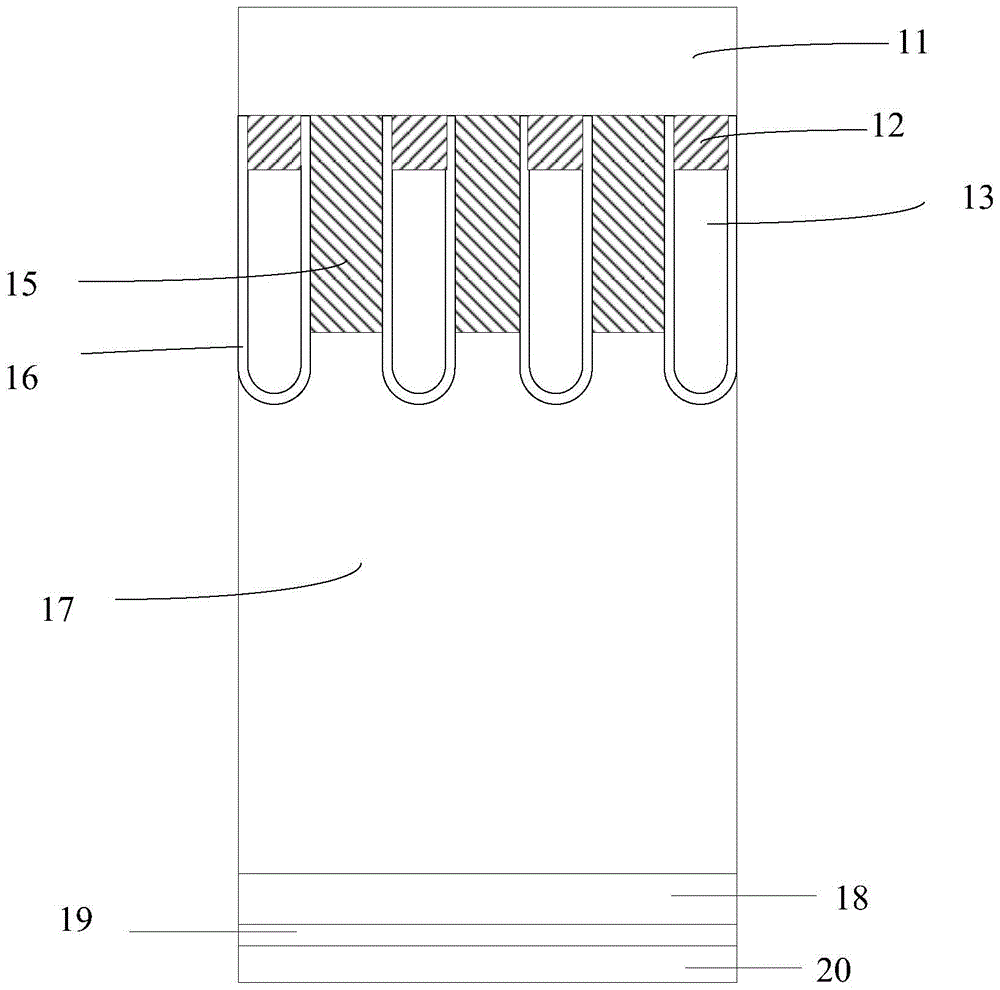

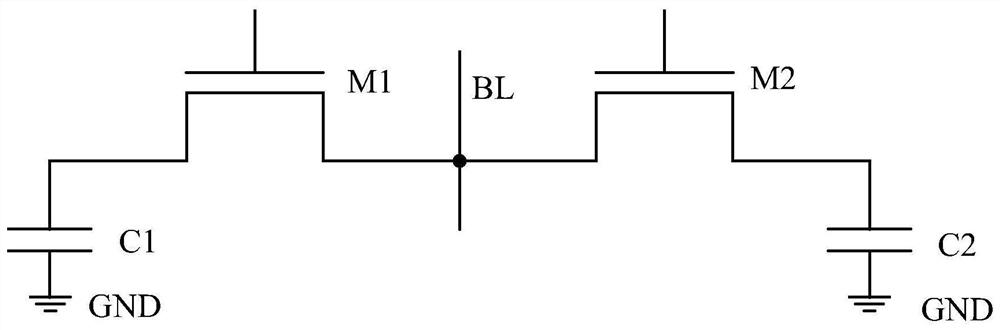

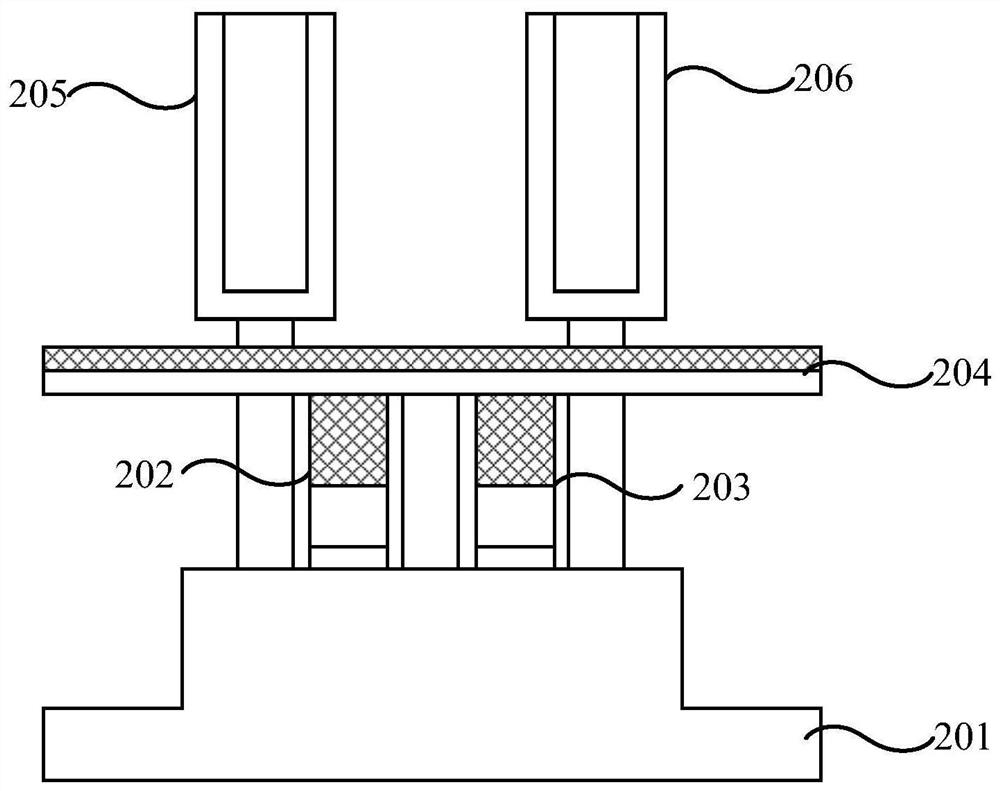

Preparation method of semiconductor structure and semiconductor structure

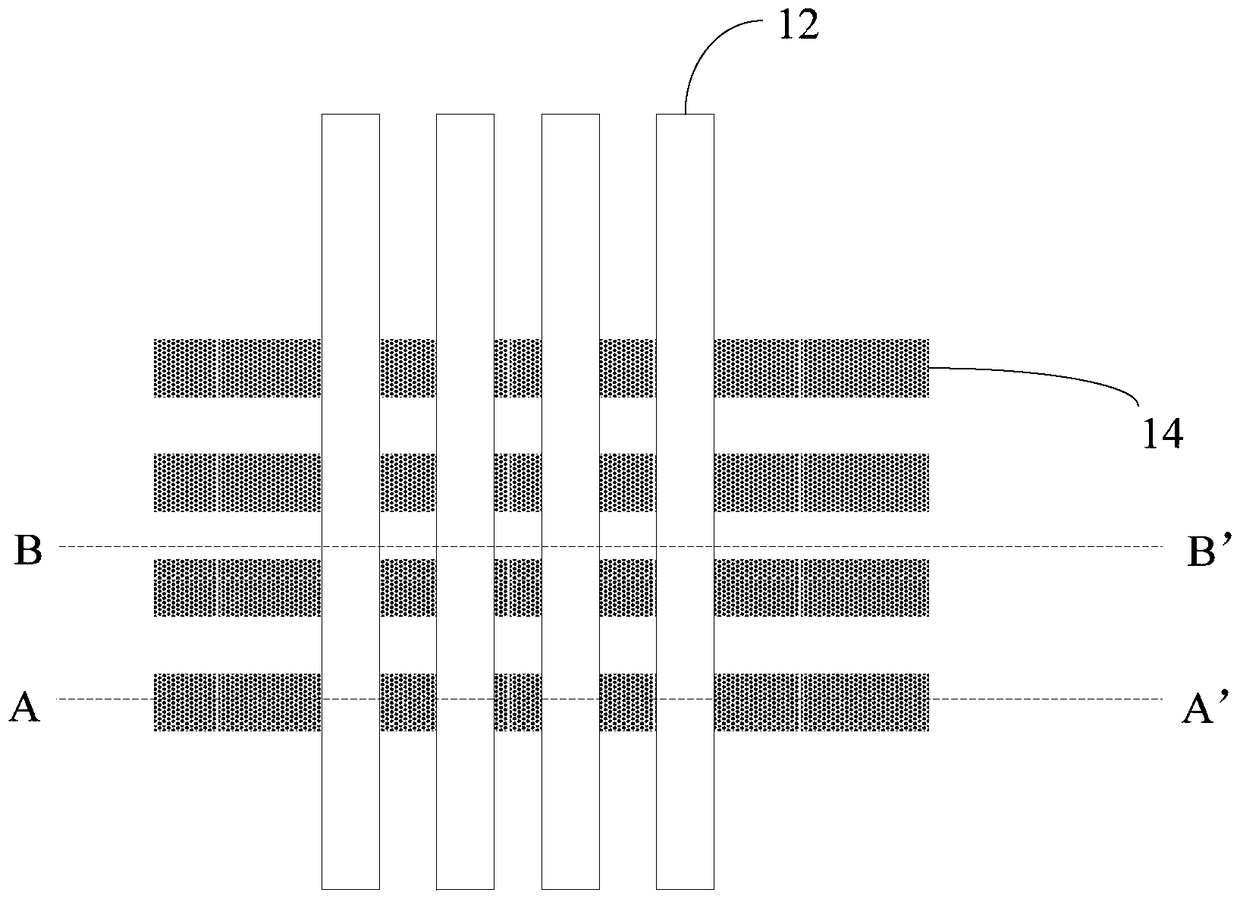

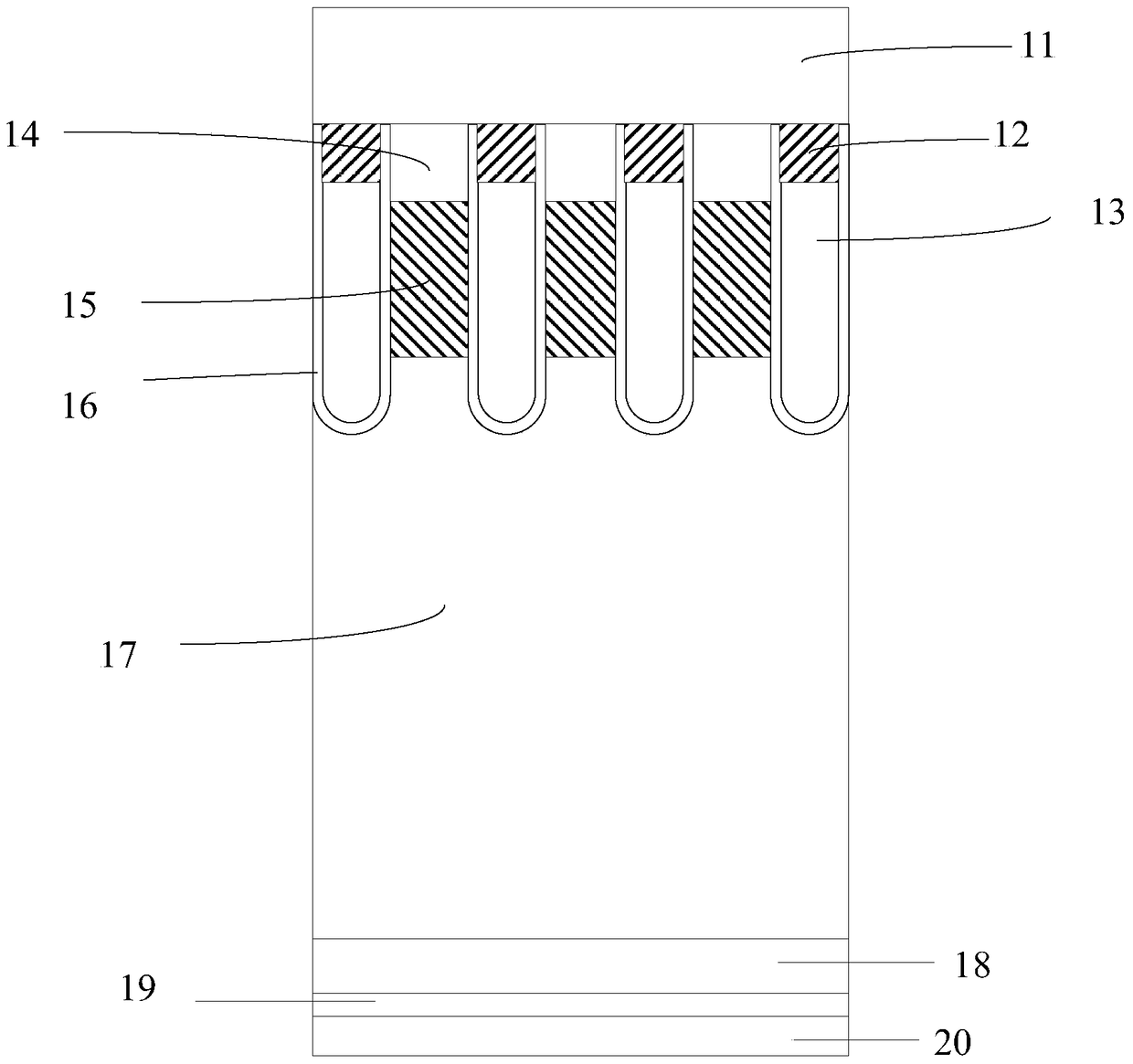

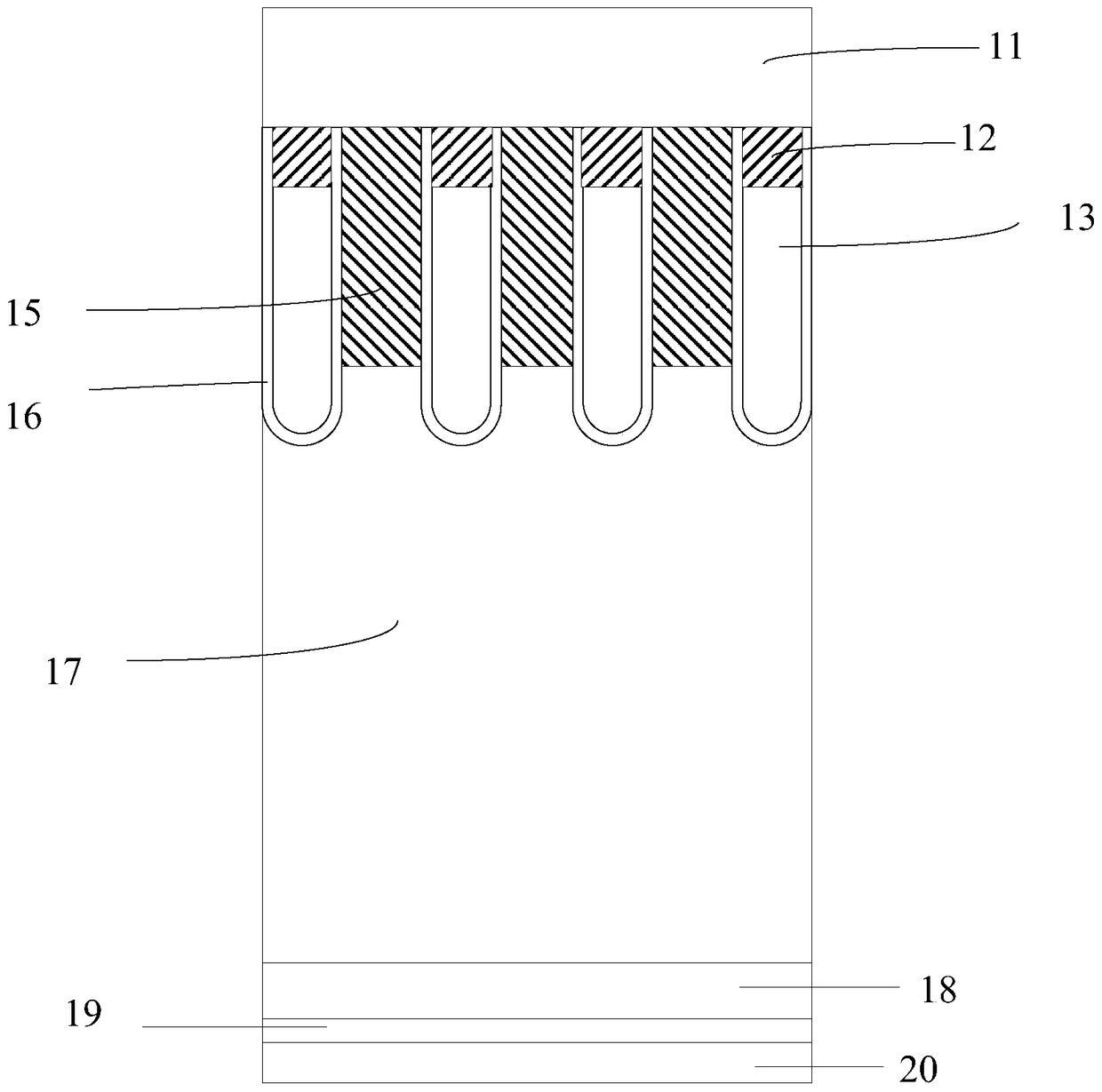

PendingCN113078116AReduce volumeIncrease unit densityTransistorSemiconductor/solid-state device manufacturingCapacitanceBit line

The invention provides a preparation method of a semiconductor structure and the semiconductor structure. The method comprises the following steps: providing a substrate; forming a first capacitor structure on the substrate; forming a first transistor structure on the first capacitor structure, wherein a source electrode or a drain electrode of the first transistor structure is electrically connected with the first capacitor structure; forming a bit line structure on the first transistor structure, wherein the bit line structure is electrically connected with a drain electrode or a source electrode of the first transistor structure; forming a second transistor structure on the bit line structure, wherein a drain electrode or a source electrode of the second transistor structure is electrically connected with the bit line structure; and forming a second capacitor structure on the second transistor structure, wherein the second capacitor structure is electrically connected with the source electrode or the drain electrode of the second transistor structure. The vertical gate-all-around field effect transistor is adopted, the size of the semiconductor structure is reduced, more storage units are obtained in the same unit area, and the unit density of the dynamic random access memory is improved.

Owner:CHANGXIN MEMORY TECH INC

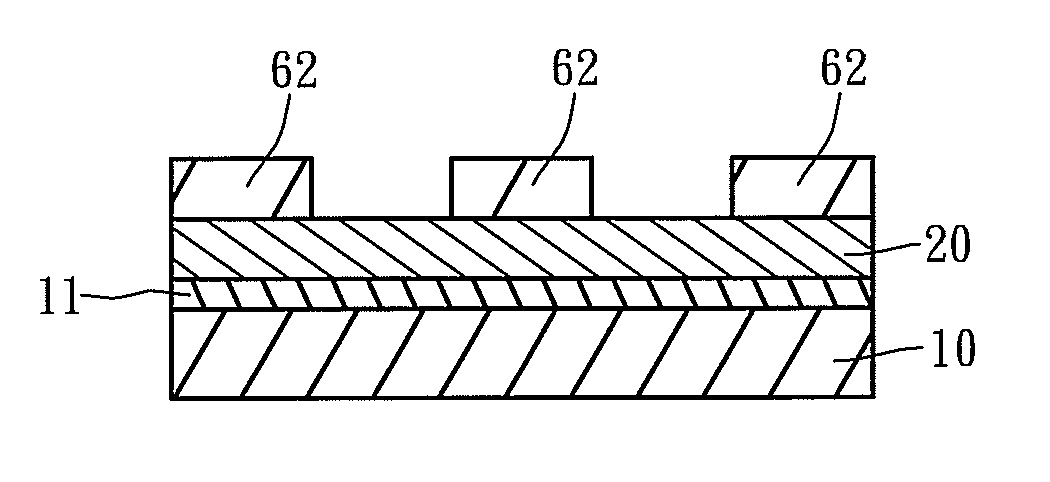

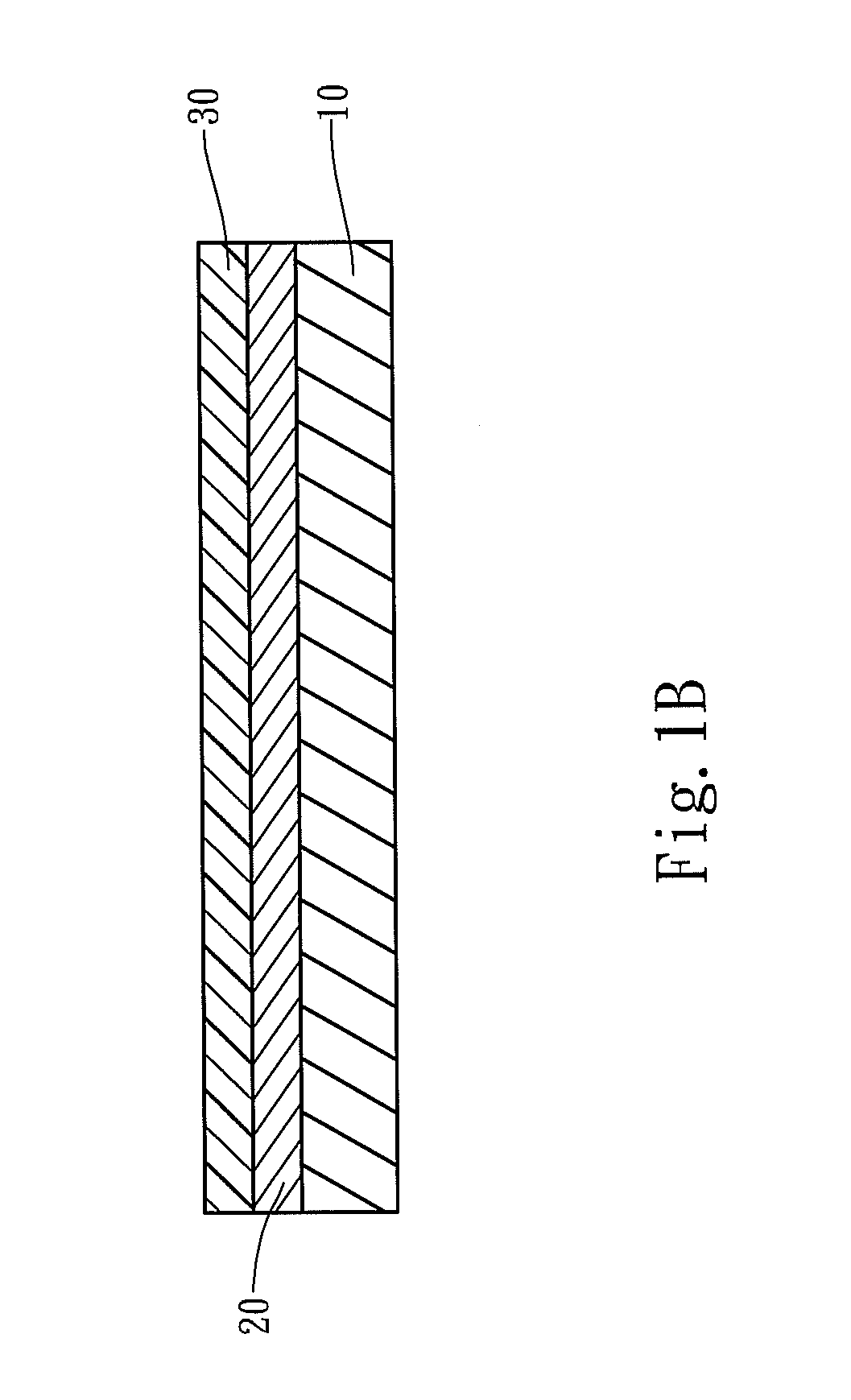

Mask ROM fabrication method

ActiveUS20130095628A1Small sizeReduce line widthSolid-state devicesSemiconductor/solid-state device manufacturingBit lineGate dielectric

A mask ROM fabrication method which comprises steps: sequentially forming a gate dielectric layer and a first photoresist layer on a substrate; letting a light having a wavelength of 365 nm pass through a first phase shift mask to photolithographically form on the first photoresist layer a plurality of first trenches having a width of 243-365 nm; doping the substrate to form a plurality of embedded bit lines having a width of 243-365 nm; removing the first photoresist layer; sequentially forming a polysilicon layer and a second photoresist layer on the gate dielectric layer; and letting the light pass through a second phase shift mask to photolithographically form a plurality of polysilicon word lines on the polysilicon layer. Thereby is reduced the line width of mask ROM to 243-365 nm and decreased the area of mask ROM.

Owner:NYQUEST +1

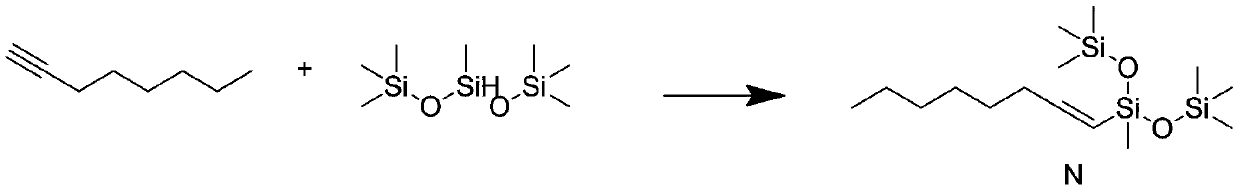

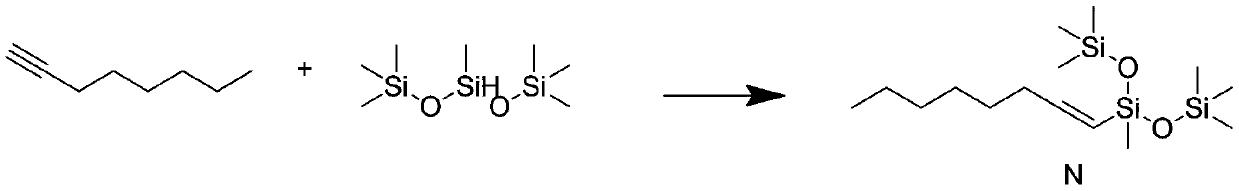

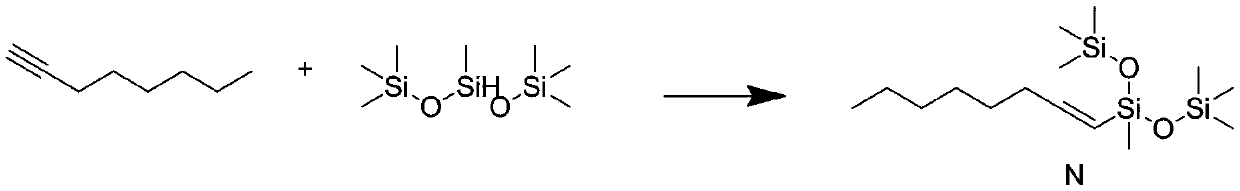

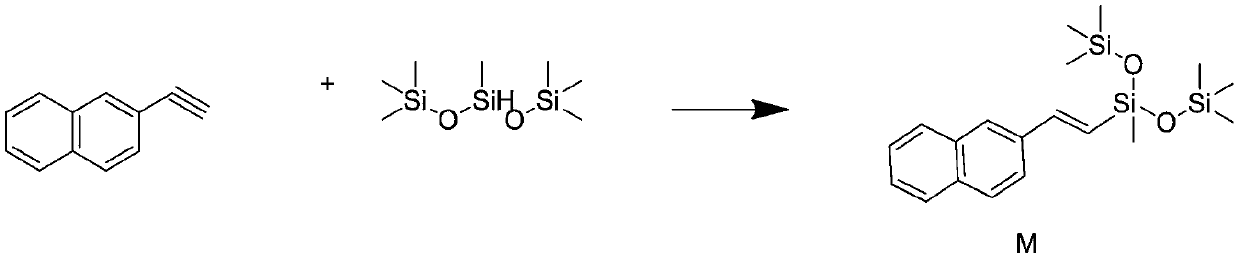

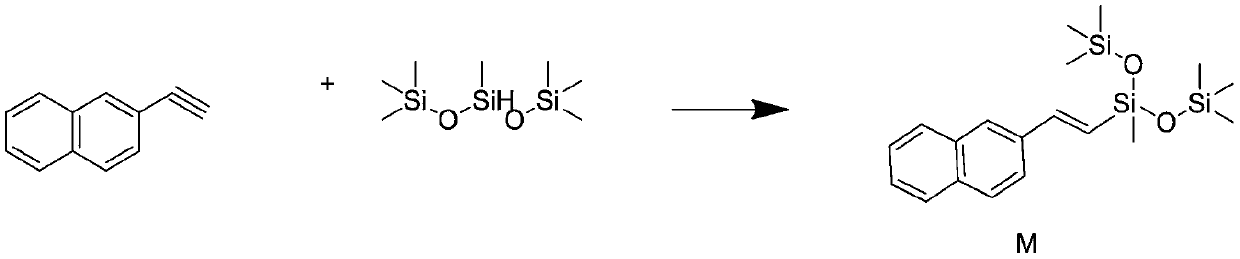

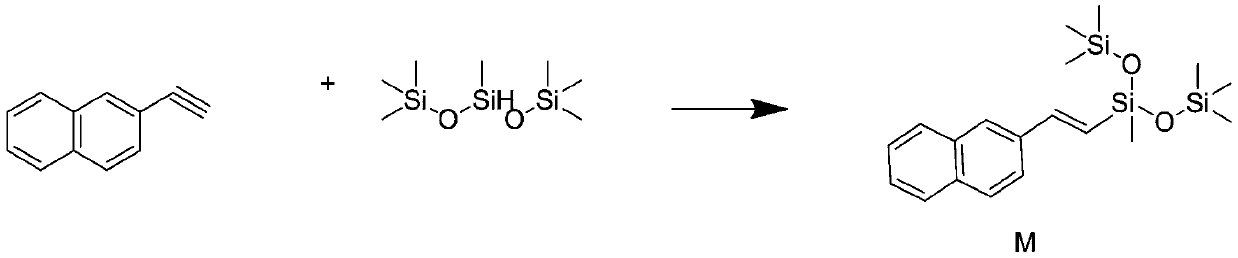

High-wear-resistance PP rope

The invention discloses a high-wear-resistance PP rope. The high-wear-resistance PP rope comprises the following raw materials in parts by weight: 100 to 150 parts of modified polypropylene, 15 to 20parts of a filler, 6 to 12 parts of ethylene propylene diene monomer, 0.5 to 1.2 parts of a plasticizer, 0.3 to 0.5 part of an antioxidant, 1.5 to 3 parts of paraffin oil and 0.5 to 1 part of a lubricant. According to the invention, polypropylene is modified, and organic silicon is introduced in a bonding manner. Specifically, an emulsion polymerization mode is adopted; a propylene monomer is pre-polymerized, then a modifier is added, and double bonds on the modifier are copolymerized with propylene so as to be embedded into polypropylene, so the polypropylene containing organic silicon is obtained; and due to introduction of the organic silicon, the unit density of a polypropylene chain segment is increased, the mechanical strength and the flexibility of the polypropylene are greatly improved, and the bearing stress of the polypropylene is enhanced, so the wear resistance of the PP rope is further improved.

Owner:界首市宏利塑料股份有限公司

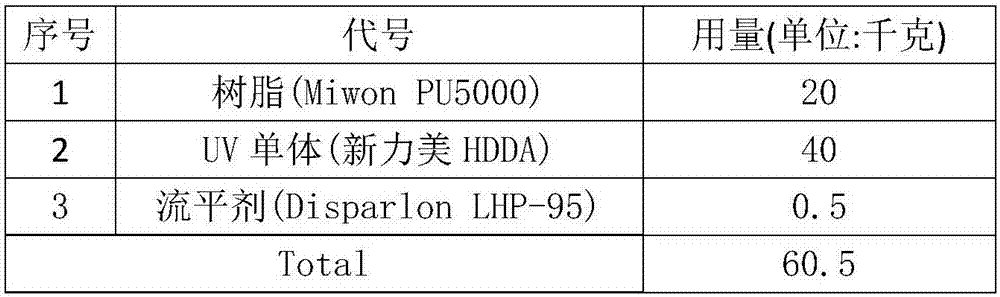

Single coating uv ultraviolet light curing color effect paint applied on plastic substrate and its preparation

ActiveCN104673064BFast film formationCompact structurePolyurea/polyurethane coatingsPolyether coatingsColor effectOrganic solvent

The invention relates to single-coated UV light cured color effect paint applied to plastic substrates and a preparation method thereof. The effect paint comprises the following components in parts by weight: 20-30 parts of light-cured resin, 40-50 parts of UV monomer, 4-8 parts of pearlescent pigment, 10-20 parts of nano paste, 3-5 parts of photoinitiator, 2-4 parts of photosensitizer, 0.5-1 part of leveling agent and 10-20 parts of organic solvent. Compared with the prior art, the effect paint provided by the invention has the properties of high UV light curing speed, high coating film surface hardness, excellent wear resistance and chemical resistance and the like, and has the advantages of color decorative effect, etc.

Owner:DONGLAI COATING TECH SHANGHAI

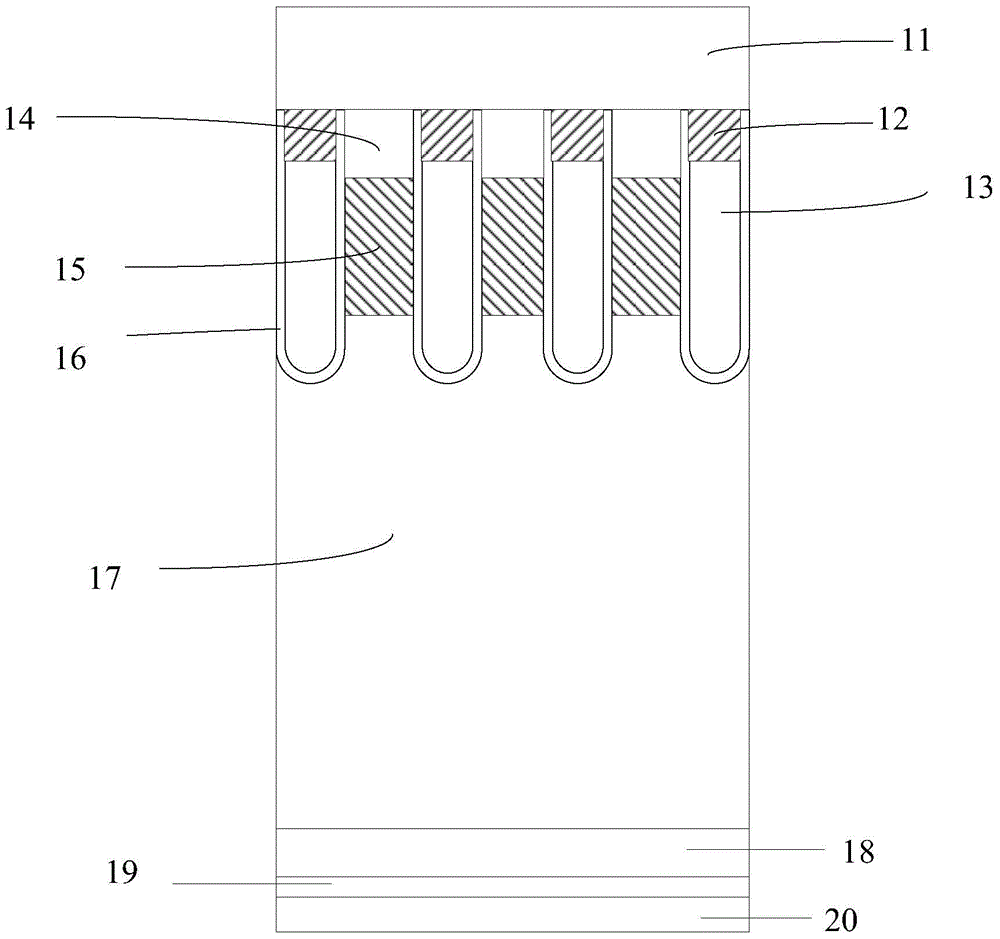

Semiconductor device with trench gate structure and manufacturing method thereof

ActiveCN106328697BReduce spacingIncrease unit densitySemiconductor devicesMetal electrodesPolysilicon gate

A semiconductor device with a trench gate structure comprises: a drift region (17), a metal electrode (11) on the drift region (17), a trench penetrating from a region below the metal electrode (11) to the drift region (17), a gate oxidation layer (16) on an inner surface of the trench, a polycrystalline silicon gate (13) in the trench, a dielectric layer (12) disposed in the trench and above the polycrystalline silicon gate (13), and a doped region at two sides of the top of the trench.

Owner:CSMC TECH FAB2 CO LTD

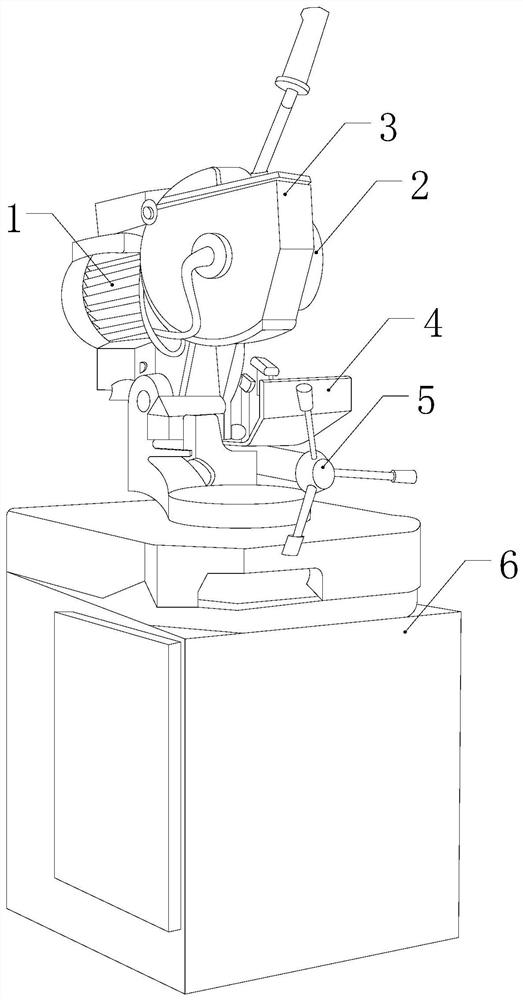

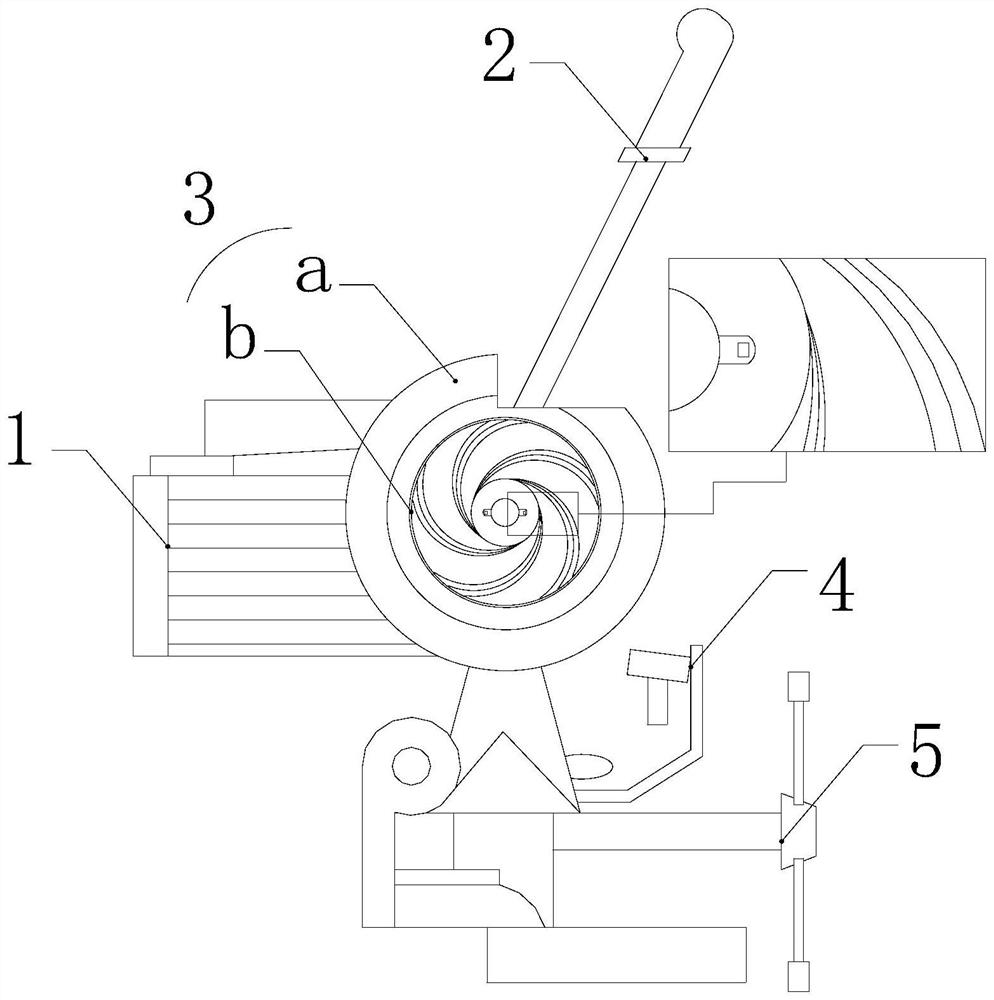

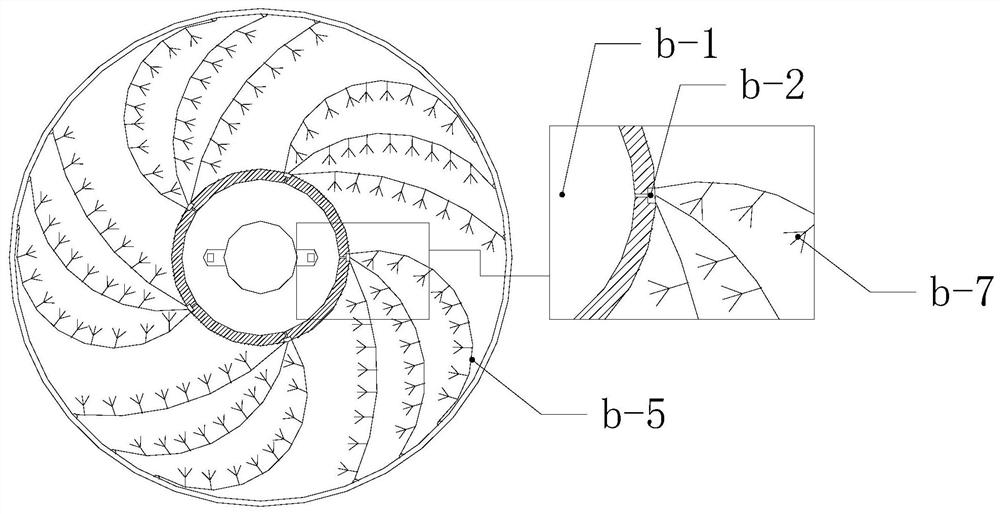

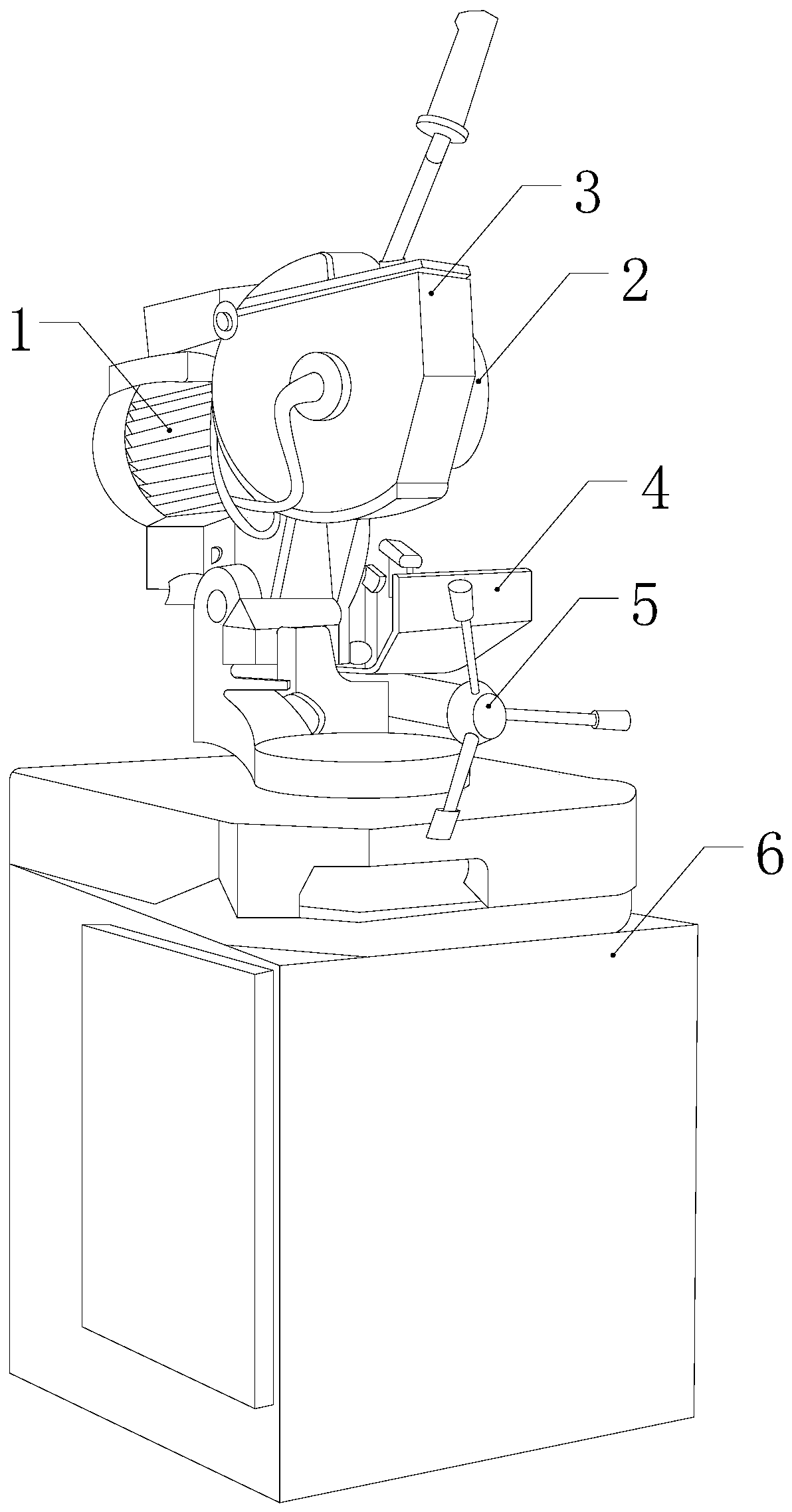

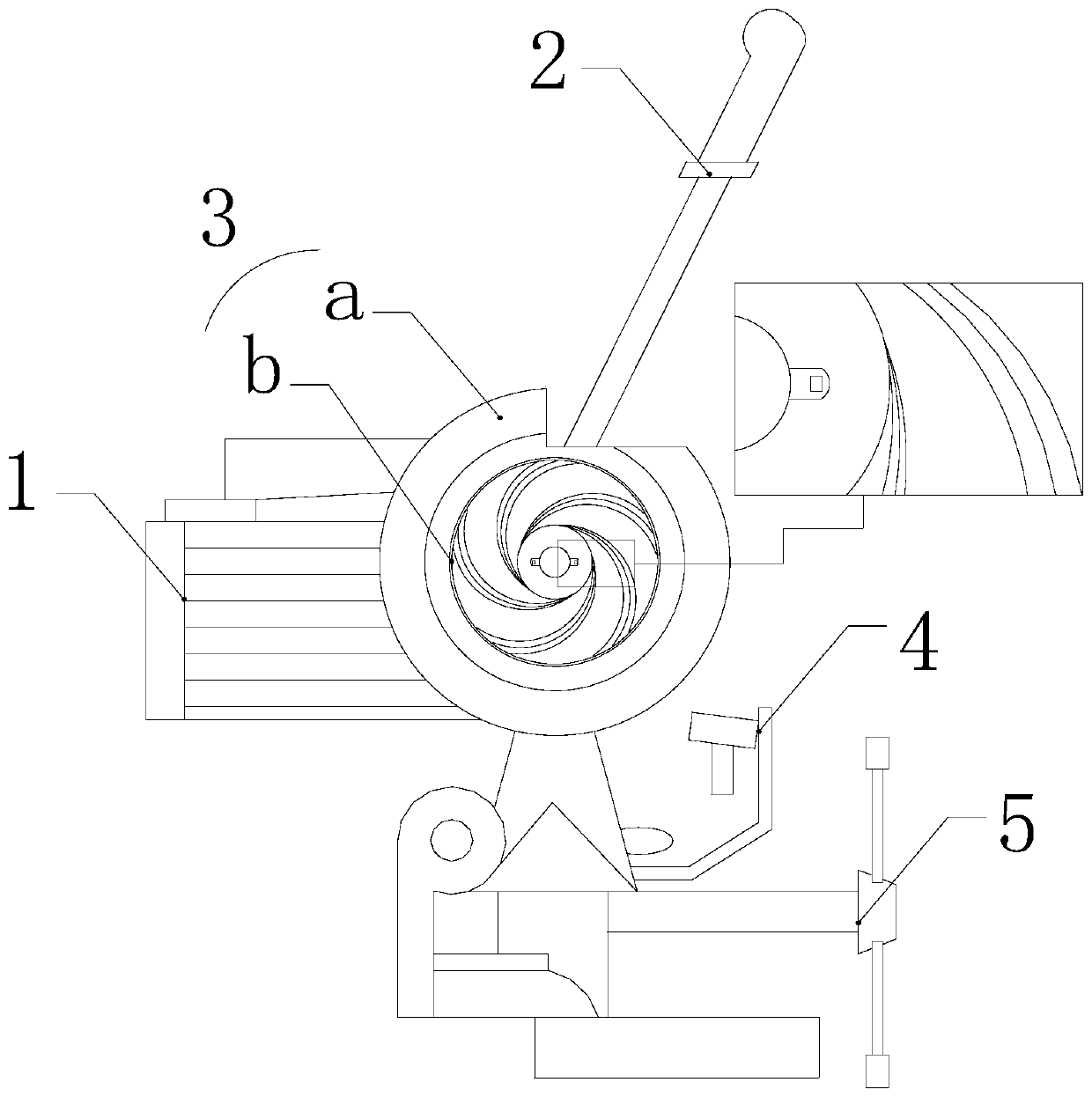

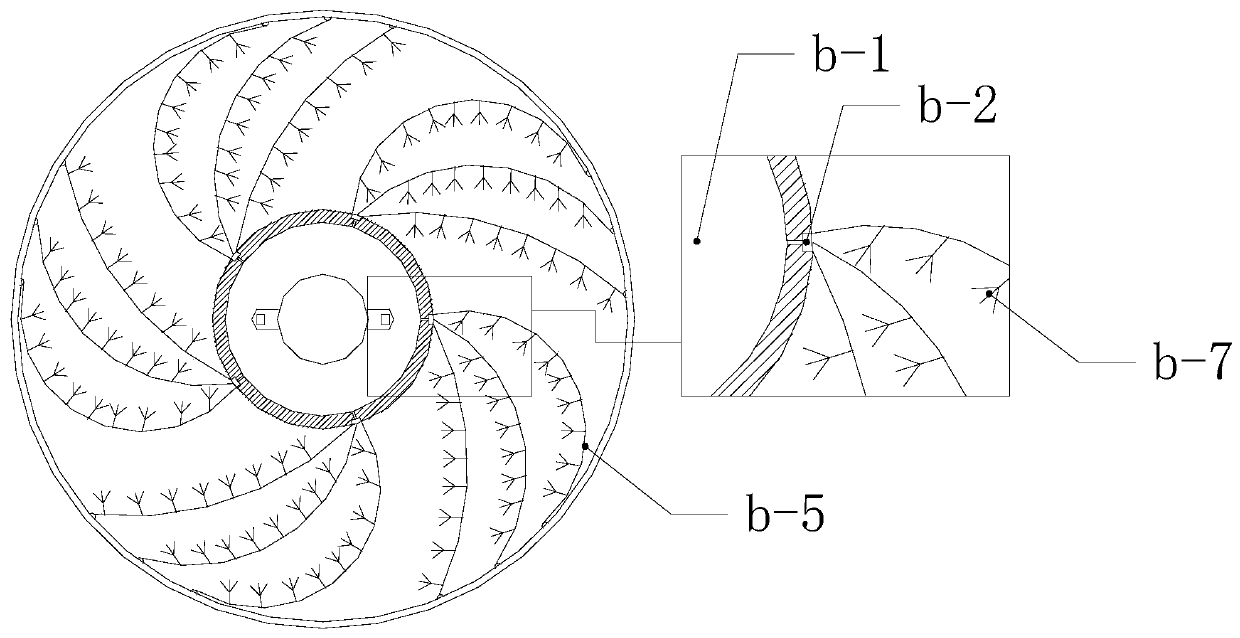

A metal cutting equipment that facilitates the collection of metal shavings

InactiveCN111300135BIncrease resistanceImprove interception effectMaintainance and safety accessoriesSteering wheelElectric machinery

Owner:新昌县灵佳机械有限公司

Mask ROM fabrication method

ActiveUS8455342B2Small sizeReduce line widthSolid-state devicesSemiconductor/solid-state device manufacturingBit lineGate dielectric

A mask ROM fabrication method which comprises steps: sequentially forming a gate dielectric layer and a first photoresist layer on a substrate; letting a light having a wavelength of 365 nm pass through a first phase shift mask to photolithographically form on the first photoresist layer a plurality of first trenches having a width of 243-365 nm; doping the substrate to form a plurality of embedded bit lines having a width of 243-365 nm; removing the first photoresist layer; sequentially forming a polysilicon layer and a second photoresist layer on the gate dielectric layer; and letting the light pass through a second phase shift mask to photolithographically form a plurality of polysilicon word lines on the polysilicon layer. Thereby is reduced the line width of mask ROM to 243-365 nm and decreased the area of mask ROM.

Owner:NYQUEST +1

High-strength and wear-proof PP plastic rope

InactiveCN111501384AIncrease unit densityHigh mechanical strengthTextile cablesPolypropyleneDouble bond

The invention discloses a high-strength and wear-proof PP plastic rope. The high-strength and wear-proof PP plastic rope is prepared from raw materials by weight: 110-140 parts of modified polypropylene, 5-8 parts of dimethyl phthalate, 6-8 parts of trimethyl ethyl acetate, 15-22 parts of filler, 0.5-1.2 parts of plasticizer, 1.5-3 parts of paroline and 0.5-1 part of lubricant. The polypropylene is modified, organosilicone and rigid functional group naphthalene rings are introduced in a bound manner, specifically, firstly, propylene monomers are pre-polymerized in an emulsion polymerization manner, then a modifier is added, double bonds on the modifier and the propylene are co-polymerized and then embedded into the polypropylene, the polypropylene with the organosilicone is obtained, due to introduction of the organosilicone, on one hand, the unit density of polypropylene chain segments is improved, the mechanical strength of the polypropylene is greatly improved, the bearing stress isenhanced, then the wear-proof performance of the PP rope is improved, and due to introduction of the rigid functional group naphthalene rings, the mechanical strength of the polypropylene is furtherimproved.

Owner:界首市宏利塑料股份有限公司

Metal cutting equipment facilitating collecting of metal scraps

InactiveCN111300135AIncrease resistanceImprove interception effectMaintainance and safety accessoriesSteering wheelElectric machinery

The invention discloses metal cutting equipment facilitating collecting of metal scraps. The structure of the equipment comprises a motor, a cutter, a curl collecting structure, a bottom frame, a steering wheel and an equipment body. The bottom frame is arranged at the top end of the equipment body. The cutter is arranged at the topmost end of the bottom frame. The curl collecting structure is installed on the side face of the cutter. The steering wheel is arranged on the bottom frame bottom directly facing the bottom frame. A motor is installed on the other side, corresponding to the steeringwheel, of the cutter. A housing covers the cutter. A curl mingling device is arranged right in the middle in the housing. The curl mingling device directly faces the cutter. According to the metal cutting equipment, the curl mingling device retracts to roll into a metal net ball of a lattice structure, the metal net ball and the housing cooperate with each other, the metal scraps generated by cutting enter the metal net ball in the cutting process, by means of layer-upon-layer design of net bars, the net bars and the metal scraps cut each other, then along with impact force of the metal scraps, the net bars and the metal scraps collide with each other, the impact force is weakened gradually, and the situation that the metal scraps penetrate through the metal ball again and collide with the housing, and noise is generated can be avoided.

Owner:新昌县灵佳机械有限公司

Memory accessing circuit and method

ActiveUS20090141574A1Reduce in quantityReduce circuit areaDigital storageAccess methodComparative test

The present invention relates to a memory accessing circuit, which is for accessing a memory circuit with 2N impedance states. The memory accessing circuit comprises a testing signal generating circuit, for generating a testing signal by detecting the impedance state of the memory circuit; a reference signal generating circuit, for generating 2N−1 reference signals by detecting the impedance states of a reference circuit having 2N−1 impedance paths; a median signal generating circuit, for generating (2N−1)−1, median signals by receiving the 2N−1 reference signals; and a comparing circuit, for comparing the testing signal and the (2N−1) median signals. The present invention further provides a memory accessing method thereof.

Owner:IND TECH RES INST