Patents

Literature

38results about How to "Consistent etch rate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

ITO-Ag-ITO etching liquid for AM-OLED display screen and preparation method

ActiveCN105176533AAdjust densityConsistent etch rateSurface treatment compositionsAcetic acidO-Phosphoric Acid

The invention discloses ITO-Ag-ITO etching liquid for an AM-OLED display screen and a preparation method. The etching liquid is prepared from phosphoric acid, acetic acid, nitric acid, additives, surfactants and pure water. The preparation method of the etching liquid comprises the steps that the rotating speed of a stirrer of a dosing tank is kept at normal temperature and pressure, the pure water, the phosphoric acid, the acetic acid, the nitric acid, the additives, the surfactants and the balance pure water are sequentially added into the dosing tank, and after full stirring is conducted, the ITO-Ag-ITO etching liquid is prepared by introducing a fully-stirred mixture into a filter for filtration. According to the ITO-Ag-ITO etching liquid for the AM-OLED display screen and the preparation method, the ITO-Ag-ITO etching liquid is small in particle size and high in purity, the etching rate to different metal is basically the same, and reaction is stable; the etching rate can be controlled by adjusting the concentrations of the phosphoric acid and the nitric acid, the surface of a substrate etched through the etching liquid is clean and tidy, residues do not exist, the intermetallic layering phenomenon does not exist, remaining lines are flat and smooth, and the etching angle is kept between 70 degrees to 90 degrees.

Owner:JIANGYIN RUNMA ELECTRONICS MATERIAL

Novel acidic molybdenum aluminum molybdenum etching liquid and its preparation process

The invention discloses a novel acidic molybdenum aluminum molybdenum etching liquid and its preparation process. The novel acidic molybdenum aluminum molybdenum etching liquid comprises phosphoric acid, acetic acid, nitric acid, metal nitrate, a cationic surfactant and pure water. The preparation process of the etching liquid includes: maintaining the rotation speed of an ingredient tank stirrer, adding the phosphoric acid, the acetic acid, the nitric acid, potassium nitrate, the pure water and the cationic surfactant sequentially into the ingredient tank, fully stirring them, then introducing the mixture into a filter to conduct filtration, thus obtaining the molybdenum aluminum molybdenum etching liquid. The molybdenum aluminum molybdenum etching liquid provided in the invention has a small particle size and high purity, has a basically consistent etching rate on different metals, and is stable in reaction. By adjusting the nitric acid concentration, the etching speed can be controllable. The substrate etched by the etching liquid has a clean and tidy surface, no residue, and no intermetallic layering phenomenon. The remaining lines are smooth, and the etching angle is maintained at 40-60 degrees.

Owner:JIANGYIN RUNMA ELECTRONICS MATERIAL

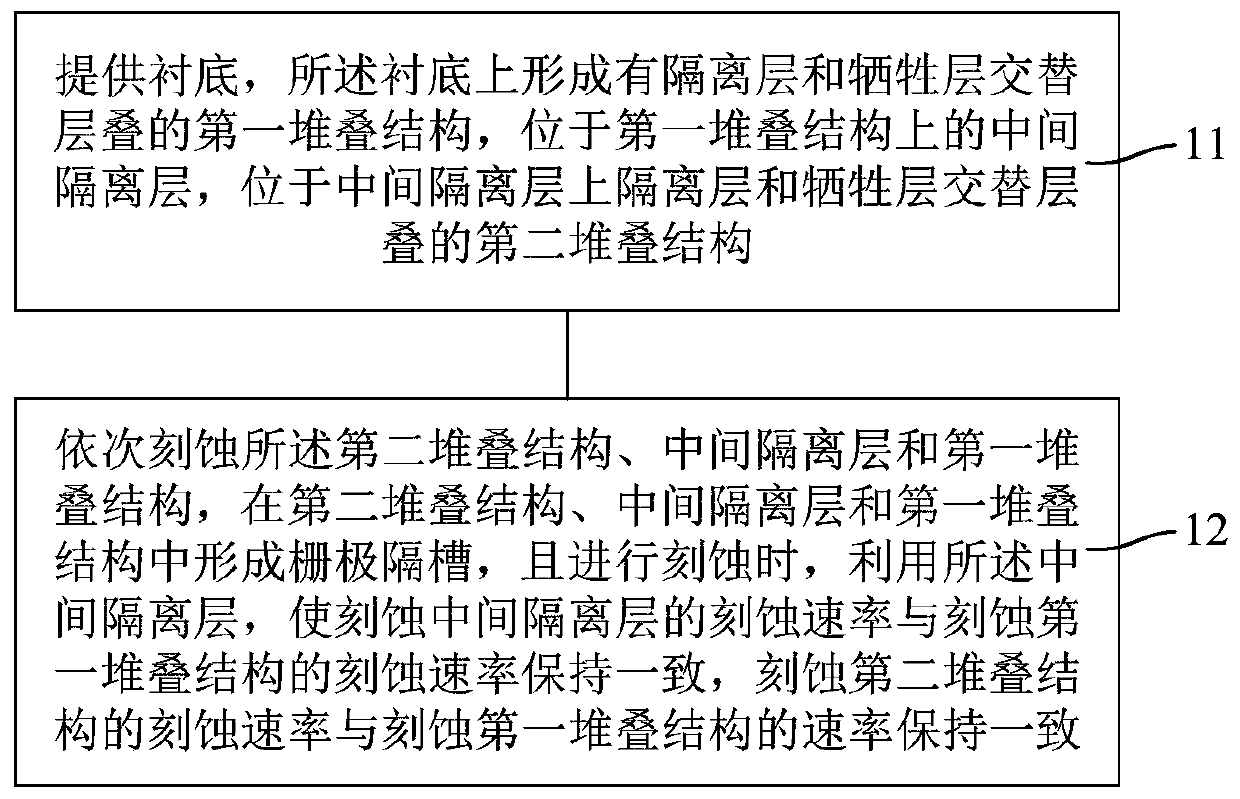

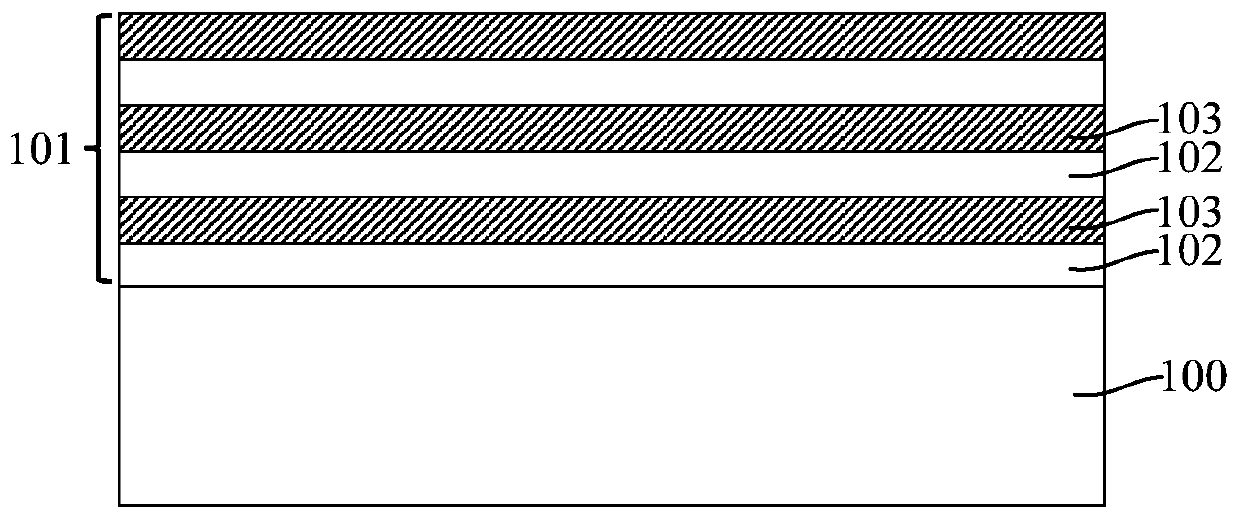

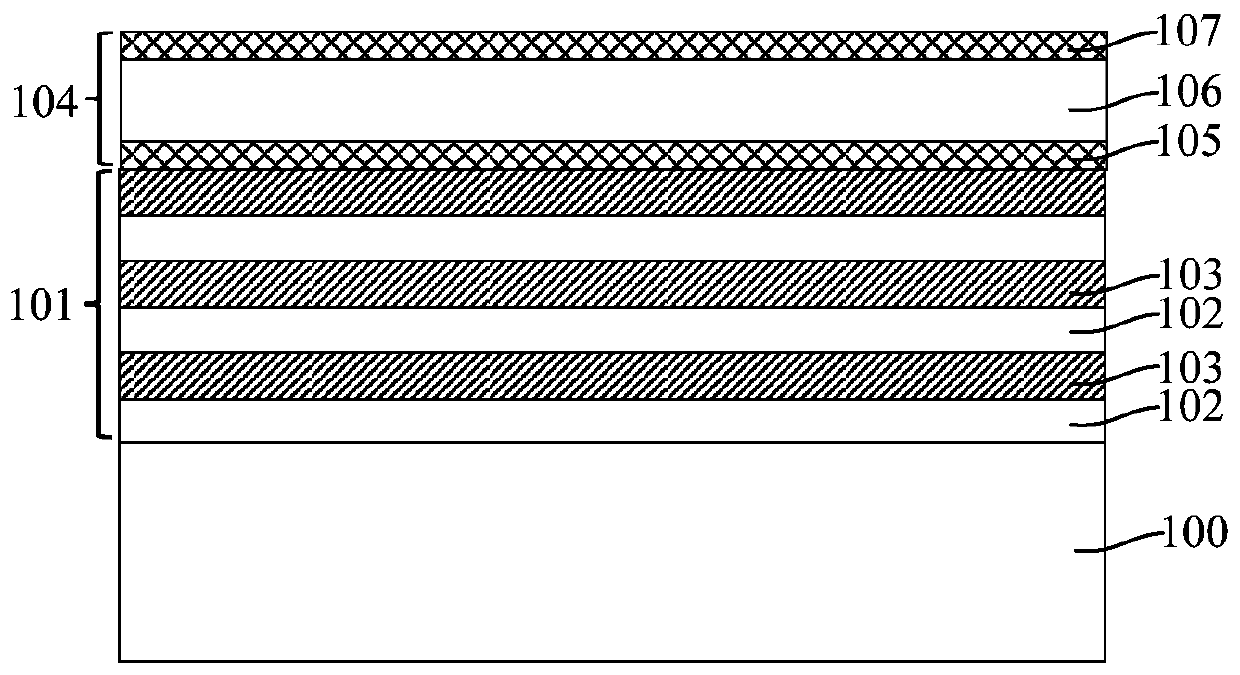

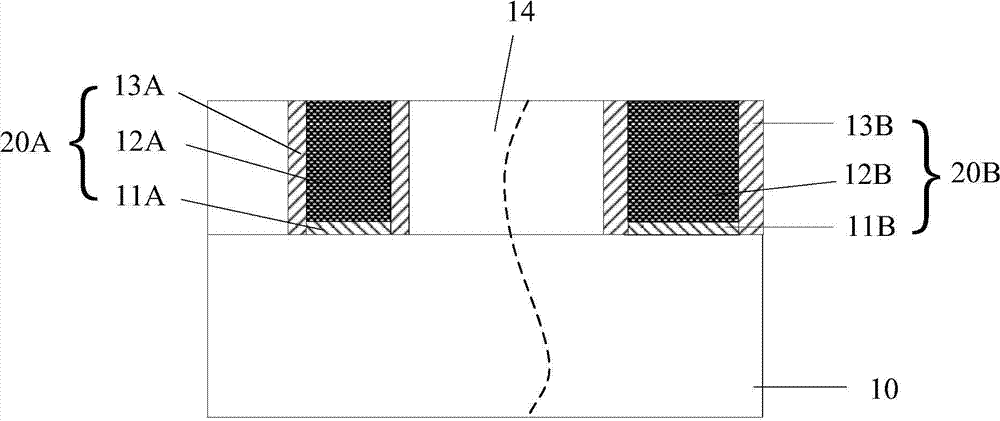

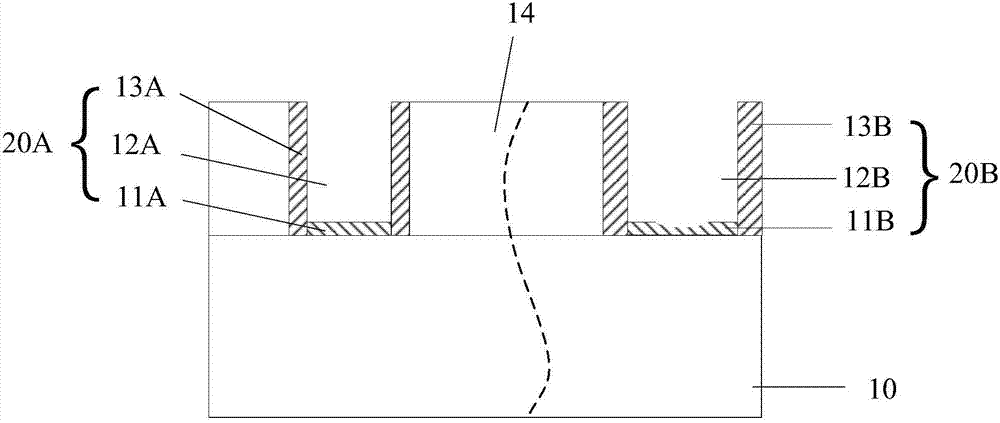

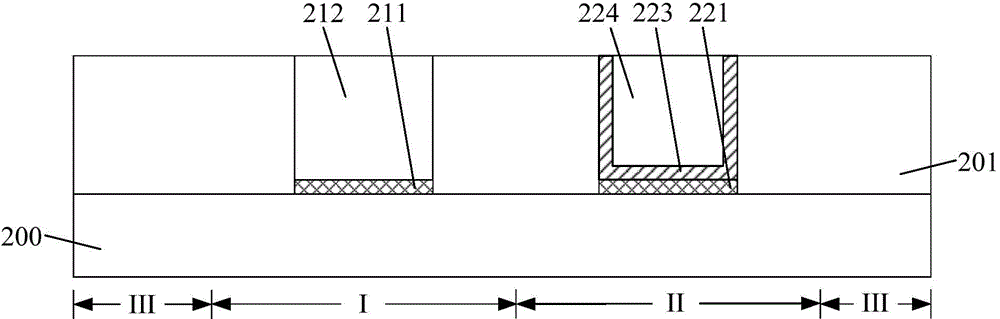

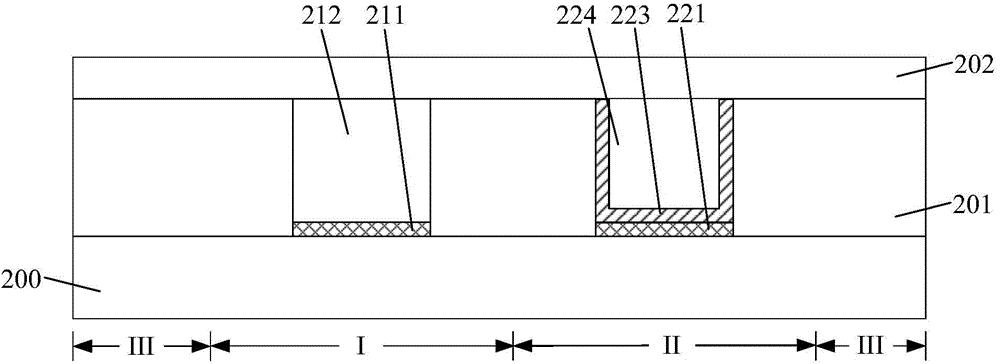

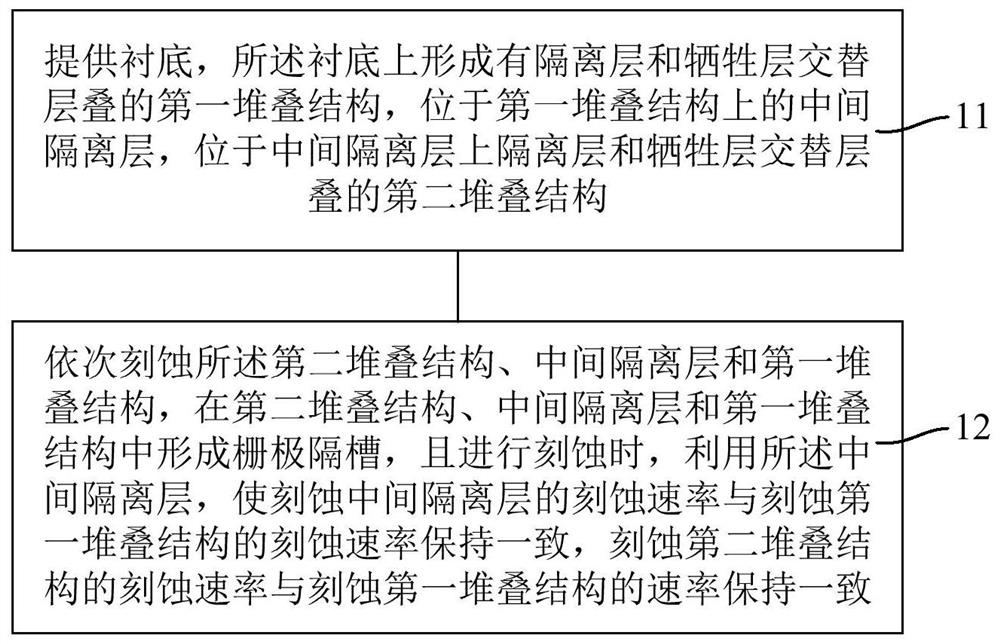

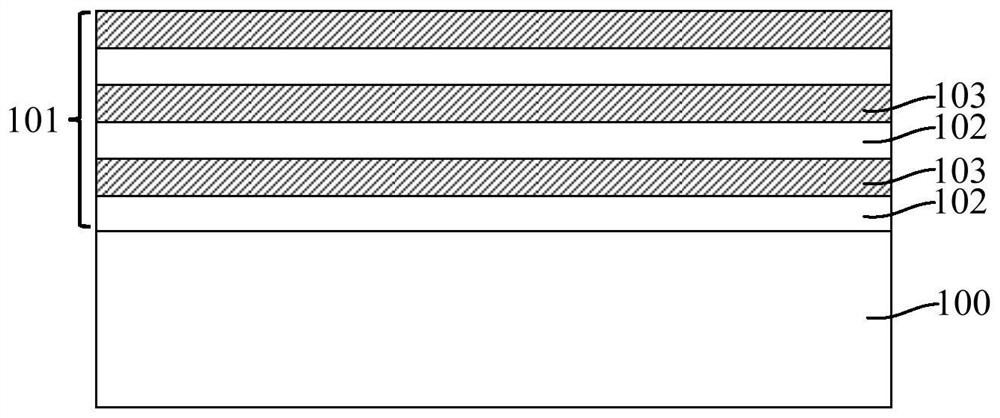

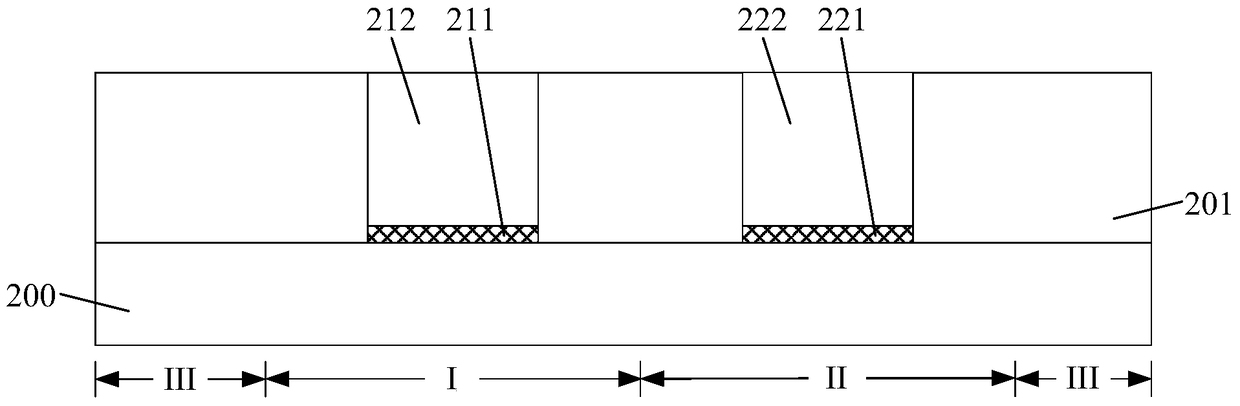

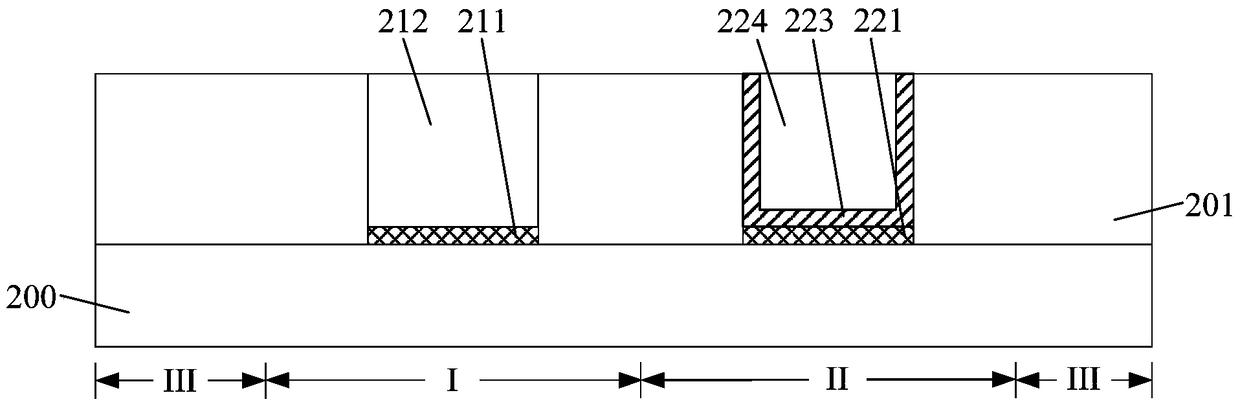

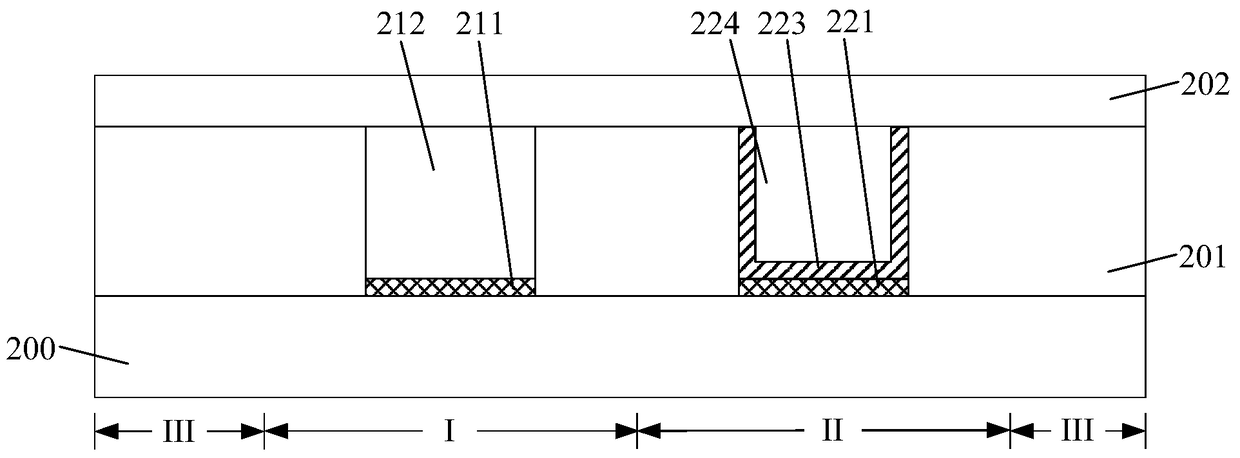

3D NAND storage and forming method thereof

ActiveCN109742038AChange etch rateConsistent etch rateSemiconductor/solid-state device testing/measurementSolid-state devicesIsolation layerEngineering

The invention discloses a 3D NAND storage and a forming method thereof. The forming method of the 3D NAND storage has the steps of forming an intermediate isolation layer between a first stacking structure and a second stacking structure; and sequentially etching the second stacking structure, the intermediate isolation layer and the first stacking structure, wherein when grid partition slots arein the second stacking structure, the middle isolation layer and the first stacking structure, by using the intermediate isolation layer, the etching speed for etching the intermediate isolation layeris consistent with that for etching the first stacking structure, and the etching speed for etching the second stacking structure is consistent with that for etching the first stacking structure, sothat the bending defect of the side wall of the grid partition slots caused when the speed for etching the intermediate insulating layer is different from the etching speeds for etching the first stacking structure and the second stacking structure can be avoided.

Owner:YANGTZE MEMORY TECH CO LTD

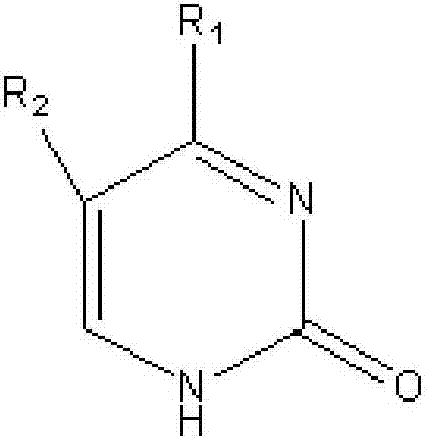

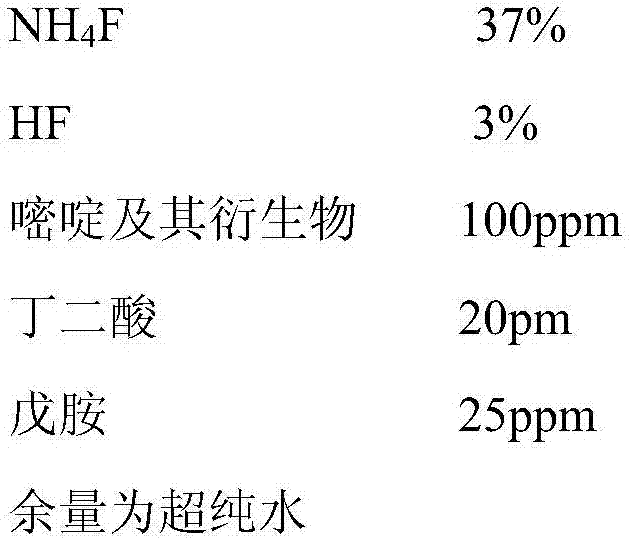

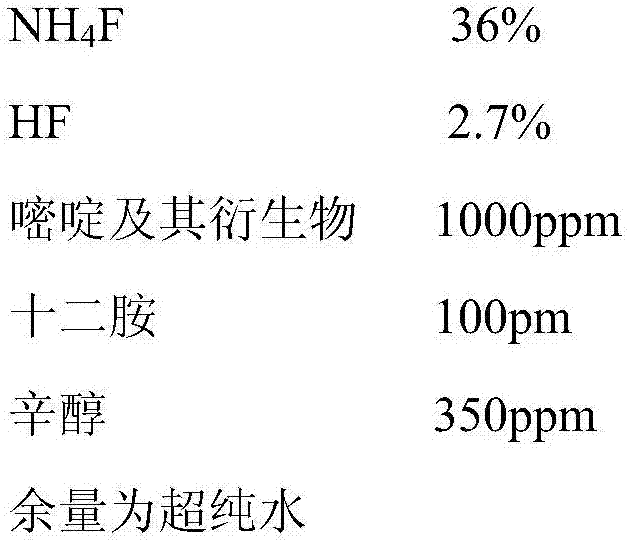

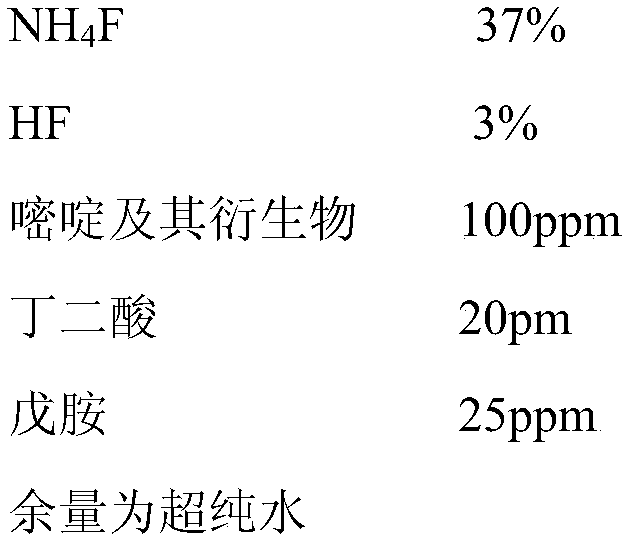

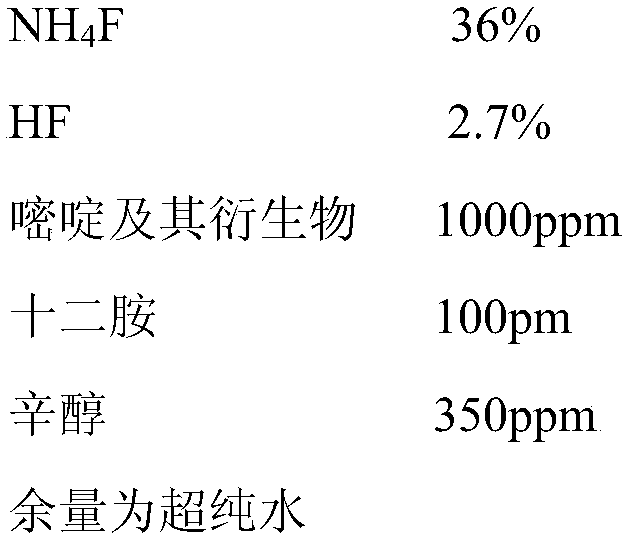

Etching liquid for silicon system multilayer films

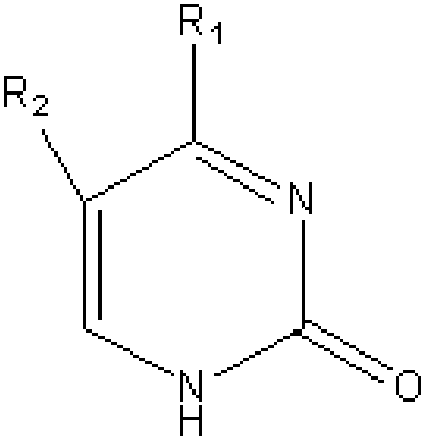

ActiveCN106854468AConsistent etch rateImprove wettabilitySurface treatment compositionsHydrofluoric acidHydrogen

The invention discloses an etching liquid for silicon system multilayer films. The etching liquid comprises a hydrofluoric acid solution, an ammonium fluoride solution, a surfactant and a compound represented by a general formula shown in the description; and in the formula, R1 is one of an amino group, hydrogen, oxygen and a hydroxyl group, and R2 is one of fluorine, chlorine, hydrogen, a hydroxyl group and a C1-C4 alkyl group. The etching liquid for silicon system multilayer films allows the etching speed of a silicon nitride layer to basically same to the etching speed of a silicon oxide layer, and has a good etching effect.

Owner:ZHEJIANG KAISN FLUOROCHEM

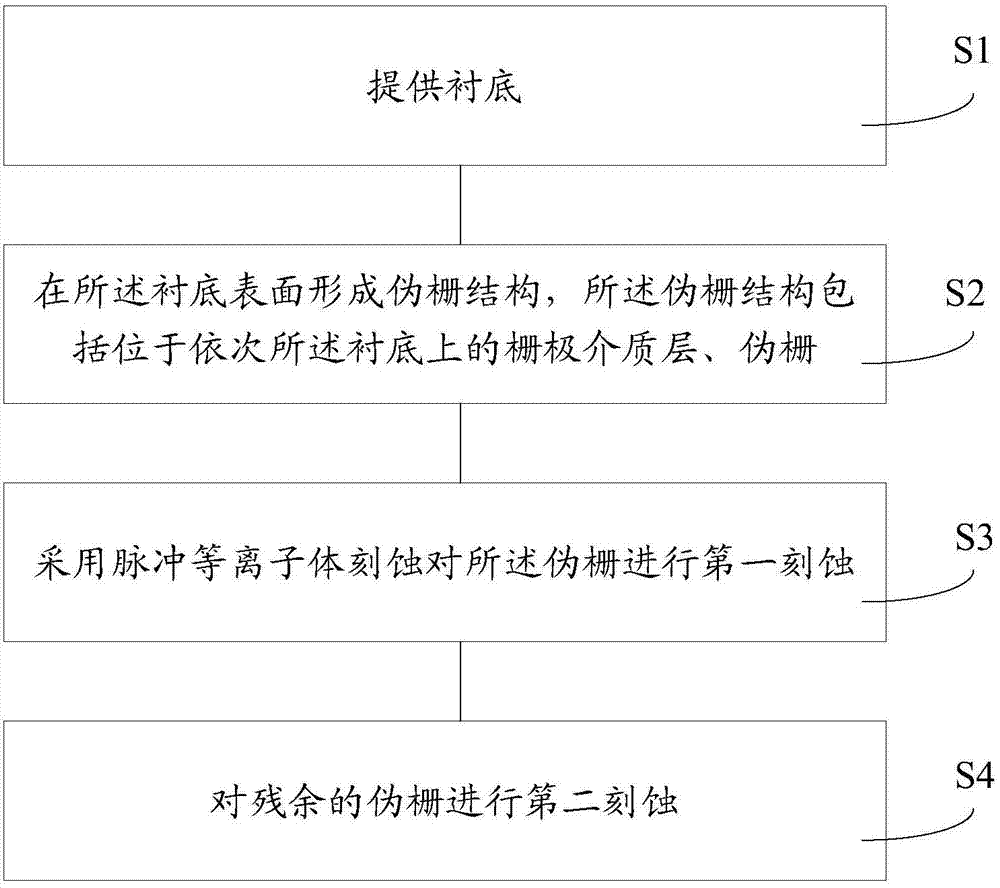

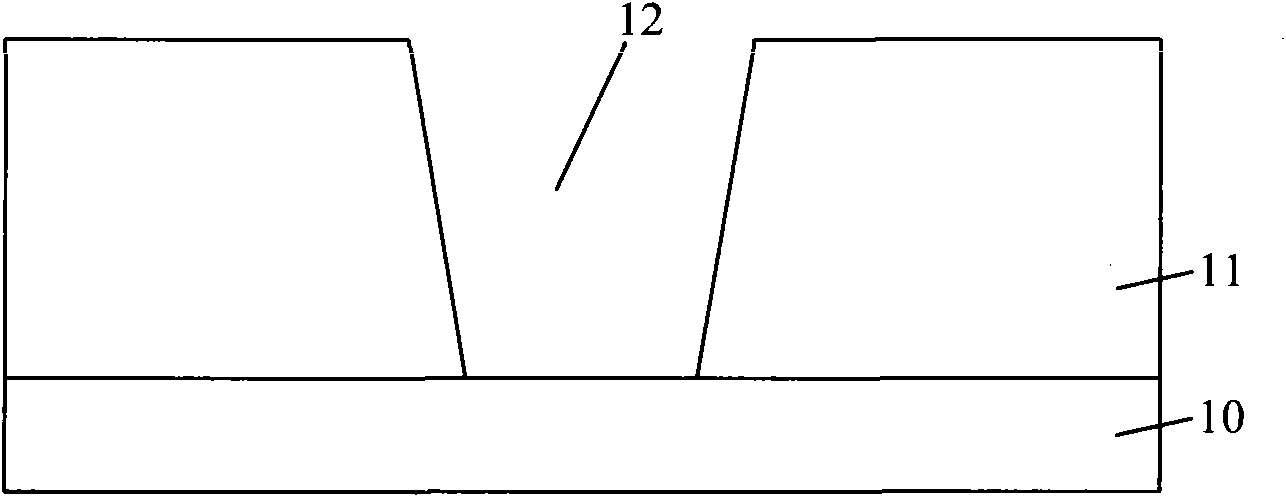

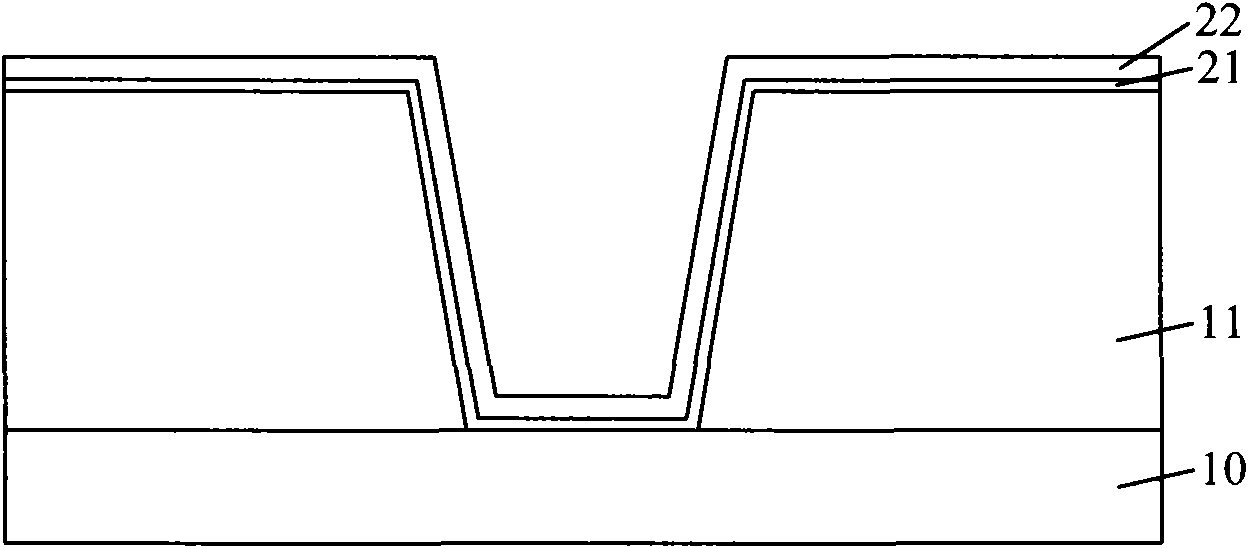

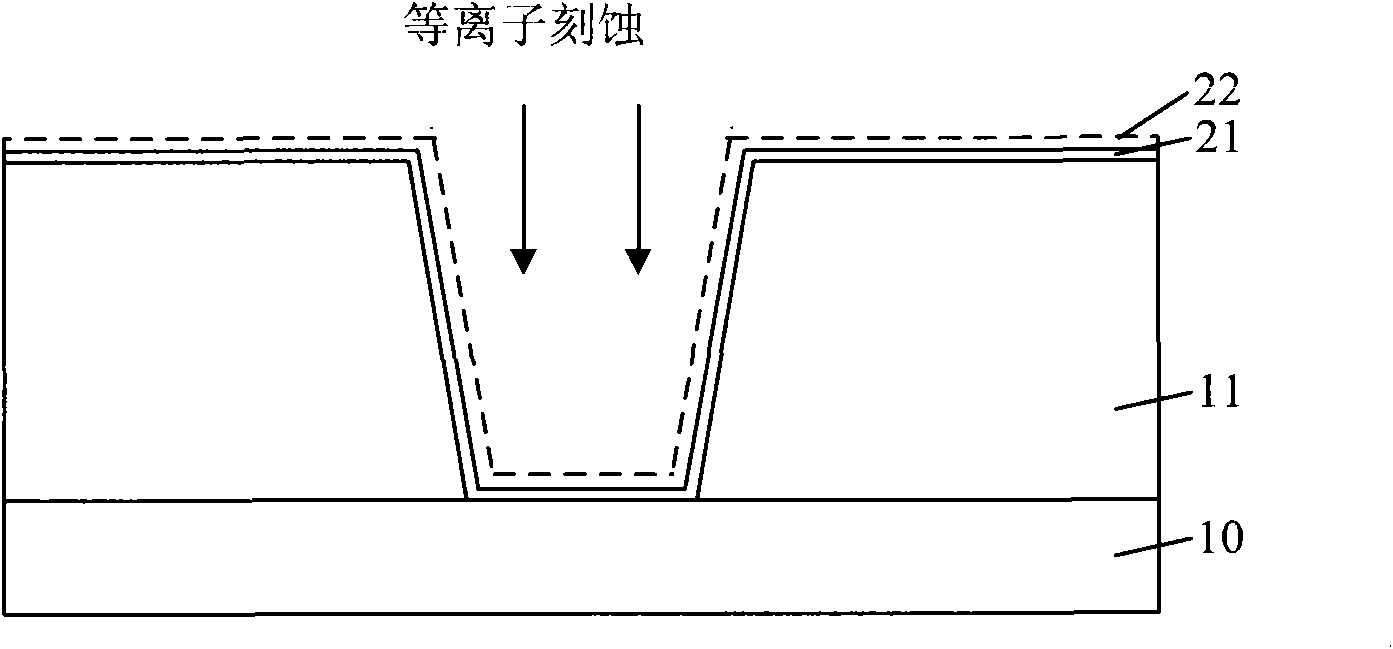

Pseudo gate removing method

ActiveCN104752181AGood lookingImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsPlasma etching

The invention provides a pseudo gate removing method. In a pseudo gate removing step, pulse plasma etching is adopted to conduct first etching on a pseudo gate, and then second etching is conducted on the residual pseudo gate. When the pulse plasma etching is adopted to conduct the first etching on the pseudo gate, an etching machine outputs source power in a pulse mode to etch the pseudo gate in an intermittent mode, source power output time and vacant time are both short, a polymer and solid produced in etching are discharged out of an opening formed through etching within the interval time of source power vacancy, the pulse plasma etching rates adopted for pseudo gates different in size are equal under the condition that no polymer blockage exists, a gate electrode dielectric layer with large-sized pseudo gates can be kept in a good shape when first etching is completed, and further the performance of the gate electrode dielectric layer can be improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

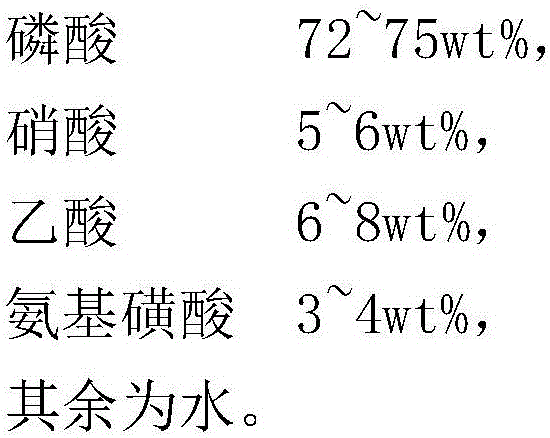

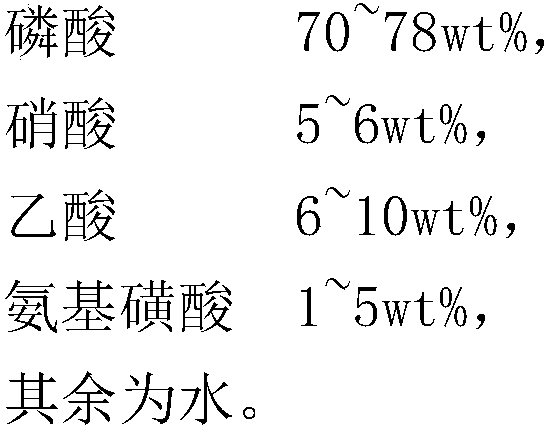

Aluminum etching agent and preparation method thereof

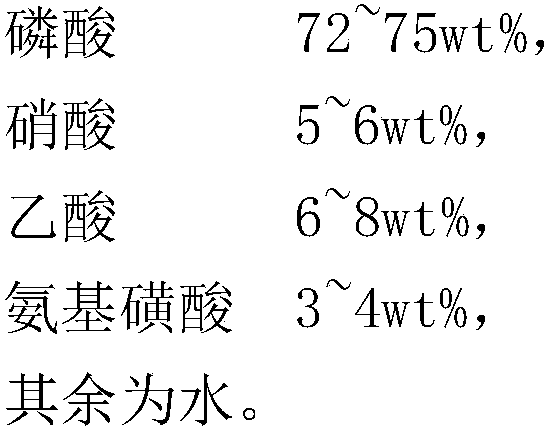

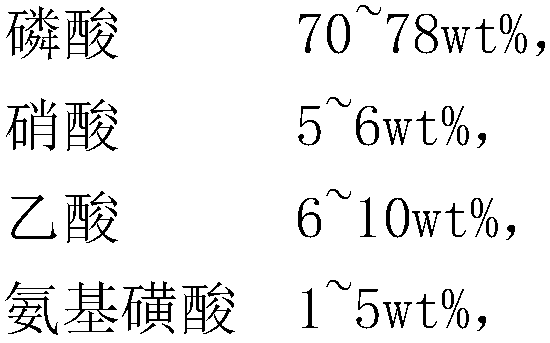

The invention belongs to the technical field of chemical preparations, and relates to an aluminum etching agent and a preparation method thereof. The formula of the aluminum etching agent comprises the following components in percentages by weight: 70-78% of phosphoric acid, 5-6% of nitric acid, 6-10% of acetic acid, 1-5% of sulfamic acid, and the balance of water. The aluminum etching liquid provided by the invention can convert a metal compound into soluble salts which are dissolved in water, speeds of etching to different metals are consistent basically, reaction is stable, the circumstance that etching efficiency and neatness of the surface of a substrate are affected by precipitate attachment is avoided, and surface dirt is removed conveniently.

Owner:SUZHOU BOYANG CHEM

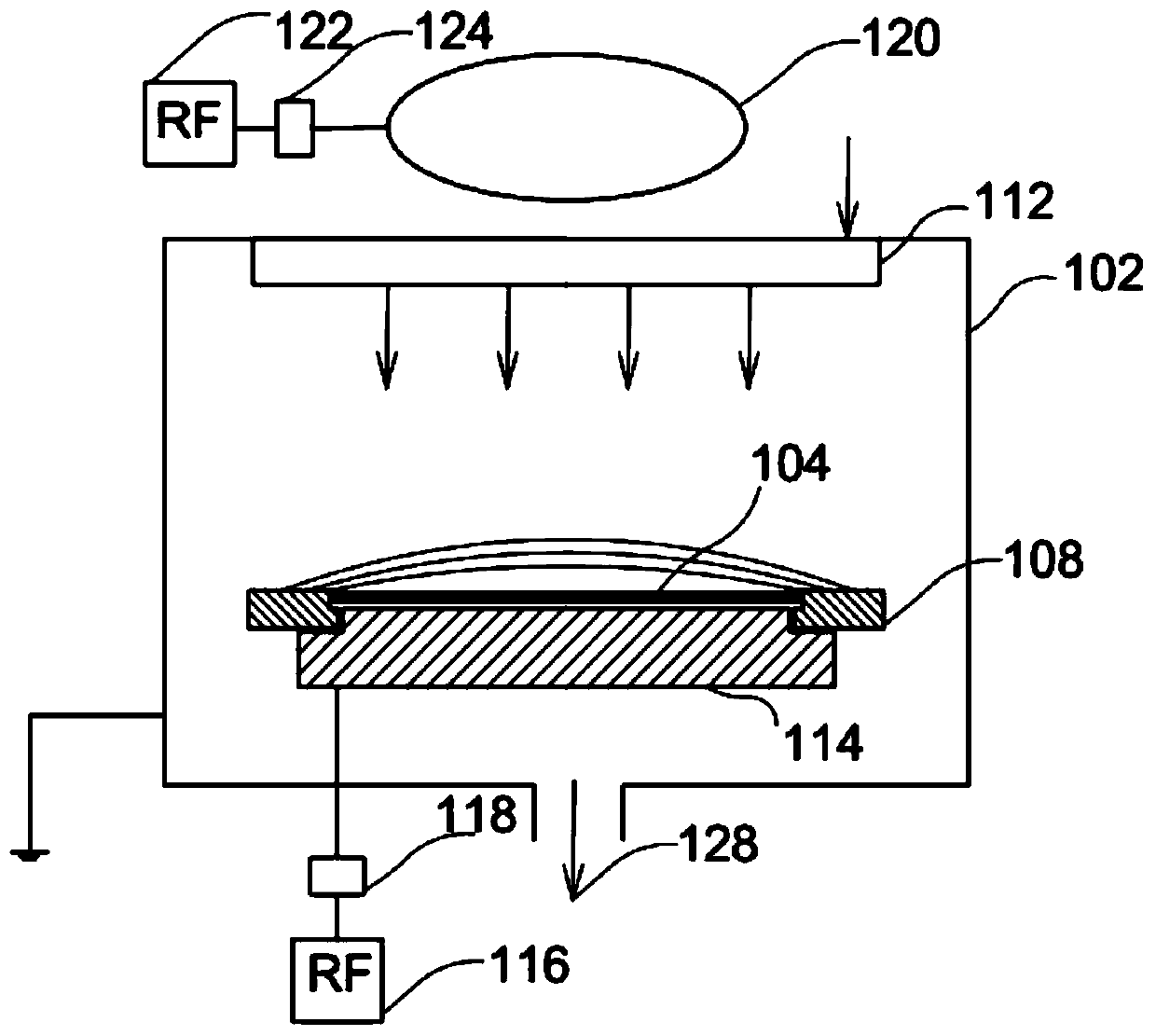

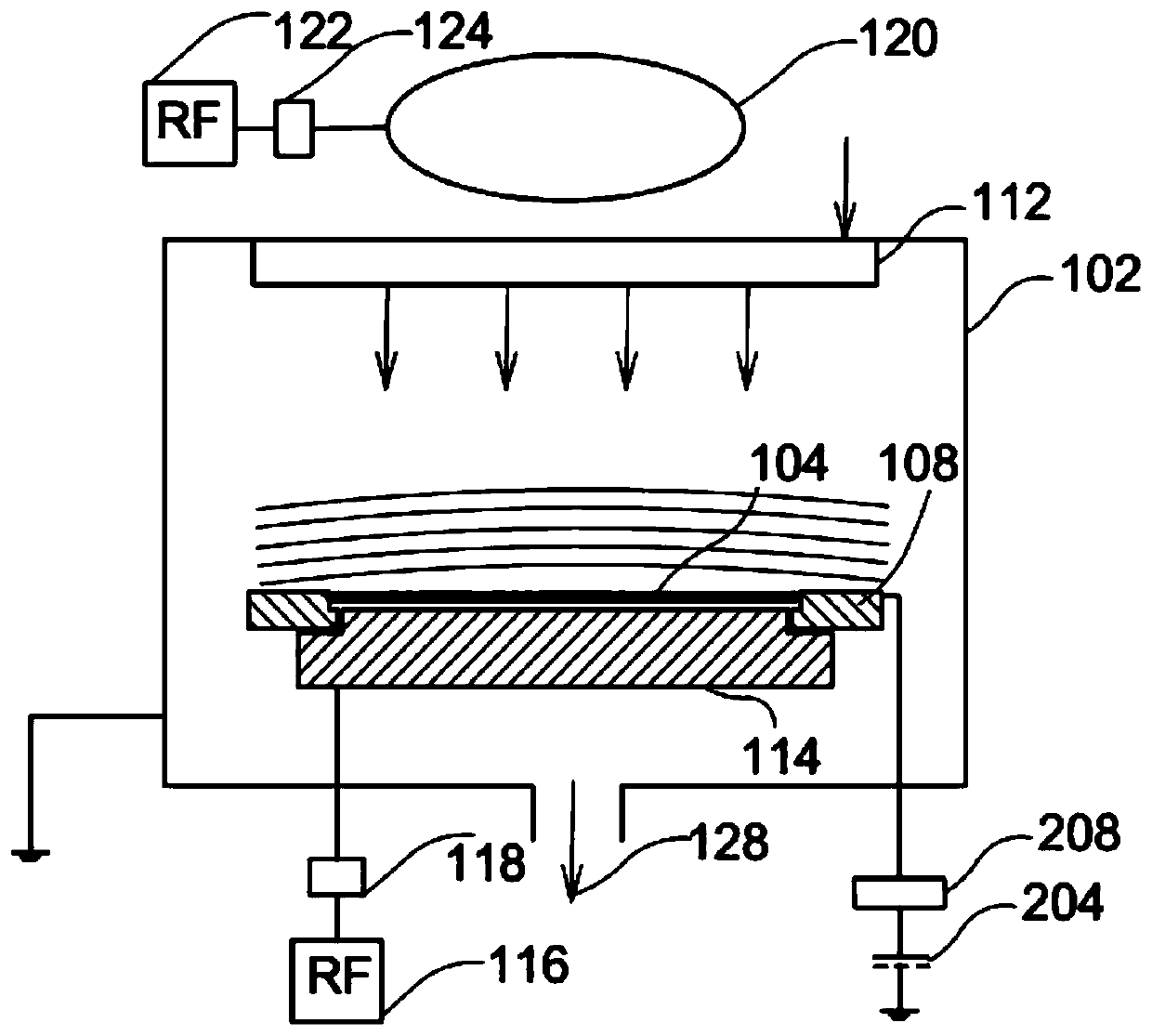

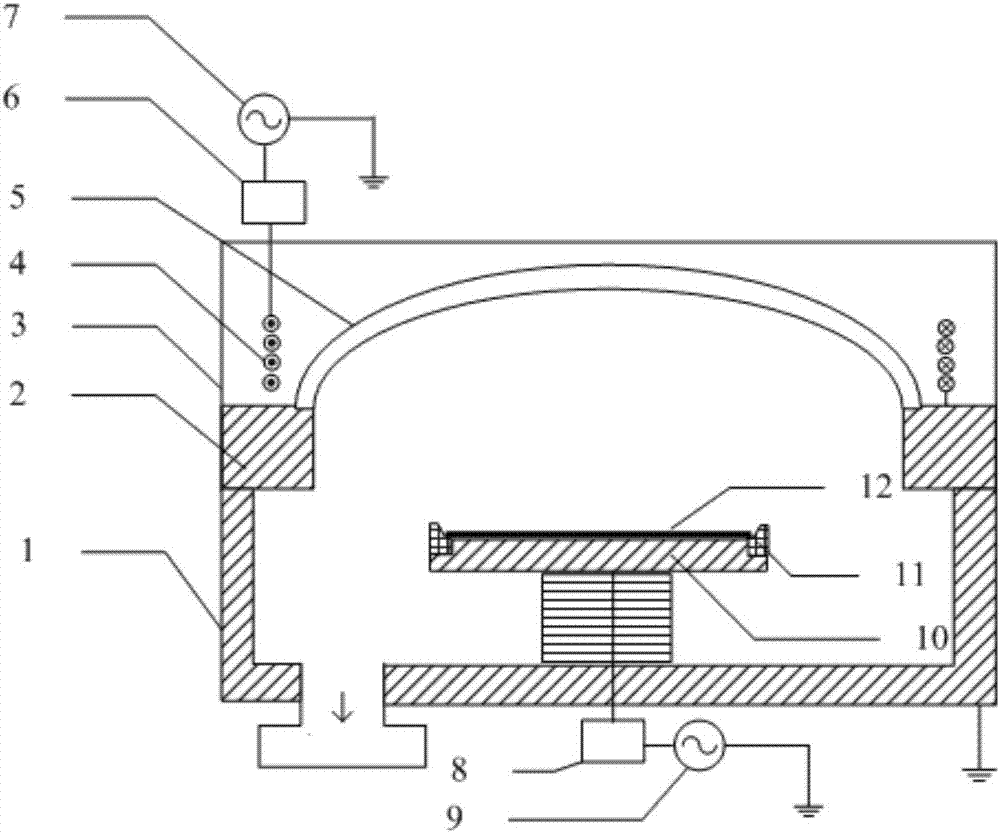

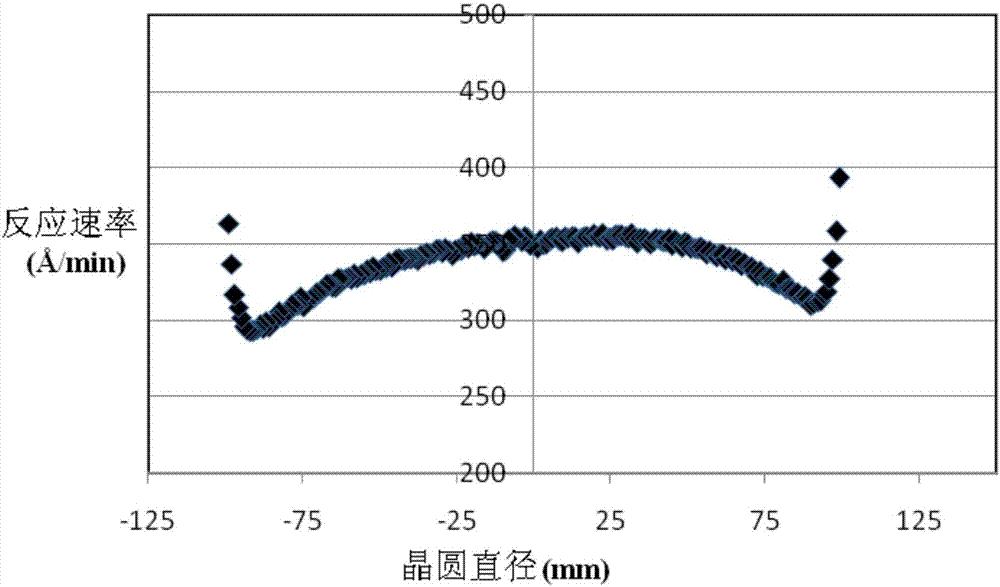

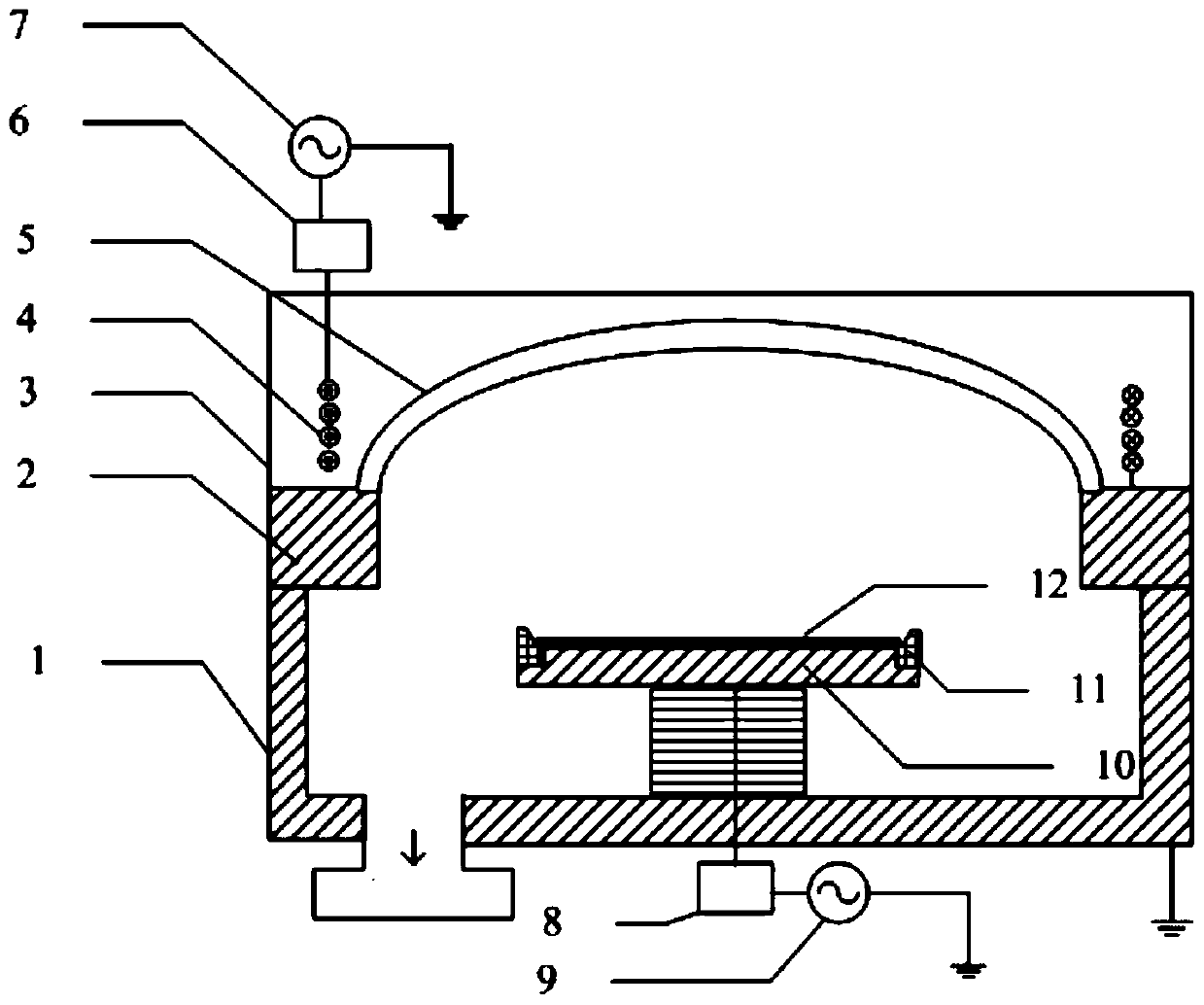

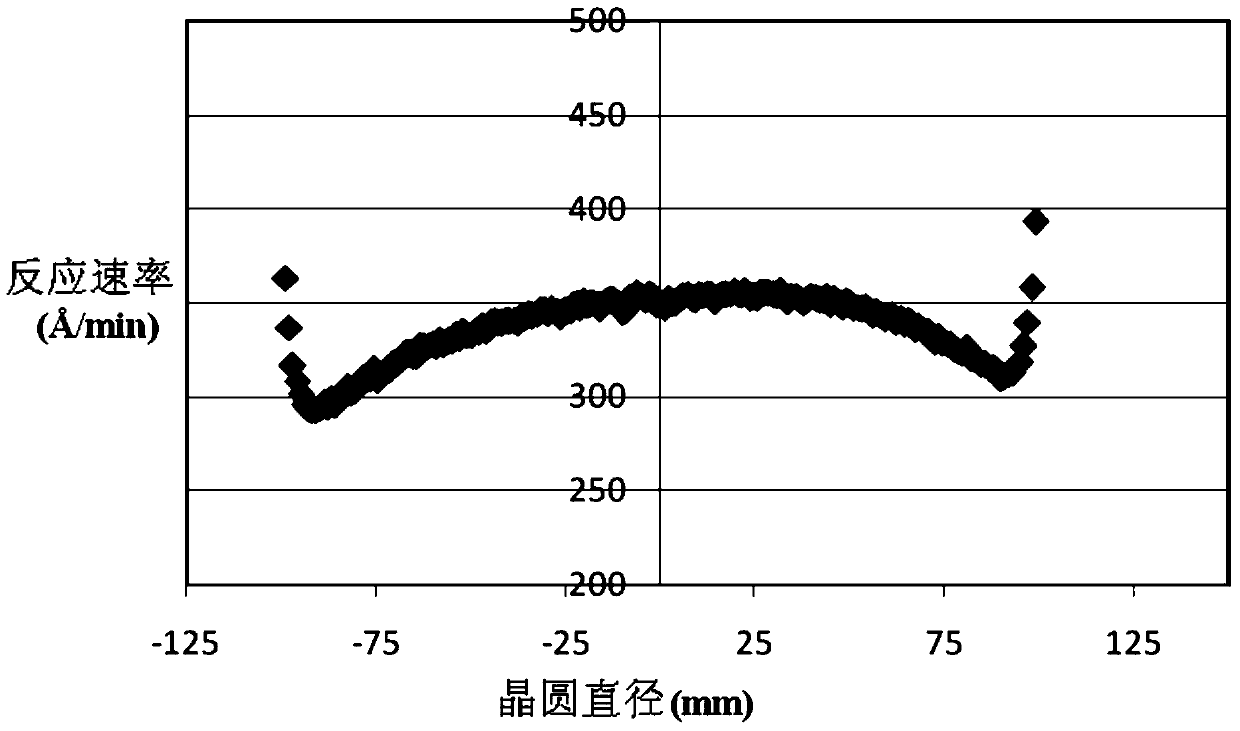

Device and method for improving plasma etching uniformity

InactiveCN111383887AImprove etch uniformityConsistent etch rateElectric discharge tubesSemiconductor/solid-state device manufacturingWaferCurrent voltage

The invention discloses a device and method for improving the plasma etching uniformity. The device comprises a direct-current power supply and a filter, wherein one end of the direct-current power supply is grounded, the other end of the direct-current power supply is connected with a focusing ring of a lower electrode of the plasma etching system through the filter, direct-current voltage is loaded on the direct-current power supply, the magnitude and polarity of the direct-current power supply are adjustable, and the filter is used for filtering alternating-current components in direct current. The polarity and the magnitude of the direct-current voltage are adjusted by loading direct-current voltage on the focusing ring of the lower electrode of the plasma etching system, so that the etching rate of the edge part of a wafer tends to be consistent with the etching rate of the center part of the wafer. The device is simple and easy to implement, the etching uniformity can be effectively improved, and the production efficiency is improved.

Owner:JIANGSU LEUVEN INSTR CO LTD

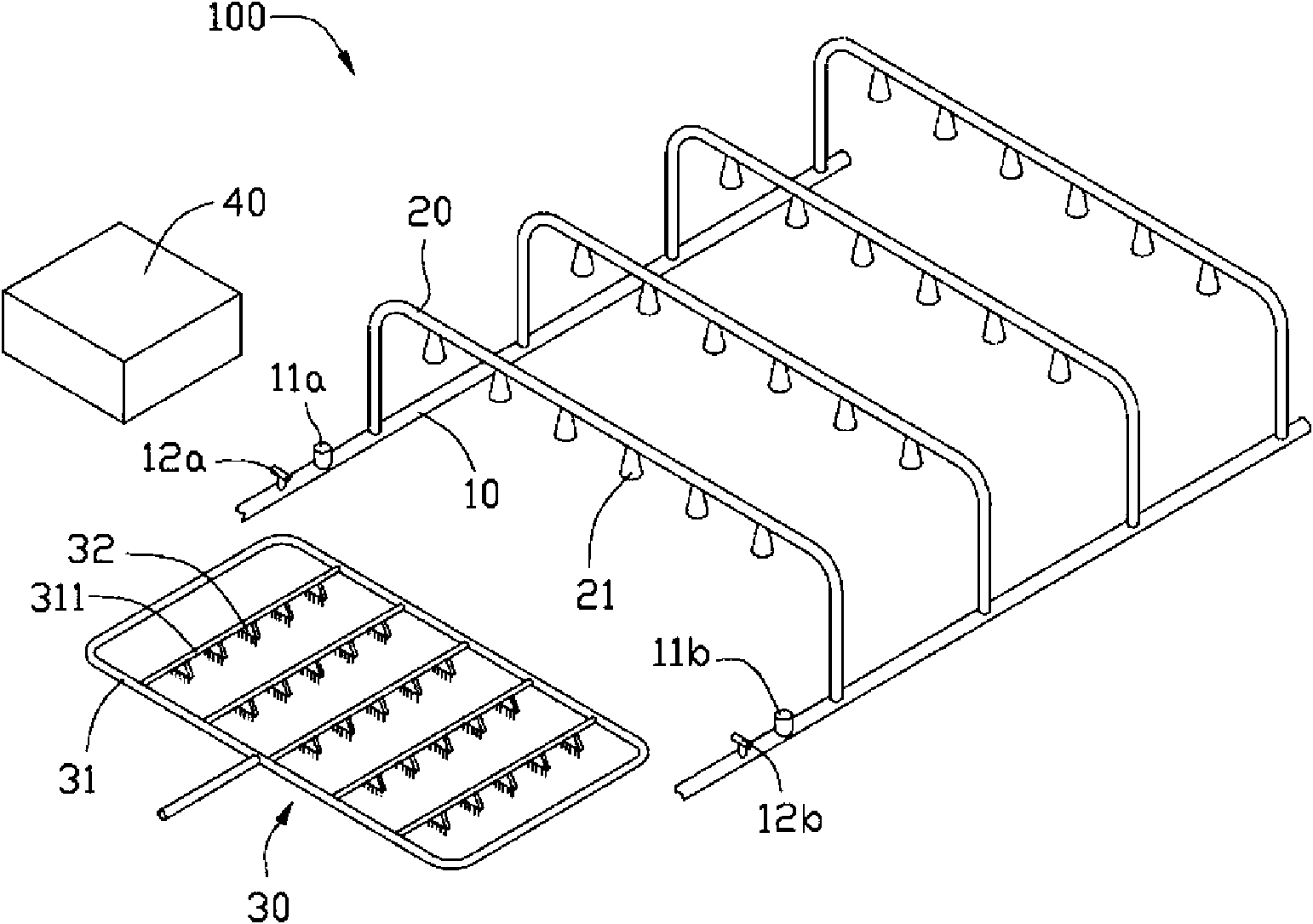

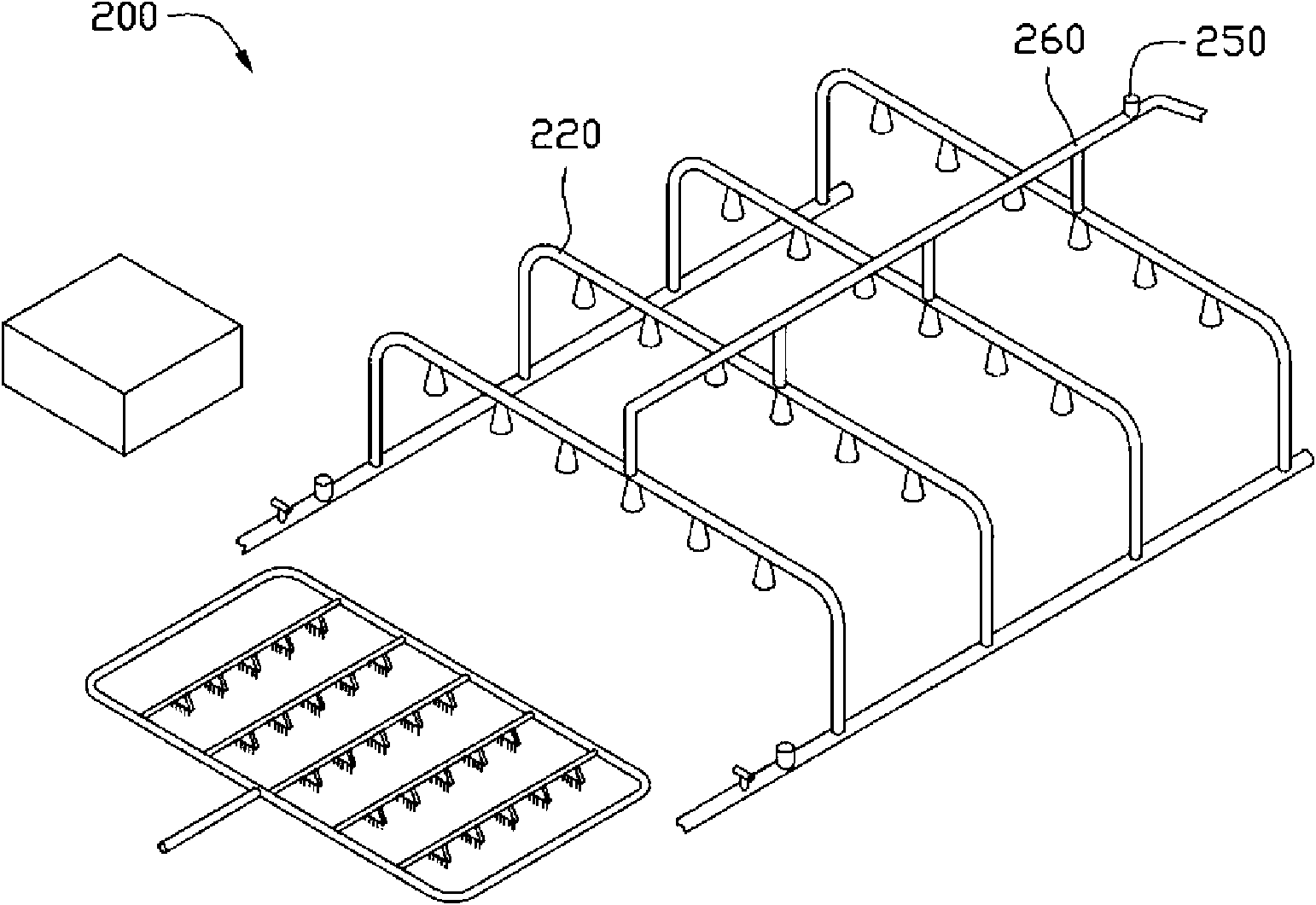

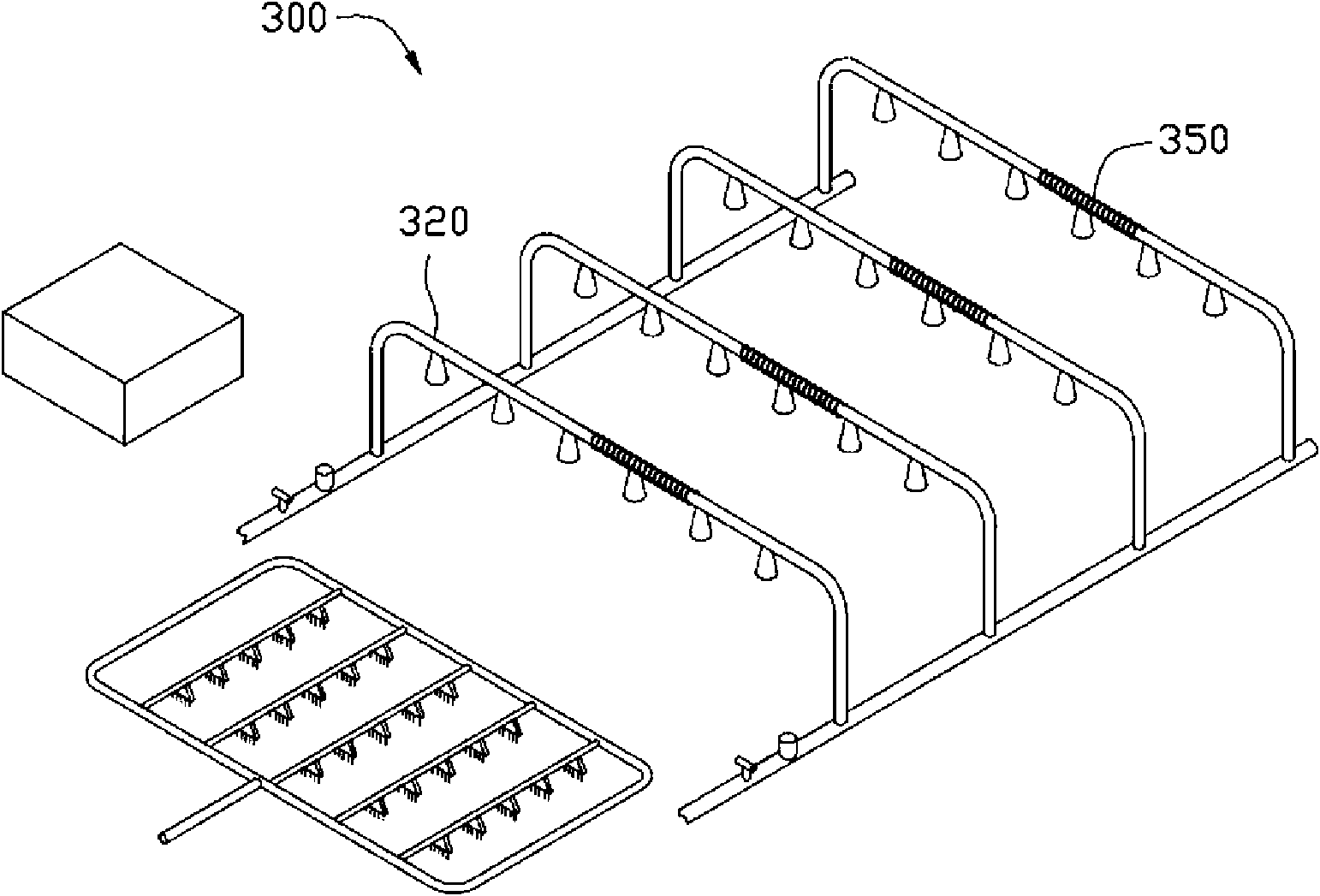

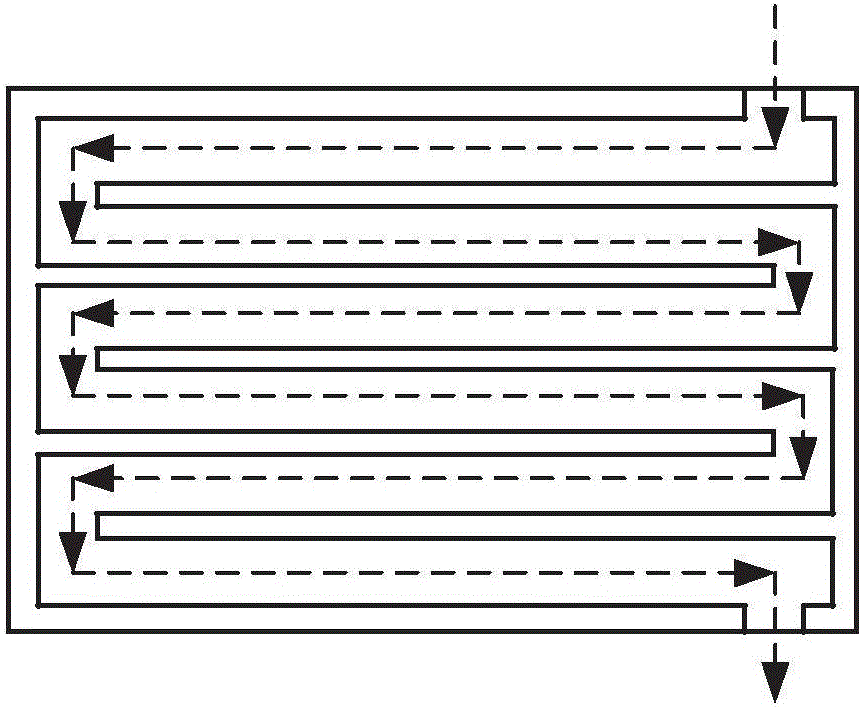

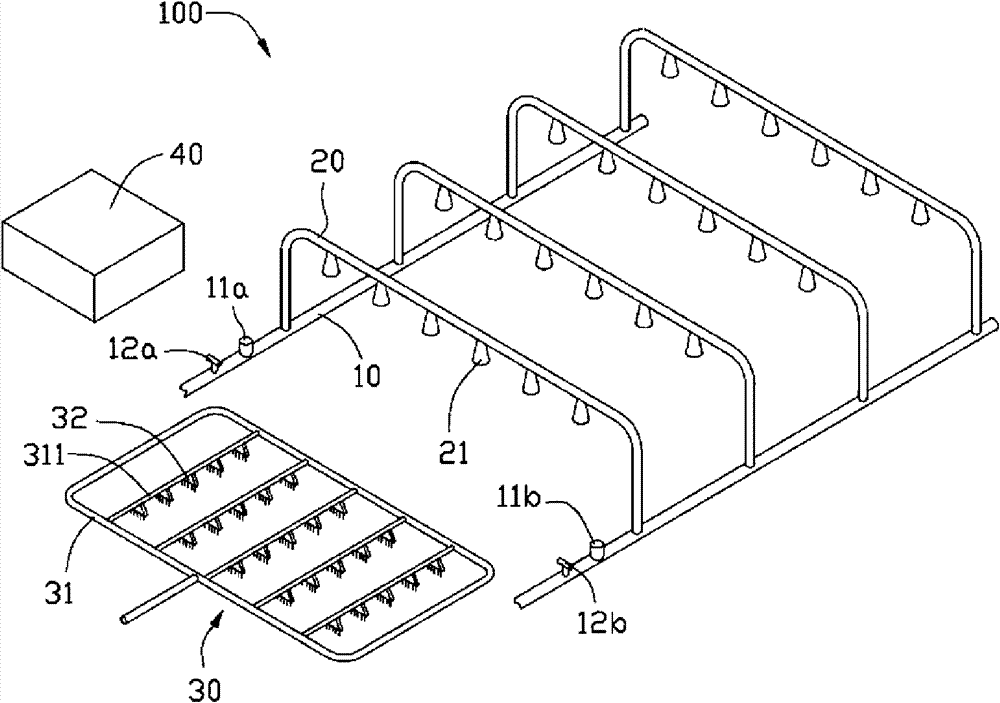

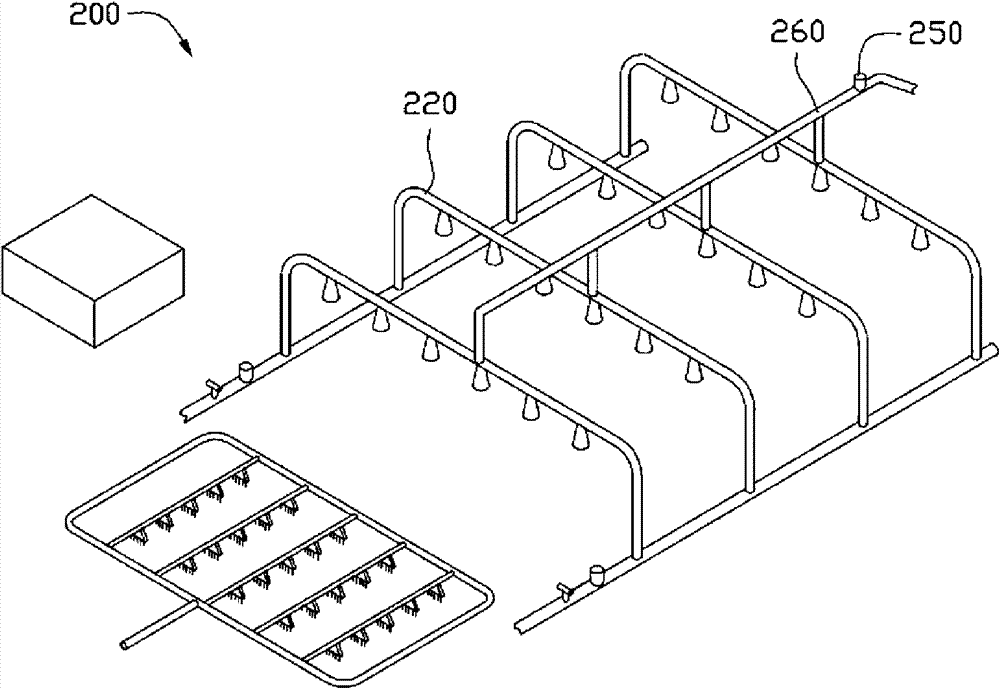

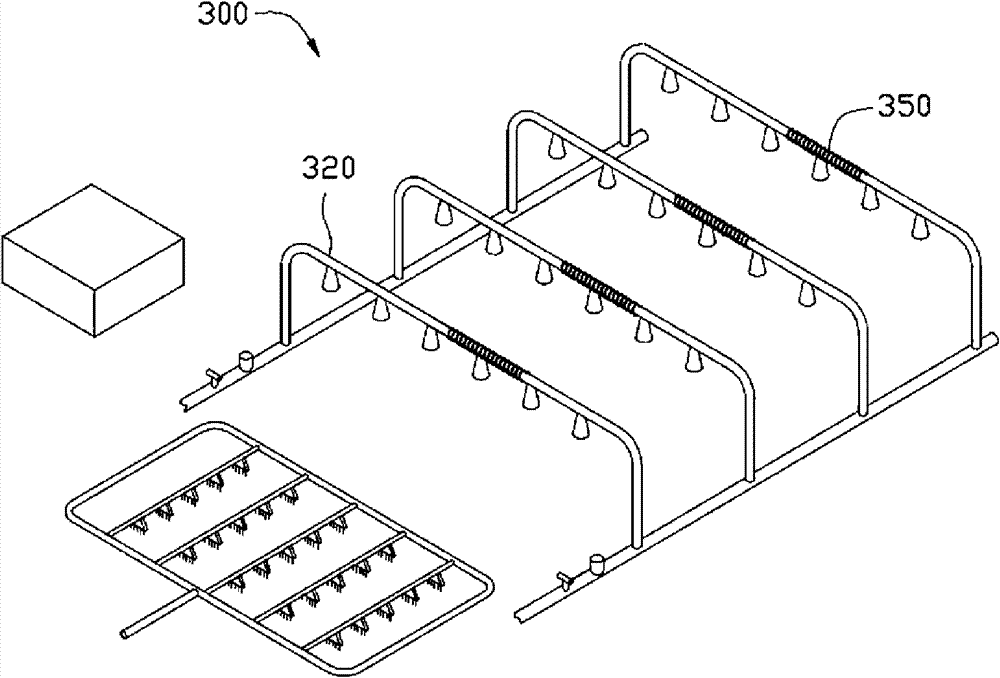

Etching device and etching method

The invention relates to an etching device and an etching method. The etching device comprises a spray pipe and a liquid scrapping device, wherein the spray pipe is provided with a plurality of spray heads; the plurality of spray heads are used for spraying etching liquid to a surface to be etched of a circuit substrate; and the liquid scrapping device is used for scrapping the etching liquid deposited in a center area of the surface to be etched out of the surface to be etched in a sliding mode. The etching method comprises the following steps of: using the plurality of spray heads arranged on the spray pipe to spray the etching liquid towards the surface to be etched of the circuit substrate; and using the liquid scrapping device to scrap the etching liquid deposited in the center area of the surface to be etched out of the surface to be etched in a sliding mode. The etching method can avoid generating water pit effect.

Owner:JIANGSU TRANSIMAGE TECH CO LTD

Copper indium gallium selenide (CIGS) thin-film solar cell window layer and preparation method thereof

ActiveCN106684184AEasy to operateConducive to productionFinal product manufacturePhotovoltaic energy generationCopper indium gallium selenide solar cellsCopper indium diselenide

The invention discloses a copper indium gallium selenide (CIGS) thin-film solar cell window layer which is composed of a lower film layer and an upper film layer from bottom to top. The lower film layer is a doped ZnO film layer, the upper film layer is an ITO film layer or a doped ZnO film layer, and when the lower and upper film layers are both doped ZnO film layers, the lower and upper film layers are different doped ZnO film layers. The invention also discloses a preparation method thereof. Two different films can be deposited with a common DC power supply without additional equipment, the operation is convenient, and production is facilitated. When the lower film layer is deposited, a different doped ZnO target material can be selected to obtain the lower film layer satisfying the production requirement by adjusting the deposition temperature, atmosphere, air pressure, power and so forth, the obtained lower film layer is combined with the continuously produced upper film layer to match with the entire battery, the production efficiency is improved in the process, the production cost is reduced, and the film quality is easy to control.

Owner:浙江尚越新能源开发有限公司

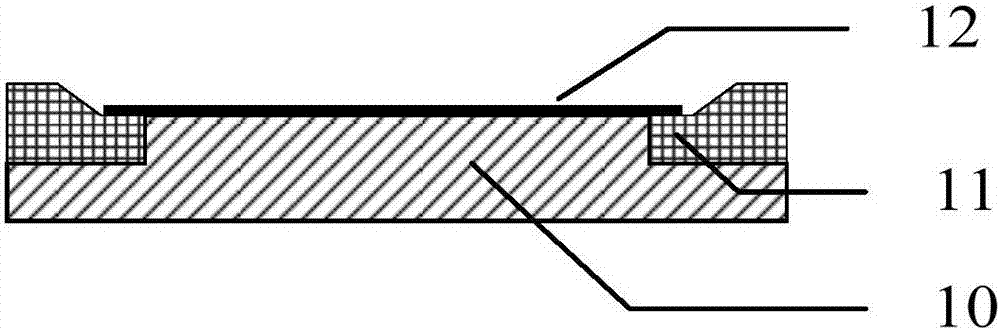

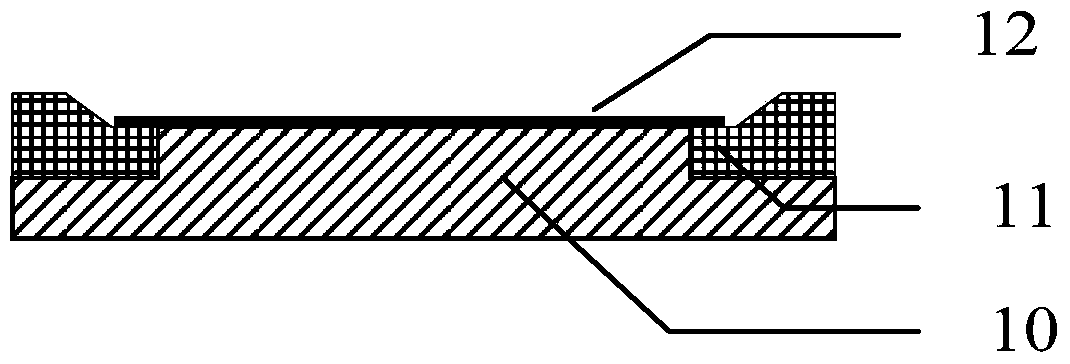

Bearing device and pre-cleaning cavity chamber

ActiveCN107464764AConsistent etch rateImprove etch uniformityElectric discharge tubesVacuum evaporation coatingNegative biasMechanical engineering

The invention discloses a bearing device and a pre-cleaning cavity chamber. The bearing device is used for bearing a top plate of a workpiece to be processed, wherein the top plate comprises a central piece and an annular piece, the annular piece encircles the central piece, the central piece and the annular piece are isolated with each other, and the etching ratios of the workpiece to be processed at different positions in a radial direction tend to be consistent by respectively loading different negative biases to the central piece and the annular piece. In the bearing device, different negative biases are loaded to the central piece and the annular piece, so that the plasma density distribution of the workpiece to be processed which is borne on the bearing device is uniform, the etching ratios of the workpiece to be processed at different positions in the radial direction tend to the consistent, and the etching uniformity of the workpiece to be processed is improved.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

Copper-molybdenum metal etching solution and application thereof

The invention discloses a copper-molybdenum metal etching solution and application thereof. The copper-molybdenum metal etching solution comprises the following components in percentage by weight: 1-21wt% of hydrogen peroxide, 0.01-10 wt% of a shape control agent, 0.01-5 wt% of an etching stabilizer, 1-13 wt% of a chelating agent, 0.01-8 wt% of a pH regulator, 0.01-2.39 percent of an etching additive and the balance of deionized water. According to the copper-molybdenum metal etching solution disclosed by the invention, the consistent etching rate on a copper-molybdenum double-layer metal structure layer can be kept in the etching process, the defect of copper hollowing corrosion caused by oxidation-reduction potential difference of copper-molybdenum double-layer metal is overcome, and a copper-molybdenum metal structure layer meeting the requirements is prepared.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

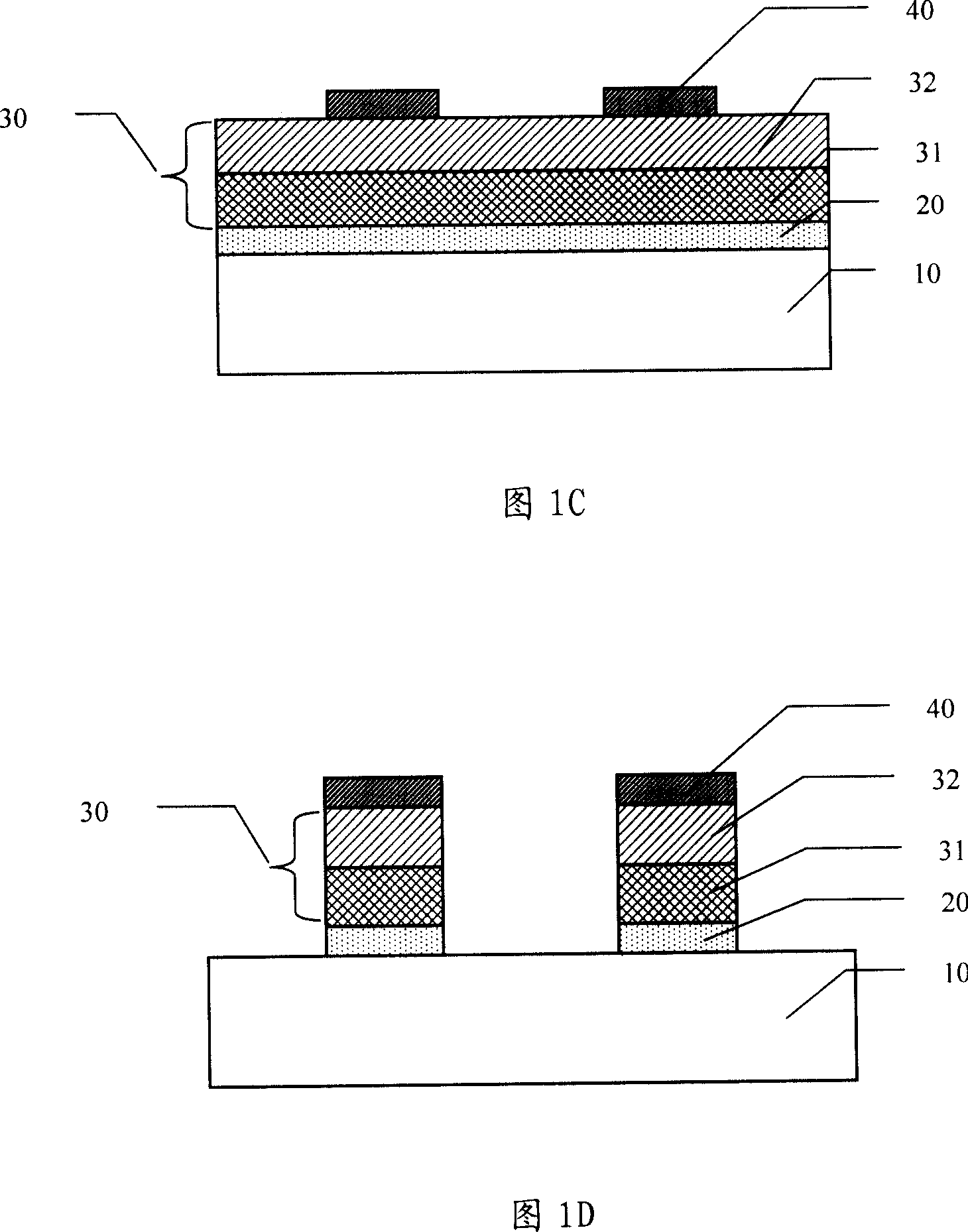

Making method for grid structure

ActiveCN101123186AConsistent etch rateControl deficienciesSemiconductor devicesResistDielectric layer

A grid structure manufacturing method comprises the following steps: depositing on substrate in a sequence with dielectric layer, conducting layer, blocking layer and patterned photoinduced corrosion resist layer; etching blocking layer; removing the patterned photoinduced corrosion resist layer; using the primary etching gas to etch the conducting layer surface; using the secondary etching gas to etch the conducting layer and the dielectric layer. By setting the etching rates of the etching gas on the conducting layer material and the conducting layer upper metal oxide layer respectively, an etching selection ratio of the etching gas on the conducting layer material and the conducting layer upper metal oxide layer can be obtained, finally, a grid structure without bottom defect can be obtained.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

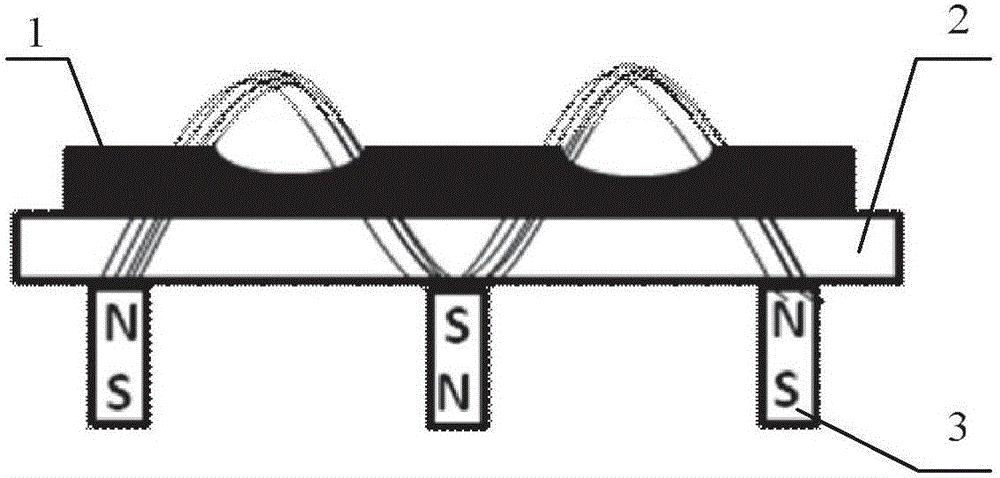

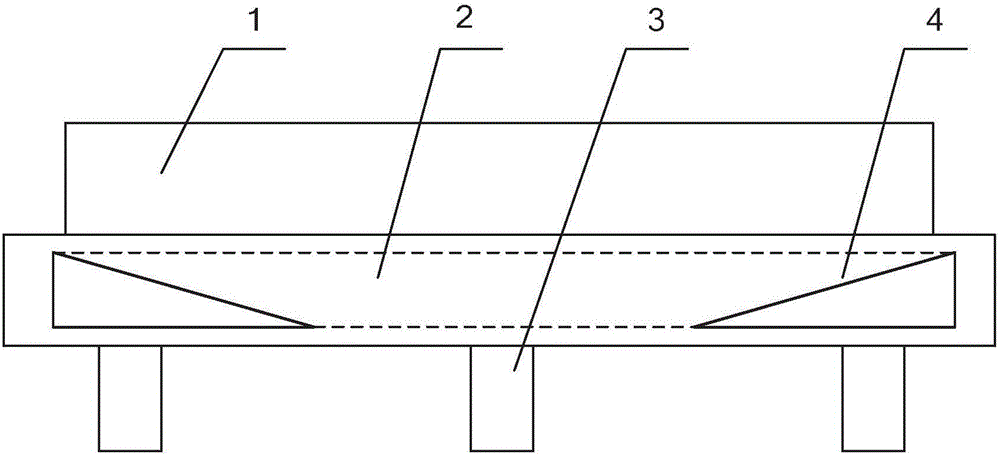

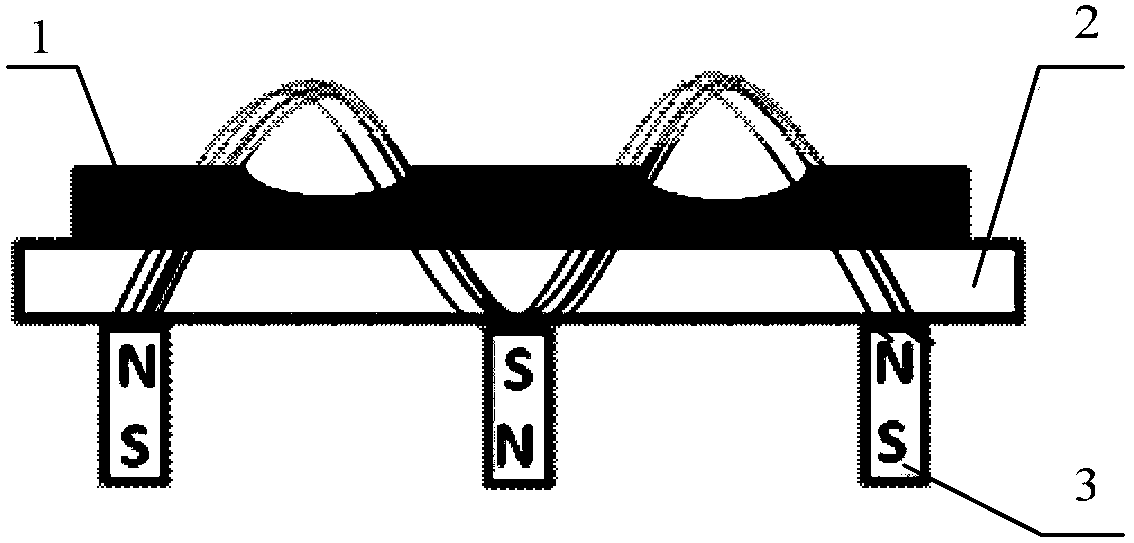

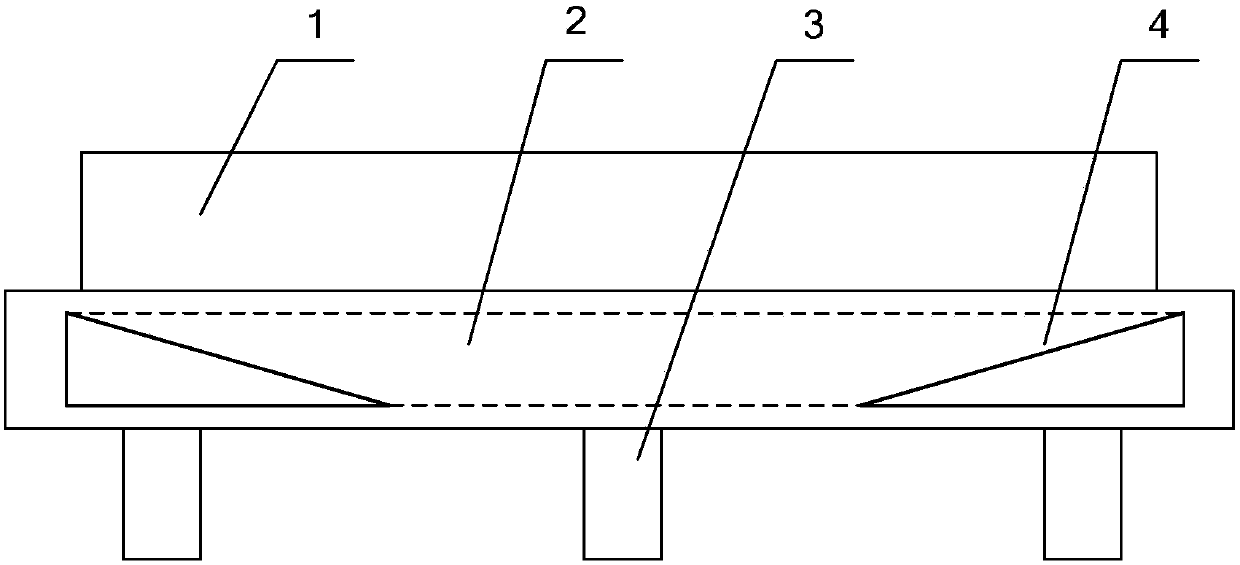

Target back plate for magnetron sputtering and magnetron sputtering device

ActiveCN105734516AConsistent etch rateExtended service lifeVacuum evaporation coatingSputtering coatingSputteringCooling fluid

The invention discloses a target back plate for magnetron sputtering and a magnetron sputtering device, relates to the technical field of magnetron sputtering, and aims to increase the utilization rate of a target material and improve the uniformity of the thickness of a film formed on a substrate to be coated. According to the target back plate for magnetron sputtering, a cooling fluid channel is formed inside the target back plate, a plurality of magnets are arranged on the back side of the target back plate, magnetic conductive pieces are arranged inside the cooling liquid channel in the target back plate; and the magnetic conductive pieces correspond to magnetic fields with the strongest magnetic intensity generated by the magnetic conductive pieces and the plurality of magnets. The target back plate for magnetron sputtering and the magnetron sputtering device, which are disclosed by the invention, are applied to planar film coating.

Owner:BOE TECH GRP CO LTD +1

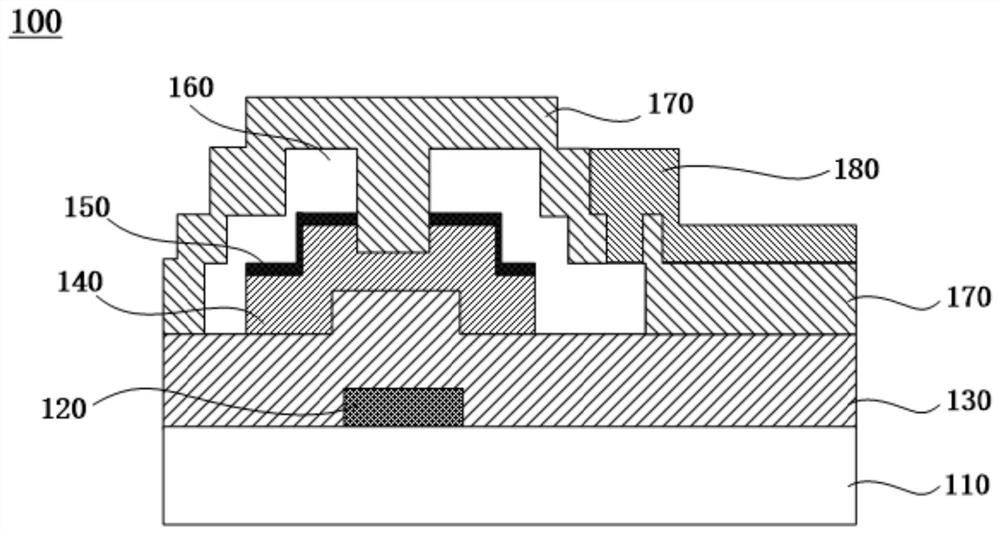

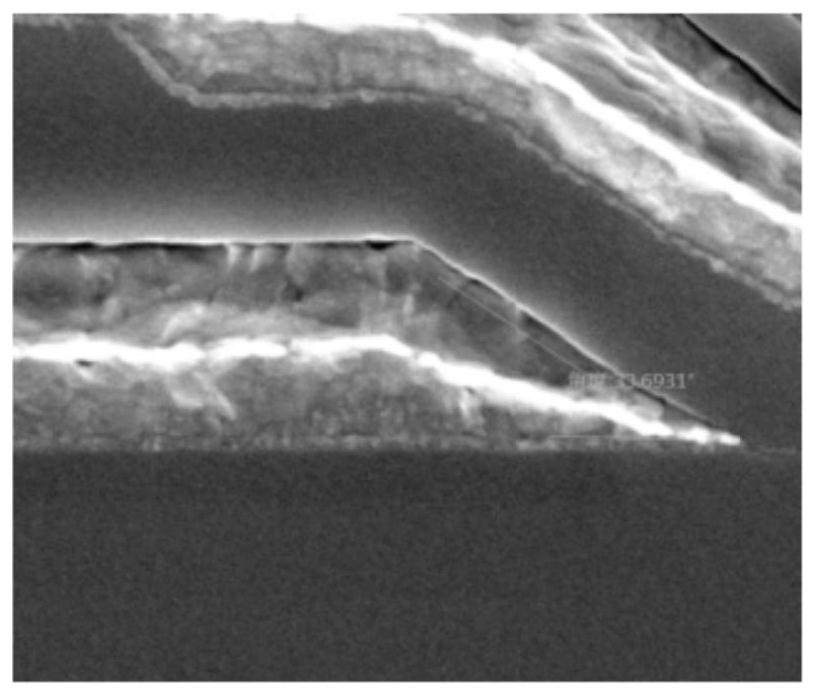

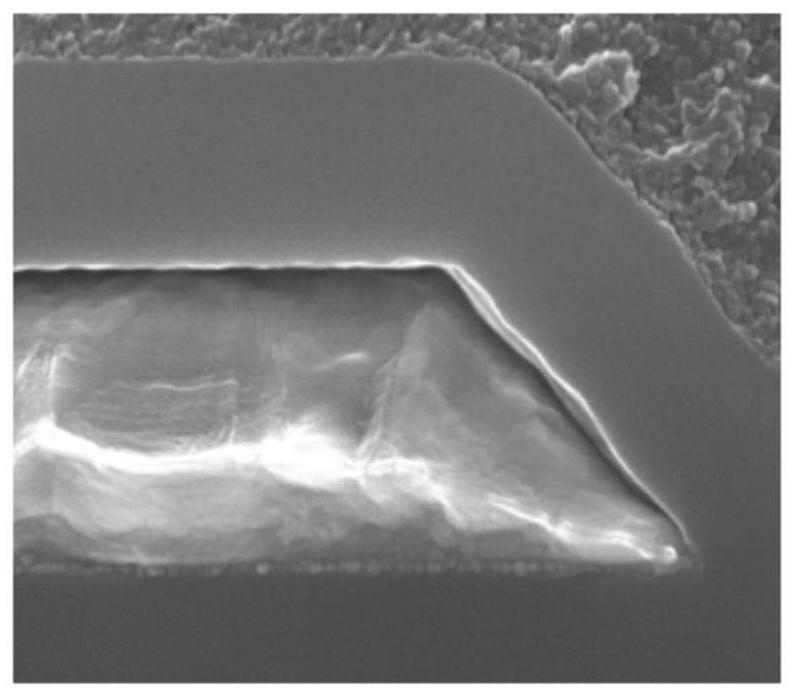

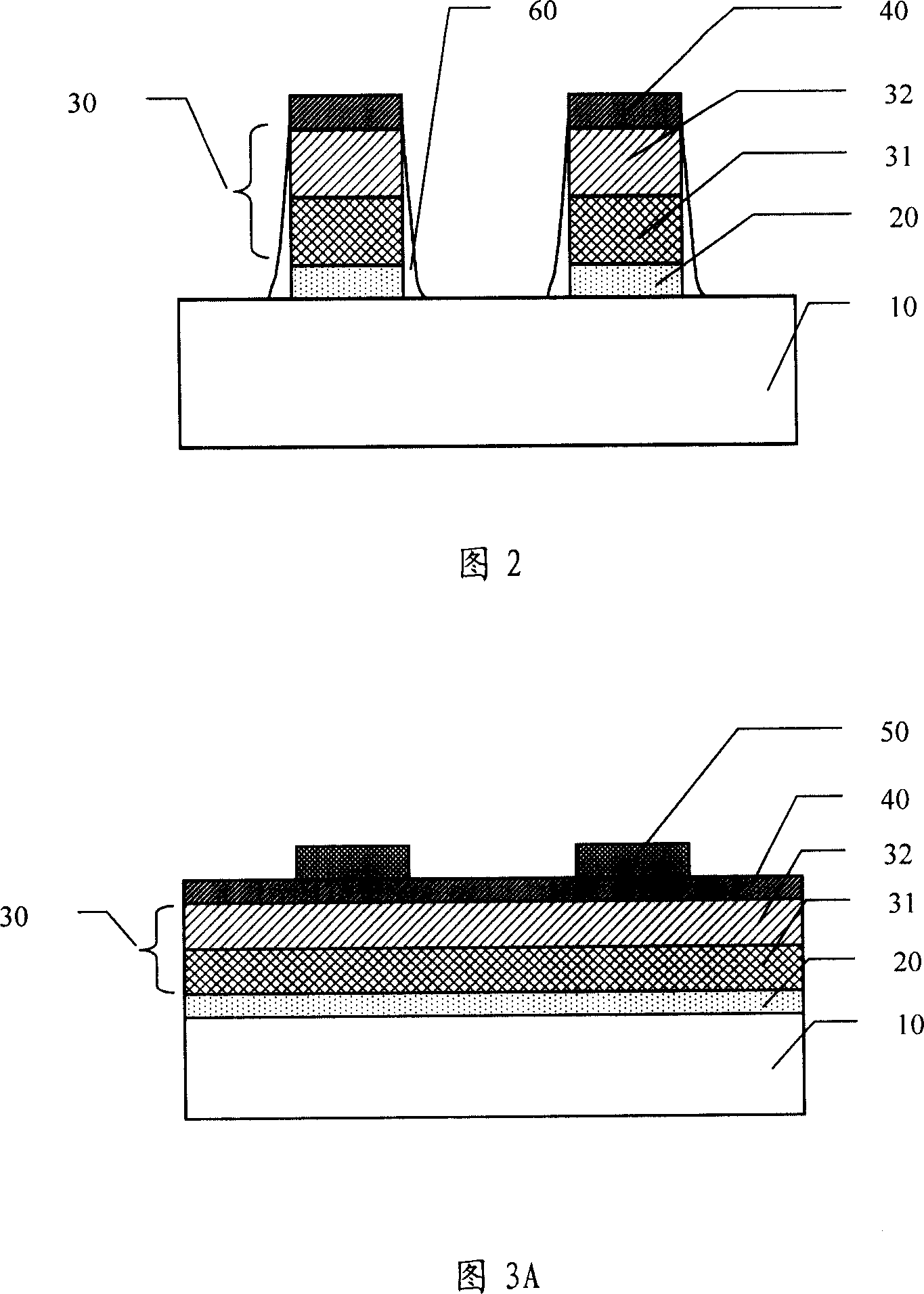

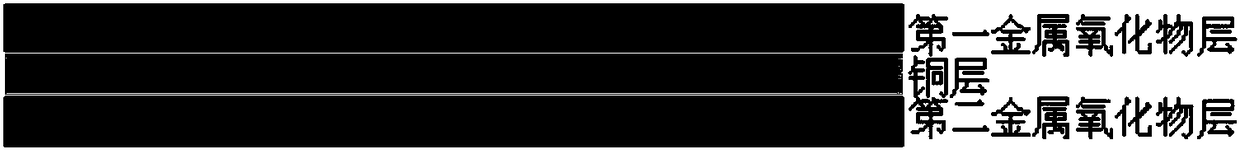

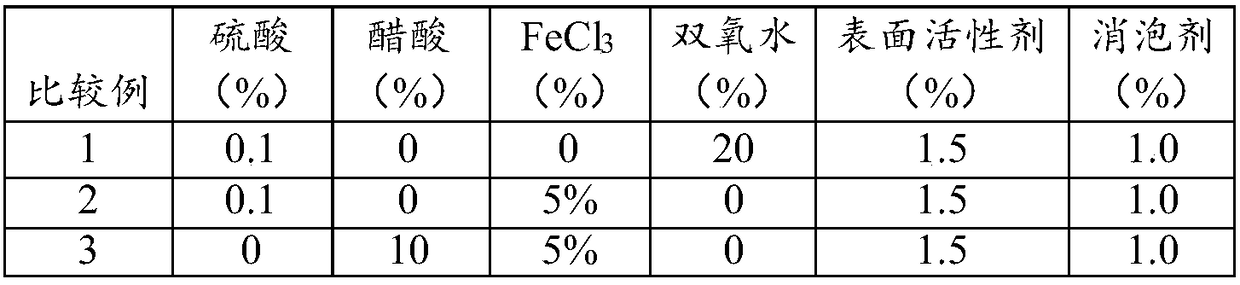

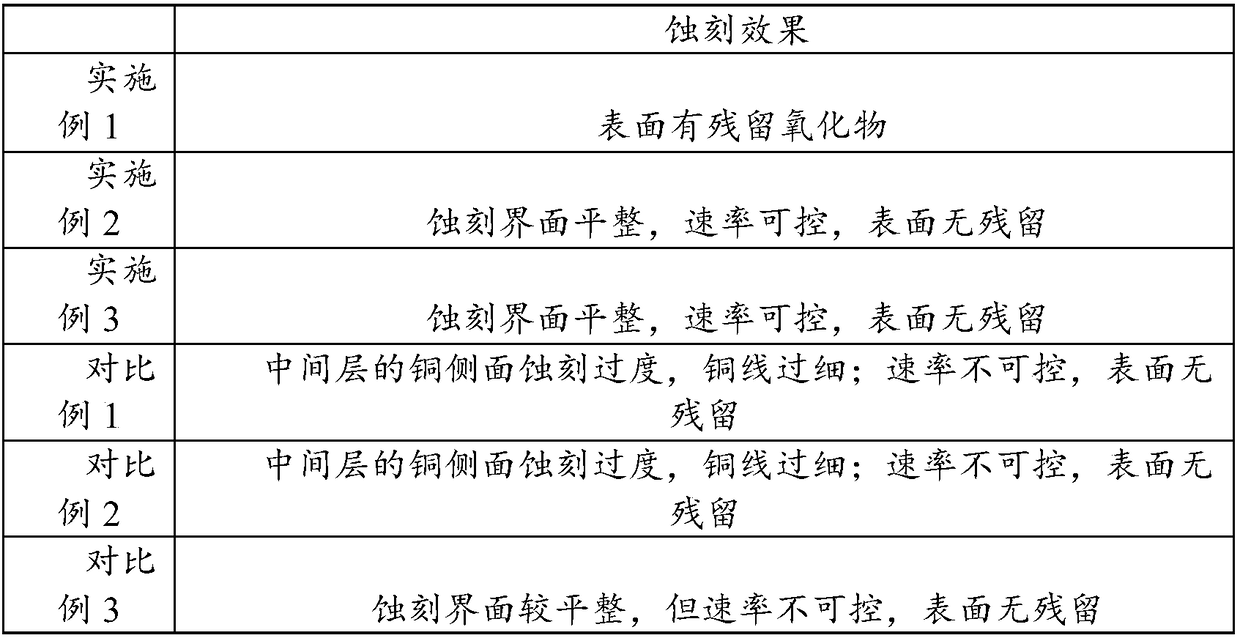

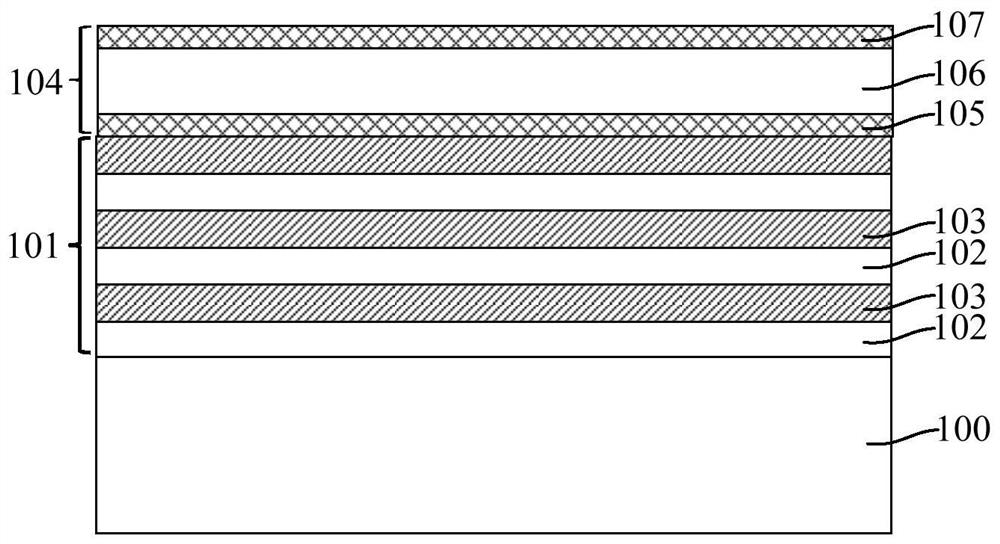

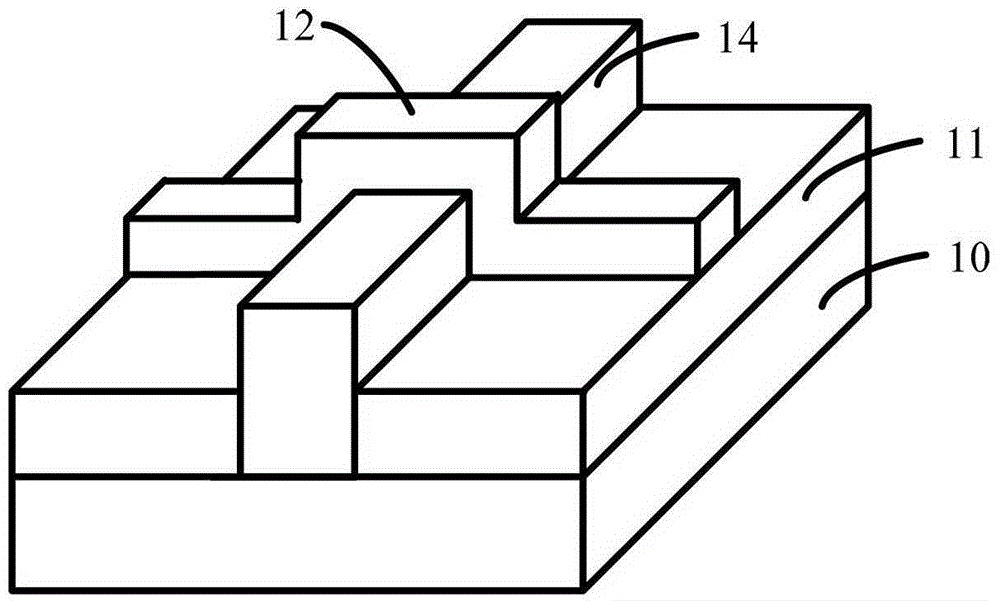

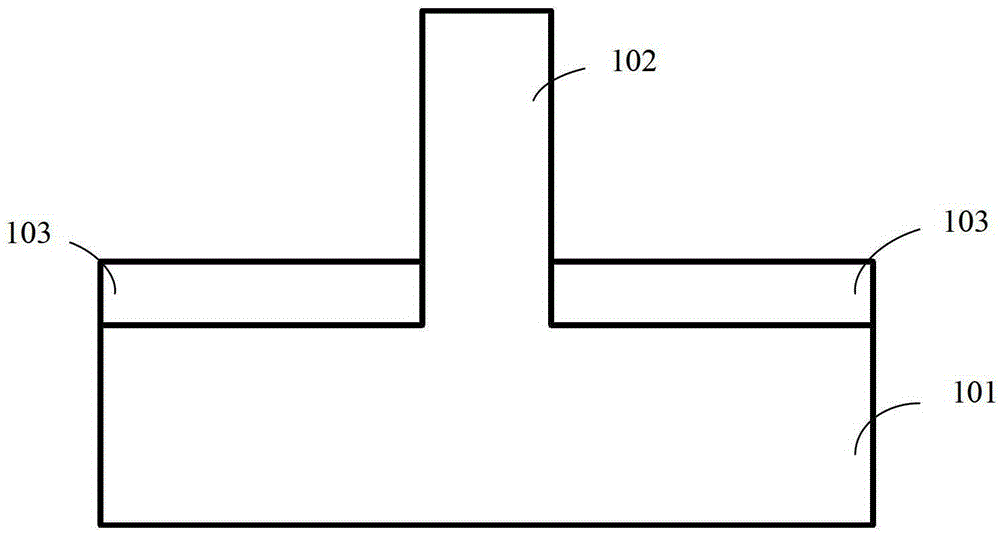

Alloy etching liquid and alloy etching method

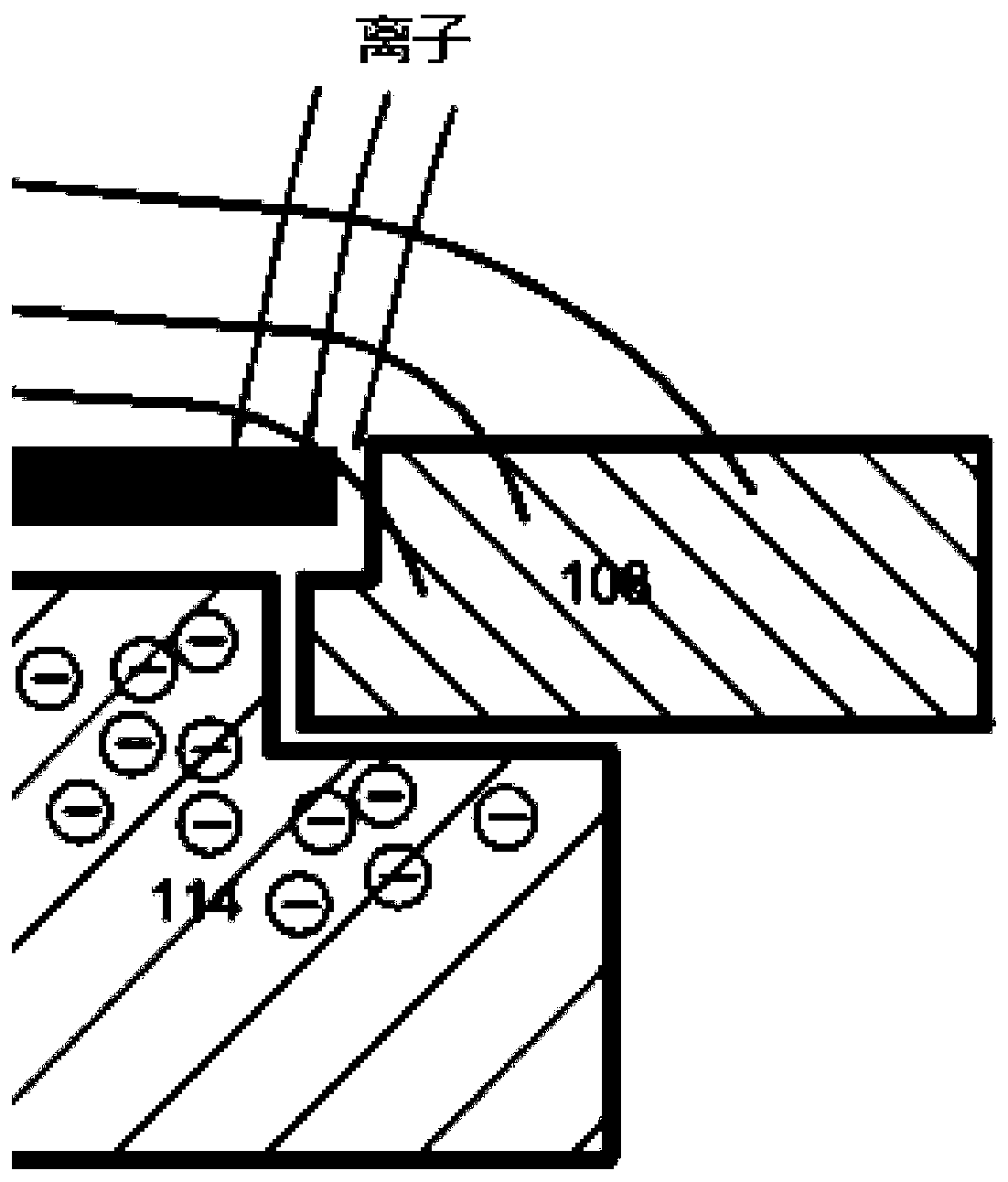

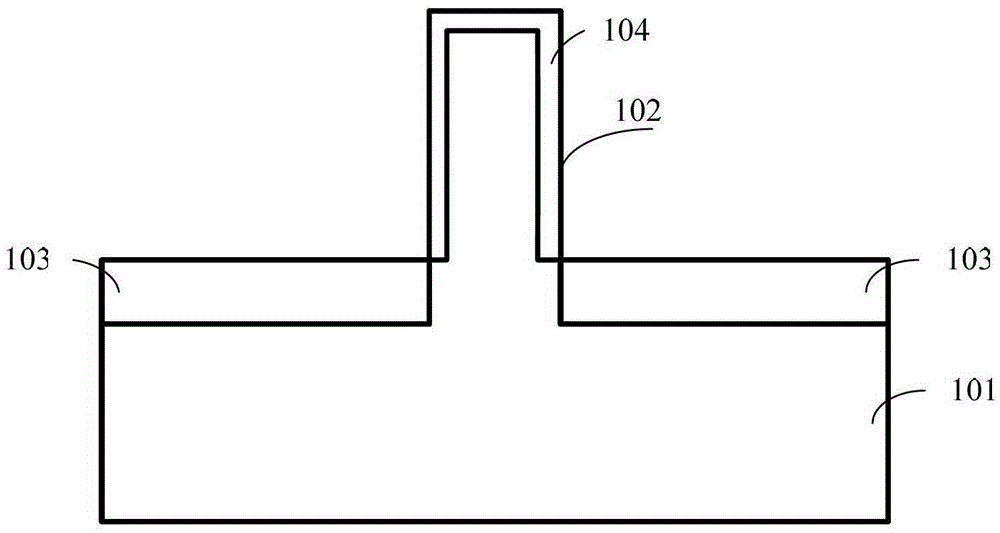

The invention provides an alloy etching liquid which comprises the following components: 5-25wt% of acetic acid, 1-35wt% of hydrogen peroxide, 0.1-5wt% of a surfactant, 0.1-5wt% of a defoamer, and thebalance deionized water. The alloy etching liquid provided by the invention has the beneficial effects that aiming at a special sandwich structure shown in figure 1, the compatibility of acetic acidand hydrogen peroxide is adopted, so that the etching rate can be effectively controlled, the rates of etching on different layers can be consistent, and the etching effect can be improved; and experimental results indicate that when the alloy etching liquid provided by the invention is adopted for etching a three-layer alloy structure shown in figure 1, a smooth etching interface can be formed, the etching rate can be controlled, and residues can be prevented from being left on the surface. The invention further provides an alloy etching method.

Owner:TRULY OPTO ELECTRONICS

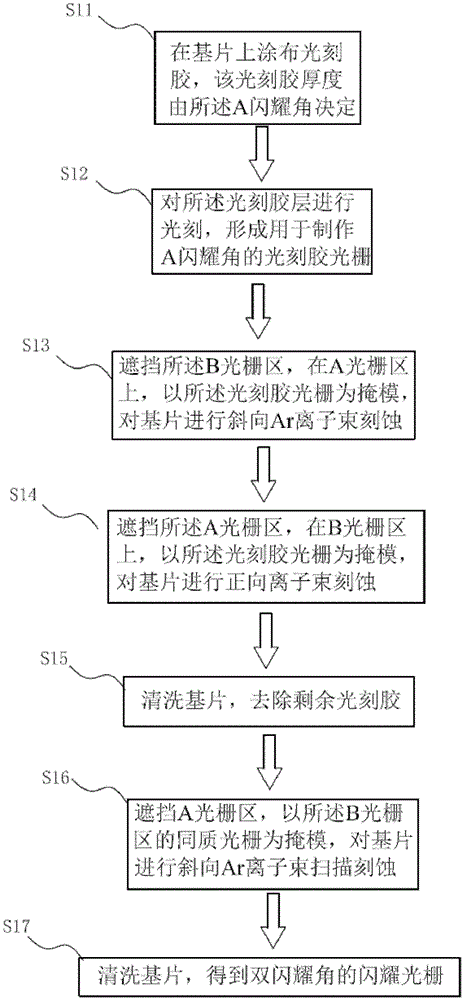

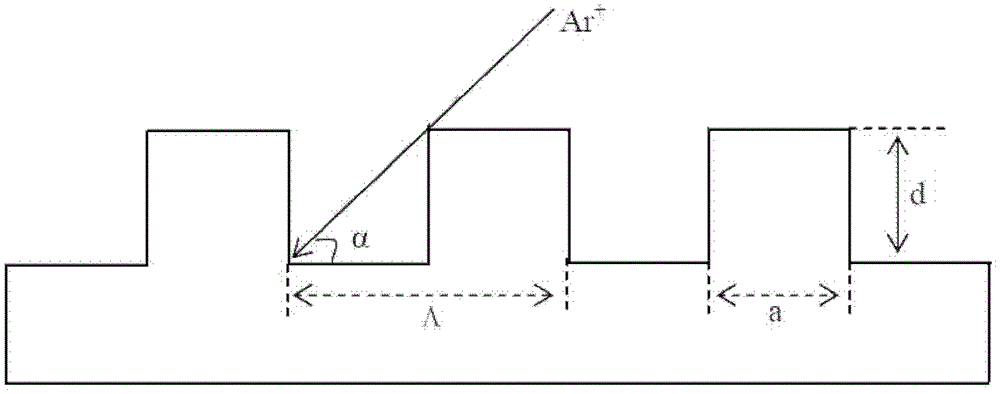

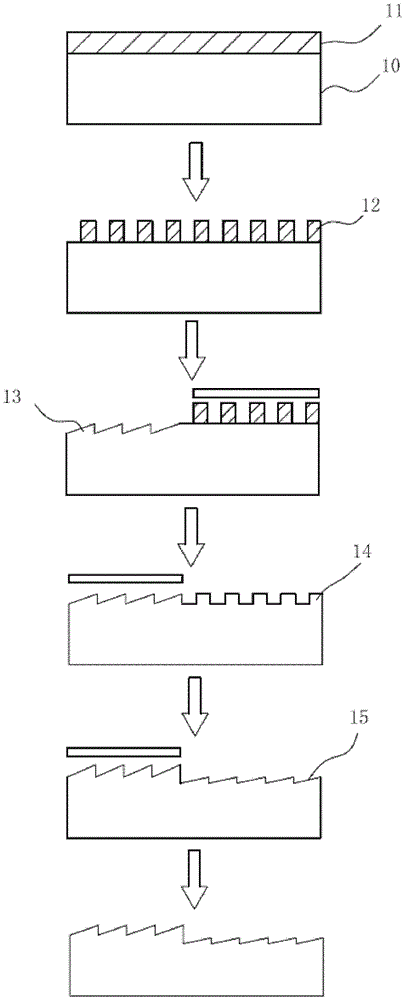

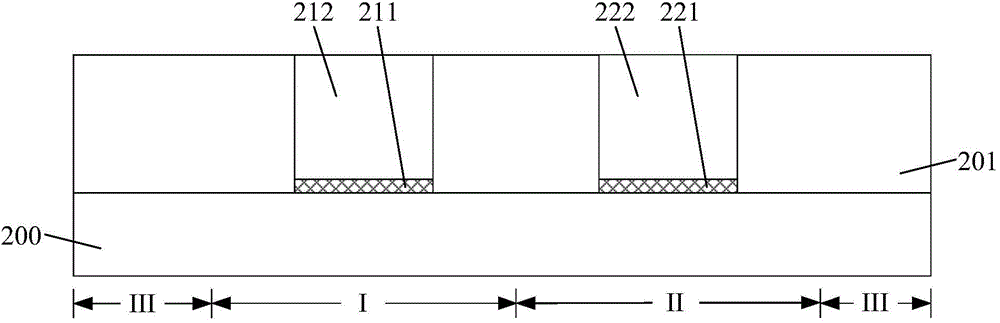

A method of manufacturing a holographic double blazed grating

ActiveCN102323634BAvoid secondary photoresist lithography processEasy to controlPhotomechanical apparatusDiffraction gratingsBlazed gratingGrating

The invention relates to a method for manufacturing a holographic double blazed grating. The two blaze angles of the holographic double blazed grating are A blaze angle and B blaze angle respectively. The homogeneous grating is used as a mask for oblique ion beam etching to achieve different control of the two blaze angles, avoiding the secondary photoresist lithography process. Since the time of forward ion beam etching can be controlled when making the homogeneous grating, the groove depth of the homogeneous grating can be precisely controlled. In addition, since the homogeneous grating mask and the substrate are formed of the same material, the etching time of the two The eclipse rate remains consistent throughout, allowing precise control of the blaze angle.

Owner:SUZHOU UNIV

TFT-LCD display screen substrate glass efficient etching liquid

The invention discloses TFT-LCD display screen substrate glass efficient etching liquid. The etching liquid consists of the following raw materials in percentage by weight: 14 to 18 percent of phosphoric acid, 16 to 20 percent of a fluorinated compound, 9 to 14 percent of nitric acid, 11 to 13 percent of hydrofluoric acid, 16 to 20 percent of potassium dichromate, 7 to 15 percent of concentrated sulfuric acid, 6 to 10 percent of phosphate, 8 to 10 percent of a surfactant and the balance of a solvent. The etching liquid can be in contact with a glass substrate completely and is permeated into the bottom of photoresist uniformly, the etching rate on different metal is basically consistent, the reaction is stable, the etched substrate is clean and tidy in surface, residues is avoided, metal layering phenomenon is avoided, and the residual lines are flat; meanwhile, after the etching liquid for the TFT-LCD display screen is thinned on the glass substrate, the precipitate impurities attached to the surface of the glass substrate are dissolved, so that the impurities on the surface of the glass substrate can be effectively removed, the qualification rate and the yield of products can beincreased, and effective guarantee can be provided for control of the thickness of the glass substrate.

Owner:长沙惠科金扬科技有限责任公司

Semiconductor device forming method

ActiveCN105826259AGood electrical propertiesReduce etchingSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical performanceDielectric layer

The invention provides a semiconductor device forming method. The method comprises steps: a substrate with a first area and a second area is provided, a first pseudo gate is formed on part of the substrate in the first area, a second metal gate is formed on part of the substrate in the second area, an interlayer dielectric layer is also formed on the surface of the substrate in the first area and in the second area, and the interlayer dielectric layer coats the side wall surface of the first pseudo gate and the side wall surface of the second metal gate; a synchronous pulse etching process is adopted to etch and remove the first pseudo gate, and a first opening is formed in the interlayer dielectric layer in the first area; a synchronous pulse method is adopted to carry out etching post-treatment on the first opening, and the treatment gas for the etching post-treatment comprises a carbon tetrafluoride gas; and a first metal gate filling the first opening is formed. The etched and removed thickness of the interlayer dielectric layer is small, the etched and removed thicknesses of the interlayer dielectric layer in a graph sparse area and a graph intensive area are consistent, and the electrical performance of the semiconductor device is thus improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

3d NAND memory and its formation method

ActiveCN109742038BPrevents bending defectsConsistent etch rateSemiconductor/solid-state device testing/measurementSolid-state devicesCrystallographyIsolation layer

A 3D NAND memory and a forming method thereof, wherein the forming method of the 3D NAND memory consists of forming an intermediate isolation layer between a first stacked structure and a second stacked structure, and sequentially etching the second stacked structure, the middle The isolation layer and the first stacked structure, when forming the gate isolation trench in the second stacked structure, the intermediate isolation layer and the first stacked structure, the intermediate isolation layer is used to make the etching rate of the intermediate isolation layer equal to the etching rate. The etching rate of the first stacked structure remains consistent, and the etching rate of the second stacked structure remains consistent with the etching rate of the first stacked structure, thereby preventing the etching rate of the intermediate insulating layer from being the same as the etching rate of the first stacked structure. When the etching rate is different from that of the second stacked structure, bending defects occur in the sidewalls of the gate trenches.

Owner:YANGTZE MEMORY TECH CO LTD

A carrying device and a pre-cleaning chamber

ActiveCN107464764BConsistent etch rateImprove etch uniformityElectric discharge tubesVacuum evaporation coatingMechanical engineeringPlasma density distribution

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

Target back plate and magnetron sputtering device for magnetron sputtering

ActiveCN105734516BConsistent etch rateExtended service lifeVacuum evaporation coatingSputtering coatingSputteringEngineering

The invention discloses a target back plate for magnetron sputtering and a magnetron sputtering device, relates to the technical field of magnetron sputtering, and aims to increase the utilization rate of a target material and improve the uniformity of the thickness of a film formed on a substrate to be coated. According to the target back plate for magnetron sputtering, a cooling fluid channel is formed inside the target back plate, a plurality of magnets are arranged on the back side of the target back plate, magnetic conductive pieces are arranged inside the cooling liquid channel in the target back plate; and the magnetic conductive pieces correspond to magnetic fields with the strongest magnetic intensity generated by the magnetic conductive pieces and the plurality of magnets. The target back plate for magnetron sputtering and the magnetron sputtering device, which are disclosed by the invention, are applied to planar film coating.

Owner:BOE TECH GRP CO LTD +1

Method of forming semiconductor device

ActiveCN105826259BGood electrical propertiesReduce etchingSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceElectrical performance

The invention provides a semiconductor device forming method. The method comprises steps: a substrate with a first area and a second area is provided, a first pseudo gate is formed on part of the substrate in the first area, a second metal gate is formed on part of the substrate in the second area, an interlayer dielectric layer is also formed on the surface of the substrate in the first area and in the second area, and the interlayer dielectric layer coats the side wall surface of the first pseudo gate and the side wall surface of the second metal gate; a synchronous pulse etching process is adopted to etch and remove the first pseudo gate, and a first opening is formed in the interlayer dielectric layer in the first area; a synchronous pulse method is adopted to carry out etching post-treatment on the first opening, and the treatment gas for the etching post-treatment comprises a carbon tetrafluoride gas; and a first metal gate filling the first opening is formed. The etched and removed thickness of the interlayer dielectric layer is small, the etched and removed thicknesses of the interlayer dielectric layer in a graph sparse area and a graph intensive area are consistent, and the electrical performance of the semiconductor device is thus improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

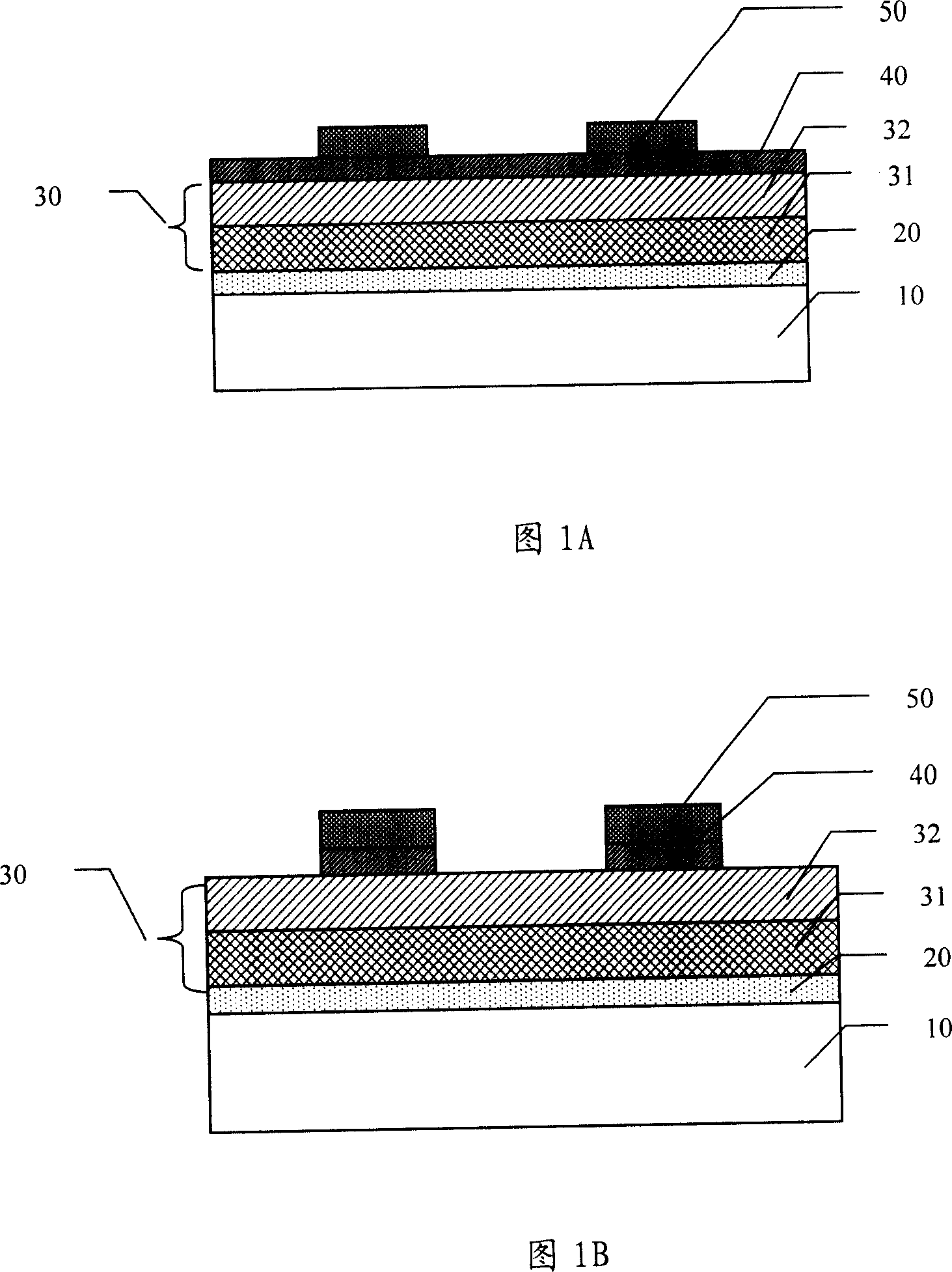

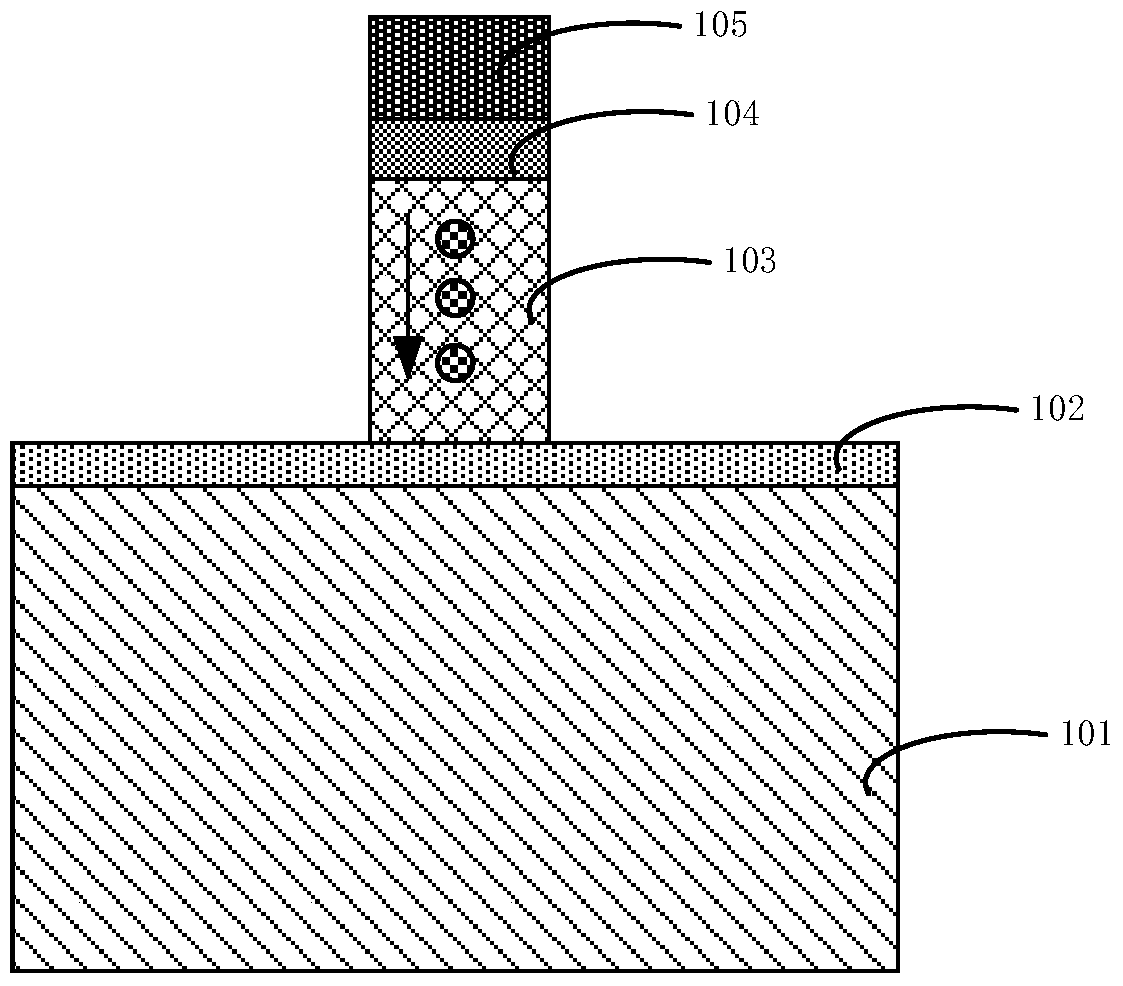

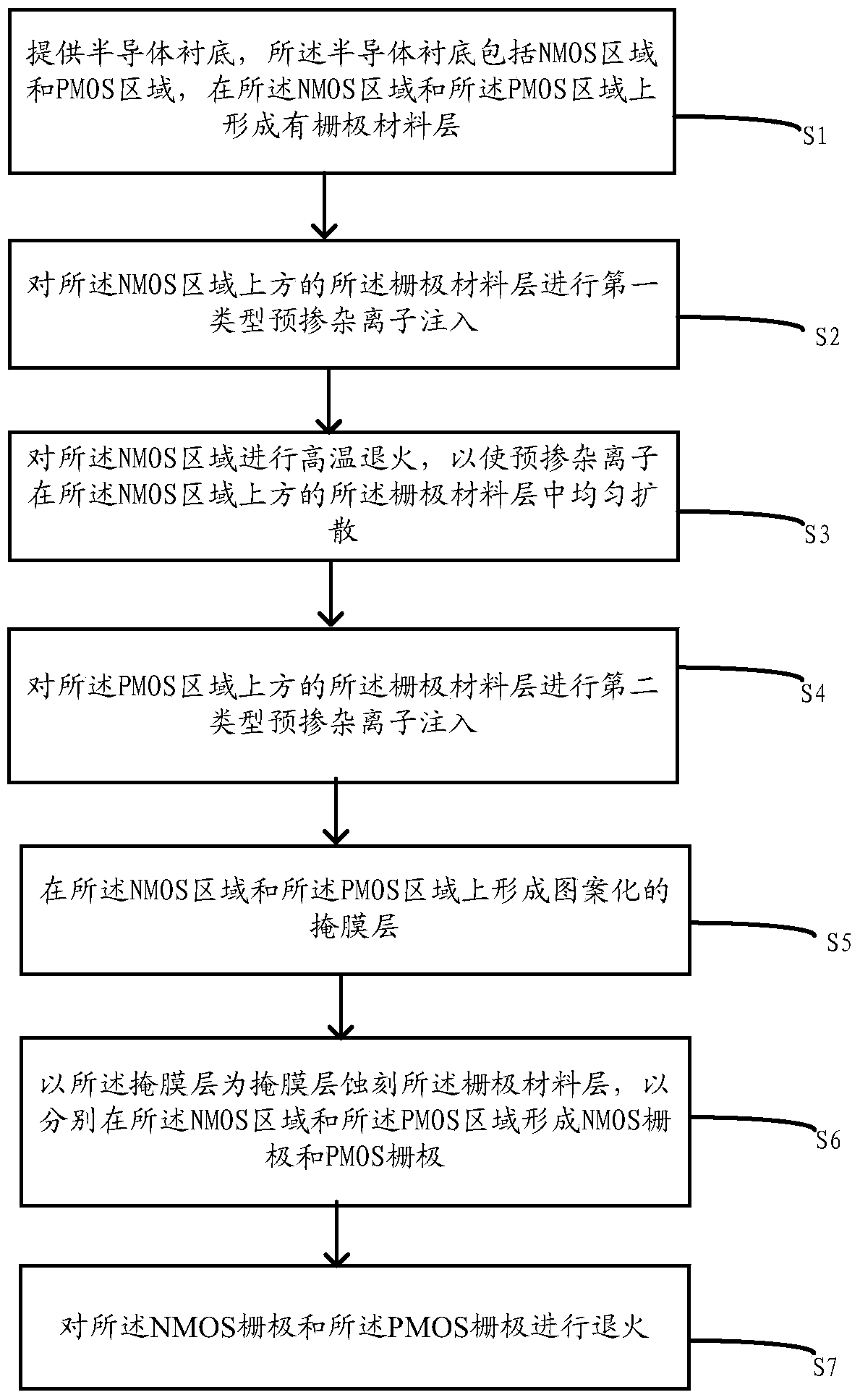

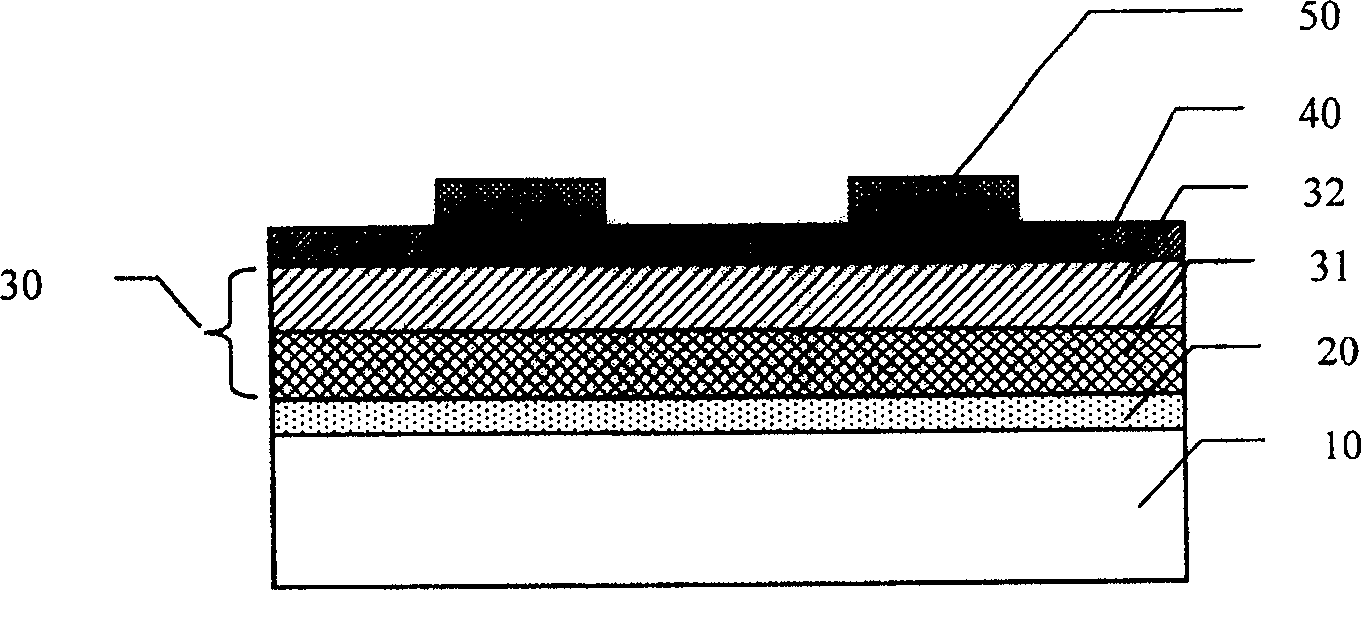

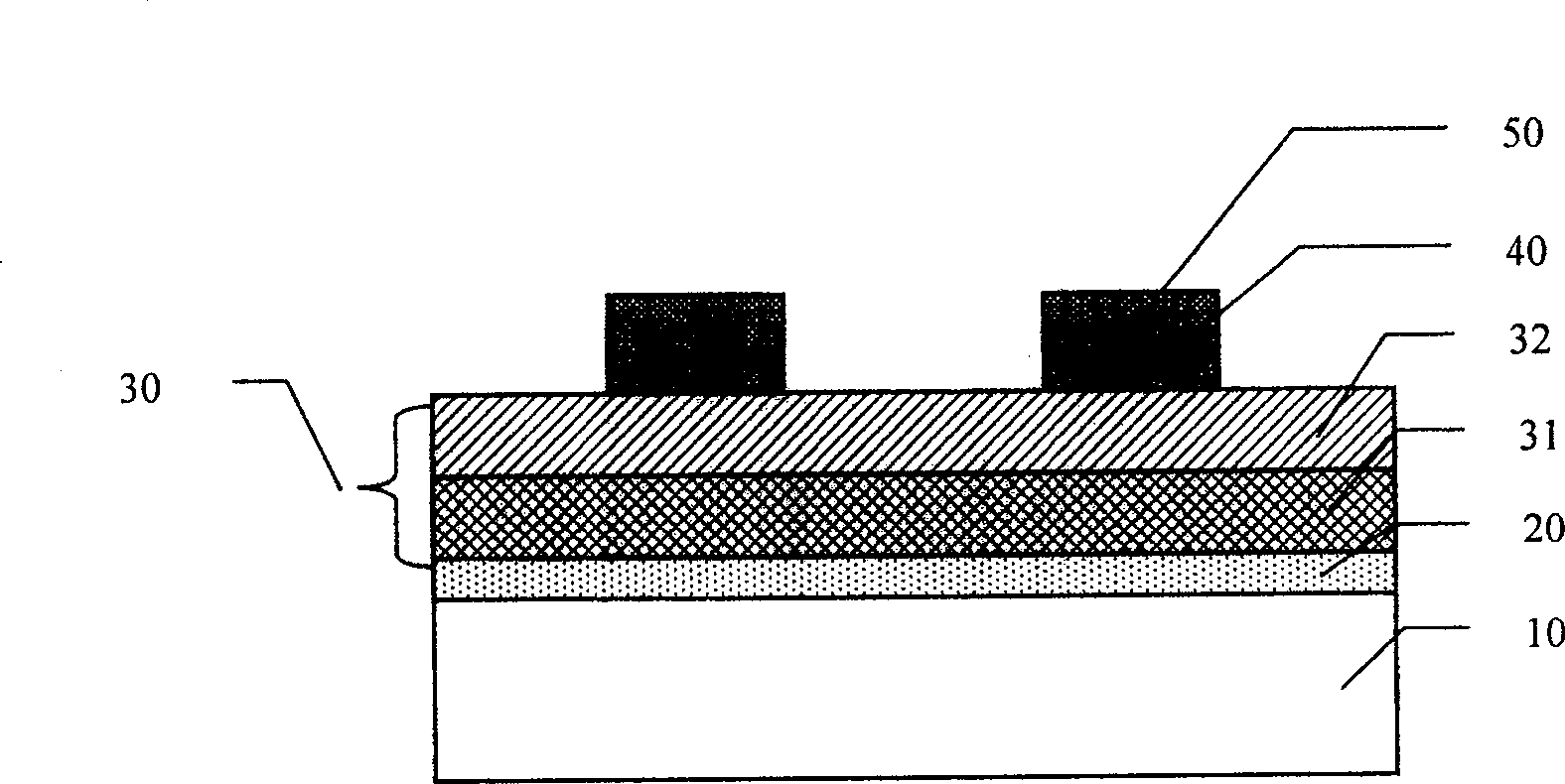

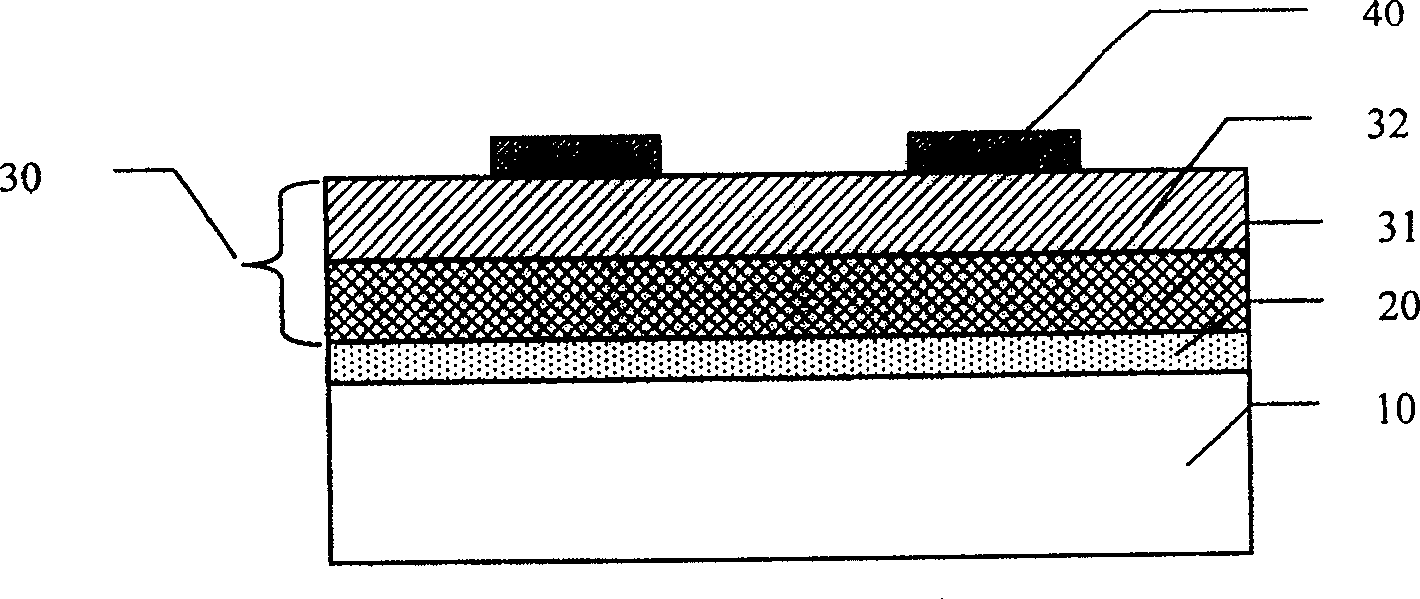

A kind of semiconductor device and its preparation method, electronic device

ActiveCN106935553BSpread evenlyPrevent proliferationTransistorSemiconductor/solid-state device manufacturingDevice materialEngineering

The invention relates to a semiconductor device and a preparation method thereof, and an electronic apparatus. The method comprises the following steps: providing a semiconductor substrate, wherein the semiconductor substrate includes an NMOS region and a PMOS region, and a gate material layer is formed on the NMOS region and the PMOS region; performing first-type pre-doped ion implantation on the gate material layer above the NMOS region; performing high-temperature annealing on the NMOS region to evenly disperse pre-doped ions in the gate material layer above the NMOS region; and performing second-type pre-doped ion implantation different from the first-type pre-doped ion implantation on the gate material layer above the PMOS region. Pre-doped ions in the PMOS region can be prevented from diffusing into the NMOS region. The threshold voltage is more stable. The performance and yield of the semiconductor device are improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Plasma etching method, device thereof and plasma etching method for diffusion barrier layers

ActiveCN102412144BEvenly distributedConsistent etch rateElectric discharge tubesSemiconductor/solid-state device manufacturingPlasma GasesDiffusion barrier

The invention provides a plasma etching method, a device thereof and a specific method applying the device to carry out plasma etching on diffusion barrier layers, wherein the plasma etching method includes the following steps: an outer electrode collar and an inner electrode collar are concentrically arranged in an etching chamber; a semiconductor wafer to be etched is arranged on the bottoms of the outer electrode collar and the inner electrode collar, and the center of the semiconductor wafer is superposed with the circle center of the outer electrode collar and the inner electrode collar; etching gas is filled into the etching chamber; the outer electrode collar and the inner electrode collar are electrified, and the current directions of the outer electrode collar and the inner electrode collar are opposite. The invention ensures that the distribution of the plasma gas of the surface of the semiconductor wafer is uniform and the etching rate at each position is equal, thus improving the thickness consistency of each diffusion barrier layer at each position on the semiconductor wafer.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

A kind of aluminum etchant and preparation method thereof

The invention belongs to the technical field of chemical preparations, and relates to an aluminum etching agent and a preparation method thereof. The formula of the aluminum etching agent comprises the following components in percentages by weight: 70-78% of phosphoric acid, 5-6% of nitric acid, 6-10% of acetic acid, 1-5% of sulfamic acid, and the balance of water. The aluminum etching liquid provided by the invention can convert a metal compound into soluble salts which are dissolved in water, speeds of etching to different metals are consistent basically, reaction is stable, the circumstance that etching efficiency and neatness of the surface of a substrate are affected by precipitate attachment is avoided, and surface dirt is removed conveniently.

Owner:SUZHOU BOYANG CHEM

Method of forming fin and method of forming fin field effect transistor

ActiveCN103594342BControl depthGuaranteed uniformitySemiconductor/solid-state device manufacturingSemiconductor devicesInsulation layerAmorphous phase

Owner:SEMICON MFG INT (SHANGHAI) CORP

Making method for grid structure

ActiveCN100539030CConsistent etch rateControl deficienciesSemiconductor devicesConductive materialsDielectric layer

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

A kind of etchant for silicon-based multilayer film

ActiveCN106854468BConsistent etch rateImprove wettabilitySurface treatment compositionsHydrofluoric acidHydrogen

The invention discloses an etching liquid for silicon system multilayer films. The etching liquid comprises a hydrofluoric acid solution, an ammonium fluoride solution, a surfactant and a compound represented by a general formula shown in the description; and in the formula, R1 is one of an amino group, hydrogen, oxygen and a hydroxyl group, and R2 is one of fluorine, chlorine, hydrogen, a hydroxyl group and a C1-C4 alkyl group. The etching liquid for silicon system multilayer films allows the etching speed of a silicon nitride layer to basically same to the etching speed of a silicon oxide layer, and has a good etching effect.

Owner:ZHEJIANG KAISN FLUOROCHEM

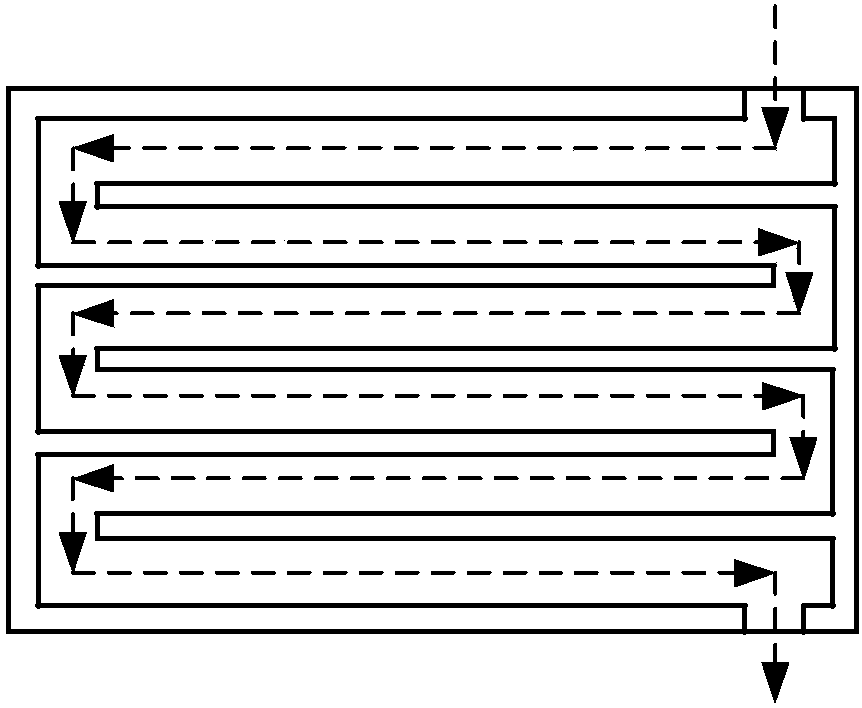

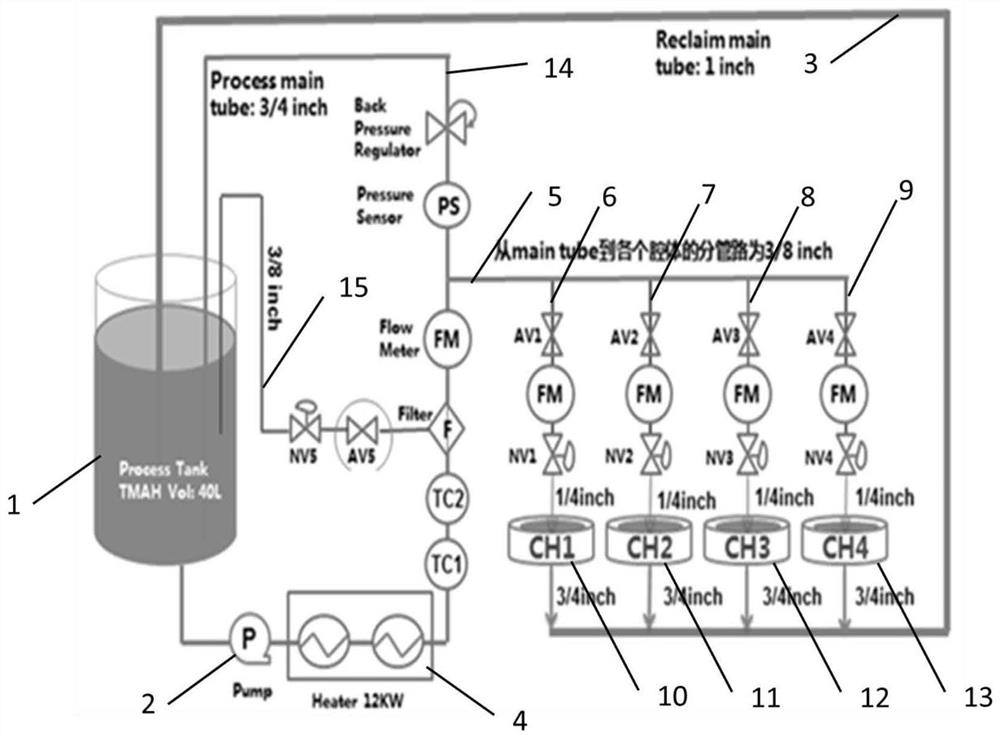

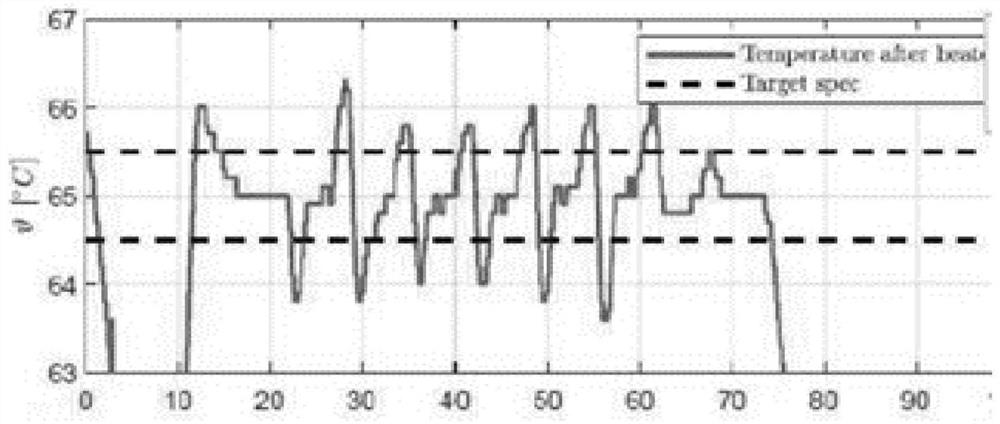

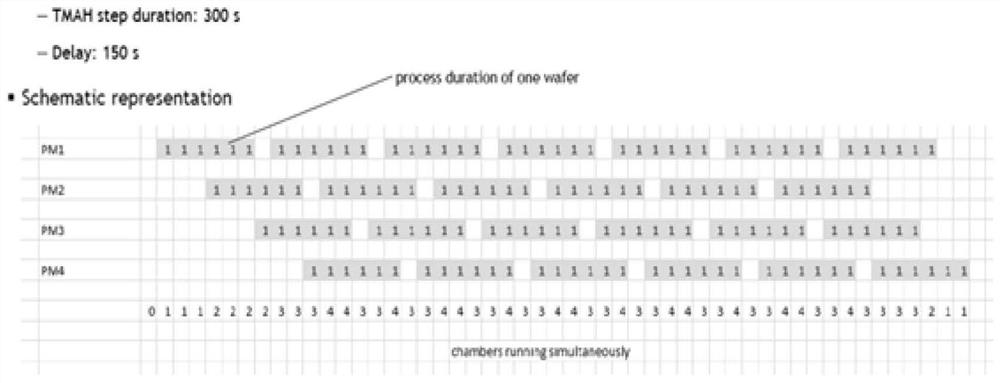

Wafer wet etching equipment

PendingCN113394135AConsistent etch rateSmall temperature fluctuationsSemiconductor/solid-state device manufacturingEtchingWafer

The invention discloses wafer wet etching equipment. The equipment comprises a storage container, and a main pipeline, a pressure relief pipeline, an auxiliary pipeline and a recovery pipeline which are respectively connected with the storage container; the main pipeline is connected with a pump, a heater and a flow meter; the pressure relief pipeline is connected with a pressure sensor and a pressure regulator; the storage container is used for storing an etching agent; the pump is used for pumping the etching agent in the storage container into the main pipeline; the heater is used for heating the etching agent to a preset temperature; the equipment further comprises a plurality of etching chambers used for etching the wafer; each etching chamber is connected with the main pipeline through a respective branch pipeline; and the equipment also comprises a control device used for controlling the etching process of each etching chamber.

Owner:SHANGHAI HUALI INTEGRATED CIRCUTE MFG CO LTD

Etching device and etching method

InactiveCN101962774BSame update rateAvoid the pool effectConductive material chemical/electrolytical removalMaterials science

The invention relates to an etching device and an etching method. The etching device comprises a spray pipe and a liquid scrapping device, wherein the spray pipe is provided with a plurality of spray heads; the plurality of spray heads are used for spraying etching liquid to a surface to be etched of a circuit substrate; and the liquid scrapping device is used for scrapping the etching liquid deposited in a center area of the surface to be etched out of the surface to be etched in a sliding mode. The etching method comprises the following steps of: using the plurality of spray heads arranged on the spray pipe to spray the etching liquid towards the surface to be etched of the circuit substrate; and using the liquid scrapping device to scrap the etching liquid deposited in the center area of the surface to be etched out of the surface to be etched in a sliding mode. The etching method can avoid generating water pit effect.

Owner:JIANGSU TRANSIMAGE TECH CO LTD

A kind of acidic molybdenum aluminum molybdenum etching solution and preparation technology thereof

The invention discloses a novel acidic molybdenum aluminum molybdenum etching liquid and its preparation process. The novel acidic molybdenum aluminum molybdenum etching liquid comprises phosphoric acid, acetic acid, nitric acid, metal nitrate, a cationic surfactant and pure water. The preparation process of the etching liquid includes: maintaining the rotation speed of an ingredient tank stirrer, adding the phosphoric acid, the acetic acid, the nitric acid, potassium nitrate, the pure water and the cationic surfactant sequentially into the ingredient tank, fully stirring them, then introducing the mixture into a filter to conduct filtration, thus obtaining the molybdenum aluminum molybdenum etching liquid. The molybdenum aluminum molybdenum etching liquid provided in the invention has a small particle size and high purity, has a basically consistent etching rate on different metals, and is stable in reaction. By adjusting the nitric acid concentration, the etching speed can be controllable. The substrate etched by the etching liquid has a clean and tidy surface, no residue, and no intermetallic layering phenomenon. The remaining lines are smooth, and the etching angle is maintained at 40-60 degrees.

Owner:JIANGYIN RUNMA ELECTRONICS MATERIAL