Patents

Literature

88results about How to "Low line resistance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

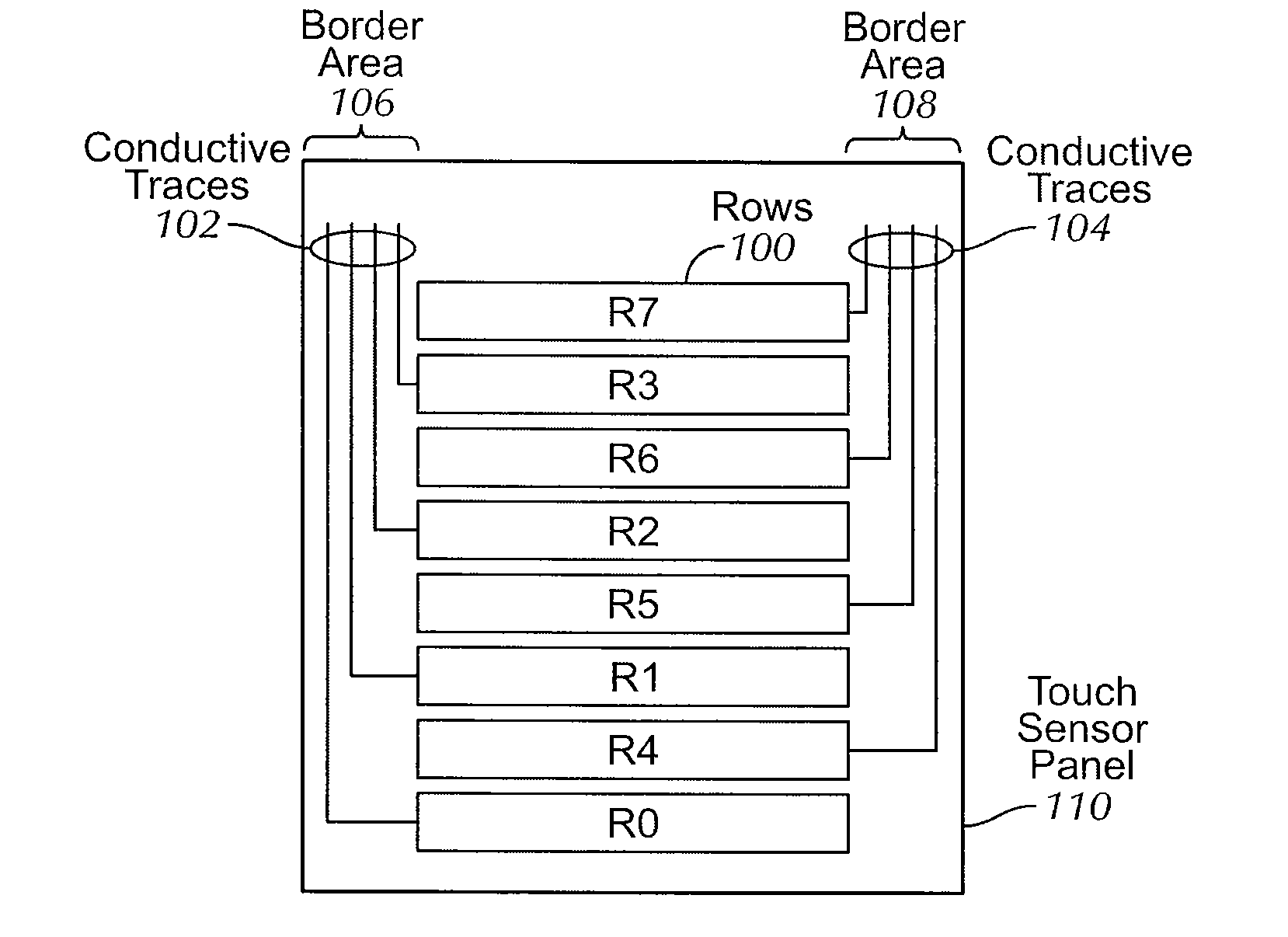

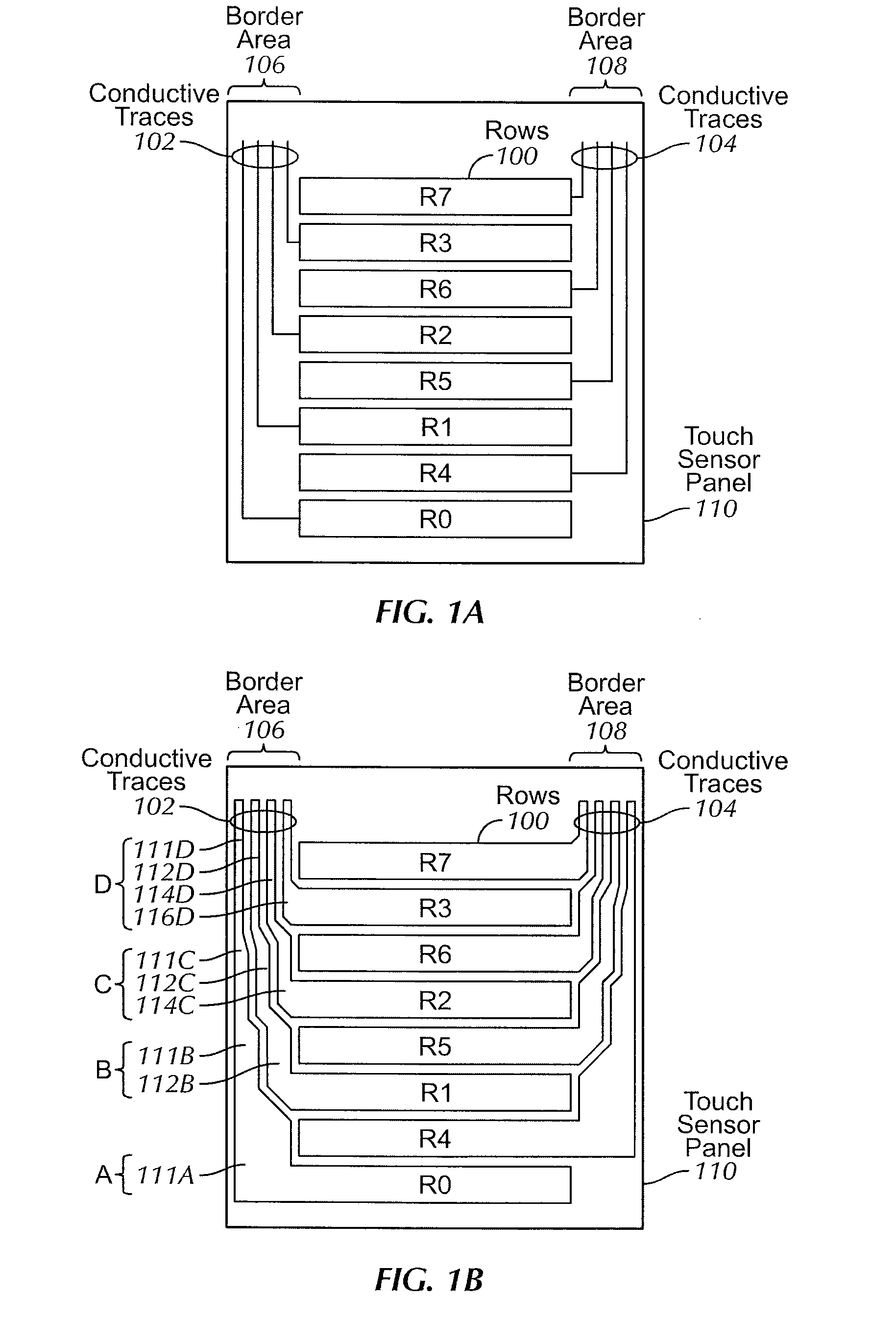

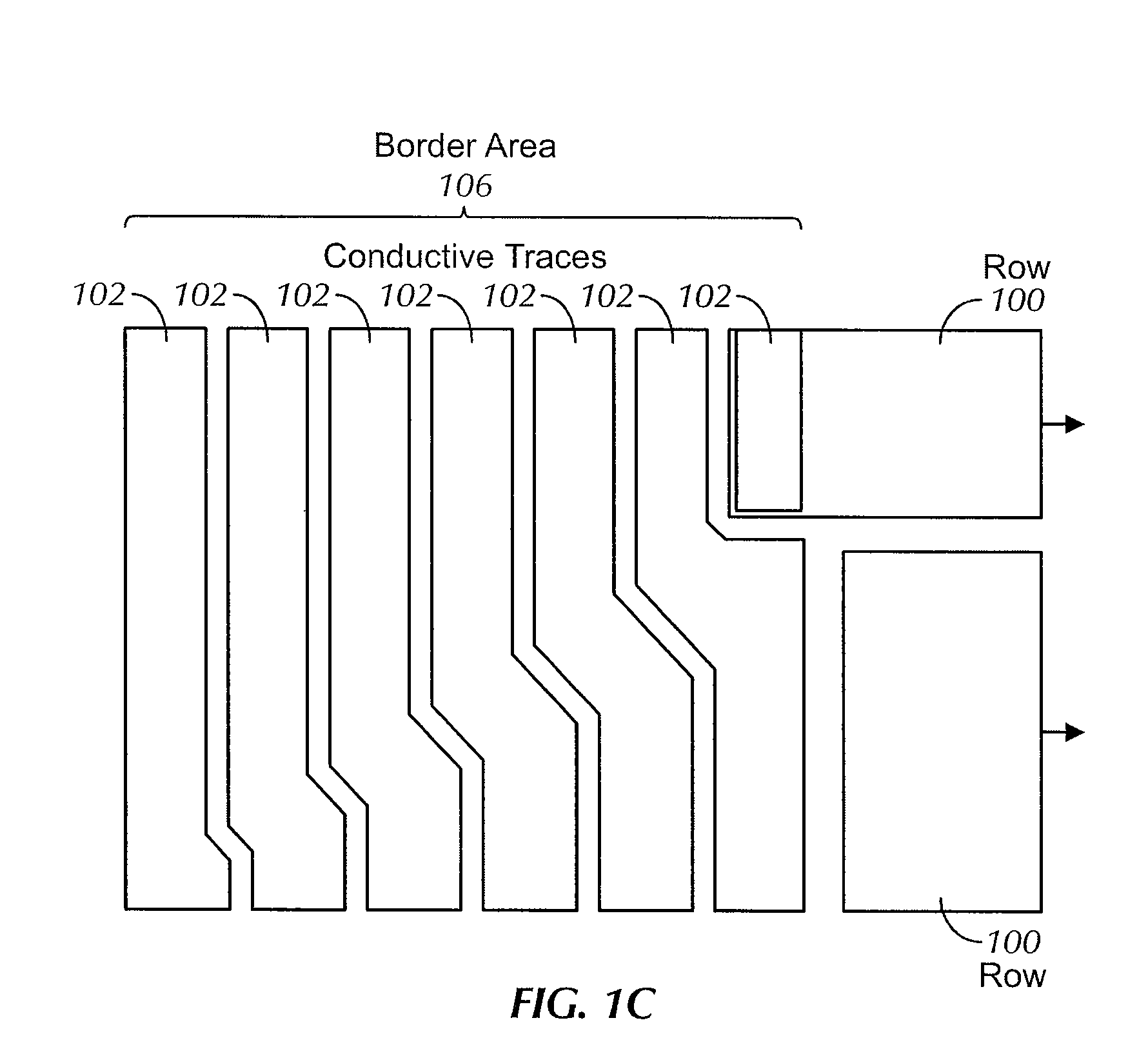

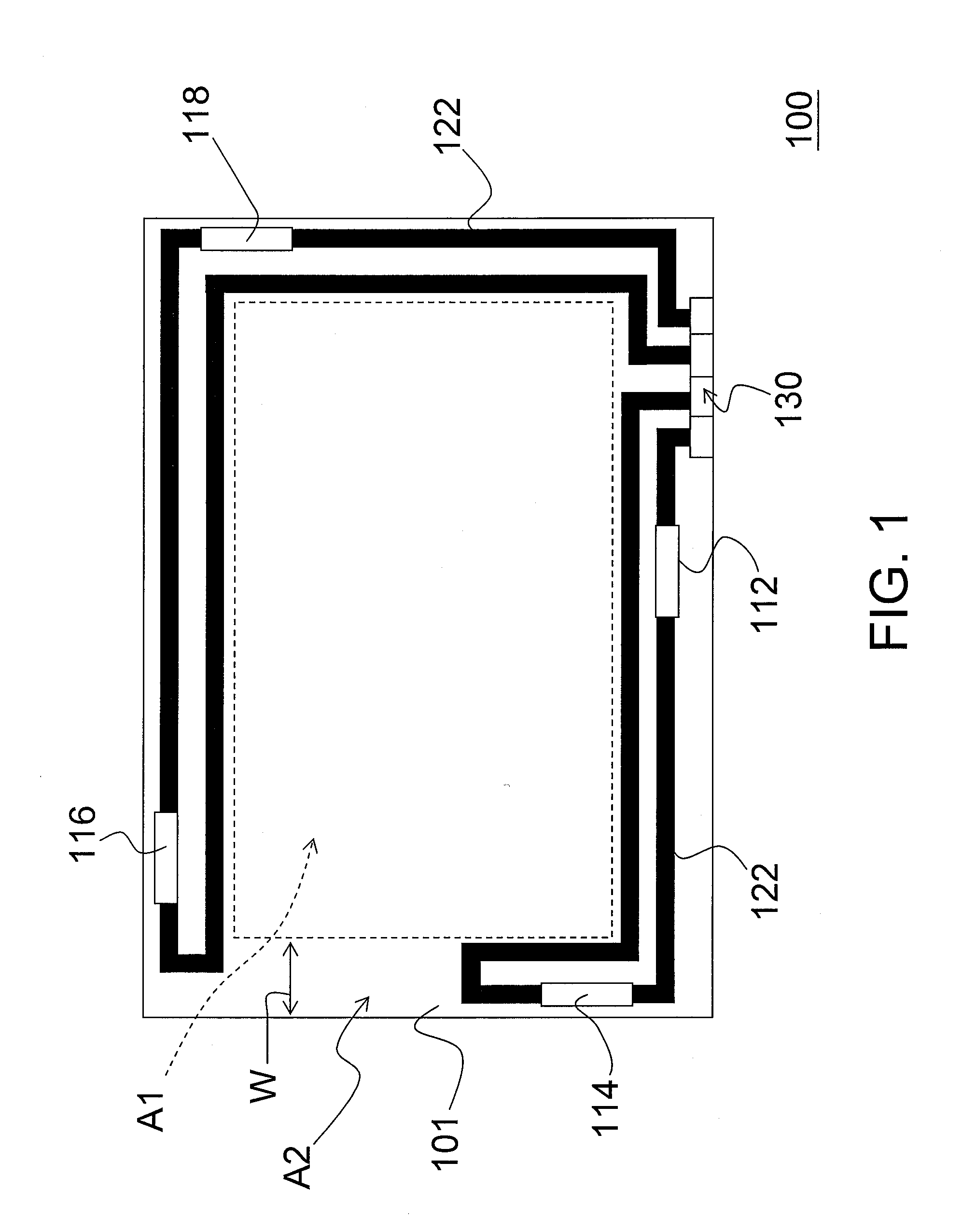

High Resistivity Metal Fan Out

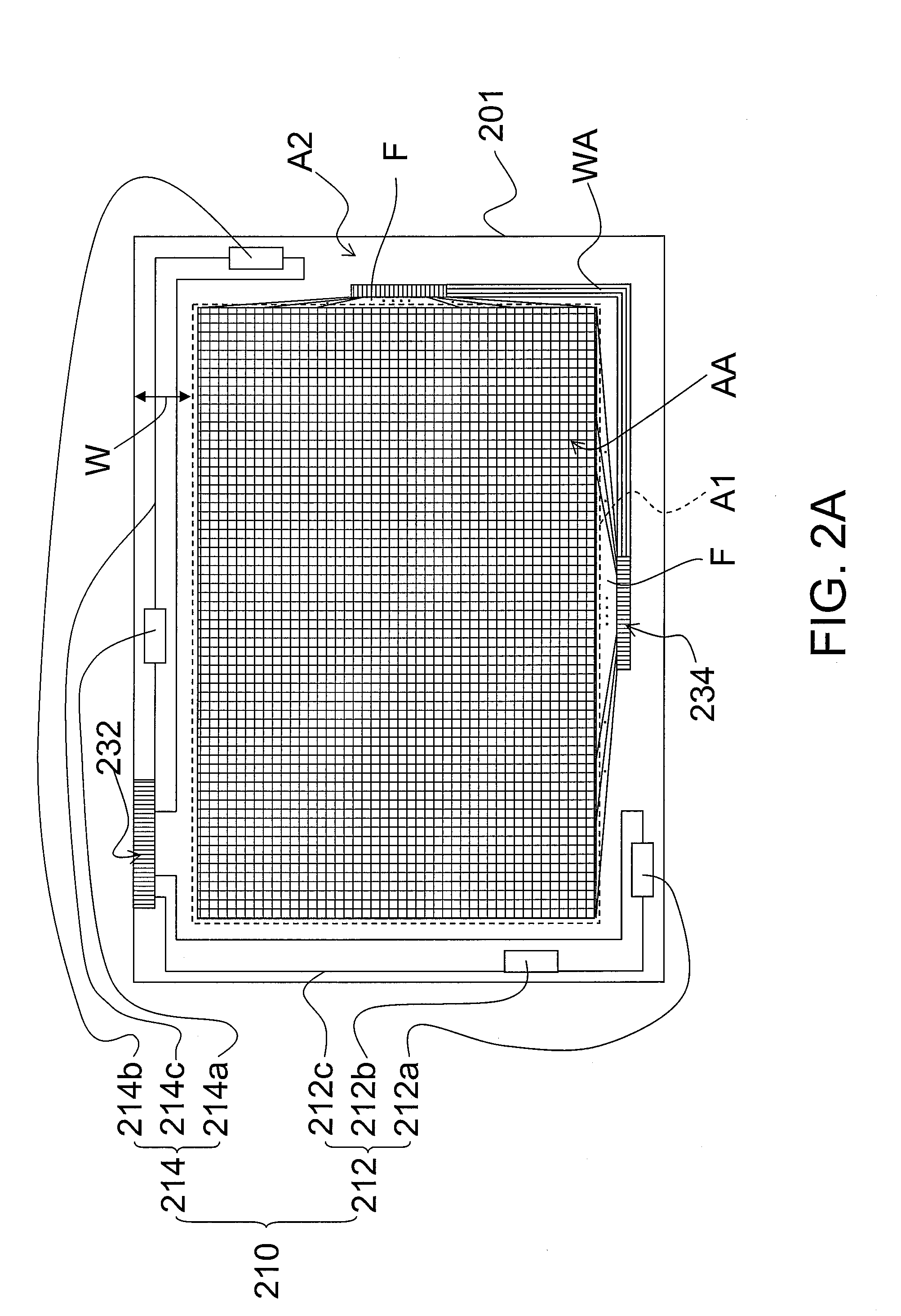

ActiveUS20090303189A1Improve reliabilityGood rejectionTransparent dielectricsConductive pattern reinforcementManufacturing cost reductionHigh resistivity

The formation of metal traces in the border areas of a touch sensor panel to provide improved reliability, better noise rejection, and lower manufacturing costs is disclosed. The metal traces can be coupled to rows on the touch sensor panel in an interleaved manner, so that any two successive rows can be coupled to metal traces in border areas on opposite sides of the touch sensor panel. In addition, by utilizing the full width available in the border areas in some embodiments, the metal traces can be formed from higher resistivity metal, which can reduce manufacturing costs and improve trace reliability. The wider traces can also provide better noise immunity from noise sources such as an LCD by providing a larger fixed-potential surface area and by more effectively coupling the drive lines to the fixed potential.

Owner:APPLE INC

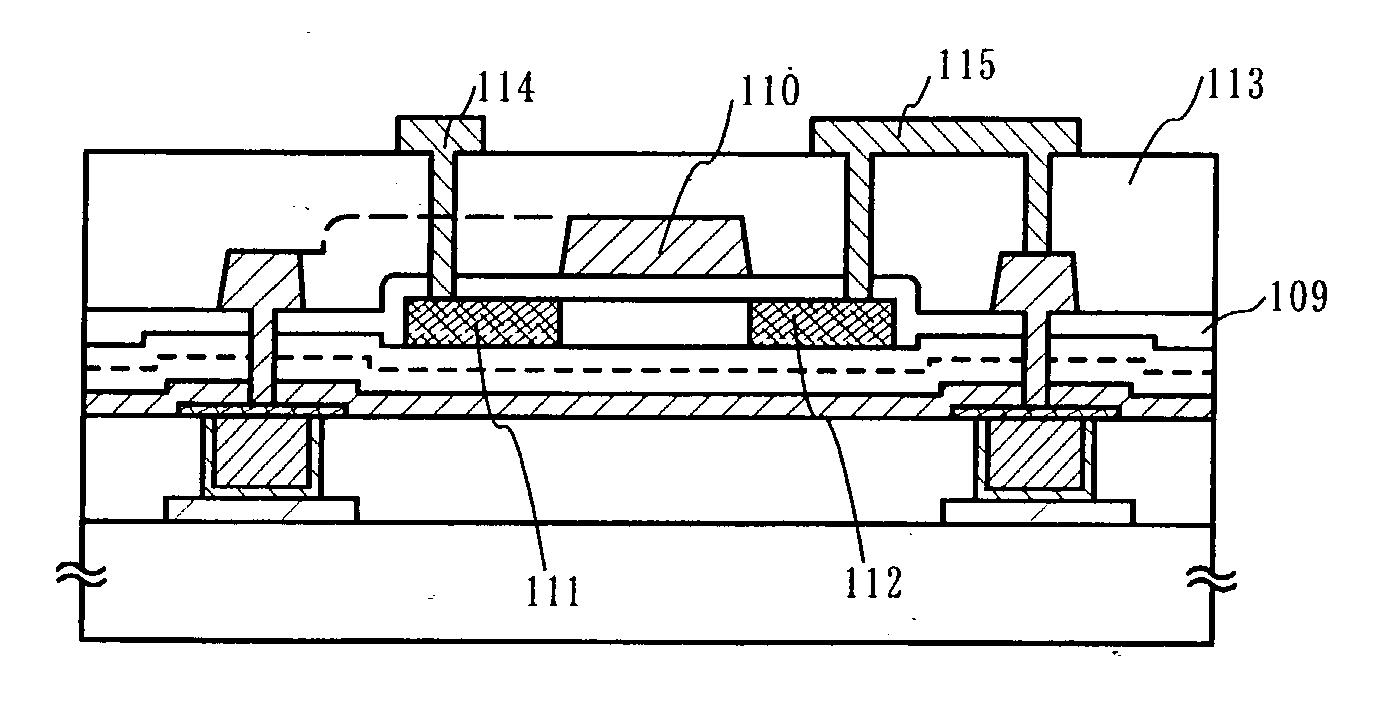

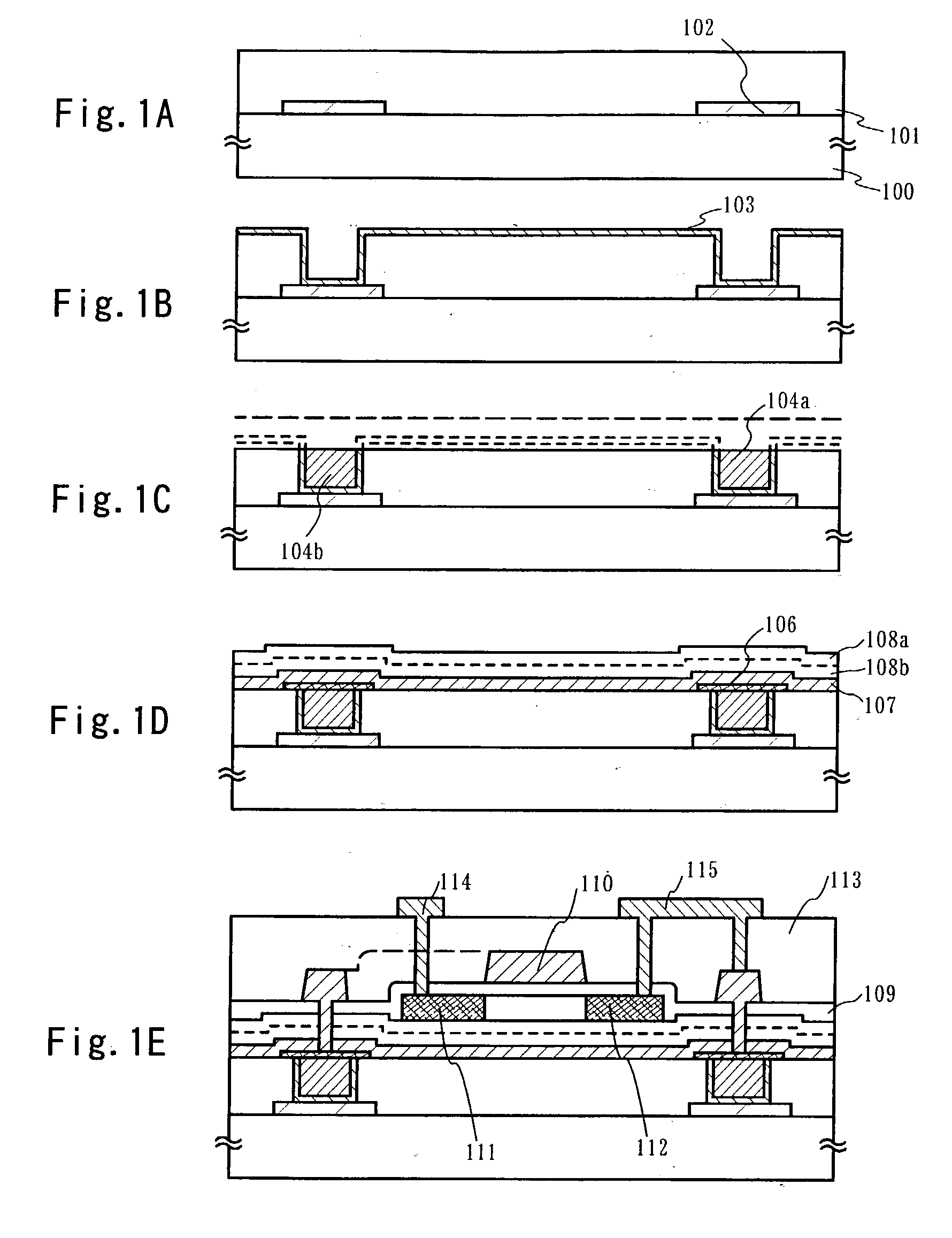

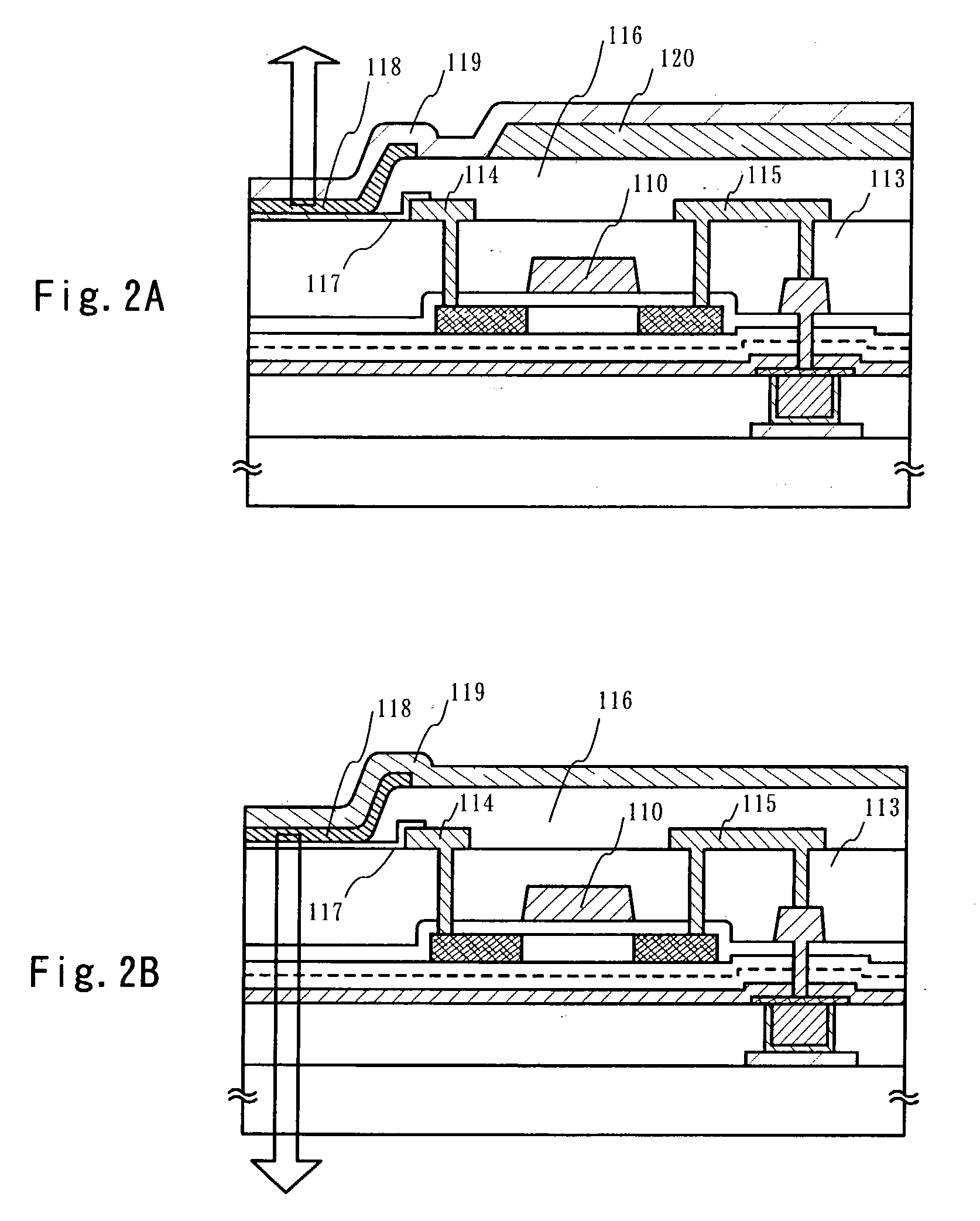

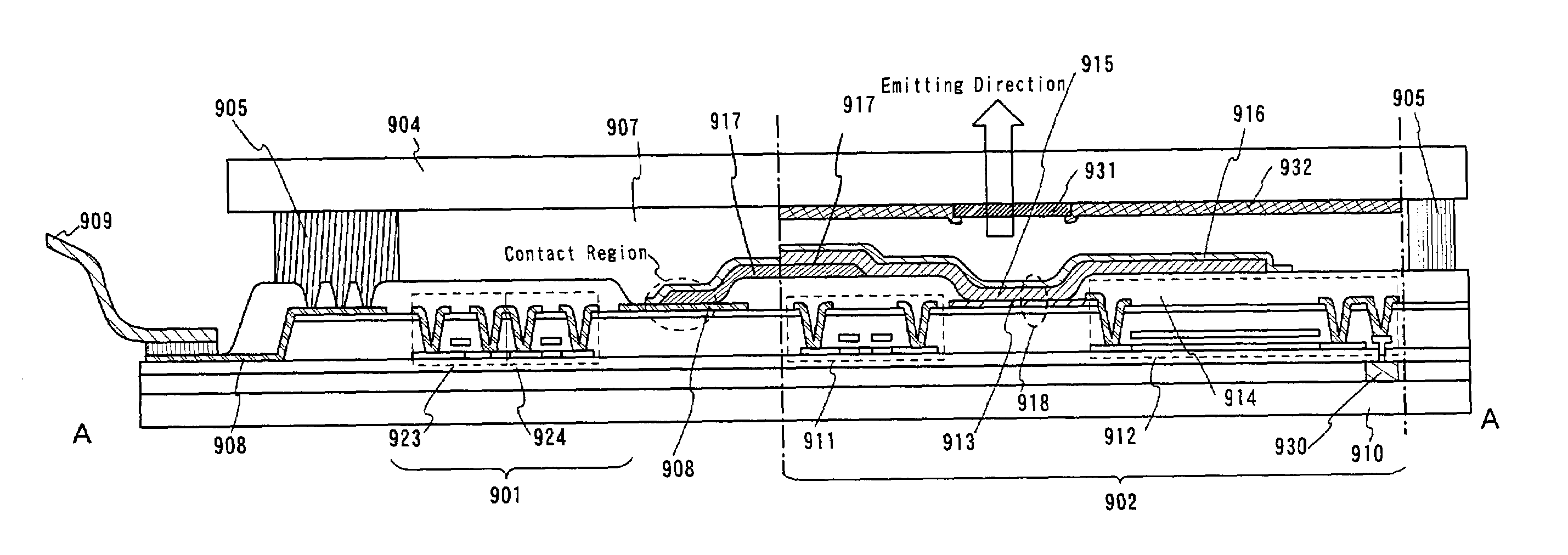

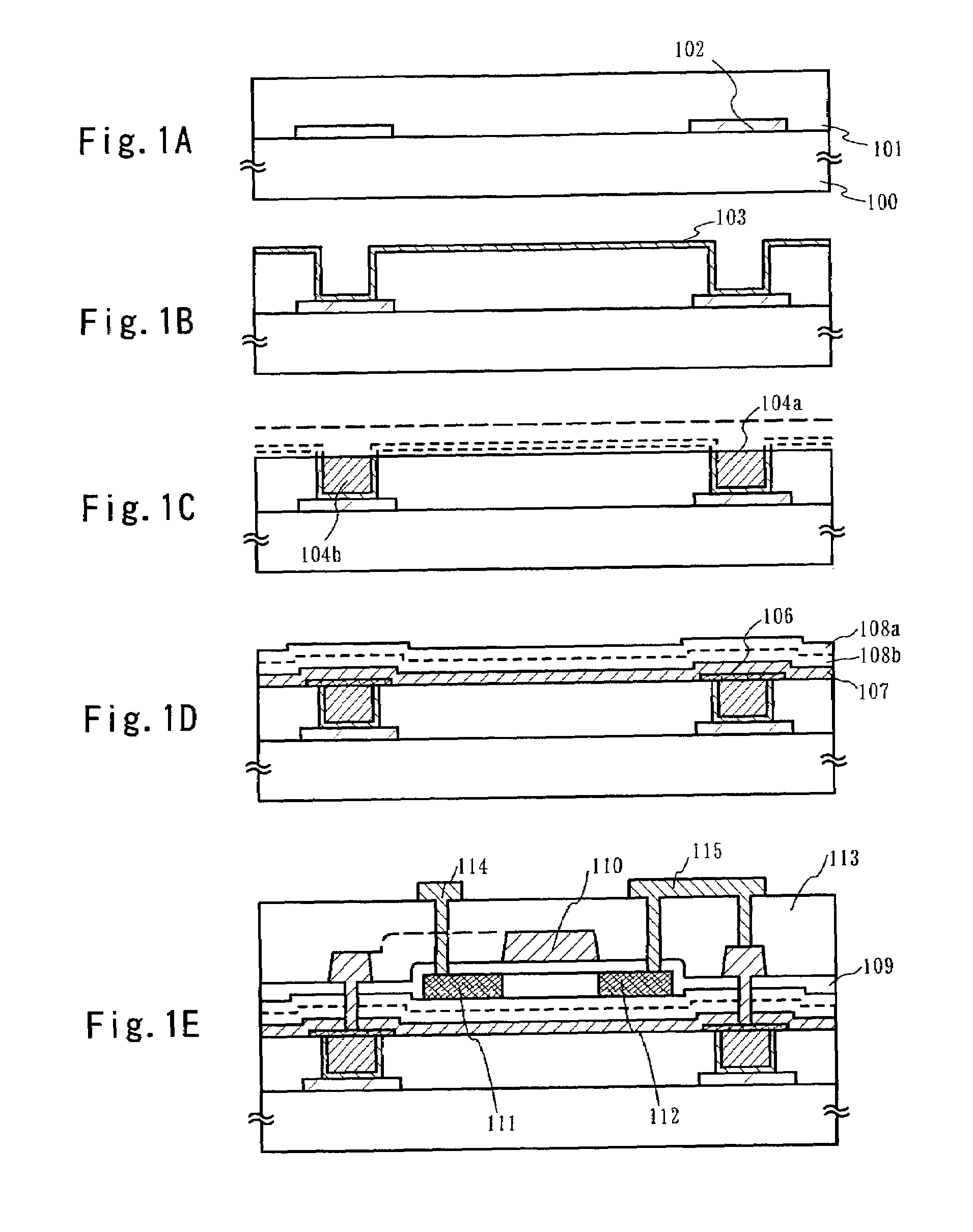

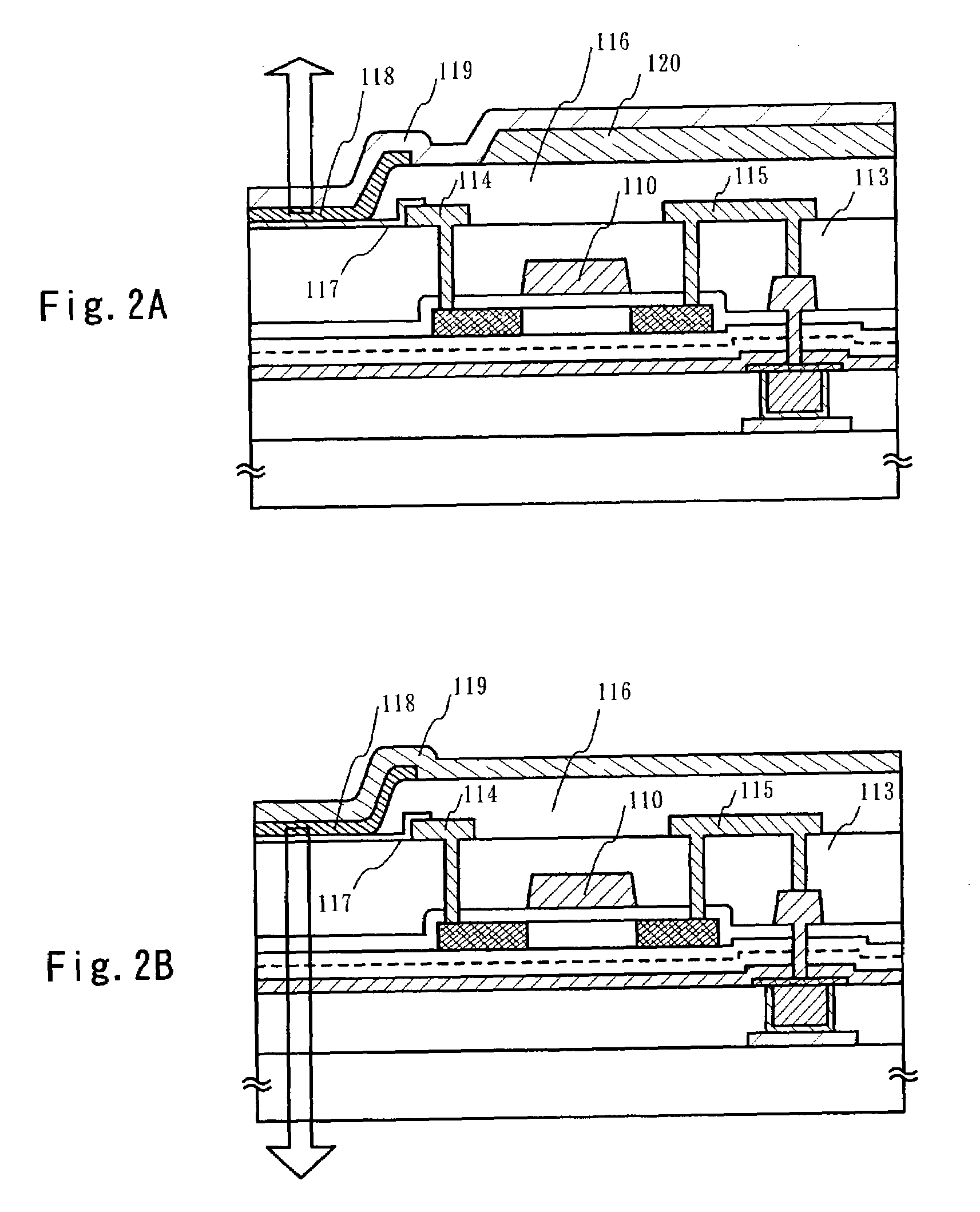

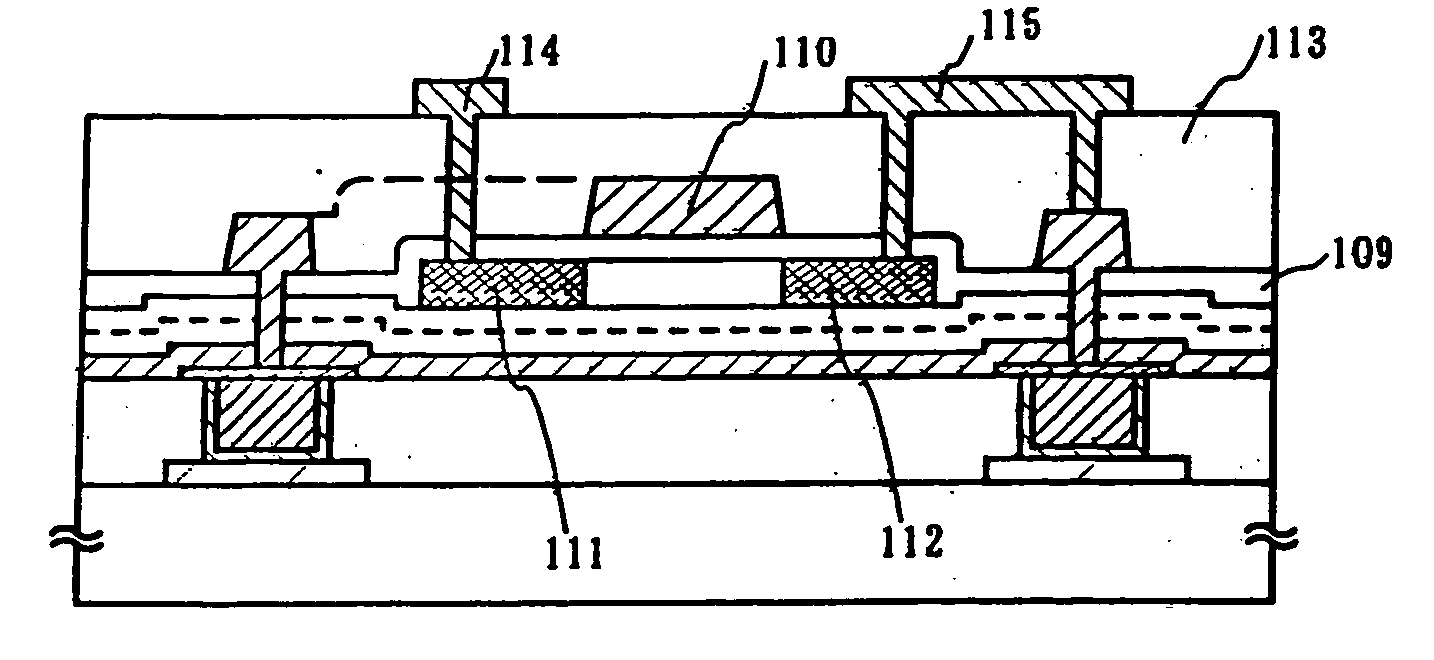

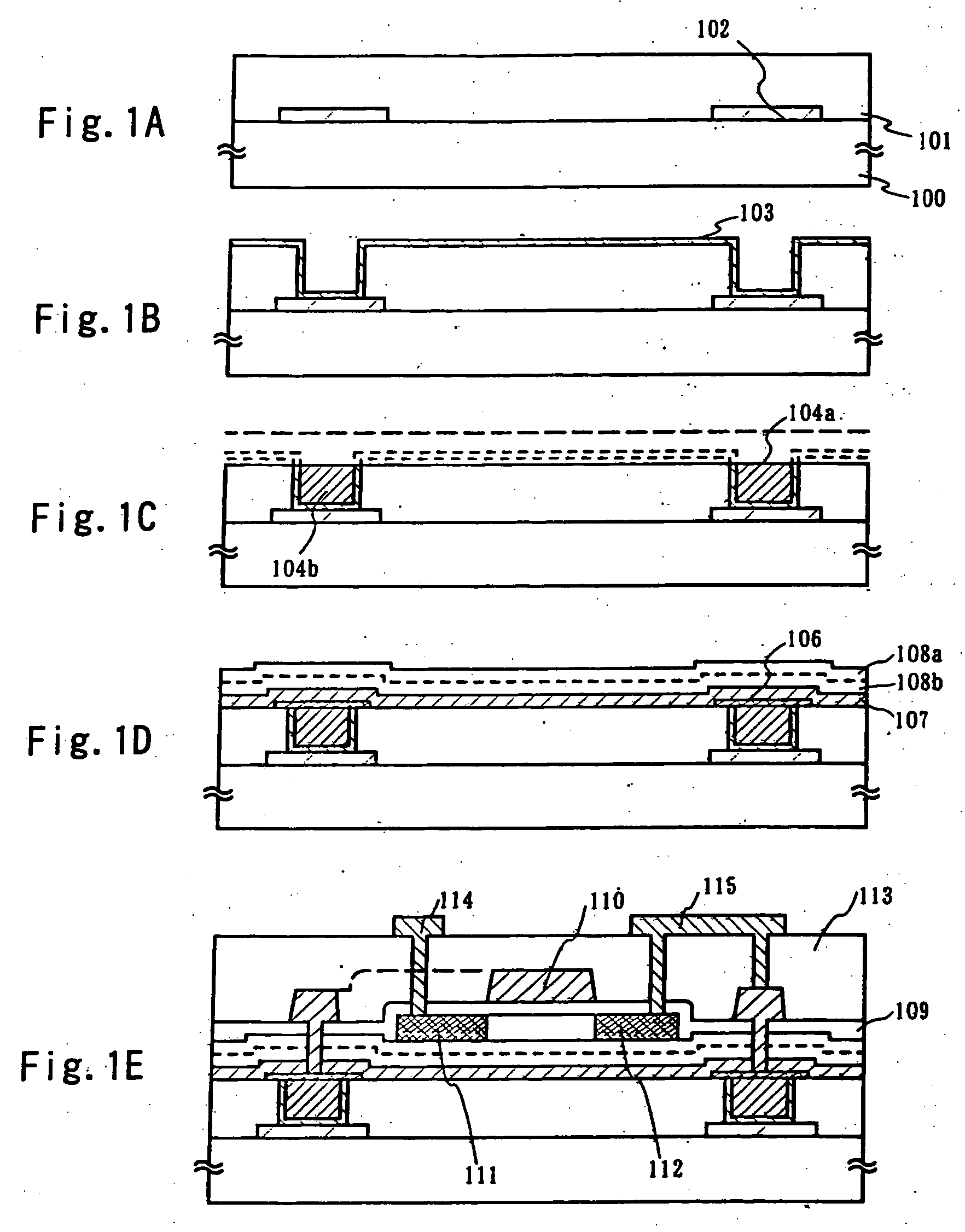

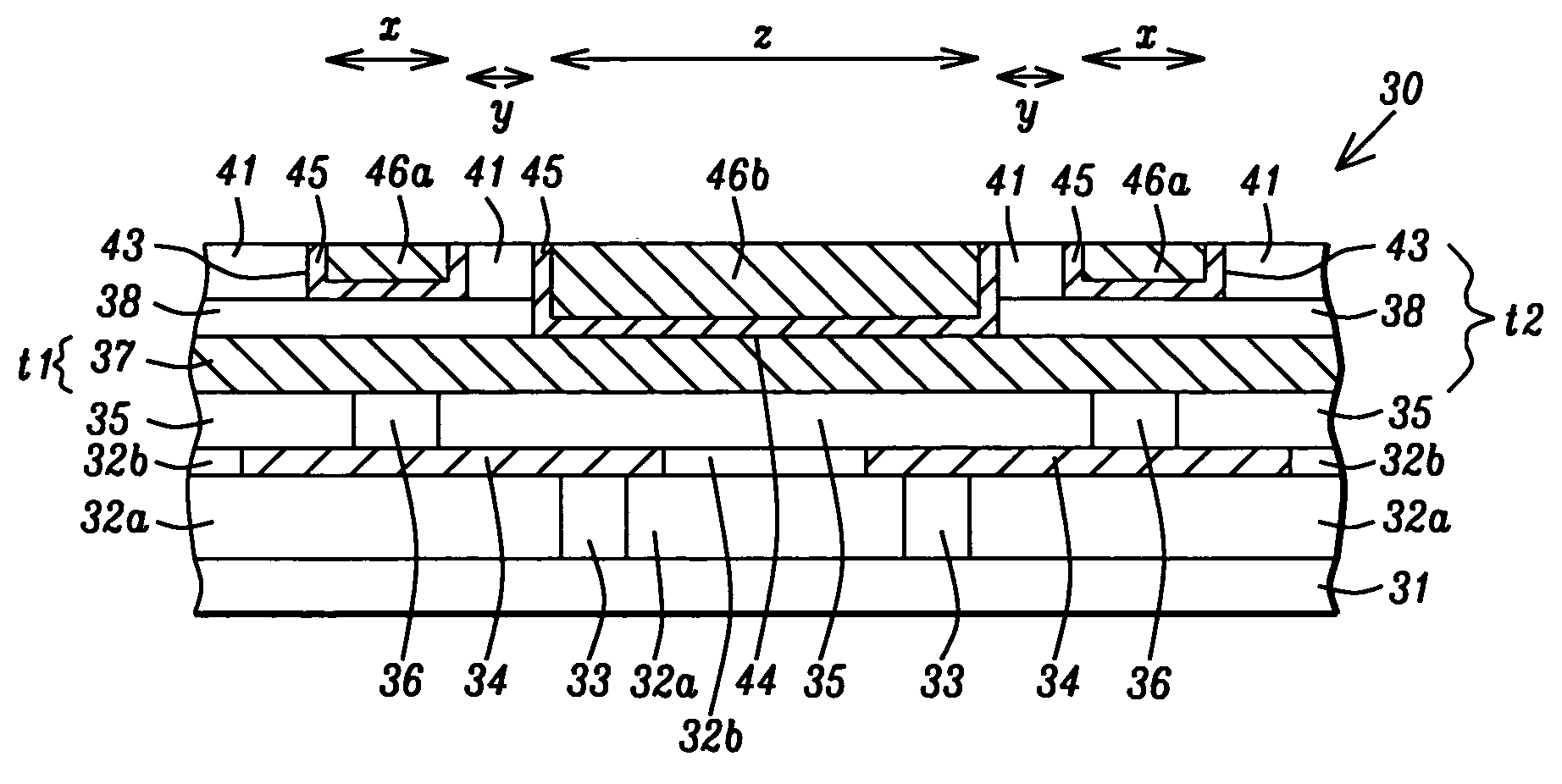

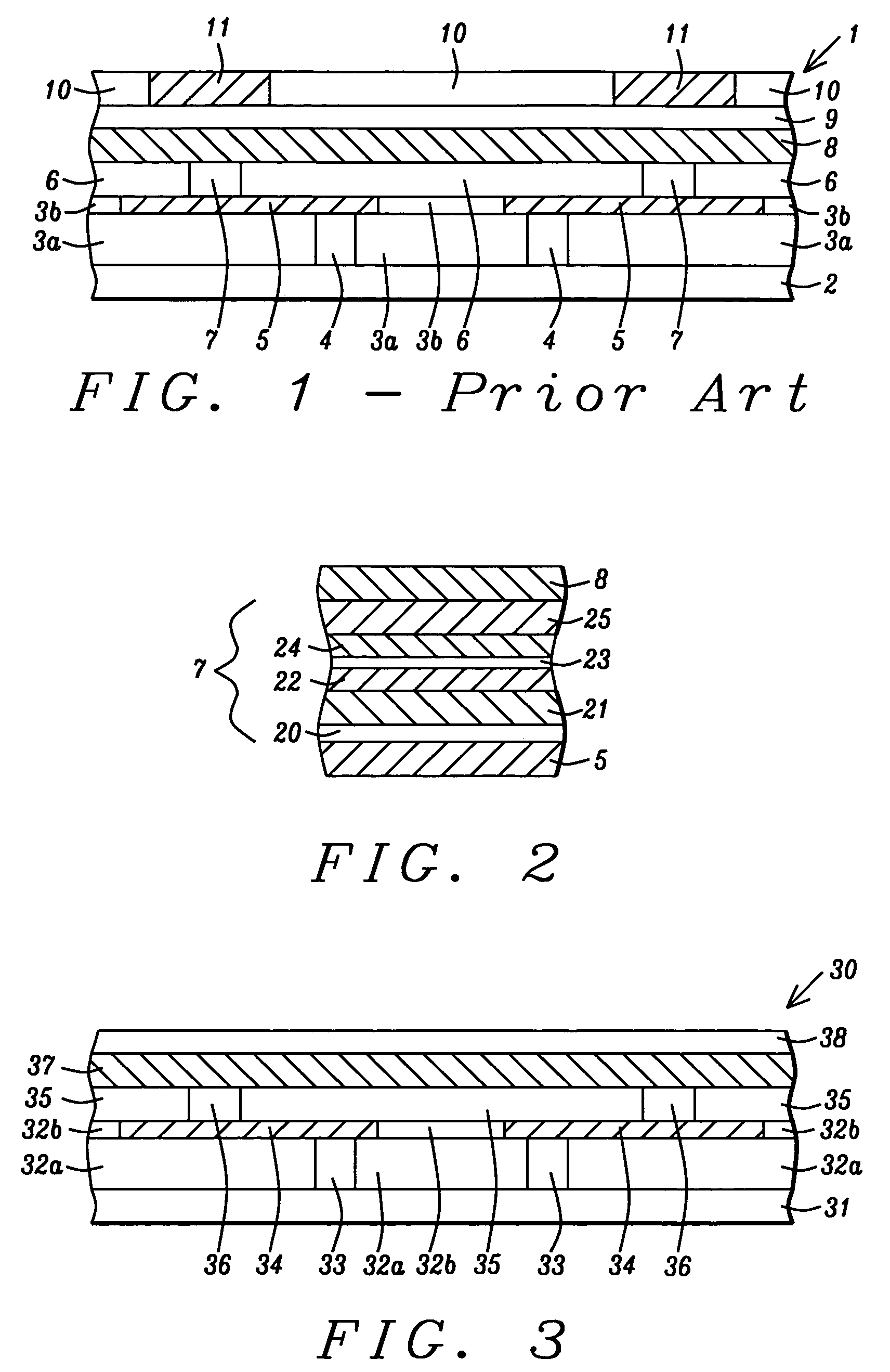

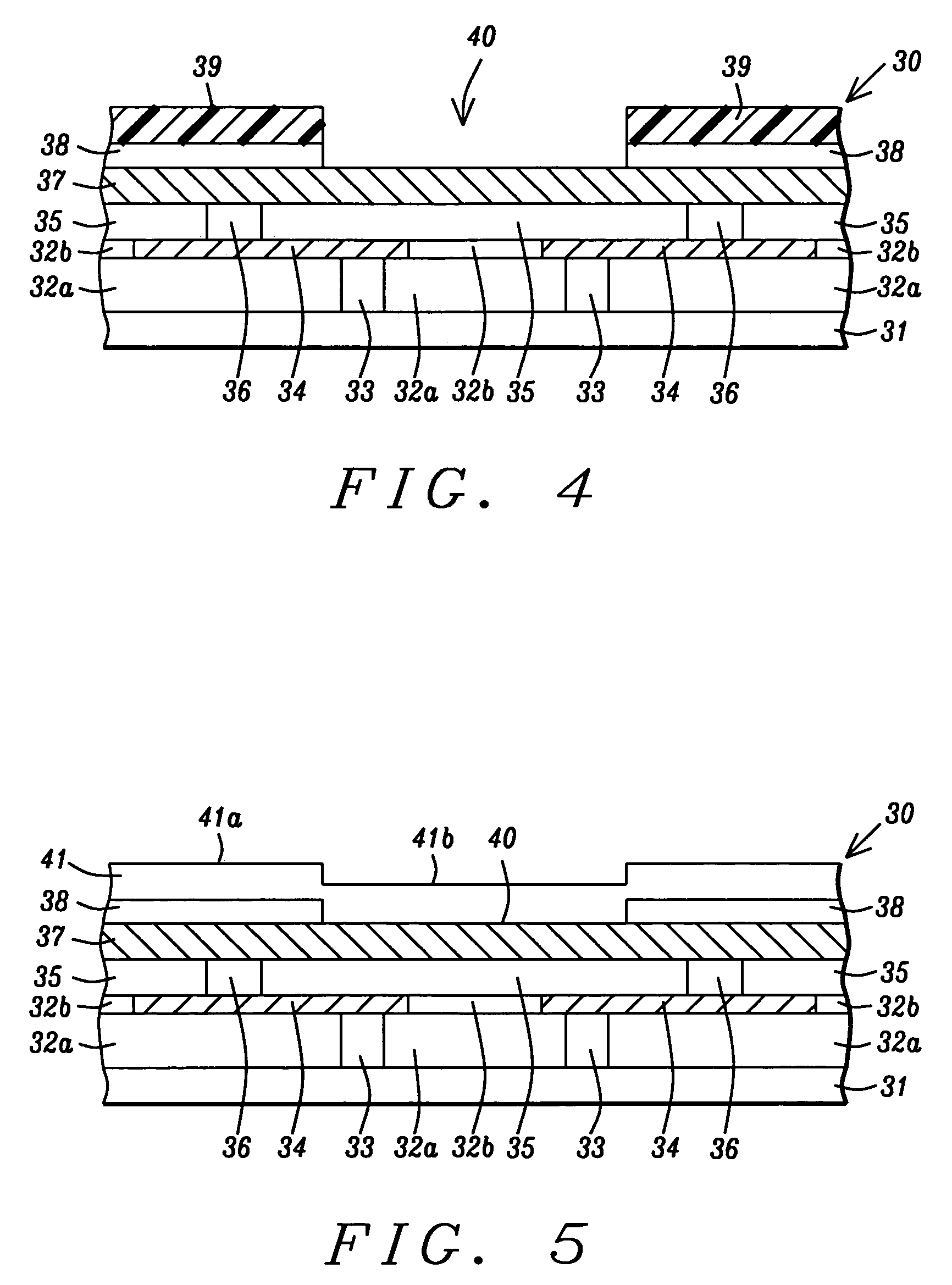

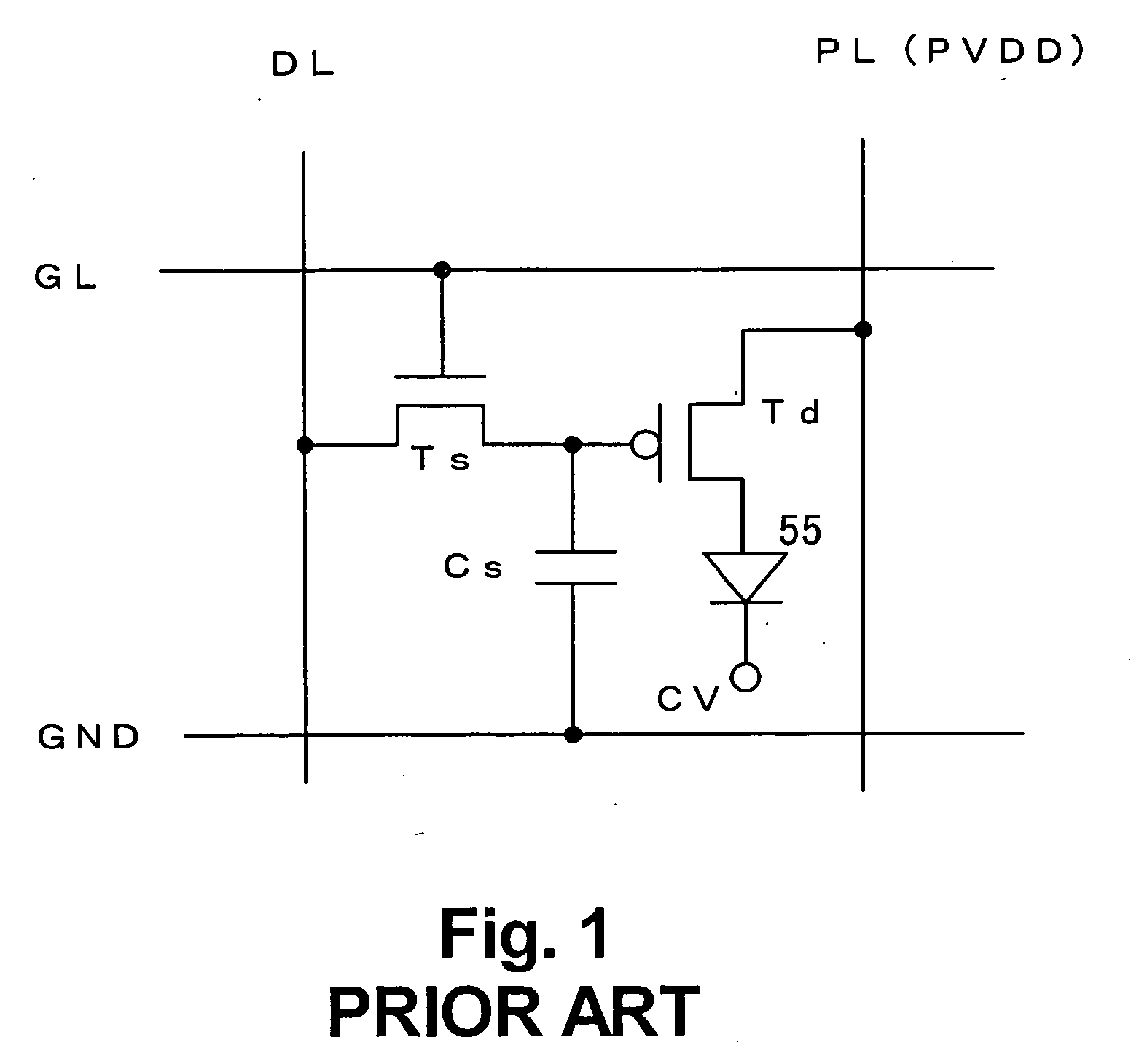

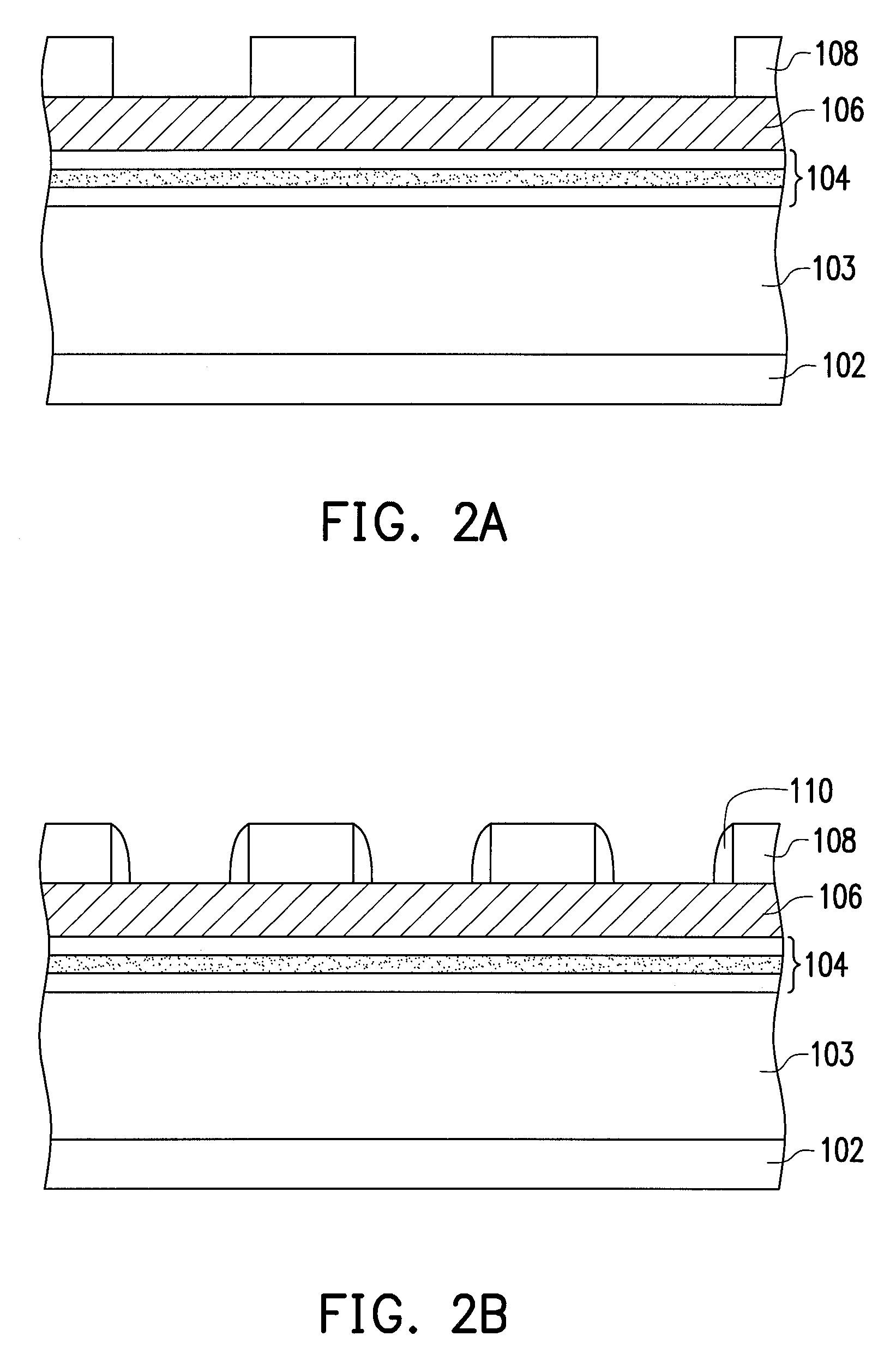

Light-emitting device, liquid-crystal display device and method for manufacturing same

InactiveUS20030193056A1Easy to displayLow line resistanceElectroluminescent light sourcesSolid-state devicesAlloyLight emitting device

The present invention provides a structure of a semiconductor device that realizes low power consumption even where increased in screen size, and a method for manufacturing the same. The invention forms an insulating layer, forms a buried interconnection (of Cu, Au, Ag, Ni, Cr, Pd, Rh, Sn, Pb or an alloy thereof) in the insulating layer. Furthermore, after planarizing the surface of the insulating layer, a metal protection film (Ti, TiN, Ta, TaN or the like) is formed in an exposed part. By using the buried interconnection in part of various lines (gate line, source line, power supply line, common line and the like) for a light-emitting device or liquid-crystal display device, line resistance is decreased.

Owner:SEMICON ENERGY LAB CO LTD

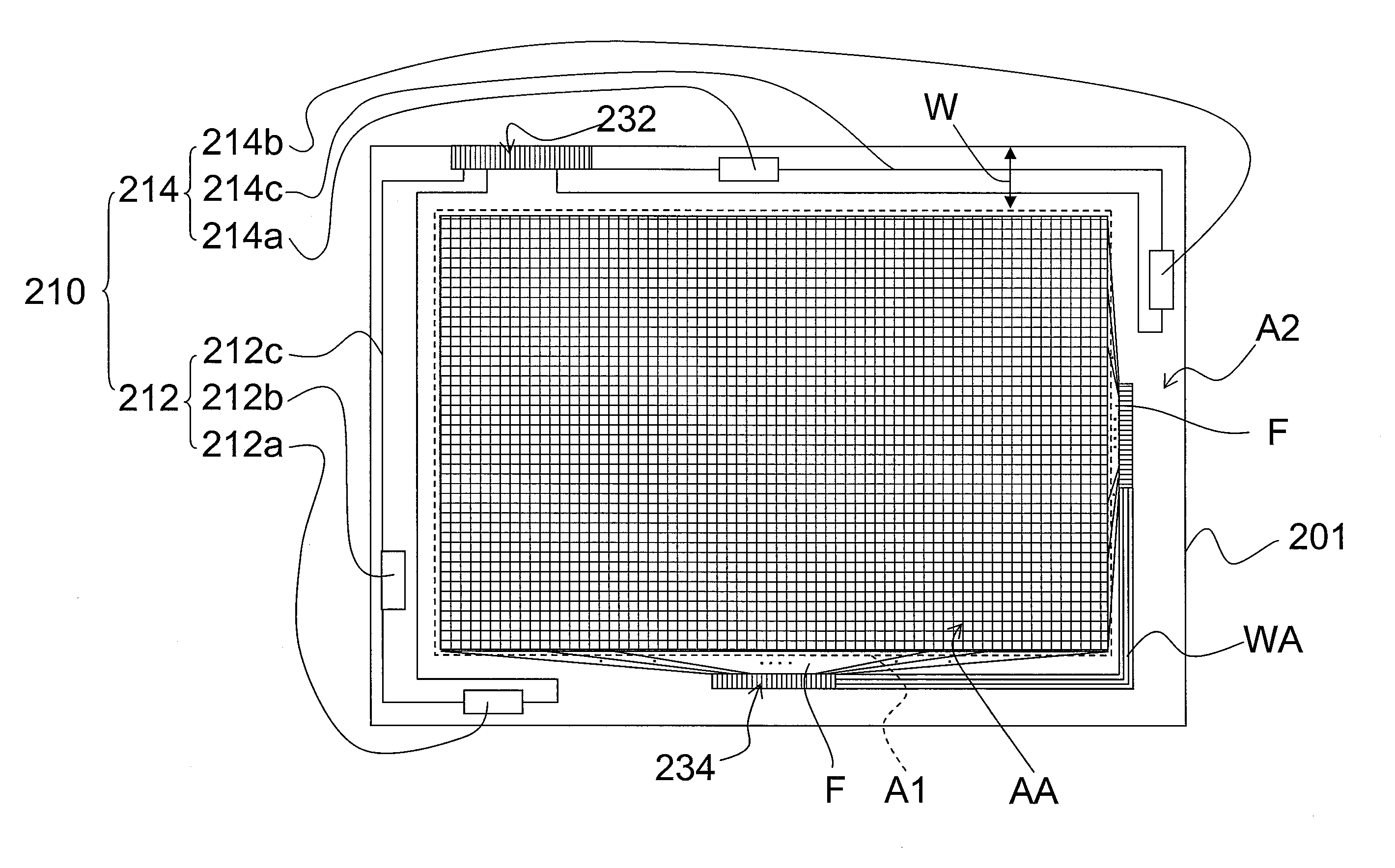

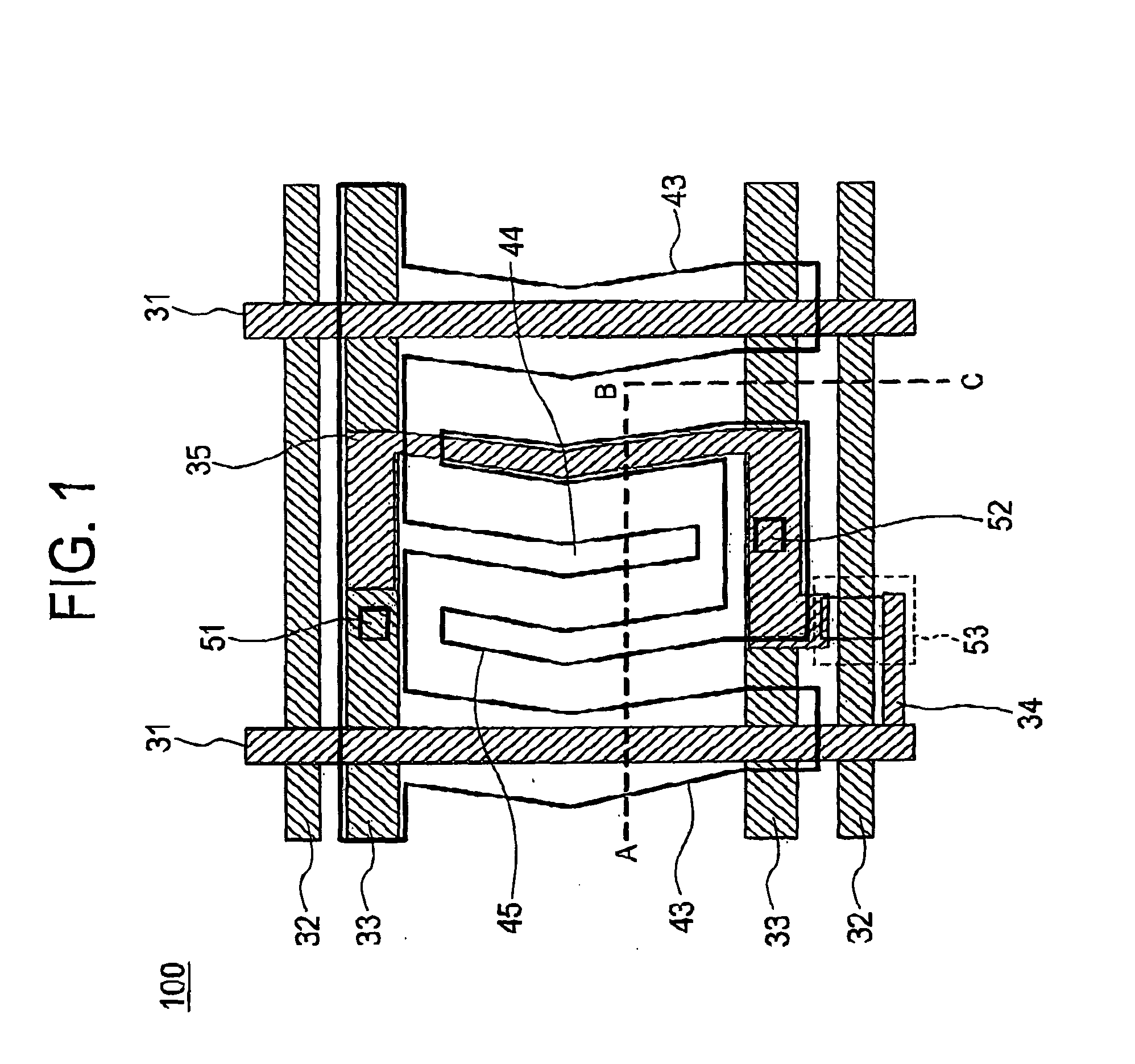

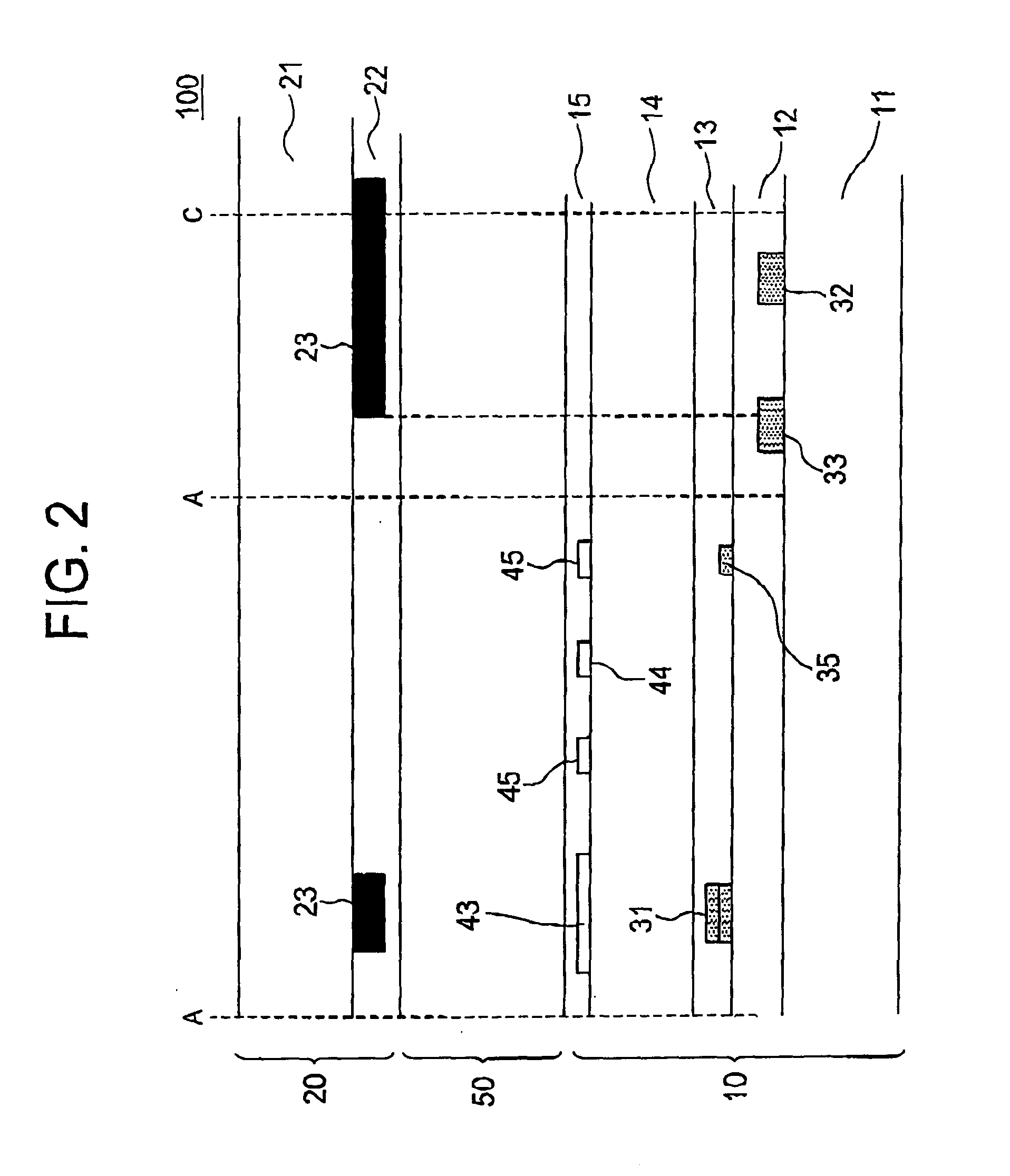

Touch display panel and display apparatus

InactiveUS20110080376A1Manufacturing precision is very highLow transmitting line resistanceStatic indicating devicesNon-linear opticsTouch SensesMedia layer

Owner:AU OPTRONICS CORP

Light-emitting device, liquid-crystal display device and method for manufacturing same

InactiveUS7045861B2Low line resistanceReduce power consumptionElectroluminescent light sourcesSolid-state devicesAlloyLight emitting device

The present invention provides a structure of a semiconductor device that realizes low power consumption even where increased in screen size, and a method for manufacturing the same. The invention forms an insulating layer, forms a buried interconnection (of Cu, Au, Ag, Ni, Cr, Pd, Rh, Sn, Pb or an alloy thereof) in the insulating layer. Furthermore, after planarizing the surface of the insulating layer, a metal protection film (Ti, TiN, Ta, TaN or the like) is formed in an exposed part. By using the buried interconnection in part of various lines (gate line, source line, power supply line, common line and the like) for a light-emitting device or liquid-crystal display device, line resistance is decreased.

Owner:SEMICON ENERGY LAB CO LTD

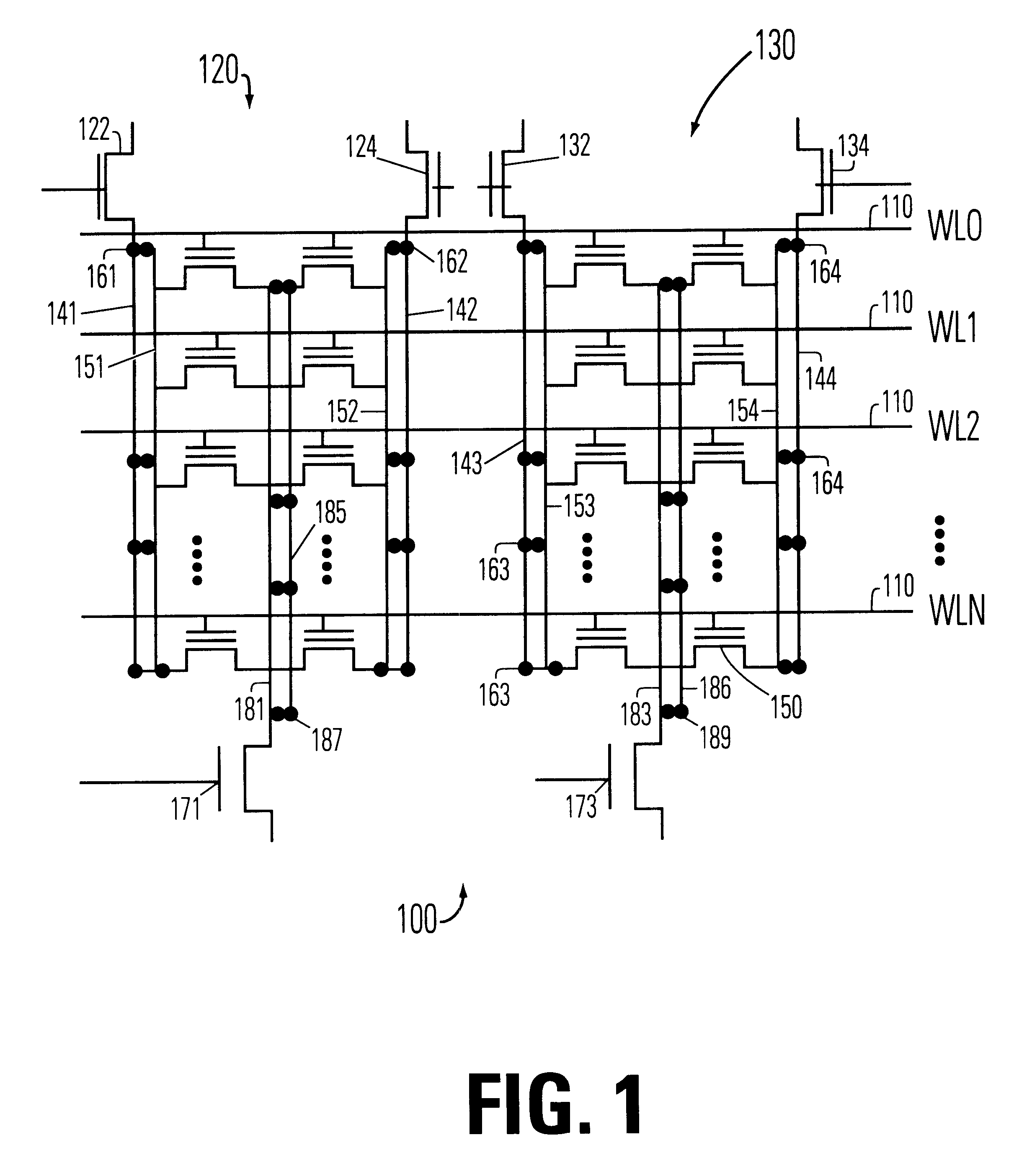

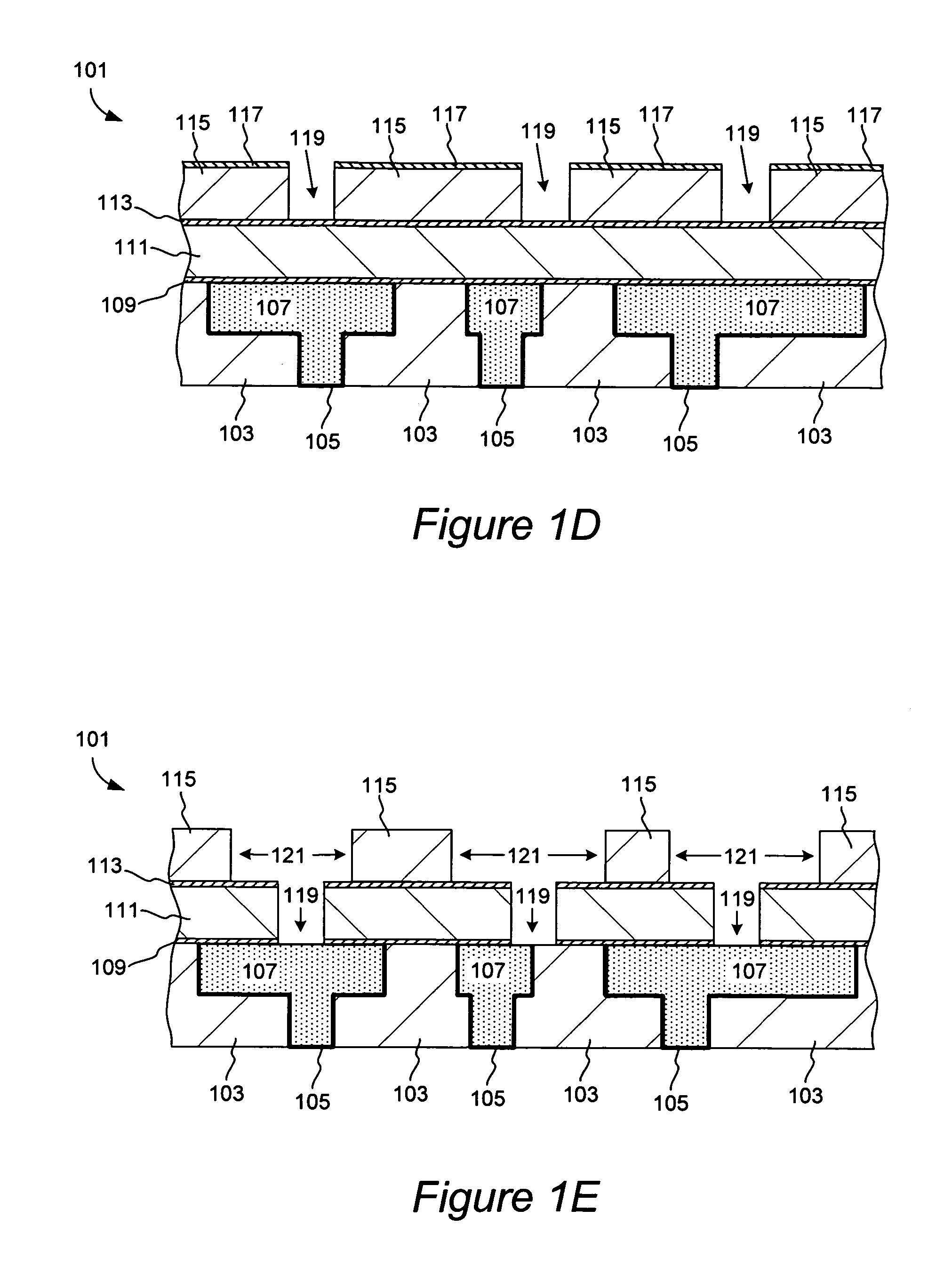

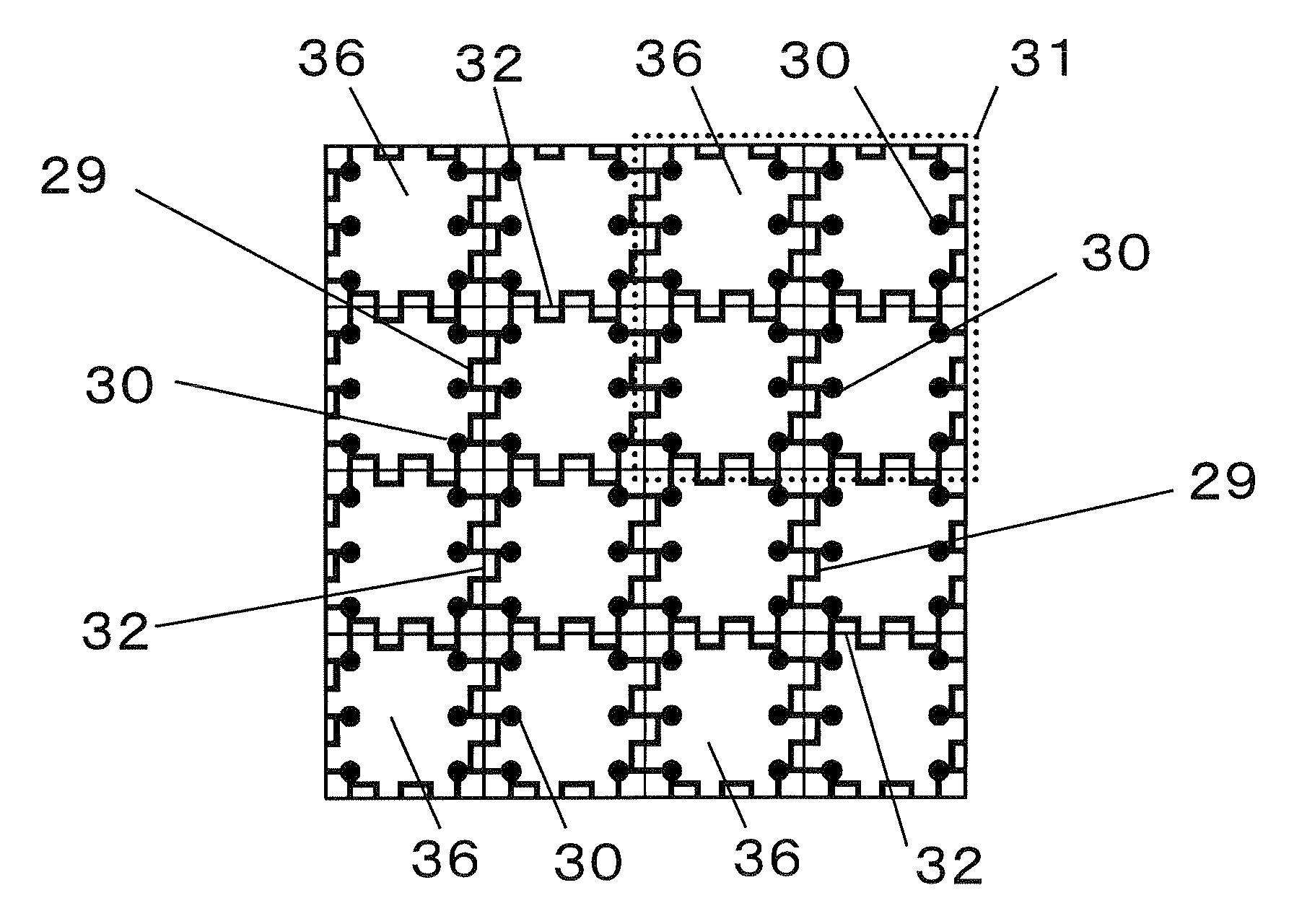

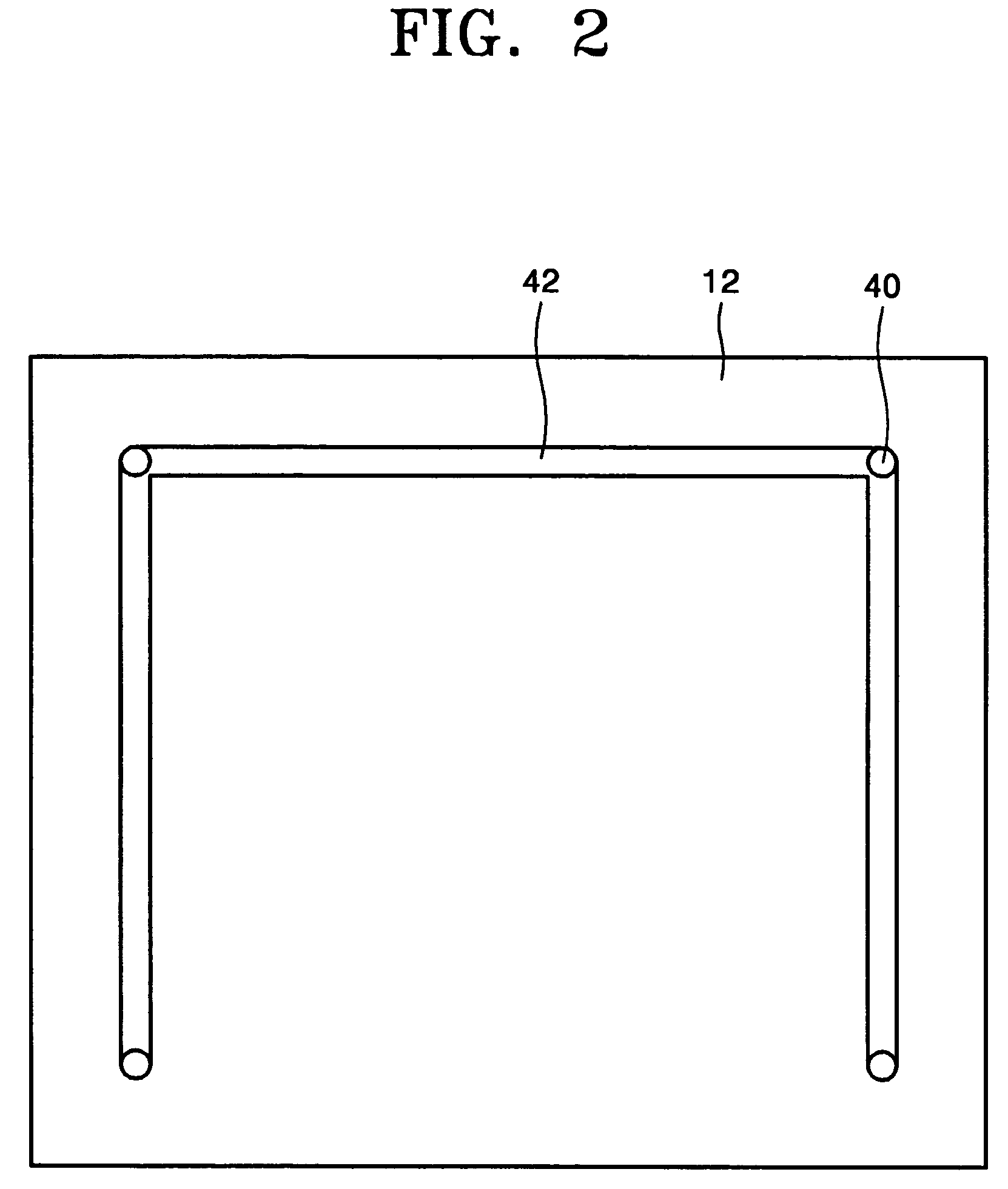

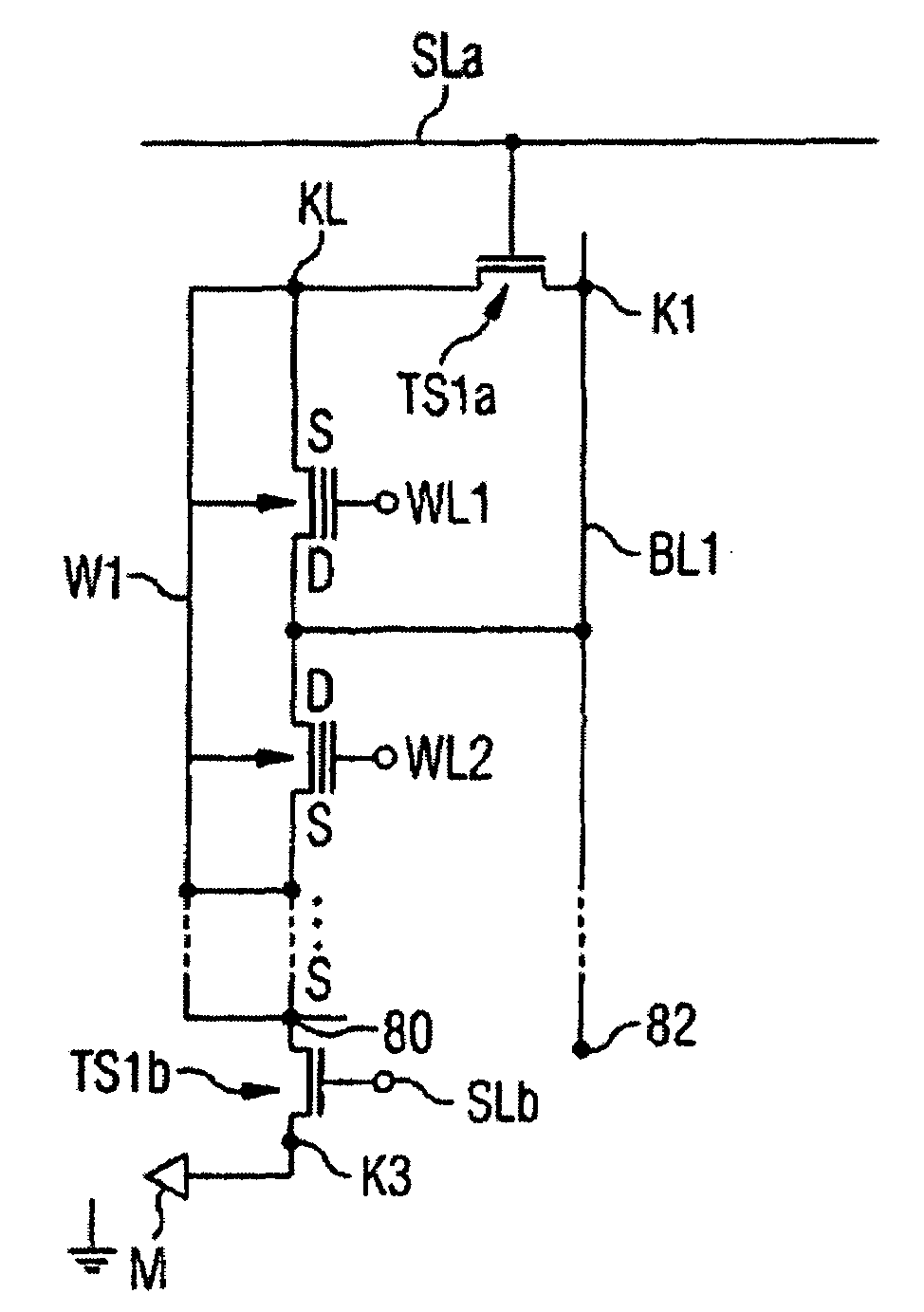

Word and bit line arrangement for a FinFET semiconductor memory

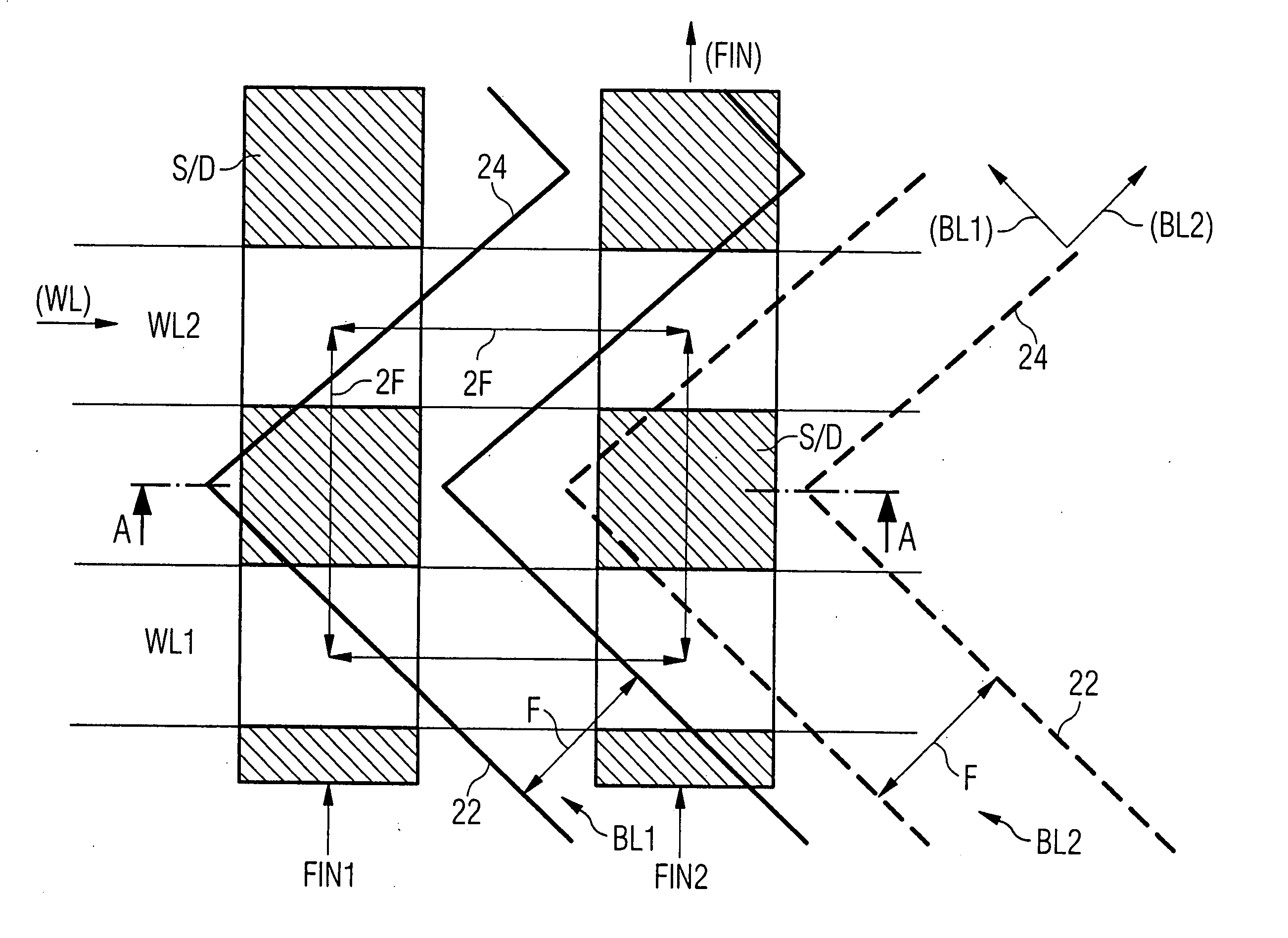

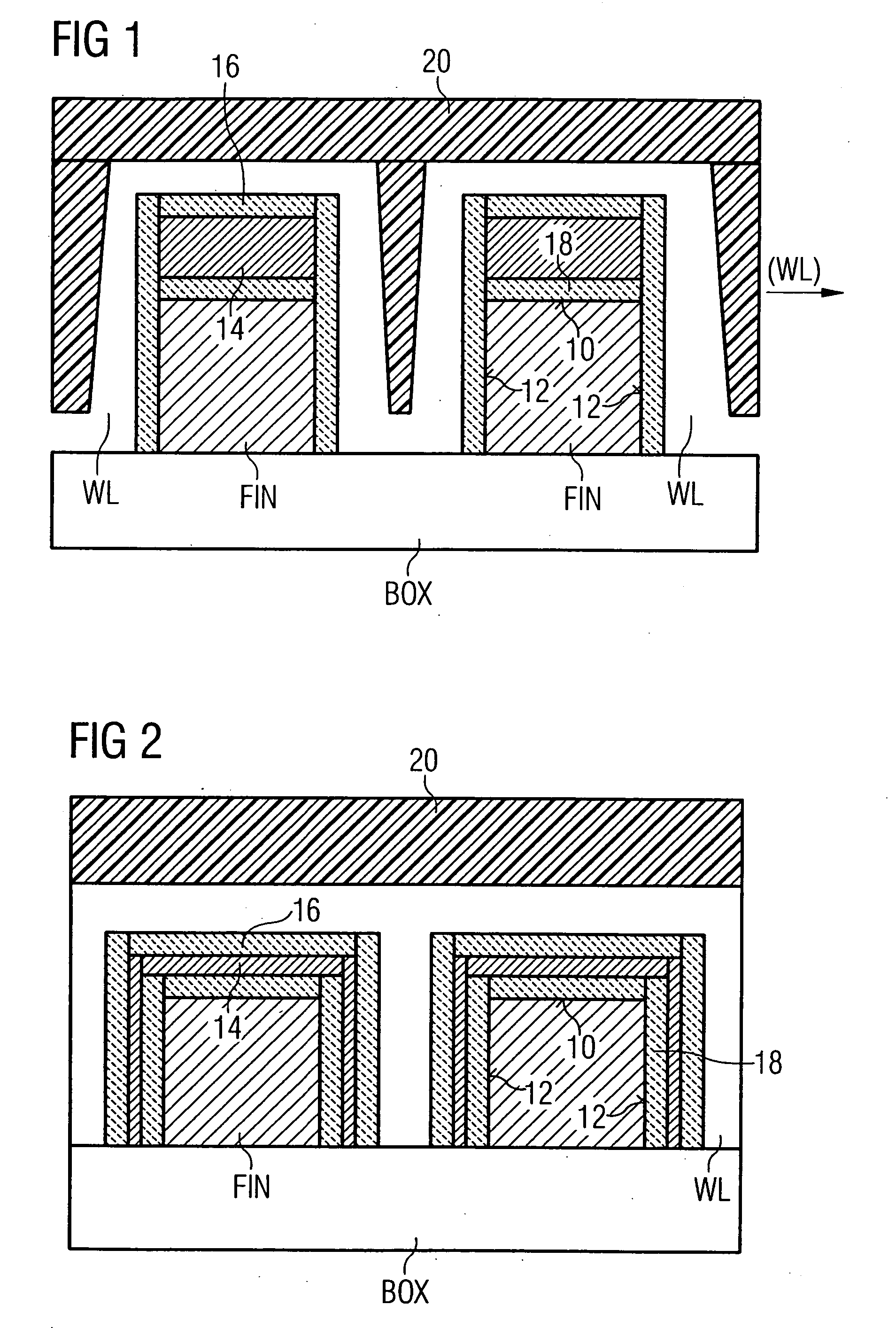

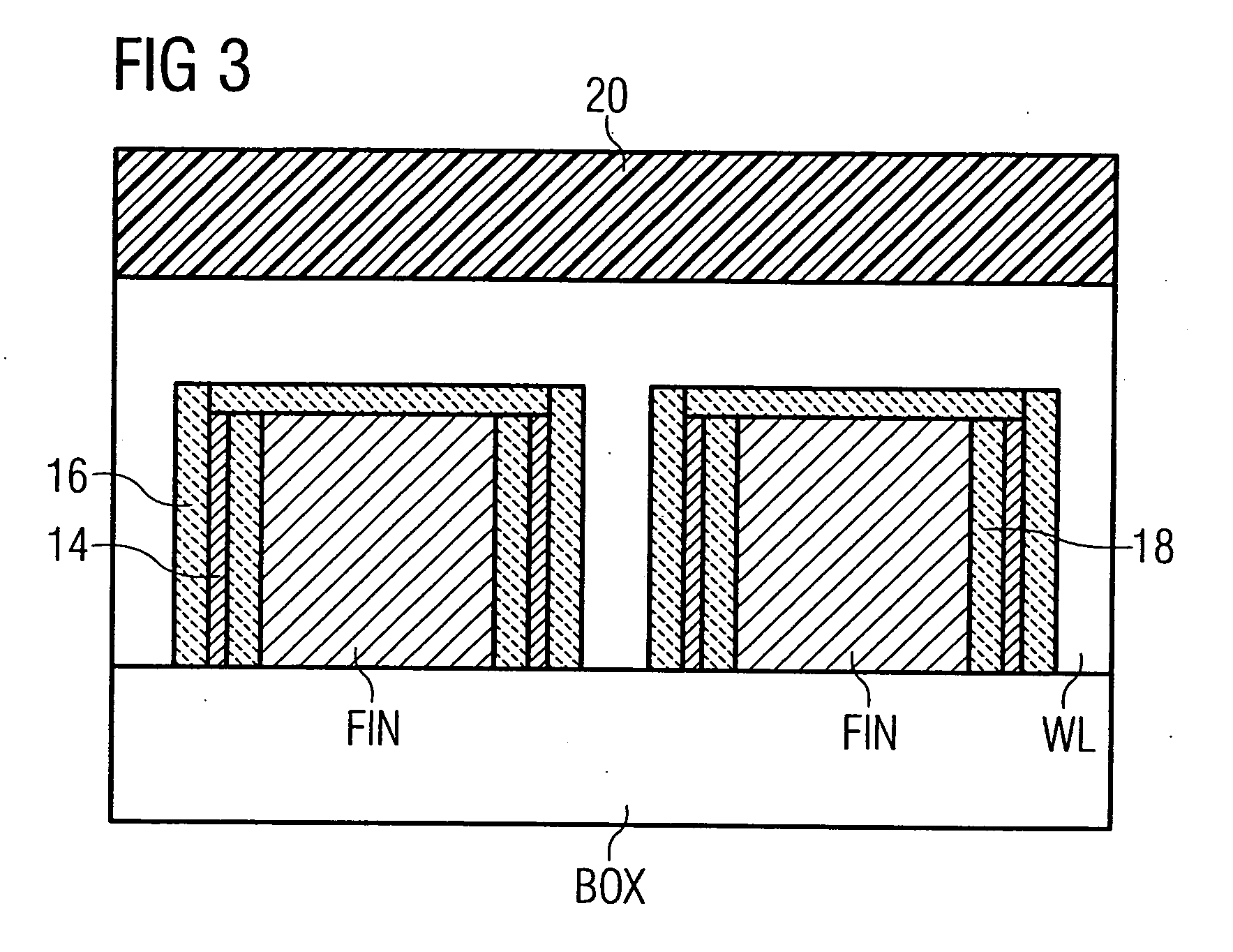

InactiveUS20050199913A1Improve good performanceImprove storage densityTransistorSolid-state devicesBit lineSemiconductor materials

The invention relates to a semiconductor memory having a multiplicity of fins made of semiconductor material which are spaced apart from one another, a multiplicity of channel regions and contact regions being formed in each of the fins, a multiplicity of word lines, a multiplicity of storage layers, at least one of the storage layers being arranged between each of the channel regions and the word line, and a multiplicity of bit lines, the longitudinal axes of first bit line portions running parallel to a first bit line direction and the longitudinal axes of second bit line portions running parallel to a second bit line direction, the second bit line direction being rotated relative to the first bit line direction, each of the bit lines being electrically connected to a multiplicity of the contact regions, wherein, between two contact regions of the same fin that are connected to one of the bit lines, a contact region is not connected to the respective bit line.

Owner:INFINEON TECH AG

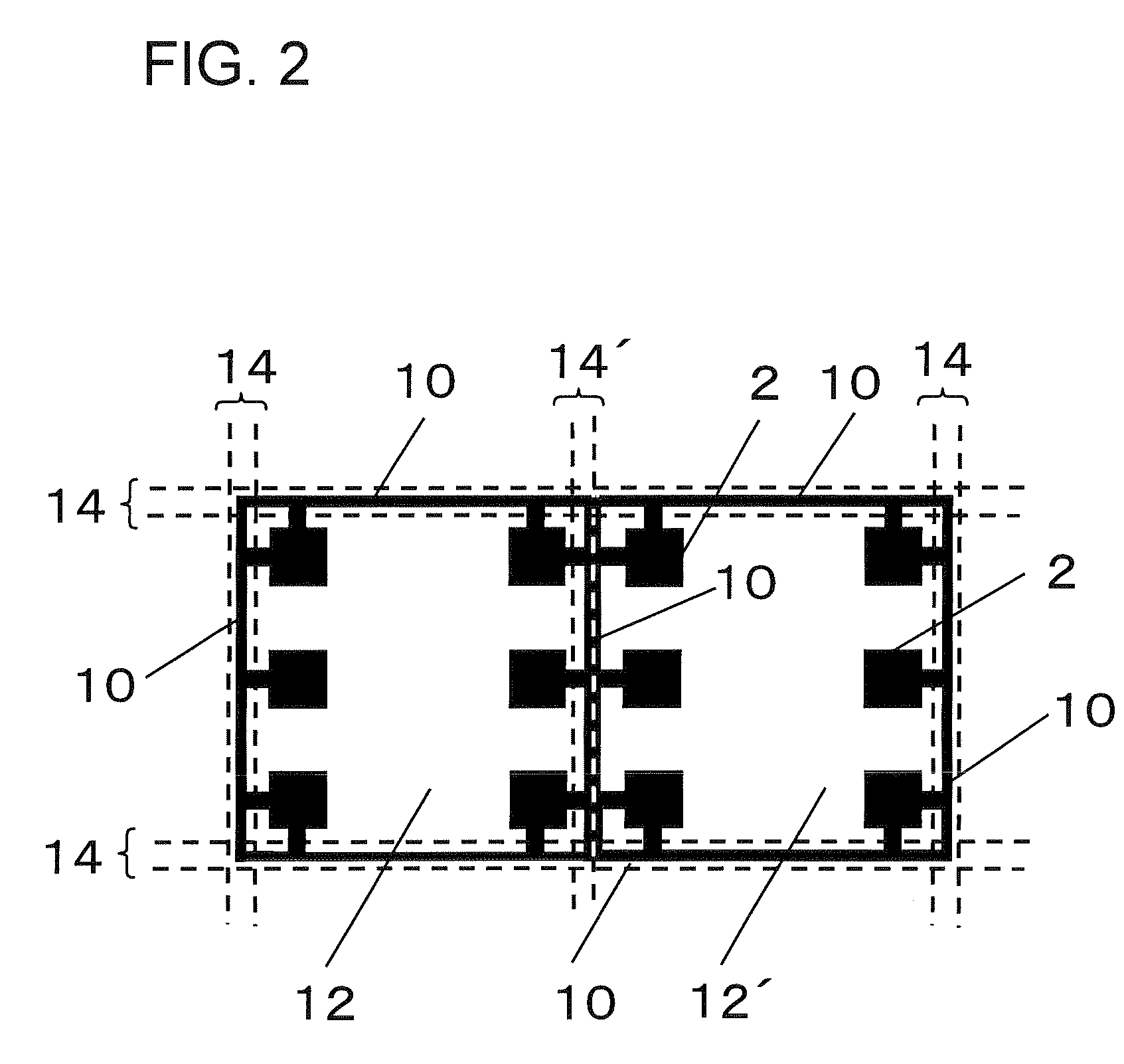

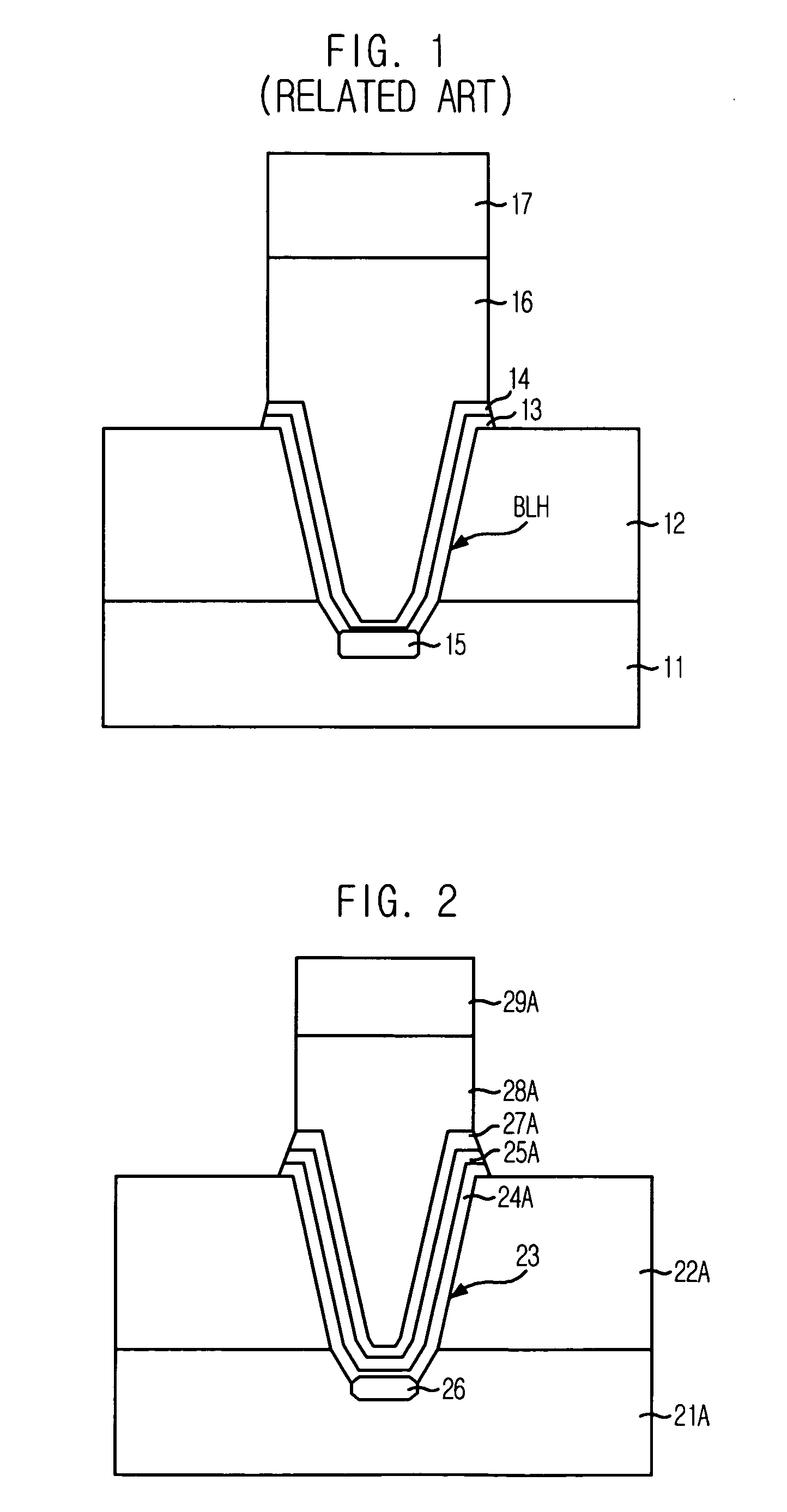

Contact array structure for buried type transistor

InactiveUS6459119B1Low line resistanceIncrease currentTransistorSolid-state devicesTime distributionHot electron

Systems and methods are described for providing an array of buried transistor cells with at least one contact array structure. A contact array structure for a buried type transistor array includes a first diffusion bit line coupled to the plurality of transistors; a first plurality of contacts coupled to the source diffusion bit line; and a first conductor coupled to the first plurality of contacts. The systems and methods provide advantages in that the diffusion line resistance is reduced, the read current and speed are reduced, and the voltage-time distribution is tightened when writing by hot electron programming.

Owner:MACRONIX INT CO LTD

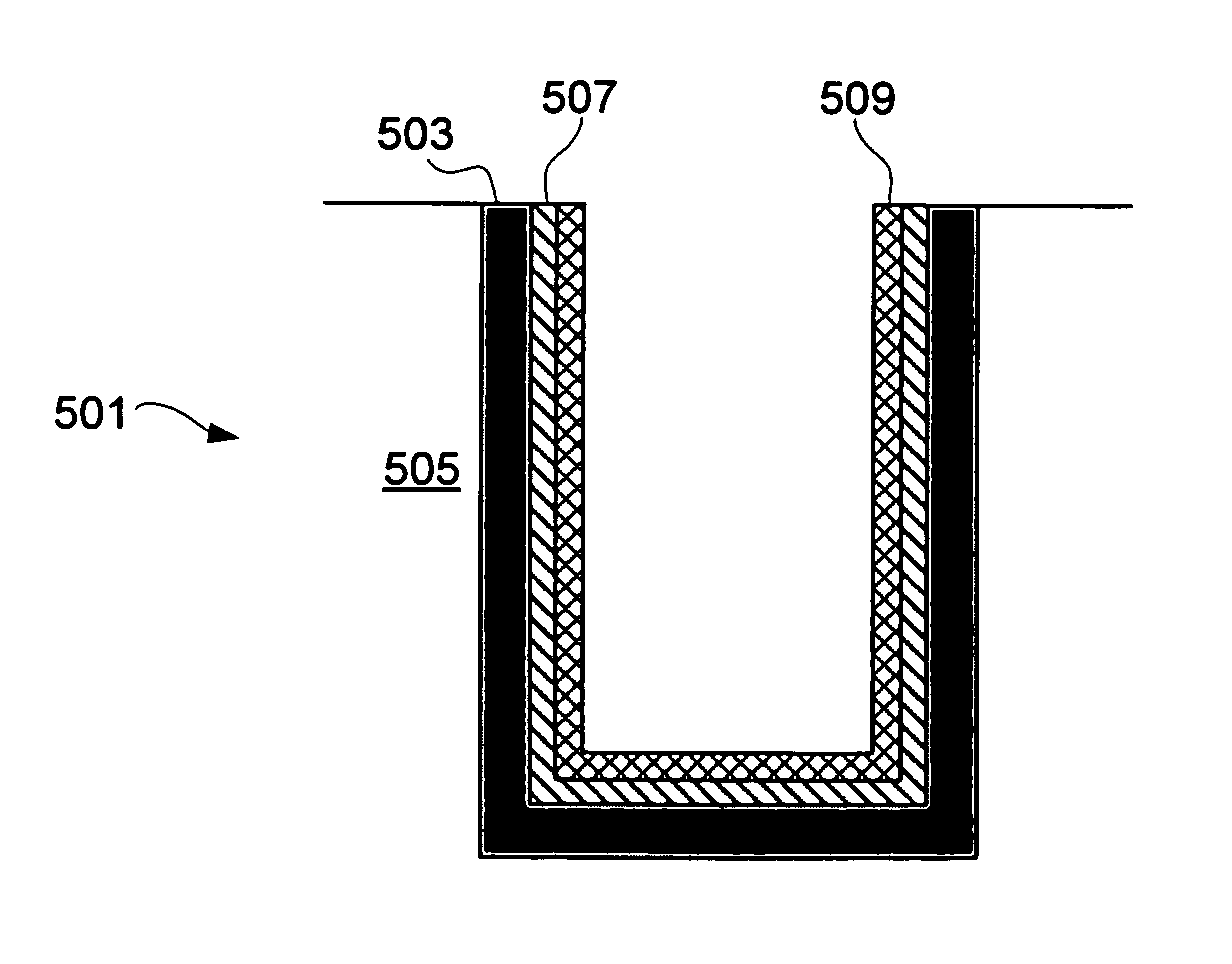

Deposition of doped copper seed layers having improved reliability

InactiveUS8017523B1Reduced line resistance increaseImprove performanceSemiconductor/solid-state device detailsSolid-state devicesLine resistanceCopper interconnect

Improved methods of depositing copper seed layers in copper interconnect structure fabrication processes are provided. Also provided are the resulting structures, which have improved electromigration performance and reduced line resistance. According to various embodiments, the methods involve depositing a copper seed bilayer on a barrier layer in a recessed feature on a partially fabricated semiconductor substrate. The bilayer has a copper alloy seed layer and a pure copper seed layer, with the pure copper seed layer is deposited on the copper alloy seed layer. The copper seed bilayers have reduced line resistance increase and better electromigration performance than conventional doped copper seed layers. Precise line resistance control is achieved by tuning the bilayer thickness to meet the desired electromigration performance.

Owner:NOVELLUS SYSTEMS

Light-emitting device, liquid-crystal display device and method for manufacturing same

InactiveUS20060186441A1Low line resistanceReduce power consumptionTransistorElectroluminescent light sourcesDevice materialAlloy

The present invention provides a structure of a semiconductor device that realizes low power consumption even where increased in screen size, and a method for manufacturing the same. The invention forms an insulating layer, forms a buried interconnection (of Cu, Au, Ag, Ni, Cr, Pd, Rh, Sn, Pb or an alloy thereof) in the insulating layer. Furthermore, after planarizing the surface of the insulating layer, a metal protection film (Ti, TiN, Ta, TaN or the like) is formed in an exposed part. By using the buried interconnection in part of various lines (gate line, source line, power supply line, common line and the like) for a light-emitting device or liquid crystal display device, line resistance is decreased.

Owner:SEMICON ENERGY LAB CO LTD

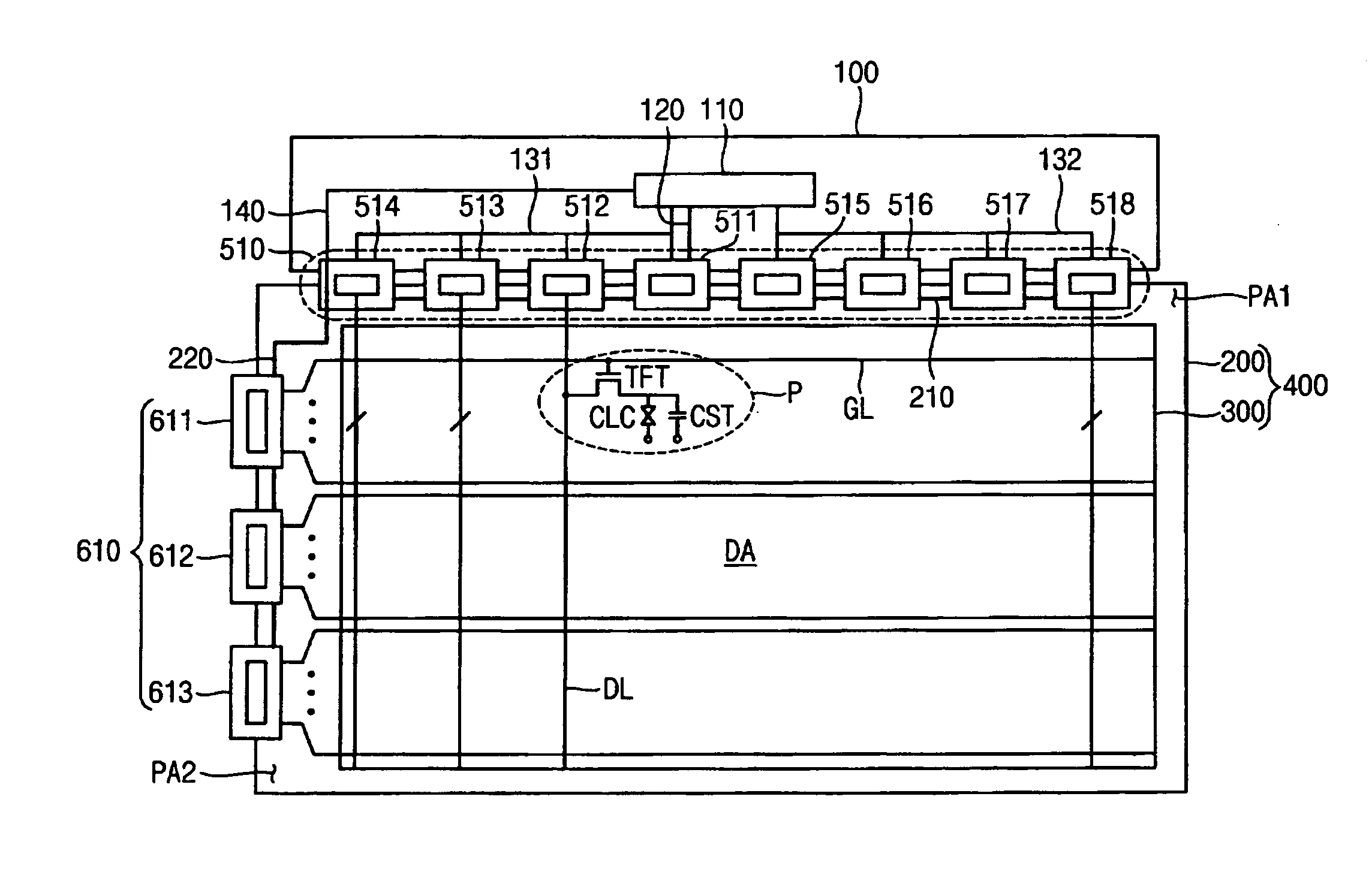

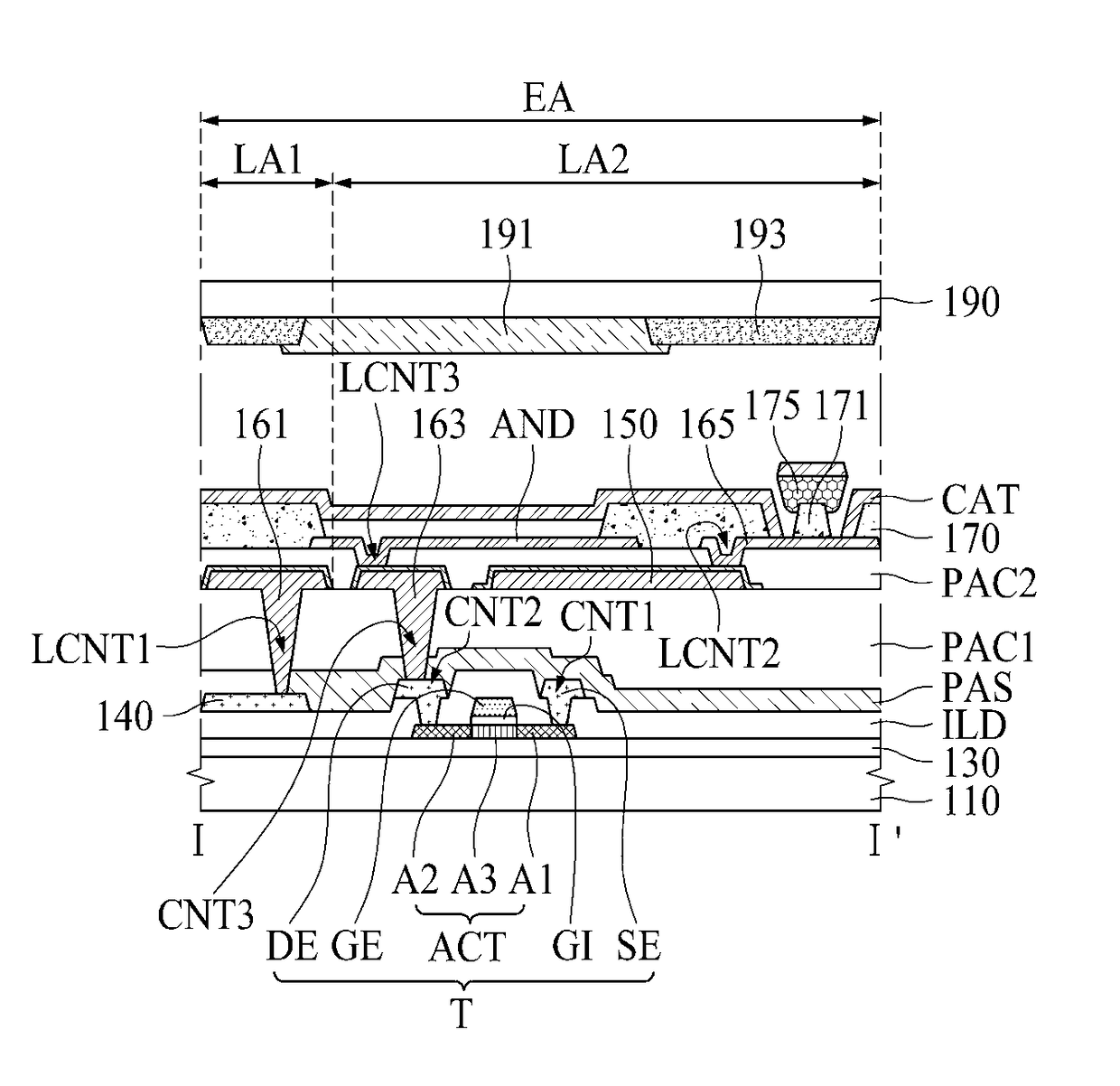

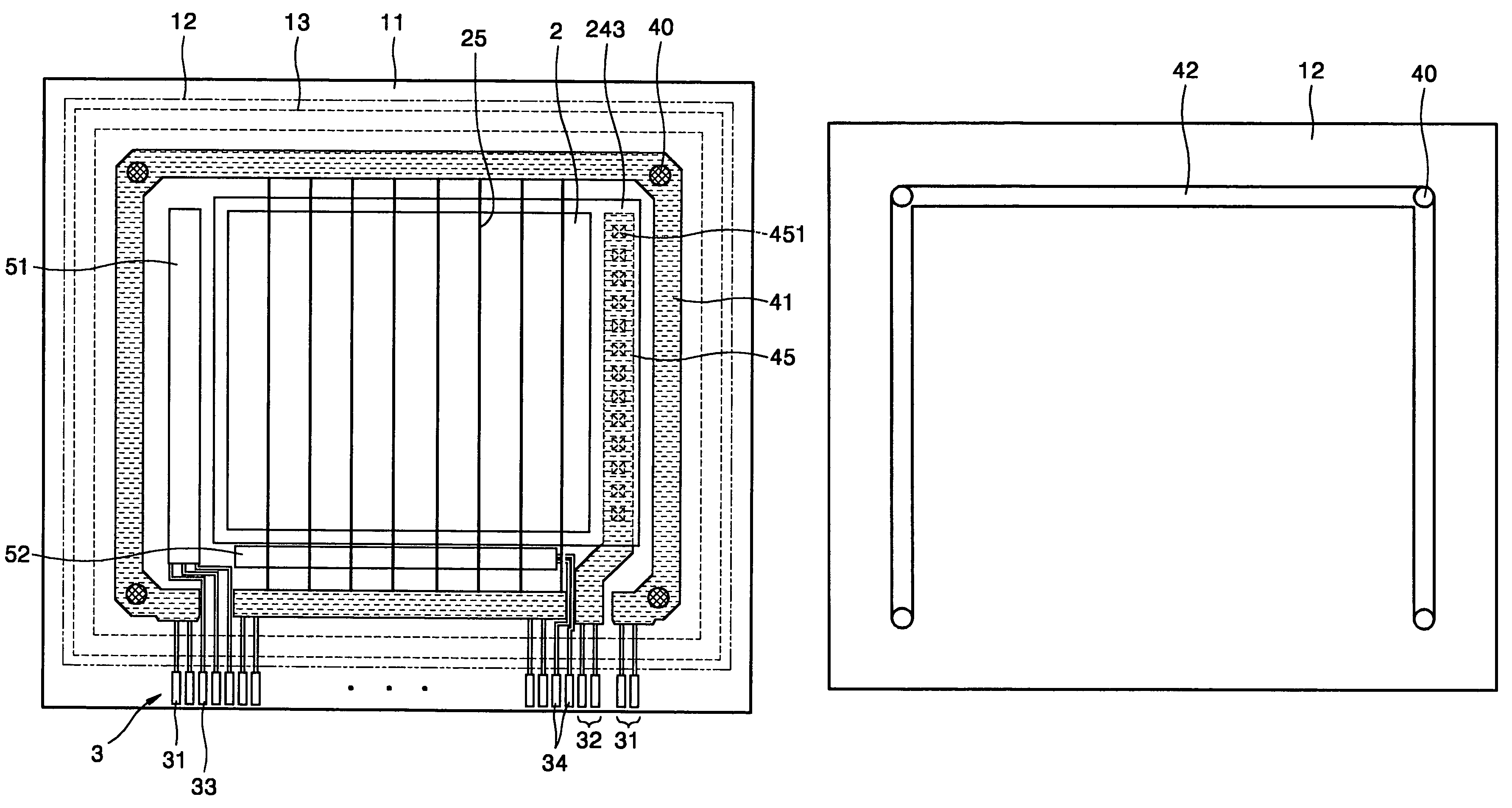

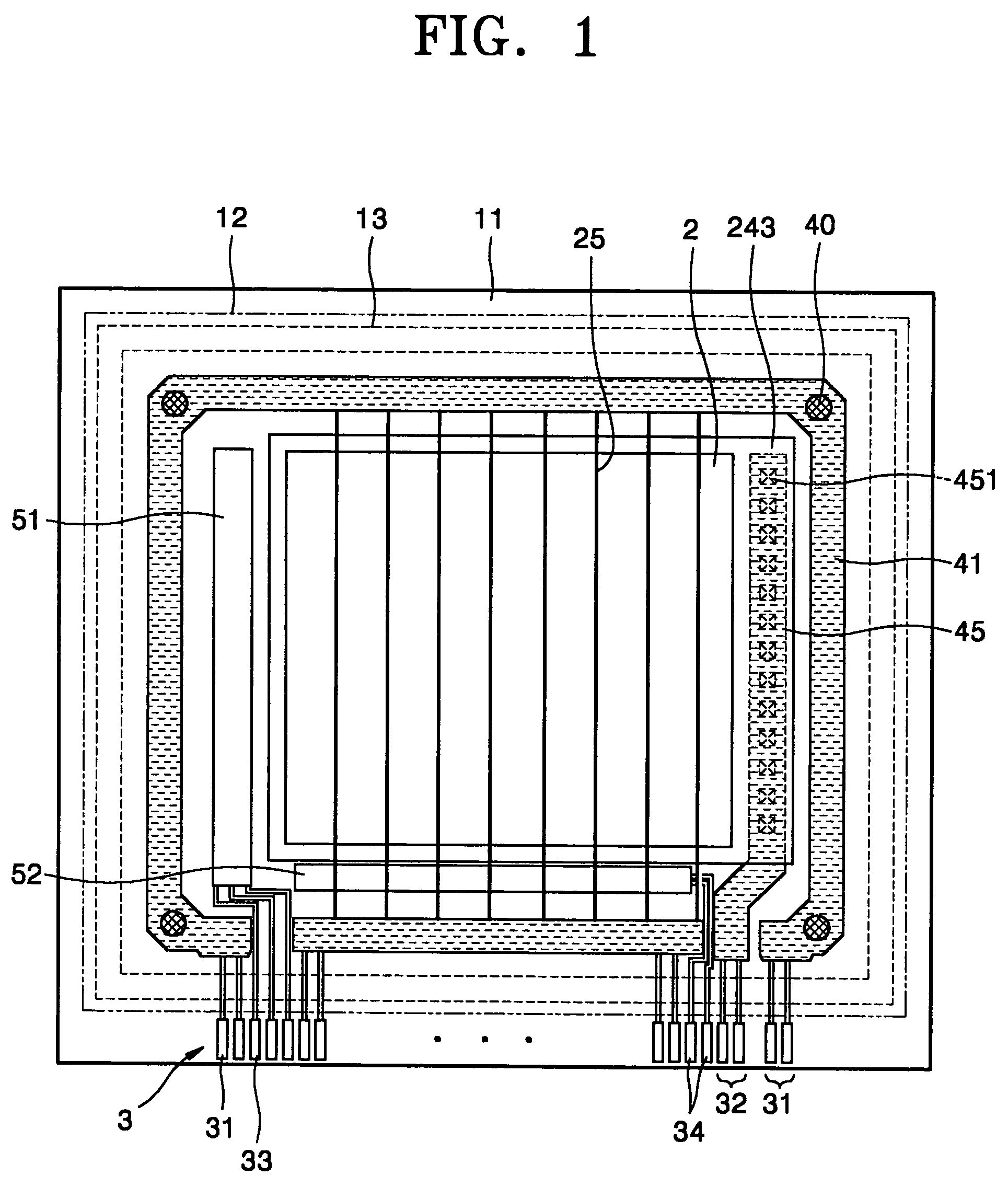

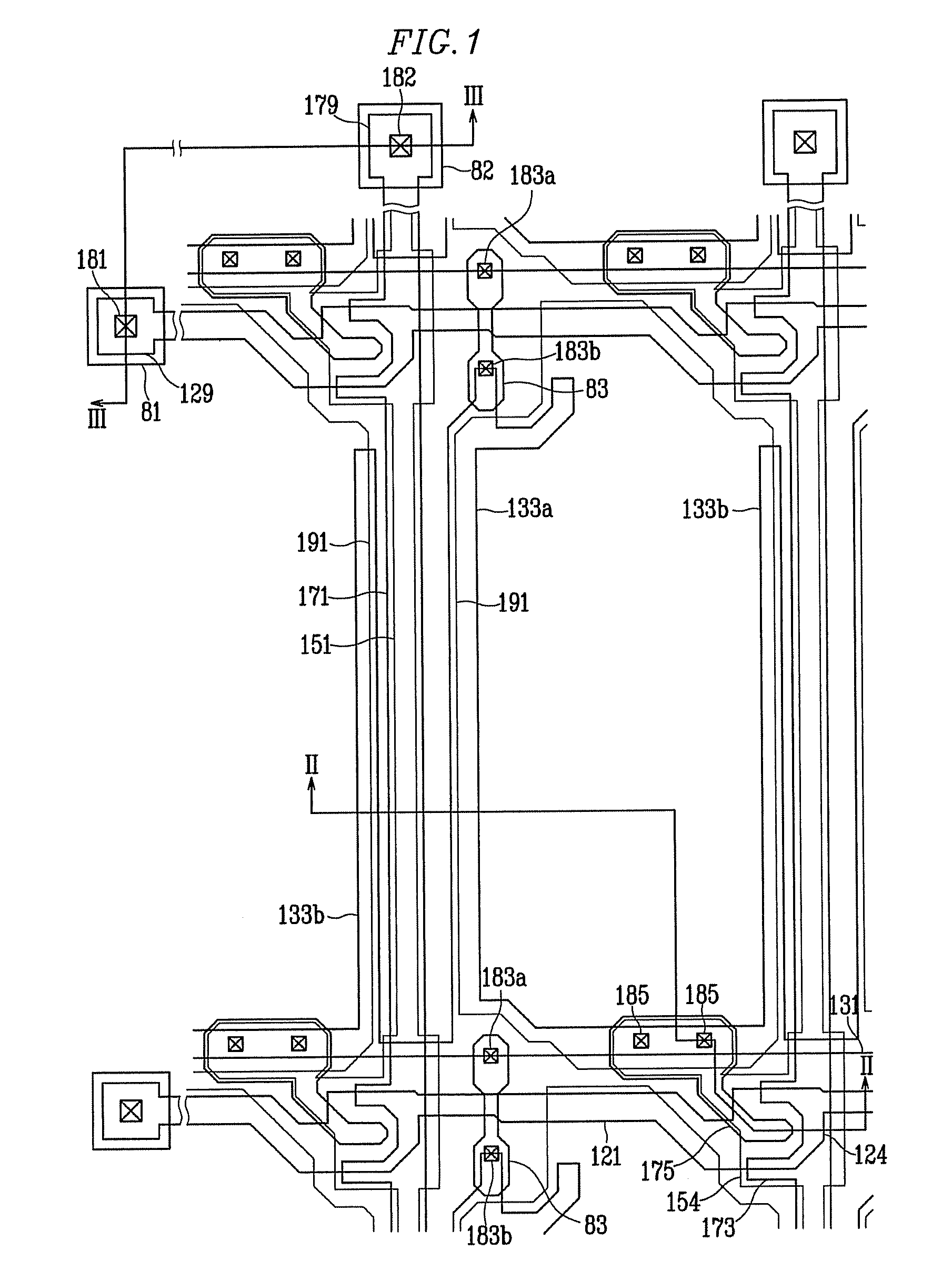

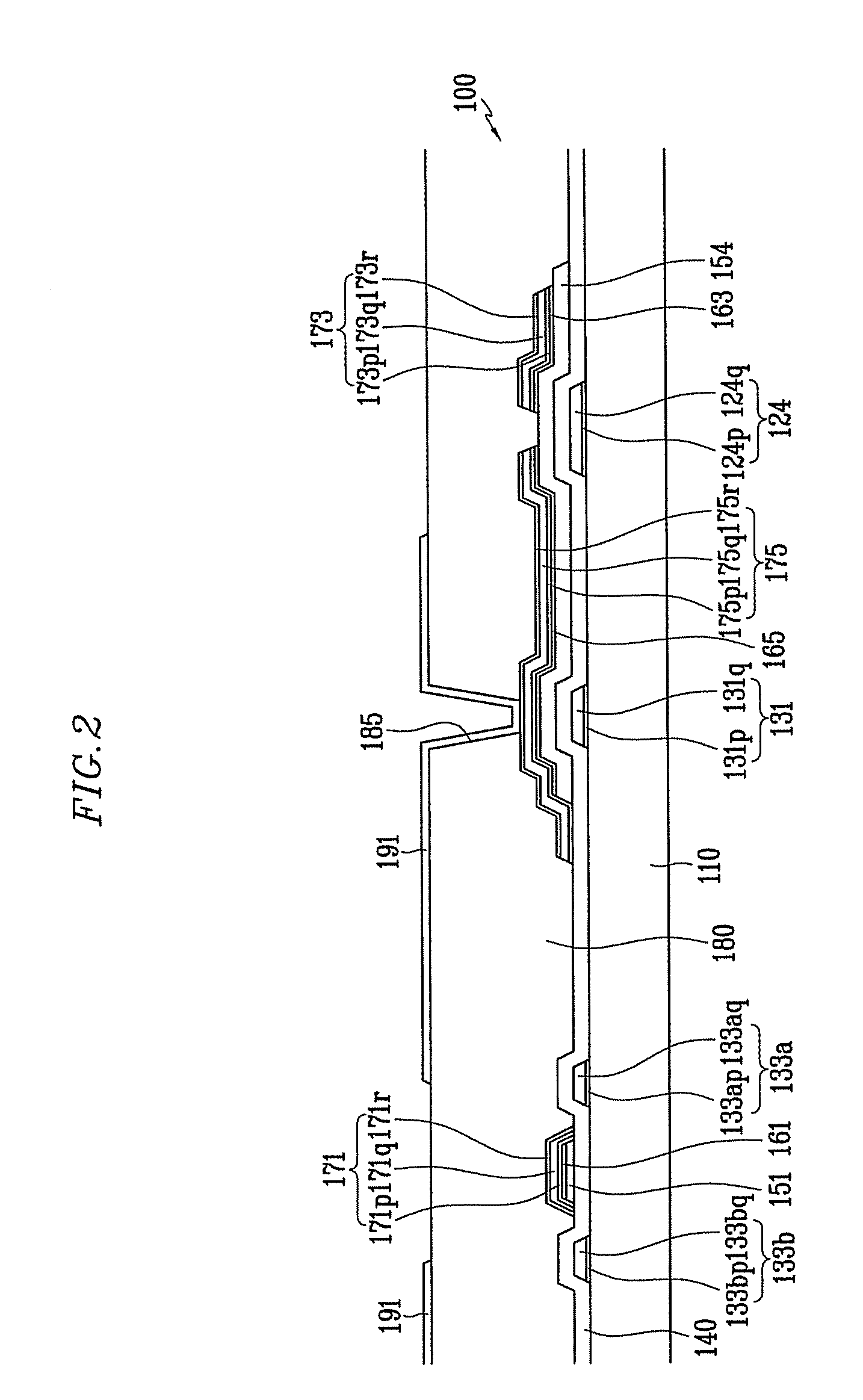

Display substrate and display device having the same

ActiveUS20080001892A1Low line resistanceStatic indicating devicesNon-linear opticsLine resistanceDisplay device

In a display substrate and a display device having the display substrate for reducing a line resistance, the display substrate includes a plurality of pixel parts, a signal line part and a signal pad part. The pixel parts are formed in a display area. The signal line part is formed in a peripheral area surrounding the display area. The signal line part includes a first line formed with a first conductive layer, and a second line formed with a second conductive layer over the first line. The second line overlaps the first line. The signal pad part includes a first pad integrally formed with the first line, and a second pad integrally formed with the second line, wherein an identical driving signal is applied to the first pad and the second pad. Accordingly, the line resistance of the signal line part may be reduced.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

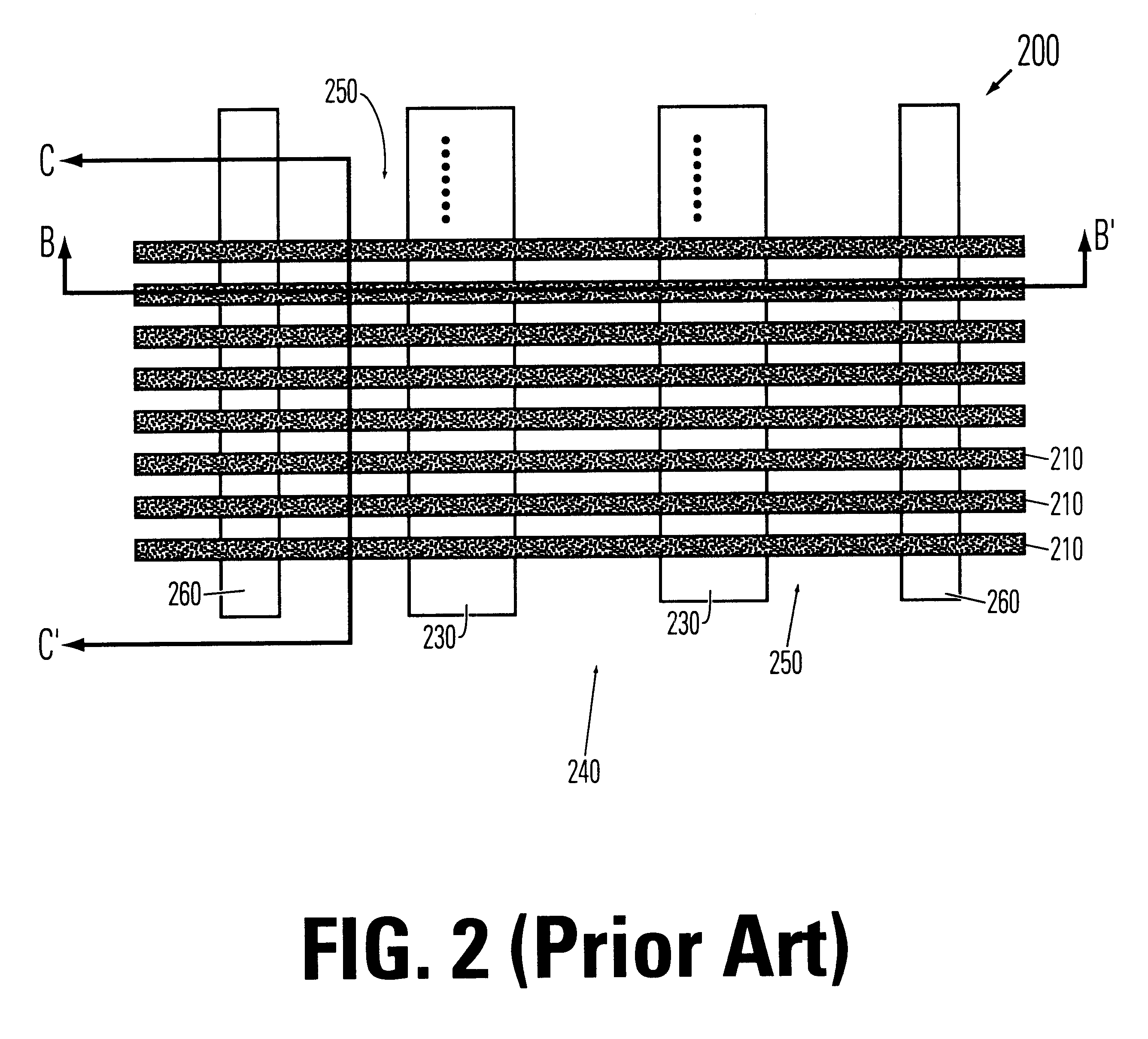

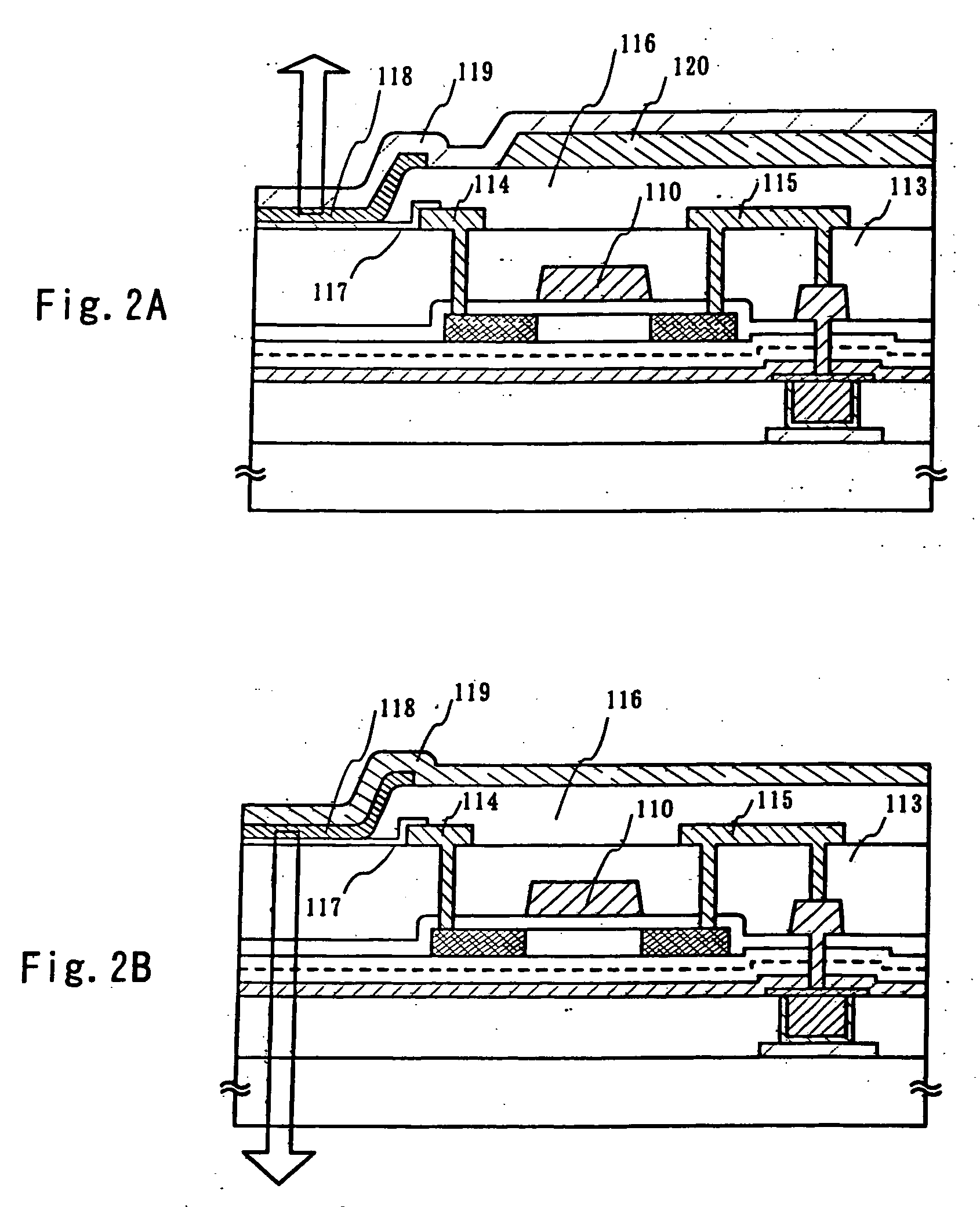

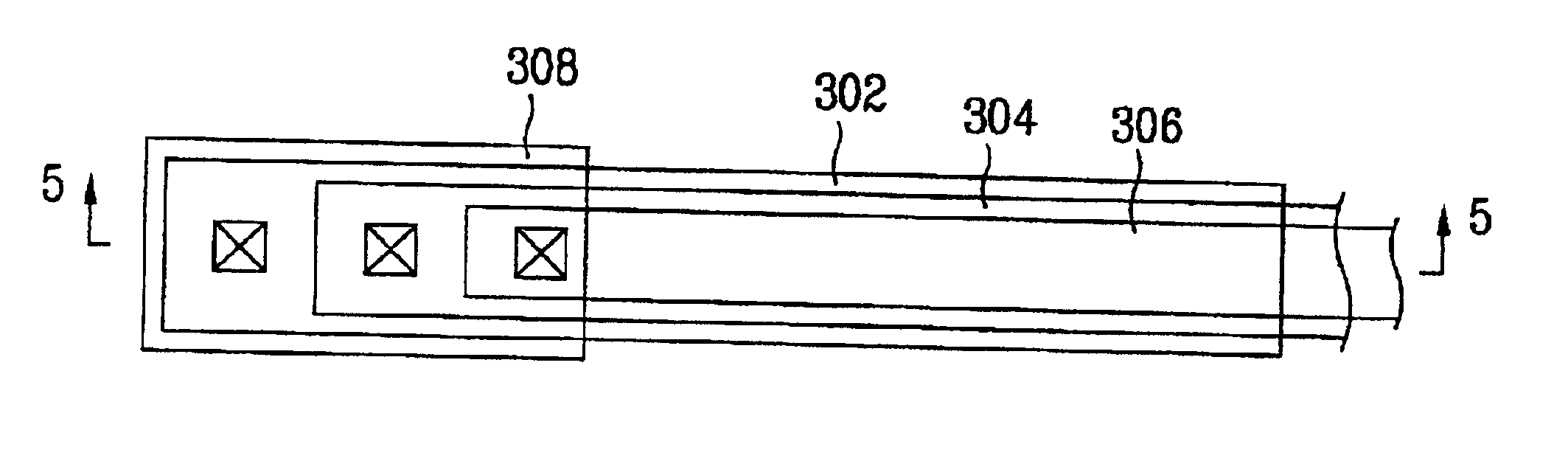

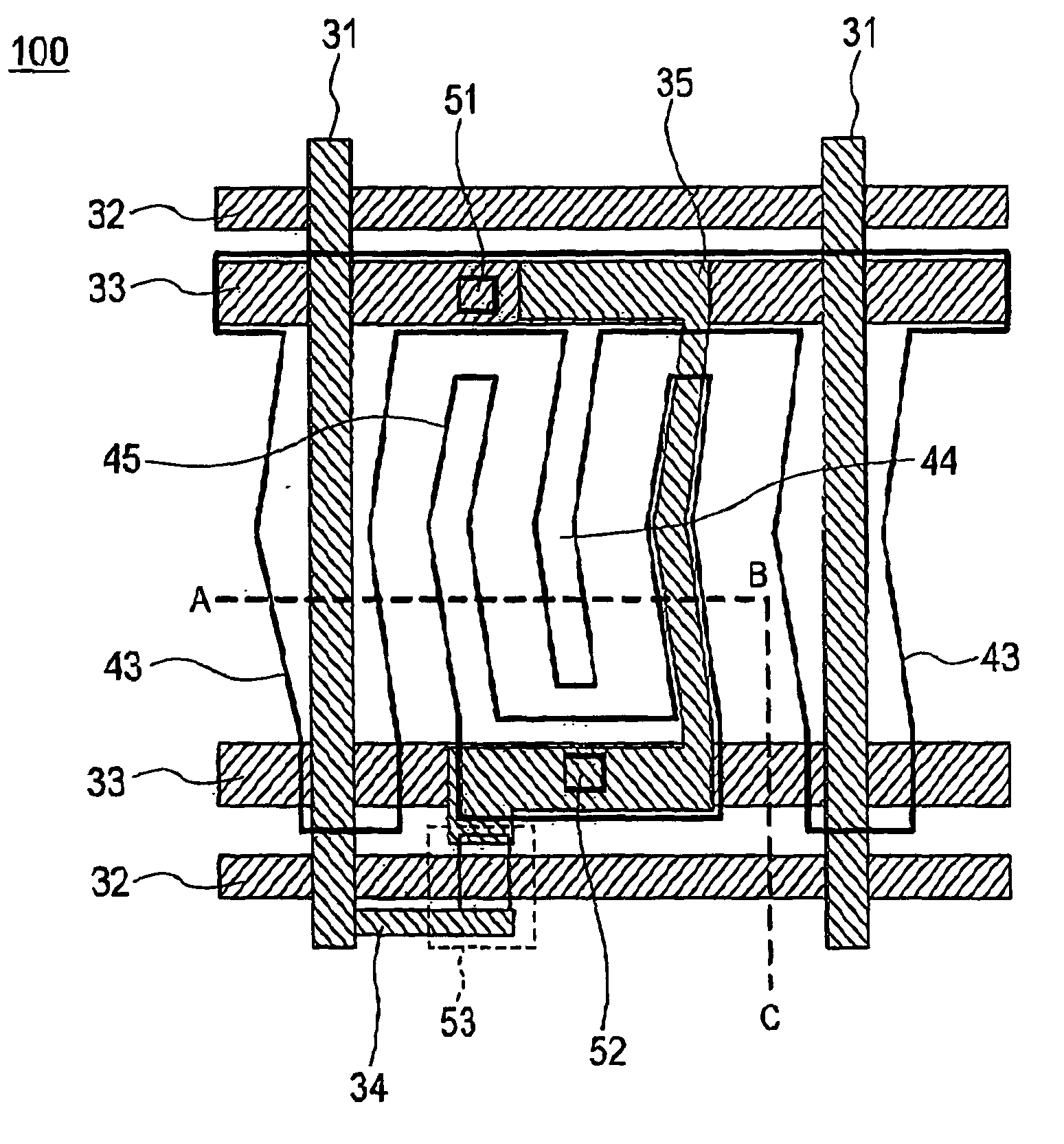

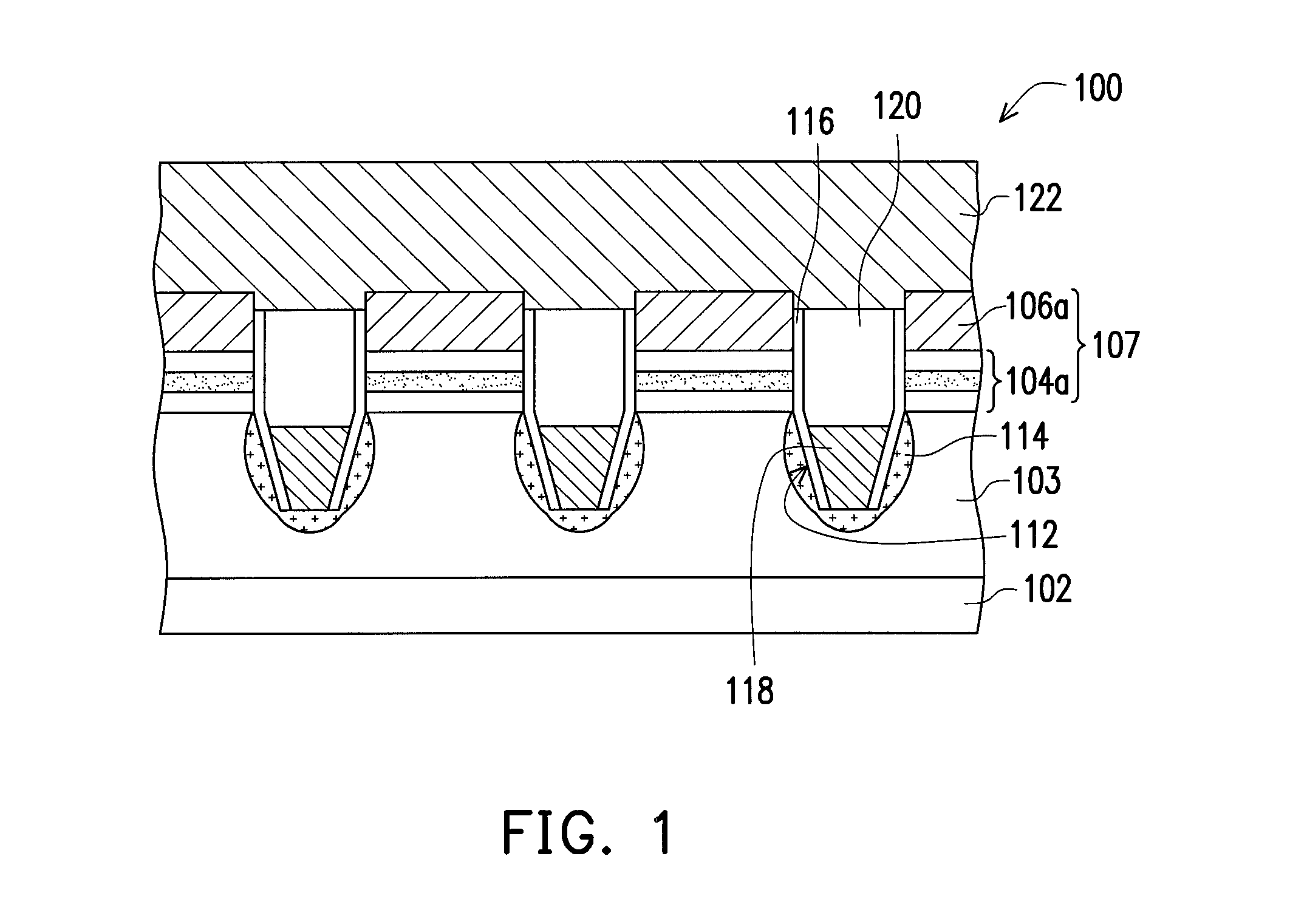

MRAM arrays with reduced bit line resistance and method to make the same

InactiveUS20050221511A1Low line resistancePerforating toolsMagnetic-field-controlled resistorsElectrical and Electronics engineeringInsulation layer

Improved MRAM arrays and a method of forming the same are disclosed in which a bit line has thinner portions formed over MTJs and thicker portions therebetween. Bottom electrodes are formed in a first insulation layer on a substrate and then MTJs and a coplanar second insulation layer are formed thereon. After a second conductive layer comprised of lower metal lines is formed above the MTJs, a trench is formed in a stack of insulation layers above portions of the lower metal lines. A barrier layer and upper metal layer are sequentially deposited and then planarized to form a filled trench that effectively increases a bit line thickness. The lower metal layer is a thin bit line in regions over MTJs. The method may also comprise forming word lines on an insulation layer that are aligned over the MTJs and perpendicular to the bit lines.

Owner:HEADWAY TECH INC +1

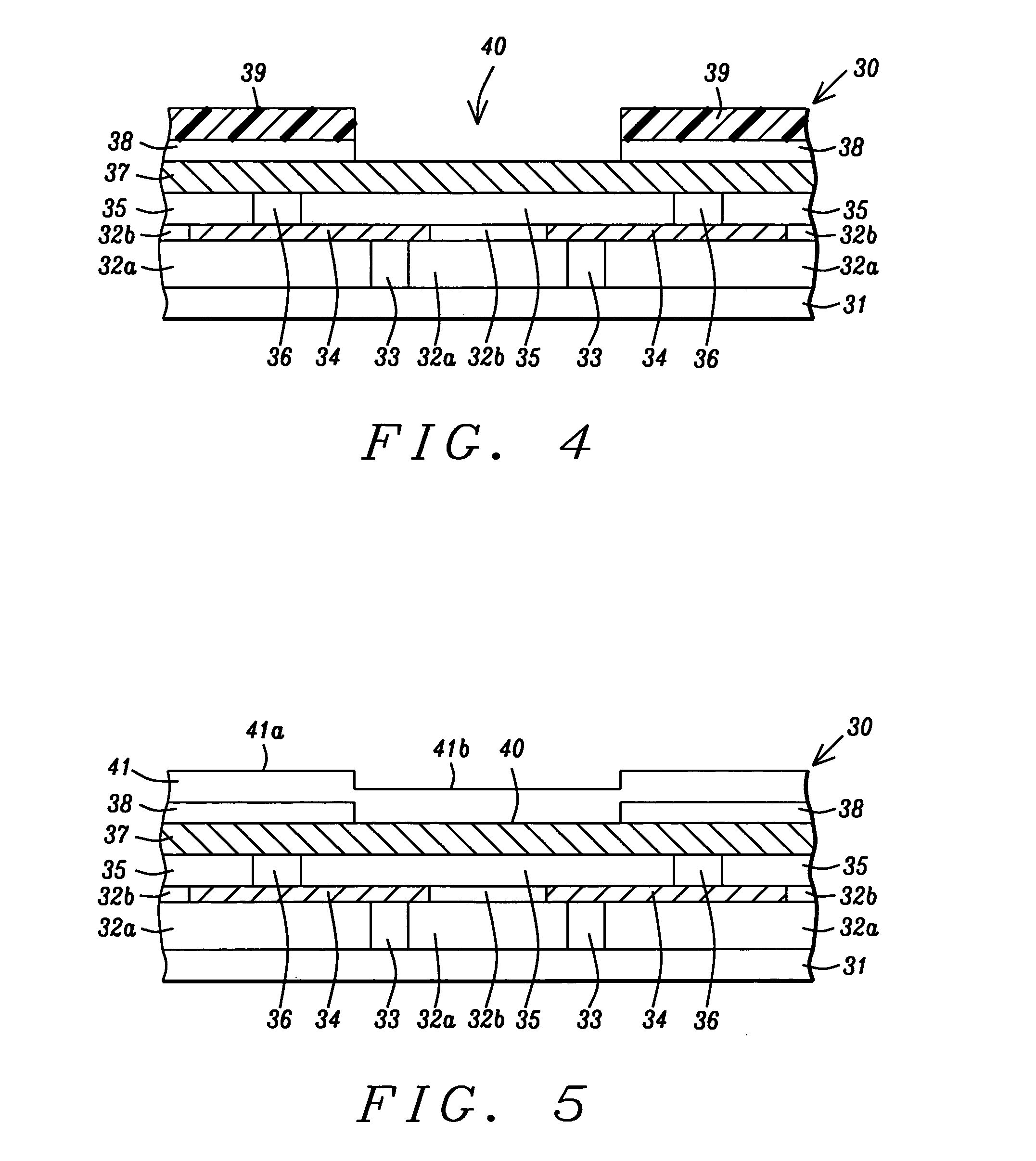

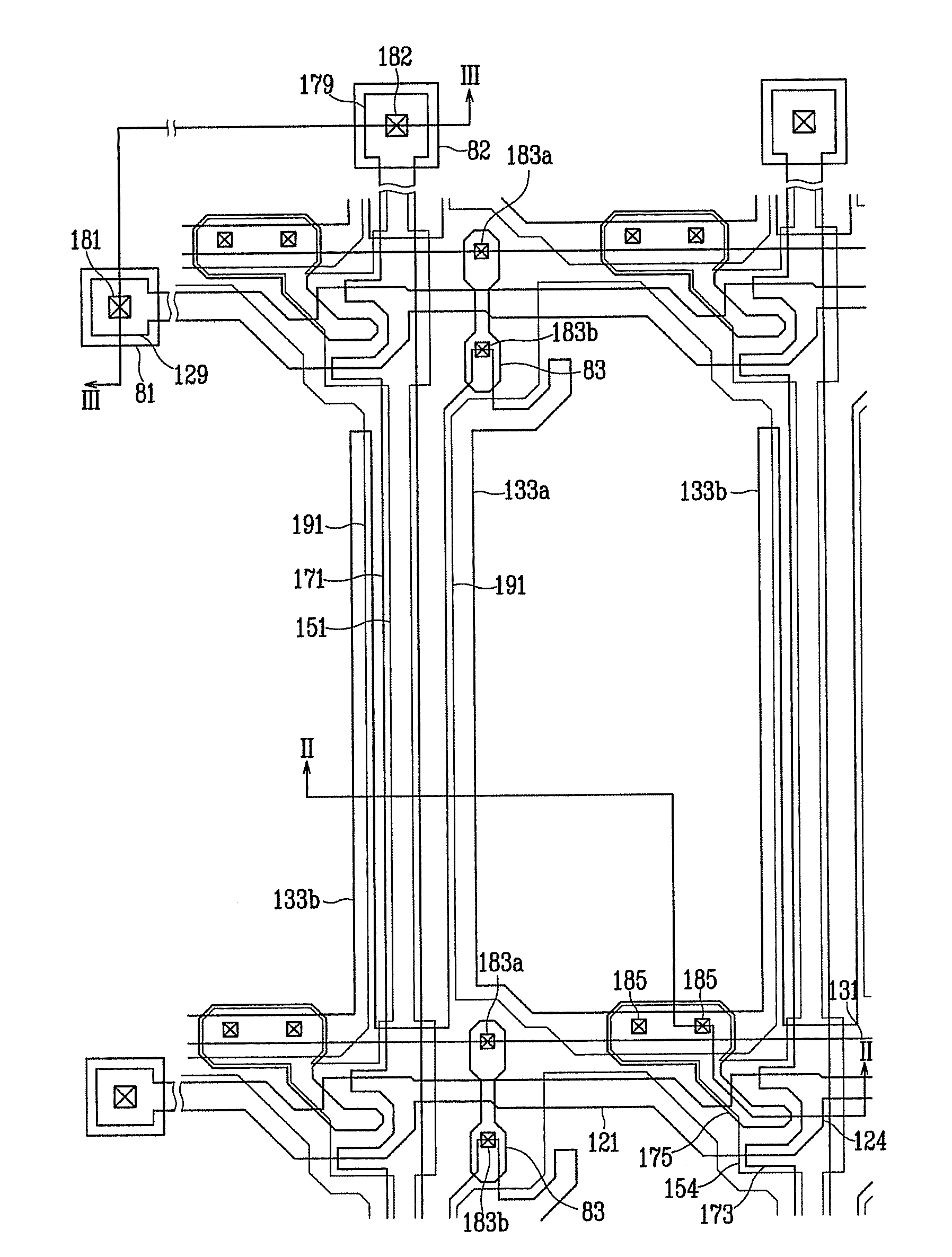

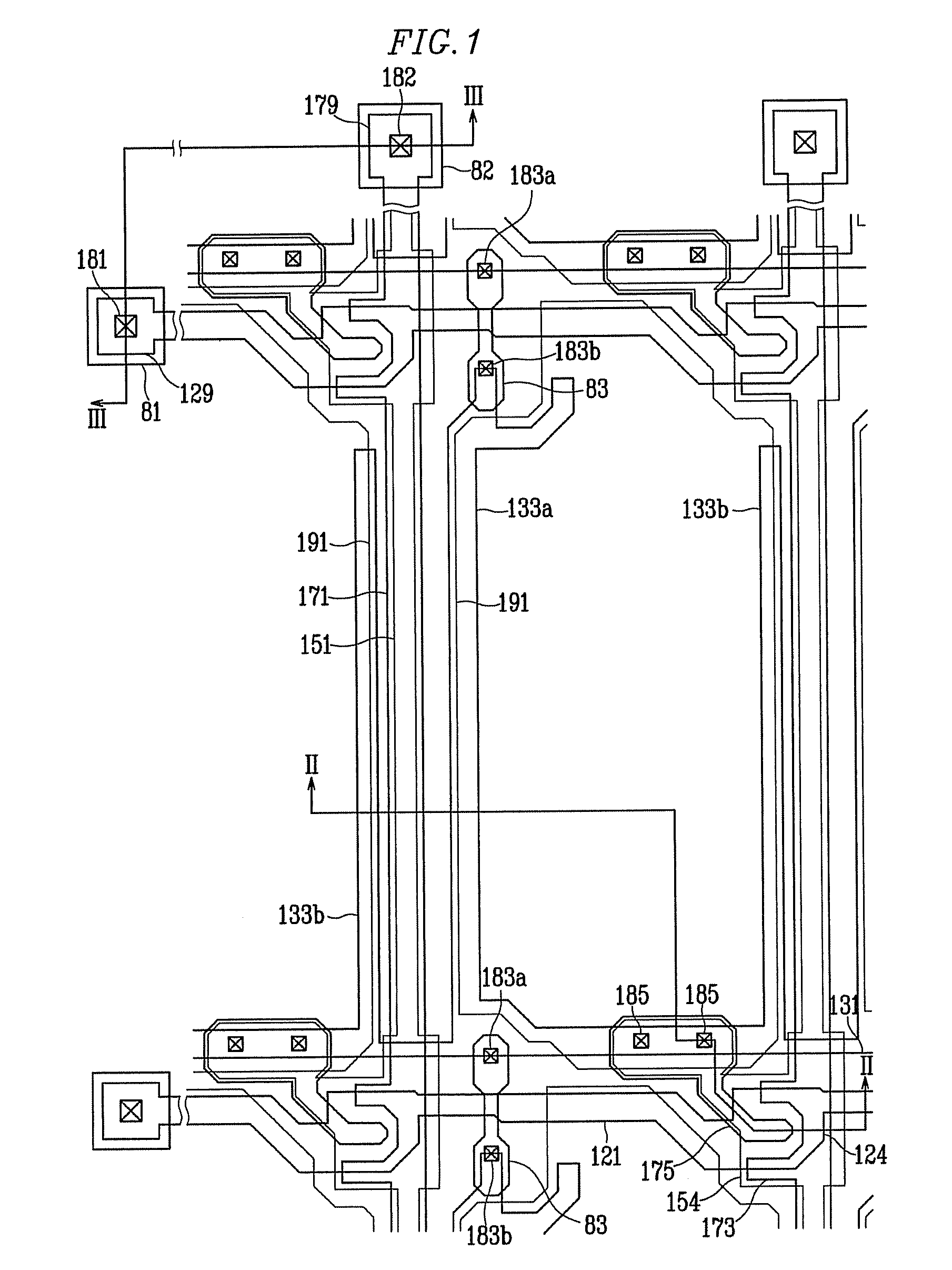

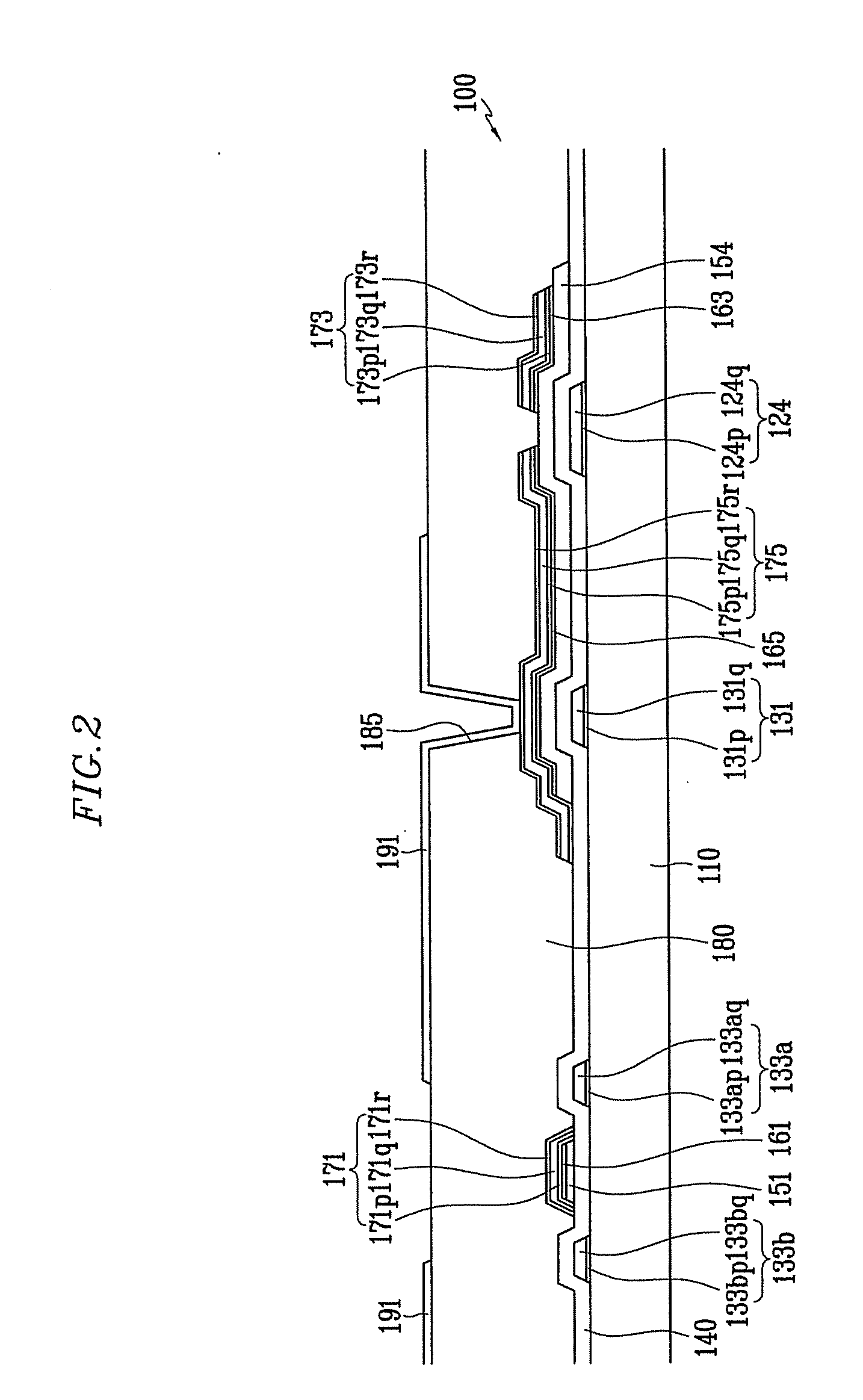

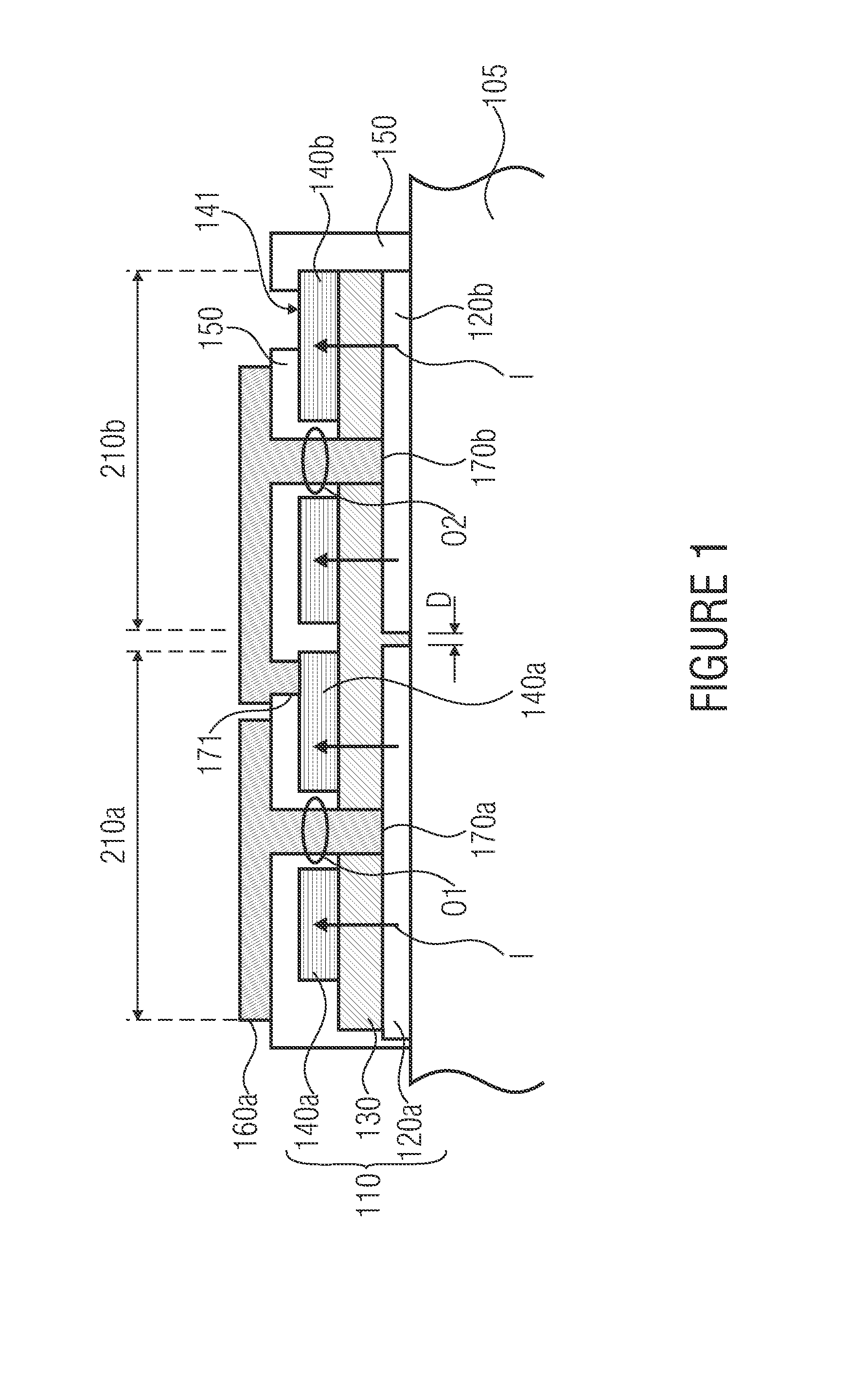

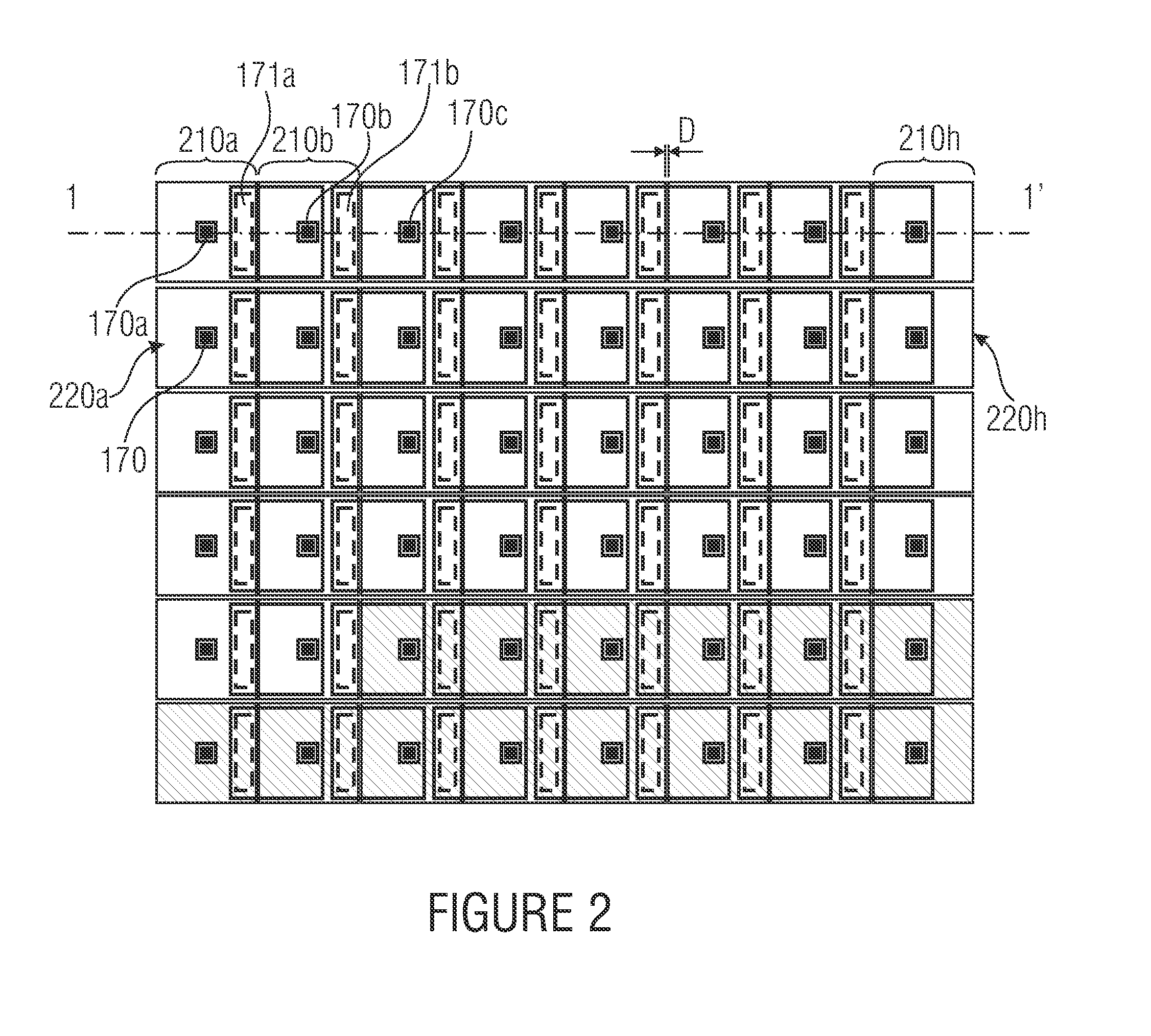

Organic Light Emitting Display Device

ActiveUS20170194415A1Lower line resistanceLow line resistanceSolid-state devicesSemiconductor/solid-state device manufacturingAuxiliary electrodeSecondary layer

Disclosed is an organic light emitting display device which includes an auxiliary line connected to a first power line and an auxiliary electrode connected to a second power line, thereby lowering a line resistance of each of the first and second power lines. The organic light emitting display device includes a substrate, a thin film transistor (TFT) disposed on the substrate, a first power line disposed in a first layer including the source electrode and the drain electrode of the TFT, a second power line disposed over the first layer, an auxiliary line disposed in a second layer including the second power line, an anode electrode disposed on the second power line and the auxiliary line and electrically connected to the drain electrode, an organic layer disposed on the anode electrode, and a cathode electrode covering the organic layer and electrically connected to the second power line.

Owner:LG DISPLAY CO LTD

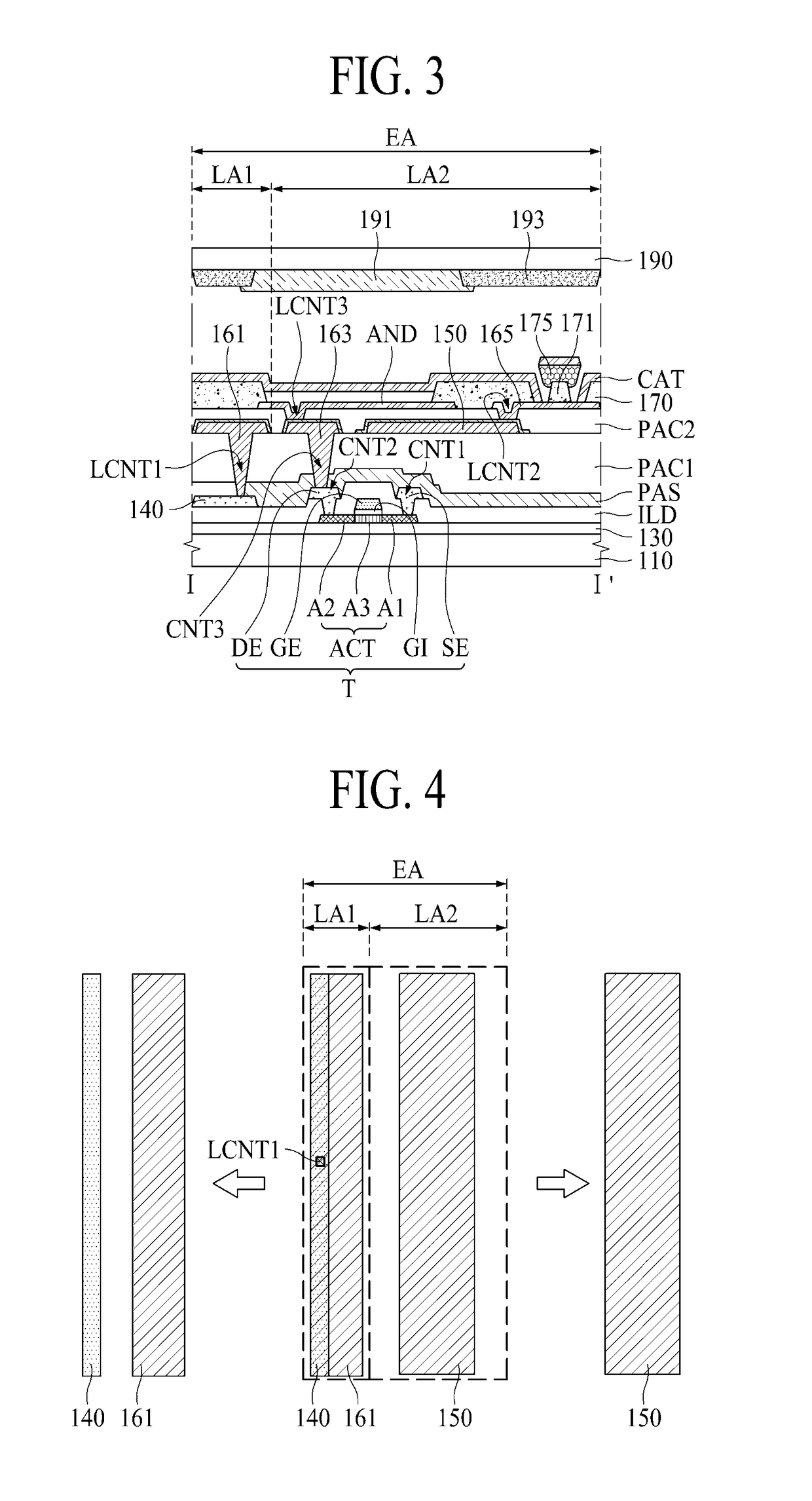

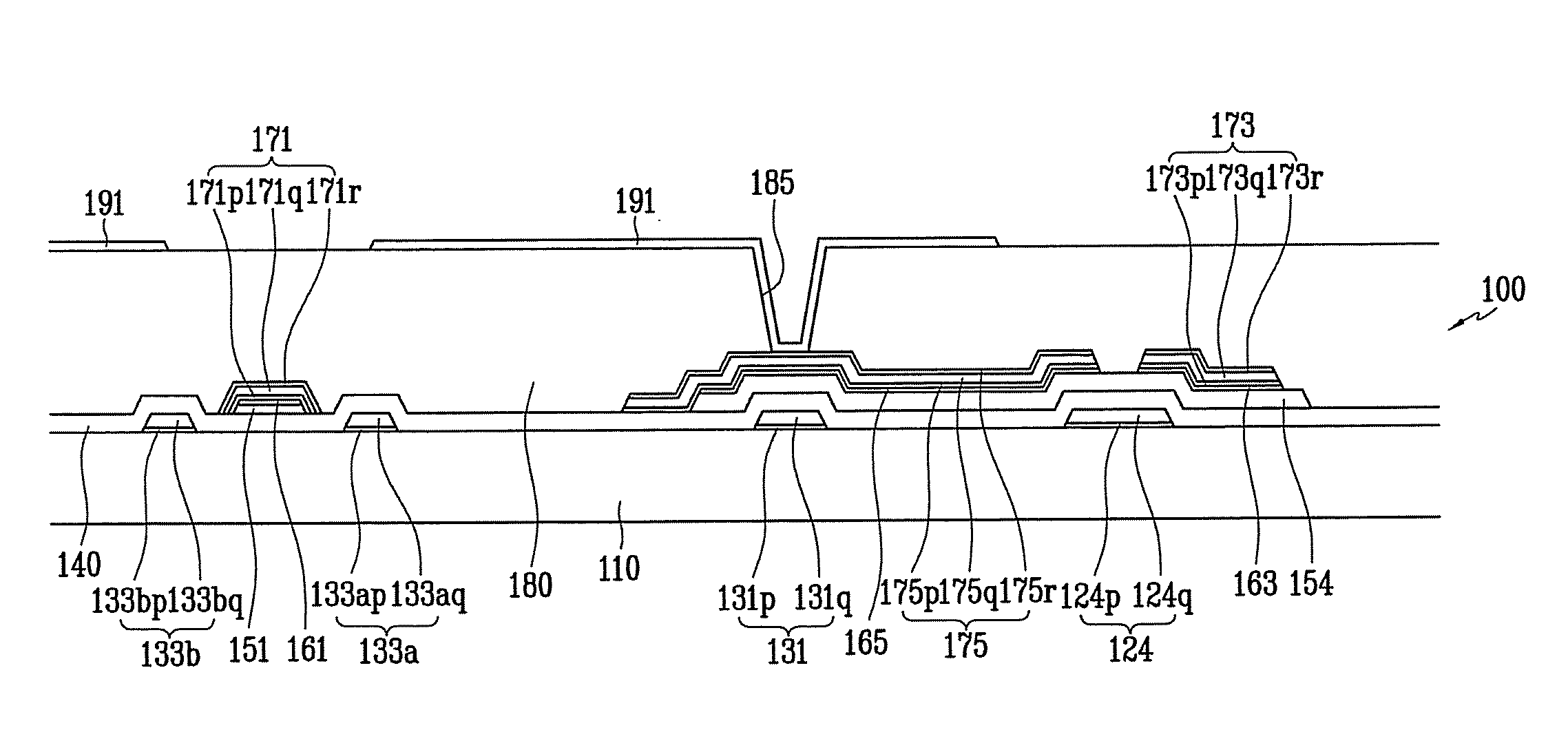

Signal line for a display device, etchant, thin film transistor panel, and method for manufacturing the same

ActiveUS20080079006A1Low reliabilityLower resistanceStatic indicating devicesSemiconductor/solid-state device detailsNiobiumDisplay device

A thin film panel includes a substrate, a gate line formed on the substrate, a gate insulating layer formed on the gate line, a semiconductor layer formed on the gate insulating layer, a data line, including a source electrode, and a drain electrode formed on the gate insulating layer or the semiconductor layer, and a pixel electrode connected to the drain electrode, wherein at least one of the gate line and the data line and drain electrode includes a first conductive layer made of a molybdenum Mo-niobium Nb alloy and a second conductive layer made of a copper Cu-containing metal.

Owner:SAMSUNG DISPLAY CO LTD

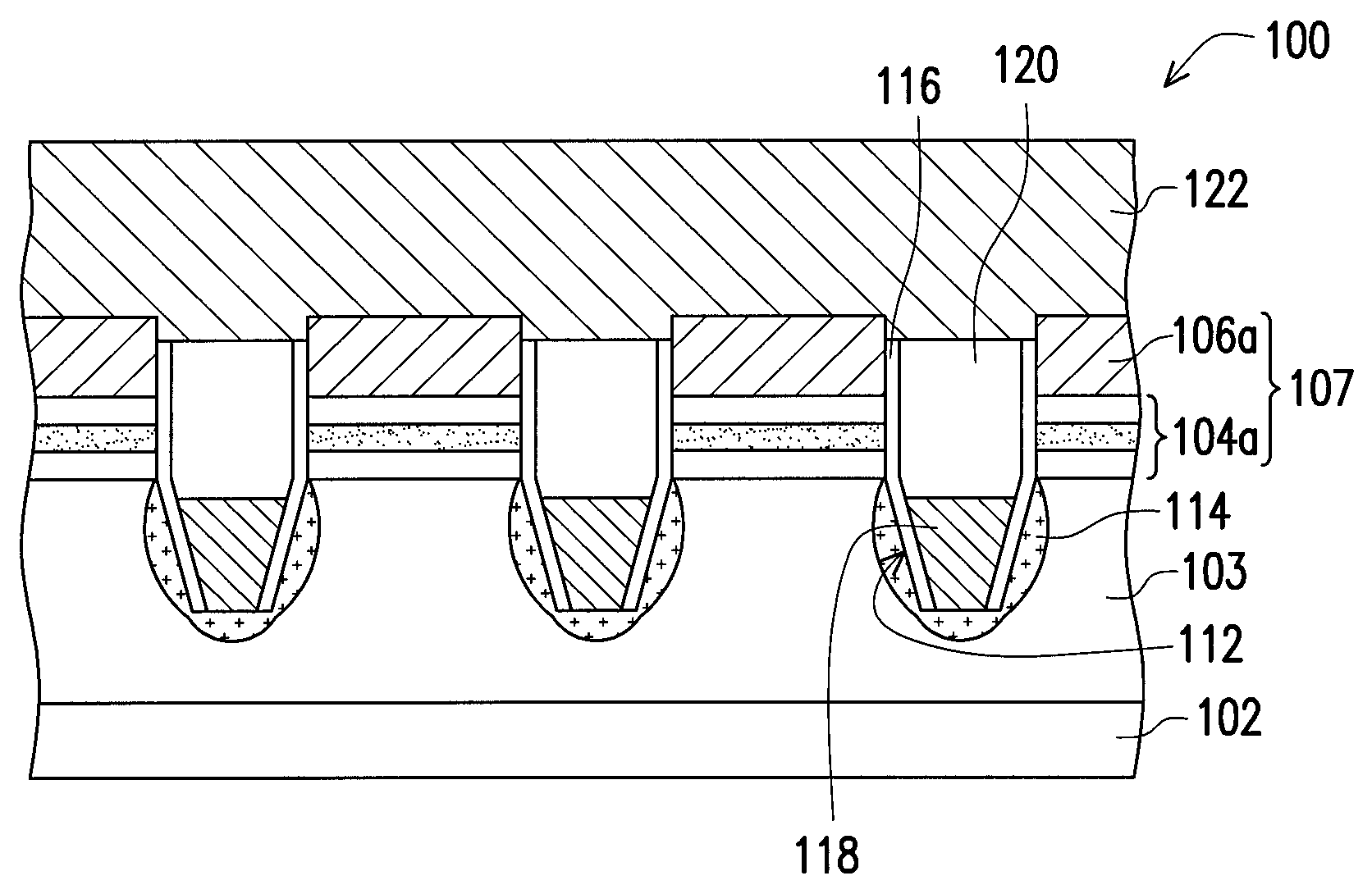

MRAM arrays with reduced bit line resistance and method to make the same

InactiveUS7071009B2Low line resistancePerforating toolsMagnetic-field-controlled resistorsBit lineInsulation layer

Improved MRAM arrays and a method of forming the same are disclosed in which a bit line has thinner portions formed over MTJs and thicker portions therebetween. Bottom electrodes are formed in a first insulation layer on a substrate and then MTJs and a coplanar second insulation layer are formed thereon. After a second conductive layer comprised of lower metal lines is formed above the MTJs, a trench is formed in a stack of insulation layers above portions of the lower metal lines. A barrier layer and upper metal layer are sequentially deposited and then planarized to form a filled trench that effectively increases a bit line thickness. The lower metal layer is a thin bit line in regions over MTJs. The method may also comprise forming word lines on an insulation layer that are aligned over the MTJs and perpendicular to the bit lines.

Owner:HEADWAY TECH INC +1

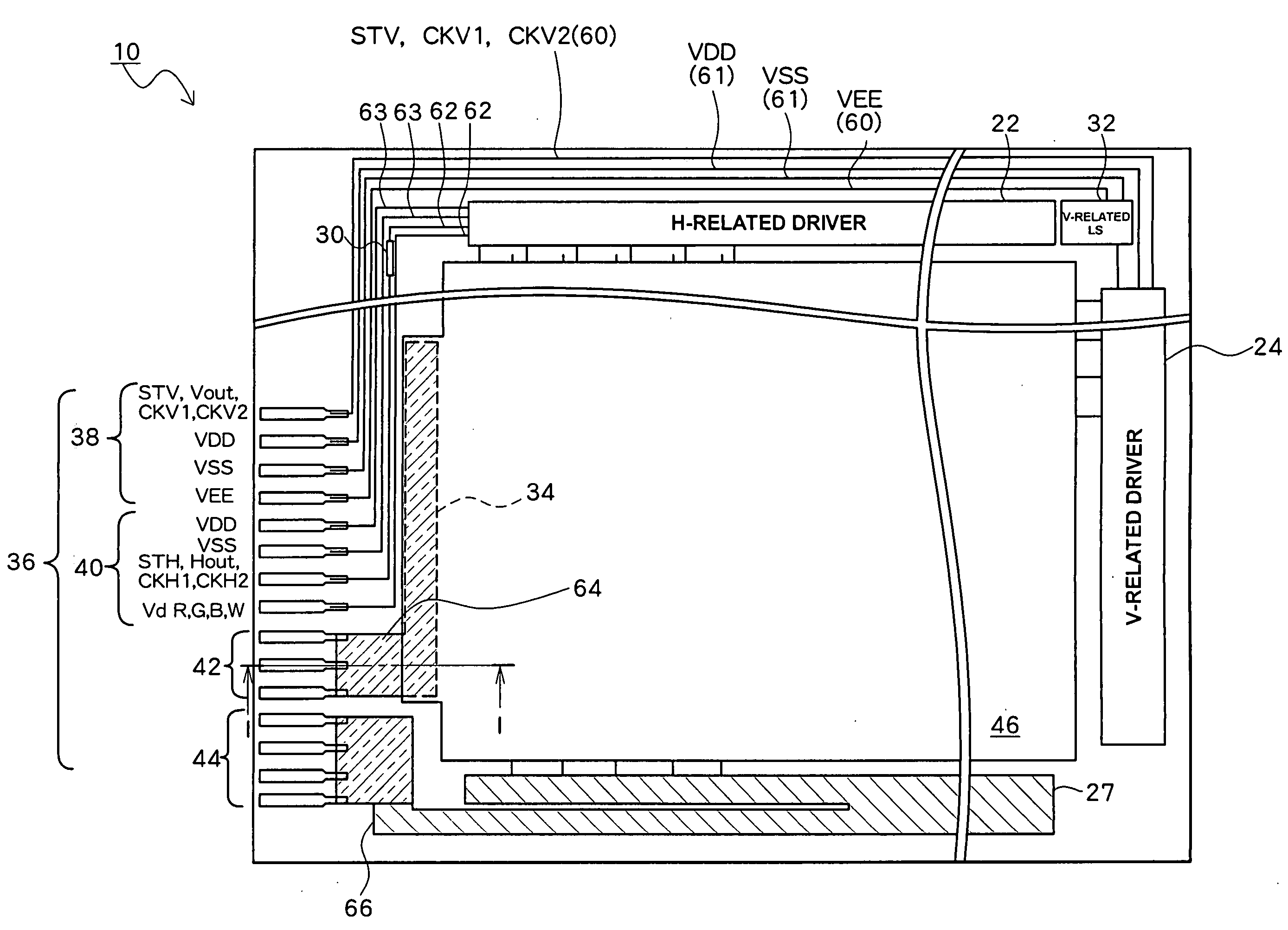

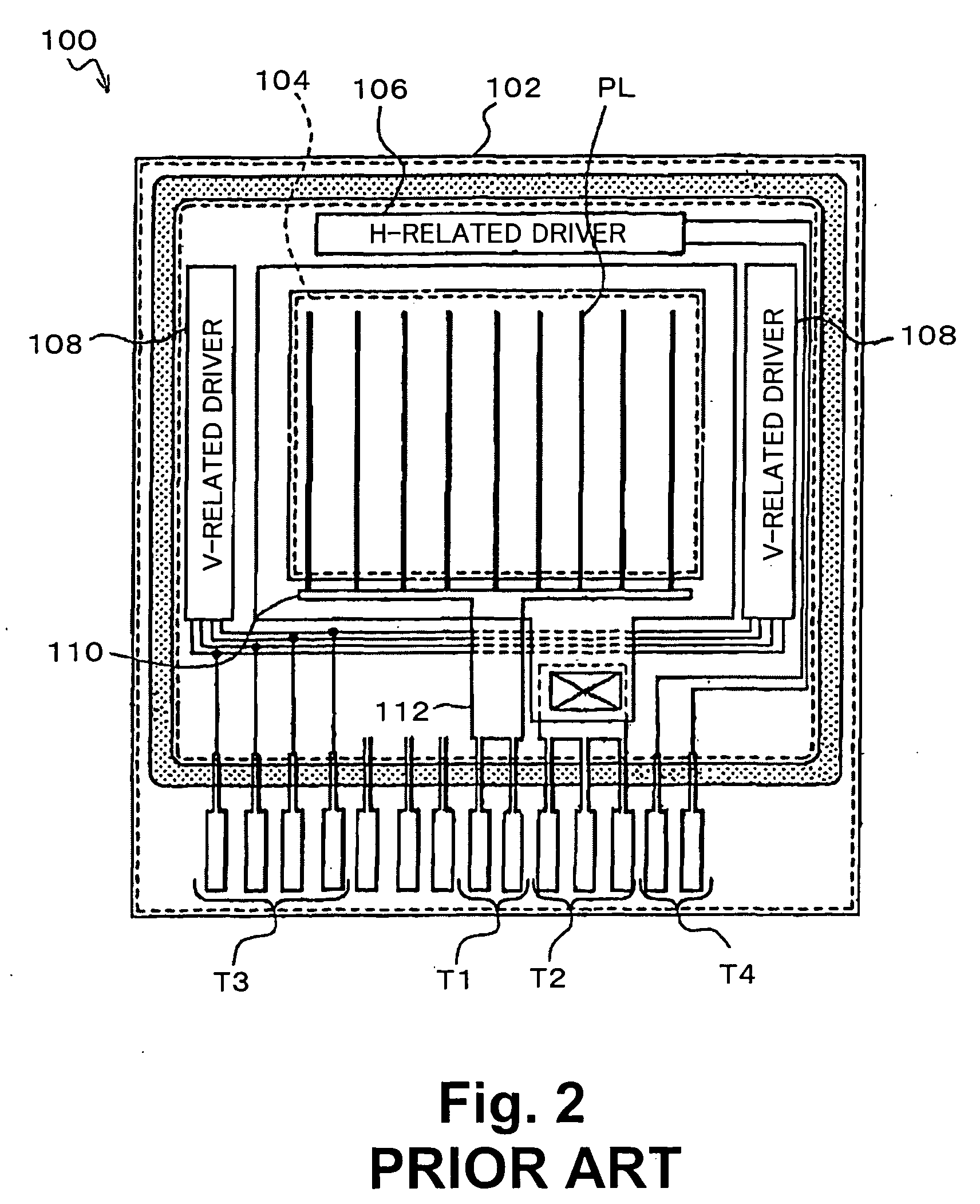

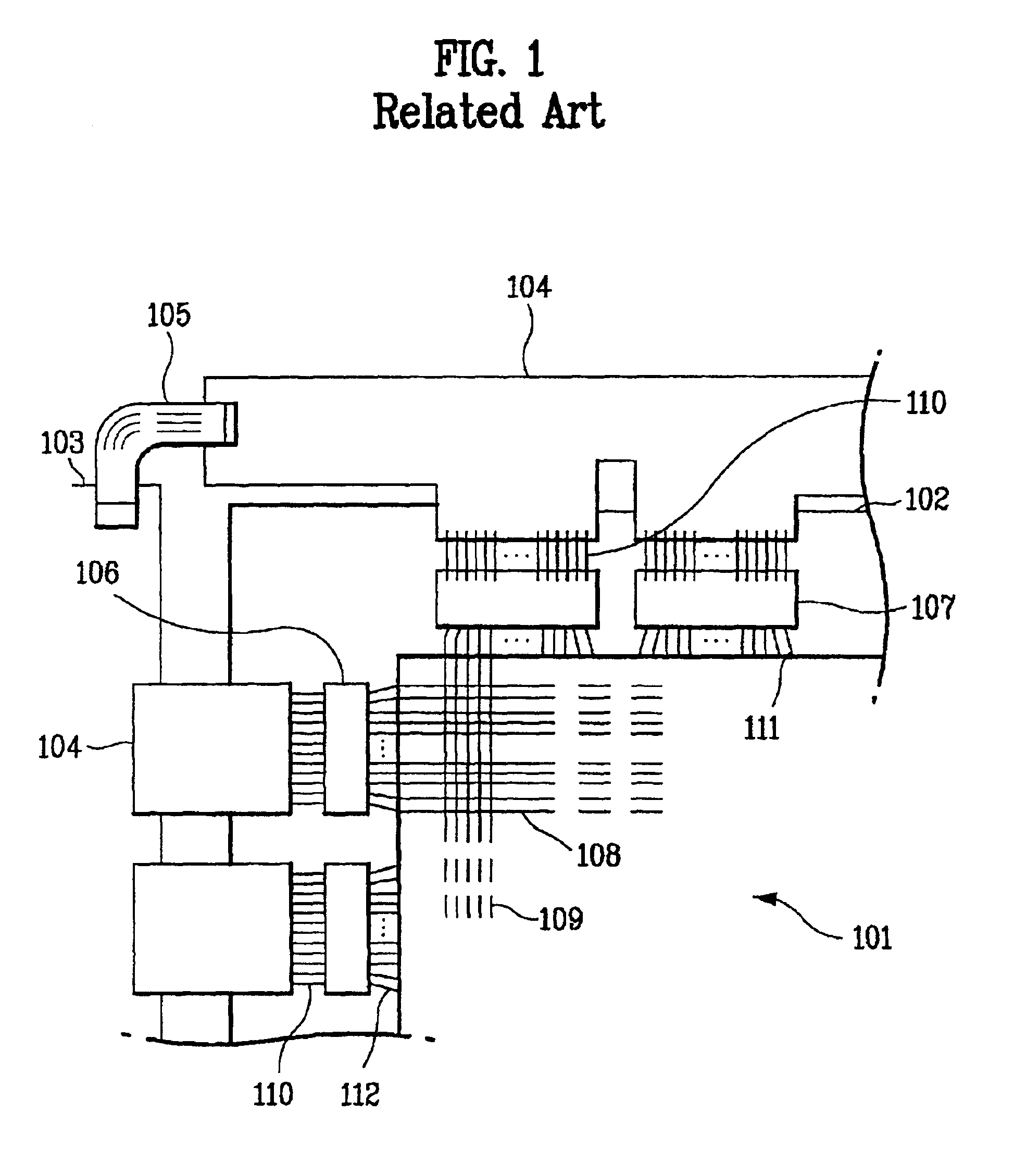

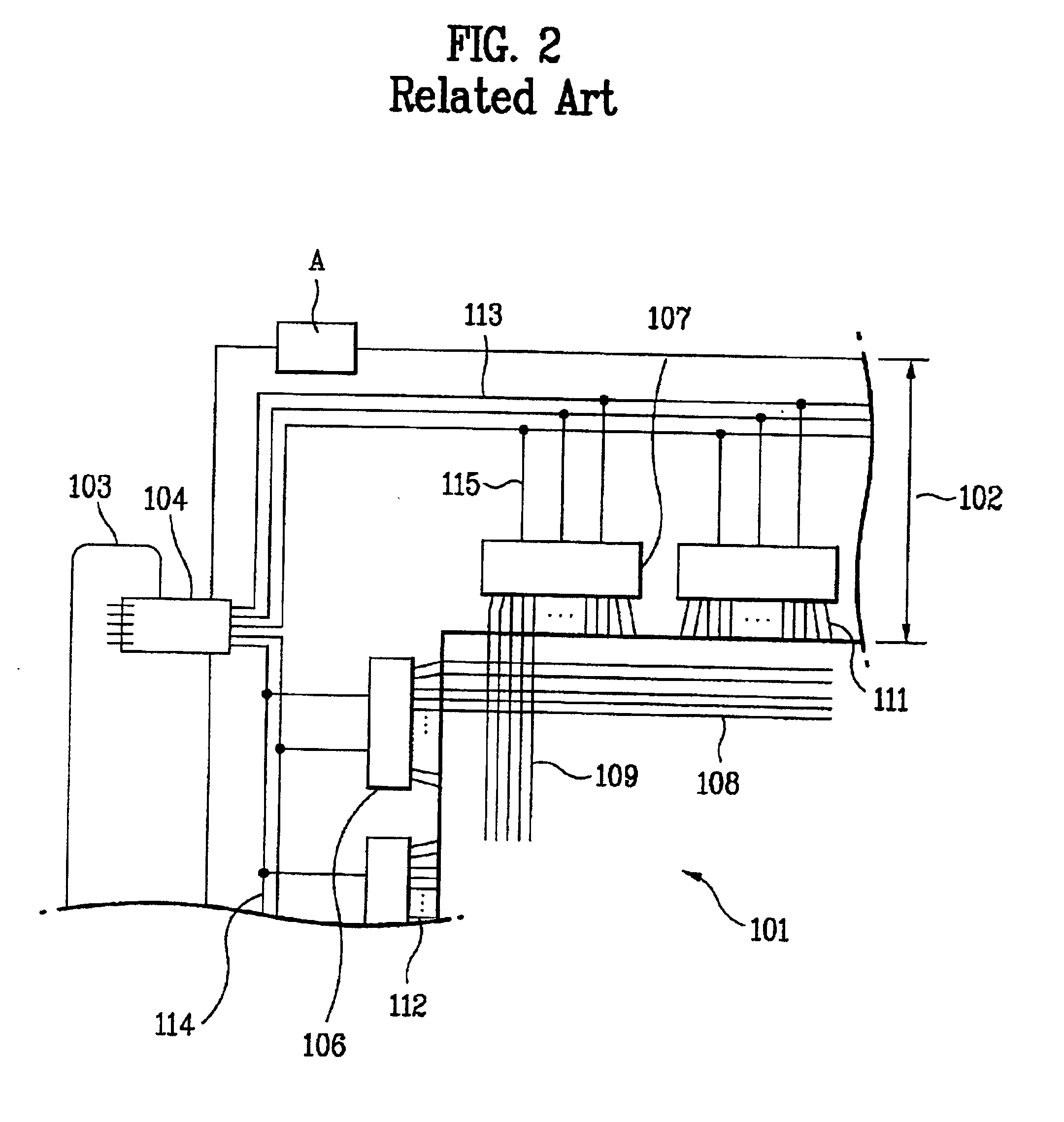

Electroluminescence display device

ActiveUS20070013629A1Reduce in quantityReduce the impactStatic indicating devicesElectroluminescent light sourcesDriver circuitDriving current

In an electroluminescence display device having, on a display panel, a display portion in which pixels are arranged in matrix, an external connection terminal is placed along a lateral side of the display panel and a vertical scan driver circuit is placed on a lateral side of the display panel which opposes the lateral side on which the external connection terminal is placed. Lines for a horizontal scan driver circuit and for the vertical scan driver circuit can be provided only on three sides of the display panel including the side on which the external connection terminal is provided, a side opposing this side, and another side. By not placing the line for the driver circuits on the remaining side, spaces can be secured on this side for a drive current line which supplies power to an electroluminescence element. With this structure, a size of a frame portion can be reduced while securing sufficient width for the drive current common line.

Owner:SANYO ELECTRIC CO LTD

Electronic component and method of manufacturing the same

InactiveUS20090212399A1Lower the resistance valueLow line resistancePiezoelectric/electrostrictive device manufacture/assemblyImpedence networksElectronic componentElectric wire

An electronic component includes a substrate, a functional element formed on the substrate, a plurality of terminals including a first terminal electrode connected to the functional element and a second terminal electrode layered on the first terminal electrode, and a feed line, one end of which is electrically connected to the first terminal electrode and the other end of which reaches an edge of the substrate, wherein the feed line includes a first portion directly reaching the edge, and a second portion branching from the first portion and then reaching the edge.

Owner:TAIYO YUDEN KK

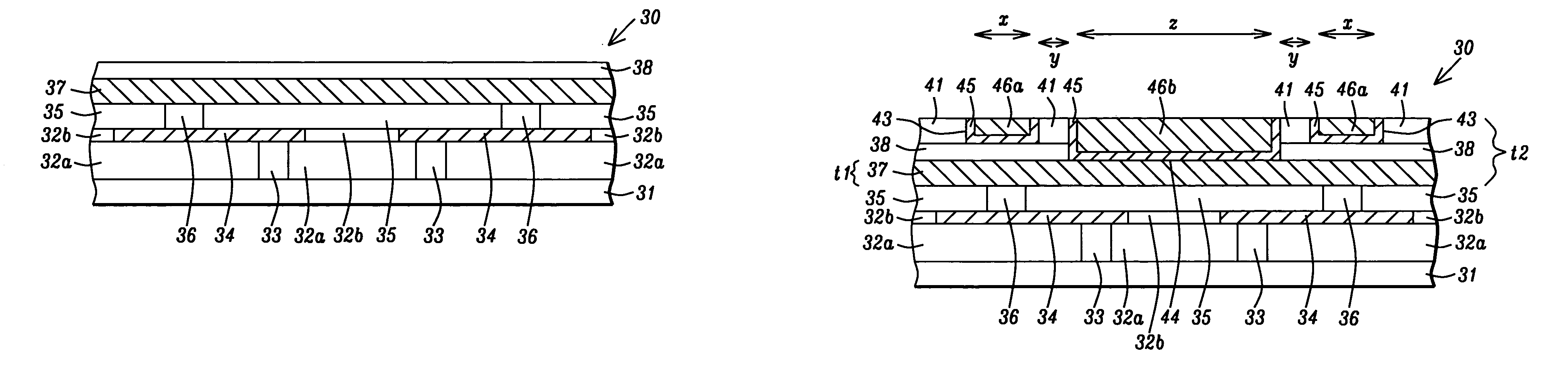

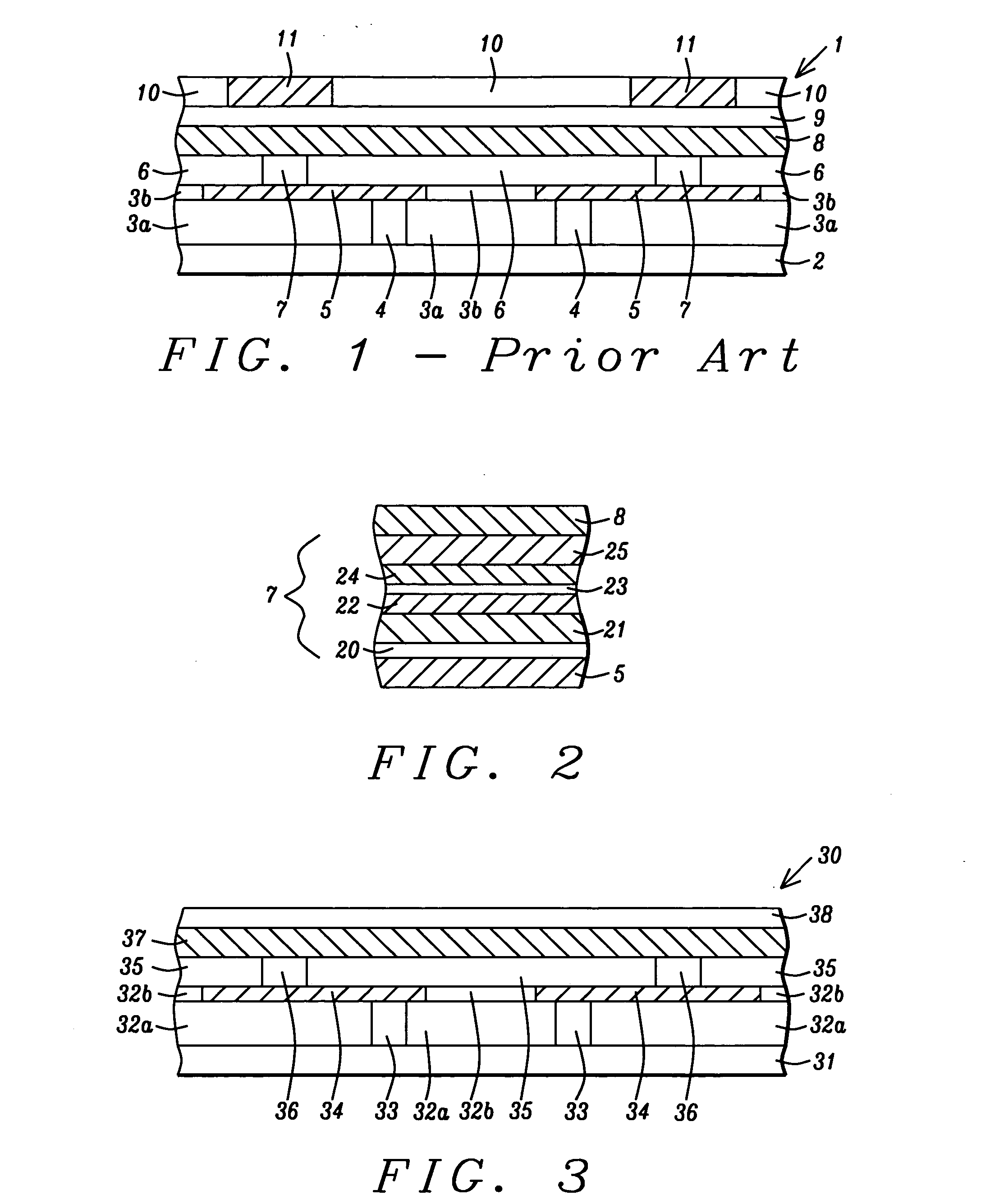

Reflective or transflective liquid crystal display device and method for manufacturing the same

InactiveUS6839120B2Low line resistanceStatic indicating devicesNon-linear opticsEngineeringLine structure

A line structure of a line on glass method in a reflective or a transflective liquid crystal display device and a method for manufacturing the same is disclosed, which offers decreased resistance by connecting a plurality of input lines in parallel. The LCD device includes a first line layer formed on a substrate, a first insulating layer formed on the substrate, having a contact hole at the first line layer, a second line layer formed on the first insulating layer, a second insulating layer formed on the substrate, having respective contact holes at the first and second line layers, a third line layer formed on the second insulating layer, a passivation layer formed on the substrate, having respective contact holes at the first, second and third line layers, and a pixel electrode on the passivation layer to electrically connect the first, second and third line layers through each contact hole.

Owner:LG DISPLAY CO LTD

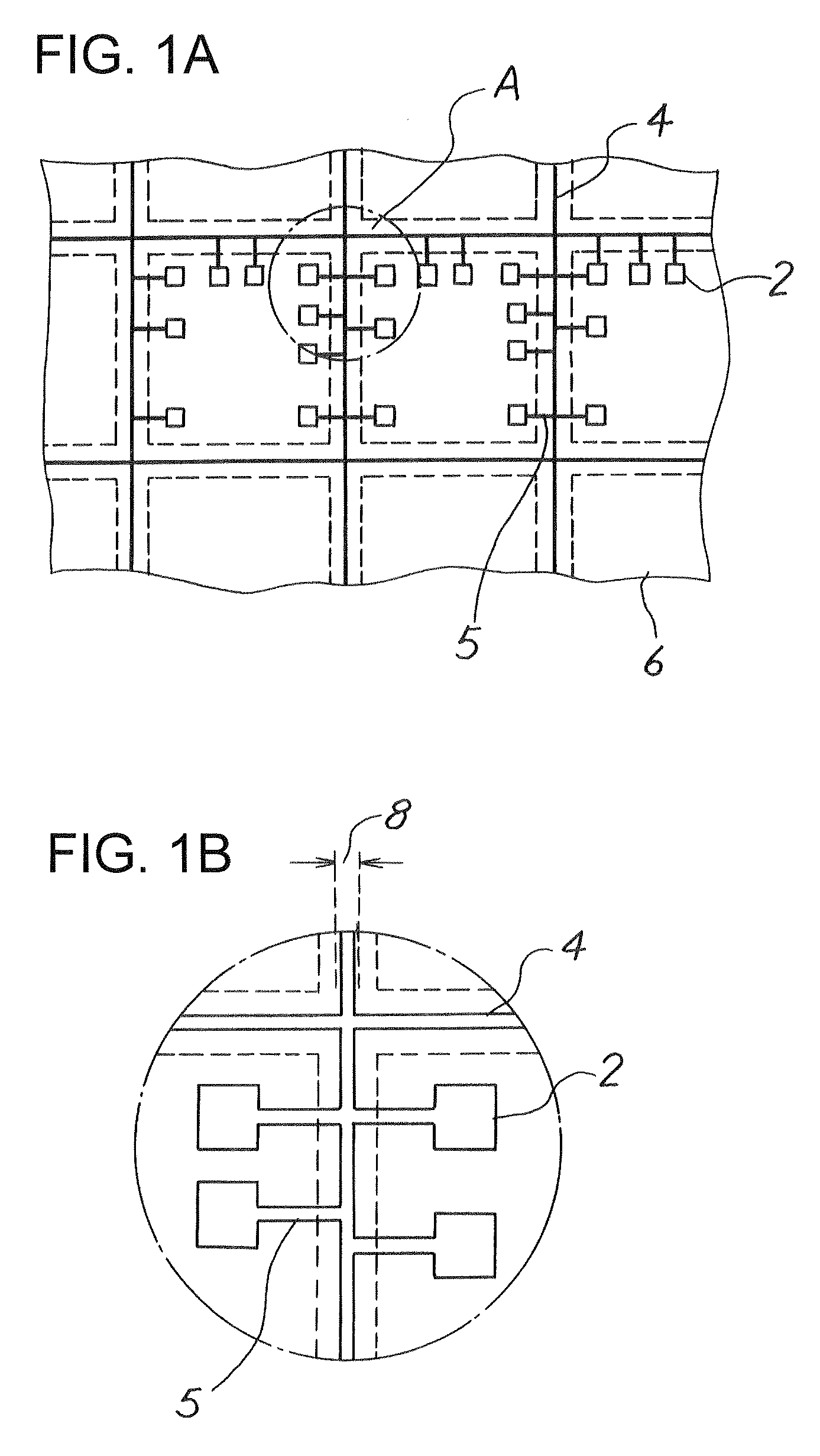

Liquid crystal display device having a higher contrast ratio

InactiveUS6950166B2Suppresses light scatteringIncrease contrastNon-linear opticsLiquid-crystal displayBlack matrix

A LCD device has a black matrix defining a plurality of pixel areas in the LCD device. An interconnect layer formed on a TFT panel includes a first interconnect line passing through the pixel area and a second interconnect line passing outside the pixel area. The first interconnect line is lower in a product of a thickness thereof by a surface reflectance thereof than the second interconnect line.

Owner:NEC LCD TECH CORP

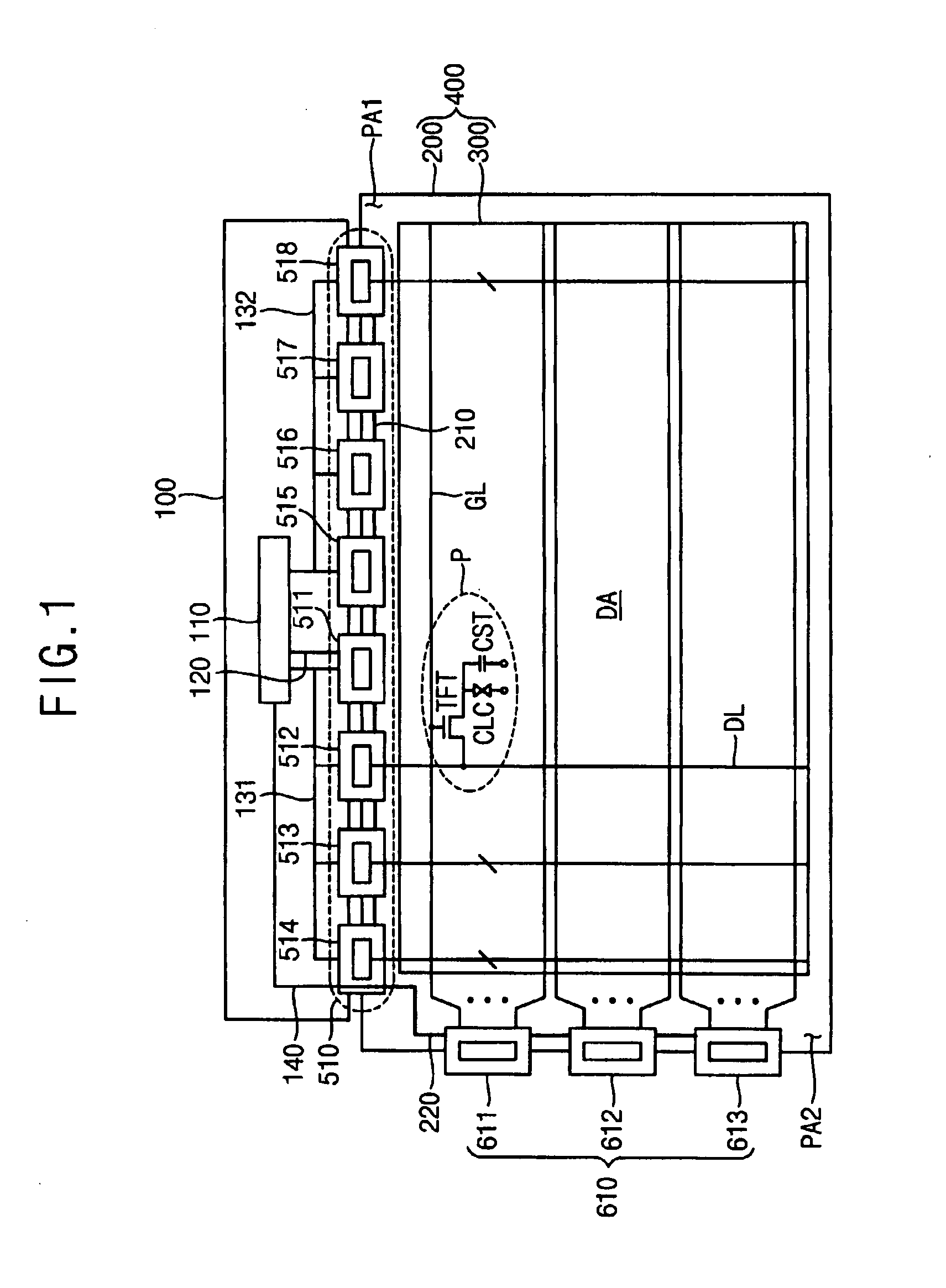

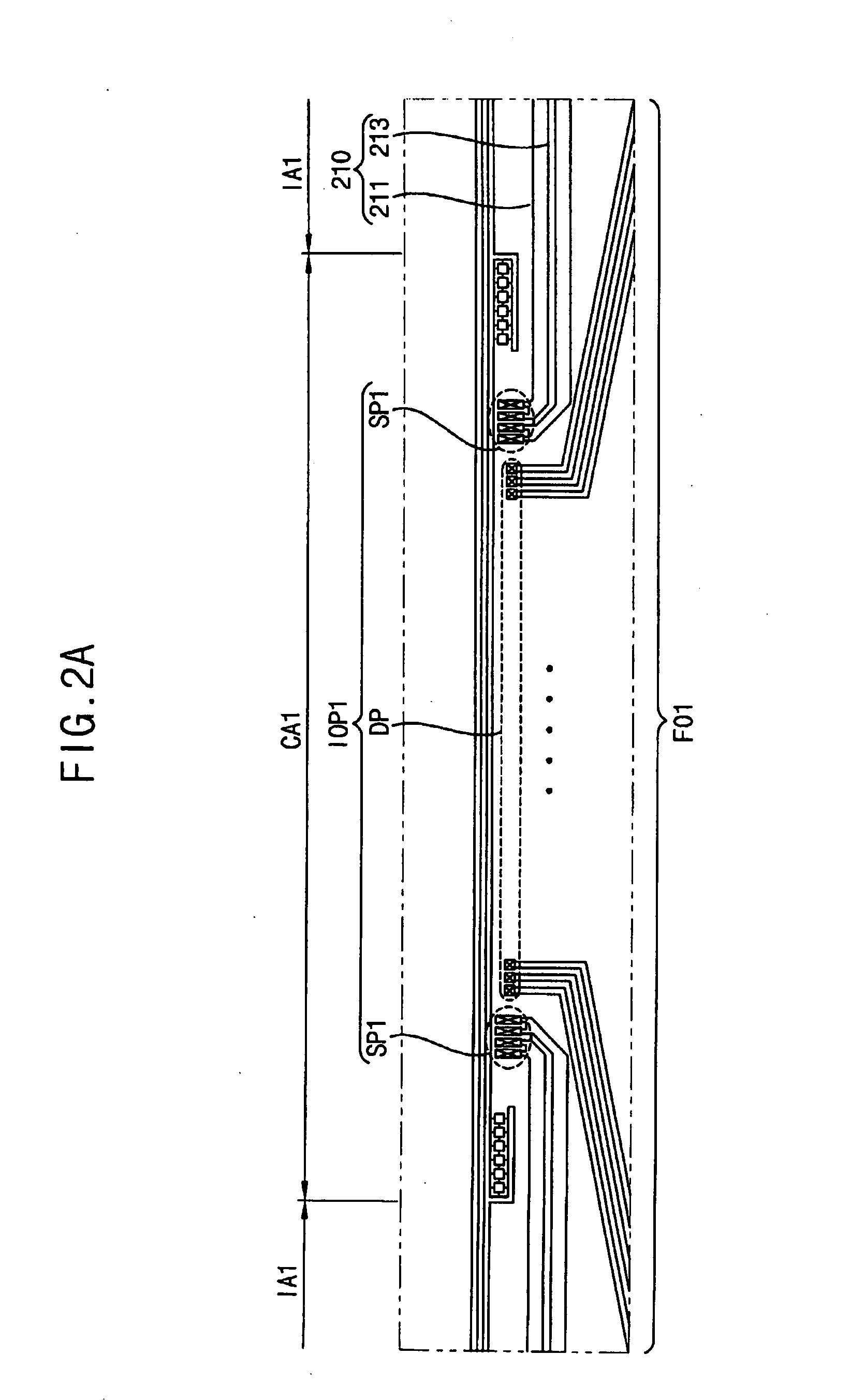

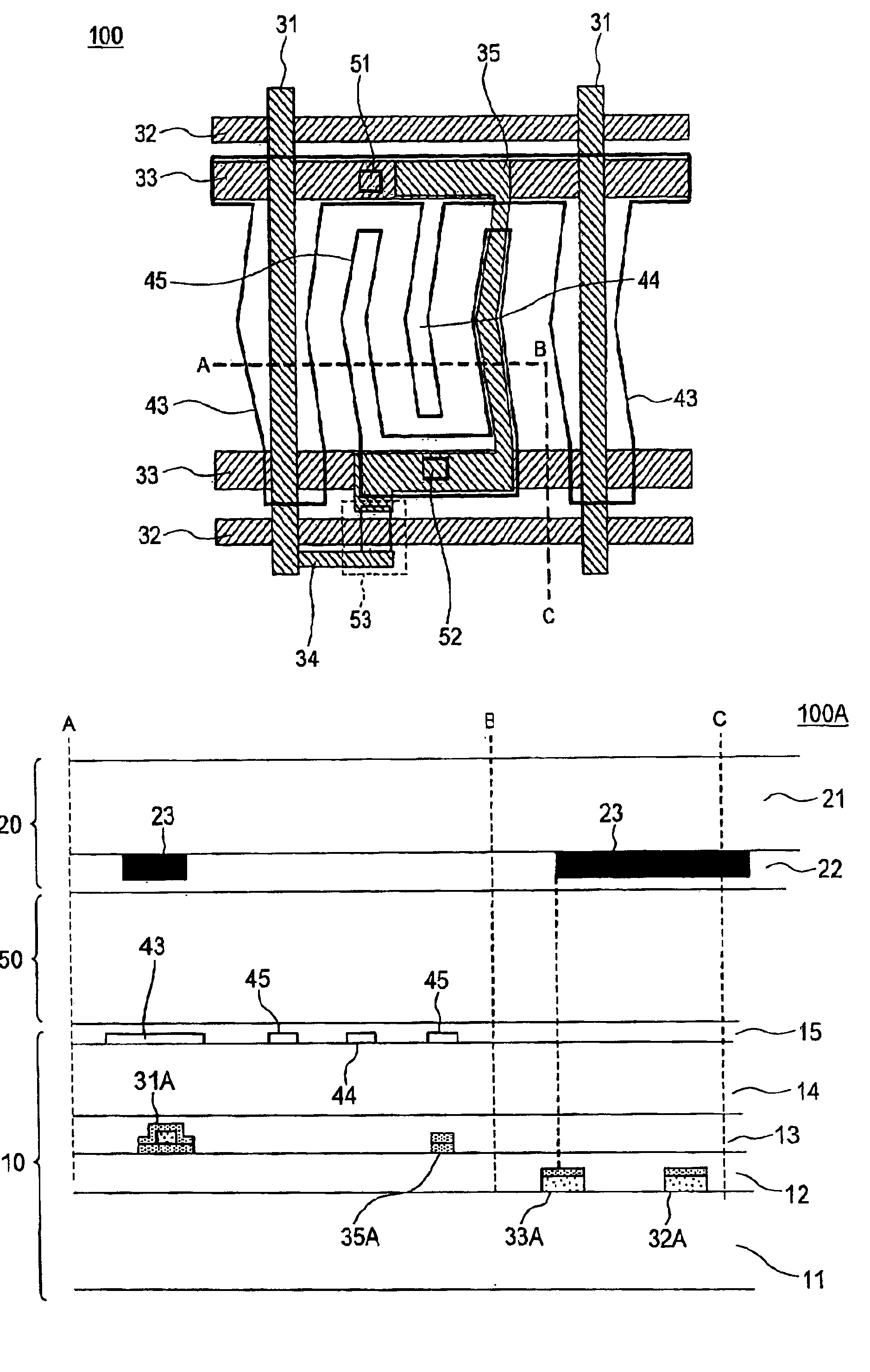

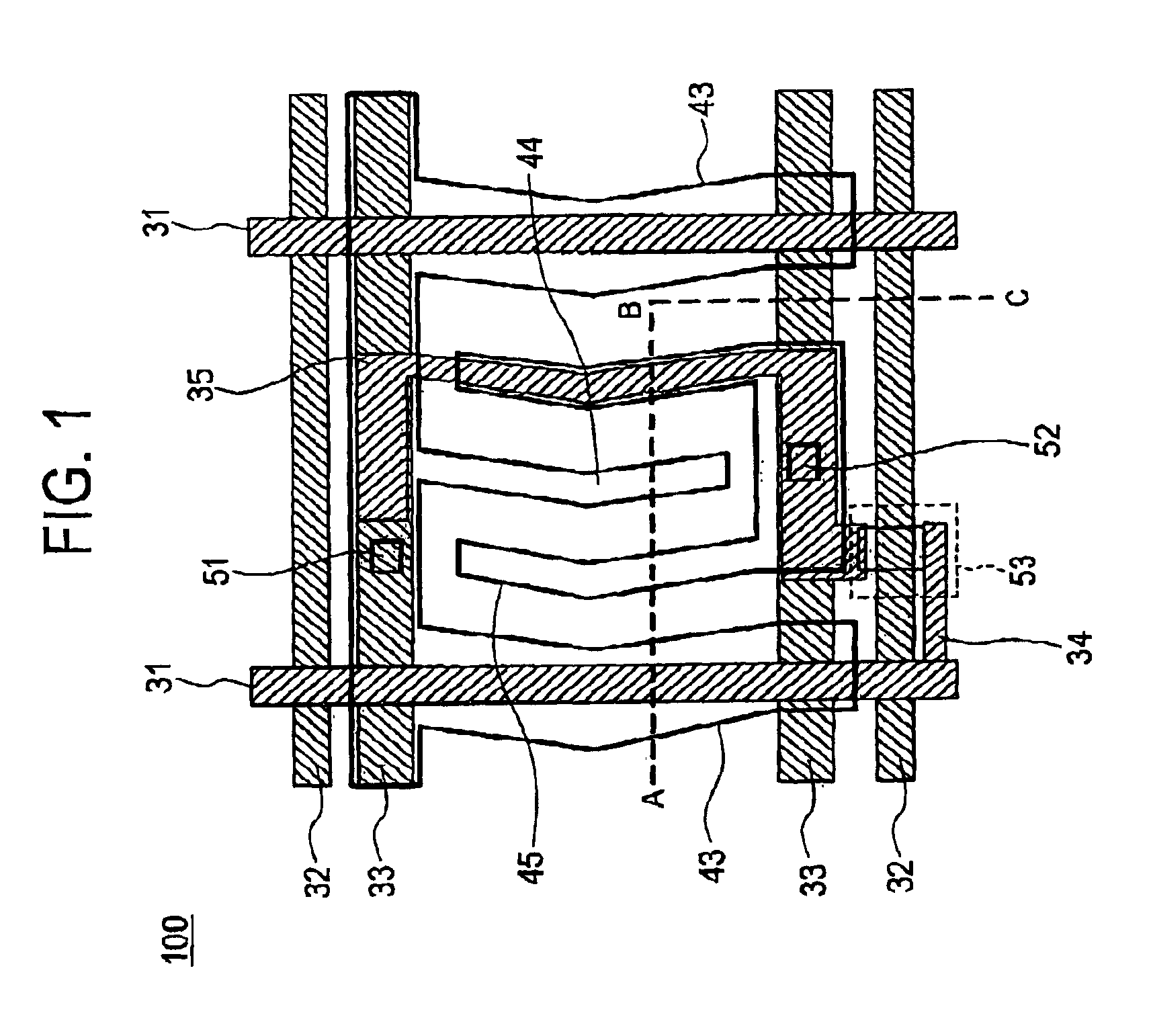

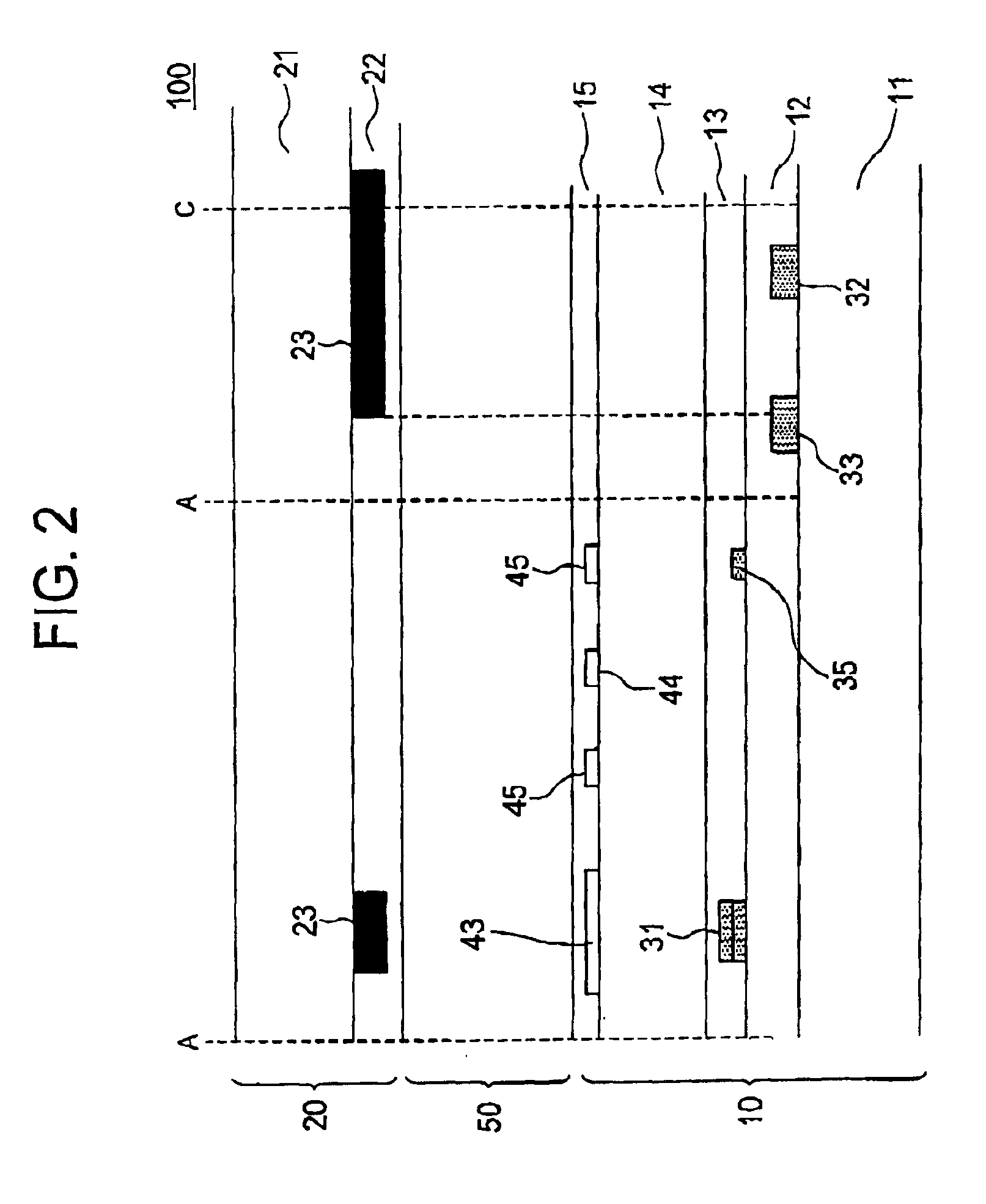

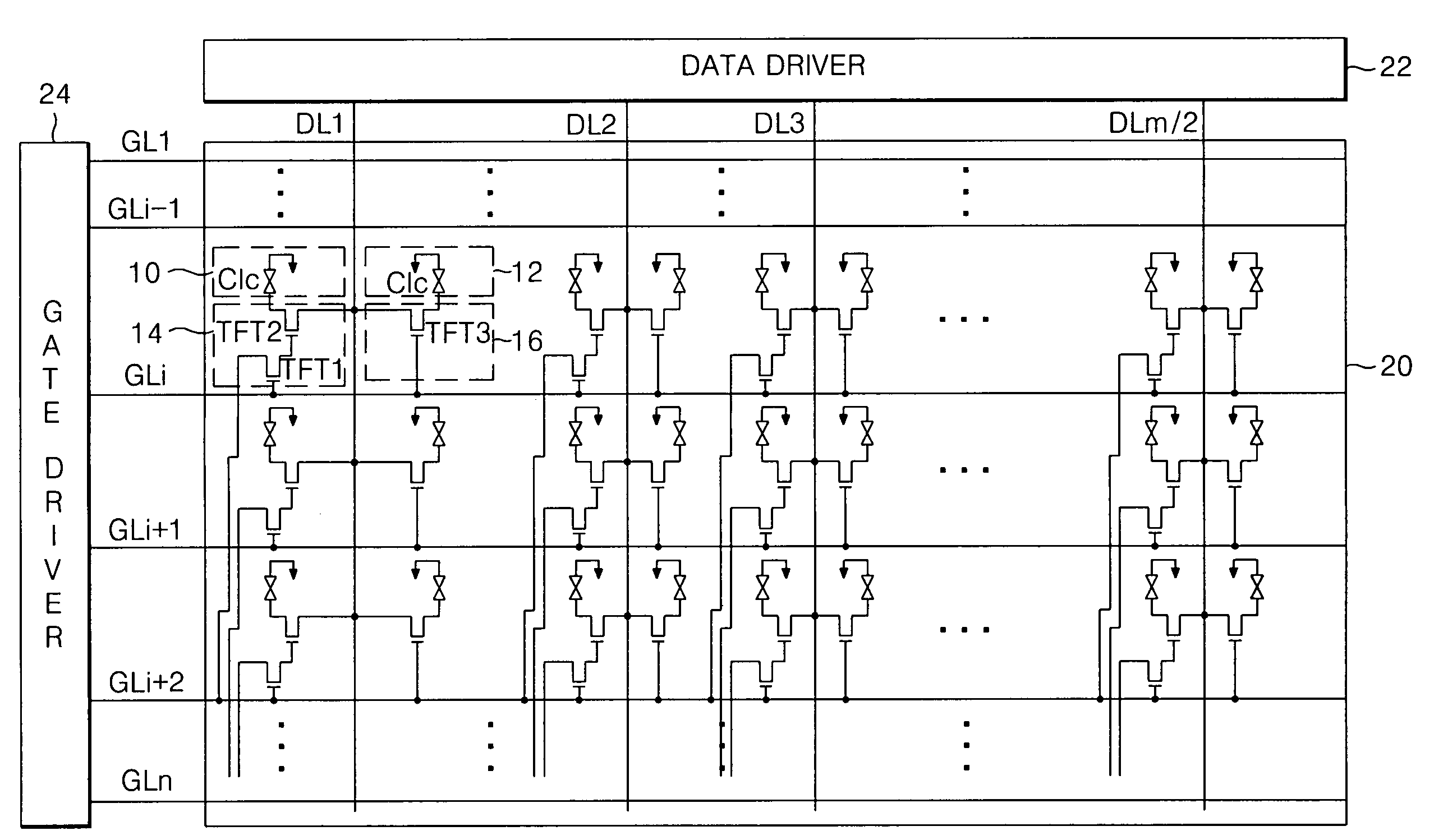

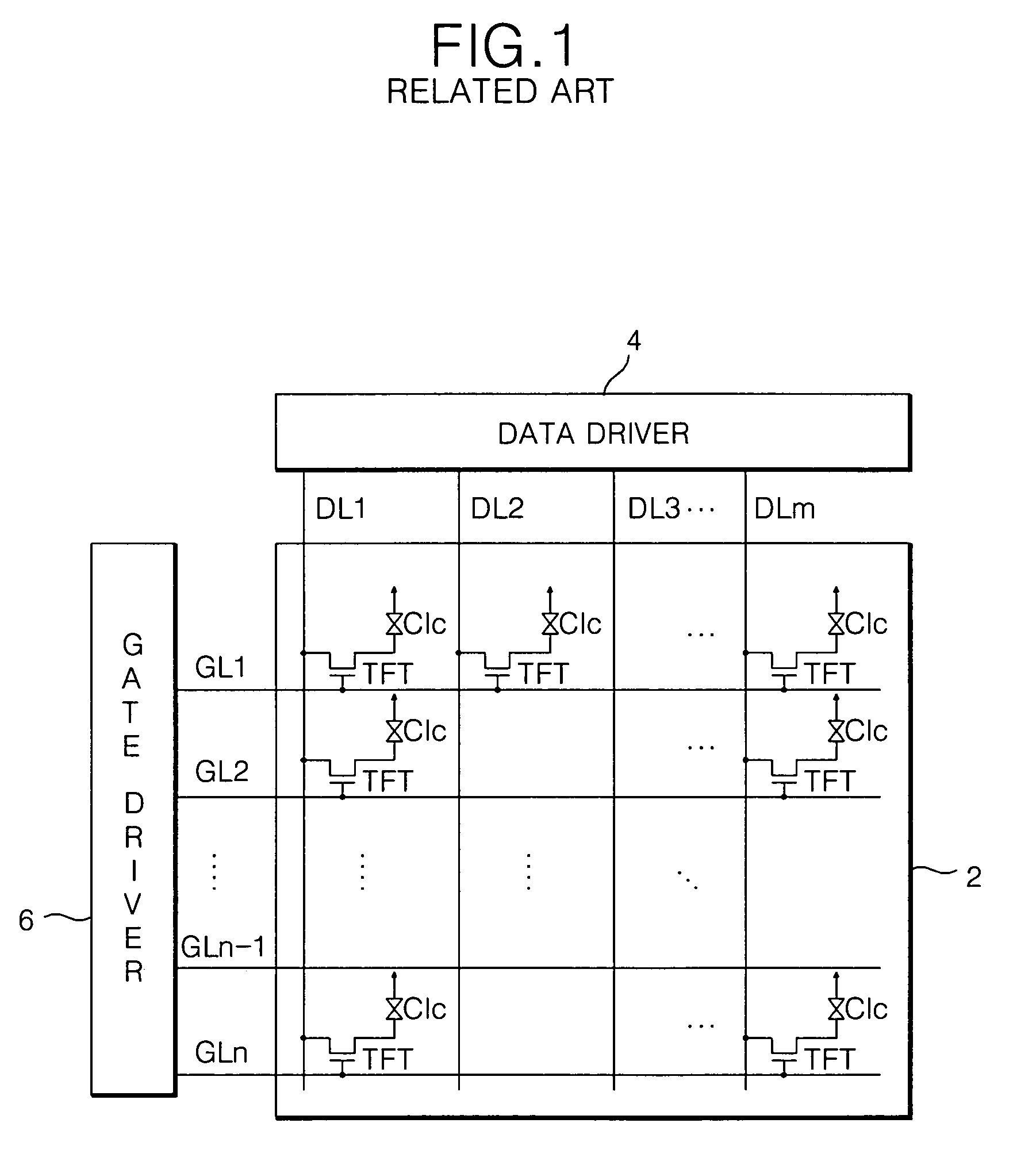

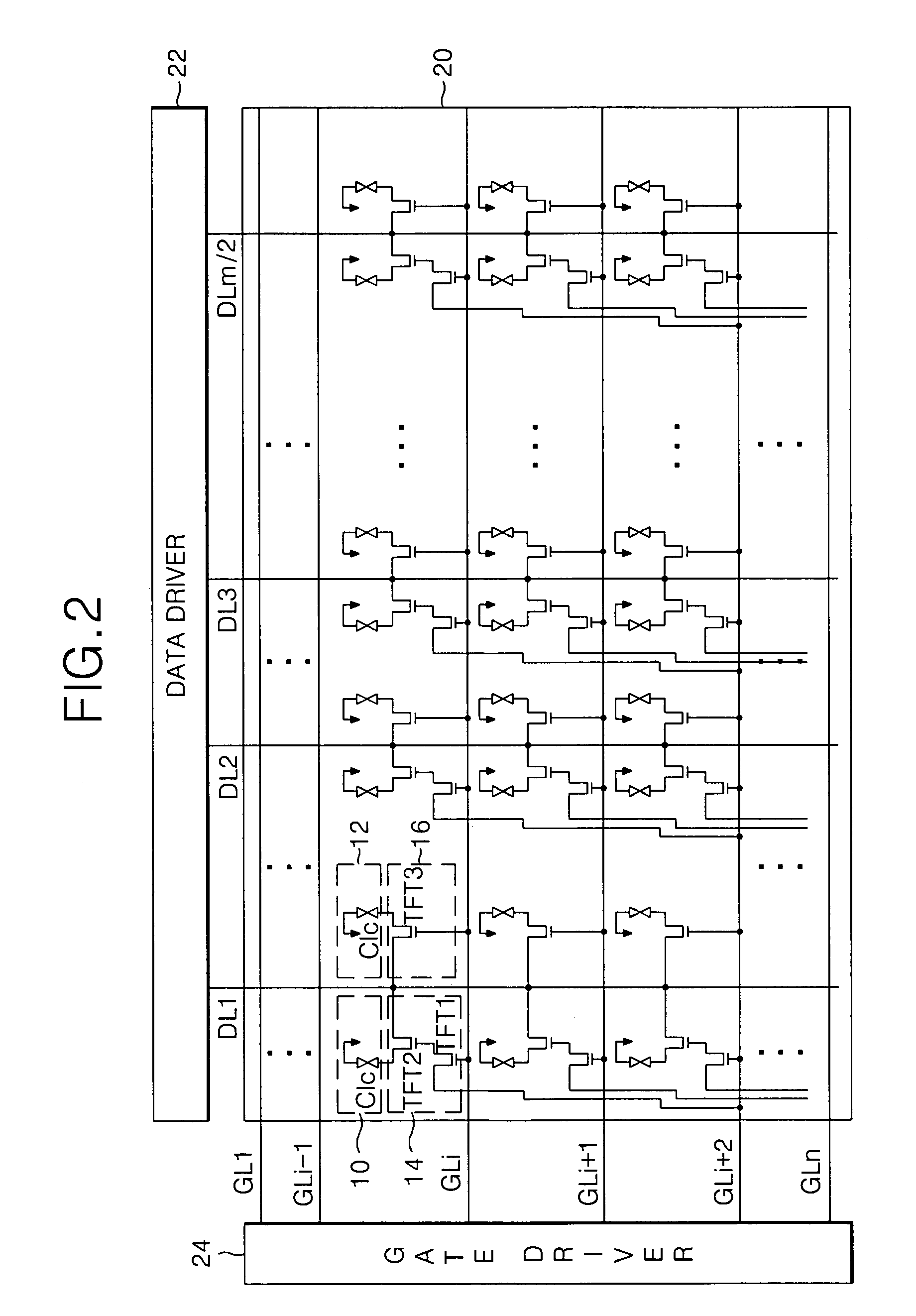

Liquid crystal display device

ActiveUS7256861B2Minimize the numberLow line resistanceStatic indicating devicesNon-linear opticsLine resistanceEngineering

A liquid crystal display device for minimizing the number of data lines and reducing a line resistance is disclosed. In the device, liquid crystal cells are provided at intersections between gate lines and data lines. At least one thin film transistor is provided at each liquid crystal cell to drive the liquid crystal cells. A source protrusion is provided at an ith horizontal line (wherein i is an integer) and is extended from any one of the thin film transistors. The source protrusion is connected, via at least one gate line, an other horizontal gate line excluding the ith horizontal line. A gate protrusion is extended from the other horizontal gate line in such a manner to be connected with the source protrusion.

Owner:LG DISPLAY CO LTD

Flat panel display having reduced line resistance

ActiveUS7397179B2Low line resistanceAvoid voltage dropControl electrodesDischarge tube luminescnet screensLine resistanceImage resolution

A flat panel display reduces the line resistance of a driving power supply line and prevents a voltage drop in the driving power supply line so as to obtain uniform resolution and luminance. The flat panel display includes a substrate, a display region formed on the substrate, the display region having a self-luminescent element and VDD lines that supply a driving potential power and / or a source current to the self-luminescent element. Further, a covering member for sealing the display region at least, the covering member being adhered to the substrate to face the substrate and a terminal region formed on one or more edges of the substrate, the terminal region having one or more driving power terminals are provided. In addition, a driving power supply line that connects the driving power terminals to the VDD lines of the display region and a bus conductive unit that is electrically connected to the driving power supply line are provided.

Owner:SAMSUNG DISPLAY CO LTD

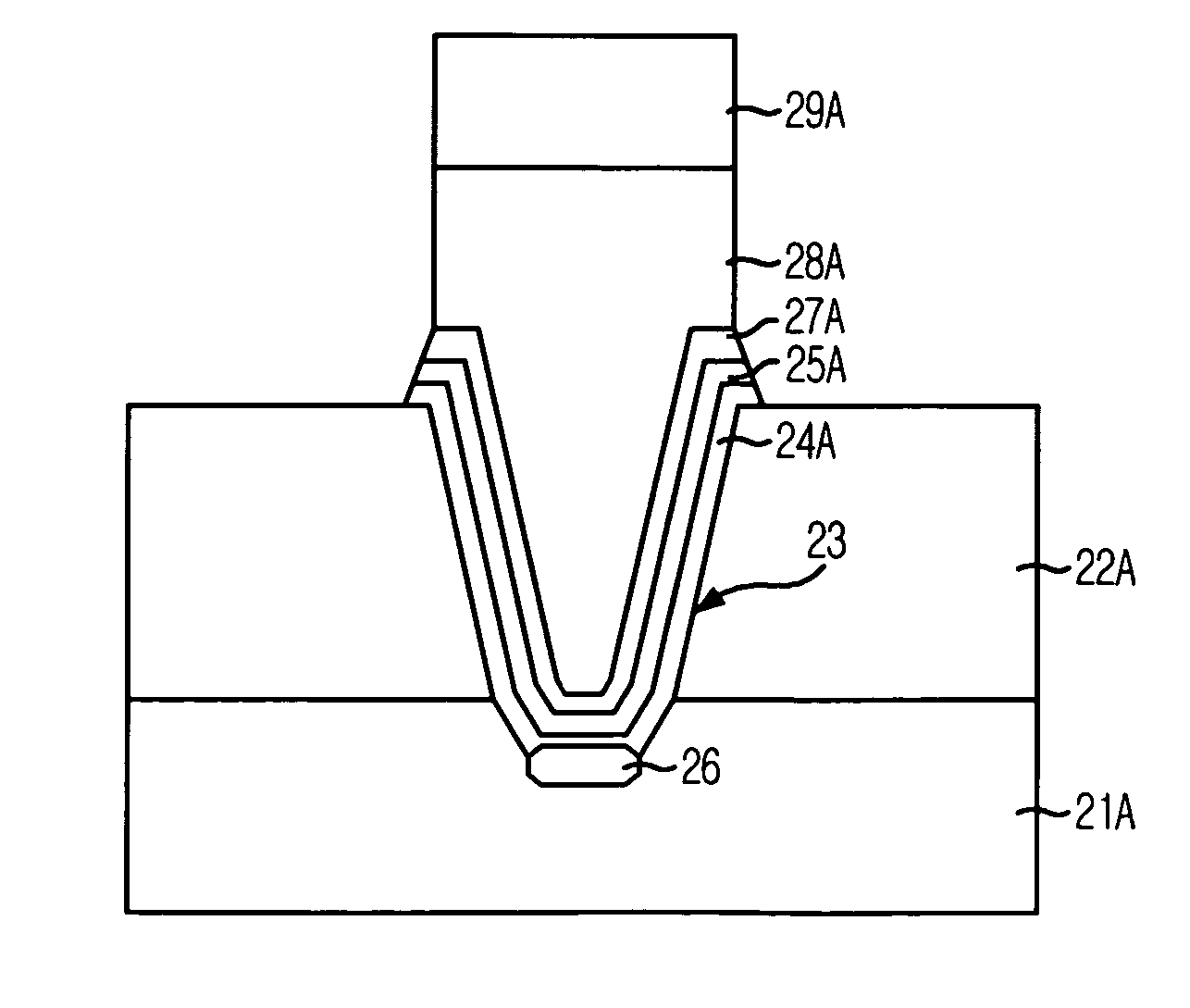

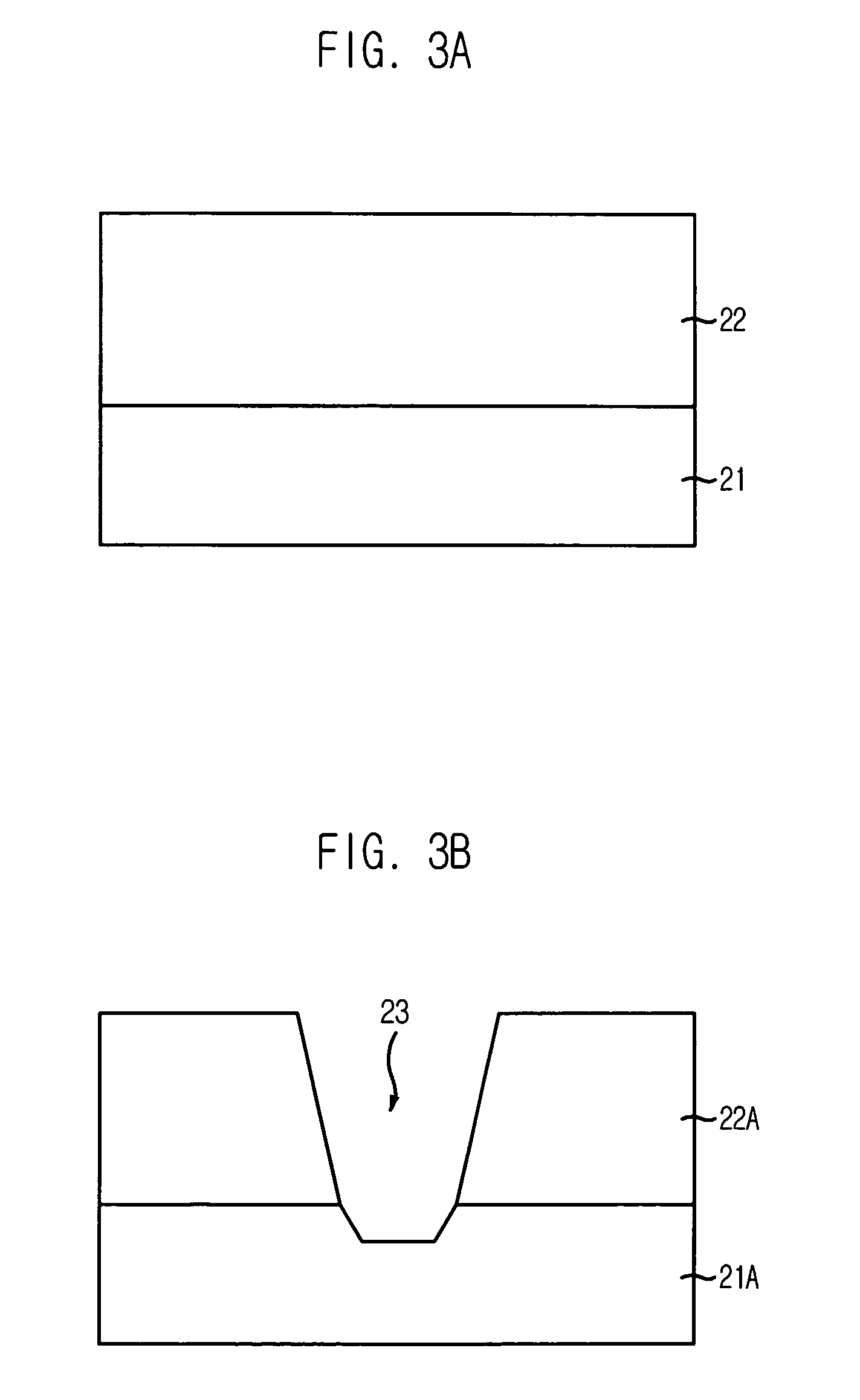

Method and fabricating semiconductor memory device

InactiveUS20070045854A1Improve operating characteristicsLow line resistanceSemiconductor/solid-state device detailsSolid-state devicesTitanium nitrideThin layer

A semiconductor memory device includes a titanium layer and a titanium nitride layer formed on a substrate, a thin layer formed on the titanium nitride layer, and a metal layer formed on the thin layer, wherein the thin layer increases a grain size of the metal layer.

Owner:SK HYNIX INC

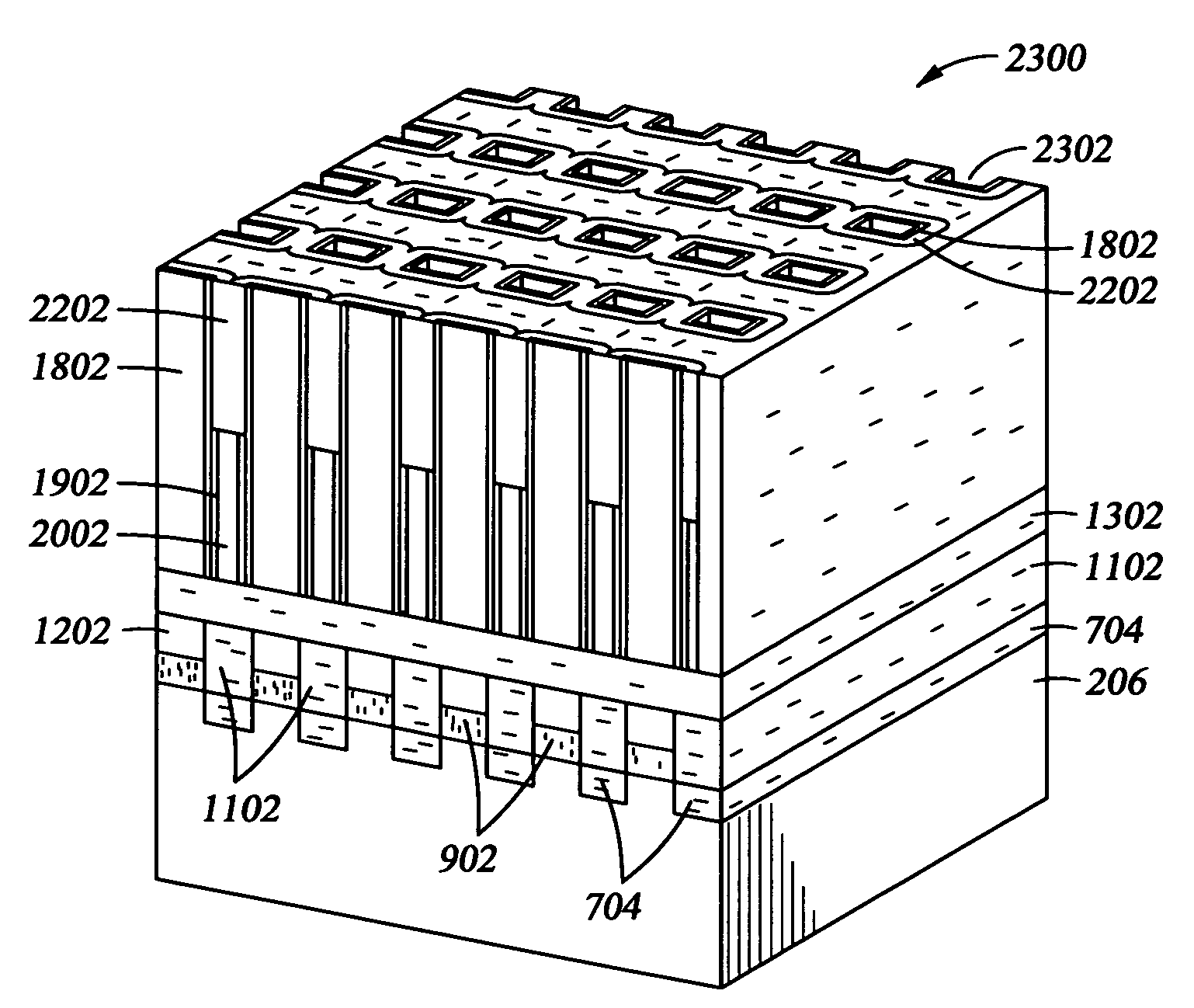

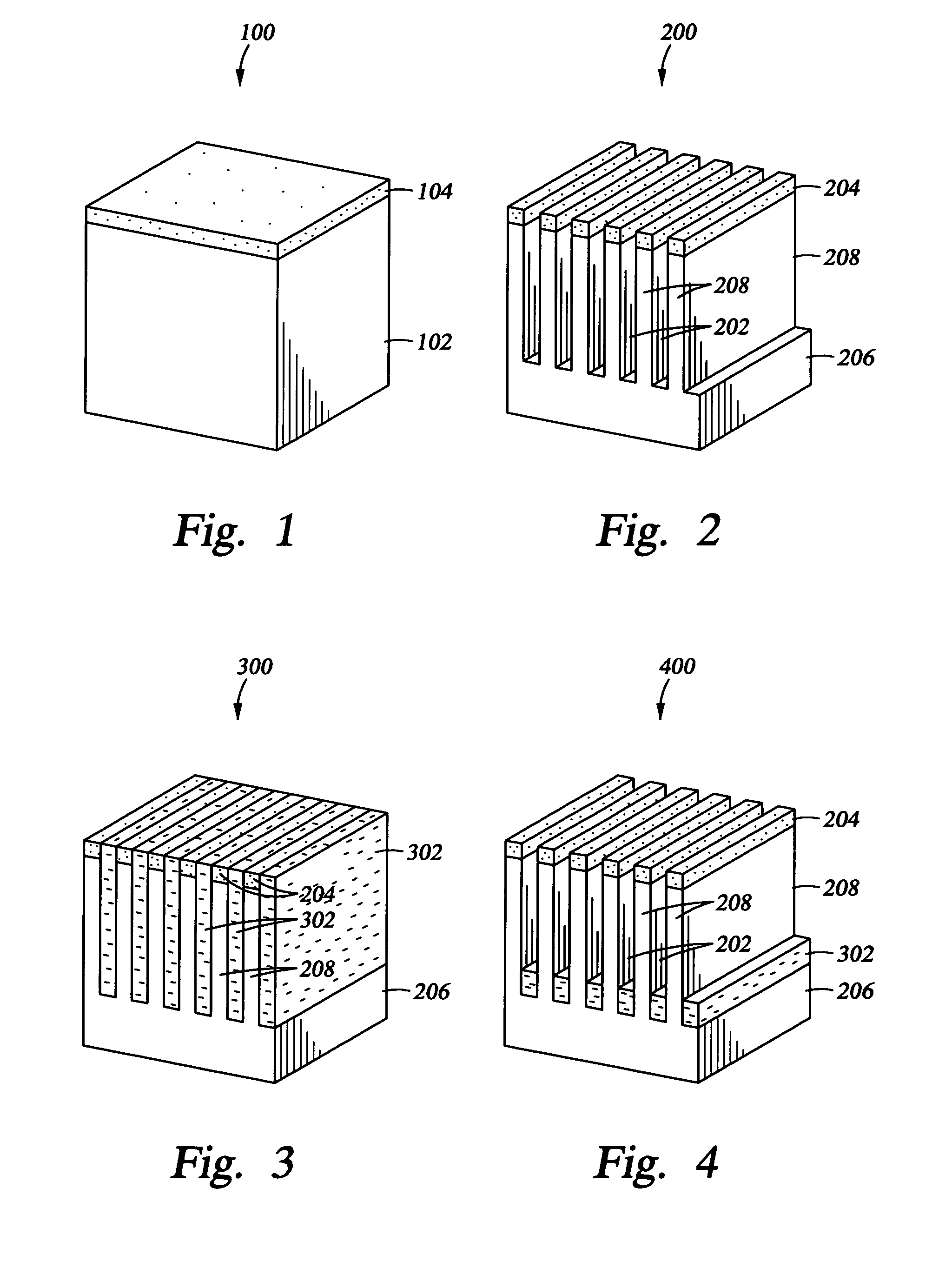

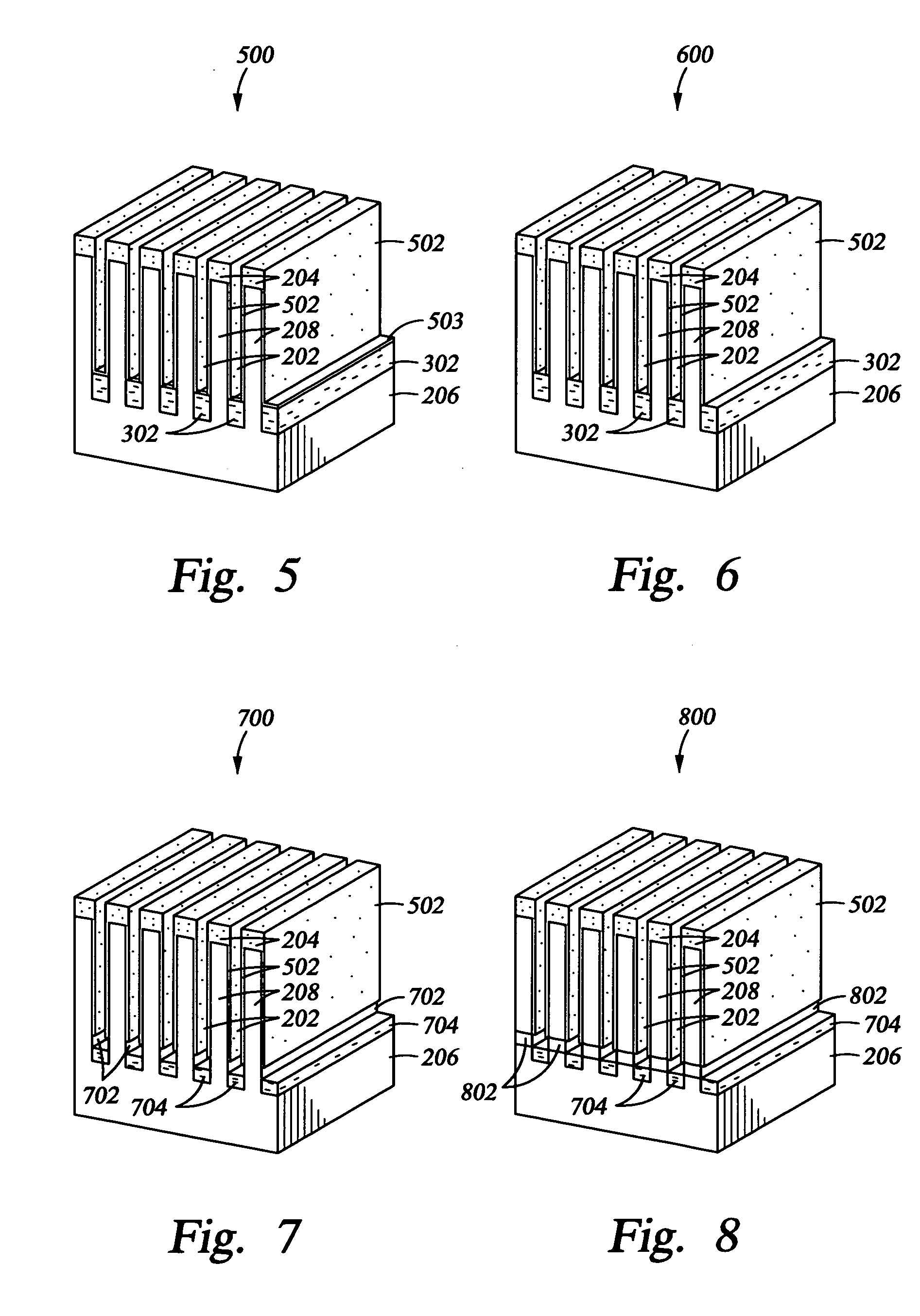

Method of fabricating a gate-all-around word line for a vertical channel DRAM

ActiveUS9023723B2Easy to processCloser packingTransistorSolid-state devicesEngineeringVertical channel

A method of fabricating a self-aligned buried wordline in a structure which contains a self-aligned buried bit line, where the overall structure which makes up a portion of a vertical channel DRAM. The materials and processes used enable self-alignment of elements of the buried wordline during the fabrication process. In addition, the materials and processes used enable for formation of individual DRAM cells which have a buried bit line width which is 16 nm or less and a perpendicular buried wordline width which is 24 nm or less.

Owner:APPLIED MATERIALS INC

Liquid crystal display device having a higher constrast ratio

ActiveUS20040057004A1High strengthLow line resistanceNon-linear opticsReflectivityLiquid-crystal display

A LCD device has a black matrix defining a plurality of pixel areas in the LCD device. An interconnect layer formed on a TFT panel includes a first interconnect line passing through the pixel area and a second interconnect line passing outside the pixel area. The first interconnect line is lower in a product of a thickness thereof by a surface reflectance thereof than the second interconnect line.

Owner:NEC LCD TECH CORP

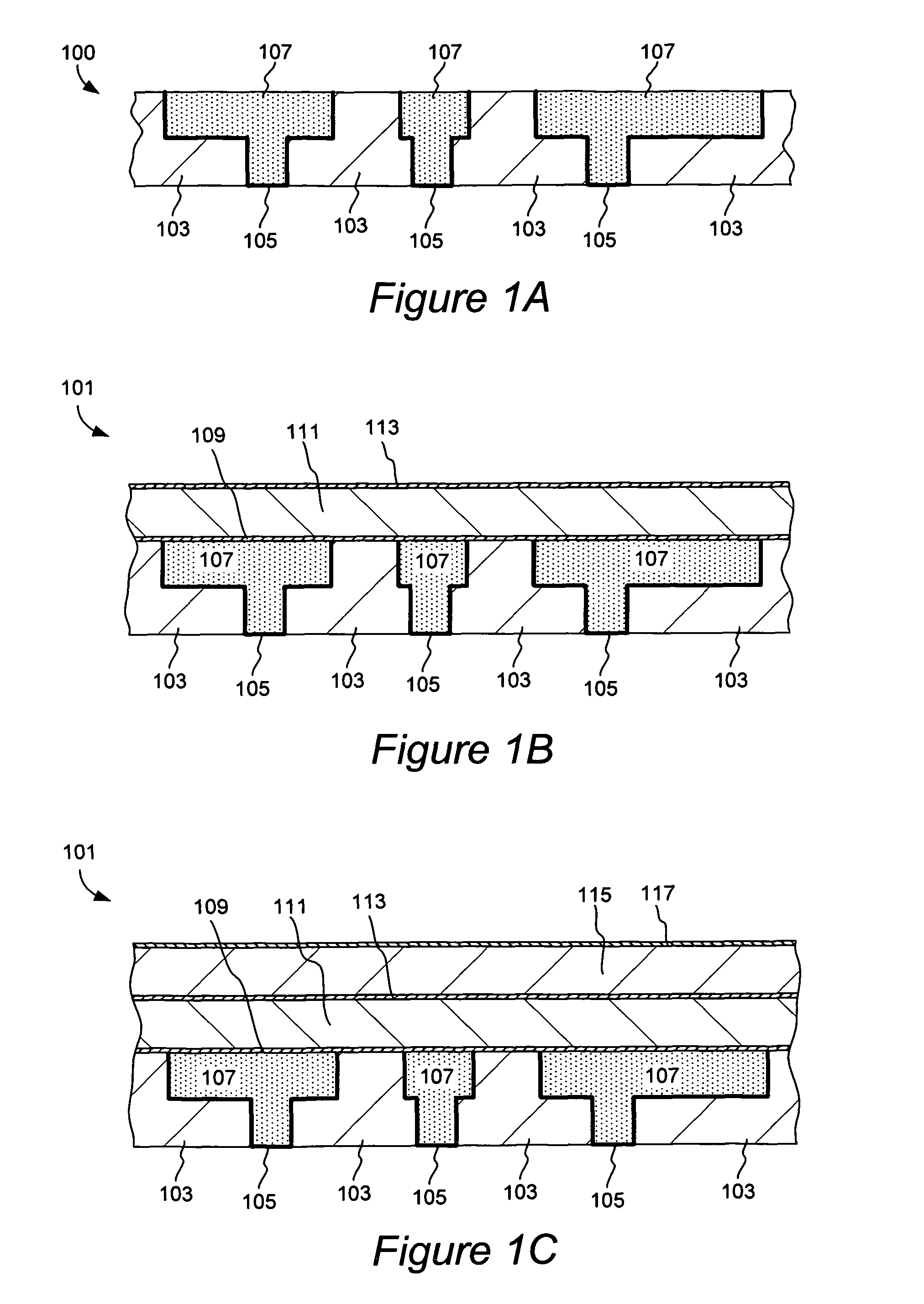

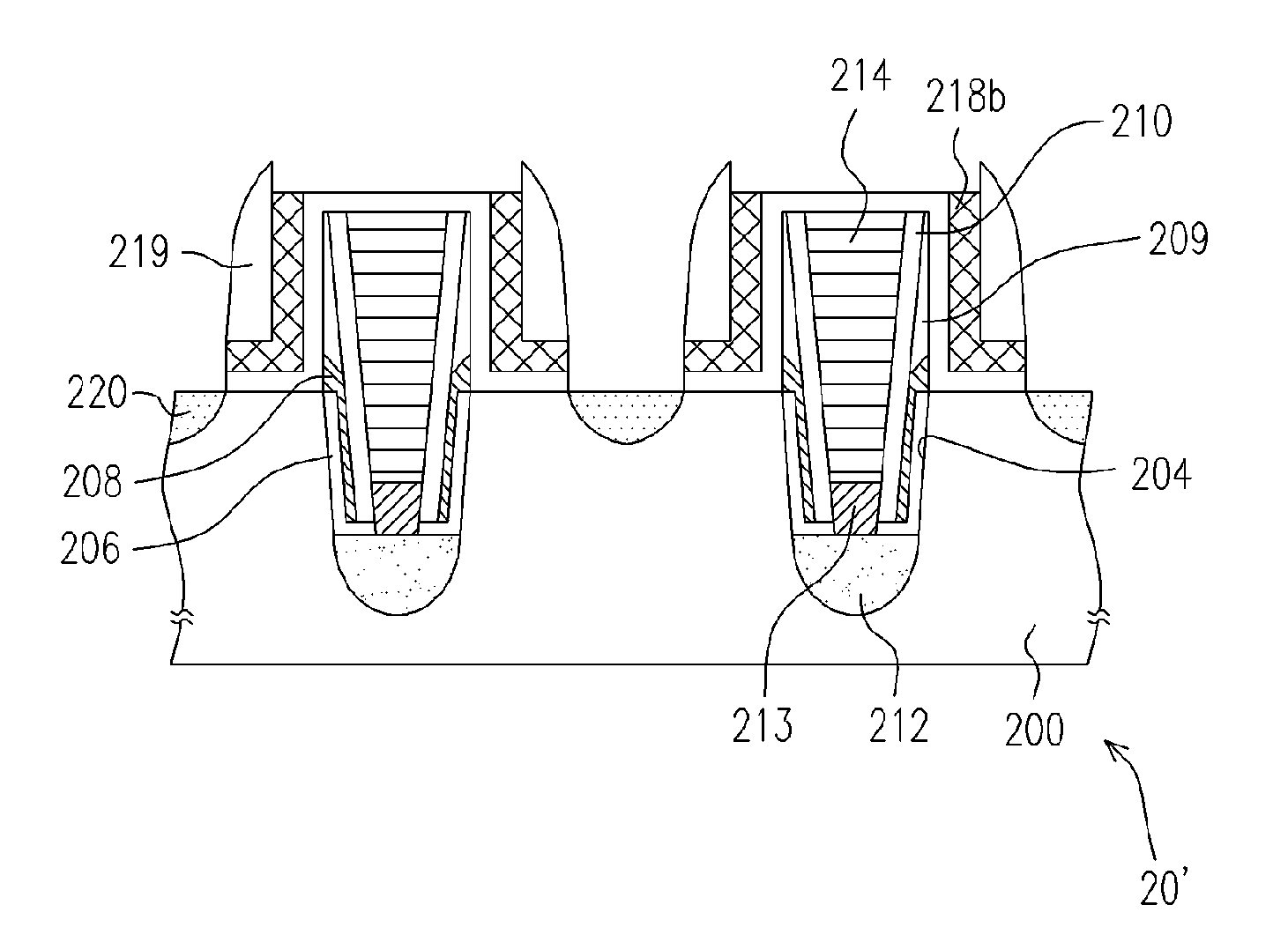

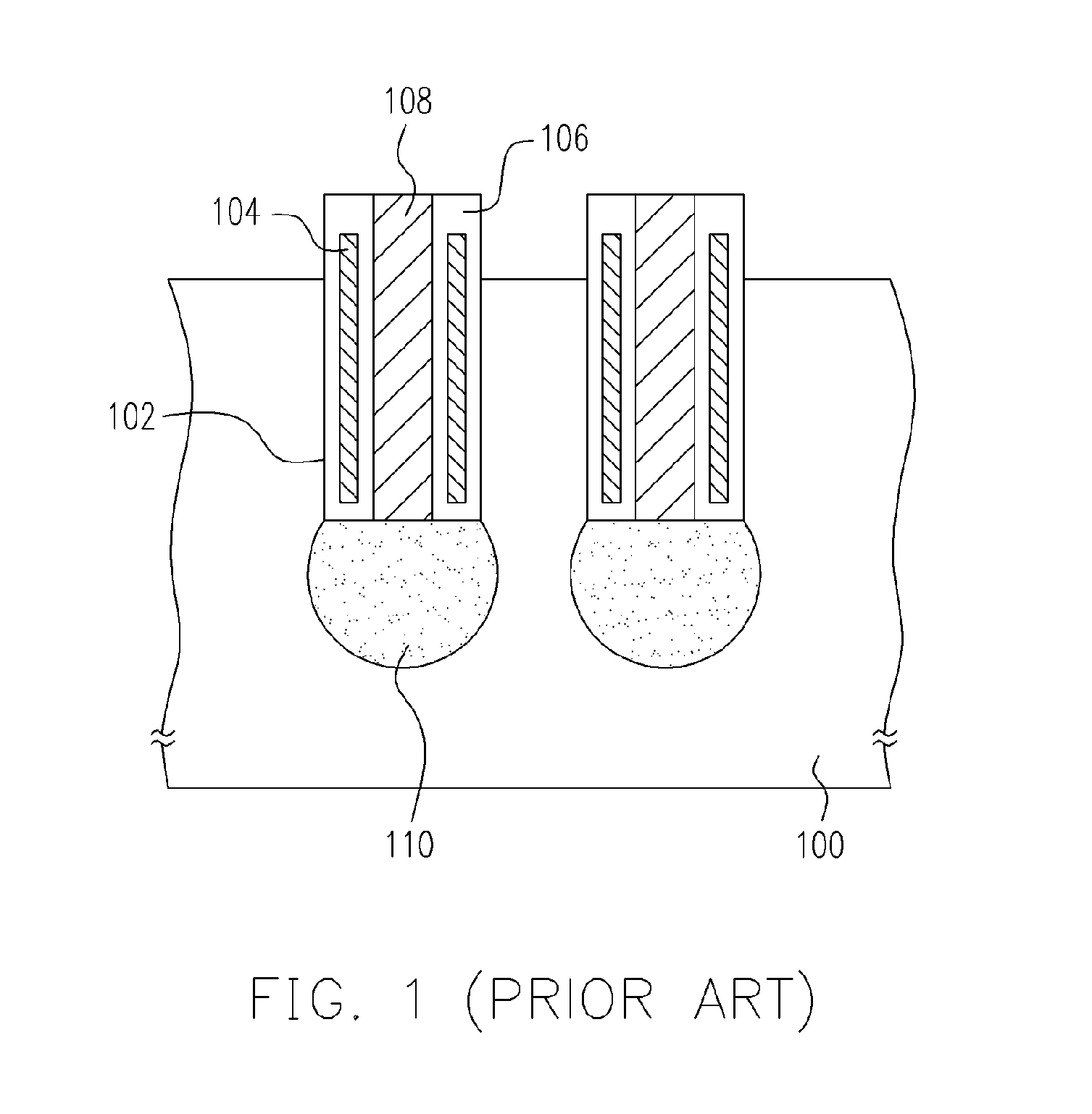

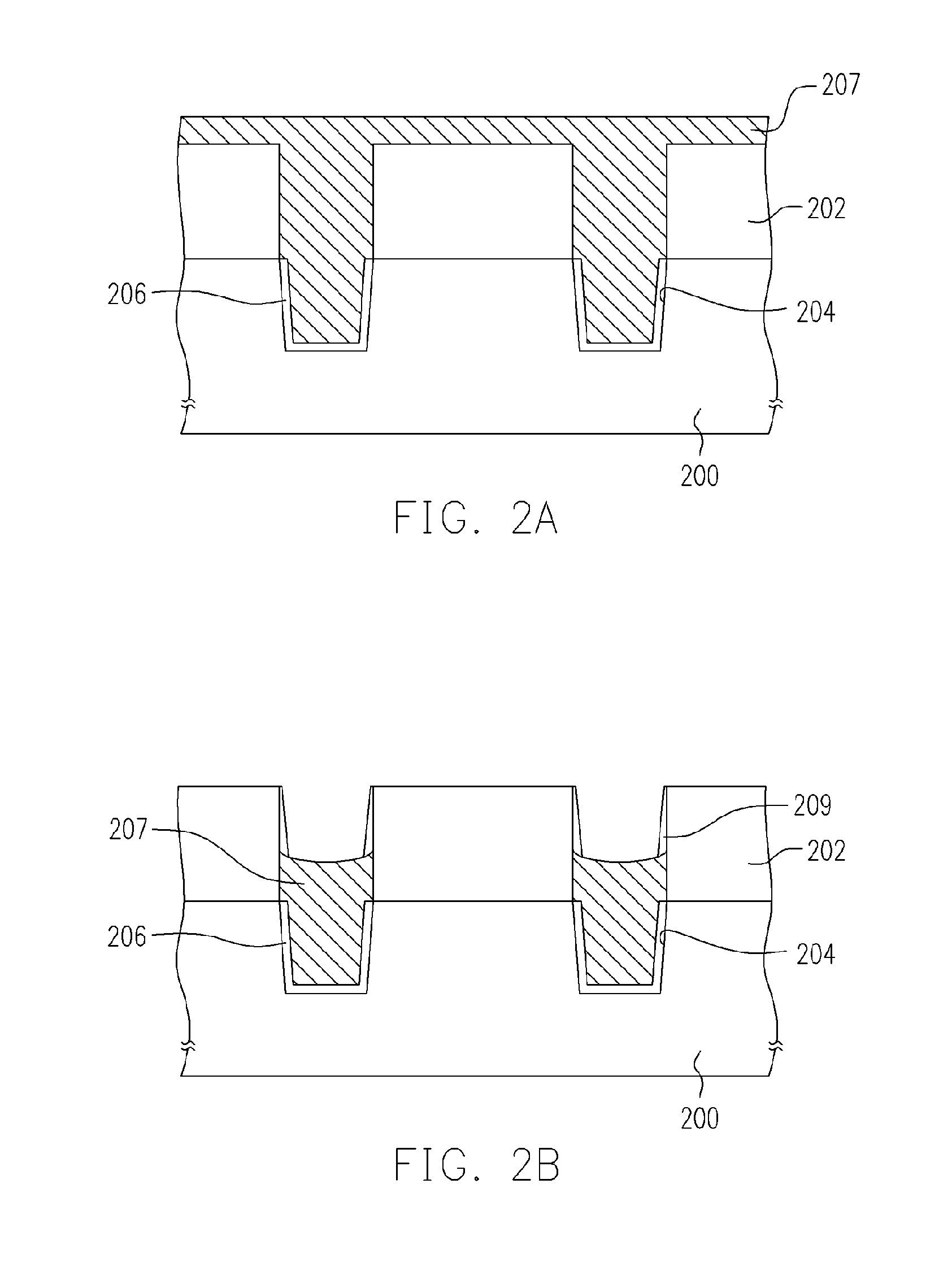

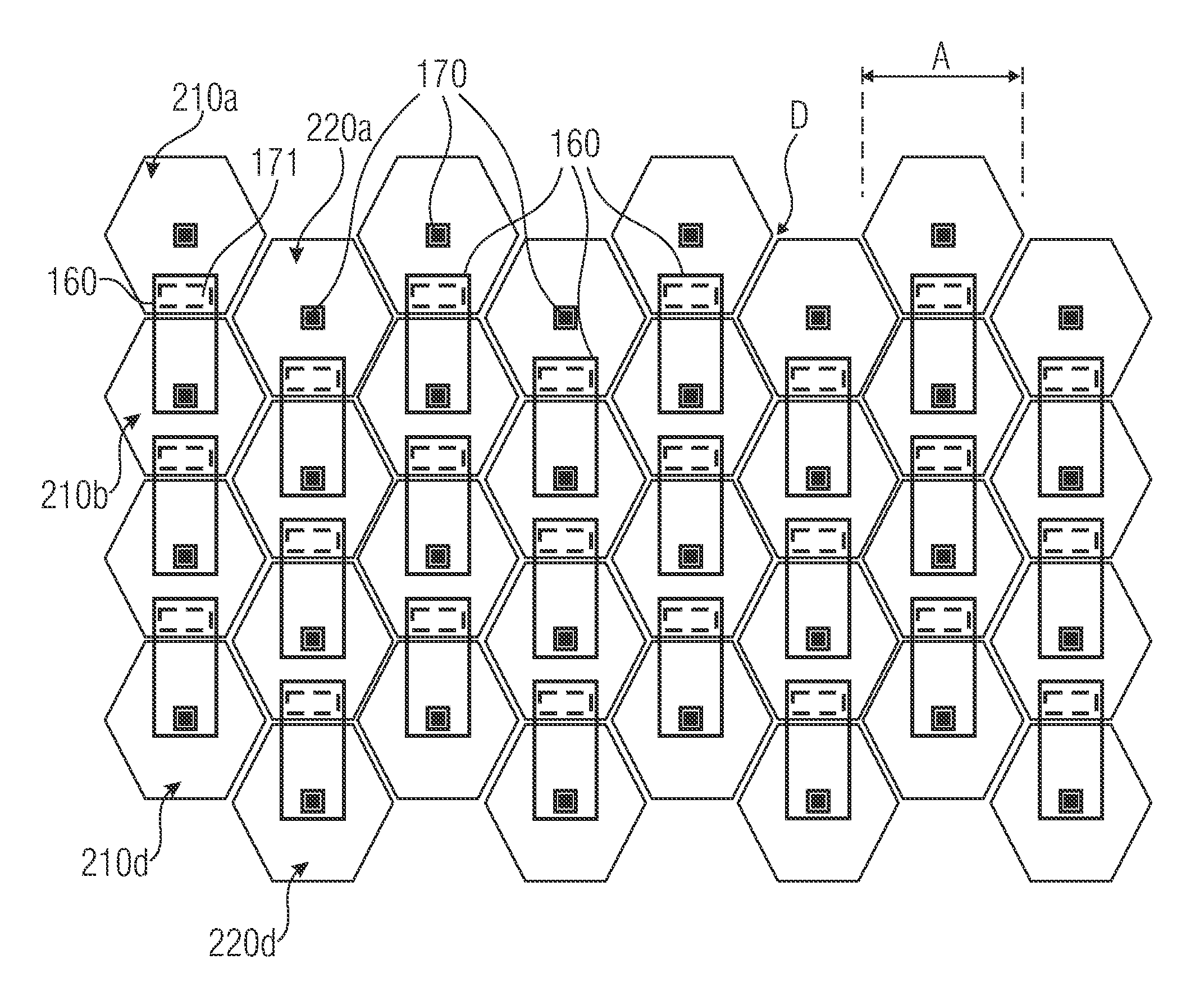

Bit line structure, semiconductor device and method of forming the same

ActiveUS8809933B2Low line resistanceAvoid loadTransistorSolid-state devicesPower semiconductor deviceEngineering

A semiconductor device including a substrate, a plurality of stacked gate structures, a plurality of doped regions, a plurality of liner layers, a plurality of conductive layers, a plurality of dielectric layers and a plurality of word lines is provided. The substrate has a plurality of trenches therein. The stacked gate structures are on the substrate between the trenches. The doped regions are in the substrate at sidewalls or bottoms of the trenches. The liner layers are on at least a portion of sidewalls of the stacked gate structures and on sidewalls of the trenches. The conductive layers are in the trenches and electrically connected to the doped regions. The dielectric layers are on the conductive layers and between the stacked gate structures. The word lines are on the substrate and electrically connected to the stacked gate structures.

Owner:MACRONIX INT CO LTD

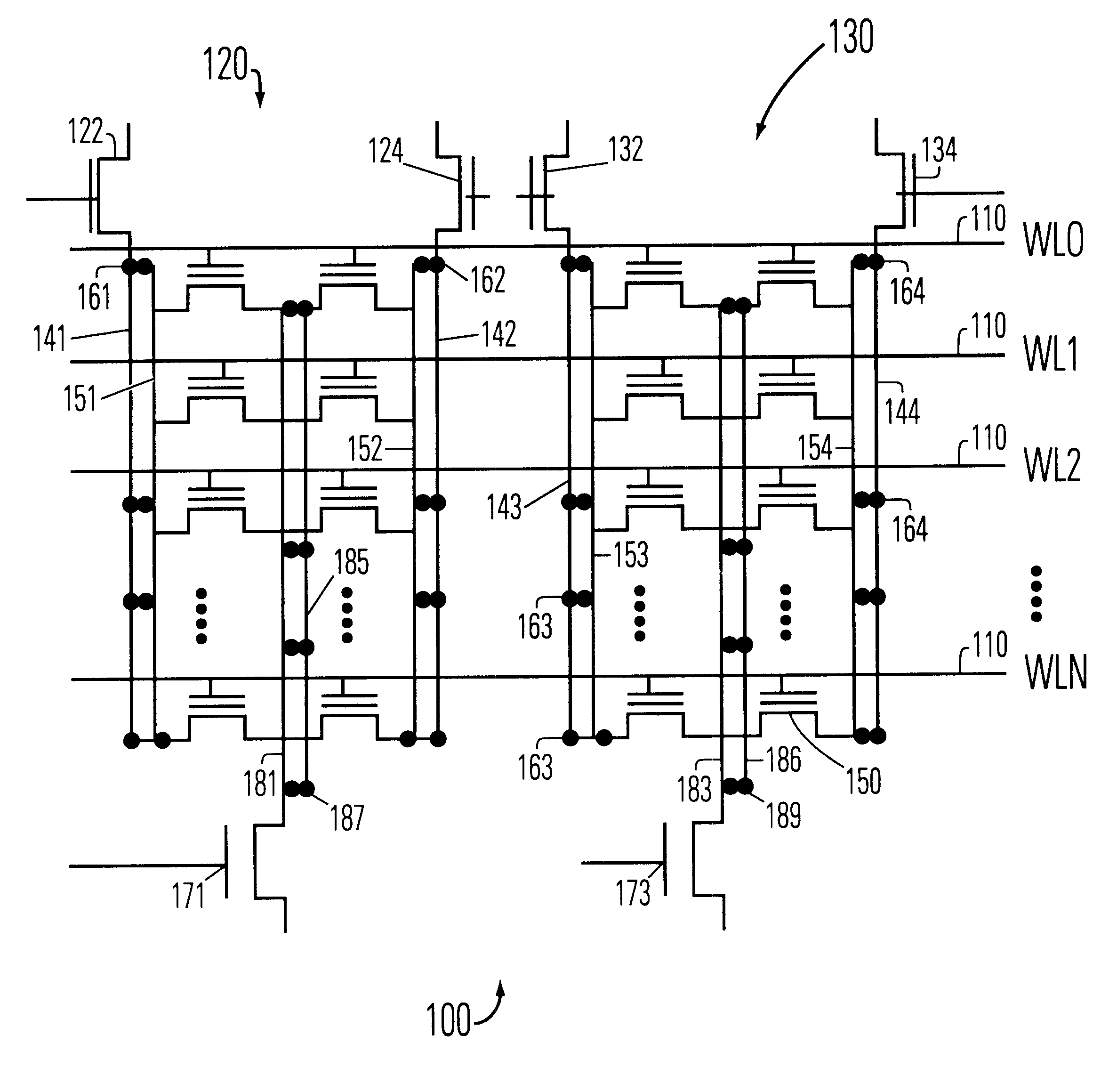

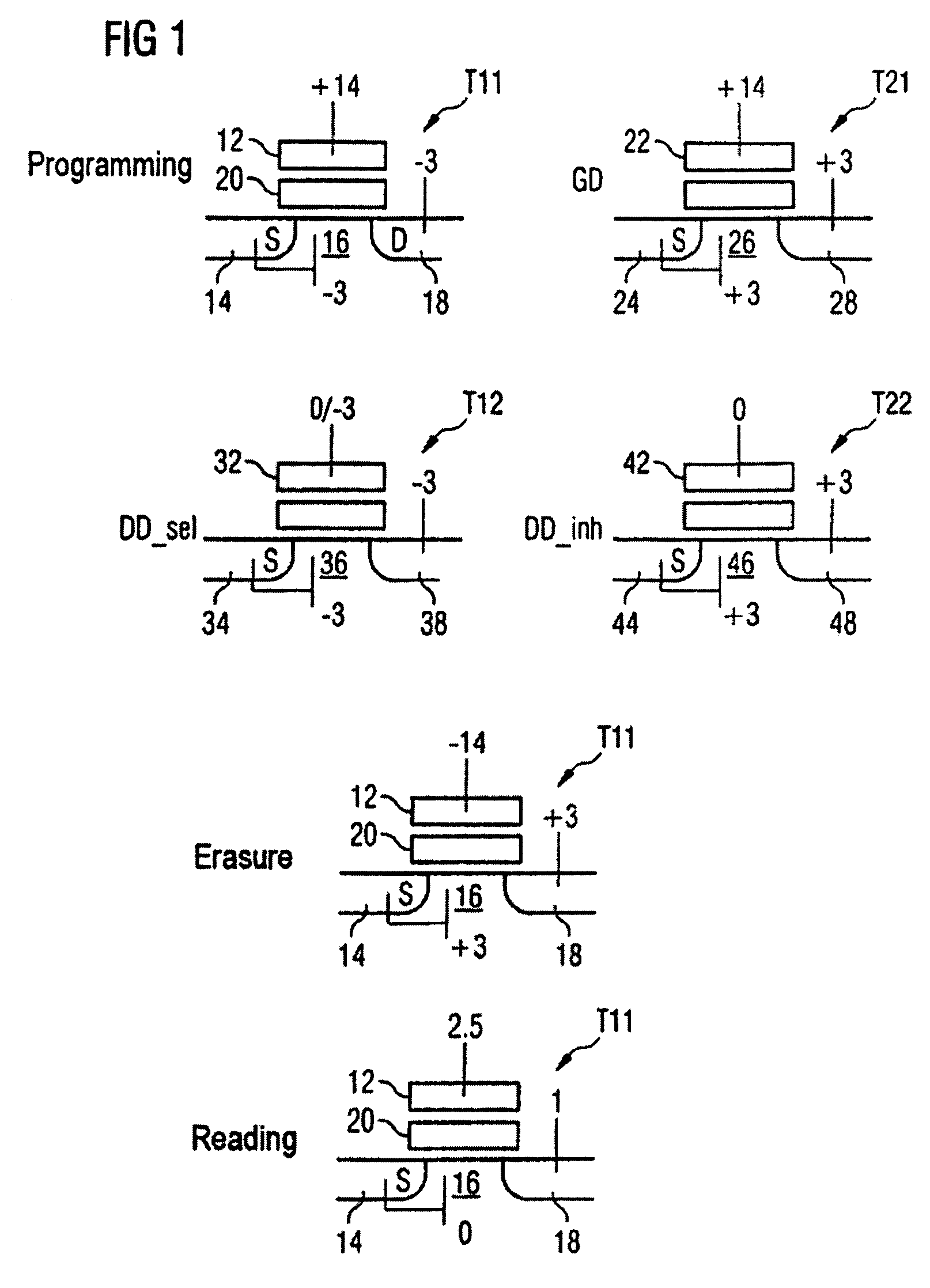

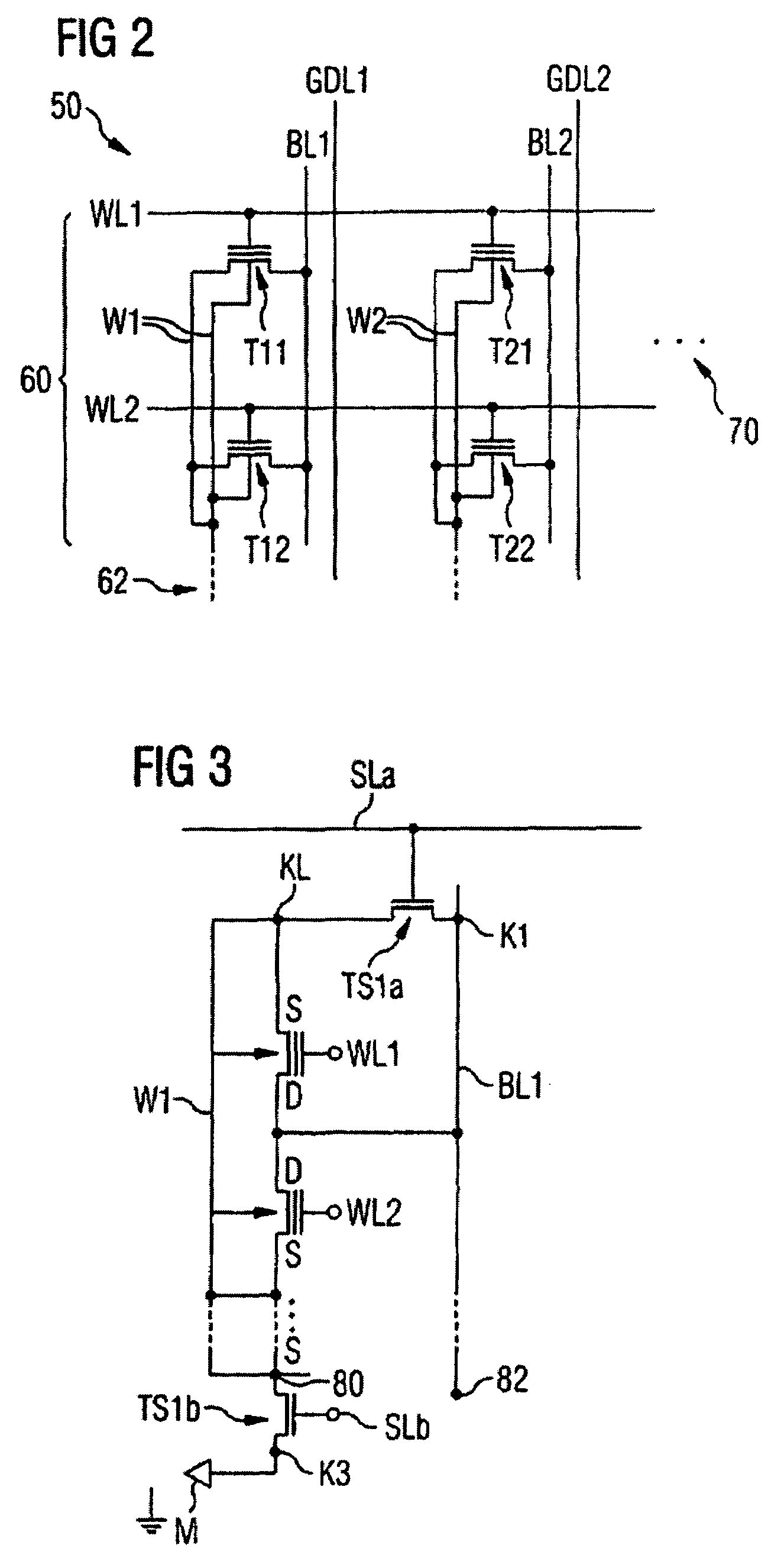

Integrated memory circuit arrangement

InactiveUS7349251B2Large sectionLow line resistanceSolid-state devicesRead-only memoriesBit lineEngineering

A memory circuit arrangement includes a switching element per column that can be used to connect or disconnect two bit lines for memory cells of a column. The switching element leads to a reduction of the chip area and / or to an improvement in the electronic properties of the memory circuit arrangement.

Owner:INFINEON TECH AG

Signal line for a display device, etchant, thin film transistor panel, and method for manufacturing the same

ActiveUS7888148B2Low reliabilityLower resistanceStatic indicating devicesSemiconductor/solid-state device detailsNiobiumDisplay device

Owner:SAMSUNG DISPLAY CO LTD

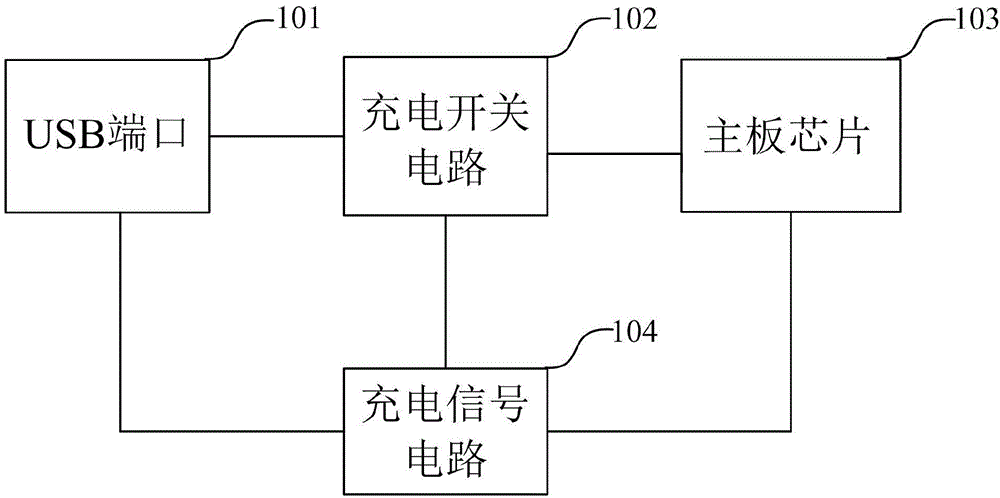

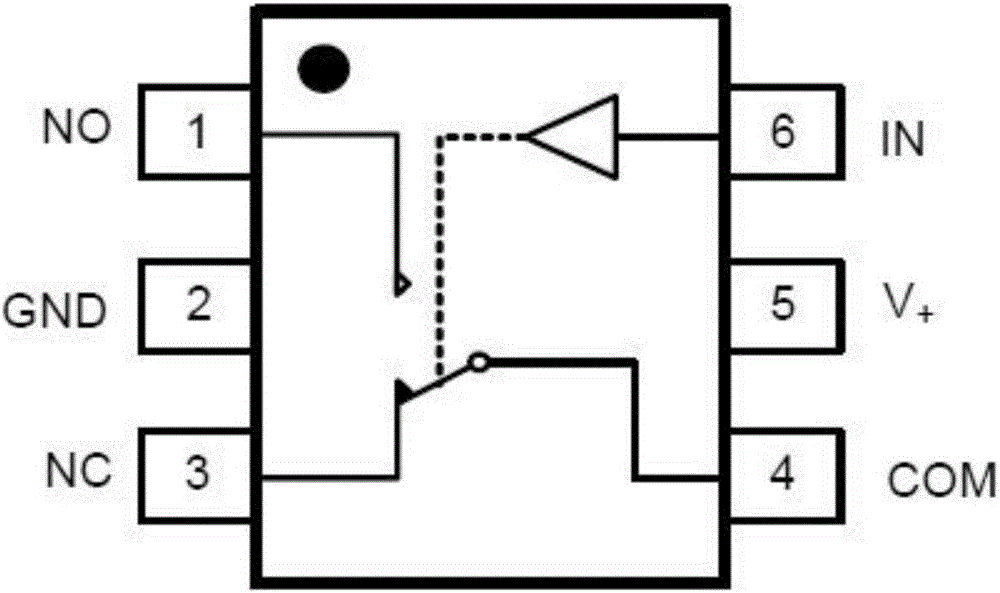

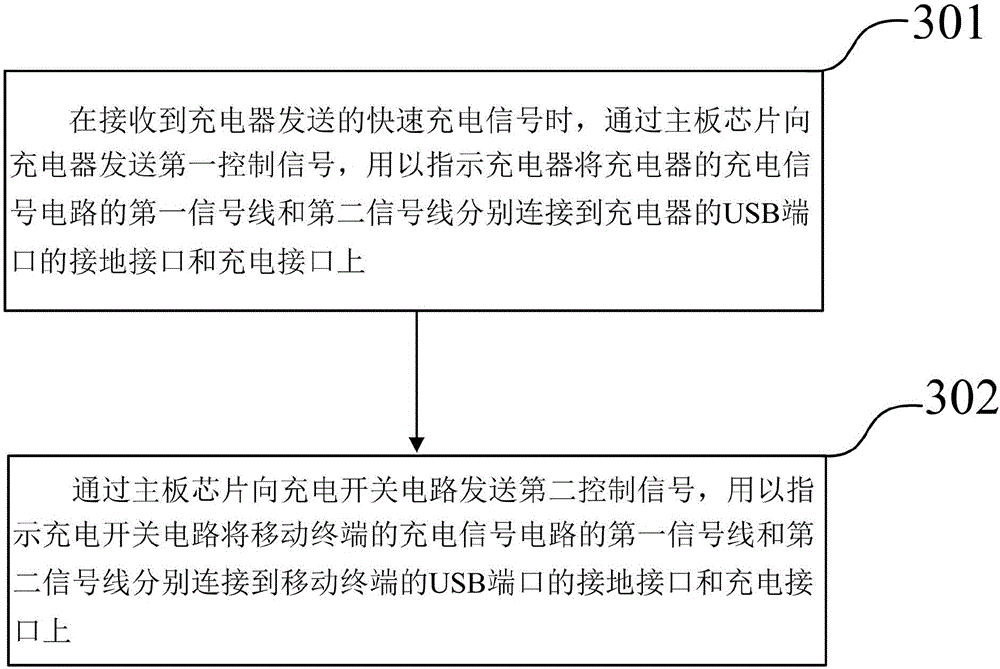

Charging method, apparatus and system for mobile terminal, and mobile terminal

PendingCN106505656AIncrease the speed of fast chargingLow line resistanceElectric powerCharging/discharging current/voltage regulationPower flowCharge current

The invention discloses a mobile terminal. The mobile terminal comprises a USB port, a main board chip, a charging signal circuit and a charging switching circuit, wherein the main board chip is used for transmitting a first control signal to a charger when a rapid charging signal from the charger is received so as to indicate the charger to connect a first signal line and a second signal lien of the charging signal circuit with a grounding interface and a charging interface of the USB port respectively, and transmitting a second control signal to the charging switching circuit; and the charging switching circuit is connected with the main board chip, the USB port and the charging signal circuit separately and used for connecting the first signal line and the second signal line of the charging signal circuit of the mobile terminal with the grounding interface and the charging interface of the USB port of the mobile terminal respectively when the second control signal is received. Therefore, the circuit resistance of the USB charging line is lowered, the charging current is greatly improved, and the rapid charging speed of the mobile terminal is increased.

Owner:QINGDAO HISENSE MOBILE COMM TECH CO LTD

Solar cell front side silver paste doped with modified grapheme and preparation method thereof

ActiveUS20180226172A1Good ohmic contactContact resistanceNon-conductive material with dispersed conductive materialPhotovoltaic energy generationSilver pasteOrganic solvent

A solar cell front side silver paste doped with modified graphene and its preparation method are disclosed. The solar cell front side silver paste doped with modified graphene comprises by weight 0.1-5 parts of modified graphene, 88-91 parts of silver powder, 5-15 parts of organic binder, 1-5 parts of organic solvent, 1-3 parts of glass powder, wherein the modified graphene is a surface modified graphene. A solar cell front side silver paste is developed, which is screen printed on a crystalline silicon wafer, sintered at a high temperature, penetrates the SiNx passivation layer in the crystalline silicon wafer, and thus forms a good ohmic contact.

Owner:NANTONG T SUN NEW ENERGY CO LTD

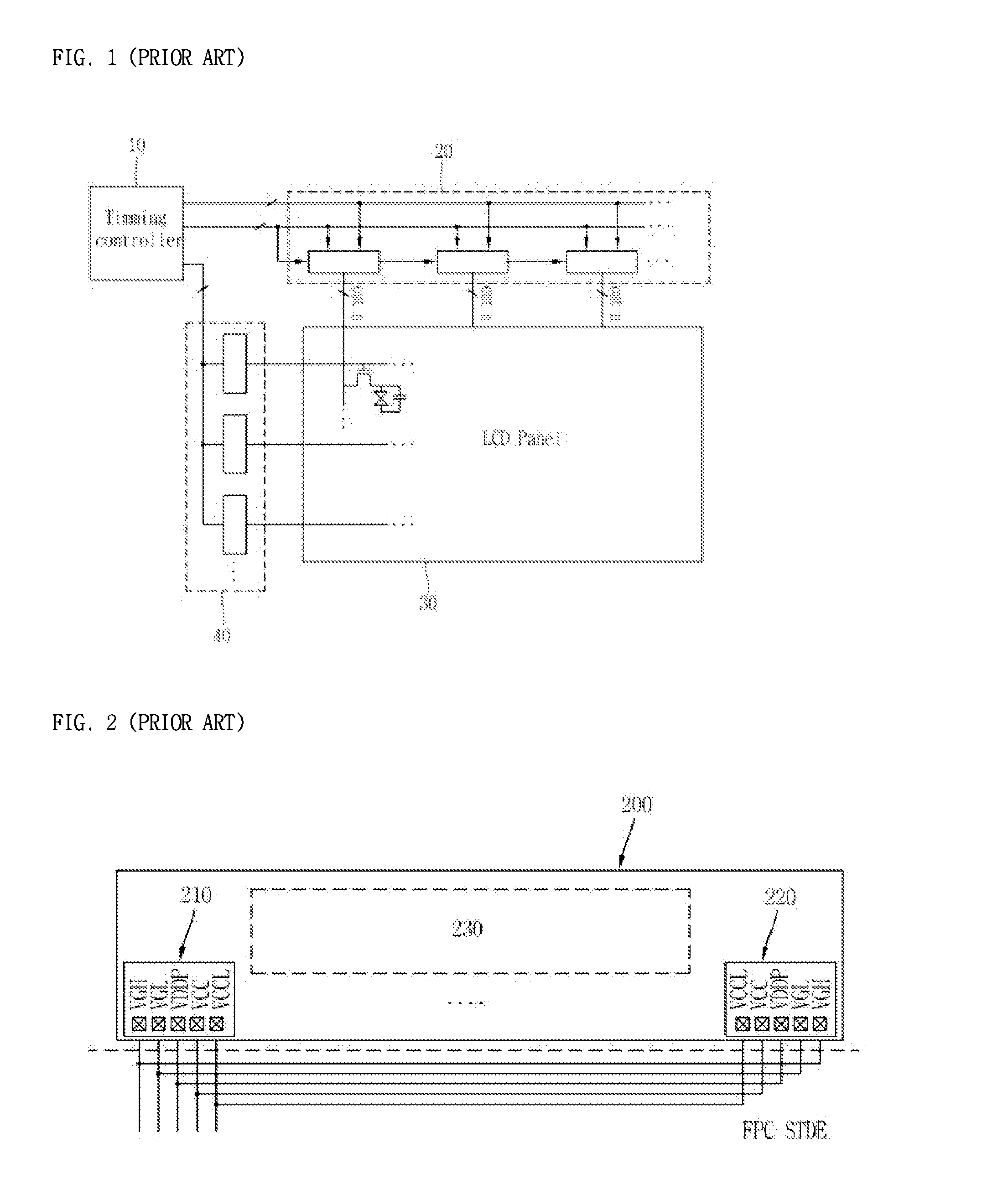

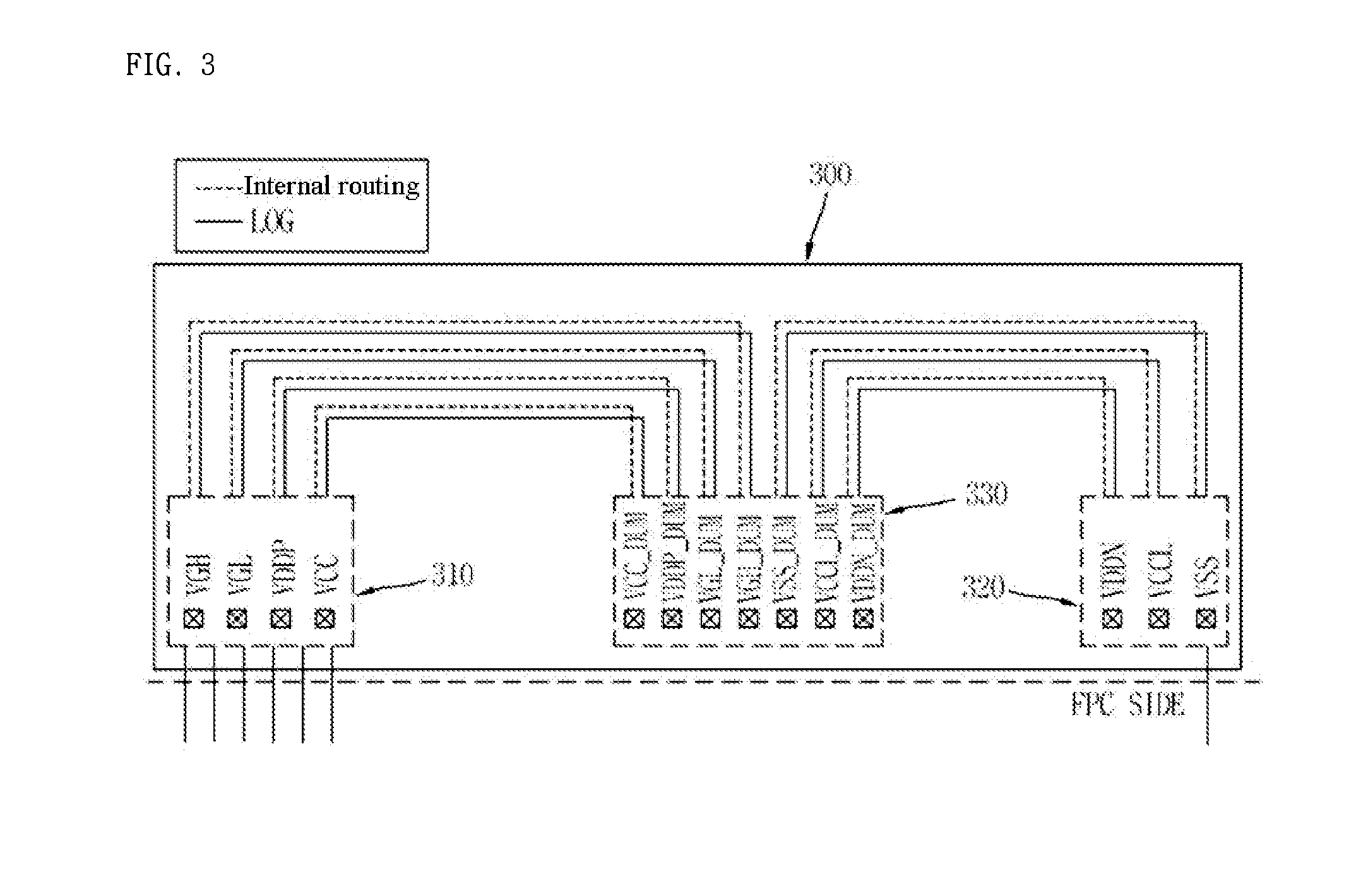

Power connection structure of driver IC chip

ActiveUS20110248972A1Simplifies the wiring processLow line resistanceCathode-ray tube indicatorsNon-linear opticsTerminal unitLiquid crystal

A power connection structure of a driver IC chip including a first power terminal unit formed on one side thereof, a second power terminal unit formed on the other side thereof, and a dummy power terminal unit formed between the first power terminal unit and the second power terminal unit. The driver IC chip is mounted to a liquid crystal panel of a liquid crystal display device in a chip-on-glass (COG) type. Both of the first power terminal unit and the dummy power terminal unit and both of the dummy power terminal unit and the second power terminal unit are connected through routing lines in the driver IC chip.

Owner:SILICON WORKS CO LTD

Non-volatile memory and fabricating method thereof

ActiveUS7102193B1Improve short channel effectPrevents effect device performanceTransistorSolid-state devicesMetal silicideMetal

A method of fabricating a non-volatile memory is provided. A substrate having a trench therein for forming a trench device is provided. Then, a doped metal silicide layer is formed on the substrate in the trench. A heating process is performed to form a source / drain area in the substrate under the doped metal silicide layer. Thereafter, a first conductive layer is formed on the doped metal silicide layer to fill up the trench.

Owner:POWERCHIP SEMICON MFG CORP

Organic opto-electric device and a method for manufacturing an organic opto-electric device

InactiveUS20110198622A1Improve conductivityLow line resistanceSolid-state devicesSemiconductor/solid-state device manufacturingOrganic layerEngineering

An organic opto-electric device has a layer stack with a base electrode, an organic layer assembly, a cover electrode and a contact layer. The organic layer assembly is arranged between the base electrode and the cover electrode and the cover electrode is arranged between the organic layer assembly and the contact layer. The cover electrode and the base electrode are structured to form several laterally adjacent optically active areas and the base electrode, the organic layer assembly, the cover electrode and the contact layer are interconnected by vias such that at least two optically active areas are connected in series so that a current flow through the at least two optically active areas passes in a direction between the base electrode and a cover electrode. The current flow between the at least two optically active areas passes through the contact layer, wherein the contact layer contacts the base electrode above one of the vias laterally in the interior of the two optically active areas.

Owner:FRAUNHOFER GESELLSCHAFT ZUR FOERDERUNG DER ANGEWANDTEN FORSCHUNG EV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com