Patents

Literature

107results about How to "Thickness variation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Glass ceramic and method of producing the same

ActiveUS20050096208A1High surface precisionThickness variationTransistorGlass tempering apparatusSolar cellGlass-ceramic

A glass ceramic comprises (in wt.-% on oxide basis): SiO2 35 to 60, B2O3>4 to 10, P2O5 0 to 10, Al2O3 16.5 to 40, TiO2 1 to 10, Ta2O5 0 to 8, Y2O3 0 to 6, ZrO21 to 10, MgO 6 to 20, CaO 0 to 10, SrO 0 to 4, BaO 0 to 8, ZnO 0 to 4, SnO2+CeO2 0 to 4, SO42−+Cl− 0 to 4, wherein the total content (SnO2+CeO2+S042−+Cl−) is between 0.01 and 4 wt.-%. The glass ceramic may be processed by the float glass method, may be transparent and is, inter alia, suitable as a substrate for thin film semiconductors, in particular for display applications, solar cells etc.

Owner:SCHOTT AG

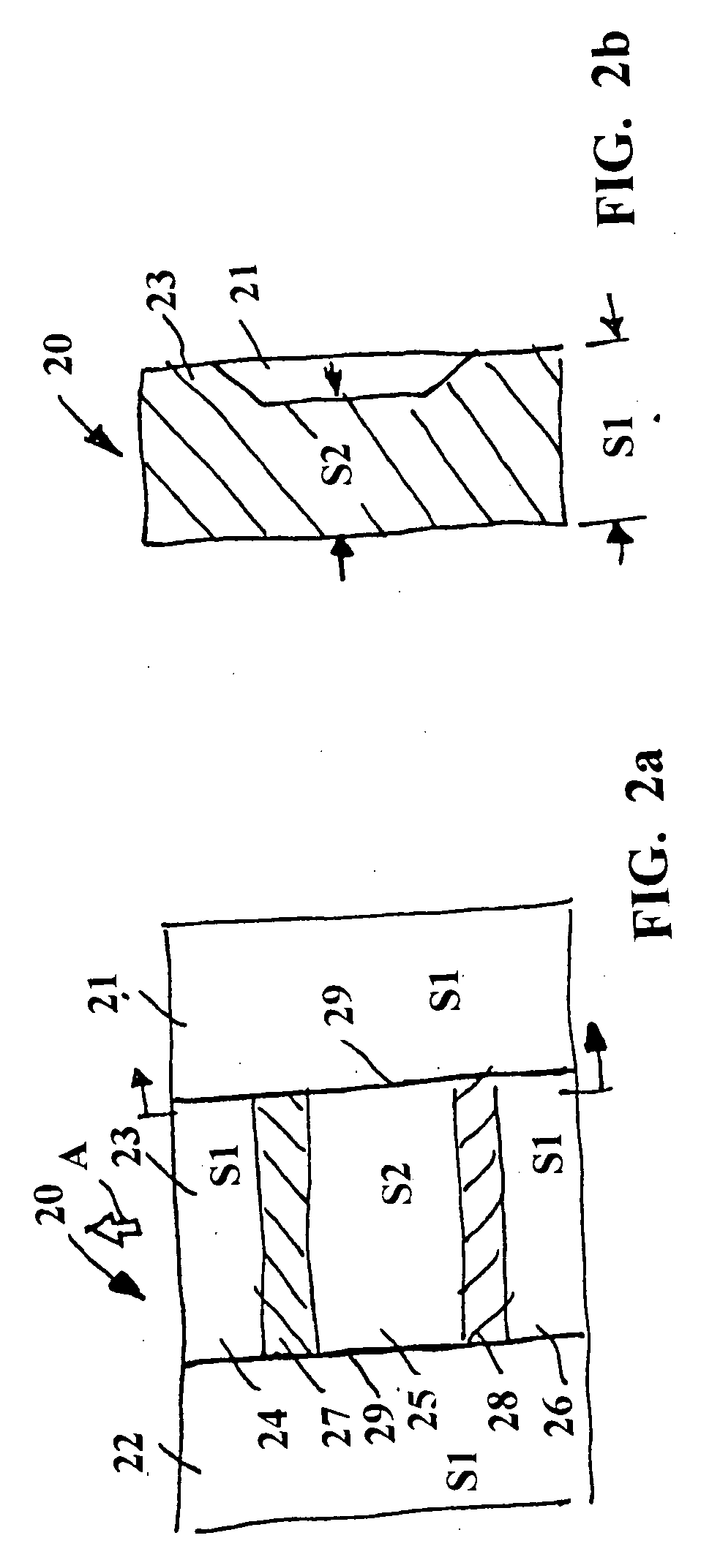

Magnetic head for perpendicular magnetic recording and method of manufacturing same

ActiveUS7375925B2Avoid problemsForming accuratelyConstruction of head windingsRecord information storageElectrical and Electronics engineeringEngineering

A pole layer incorporates: a first portion having an end face located in a medium facing surface; and a second portion having a thickness greater than that of the first portion. A surface of the first portion closer to a substrate is located farther from the substrate than a surface of the second portion closer to the substrate. A surface of the first portion farther from the substrate is located closer to the substrate than a surface of the second portion farther from the substrate. At least a portion of the pole layer is placed in an encasing groove formed in a region extending from a first encasing layer through a second encasing layer to a nonmagnetic metal layer.

Owner:HEADWAY TECH INC

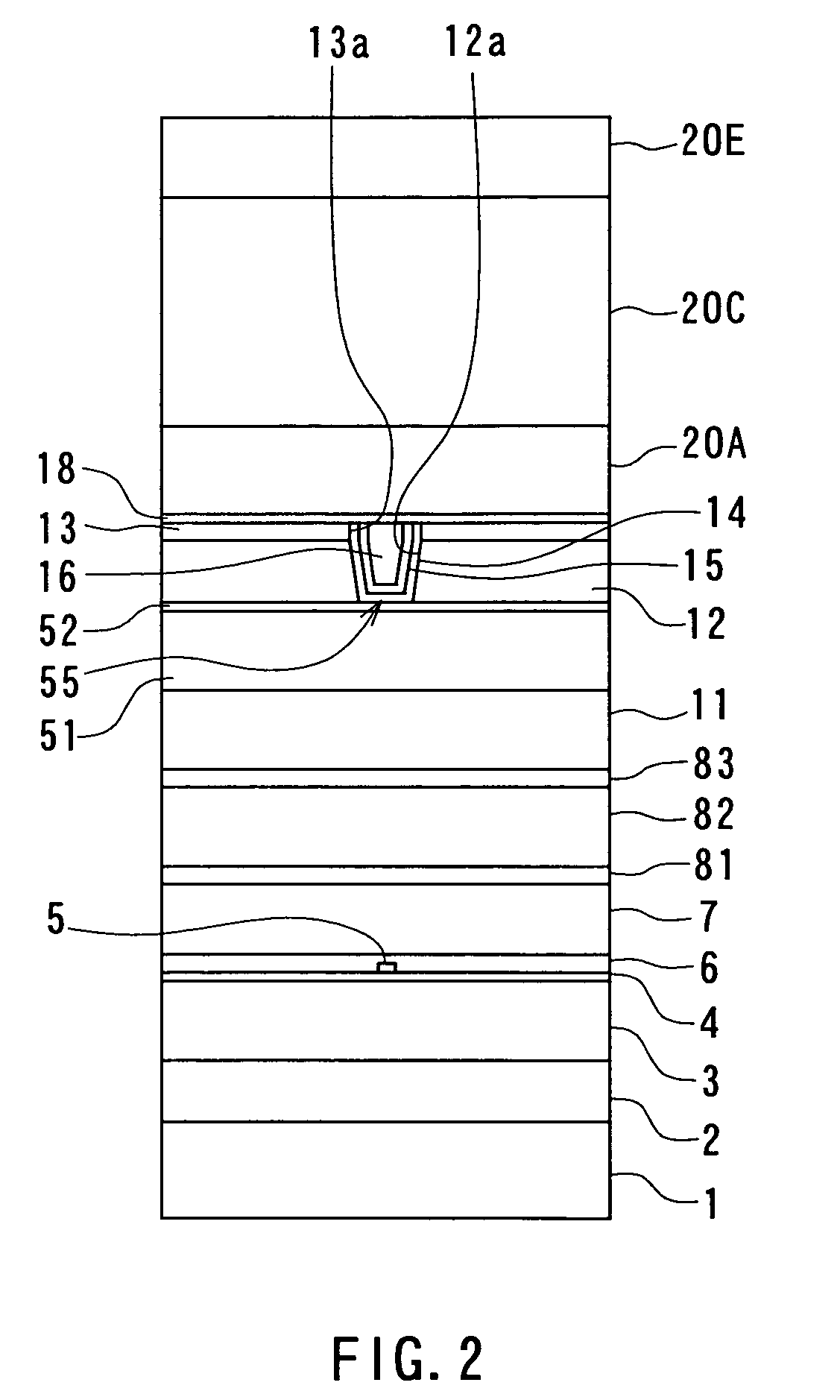

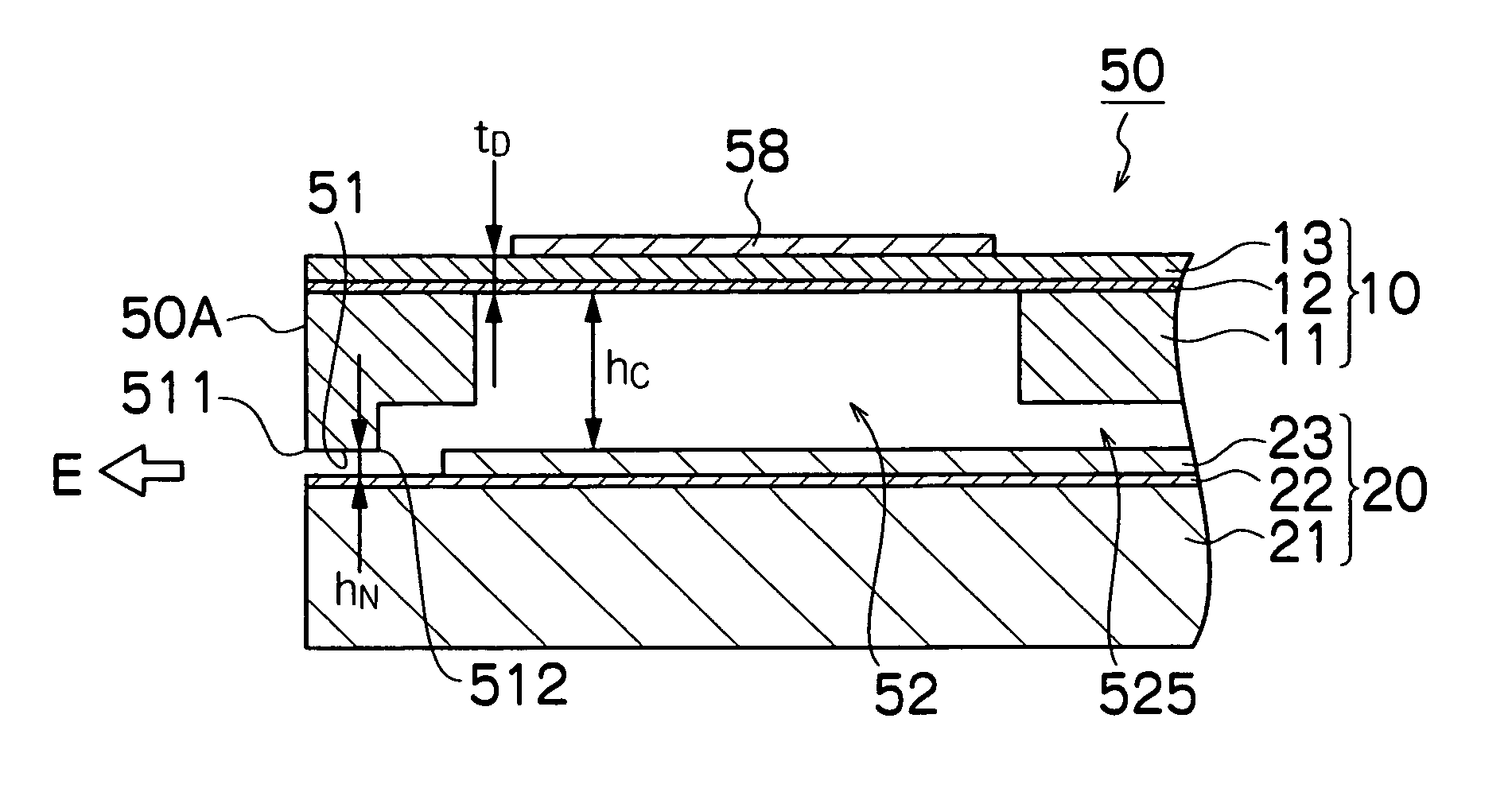

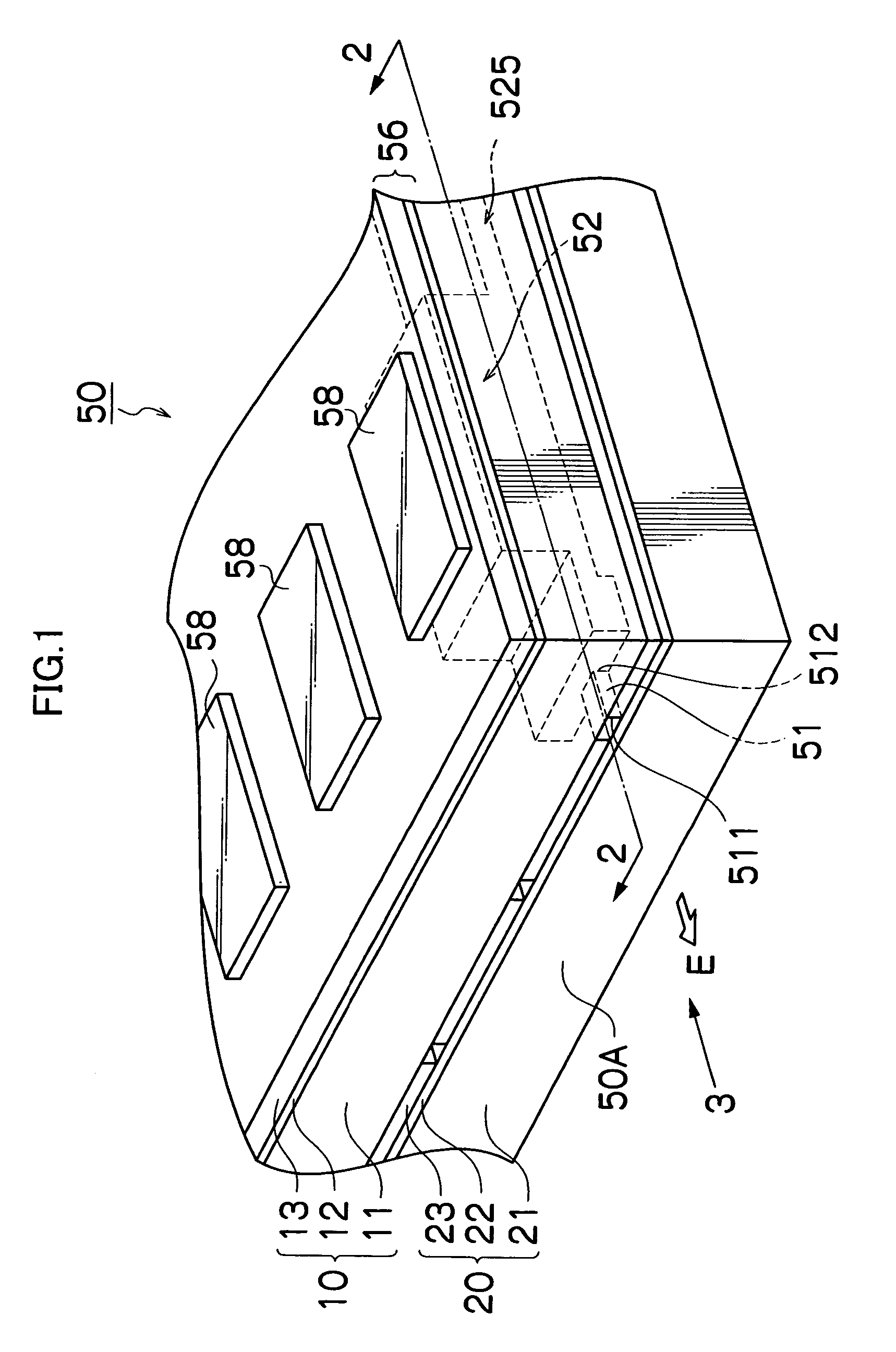

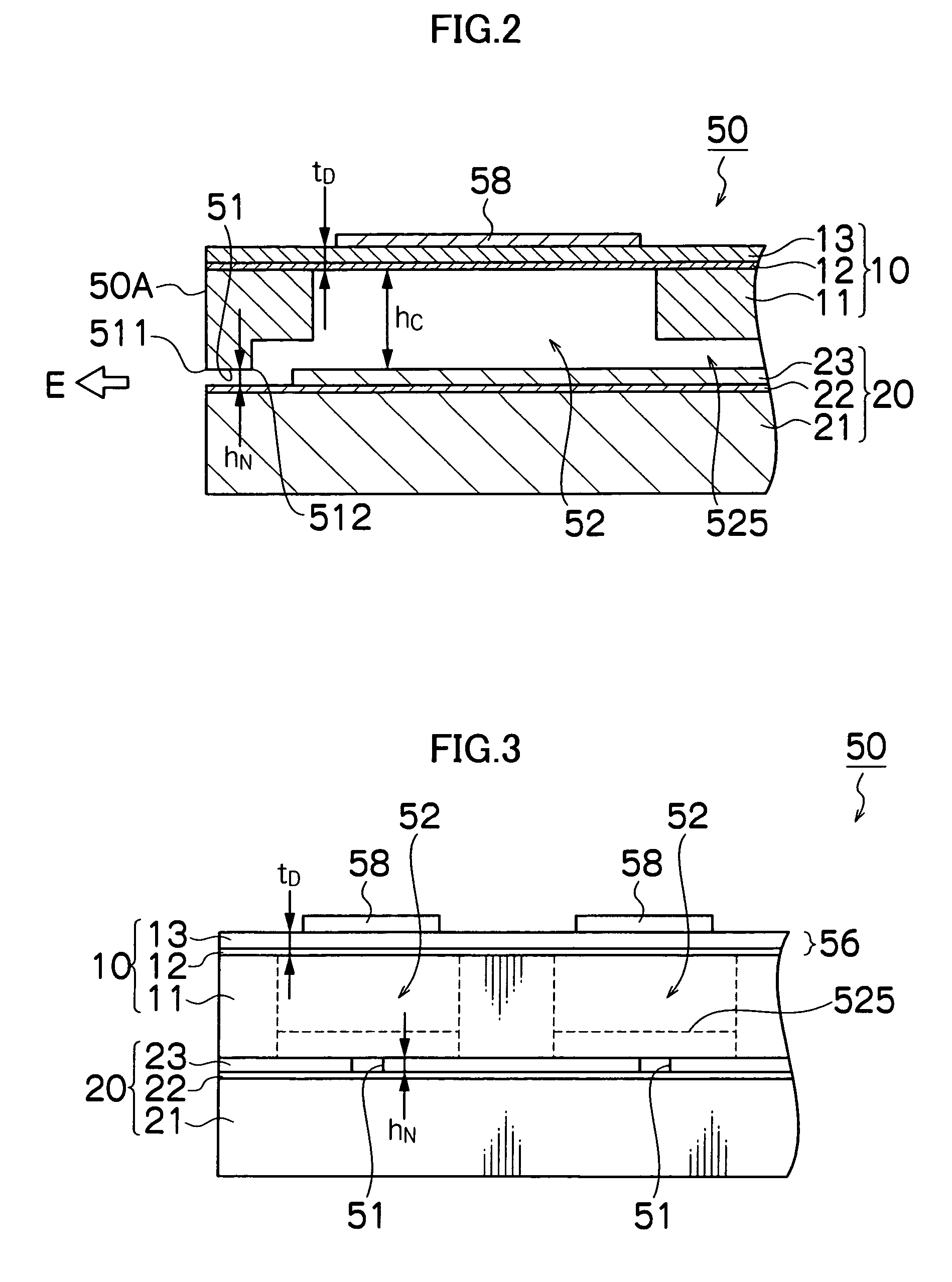

Liquid ejection head and manufacturing method thereof

InactiveUS20070064062A1Reduce variationThickness variationPrintingLiquid jetElectrical and Electronics engineering

The liquid ejection head includes: a first SOI substrate which has a first active layer, a first dielectric layer and a first supporting layer; a second SOI substrate which has a second active layer, a second dielectric layer and a second supporting layer, the second active layer being bonded to the first supporting layer; and a nozzle which is formed between the first supporting layer and the second dielectric layer, the nozzle ejecting liquid in an ejection direction perpendicular to a thickness direction of the first SOI substrate and the second SOI substrate, a cross-sectional width of the nozzle perpendicular to the ejection direction being defined by a thickness of the second active layer.

Owner:FUJIFILM CORP

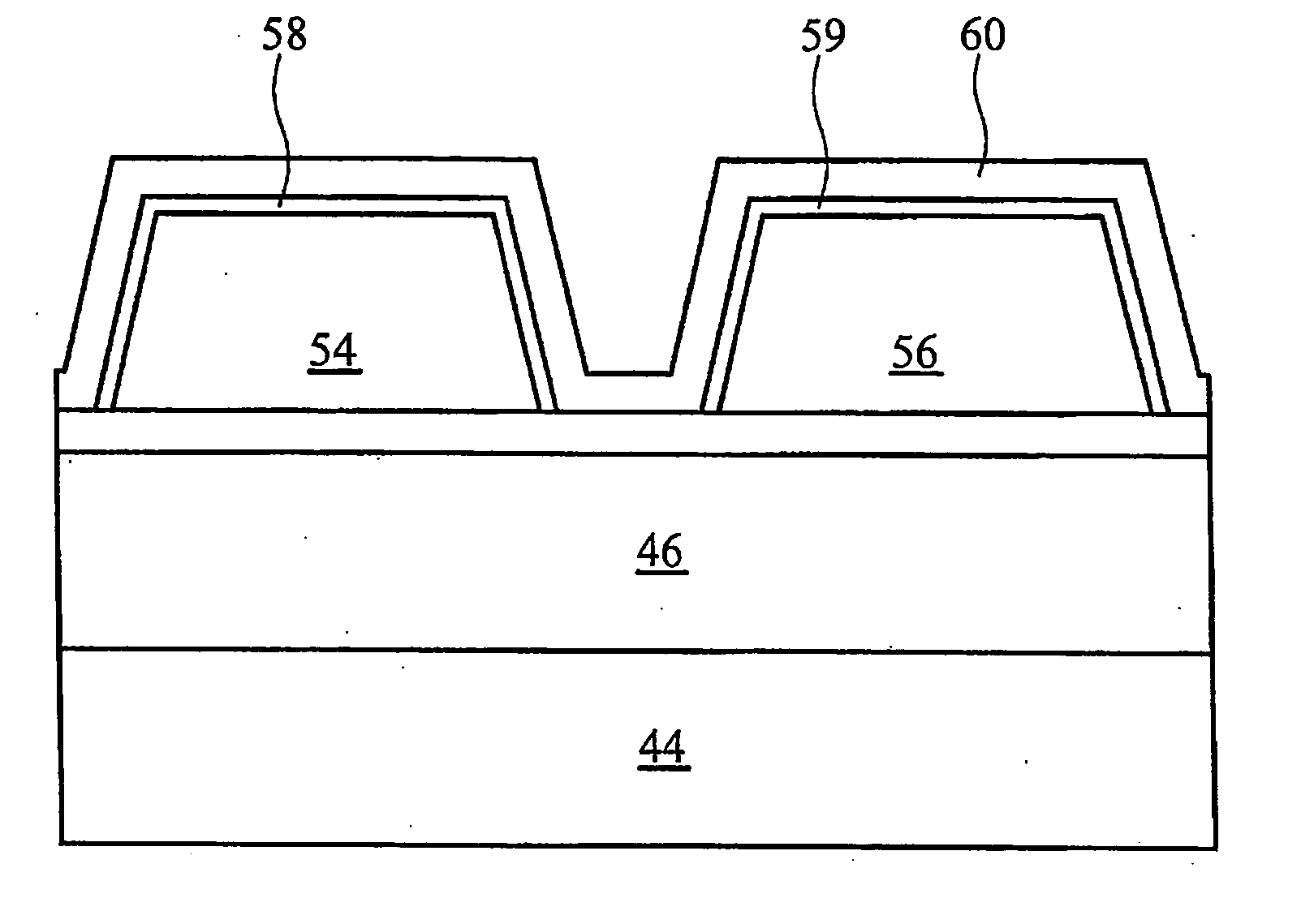

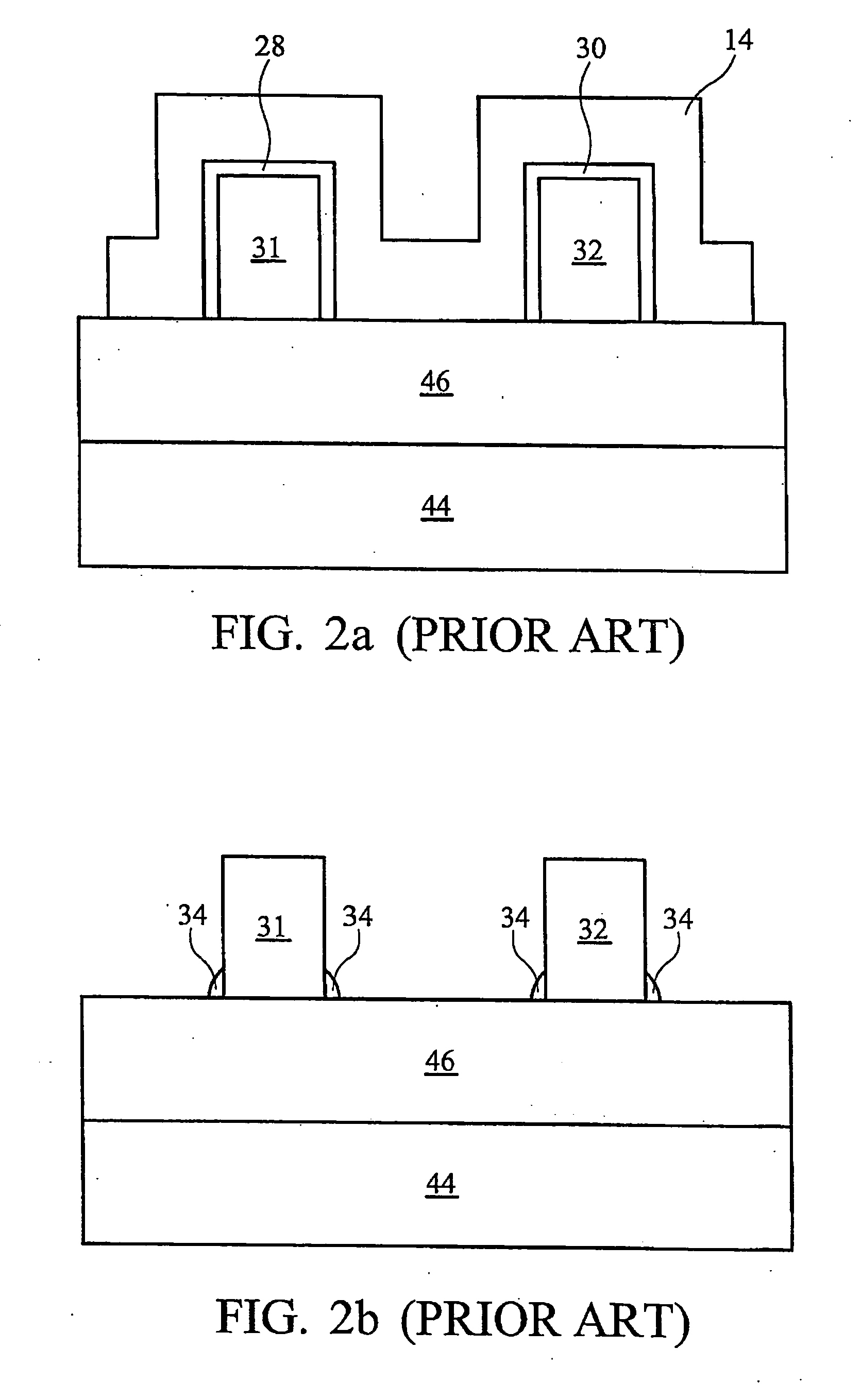

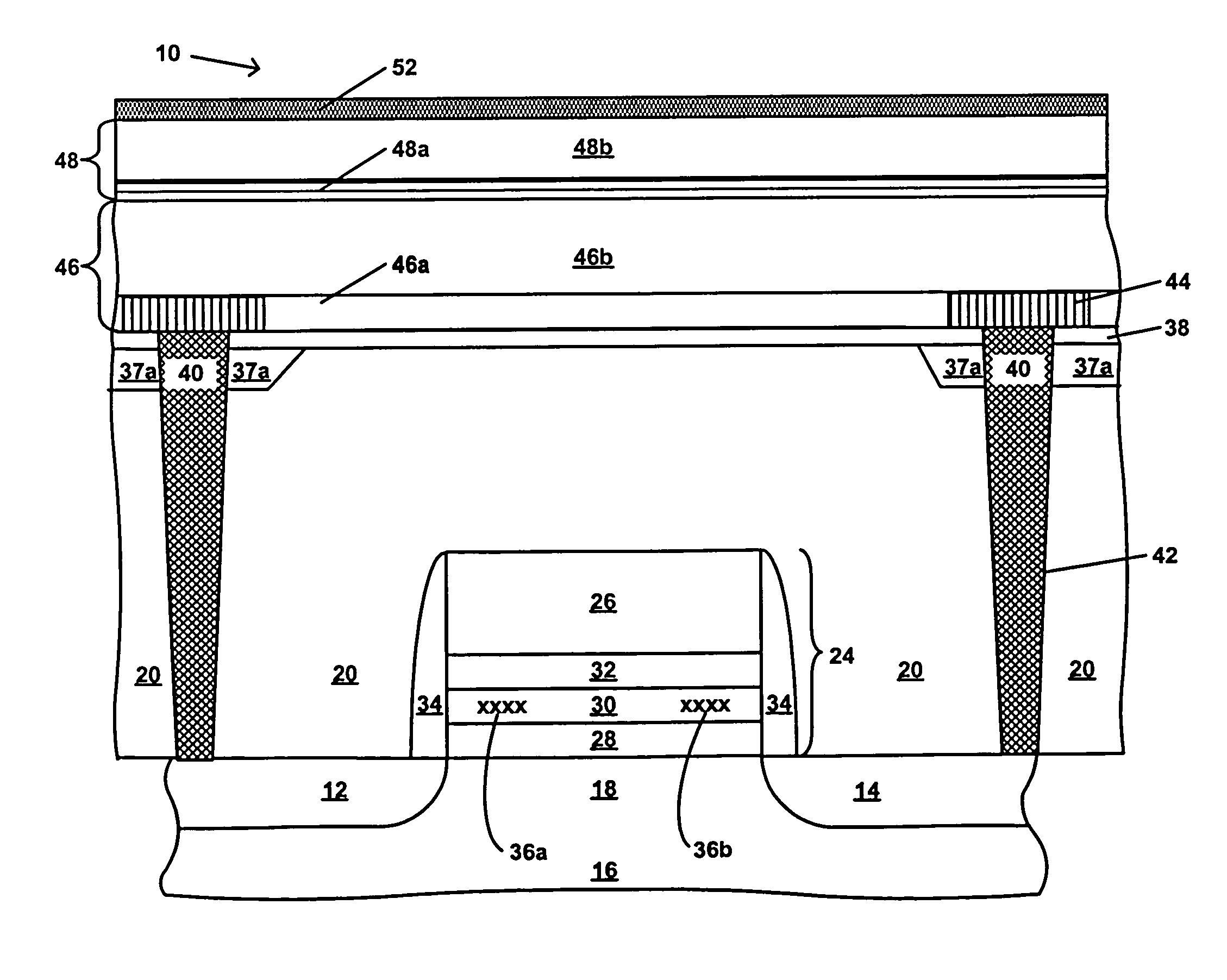

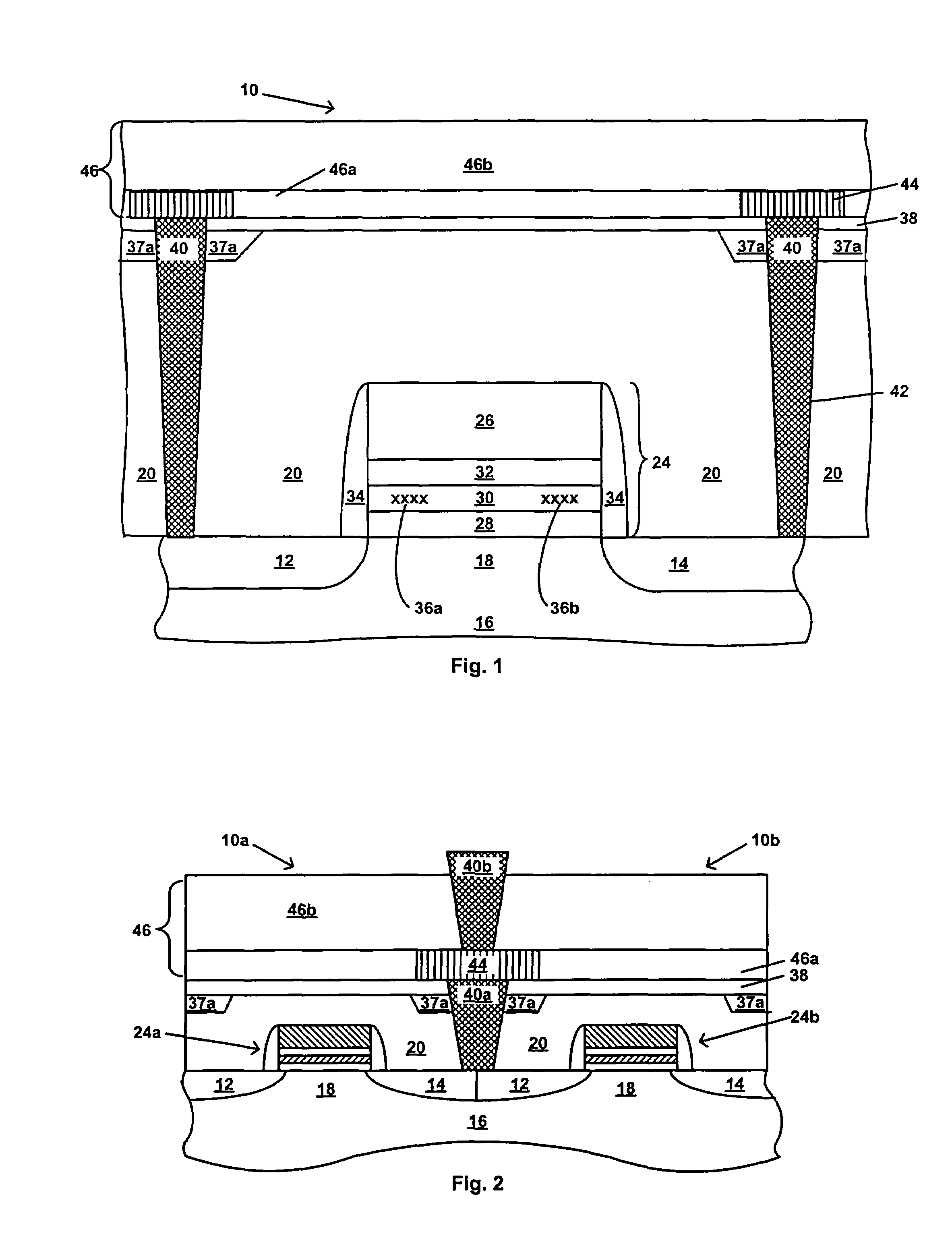

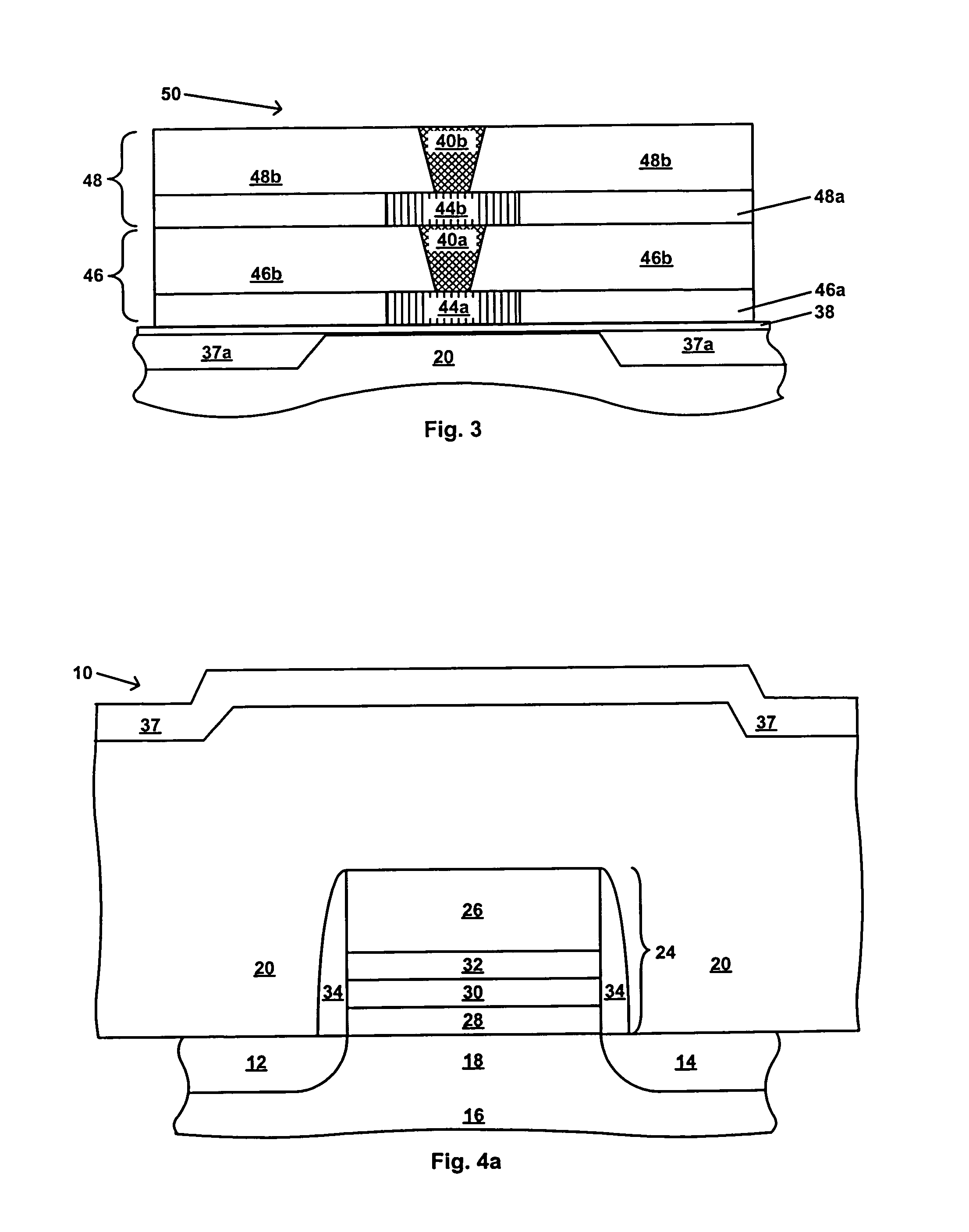

Apparatus and method for multiple-gate semiconductor device with angled sidewalls

ActiveUS20050253203A1Thickness variationReduce needTransistorSolid-state devicesEngineeringSemiconductor

A multiple-gate transistor has an active region with a side that forms an interior angle with the base of the active region of less than 80°. A process for fabricating a FinFET includes the steps of etching a silicon-on-insulator wafer to form an active region, including the source, channel, and drain, with vertically angled sidewalls.

Owner:TAIWAN SEMICON MFG CO LTD

Sealed prismatic battery

InactiveUS20060292437A1Stable pressureImprove securitySmall-sized cells cases/jacketsLarge-sized cells cases/jacketsInternal pressureEngineering

A sealed prismatic battery includes a laterally elongated cap that closes the upper surface of the opening of a battery can 1 and a safety vent that is provided at the cap and opens when the battery internal pressure abnormally rises. The safety vent has a looped groove that is formed recessed and located nearer to the left end of the cap on the outer surface side of the cap. The looped groove is annularly formed of front, rear, left and right groove portions into a laterally elongated prismatic shape, and the thickness of the bottom wall of the end side groove portion is thicker than that of the bottom walls of the other groove portions. The center side groove portion of the looped groove is formed into a circular arc shape curved convex toward the center side of the cap.

Owner:HITACHT MAXELL LTD

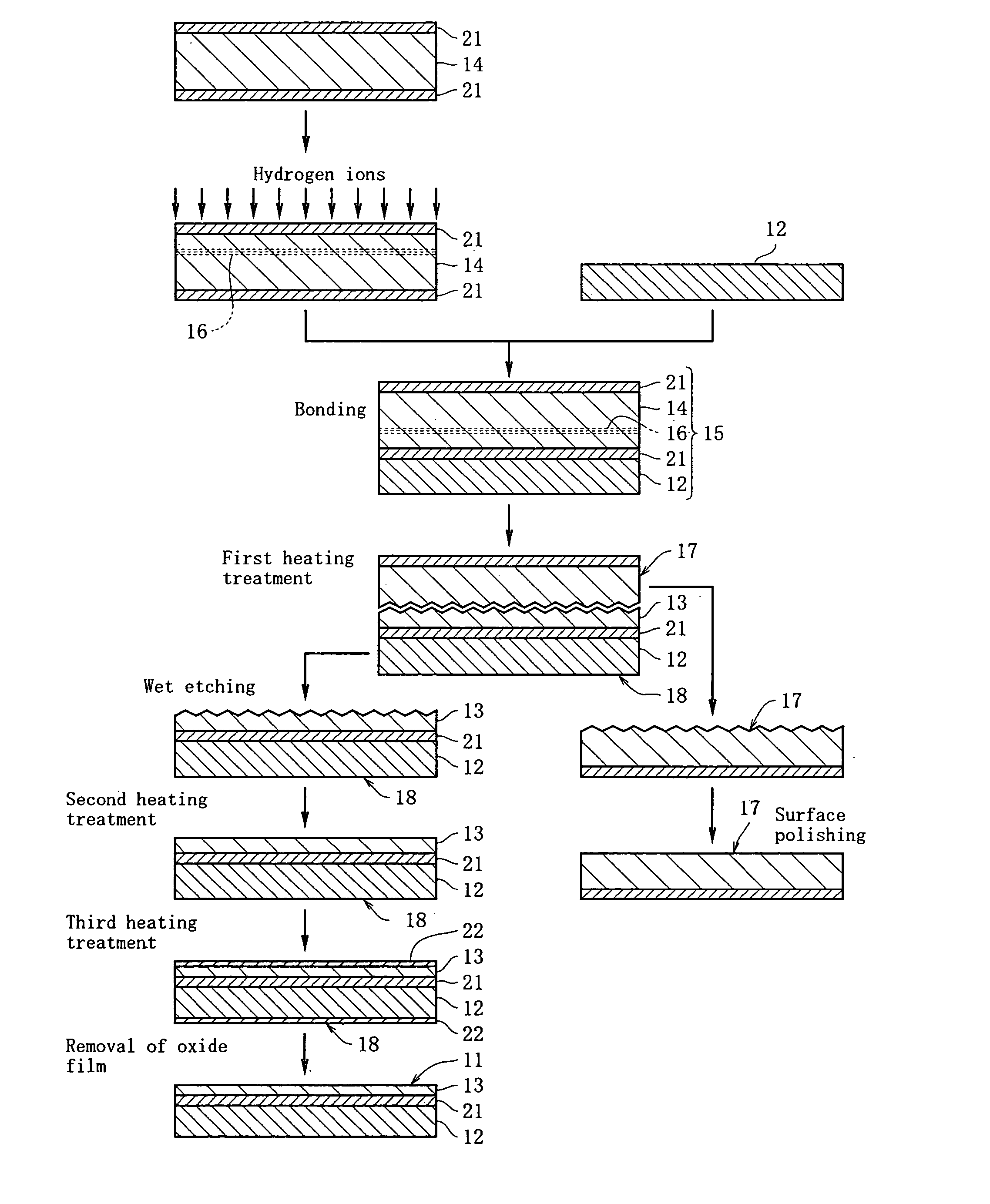

Method for manufacturing SOI substrate

ActiveUS20060177993A1Variation in thickness of the SOI layer is effectively suppressedThickness variationSemiconductor/solid-state device manufacturingEtchingHydrogen

The object of the invention is to provide a method for manufacturing an SOI layer which is devoid of damages, has a reduced variation in thickness, and is uniform in thickness. The object is met by providing a method for manufacturing an SOI substrate comprising the steps of forming an oxide film at least on one surface of a first silicon substrate, implanting hydrogen ions from the surface of the first silicon substrate thereby forming an ion-implantation zone in the interior of the first silicon substrate, bonding the first silicon substrate over a second silicon substrate with the oxide film interposed thereby forming a laminated assembly, subjecting the laminated assembly to a first heating treatment consisting of heating at a specified temperature, so that the first silicon substrate is split at the ion-implantation zone thereby manufacturing a bonded substrate, flattening the exposed surface of the SOI layer by subjecting the bonded substrate to wet etching, subjecting the bonded substrate to a second heating treatment consisting of heating at 750 to 900° C. in an oxidative atmosphere thereby reducing damages inflicted to the SOI layer, and subjecting the resulting bonded substrate to a third heating treatment consisting of heating at 900 to 1200° C. thereby enhancing the bonding strength of the bonded substrate.

Owner:SUMCO CORP

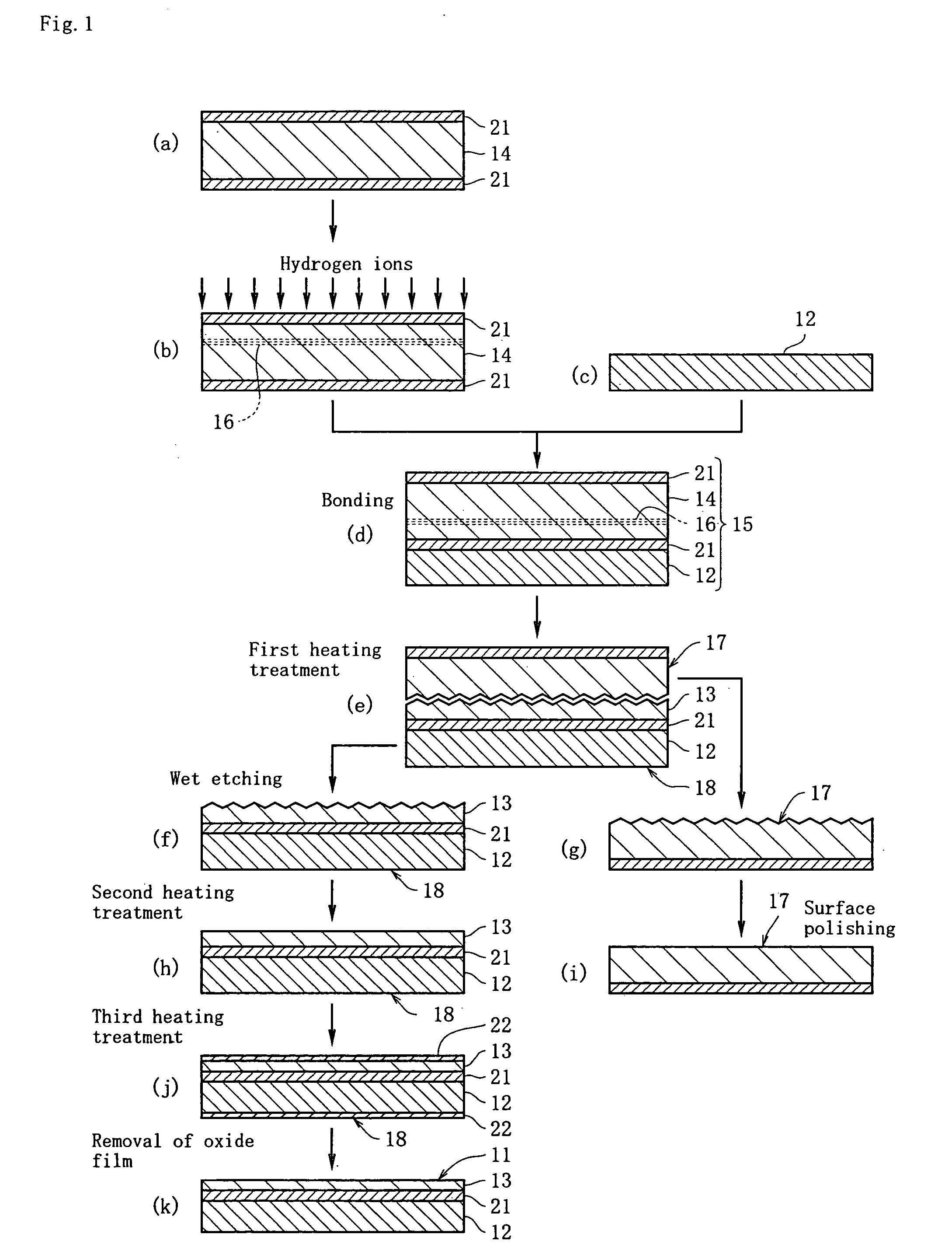

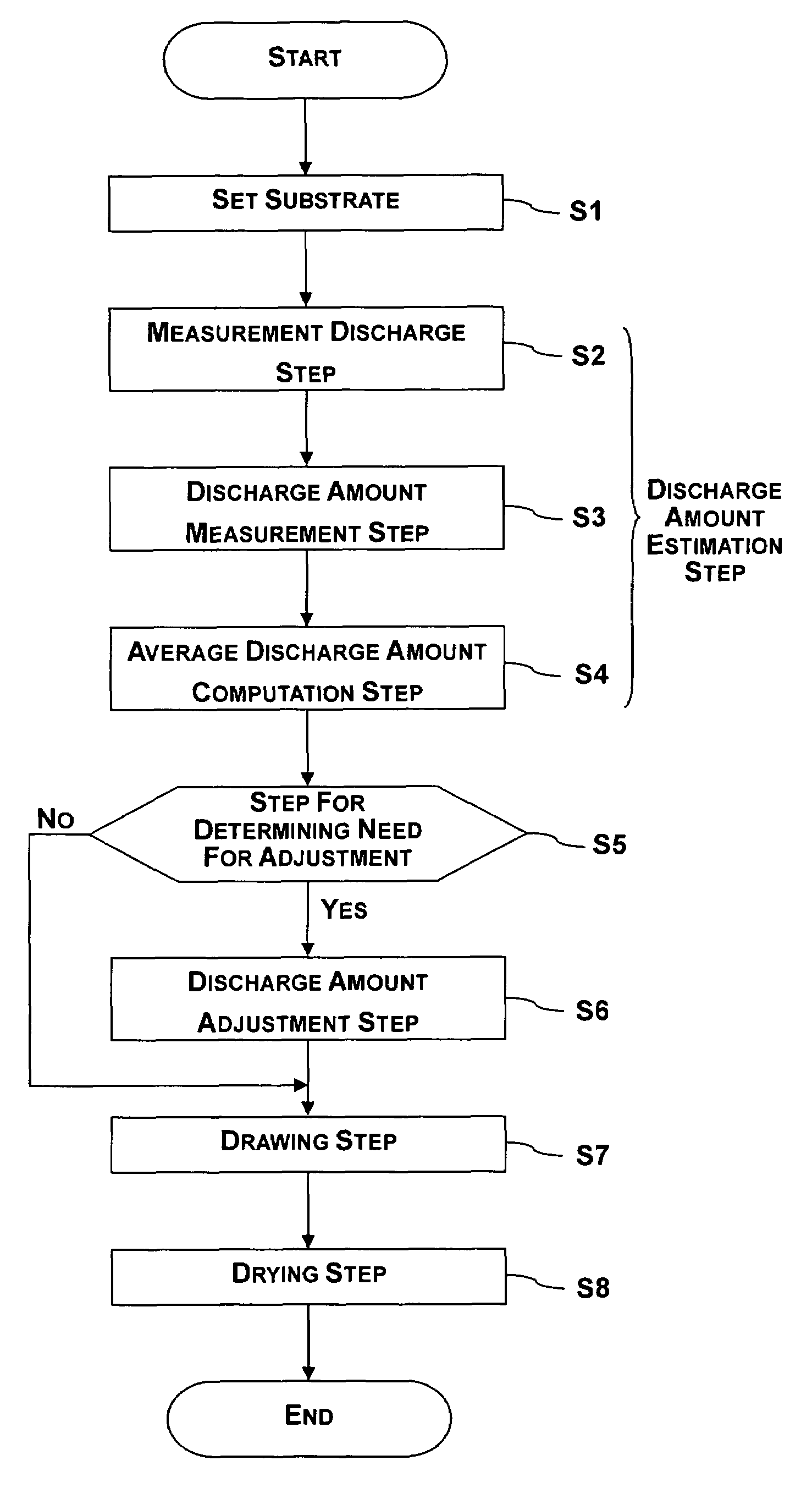

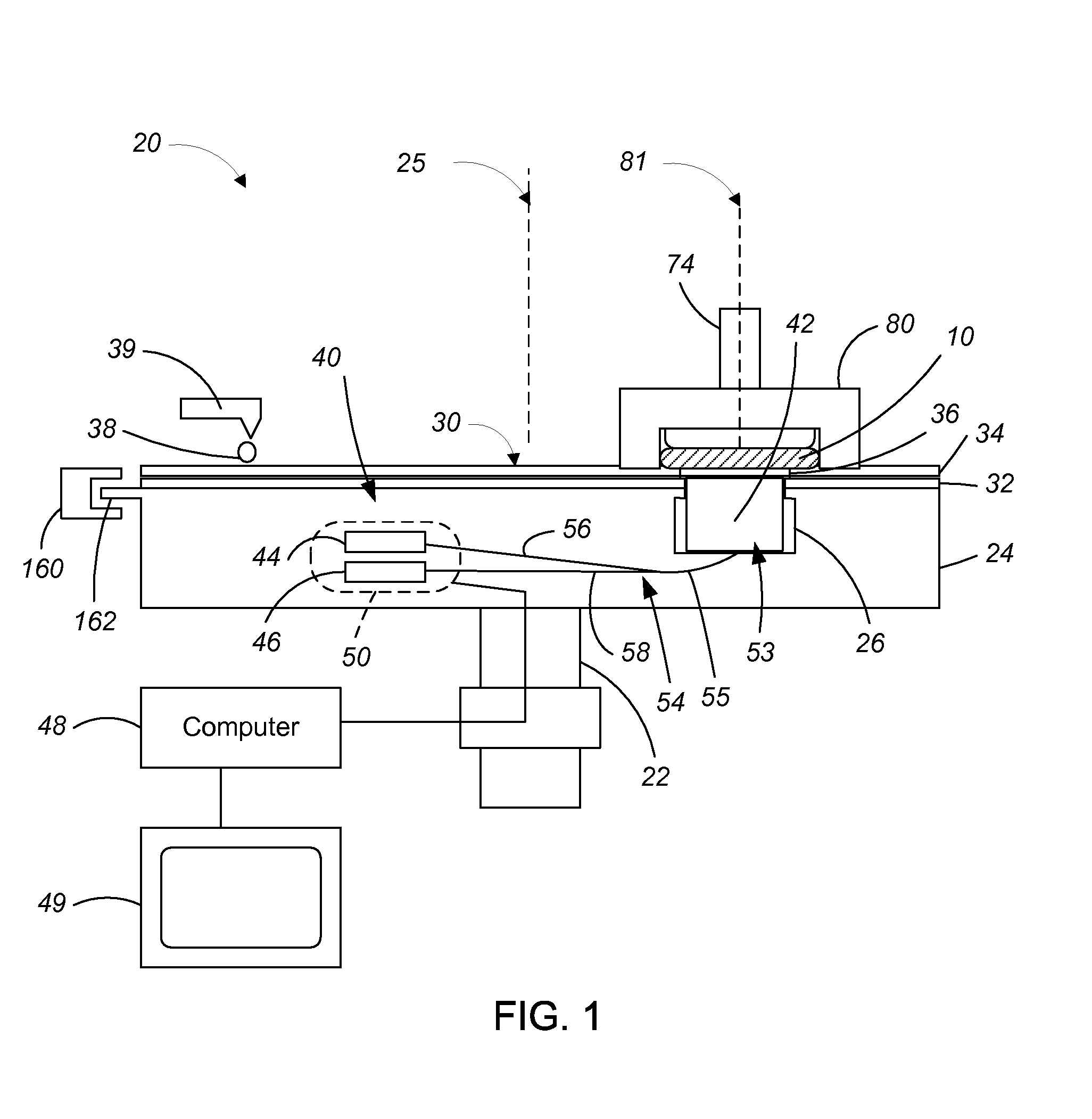

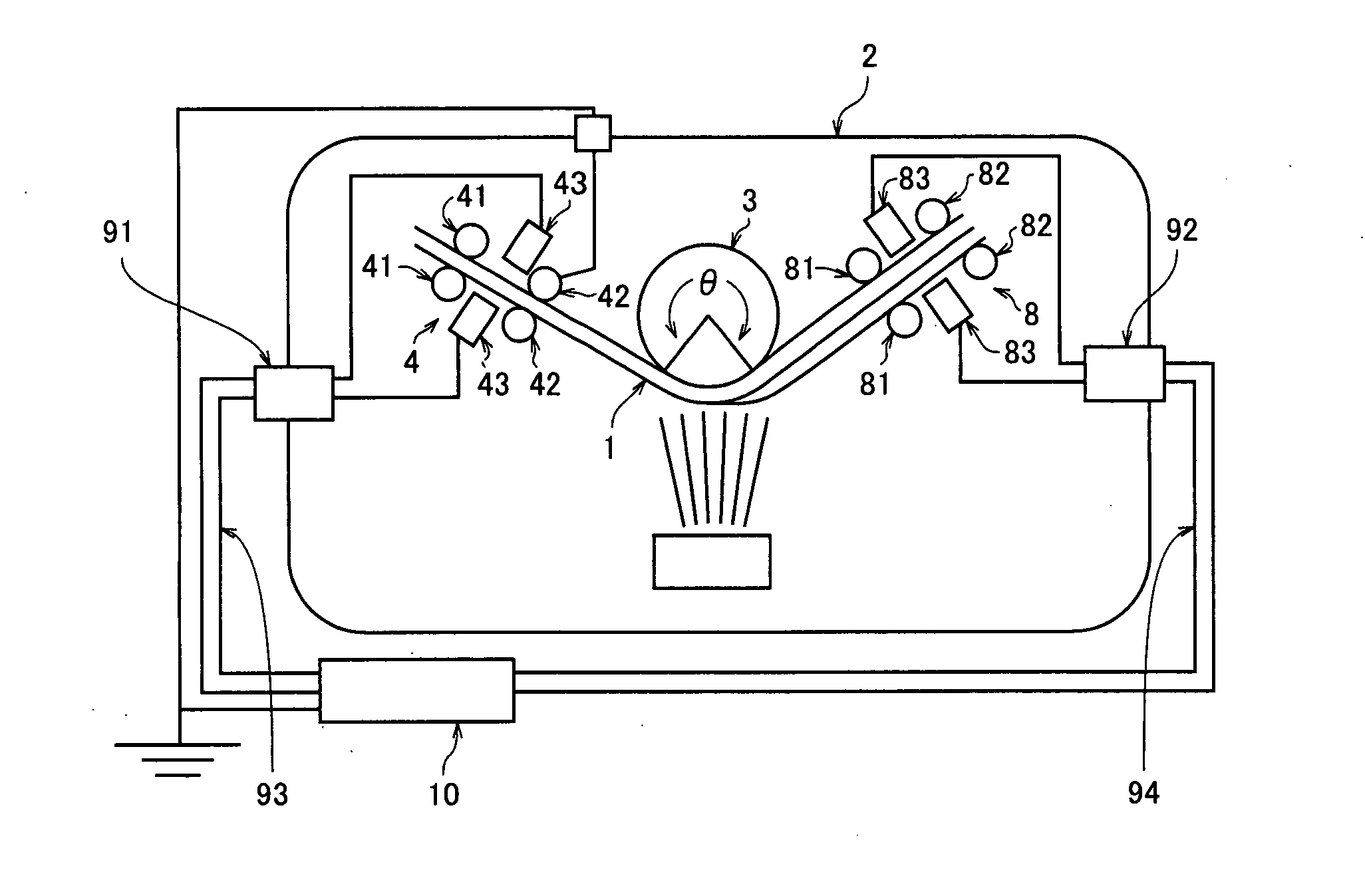

Discharge amount measurement method, pattern formation method, device, electro-optical device, and electronic instrument

ActiveUS20070109342A1Stable characteristicEasy to measureLiquid surface applicatorsCoatingsDischarge dataMeasurable quantity

A discharge amount measurement method is configured to measure a discharge amount of a liquid discharged from at least one nozzle of a droplet discharge head. The discharge amount measurement method includes discharging the liquid as a droplet from the at least one nozzle of the droplet discharge head by a number of discharges that is set to obtain a measurable quantity by driving the droplet discharge head based on measurement discharge data that is substantially identical to data used when a drawing pattern is formed by discharging the liquid from the at least one nozzle of the droplet discharge head, measuring the discharge amount of the liquid discharged from the at least one nozzle of the droplet discharge head, and calculating an average discharge amount based on the discharge amount and the number of discharges.

Owner:KATEEVA

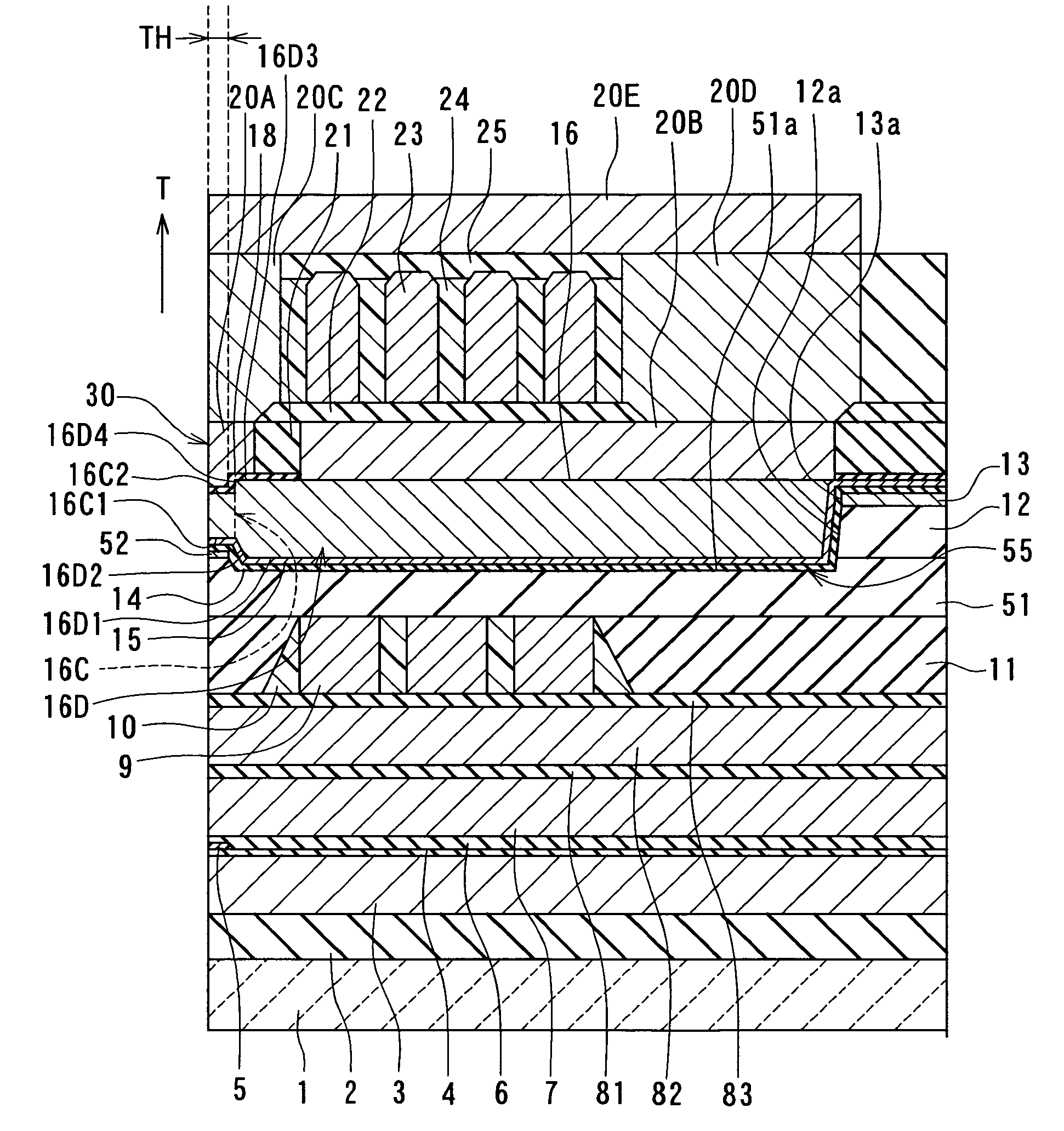

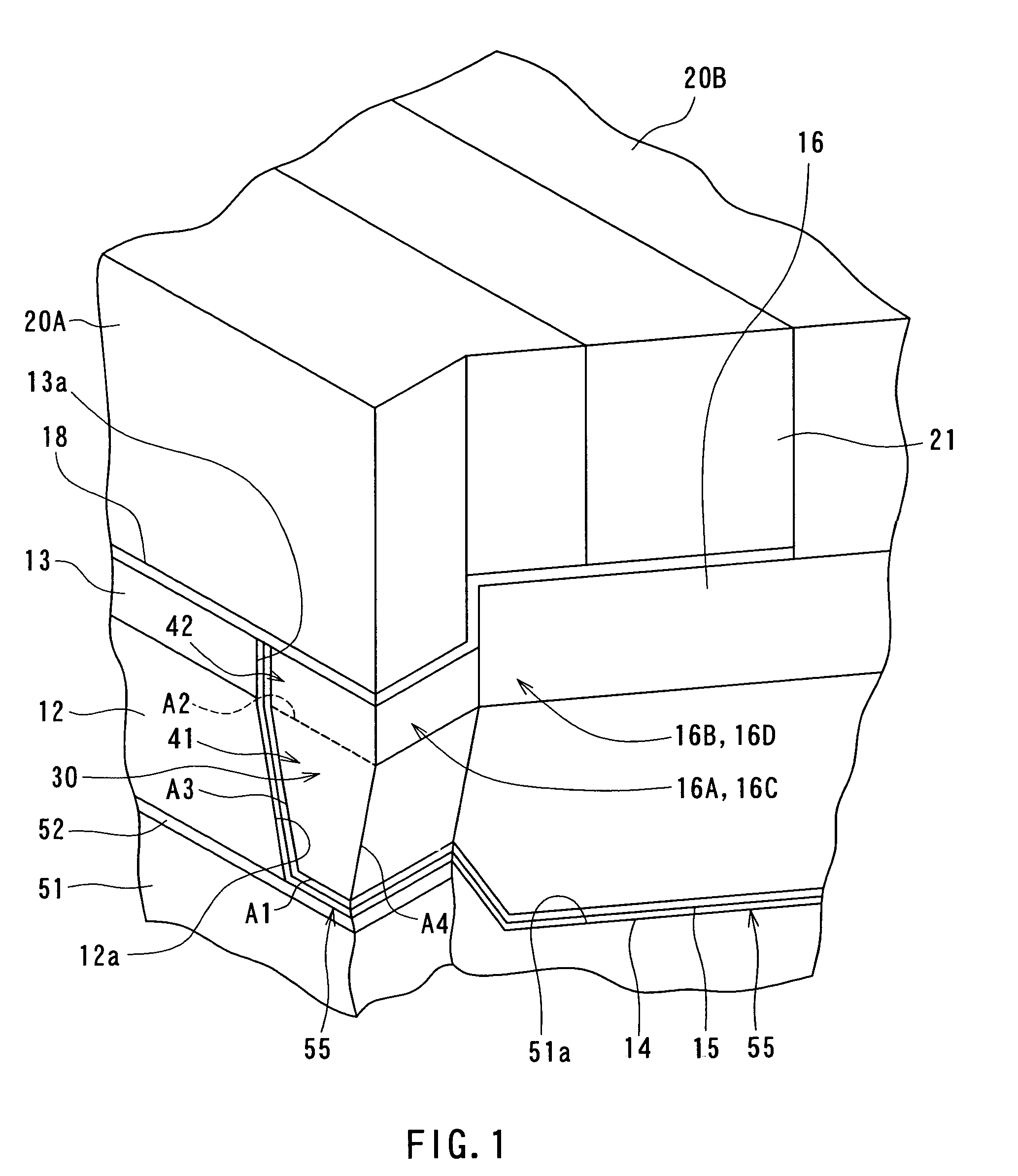

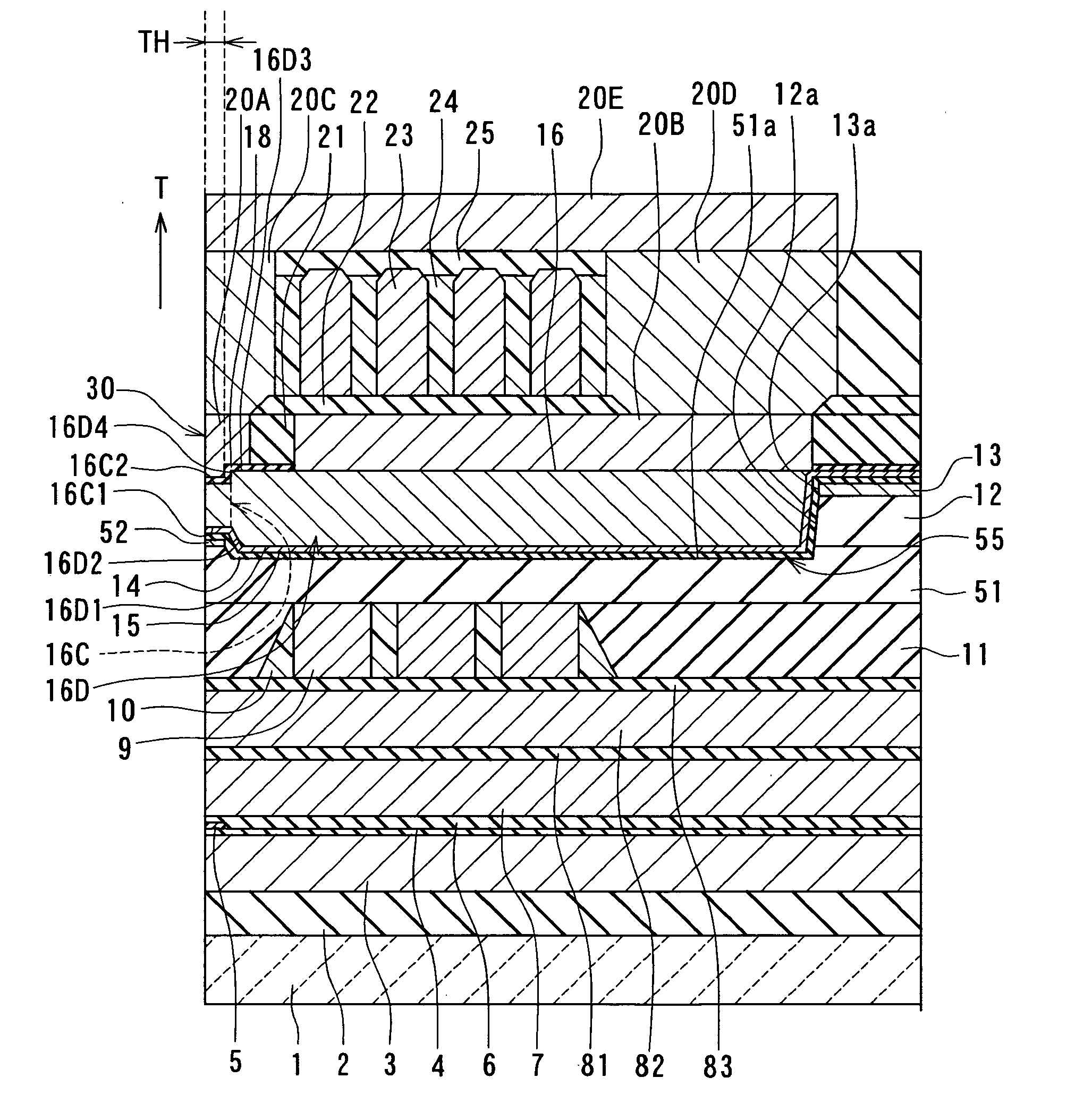

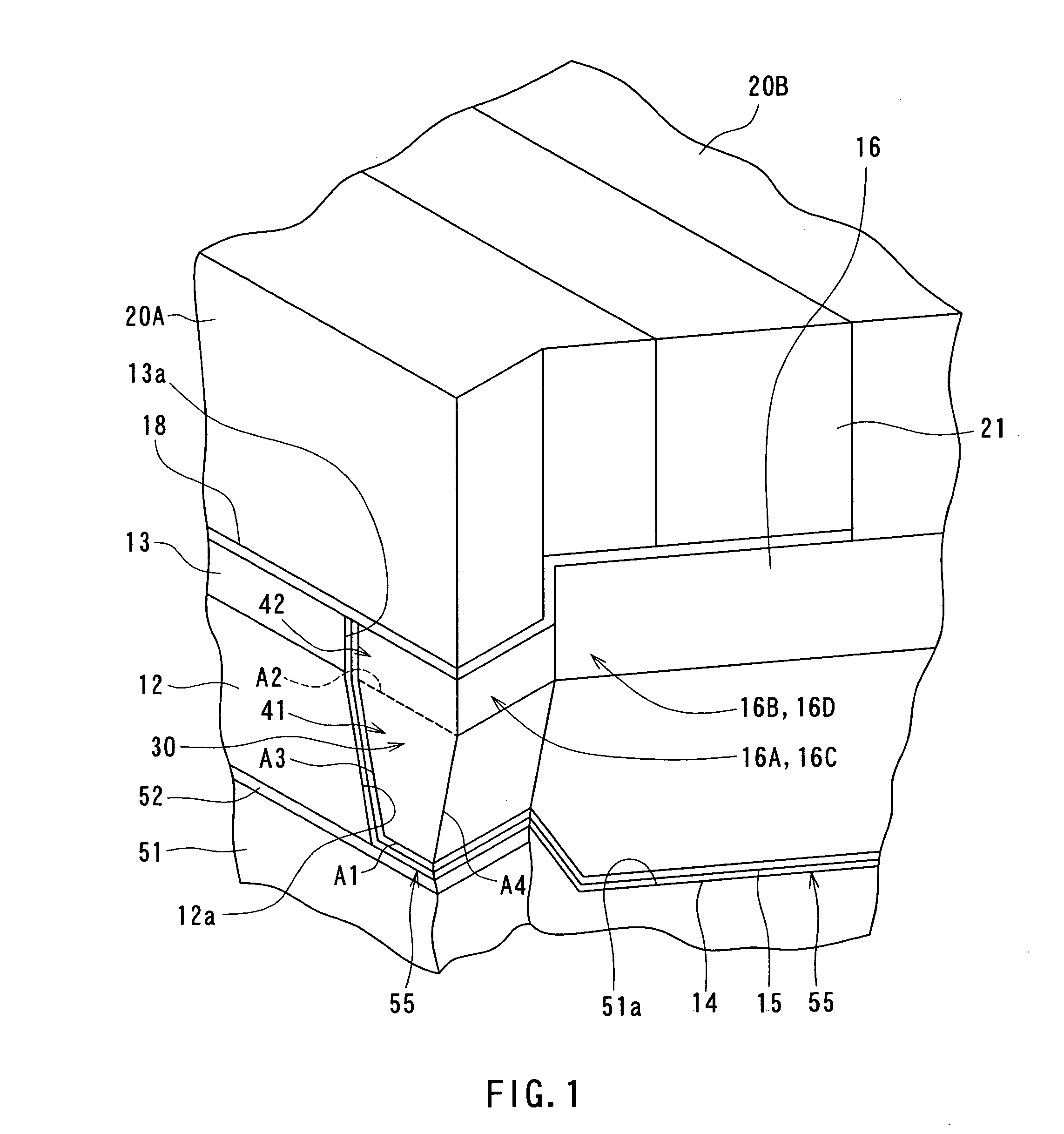

Magnetic head for perpendicular magnetic recording and method of manufacturing same

ActiveUS20060268456A1Avoid problemsForming accuratelyConstruction of head windingsRecord information storageEngineeringElectrical and Electronics engineering

A pole layer incorporates: a first portion having an end face located in a medium facing surface; and a second portion having a thickness greater than that of the first portion. A surface of the first portion closer to a substrate is located farther from the substrate than a surface of the second portion closer to the substrate. A surface of the first portion farther from the substrate is located closer to the substrate than a surface of the second portion farther from the substrate. At least a portion of the pole layer is placed in an encasing groove formed in a region extending from a first encasing layer through a second encasing layer to a nonmagnetic metal layer.

Owner:HEADWAY TECH INC

Discharge amount measurement method, pattern formation method, device, electro-optical device, and electronic instrument

ActiveUS7699428B2Easy to measureGood precisionLiquid surface applicatorsCoatingsElectronic instrumentEngineering

Owner:KATEEVA

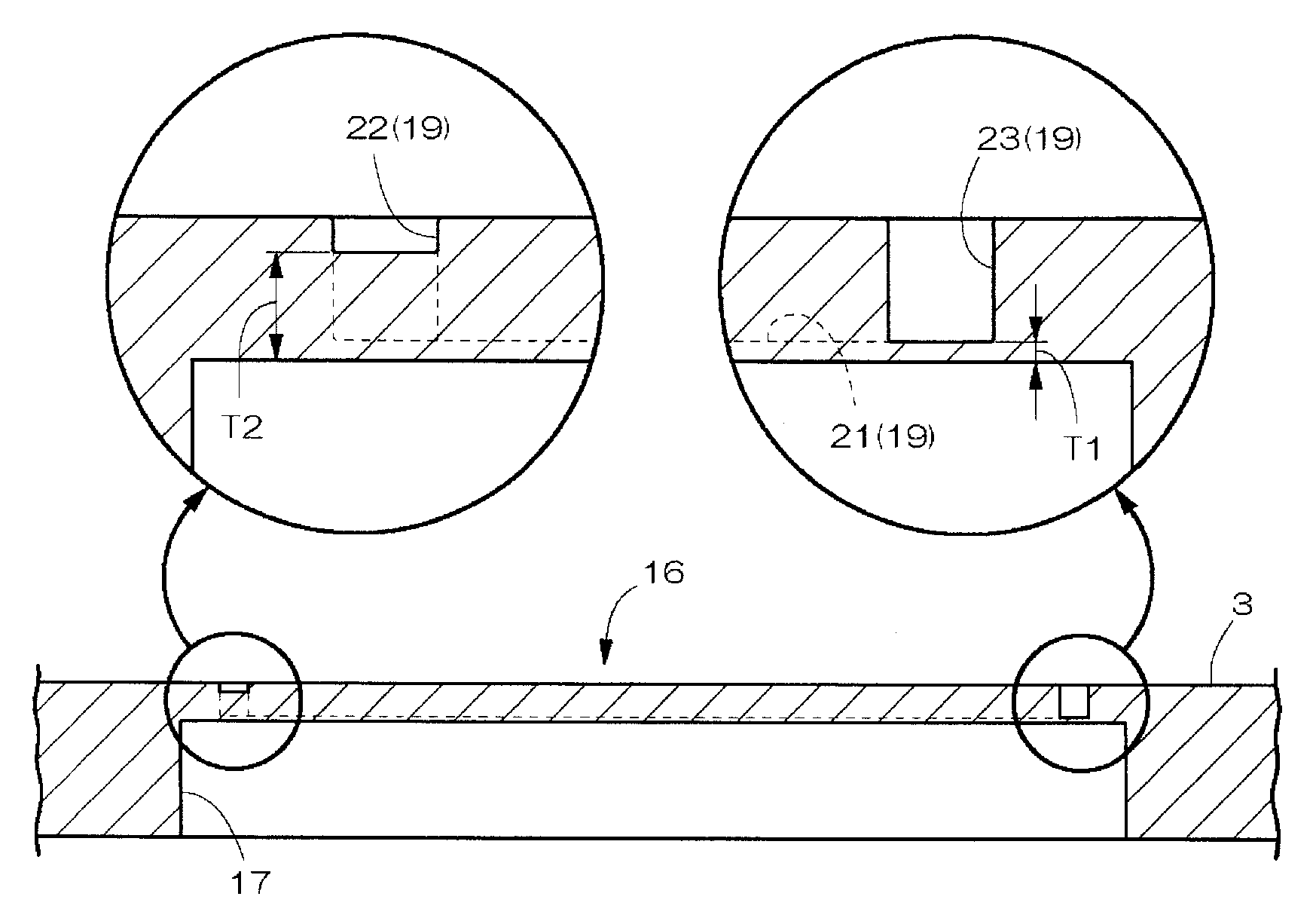

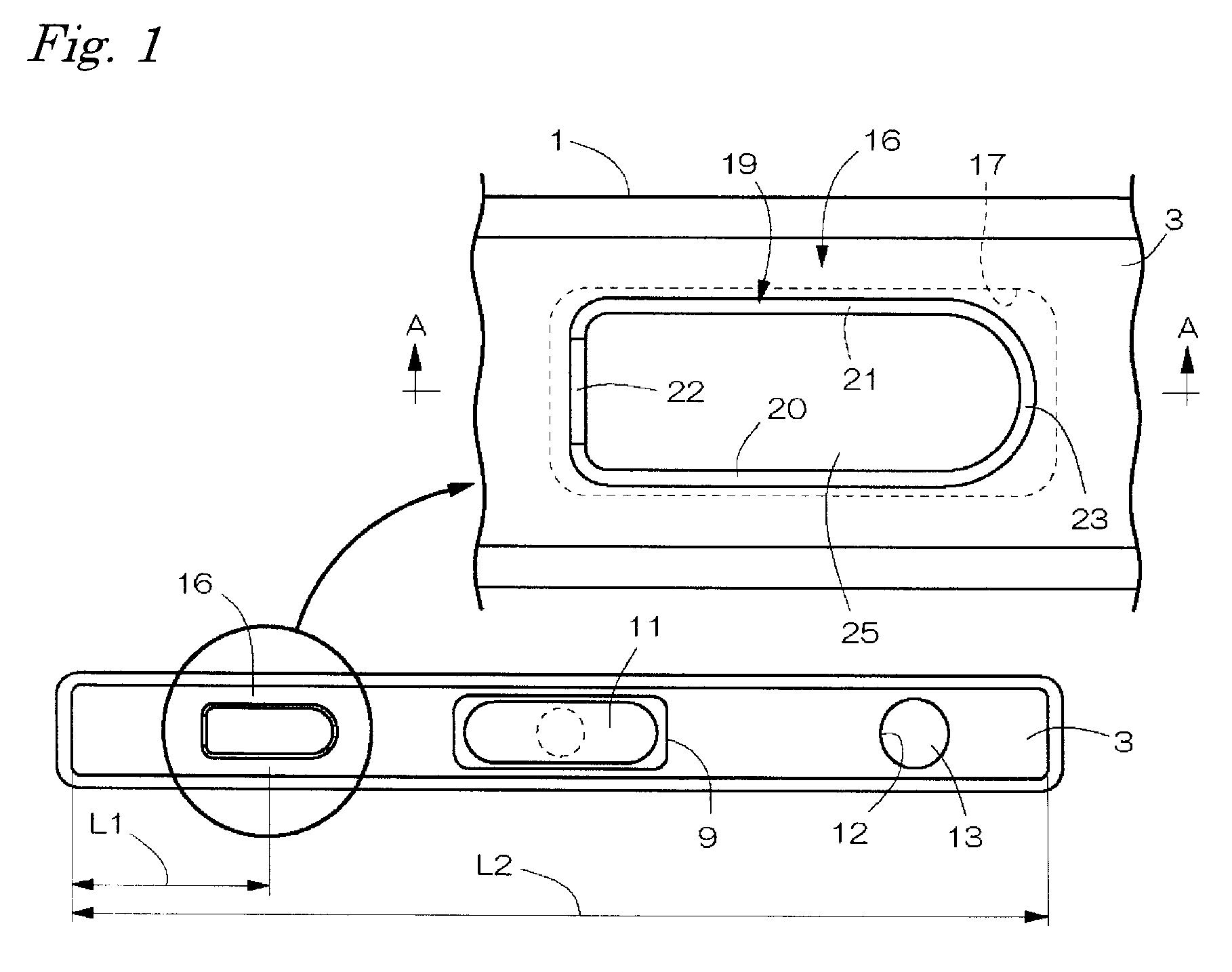

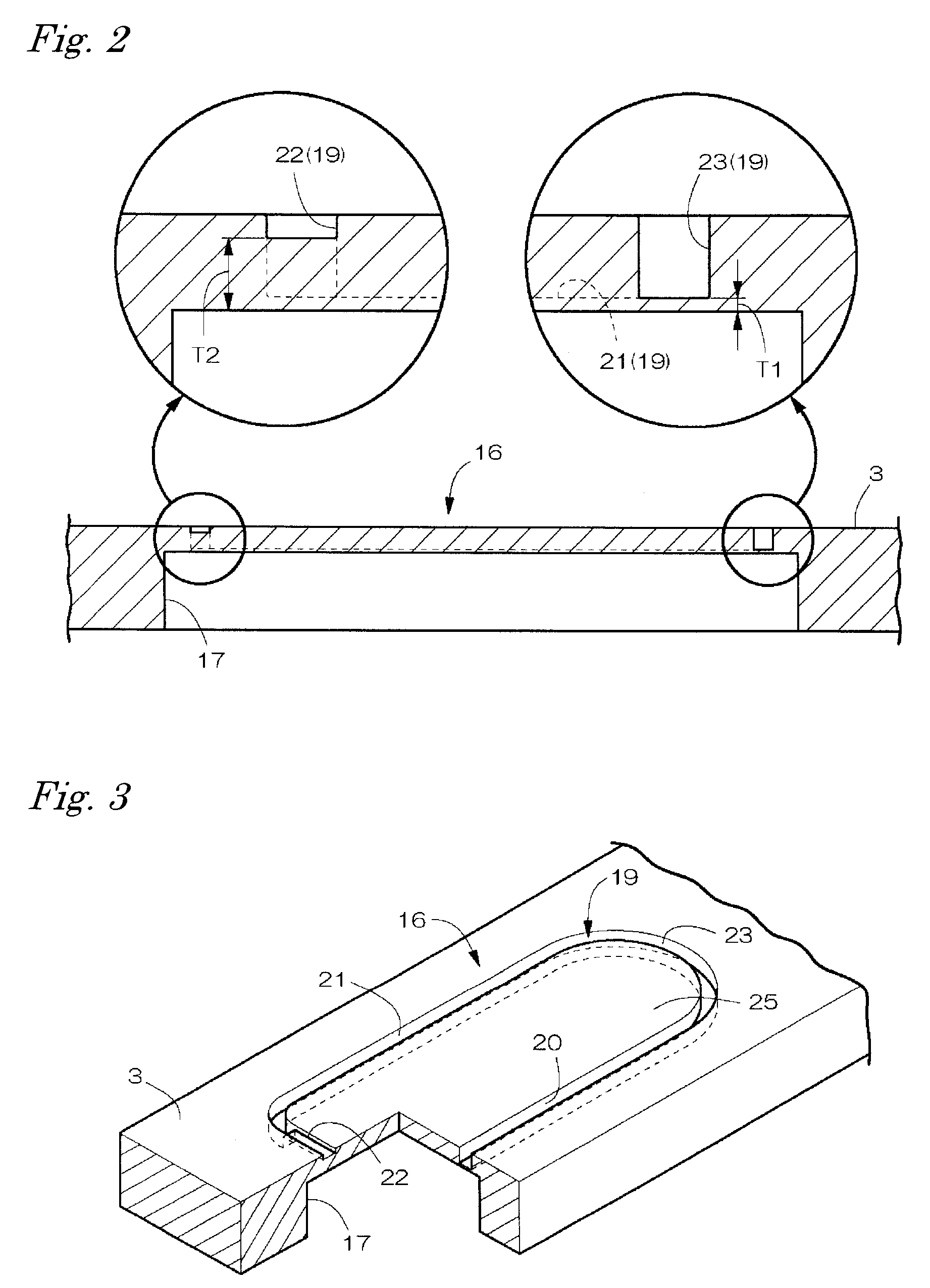

Base fabric for hollow-woven air bag and air bag

InactiveUS20020130503A1FlatnessImprove weaving performancePedestrian/occupant safety arrangementMulti-ply fabricsMechanical engineering

Owner:TOYO TOYOBO CO LTD

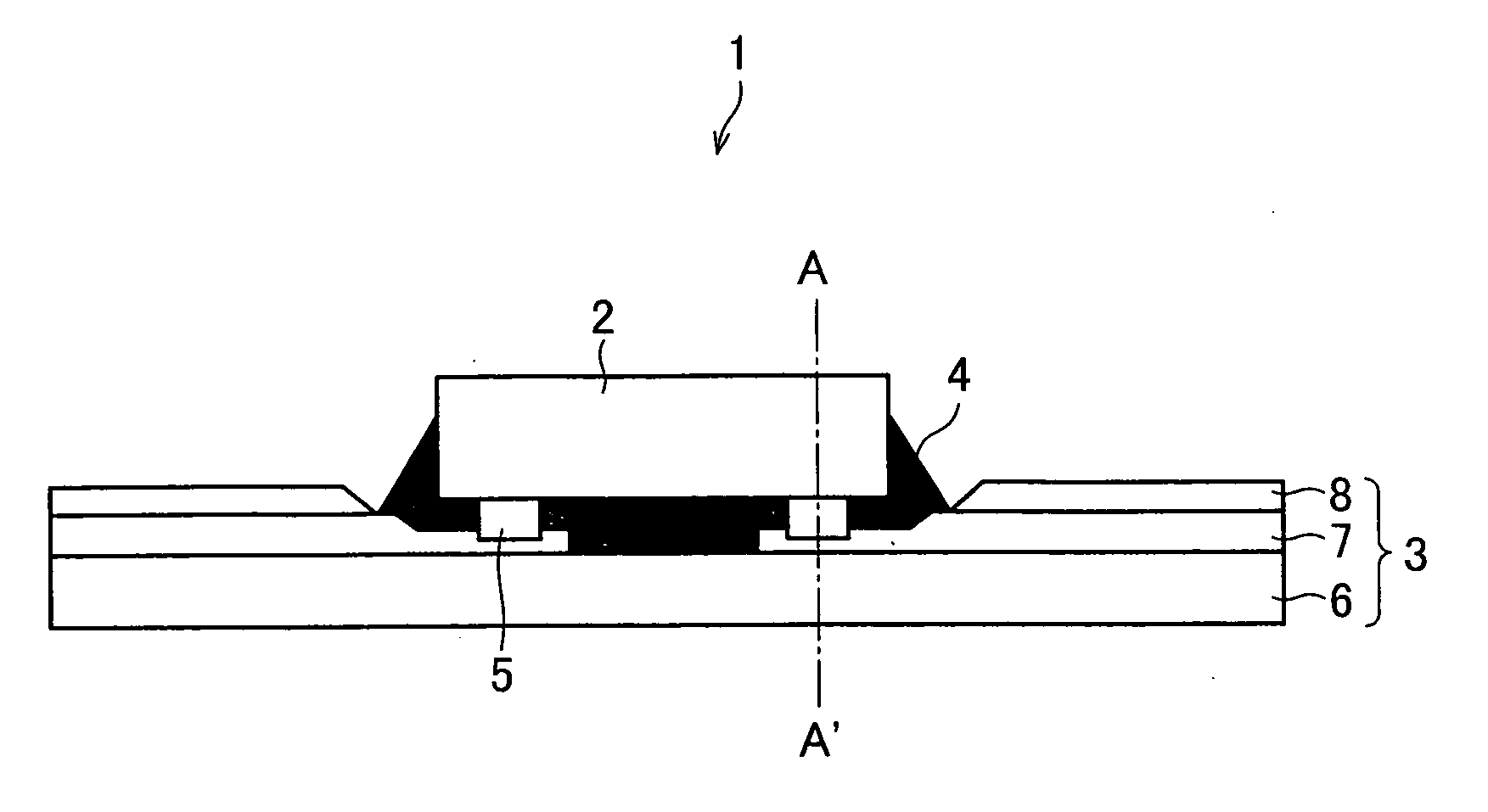

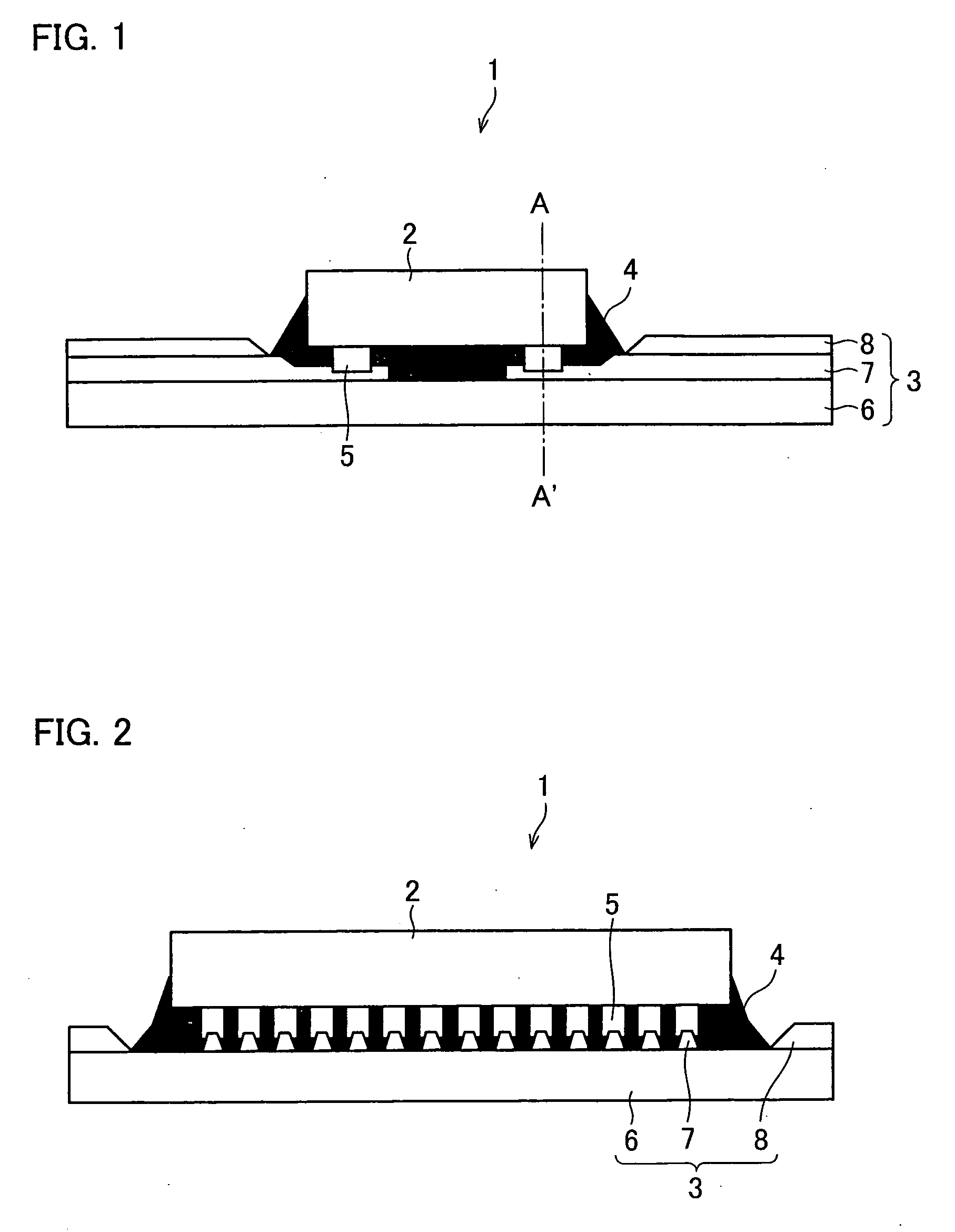

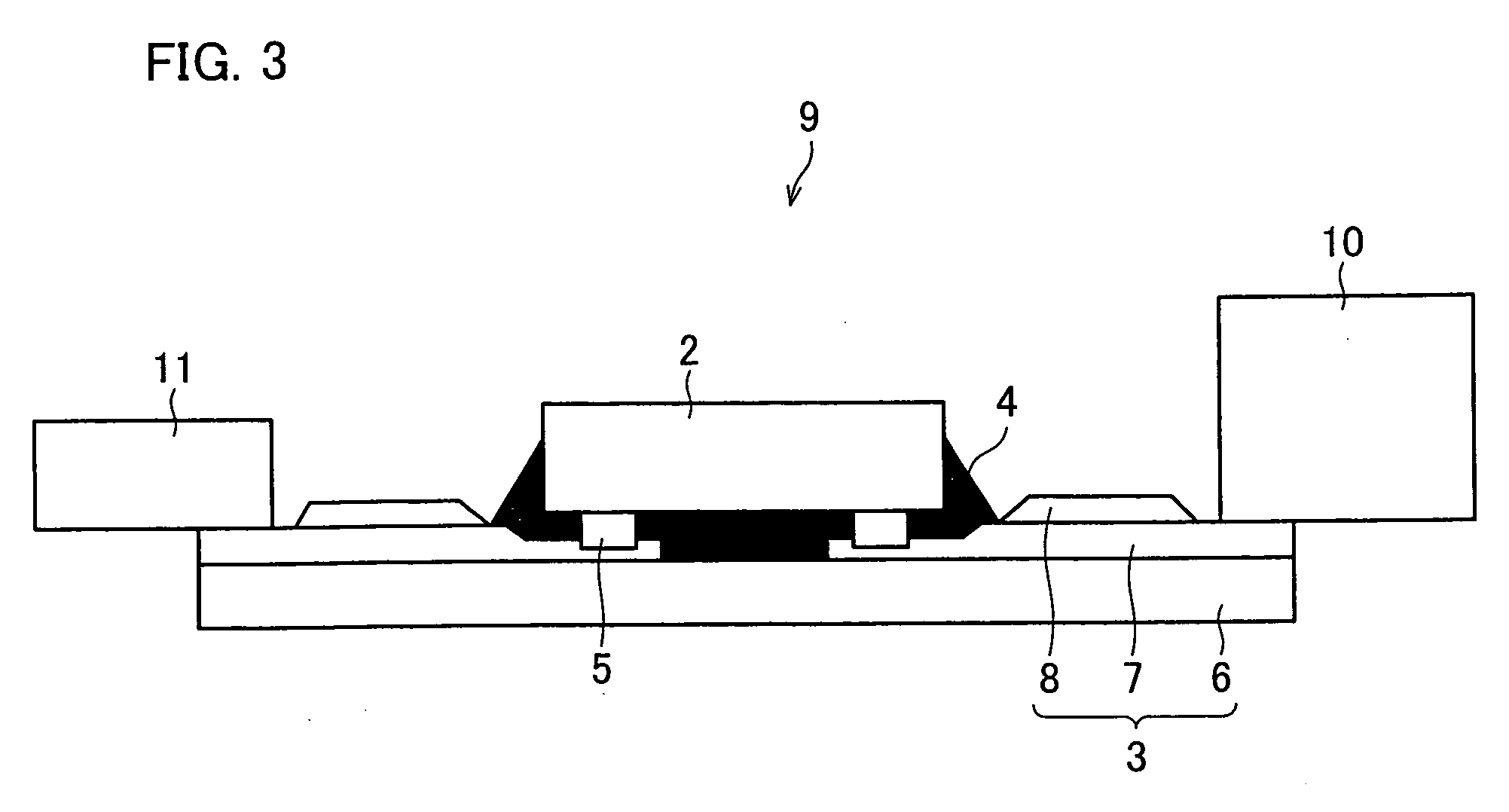

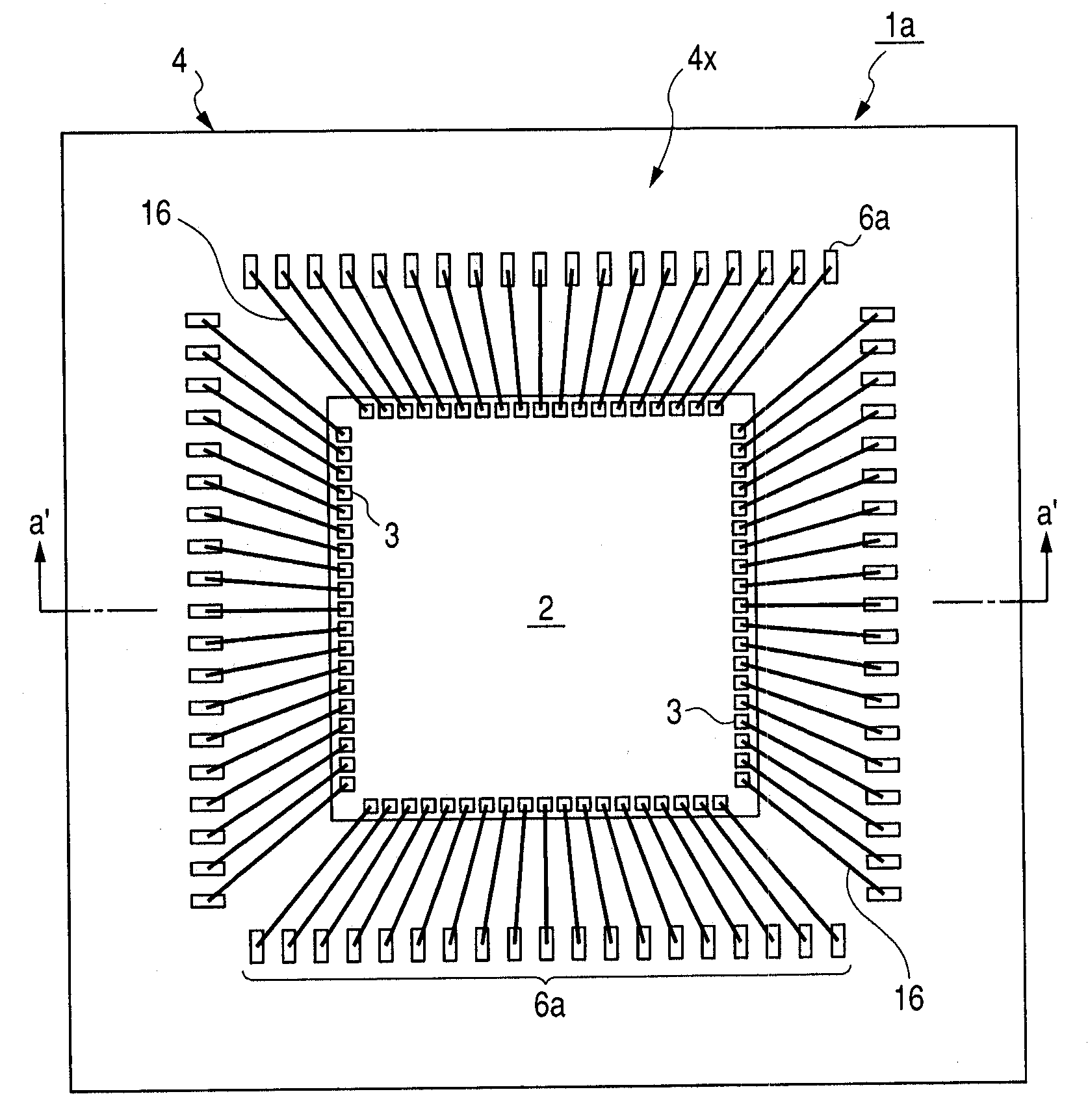

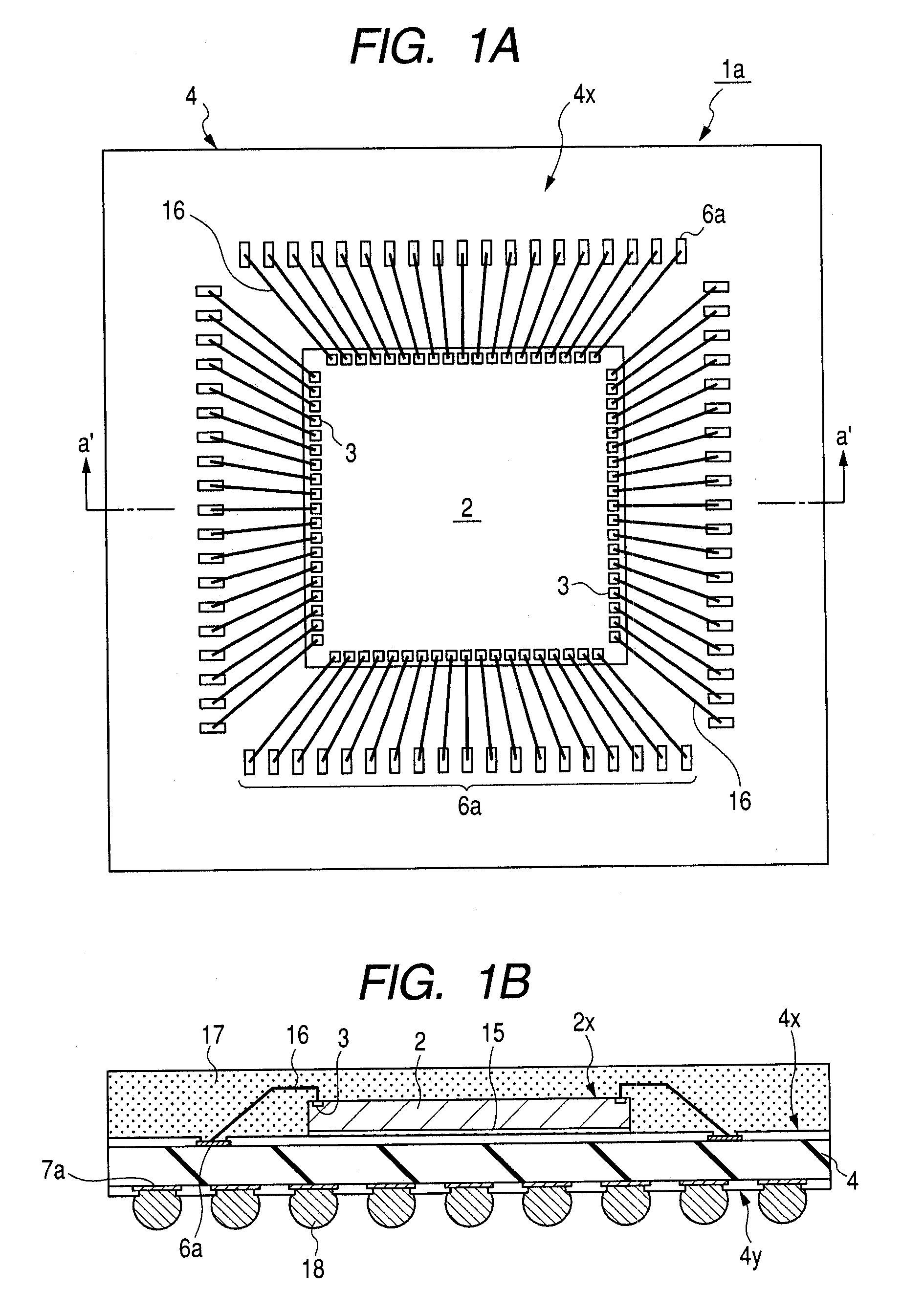

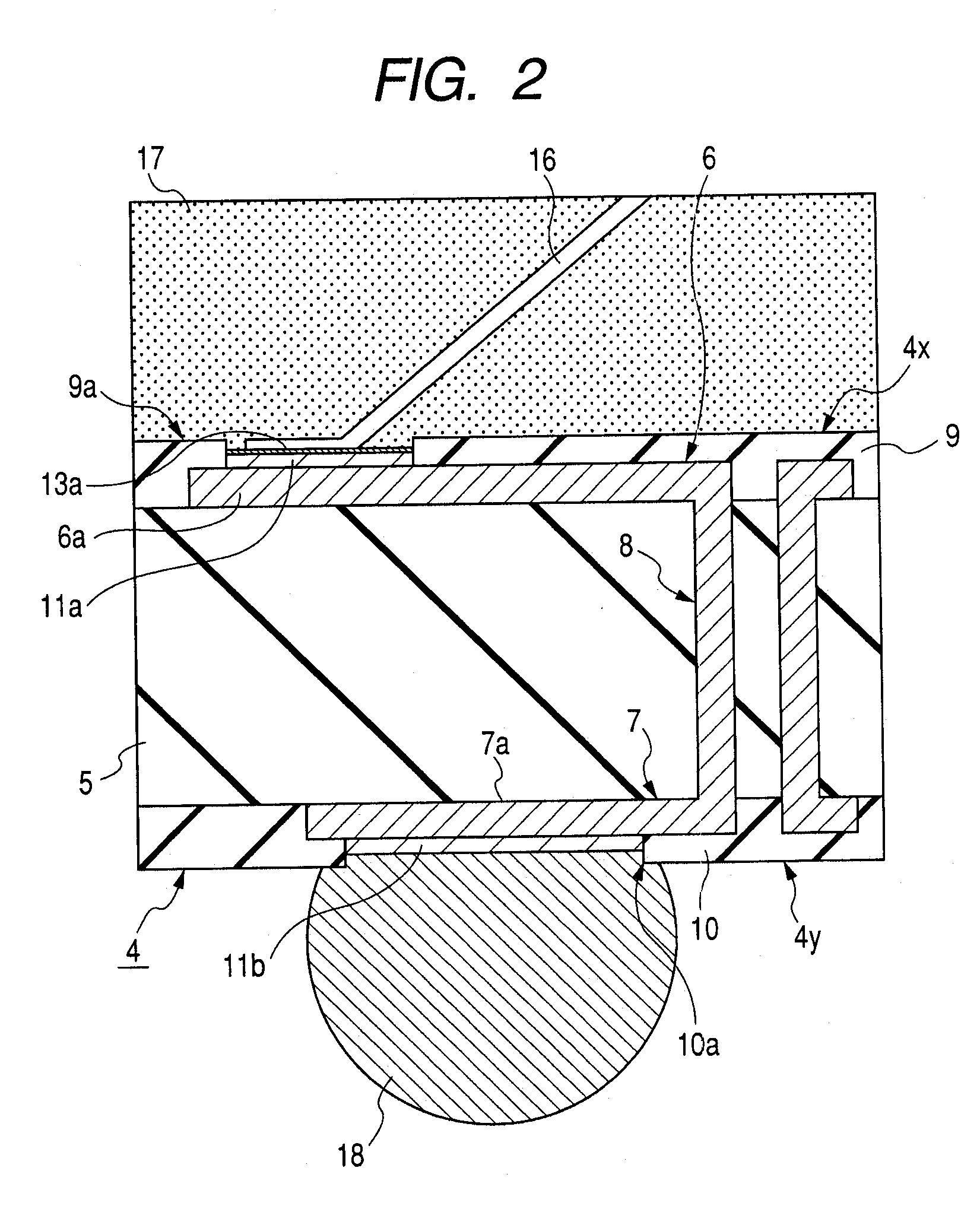

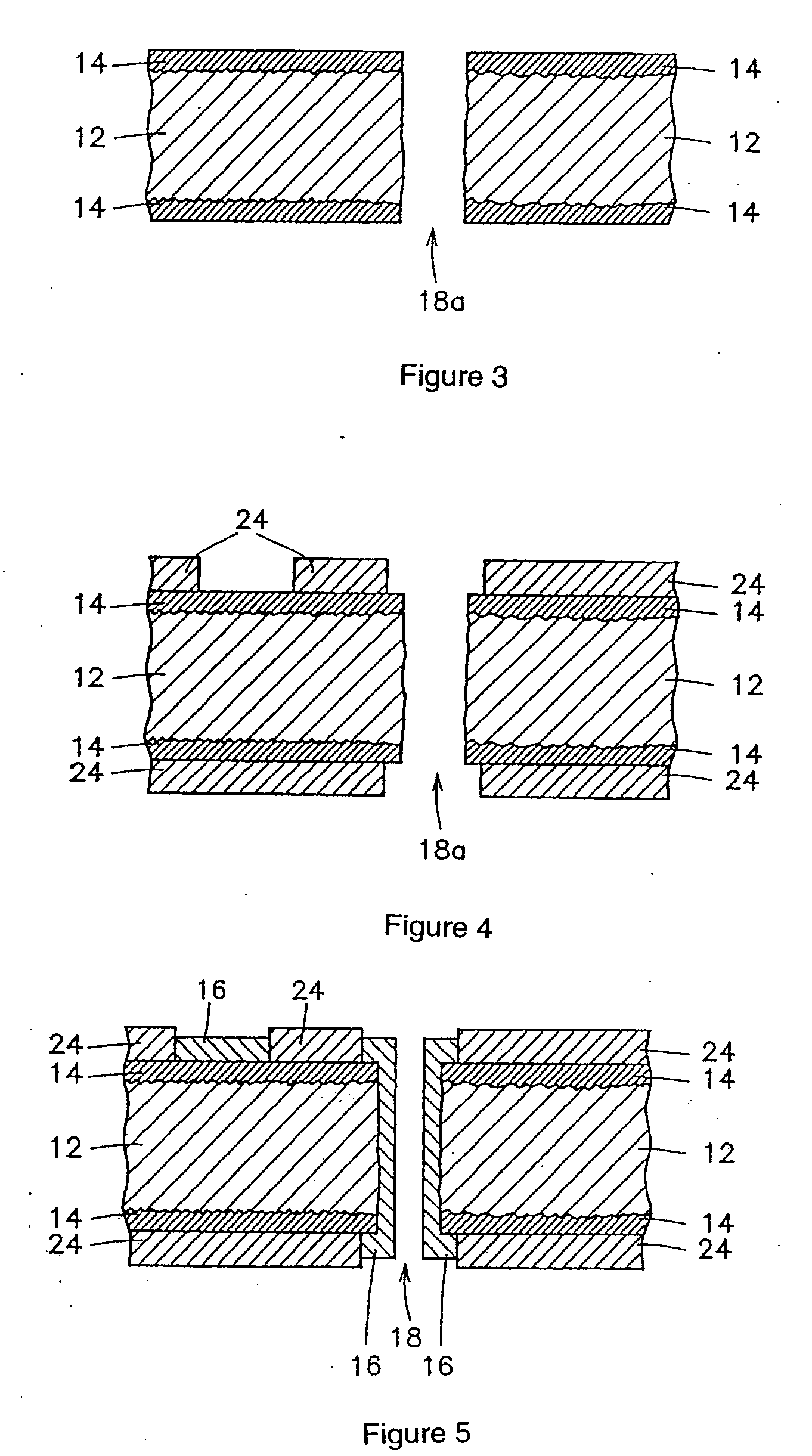

Flexible wiring substrate, semiconductor device and electronic device using flexible wiring substrate, and fabricating method of flexible wiring substrate

ActiveUS20060097368A1Good body shapeReduce variationFinal product manufactureSemiconductor/solid-state device detailsDevice materialEngineering

A flexible wiring substrate is provided which realizes a fine pitch of a wiring pattern and improves mechanical strength of the wiring pattern so as to prevent breaks or exfoliation of the wiring pattern. A flexible wiring substrate 3 of the present invention includes an insulation tape 6, and a wiring pattern 7 formed on the insulation tape 6. A thickness of the wiring pattern 7 is made thinner in a mounting region, where a semiconductor element is connected to, than in a non-mounting region.

Owner:SHENZHEN TOREY MICROELECTRONIC TECH CO LTD

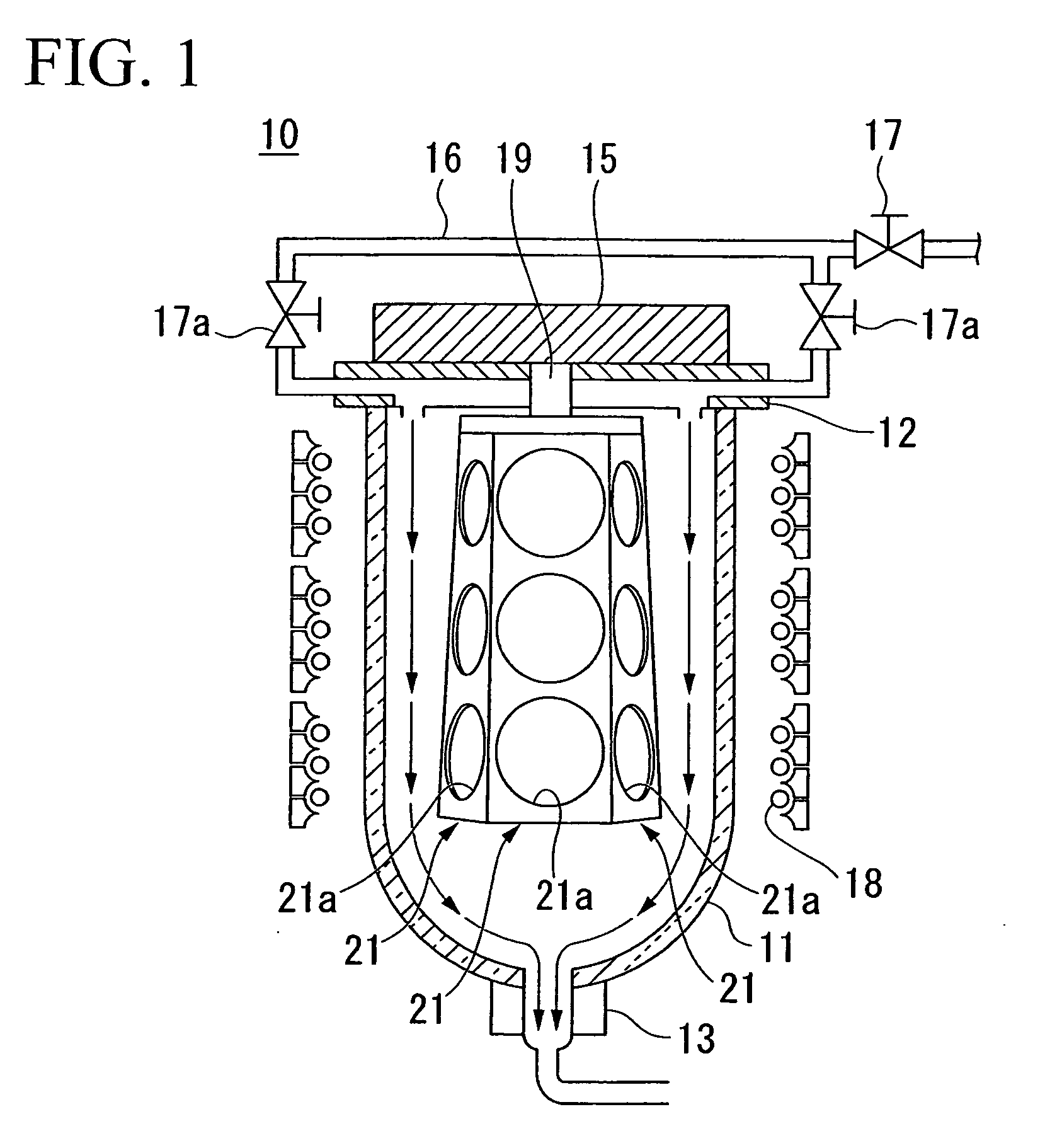

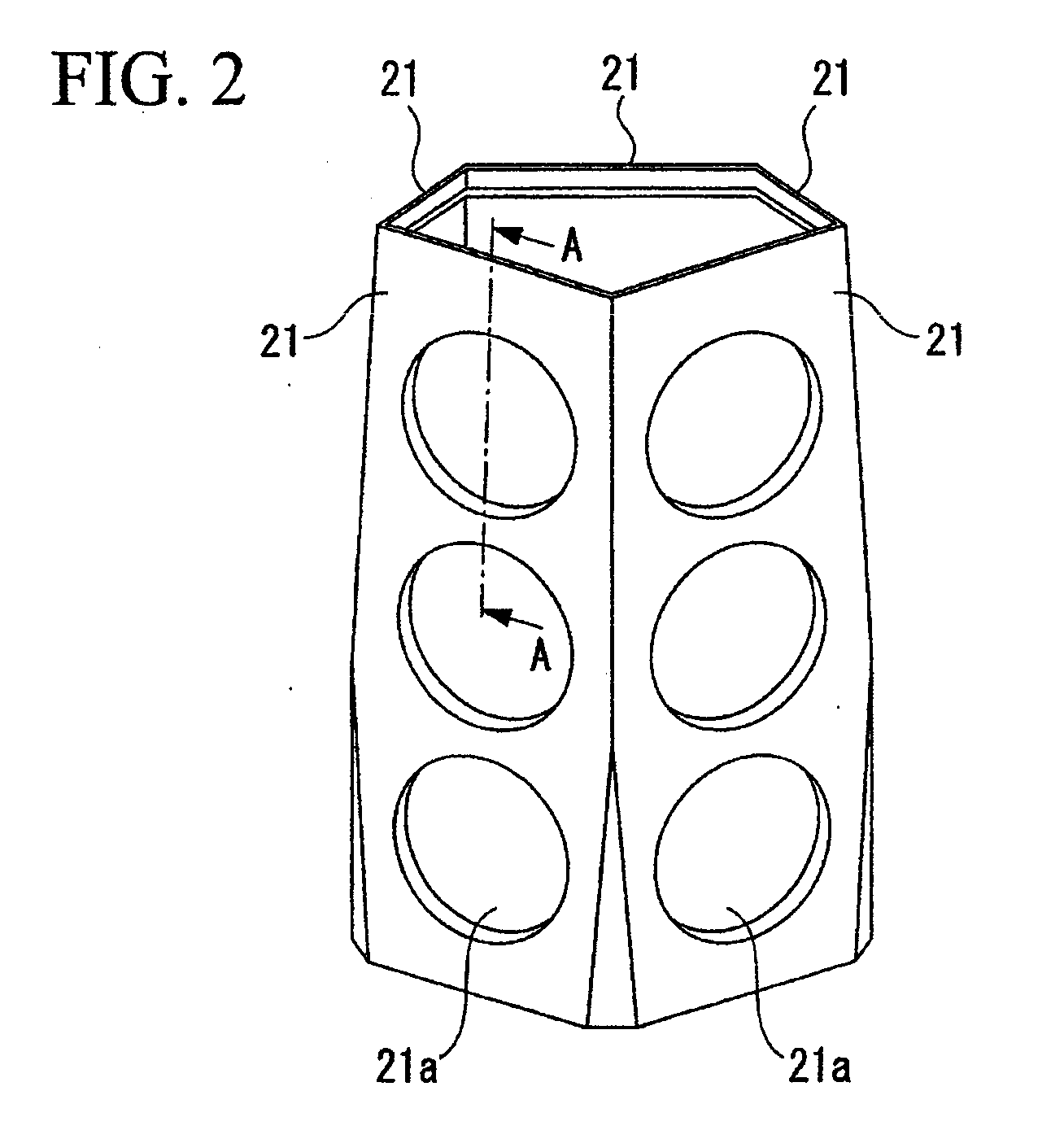

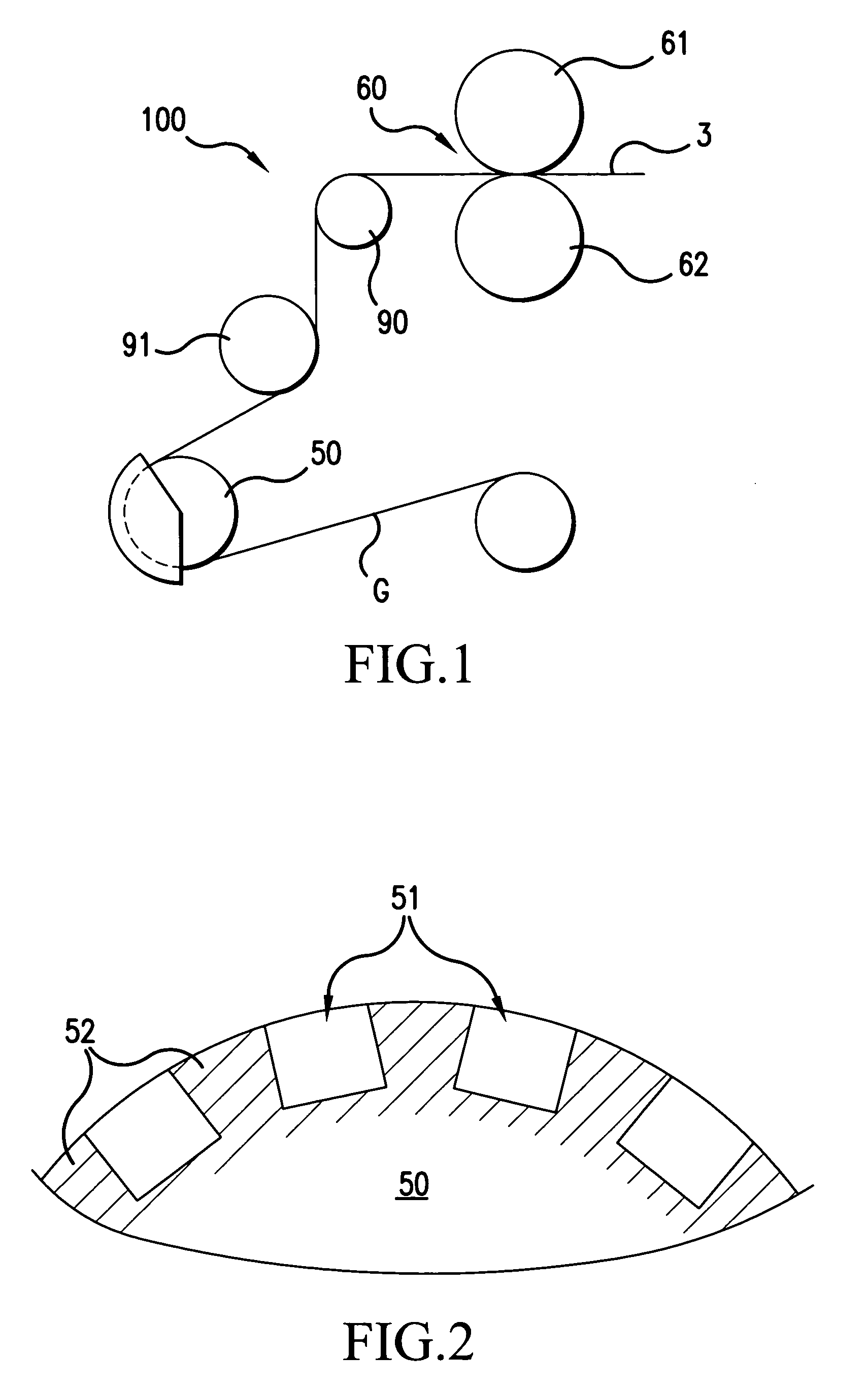

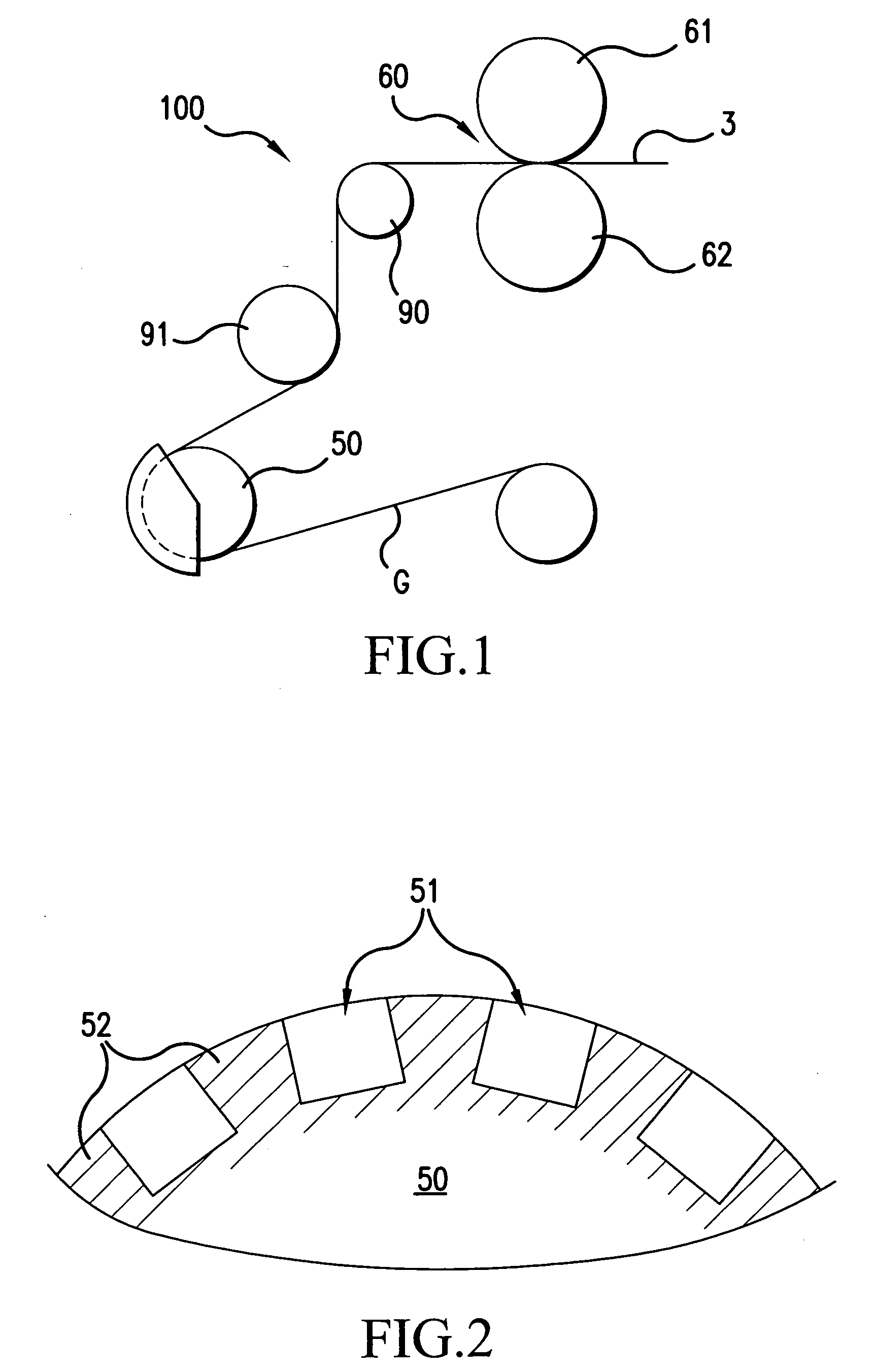

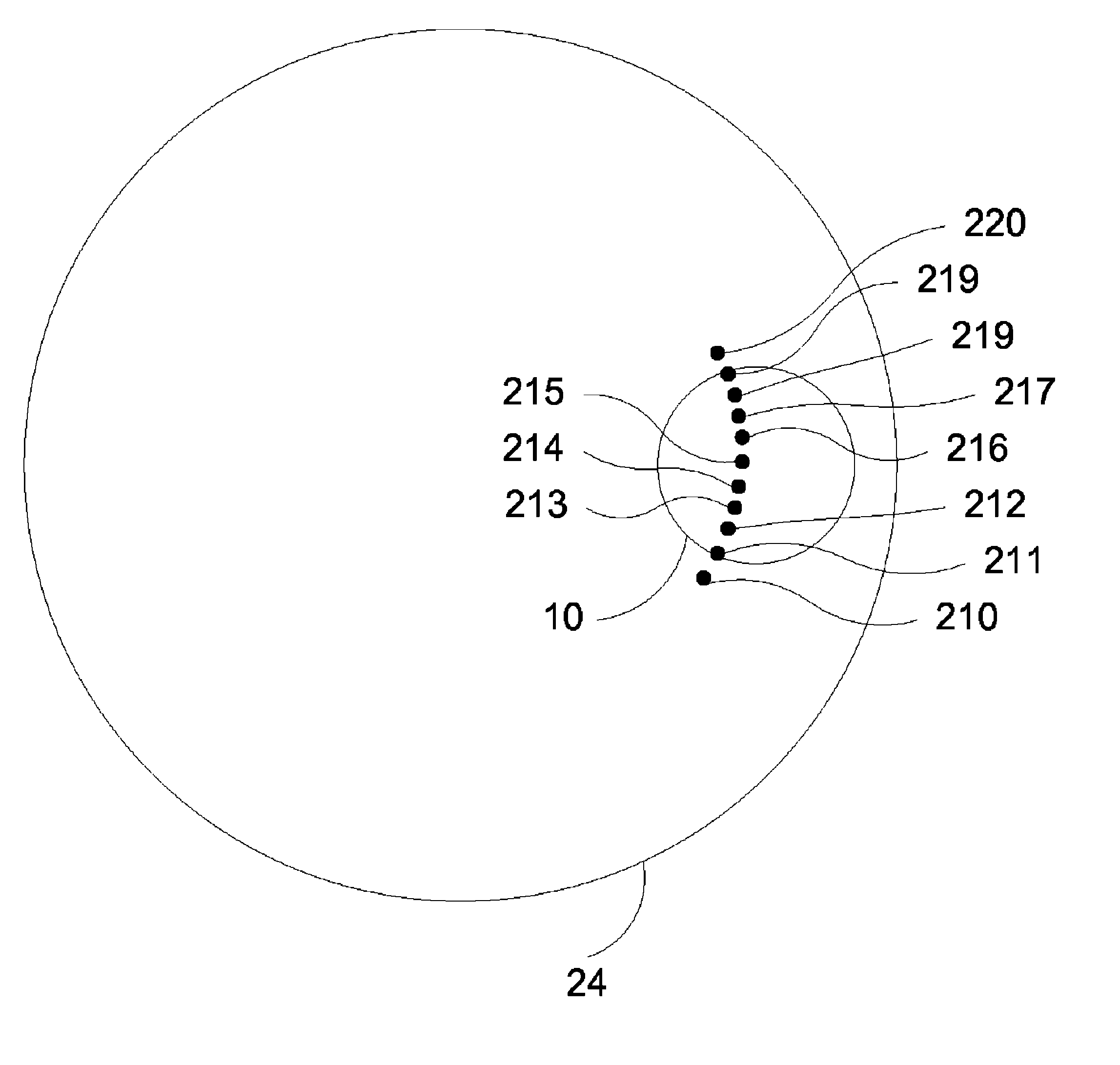

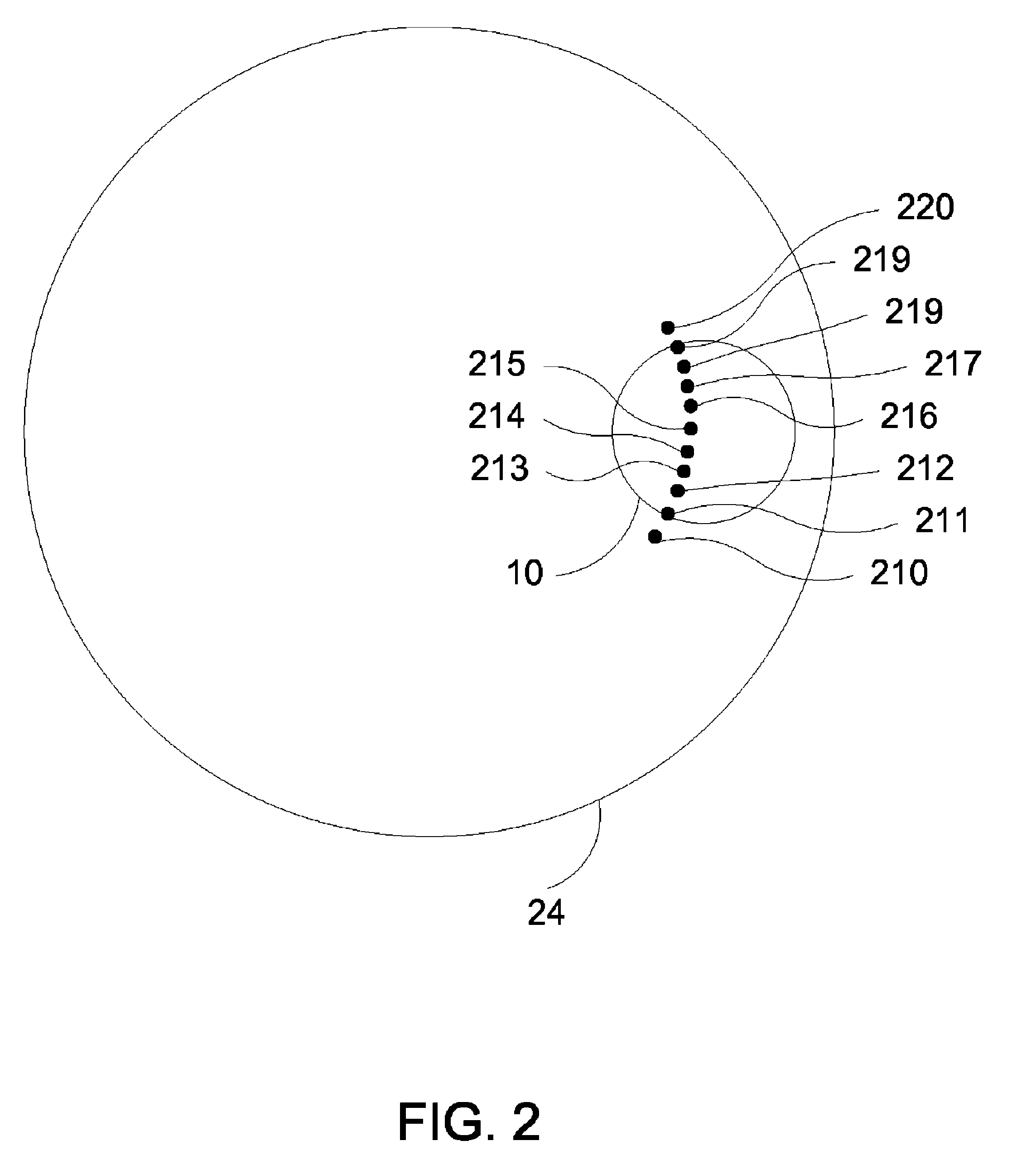

Susceptor for epitaxial layer forming apparatus, epitaxial layer forming apparatus, epitaxial wafer, and method of manufacturing epitaxial wafer

InactiveUS20090127672A1Little change in thicknessUniform etchingSemiconductor/solid-state device detailsSolid-state devicesSusceptorEngineering

A susceptor for epitaxial layer forming apparatus provided in a layer forming chamber of an epitaxial layer forming apparatus includes: a recessed portion which is provided to accommodate a semiconductor wafer therein and has an approximately circular shape in plan view; and a protruding portion which is provided in the recessed portion in order to support the semiconductor wafer and has an approximately circular shape in plan view. The diameter of the protruding portion is smaller than that of the recessed portion, and the diameter of the protruding portion is set to be a size allowing reaction gas supplied for vapor-phase growth reaction to circulate through an entire boundary between the protruding portion and the semiconductor wafer when the semiconductor wafer is placed in the recessed portion.

Owner:SUMCO CORP

Glass ceramic and method of producing the same

ActiveUS7300896B2High surface precisionThickness variationTransistorGlass tempering apparatusSolar cellGlass-ceramic

A glass ceramic comprises (in wt.-% on oxide basis): SiO2 35 to 60, B2O3>4 to 10, P2O5 0 to 10, Al2O3 16.5 to 40, TiO2 1 to 10, Ta2O5 0 to 8, Y2O3 0 to 6, ZrO2 1 to 10, MgO 6 to 20, CaO 0 to 10, SrO 0 to 4, BaO 0 to 8, ZnO 0 to 4, SnO2+CeO2 0 to 4, SO42−+Cl− 0 to 4, wherein the total content (SnO2+CeO2+SO42−+Cl−) is between 0.01 and 4 wt.-%. The glass ceramic may be processed by the float glass method, may be transparent and is, inter alia, suitable as a substrate for thin film semiconductors, in particular for display applications, solar cells etc.

Owner:SCHOTT AG

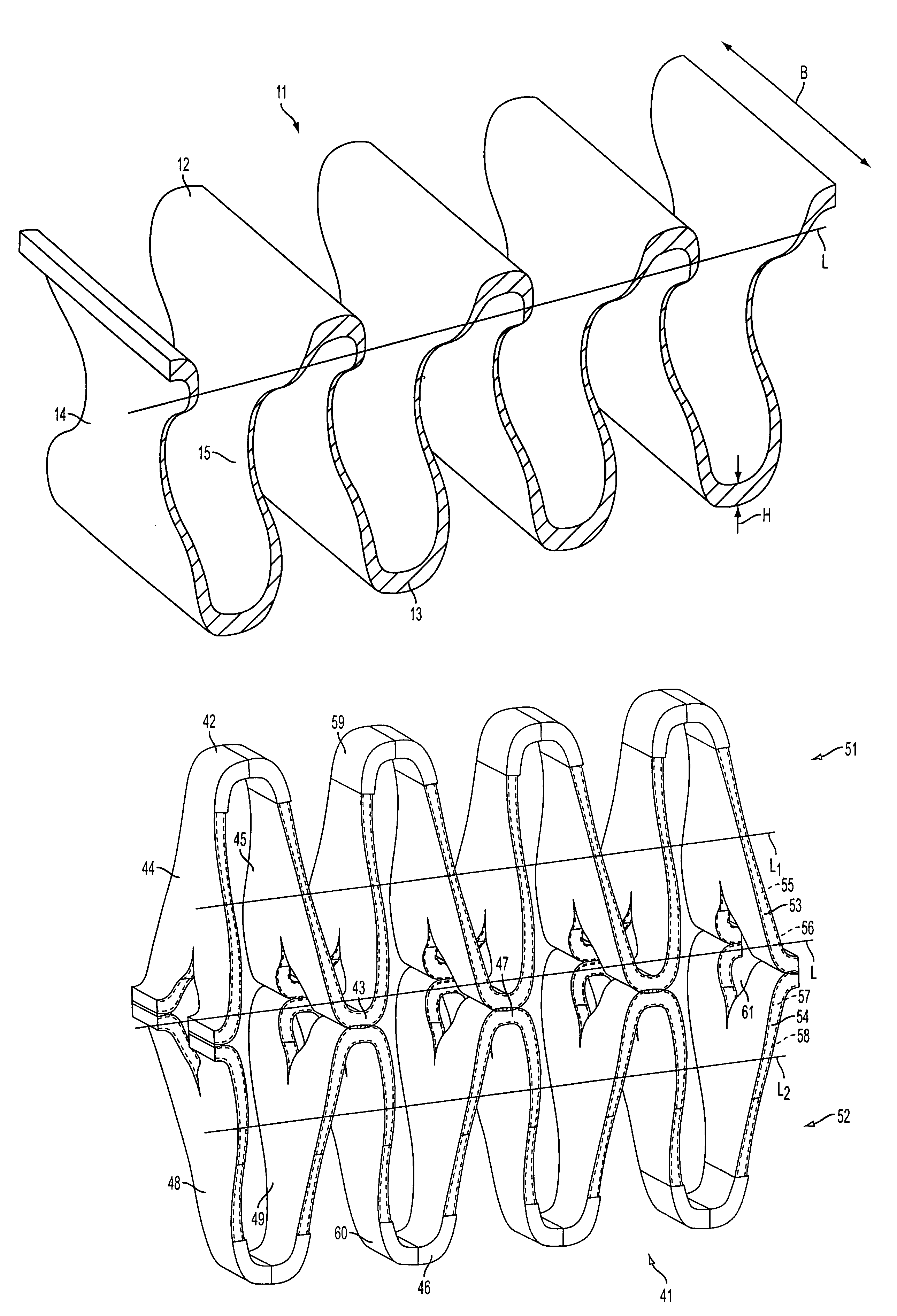

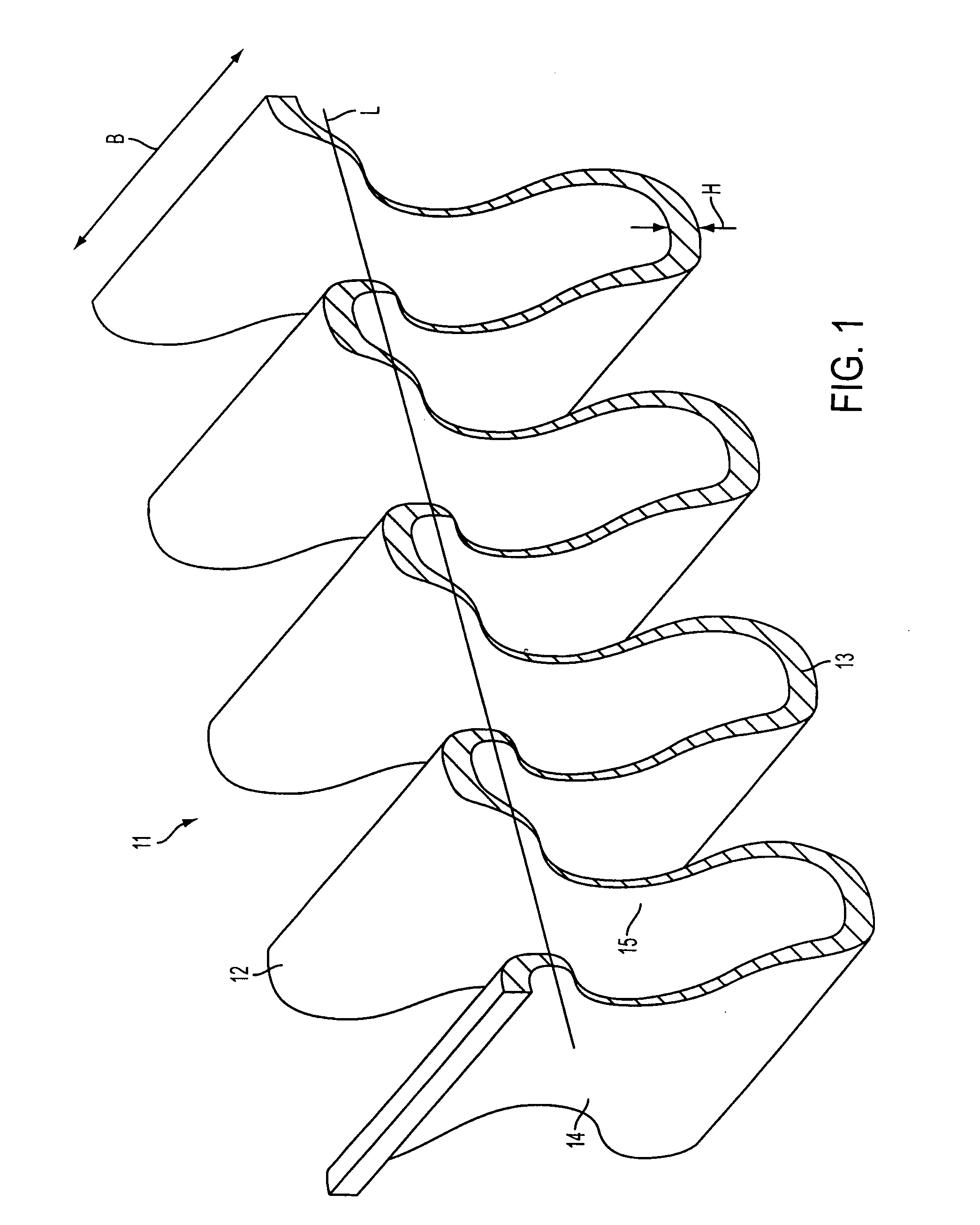

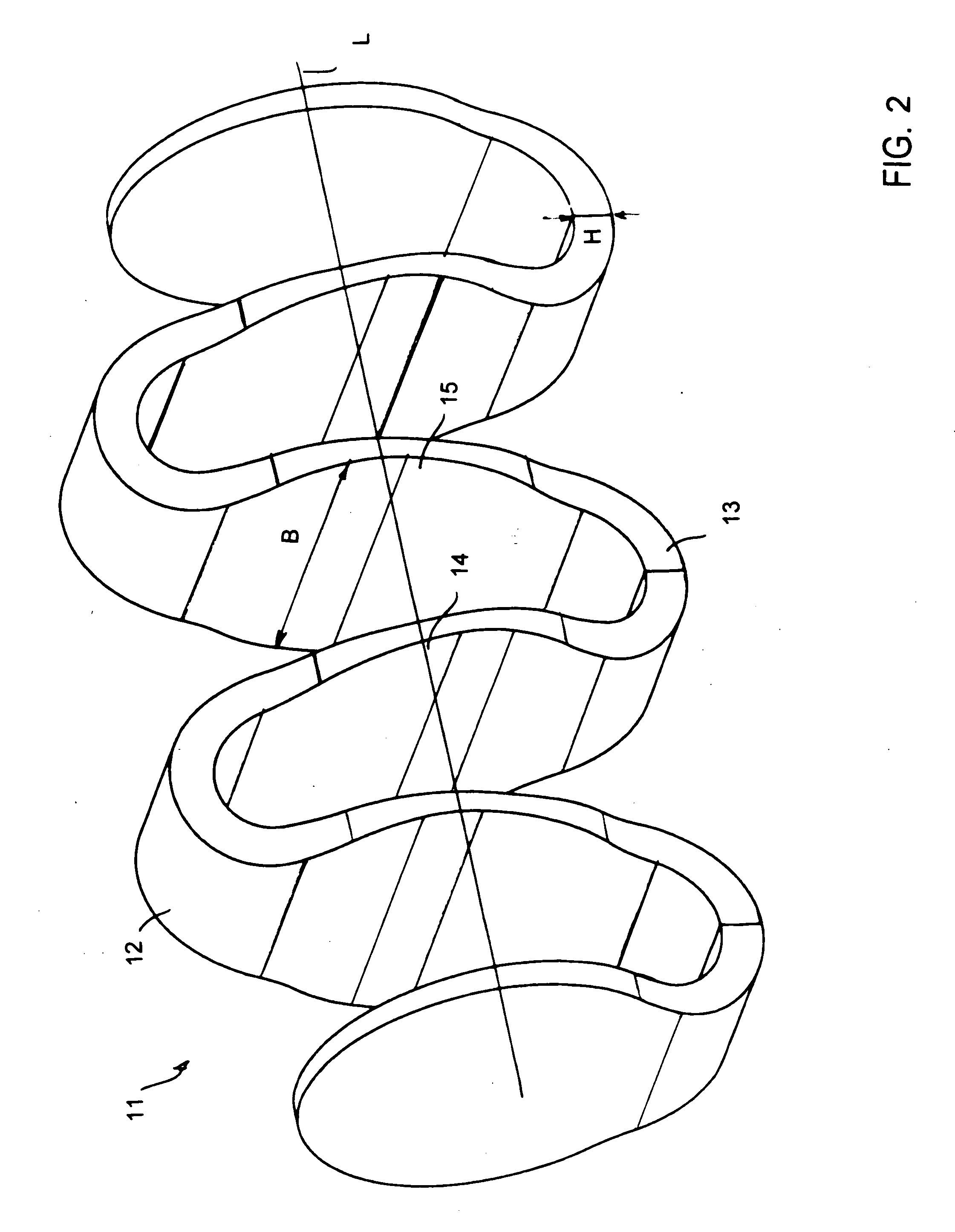

Motor vehicle spring comprising fiber composite material

InactiveUS20090200721A1Width variationThickness variationResilient suspensionsVehicle springsMobile vehicleMassive gravity

A band spring including fiber composite material and extending in an undulating way, wherein a spring band can be provided to meander in the form of one single wave train composed of reversal regions and intermediate portions around a longitudinal center line L which can substantially correspond to the direction of force introduction K, and wherein, there can be provided an increased resistance moment of the spring band in the reversal regions of the wave train.

Owner:MUHR UND BENNDER KG

Manufacturing method of printed circuit board

InactiveUS7726016B2Adjustable aspect ratioEliminate variationPrinted circuit aspectsConductive pattern formationMetal foilEngineering

The present invention provides a method of manufacturing a printed circuit board. The method includes the steps of preparing an insulating substrate having a front surface and a back surface and a layer of metal foil formed on each of the front surface and the back surface; selectively forming a plating layer for forming a land on at least one of the metal foils; adjusting a thickness of the plating layer; and forming the metal foils into lines.

Owner:GLOBALFOUNDRIES U S INC

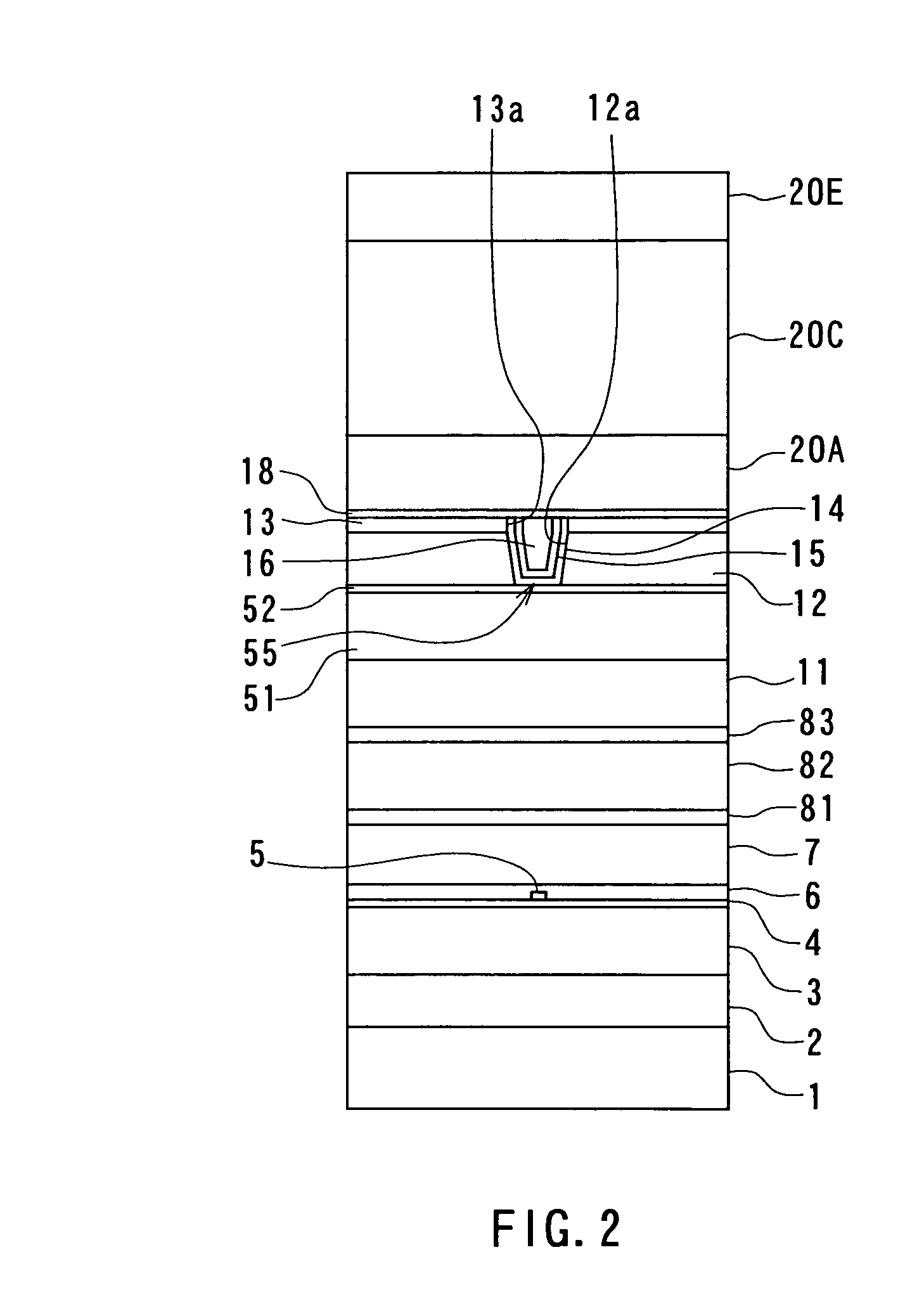

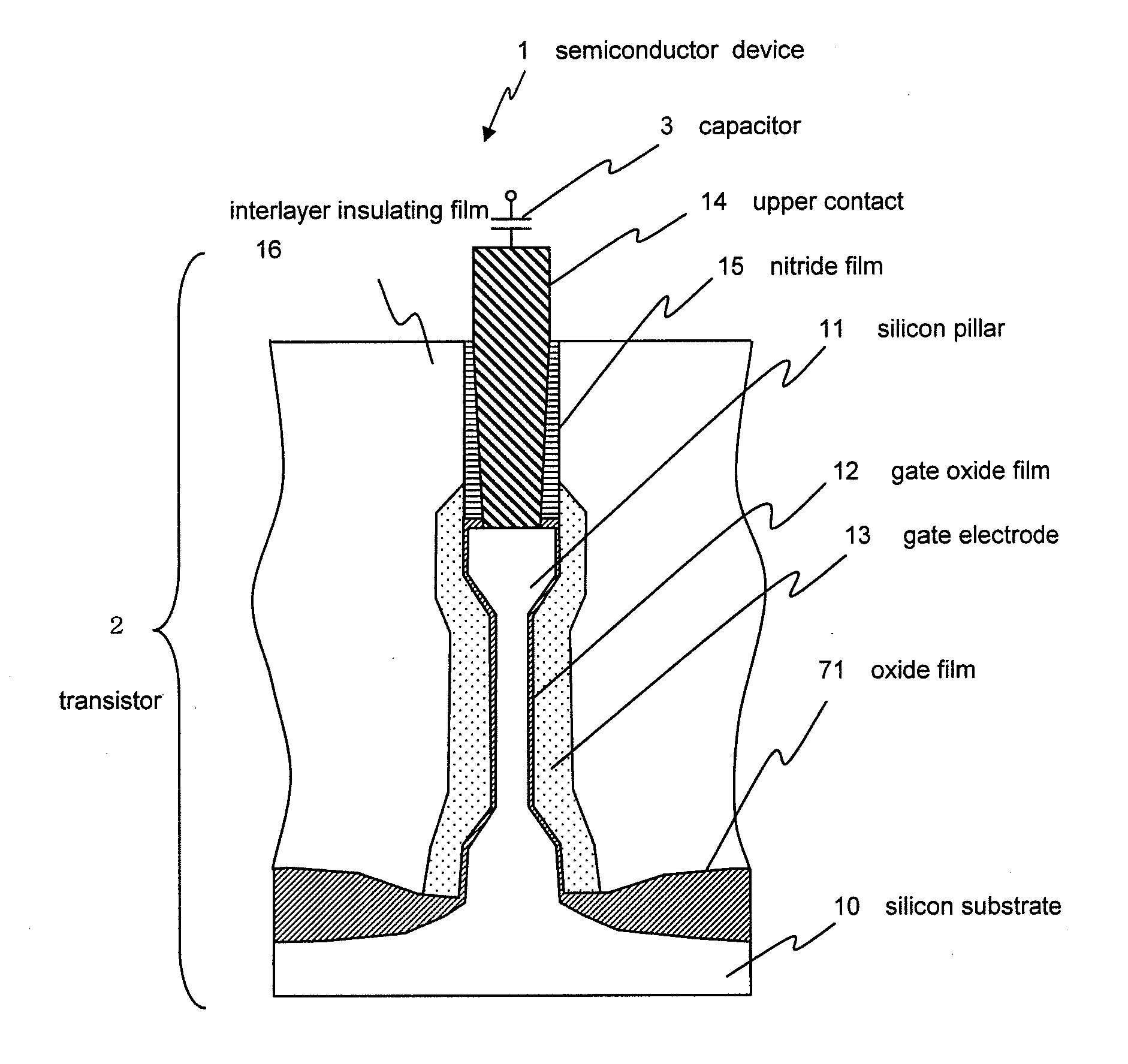

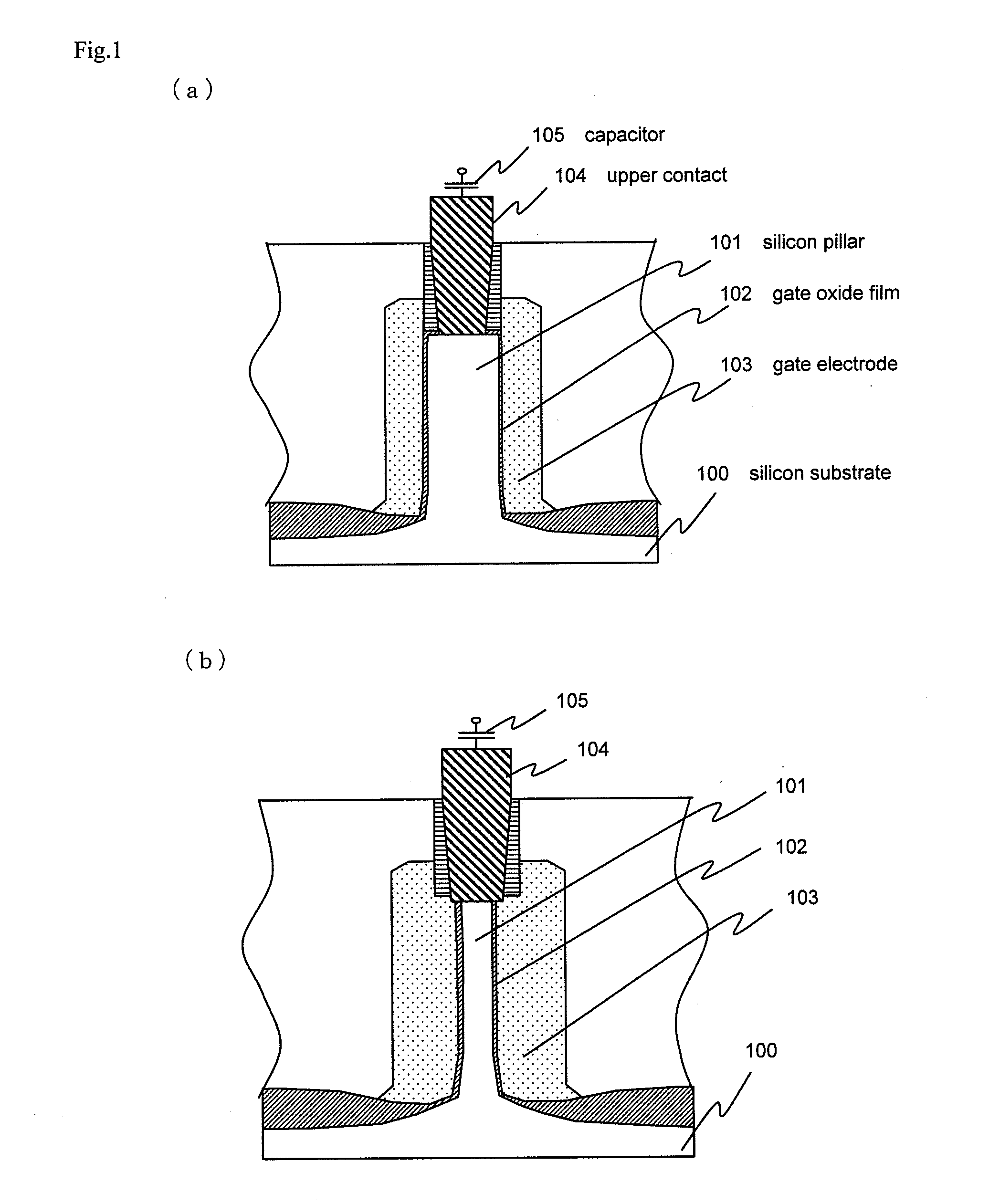

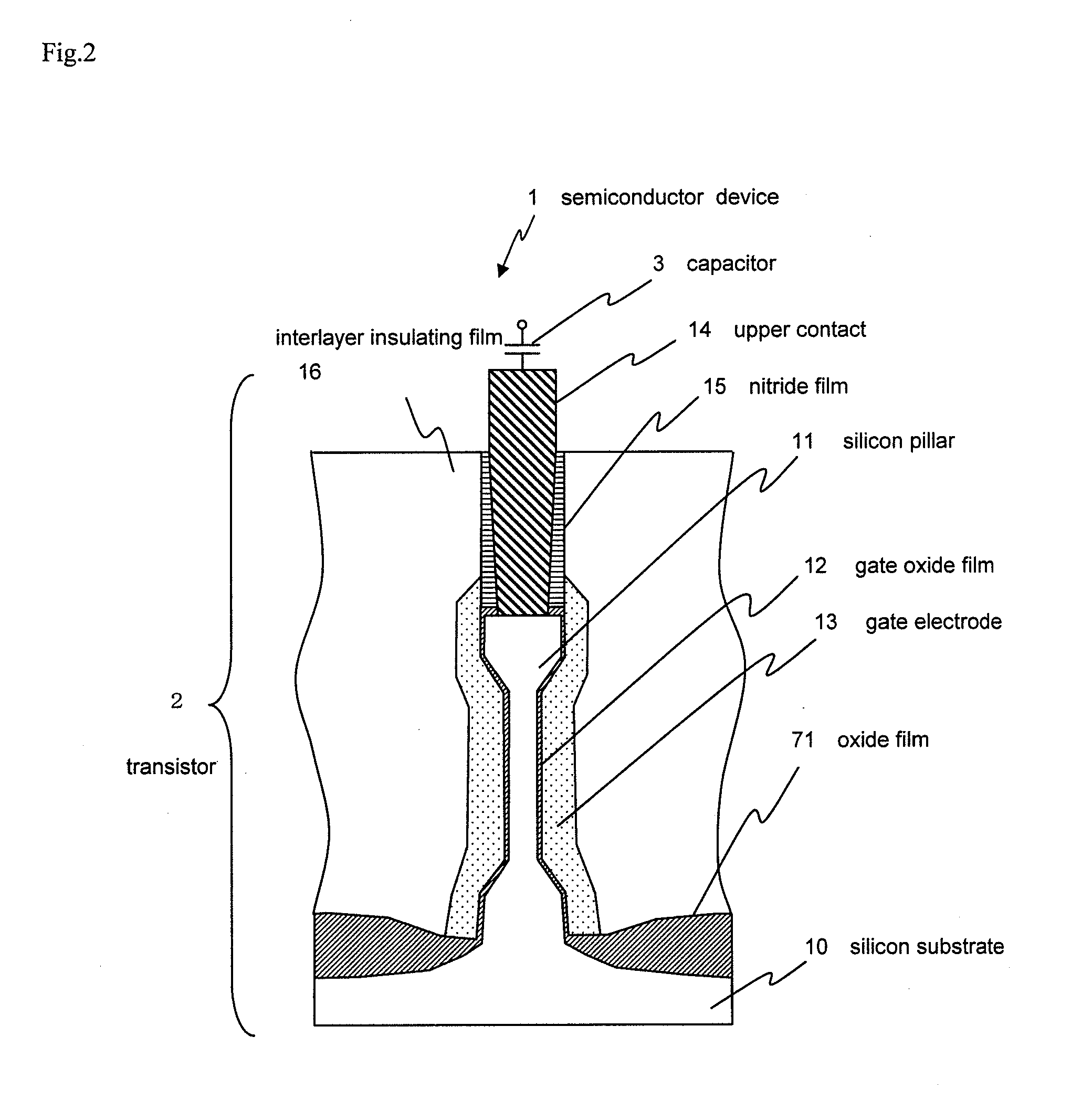

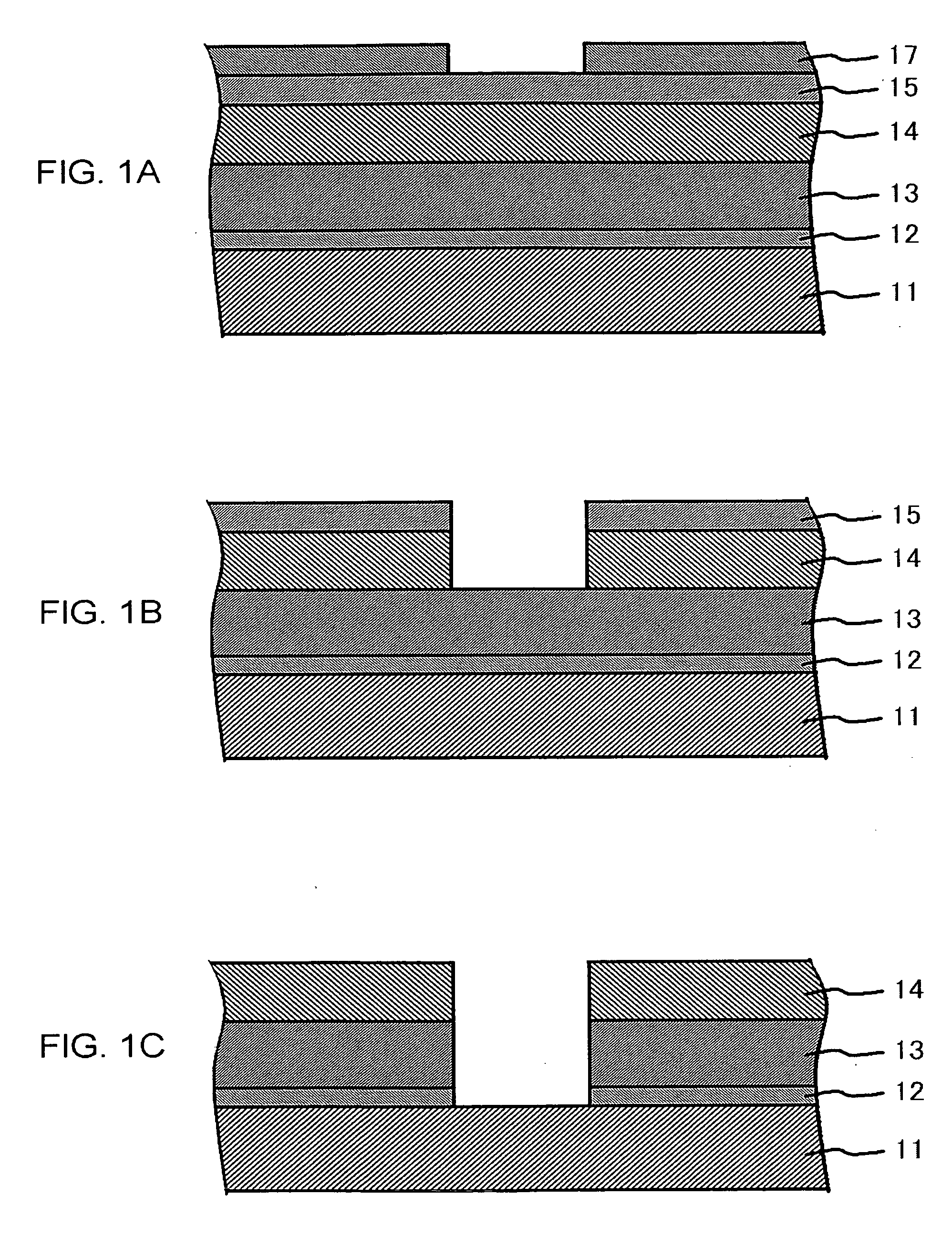

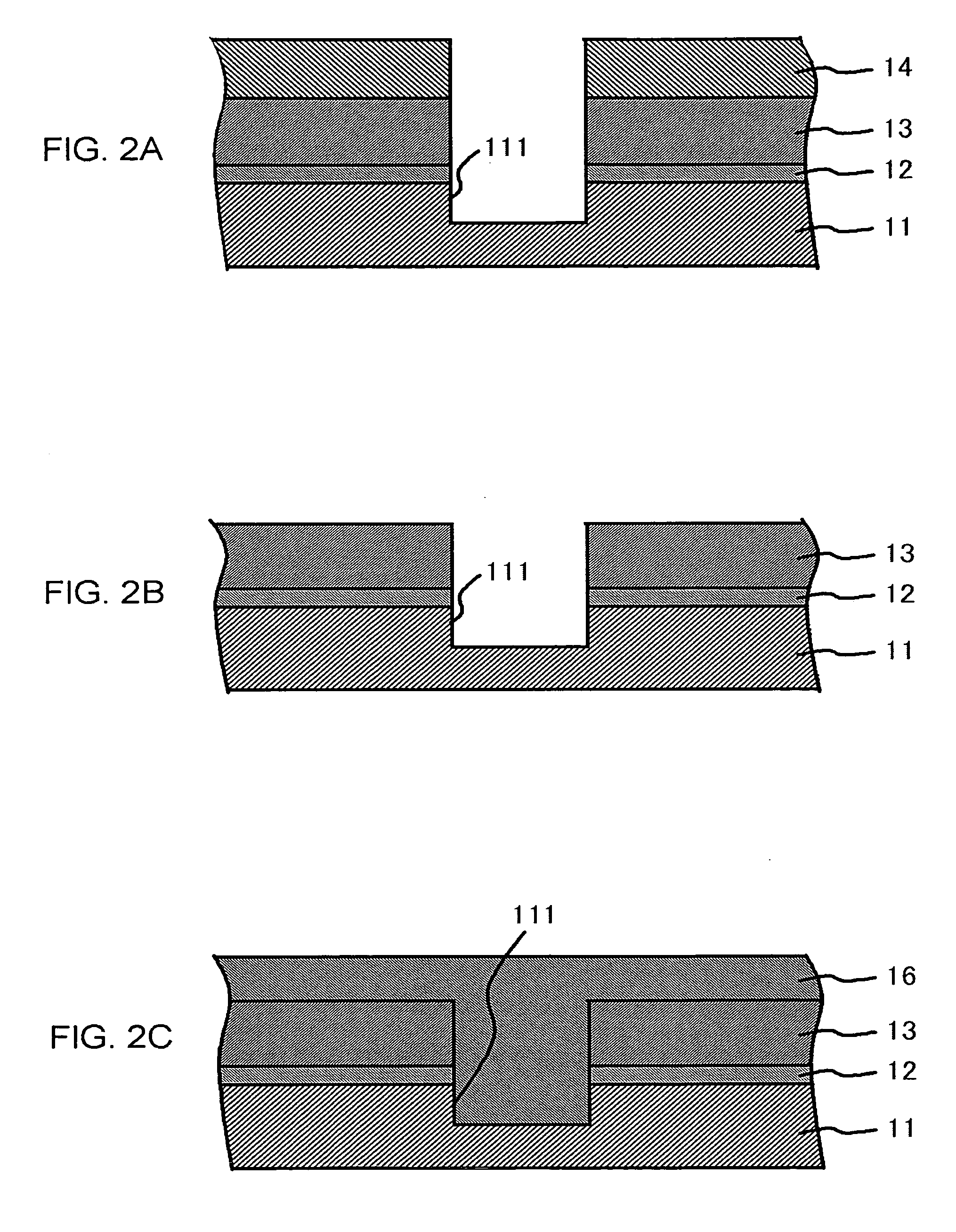

Semiconductor device and method of manufacturing the semiconductor device

InactiveUS20120025286A1Uniform damageSuppress mutationTransistorSolid-state devicesDevice materialEngineering

A method of manufacturing a semiconductor device includes forming silicon pillar 11 on substrate 10, forming a protective film which covers an upper end portion and a lower end portion of a side surface of silicon pillar 11, forming a constricted portion by anisotropic etching in a portion of the side surface of silicon pillar 11 which is not covered with the protective film after forming the protective film, removing the protective film after forming the constricted portion, forming gate oxide film 12 which covers the side surface of silicon pillar 11 in which the constricted portion is formed, and forming gate electrode 13 which covers gate oxide film 12.

Owner:PS4 LUXCO SARL

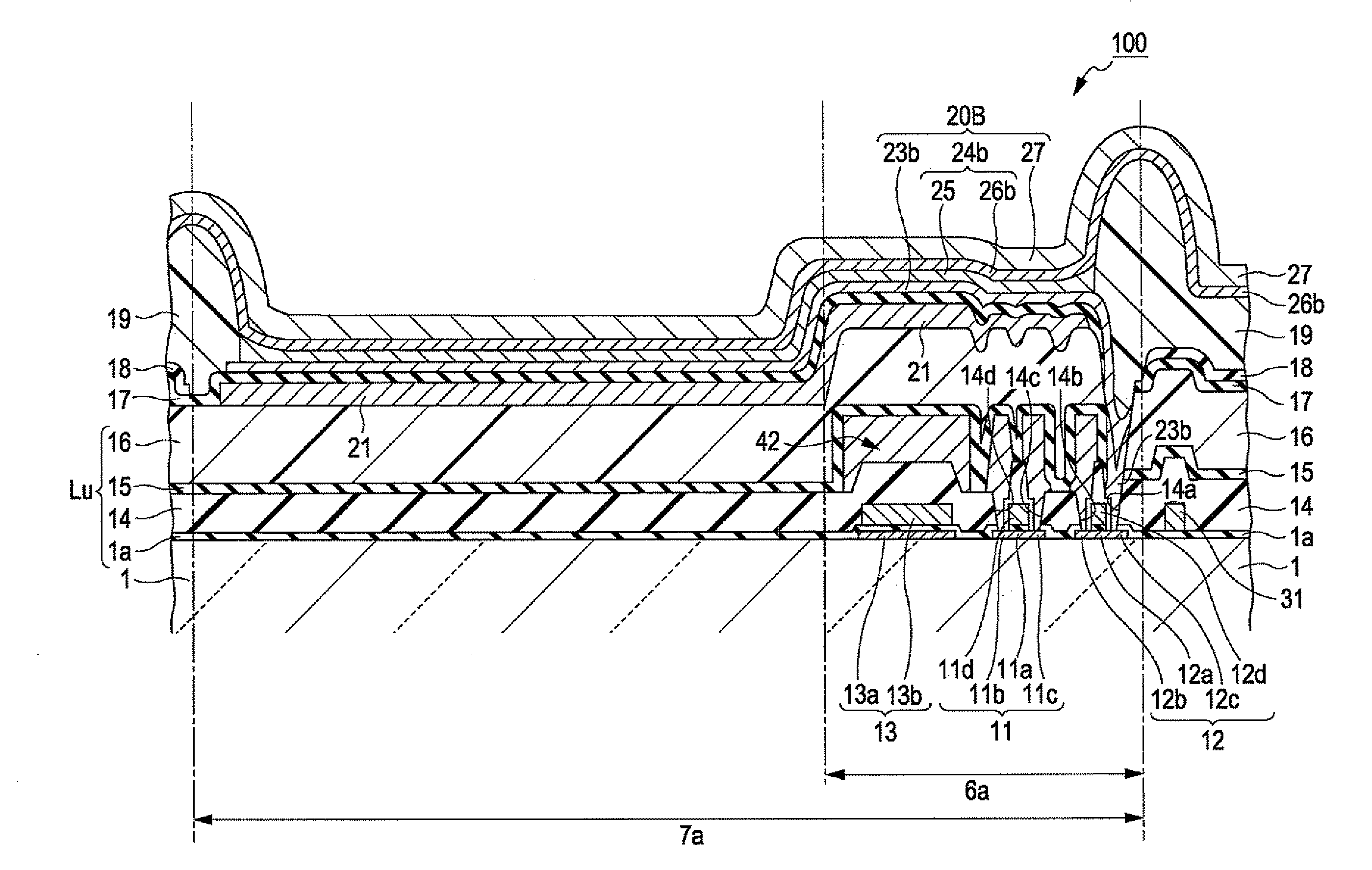

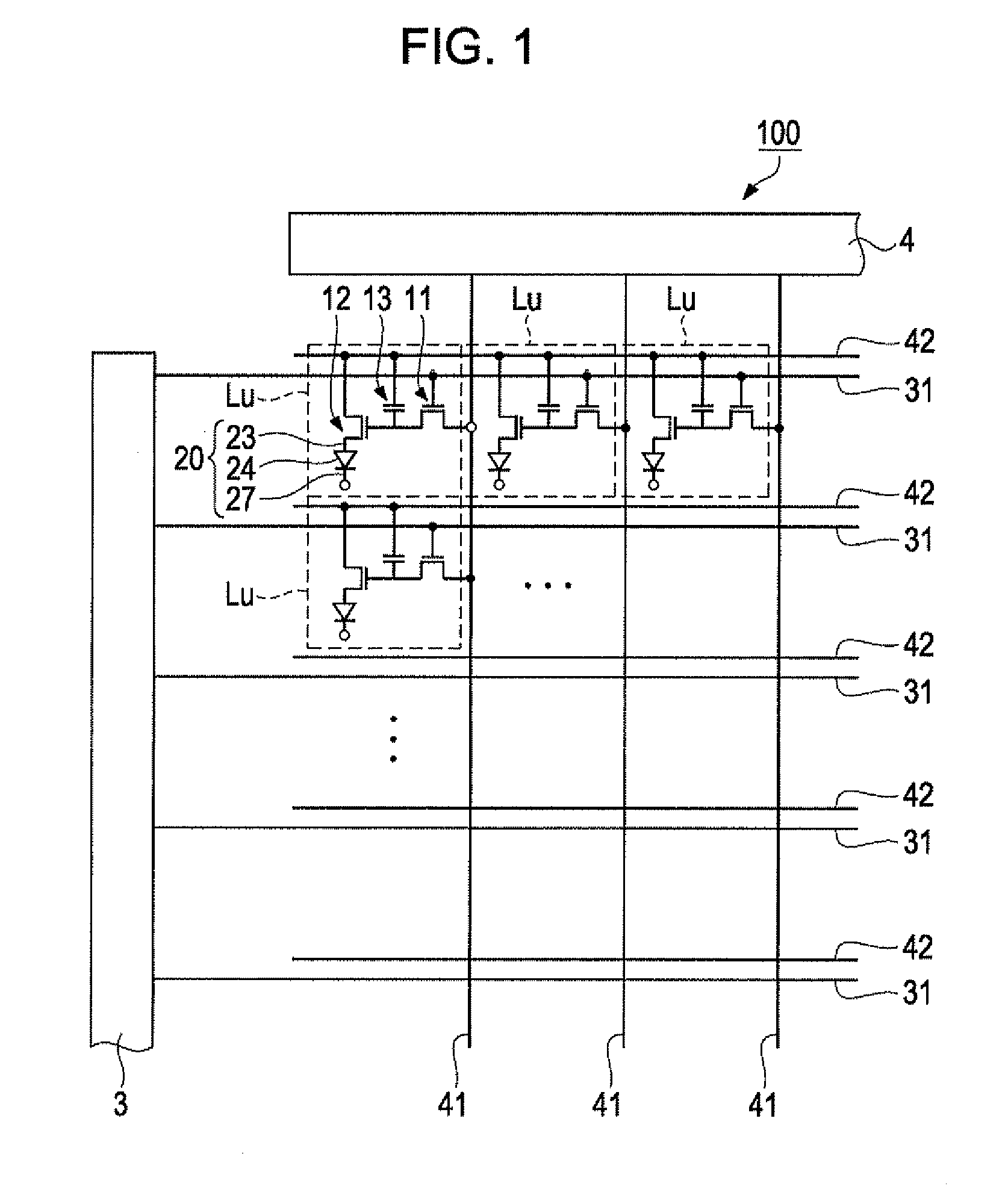

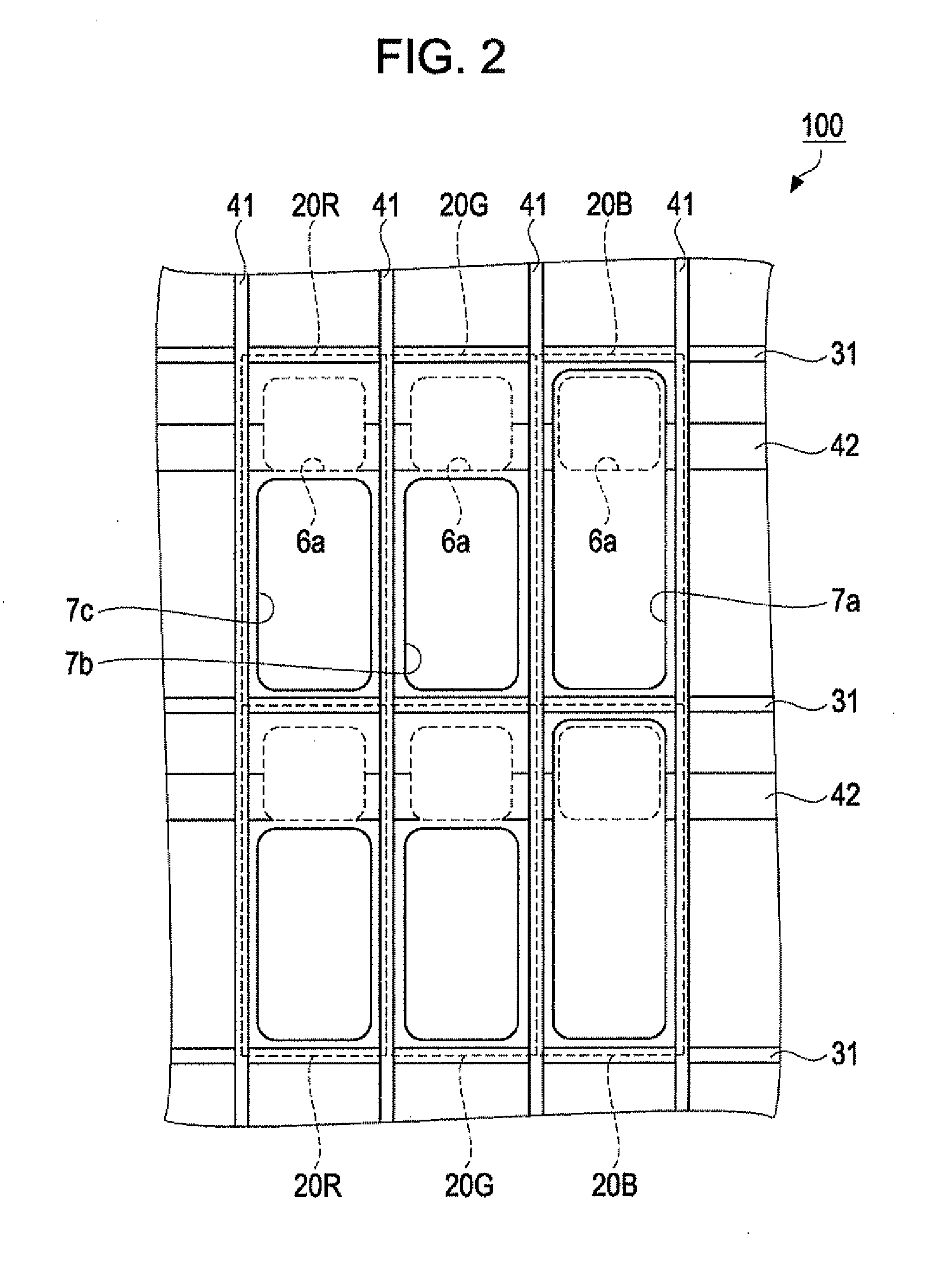

Organic el device, method for manufacturing organic el device, and electronic device

ActiveUS20110101888A1Little changeClearElectroluminescent light sourcesSolid-state devicesEngineeringElectron

An organic EL device includes a first organic EL element and a second organic EL element on an underlying layer that includes a first drive circuit unit for driving the first organic EL element and a second drive circuit unit for driving the second organic EL element. The organic EL device includes a partition on the underlying layer defining a first region including a first light-emitting layer of the first organic EL element and a second region including a second light-emitting layer of the second organic EL element. The partition defines the first film-forming region such that the first film-forming region includes the first drive circuit unit and the second film-forming region such that the second film-forming region does not include at least part of the second drive circuit unit. The first light-emitting layer is formed by a different method from that used for the second light-emitting layer.

Owner:SEIKO EPSON CORP

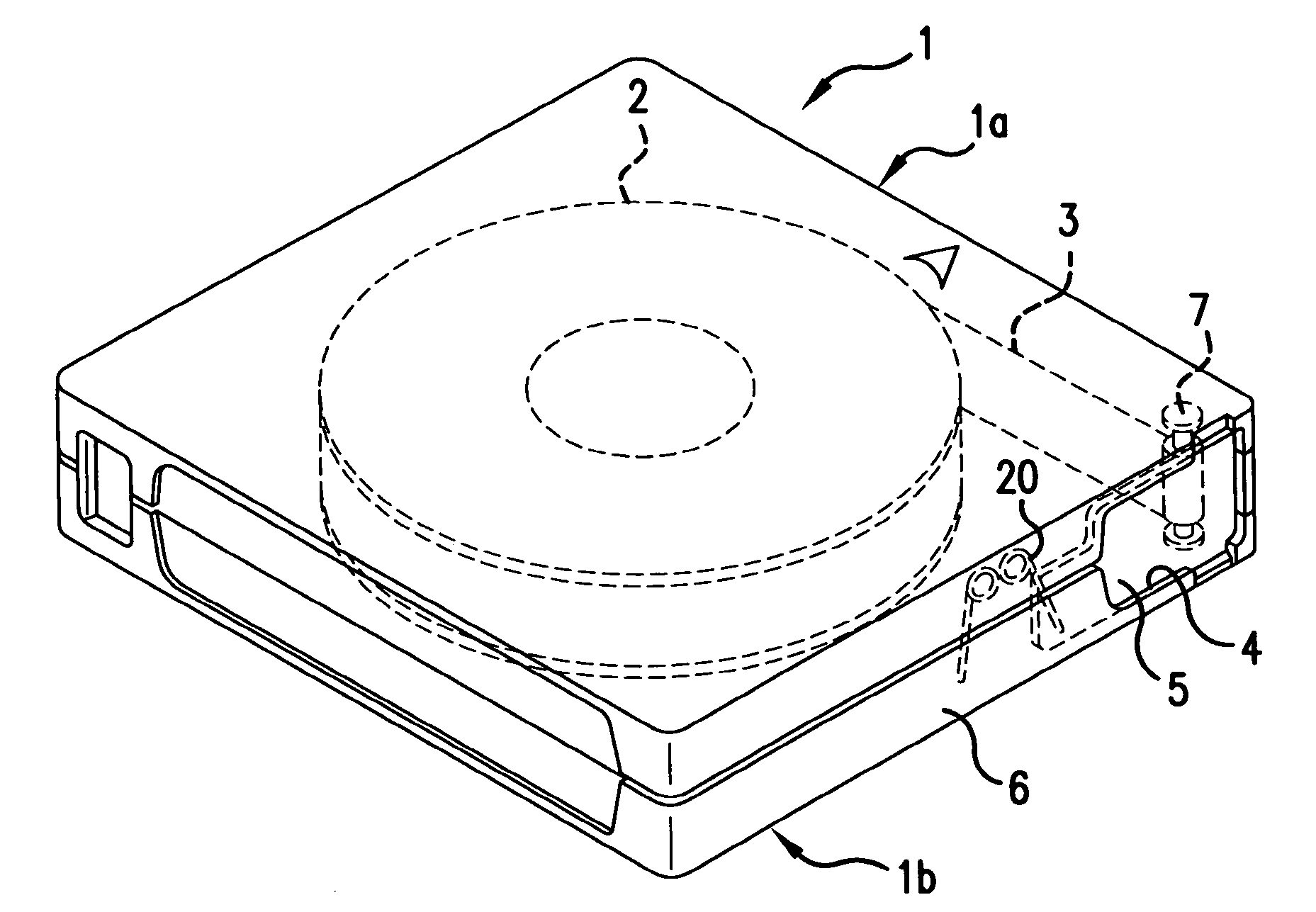

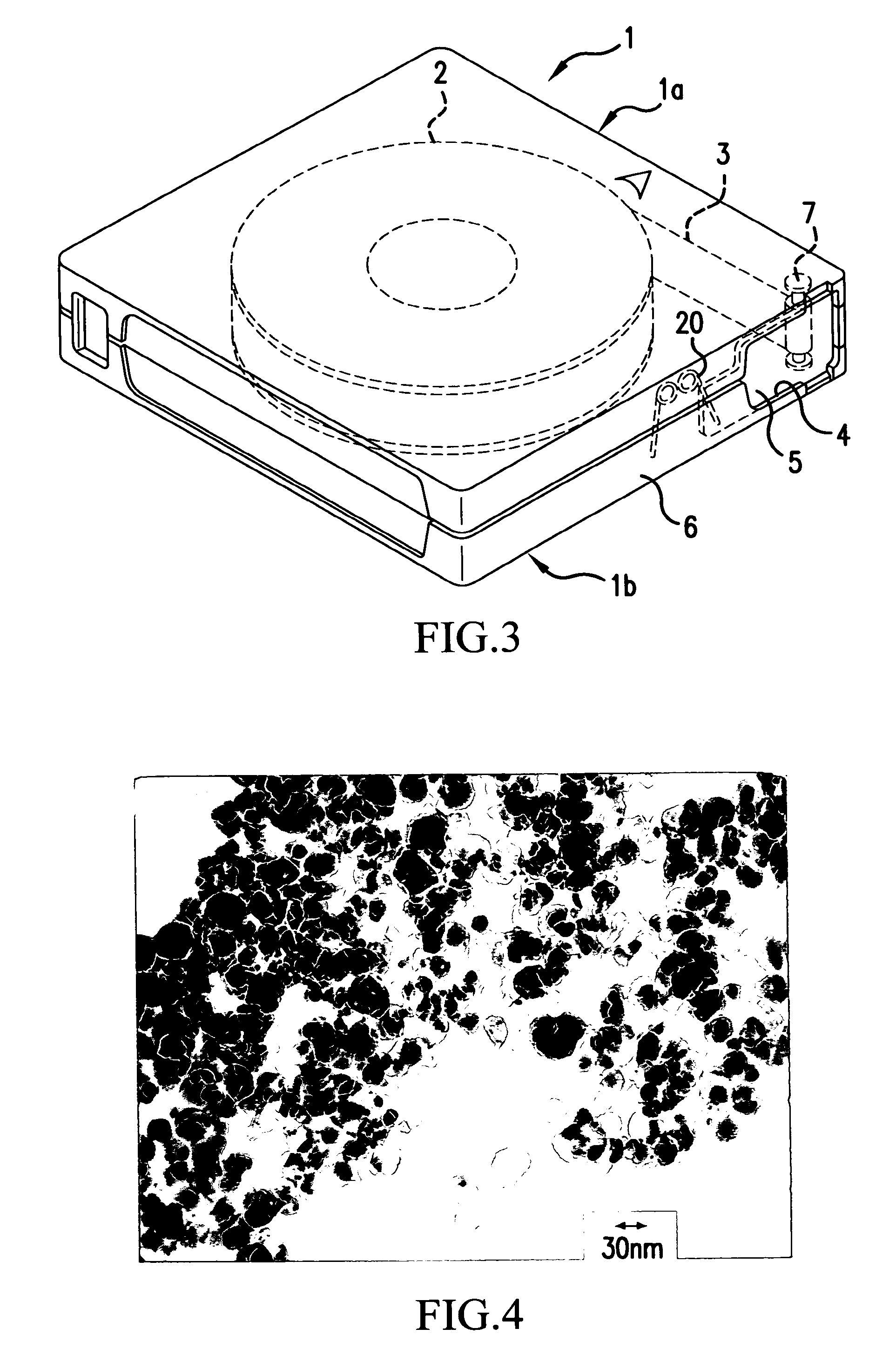

Magnetic tape and magnetic tape cartridge

InactiveUS7494728B2Reduce distortionThickness variationMagnetic materials for record carriersRecord information storageMagnetic tapeNon magnetic

Owner:FUJIFILM CORP

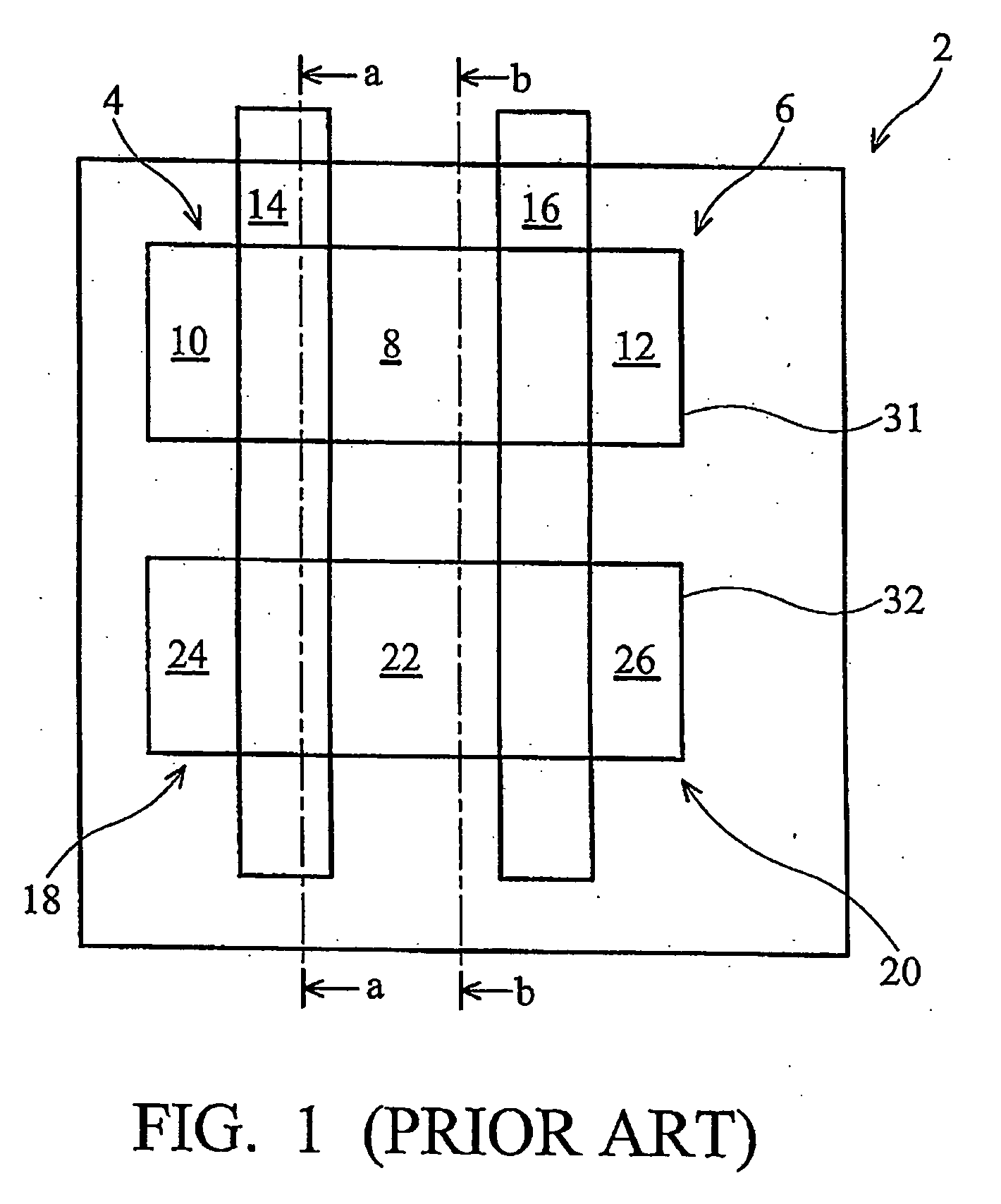

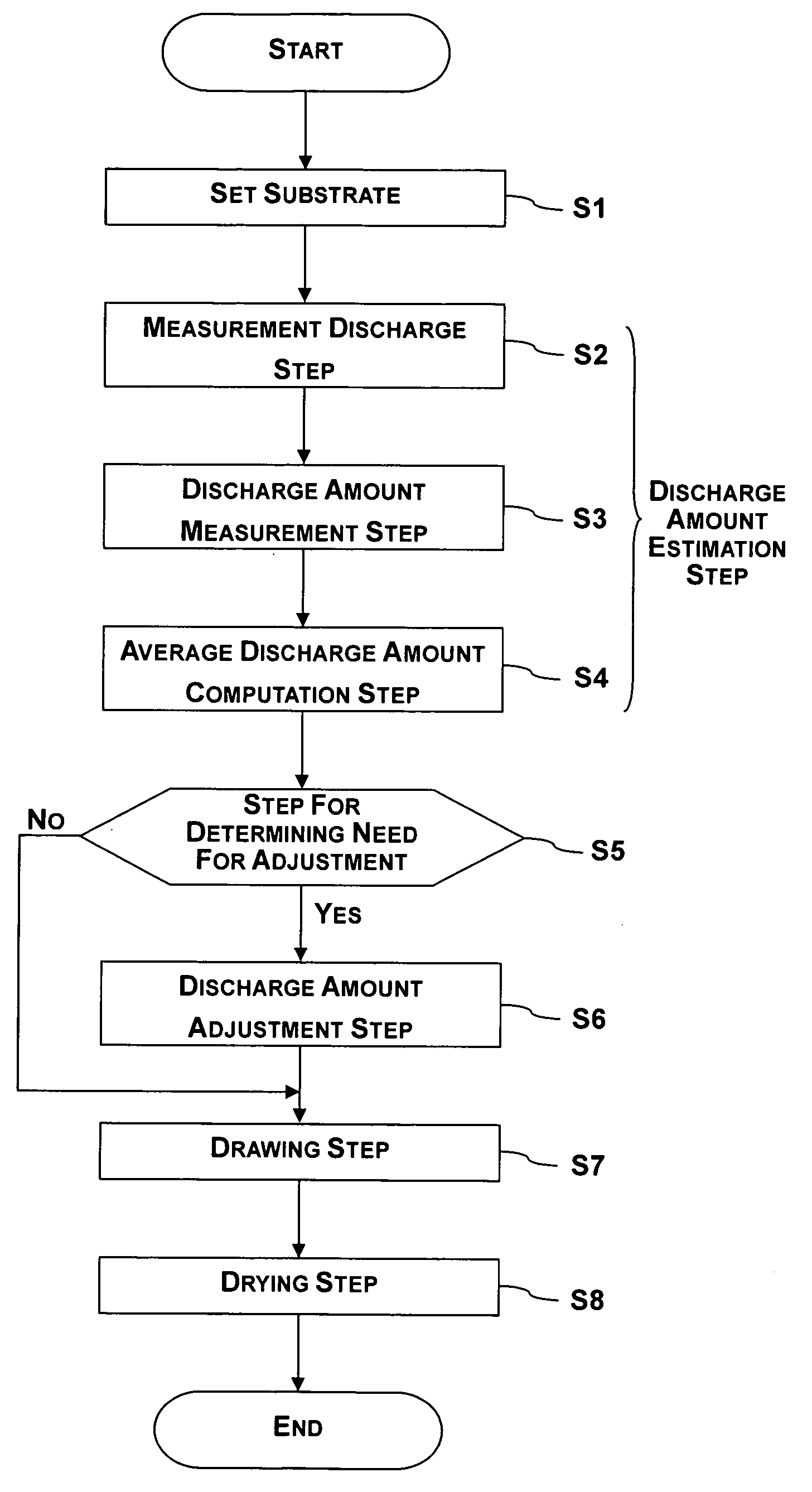

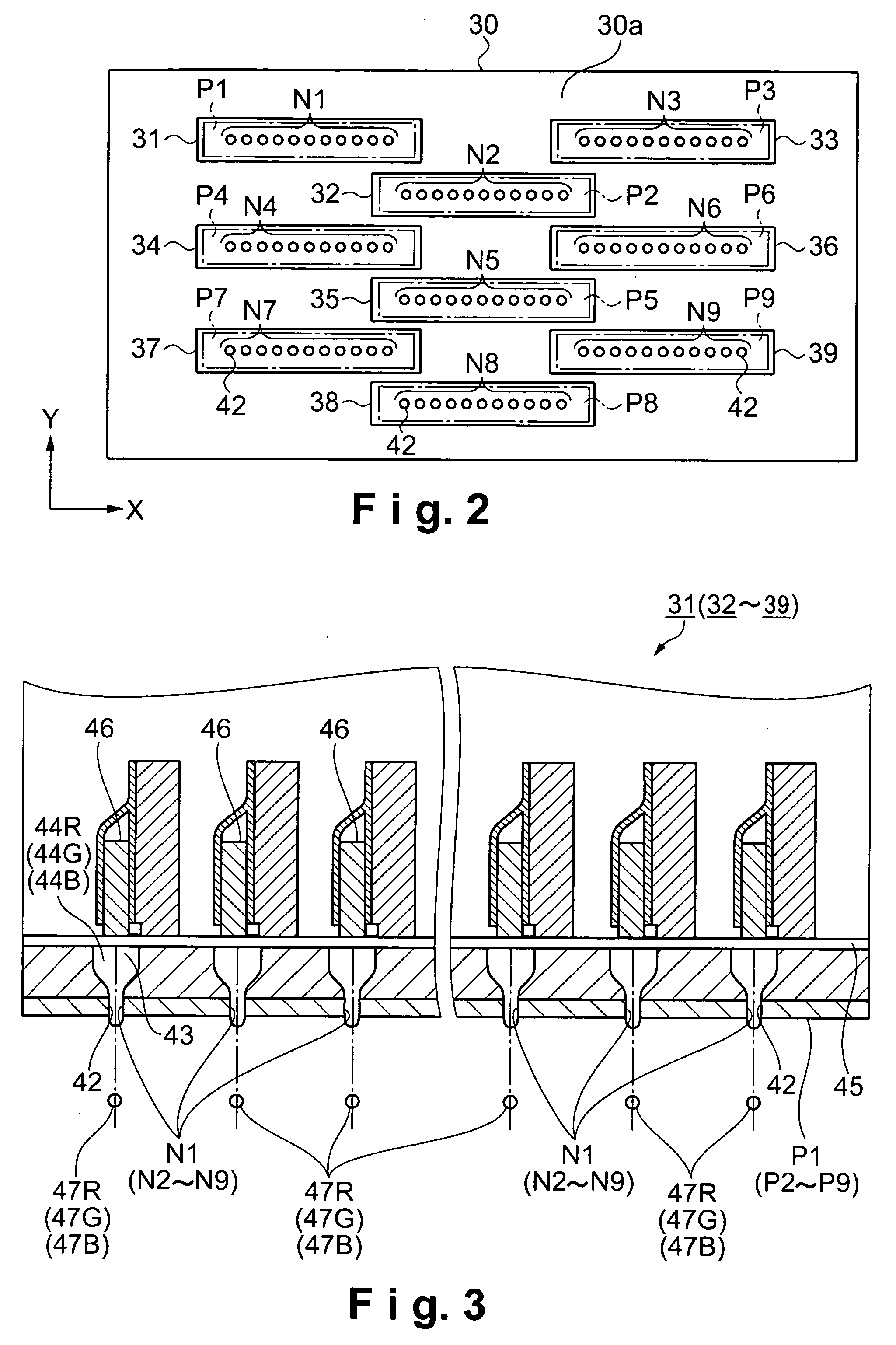

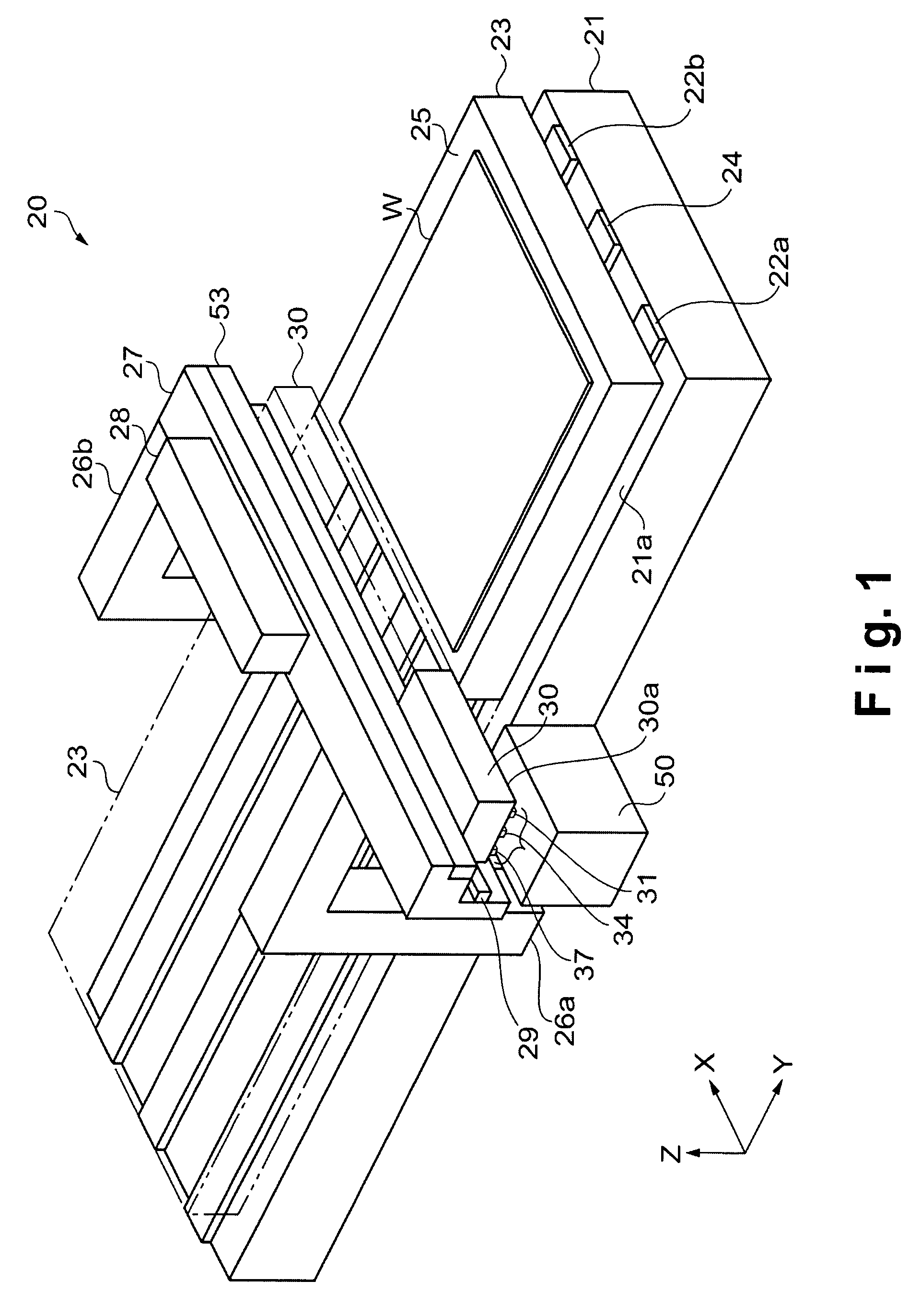

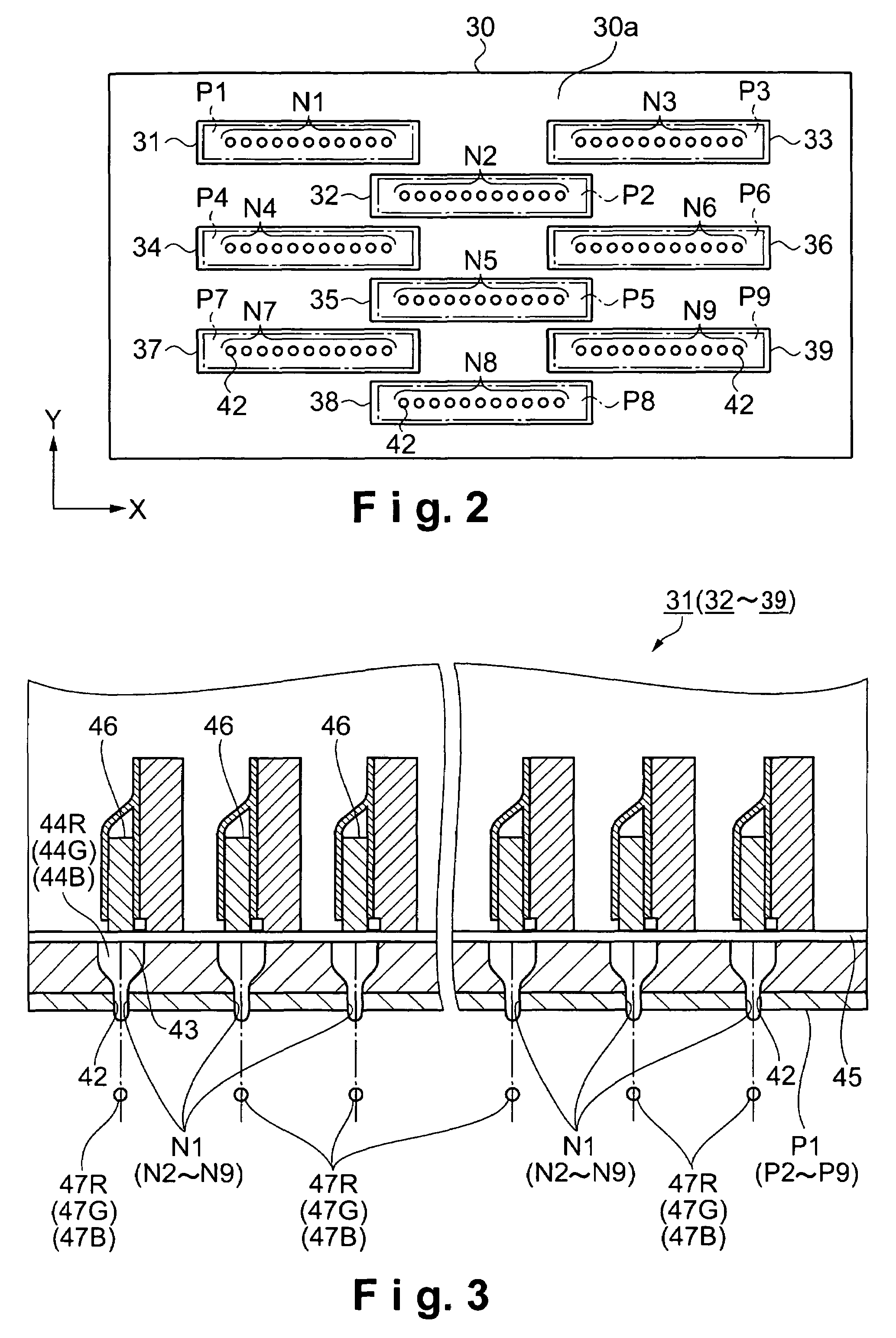

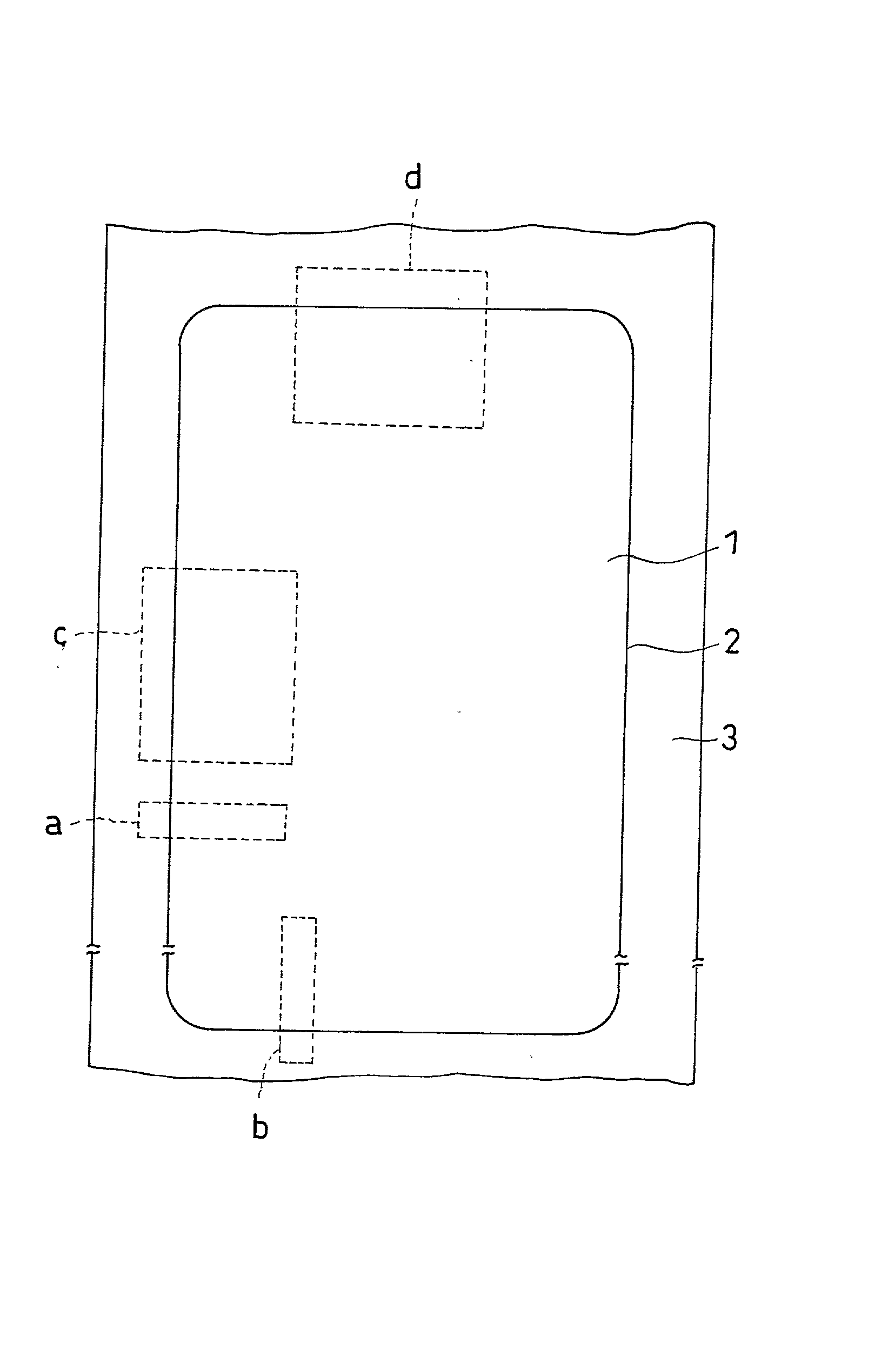

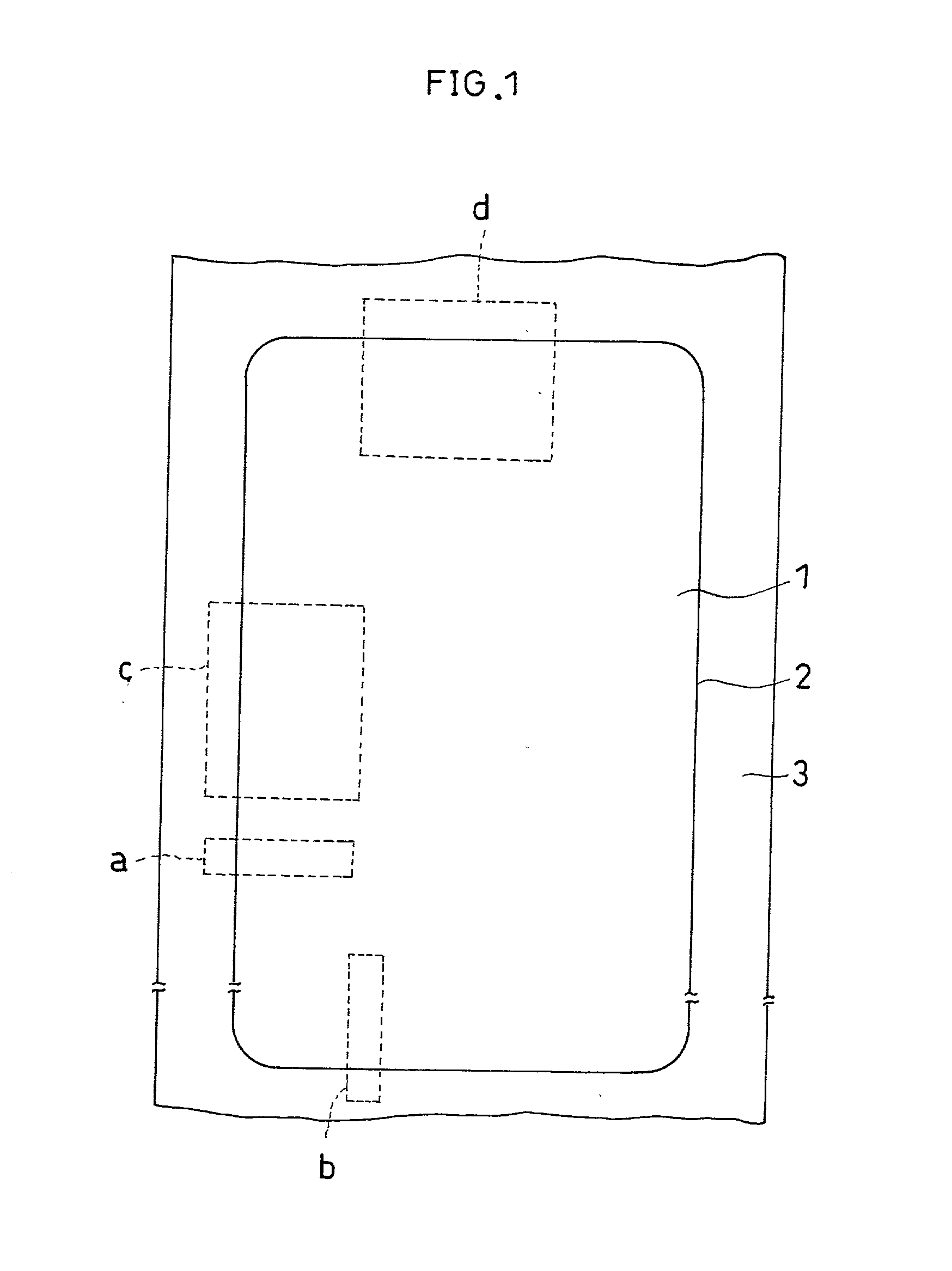

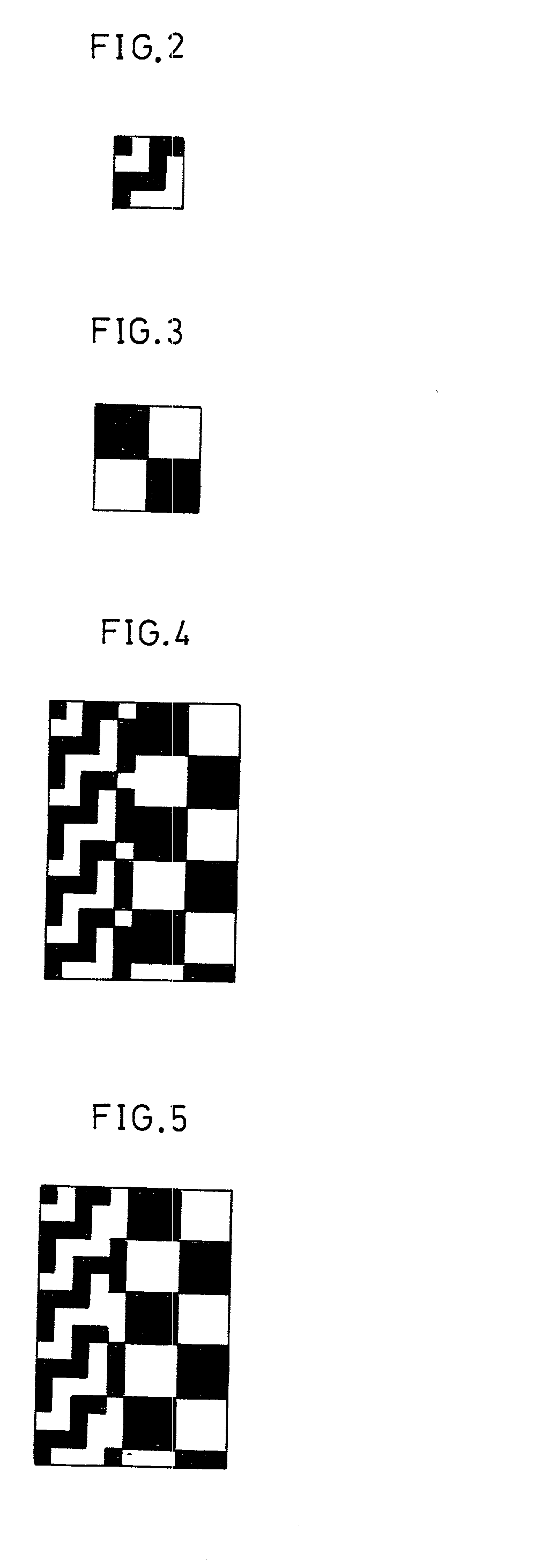

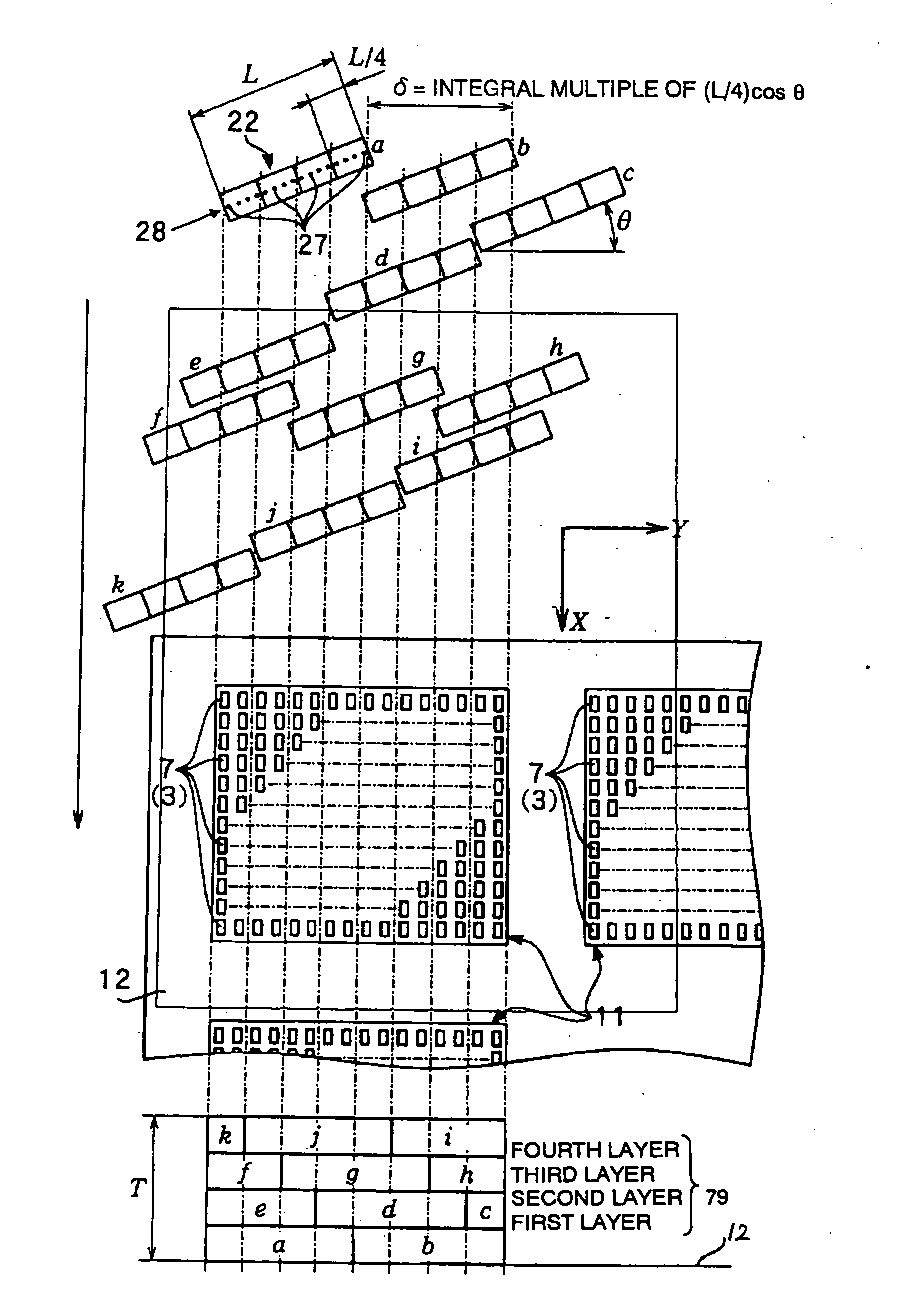

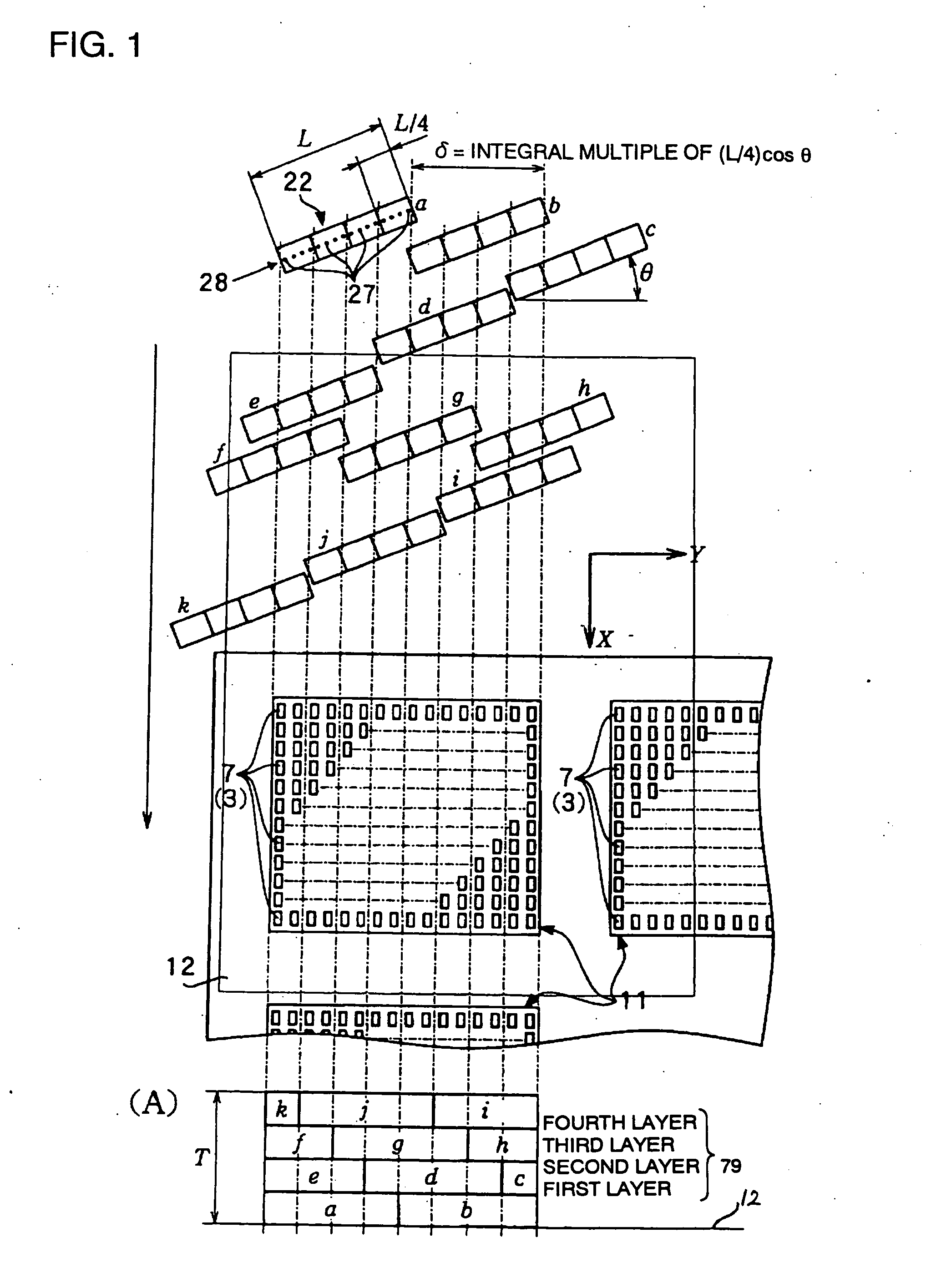

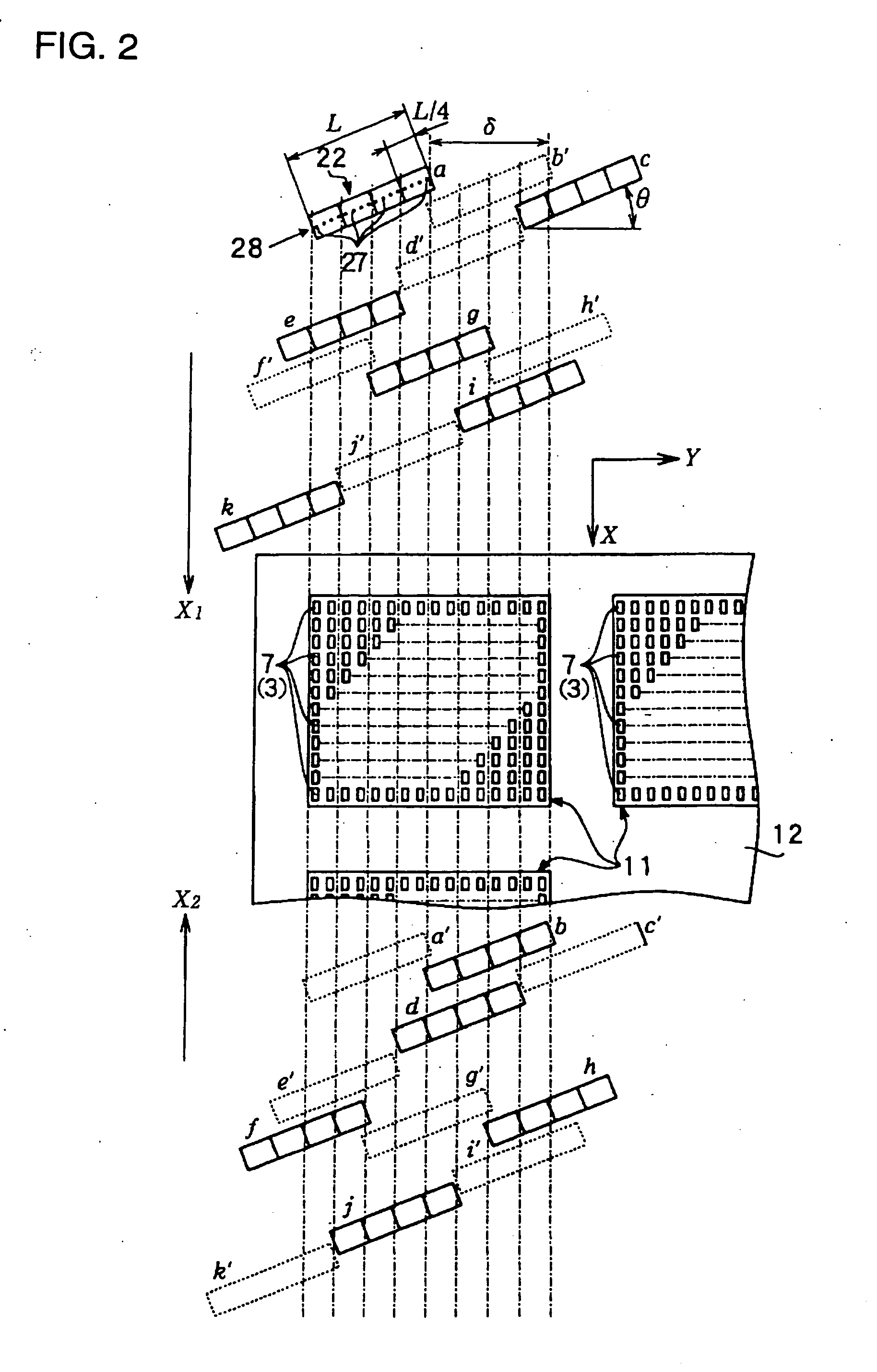

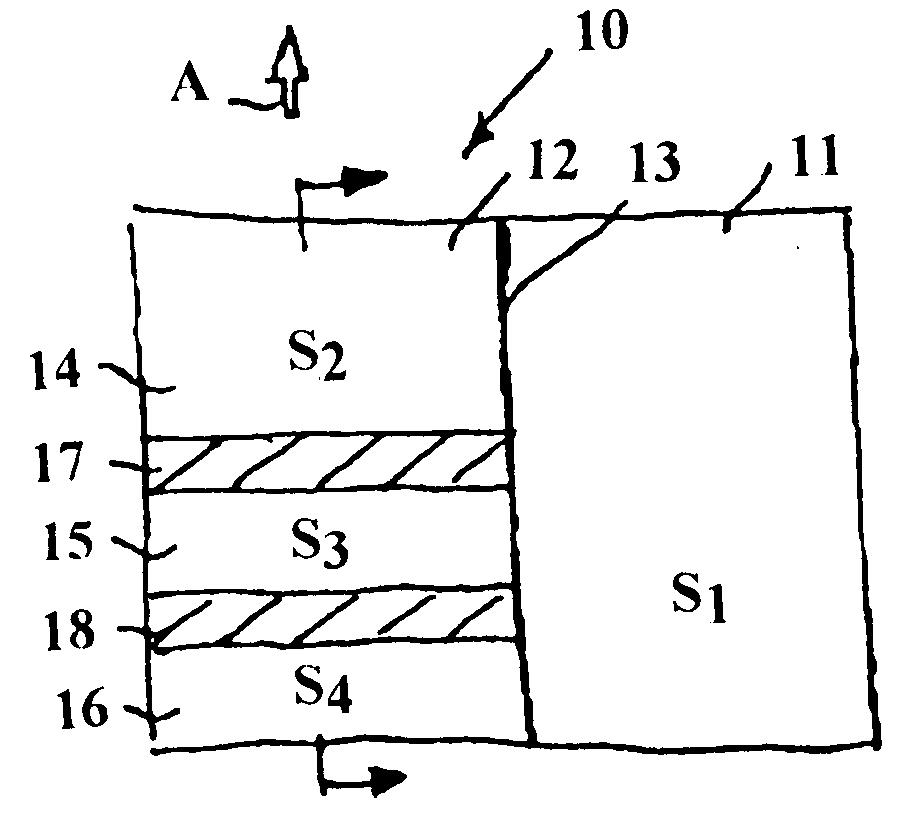

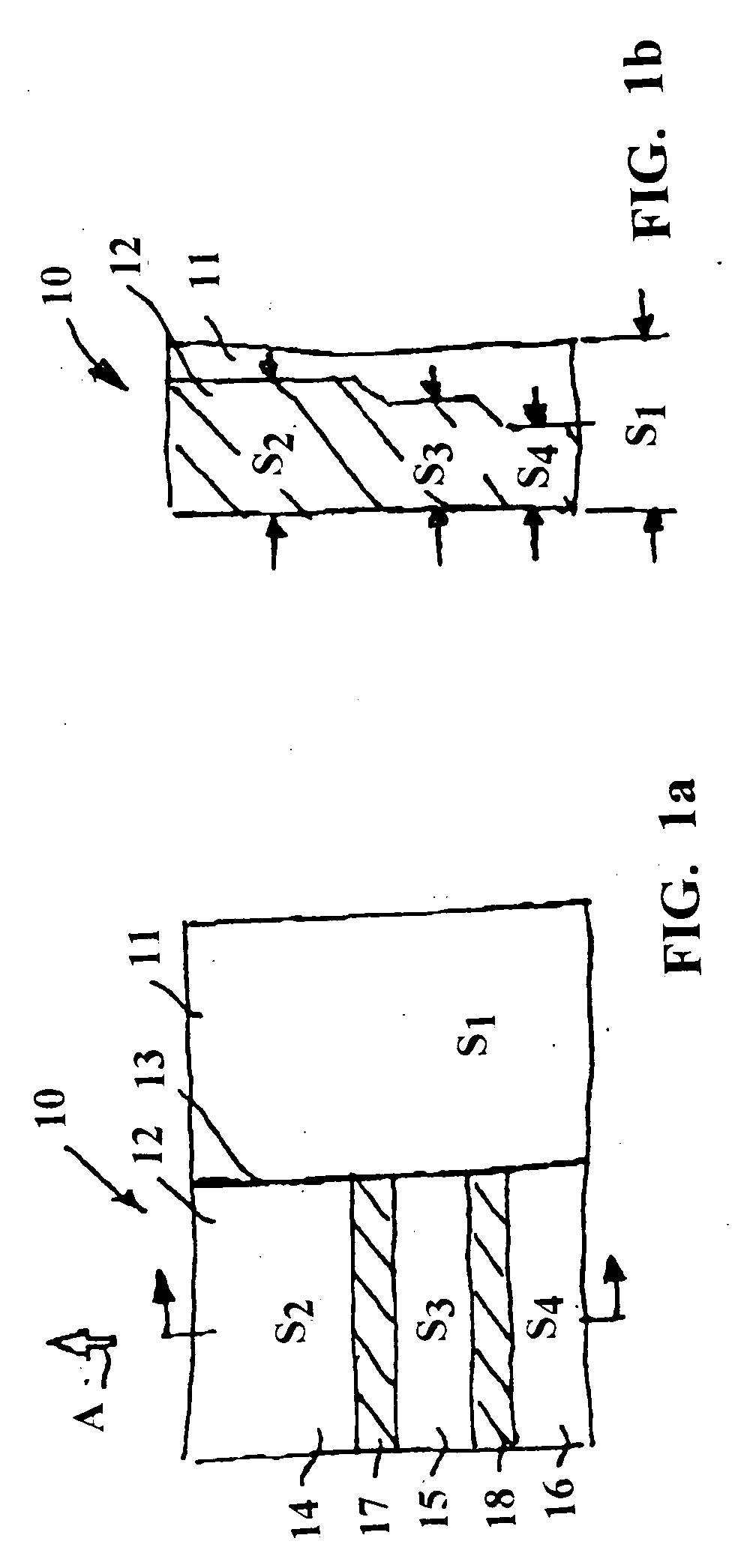

Method and apparatus for producing color filter, method and apparatus for manufacturing liquid crystal device, method and apparatus for manufacturing EL device, method of discharging material, apparatus for controlling head and electronic apparatus

ActiveUS20050003283A1Thickness variationNo wasteInking apparatusElectroluminescent light sourcesDot matrixOptical property

The invention makes uniform, in a plane, optical properties of optical members, such as the distribution properties of light transmission of a color filter, the color display properties of a liquid crystal device, and the light emission properties of an EL luminescent plane. During main scanning of color filter formation areas of a board in the X direction with an ink jet head having a nozzle row formed of a plurality of nozzles arranged in a row, a filter material is selectively discharged from the plurality of the nozzles to each of filer element areas arranged in a dot matrix to form filter elements, producing a color filter. First, the nozzle row is moved to positions “a” and “b” by main scanning in the X direction to enhance wettability of the surface of the areas and then main scanning is executed at each of the positions while successively moving the nozzle row to positions “c” through “k” by sub-scanning, thereby repeatedly discharging ink in the same portion of the areas.

Owner:SEIKO EPSON CORP

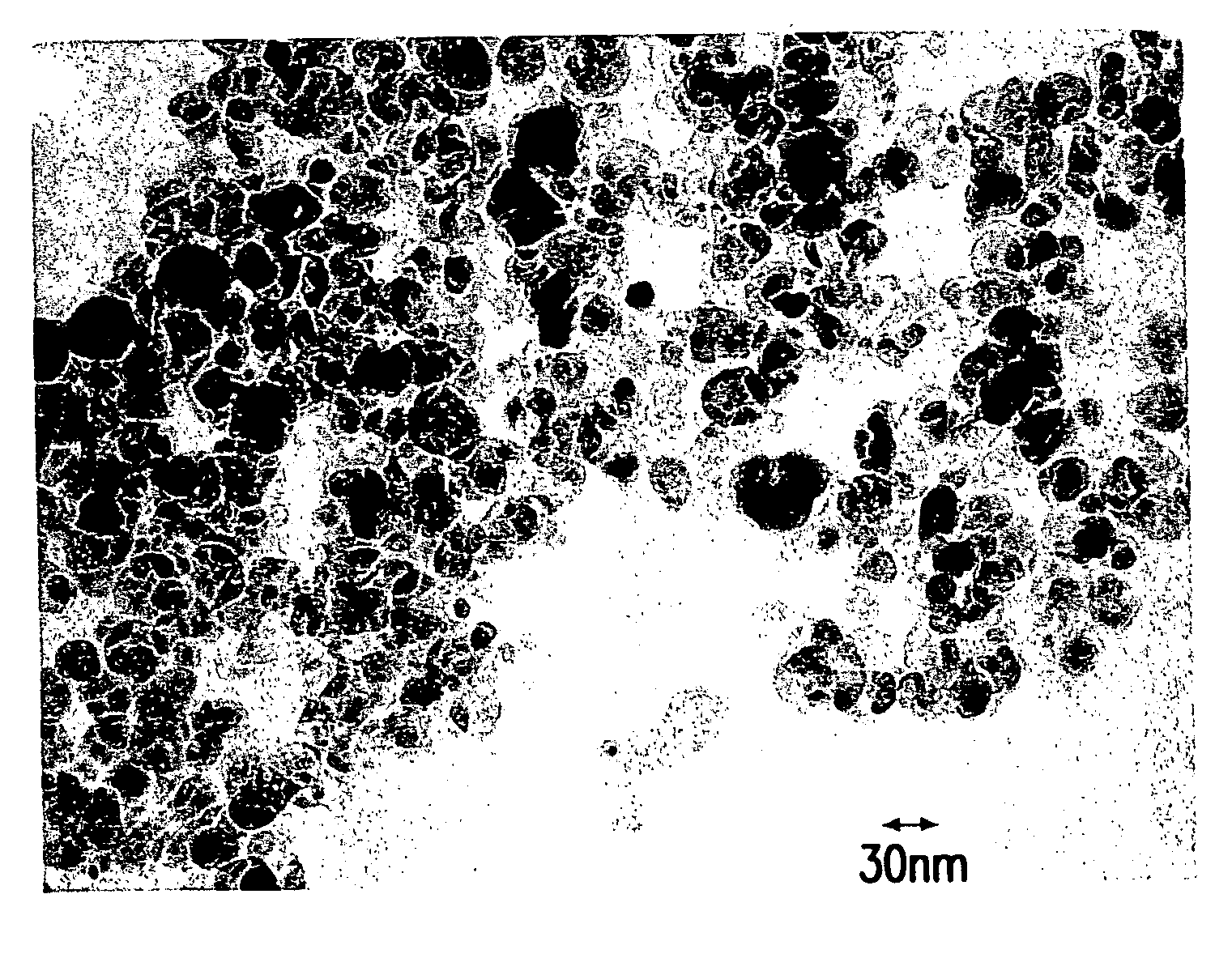

Magnetic tape and magnetic tape cartridge

InactiveUS20060003191A1Improve recording densityReduce distortionMagnetic materials for record carriersRecord information storageMagnetic tapeNon magnetic

A magnetic tape comprising a non-magnetic support, a magnetic layer containing magnetic powder which is formed on one side of the non-magnetic support, a primer layer containing non-magnetic powder which is formed between the non-magnetic support and the magnetic layer, and a backcoat layer containing non-magnetic powder which is formed on the other side of the non-magnetic support, wherein the magnetic layer contains the magnetic powder which comprises plate, granular or ellipsoidal magnetic particles with a particle diameter of 5 to 50 nm, and has a thickness of 0.09 μm or less, and wherein at least one of the primer layer and the backcoat layer contains non-magnetic plate particles with a particle diameter of 10 to 100 nm.

Owner:KUSE SADAMU +3

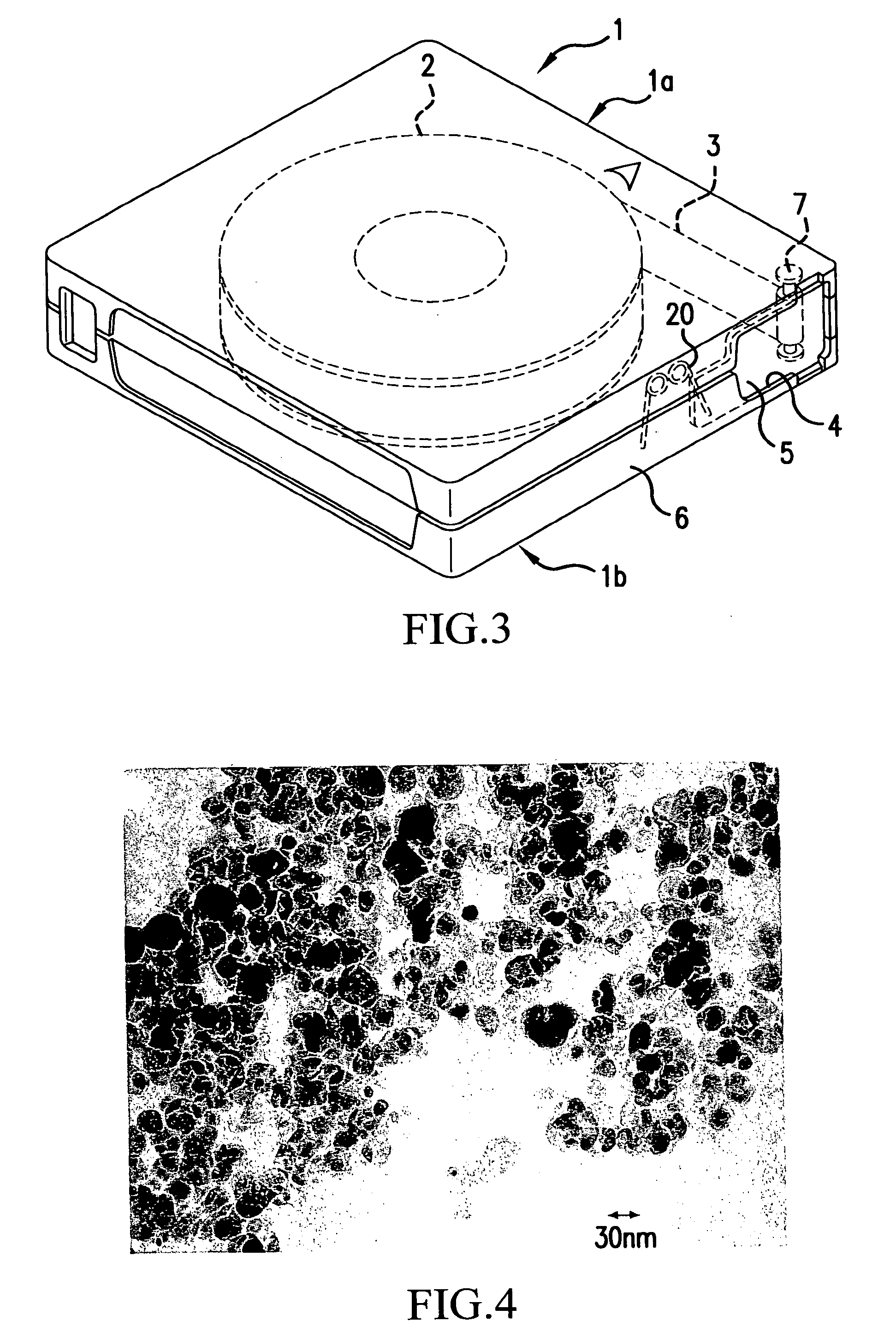

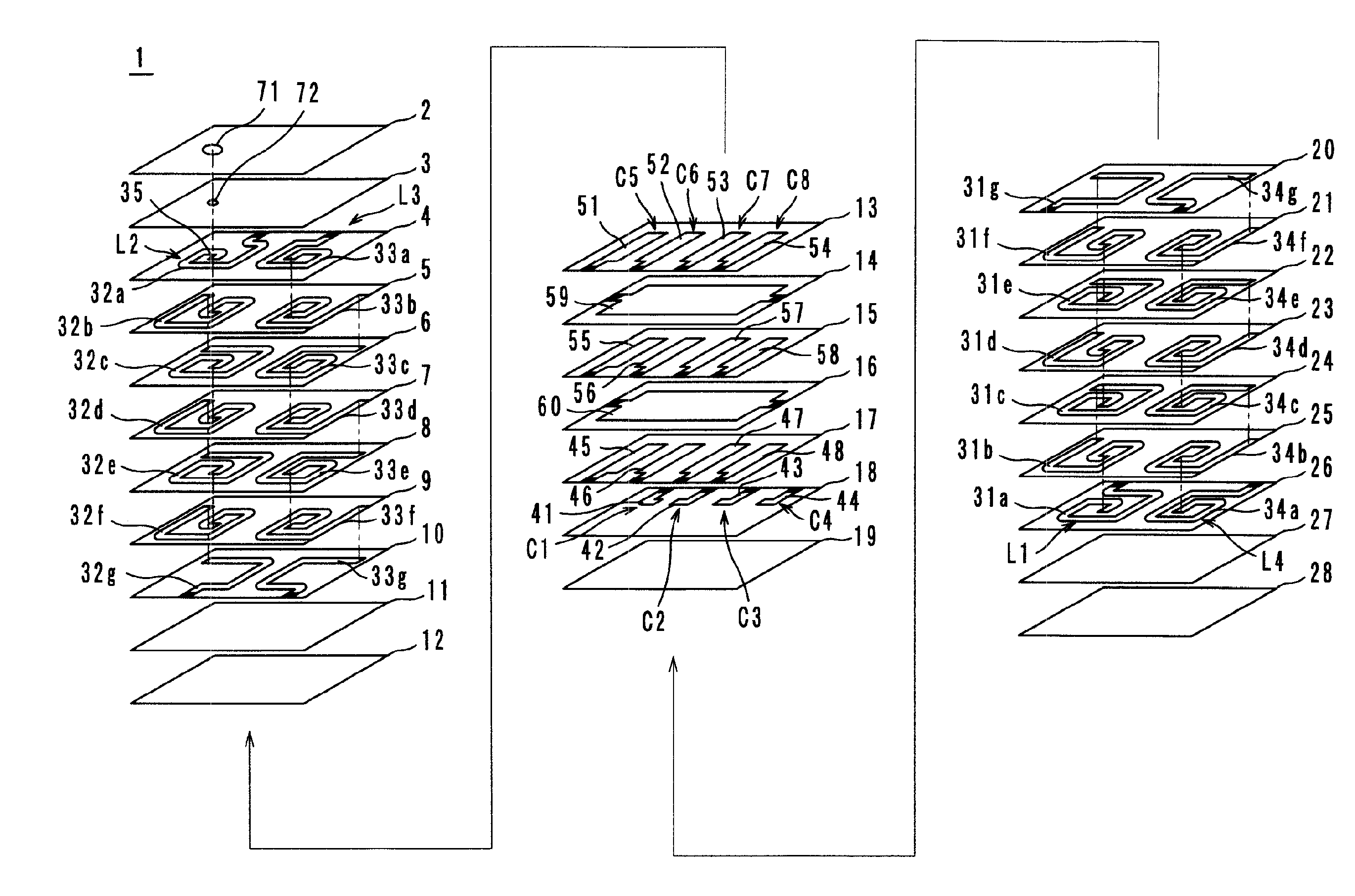

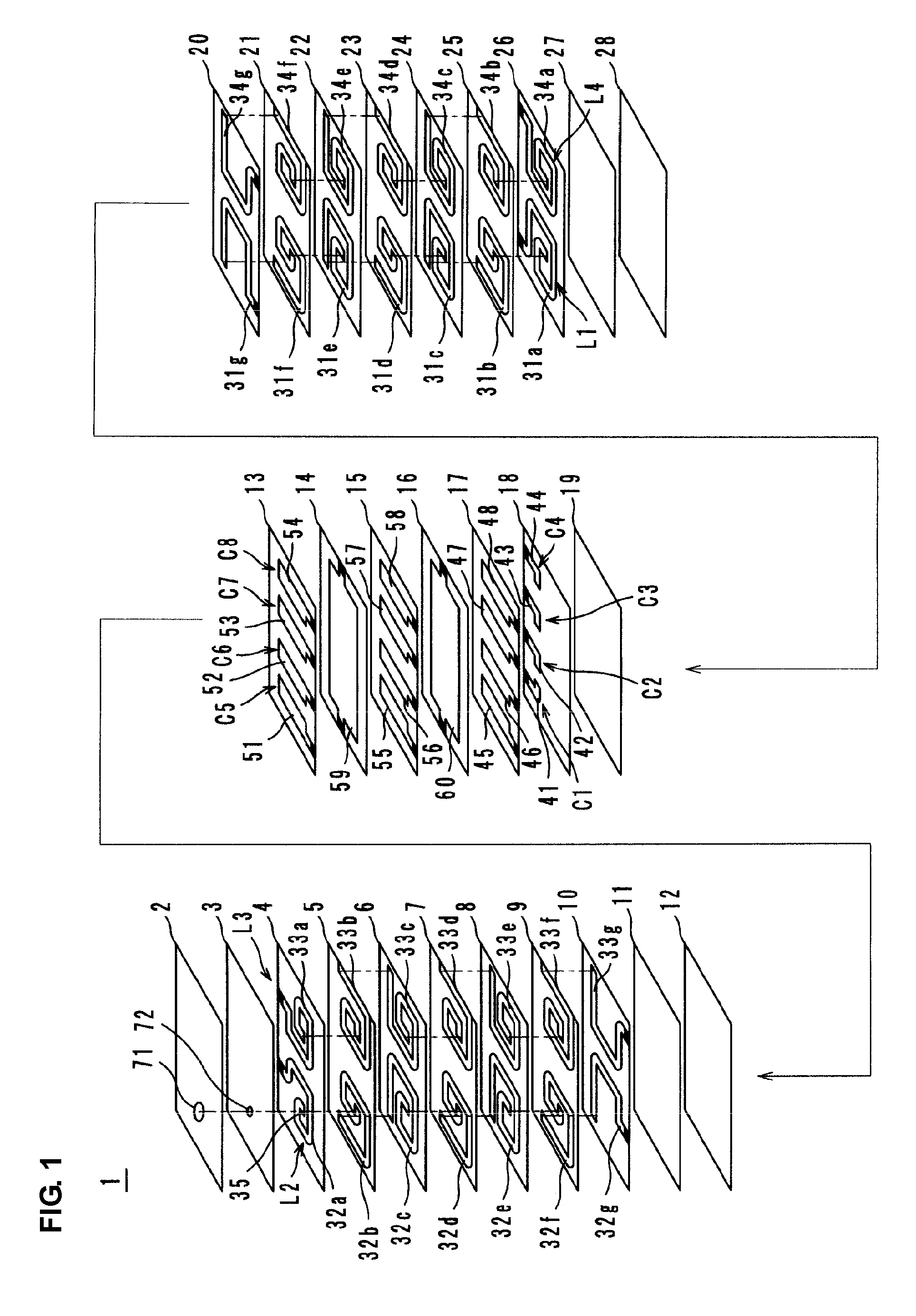

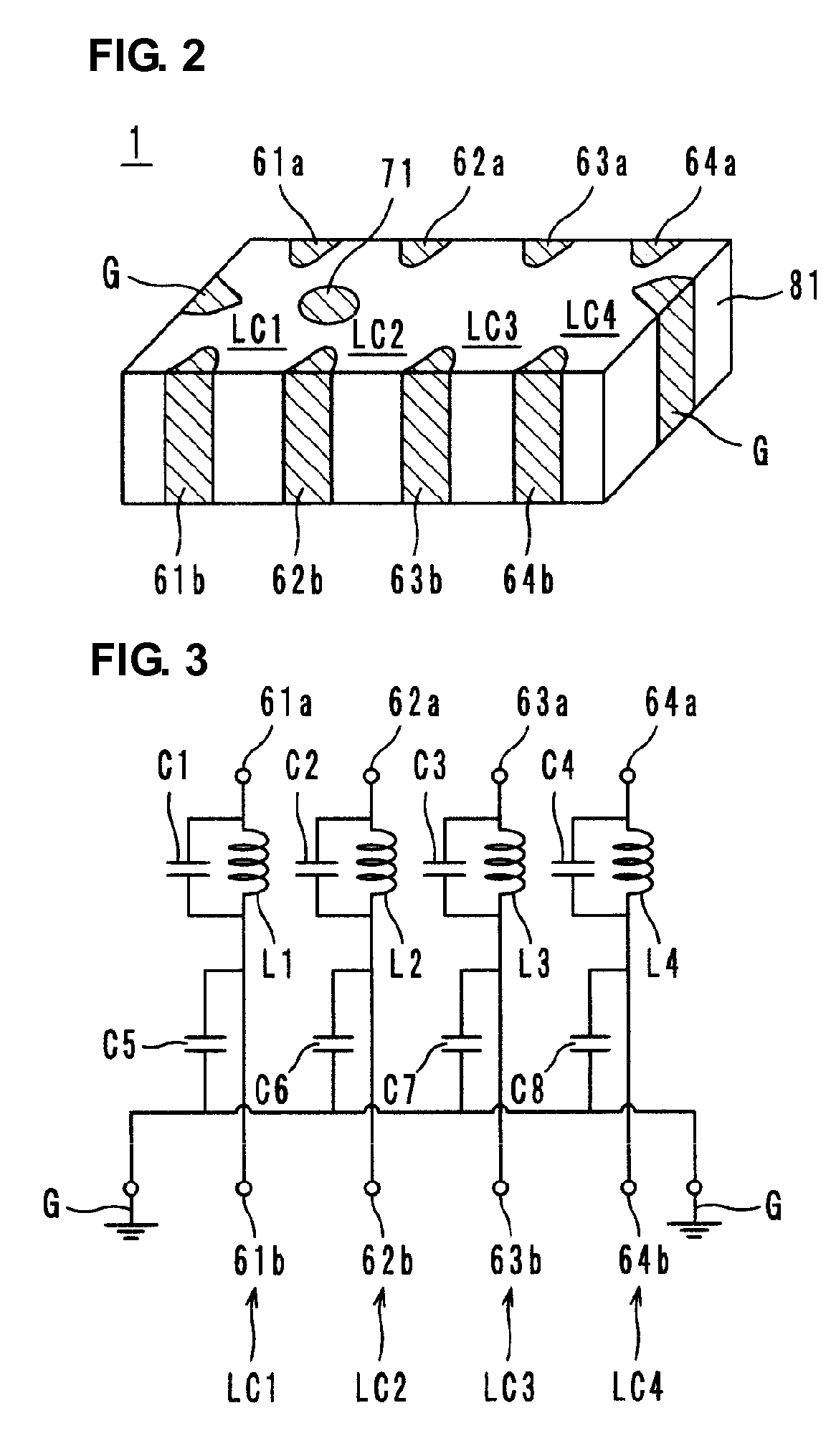

Multilayer electronic component and multilayer array electronic component

ActiveUS20090134956A1Reliable formingReduce componentsMultiple-port networksStacked capacitorsElectrical conductorHelical coil

A multilayer array electronic component includes a multilayer composite including a helical coil and a capacitor that are defined by stacking a coil conductor, a capacitor conductor, and a ceramic sheet on one another. External electrodes are arranged on the surface of the multilayer composite and electrically connected to the helical coil or the capacitor. A direction identification mark is arranged on the upper surface of the multilayer composite and electrically connected to any of the external electrodes through the helical coil or the capacitor.

Owner:MURATA MFG CO LTD

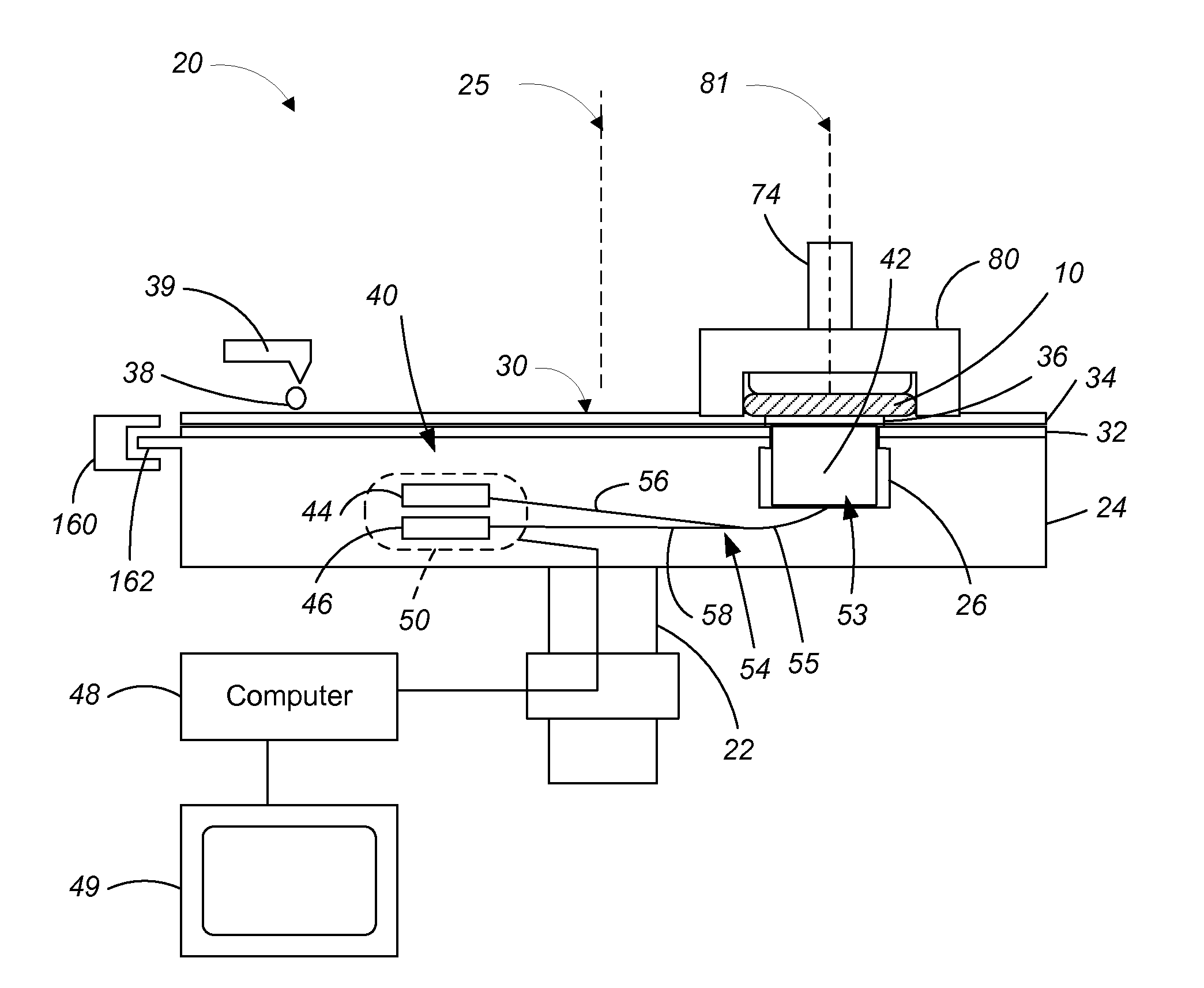

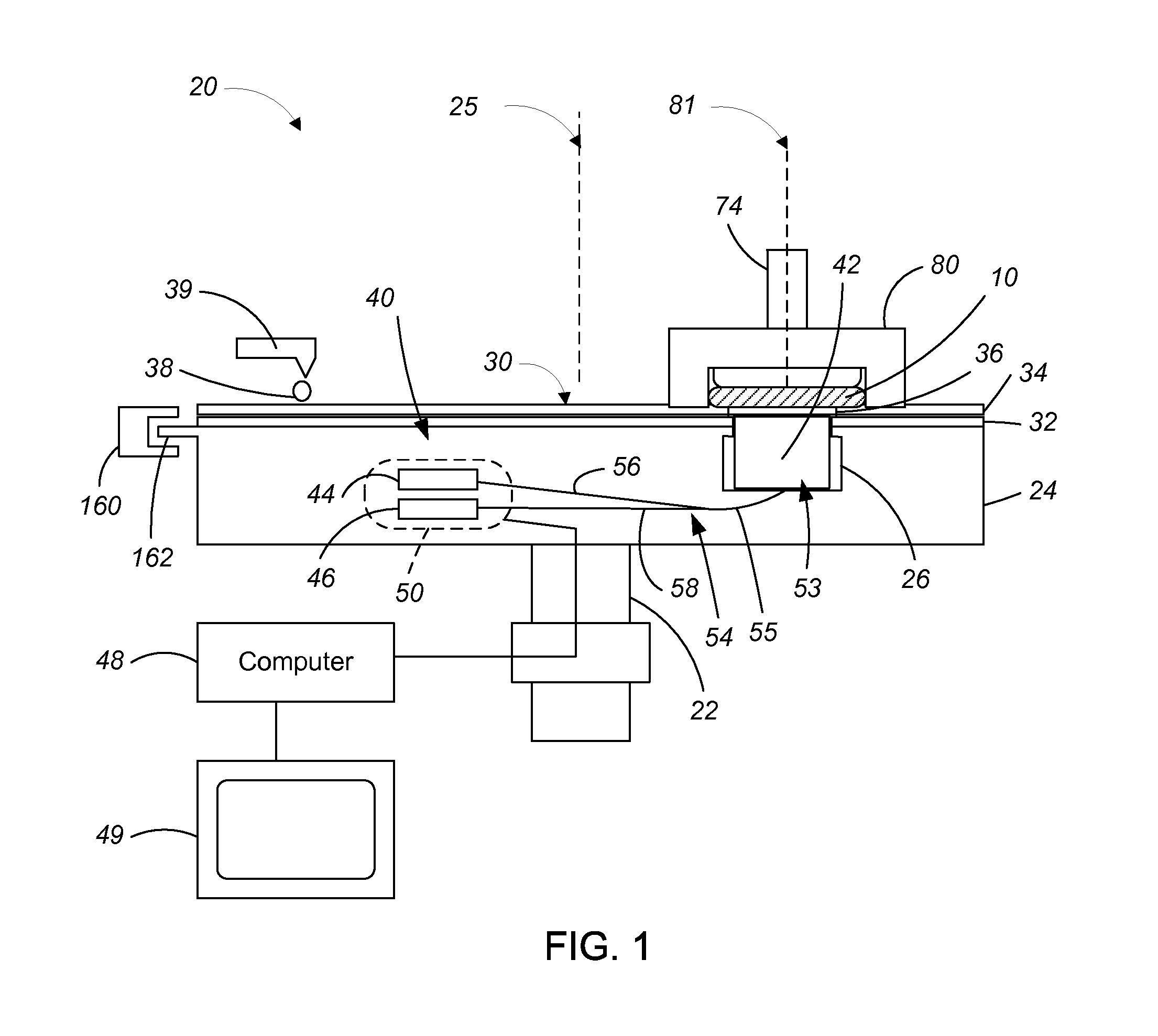

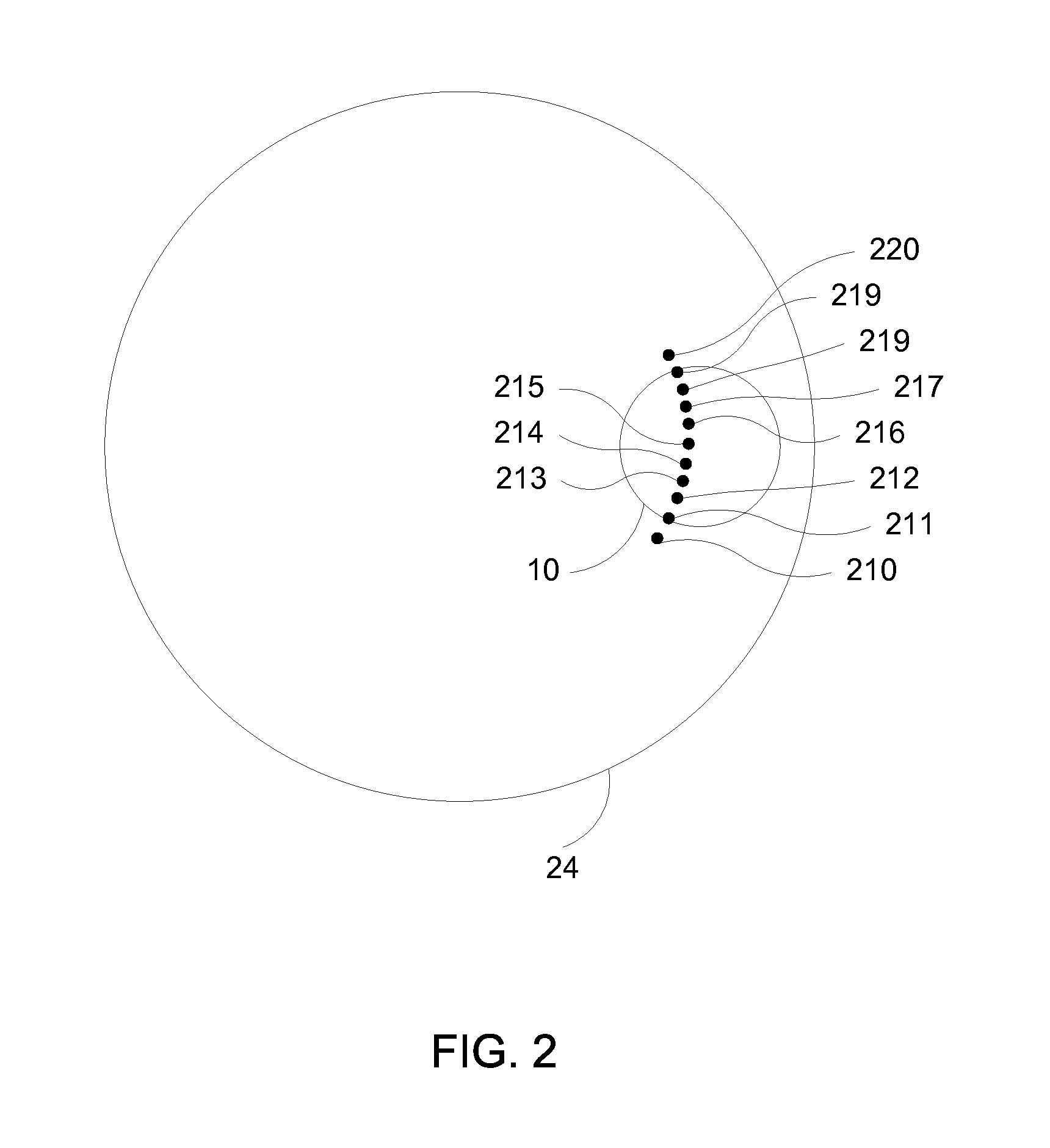

High throughput measurement system

InactiveUS7952708B2Improve accuracyIncrease speedSpectrum investigationSemiconductor/solid-state device testing/measurementMonitoring systemThroughput

A substrate processing system includes a processing module to process a substrate, a factory interface module configured to accommodate at least one cassette for holding the substrate, a spectrographic monitoring system positioned in or adjoining the factory interface module, and a substrate handler to transfer the substrate between the at least one cassette, the spectrographic monitoring system and the processing module.

Owner:APPLIED MATERIALS INC

Manufacturing method of semiconductor device

InactiveUS20070202682A1Improve welding strengthHigh densitySemiconductor/solid-state device detailsSolid-state devicesSemiconductorMaterials science

Improvement in shock-resistant strength of a soldered joint is aimed at, and the variation in the plating film formed on an electrode pad is reduced.In the step which forms a plating film (for example, Ni film) by an electrolytic plating method on the surface of an electrode pad, the first layer is formed in the front surface of the electrode pad with the first current density, and the second layer is formed in the front surface of the first layer with the second current density higher than the first current density after that.

Owner:RENESAS TECH CORP

Hybrid-produced sheet metal element and method of producing same

InactiveUS20050244667A1Thickness variationLayered productsRoll mill control devicesMetalComposite material

Owner:MUHR UND BENNDER KG

Methods and apparatus for generating a library of spectra

InactiveUS20110046918A1Improve accuracyIncrease speedSemiconductor/solid-state device testing/measurementDigital computer detailsMeasurement pointEngineering

A method of generating a library from a reference substrate for use in processing product wafers is described. The method includes measuring substrate characteristics at a plurality of well-defined points of a reference substrate, measuring spectra at plurality of measurement points of the reference substrate, there being more measurement points than well-defined points, and associating measured spectra with measured substrate characteristics.

Owner:APPLIED MATERIALS INC

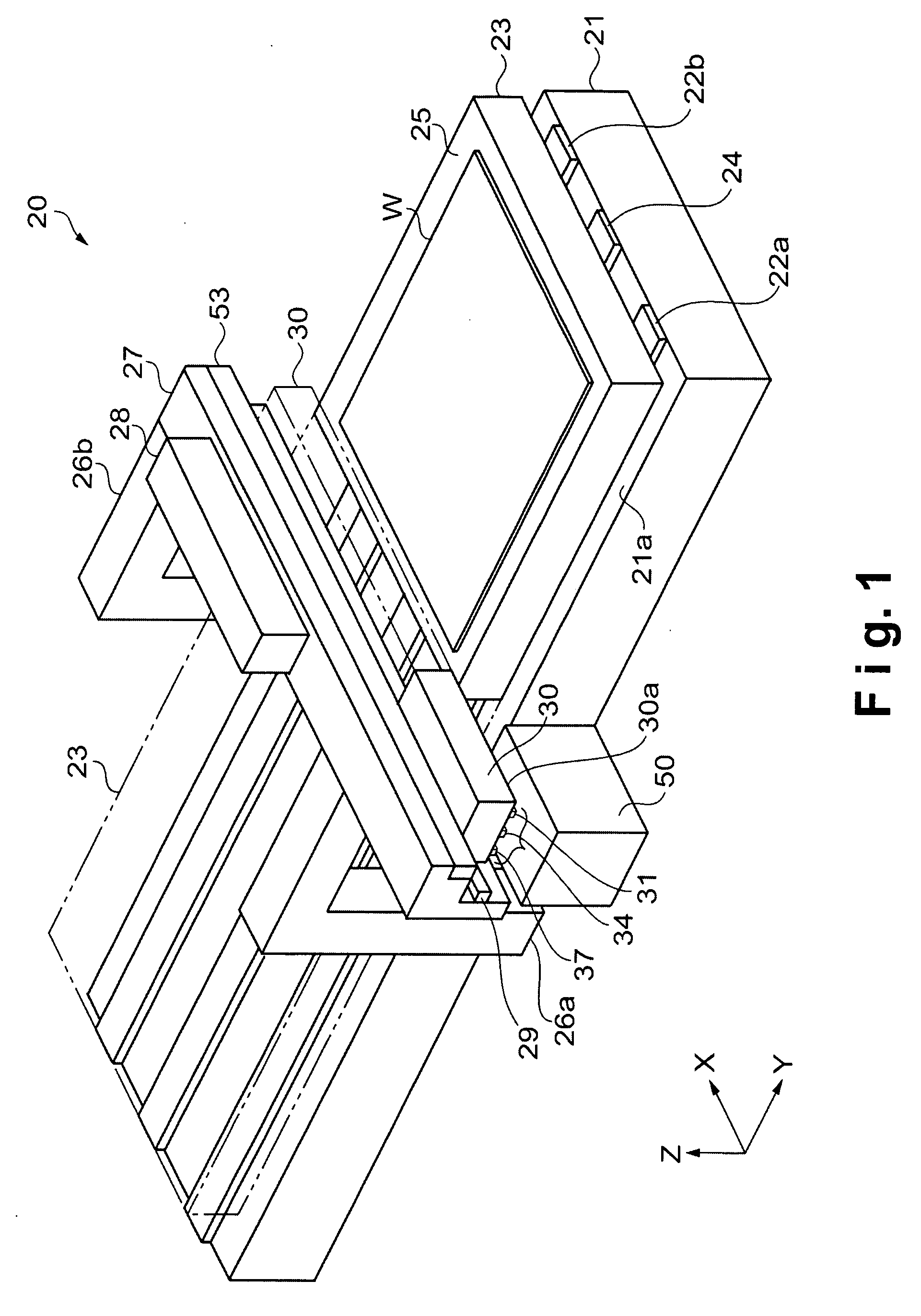

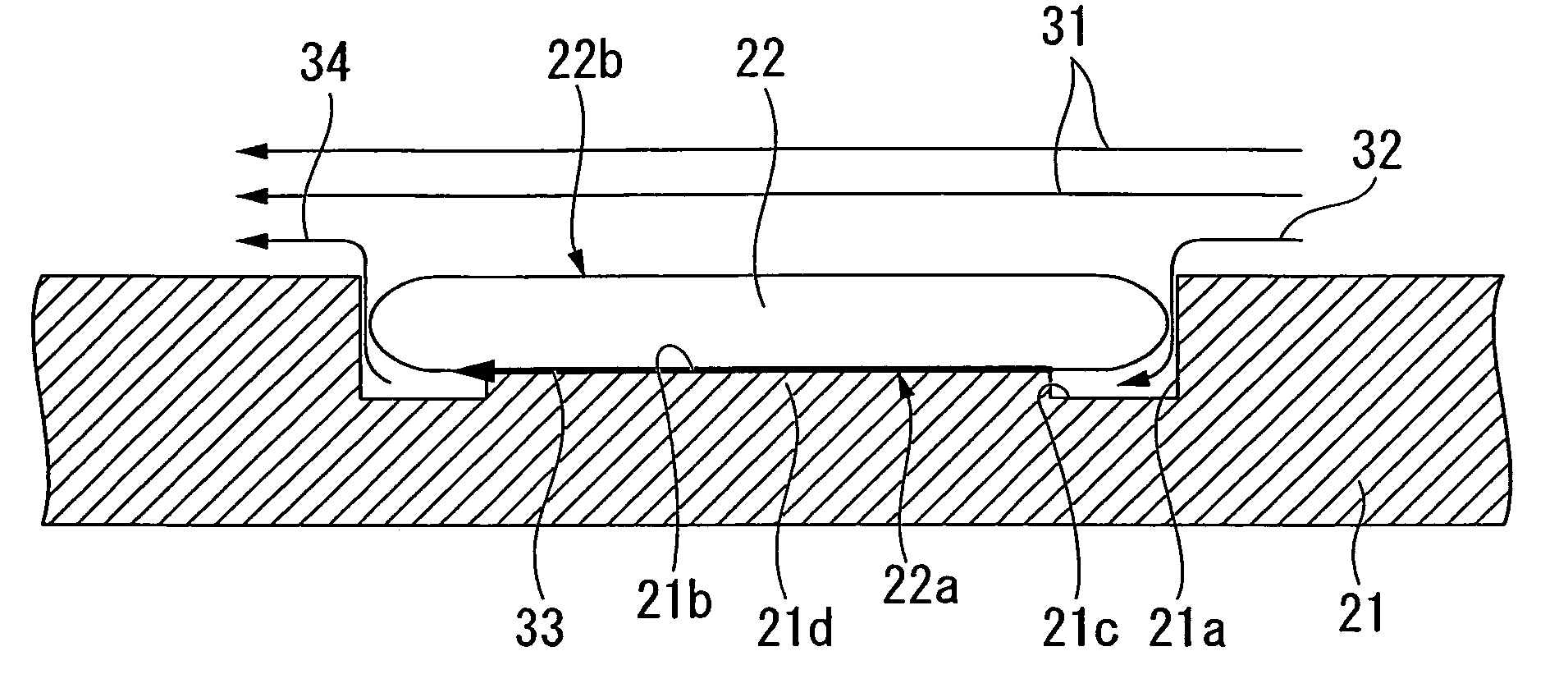

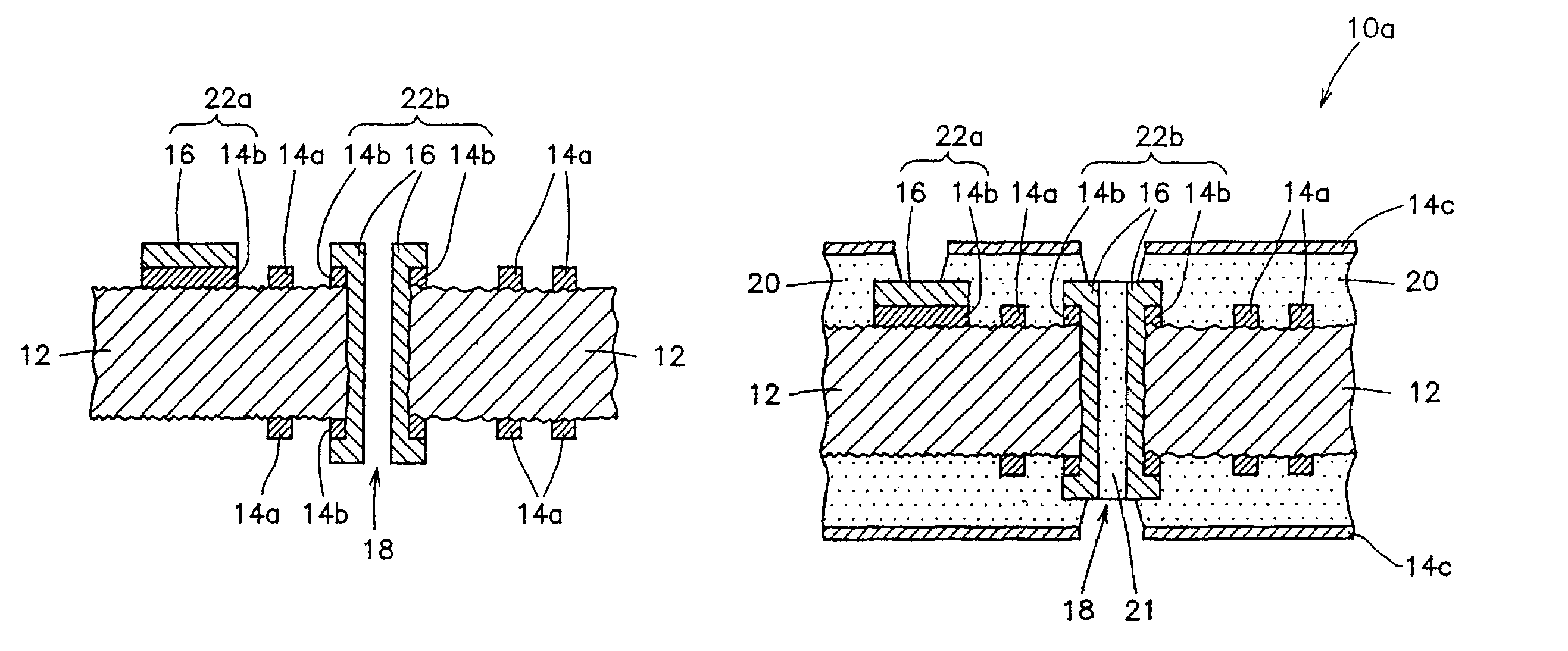

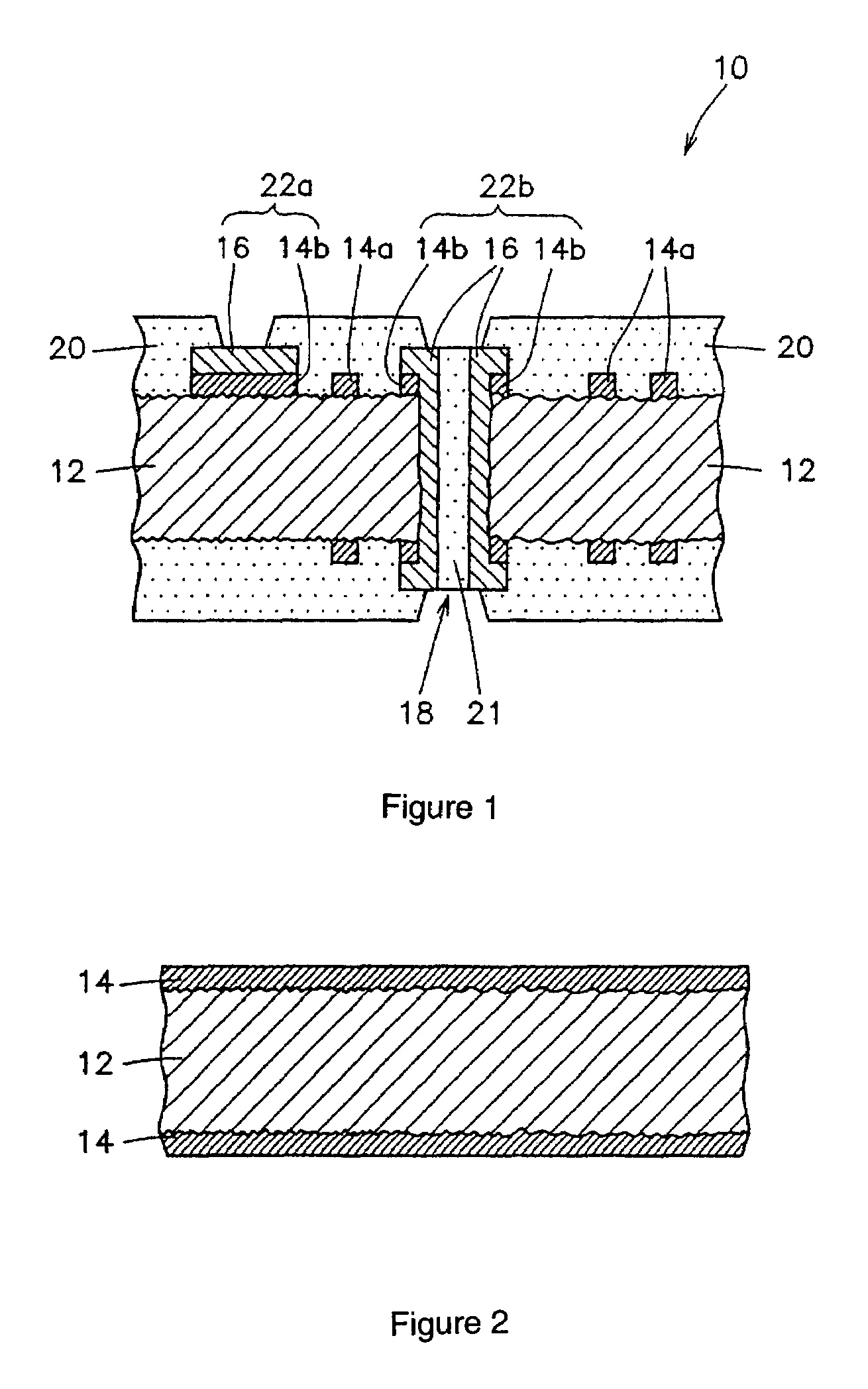

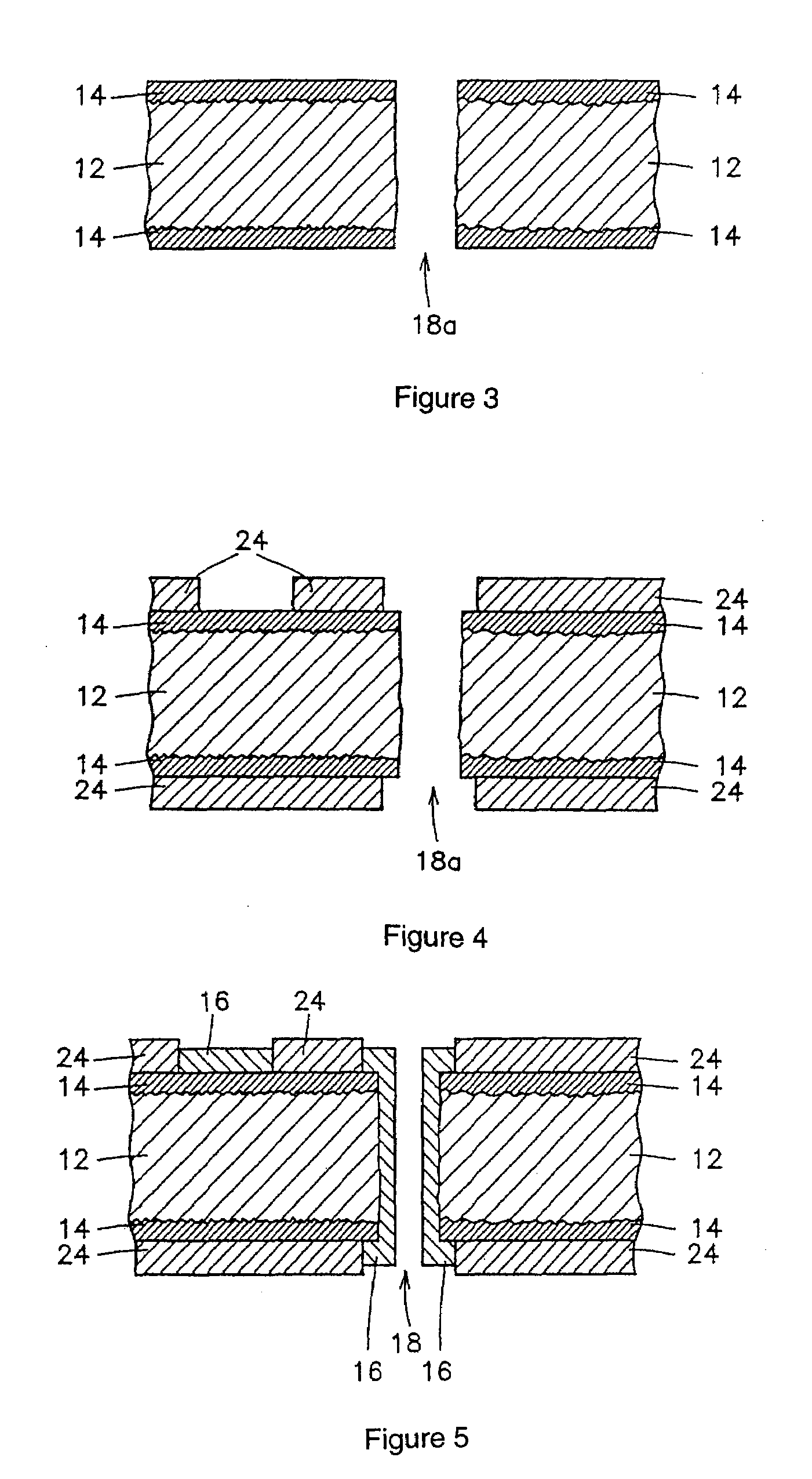

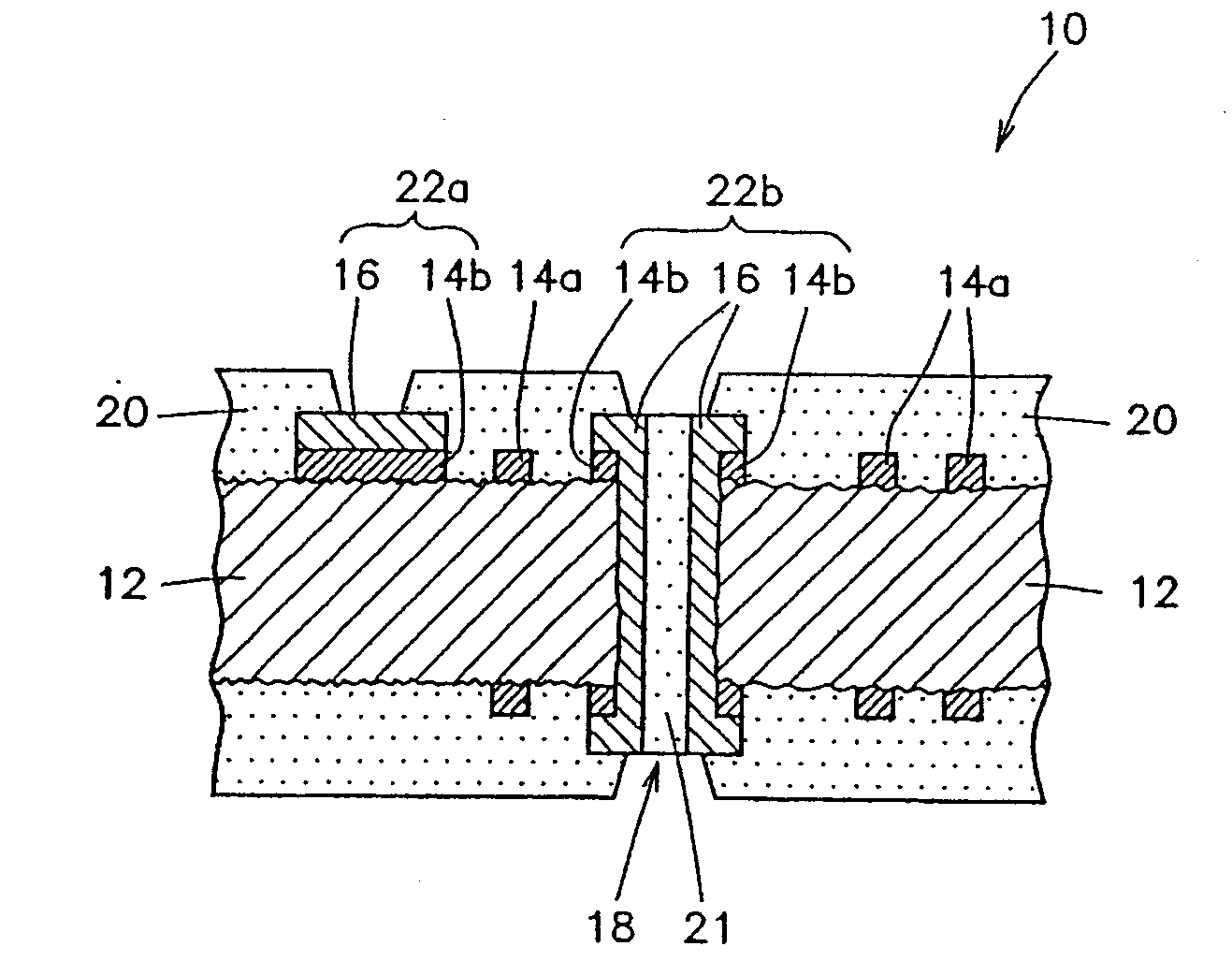

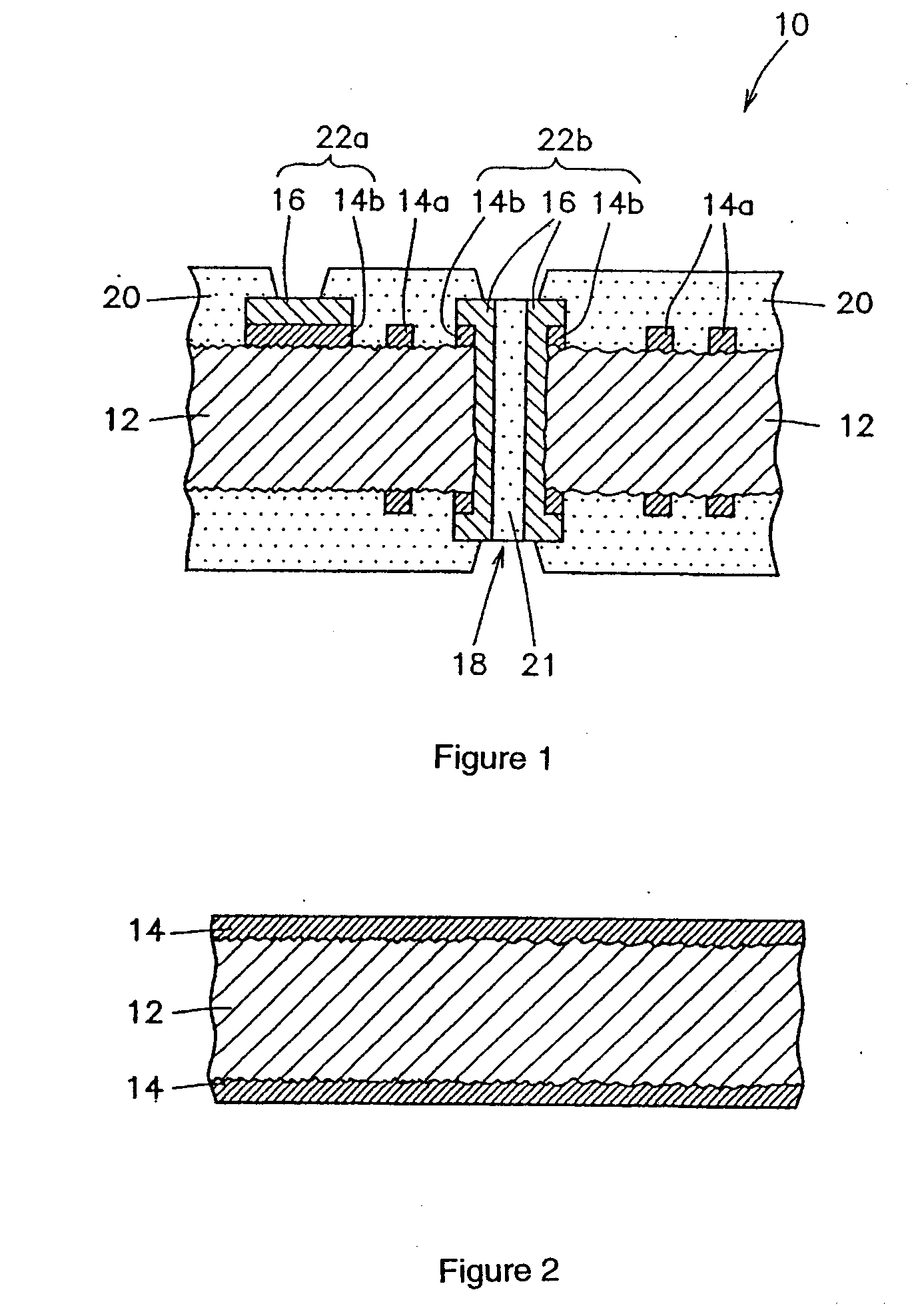

Printed circuit board manufacturing method and printed circuit board

InactiveUS20080257597A1Reduce depthEasy to makePrinted circuit aspectsConductive pattern formationFine lineMetal foil

The present invention provides a method of manufacturing printed a circuit board capable of formation of via holes having a low aspect ratio and formation of fine lines, and a printed circuit board manufactured by the method. The method of manufacturing a printed circuit board 10 according to the present invention includes a step of selectively forming a plating layer 16 for lands 22a and 22b on a metal foil 14 on the printed circuit board 10, a step of adjusting the thickness of the plating layer 16, and a step of forming the metal foil 14 into lines 14a. The aspect ratio of via holes 28 formed on lands 22a and 22b can be adjusted by adjusting the thickness of the lands 22a and 22b.

Owner:GLOBALFOUNDRIES INC

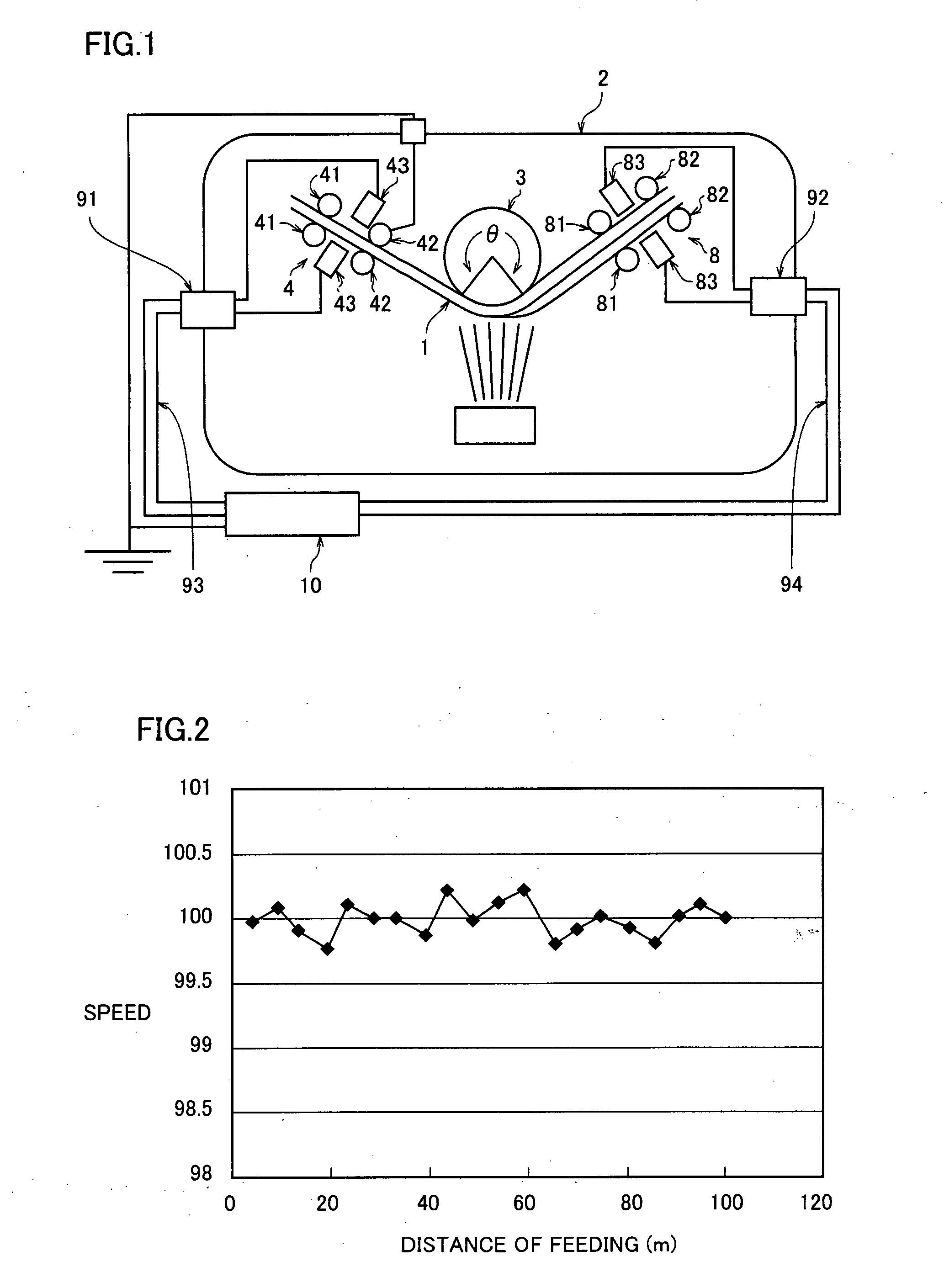

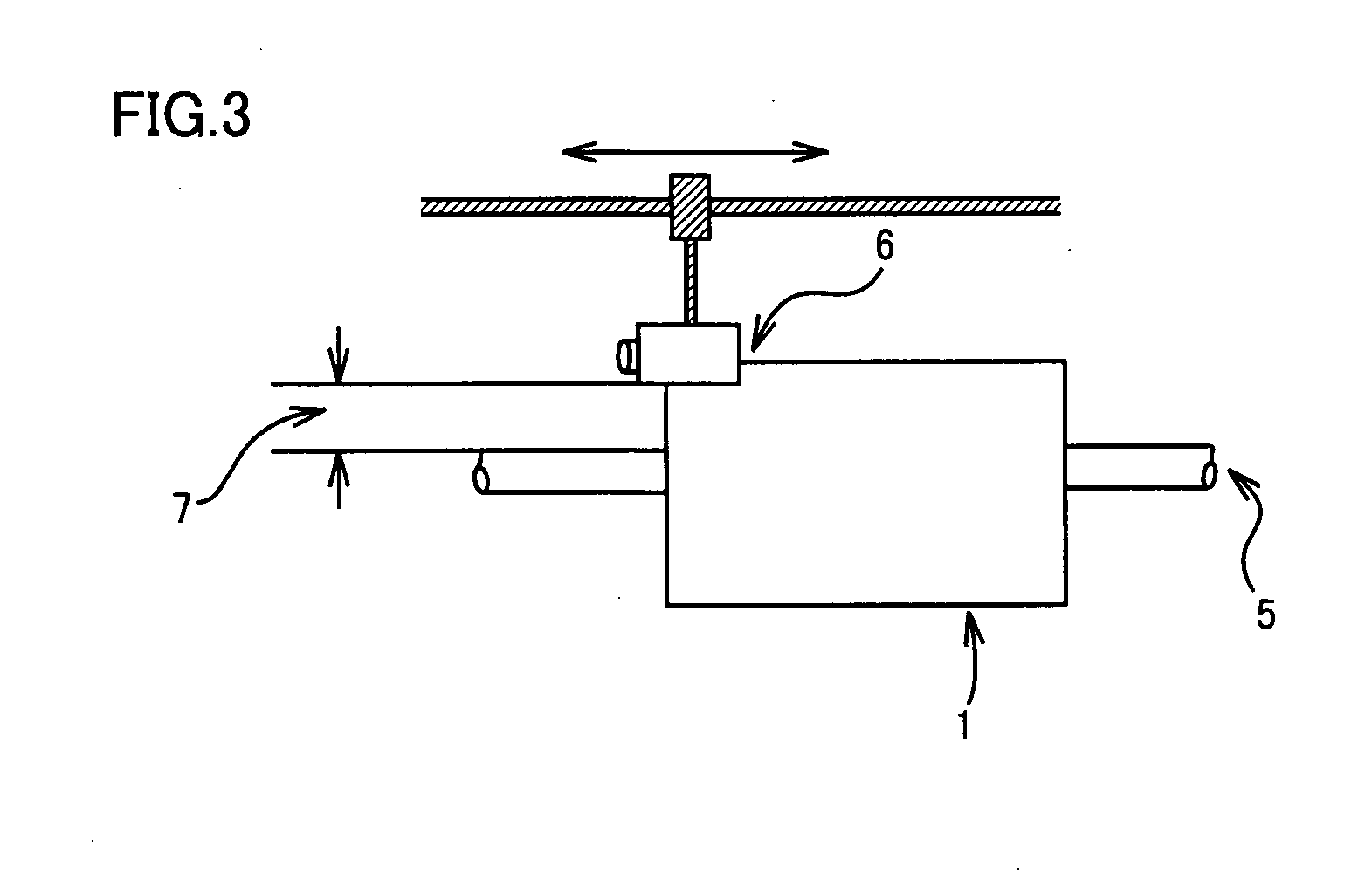

Coating layer thickness measurement mechanism and coating layer forming apparatus using the same

InactiveUS20070261638A1Suppressing variation in a speed of feeding a base materialMinimize impactLiquid surface applicatorsVacuum evaporation coatingCapacitanceEngineering

In a measurement mechanism for continuously measuring a thickness of a coating layer, provided in an apparatus for forming the coating layer on a conductive elongate base material in a coating treatment base station while the base material is fed, a sensing portion for measuring a capacitance value of the coating layer is arranged before and after the base station, and tension applied to the base material at the sensing portion is set to be greater than tension applied to the base material at the base station. Thus, in forming the coating layer on the elongate base material while the base material is continuously fed, variation in a feeding speed is suppressed, influence of sway of a measurement surface in a direction of thickness at the thickness sensing portion during feeding is minimized, and a thickness of the coating layer can be measured with higher accuracy.

Owner:SUMITOMO ELECTRIC IND LTD

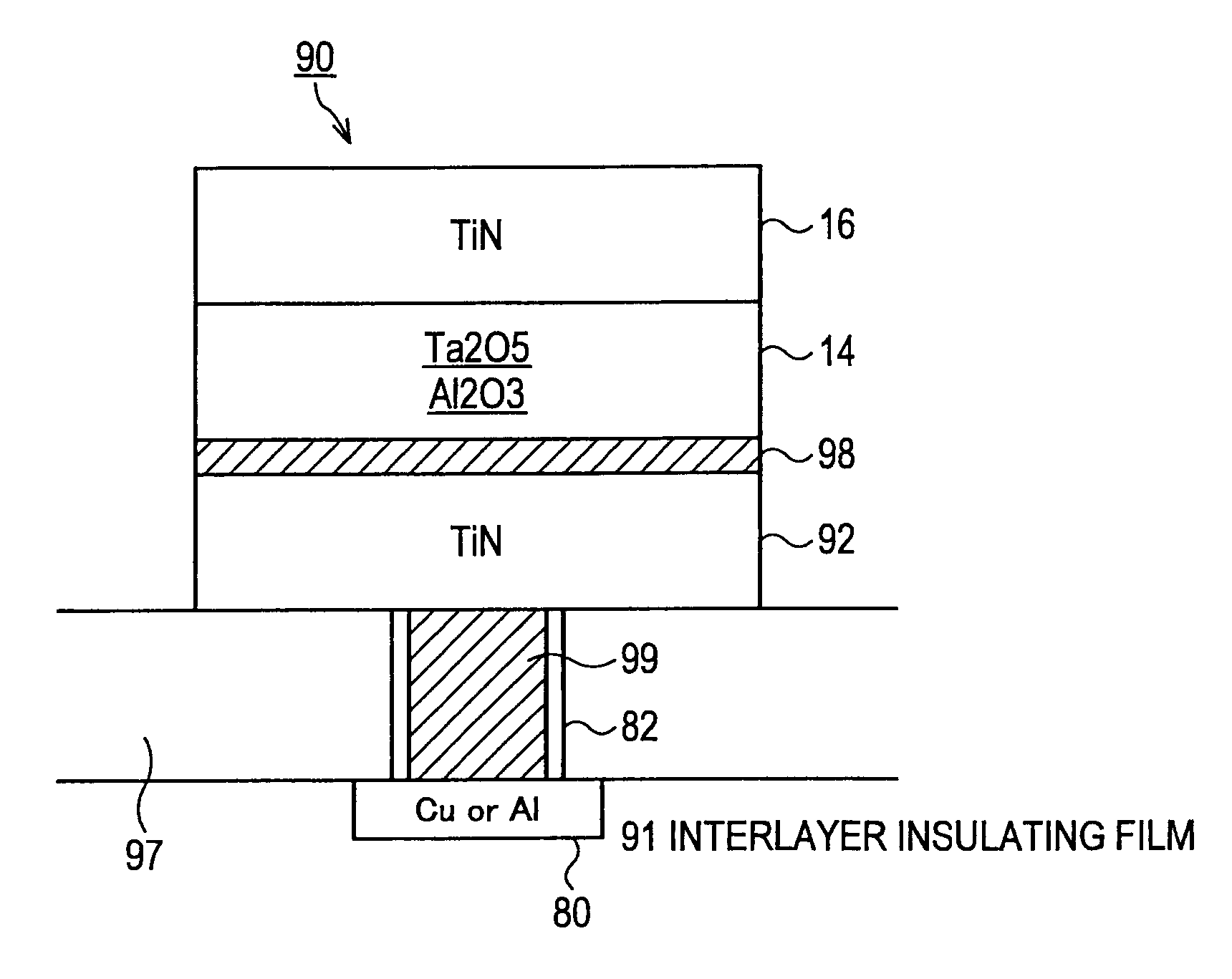

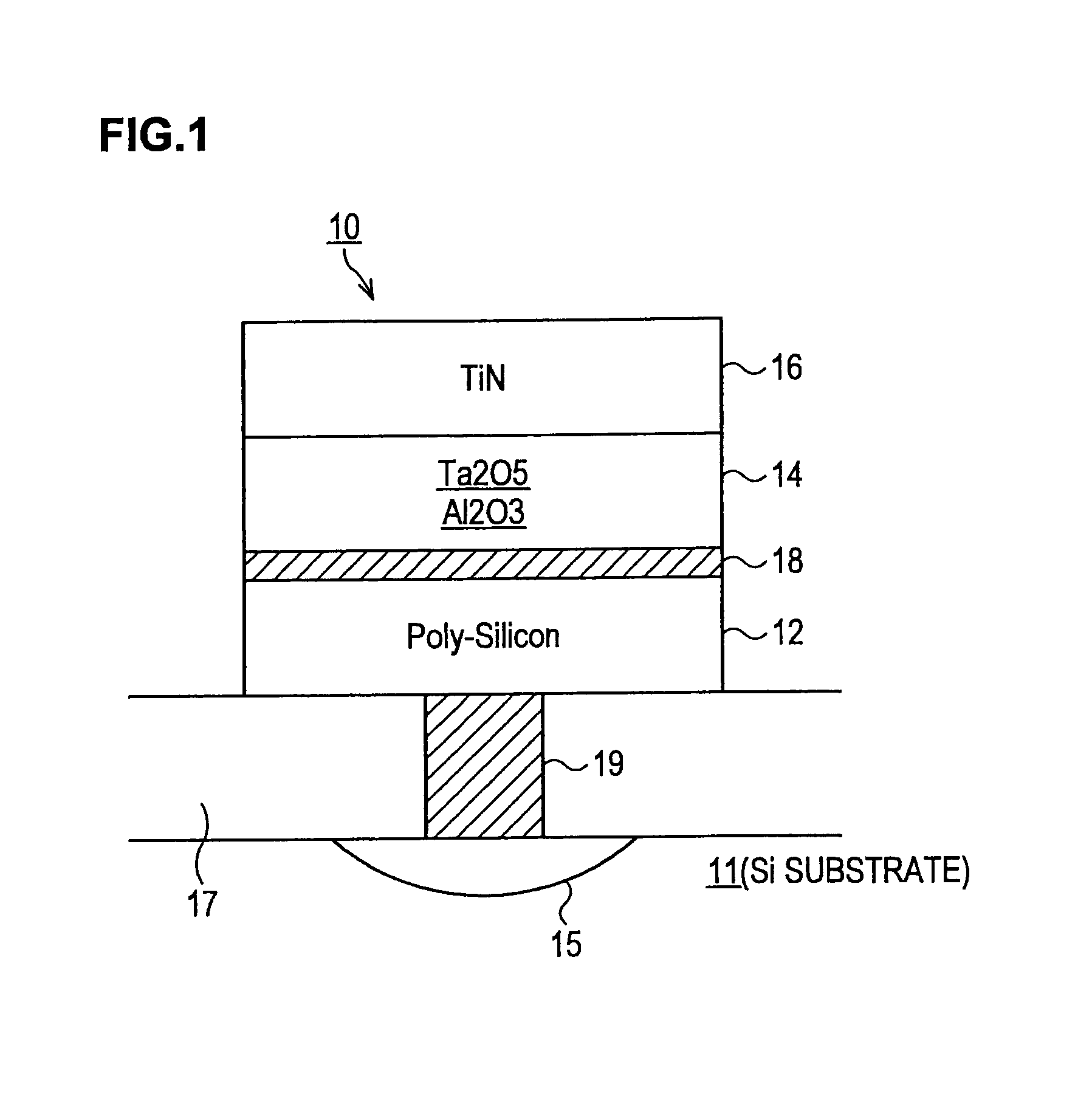

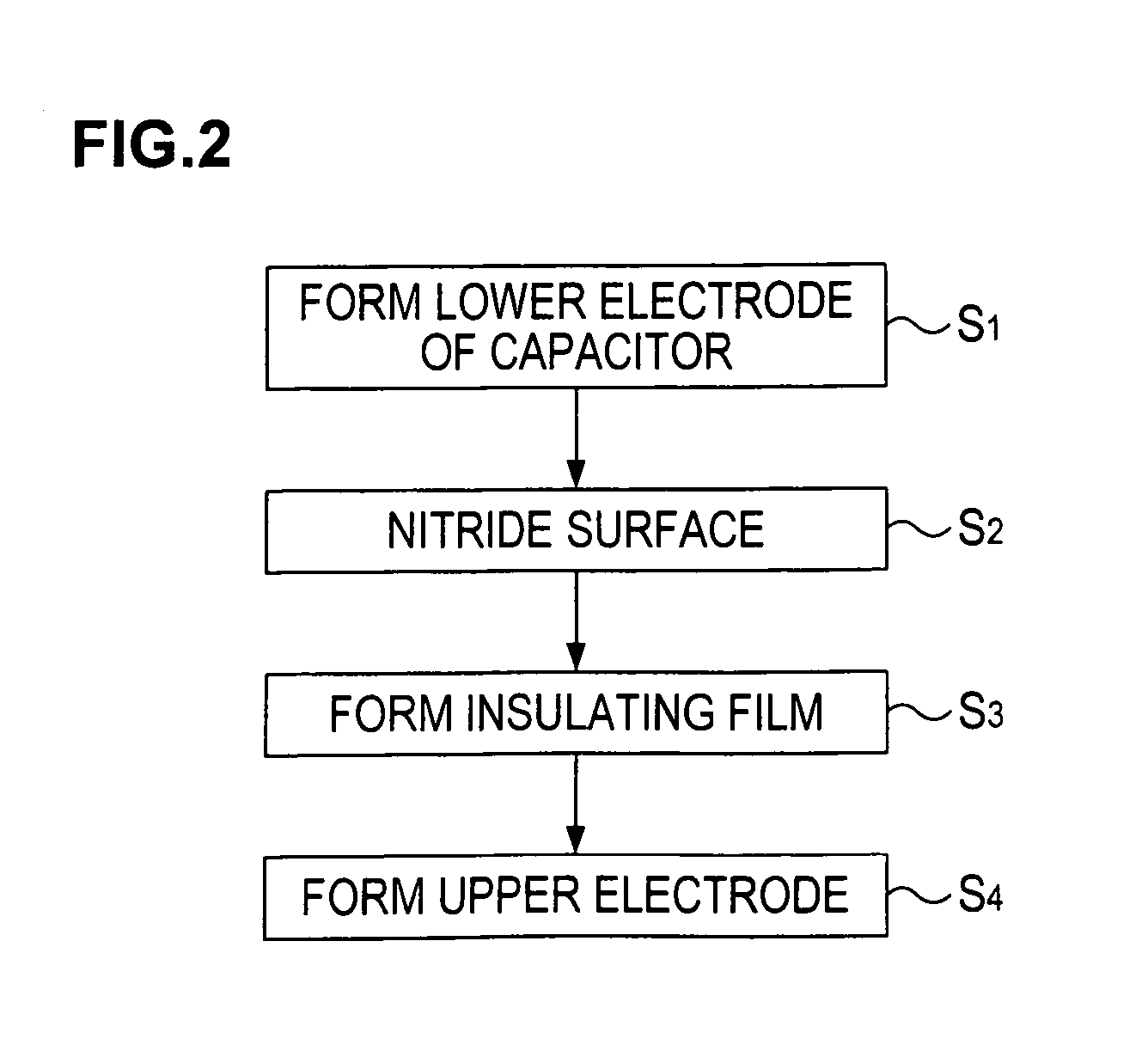

Manufacturing method of semiconductor device, semiconductor manufacturing apparatus, plasma nitridation method, computer recording medium, and program

InactiveUS7524774B2Improve the immunityReduce leakage currentSolid-state devicesSemiconductor/solid-state device manufacturingPlasma nitridationCapacitor

An object of the present invention is to prevent an increase in film thickness and inhibit a reduction in capacity of a capacitor. In a semiconductor device having a capacitor, the capacitor includes a lower electrode, an upper electrode, and an insulating film interposed between the lower electrode and the upper electrode. A surface of the lower electrode on an insulating layer side is nitrided. If the lower electrode is made of polysilicon, nitriding the surface thereof increases oxidation resistance at the time of heat treatment in a post process. Particularly in a DRAM, the capacity of the capacitor is large, and therefore, this effect is significant. Further, leakage current inside the capacitor is also reduced.

Owner:TOKYO ELECTRON LTD

Flash memory cell with UV protective layer

ActiveUS6989563B1Reduce thickness variationProtection from damageTransistorSemiconductor/solid-state device detailsUv protectiveUltraviolet

A method of protecting a charge trapping dielectric flash memory cell from UV-induced charging, including fabricating a charge trapping dielectric flash memory cell in a semiconductor device; depositing and planarizing an interlevel dielectric layer over the charge trapping dielectric flash memory cell and depositing over the planarized interlevel dielectric layer at least one UV-protective layer, the UV-protective layer including a substantially UV-opaque material.

Owner:INFINEON TECH LLC

Method for manufacturing semiconductor device

InactiveUS20070087520A1Desired thicknessLess variationSemiconductor/solid-state device manufacturingDevice materialSemiconductor

A semiconductor device includes an element isolation film, which exhibits less variations in the height dimension from the surface of the substrate and has a desired height dimension from the surface of the substrate. A process for manufacturing a semiconductor device includes: providing a predetermined pattern of a silicon nitride film and a protective film which covers the silicon nitride film, on a semiconductor substrate; selectively etching the semiconductor substrate using the protective film as a mask to form a trenched portion; removing the protective film to expose the silicon nitride film; depositing an element isolation film, so as to fill the trenched portion therewith and cover the silicon nitride film; removing the element isolation film formed on the silicon nitride film by polishing thereof until the silicon nitride film is exposed; and removing the silicon nitride film.

Owner:RENESAS ELECTRONICS CORP