Patents

Literature

62 results about "Adaptive logic" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

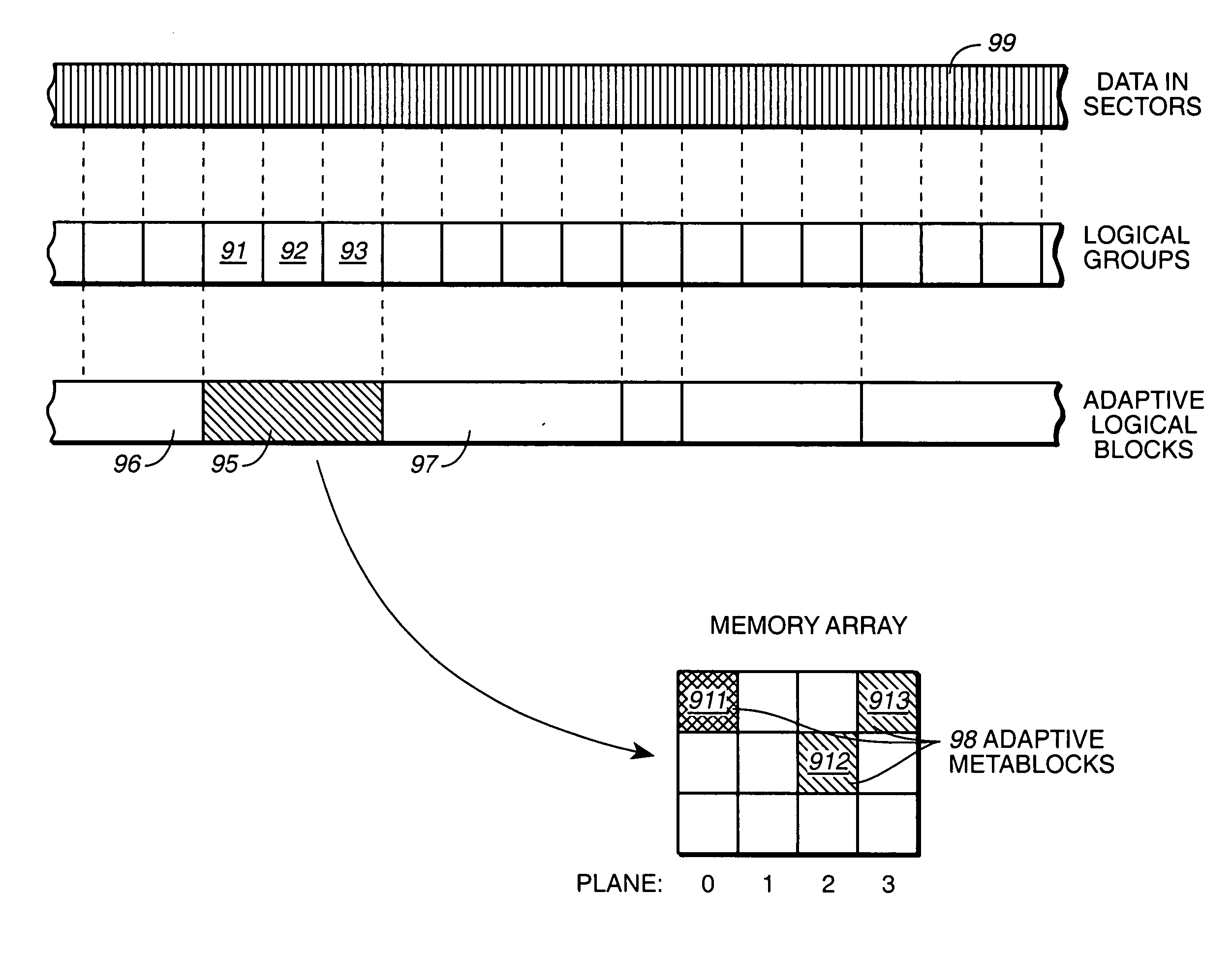

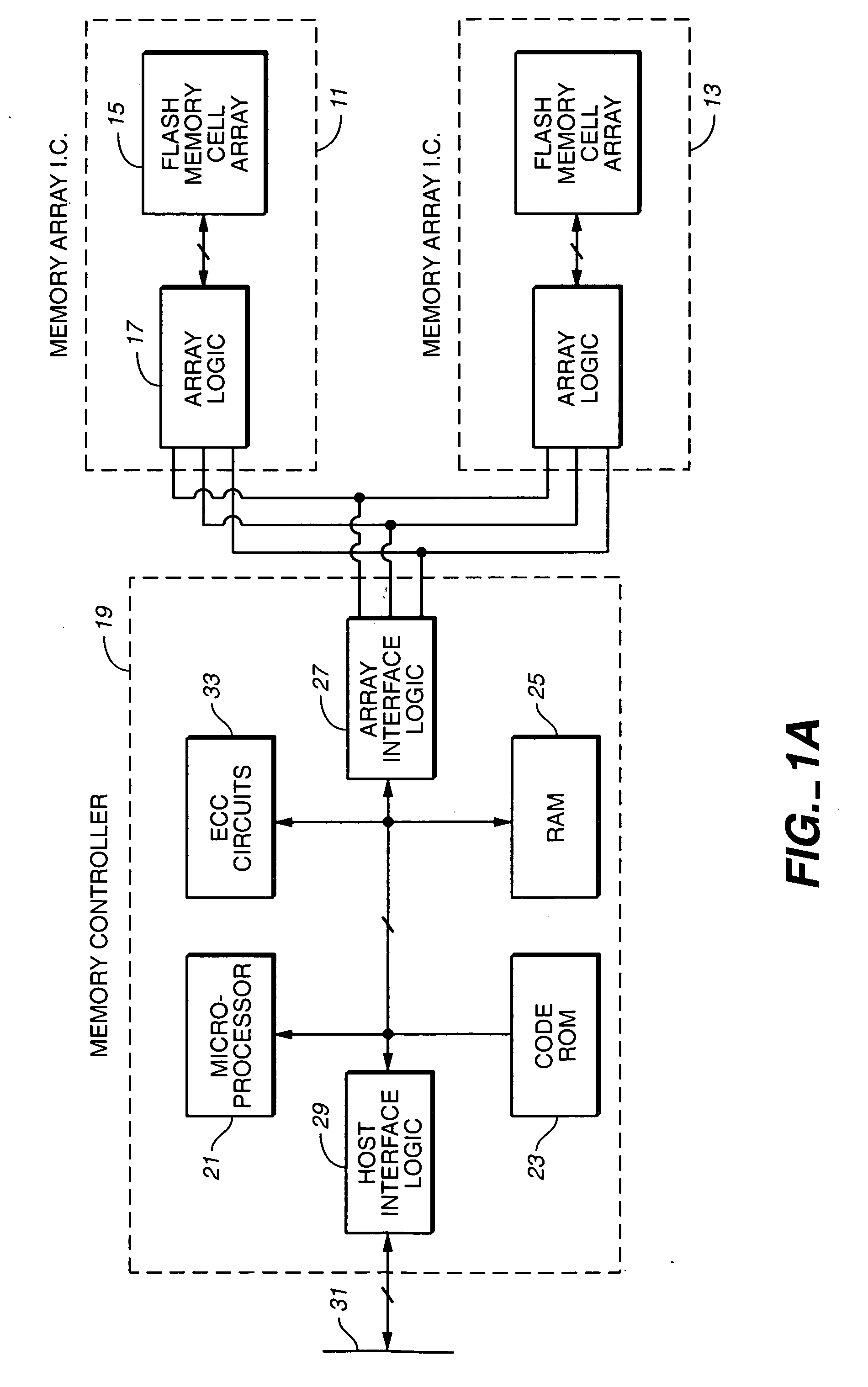

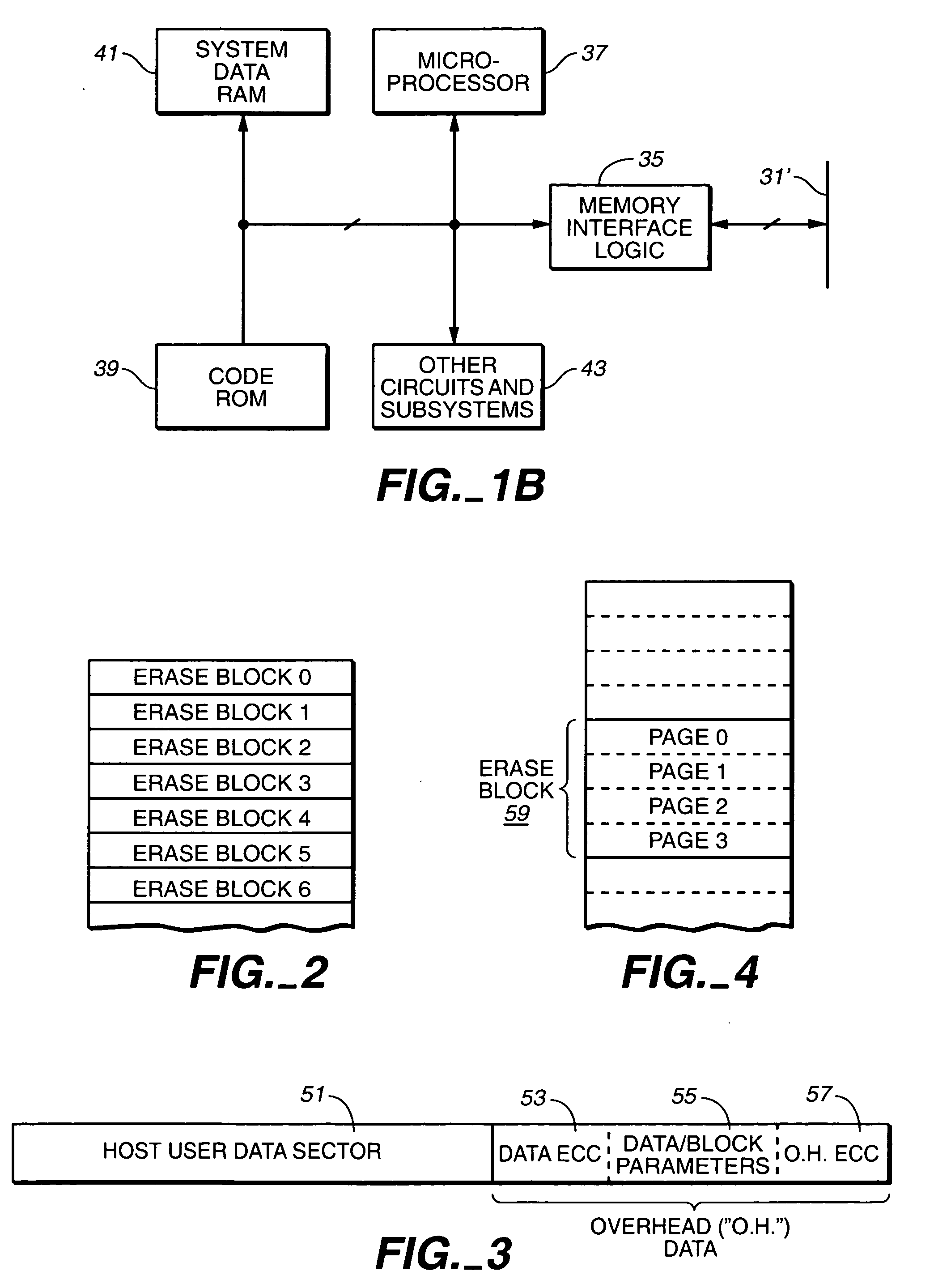

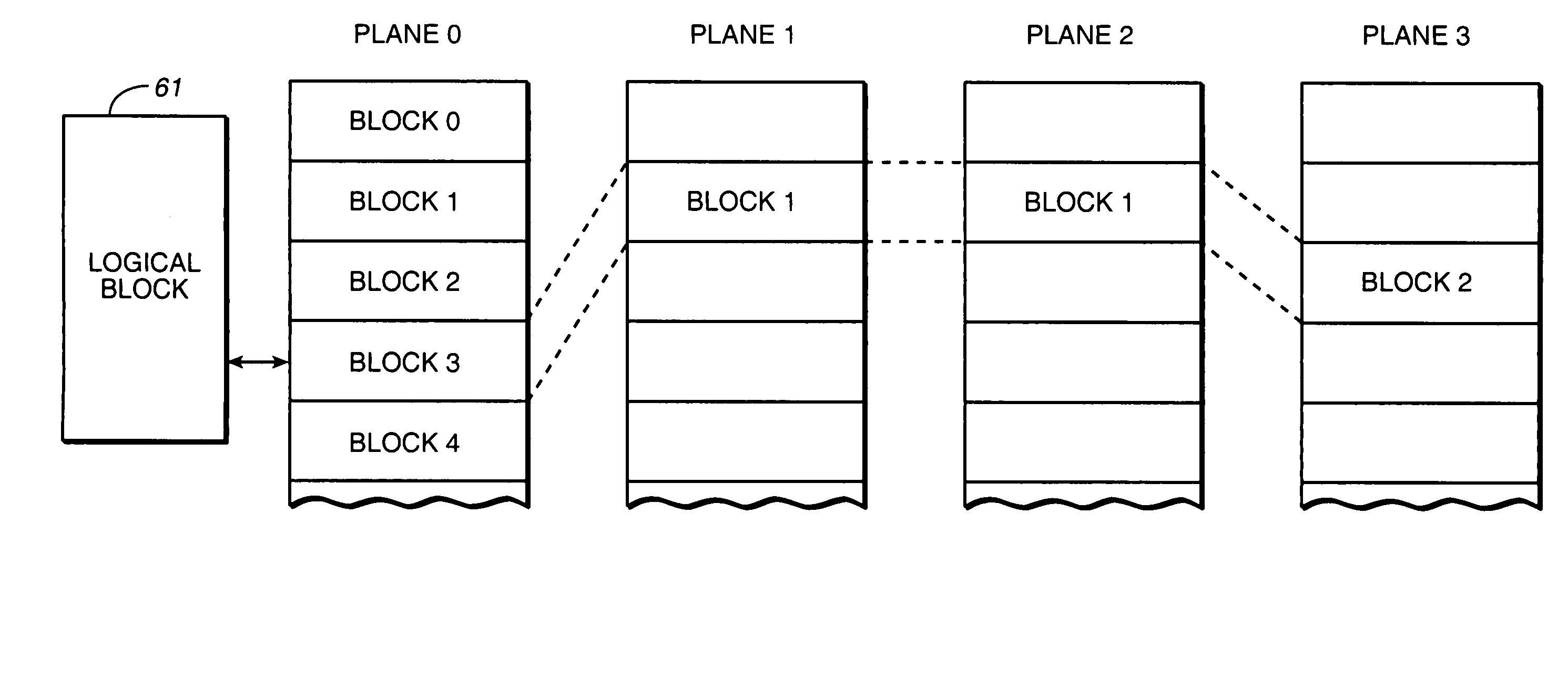

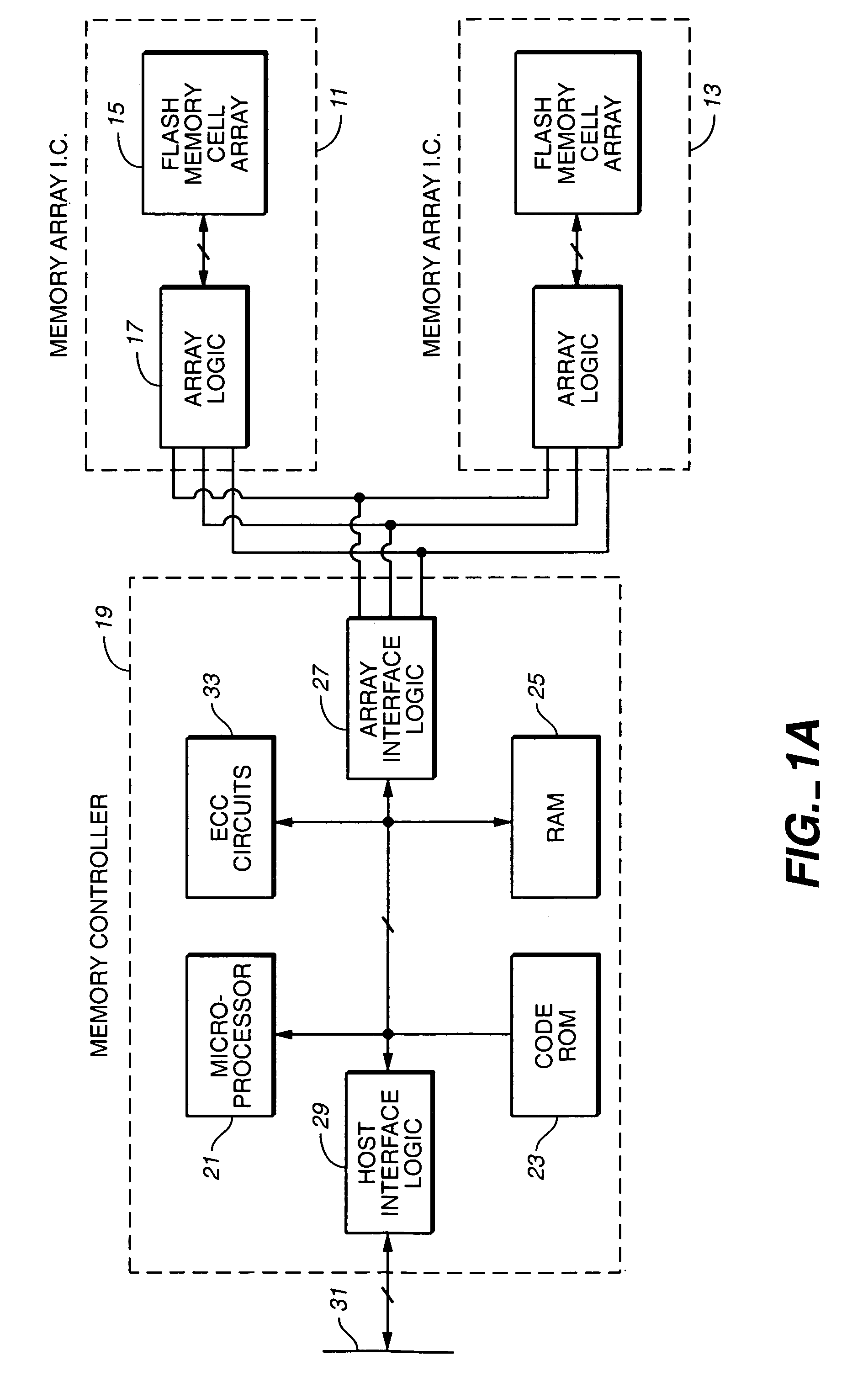

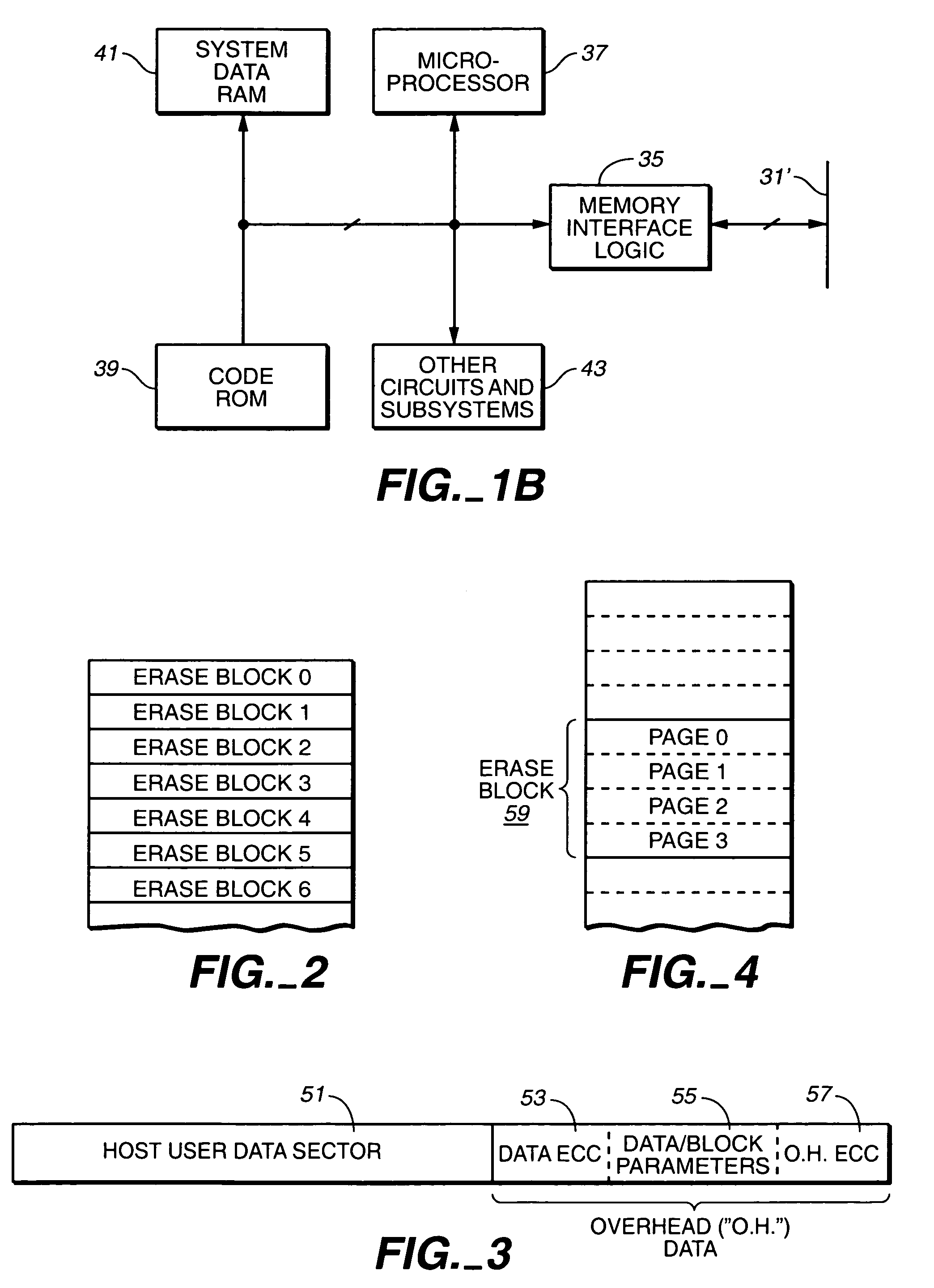

Adaptive metablocks

ActiveUS20050144357A1Reduce the impactEfficient updateMemory architecture accessing/allocationMemory adressing/allocation/relocationData selectionTheoretical computer science

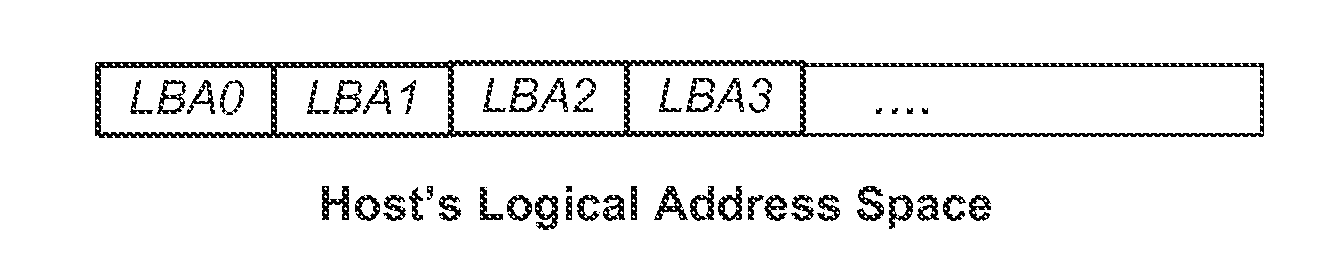

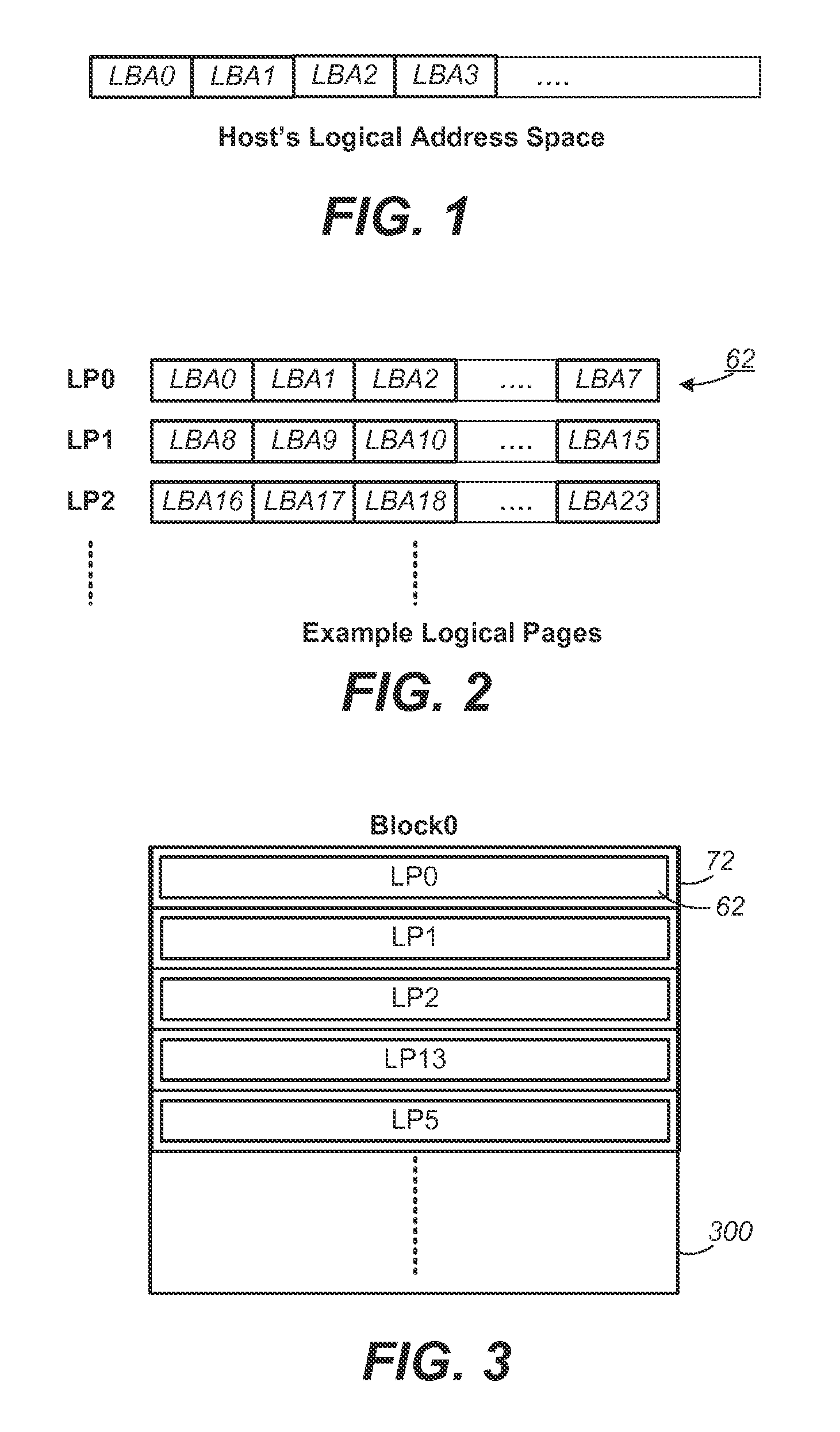

In a memory system having multiple erase blocks in multiple planes, a selected number of erase blocks are programmed together as an adaptive metablock. The number of erase blocks in an adaptive metablock is chosen according to the data to be programmed. Logical address space is divided into logical groups, a logical group having the same size as one erase block. Adaptive logical blocks are formed from logical groups. One adaptive logical block is stored in one adaptive metablock.

Owner:SANDISK TECH LLC

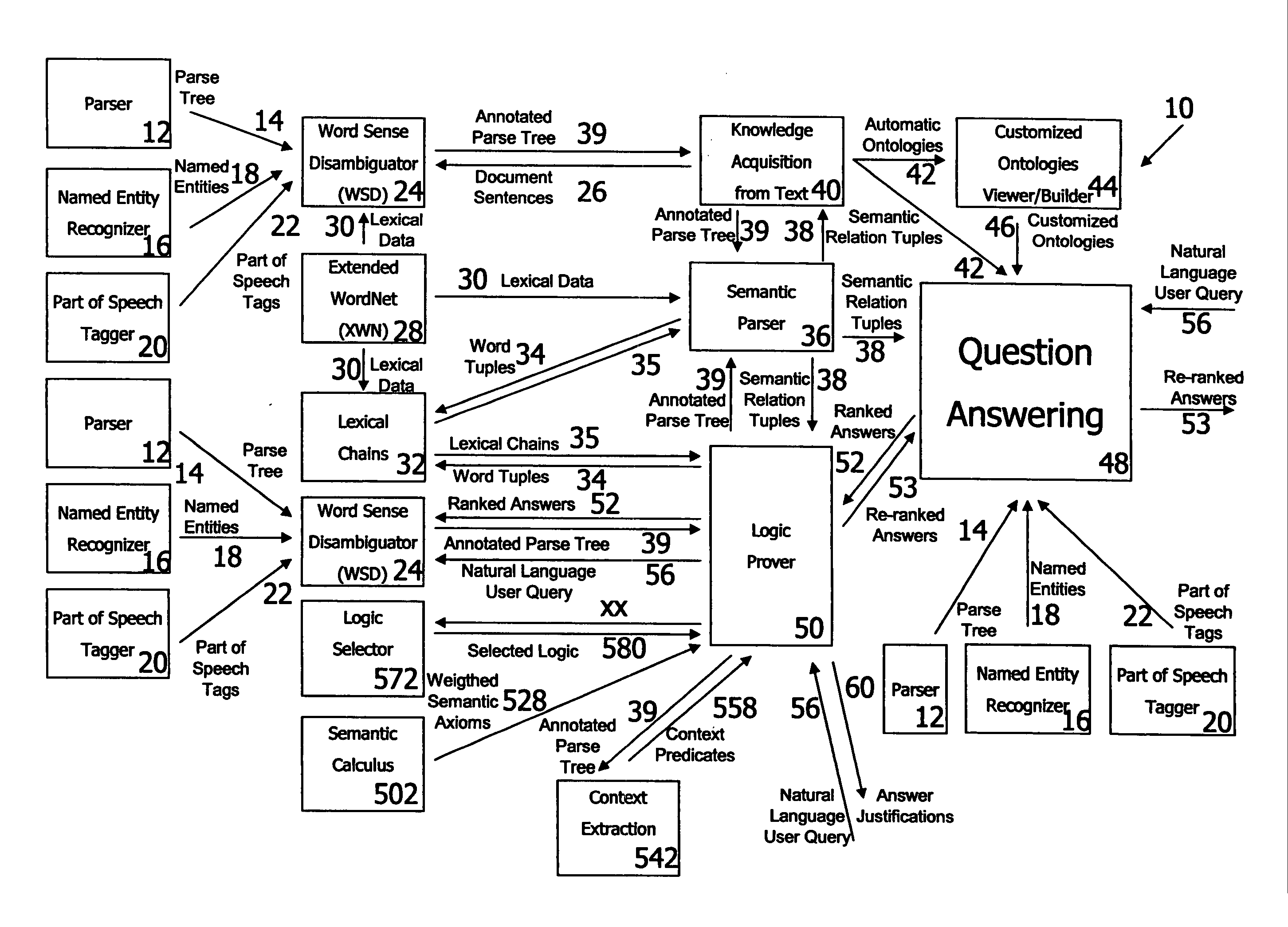

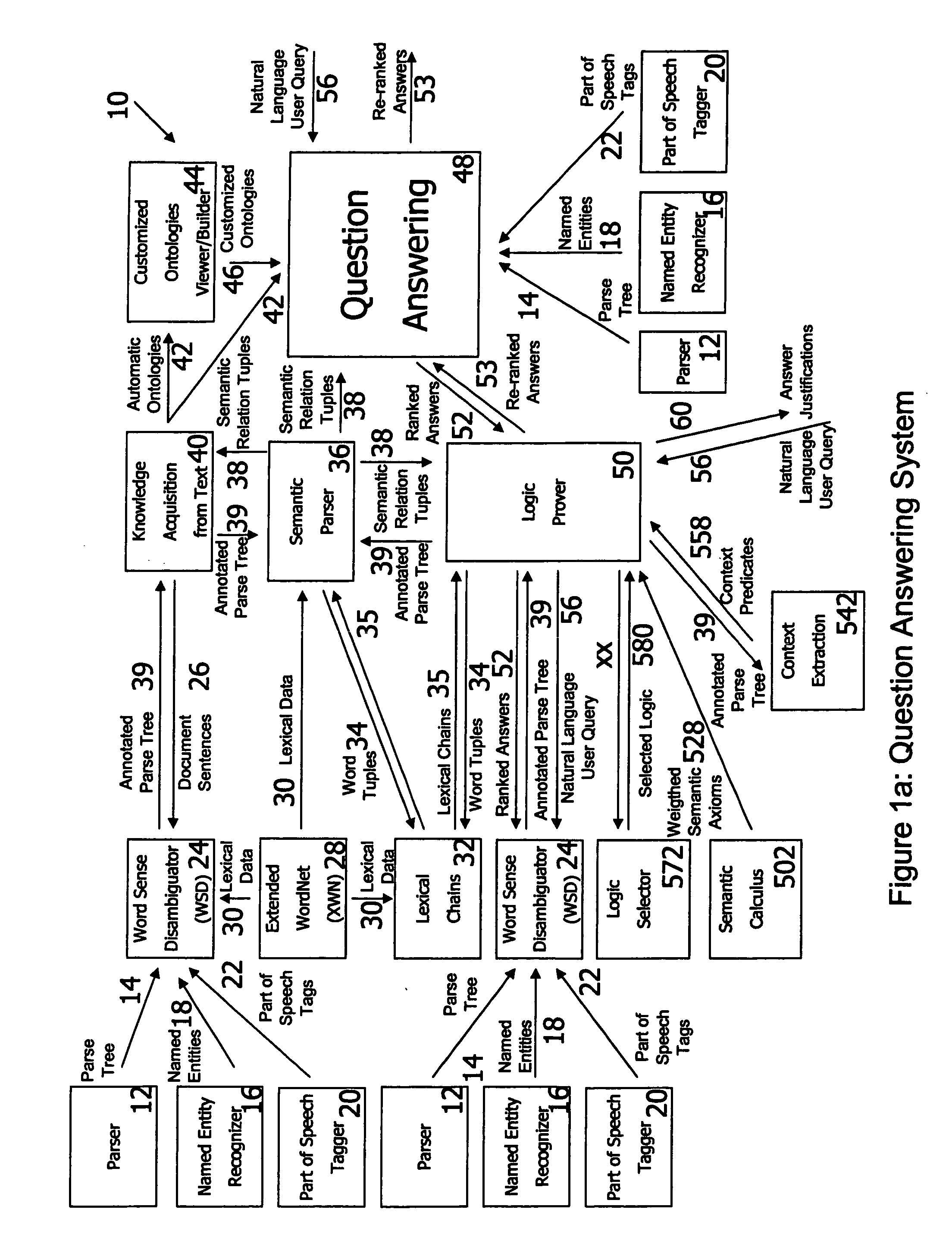

Natural language question answering system and method utilizing multi-modal logic

InactiveUS20060053000A1Digital data information retrievalSemantic analysisNatural language question answeringModal logic

A multi-modal natural language question answering system and method comprises receiving a question logic form, at least one answer logic form, and utilizing semantic relations, contextual information, and adaptable logic.

Owner:LYMBA CORP

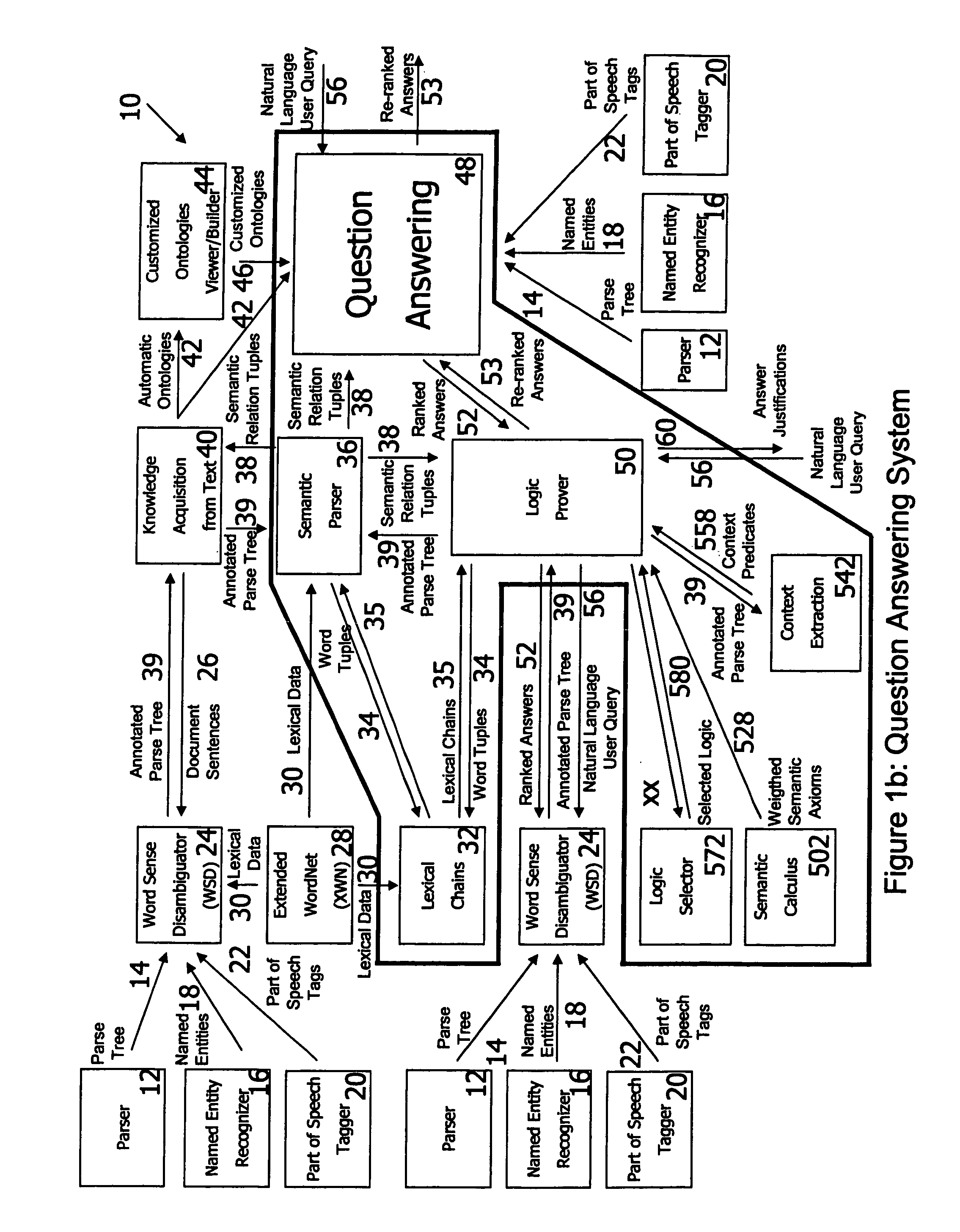

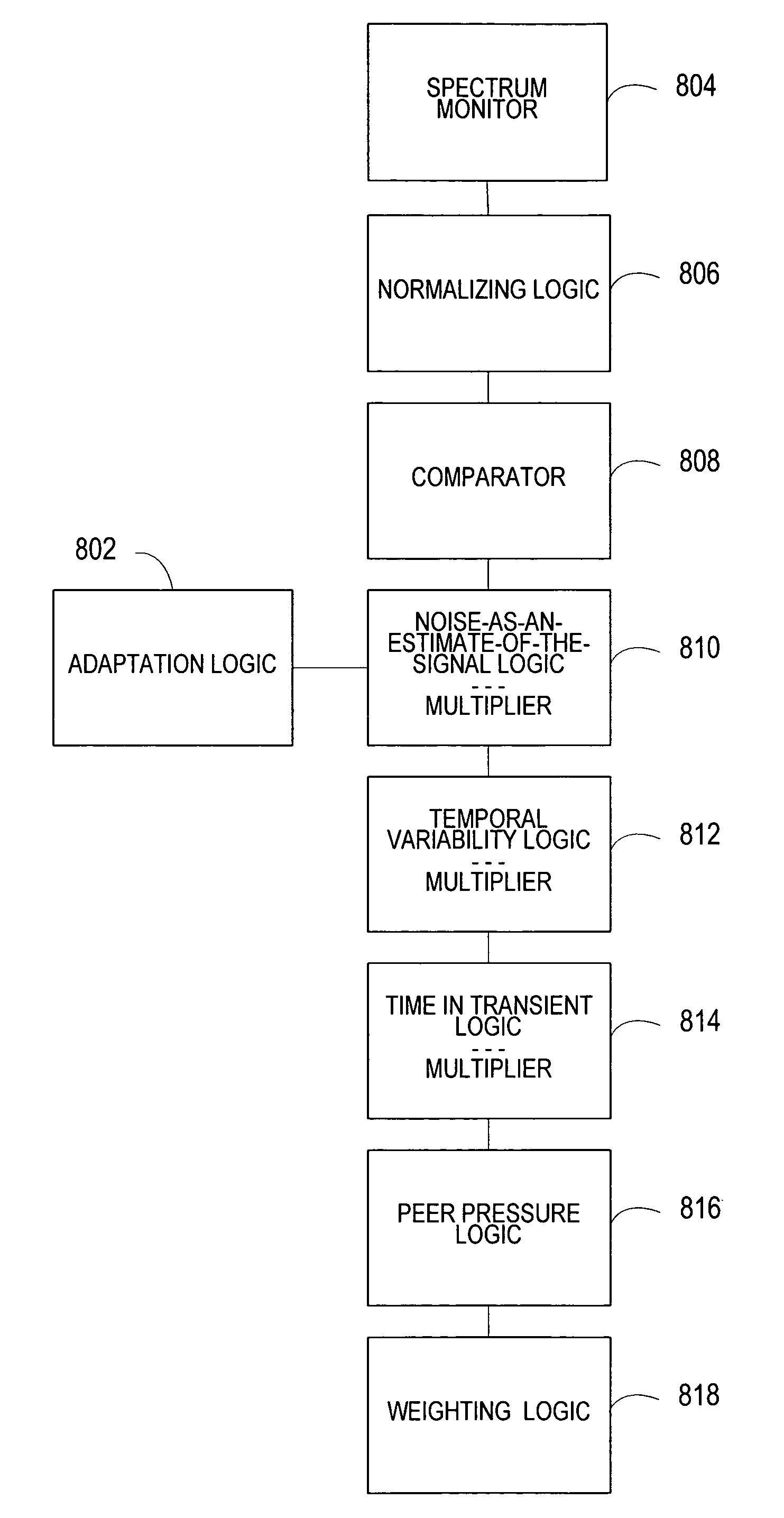

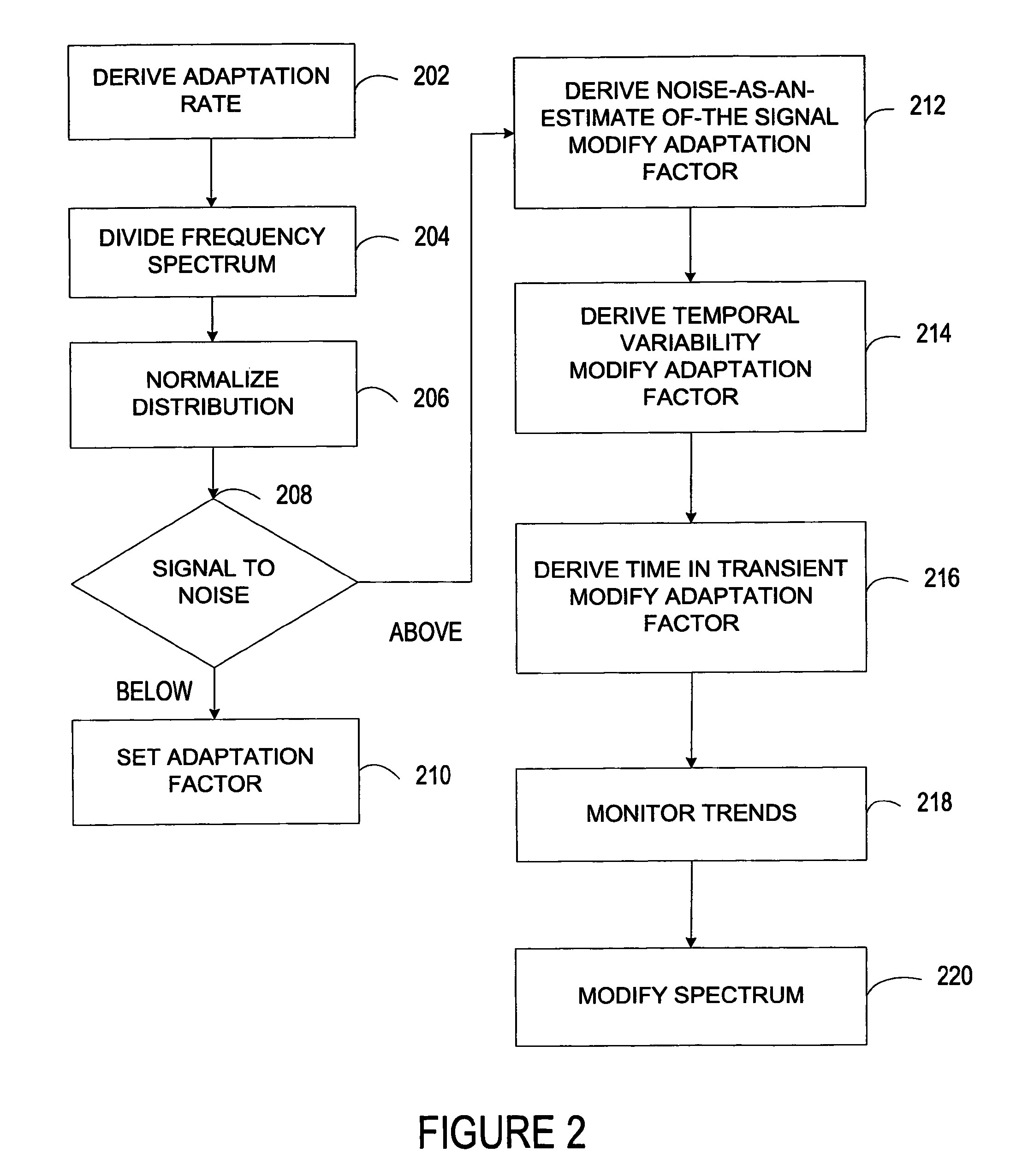

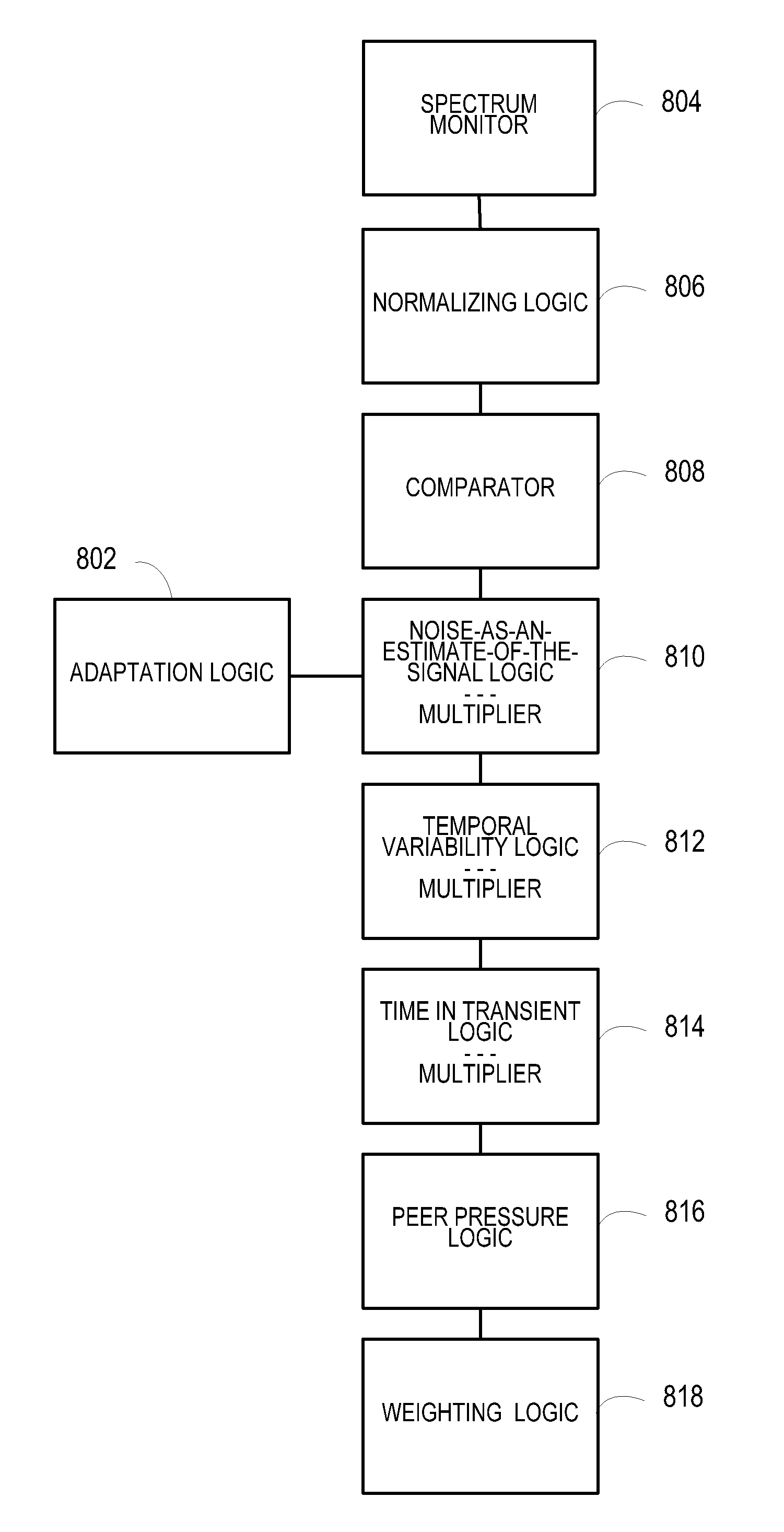

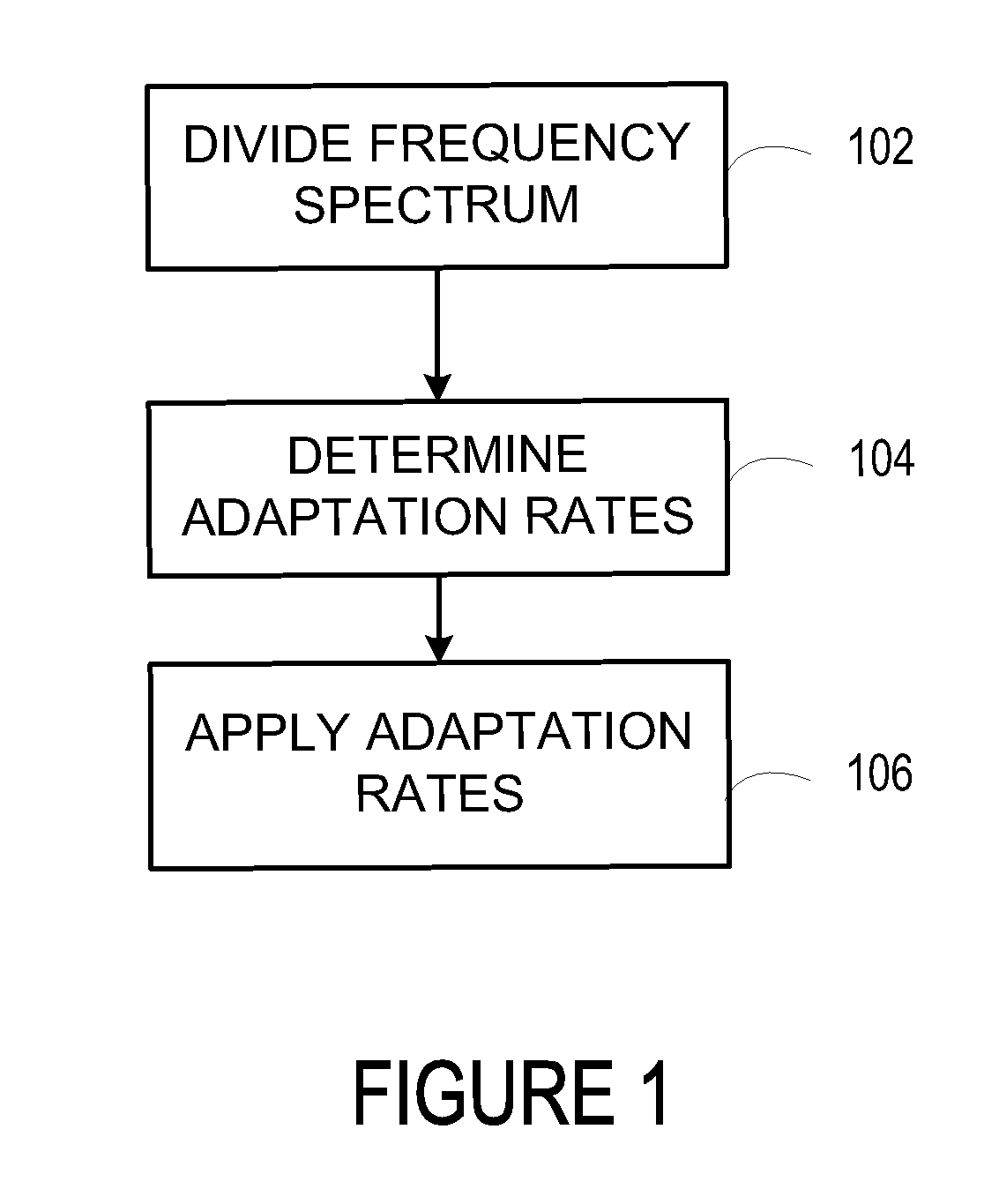

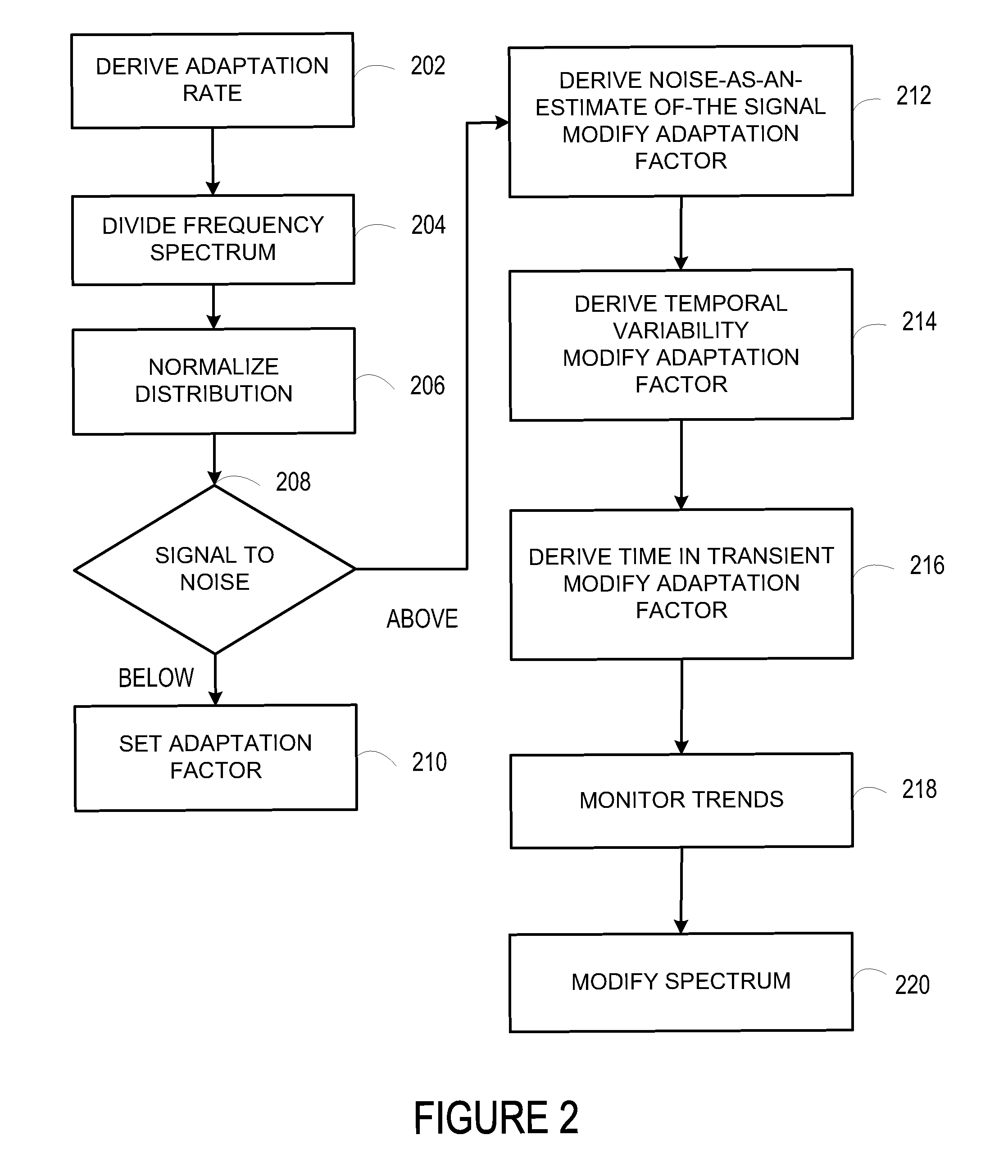

Robust noise estimation

ActiveUS7844453B2Improved noise estimationGood estimateSpeech analysisFrequency spectrumImage resolution

An enhancement system improves the estimate of noise from a received signal. The system includes a spectrum monitor that divides a portion of the signal at more than one frequency resolution. Adaptation logic derives a noise adaptation factor of the received signal. A plurality of devices tracks the characteristics of an estimated noise in the received signal and modifies multiple noise adaptation rates. Weighting logic applies the modified noise adaptation rates derived from the signal divided at a first frequency resolution to the signal divided at a second frequency resolution.

Owner:MALIKIE INNOVATIONS LTD

Adaptive metablocks

ActiveUS7433993B2Efficient updateHigh degree of parallelismMemory architecture accessing/allocationMemory adressing/allocation/relocationData selectionTheoretical computer science

In a memory system having multiple erase blocks in multiple planes, a selected number of erase blocks are programmed together as an adaptive metablock. The number of erase blocks in an adaptive metablock is chosen according to the data to be programmed. Logical address space is divided into logical groups, a logical group having the same size as one erase block. Adaptive logical blocks are formed from logical groups. One adaptive logical block is stored in one adaptive metablock.

Owner:SANDISK TECH LLC

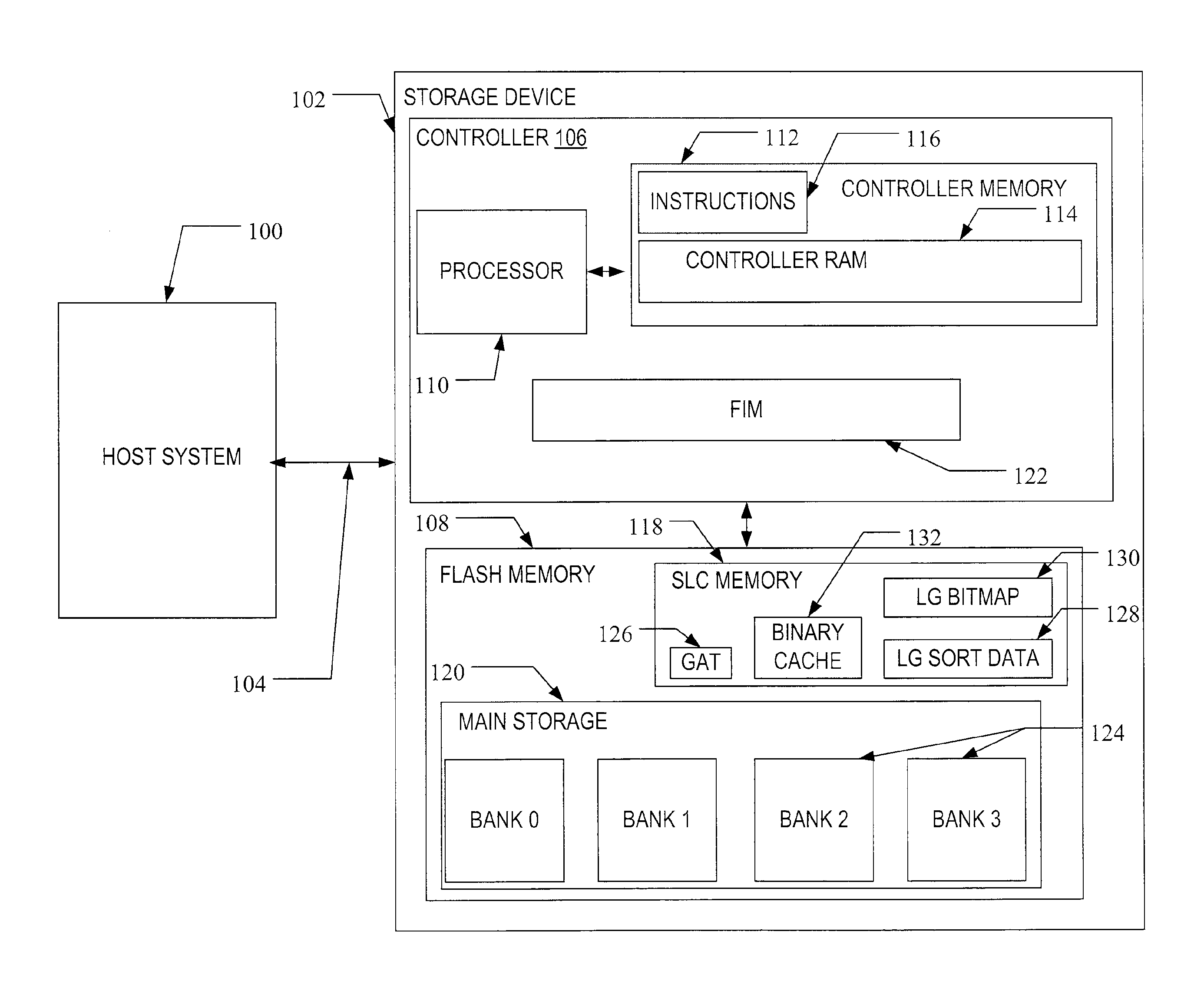

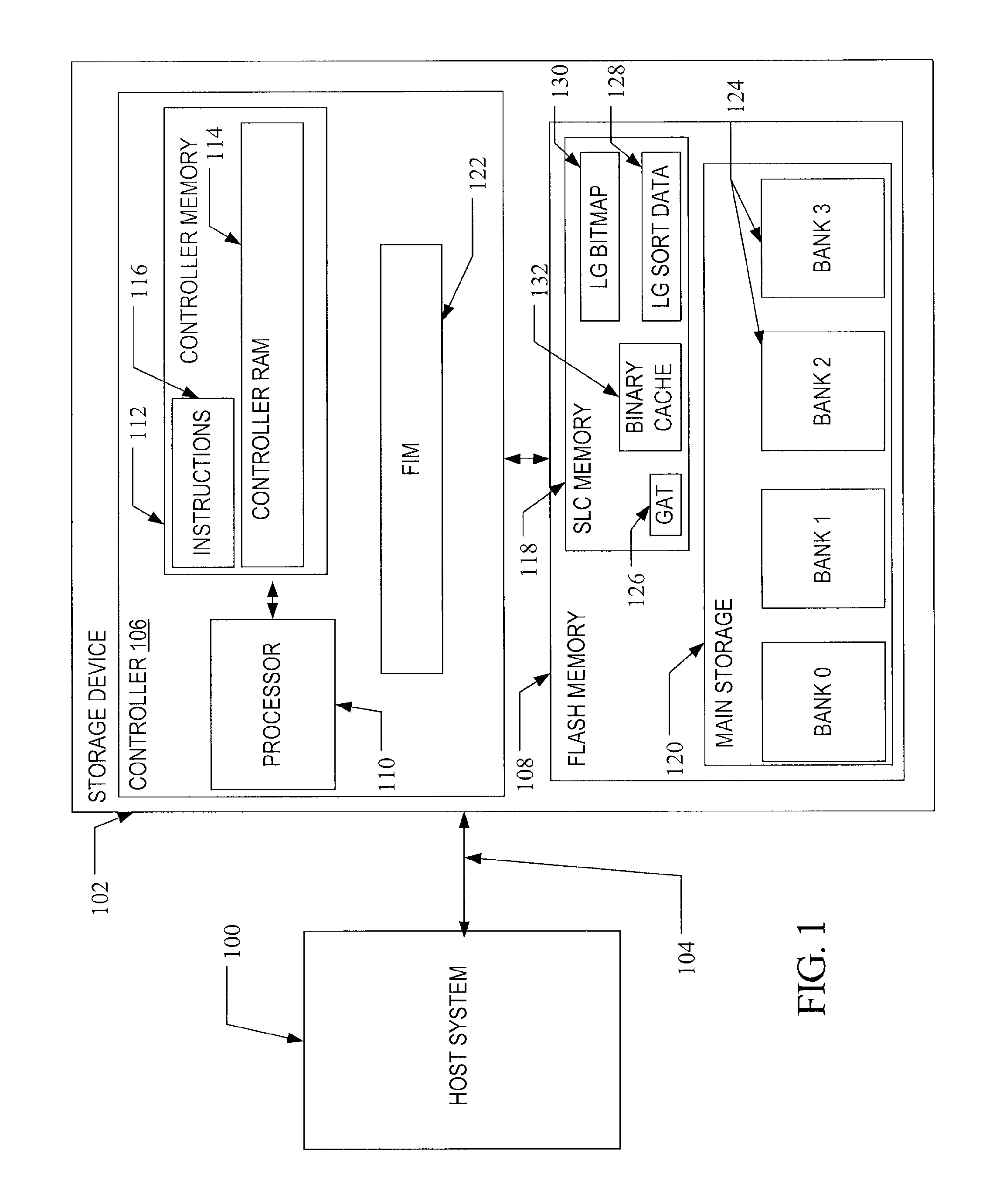

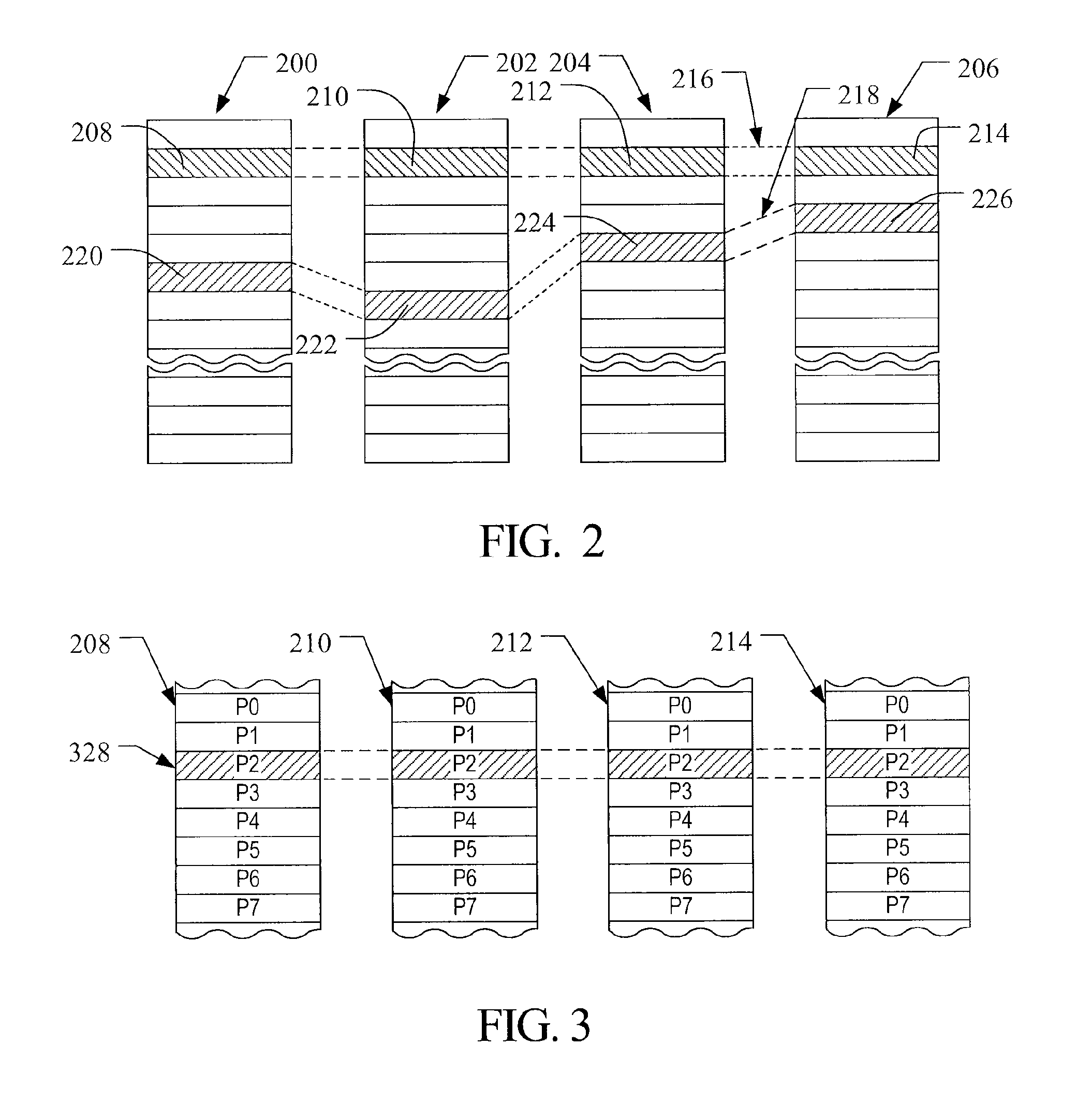

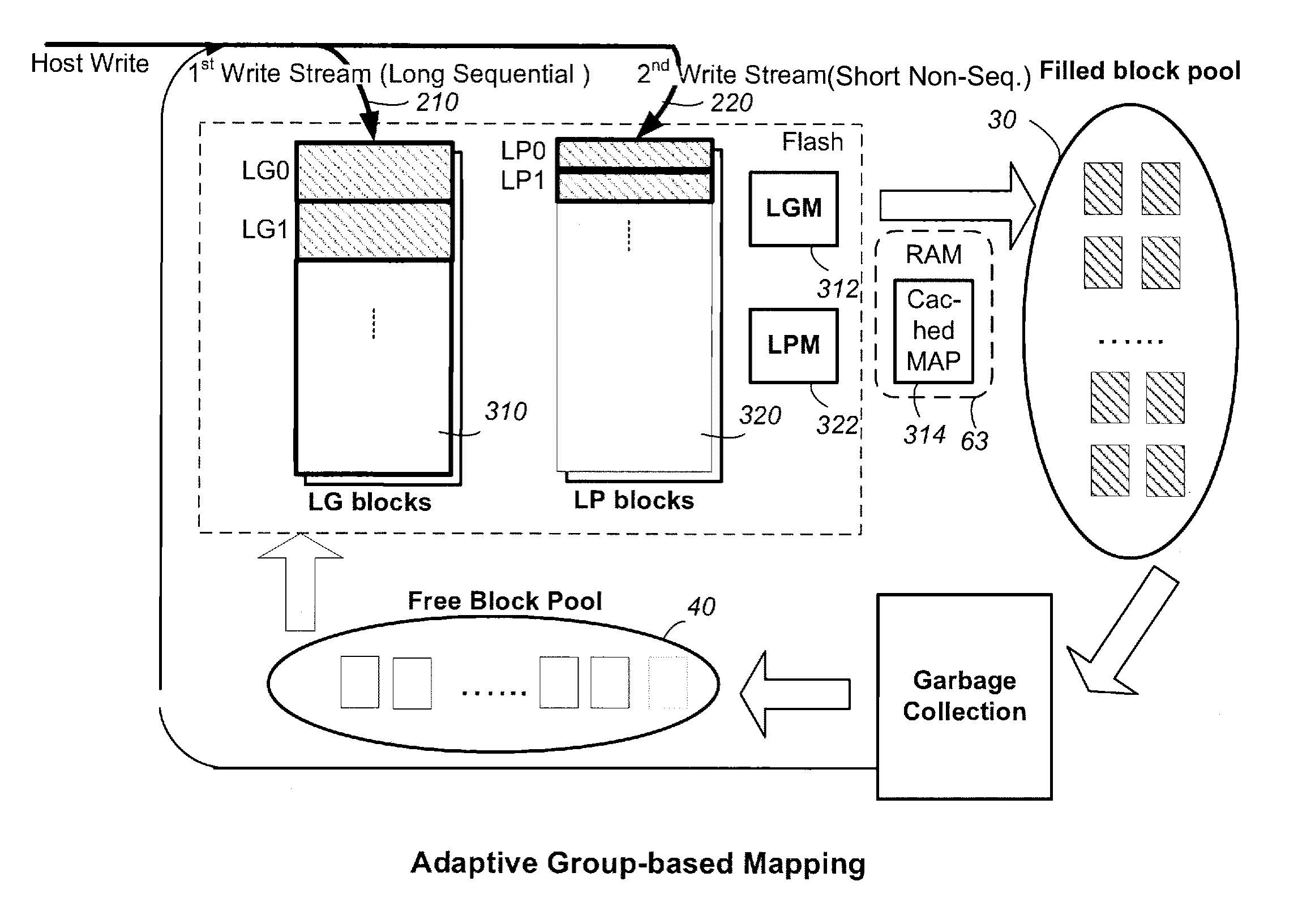

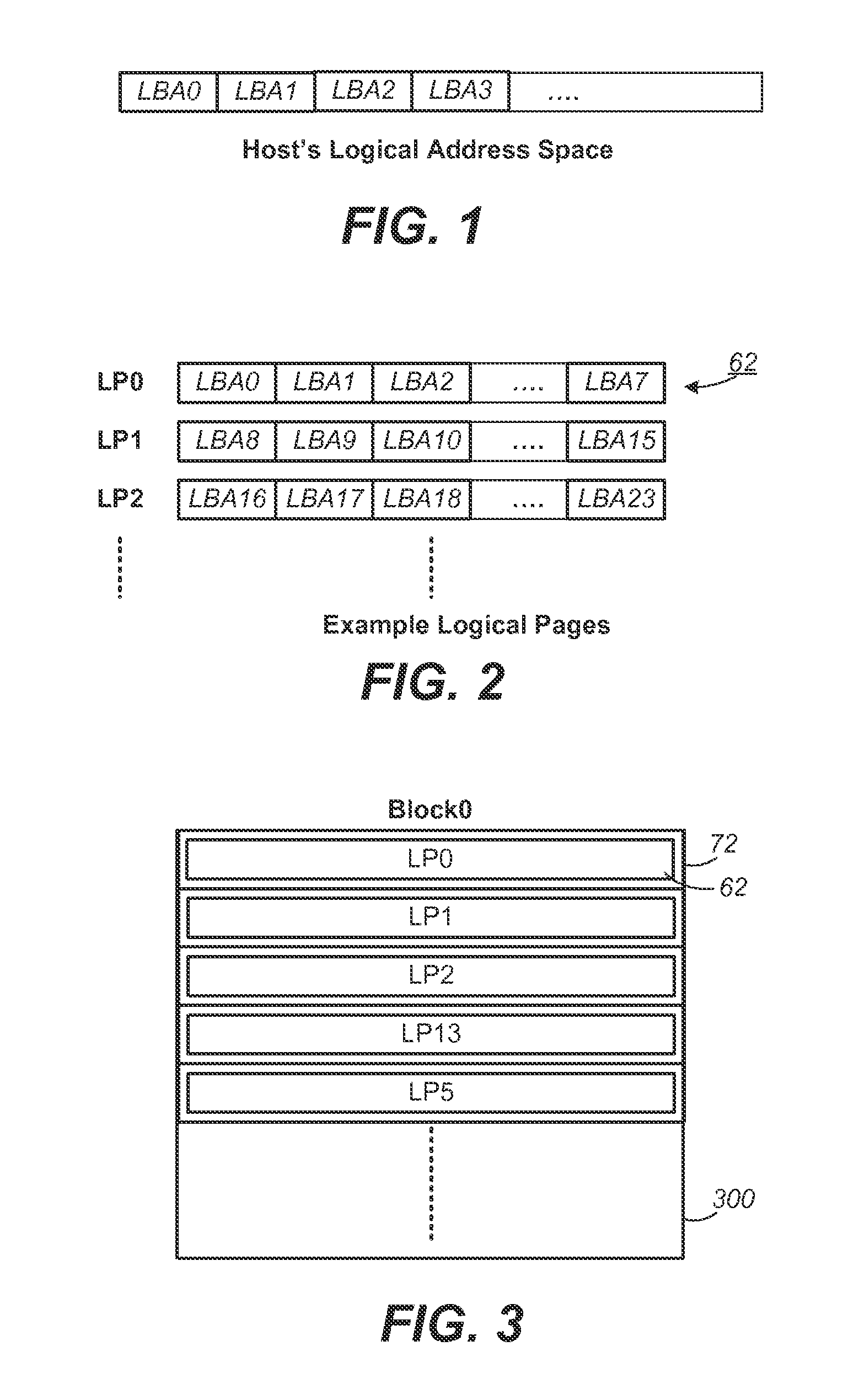

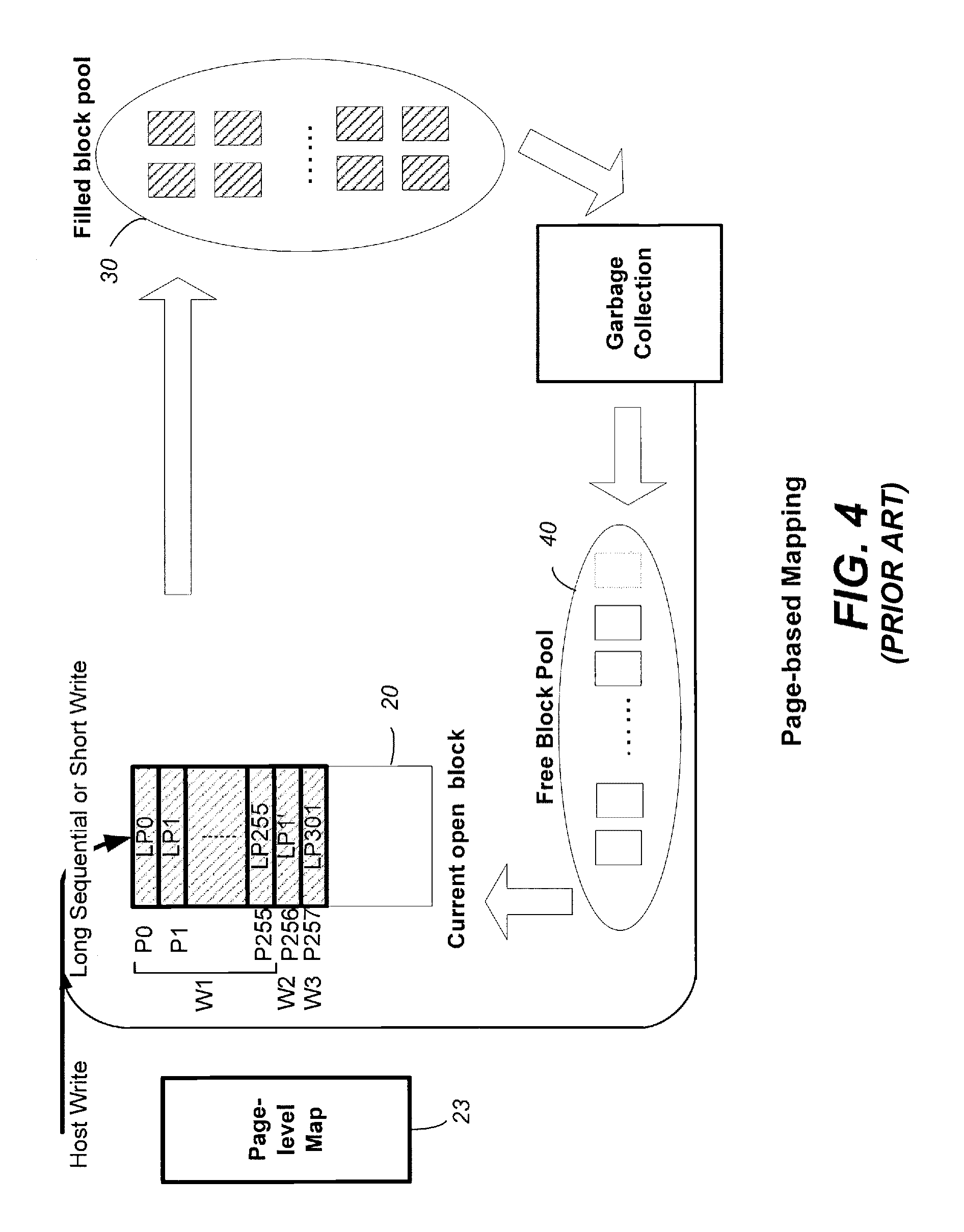

Non-volatile memory and method with adaptive logical groups

ActiveUS20150186270A1Small sizeReduce in quantityMemory architecture accessing/allocationMemory adressing/allocation/relocationPhysical addressSelf adaptive

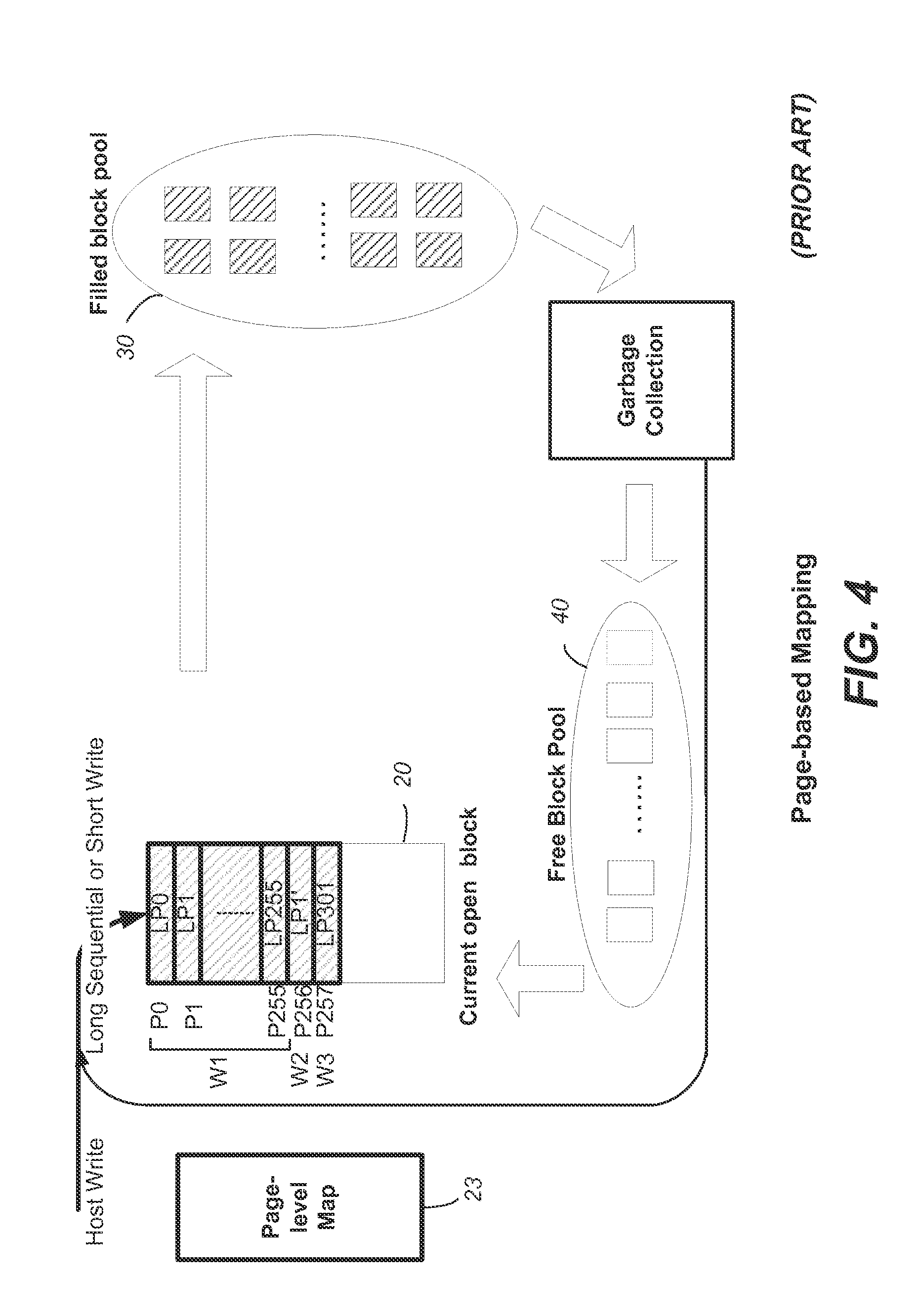

A nonvolatile memory is organized into blocks as erase units and physical pages as read / write units. A host addresses data by logical pages, which are storable in corresponding physical pages. Groups of logical pages are further aggregated into ogical groups as addressing units. The memory writes host data in either first or second write streams, writing to respective blocks either logical-group by logical-group or logical-page by logical-page in order to reduce the size of logical-to-physical-address maps that are cached in a controller RAM. Only one block at a time needs be open in the second stream to accept logical pages from multiple logical groups that are active. Garbage collection is performed on the blocks from each write stream independently without data copying between the two streams.

Owner:SANDISK TECH LLC

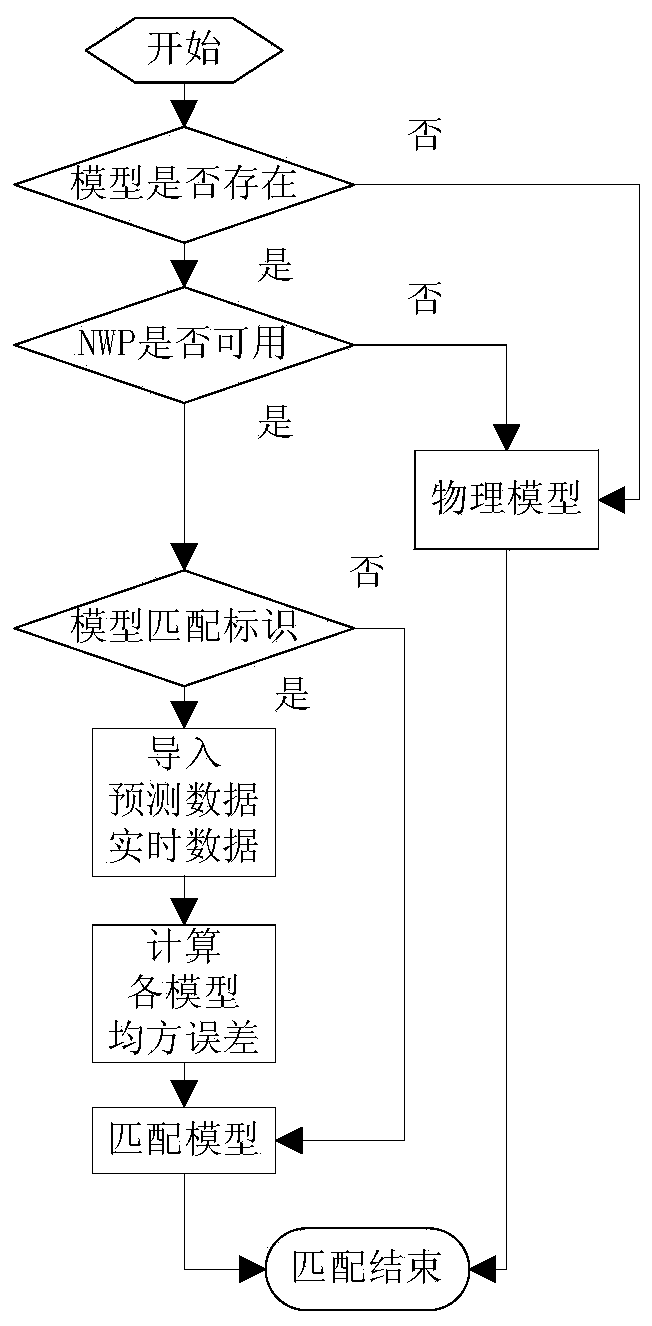

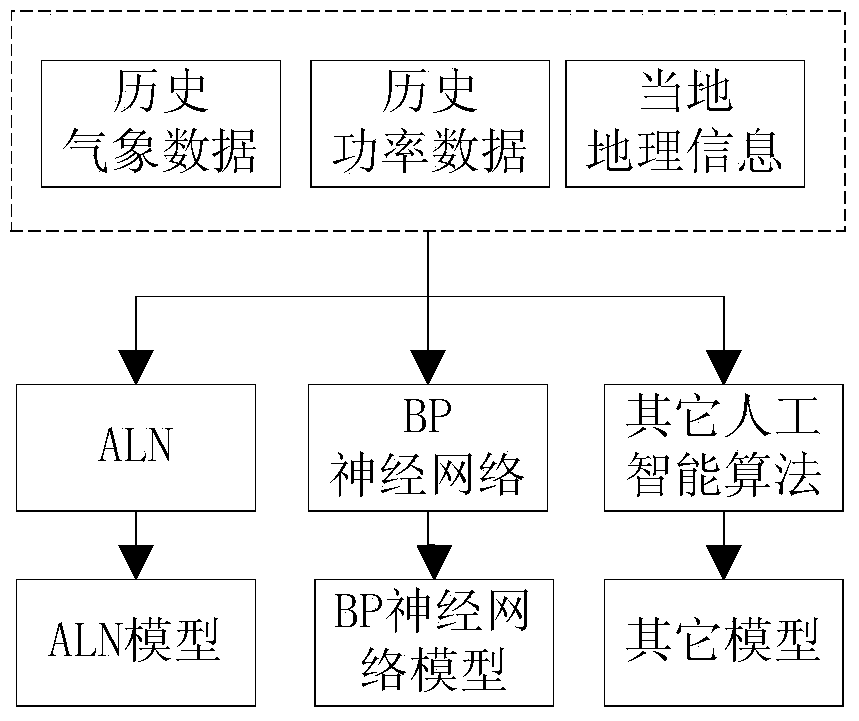

Wind and photovoltaic generation power prediction system with multiple prediction modes

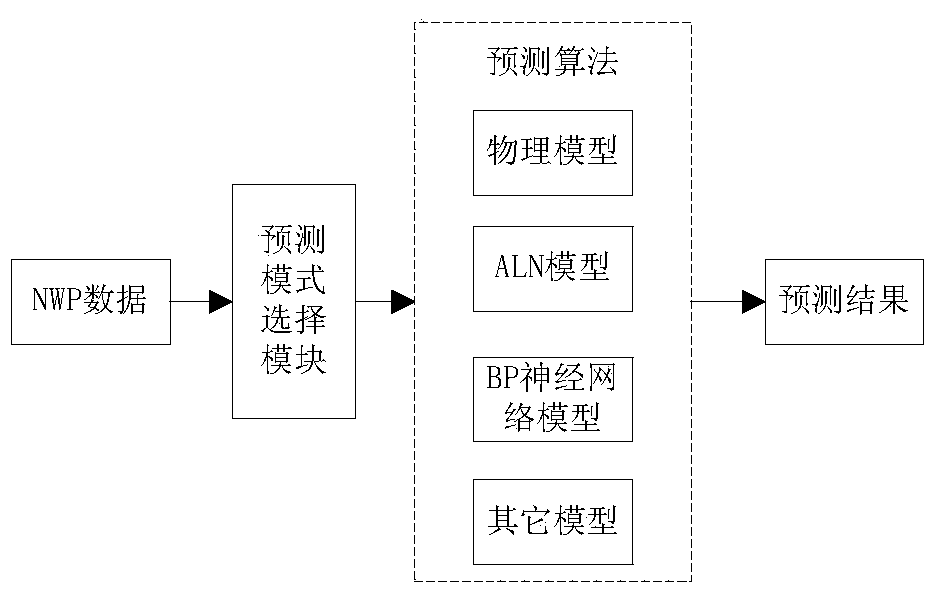

InactiveCN103699944APower Prediction GuaranteeCalculation speedForecastingPrediction algorithmsPredictive methods

The invention discloses a wind and photovoltaic generation power prediction system with multiple prediction modes. The system is characterized by comprising a numerical value weather prediction data acquisition module for inputting numerical value weather forecast data serving as basic data of a prediction algorithm, a prediction mode selection module used for selecting a proper prediction algorithm to predict the power of a wind power plant or a photovoltaic power plant, a prediction algorithm module used for predicting the power of the wind power plant or the photovoltaic power plant and comprising a physical model, an adaptive logic network algorithm model and a BP neural network model, and a prediction result storage module for storing result data predicted by the prediction algorithm module. According to the method, the numerical value weather forecast data is used as input data of the prediction algorithm, the most proper prediction method is selected through the mode selection module, and a power prediction result is obtained.

Owner:GUODIAN NANJING AUTOMATION

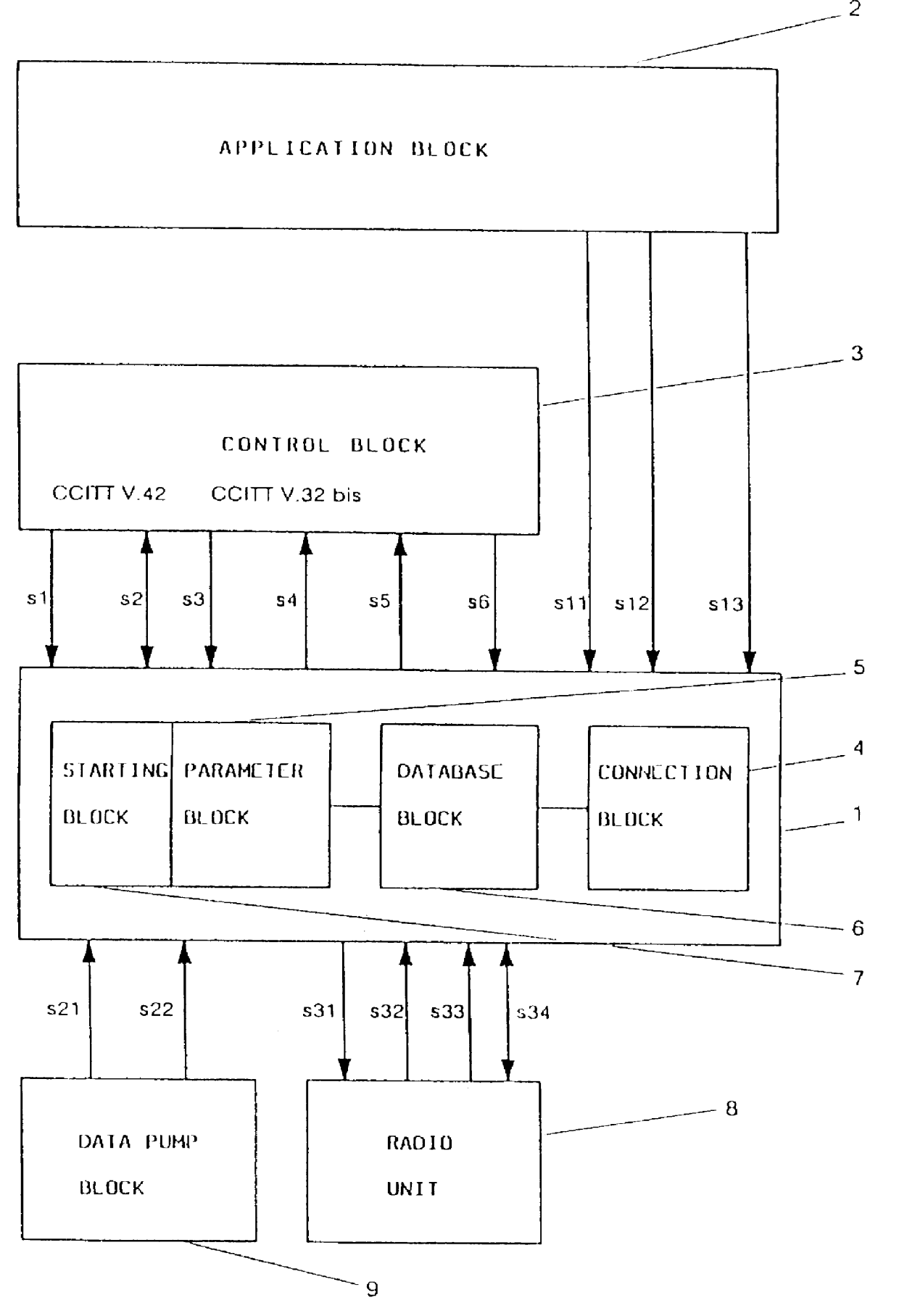

Method and equipment for the control of a data transfer connection

InactiveUS6067534AEstablishment and maintenance of the connection faster and more reliableDigital computer detailsTelephonic communicationModem deviceControl data

In data transfer connections with disturbances, e.g. in cellular networks, it is possible to establish and maintain an optimal connection using the solution according to the present invention. The optimal parameters for each data transfer connection are saved in the modem database. When the user next calls a number, the data of which has been saved, the parameters saved in the database are first used for the connection control. Interference occurring during the data transfer is handled with the help of the database with adaptive logic searching for the optimal data transfer rate and other connection parameters.

Owner:NOKIA TECHNOLOGLES OY

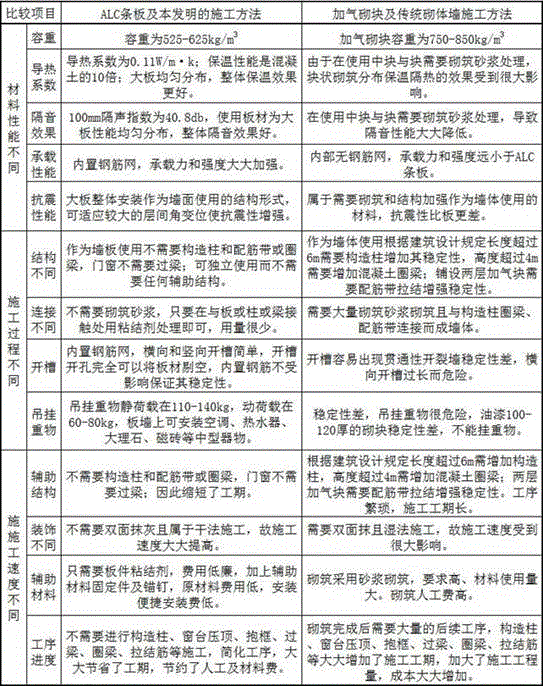

Construction method for fabricated type partition wall based on ALC board

The invention discloses a construction method for a fabricated type partition wall based on an ALC (Adaptive Logic Circuit) board, relating to the technical field of fabricated wall construction. According to the invention, the ALC board can be used in the frequently flooded or easily wetted places, such as a bathroom and a kitchen; in a construction process, no structural column or lintel is additionally arranged on the door and window parts; tools, materials and manpower are saved, so that the purposes of relieving labor intensity and shortening construction period can be achieved; the manual horizontal and longitudinal pressing manner is adopted for mounting battens, so that the combination between the binder and the panel as well as concrete surface is benefited, no higher stress exists on the wall and the joint after the binder is solidified and contracted and the possibility of generating cracks on the wall and the joint is greatly reduced; the anti-cracking treating step is performed at last and anti-cracking cloth is used for reinforcing the joint, so that the connecting effect of the joint is further guaranteed; the mounting for the ALC board is further adjusted and corrected in the construction process, so that the mounting precision of the wall is further guaranteed, the wall is prevented from cracking and the forming quality of the wall is promoted.

Owner:CHINA CONSTR SEVENTH ENG DIVISION CORP LTD

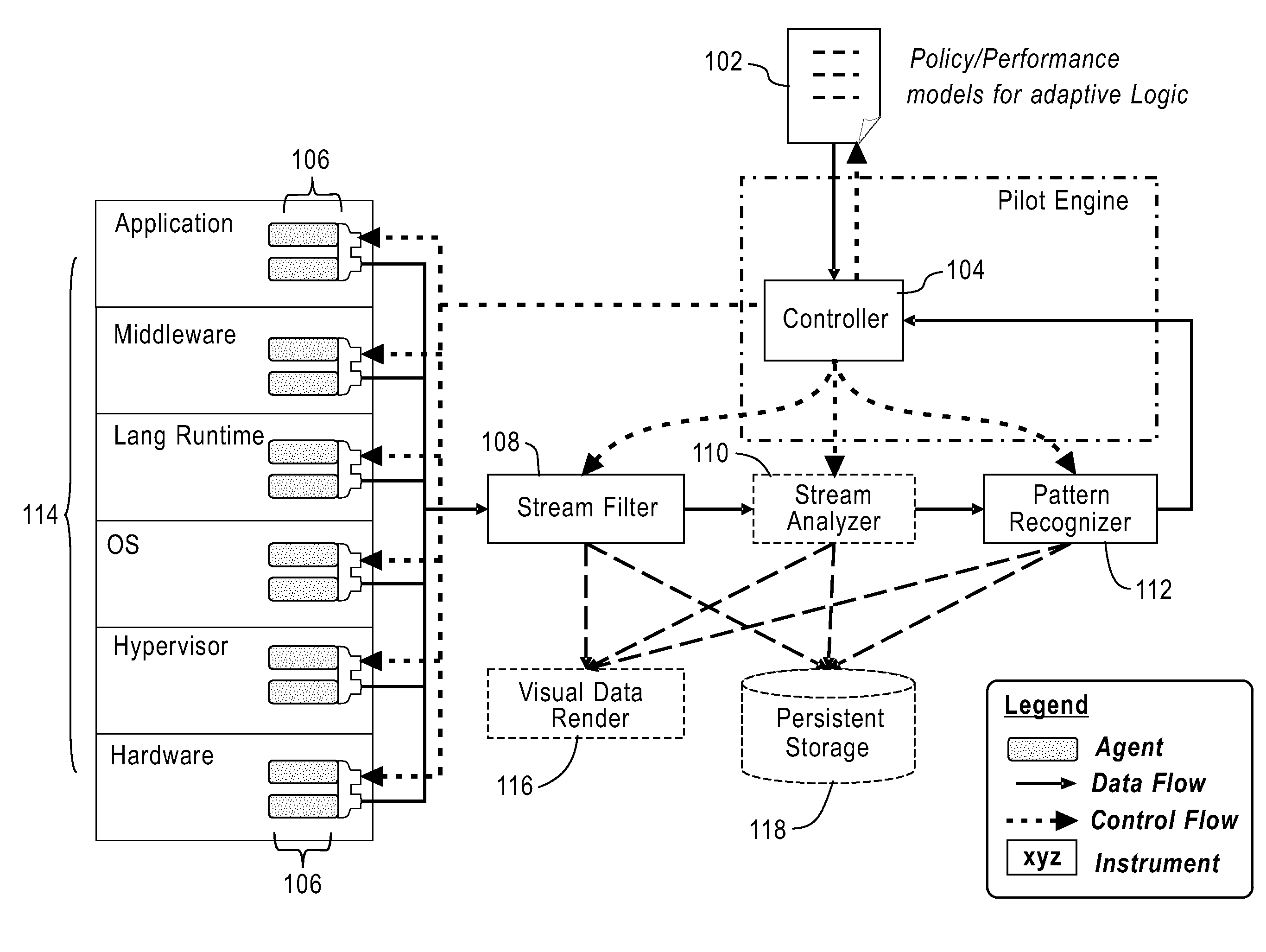

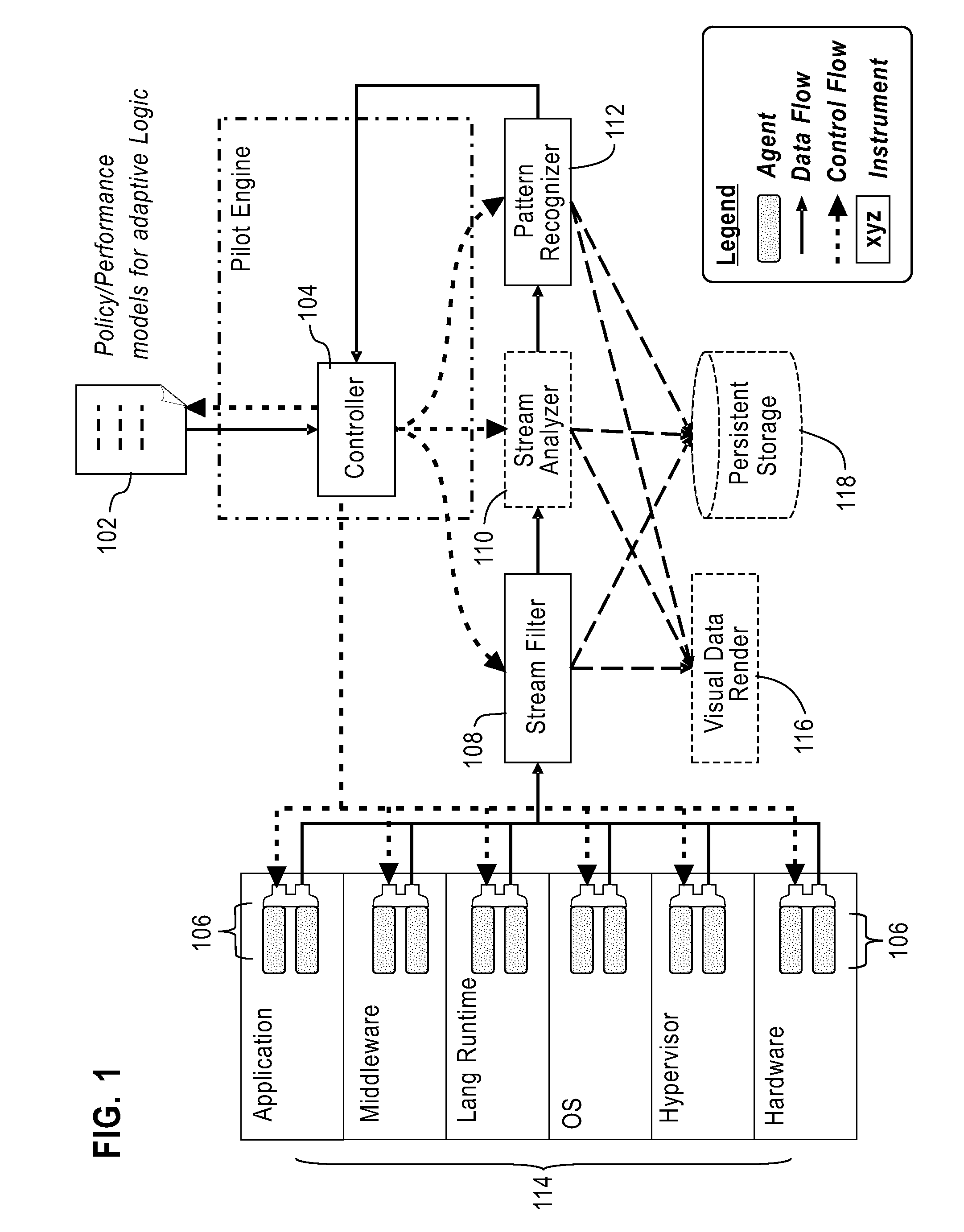

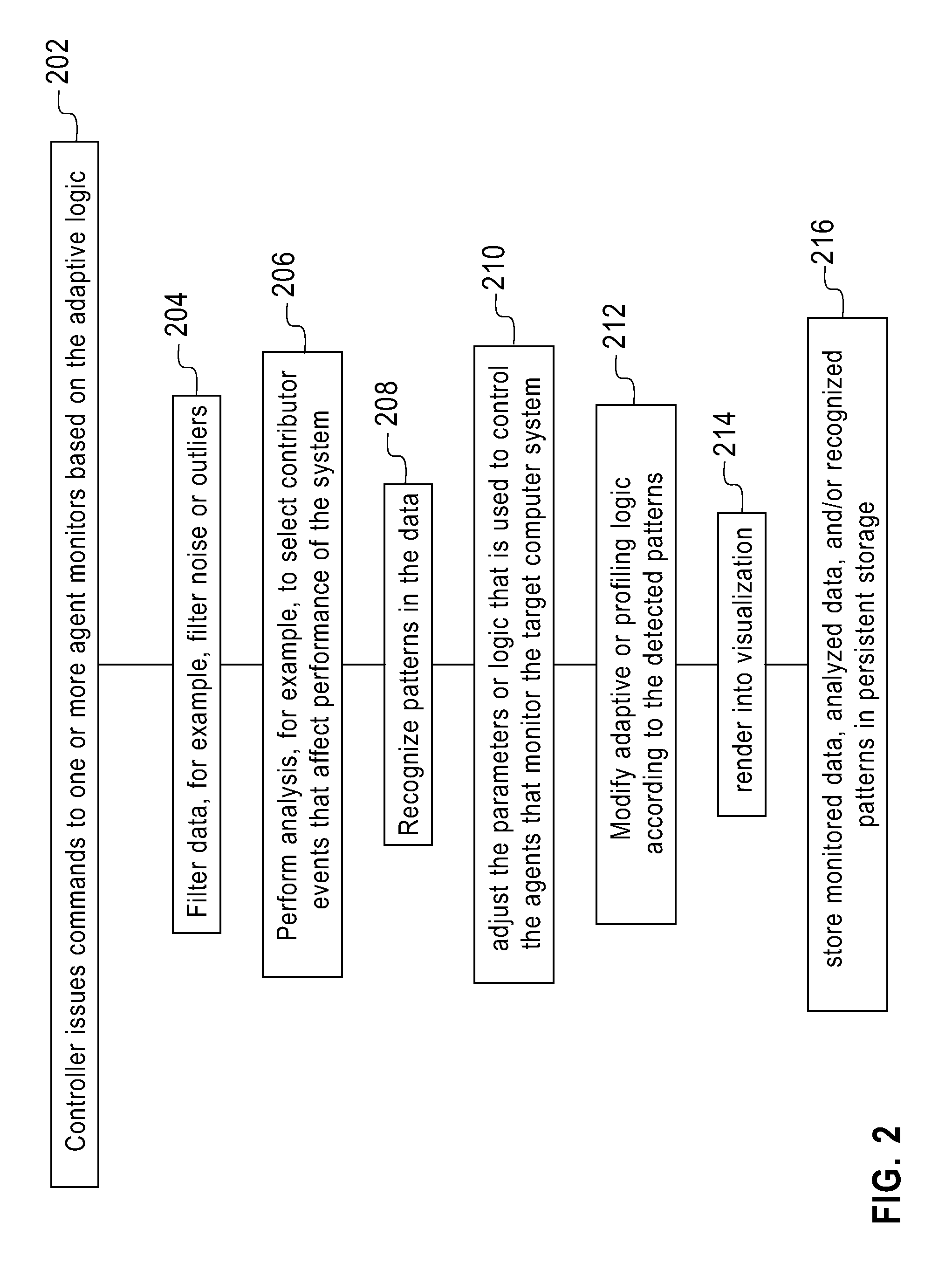

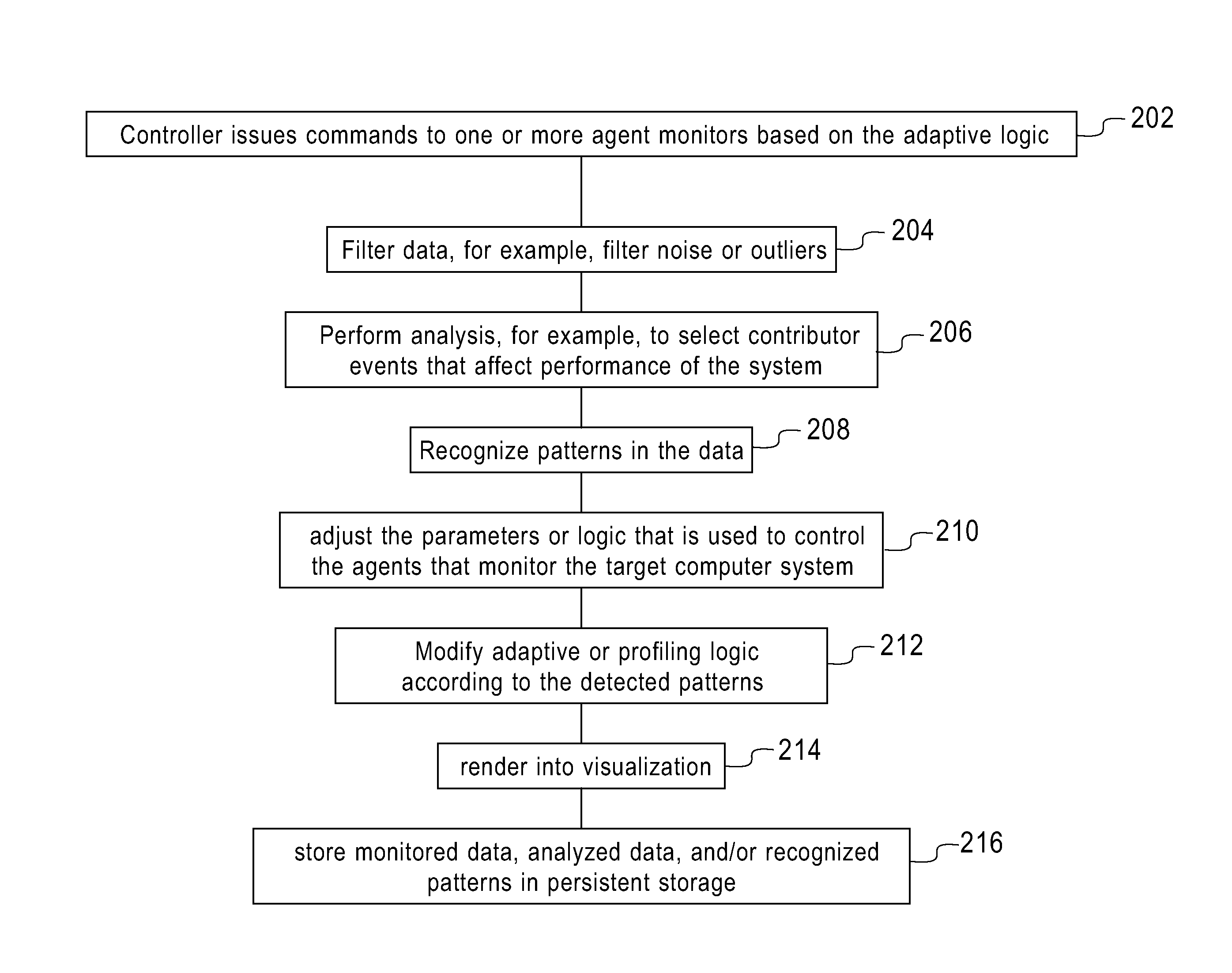

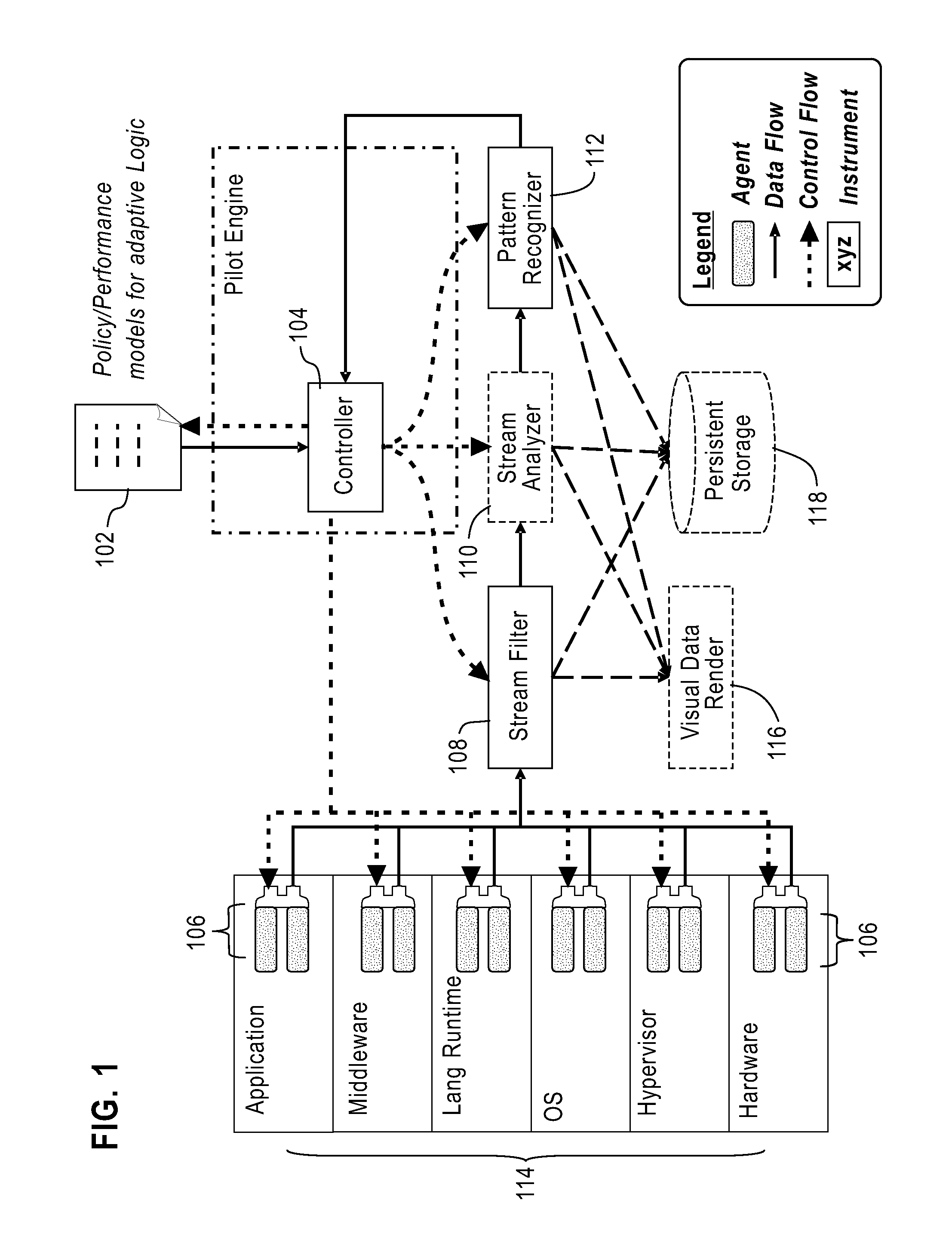

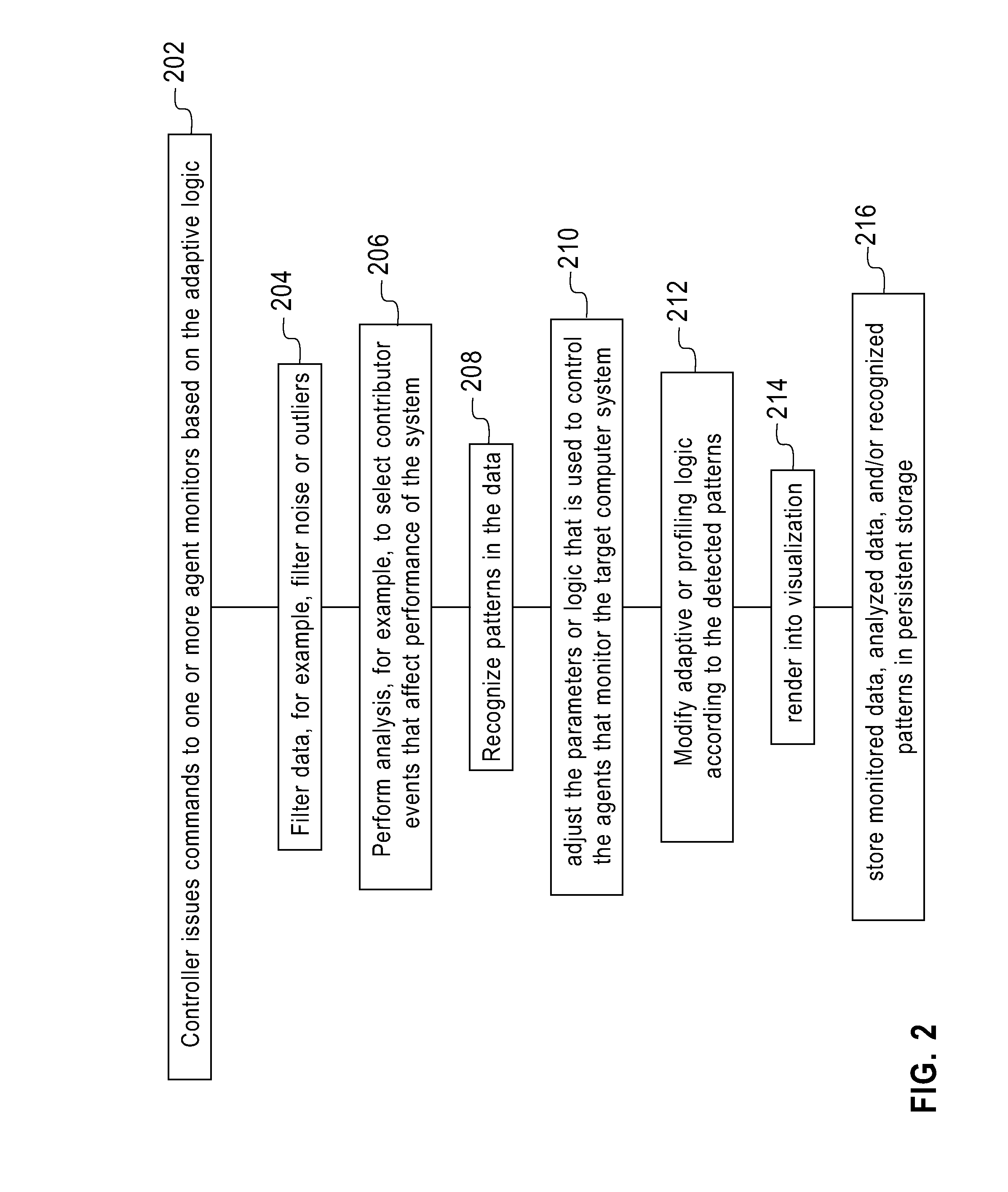

Mechanism for adaptive profiling for performance analysis

InactiveUS20090300166A1Error detection/correctionDigital computer detailsComputerized systemSelf adaptive

Adaptive profiling for performance analysis of a computer system controls one or more agents to monitor a plurality of events occurring in a target computer system based on an adaptive logic. Collected data may be filtered and analyzed to determine one or more contributor events that attribute to performance of the target computer system. One or more patterns are observed or detected in said collected data, behavior of said one or more agents are adjusted based on said detected one or more patterns. The adaptive logic may be further reconfigured based on said detected one or more patterns.

Owner:IBM CORP

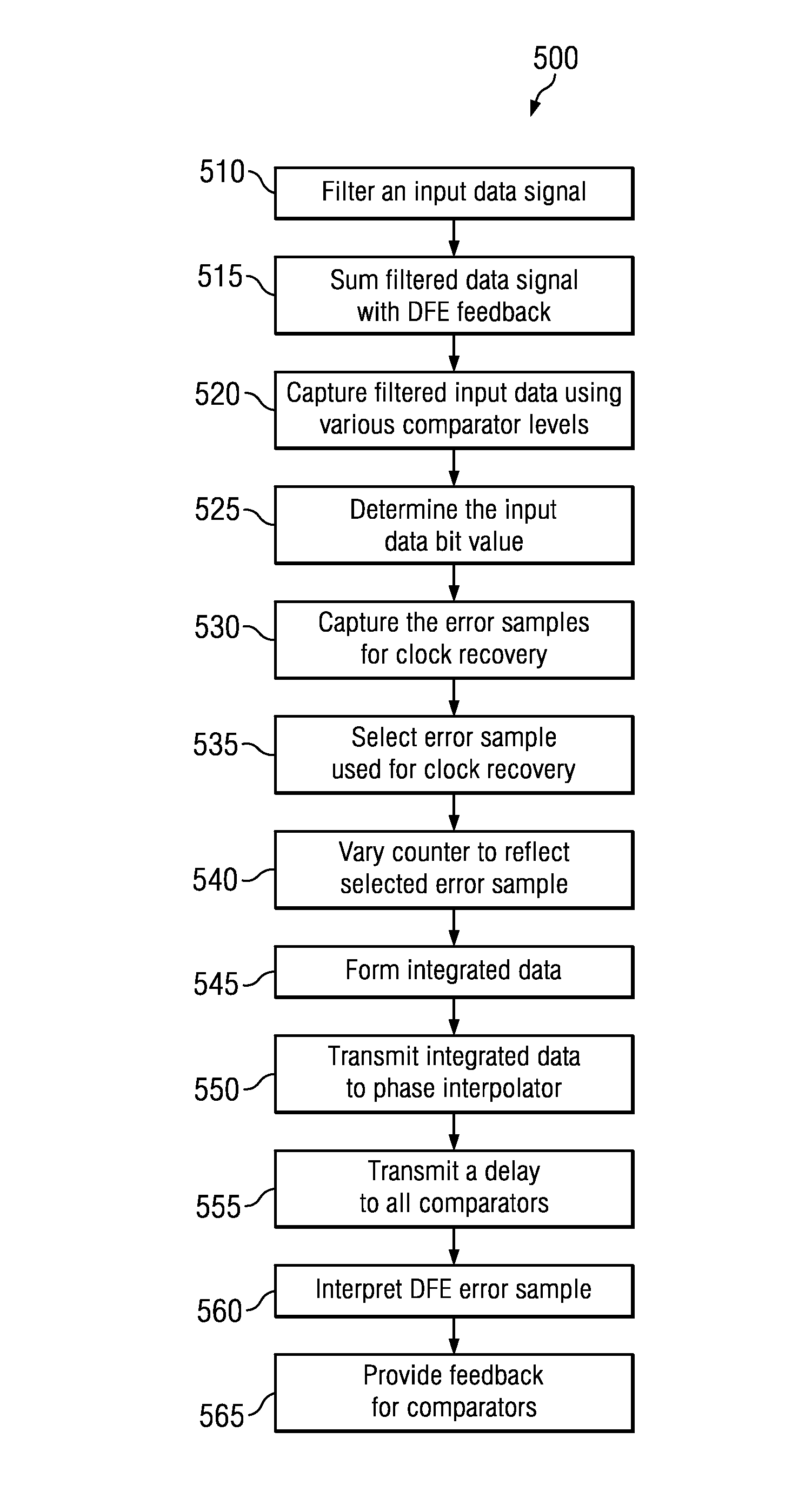

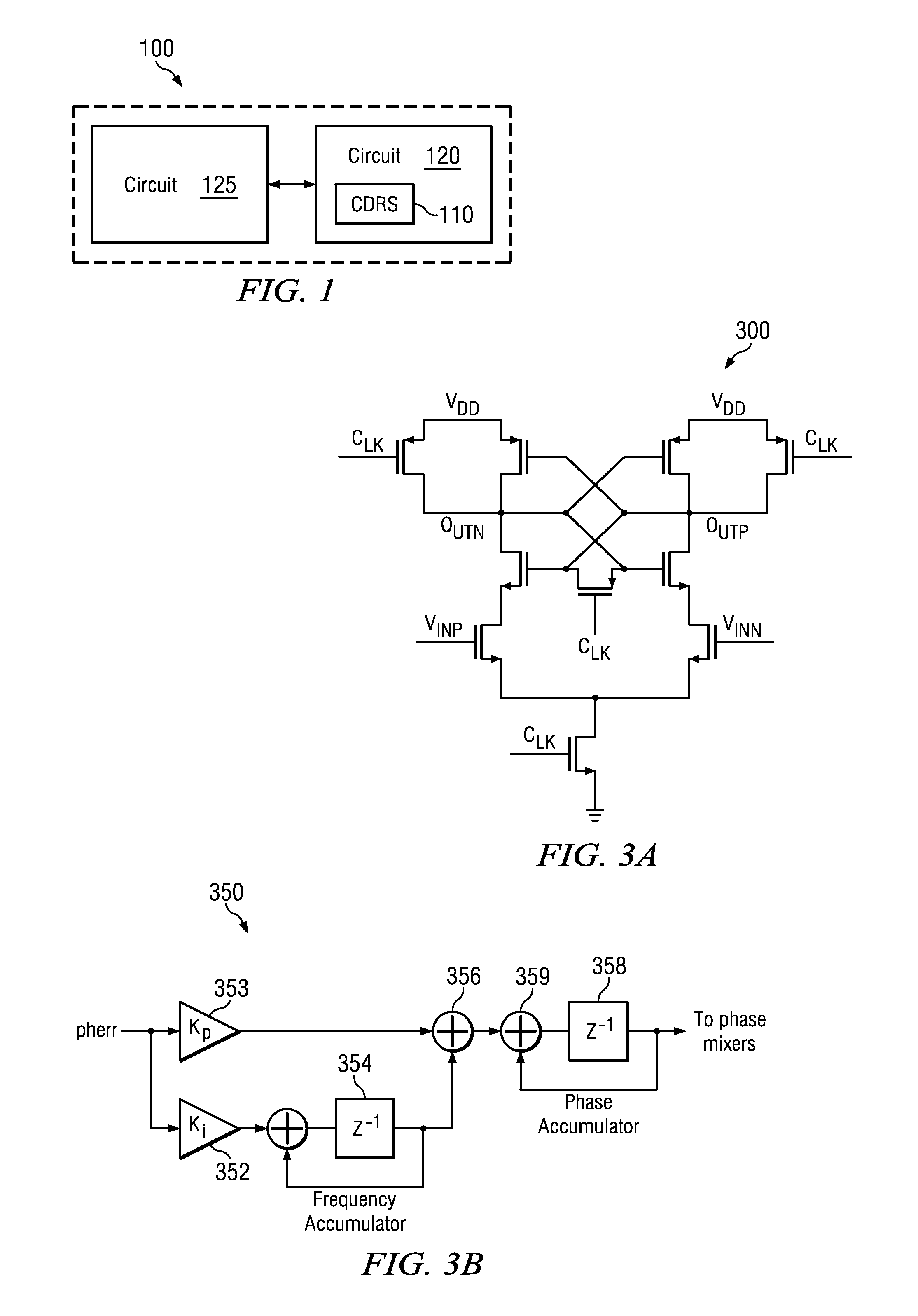

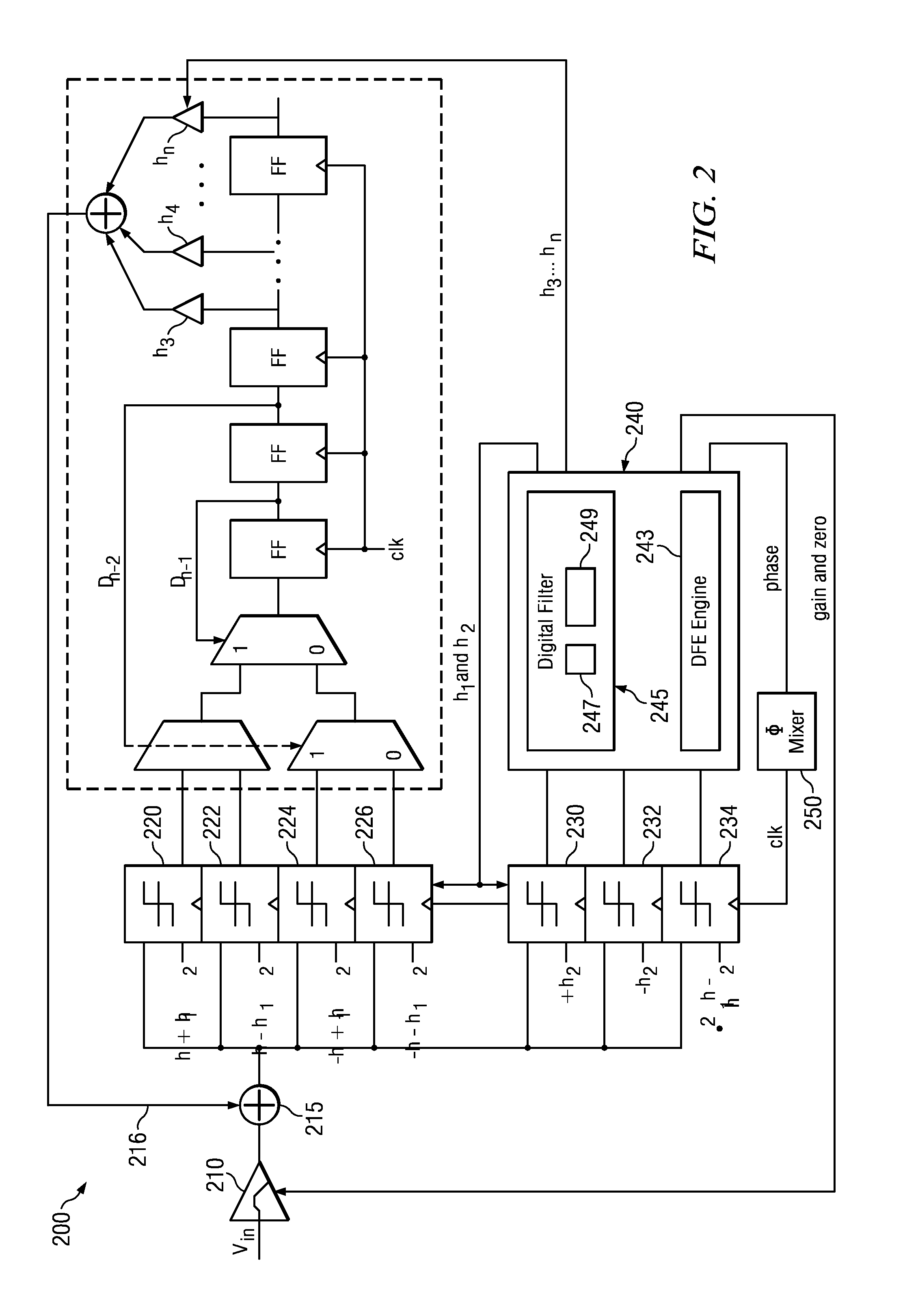

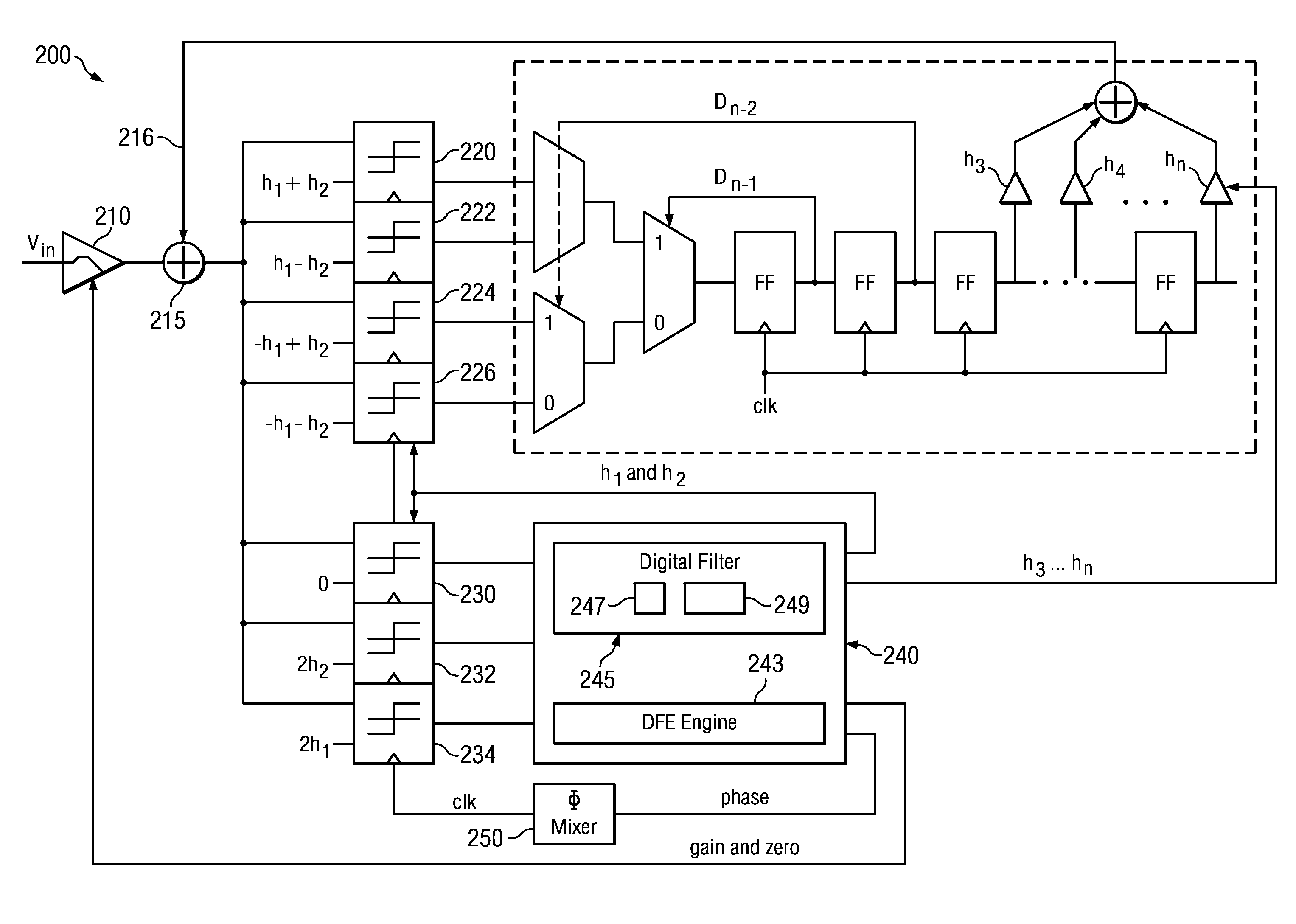

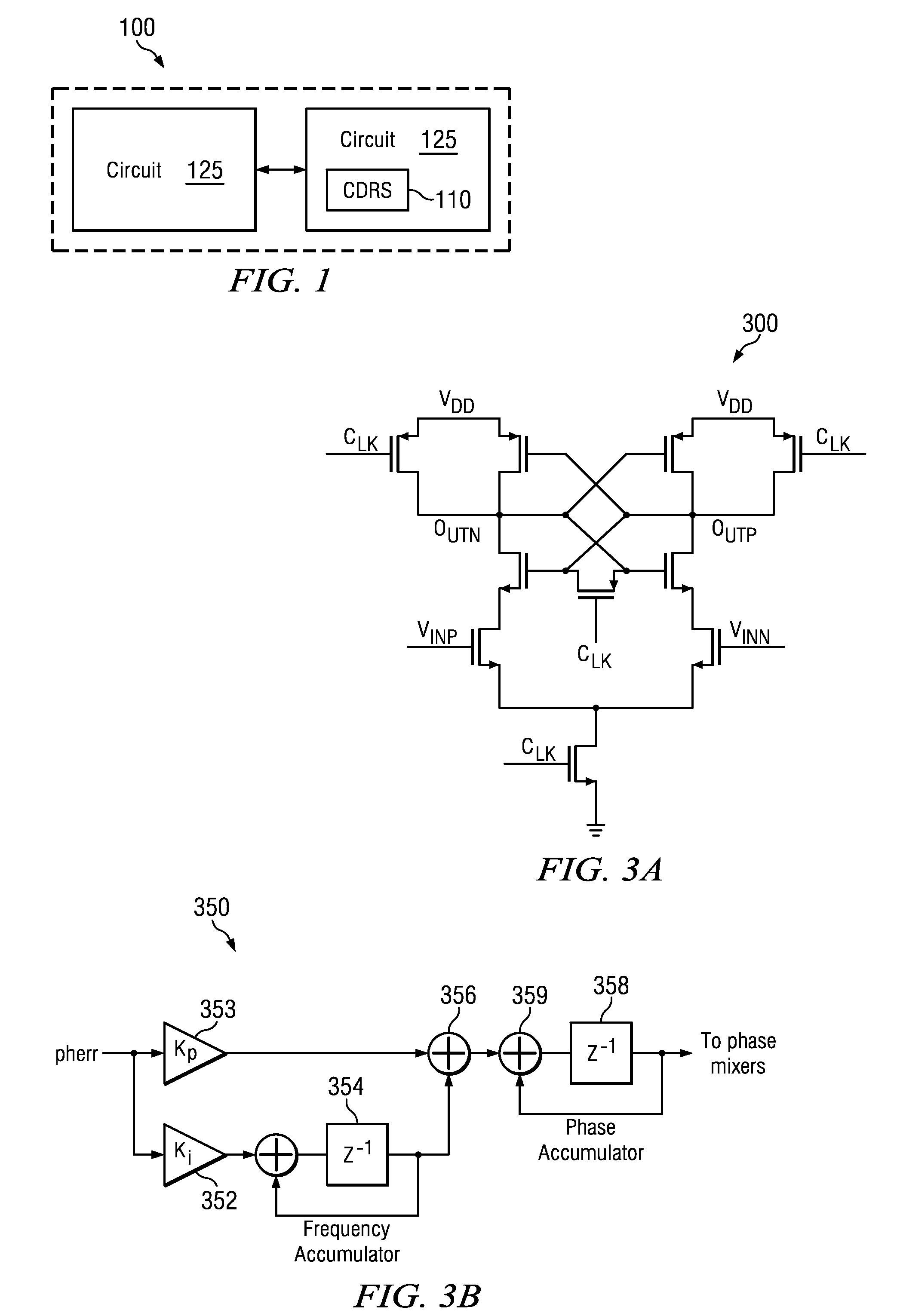

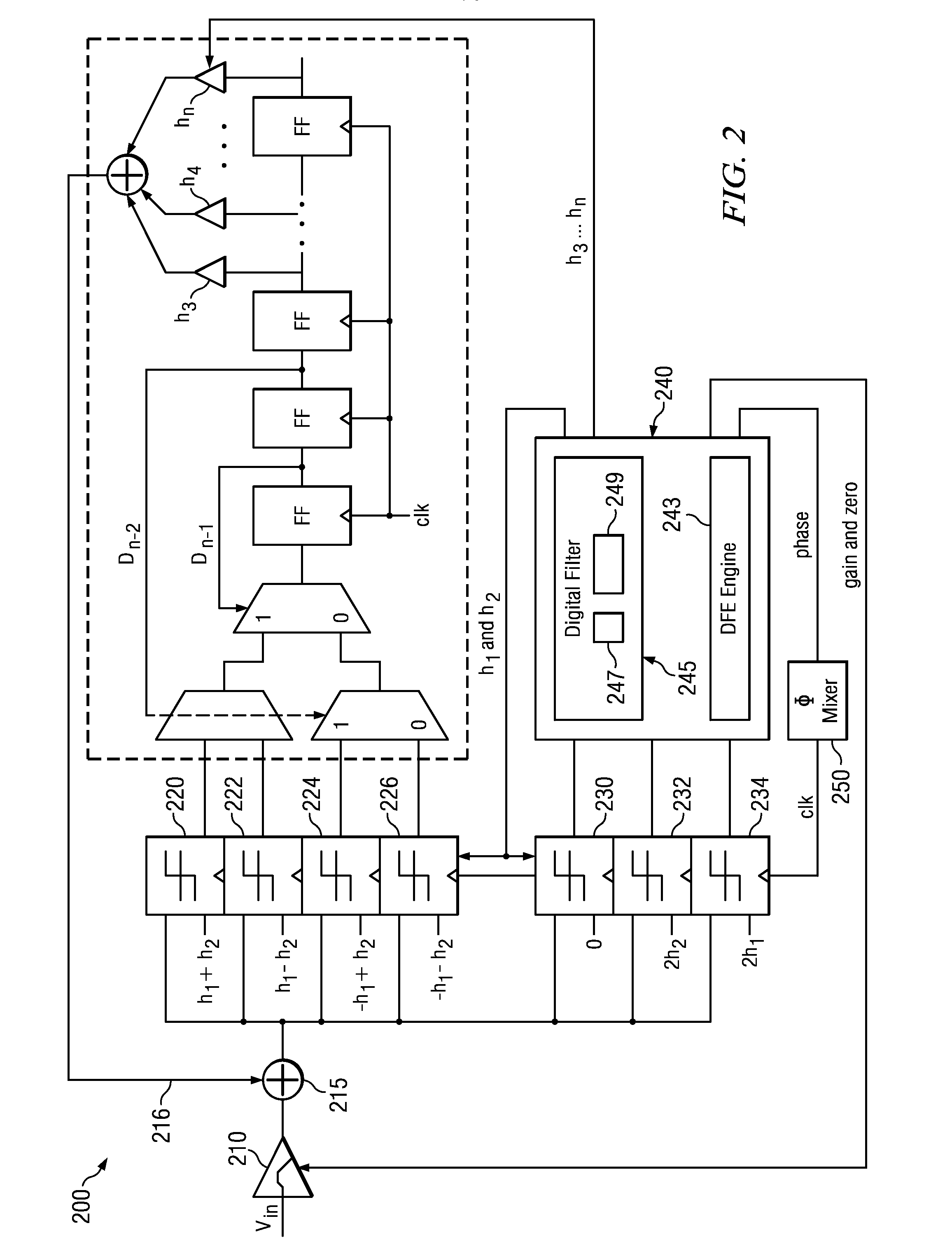

Clock Data Recovery System

A clock data recovery system is described. It includes a high pass filter for transmitting a filtered data signal in response to receiving an input data signal; an adder for summing the filtered data signal with a feedback signal, wherein the adder produces a summed input signal; a plurality of clocked data comparators for receiving the summed input signal, wherein the clocked data comparators determine an input data bit value; a plurality of clocked error comparators for receiving an error signal associated with clock recovery; an equalization and adaptation logic for selecting an error sample such that a phase associated with the error sample is locked at a second post cursor; and a phase mixer for transmitting a delay in response to receiving the phase and the delay is transmitted to the clocked-data comparators and the clocked-error comparators.

Owner:TEXAS INSTR INC

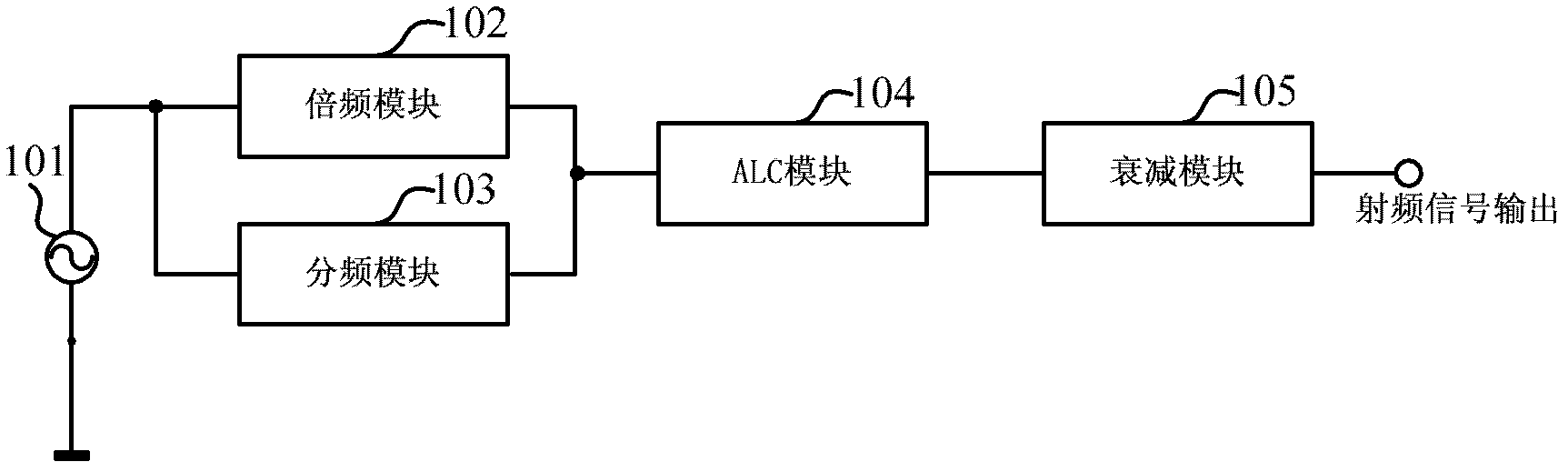

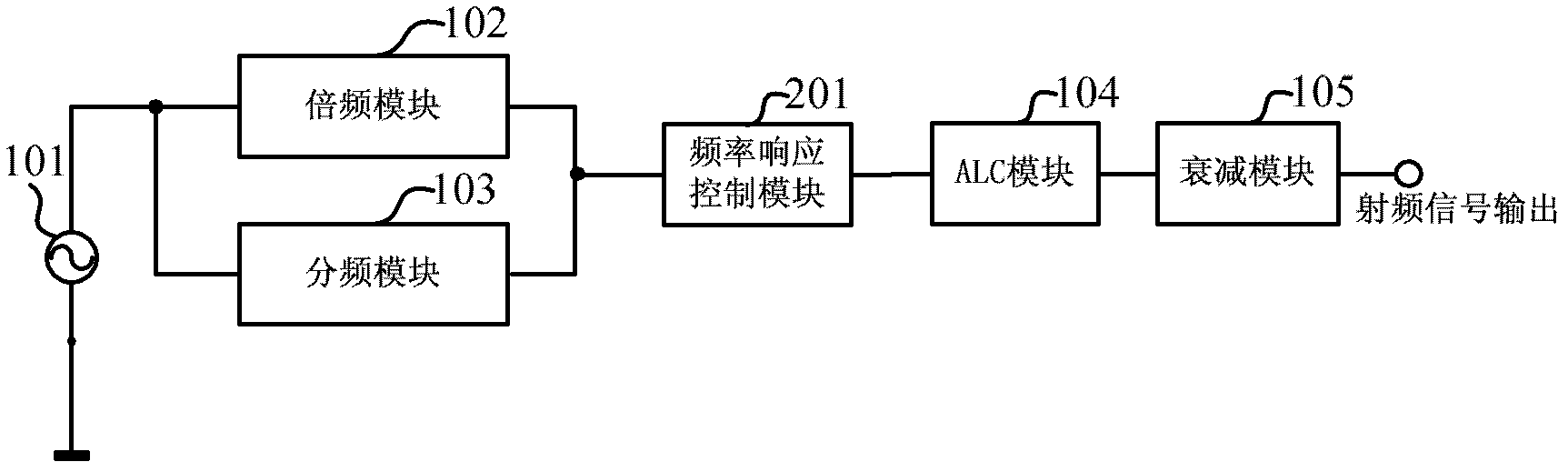

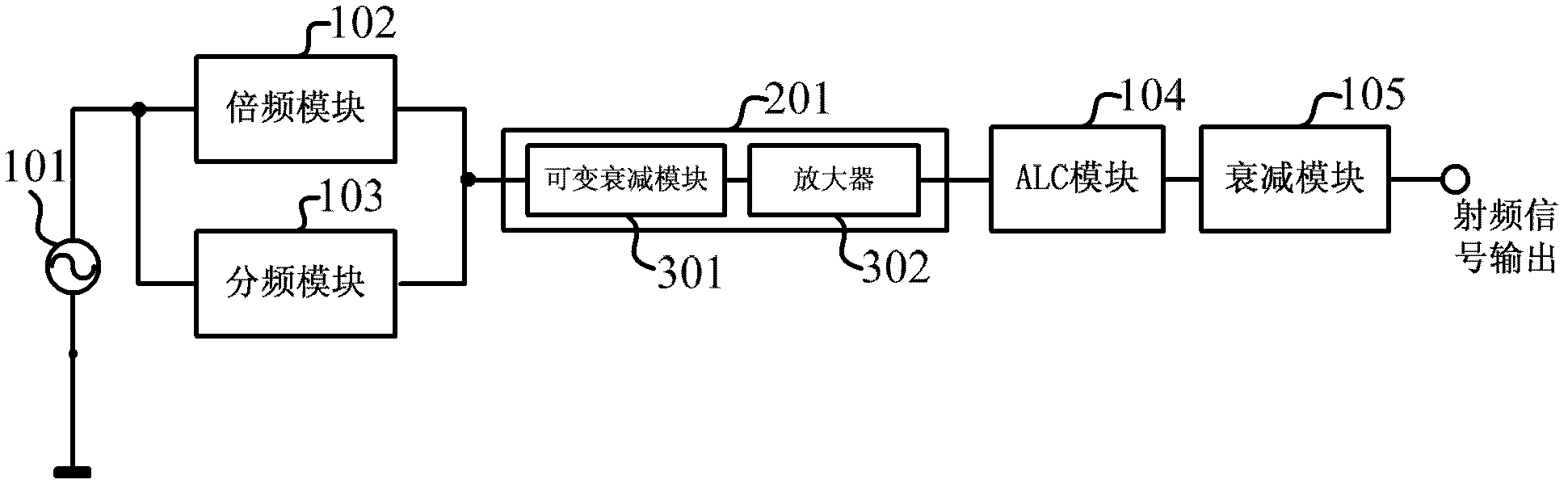

Radio frequency signal source

ActiveCN103178798AReduced dynamic range requirementsReduce design difficultyGain controlTransmissionUltrasound attenuationAudio power amplifier

The invention provides a radio frequency signal source which comprises a signal oscillator, a frequency multiplication module, a frequency demultiplication module, an Adaptive Logic Circuit (ALC) module, an attenuation module and a frequency response control module, wherein the signal input end of the frequency response control module is connected with the output end of the frequency multiplication module and the output end of the frequency demultiplication module, and the signal output end of the frequency response control module is connected with the input end of the ALC module. The frequency response control module comprises a changeable attenuation module and an amplifier, wherein the changeable attenuation module receives input signals and is used for adjusting the amplitude of the input signals to be in a preset range; and the signal input end of the amplifier is connected with the output end of the changeable attenuation module, and the amplifier is used for compensating inserting loss of the changeable attenuation module. The radio frequency signal source can adjust frequency response caused by radio frequency link by being additionally provided with the frequency response control module, greatly reduces requirements for ALC dynamic range, reduces design difficulty and saves design and debugging time.

Owner:RIGOL

Clock Data Recovery System

A clock data recovery system is described. It includes a high pass filter for transmitting a filtered data signal in response to receiving an input data signal; an adder for summing the filtered data signal with a feedback signal, wherein the adder produces a summed input signal; a plurality of clocked data comparators for receiving the summed input signal, wherein the clocked data comparators determine an input data bit value; a plurality of clocked error comparators for receiving an error signal associated with clock recovery and DFE tap adaption; an equalization and adaptation logic for selecting an error sample such that a phase associated with the error sample is locked at h0=h1+h2; and a phase mixer for transmitting a delay in response to receiving the phase and the delay is transmitted to the clocked-data comparators and the clocked-error comparators.

Owner:TEXAS INSTR INC

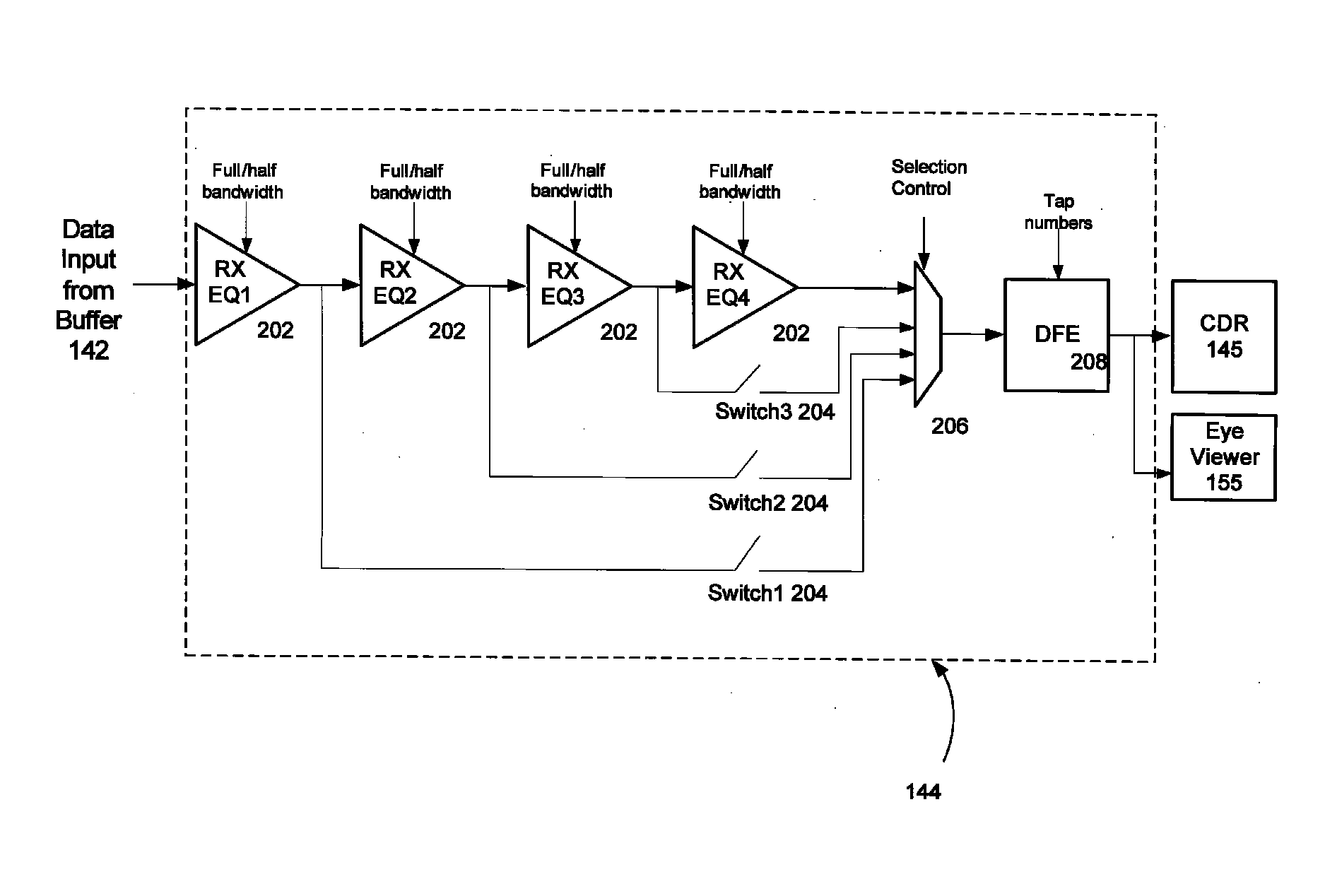

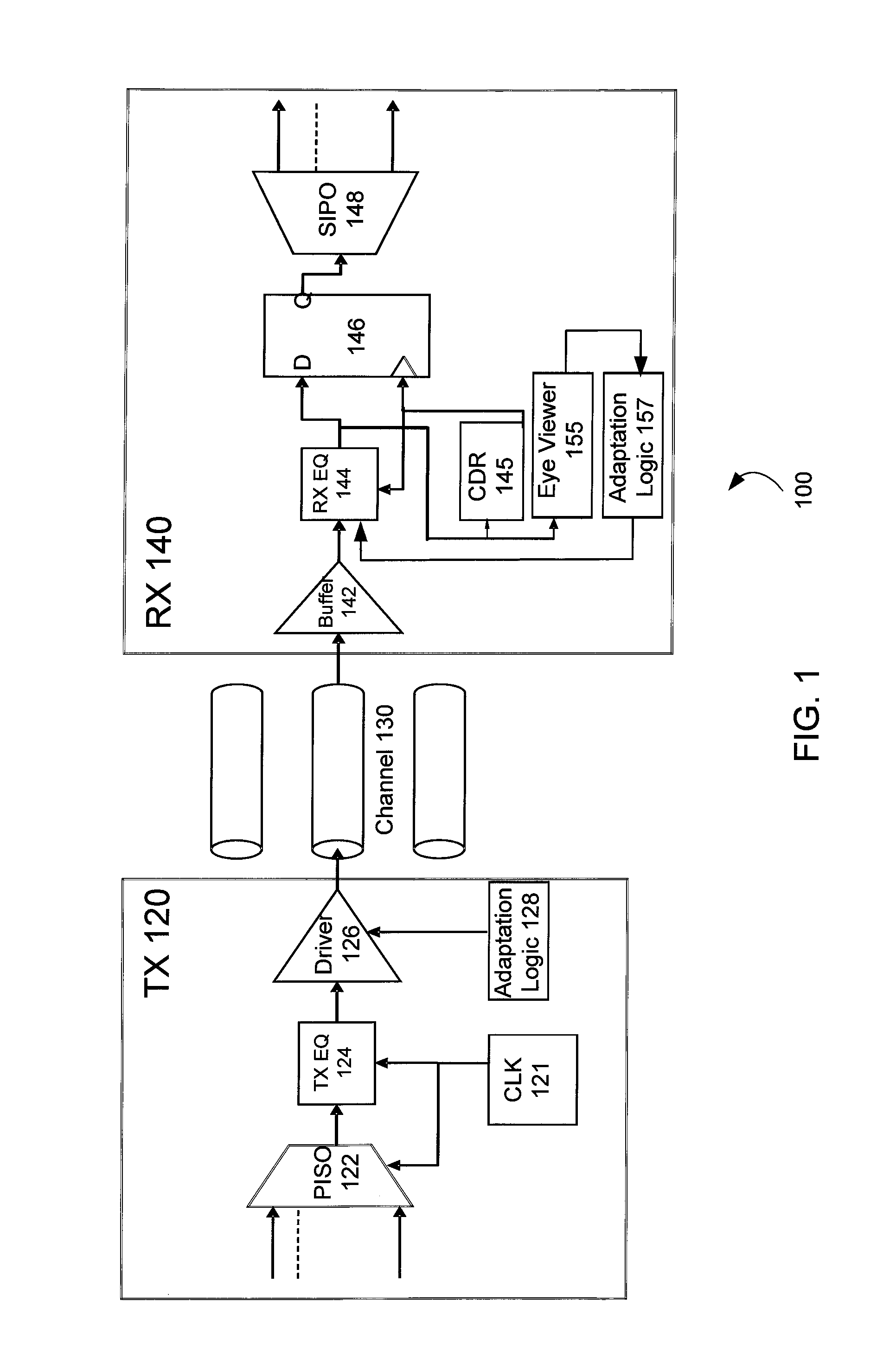

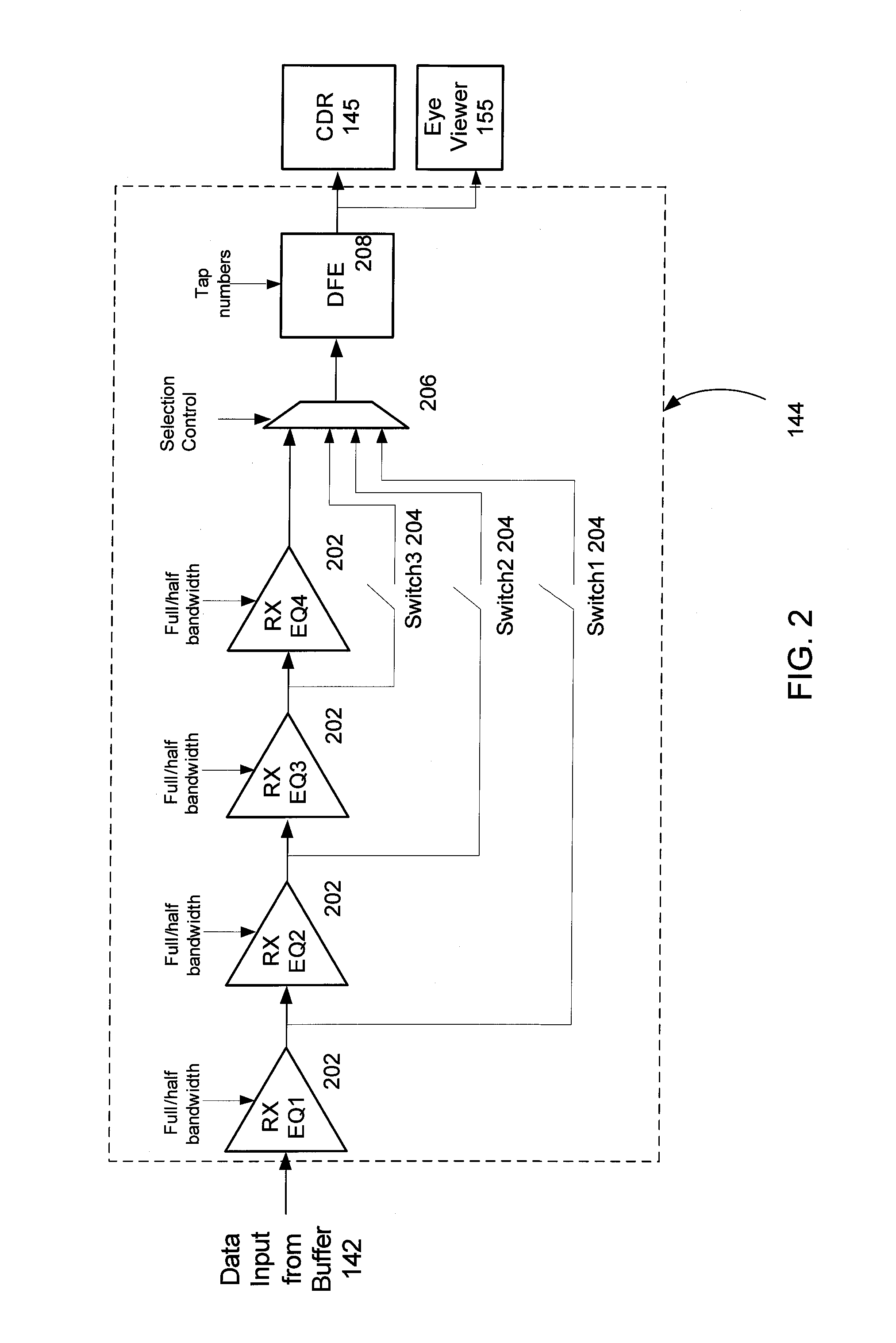

Apparatus and methods for transceiver power adaptation

ActiveUS8611403B1Differential output voltage is increasedDigital data processing detailsDuplex signal operationTransceiverData signal

Disclosed are apparatus and methods to advantageously manage transceiver power in an automated manner using adaptation logic that may be implemented on a same integrated circuit as the transceiver circuitry. In one embodiment, a power-consuming component of the transceiver is turned on at a lowest power setting. A determination is made as to whether a first set of eye opening data for a serial data signal meets preset criteria. If the preset criteria are not met by the first set of eye opening data, then the power-consuming component is changed to a second lowest power setting. Another embodiment relates to an integrated circuit including a receiver buffer, a receiver equalization circuit, an eye viewer circuit and adaptation logic. The adaptation logic is configured to obtain the eye opening data and to adapt the receiver equalization circuit to conserve power used. Other embodiments, aspects and features are also disclosed.

Owner:ALTERA CORP

Adaptive Logical Group Sorting to Prevent Drive Fragmentation

A method and system are disclosed for controlling the storage of data in a storage device to reduce fragmentation. The method may include a controller of a storage device receiving data for storage in non-volatile memory and determining if a threshold amount of data has been received. When the threshold amount of data is received, the non-volatile memory is scanned for sequentially numbered logical groups of data previously written in noncontiguous locations in the non-volatile memory. When a threshold amount of such sequentially numbered logical groups is found, the controller re-writes the sequentially numbered logical groups of data contiguously into a new block. The system may include a storage device with a controller configured to perform the method noted above, where the thresholds for scanning the memory for fragmented data and removing fragmentation by re-writing the fragmented data into new blocks may be fixed or variable.

Owner:SANDISK TECH LLC

Non-volatile memory and method with adaptive logical groups

ActiveUS9466383B2Small sizeReduce in quantityMemory architecture accessing/allocationMemory adressing/allocation/relocationRandom access memoryPhysical address

A nonvolatile memory is organized into blocks as erase units and physical pages as read / write units. A host addresses data by logical pages, which are storable in corresponding physical pages. Groups of logical pages may be further aggregated into logical groups as addressing units. The memory writes host data in either first or second write streams, writing to respective blocks either logical-group by logical-group or logical-page by logical-page in order to reduce the size of logical-to-physical-address maps that are cached in a controller random-access memory (RAM). A group-level map may be used to track logical groups. A page-level map may be used to track logical pages. Only one block at a time needs be open in the second stream to accept logical pages from multiple logical groups that are active. Garbage collection is performed on the blocks from each write stream independently without data copying between the two streams.

Owner:SANDISK TECH LLC

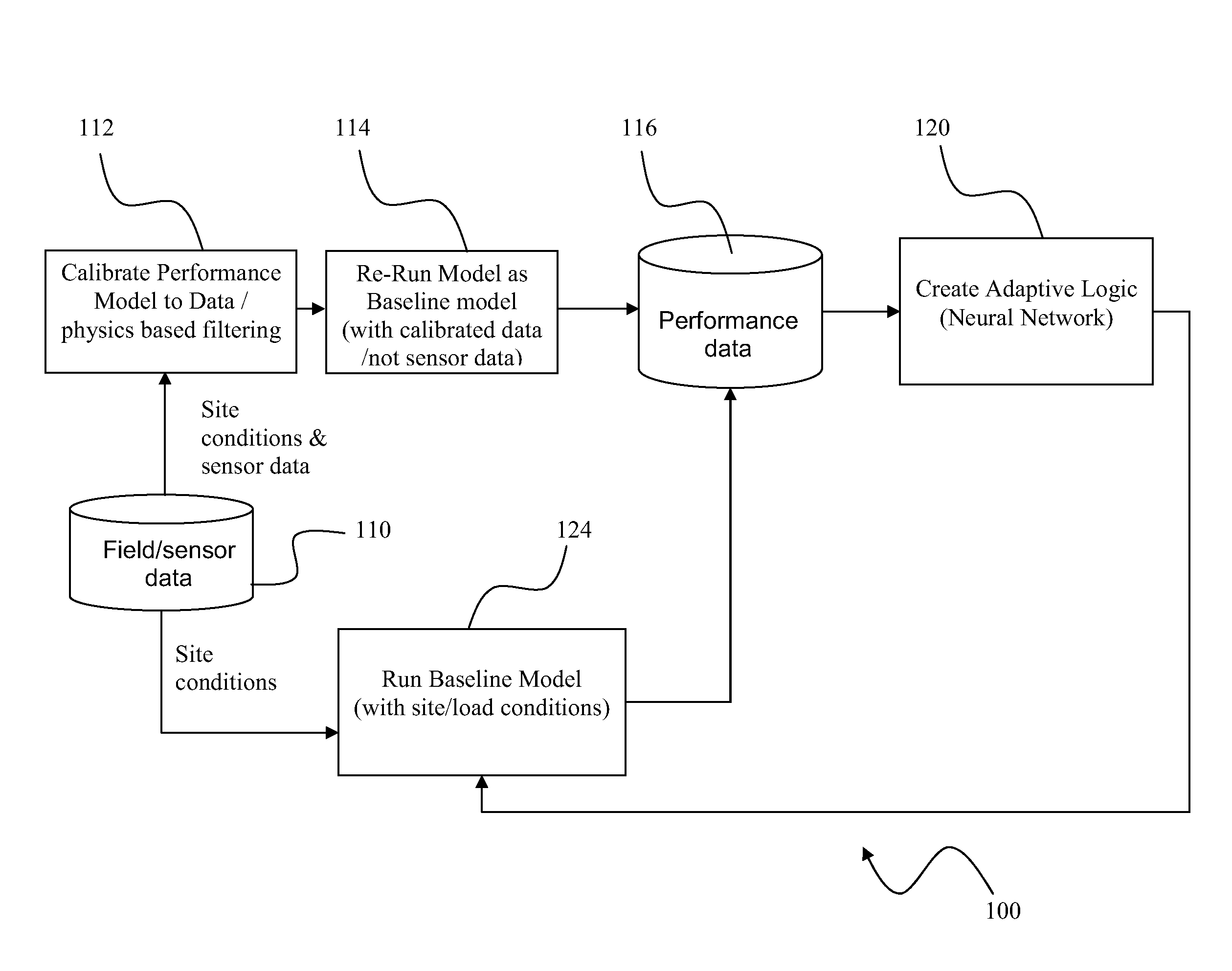

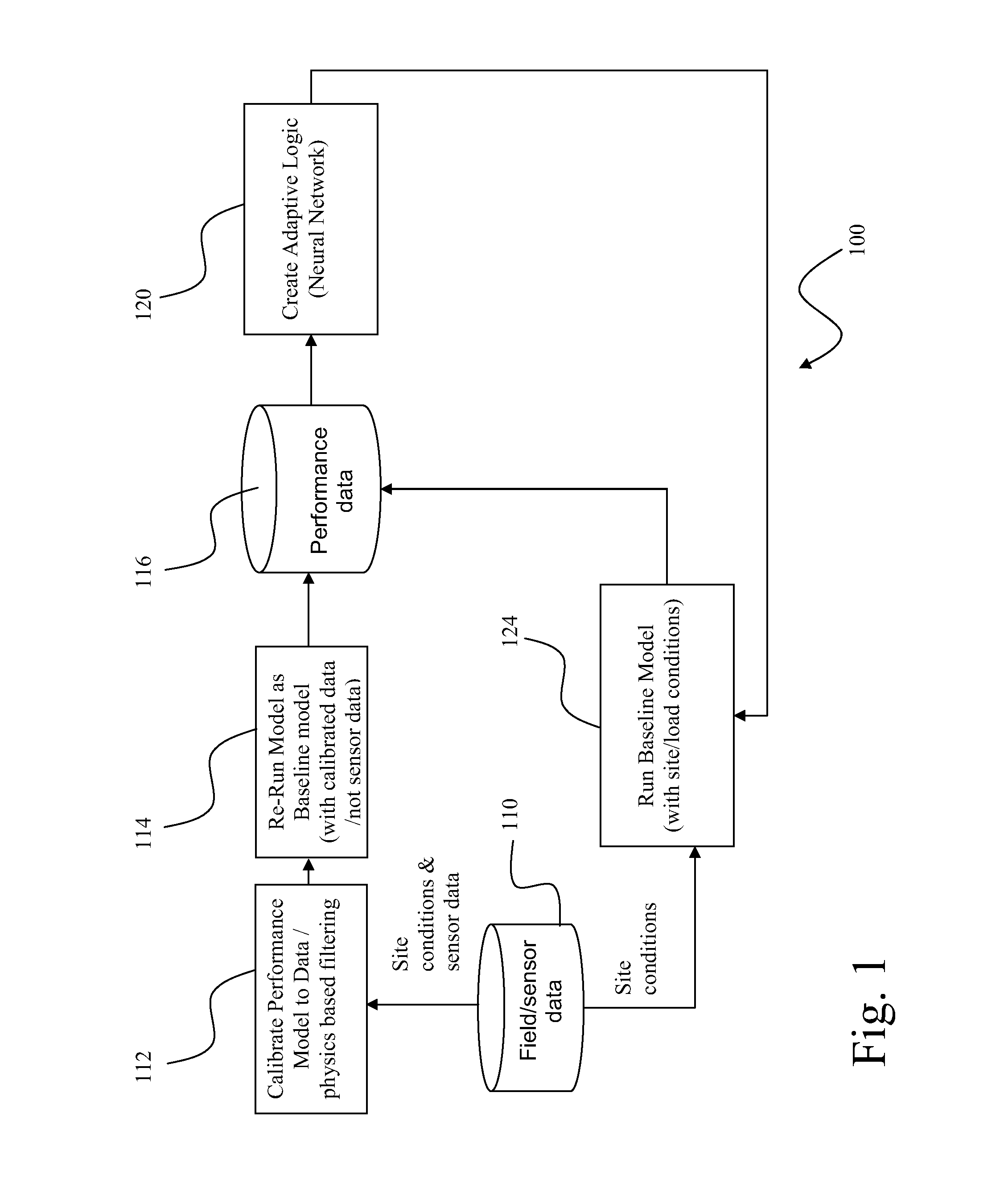

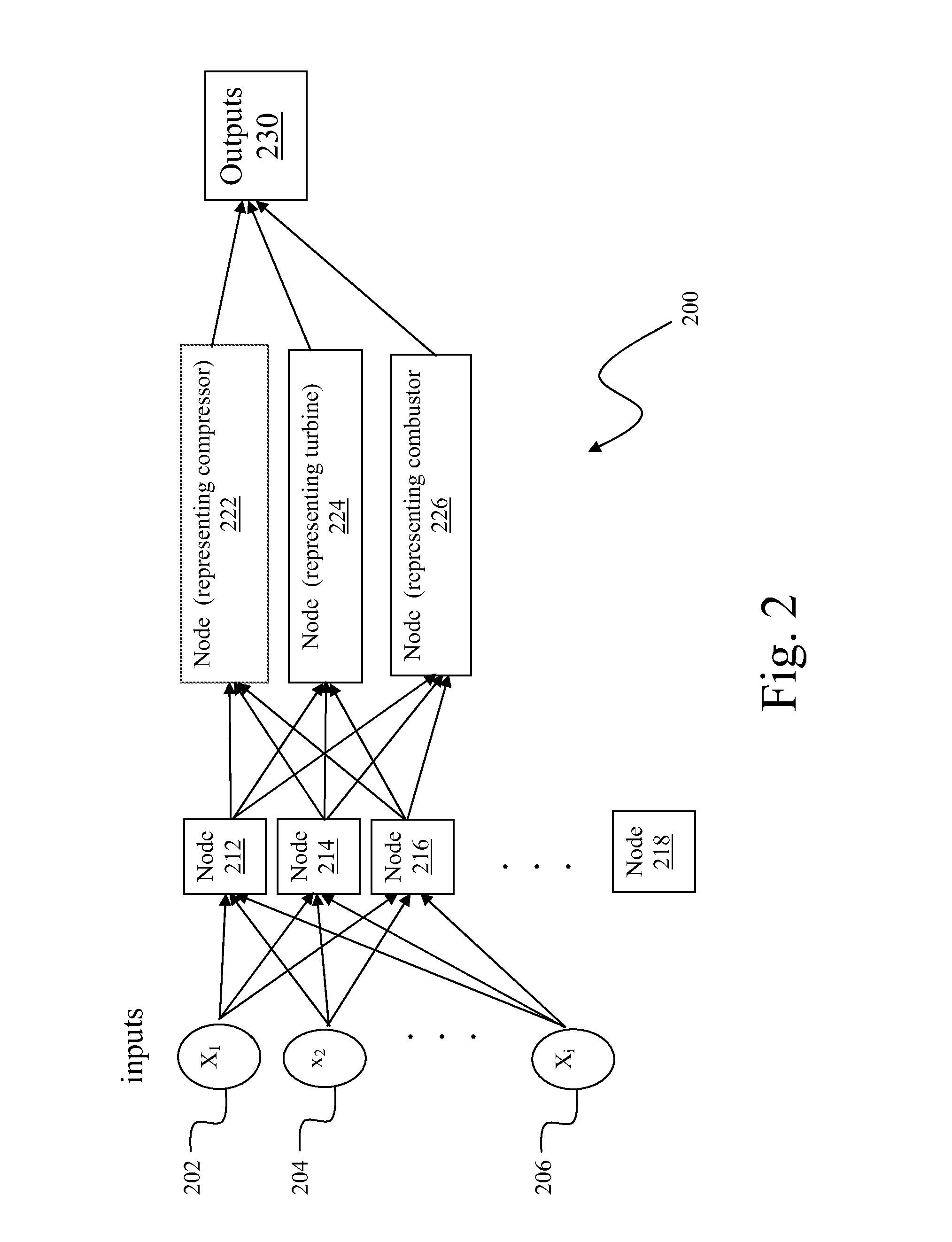

Process for adaptive modeling of performance degradation

The present subject matter is directed to methods and systems for providing adaptive modeling of performance degradation in a system, particularly, a gas turbine system. A performance model is provided and operated as both a calibration model and a baseline model. Data produced during both operations is stored and differences there between is used in adaptive logic, which may correspond to a neural network, to predict performance degradation to control operation of a system baseline model. Data from operation of the system baseline model may also be stored and used with data from the calibration model and baseline model in the adaptive logic.

Owner:GENERAL ELECTRIC CO

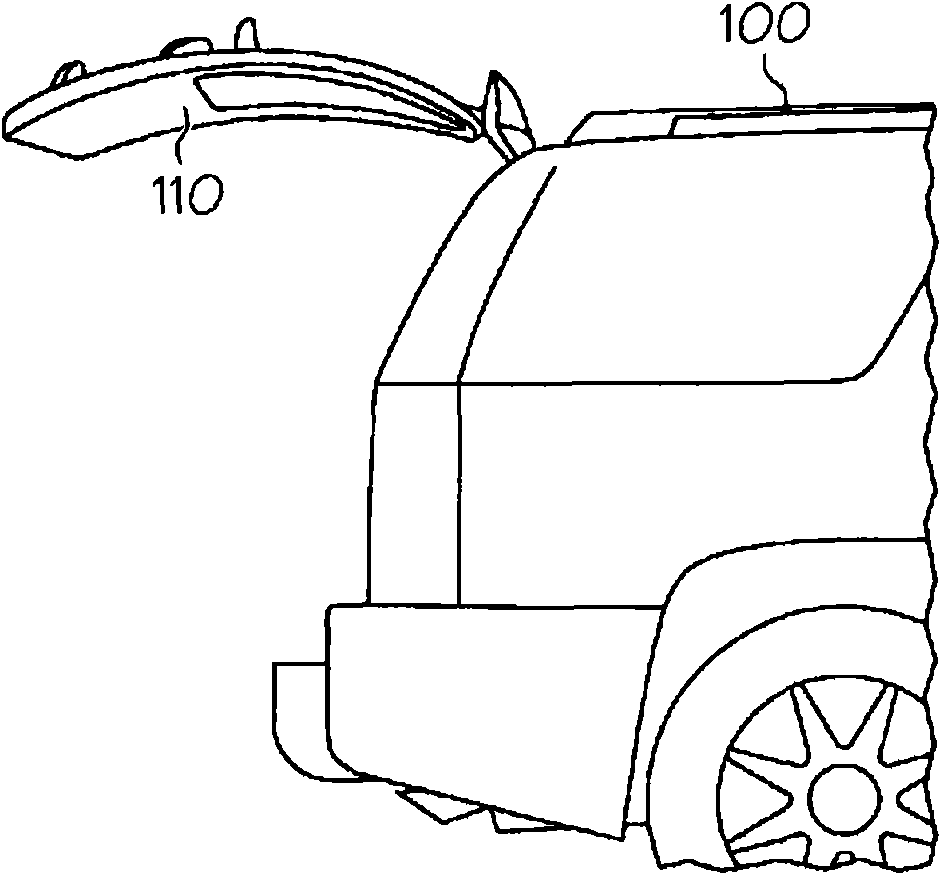

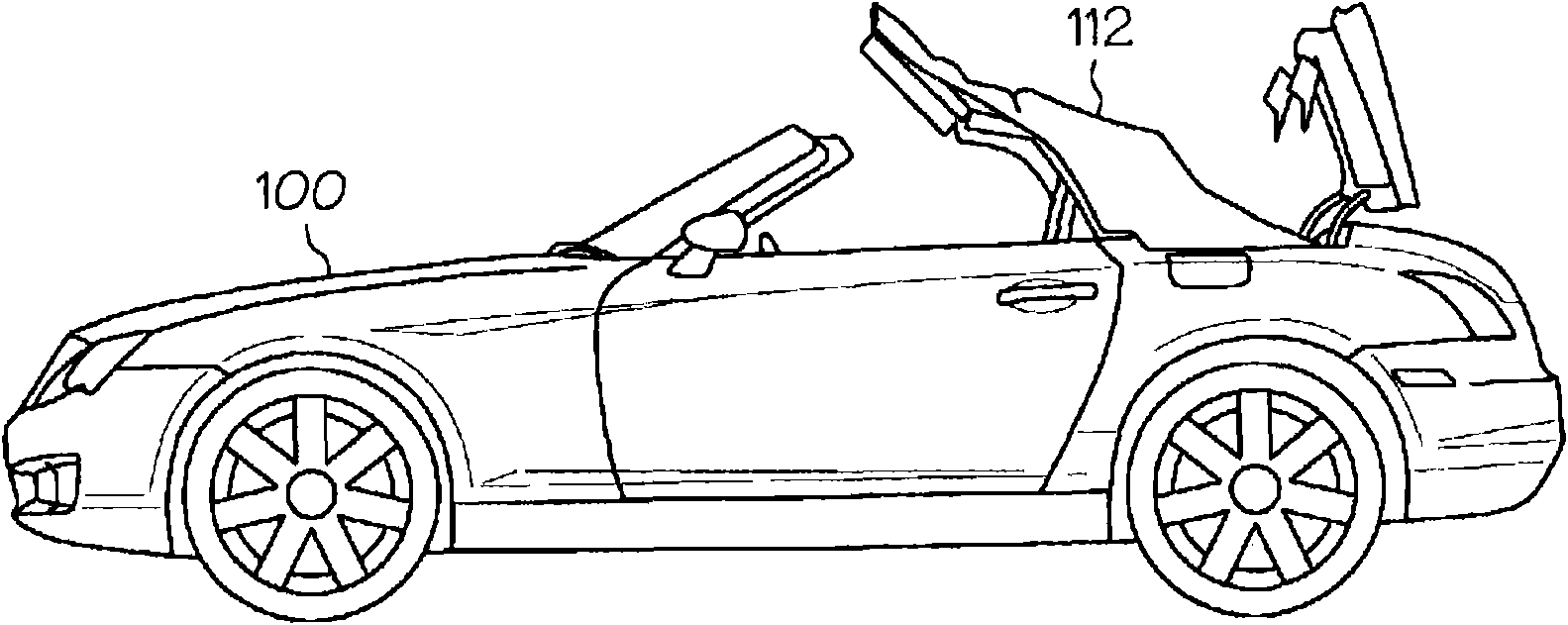

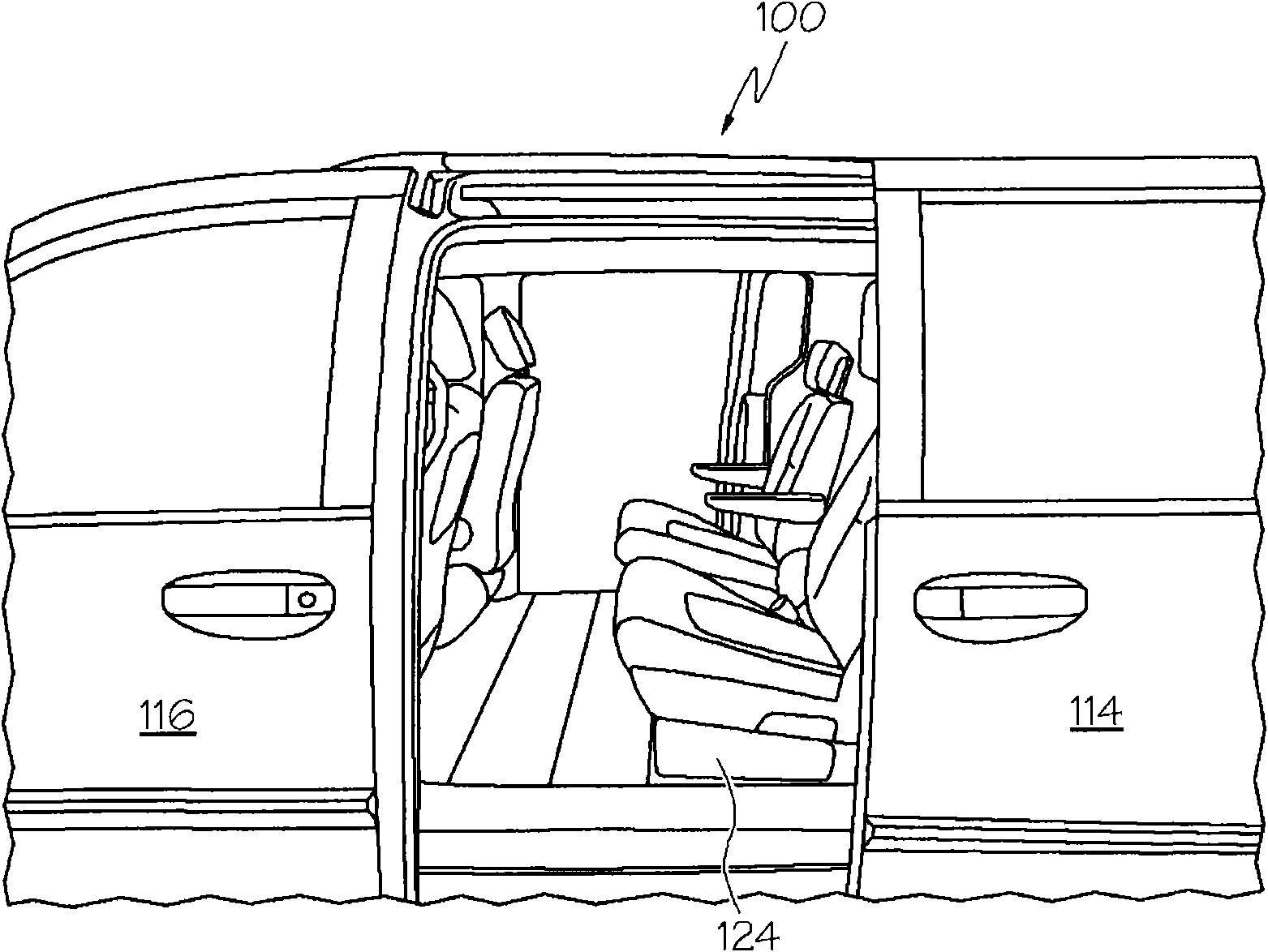

Adaptive control system for automated vehicle applications

An apparatus is provided for controlling an automated closure panel in a vehicle. The apparatus includes a command module configured to generate a control signal. A motor is configured to actuate the automated closure panel based upon the control signal. A motor sensor is configured to measure an output characteristic of the motor, with the motor sensor having a motor sensor output signal. An adaptive logic module is coupled to the command module and to the motor sensor. The adaptive logic module is configured to provide an output to the command module to thereby adjust the control signal, wherein the adaptive logic module is configured to determine when the automated closure panel is obstructed by an obstacle based upon the motor sensor output signal.

Owner:GM GLOBAL TECH OPERATIONS LLC

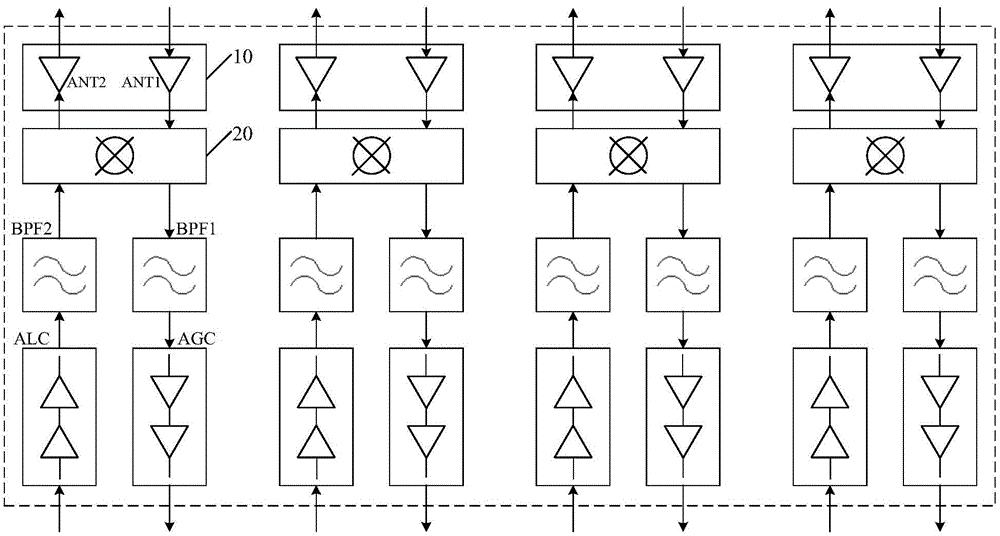

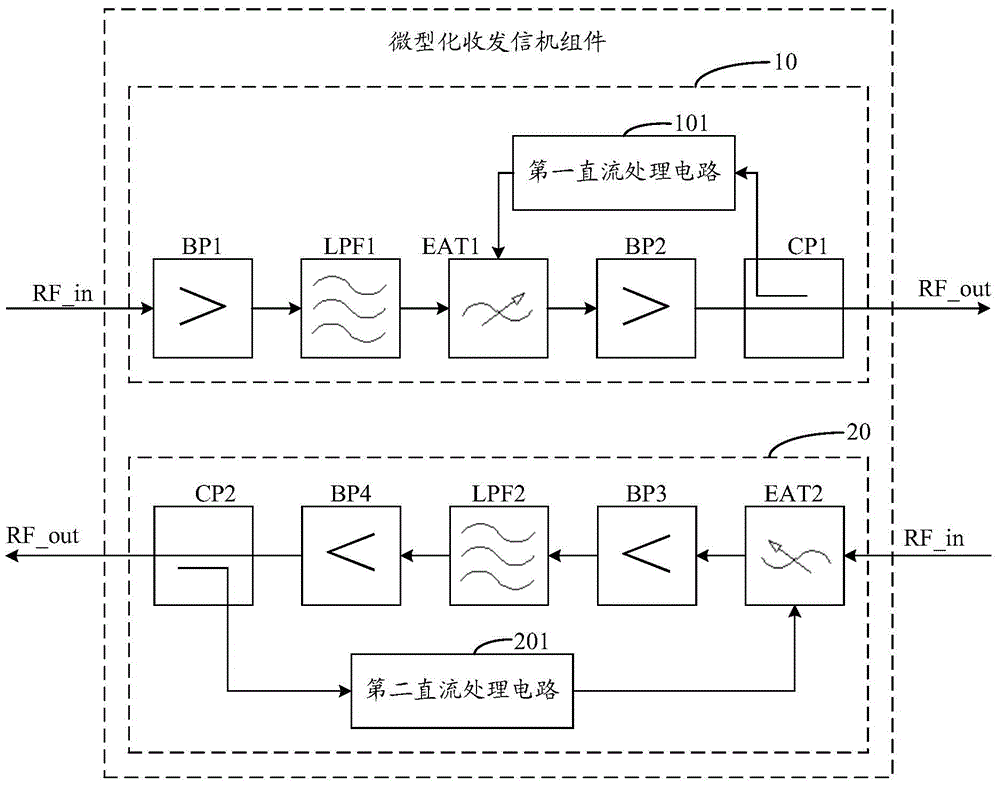

Micro structure MiMo radio frequency front end assembly

InactiveCN104702308AReduce volumeIncrease in sizeSpatial transmit diversityMicro structureTransceiver

The invention discloses a micro structure MiMo radio frequency front end assembly. The micro structure MiMo radio frequency front end assembly comprises even groups of radio frequency front end transceiver assemblies including a micro transceiver antenna, a polarization transformer, a first channel filter, a second channel filter, an AGC (automatic gain control) receiving module and an ALC (adaptive logic circuit) emitting module, wherein the micro transceiver antenna is connected with an input end of the AGC receiving module through the polarization converter, the first channel filter and the AGC receiving module in sequence; an output end of the ALC emitting module is connected with the micro transceiver antenna through the second channel filter and the polarization transformer in sequence; the AGC receiving module comprises a first balance amplifier, a first electrically controlled attenuator, a second balance amplifier, a first coupler and a first direct-current processing circuit; the ALC emitting module comprises a second electrically controlled attenuator, a third balance amplifier, a fourth balance amplifier, a second coupler and a second direct-current processing circuit. The micro structure MiMo radio frequency front end assembly is high in integration degree and capable of greatly reducing the size of the MiMo radio frequency front end assembly, and has the advantages of being high in linearity, high in gain and the like.

Owner:庄昆杰

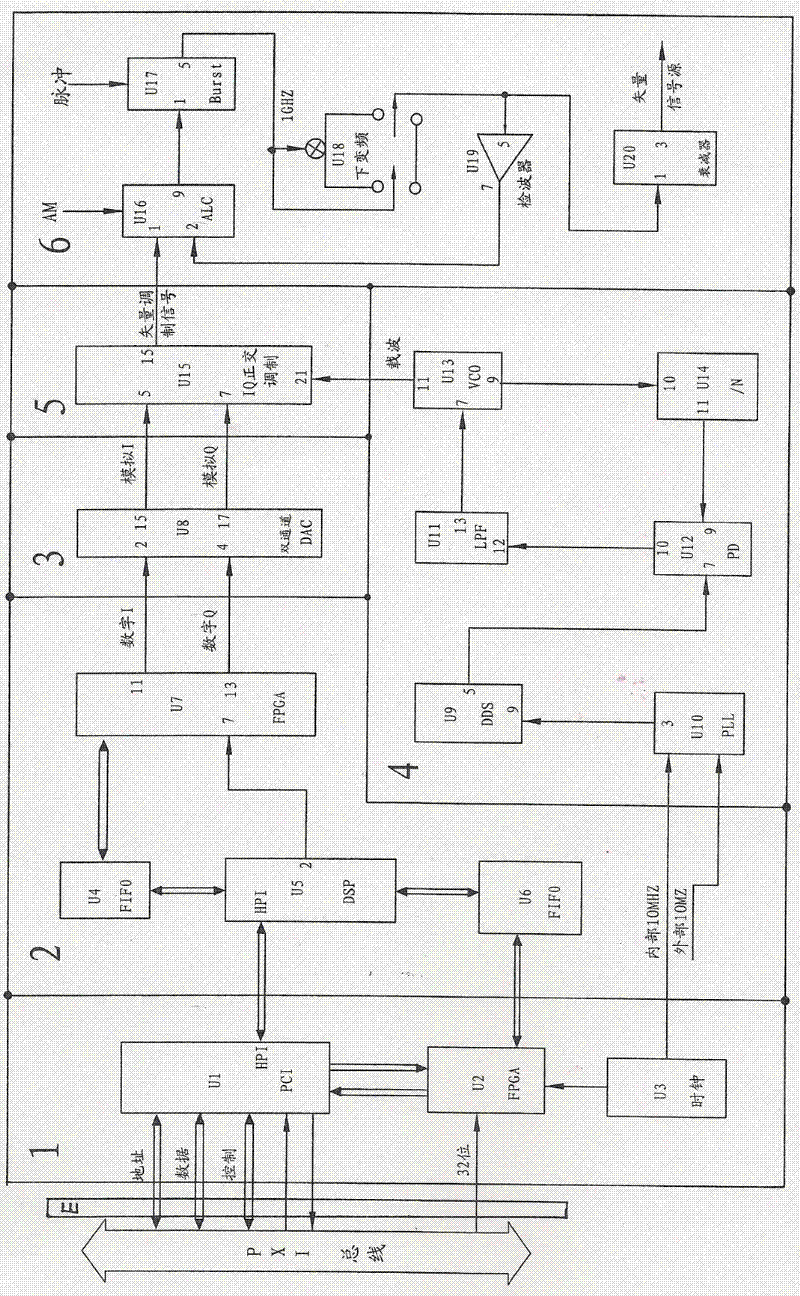

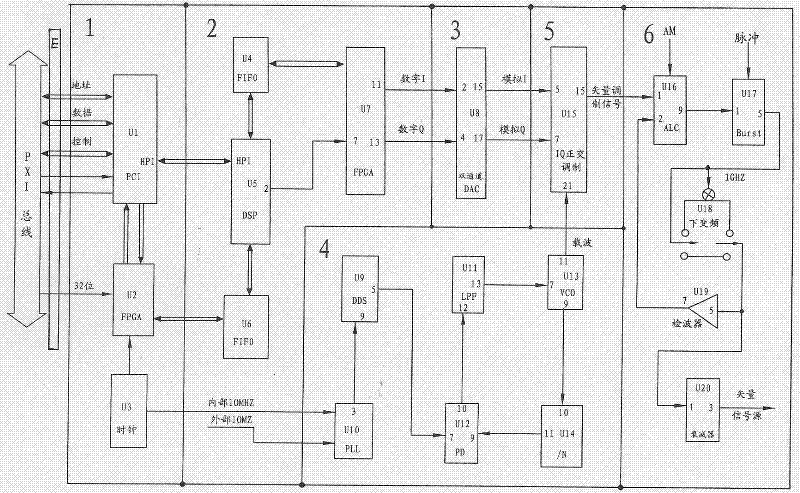

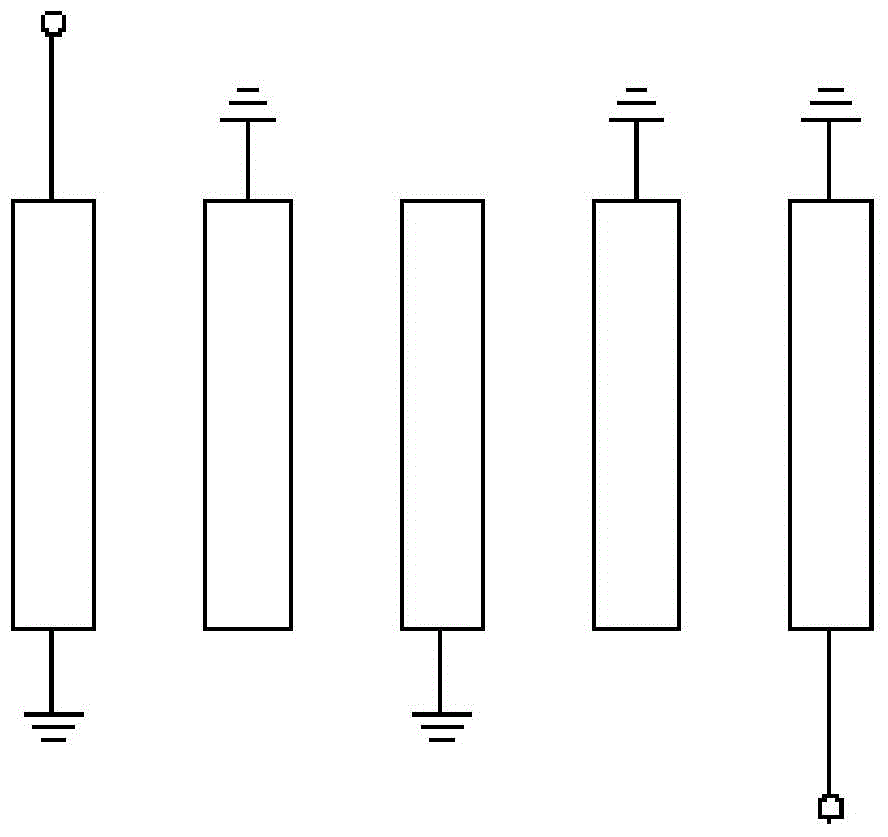

Vector signal source plug-in card-type structural module based on PCI extension for instrumentation (PXI) bus

InactiveCN102386894ACompact structureReasonable layoutSingle output arrangementsMathematical modelPCI eXtensions for Instrumentation

The invention relates to a vector signal source plug-in card-type structural module based on a PCI extension for instrumentation (PXI) bus, which comprises a PXI interface circuit 1, a baseband signal generating circuit 2, a digital-to-analogue conversion circuit 3, a frequency synthesis circuit 4, an in-phase quadrature (IQ) vector modulation circuit 5 and an adaptive logic circuit (ALC) control and vector signal source output circuit 6 which are combined with an external plug-in card E to form a modular structural integrity. According to the software radio technology and the modular structural design principle of an integrated circuit, a mathematical model is established; a microwave and a high-speed digital processing chip are adopted to set required vector signal source frequency, amplitude and power to perform real-time calculation to generate modulation output. Technologically, the optimal shielding, grounding, decoupling, filtering and leakage prevention optimization design is adopted to realize the characteristics of reasonable layout, compact structure, skillful installation, wide expansibility, high adaptability, high reliability and the like, and the requirements of automatic testing and analysis of a traditional digital communication system are completely met, and the need of the development of the communication technology is adapted.

Owner:63963 TROOP OF THE PLA +1

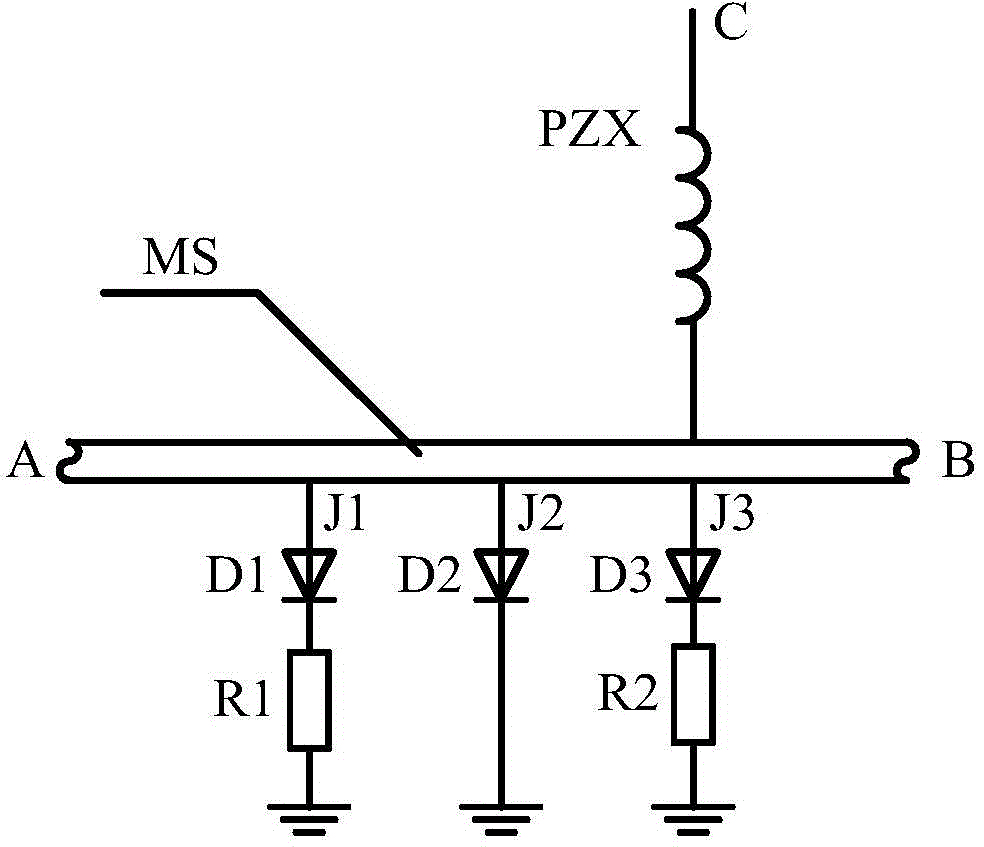

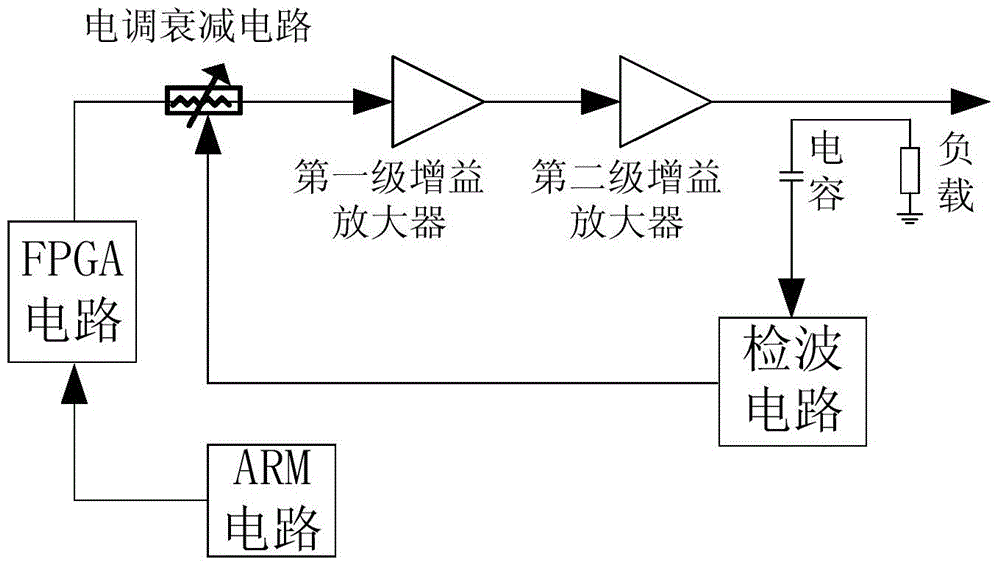

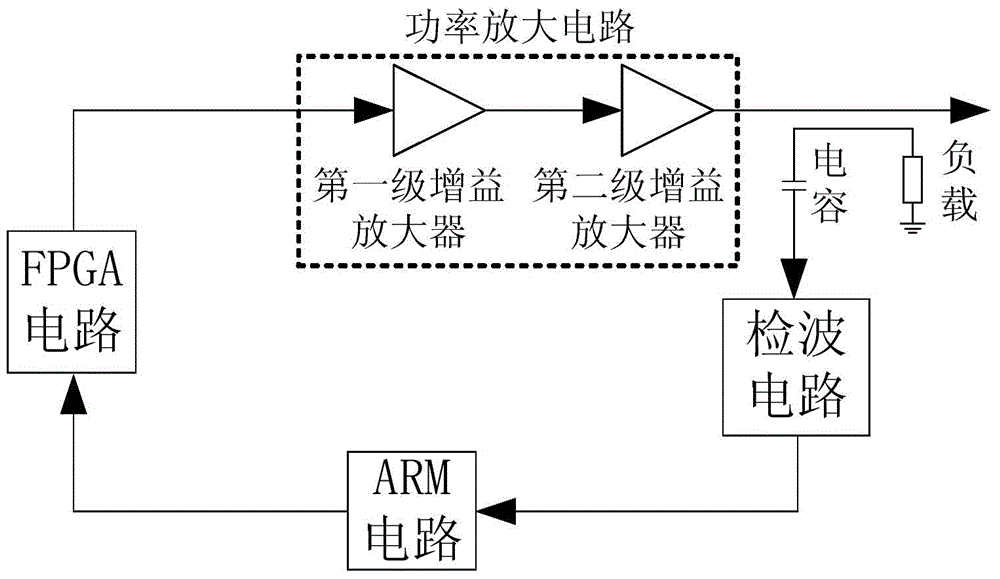

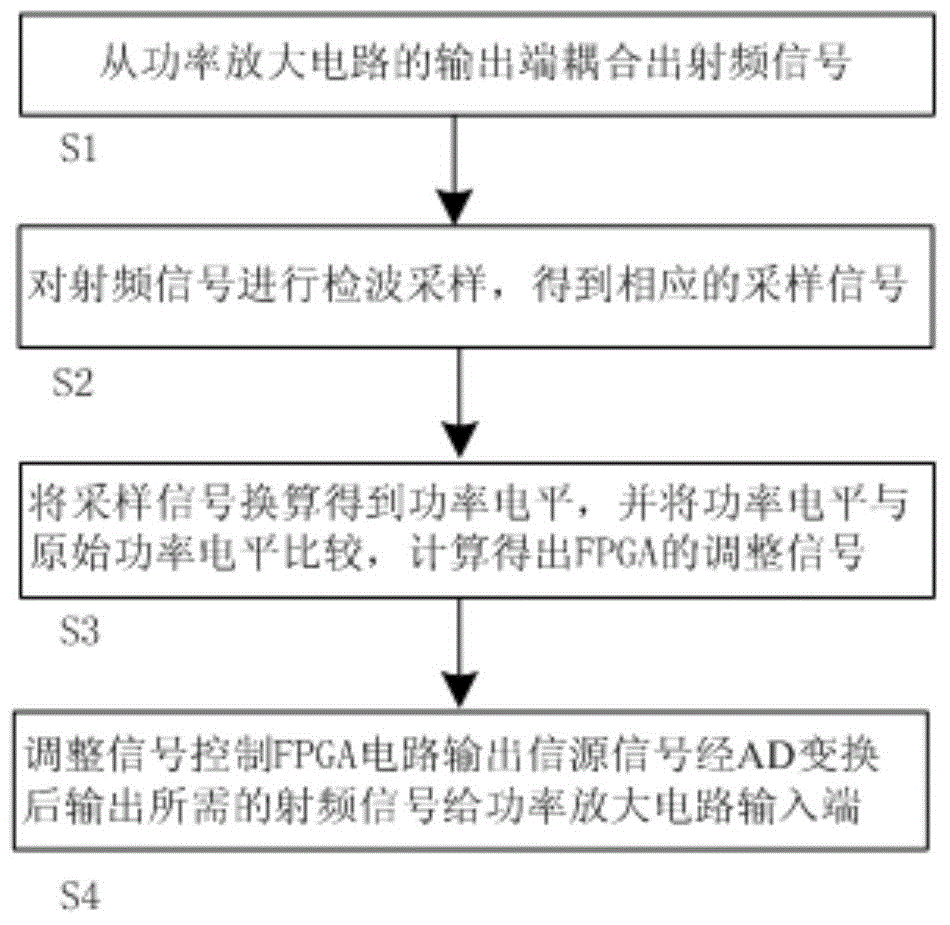

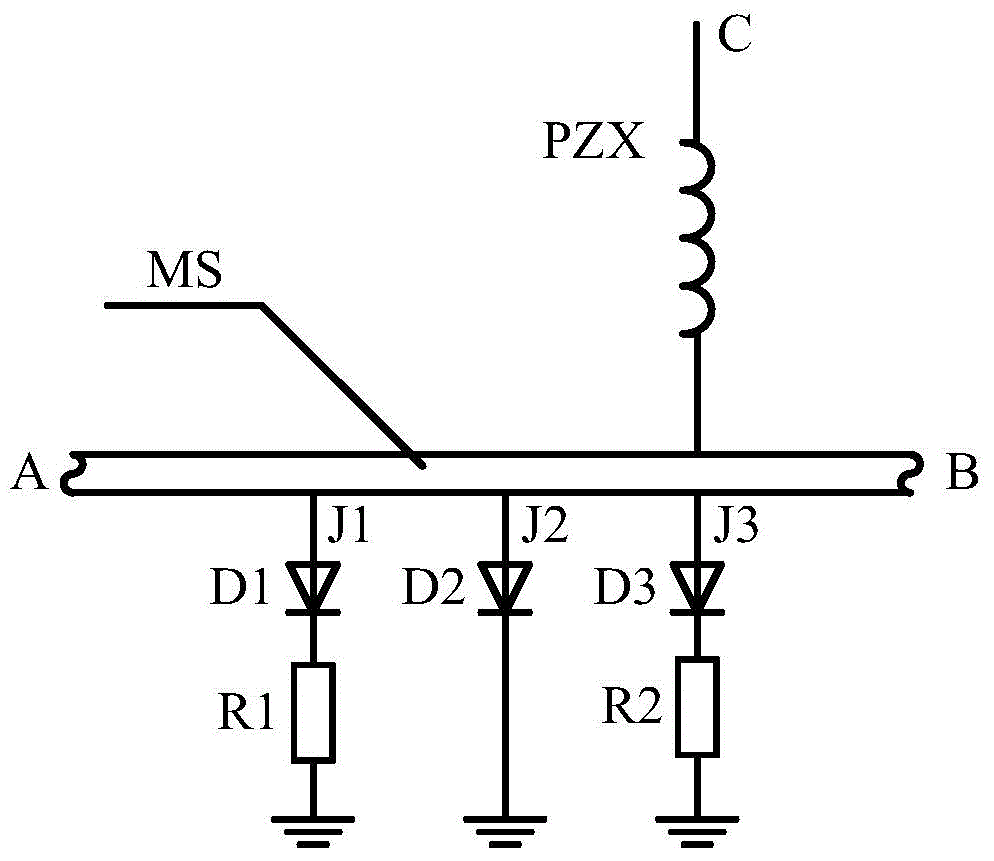

Field programmable gate array (FPGA) based automatic power control circuit and method

InactiveCN105491655ASimple designIncreased control depthPower managementDetector circuitsField-programmable gate array

The invention discloses a field programmable gate array (FPGA) based automatic power control circuit and method. The loop-locked power control circuit comprises a power amplification circuit, a coupling circuit, a detector circuit, an ARM circuit and an FPGA circuit. An output radio frequency signal of the power amplification circuit is coupled by the coupling circuit and then is output to the detector circuit, and the detector circuit samples the radio frequency signal and outputs an obtained sampling signal to the ARM circuit; and the ARM circuit compares a power level obtained through conversion of the sampling signal with an original power level, calculates to obtain an adjustment signal of the FPGA circuit and gives the adjustment signal to the PFGA circuit, and controls the PFGA circuit to output a required radio frequency signal to the input end of the power amplification circuit. According to the FPGA based automatic power control circuit and method, an electronic speed control attenuation circuit is saved, and data collected by the ARM is directly fed back to the FPGA circuit, thereby controlling the output power, improving control accuracy and speed, simplifying circuit design and increasing initial control depth of an adaptive logic circuit (ALC).

Owner:PROSE TECH CO LTD

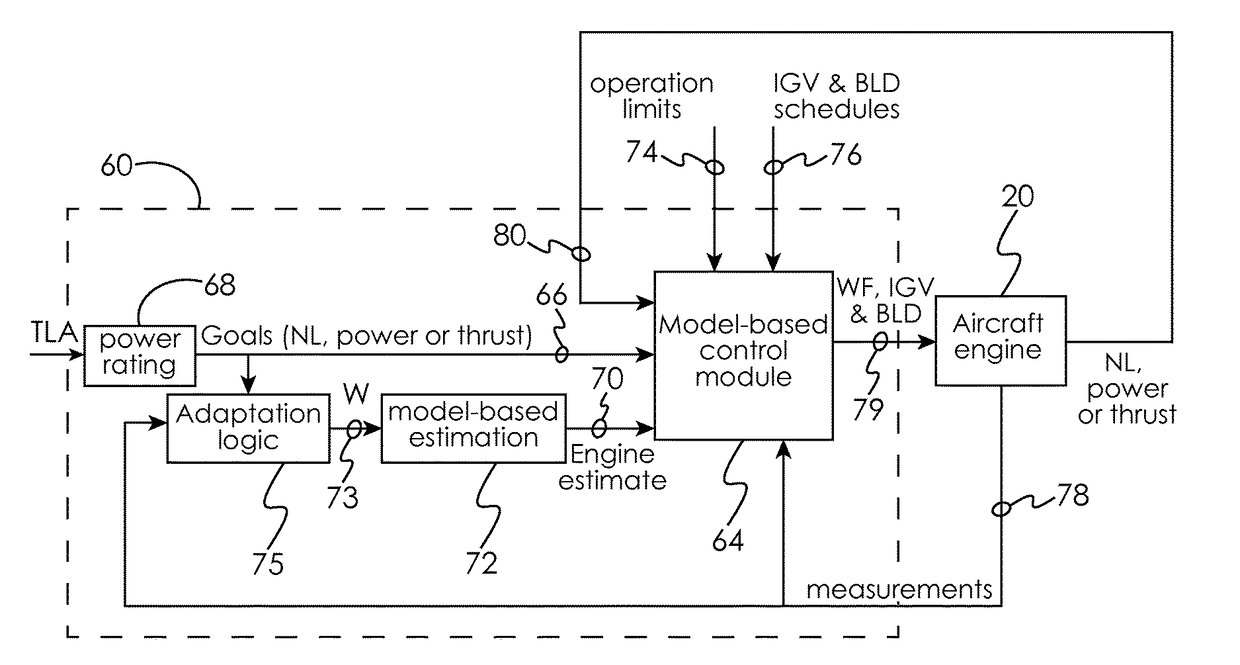

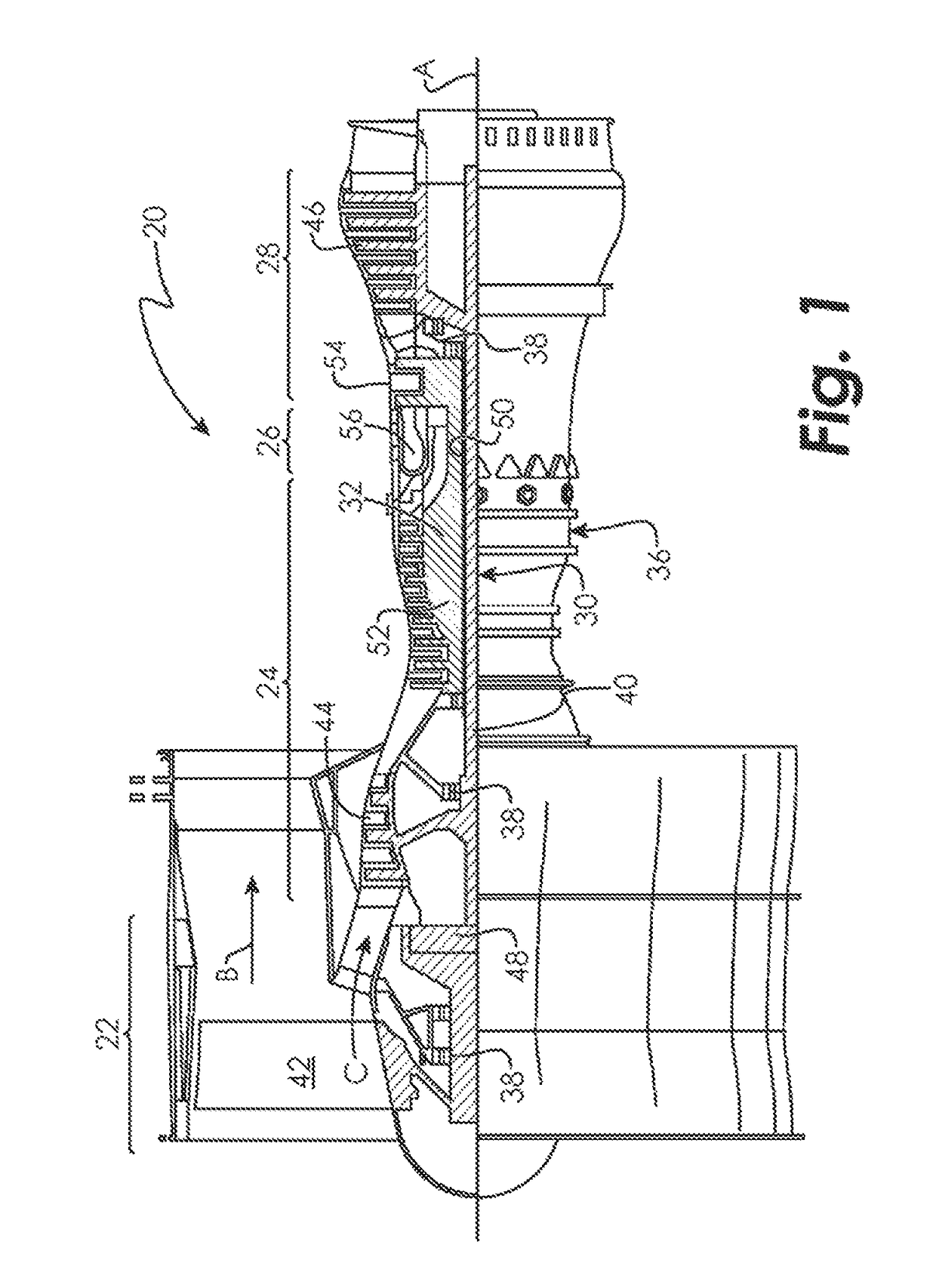

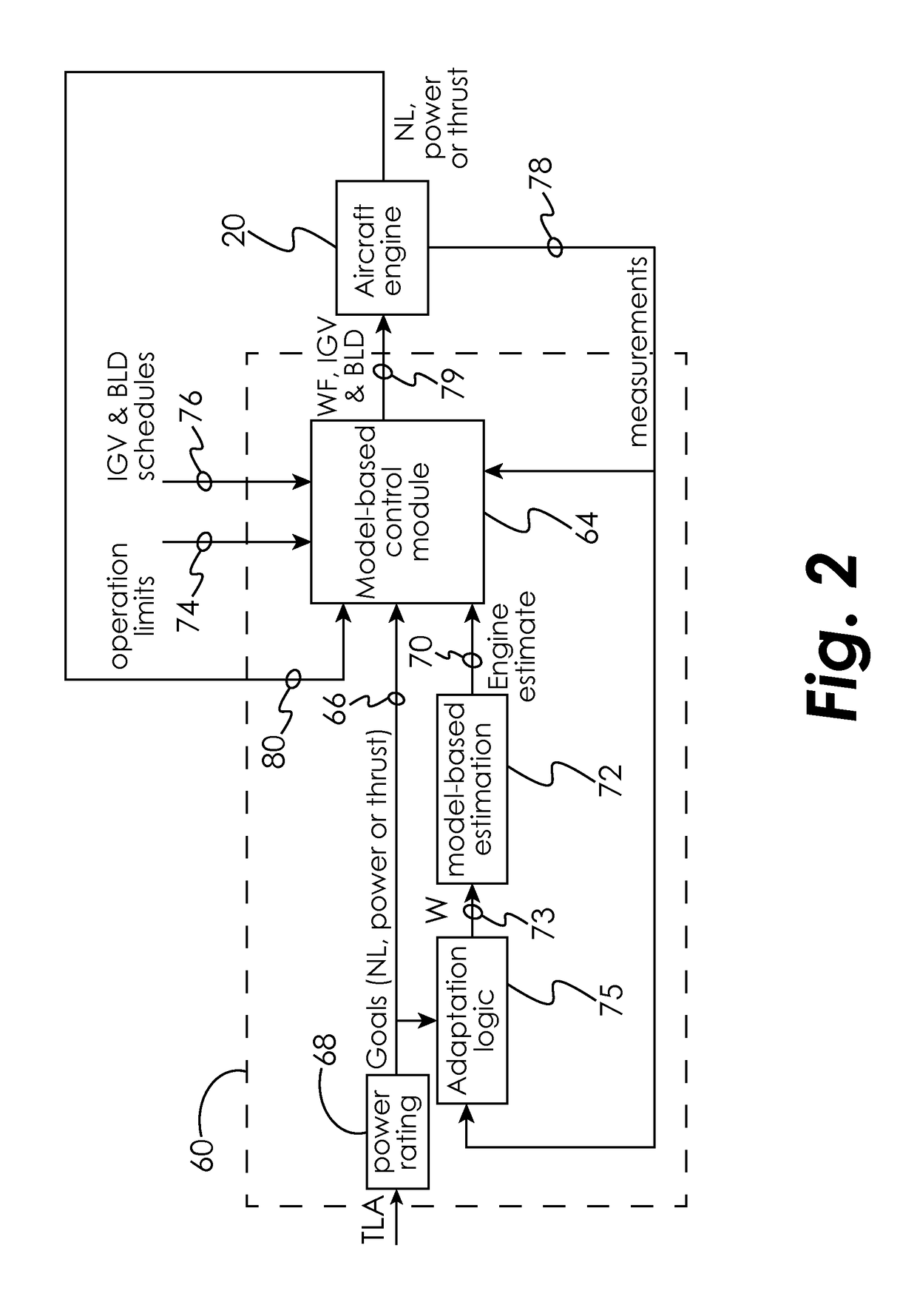

System and method for controlling a gas turbine engine

A control system for a gas turbine engine including a power turbine is disclosed. The control system may include a control module to receive engine operating goals and an estimated current engine state, wherein the estimated current engine state is produced by a model-based estimation module using a bandwidth signal produced by an adaptation logic module. The control module is operative to determine fuel flow, inlet guide vane schedules and stability bleed schedules based at least in part on the received engine operating goals and the estimated current engine state, and to send signals to a gas generator of the gas turbine engine in order to control the gas generator according to the determined fuel flow, inlet guide vane schedules and stability bleed schedules.

Owner:RTX CORP

Mechanism for adaptive profiling for performance analysis

InactiveUS8527624B2Electronic circuit testingError detection/correctionComputerized systemSelf adaptive

Adaptive profiling for performance analysis of a computer system controls one or more agents to monitor a plurality of events occurring in a target computer system based on an adaptive logic. Collected data may be filtered and analyzed to determine one or more contributor events that attribute to performance of the target computer system. One or more patterns are observed or detected in said collected data, behavior of said one or more agents are adjusted based on said detected one or more patterns. The adaptive logic may be further reconfigured based on said detected one or more patterns.

Owner:INT BUSINESS MASCH CORP

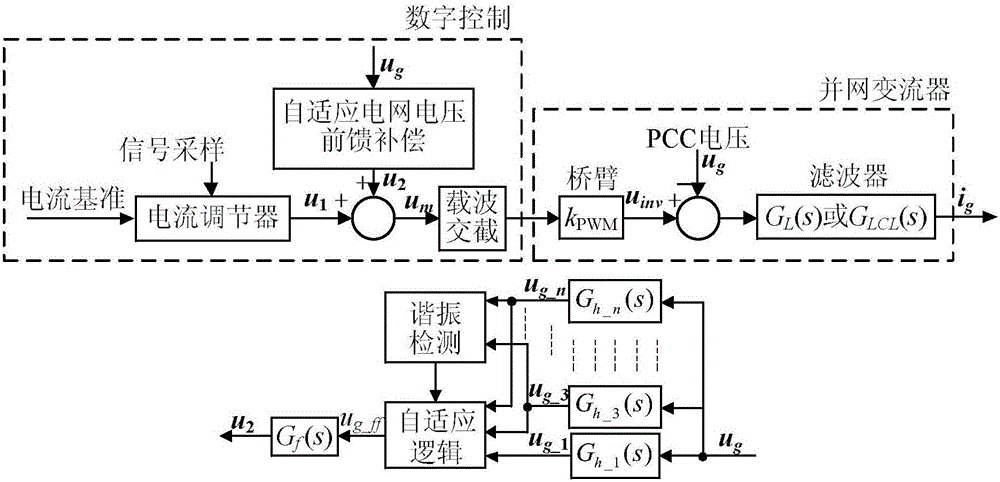

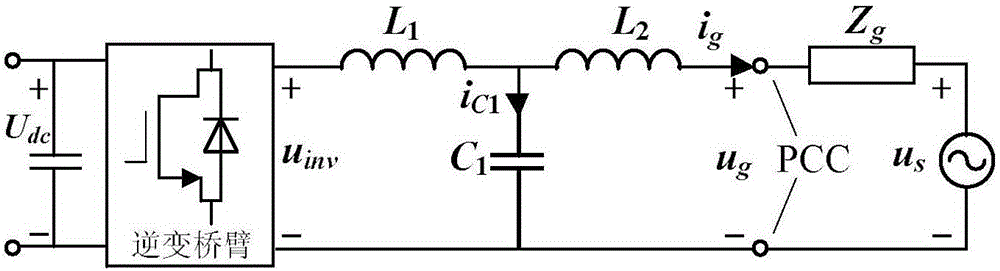

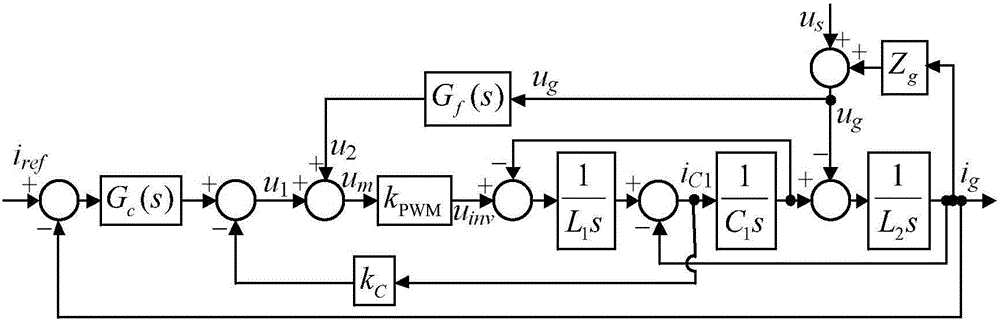

Adaptive network voltage feed-forward compensation method for grid-connected inverter

ActiveCN106300354AImprove stabilityExcellent grid side current qualitySingle network parallel feeding arrangementsHarmonic reduction arrangementBand-pass filterEngineering

The invention discloses an adaptive network voltage feed-forward compensation method for a grid-connected inverter and belongs to the field of current control of the grid-connected inverter (including an inverter and a rectifier). The method comprises the following steps that the network voltage of a point of common coupling is sampled and the voltage is taken as an input signal for adaptive network voltage feed-forward compensation of the grid-connected inverter, the input signal generates one group of output signals through one group of parallel band-pass filters at the harmonic frequency, and independent output signals in the group of output signals are added to generate a voltage signal used for feed-forward compensation; and meanwhile, resonance detection is carried out on the independent output signals, and when the amplitude of one output signal is suddenly increased, the related output signal is eliminated from the voltage signal used for feed-forward compensation according to the adaptive logic. The method has the advantages of strong adaptability for large-range varying network impedance, excellent grid-side current quality and convenience for design.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

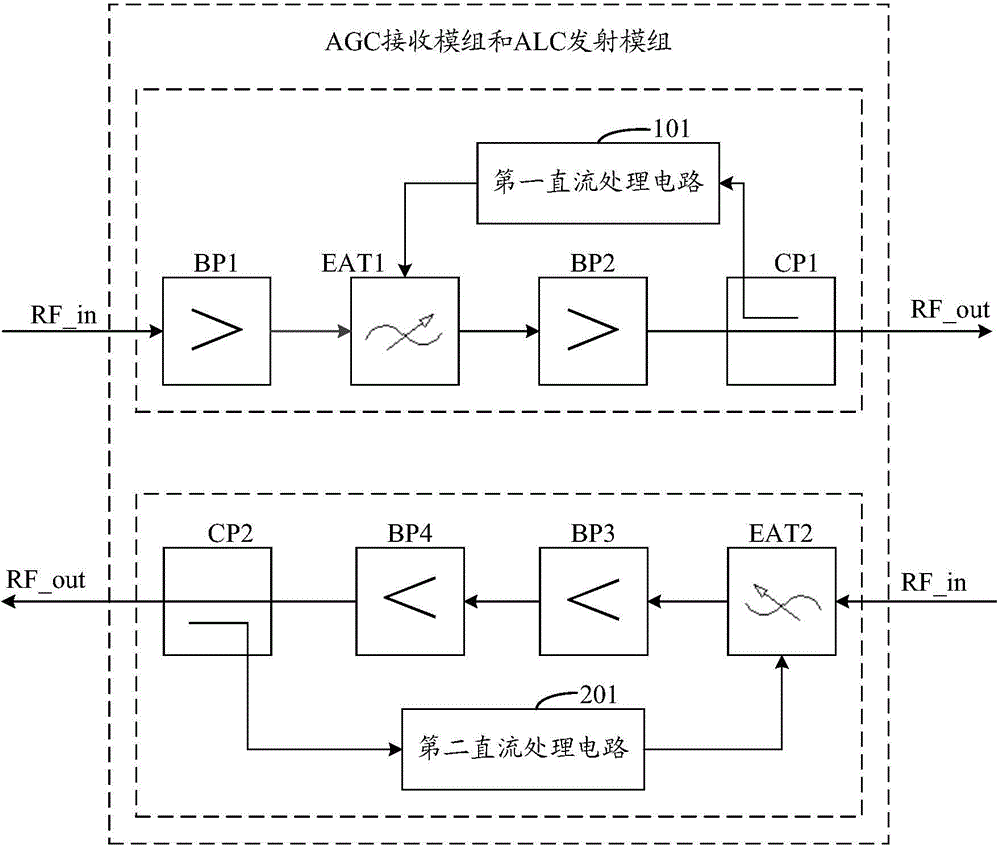

Micro transceiver assembly

The invention discloses a micro transceiver assembly. The micro transceiver assembly comprises an AGC (automatic gain control) receiving module and an ALC (adaptive logic circuit) emitting module, wherein the AGC receiving module comprises a first balance amplifier, a first micro belt filter, a first electrically controlled attenuator, a second balance amplifier, a first coupler and a first direct-current processing circuit; the ALG emitting module comprises a second electrically controlled attenuator, a third balance amplifier, a second micro belt filter, a fourth balance amplifier, a second coupler and a second direct-current processing circuit; the first balance amplifier, the second balance amplifier, the third balance amplifier, the fourth balance amplifier, the first micro belt filter, the second micro belt filter, the first electrically controlled attenuator, the second electrically controlled attenuator, the first coupler and the second coupler are manufactured on a ceramic base plate through a superfine micro belt film process. The micro transceiver assembly is integrated on a circuit in the form of a distribution parameter, so that peripheral assemblies are reduced, the integration degree of the whole transceiver assembly is relatively high and the size of the transceiver is greatly reduced.

Owner:庄昆杰

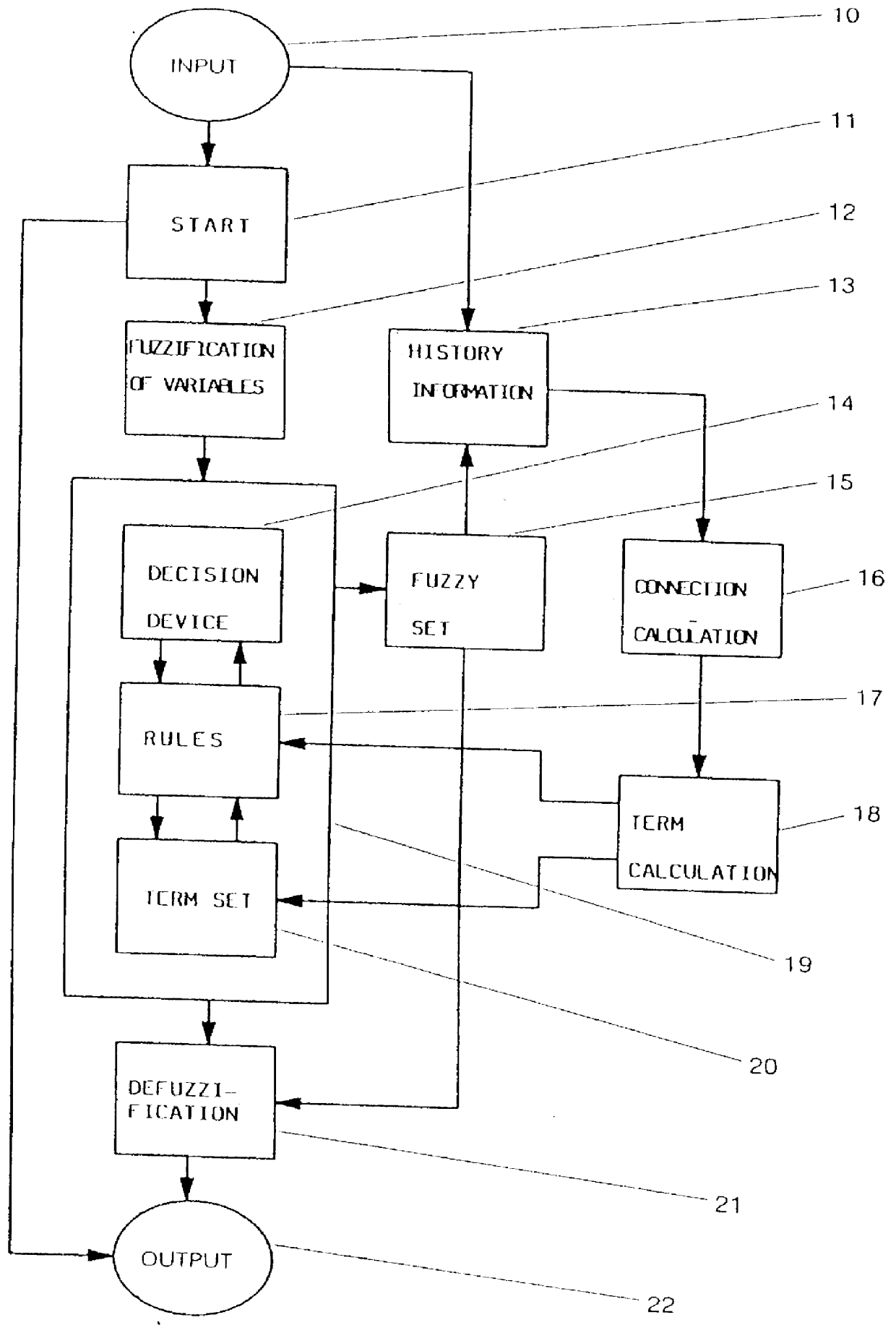

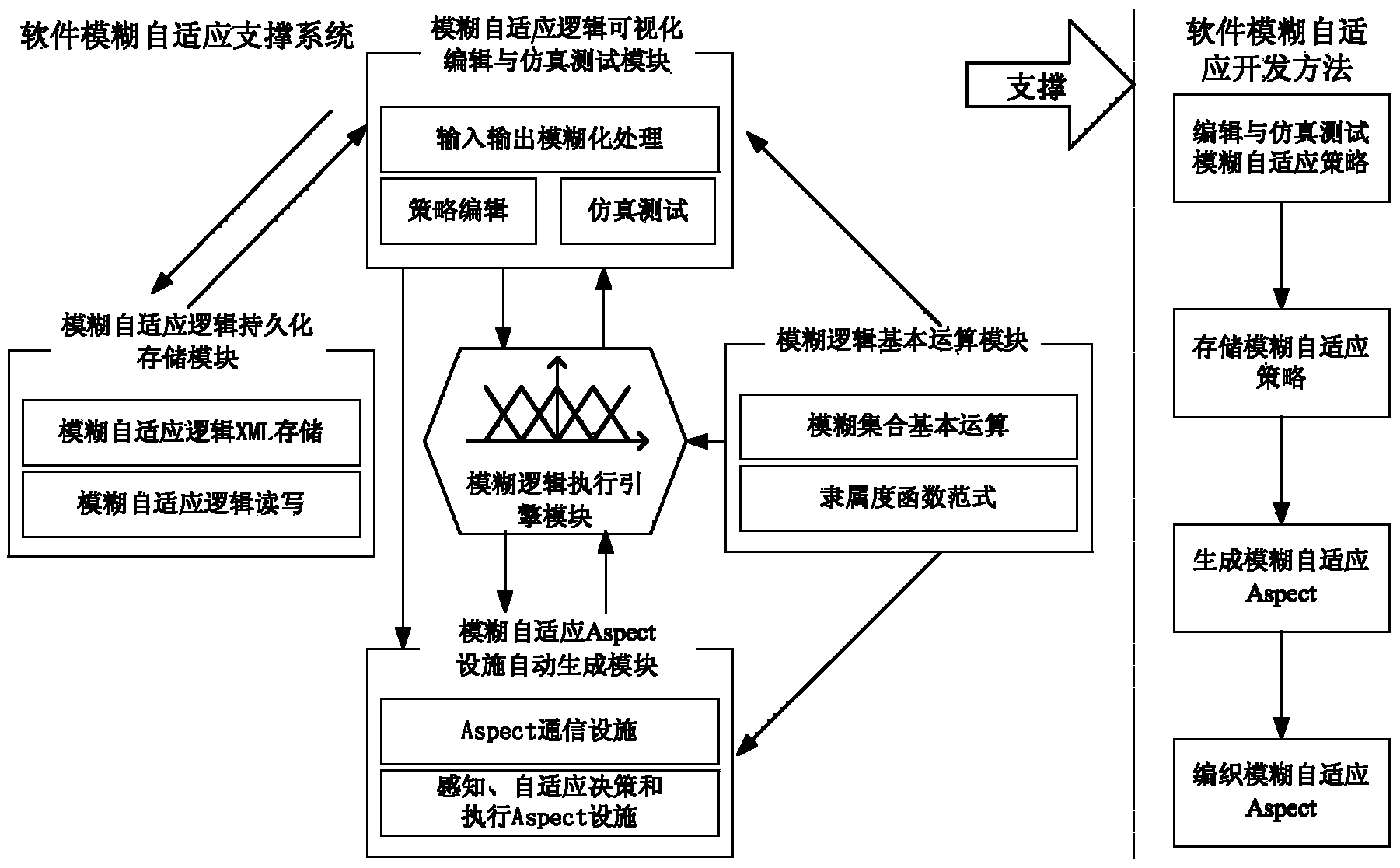

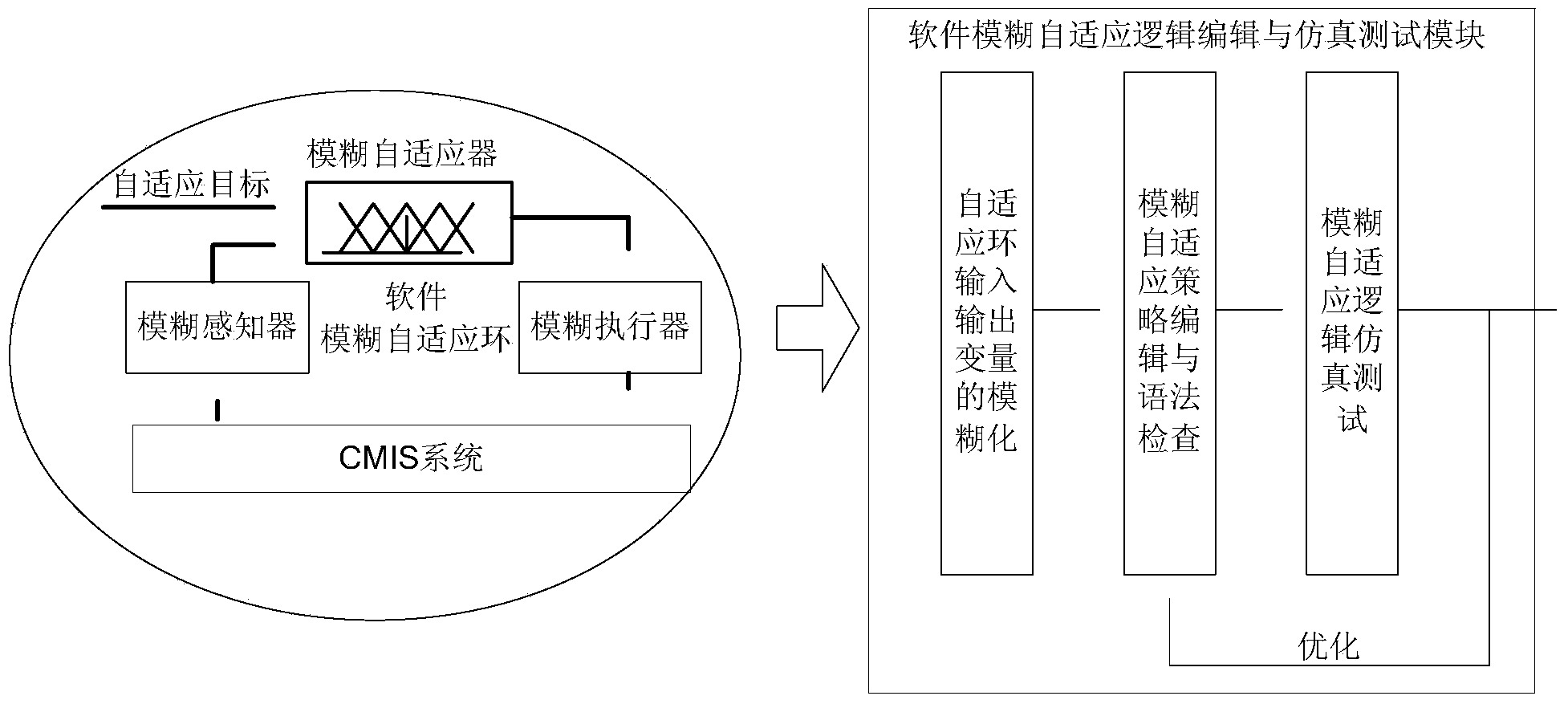

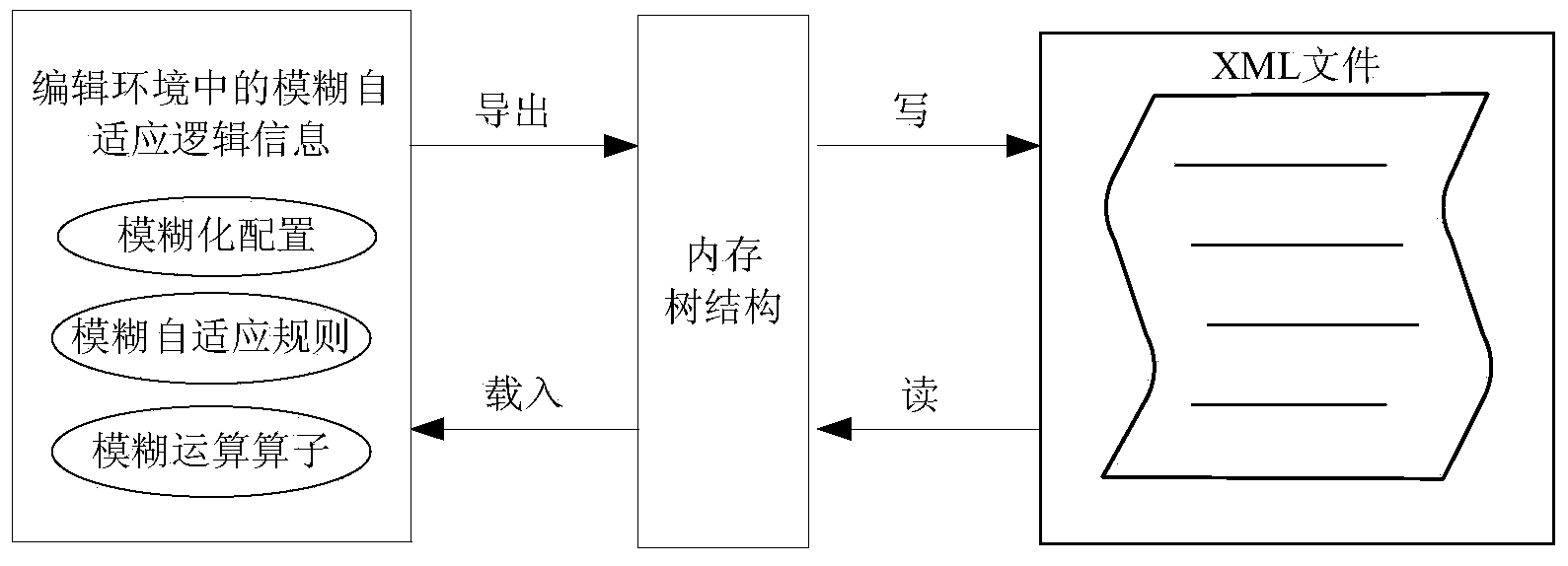

Software fuzzy adaptive support system and development method

ActiveCN103955368AEasy to carry outEasy to shareSpecific program execution arrangementsSyntaxFuzzy adaptive

The invention discloses a software fuzzy adaptive support system and a development method. The system comprises a software fuzzy adaptive visualized editing and simulation testing module, a software fuzzy adaptive logic persistence storage module, a fuzzy adaptive Aspect facility automatic generating module, a fuzzy logic basic operation module and a fuzzy logic execution engine module. The method is based on the system, supplies a domain specific language to realize the editing of software fuzzy adaptive strategies, performs syntax check to the fuzzy adaptive strategies, then performs visualized emulation and testing to fuzzy adaptive logics, finally automatically converts the fuzzy adaptive logics based on the domain specific language into executable programming language Aspect codes, and can knit automatically generated Aspect into object software through a universal Aspect knitting system. The system and the method shield complex fuzzy control technical details, and provide visualized and automatic support means for software fuzzy adaptive development.

Owner:PLA UNIV OF SCI & TECH

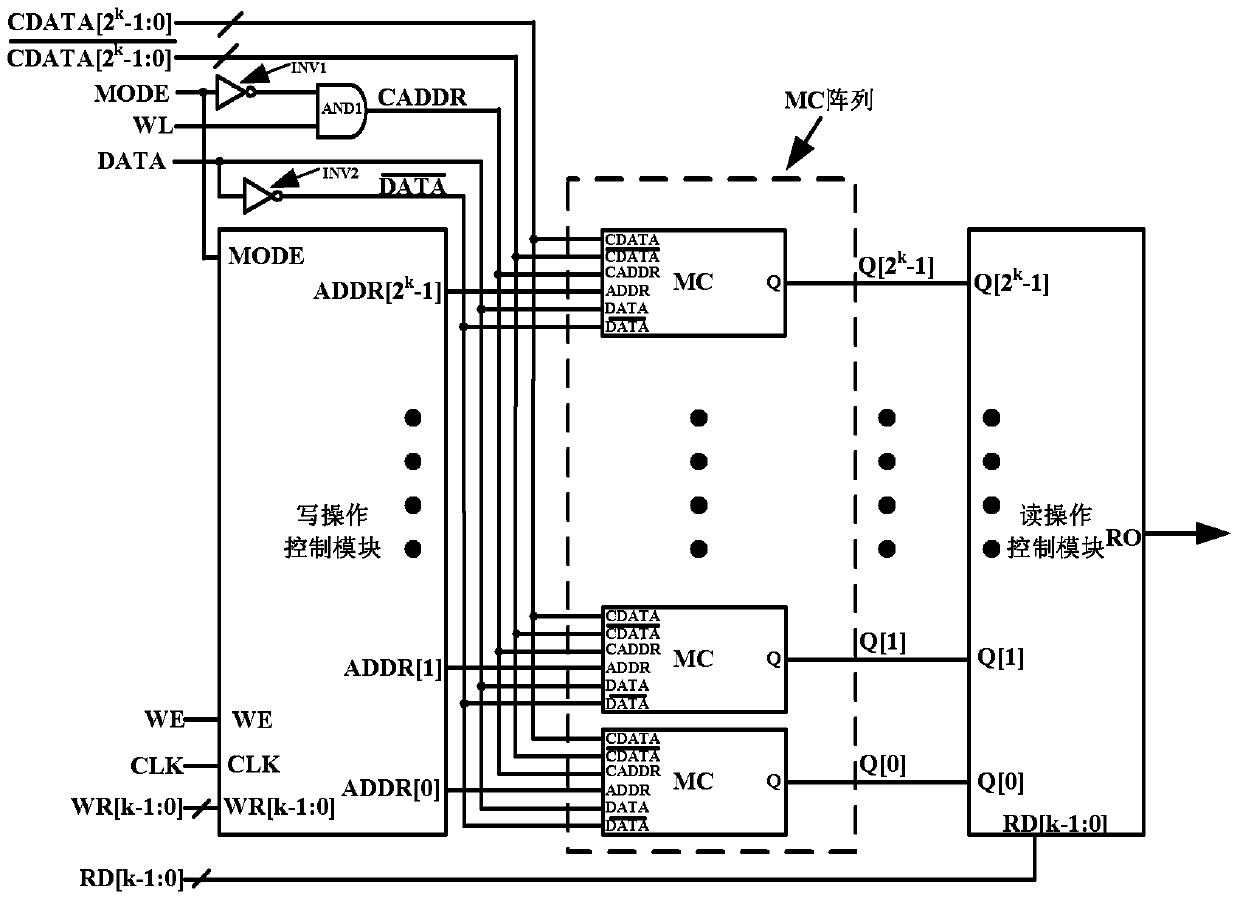

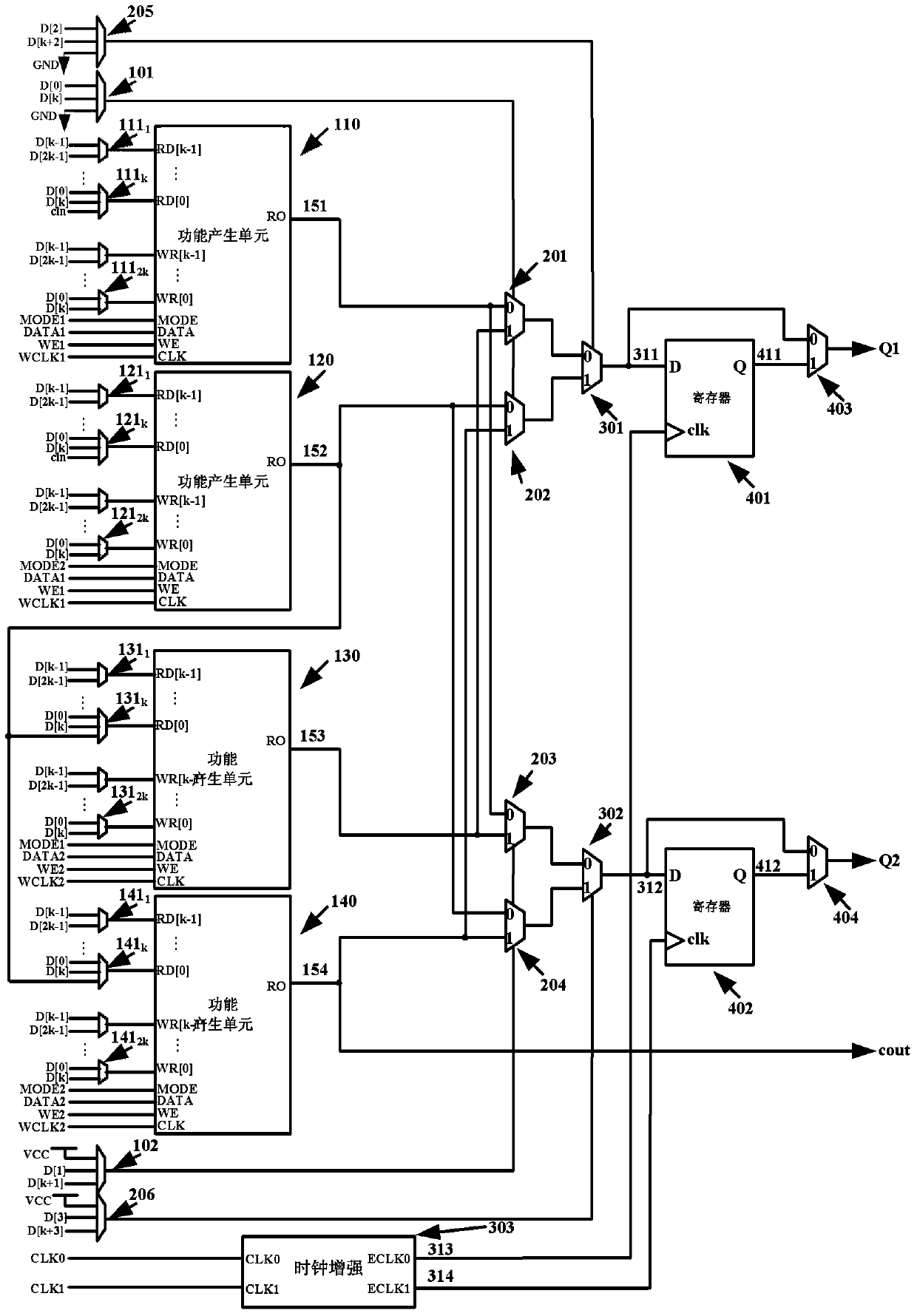

Programmable signal processing unit

ActiveCN103631754AImplement read/write operationsImplement logical operationsGeneral purpose stored program computerMultiplexerLogical operations

The invention provides a programmable signal processing unit based on a function generating unit. According to the programmable signal processing unit, the function generating unit which has an logical operation function and a data storage function is adopted and is connected with a flexible multiplexer in a matched mode, as a result, the programmable signal processing unit can be used for storing configuration data to achieve independent self-adaptive logic operation and storing user data to achieve reading / writing operation of a fine-grained data memory on one hand and can achieve mixed operation of the self-adaptive logic operation and the reading / writing operation of the fine-grained data memory on the other hand, and therefore the resource use efficiency of a programmable chip is greatly improved.

Owner:EHIWAY MICROELECTRONIC SCI & TECH SUZHOU CO LTD

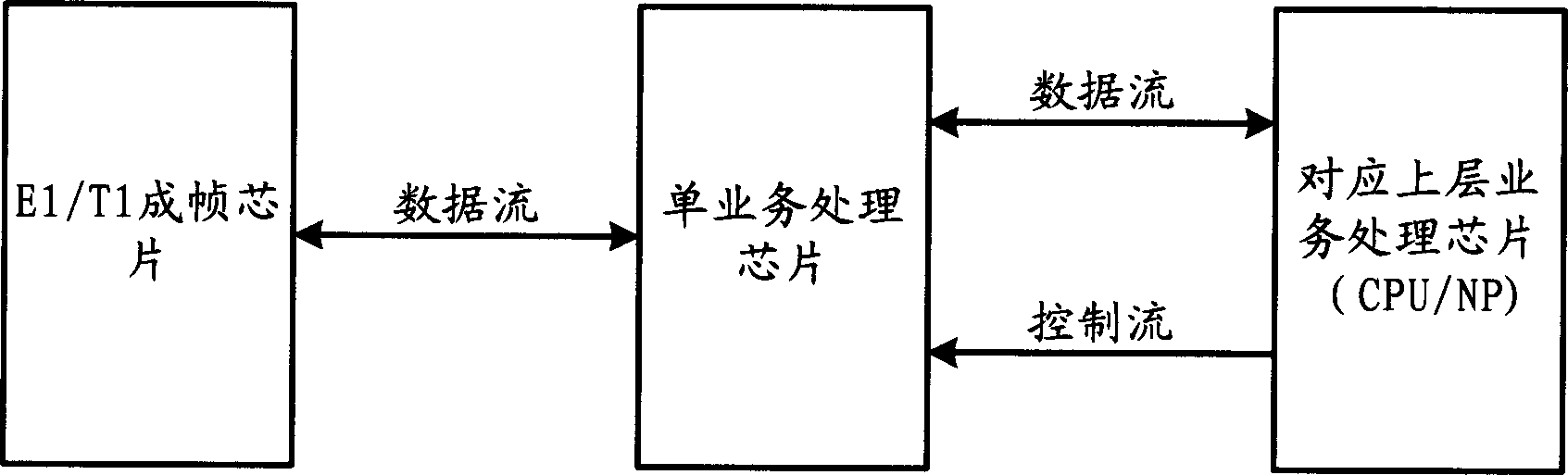

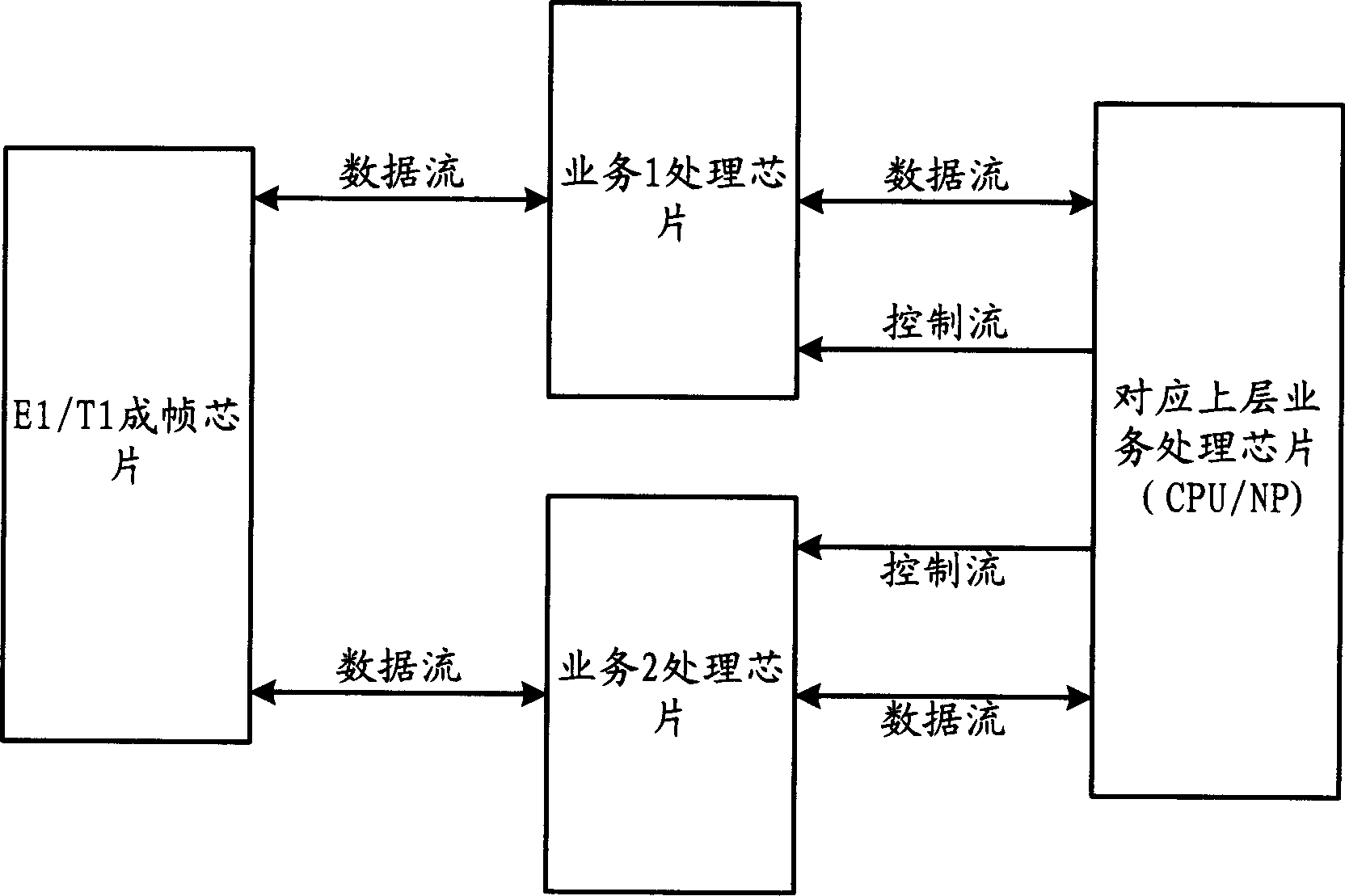

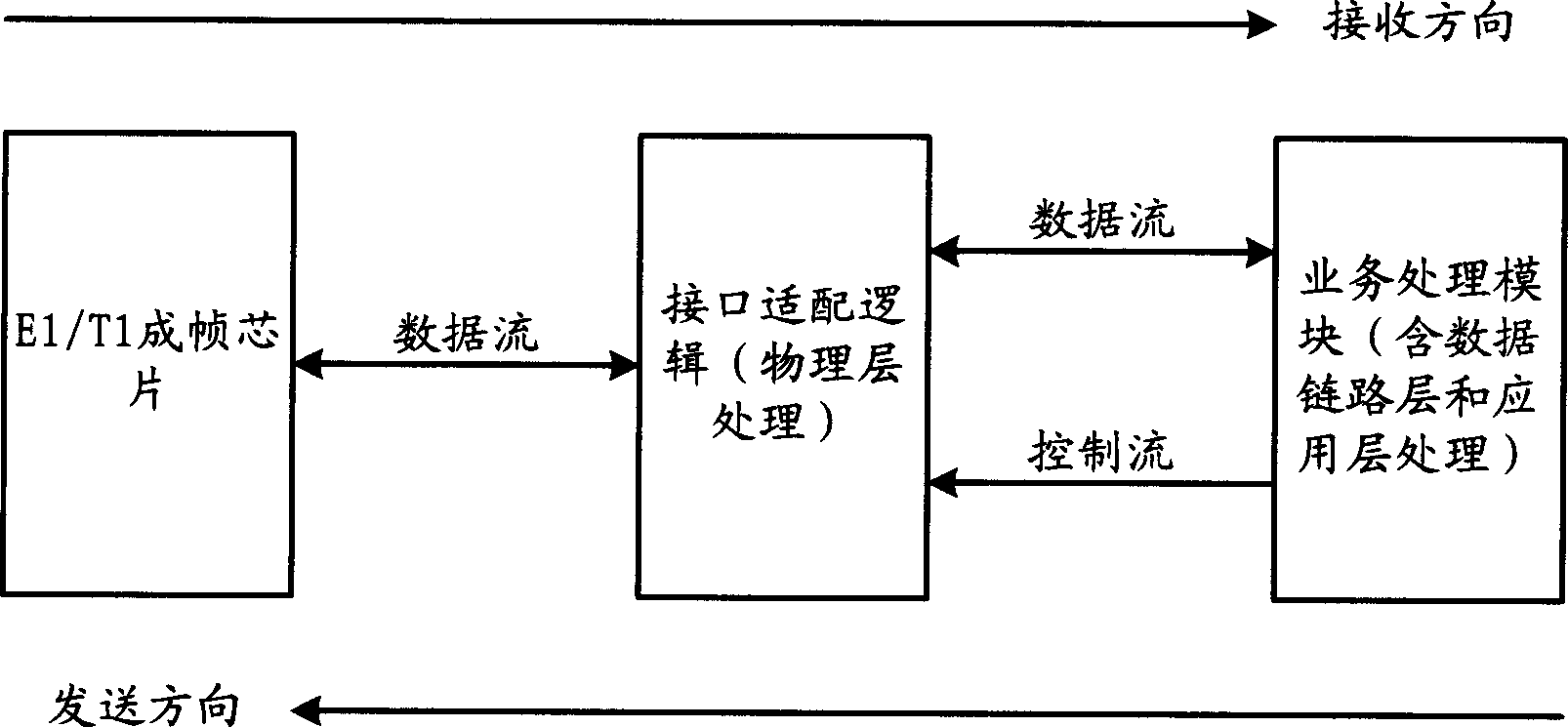

Multiple service device and its signal processing method based on primary group

The present invention discloses E1 / T1based multiple business equipment and signal processing method, to make same equipment capable of supporting variety E1 / T1 interface based service type, referring to E1 / T1 application technology. The present invention uniformly realizes service data link layer and application layer processing in service process module, wherein containing current technology single service process chip all function, and increasing interface adaptive logic used for uniformly adapting multiple operation multiple operation to E1 / T1 frame chip physical layer interface to service process module physical layer interface. Service process module correlation processing function can be realized in hard ware mode by ASIC chip, also in software mode by CPU, NP, DSP etc processor. Interface adaptive logic also can added in physical layer with time slot crossing, time slot merging, inserting random error, and replacing assigned content etc processing.

Owner:HUAWEI TECH CO LTD

Robust Noise Estimation

An enhancement system improves the estimate of noise from a received signal. The system includes a spectrum monitor that divides a portion of the signal at more than one frequency resolution. Adaptation logic derives a noise adaptation factor of the received signal. A plurality of devices tracks the characteristics of an estimated noise in the received signal and modifies multiple noise adaptation rates. Weighting logic applies the modified noise adaptation rates derived from the signal divided at a first frequency resolution to the signal divided at a second frequency resolution.

Owner:MALIKIE INNOVATIONS LTD

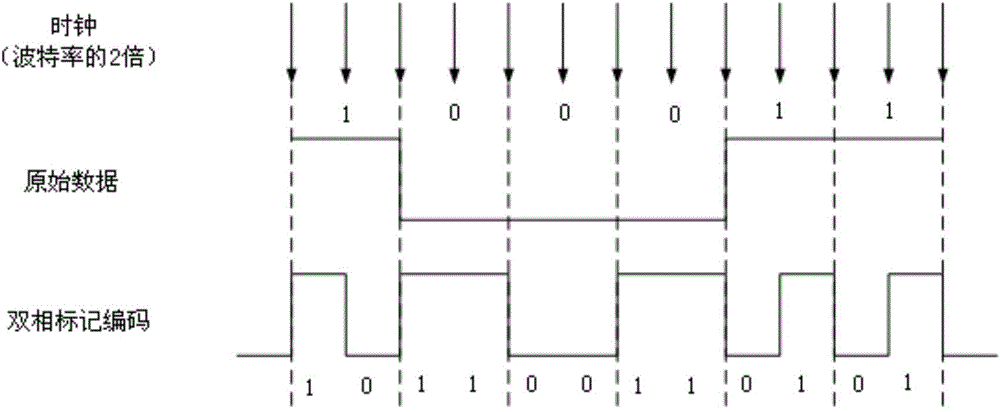

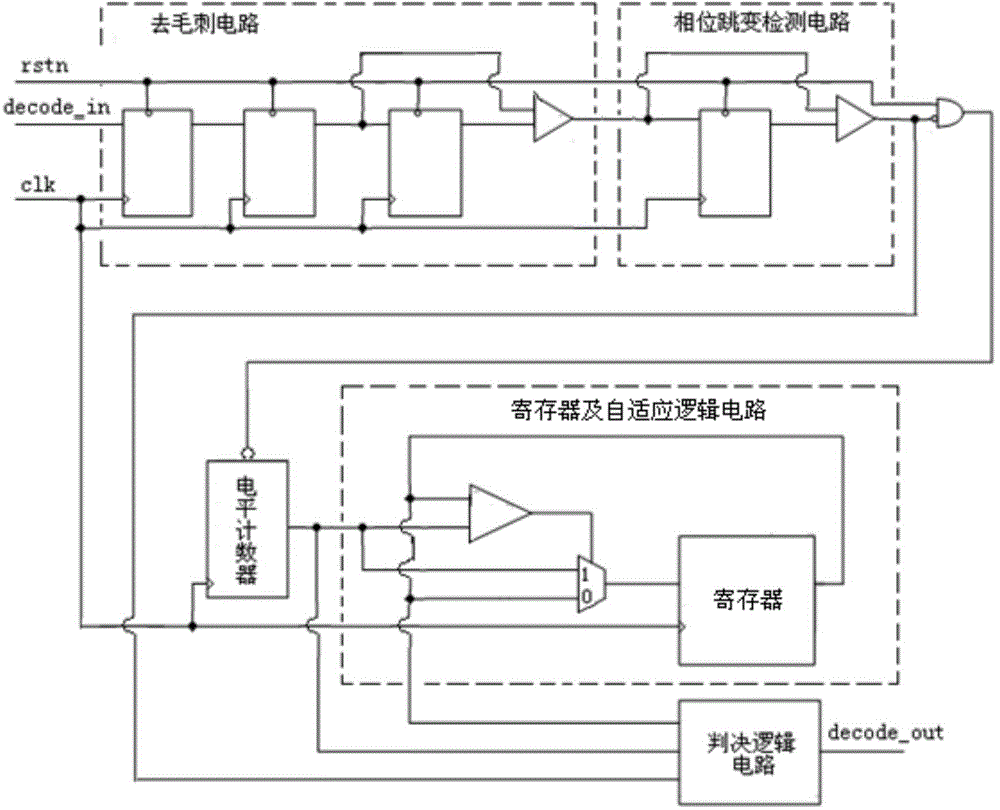

Asynchronous decoder and asynchronous decoding method for BMC (Biphase Mark Coding) signal

ActiveCN104639176AImprove receiving data performanceAvoid mistakesCode conversionCoding detailsProcessor registerPhase change

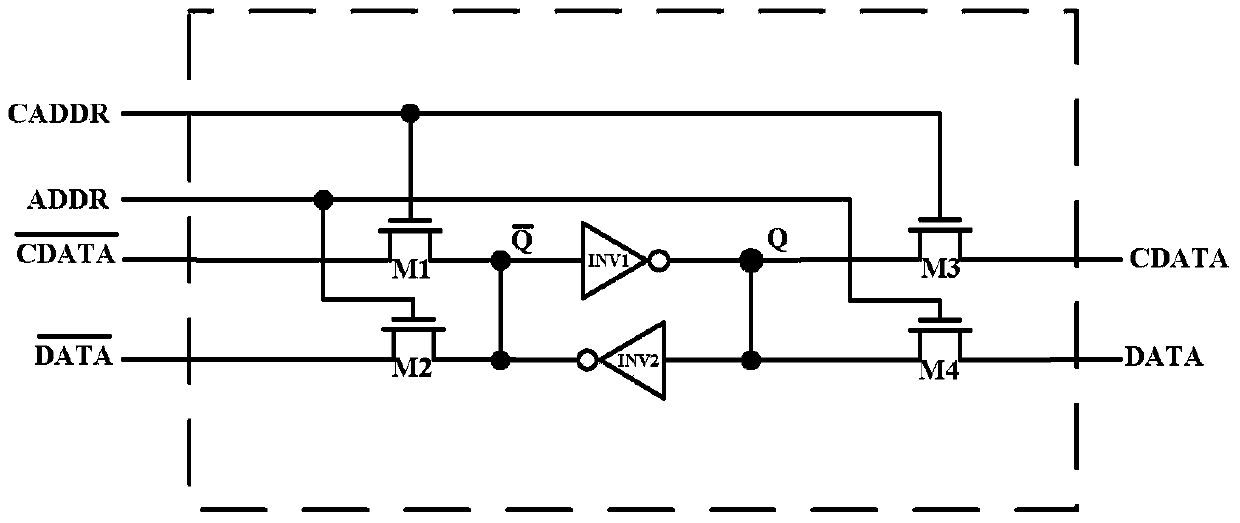

The invention discloses an asynchronous decoder for a BMC (Biphase Mark Coding) signal. The asynchronous decoder comprises a deburring circuit, a phase jump detection circuit, a level counter, a register, an adaptive logic circuit and a judgment logic circuit, wherein the phase jump detection circuit is used for detecting the edge of the phase change of the BMC signal, and taking the edge of the phase change as a judgment point of data, a reset point of the level counter and an update point of a half-bit sample point quantity; the level counter is used for recording the sample point quantity of each level; at the judgment point of the data, a judgment on whether 0 or 1 is received is made through comparison of the size relation between the level counter and the half-bit sample point quantity; and the half-bit sample point quantity is acquired through the adaptive logic circuit. The invention further discloses an asynchronous decoding method for the BMC signal. Through adoption of the asynchronous decoder and the asynchronous decoding method, the reception performance of the asynchronous decoder for the BMC signal can be improved, and reception data errors are avoided.

Owner:SHANGHAI HUAHONG INTEGRATED CIRCUIT

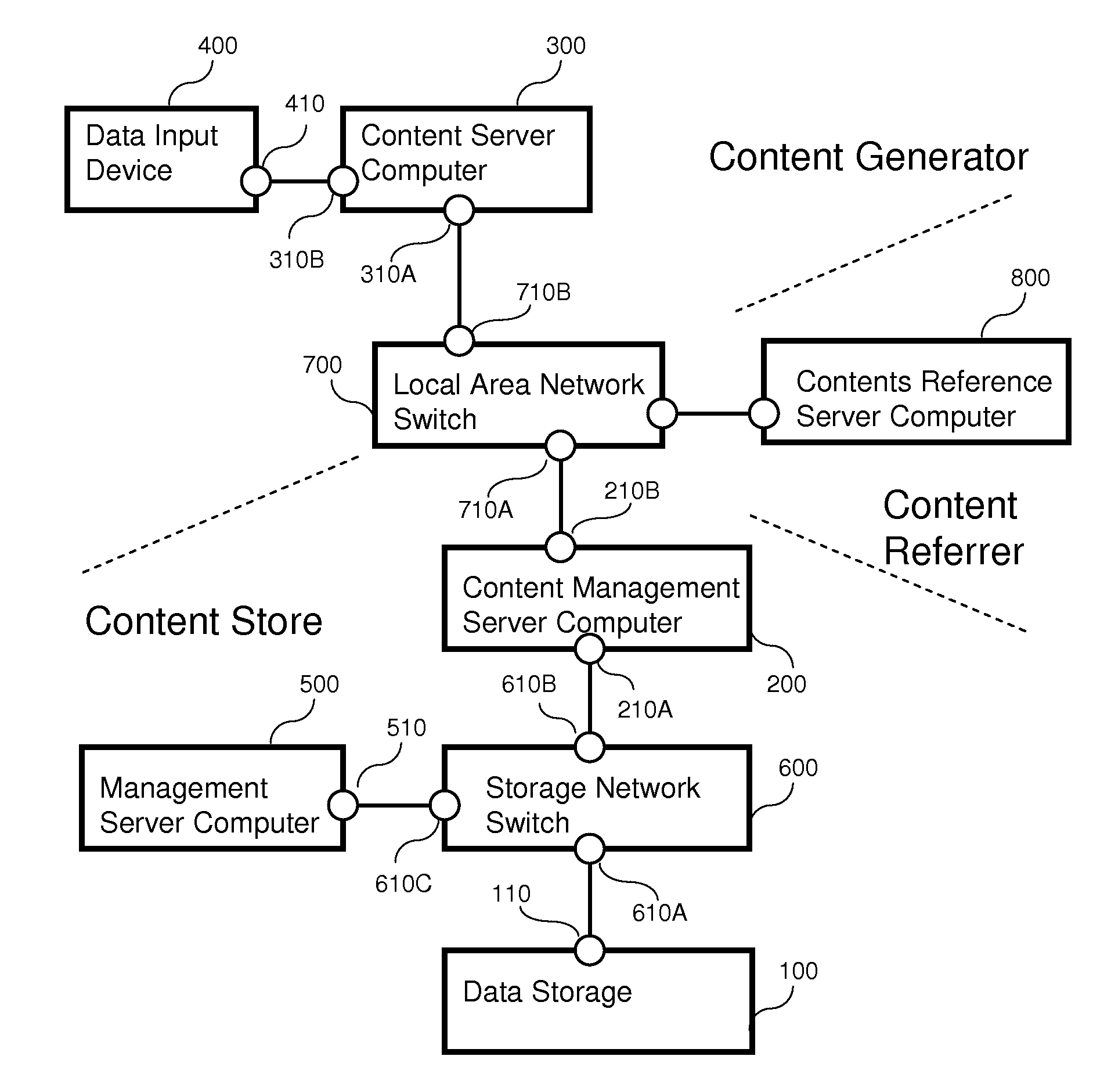

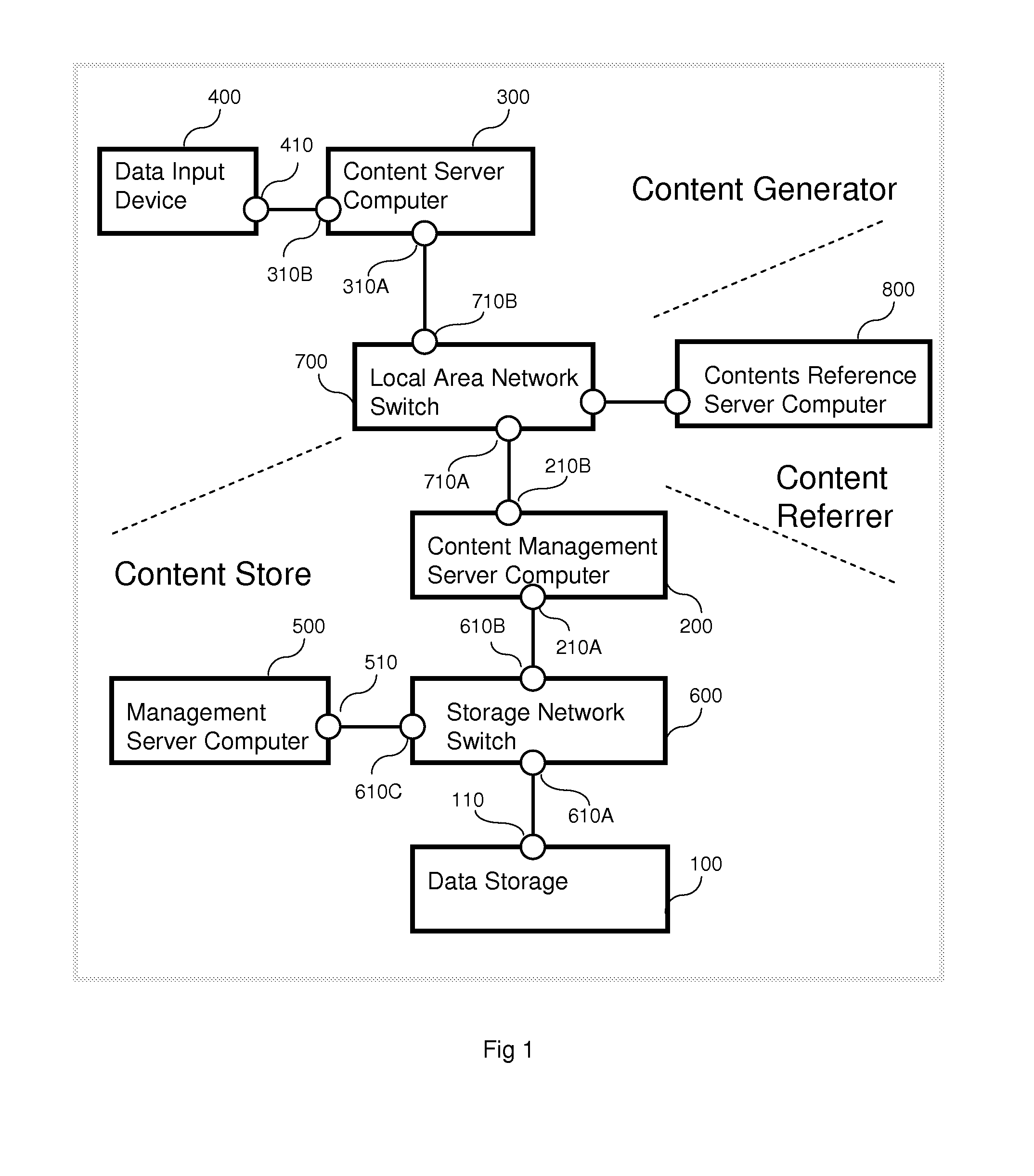

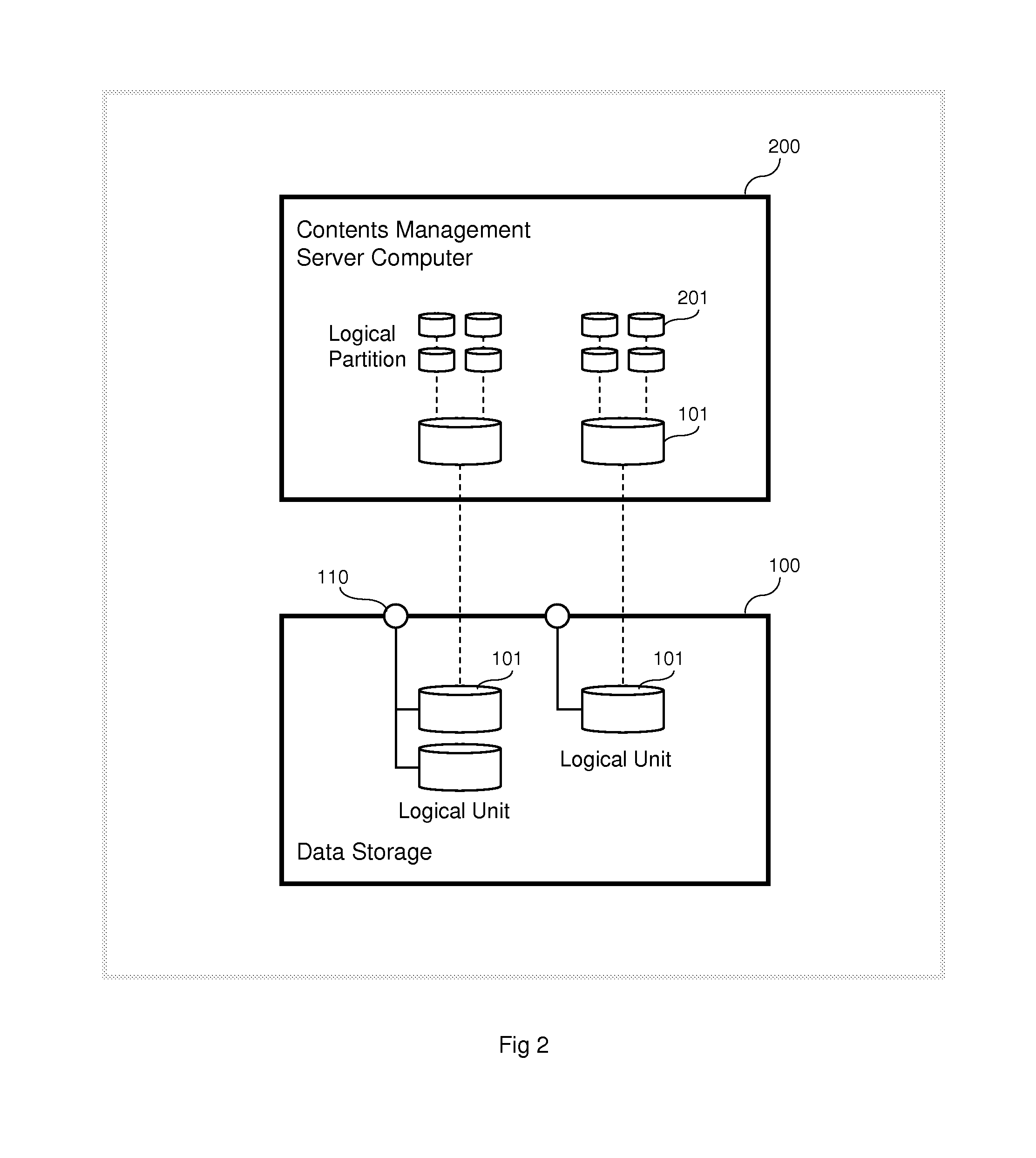

Efficient data storage method for multiple file contents

InactiveUS20120246205A1Improve production efficiencyImprove performanceDigital data information retrievalSpecial data processing applicationsData storeContent management

Embodiments of the invention provide efficient data storage for multiple file contents. In specific embodiments, a content management computer is coupled via a network to a storage system, and comprises a processor, a memory, and a content compose / decompose module. The content compose / decompose module is configured to: decompose a file into multiple parts of data and store the multiple parts into adaptive logical storage partitions; and in response to a read request for the file, re-compose the multiple parts into an original file and send the original file. The file is decomposed into the multiple parts based on both structure and characteristics of the data in the file. The multiple parts are stored into different media provided by the adaptive logical storage partitions according to the structure and characteristics of the data in the multiple parts.

Owner:HITACHI LTD