Patents

Literature

40results about How to "Delay characteristic" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

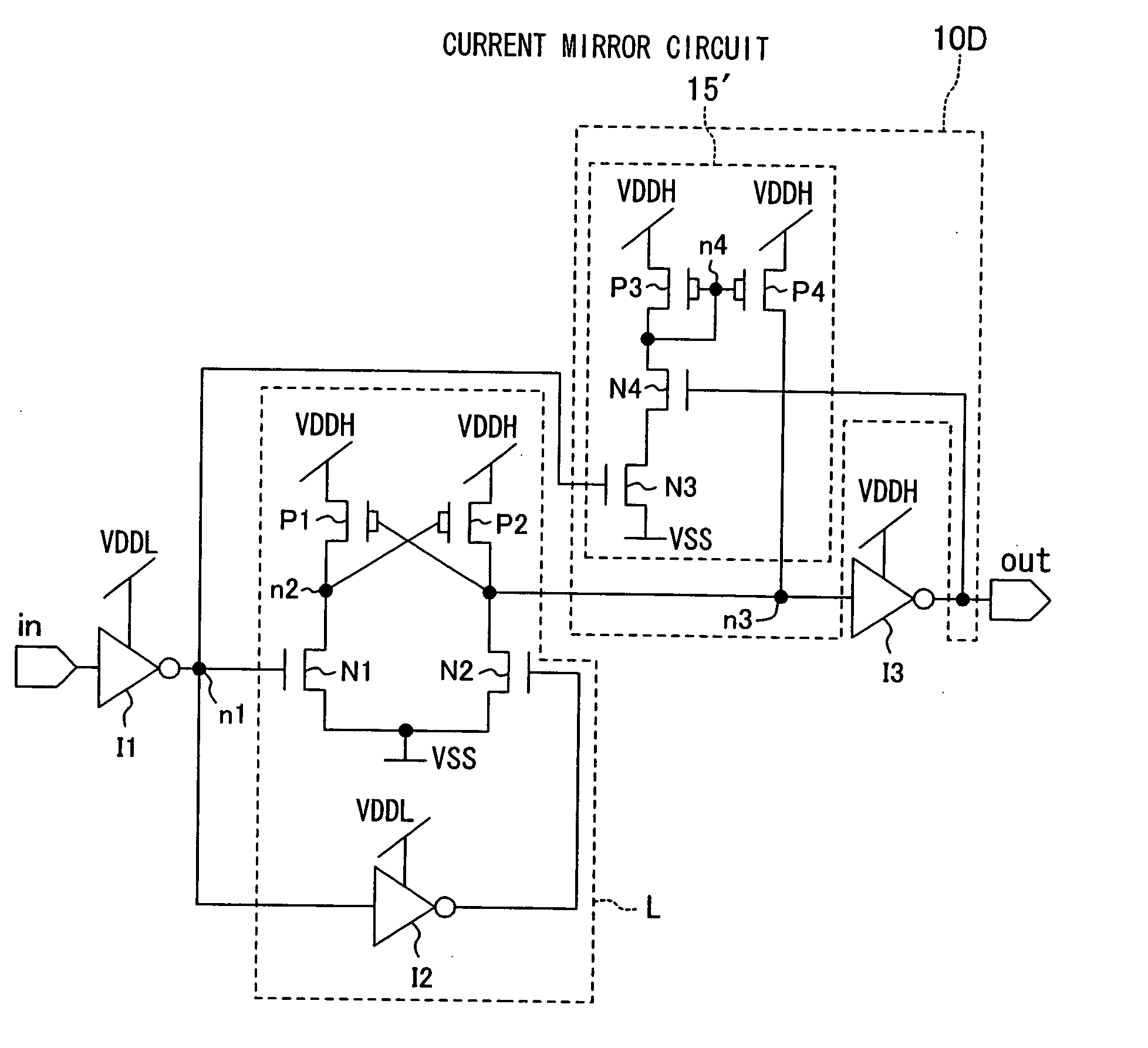

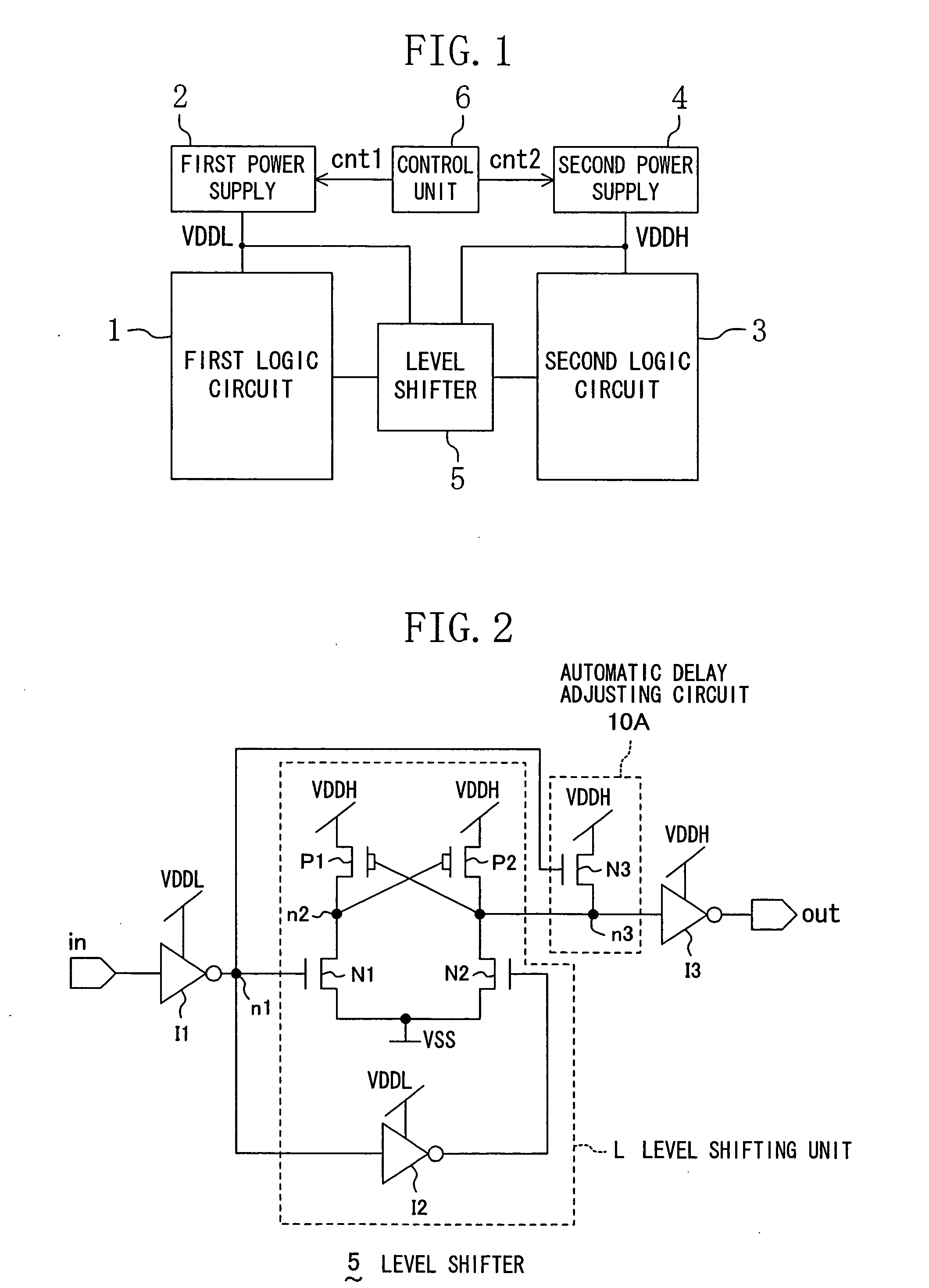

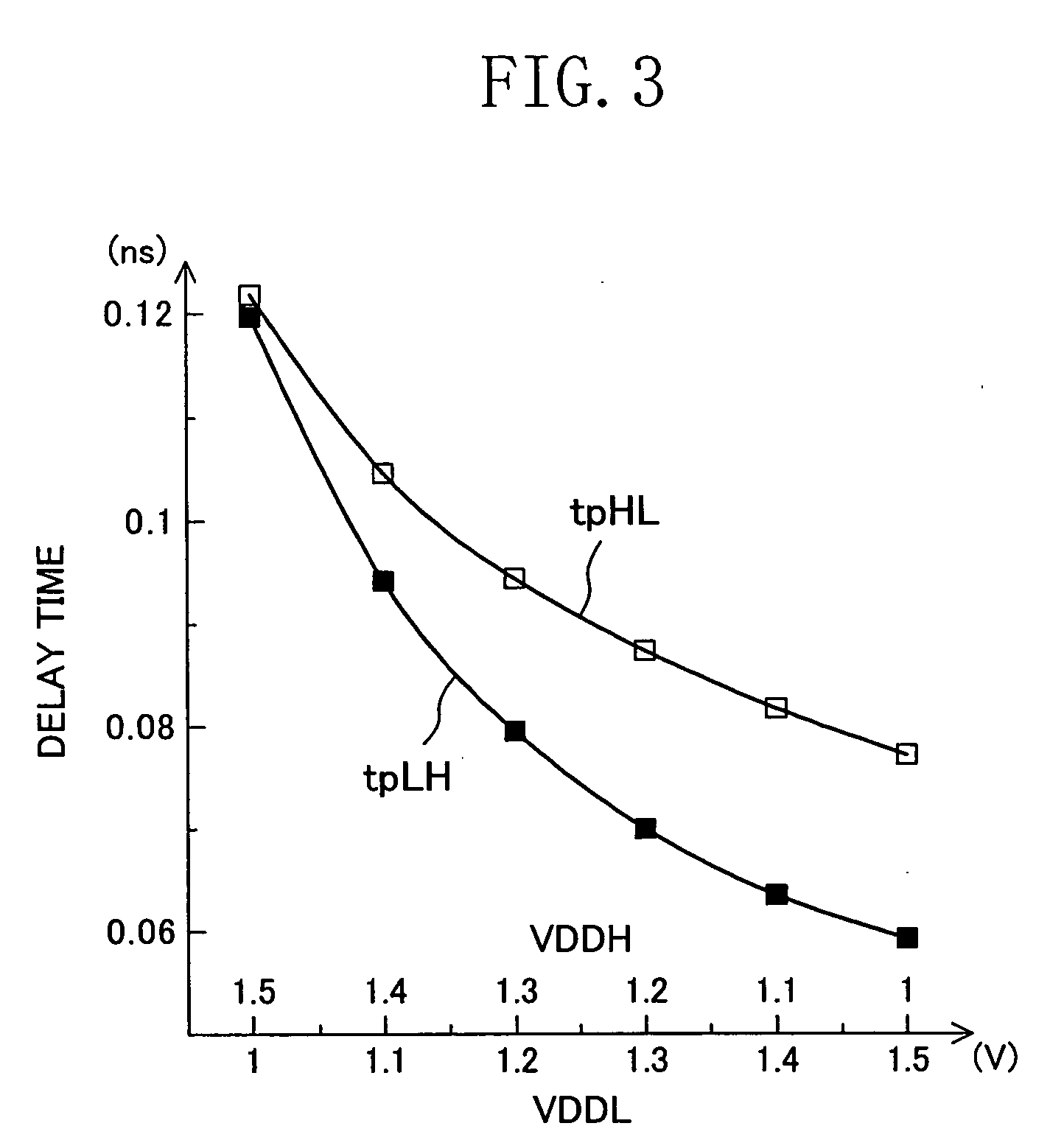

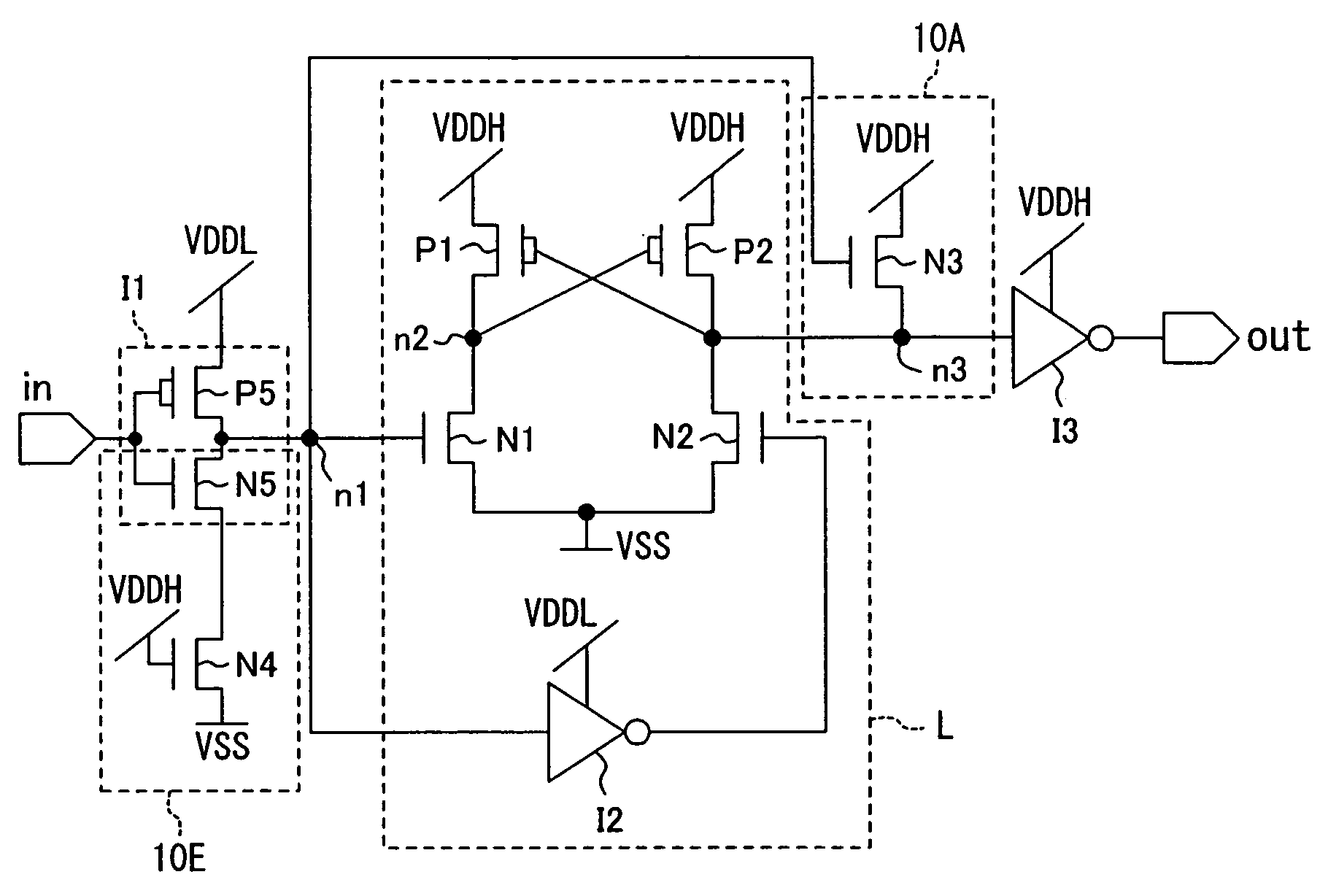

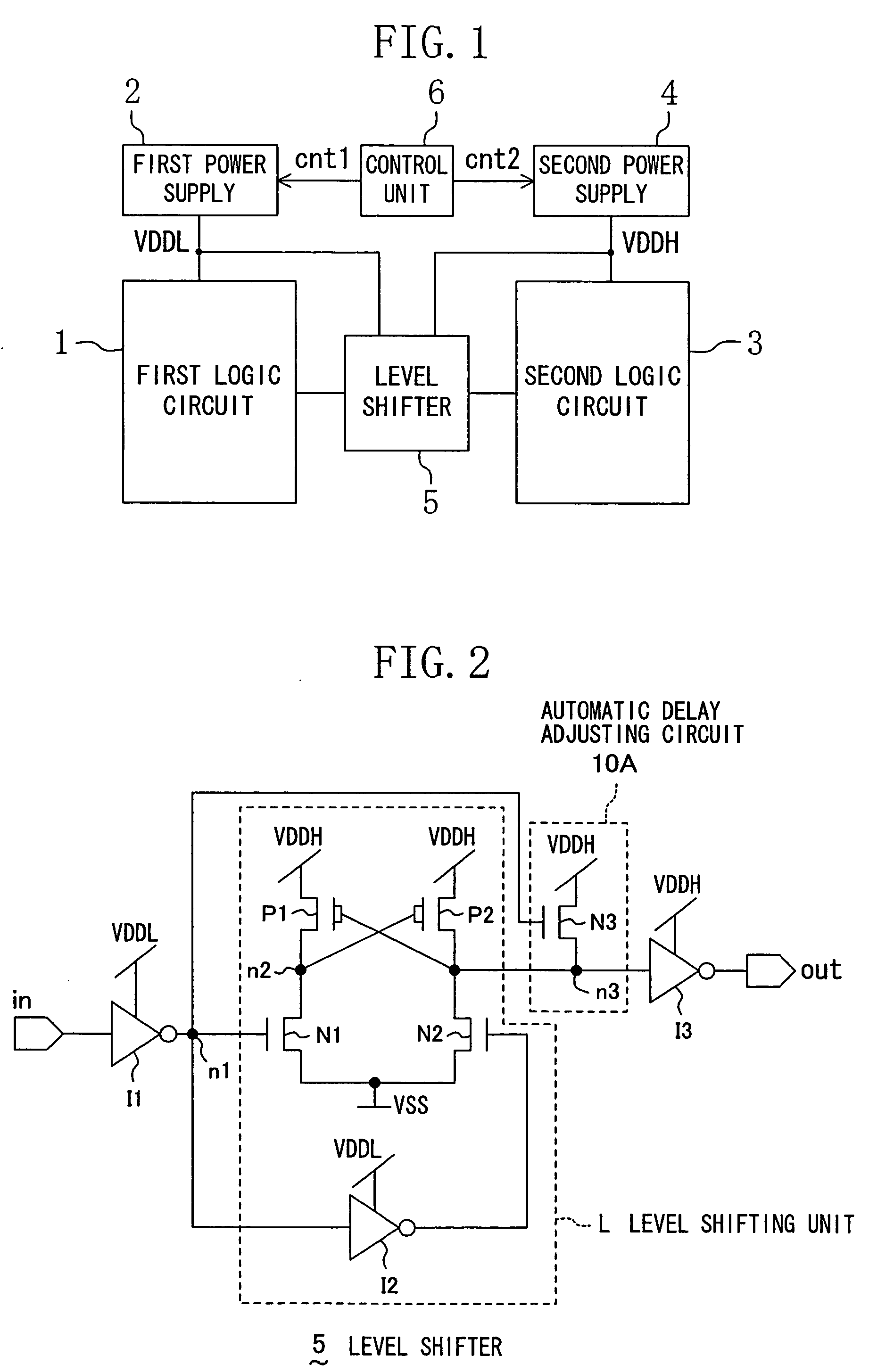

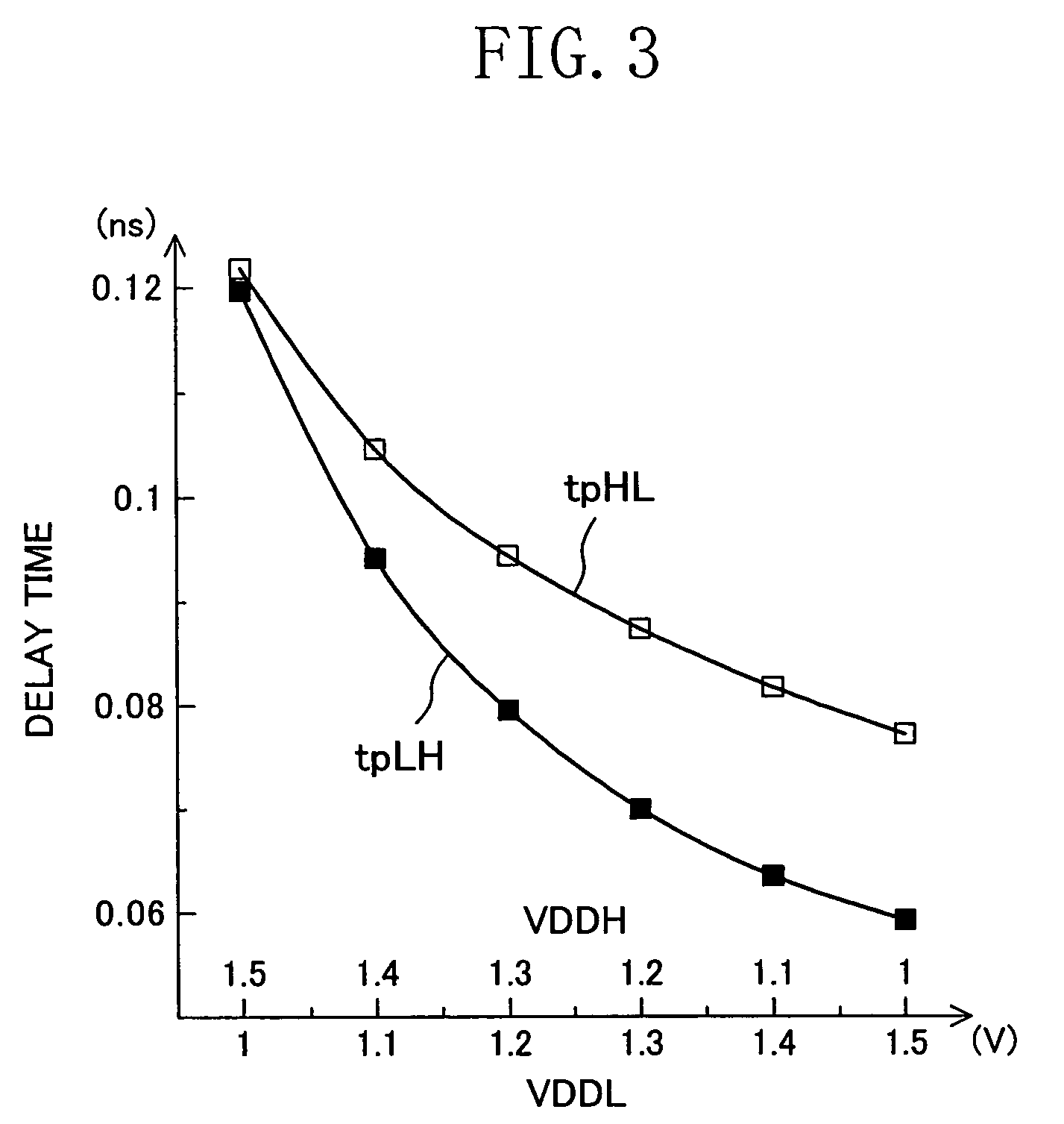

Level shifter having automatic delay adjusting function

InactiveUS20050258887A1Increase the number ofReduce decreasePulse automatic controlInstant pulse delivery arrangementsLevel shiftingDelayed time

In a level shifter, in the case where the amplitude voltage of an input signal (i.e., a first power voltage VDDL) input to an input terminal is changed to be higher and the amplitude voltage of an output signal (i.e., a second power voltage VDDH) output from an output terminal is changed to be lower, a fall delay time of the signal output from the output terminal tends to be longer than a rise delay time of the signal. However, an inverted input signal obtained by an inverter is input to a level shifting unit and also to the gate of an N-type transistor, and therefore, the N-type transistor is turned on at the fall of the input signal input to the input terminal, so as to supply a current based on the second power voltage VDDH to an output node of the level shifting unit for assisting the shift into H level performed in the level shifting unit. Accordingly, even when at least one of the amplitude voltage of the input signal and the amplitude voltage of the output signal is changed, balance between the fall delay time characteristic and the rise delay time characteristic of the output signal can be satisfactorily kept.

Owner:SOCIONEXT INC

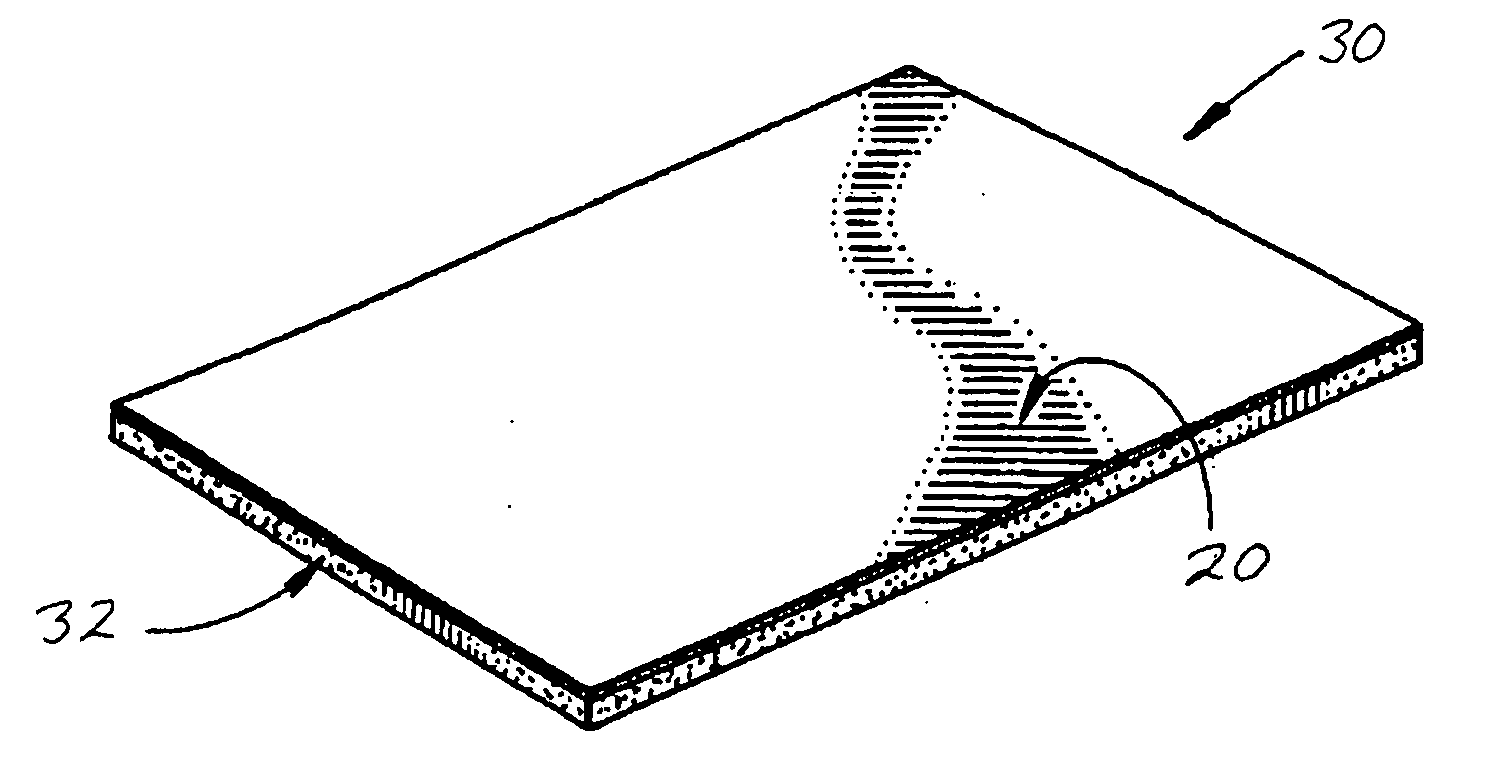

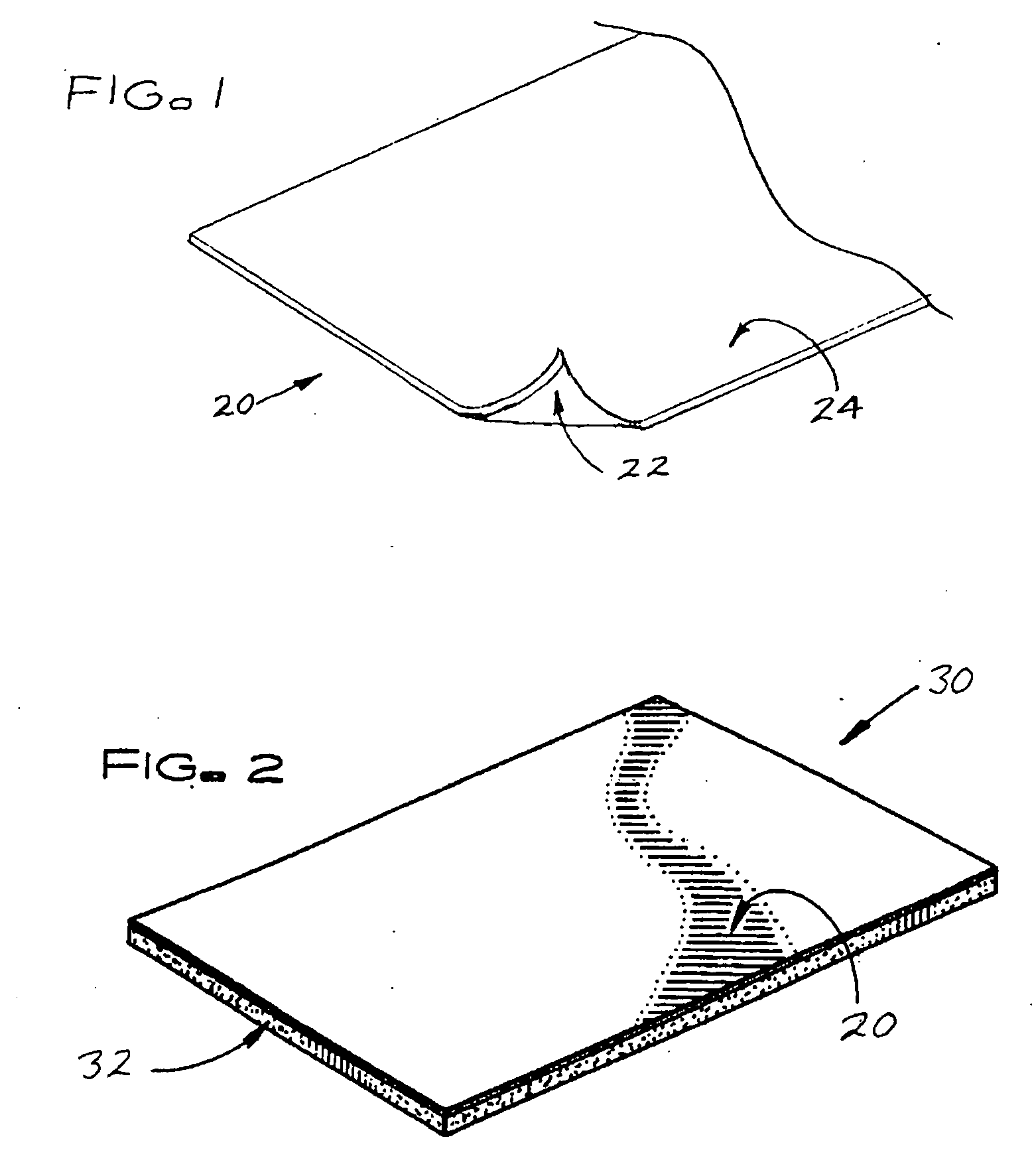

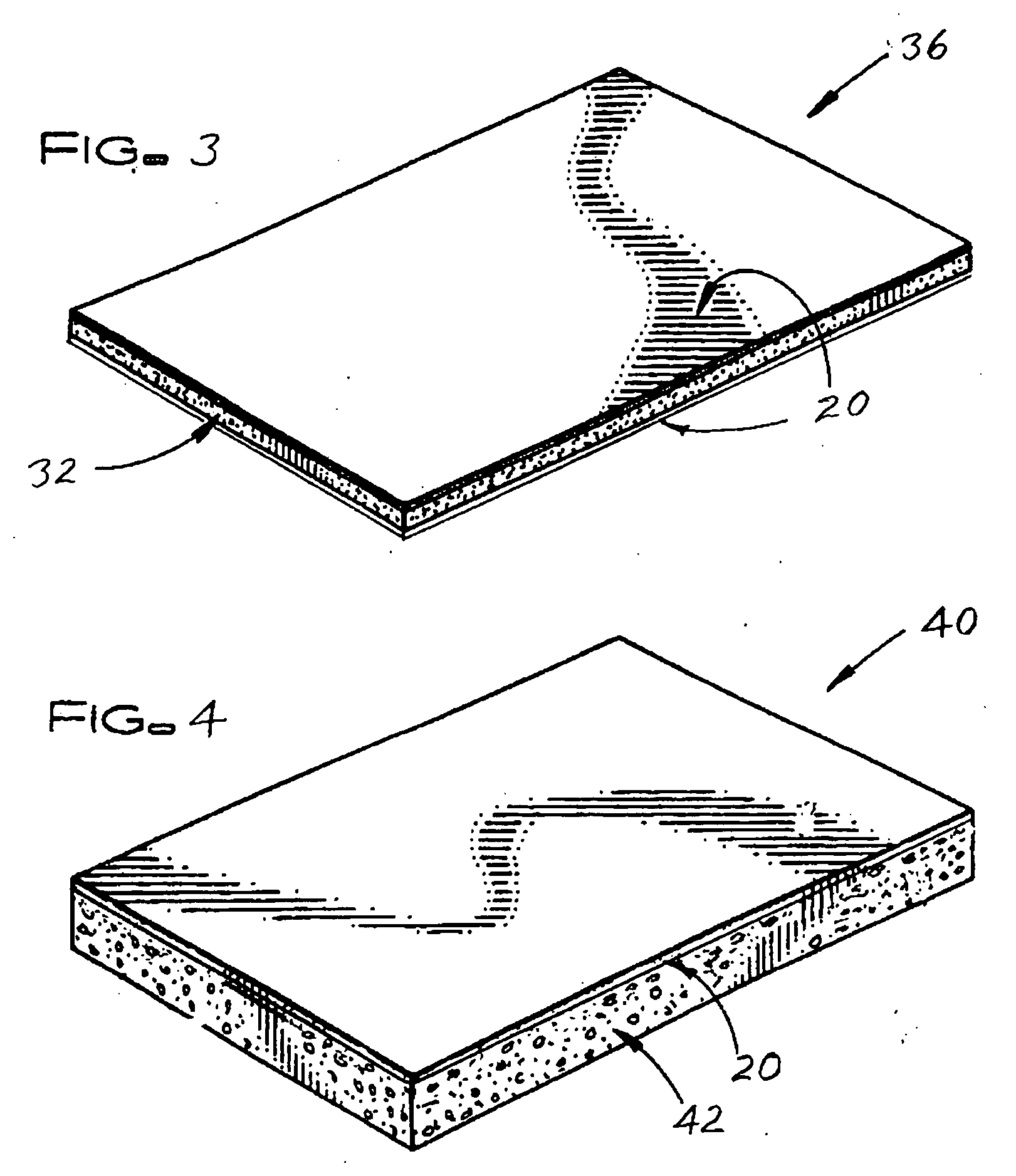

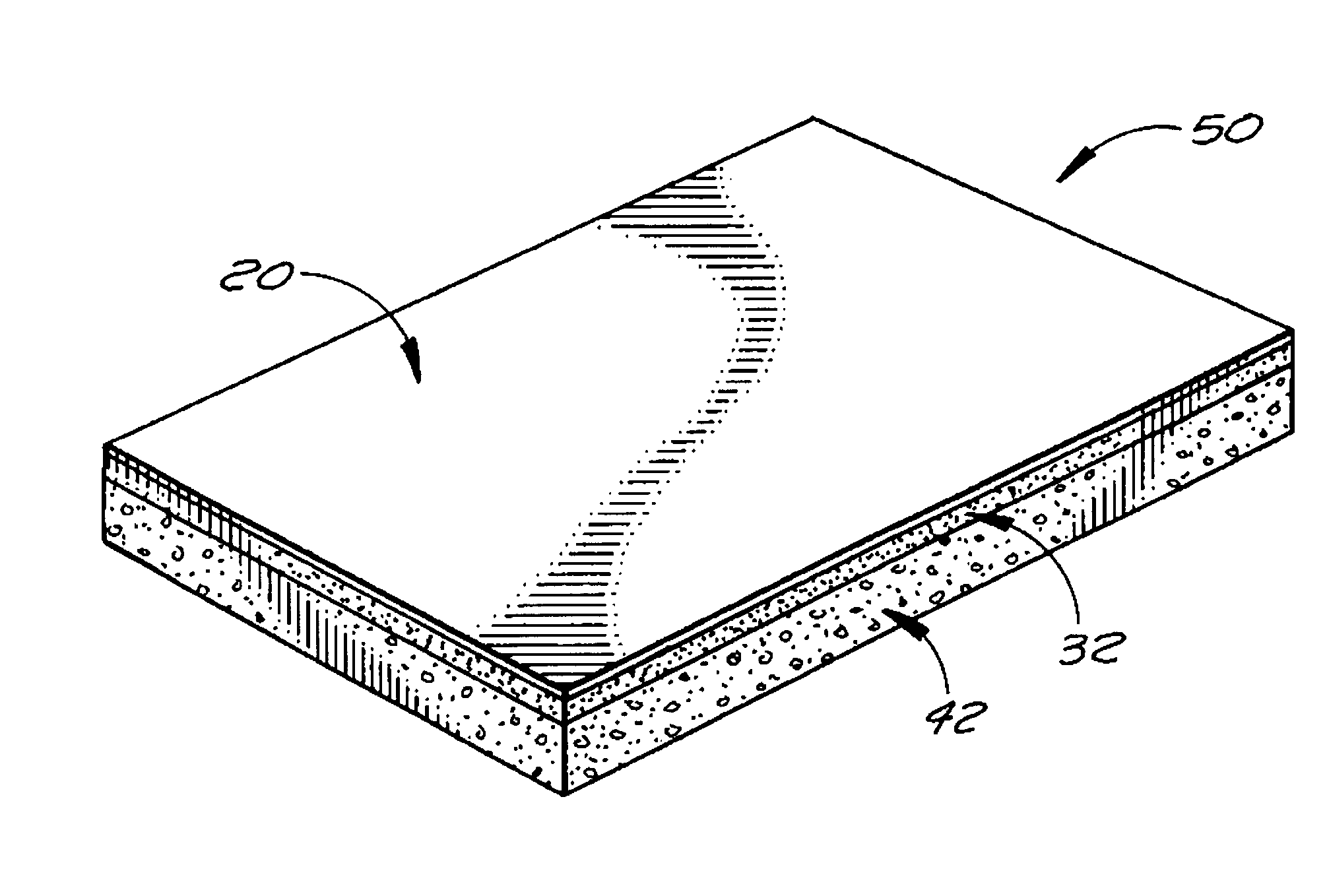

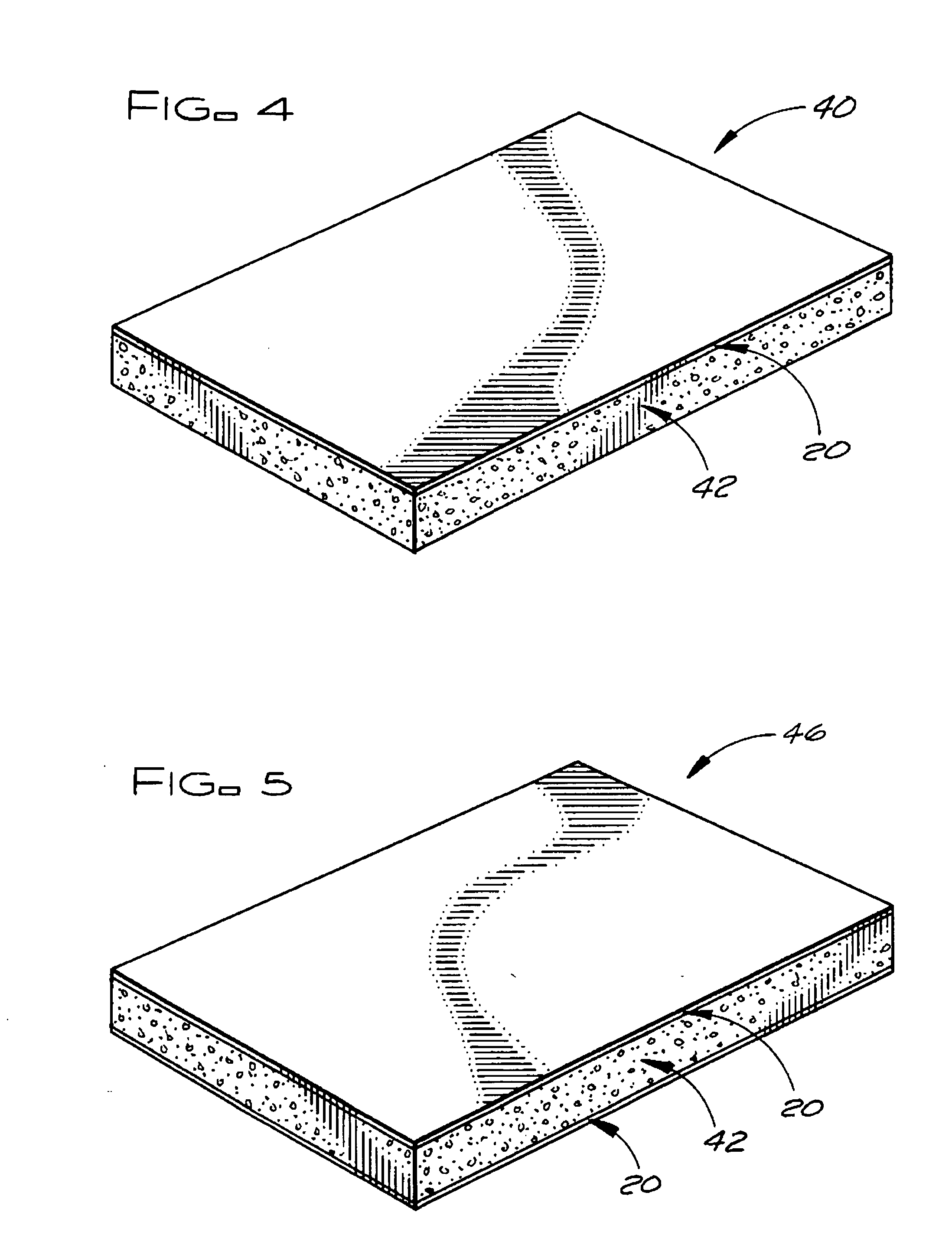

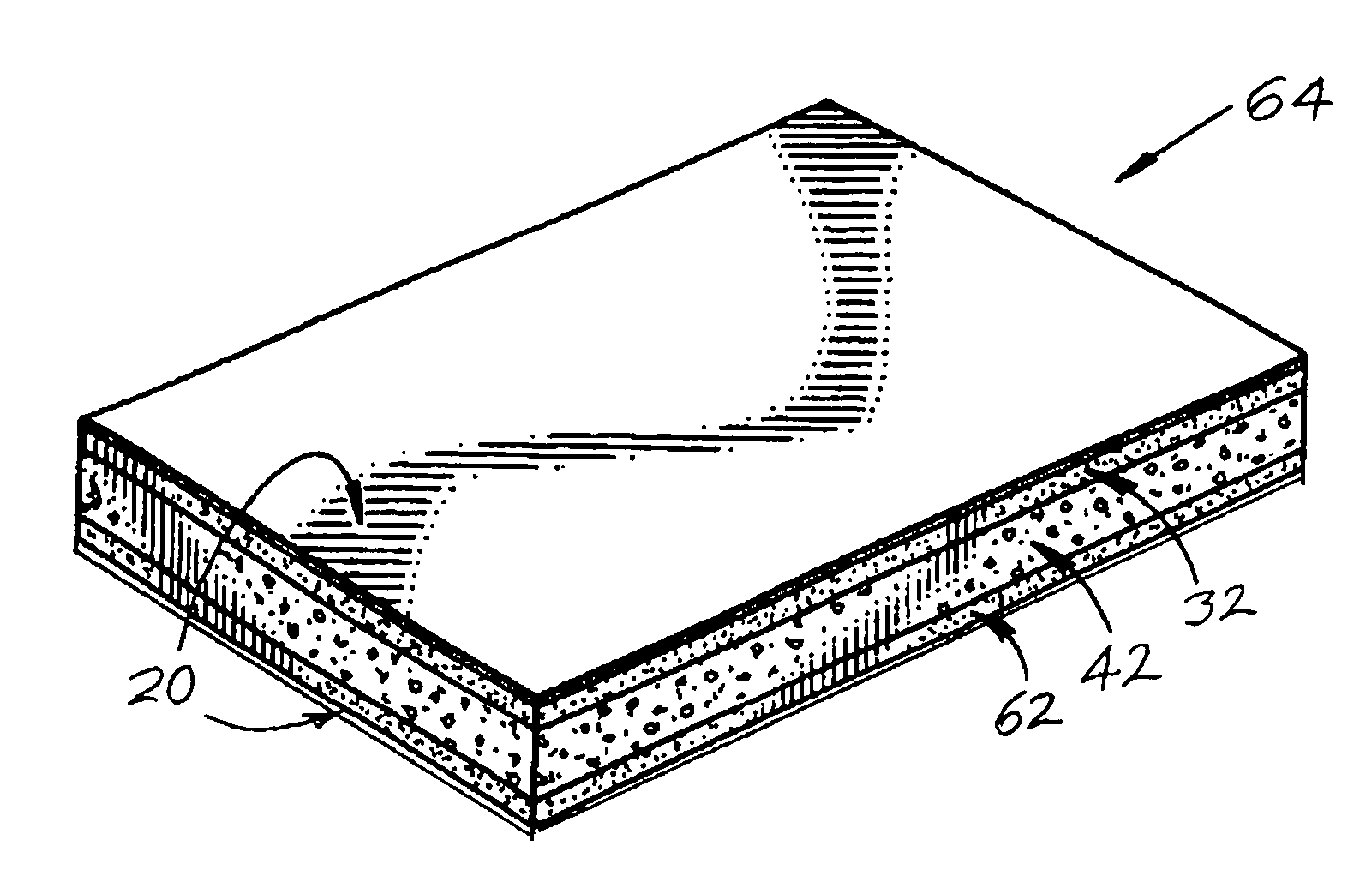

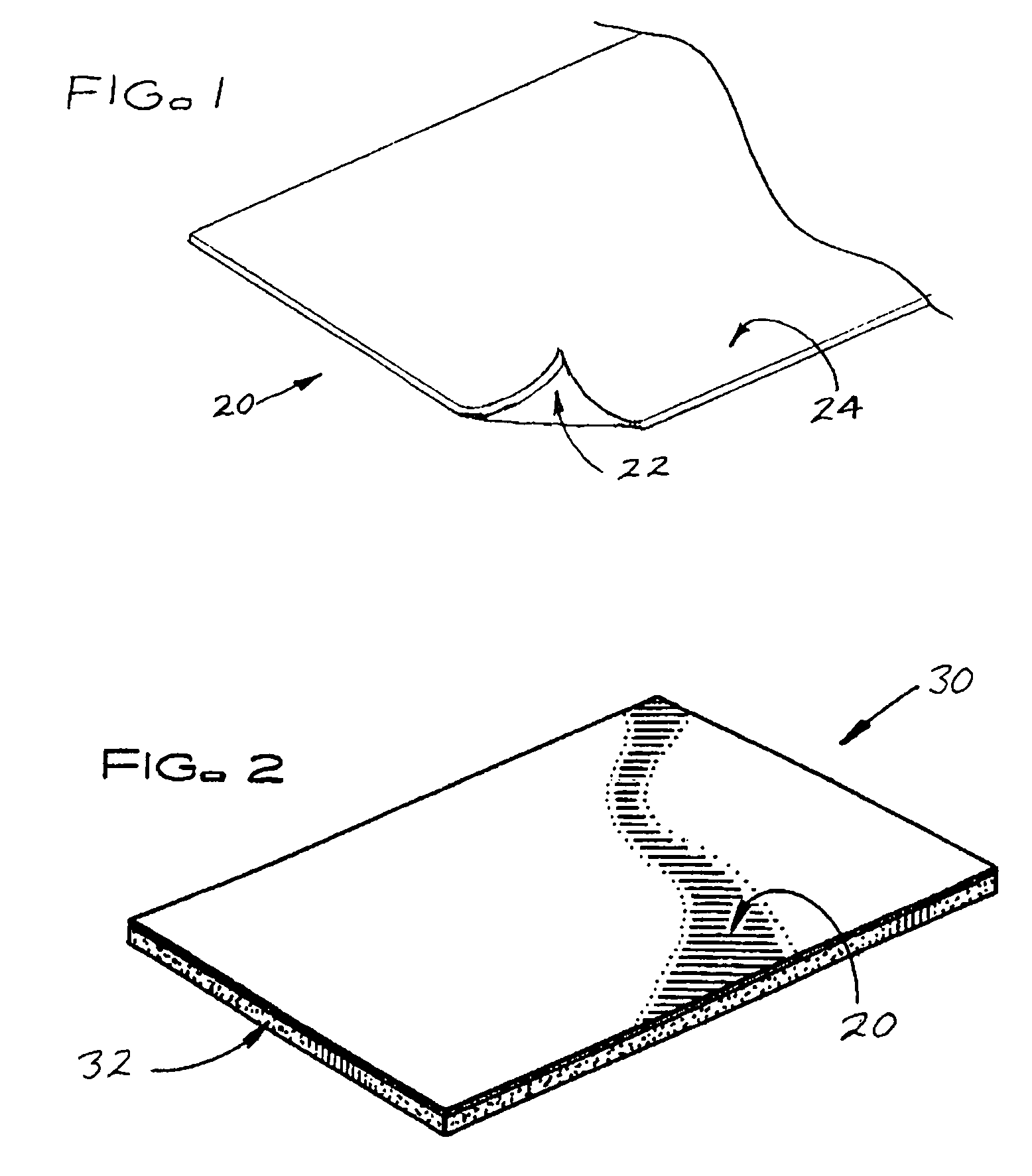

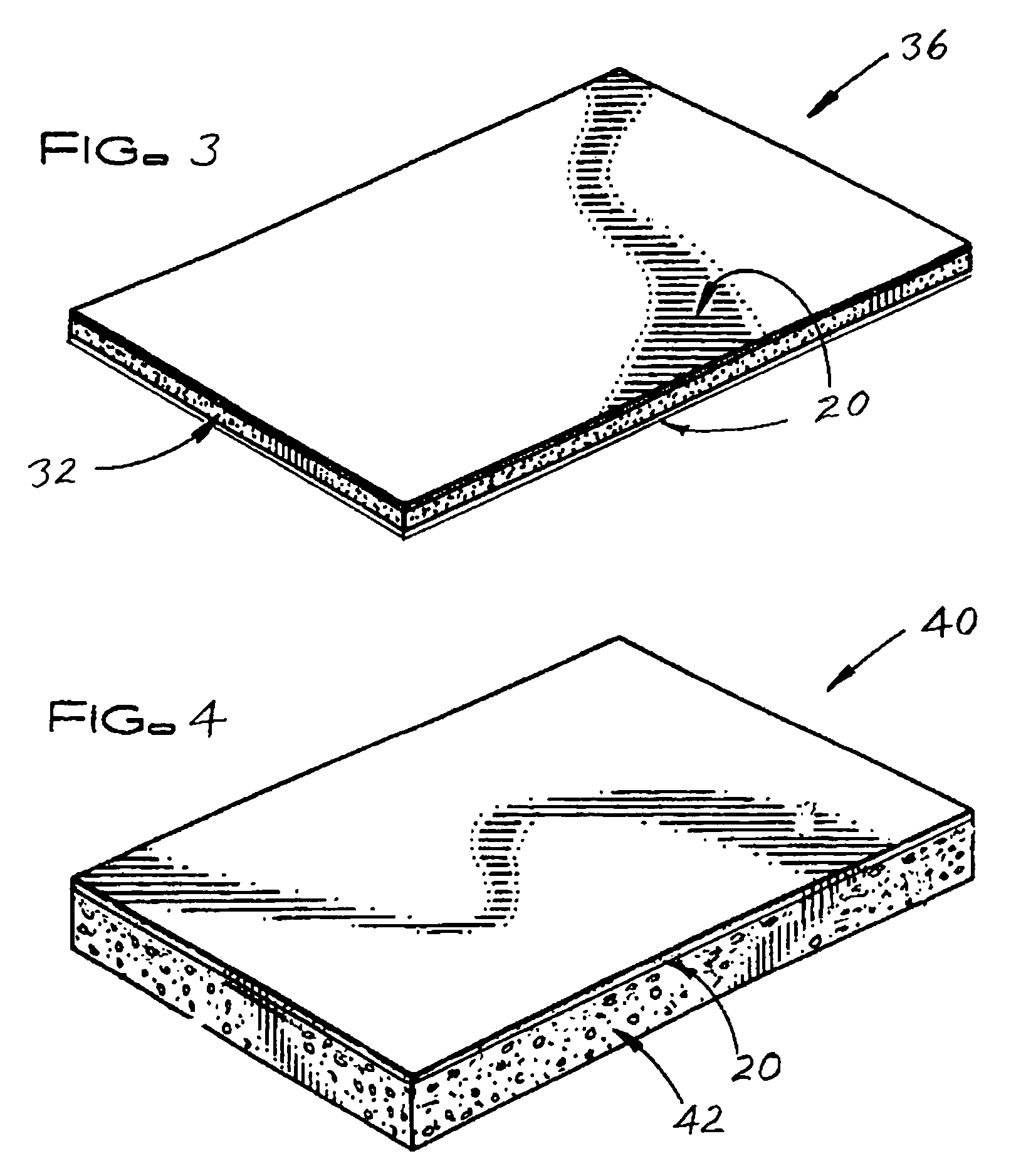

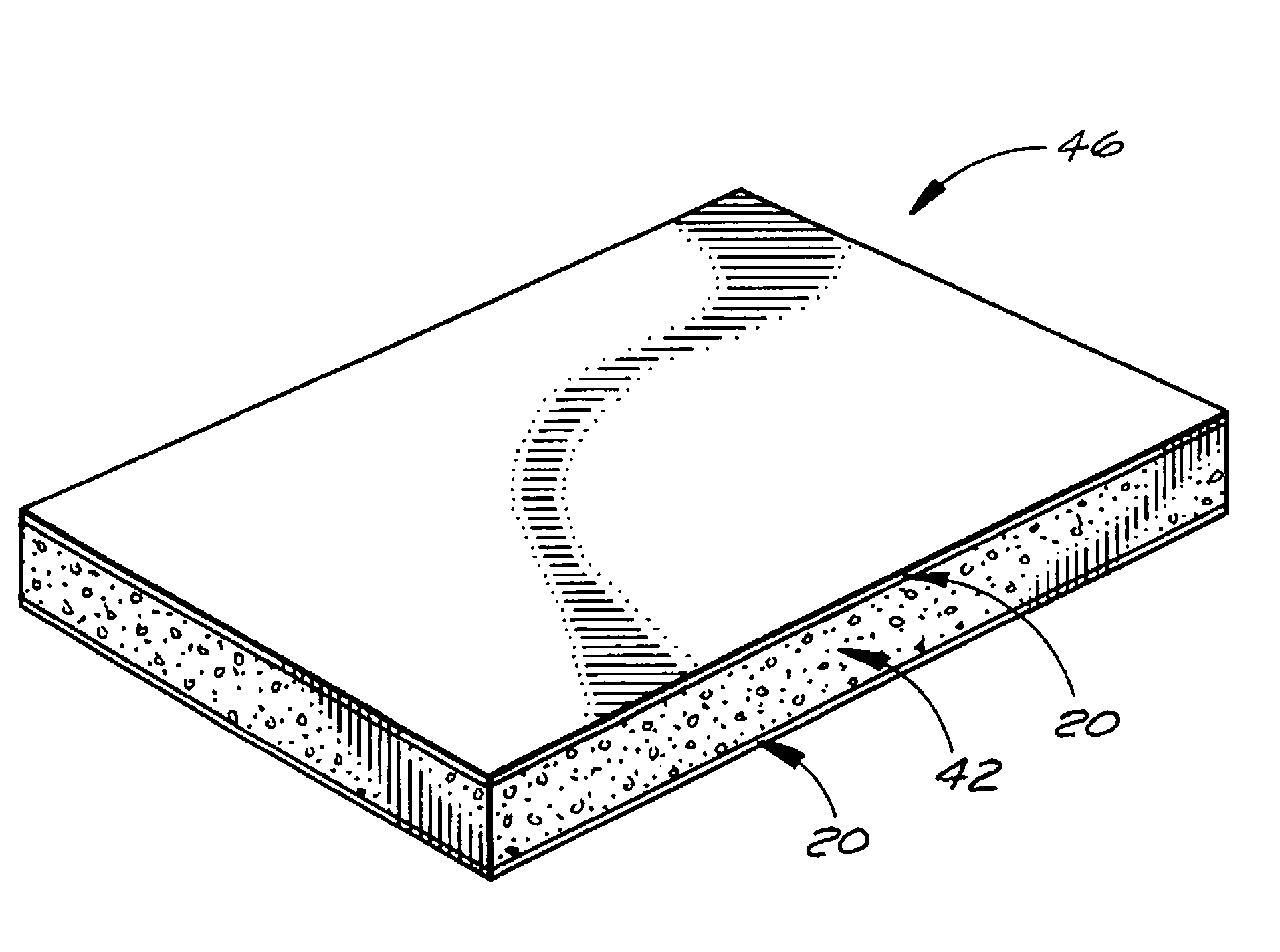

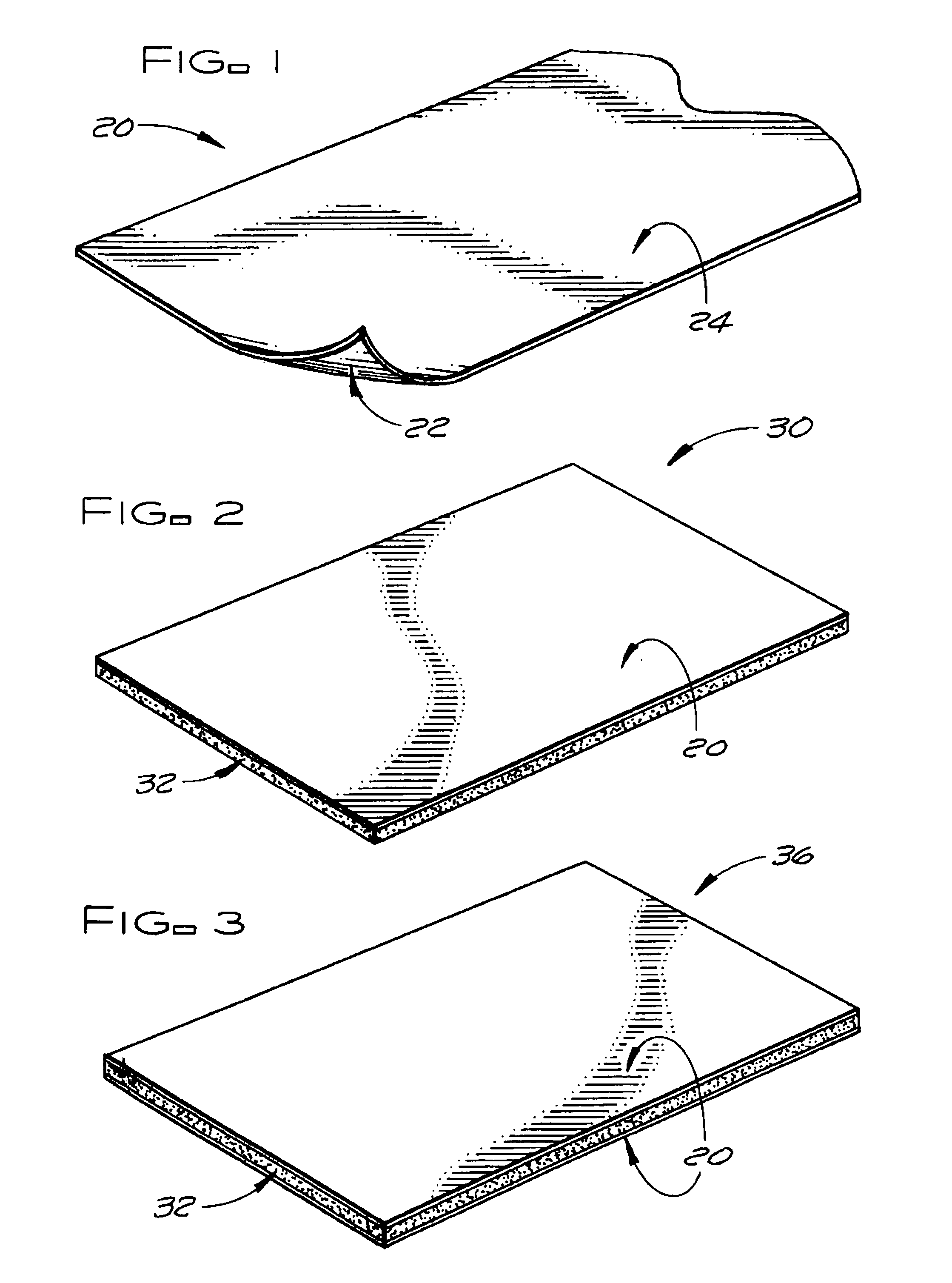

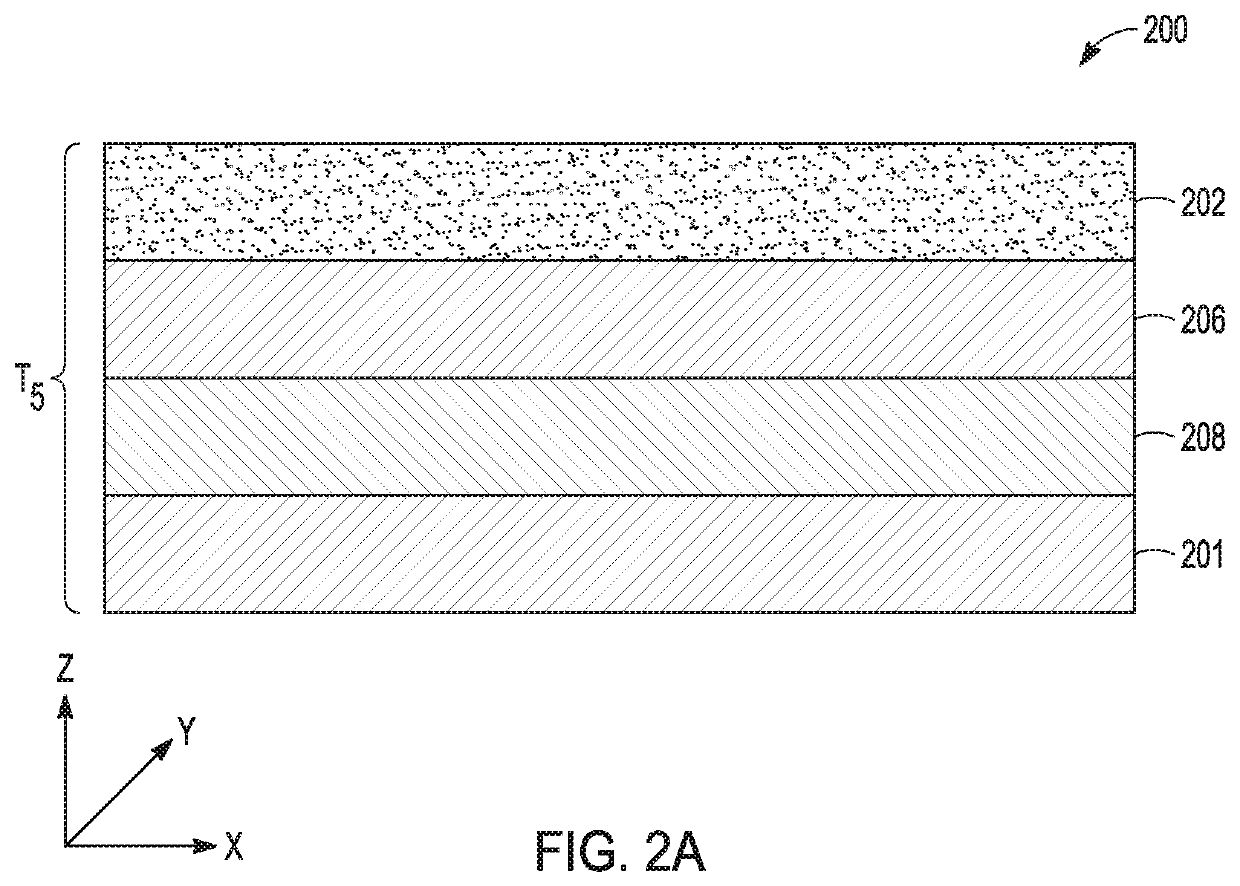

Facer and faced polymeric roofing board

ActiveUS20060275561A1Improve propertiesReduce spreadRoof covering using slabs/sheetsSynthetic resin layered productsGlass fiberWater vapor

A prefabricated, faced roofing board composite includes a first board layer made of a polymeric material or a predominantly polymeric material and a fire and weather resistant fiberglass-based facer bonded to a top major surface of the first board layer and forming a top major surface of the composite. The fiberglass-based facer is substantially impervious to the passage of hot gases of combustion, water, and water vapor through the thickness of the fiberglass-based facer. The faced composite can be a cover board, an insulation board; can include cover board and insulation board layers; and can include cover board, insulation board, and baseboard layers. A second fiberglass-based facer that is substantially impervious to the passage of hot gases of combustion through its thickness can form a bottom major surface of the composite. The polymeric material or predominantly polymeric material of the board layer to which each fiberglass-based facer is bonded penetrates part of the way through, but not completely through, the fiberglass-based facer.

Owner:JOHNS MANVILLE CORP

Facer and faced polymeric roofing board

ActiveUS20060276093A1Reduced flame spread characteristicImprove propertiesRoof covering using slabs/sheetsSynthetic resin layered productsGlass fiberCombustion

A prefabricated, faced roofing board composite includes a first board layer made of a polymeric material or a predominantly polymeric material and a fire and weather resistant fiberglass-based facer bonded to a top major surface of the first board layer and forming a top major surface of the composite. The fiberglass-based facer is substantially impervious to the passage of hot gases of combustion, water, and water vapor through the thickness of the fiberglass-based facer. The faced composite can be a cover board, an insulation board; can include cover board and insulation board layers; and can include cover board, insulation board, and baseboard layers. A second fiberglass-based facer that is substantially impervious to the passage of hot gases of combustion through its thickness can form a bottom major surface of the composite. The polymeric material or predominantly polymeric material of the board layer to which each fiberglass-based facer is bonded penetrates part of the way through, but not completely through, the fiberglass-based facer.

Owner:JOHNS MANVILLE CORP

Facer and faced polymeric roofing board

ActiveUS7749598B2Improve propertiesReduce spreadRoof covering using slabs/sheetsSynthetic resin layered productsGlass fiberCombustion

A prefabricated, faced roofing board composite includes a first board layer made of a polymeric material or a predominantly polymeric material and a fire and weather resistant fiberglass-based facer bonded to a top major surface of the first board layer and forming a top major surface of the composite. The fiberglass-based facer is substantially impervious to the passage of hot gases of combustion, water, and water vapor through the thickness of the fiberglass-based facer. The faced composite can be a cover board, an insulation board; can include cover board and insulation board layers; and can include cover board, insulation board, and baseboard layers. A second fiberglass-based facer that is substantially impervious to the passage of hot gases of combustion through its thickness can form a bottom major surface of the composite. The polymeric material or predominantly polymeric material of the board layer to which each fiberglass-based facer is bonded penetrates part of the way through, but not completely through, the fiberglass-based facer.

Owner:JOHNS MANVILLE CORP

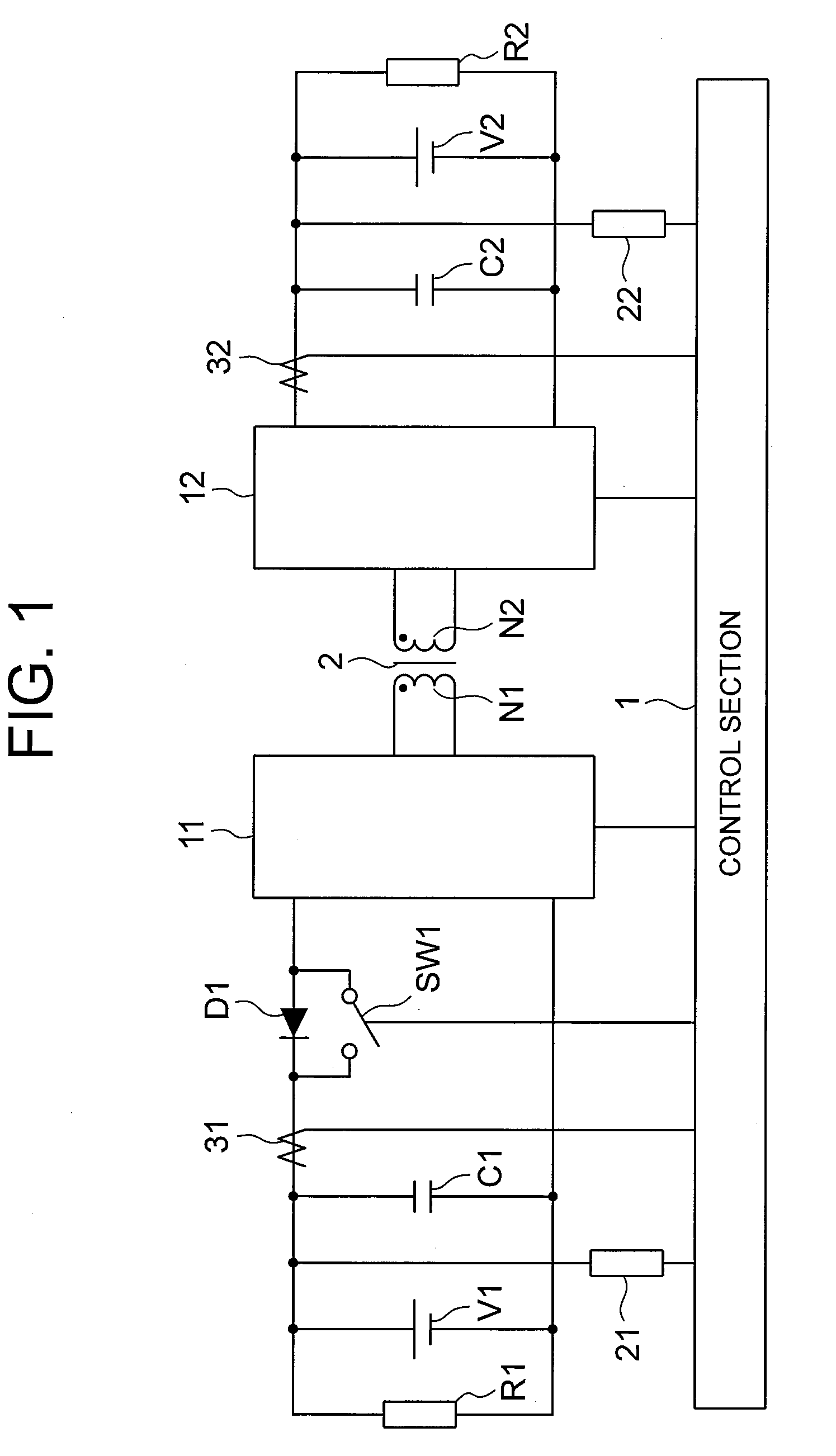

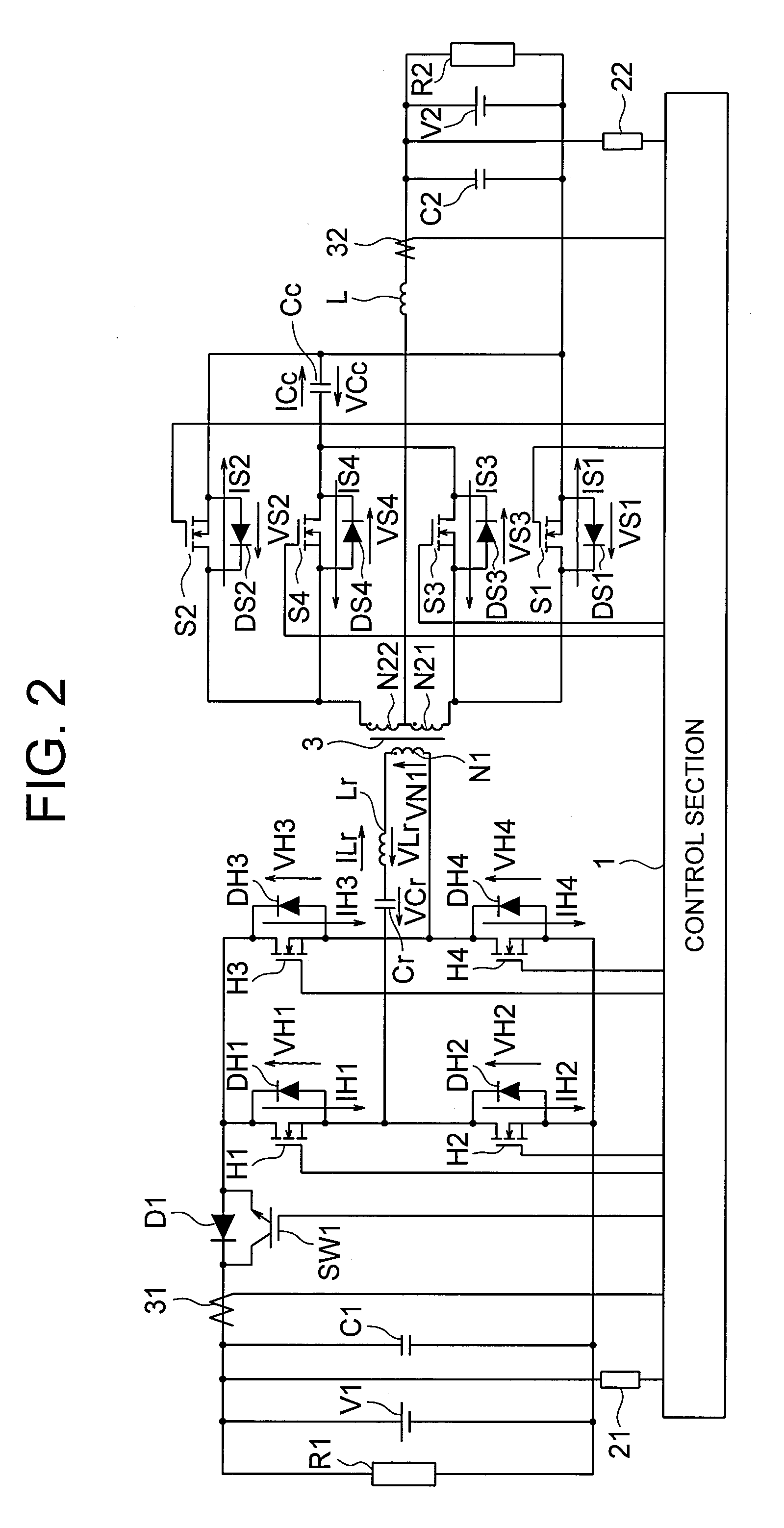

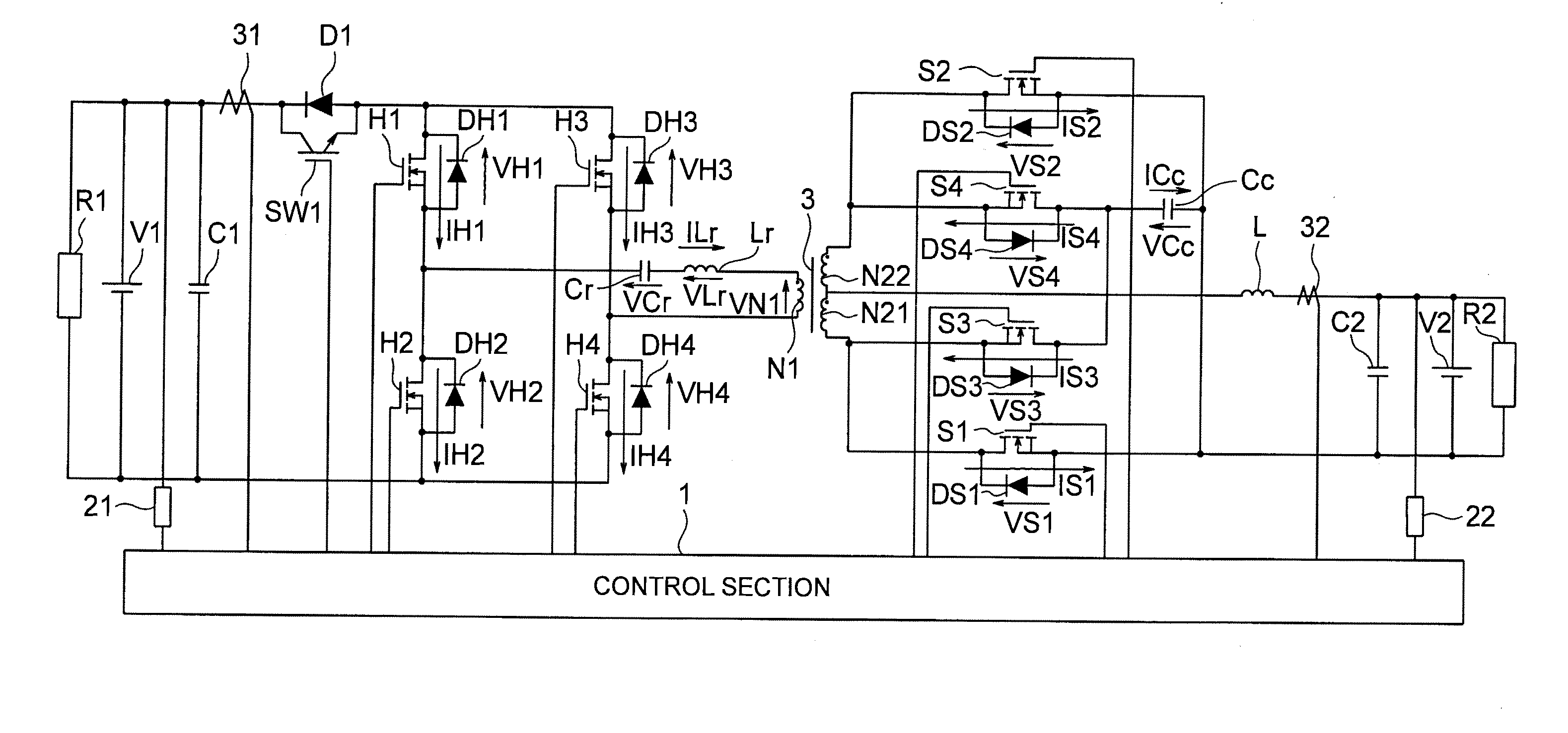

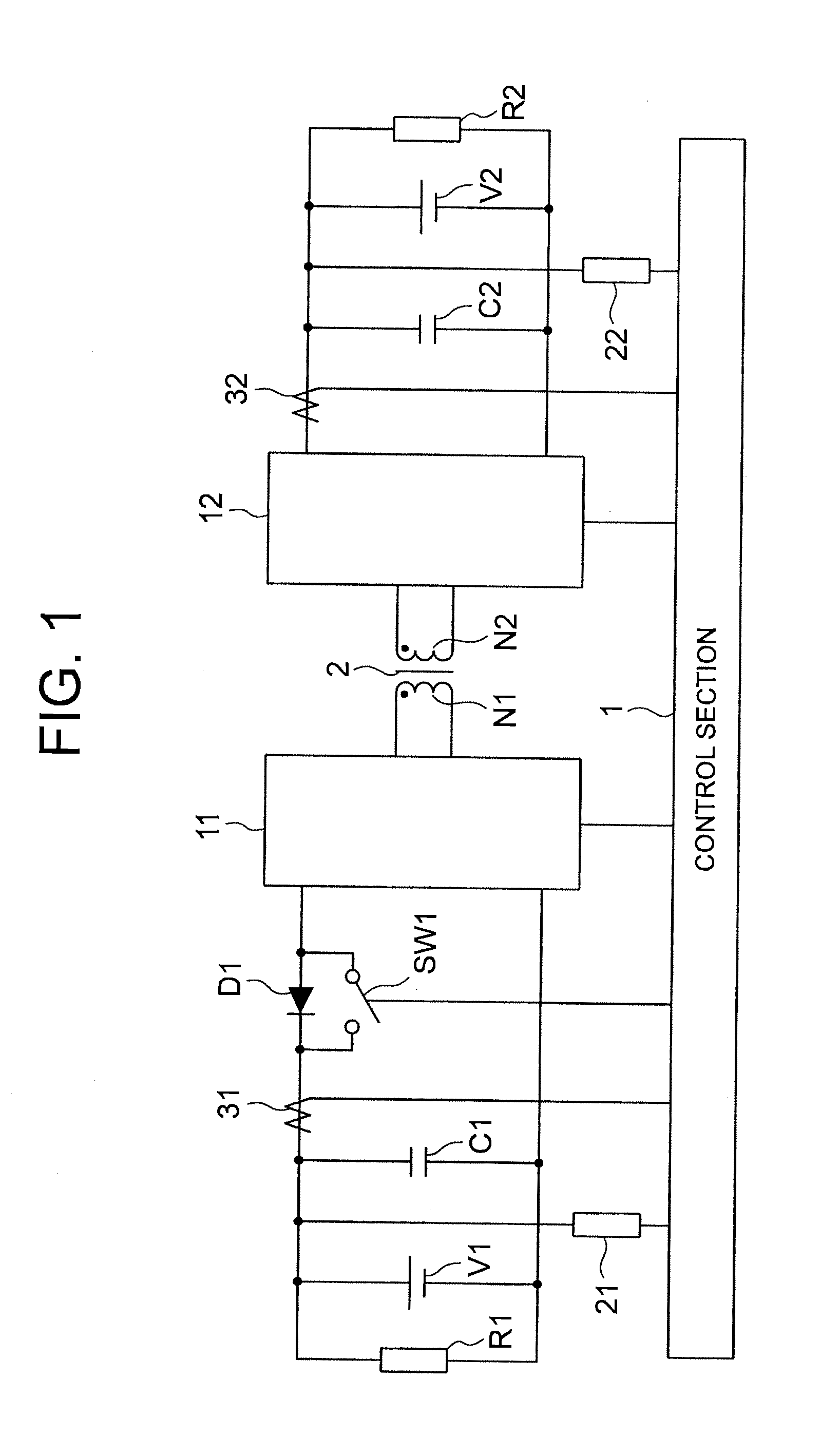

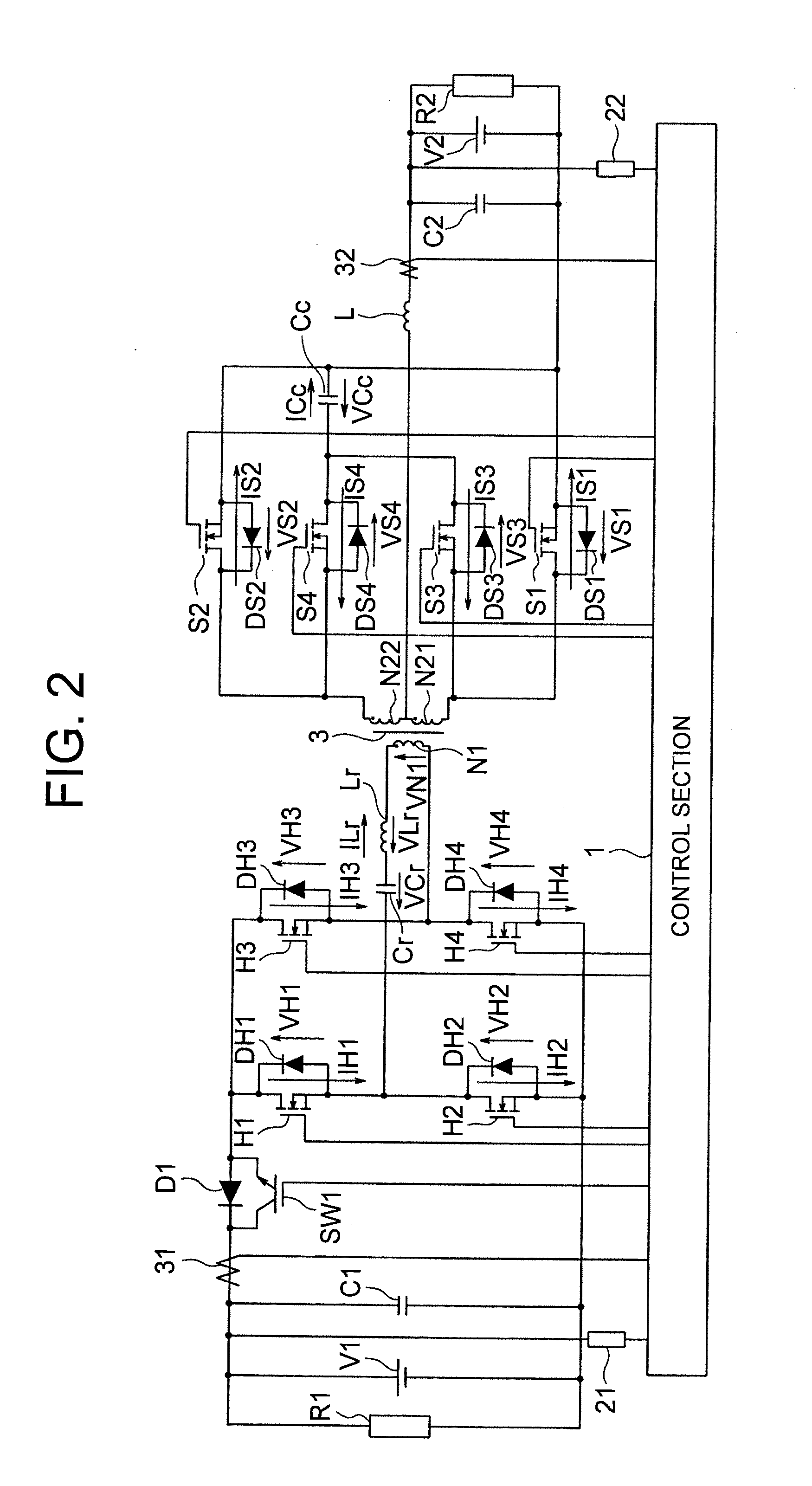

Bidirectional dc-dc converter and control method thereof

ActiveUS20100052423A1Delay characteristicReduce the impactBatteries circuit arrangementsApparatus with intermediate ac conversionElectric power transmissionDc dc converter

Disclosed is a small-size, high-efficiency, isolated, bidirectional DC-DC converter. The bidirectional DC-DC converter includes a transformer in which windings are magnetically coupled, switching circuits, a diode which is connected in parallel with a switch, smoothing capacitors, and a control section. First and second DC power supplies, which are connected in parallel with the smoothing capacitors, respectively, provide bidirectional electrical power transfer. When electrical power is to be transferred from the first DC power supply to the second DC power supply, the switch is maintained in the ON state. When, on the other hand, electrical power is to be transferred from the second DC power supply to the first DC power supply, the switch is maintained in the OFF state to prevent a reverse electrical power flow from the first DC power supply.

Owner:HITACHI INFORMATION & TELECOMM ENG LTD

Facer and faced polymeric roofing board

ActiveUS7785703B2Improve propertiesReduce spreadRoof covering using slabs/sheetsSynthetic resin layered productsGlass fiberCombustion

A prefabricated, faced roofing board composite includes a first board layer made of a polymeric material or a predominantly polymeric material and a fire and weather resistant fiberglass-based facer bonded to a top major surface of the first board layer and forming a top major surface of the composite. The fiberglass-based facer is substantially impervious to the passage of hot gases of combustion, water, and water vapor through the thickness of the fiberglass-based facer. The faced composite can be a cover board, an insulation board; can include cover board and insulation board layers; and can include cover board, insulation board, and baseboard layers. A second fiberglass-based facer that is substantially impervious to the passage of hot gases of combustion through its thickness can form a bottom major surface of the composite. The polymeric material or predominantly polymeric material of the board layer to which each fiberglass-based facer is bonded penetrates part of the way through, but not completely through, the fiberglass-based facer.

Owner:JOHNS MANVILLE CORP

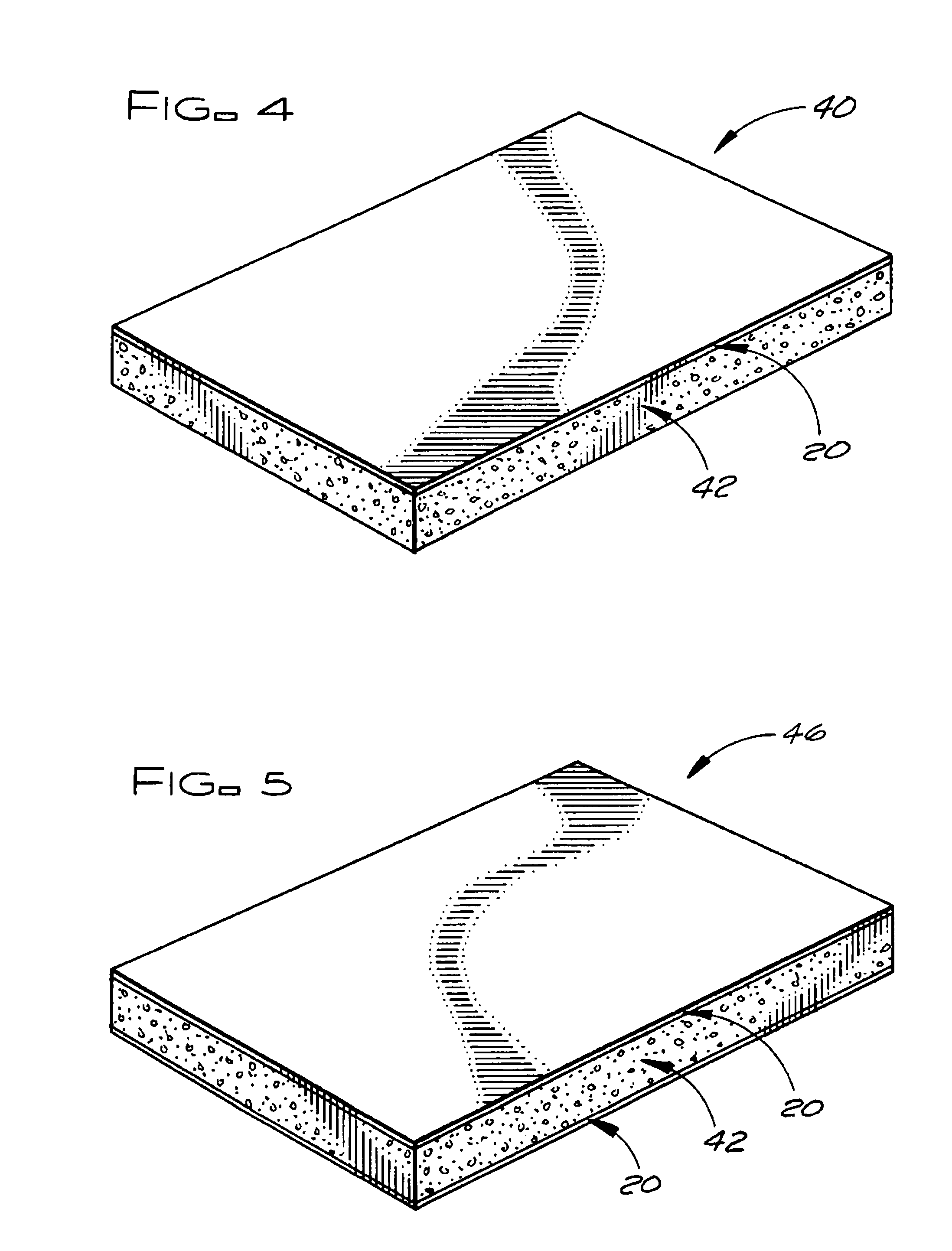

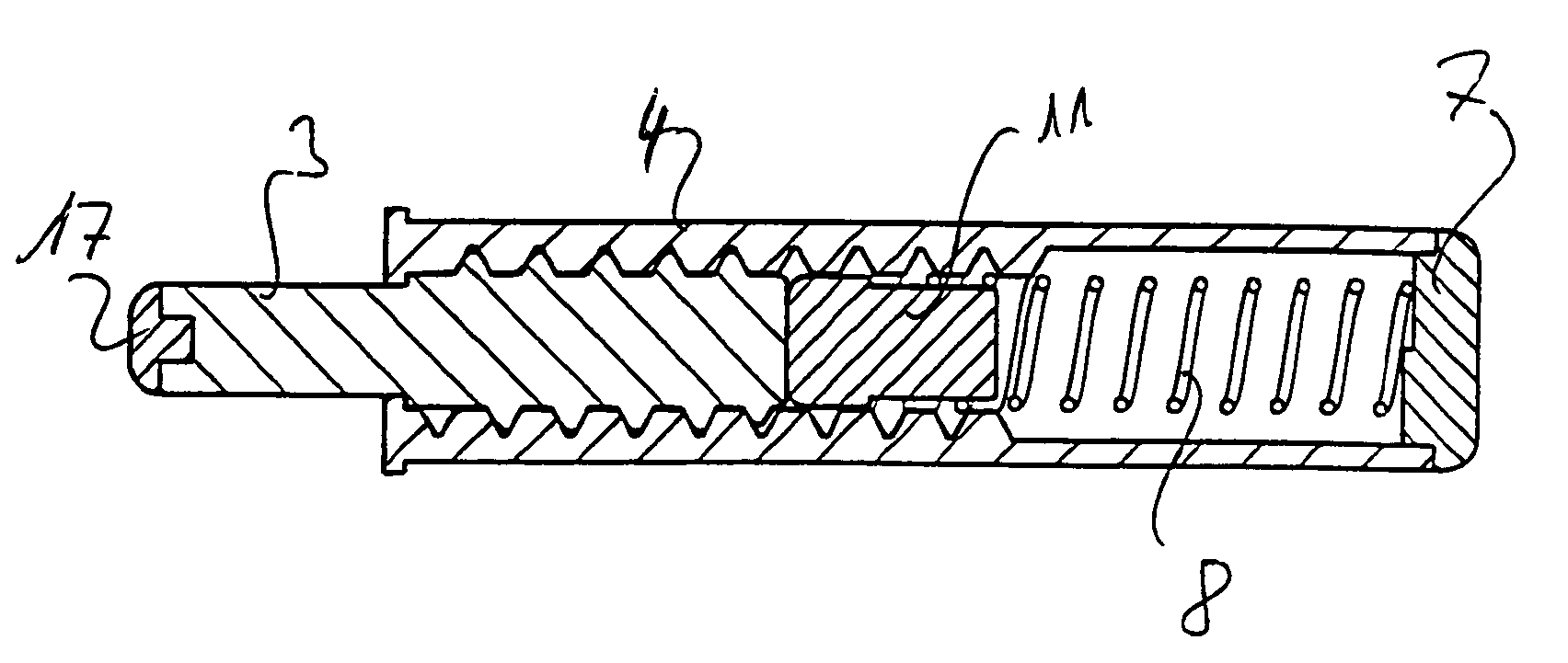

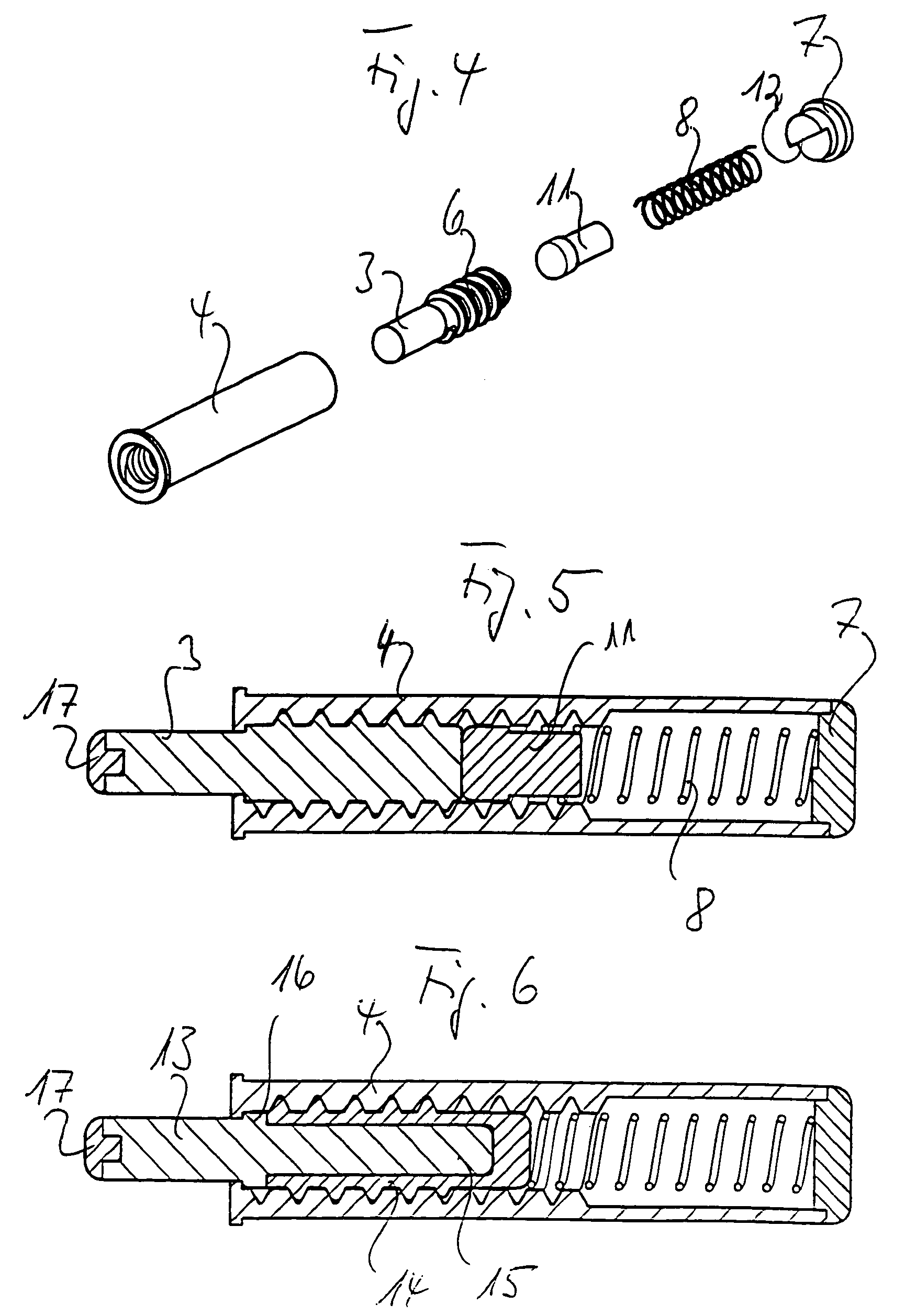

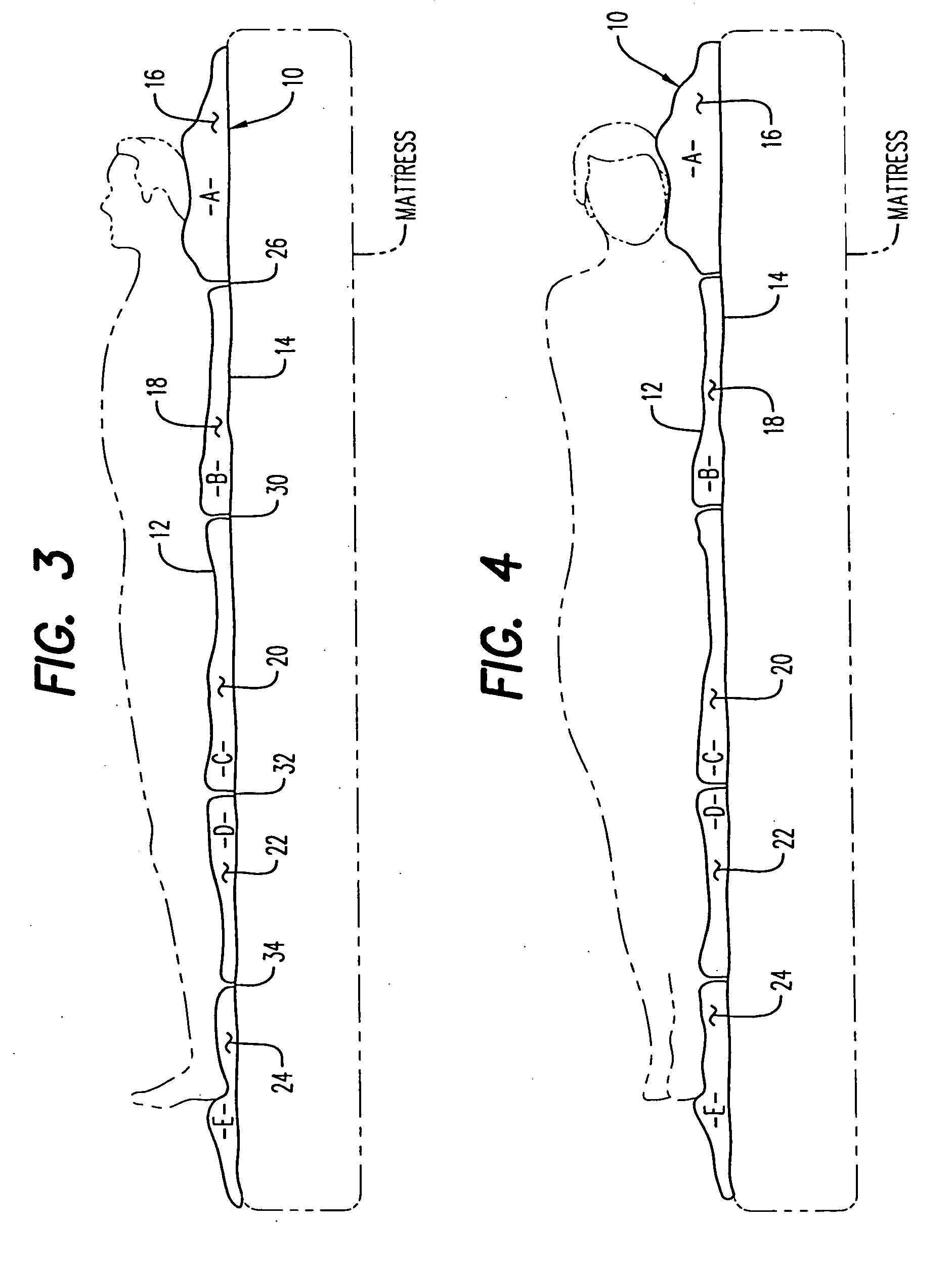

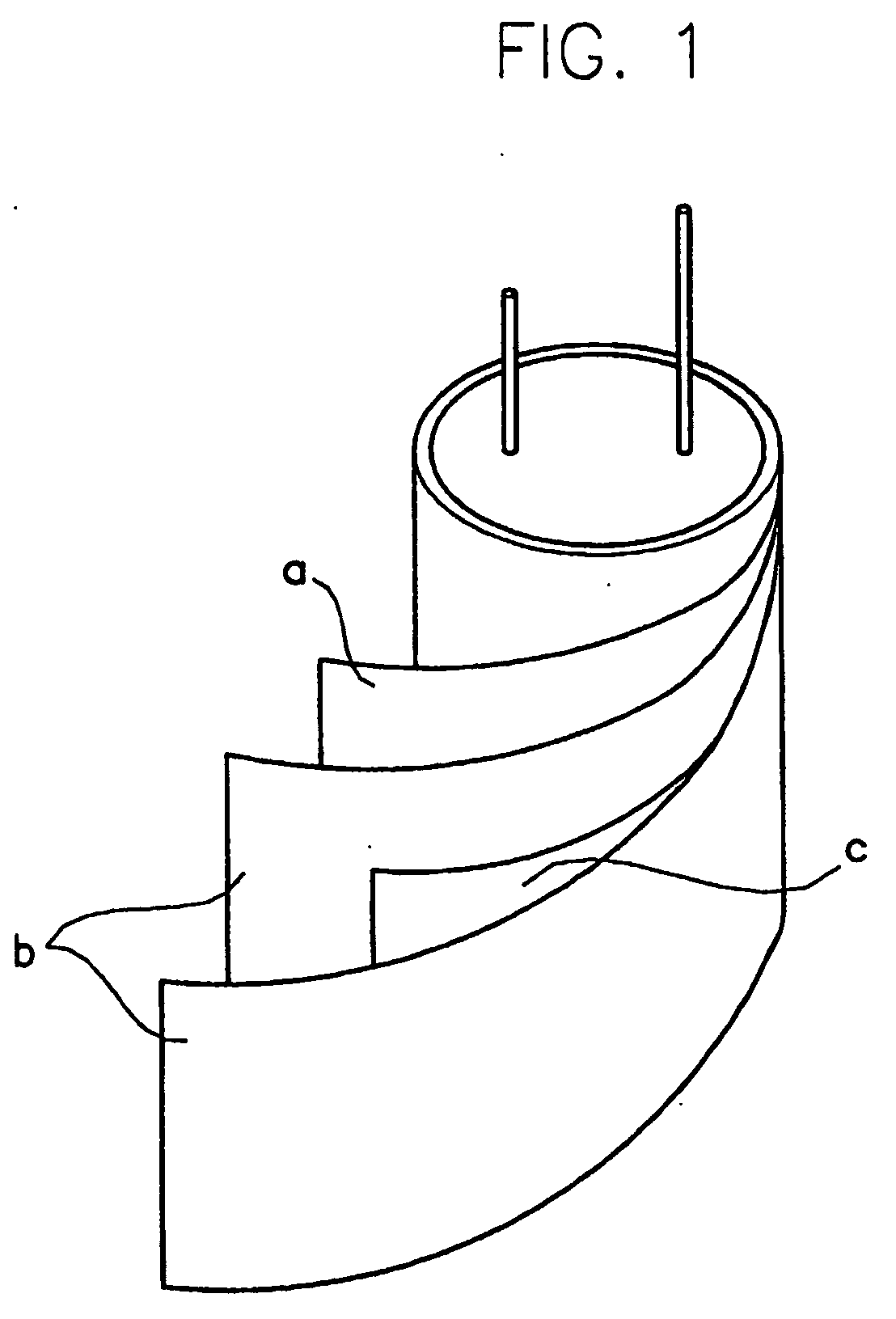

Spiral-action damper

InactiveUS7234569B2Improve braking effectLarge braking forceSpringsBuilding braking devicesSpring forceSelf locking

The invention relates to a damping device for movable furniture parts, for example for doors or drawers, comprising a piston or plunger which is slidably guided in a hollow body, e.g. a cylinder, with said piston or plunger being impinged upon by spring force into its pushed-out position. According to the invention, the hollow body comprises at least one section of a spiral-shaped stay of the internal screw thread, and / or the piston or plunger comprises at least one section of a spiral-shaped stay of the external screw thread. The stays of the screw threads are glidingly supported one on top of the other, or cams or journals of the hollow body or of the piston or plunger are supported on a screw-thread section of the other component. The pitch of the stays of the screw threads is greater than the pitch at which self-locking occurs.

Owner:ARTURO SALICE

Nonhygroscopic thermally stable aluminum hydroxide

InactiveUS6280839B1Improve thermal stabilityImprove flame retardant propertiesGlass/slag layered productsWood layered productsEngineeringFire retardant

A nonhygroscopic thermally stable aluminum hydroxide, which is particularly useful for the preparation of thermally stable and fire retardant laminates for printed circuit boards.

Owner:ALUSUISSE MARTINSWERK

Level shifter having automatic delay adjusting function

InactiveUS7148735B2Increase the number ofReduce decreasePulse automatic controlInstant pulse delivery arrangementsLevel shiftingDelayed time

In a level shifter, in the case where the amplitude voltage of an input signal (i.e., a first power voltage VDDL) input to an input terminal is changed to be higher and the amplitude voltage of an output signal (i.e., a second power voltage VDDH) output from an output terminal is changed to be lower, a fall delay time of the signal output from the output terminal tends to be longer than a rise delay time of the signal. However, an inverted input signal obtained by an inverter is input to a level shifting unit and also to the gate of an N-type transistor, and therefore, the N-type transistor is turned on at the fall of the input signal input to the input terminal, so as to supply a current based on the second power voltage VDDH to an output node of the level shifting unit for assisting the shift into H level performed in the level shifting unit. Accordingly, even when at least one of the amplitude voltage of the input signal and the amplitude voltage of the output signal is changed, balance between the fall delay time characteristic and the rise delay time characteristic of the output signal can be satisfactorily kept.

Owner:SOCIONEXT INC

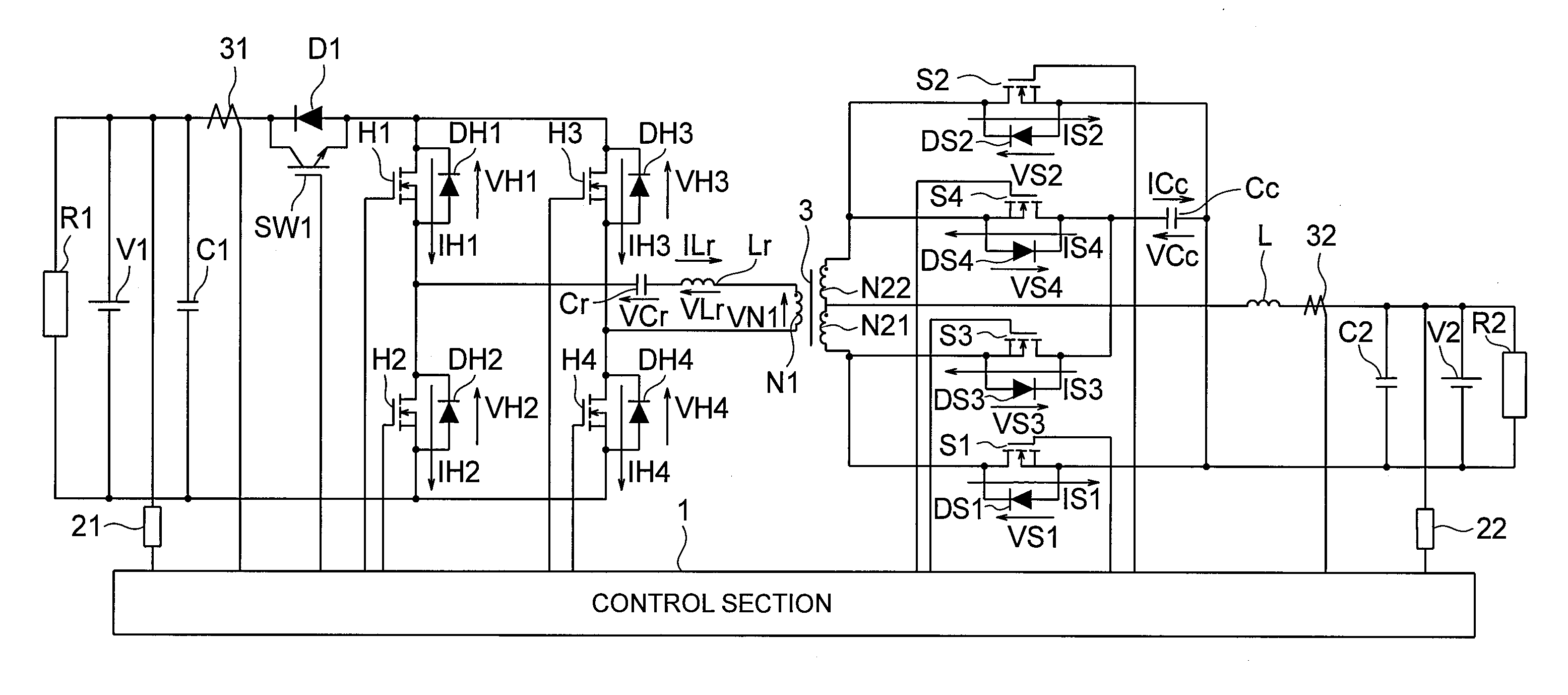

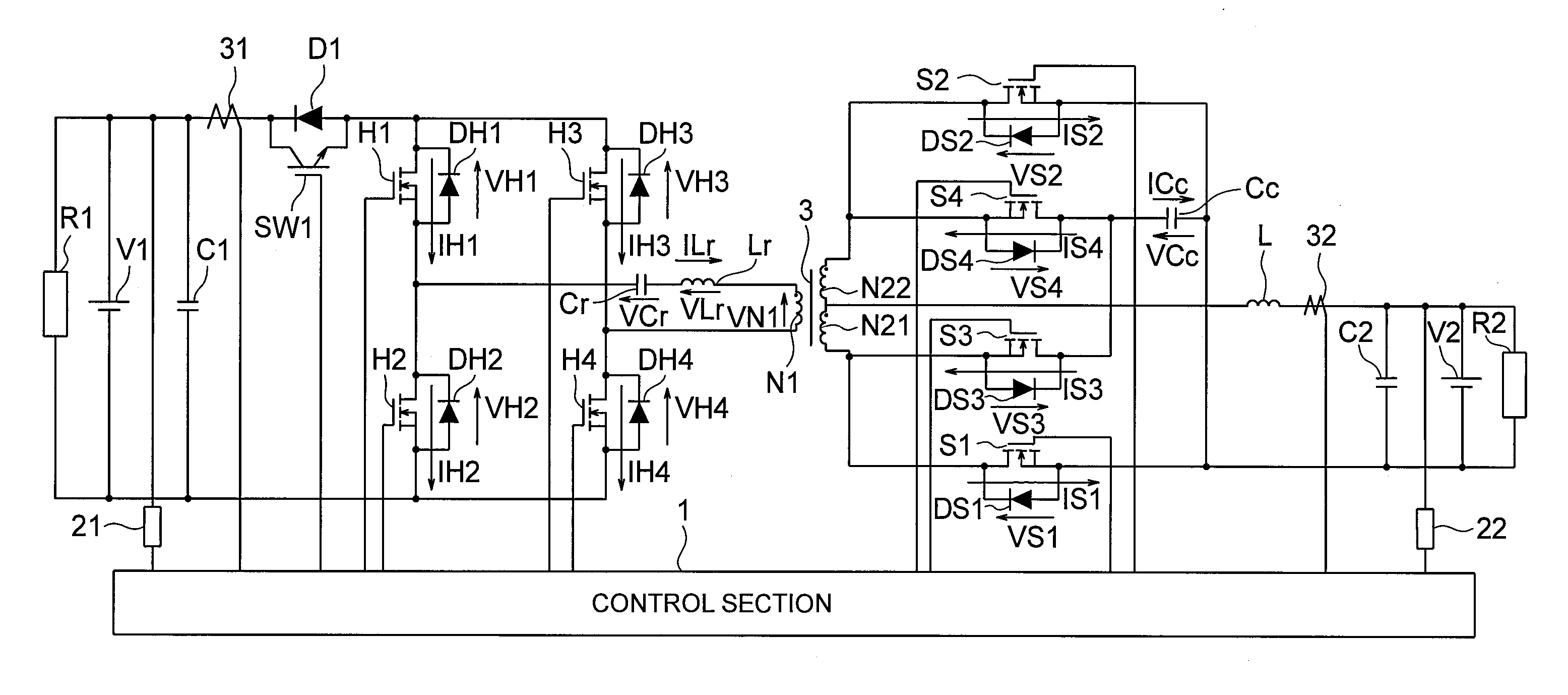

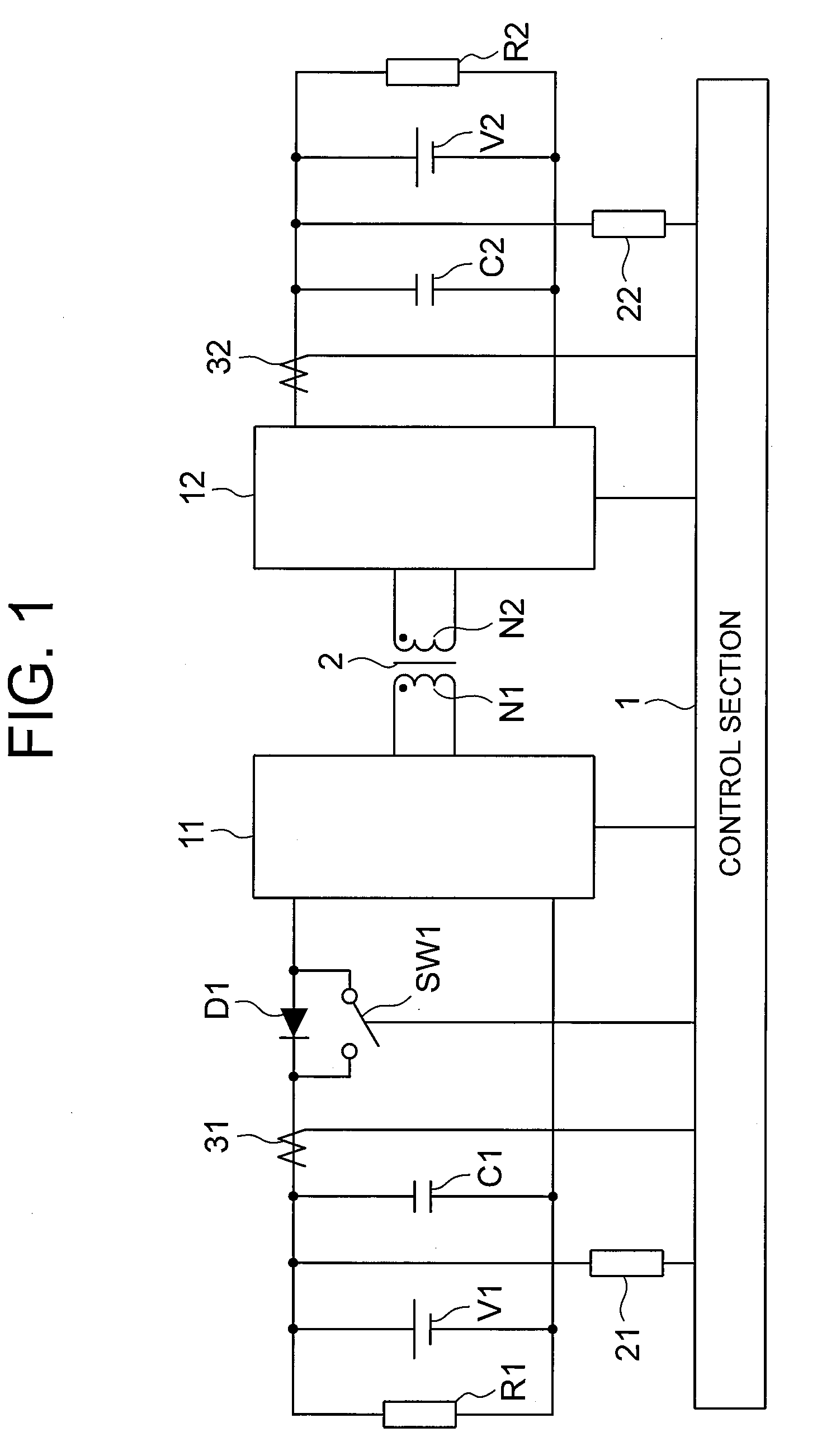

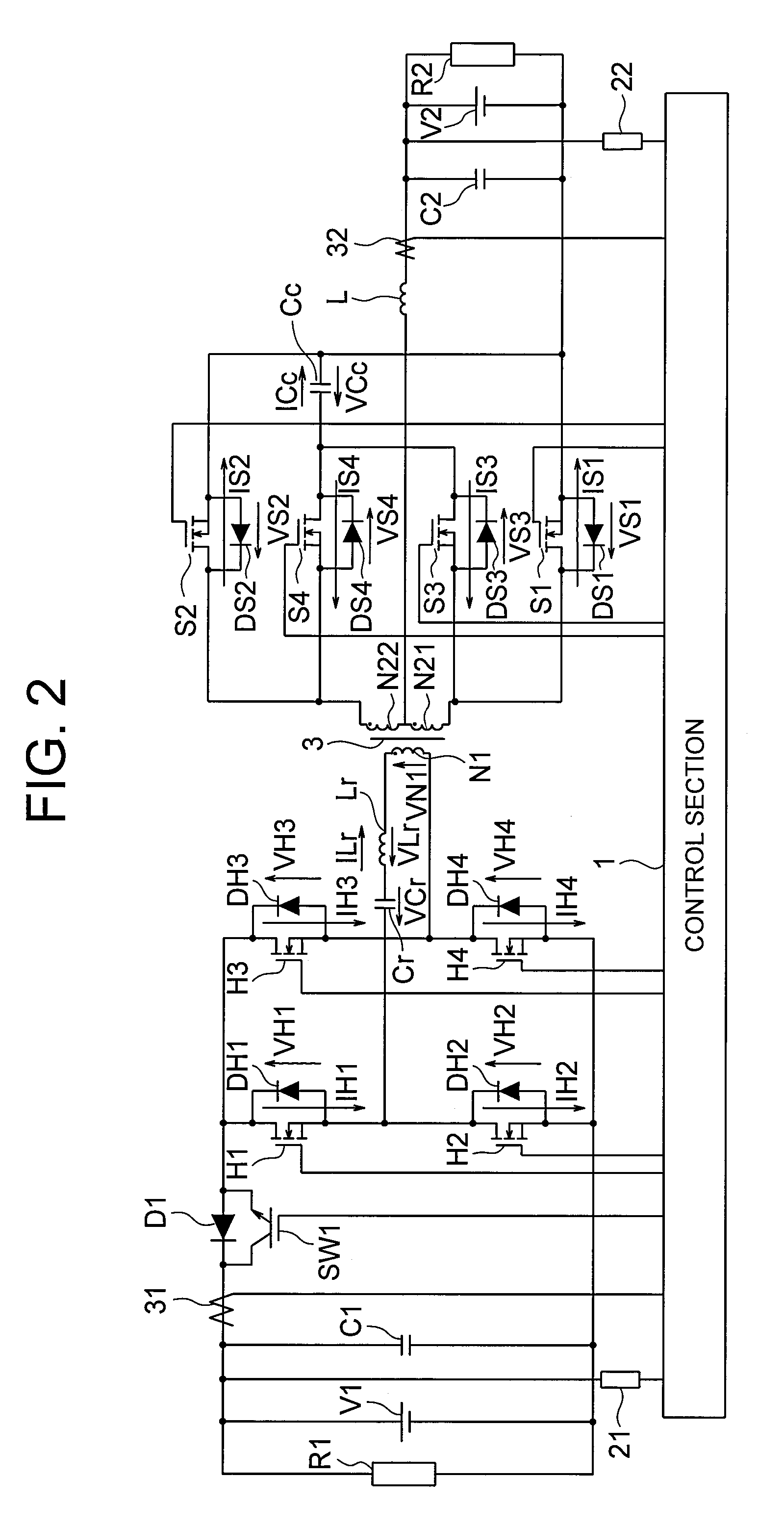

Bidirectional dc-dc converter and control method thereof

ActiveUS20120098341A1Improve efficiencyDownsizingDc source parallel operationApparatus with intermediate ac conversionElectric power transmissionDc dc converter

Disclosed is a small-size, high-efficiency, isolated, bidirectional DC-DC converter. The bidirectional DC-DC converter includes a transformer in which windings are magnetically coupled, switching circuits, a diode which is connected in parallel with a switch, smoothing capacitors, and a control section. First and second DC power supplies, which are connected in parallel with the smoothing capacitors, respectively, provide bidirectional electrical power transfer. When electrical power is to be transferred from the first DC power supply to the second DC power supply, the switch is maintained in the ON state. When, on the other hand, electrical power is to be transferred from the second DC power supply to the first DC power supply, the switch is maintained in the OFF state to prevent a reverse electrical power flow from the first DC power supply.

Owner:HITACHI INFORMATION & TELECOMM ENG LTD

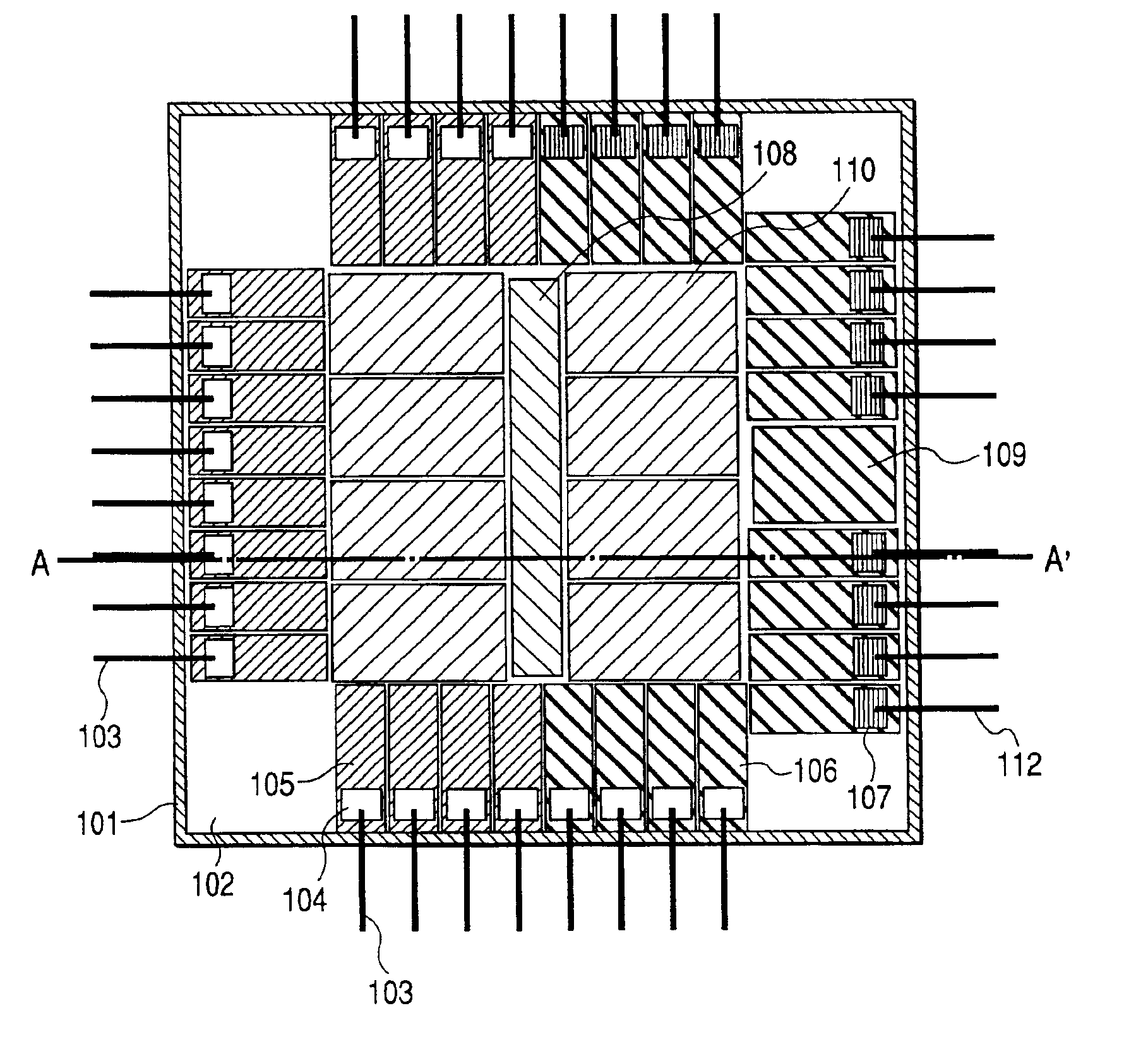

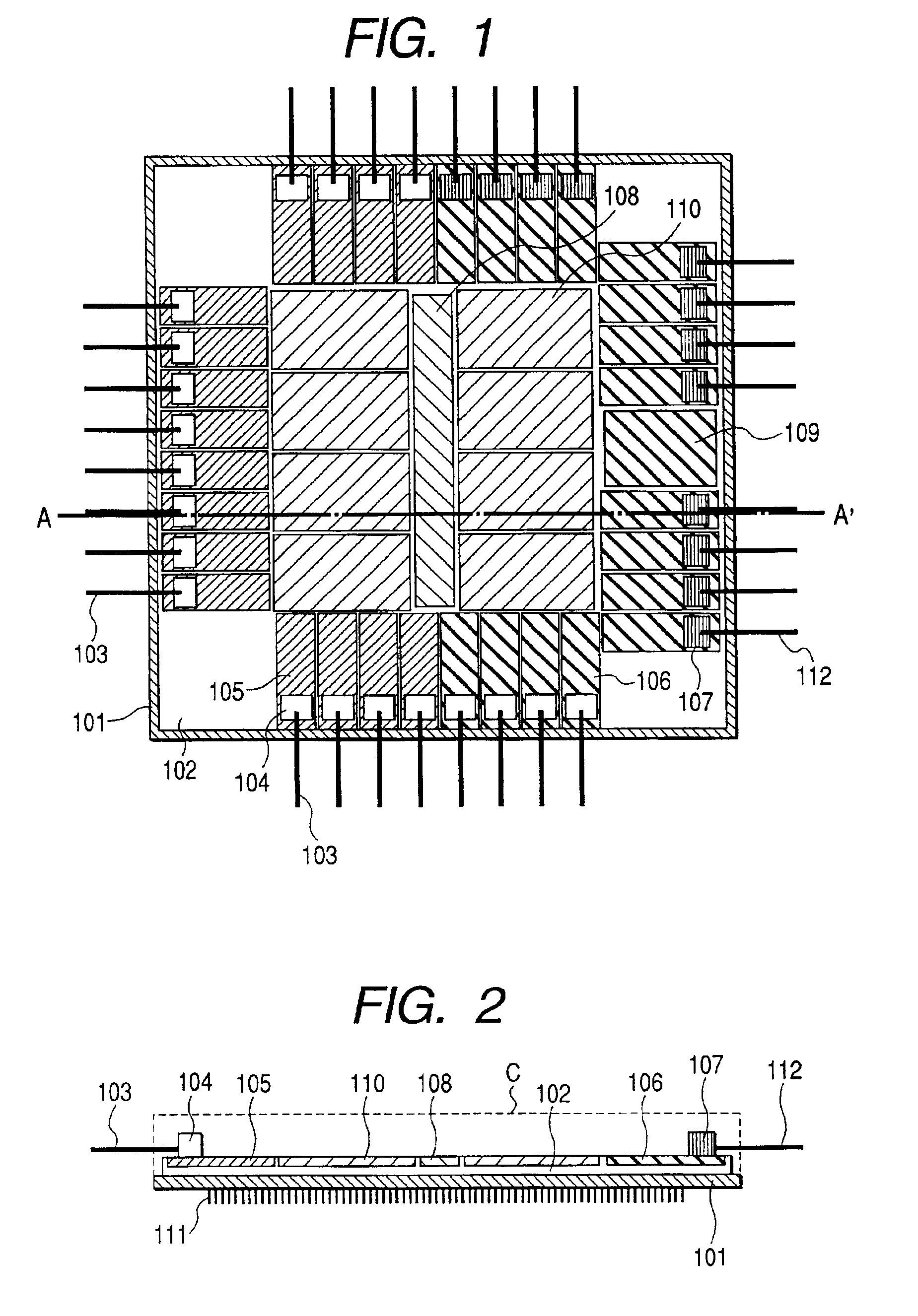

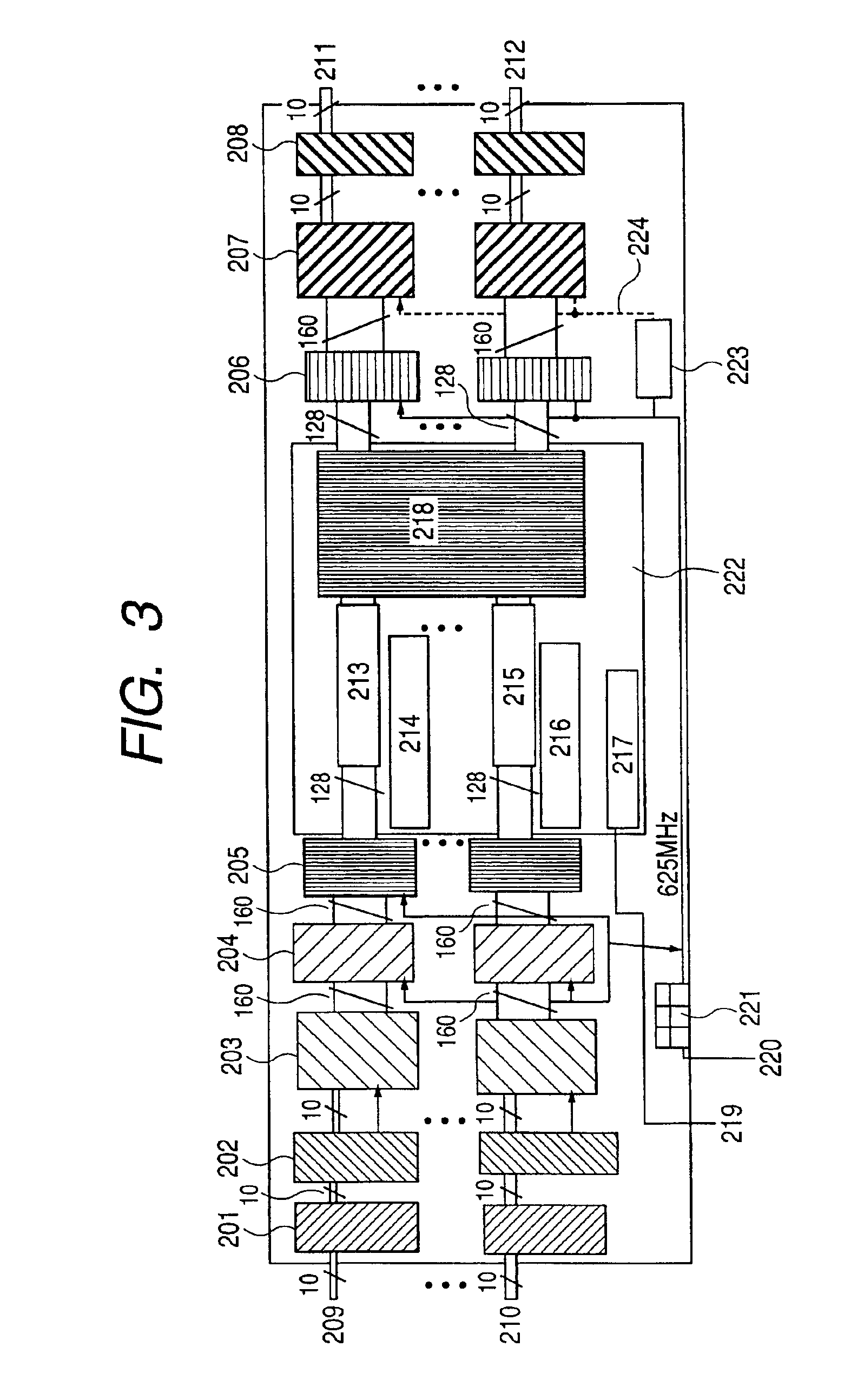

Wavelength division multiplexed optical interconnection device

InactiveUS6907198B2Reduce troubleEfficient use ofSolid-state devicesVisual presentation using printersDriver circuitCMOS

A high-speed and small-sized optical interconnection device uses wavelength-multiplexed light suitable therefor in order to make compatible between an increase in high-speed communication capacity of the optical interconnection device and an increase in high-speed communication distance thereof. A signal processing LSI is placed within a central portion of a main surface of a semiconductor substrate, and input / output units for transmitting and receiving optical wavelength-multiplexed lights are multi-chip integrated on the periphery of the main surface of the semiconductor substrate into a single package, and a wiring length can be reduced and a physical signal band for each connecting wiring can be enlarged. Further, the signal processing LSI is made up of CMOS and a driver circuit for each optical transmitting / receiving element is comprised of a Si—Ge transistor circuit, whereby a modulated signal band can be enlarged and the performance of the input / output optical signals from the device can be improved.

Owner:HITACHI LTD

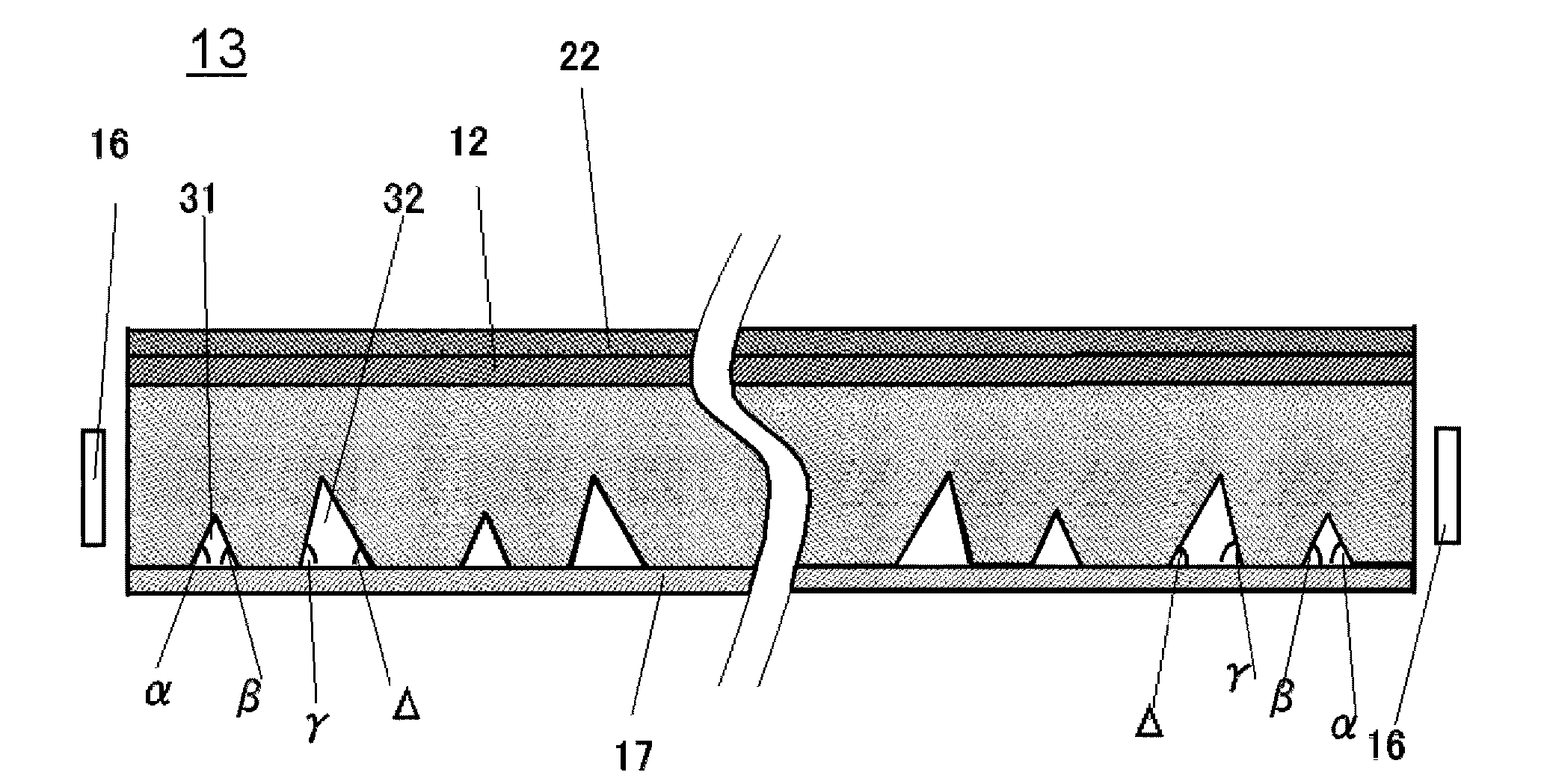

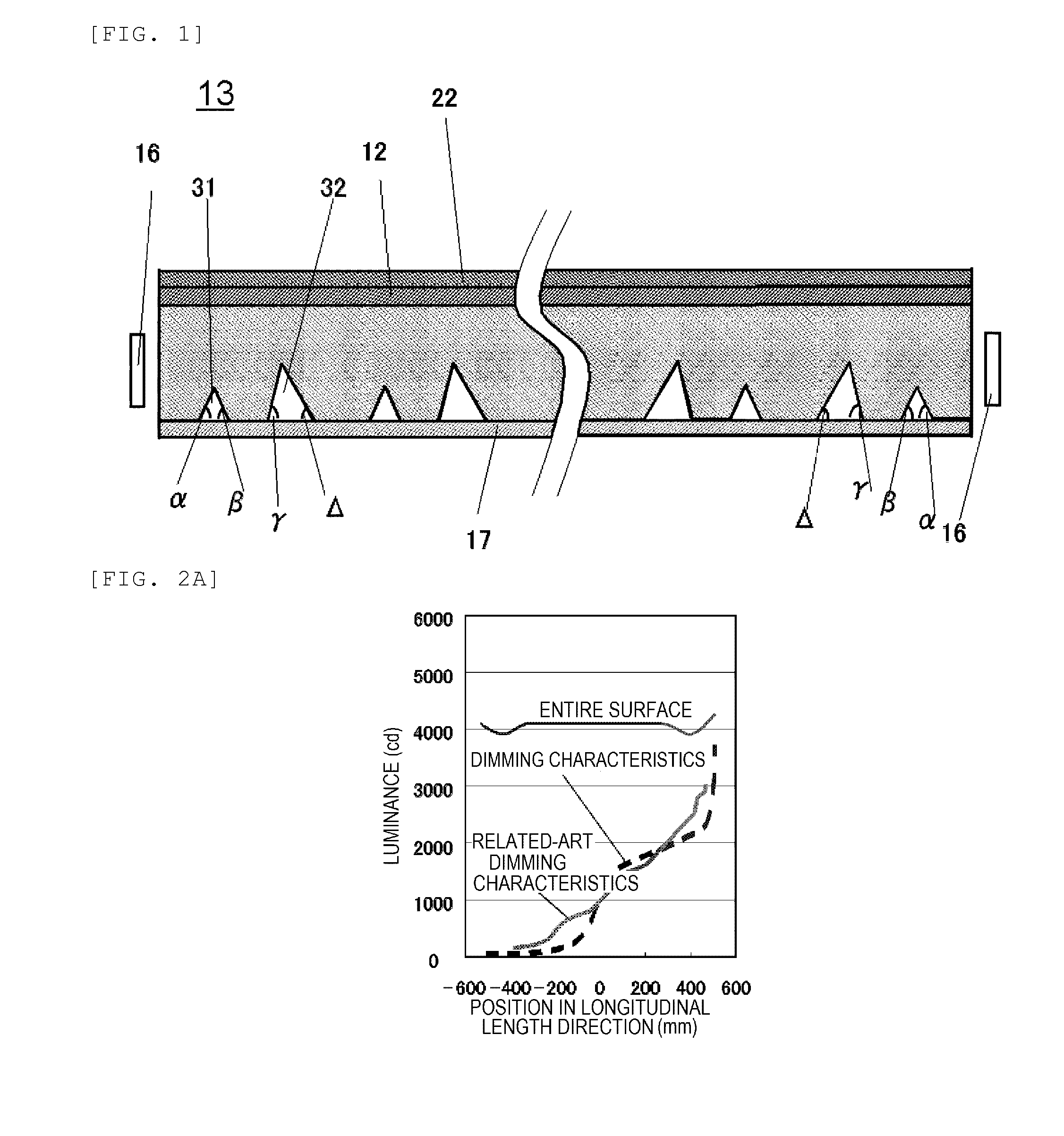

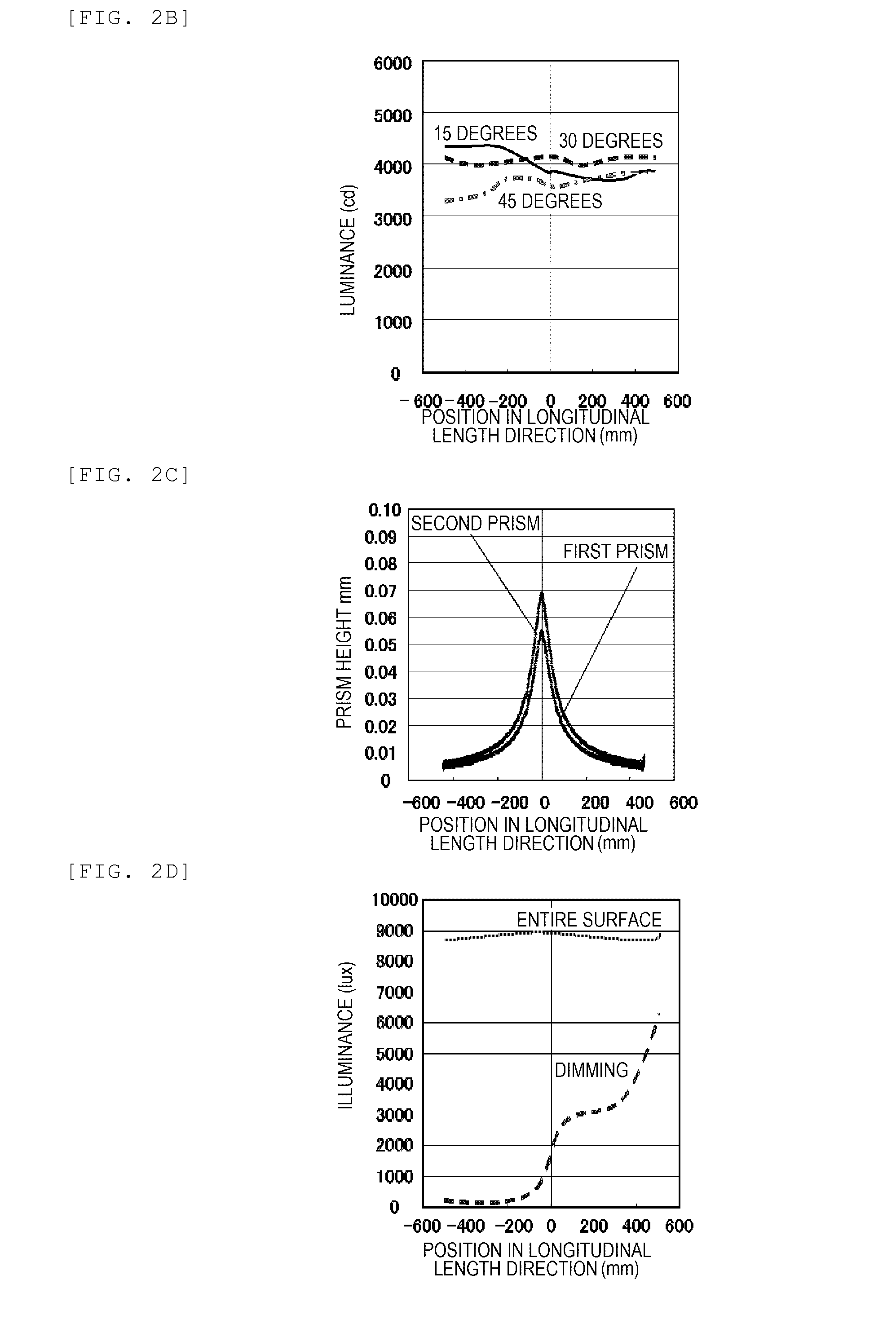

Light source device

ActiveUS20150293296A1Secures viewing angle characteristicIncrease front brightnessMechanical apparatusLight guides for lighting systemsLight guideOptoelectronics

A light source device including a light guide plate and a light source, in which the light guide plate includes an incident surface on which light emitted from the light source is incident, an emission surface emitting light incident from the incident surface, and a propagating reflection surface which is a surface opposite to the emission surface and which propagates and reflects the light incident from the incident surface toward the emission surface, the propagating reflection surface has approximately V-shaped grooves and the V-shaped grooves have two kinds of grooves.

Owner:PANASONIC INTELLECTUAL PROPERTY MANAGEMENT CO LTD

Bidirectional dc-dc converter and control method thereof

ActiveUS8378646B2Improve efficiencyDownsizingBatteries circuit arrangementsDc source parallel operationElectric power transmissionDc dc converter

Disclosed is a small-size, high-efficiency, isolated, bidirectional DC-DC converter. The bidirectional DC-DC converter includes a transformer in which windings are magnetically coupled, switching circuits, a diode which is connected in parallel with a switch, smoothing capacitors, and a control section. First and second DC power supplies, which are connected in parallel with the smoothing capacitors, respectively, provide bidirectional electrical power transfer. When electrical power is to be transferred from the first DC power supply to the second DC power supply, the switch is maintained in the ON state. When, on the other hand, electrical power is to be transferred from the second DC power supply to the first DC power supply, the switch is maintained in the OFF state to prevent a reverse electrical power flow from the first DC power supply.

Owner:HITACHI INFORMATION & TELECOMM ENG LTD

Optical filter

ActiveUS20150205142A1Wide viewing angleStable maintenanceLiquid crystal compositionsOptical filtersDisplay deviceComputer science

Provided is an optical filter and a display device. The illustrative optical filter may be applied to a stereoscopic image display device so that the stereoscopic image display device can display a 3D image at a wide viewing angle without loss of brightness.

Owner:LG CHEM LTD

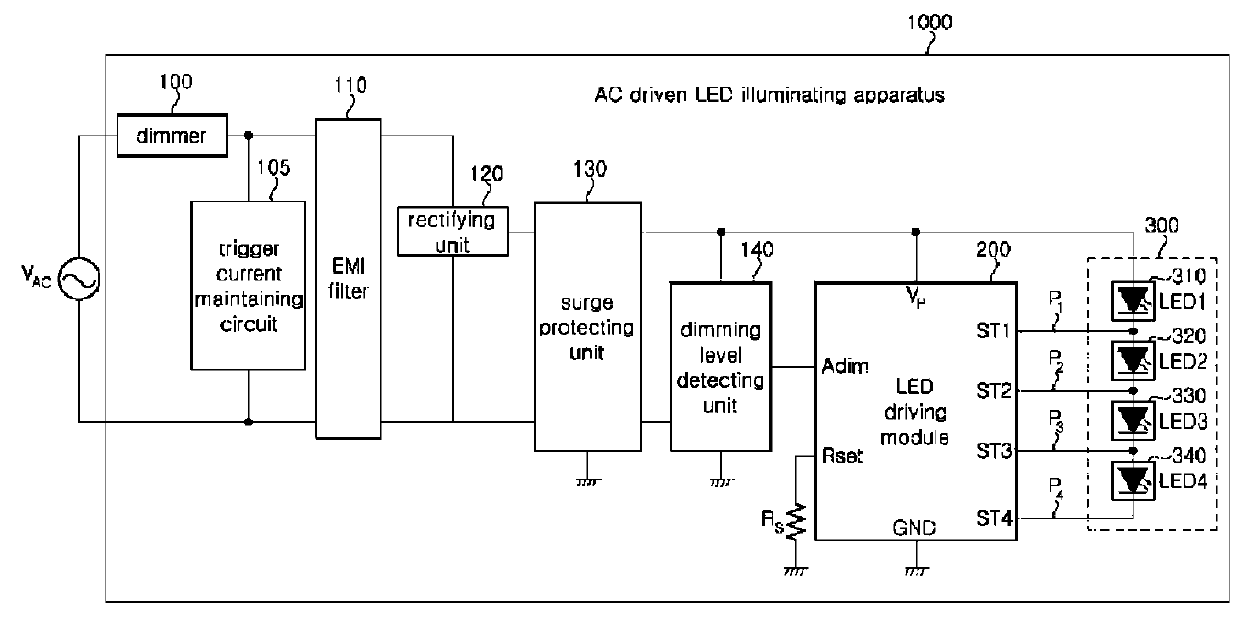

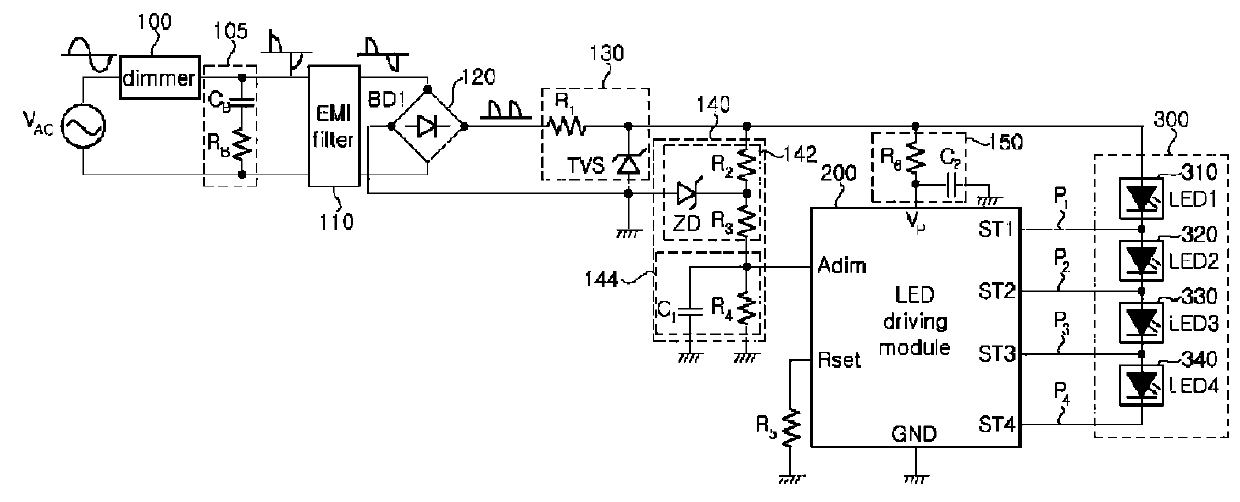

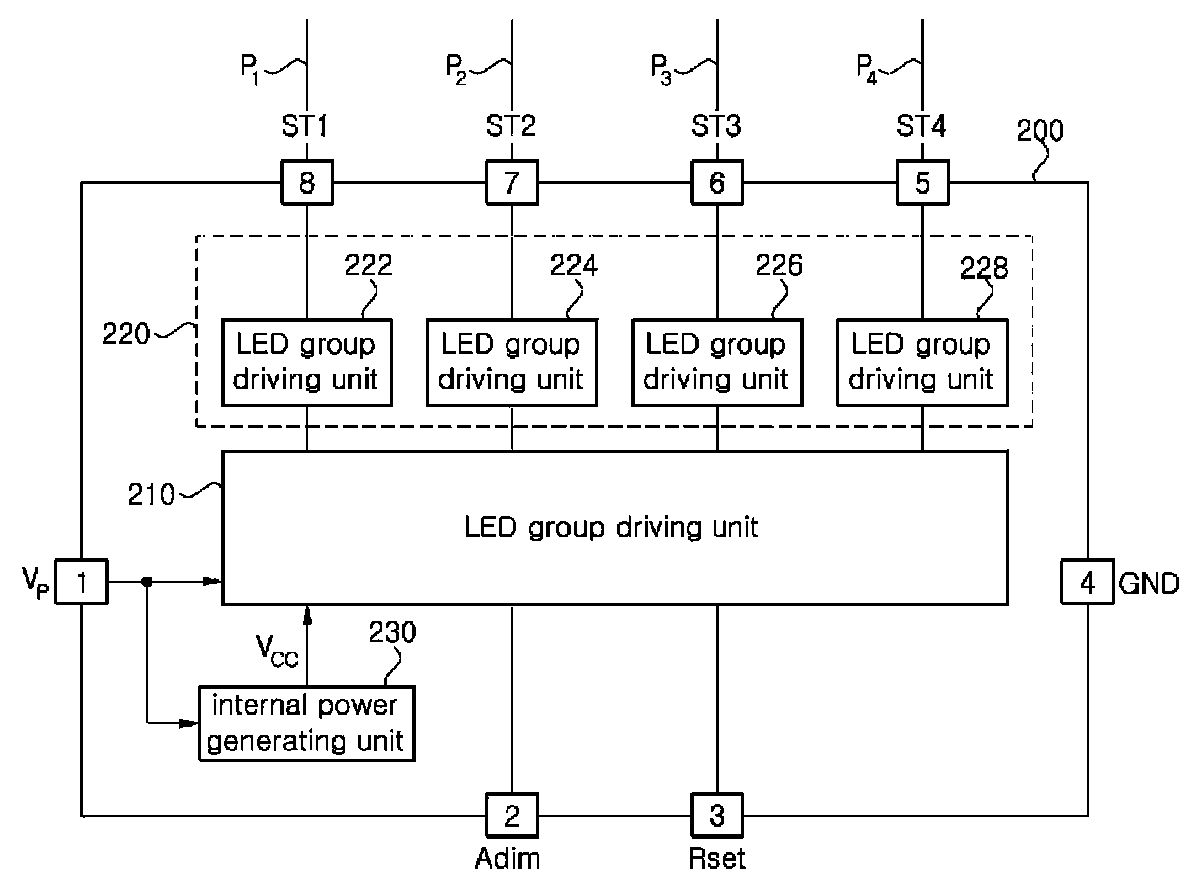

Dimmable AC driven LED illuminating apparatus

ActiveUS9345094B2Delay characteristicExcellent dimming characteristicElectrical apparatusElectroluminescent light sourcesTRIACDimmer

A dimmable alternating current (AC) driven light emitting diode (LED) illuminating apparatus including a TRIAC dimmer configured to perform a dimming control using a phase control.

Owner:SEOUL SEMICONDUCTOR

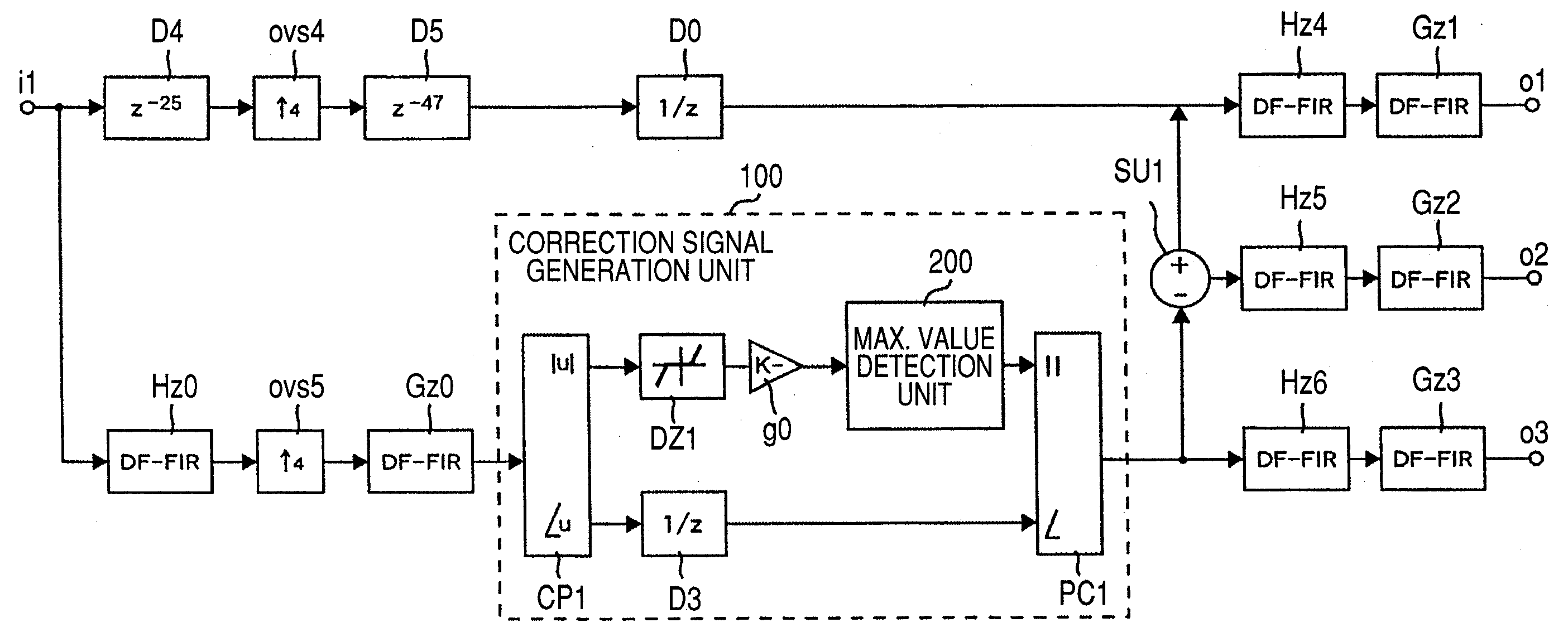

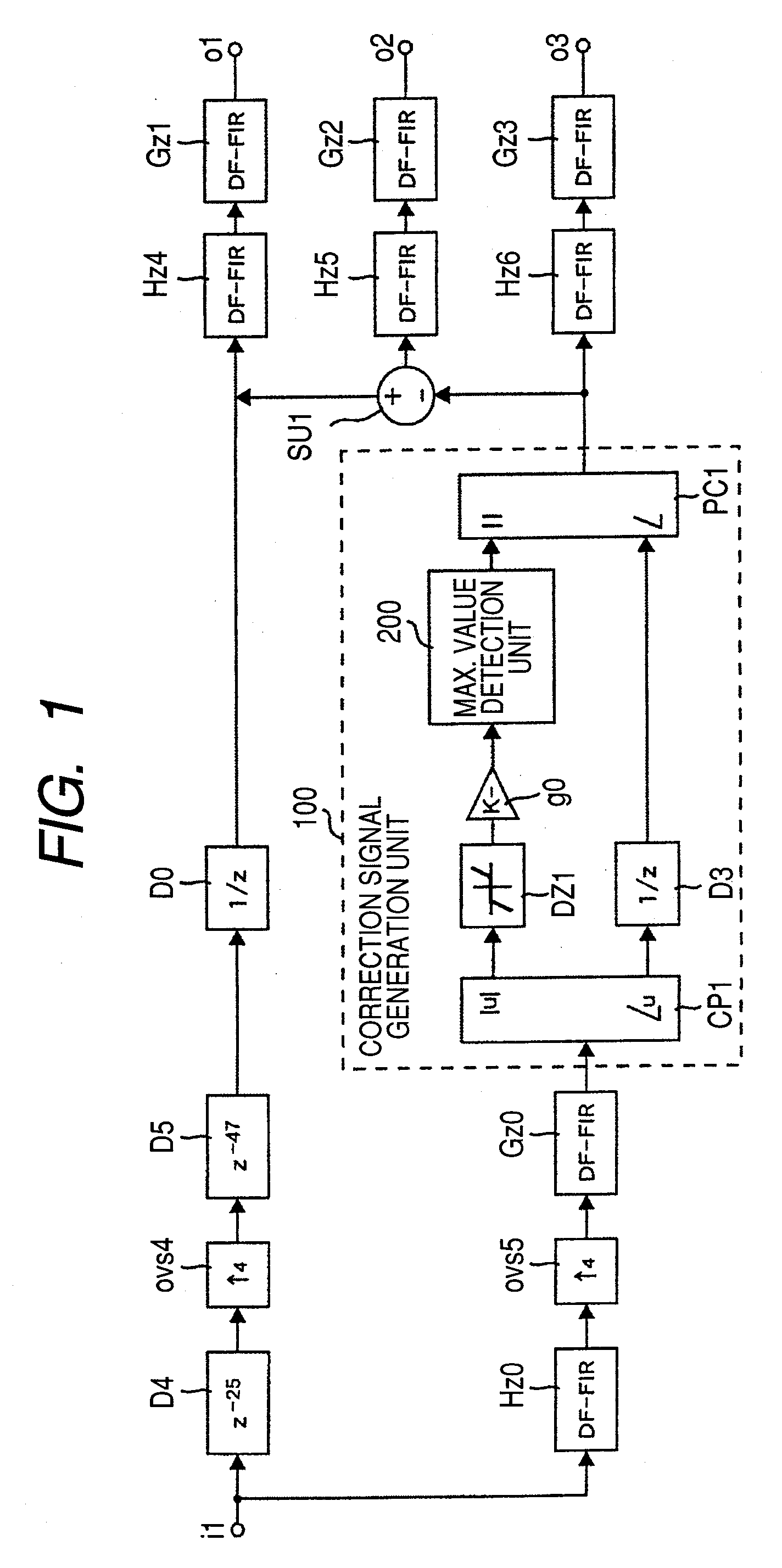

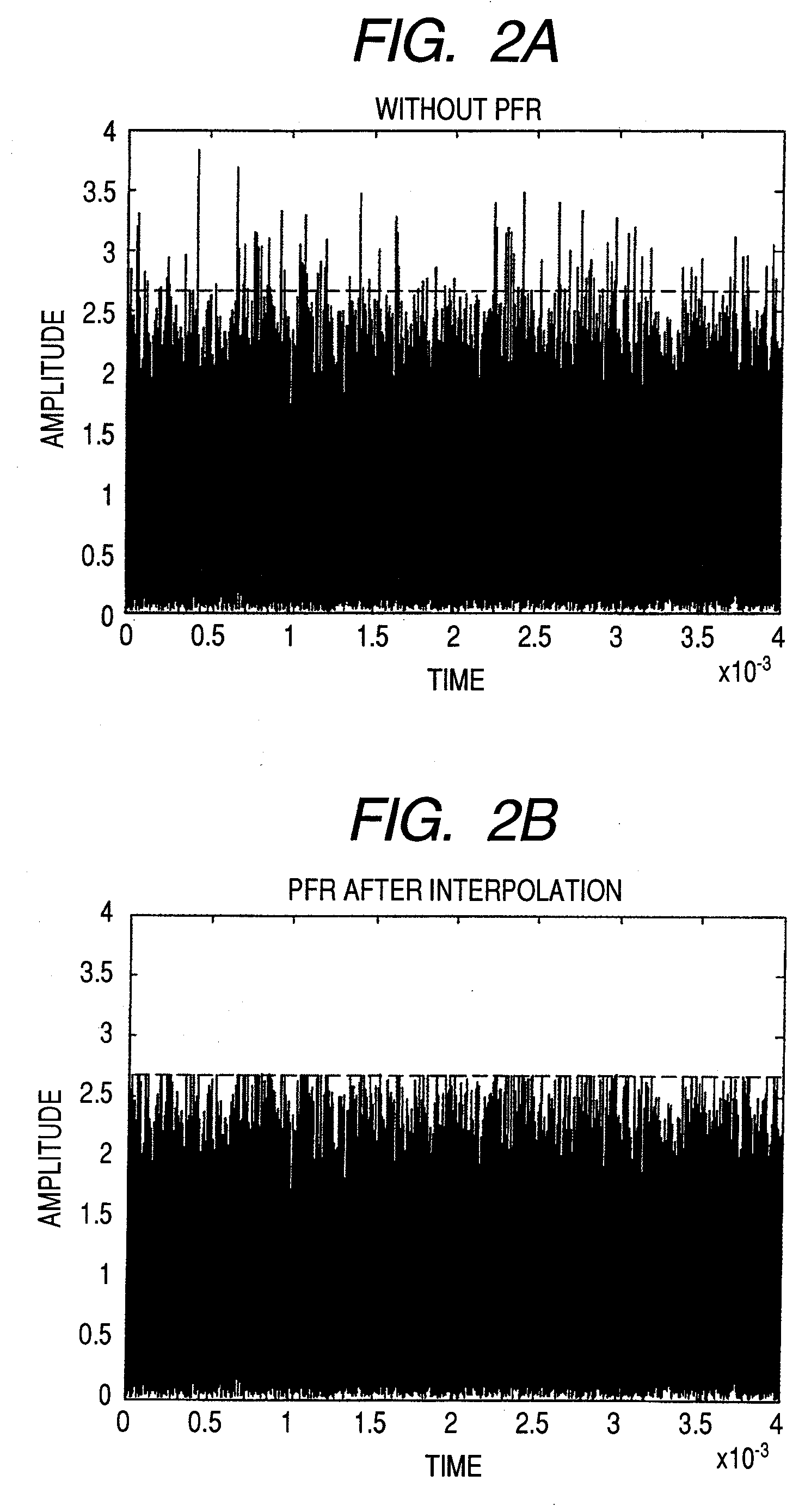

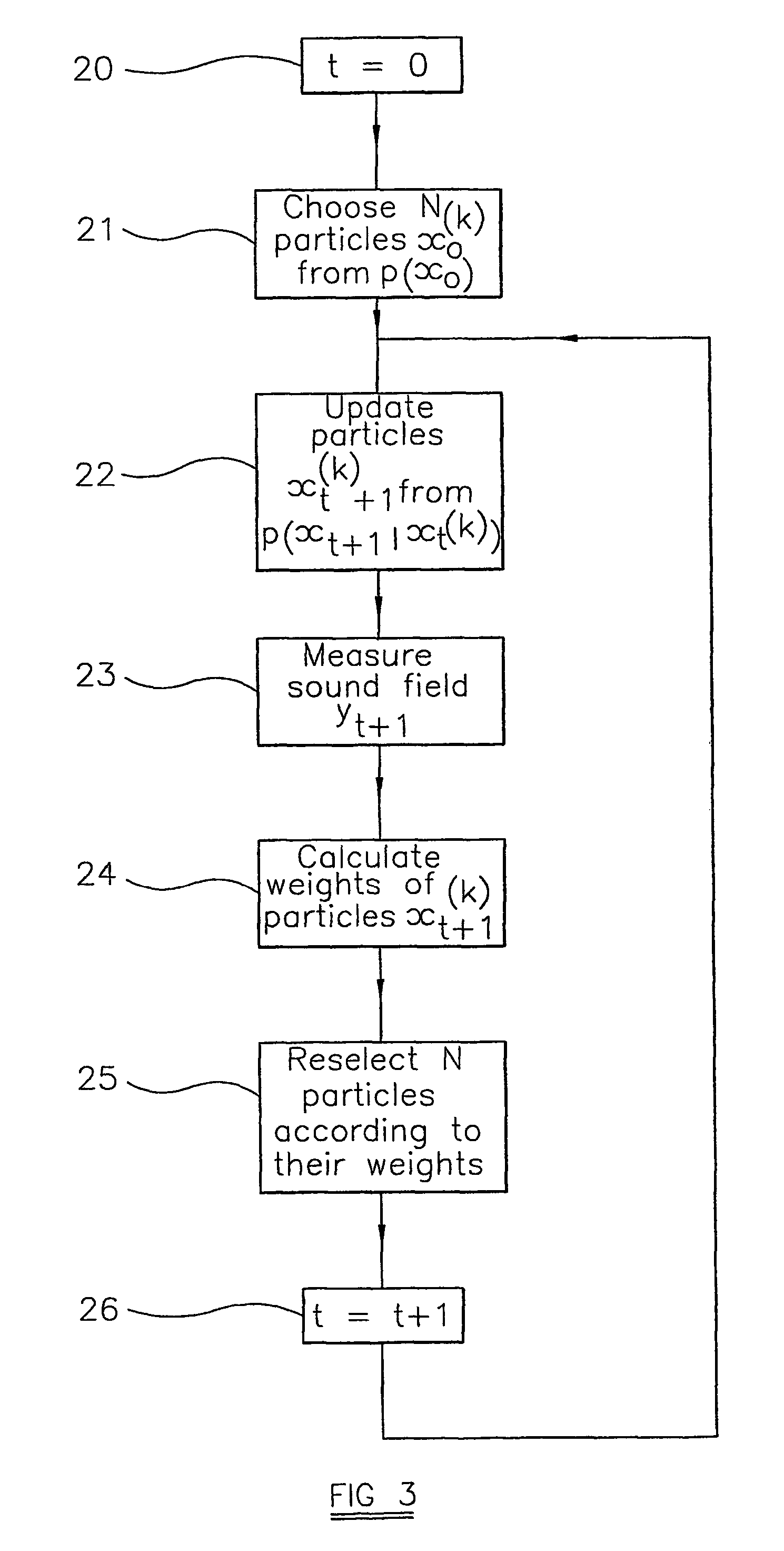

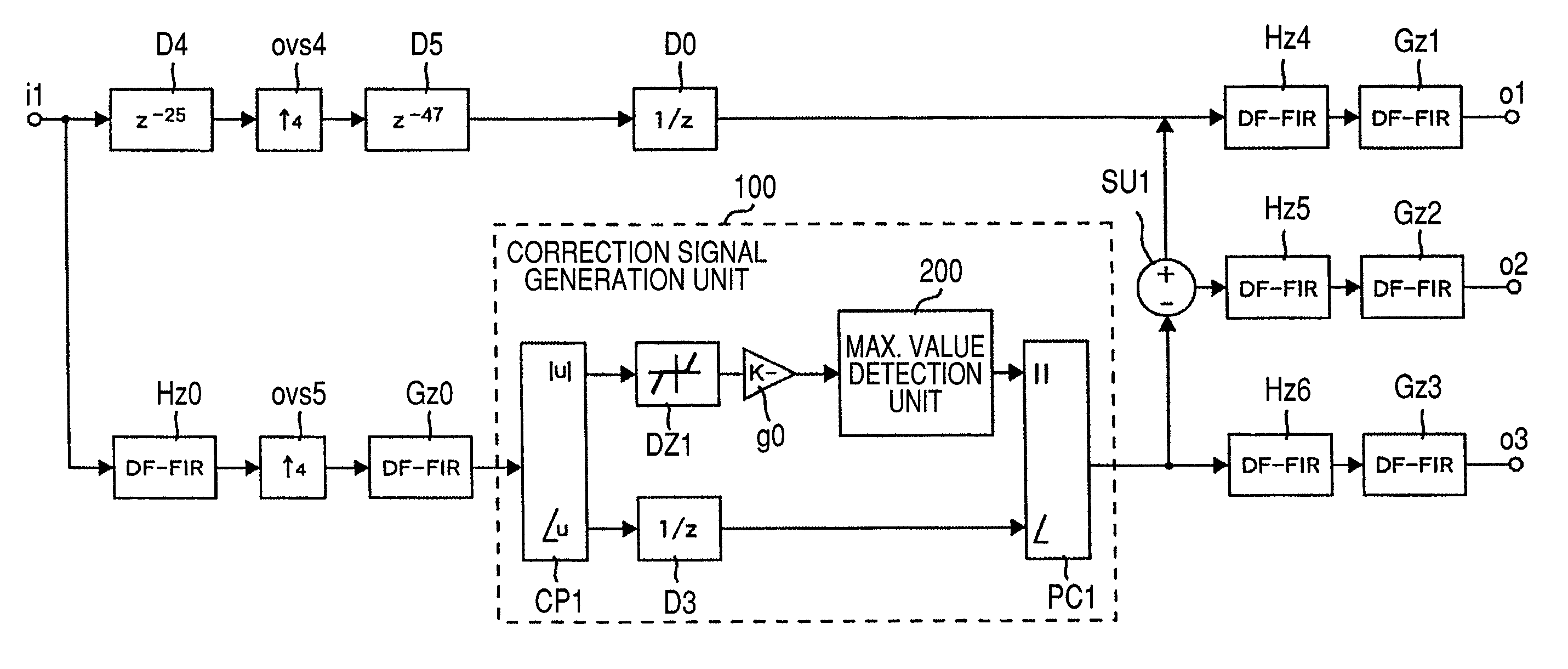

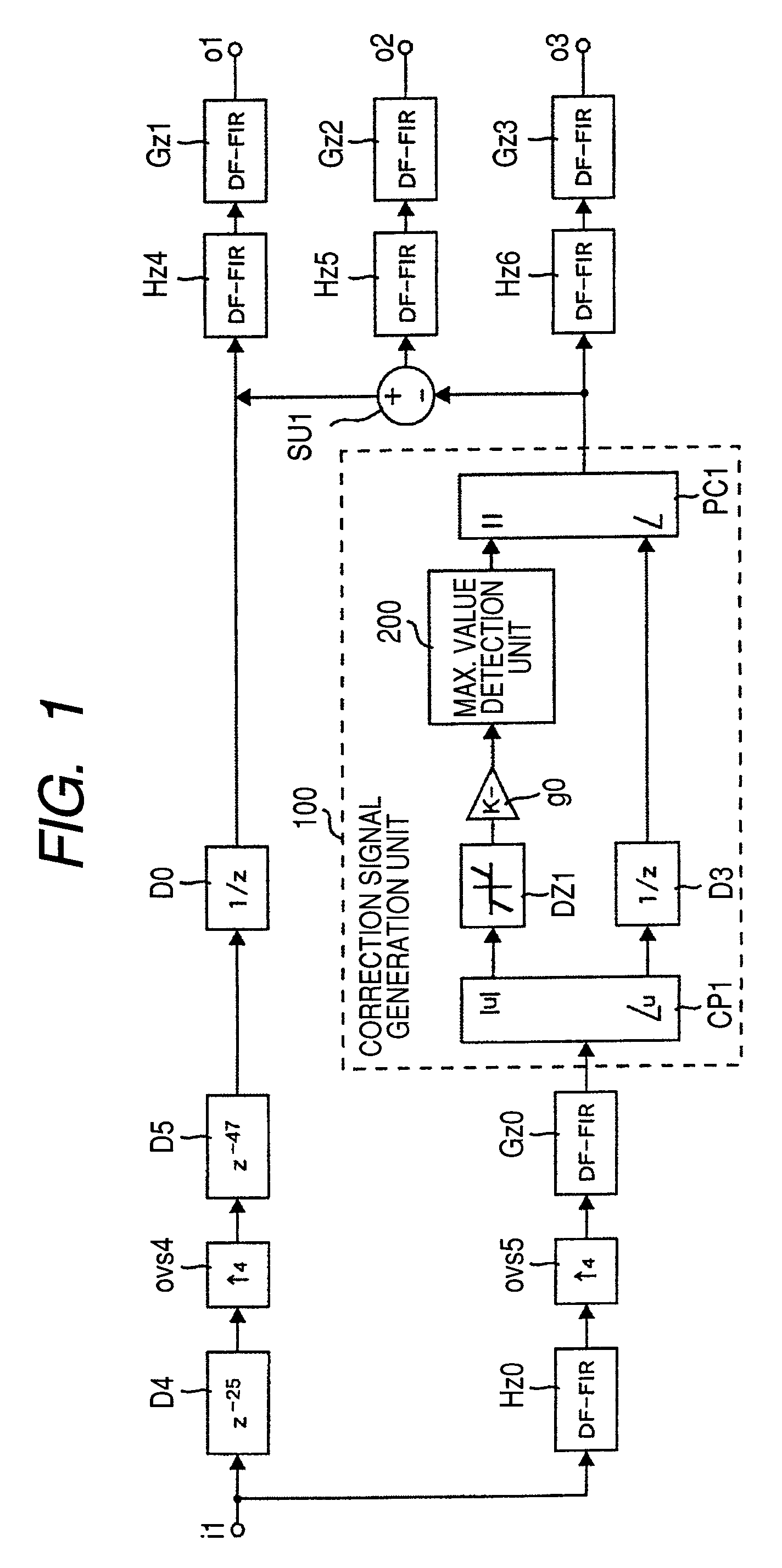

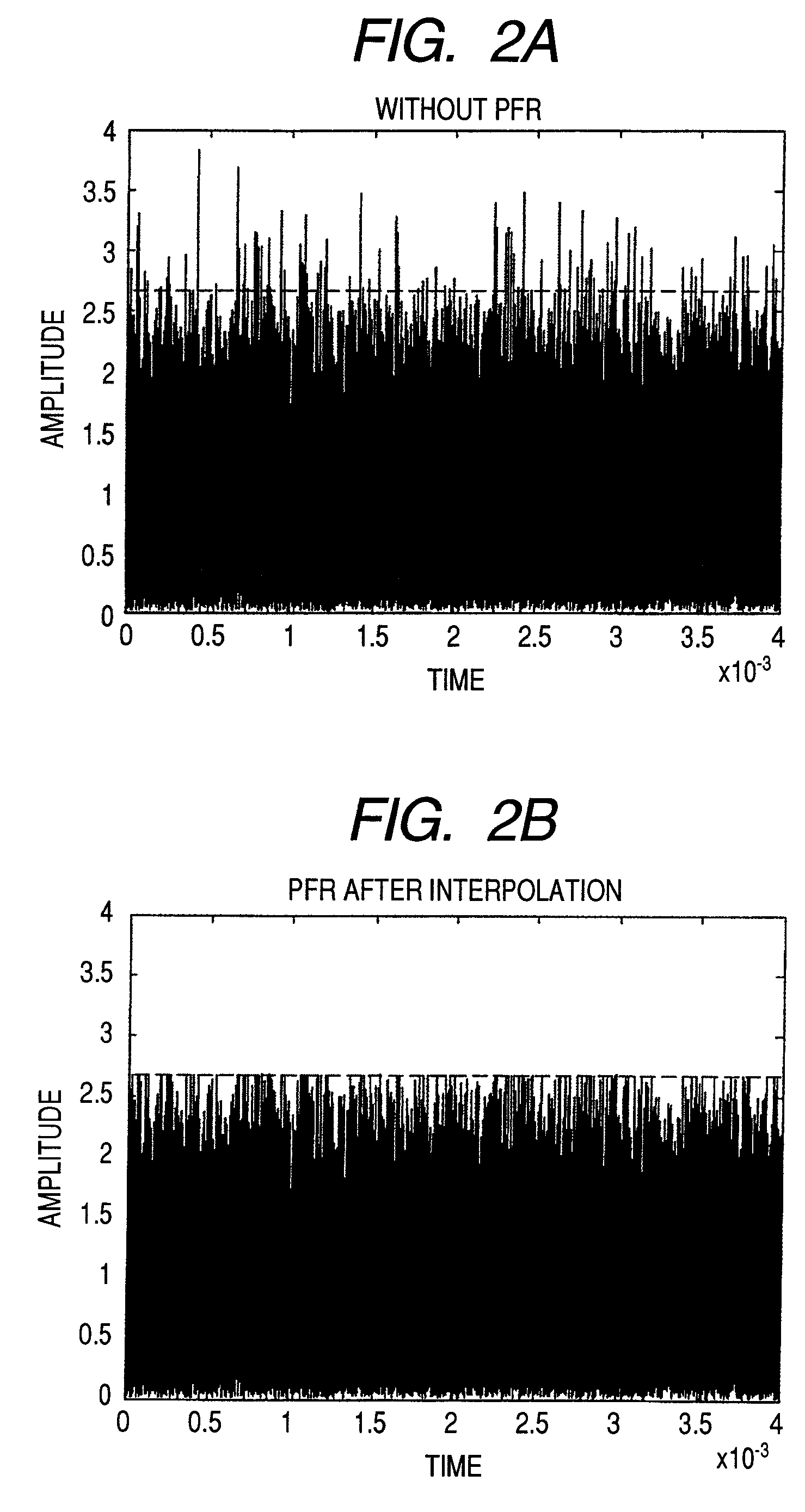

Peak factor reduction unit and baseband signal processing device

InactiveUS20080095284A1Reduce generationReduce phase distortionModulated-carrier systemsFrequency-division multiplexEngineeringPeak value

A peak factor reduction unit that never allow peak factor reproduction even when interpolation is done in a succeeding stage. The unit detects a local maximum value of amplitude components from an input complex signal and supplies a complex signal that passes a band limiting baseband filter and an interpolation filter to a correction signal generation unit for generating a correction signal used for peak factor reduction and reduces a peak factor of the input complex signal with use of the correction signal generated from an interpolated complex signal.

Owner:HITACHI LTD

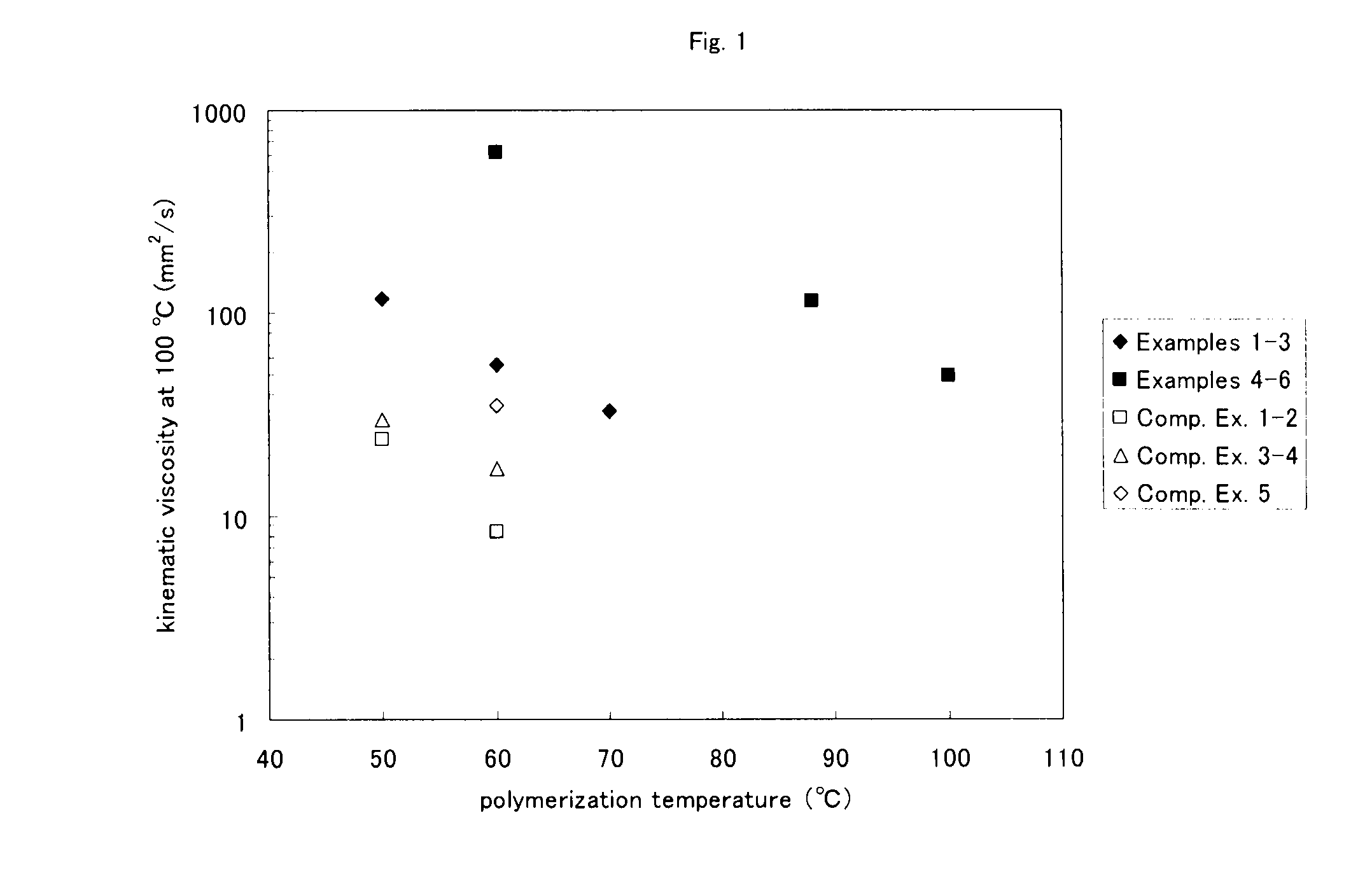

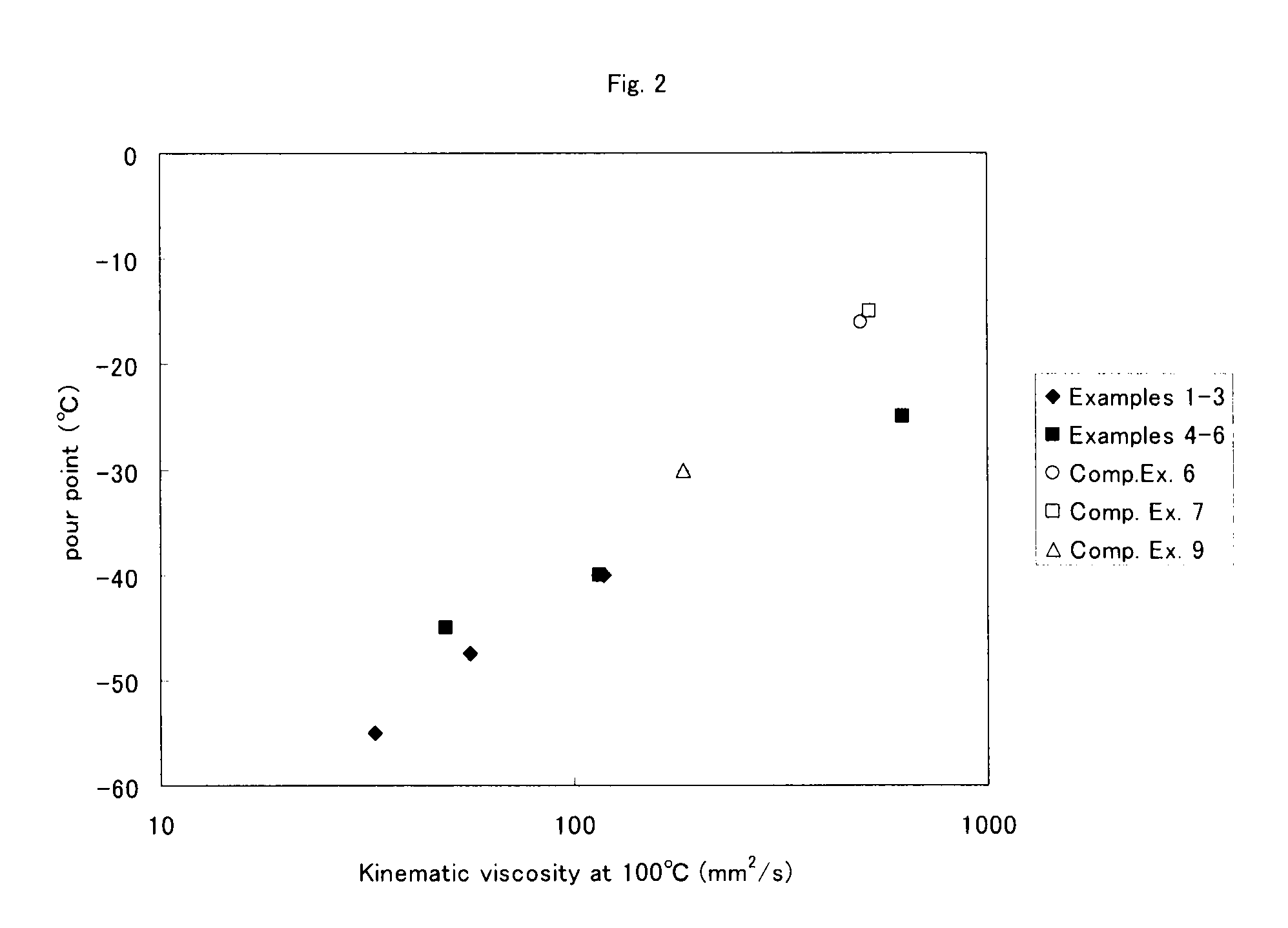

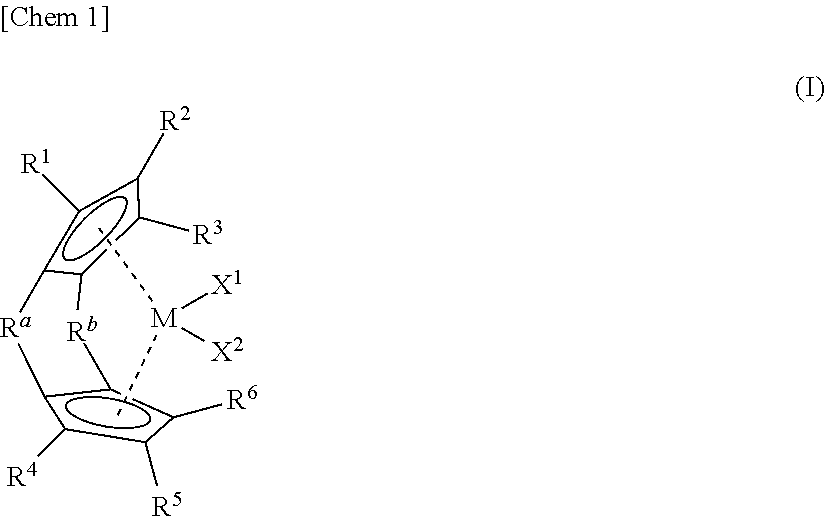

Process for producing alpha-olefin polymer, alpha-olefin polymer, and lubricating oil composition

ActiveUS20120040878A1Delay scalingEasy to manufactureLiquid carbonaceous fuelsAdditivesChemical compositionAlpha-olefin

Provided is a method of producing an α-olefin polymer including a step of polymerizing one or more kinds of α-olefins each having 6 to 20 carbon atoms with a catalyst obtained by using a specific transition metal compound. By the method, an α-olefin polymer having a viscosity suitable for use in a lubricating oil can be produced on an industrial scale with ease, and further, the characteristics of the product can be widely changed through the control of reaction conditions.

Owner:IDEMITSU KOSAN CO LTD

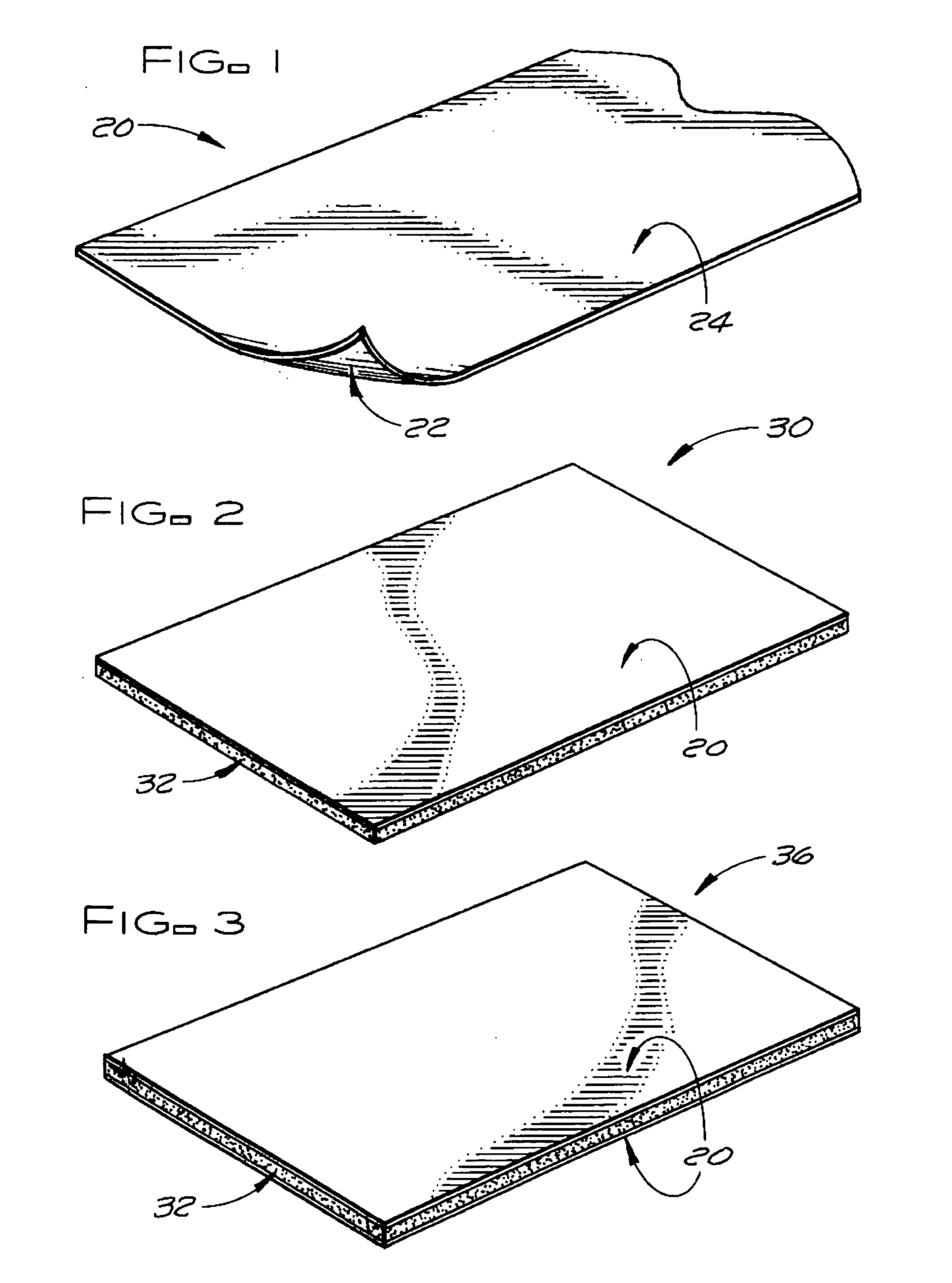

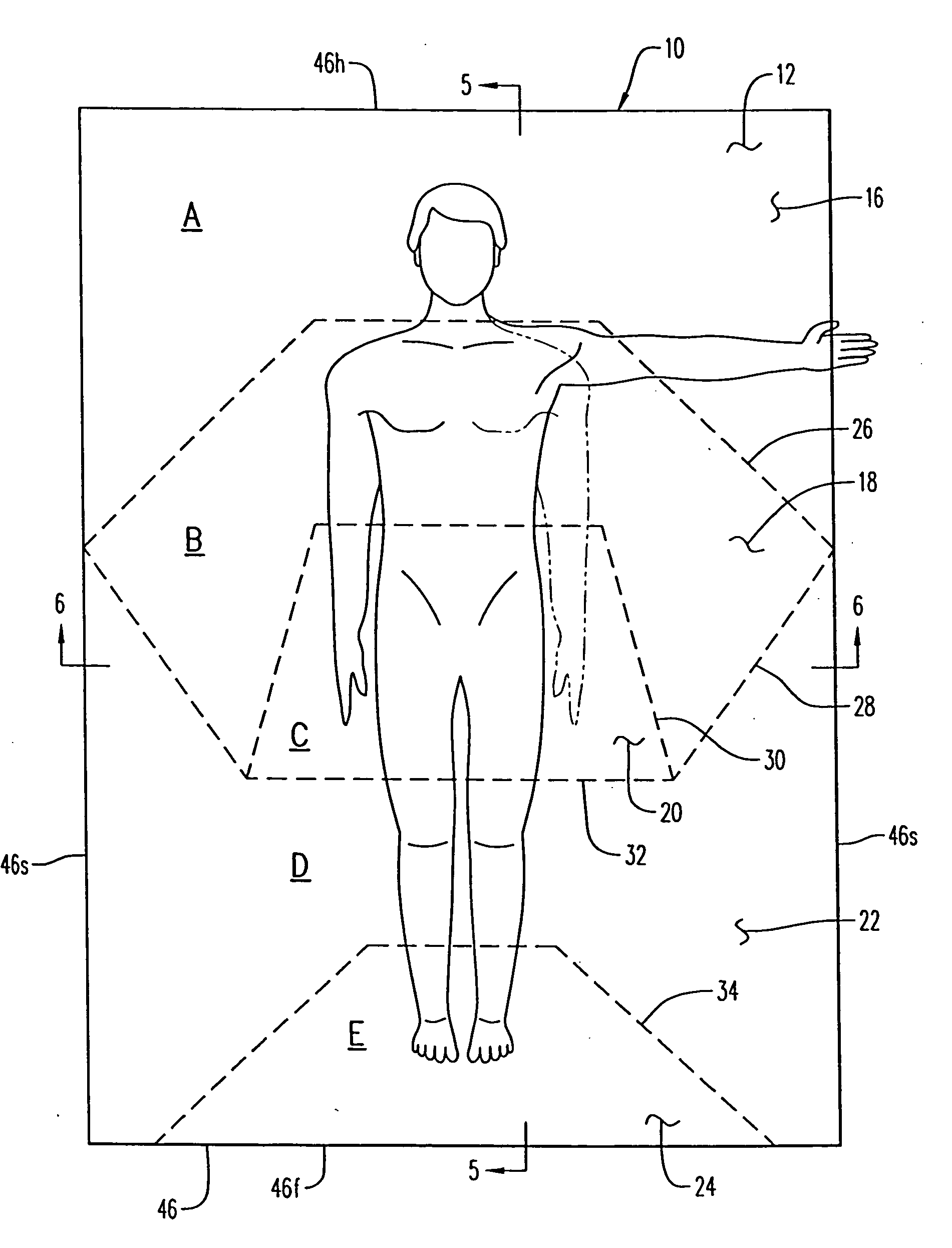

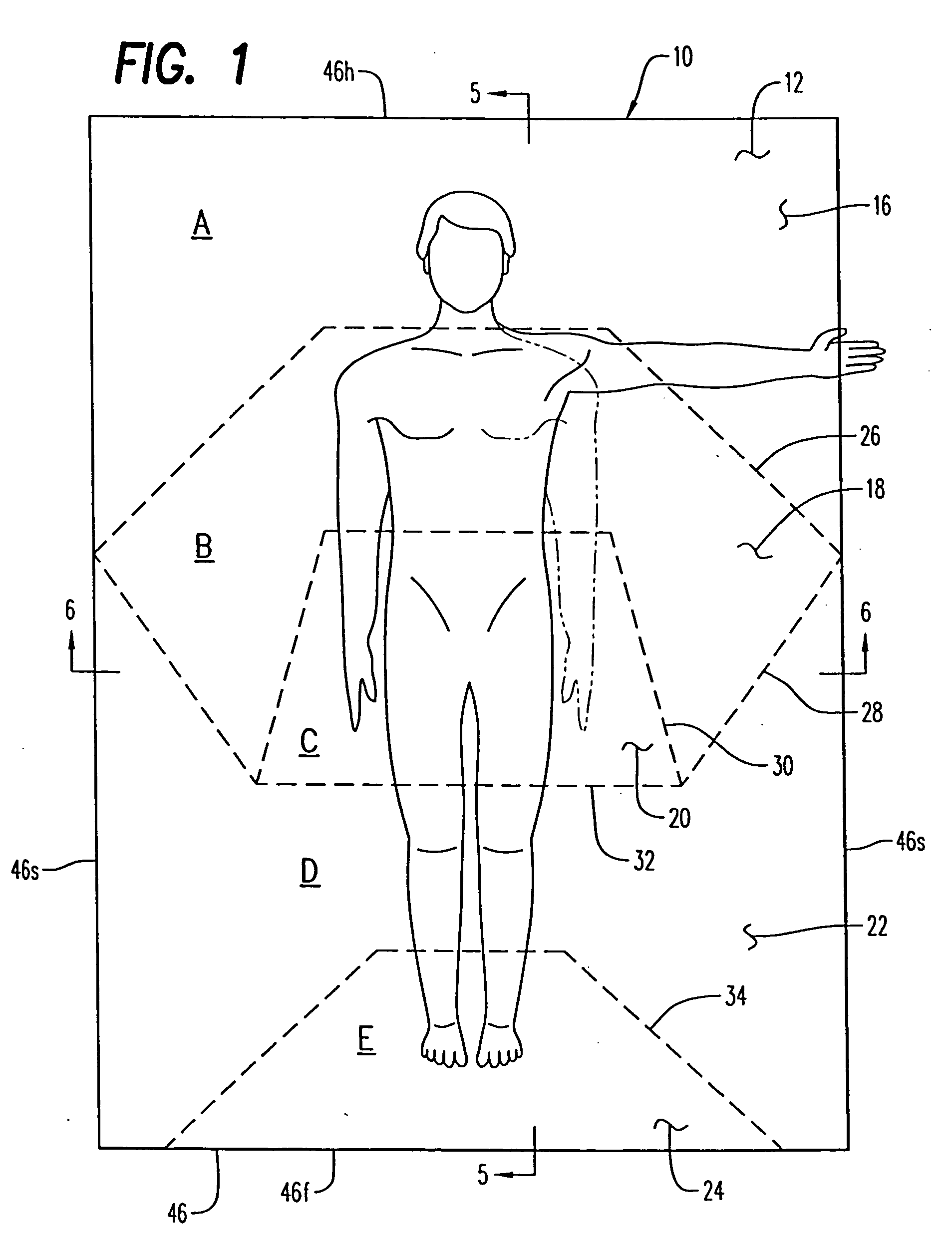

Mattress pad

ActiveUS20070113349A1Improve comfortDelay characteristicStuffed mattressesSpring mattressesEngineeringClosed cell

A mattress pad positionable atop a rectangular mattress which better accommodates diverse weights and sizes of the human anatomy for enhanced comfort. The mattress pad includes a flexible bottom sheet having a size and shape substantially similar to that of a top surface of the mattress. A flexible fabric top sheet is connected to the bottom sheet by peripheral stitching along common perimeter side, head and foot margins. A plurality of generally side-by-side body supporting chambers are each defined by peripheral stitching and spaced lines of continuous stitching which interconnect the top and bottom sheets. Each chamber is filled with an open or closed cell urethane foam material. Preselected nominal thicknesses of each of the chambers provides the comfort and accommodation to each portion of the human anatomy.

Owner:OPRANDI ARTHUR V

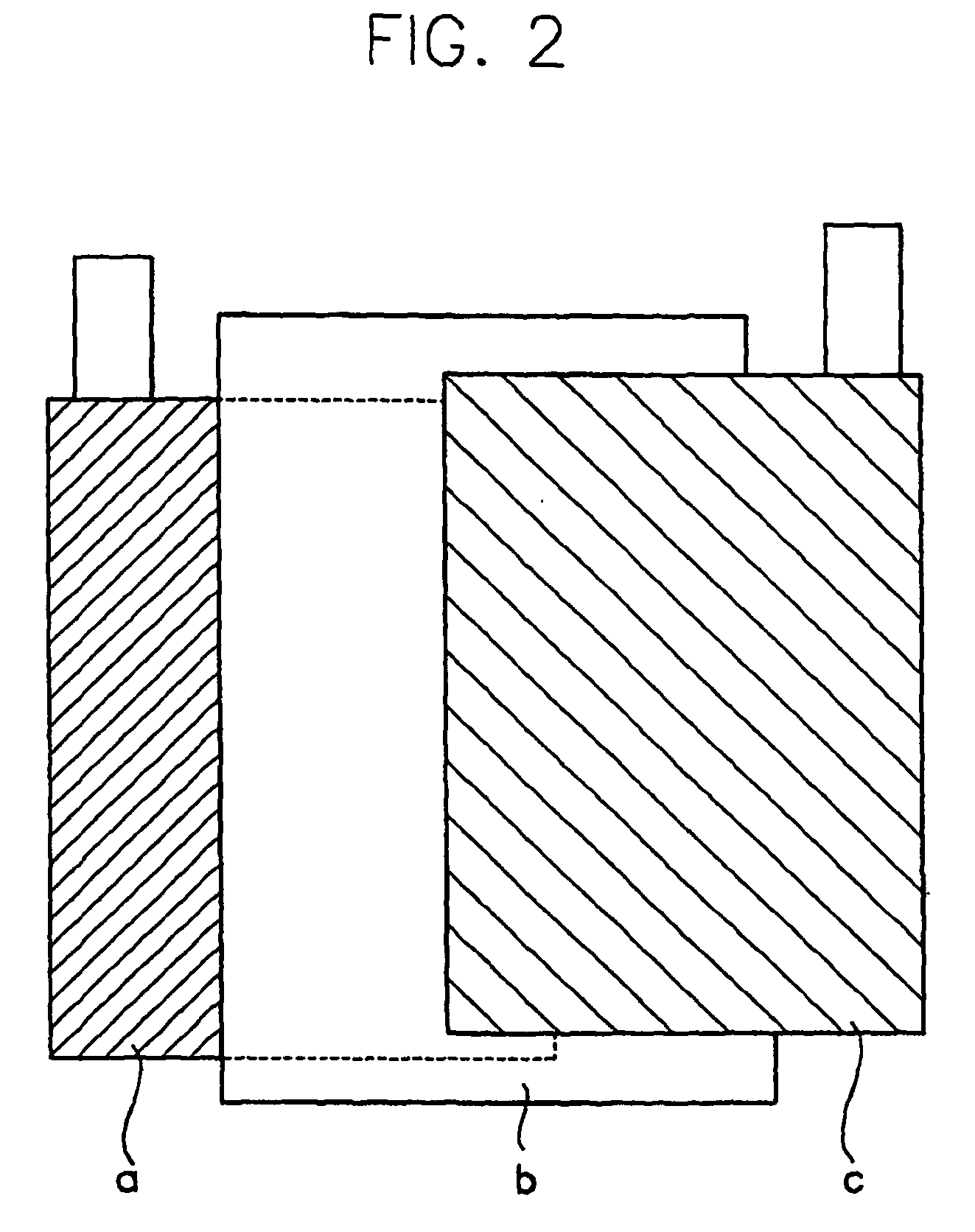

Electric energy storage system

InactiveUS20050105247A1Improve cycle lifeRapid charging-discharging characteristicCapacitor and primary/secondary cellsHybrid capacitor electrodesHigh resistanceHigh energy

An electric energy storage system having a novel structure which exhibits a ling cycle life, rapid charging-discharging characteristics and a high energy density. The electric energy storage system comprises: an anode comprised of a first material that performs interalation-deintercalation of cation as an anode active material; a cathode comprised of a second material that may form an electric doublelayer with anion as a cathode active materials; and a electrolyte including lithium salt, the electrolyte including the cation and anion. Due to a high difference between anode and cathode in capacity to store the electric energy, most electrochemical impact that occurs in the process of intercalation-deintercalation of electric energy is absorbed into cathode and active material used for anode is activated carbon having a very high resistance to electrochemical and structural impact, so that its operation life is elongated and it has rapid charging-discharging characteristics. The electric energy storage system can complement the defects of a conventional technology.

Owner:NESS CAPACITOR CO LTD

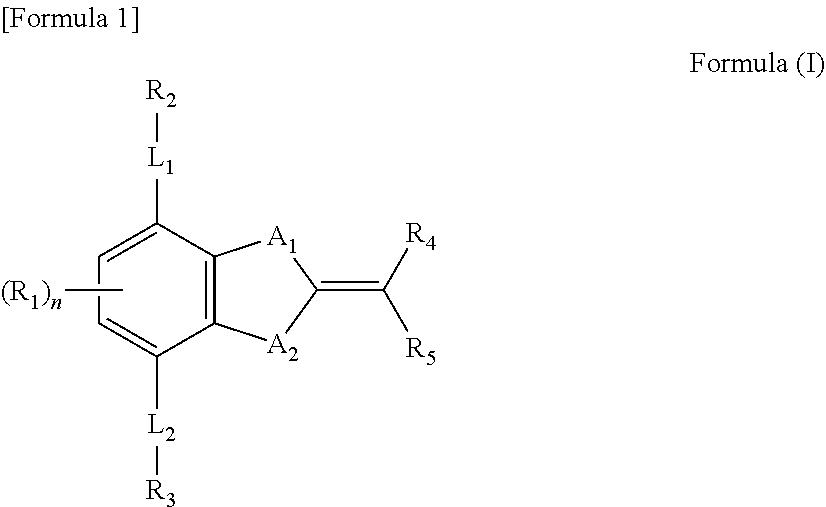

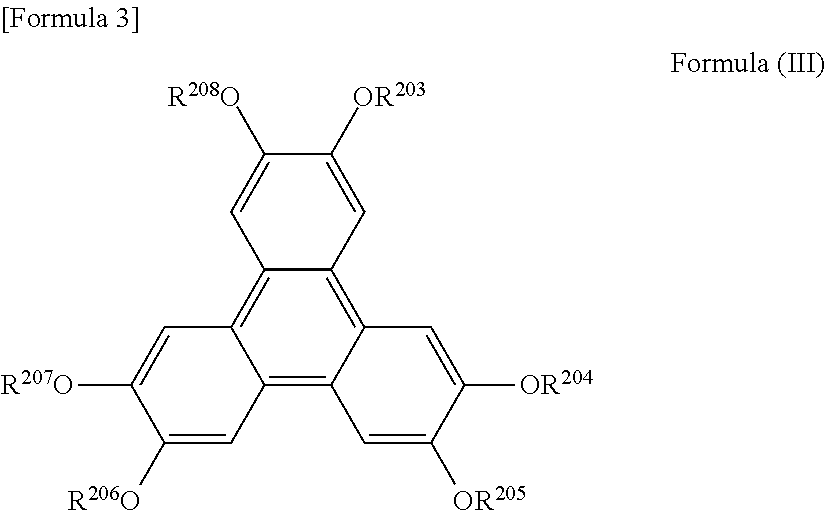

Method of preparing retardation film, polarizing plate, and liquid crystal display

InactiveUS20150114257A1Superior retardation characteristicImprove moisture resistanceOptical articlesOrganic non-macromolecular adhesiveAcetic acidPolymer science

A method of preparing a retardation film includes cellulose acetate having an average degree of acetylation of 2.0 to 2.5 and having a moisture content of 1.0 mass % or less, where the retardation film includes a compound having a Van der Waals volume of 450 to 1000 Å3. The retardation film is prepared by a dope preparing step of dissolving cellulose acetate having an average degree of acetylation within the range of 2.0 to 2.5 to prepare a dope; a film product forming step of casting the dope onto a metal belt to form a film product; a film product peeling step of peeling off the film product from the metal belt; a drawing step of drawing the peeled film product; and a drying step at a drying temperature of 140° C. or more.

Owner:KONICA MINOLTA INC

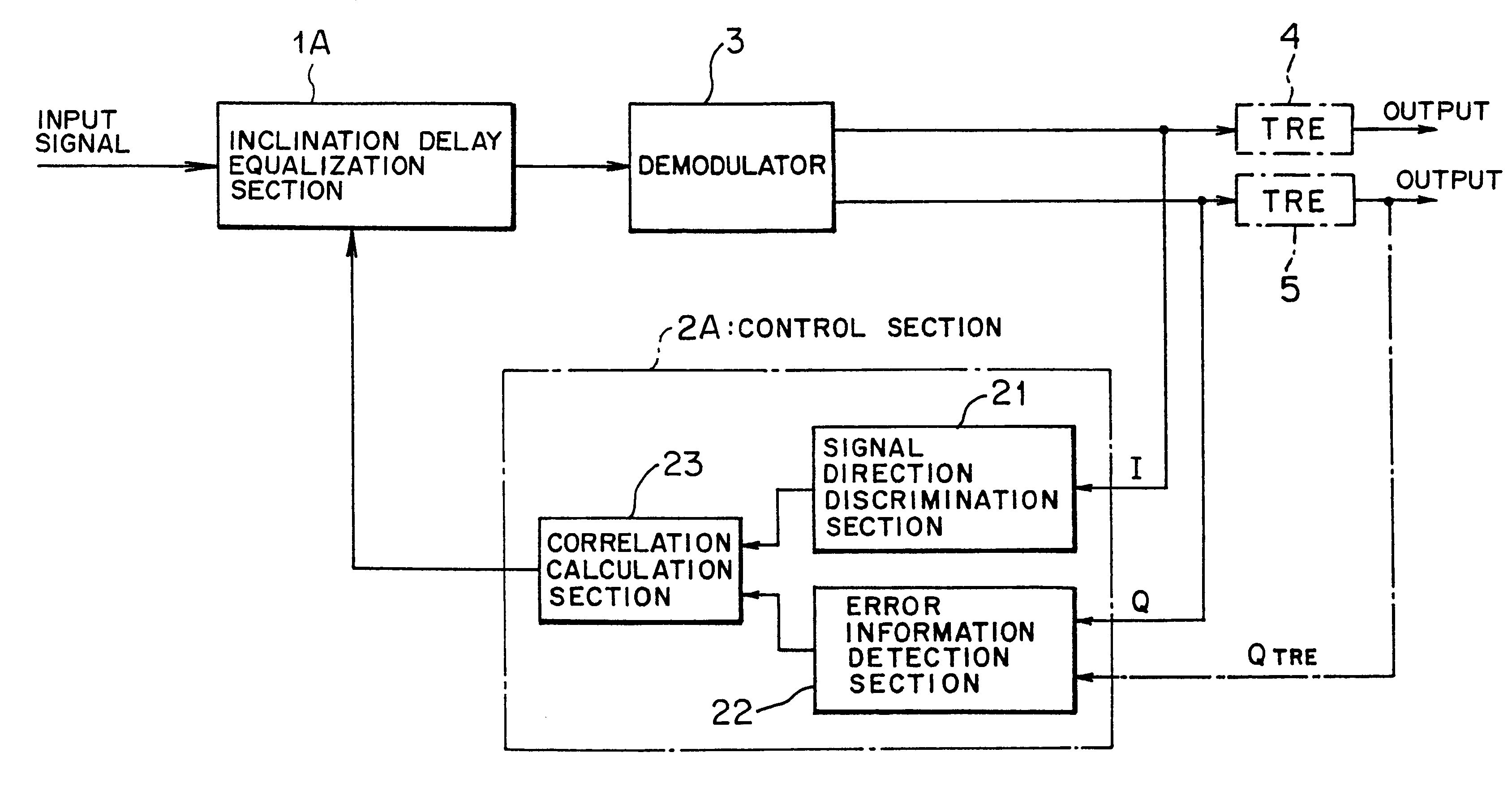

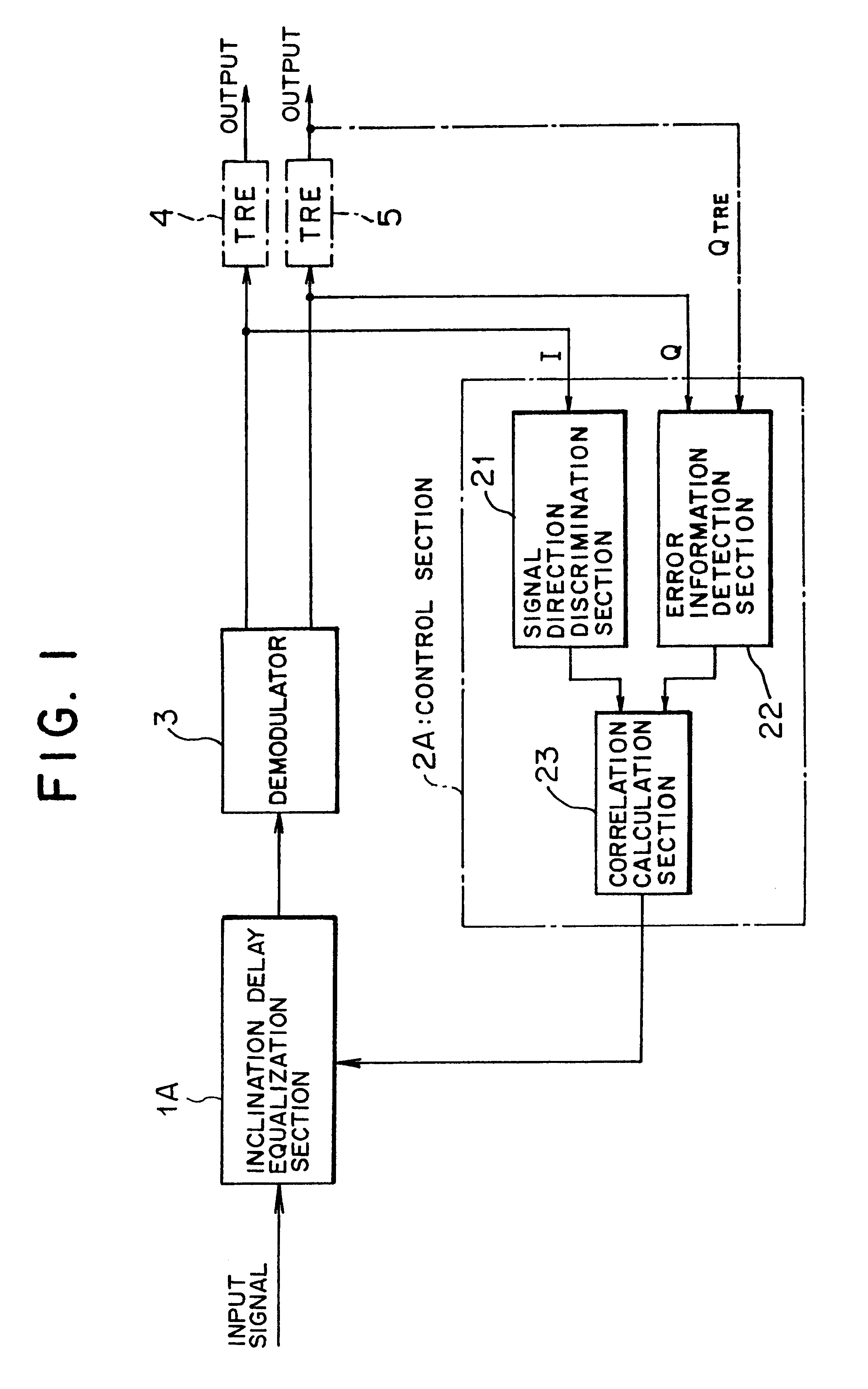

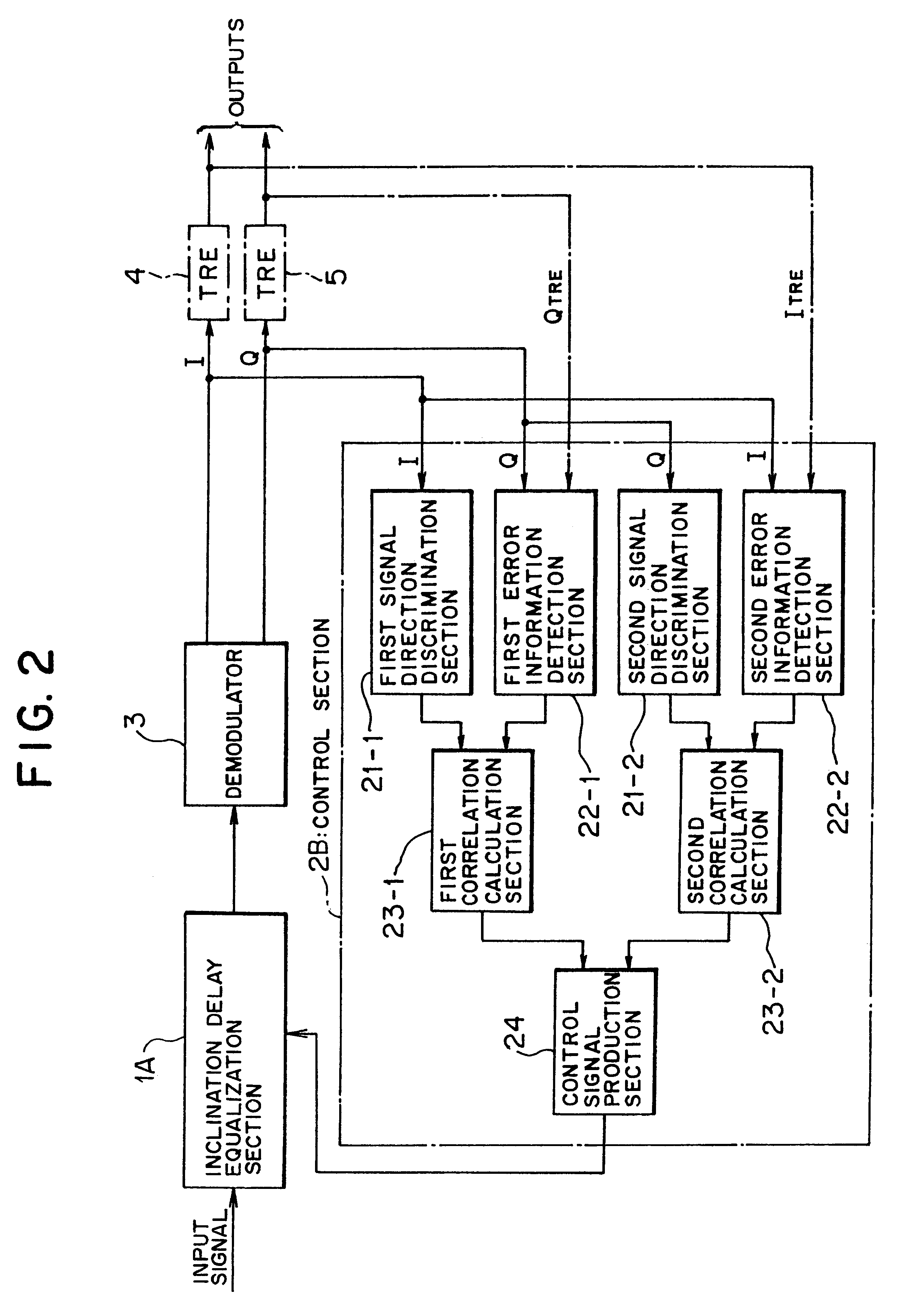

Automatic delay equalizer and automatic delay equalization method as well as automatic delay and amplitude equalizer and automatic delay and amplitude equalization method

InactiveUS6516028B1Delay characteristicSmall sizeMultiple-port networksTransmission control/equlisationControl signalEqualization

The invention provides an automatic delay equalizer and an automatic delay equalization method which can detect a delay characteristic (delay distortion) of an input signal and automatically compensate for the delay characteristic. The equalizer includes an inclination delay equalization section for compensating for the delay characteristic of the input signal in accordance with an inclination delay characteristic, and a control section for discriminating a direction of variation of a value of a first one of a pair of digital demodulated signals of the input signal, detecting error information from a second one of the digital demodulated signals which is orthogonal to the first signal and outputting a control signal for the inclination delay equalization section based on a correlation between the error information and the direction of variation of the value of the first signal.

Owner:FUJITSU LTD

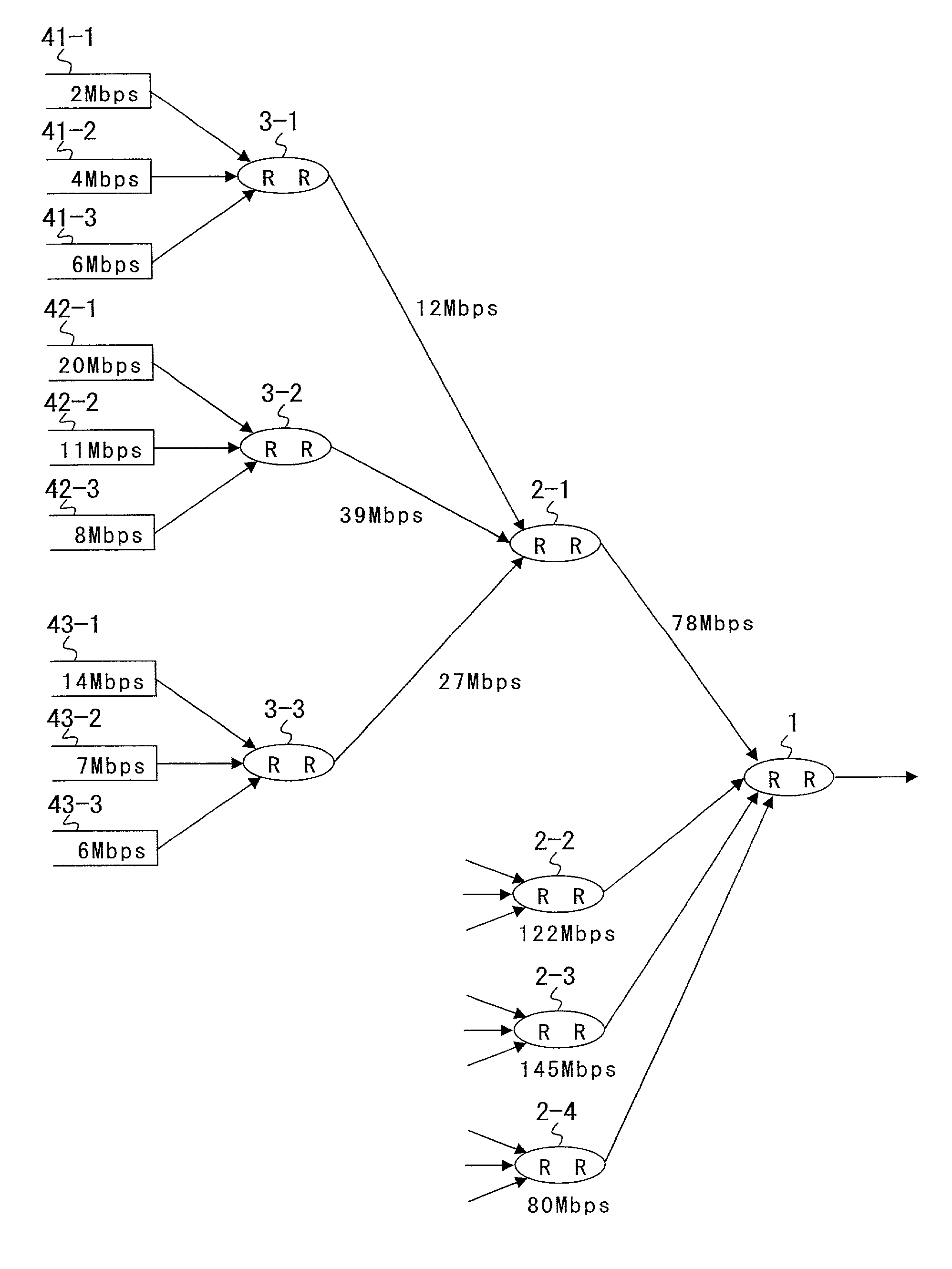

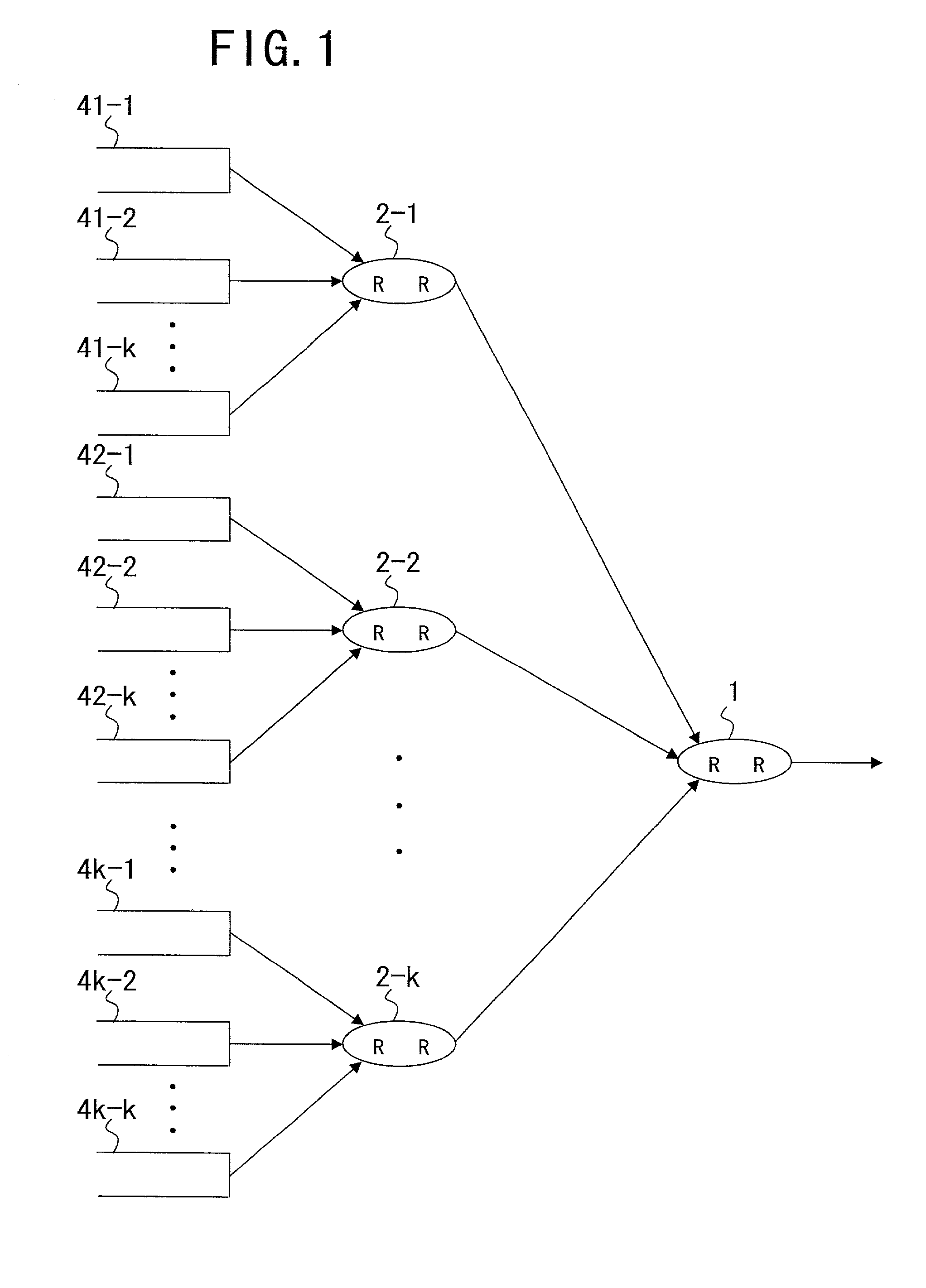

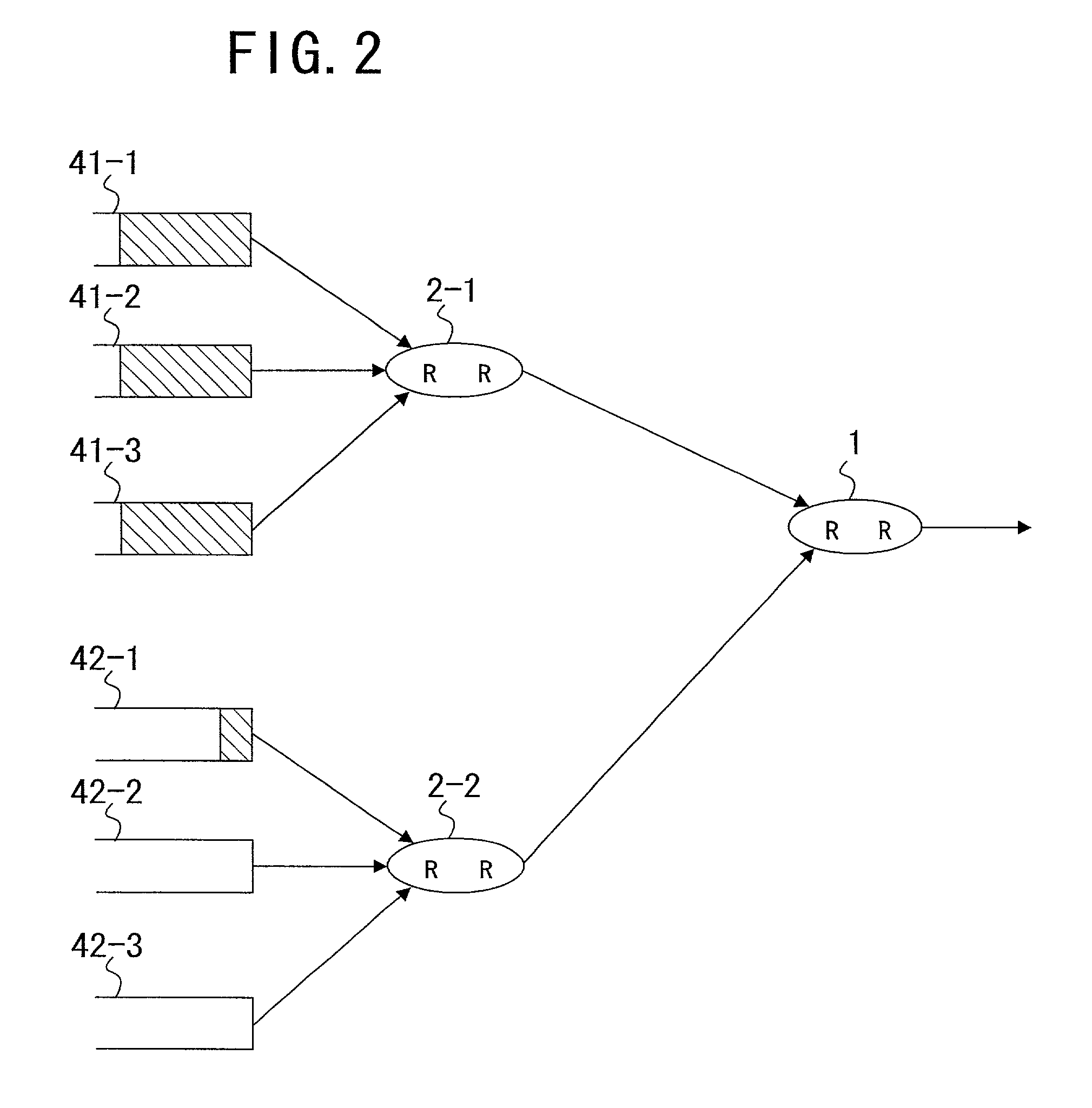

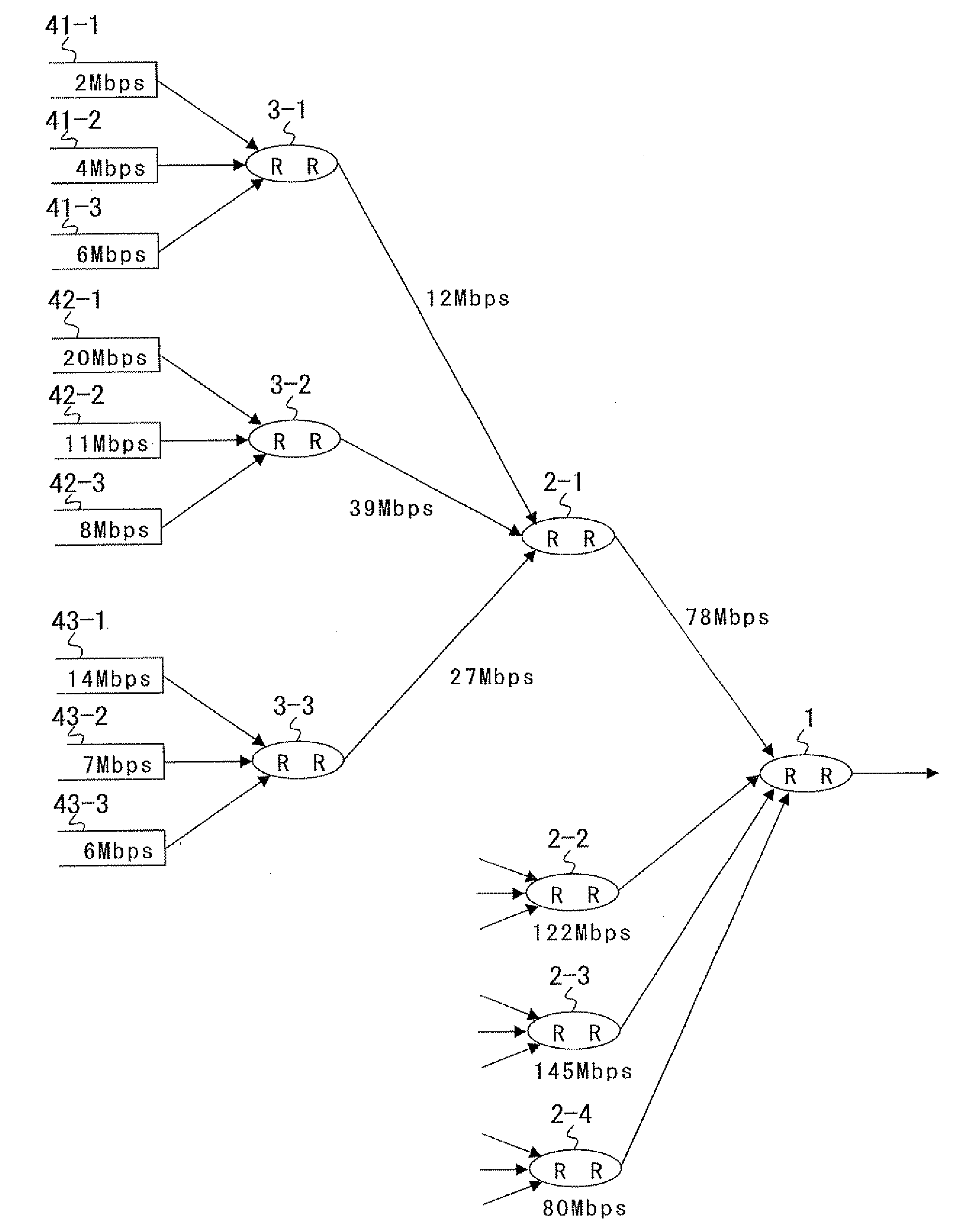

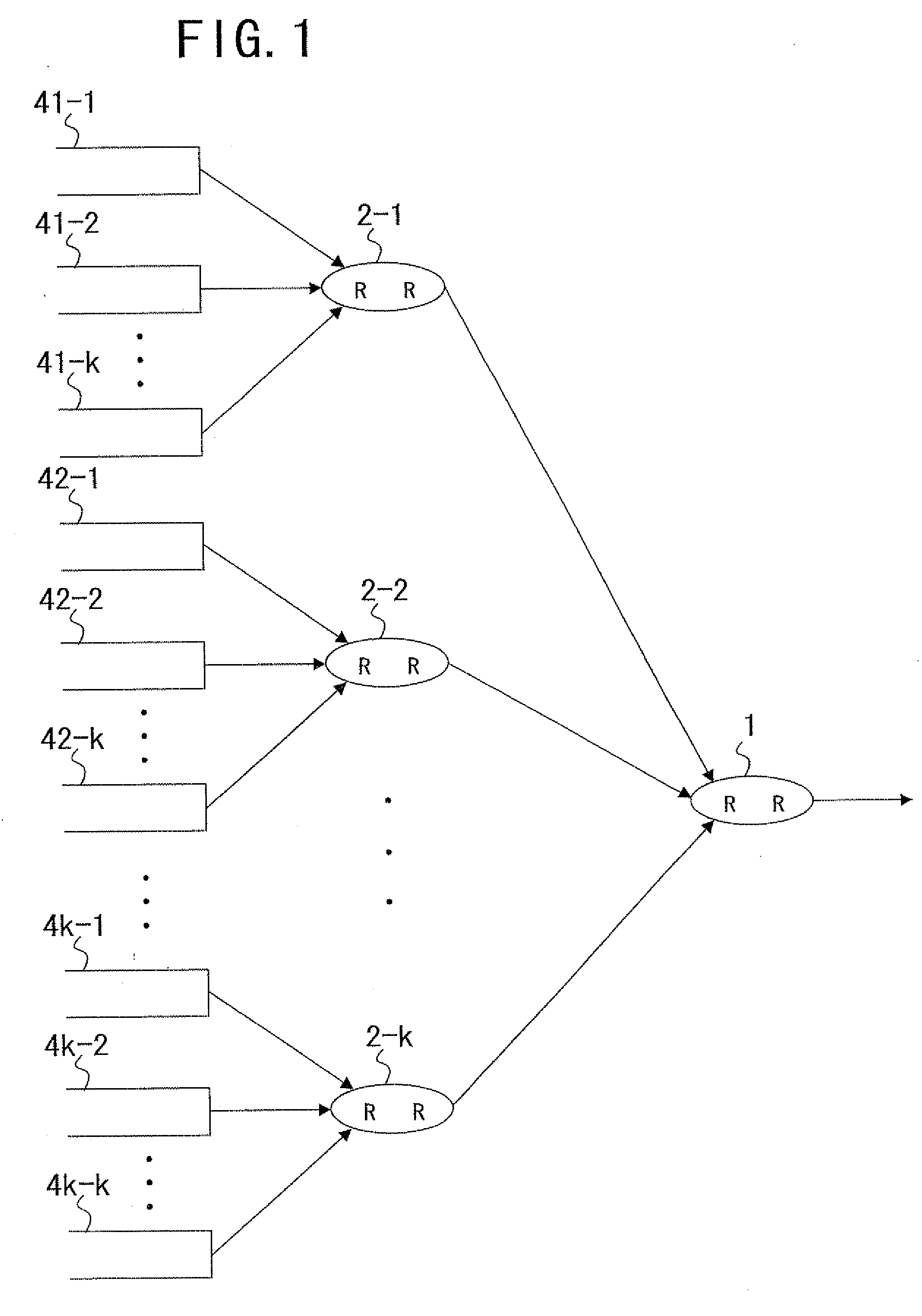

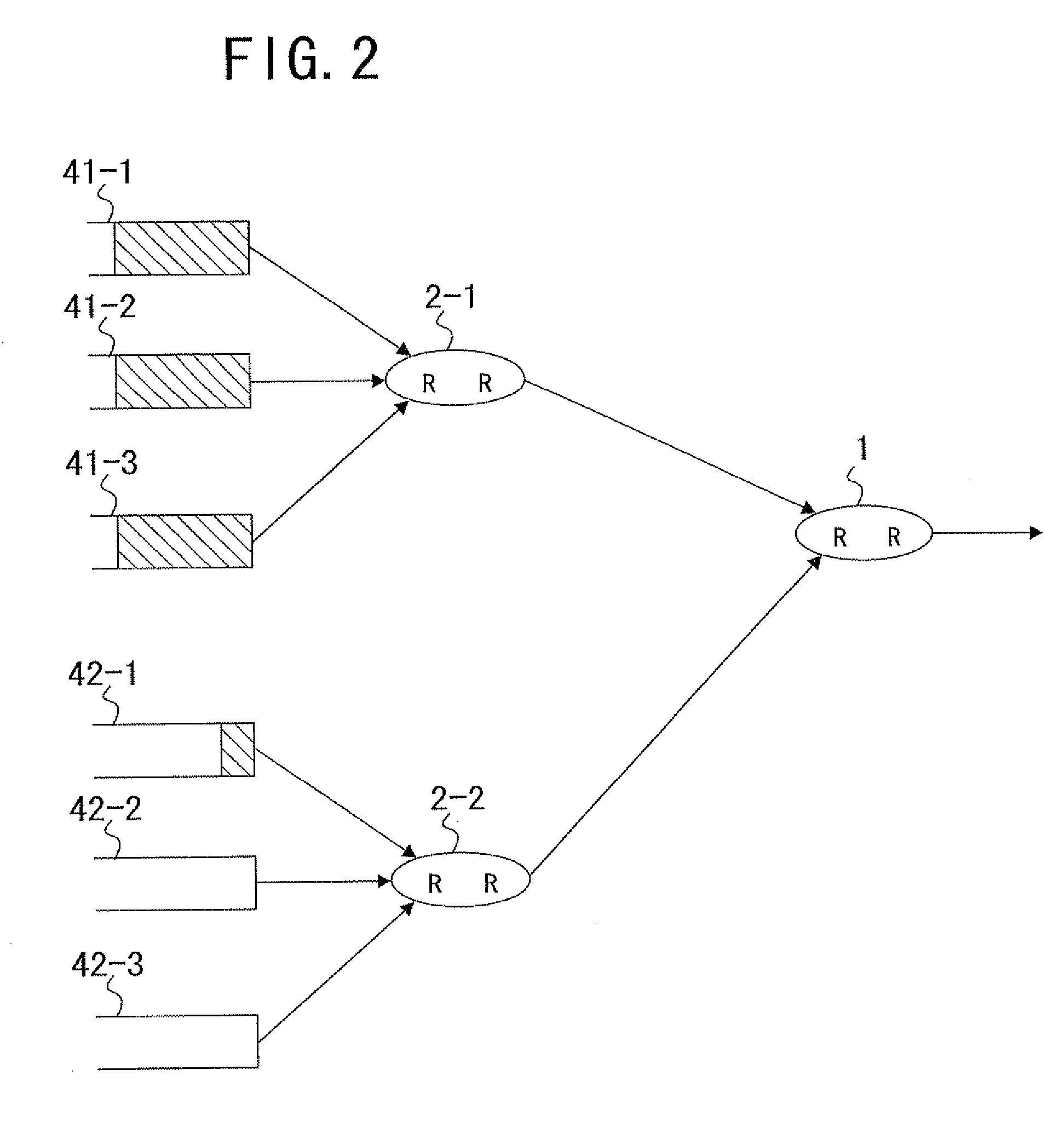

Arbitration method and arbiter circuit

InactiveUS7065049B2Simple configurationDelay characteristicError preventionFrequency-division multiplex detailsComputer architectureData transmission

The invention provides an arbitration method and an arbiter circuit in which sets of storage members having an associated output rate, and sets of arbitration members to be successively linked in multi-stage subordinate / superior relation and arbitrate data transfer from the storage members. One of the sets of the arbitration members may include first arbitration members to respectively connect to the storage members, each first arbitration member having an associated transfer rate corresponding to a sum of the output rates associated with the storage members of the set to which the first arbitration member connects. One or more other sets of the arbitration members may include arbitration members that are superior to the first arbitration members and have an associated transfer rate corresponding to a sum of the transfer rates associated with immediately subordinate arbitration members and have information identifying a rank order subordinate arbitration members having the lowest associated transfer rates among the immediately subordinate arbitration members.

Owner:JUMIPER NETWORKS INC

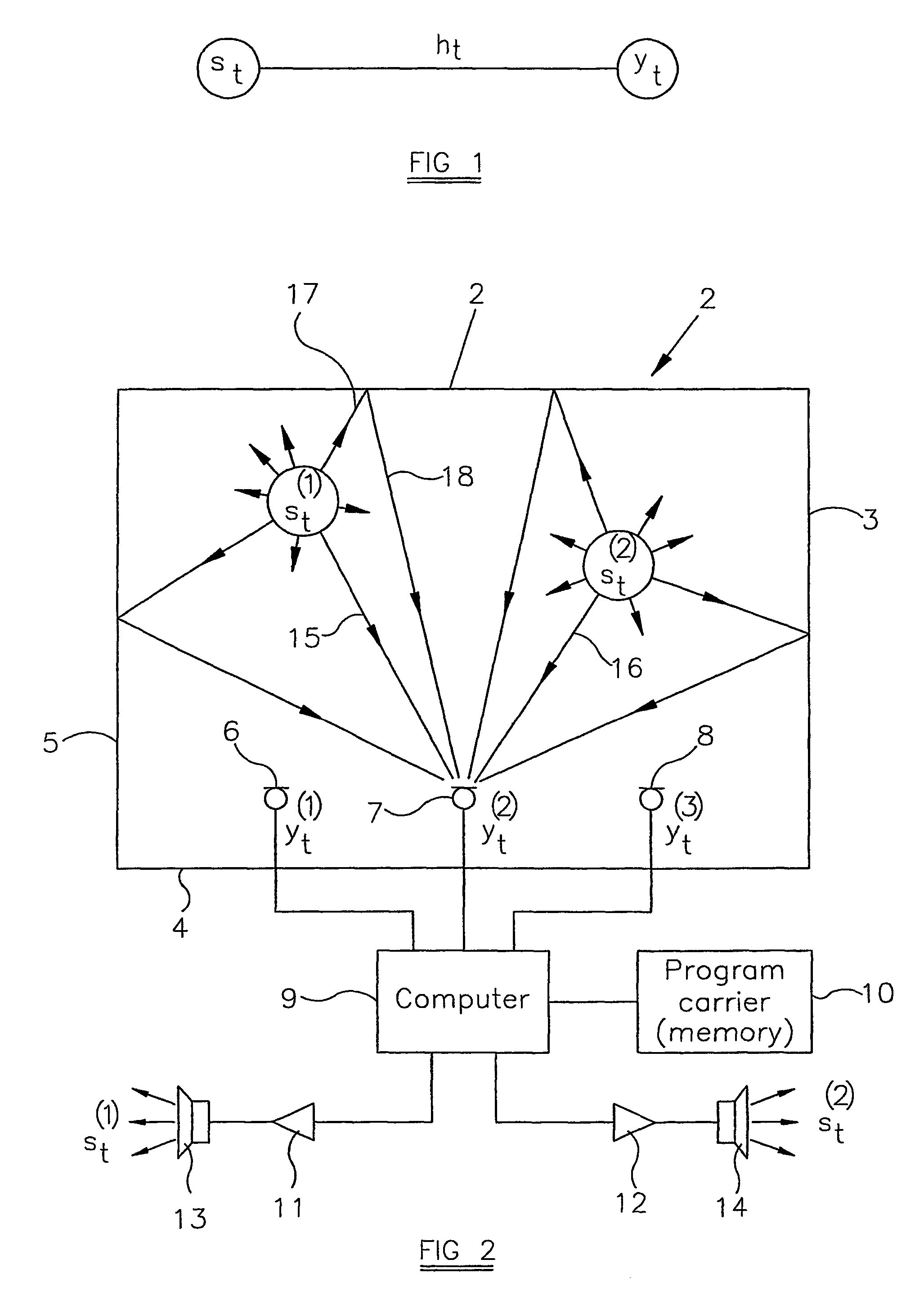

Method for extracting a signal

InactiveUS7110722B2Many problemExtraction of moreTransmission control/equlisationTransmission monitoringState spaceElectrical and Electronics engineering

A method is provided of extracting desired signals st from contaminated signals yt measured via respective communication channels. The system comprising the desired signals st and the channels is modelled as a state space model. In the model, the desired signals have time-varying characteristics which vary more quickly than second time-varying characteristics of the channels.

Owner:AT&T LABS

Peak factor reduction unit and baseband signal processing device

InactiveUS7817746B2Specific retardationIncrease speedModulated-carrier systemsFrequency-division multiplexPeak valueEngineering

A peak factor reduction unit that never allow peak factor reproduction even when interpolation is done in a succeeding stage. The unit detects a local maximum value of amplitude components from an input complex signal and supplies a complex signal that passes a band limiting baseband filter and an interpolation filter to a correction signal generation unit for generating a correction signal used for peak factor reduction and reduces a peak factor of the input complex signal with use of the correction signal generated from an interpolated complex signal.

Owner:HITACHI LTD

Flame retardant polycarbonate based composition including carbon

InactiveUS20090227707A1Improve flame retardant performanceHigh impact strengthPolycarbonateImpact resistance

A flame retardant thermoplastic composition that includes a polycarbonate or polycarbonate blend resin, a non-brominated, non-chlorinated flame retardant package, a carbon-containing synergist, such as carbon black and an optional reinforcing filler. The composition provides high impact resistance, improved flame retardant characteristics, and / or good processing during injection molding (i.e. mold-ability), while complying with regulations that restrict the use of halogenated materials. These compositions may be used, for example, to injection-mold big or complex parts that are used in objects that are beneficially flame-resistant and / or do not break when an accidental impact occurs during usage or transportation.

Owner:SABIC INNOVATIVE PLASTICS IP BV

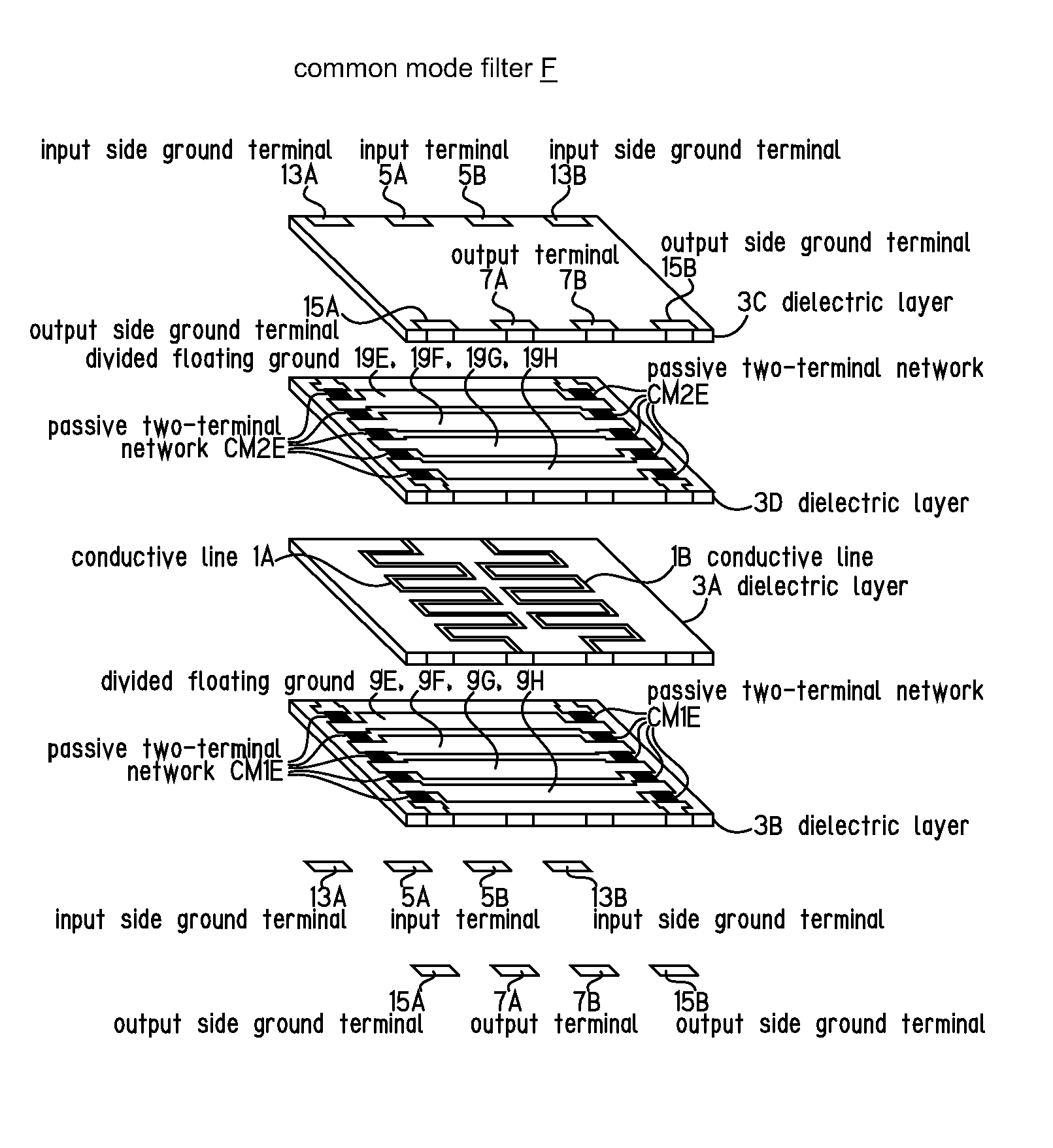

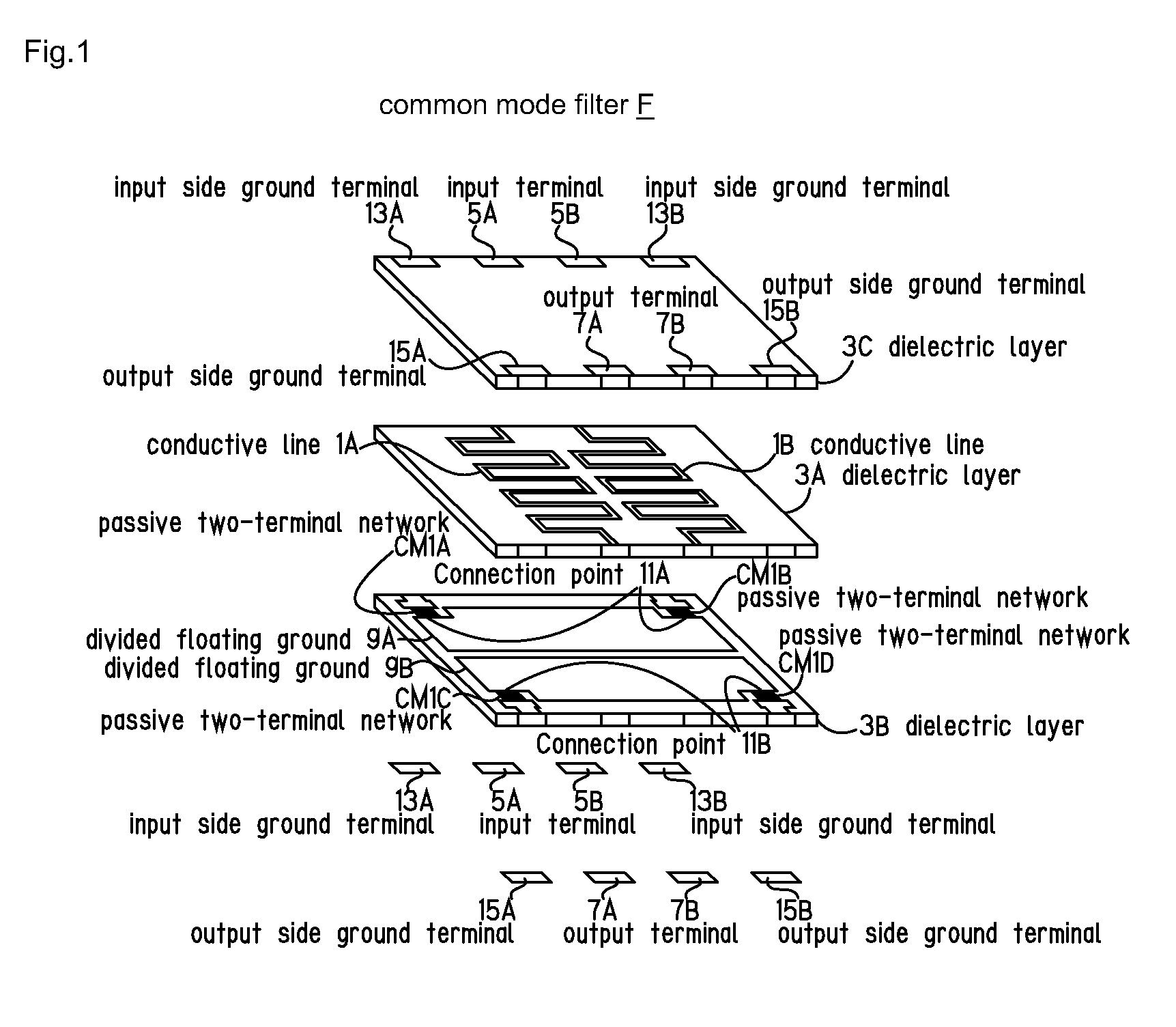

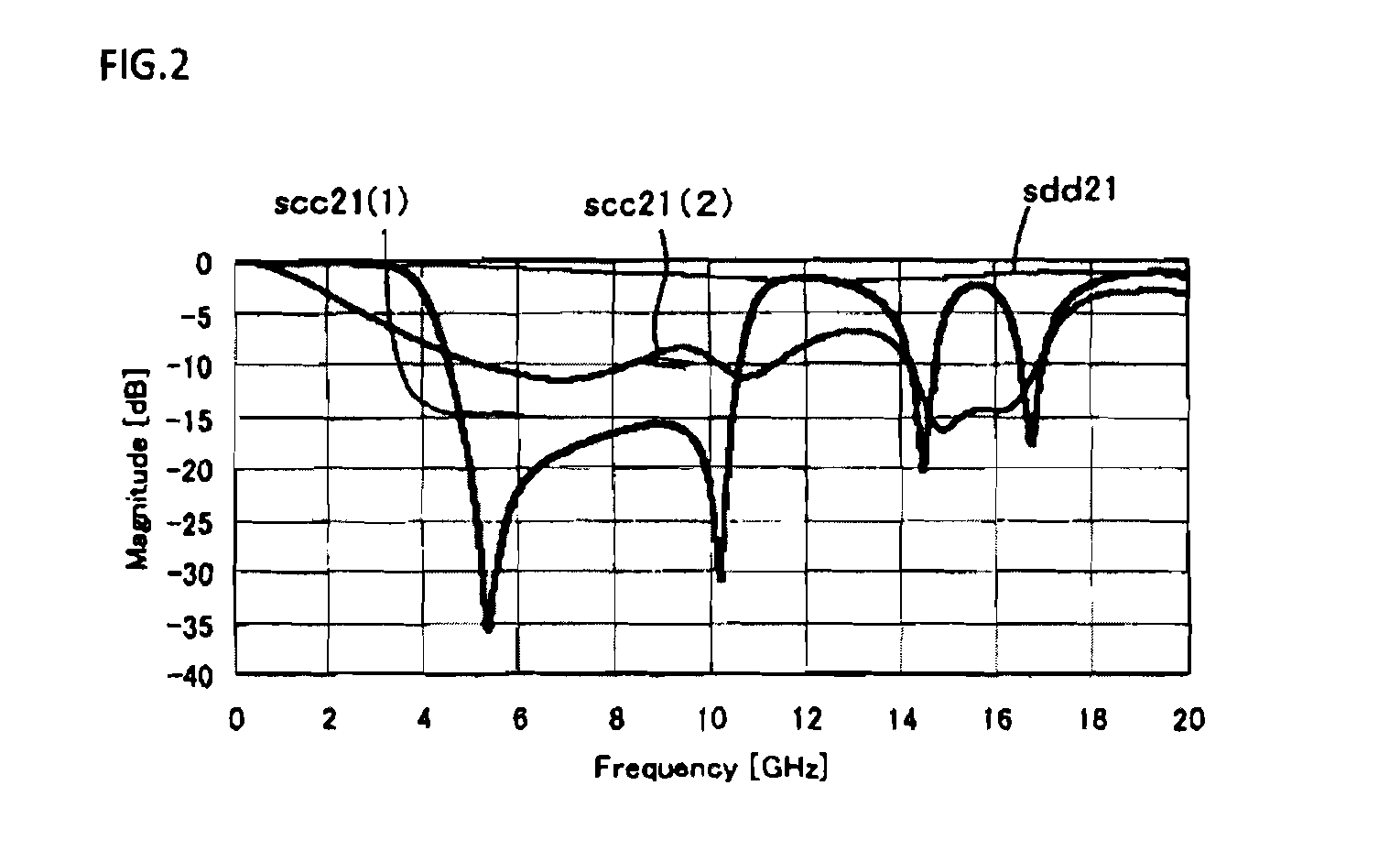

Common mode filter

ActiveUS8922303B2Simple structureReduced characteristicsMultiple-port networksCurrent interference reductionUltra high speedDifferential signaling

To sufficiently attenuate a common mode signal by passing an ultra-high speed differential signal through an ultra-high speed differential transmission line. A common mode filter comprises: a pair of conductive lines formed on a first dielectric layer to transmit a differential signal; a plurality of first divided floating grounds in a state of being separated from an external ground potential, and facing the conductive lines, with the first dielectric layer interposed between them, and formed by being divided into a plurality of numbers in a length direction of the conductive lines, and forming a distribution constant type differential transmission line for the differential signal, together with the conductive lines; and a first passive two-terminal network connected between the first divided floating grounds located at least at an input side or an output side of the first divided floating grounds, and the external ground potential.

Owner:ELMEC

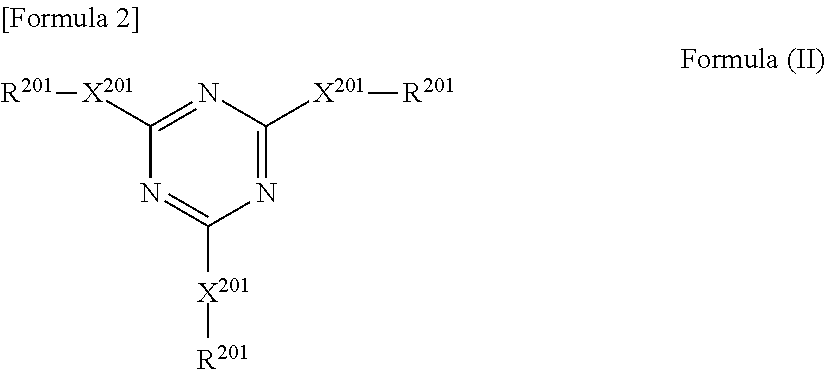

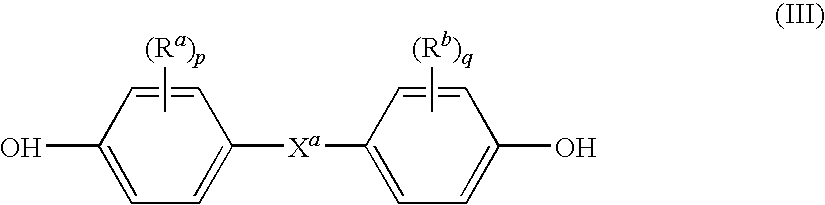

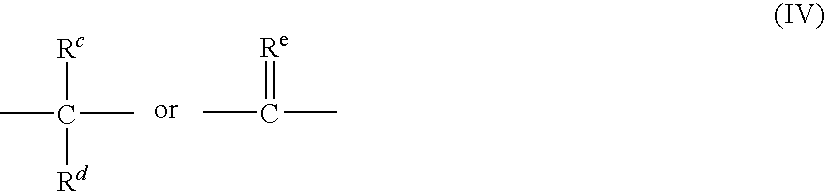

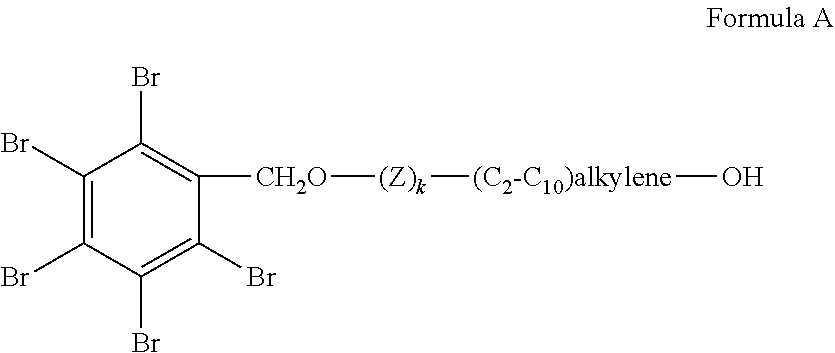

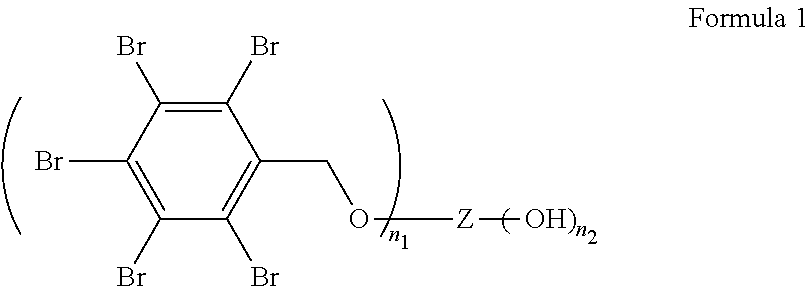

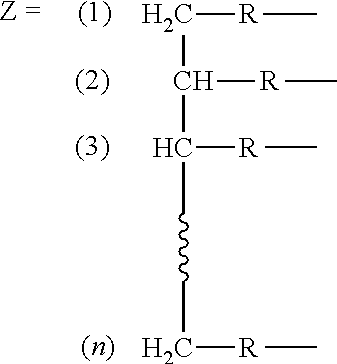

Flame retardants, processes for their preparation and uses thereof in polyurethane and polyisocyanurate foams

ActiveUS20140303271A1Highly satisfactory flame retarding characteristicImprove compatibilityOrganic chemistryOrganic compound preparationPolyisocyanurateFire retardant

The invention provides pentabromobenzyl moiety containing hydroxy-functional compounds which are useful as flame-retardants in flexible and rigid polyurethane foams and also in rigid polyisocyanurate foams. Processes for preparing the compounds, polyurethane and polyisocyanurate foams containing the compounds are also provided by the invention.

Owner:BROMINE COMPOUNDS

Arbitration method for output cells of ATM and arbiter circuit

InactiveUS20060193324A1Simple configurationDelay characteristicError preventionTransmission systemsDistributed computingLower order

The invention provides an arbitration method and an arbiter circuit by which equal arbitration of output cells can be achieved with a comparatively simple configuration even where a very great number of queues are involved. The arbiter circuit includes a plurality of queues for storing output cells, and a plurality of round robins for successively providing the right of outputting output cells to the queues. The round robins are arranged in a multi-stage tree link configuration, and the queues are distributed under those of the round robins which are in the lowest order stage. Each of the round robins in the lowest order stage has a rate information holding function of holding rate information representative of a rate of cells inputted thereto. Meanwhile, each of the round robins in the higher order stage or stages has a rate information holding function of holding rate information regarding those of the round robins which are subordinate to the round robin and a subordinate selection function of selecting one of the subordinate round robins based on the rate information of the subordinate round robins. A queue is added as a subordinate to the selected round robin in the lowest order stage when a connection is to be added newly.

Owner:JUMIPER NETWORKS INC

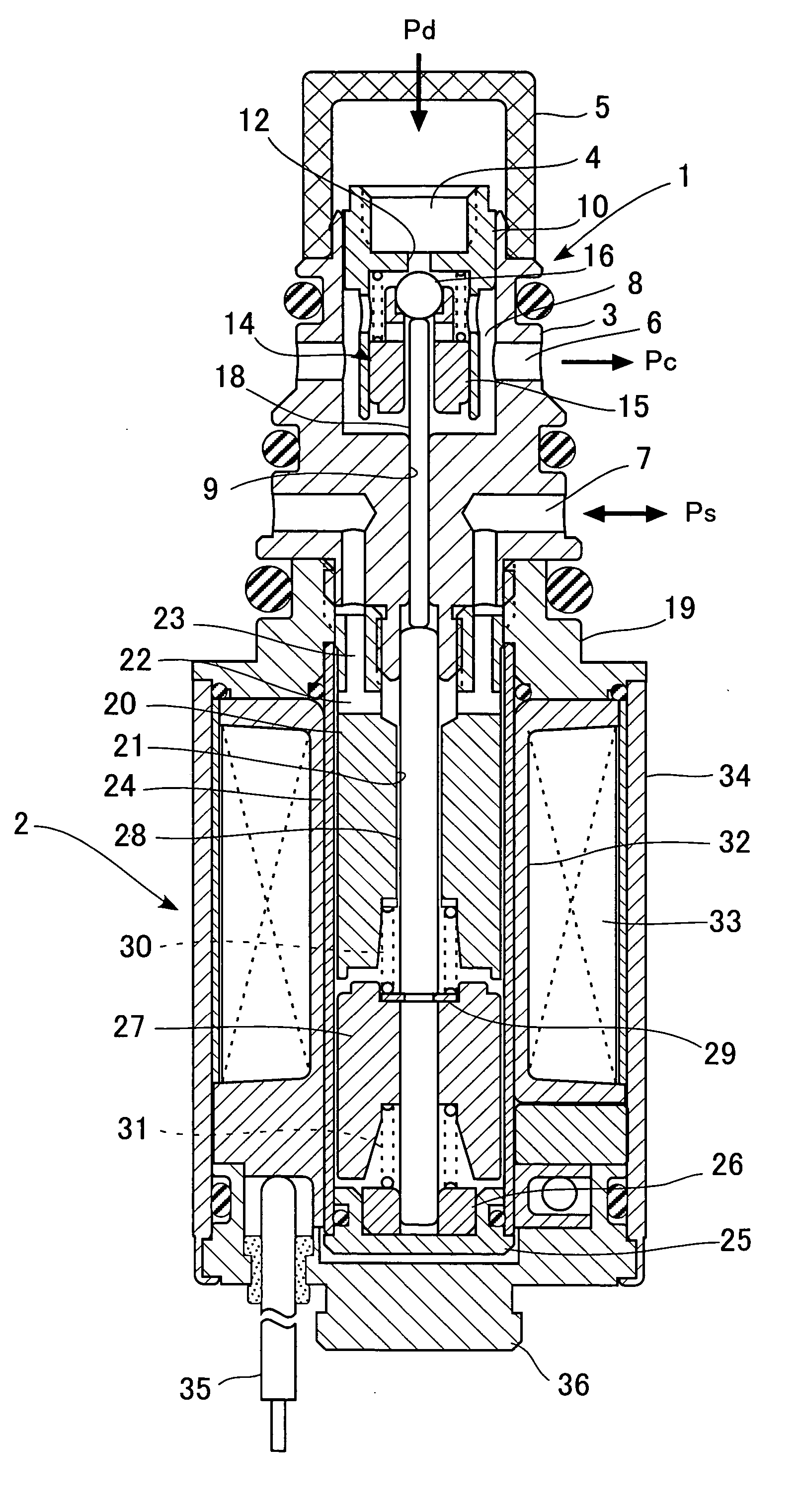

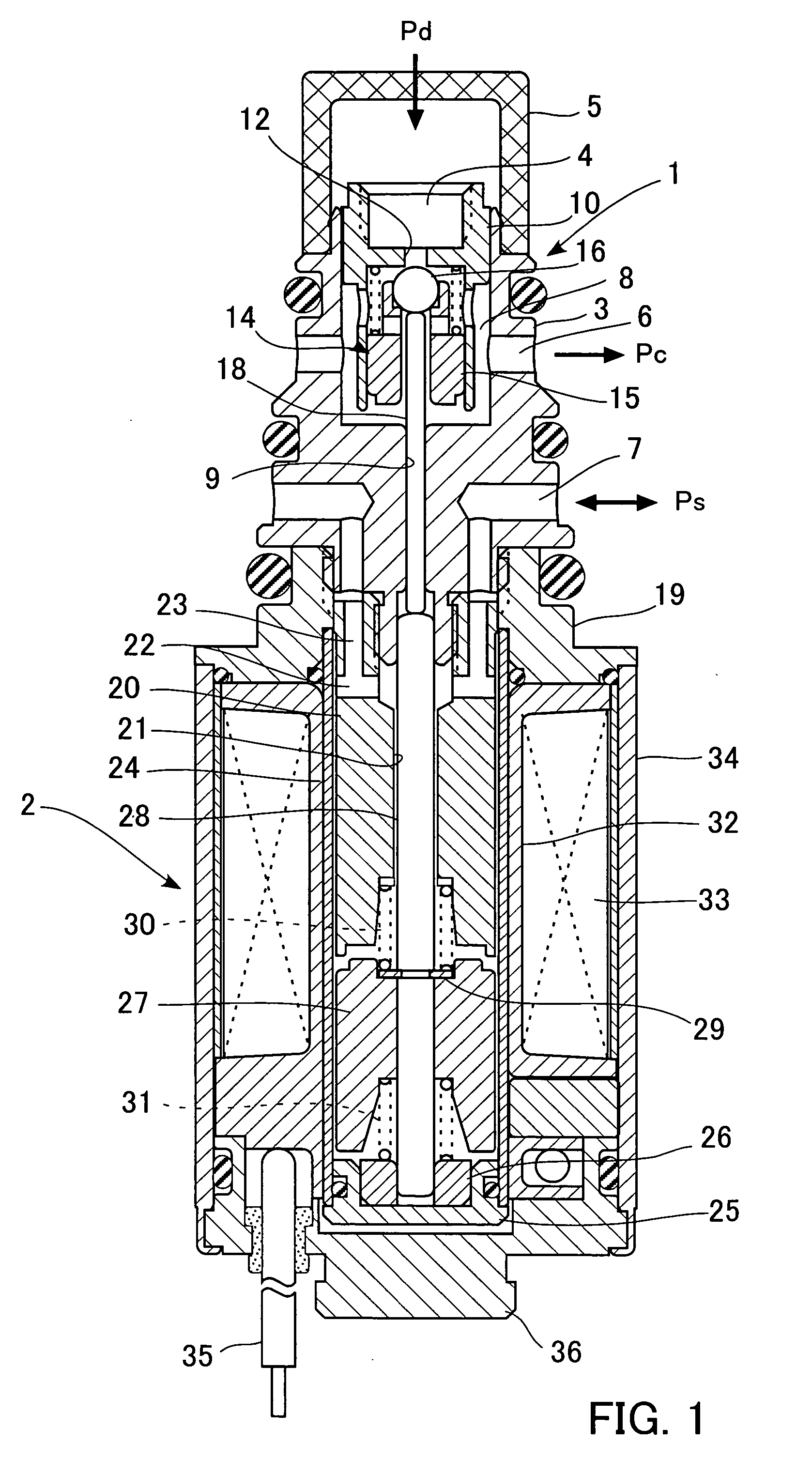

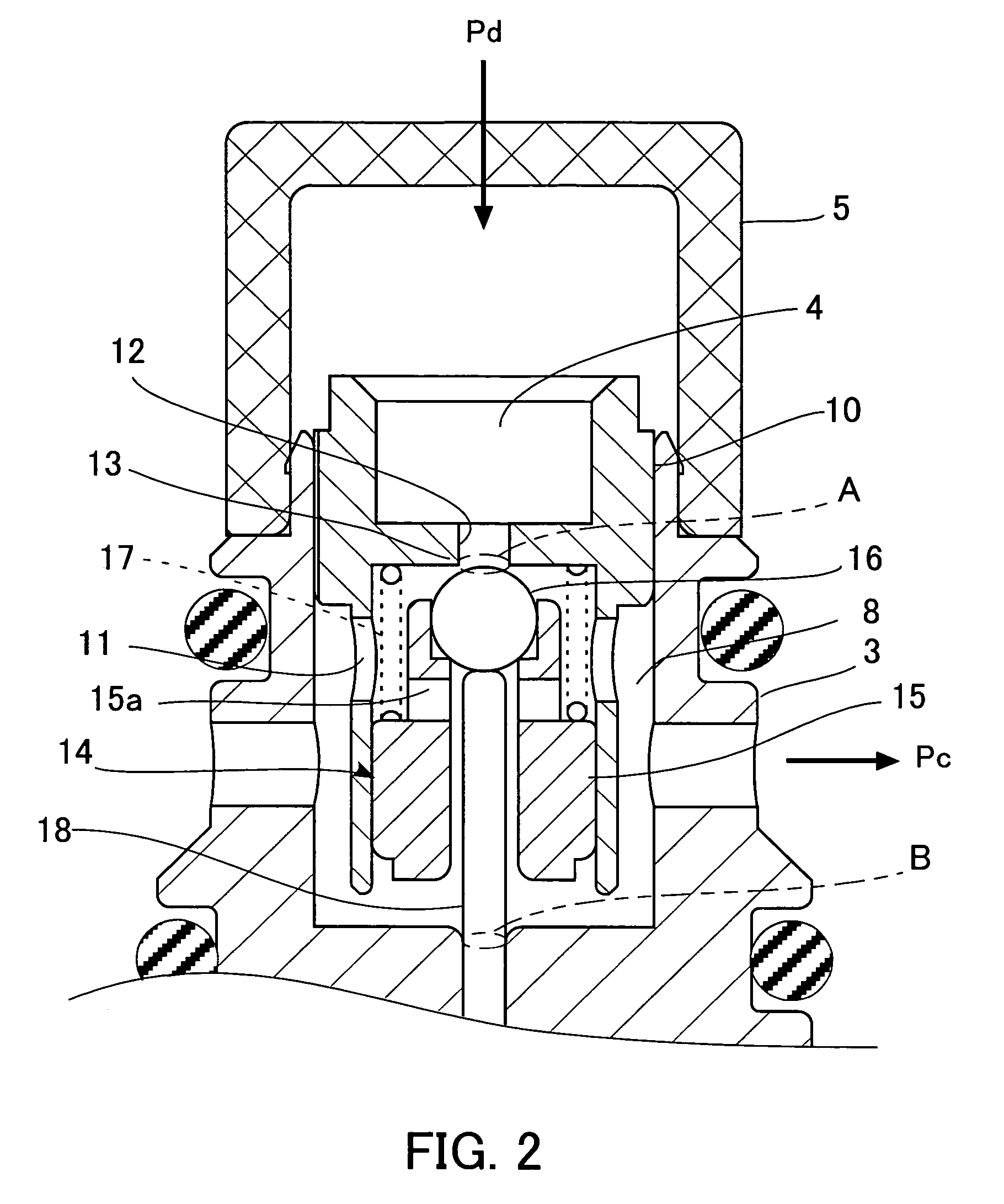

Control valve for variable displacement compressor

InactiveUS20060039798A1Delay characteristicPositive displacement pump componentsMulti-stage pumpsDifferential pressureControl valves

To provide a control valve for a variable displacement compressor, based on a Pd−Ps differential pressure control method, which is capable of setting characteristics concerning the degree of influence of crank pressure on a change in the differential pressure between discharge pressure and suction pressure, to desired characteristics with ease. A control valve for a variable displacement compressor adjusts the difference between an effective pressure-receiving area A on a discharge pressure side of an intermediate in which a valve element and a shaft are integral with each other and an effective pressure-receiving area B on a suction pressure side of the intermediate, as required. This makes it possible to obtain desired differential pressure·crank pressure characteristics according to the specifications of the control valve. Changes in the effective pressure-receiving areas have almost no influence on electric current·differential pressure characteristics, i.e. the relationship between the value of electric current supplied to a solenoid and the differential pressure between discharge pressure and suction pressure, and hence it is possible to realize the changes in the effective pressure-receiving areas with ease.

Owner:TGK

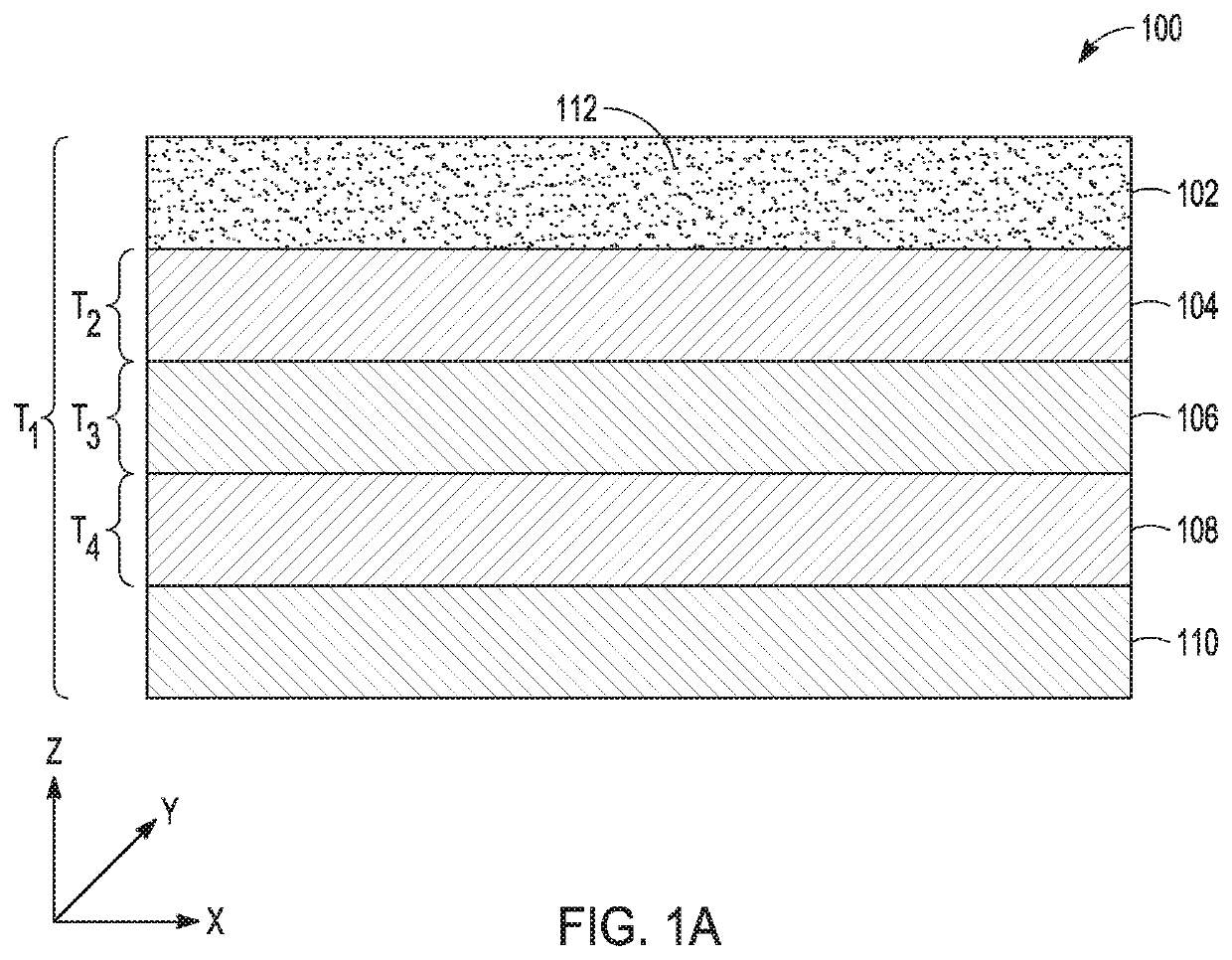

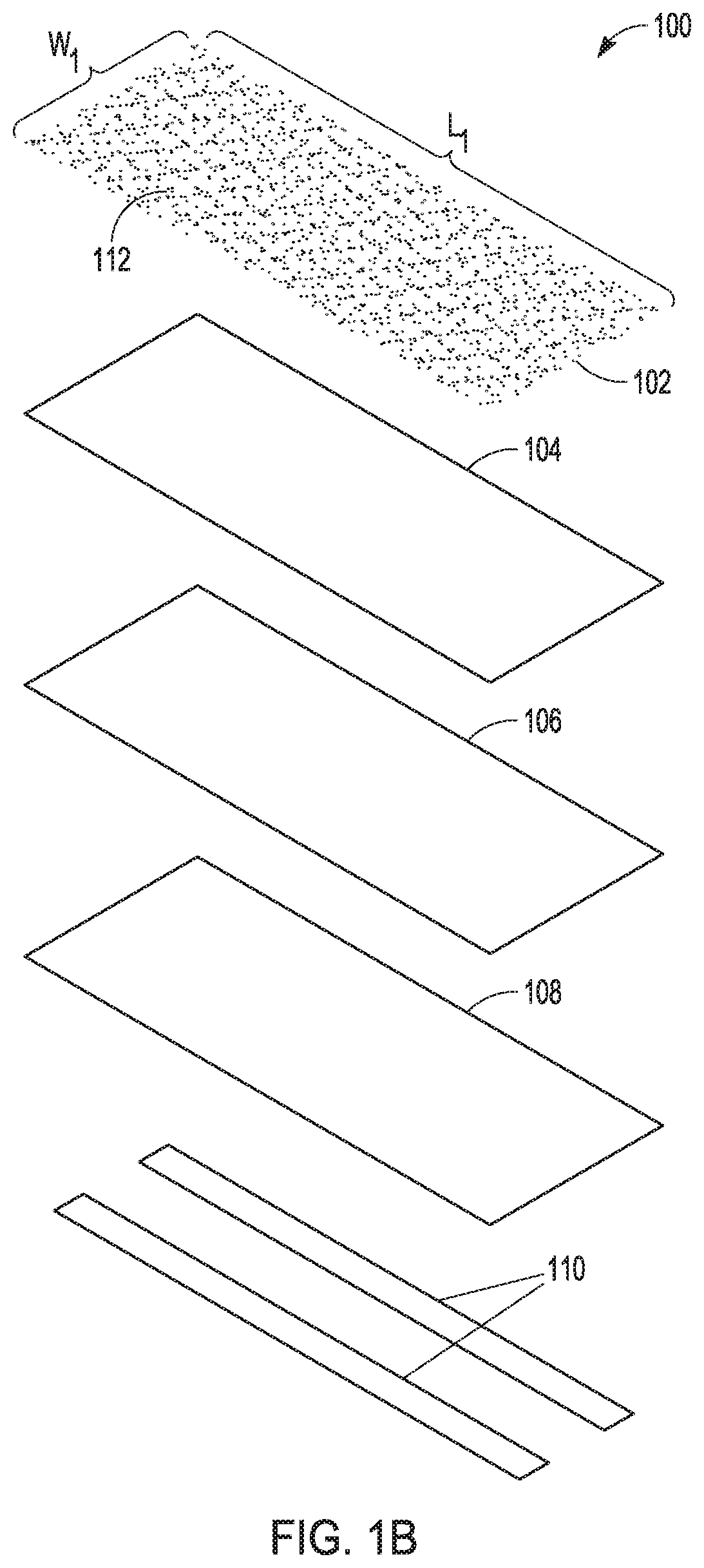

Composite shingle including polyketone

ActiveUS10655329B1Reduce weightReduce shipping costsRoof covering using tiles/slatesSynthetic resin layered productsPolymer sciencePolyketone

Various embodiments disclosed relate to a composite shingle. The composite shingle includes a particle layer and a polyketone layer proximate to the particle layer.

Owner:VIAFLEX INC