Patents

Literature

147results about How to "Convenient and efficient" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

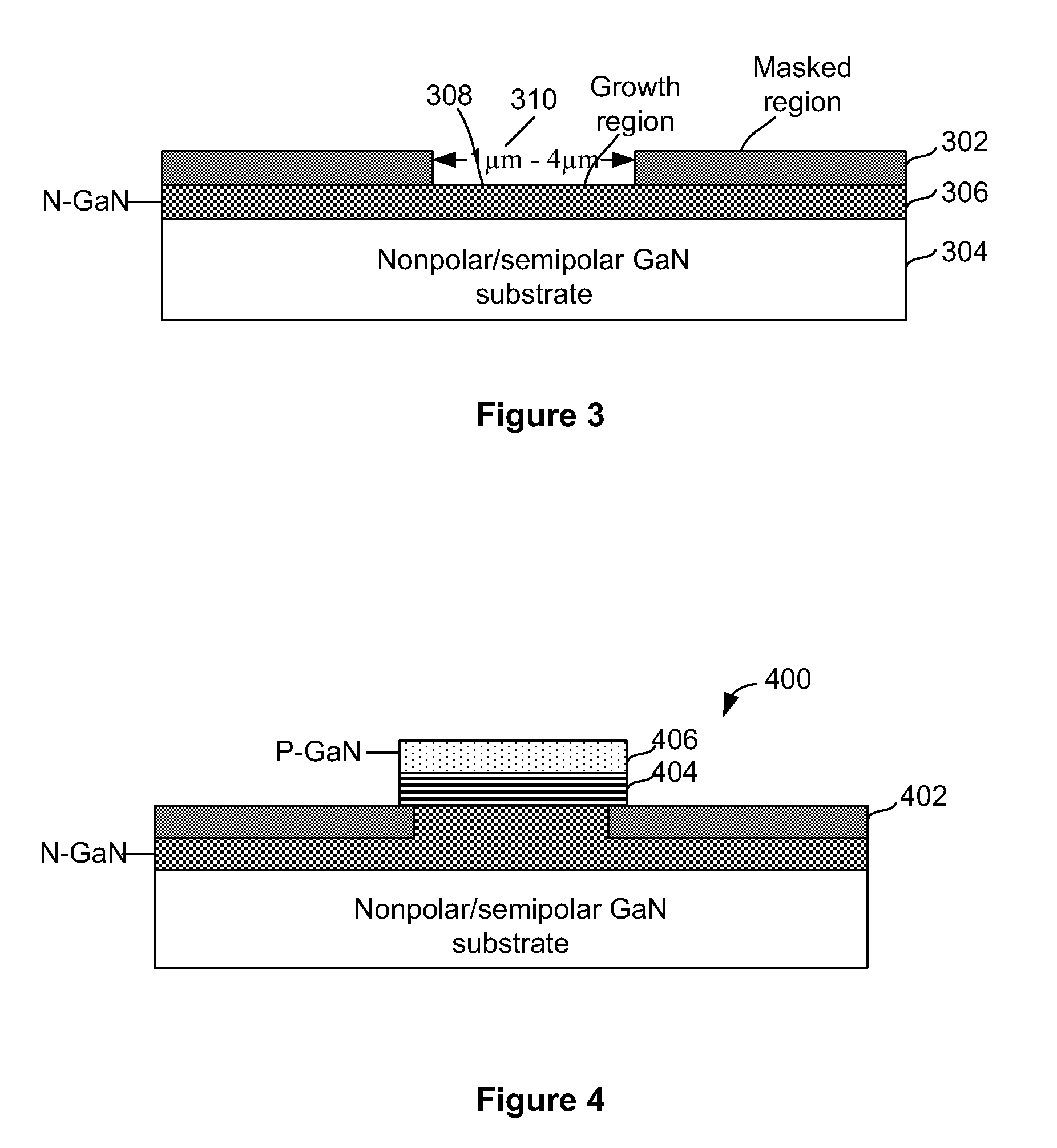

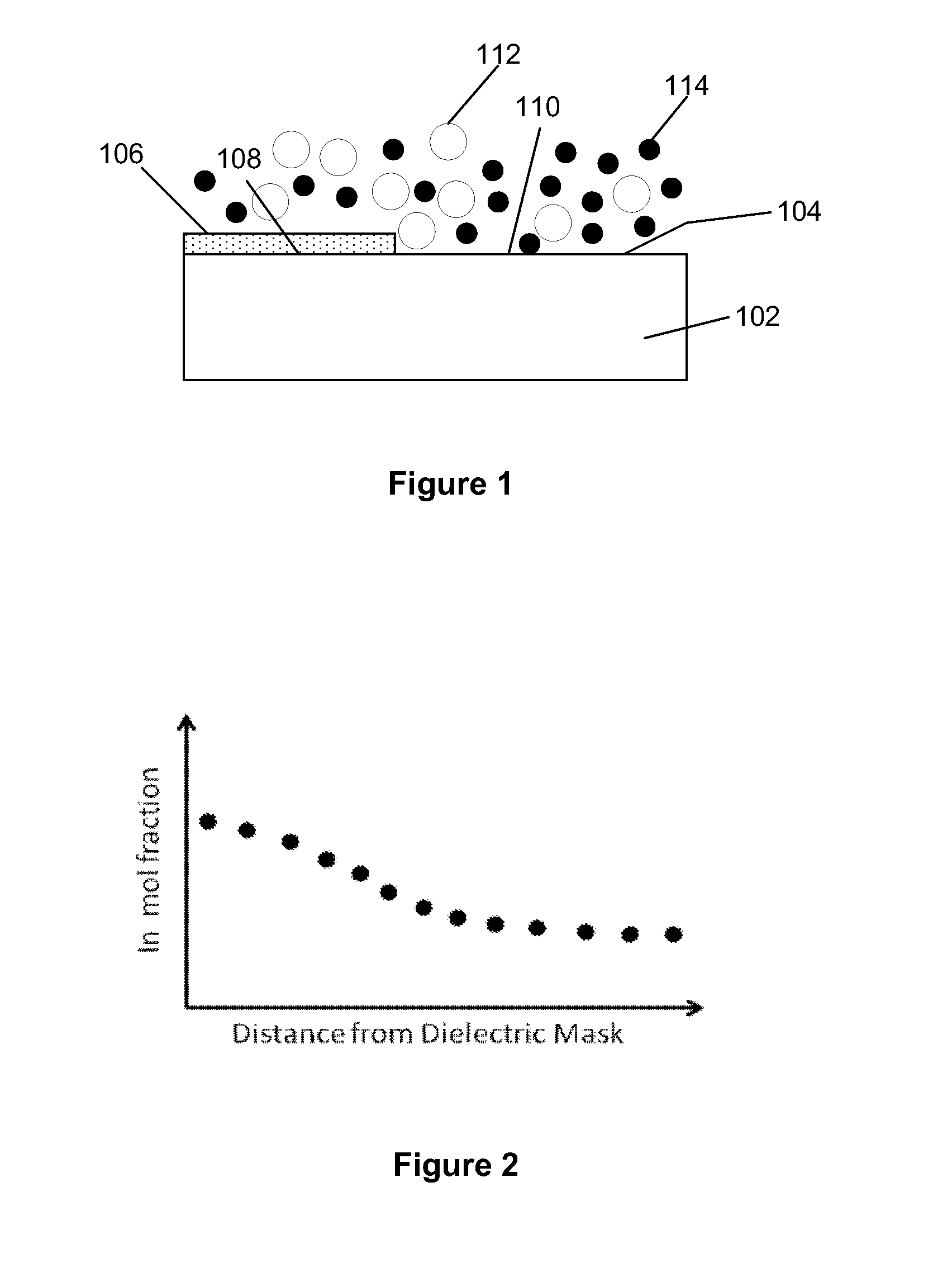

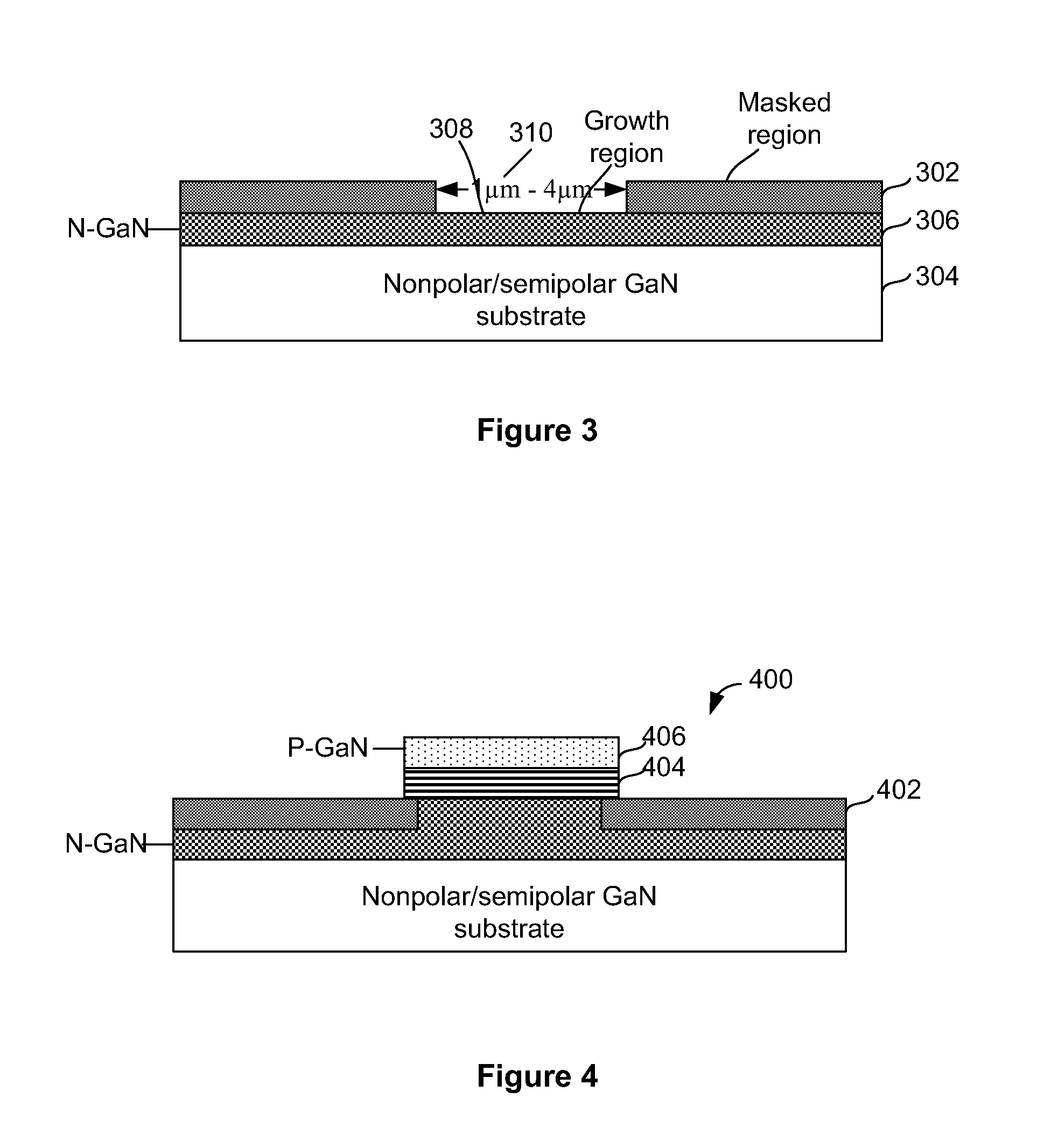

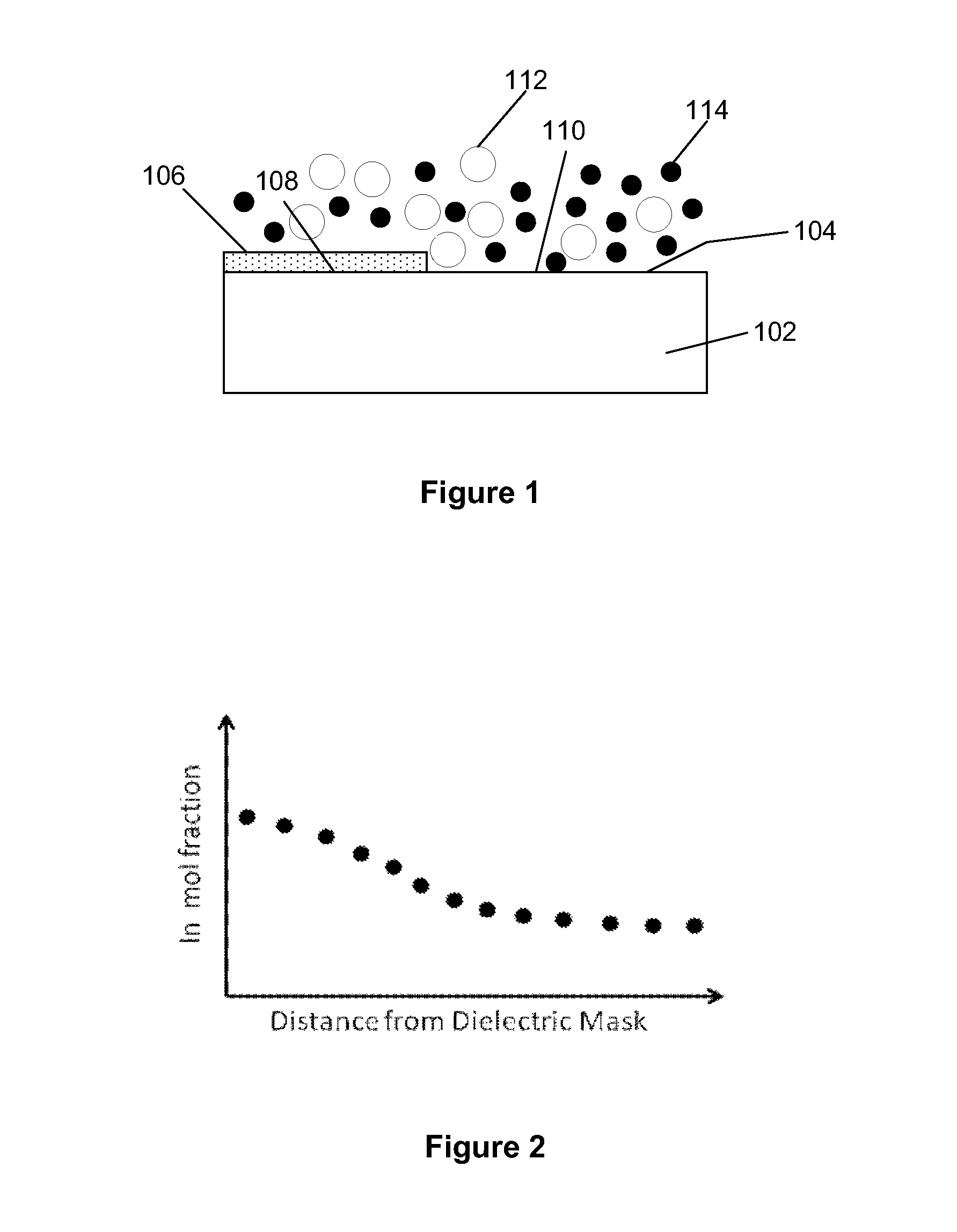

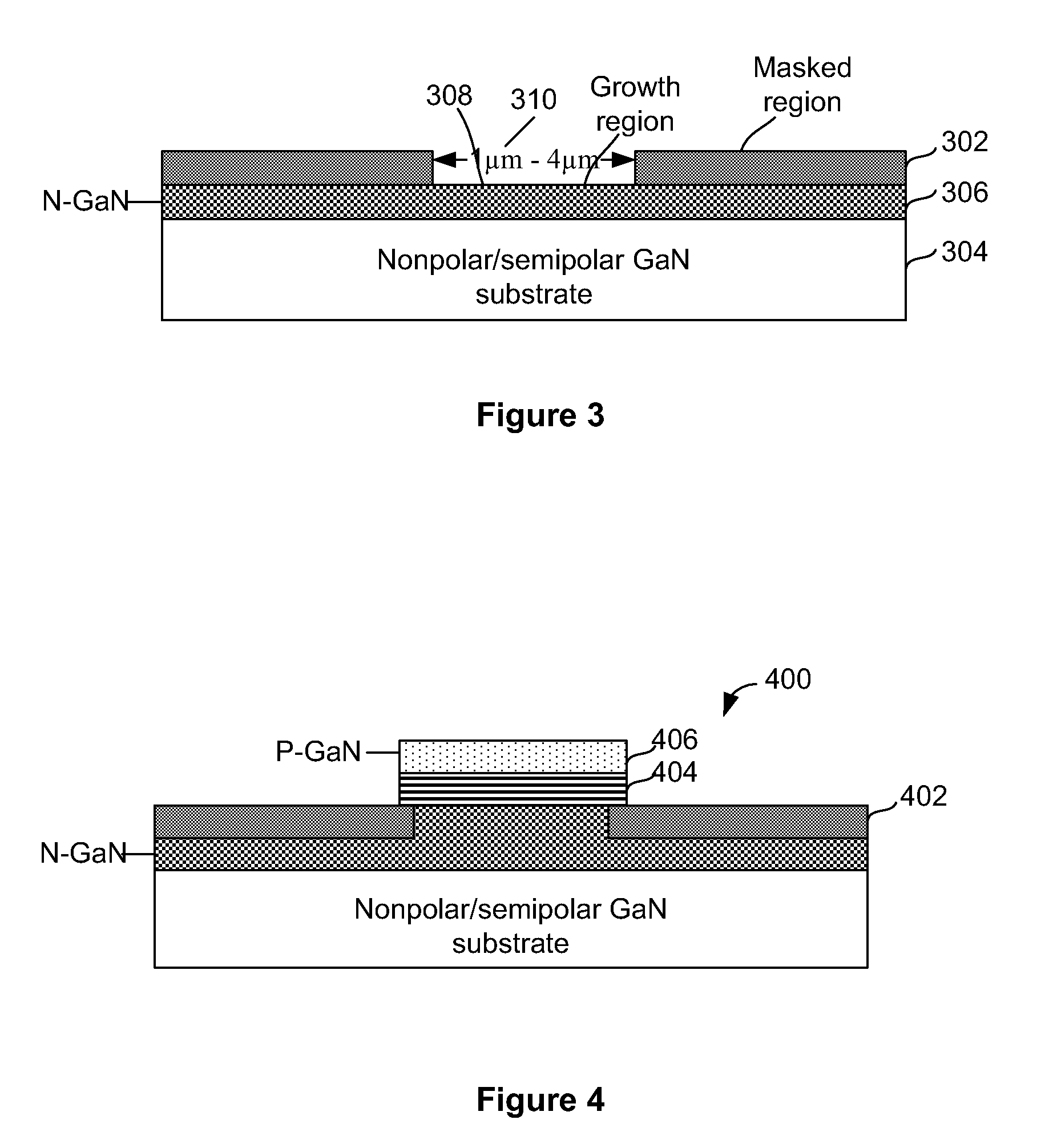

Selective area epitaxy growth method and structure for multi-colored devices

InactiveUS20090309110A1Improve the level ofImprove surface mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesIndiumSelective area epitaxy

A multicolored LED device made of a semipolar material having different indium containing regions provided on different spatial features of GaN material. Other materials such as non-polar materials can also be used.

Owner:SLT TECH

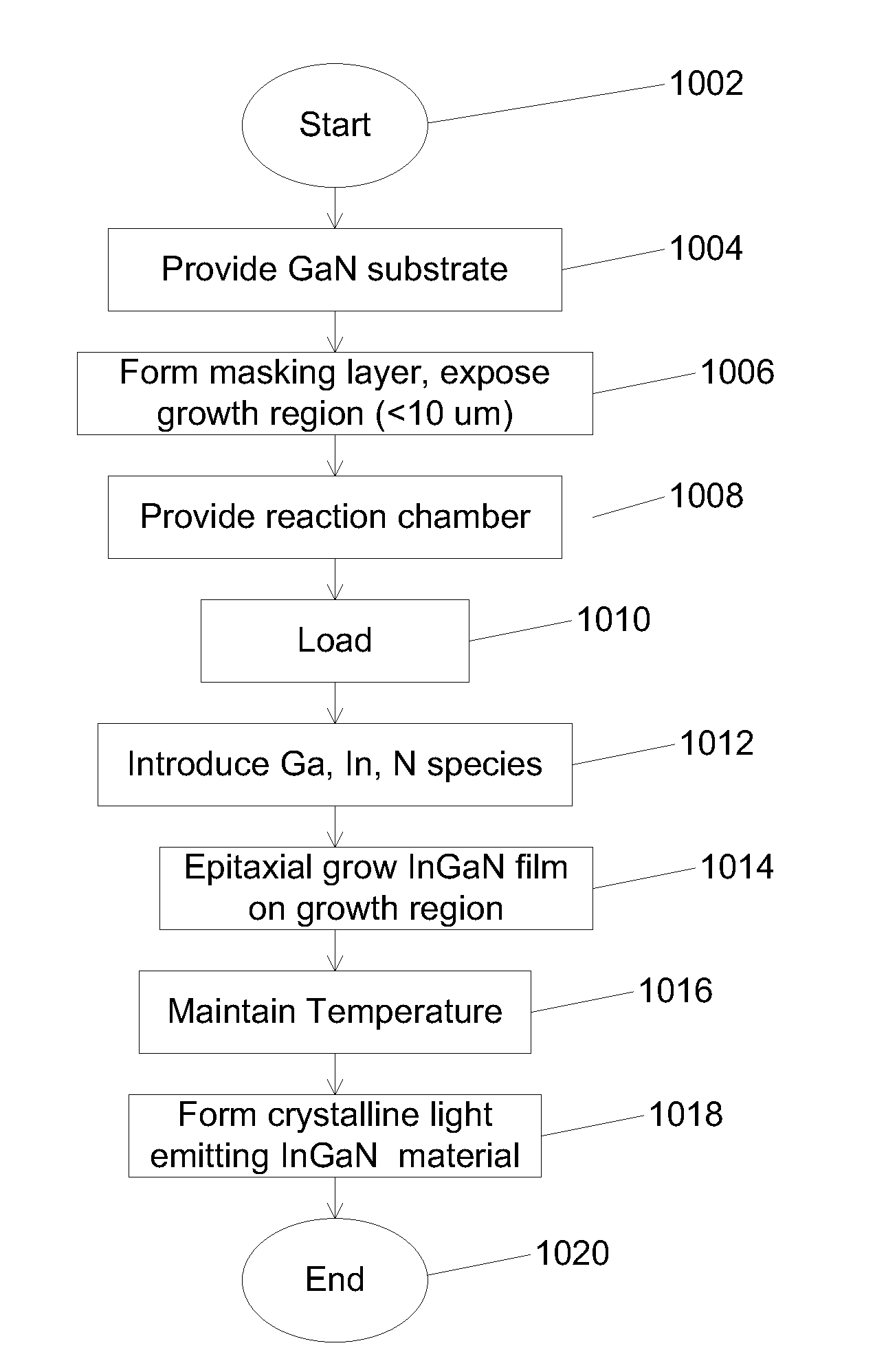

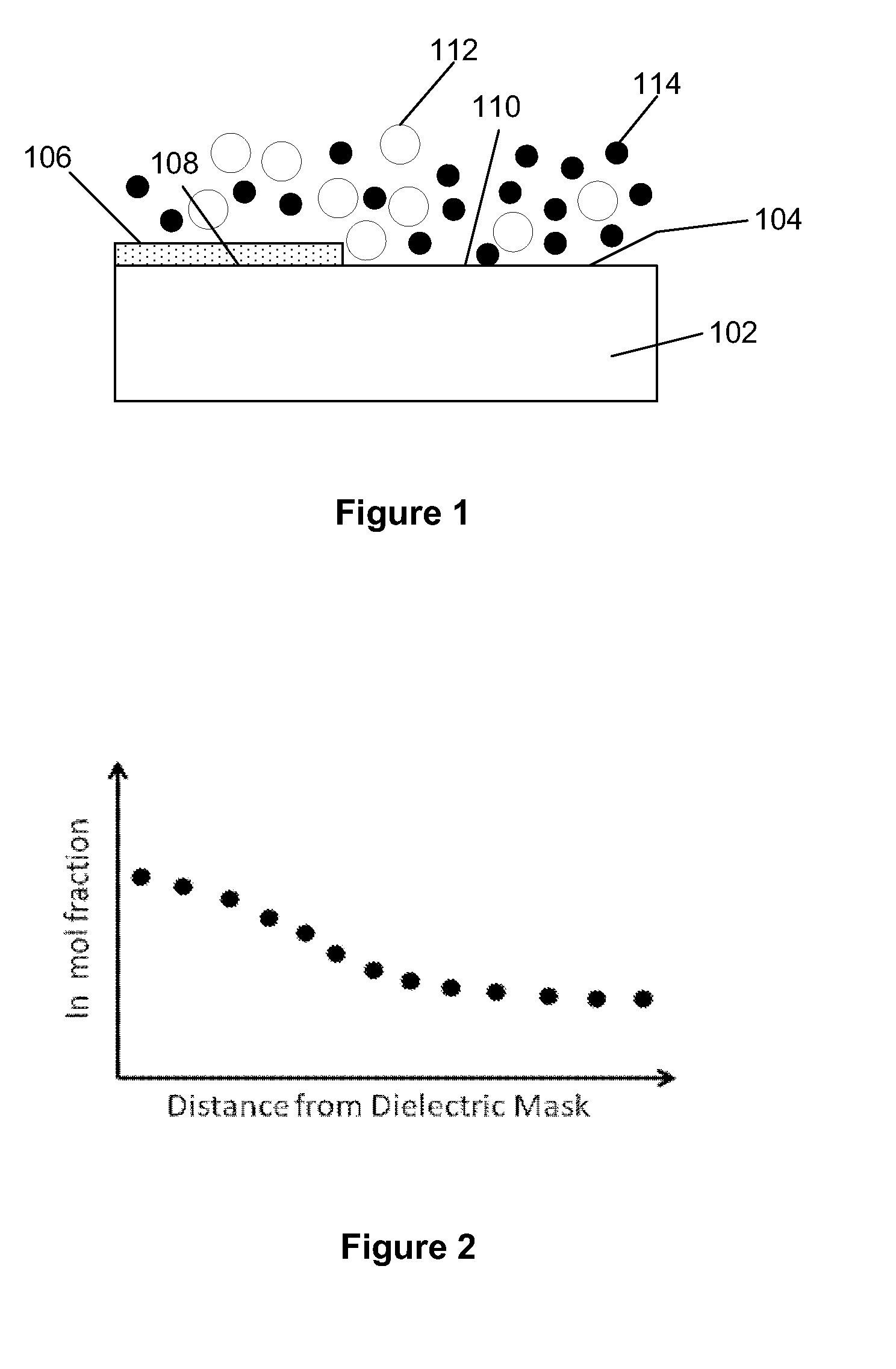

Selective area epitaxy growth method and structure

InactiveUS20090309127A1Improve the level ofSmall sizePolycrystalline material growthNanoinformaticsIndiumPhotoluminescence

A gallium containing crystalline material. The material comprises a bulk semi-polar gallium indium containing crystalline material having a thickness of about 20 nanometers to about 1000 nanometers. The material includes a spatial width dimension of no greater than about 10 microns characterizing the thickness of the bulk semi-polar gallium indium containing crystalline material. The material includes a photoluminescent characteristic of the crystalline material having a first wavelength, which is at least five nanometers greater than a second wavelength, which is derived from an indium gallium containing crystalline material grown on a growth region of greater than about 15 microns.

Owner:SORAA +1

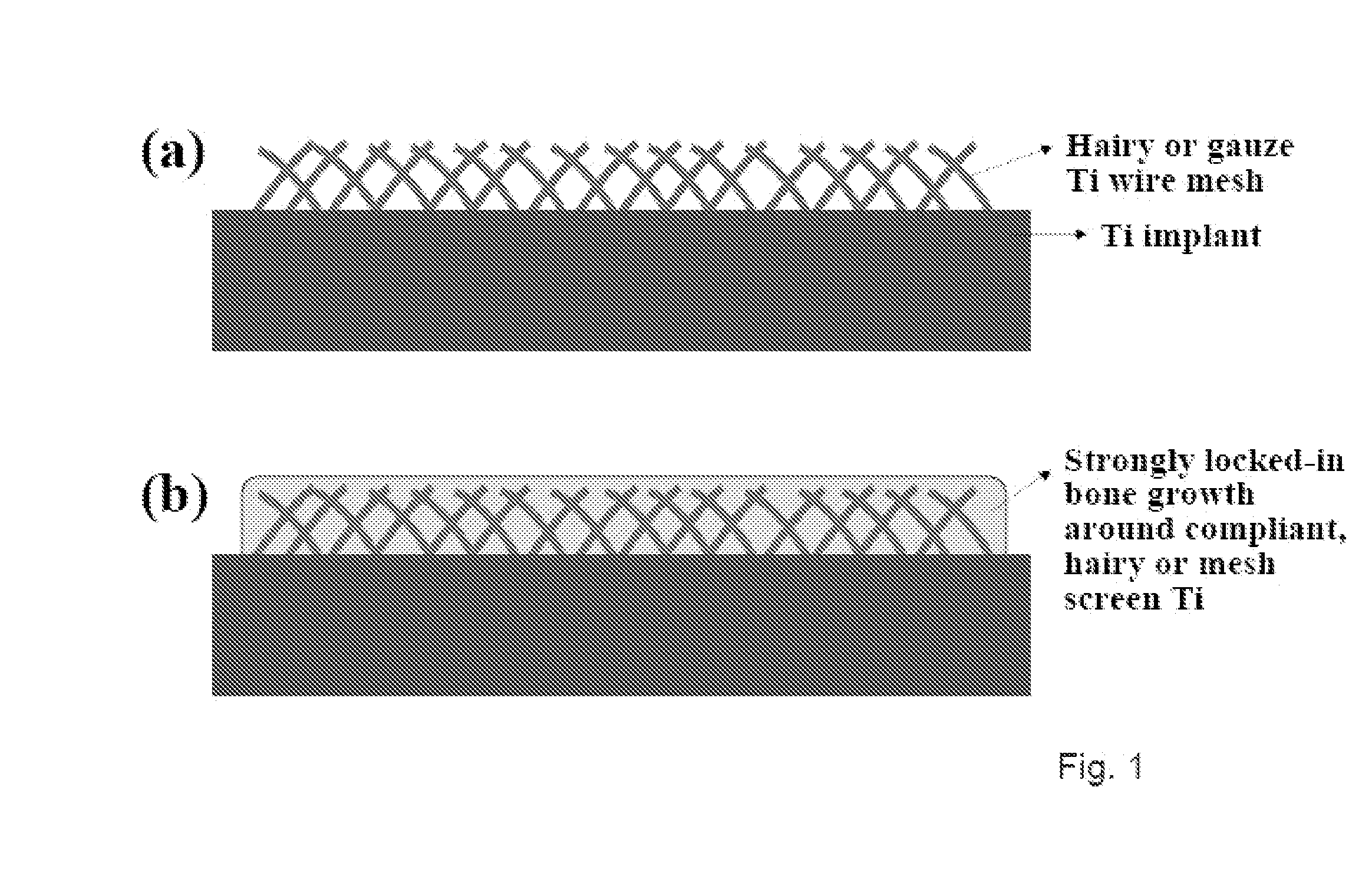

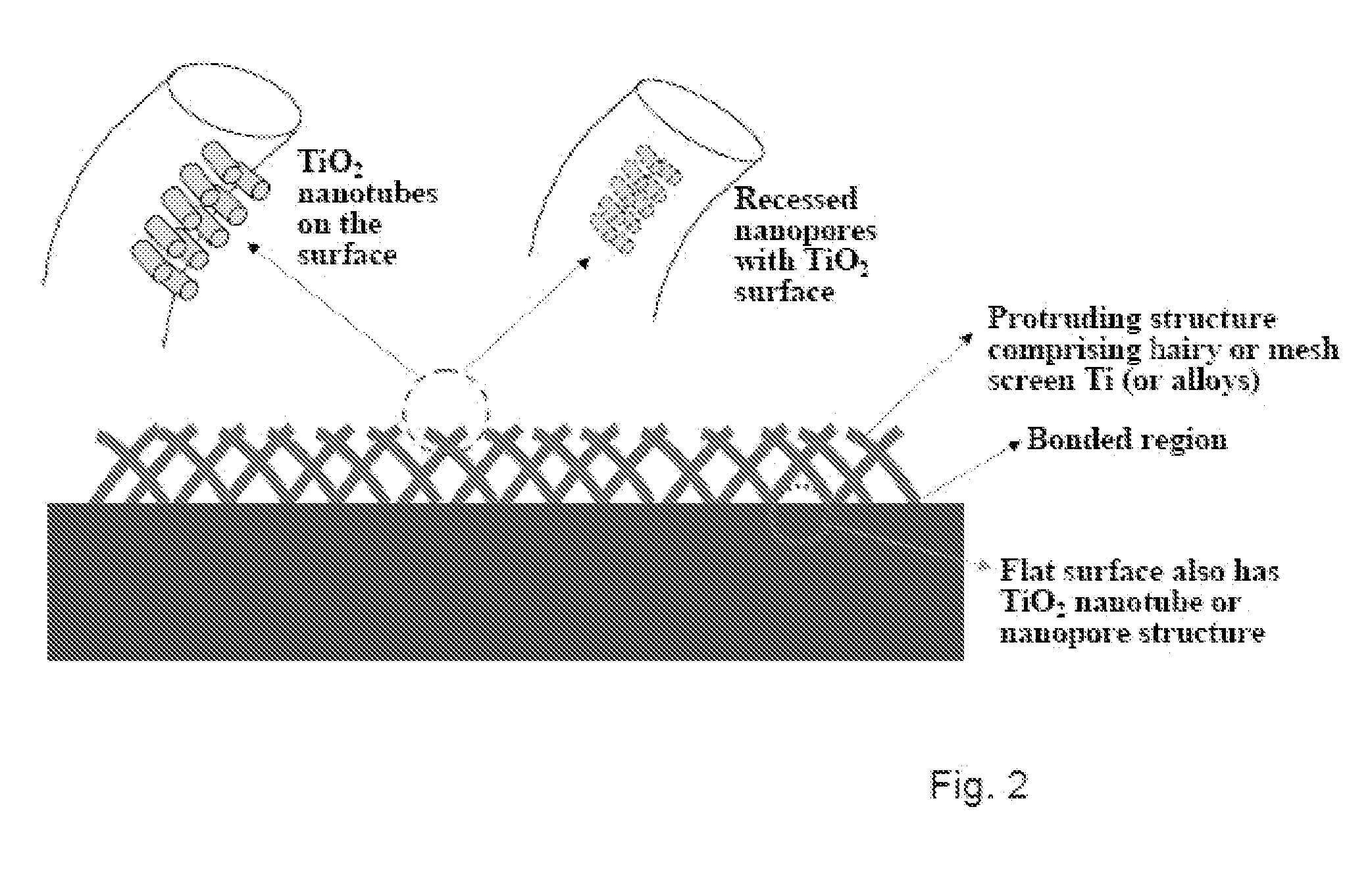

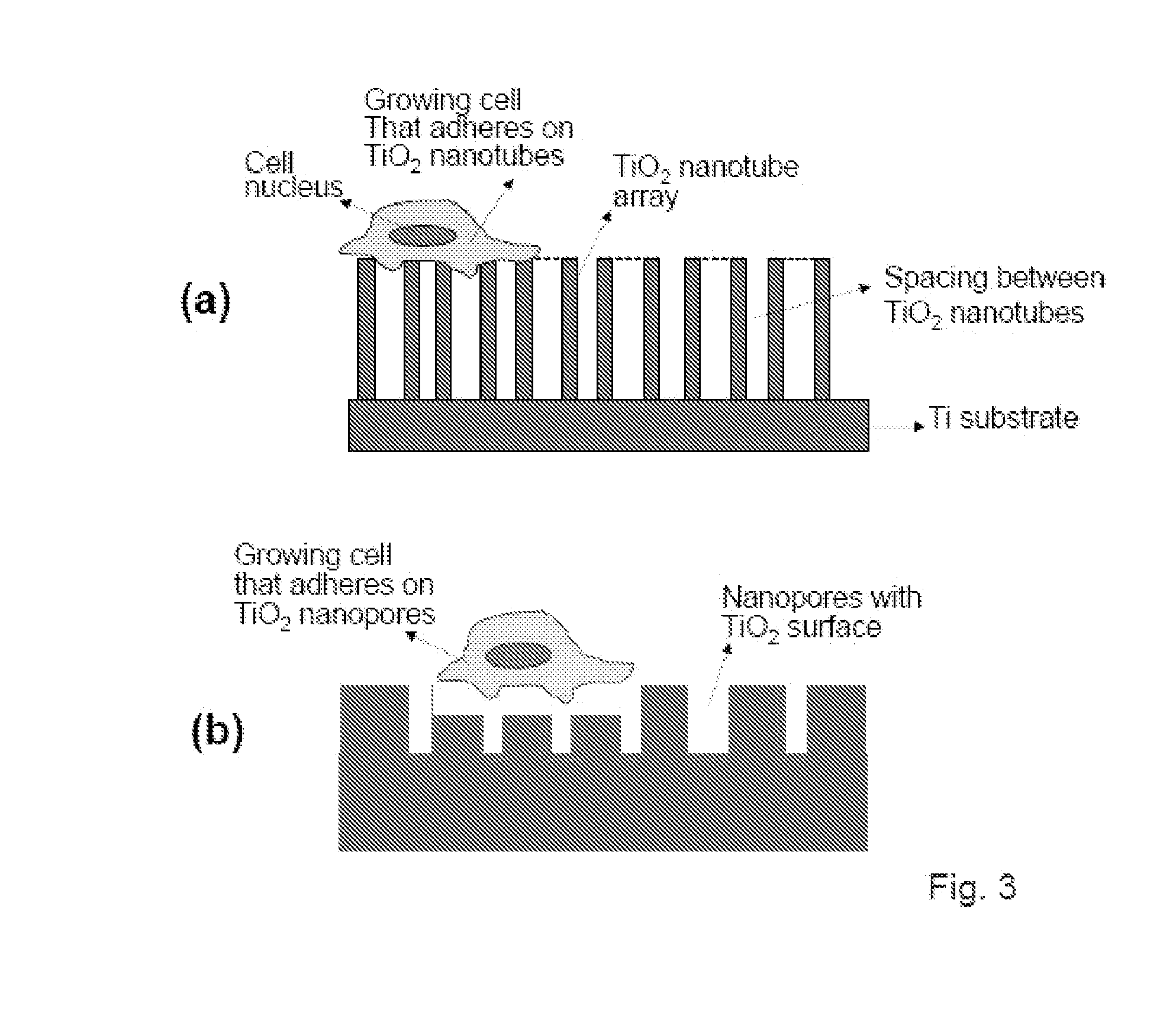

Articles comprising large-surface-area bio-compatible materials and methods for making and using them

ActiveUS20100303722A1Improve cell adhesionAccelerated cell growth characteristicImmobilised enzymesBioreactor/fermenter combinationsCell culture mediaBone growth

The present invention provides articles of manufacture comprising biocompatible nanostructures comprising significantly increased surface area for, e.g., organ, tissue and / or cell growth, e.g., for bone, tooth, kidney or liver growth, and uses thereof, e.g., for in vitro testing of drugs, chemicals or toxins, or as in vivo implants, including their use in making and using artificial tissues and organs, and related, diagnostic, screening, research and development and therapeutic uses, e.g., as drug delivery devices. The present invention provides biocompatible nanostructures with significantly increased surface area, such as with nanotube and nanopore array on the surface of metallic, ceramic, or polymer materials for enhanced cell and bone growth, for in vitro and in vivo testing, cleansing reaction, implants and therapeutics. The present invention provides optically transparent or translucent cell-culturing substrates. The present invention provides biocompatible and cell-growth-enhancing culture substrates comprising elastically compliant protruding nanostructure substrates coated with Ti, TiO2 or related metal and metal oxide films.

Owner:RGT UNIV OF CALIFORNIA

Microplate thermal shift assay for ligand development and multi-variable protein chemistry optimization

InactiveUS6020141AConvenient and efficientAccurate informationCompound screeningHeating or cooling apparatusThermal shift assayProtein chemistry

The present invention is a method for ranking the affinity of each of a multiplicity of different molecules for a target molecule which is capable of denaturing due to a thermal change. The method comprises contacting the target molecule with one molecule of the multiplicity of different molecules in each of a multiplicity of containers, simultaneously heating the multiplicity of containers, measuring in each of the containers a physical change associated with the thermal denaturation of the target molecule resulting from the heating in each of the containers, generating a thermal denaturation curve for the target molecule as a function of temperature for each of the containers and determining a midpoint temperature (T.sub.m) therefrom, comparing the T.sub.m of each of the thermal denaturation curves with the T.sub.m of a thermal denaturation curve obtained for the target molecule in the absence of any of the molecules in the multiplicity of different molecules, and ranking the affinities of the multiplicity of different molecules according the change in T.sub.m of each of the thermal denaturation curves.

Owner:LIFE TECH CORP

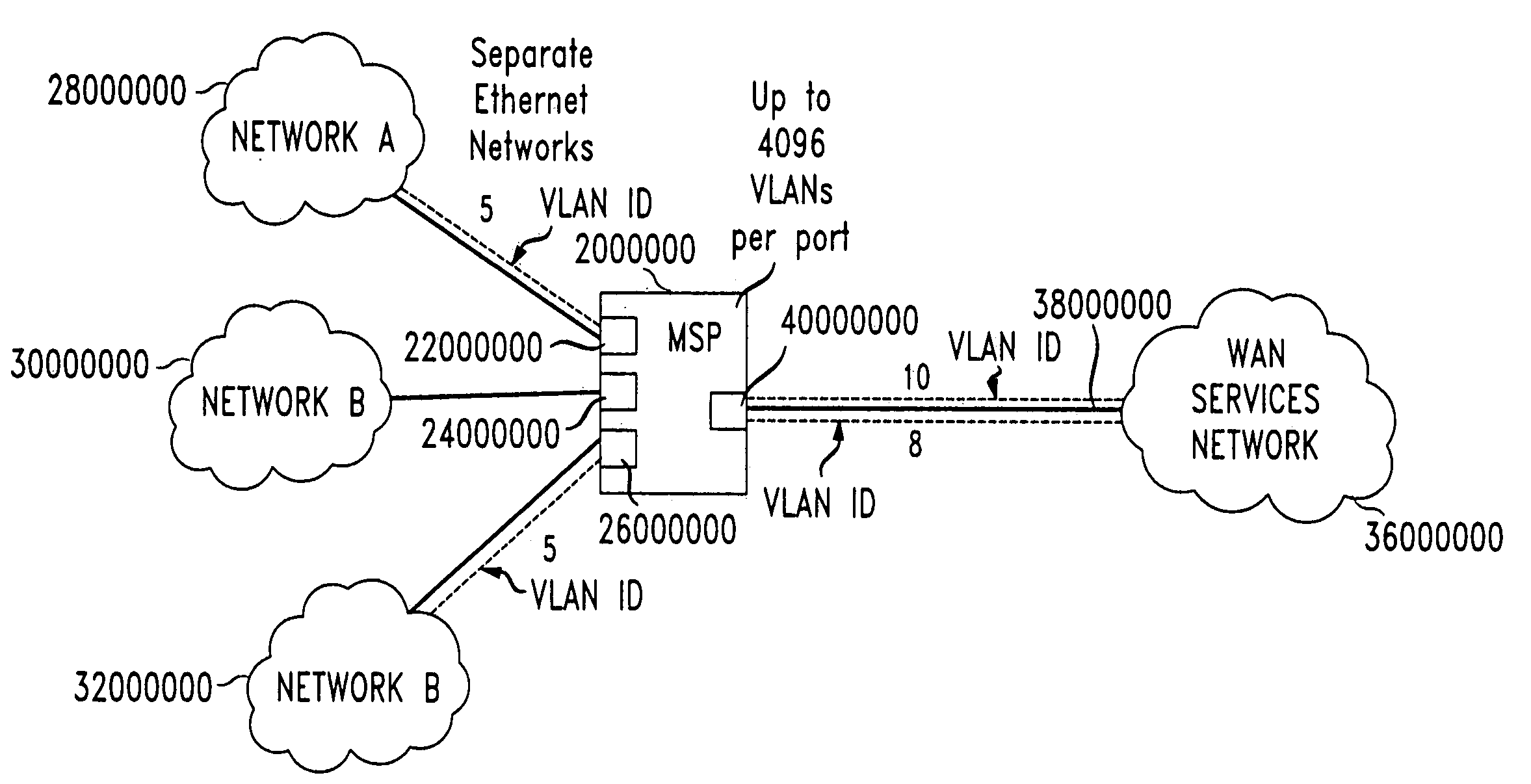

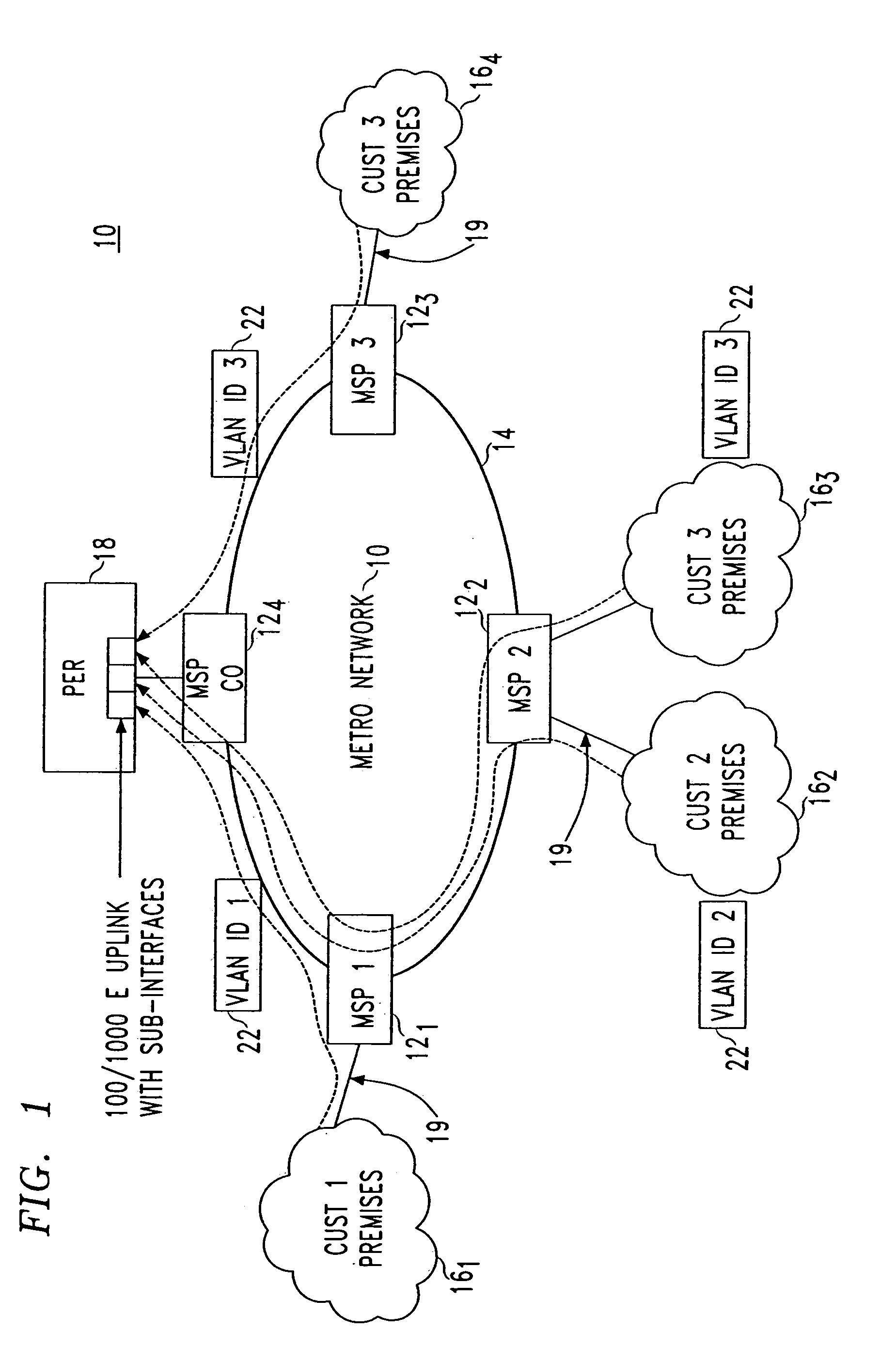

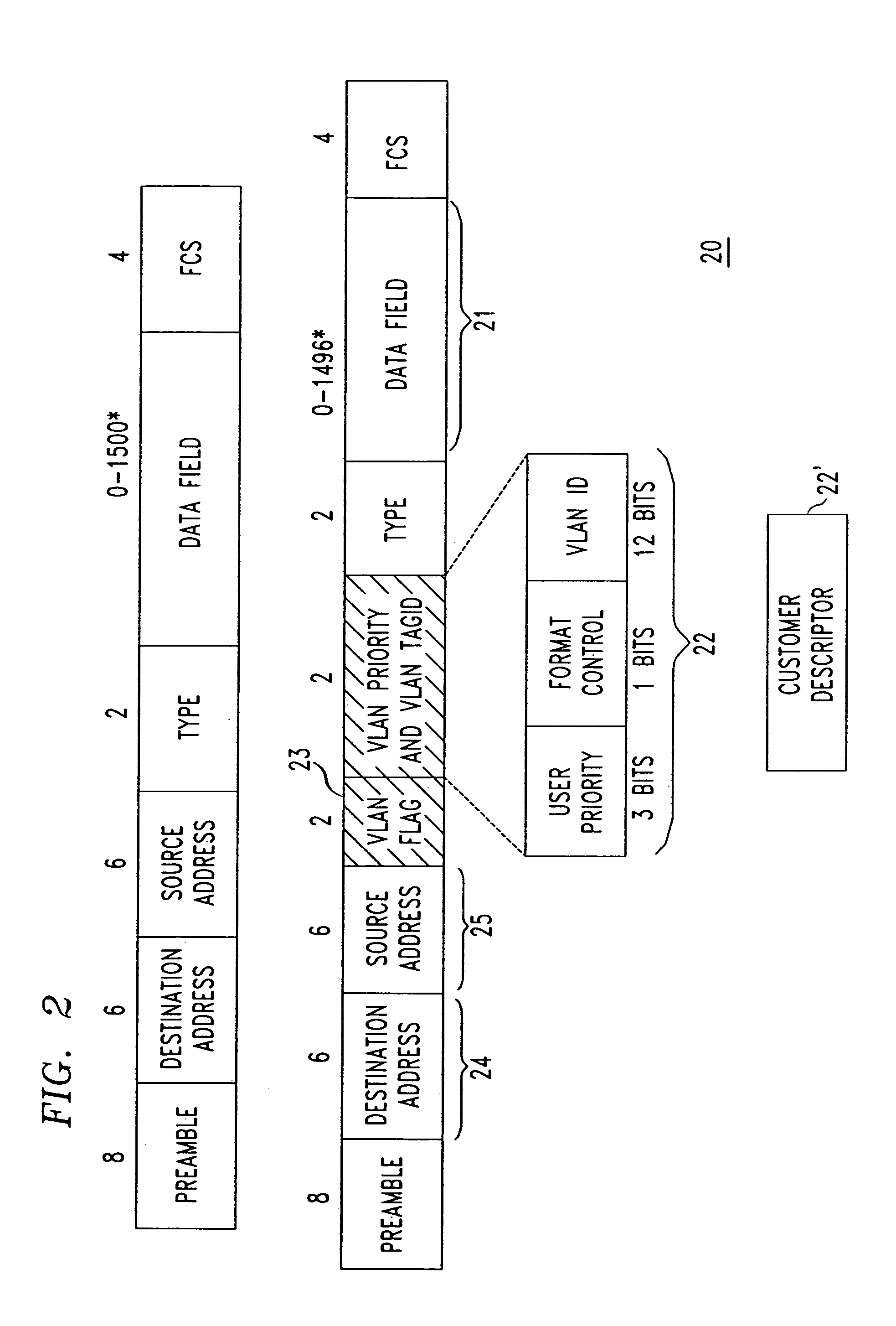

Technique for ethernet access to packet-based services

ActiveUS7092389B2Convenient and efficientThe process is convenient and fastNetworks interconnectionMetropolitian area networksTraffic volumeReceipt

An Ethernet Metropolitan Area Network (10) provides connectivity to one or more customer premises (161,162,163) to packet-based services, such as ATM, Frame Relay, or IP, while advantageously providing a mechanism for assuring security and regulation of customer traffic. Upon receipt of each customer-generated information frame (20), an ingress Multi-Service Platform (MSP) (122) “tags” the frame with a customer descriptor (22′) that specifically identifies the recipient customer. In practice, the MSP tags each frame by overwriting the Virtual Local Area Network (VLAN) identifier (22) with the customer descriptor. Using the customer descriptor in each frame, a recipient Provider Edge Router (PER) (18) or ATM switch can map the information as appropriate to direct the information to the specific customer at its receiving site. In addition, the customer descriptor (22′) may also include Quality of Service (QoS) information, allowing the recipient Provider Edge Router (PER) (18) or ATM switch to afford the appropriate QoS level accordingly. Each Ethernet switch may advantageously overwrite the VLAN identifier at an incoming port with a second tag associated with an egress port to increase the scale associated with single switch.

Owner:AMERICAN TELEPHONE & TELEGRAPH CO

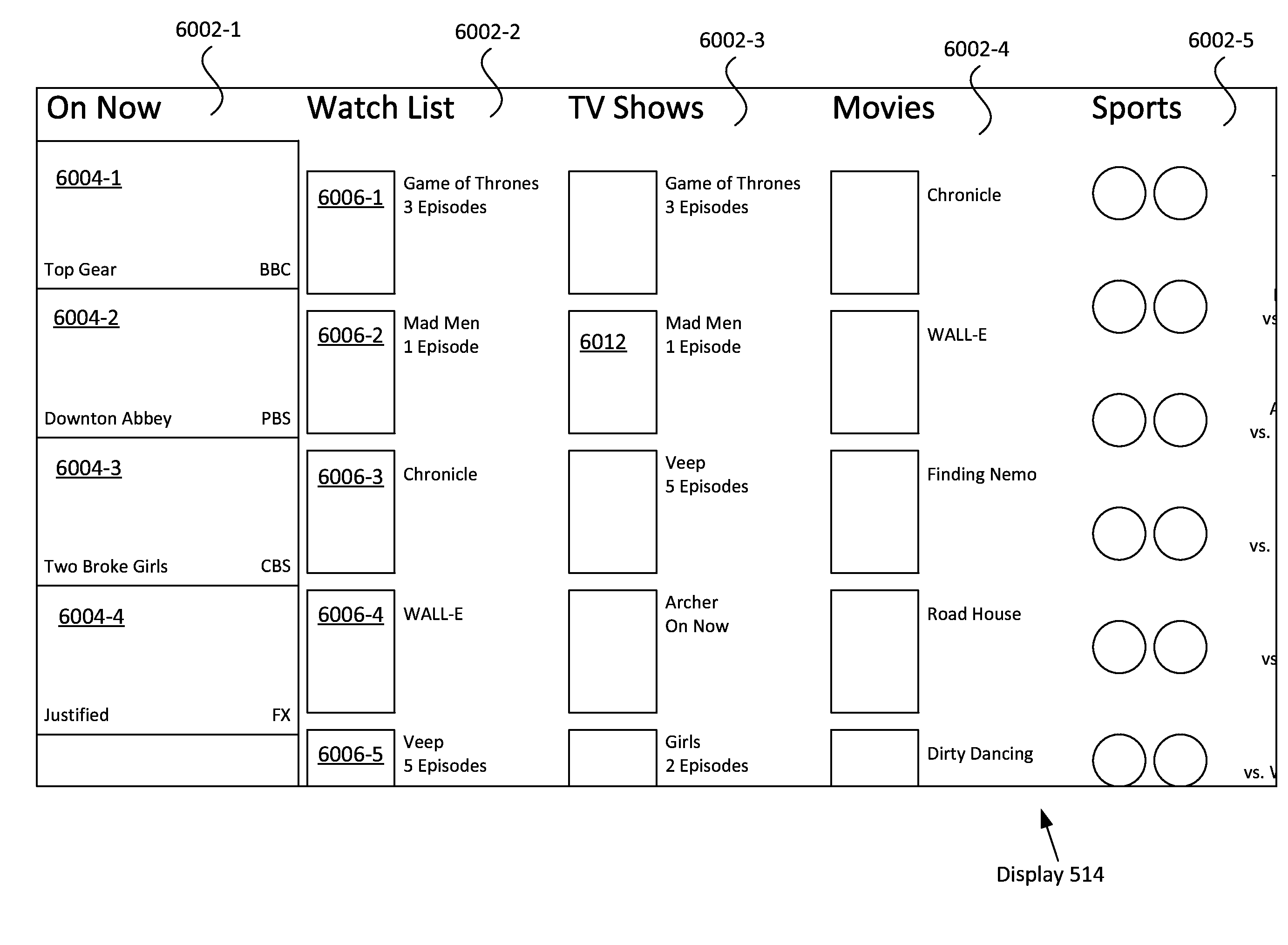

Column interface for navigating in a user interface

ActiveUS20150370920A1Fast and efficientConvenient and efficientDigital data information retrievalDigital data processing detailsDisplay deviceElectronic equipment

The invention is directed to an electronic device. The electronic device provides, for display on a display device, a user interface including a first set of columns, two or more columns in the first set of columns each including two or more menu items. The electronic device receives a selection input. In response to receiving the selection input, in accordance with a determination that the selection input corresponds to selection of a first column the electronic device provides, for display on the display device, a second set of columns, two or more of the columns in the second set of columns corresponding to different subsets of menu items that were displayed in the first column that was selected in response to the selection input.

Owner:APPLE INC

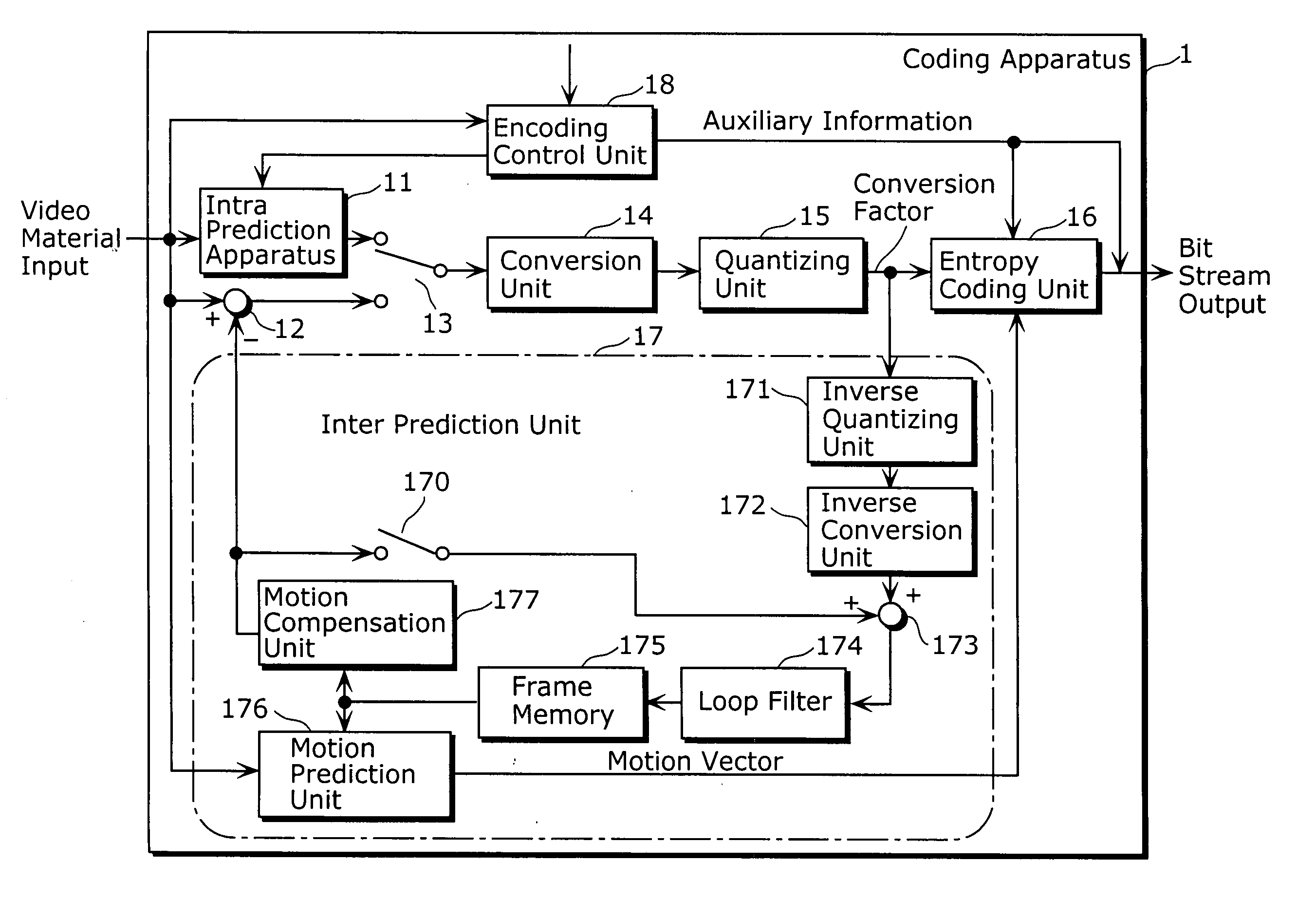

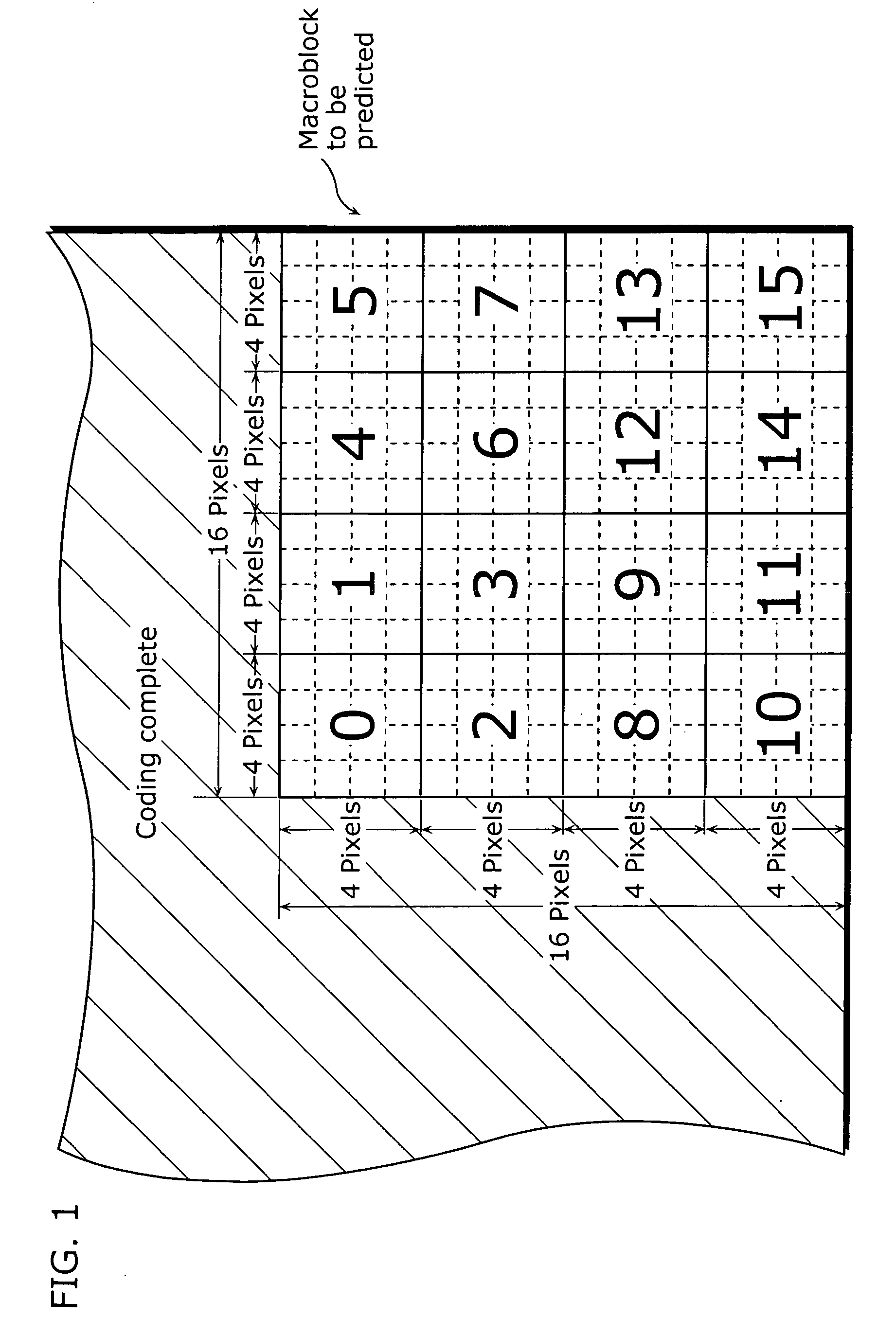

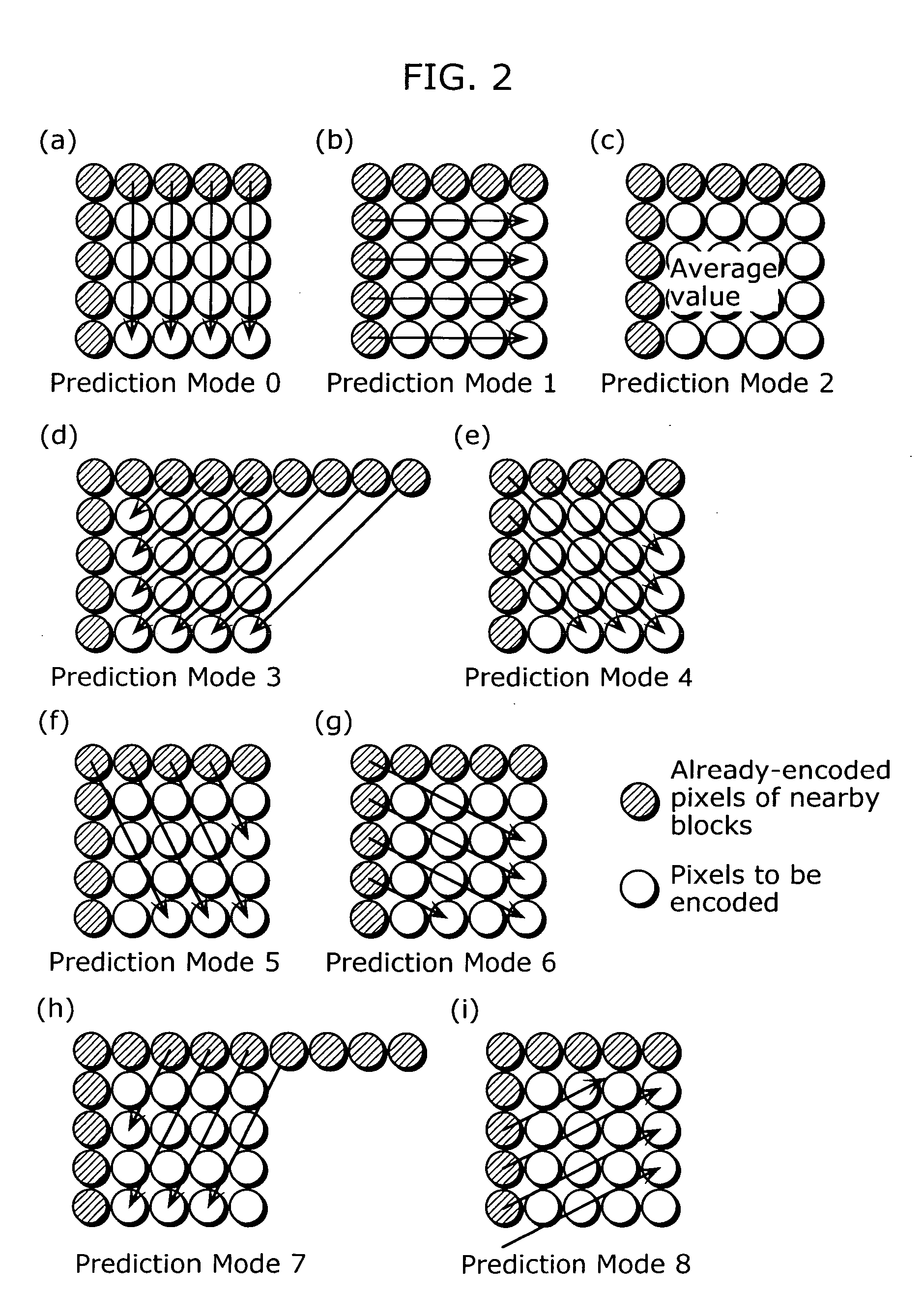

Intra prediction apparatus

InactiveUS20060120456A1Improve efficiencyImprove picture qualityColor television with pulse code modulationColor television with bandwidth reductionParallel computingExecution unit

An intra prediction apparatus includes: a candidate narrowing-down unit which narrows down, from a plurality of intra prediction directions, an intra prediction direction candidate which is applied to a block of multiple pixels that constitutes a video in accordance with a characteristic of the video; and an intra prediction execution unit which executes intra prediction in the intra prediction direction narrowed down by said candidate narrowing-down unit. Through this, computational load can be lightened while contributing to improvement in picture quality and encoding efficiency.

Owner:GK BRIDGE 1

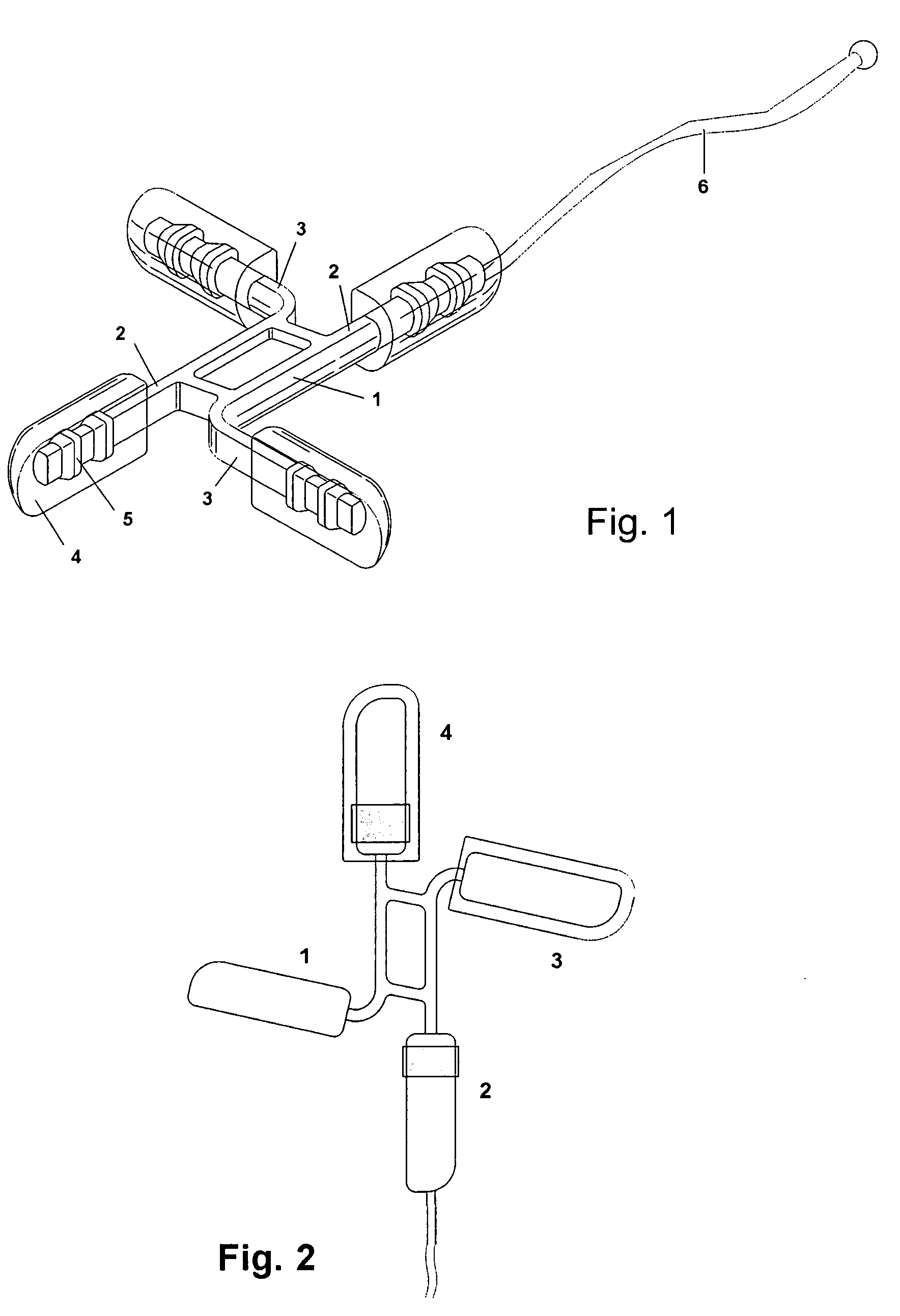

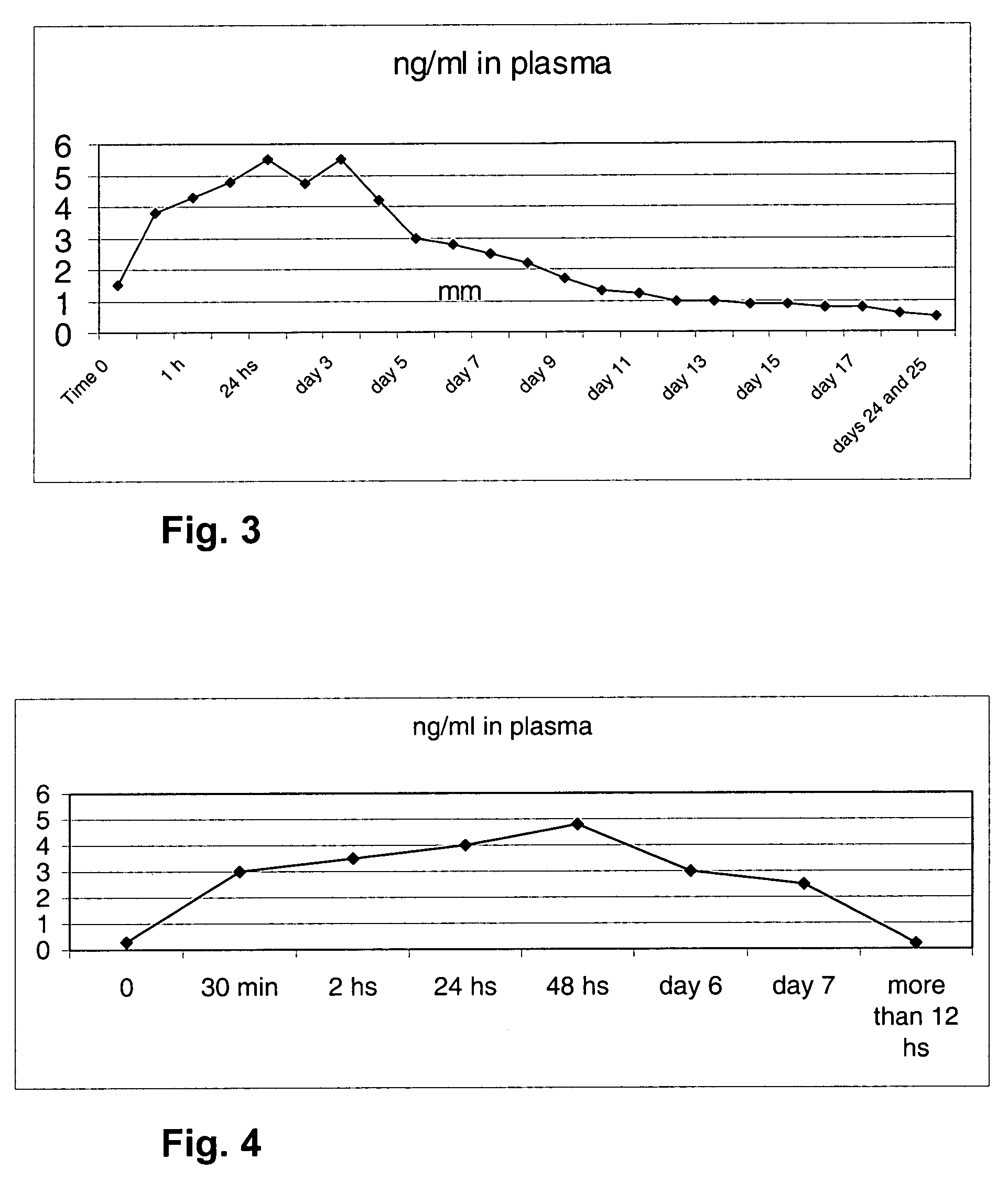

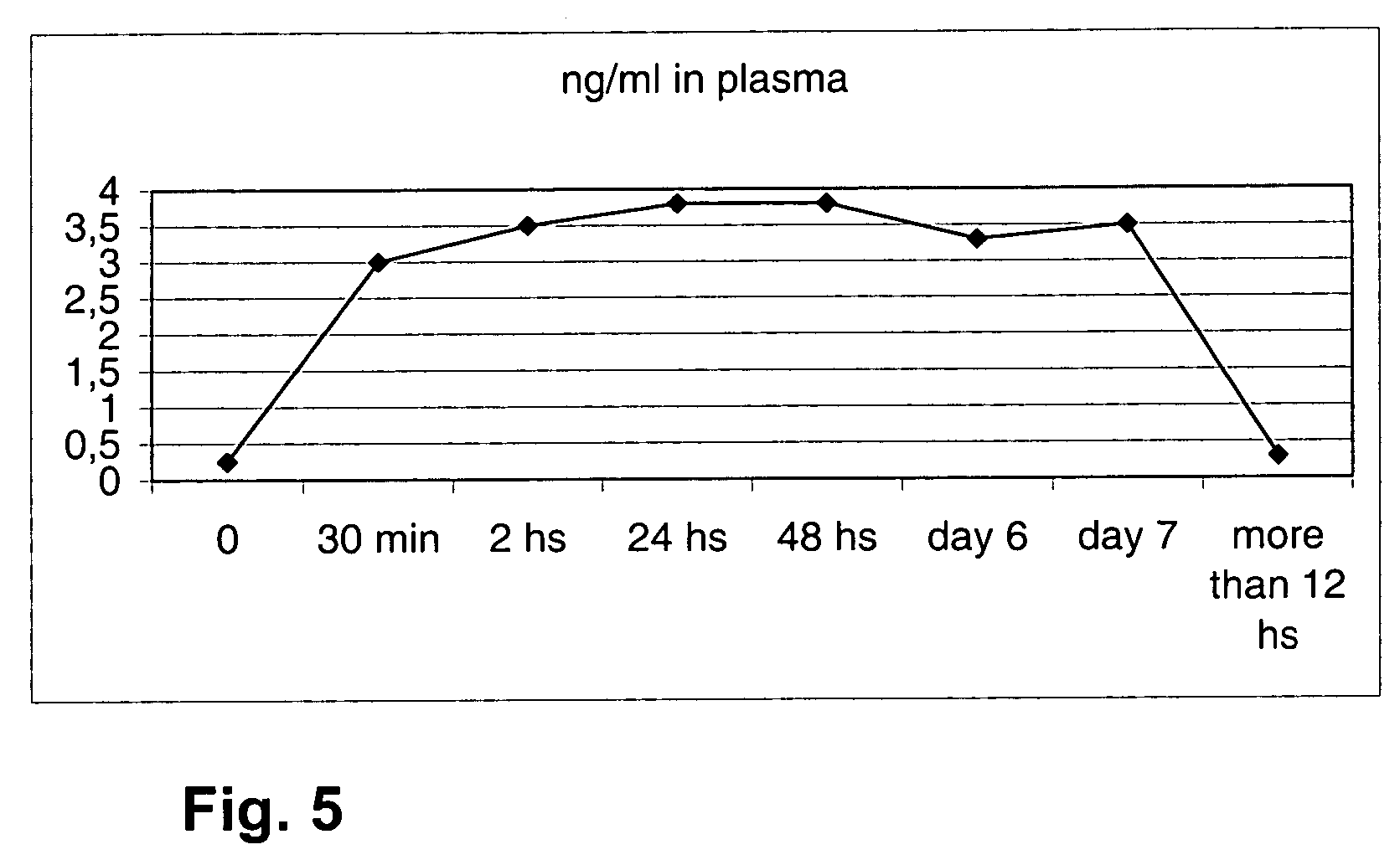

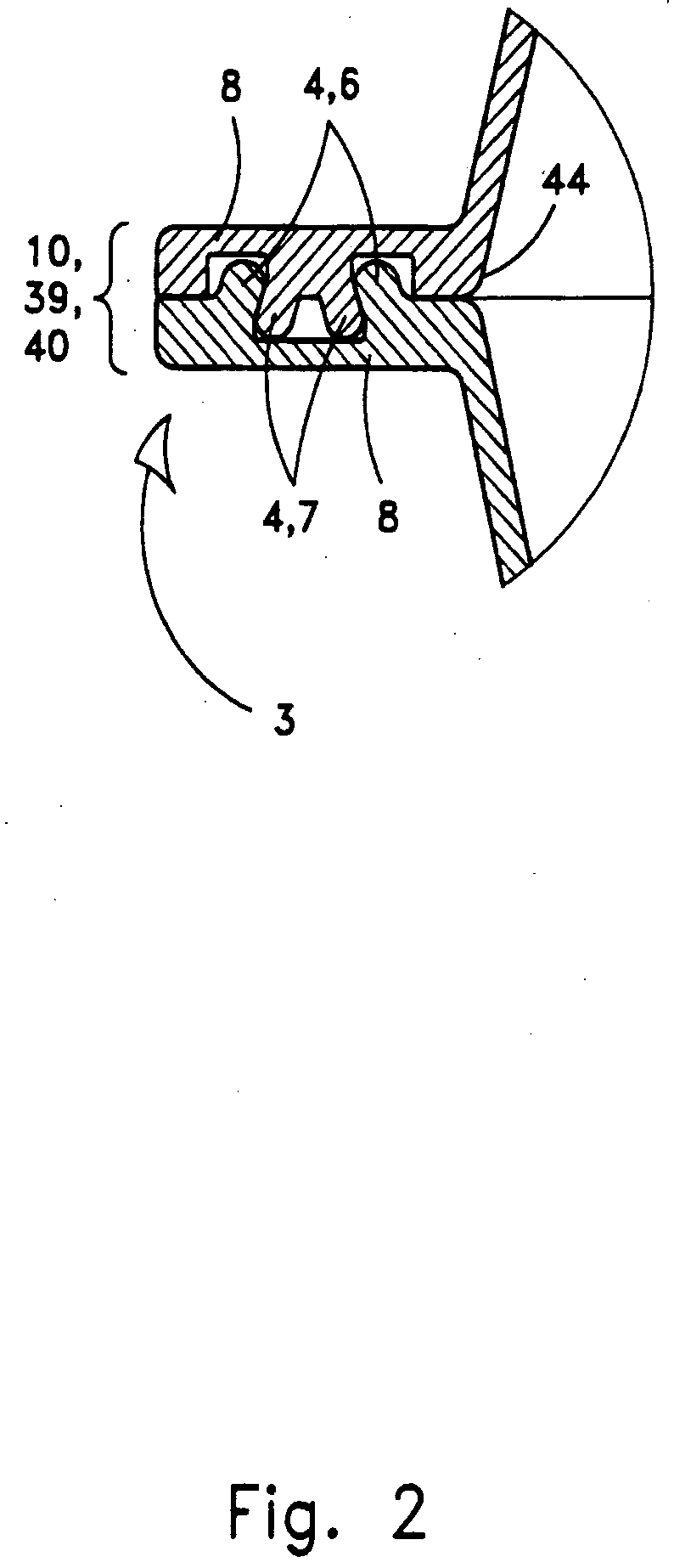

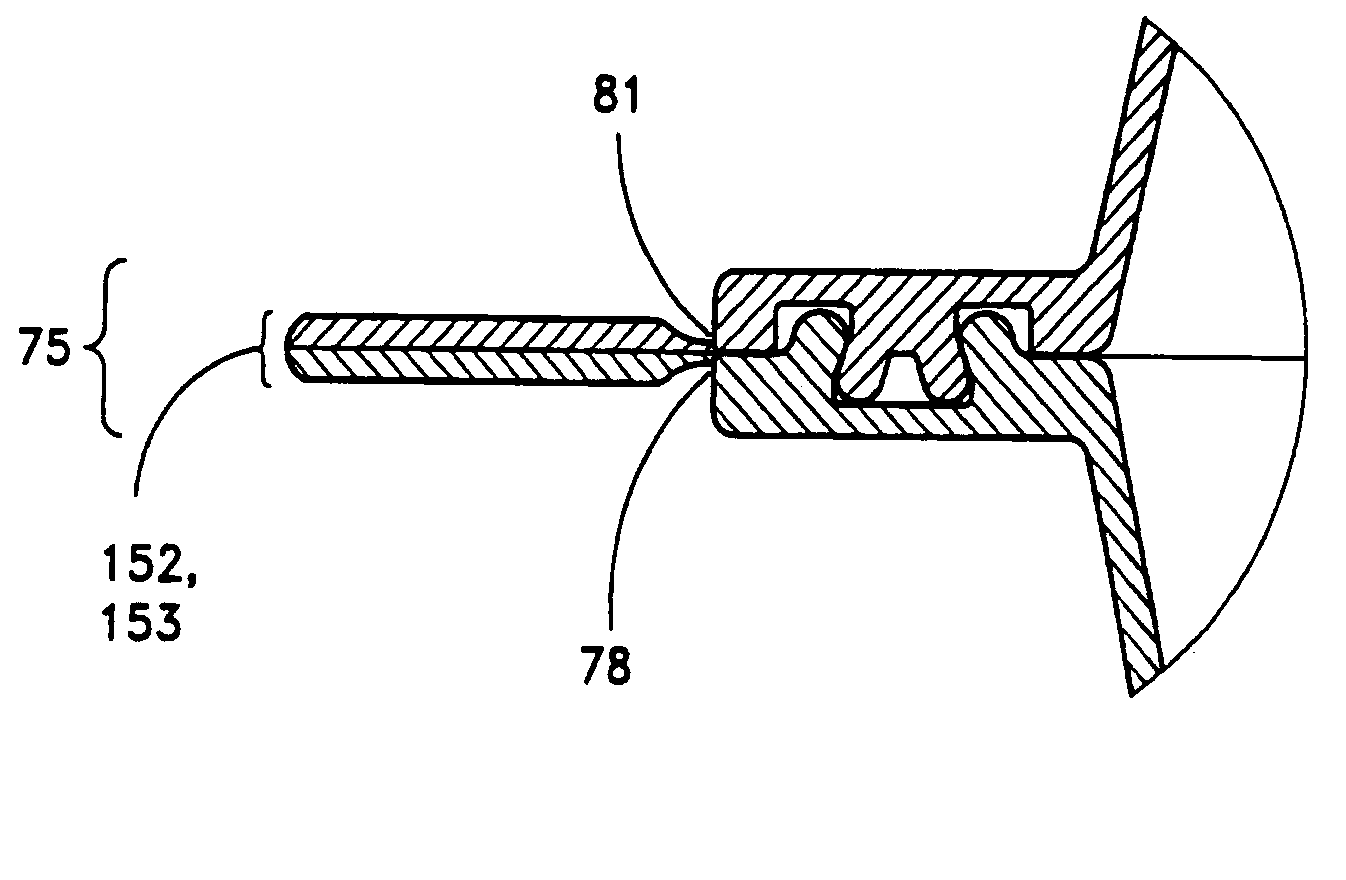

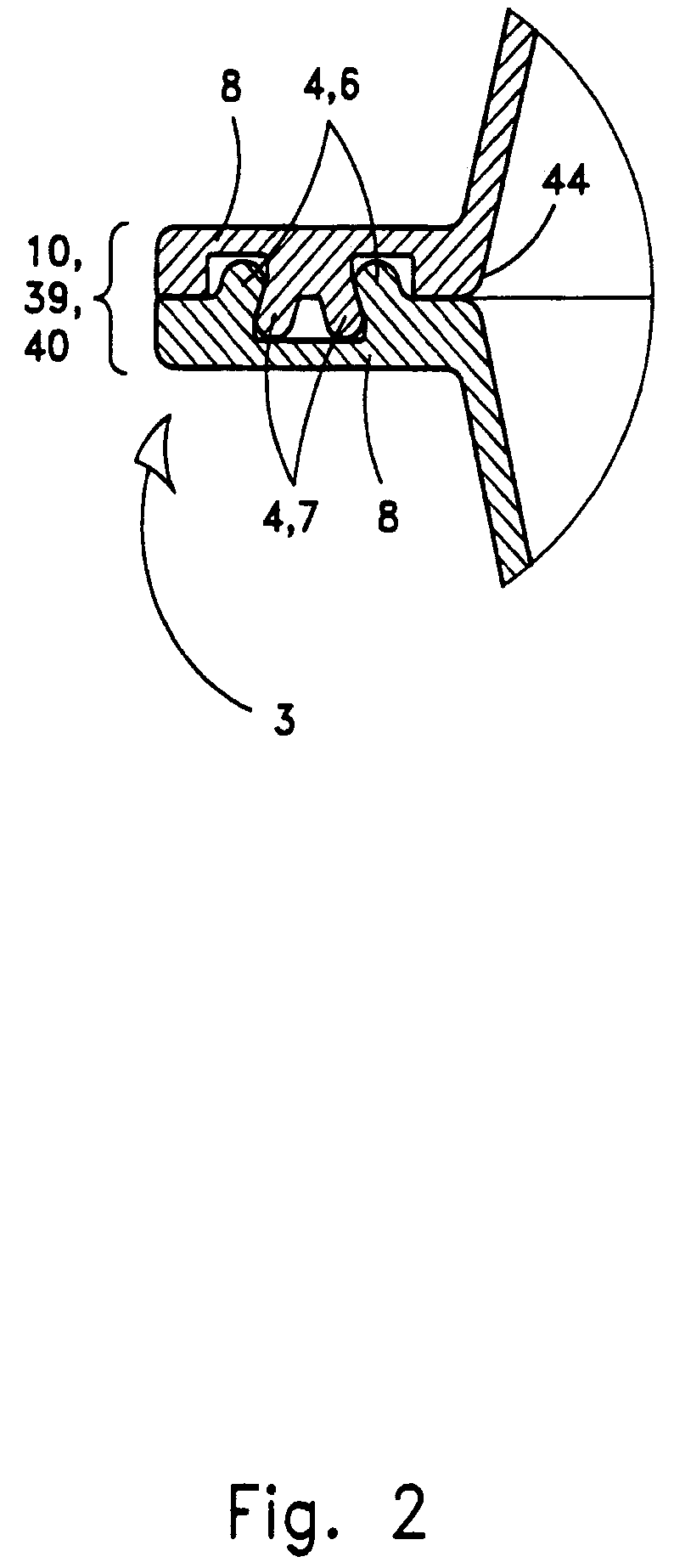

Device for the controlled administration of substances to be inserted in a body cavity

InactiveUS20060051391A1Optimize management modeImprove nutritional managementPharmaceutical delivery mechanismTamponsManufacturing technologyBiomedical engineering

Device for the controlled administration of substances to be inserted in a body cavity, characterized by: an anchoring medium allowing for a firm anchorage of the device in said body cavity; at least one substance support medium for the release of at least one substance into the body cavity following a specific protocol and in which each substance to be administered comprises an independent protocol that establishes a release kinetics with one or more substance administration stages, being each stage defined by a different release kinetics. These devices are useful to develop a simple or complex treatment protocol in mammals. The formulations applicable to the substance support media as well as the appropriate manufacturing processes are also provided.

Owner:DVOSKIN VICTOR OSCAR +2

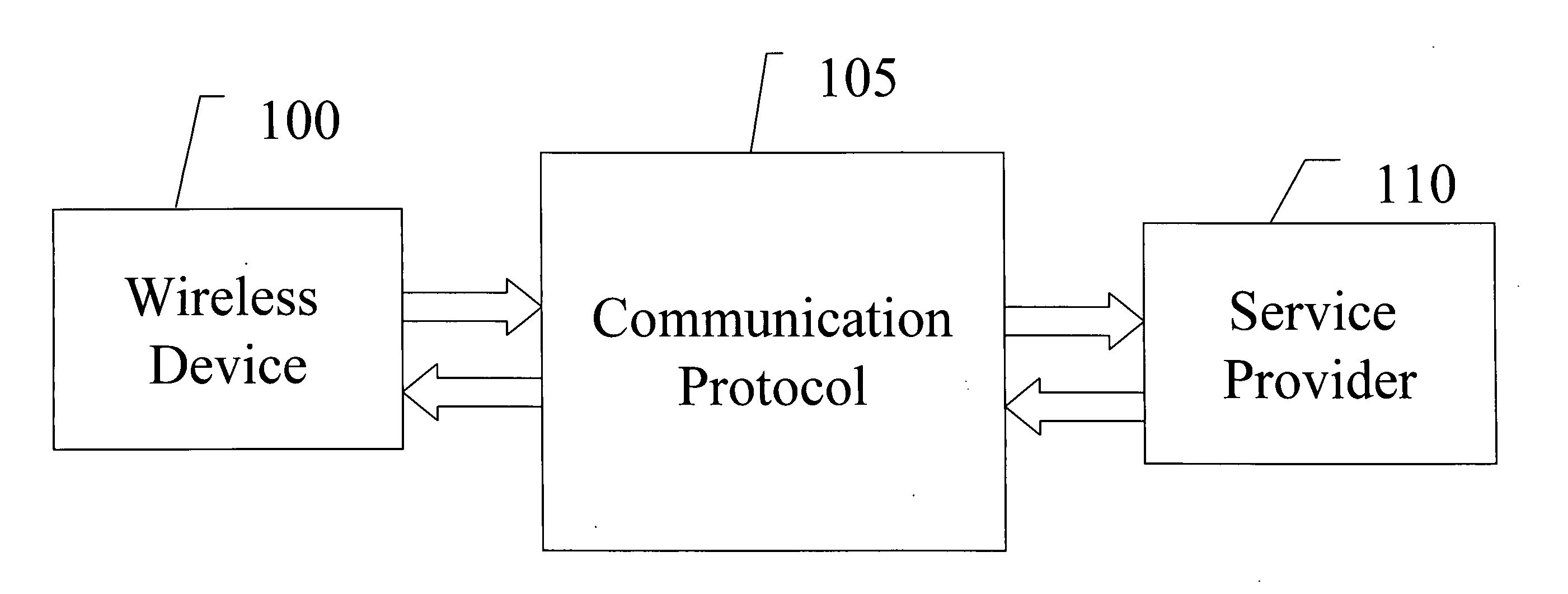

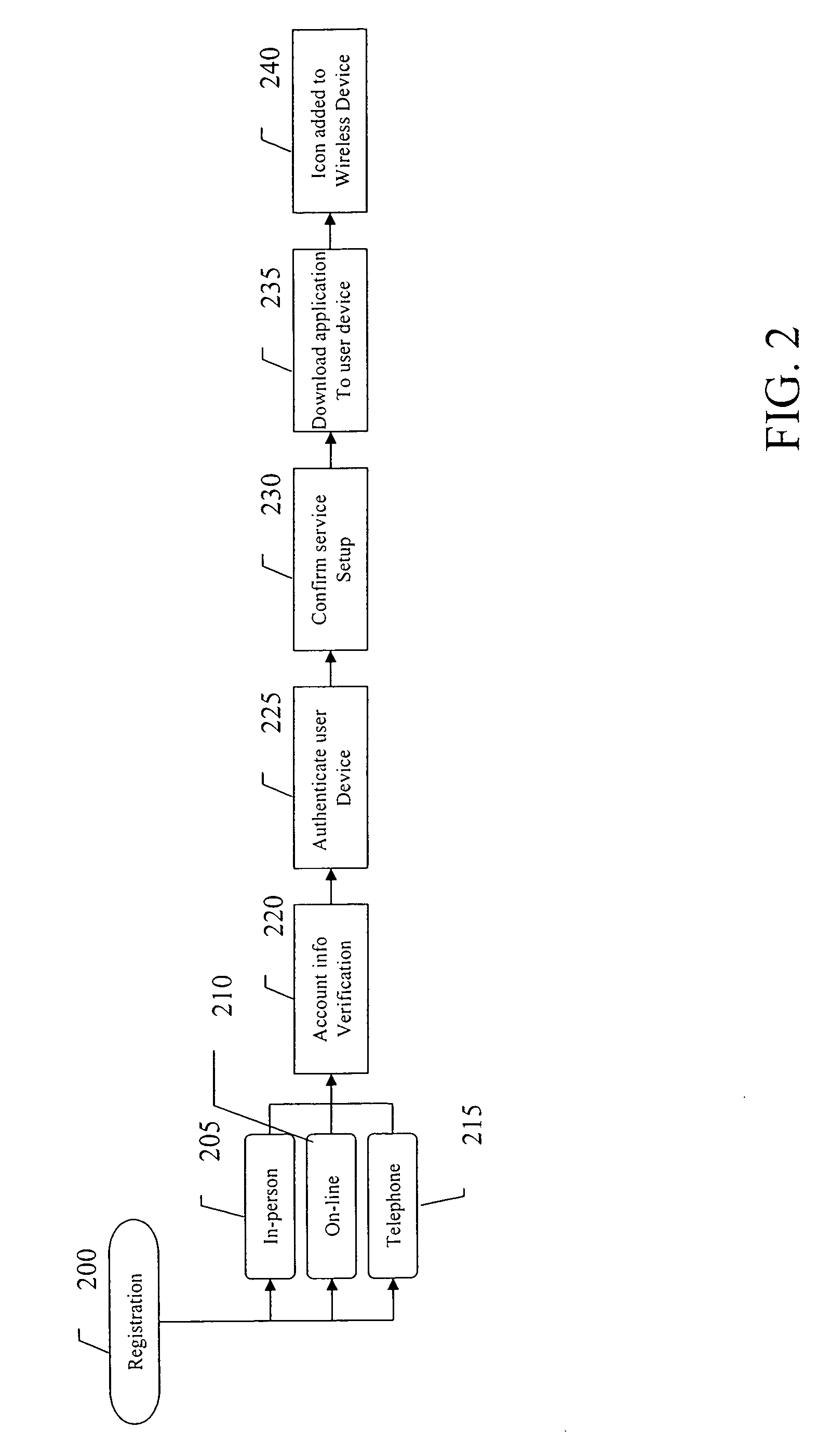

Method and system for conducting financial and non-financial transactions using a wireless device

InactiveUS20070053518A1Efficient and convenient methodEasy to completeAcutation objectsFinanceDisplay deviceFinancial transaction

The present invention relates to a method for conducting transactions, such as standard banking transactions, using a wireless device, such as a cellular telephone, personal digital assistant, and other web-enabled wireless devices utilizing software downloaded to the wireless device. The software provides a user with interface screens on the display of the wireless device for facilitating information requests to a service provider having access to at least one account of the user.

Owner:CITICORP CREDIT SERVICES INC (USA)

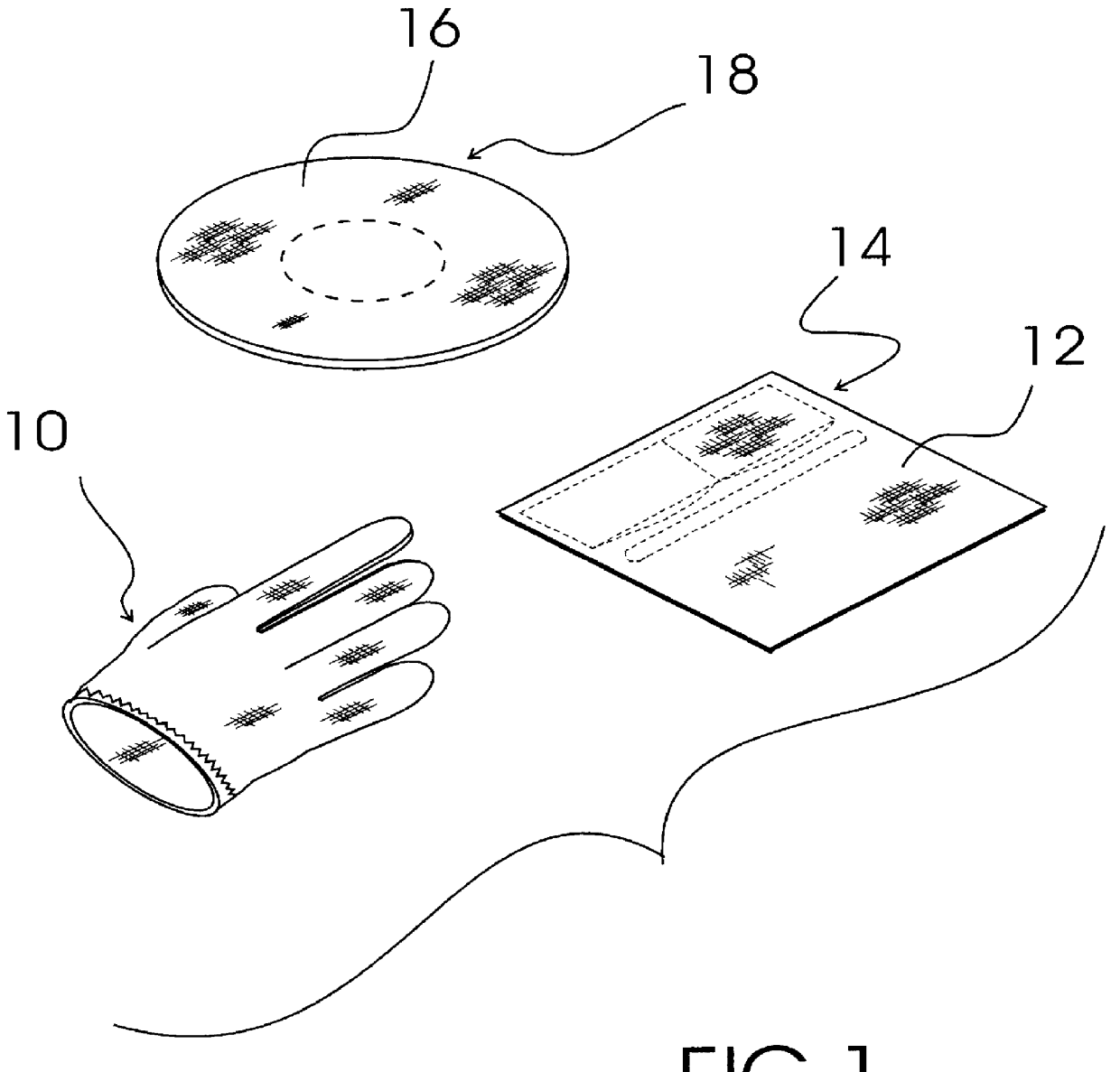

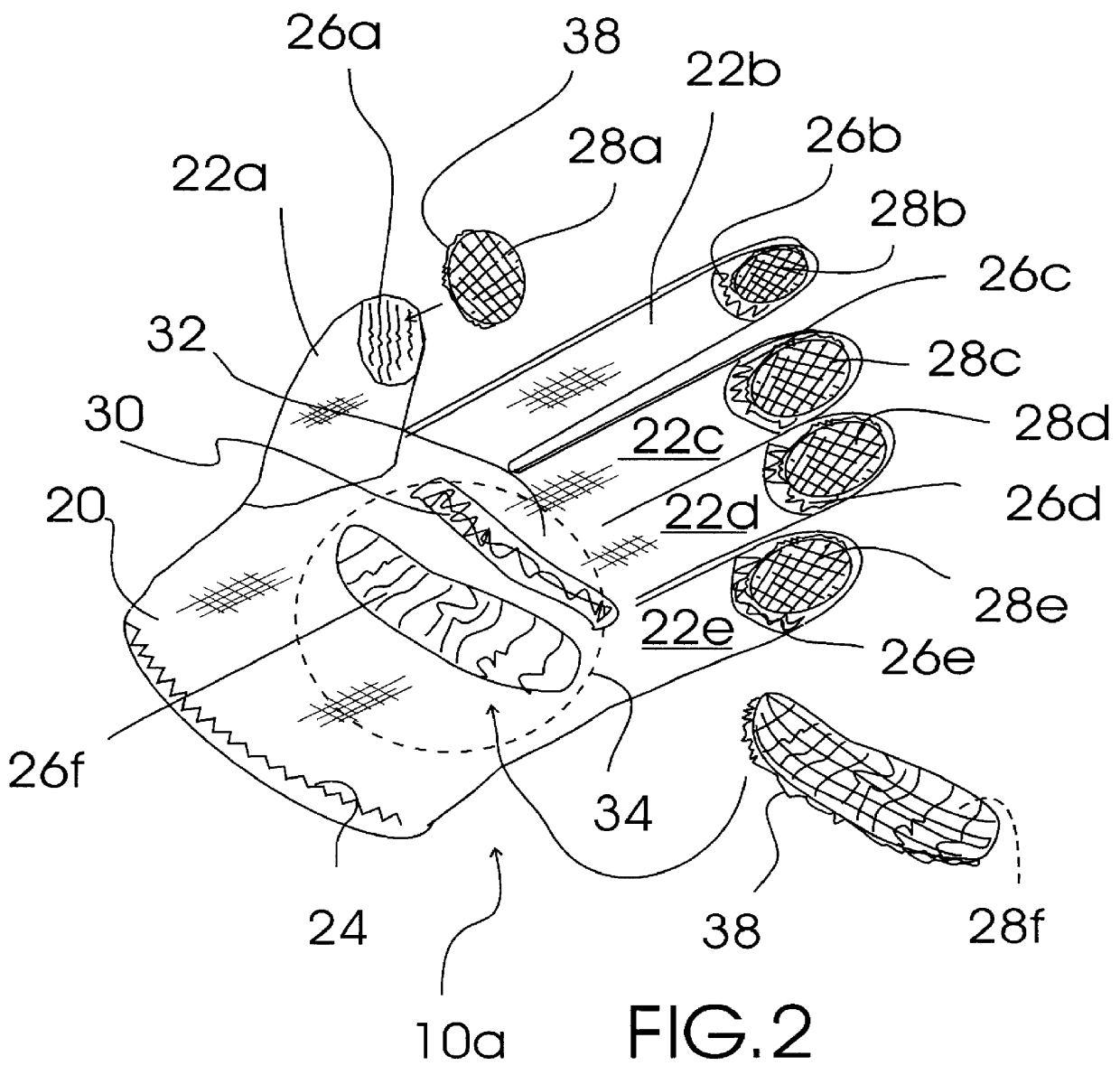

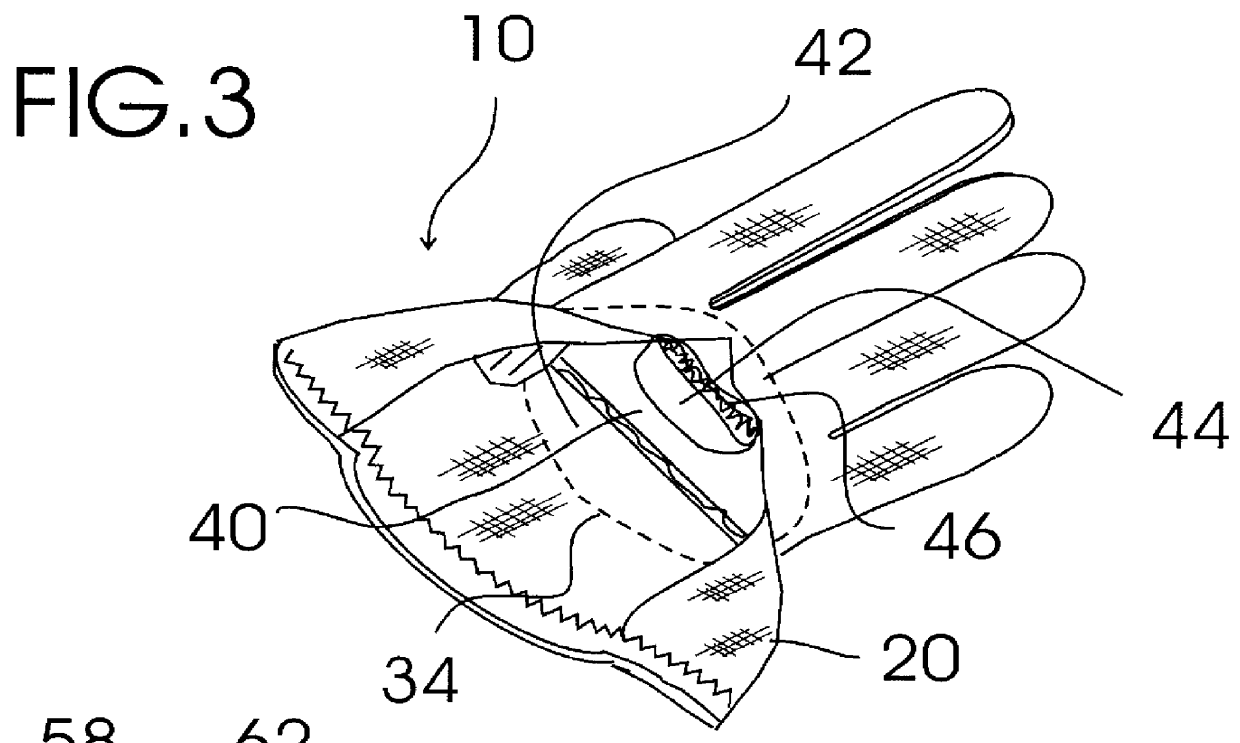

Cleaning system

InactiveUS6098234AConvenient and efficientThe process is convenient and fastBoard cleaning devicesCarpet cleanersScrubberWrist

A cleaning system that is convenient and efficient. The cleaning system includes a glove assembly, a wash cloth assembly, and a buffer cloth assembly. The glove assembly includes a cloth glove shell with an elastic wrist band, six hook and pile scrubber fastening sections, six detachable scrub sections, an elongated accessory hook and pile fastener strip secured to the palm area of the glove shell, and a glove assembly soap receiving compartment within the glove shell that is accessible through an access opening formed through an interior palm surface of the glove shell and having a hook and pile closure sealing flap for sealing the access opening.

Owner:JACKSON JR ANDREW

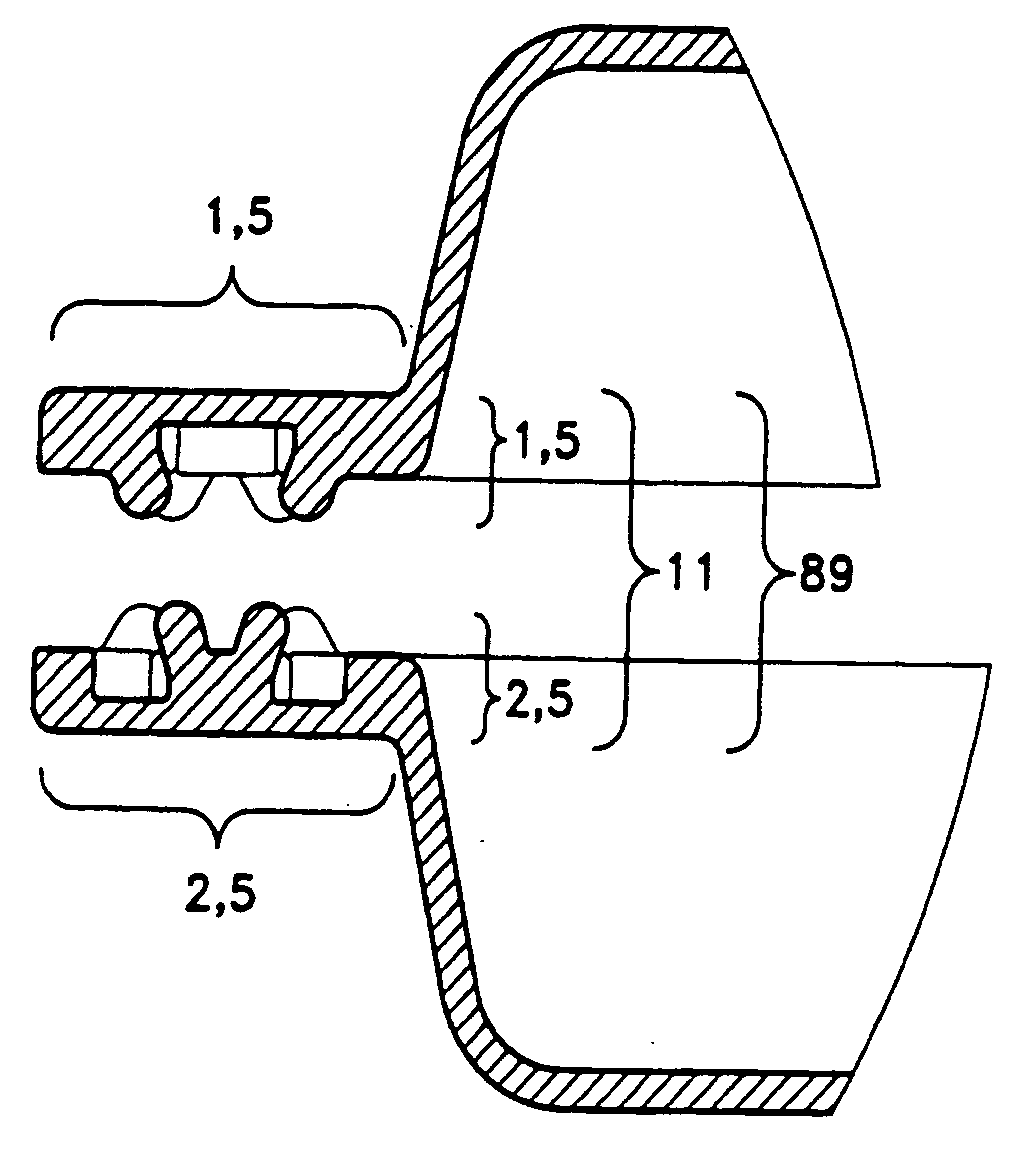

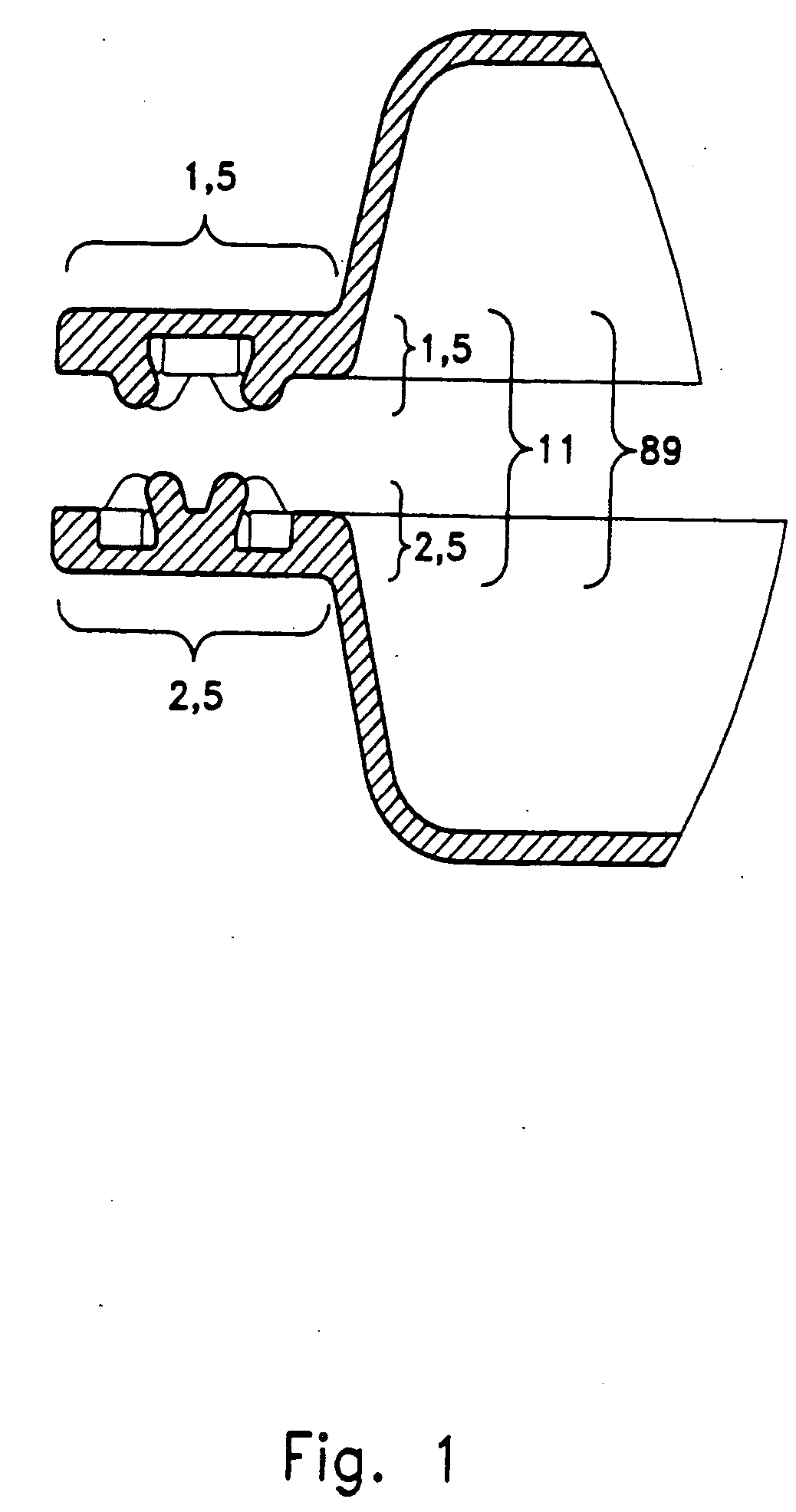

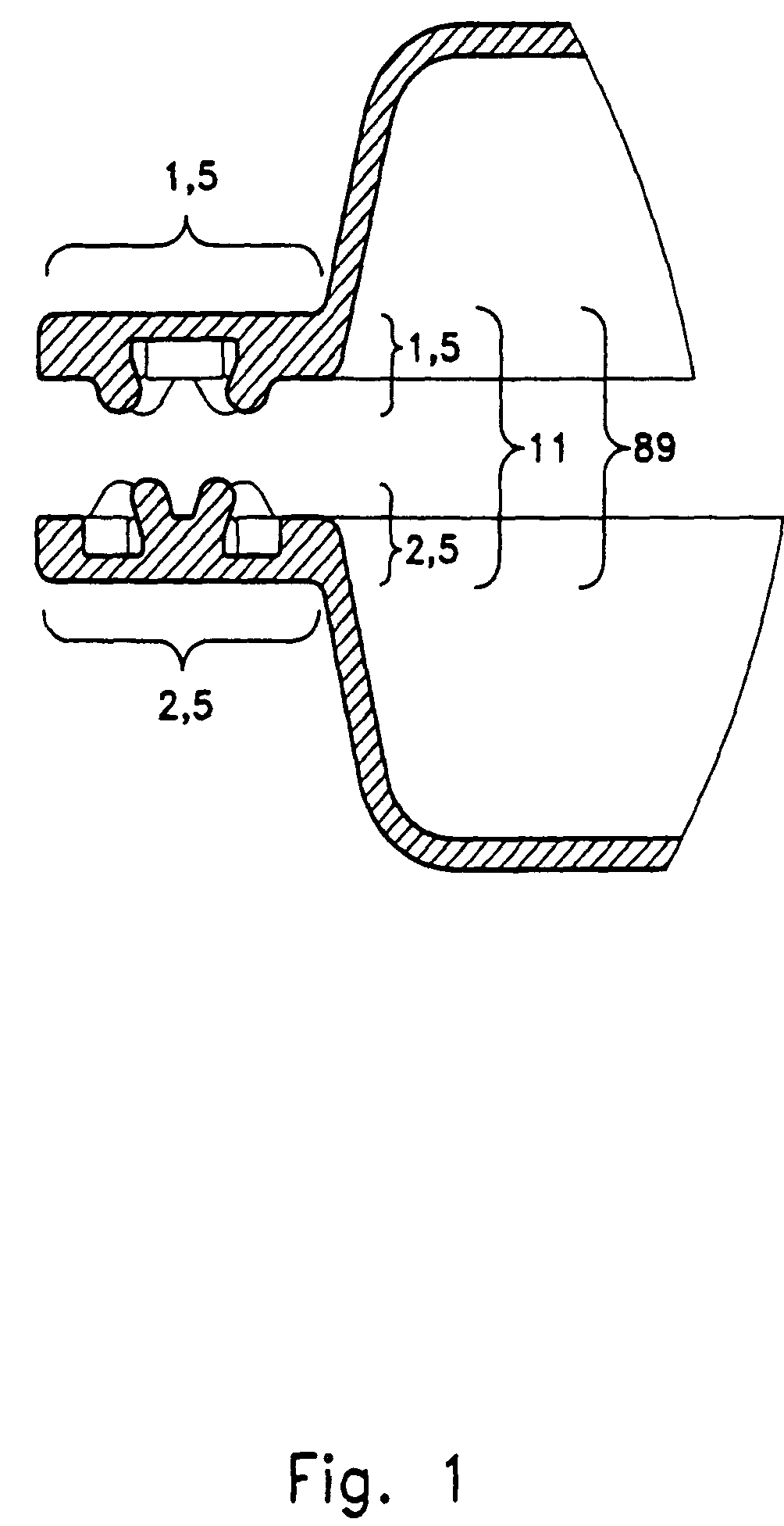

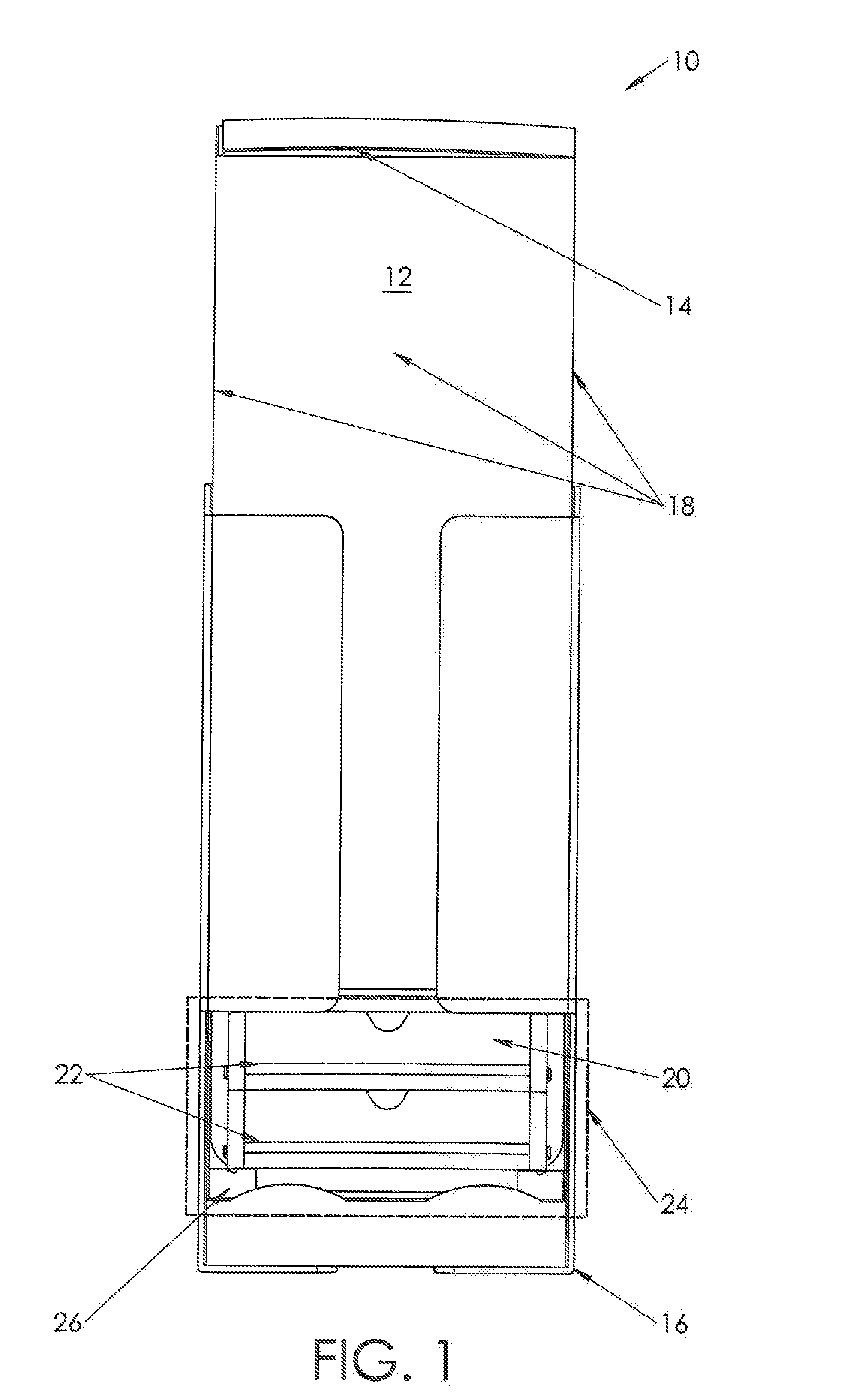

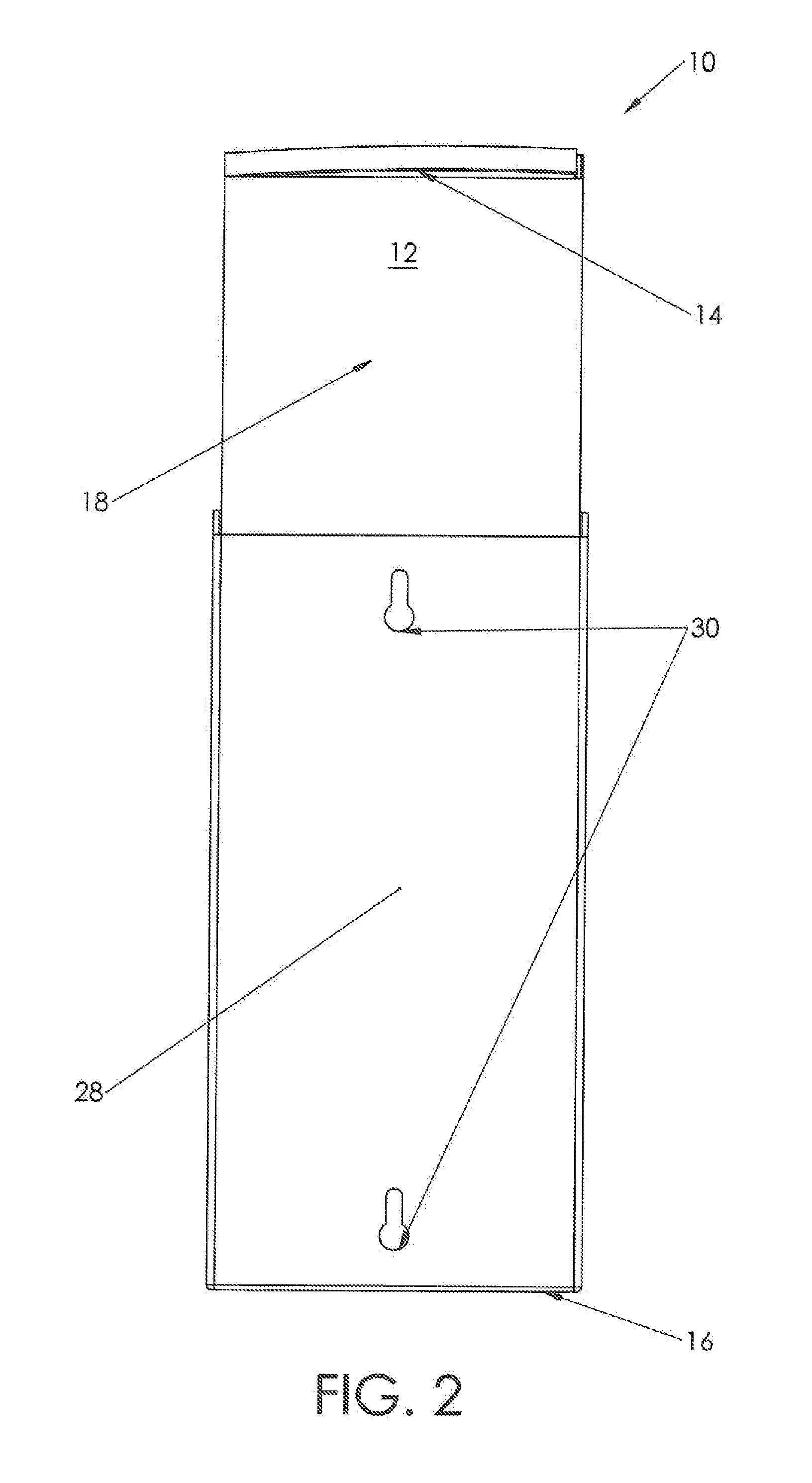

Latchable container system

InactiveUS20070095848A1Increase efficiencyIncrease safetyPackage recyclingCapsMechanical engineeringEngineering

A latching system including both apparatus and methods addresses the need for a reusable latch that is identical on either side of a container opening, thereby facilitating container manufacture. Also disclosed are apparatus and methods for assuring the quality of latchable container enclosed contents and enhancing the safety of container users by providing an unopened condition assurance element such as a tab that is removable from a reusable container latch. A novel latching system with a split insertion clement on a first latch side and unitary receptor element on a second latch side is also disclosed. A preferred embodiment involves an elastically obstructed latch as used on a squeeze-openable container.

Owner:INT MOLDED PACKAGING CORP

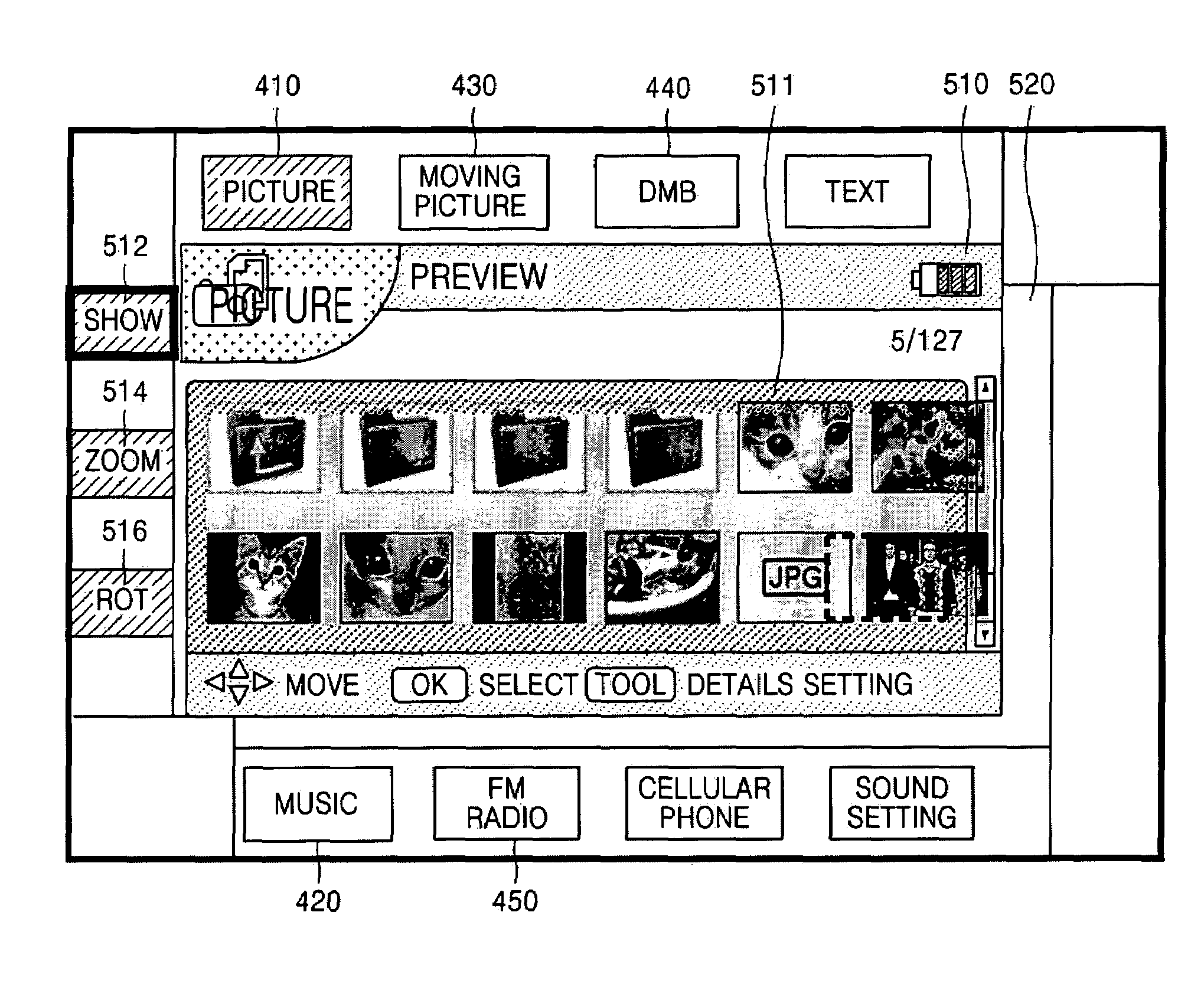

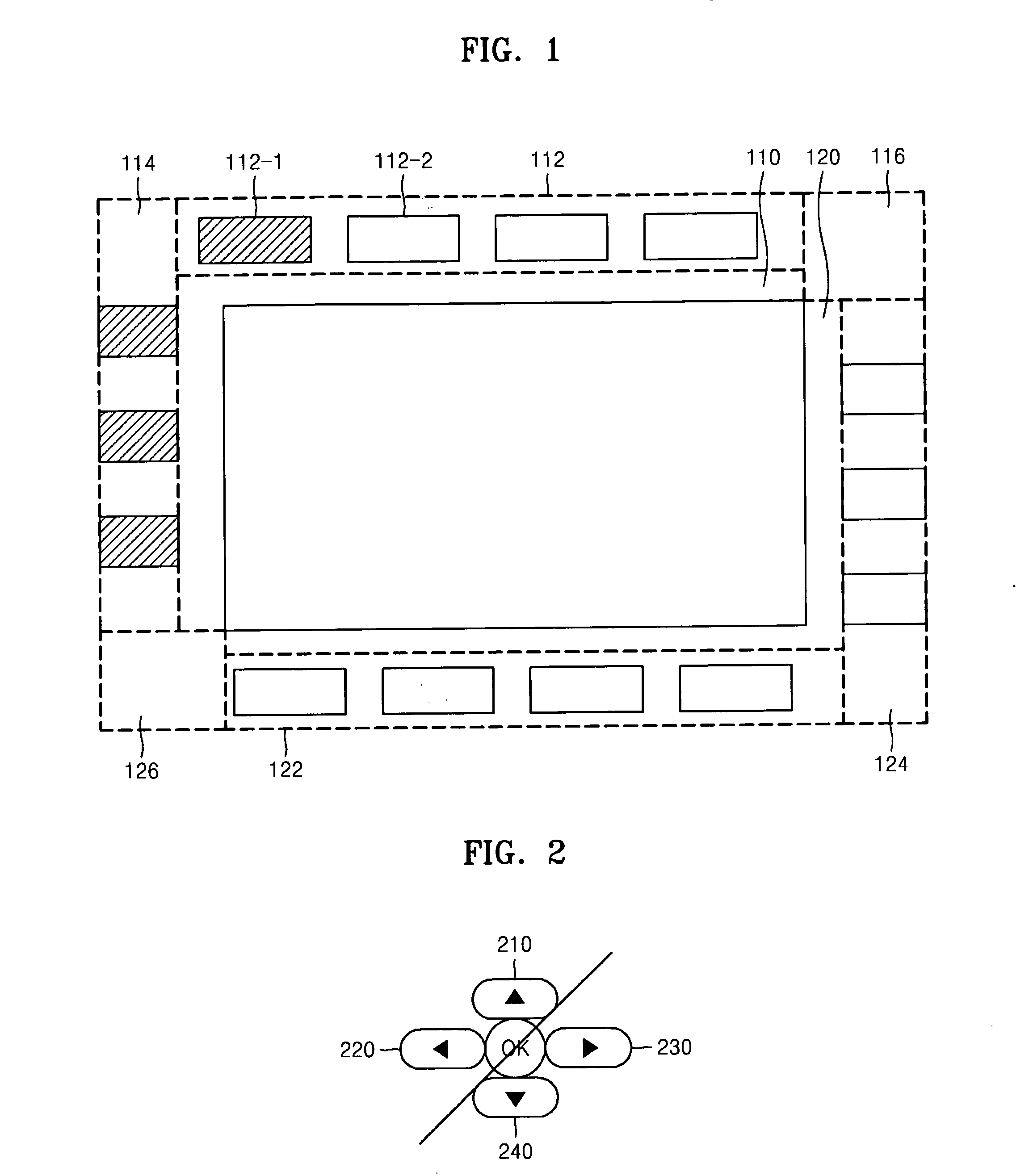

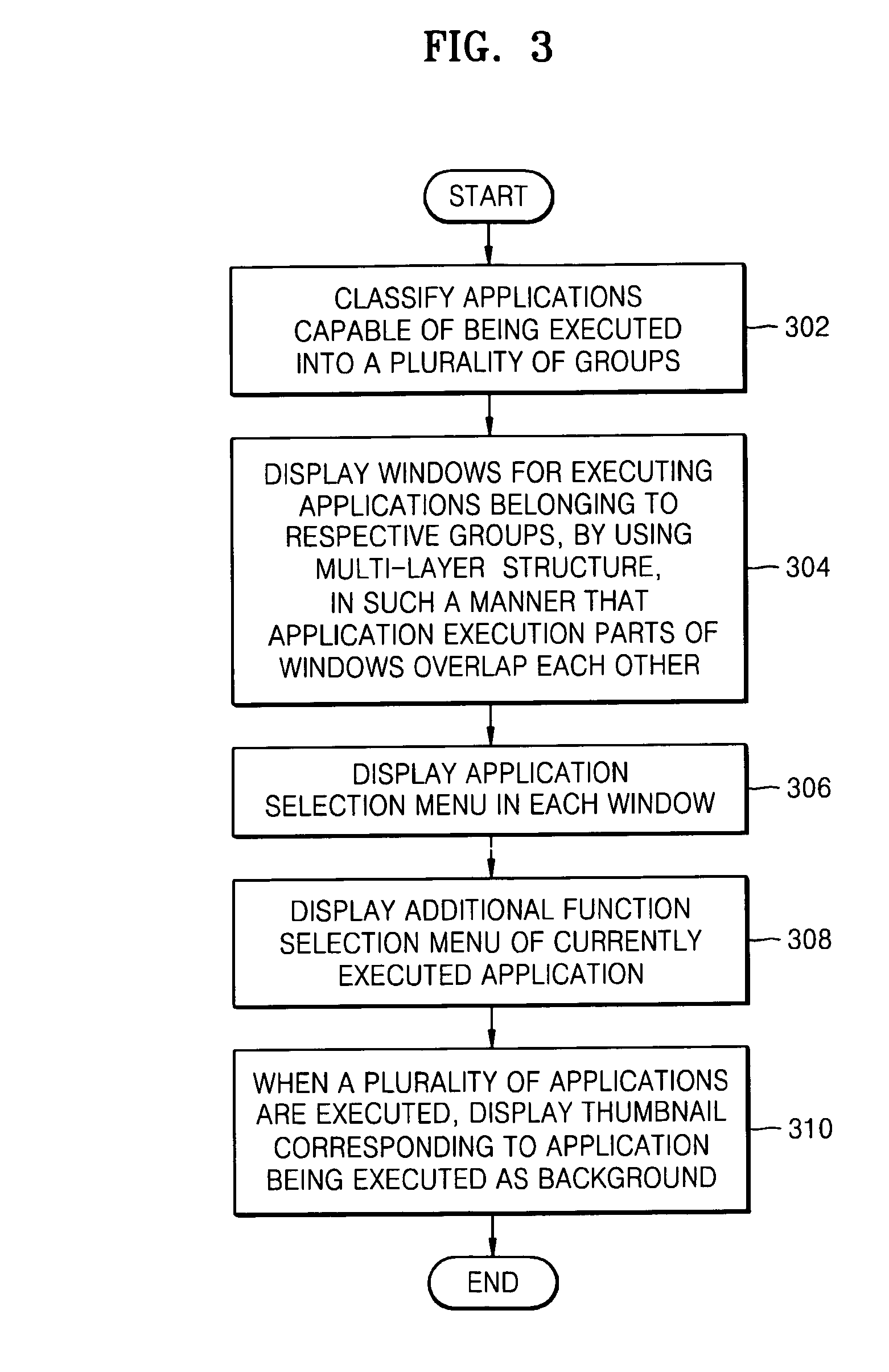

User interface method of multi-tasking and computer readable recording medium storing program for executing the method

ActiveUS20070220440A1Convenient and efficientEfficient and convenient to useTelevision system detailsData processing applicationsMultiple applicationsComputer hardware

Provided are a user interface method of enabling a user to conveniently use a terminal allowing multi-tasking, and a computer readable recording medium storing the method. The user interface method includes classifying applications capable of being executed by the apparatus into groups, in such a manner as to classify one or more applications that perform similar functions into the same group; and displaying a window for executing a corresponding application, for each of the groups.

Owner:SAMSUNG ELECTRONICS CO LTD

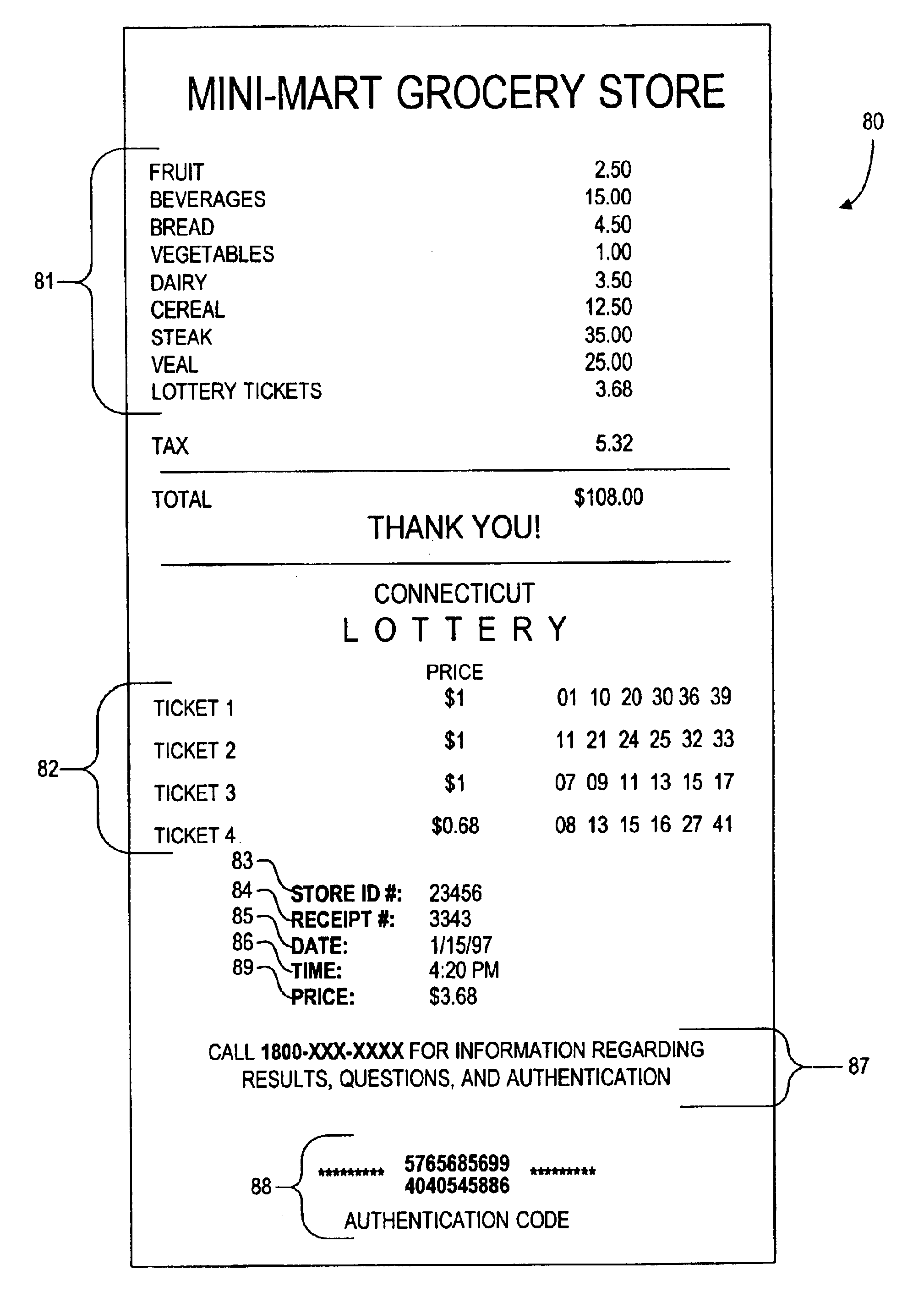

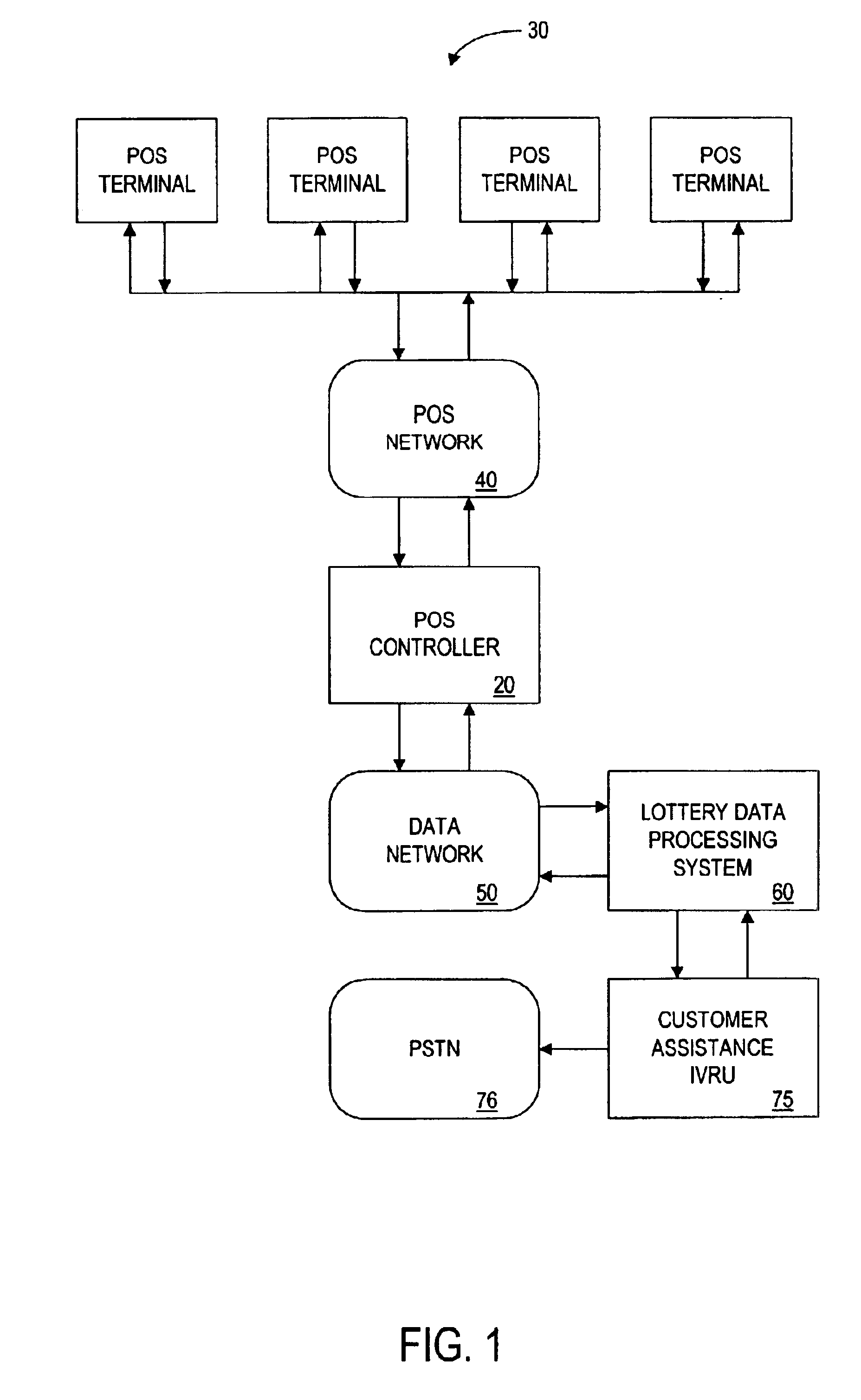

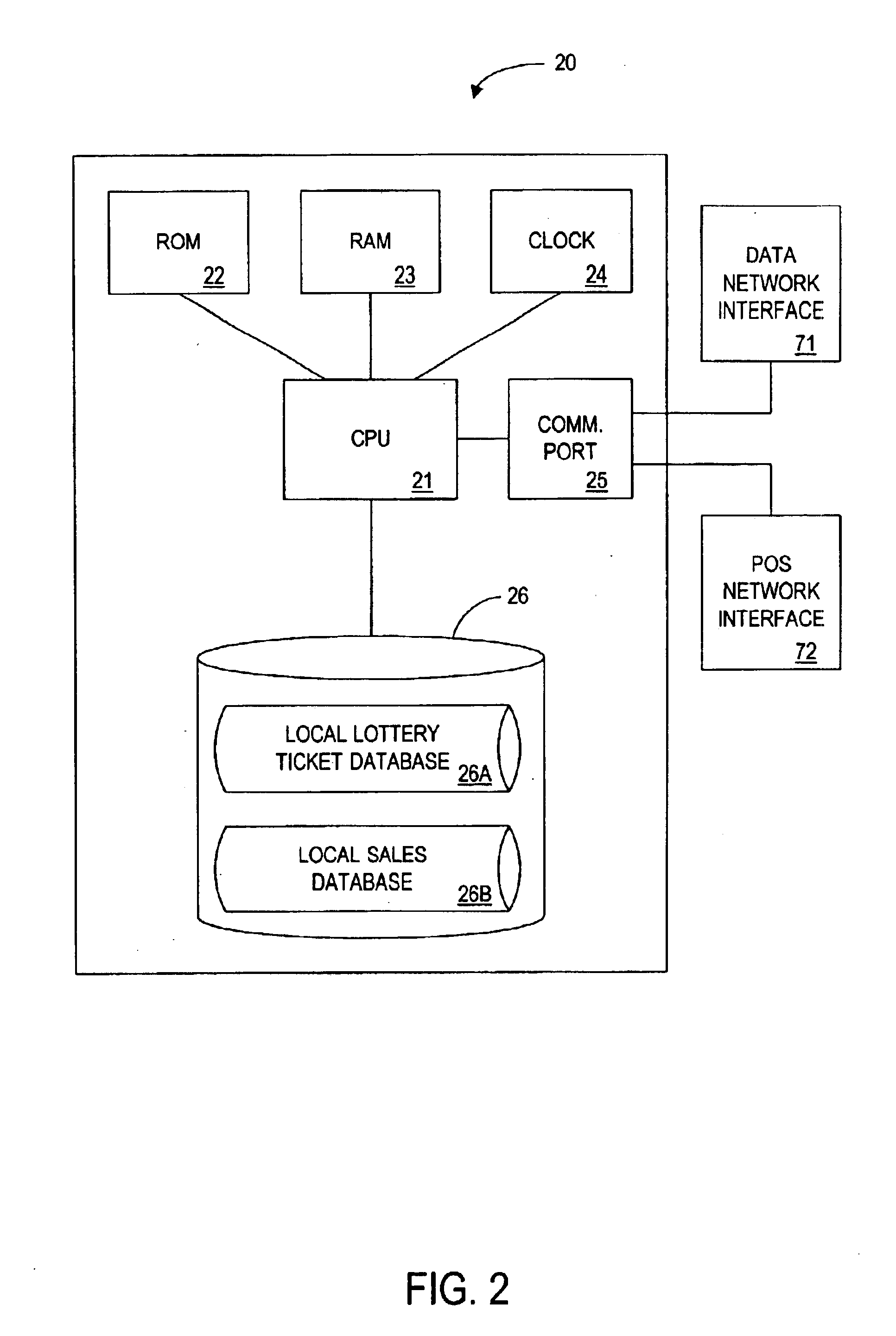

System and method for performing lottery ticket transactions utilizing point-of-sale terminals

InactiveUS6887153B2Convenient and efficientGreat accessLottery apparatusApparatus with change-givingReceiptHandling system

A system and method for performing integrated lottery ticket and merchandise transactions using a point-of-sale terminal that generates a single sales receipt containing all pertinent lottery ticket and merchandise transaction information. The lottery tickets generated include fractional value and “quick-pick” lottery tickets. A group of point-of-sale terminals are connected to a POS controller which communicates with a lottery data processing system. An encrypted authentication code also printed on the sales receipt allows the lottery player to verify all lottery ticket transaction information, as needed.

Owner:INVENTOR HLDG +1

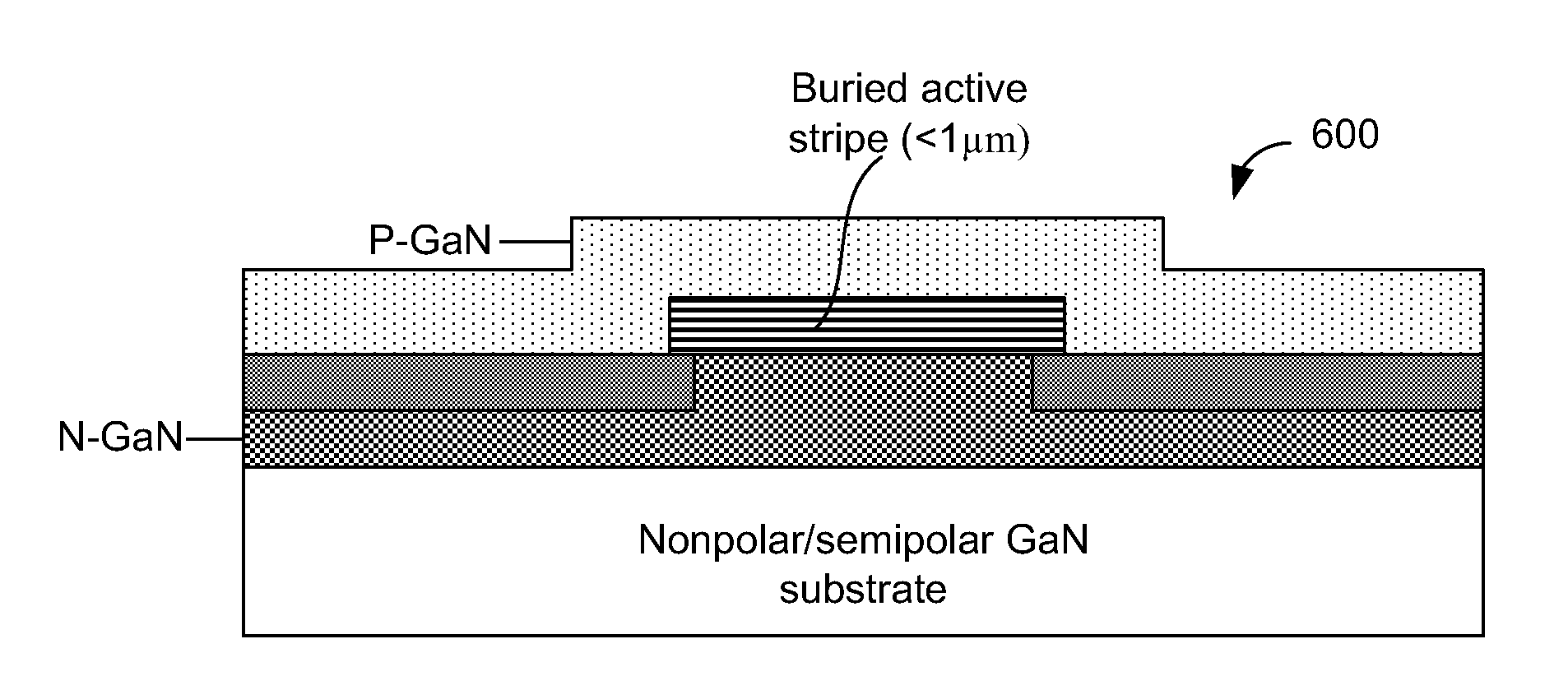

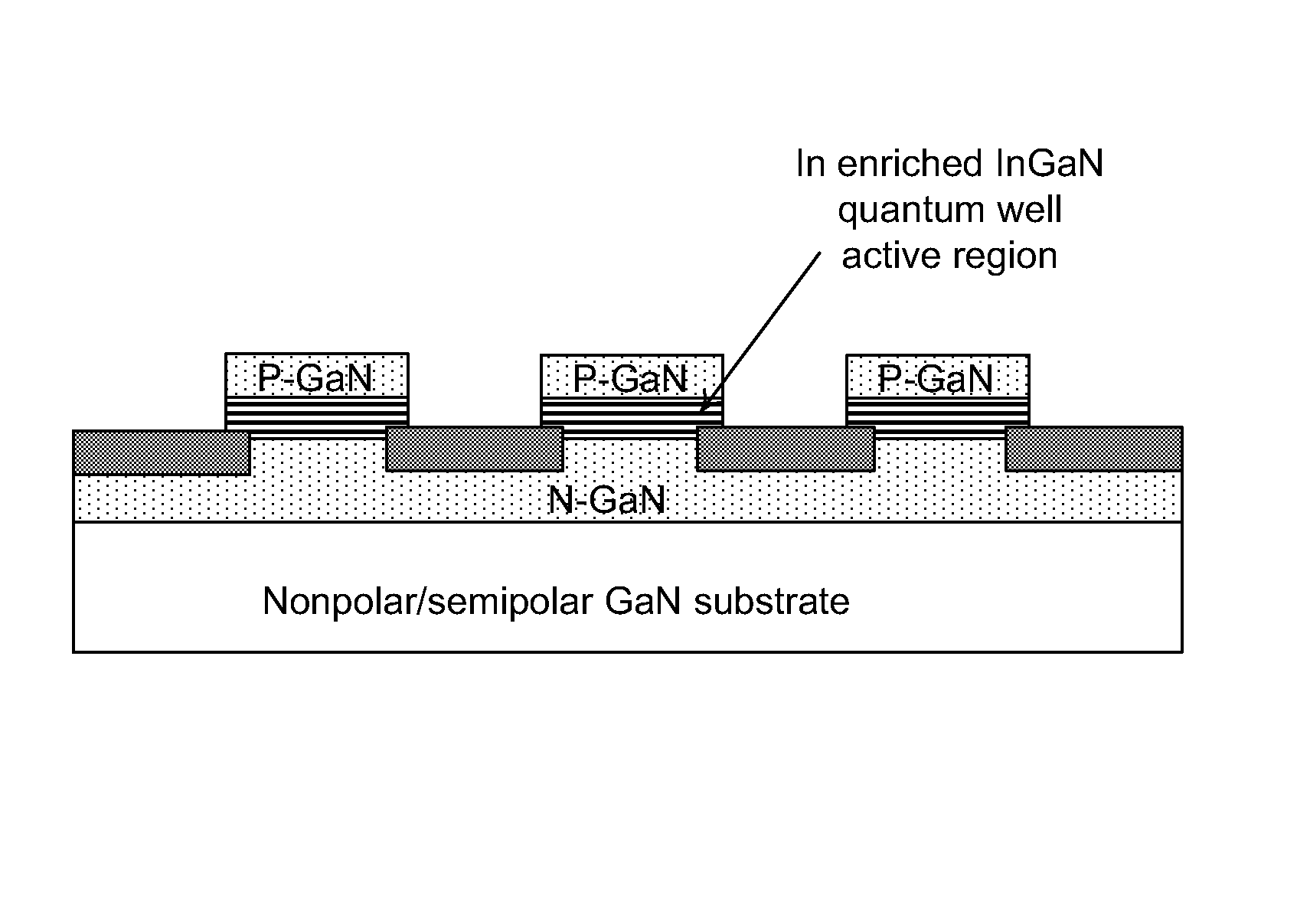

Solid-state optical device having enhanced indium content in active regions

InactiveUS8847249B2Improve the level ofSmall sizeSemiconductor/solid-state device manufacturingSemiconductor devicesIndiumOptics

A multicolored LED device made of a semipolar material having different indium containing regions provided on different spatial features of GaN material. Other materials such as non-polar materials can also be used.

Owner:SLT TECH

Latchable container system

InactiveUS7819279B2Convenient and efficientImprove securityCapsPackage recyclingEngineeringMechanical engineering

A latching system including both apparatus and methods addresses the need for a reusable latch that is identical on either side of a container opening, thereby facilitating container manufacture. Also disclosed are apparatus and methods for assuring the quality of latch able container enclosed contents and enhancing the safety of container users by providing an unopened condition assurance element such as a tab that is removable from a reusable container latch. A novel latching system with a split insertion clement on a first latch side and unitary receptor element on a second latch side is also disclosed. A preferred embodiment involves an elastically obstructed latch as used on a squeeze-openable container.

Owner:INT MOLDED PACKAGING CORP

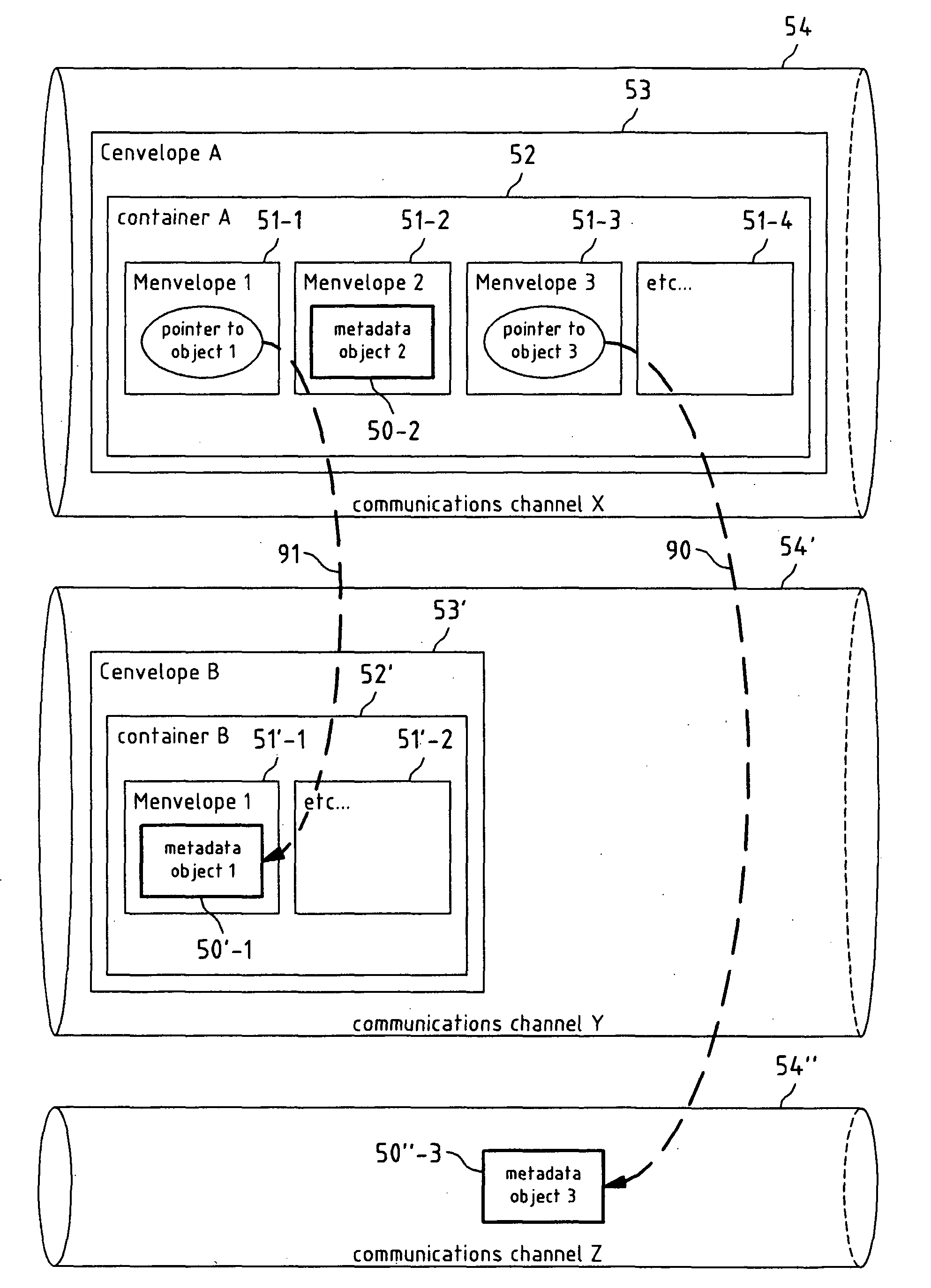

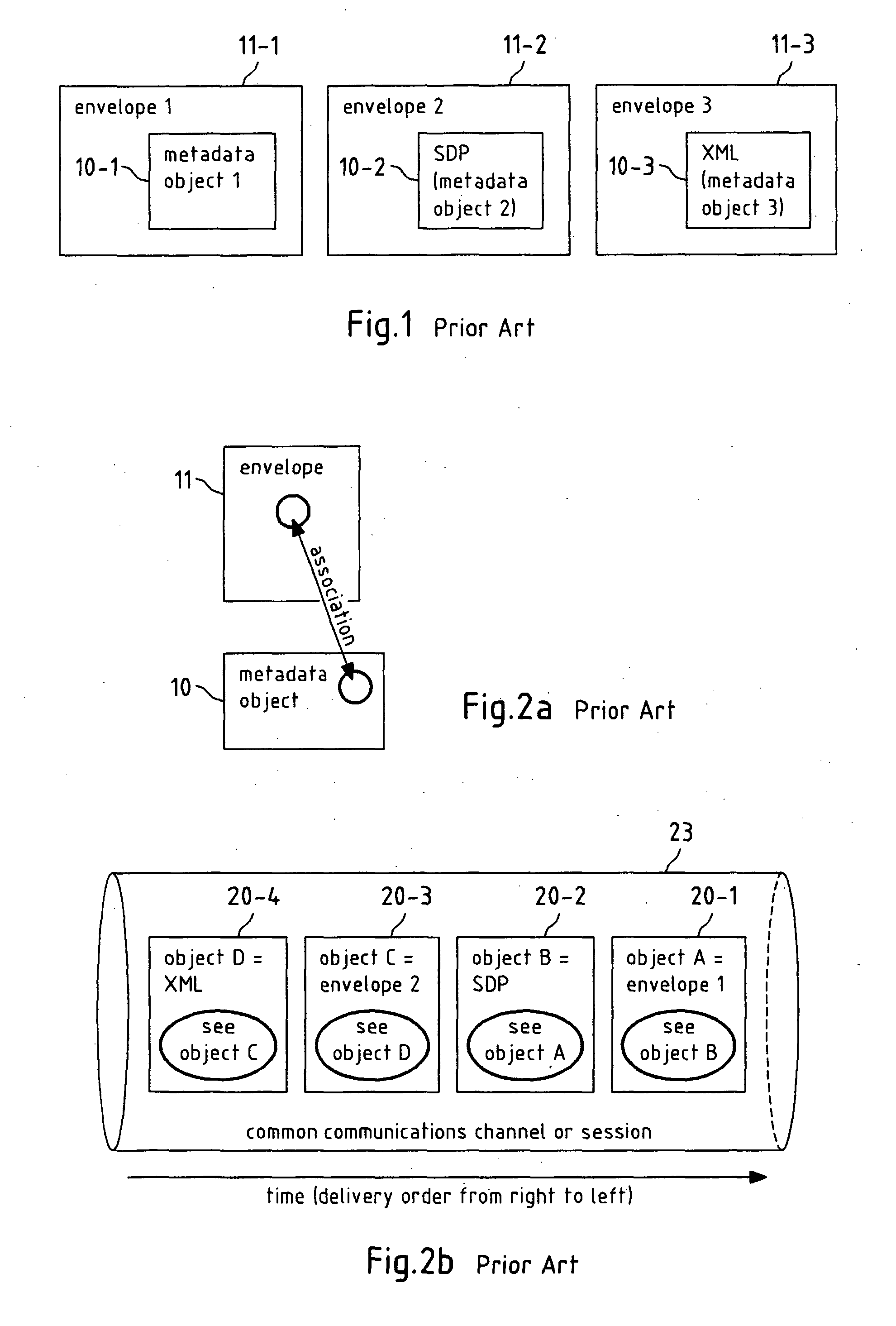

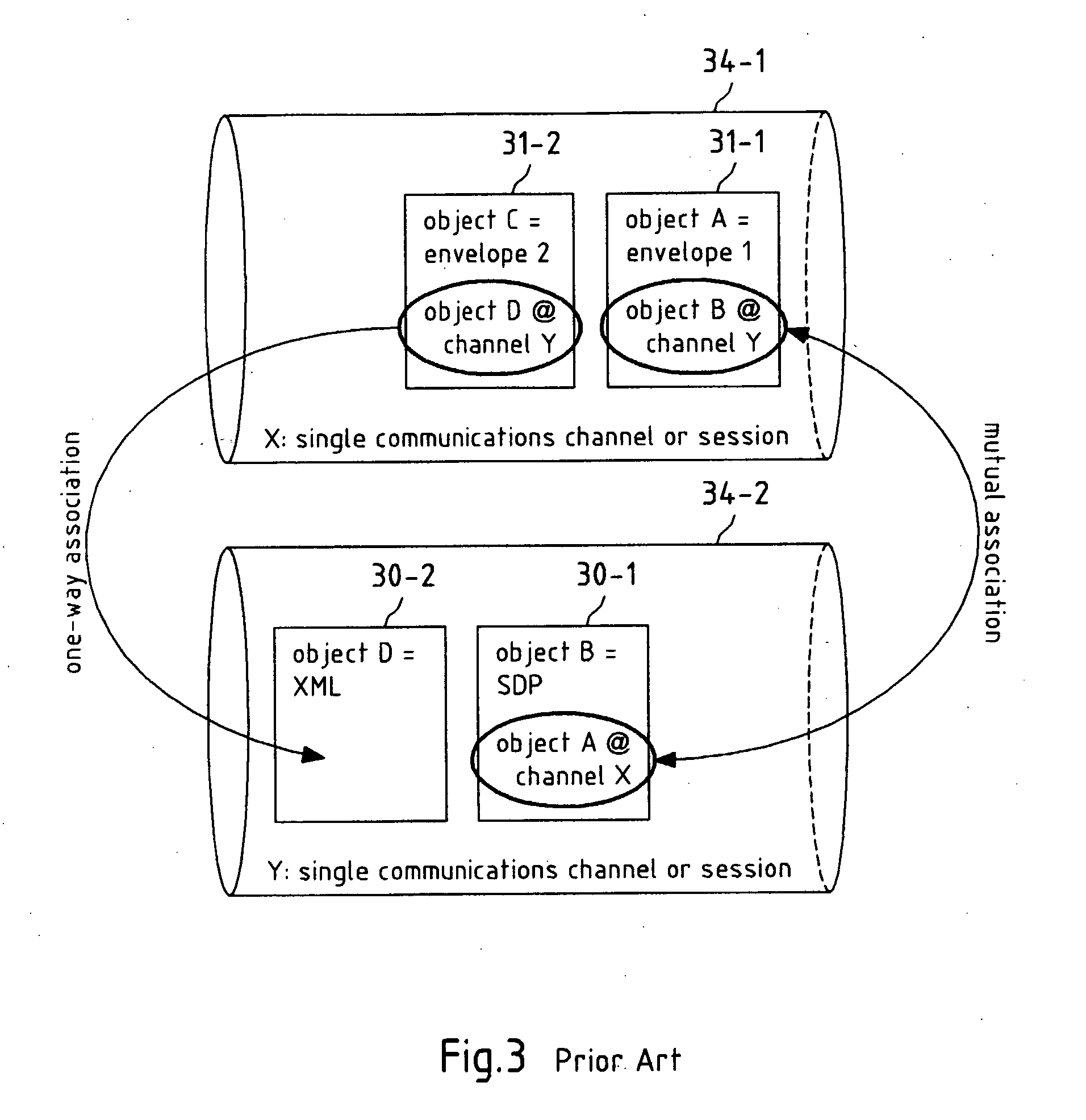

Transfer of Data Objects

InactiveUS20080137688A1Efficient transferReduce transmission overheadDigital computer detailsTime-division multiplexData packSoftware engineering

A method, computer program / product, system, transmitter and receiver suited for the transfer of at least one data object (50) to the receiver (101) are shown, wherein the at least one data object is associated with a respective data envelope (51) that serves for at least one of identifying, versioning and time bounding the at least one data object, the method embedding (110) the at least one data envelope and a representation of the at least one data object into a compound container object (52), and transferring (112) the compound containerobject to the receiver. The at least one data object may be a metadata object that represents a description of services and / or content that can be used by the receiver, and the compound container object is furnished with a compound container envelope (53) that serves for at least one of identifying, versioning and time bounding of the compound container object.

Owner:NOKIA CORP

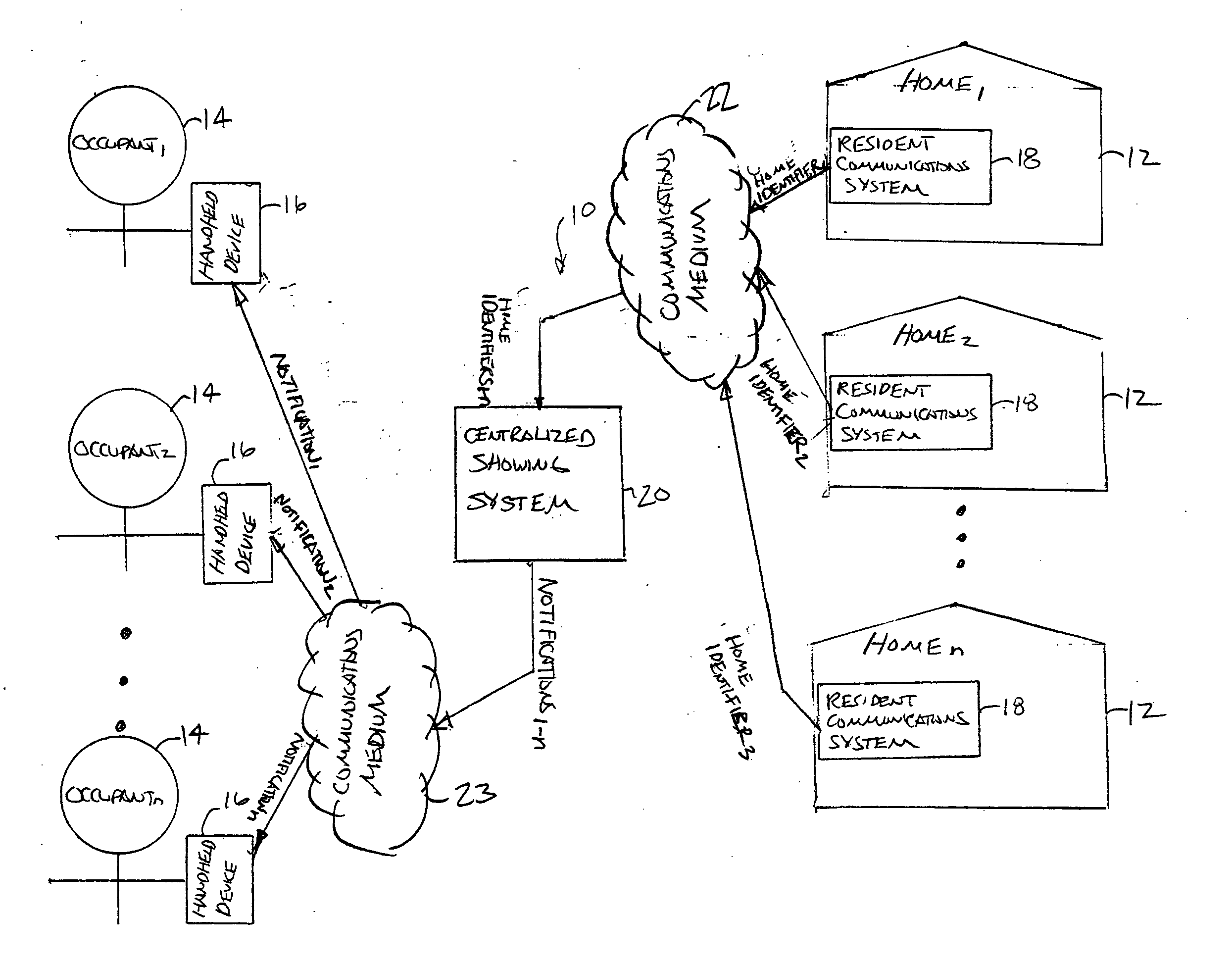

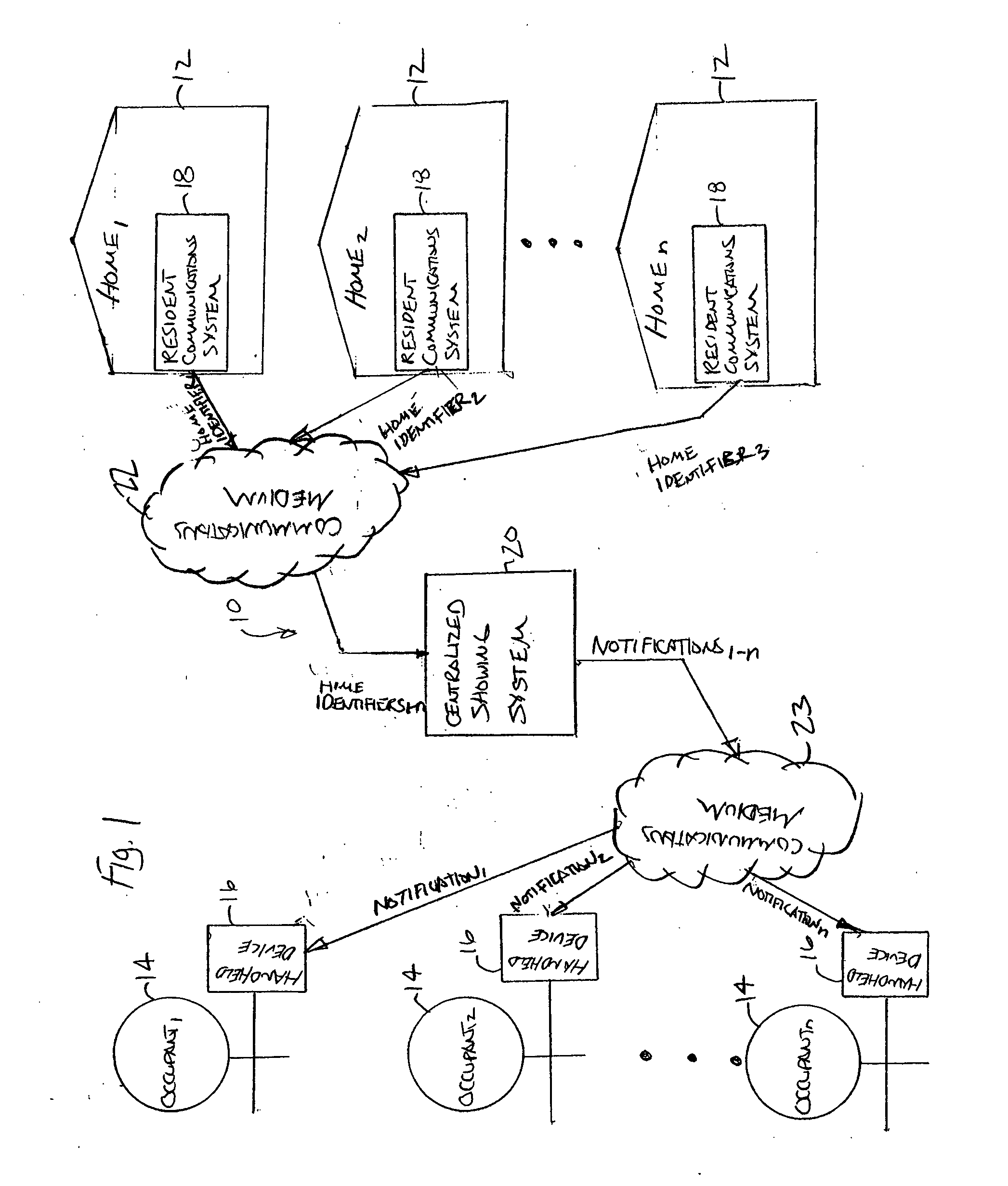

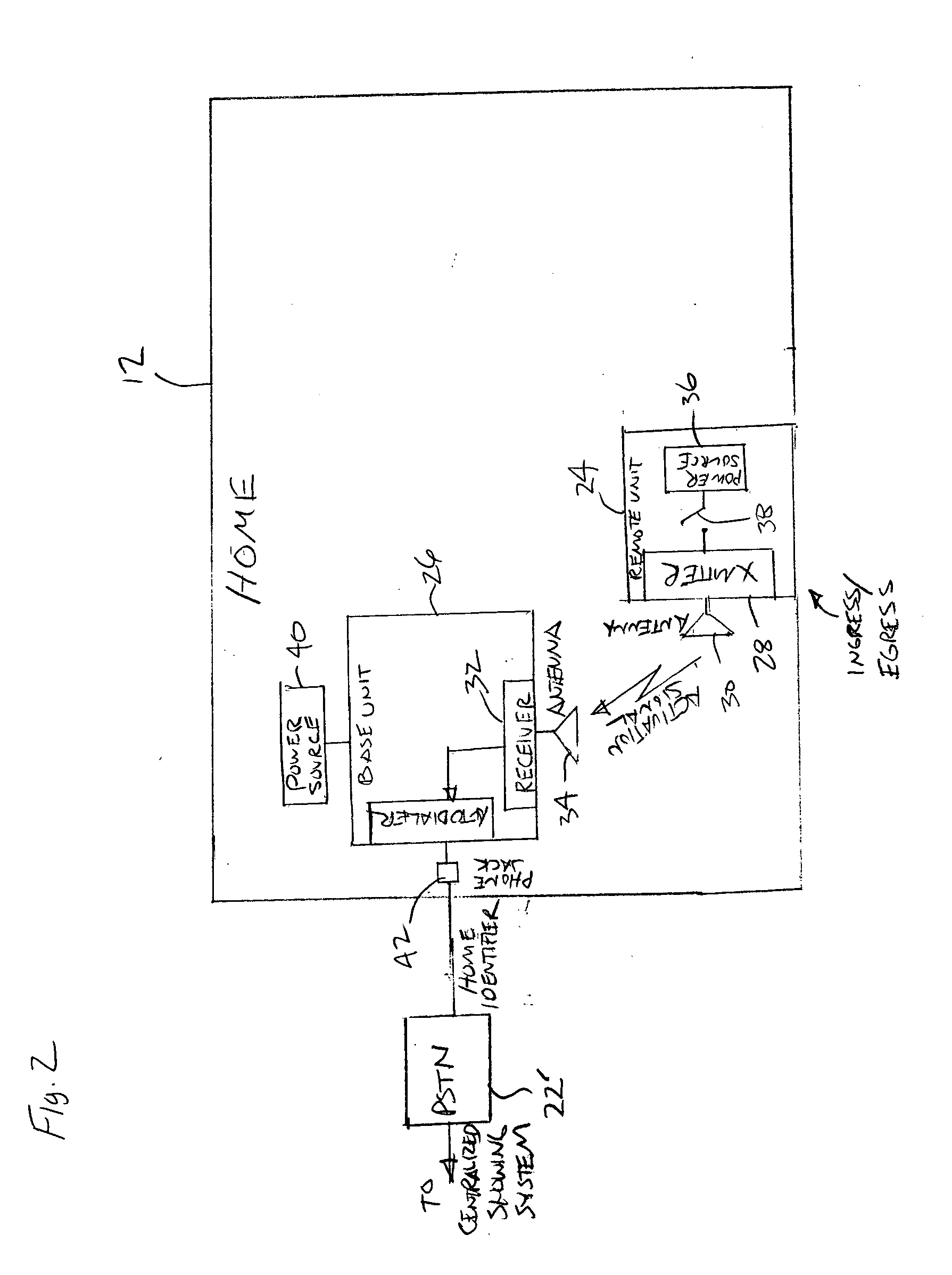

Centralized system and method for notifying occupant of completion of home showing

InactiveUS20060106628A1Convenient and efficientOptimize locationBuying/selling/leasing transactionsTelecommunicationsLogical address

Methods and systems for facilitating sale of a home in which an occupant is absent are provided. A resident communications system is installed at the home. Upon completion of a showing at the home by a real estate agent, a signal is transmitted from the resident communication system. The signal can be a home identifier that is subsequently received by a centralized showing system, which correlates the home identifier with a logical address of a handheld communications device carried by the occupant, and contacts and informs the occupant via the handheld communications device that the home showing has been completed. Or the signal can be a notification signal that is transmitted directly to the handheld communications device for notifying the occupant that the home showing has been completed. The resident communications system may have a base unit and a remote unit, such as a lockbox, that can be placed near the ingress / egress of the home and actuated to transmit an activation signal to the base unit, which then transmits the signal to centralized showing system or directly to the handheld communications device.

Owner:CENTIZED SHOWING SERVICE

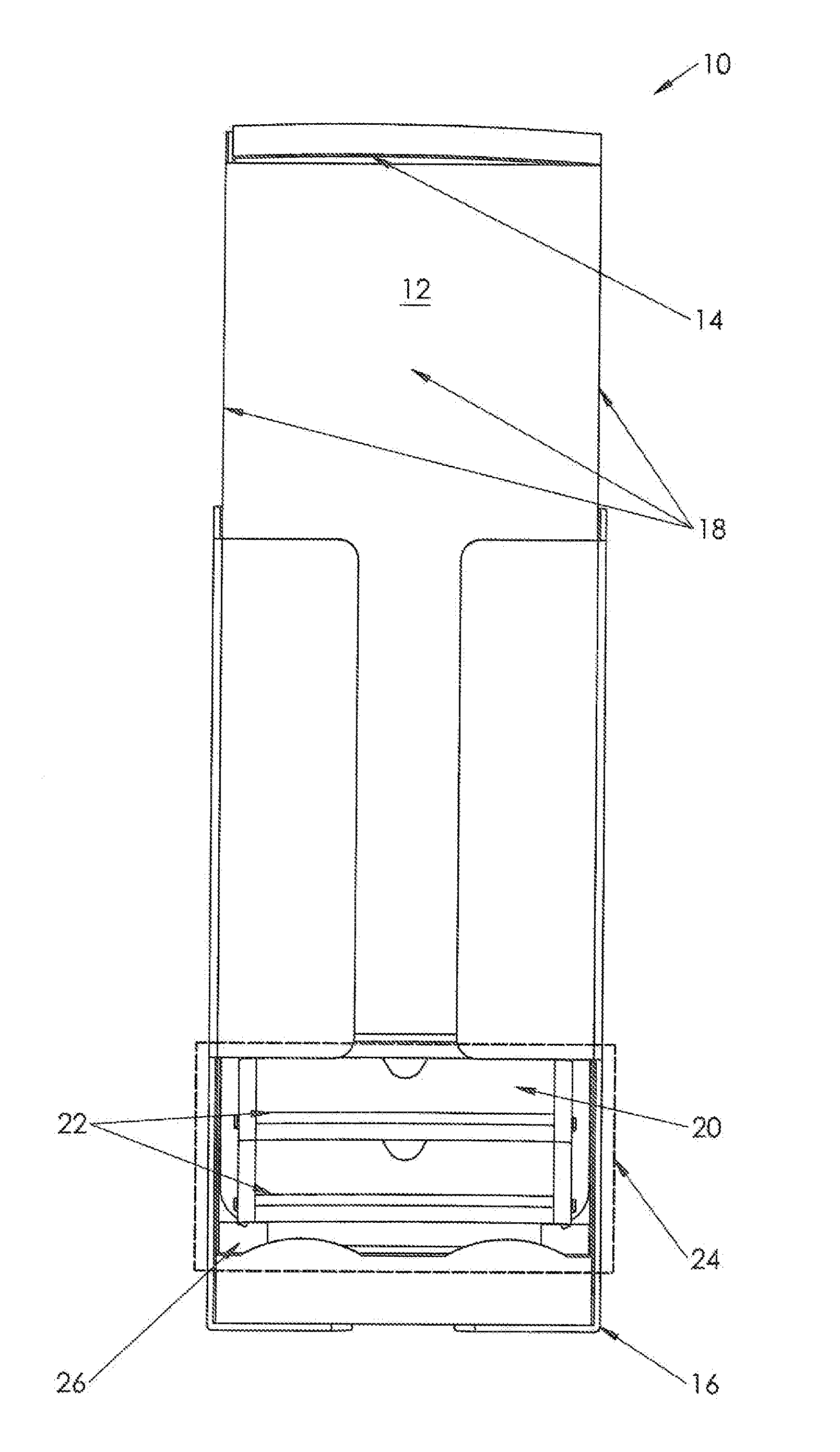

Dispenser-Packaging For Protective Eyewear

ActiveUS20150203282A1Avoid rapid distributionEase of useCoin-freed apparatus detailsDe-stacking articlesMechanical engineeringMedical care

Aspects of the invention provide a dispenser-package for storing protective eyewear glasses comprising an exterior box having a top, a bottom and four sidewalls along a first length, and an interior retention mechanism for holding a plurality of protective eyewear glasses along a second length. The exterior box completely receives the interior retention mechanism and securely holds the plurality of protective eyewear glasses in place. The exterior box includes a detachable area in proximity to the bottom to allow accessing one or more of the protective eyewear glasses held in place. As a result, a more convenient and efficient way to store and distribute protective eyewear glasses encourages healthcare professionals and patients to wear them and maintain personal safety.

Owner:TIDI PROD LLC

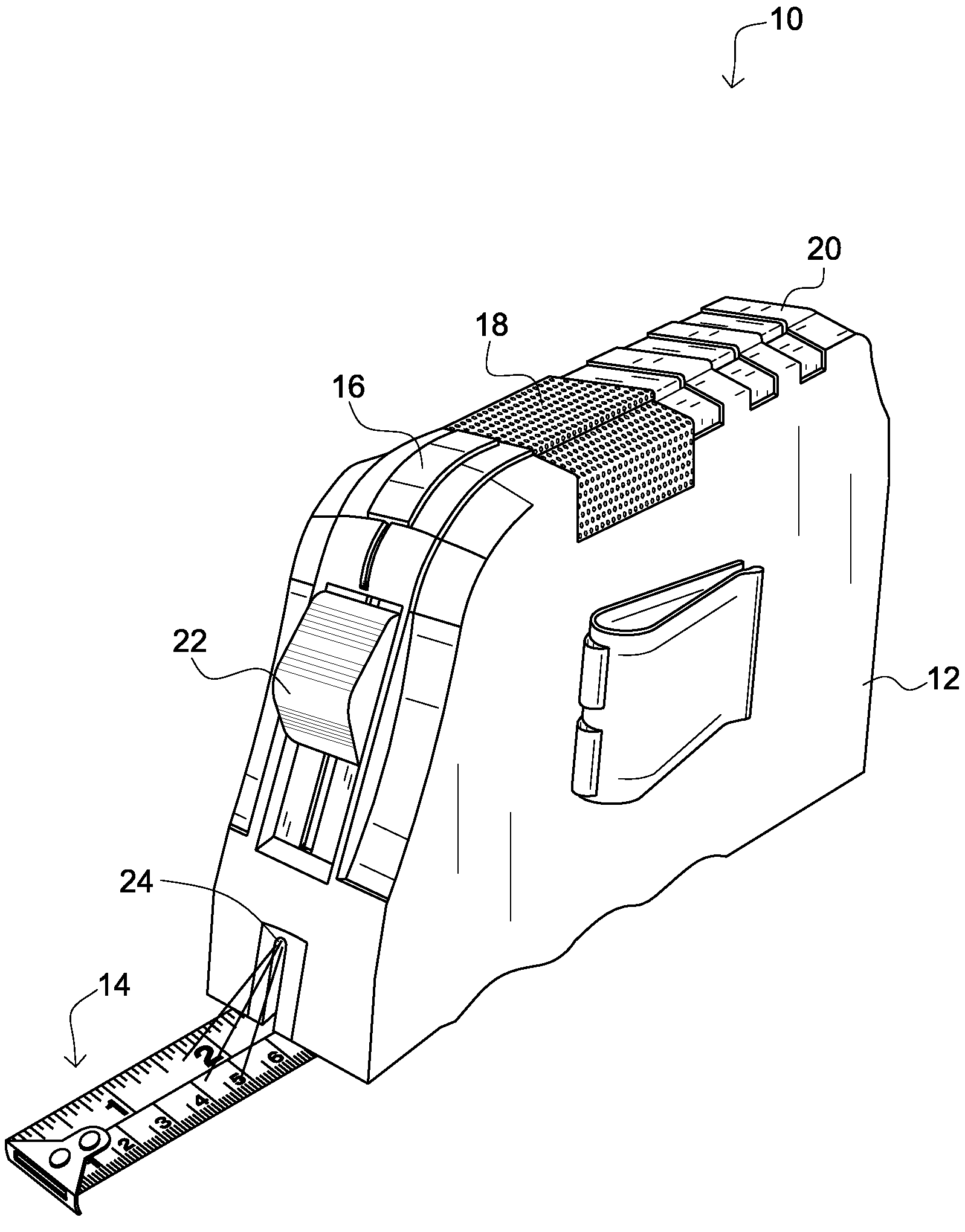

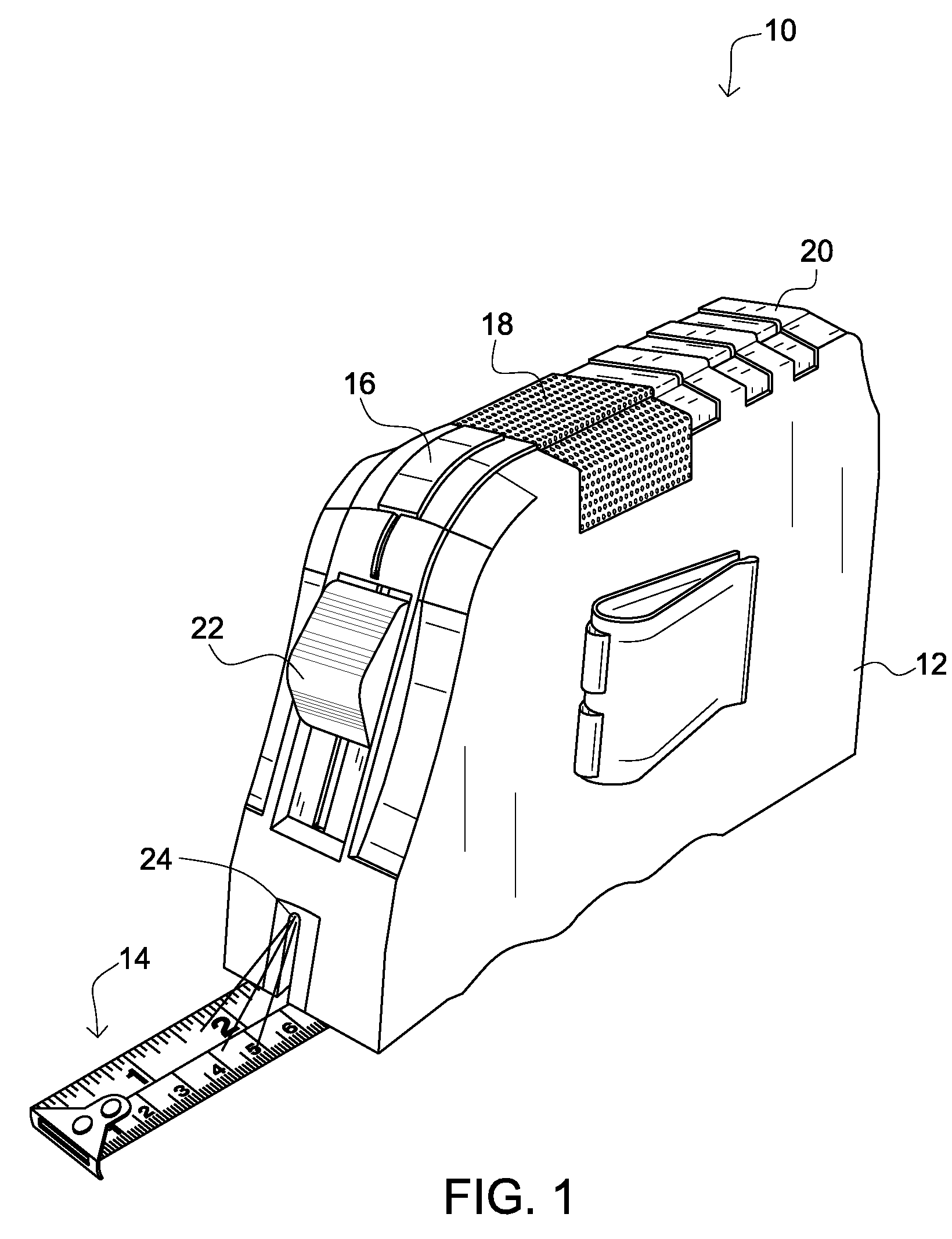

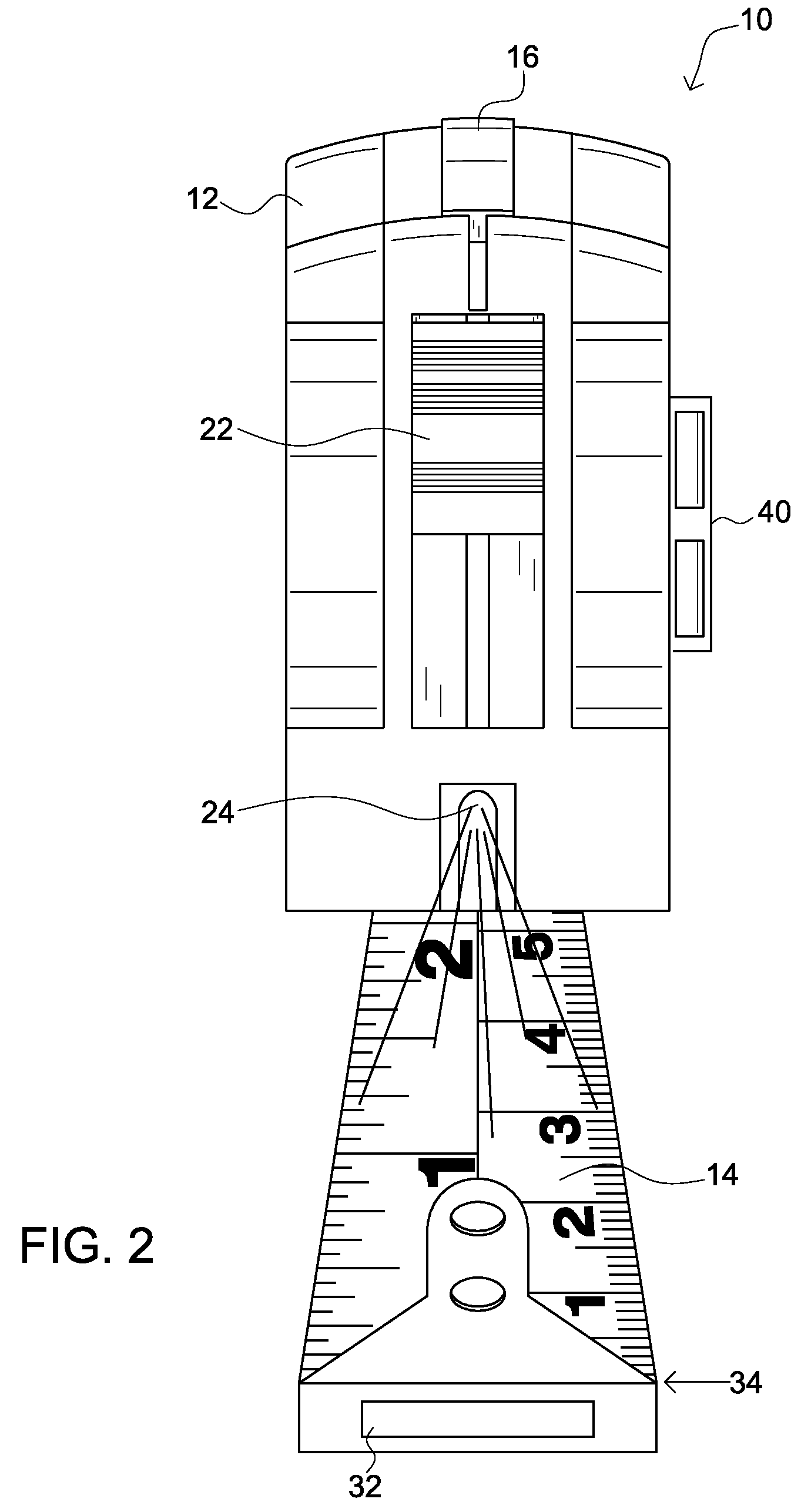

Tape measure

InactiveUS20090307920A1Convenient and efficientThe process is convenient and fastMeasuring tapesTape measureLoudspeaker

There is a tape measure configured for one-hand operation. The tape measure includes a protective casing and a coiled measuring tape. The tape measure includes an audio recorder and a speaker module coupled to the protective casing, wherein the speaker module is configured to audibly broadcast recorded audio information. The tape measure also includes a locking mechanism and a light module; wherein the light module is configured to activate when the locking mechanism is actuated, thereby disposing light over a portion of the measuring tape. The tape measure includes a control module in communication with each of the audio recorder, speaker module, light module, and magnetic locking mechanism, configured to provide controls thereto for each. The control module is disposed substantially above the magnetic locking mechanism on the protective housing and operable with a single digit of a hand, while the hand is grasping the protective casing.

Owner:SCHRAGE SIDNEY LOUIS

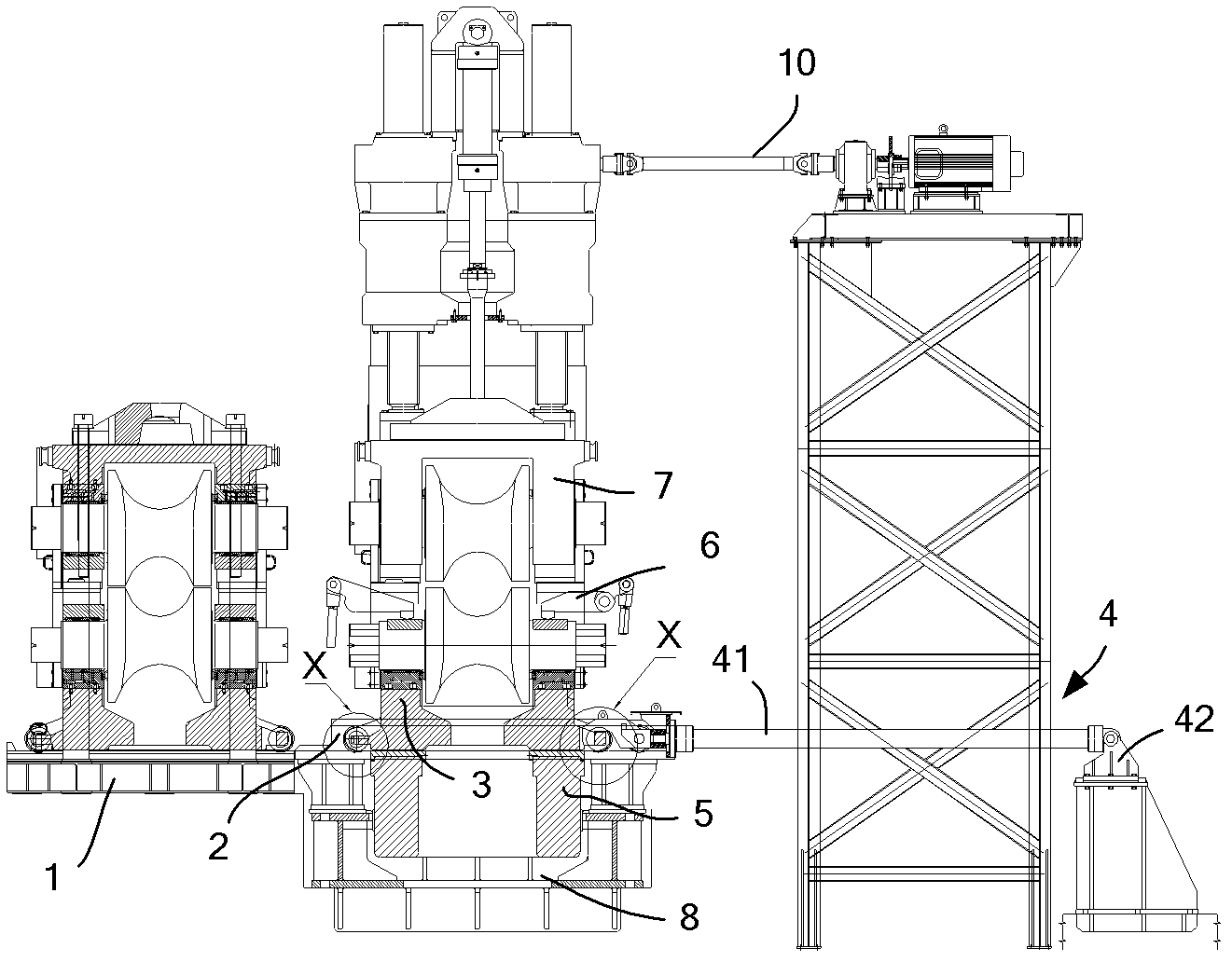

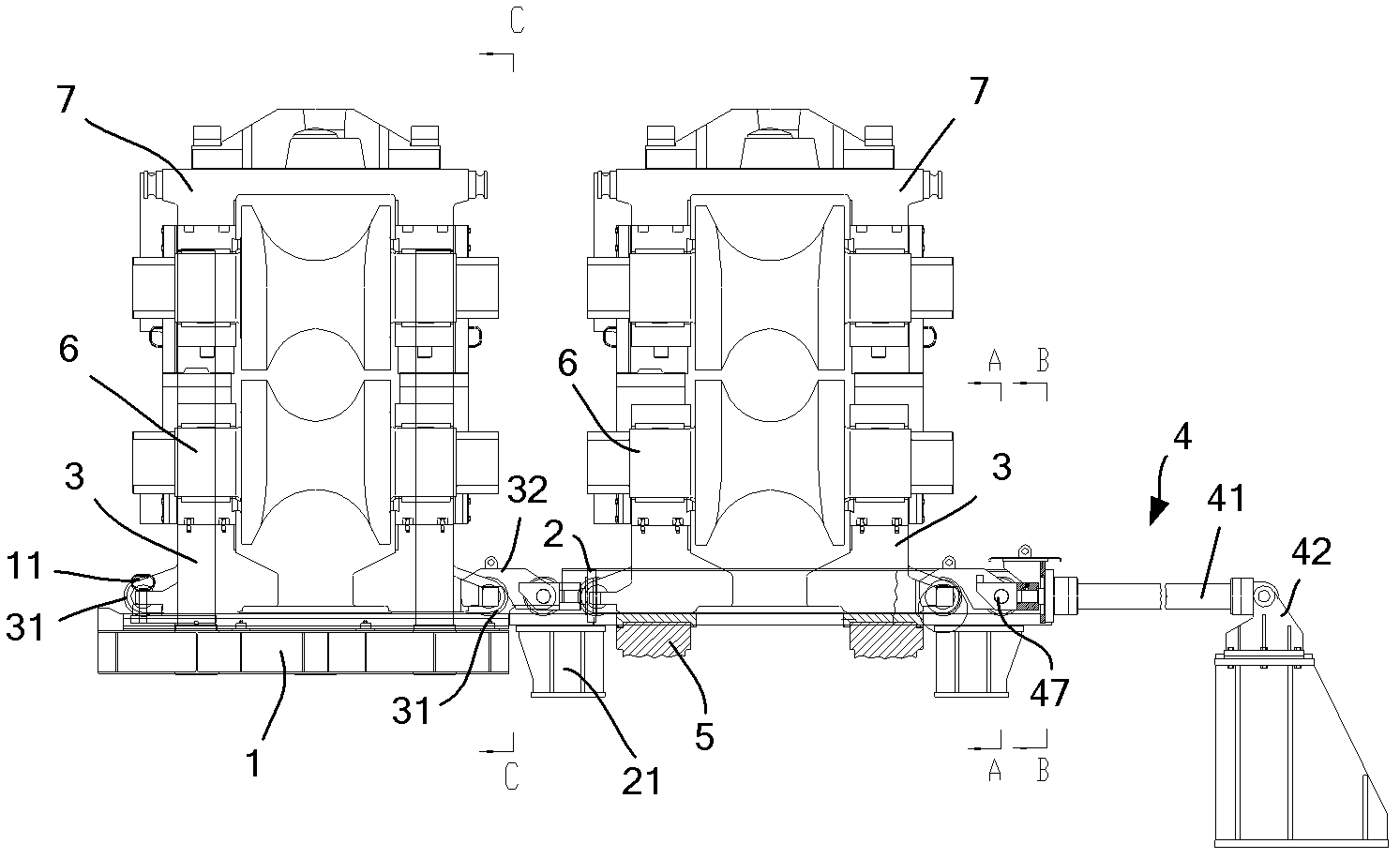

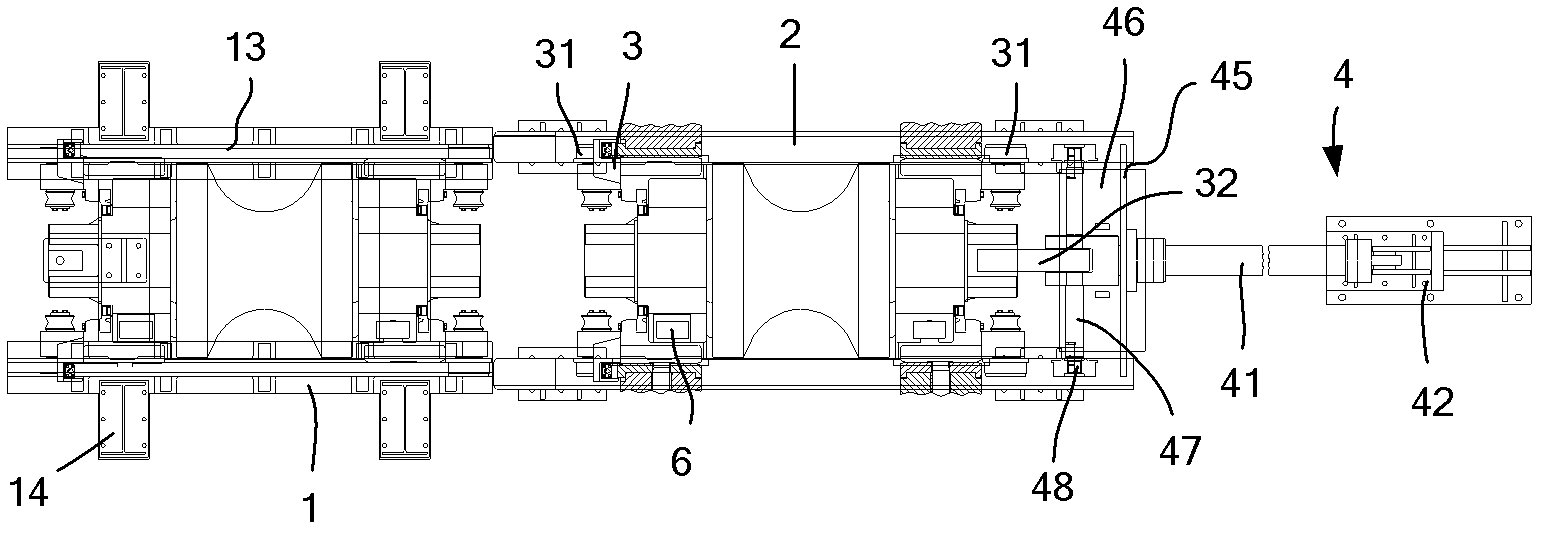

Device for replacing rollers of pilger seamless tube mill

ActiveCN102441575ASo as not to damageReduce frictional resistanceMetal rolling stand detailsMetal rolling arrangementsPush pullIdler-wheel

Owner:TAIYUAN HEAVY IND

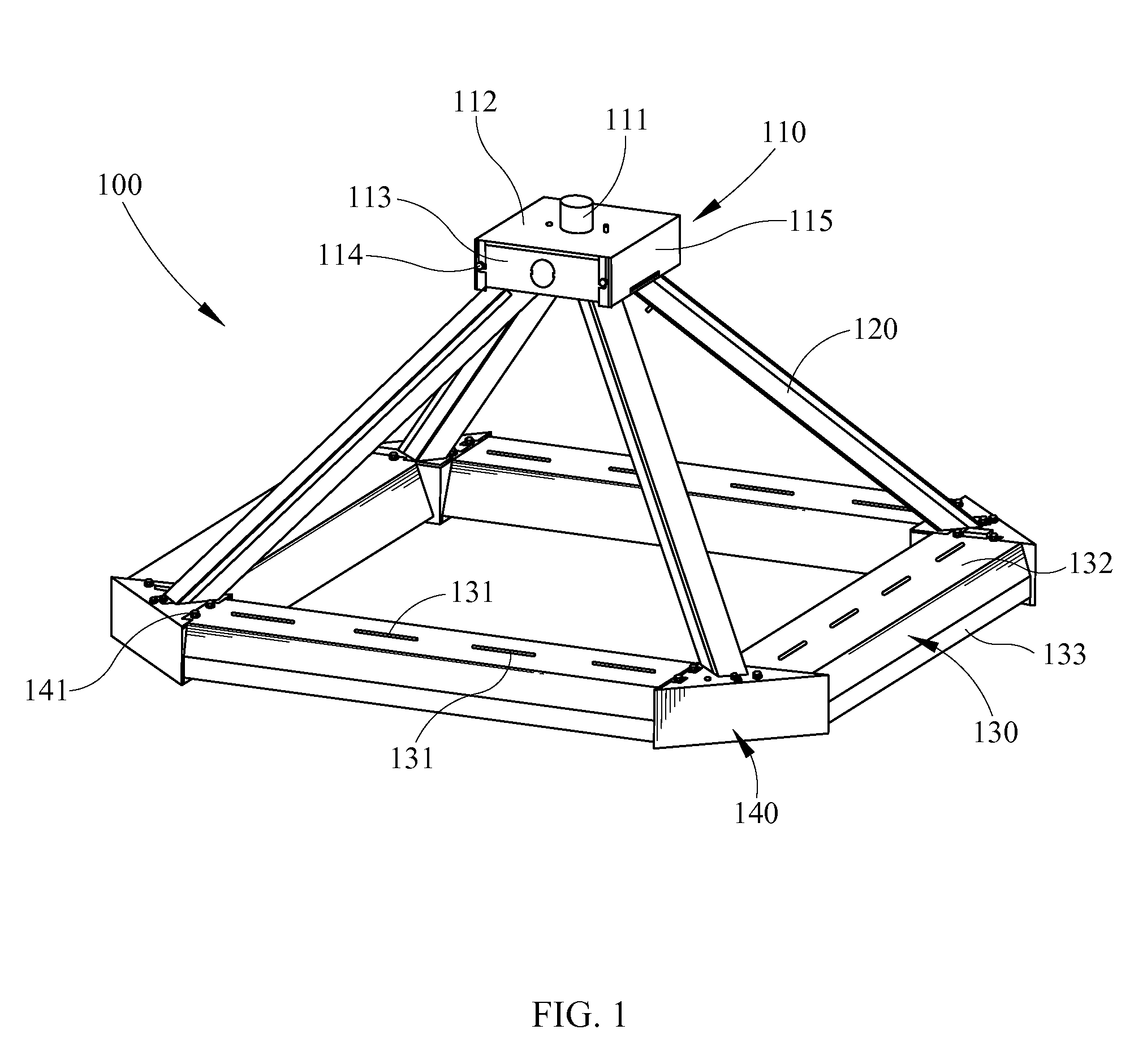

Fluorescent lamp luminaire

InactiveUS7506994B1Improve lamp efficiencyWide spacing to mounting height ratioLighting applicationsMechanical apparatusEngineeringLight-emitting diode

The luminaire of the present invention comprises at least two channel reflectors geometrically arranged in substantially a common plane forming a light emitting region, each channel reflector has one fluorescent lamp holder extending therein and each channel reflector has a channel reflector retaining arm having a ballast therein and extending to a luminaire supporting base.

Owner:GENLYTE THOMAS GRP LLC

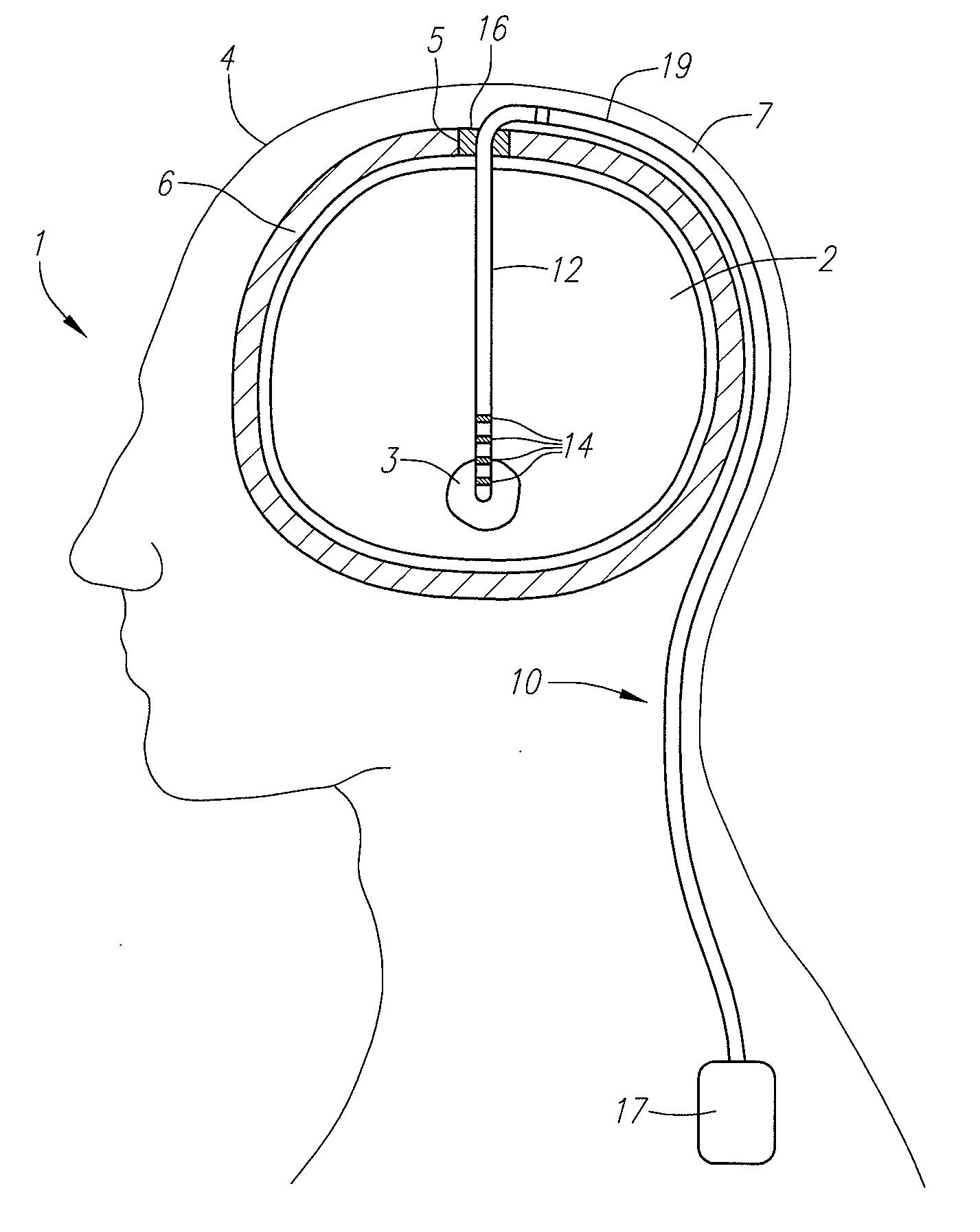

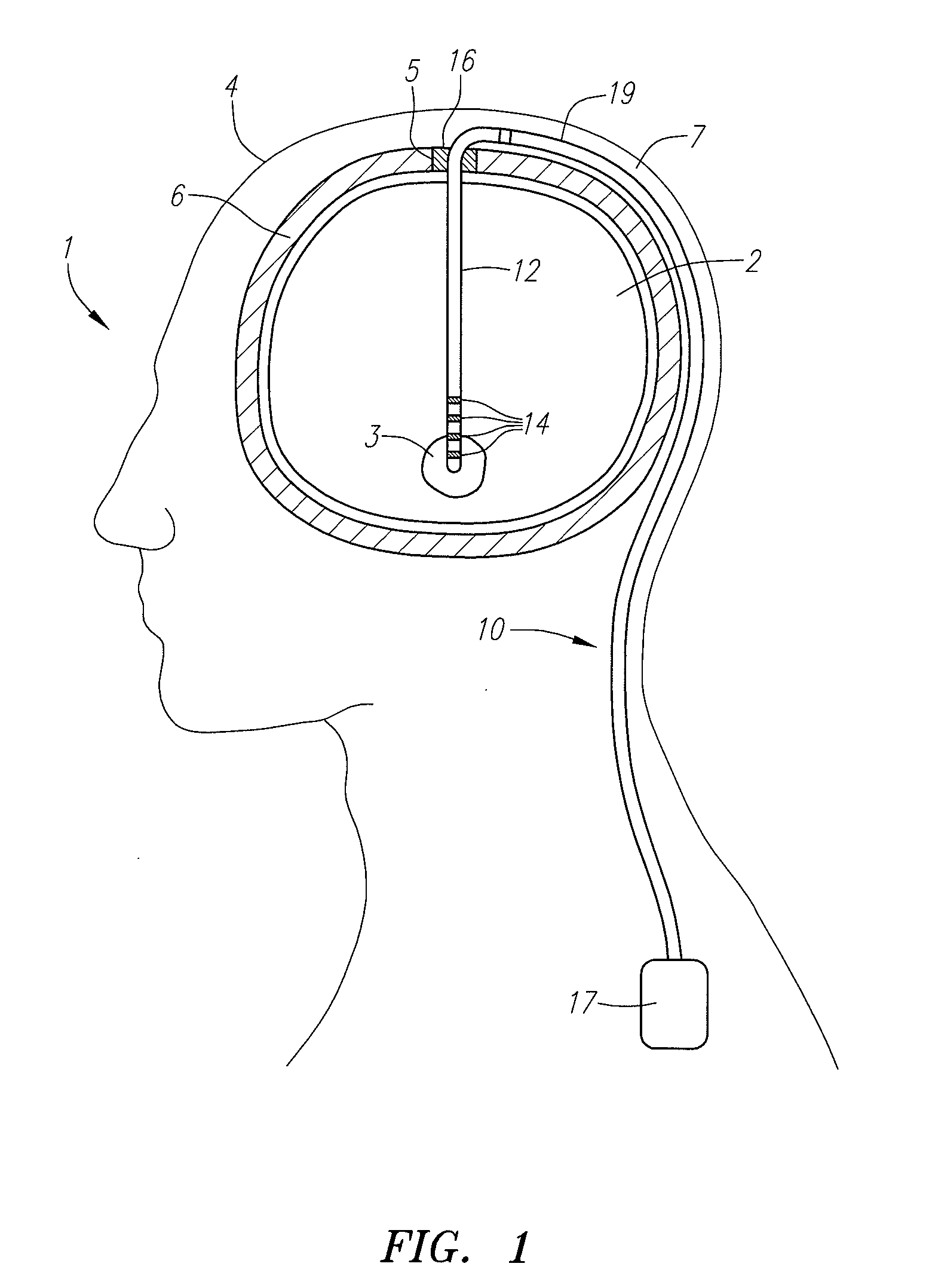

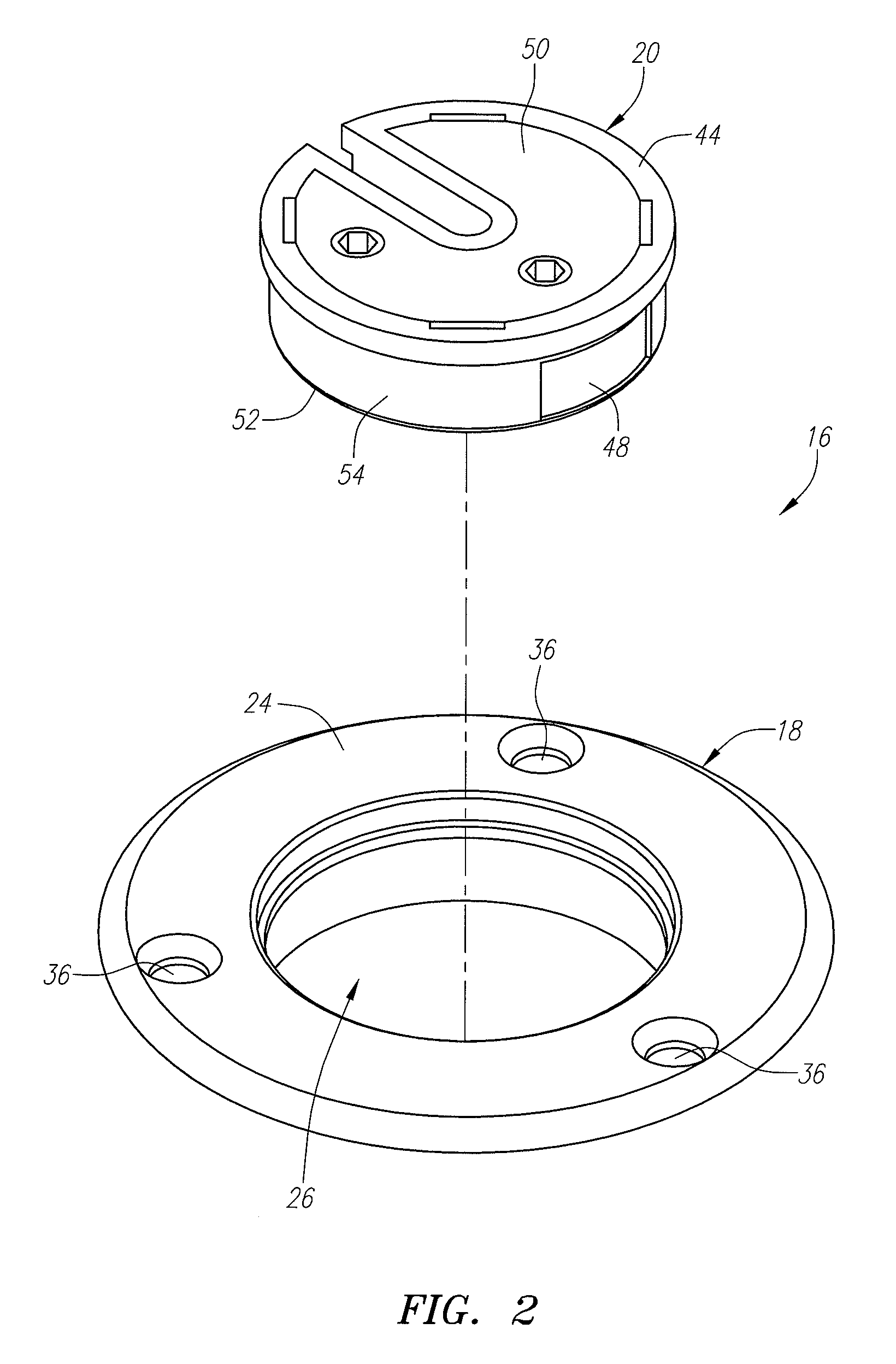

Cam lock burr hole plug for securing retainer/plug base

ActiveUS20100023020A1Convenient and efficientEasy to fixDiagnosticsSurgical instrument supportCamBiomedical engineering

A burr hole plug comprises a plug base configured for being mounted around a cranial burr hole. The plug base includes an aperture through which an elongated medical device exiting the burr hole may pass. The burr hole plug further comprises a retainer configured for being mounted within the aperture of the plug base. The retainer includes a retainer support, a slot formed in the retainer support for receiving the medical device, and a clamping mechanism having a movable clamping element and a cam configured for being rotated relative to the retainer support to linearly translate the movable clamping element into the slot, thereby securing the medical device. The retainer further comprises another clamping mechanism having another movable clamping element and another cam configured for being rotated relative to the retainer support to linearly translate the other movable clamping element, thereby laterally securing the retainer within the plug base.

Owner:BOSTON SCI NEUROMODULATION CORP

Method of determining substrate contained in hemoglobin-containing sample

InactiveUS20070154976A1Accurate measurementReduce distractionsMicrobiological testing/measurementBiological testingActive agentSuccinic acid

The present invention provides a convenient, efficient method for determining a substrate contained in a hemoglobin-containing sample and a reagent therefor, which can be employed for a variety of automatic analyzers while reducing interference of hemoglobin contained in the sample. A method for determining a substrate contained in a hemoglobin-containing sample through reaction of an oxidase with the substrate and optical measurement of the produced hydrogen peroxide by use of a peroxidase and an oxidizable color producing reagent, characterized in that the hemoglobin-containing sample is treated with an anionic surfactant selected from among a polyoxyethylene alkyl ether sulfate salt, a polyoxyethylene alkylphenyl ether sulfate salt, a polyoxyethylene alkyl ether phosphate, a polyoxyethylene alkyl sulfosuccinate, a polyoxyethylene alkyl ether carboxylate salt, a polyoxyethylene alkyl ether sulfonate salt, triethanolamine lauryl sulfate, an alkyl sulfosuccinate, and an alkylphenyl ether sulfonate salt.

Owner:SEKISUI MEDICAL CO LTD

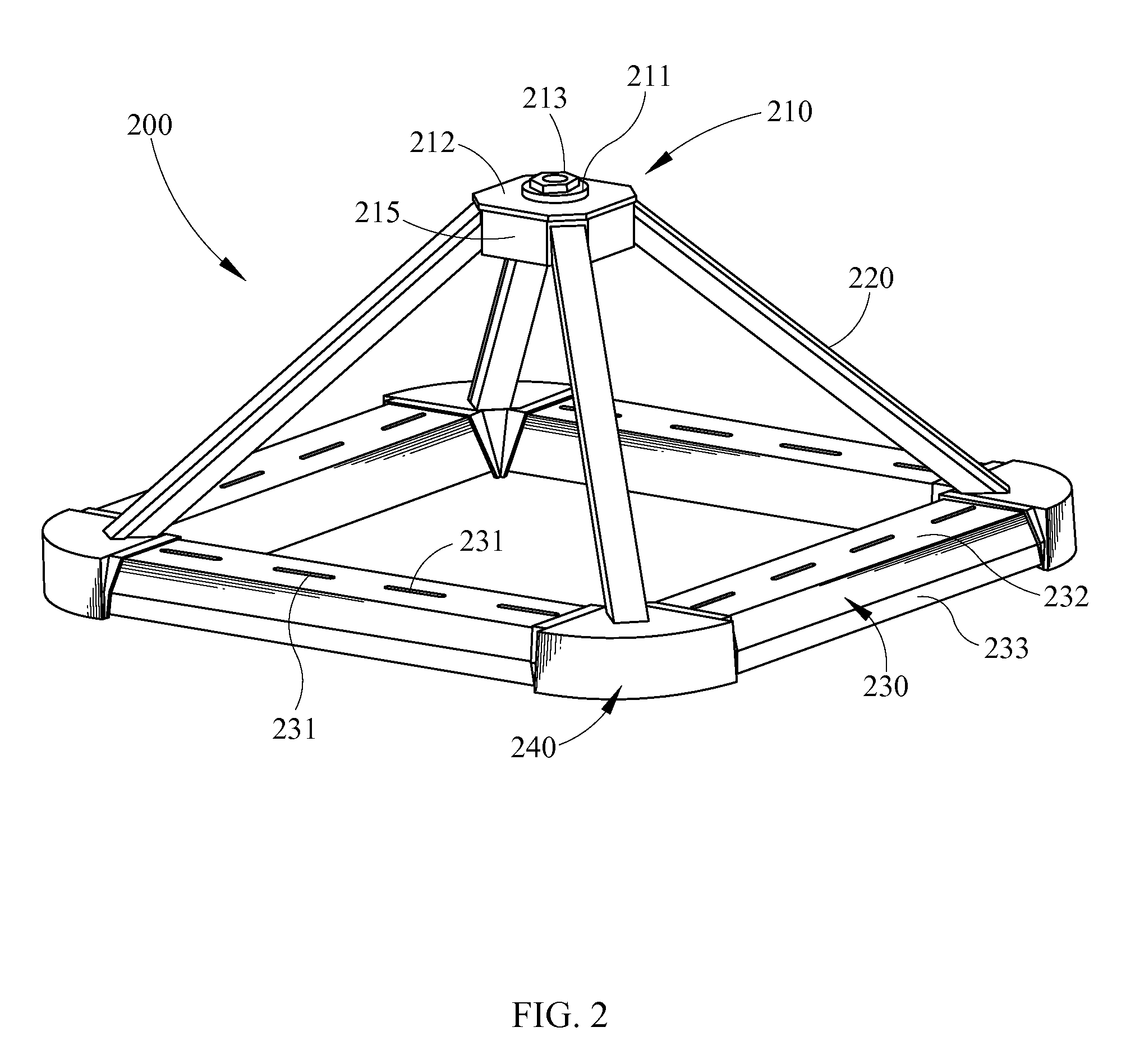

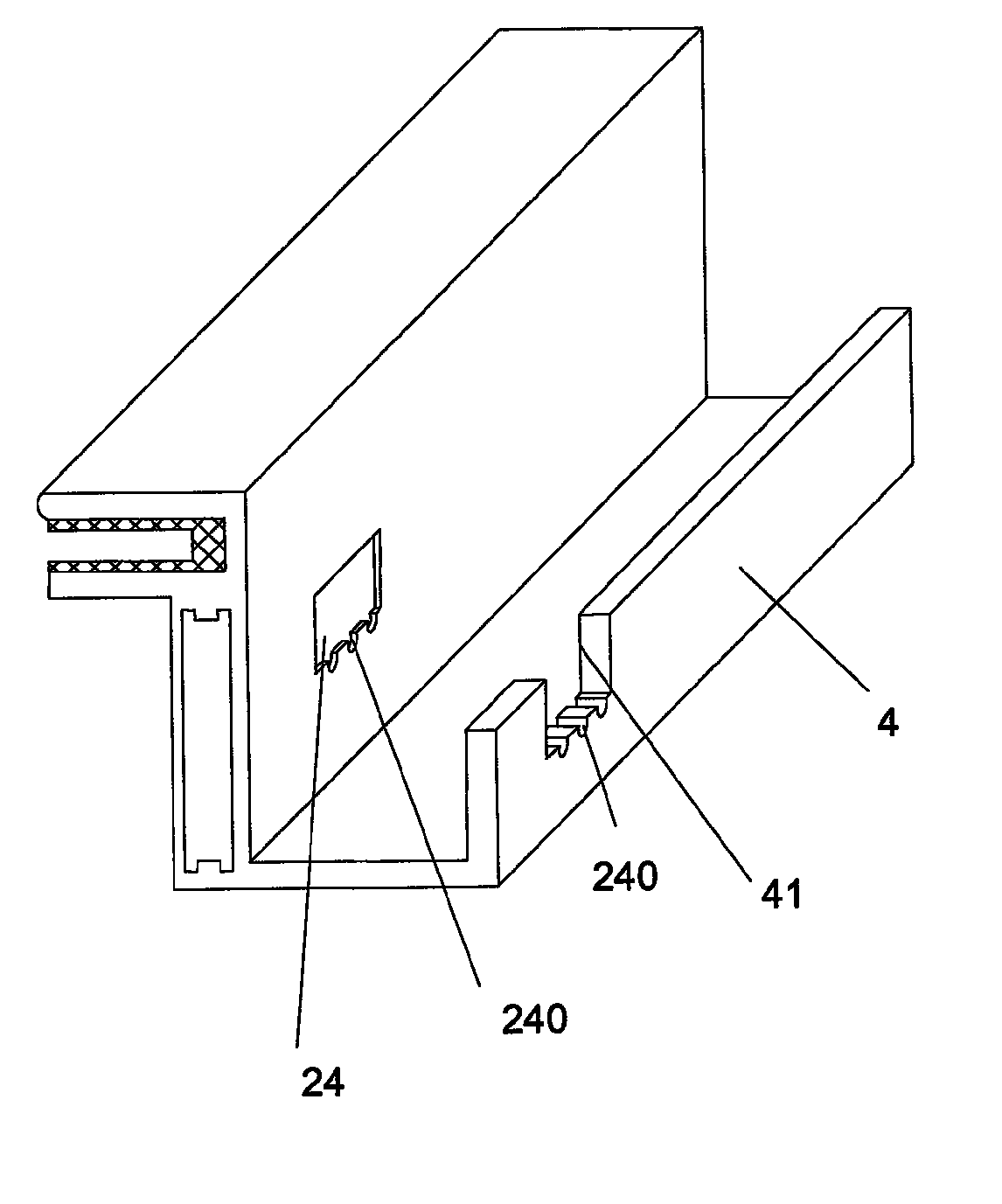

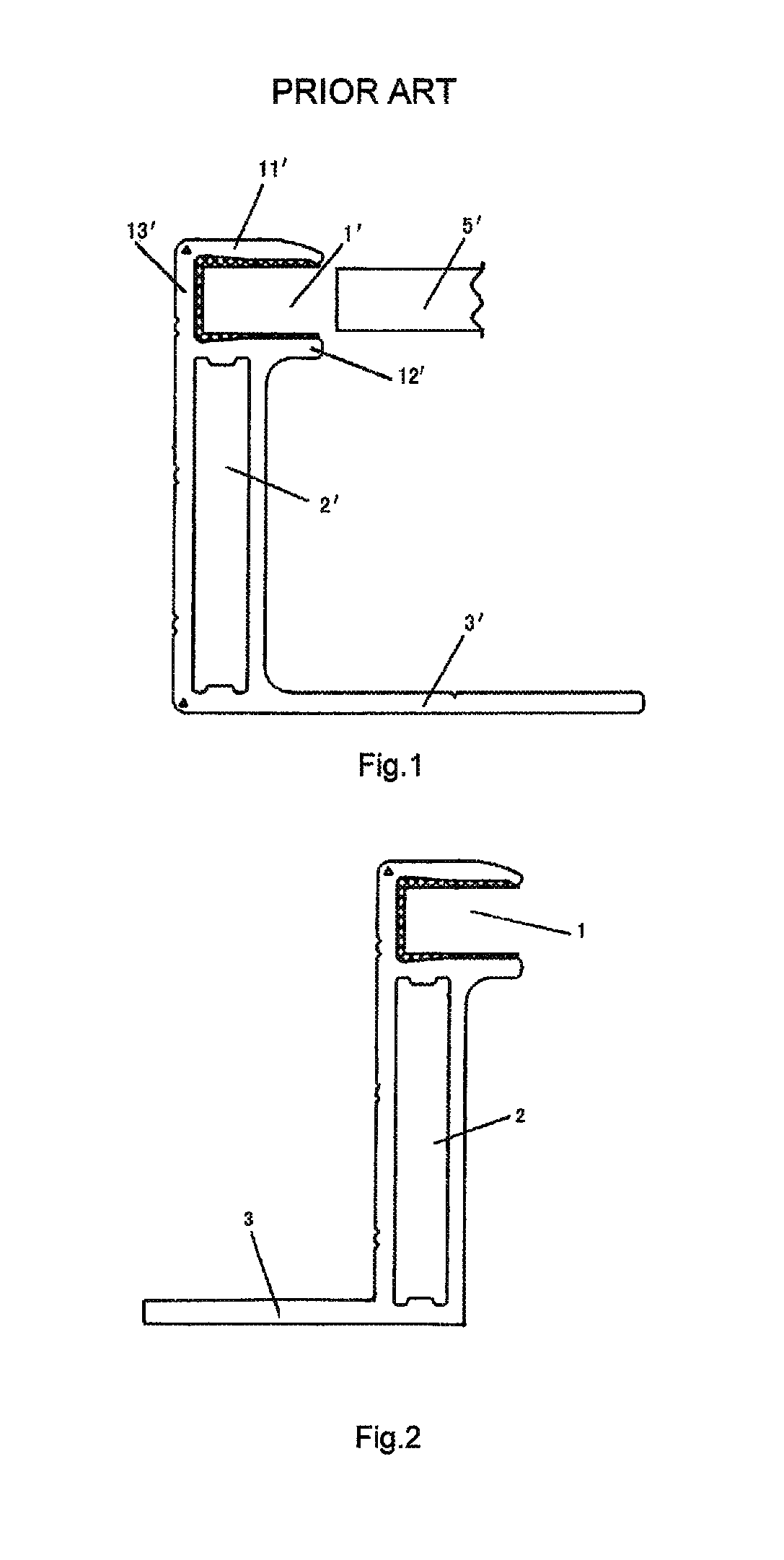

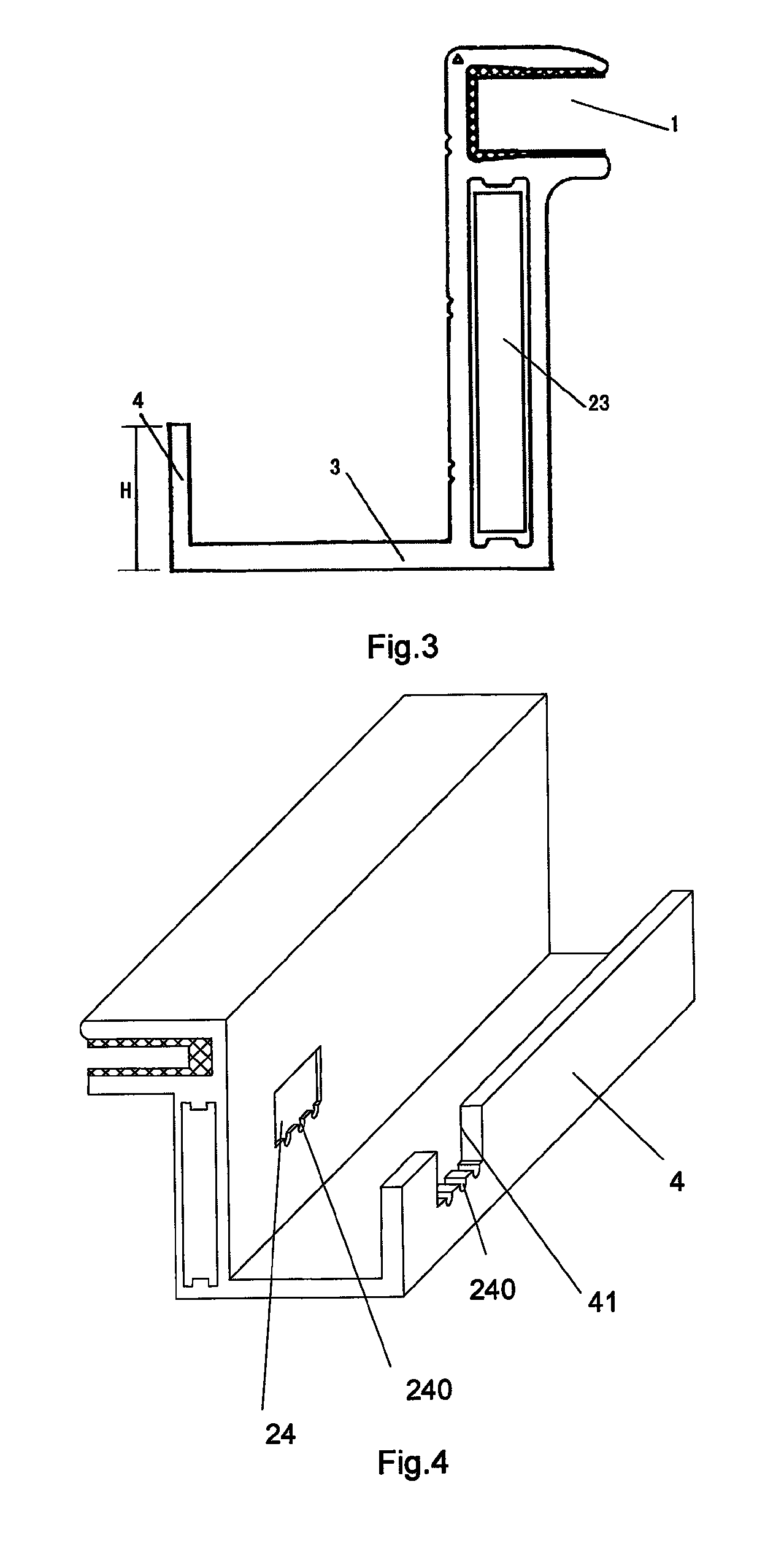

PV module frame, PV module and installation system thereof

InactiveUS8272189B2Quick installationReduce in quantityPhotovoltaic supportsSolar heating energyComputer moduleEngineering

A PV module frame, includes a module recess, a sidewall vertical to the module recess and a bottom portion vertical to the sidewall. The bottom portion extends from the bottom of the sidewall along the opposite direction of the recess of the module recess. A PV module having the PV module frame and a PV module installation system for installing the PV module onto a support, wherein the bottom portions of the adjacent solar cell assemblies are socket jointed and fixed to at least one installation beam which is fixed to the support. The beneficial effect of the present invention is that: fast installation of a PV module could be realized only by using the improved frame and one installation beam, Which reduces the quantity of the members in an installation system module and makes the installation more efficient, easier and more economical.

Owner:WUXI SUNTECH POWER CO LTD

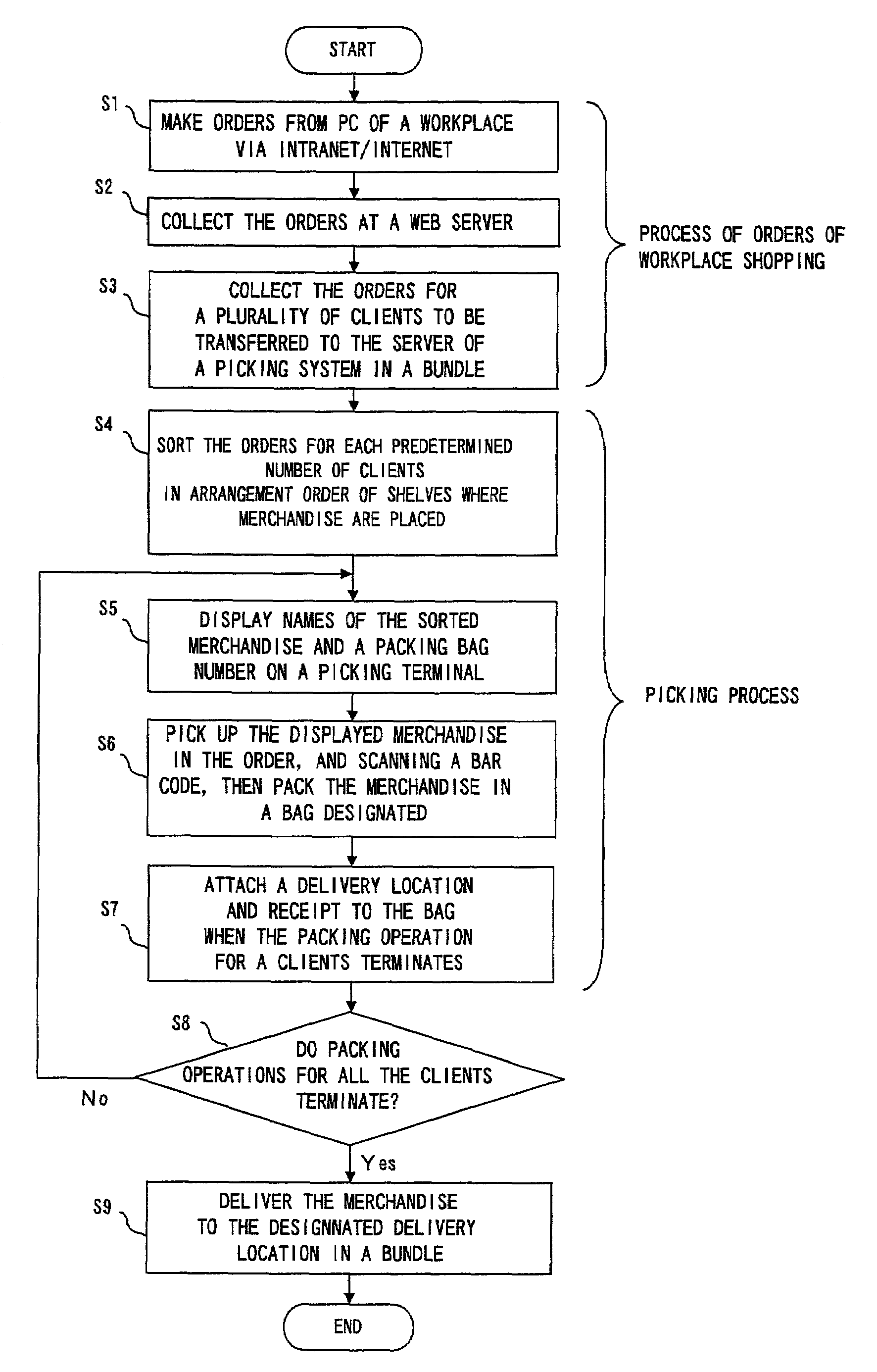

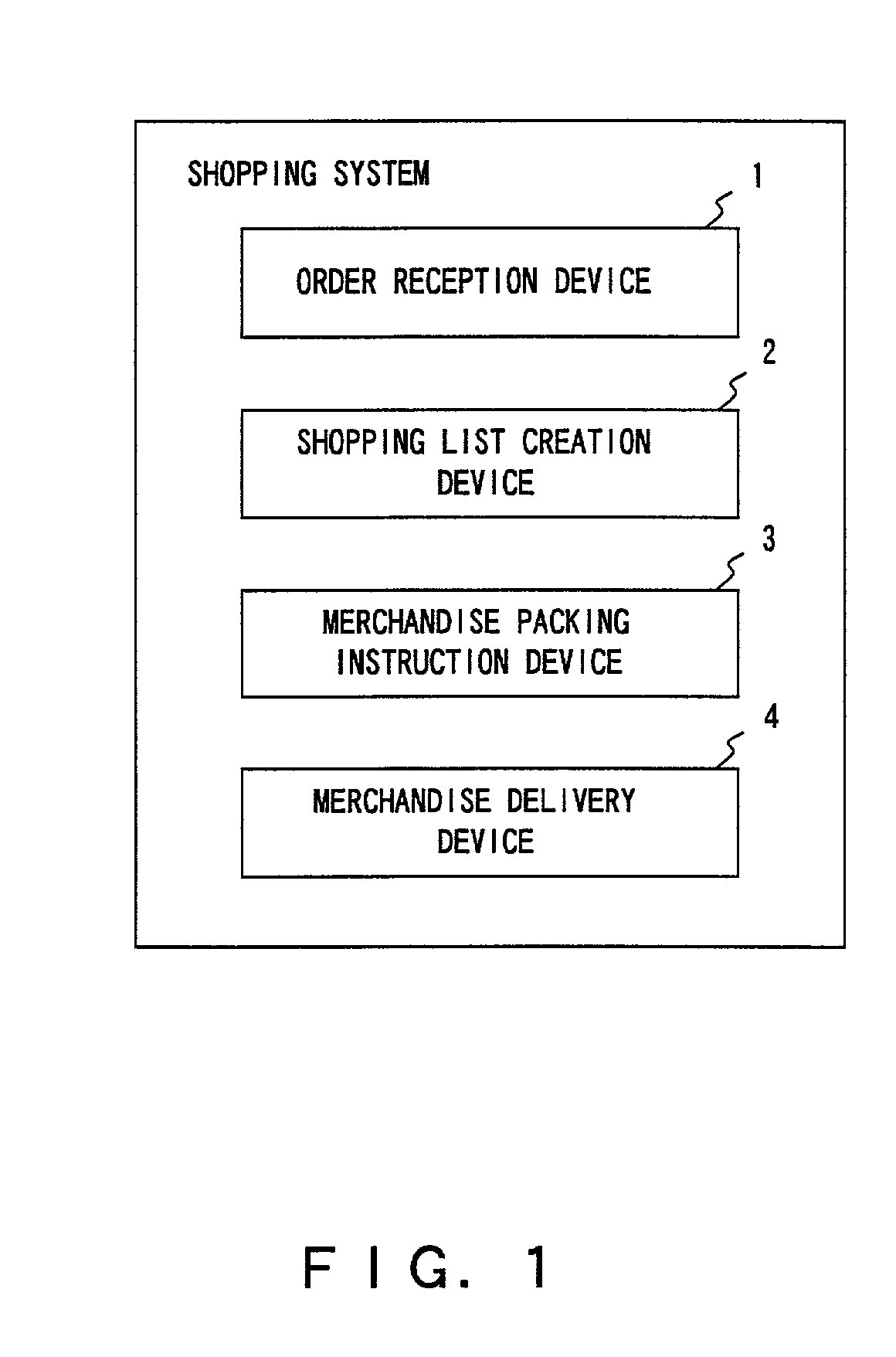

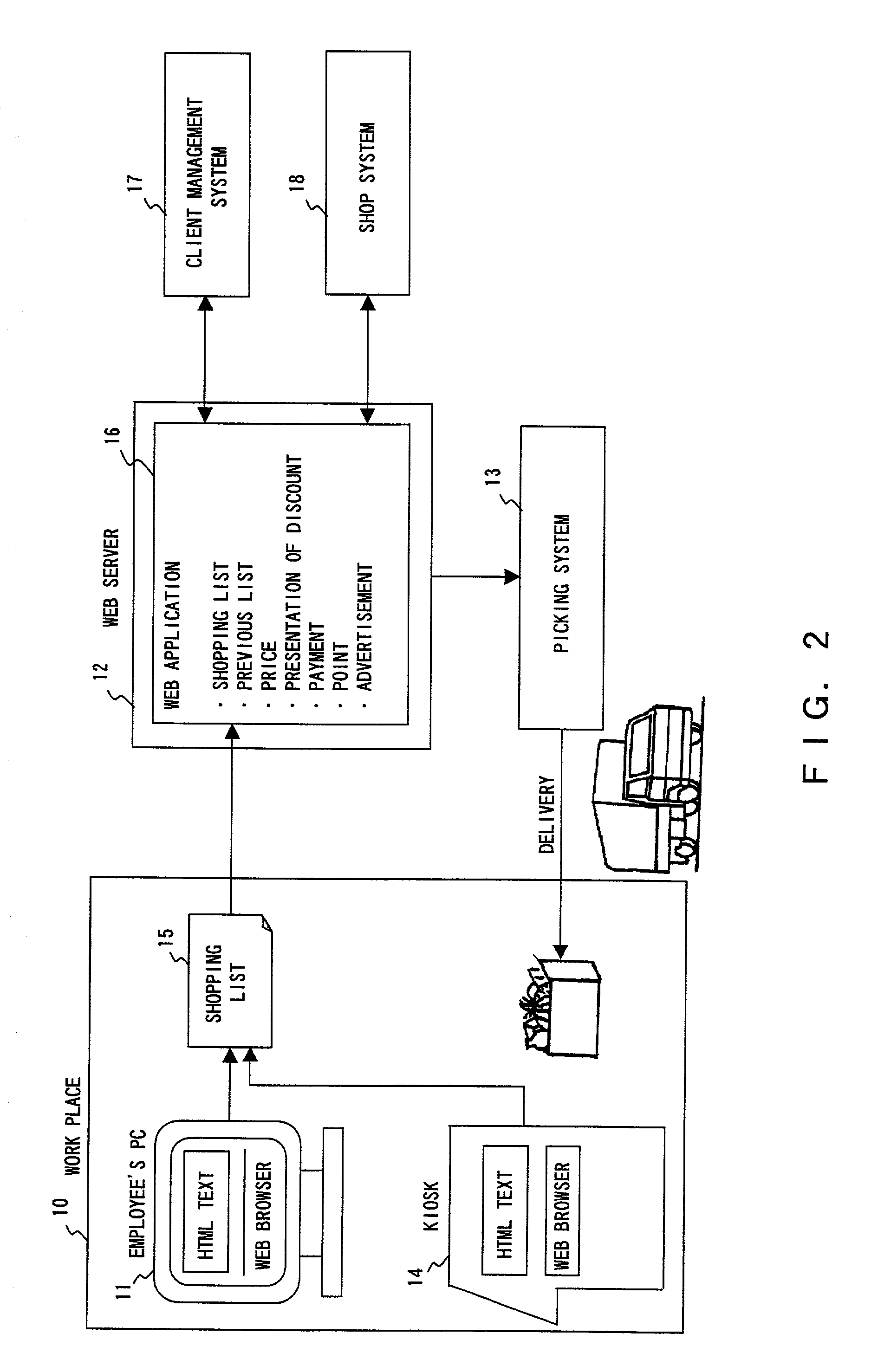

Workplace shopping system and merchandise picking system, and shopping method and picking method thereof

InactiveUS7171377B2Convenient and efficientPromote effectiveHand manipulated computer devicesFeeding apparatusPerishable foodDelivery location

It is an object of the present invention to provide a system to receive orders of merchandise such as merchandise sold in a supermarket from a large number of employees, for example, of a workplace, and to deliver the ordered merchandise in a bundle, thereby enhancing the employees' convenience and the efficiency of business.The system is provided with an order reception unit receiving an order of merchandise that can include perishable foods, a shopping list creation unit receiving one or more shopping lists corresponding to the orders from clients, a merchandise packing instruction unit receiving one or more shopping lists, and instructing picking and packing of the ordered merchandise corresponding to one or more clients, to a packing worker, and a merchandise delivery unit delivering the packed merchandise to the delivery locations corresponding to one or more clients.

Owner:FUJITSU LTD

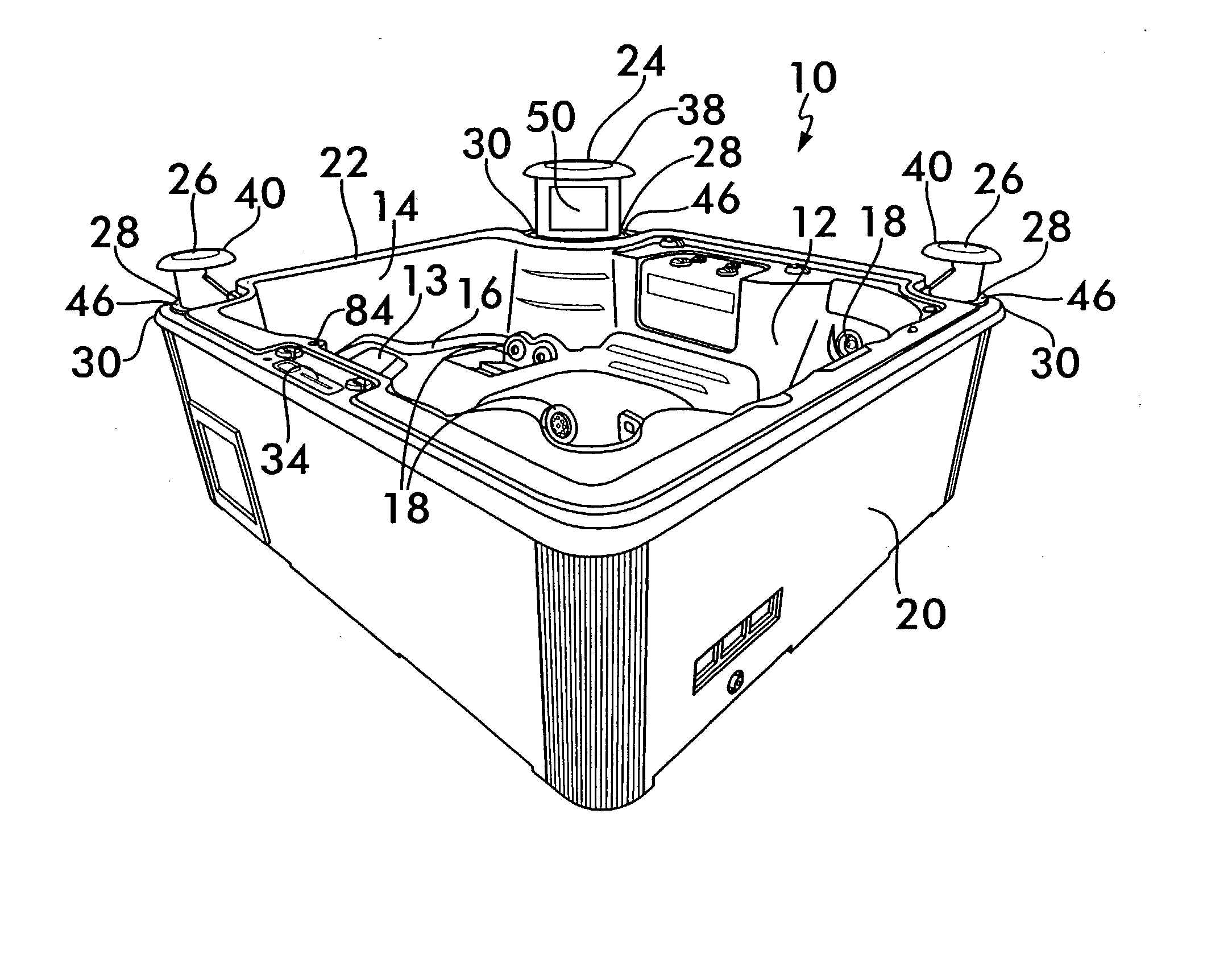

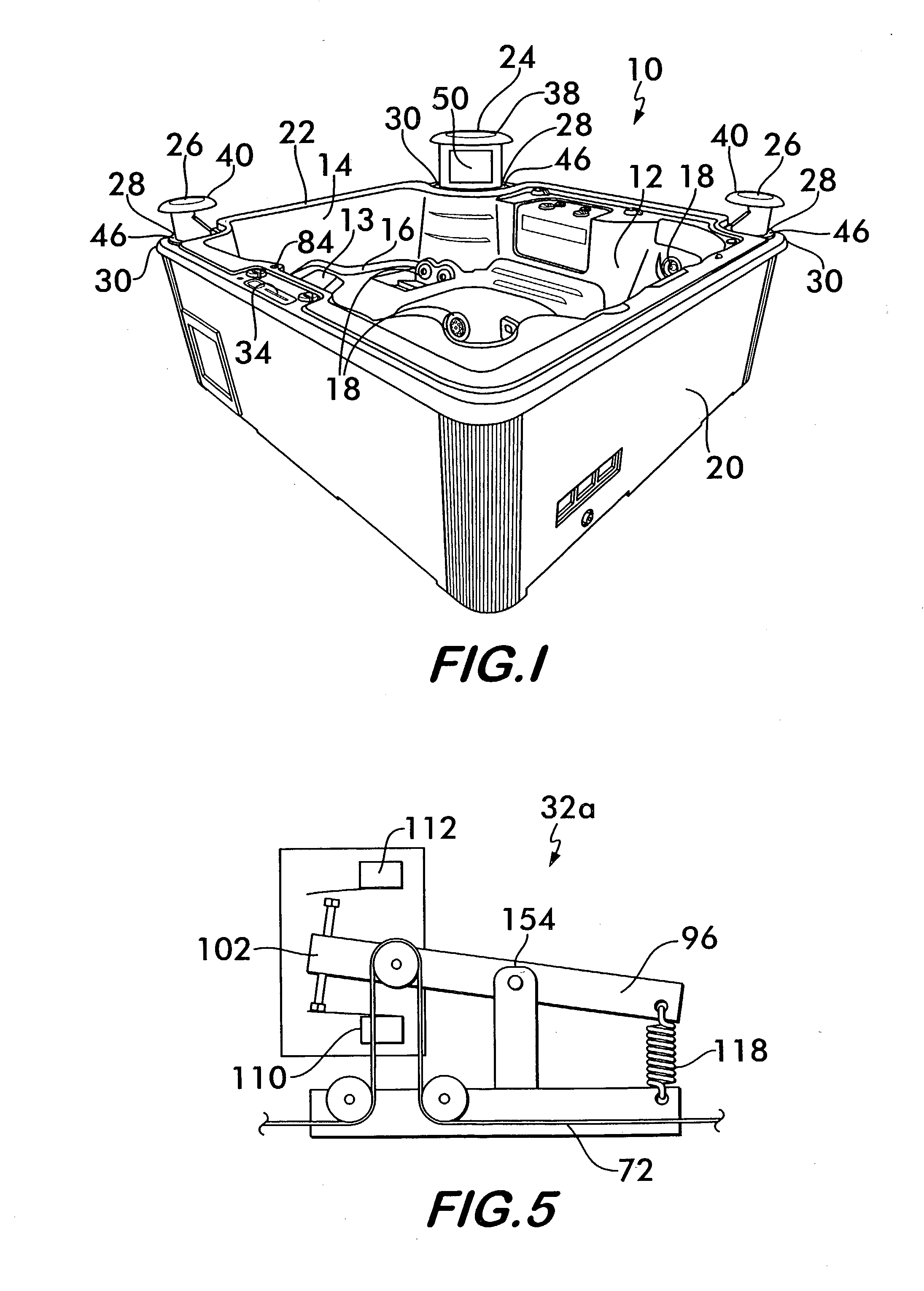

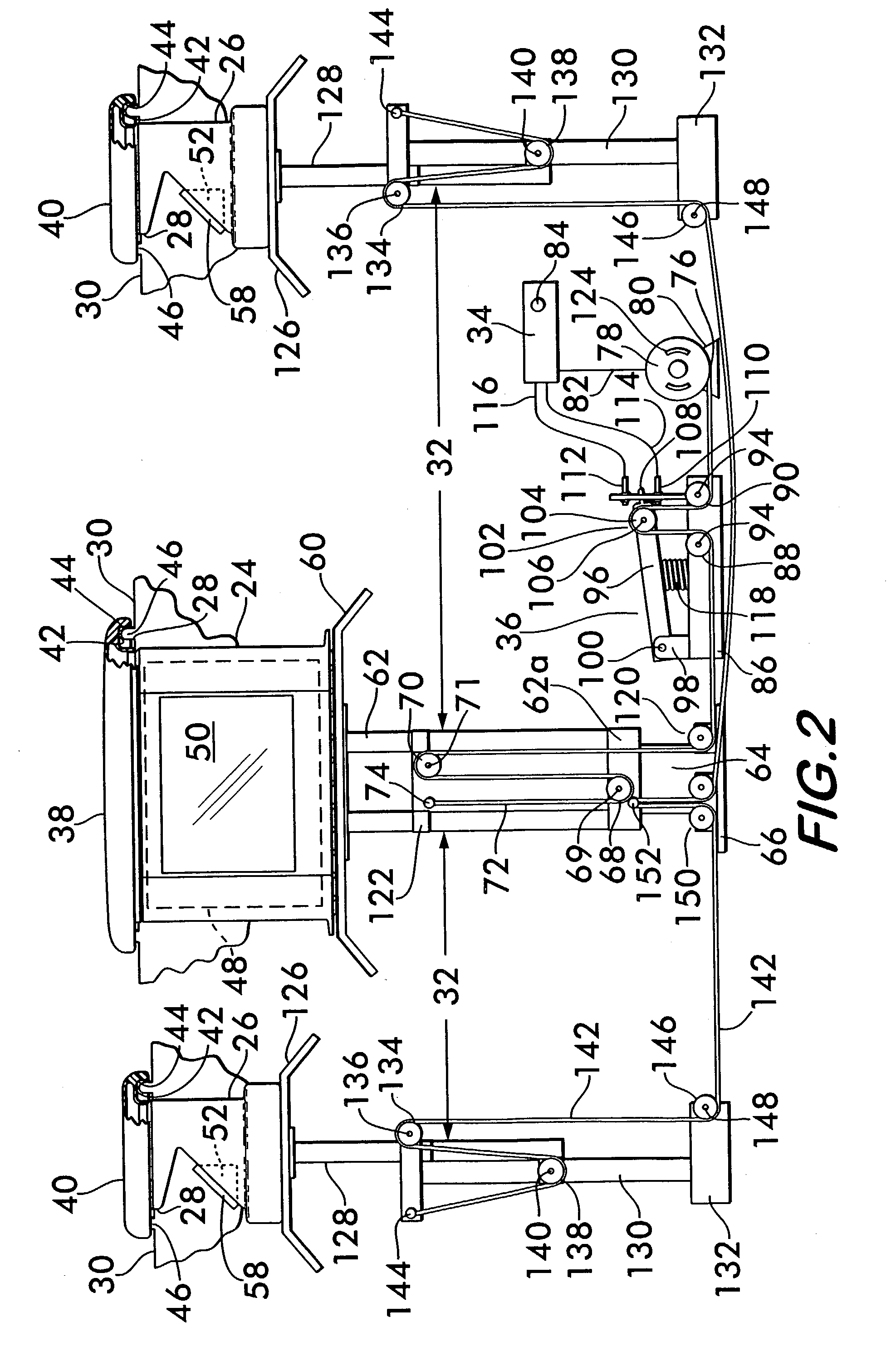

Combination spa and entertainment system

A combination spa and electronic entertainment system is disclosed. The spa includes a tub with an upper edge from which horizontal surfaces extend. The surfaces have apertures through which water-tight housings may be raised and lowered. The housings hold components of the entertainment system and have tops larger in size than the apertures to form sealing areas engageable with the horizontal surfaces surrounding the apertures for sealing the apertures and the water-tight housings. A moving mechanism is provided to raise and lower the housings. The mechanism has a platform supported on a carriage movable vertically along a support column. A motor raises and lowers the platforms through a cable and pulley system. A motion limiting device having a pivoting arm which engages sensors communicating with the motor through a control system shuts the motor off in response to predetermined upper and lower limits of cable tension.

Owner:MASTER SPAS

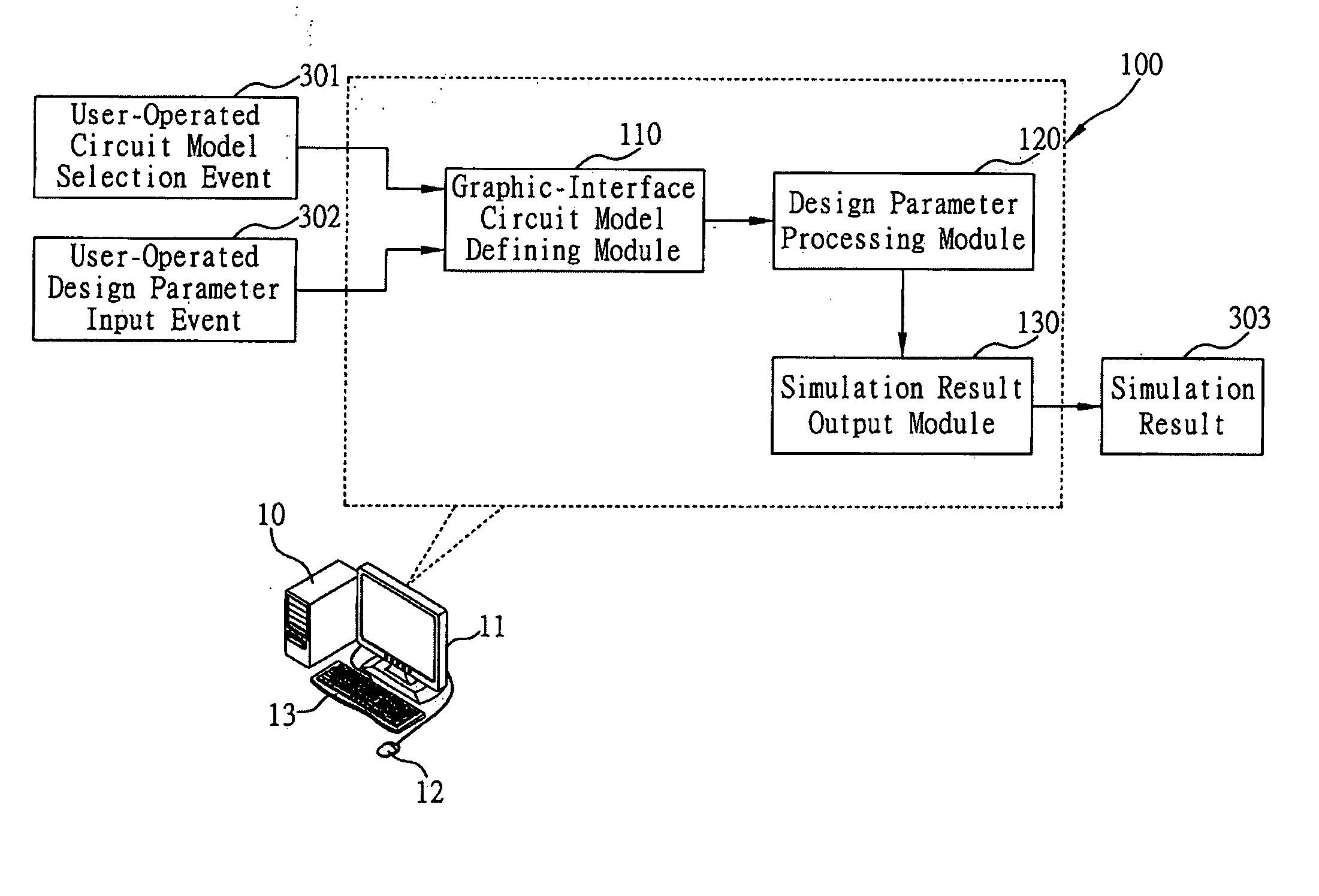

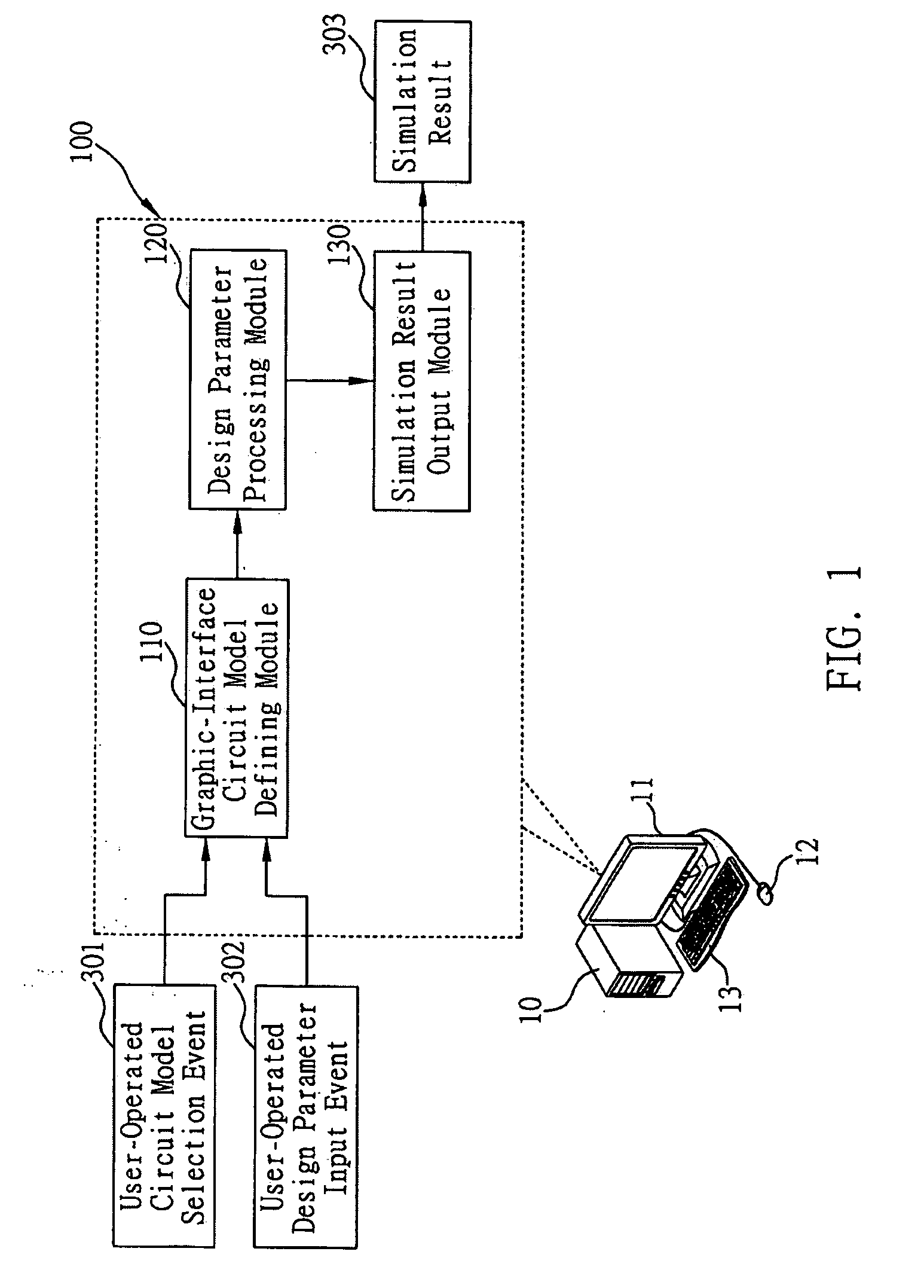

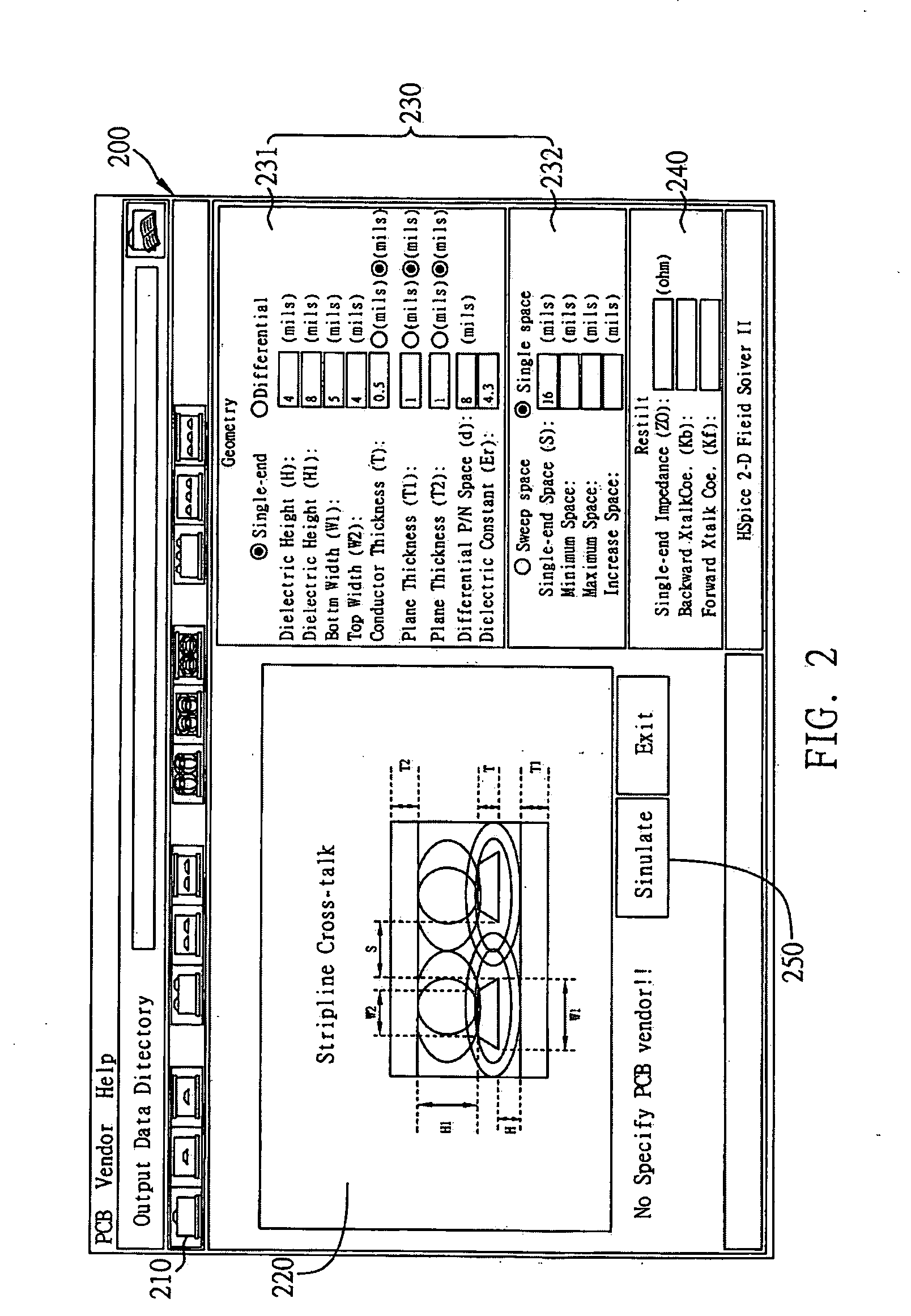

Computer-aided ultrahigh-frequency circuit model simulation method and system

InactiveUS20070233443A1Convenient and efficientSimulation of high-speed digital circuit models more convenient and efficientComputer aided designSpecial data processing applicationsComputer architectureComputer-aided

A computer-aided ultrahigh-frequency circuit model simulation method and system is proposed, which is designed for use in conjunction with a computer platform for providing a user-operated ultrahigh-frequency circuit model simulation function, which is characterized by the provision of a graphic interface that allows the user to select a desired circuit model and input a set of design parameters about the selected circuit model, and whereupon a set of operating characteristics data can be automatically determined through simulation. This feature allows the circuit design engineer unnecessary to write lengthy circuit model description files for the description of the intended circuit models, thereby making the simulation of high-speed digital circuit models more convenient and efficient.

Owner:INVENTEC CORP

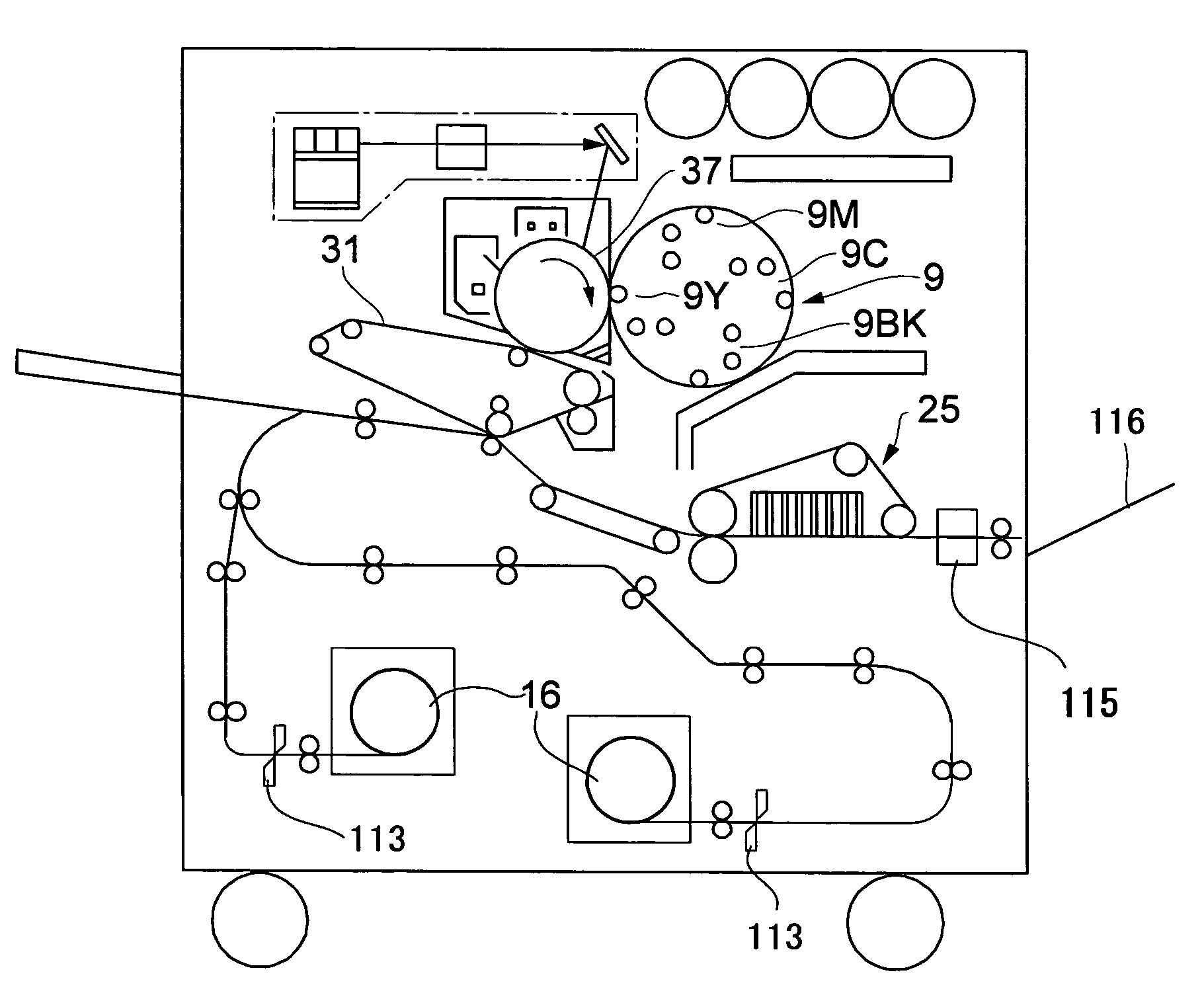

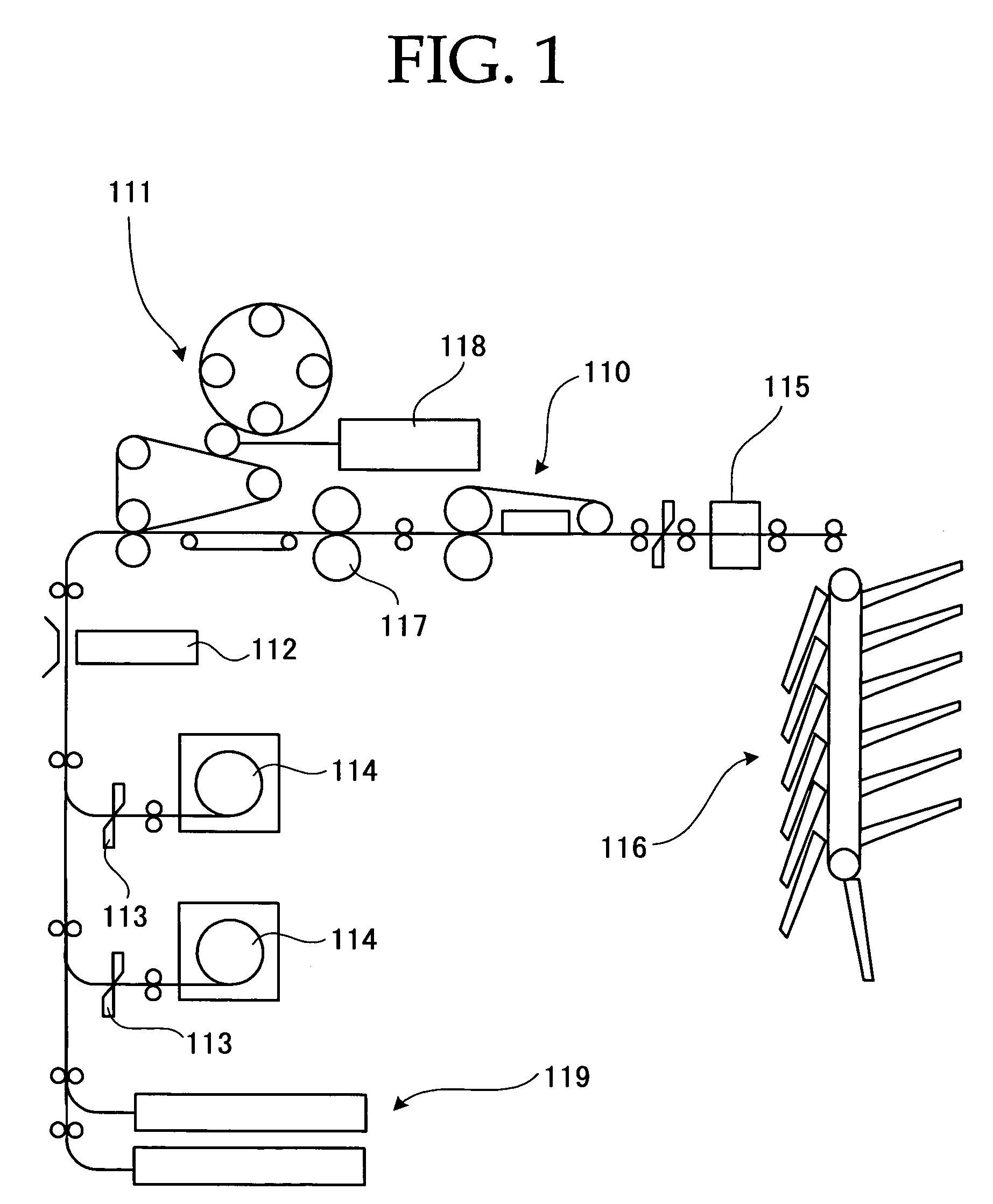

Image forming apparatus, image forming system, and electrophotographic print

ActiveUS7233765B2Save powerSave spaceElectrographic process apparatusComputer graphics (images)Latent image

An image forming apparatus includes a forming unit configured to form a latent electrostatic image on a latent electrostatic image bearing member based on a digital image; a developing unit configured to develop the latent electrostatic image with a toner to form a visible image; a transferring unit configured to transfer the visible image to one of an electrophotographic image receiving roll and an electrophotographic image receiving sheet; and a smoothing and fixing unit configured to smooth and fix the transferred image on one of the electrophotographic image receiving roll and the electrophotographic image receiving sheet to thereby form a series of electrophotographic prints and an electrophotographic print. In the apparatus, the hardware including the media, printer and unit for aftertreatment optimally matches with the toner, and the apparatus can produce high-quality images equal to silver-halide photographs.

Owner:FUJIFILM HLDG CORP +1

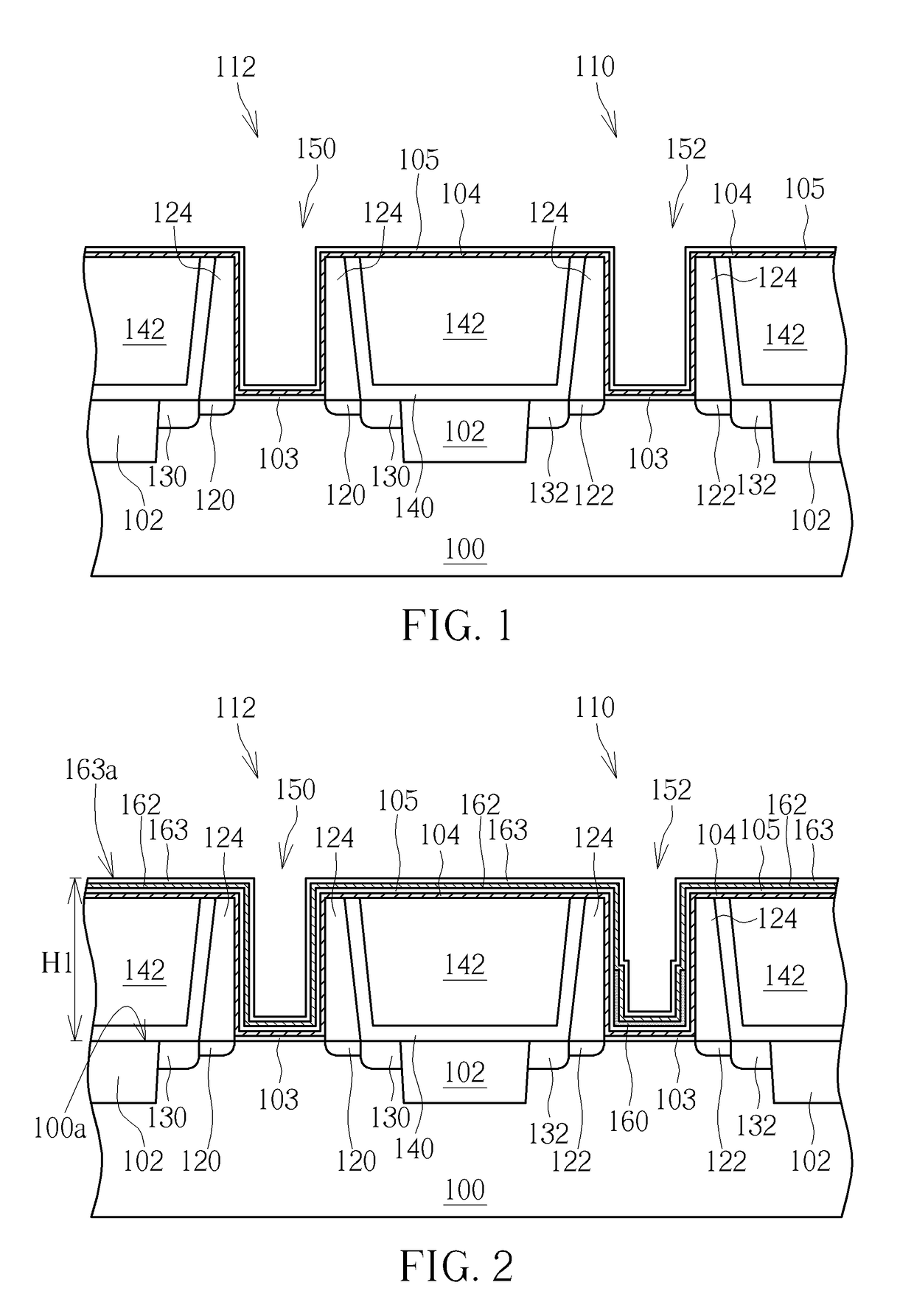

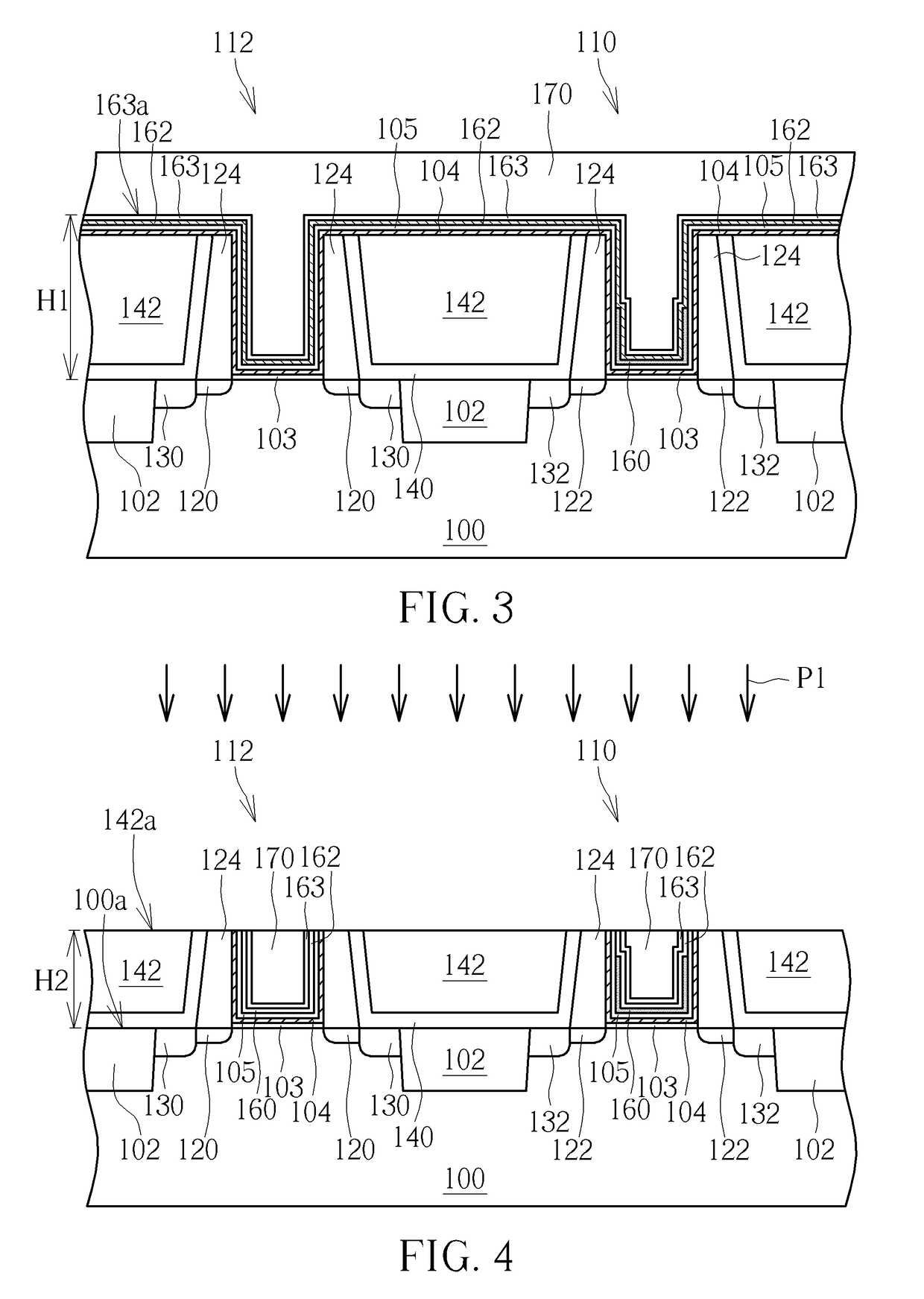

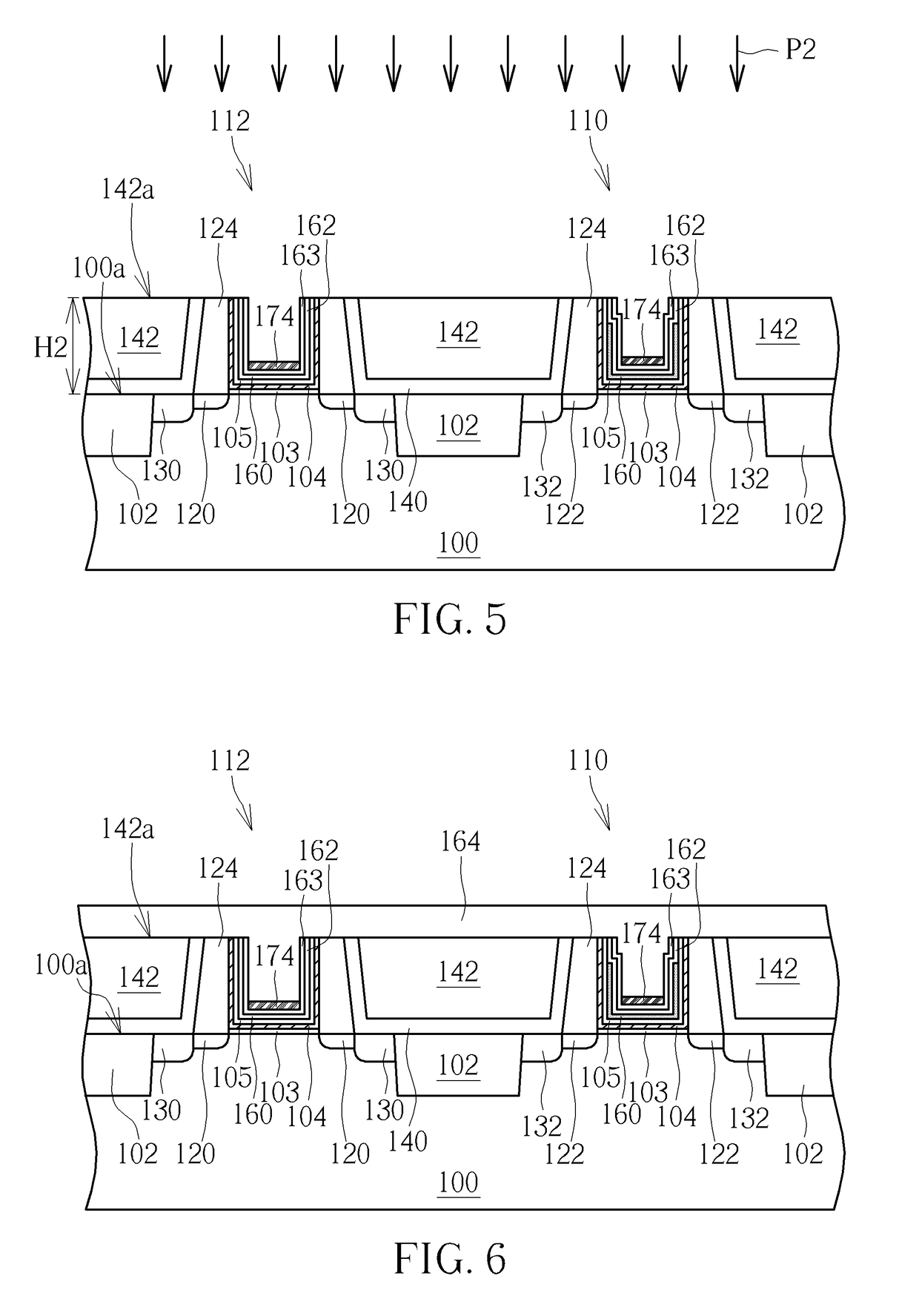

Semiconductor device having metal gate

ActiveUS20180358448A1Convenient and efficientReduce aspect ratioSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceWork function

The present invention provides a method of manufacturing a gate stack structure. The method comprises providing a substrate. A dielectric layer is then formed on the substrate and a gate trench is formed in the dielectric layer. A bottom barrier layer, a first work function metal layer and a top barrier layer are formed in the gate trench in sequence. Afterwards, a silicon formation layer is formed on the top barrier layer and filling the gate trench. A planarization process is performed, to remove a portion of the silicon formation layer, a portion of the bottom barrier layer, a portion of the first work function metal layer, and a portion of the top barrier layer. Next, the remaining silicon formation layer is removed completely, and a conductive layer is filled in the gate trench.

Owner:UNITED MICROELECTRONICS CORP

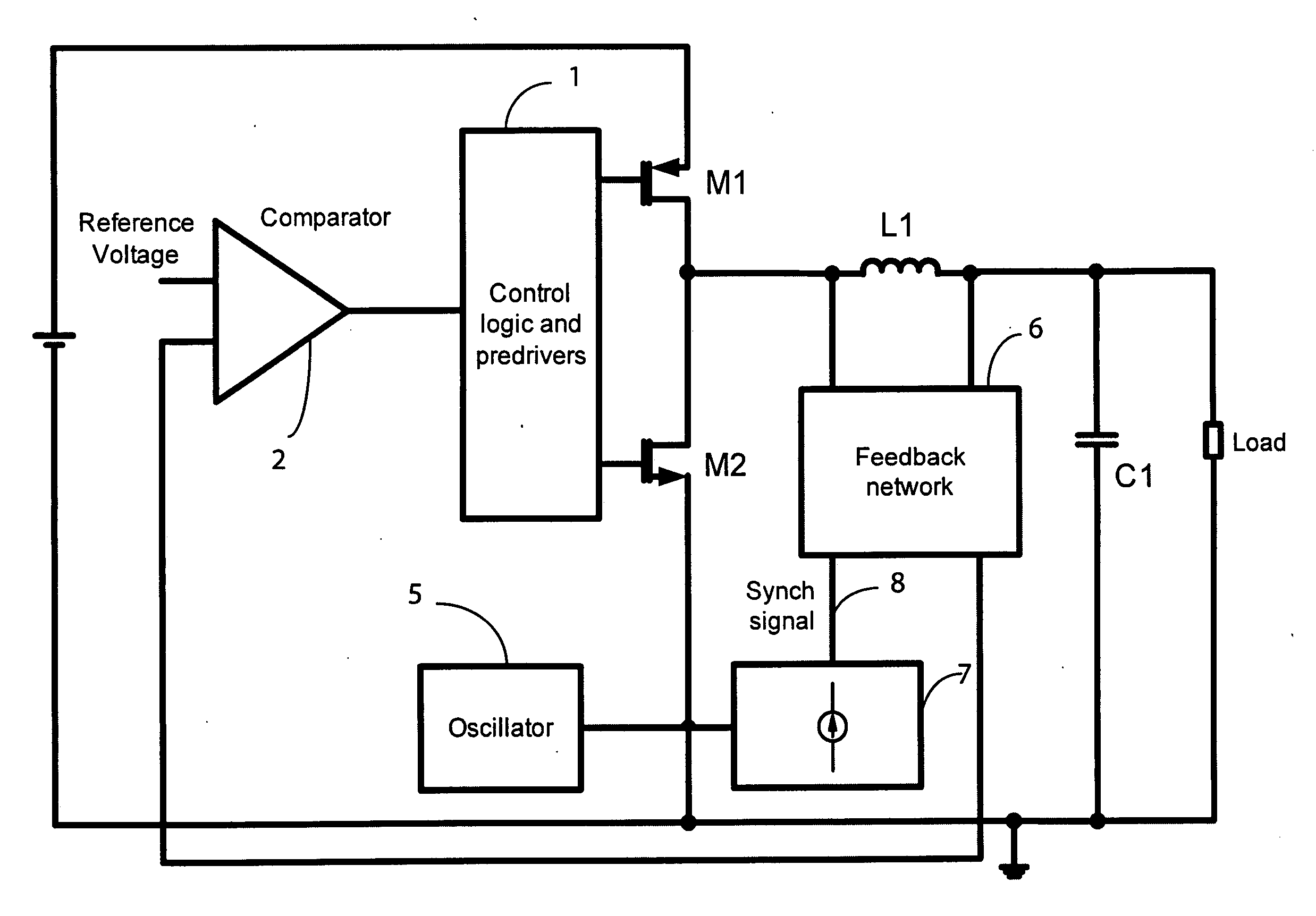

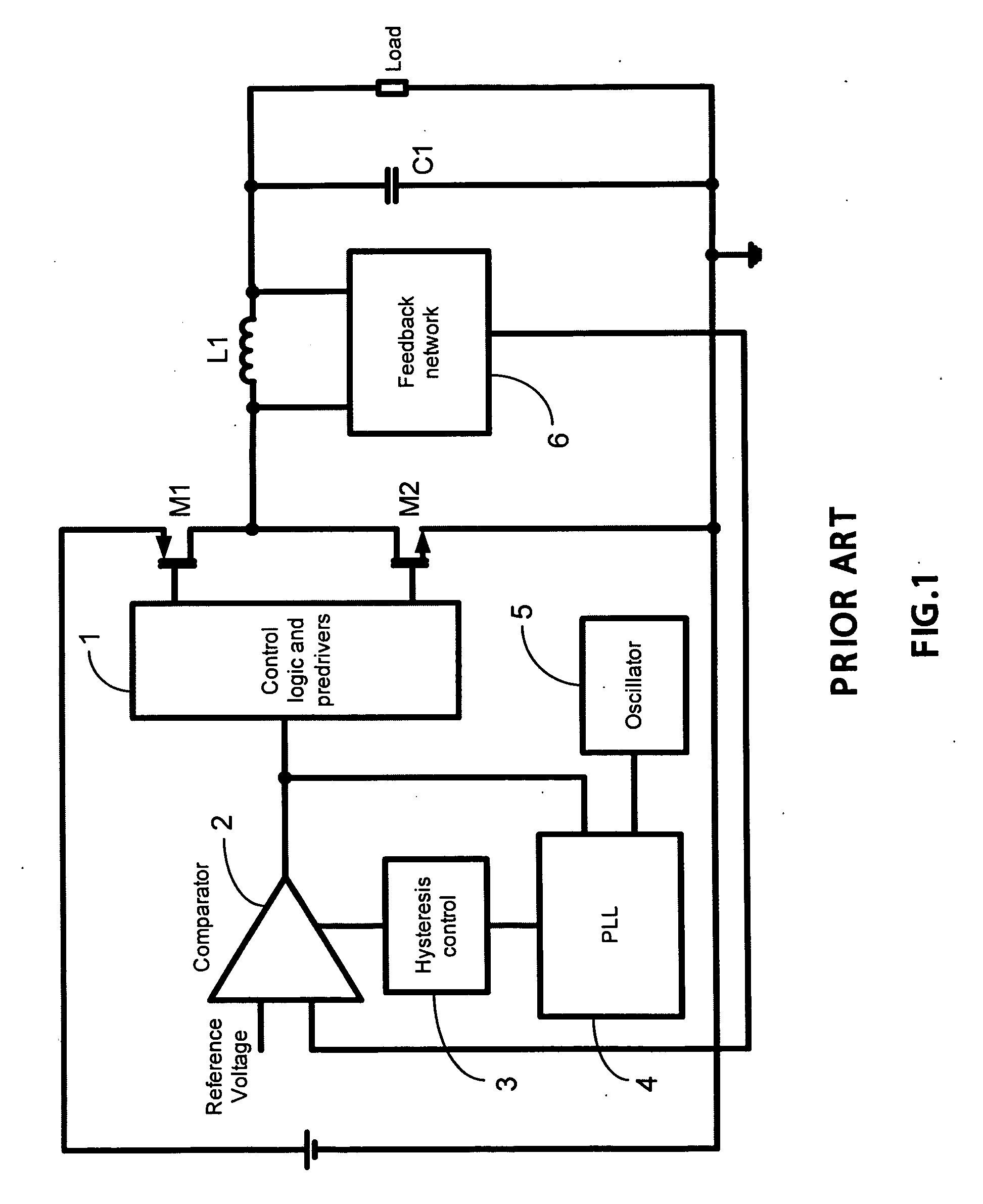

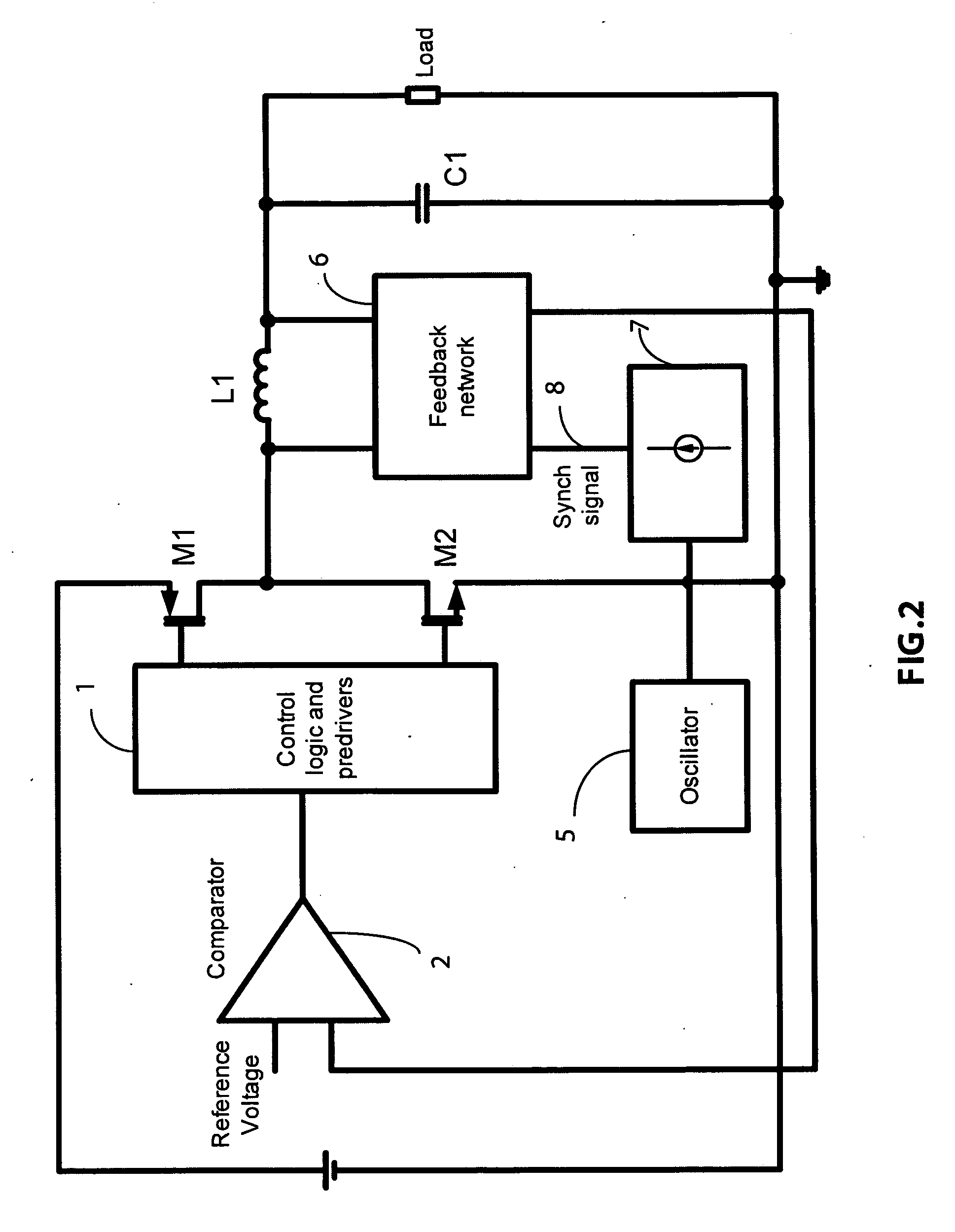

Synchronization of hysteretic power converters

ActiveUS20130015829A1Quickly switchQuick switchDc-dc conversionElectric variable regulationDelay-locked loopEngineering

A novel method to synchronize the switching frequency of hysteretic power converters is presented. The method includes the generation of a clock signal and the injection of a periodic disturbance signal operating at the frequency of the generated clock in the main loop of the converter to synchronize the hysteretic power converter to switch at the frequency of the clock.The presented approach provides significant advantages with respect to the more traditional means of utilizing Frequency Lock Loop, Phase Lock Loop or Delay Lock Loop circuits, mainly for its simplicity, faster locking and much reduced phase error.The switching frequency can be higher or lower than the free running frequency of the power converter provided that the free running frequency is close enough to the desired switching frequency.The method is presented for buck and boost hysteretic high frequency switching power converters.

Owner:QUALCOMM INC