Patents

Literature

99results about How to "Keep linear" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

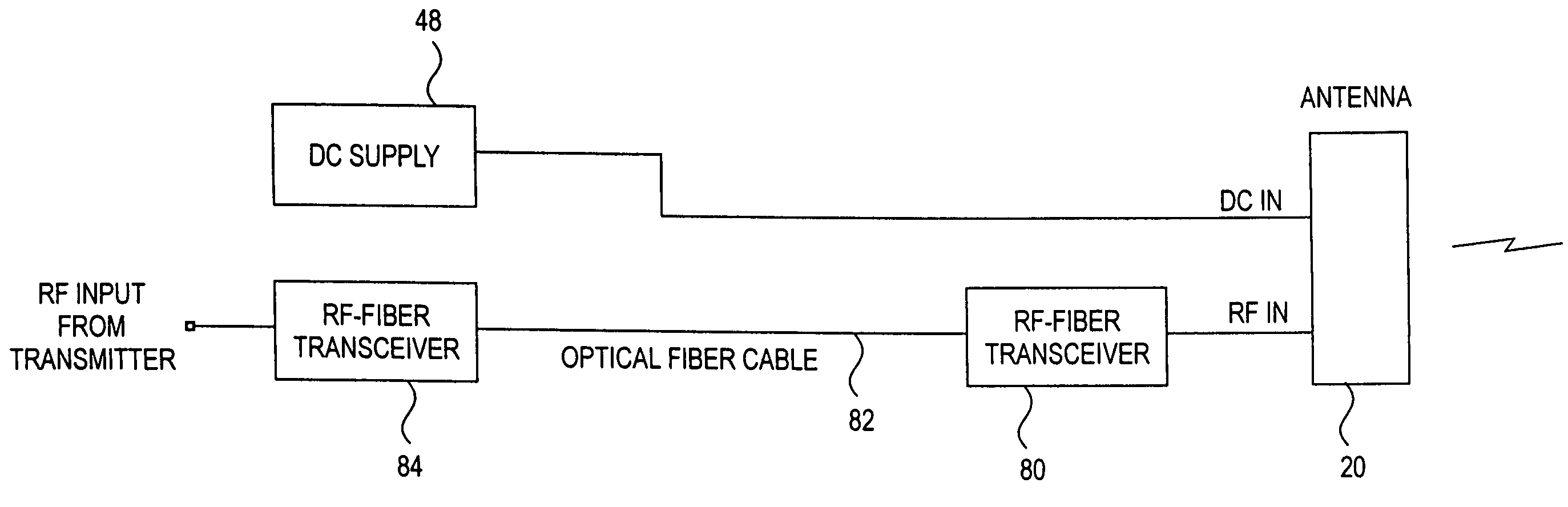

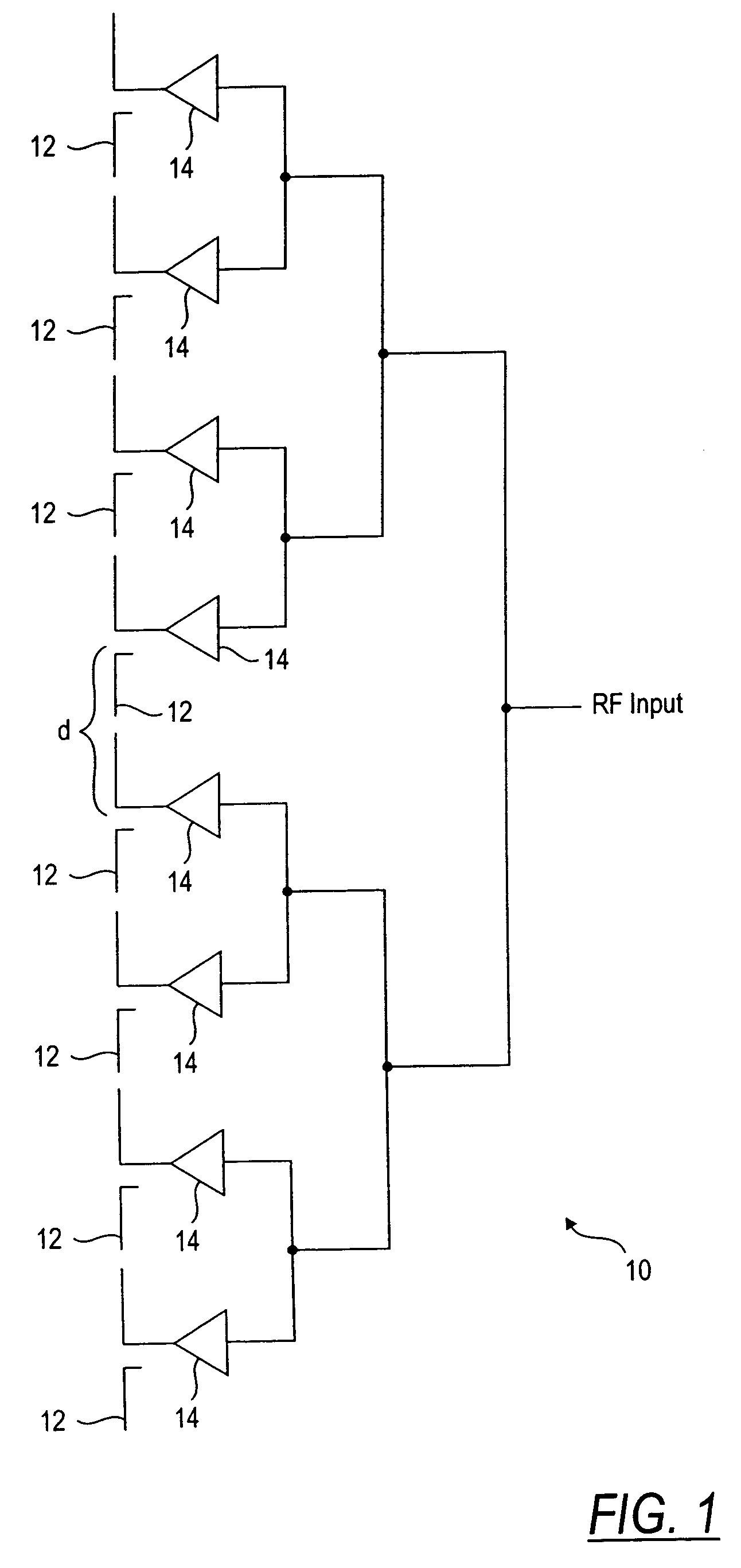

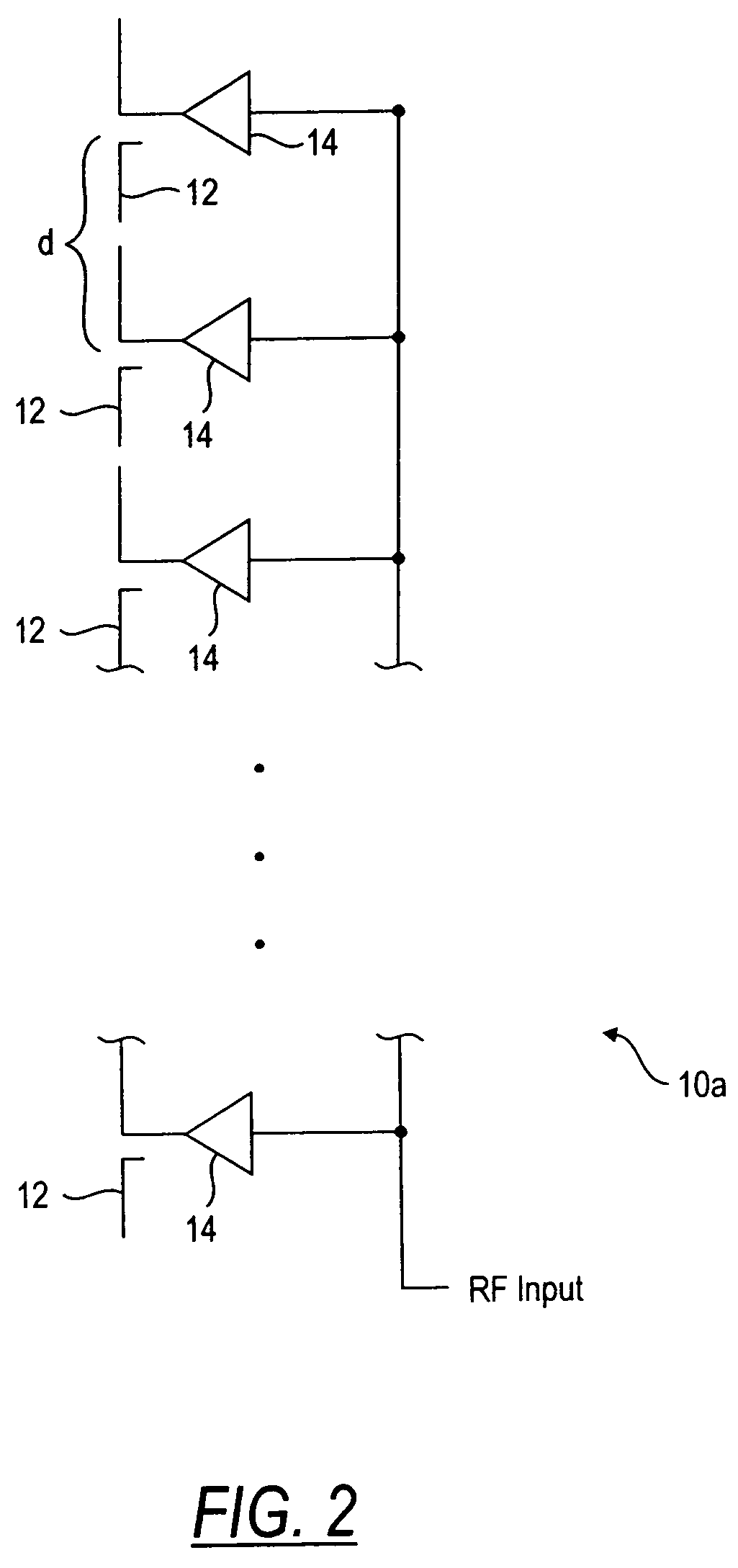

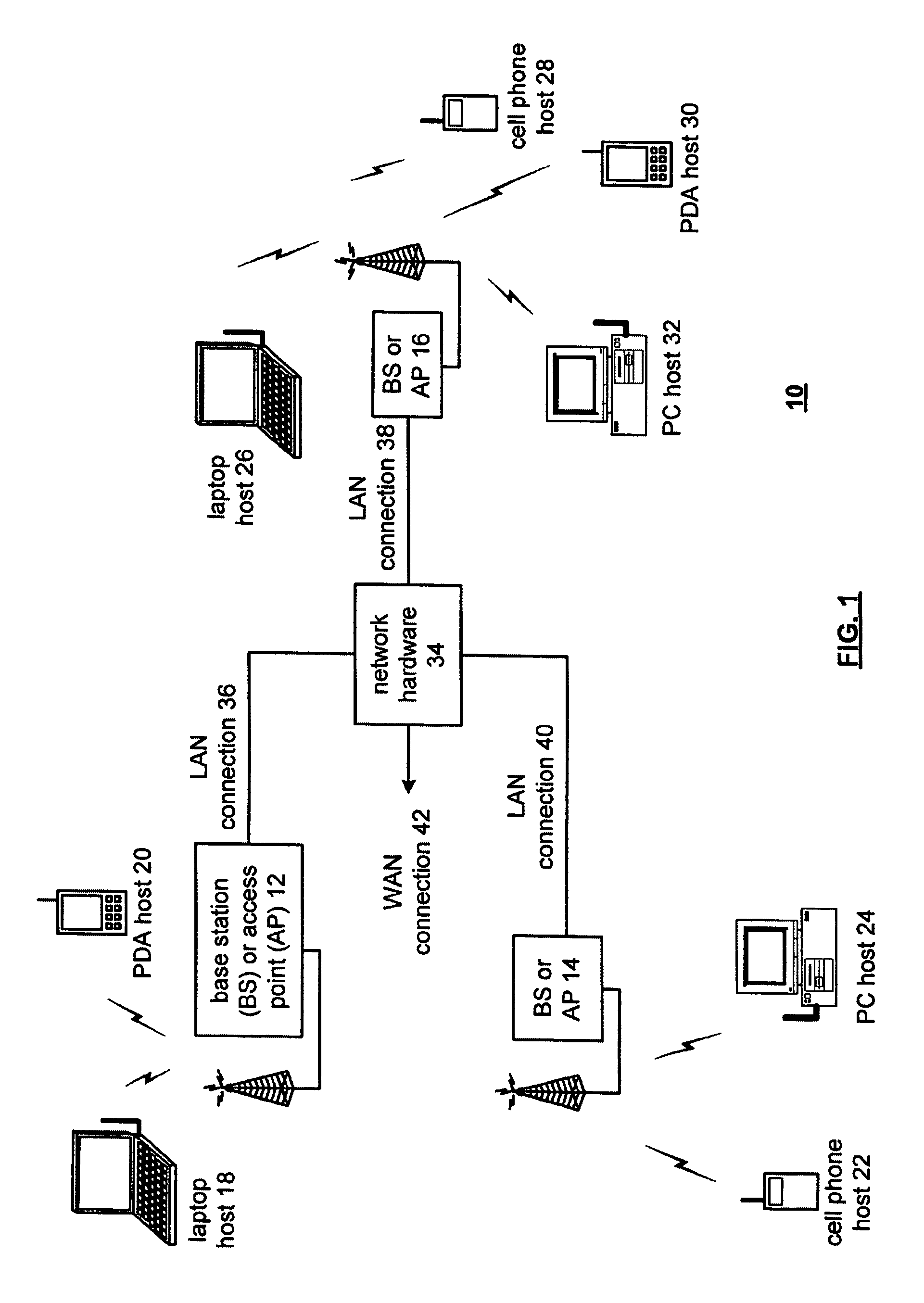

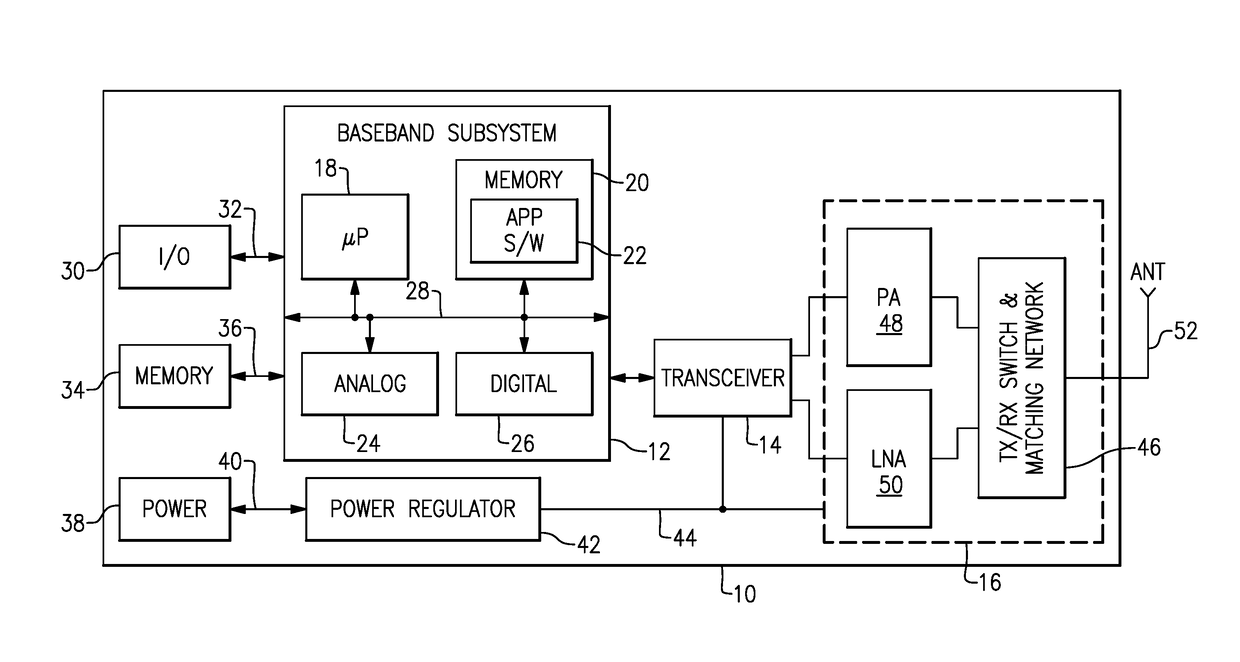

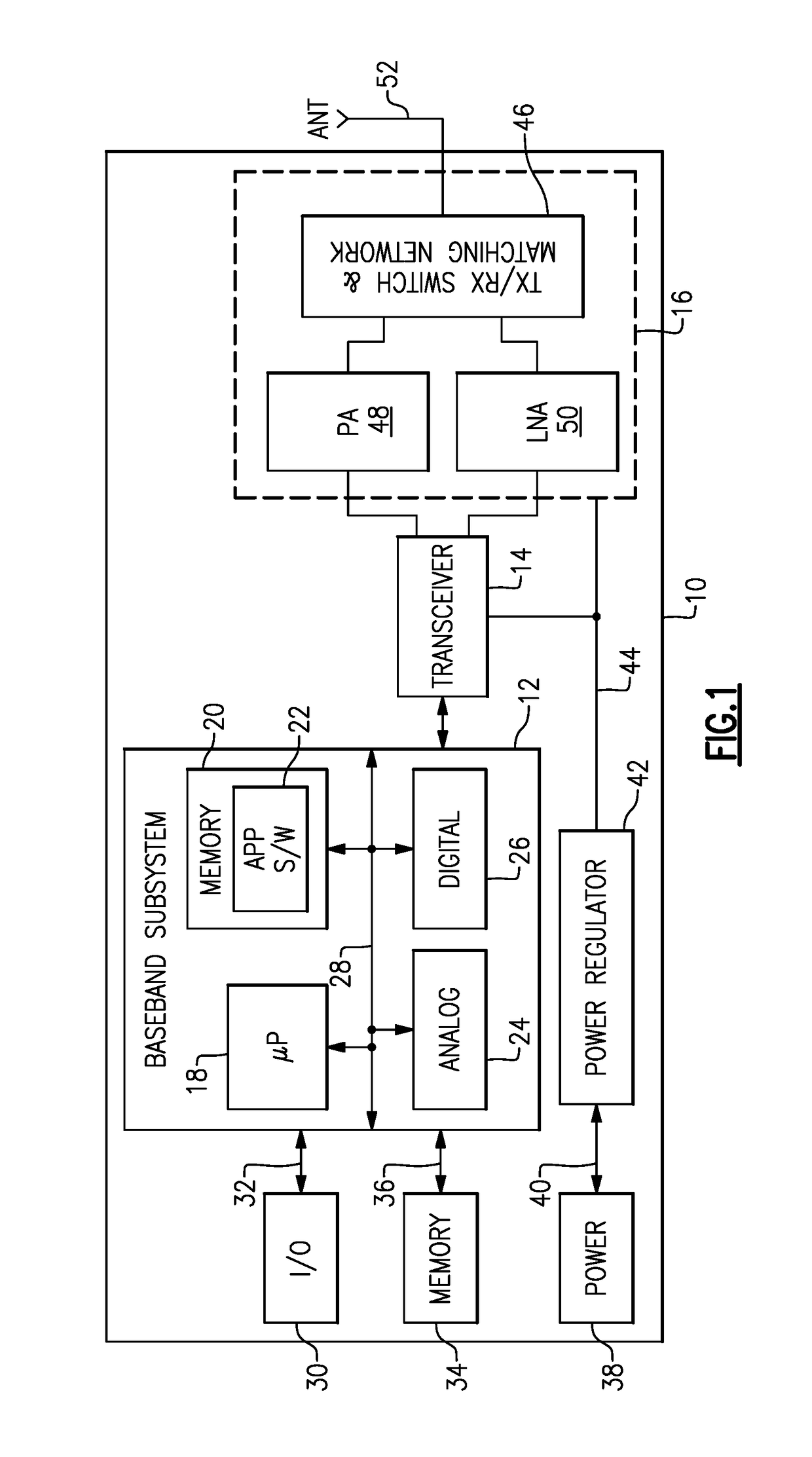

Antenna structure and installation

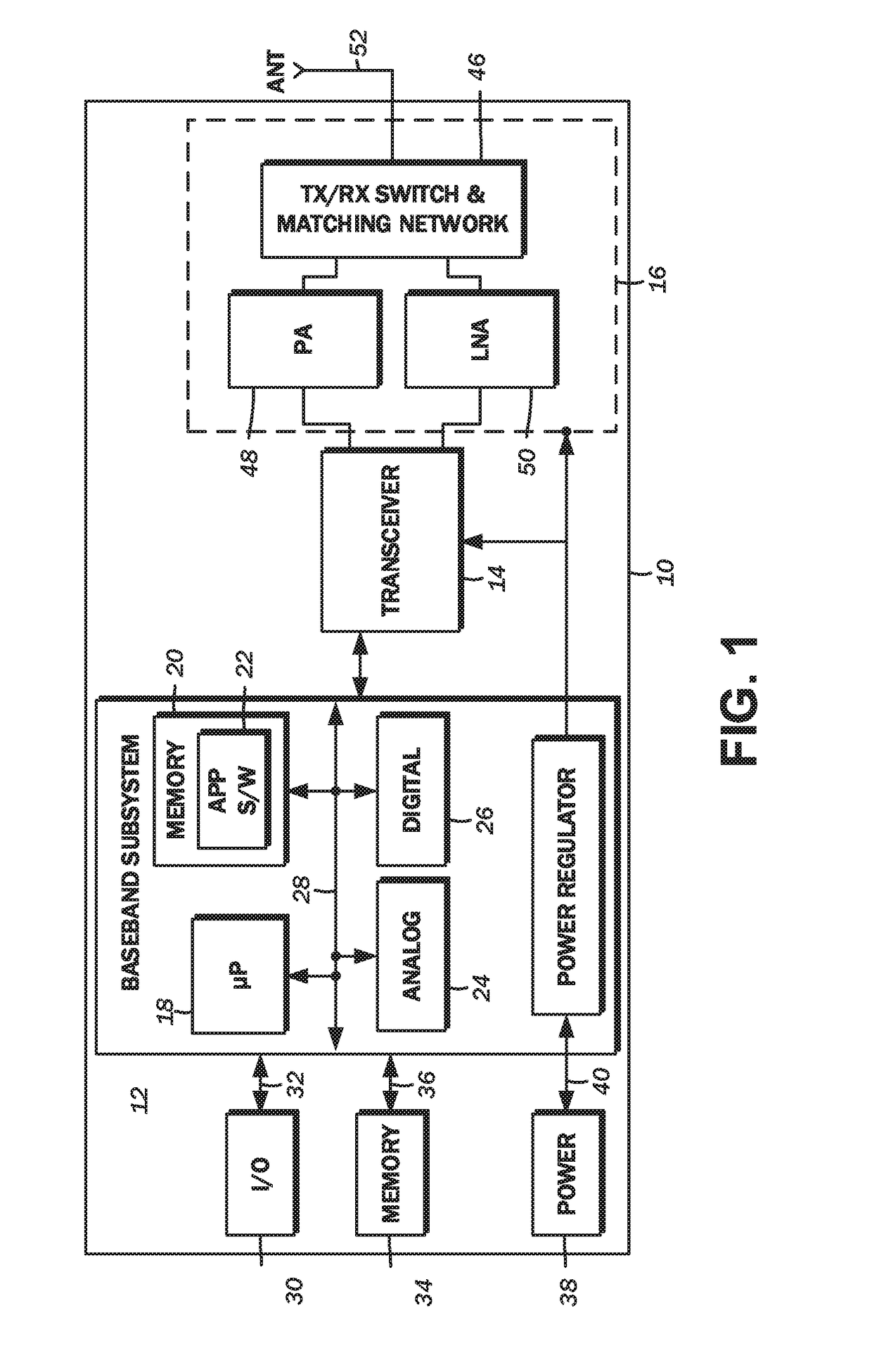

InactiveUS7053838B2Low costLow powerAntenna supports/mountingsIndividually energised antenna arraysFiberTransceiver

An antenna system installation comprising a tower / support structure, and an antenna structure mounted at the top of said tower / support structure, said antenna structure comprises a plurality of antenna elements, a plurality of power amplifiers, each power amplifier being operatively coupled with one of said antenna elements and mounted closely adjacent to the associated antenna element, such that no appreciable power loss occurs between the power amplifier and the associated antenna element, each said power amplifier comprising a relatively low power, relatively low cost per watt linear power amplifier chip, a first RF to fiber transceiver mounted at the top of said tower / support structure and operatively coupled with said antenna structure, and a second RF to fiber transceiver mounted adjacent a base portion of said tower / support structure and coupled with said first RF transceiver by an optical fiber cable.

Owner:COMMSCOPE TECH LLC

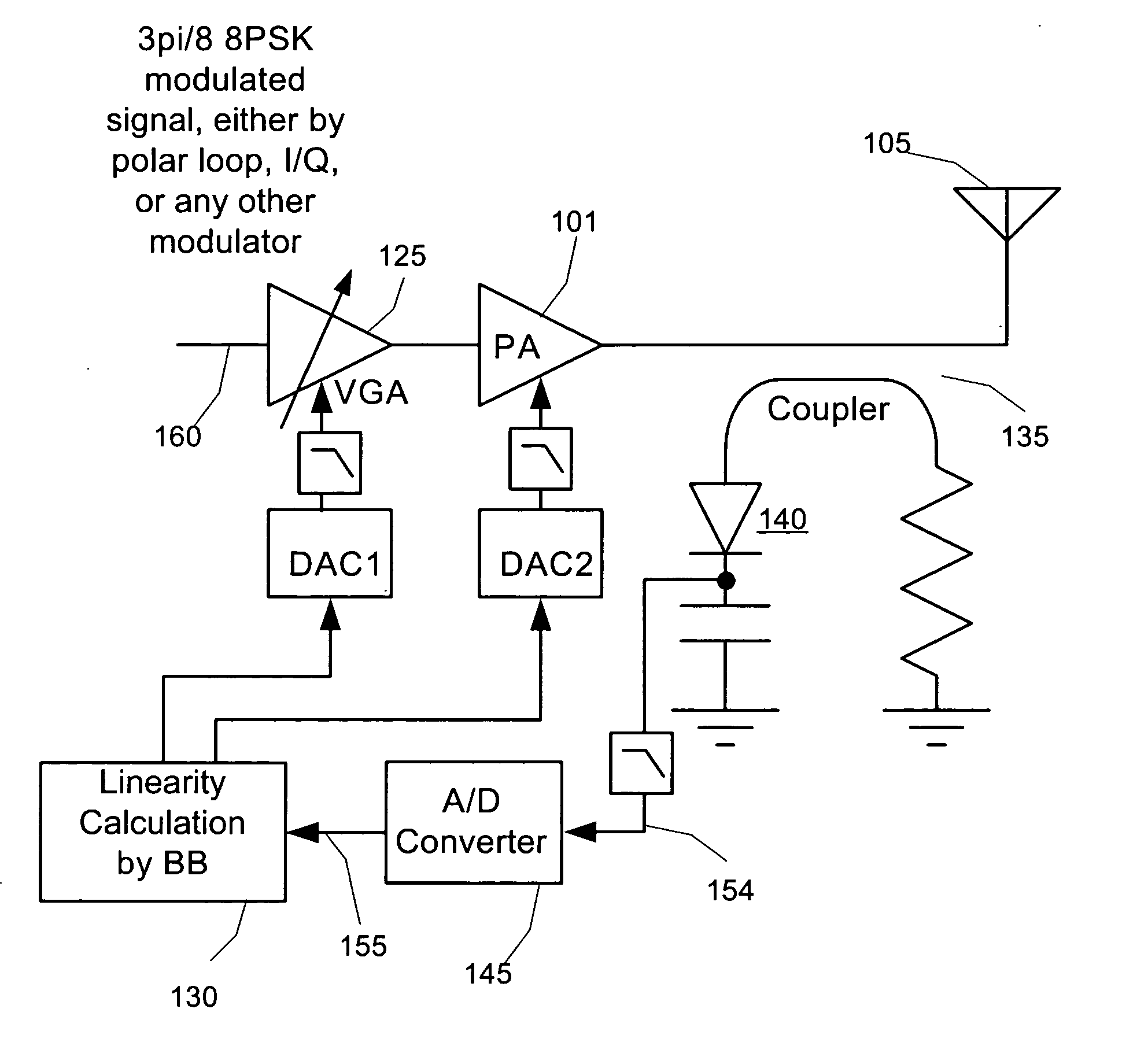

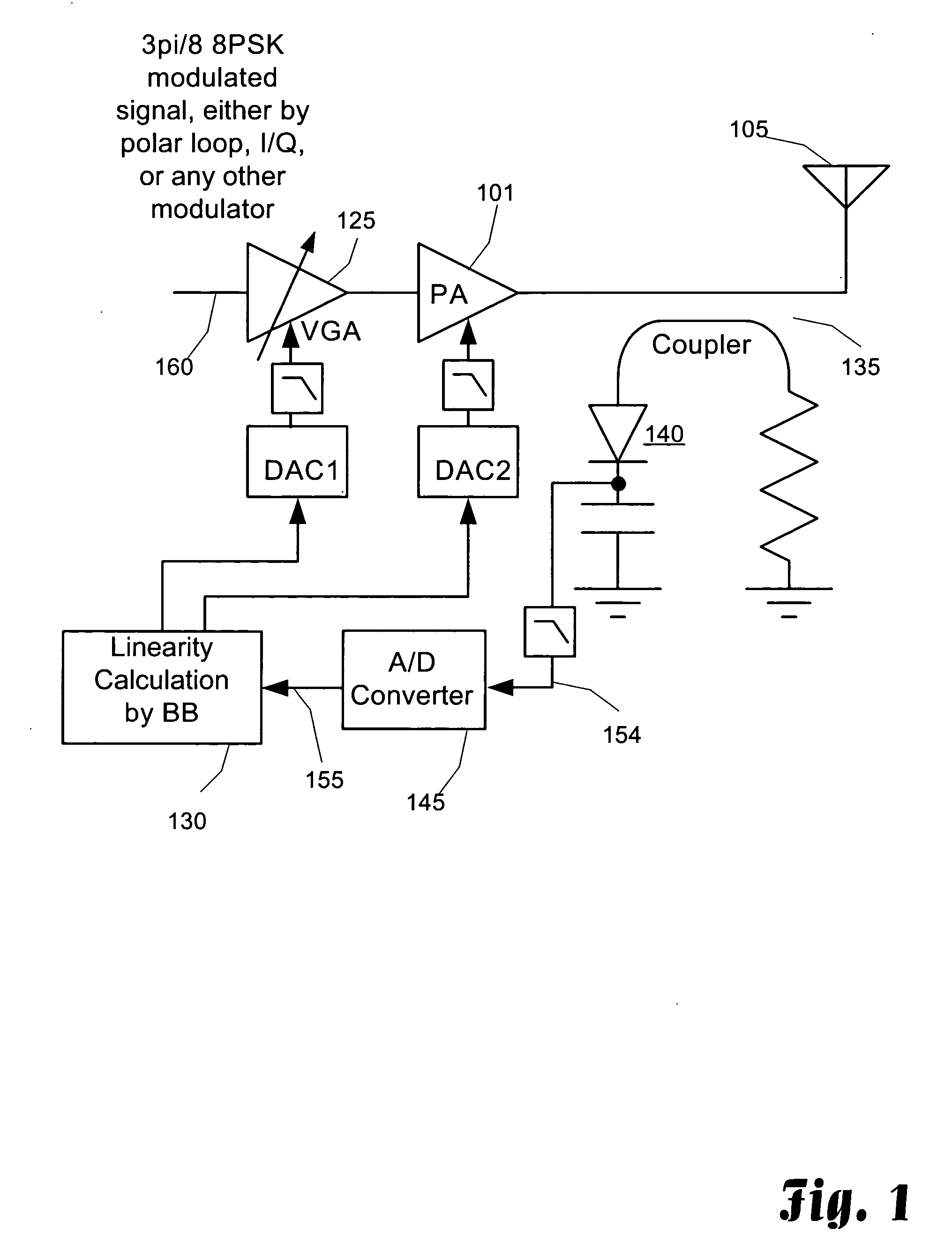

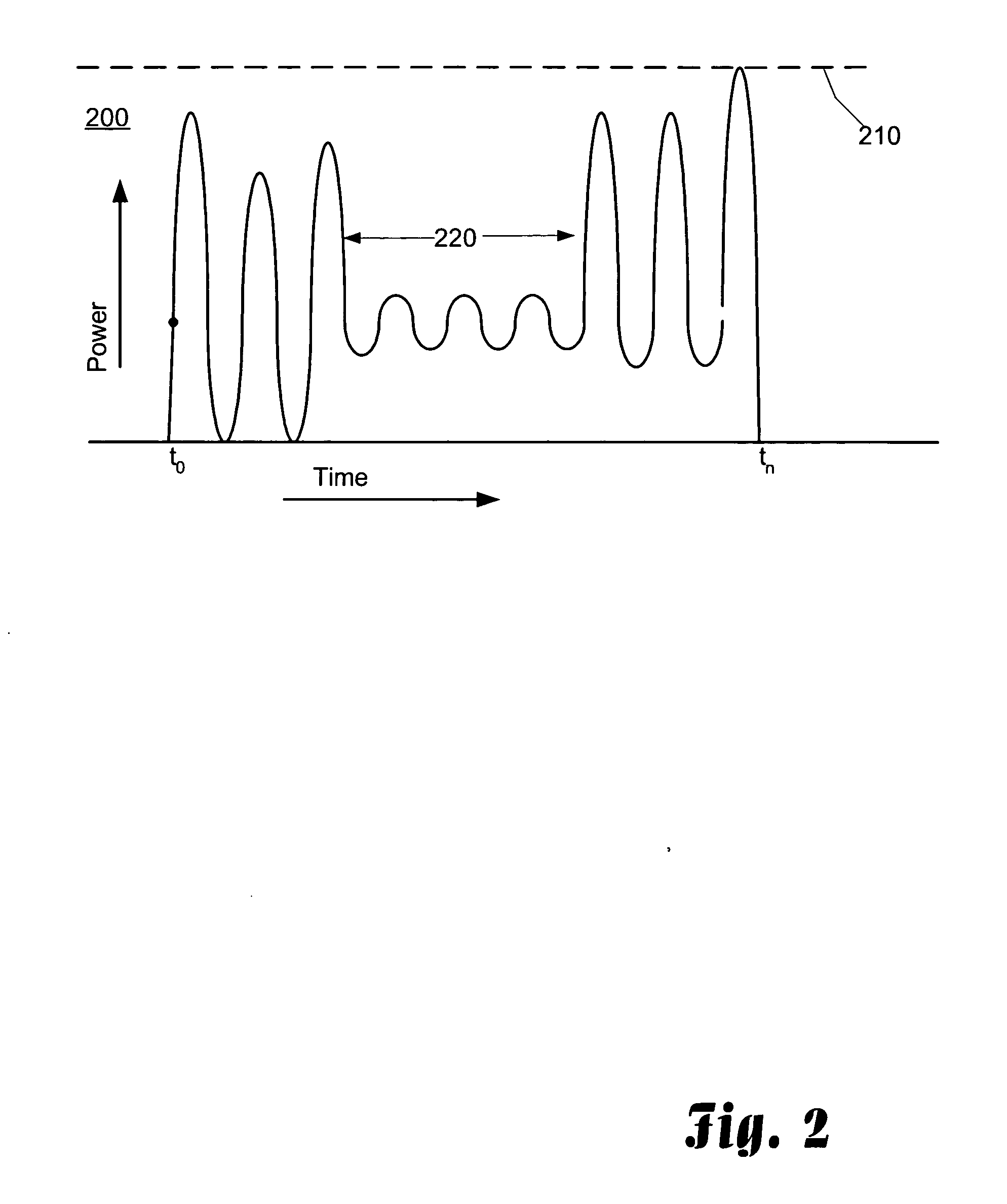

Detecting and maintaining linearity in a power amplifier system through comparing peak and RMS power levels

InactiveUS20050227646A1Raise the ratioRestore linearityResonant long antennasSupply voltage varying controlAudio power amplifierLinear region

Small portable communication devices that support multiple modulation techniques cannot gain the benefits of using an isolator at the output of a power amplifier to provide stability in the load impedance. However, for communication devices that include amplitude modulation schemes, maintaining linear operation of the power amplifier is still required. In the presence of unstable load impedance, this can be a difficult task. As a solution, the linearity of the power amplifier is detected by determining the peak power of the output signal and the average or root-mean-square of a portion of the output signal, such as a mid-amble). The ratio of the peak power and the average power of the output signal are used to determine if the power amplifier is operating in the linear region. If the ratio is too high, then the power amplifier may be operating in the linear region. By adjusting the power level of the input signal to the power amplifier when the ratio increases, linearity of the power amplifier is maintained.

Owner:PANASONIC CORP

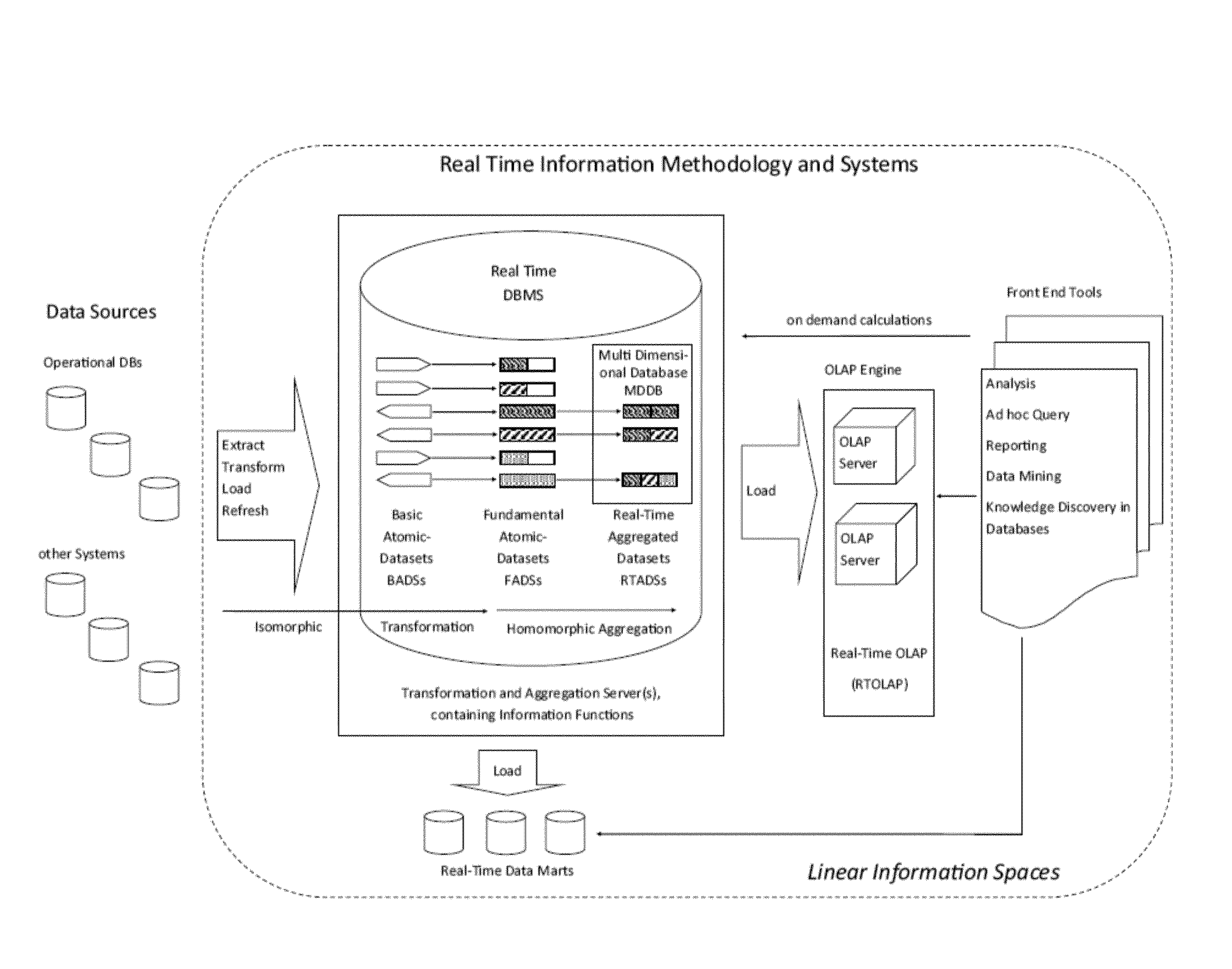

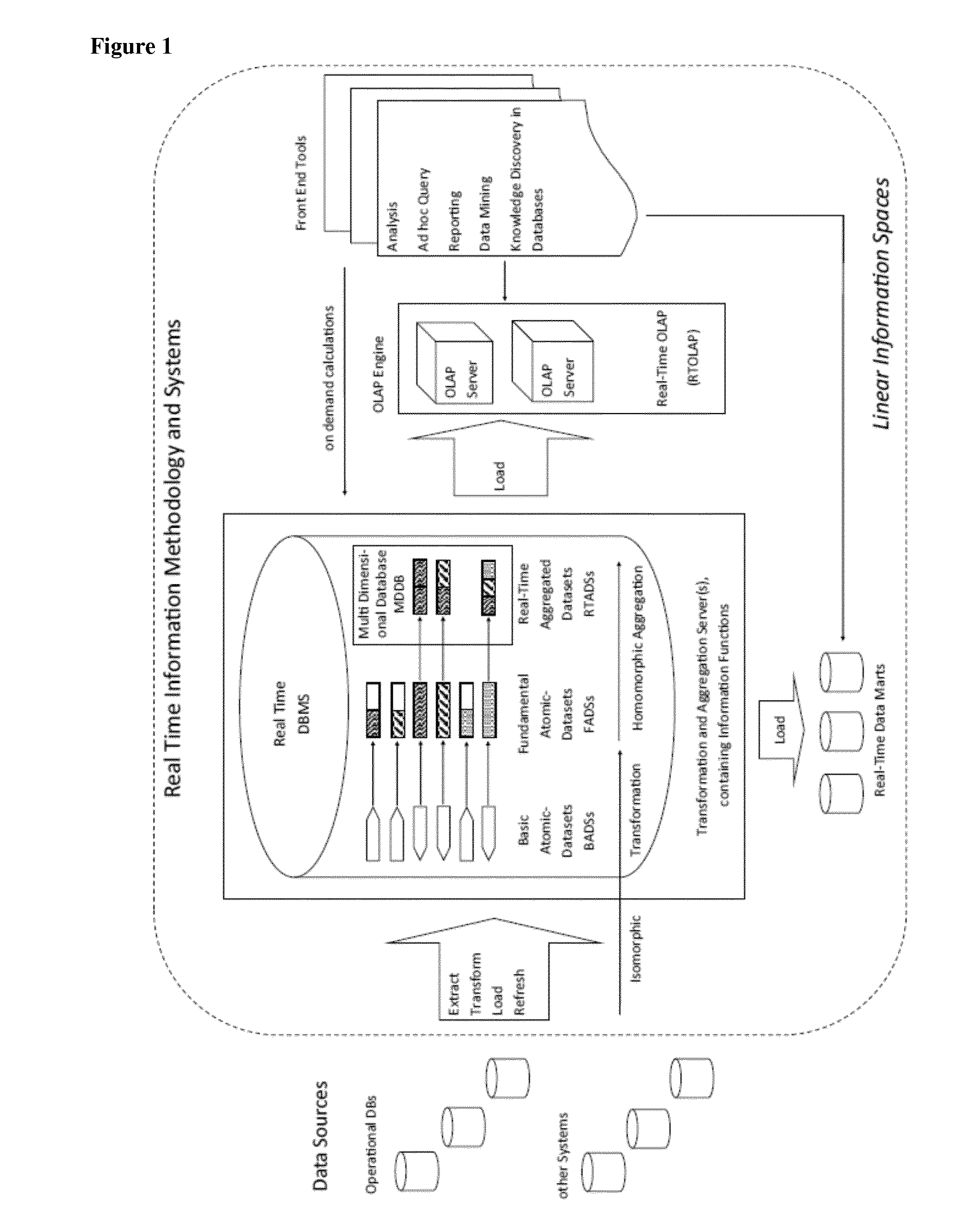

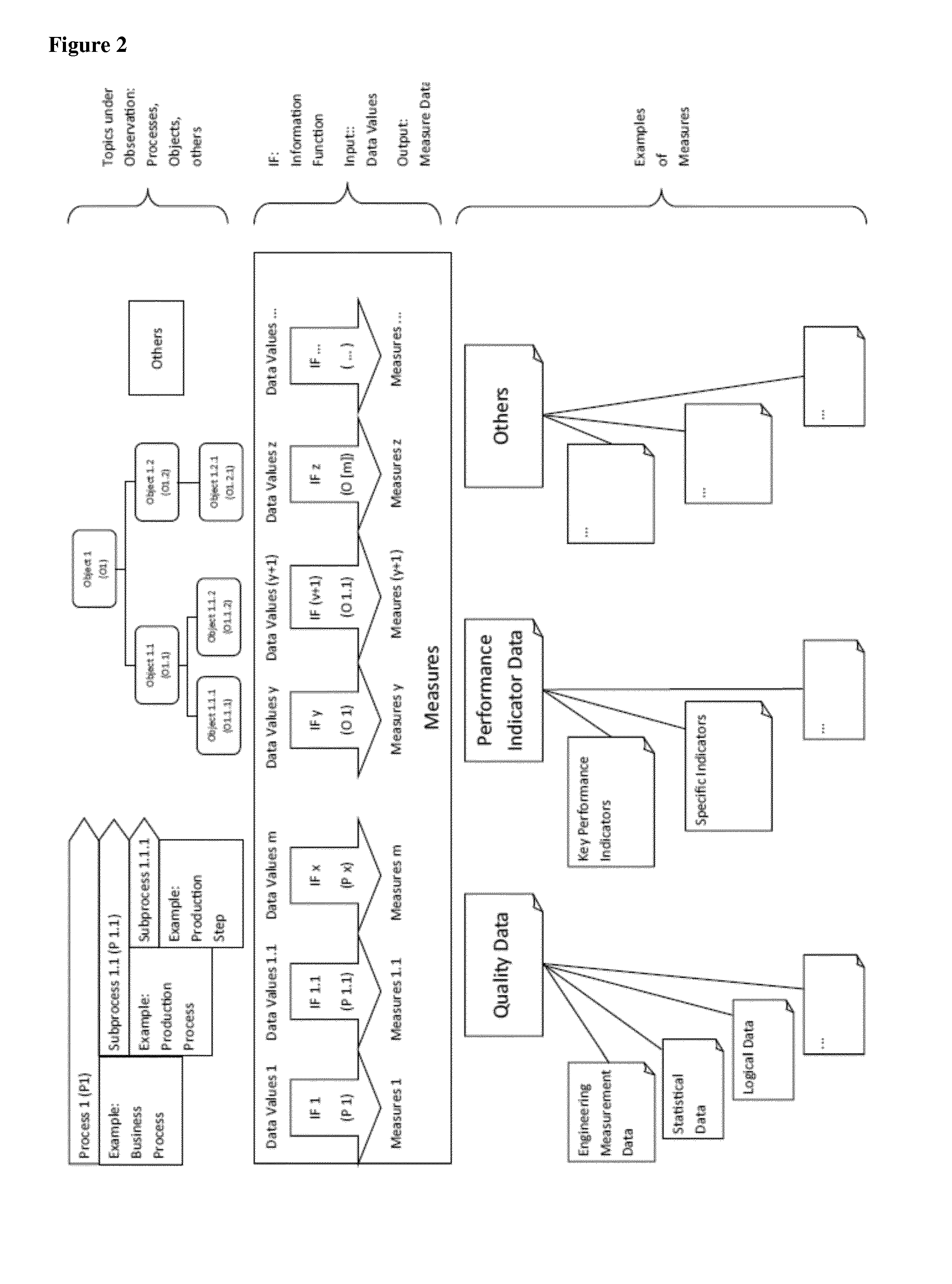

Real-time information systems and methodology based on continuous homomorphic processing in linear information spaces

InactiveUS20170032016A1Keep linearMulti-dimensional databasesResourcesTime informationInformation space

The present invention relates to the field of information system technology. More particularly, the present invention relates to methods and systems for Real-Time information processing, including Real-Time Data Warehousing, using Real-Time in-formation aggregation (including calculation of the performance indicators and the like) based on continuous homomorphic processing, thus preserving the linearity of the underlying structures. The present invention further relates to a computer program product adapted to perform the method of the invention, to a computer-readable storage medium comprising said computer program product and a data processing system, which enables Real-Time information processing according to the methods of the invention.

Owner:SYST SYSTNTWICKLUNG DIP INF MANFRED AUSTEN

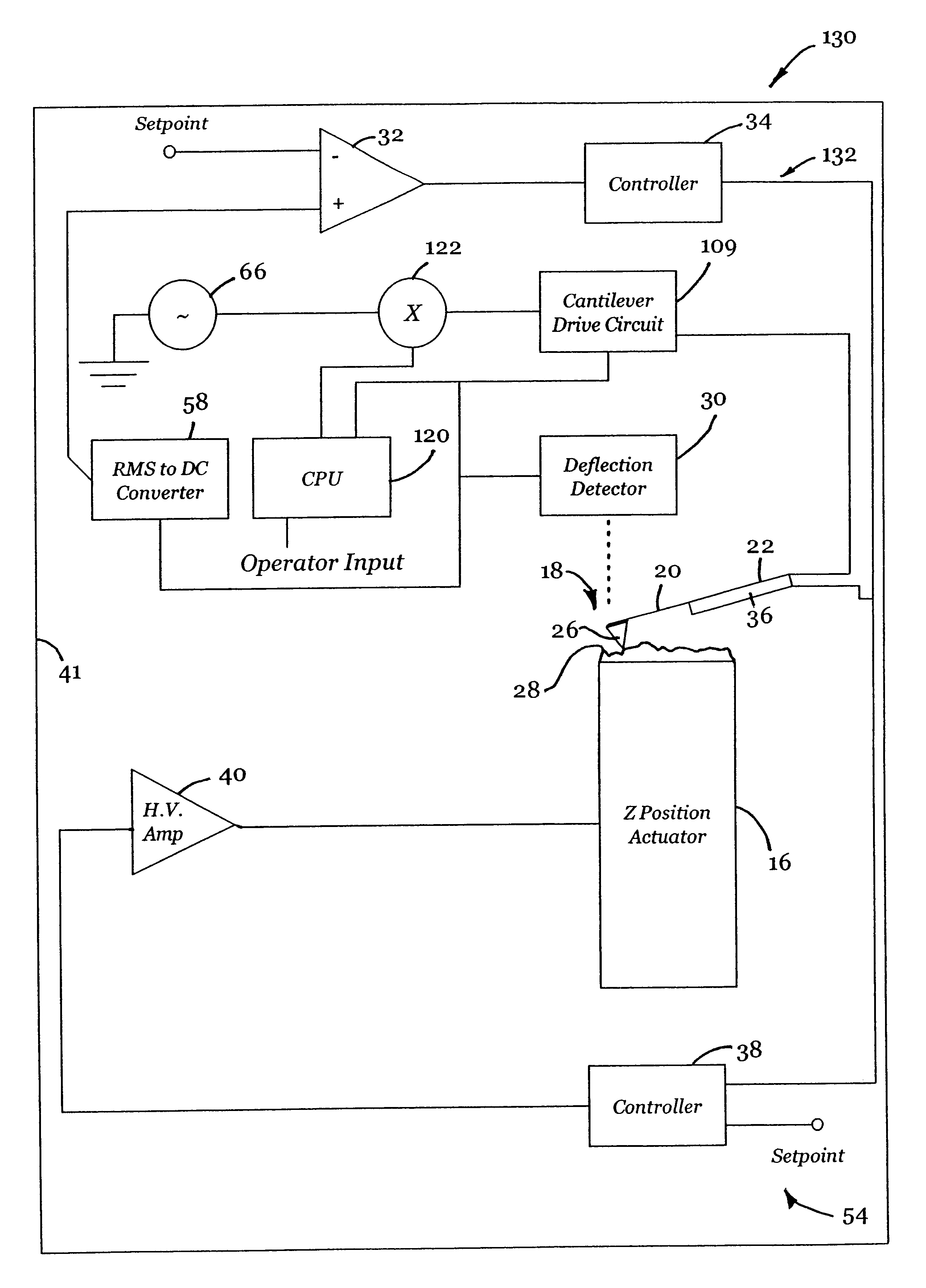

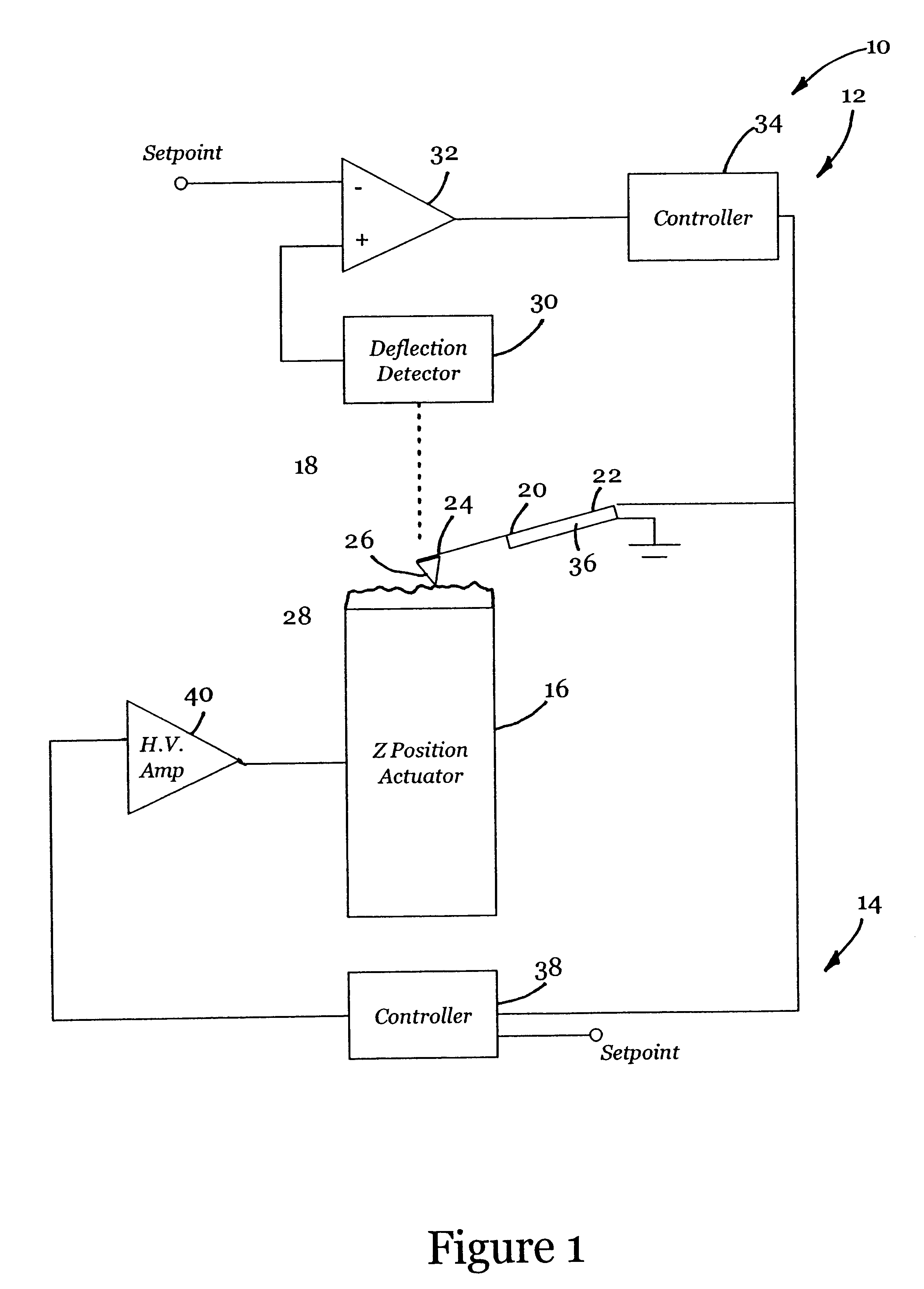

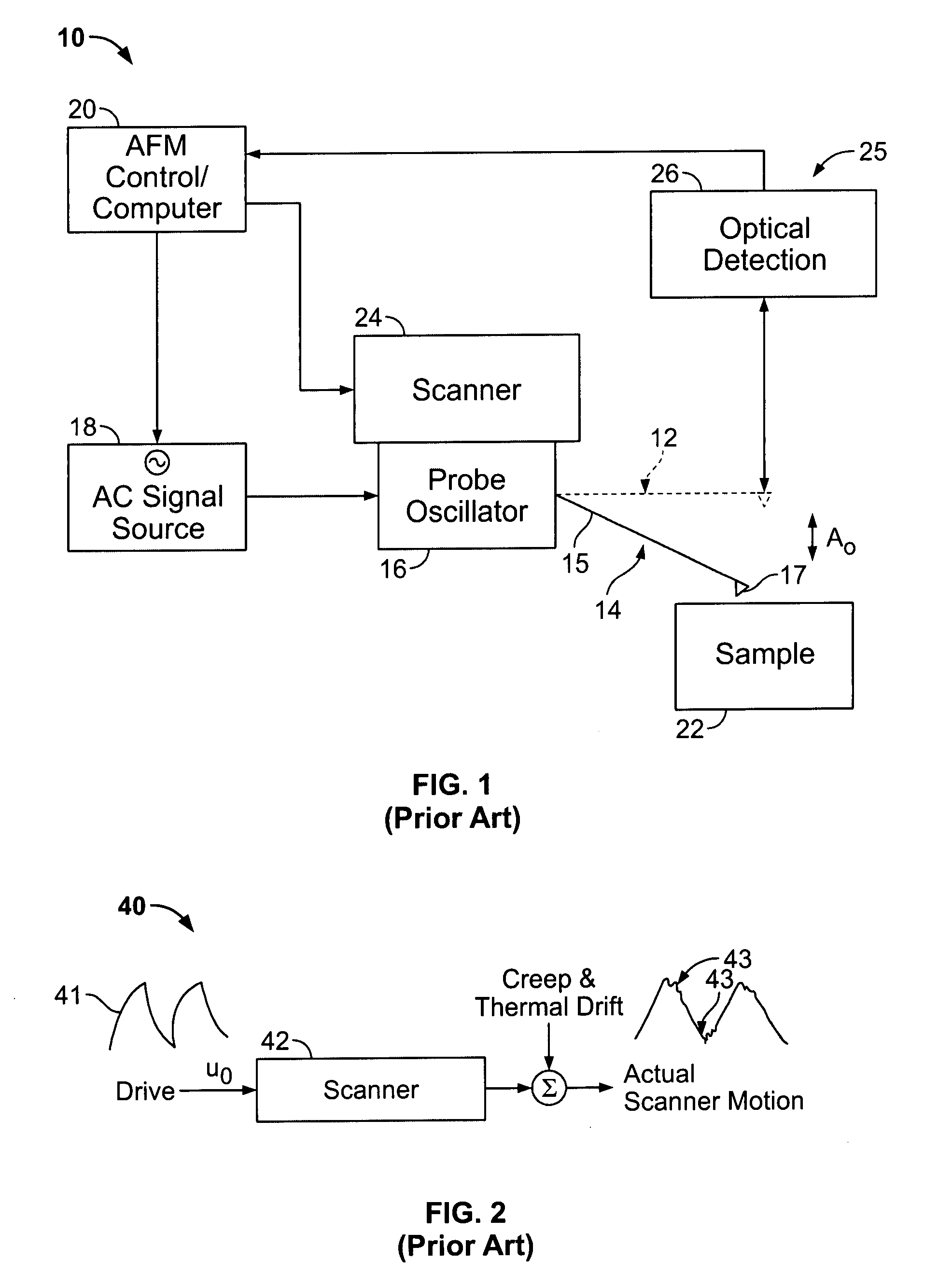

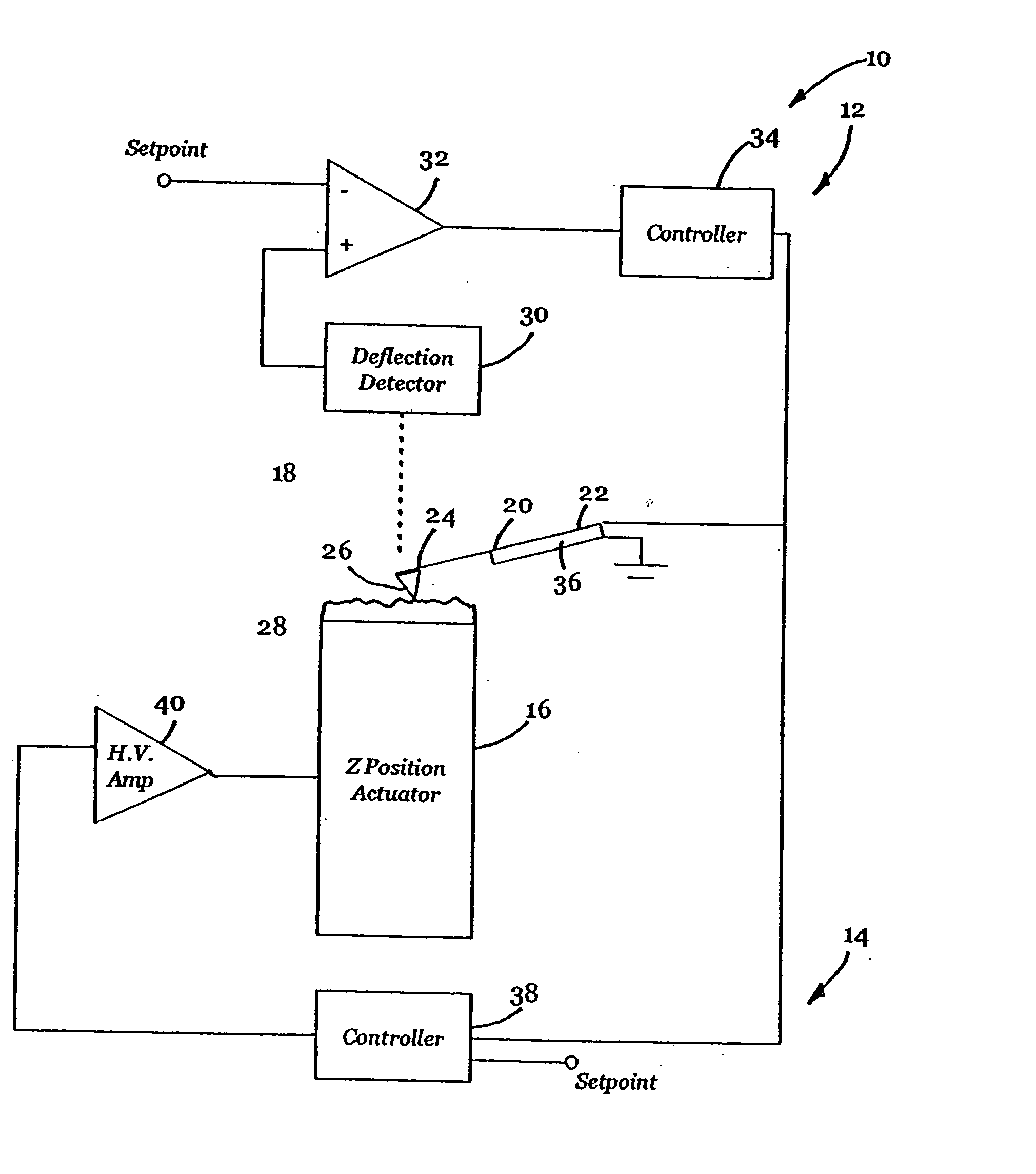

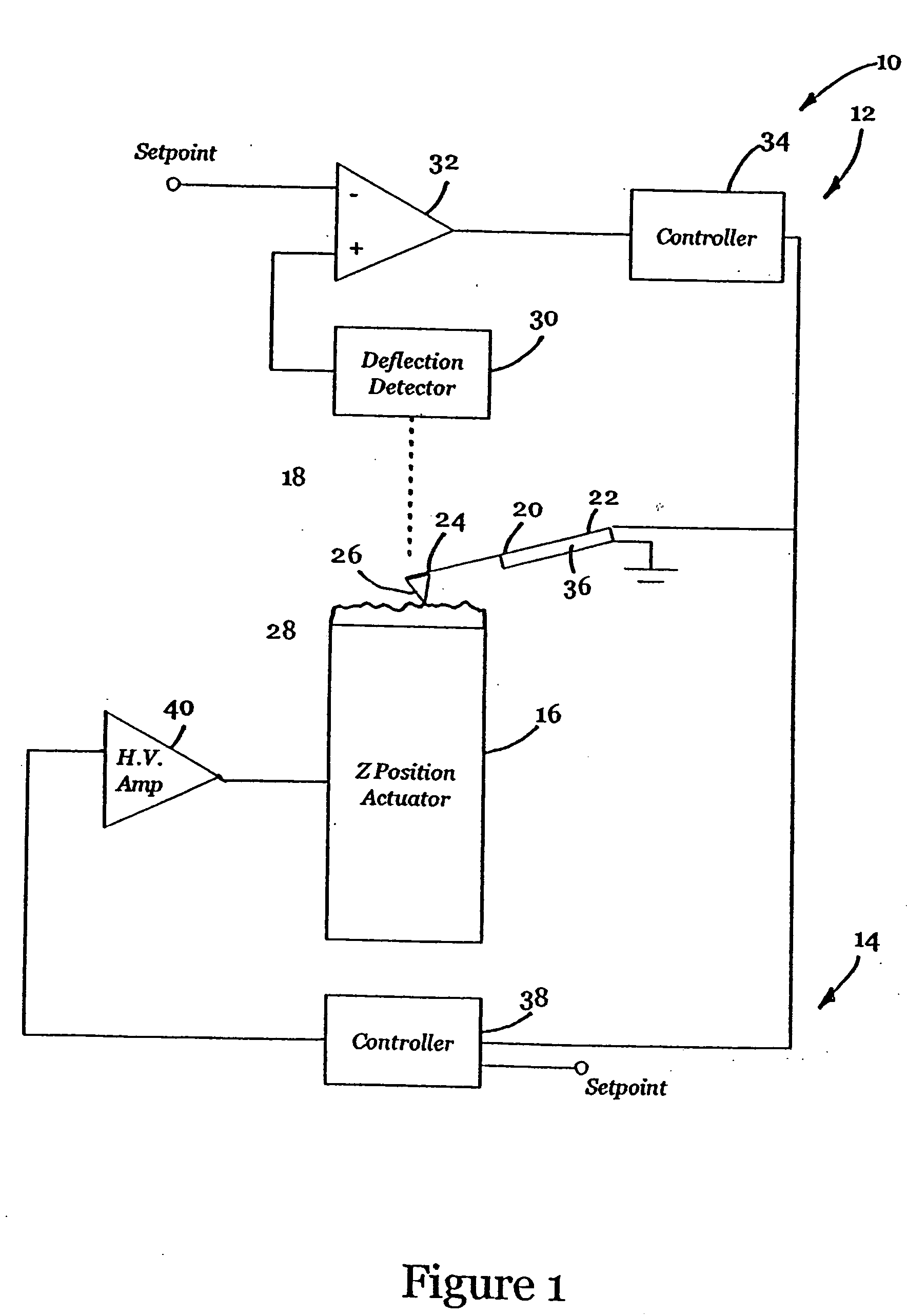

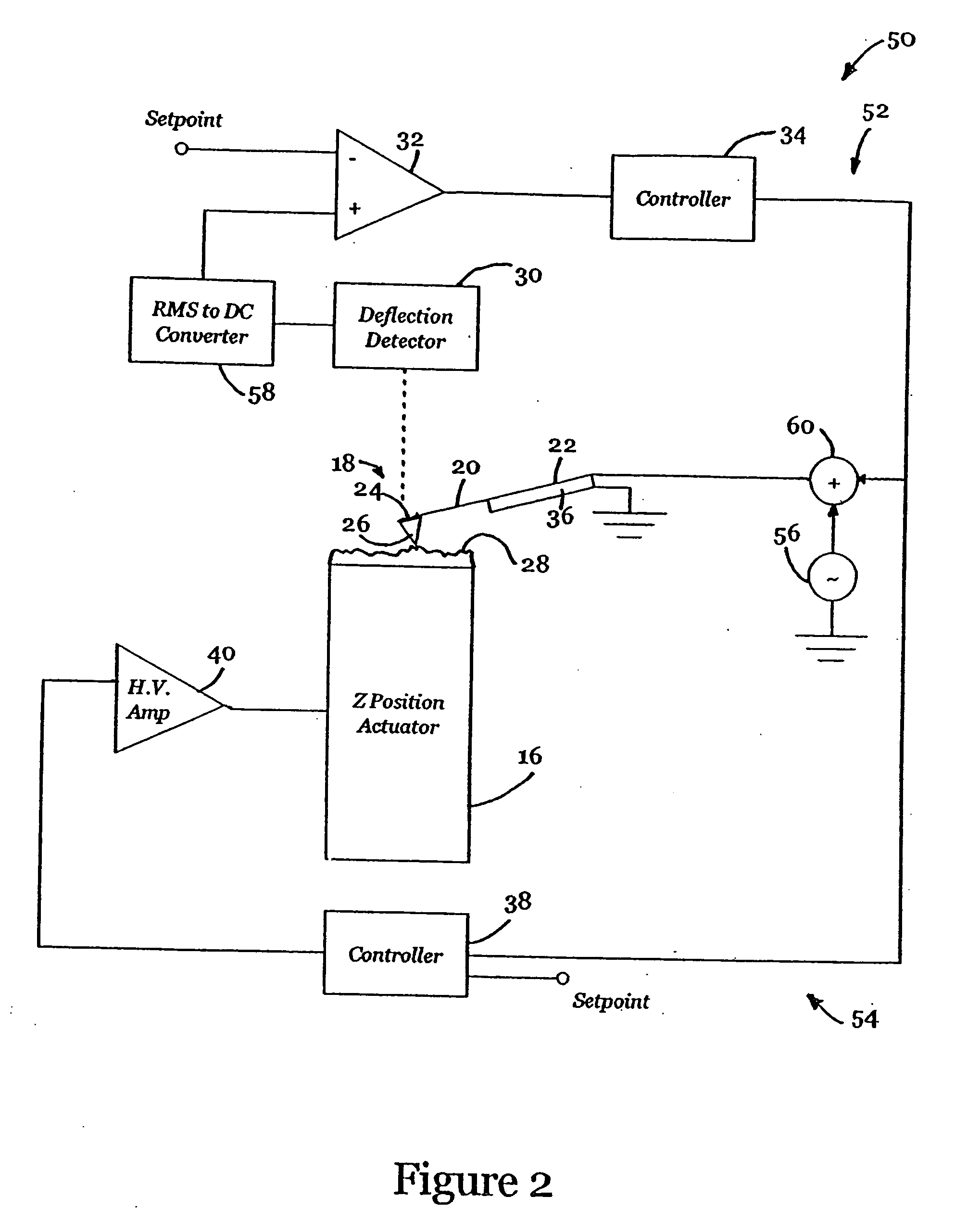

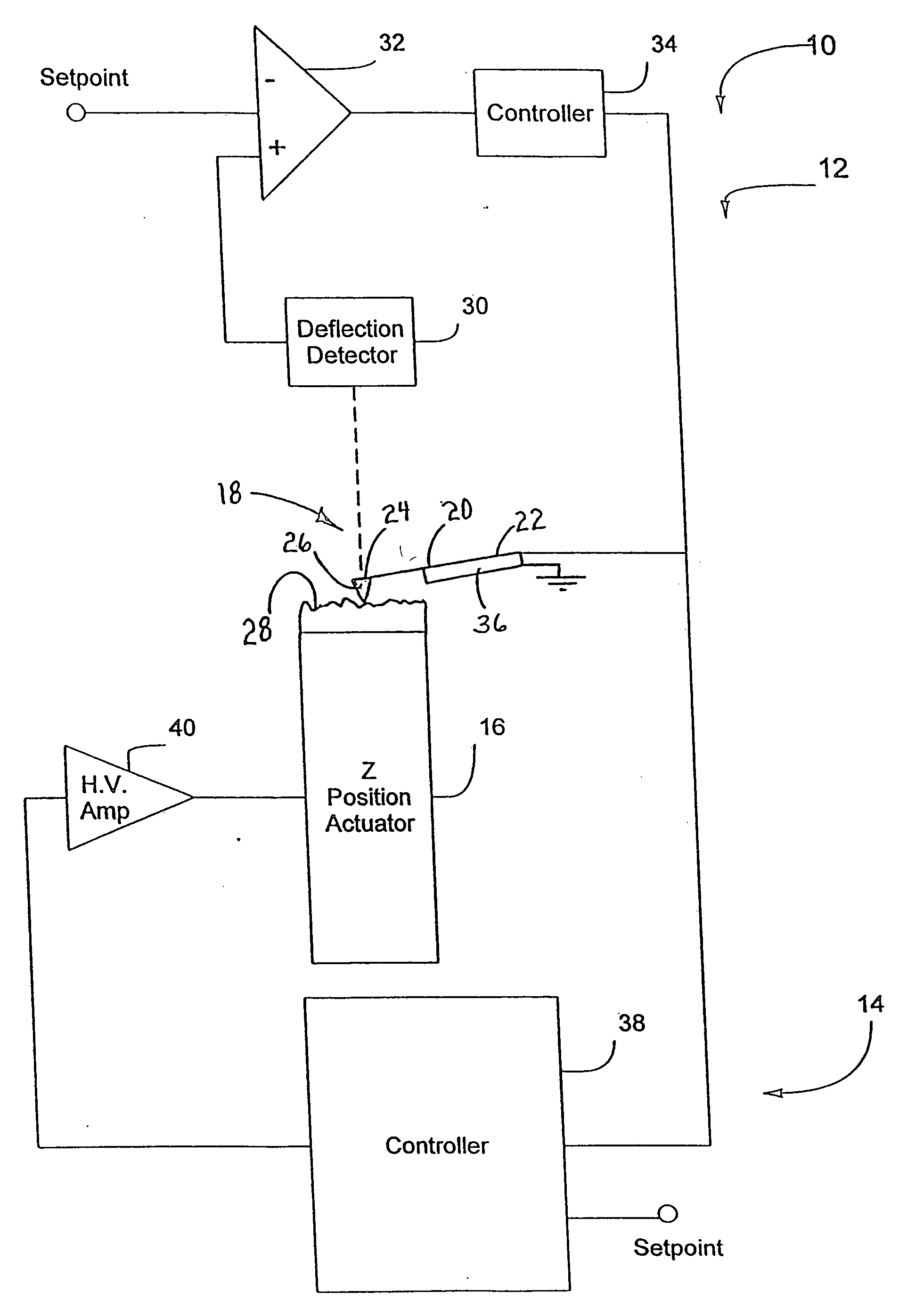

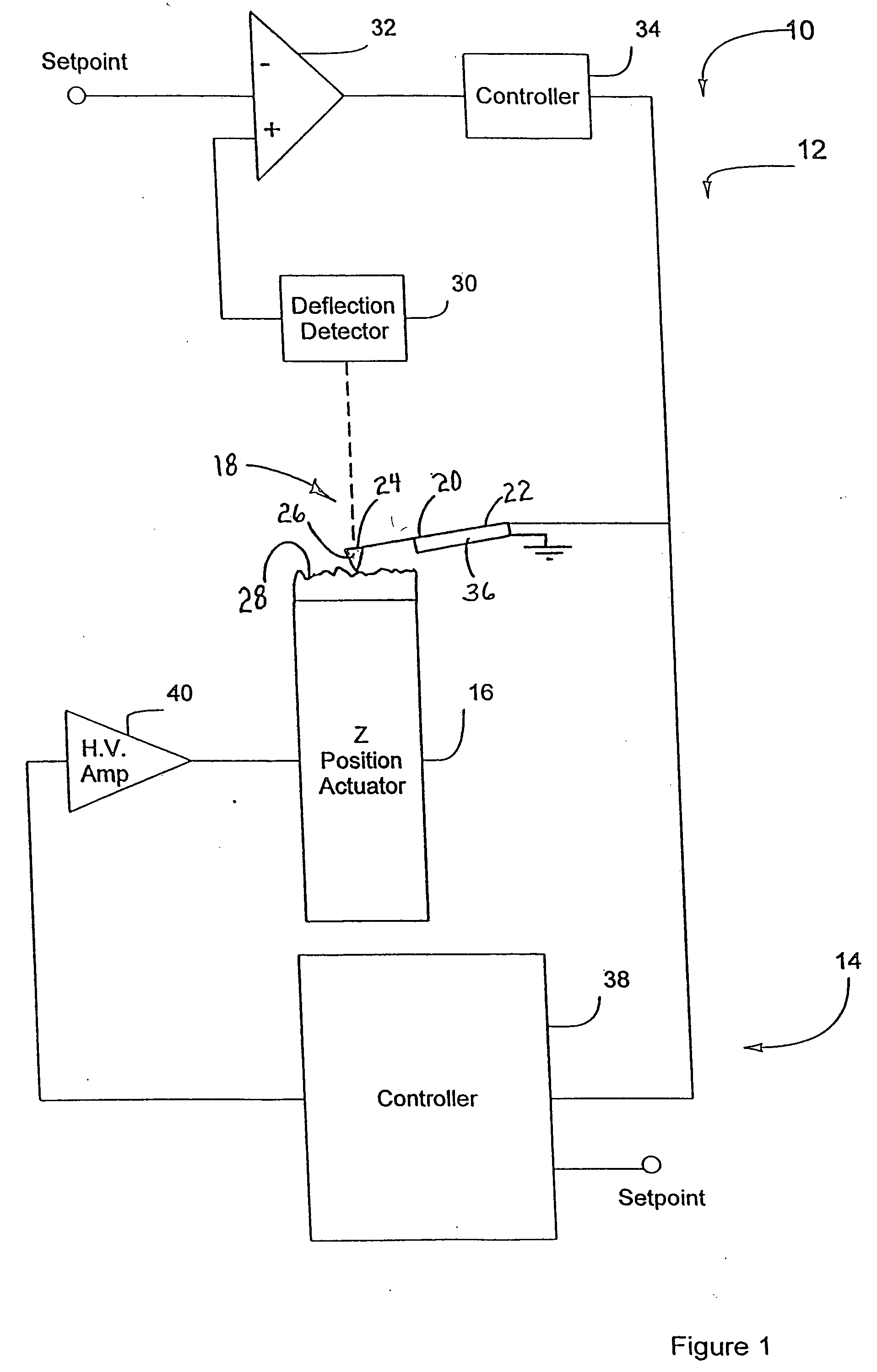

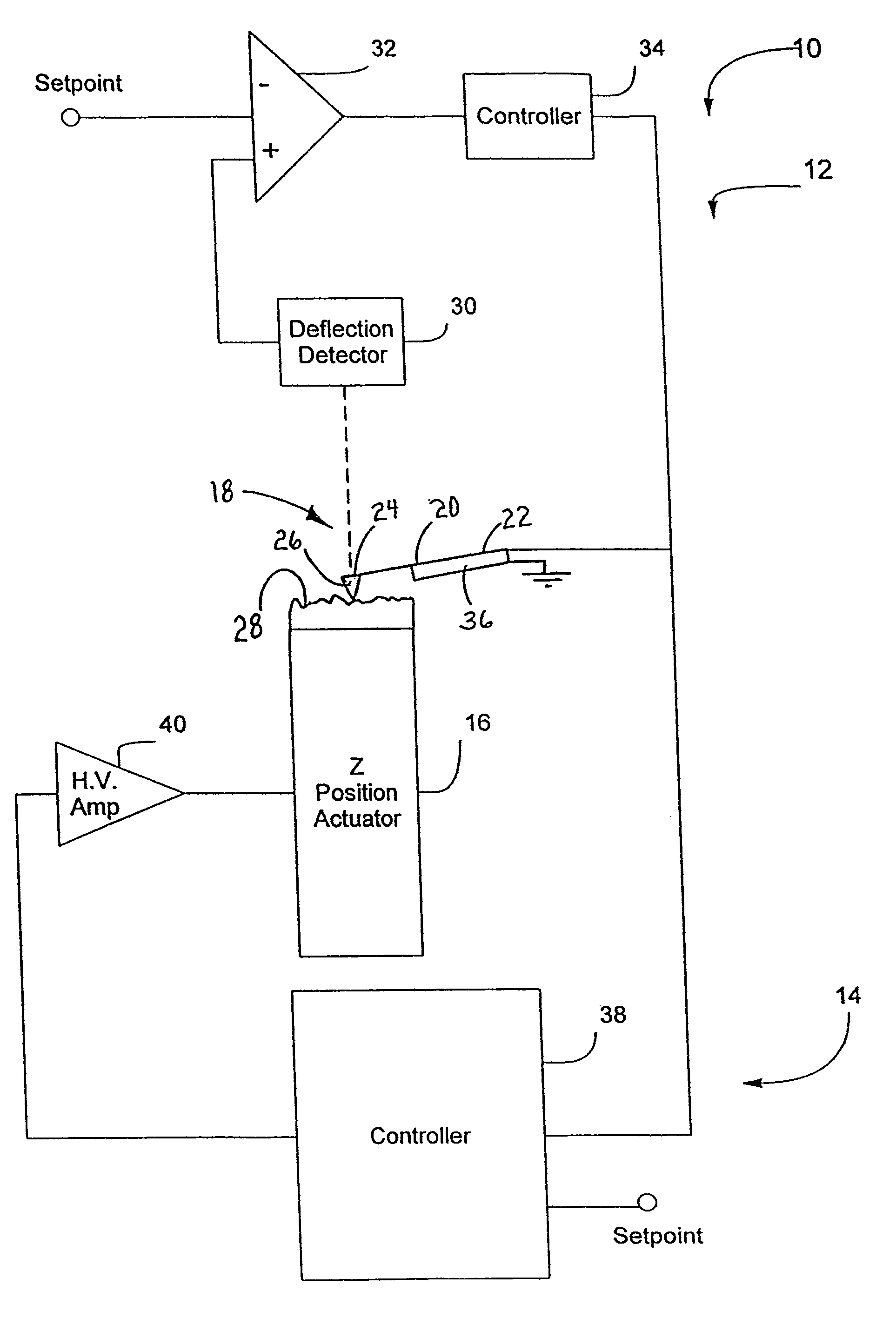

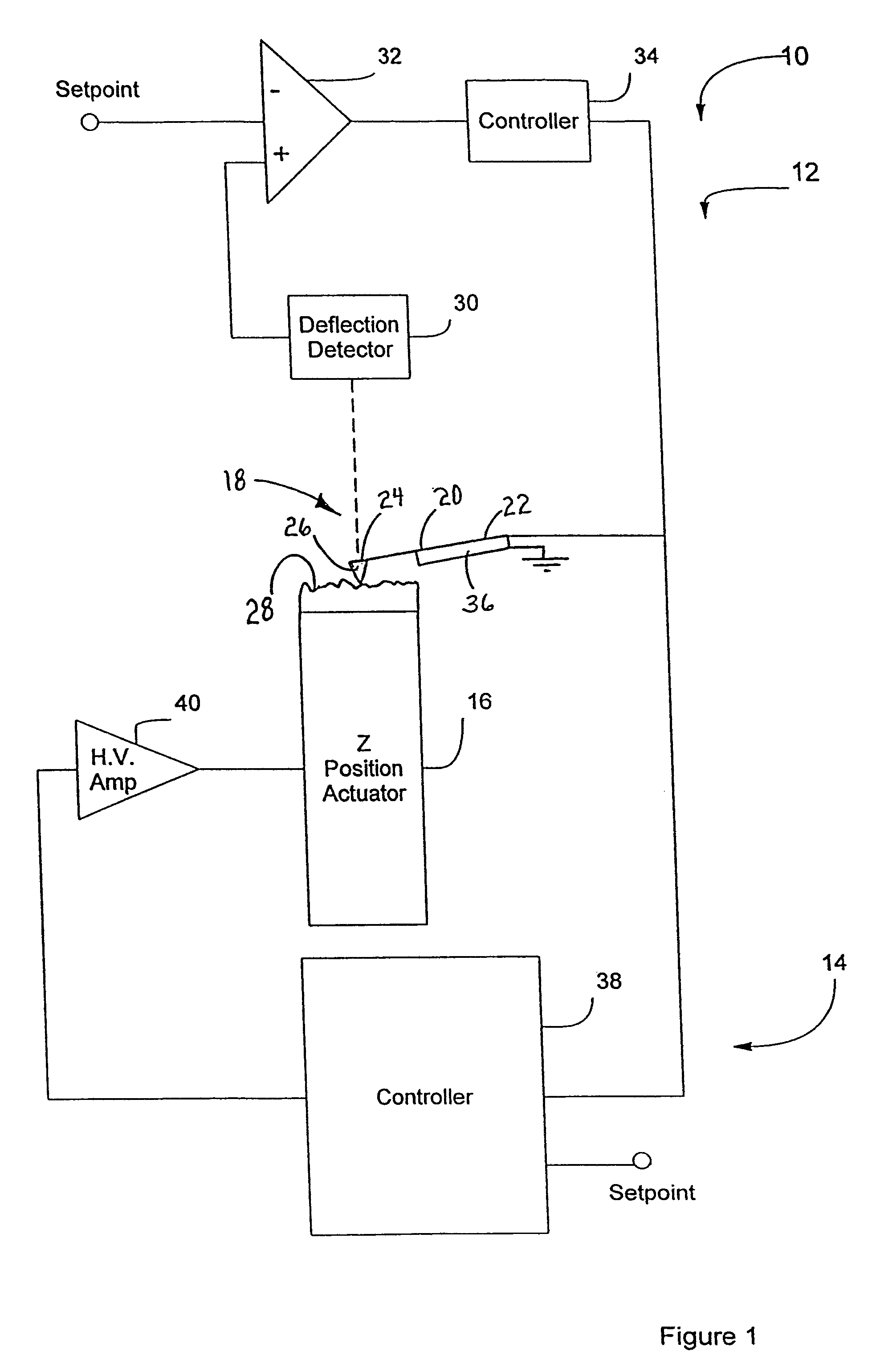

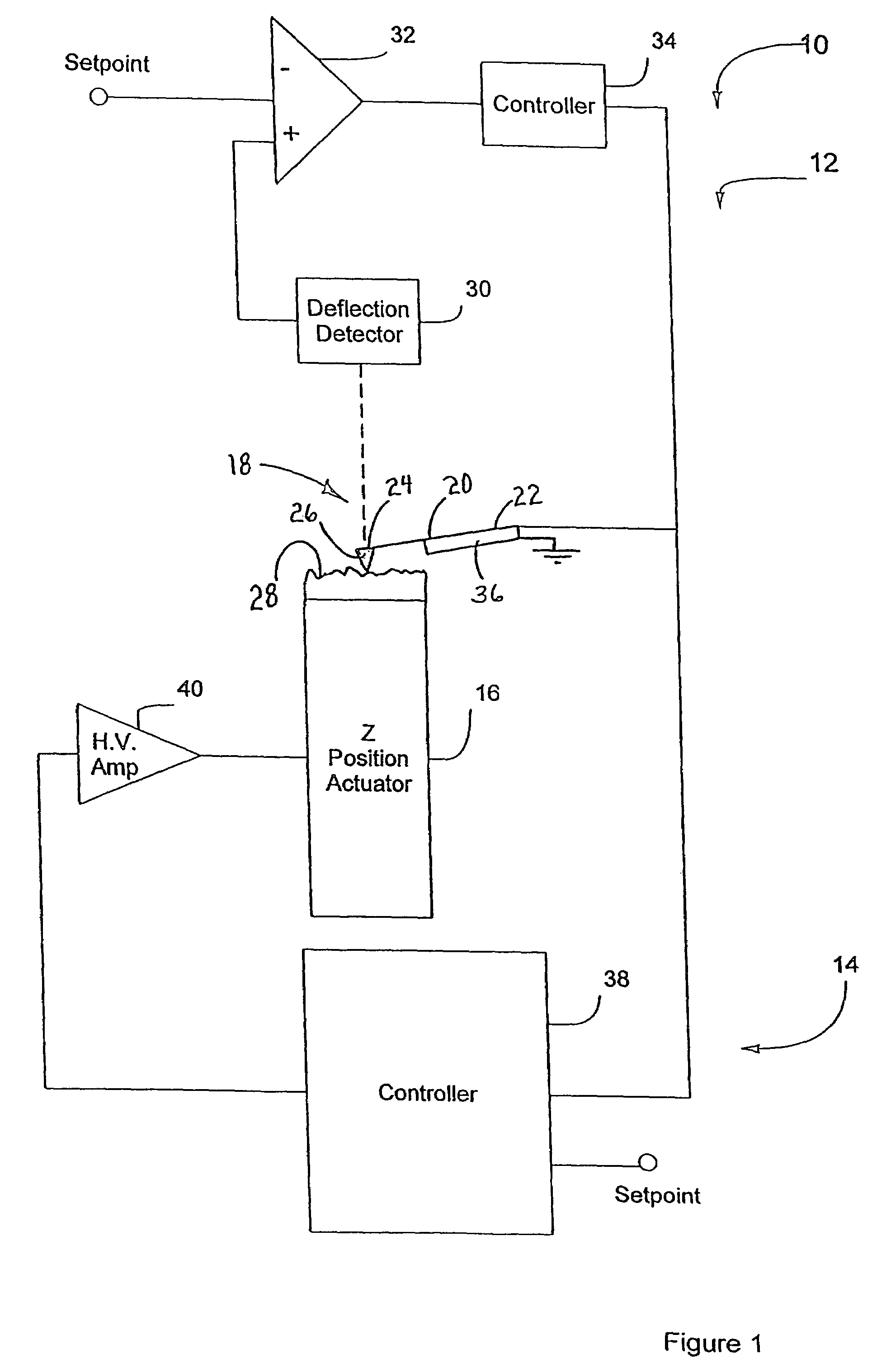

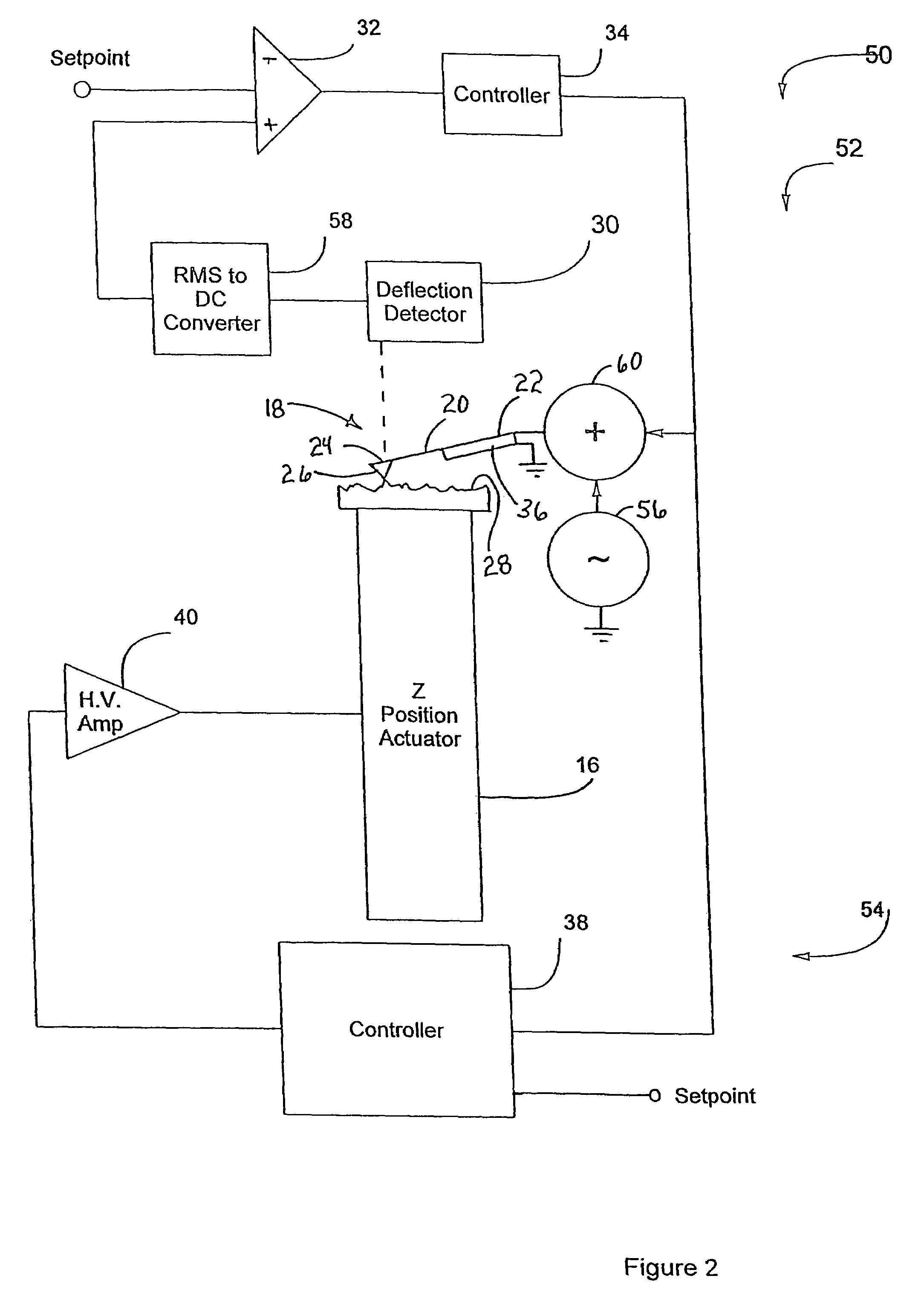

Active probe for an atomic force microscope and method of use thereof

InactiveUS6530266B1High-speed imagingAccurate Z position measurementNanotechElectric discharge tubesFrequency oscillationCantilever

An AFM that combines an AFM Z position actuator and a self-actuated Z position cantilever (both operable in cyclical mode and contact mode), with appropriate nested feedback control circuitry to achieve high-speed imaging and accurate Z position measurements. A preferred embodiment of an AFM for analyzing a surface of a sample in either ambient air or fluid includes a self-actuated cantilever having a Z-positioning element integrated therewith and an oscillator that oscillates the self-actuated cantilever at a frequency generally equal to a resonant frequency of the self-actuated cantilever and at an oscillation amplitude generally equal to a setpoint value. The AFM includes a first feedback circuit nested within a second feedback circuit, wherein the first feedback circuit generates a cantilever control signal in response to vertical displacement of the self-actuated cantilever during a scanning operation, and the second feedback circuit is responsive to the cantilever control signal to generate a position control signal. A Z position actuator is also included within the second feedback circuit and is responsive to the position control signal to position the sample. In operation, preferably, the cantilever control signal alone is indicative of the topography of the sample surface. In a further embodiment, the first feedback circuit includes an active damping circuit for modifying the quality factor ("Q") of the cantilever resonance to optimize the bandwidth of the cantilever response.

Owner:BRUKER NANO INC

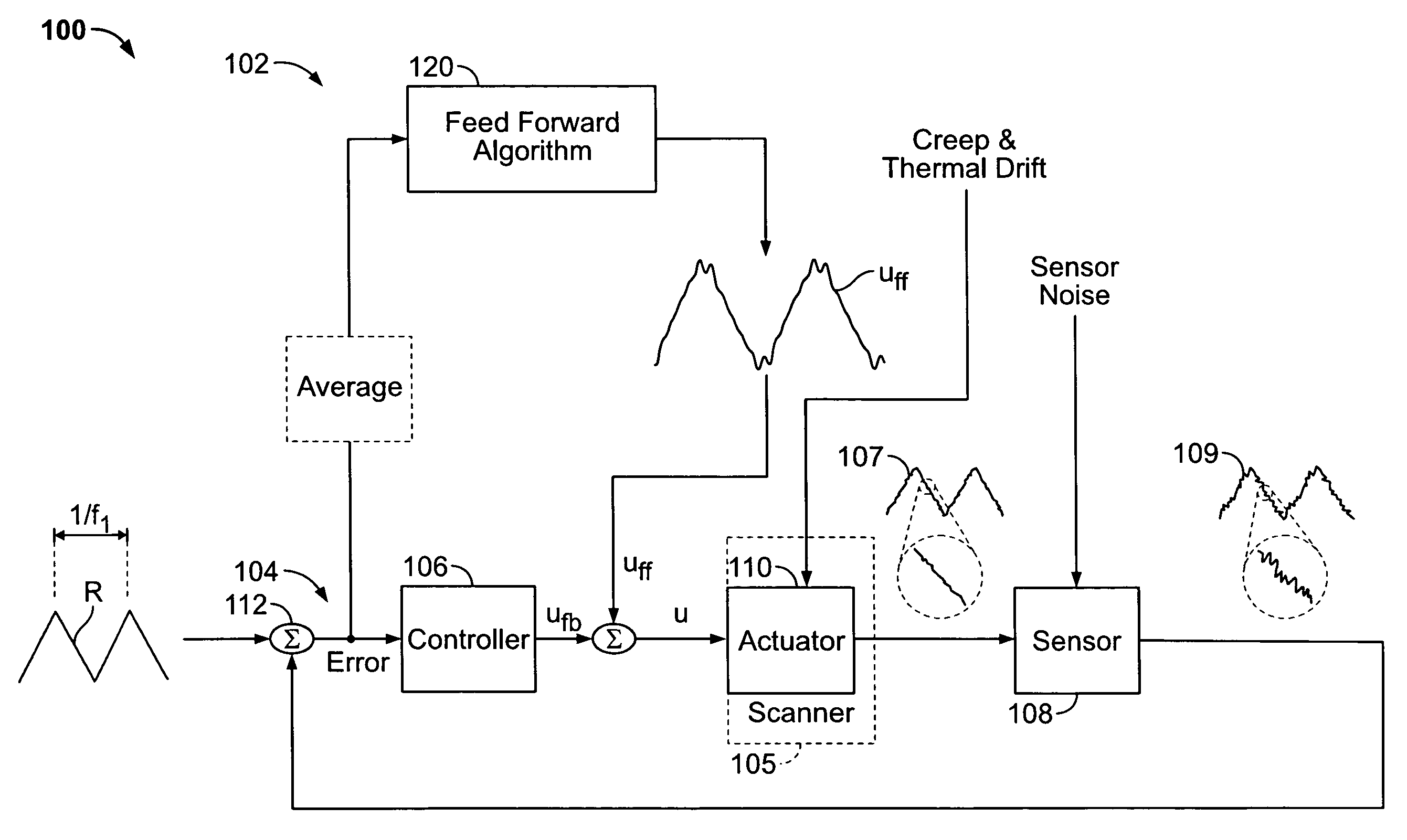

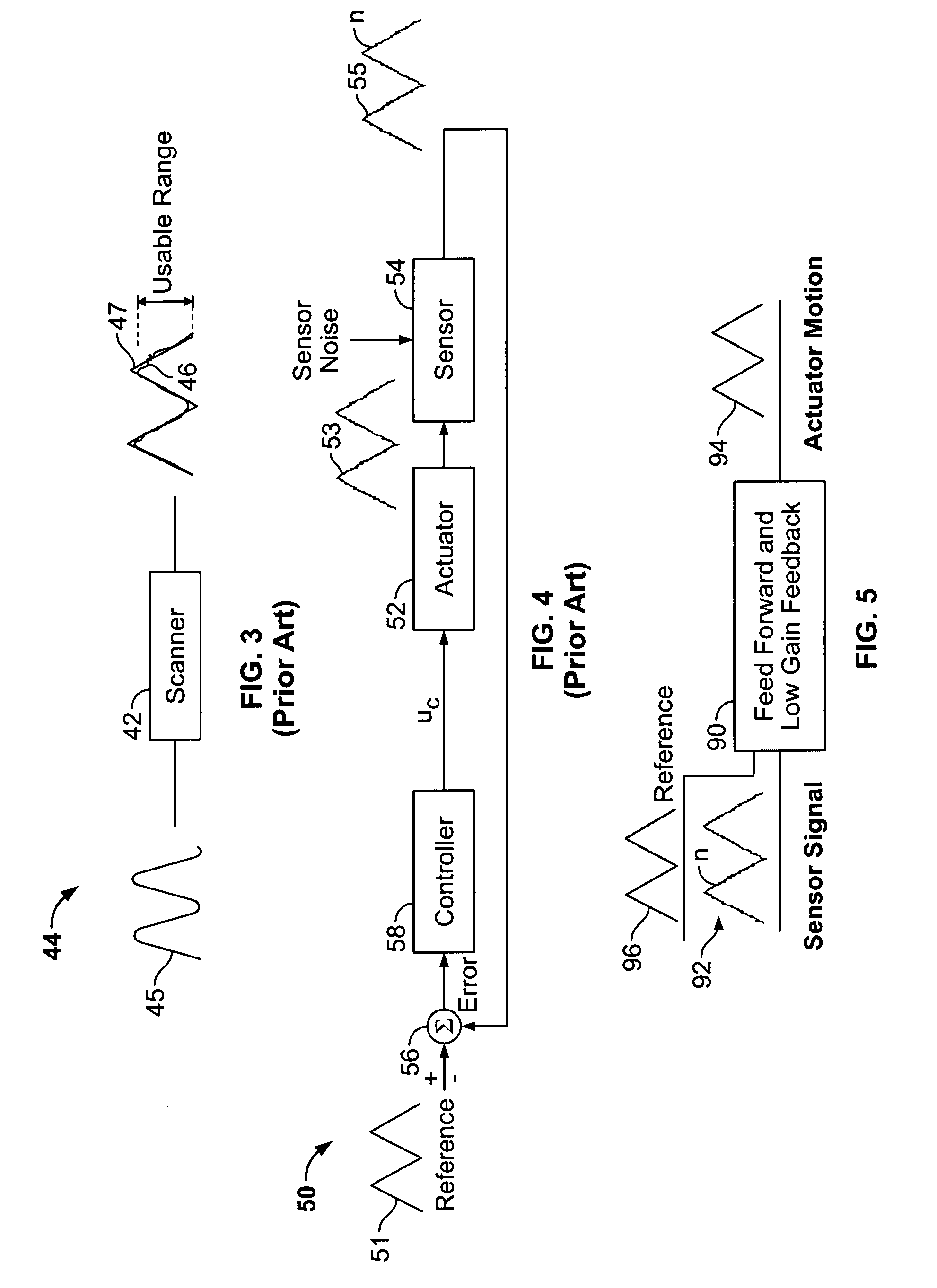

Closed loop controller and method for fast scanning probe microscopy

ActiveUS20080277582A1High frequency noiseReduce high frequency noiseMaterial analysis using wave/particle radiationNanotechnologyFast scanningMicroscope

A method of operating a metrology instrument includes generating relative motion between a probe and a sample at a scan frequency using an actuator. The method also includes detecting motion of the actuator using a position sensor that exhibits noise in the detected motion, and controlling the position of the actuator using a feedback loop and a feed forward algorithm. In this embodiment, the controlling step attenuates noise in the actuator position compared to noise exhibited by the position sensor over the scan bandwidth. Scan frequencies up to a third of the first scanner resonance frequency or greater than 300 Hz are possible.

Owner:BRUKER NANO INC

Active probe for an atomic force microscope and method for use thereof

InactiveUS20050066714A1High-speed imagingAccurate measurementNanotechElectric discharge tubesControl signalFeedback circuits

An AFM that combines an AFM Z position actuator and a self-actuated Z position cantilever (both operable in cyclical mode and contact mode), with appropriate nested feedback control circuitry to achieve high-speed imaging and accurate Z position measurements. A preferred embodiment of an AFM for analyzing a surface of a sample in either ambient air or fluid includes a self-actuated cantilever having a Z-positioning element integrated therewith and an oscillator that oscillates the self-actuated cantilever at a frequency generally equal to a resonant frequency of the self-actuated cantilever and at an oscillation amplitude generally equal to a setpoint value. The AFM includes a first feedback circuit nested within a second feedback circuit, wherein the first feedback circuit generates a cantilever control signal in response to vertical displacement of the self-actuated cantilever during a scanning operation, and the second feedback circuit is responsive to the cantilever control signal to generate a position control signal. A Z position actuator is also included within the second feedback circuit and is responsive to the position control signal to position the sample. In operation, preferably, the cantilever control signal alone is indicative of the topography of the sample surface. In a further embodiment, the first feedback circuit includes an active damping circuit for modifying the quality factor (“Q”) of the cantilever resonance to optimize the bandwidth of the cantilever response.

Owner:BRUKER NANO INC

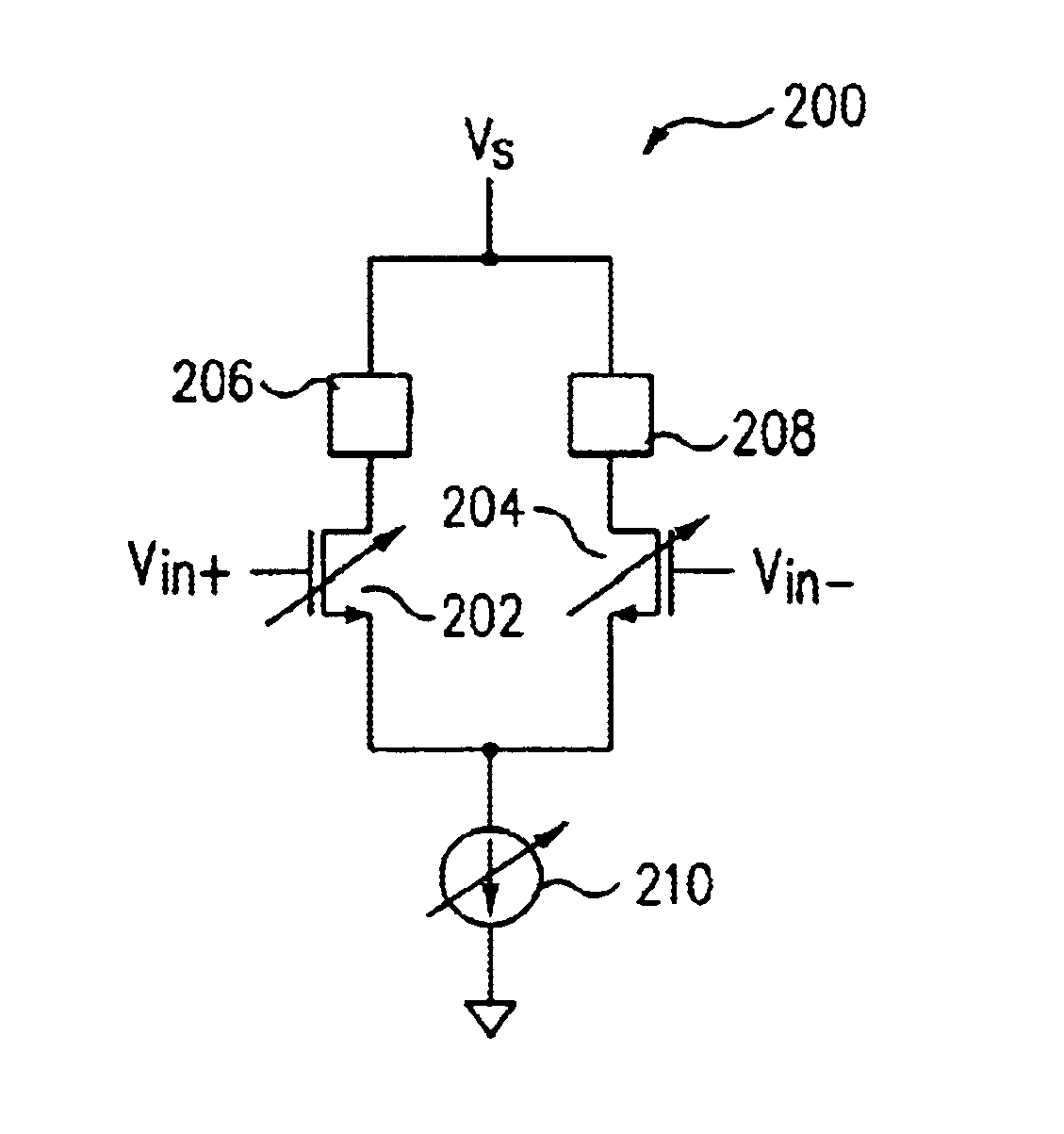

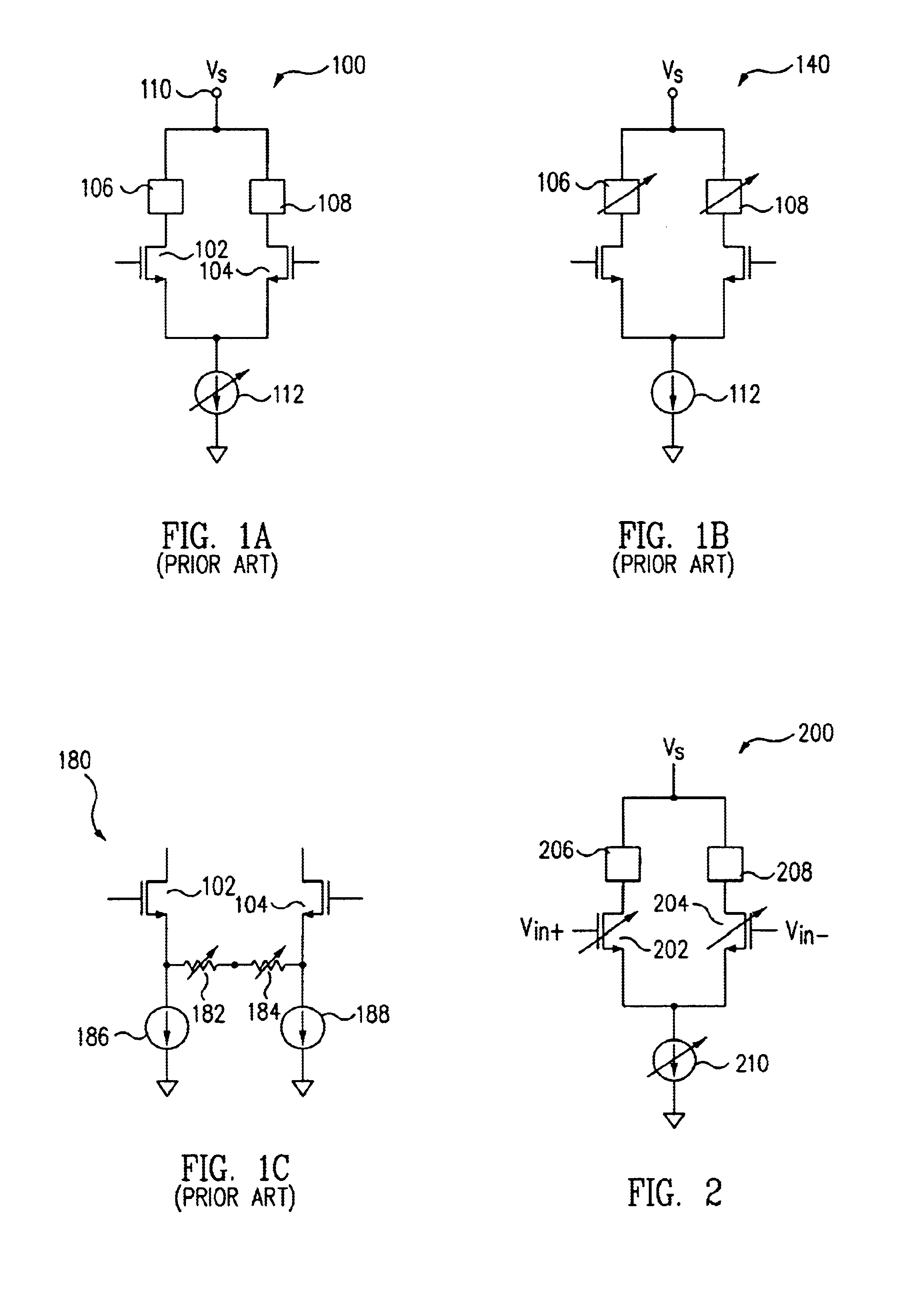

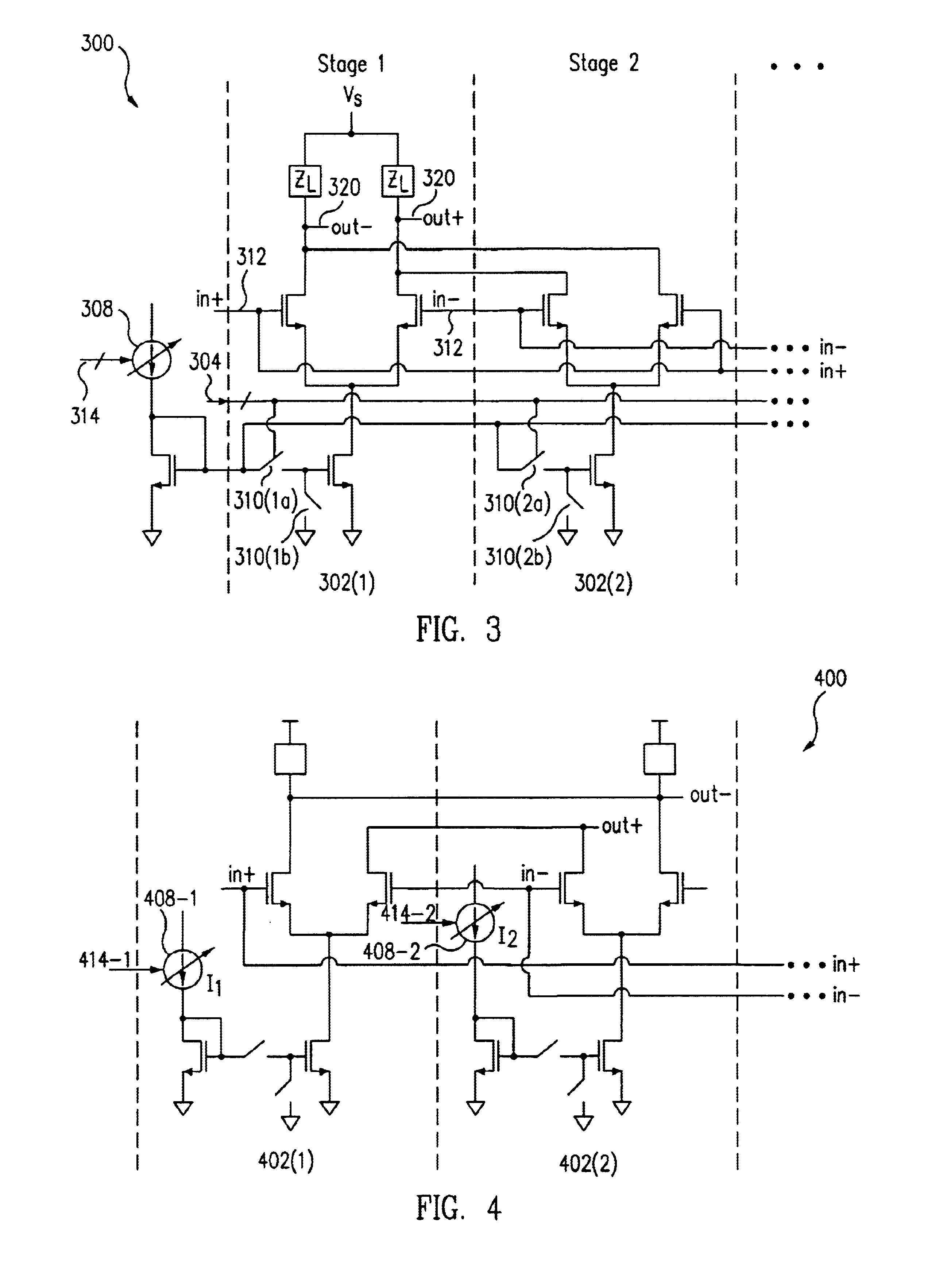

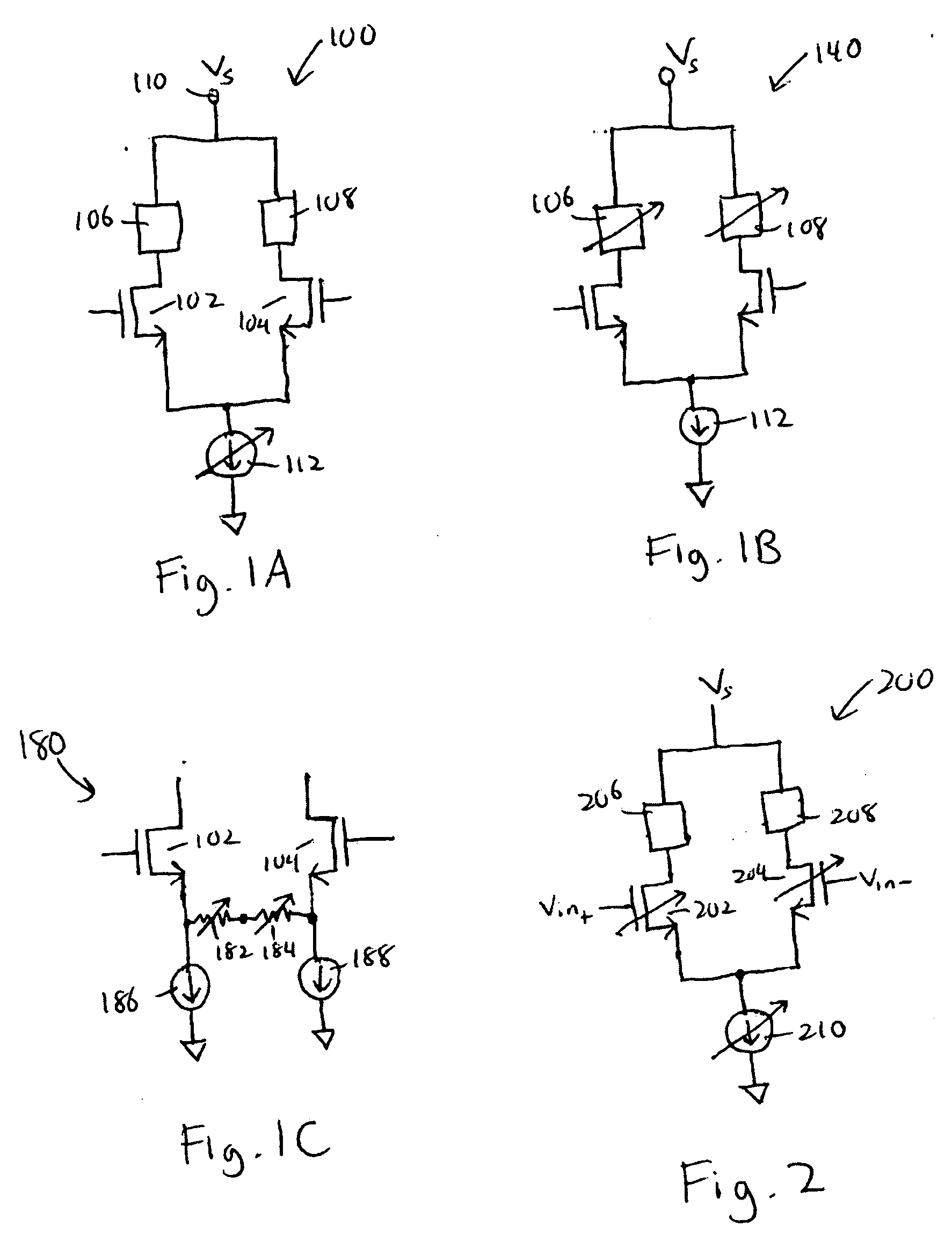

Digitally controlled transconductance cell

ActiveUS6985036B2Improve controllabilityKeep linearDifferential amplifiersDc-amplifiers with dc-coupled stagesTransconductanceCurrent source

A digitally controlled transconductance cell includes a differential transistor pair coupled to load elements (either passive or active with resistive or impedance loads) and a variable bias current source, where the transconductance or gain is digitally varied by changing the aspect ratio of the transistors and the bias current.

Owner:SCINTERA NETWORKS

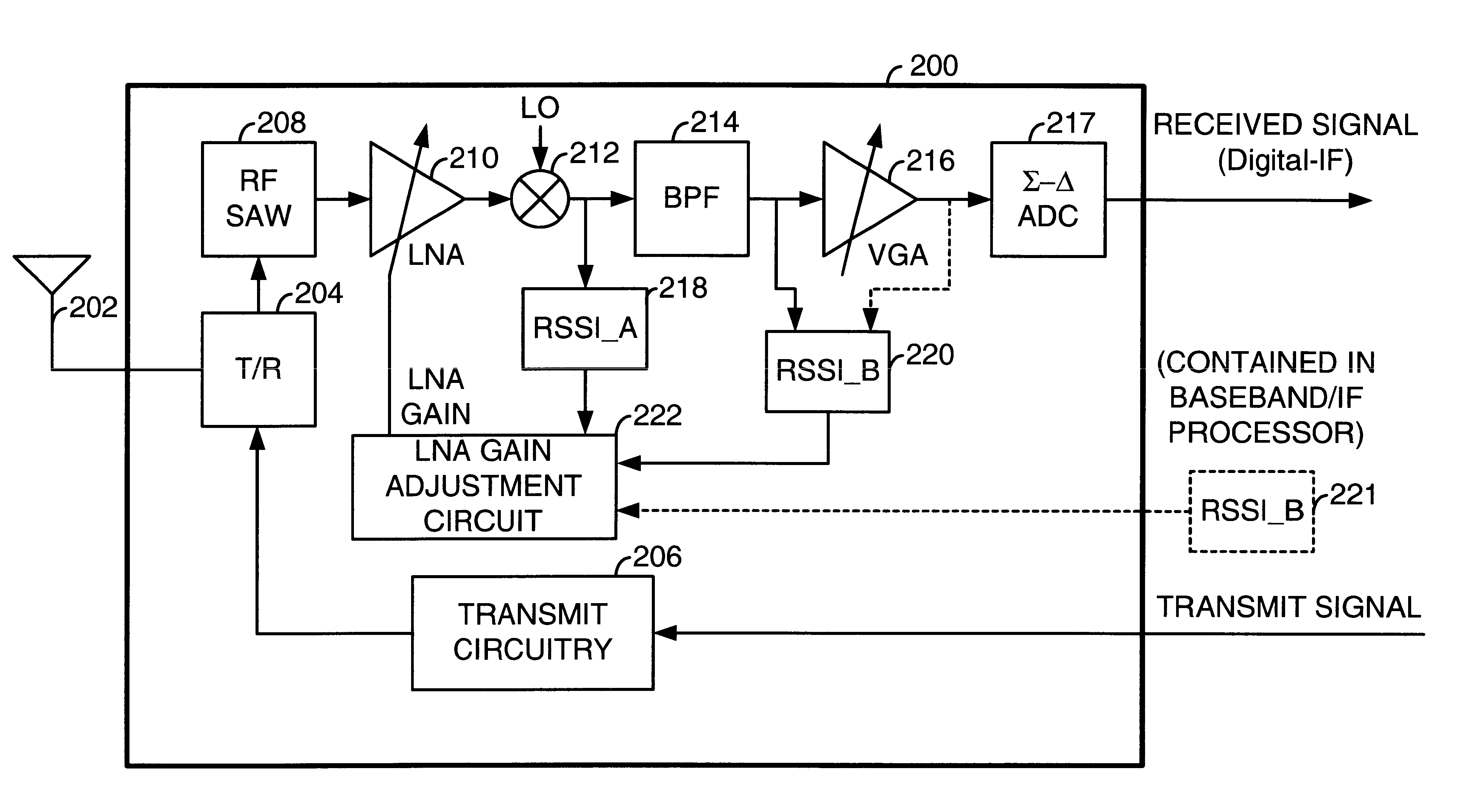

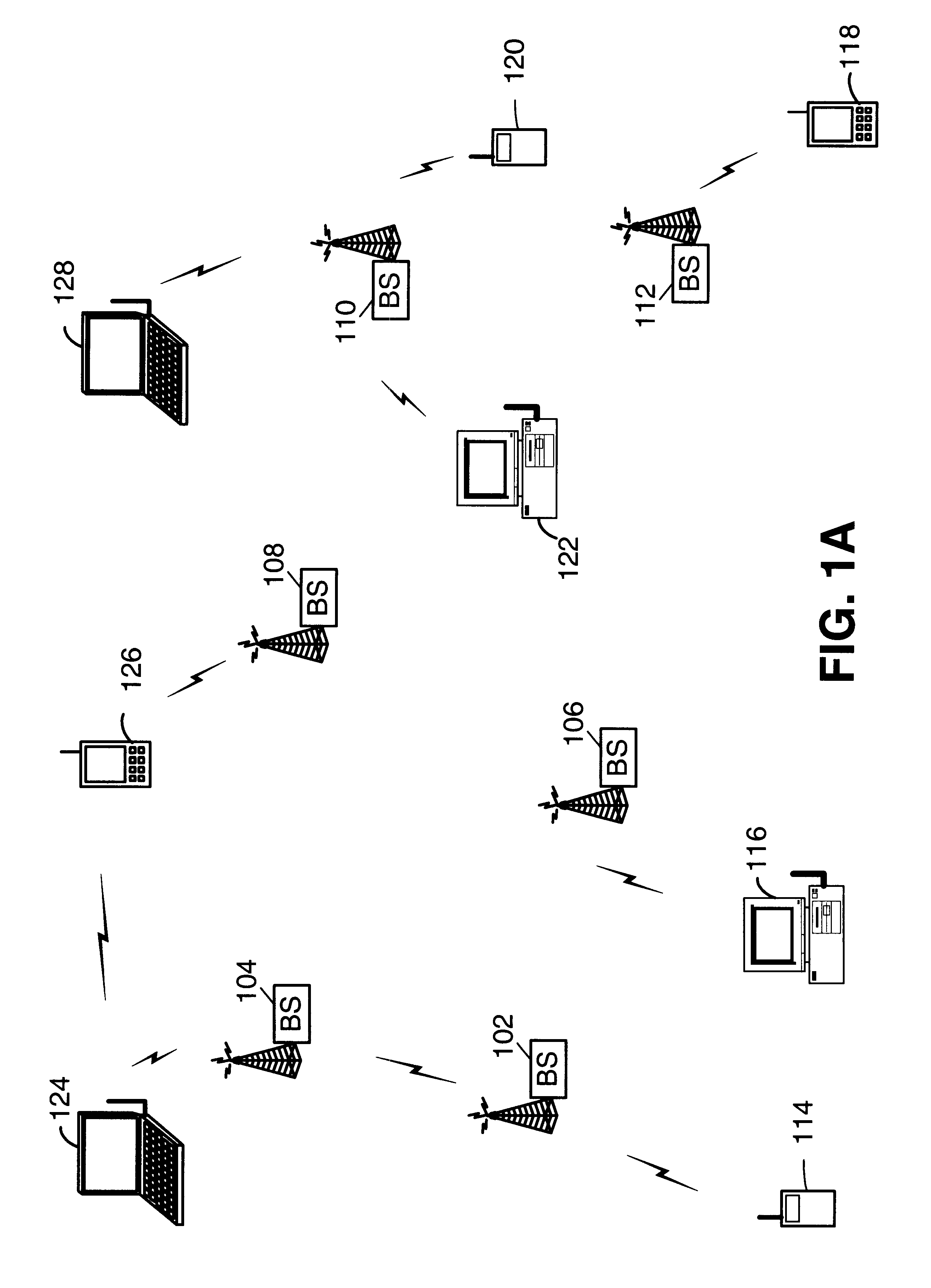

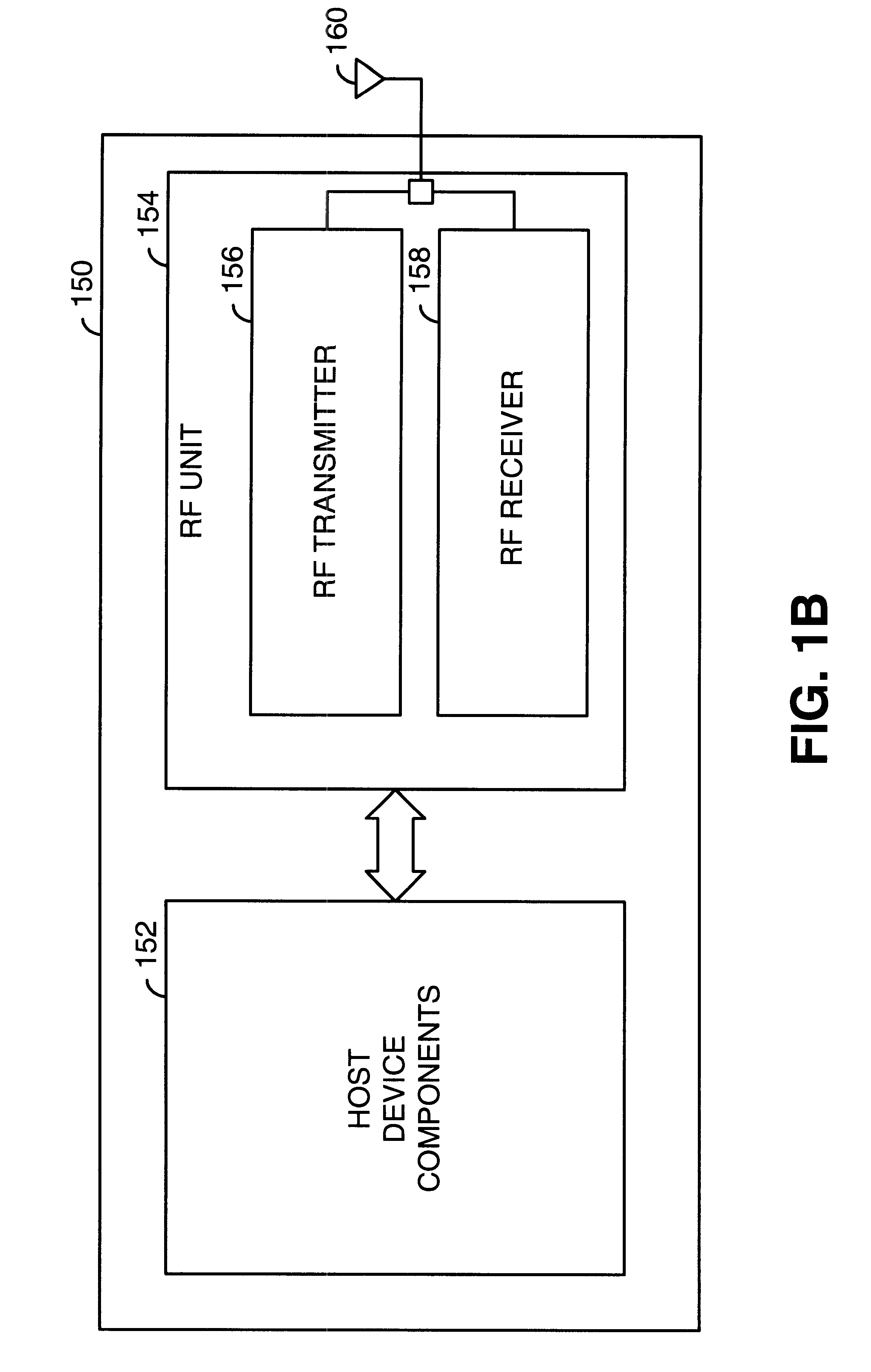

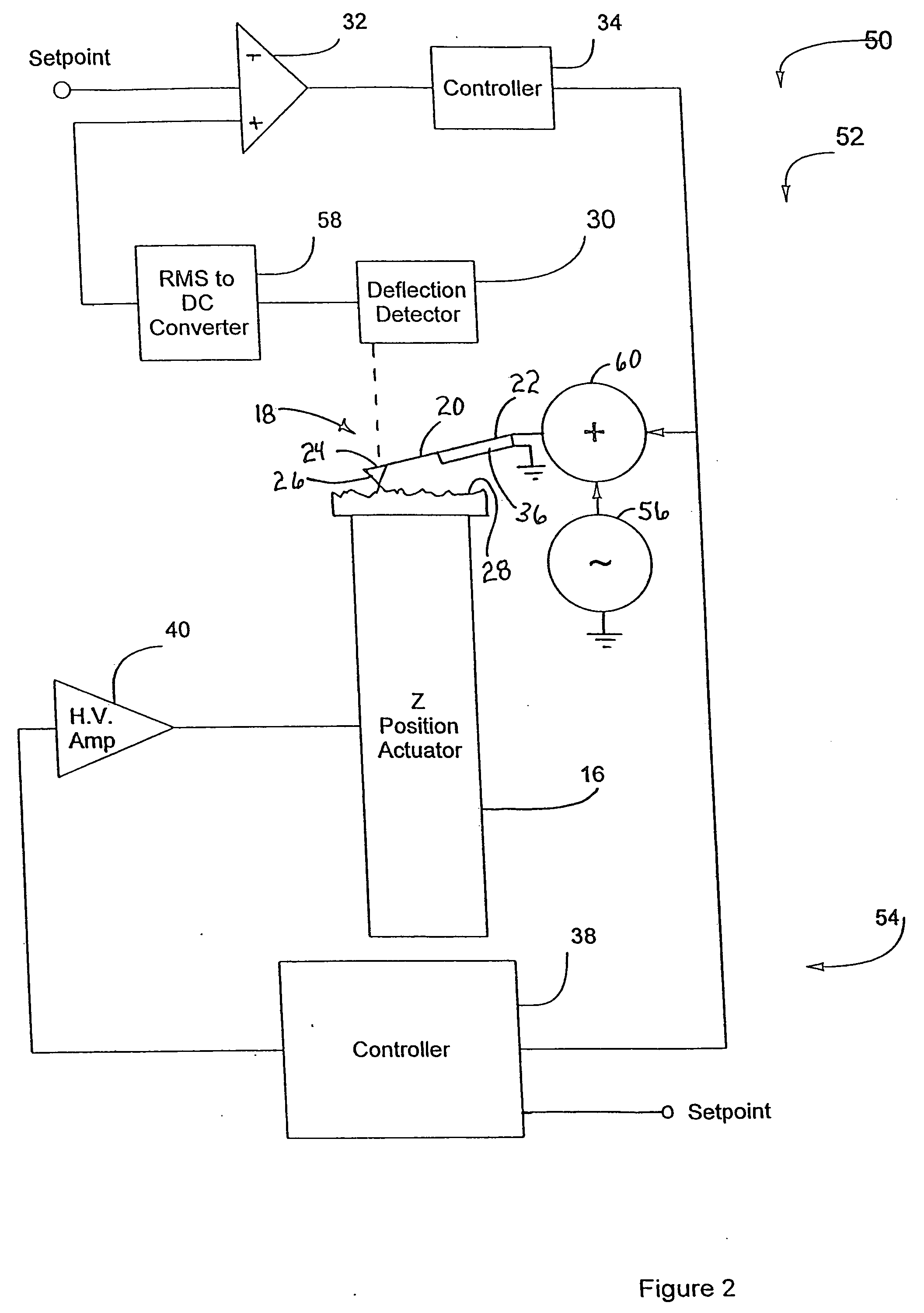

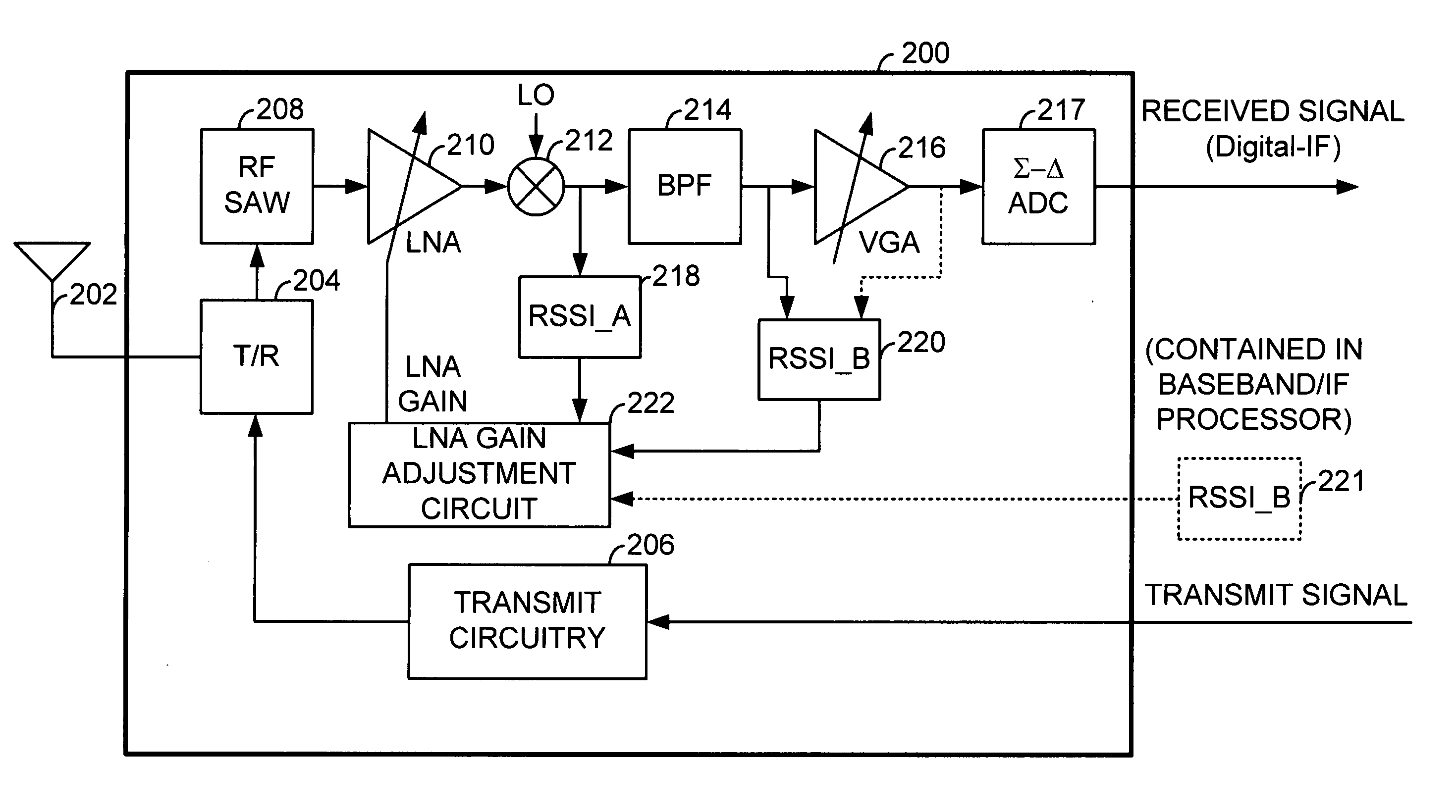

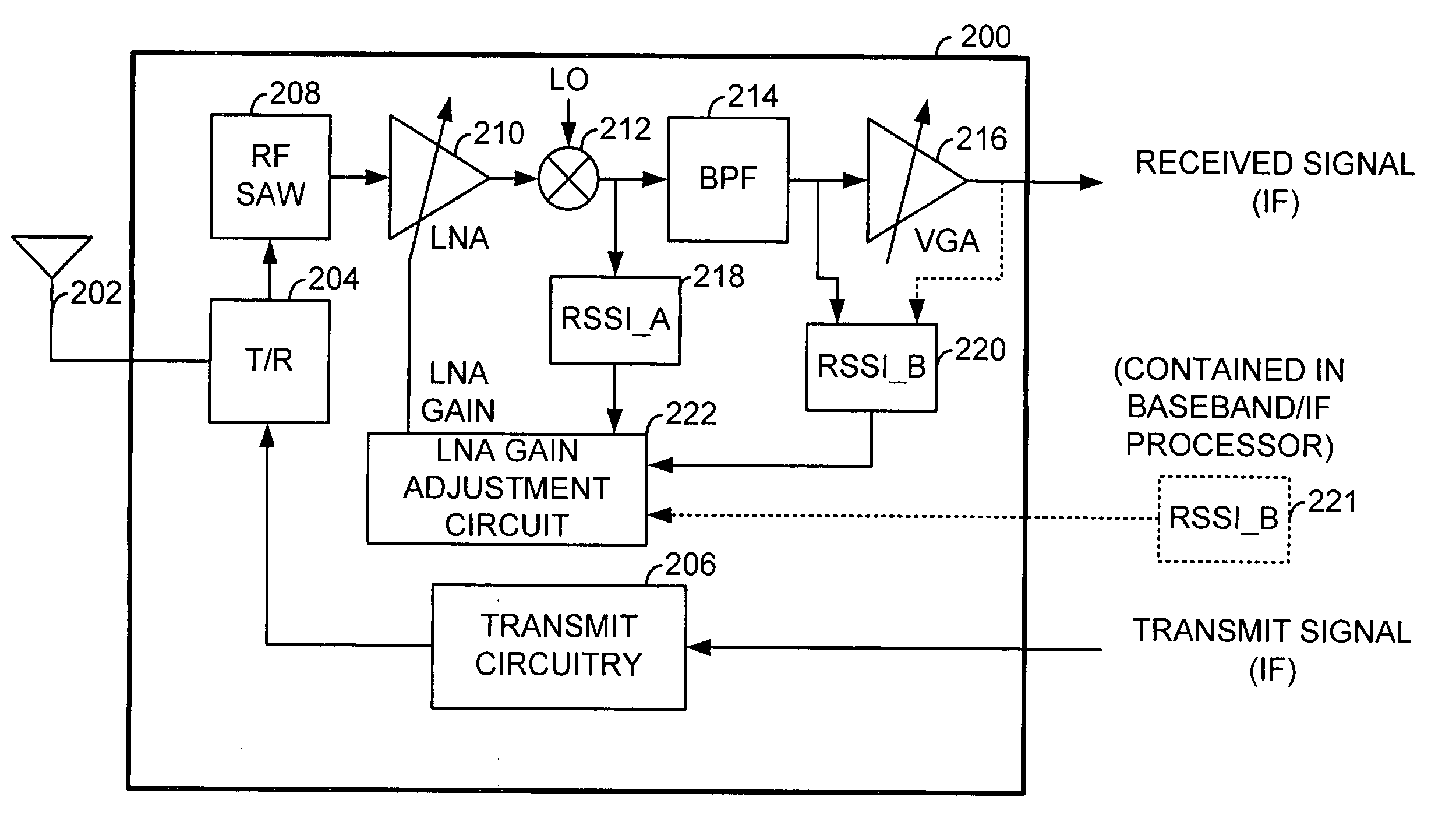

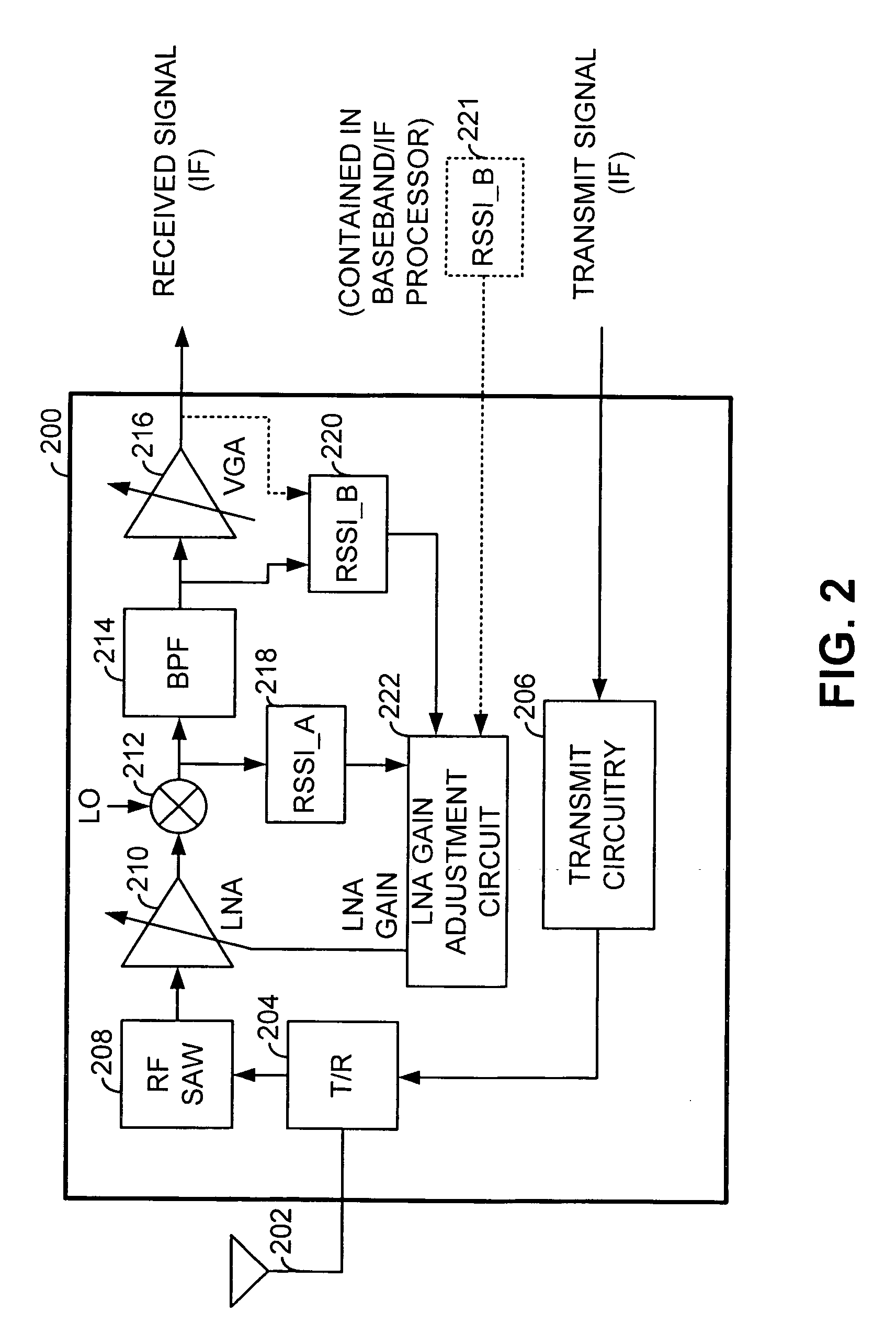

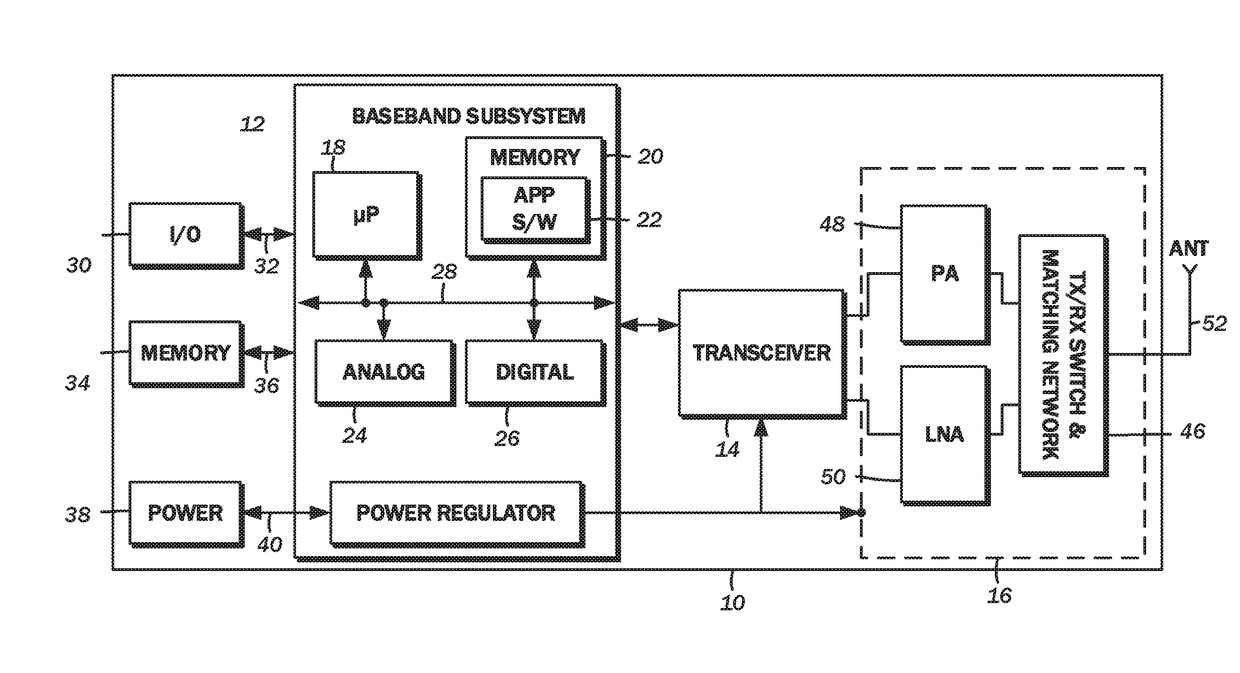

Timing based LNA gain adjustment in an RF receiver to compensate for intermodulation interference

InactiveUS6873832B2Keep linearMaximize signal to noise ratioAmplifier modifications to reduce non-linear distortionGain controlLinear regionSignal-to-noise ratio (imaging)

A Radio Frequency (RF) receiver includes a low noise amplifier (LNA) and a mixer coupled to the output of the LNA. The gain of the LNA is adjusted to maximize signal-to-noise ratio of the mixer and to force the mixer to operate well within its linear region when an intermodulation interference component is present. The RF receiver includes a first received signal strength indicator (RSSI_A) coupled to the output of the mixer that measures the strength of the wideband signal at that point. A second received signal strength indicator (RSSI_B) couples after the BPF and measures the strength of the narrowband signal. The LNA gain is set based upon these signal strengths. LNA gain is determined during a guard period preceding an intended time slot of a current frame and during a guard period following an intended time slot of a prior frame. The lesser of these two LNA gains is used for the intended time slot of the current frame.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

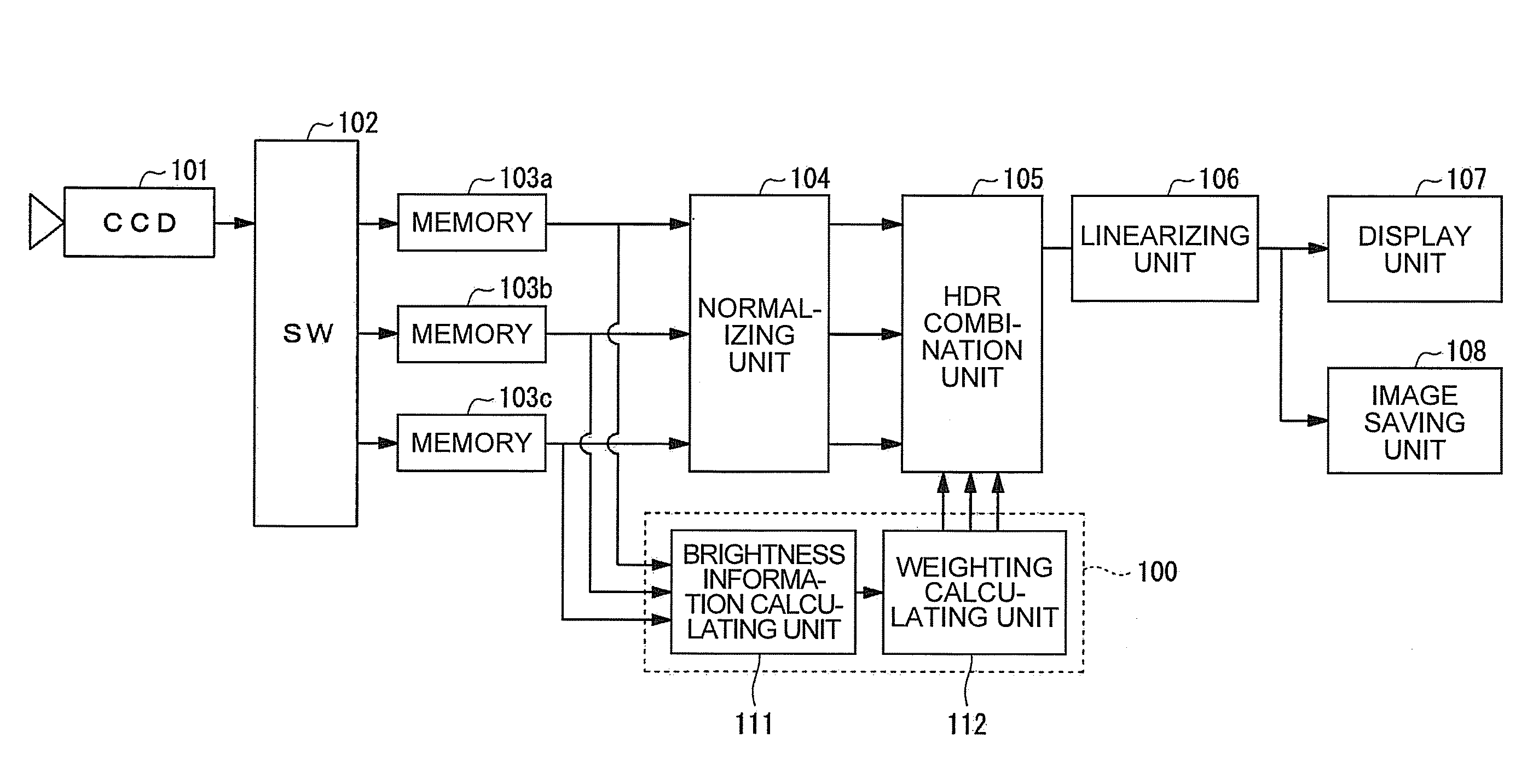

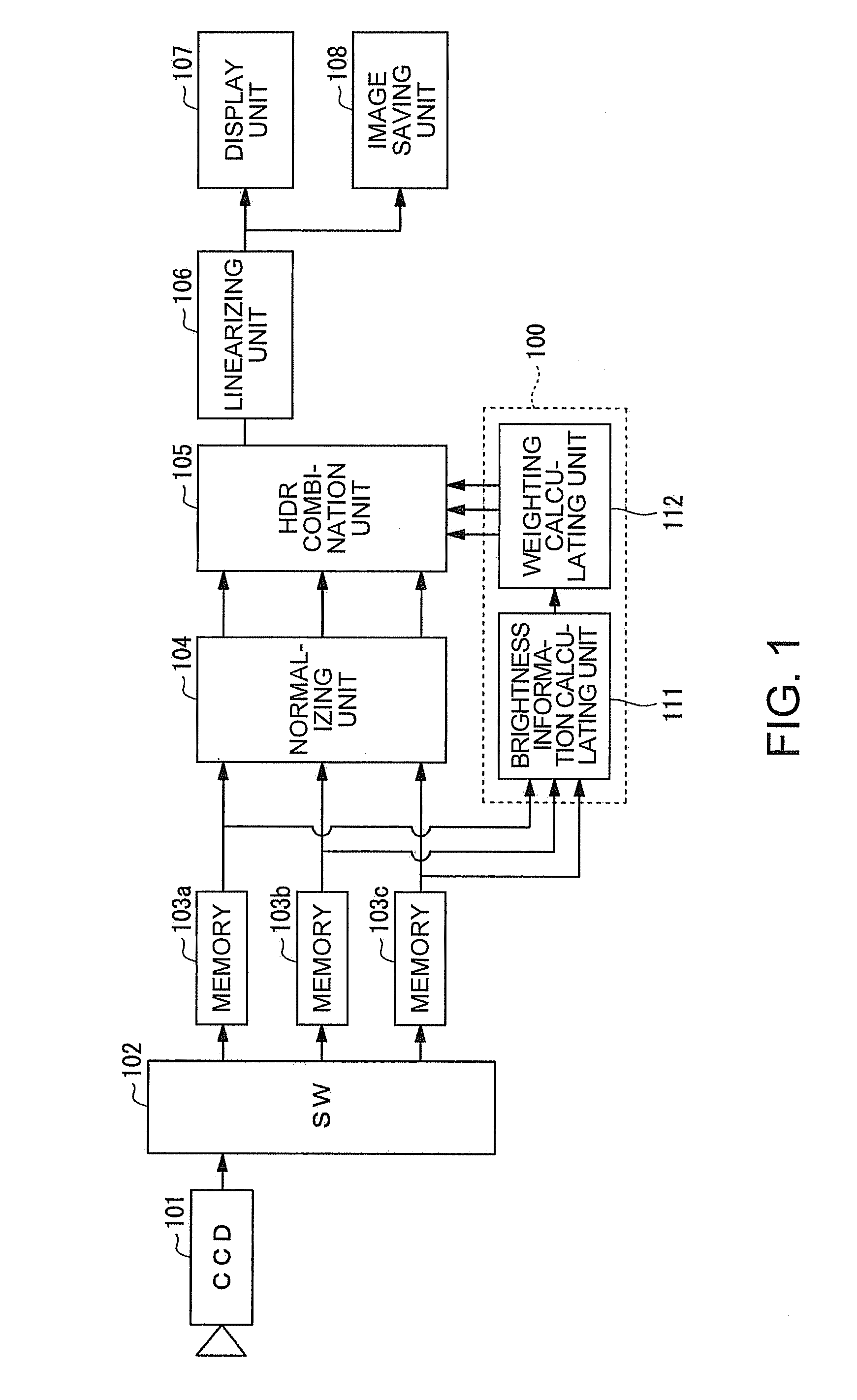

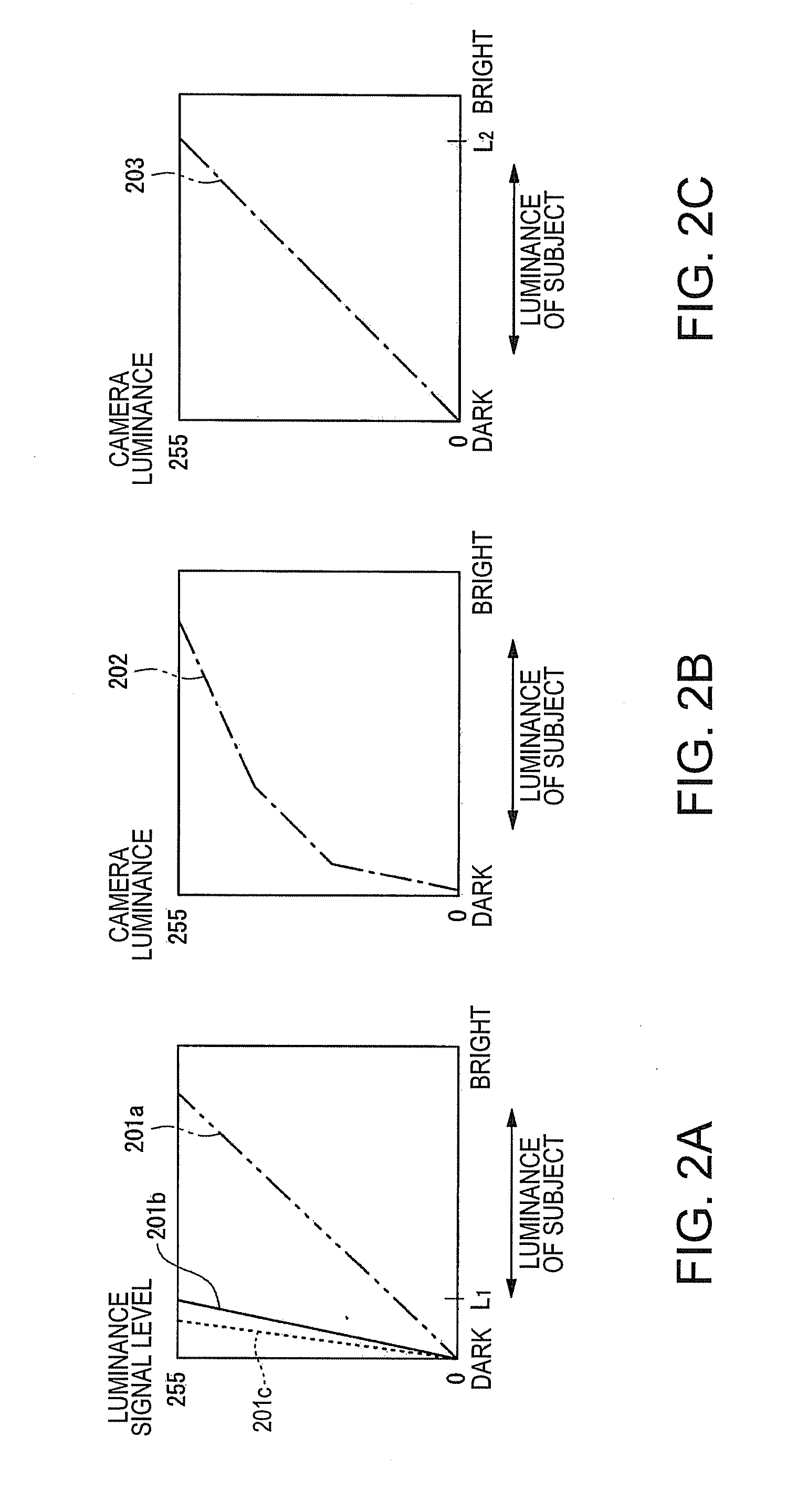

Image processing apparatus and image processing method

InactiveUS20090046947A1Improve image qualityReduce noiseTelevision system detailsImage enhancementImaging processingLightness

An image processing apparatus that generates a combined image by combining plural image data acquired as a result of digitizing plural images acquired by shooting with different quantities of exposure, includes a weighting unit that adds weight to adjust proportion of combination of the image data, to at least one of the plural image data. The weighting unit includes a luminance data generating unit that combines data related to luminance of the plural image data and thus generates combined luminance data, and a weight deciding unit that decides the weight added to the image data in accordance with the combined luminance data generated by the luminance data generating unit.

Owner:SEIKO EPSON CORP

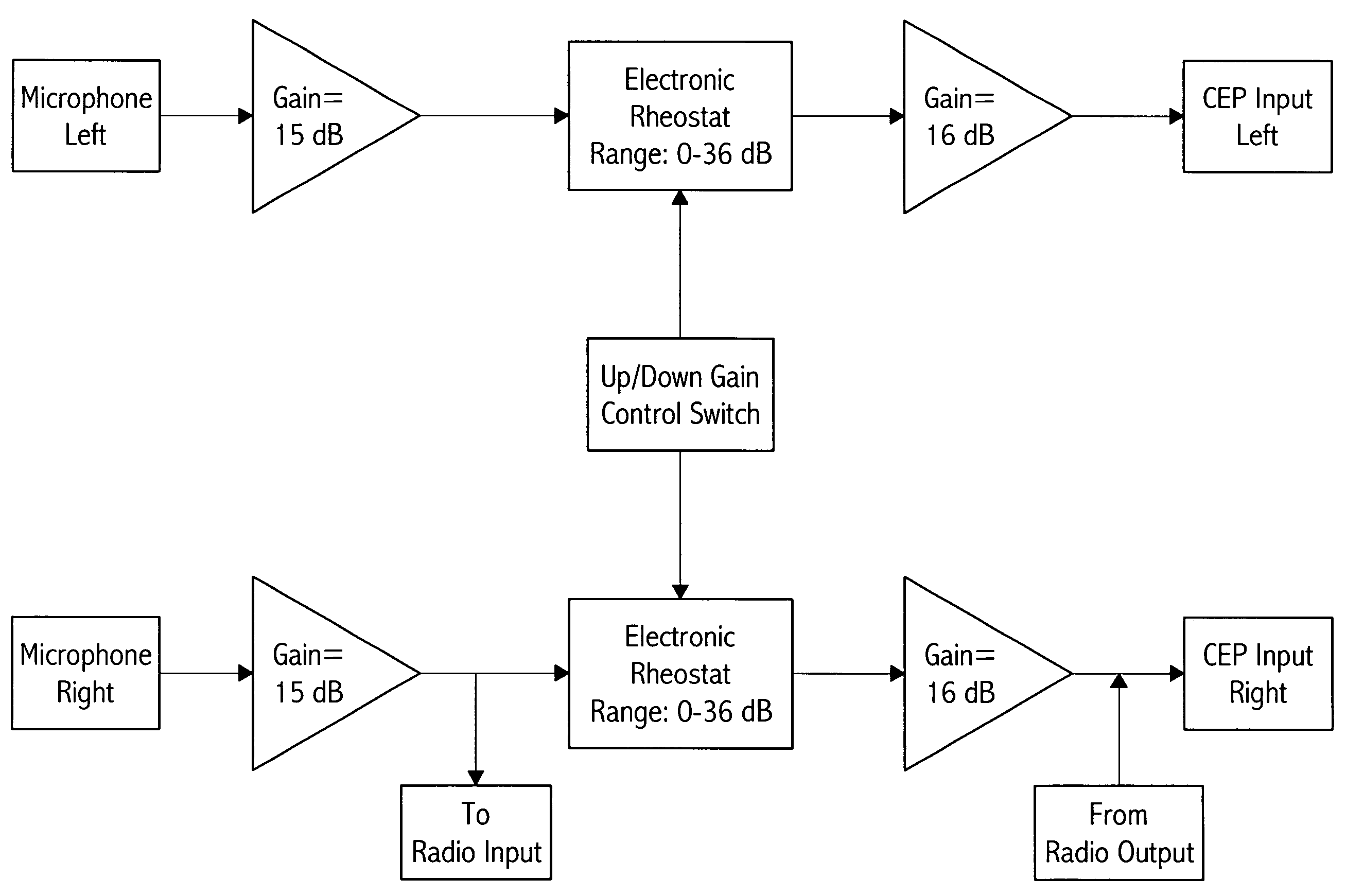

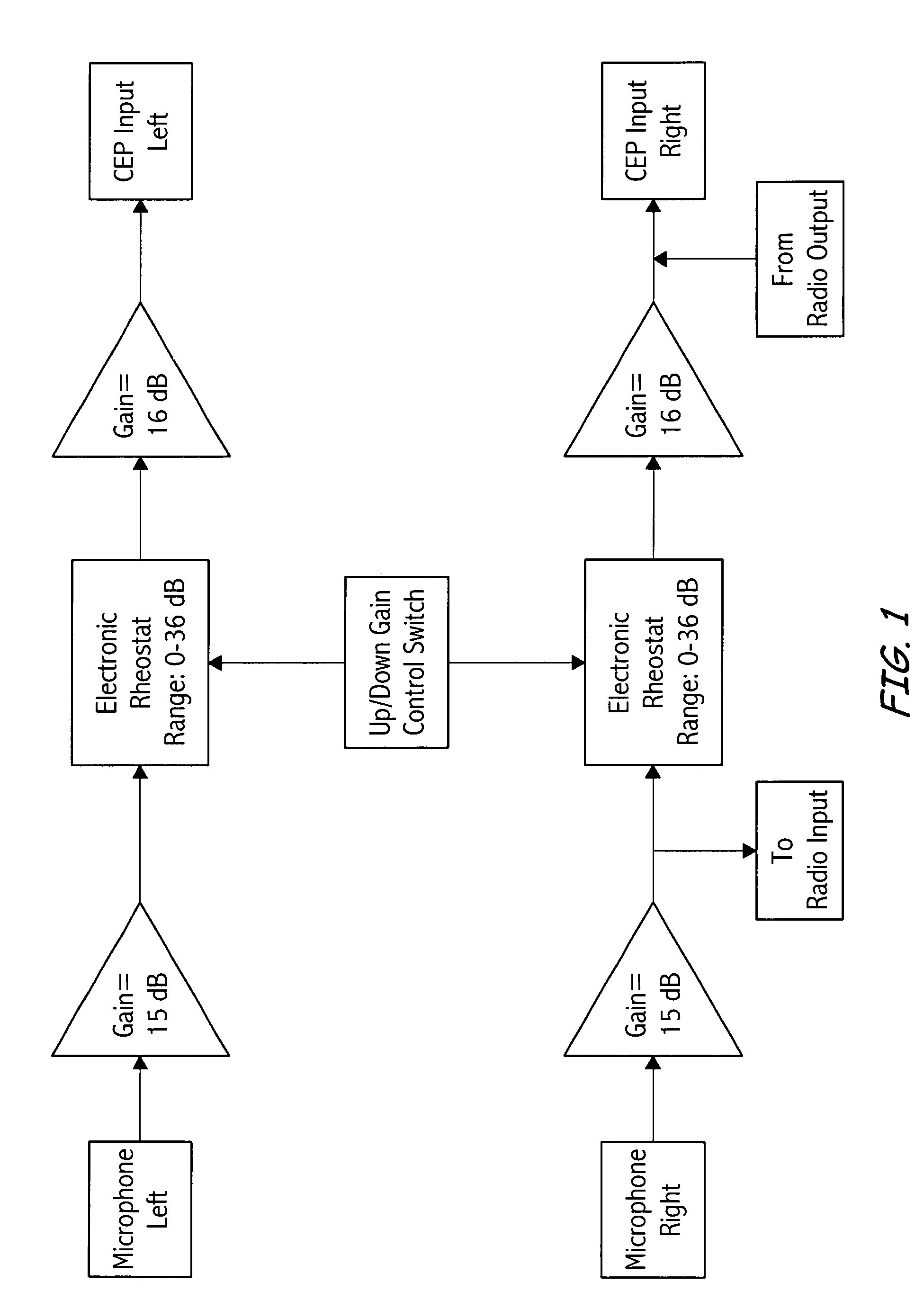

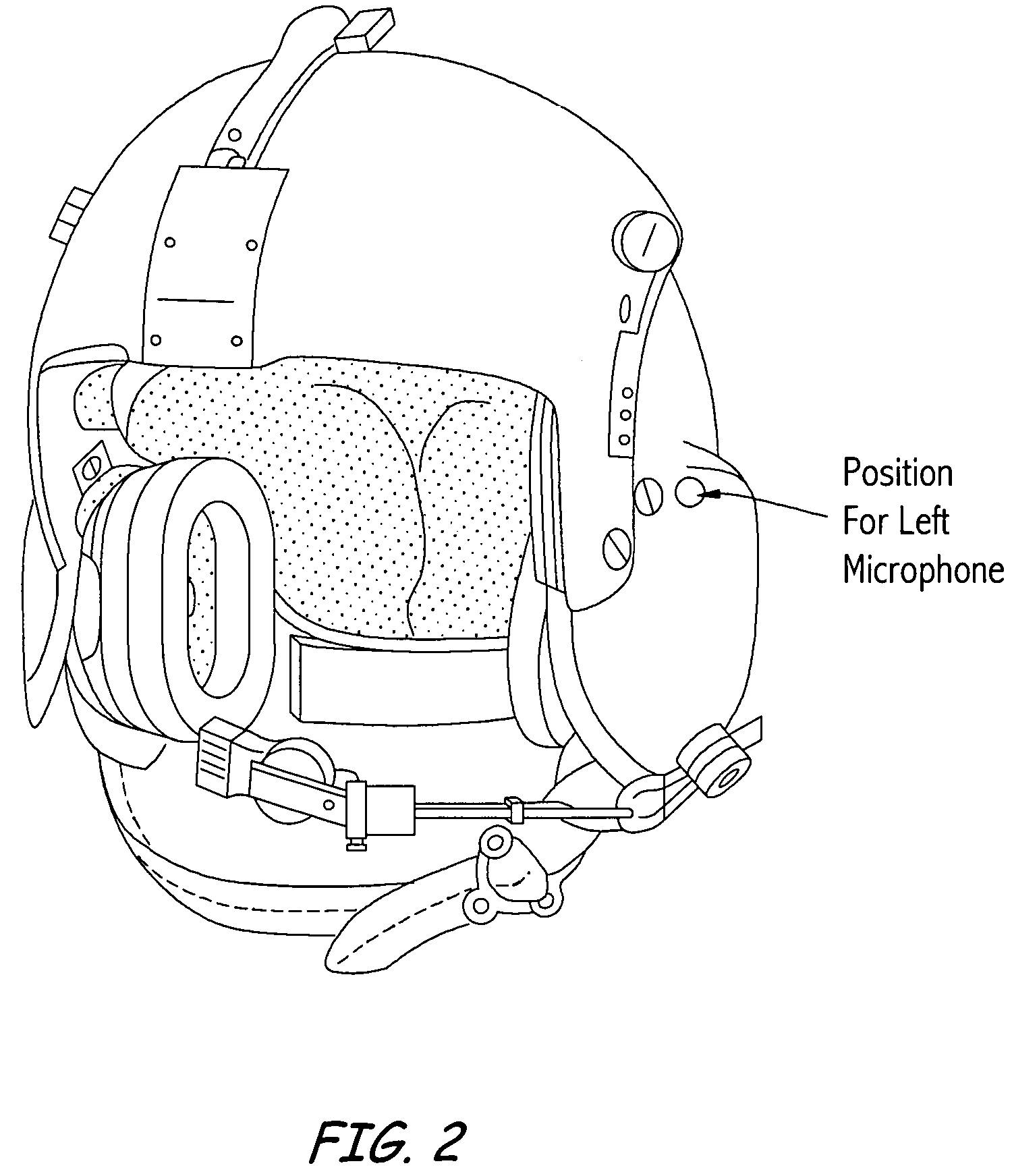

Apparatus for communication and reconnaissance coupled with protection of the auditory system

ActiveUS7352871B1Improve fidelityMinimize impactEar treatmentLimiting amplitude without controlling loopSound detectionVoice communication

A method and apparatus are disclosed for listening to ambient sounds, engage in face-to-face communication, listen to and transmit voice communications, while also protecting the auditory system from hazardous sound pressure levels. Increased gain permits the user to maximize his sound detection ability during “reconnaissance and sentry” activities, thereby increasing the user's ability to detect and localize low level sounds such as, for example, enemy movement or activity. The throughput of the system is linear creating high fidelity of sound until the output level for a particular setting of the final gain reaches the limits established by the power supply. At that point, the output reaches a hard limit. This supply voltage also limits the output to the ear for any instantaneous increase in sound pressure levels. The invention includes barriers to attenuate ambient sounds from entering the ear canal and means for providing sound to the occluded portion of the ear canal. Therefore, hazardous impact noise (e.g., weapons blast, small arms fire, etc.) does not pass through the invention while ambient sounds and conversation are received at a level suitable for the auditory system.

Owner:MOZO BEN T

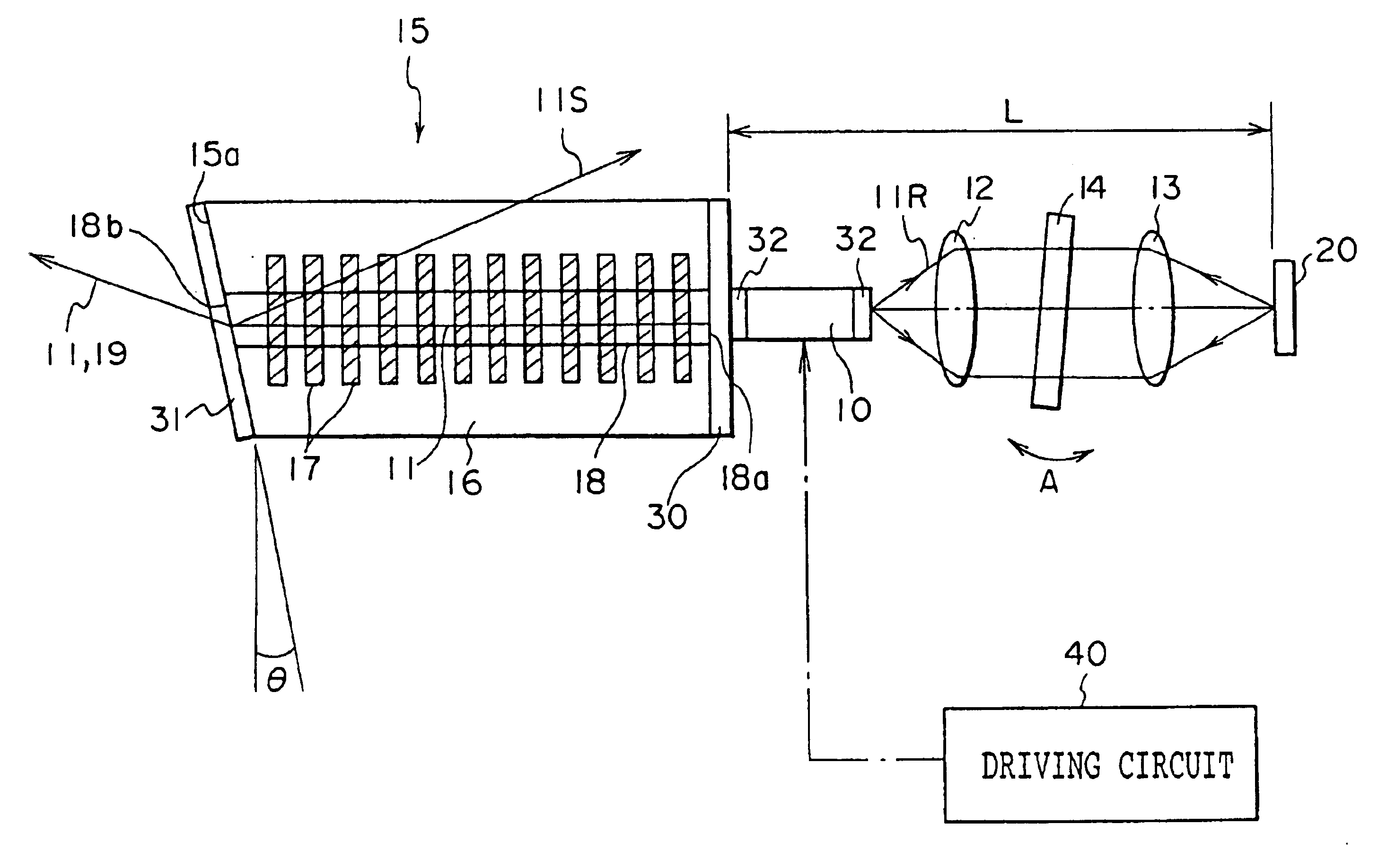

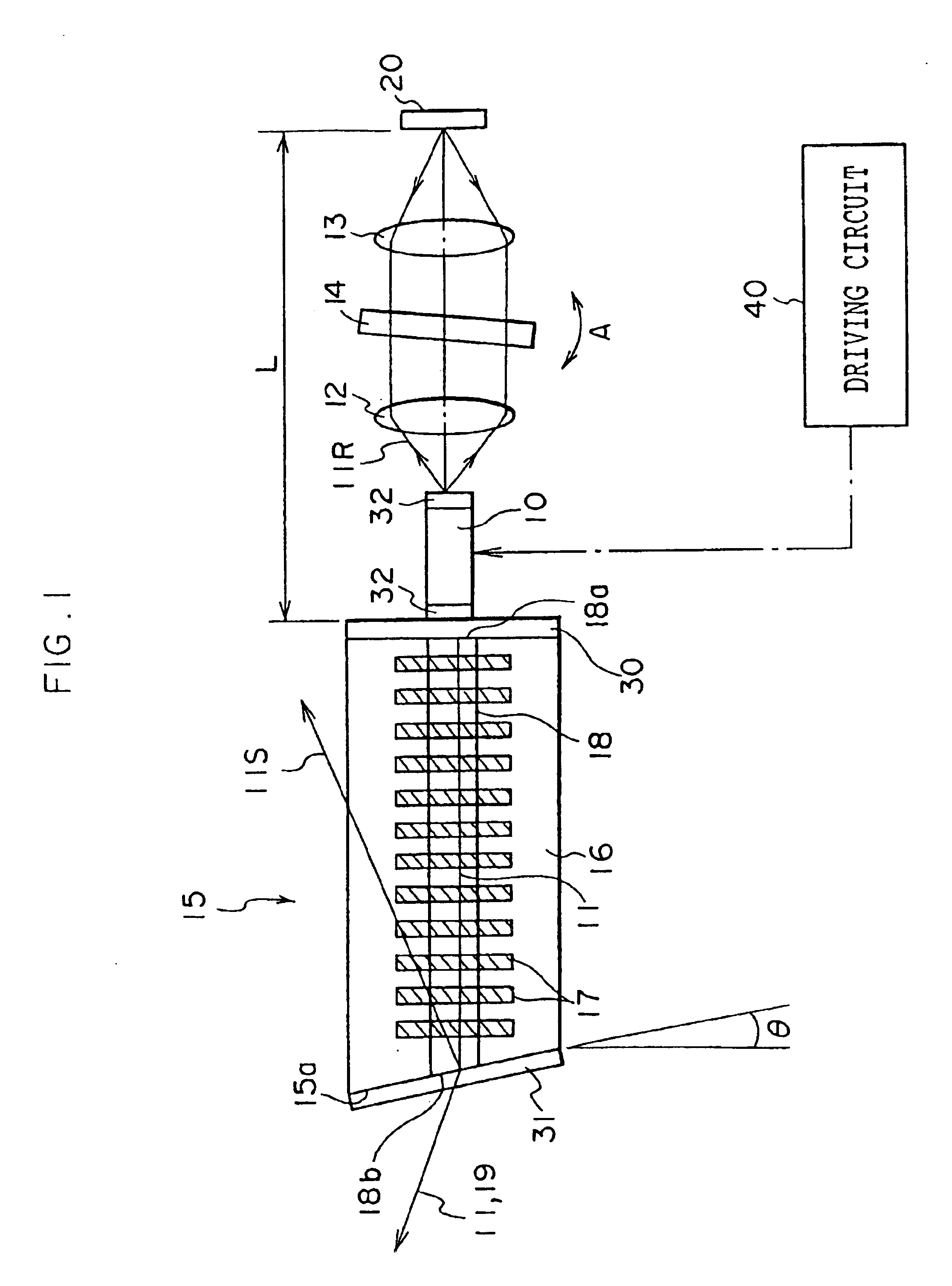

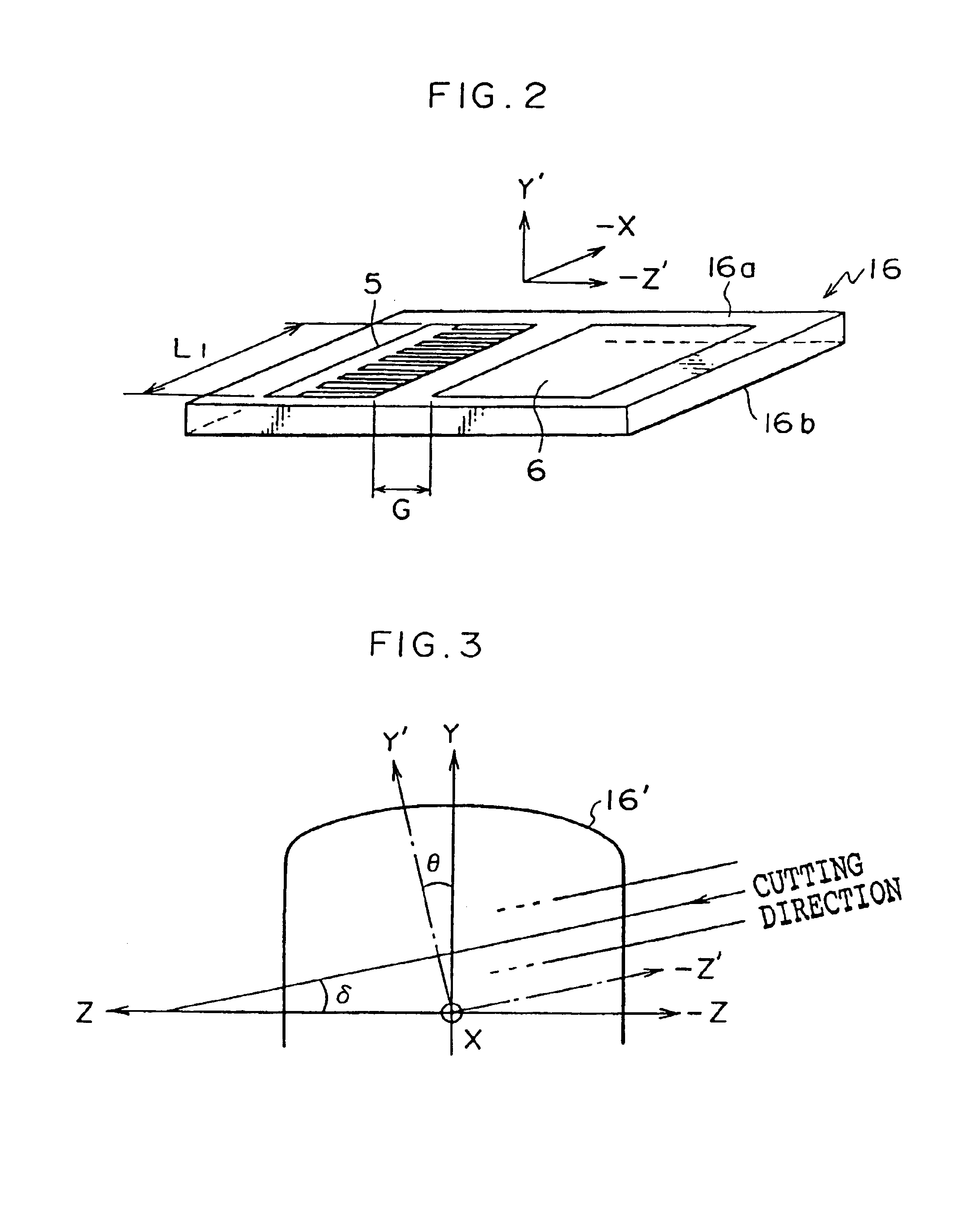

Light wavelength converting system

InactiveUS6839365B1Avoid interferenceKeep linearLaser optical resonator constructionNon-linear opticsBand-pass filterComputer module

A light wavelength converting element which can reduce an amount of light fed-back to a semiconductor laser. The light wavelength converting element converts a wavelength of a fundamental wave which enters from a first end surface side of an optical waveguide to thereby emit a converted wavelength wave from a second end surface side thereof. The second end surface is inclined with respect to the side surface of the optical waveguide. Also provided is a wavelength stabilized laser having a semiconductor laser, a device which feeds a laser beam emitted from the semiconductor laser back to the semiconductor laser, and a band-pass filter. An optical length between the semiconductor laser and the device is made to be longer than a coherent length of the semiconductor laser, thus improving linearity of a current vs. light output characteristic. Further, a light wavelength converting unit and a light wavelength converting module are provided in which, since an LD-SHG unit formed by a semiconductor laser and a light wavelength converting element is hermetically sealed in a package, the LD-SHG unit can be manufactured easily and has excellent stability over time.

Owner:FUJIFILM HLDG CORP +1

Dynamic activation for an atomic force microscope and method of use thereof

InactiveUS20060191329A1Increase speedIncrease usageNanotechScanning probe microscopyPhotodetectorLight beam

A scanning probe microscope method and apparatus that modifies imaging dynamics using an active drive technique to optimize the bandwidth of amplitude detection. The deflection is preferably measured by an optical detection system including a laser and a photodetector, which measures cantilever deflection by an optical beam bounce technique or another conventional technique. The detected deflection of the cantilever is subsequently demodulated to give a signal proportional to the amplitude of oscillation of the cantilever, which is thereafter used to drive the cantilever.

Owner:BRUKER NANO INC

Timing based LNA gain adjustment in an RF receiver to compensate for intermodulation interference

InactiveUS20050079842A1Keep linearMaximize signal to noise ratioAmplifier modifications to reduce non-linear distortionResonant long antennasLinear regionSignal-to-noise ratio (imaging)

A Radio Frequency (RF) receiver includes a low noise amplifier (LNA) and a mixer coupled to the output of the LNA. The gain of the LNA is adjusted to maximize signal-to-noise ratio of the mixer and to force the mixer to operate well within its linear region when an intermodulation interference component is present. The RF receiver includes a first received signal strength indicator (RSSI_A) coupled to the output of the mixer that measures the strength of the wideband signal at that point. A second received signal strength indicator (RSSI_B) couples after the BPF and measures the strength of the narrowband signal. The LNA gain is set based upon these signal strengths. LNA gain is determined during a guard period preceding an intended time slot of a current frame and during a guard period following an intended time slot of a prior frame. The lesser of these two LNA gains is used for the intended time slot of the current frame.

Owner:AVAGO TECH INT SALES PTE LTD

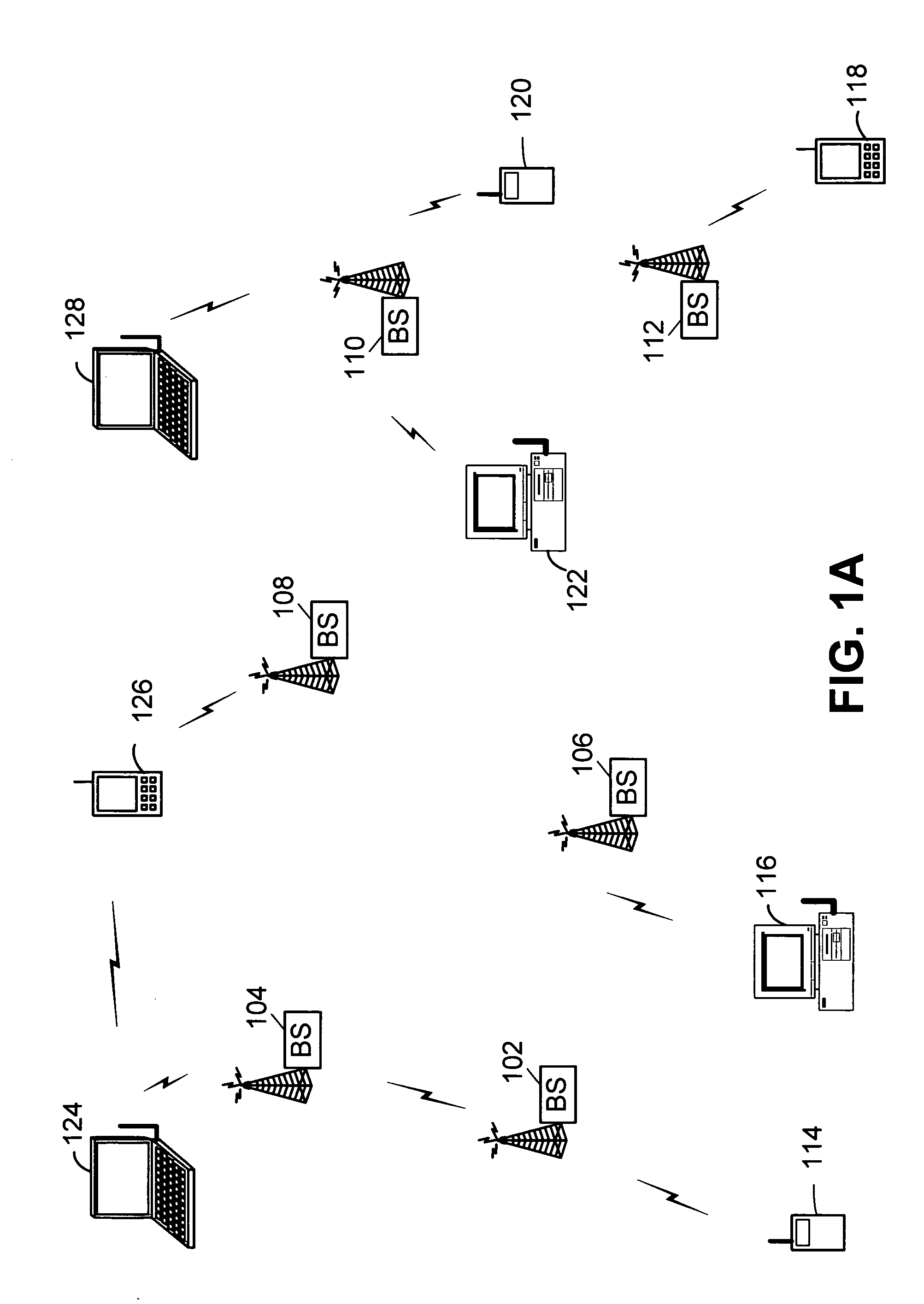

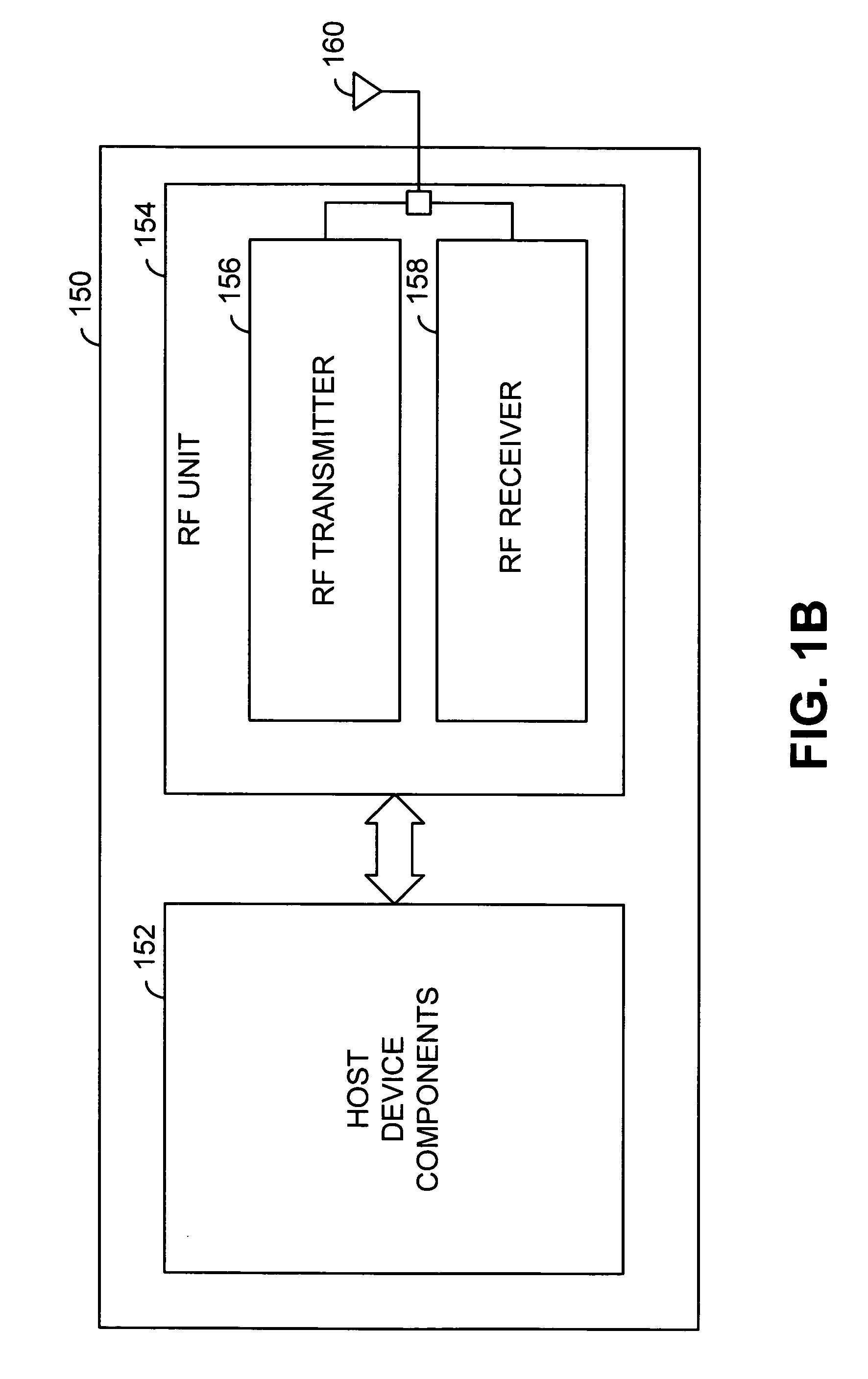

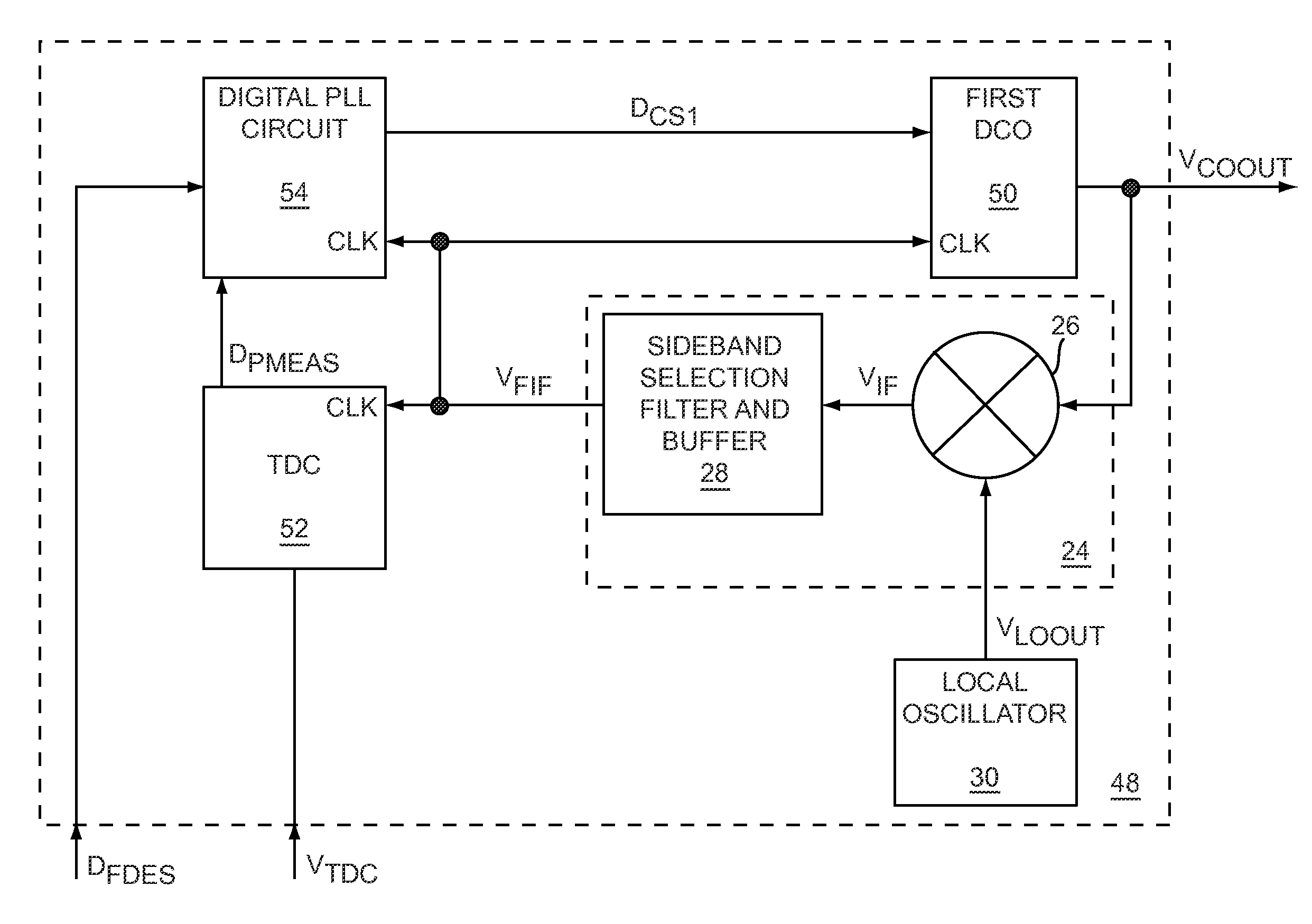

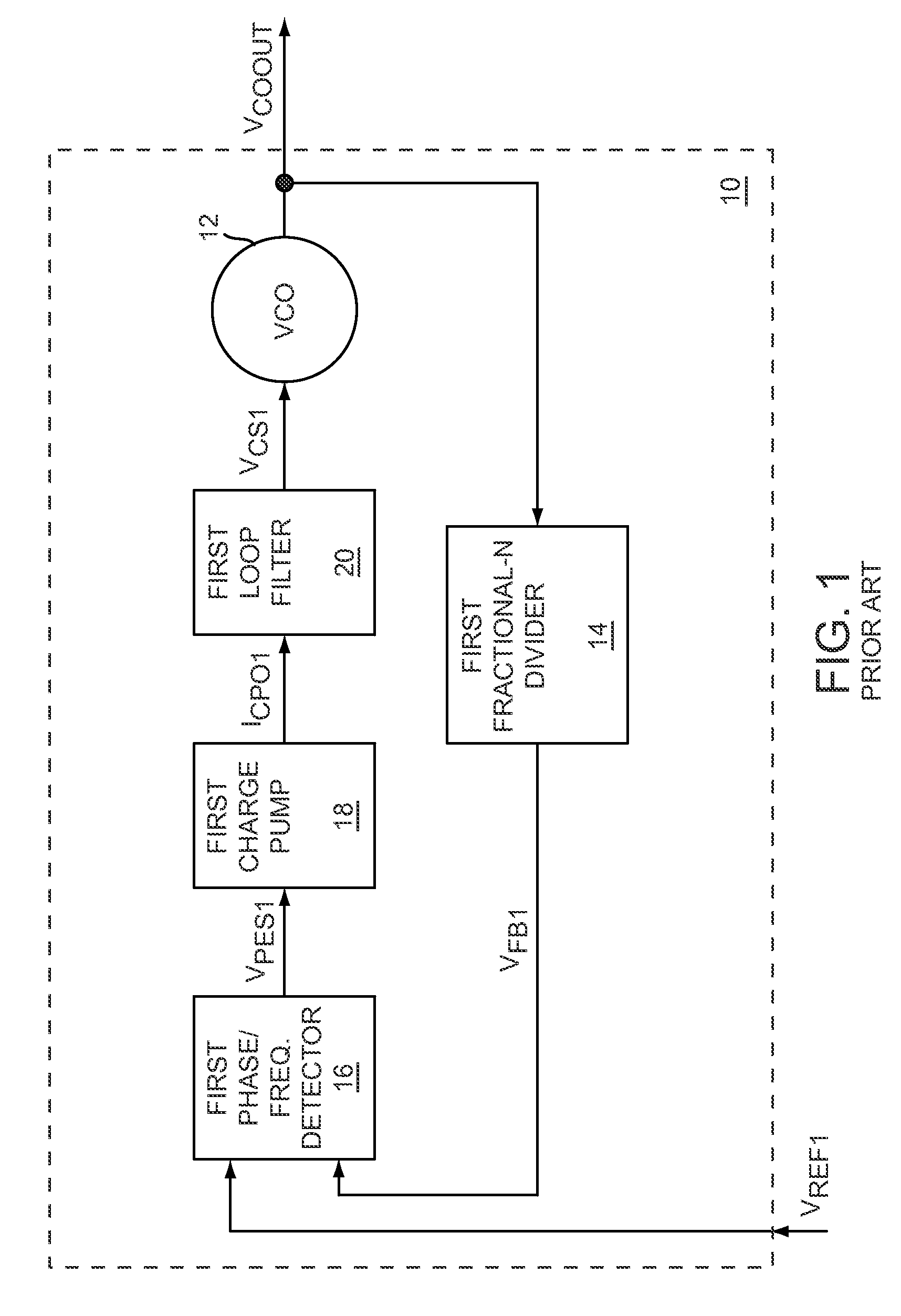

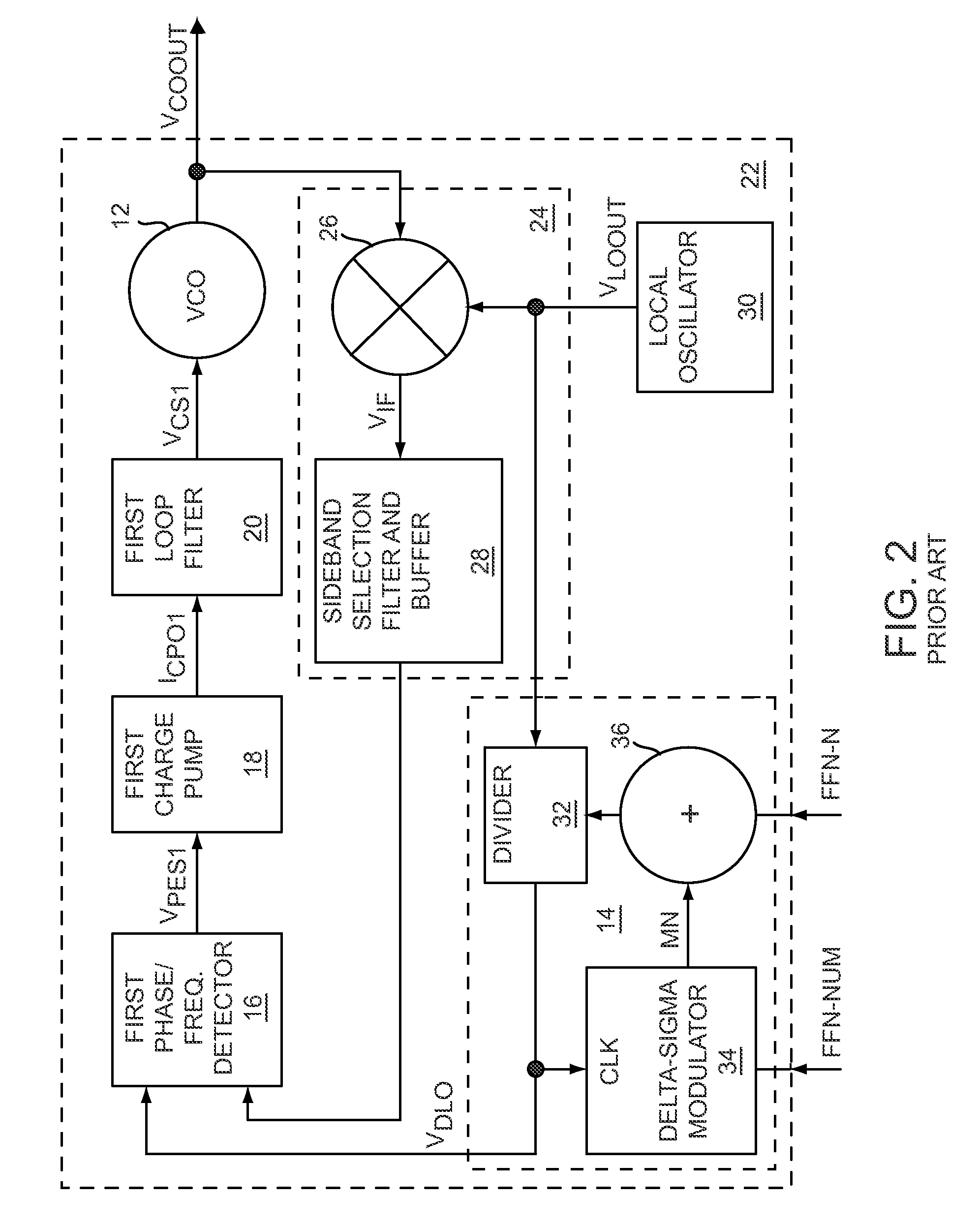

Digital offset phase-locked loop

ActiveUS7746178B1Reducing loop gainKeep linearPulse automatic controlDigital feedbackDigital control oscillator

The present invention relates to a digital offset phase-locked loop (DOPLL), which may have advantages of size, simplicity, performance, design portability, or any combination thereof, compared to analog-based phase-locked loops (PLLs). The DOPLL may include a digital controlled oscillator (DCO), which provides a controllable frequency output signal based on a digital control signal, a radio frequency (RF) mixer circuit, which provides a reduced-frequency feedback signal based on the controllable frequency output signal without reducing loop gain, a time-to-digital converter (TDC), which provides a digital feedback signal that is a time representation of the reduced-frequency feedback signal, and digital PLL circuitry, which provides the digital control signal based on the digital feedback signal and a digital setpoint signal.

Owner:QORVO US INC

LNA gain adjustment in an RF receiver to compensate for intermodulation interference

InactiveUS20070010224A1Keep linearMaximize signal to noise ratioAmplifier modifications to reduce non-linear distortionGain controlLinear regionSignal-to-noise ratio (imaging)

A Radio Frequency (RF) receiver includes a low noise amplifier (LNA) and a mixer coupled to the output of the LNA. The gain of the LNA is adjusted to maximize signal-to-noise ratio of the mixer and to force the mixer to operate well within its linear region when an intermodulation interference component is present. The RF receiver includes a first received signal strength indicator (RSSI_A) coupled to the output of the mixer that measures the strength of the wideband signal at that point. A second received signal strength indicator (RSSI_B) couples after the BPF and measures the strength of the narrowband signal. The LNA gain is set based upon these signal strengths. By altering the gain of the LNA by one step and measuring the difference between a prior RSSI_B reading and a subsequent RSSI_B′ reading will indicate whether intermodulation interference is present.

Owner:AVAGO TECH INT SALES PTE LTD

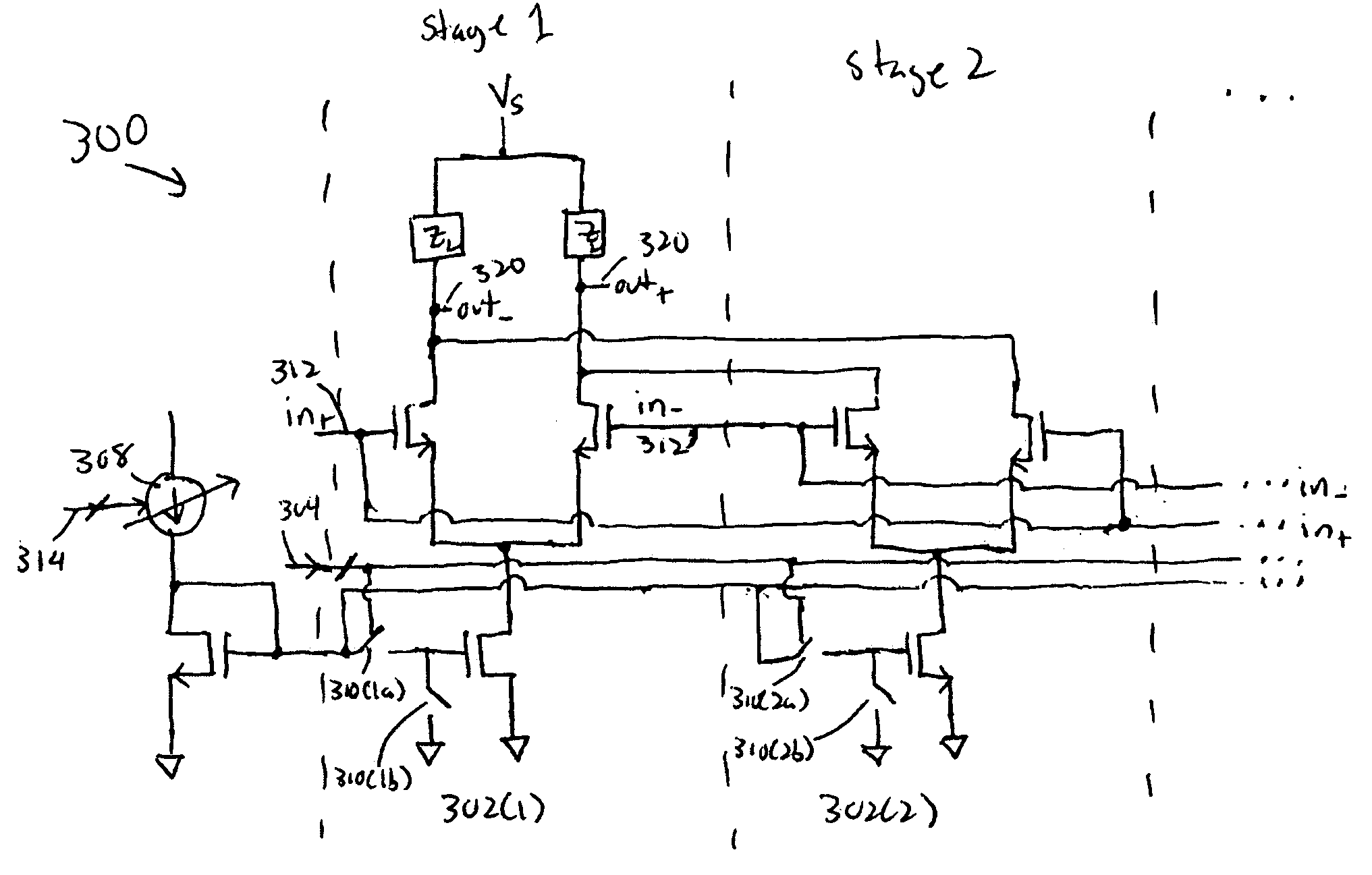

Digitally controlled transconductance cell

ActiveUS20050110569A1Improve controllabilityKeep linearDifferential amplifiersDc-amplifiers with dc-coupled stagesTransconductanceCurrent source

A digitally controlled transconductance cell includes a differential transistor pair coupled to load elements (either passive or active with resistive or impedance loads) and a variable bias current source, where the transconductance or gain is digitally varied by changing the aspect ratio of the transistors and the bias current.

Owner:SCINTERA NETWORKS

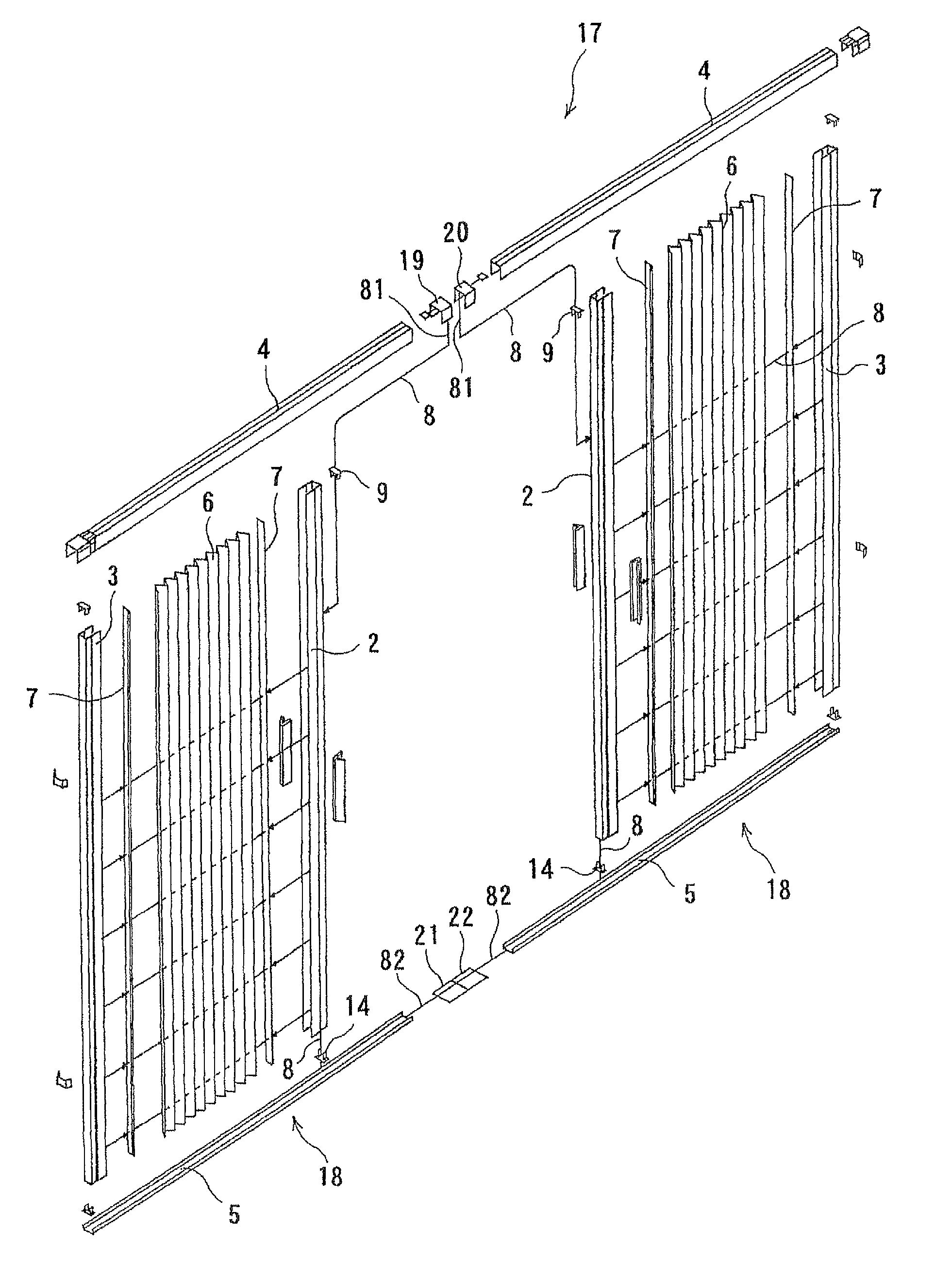

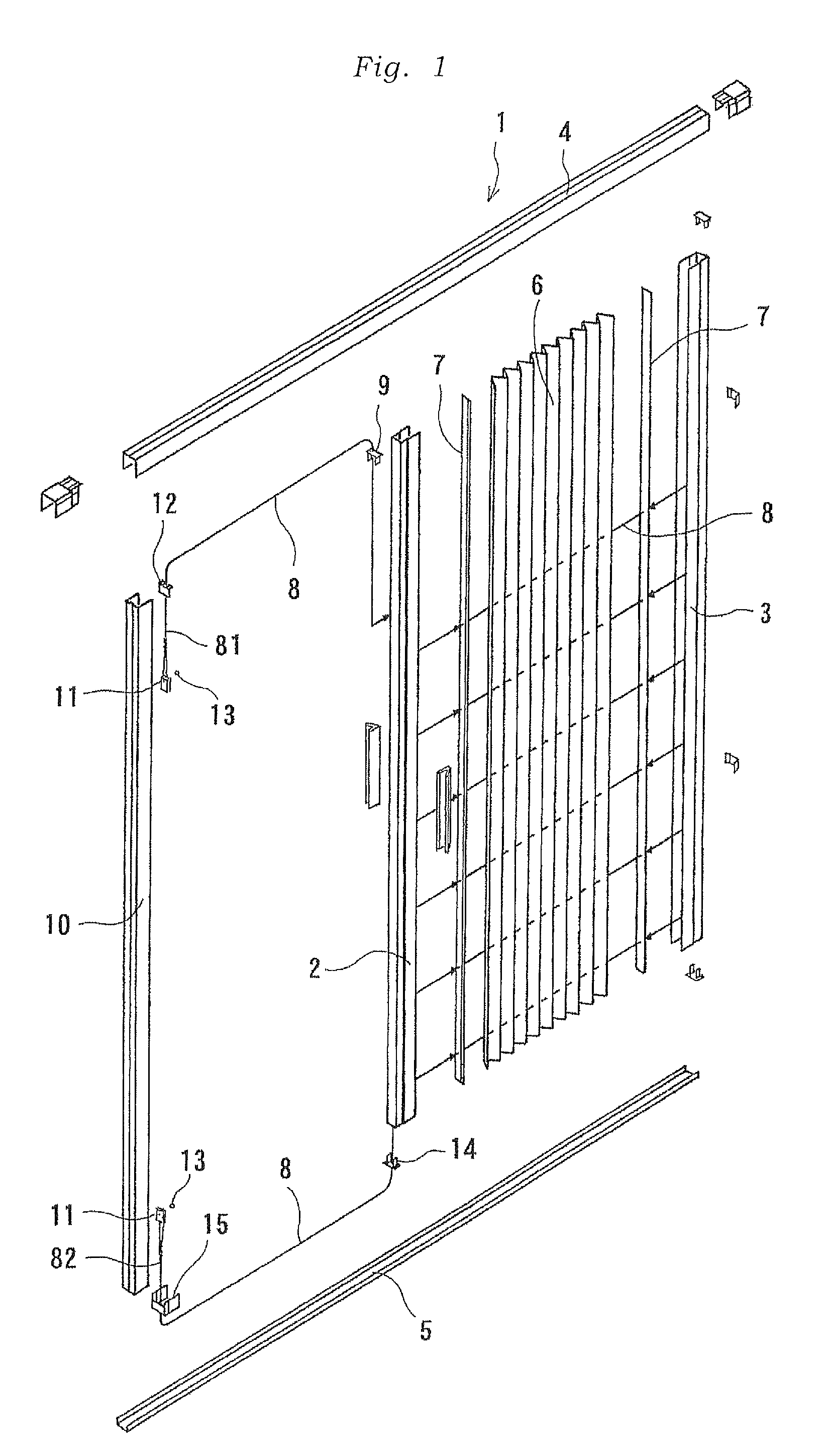

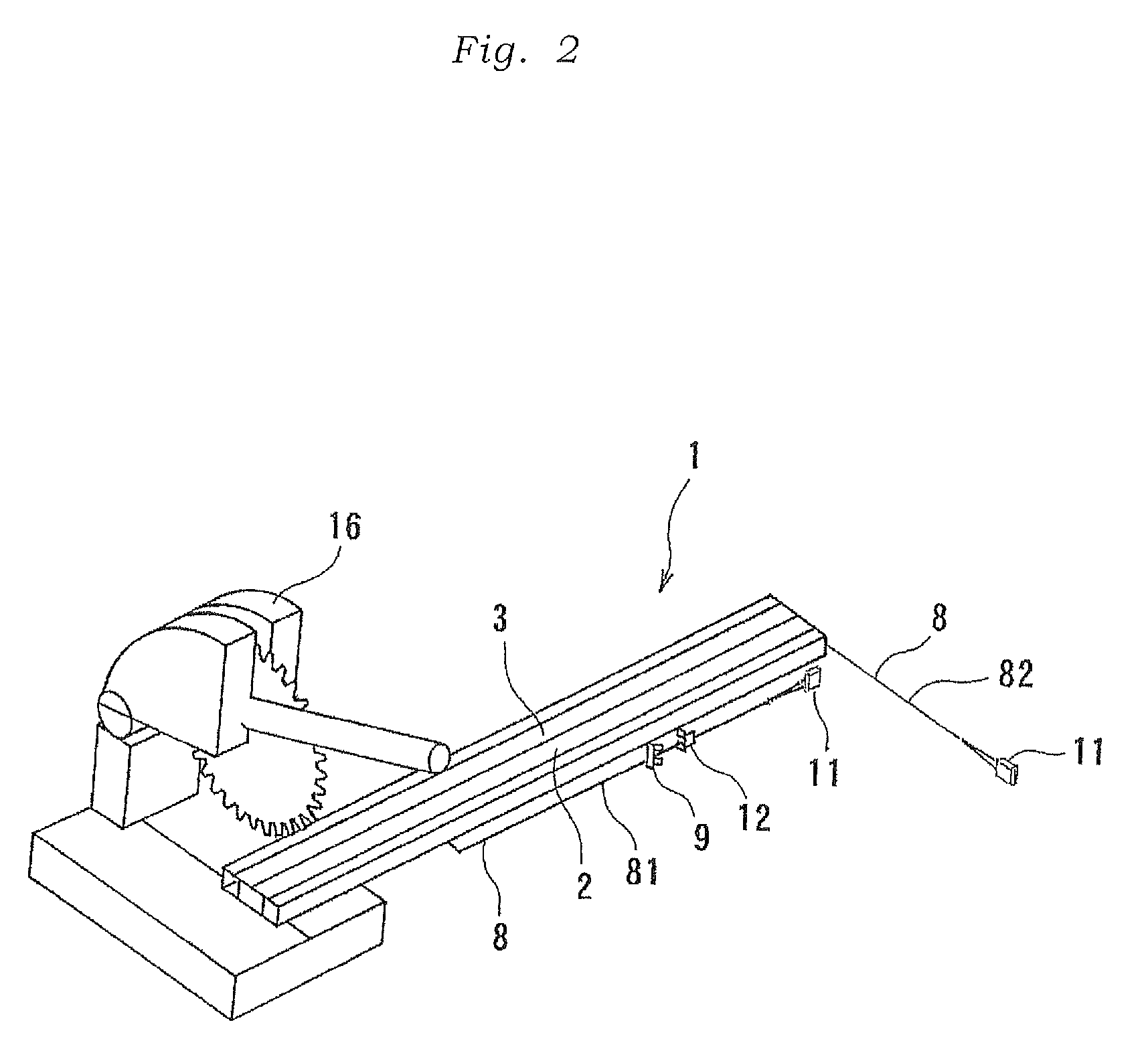

Screen device

A shrinkable and extensible screen is mounted between a pair of screen-mounting frame portions arranged bilaterally to confront each other and at least one being slidably movable. A tension member extending through the screen for supporting it in shrinking and extending directions is routed in the screen-mounting frame portions. The tension member is extracted at the portion close to the central portion from the upper end portion of the slidably movable screen-mounting frame portions, to the outside on the side opposite to the screen mounting side.

Owner:METACO INC

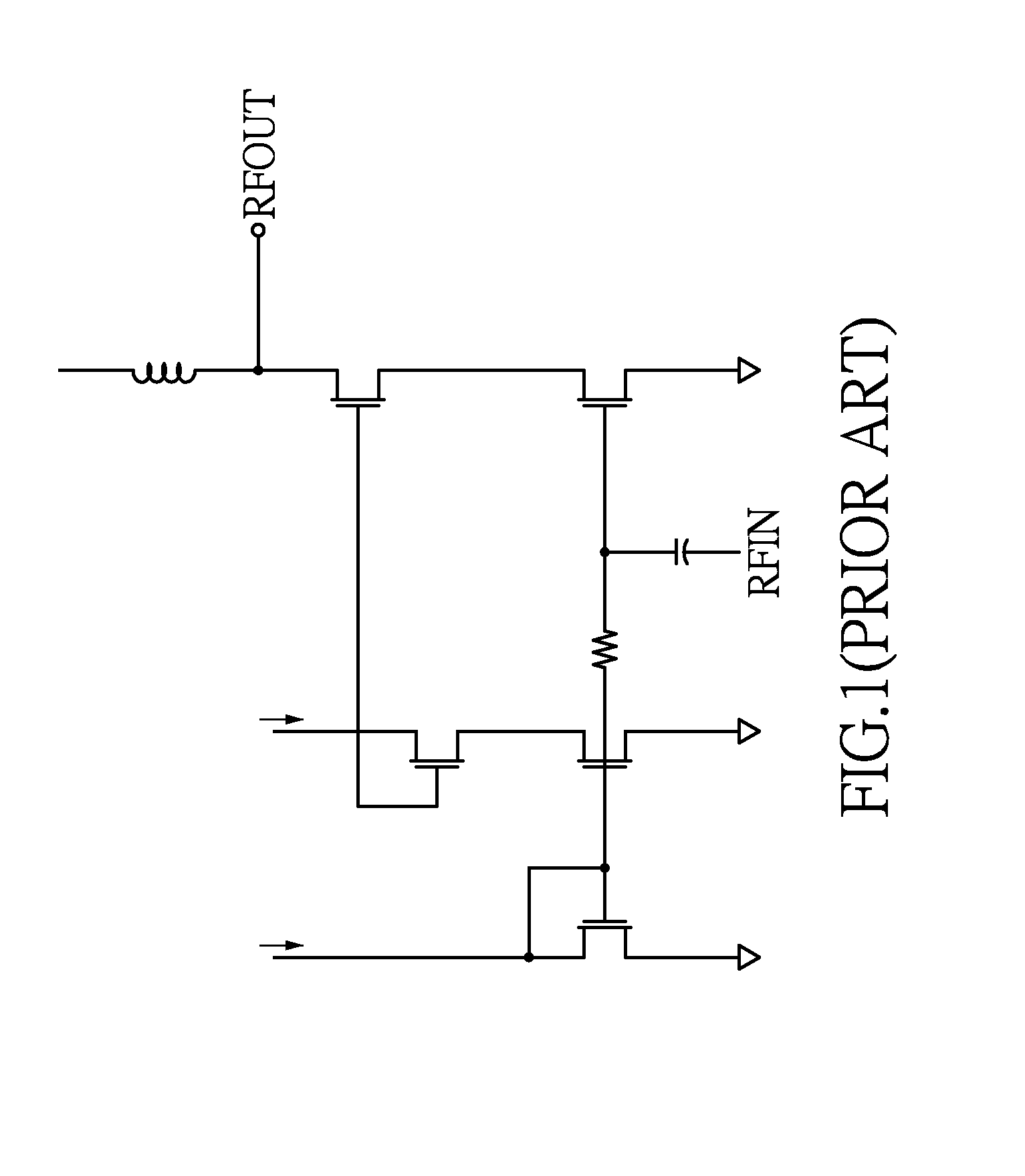

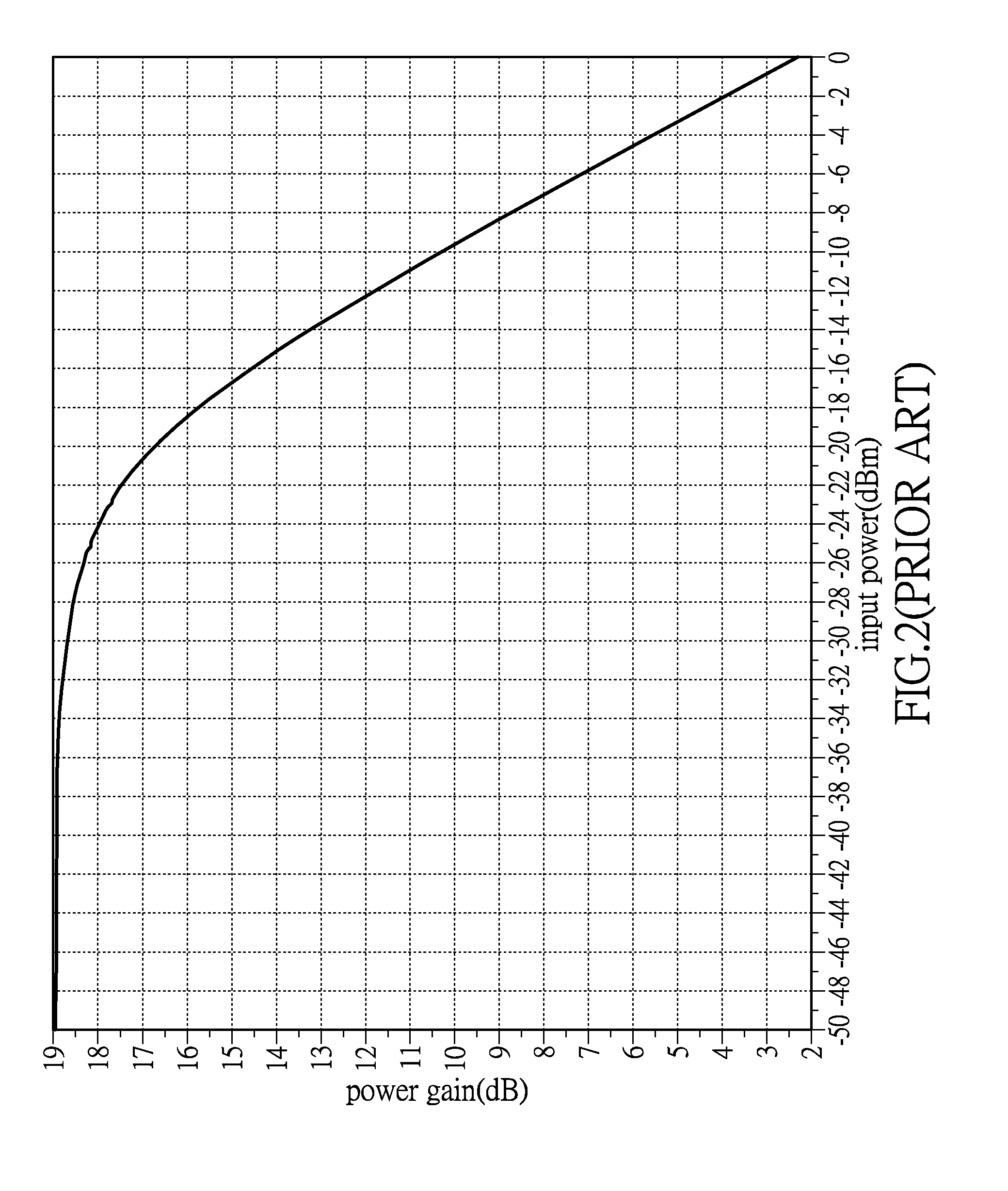

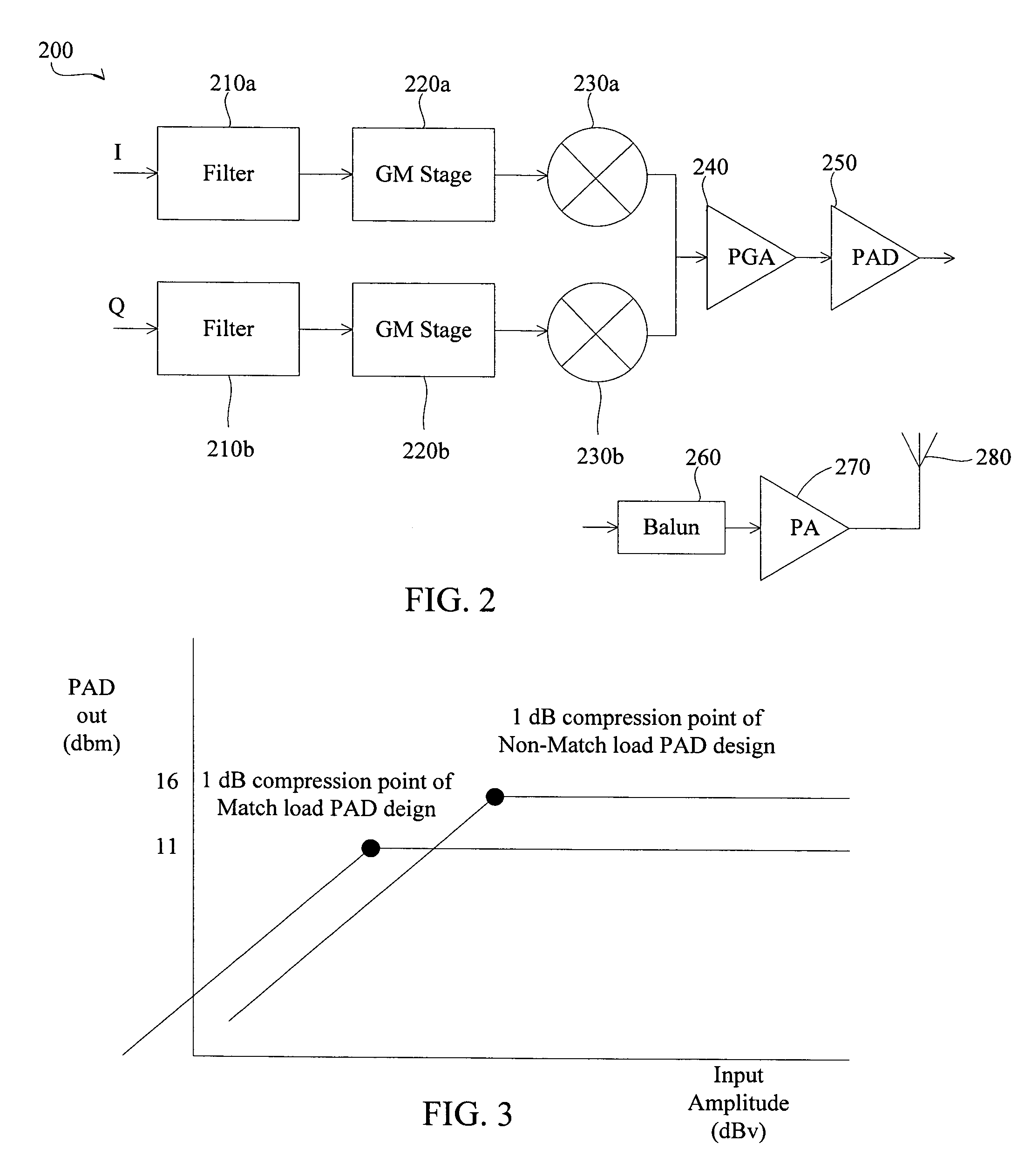

Low noise amplifier and receiver

ActiveUS20150280672A1High linearity low noise amplifierHigh P1dBHigh frequency amplifiersGain controlPower flowAudio power amplifier

A low noise amplifier is disclosed. The low noise amplifier comprises a current mirror circuit, a bias circuit, a cascode amplifying circuit and a power gain compensating circuit. The current mirror circuit is used for providing a first current and third current. The bias circuit is used for receiving a first current and third current and outputting a first bias voltage and a second bias voltage according to the first current and third current. The cascode amplifying circuit respectively receives the first bias voltage and the second bias voltage, and accordingly to work at an operation bias point. The power gain compensating circuit is used for receiving a RF output signal and accordingly outputs a gain compensating signal to the current mirror circuit so as to dynamically adjust current value of the first current and third current and further to compensates power gain of the low noise amplifier in order to increase 1 dB gain compression point (P1dB).

Owner:ADVANCED SEMICON ENG INC

Dynamic activation for an atomic force microscope and method of use thereof

InactiveUS7036357B2Improve ease of useIncrease speedNanotechSurface/boundary effectPhotodetectorLight beam

A scanning probe microscope method and apparatus that modifies imaging dynamics using an active drive technique to optimize the bandwidth of amplitude detection. The deflection is preferably measured by an optical detection system including a laser and a photodetector, which measures cantilever deflection by an optical beam bounce technique or another conventional technique. The detected deflection of the cantilever is subsequently demodulated to give a signal proportional to the amplitude of oscillation of the cantilever, which is thereafter used to drive the cantilever.

Owner:BRUKER NANO INC

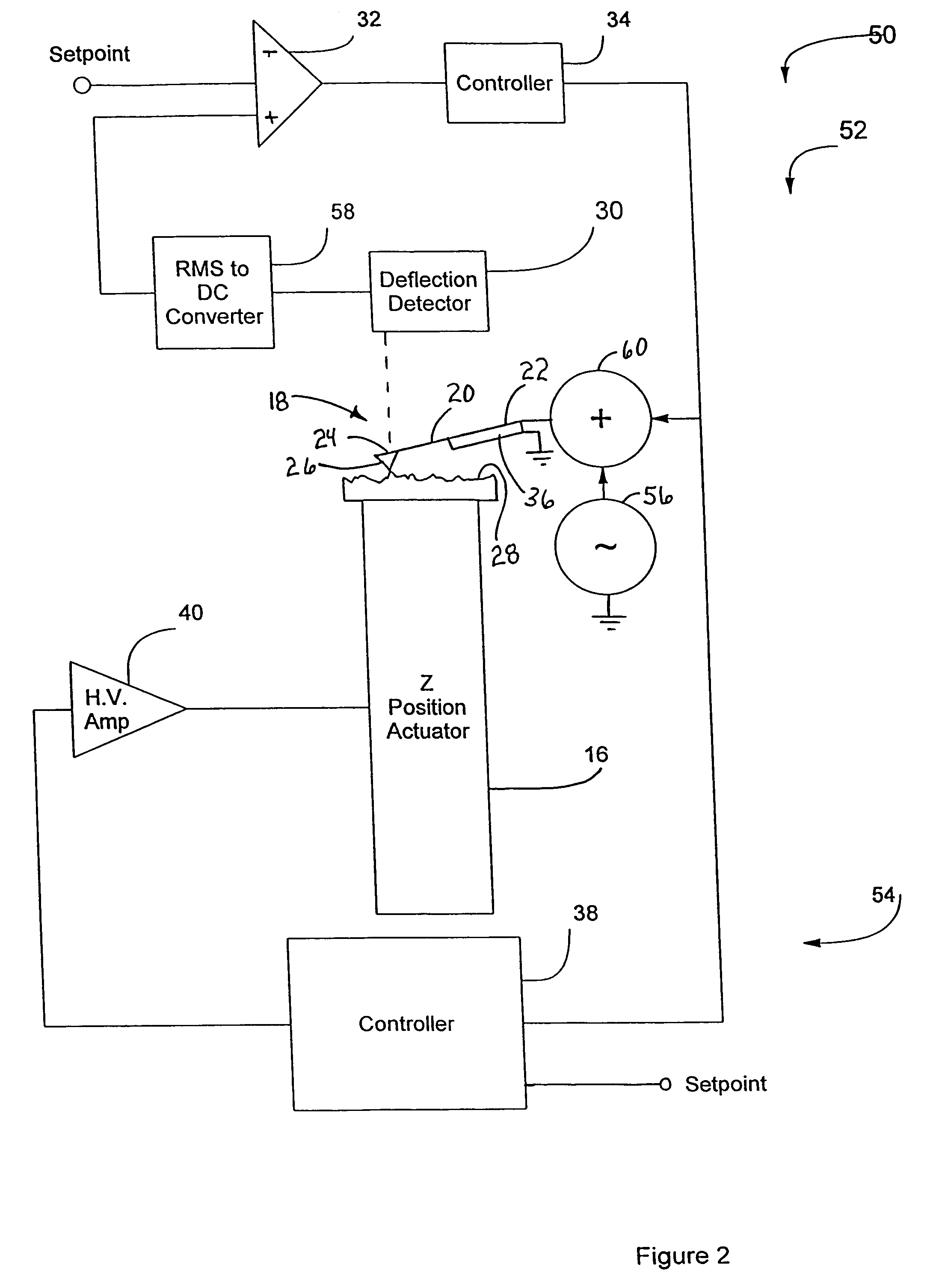

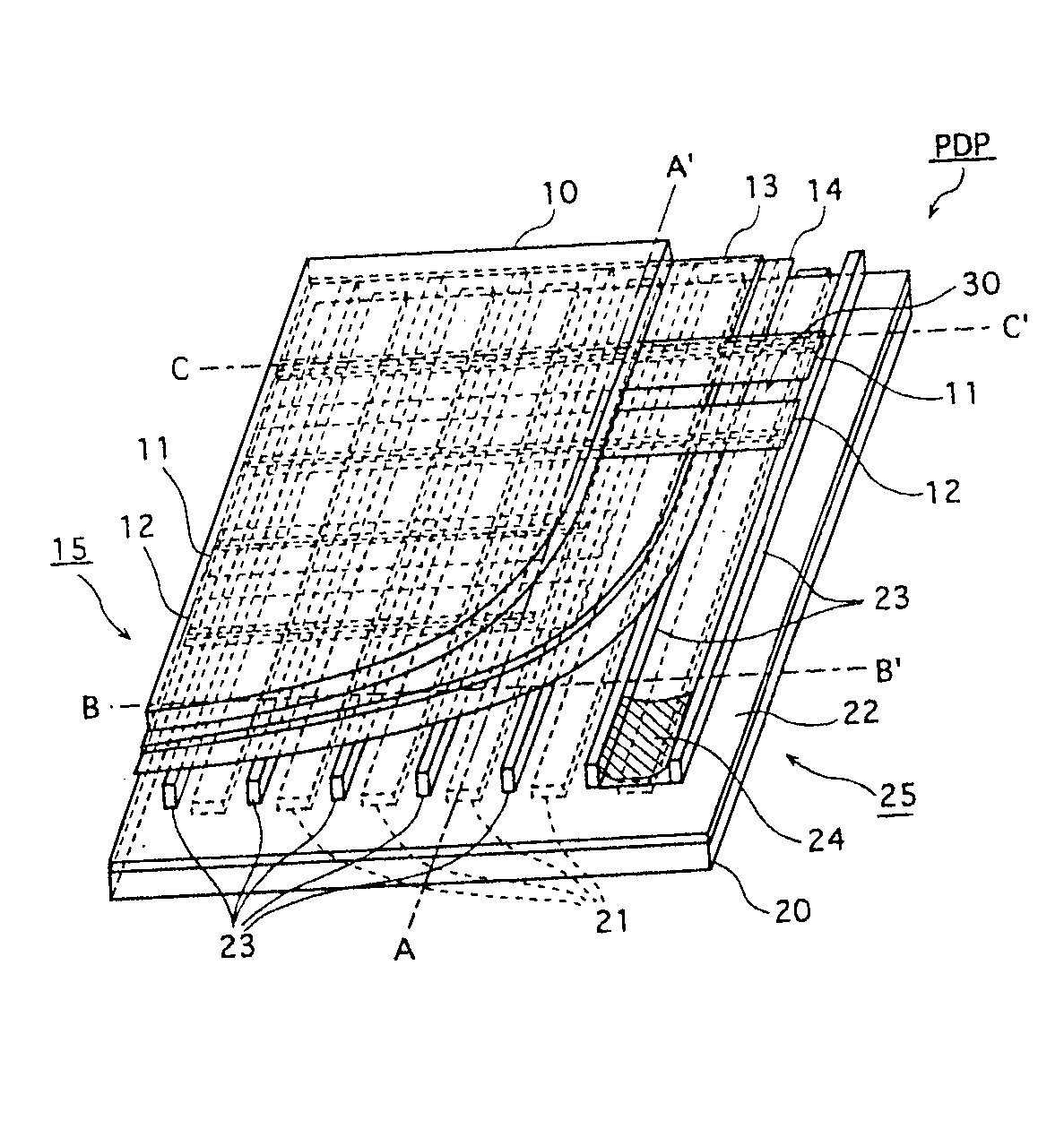

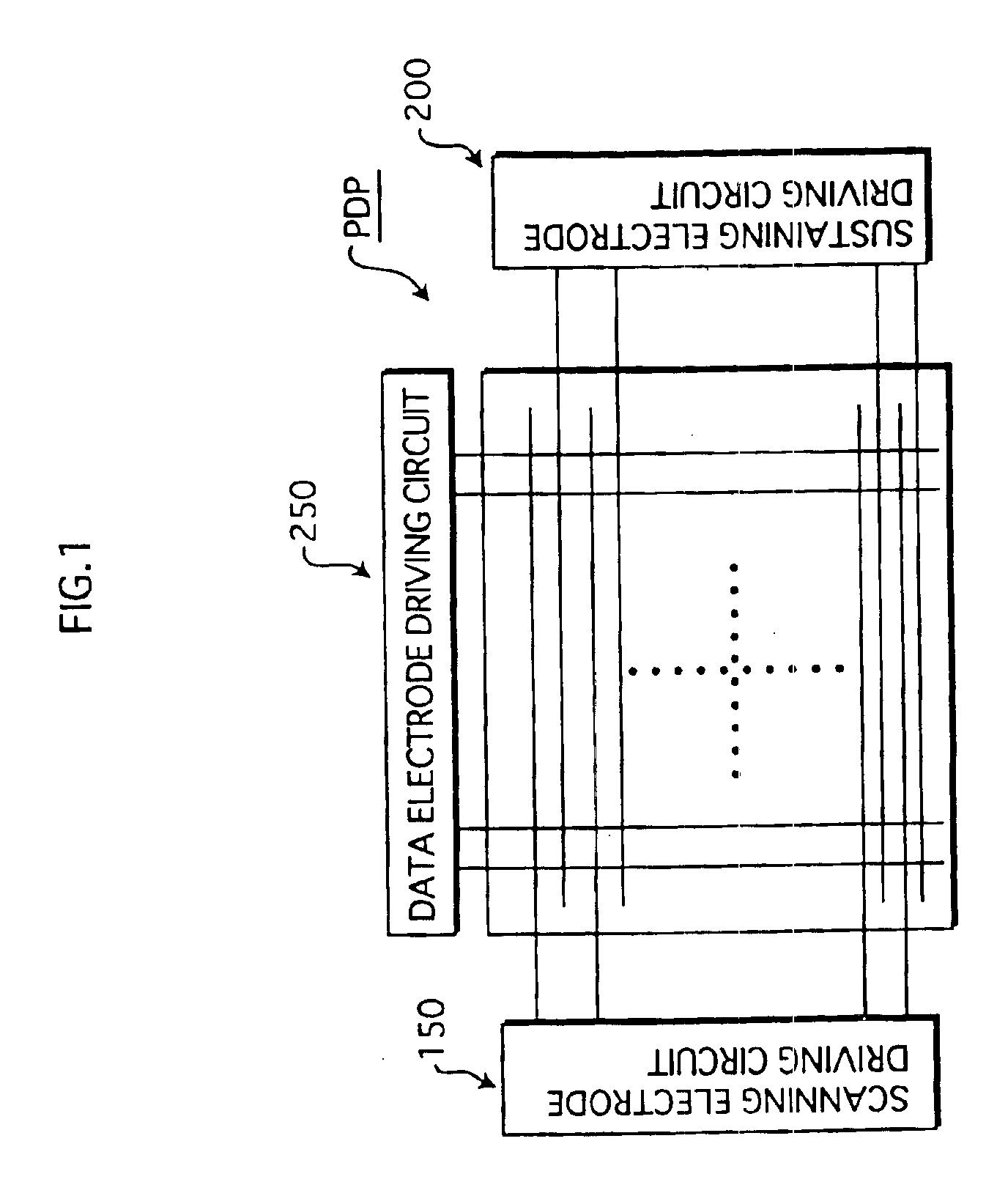

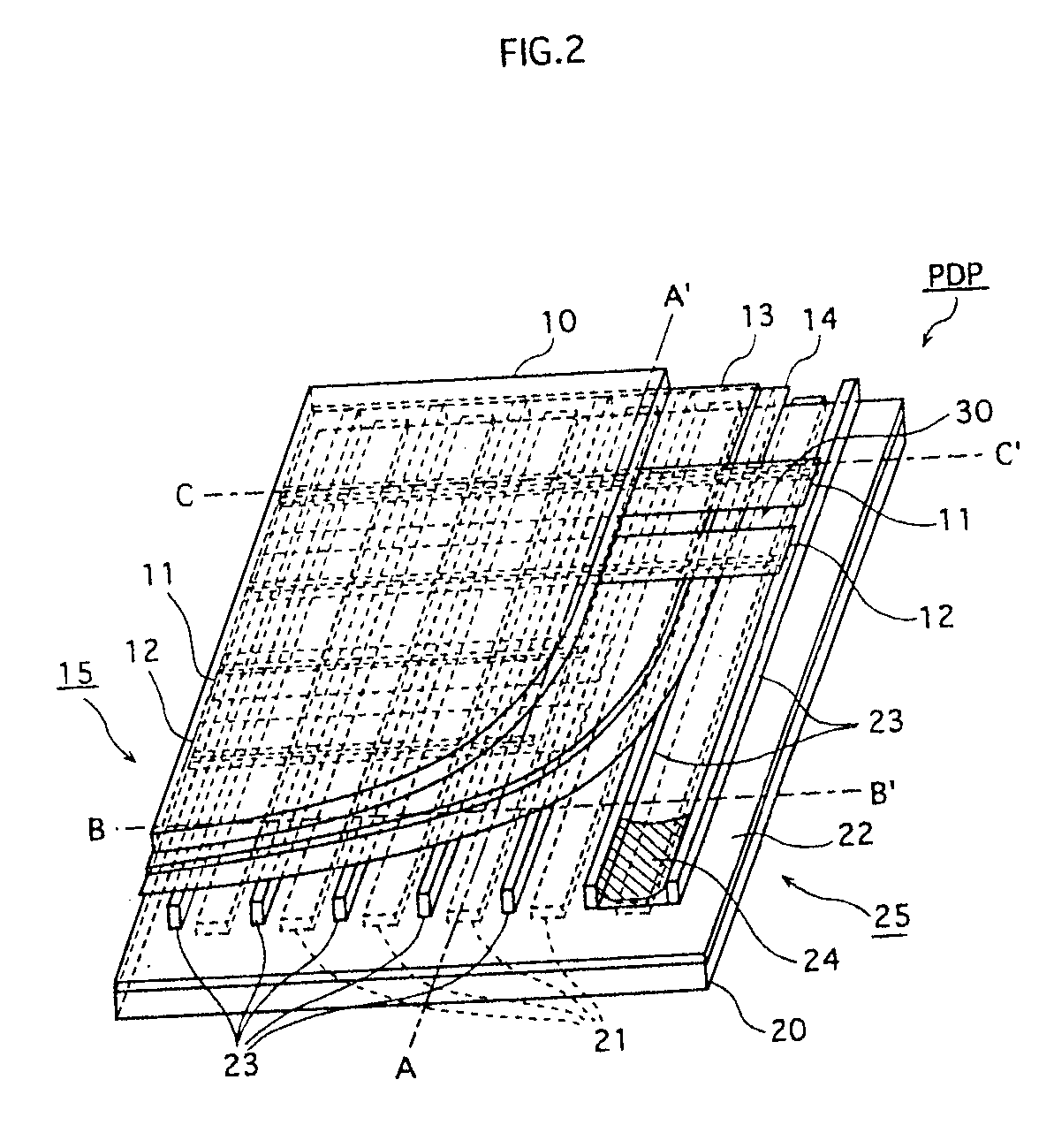

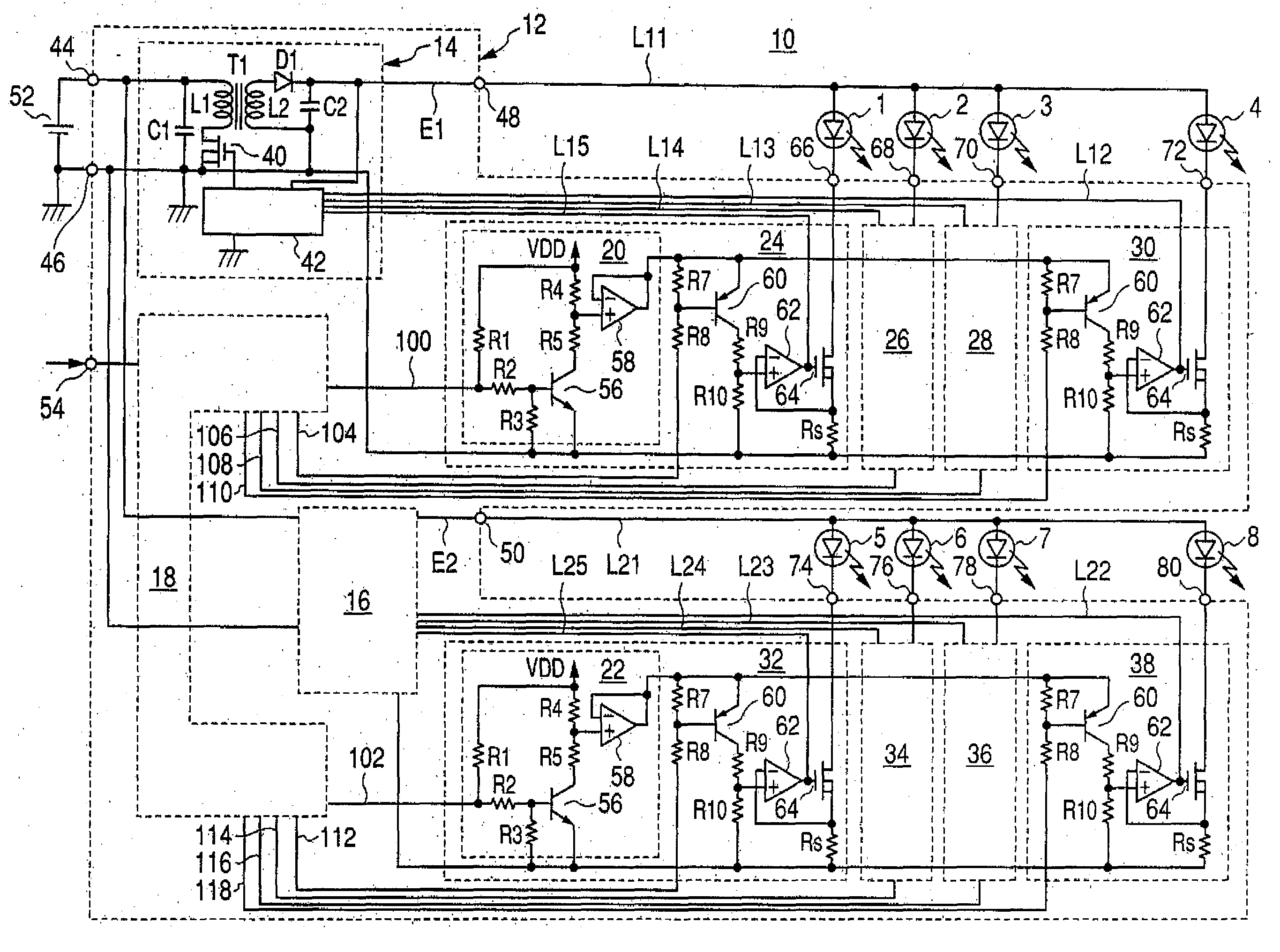

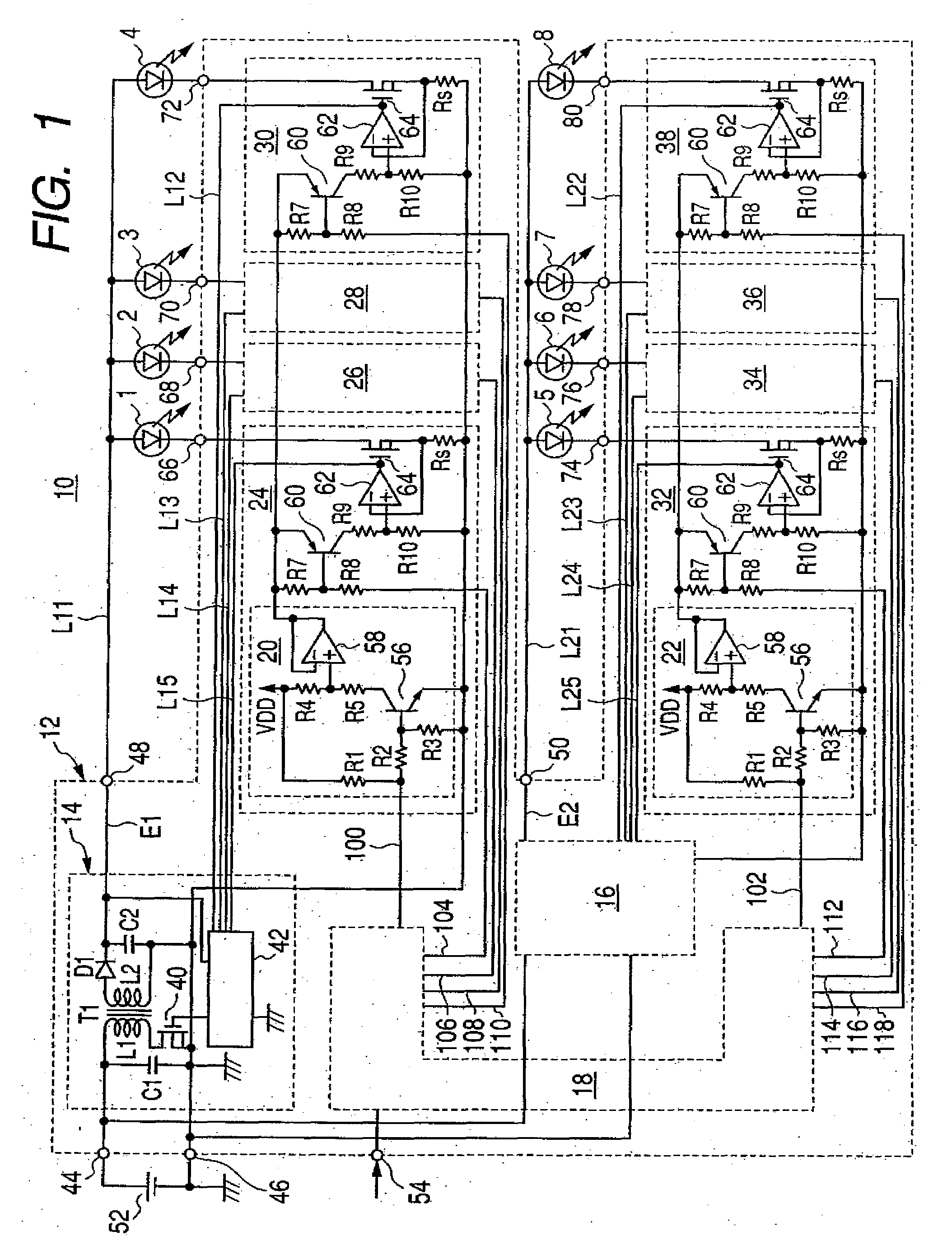

Plasma display unit and production method thereof

InactiveUS6891331B2Avoid high pressureReduced Linearity RequirementsSustain/scan electrodesAlternating current plasma display panelsCooking & bakingDissolution

An object of the present invention is to provide a method for manufacturing electrodes that can effectively suppress edge-curl when metal electrodes such as bus electrodes and data electrodes are patterned mainly by a photolithography method.In order to achieve the above object, in the manufacturing method in the present invention, an amount of undercut generated by difference in a degree of dissolution caused by developing solution is controlled, and baking is performed at a temperature such that glass in a protrusion formed at side edges becomes soft so as to touch a substrate by gravity. With such method for manufacturing, it becomes possible to make the side edges rounded whose curvature changes continuously.

Owner:PANASONIC CORP

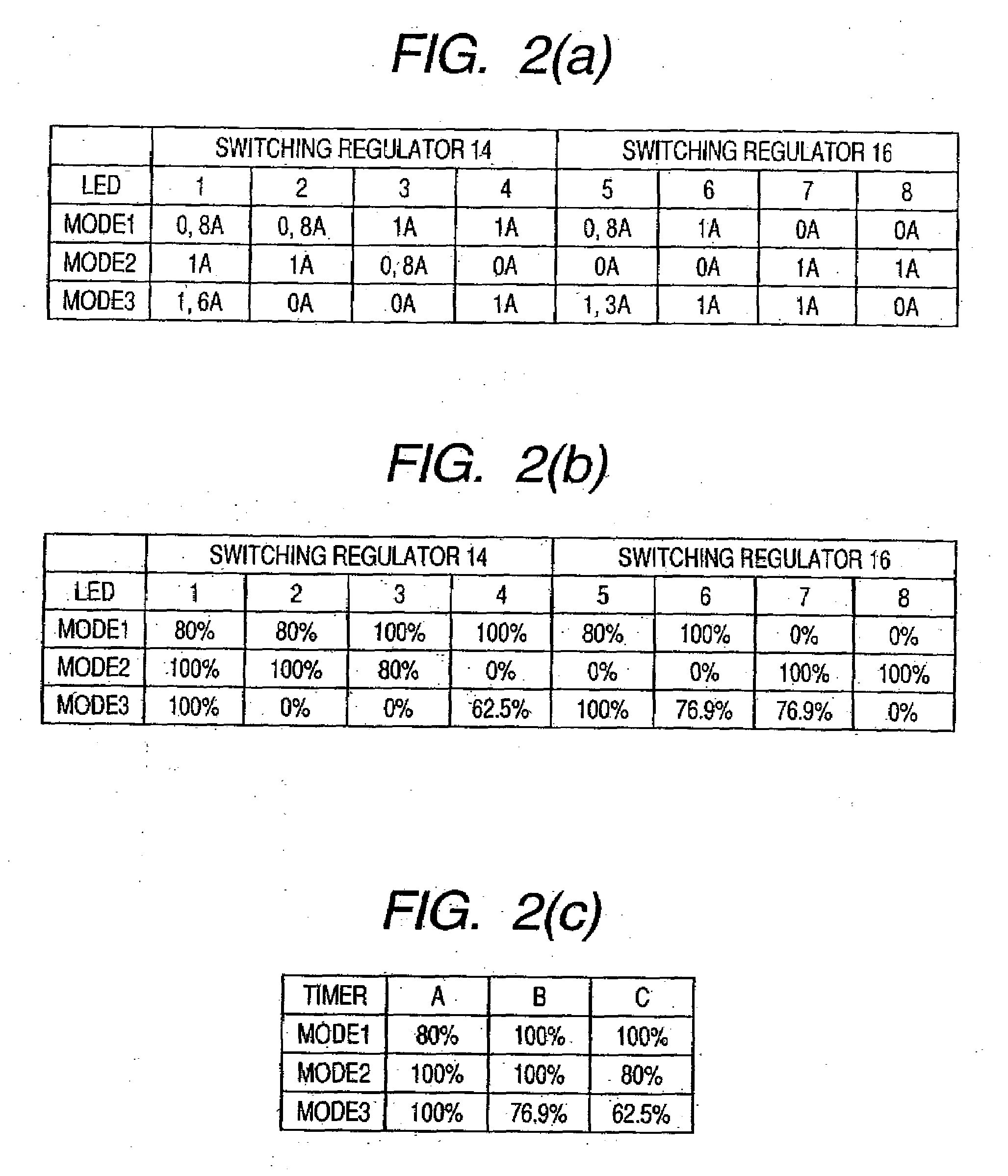

Lighting controlling device of vehicle lighting equipment

InactiveUS20090072764A1Reduce switchingAccurate currentElectrical apparatusElectroluminescent light sourcesMultiple stagesLight source

A lighting controlling device of vehicle lighting equipment includes switching regulators for supplying a current to a plurality of semiconductor light sources respectively; a plurality of current driving portions, having switching elements connected to the semiconductor light sources for controlling ON / OFF of the semiconductor light sources, for current-driving the semiconductor light sources at a maximum current value or a current value smaller than the maximum current value in response to respective operating states of the switching elements; current setting portion for setting a maximum current value applied in current-driving the current driving portion or a maximum current value of currents fed from the switching regulators to the semiconductor light sources separately in plural stages in response to respective assignments; and a controlling portion for controlling the current driving portion and the current setting portion in response to a plurality of lighting modes based on communication information from an external device. The controlling portion assigns the maximum current value corresponding to each lighting mode to the current setting portion for every lighting mode, and assigns ON / OFF periods of the switching elements to the current driving portion for every lighting mode.

Owner:KOITO MFG CO LTD

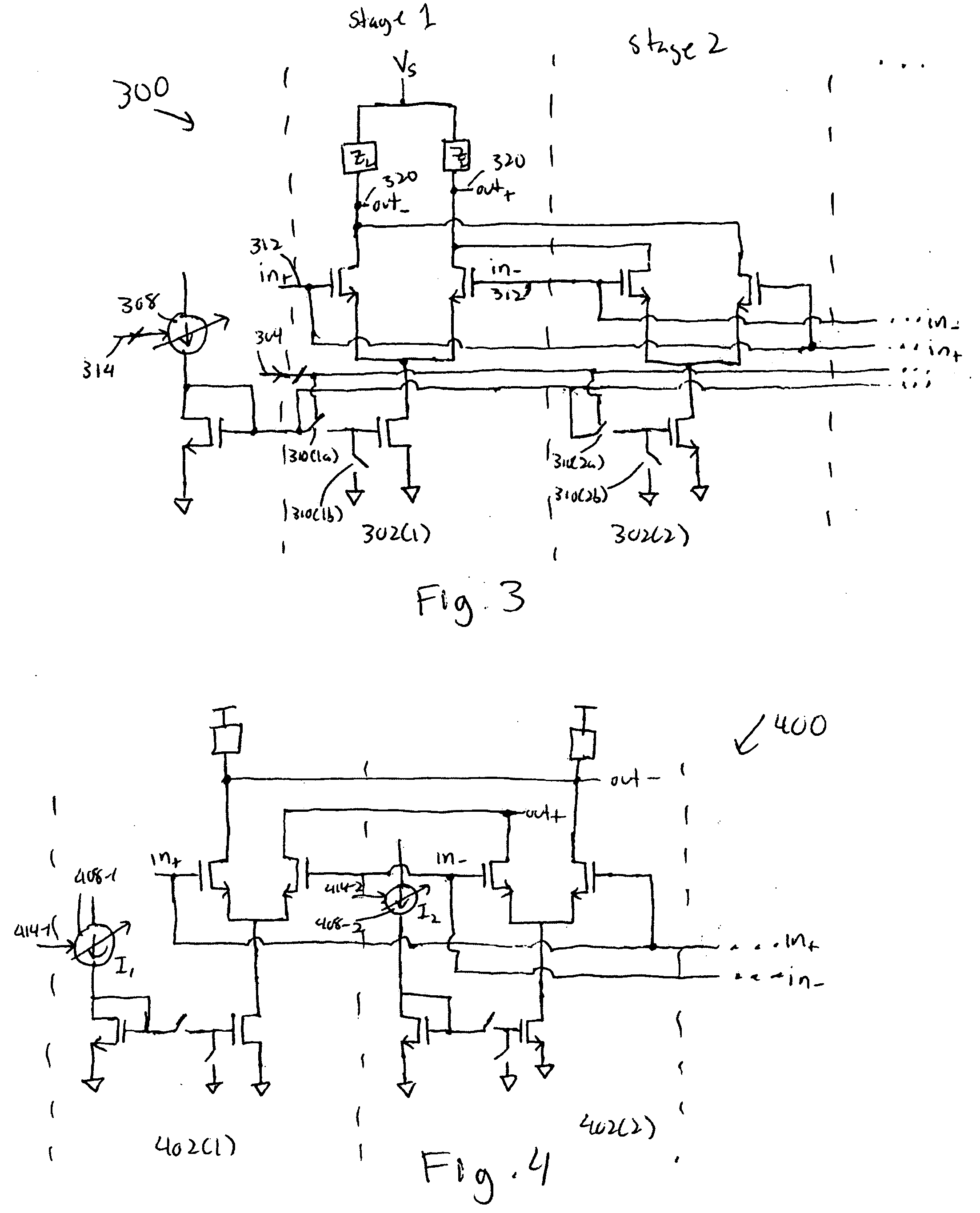

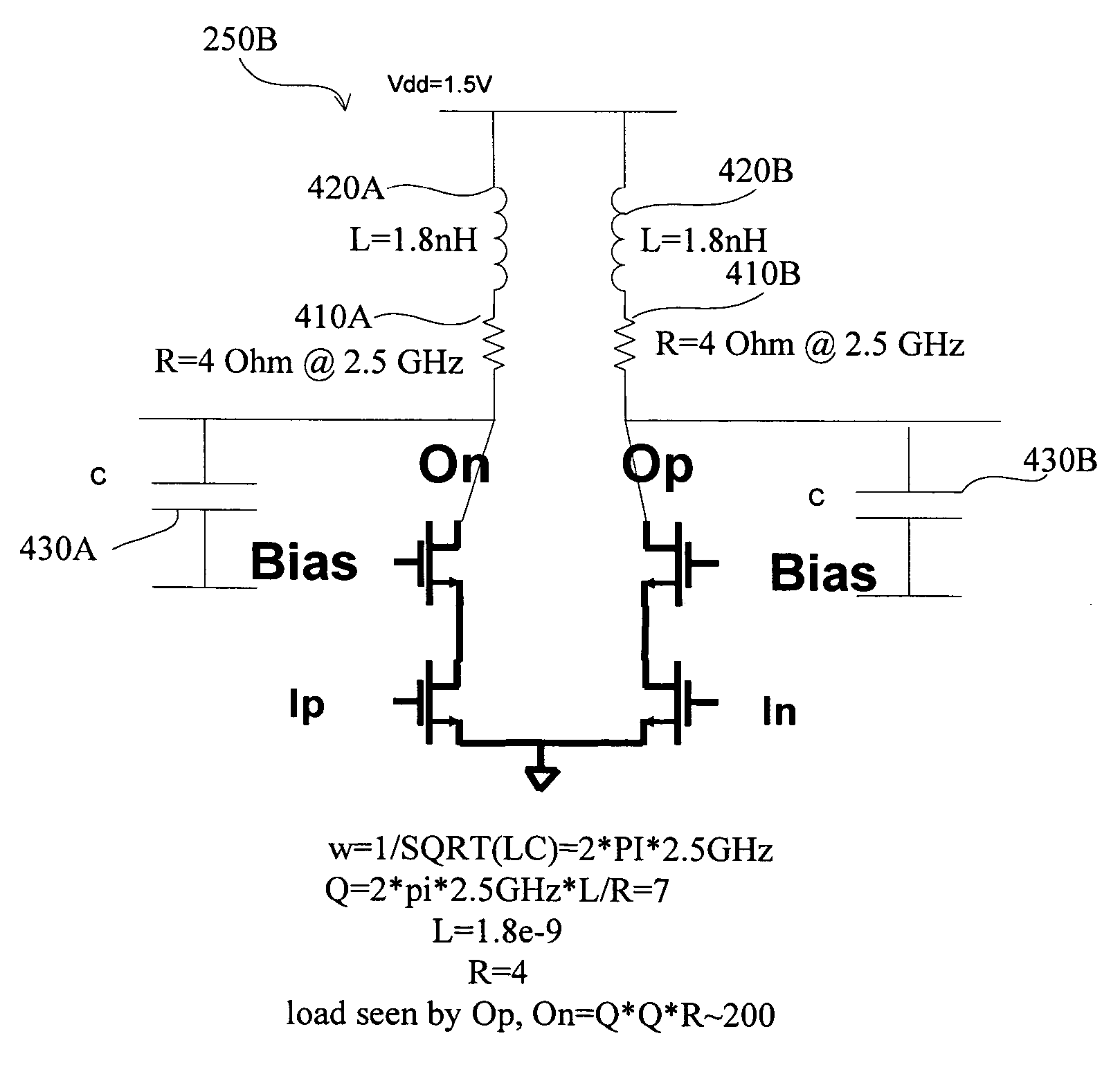

Differential power amplifier and method in class AB mode

InactiveUS7145390B2Keep linearTotal current dropHigh frequency amplifiersDifferential amplifiersAudio power amplifierCurrent consumption

Owner:AVAGO TECH INT SALES PTE LTD

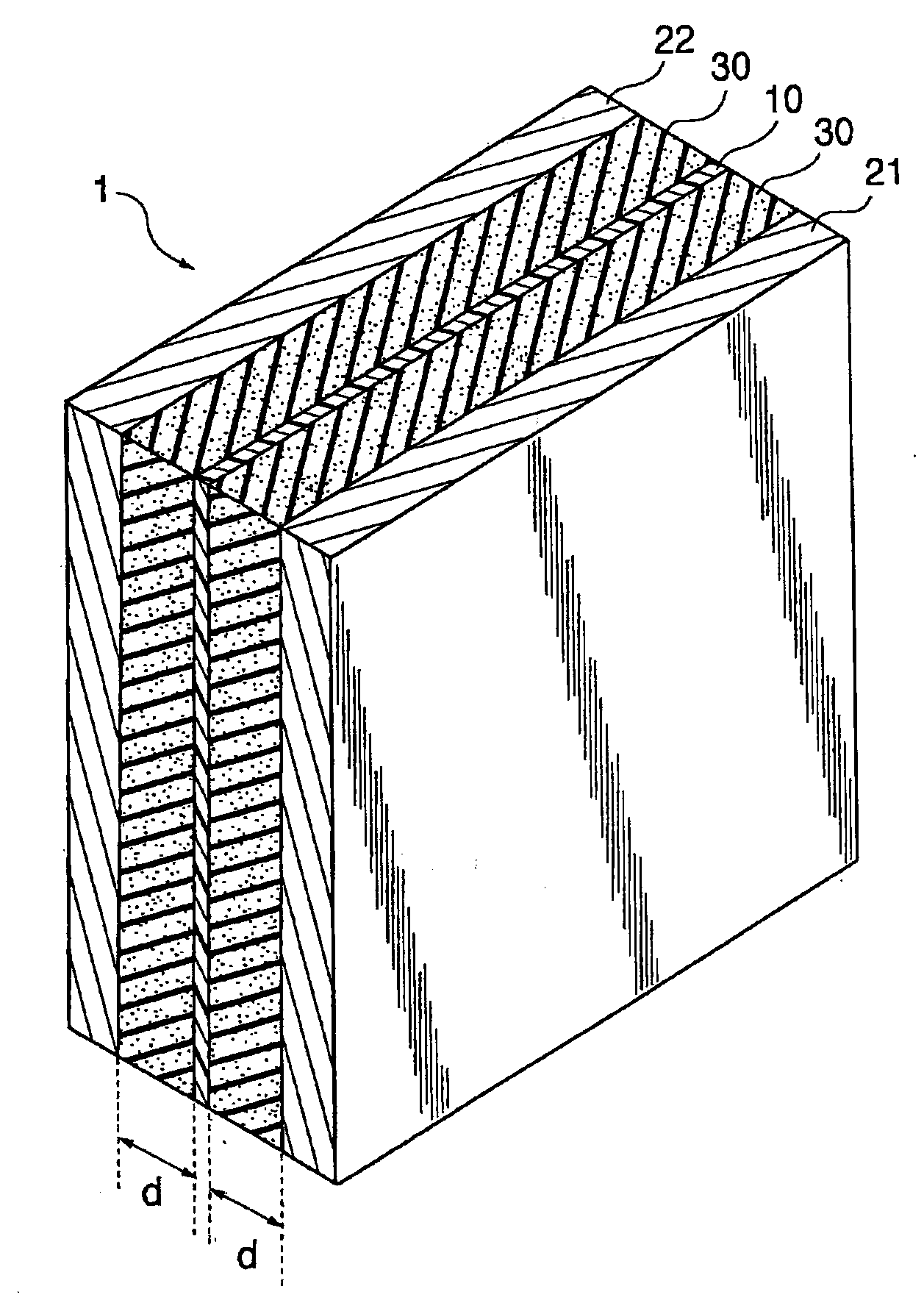

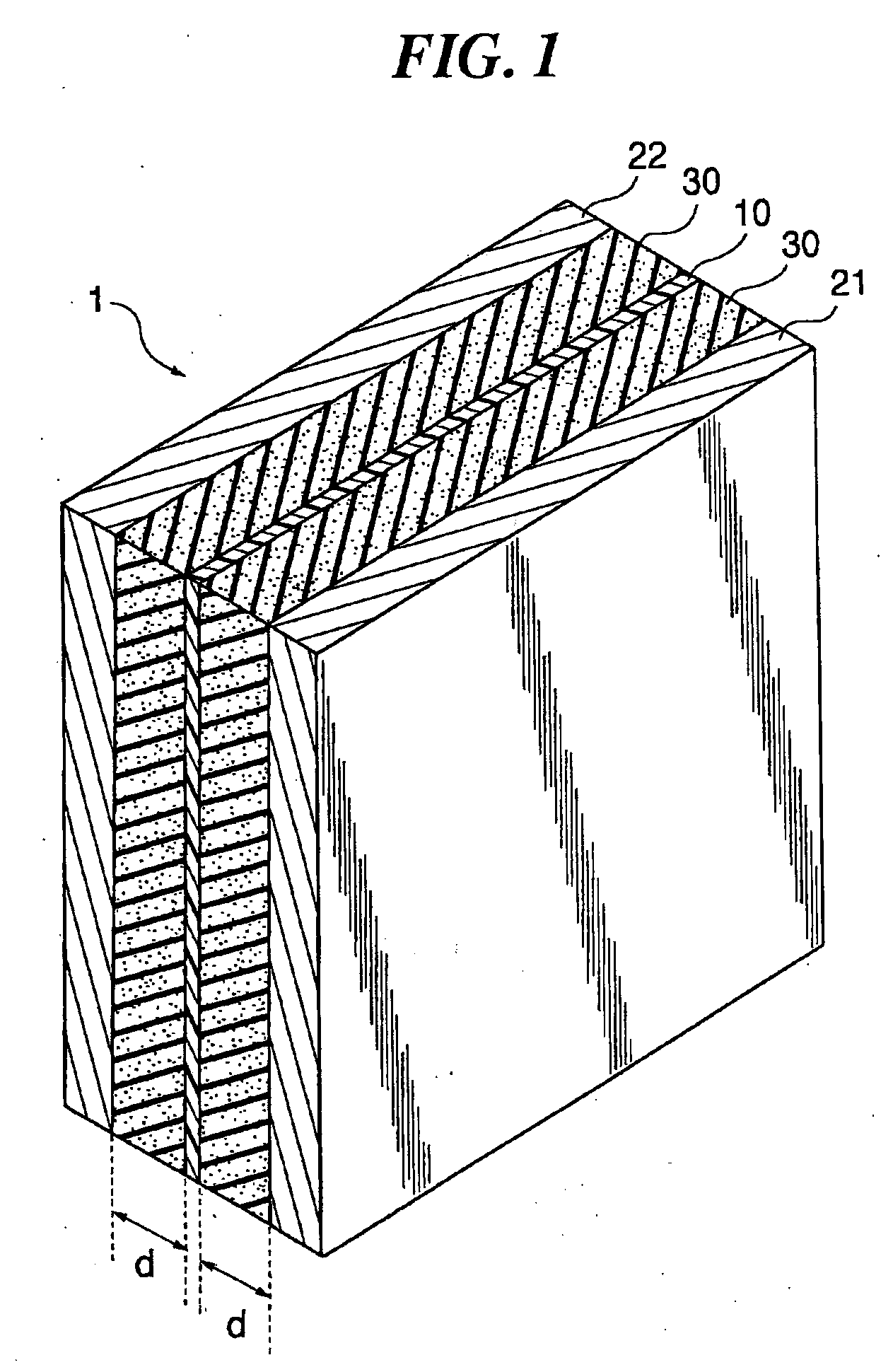

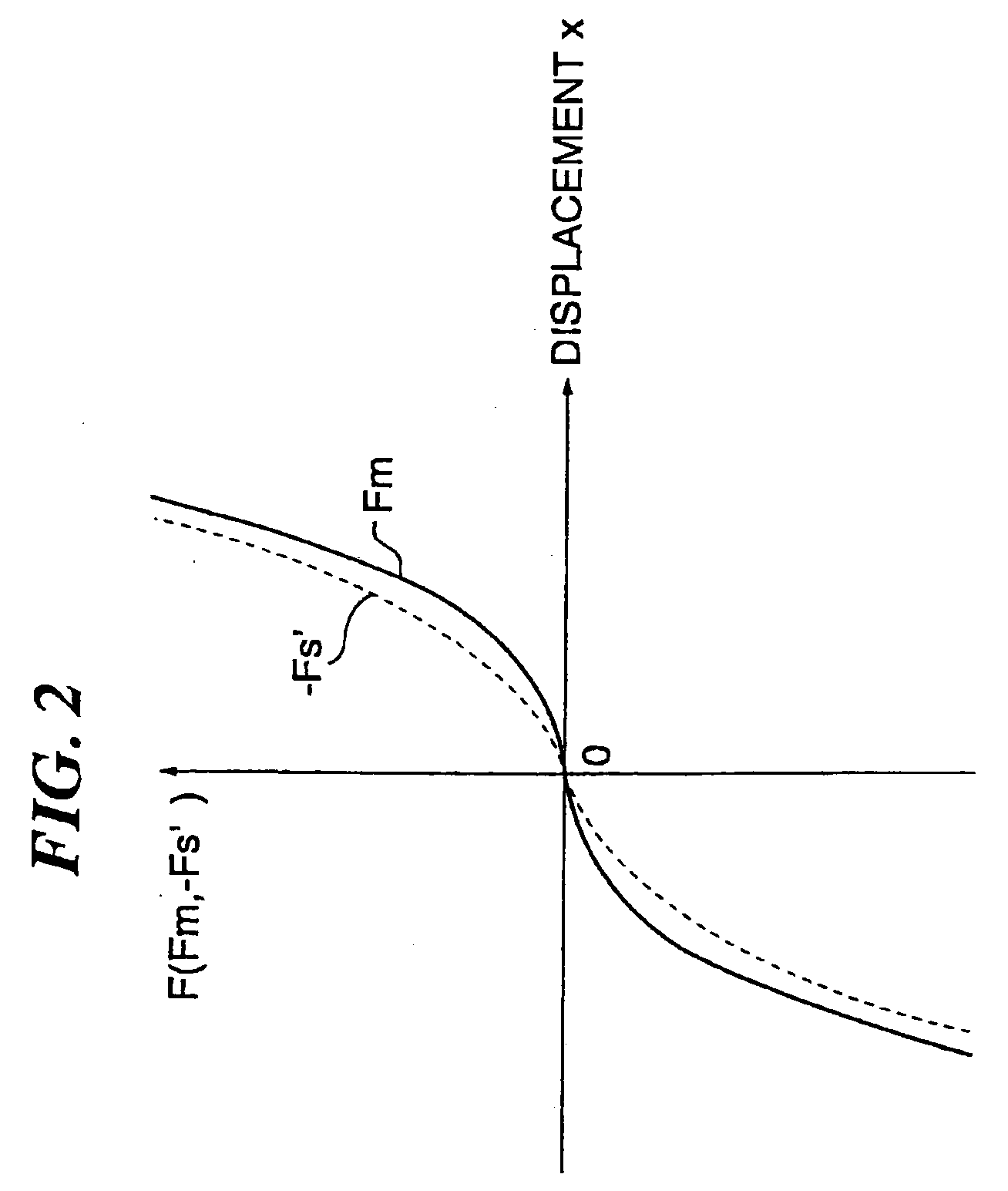

Electrostatic speaker

InactiveUS20070274545A1Keep linearElectrostatic transducer loudspeakersDeaf-aid setsEngineeringLinearity

An electrostatic speaker capable of relaxing a restriction on the allowable amplitude of a diaphragm while maintaining the linearity of a force acting on the diaphragm. The electrostatic speaker mainly includes electrodes opposed to each other, a diaphragm, and elastic members interposed between the diaphragm and the electrodes. The elastic members have an elastic characteristic that generates a restorative force corresponding to higher order terms of an electrostatic force generated by the electrodes and acting on the diaphragm.

Owner:YAMAHA CORP

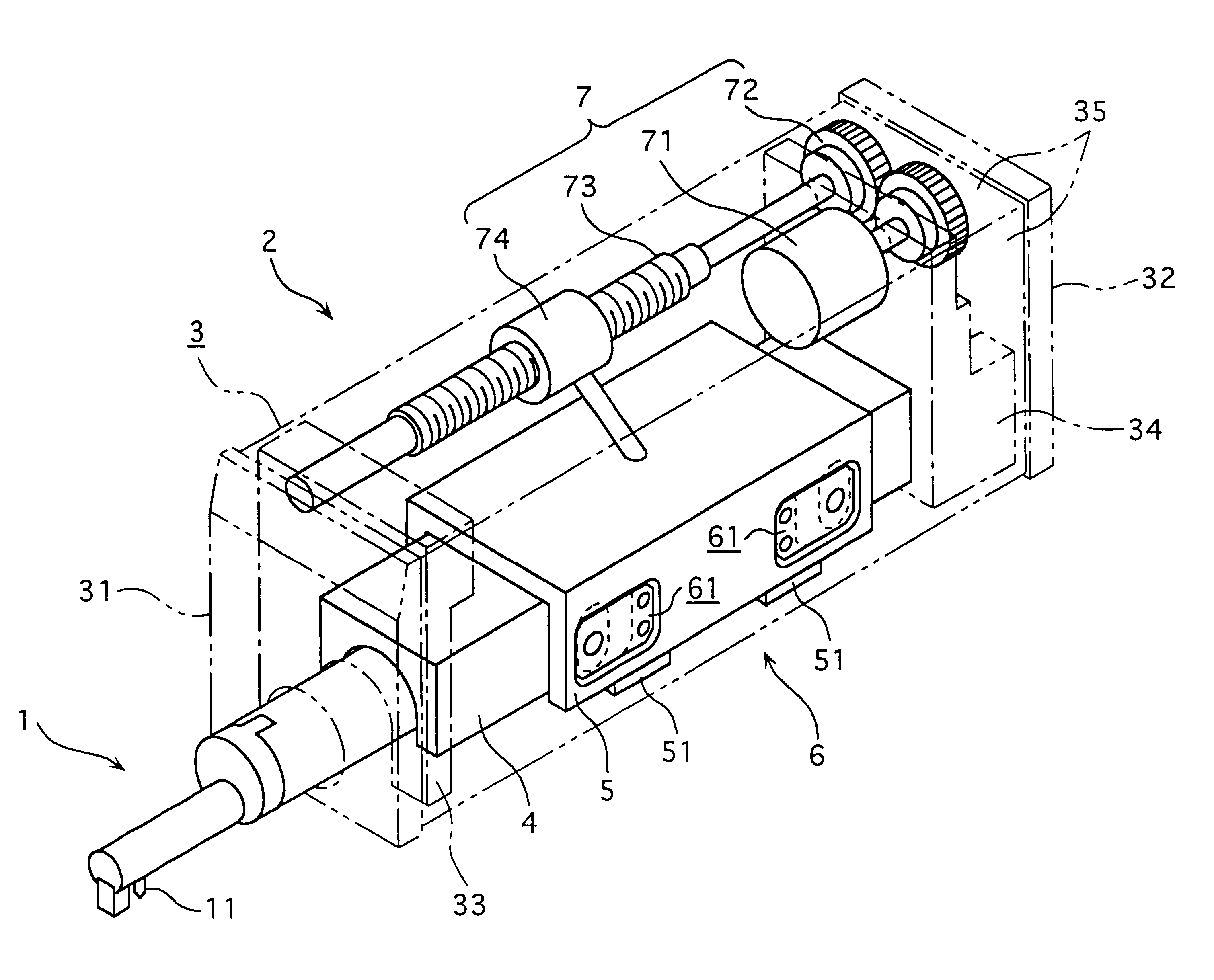

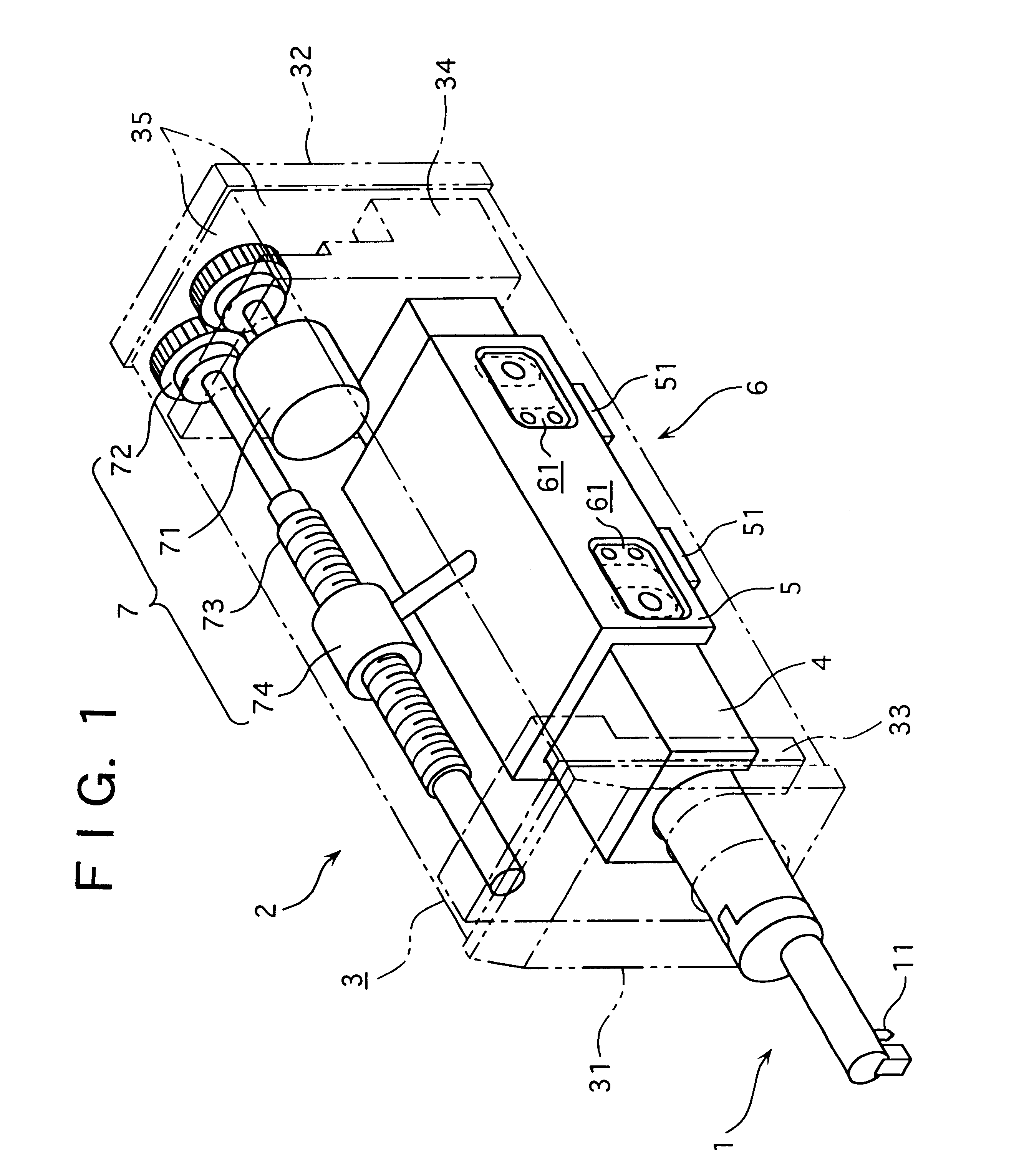

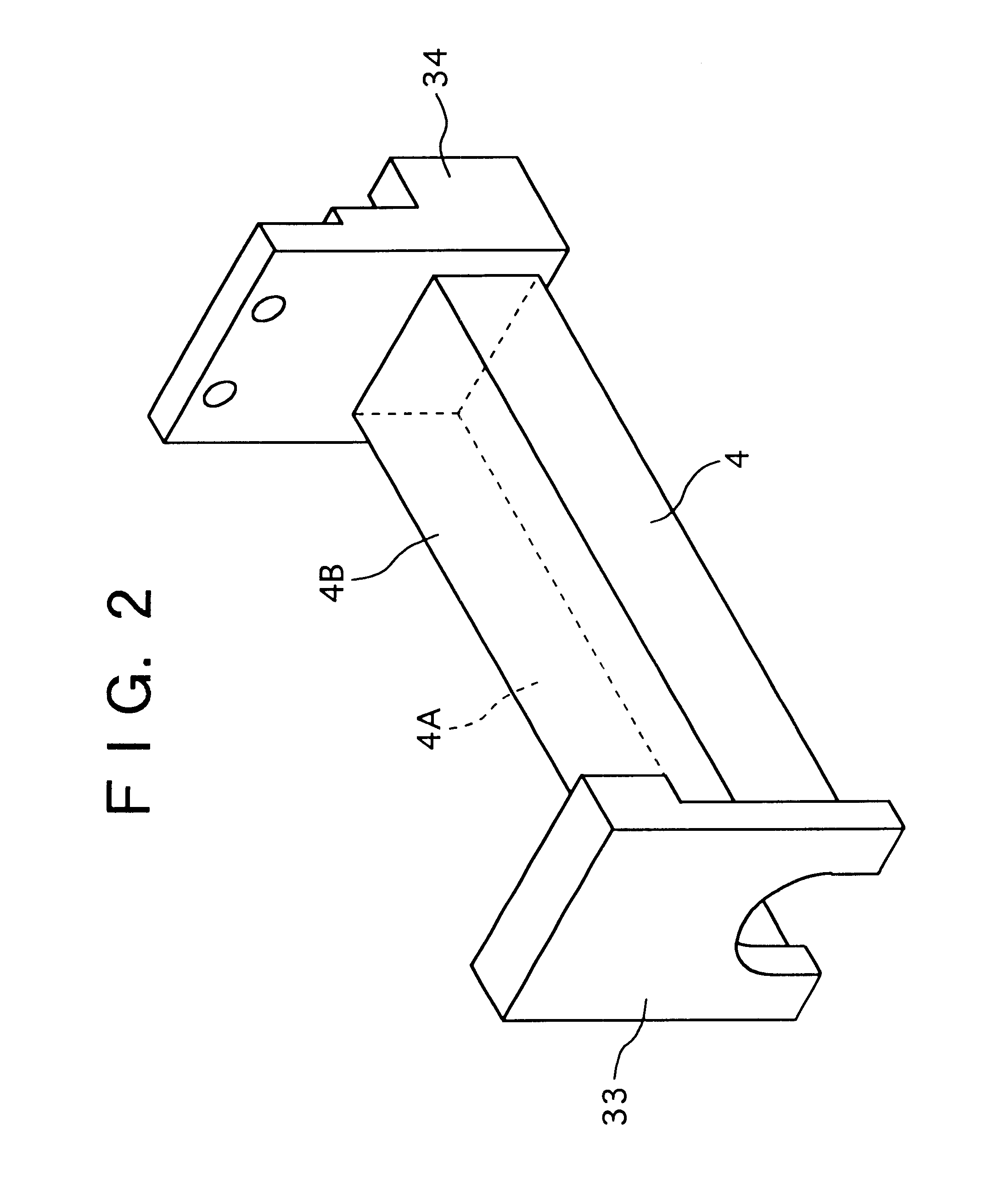

Drive unit

A slider holding a measuring tool moves along an approximately reverse U-shaped guide rail provided in parallel with a moving direction of the measuring tool without being rotated. Accordingly, a cross section of the guide rail can be enlarged without increasing the size of the entirety of a drive unit. As a result, high rigidity can be obtained while reducing the size and weight of the drive unit as compared to a conventional arrangement having two shafts. Further, linearity of the slider and the measuring tool moving along a reference surface of the guide rail can be attained with high accuracy. Further, since a pre-load means for biasing the slider toward a guide rail is provided, a position or orientation of the slider and the measuring tool can be stabilized, thus securely repeating movement of the measuring tool.

Owner:MITUTOYO CORP

Wide dynamic range broadband current mode linear detector circuits for high power radio frequency power amplifier

ActiveUS20170160318A1Reduce complexityKeep linearElectric devicesCurrent/voltage measurementDetector circuitsPower detector

A power detector with a detection signal input connectible to a source of a radio frequency signal and a detected power level output has a differential amplifier detector circuit with an input connected to the detection signal input and an output corresponding to the detected power level output. A feedback network is connected to the input and the output of the differential amplifier detector circuit. A mirror circuit is connected to the differential amplifier detector circuit. A root mean square current corresponding to a power level of the radio frequency signal from the source is mirrored and integrated, with a direct current voltage level being generated therefrom and output to the detected power level output.

Owner:SKYWORKS SOLUTIONS INC

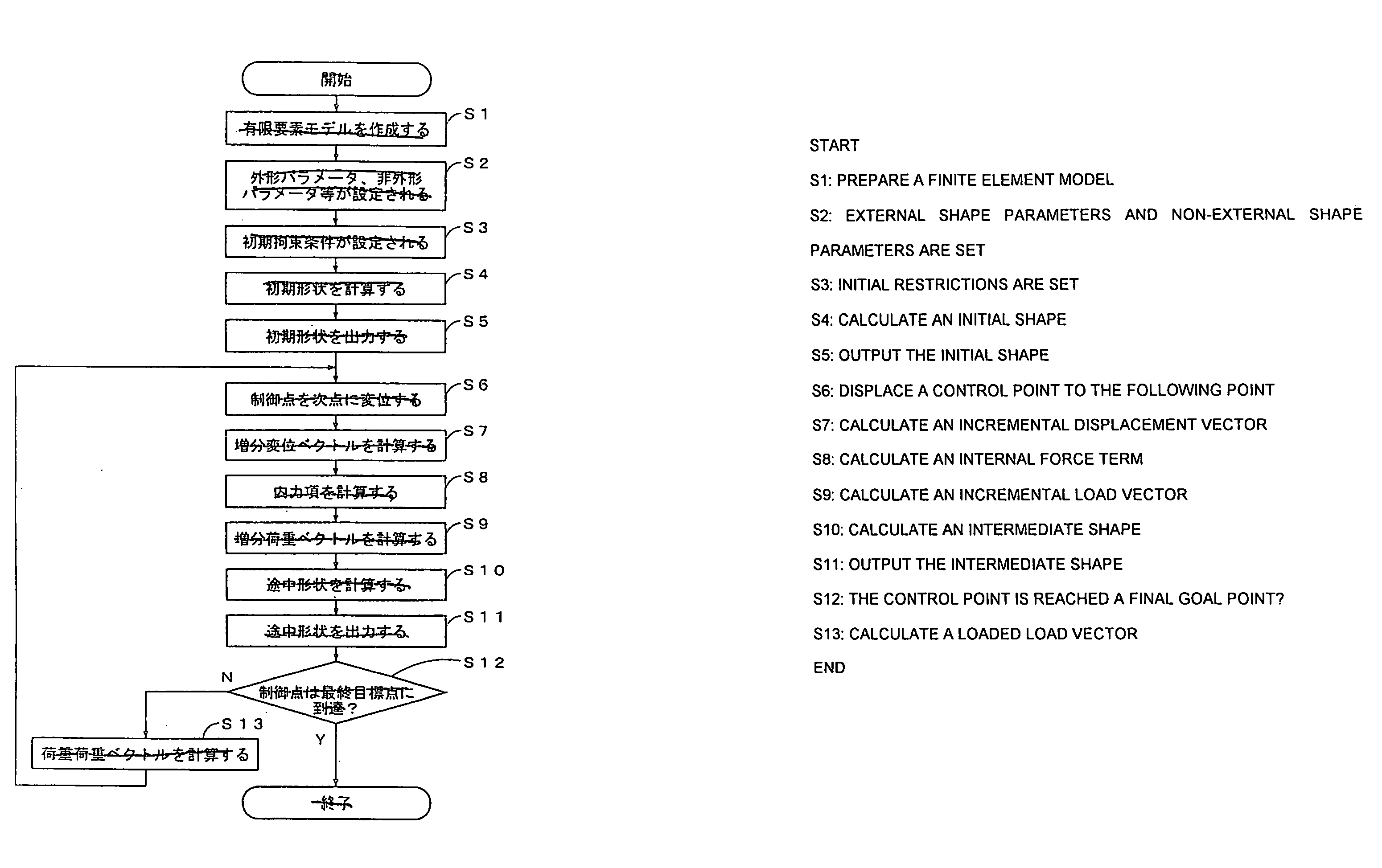

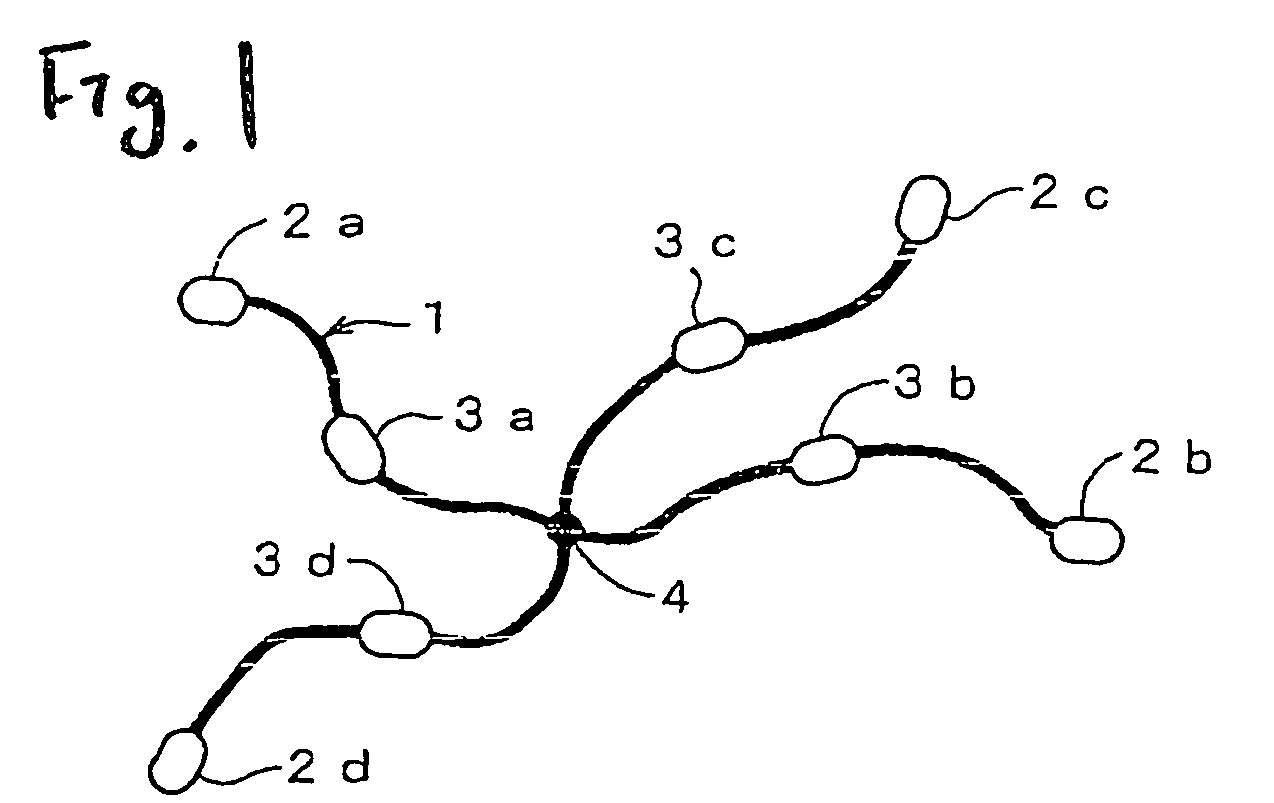

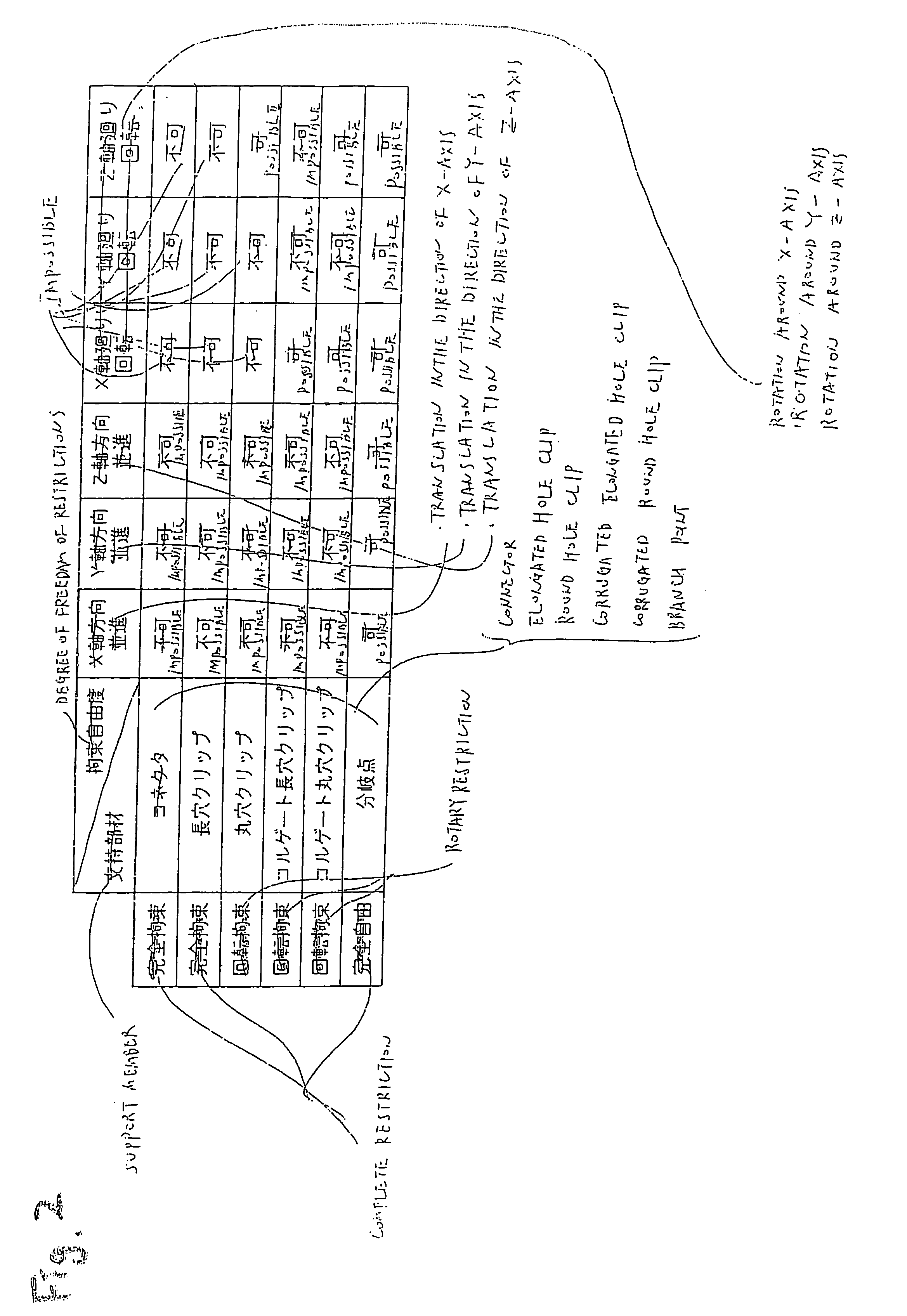

Method of calculating predictive shape of wire structure, calculation apparatus, and computer-readable recording medium

ActiveUS20060020434A1Predictive shapeRealistic predictive shapeDetecting faulty computer hardwareComputation using non-denominational number representationEngineeringCell Computing

A calculating apparatus includes a finite element model creating unit that creates a finite element model of the wire structure, a setting unit that sets physical properties, restriction conditions and loads of the wire structure to the finite element model, a predictive shape calculating unit that calculates a predictive shape of the finite element model in a physically balanced condition, an outputting unit that outputs the predictive shape of the finite element model, a load calculating unit that calculates the loads which are applied to the respective joints of the finite element model, a displacing unit that displaces a predetermined control point on the finite element model. The predictive shape calculating unit calculates the predictive shape of the finite element model in which the control point is displaced, based on the loads applied to the finite element model prior to the displacement of the control point.

Owner:YAZAKI CORP

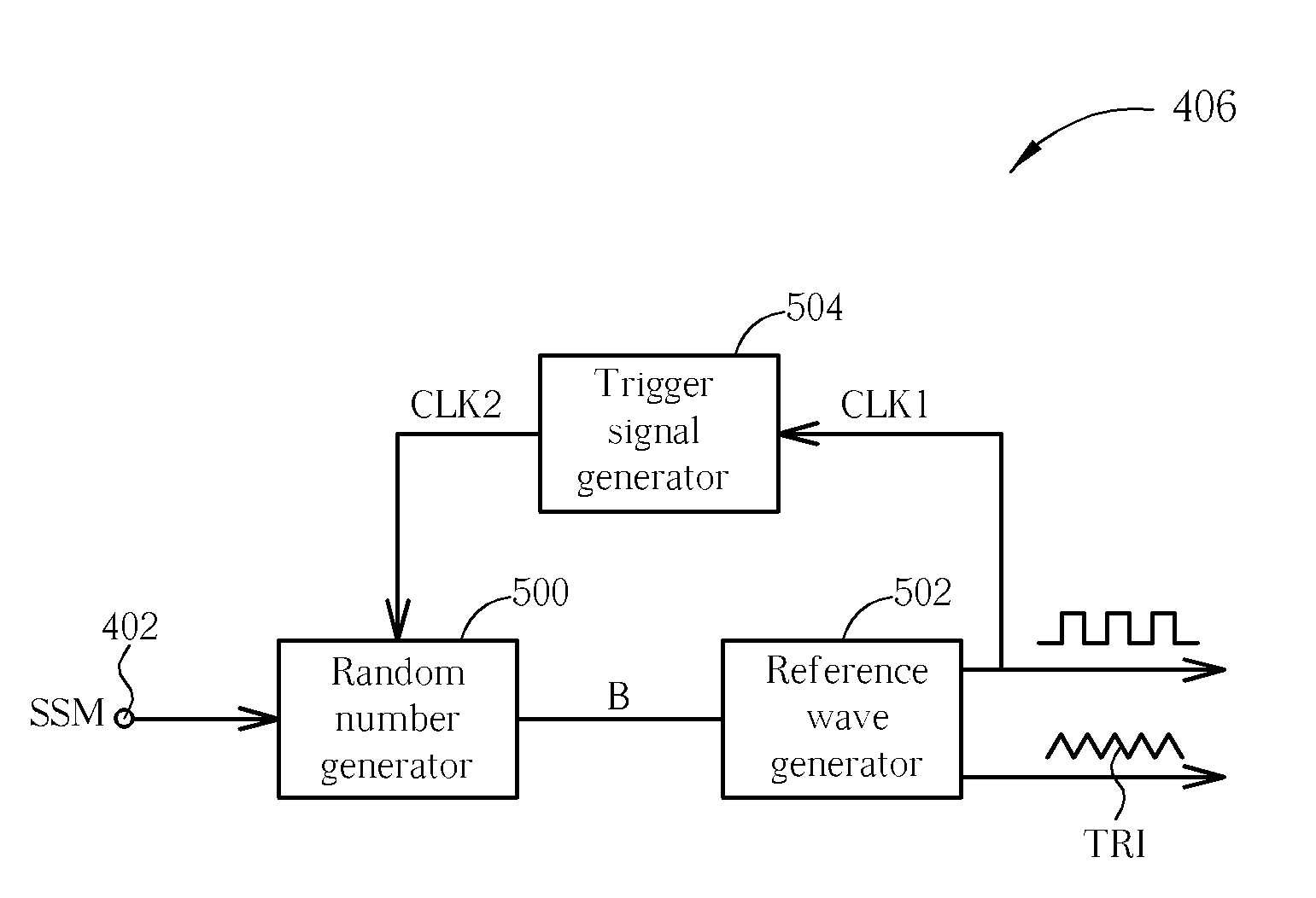

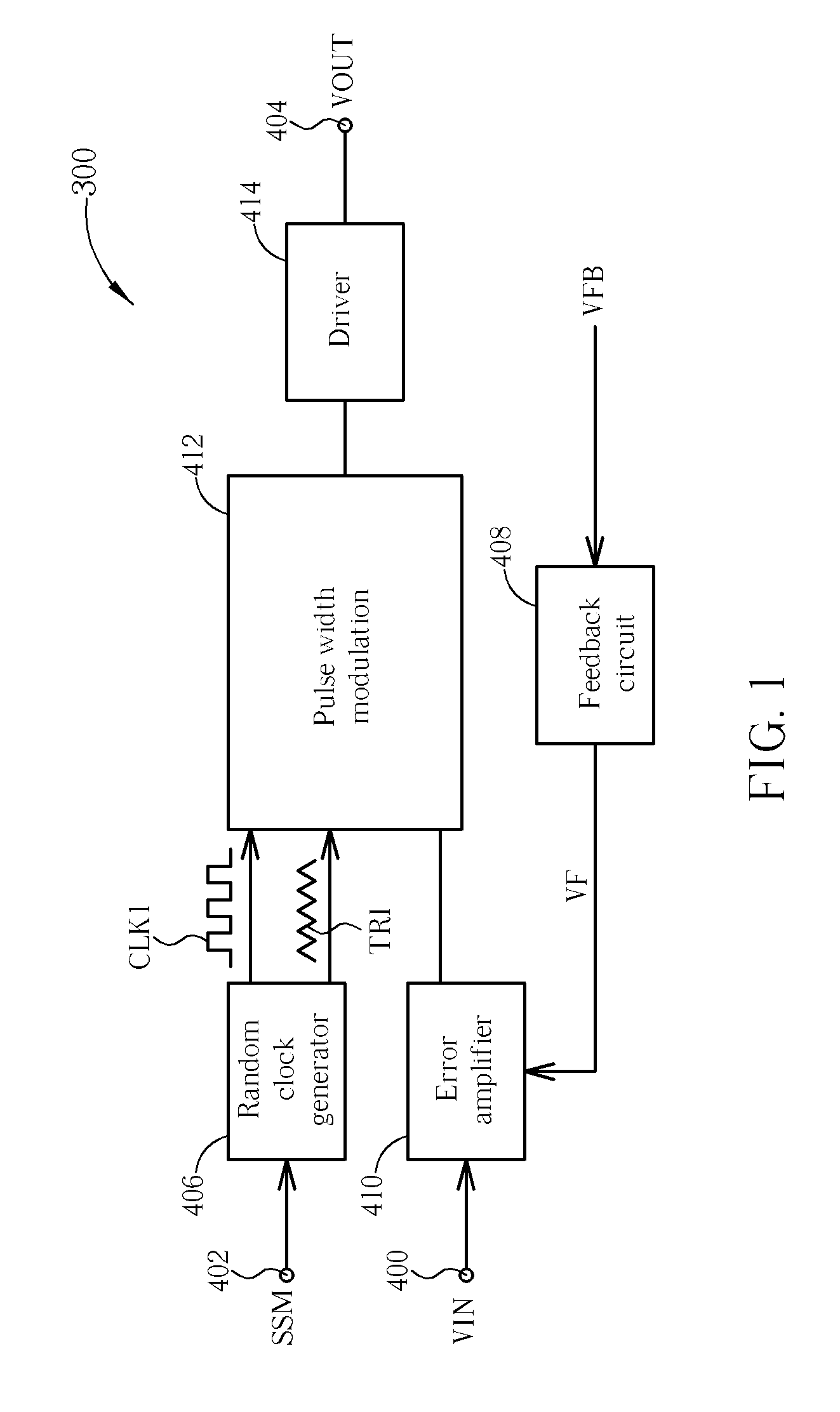

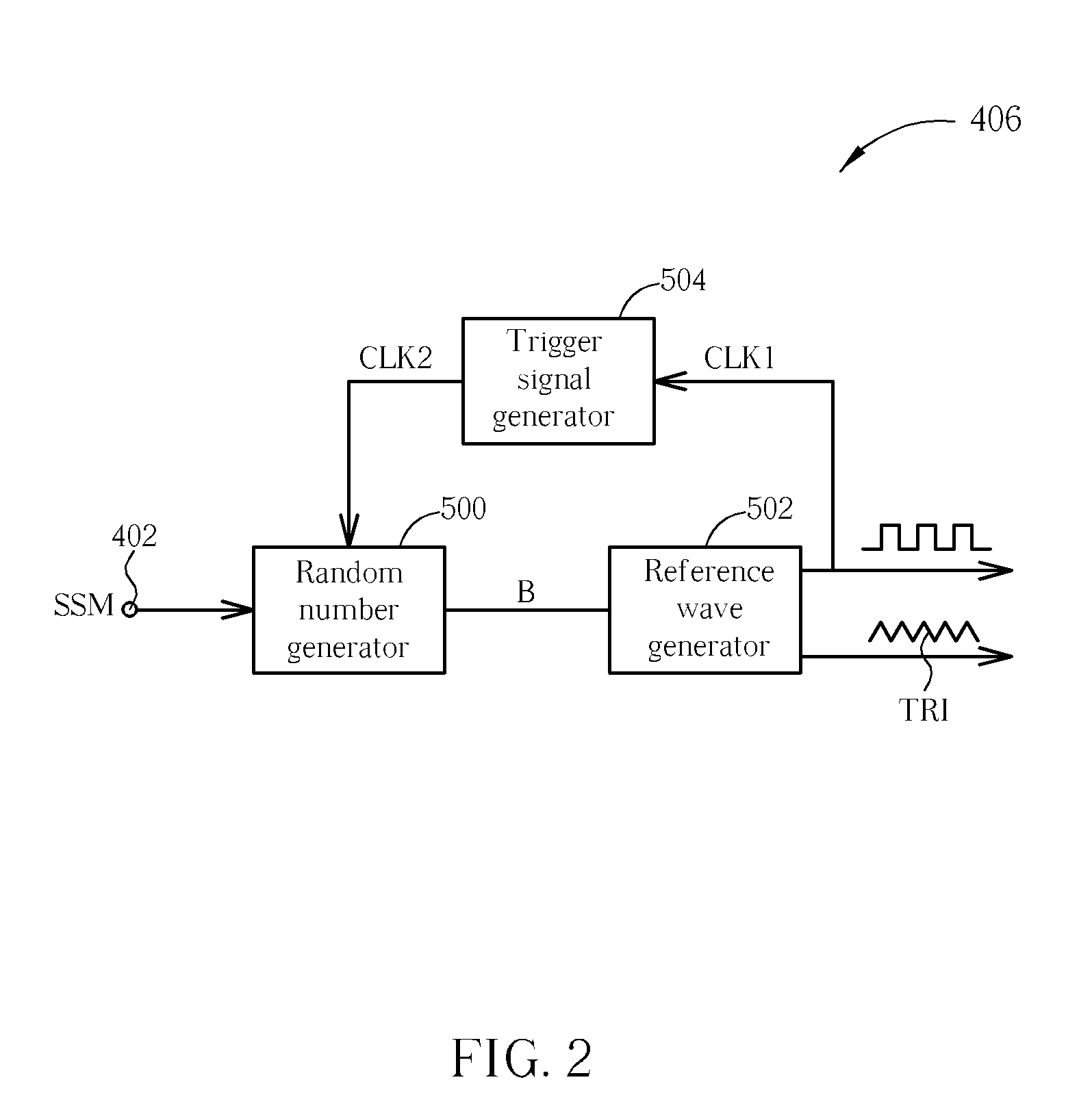

Spread Spectrum Device and Related Random Clock Generator for a Switching Amplifier

ActiveUS20080303572A1Output signal distortionLow costMultiple input and output pulse circuitsInstant pulse delivery arrangementsSquare waveformAudio power amplifier

A random clock generator for a spread spectrum modulating device includes a random number generator for generating a plurality of random number signals according to a first square wave signal and a control signal, a reference wave generator coupled to the random number generator for generating a triangular signal and a second square wave signal according to the plurality of random number signals, and a trigger signal generator coupled to the random number generator and the reference wave generator, for generating the first square wave signal according to the second square wave signal.

Owner:ANPEC ELECTRONICS CORPORATION

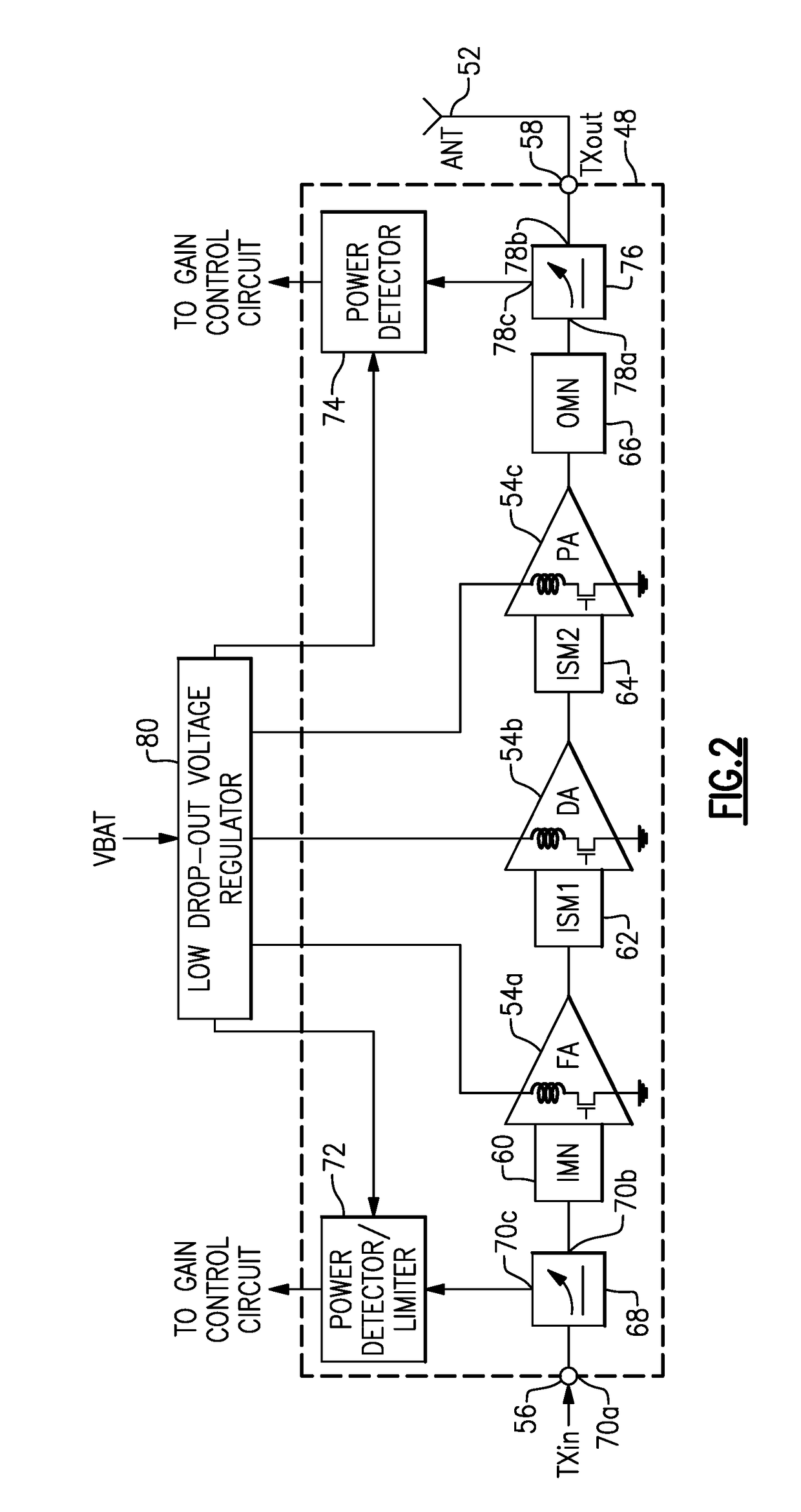

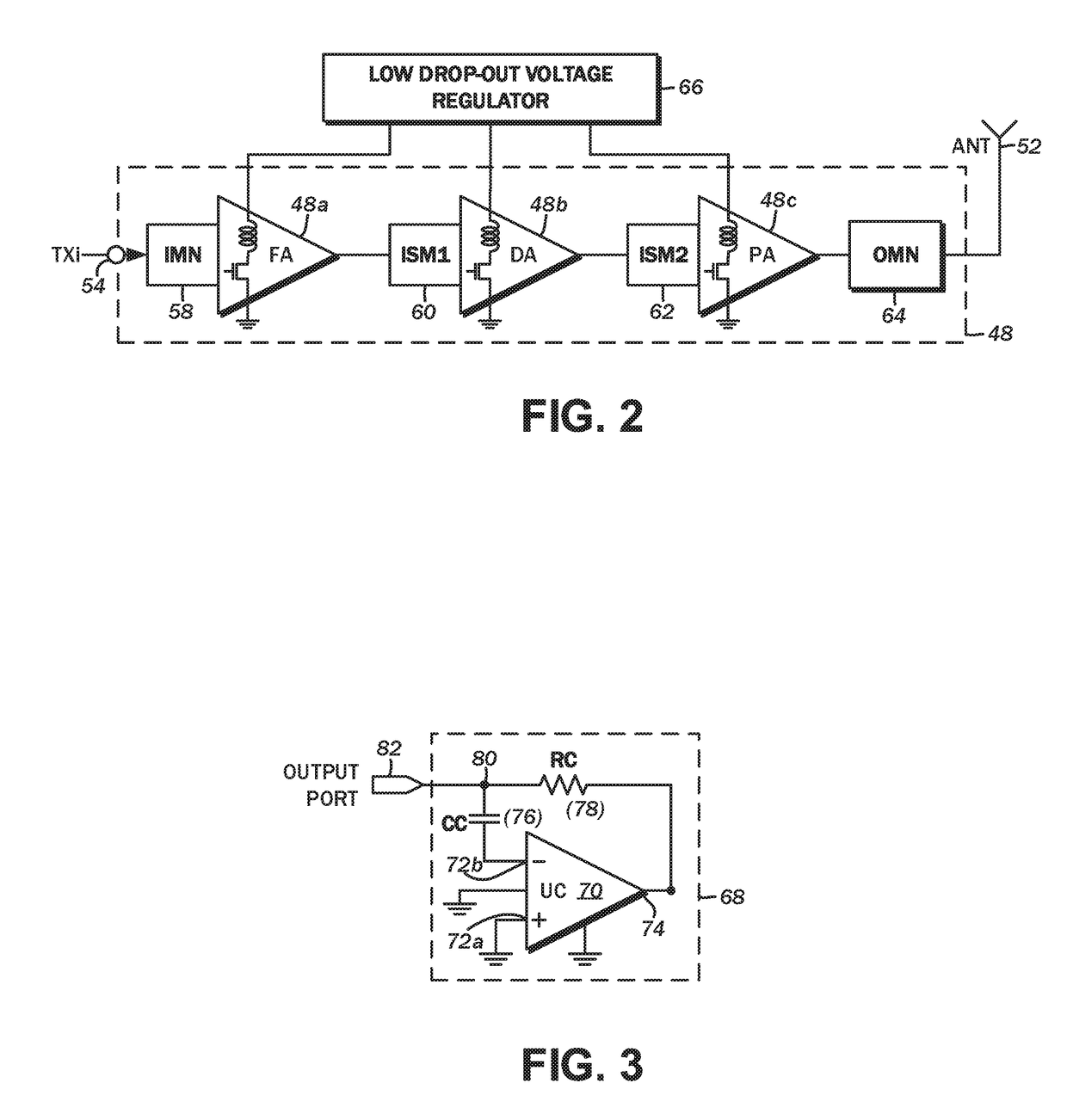

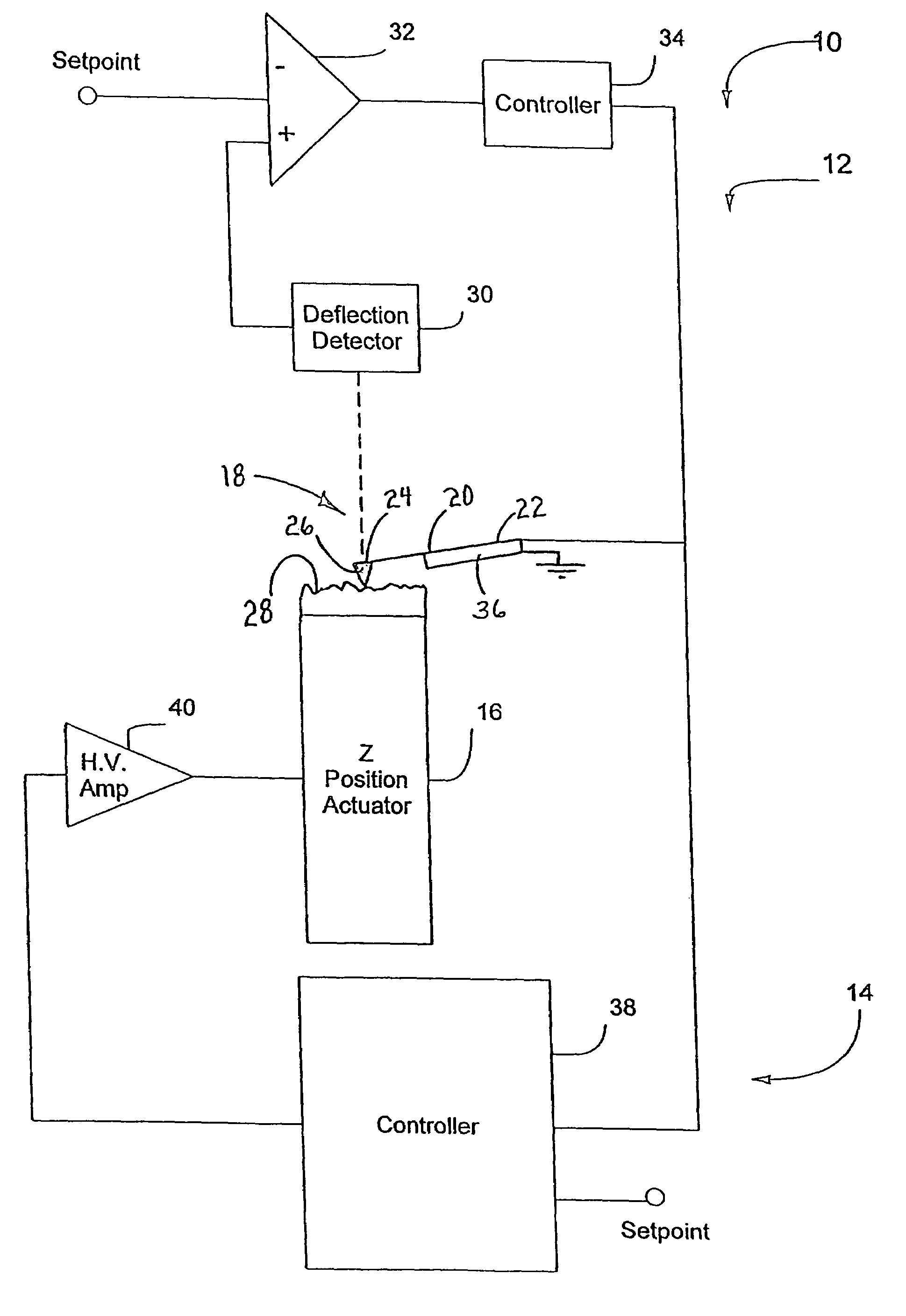

Low dropout voltage regulator for highly linear radio frequency power amplifiers

ActiveUS20170163218A1Keep linearPower managementAmplifier modifications to reduce non-linear distortionCapacitanceAudio power amplifier

A radio frequency amplifier circuit has a signal input and a signal output. A primary amplifier is connected to the signal input and the signal output. A low dropout voltage regulator is connectible to an external power supply and to the primary amplifier, and generates a set voltage to bias the primary amplifier from a variable voltage provided by the external power supply. An equivalent capacitance circuit is connected to the primary amplifier and to the low dropout voltage regulator. The equivalent capacitance circuit defines a low dropout voltage regulator output capacitance in a nano-Farad to micro-Farad range absent any passive capacitor components corresponding thereto to maintain linearity of the primary amplifier.

Owner:SKYWORKS SOLUTIONS INC

Dynamic activation for an atomic force microscope and method of use thereof

InactiveUS7204131B2Increase speedIncrease usageNanotechSurface/boundary effectPhotodetectorLight beam

A scanning probe microscope method and apparatus that modifies imaging dynamics using an active drive technique to optimize the bandwidth of amplitude detection. The deflection is preferably measured by an optical detection system including a laser and a photodetector, which measures cantilever deflection by an optical beam bounce technique or another conventional technique. The detected deflection of the cantilever is subsequently demodulated to give a signal proportional to the amplitude of oscillation of the cantilever, which is thereafter used to drive the cantilever.

Owner:BRUKER NANO INC

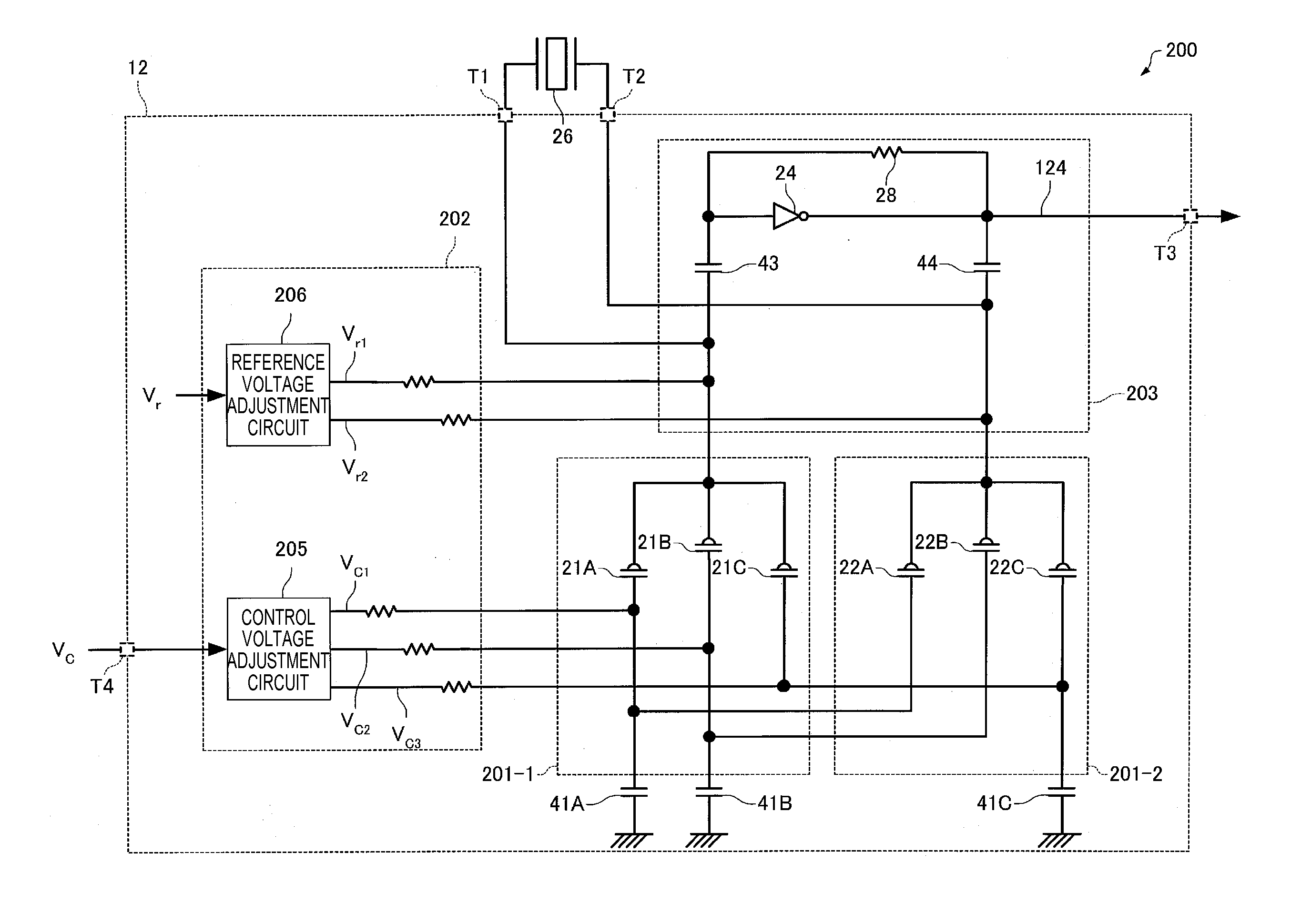

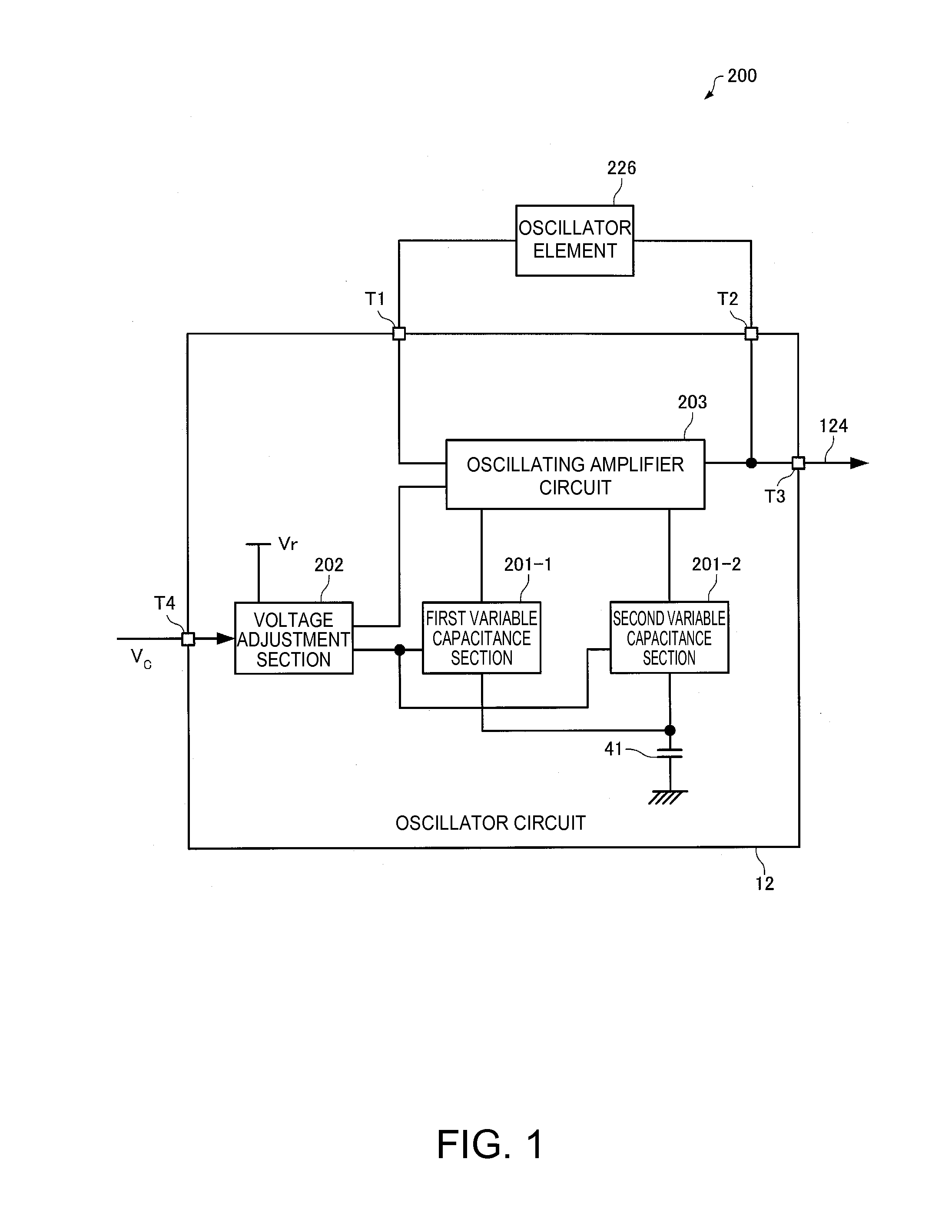

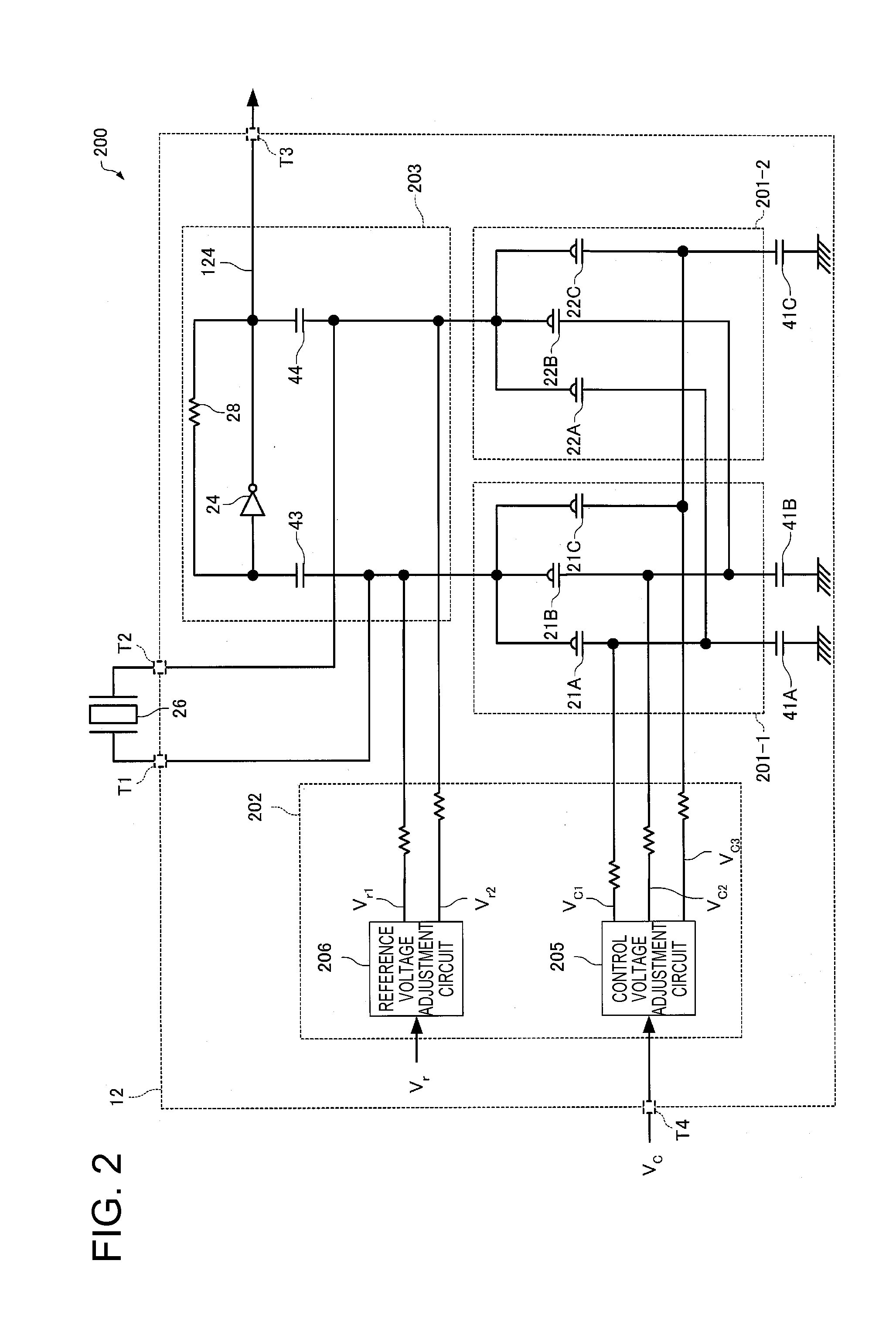

Oscillator circuit, oscillator, electronic apparatus, and moving object

InactiveUS20150145611A1Increase width of variationReduce circuit sizeOscillations generatorsCapacitanceAudio power amplifier

An oscillator circuit includes an oscillating amplifier circuit to which an oscillator element is connected, and which generates an oscillation signal, and a plurality of MOS type variable capacitance elements each having two terminals, one of which is electrically connected to the oscillating amplifier circuit, the MOS type variable capacitance elements have respective threshold voltages different from each other, a control voltage is applied to one of the terminals of each of the MOS type variable capacitance elements, and a reference voltage is applied to the other of the terminals of each of the MOS type variable capacitance elements. It is also possible for the MOS type variable capacitance elements to be different from each other in dope amount of impurities to a semiconductor layer below a gate electrode.

Owner:SEIKO EPSON CORP