Patents

Literature

37results about How to "Eliminate bias effects" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Methods and apparatus for measurinfg the effect of online advertising on online user behavior

InactiveUS20070260519A1Eliminate the effects ofEliminate bias effectsAdvertisementsThird partyNative advertising

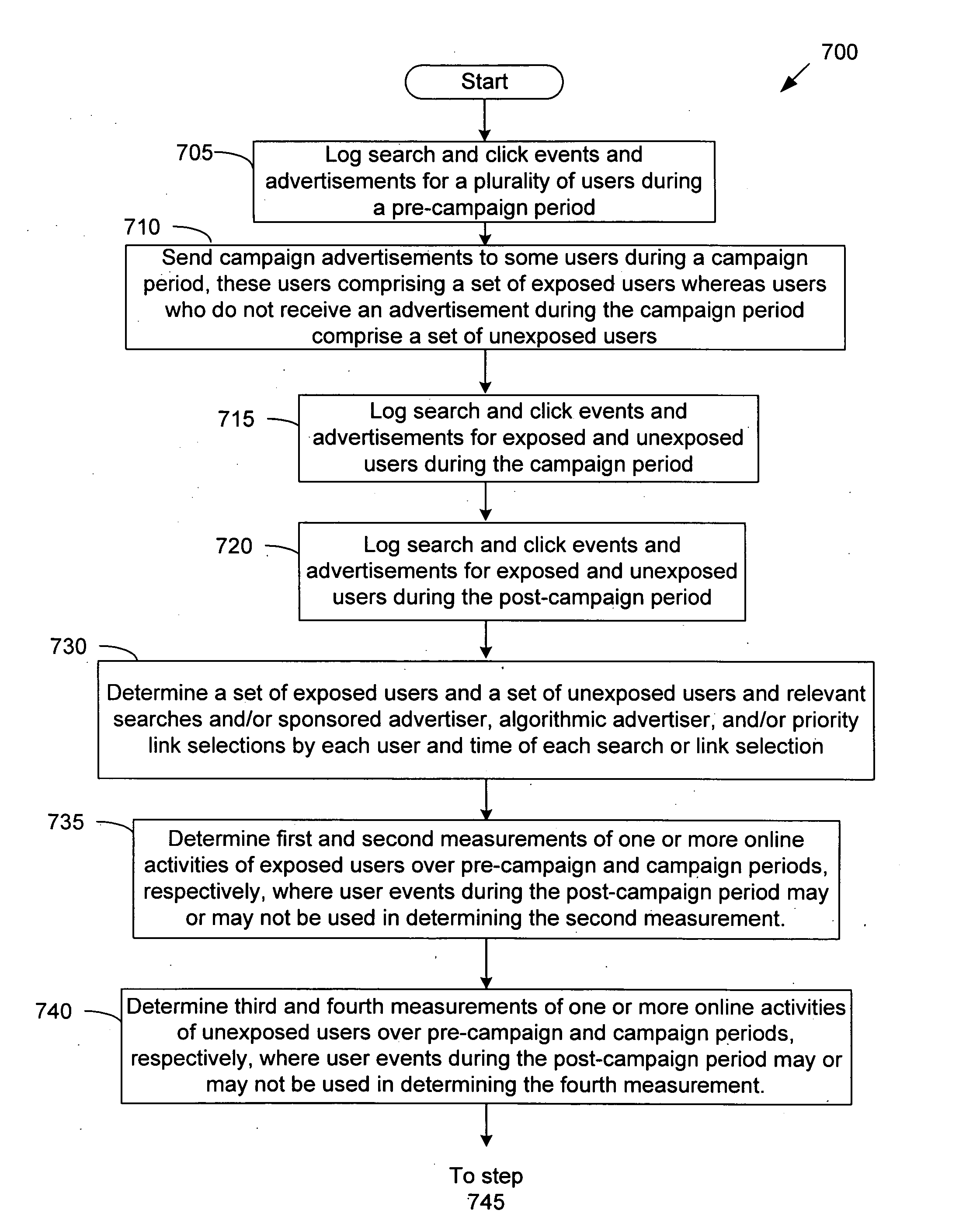

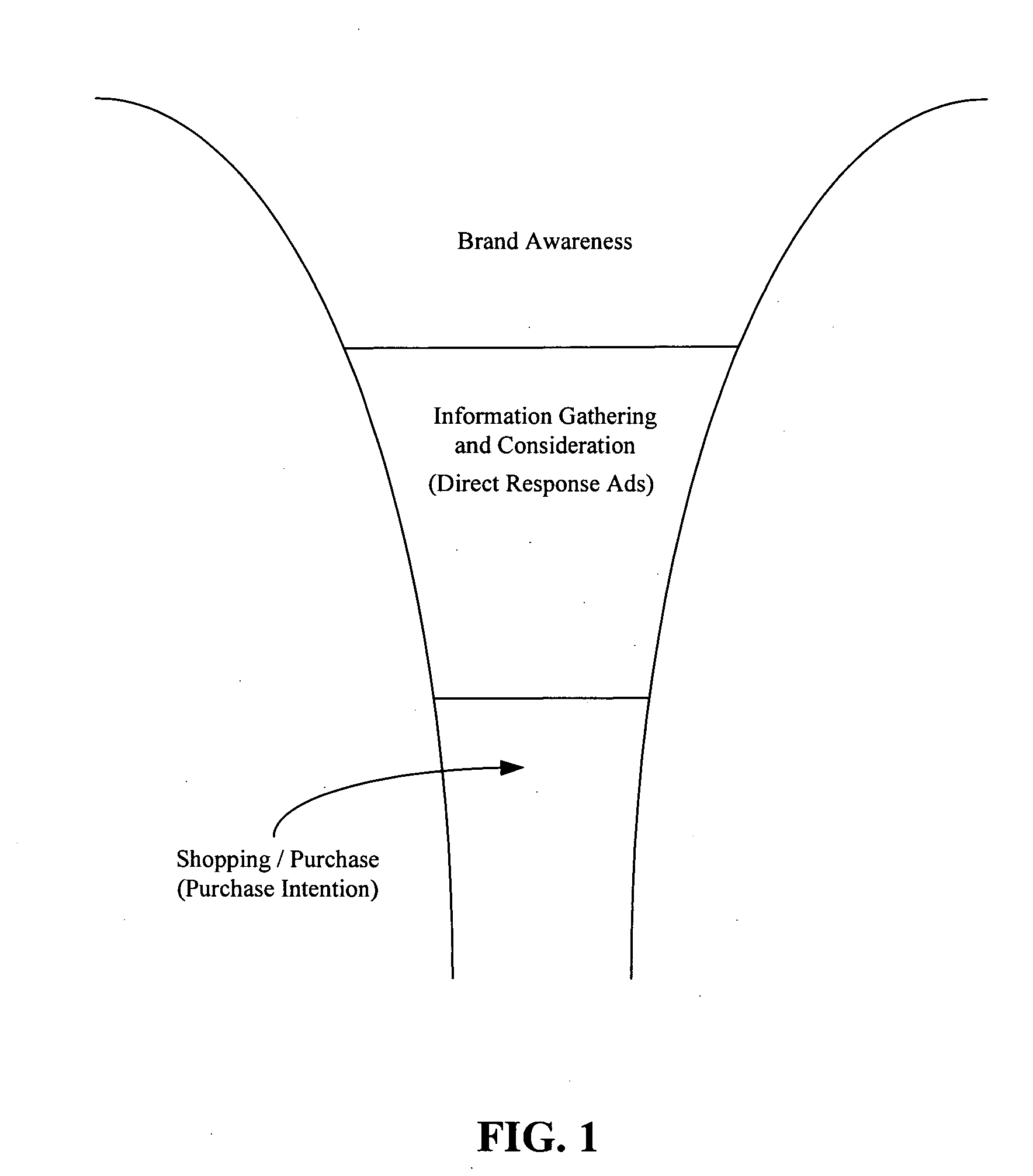

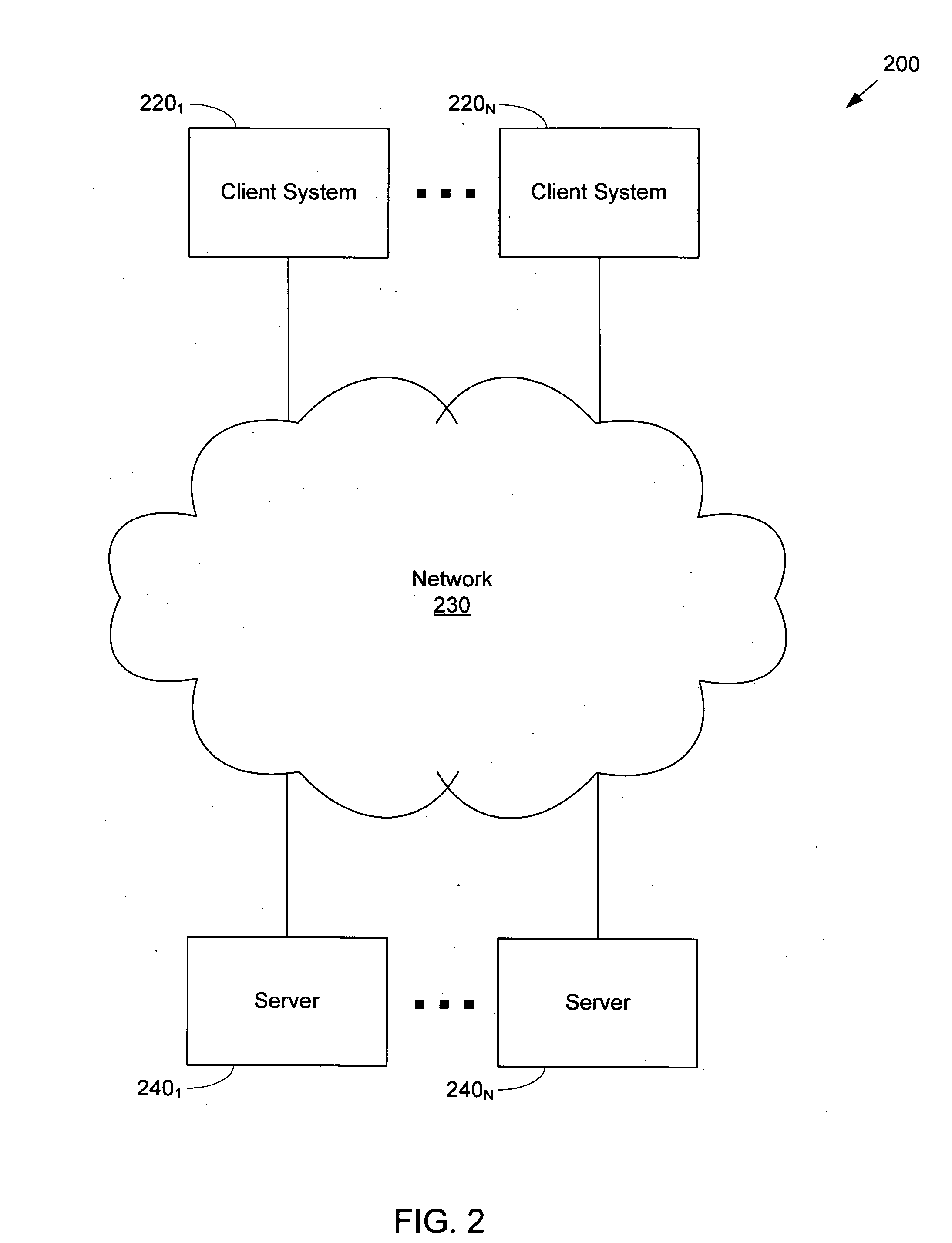

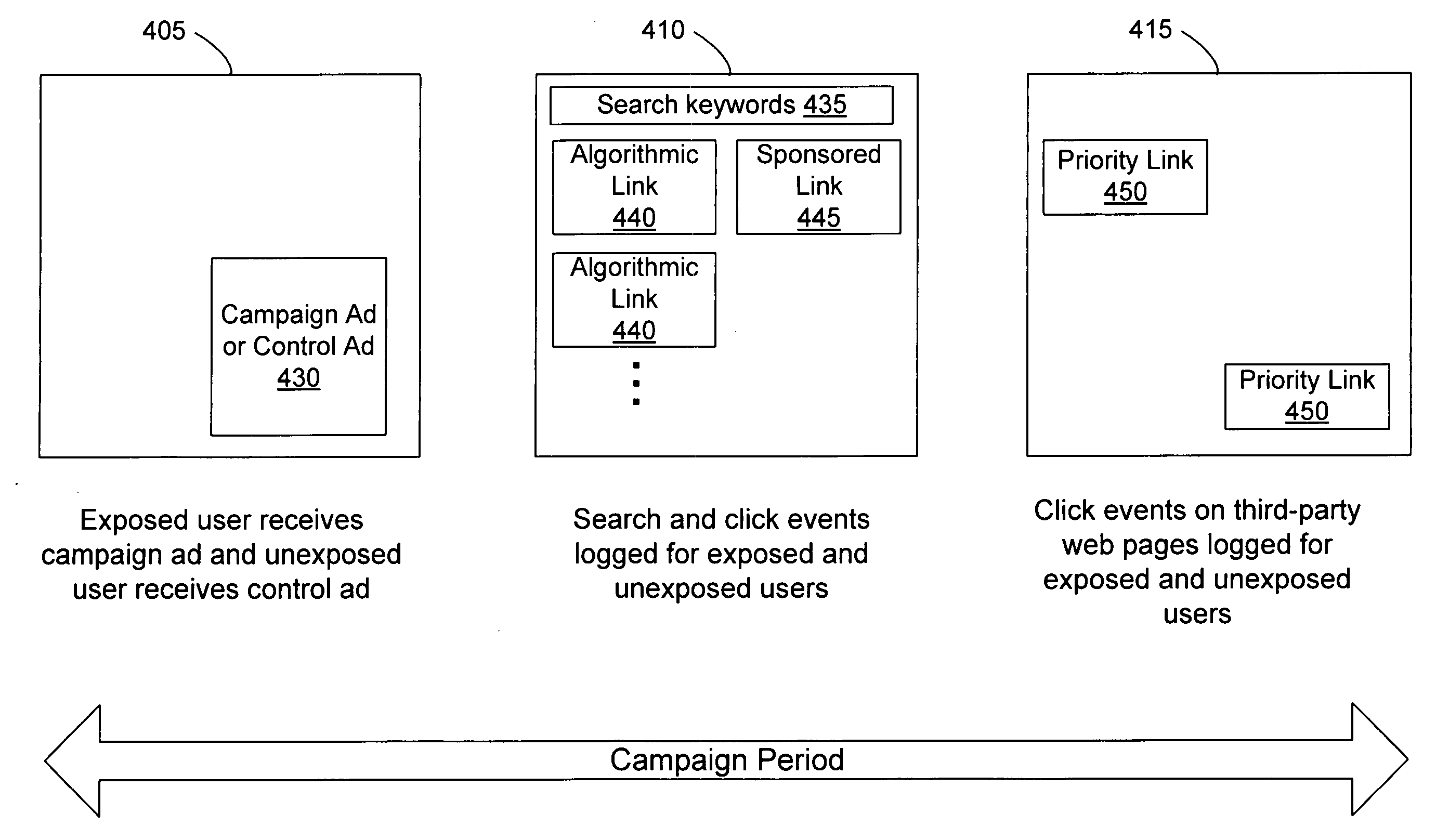

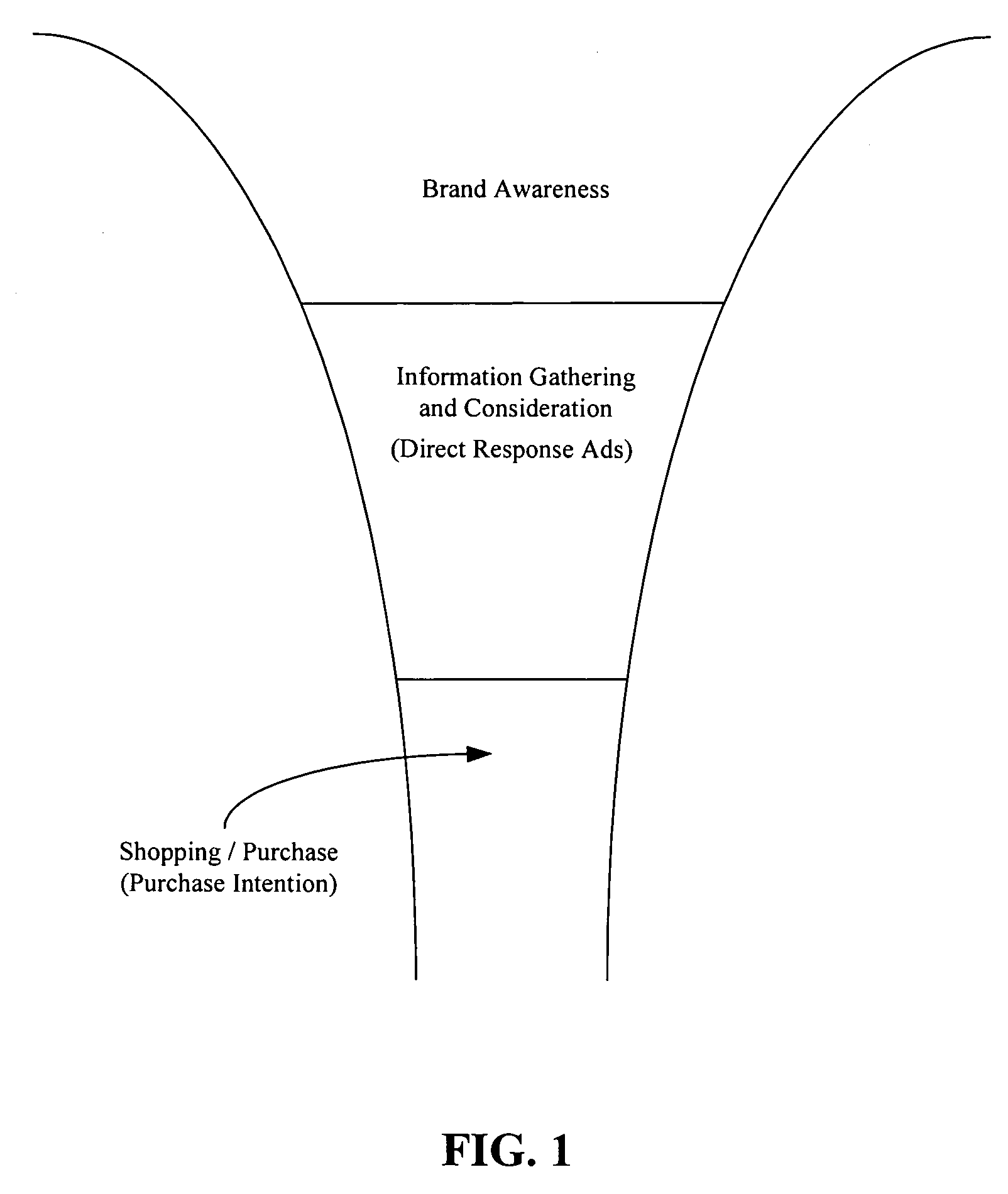

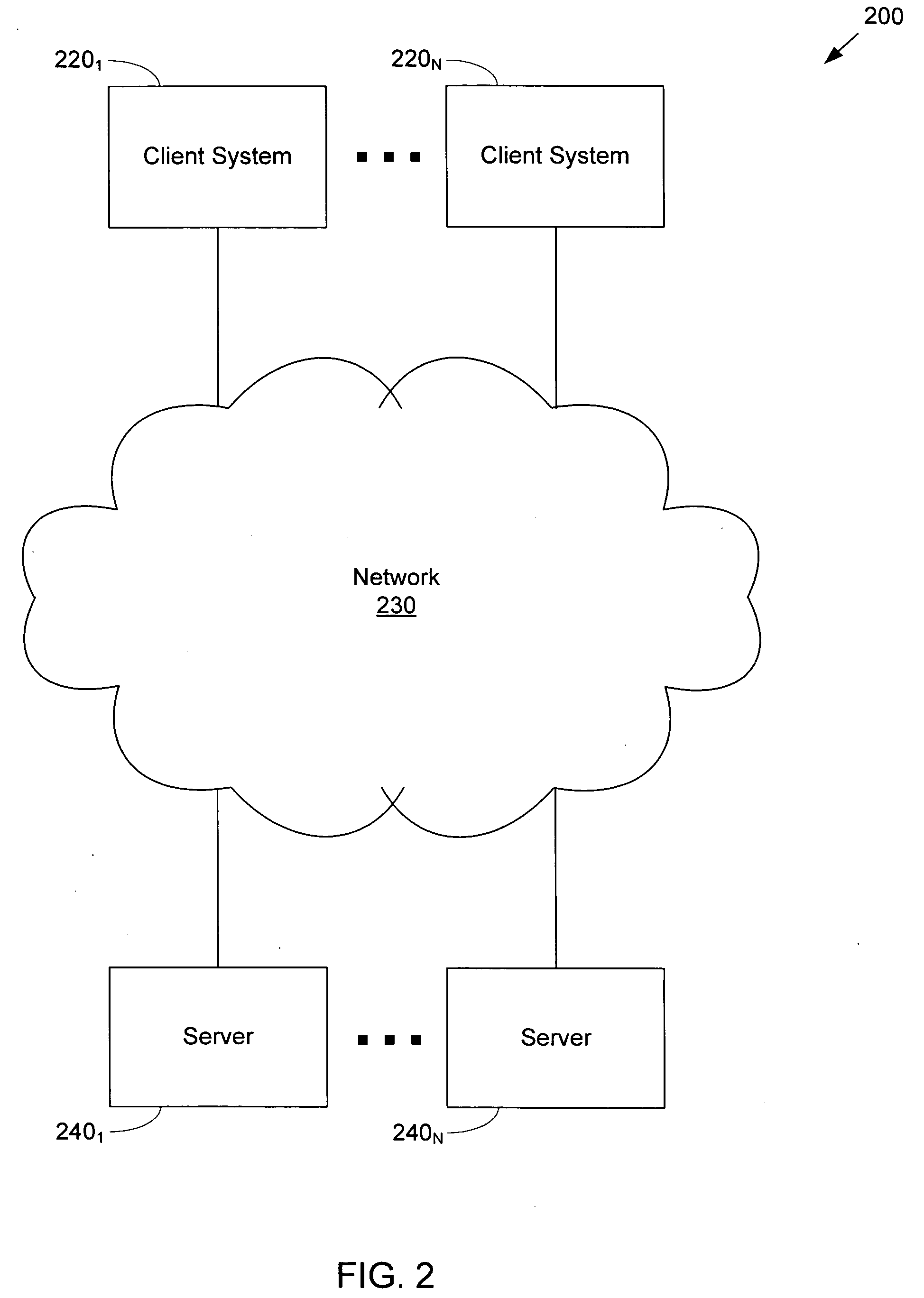

Described herein are methods and apparatus for measuring the effect of an online advertisement campaign on online behavior (searches relevant to the campaign and / or click activity on particular sponsored, algorithmic, and / or third-party links) of exposed users who have received a campaign advertisement. Online events of exposed and unexposed users are logged during a pre-campaign period (before any users receive any campaign advertisements) and a campaign period (when exposed users receive a campaign advertisement). A variety of behavior measurements and metrics may be determined using the logged user events. A metric may indicate the difference of an online activity between exposed and unexposed users during the campaign period or between exposed users during the pre-campaign and campaign periods. A metric may indicate the campaign's effect on an online activity by exposed users during the pre-campaign and campaign period in comparison to the online activity by unexposed users during the same periods.

Owner:OATH INC

Methods and apparatus for measuring the effect of online advertising on online user behavior

InactiveUS20070260512A1Eliminate the effects ofEliminate bias effectsAdvertisementsThird partyOnline advertising

Described herein are methods and apparatus for measuring the effect of an online advertisement campaign on online behavior (searches relevant to the campaign and / or click activity on particular sponsored, algorithmic, and / or third-party links) of exposed users who have received a campaign advertisement. Online events of exposed and unexposed users are logged during a pre-campaign period (before any users receive any campaign advertisements) and a campaign period (when exposed users receive a campaign advertisement). A variety of behavior measurements and metrics may be determined using the logged user events. A metric may indicate the difference of an online activity between exposed and unexposed users during the campaign period or between exposed users during the pre-campaign and campaign periods. A metric may indicate the campaign's effect on an online activity by exposed users during the pre-campaign and campaign period in comparison to the online activity by unexposed users during the same periods.

Owner:OATH INC

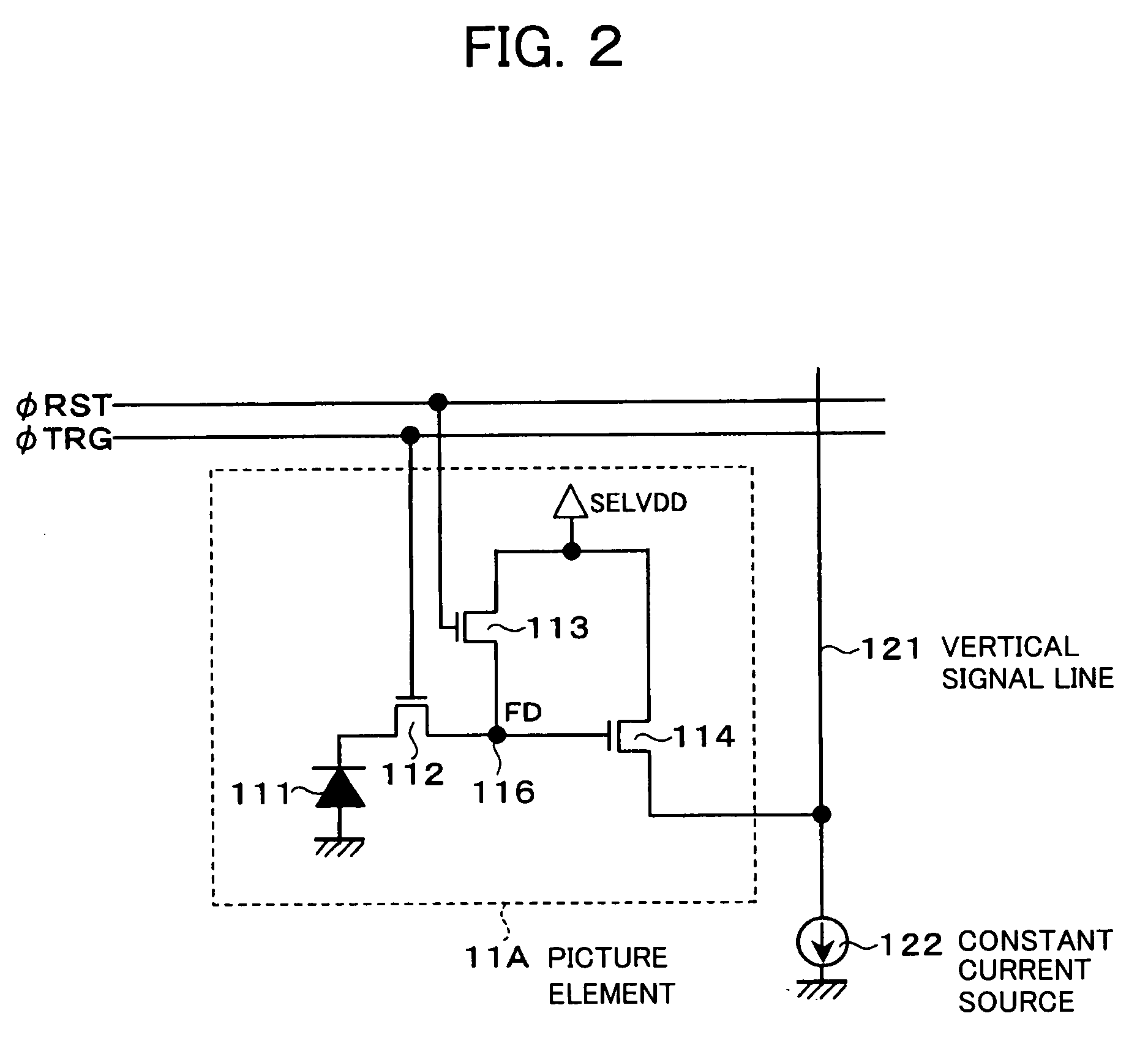

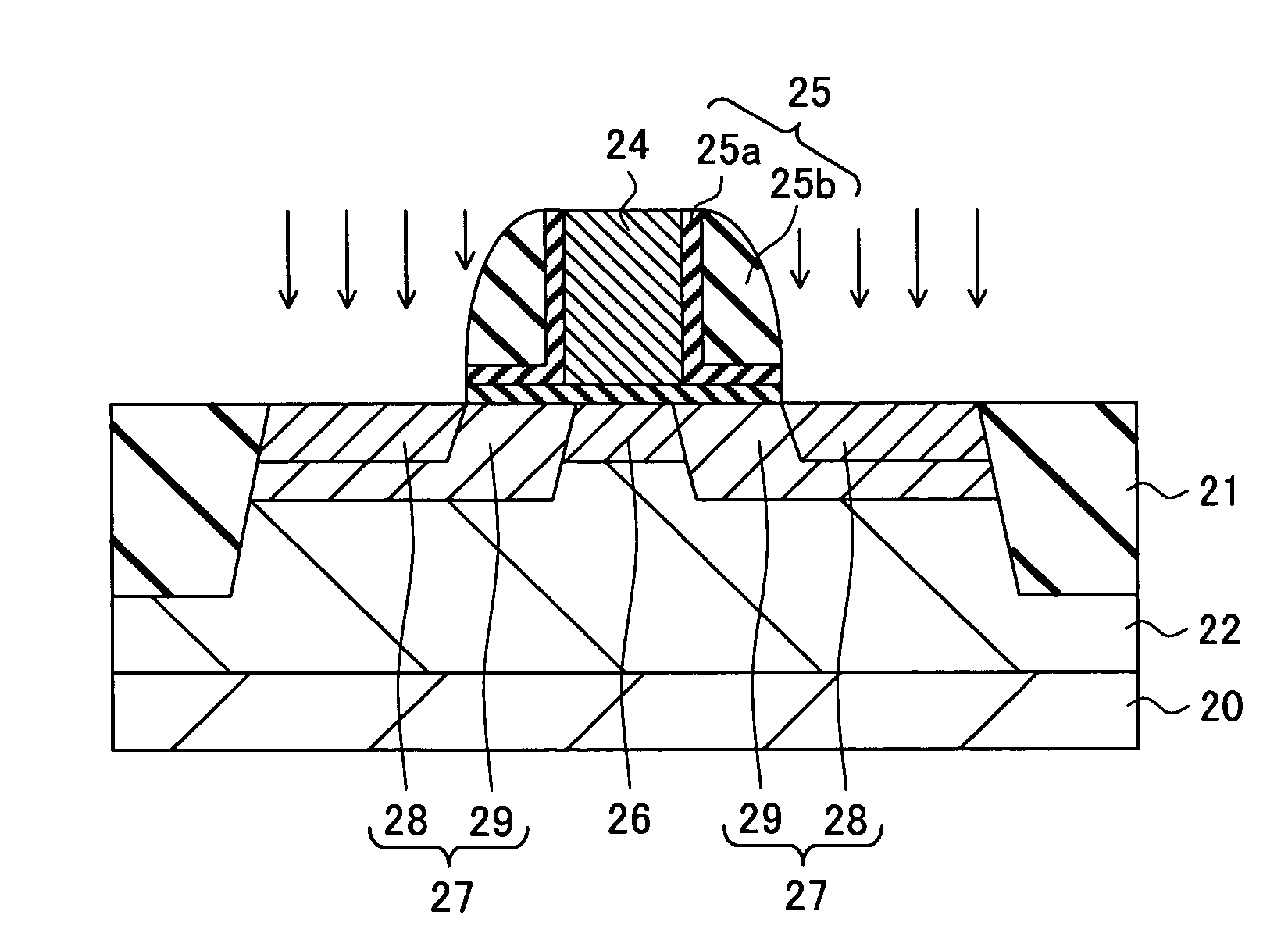

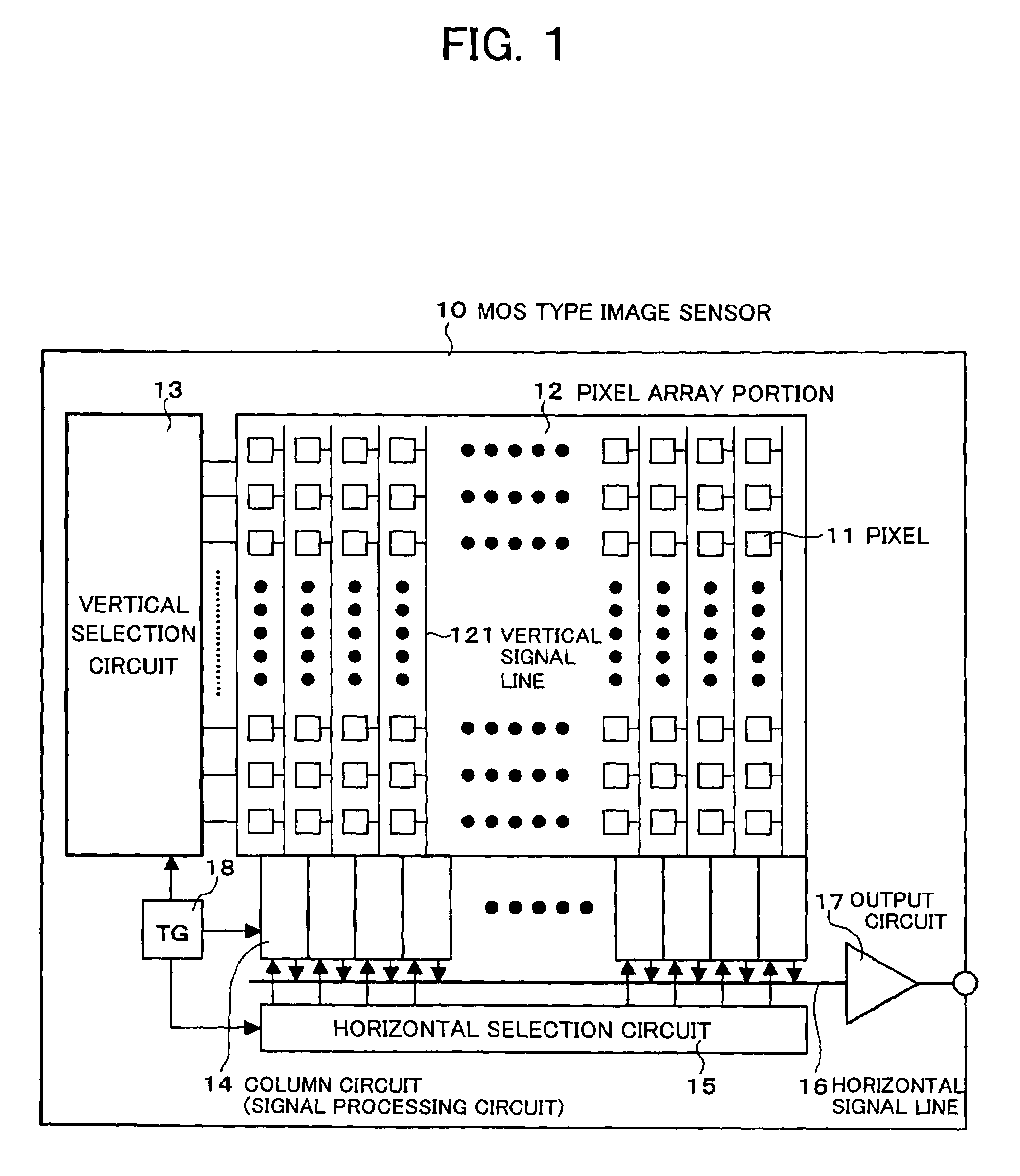

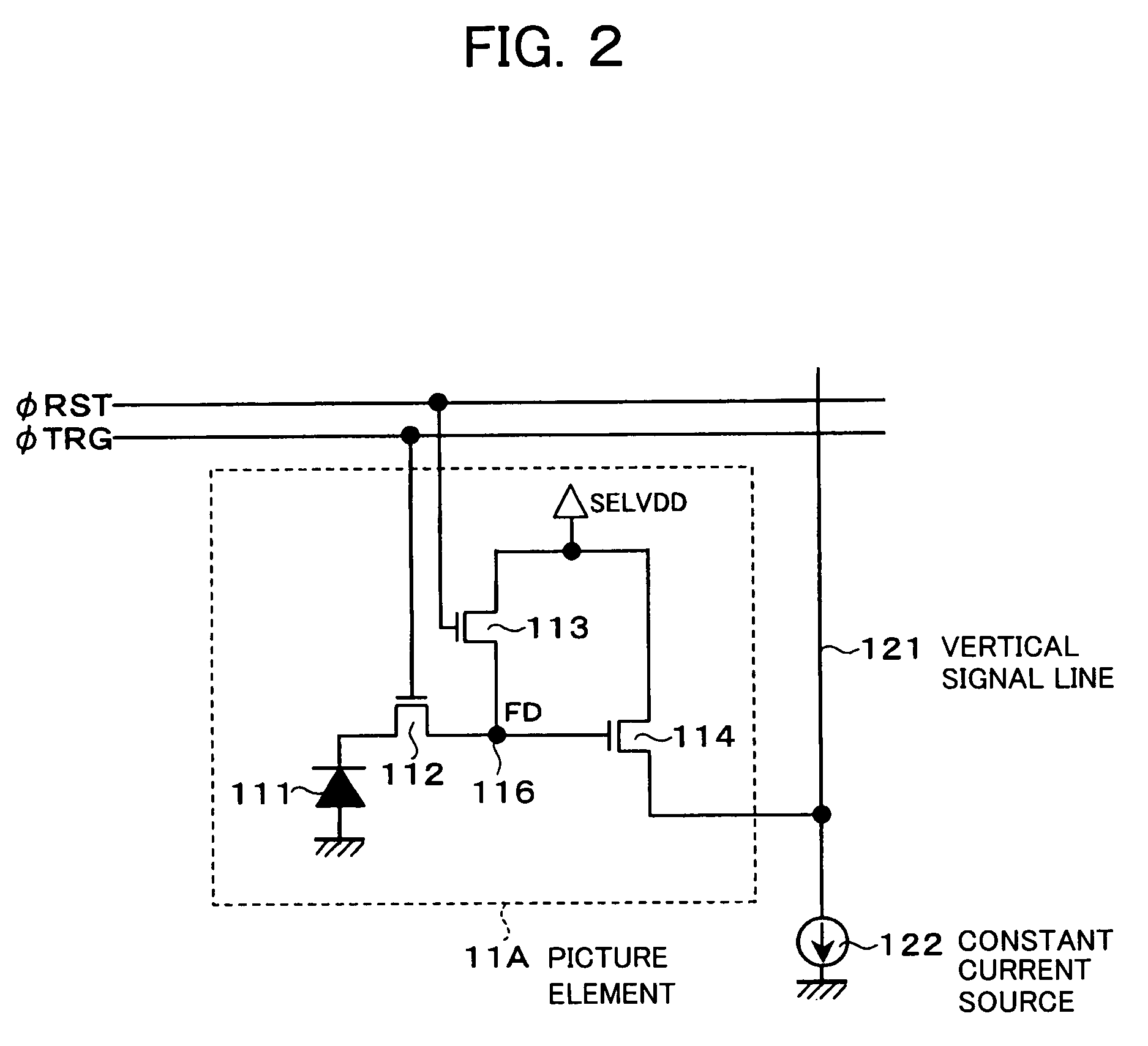

Semiconductor device and method of producing same

InactiveUS20060275990A1Reduce noiseImprove linearityTransistorTelevision system detailsDevice materialSemiconductor

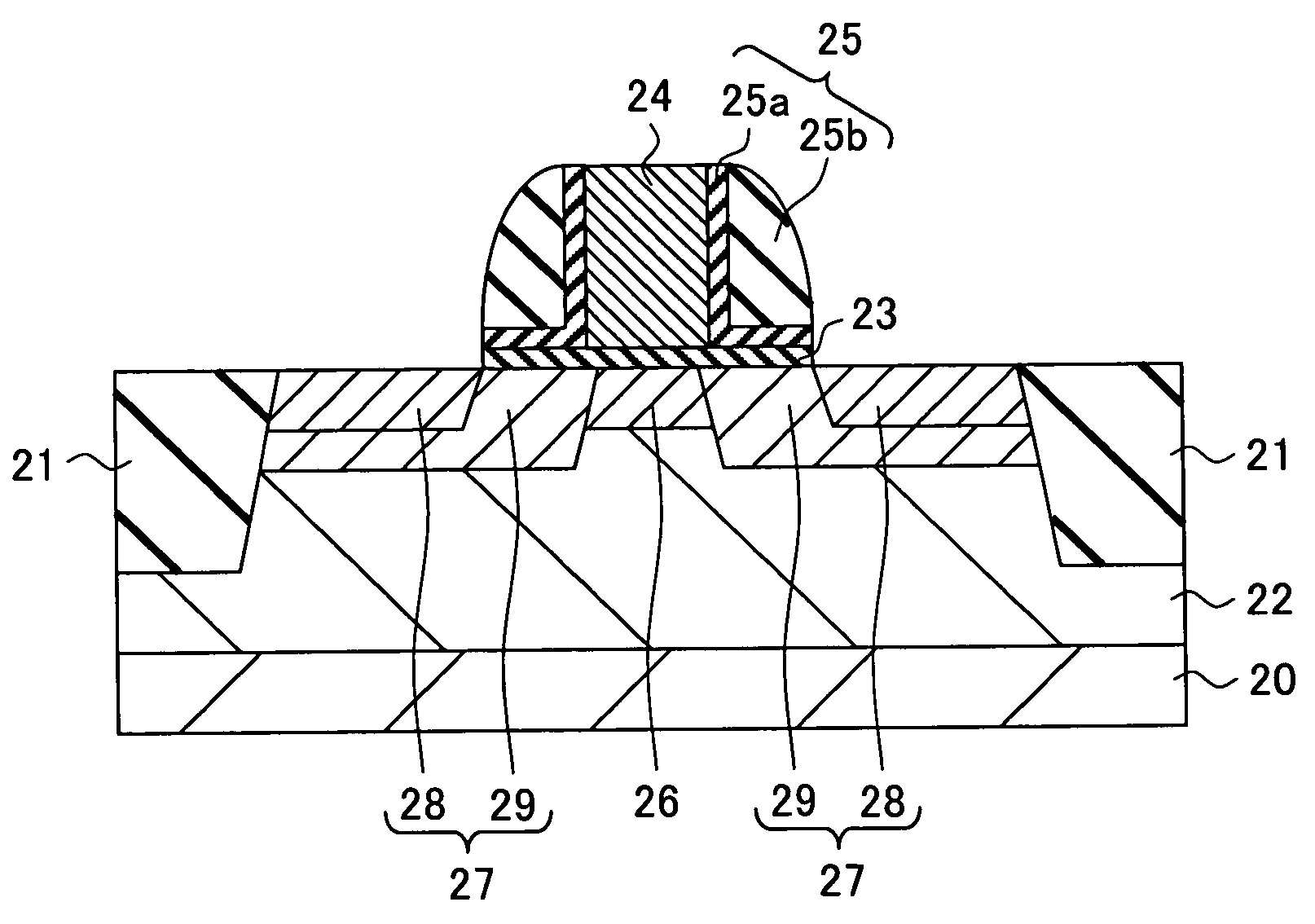

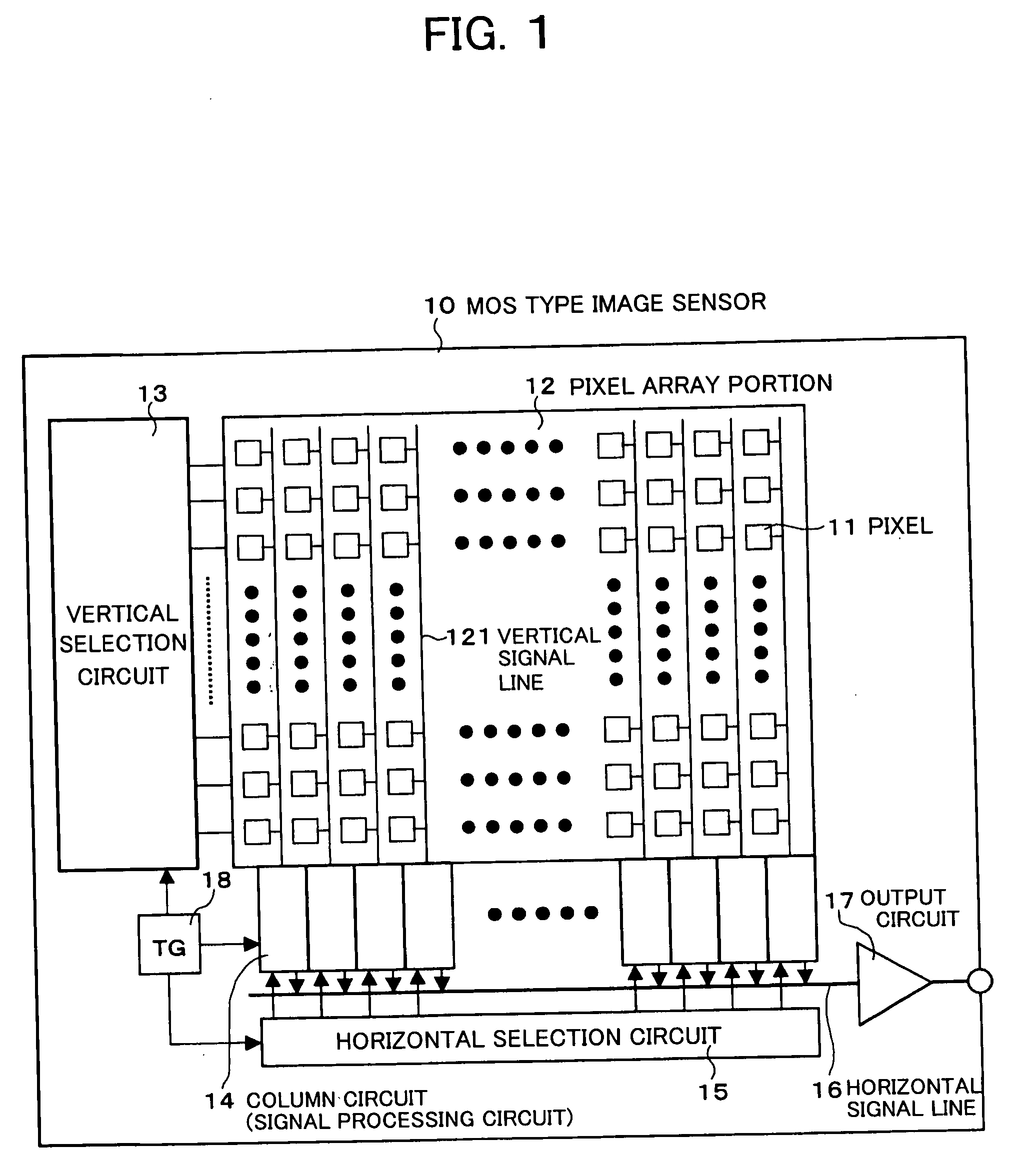

A semiconductor device suitable for a source-follower circuit, provided with a gate electrode formed on a semiconductor substrate via a gate insulation film, a first conductivity type layer formed in the semiconductor substrate under a conductive portion of the gate electrode and containing a first conductivity type impurity, first source / drain regions of the first conductivity type impurity formed in the semiconductor substrate and extended from edge portions of the gate electrode, and second source / drain regions having a first conductivity type impurity concentration lower than that in the first source / drain regions and formed adjoining the gate insulation film and the first source / drain regions in the semiconductor substrate so as to overlap portions of the conductive portion of the gate electrode.

Owner:SONY SEMICON SOLUTIONS CORP

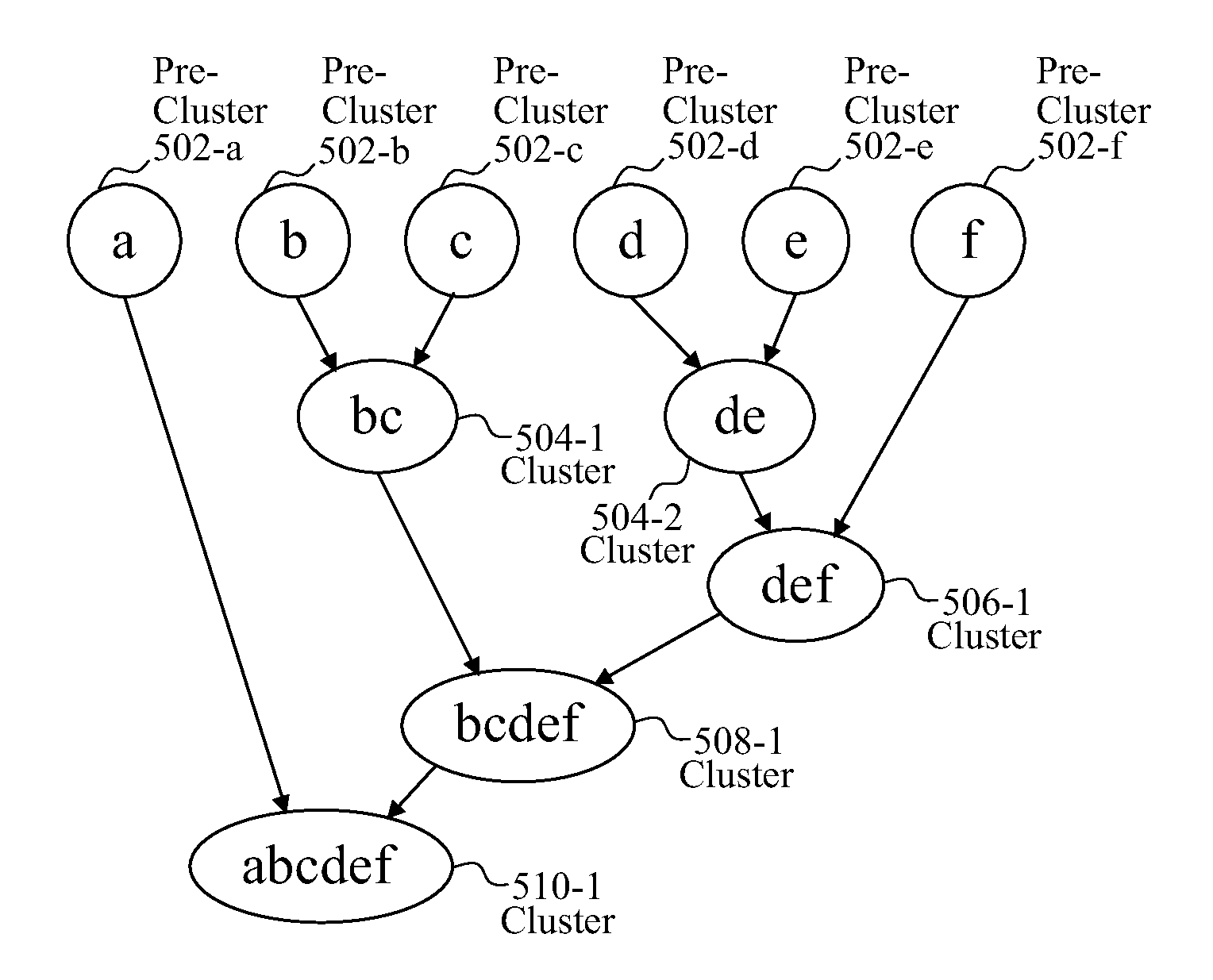

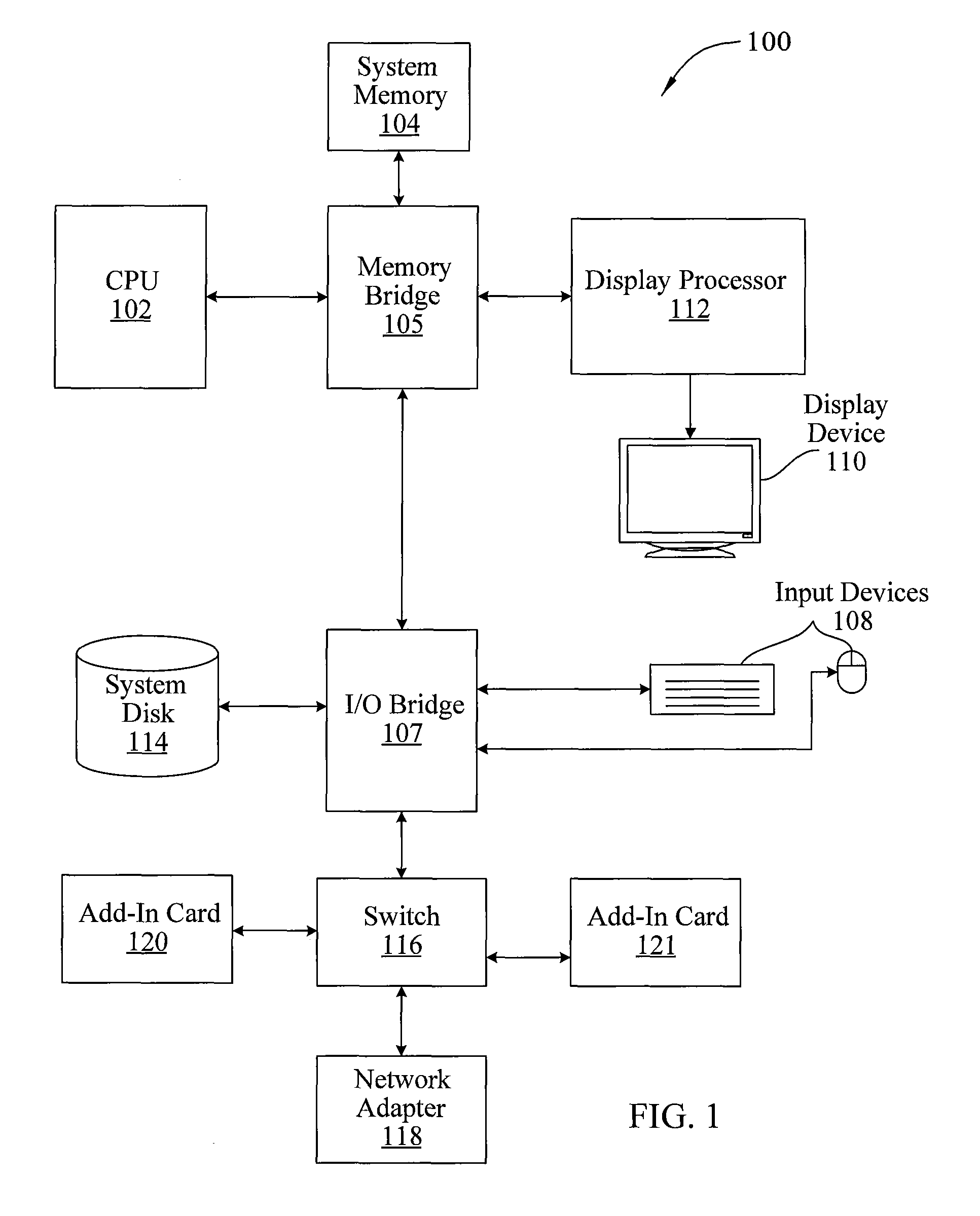

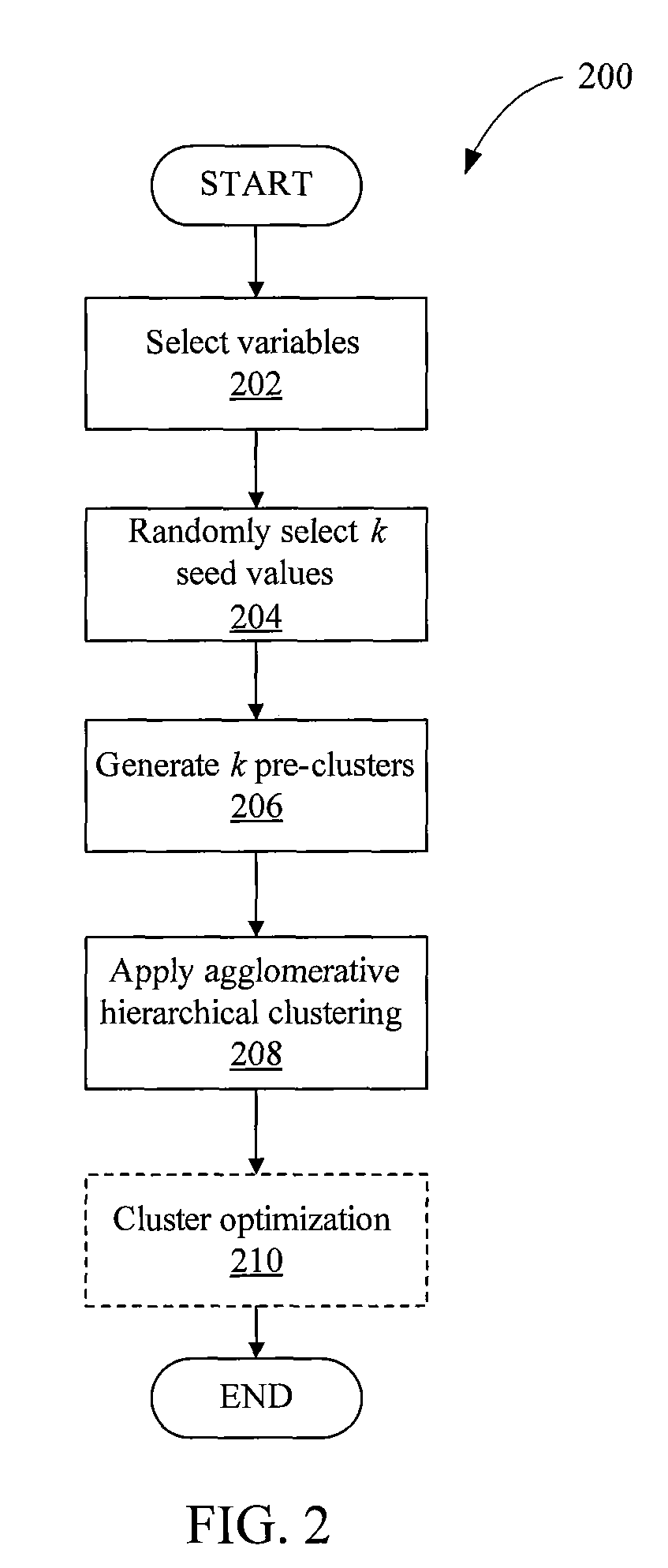

System and method for hybrid hierarchical segmentation

ActiveUS8402027B1Prevent deviationMaximizing similarityDigital data processing detailsCharacter and pattern recognitionHierarchical cluster algorithmValue set

A computer-implemented method for clustering a plurality of observations included in a dataset. The method includes selecting a subset of variables from a set of variables, where each variable in the subset is associated with each observation in the dataset; for each of a first number of times, randomly selecting an initial value for each variable in the subset to generate a seed value set that includes an initial value for each variable in the subset; generating a number of pre-clusters equal to the first number based on a similarity between each observation in the dataset and each of the first number of seed value sets; and applying a hierarchical clustering algorithm to the first number of pre-clusters to derive a second number of clusters.

Owner:DISNEY ENTERPRISES INC

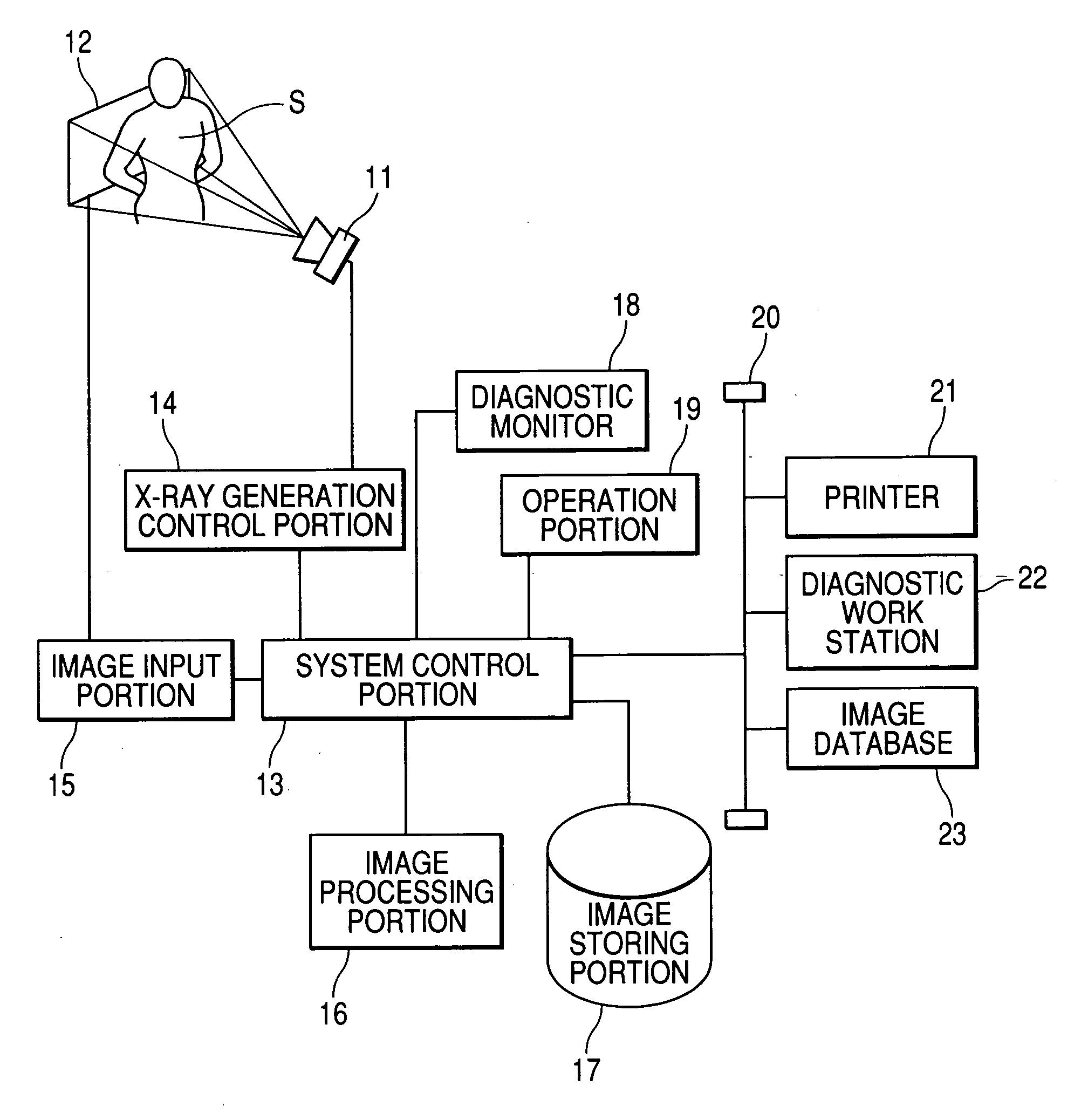

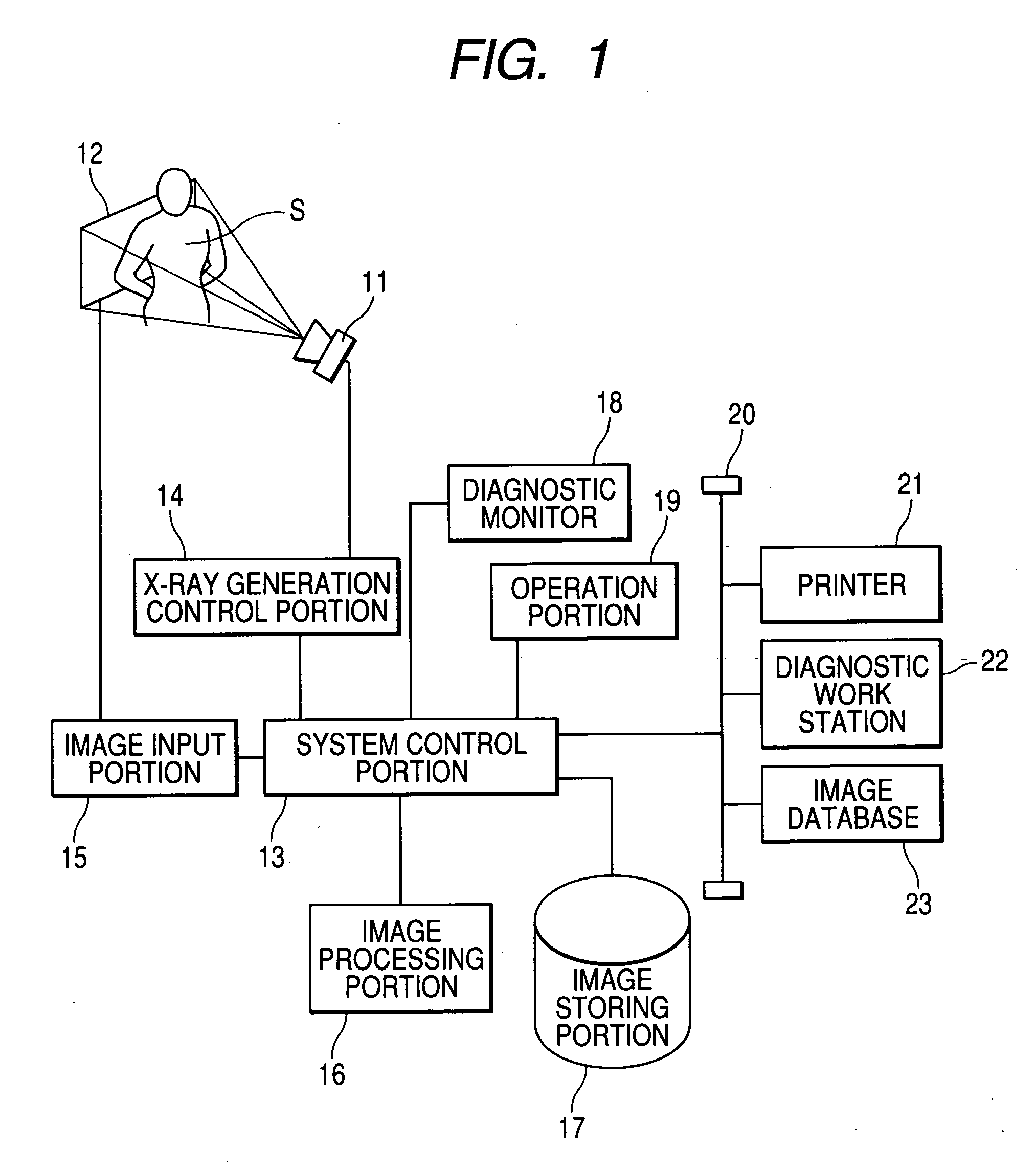

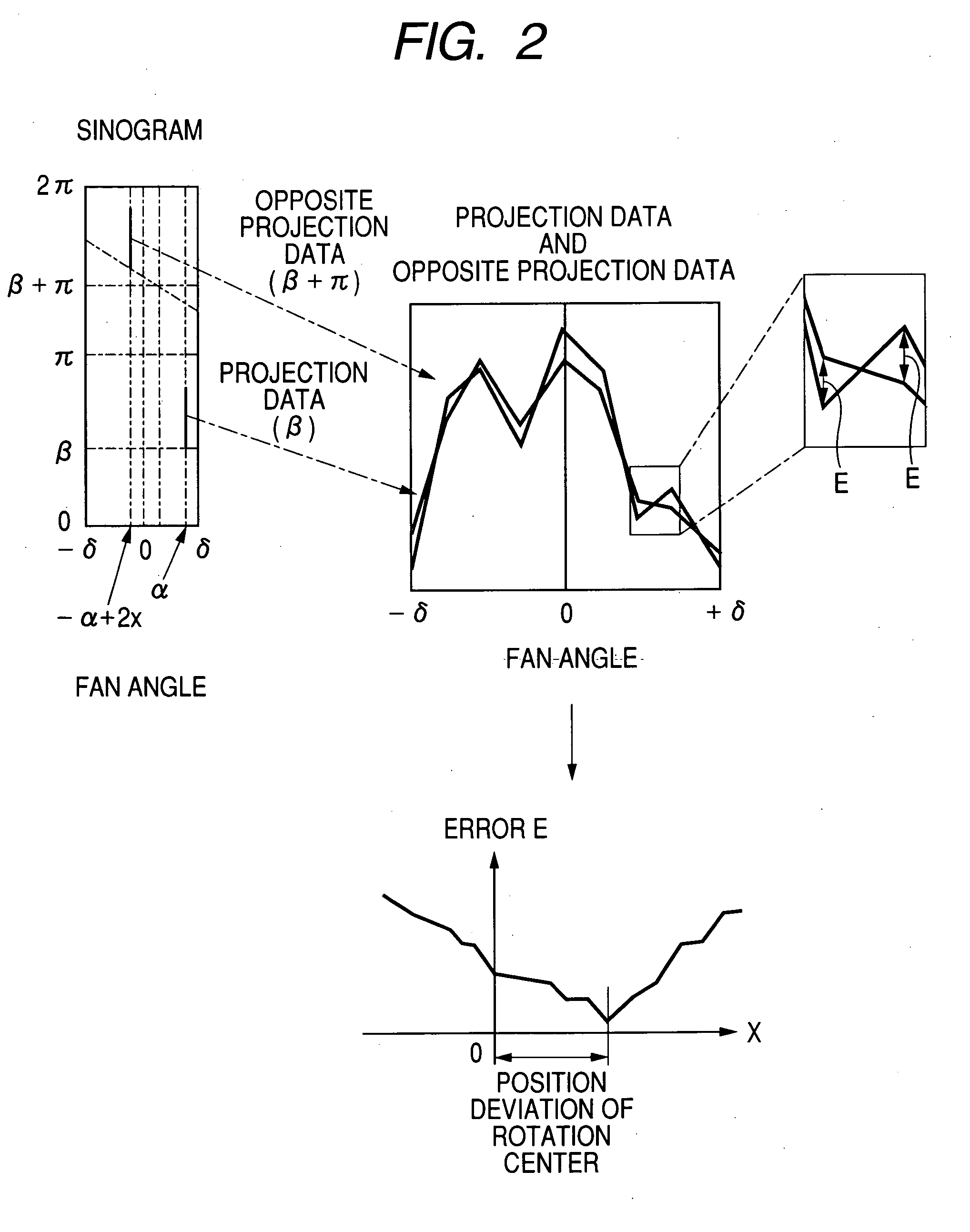

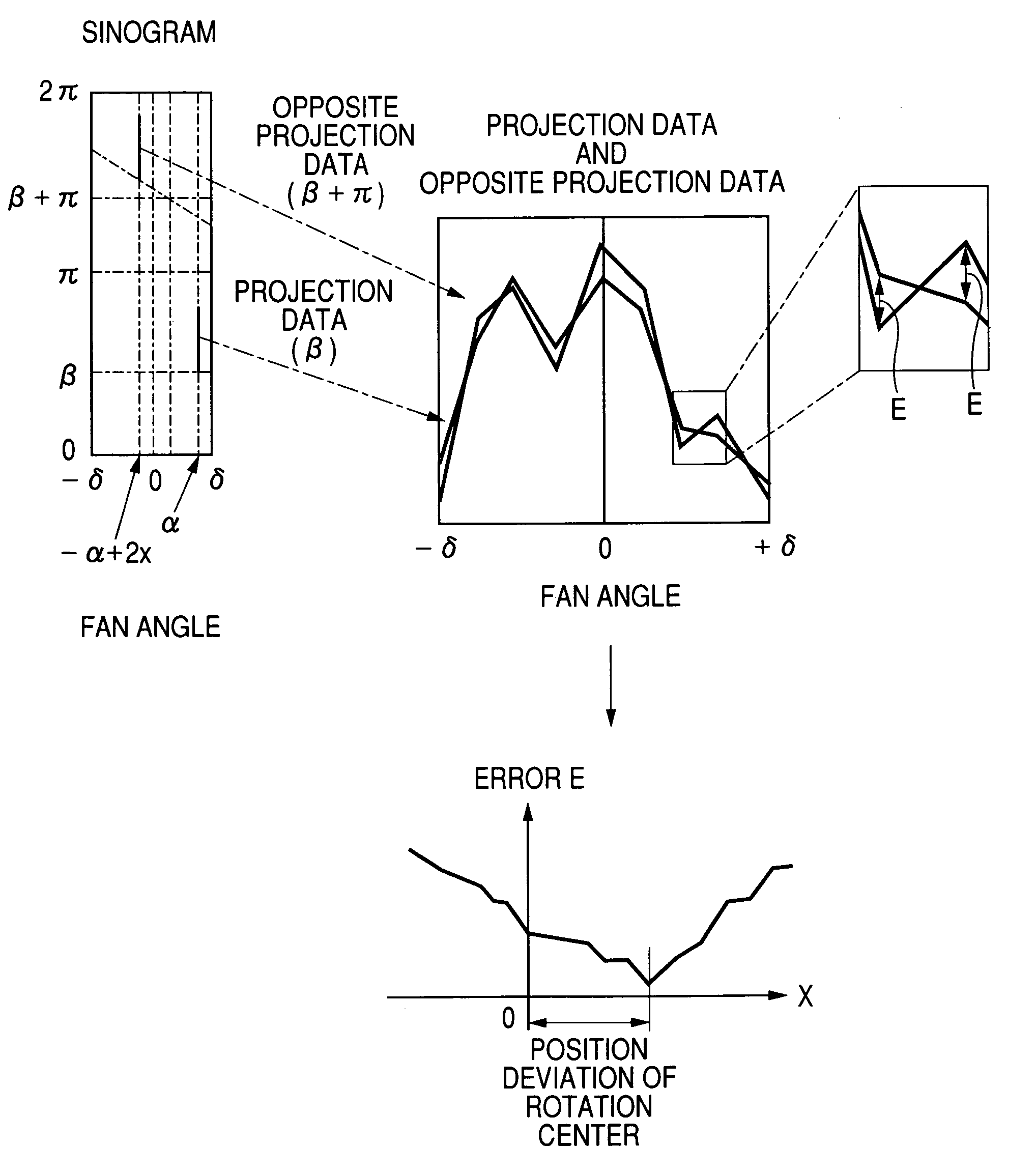

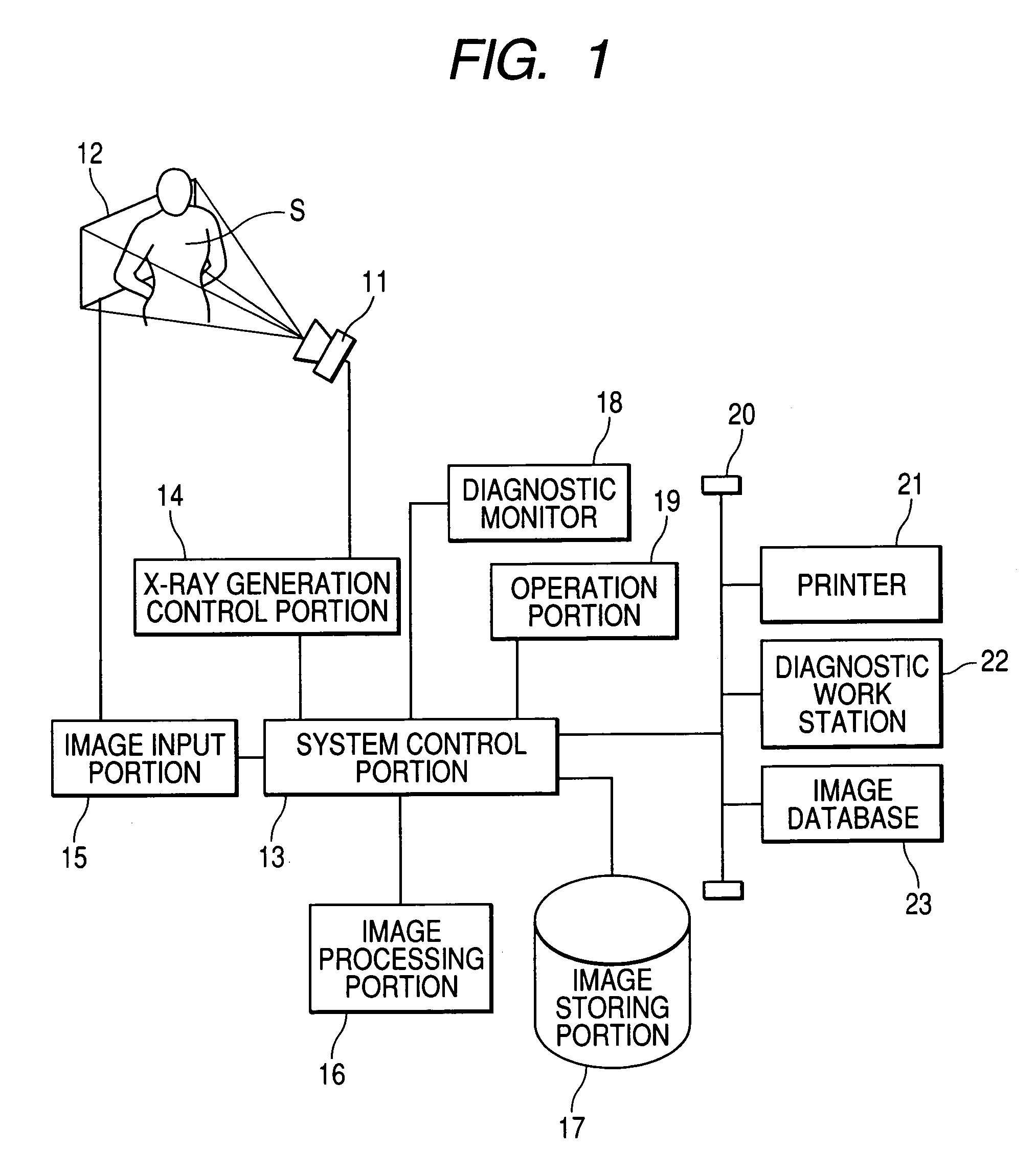

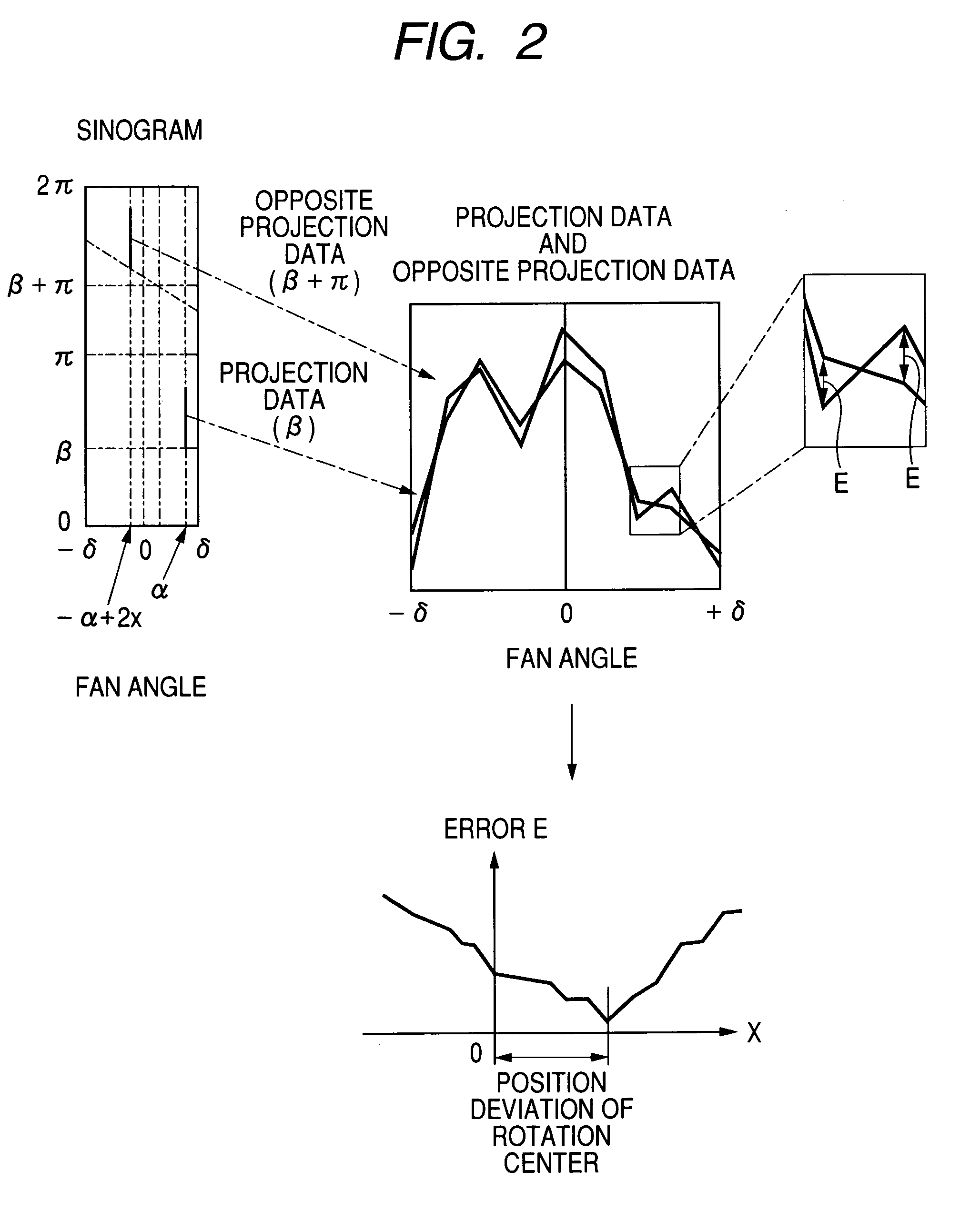

X-ray CT apparatus and image-taking method therefor

InactiveUS20050276375A1Reduce the impactEliminate bias effectsMaterial analysis using wave/particle radiationRadiation/particle handlingX-rayComputer science

Time-series data over the range of a projection angle is created from a sinogram. Then, time-series data made up of opposite data corresponding to the time-series data over the range of a projection angle is created. Based on the amount of the error between the two types of time-series data, the amount of position deviation of a revolution axis is calculated.

Owner:CANON KK

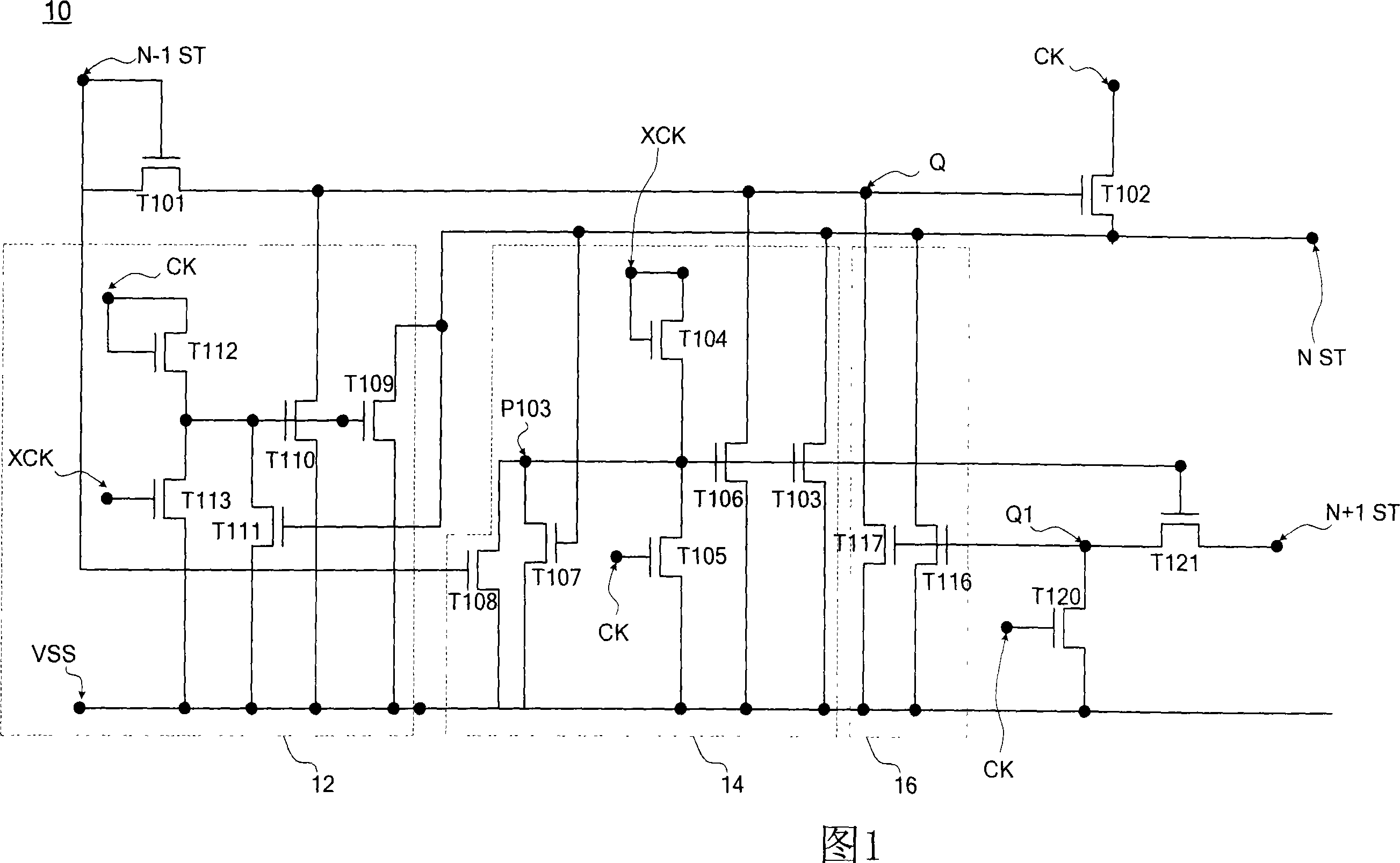

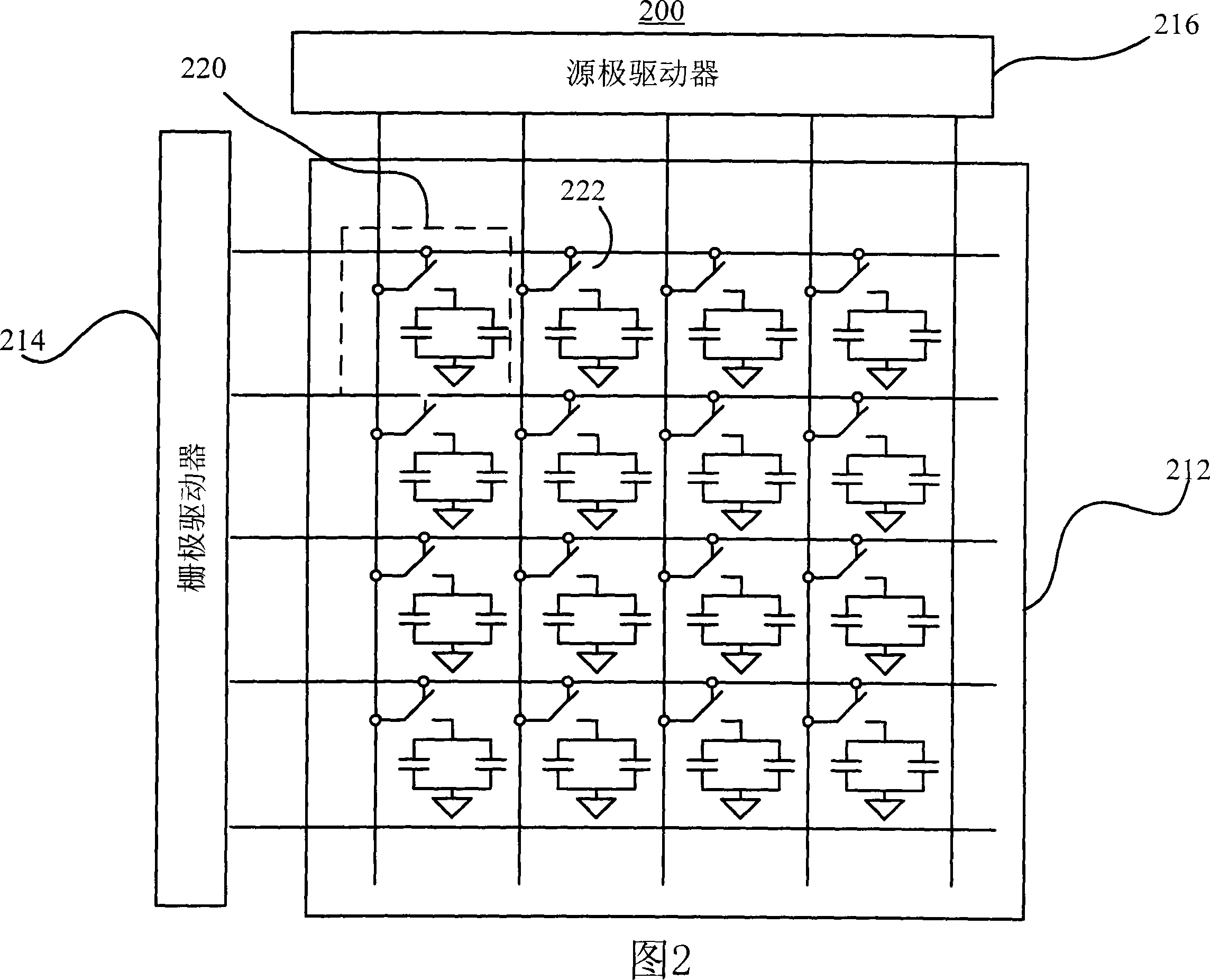

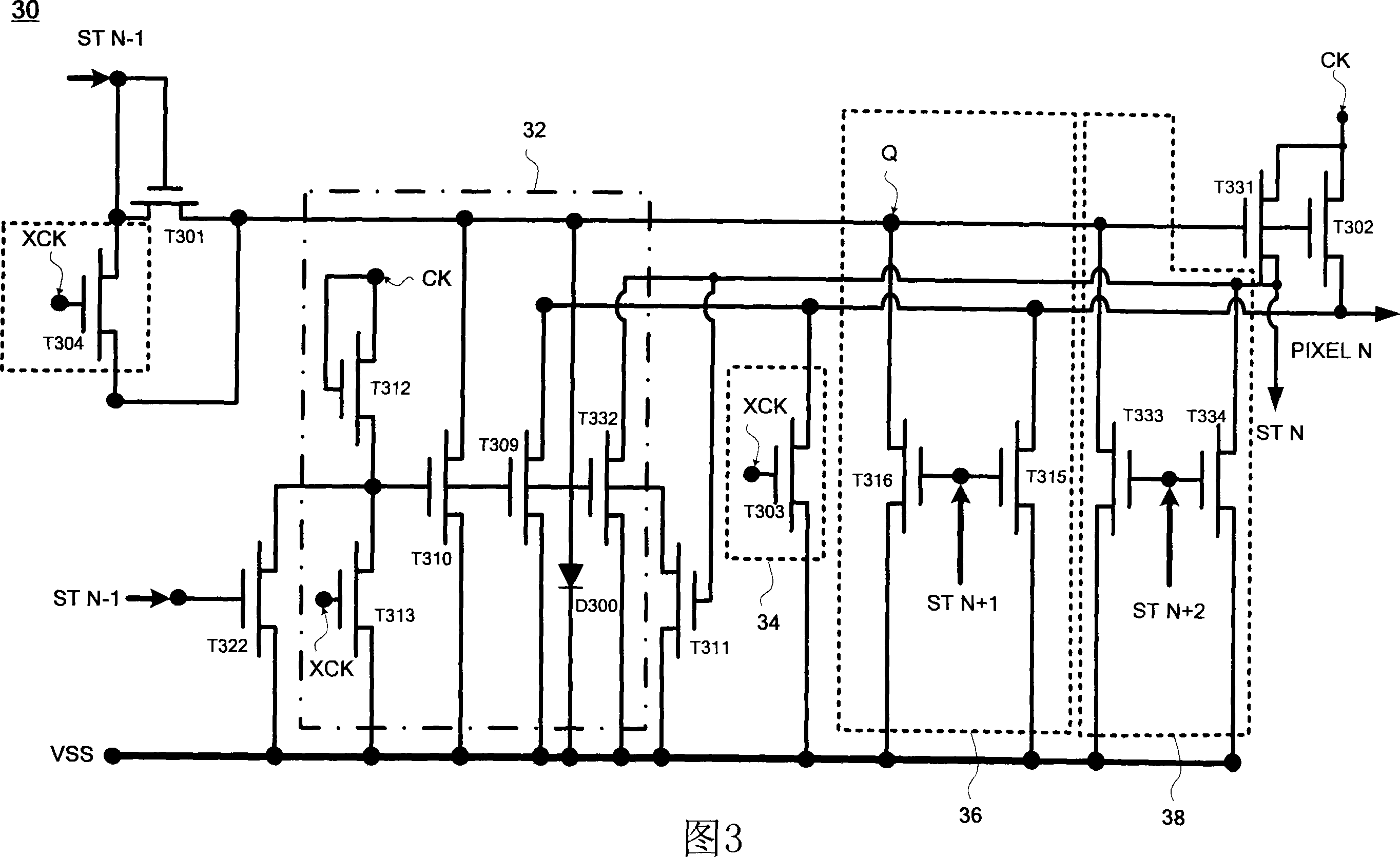

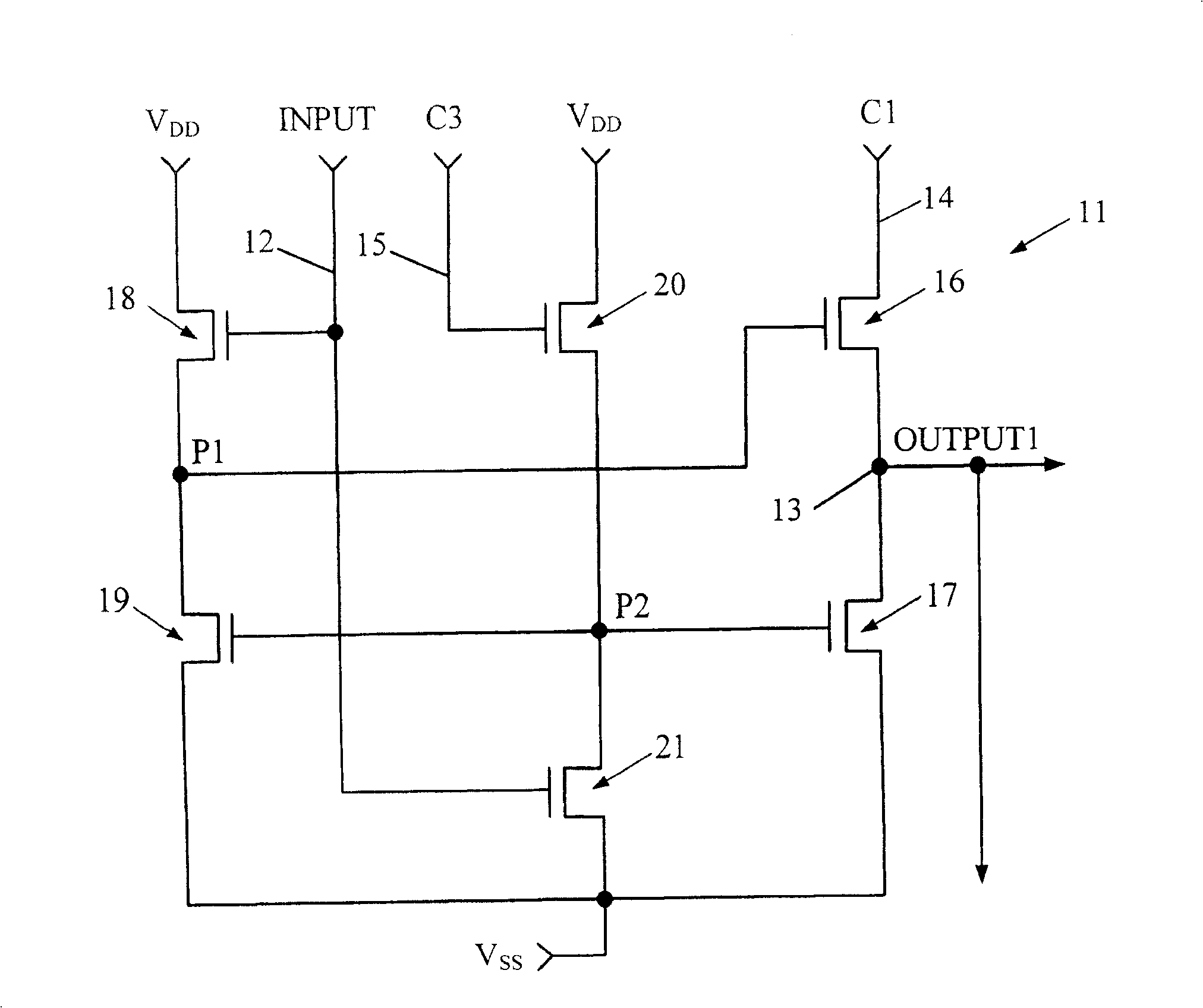

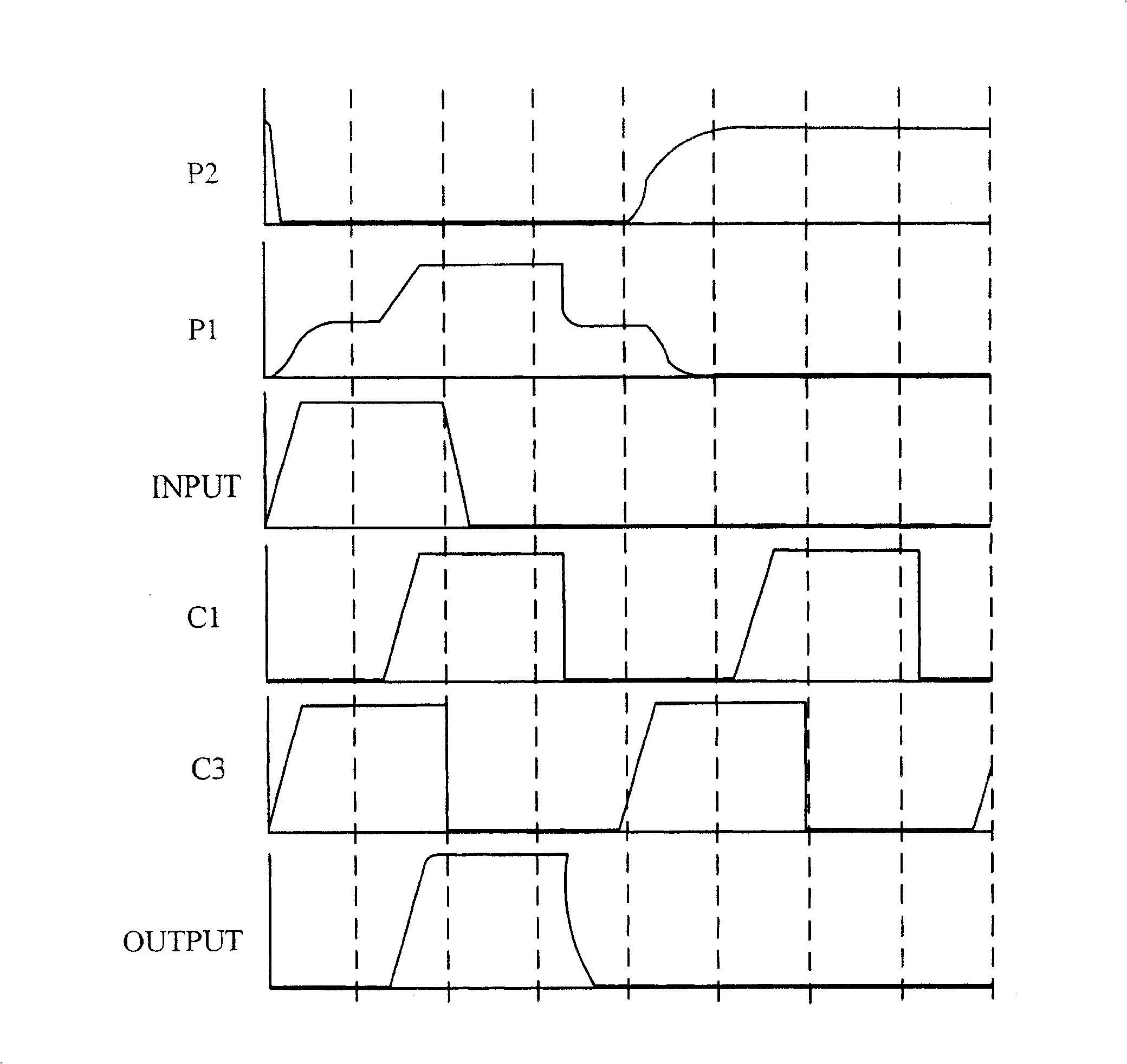

Displacement register capable of reducing voltage bias effective voltage

ActiveCN101042937AReduce bias effectsIncreased steady state timeStatic indicating devicesDigital storageVoltageShift register

This invention discloses one displacement register, which comprises one first frequency signal pull down module, one second frequency signal pull down module, one first main pull down module, one second pull down module and one discharge circuit, wherein, when the first and second pull down modules generate abnormal circuit to make the register not capable of discharge, the discharge circuit can proceed to lower the register circuit bias effect.

Owner:AU OPTRONICS CORP

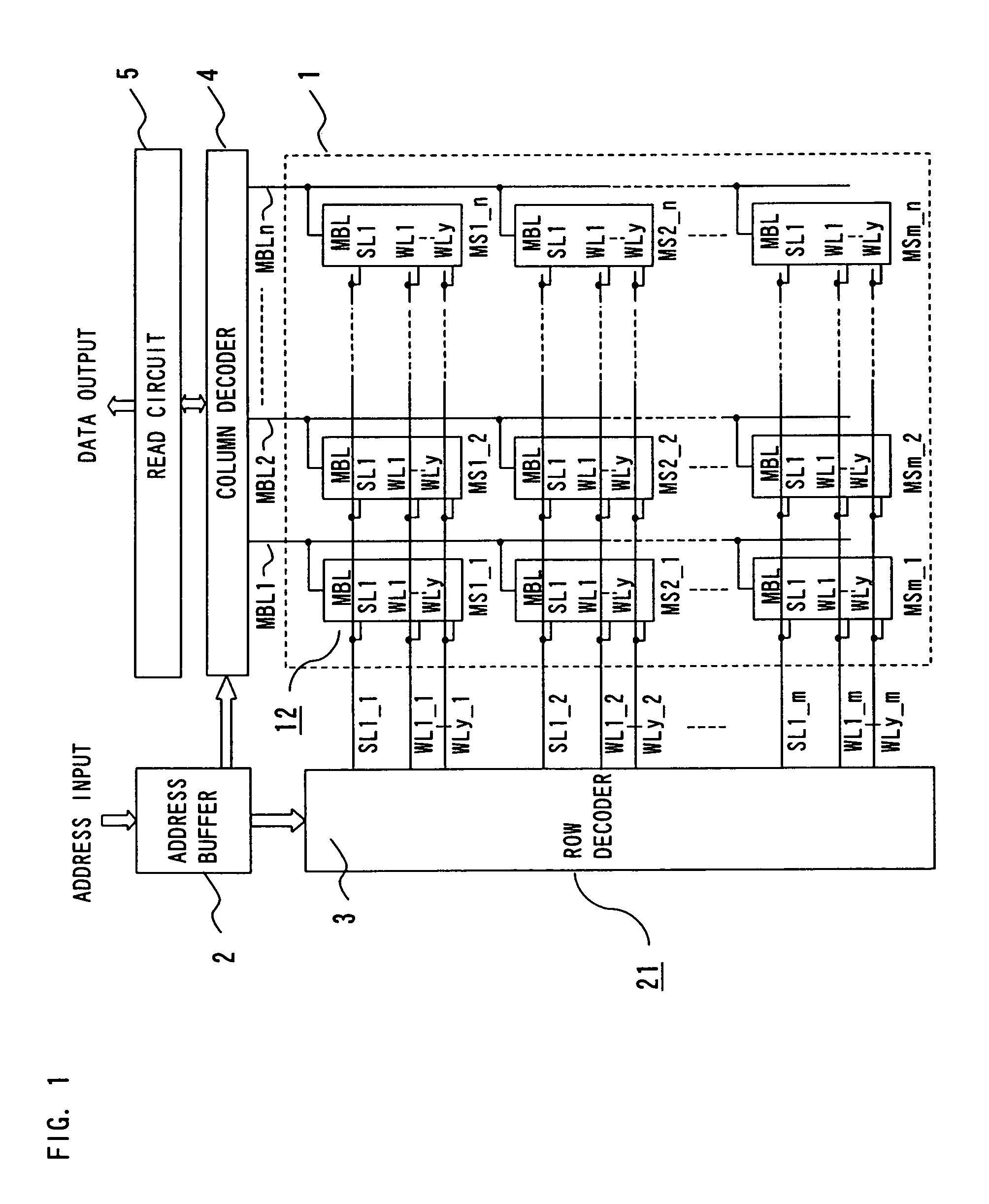

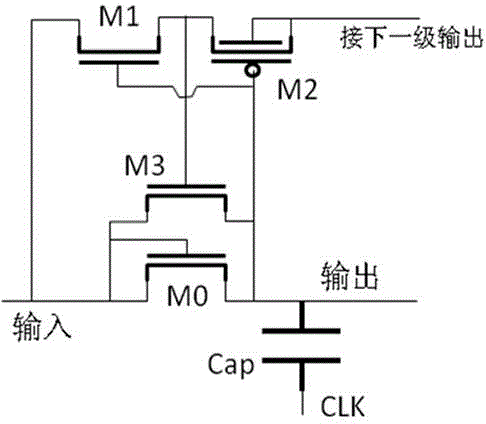

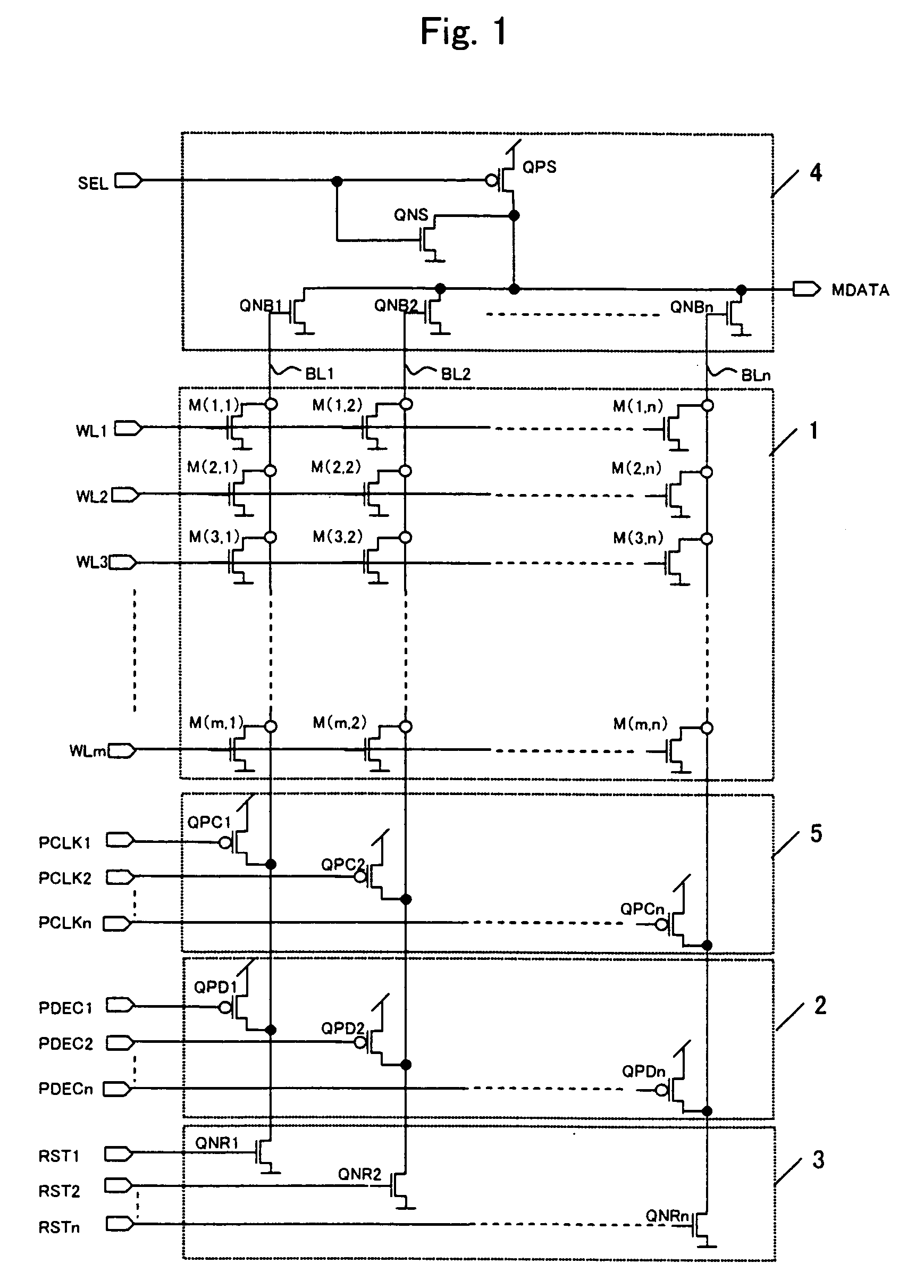

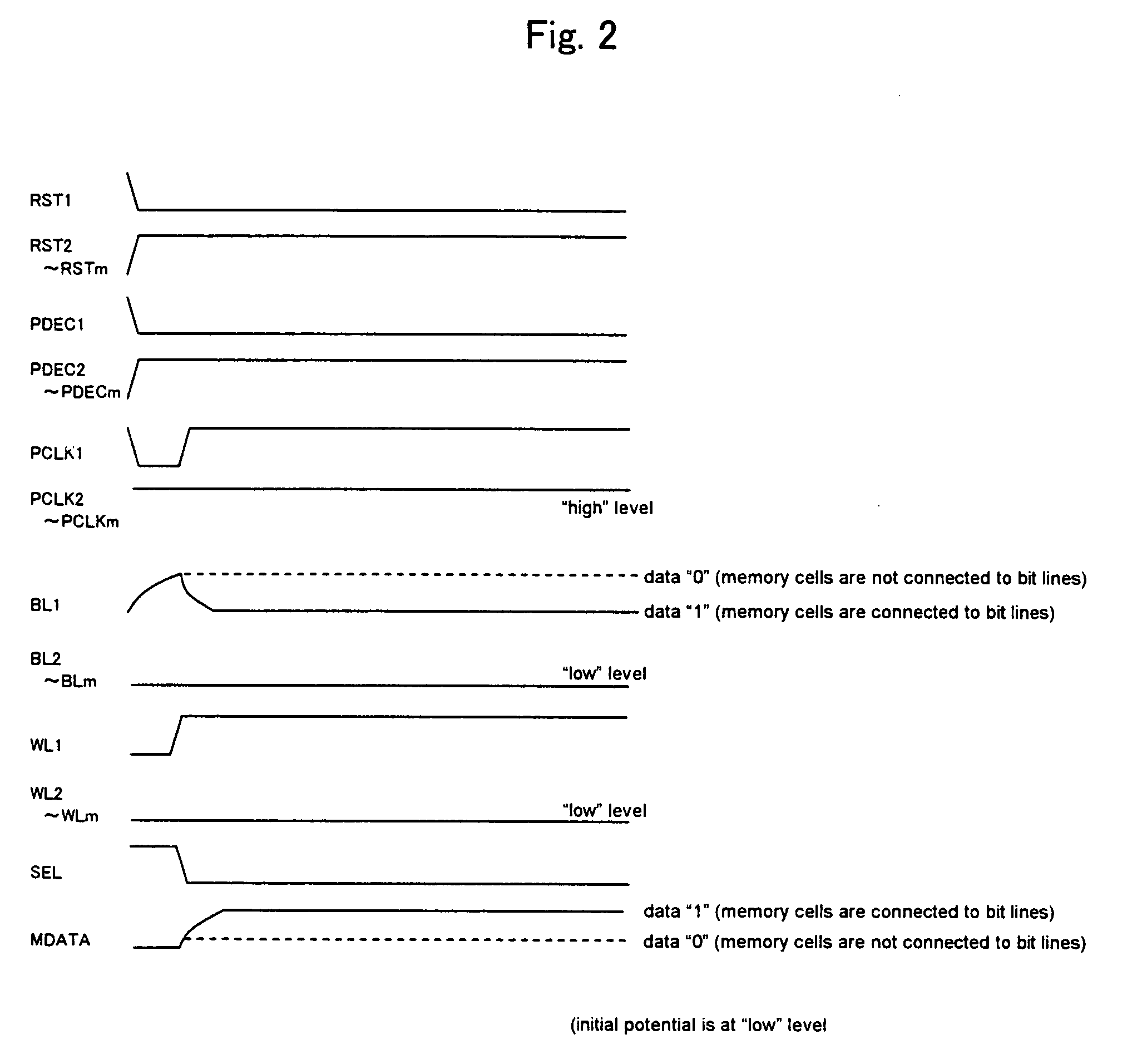

Semiconductor memory device

Owner:SOCIONEXT INC

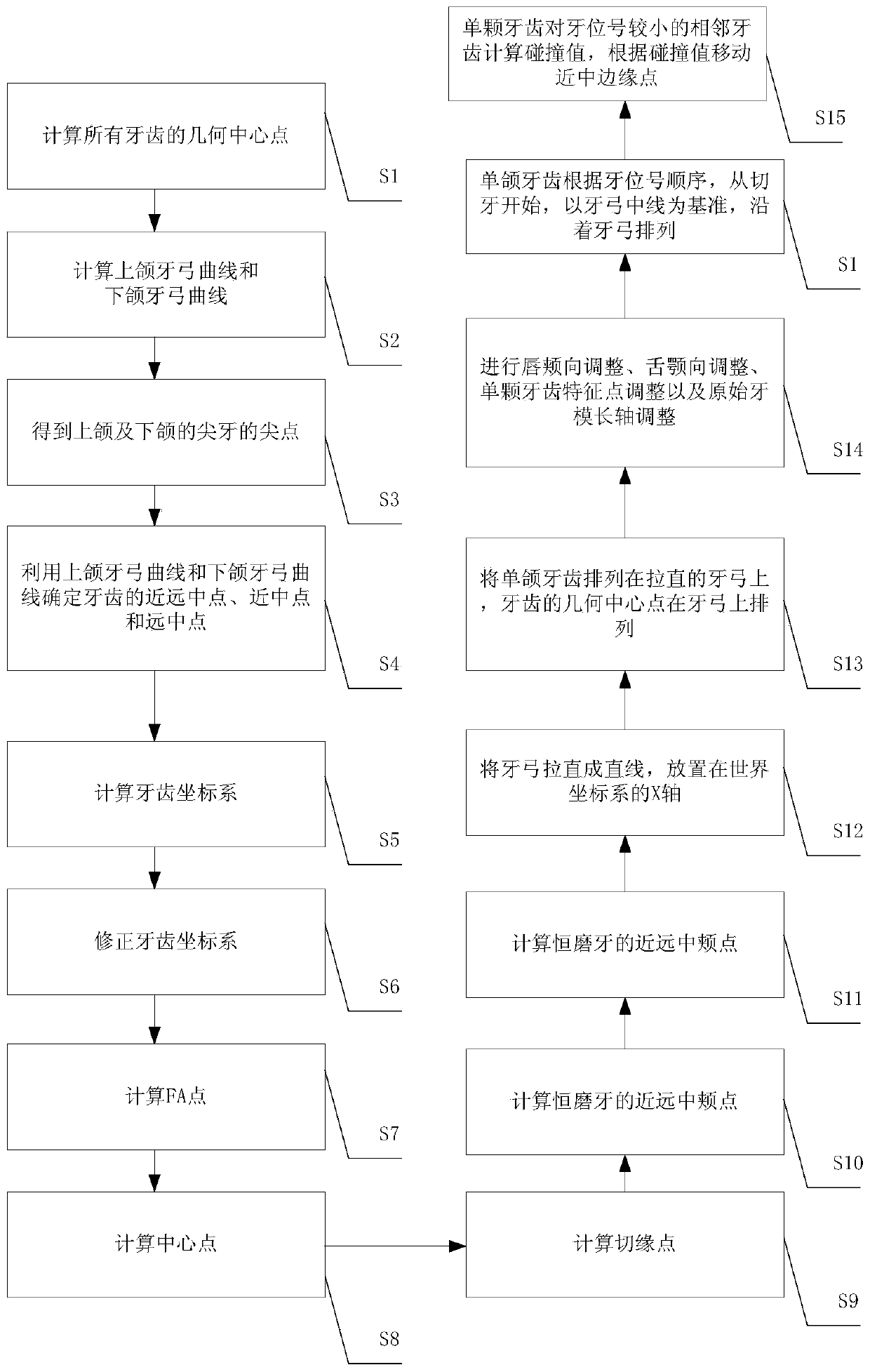

Method for teeth model parameterization

ActiveCN110164558AReduce dependenceImprove accuracyMedical simulationSustainable transportationLong axisMiddle line

The invention discloses a method for teeth model parameterization. The method comprises the steps of calculating geometric center points of all teeth; fitting an upper jaw dentofacial plane and a lower jaw dentofacial plane, and calculating an upper jaw dental arch curve and a lower jaw dental arch curve; determining tip points of canine teeth of the upper jaw and the lower jaw; determining far-near-middle points, near-middle points and far-middle points of the teeth; determining a teeth coordinate system according to the tip points, the far-near-middle points, the near-middle points and the far-middle points; calculating FA points, central points and cutting edge points of the teeth, and the near-far-middle cheek points of accessional teeth; performing lip cheek-direction adjustment, tongue jaw-direction adjustment, single-tooth characteristic point adjustment and original tooth die long-axis adjustment; arranging the teeth at a single jaw according to a tooth position number sequencefrom incisor teeth along a dental arch through using the middle line of the dental arch as a reference; calculating a collision value between the single tooth and the adjacent tooth with a relativelysmall tooth position number, and moving a near-middle edge point according to the collision value. The method of the invention effectively improves accuracy and rationality of the parameters after teeth model parameterization.

Owner:INNOVATIVE MATERIAL & DEVICES

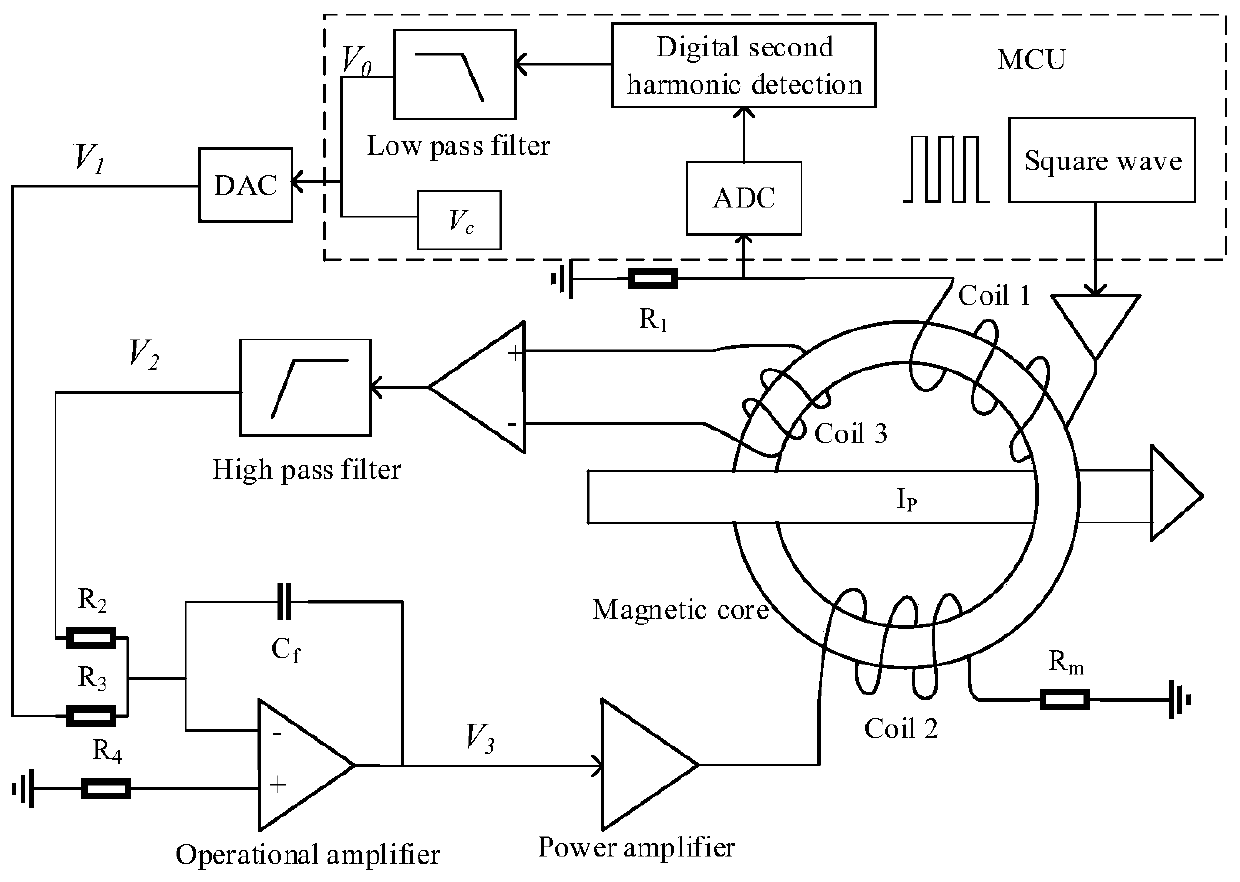

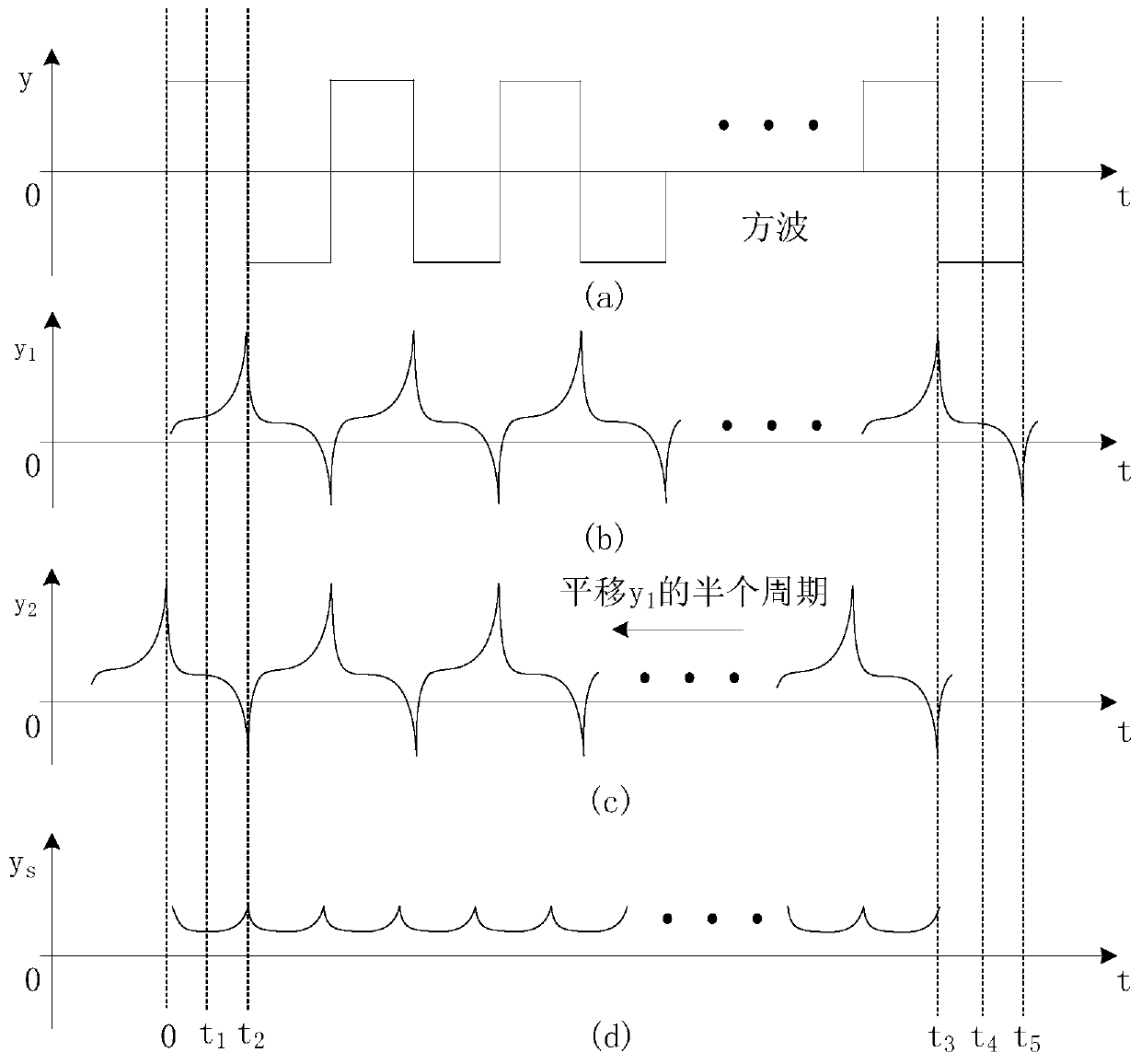

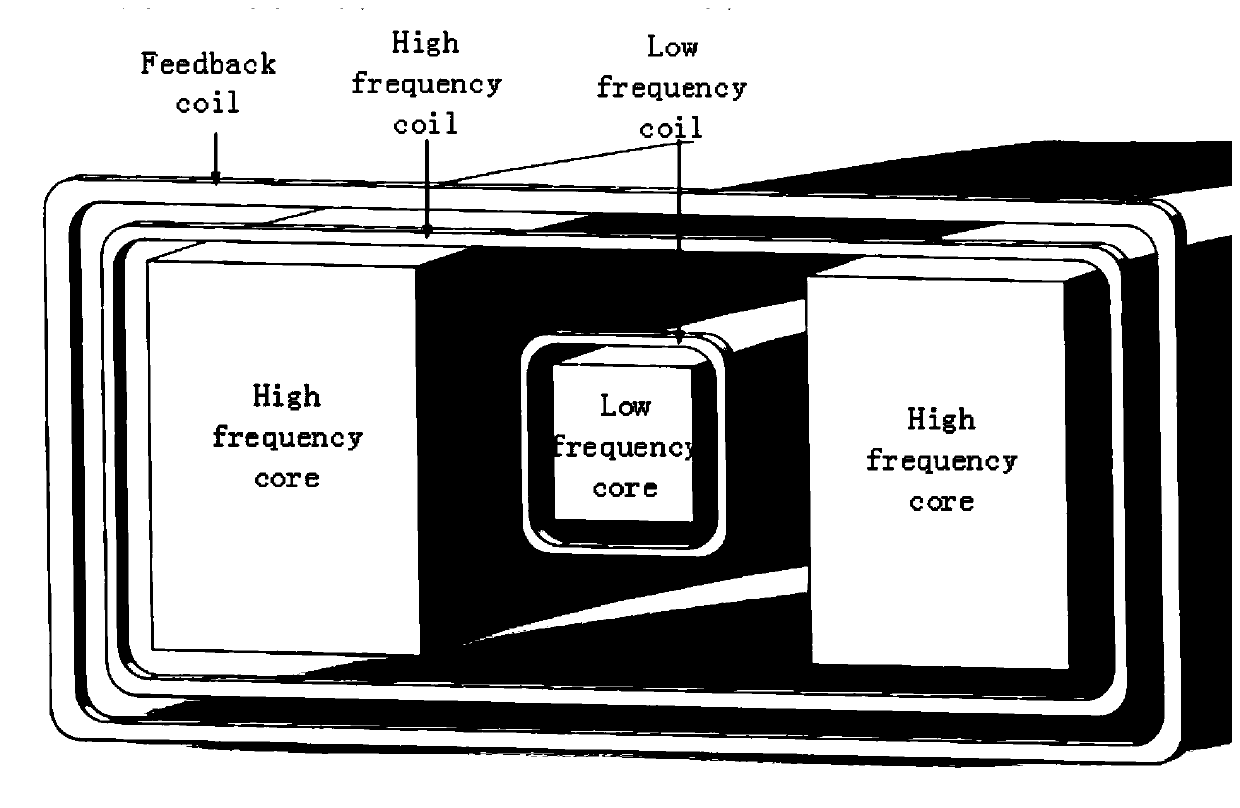

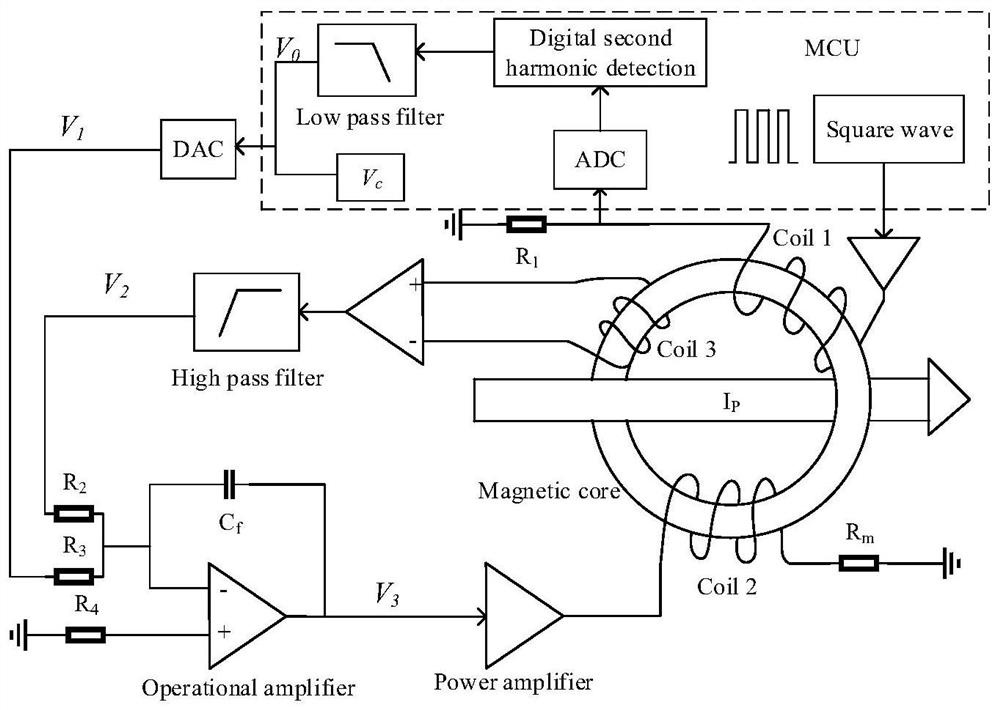

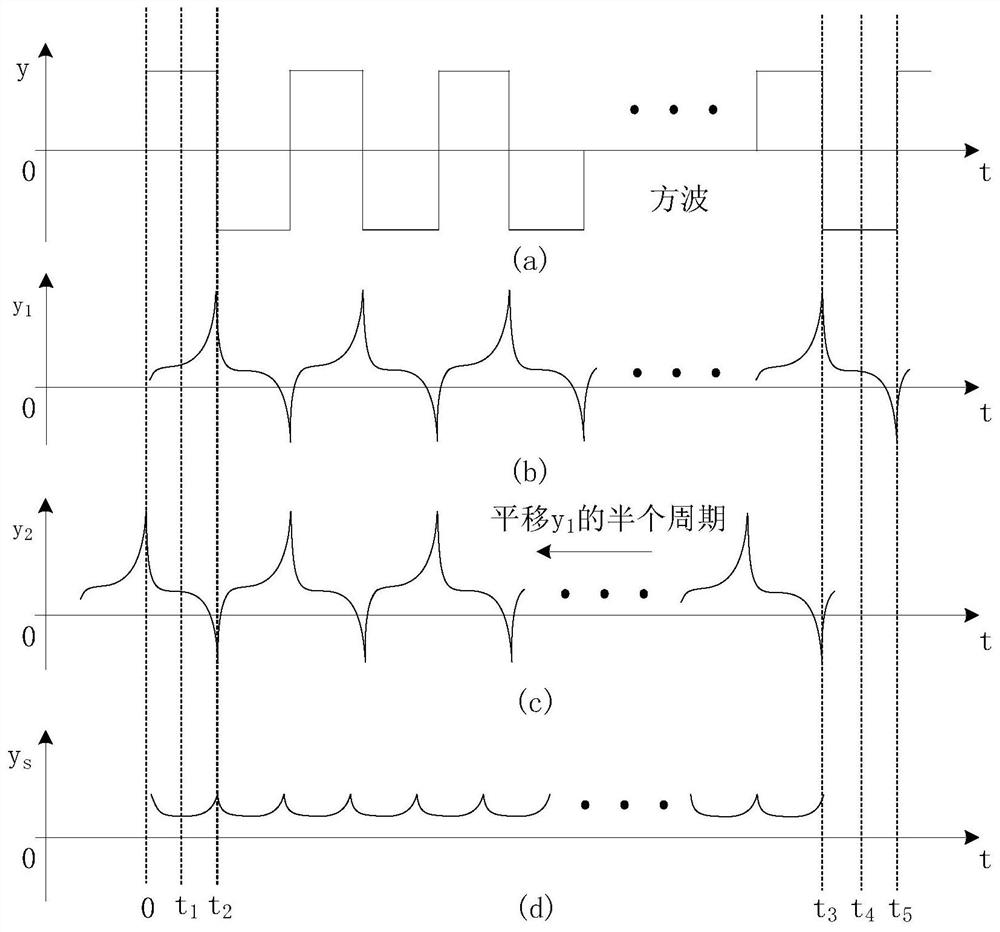

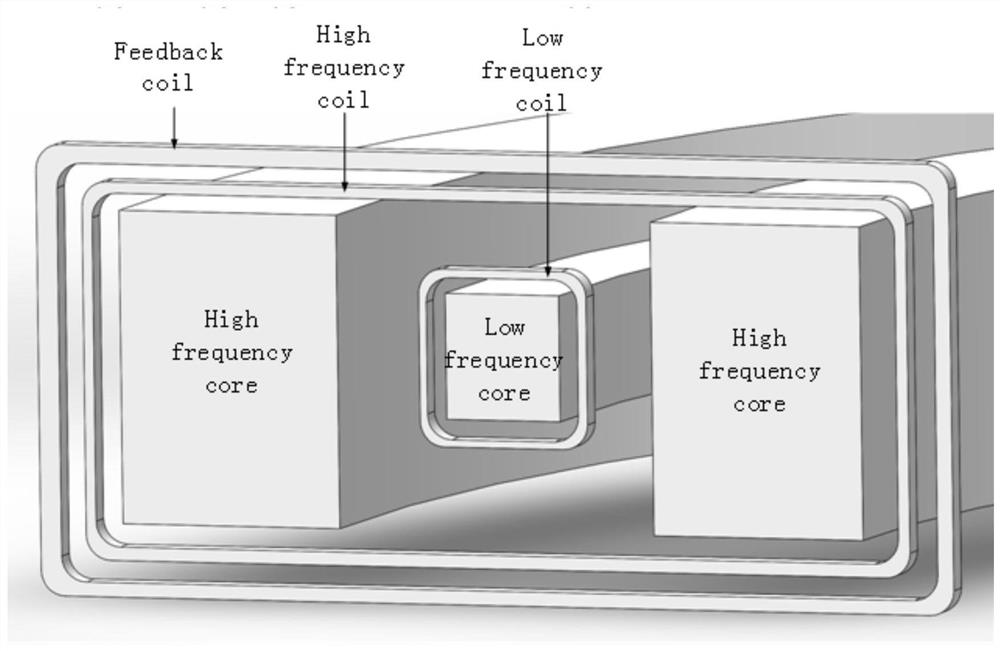

Fluxgate large-current sensor based on digital second harmonic detection and ripple compensation

ActiveCN110988430AEliminate bias effectsImprove measurement accuracyVoltage/current isolationMeasurement using digital techniquesCurrent sensorHemt circuits

The invention provides a fluxgate large-current sensor based on digital second harmonic detection and ripple compensation, and the sensor is characterized in that the sensor comprises a low-frequencymeasurement coil, a feedback coil, and a high-frequency measurement coil, which are wound on an annular magnetic core. According to the invention, the direct current component and the alternating current component in the current can be measured at the same time. The measurement accuracy is high, the linearity is good, the temperature stability is high, and the beneficial effects are shown as follows: (1) the sensor has digital quantity output and analog quantity output; (2) zero drift digital correction is carried out, and the influence of device output current bias caused by an analog circuitis reduced; and (3) ripple output is inhibited.

Owner:SHANGHAI TECH UNIV +1

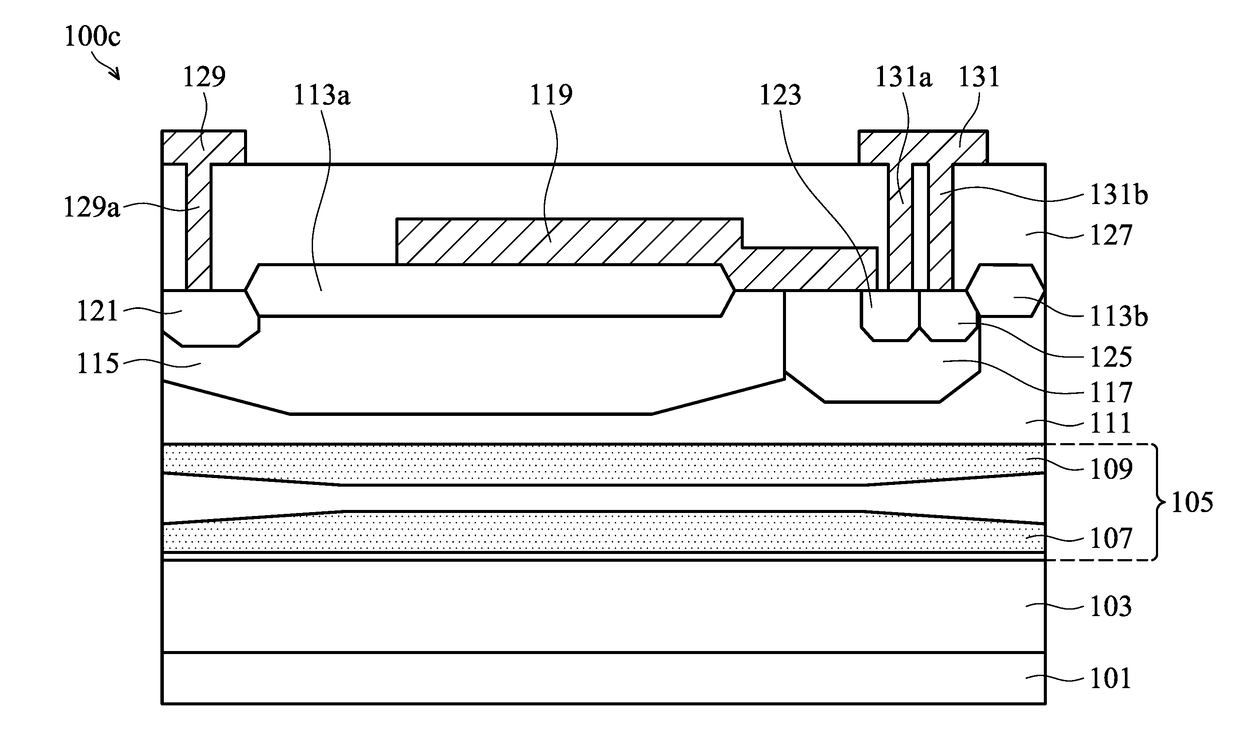

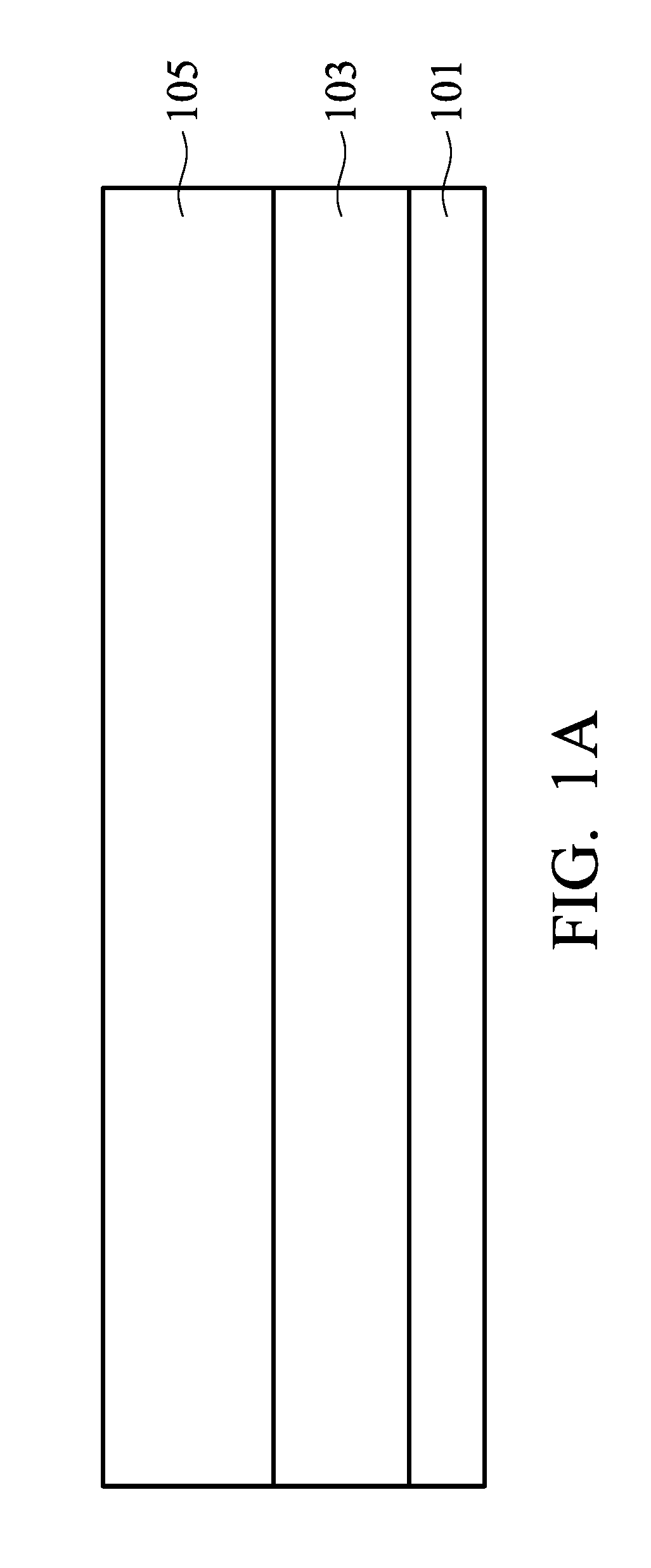

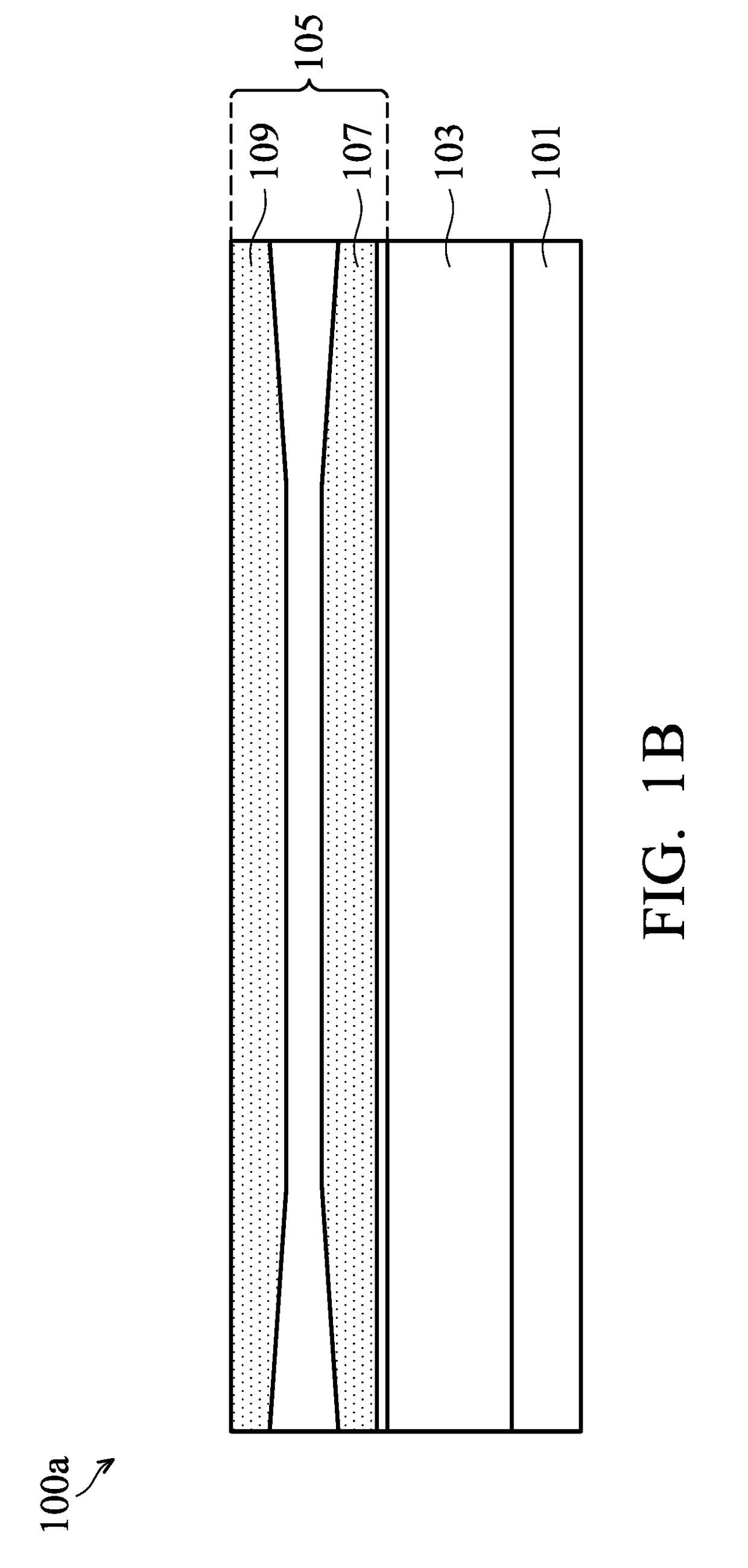

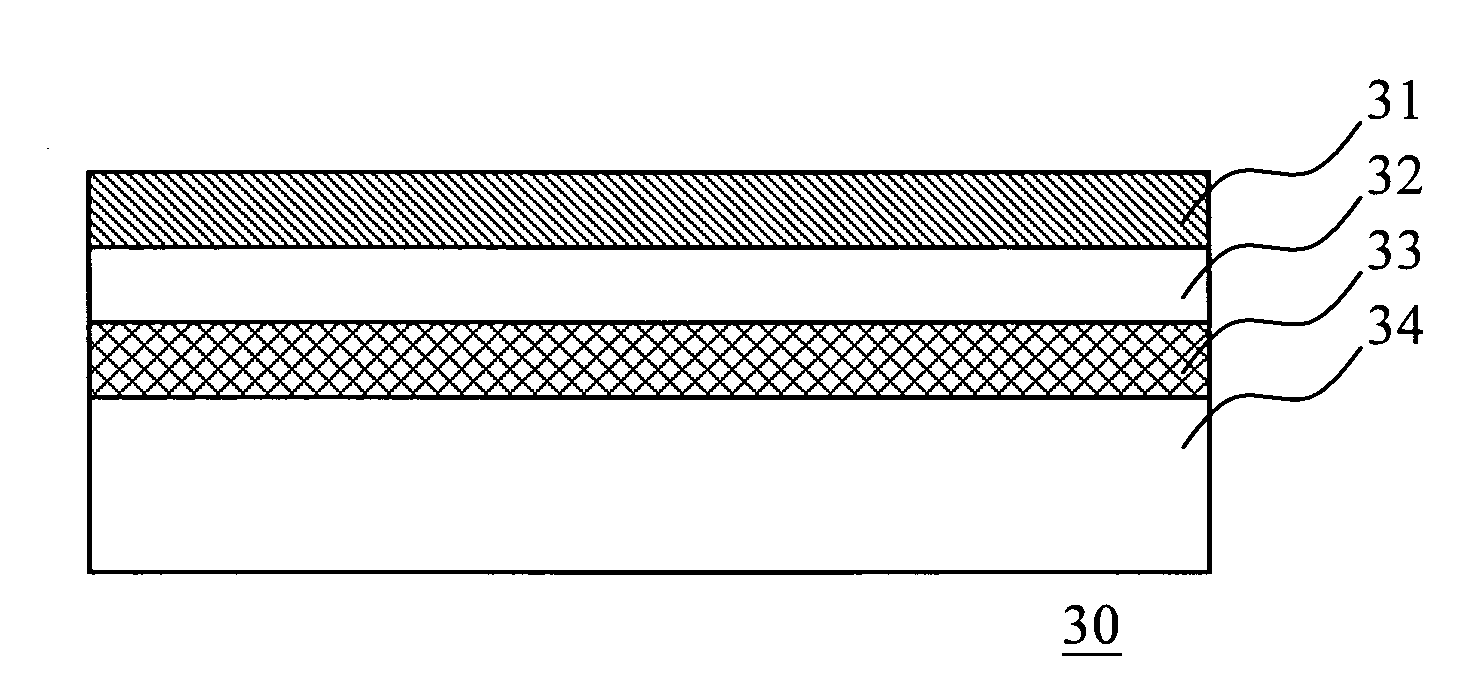

Semiconductor substrate structures, semiconductor devices and methods for forming the same

ActiveUS20180130907A1Eliminate bias effectsSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor packageSemiconductor device

A semiconductor substrate structure includes a substrate having a first conductivity type, an oxide layer disposed on the substrate, and a semiconductor layer disposed on the oxide layer. The semiconductor substrate structure also includes a first buried layer disposed in the semiconductor layer, having a second conductivity type opposite to the first conductivity type. The semiconductor substrate structure further includes a second buried layer disposed in the semiconductor layer and above the first buried layer, having the first conductivity type, wherein the first buried layer and the second buried layer are separated by a distance.

Owner:VANGUARD INTERNATIONAL SEMICONDUCTOR CORPORATION

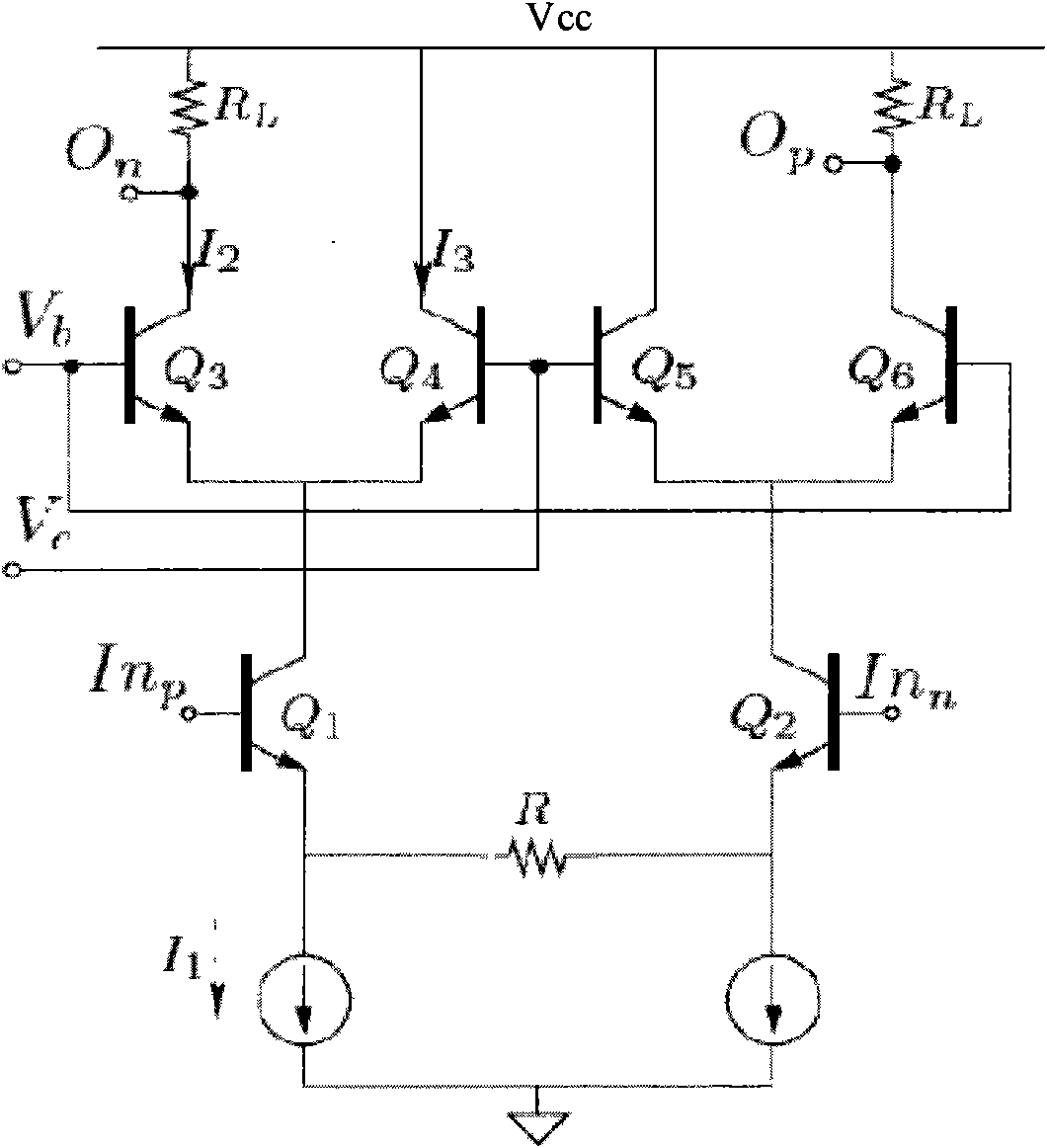

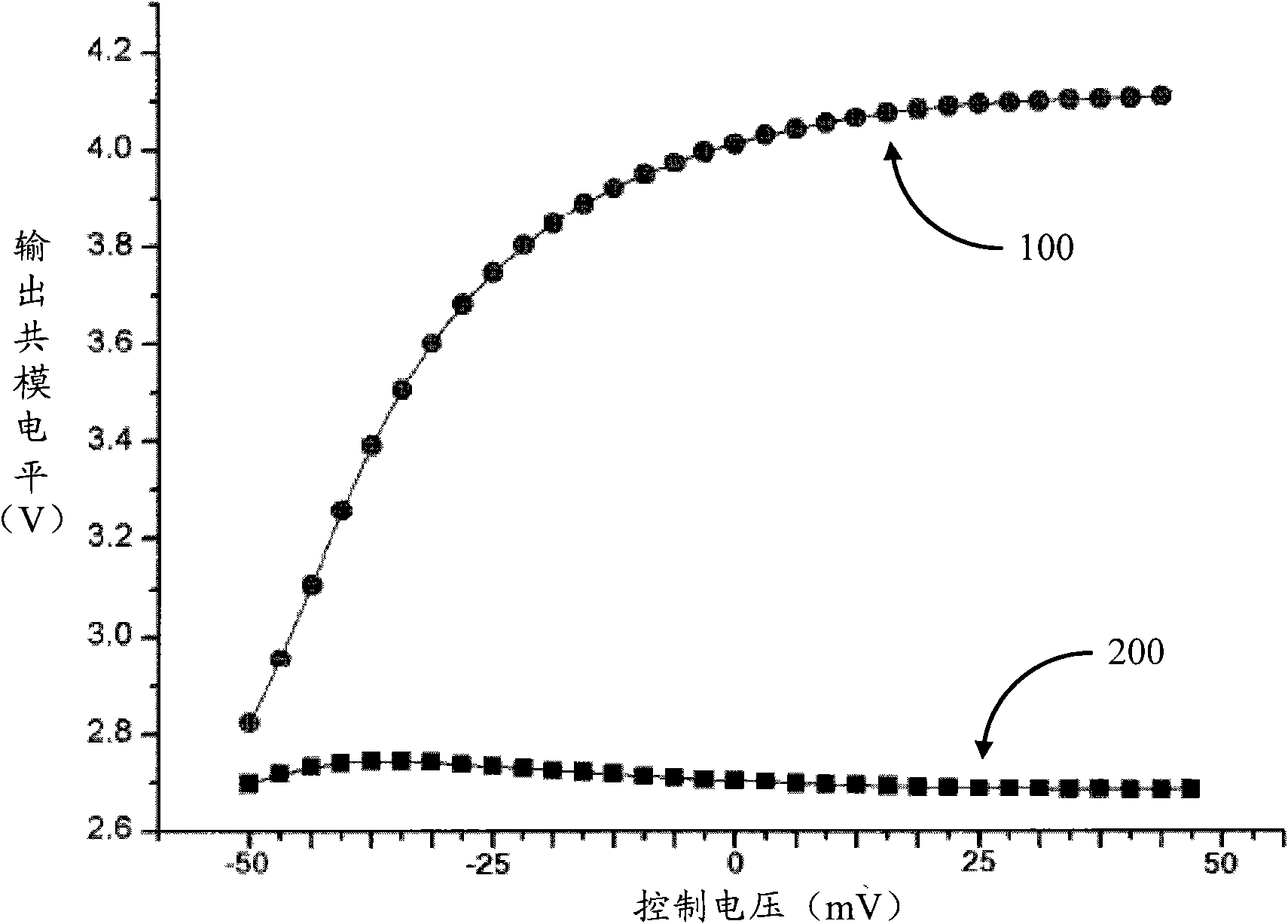

Variable gain amplifier

InactiveCN101567669AStable output currentMinimizes variation in common-mode output levelAmplifier modifications to raise efficiencyDifferential amplifiersAudio power amplifierVariable-gain amplifier

The invention discloses a variable gain amplifier, which comprises a current adjustable amplifying circuit and a compensating circuit; wherein the current adjustable amplifying circuit can change the gain according to a control voltage; while the output terminal of the compensating circuit is connected with the output terminal of the current adjustable amplifying circuit, and provides direct compensating current to the adjustable amplifying circuit; the sum of the direct compensating current and the output current of the current adjustable amplifying circuit is equal to the current source current of the current adjustable amplifying circuit. The output current of the variable gain amplifier is relatively stable, which reduces the change of a common mode output level, thereby reducing the influence on the next-stage circuit offset.

Owner:苏州中科半导体集成技术研发中心有限公司

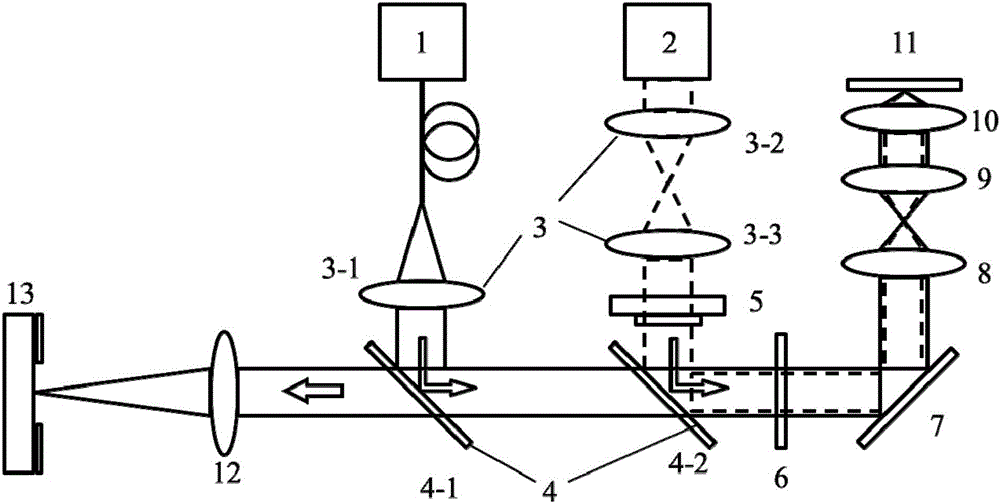

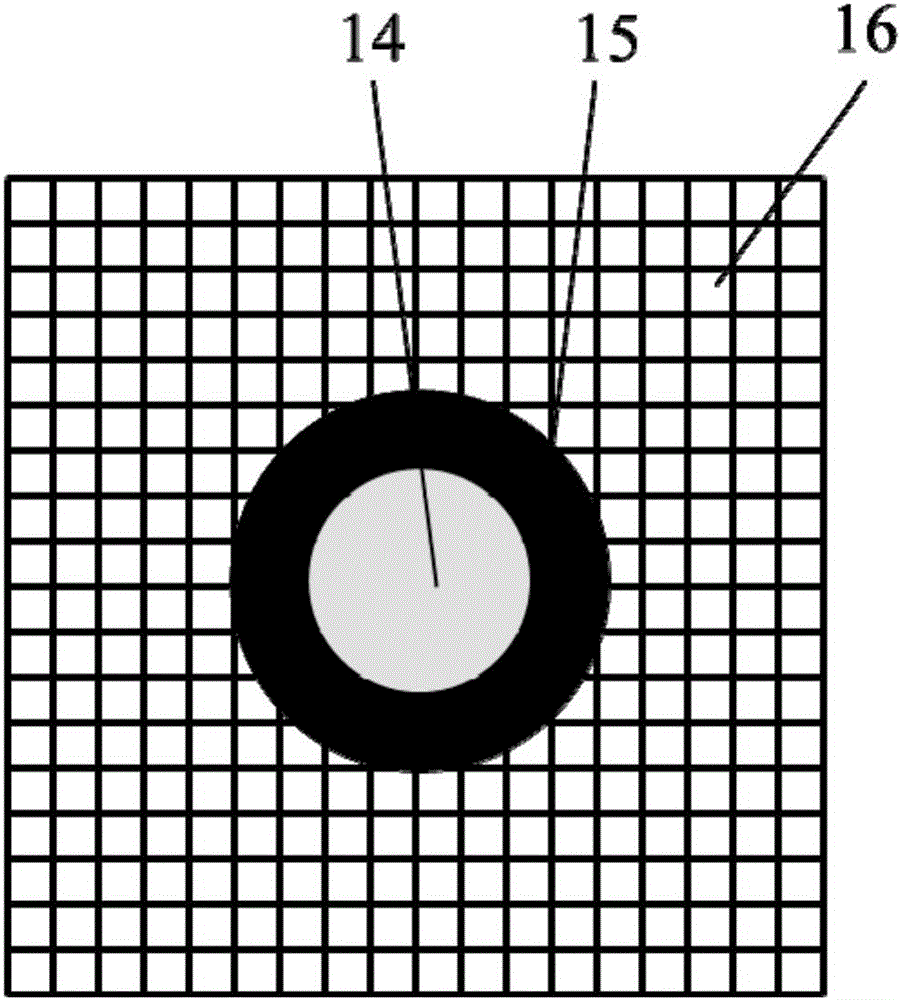

Area array detection type stimulated radiation loss imaging system

InactiveCN106124472AEasy to monitorEasy to adjustFluorescence/phosphorescenceRadiation lossGalvanometer

An area array detection stimulated radiation depletion imaging system, including an excitation light source for generating excitation light, a depletion light source for generating depletion light, a beam expander system, a vortex phase modulation plate, a dichromatic mirror, and a wave plate , scanning galvanometer, scanning lens, tube lens, objective lens, nano-shift stage, telephoto converging lens and area array detector, the excitation light after beam expansion by the beam expander system and the beam expander system, vortex phase The lost light after beam expansion and phase modulation by the modulation plate enters the dichroic mirror and then enters the wave plate. After scanning the lens, tube lens and objective lens, focus on the inside of the sample at the nano-shift stage, and the optical signal generated by the excitation light and loss light focused on the inside of the sample at the nano-shift stage passes through the detection optical path and the telephoto converging lens Converged on the area array detector for imaging. The application is simple and convenient to operate and has high utilization rate of light energy.

Owner:SUZHOU INST OF BIOMEDICAL ENG & TECH CHINESE ACADEMY OF SCI

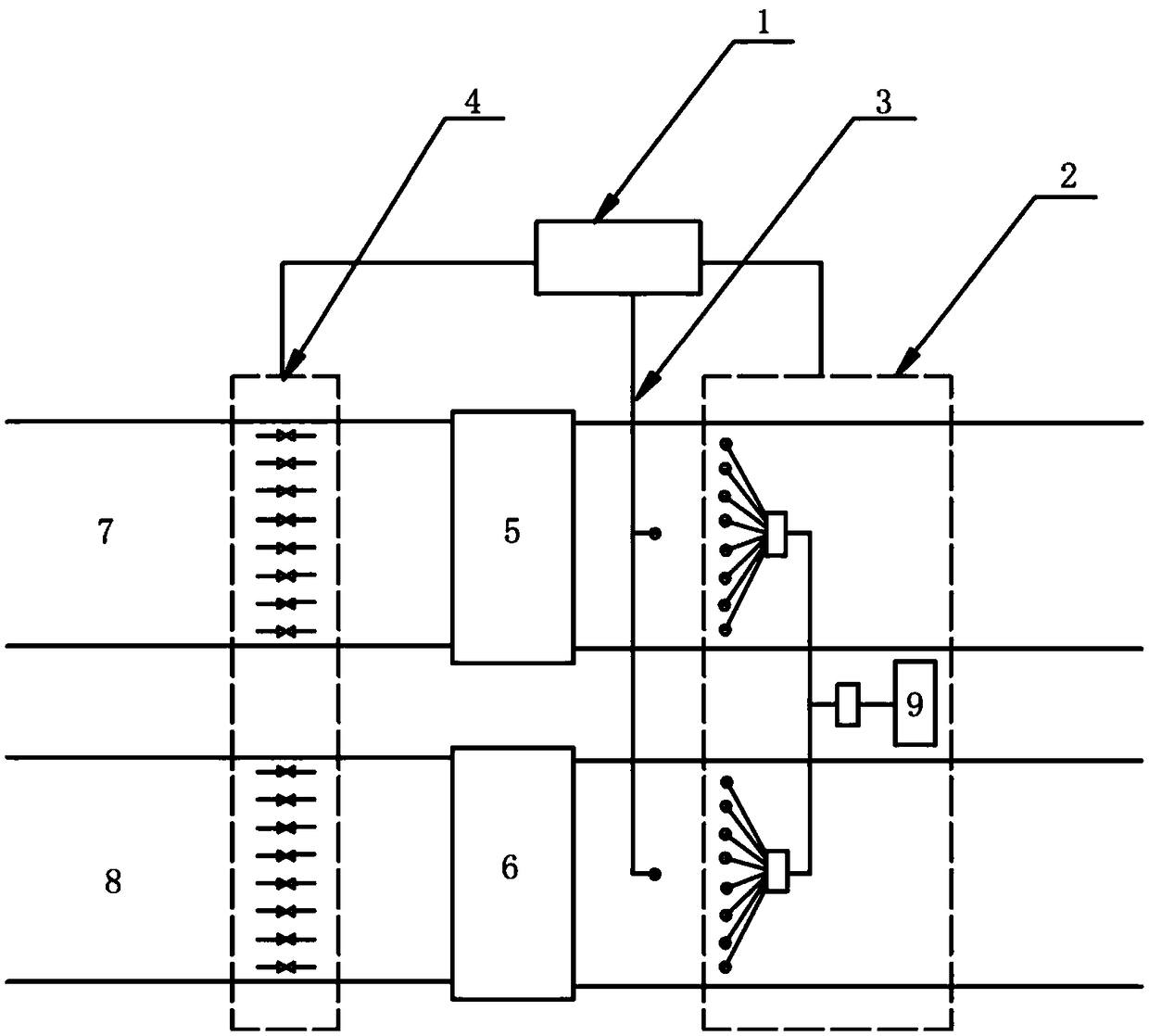

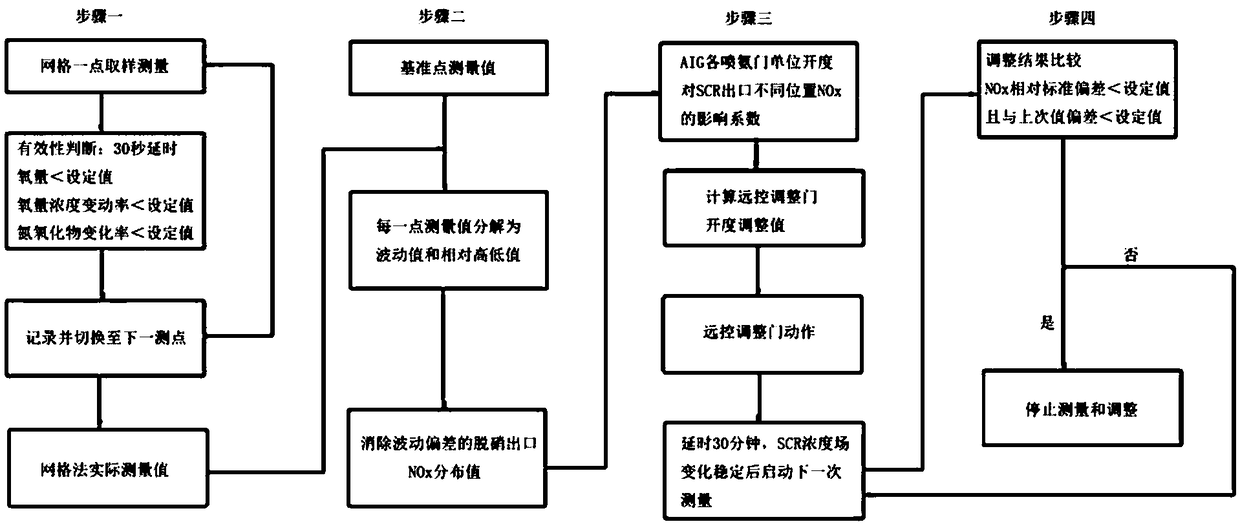

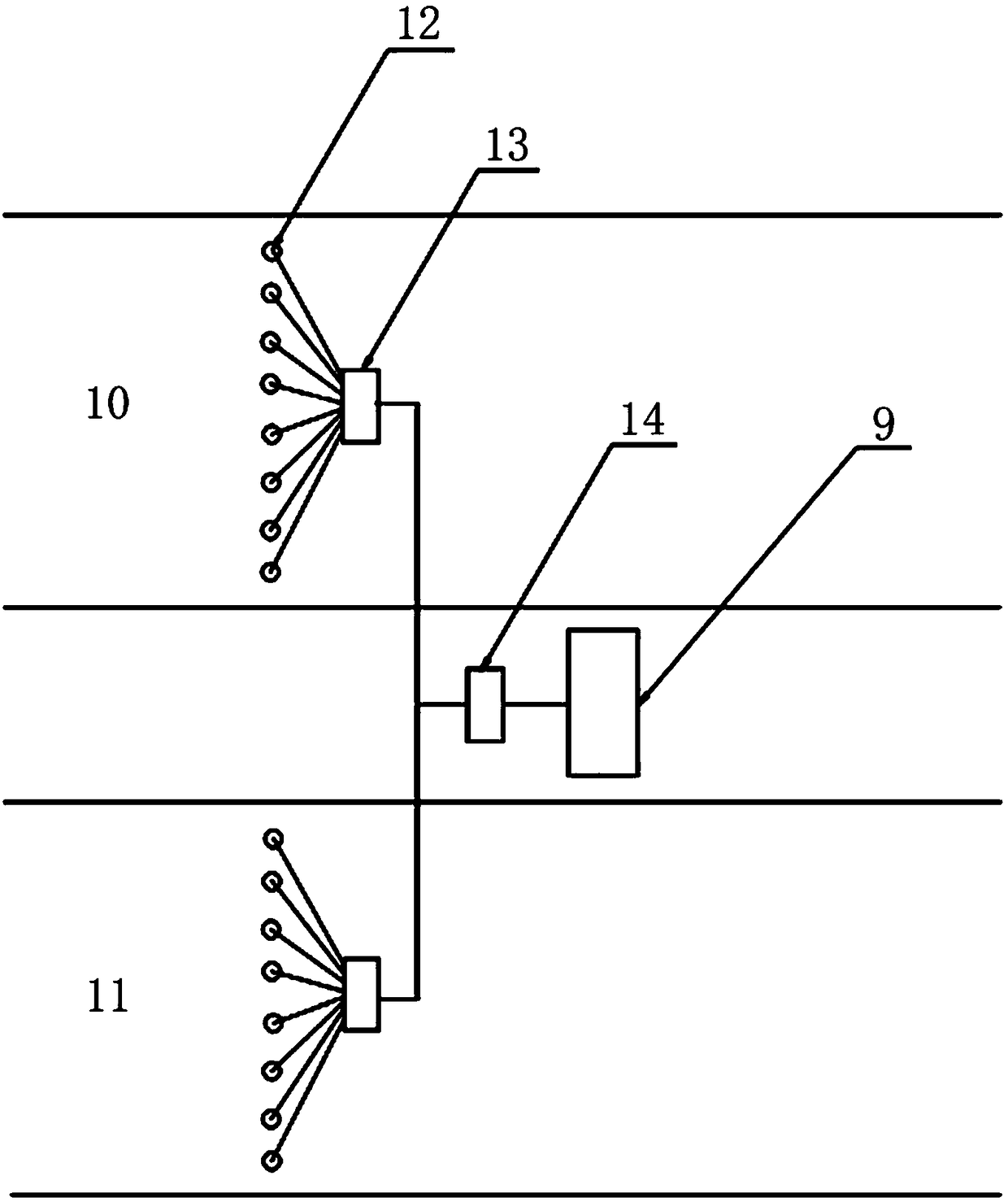

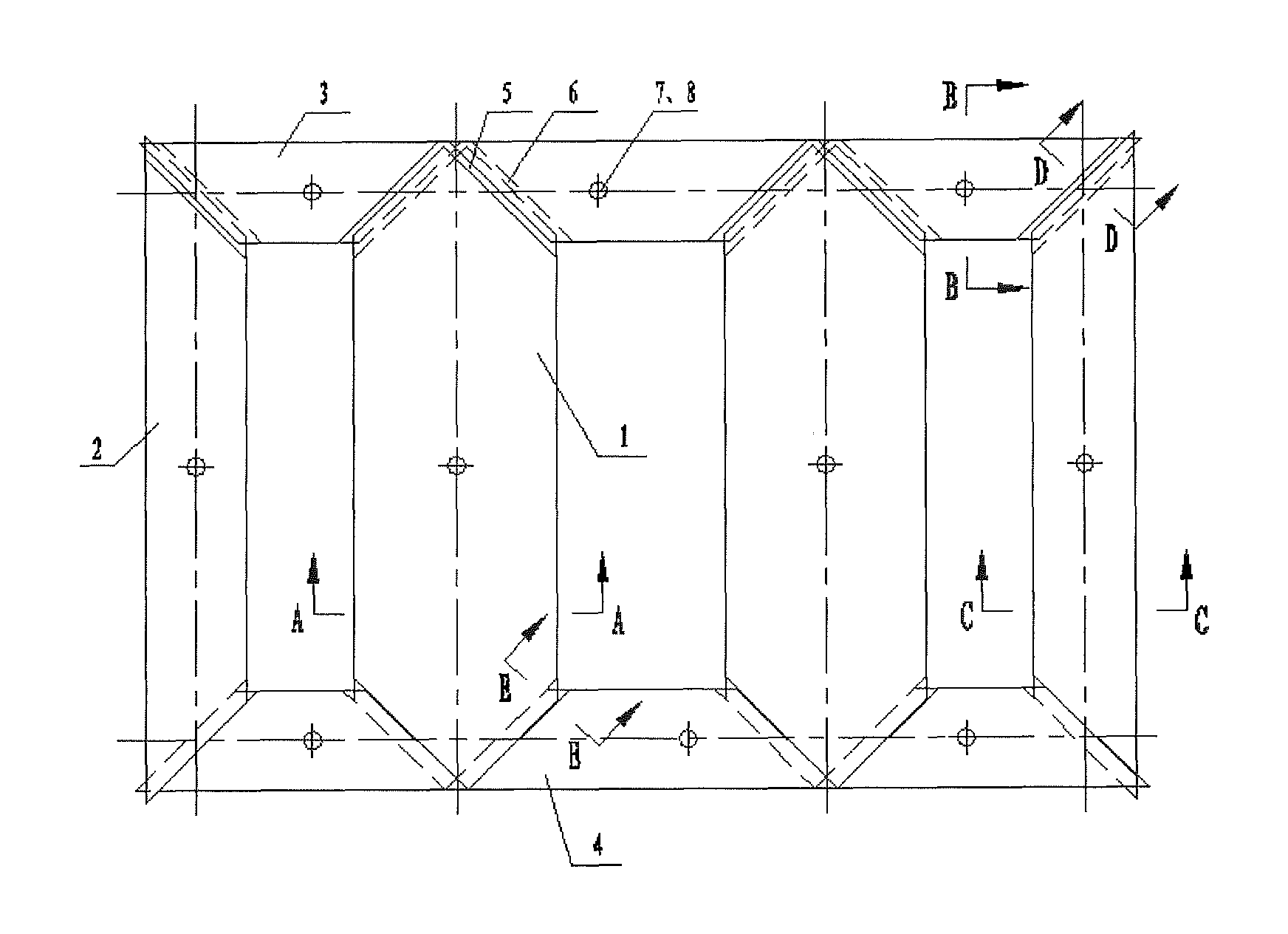

Denitration uniformity measurement optimizing system and method under fluctuating loads

InactiveCN109260948AEliminate the bias effects of fluctuationsEliminate bias effectsGas treatmentControlling ratio of multiple fluid flowsControl systemRemote control

The invention relates to a denitration uniformity measurement optimizing system and method under fluctuating loads. The system comprises two flue inlets formed in a side A and a side B respectively and two SCR reactors arranged between two flue outlets, remote control adjusting doors (4) are formed between the two flue inlets and the two SCR reactors, grid method tour measuring devices (2) are arranged between the two flue outlets and the two SCR reactors, reference point calibration loops (3) are arranged between the two flue outlets and the two grid method tour measuring devices, and a uniformity analysis control system (1) is further arranged and connected with the remote control adjusting doors (4), the reference point calibration loops (3) and the grid method tour measuring devices (2) separately. According to the system and method, through the reference point calibration loops, the deviation influence of NOx overall fluctuation is removed, through the uniformity measurement result, the relative amplitude of NOx values at different position points is accurately reflected, and misjudgment and wrong adjustment caused by the influence of fluctuation are avoided.

Owner:HUADIAN POWER INTERNATIONAL CORPORATION LTD +1

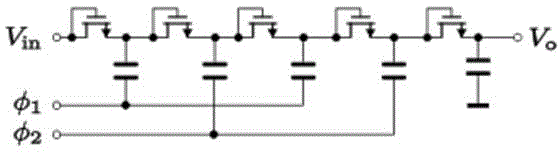

Charge pump circuit of charge transfer structure suitable for low-voltage operation

InactiveCN104821714AImprove conduction abilityReduces substrate bias effectsApparatus without intermediate ac conversionCapacitanceEnergy storage

The invention relates to a charge pump circuit of a charge transfer structure CTS suitable for low-voltage operation. The charge pump circuit comprises a plurality of cascaded CTS charge pump sub-units. Each stage of CTS charge pump sub-unit comprises the components of a first NMOS transistor as a transmission switch, the drain electrode of the first NMOS transistor is connected with the input end of this stage, and the source electrode is connected with the output end of this stage; a second NMOS transistor of which the drain electrode is connected with the input end of this stage, the source electrode is connected with the gate electrode of the first NMOS transistor, and the gate electrode is connected with the output end of this stage; a PMOS transistor of which the source electrode is connected with the gate electrode of the first NMOS transistor, the drain electrode is connected with the output end of a next stage, and the gate electrode is connected with the output end of this stage; and a random phase clock signal in a pair of phase clock signals, wherein the random phase clock signal is transmitted to the output end of this stage through an energy storage lifting capacitor. The charge pump circuit is based on the improvement of the existing CTS charge pump sub-unit and a cascaded circuit, and increases the gate electrode voltage of the NMOS transistor as a transmission switch through a simpler structure. Furthermore the charge pump circuit has functions of reducing side effect of a substrate bias effect and simplifying design for a circuit board diagram.

Owner:GIANTEC SEMICON LTD

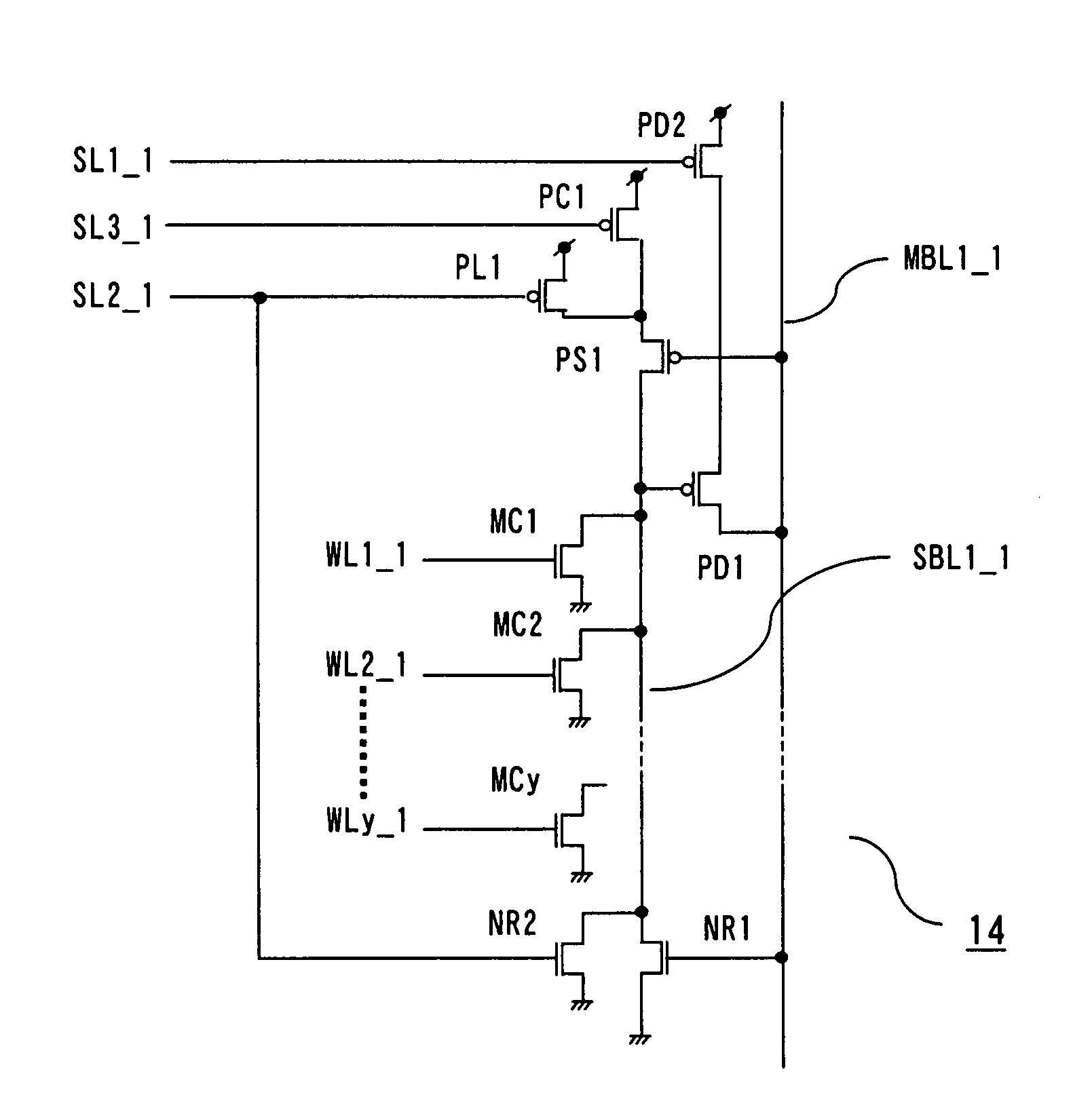

Semiconductor memory device

InactiveUS20060158942A1Stable reading operationEliminate bias effectsRead-only memoriesDigital storageBit lineTransmission gate

A semiconductor memory device includes a memory cell array, a charge circuit which compensates for OFF leakage current developed at selected bit lines, a reset circuit having a ground potential corresponding to a potential at non-selected bit lines, a read circuit constituted by a plurality of transistors whose gates are connected to the bit lines, and a bit line precharge circuit which charges the selected bit lines for a fixed time period. As a result of adopting such a configuration, there is no need to provide a transmission gate, such as a column decoder, to a charging path between the read circuit and the bit lines, so that a low-power supply voltage operation can be effected without the influence of a substrate bias effect.

Owner:SOCIONEXT INC

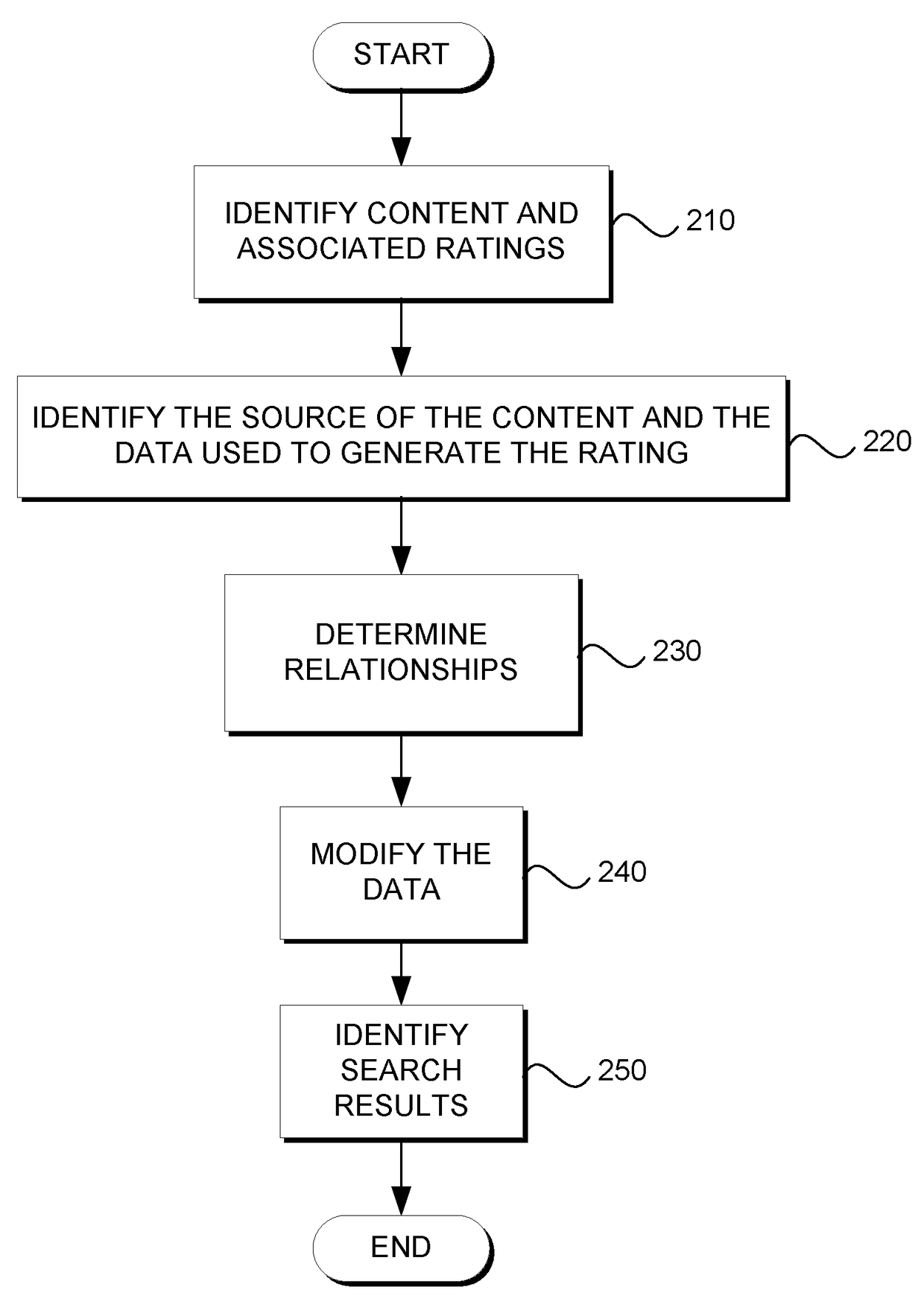

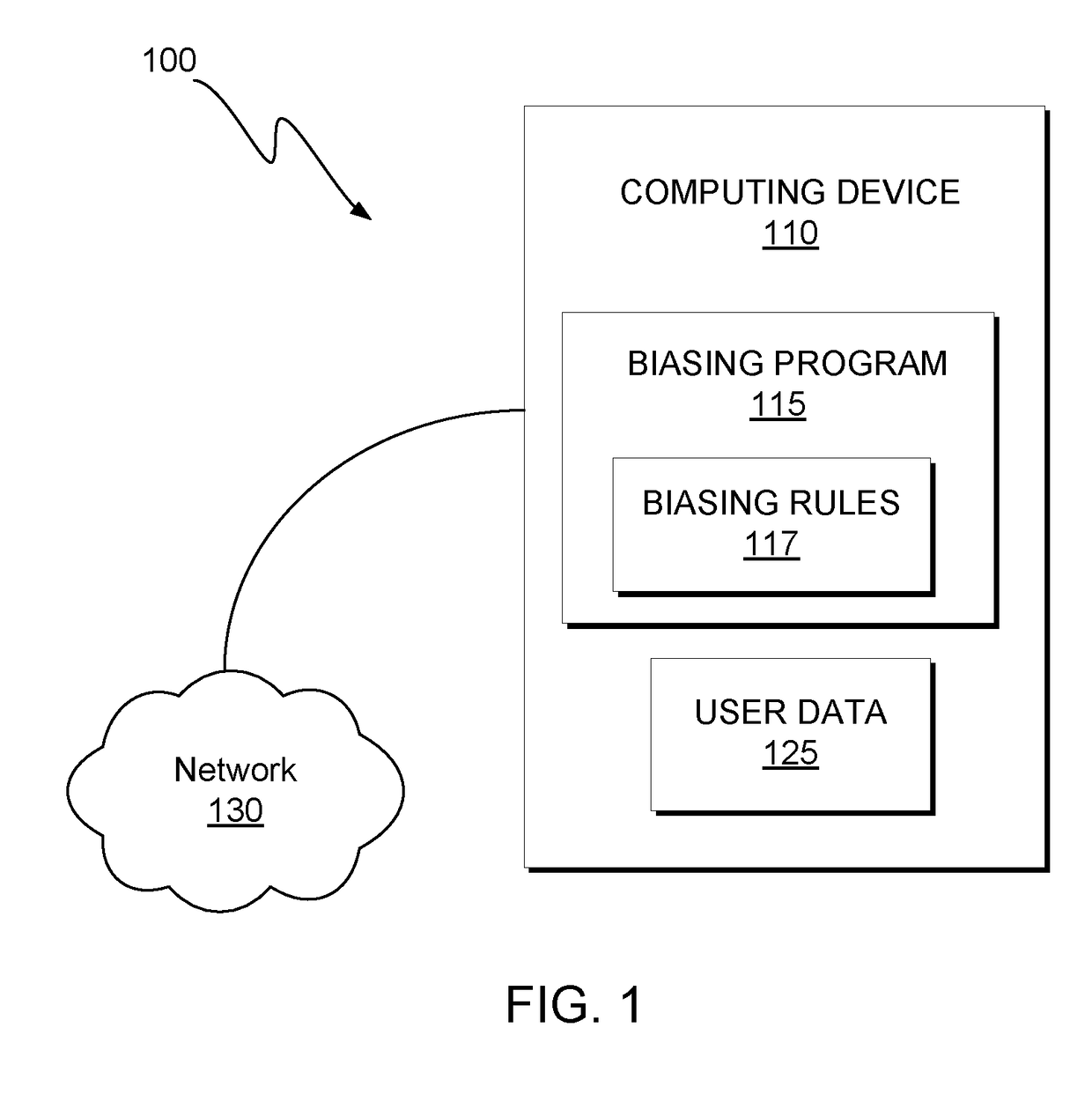

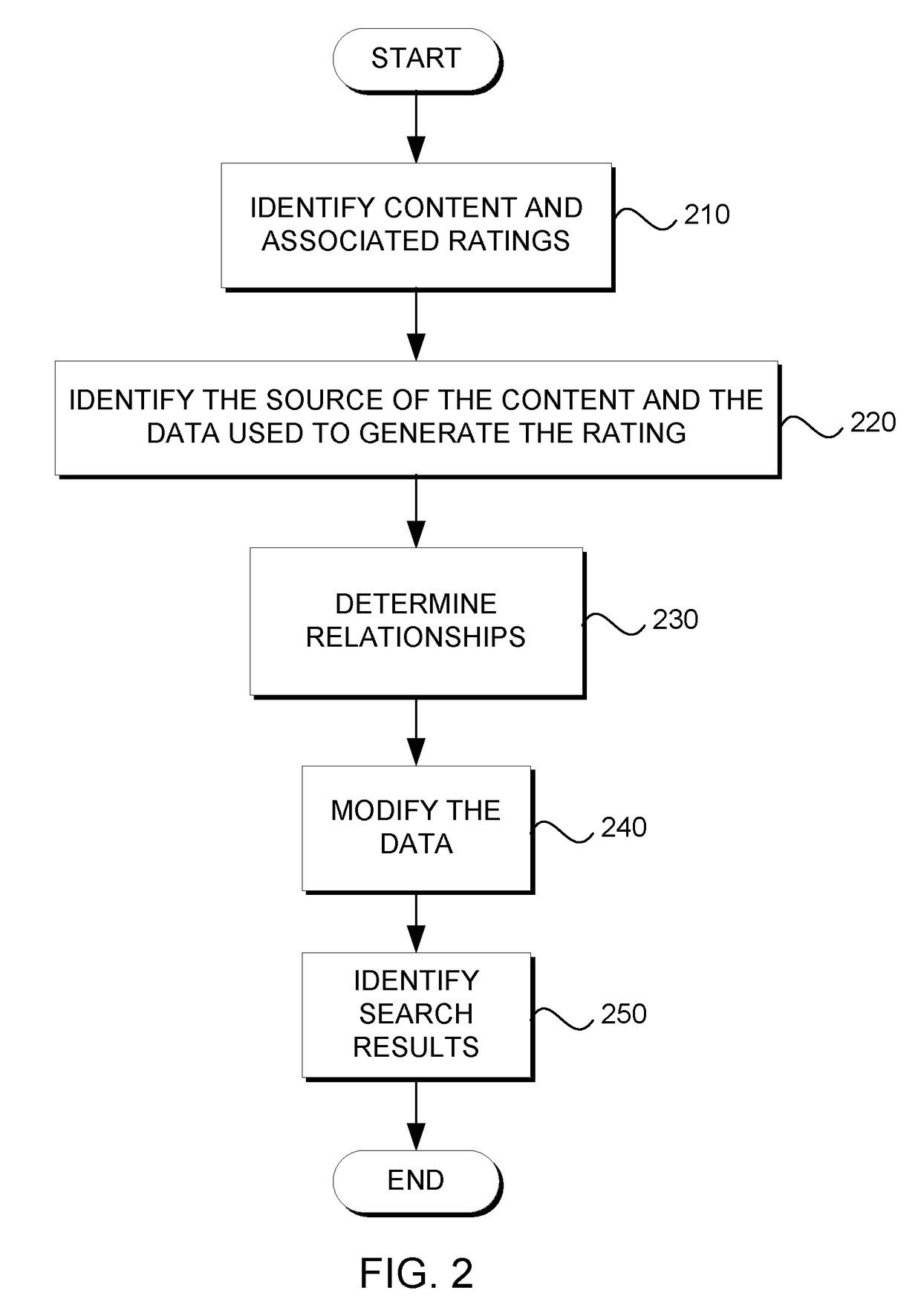

Bias correction in content score

InactiveUS20170185652A1Reduce biasEliminate bias effectsDigital data information retrievalInference methodsData miningData science

One or more processors reduce bias in a score of a content. The one or more processors determine a predicted pattern of behavior of a user that provided a portion of data used to generate an initial rating of content. The one or more processors generate a modified rating of the content based on a degree of matching between the predicted pattern of behavior of the user and an action of the user that provided the portion of data.

Owner:IBM CORP

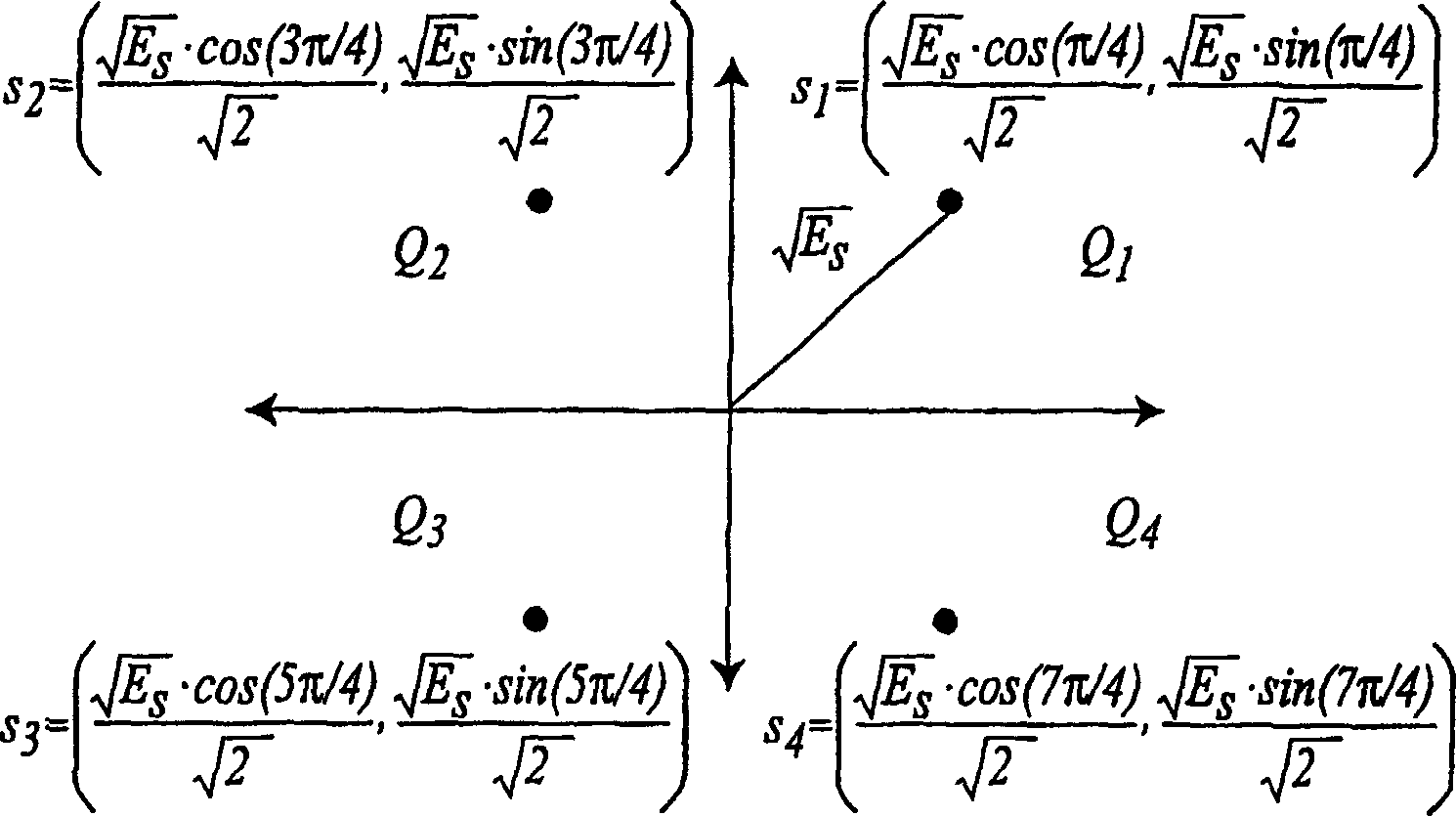

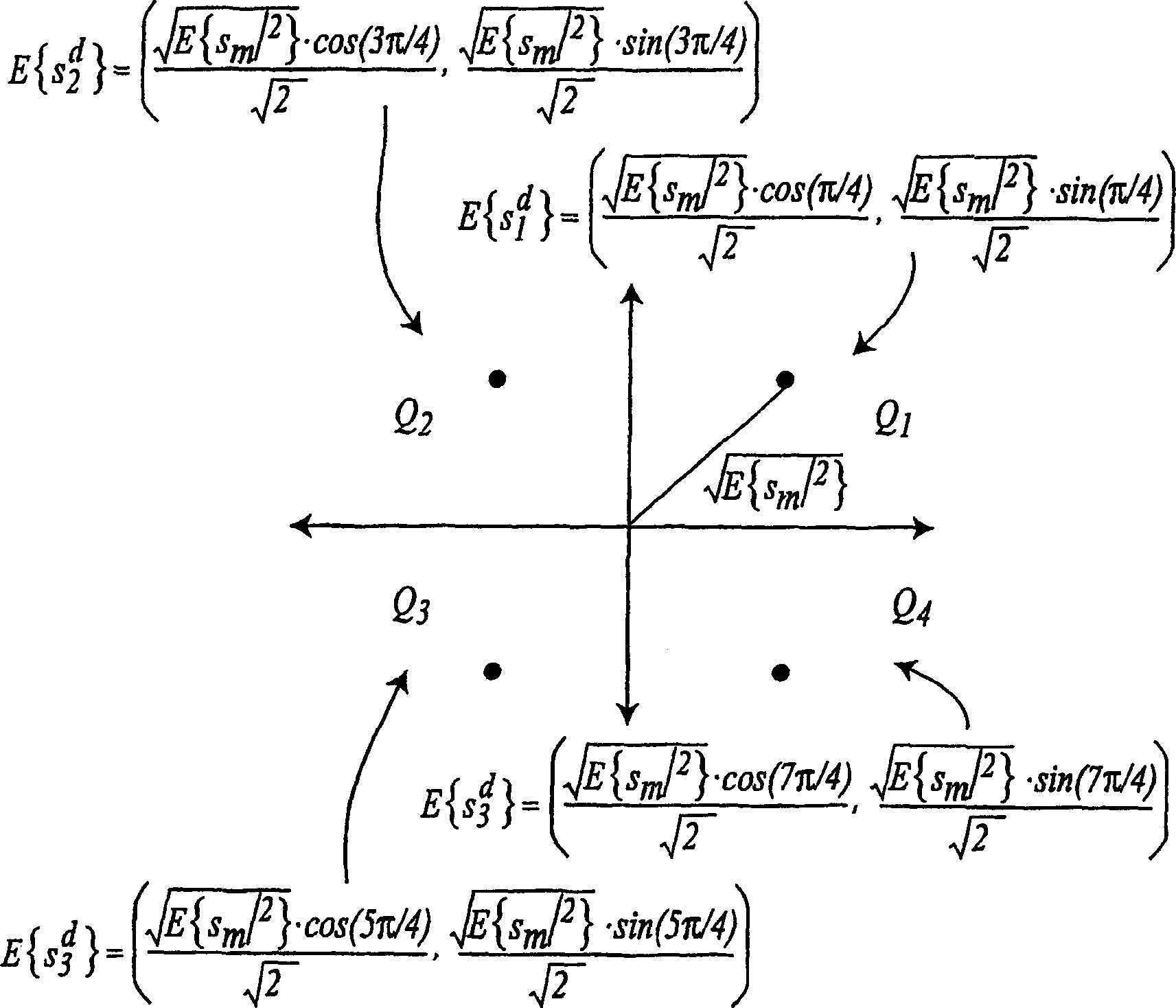

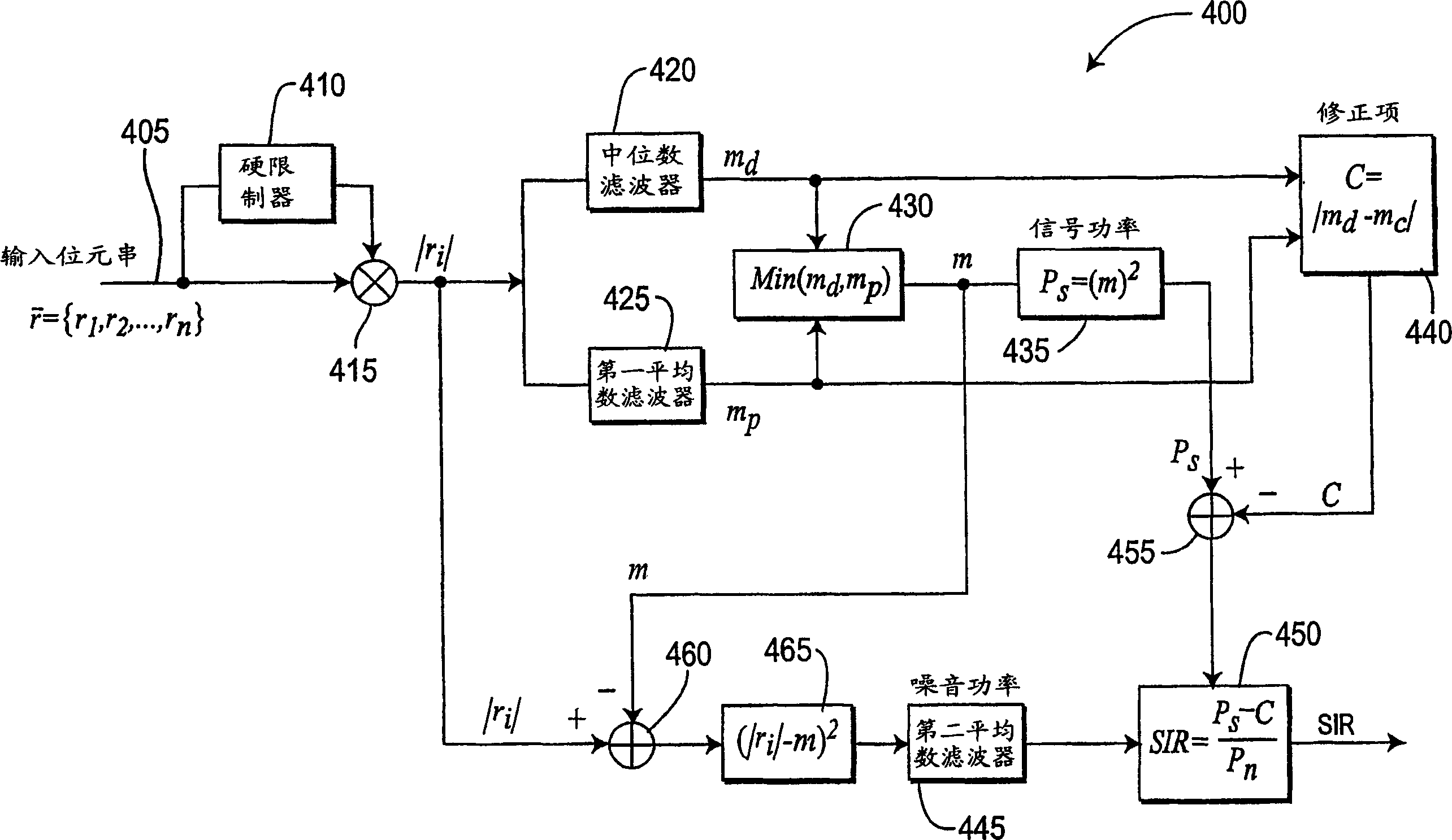

Method and apparatus for determining signal-to-interference ratio with reduced bias effect

InactiveCN1711709AReliable estimateAccurate estimateTransmission control/equalisingCriteria allocationCommunications systemMulti user detection

A method and apparatus for performing Signal-to-Interference Ratio (SIR) estimation in a wireless communication system using a demodulator output, such as a Rake output or a Multi-User Detection (MUD) receiver output . The demodulator output is provided to a SIR estimator to perform the SIR estimation based on estimated average signal power and estimated effective interference power. The estimated average signal power is based on a minimum function for determining a minimum value between a median-based average power value and a mean-based average power value. The SIR estimator reduces the bias effect in SIR estimation, and can be used in BPSK and QPSK modulation modes and higher order modulation modes such as 8-PSK and 16-QAM. A correction function term is used as the mean and median to further reduce the bias effect.

Owner:INTERDIGITAL TECH CORP

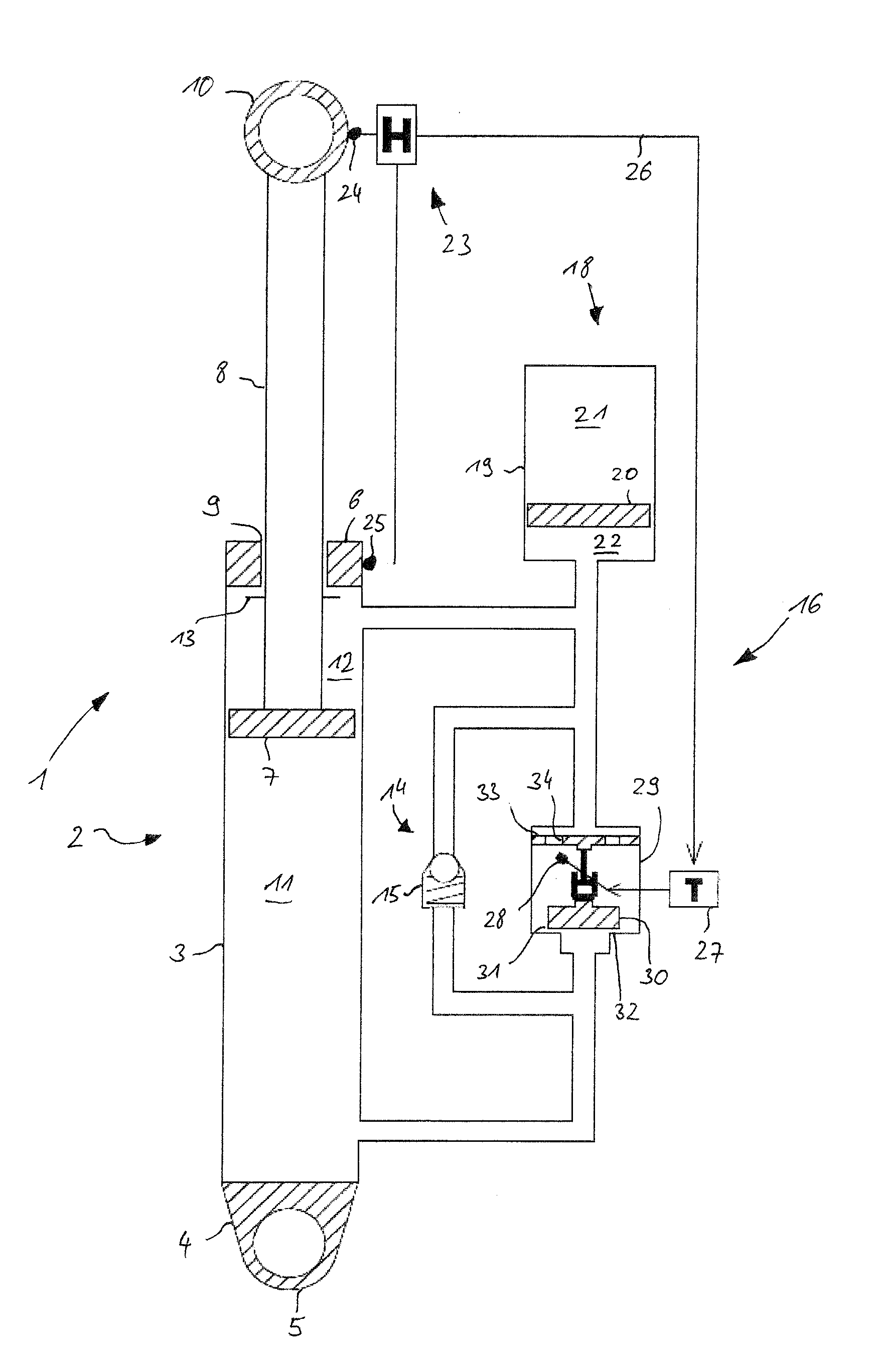

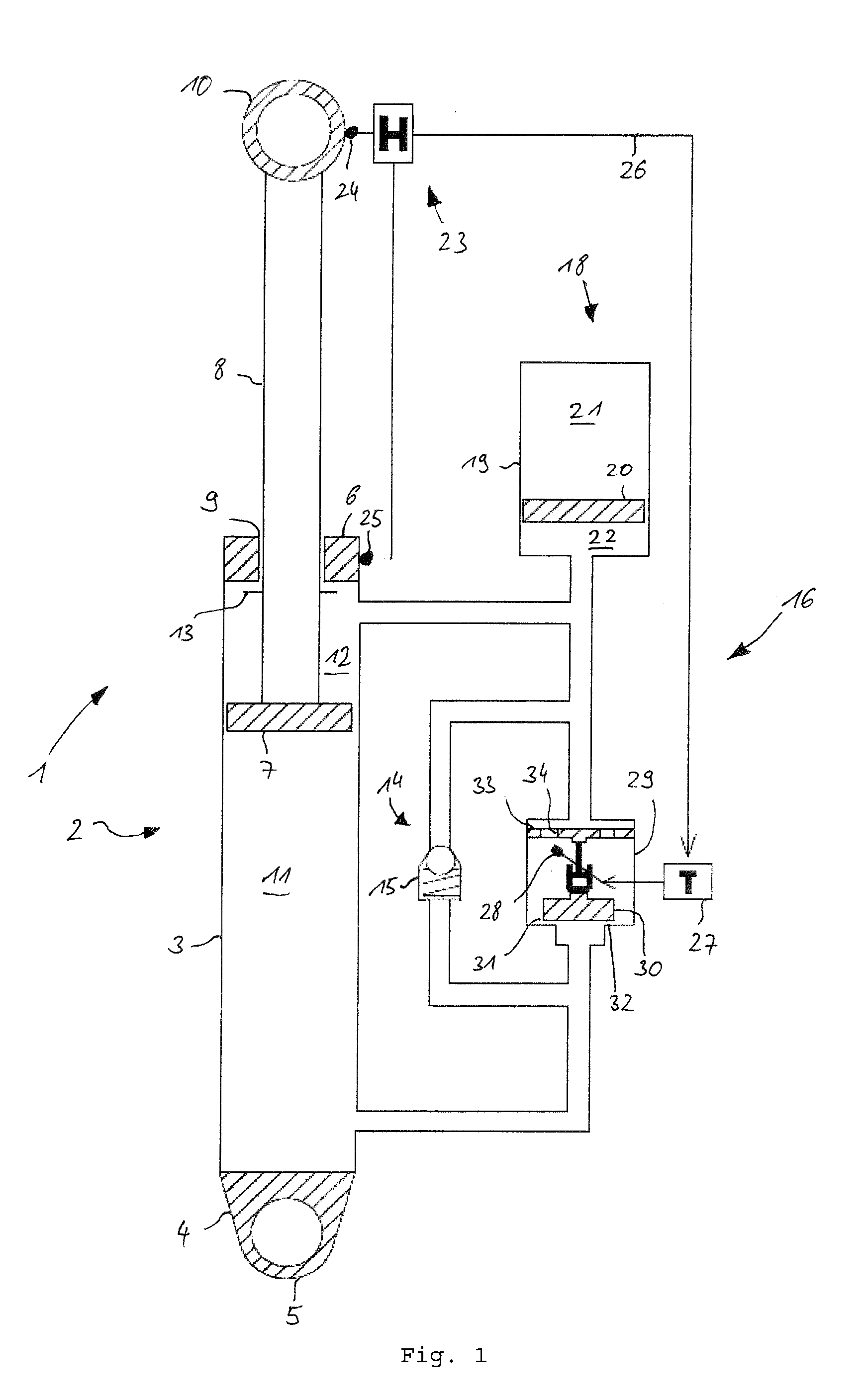

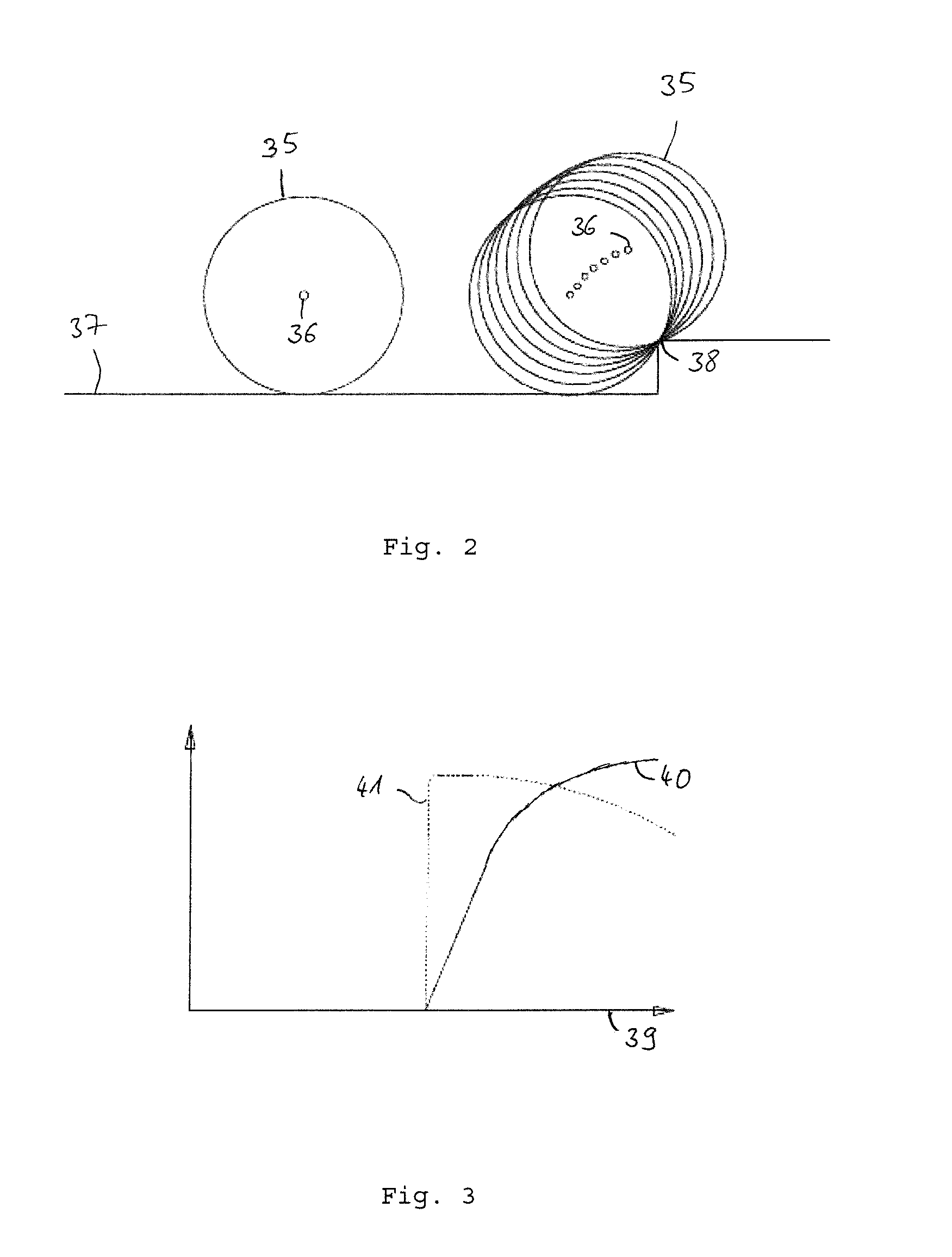

Damping strut with a hydraulic shock absorber and method for operating the damping strut

ActiveUS20160265616A1Reduced strengthEliminate bias effectsSpringsSprings/dampers functional characteristicsThrottleHydraulic shock

A damping strut with a hydraulic shock absorber has a damping volume filled with an incompressible damping fluid, a retract detection device, and a compression stage throttle having a disk valve with a valve disk. The damping fluid flows through the compression stage throttle during a retraction of the shock absorber and generates a damping strut resistance force. A biasing means for biasing the valve disk against a through flow direction of the disk valve has a force-distance-characteristic curve in a range of the valve stroke of the valve disk, a first derivative of which is substantially zero and has a value (K). A bias regulator couples the biasing means with the valve disk and is interconnected with the retract detection device. When the retraction of the shock absorber starts, the value (K) is raised during a first period of time starting at a single start value.

Owner:RIPA THOMAS

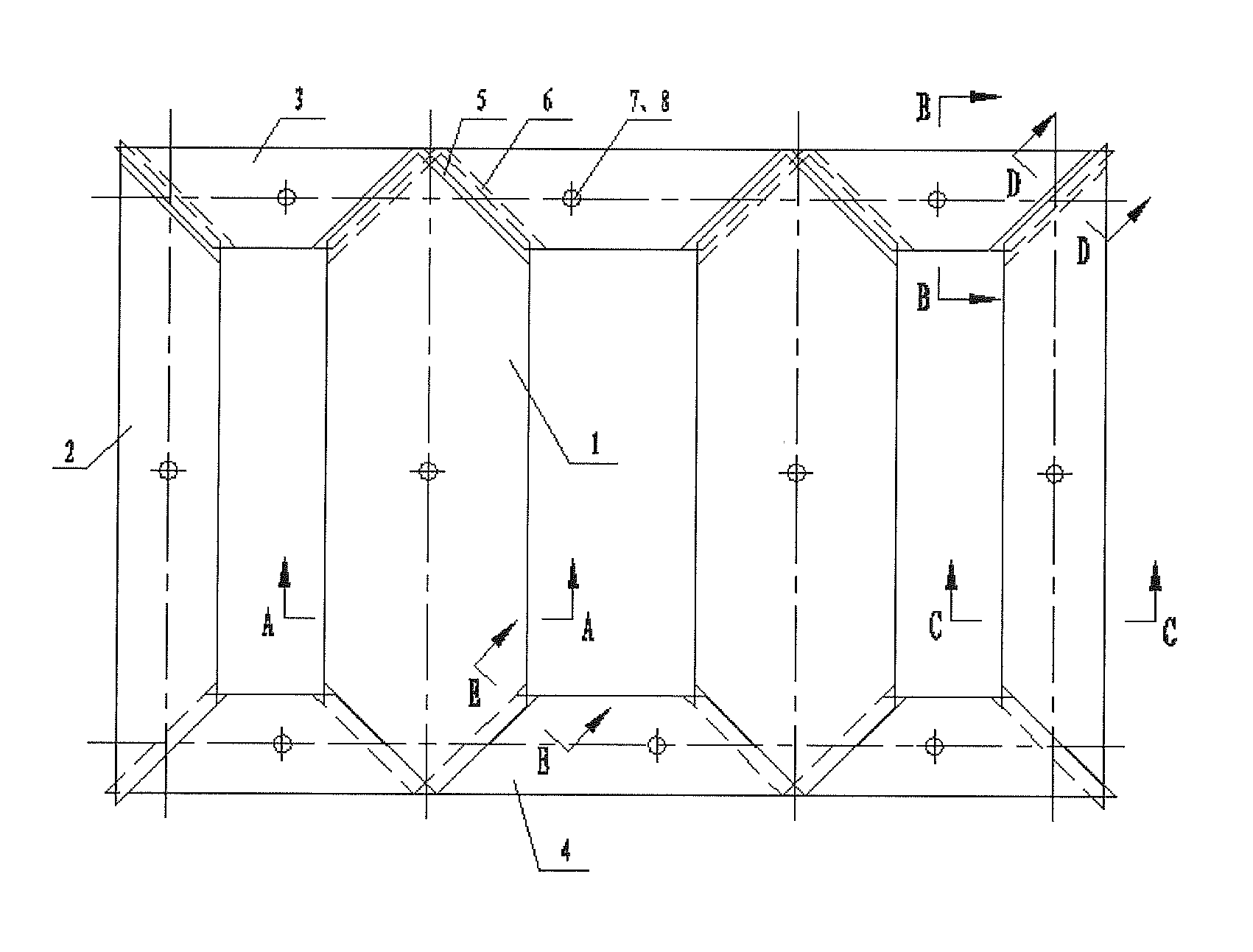

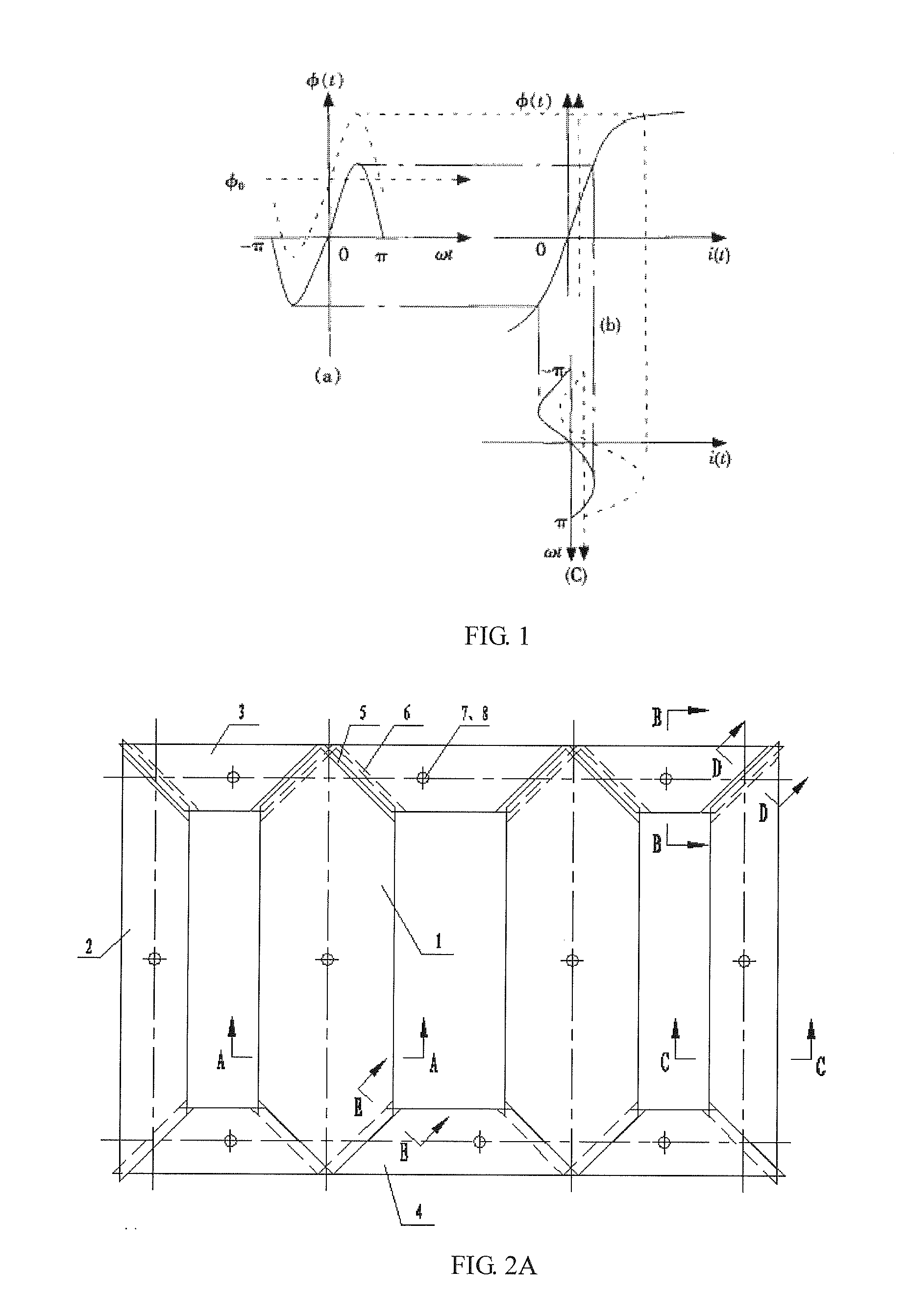

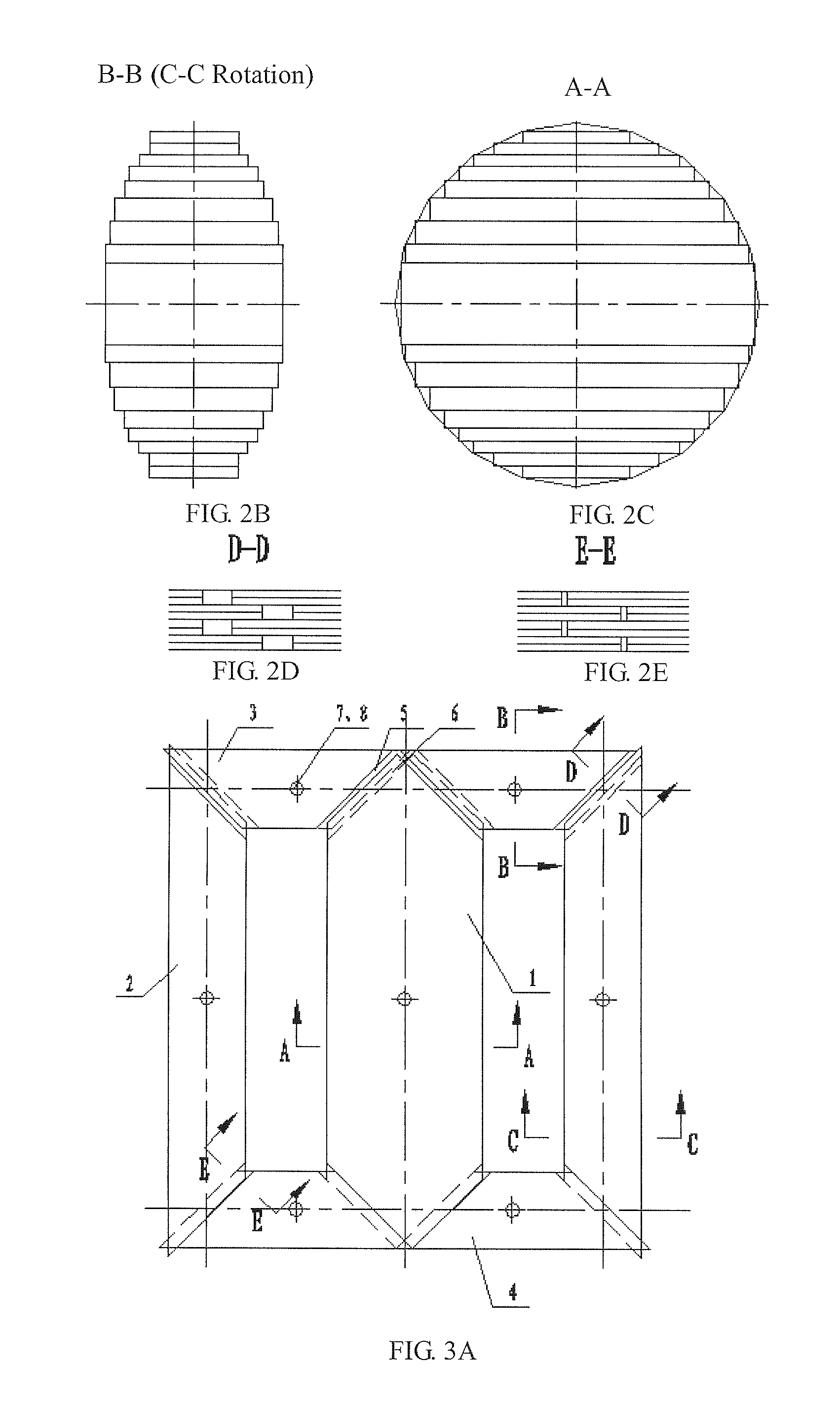

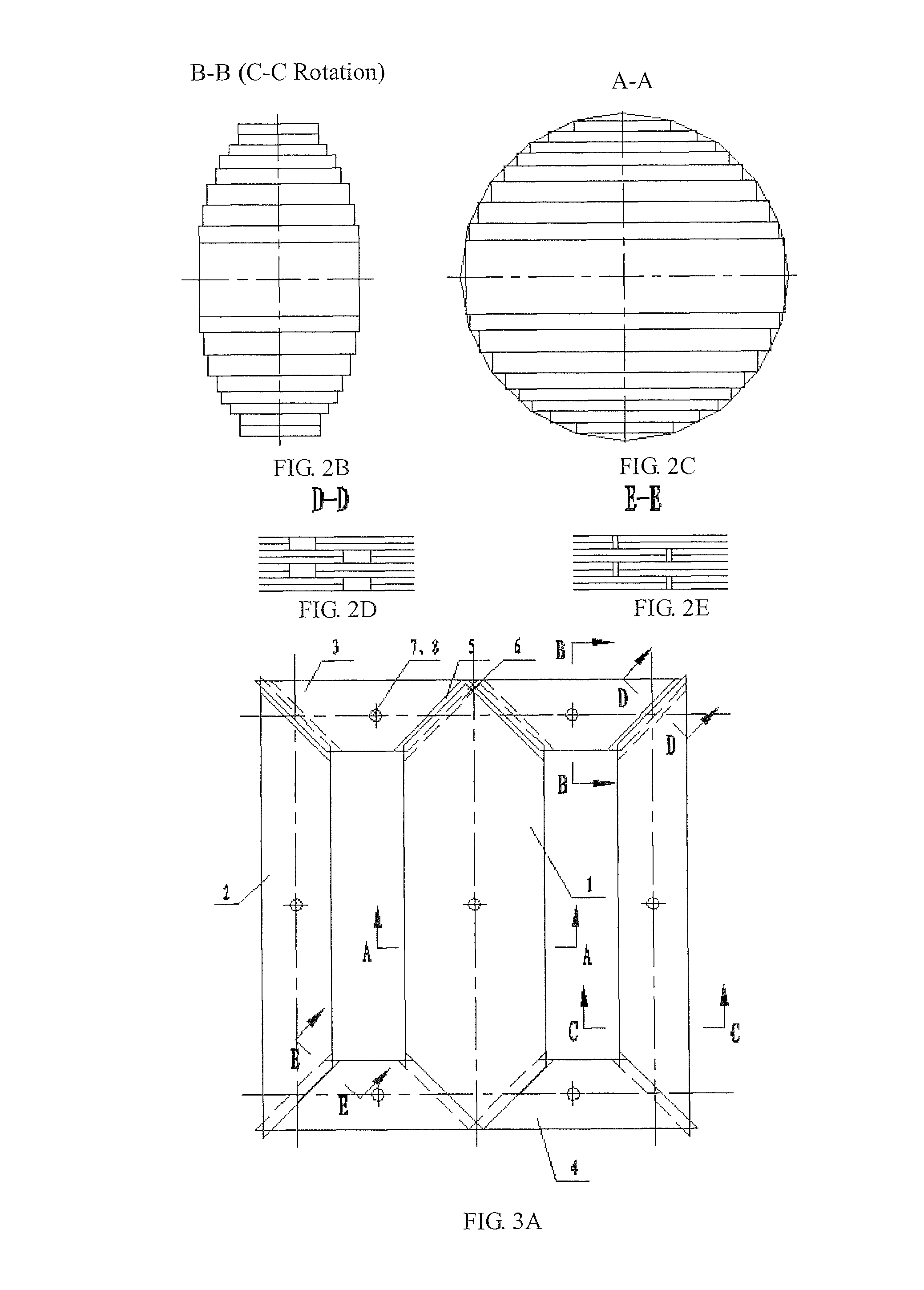

Method for Achieving Converter Transformer for Suppressing DC Bias Magnet

ActiveUS20120090164A1Eliminate bias effectsReduce impactInductances/transformers/magnets manufactureElectromagnetsTransformerMagnet

A method for achieving converter transformer for suppressing DC bias magnet comprises increasing the seaming width of the transformer core lamination, which comprises in detail calculating the width and the height of each stage of lamination according to the reserved seaming width of the lamination, the sectional area of the core, the space between columns, and the height of the window, shearing the lamination based on the width and the height of the lamination obtained by calculating, overlapping two pieces of laminations into one piece of lamination according to the order of stages, placing them on the core frame alternately by stages, and after overlapping all the laminations, fastening each stage of lamination.

Owner:TBEA SHENYANG TRANSFORMER GRP CO LTD

X-ray CT apparatus and image-taking method therefor

InactiveUS7555096B2Eliminate bias effectsMaterial analysis using wave/particle radiationRadiation/particle handlingComputer graphics (images)Radiology

Time-series data over the range of a projection angle is created from a sinogram. Then, time-series data made up of opposite data corresponding to the time-series data over the range of a projection angle is created. Based on the amount of the error between the two types of time-series data, the amount of position deviation of a revolution axis is calculated.

Owner:CANON KK

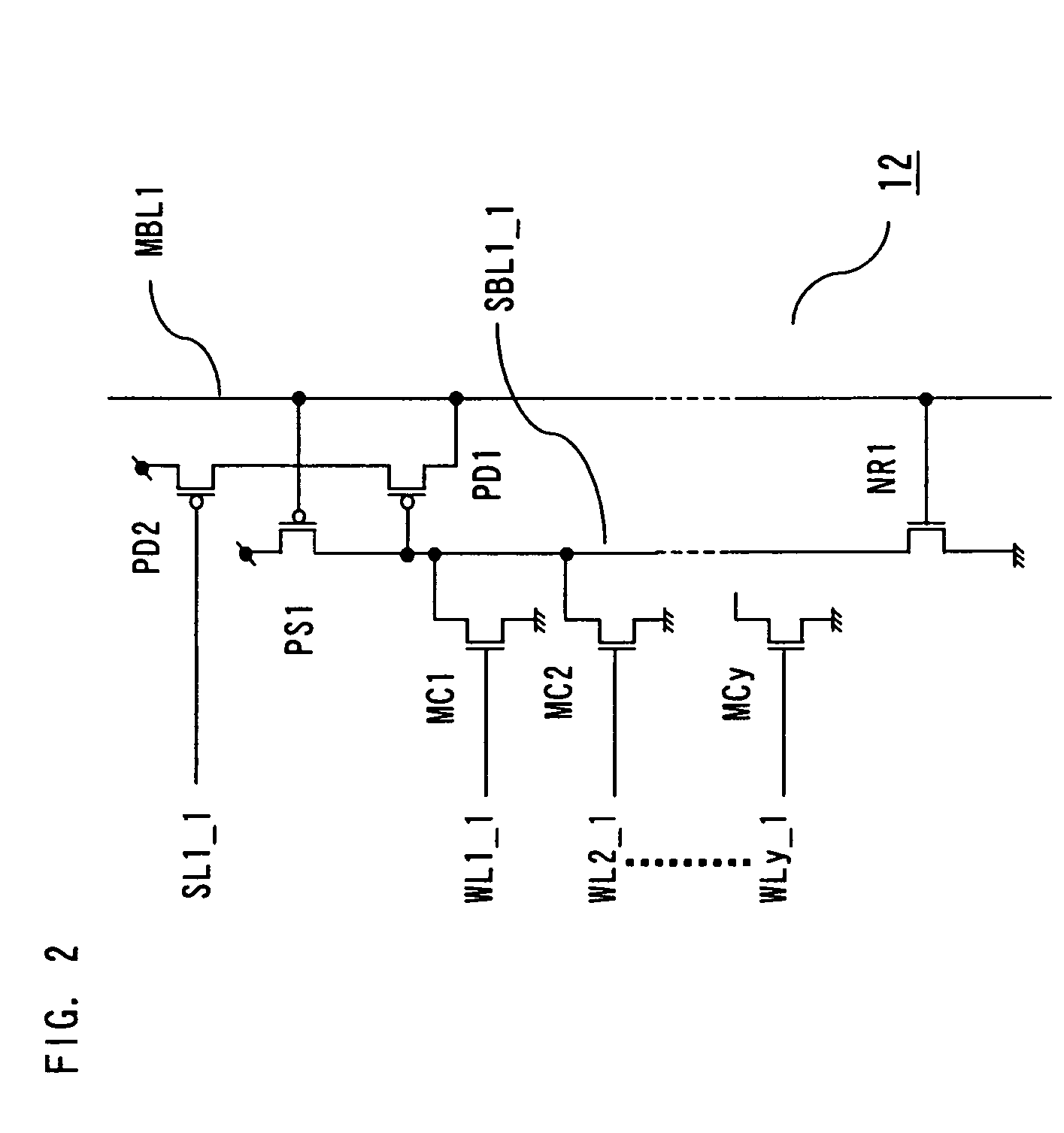

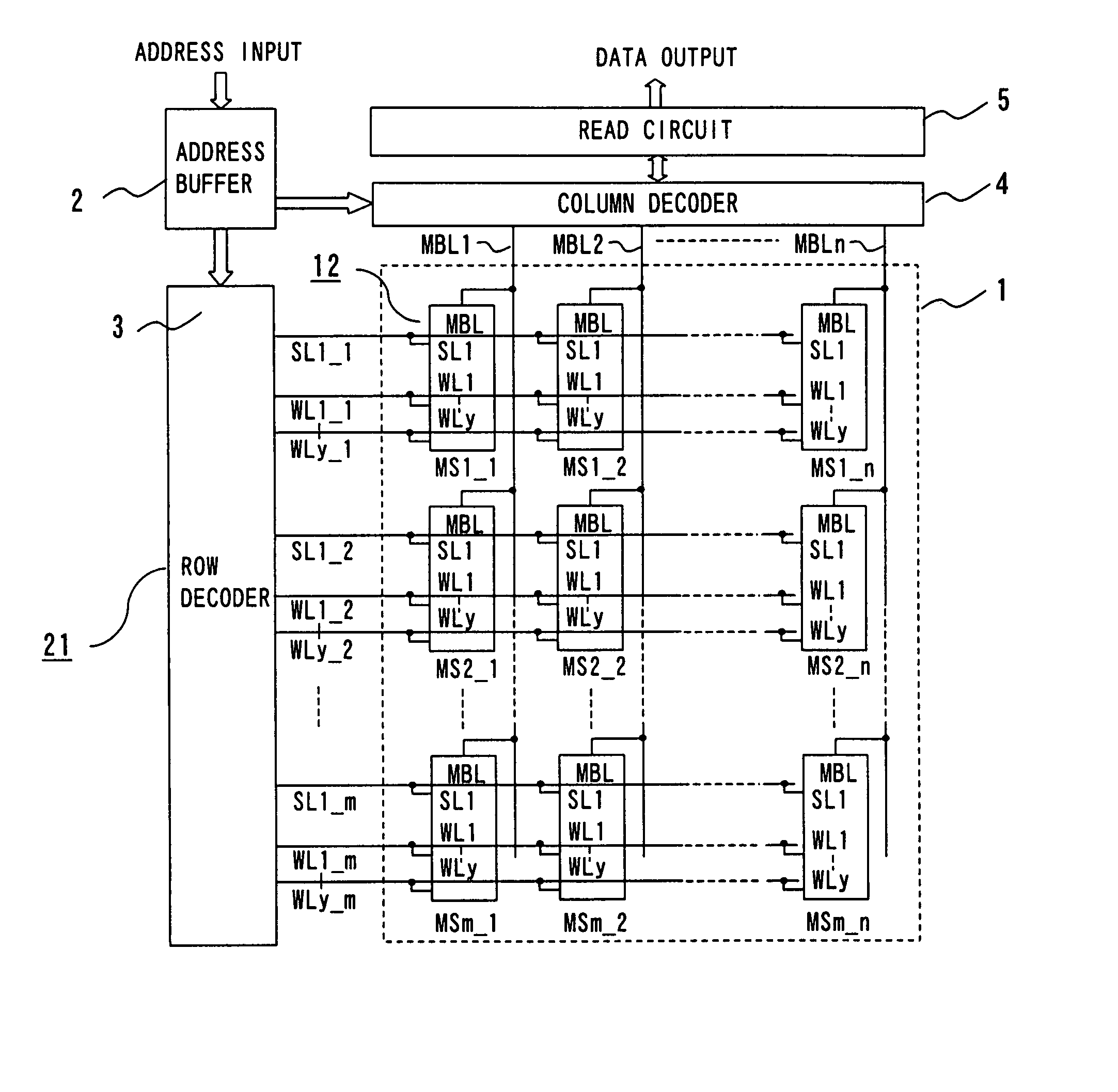

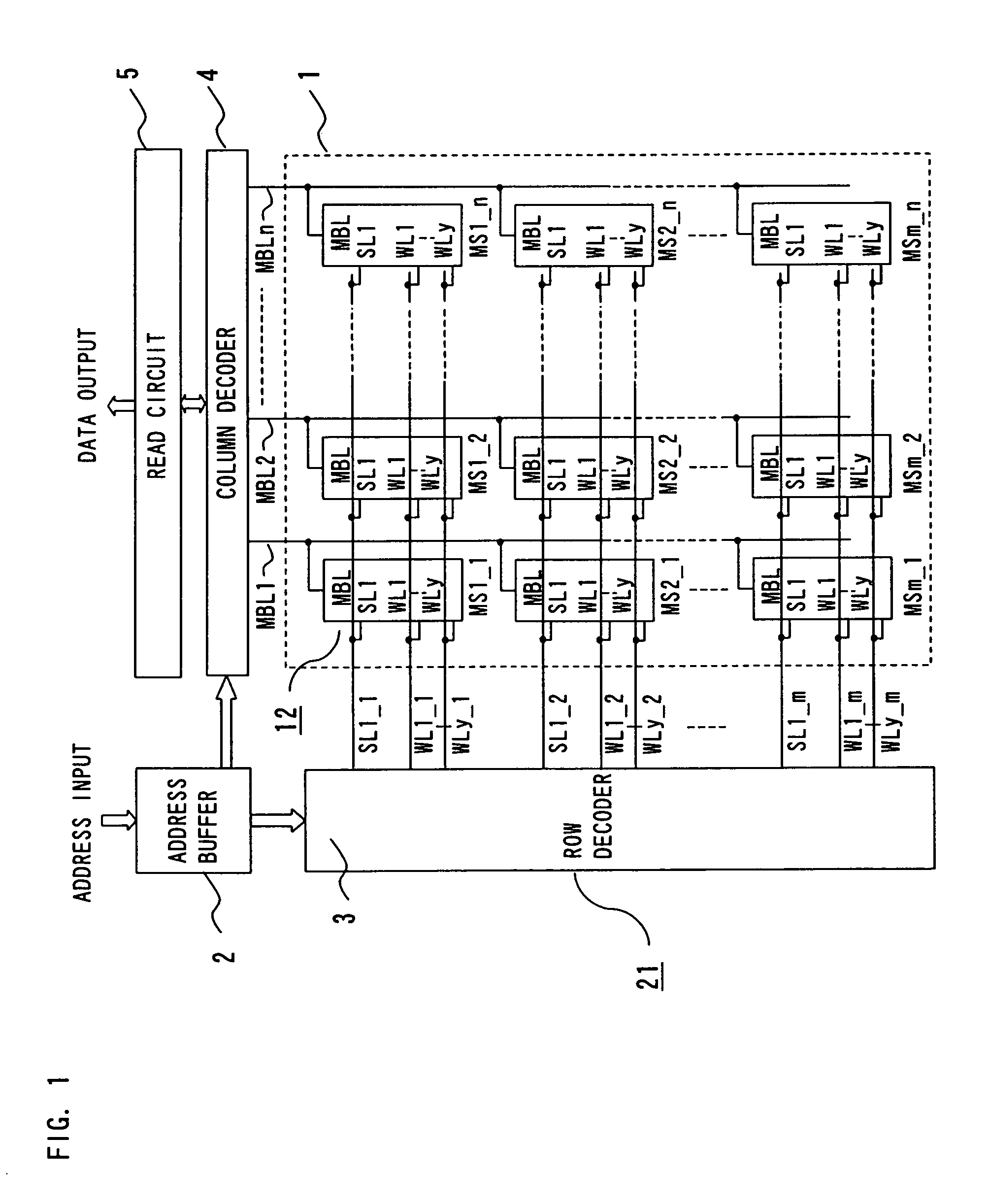

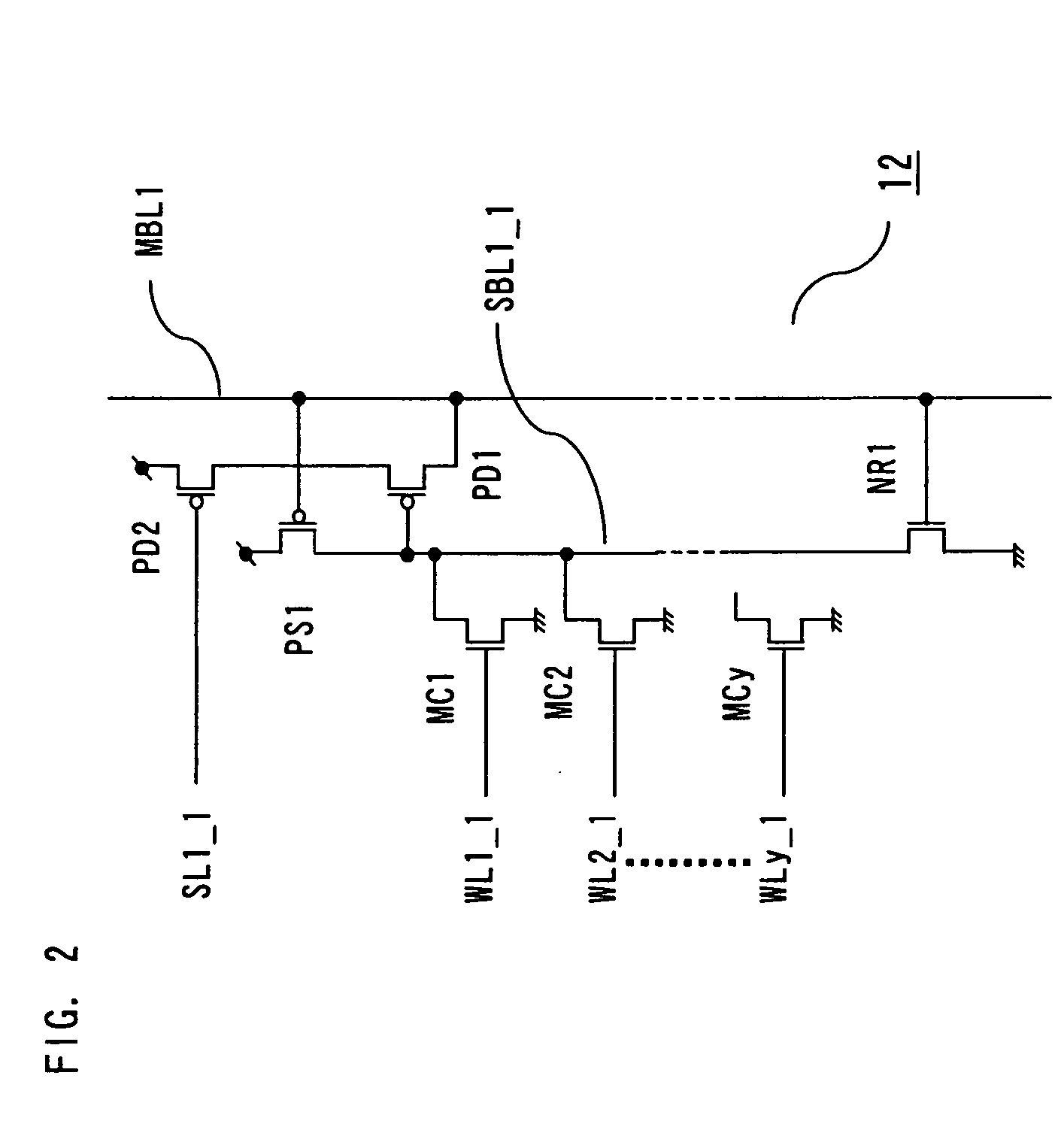

Semiconductor memory device

ActiveUS20060239109A1Favourable costLow voltageRead-only memoriesDigital storageSemiconductor memorySemiconductor

A semiconductor memory device is provided which has a hierarchical bit line structure and can perform a high-speed read operation even with a low voltage. A subarray 12 includes a first MOS transistor PD1 for charging a main bit line MBL1 and a second MOS transistor PS1 for charging a sub-bit line SBL1—1. The source electrode of the second MOS transistor PS1 is connected to a power source voltage, and the source electrode of the first MOS transistor PD1 is connected via a fourth MOS transistor PD2 to the power source voltage. Since there is not a resistance between the main bit line MBL1 and the sub-bit line SBL1—1, which is present if a transistor is used to achieve conduction therebetween, discharging of the main bit line and charging of the sub-bit line can be performed with high speed.

Owner:SOCIONEXT INC

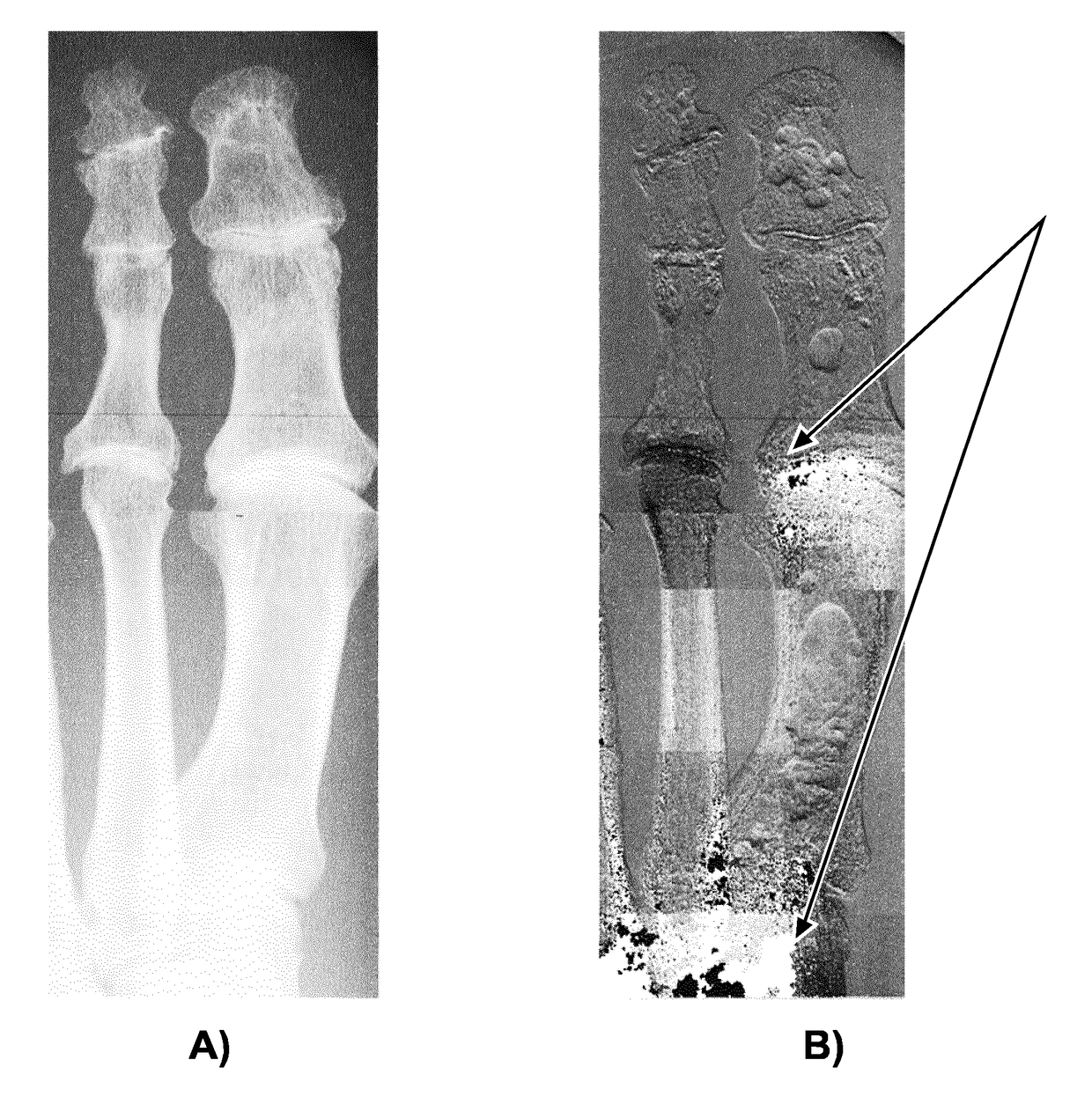

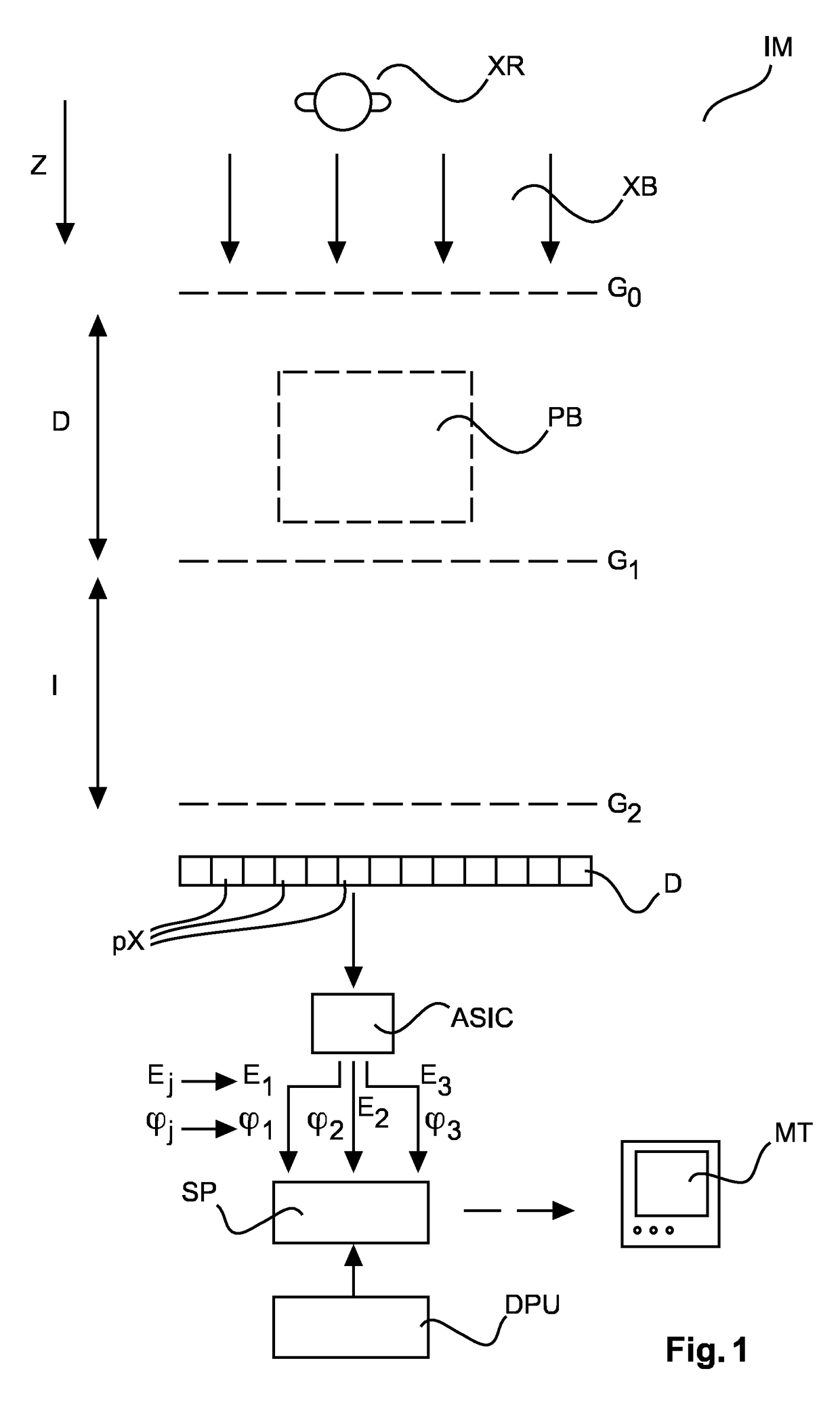

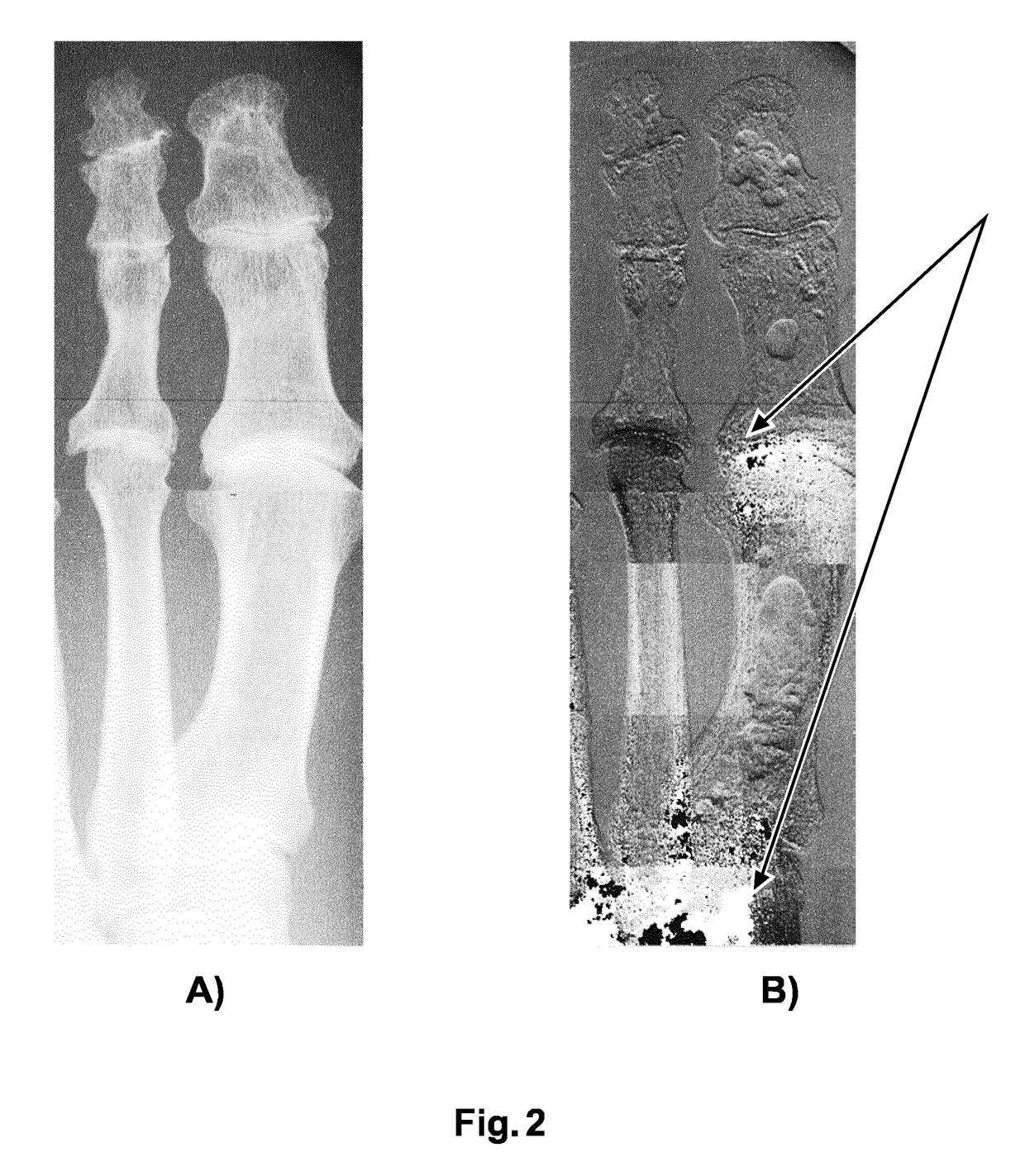

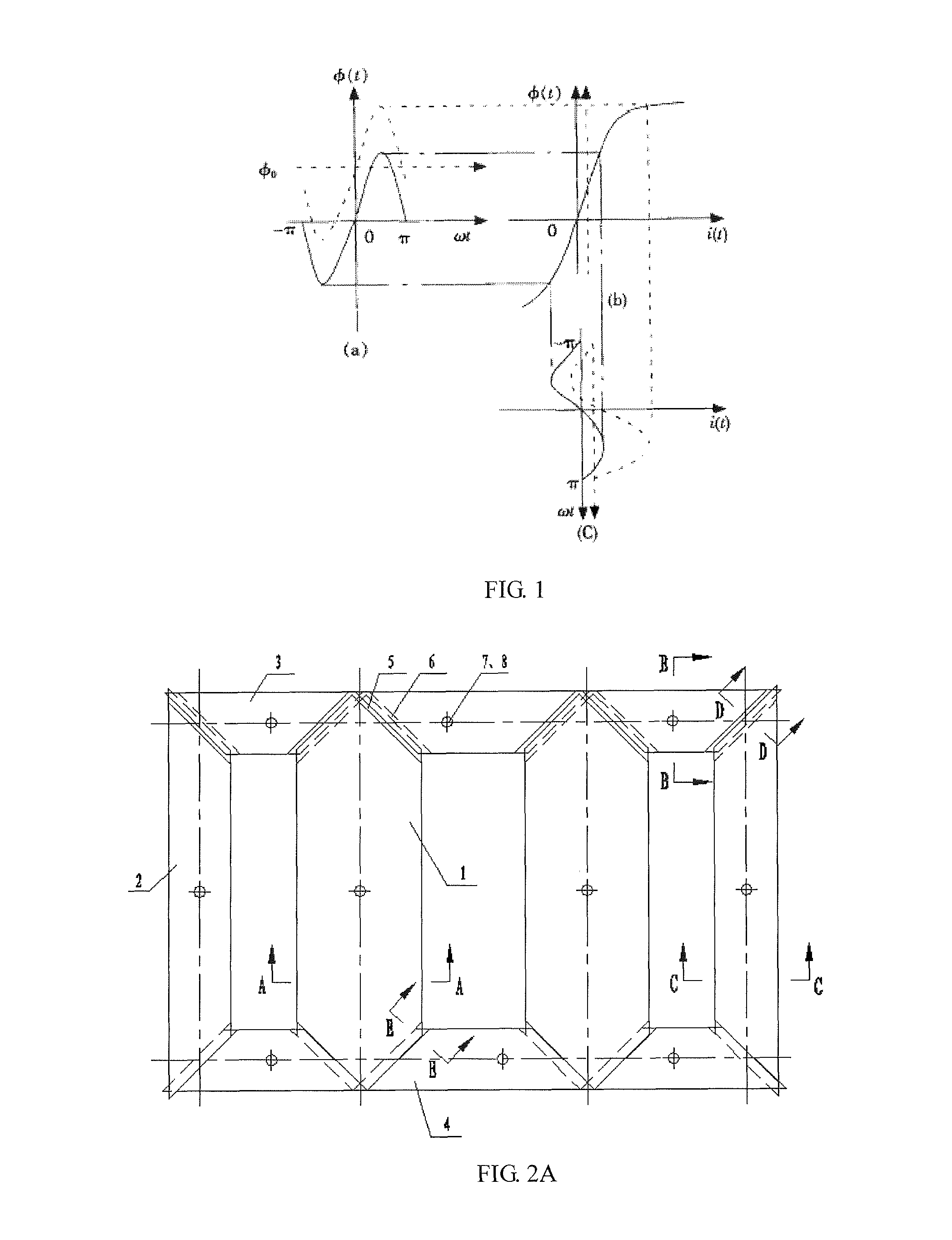

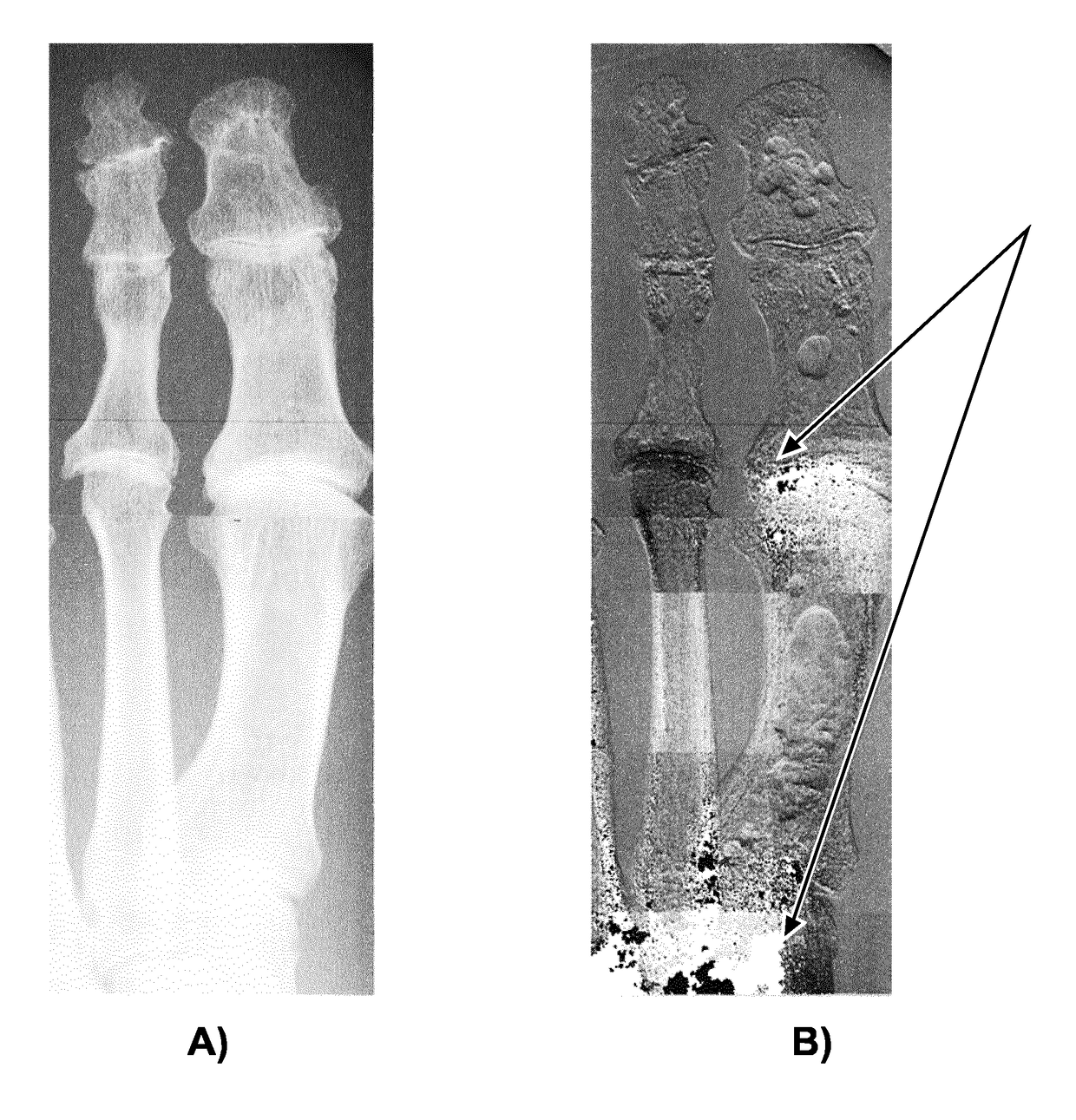

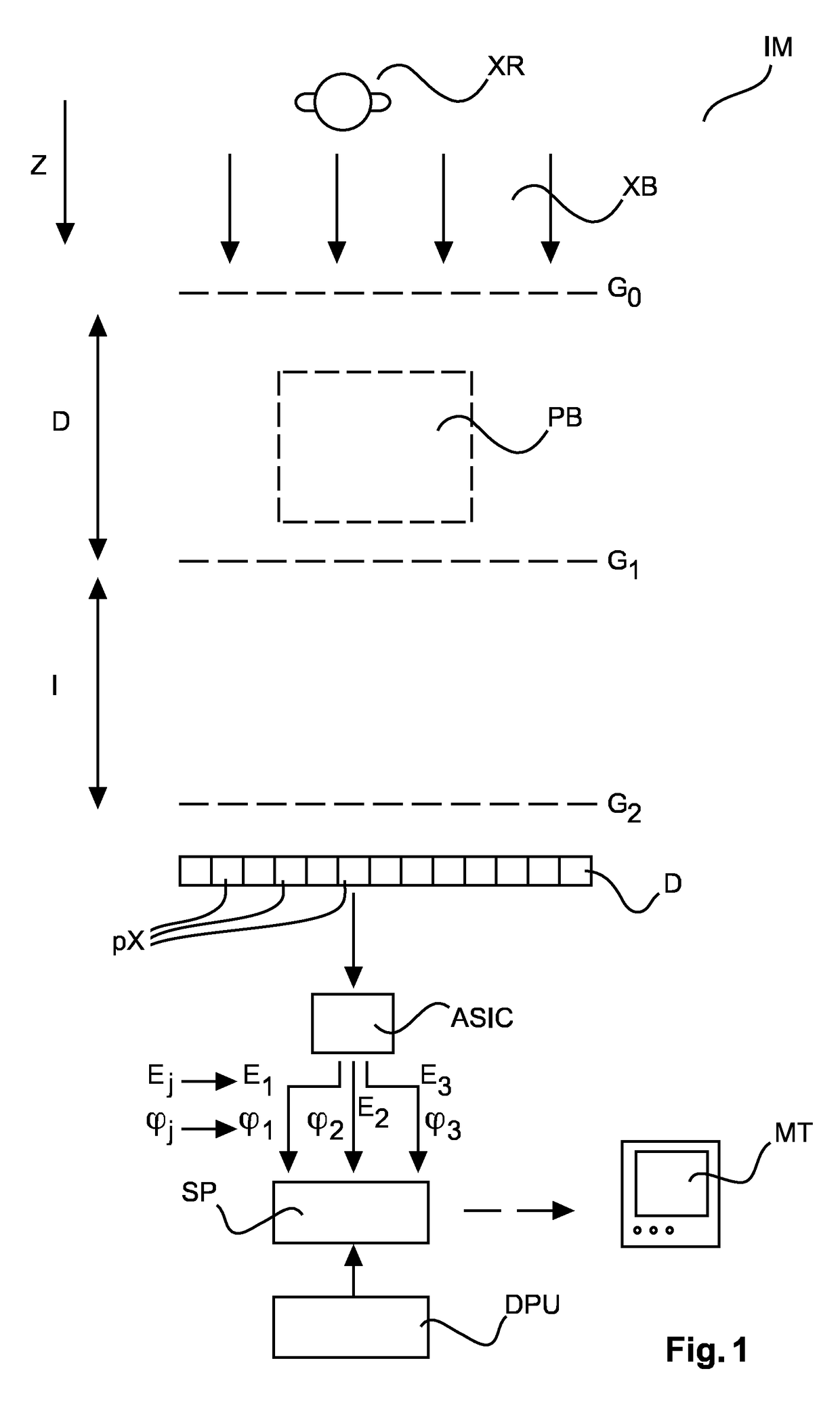

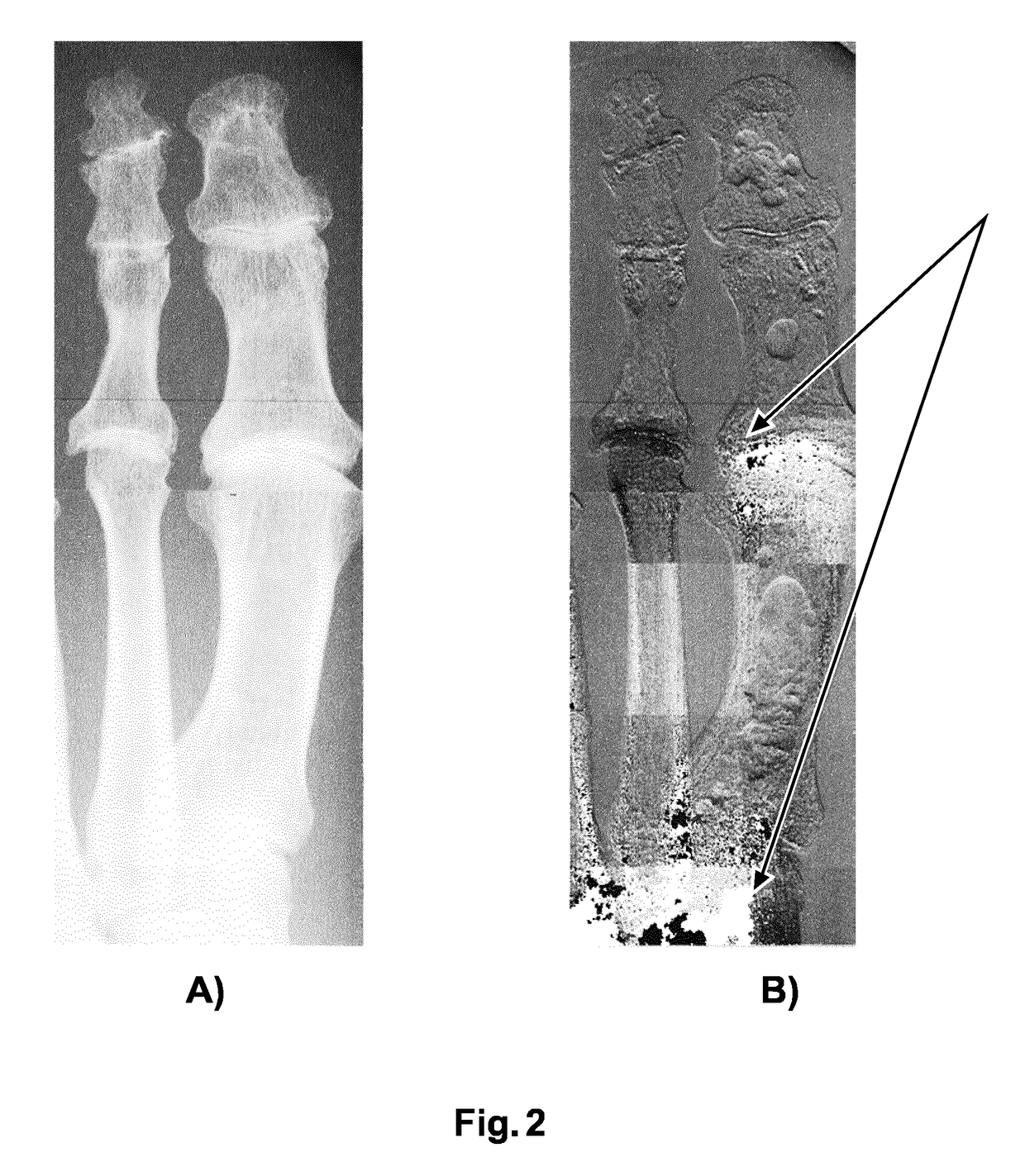

Bias-free regularization for spectral phase-unwrapping in differential phase contrast imaging

ActiveUS20170091933A1Improve accuracyAvoiding orImage enhancementReconstruction from projectionPhase shiftedPhase unwrapping

Methods and related apparatus (SP) to correct phase shift image data for phase wrapping artifacts. The data is detected at a detector (D) of an imaging system (IM) including interferometric equipment (G0, G1, G2). In a phase unwrapping method that involves optimizing an objective function with regularization, a two-sage approach is proposed. The measured data is processed in one stage with regularization and in the other stage without regularization. This allows improving the accuracy of the corrected (phase unwrapped) phase shift data because an undesirable bias caused by the regularization can be avoided.

Owner:KONINKLJIJKE PHILIPS NV

Semiconductor device and method of producing same

InactiveUS7718498B2Reduced characteristicsReduce impurity concentrationTransistorTelevision system detailsSemiconductorImpurity

A semiconductor device suitable for a source-follower circuit, provided with a gate electrode formed on a semiconductor substrate via a gate insulation film, a first conductivity type layer formed in the semiconductor substrate under a conductive portion of the gate electrode and containing a first conductivity type impurity, first source / drain regions of the first conductivity type impurity formed in the semiconductor substrate and extended from edge portions of the gate electrode, and second source / drain regions having a first conductivity type impurity concentration lower than that in the first source / drain regions and formed adjoining the gate insulation film and the first source / drain regions in the semiconductor substrate so as to overlap portions of the conductive portion of the gate electrode.

Owner:SONY SEMICON SOLUTIONS CORP

Method for achieving converter transformer for DC magnetic bias

ActiveUS9142349B2Eliminate bias effectsReduce impactInductances/transformers/magnets manufactureElectromagnetsTransformerMagnet

Owner:TBEA SHENYANG TRANSFORMER GRP CO LTD

Method for fabricating thin film transistors

InactiveUS20080254578A1Promote electric performanceIncrease uniformitySolid-state devicesSemiconductor/solid-state device manufacturingPhysicsLaser annealing

A method for fabricating thin film transistors is disclosed. An amorphous silicon film is formed on a substrated and selectively irradiated with a laser beam for lateral growth to form a plurality of polysilicon regions. The whole surface of the substrate is then oxidized and irradiated with exicer laser annealing.

Owner:CHUNGHWA PICTURE TUBES LTD

Chemical oxidation technology of gold film of porous ZM6 magnesium alloy spare part

InactiveCN109161878AReduce the amount of feedErosion mitigationMetallic material coating processesGold filmSurface finishing

The invention belongs to the field of surface treatment of a magnesium alloy spare part and particularly relates to a chemical oxidation technology of a gold film of a porous ZM6 magnesium alloy sparepart. The technology comprises the following steps: step I: preparing ZM6 magnesium alloy chemical oxidation tank liquor, step II: performing chemical oxidation, and step III: detecting dimensional precision of pores before and after the chemical oxidation. According to the technology, contents of ingredients of the tank liquor are adjusted; an acid mist inhibitor preventing volatilization of acetic acid during heating is added; the gold film can be obtained by oxidizing the porous ZM6 magnesium alloy spare part with a chemical oxidation solution formula; a film layer is uniform; the obtainedgold film layer is high in repeatability during testing; the influence on pore precision is small; and the influence of the surface treatment on the dimension and appearance of the porous magnesium alloy spare part is comprehensively reduced.

Owner:BEIJING XINGHANG MECHANICAL ELECTRICAL EQUIP

Bias-free regularization for spectral phase-unwrapping in differential phase contrast imaging

ActiveUS10037600B2Avoiding orEliminate bias effectsImage enhancementReconstruction from projectionPhase shiftedPhason

Methods and related apparatus (SP) to correct phase shift image data for phase wrapping artifacts. The data is detected at a detector (D) of an imaging system (IM) including interferometric equipment (G0, G1, G2). In a phase unwrapping method that involves optimizing an objective function with regularization, a two-sage approach is proposed. The measured data is processed in one stage with regularization and in the other stage without regularization. This allows improving the accuracy of the corrected (phase unwrapped) phase shift data because an undesirable bias caused by the regularization can be avoided.

Owner:KONINKLJIJKE PHILIPS NV

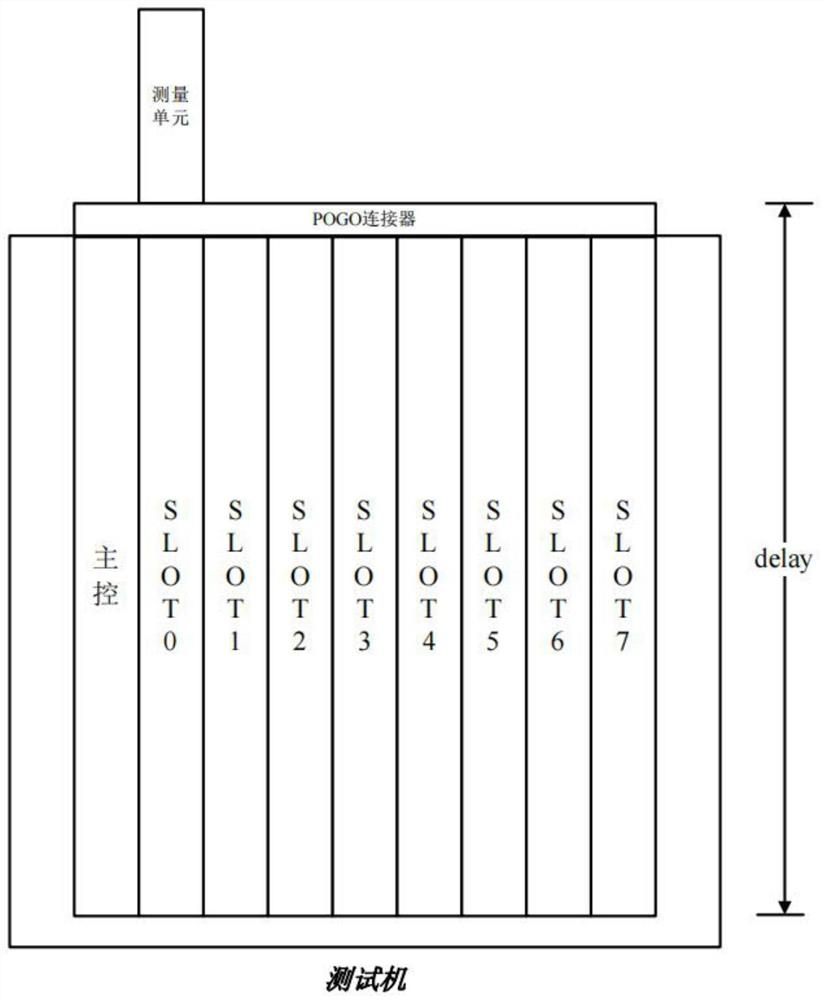

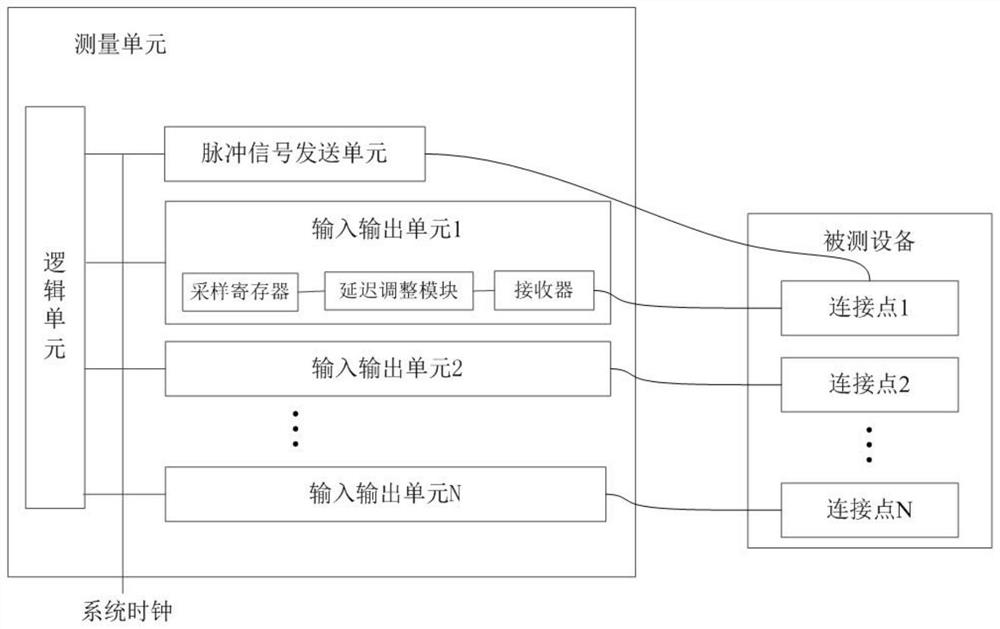

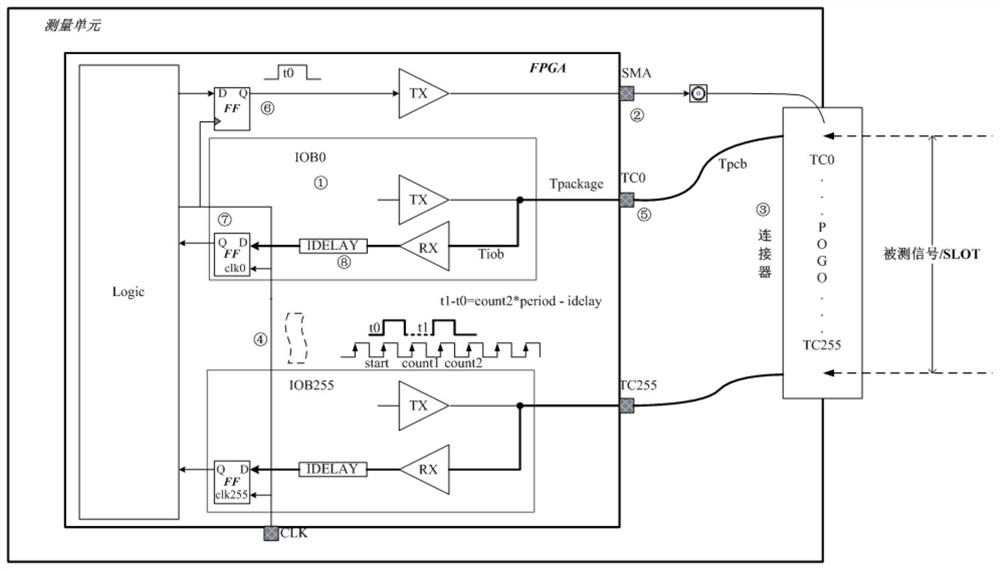

FPGA measuring unit and channel delay compensation method and device based on FPGA measuring unit

PendingCN113986633AEliminate bias effectsHigh measurement accuracyFunctional testingFaulty hardware testing methodsEngineeringReceiver

The invention provides an FPGA measuring unit and a channel delay compensation method and device based on the FPGA measuring unit. The measuring unit comprises a logic unit, a pulse signal sending unit and a plurality of input and output units, wherein the pulse signal sending unit and the input and output units are connected with the logic unit. Each input and output unit comprises a receiver, a delay adjustment module and a sampling register which are connected in sequence; the sampling register and the pulse signal sending unit are connected with the same system clock; the pulse signal sending unit is connected with a plurality of connection points in the tested equipment; the plurality of connection points are respectively connected with the plurality of receivers in a one-to-one correspondence manner; a complete path from one connection point to one sampling register is a channel; and the delay adjustment module is used for compensating delay deviation between the channels. According to the invention, the delay among multiple channels can be accurately compensated, so that the deviation influence of the measurement unit itself is eliminated, and the self-calibration of the measurement unit is completed.

Owner:HANGZHOU CHANGCHUAN TECH CO LTD

Fluxgate High Current Sensor Based on Digital Second Harmonic Detection and Ripple Compensation

ActiveCN110988430BEliminate bias effectsImprove measurement accuracyVoltage/current isolationMeasurement using digital techniquesAc componentsWave detection

The invention provides a fluxgate high current sensor based on digital second harmonic wave detection and ripple compensation, which is characterized in that it includes a low frequency measurement coil, a feedback coil and a high frequency measurement coil wound on a ring magnetic core. The invention can simultaneously measure the DC component and the AC component in the current, and has high measurement accuracy, good linearity and high temperature stability. The beneficial effects are as follows: (1) the sensor has both digital output and analog output; (2) ) Zero drift digital correction to reduce the influence of the output current bias of the device brought by the analog circuit; (3) Suppress the output ripple.

Owner:SHANGHAI TECH UNIV +1

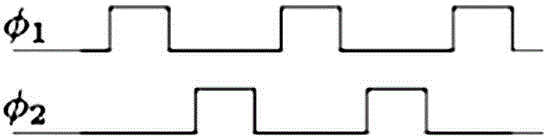

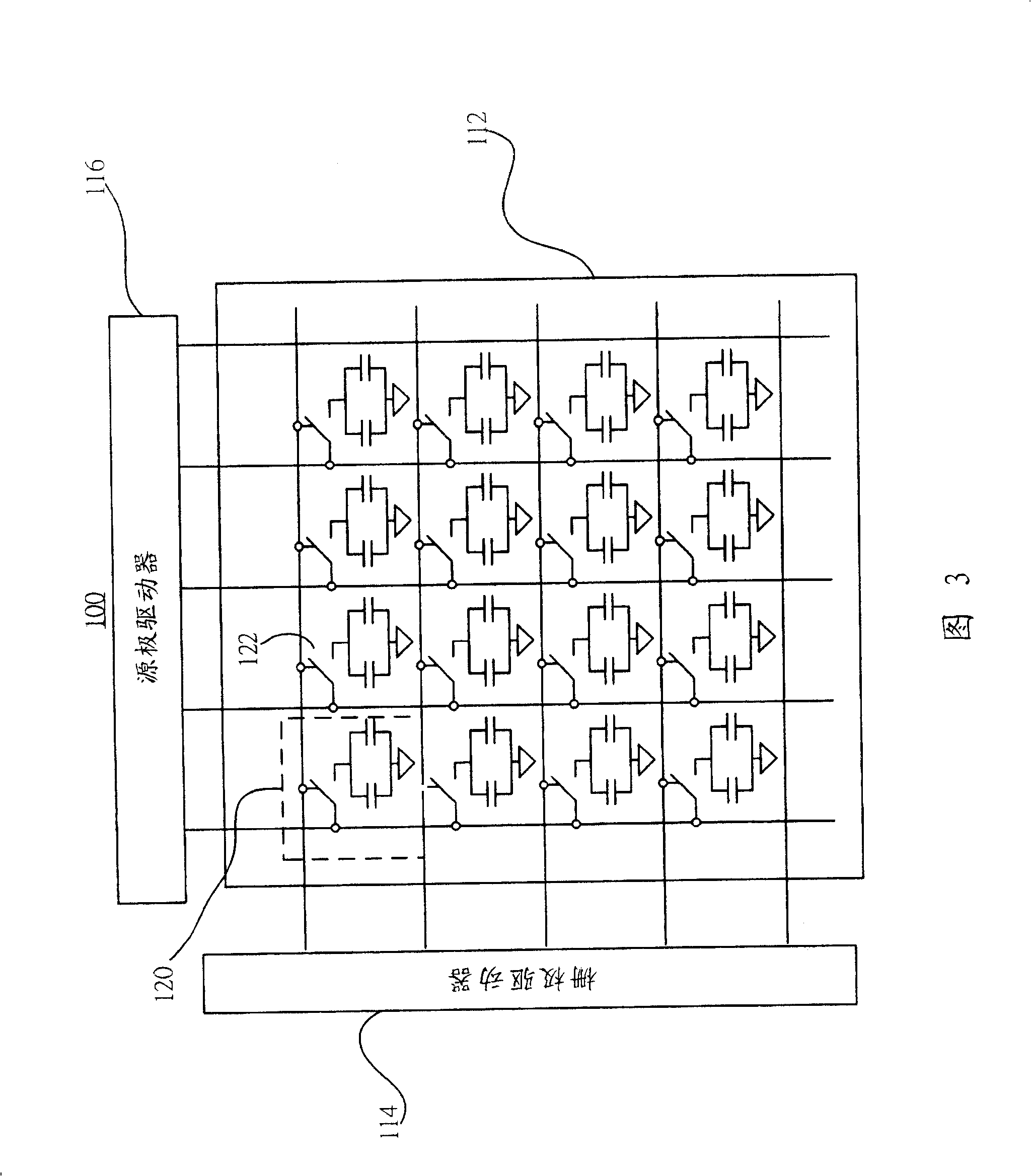

Shifting register reducing bias voltage effect

ActiveCN100437831CEliminate bias effectsImprove AC signal coupling effectStatic indicating devicesDigital storageShift registerProcessor register

The related shift register comprises multilevel registers, every of which includes an output circuit to output a first drive signal, a first switch circuit to draw the circuit to a low potential before the drive signal, and a second switch circuit for signal receiving. Wherein, the first circuit applies potential of the input signal to hold charge in its parasitic capacitor and keep opening before the drive signal.

Owner:AU OPTRONICS CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com