Patents

Literature

122results about How to "Minimize work" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

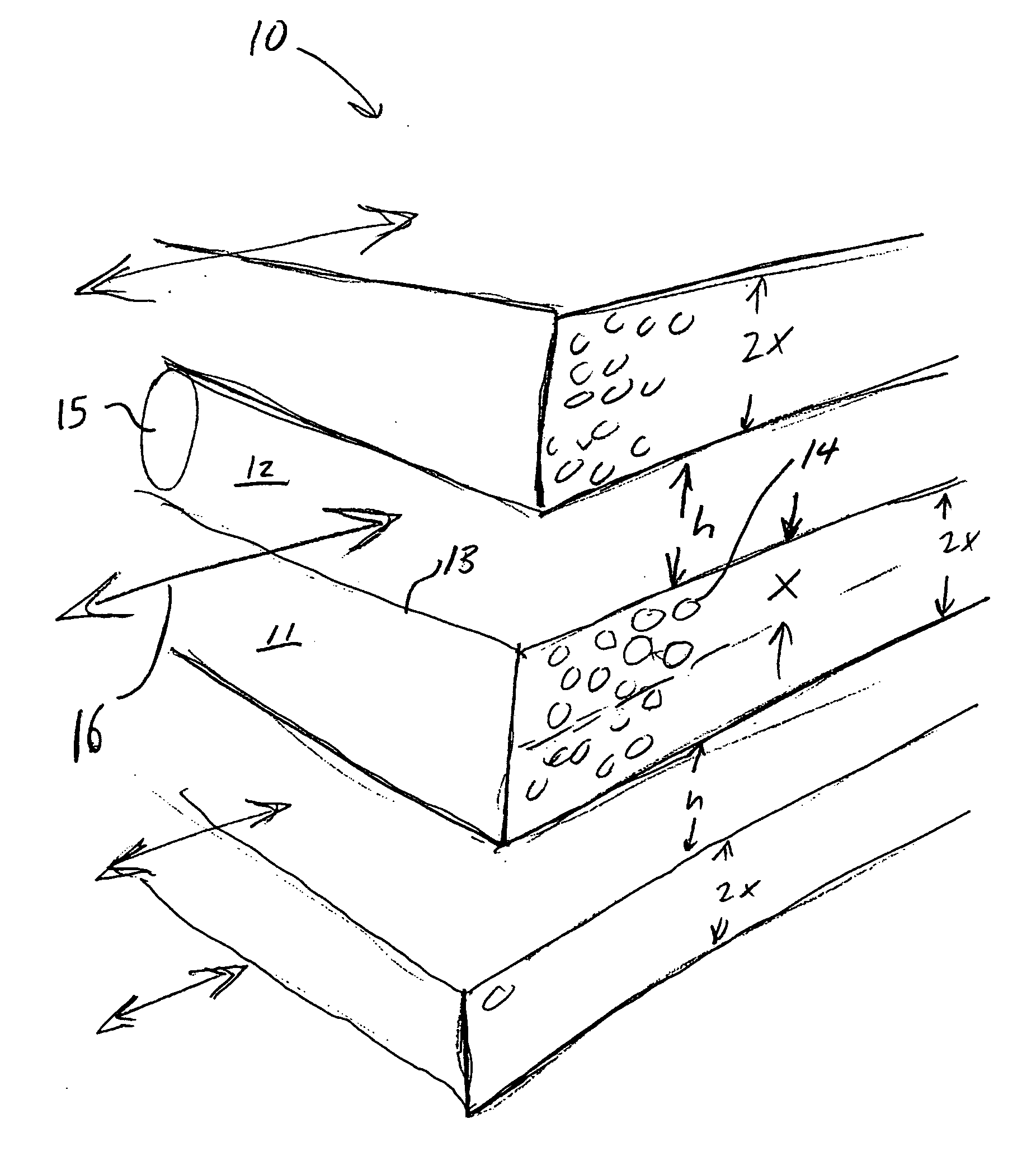

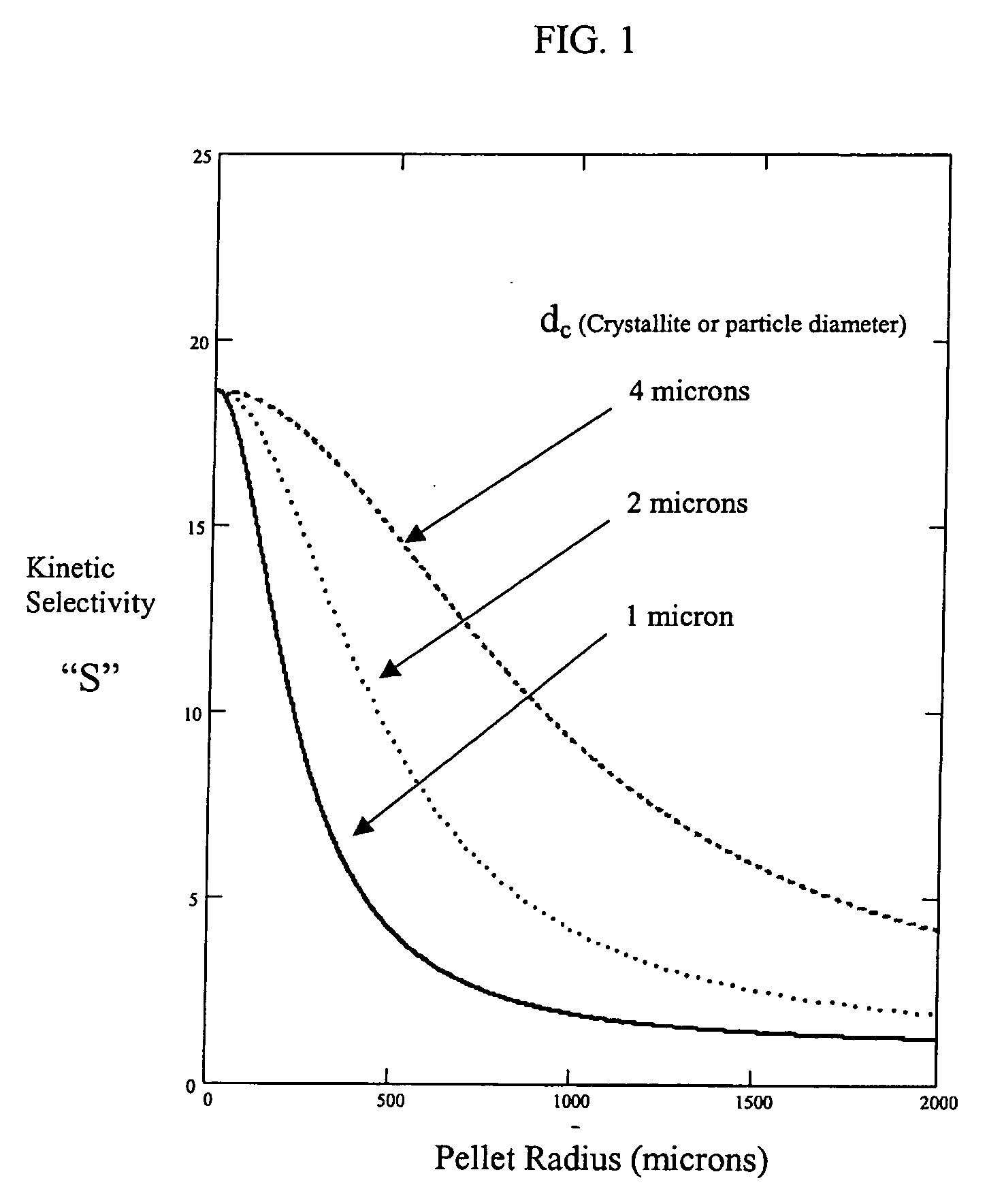

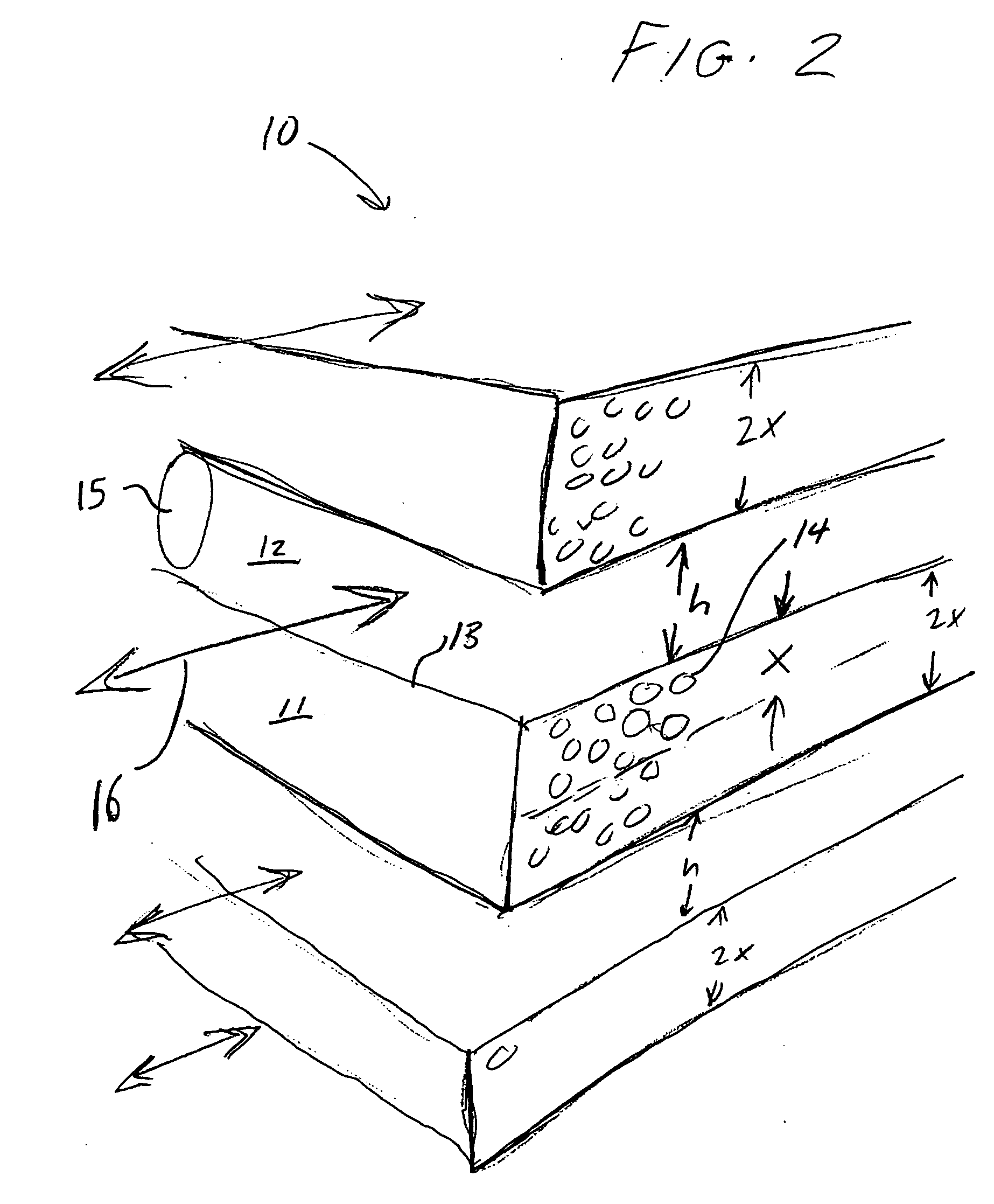

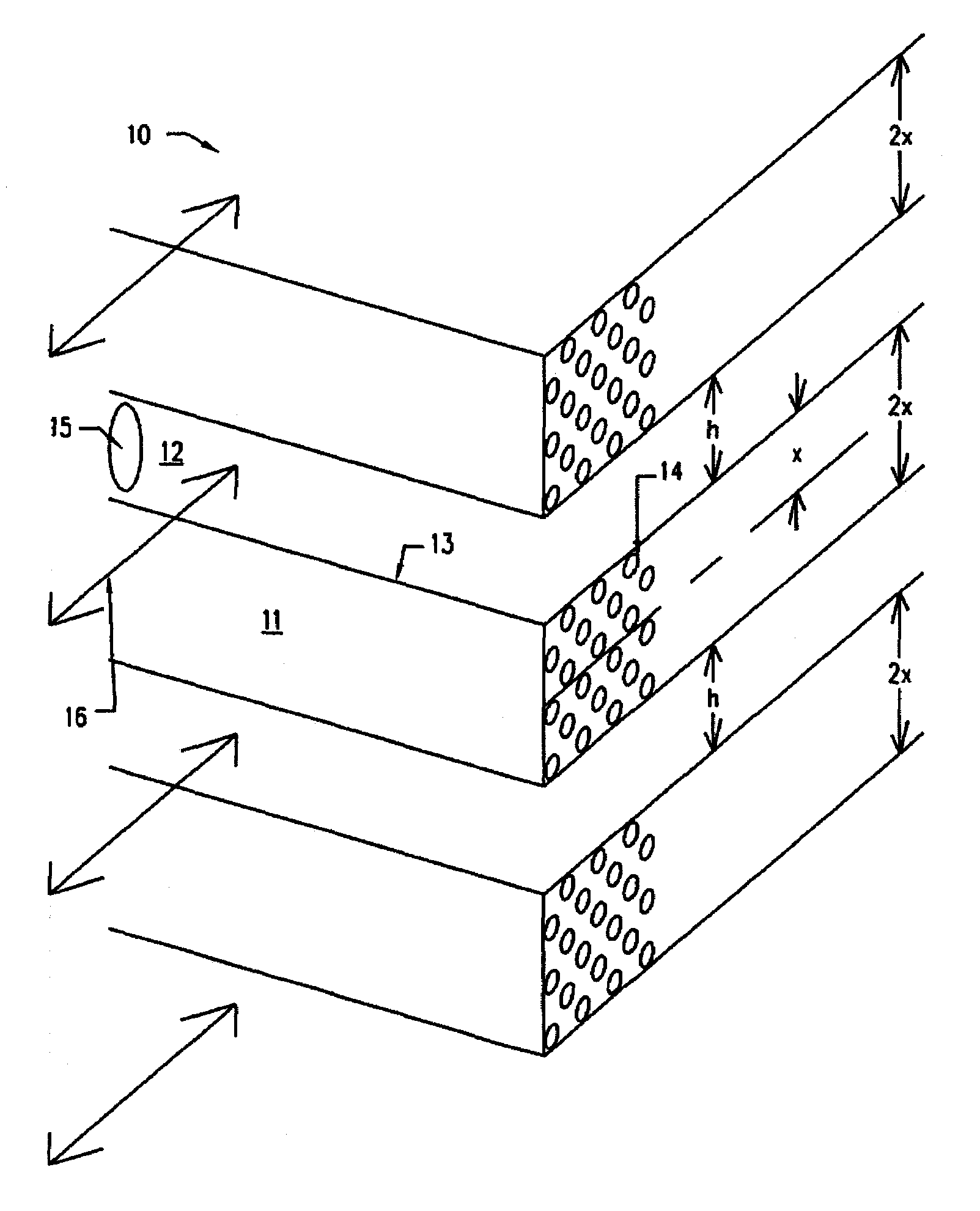

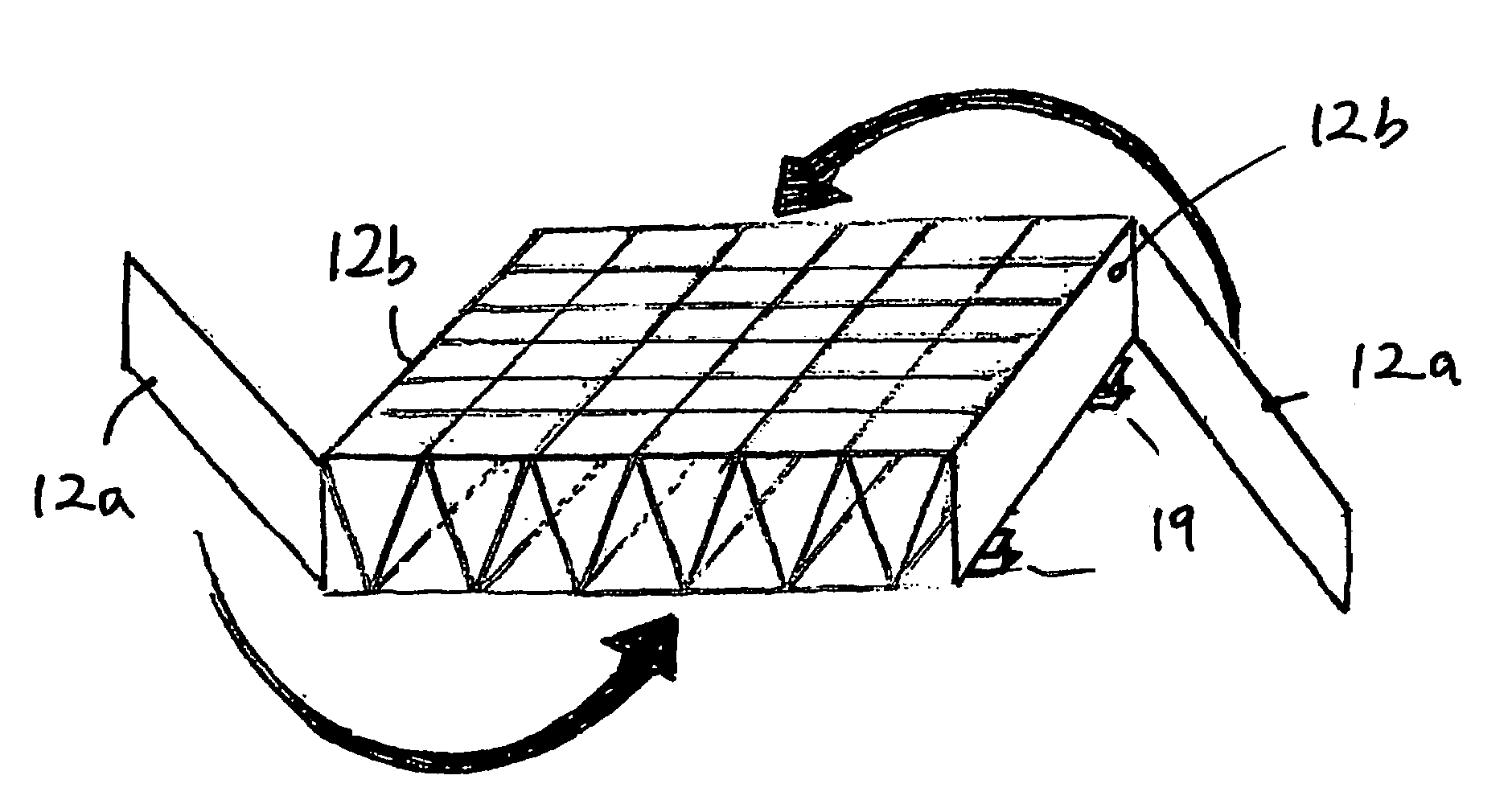

Engineered adsorbent structures for kinetic separation

ActiveUS20060169142A1Easy to controlHigh selectivityGas treatmentMethane captureProduction rateSorbent

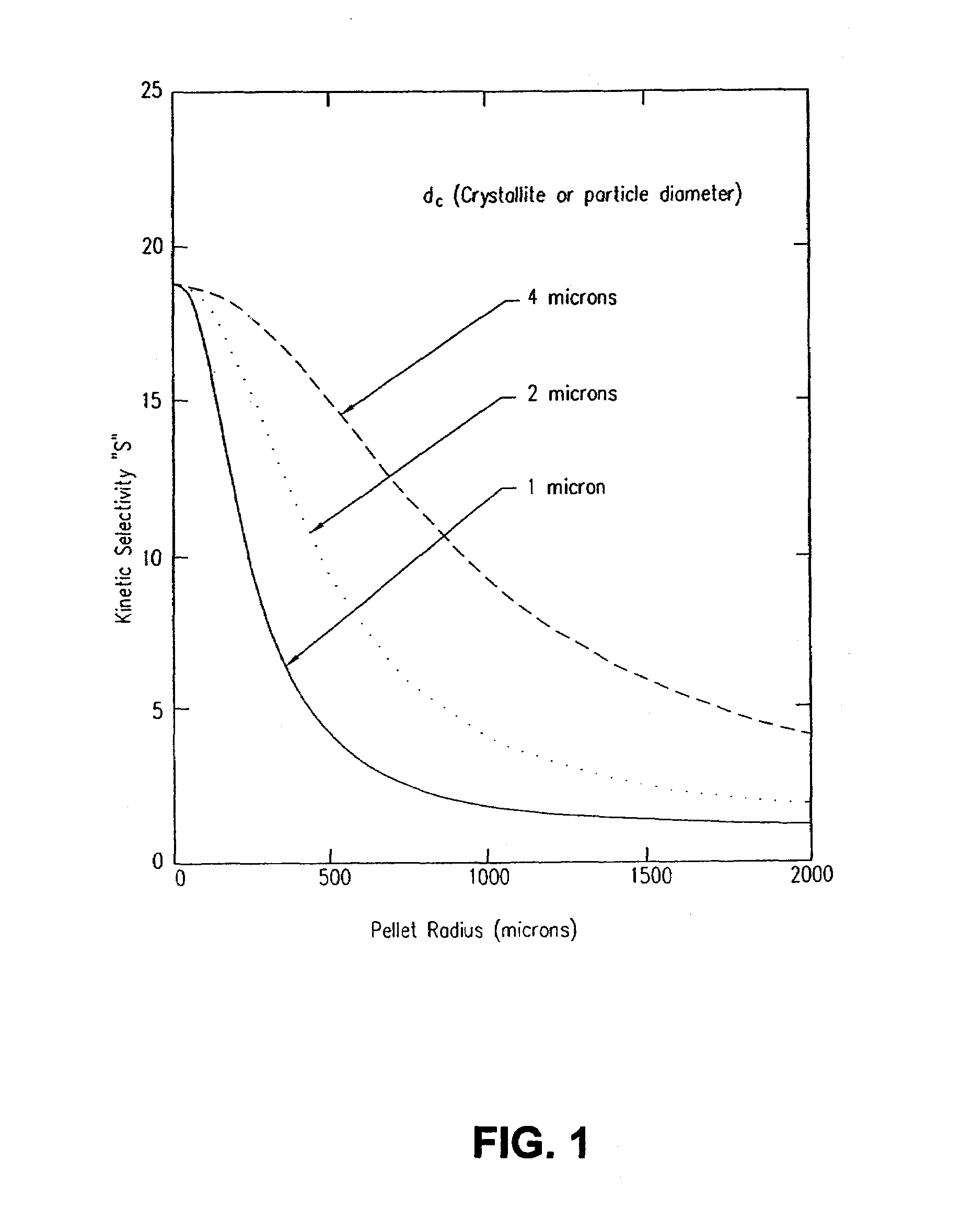

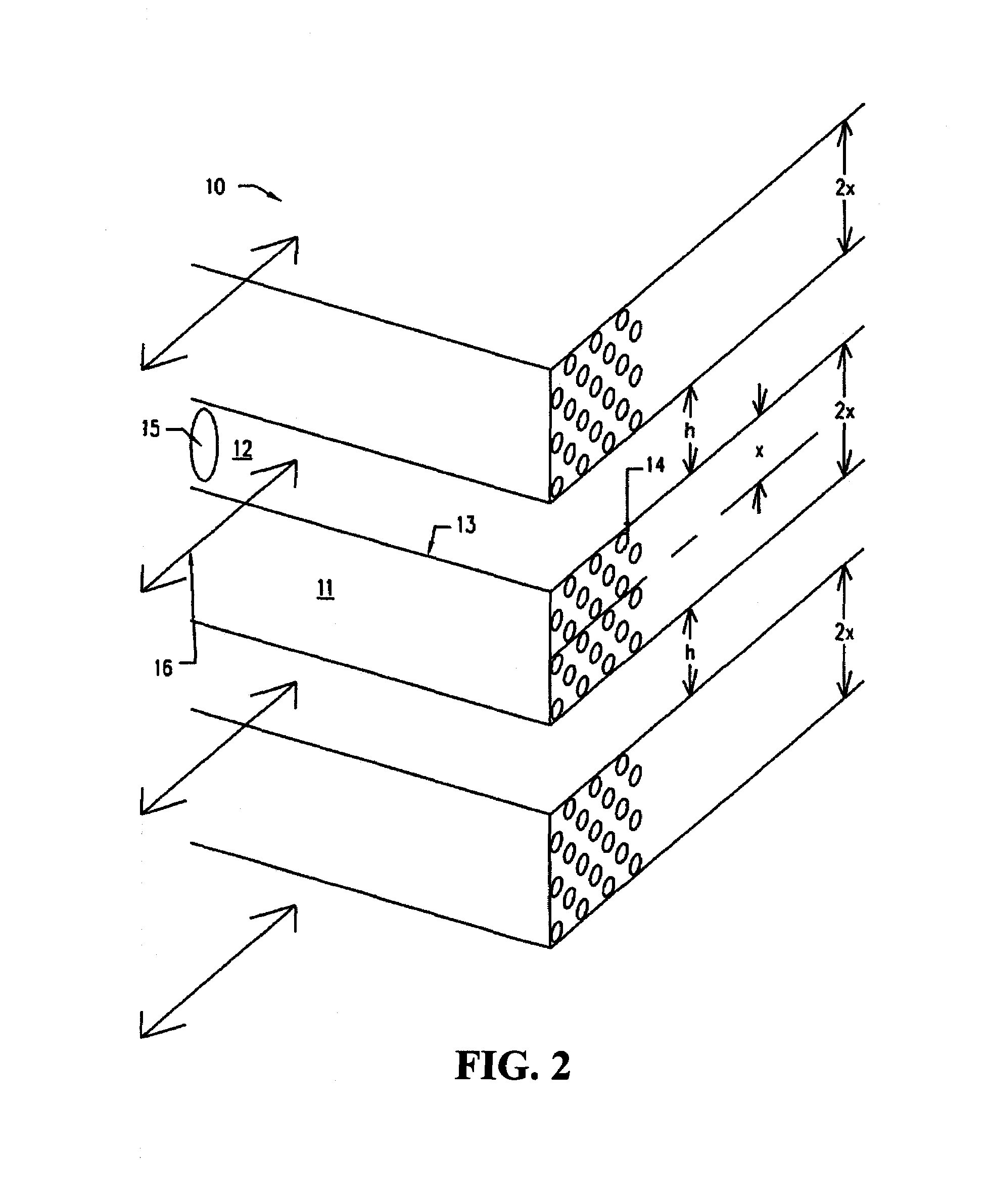

Improved adsorbent sheet based parallel passage adsorbent structures for enhancing the kinetic selectivity of certain kinetic-controlled adsorption processes, such as PSA, TSA and PPSA processes, and combinations thereof, are provided. The enhancements in kinetic selectivity made possible through the implementation of the present inventive improved adsorbent structures may unexpectedly enable significant intensification of selected kinetic adsorption processes relative to attainable performance with conventional adsorbent materials in beaded or extruded form. Such process intensification enabled by the present inventive adsorbent structures may provide for increased adsorption cycle frequencies, and increased gas flow velocities within the adsorbent beds, which may increase the productivity and / or recovery of a kinetic adsorption system incorporating the inventive adsorbent structures.

Owner:AIR PROD & CHEM INC

Engineered adsorbent structures for kinetic separation

ActiveUS7645324B2High selectivityIncrease cycle frequencyGas treatmentMethane captureProduction rateSorbent

Improved adsorbent sheet based parallel passage adsorbent structures for enhancing the kinetic selectivity of certain kinetic-controlled adsorption processes, such as PSA, TSA and PPSA processes, and combinations thereof, are provided. The enhancements in kinetic selectivity made possible through the implementation of the present inventive improved adsorbent structures may unexpectedly enable significant intensification of selected kinetic adsorption processes relative to attainable performance with conventional adsorbent materials in beaded or extruded form. Such process intensification enabled by the present inventive adsorbent structures may provide for increased adsorption cycle frequencies, and increased gas flow velocities within the adsorbent beds, which may increase the productivity and / or recovery of a kinetic adsorption system incorporating the inventive adsorbent structures.

Owner:AIR PROD & CHEM INC

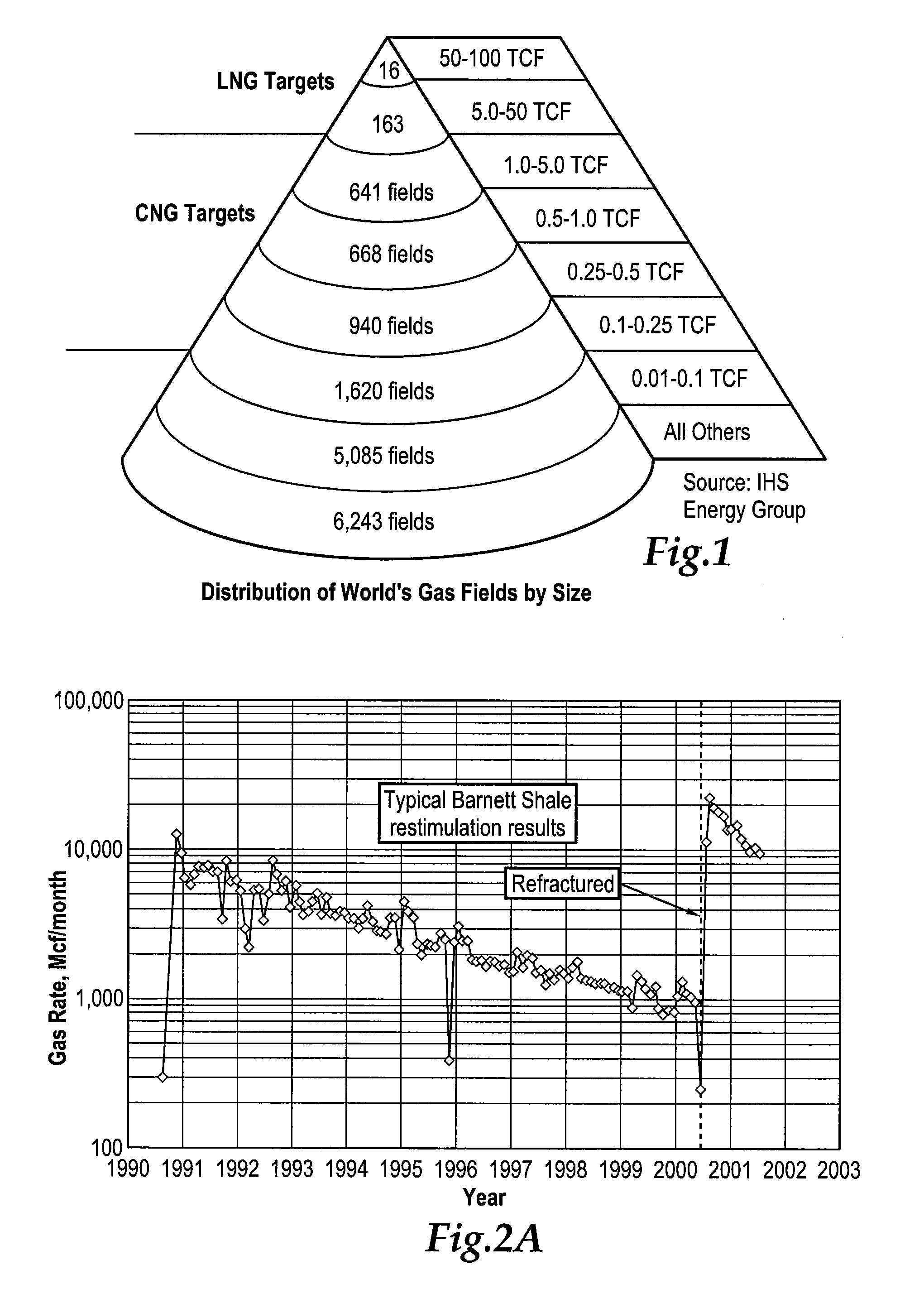

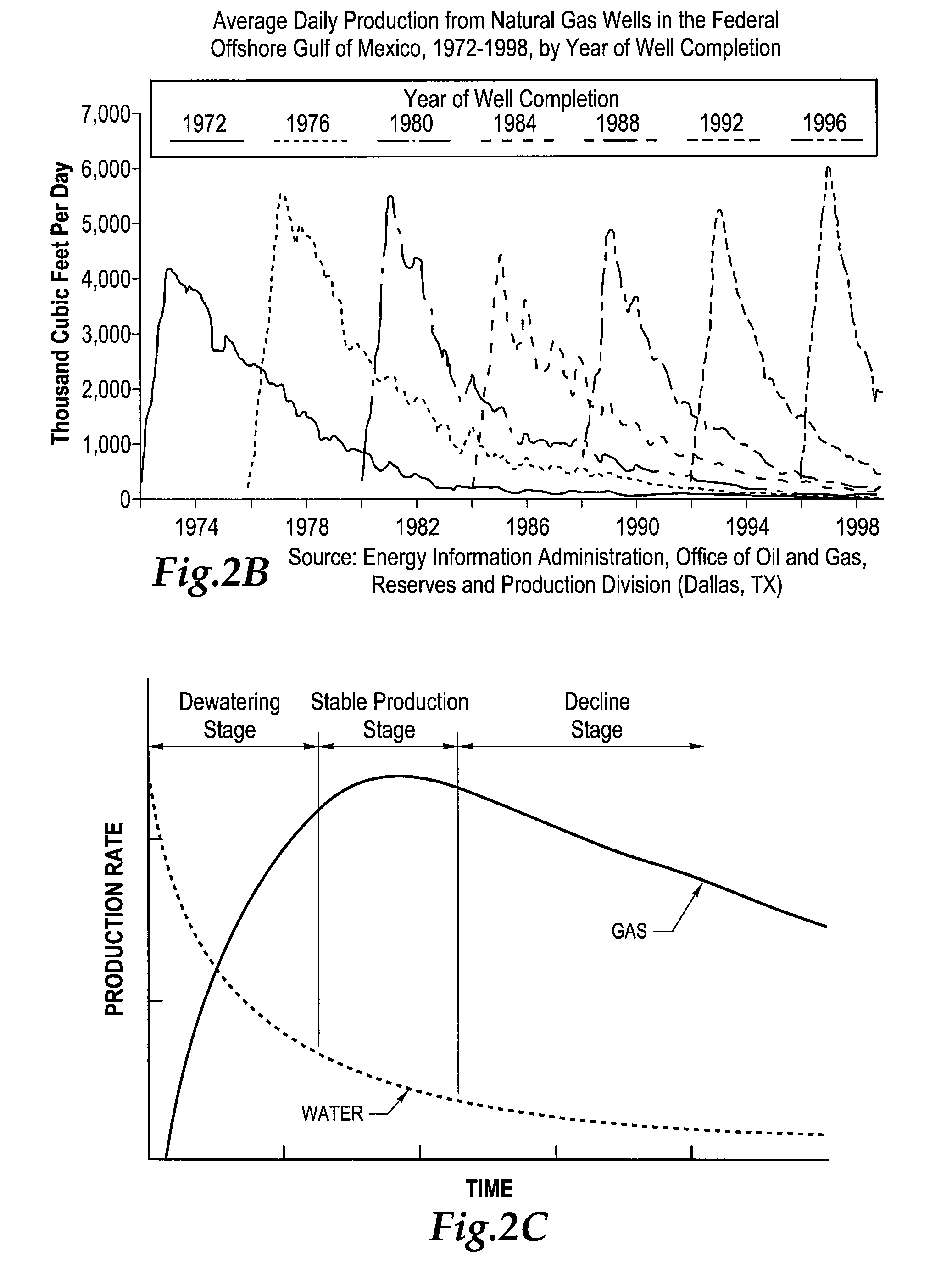

Tracking feedstock production with micro scale gas-to-liquid units

ActiveUS8293805B2Minimize workOrganic compound preparationOxygen compounds preparation by reductionCarbon numberLiquid product

A method of tracking production from an NG source that includes the steps of providing one or more micro-scale GTL units, feeding NG from the source to the micro-scale GTL units, operating the micro-scale GTL units and adjusting the number of micro-scale GTL units employed to track or match the production from the source is provided. In some aspects of the invention, the micro-scale GTL unit includes both syngas manufacture and liquid product synthesis. The liquid product synthesis step may produce methanol, mixed higher carbon number alcohols, dimethyl ether, Fischer-Tropsch liquids, and / or any combination of these products.

Owner:SCHLUMBERGER TECH CORP

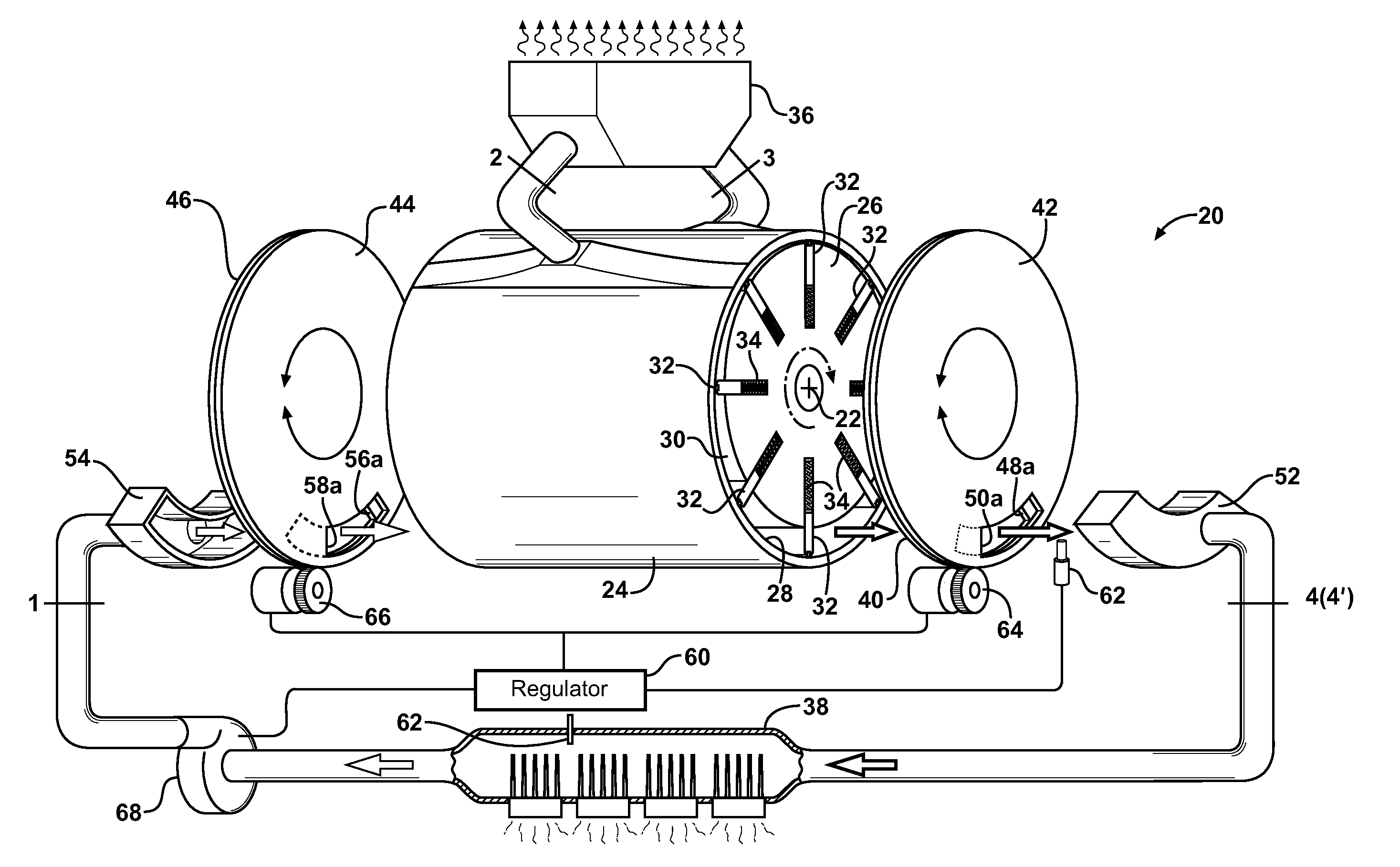

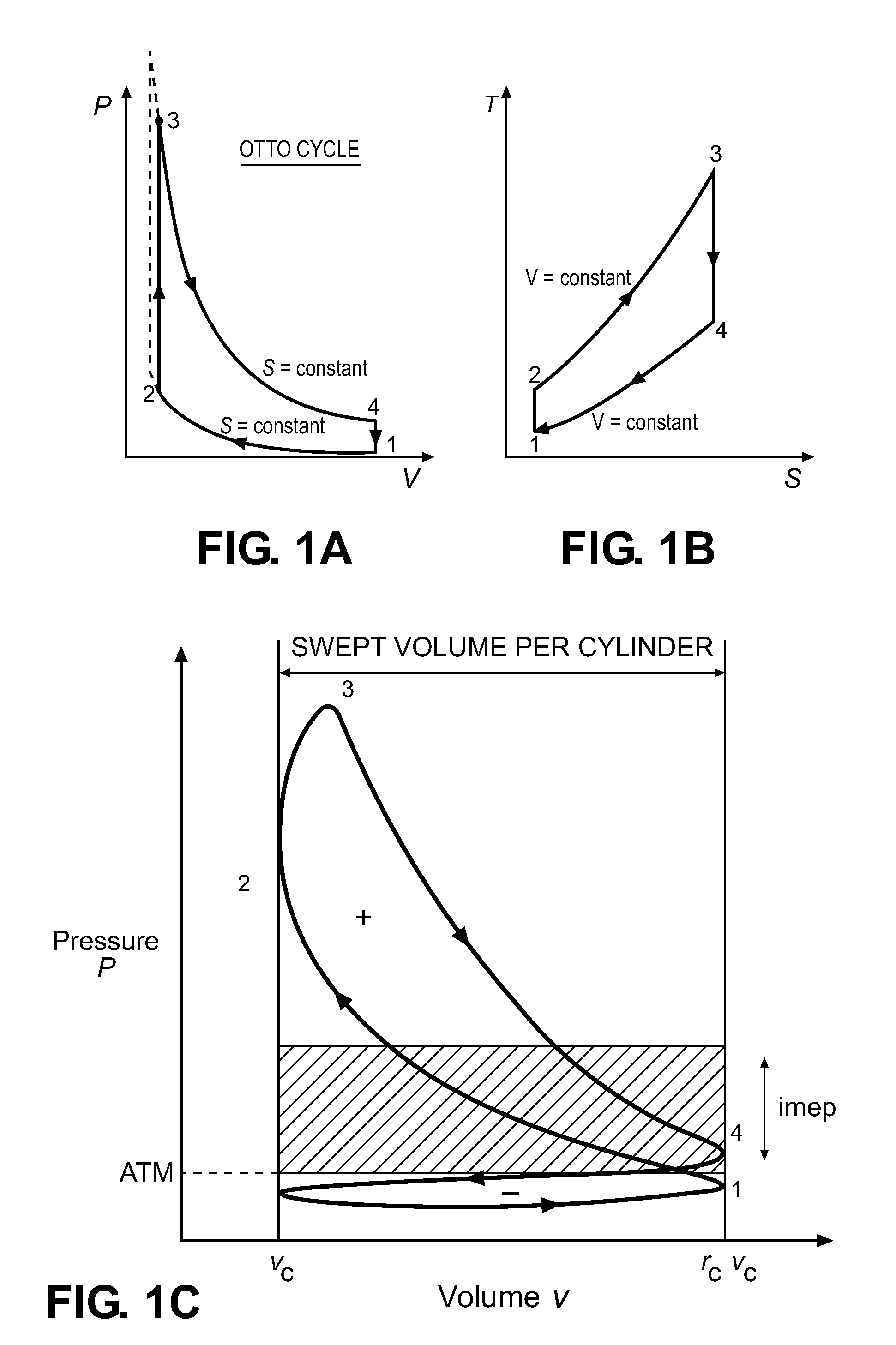

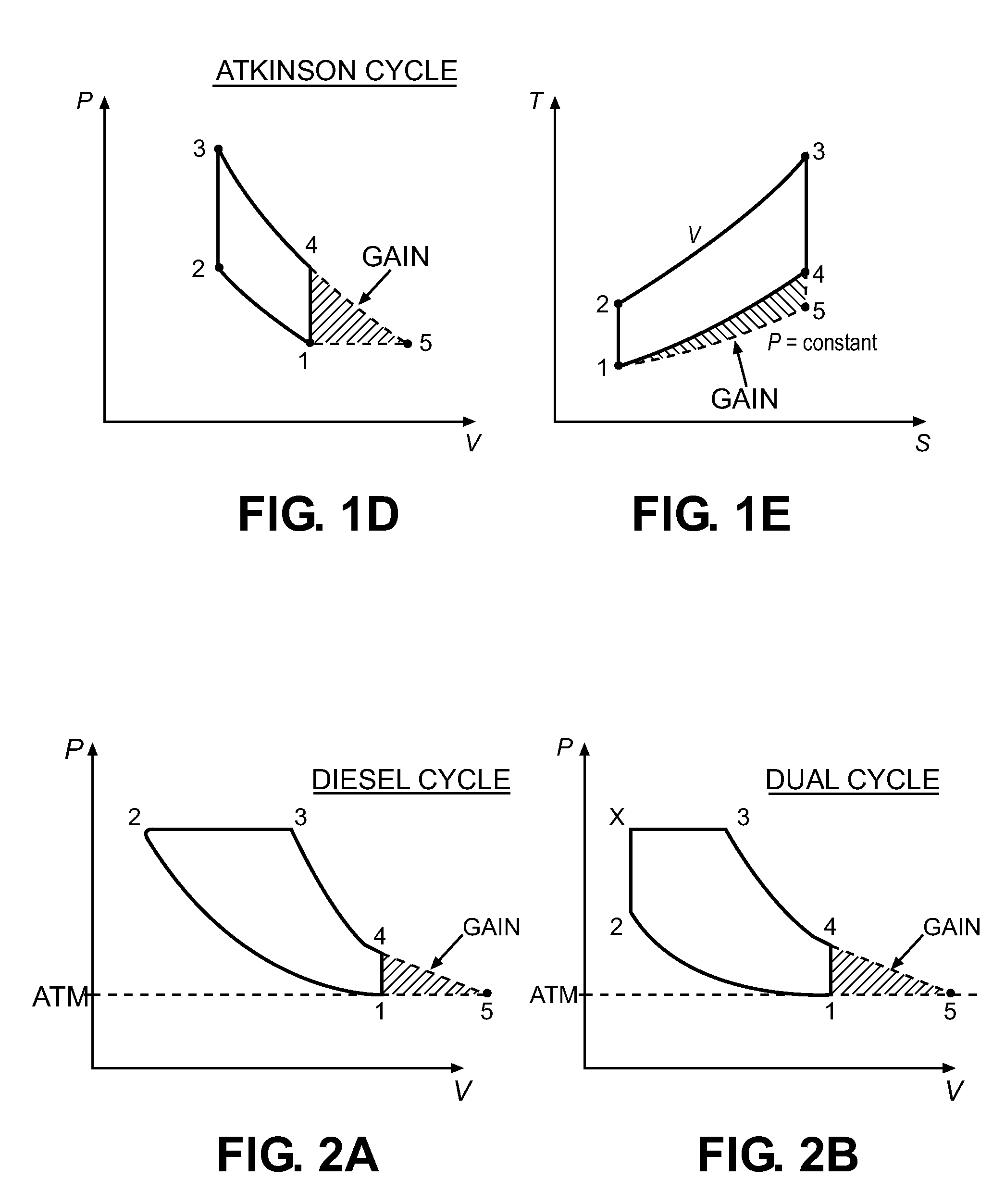

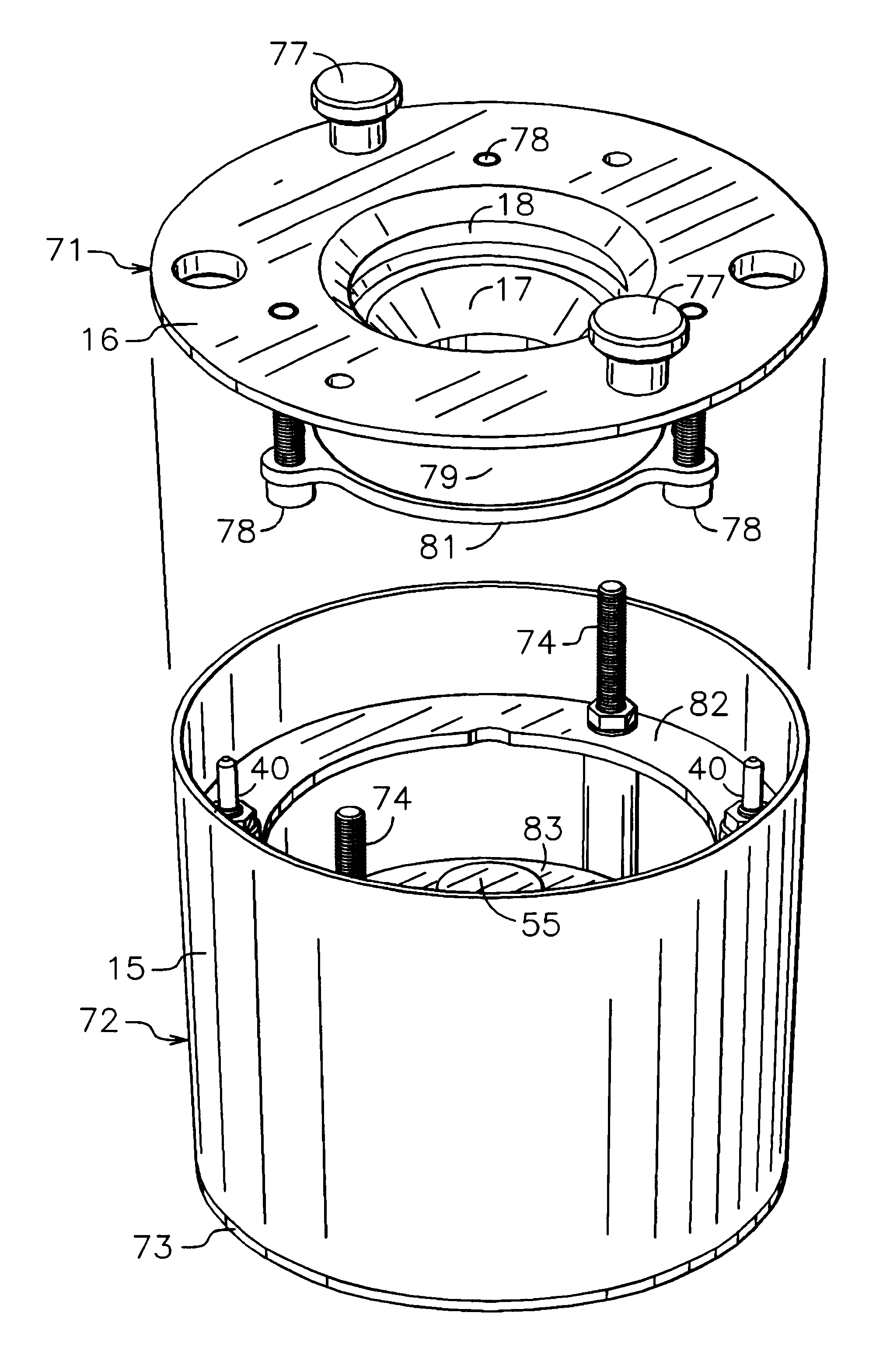

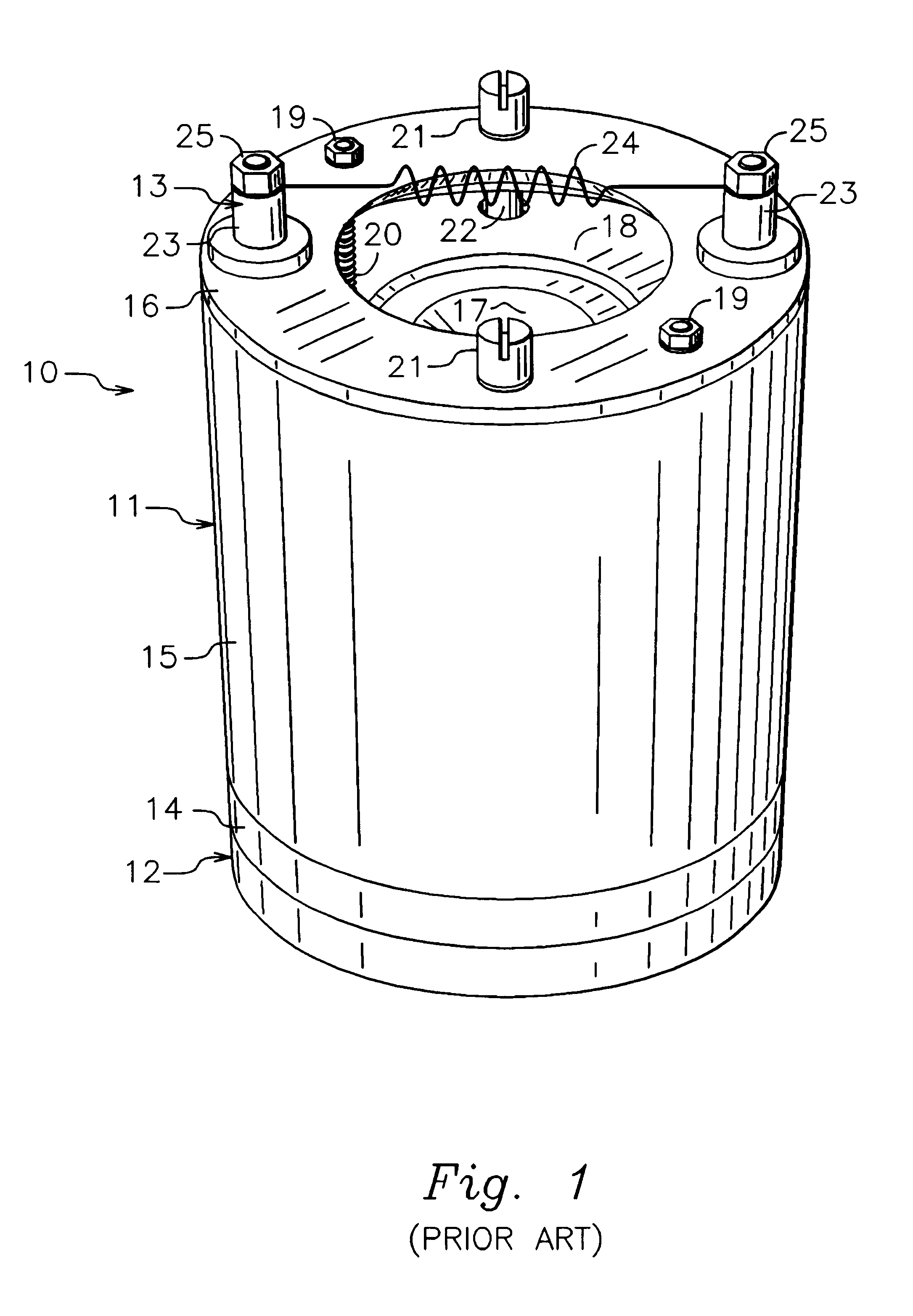

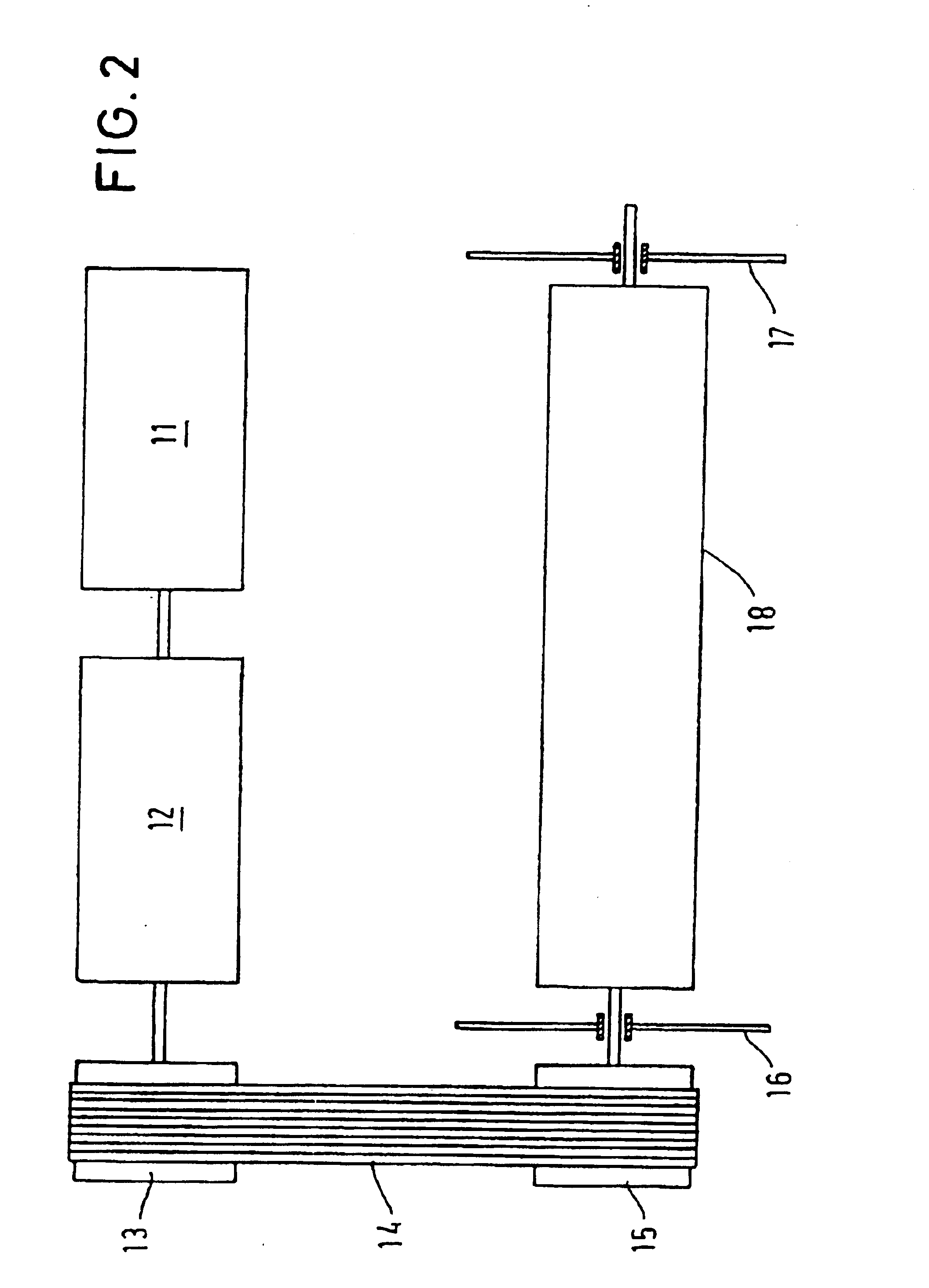

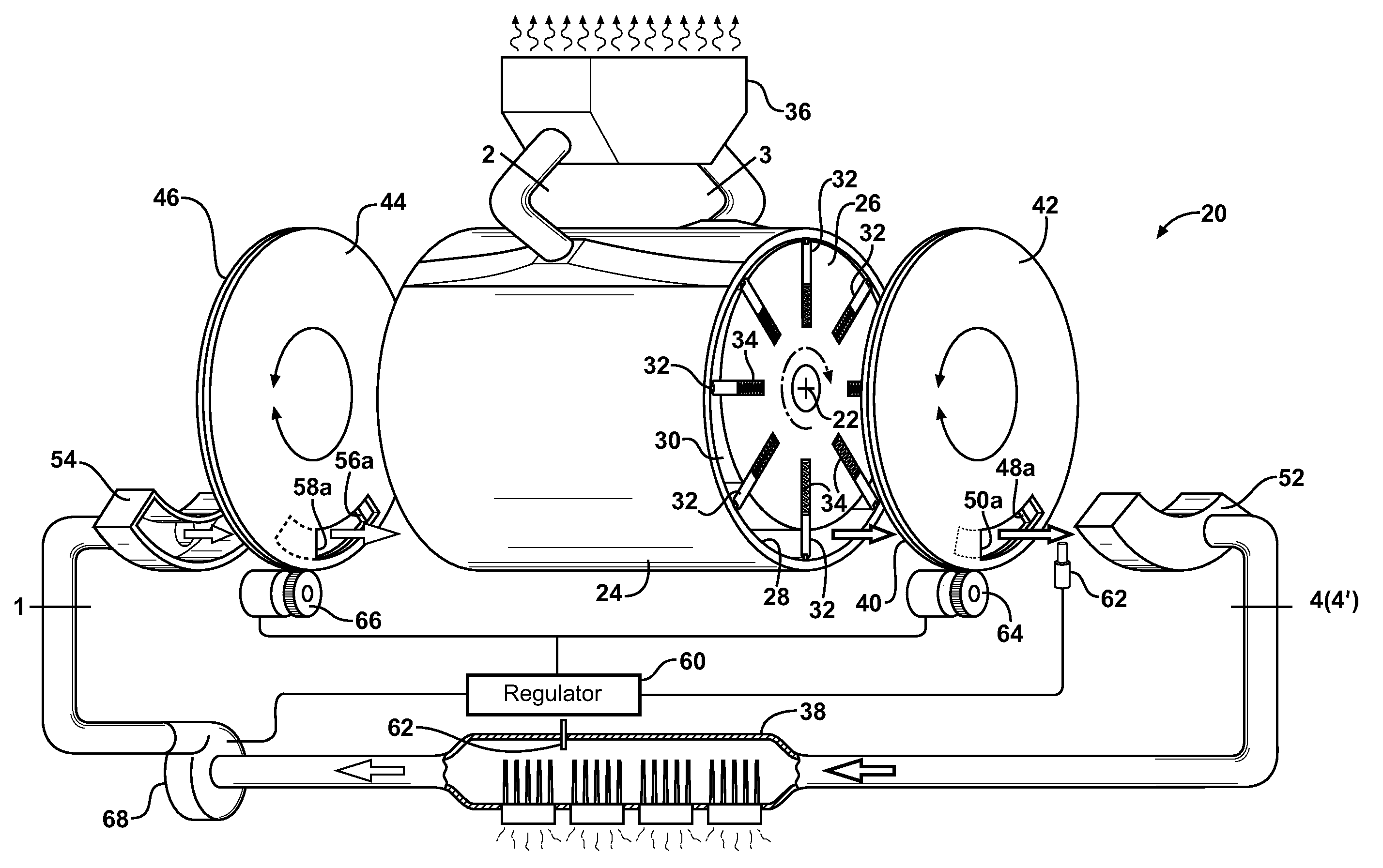

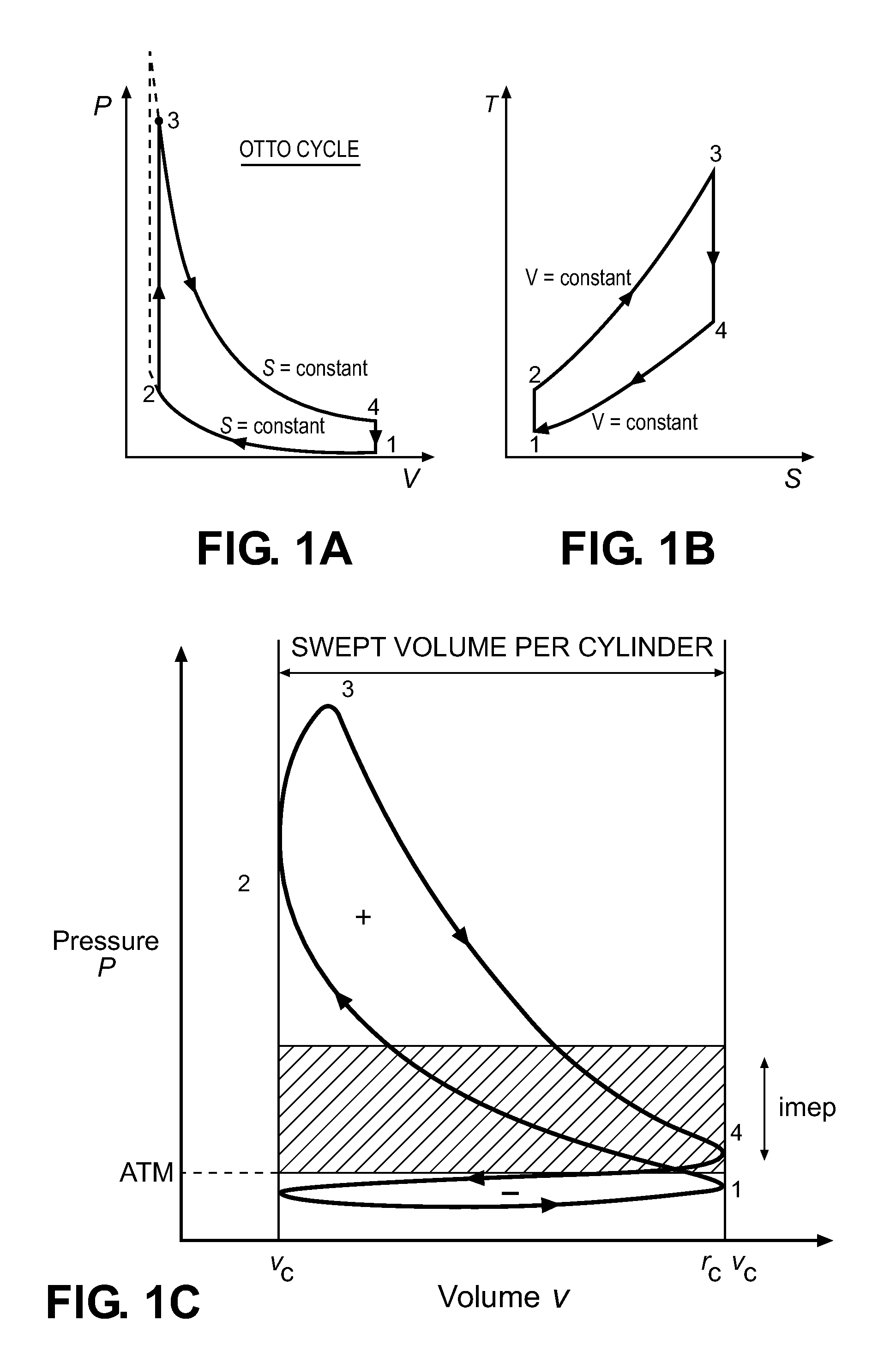

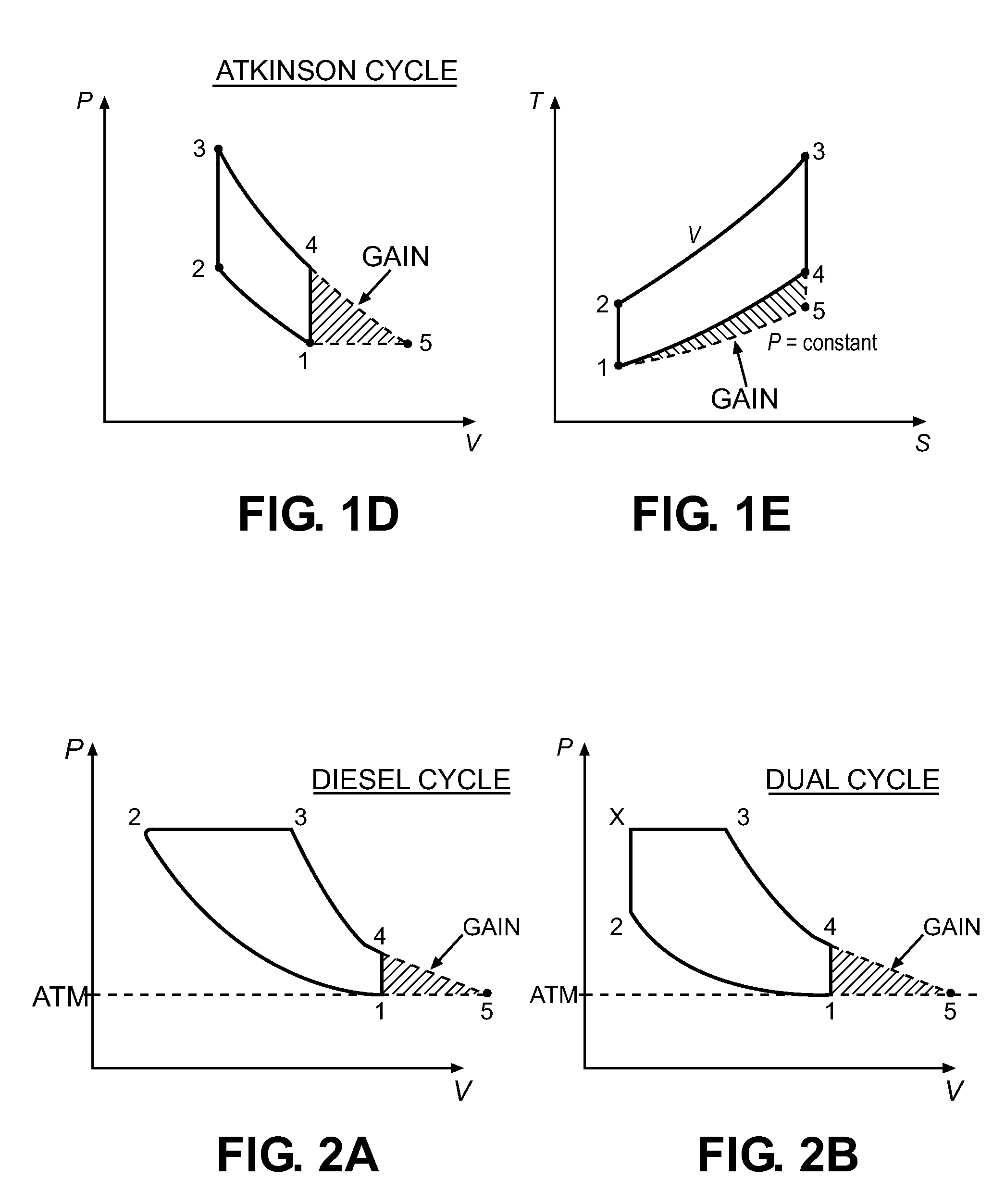

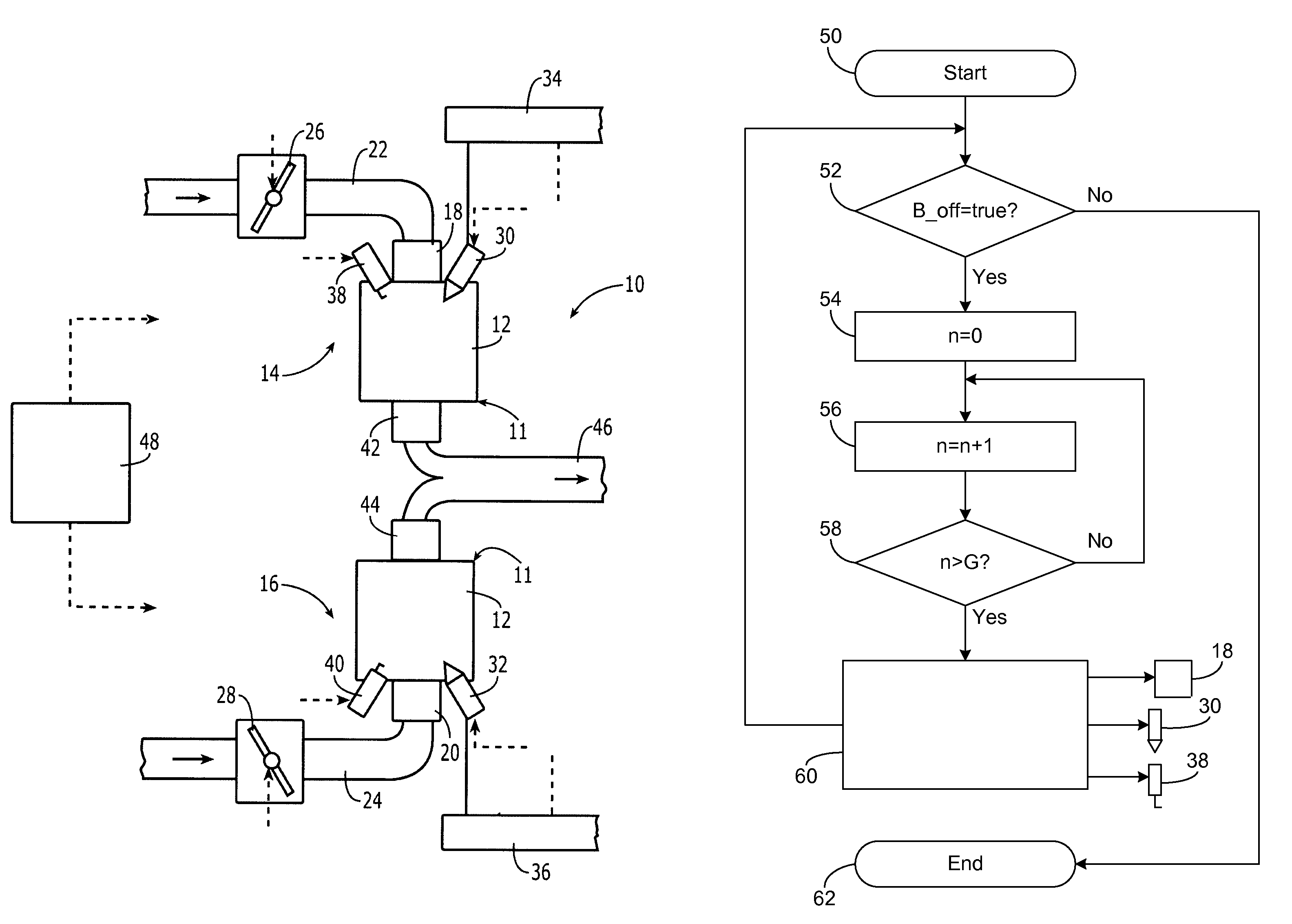

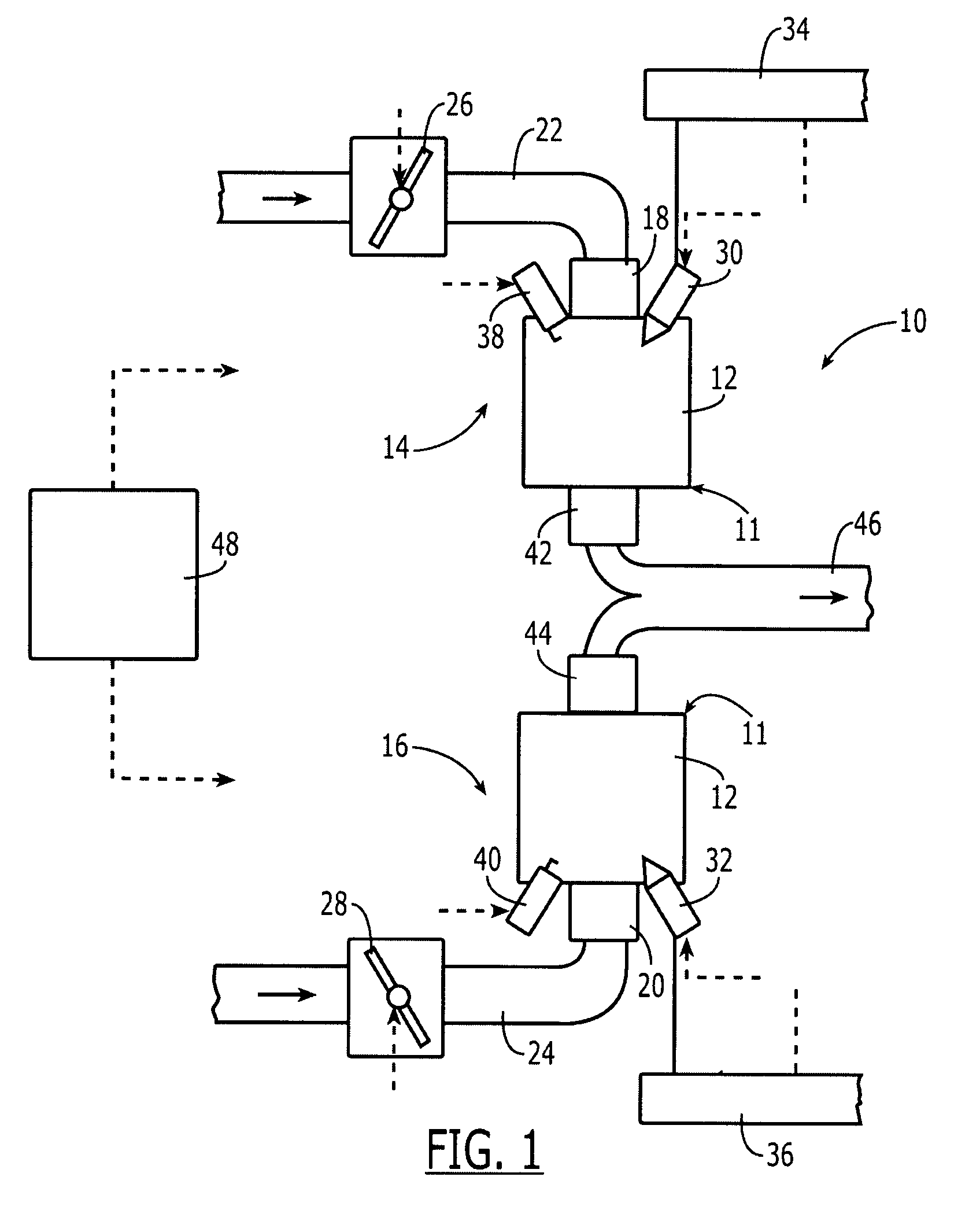

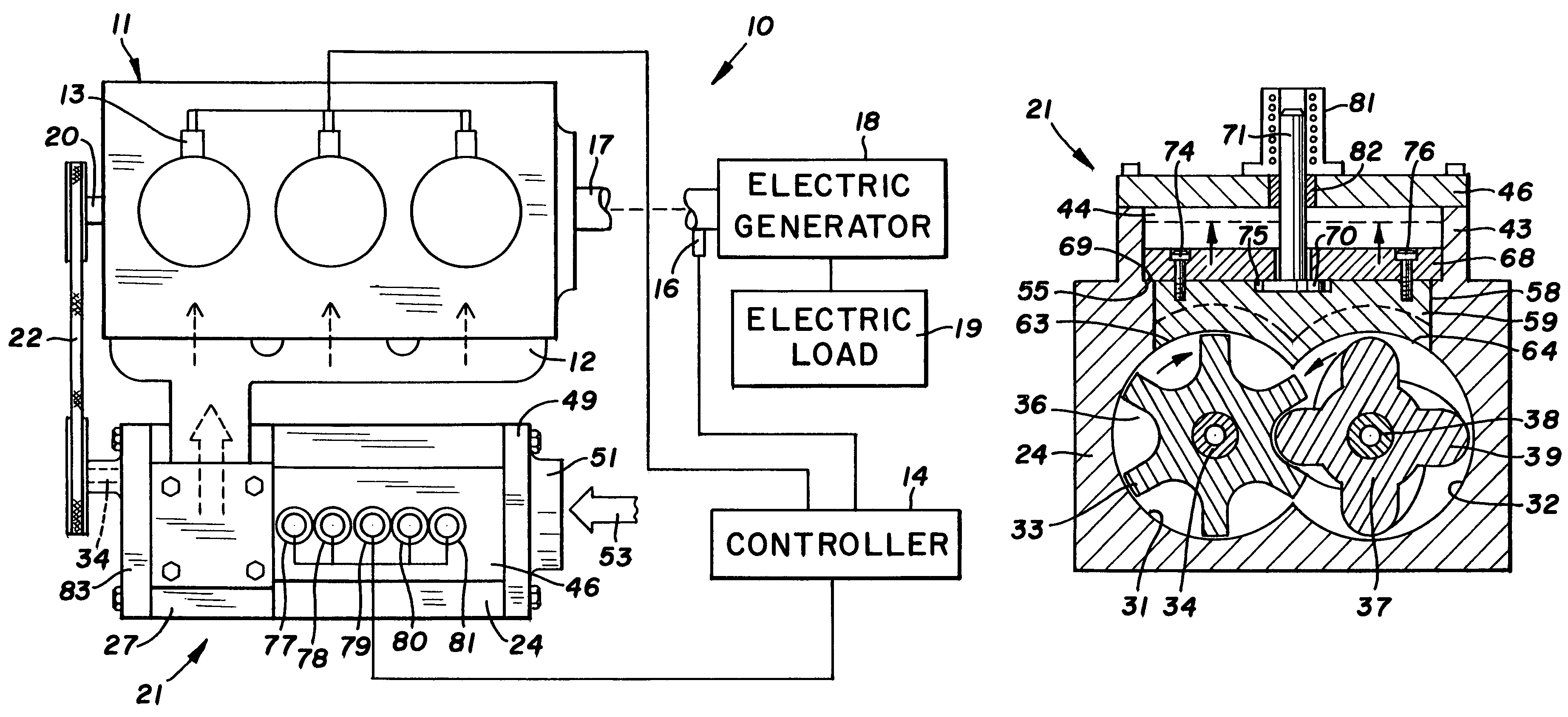

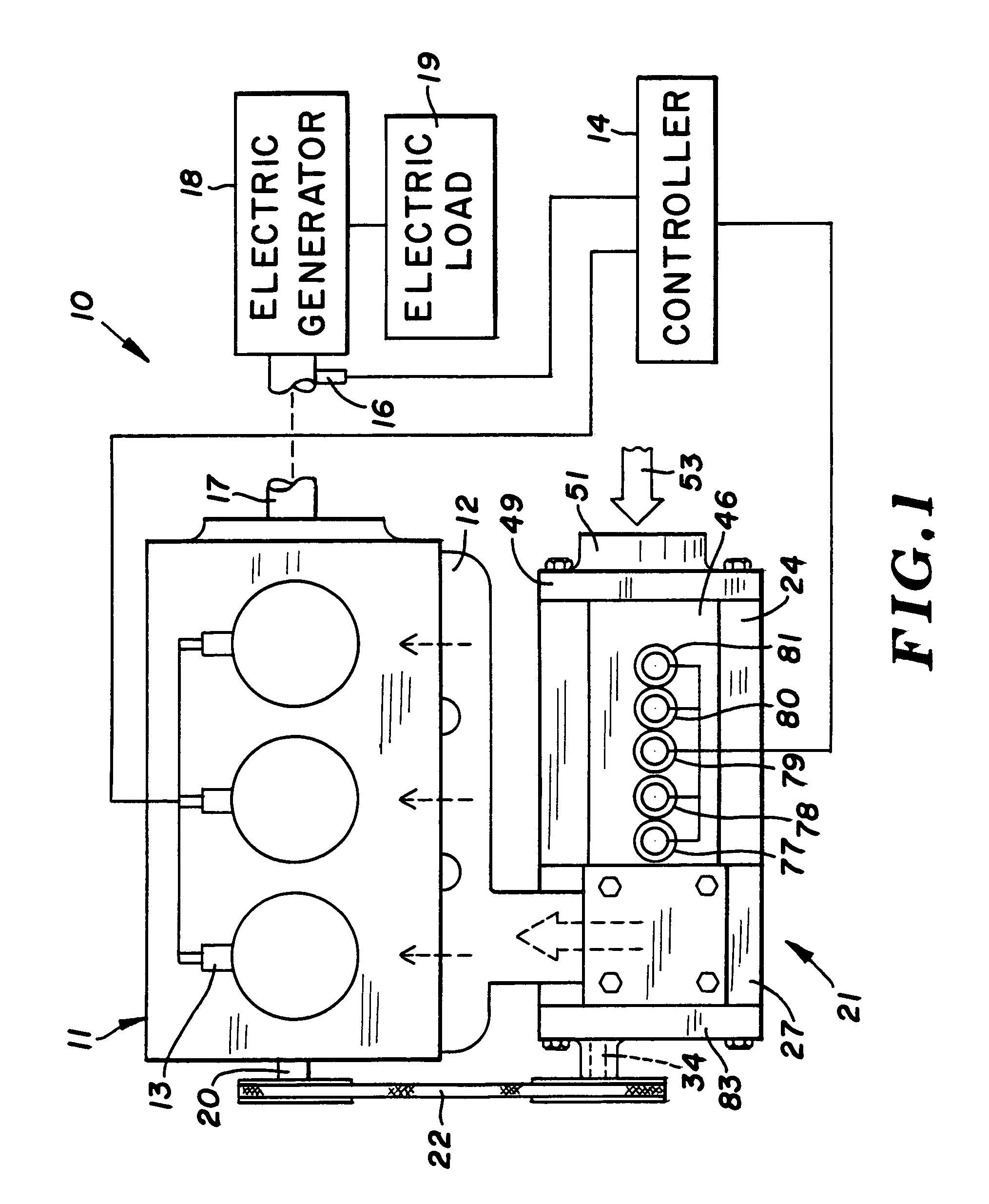

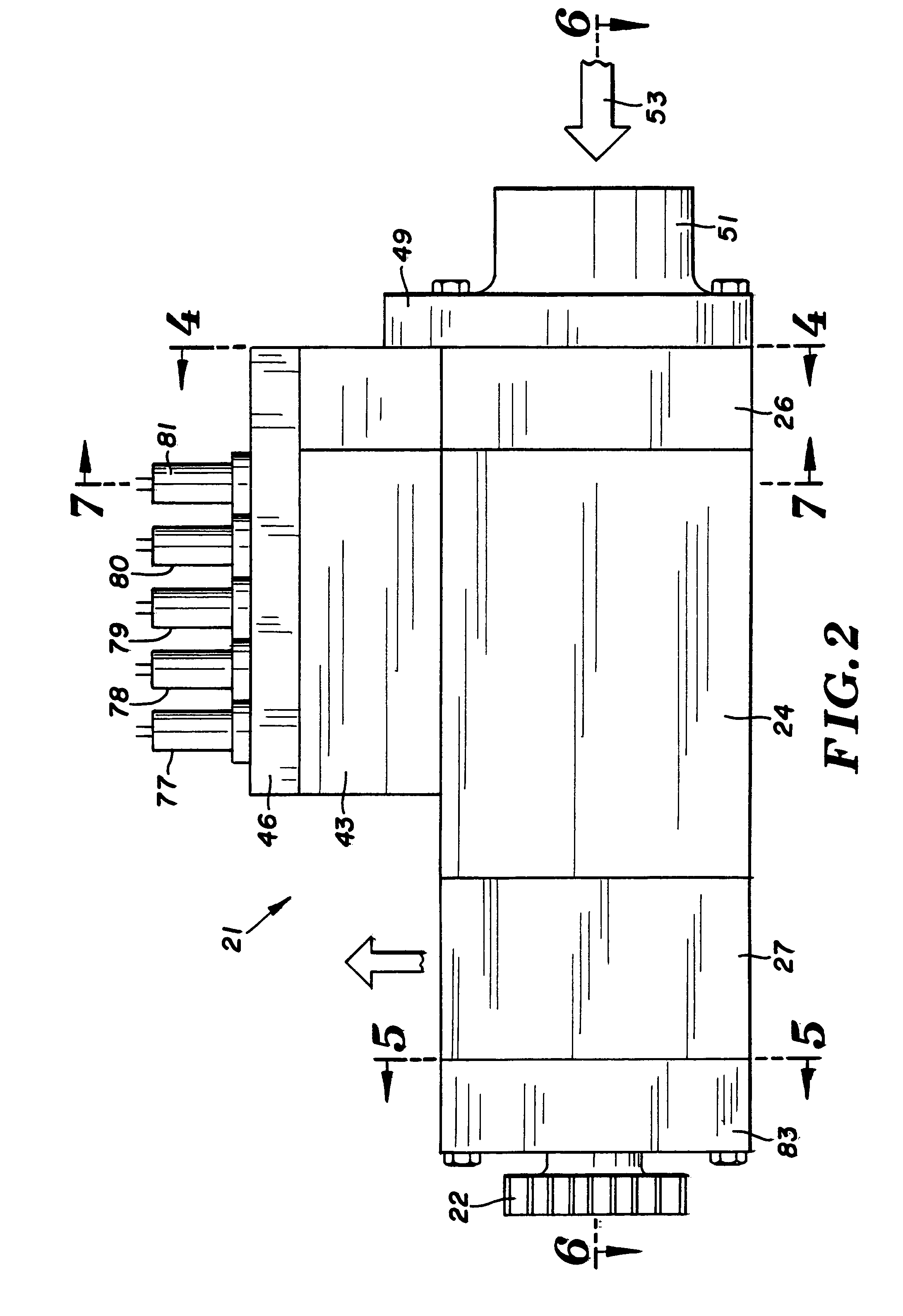

High efficiency positive displacement thermodynamic system

ActiveUS8424284B2Without decreasing volumetric efficiencySave heatInternal combustion piston enginesCombination enginesPower modeWorking fluid

Devices and methods for moving a working fluid through a controlled thermodynamic cycle in a positive displacement fluid-handling device (20, 20′, 20″) with minimal energy input include continuously varying the relative compression and expansion ratios of the working fluid in respective compressor and expander sections without diminishing volumetric efficiency. In one embodiment, a rotating valve plate arrangement (40, 42, 44, 46) is provided with moveable apertures or windows (48, 50, 56, 58) for conducting the passage of the working fluid in a manner which enables on-the-fly management of the thermodynamic efficiency of the device (20) under varying conditions in order to maximize the amount of mechanical work needed to move the target quantity of heat absorbed and released by the working fluid. When operated in refrigeration modes, the work required to move the heat is minimized. In power modes, the work extracted for the given input heat is maximized.

Owner:STAFFEND GILBERT

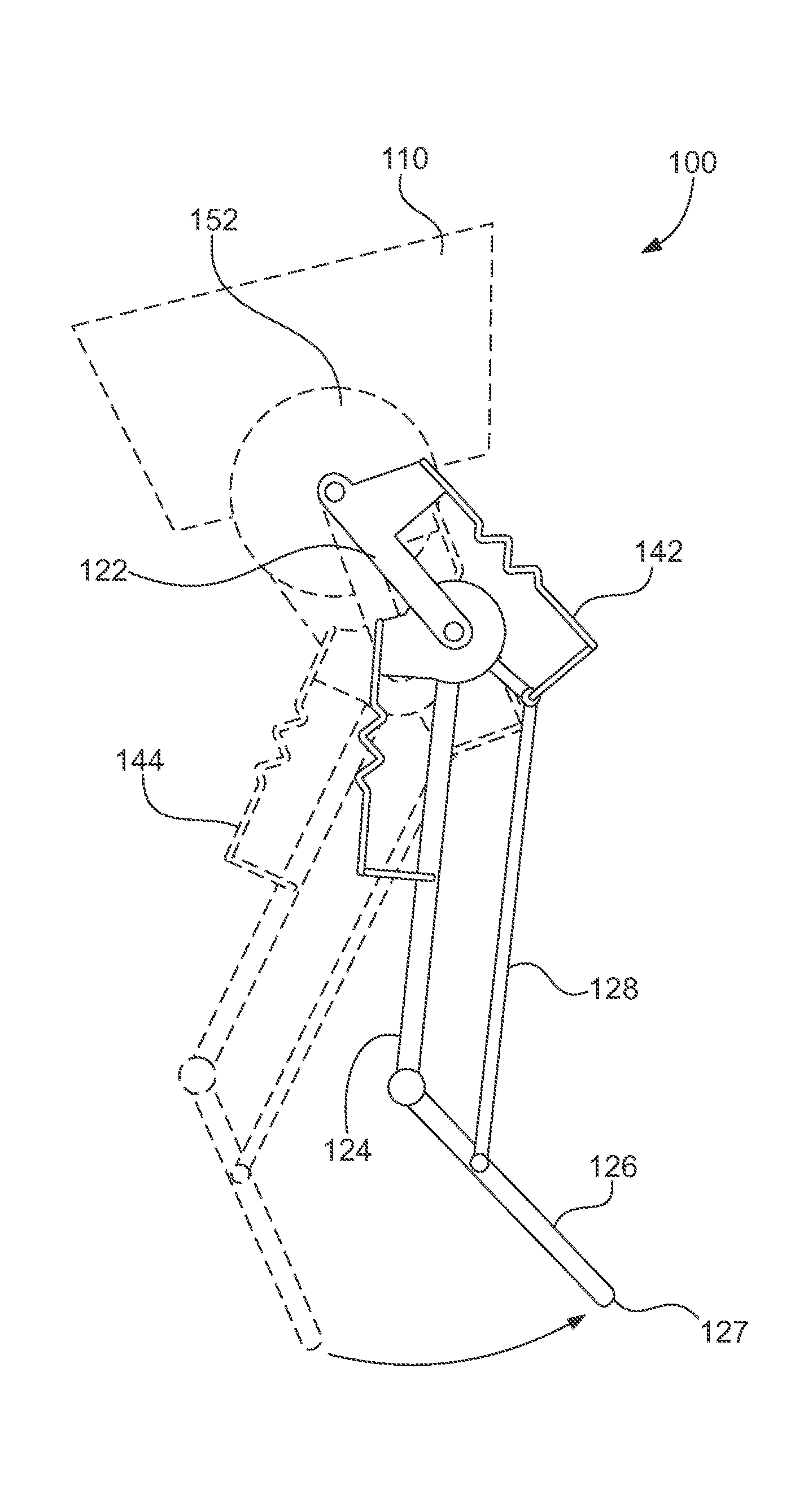

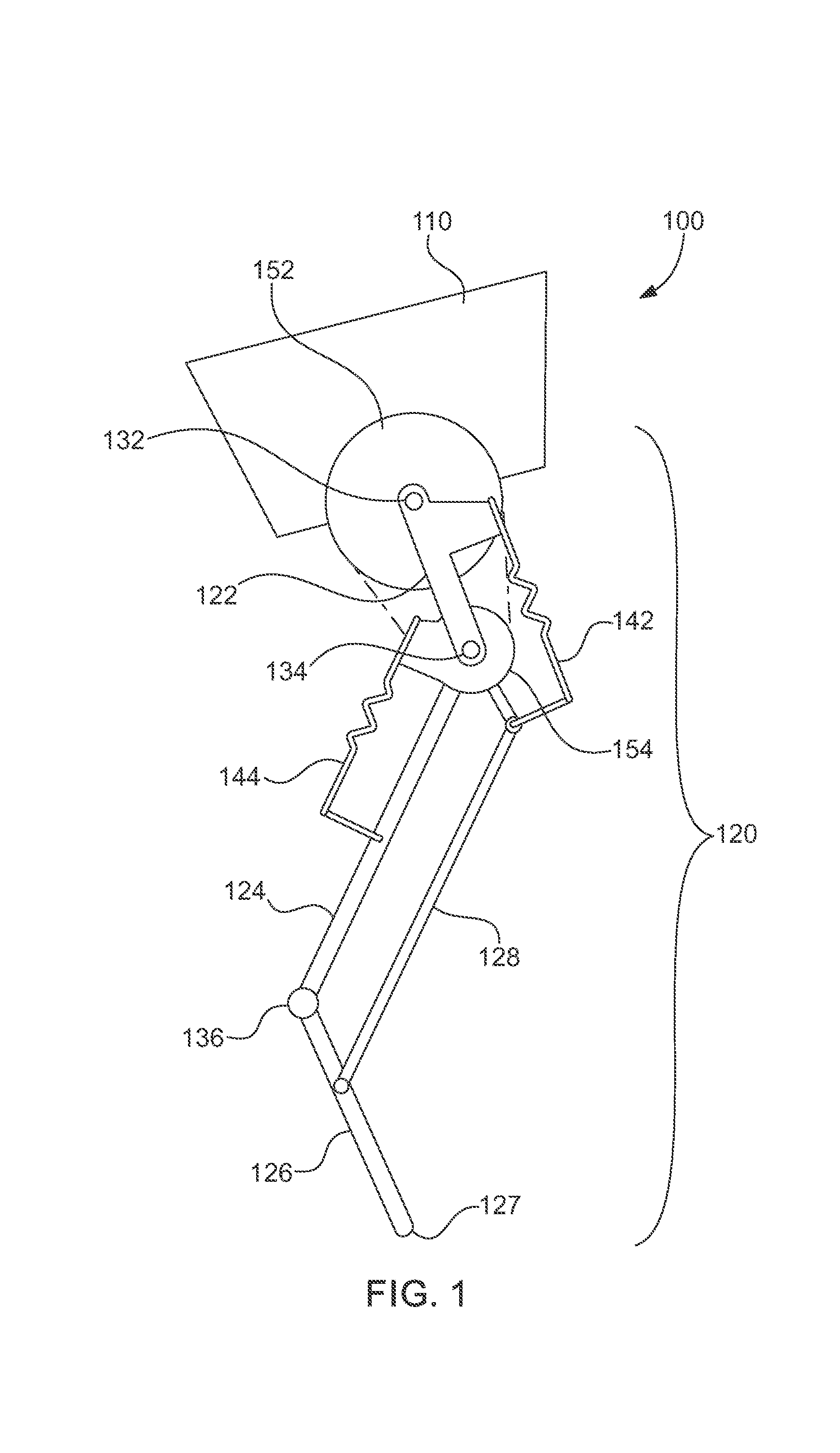

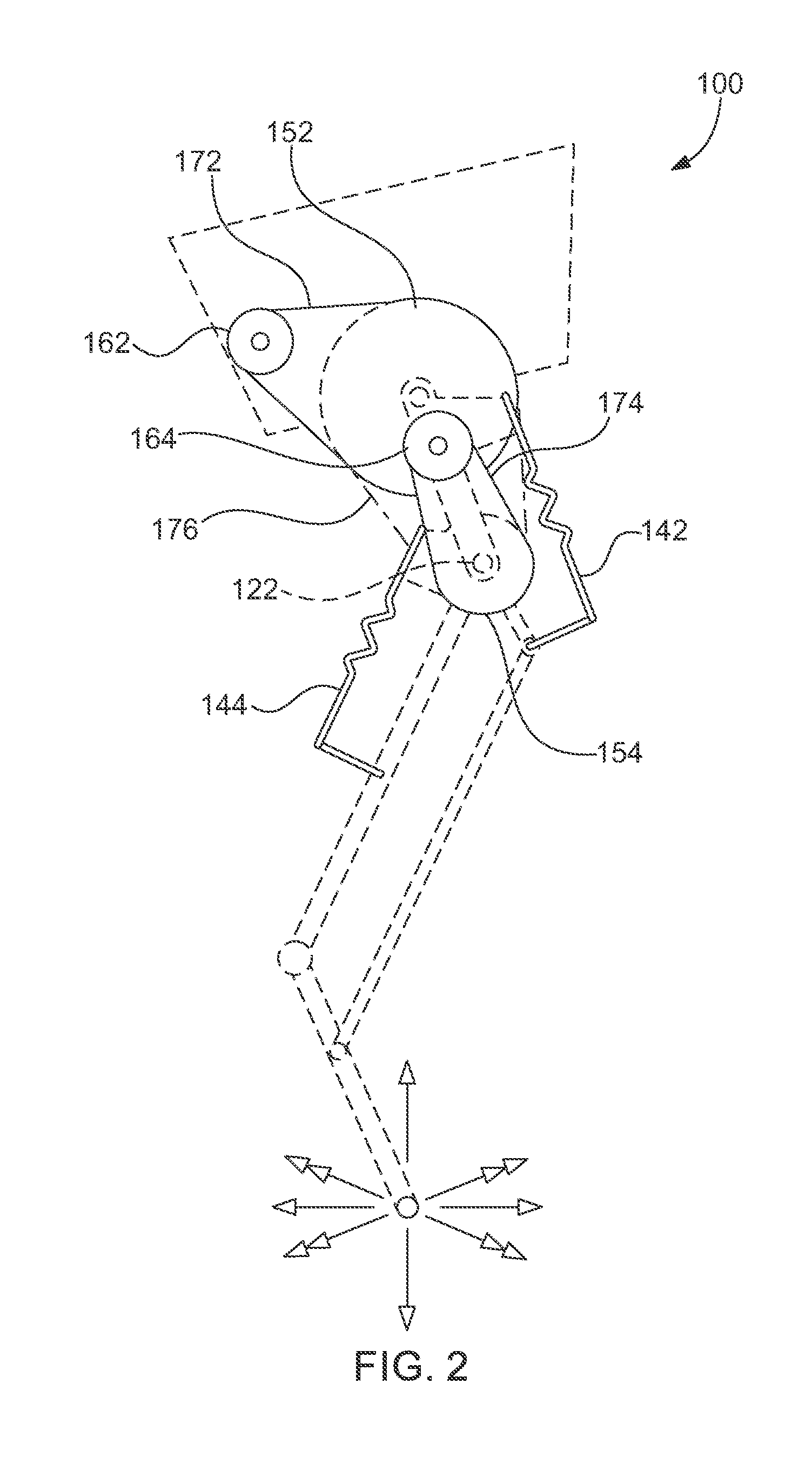

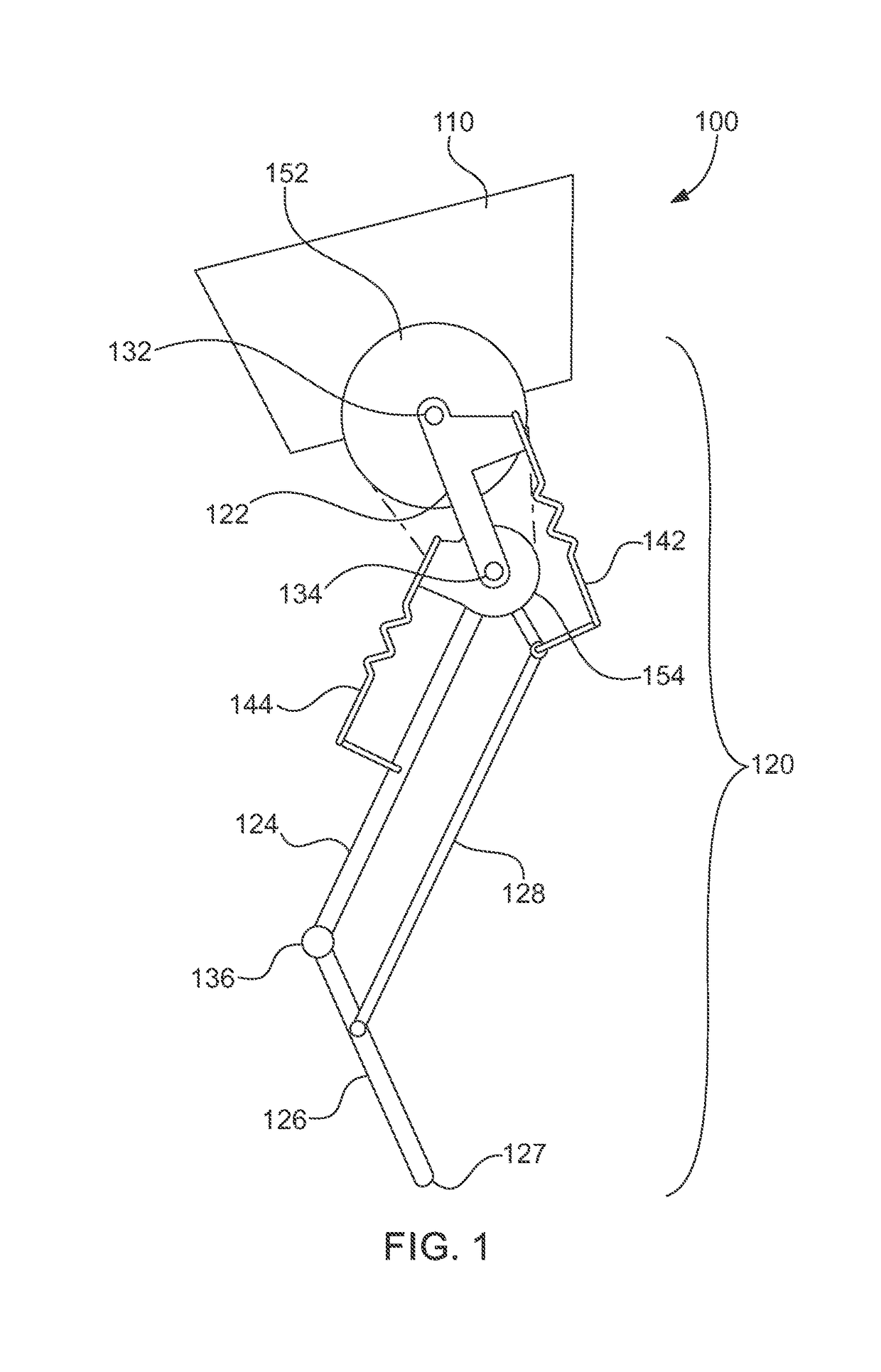

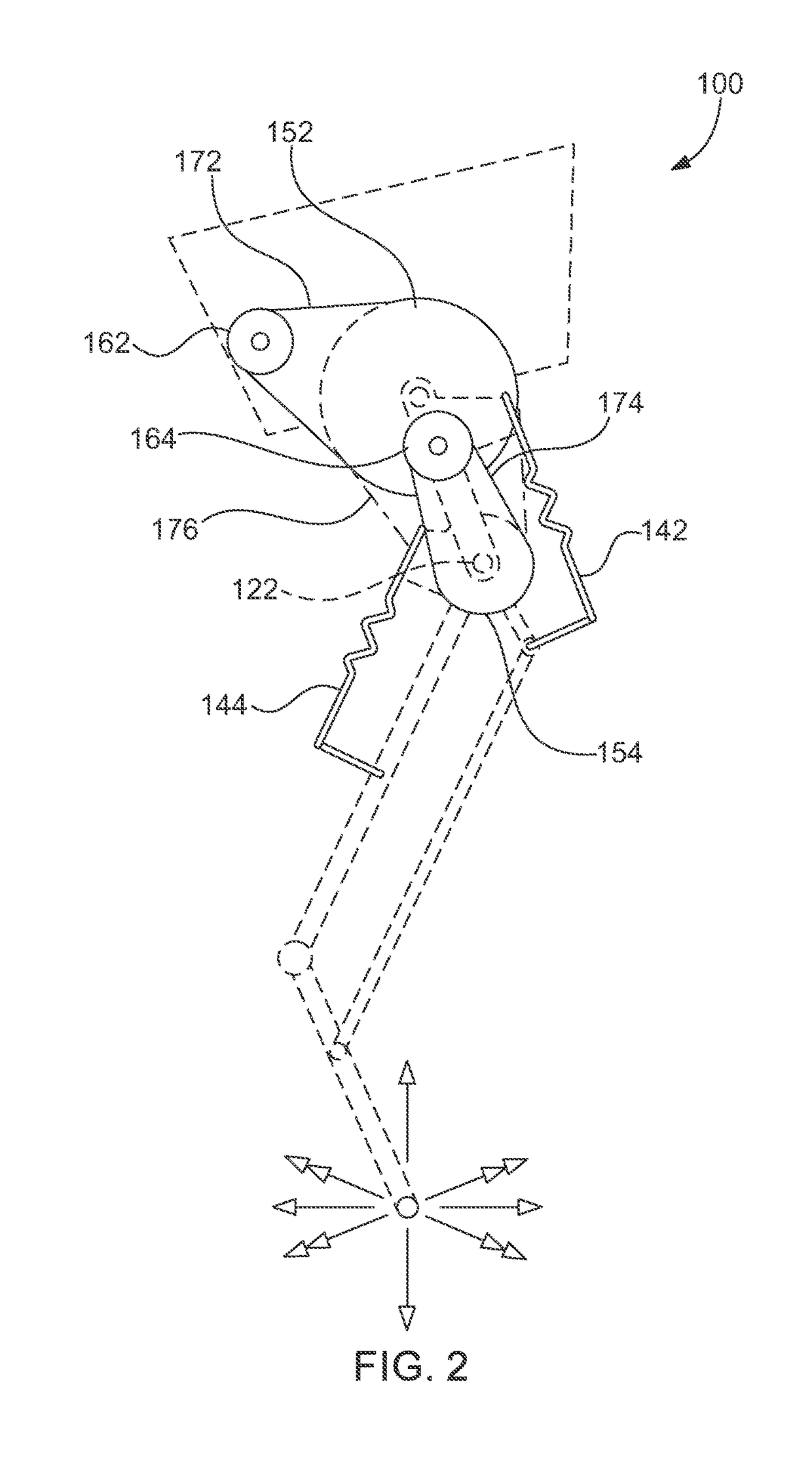

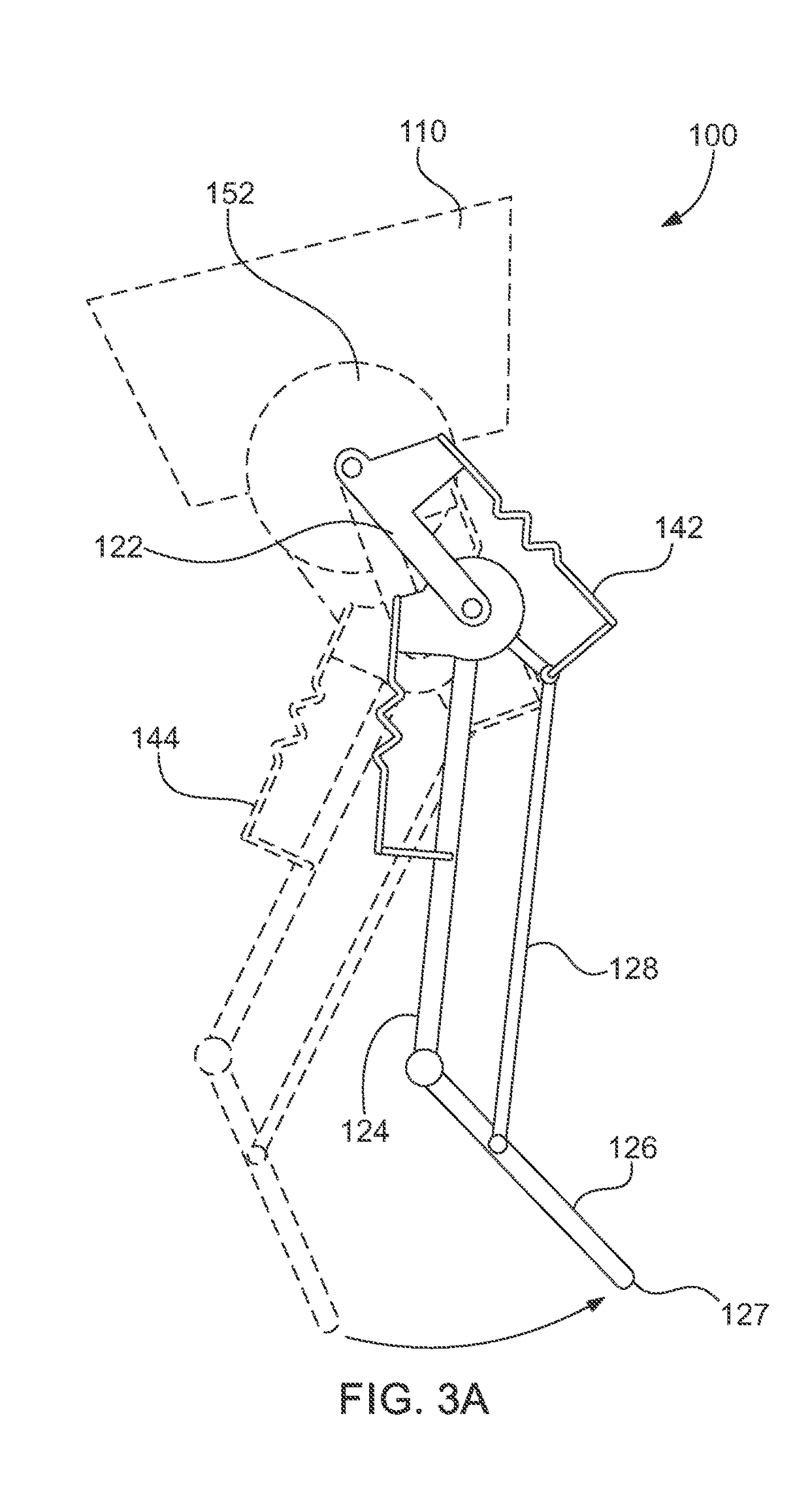

Leg configuration for spring-mass legged locomotion

ActiveUS20160347387A1Inherent stability be improveBalance stabilityRobotVehiclesEngineeringRobot leg

Devices and methods for legged locomotion, including a robotic leg for spring-mass legged locomotion incorporating passive dynamics.

Owner:THE STATE OF OREGON ACTING BY & THROUGH THE OREGON STATE BOARD OF HIGHER EDUCATION ON BEHALF OF OREGON STATE UNIV

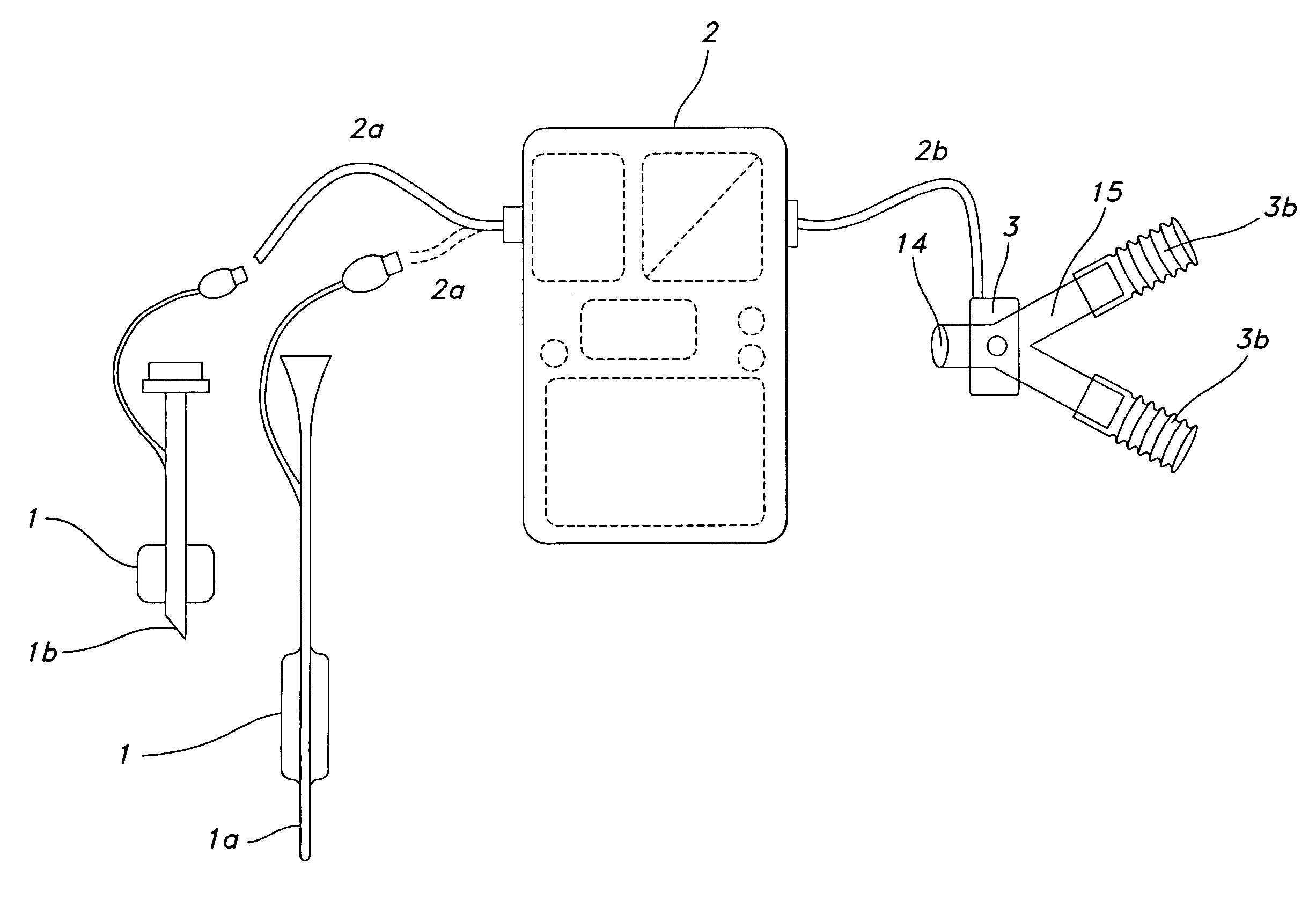

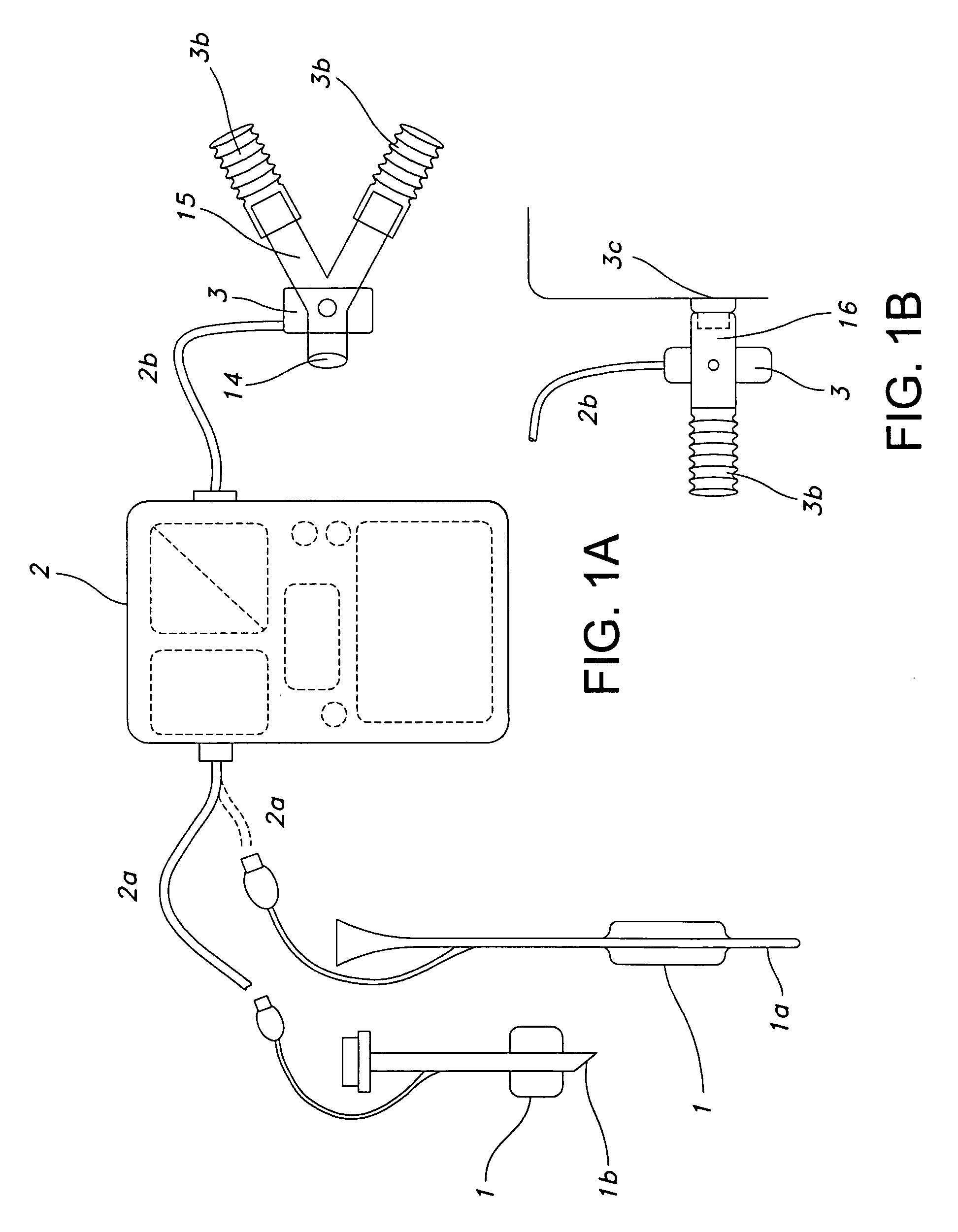

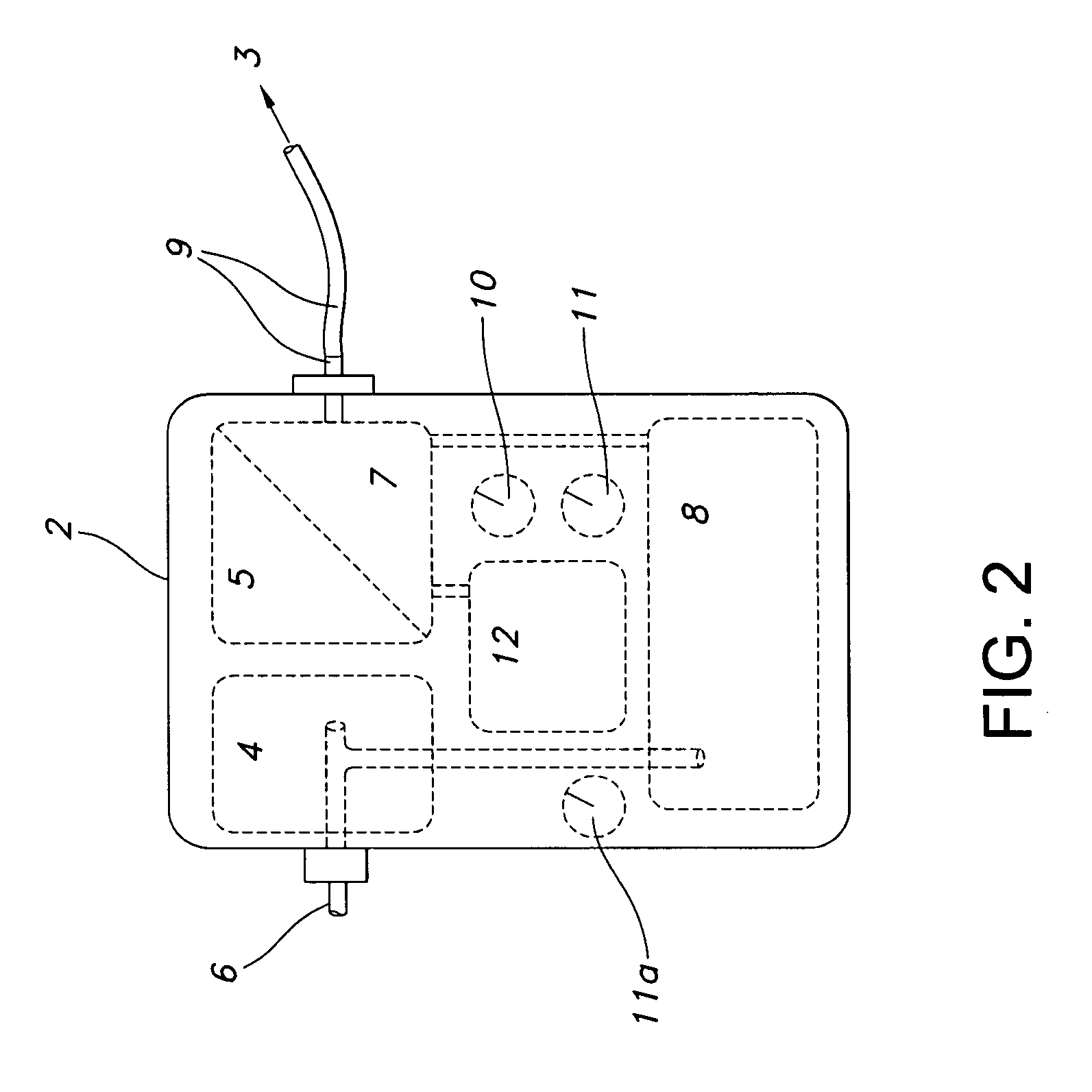

Method of triggering a ventilator

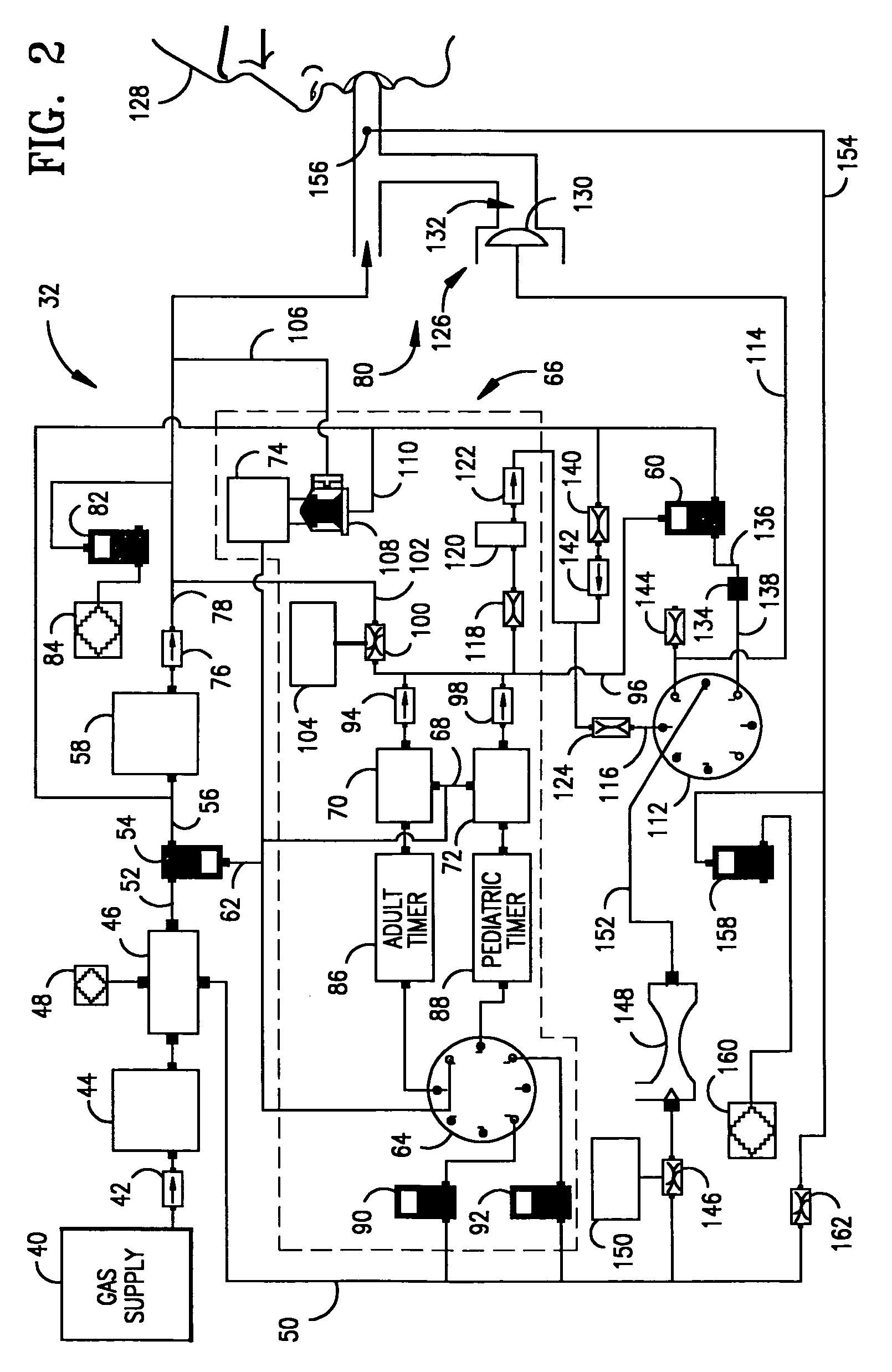

InactiveUS20090120439A1Patient weaning acceleratedMinimize workTracheal tubesOperating means/releasing devices for valvesNoseEndotracheal tube

There is provided a method for controlling breathing gas flow of a ventilator for assisted or controlled ventilation of a patient as a function of a intra-thoracic airway pressure of the patient using a tracheal tube or naso-gastric tube. The intra-thoracic pressure is transmitted to a controller and the information detected is used to control a valve to vent gas from the inhalation tubing of the ventilator, thus triggering an inhalation cycle in the ventilator.

Owner:KIMBERLY-CLARK WORLDWIDE INC

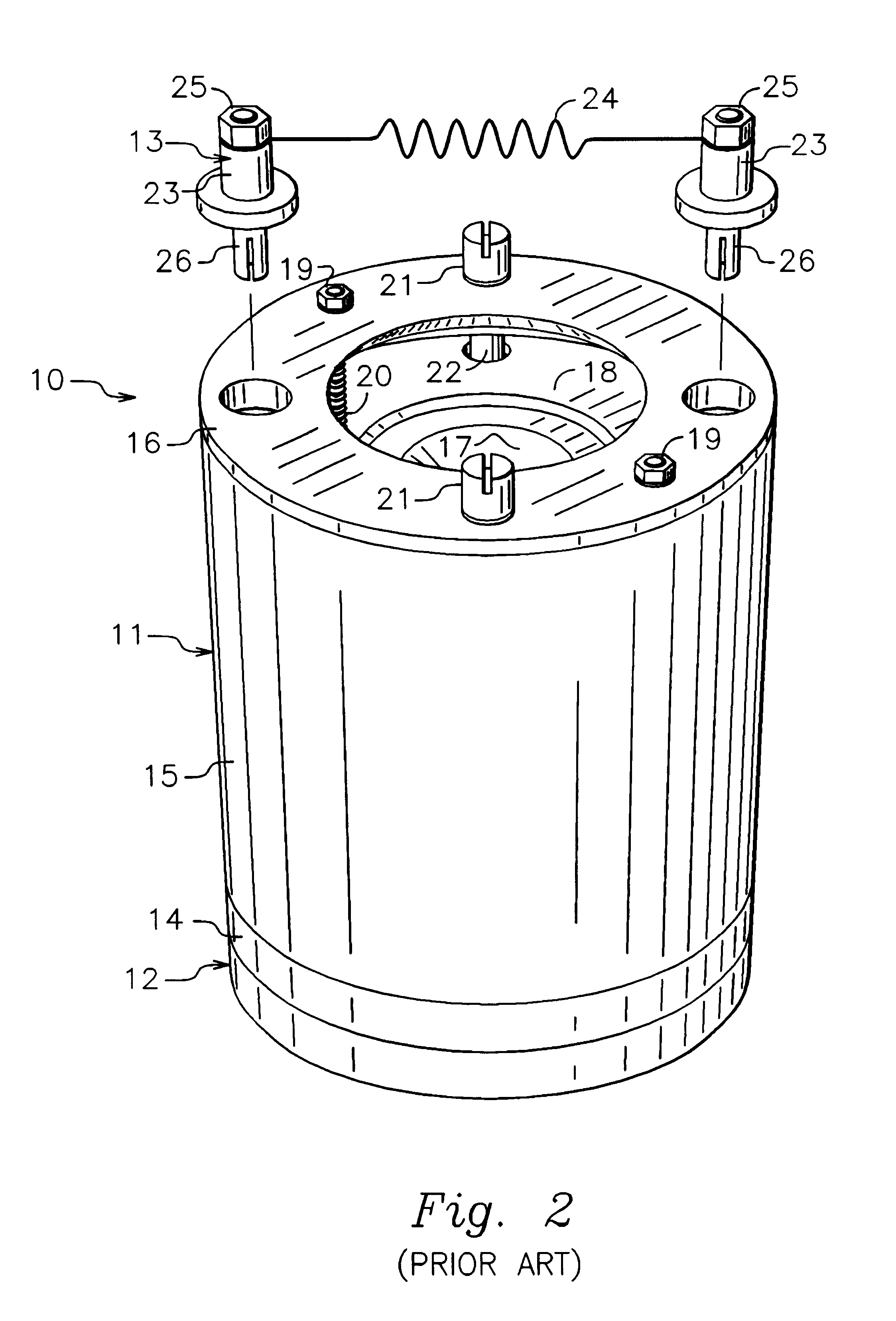

Modular gridless ion source

InactiveUS6608431B1Minimize workReduce lossesElectric arc lampsMachines/enginesModularityReduced size

In accordance with one embodiment of the present invention, the ion-beam apparatus takes the form of an end-Hall ion source in which the detachable anode module incorporates the outer pole piece and includes an enclosure around the anode that both minimizes the loss of working gas and confines sputter contamination to the interior of this enclosure. This detachable anode module is substantially smaller than the entire end-Hall ion source, weighs substantially less, and can be duplicated for significantly less cost than the duplication of the entire ion source. In general, the components of the magnetic circuit determine the overall size, weight, and much of the cost of a gridless ion source. The reduced size, weight, and cost of the detachable anode module compared to the entire ion source is due to most of the magnetic circuit being excluded from the detachable module.

Owner:KAUFMAN & ROBINSON

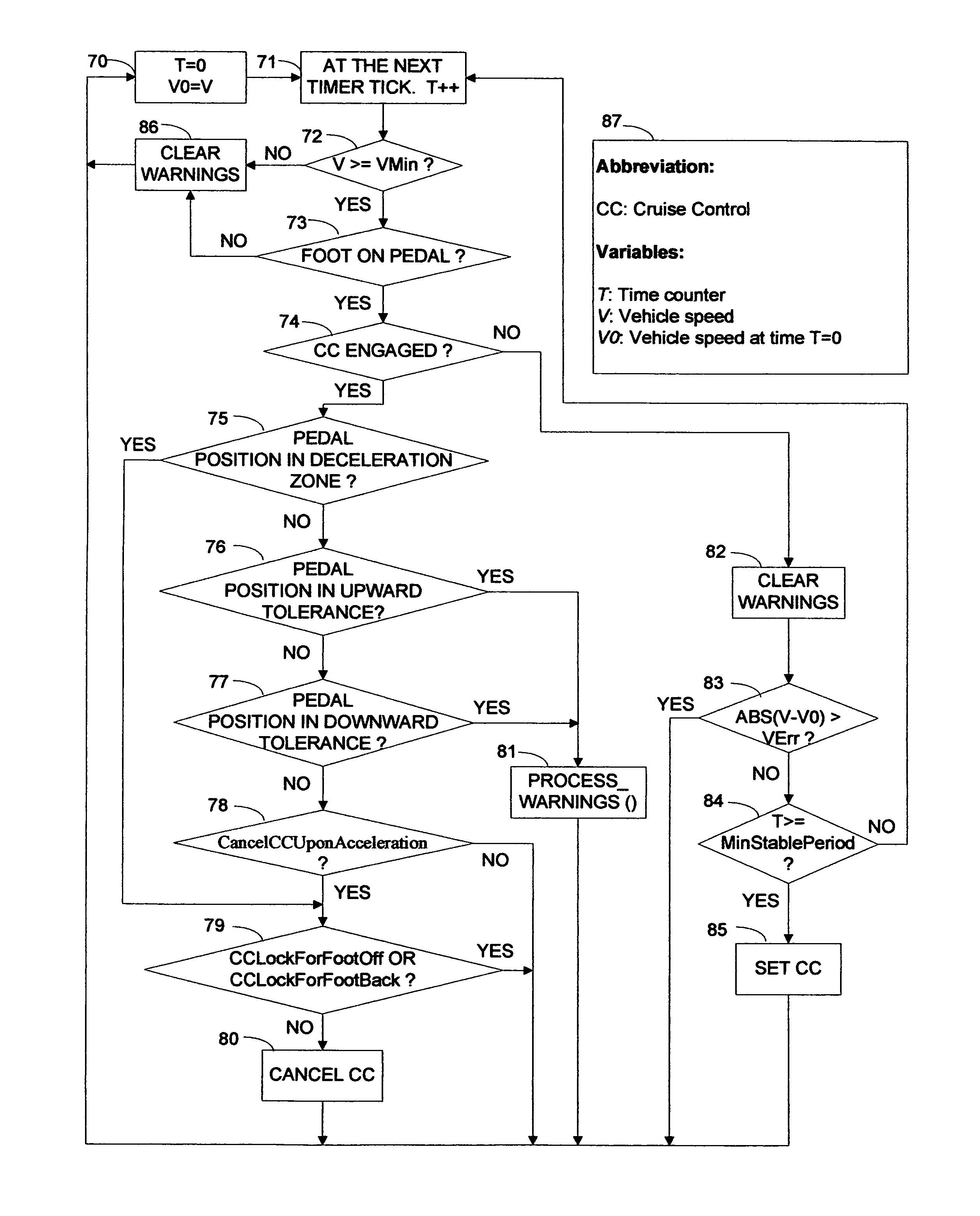

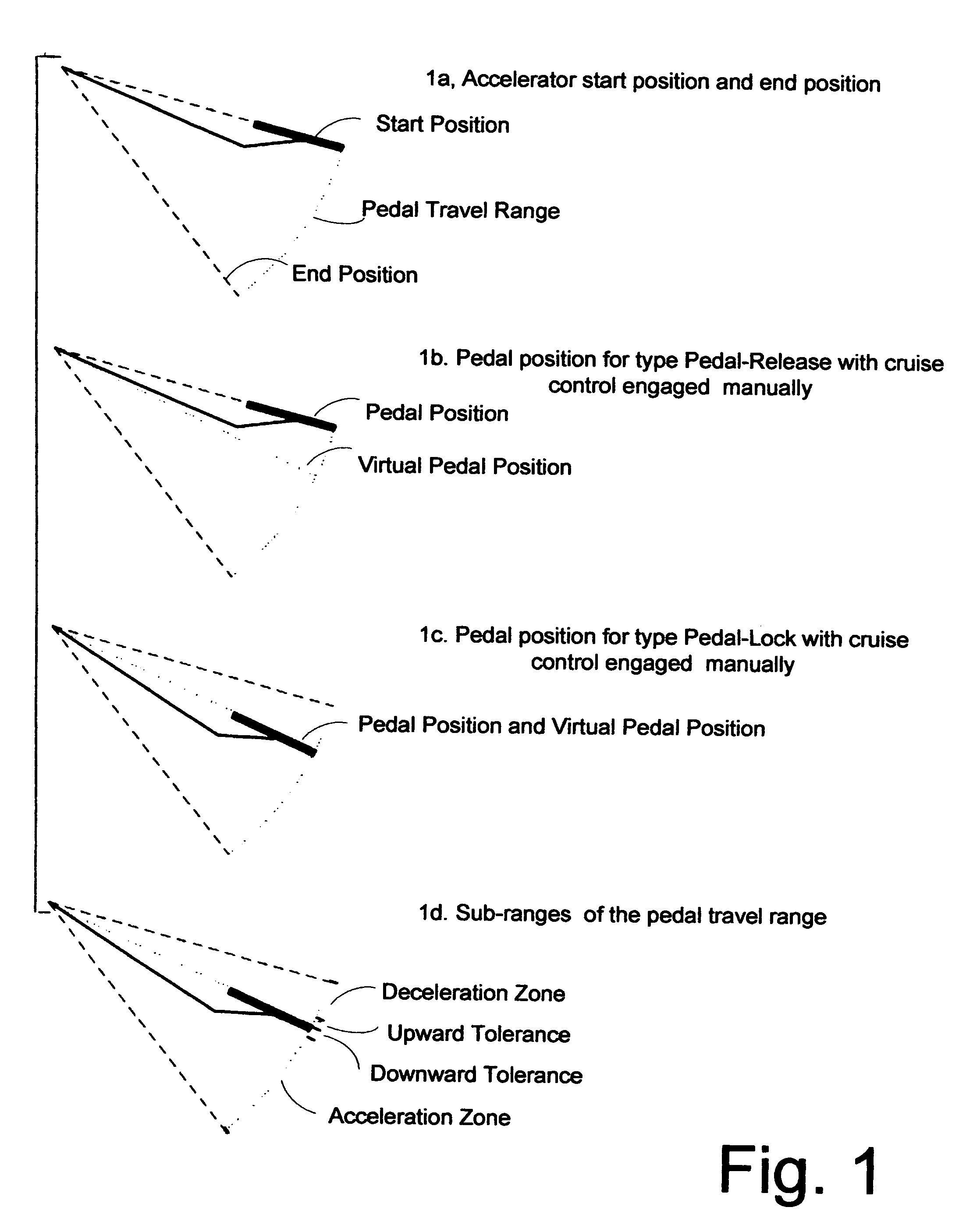

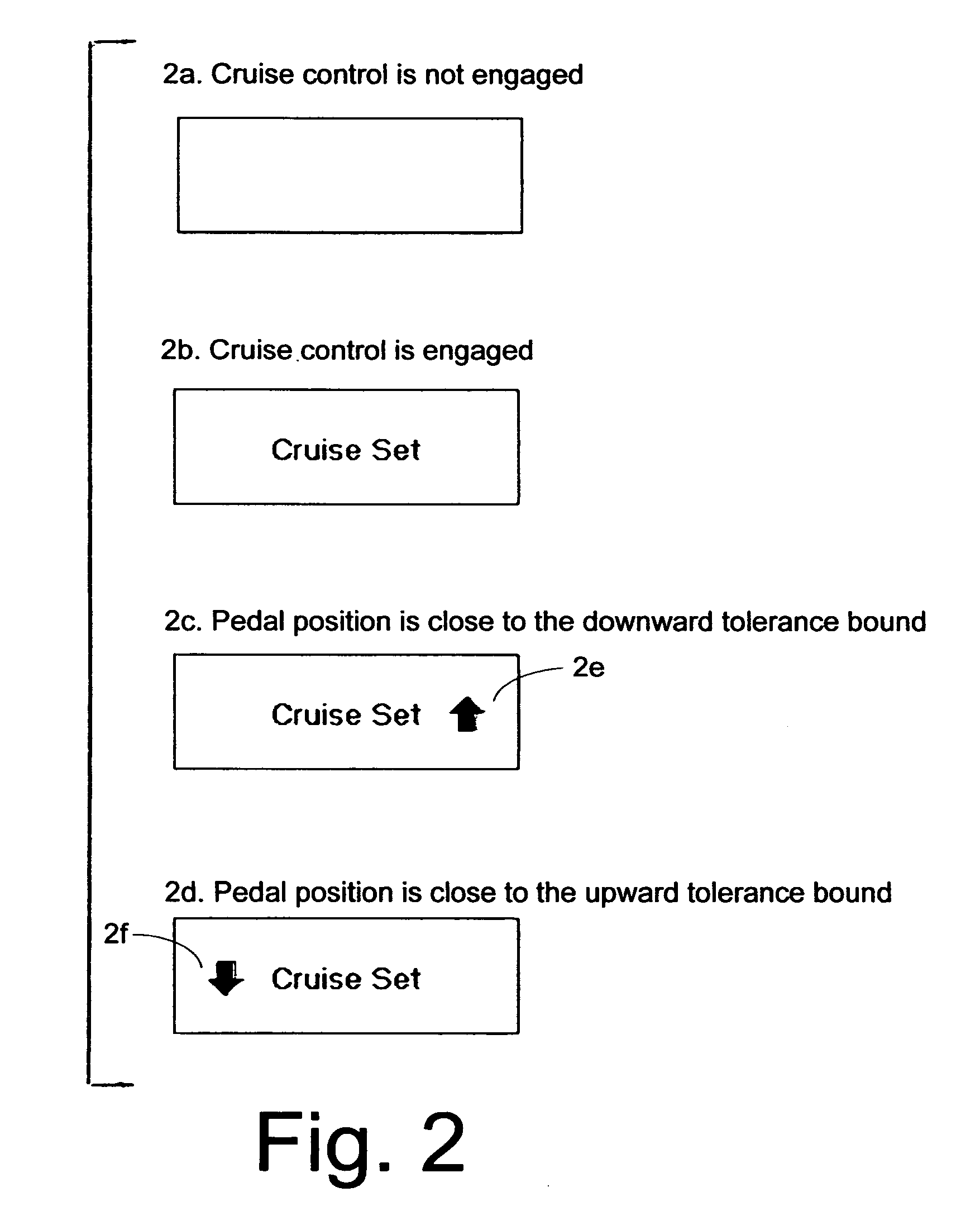

Speed stabilizer for automatically turning conventional cruise controls on/off in dense low speed traffic to save fuel

InactiveUS7706953B1Filter out instabilityMaximizing periodControlling membersVehicle fittingsDriver/operatorLED display

The stabilizer works with any conventional cruise control (CC) and permits automatic CC in slower heavy traffic as it eliminates laborious frequent manual actuation of CC control buttons otherwise needed in such heavy traffic. More frequent automatic CC operation at slower speeds increases fuel efficiency. When the vehicle maintains a speed above a minimum speed and exceeds a brief preset period, the speed stabilizer sets the cruise control at that speed. When the cruise control is thus engaged, the driver's foot can move the accelerator pedal within a small tolerance range without canceling the cruise control. When the pedal is close to the bounds of the tolerance range, a warning signal such as a flashing LED display, is generated by the speed stabilizer to inform the driver that further movement of the pedal will cause acceleration / deceleration, automatically canceling cruise control. Actuation of conventional CC control buttons restores conventional CC.

Owner:SUN JUN SHI

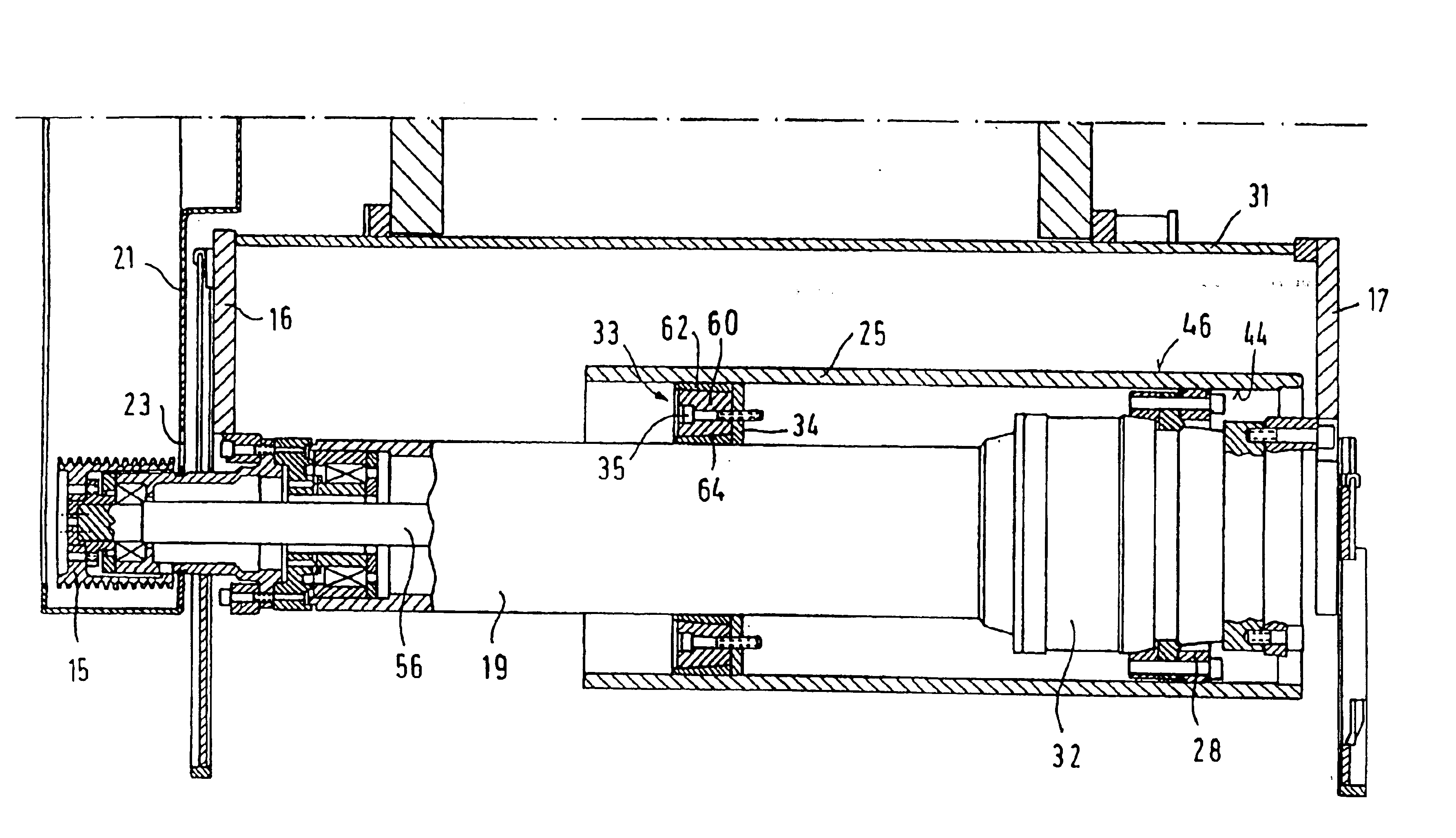

Construction machine and milling roller

InactiveUS6877818B1Quick exchangeEasy to operateMechanical machines/dredgersTilling equipmentsEngineeringMachine

In a construction machine comprising a machine frame (2) having a milling roller (18) arranged for rotation therein, the milling roller (18) comprising a roller base body (19) driven by a milling roller drive device (11 to 15) via a transmission unit (32), and a milling tube (25) to be coaxially mounted on the roller base body (19) and to be attached in a manner allowing exchange thereof, with the milling tube (25) carrying cutting tools on its outer surface (46), it is provided that the milling tube (25) comprises fastening elements (28), radially projecting from the inner surface (44), by which the milling tube (25) can be mounted in a rotationally fixed manner to the roller base body (19) or to a member connected to the roller base body (19).

Owner:WIRTGEN GMBH

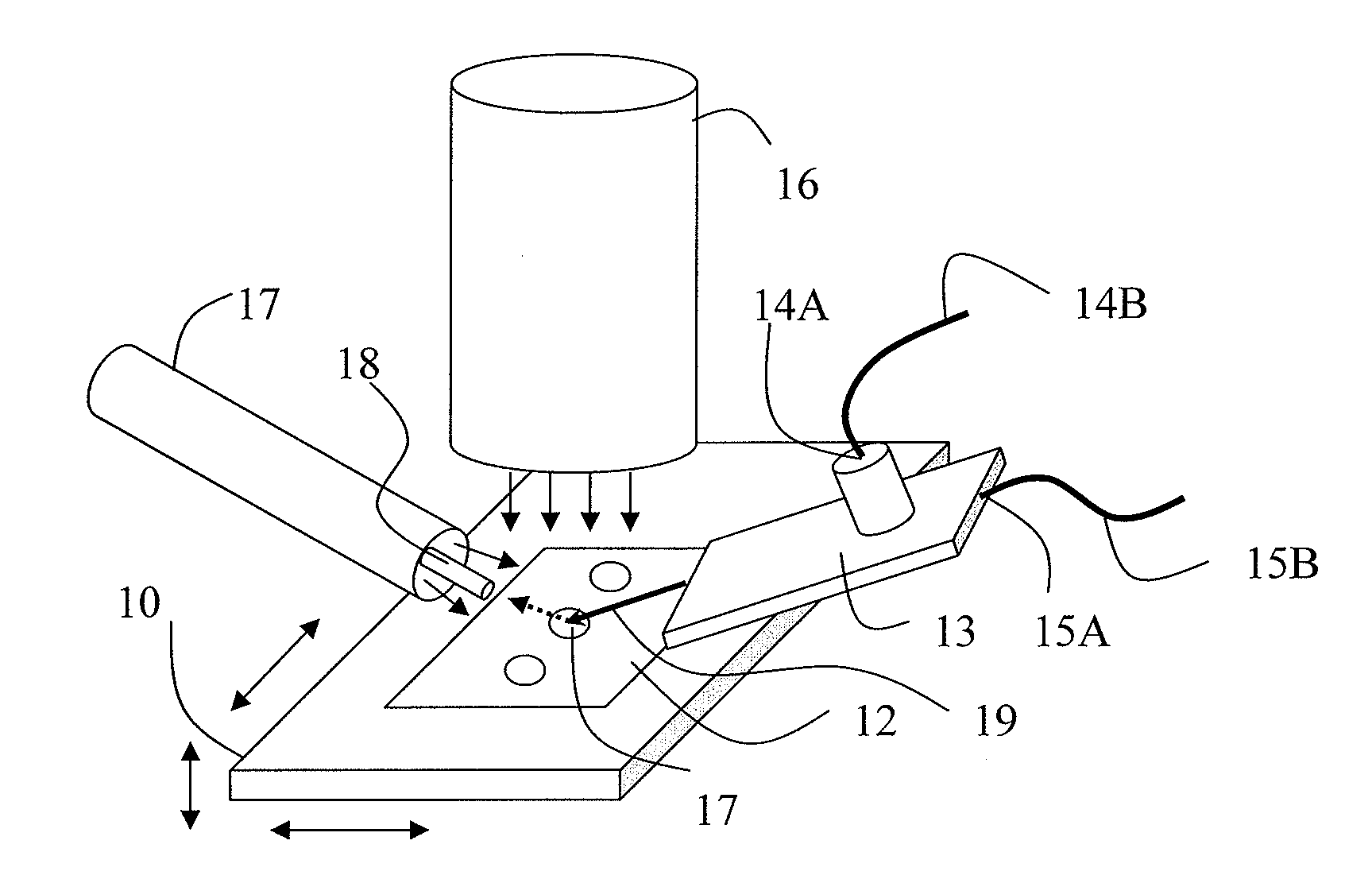

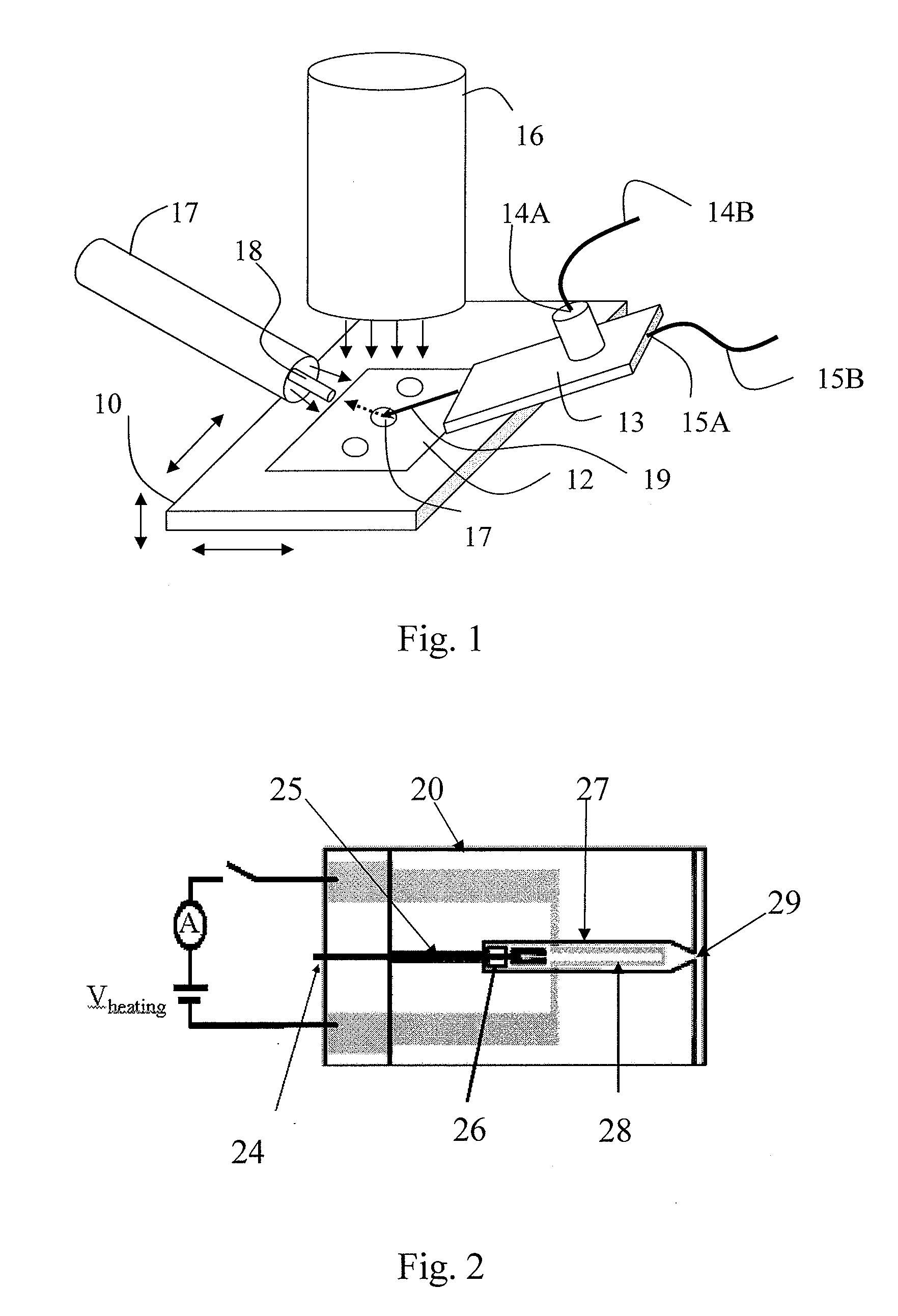

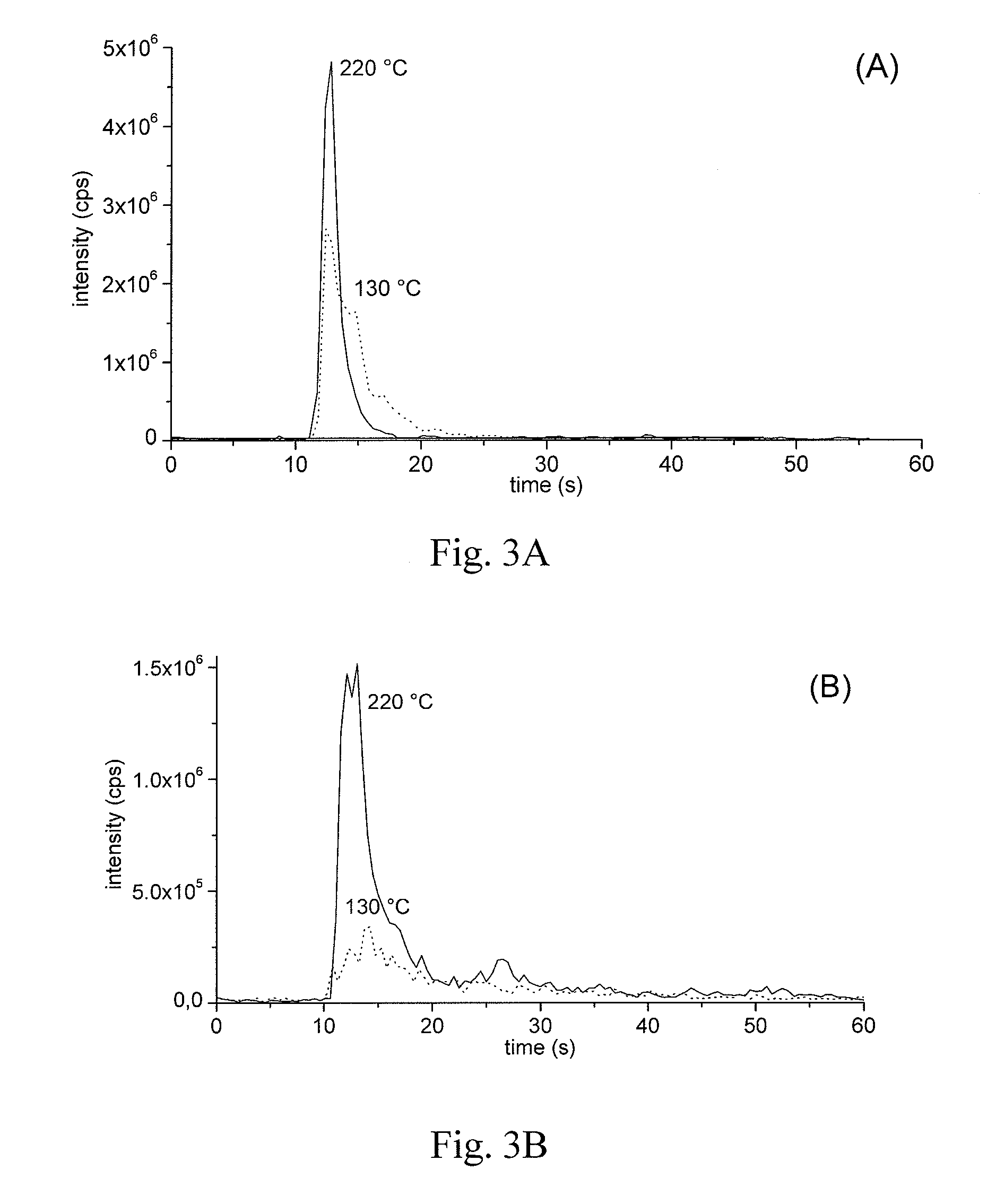

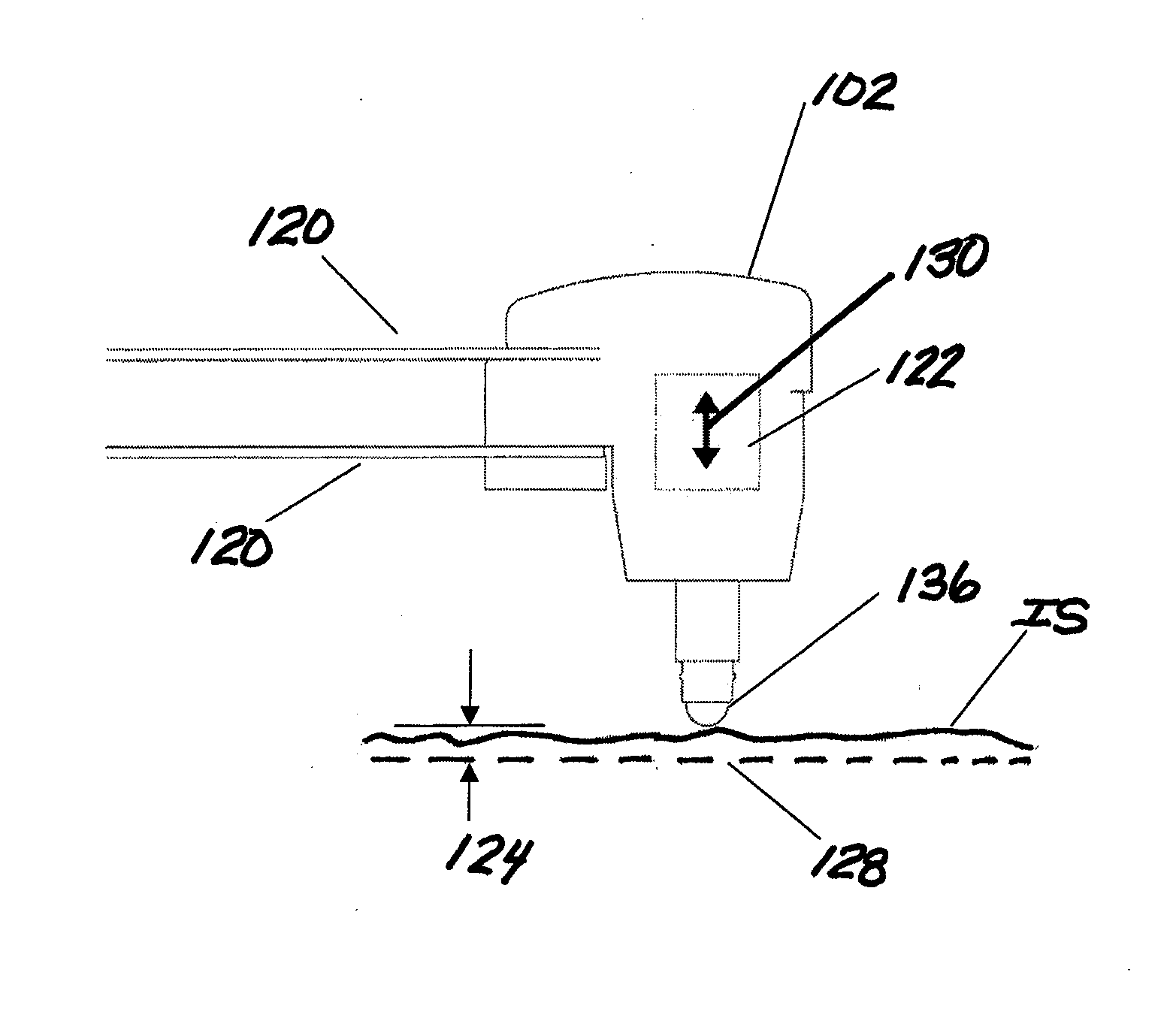

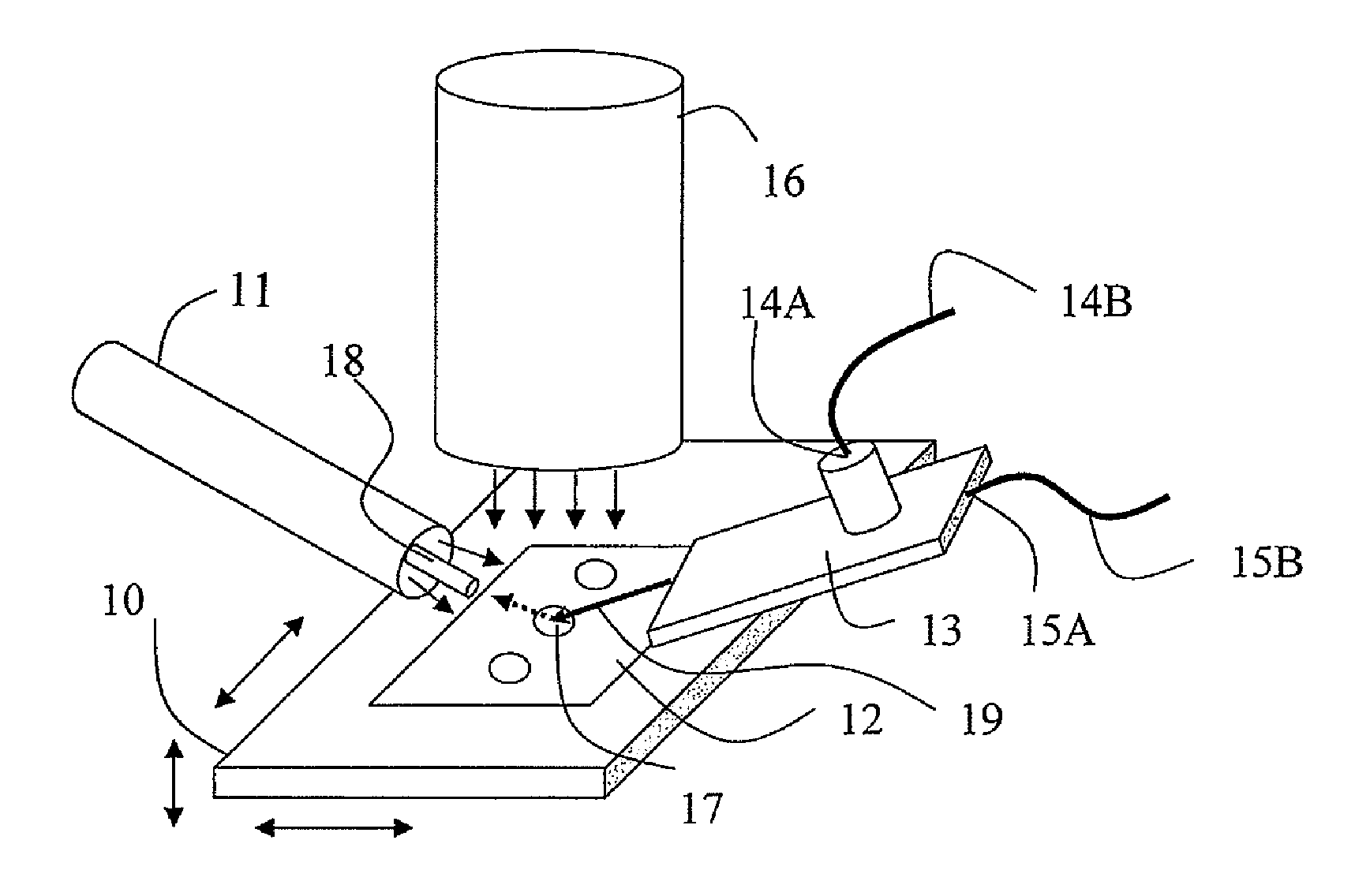

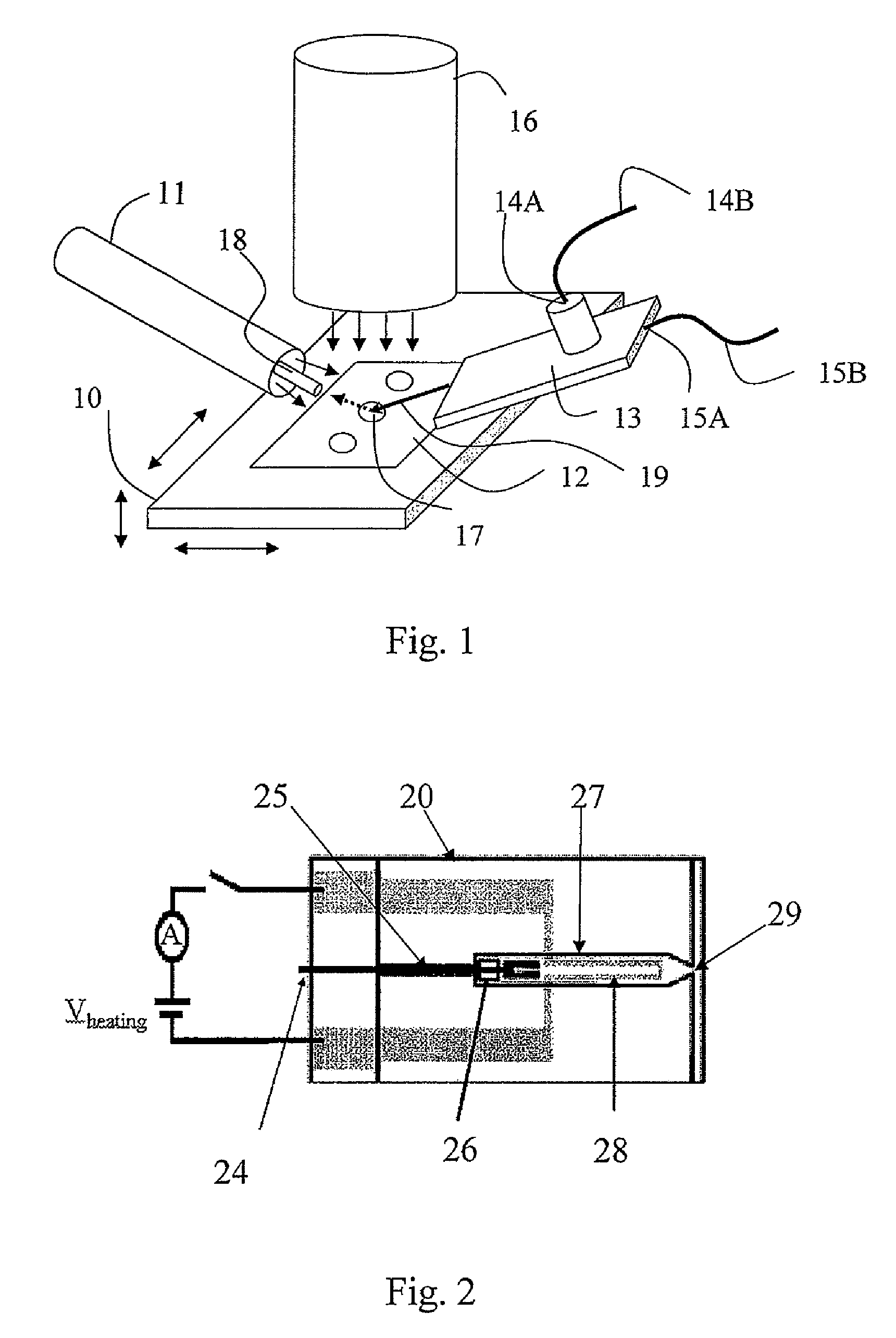

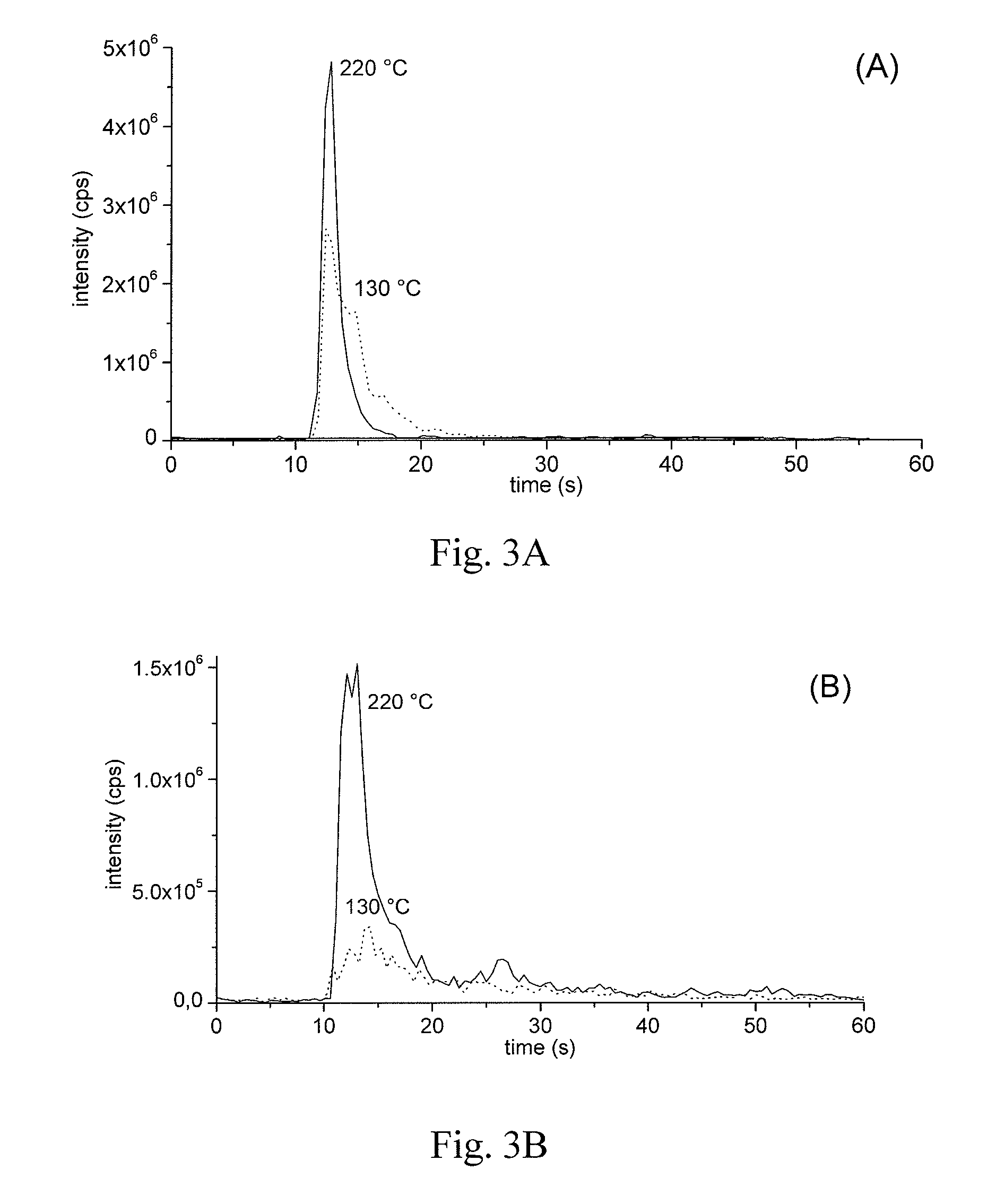

Method and system for desorbing and ionizing chemical compounds from surfaces

InactiveUS20090159790A1Efficient productionSimple technologyParticle separator tubesIsotope separationAnalyteDesorption

The invention relates to a method and system for ionizing analyte-containing sample lying on a surface of a substrate. The method comprises directing to the sample a heated flow of desorption gas in order to desorb analyte from the surface, and simultaneously directing to the sample light capable of ionizing the desorbed analyte in the presence of the desorption gas. The invention provides a method and system suitable for efficiently producing ions of neutral and nonpolar molecules on surfaces, for example for mass spectrometric purposes.

Owner:LICENTIA OY

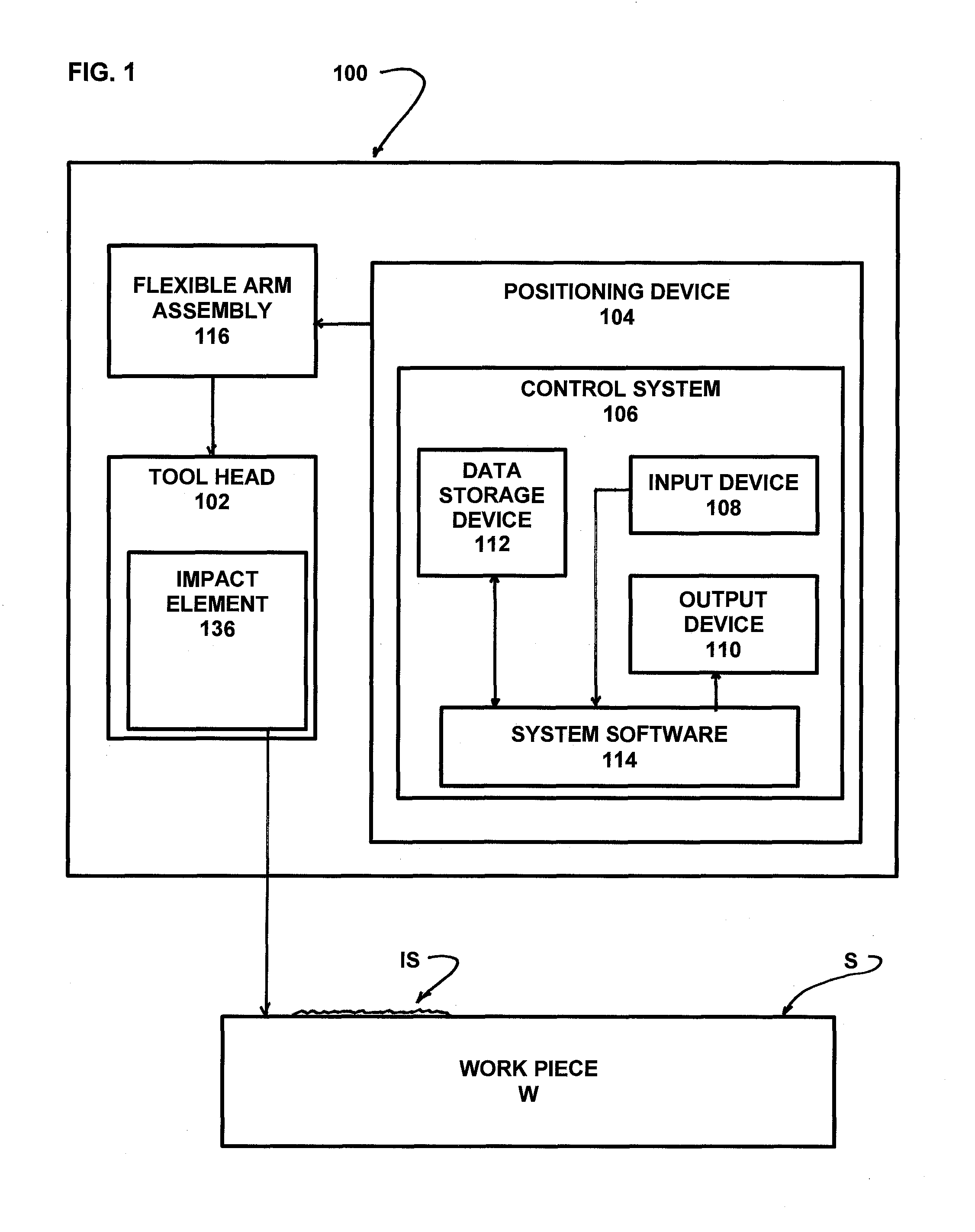

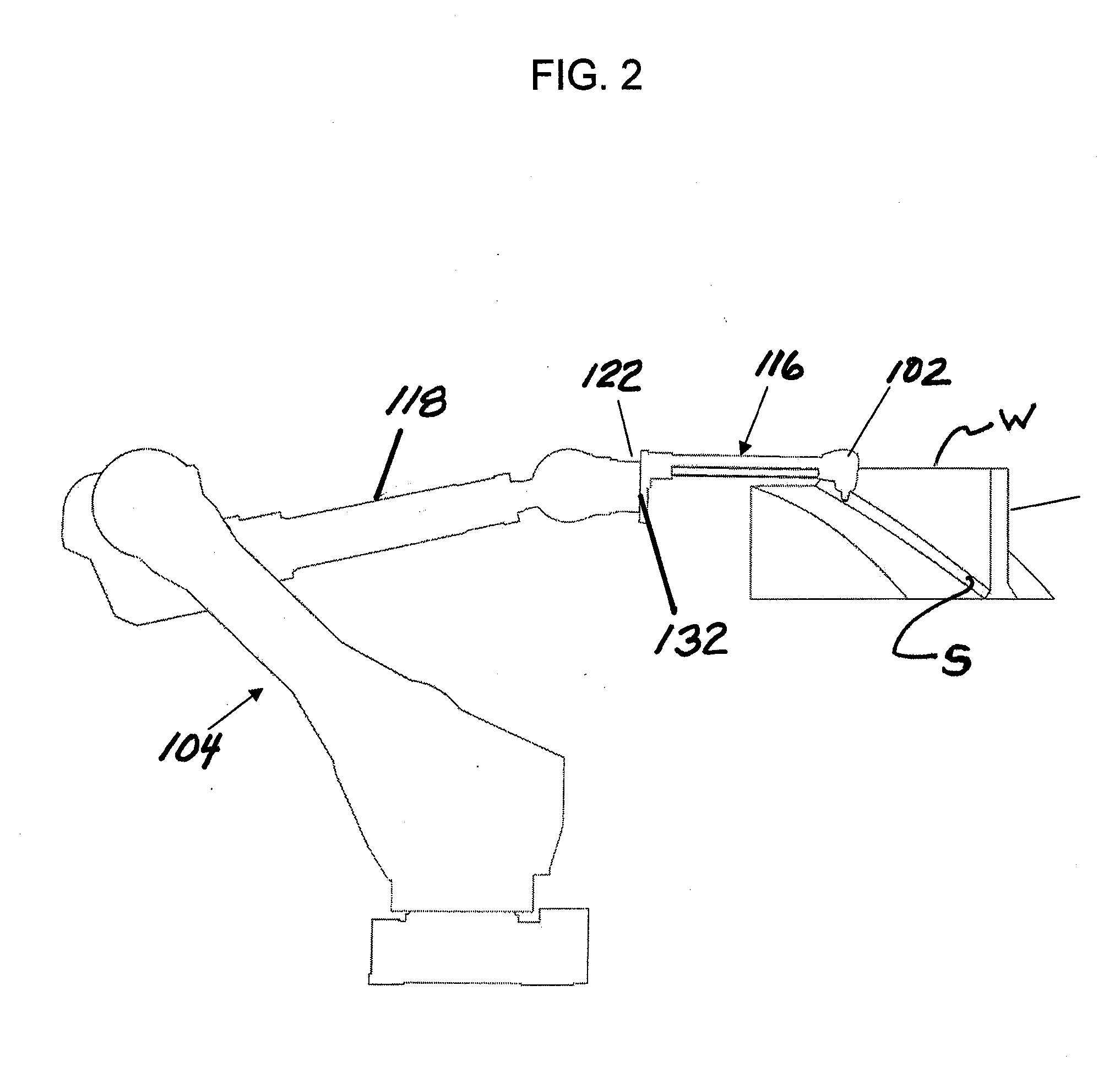

Method and compression apparatus for introducing residual compression into a component having a regular or an irregular shaped surface

ActiveUS20140007394A1Freedom of movementDeformation MinimizationBurnishing machinesGrinding machinesCompression deviceClosed loop

A method and apparatus for improving the fatigue and stress corrosion cracking performance of irregular surfaces, such as welds assemblies of components, using a positioning system, such as a robotic or CNC machine, to position a tool head for inducing compression along and into the surface of a workpiece to automatically follow the surface irregularities. The method and apparatus operates to follow a virtual control surface located below the actual surface of the workpiece thereby allowing the irregular topography surface to be uniformly processed with closed loop process control.

Owner:SURFACE TECH HLDG

Method and system for desorbing and ionizing chemical compounds from surfaces

InactiveUS8044346B2Efficient productionEasy to changeParticle separator tubesIsotope separationAnalyteChemical compound

The invention relates to a method and system for ionizing analyte-containing sample lying on a surface of a substrate. The method comprises directing to the sample a heated flow of desorption gas in order to desorb analyte from the surface, and simultaneously directing to the sample light capable of ionizing the desorbed analyte in the presence of the desorption gas. The invention provides a method and system suitable for efficiently producing ions of neutral and nonpolar molecules on surfaces, for example for mass spectrometric purposes.

Owner:LICENTIA OY

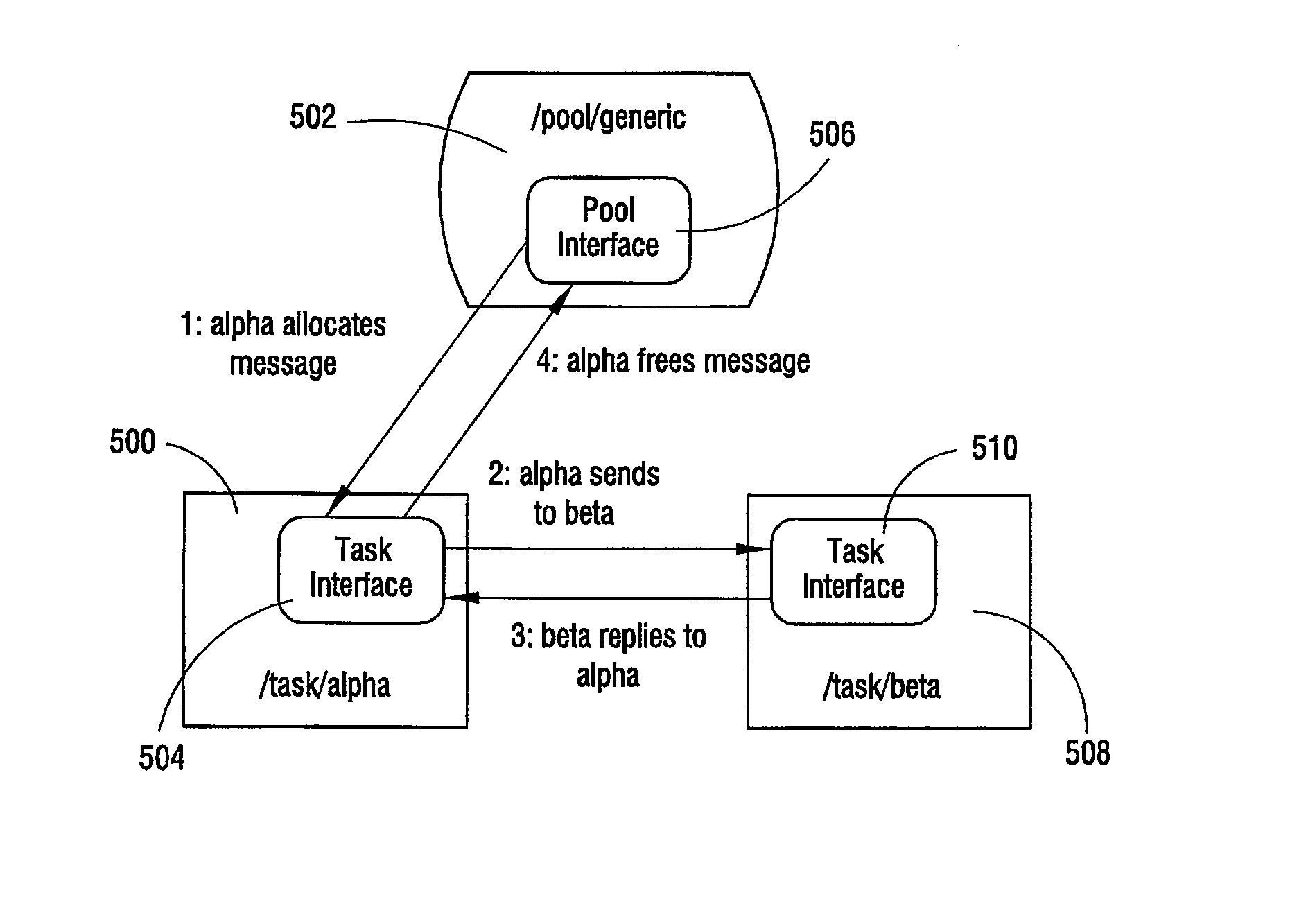

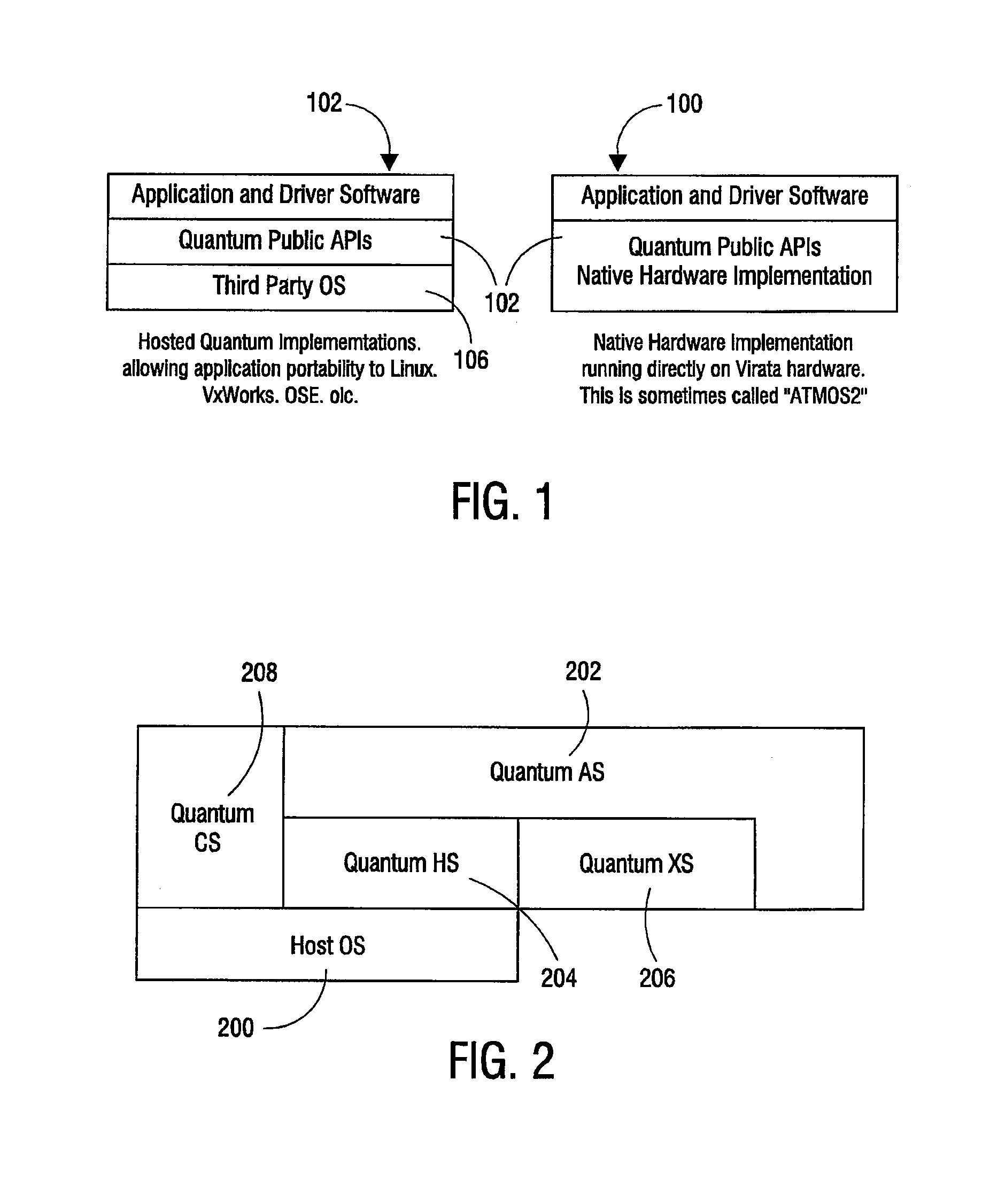

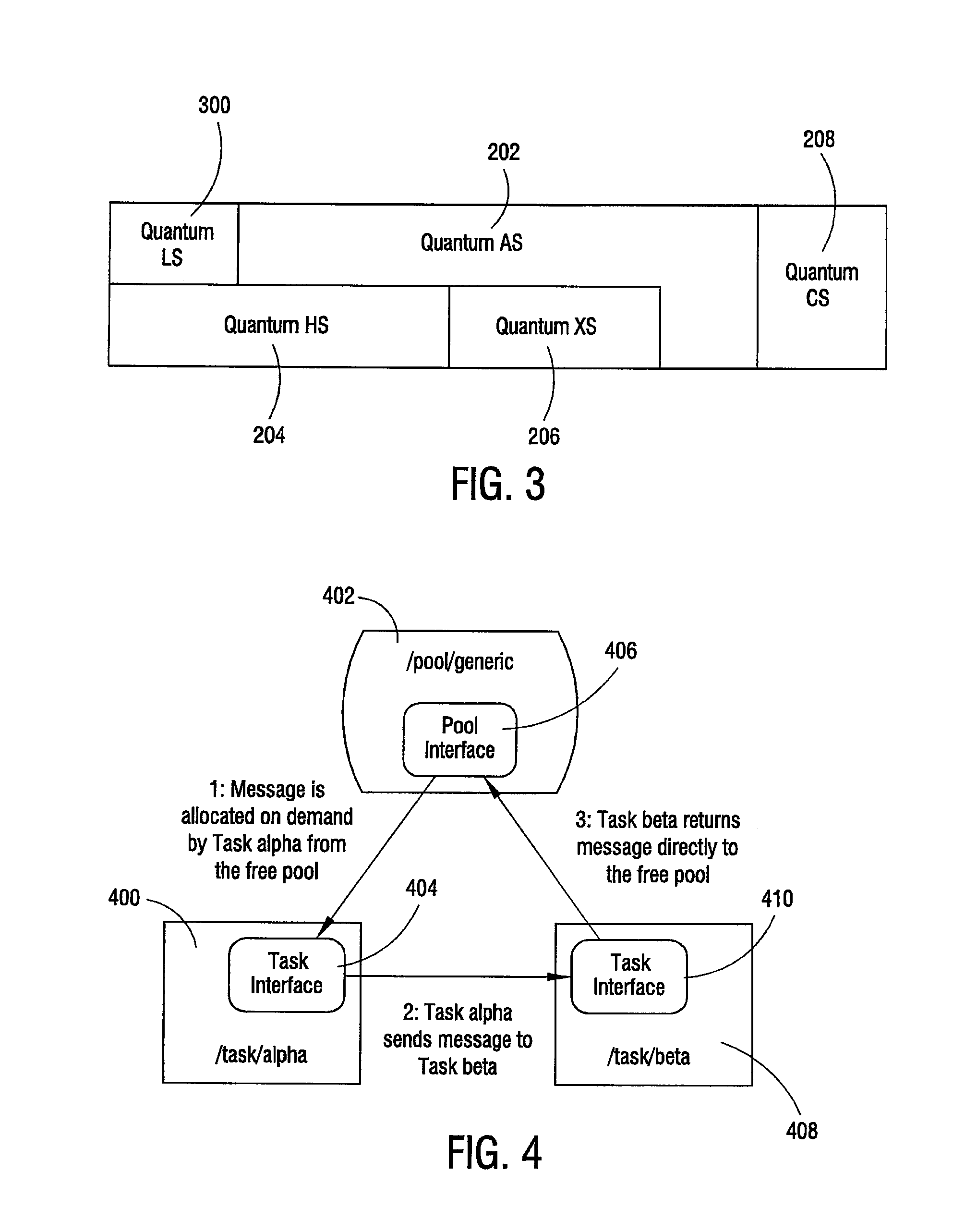

Systems and methods for managing shared resources in a computer system

InactiveUS8028298B2Improve performanceSimple designMultiprogramming arrangementsSoftware simulation/interpretation/emulationOperational systemShared resource

An operating system is provided wherein a plurality of objects are established and registered in response to requests from hardware or software associated with the computer system. The objects include at least one type, at least one attribute, and a handle. The plurality of objects are then manipulated to effect processing and exchange of information.

Owner:SYNAPTICS INC

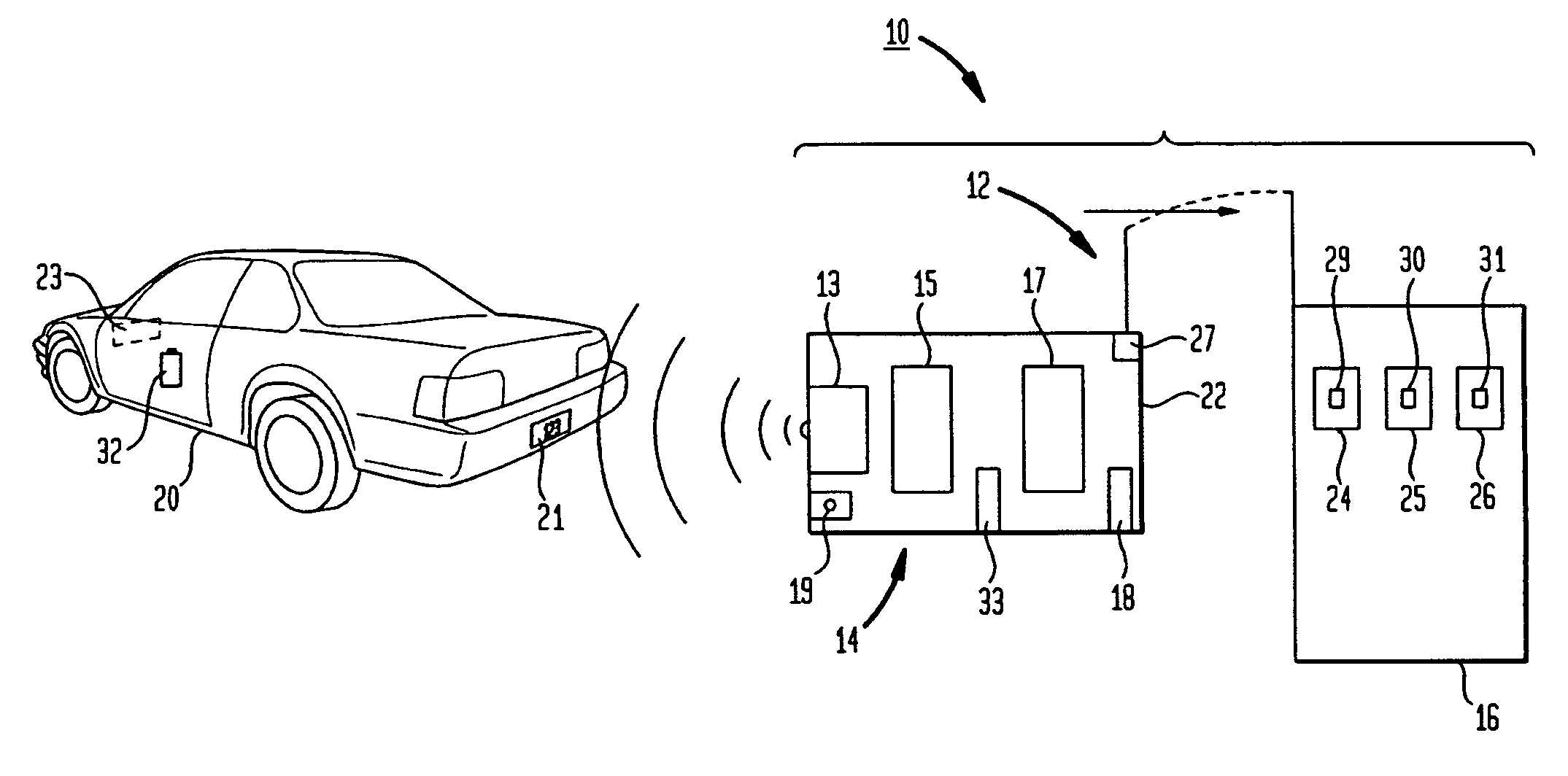

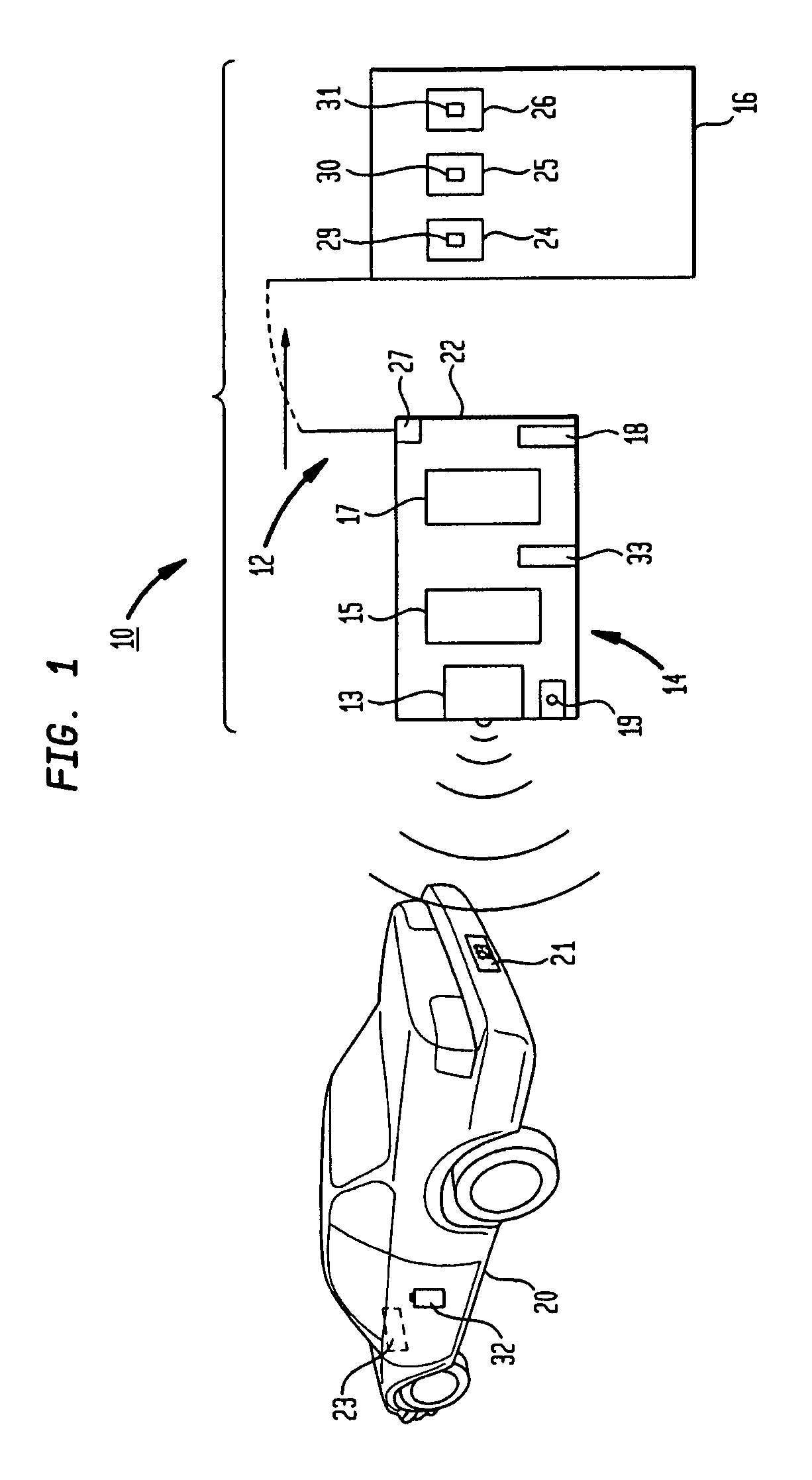

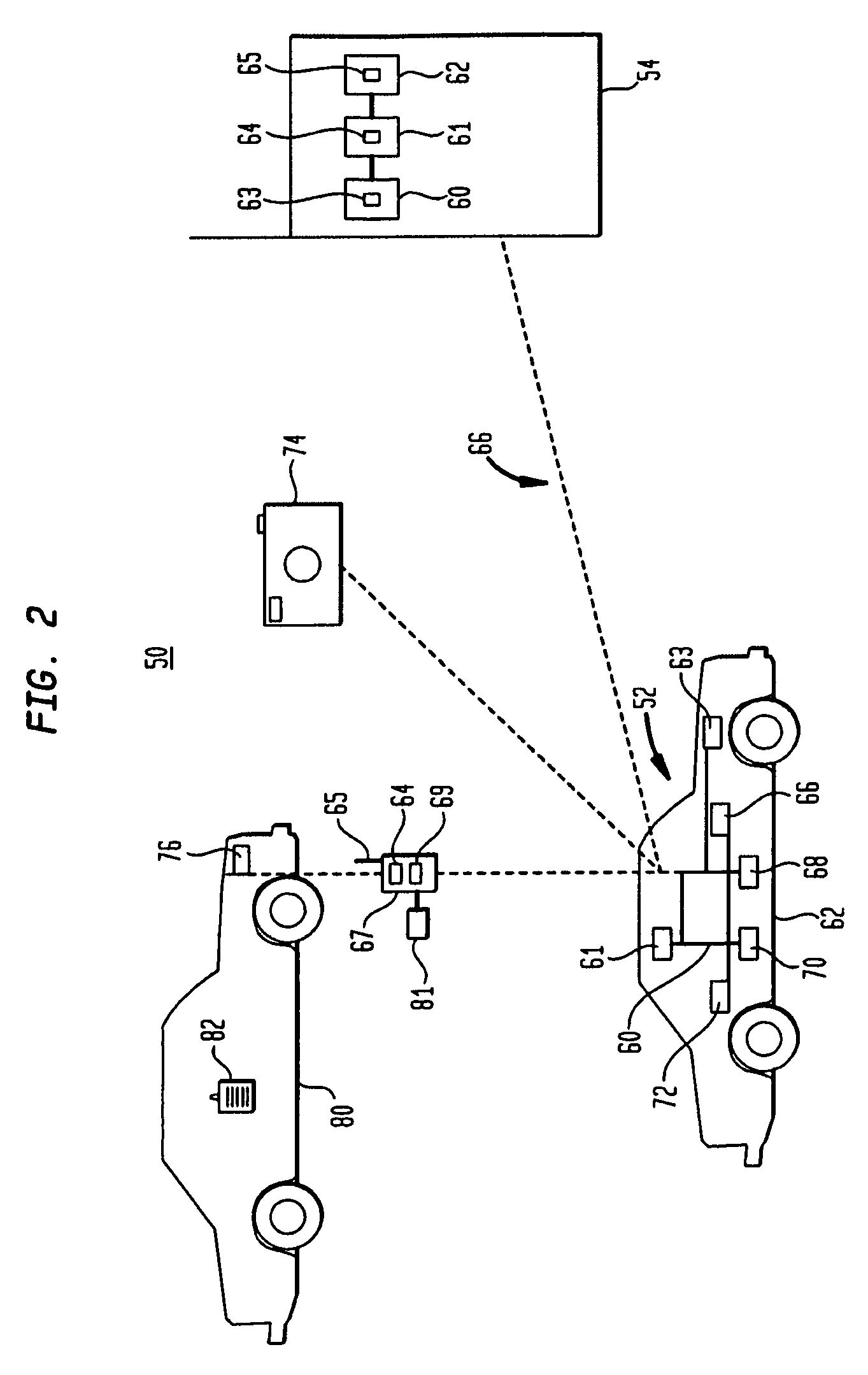

Vehicle Violation Enforcement System And Method

ActiveUS20080238719A1Efficient collectionMinimizing work flow/loadTicket-issuing apparatusRoad vehicles traffic controlTelecommunications linkMobile data terminal

A vehicle violation enforcement and noticing system that includes a first server and a second server. The first server contains a vehicle information database that is in communication with the second server. The second server is a mobile data terminal that allows for the identification of vehicles and retrieves the vehicle information pertaining to the identified vehicles from the first server via a communications link. Once the vehicle information has been received, appropriate enforcement tactics are prepared based upon the received vehicle information. The appropriate enforcement tactics may include printing a notice informing a vehicle user of the current and outstanding debt associated with the vehicle for placement directly on the vehicle, writing a notice as per instructions displayed by the second server, for placement directly on the vehicle, booting the vehicle, towing the vehicle and / or informing a second agency of the vehicle location so that the second agency may take appropriate action.

Owner:IPT

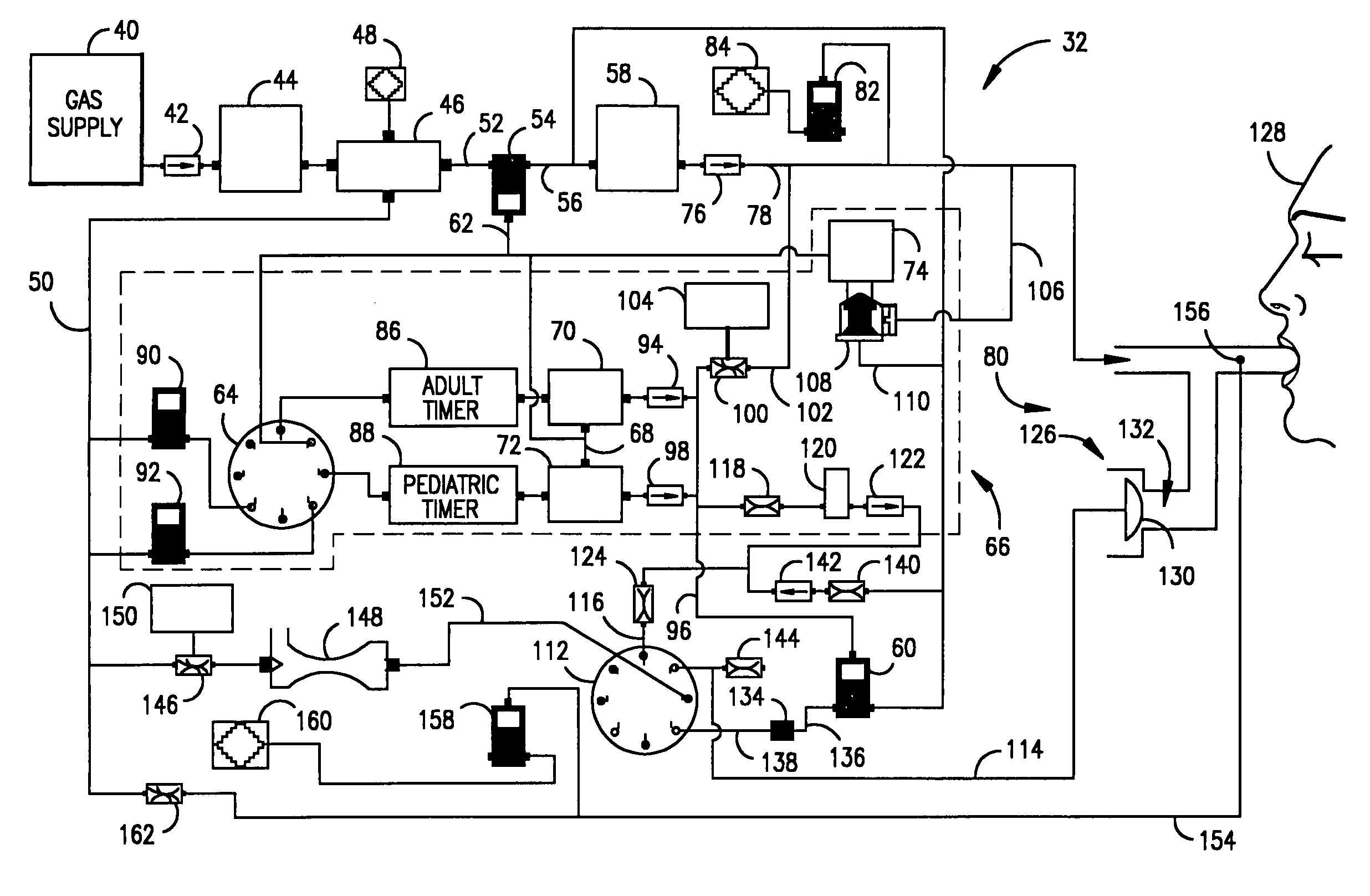

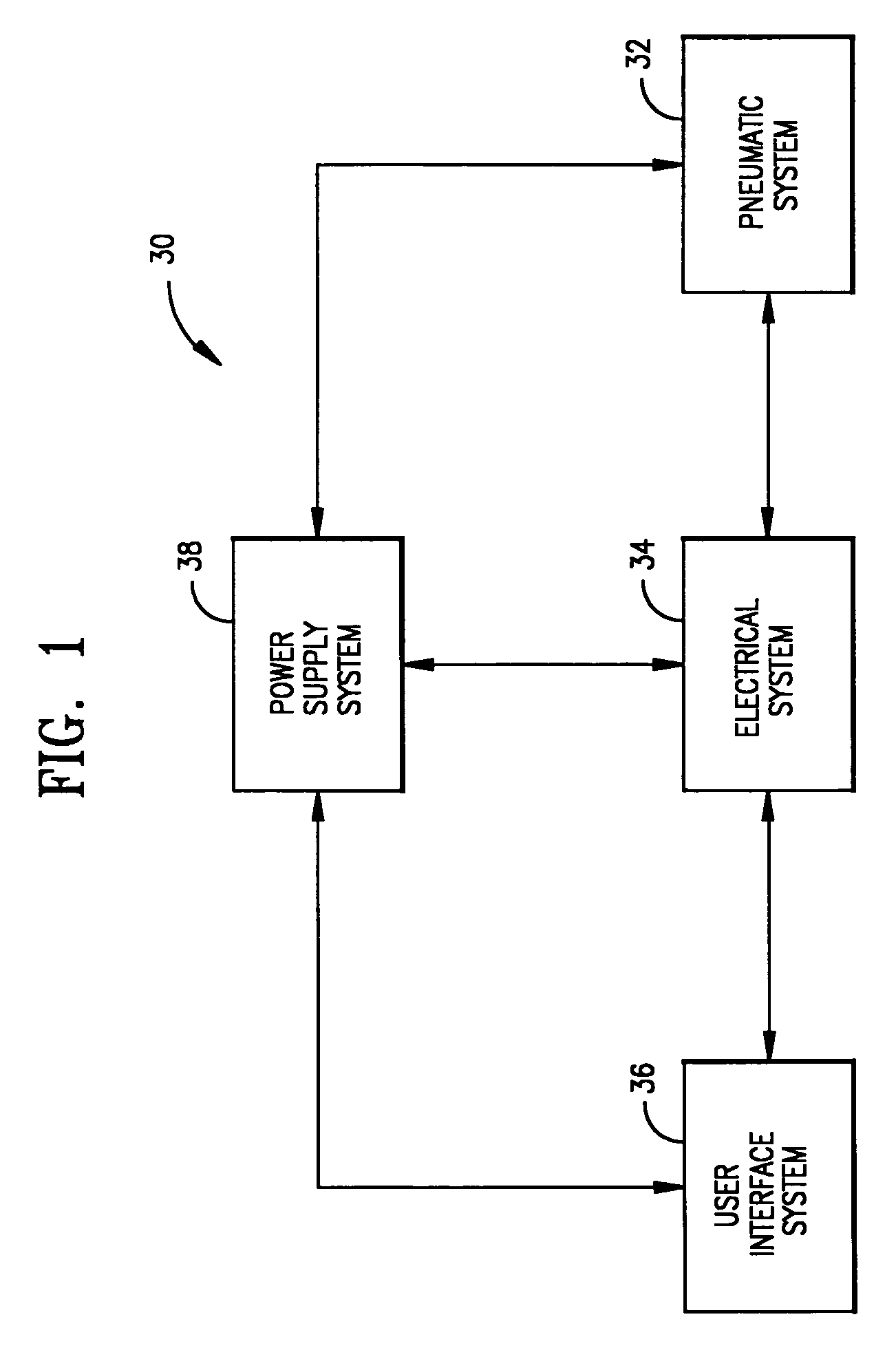

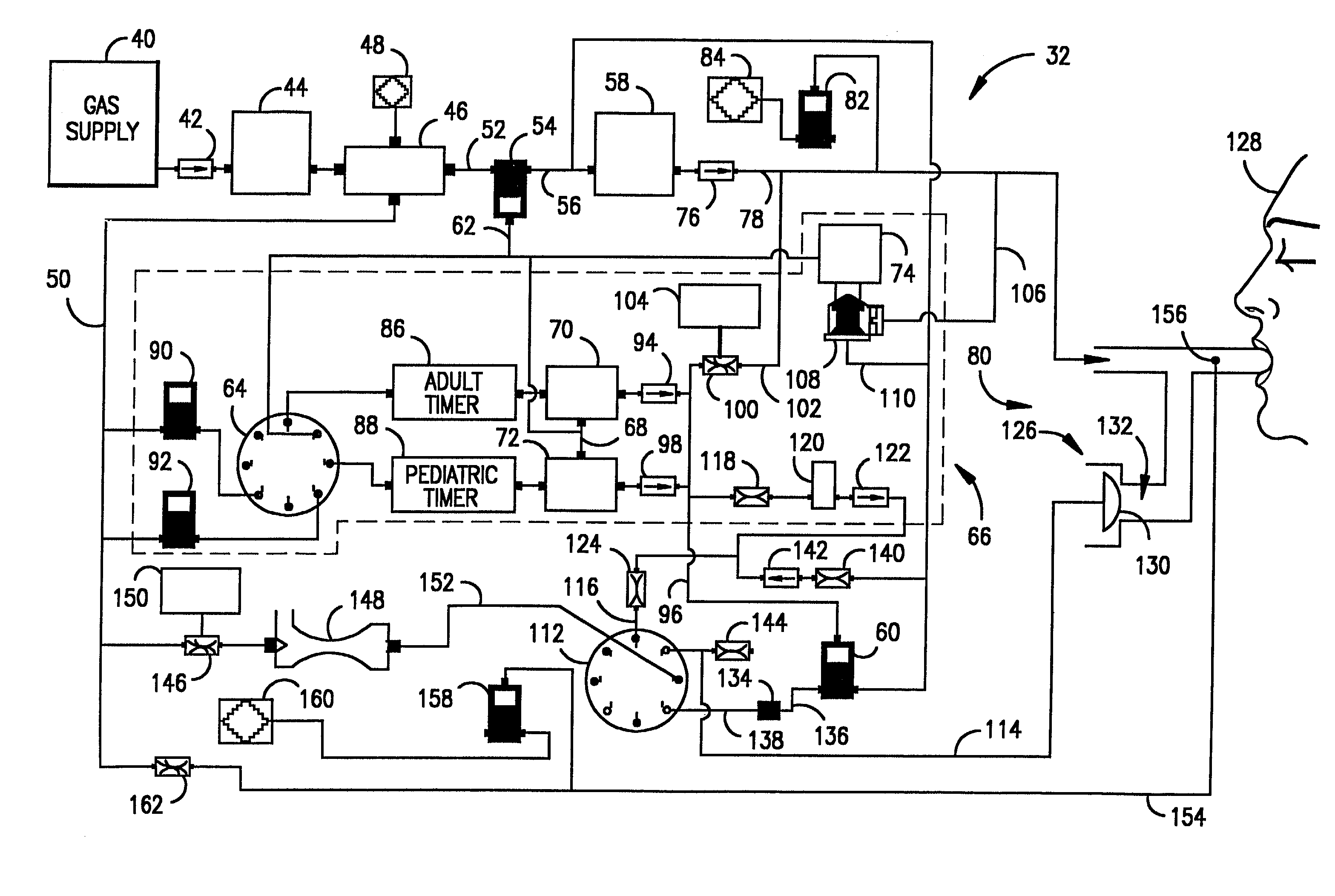

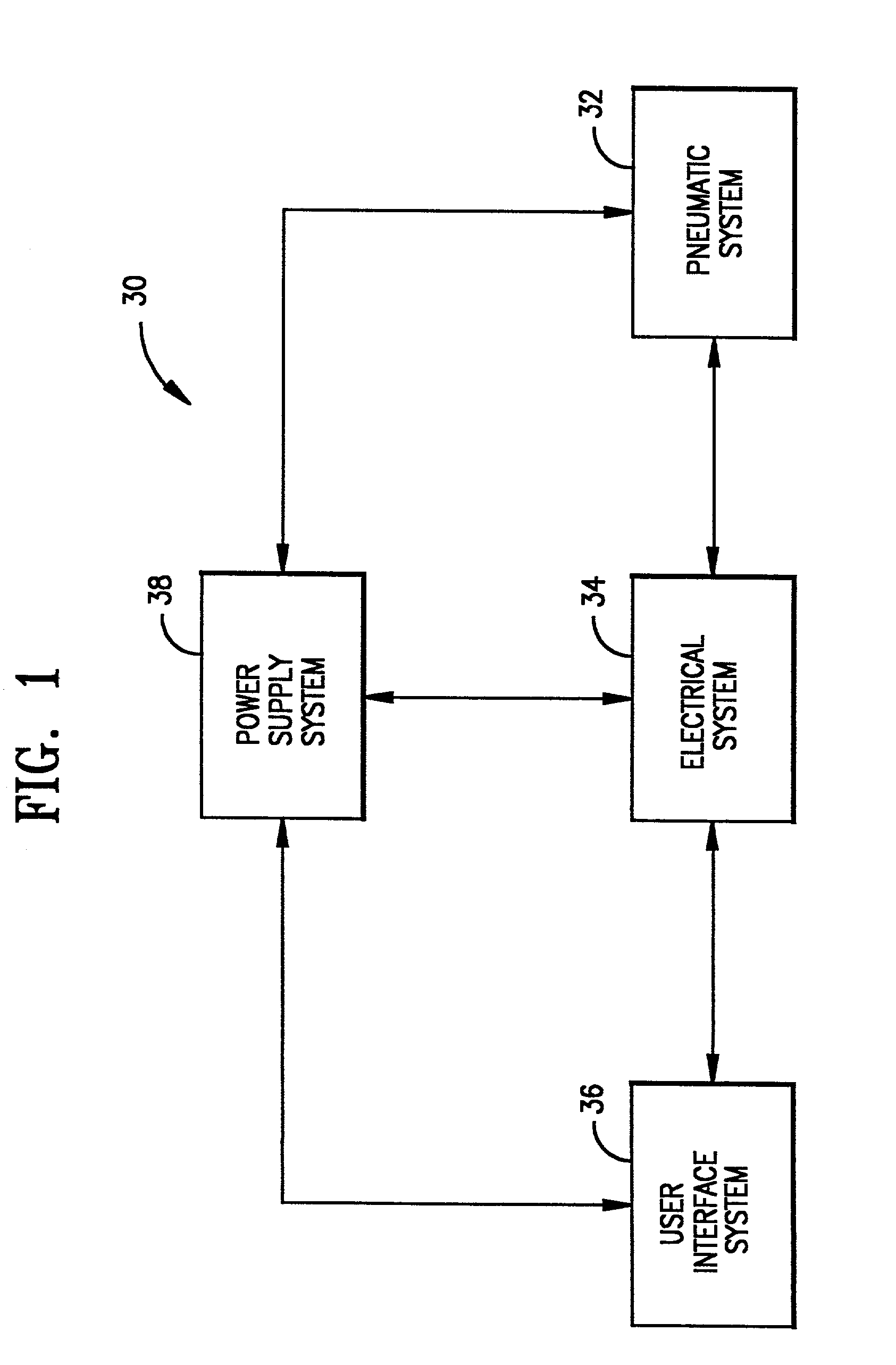

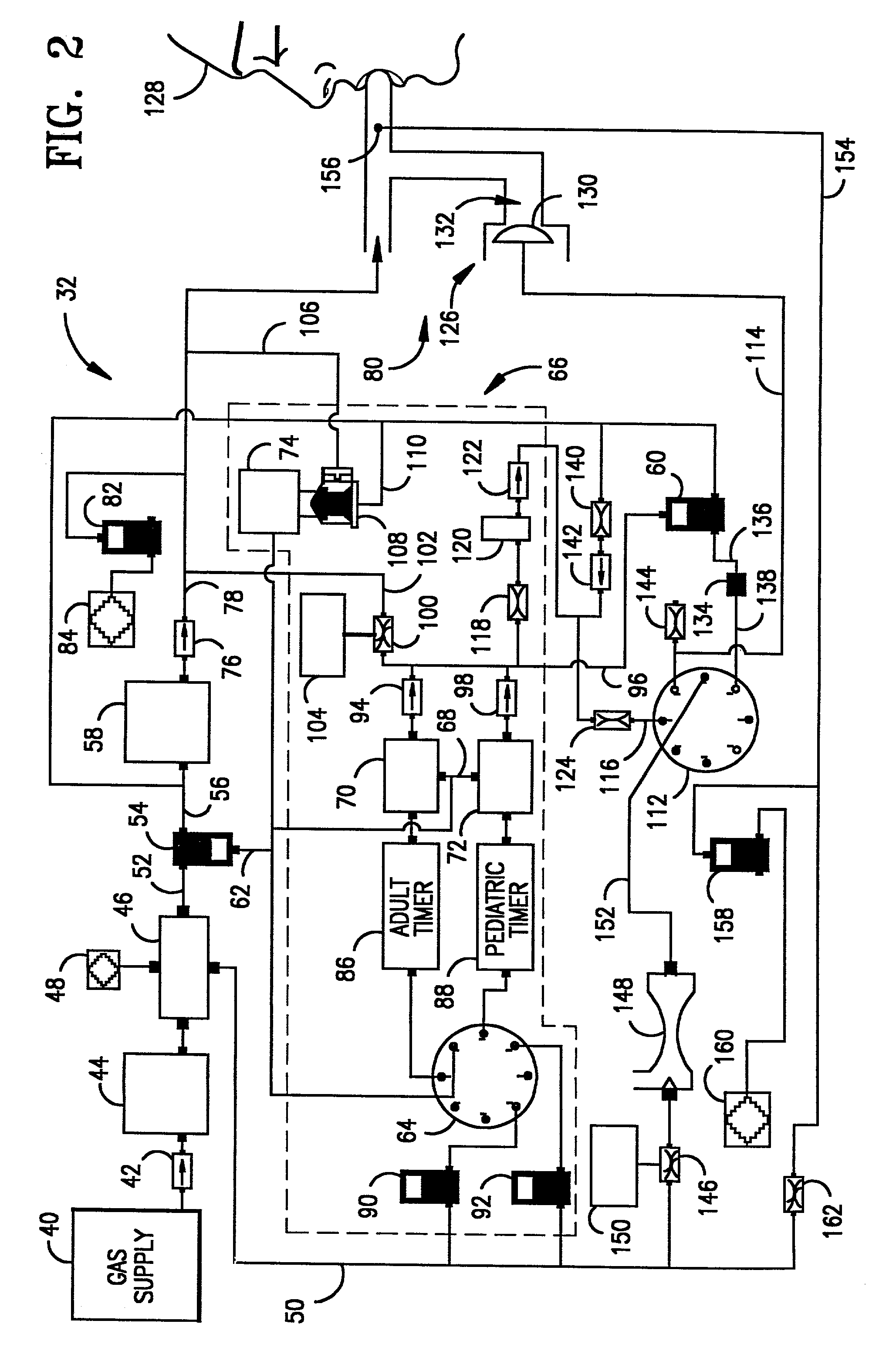

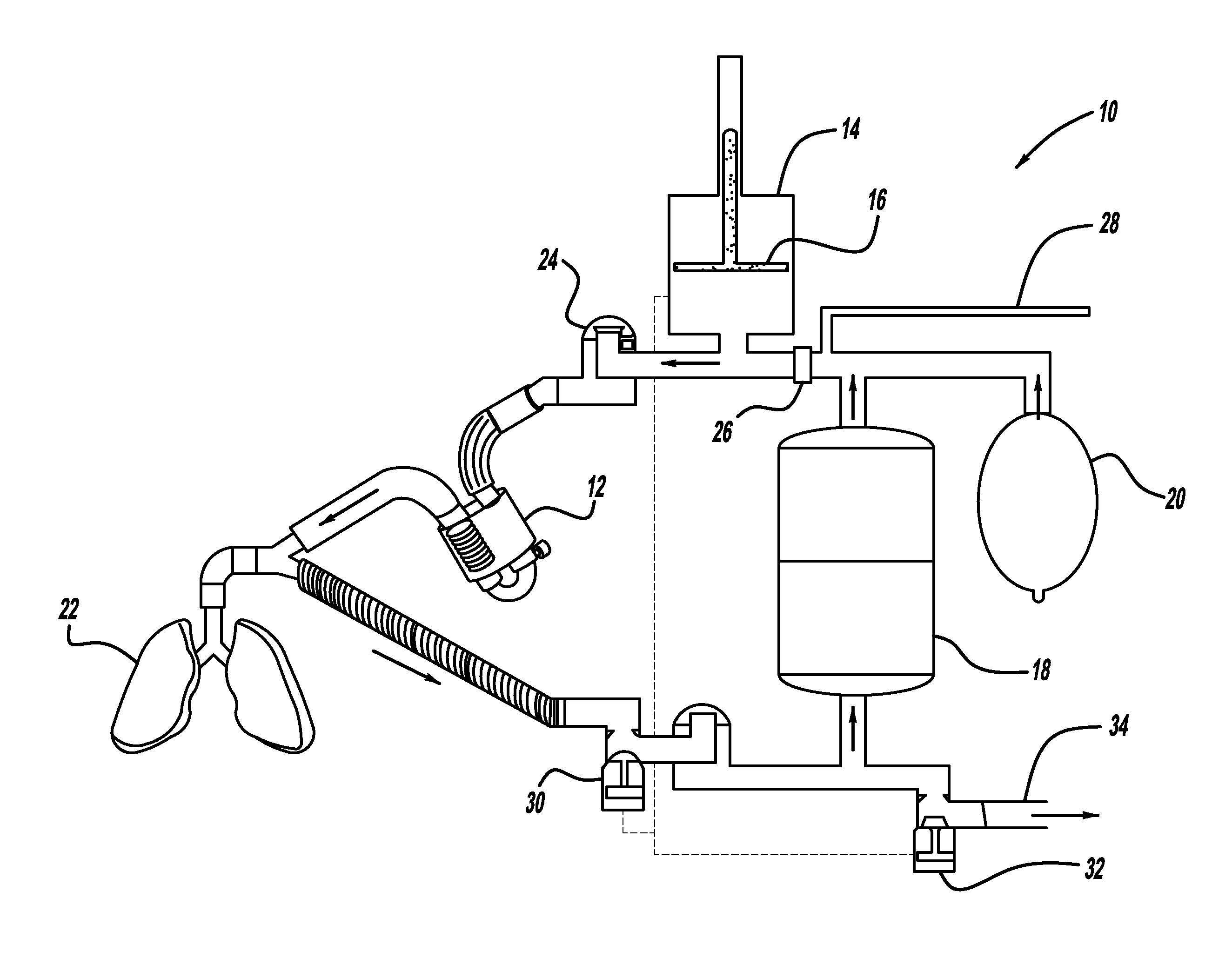

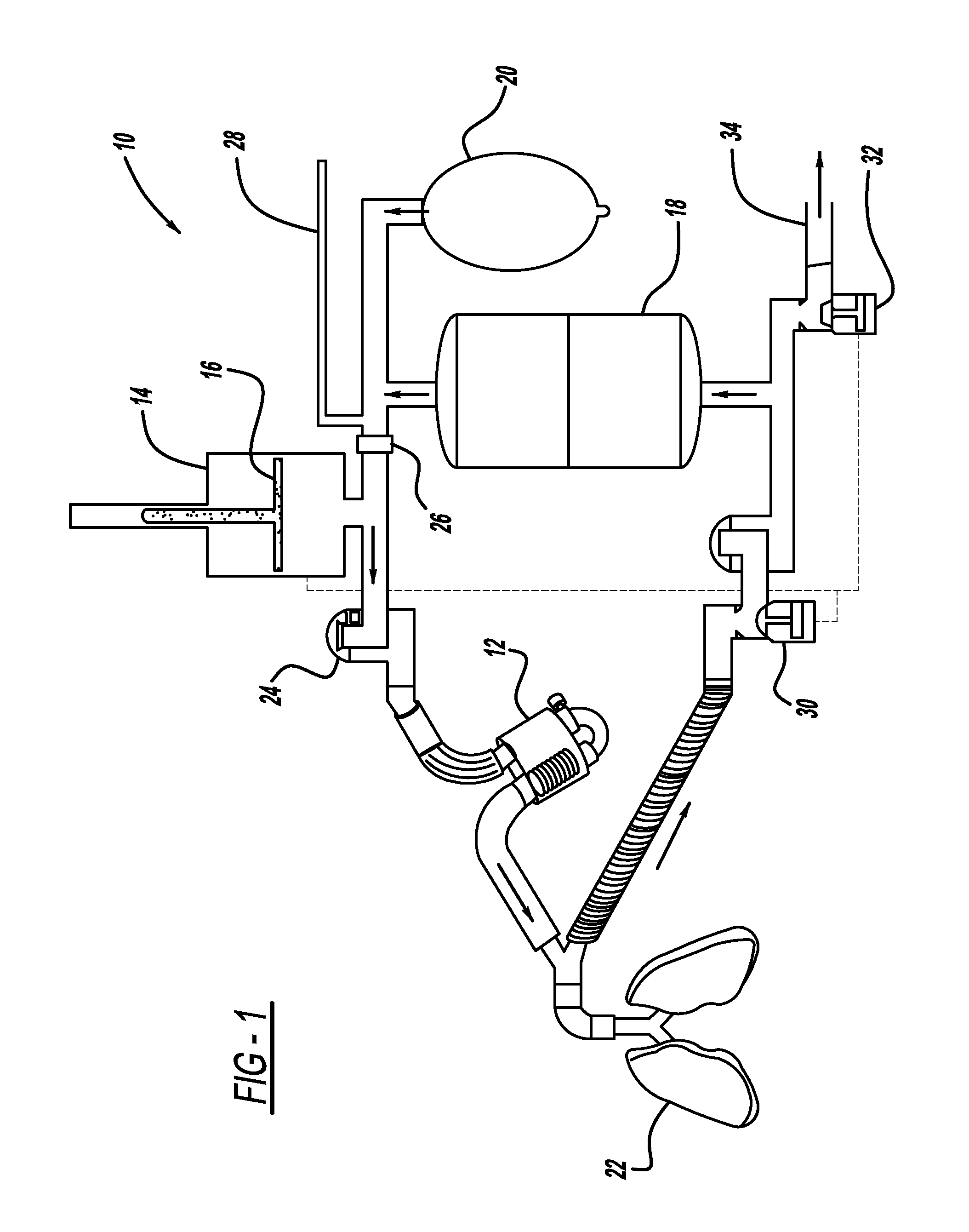

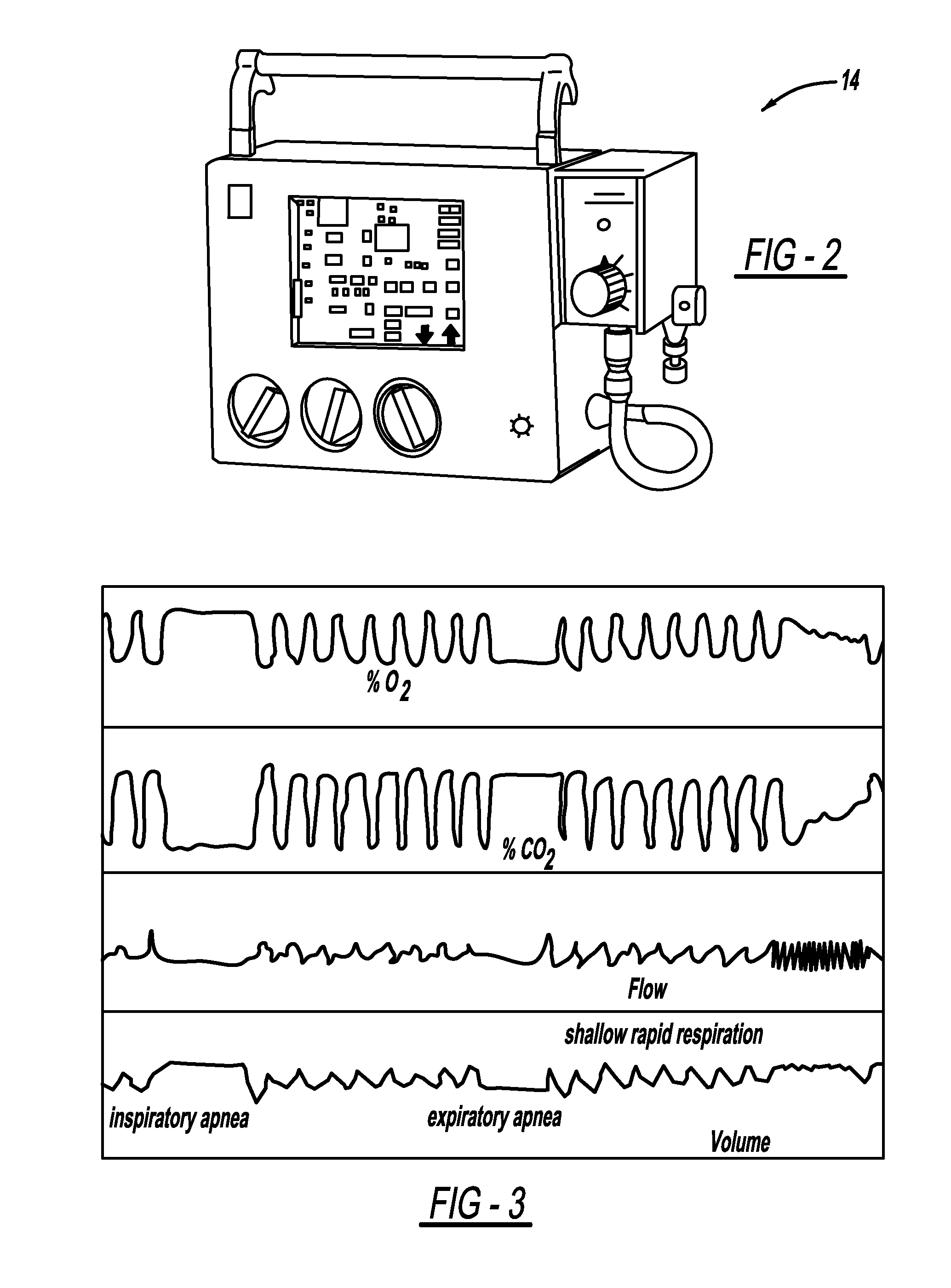

Ventilatory method utilizing body length-based parameter calculations

InactiveUS6976487B1Work lessAvoid dangerRespiratorsOperating means/releasing devices for valvesEngineeringBasic mode

A method and apparatus for operating a ventilator in a primary electronic mode or in a back-up pneumatic mode during primary electronic mode failure. A method and apparatus for operating a ventilator in an advanced mode, having a number of ventilatory modes, or in a basic mode, having a limited number of ventilatory modes is also disclosed.

Owner:UNIV OF FLORIDA RES FOUNDATION INC

High efficiency positive displacement thermodynamic system

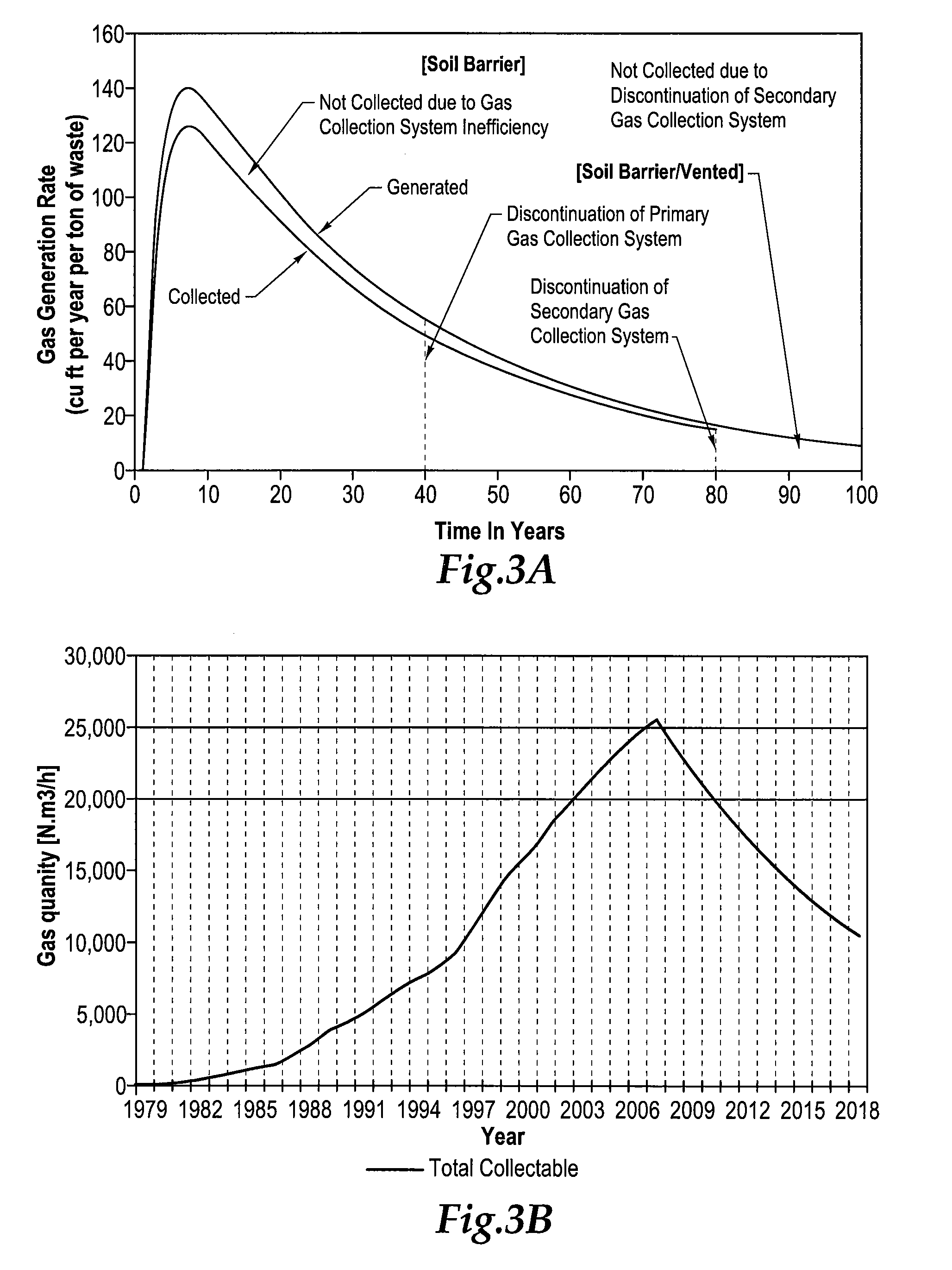

ActiveUS20100050628A1Without decreasing volumetric efficiencySave heatInternal combustion piston enginesCombination enginesPower modeWorking fluid

Devices and methods for moving a working fluid through a controlled thermodynamic cycle in a positive displacement fluid-handling device (20, 20′, 20″) with minimal energy input include continuously varying the relative compression and expansion ratios of the working fluid in respective compressor and expander sections without diminishing volumetric efficiency. In one embodiment, a rotating valve plate arrangement (40, 42, 44, 46) is provided with moveable apertures or windows (48, 50, 56, 58) for conducting the passage of the working fluid in a manner which enables on-the-fly management of the thermodynamic efficiency of the device (20) under varying conditions in order to maximize the amount of mechanical work needed to move the target quantity of heat absorbed and released by the working fluid. When operated in refrigeration modes, the work required to move the heat is minimized. In power modes, the work extracted for the given input heat is maximized.

Owner:STAFFEND GILBERT

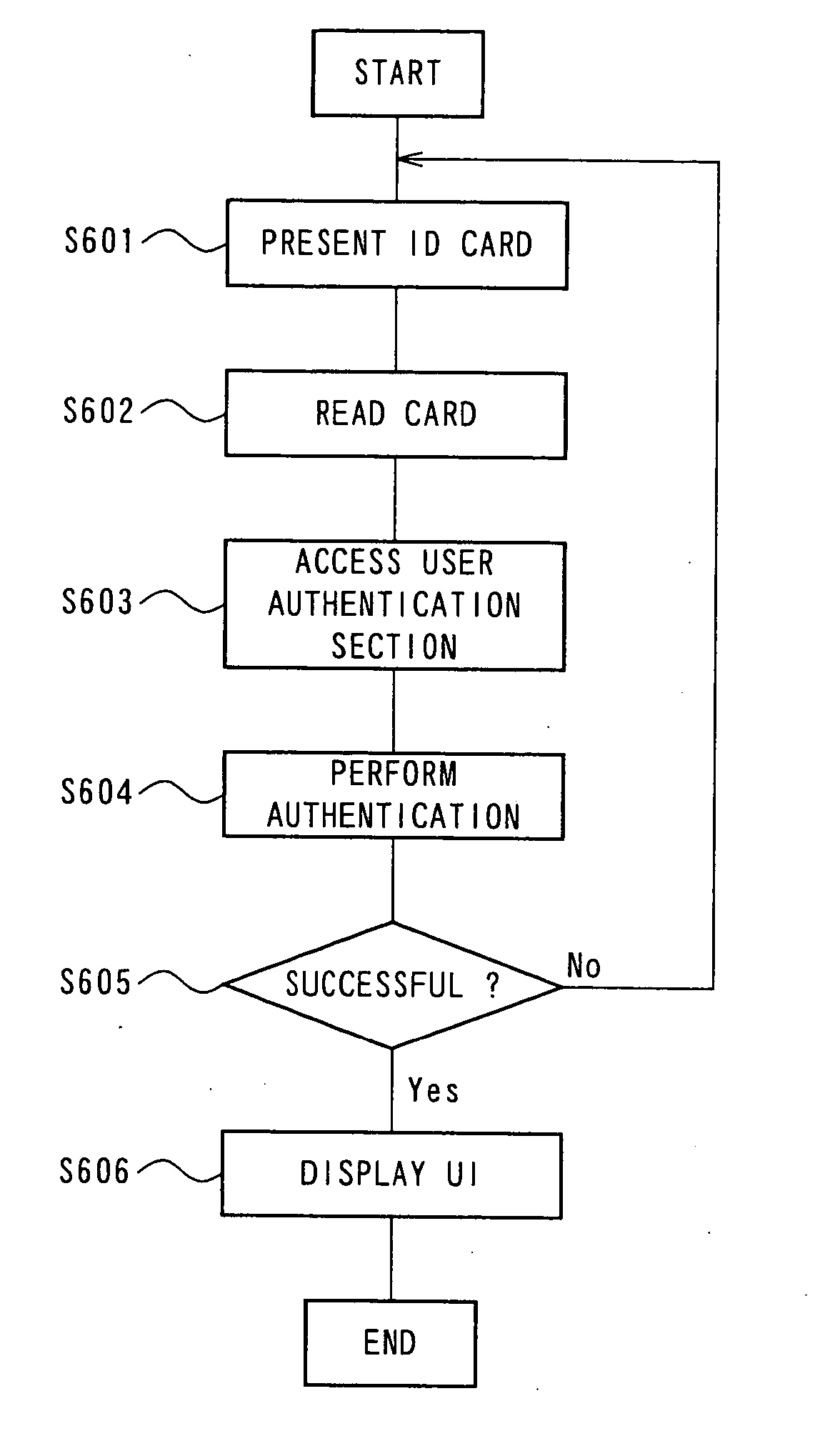

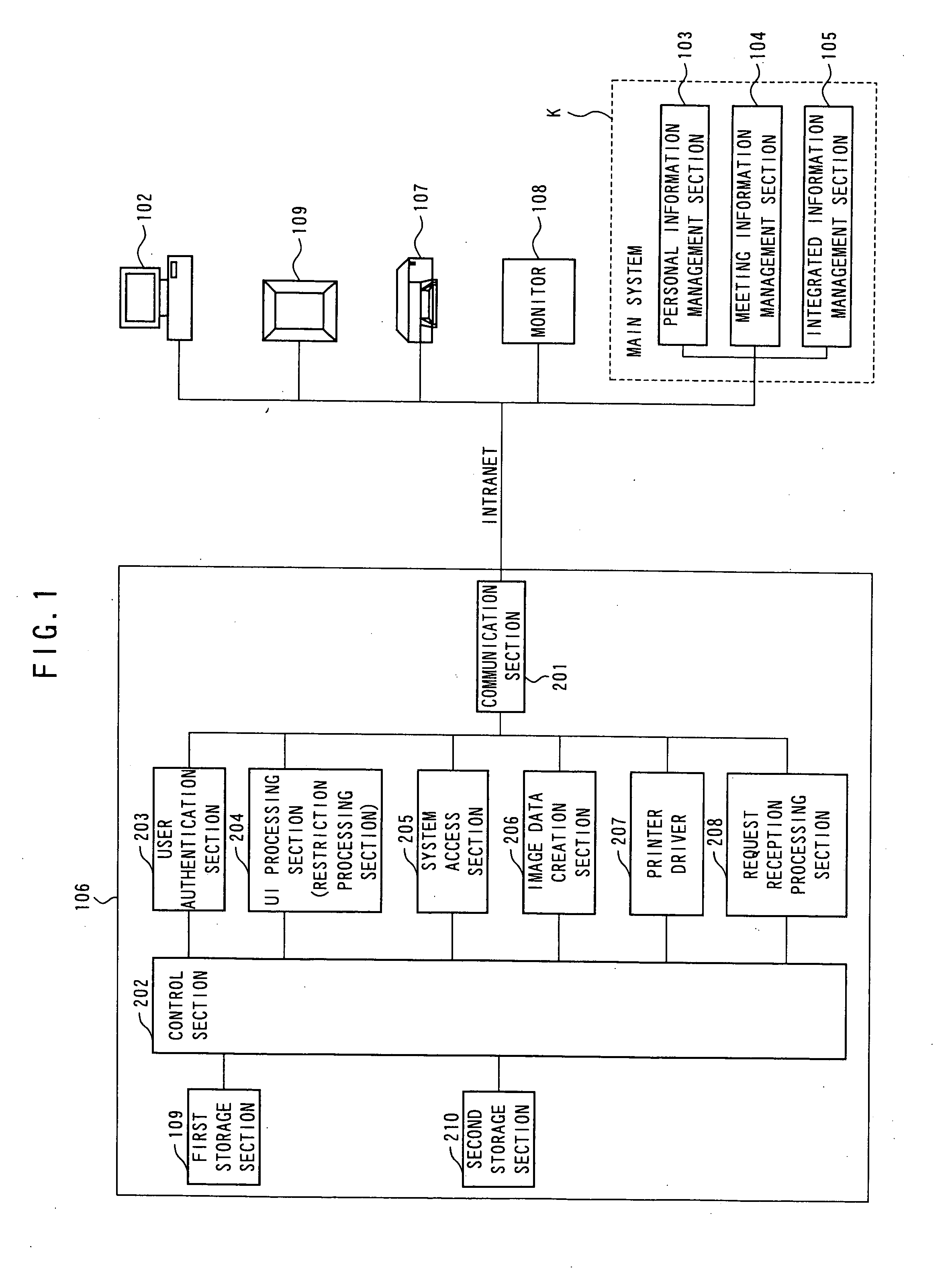

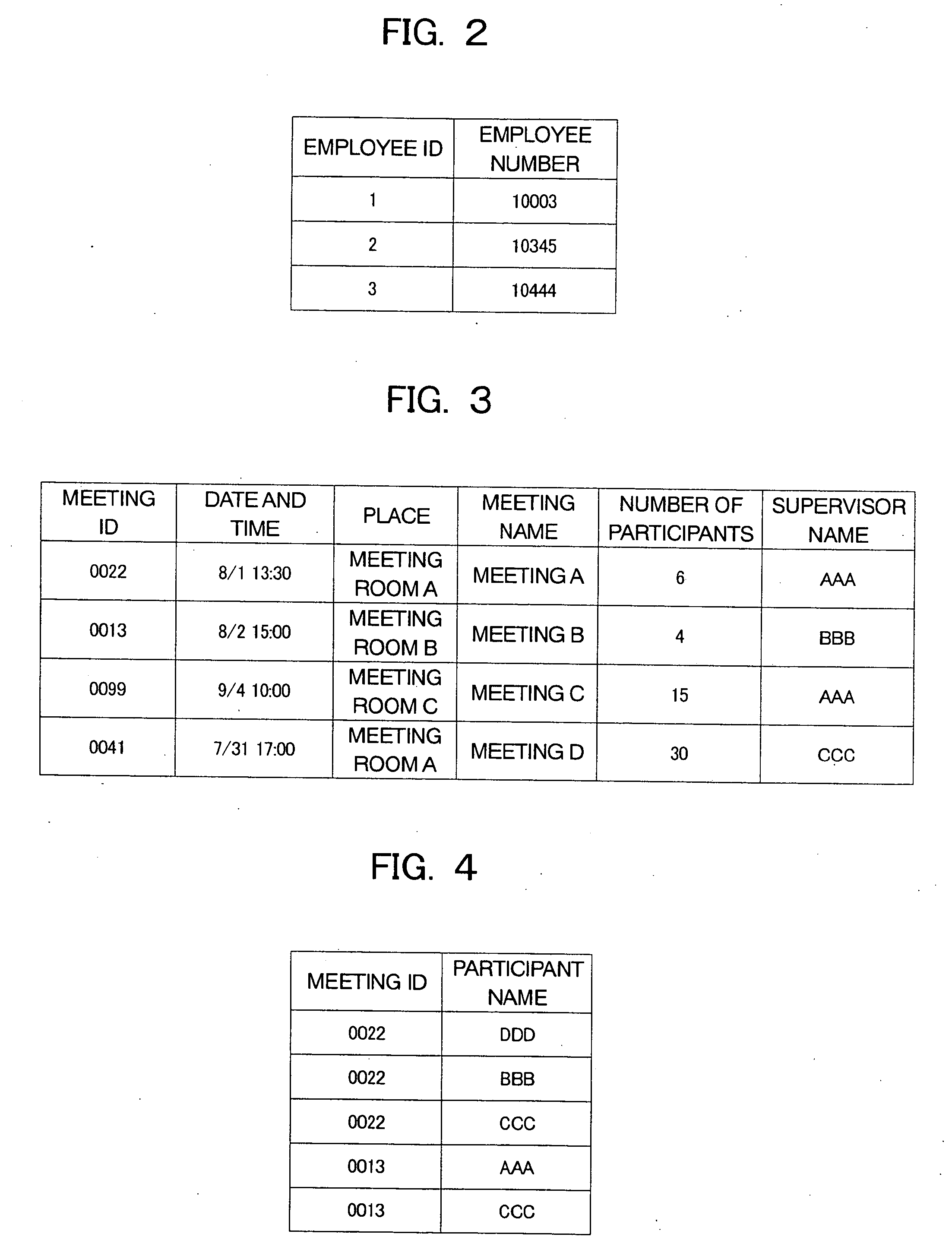

Image processing apparatus, image processing method and image processing program

InactiveUS20050204145A1Efficiently discriminate and processMinimizing human work and operationReservationsUser identity/authority verificationUser authenticationComputer graphics (images)

An image processing apparatus, an image processing method and an image processing program is provided which efficiently discriminate and process varying pieces of image data for materials corresponding to individual participants to a meeting, while minimizing the human work or operation required. The apparatus includes a user authentication section that acquires ID information to identify each user from among a plurality of users, and performs user authentication based on the ID information; a setting information acquisition section that acquires information for image formation associated with the users authenticated by the user authentication section; and an image data creation section creates image data for images to be formed on sheets of paper based on the setting information acquired by the setting information acquisition section.

Owner:KK TOSHIBA +1

Hybrid microprocessor controlled ventilator unit

InactiveUS7156095B2Restricting trainingReduce stepsRespiratorsOperating means/releasing devices for valvesEngineeringBasic mode

A method and apparatus for operating a ventilator in a primary electronic mode or in a back-up pneumatic mode during primary electronic mode failure. A method and apparatus for operating a ventilator in an advanced mode, having a number of ventilatory modes, or in a basic mode, having a limited number of ventilatory modes is also disclosed.

Owner:UNIV OF FLORIDA RES FOUNDATION INC

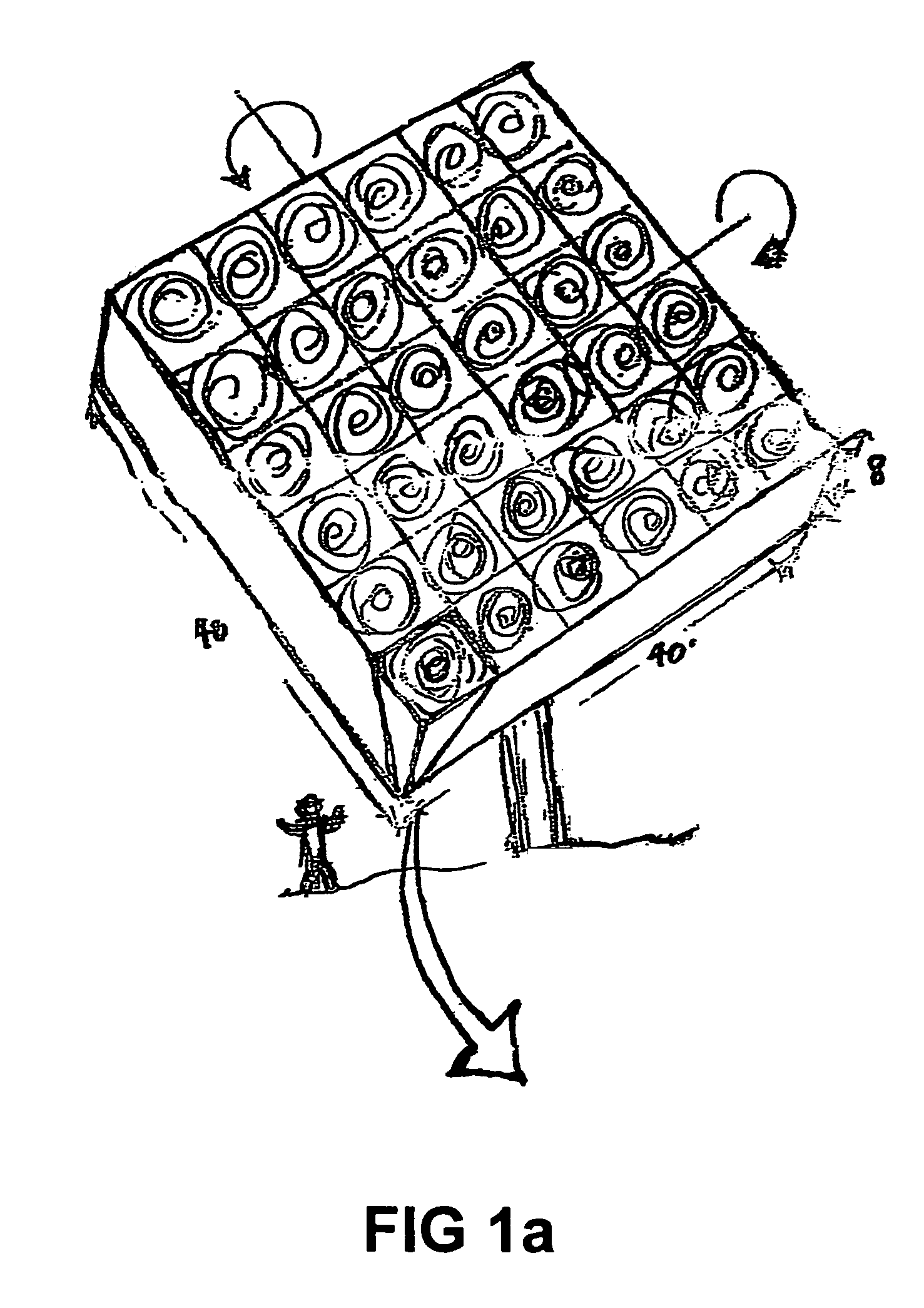

Solfire solar concentrator and pointer structure

InactiveUS7658071B1Low costStable removalAuxillary drivesSolar heating energyFresnel lensSolar generator

Solar generators have Fresnel lenses and spaced heat absorbers or photovoltaic cells for receiving focused solar rays. Heat is removed from their backs by boiling liquid in conical receivers. Pins or fins extend rearward into the receivers from the heat absorbers or photovoltaic cells. Liquid supply to the receivers is controlled by valves and floats or sensors. Tubes remove steam or vapor from the receivers for driving generators or for cooling photovoltaic cells. Hinged tubes which form the foldable support conduct the steam to generators and condense the vapor. Liquid is returned to a holding tank, is pumped to a distribution tank and is conducted by some of the structural tubes back to the valved receivers.

Owner:MCDERMOTT PATRICK P

Method for operating an internal combustion engine

InactiveUS7581531B2Reduce consumptionEmission reductionElectrical controlOutput powerExternal combustion engineInternal combustion engine

Owner:ROBERT BOSCH GMBH

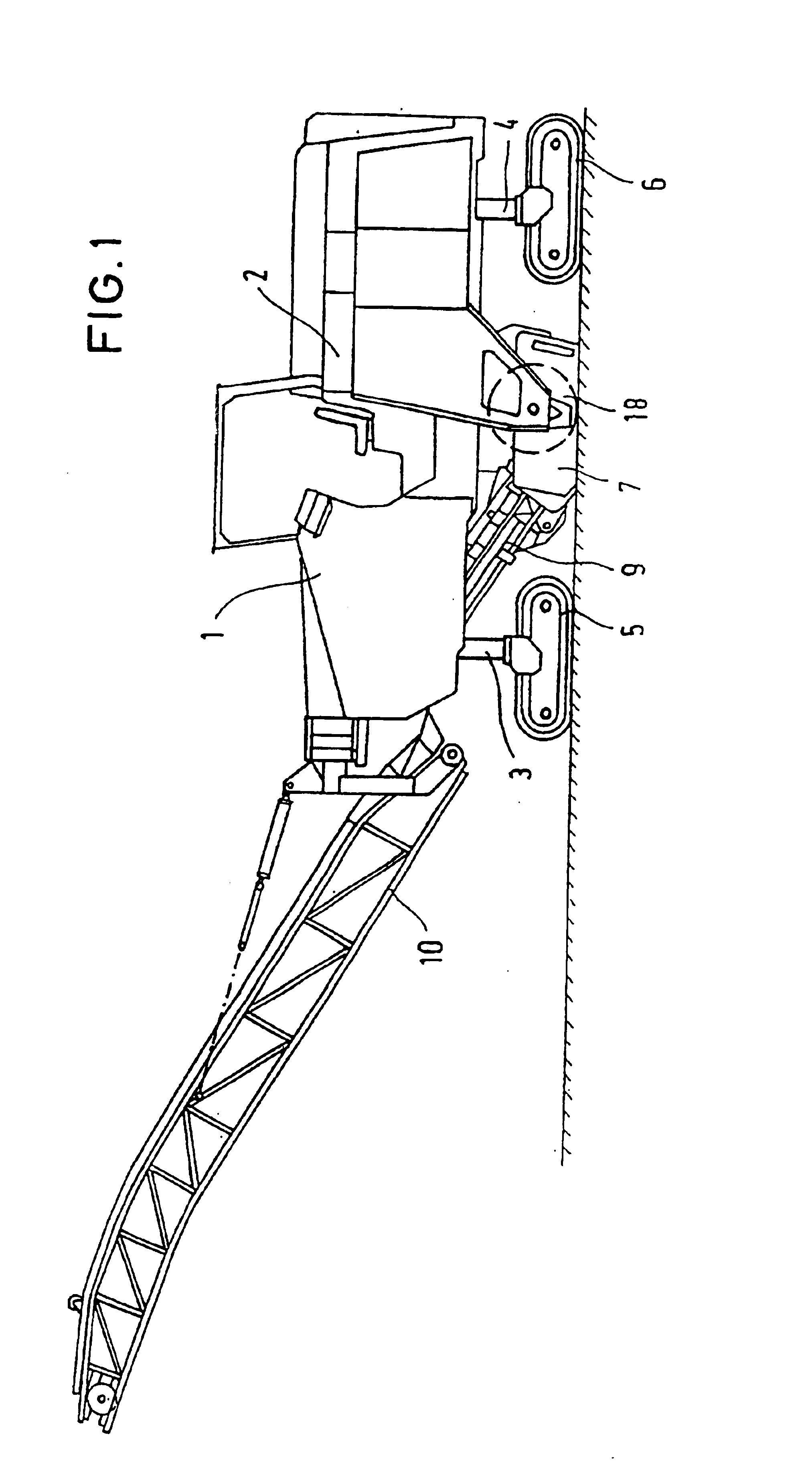

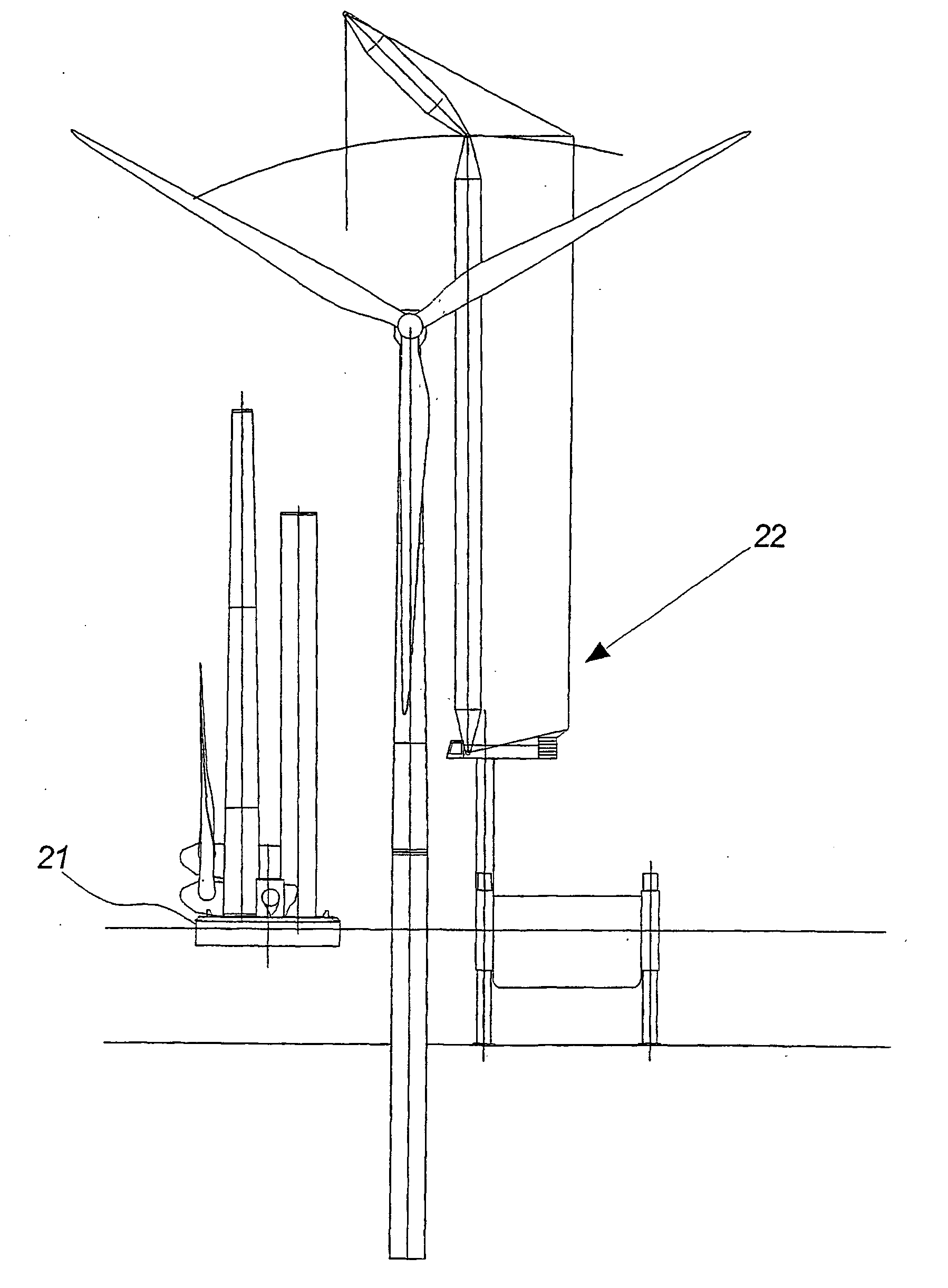

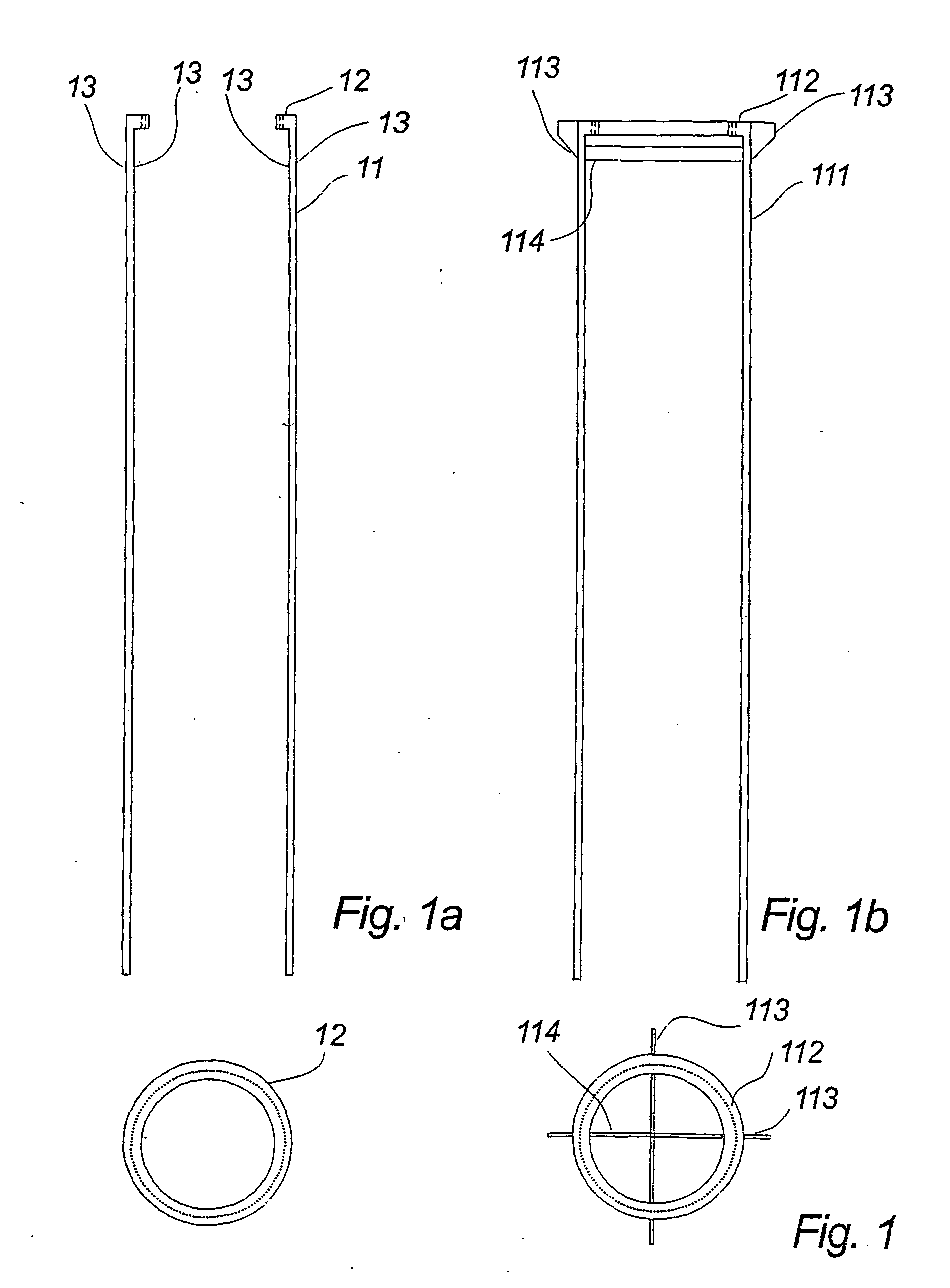

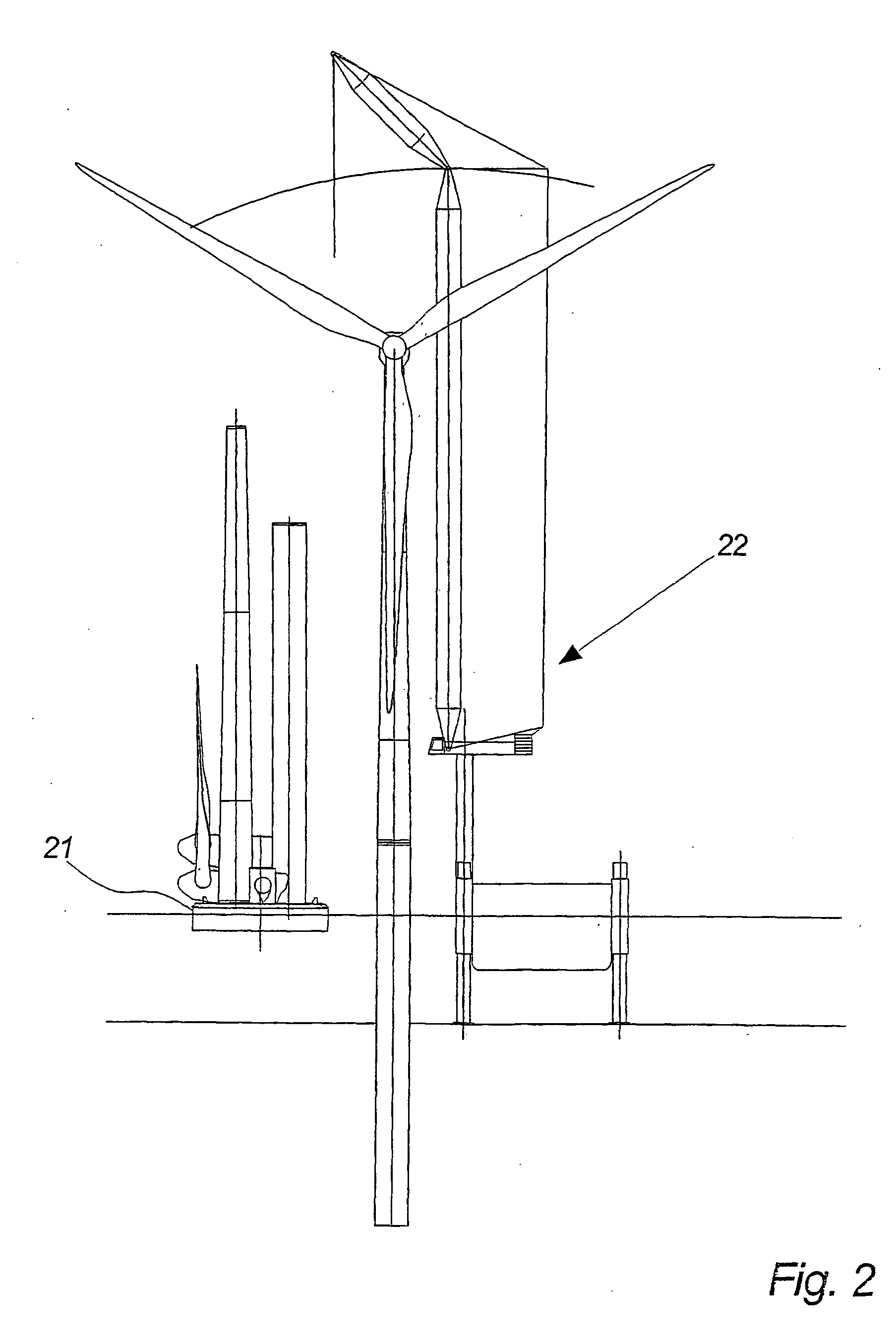

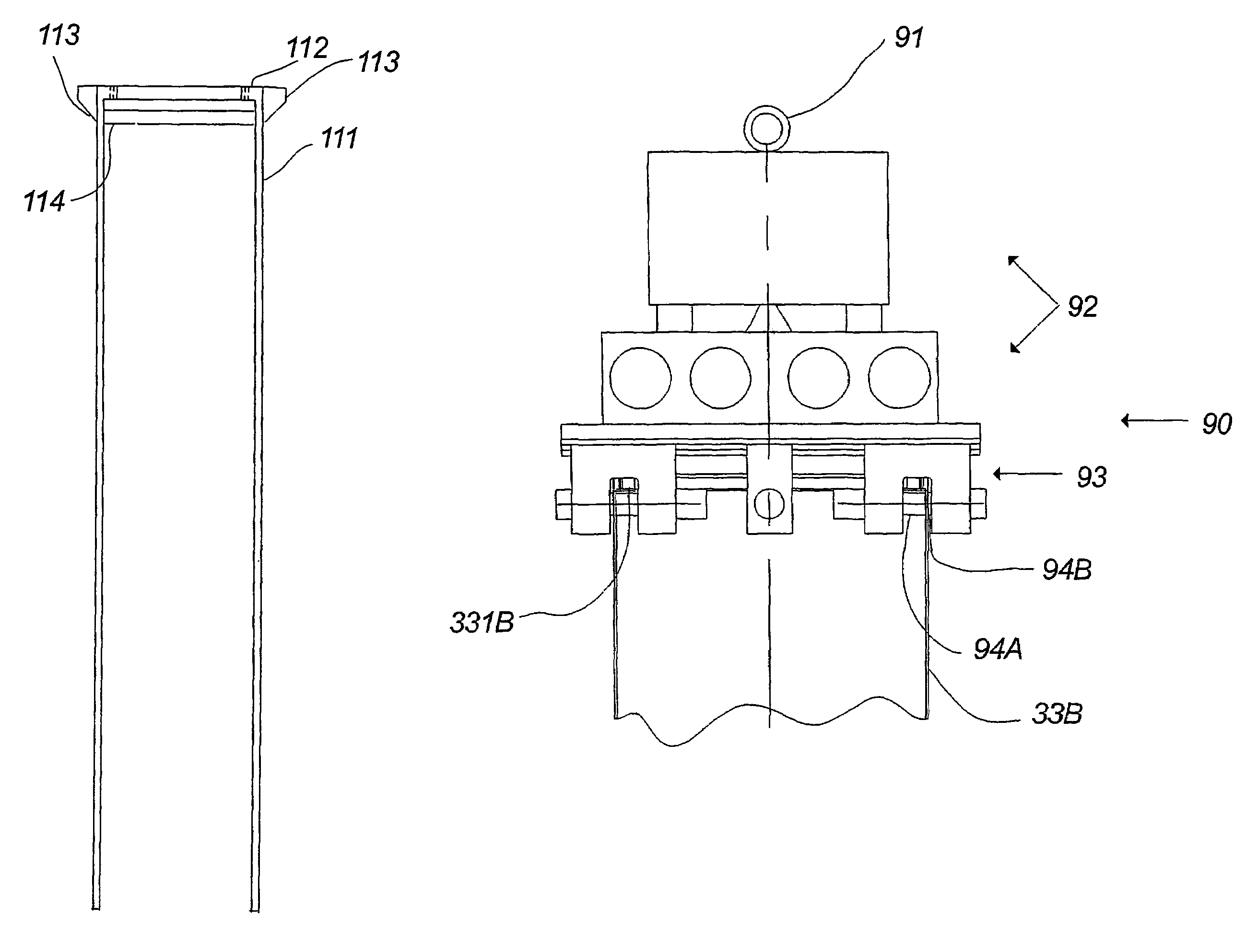

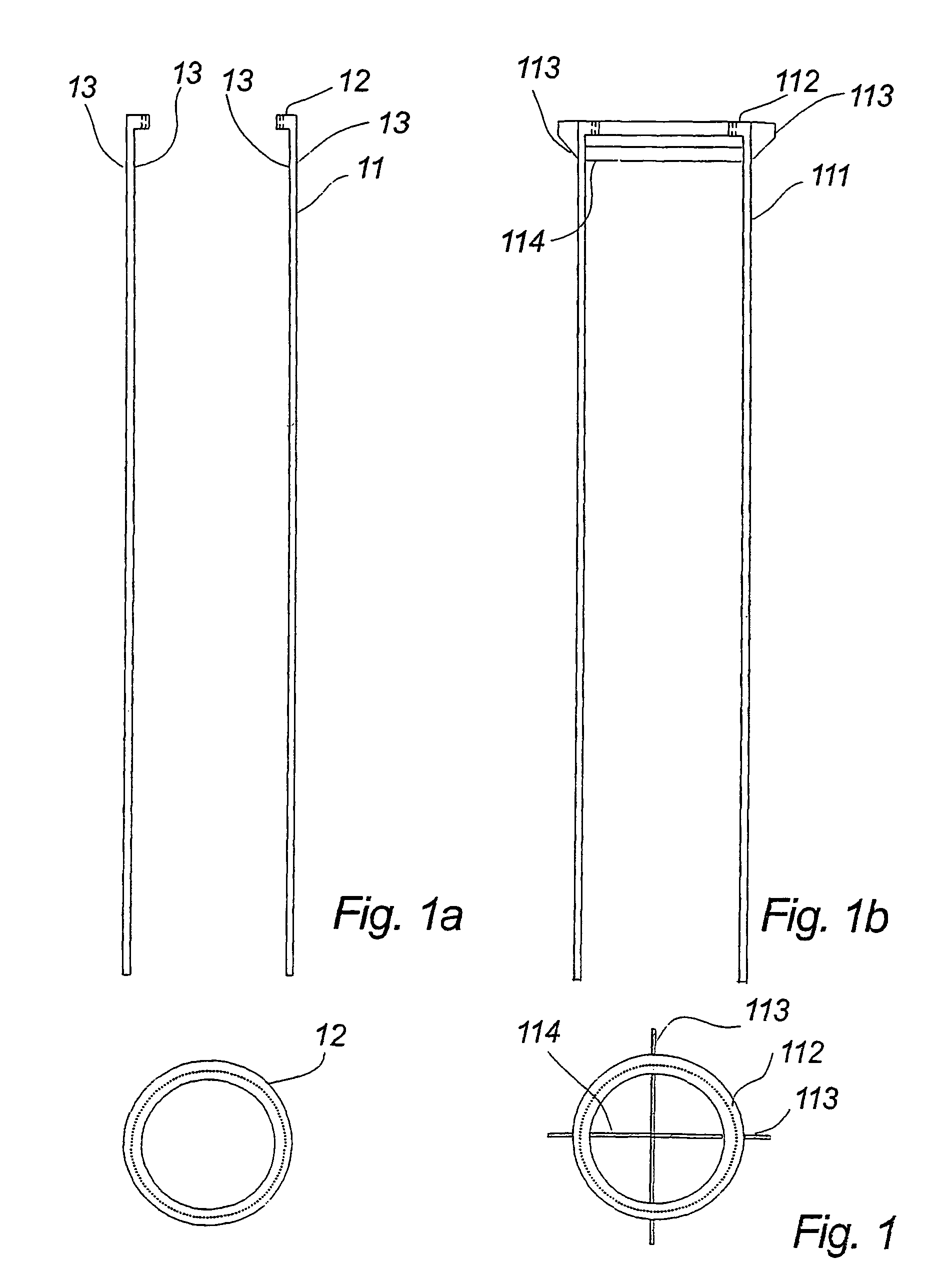

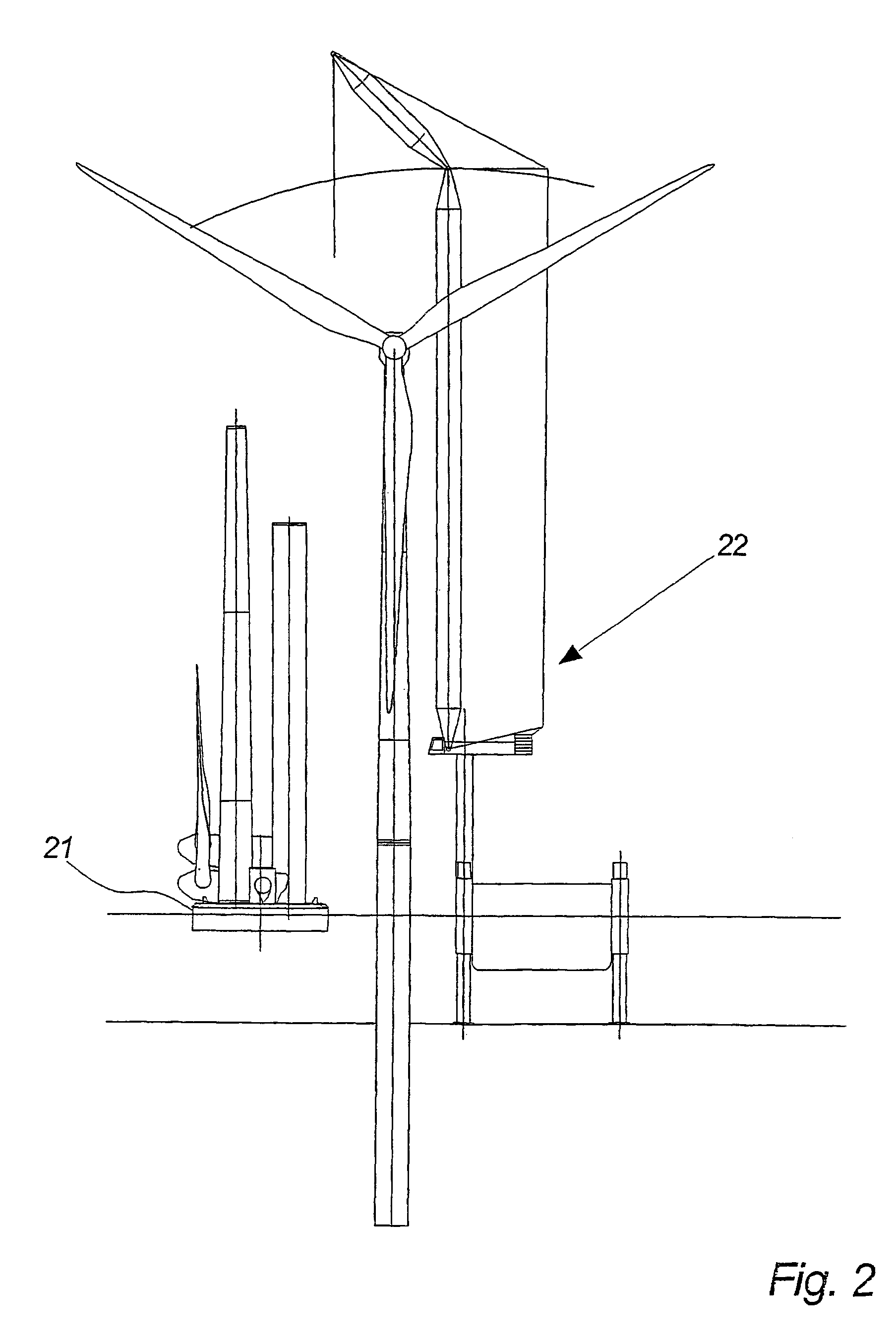

Methods of mounting a wind turbine, a wind turbine foundation and a wind turbine assembly

The invention relates to a method of mounting a wind turbine at a mounting location, said method comprising the steps of providing a foundation (33A, 33B), said foundation comprising a foundation body and pre-fitted upper attachment means vibrating at least a part of the foundation into the earth by transferring of vibrations into the structure of the foundation, mounting at least a part of said wind turbine to said upper attachment means (12) of said foundation. According to the invention, large scale wind turbines, especially offshore wind turbines, may be transported and mounted at the site in a cost-effective and expedient way.

Owner:VESTAS WIND SYST AS

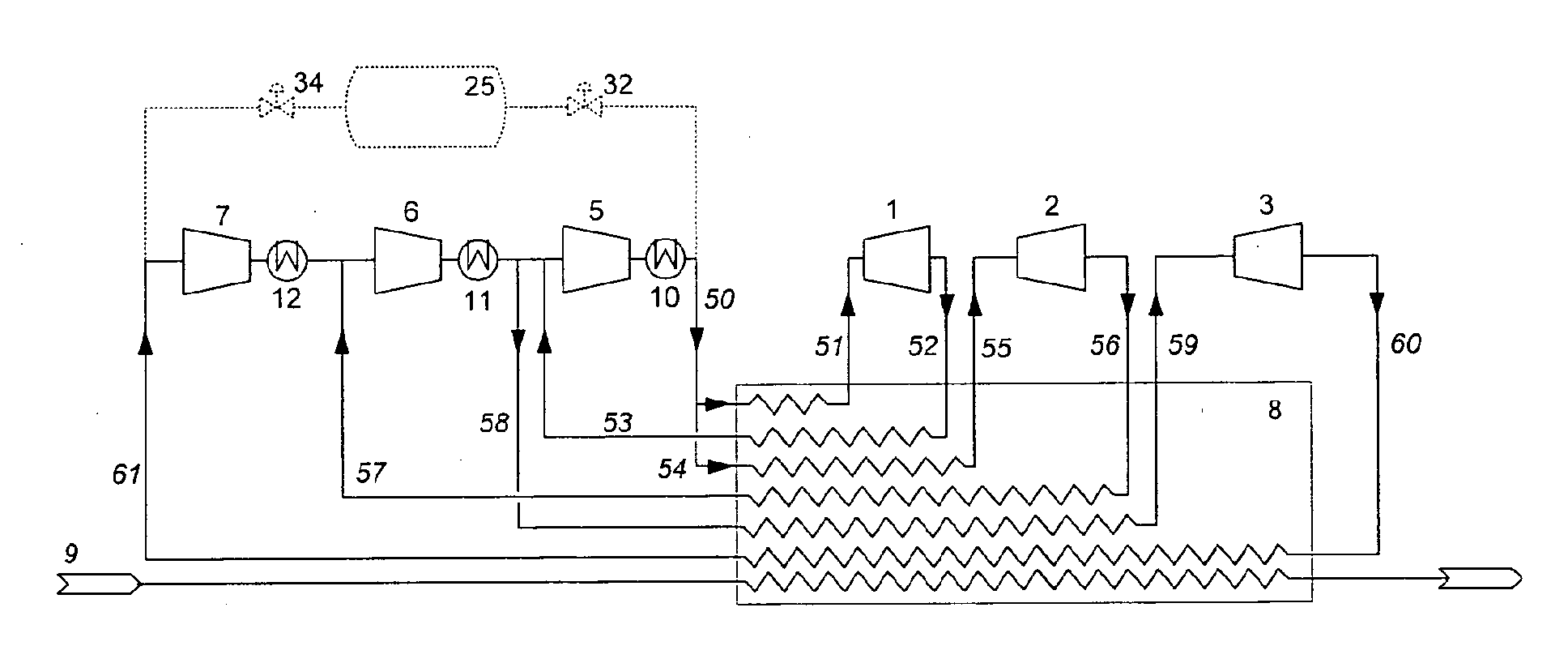

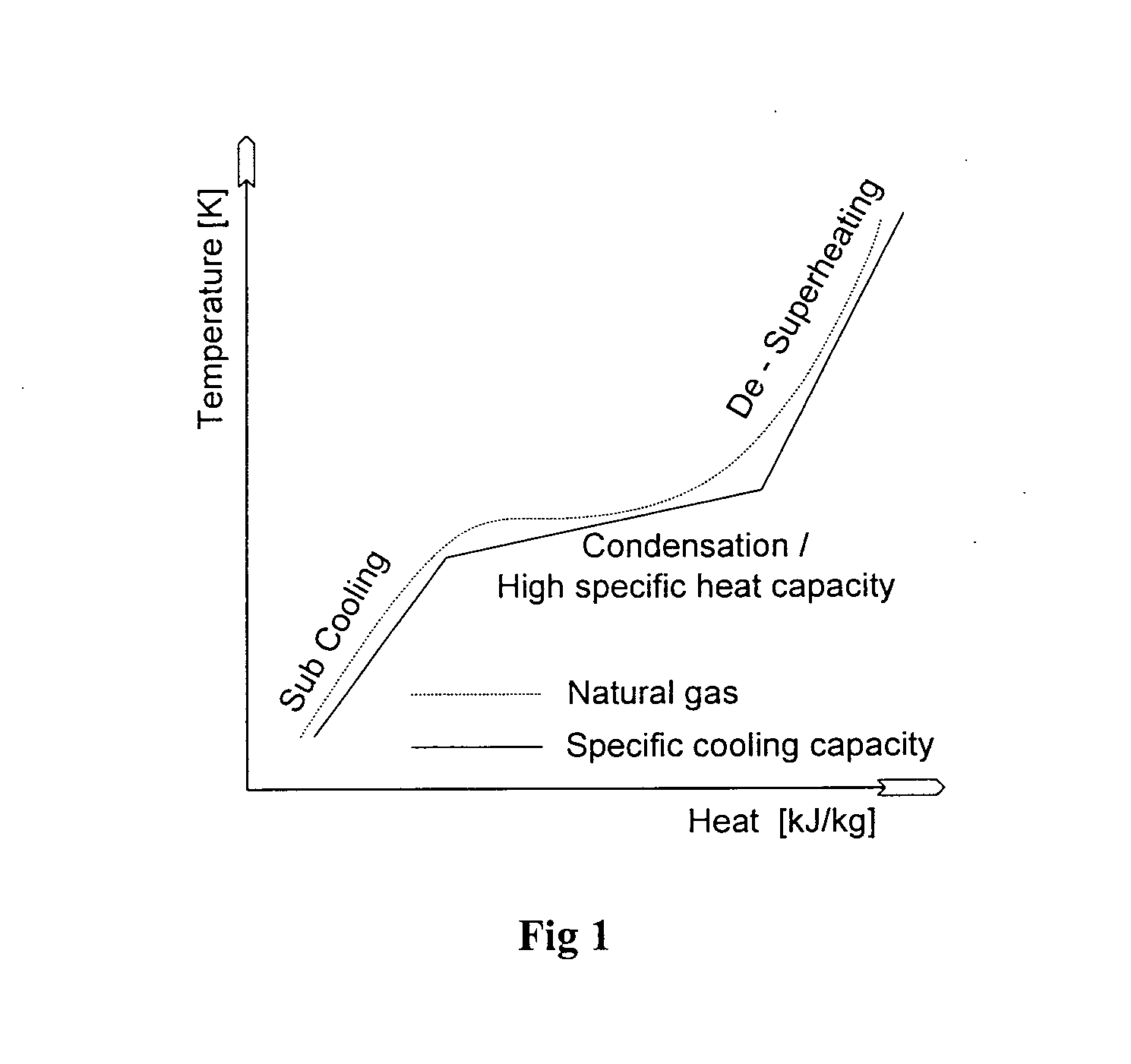

Method and system for optimized LNG production

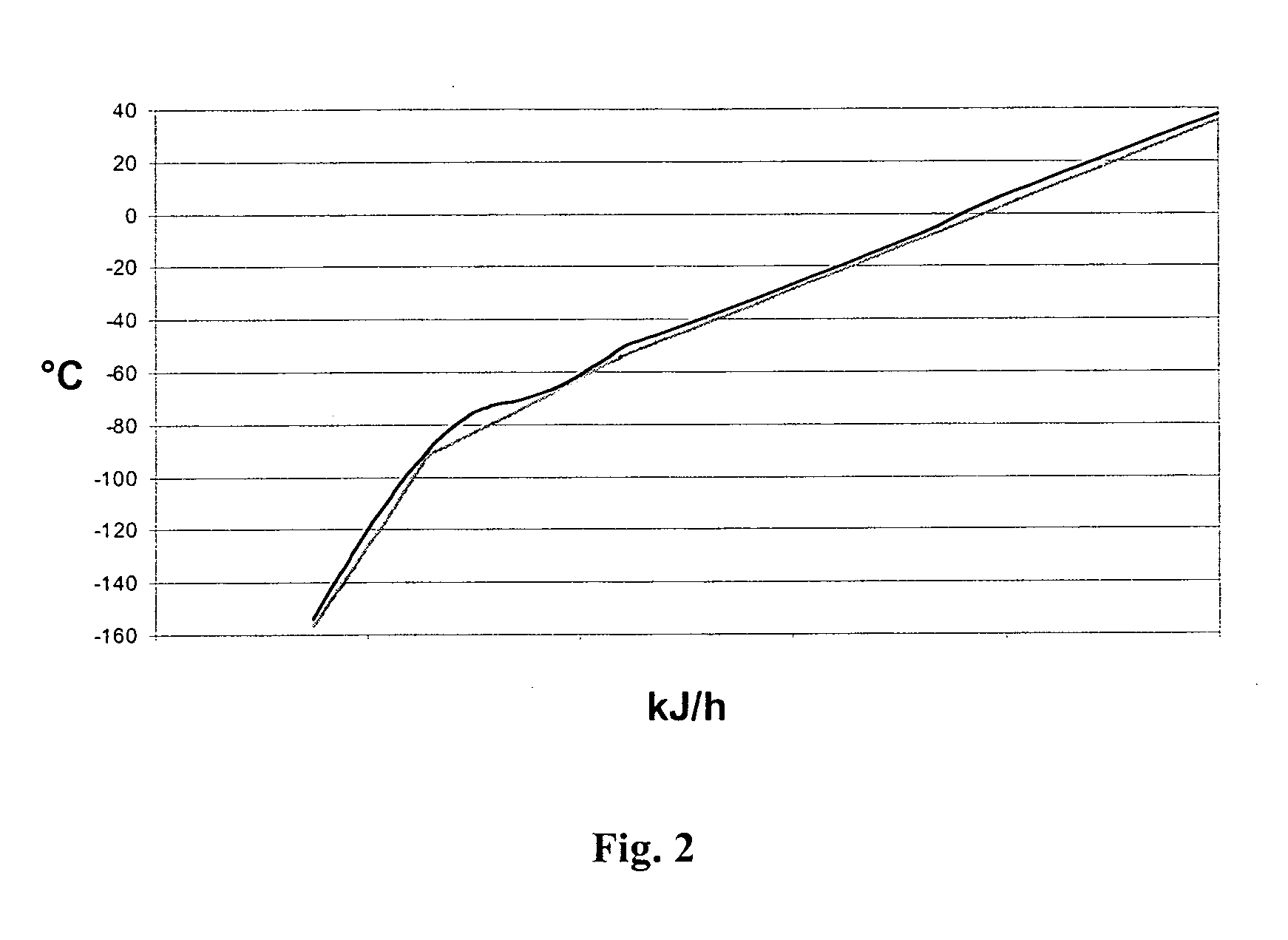

ActiveUS20110203312A1Improve system efficiencyReduced dimensionSolidificationLiquefactionCompressed natural gasHeat rejection

A method and system for producing liquefied and sub-cooled natural gas by means of a refrigeration assembly using a single phase gaseous refrigerant comprising: at least two expanders (1-3); a compressor assembly (5-7); a heat exchanger assembly (8) for heat absorption from natural gas; and a heat rejection assembly (10-12). The novel features according to the present invention are arranging the expanders (1-3) in expander loops; using only one and the same refrigerant in all loops; passing an expanded refrigerant flow from the respective expander into the heat exchanger assembly (8), each being at a mass flow and temperature level adapted to de-superheating, condensation or cooling of dense phase and / or sub-cooling of natural gas; and serving the refrigerant to the respective expander in a compressed flow by means of the compressor assembly having compressors or compressor stages enabling adapted inlet and outlet pressures for the respective expander.

Owner:WARTSILA OIL & GAS SYST

Hyperthermia Assisted Radiation Therapy

ActiveUS20100294279A1Local tumor controlImprove clinical outcomesRespiratorsOther heat production devicesBreathing systemRadiation therapy

A breathing system for hyperthermic assisted radiation therapy includes at least one heating element that modulates the temperature of air inhaled by a patient, at least one cooling element that modulates the humidity of the air inhaled by a patient, and a controller that maintains the desired humidity and temperature.

Owner:WILLIAM BEAUMONT HOSPITAL

Methods of mounting a wind turbine, a wind turbine foundation and a wind turbine assembly

InactiveUS7281902B2Minimize workSignificant simplificationEngine manufactureFinal product manufactureTurbineWind force

Owner:VESTAS WIND SYST AS

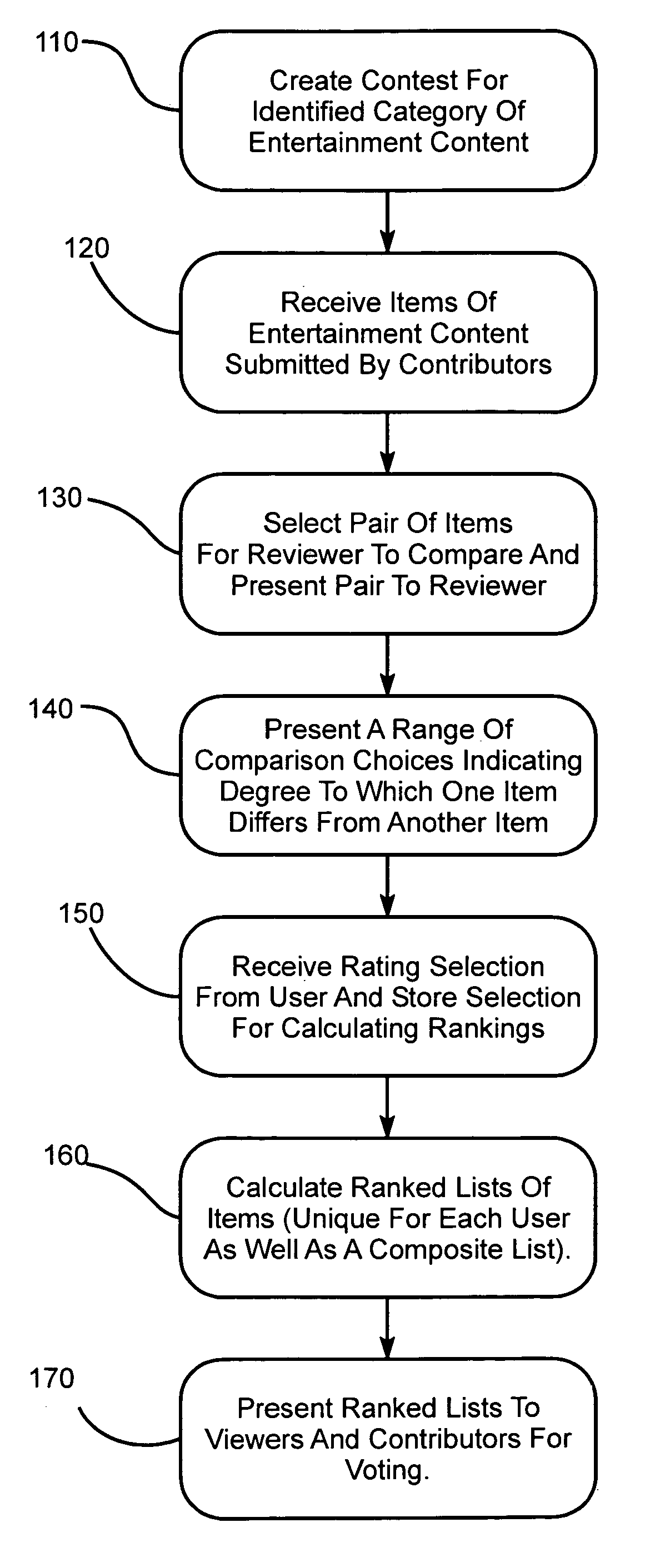

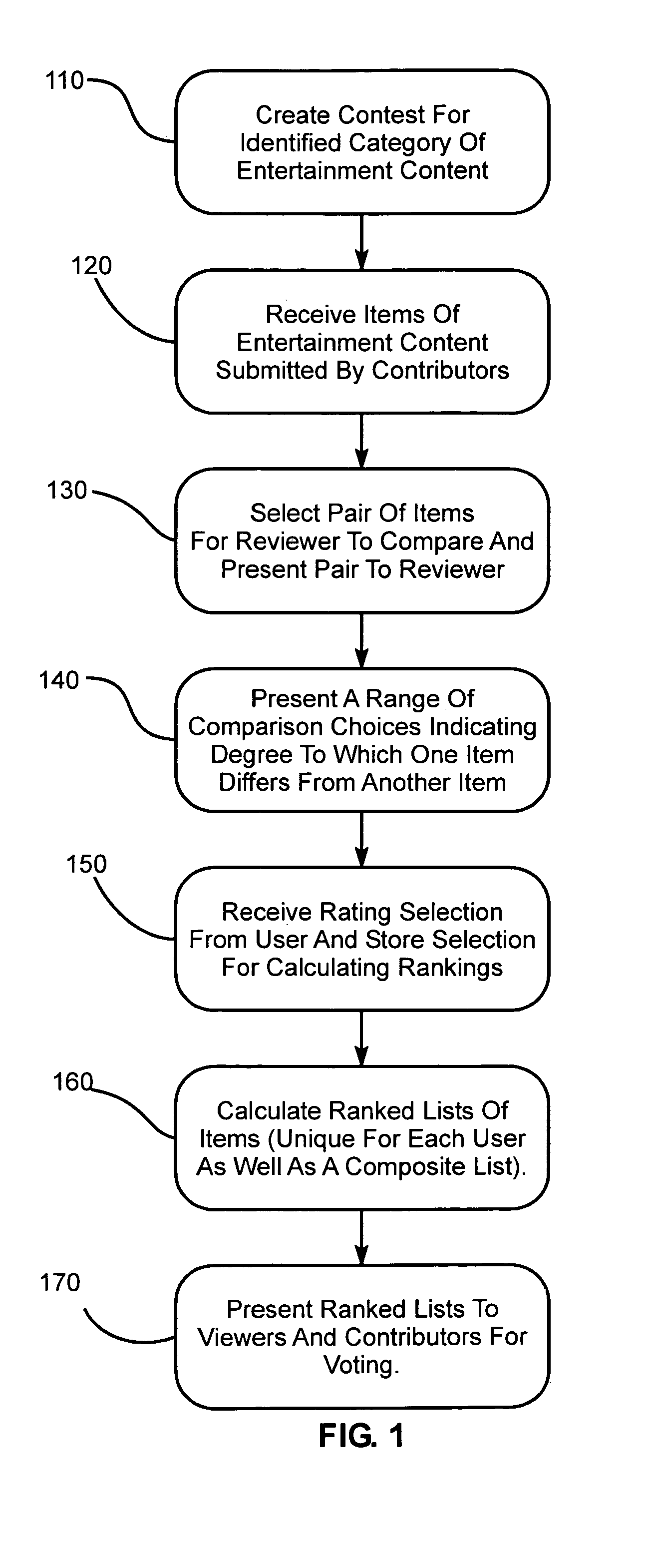

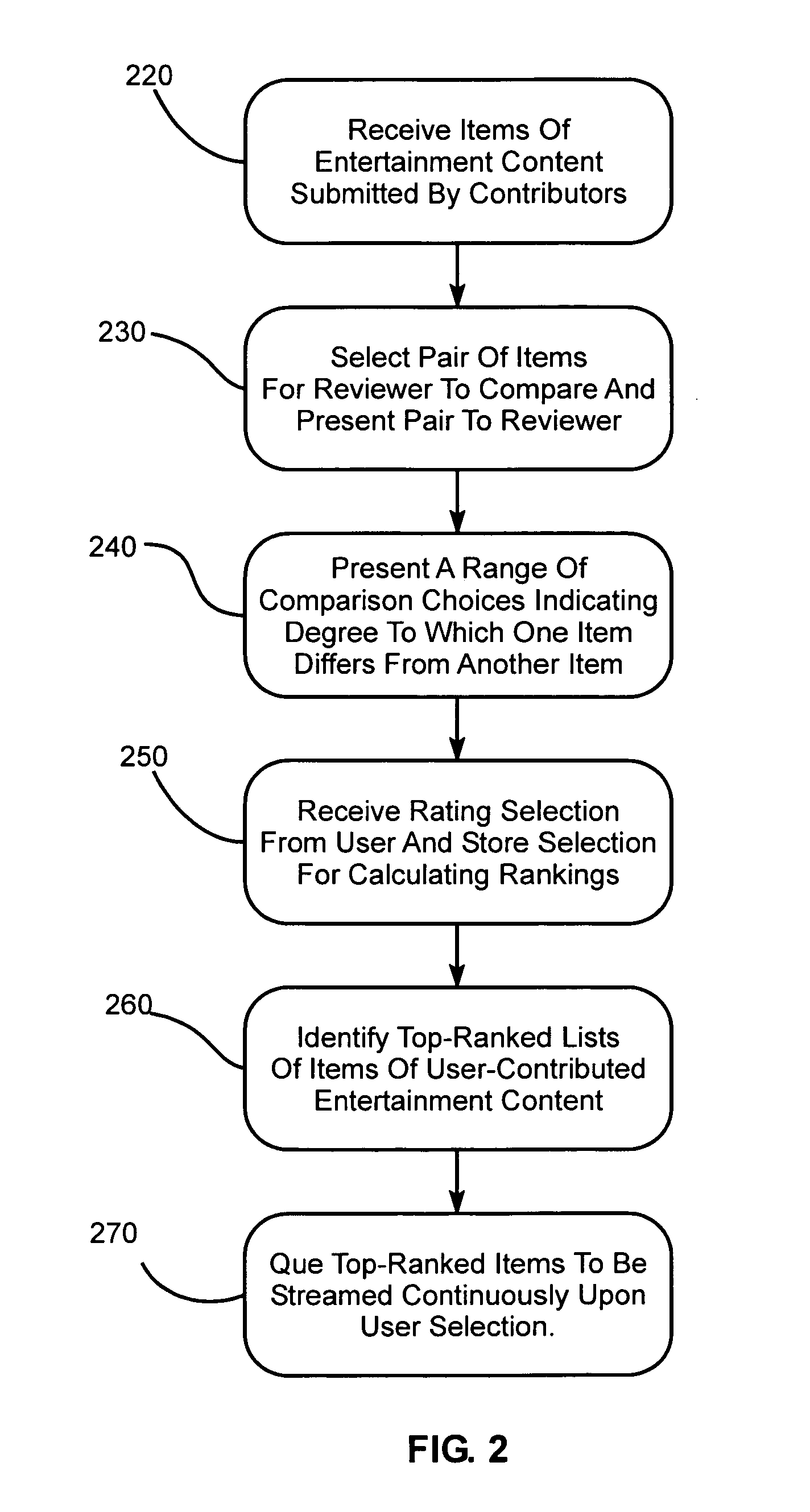

Online entertainment network for user-contributed content

InactiveUS7827054B2Reduce in quantityHighly accurateMarket predictionsVoting apparatusSocial webMultimedia

The invention includes a system for providing an online entertainment network for user-contributed entertainment content. The system quickly and accurately identifies quality content from a vast pool of user-contributed content. User-contributed content is rated by those who contribute and those who view content. Fraud detection devices automatically detect and remove fraudulent ratings. Contests and prizes associated with specific categories of content provide incentives for contributors to provide quality content and rate many pairs of items. Contests may be localized by geography, organization, social network, and other relationships. Identified top-rated content is made available individually, or as a continuous stream of user-contributed entertainment content.

Owner:OUSGE

System and method for distributed project outsourcing

InactiveUS20050240916A1Fast trainingImprove skillsProgram controlResourcesQuality assuranceWork product

Embodiments of the invention provide a system and method for distributed projects comprising computer systems and employing outsourced labor to be initiated, worked and completed. A distributed project that has been divided into pieces may be worked by disparate groups of workers. This is accomplished by copying data to each distributed work site. The data is then worked with by the remote workers. Once the data is at the remote site both local and remote workers can divide and conquer the task at hand by further subdividing the project tasks that are worked on by each group of workers. Embodiments of the invention may transfer operations between sites instead of raw output data so that each site's work efforts can be added to the work product with minimal bandwidth. In at least one embodiment of the invention, the labor may be performed primarily by at least one site with at least one other site performing quality assurance primarily.

Owner:LEGEND FILMS INC

Diesel engine and supercharger

InactiveUS7726285B1Facilitate cold startingLow parasitic lossRotary/oscillating piston combinations for elastic fluidsElectrical controlTwo-stroke diesel engineDiesel engine

A four stroke diesel engine combined with a supercharger is operable to supply varying amounts of air to the engine responsive to the load on the engine. The supercharger has a pair of rotors driven by the engine operable to move air to the engine. Gates associated with the rotors control the amount of air and pressure of the air moved by the rotors to the diesel engine.

Owner:HANSEN ENGINE

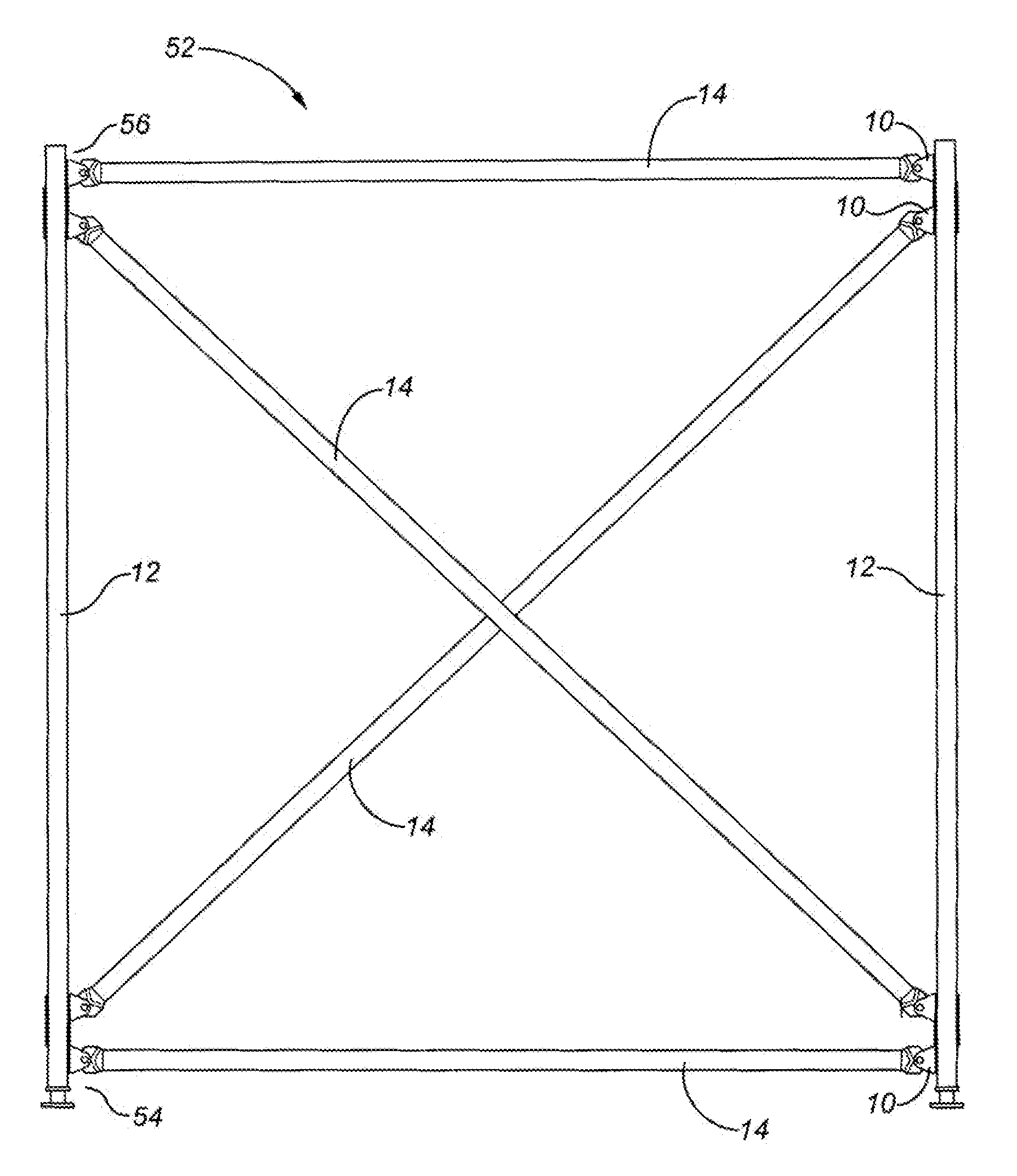

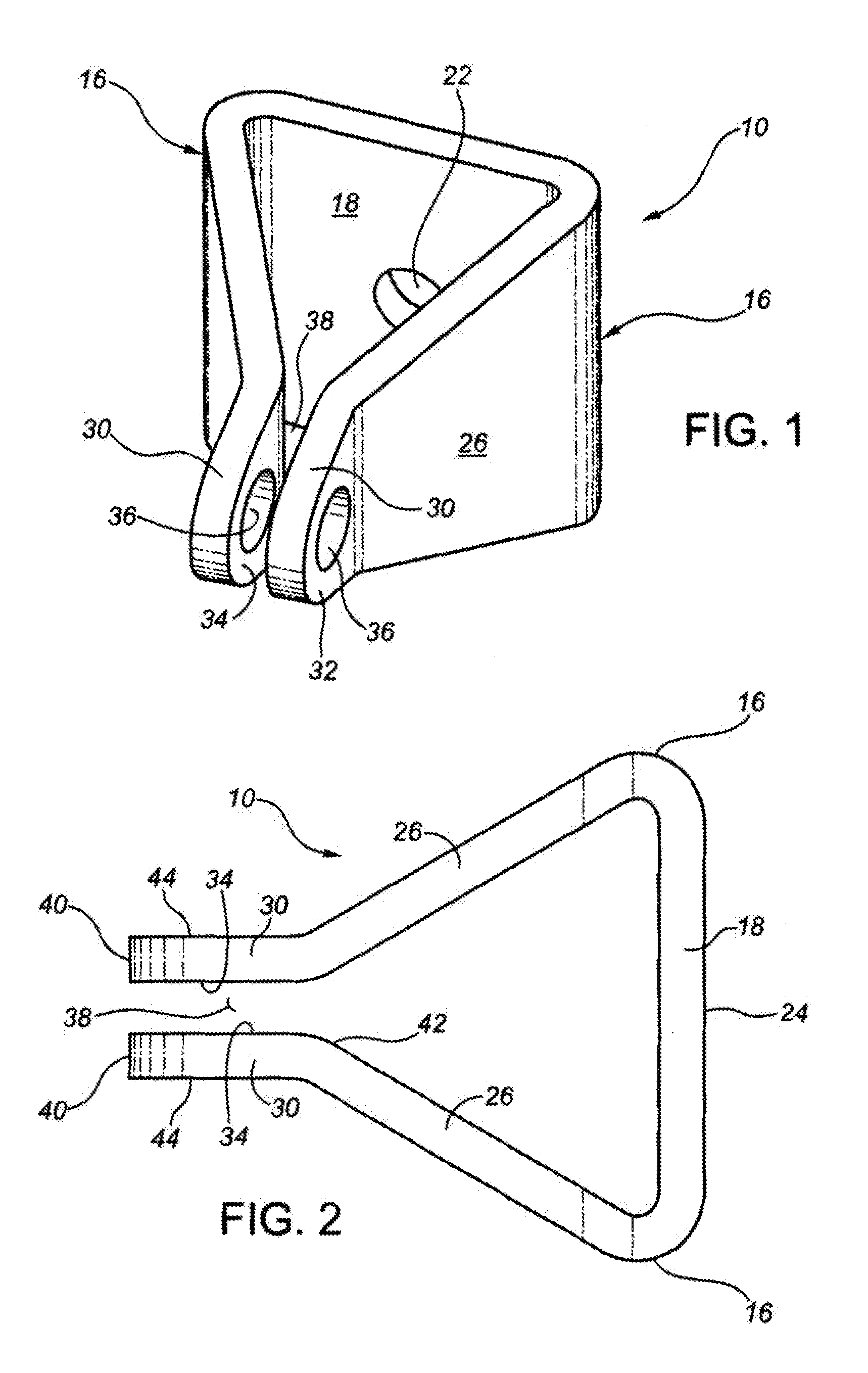

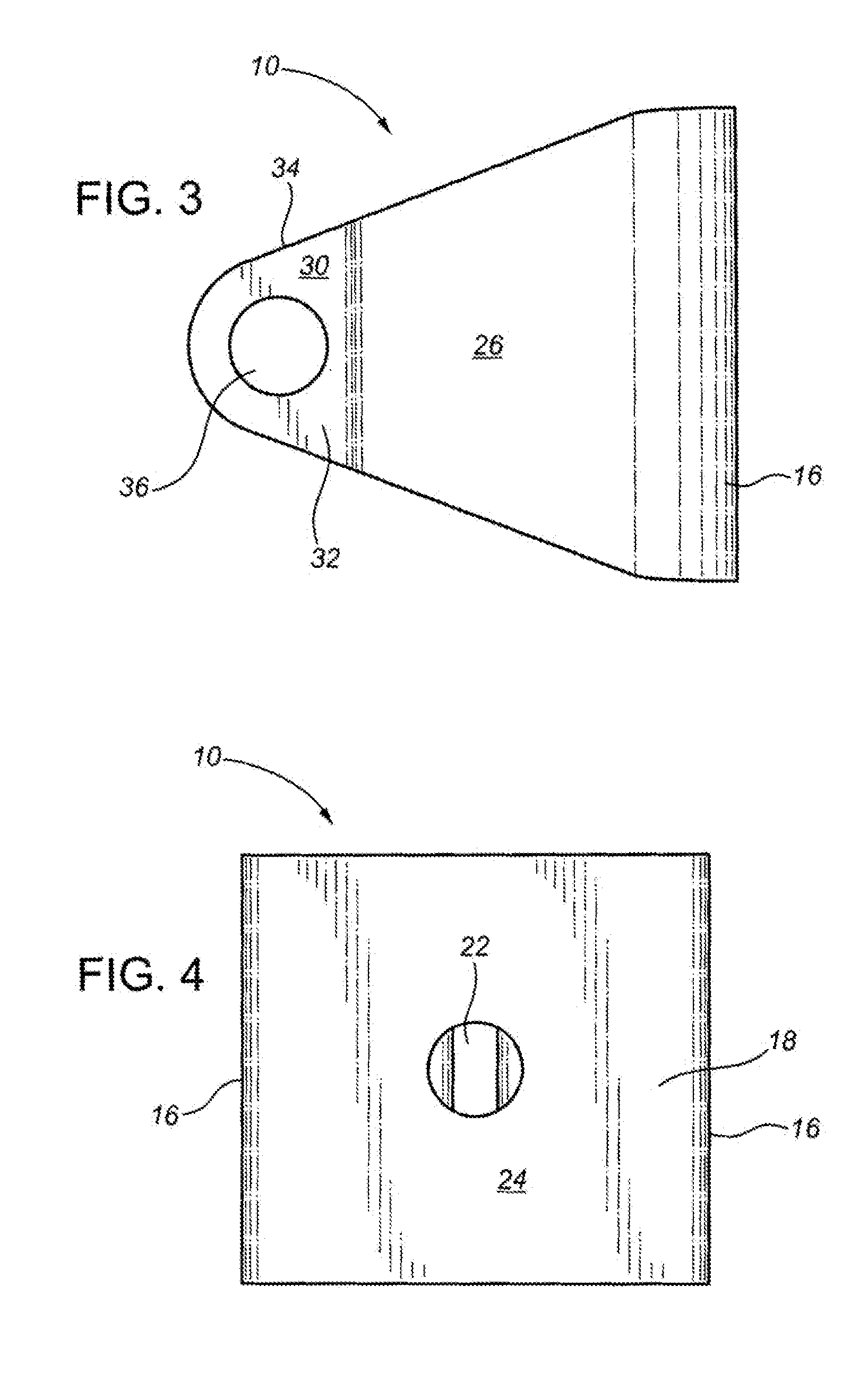

Scaffold Support Bracket and Assembly

A scaffold bracket has a vertical planar base member defining an aperture adapted to receive a fastener for connecting to a vertical support member. The base member has two arms extending forwardly from opposing sides of the base member to form a mouth or a slit sufficiently wide to accept a brace end of a cross member. Mutually aligned openings on the two arms are configured to receive a fastener for releasable connection to the brace end and allowing the cross member to pivot on the arm. Slots are provided on the arms and work in combination with a pin extending through the slots and the brace end to limit the pivotal movement of the cross member with respect to the bracket. A clamshell half clamp fastened to the base member allows the bracket to be releasably attached to a vertical support tube of a scaffold assembly at any location to provide increased flexibility in assembling the scaffold assembly.

Owner:SIMOES PORFIRIO

Leg configuration for spring-mass legged locomotion

ActiveUS10189519B2Relatively large bandwidthHigh force controlRobotVehiclesPassive dynamicsEngineering

Owner:THE STATE OF OREGON ACTING BY & THROUGH THE OREGON STATE BOARD OF HIGHER EDUCATION ON BEHALF OF OREGON STATE UNIV

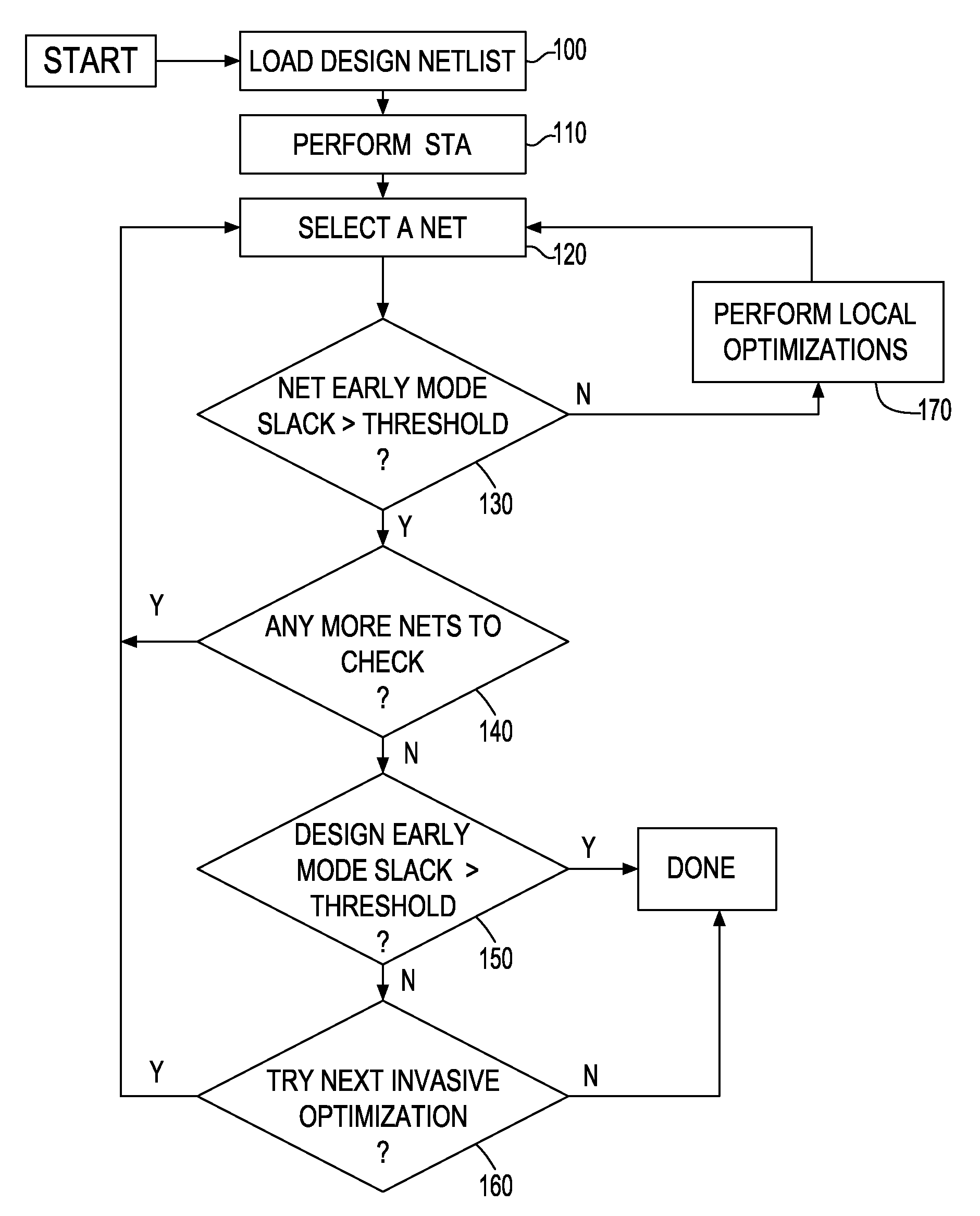

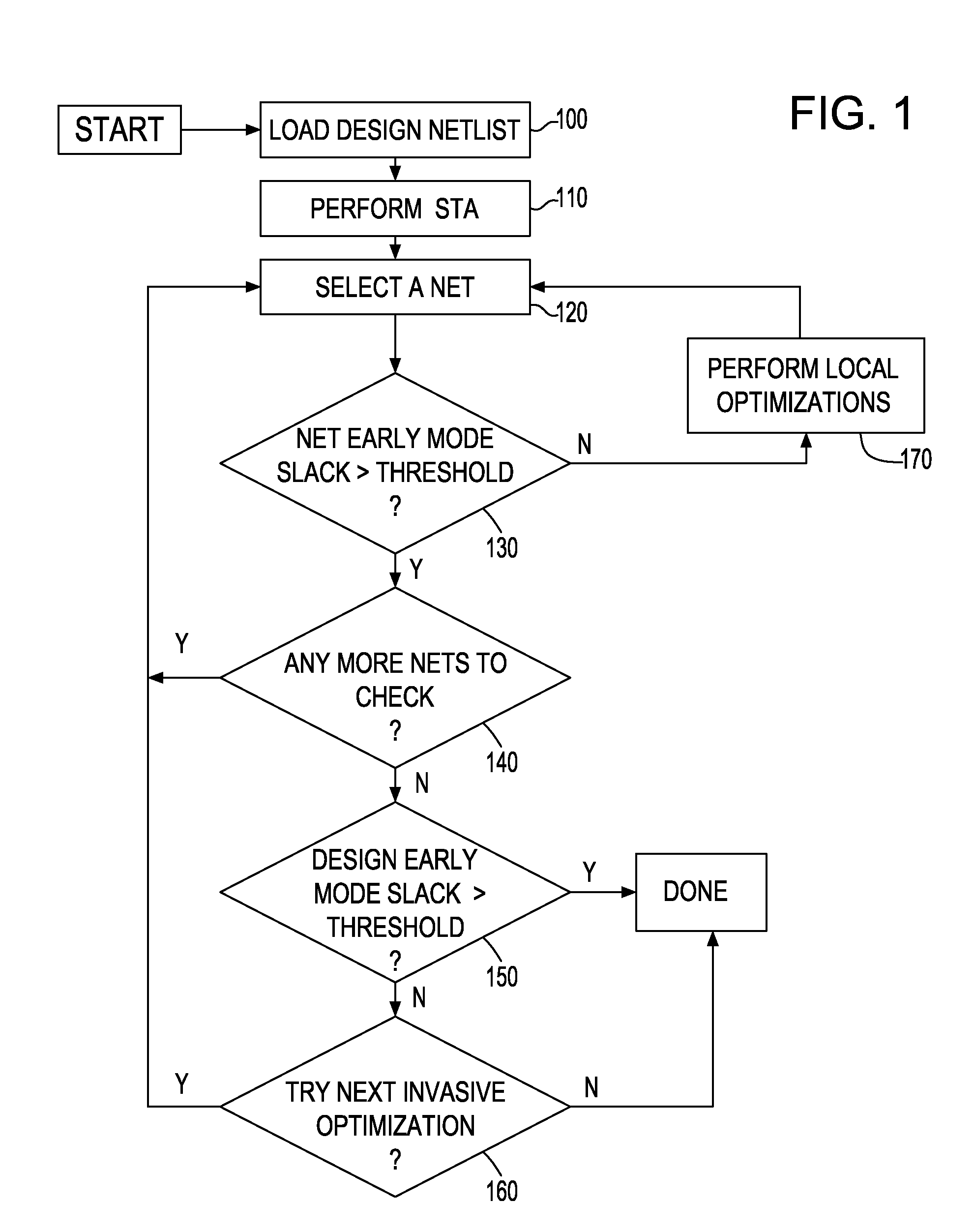

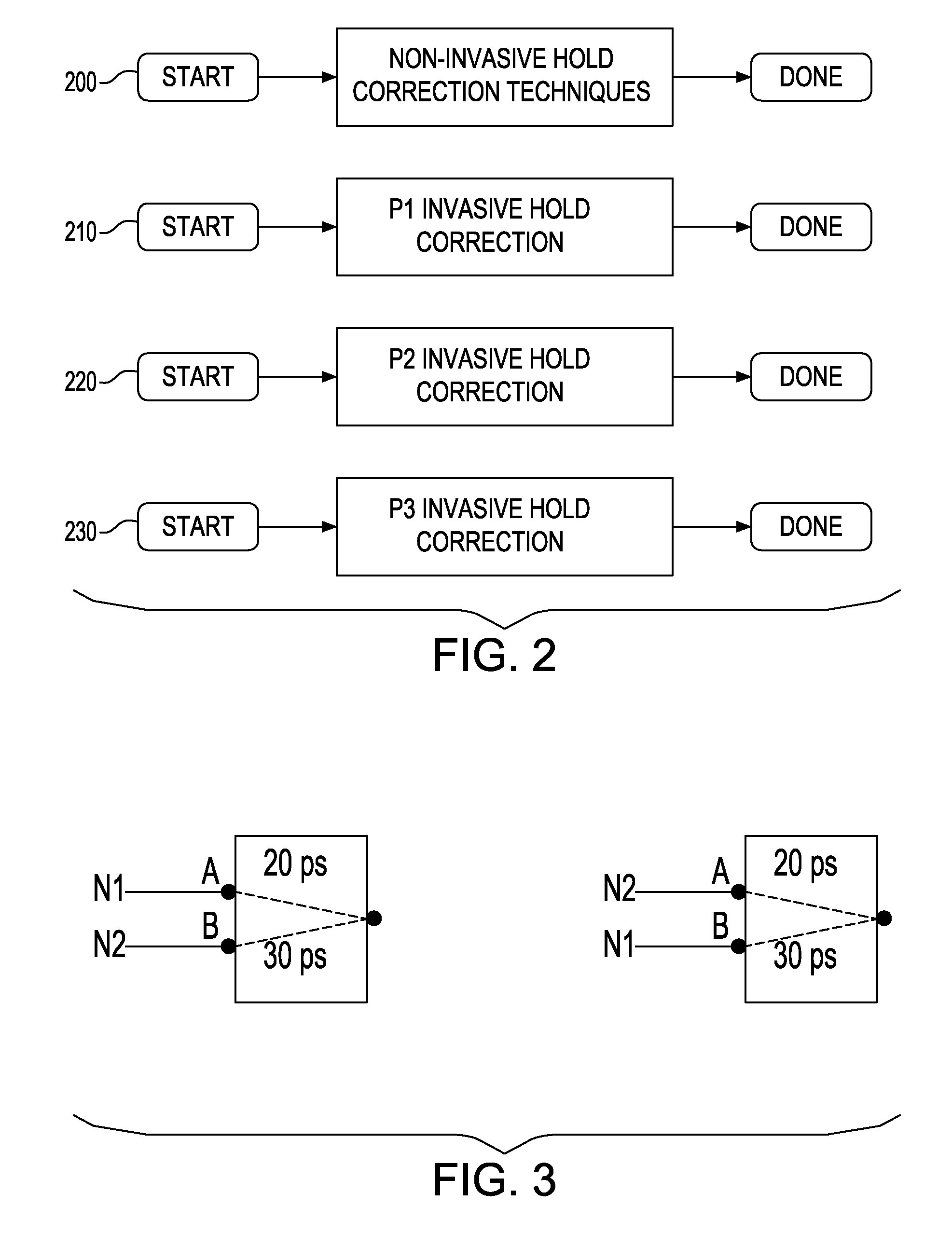

Method of minimizing early-mode violations causing minimum impact to a chip design

InactiveUS7996812B2Minimize disruptionAccurate timingComputer aided designSoftware simulation/interpretation/emulationFast pathEngineering

A system and a method for correcting early-mode timing violations that operate across the process space of a circuit design. Optimizations are performed to replace padding that increase path delays on fast paths. At the stage in the design process where early-mode violations are addressed, placement, late-mode timing closure, routing, and detailed electrical and timing analysis are assumed to have been completed. The optimizations are designed to be effective in delaying fast paths while minimizing the impact on already-completed work on the chip, in contrast to relying only on adding pads that can have a negative impact on all of these quantities. The optimizations are classified according to their invasiveness and are followed by their deployment. The deployment is designed to minimize using delay pads, reduce design disruptions, and minimize effects on other aspects of the design.

Owner:MENTOR GRAPHICS CORP