Patents

Literature

32results about How to "Step of become large" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

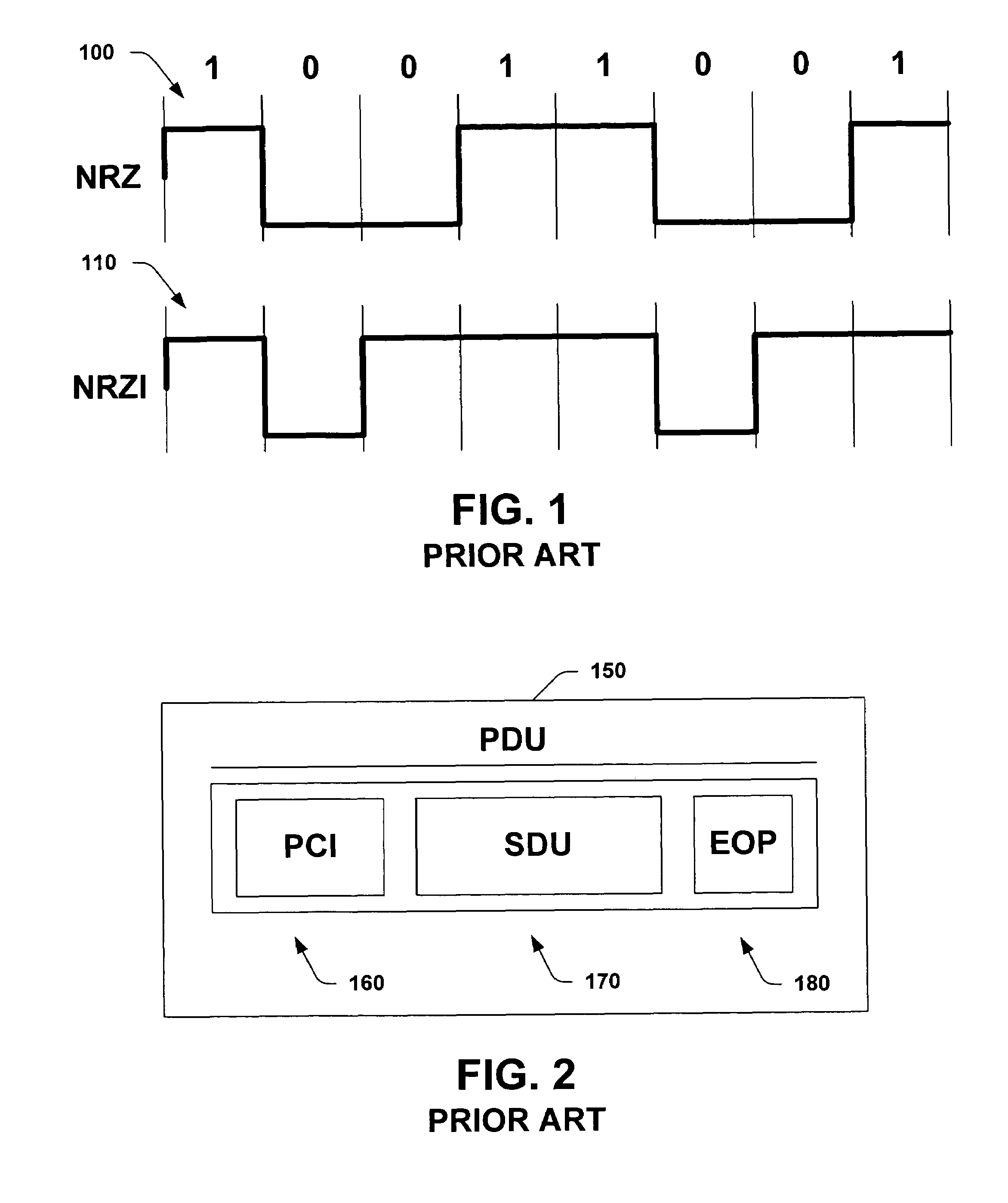

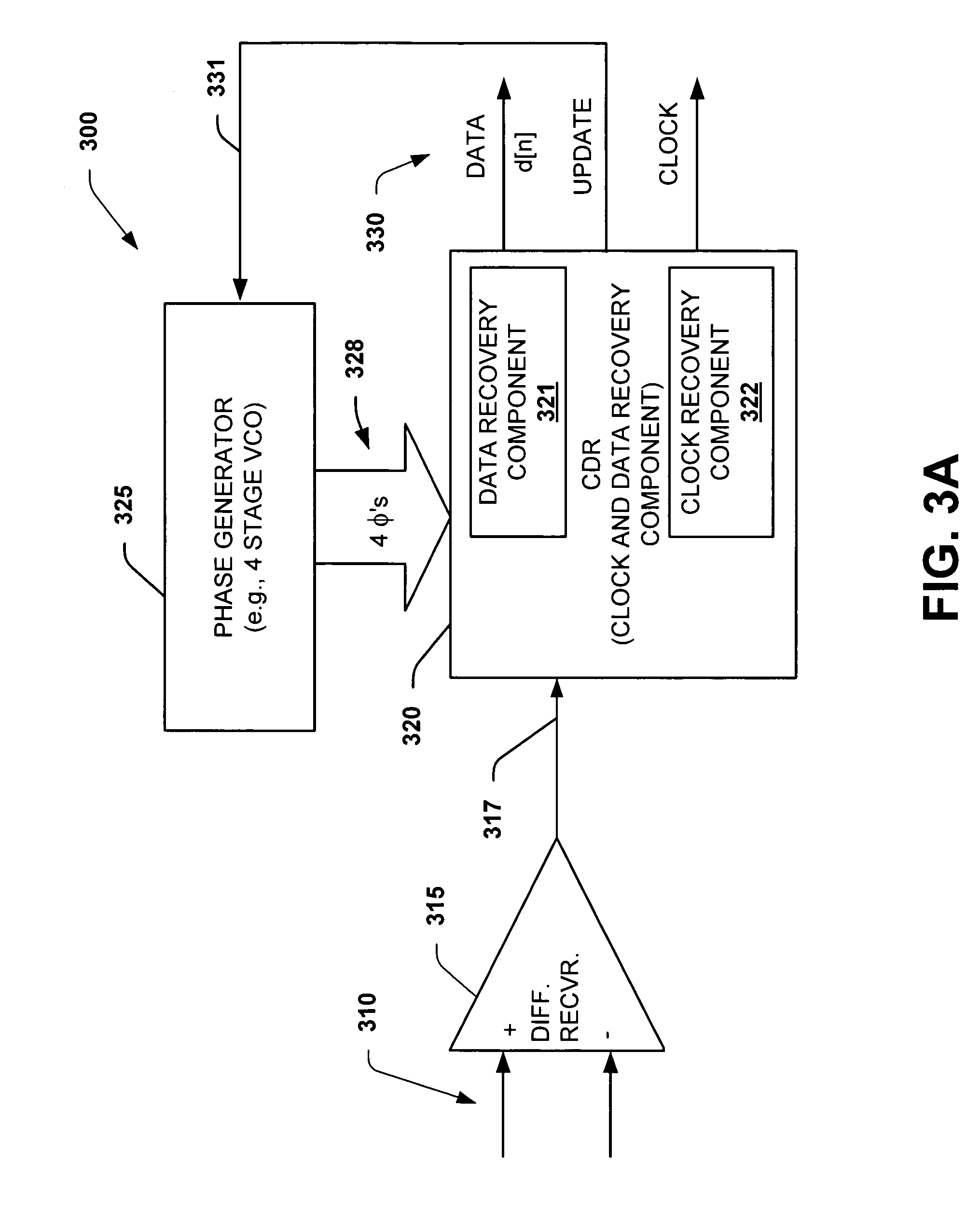

Interpolator based clock and data recovery (CDR) circuit with digitally programmable BW and tracking capability

ActiveUS20050180536A1High bandwidthLower latencyPulse automatic controlSynchronising arrangementPhase correctionData stream

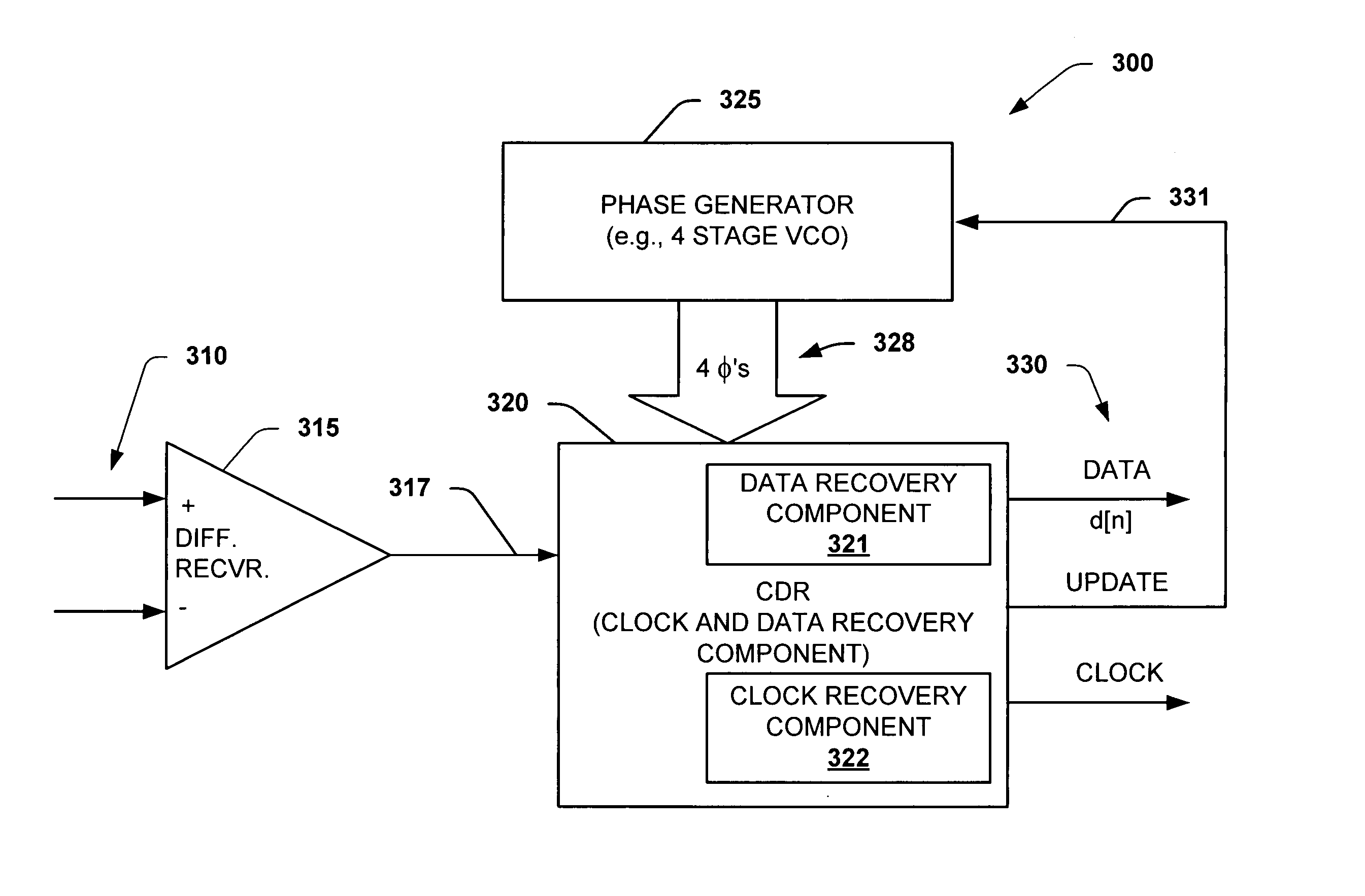

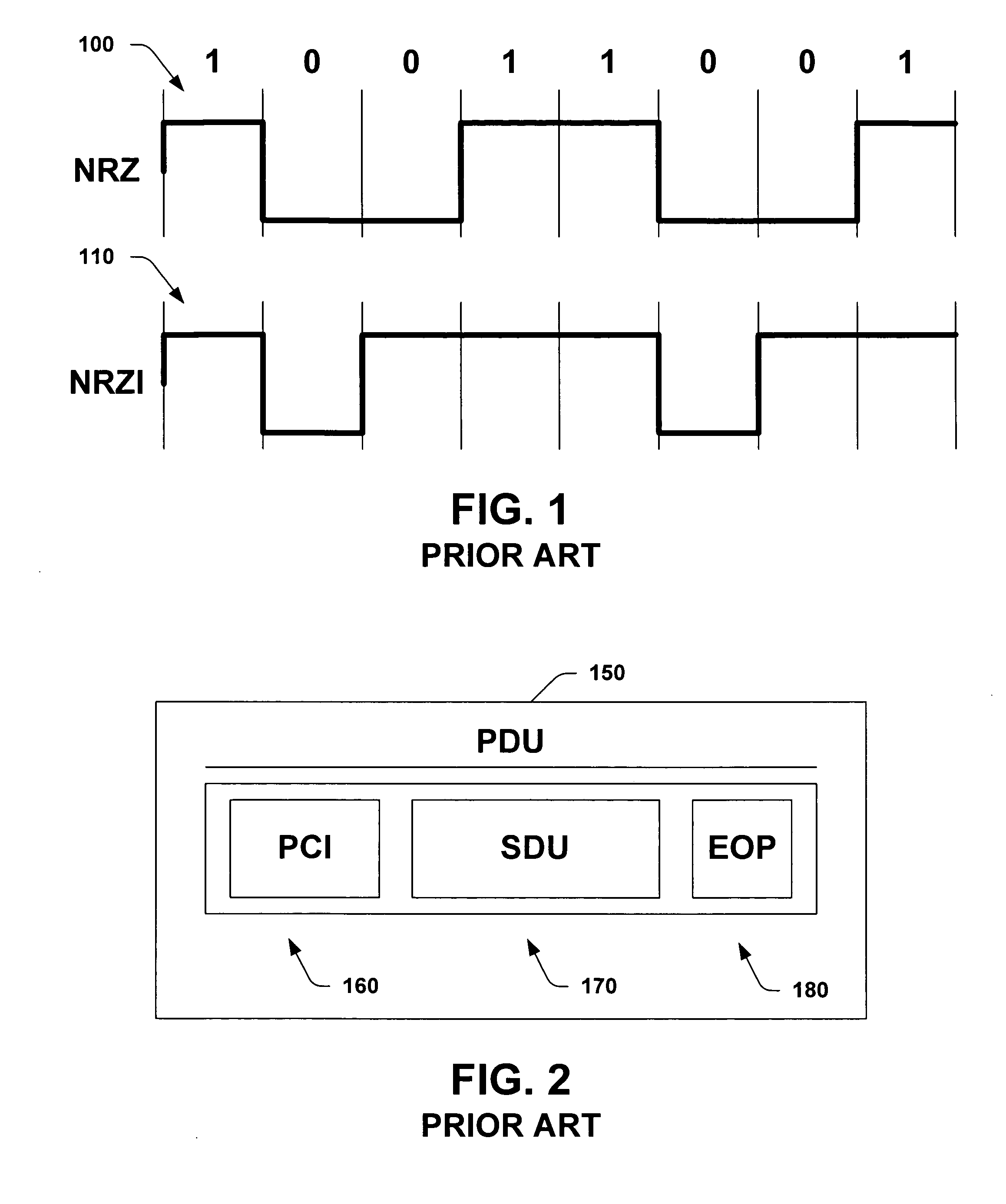

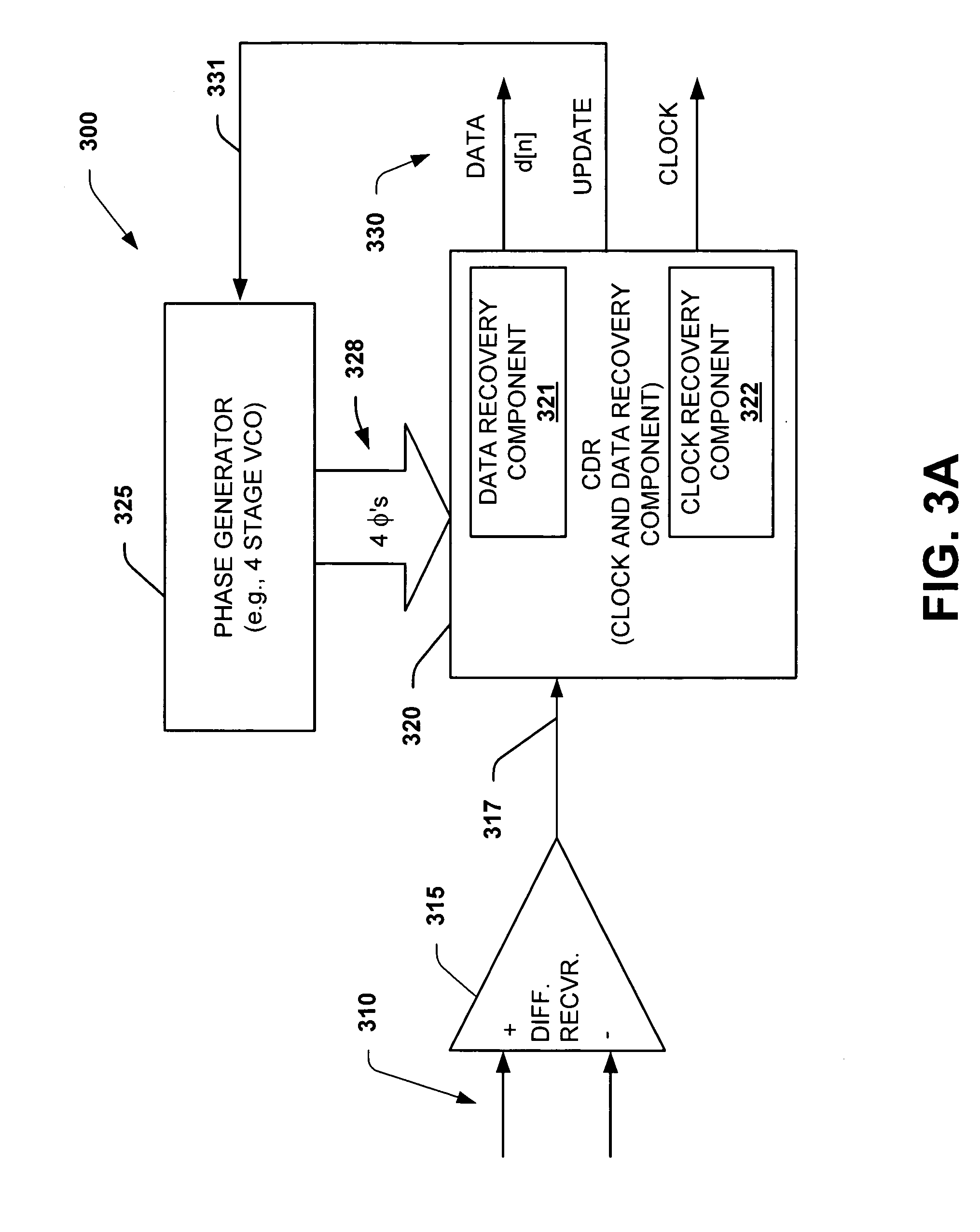

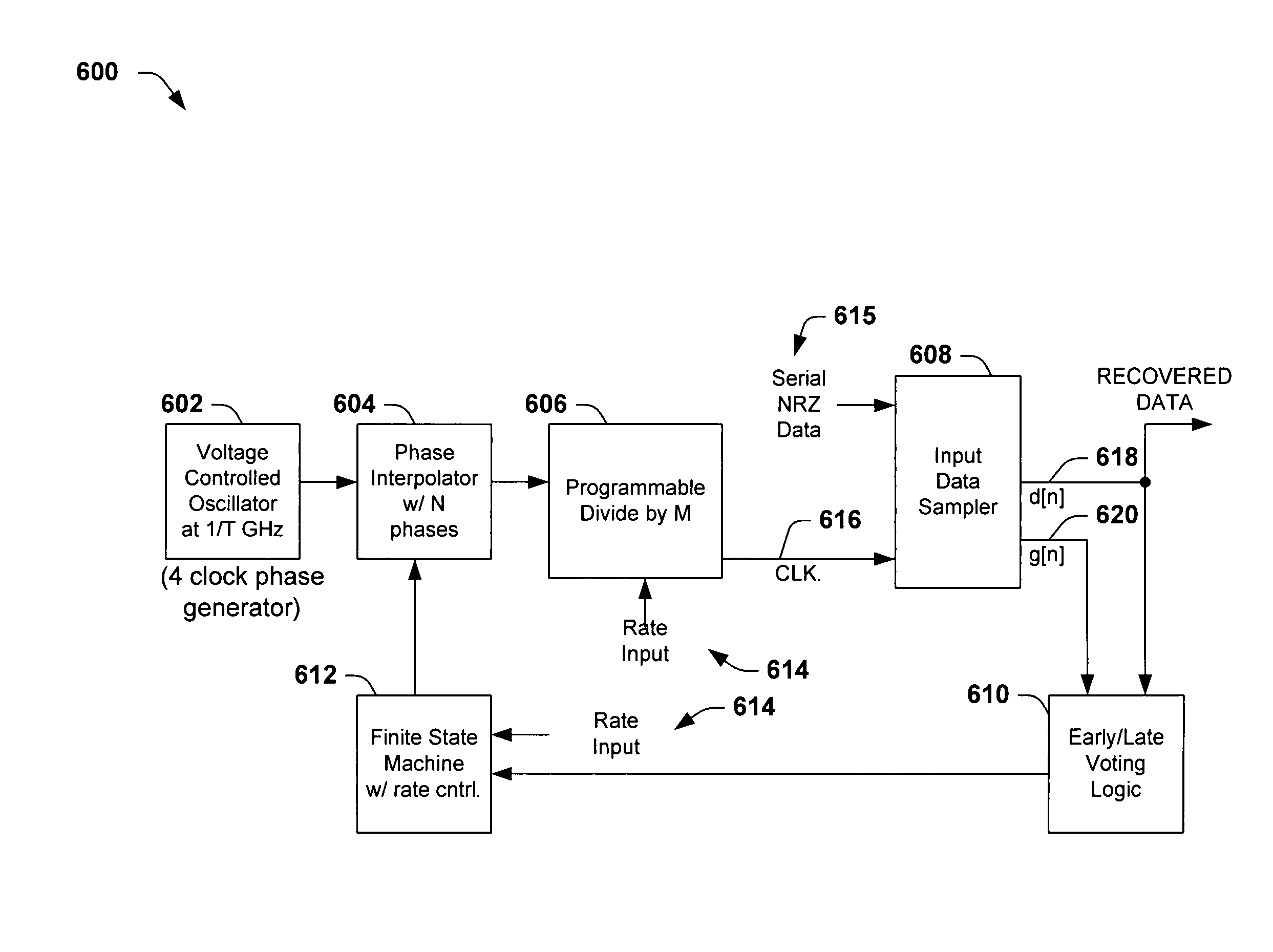

The present invention facilitates clock and data recovery (330,716 / 718) for serial data streams (317,715) by providing a mechanism that can be employed to maintain a fixed tracking capability of an interpolator based CDR circuit (300,700) at multiple data rates (e.g., 800). The present invention further provides a wide data rate range CDR circuit (300,700), yet uses an interpolator design optimized for a fixed frequency. The invention employs a rate programmable divider circuit (606,656,706) that operates over a wide range of clock and data rates (e.g., 800) to provide various phase correction step sizes (e.g., 800) at a fixed VCO clock frequency. The divider (606,656,706) and a finite state machine (FSM) (612,662,712) of the exemplary CDR circuit (600,650,700) are manually programmed based on the data rate (614,667). Alternately, the data rate may be detected from a recovered serial data stream (718) during CDR operations (on-the-fly) utilizing a frequency detection circuit (725) to automatically program the divider (706) and FSM (712) to provide CDR circuit operation at the nearest base clock rate (716).

Owner:TEXAS INSTR INC

Interpolator based clock and data recovery (CDR) circuit with digitally programmable BW and tracking capability

ActiveUS7315596B2Easy to operateWide data rate rangePulse automatic controlSynchronising arrangementPhase correctionData stream

Owner:TEXAS INSTR INC

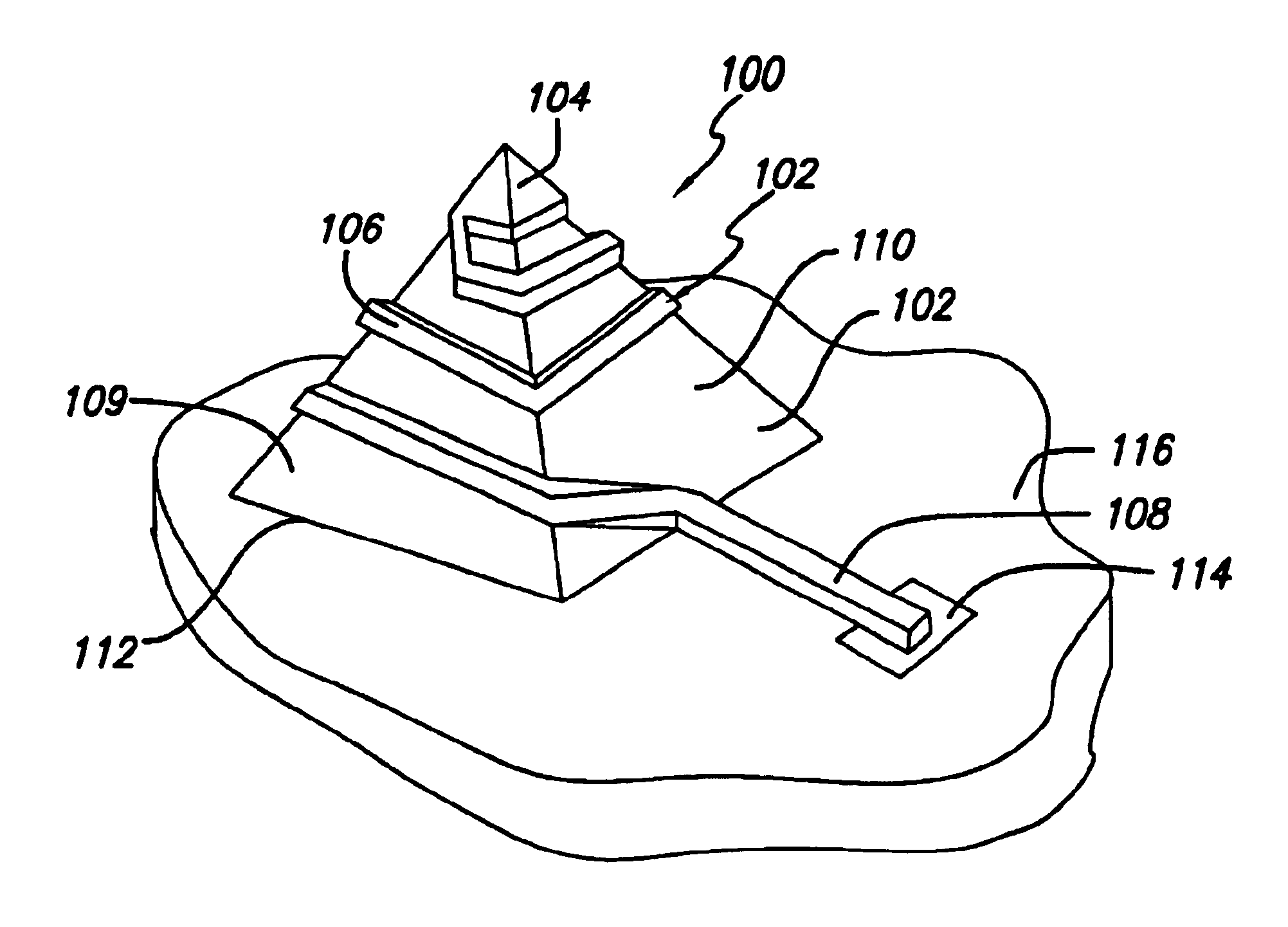

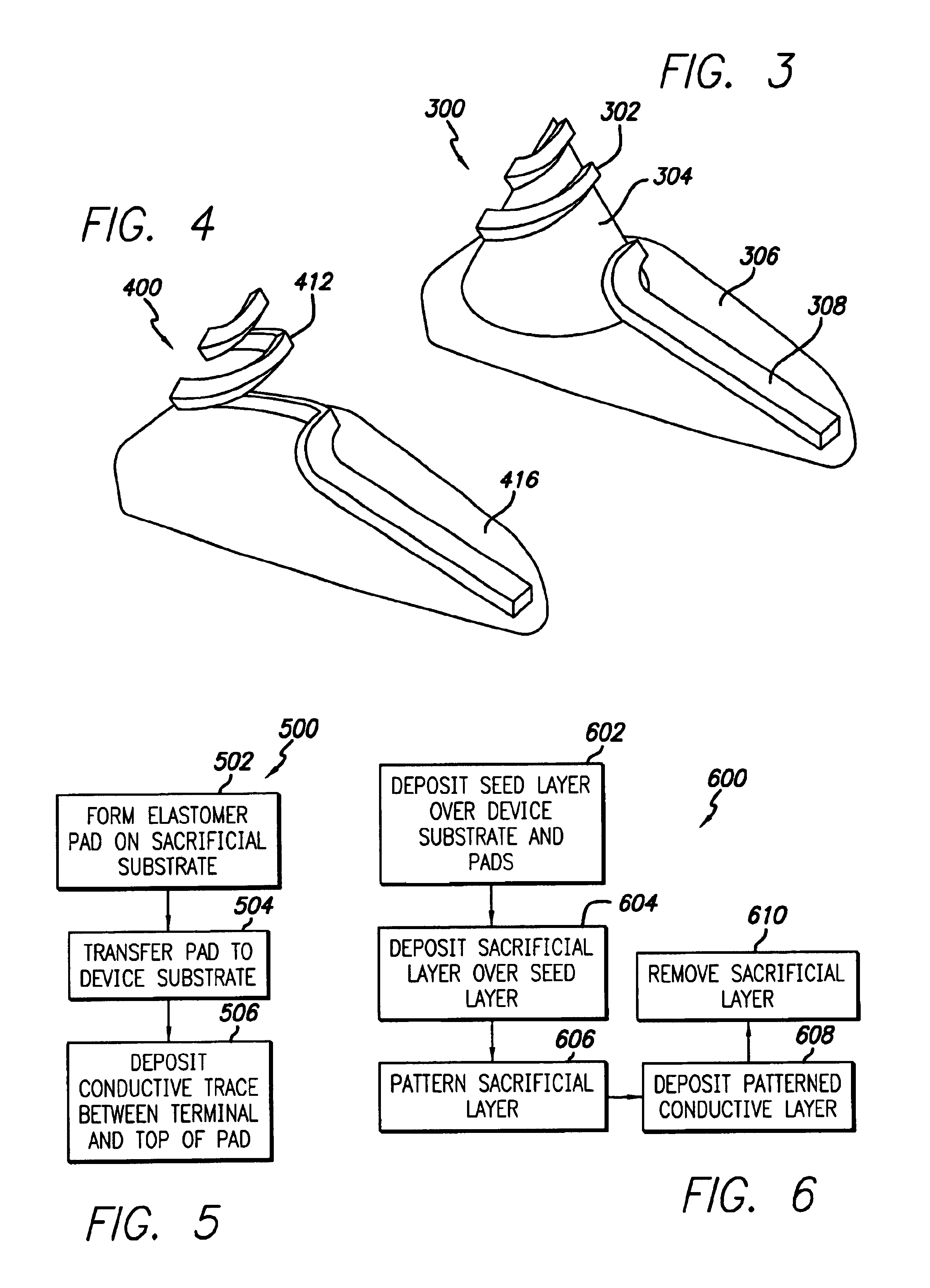

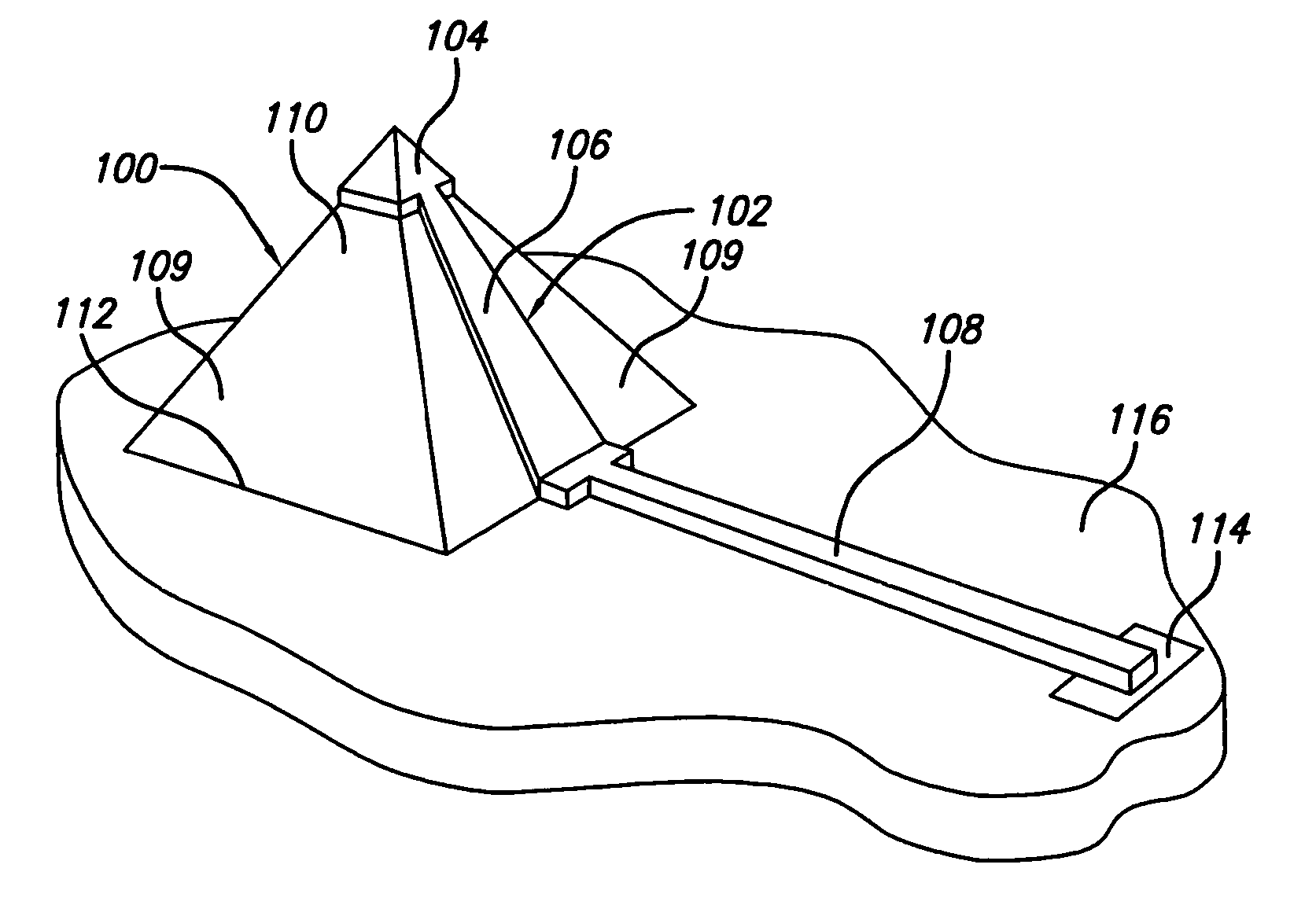

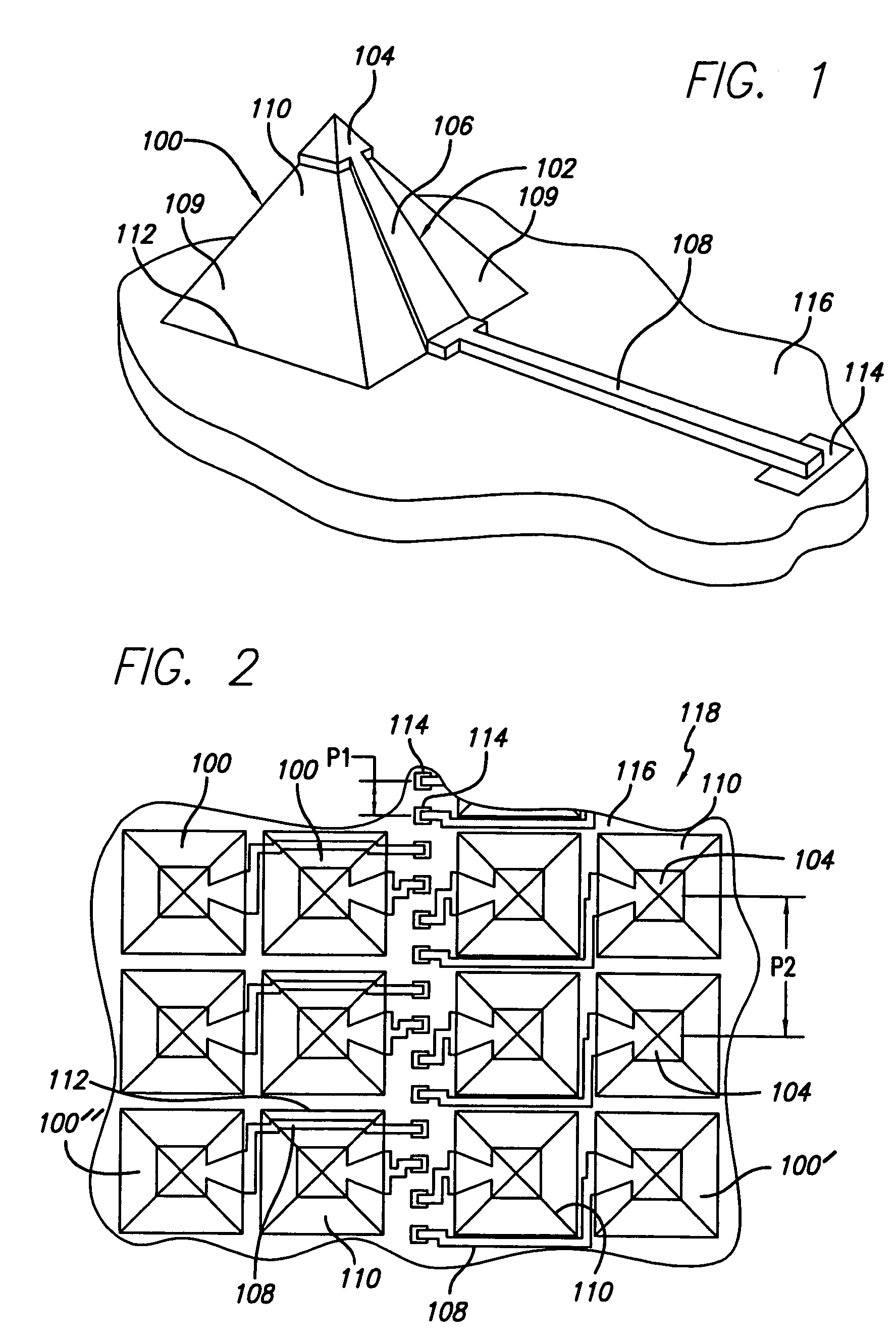

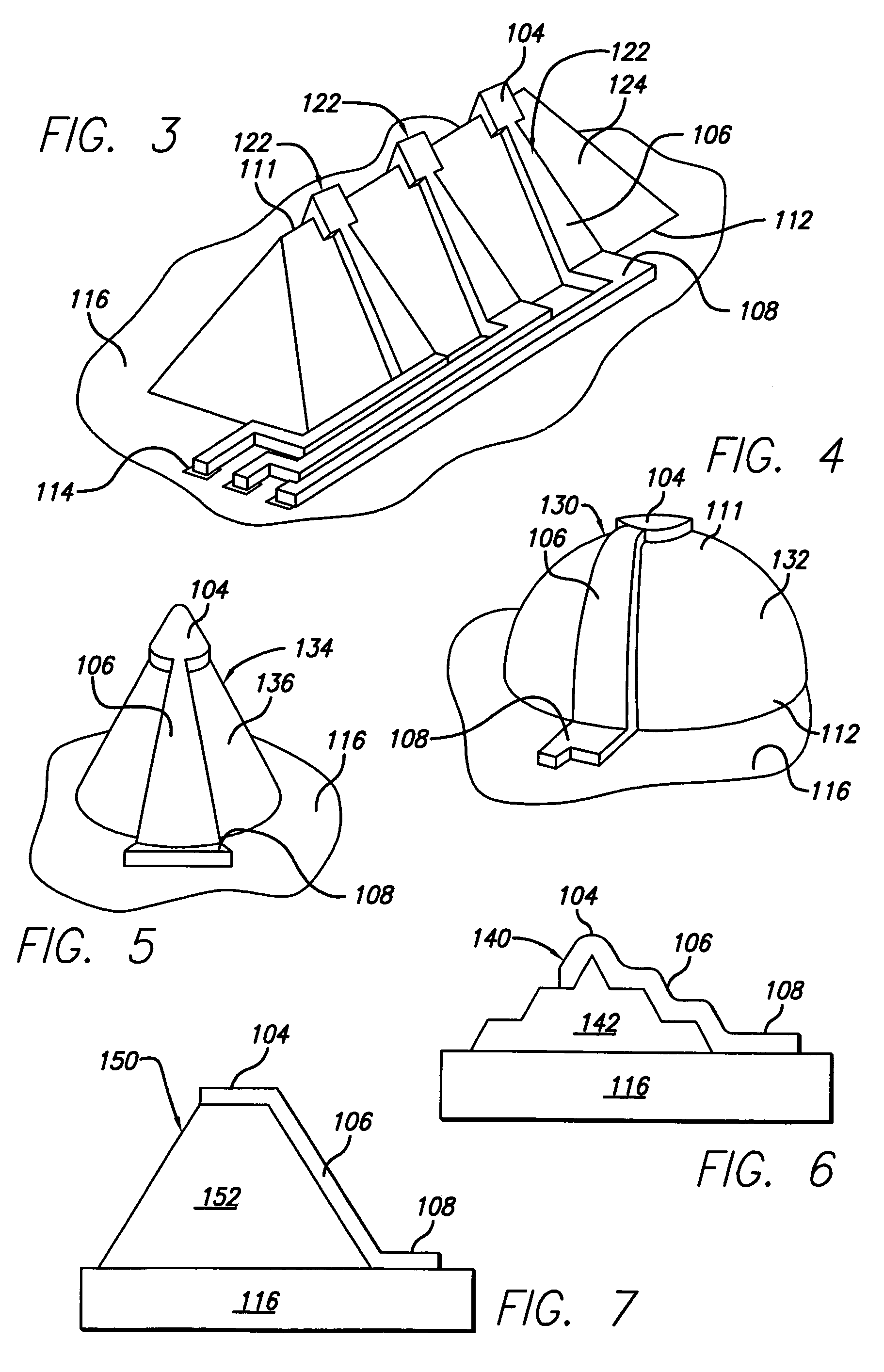

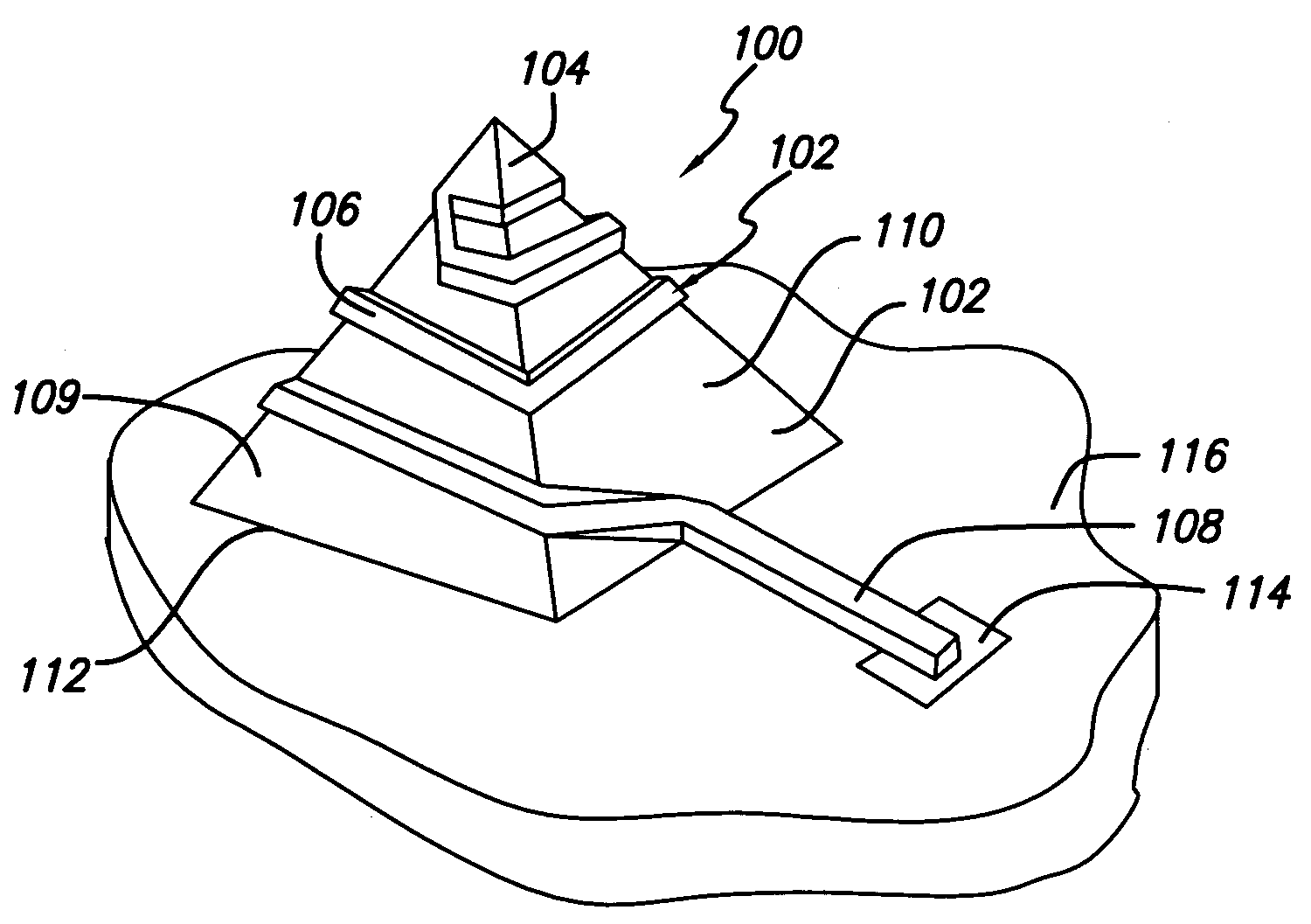

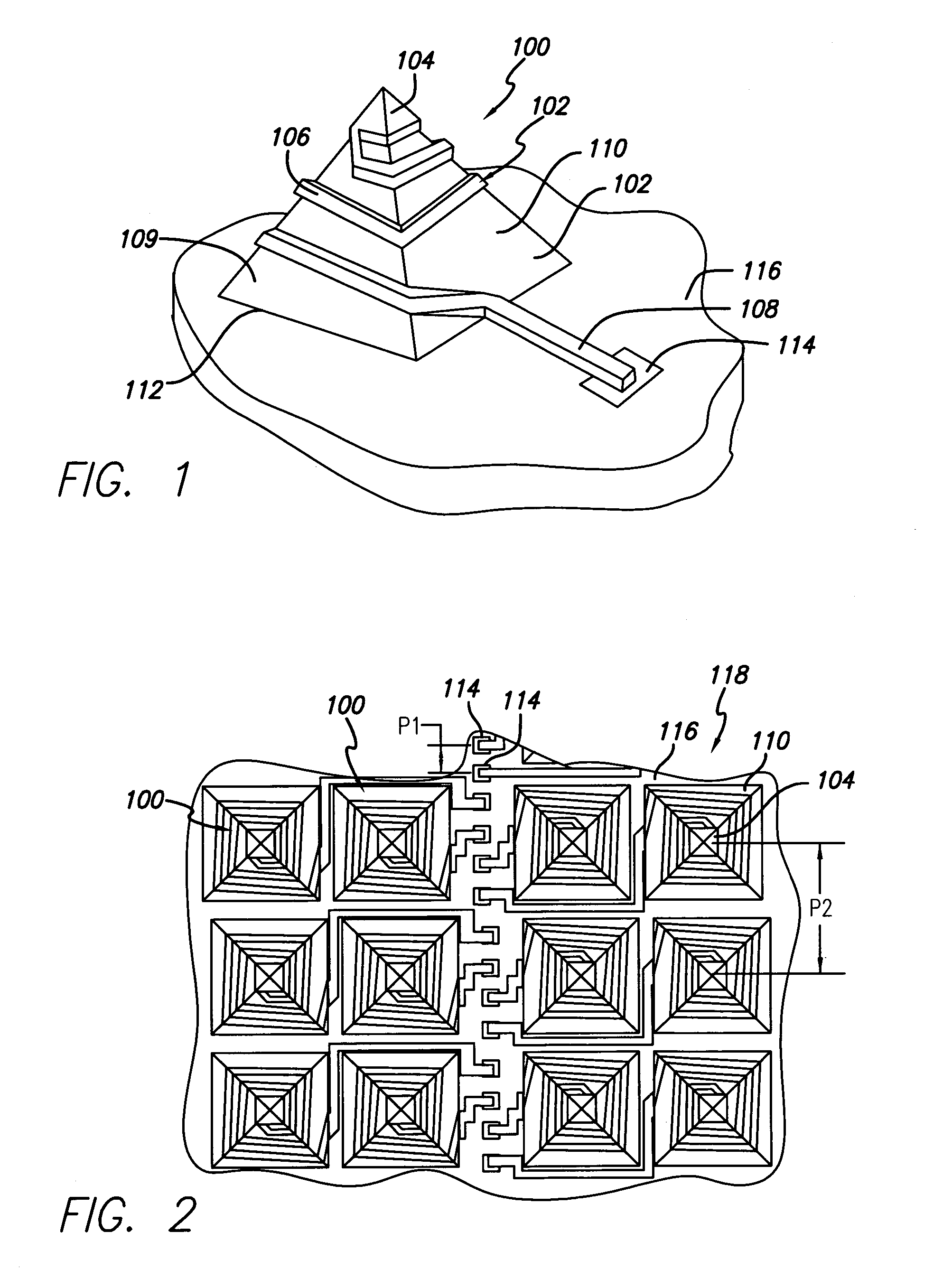

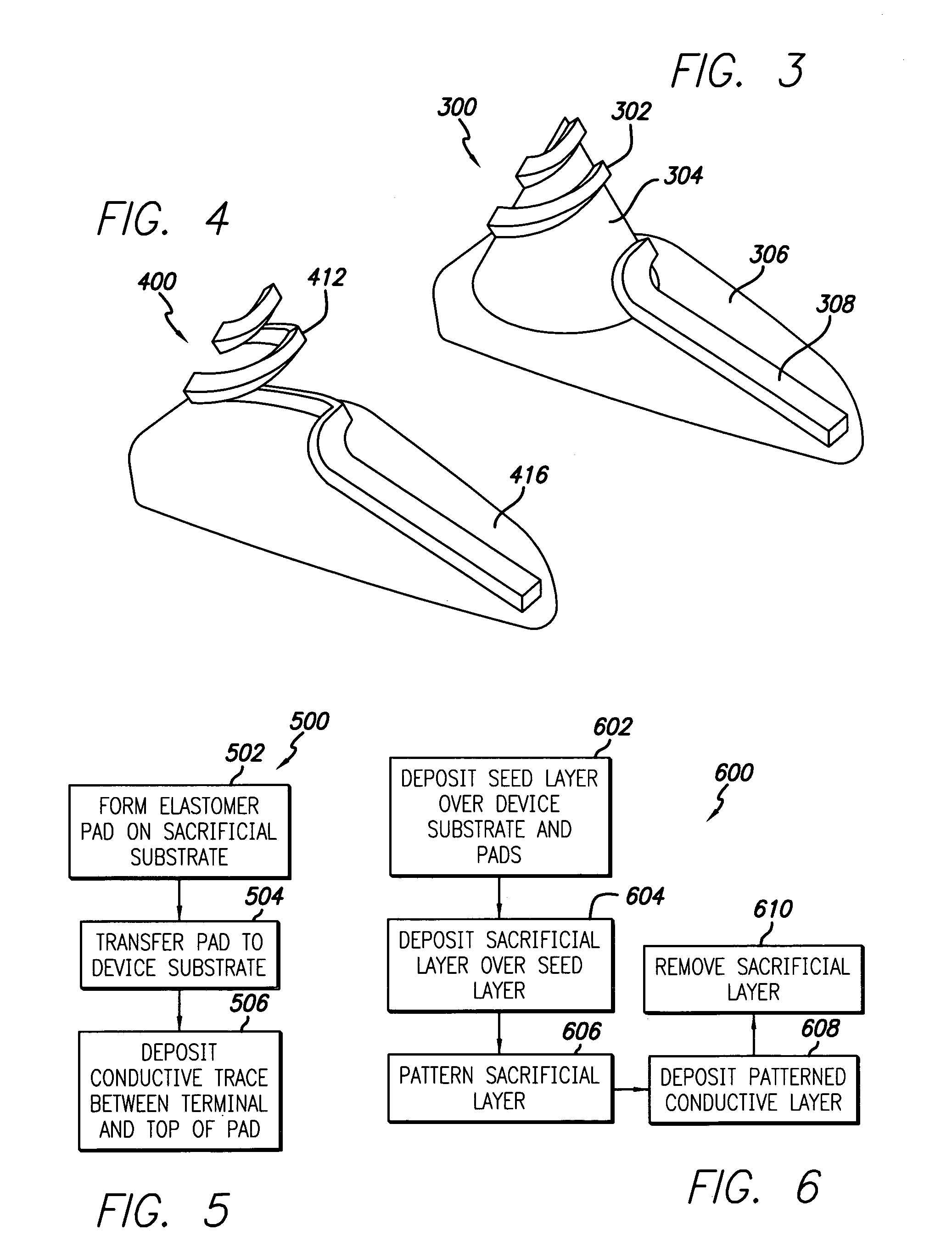

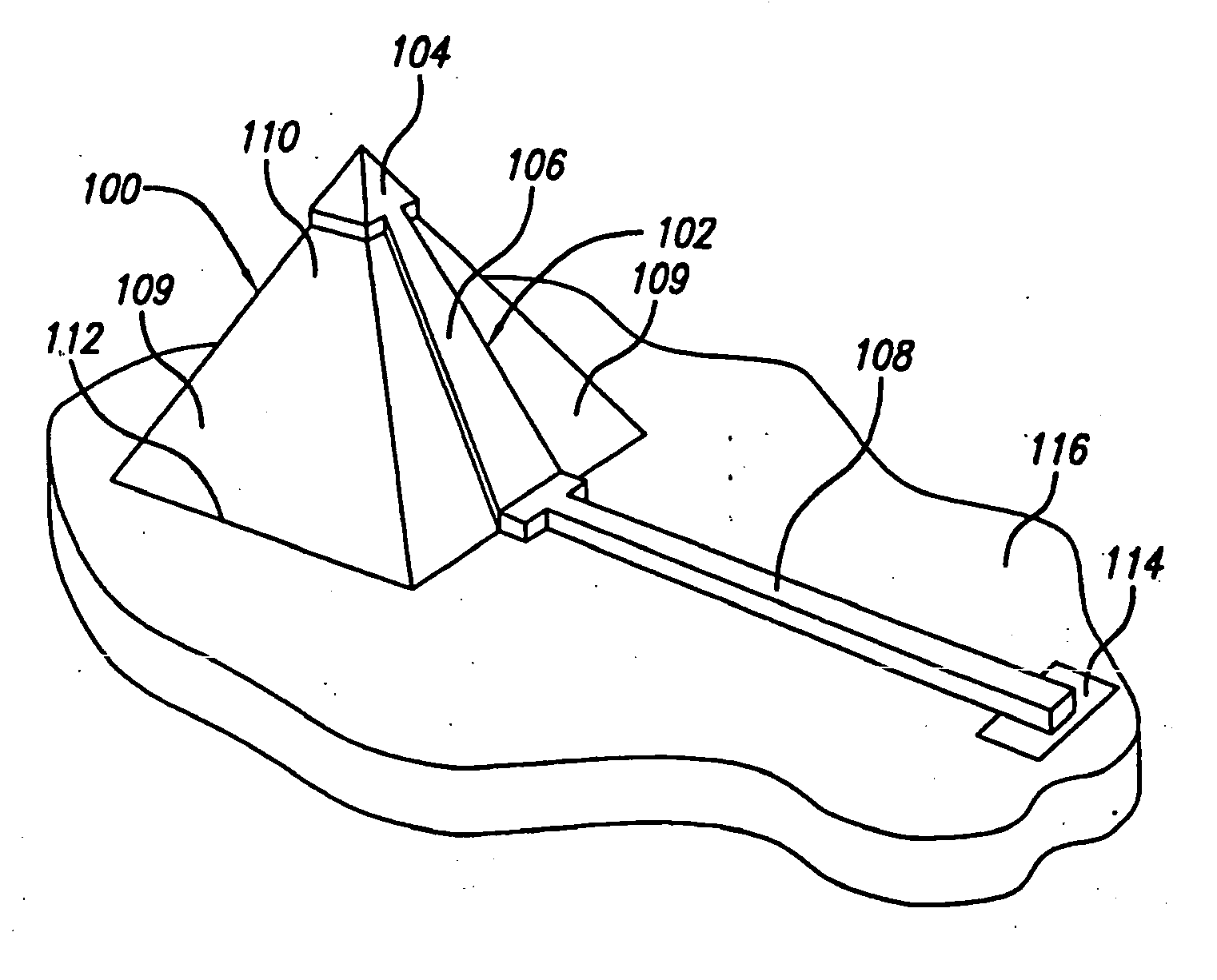

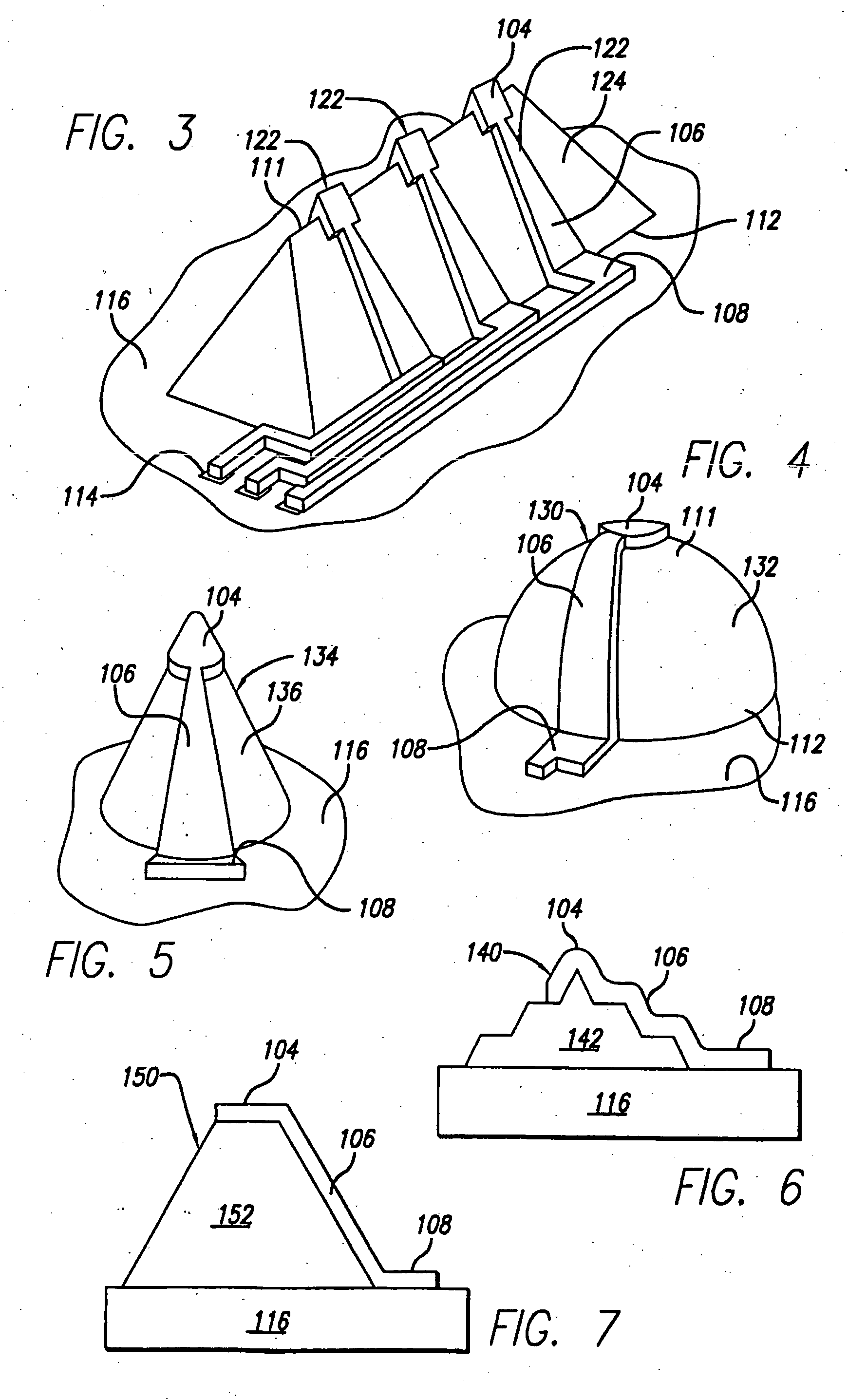

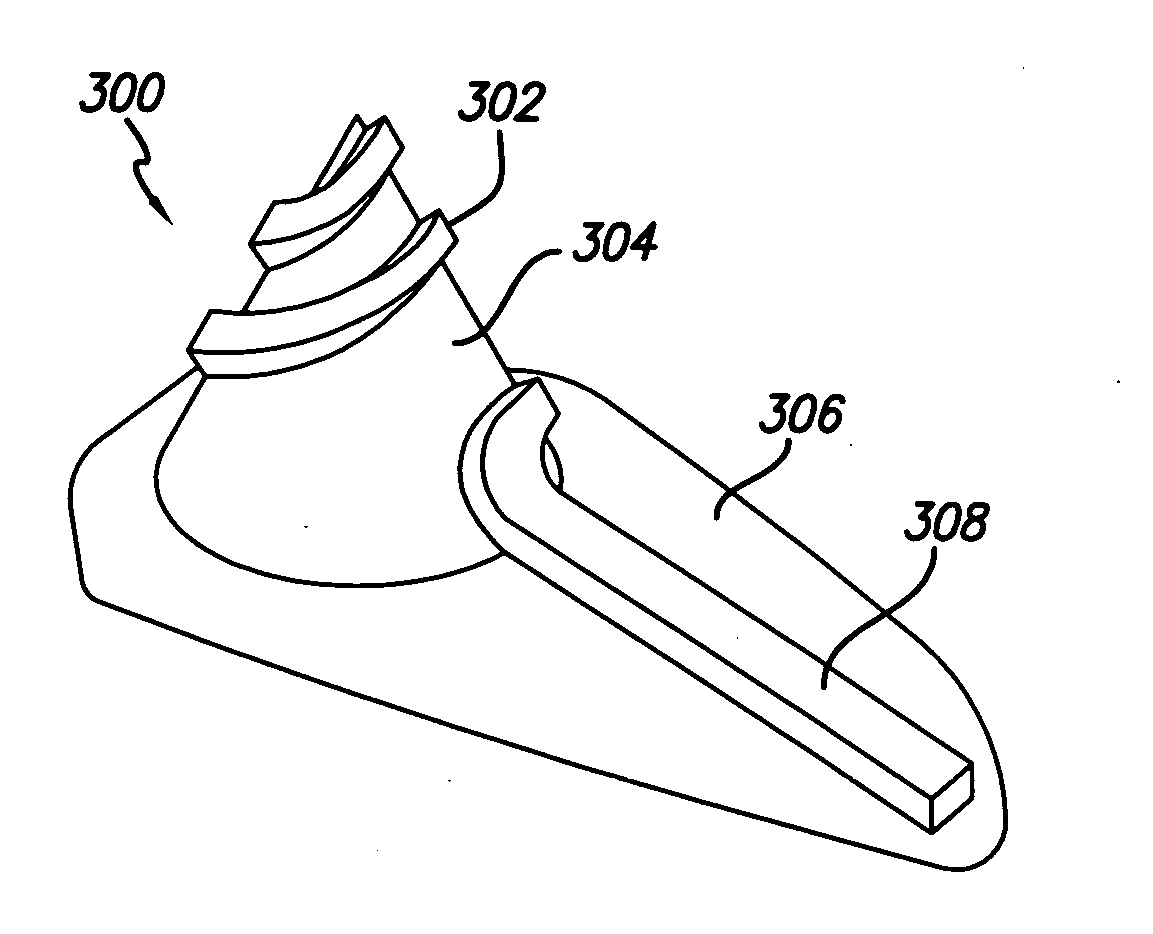

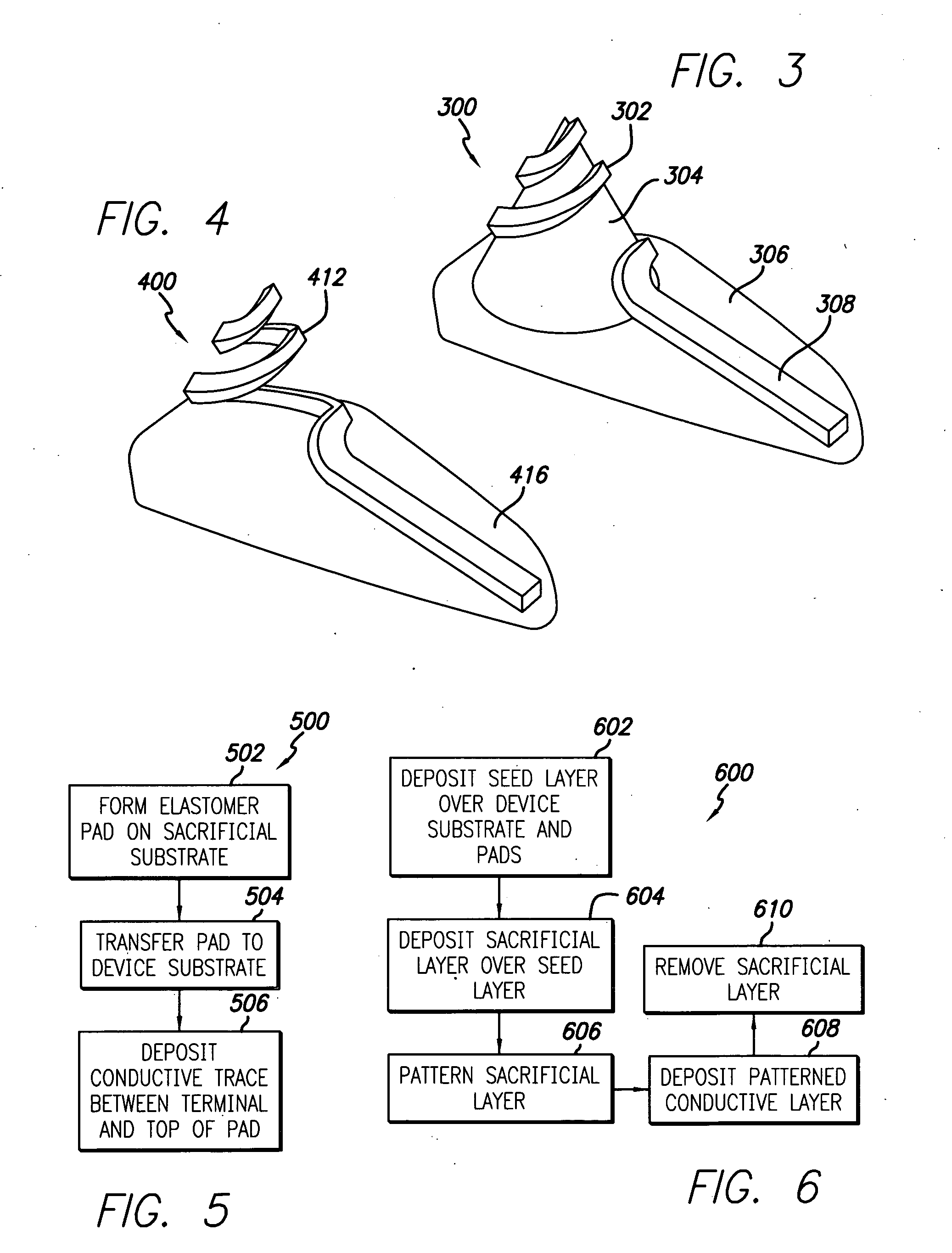

Helical microelectronic contact and method for fabricating same

InactiveUS6948940B2Step of become largeContact member manufacturingElectronic circuit testingEngineeringHelix

A microelectronic spring contact for making electrical contact between a device and a mating substrate and method of making the same are disclosed. The spring contact has a compliant pad adhered to a substrate of the device and spaced apart from a terminal of the device. The compliant pad has a base adhered to the substrate, and side surfaces extending away from the substrate and tapering to a smaller end area distal from the substrate. A trace extends from the terminal of the device in a coil pattern over the compliant pad to its end area, forming a helix. At least a portion of the compliant pad end area is covered by the trace, and a portion of the trace that is over the compliant pad is supported by the compliant pad. In an alternative embodiment, the pad is removed to leave a freestanding helical contact.

Owner:FORMFACTOR INC

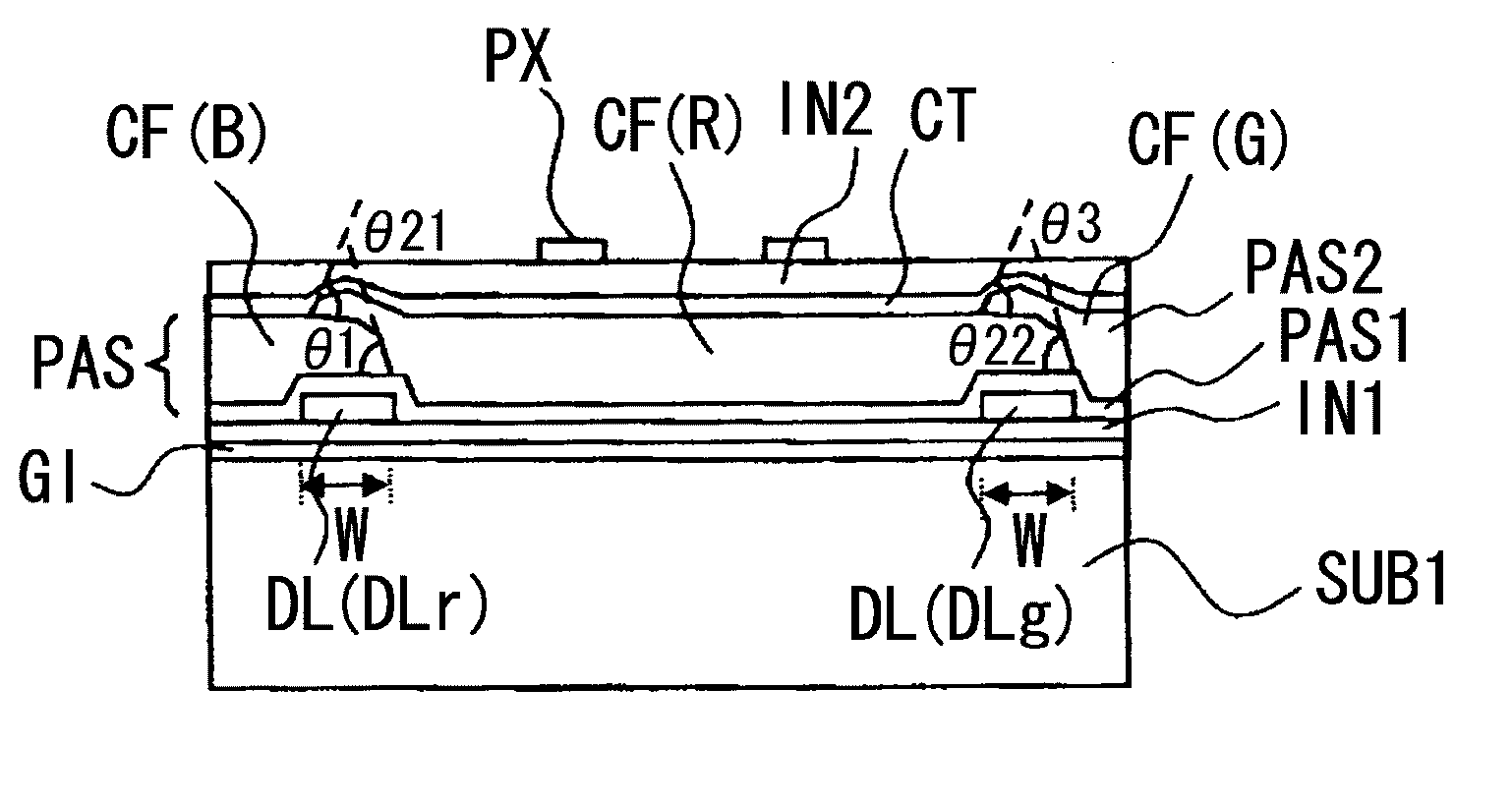

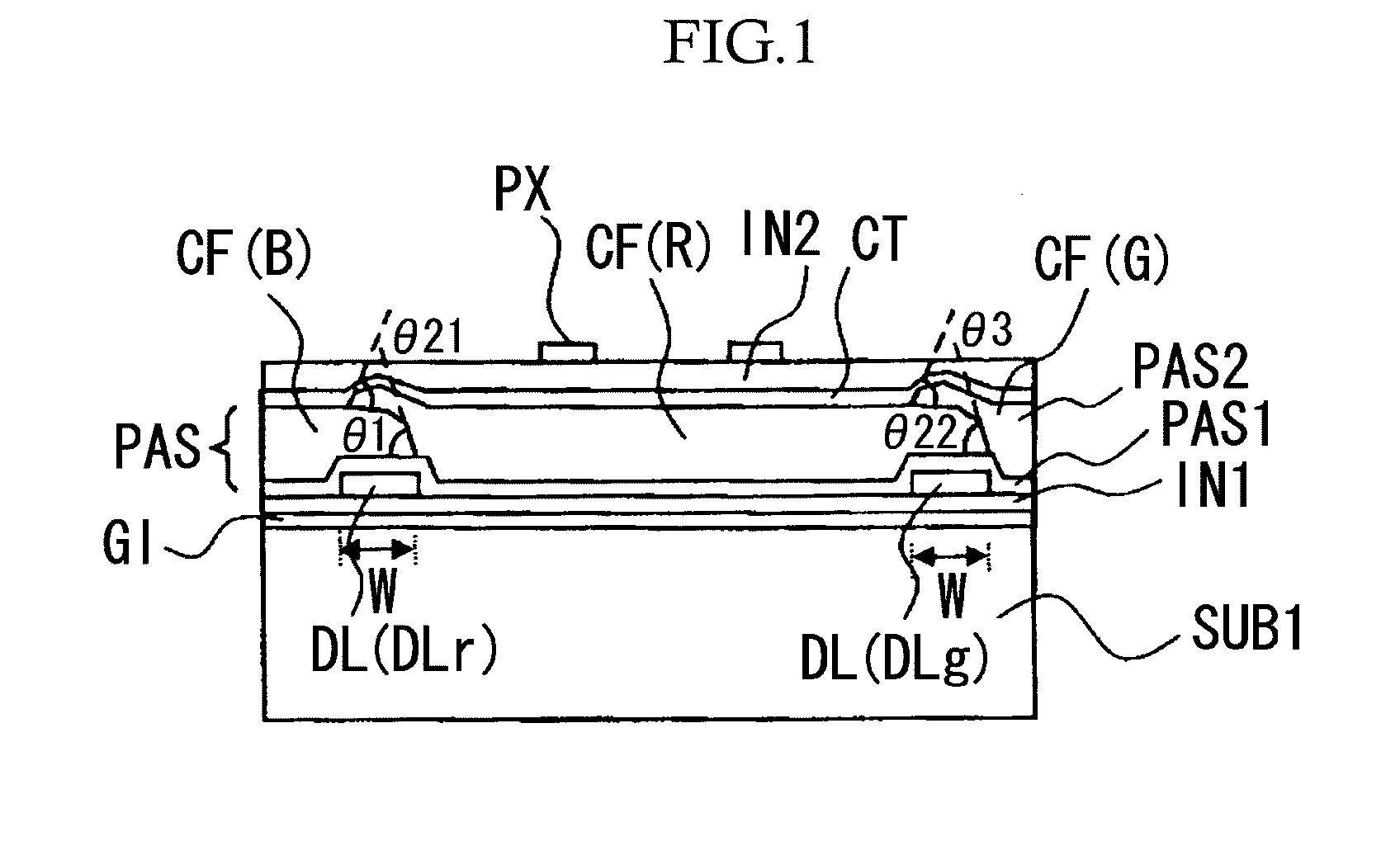

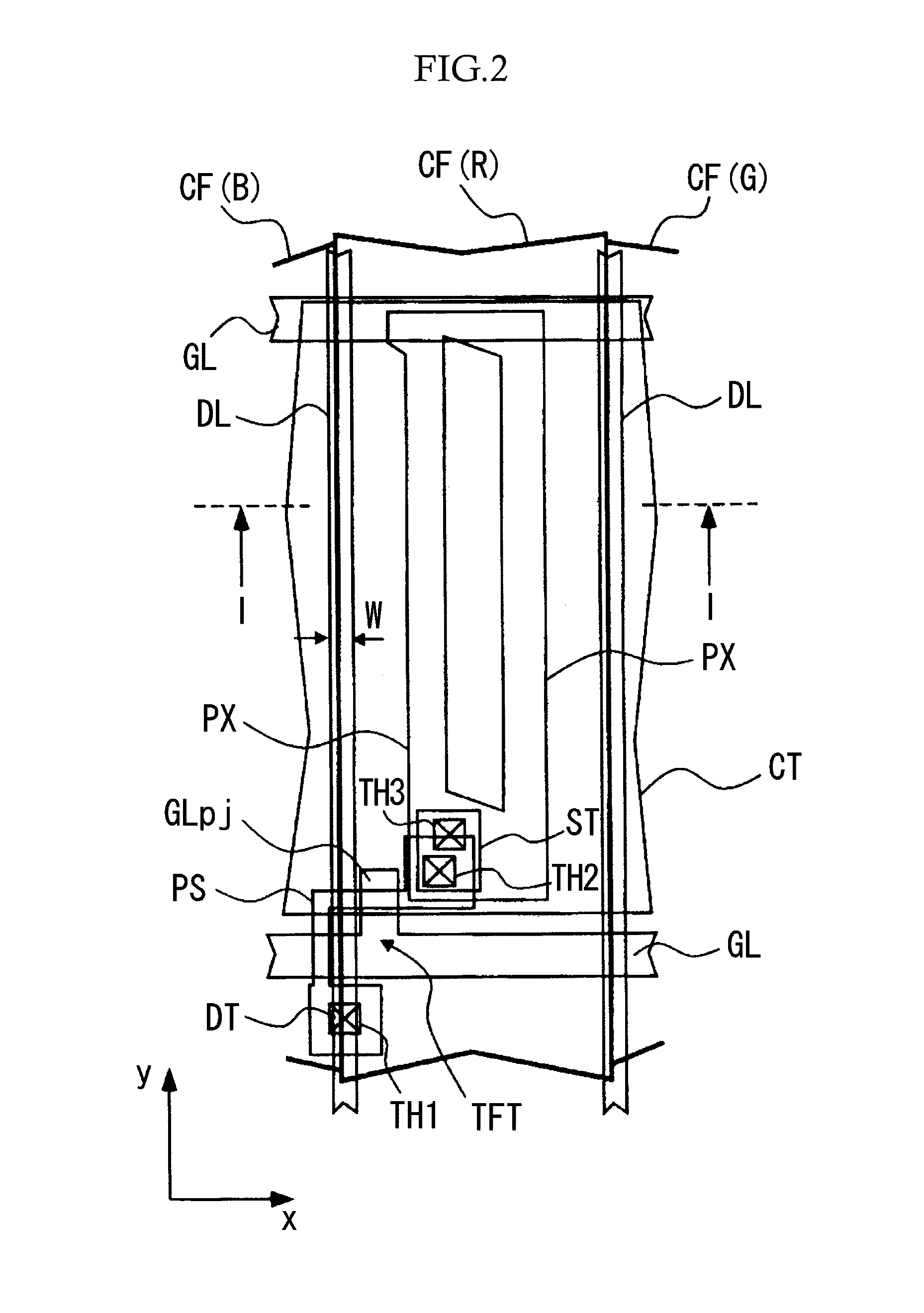

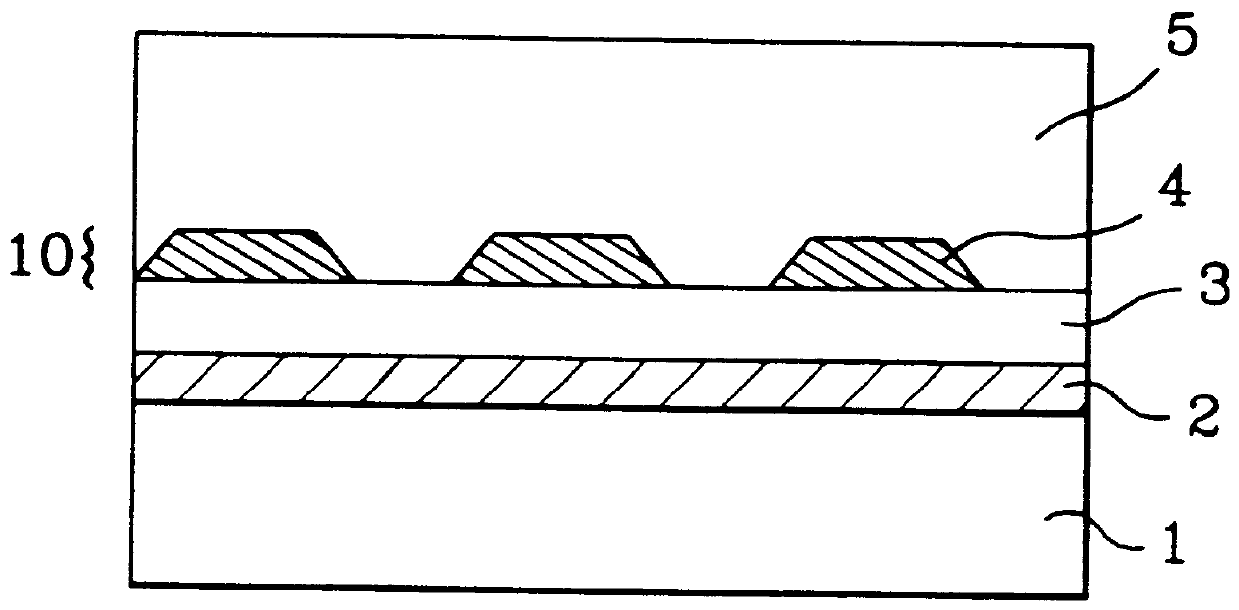

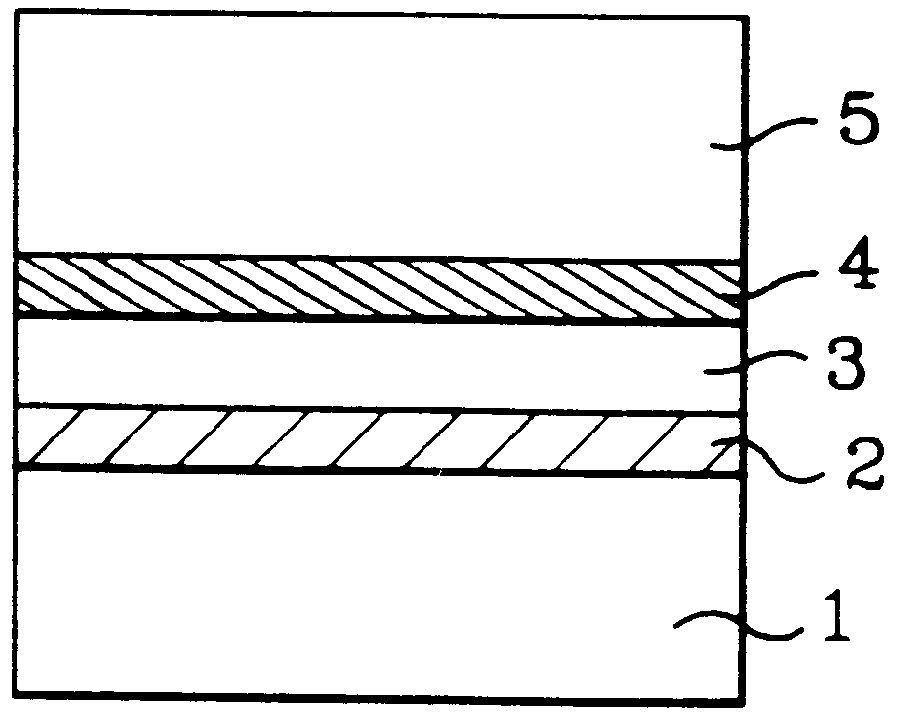

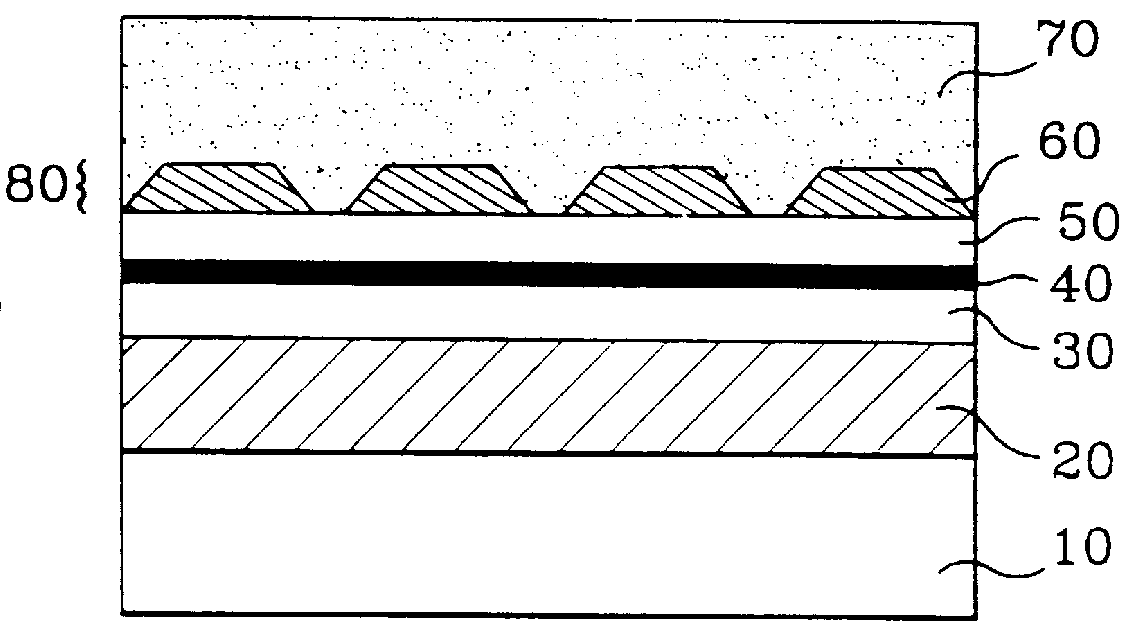

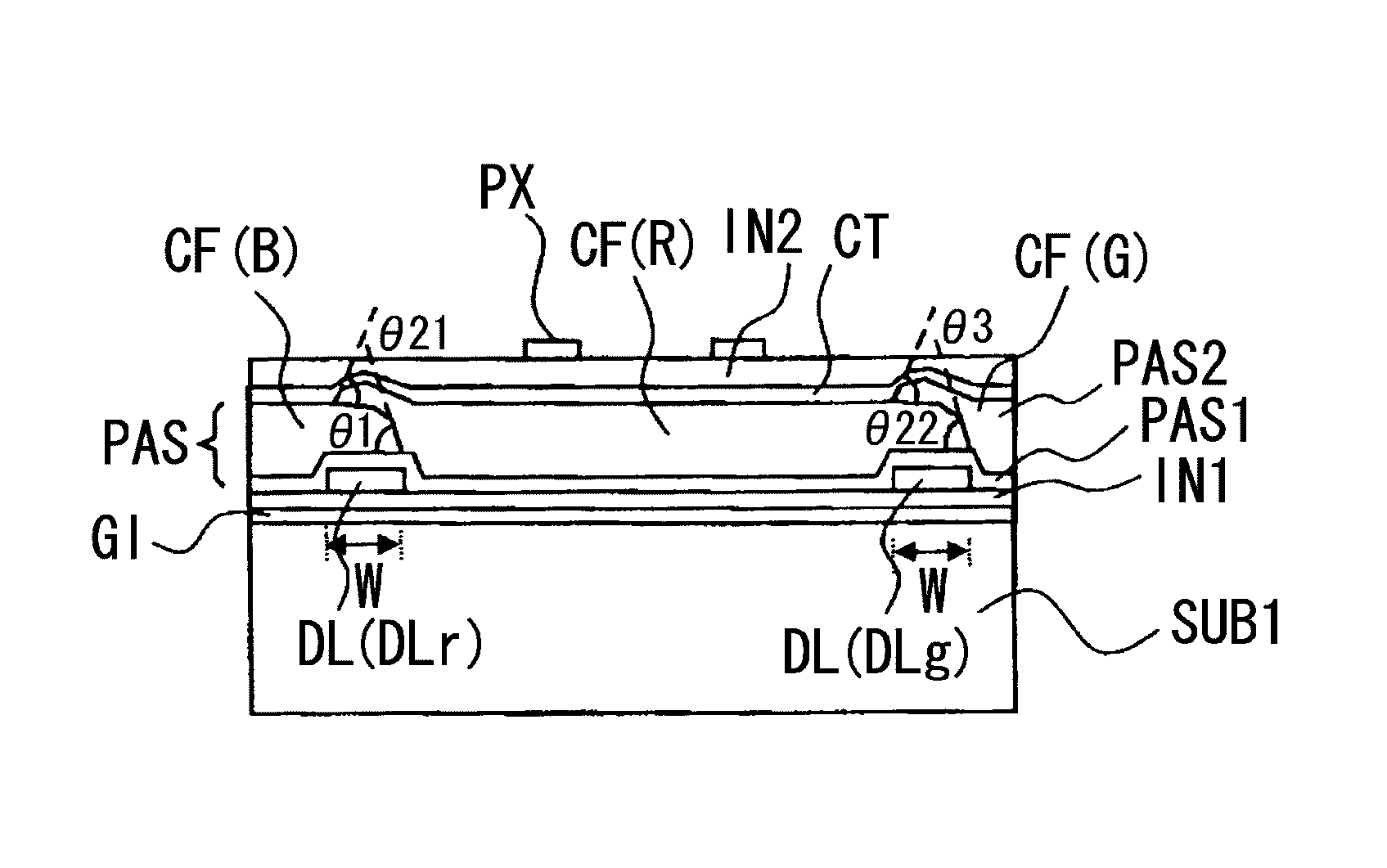

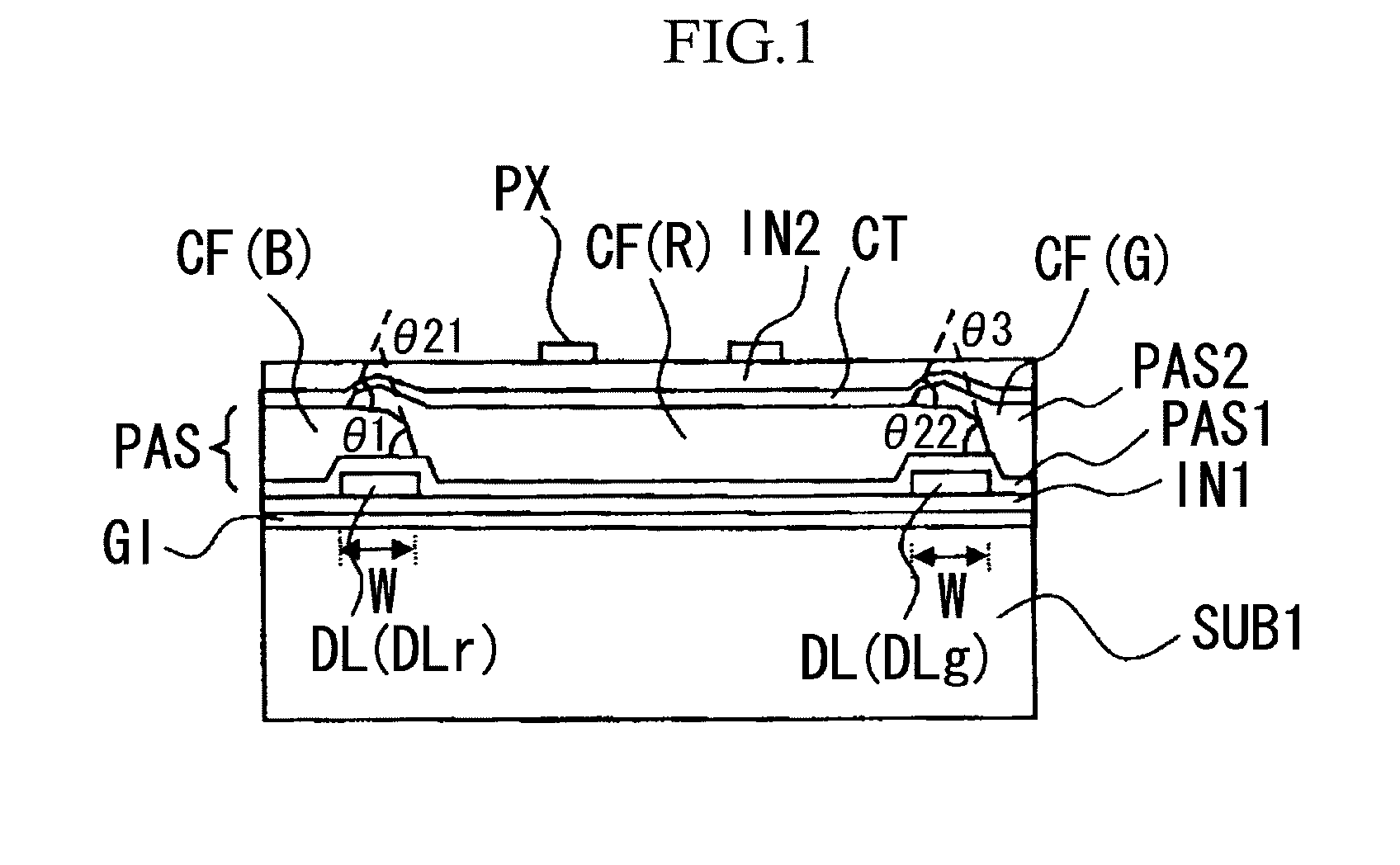

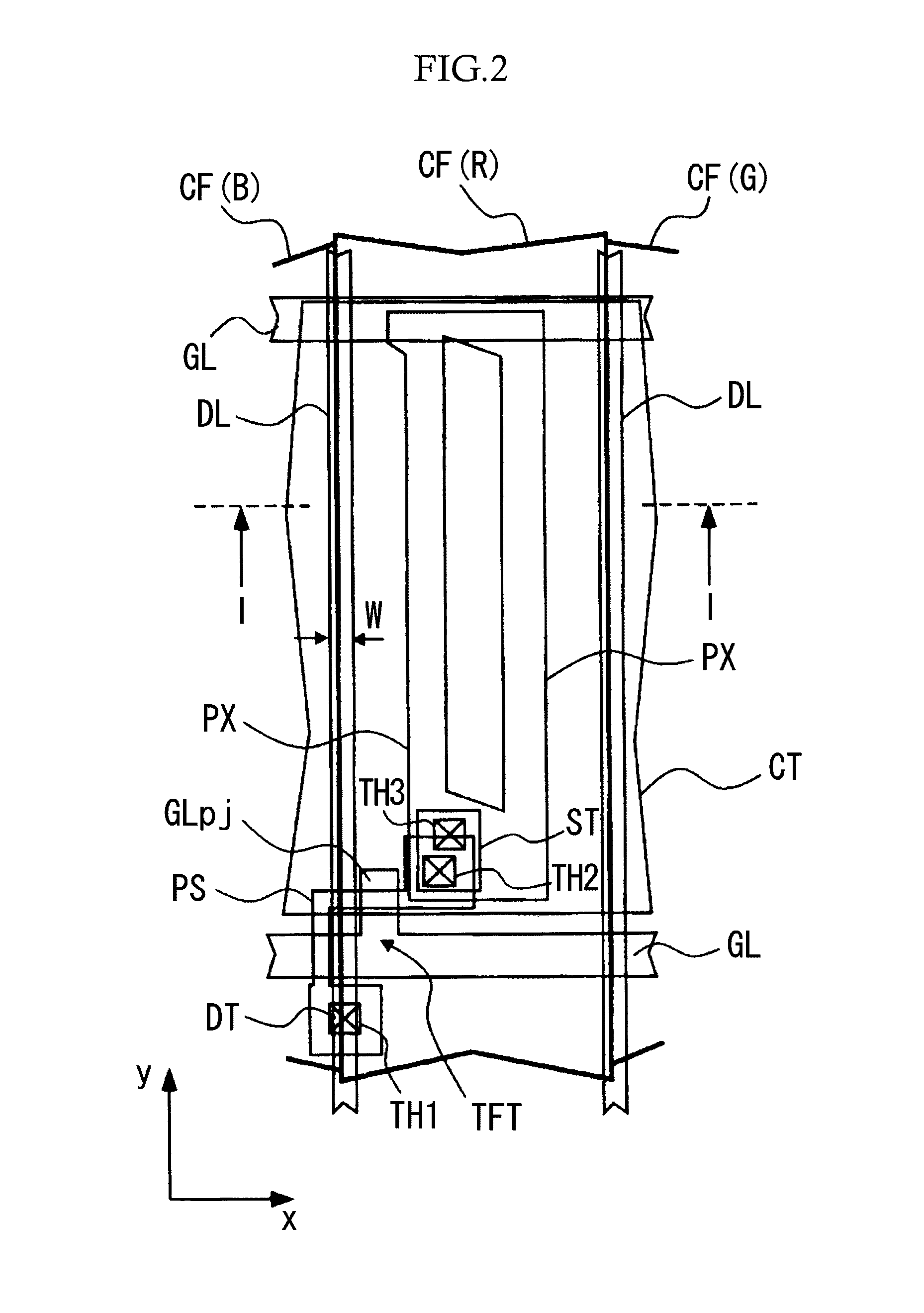

Liquid crystal display device and manufacturing method for same

ActiveUS20100321283A1Small aperture ratioStep of become largeLiquid crystal compositionsStatic indicating devicesLiquid-crystal displayColor filter array

A liquid crystal display device with a higher aperture ratio is provided. According to one embodiment of the present invention, second color filters are formed so as to overlap with first color filters when adjacent color filters having different colors are formed on the TFT substrate side, so that the angle of the first tapers where said first color filters overlap and the angle of the second tapers where said second color filters overlap are set to 45° or more and 90° or less.

Owner:PANASONIC LIQUID CRYSTAL DISPLAY CO LTD

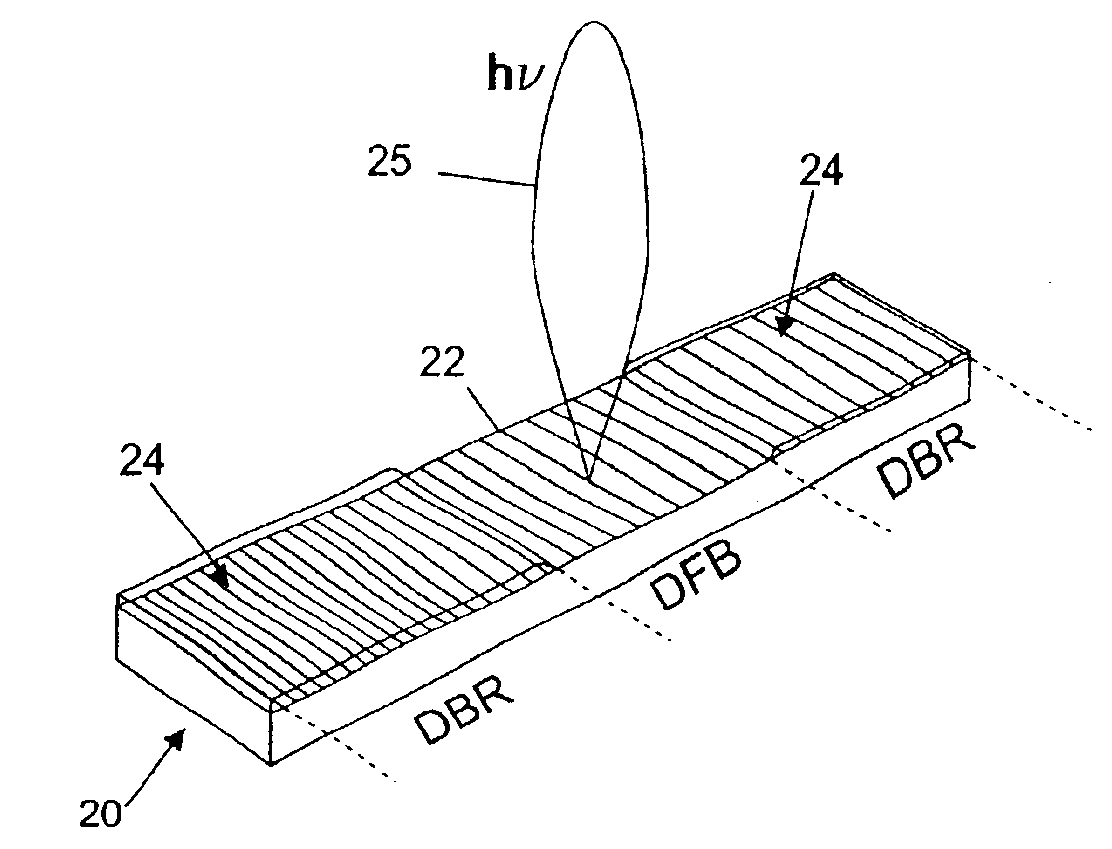

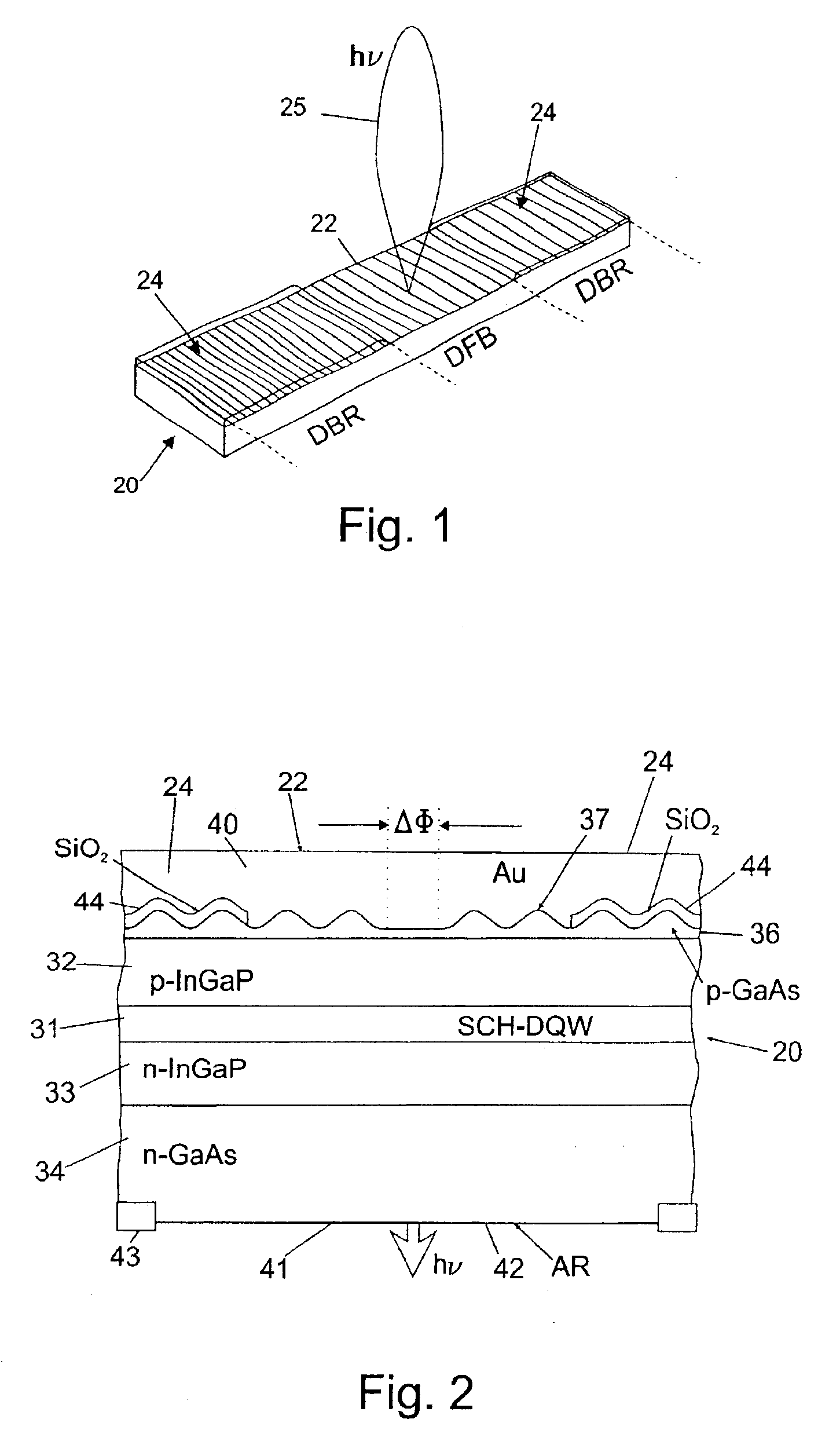

Semiconductor Bragg reflector and a method of fabricating said reflector

InactiveUS6023354ASmall sizeImprove the overall coefficientOptical wave guidanceLaser optical resonator constructionGratingSemiconductor

A semiconductor Bragg reflector and to a method of fabricating it. The reflector comprises a plurality of stacked layers on a substrate of a III-V type material, one of the stacked layers forming a holographic grating. The layer forming the grating comprises an alternating succession of air pockets and of III-V type material. Such a reflector is particularly suitable for use in laser devices.

Owner:OCLARO NORTH AMERICA

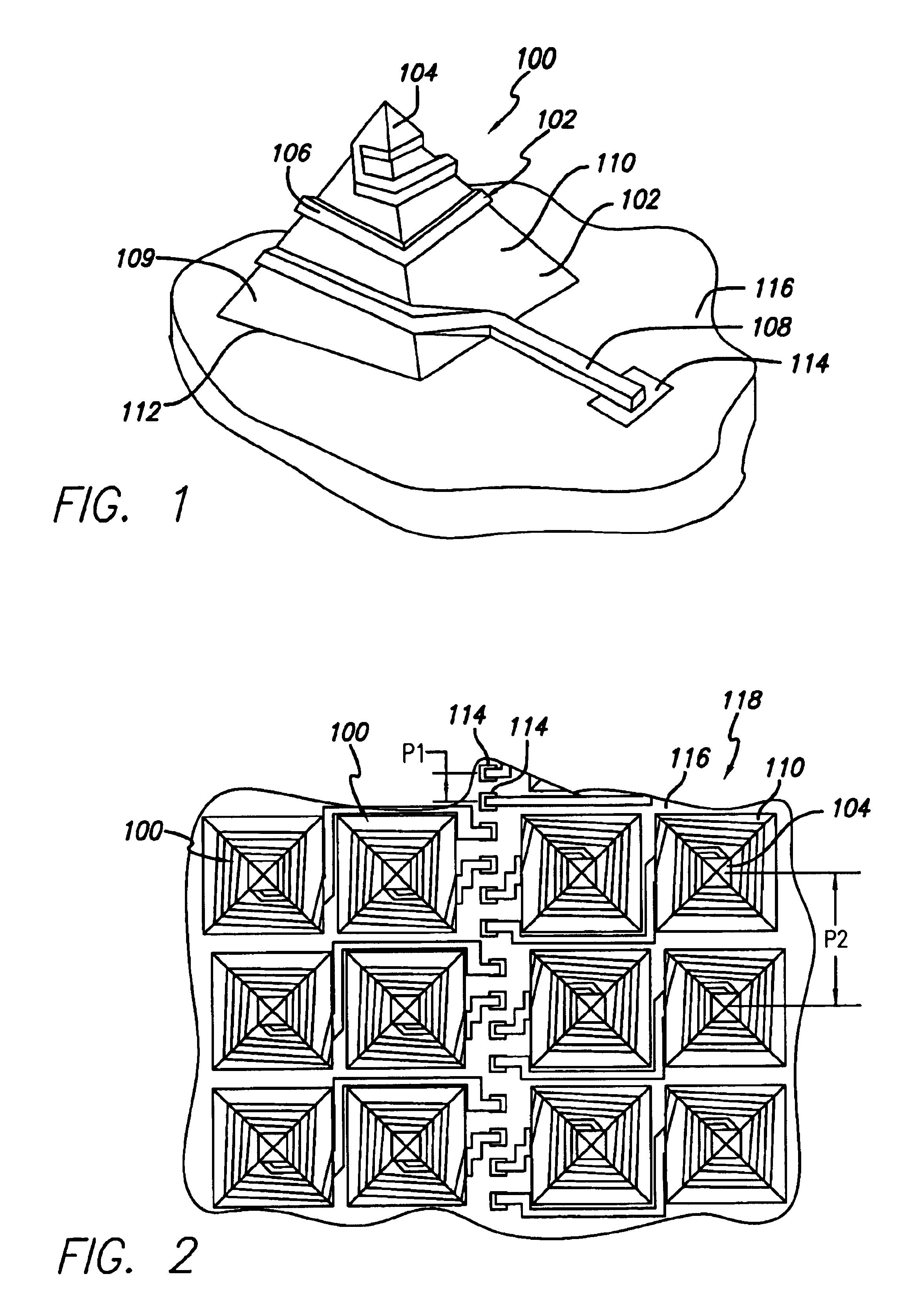

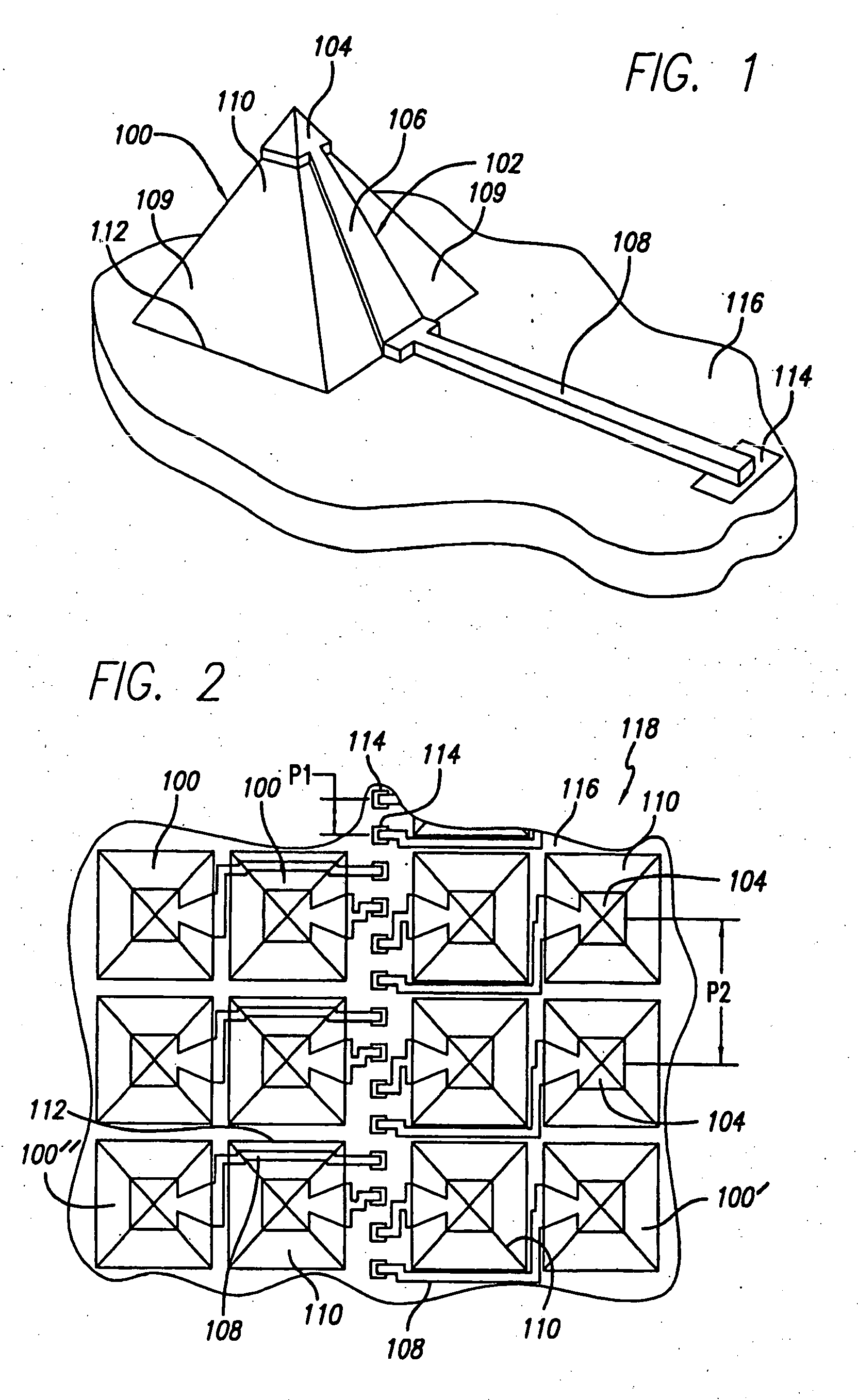

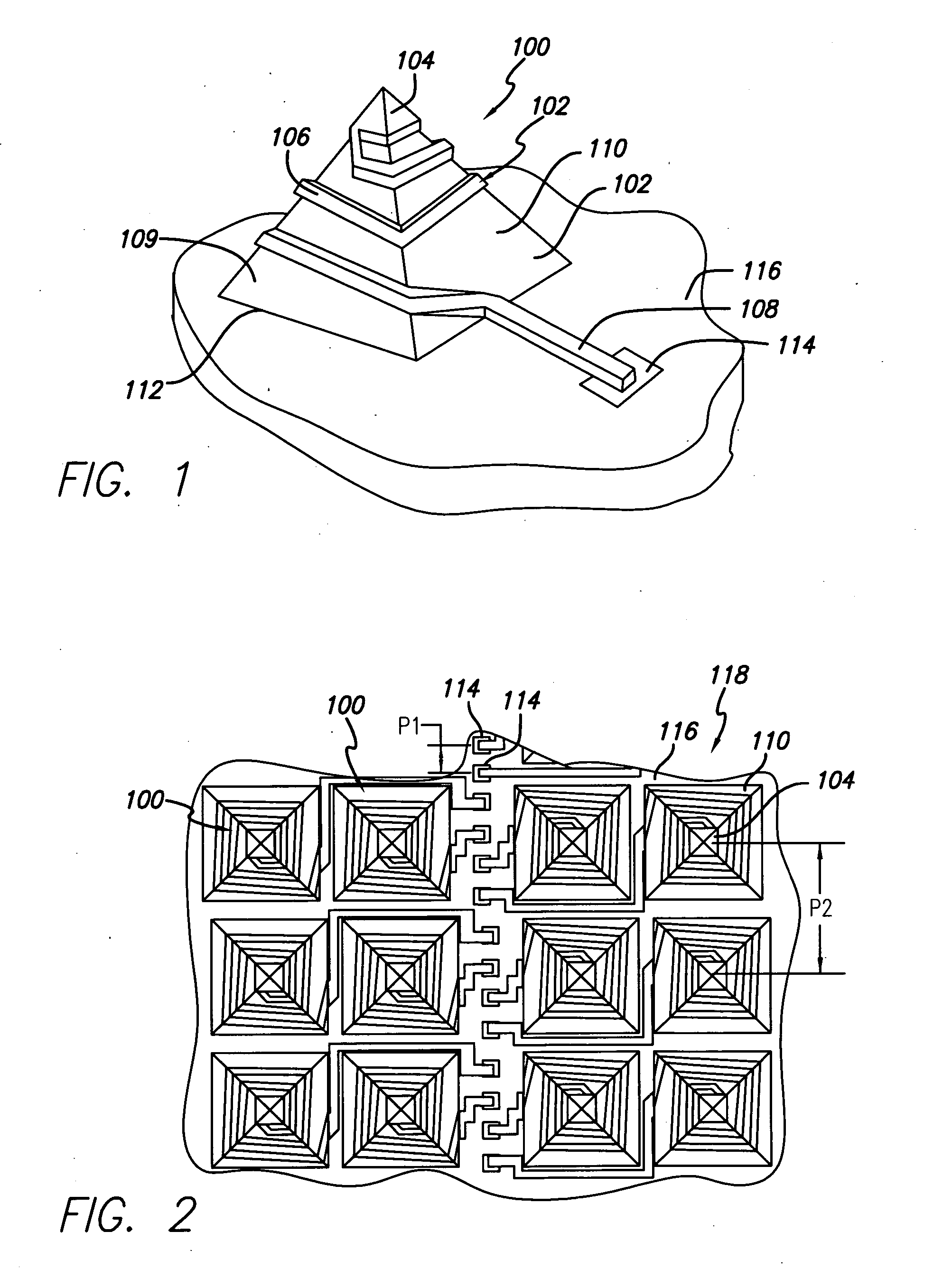

Layered microelectronic contact and method for fabricating same

InactiveUS7005751B2Eliminate requirementsGood strength and stiffnessPrinted circuit assemblingElectrically conductive connectionsDistal portionElectrical contacts

A microelectronic spring contact for making electrical contact between a device and a mating substrate and method of making the same are disclosed. The spring contact has a compliant pad adhered to a substrate of the device and spaced apart from a terminal of the device. The compliant pad has a base adhered to the substrate, and side surfaces extending away from the substrate and tapering to a smaller end area distal from the substrate. A trace extends from the terminal of the device over the compliant pad to its end area. At least a portion of the compliant pad end area is covered by the trace, and a portion of the trace that is over the compliant pad is supported by the compliant pad. A horizontal microelectronic spring contact and method of making the same are also disclosed. The horizontal spring contact has a rigid trace attached at a first end to a terminal of a substrate. The trace is free from attachment at its second end, and extends from the terminal in a direction substantially parallel to a surface of the substrate to the second end. At least a distal portion of the trace extending to the second end is spaced apart from the surface of the substrate. The spaced-apart distal portion is flexible in a plane parallel to the substrate.

Owner:FORMFACTOR INC

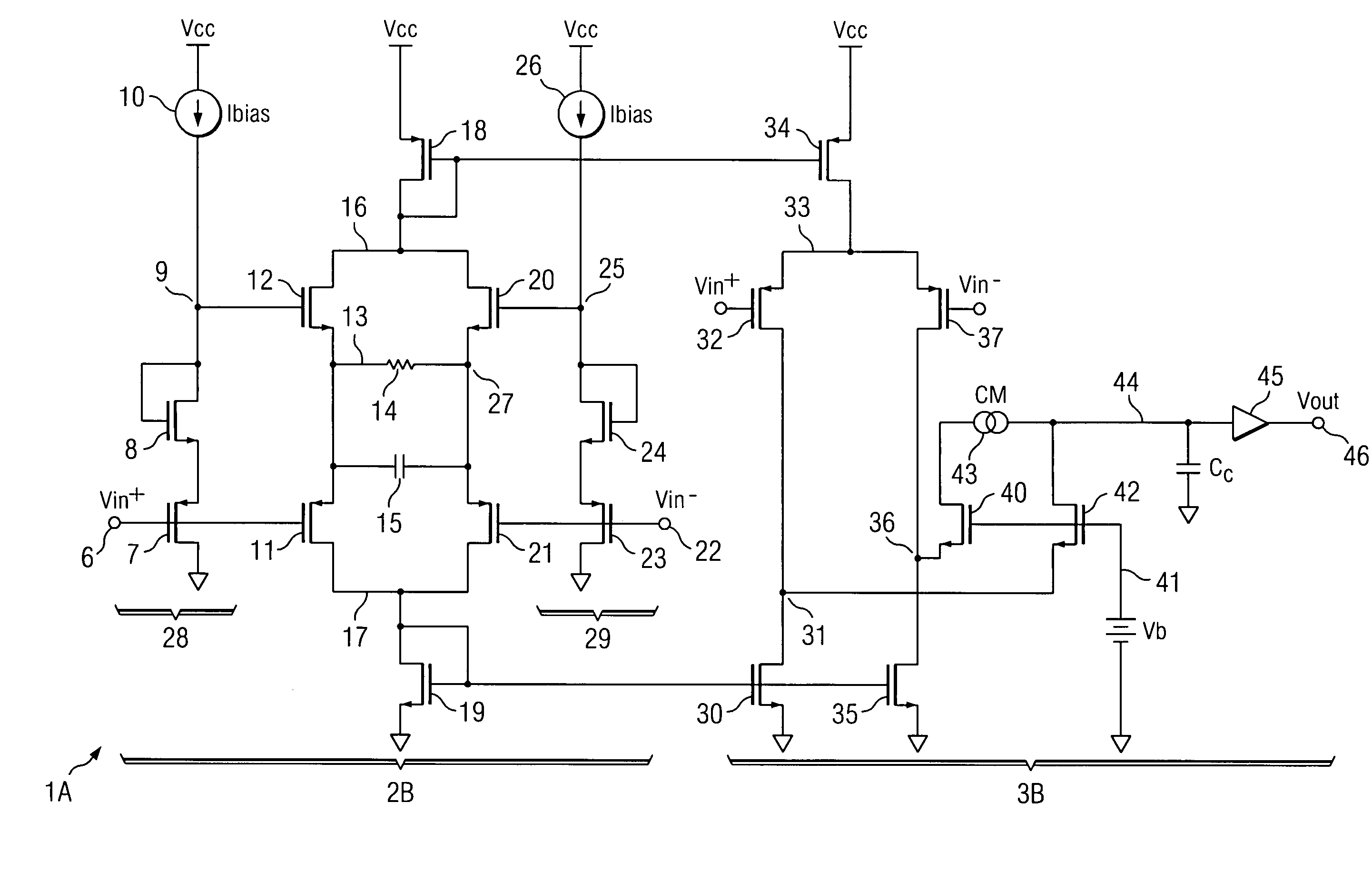

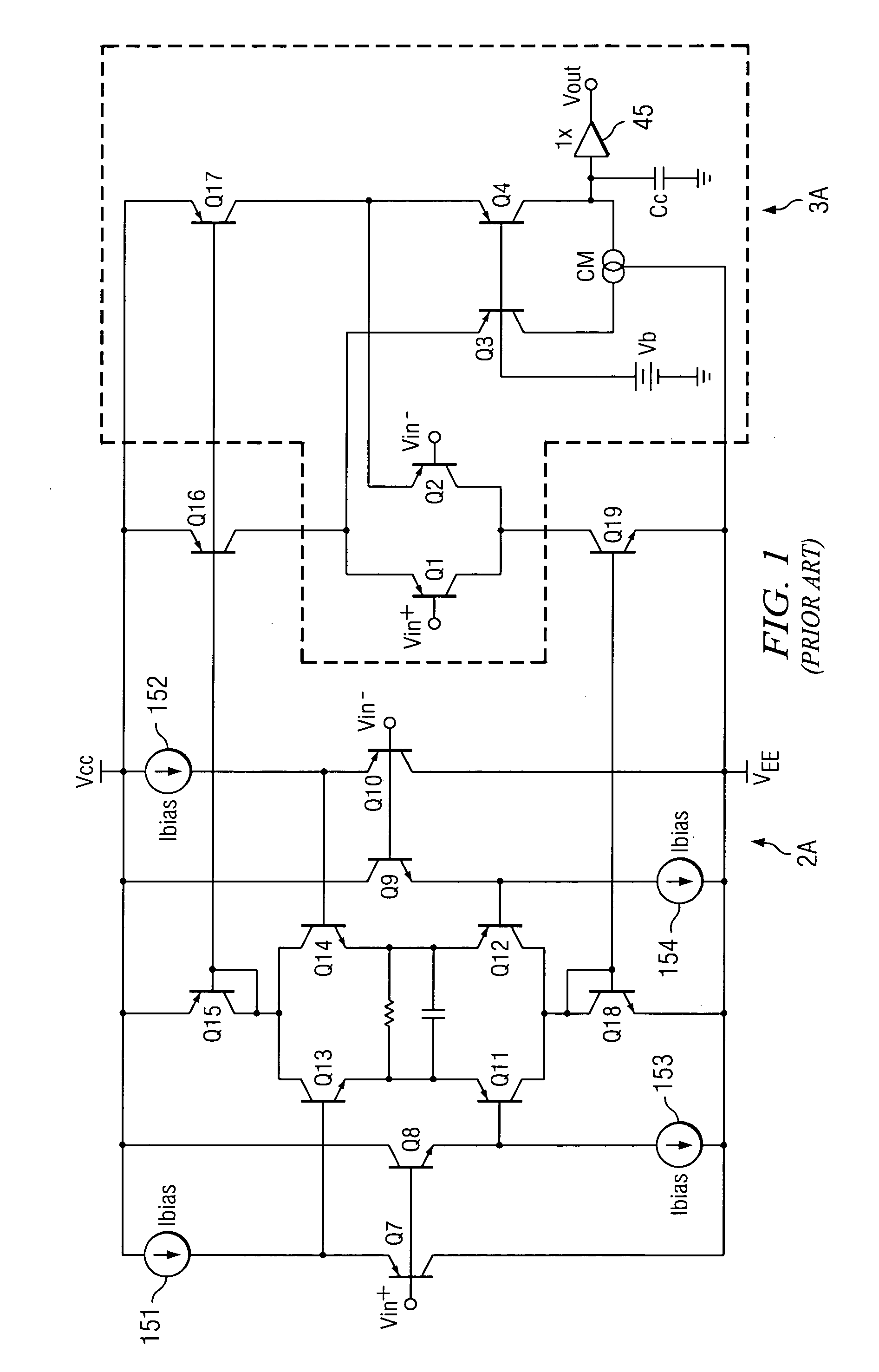

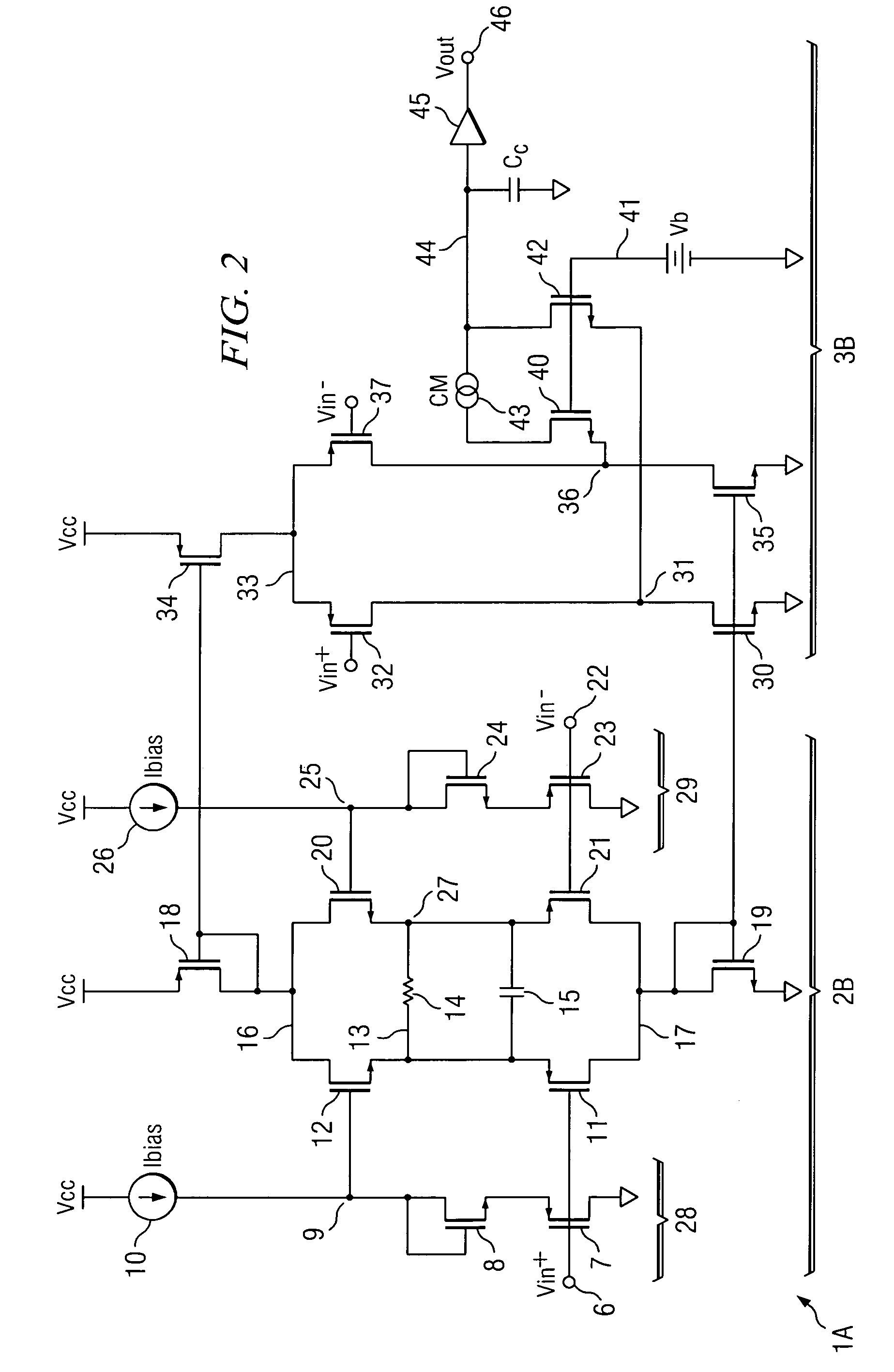

CMOS class AB folded cascode operational amplifier for high-speed applications

ActiveUS7176760B2Reduce noiseTurn fasterDifferential amplifiersDc-amplifiers with dc-coupled stagesCMOSAudio power amplifier

Owner:TEXAS INSTR INC

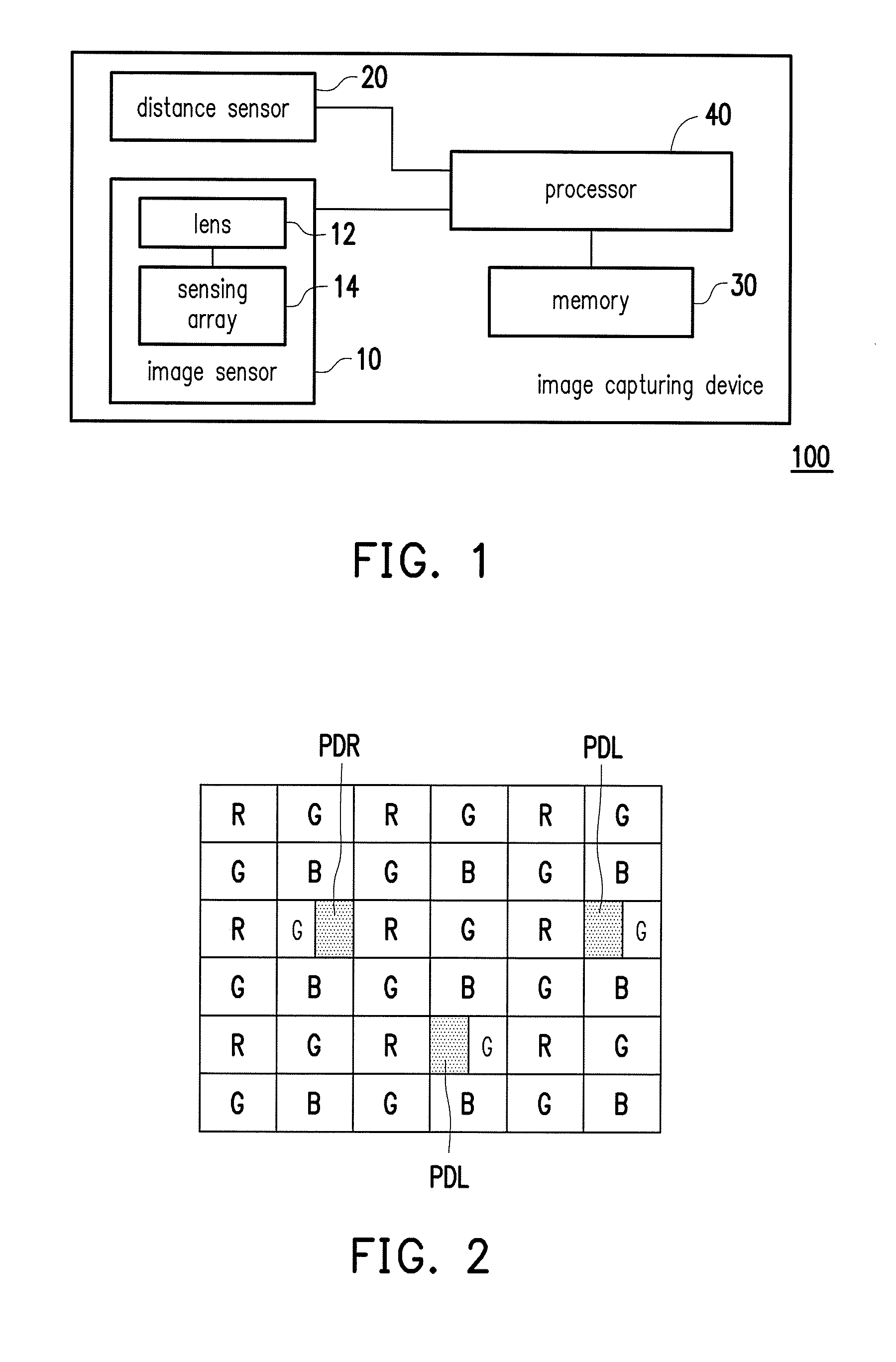

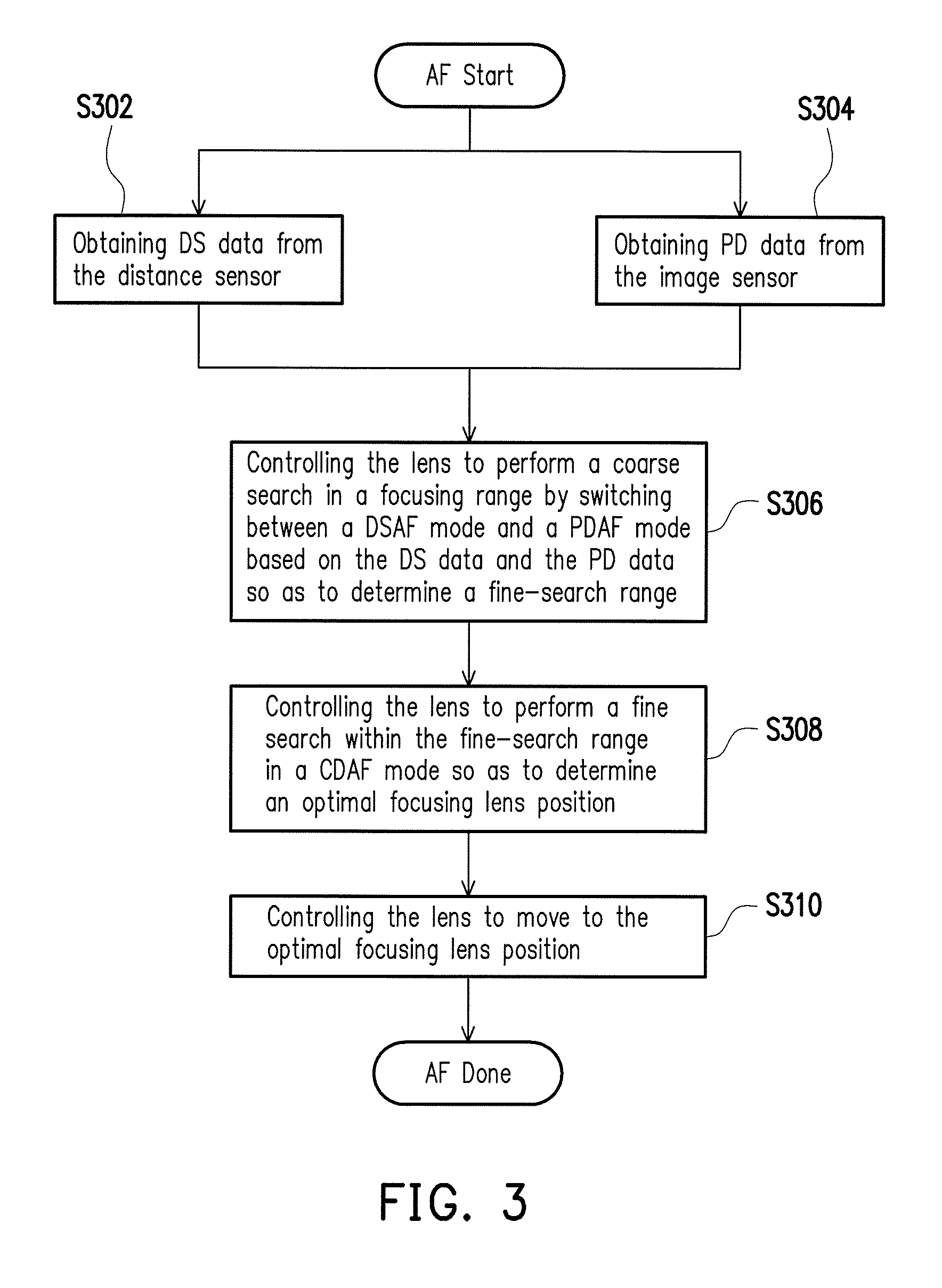

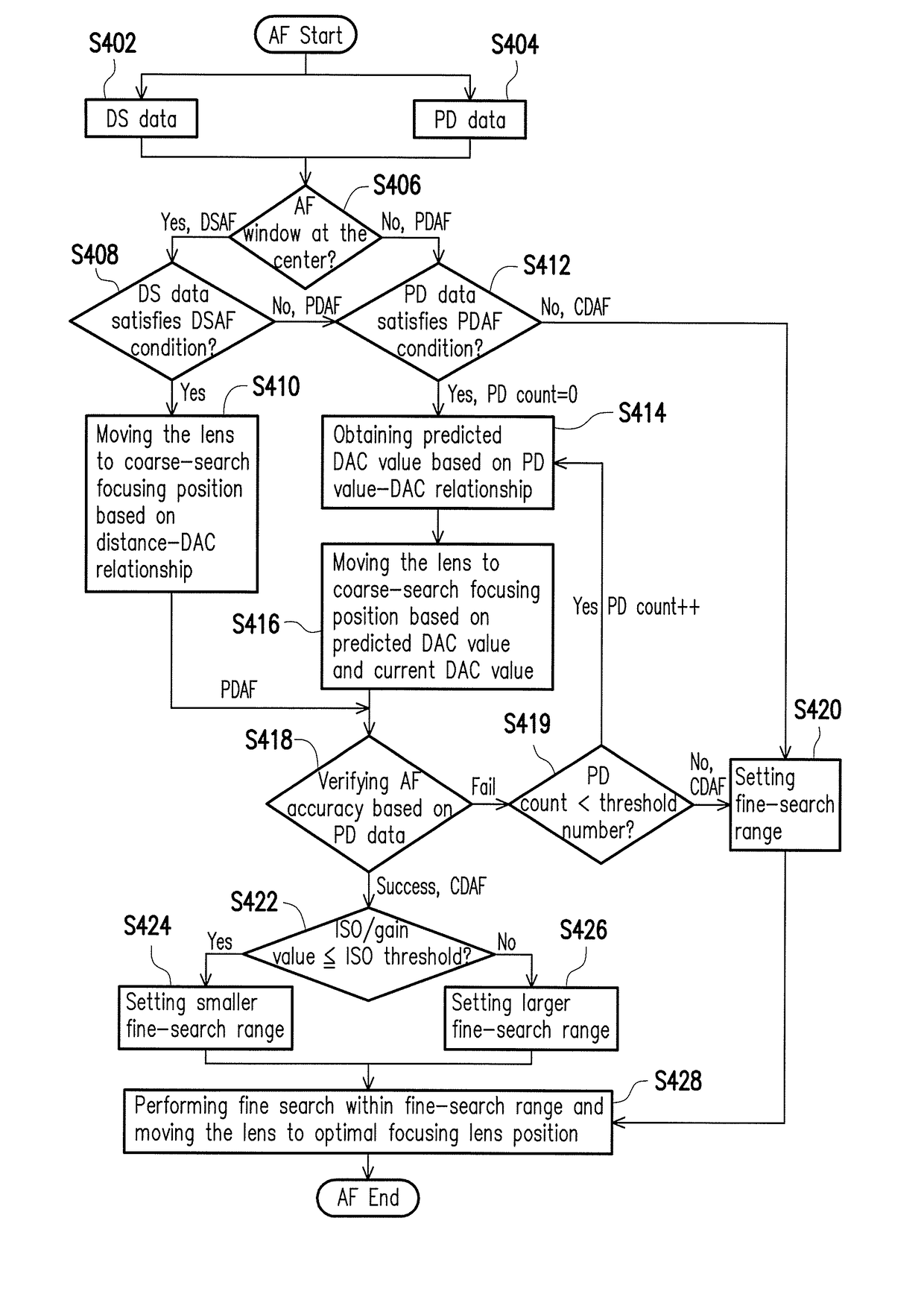

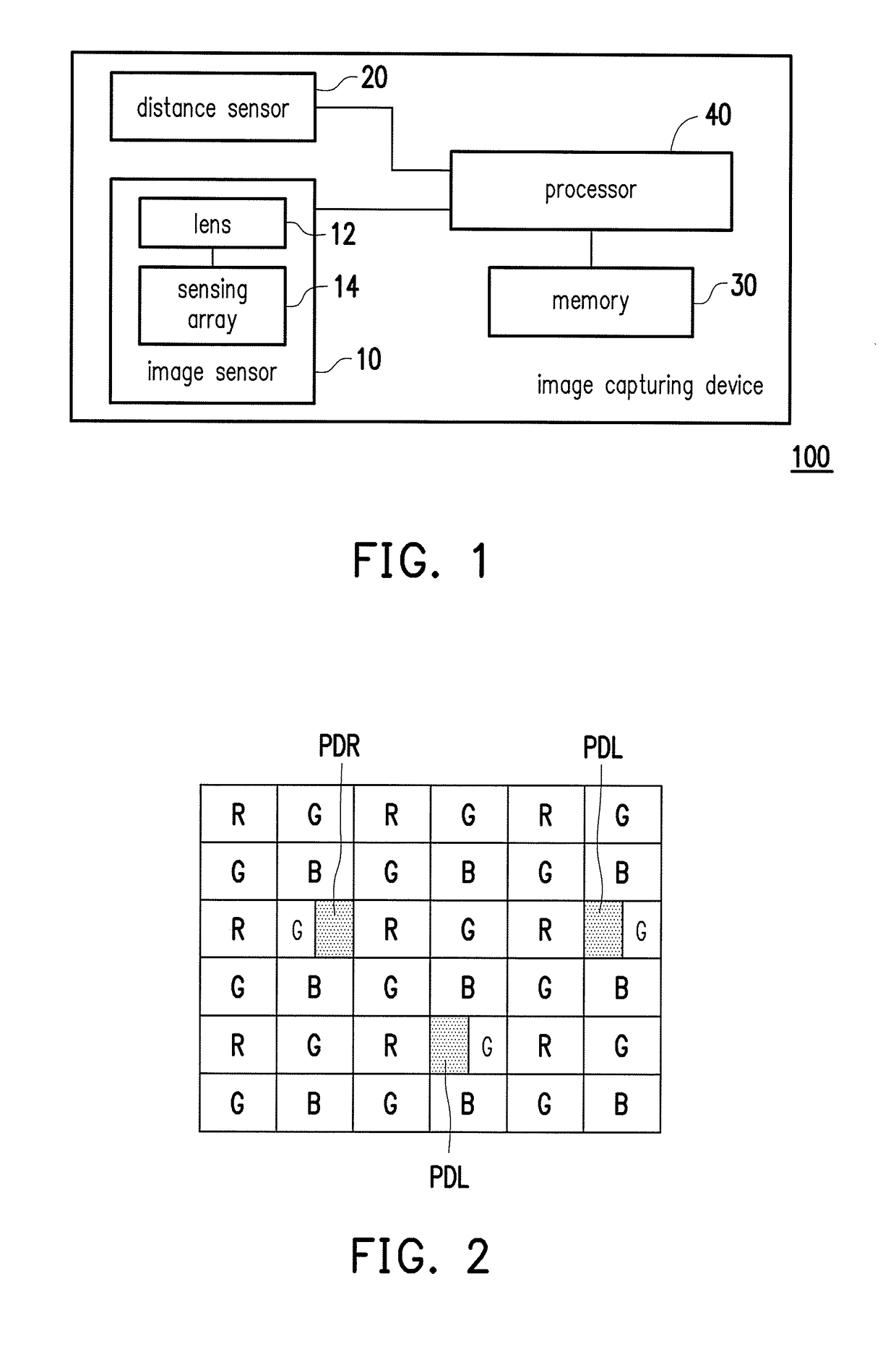

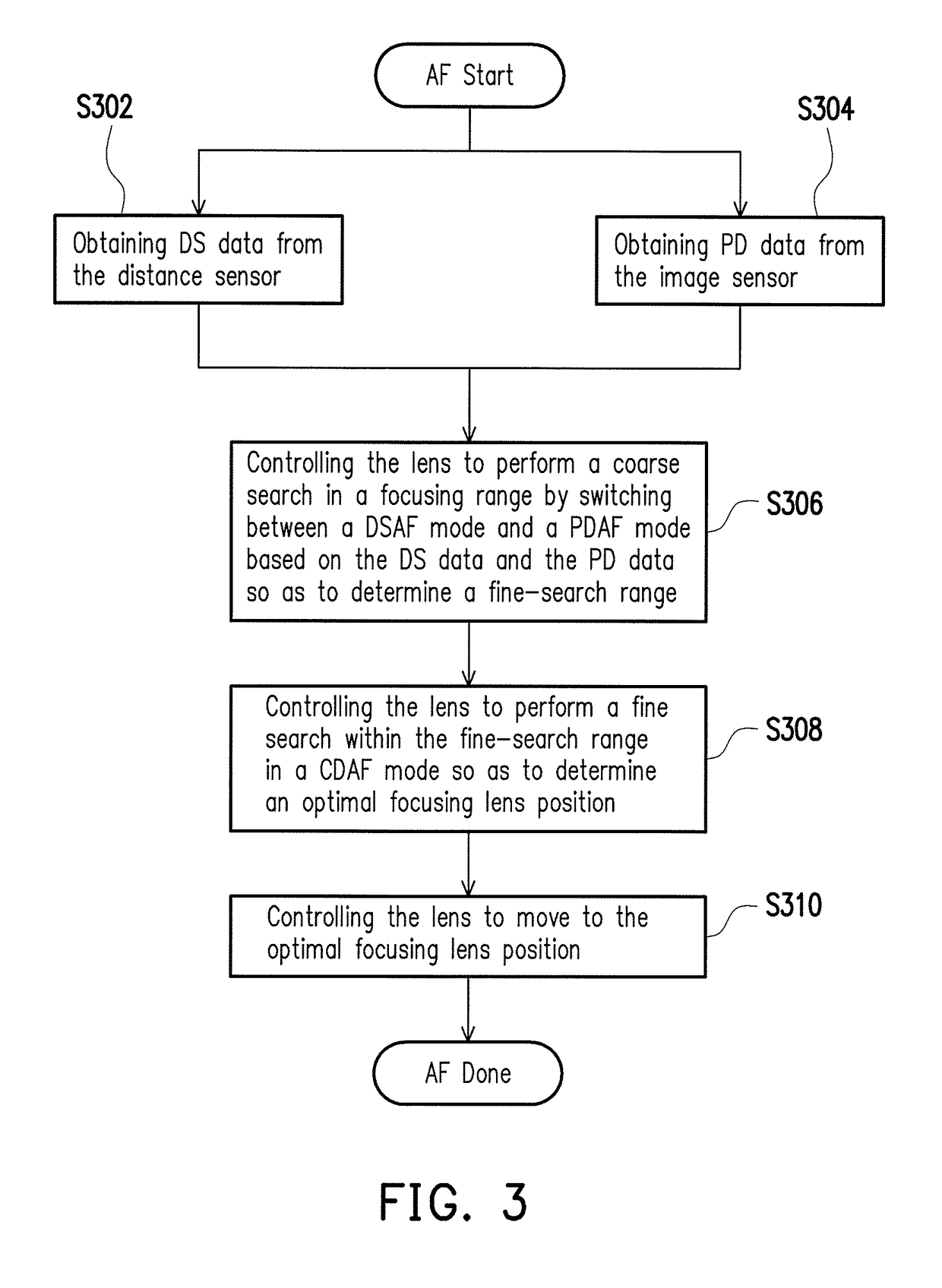

Image capturing device and auto-focus method thereof

ActiveUS20170017136A1Efficient procedureImprove user experienceTelevision system detailsSteroscopic systemsAutofocusDistance sensors

The disclosure proposes an auto-focus method and an image capturing device including a distance sensor and an image sensor having a lens and a sensing array. The method includes the following steps. First, distance sensor data and phase detection data are respectively obtained from the distance sensor and the sensing array. The lens is controlled to perform a course search within a focusing range by switching between a distance sensor auto-focus mode and a phase detection auto-focus mode based on the distance sensor data and the phase detection data so as to determine a fine-search range. The lens is further controlled to perform a fine search within the fine-search range in a contrast detection auto-focus mode so as to determine an optimal focusing lens position. Next, the lens is controlled to move to the optimal focusing lens position.

Owner:HTC CORP

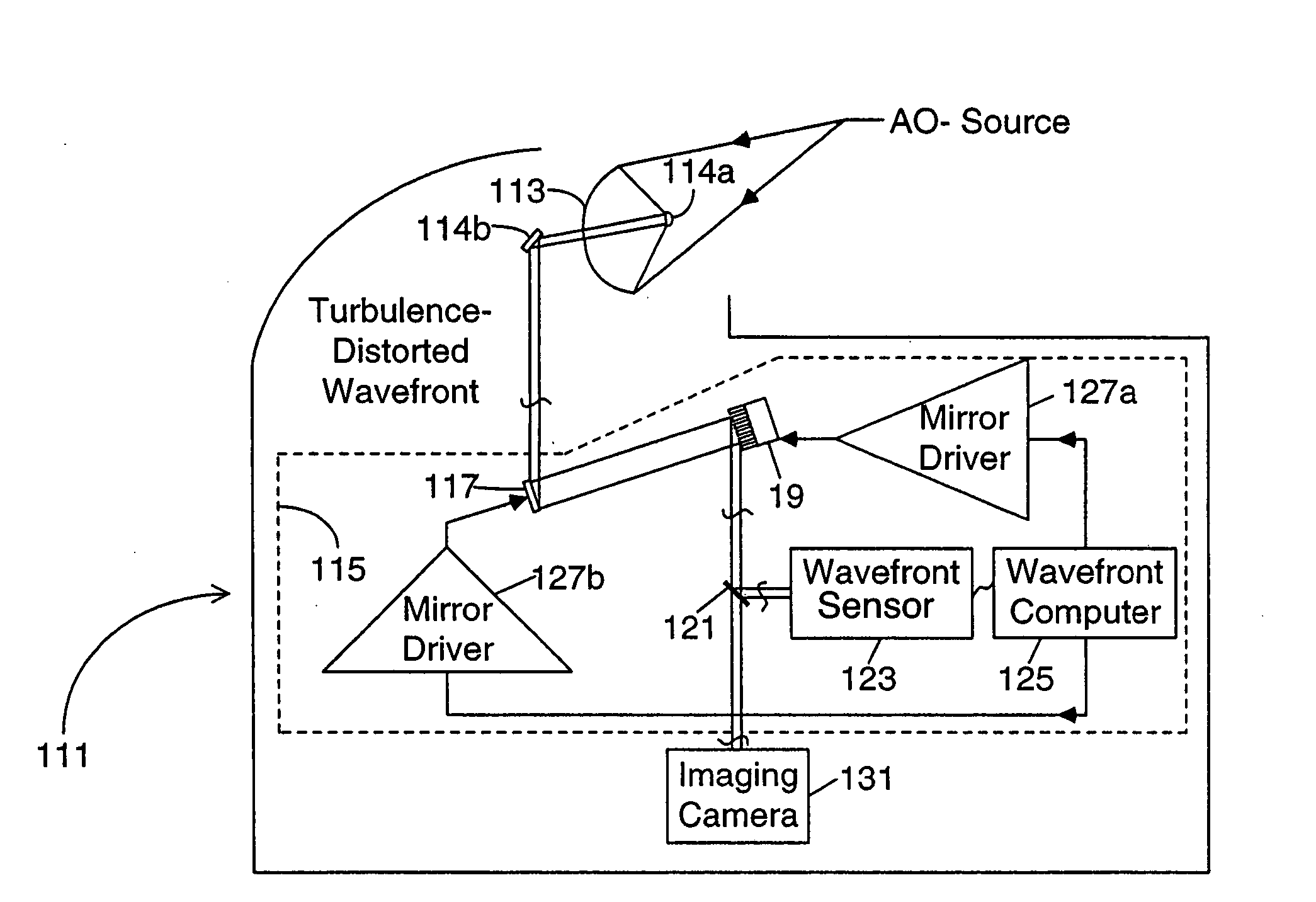

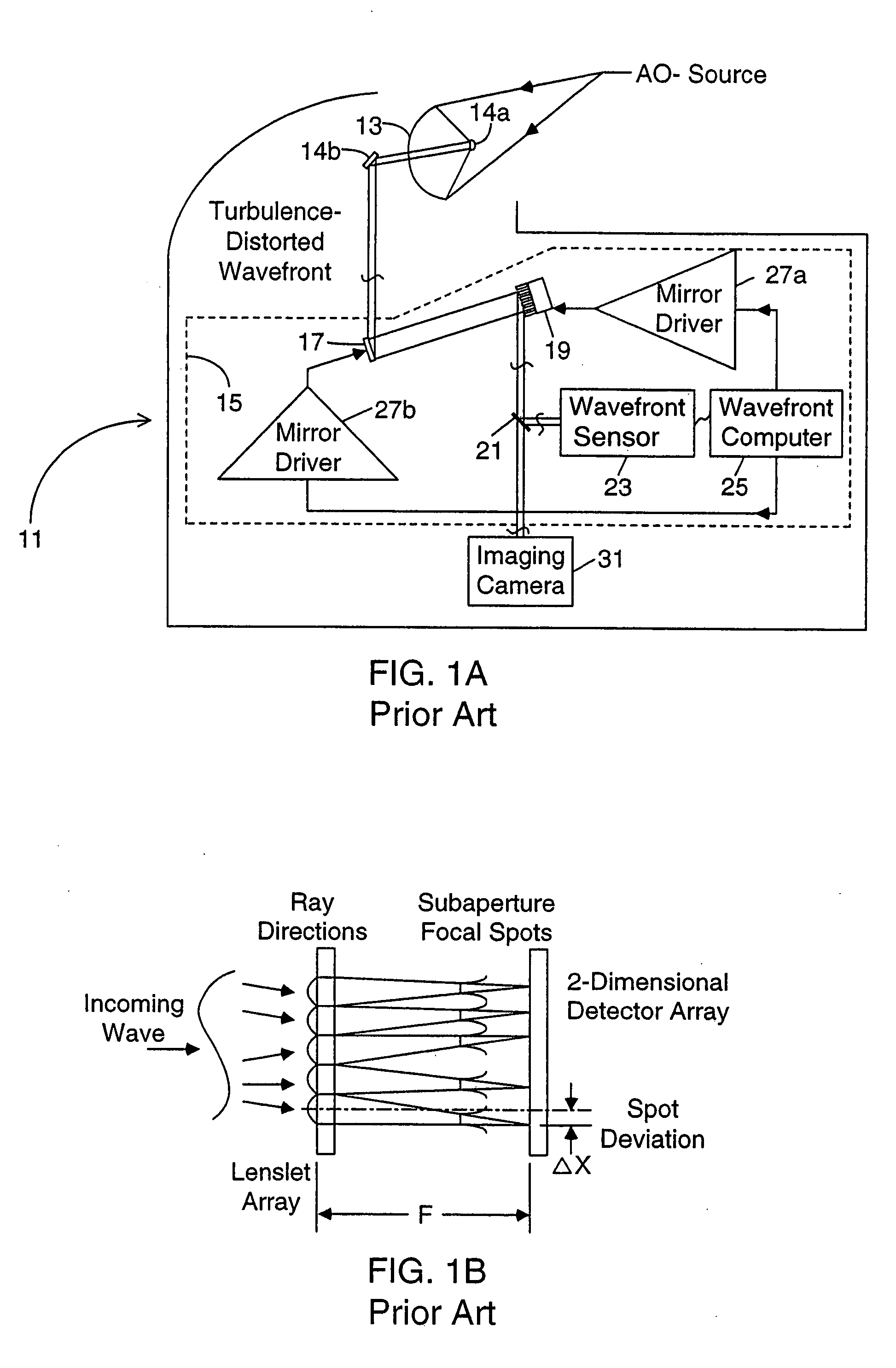

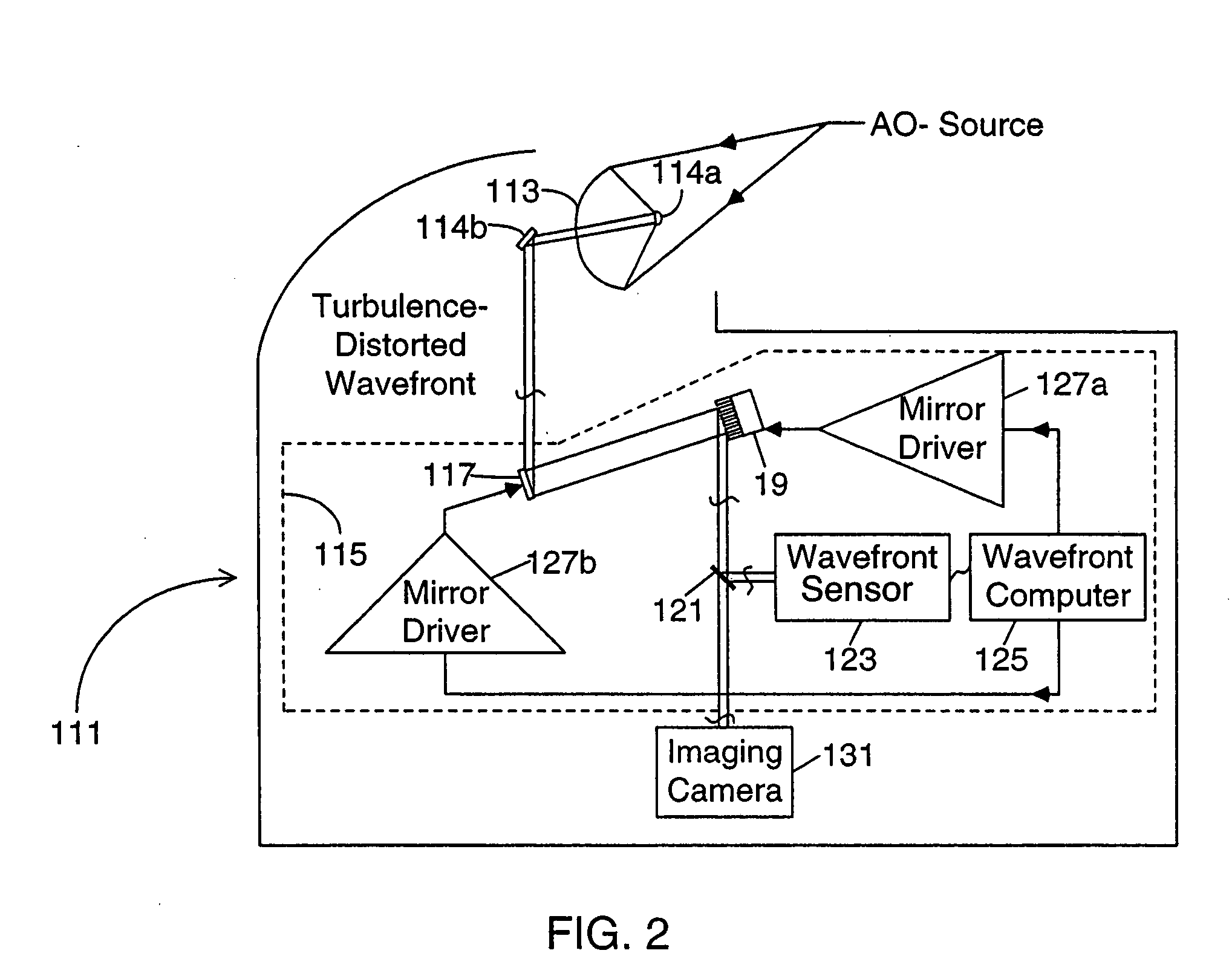

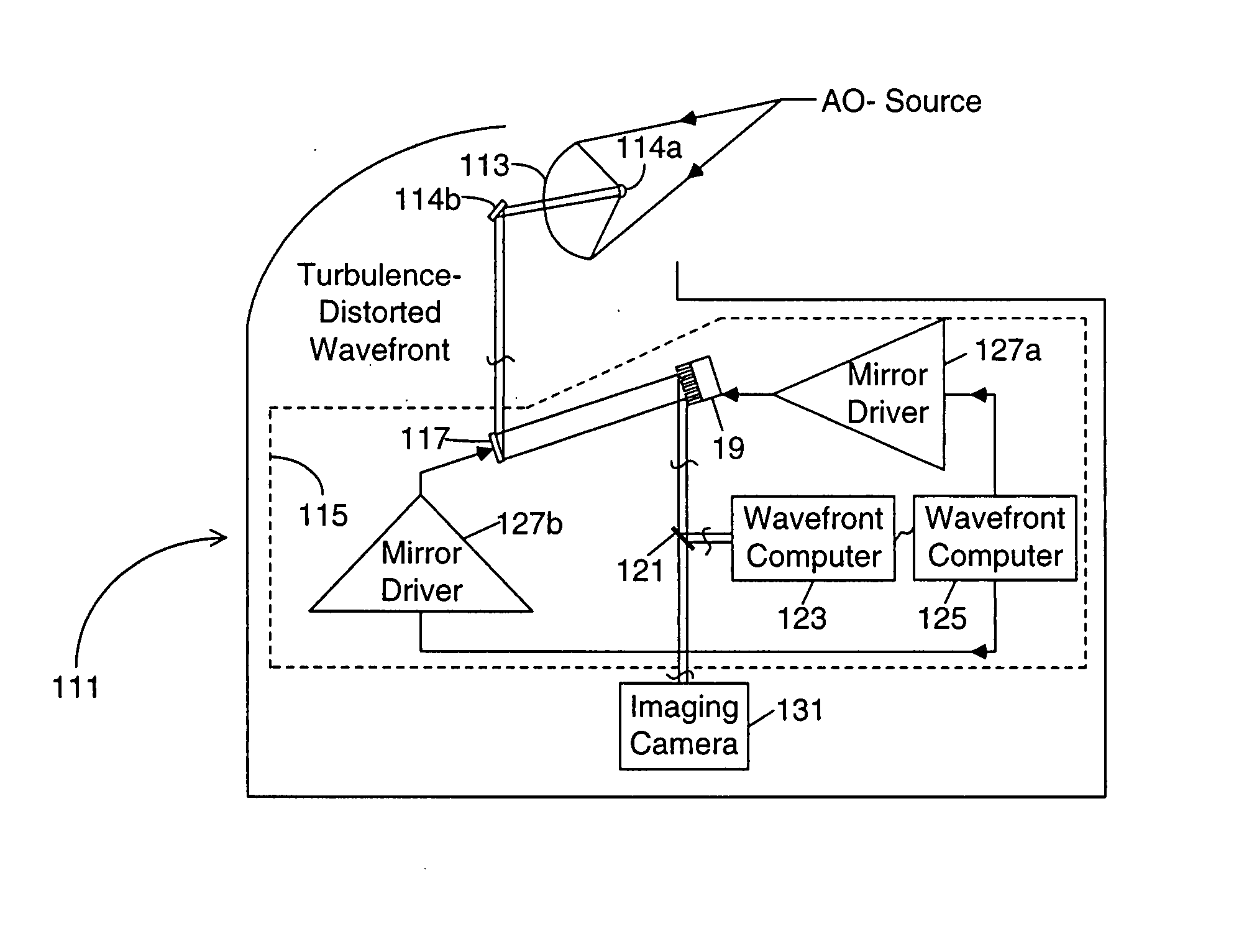

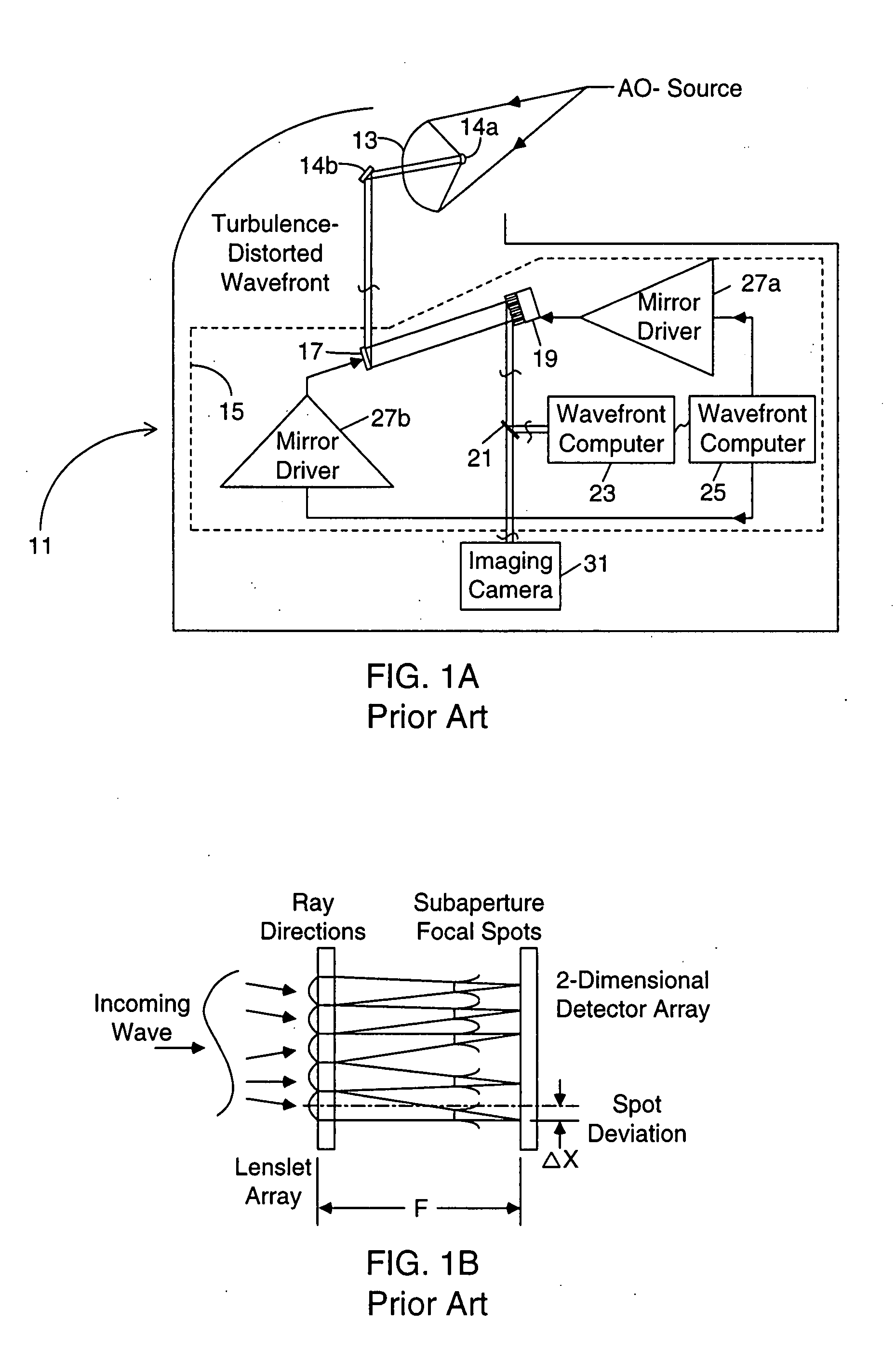

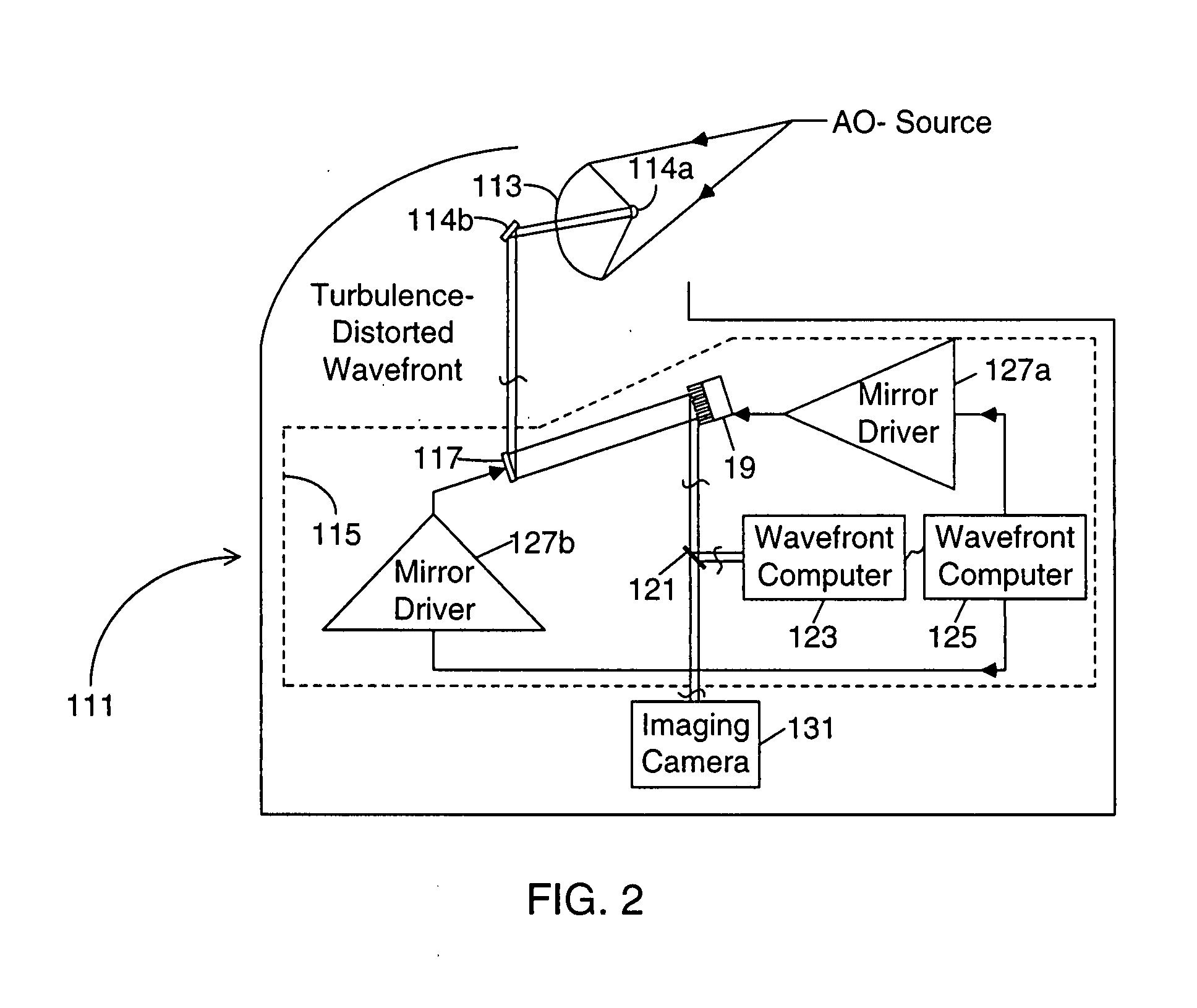

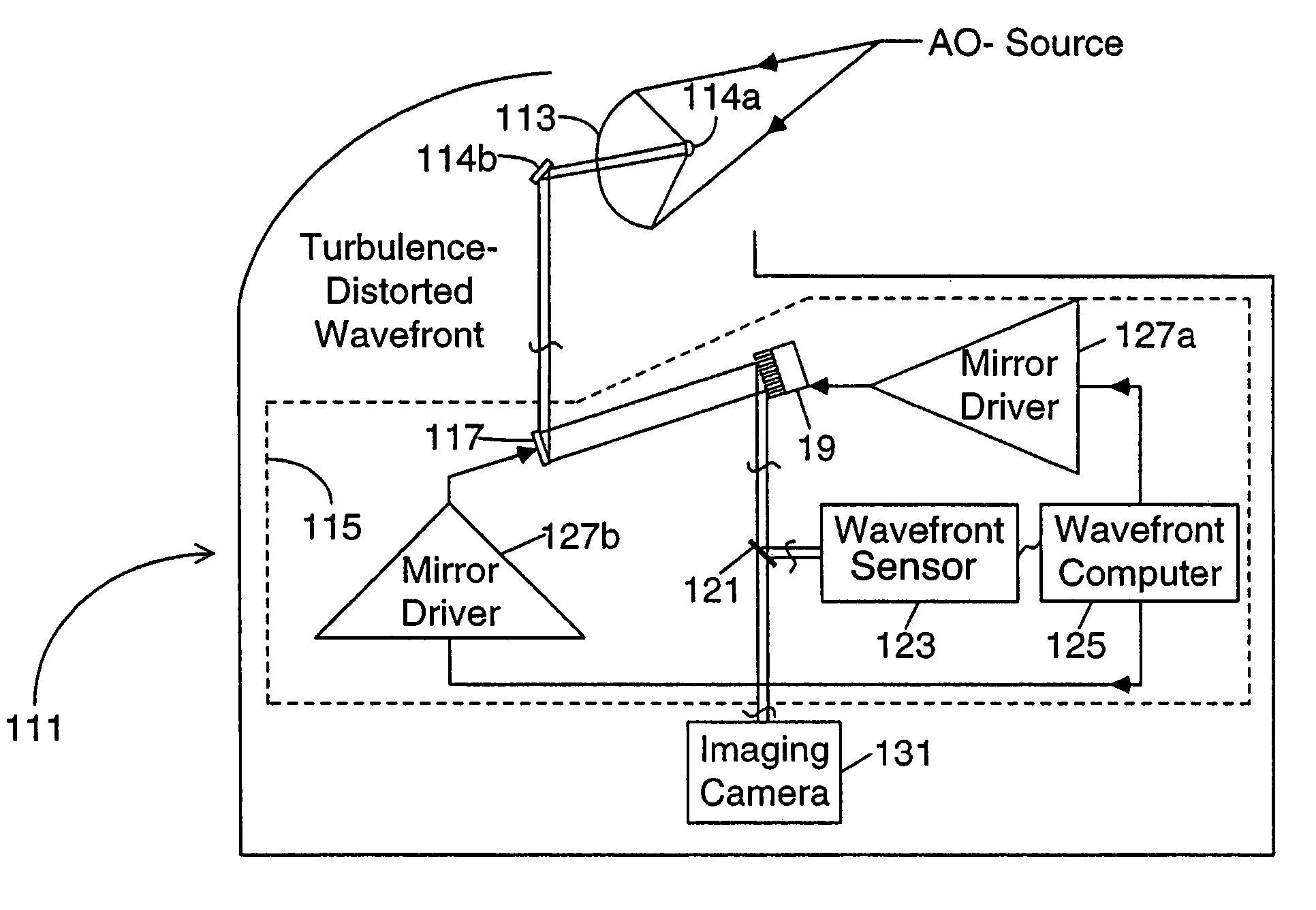

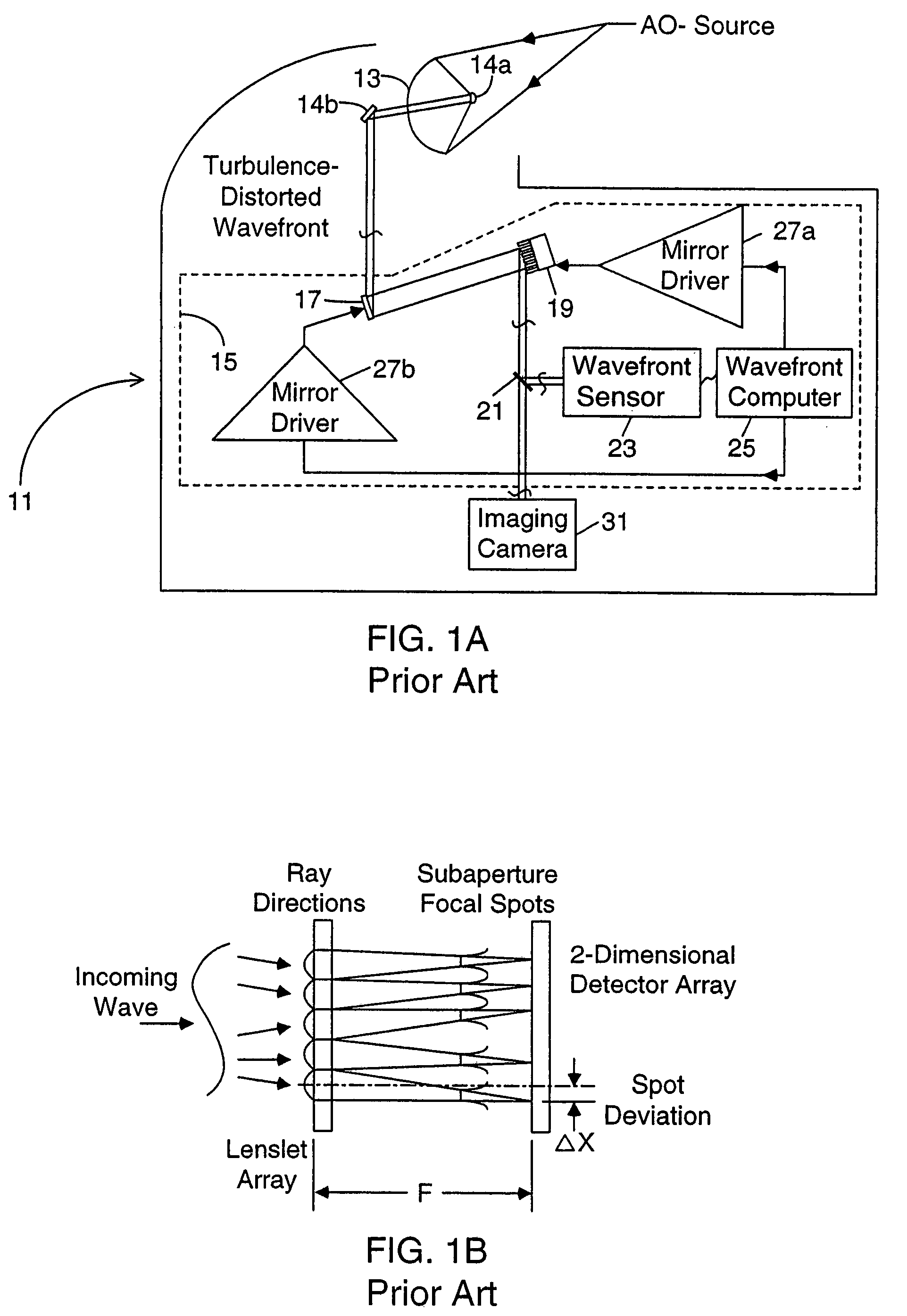

Method and apparatus for wavefront measurement that resolves the 2-pi ambiguity in such measurement and adaptive optics systems utilizing same

InactiveUS20050098707A1Step of become largeImprove tolerancePhotometry using reference valueOptical measurementsWavefront sensorAmbiguity

An improved wavefront sensor for characterizing phase distortions in incident light including optical elements that spatially sample the incident light and form a dispersed spot with a fringe pattern corresponding to samples of the incident light. An imaging device captures an image of the dispersed spot with said fringe pattern formed by said optical elements. And an image processor that analyzes the spectral components of the fringe pattern of a given dispersed spot to derive a measure of the local phase distortion without ambiguity in the corresponding sample of incident light. The optical elements may comprise refractive elements, diffractive elements or a combination thereof (such as a grism). The wavefront sensor may be part of an adaptive optic system (such as a large-aperture space telescope) to enable the measurement and correction of large phase steps across adjacent mirror segments of a deformable mirror.

Owner:NORTHROP GRUMMAN SYST CORP

Helical microelectronic contact and method for fabricating same

InactiveUS7131848B2Step of become largeContact member manufacturingElectronic circuit testingHelixElectrical contacts

A microelectronic spring contact for making electrical contact between a device and a mating substrate and method of making the same are disclosed. The spring contact has a compliant pad adhered to a substrate of the device and spaced apart from a terminal of the device. The compliant pad has a base adhered to the substrate, and side surfaces extending away from the substrate and tapering to a smaller end area distal from the substrate. A trace extends from the terminal of the device in a coil pattern over the compliant pad to its end area, forming a helix. At least a portion of the compliant pad end area is covered by the trace, and a portion of the trace that is over the compliant pad is supported by the compliant pad. In an alternative embodiment, the pad is removed to leave a freestanding helical contact.

Owner:FORMFACTOR INC

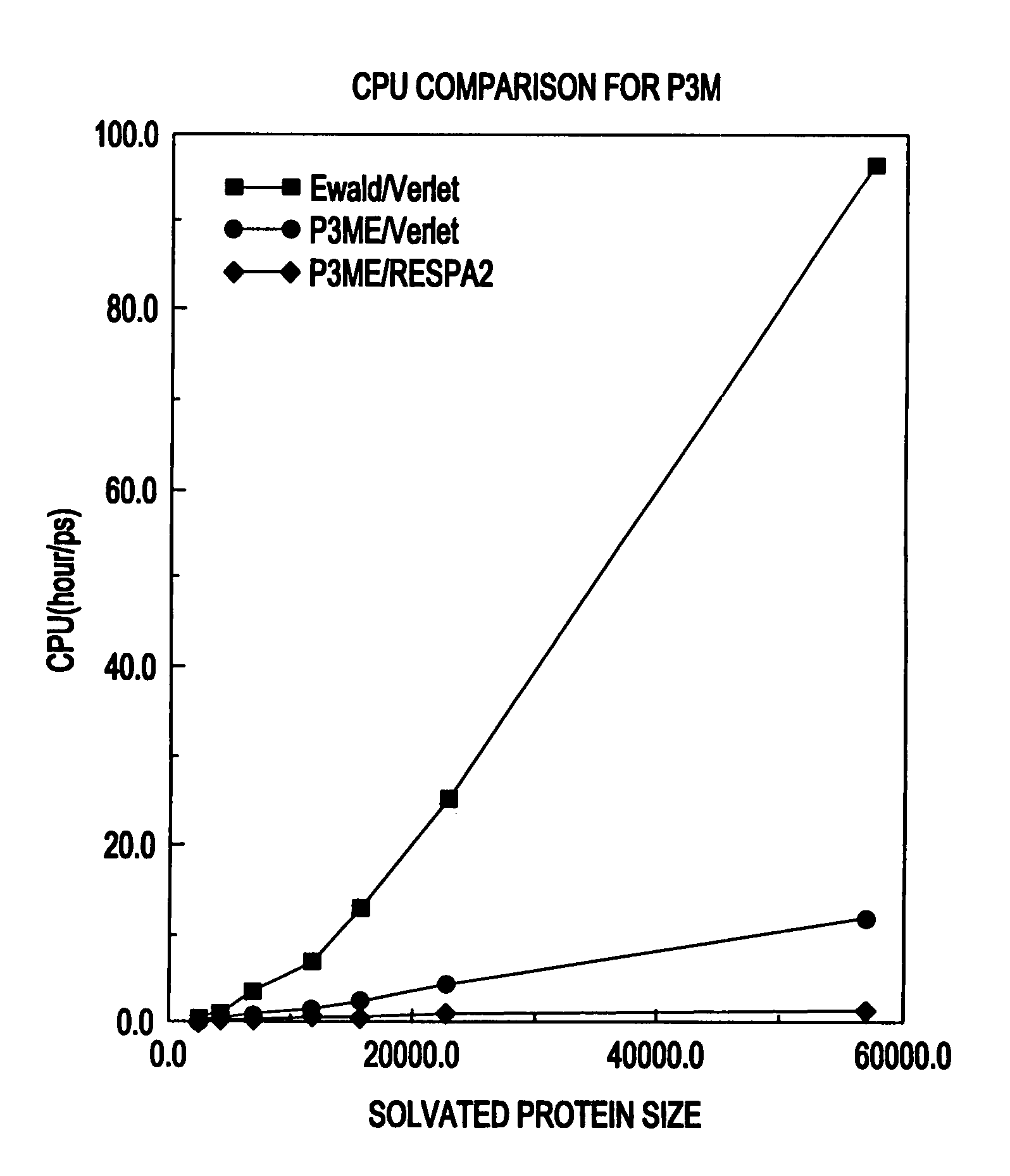

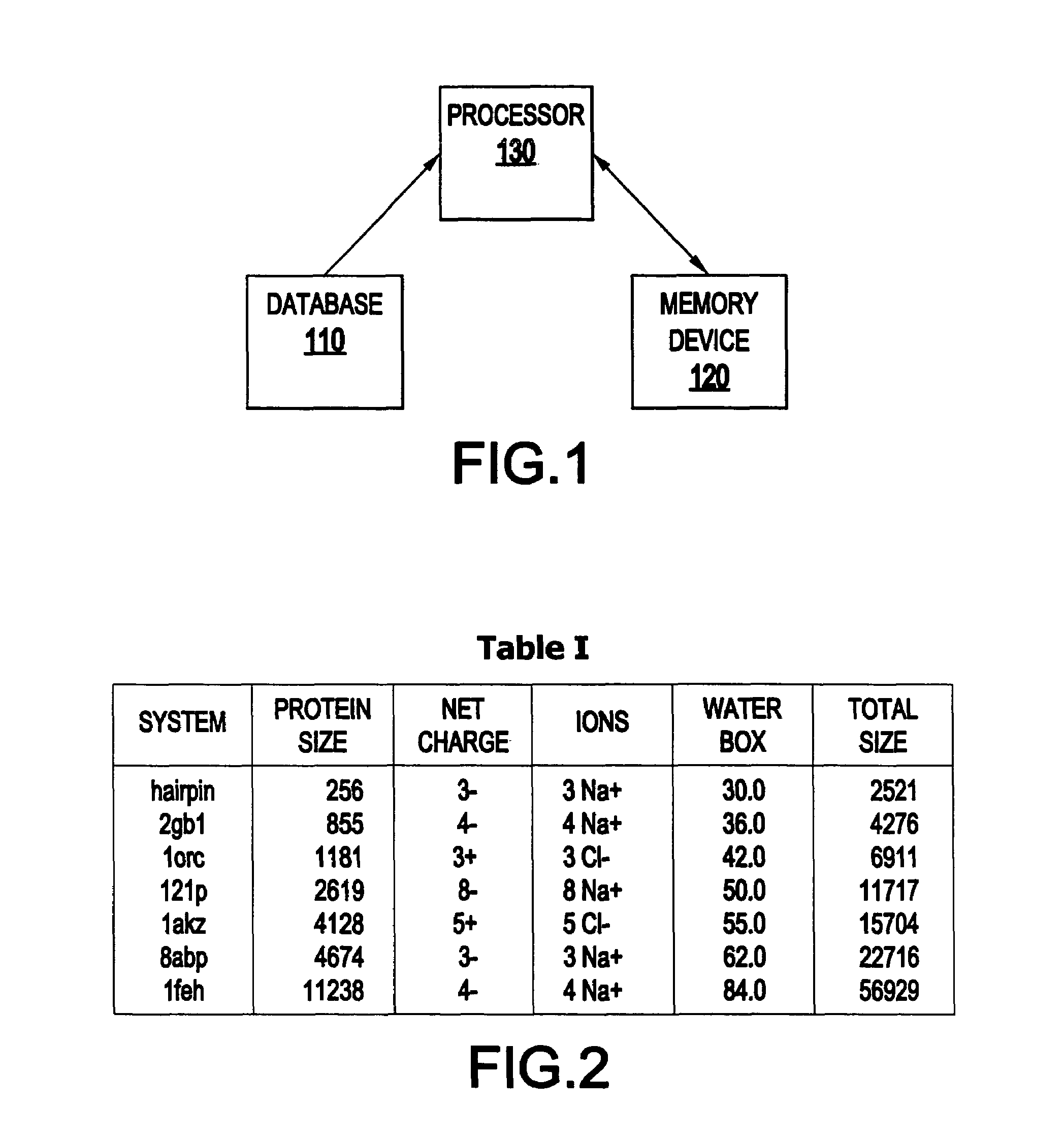

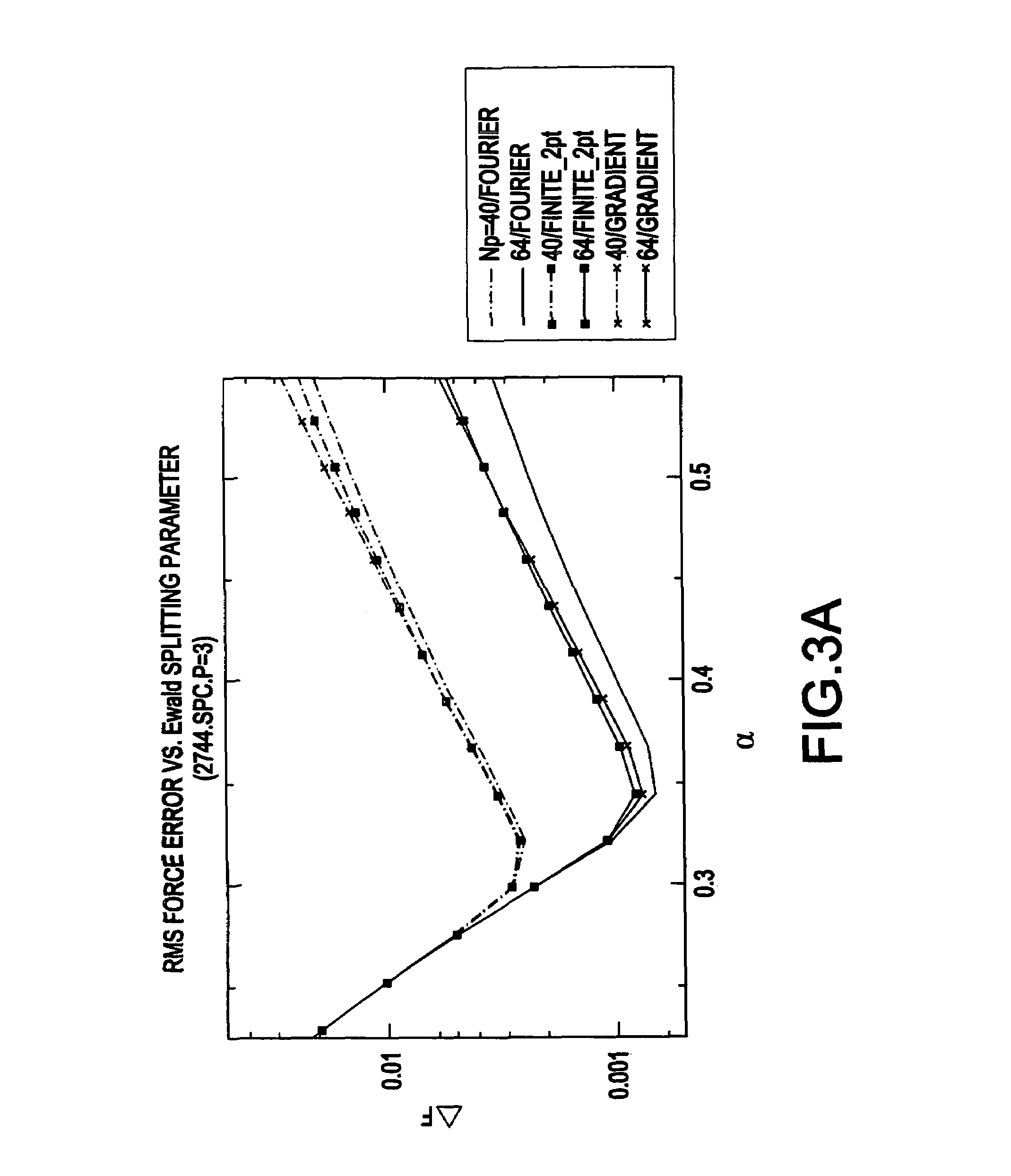

System and method for molecular dynamic simulation

InactiveUS7096167B2Doubles speedStep of become largeComputation using non-denominational number representationBiological testingProtein solutionProtein molecules

A system and method for molecular dynamic simulation includes a database for storing data pertaining to at least one biomolecular system, a memory device for storing instructions for performing at least one algorithm having an electrostatic interaction calculating function and a multiple time step function, and subdividing forces on a basis of distance over which the forces act, and a processor for processing the data by executing the instructions in order to propagate the biomolecular system from a first set of coordinates to a second set of coordinates. The system and method significantly speed up the molecular dynamics simulation of biomolecular systems in which there are long-range and short-range electrostatic interactions and in which there are fast and slow motions, and make practicable the simulation of large protein solutions and thus, can be used to simulate protein folding and the binding of substrates to protein molecules.

Owner:LINKEDIN

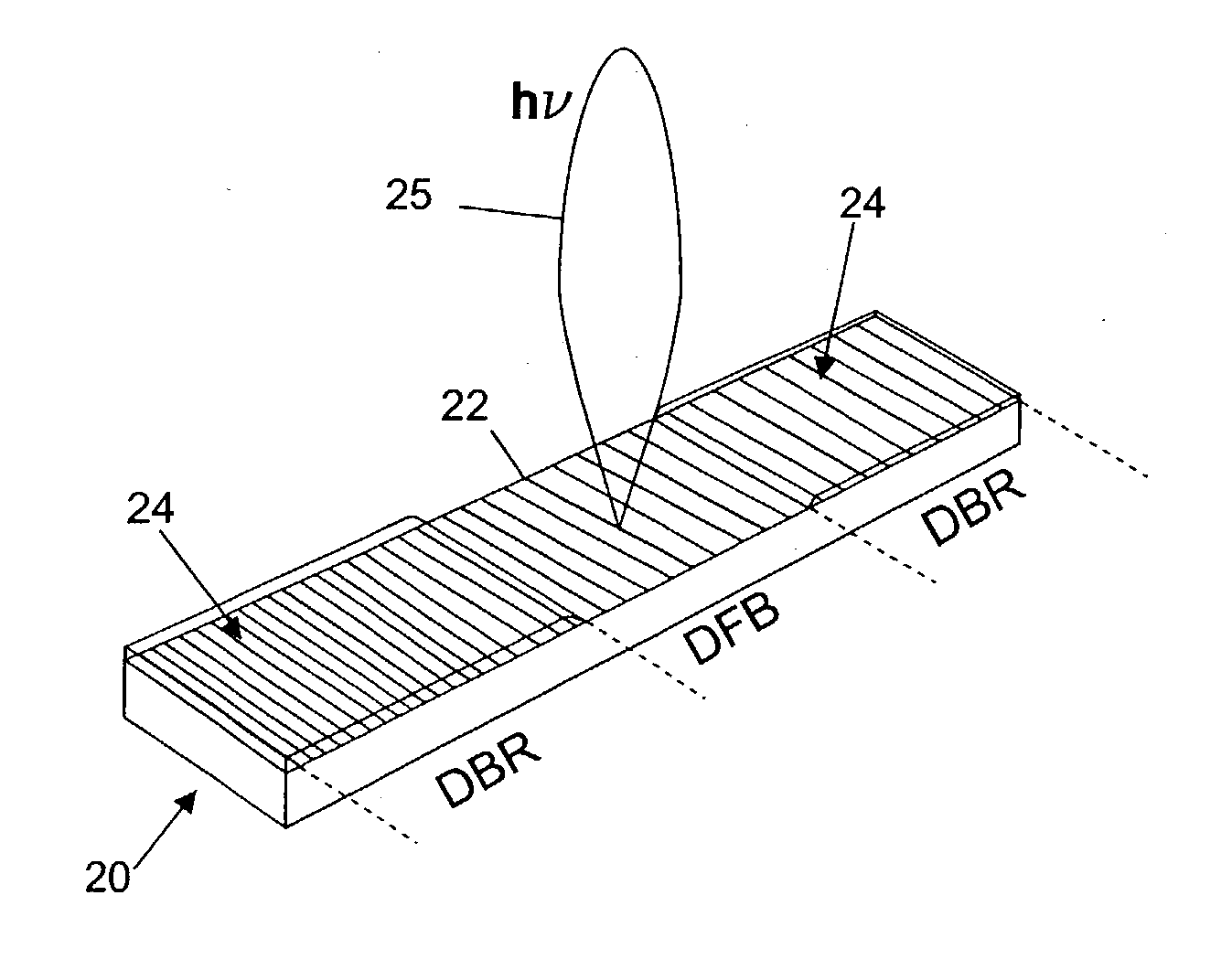

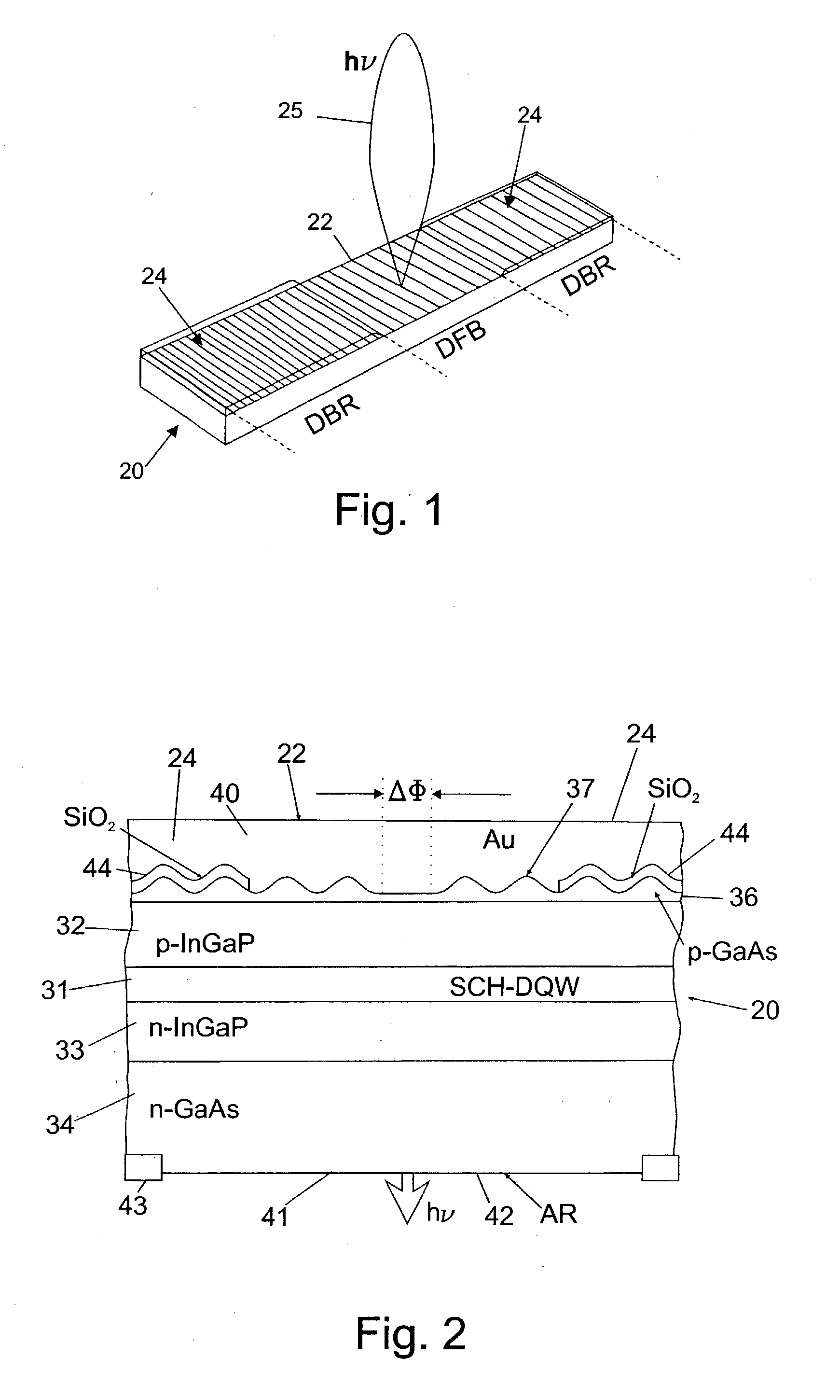

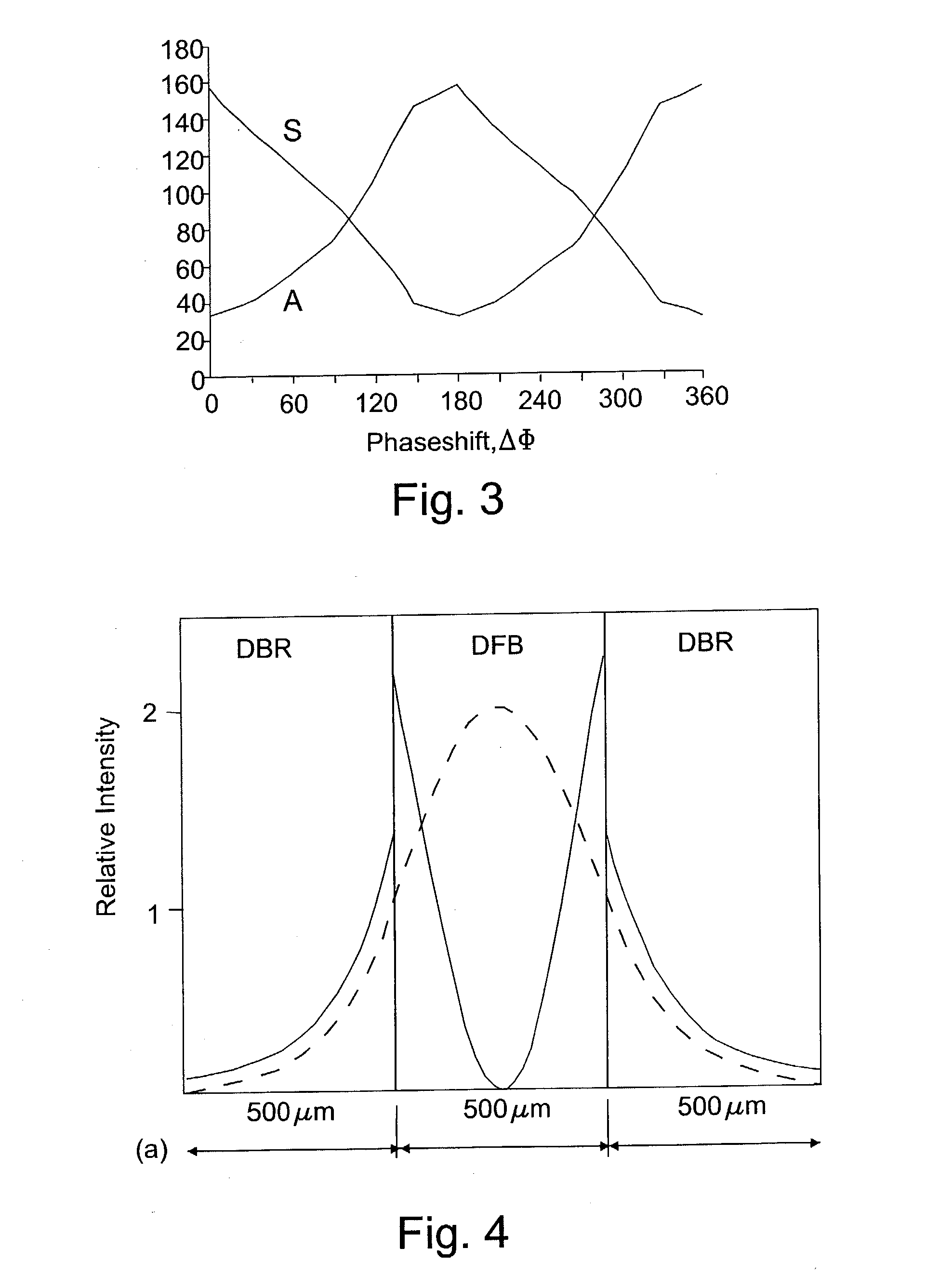

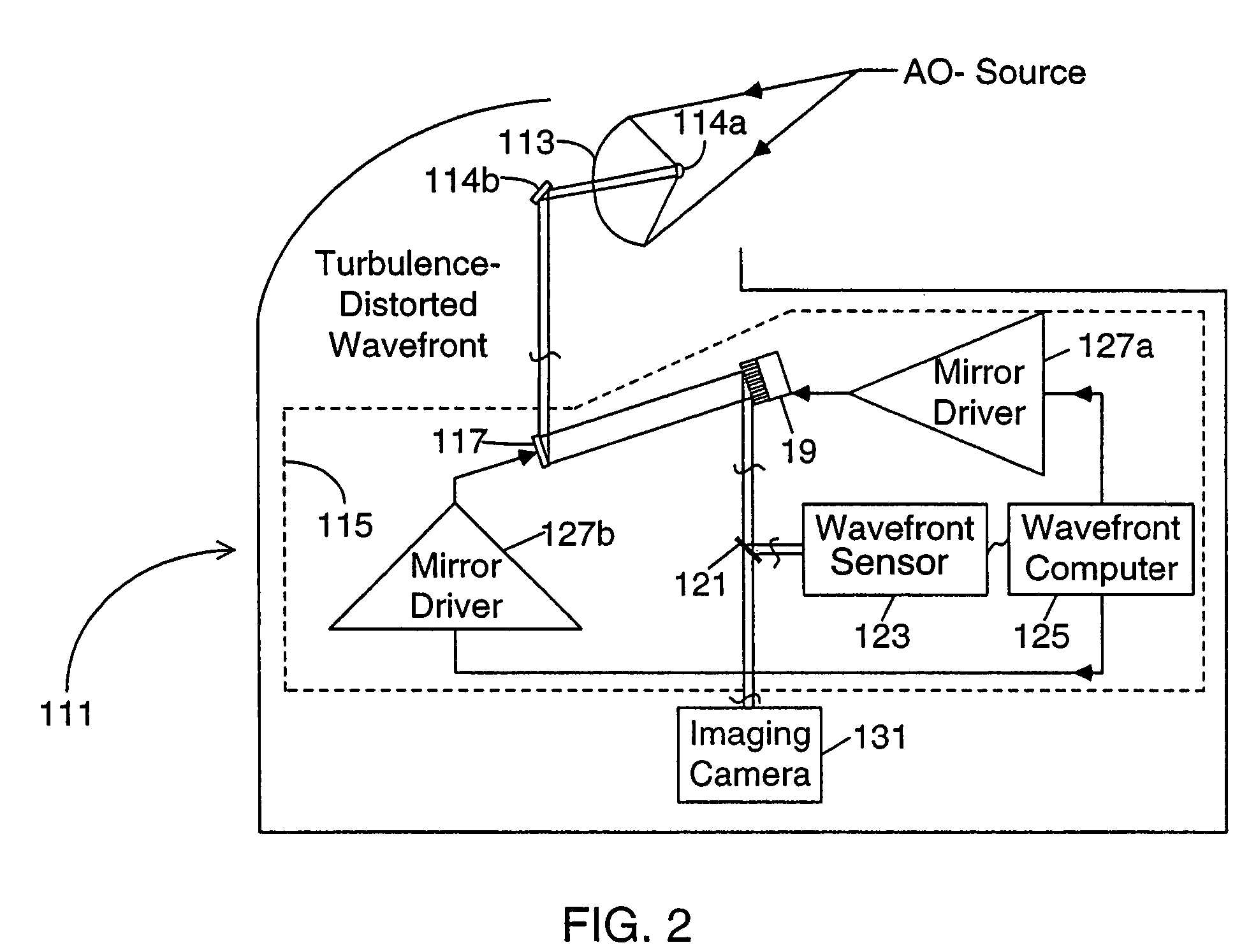

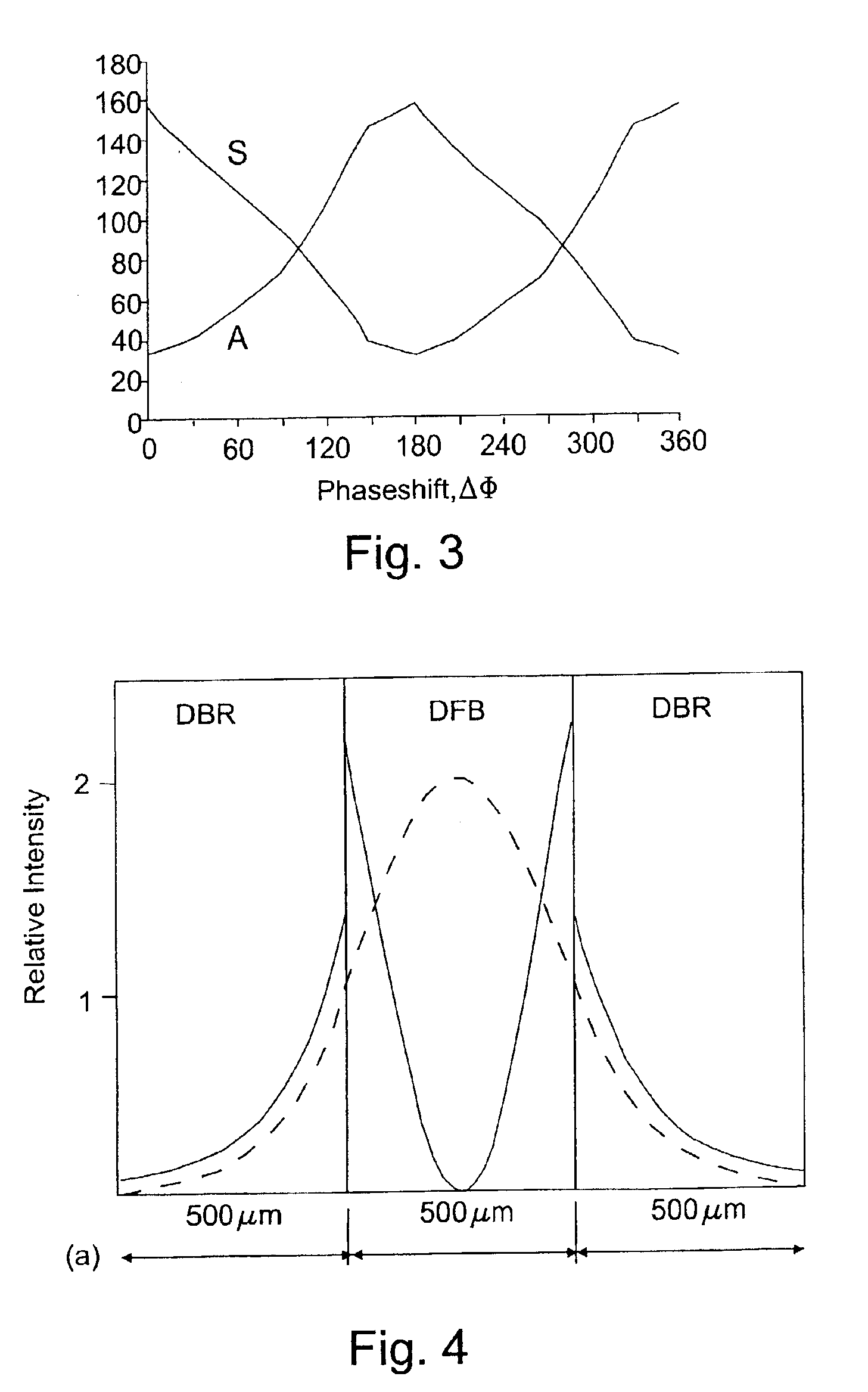

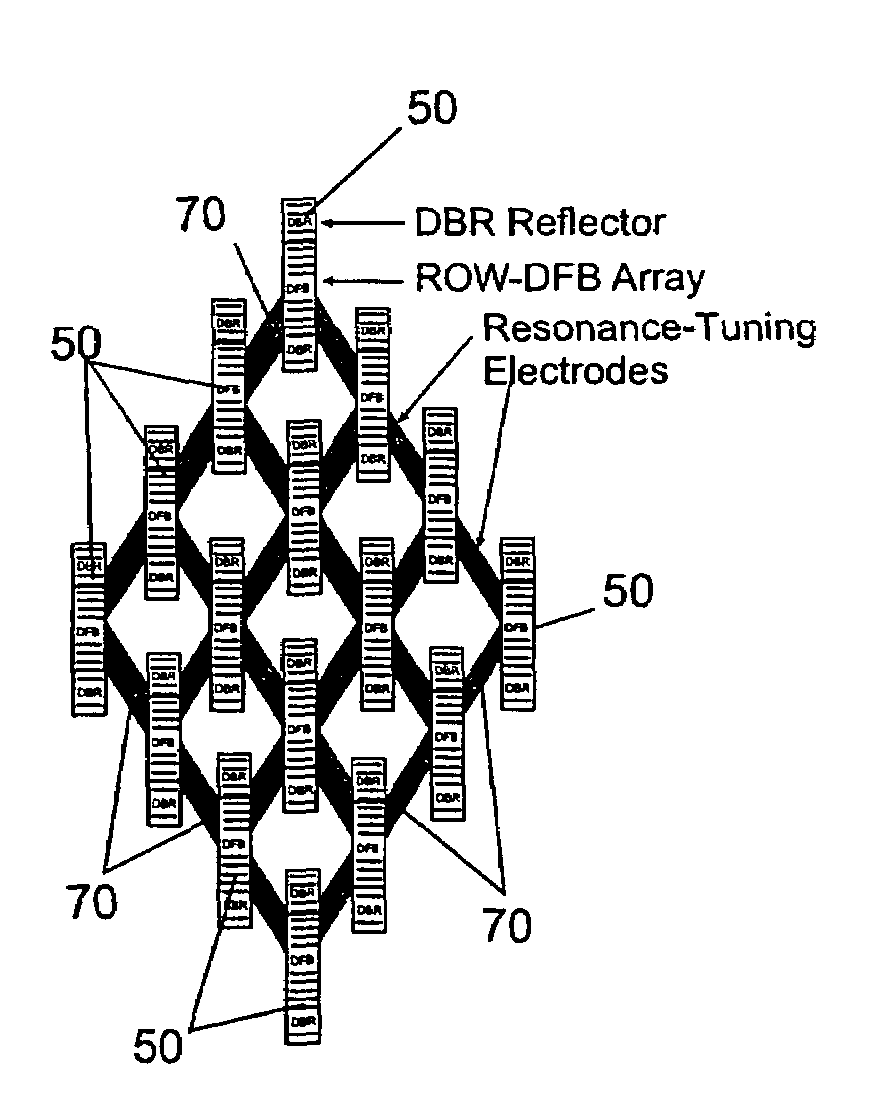

High coherent power, two-dimensional surface-emitting semiconductor diode array laser

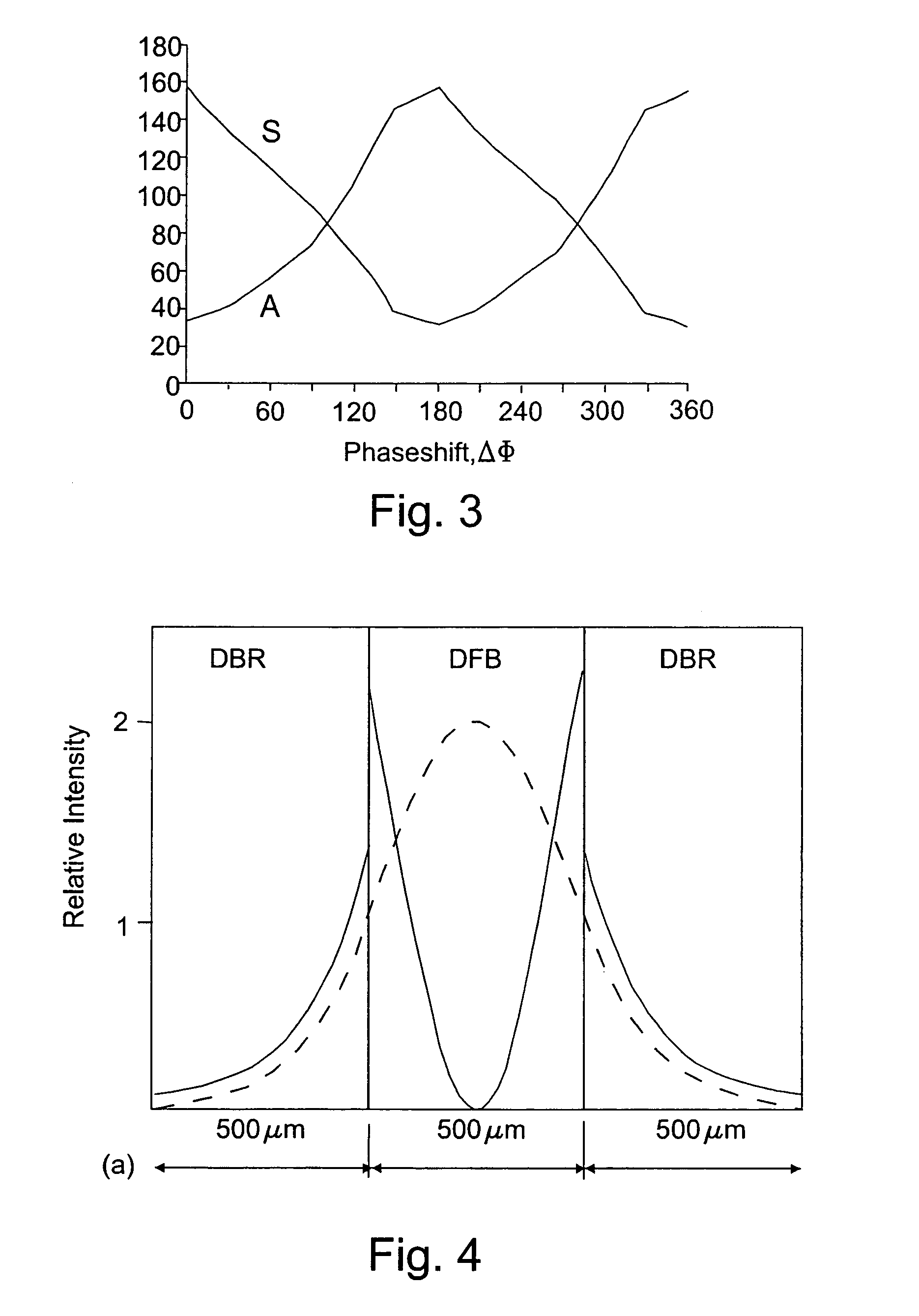

InactiveUS20050031002A1No penalty in device efficiencyImprove efficiencyLaser optical resonator constructionSemiconductor laser arrangementsGratingPhase shifted

A semiconductor laser is formed on a semiconductor substrate with an array of laterally spaced laser device elements each including a second order distributed feedback grating bounded by distributed Bragg reflector gratings and a central phase shift in the distributed feedback grating. The device elements in which the distributed feedback grating and the distributed Bragg reflector gratings are formed have a lower effective index than the index of the interelement regions and are spaced so as to form an antiguided array. A two-dimensional semiconductor array laser may be formed of four or more of the semiconductor array devices arranged on the substrate to provide long range coherent coupling via traveling waves of light between the device elements.

Owner:WISCONSIN ALUMNI RES FOUND

Method and apparatus for wavefront measurement that resolves the 2-pi ambiguity in such measurement and adaptive optics systems utilizing same

InactiveUS20070194207A1Step of become largeImprove toleranceOptical measurementsPhotometry using reference valueWavefront sensorAmbiguity

An improved wavefront sensor for characterizing phase distortions in incident light including optical elements that spatially sample the incident light and form a dispersed spot with a fringe pattern corresponding to samples of the incident light. An imaging device captures an image of the dispersed spot with said fringe pattern formed by said optical elements. And an image processor that analyzes the spectral components of the fringe pattern of a given dispersed spot to derive a measure of the local phase distortion without ambiguity in the corresponding sample of incident light. The optical elements may comprise refractive elements, diffractive elements or a combination thereof (such as a grism). The wavefront sensor may be part of an adaptive optic system (such as a large-aperture space telescope) to enable the measurement and correction of large phase steps across adjacent mirror segments of a deformable mirror.

Owner:METROLOGIC INSTR INC

Optical instrument employing a wavefront sensor capable of coarse and fine phase measurement capabilities during first and second modes of operation

InactiveUS7161128B2Step of become largeImprove tolerancePhotometry using reference valueOptical measurementsWavefront sensorAmbiguity

An improved wavefront sensor for characterizing phase distortions in incident light including optical elements that spatially sample the incident light and form a dispersed spot with a fringe pattern corresponding to samples of the incident light. An imaging device captures an image of the dispersed spot with said fringe pattern formed by said optical elements. And an image processor that analyzes the spectral components of the fringe pattern of a given dispersed spot to derive a measure of the local phase distortion without ambiguity in the corresponding sample of incident light. The optical elements may comprise refractive elements, diffractive elements or a combination thereof (such as a grism). The wavefront sensor may be part of an adaptive optic system (such as a large-aperture space telescope) to enable the measurement and correction of large phase steps across adjacent mirror segments of a deformable mirror.

Owner:NORTHROP GRUMMAN SYST CORP

High coherent power, two-dimensional surface-emitting semiconductor diode array laser

InactiveUS6885686B2No penalty in device efficiencyStep of become largeLaser optical resonator constructionSemiconductor laser arrangementsGratingPhase shifted

A semiconductor laser is formed on a semiconductor substrate with an array of laterally spaced laser device elements each including a second order distributed feedback grating bounded by distributed Bragg reflector gratings and a central phase shift in the distributed feedback grating. The device elements in which the distributed feedback grating and the distributed Bragg reflector gratings are formed have a lower effective index than the index of the interelement regions and are spaced so as to form an antiguided array. A two-dimensional semiconductor array laser may be formed of four or more of the semiconductor array devices arranged on the substrate to provide long range coherent coupling via traveling waves of light between the device elements.

Owner:WISCONSIN ALUMNI RES FOUND

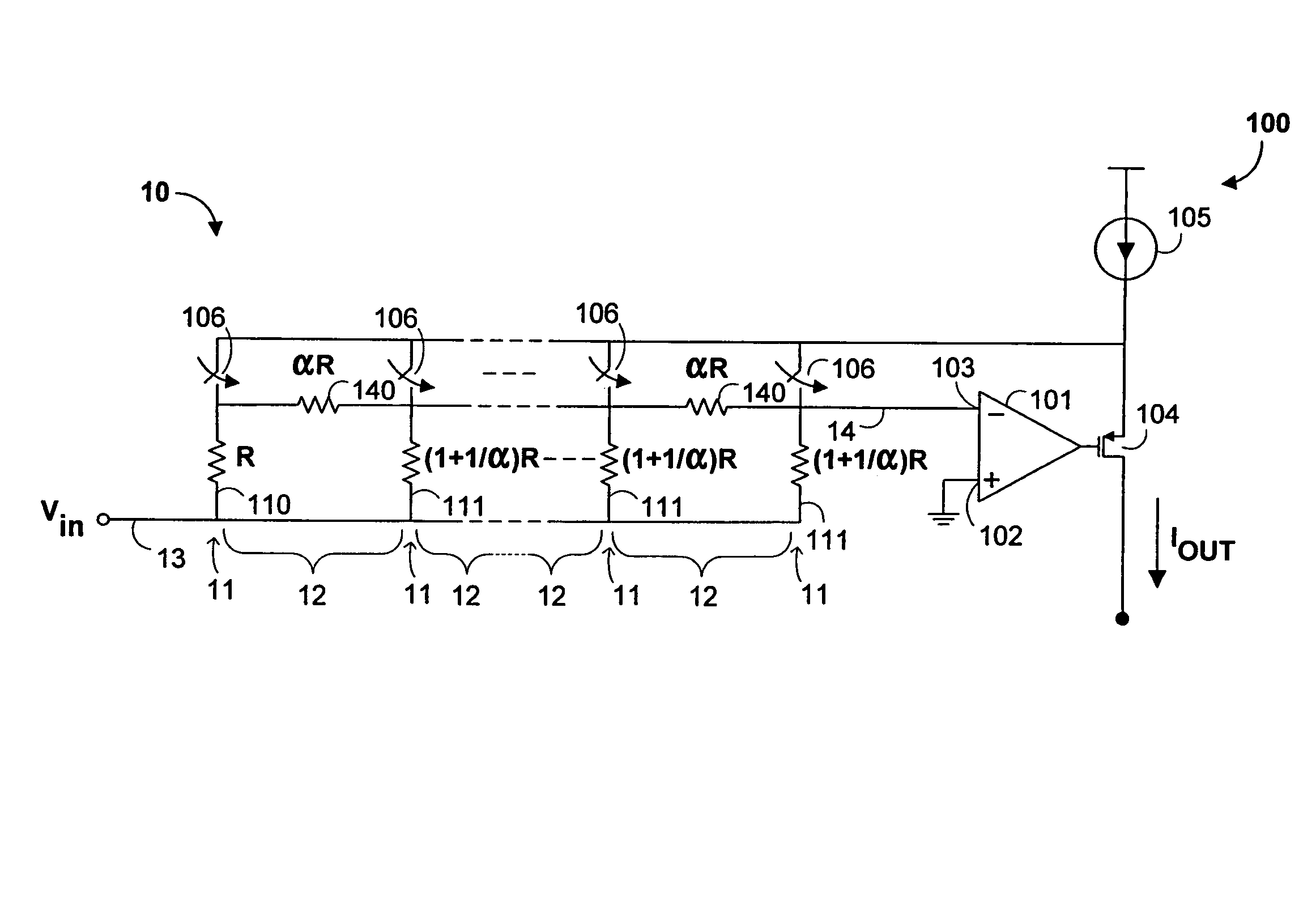

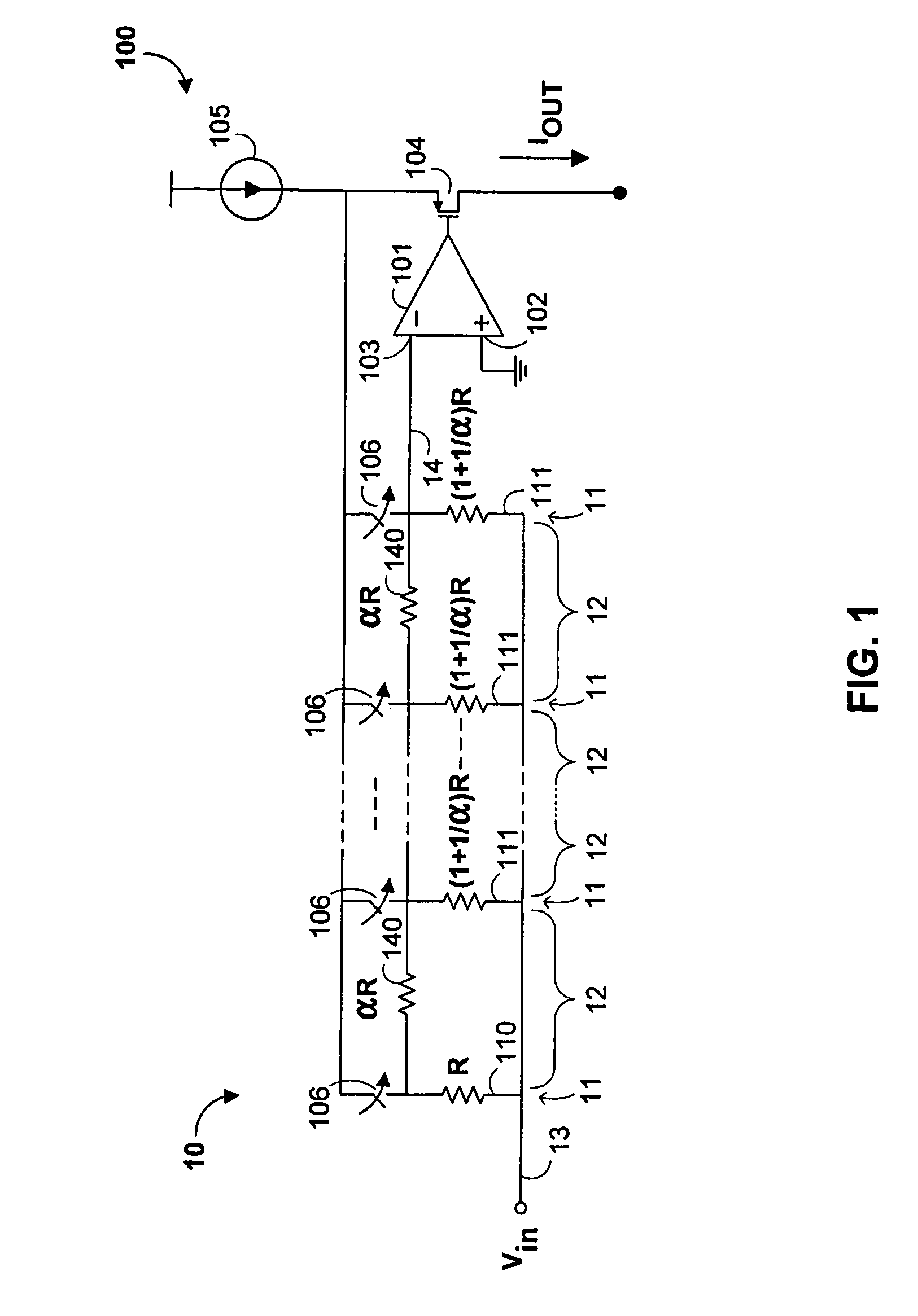

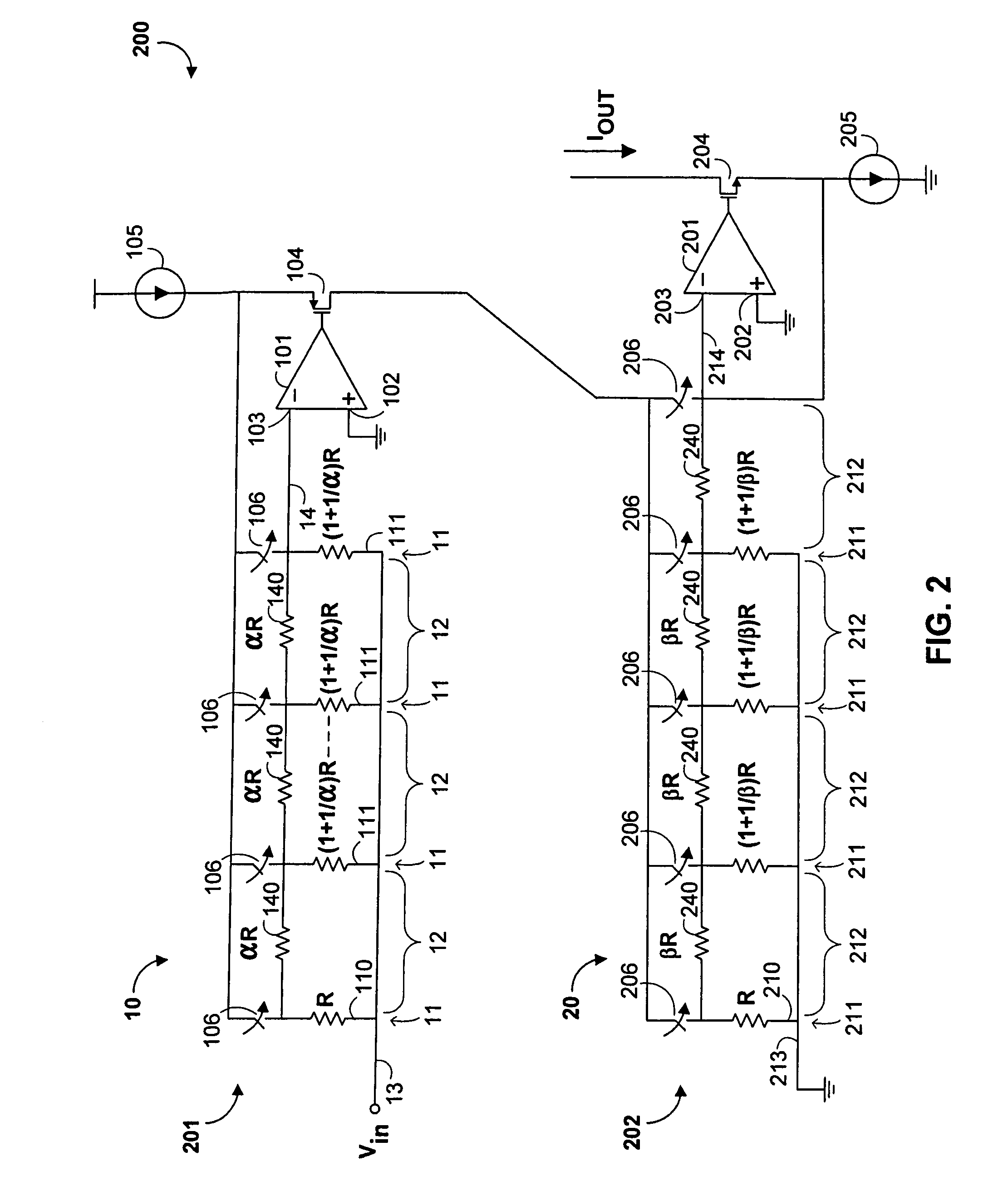

Linear-in-dB variable gain amplifier using geometric ladder circuit

ActiveUS7339434B1Increase rangeSave areaGain controlAmplifier with semiconductor-devices/discharge-tubesElectrical resistance and conductanceVariable-gain amplifier

A variable gain amplifier uses a geometric ladder circuit that produces a transfer function having substantially uniform steps measured in dB. Where the ladder has a plurality of substantially identical resistor rungs of a first resistance, one stile that is a conductor connecting the rungs, and another having a series of substantially identical resistors of a second resistance, then for identical inputs at different rungs, the output signal at an end of the ladder is attenuated by a number of substantially equal steps, one for each rung between input and output. For a ladder with a base rung R, an output at an end opposite the base rung, stile resistors of resistance αR, and other rungs all of resistance (1+(1 / α))R, the step size is 20 log10(1+α). By using such ladders in op-amp feedback loops, chaining different stages with different values of α, coarse and fine gain adjustment can be provided.

Owner:MARVELL ASIA PTE LTD

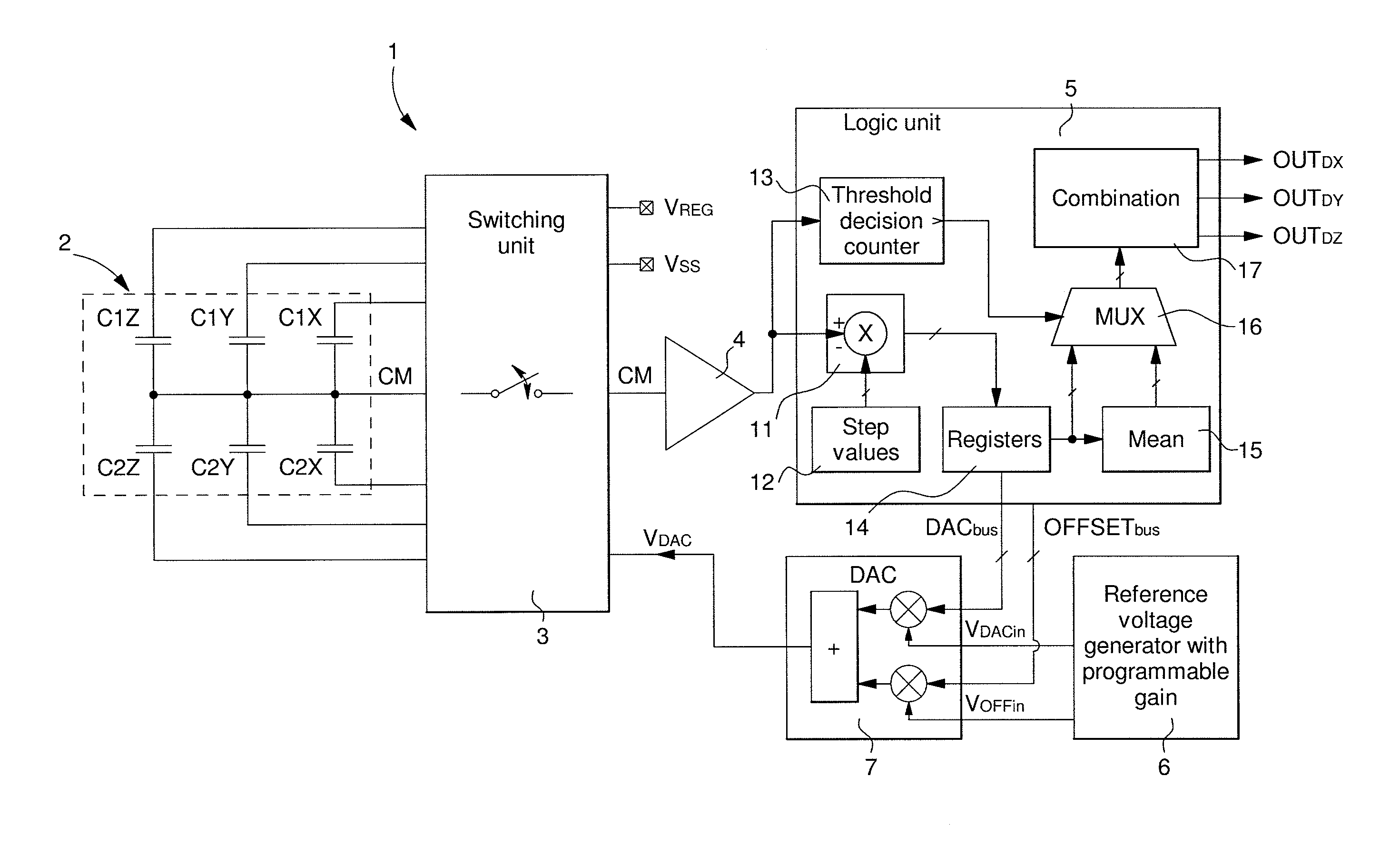

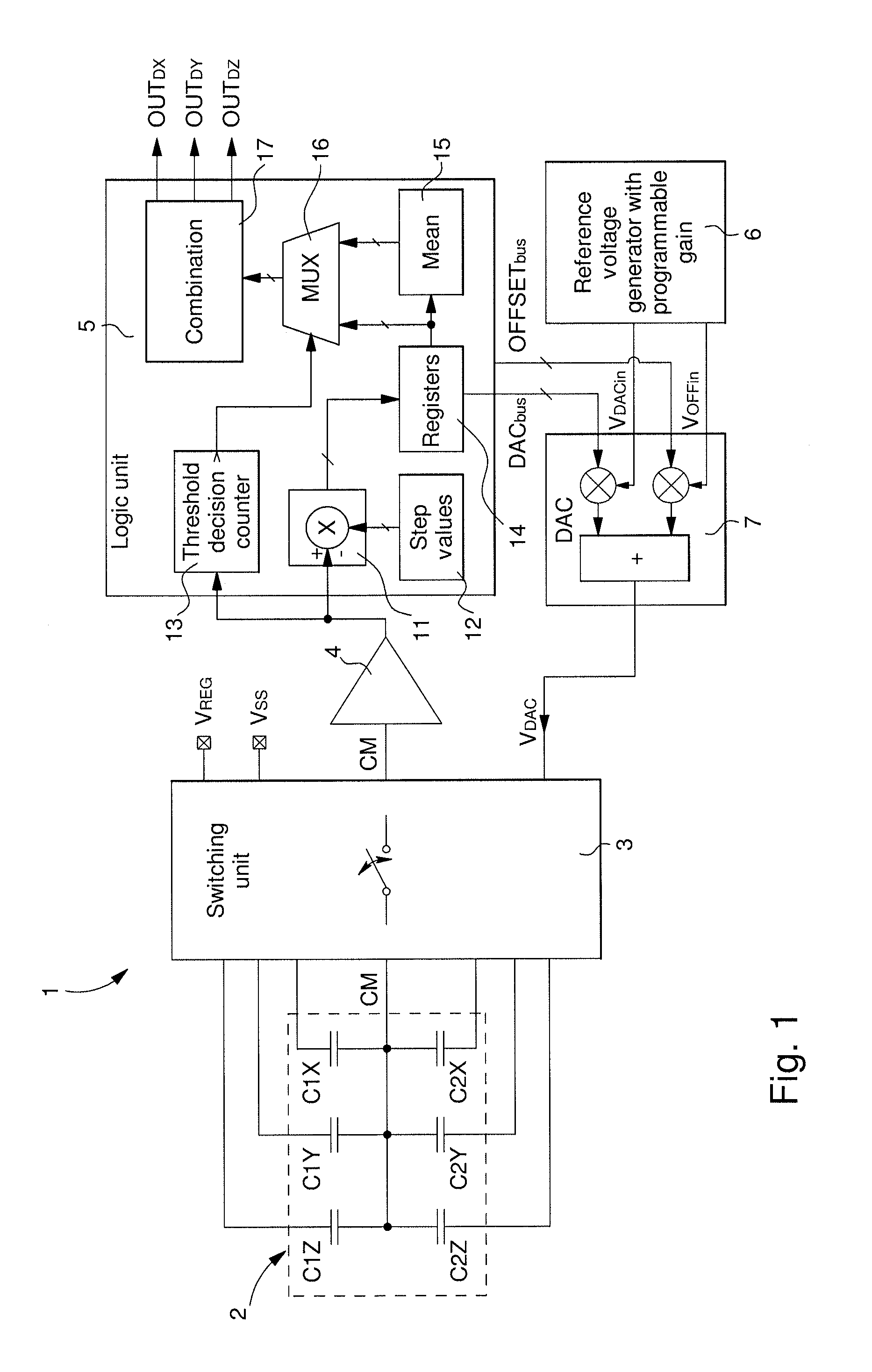

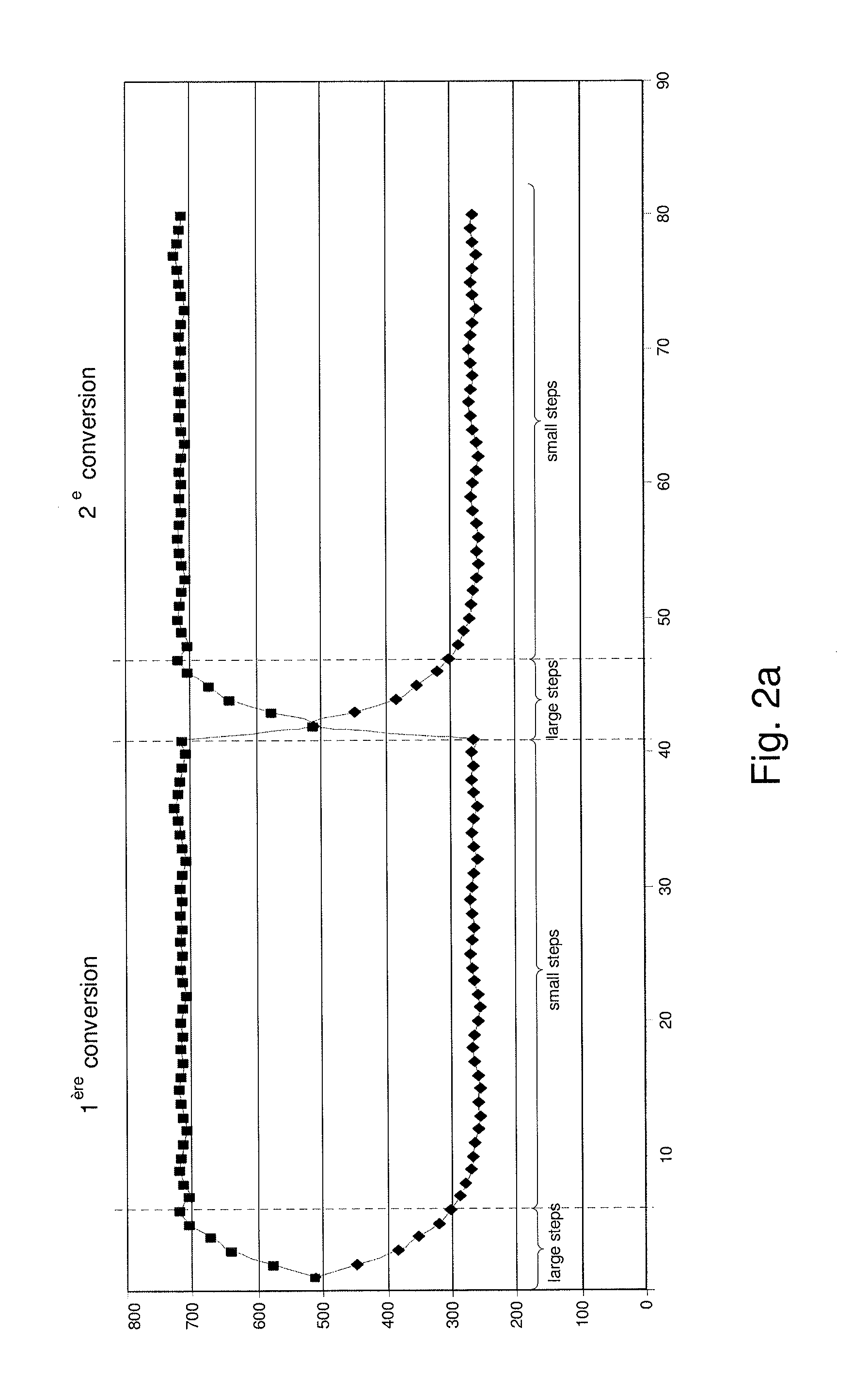

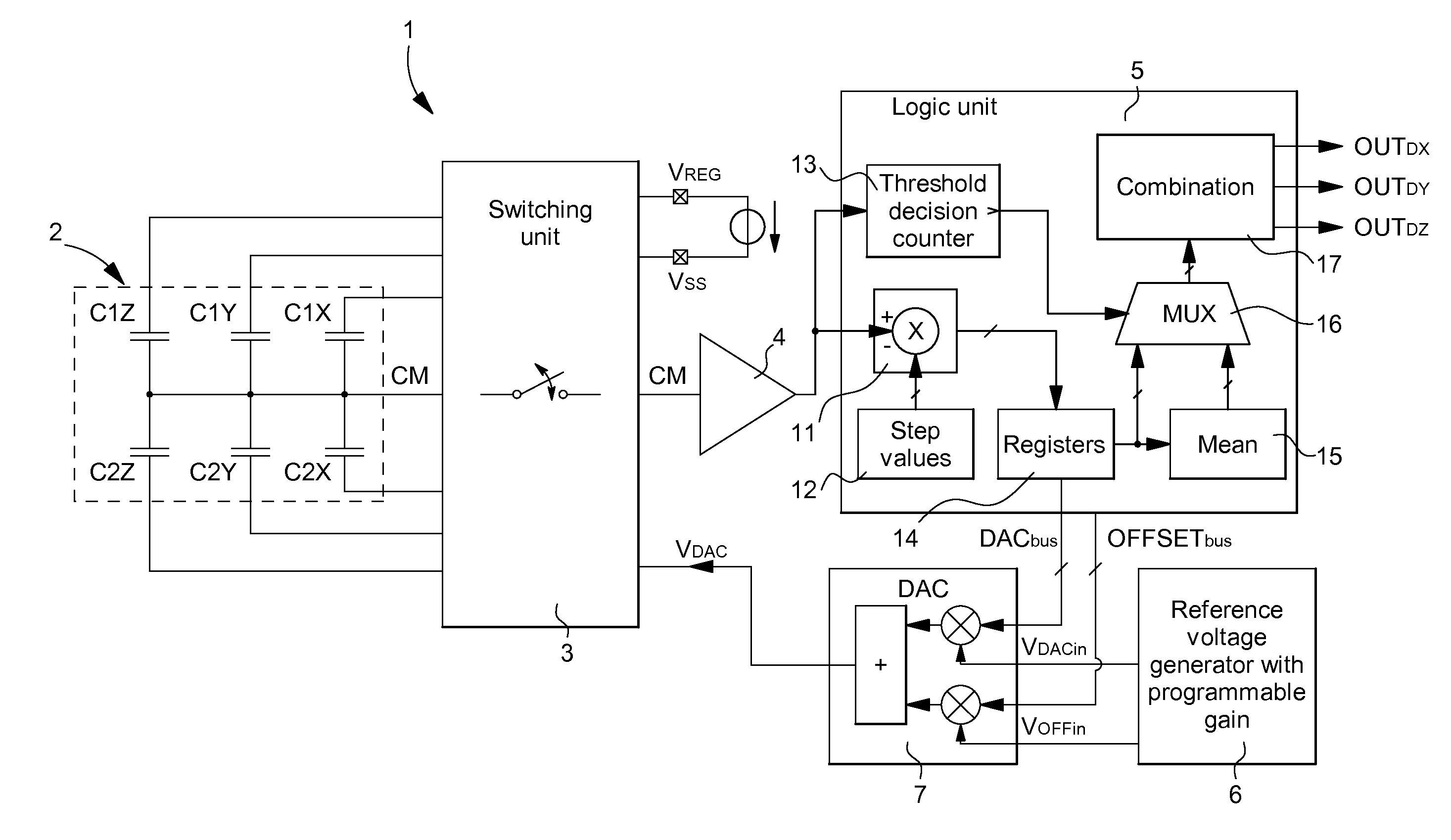

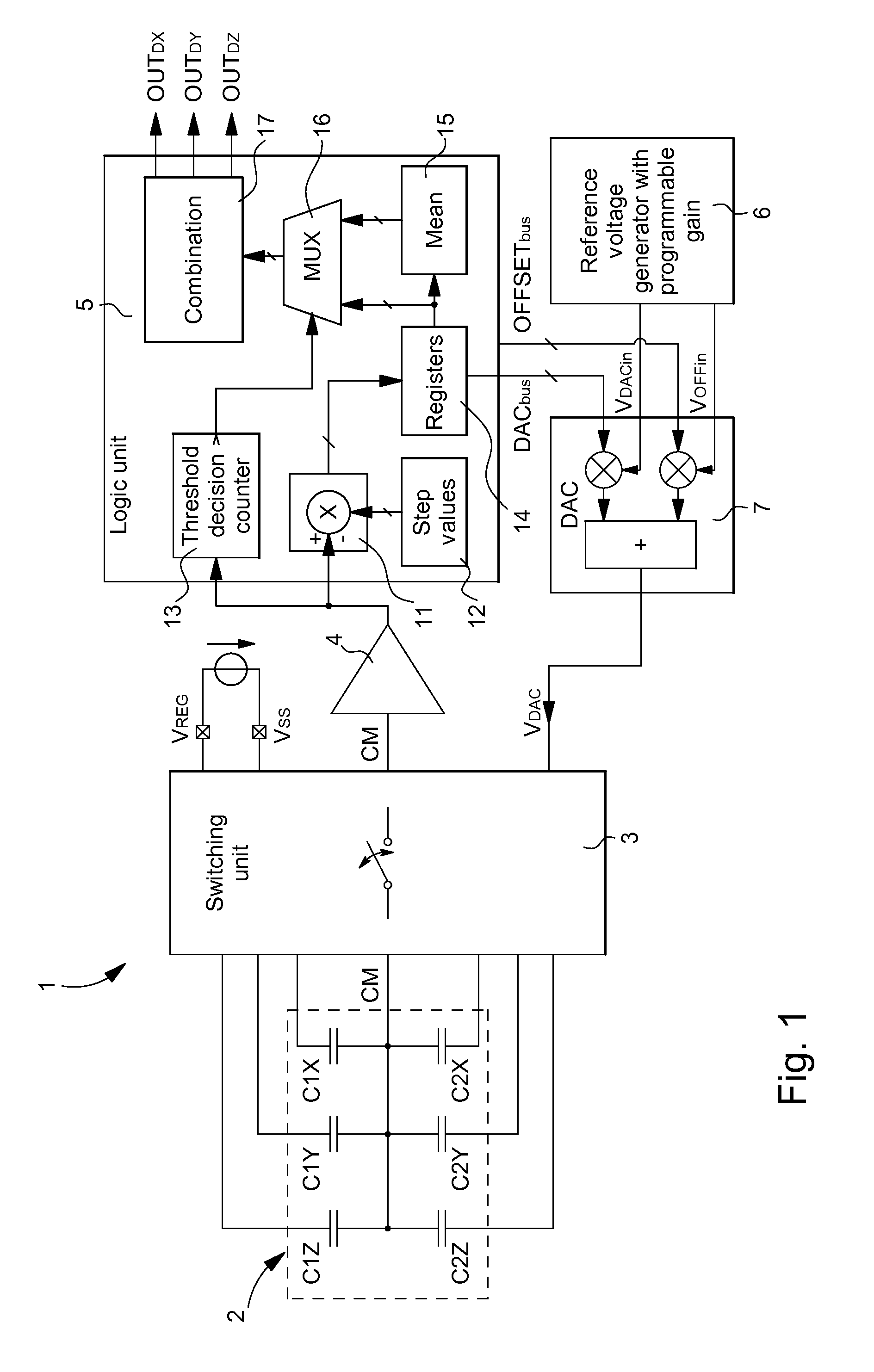

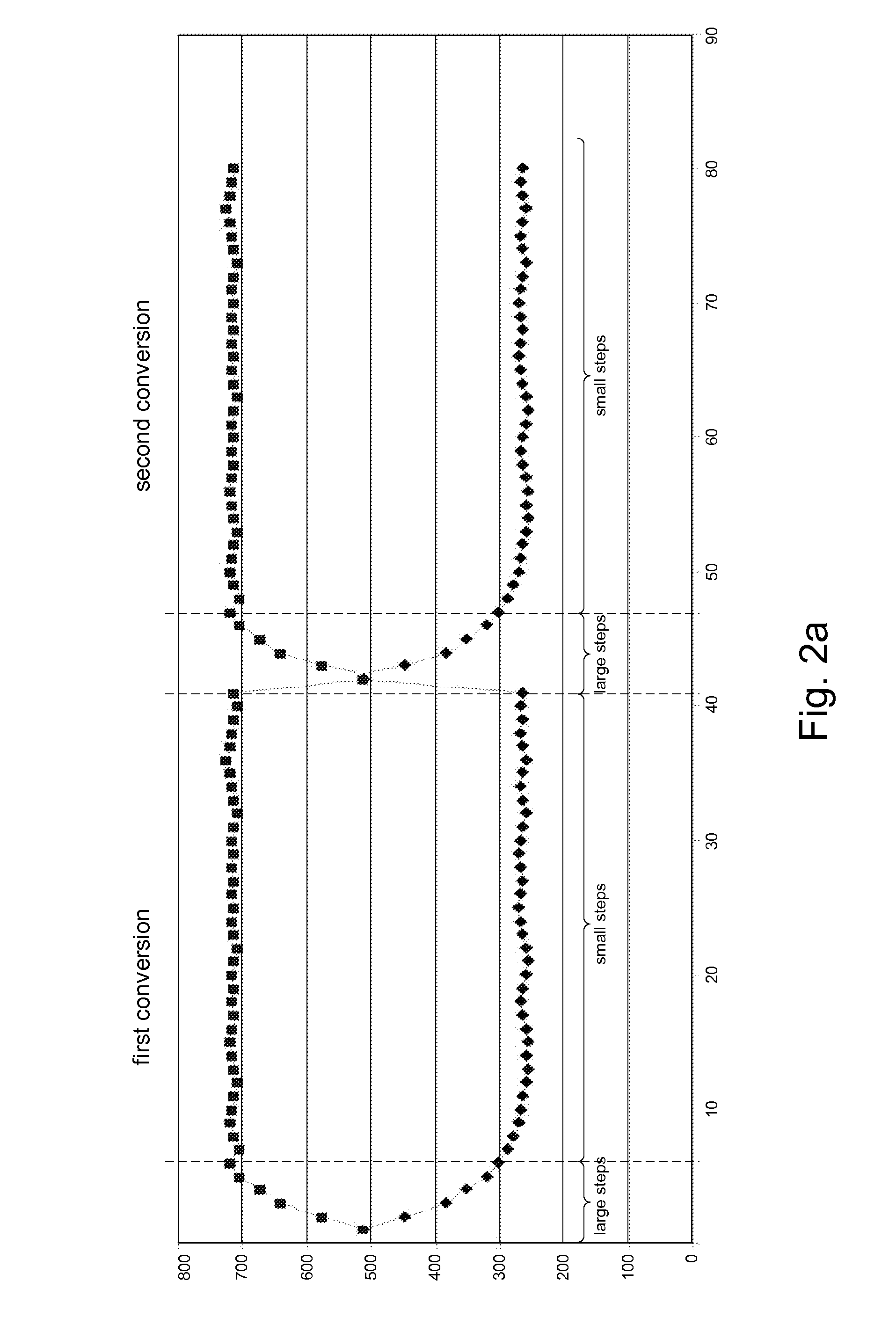

Method of measuring a physical parameter and electronic interface circuit for a capacitive sensor for implementing the same

ActiveUS20130187668A1Provide quicklyLimited redundancyCapacitance measurementsAcceleration measurementCapacitive sensingEngineering

The method is for measuring a physical parameter by an electronic circuit connected to a two differential capacitor sensor having two fixed electrodes and a common moving electrode. The electronic circuit supplies first and second digital measuring signals. Each measuring cycle consists on biasing the electrodes by the measuring voltage based on the first digital signal, connecting the fixed electrodes to a supply voltage source for a first biasing, biasing the electrodes by the measuring voltage based on the second digital measuring signal, and inversely connecting the fixed electrodes to a supply voltage source for a second biasing. In first successive measuring cycles, the first and second digital signals are adapted to each cycle by a large step value. In second successive measuring cycles, the first and second digital signals are adapted to each cycle by a small step value until the end of the conversion.

Owner:EM MICROELECTRONIC-MARIN

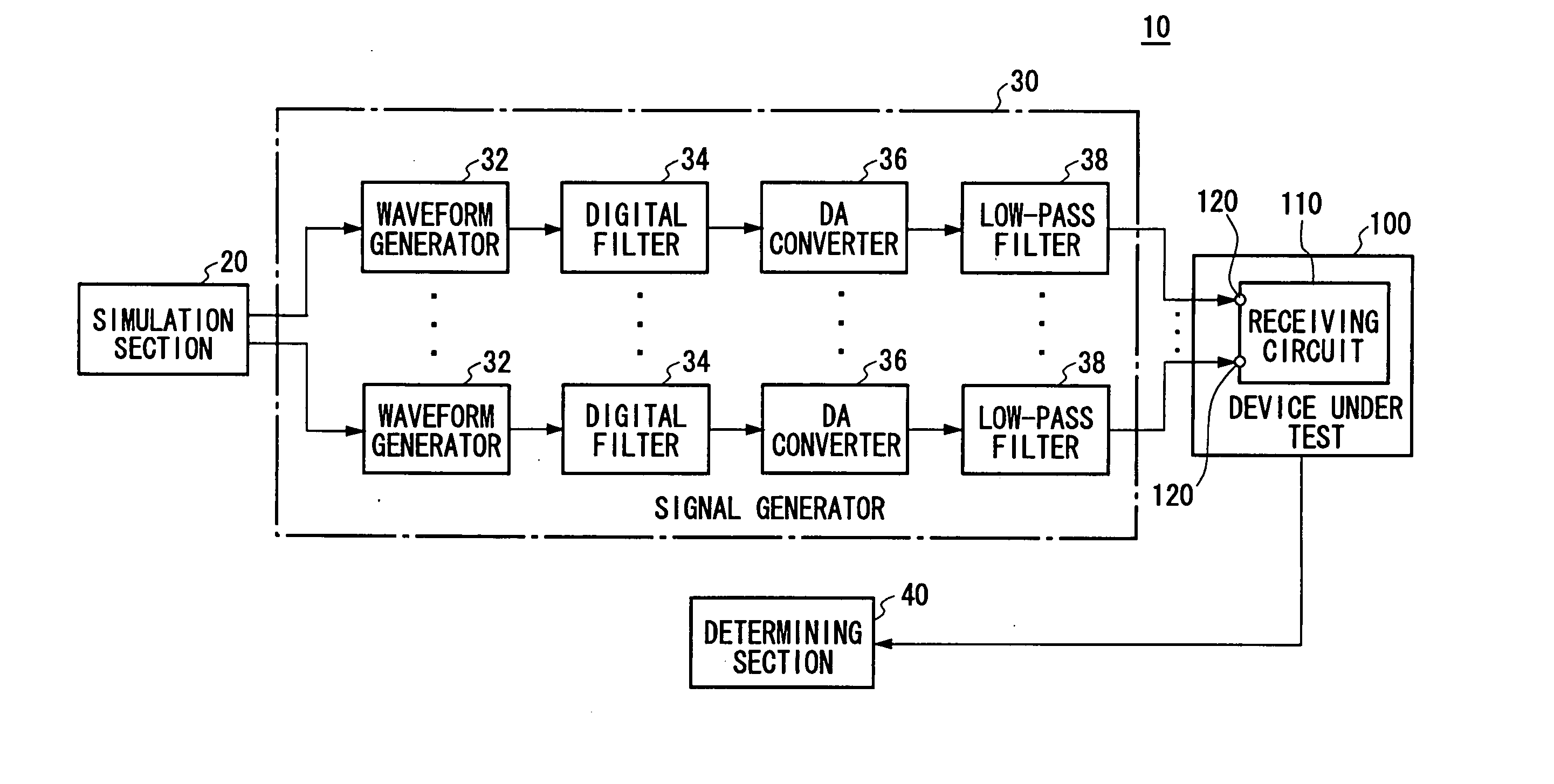

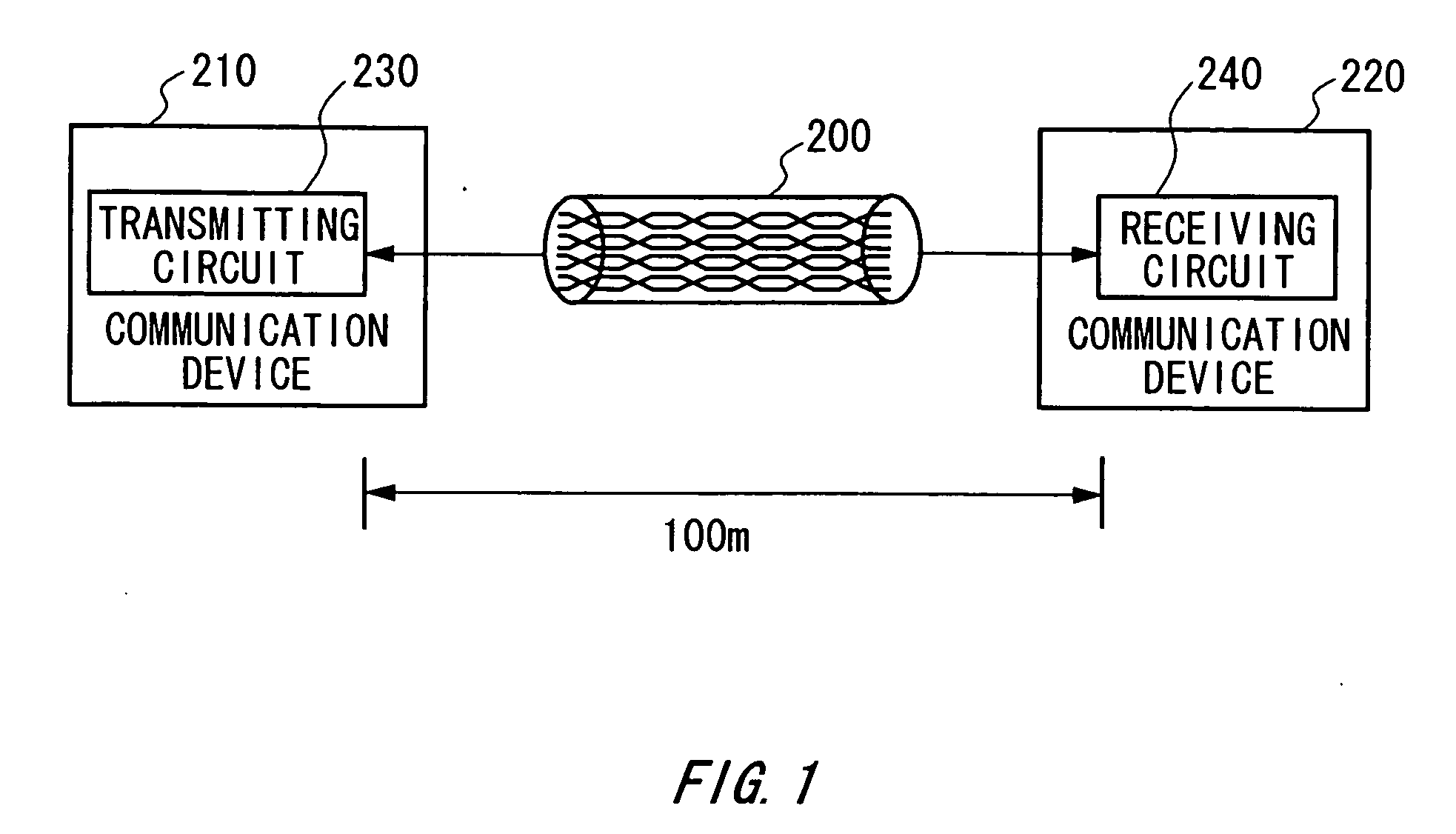

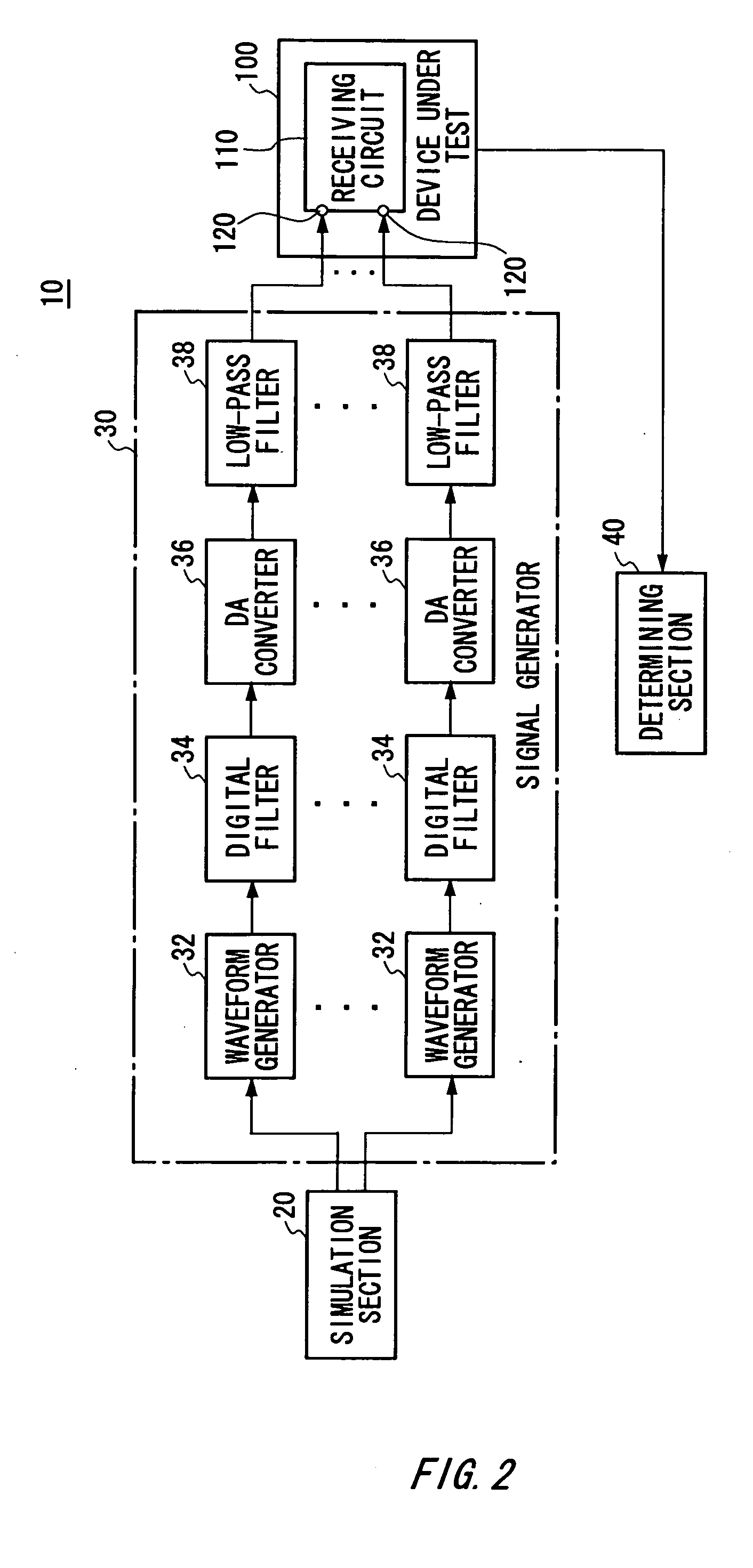

Test apparatus and test method

InactiveUS20070230355A1Step of become largeError preventionFrequency-division multiplex detailsUltrasound attenuationCable transmission

A test apparatus for testing a device under test including a receiving circuit for receiving signals transmitted through a communication cable is provided. The test apparatus includes: an waveform generating section for outputting waveform data to define an waveform to be provided to an input terminal of a receiving circuit; a digital filter having the filter characteristic substantially reverse to the attenuation characteristic of the communication cable, for outputting amplified waveform data obtained by amplifying the waveform data; a DA converter for converting the amplified waveform data to an analog waveform; and a low-pass filer having the attenuation characteristic substantially the same as that of the communication cable, for attenuating the analog waveform and providing the same to the receiving circuit.

Owner:ADVANTEST CORP

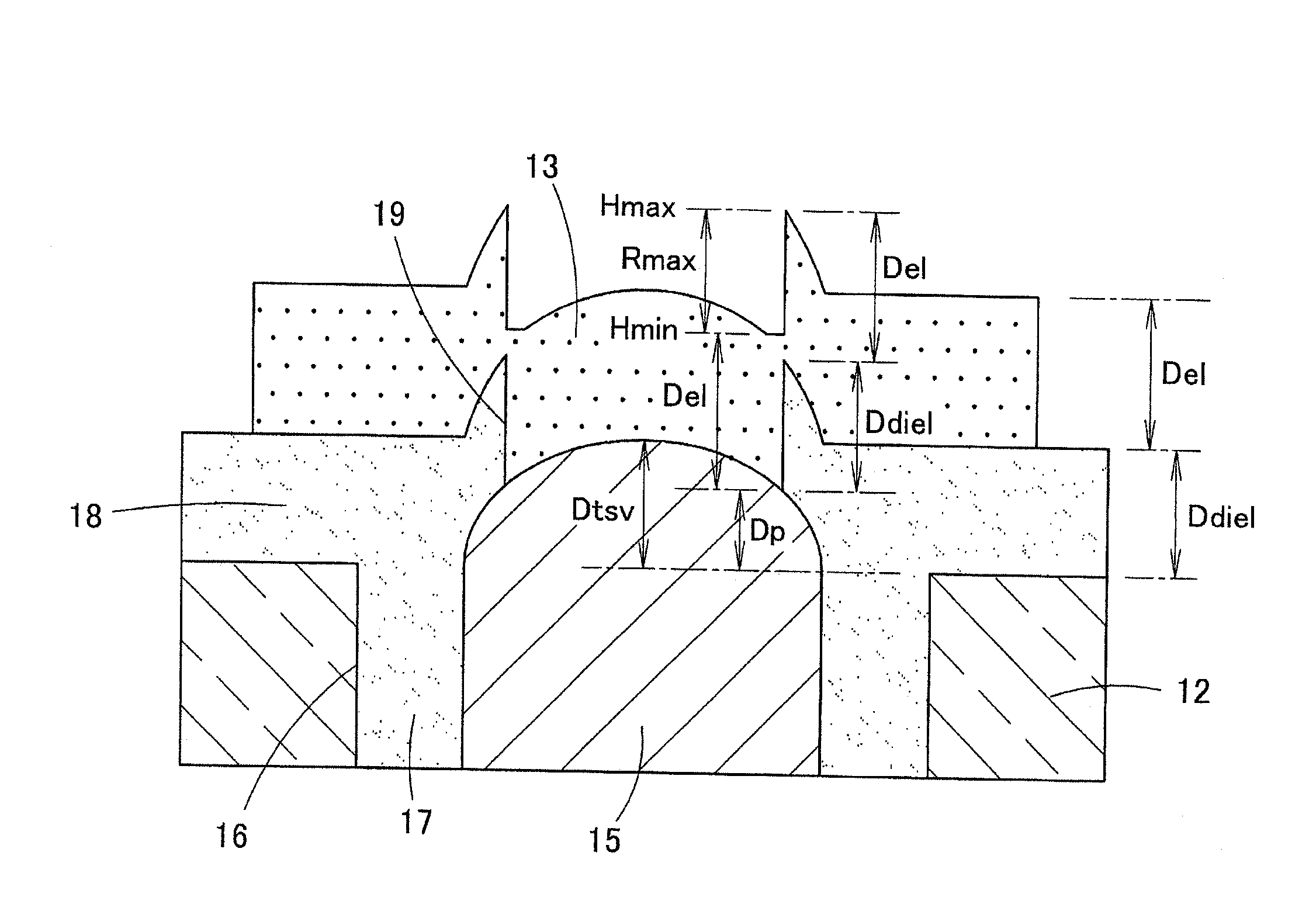

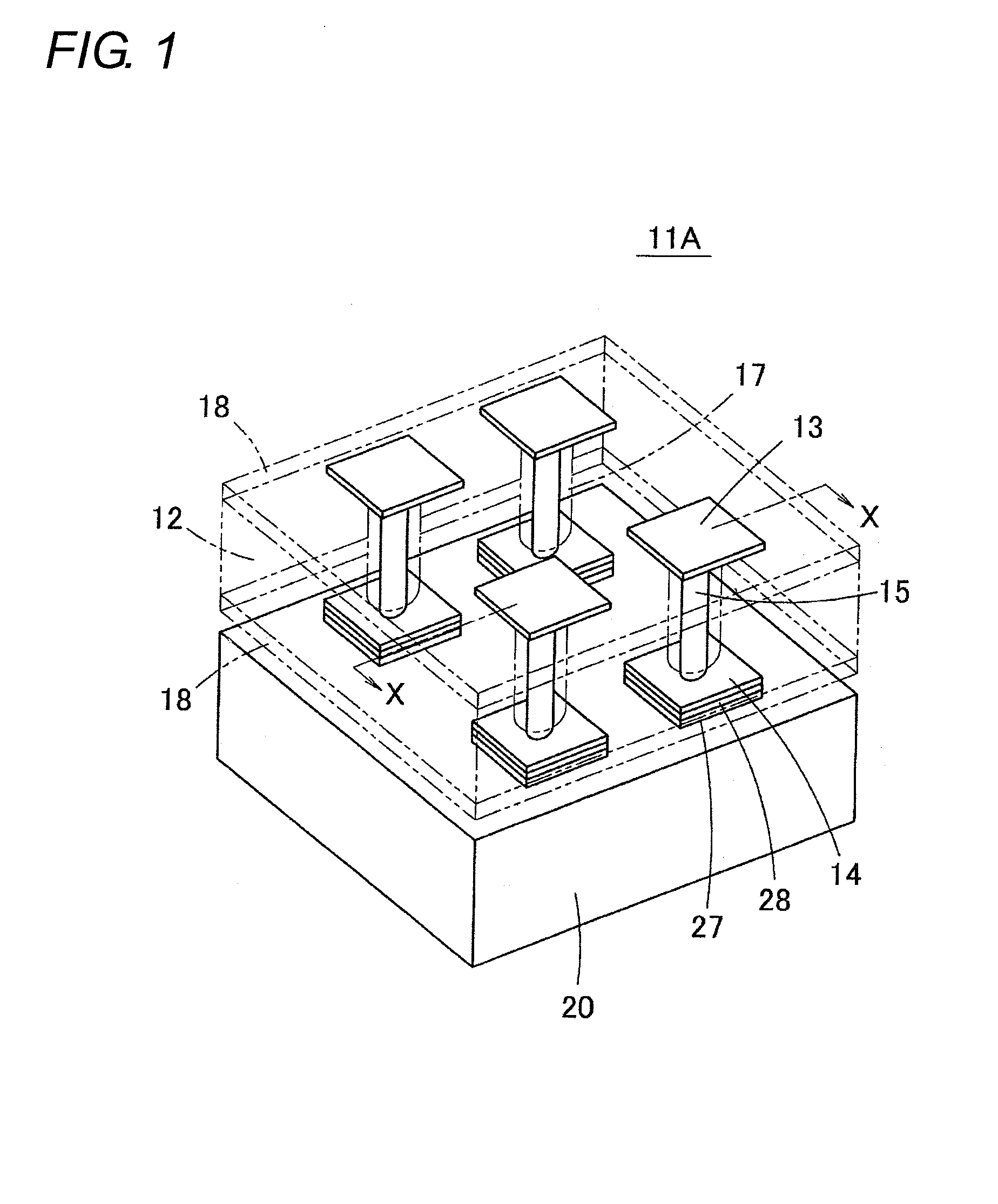

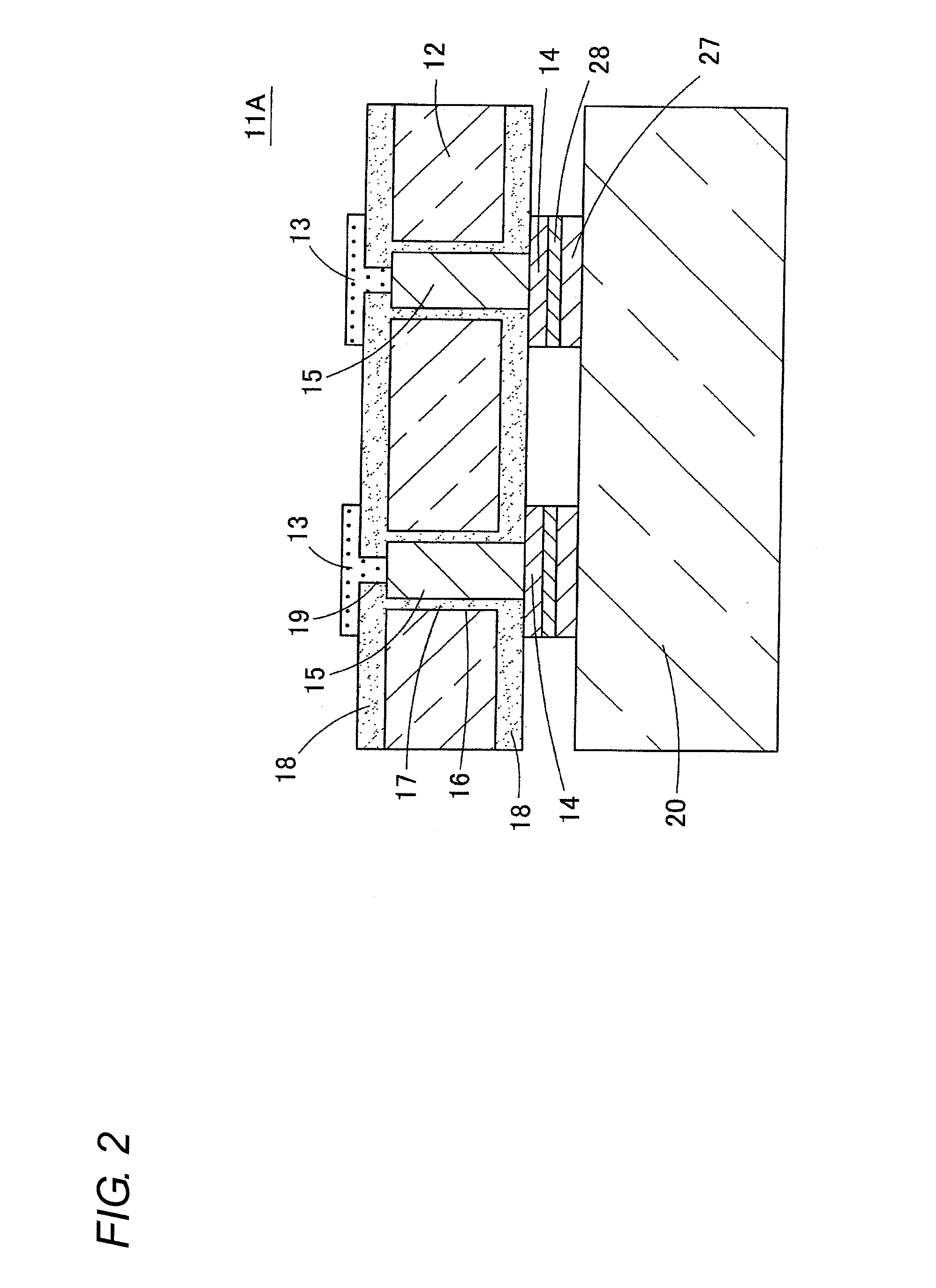

Electrode portion structure

InactiveUS20110220406A1Improve mass productionReduce resistanceSemiconductor/solid-state device detailsSolid-state devicesEngineeringContact hole

In an electrode portion structure in which an electrode is formed in an end portion of a through-wiring, disconnection is prevented in an electrode portion. A through-hole that vertically pierces a substrate is made in the substrate, and a through-electrode is provided in the through-hole. The through-electrode is projected in s curved-surface manner from an upper surface of the substrate. The upper surface of the substrate 12 is coated with an insulating film, and a contact hole is made in the insulating film while aligned with the through-electrode. An opening diameter of the contact hole is lower than a sectional diameter of the through-electrode, and surroundings of an upper surface of the through-electrode are coated with the contact hole. A thickness Ddiel of the insulating film is equal to or lower than a projection length Dp of the through-electrode from the upper surface of the substrate at an opening edge of the contact hole. Additionally, assuming that Dtsv is a projection length (maximum projection length) of an apex of the through-electrode from the upper surface of the substrate, the projection length Dtsv is adjusted so as to become 0≦Dtsv≦Ddiel+Dp (Dp>0).

Owner:ORMON CORP

Layered microelectronic contact and method for fabricating same

InactiveUS20060138677A1Good strength and stiffnessStep of become largePrinted circuit assemblingSemiconductor/solid-state device detailsDistal portionEngineering

A microelectronic spring contact for making electrical contact between a device and a mating substrate and method of making the same are disclosed. The spring contact has a compliant pad adhered to a substrate of the device and spaced apart from a terminal of the device. The compliant pad has a base adhered to the substrate, and side surfaces extending away from the substrate and tapering to a smaller end area distal from the substrate. A trace extends from the terminal of the device over the compliant pad to its end area. At least a portion of the compliant pad end area is covered by the trace, and a portion of the trace that is over the compliant pad is supported by the compliant pad. A horizontal microelectronic spring contact and method of making the same are also disclosed. The horizontal spring contact has a rigid trace attached at a first end to a terminal of a substrate. The trace is free from attachment at its second end, and extends from the terminal in a direction substantially parallel to a surface of the substrate to the second end. At least a distal portion of the trace extending to the second end is spaced apart from the surface of the substrate. The spaced-apart distal portion is flexible in a plane parallel to the substrate.

Owner:FORMFACTOR INC

Helical microelectronic contact and method for fabricating same

InactiveUS20060024989A1Step of become largeContact member manufacturingElectronic circuit testingEngineeringMechanical engineering

A microelectronic spring contact for making electrical contact between a device and a mating substrate and method of making the same are disclosed. The spring contact has a compliant pad adhered to a substrate of the device and spaced apart from a terminal of the device. The compliant pad has a base adhered to the substrate, and side surfaces extending away from the substrate and tapering to a smaller end area distal from the substrate. A trace extends from the terminal of the device in a coil pattern over the compliant pad to its end area, forming a helix. At least a portion of the compliant pad end area is covered by the trace, and a portion of the trace that is over the compliant pad is supported by the compliant pad. In an alternative embodiment, the pad is removed to leave a freestanding helical contact.

Owner:FORMFACTOR INC

High coherent power, two-dimensional surface-emitting semiconductor diode array laser

ActiveUS7457340B2No penalty in device efficiencyStep of become largeLaser optical resonator constructionSemiconductor laser arrangementsGratingDistributed Bragg reflector

A semiconductor laser is formed on a semiconductor substrate with an array of laterally spaced laser device elements each including a second order distributed feedback grating bounded by distributed Bragg reflector gratings. The device elements in which the distributed feedback grating and the distributed Bragg reflector gratings are formed have a lower effective index than the index of the interelement regions and are spaced so as to form an antiguided array.

Owner:WISCONSIN ALUMNI RES FOUND

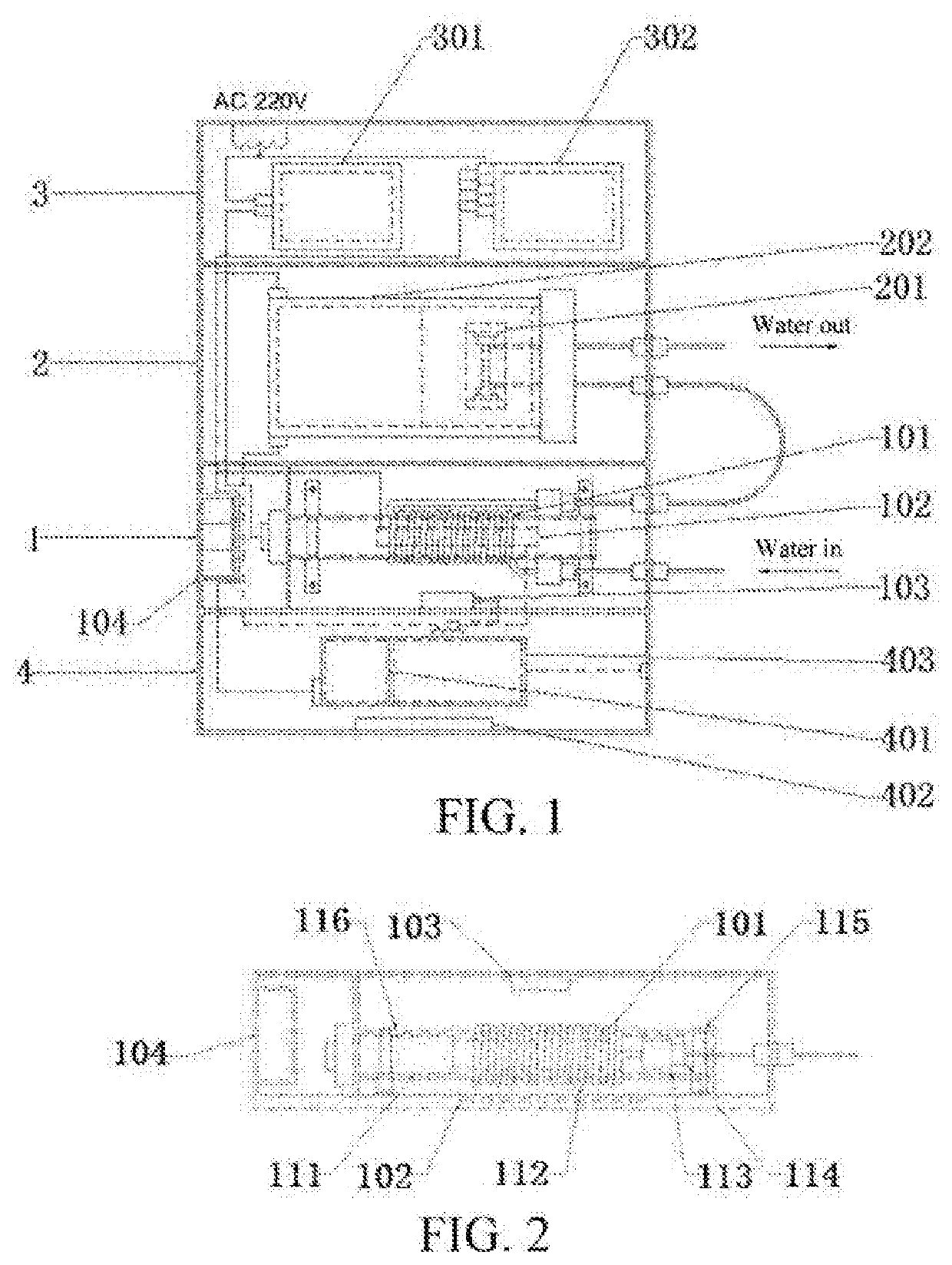

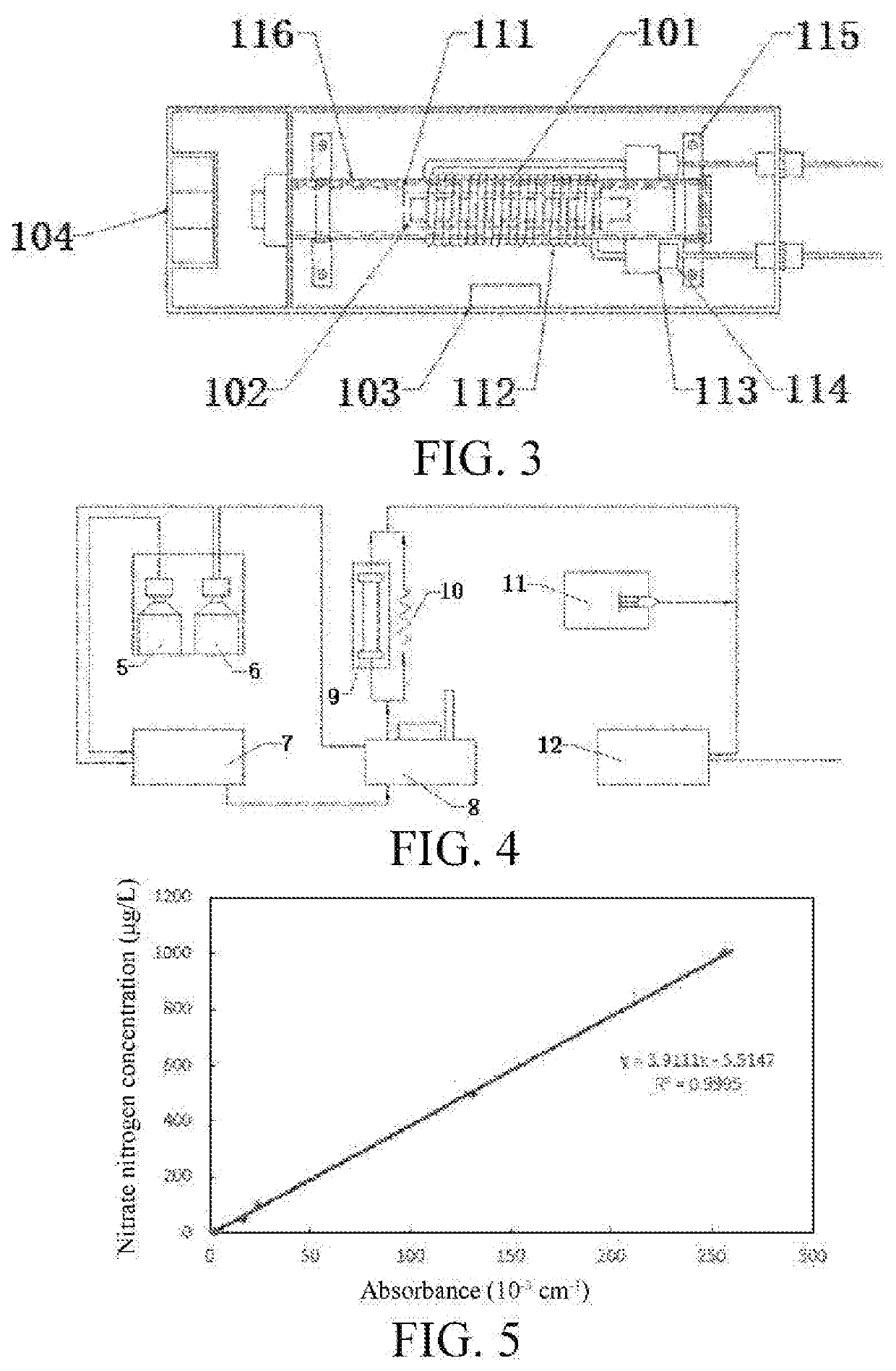

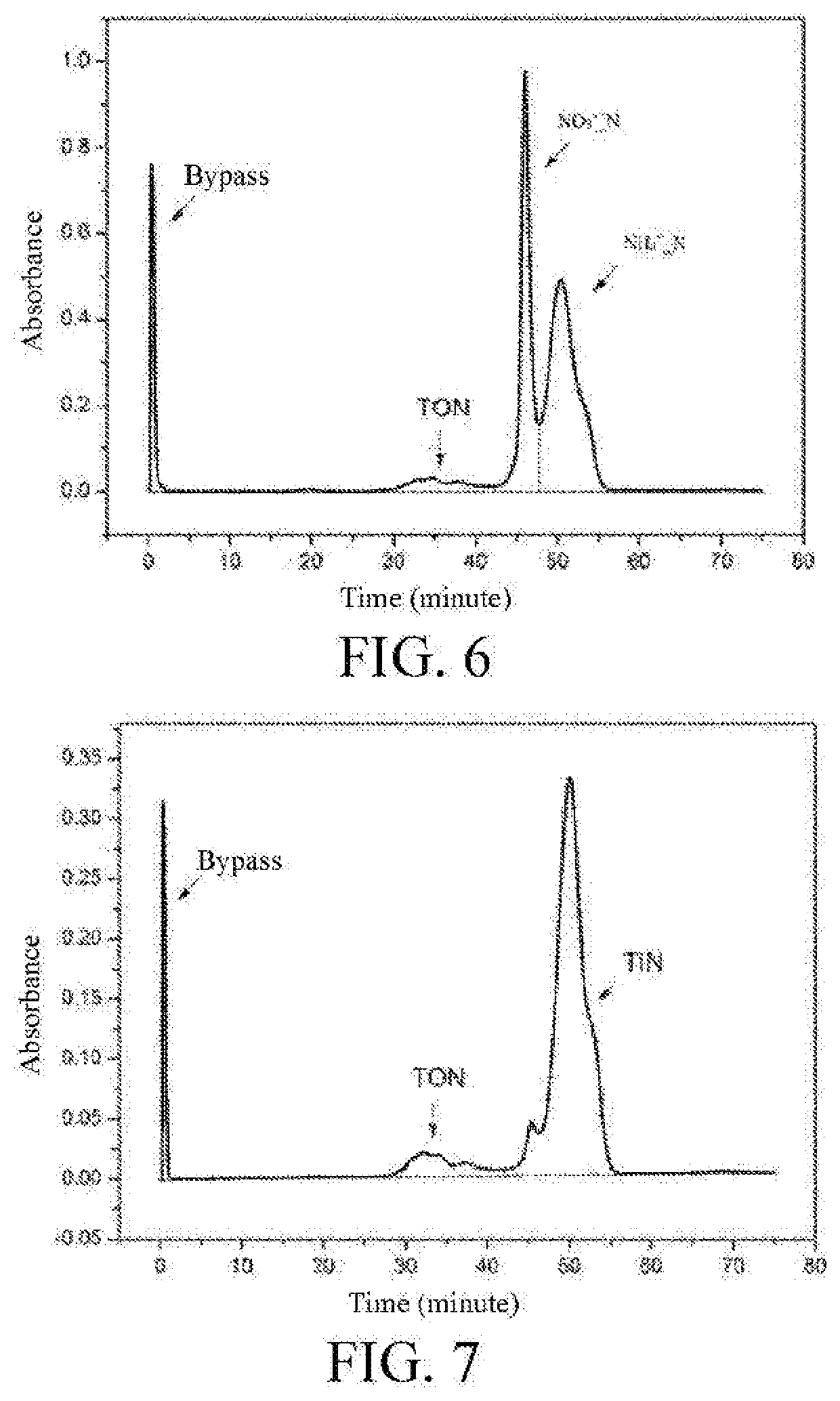

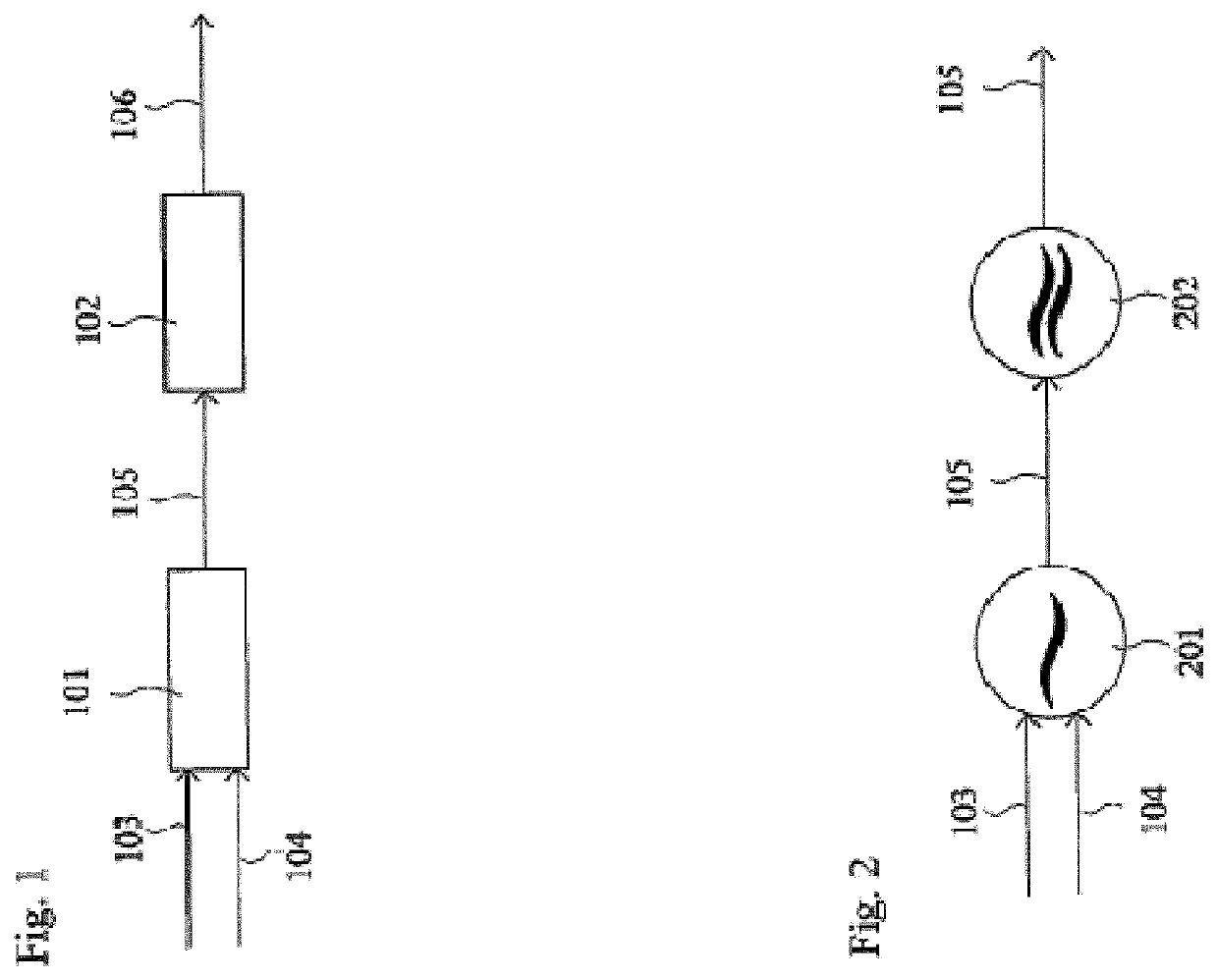

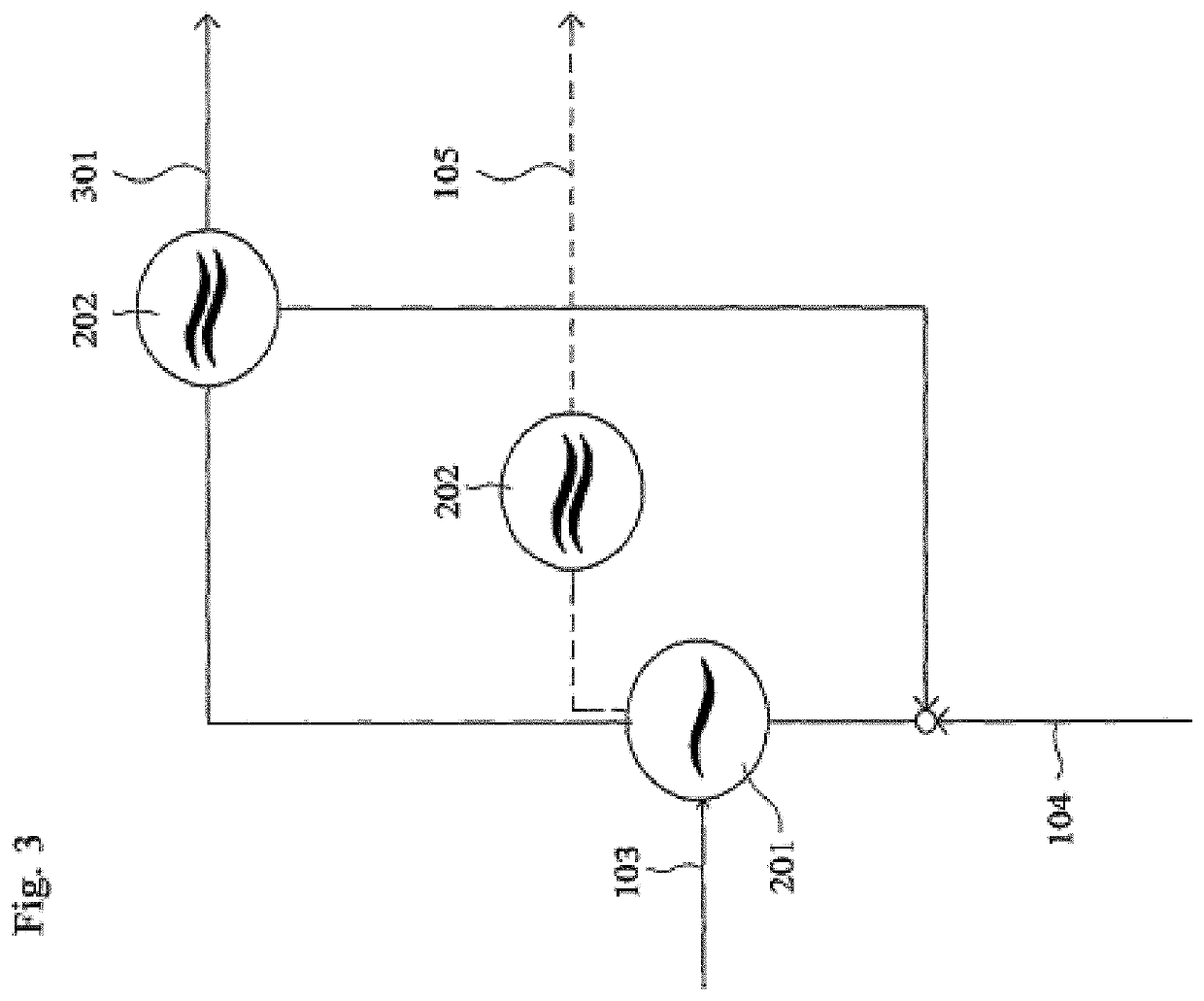

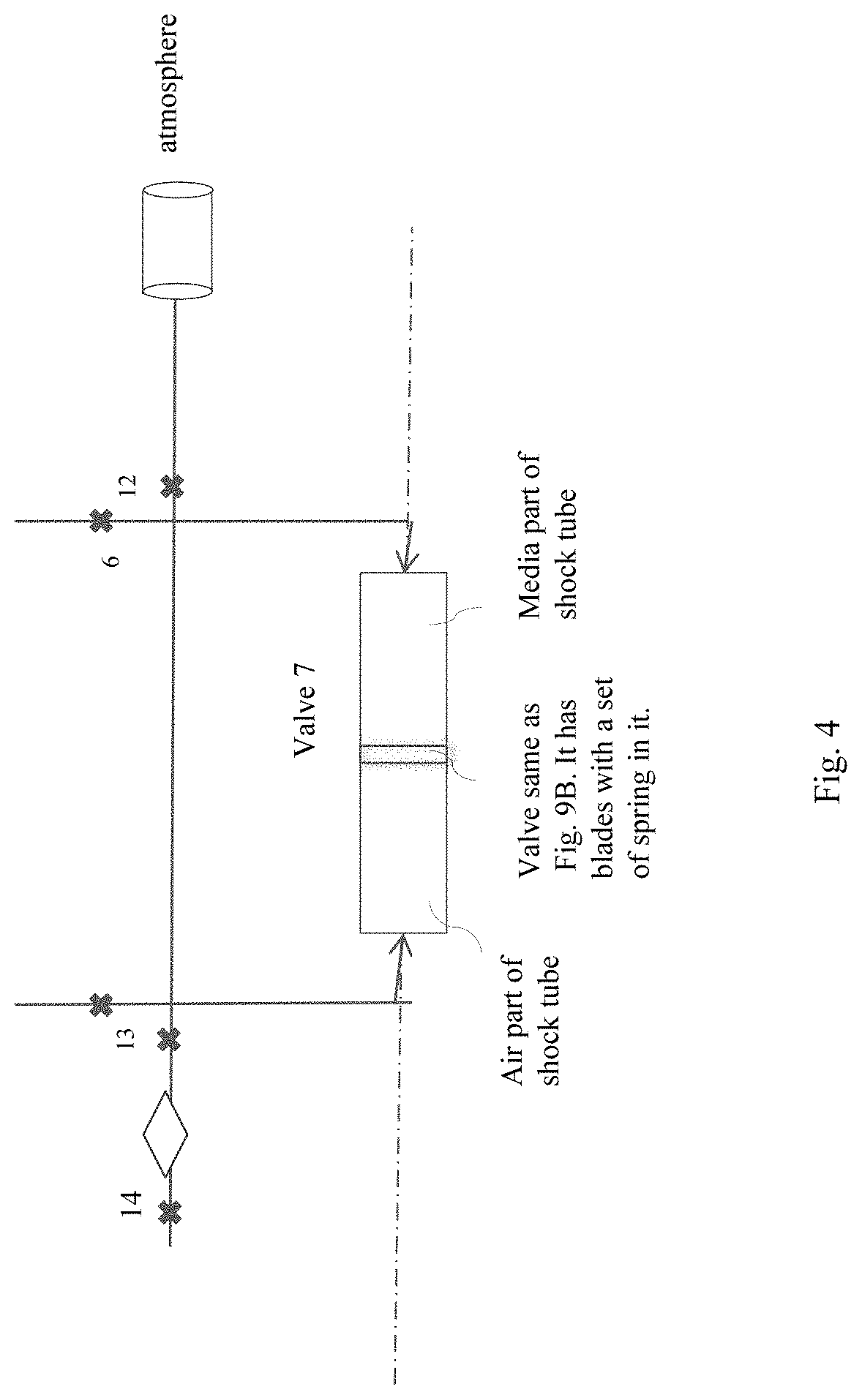

Size exclusion chromatography-combined nitrogen detector and application method

PendingUS20210018476A1Accurate quantitative analysisThe result is accurate and reliableComponent separationColor/spectral properties measurementsChromatographic separationUltraviolet

Disclosed are a size exclusion chromatography-combined nitrogen detector and an application method thereof, which belong to the field of detection and analysis of water quality. The detector comprises an oxidation system (1), a nitrate detection system (2), a power supply system (3), and a signal processing and control system (4), wherein after being separated by size exclusion chromatography, a sample to be detected enters into the oxidation system (1) to undergo oxidation treatment, and after nitrogenous compound in the sample is converted into nitrate, the sample is detected in the nitrate detection system (2) by ultraviolet (UV) absorbance method. The power supply system (3) supplies power to the detector, and the signal processing and control system (4) is responsible for processing and controlling signals of the oxidation system (1) and the nitrate detection system (2). The detector can achieve quantitative analyses of total nitrogen, organic nitrogen, nitrate nitrogen, and ammonia nitrogen, has the advantages of easiness in operation, being rich in information, etc. and thereby effectively prevents the problems of relatively large error and negative value resulting from the subtraction calculation in conventional organic nitrogen analysis methods.

Owner:NANJING UNIV +1

Grading System

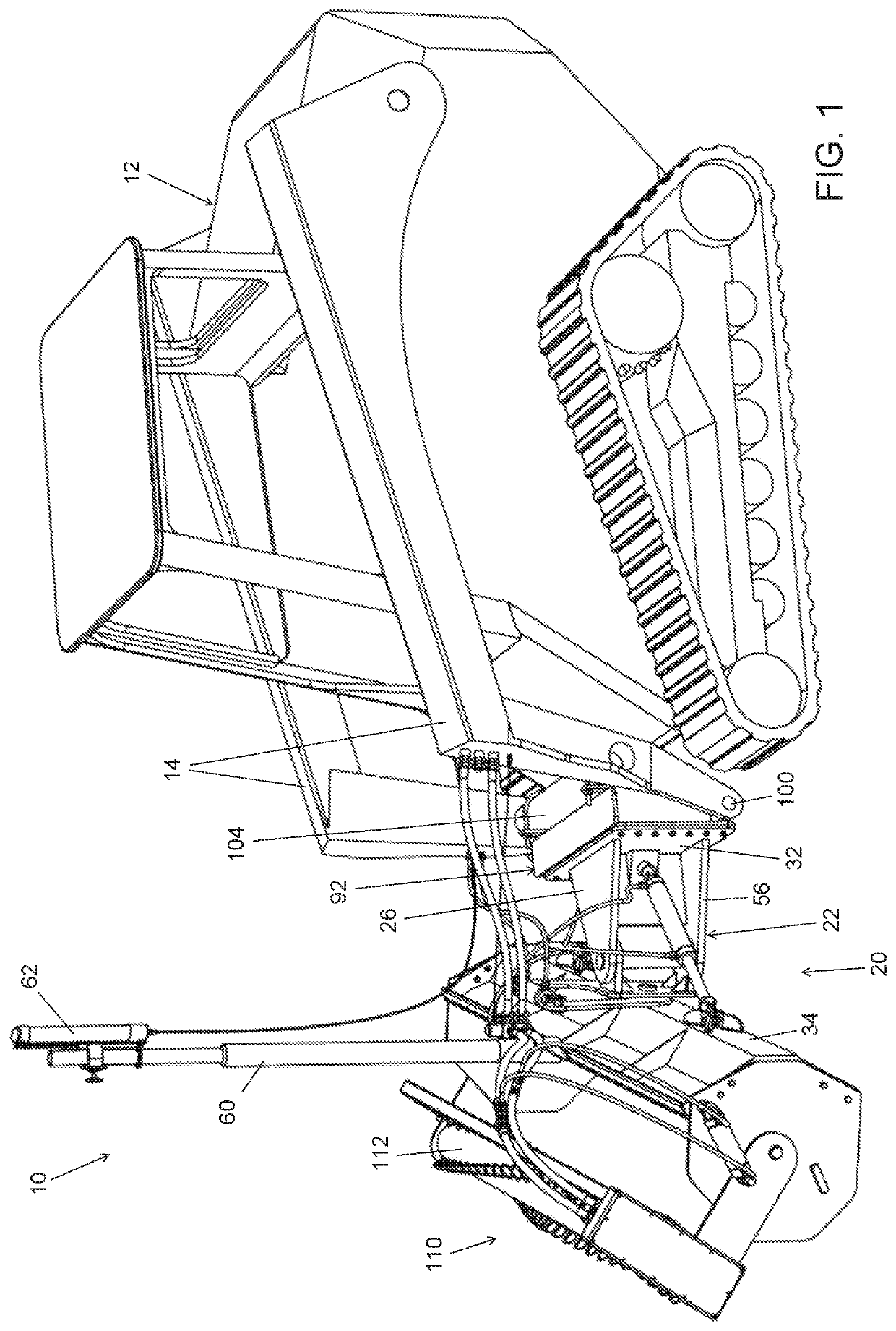

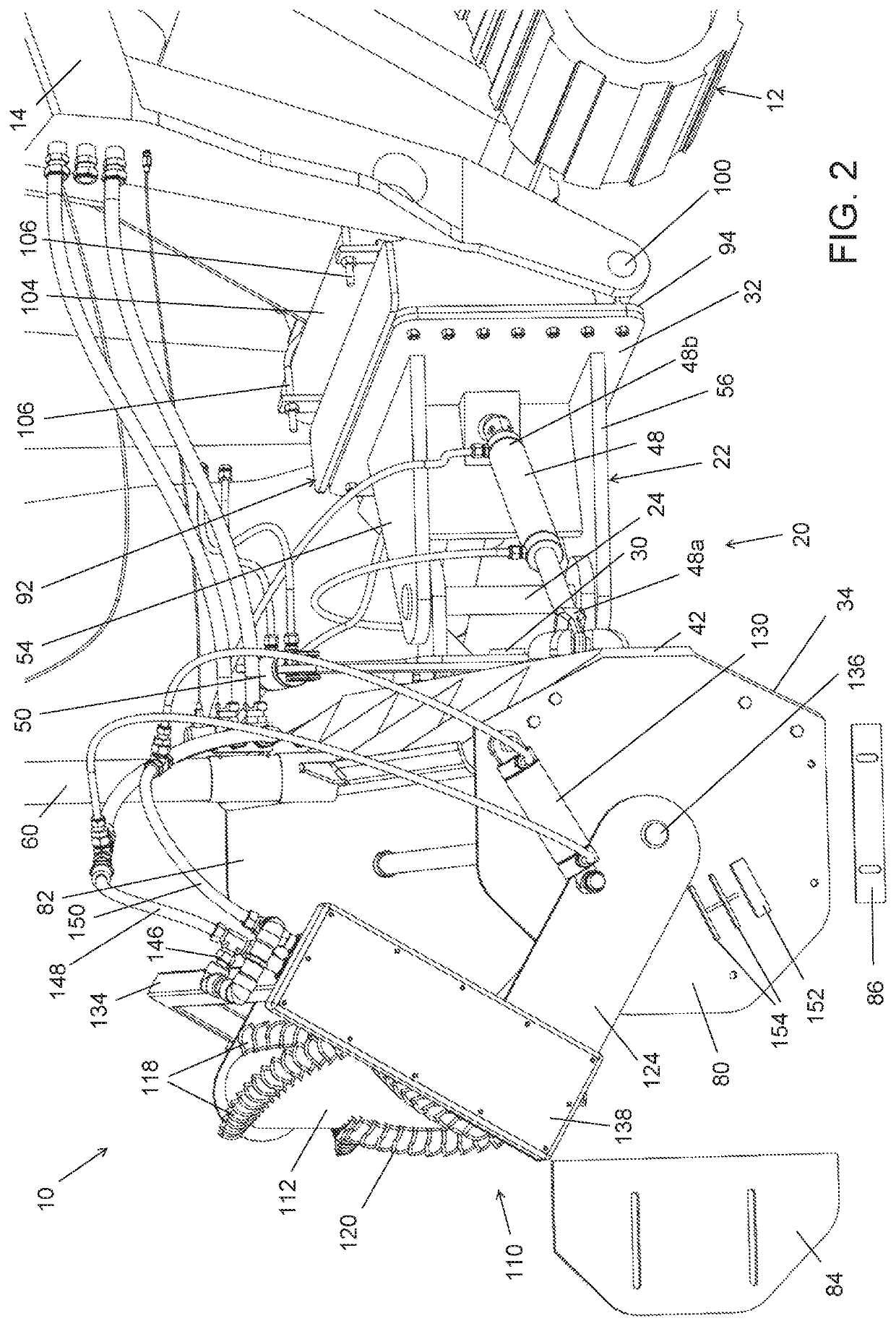

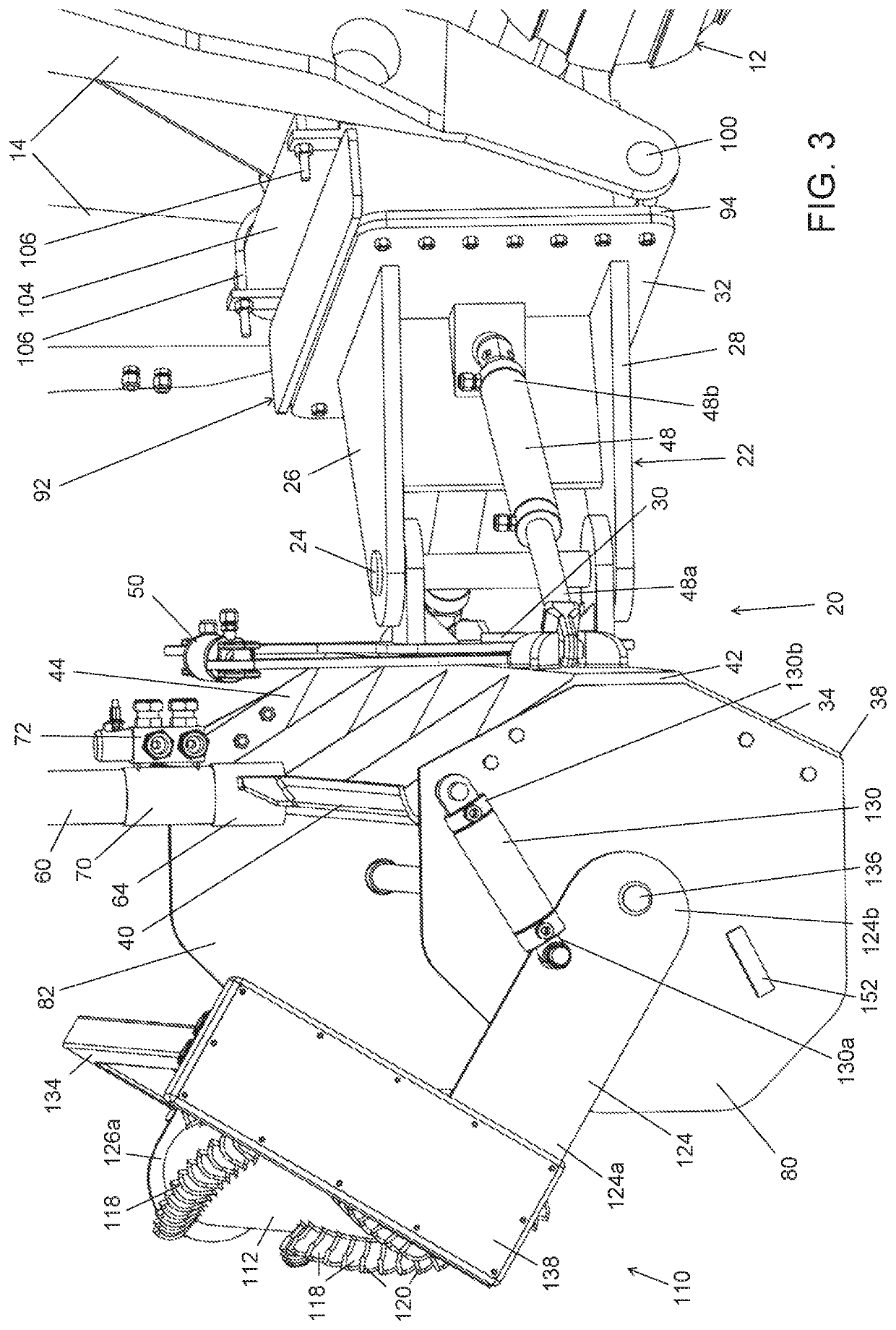

ActiveUS20210355647A1Improve performanceLess bounceMechanical machines/dredgersSoil preservationStructural engineeringActuator

A grading system for connection to a vehicle having vertically movable arms, the grading system including a grading blade assembly having a frame having a first pivot extending upward, a second pivot extending forward, a blade connected to the frame via the first pivot and the second pivot, a blade yaw actuator and a blade roll actuator, wherein the frame is configured to have the first pivot extend substantially vertically and the second pivot extend substantially longitudinally when the grading blade assembly is connected to the vehicle and the blade and vehicle are in a level position on a ground surface and the vertically movable arms of the vehicle are in a first raised position above a lowest most position.

Owner:SC GRADE LLC

Method of measuring a physical parameter and electronic interface circuit for a capacitive sensor for implementing the same

ActiveUS9075094B2The output signal is accurateFast supplyCapacitance measurementsAcceleration measurementHemt circuitsComputational physics

Owner:EM MICROELECTRONIC-MARIN

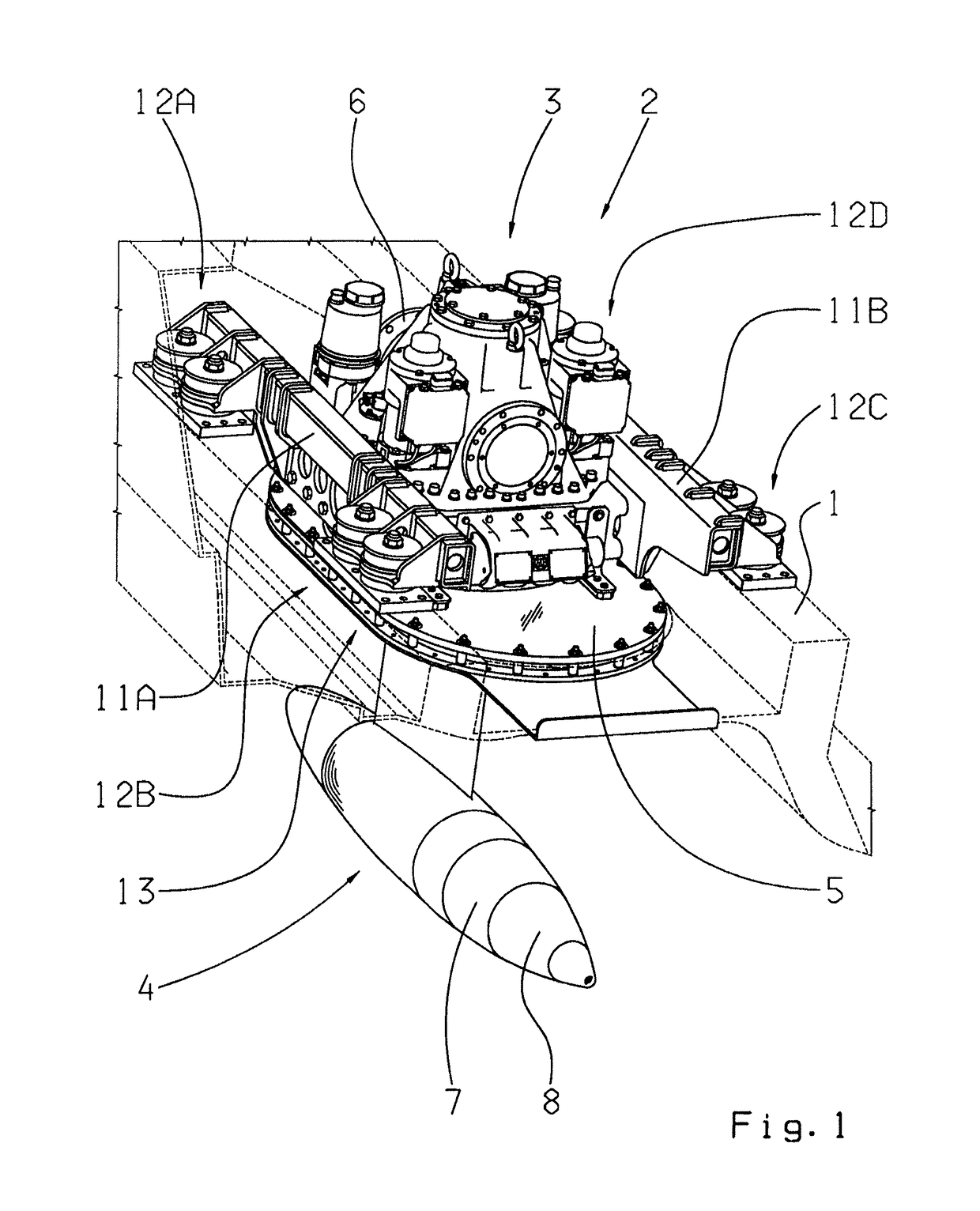

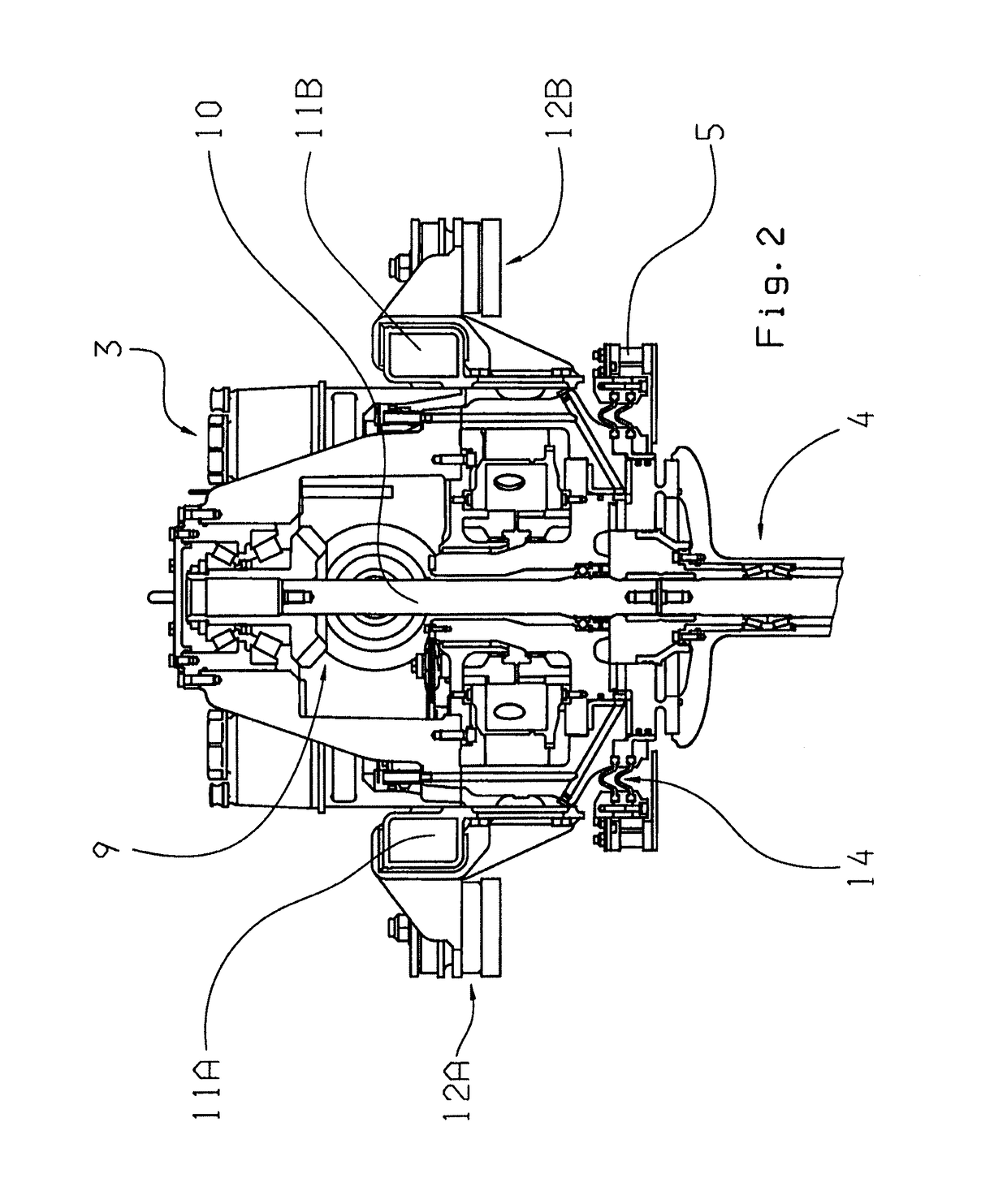

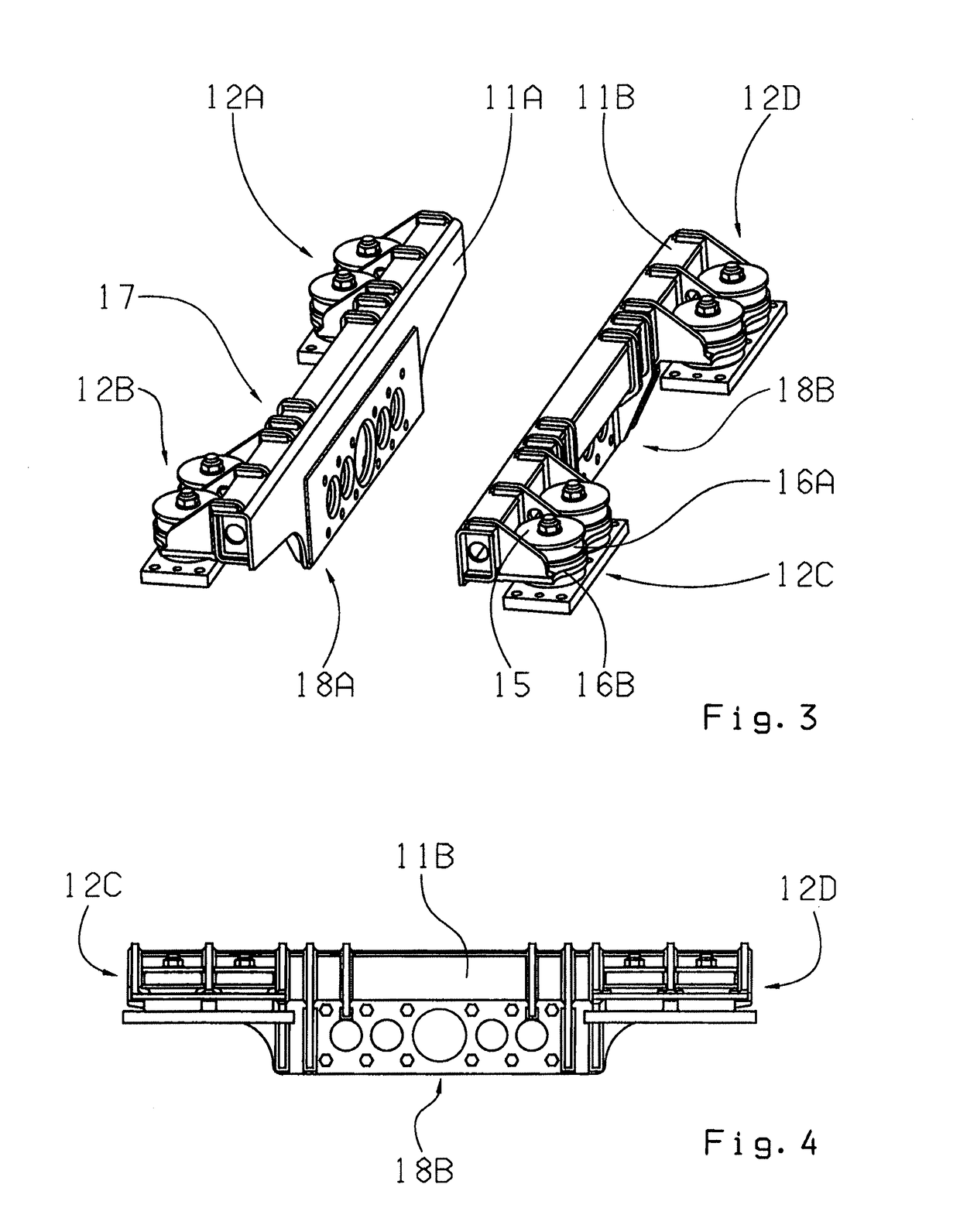

Drive arrangement for an inboard-outboard drive engine of a watercraft

InactiveUS8469755B2Reduce loadSimple designPropulsion power plantsPropulsive elementsDrivetrainElectric machinery

A drive arrangement for an inboard-outboard drive engine of a watercraft, comprising a drive unit (2) with an upper part (3) arranged in a hull (1) of the watercraft and a lower part (4) which projects through a sealed opening in the hull (1) into the surrounding water such that a drivetrain extends through the drive unit (2). At least one propeller is supported by the lower part (4) and can be driven by a motor coupled to drive the upper part (3). The upper part (3) is in contact with a carrier system which, by virtue of a plurality of supporting units (12A-12D), supports reaction forces and torques produced in the drive unit (2) in the longitudinal, transverse and vertical directions relative to the hull (1).

Owner:ZF FRIEDRICHSHAFEN AG

Liquid crystal display device and manufacturing method for same

ActiveUS8953122B2Small aperture ratioStep of become largeLiquid crystal compositionsStatic indicating devicesLiquid-crystal displayColor filter array

Owner:PANASONIC INTELLECTUAL PROPERTY CORP OF AMERICA

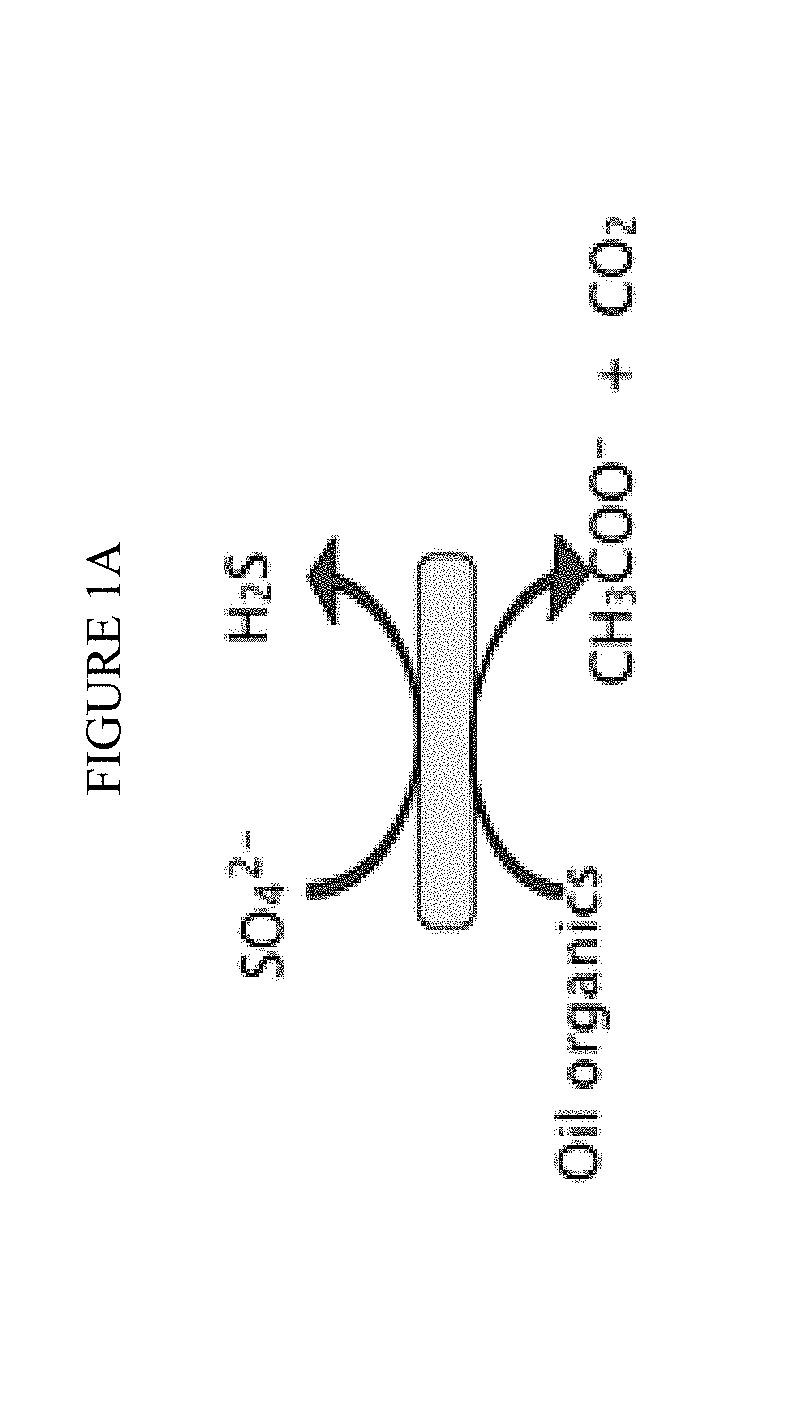

Optimal feedback heat energy internal combustion engine and applications

ActiveUS10900443B2Step of become largeIncrease pressureEfficient propulsion technologiesIntermittent jet plantsHeat flowEngineering

An internal combustion engine wherein a thermo potential heat flow in combustion is maximized by providing a feedback of an optimized amount of thermo potential heat flow that is modulated in the exhaust media, into the air intake, and a method of providing feedback comprises producing a shock wave of pulse of exhaust media and pulse of intake air on the opposite side of a high temperature shock tube thereby transferring the thermo potential heat energy flow from the exhaust media to the air intake.

Owner:DE ZHEN CORP

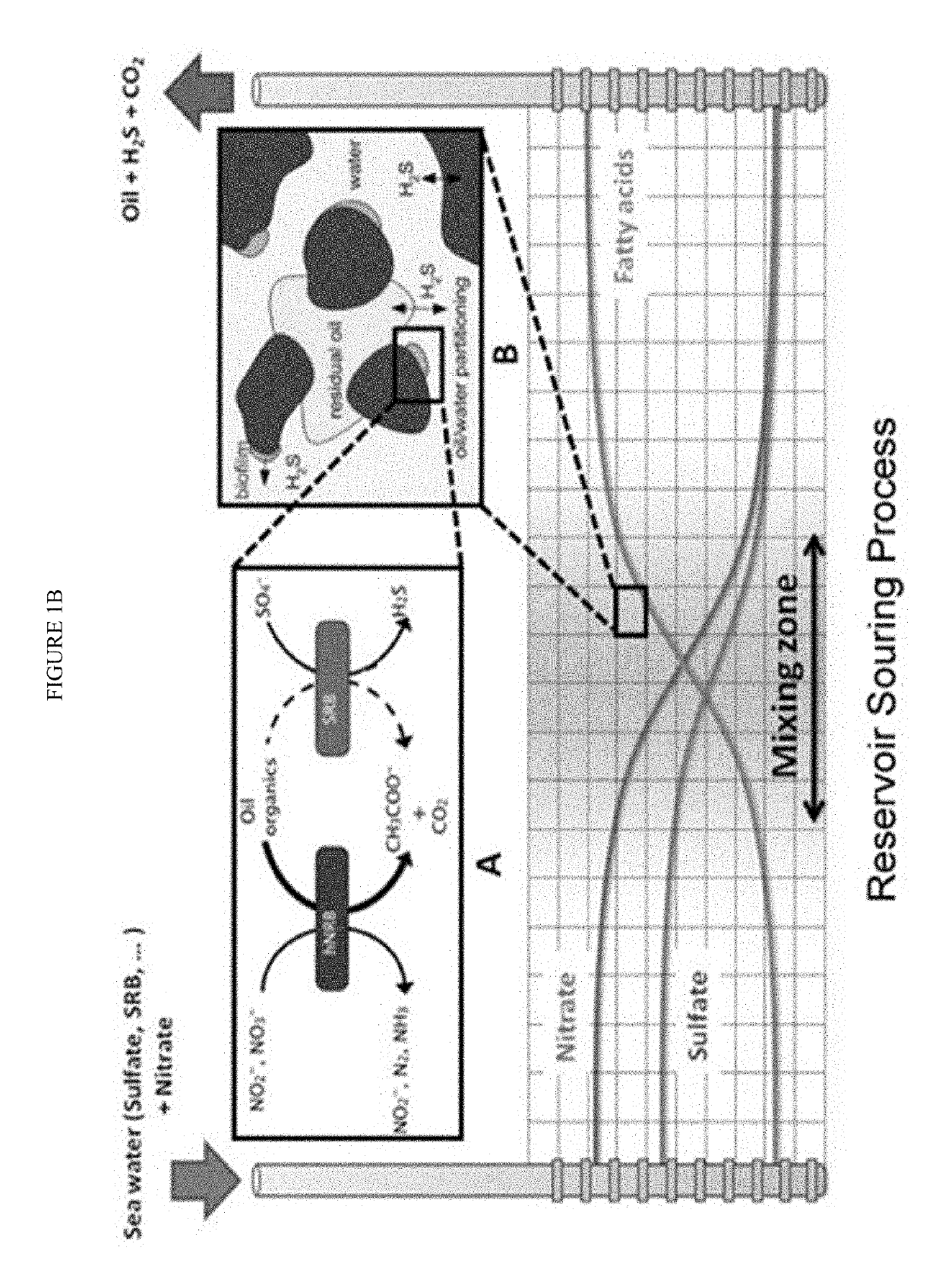

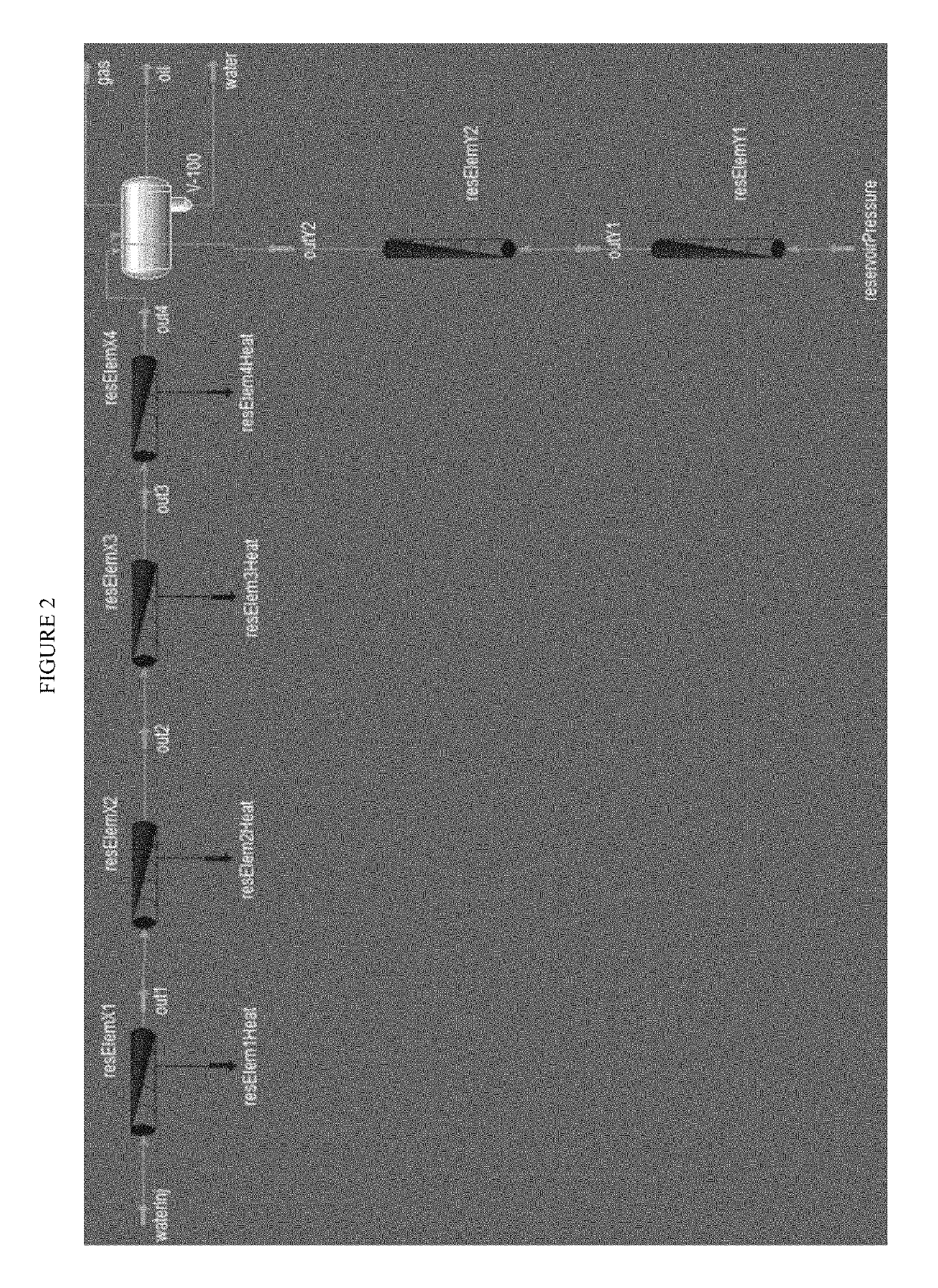

Reservoir souring forecasting

ActiveUS10635762B2Efficient solutionStep of become largeSurveyConstructionsGeophysicsObject-orientation

A method for modeling reservoir souring using object-oriented numerical solutions separate from reservoir topography is described. Specifically, flow physics are separated into one or more objects, along with one or more H2S generation mechanisms, for modeling on time and spatial scales separate from field scale modeling.

Owner:CONOCOPHILLIPS CO

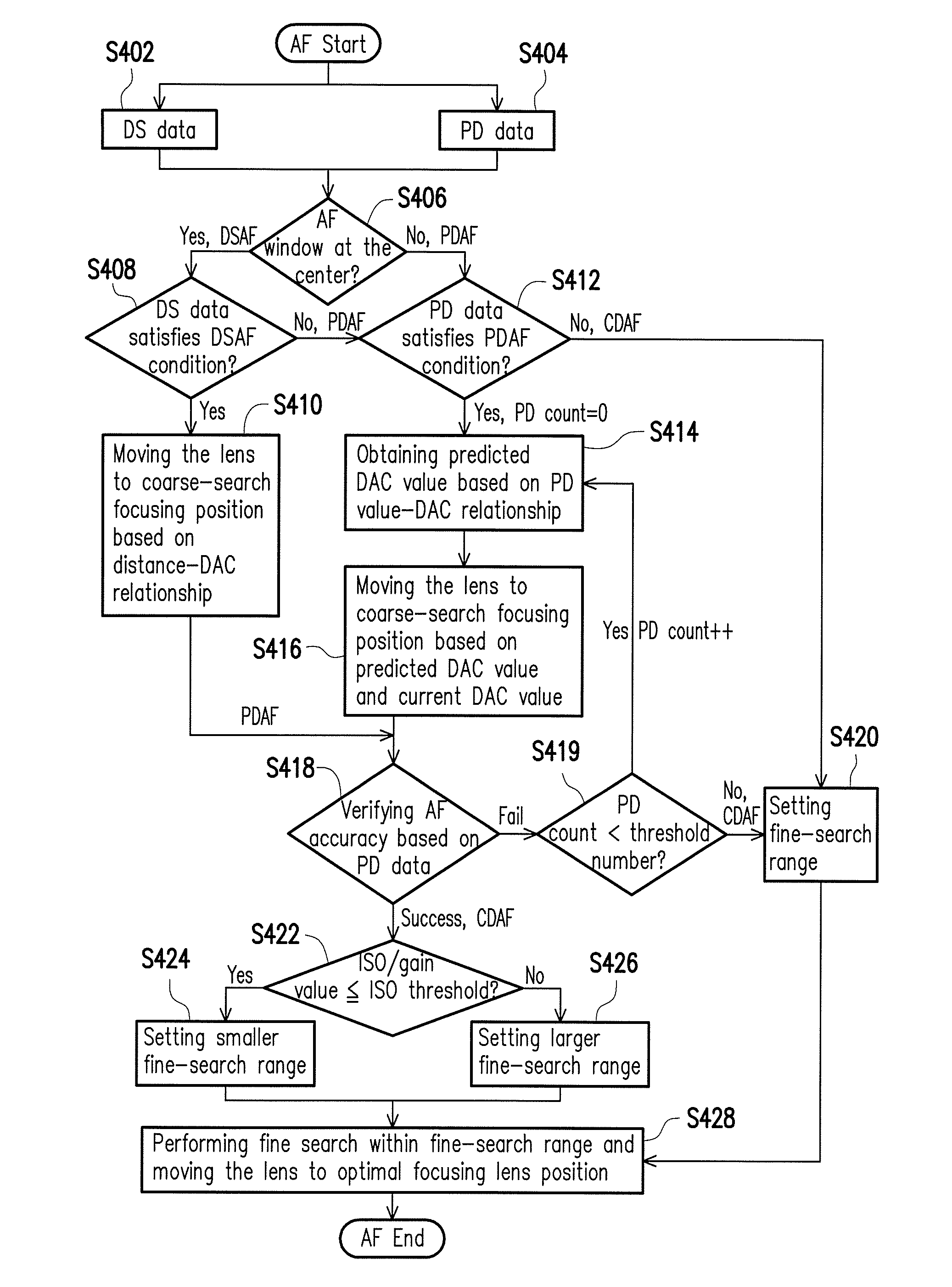

Image capturing device and hybrid auto-focus method thereof

ActiveUS9866745B2Efficient procedureImprove user experienceTelevision system detailsColor television detailsCamera lensAutofocus

The disclosure proposes an auto-focus method and an image capturing device including a distance sensor and an image sensor having a lens and a sensing array. The method includes the following steps. First, distance sensor data and phase detection data are respectively obtained from the distance sensor and the sensing array. The lens is controlled to perform a course search within a focusing range by switching between a distance sensor auto-focus mode and a phase detection auto-focus mode based on the distance sensor data and the phase detection data so as to determine a fine-search range. The lens is further controlled to perform a fine search within the fine-search range in a contrast detection auto-focus mode so as to determine an optimal focusing lens position. Next, the lens is controlled to move to the optimal focusing lens position.

Owner:HTC CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com