Patents

Literature

91results about How to "Further manufacturing cost" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Filtering face-piece respirator having parallel line weld pattern in mask body

ActiveUS20110094515A1Reduce usageDeformation MinimizationBreathing filtersBreathing masksRespiratorEngineering

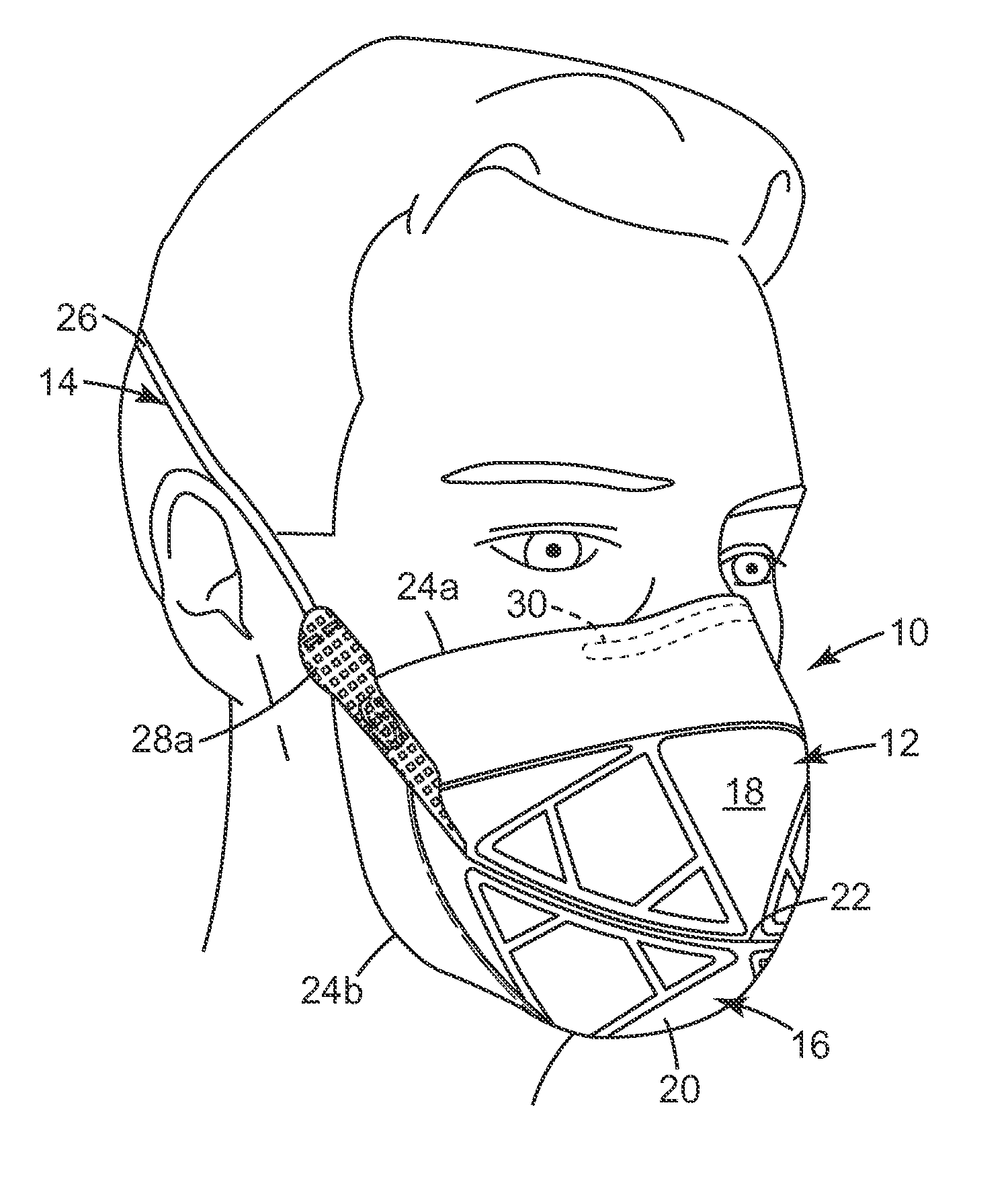

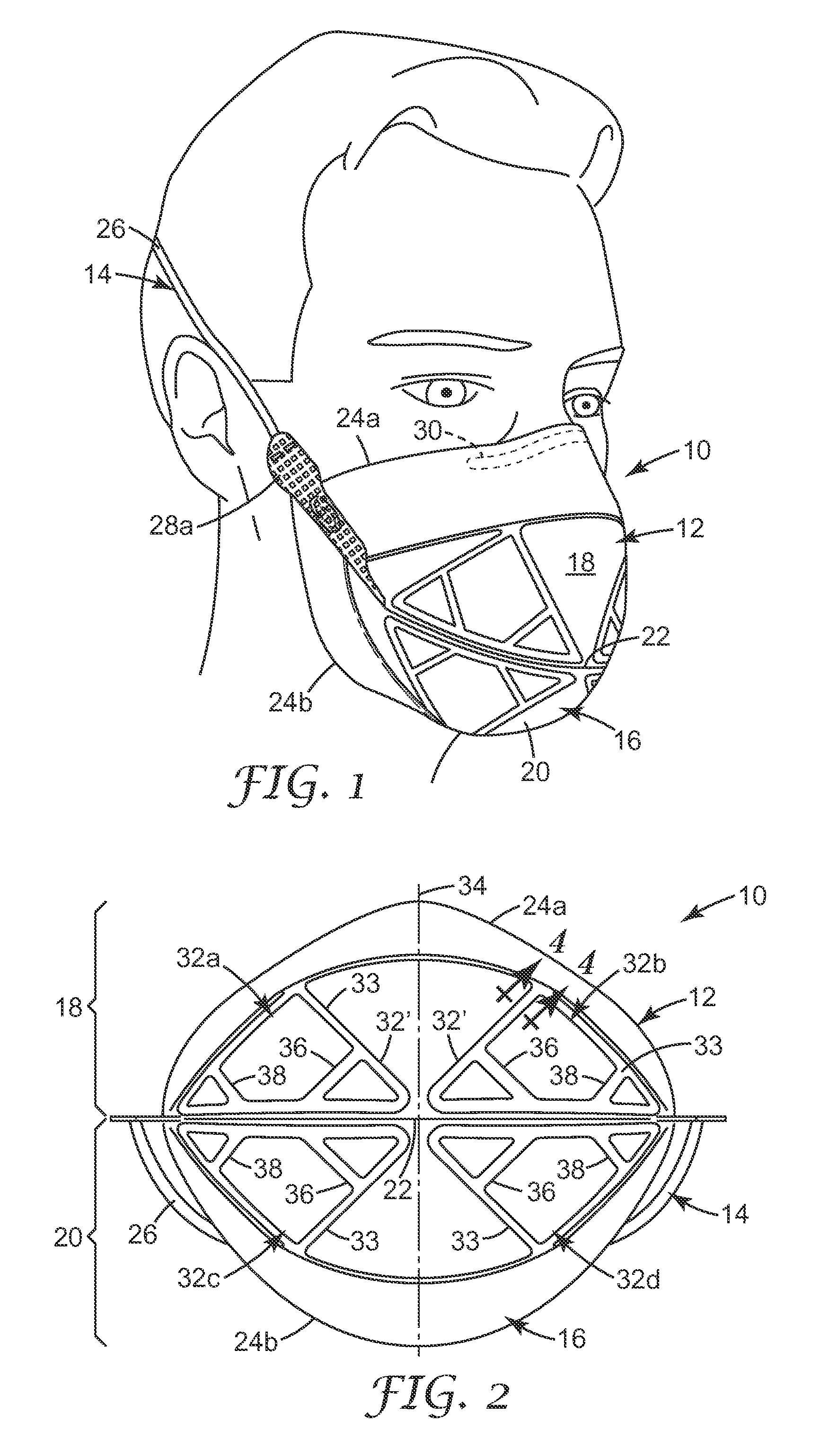

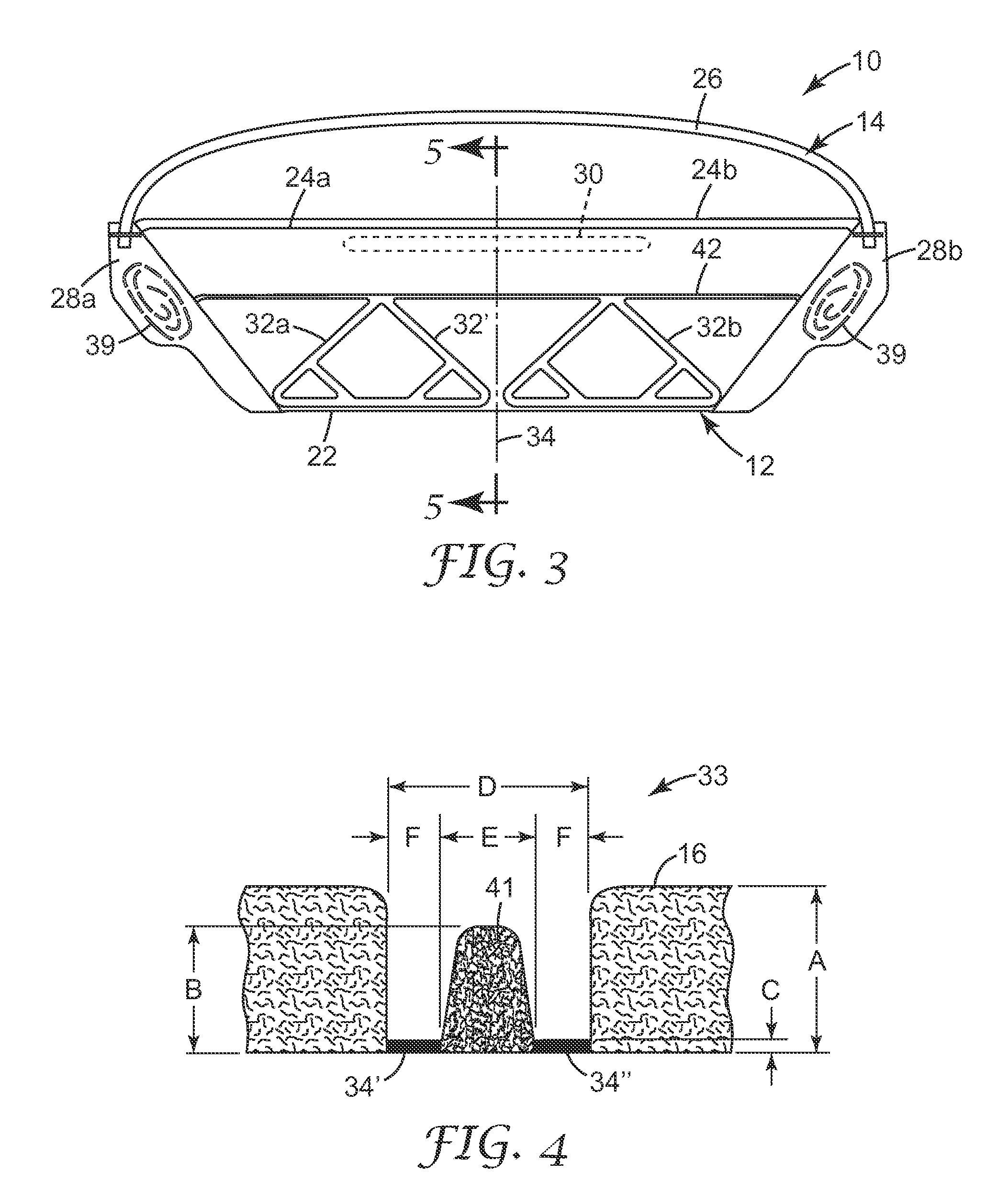

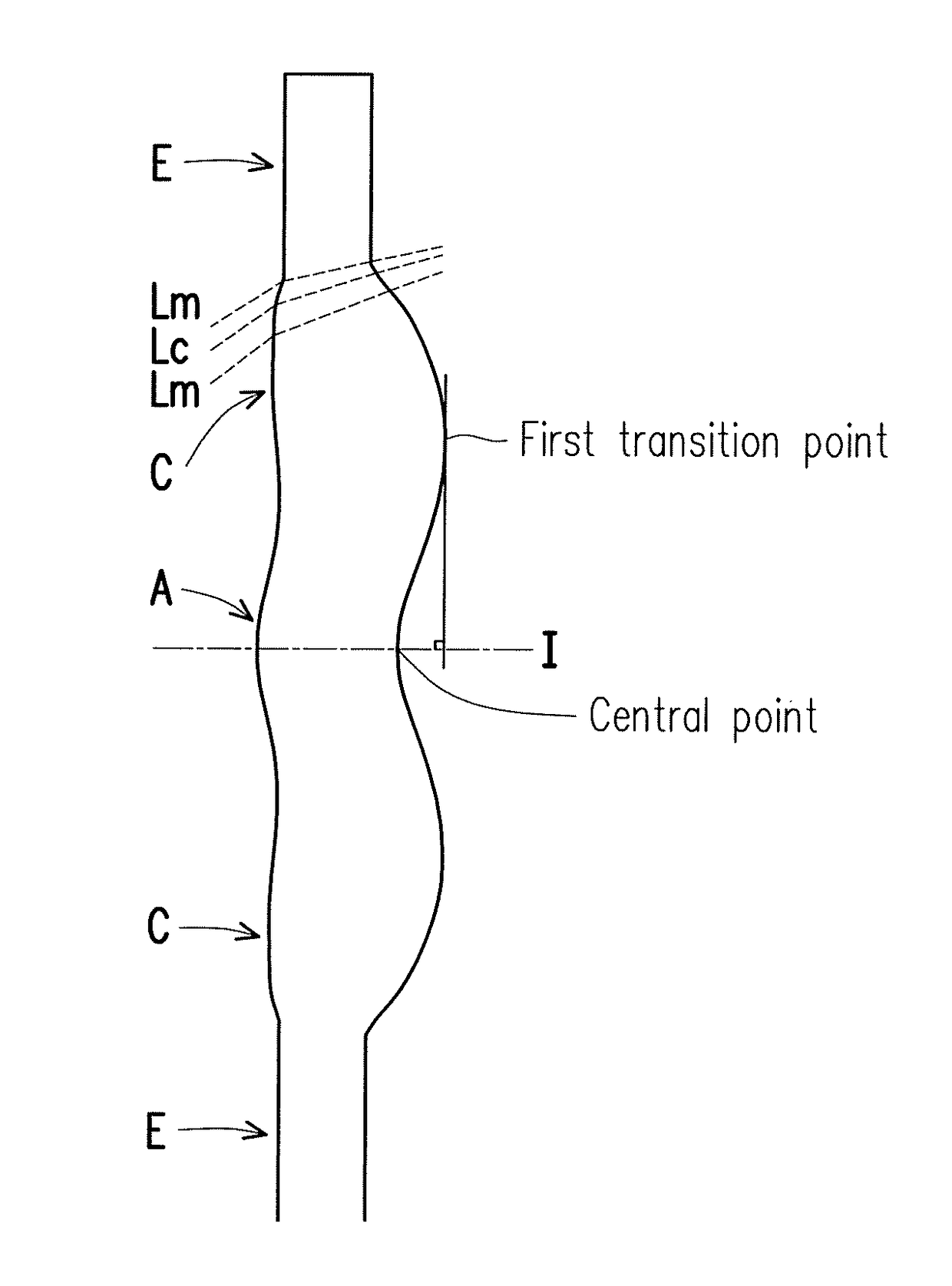

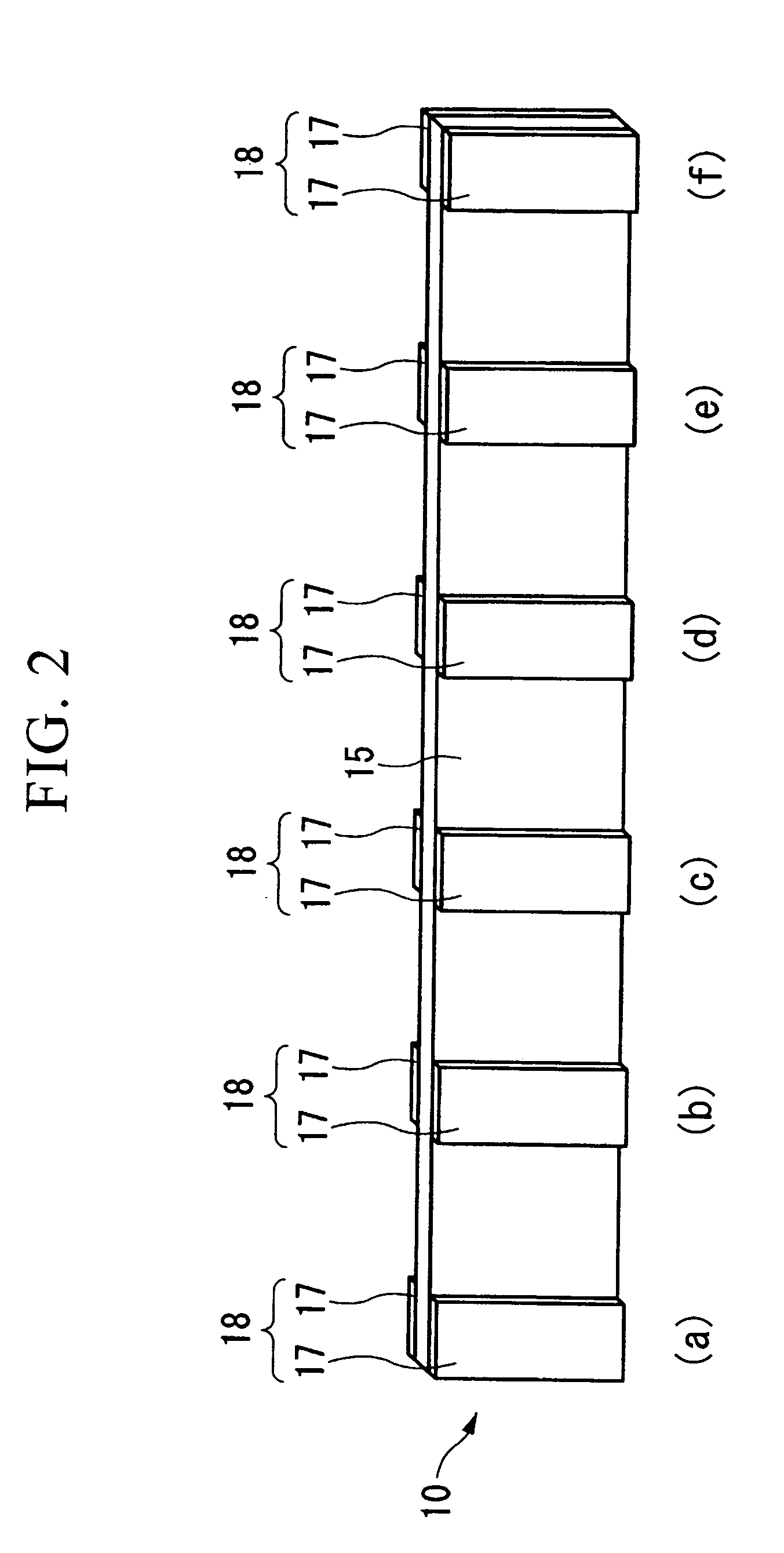

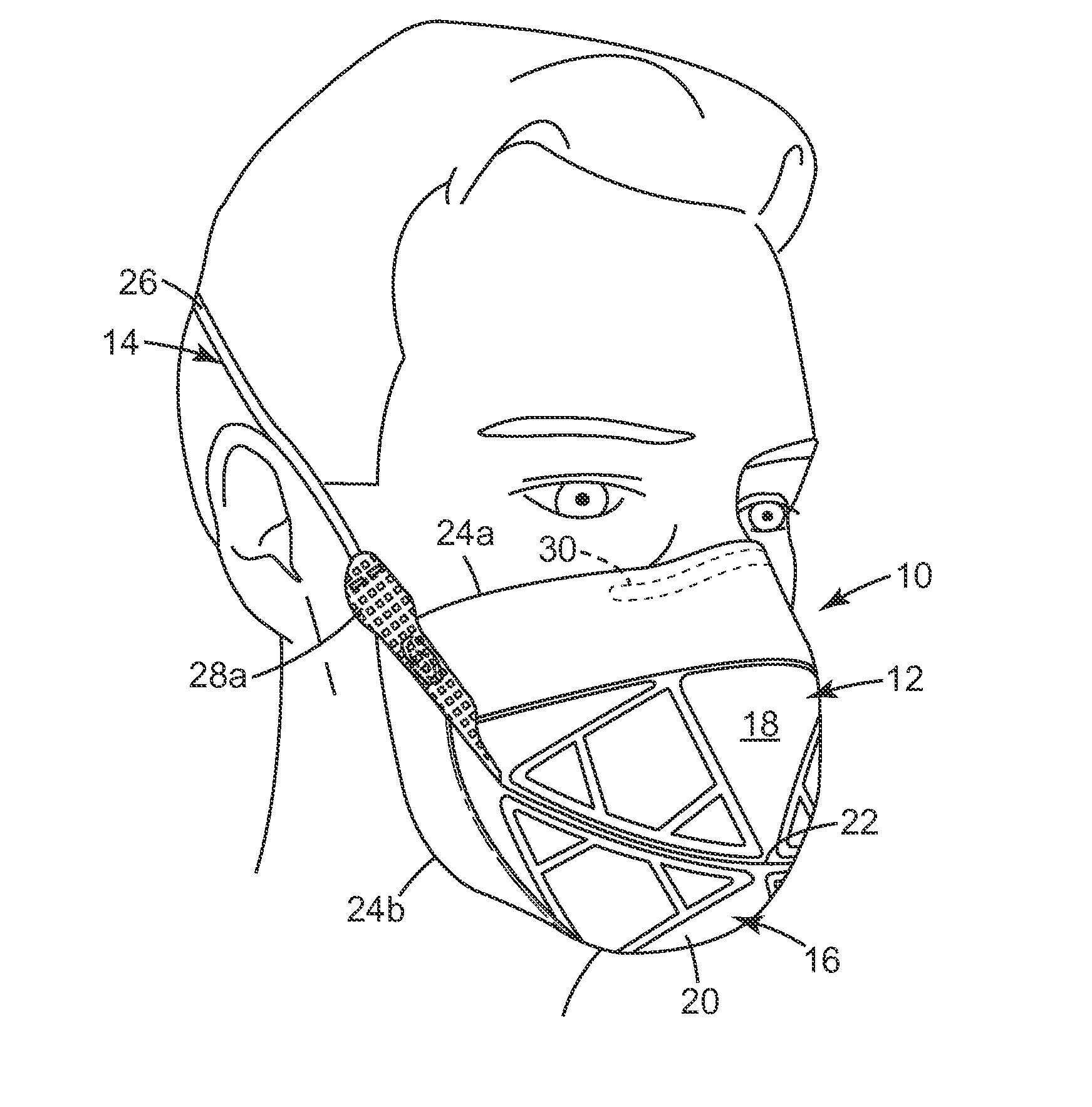

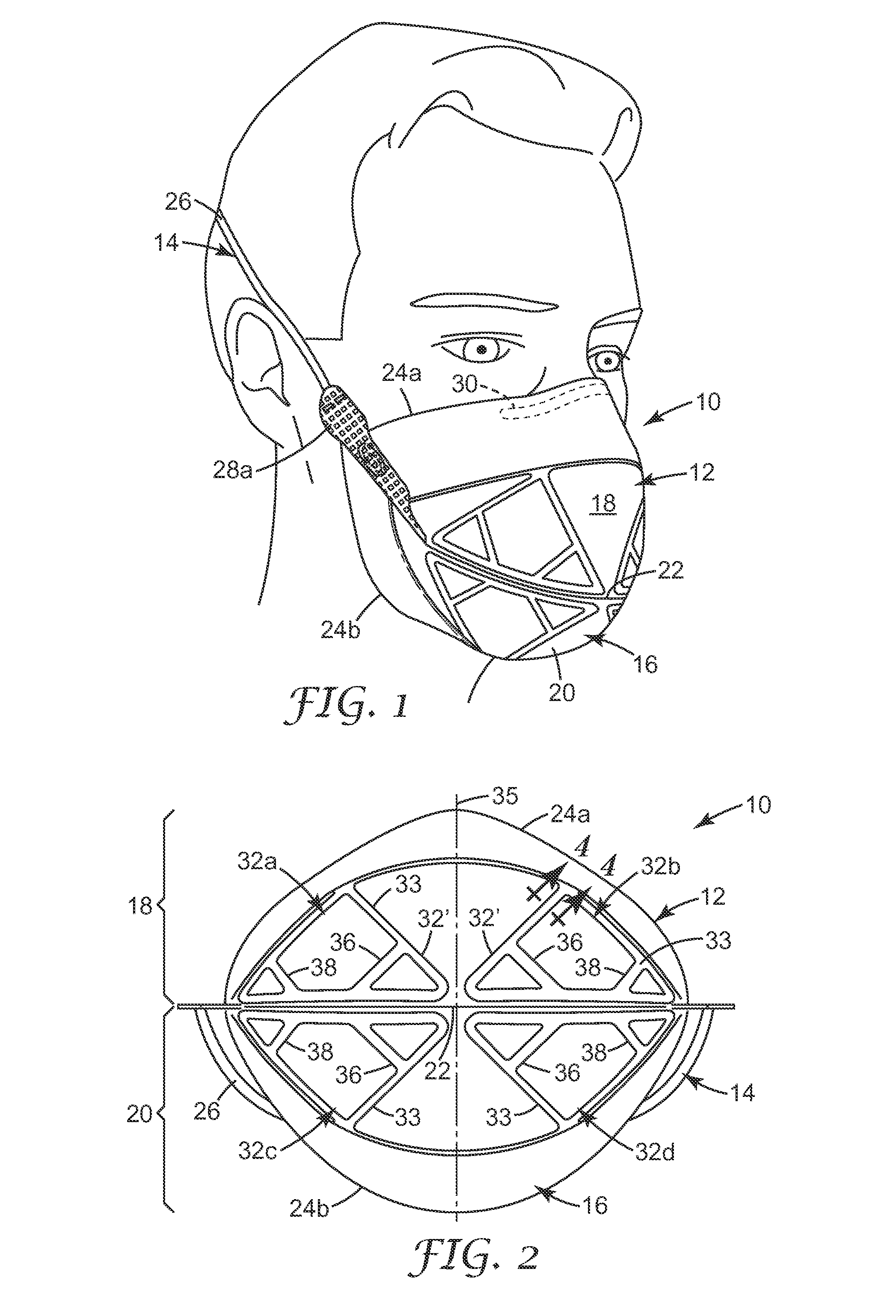

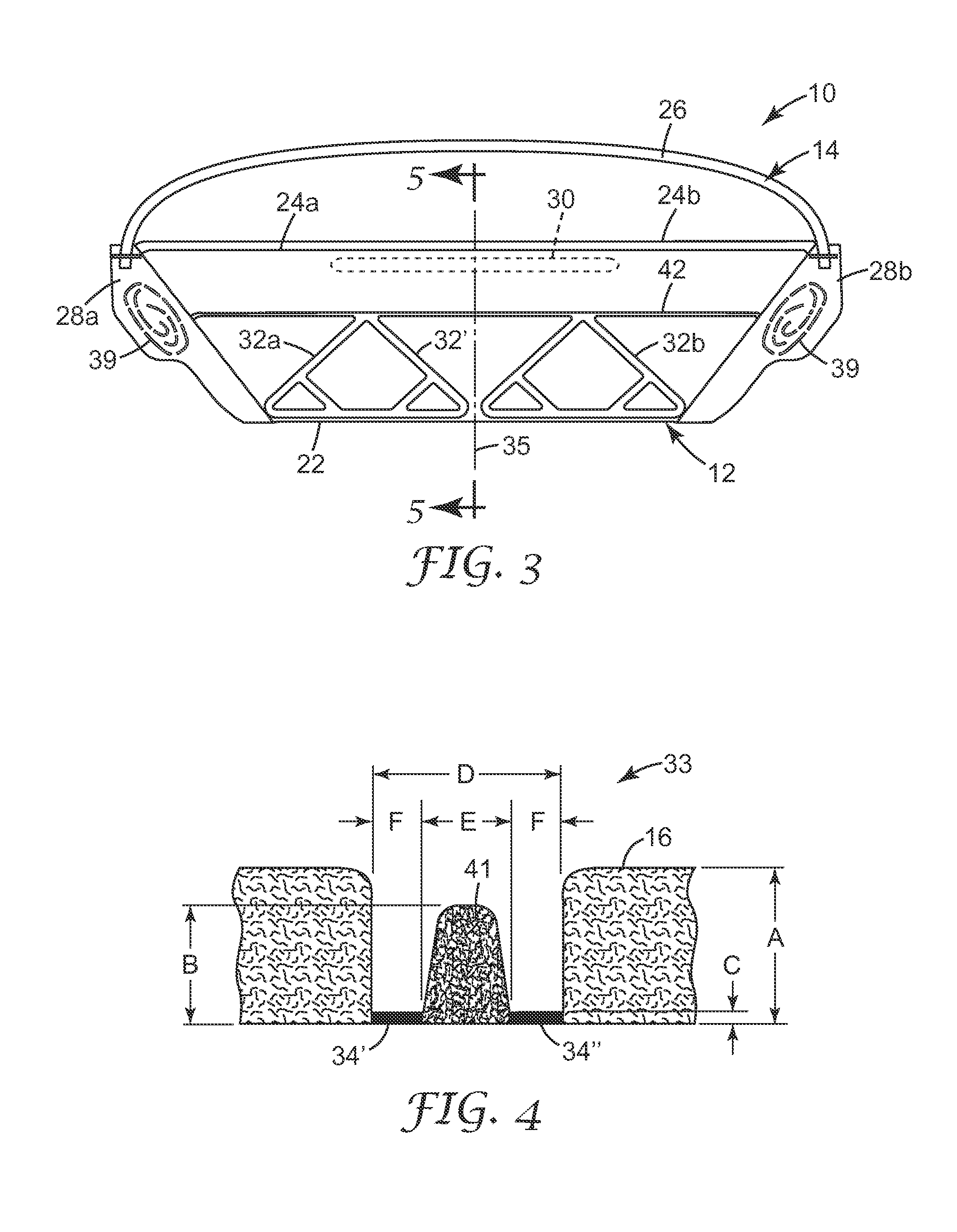

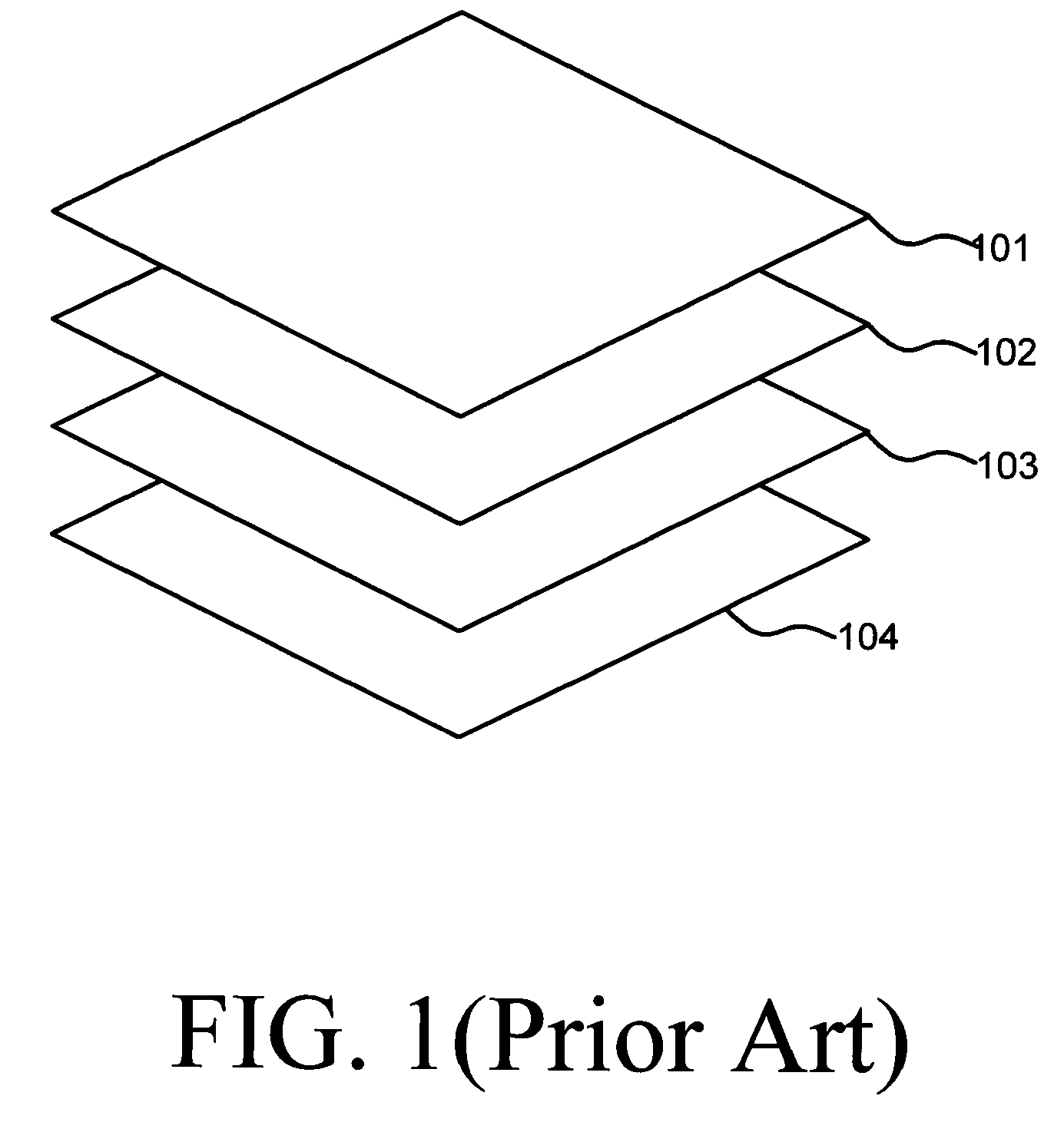

A respirator 10 that has a harness 14 and a mask body 12 that is joined to the harness 14. The mask body 12 includes a filtering structure 16 that may contain a plurality of layers of nonwoven fibrous material 58, 60, 62. The layers of nonwoven fibrous material 58, 60, 62 have a thickness A and are welded together by at least two parallel weld lines 34′, 34″ that are spaced at 0.5 to 6 times A. A mask body that uses parallel weld lines may exhibit better resistance to collapse and may be manufactured at faster speeds than similar structures which use single weld lines of comparable width.

Owner:3M INNOVATIVE PROPERTIES CO

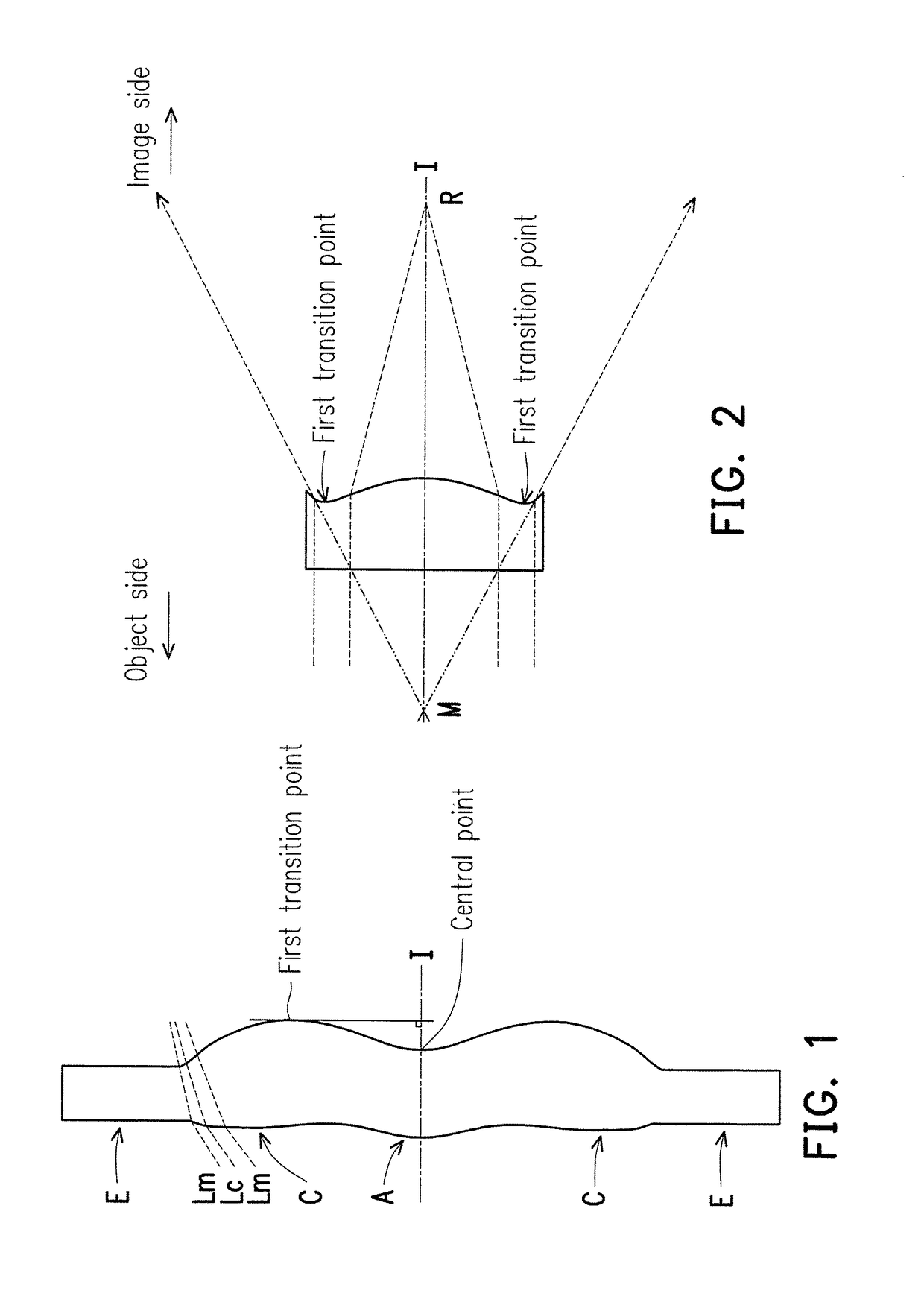

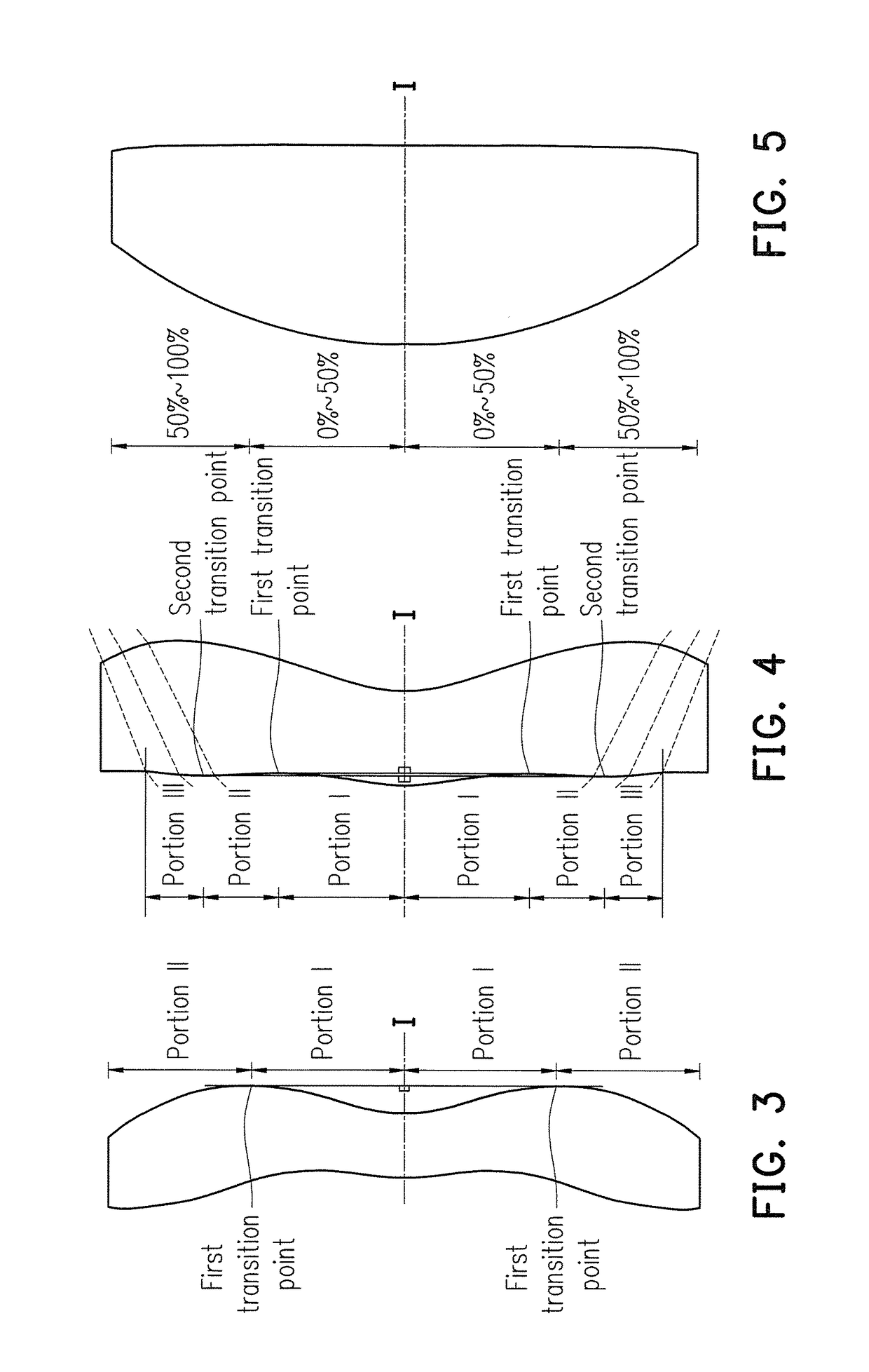

Optical imaging lens

InactiveUS20180067283A1Large field of viewPreferable and stable optical image qualityOptical filtersOphthalmologyOptical axis

An optical imaging lens including an aperture stop, a first lens element, a second lens element, a third lens element, a fourth lens element, a fifth lens element and a sixth lens element arranged in sequence from an object side to an image side along an optical axis is provided. Each lens element includes an object-side surface and an image-side surface. The material of the first lens element is plastic. The object-side surface of the second lens element has a concave portion in a vicinity of the optical axis. The image-side surface of the second lens element has a concave portion in a vicinity of a periphery of the second lens element. The object-side surface of the third lens element has a concave portion in a vicinity of a periphery of the third lens element. The image-side surface of the third lens element has a concave portion in a vicinity of the optical axis. The fourth lens element has positive refractive power. The image-side surface of the fifth lens element has a convex portion in a vicinity of the optical axis. The material of the sixth lens element is plastic.

Owner:GENIUS ELECTRONICS OPTICAL XIAMEN

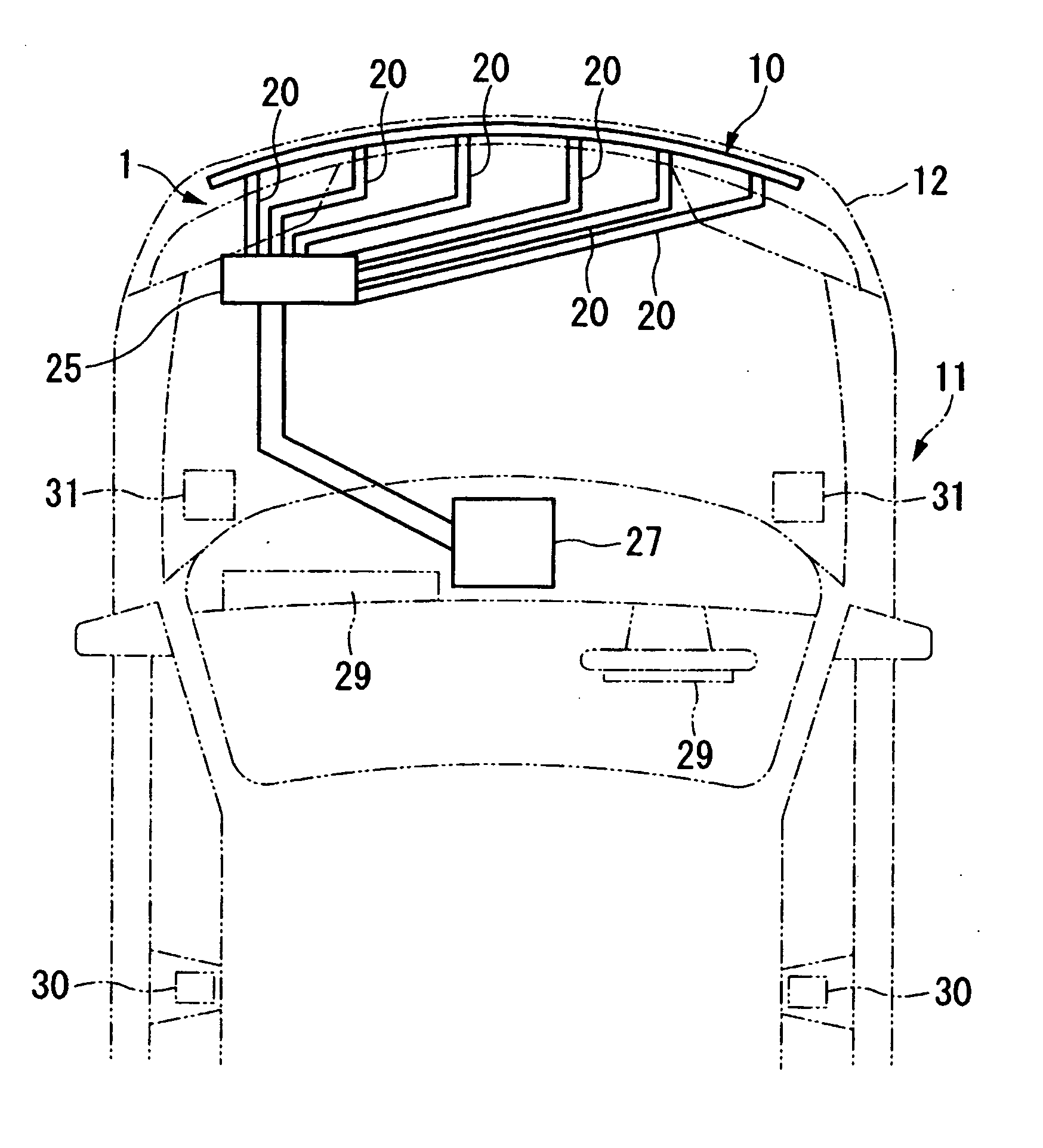

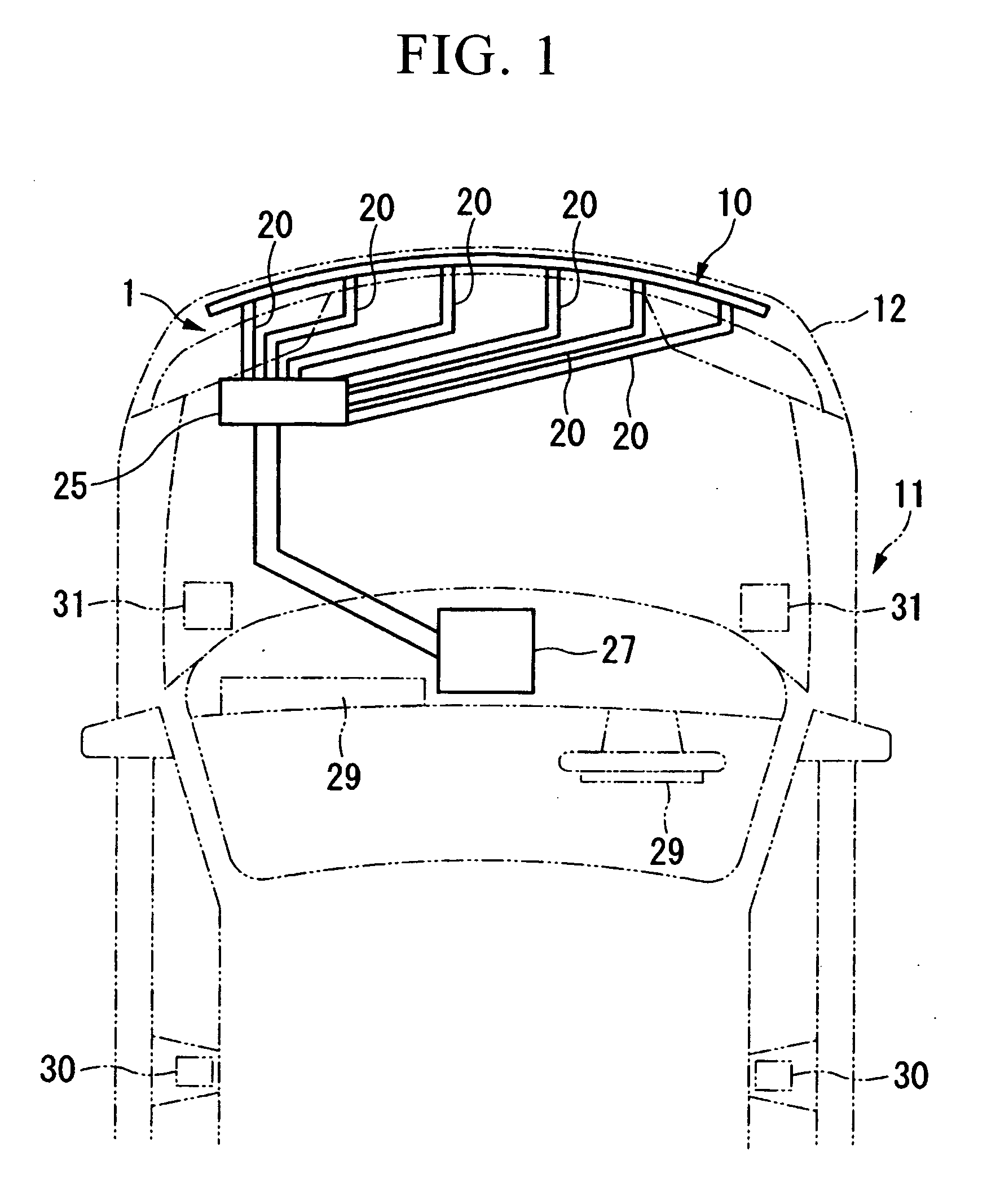

Collision detection sensor for vehicle and collision detection device for vehicle

InactiveUS20050104721A1Reduce numberReduce manufacturing costAcceleration measurement using interia forcesPedestrian/occupant safety arrangementVoltageEngineering

A collision detection sensor for a vehicle of the present invention includes a single piezoelectric film which is flat, plural pairs of electrodes which sandwich the piezoelectric film and measure voltages between the electrodes, and spaces provided between the plural pairs of electrodes.

Owner:HONDA MOTOR CO LTD

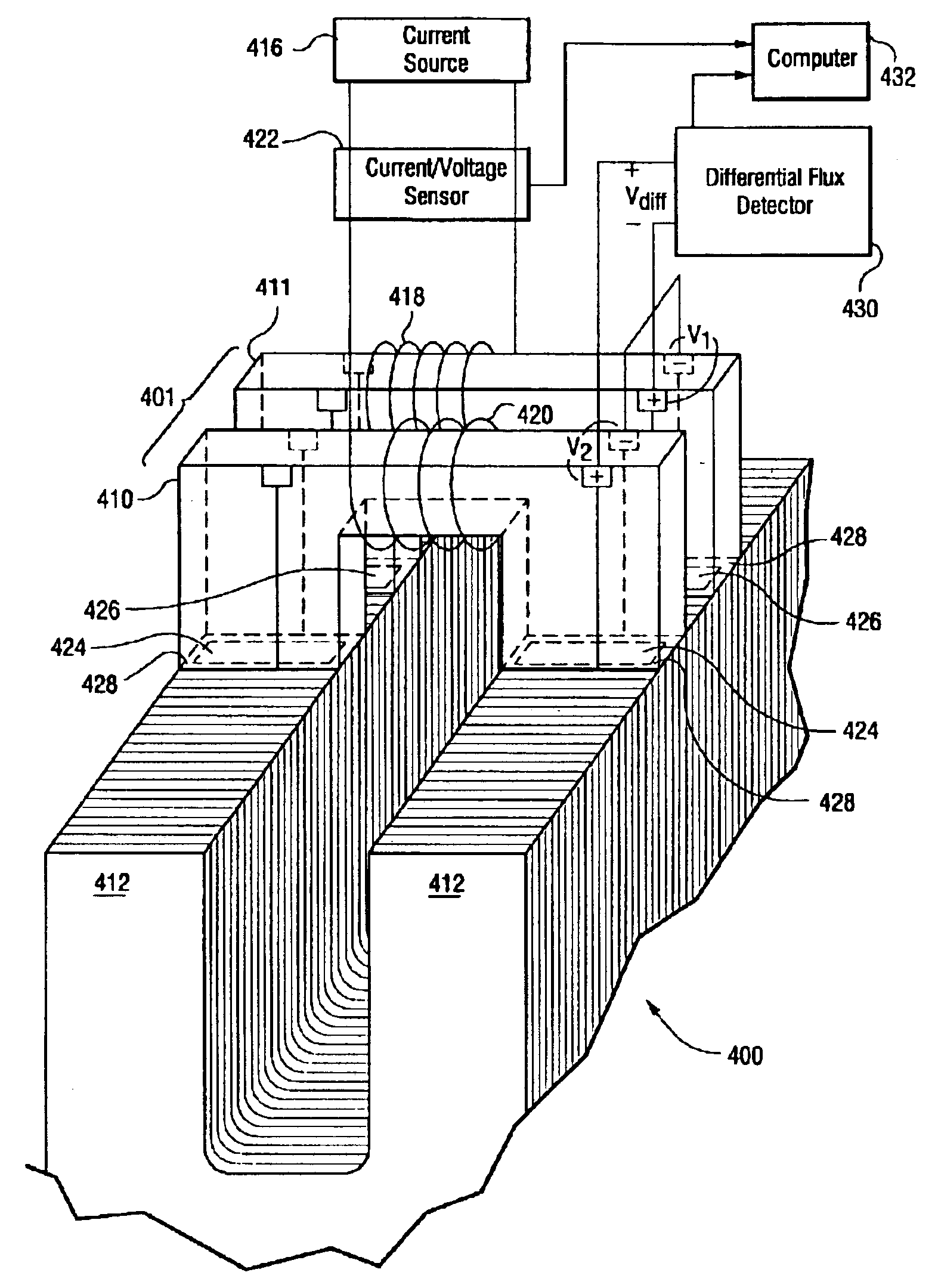

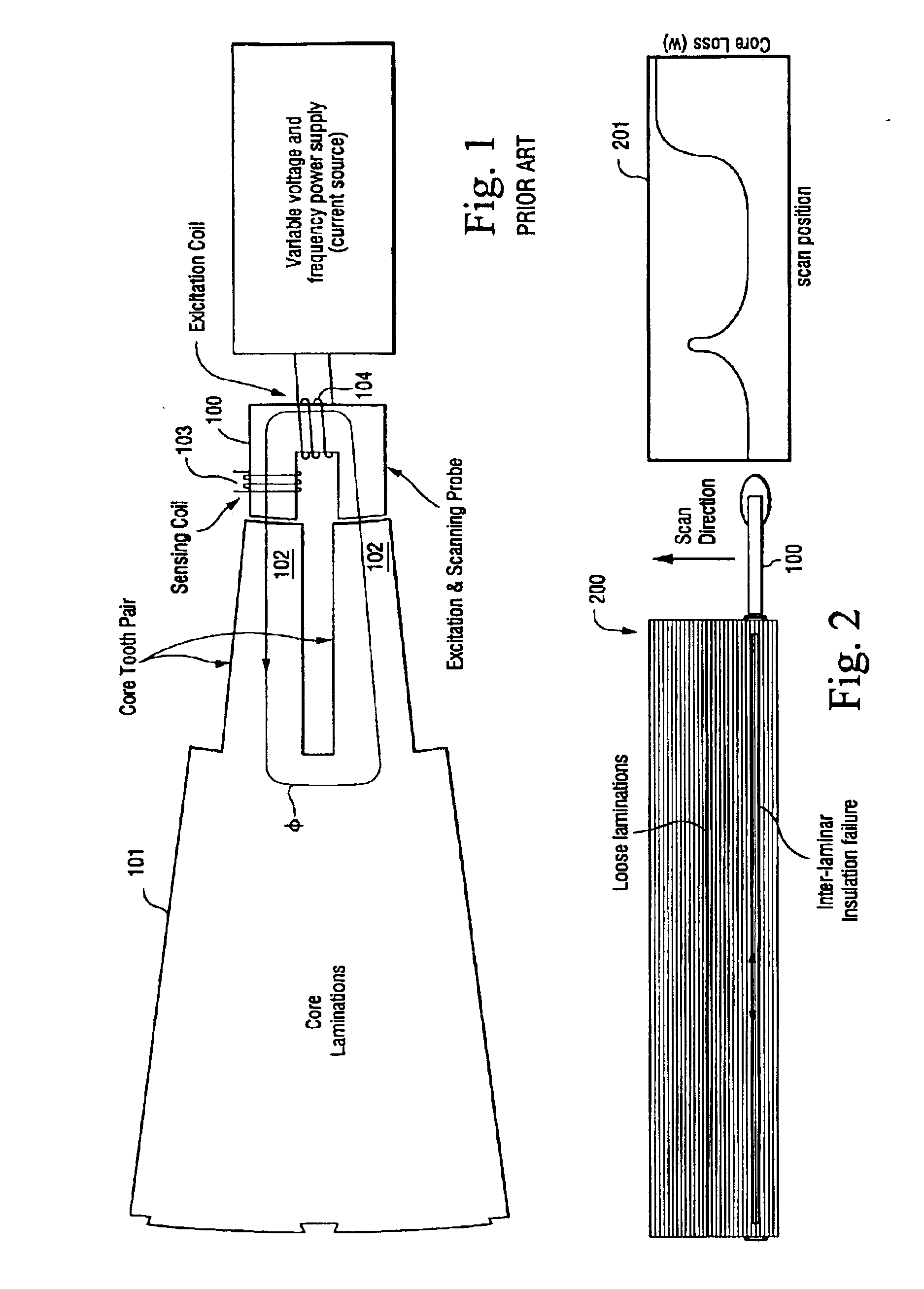

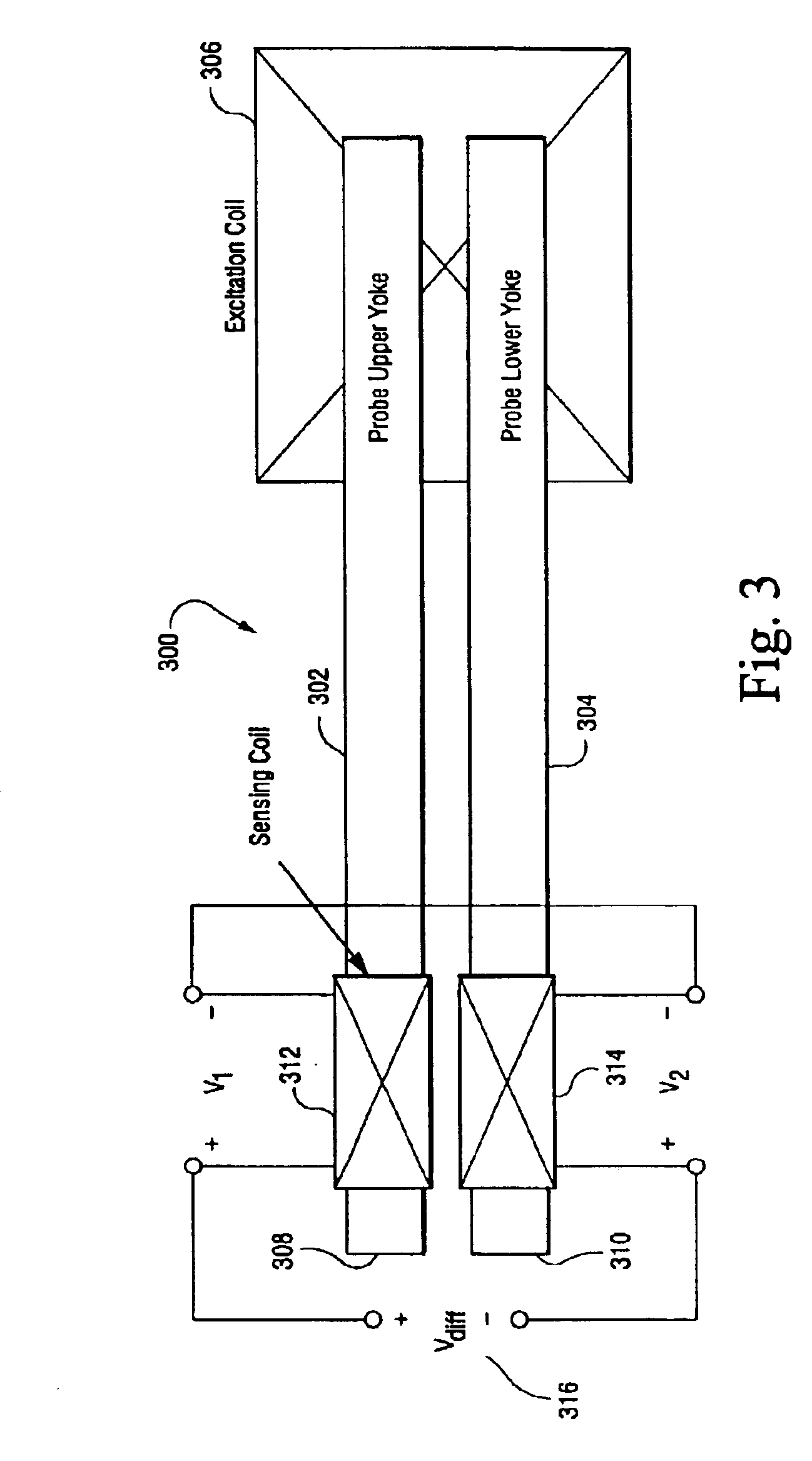

Differential sensor apparatus and method for laminated core fault detection

InactiveUS6873152B2Reduce manufacturing costHigh precisionMagnetic field measurement using flux-gate principleMagnetic property measurementsConductor CoilMagnetic flux

A differential probe is scanned along a stator core tooth portion to detect lamination faults. The probe utilizes two magnetic flux injection yokes arranged side-by-side in relatively close proximity, each yoke having two arm portions and two core-tooth flux-injection surfaces, each yoke being wound with an excitation coil winding and at least one yoke-arm of each yoke having a magnetic flux sensor. Current is supplied to the excitation coil windings on each yoke to inject magnetic flux into the stator core laminations while the probe is moved in a scanning process along the core teeth across the laminations. The magnetic flux differential detected at adjacent regions in the core by flux sensors on each of the two yokes is used to incrementally evaluate the core for laminations faults. The output produced by the differential probe may be converted to a digital signal and provided to a computer system for storage and future analysis.

Owner:GENERAL ELECTRIC CO

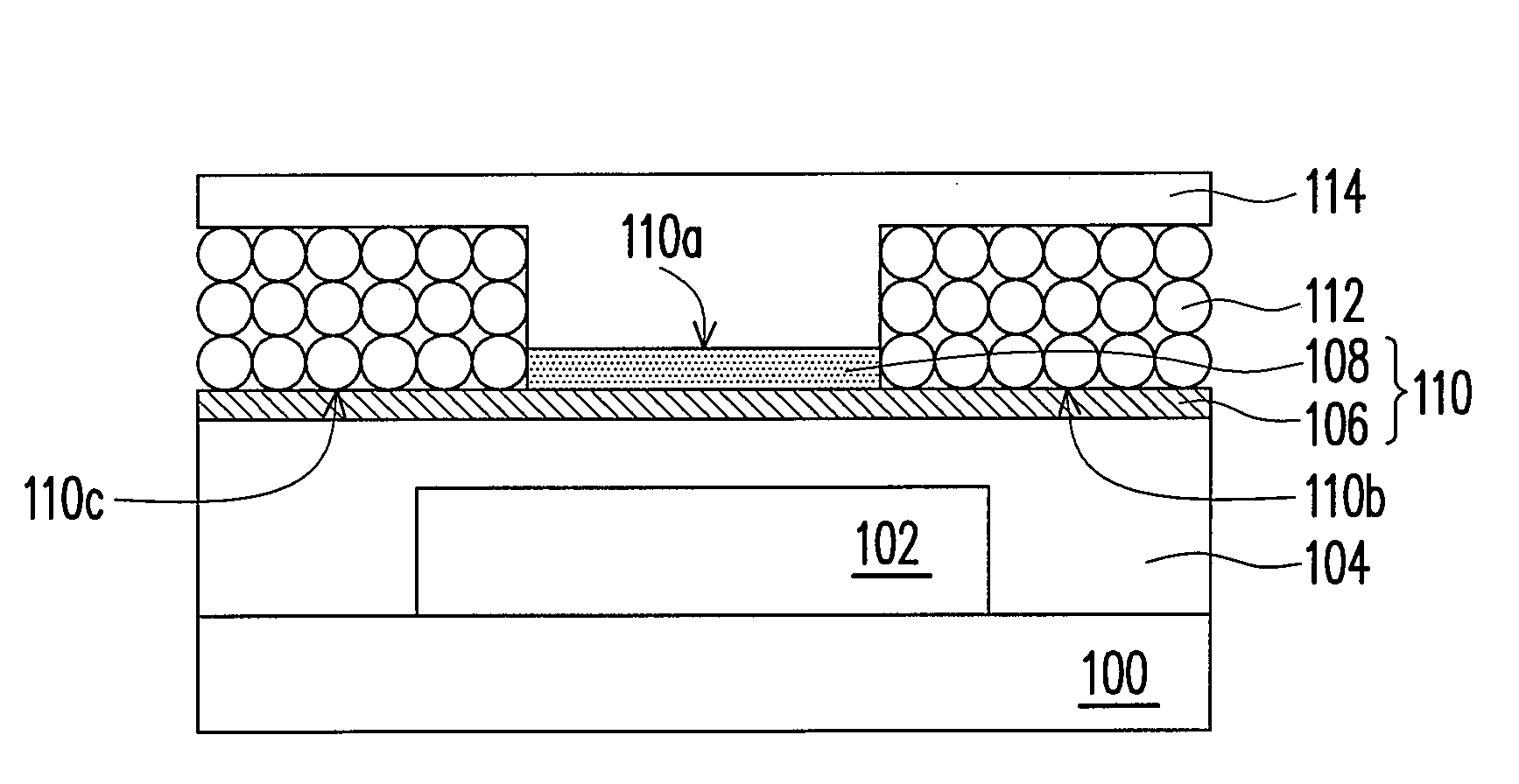

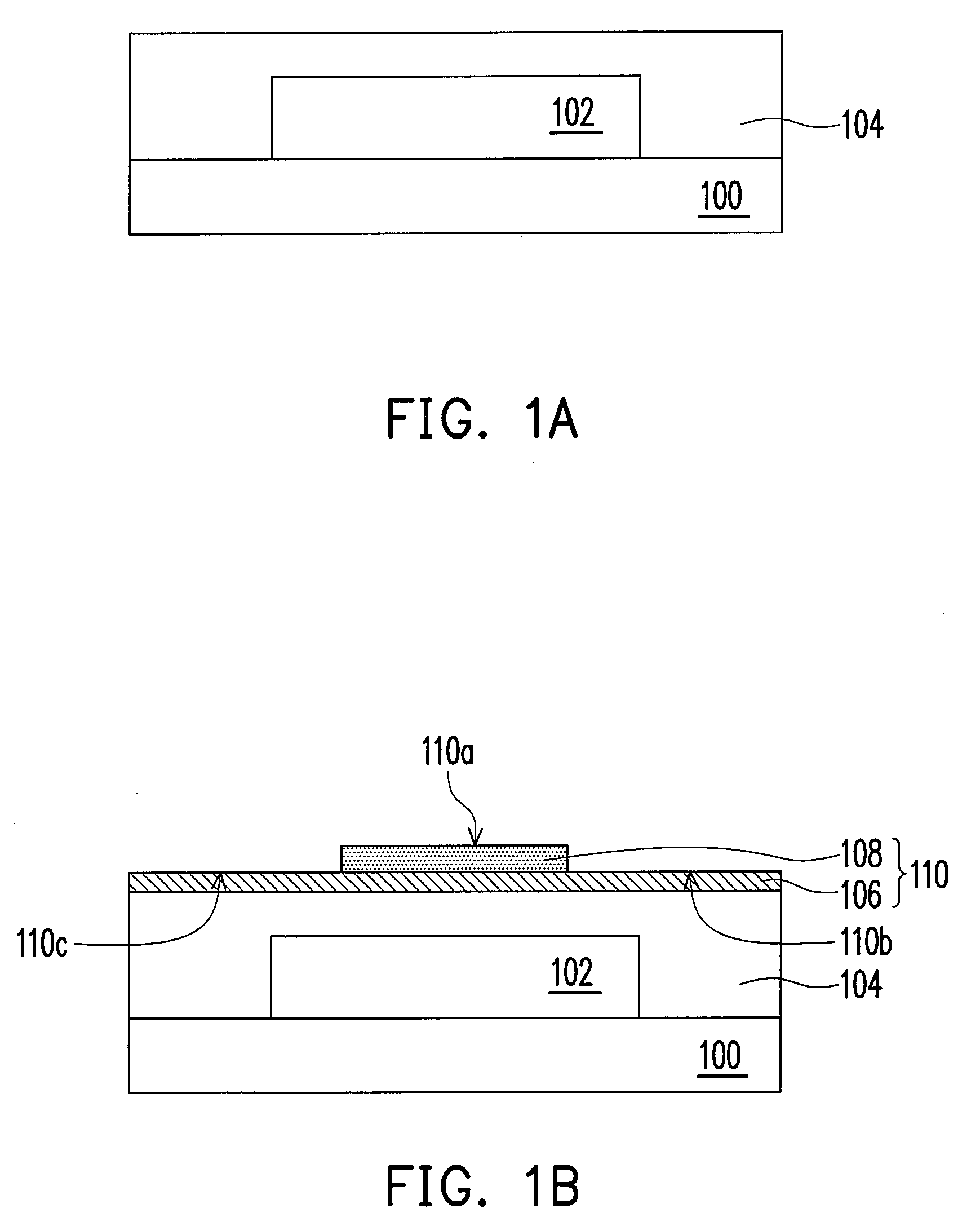

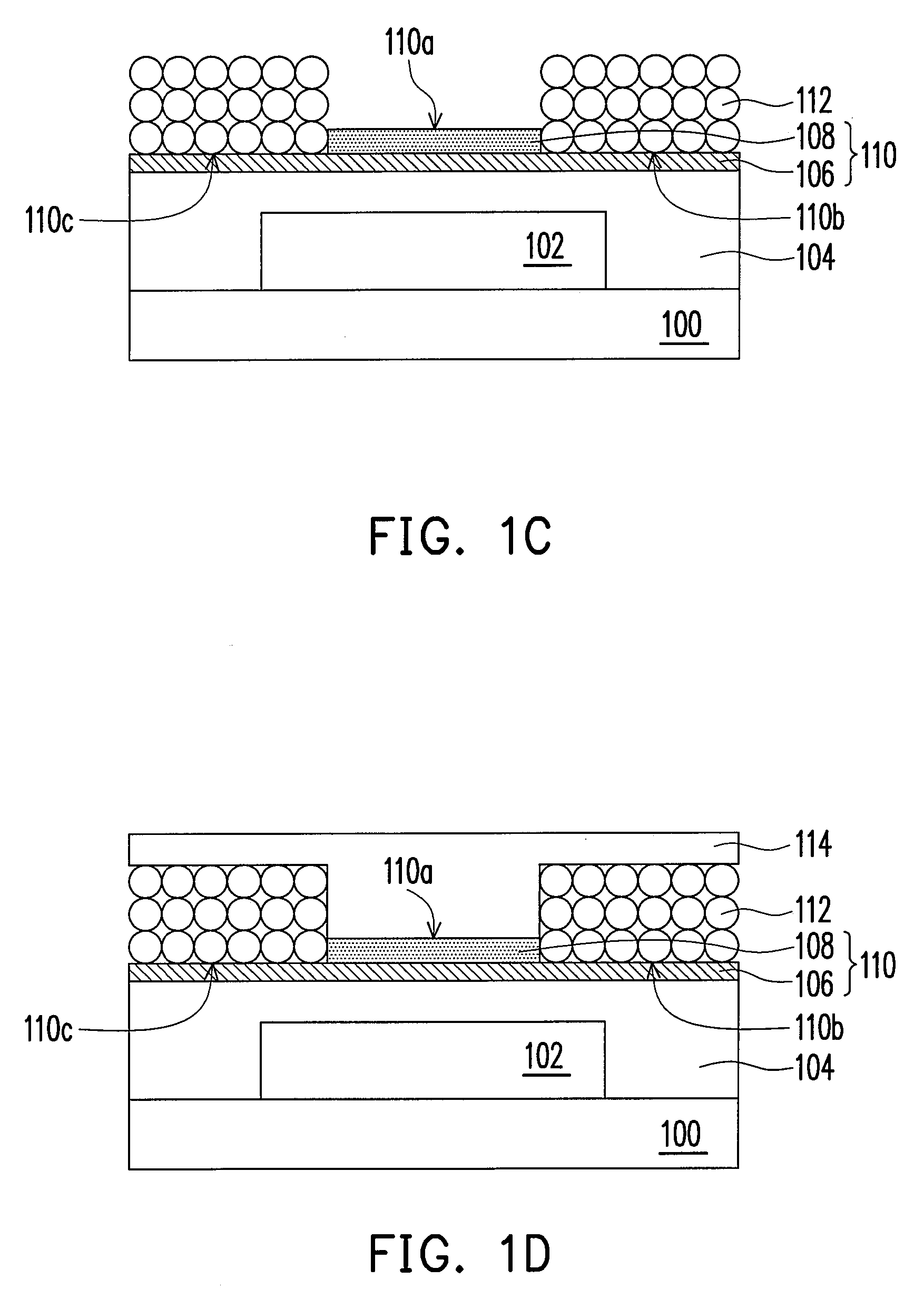

Organic thin film transistor and method for manufacturing the same

ActiveUS20080157064A1Improve adhesionImprove device performanceSolid-state devicesSemiconductor/solid-state device manufacturingOrganic filmGate insulator

An organic thin film transistor including a substrate, a gate, a gate insulator, an adhesive layer, a metal nano-particle layer and an organic semiconductor layer is provided. The gate is disposed on the substrate. The gate insulator is disposed on the gate and the substrate. The adhesive layer is disposed on the gate insulator. Besides, the adhesive layer has a hydrophobic surface above the gate and a first hydrophilic surface and a second hydrophilic surface on two sides of the hydrophobic surface. A surface of the metal nano-particle layer is modified by a hydrophilic group, and the metal nano-particle layer is disposed on the first and the second hydrophilic surfaces of the adhesive layer as a source and a drain, respectively. The organic semiconductor layer is disposed on the hydrophobic surface of the adhesive layer and on the metal nano-particle layer.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

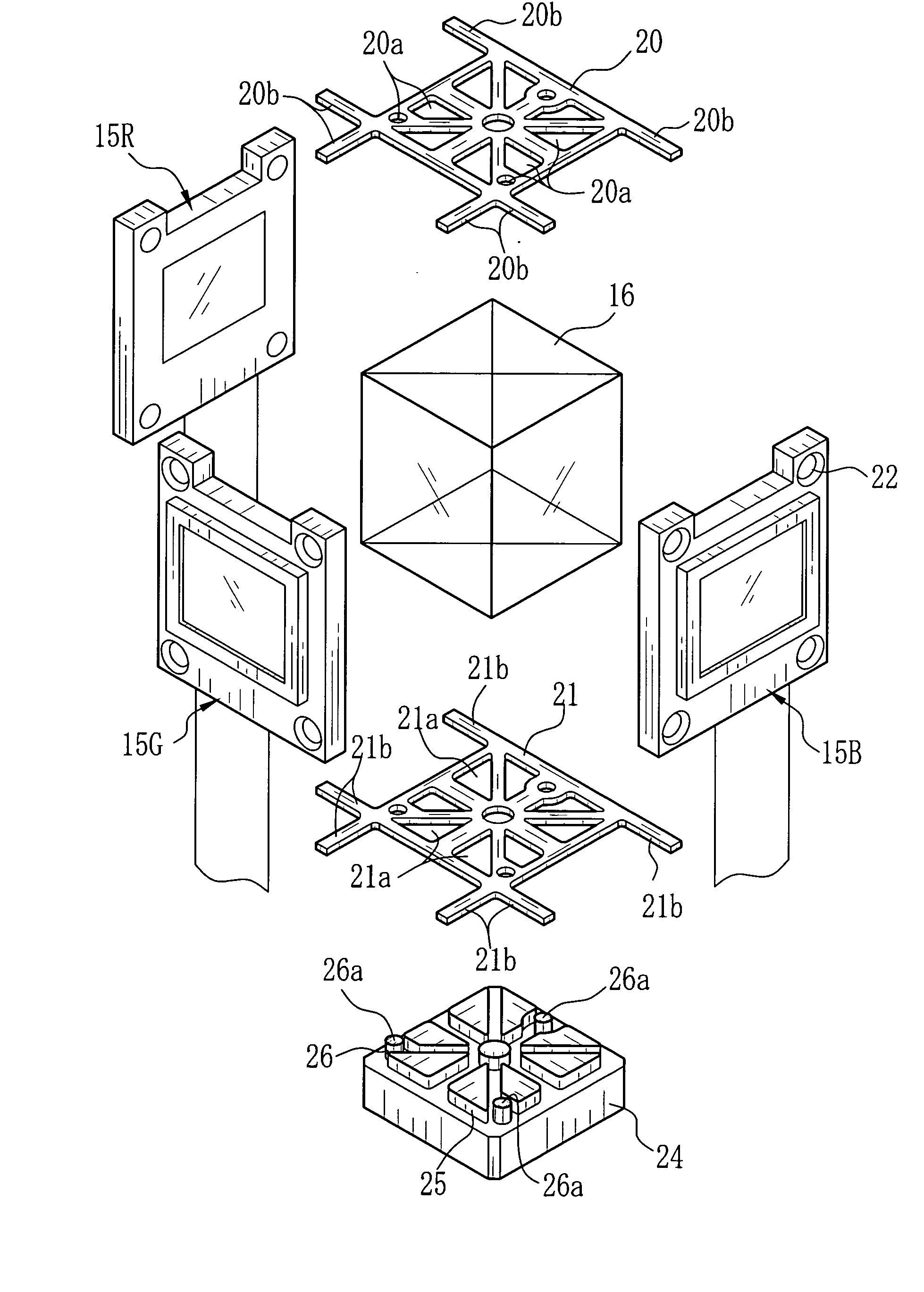

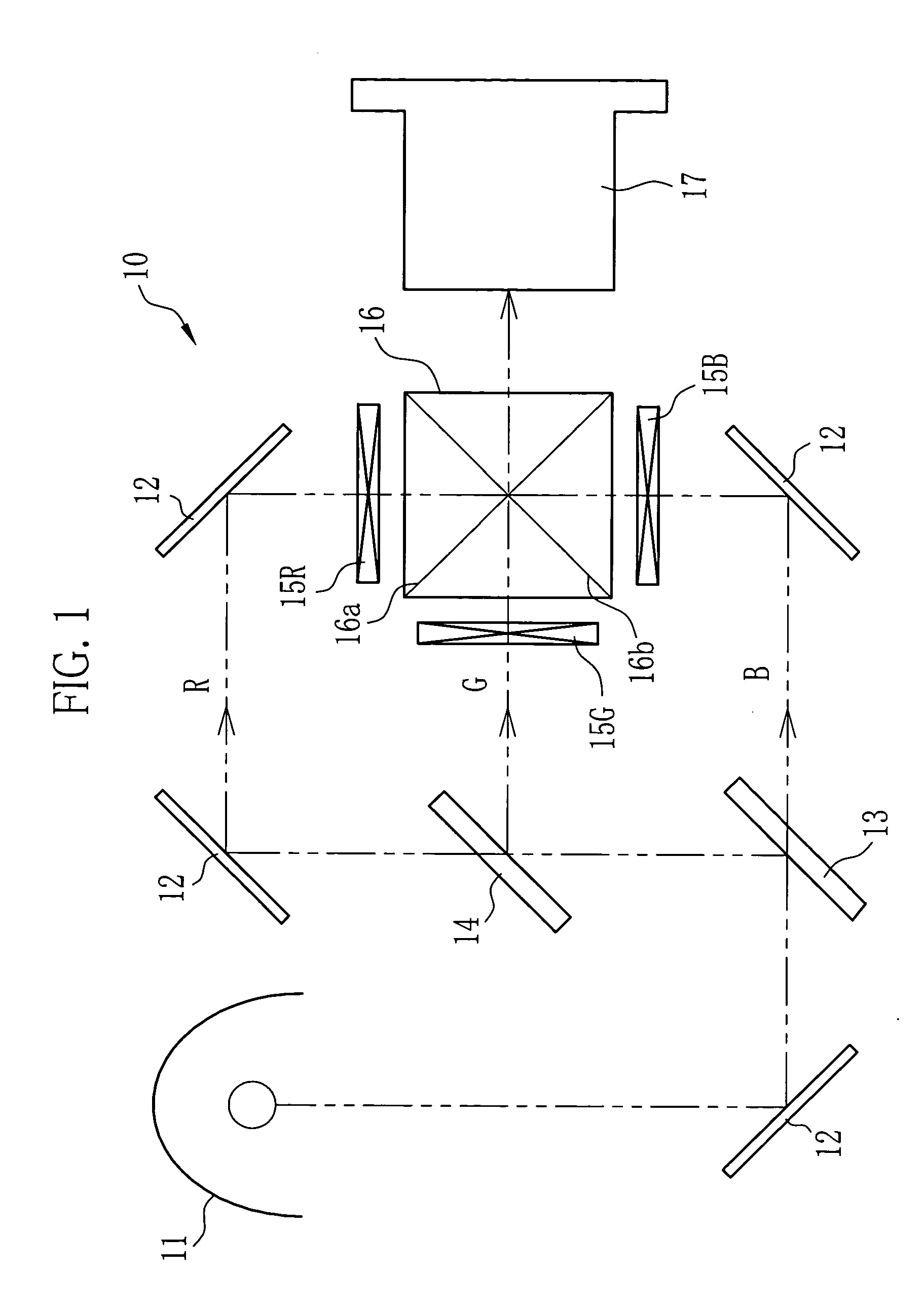

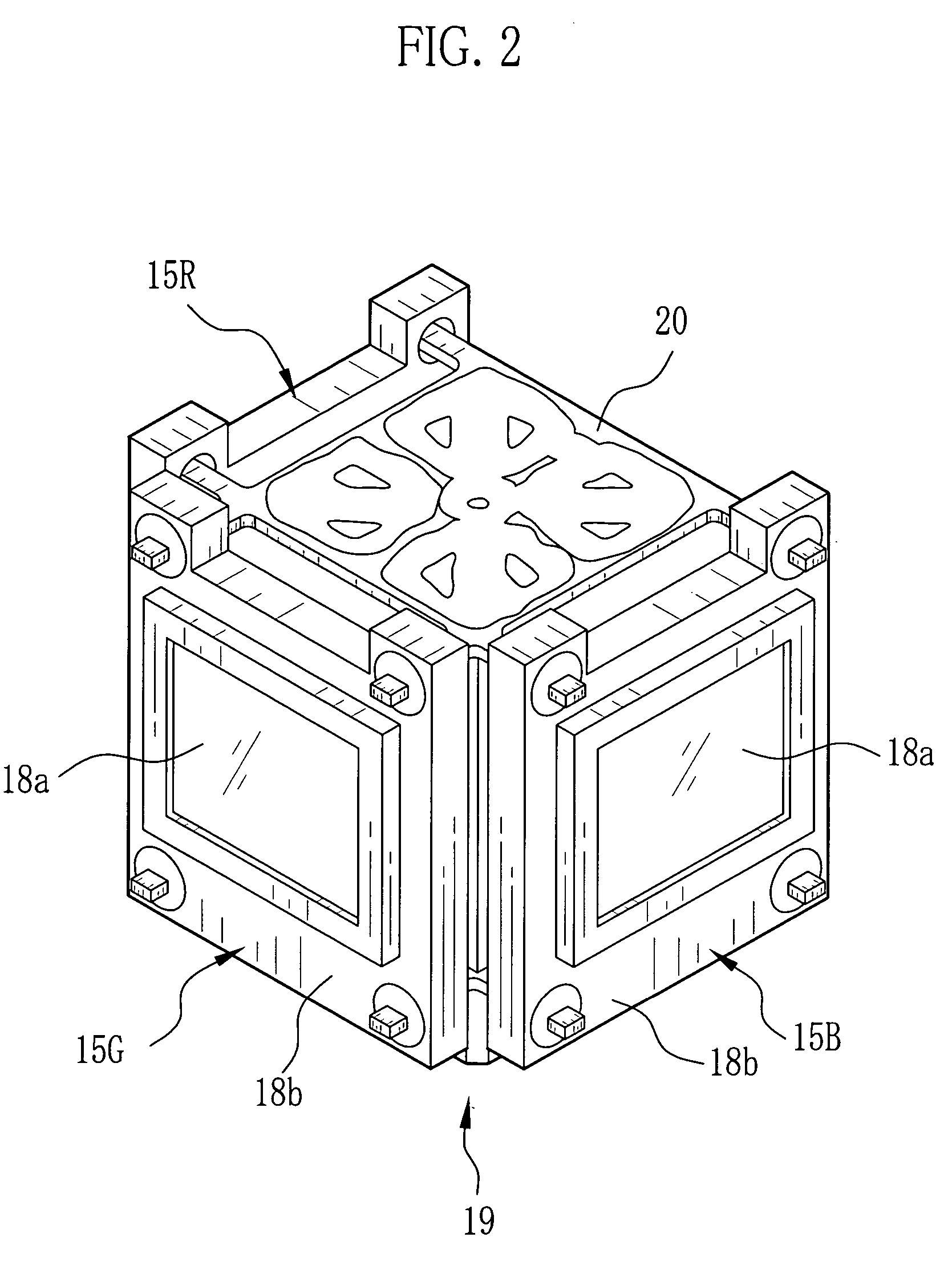

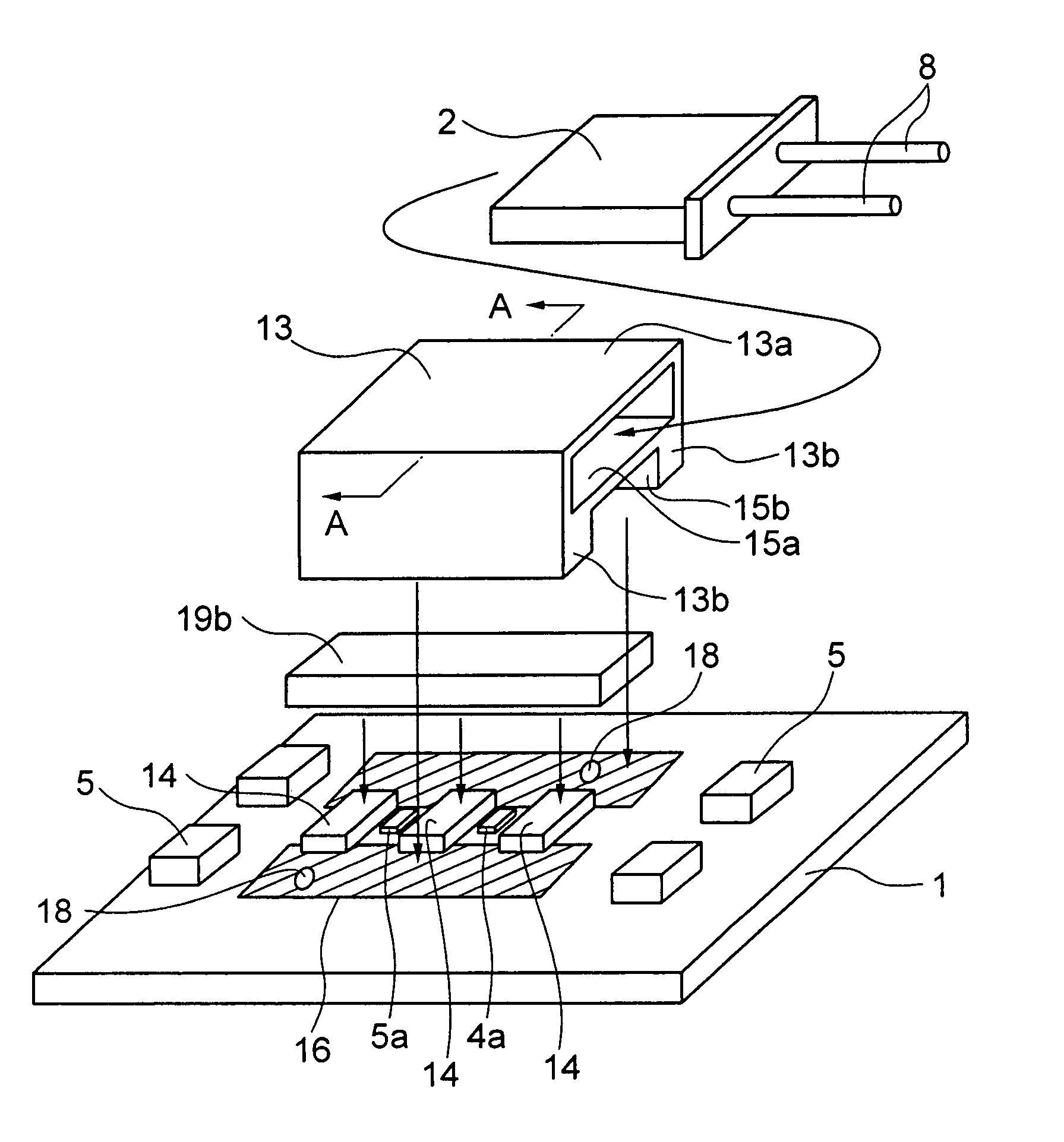

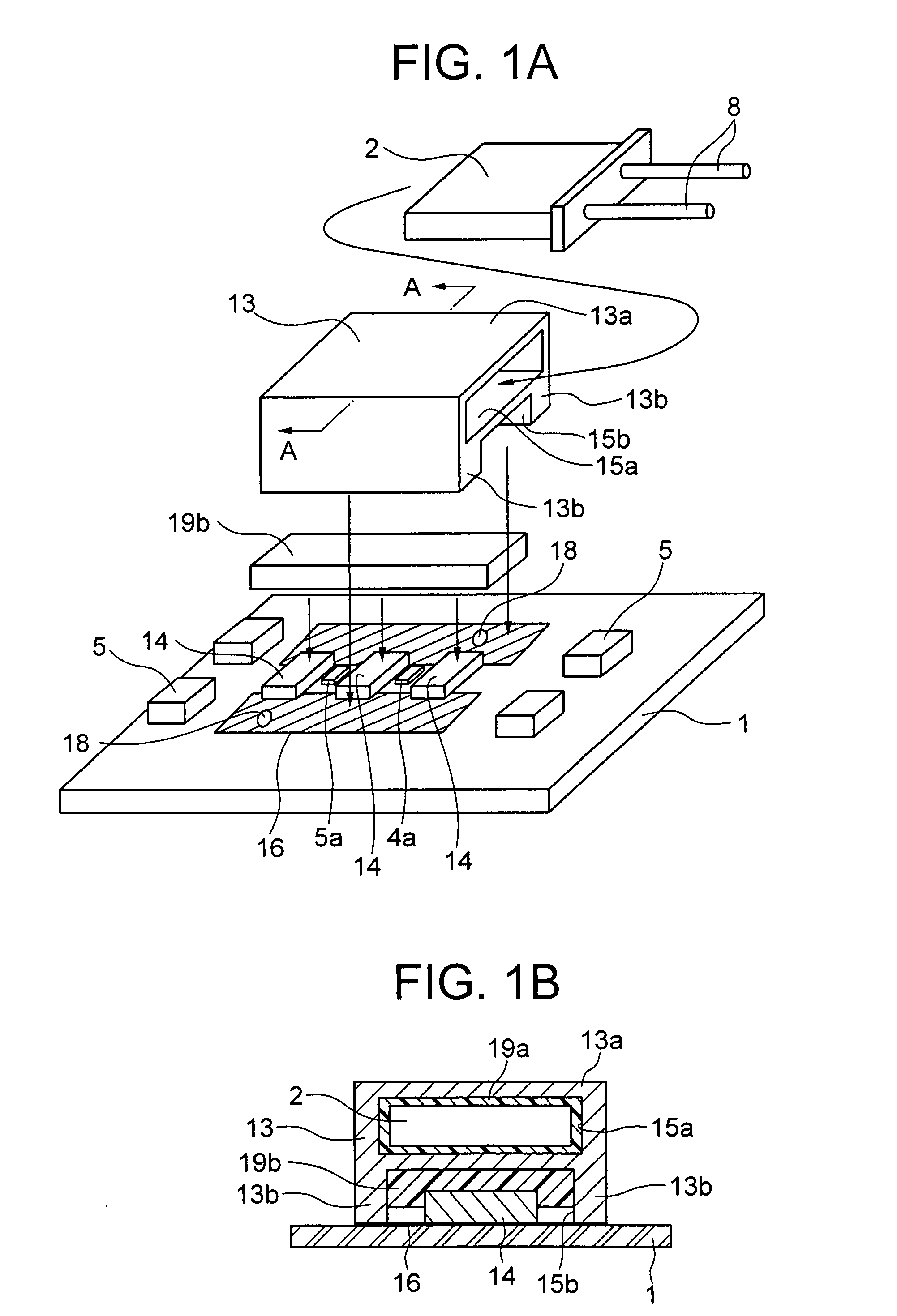

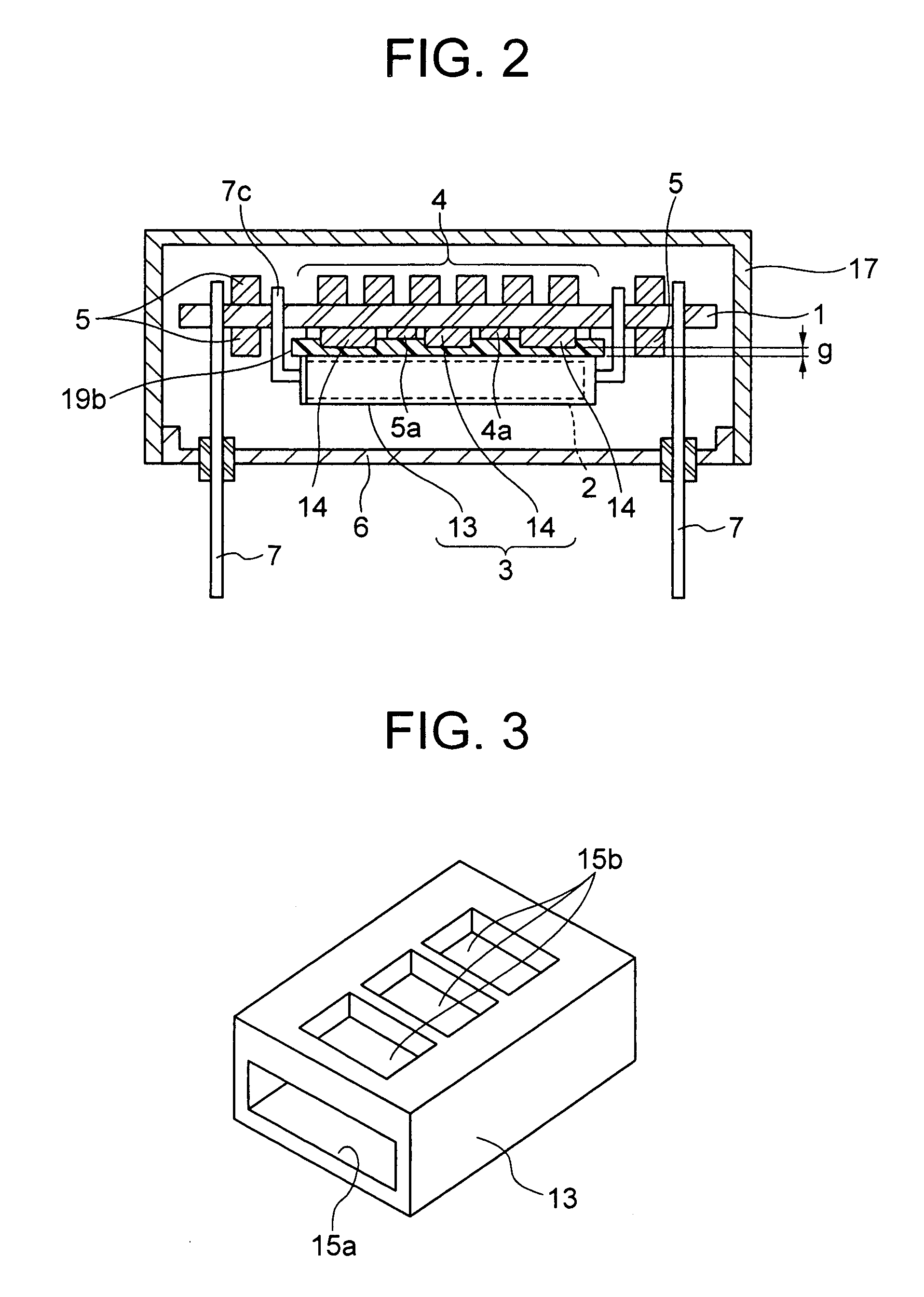

Projector

InactiveUS20050162621A1Shorten the timePrecise positioningPrismsProjectorsLiquid-crystal displayDichroic prism

In a base plate, projections for being inserted into openings in a lower bracket, and for supporting a bottom surface of a cross-dichroic prism, are provided. The lower bracket and the cross-dichroic prism are fixed to the base plate by adhesive agent filled into a clearance between the lower bracket and the bottom surface of the cross-dichroic prism supported on the projections. Holes are provided on a liquid-crystal panel, and holding arms provided on an upper bracket and the lower bracket are inserted into the holes. Then the adhesive agent is applied into the holes to fix the liquid-crystal display to the upper and lower brackets.

Owner:FUJI PHOTO OPTICAL CO LTD

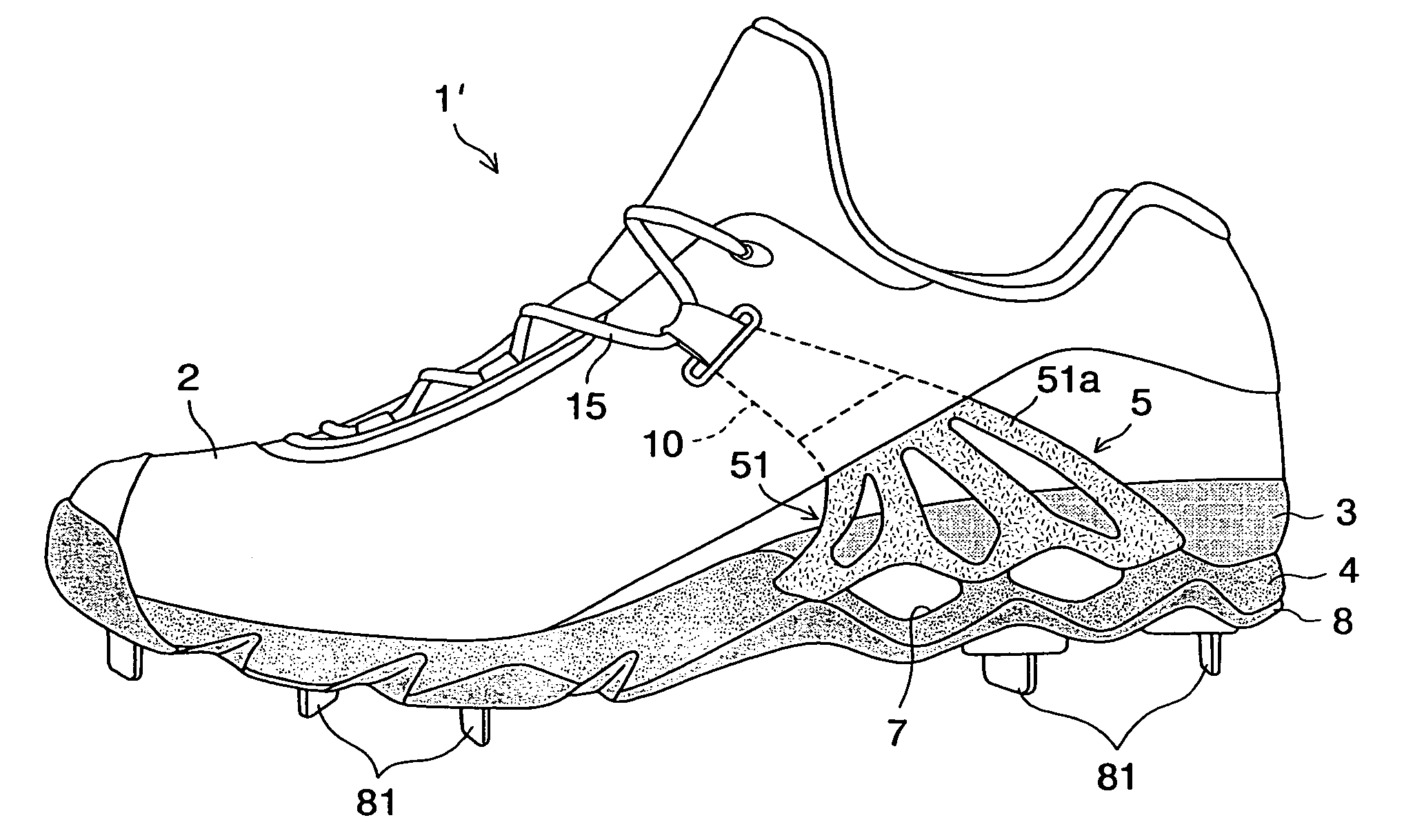

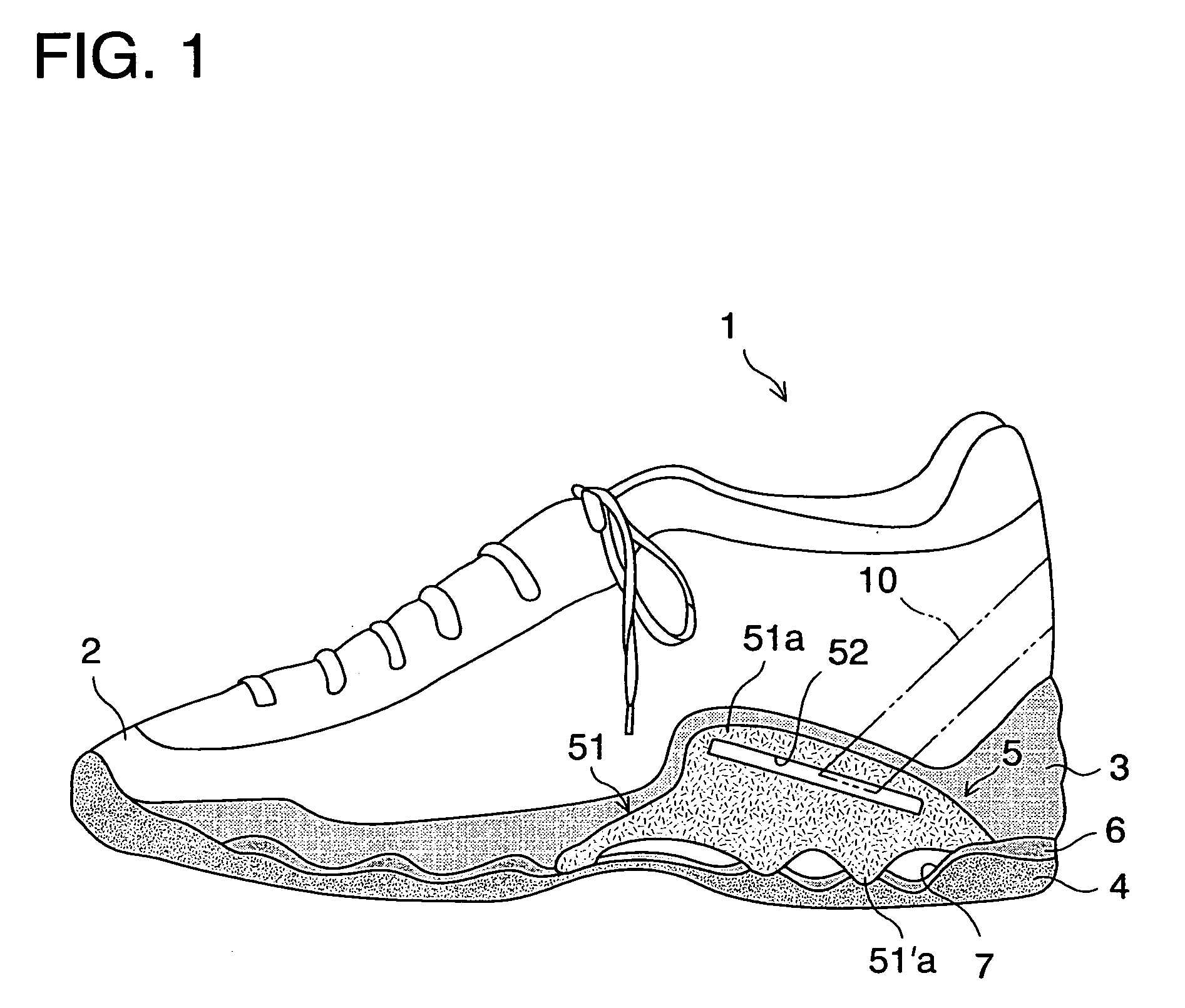

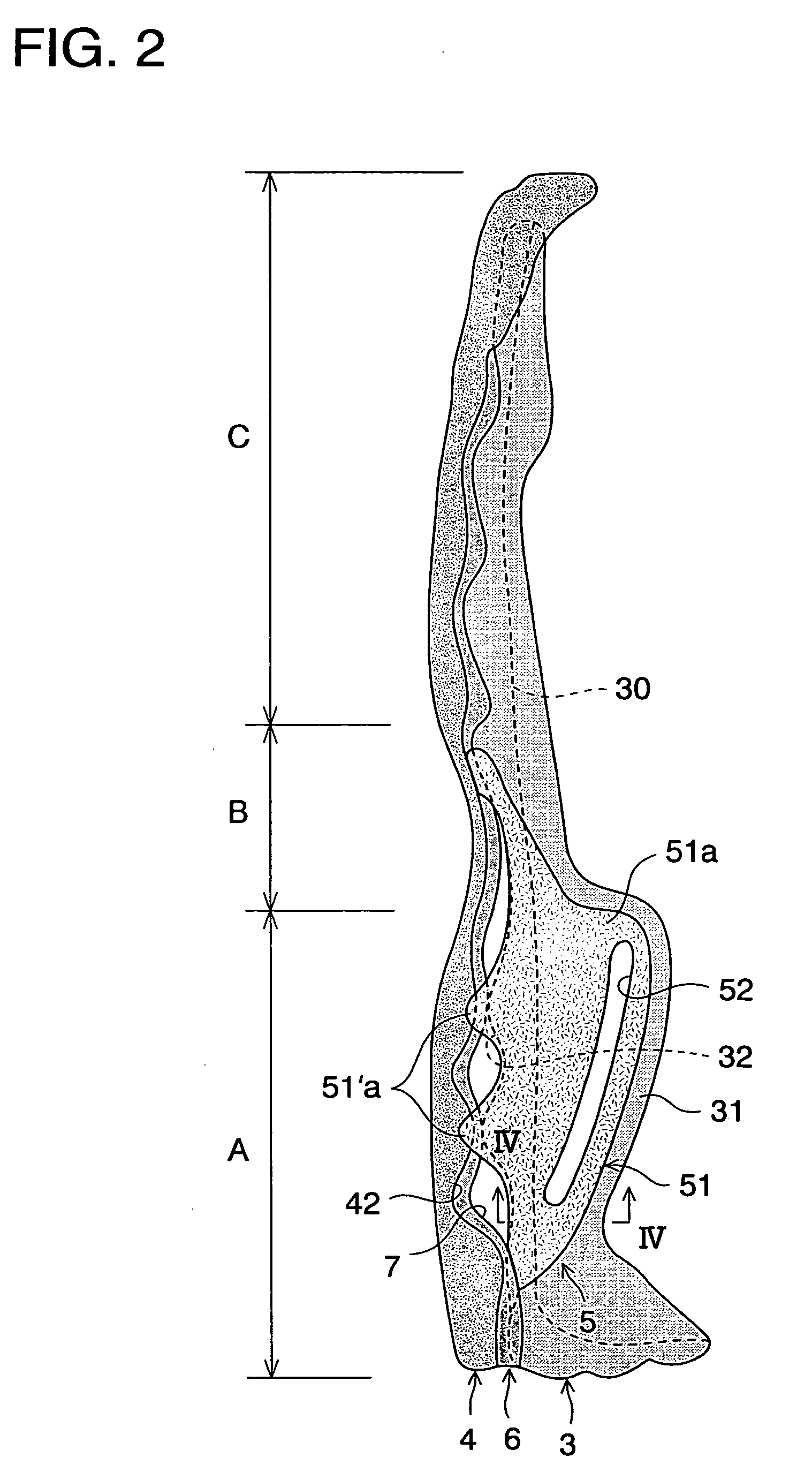

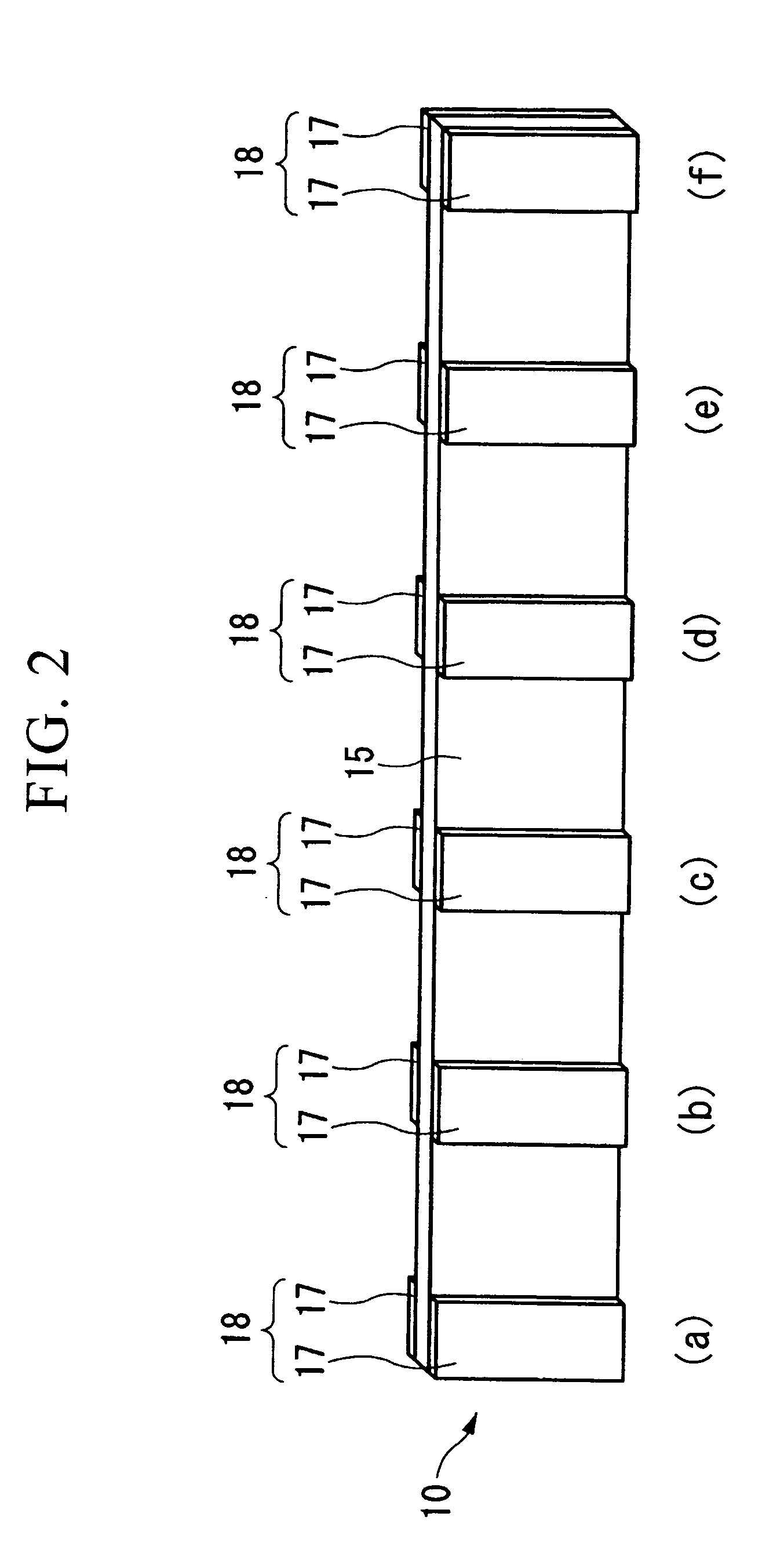

Midsole structure for an athletic shoe

InactiveUS20050217145A1Well formedFurther manufacturing costSolesFasteningsEngineeringManufacturing cost reduction

A midsole structure for an athletic shoe includes an upper midsole (3) formed of a soft elastic material, a lower midsole (4) disposed under the upper midsole (3) and formed of a soft elastic material, and a wavy plate assembly (5) interposed between the upper midsole (3) and the lower midsoles (4). The wavy plate assembly (5) is comprised of a wavy board (50) and a pair of sidewall members (51) provided discretely from the wavy board (50) and disposed on opposite sides of the wavy board (50). Each of the sidewall members (51) is composed of a wavy bottom-portion (51b) overlapping the wavy board (50) and an upraised portion (51a) extending upwardly from the wavy bottom portion (51b) to face a side surface of the upper midsole (3). Provision of the wavy board (50) and the sidewall members (51) discretely from each other simplifies a layout of a mold for forming the wavy plate assembly (5), thereby reducing a manufacturing cost.

Owner:MIZUNO CORPORATION

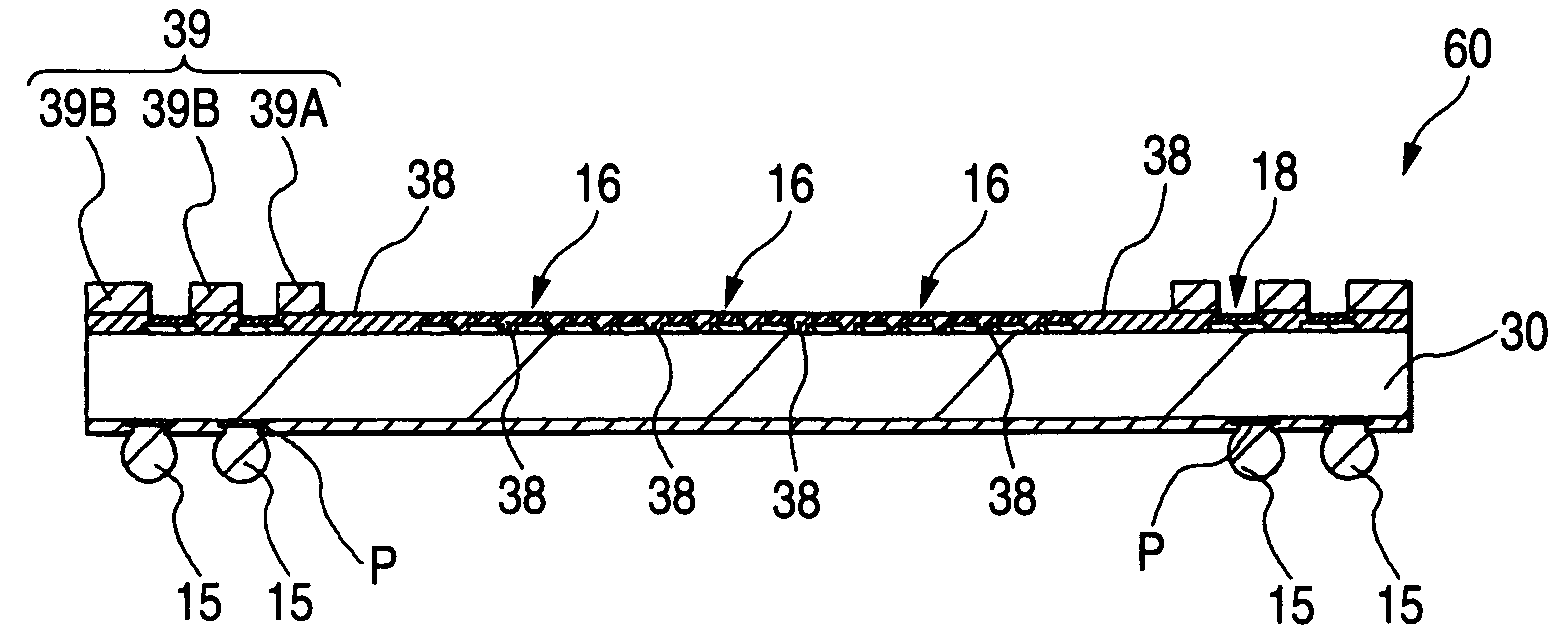

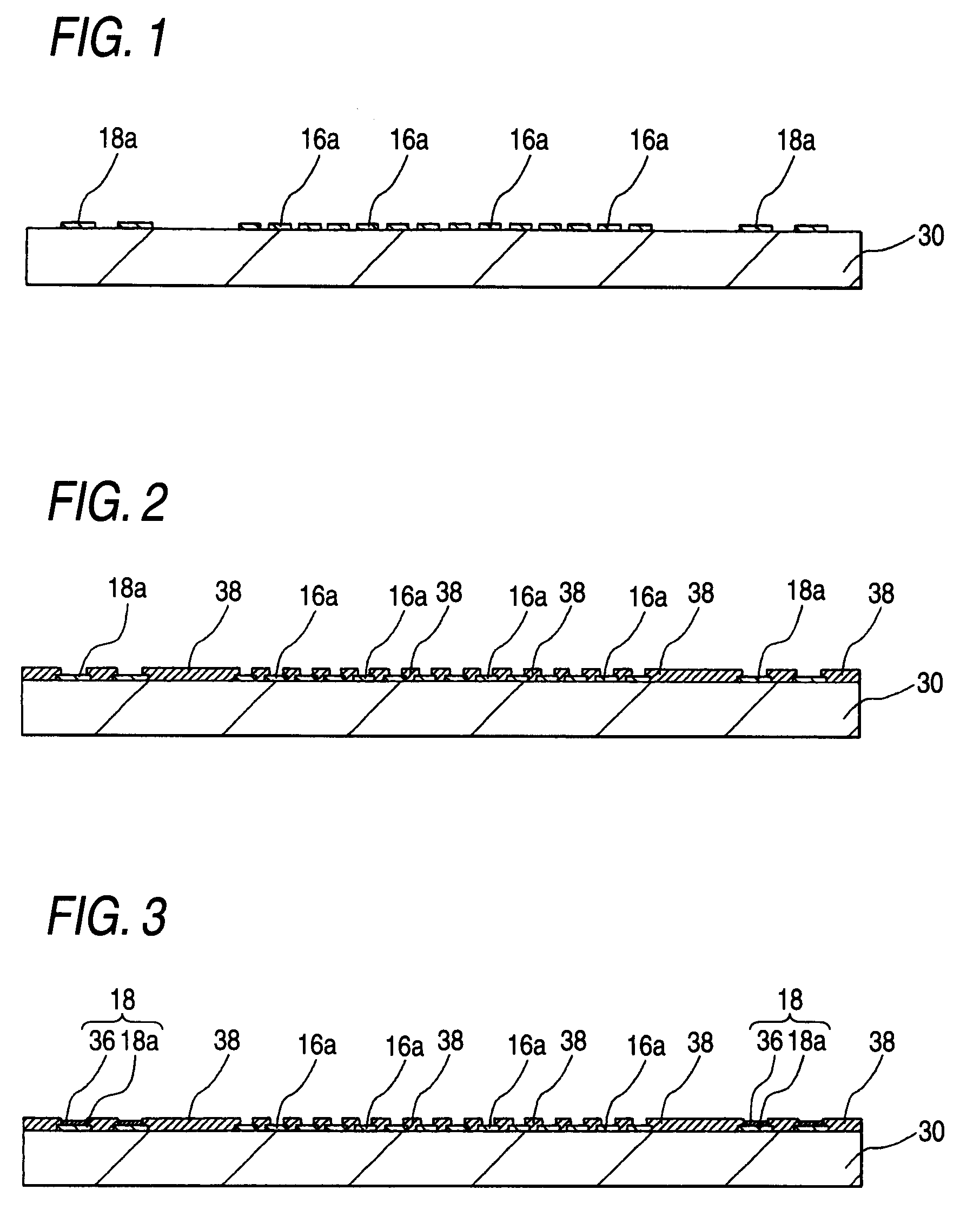

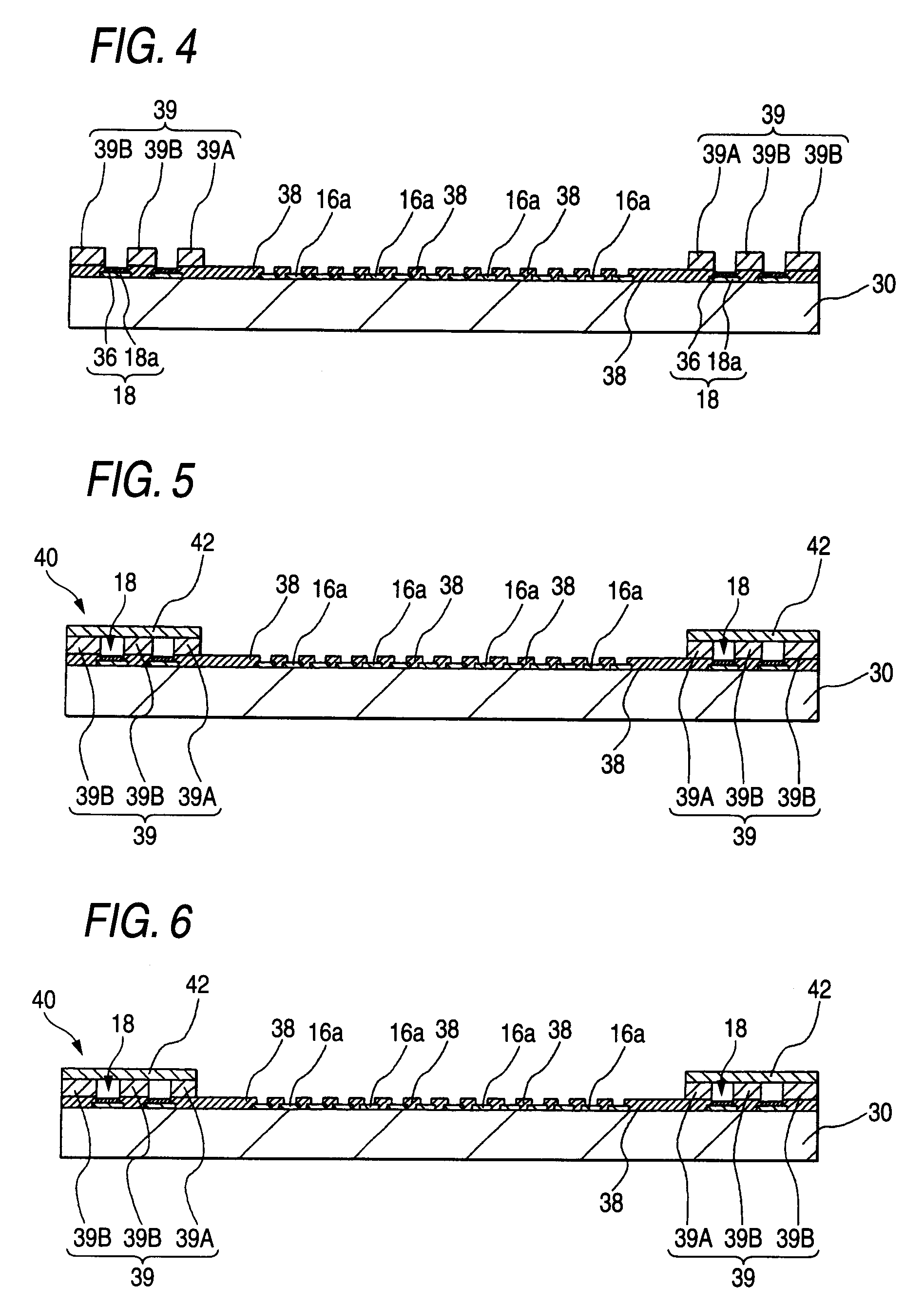

Semiconductor package and semiconductor device using the same

InactiveUS20090001606A1Reliably carry-outEliminate warpingSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageEngineering

A semiconductor package 60 in which a region where a land pad 18 is formed is provided on an outer side of a region in which a flip-chip connecting pad 16 is formed, wherein a protecting member 39 is formed to expose the land pad 18 in the region in which the land pad 18 is formed, and the protecting member 39 includes a frame-shaped structure portion 39A disposed to surround the flip-chip connecting pad 16 and a support film portion 39B disposed on an outer side of the frame-shaped structure portion 39A, and a semiconductor device 70 using the semiconductor package 60.

Owner:SHINKO ELECTRIC IND CO LTD

Water repellent cellulose preservative

InactiveUS20060086283A1Further manufacturing costShorten production timeAntifouling/underwater paintsWood treatment detailsWaxWater soluble

The wood preservative is a compound that includes a water soluble wax that has a chemically basic pH that is about 9.5 to 13.5. The compound is blended with the wood being preserved. Subsequently, a silicate polymer with a basic pH that is chemically compatible with the wax pH and a viscosity of about 1 centipoise is further blended with the wood to form a matrix of wax and preservative that permeates the structure of the wood without chemically combining with the wood. The chips that form wood products of which oriented stand board is typical, are first dried to a moisture content of about 4% by weight and then blended with a resin to form with the wax a water repellant matrix for the wood preservative.

Owner:PREMIER WOOD TREATING

Filtering face-piece respirator having parallel line weld pattern in mask body

ActiveUS8528560B2Reduce usageDeformation MinimizationBreathing filtersBreathing masksRespiratorEngineering

Owner:3M INNOVATIVE PROPERTIES CO

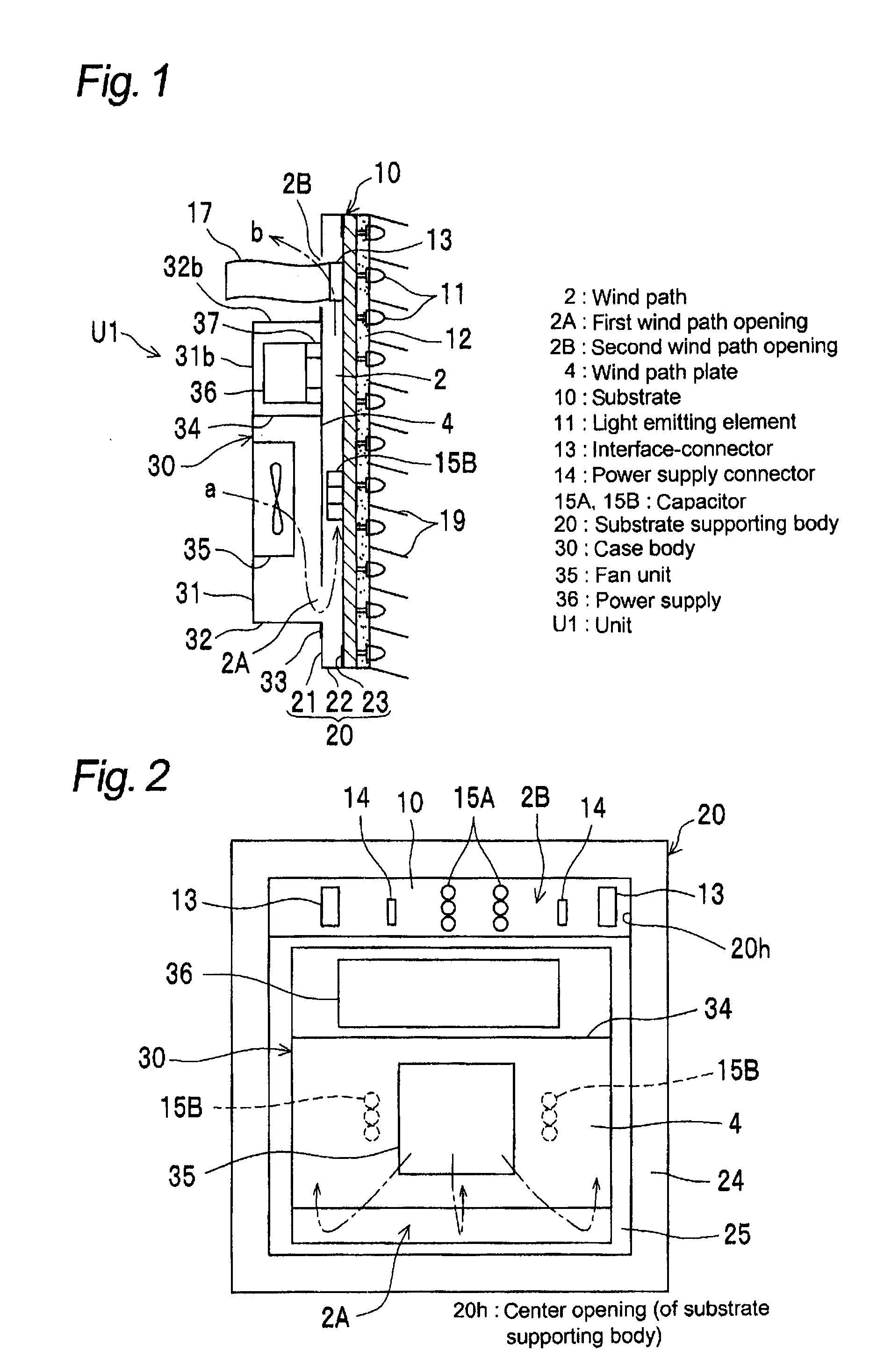

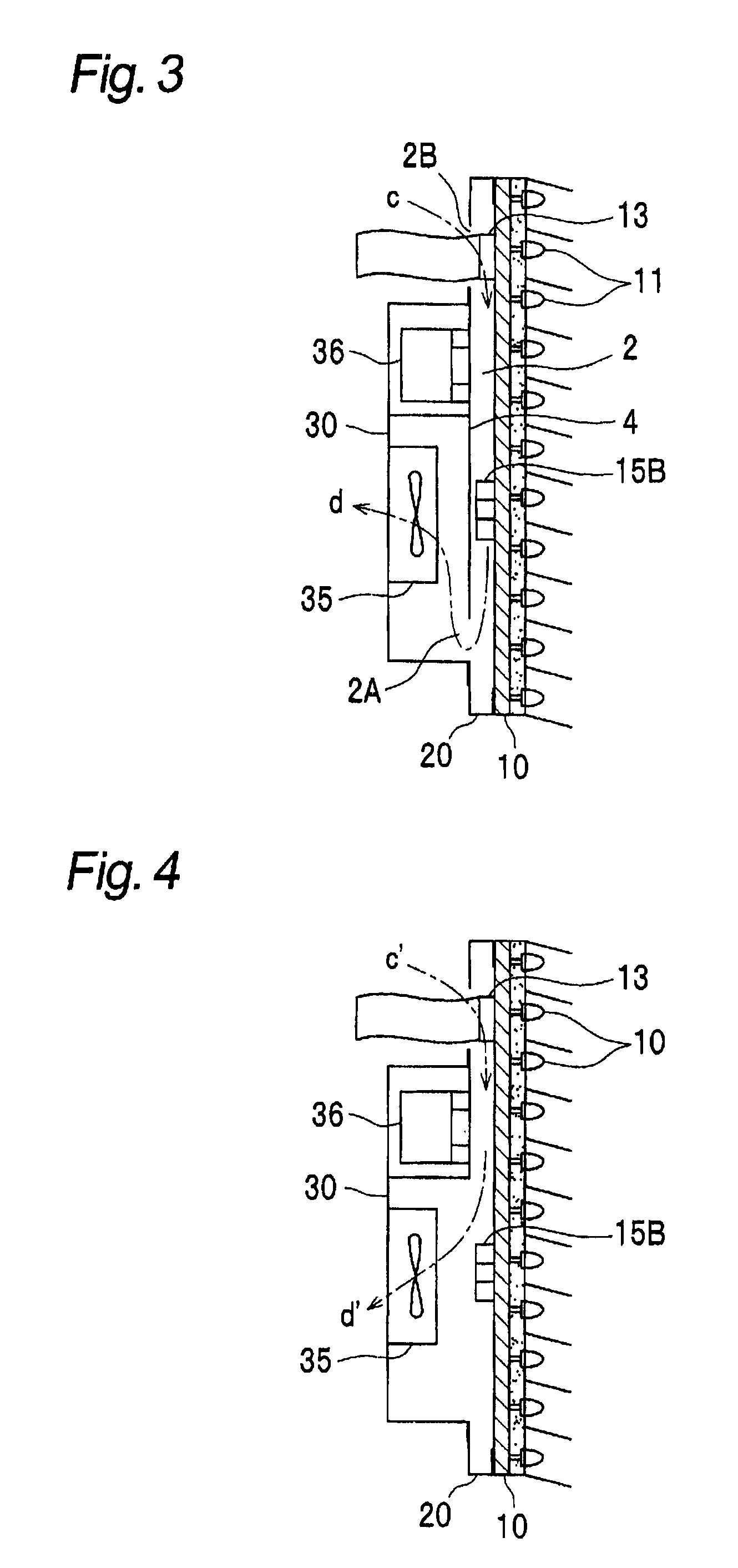

Display device

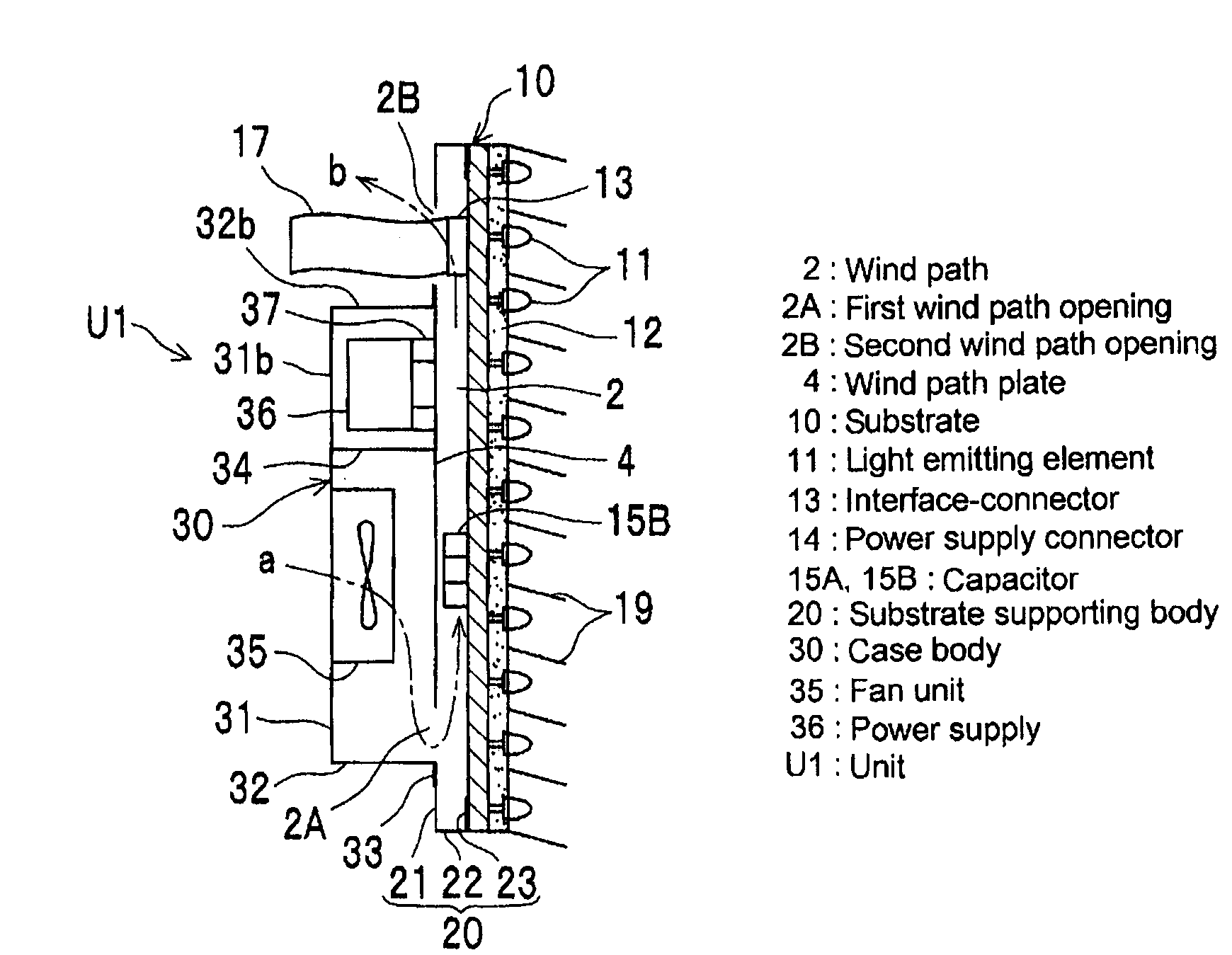

ActiveUS20080170015A1Improve cooling effectAvoid simple structuresStatic indicating devicesDigital data processing detailsDisplay deviceEngineering

A display device includes a substrate having light emitting elements for display on a front surface; a substrate supporting body having an opening in the center and positioned on the back surface side of the substrate to support a peripheral region of the substrate; a case body positioned on the back surface side of the substrate supporting body and covering a part of the center opening; a fan unit arranged in the case body; a wind path plate arranged between the fan unit and the back surface of the substrate and forming a wind path to pass airflow generated by driving the fan unit only on the back surface side of the substrate; and a power supply arranged in the case body and on the back surface of the wind path plate; and wherein the airflow impinges the wind path plate through the fan, thereafter passes through the wind path and is discharged to the outside from the back side of the wind path plate. According to the present invention, it is possible to cool down a substrate uniformly and efficiently in a display device using light emitting elements arranged on the substrate without raising cost or complicating the structure.

Owner:MITSUBISHI ELECTRIC CORP

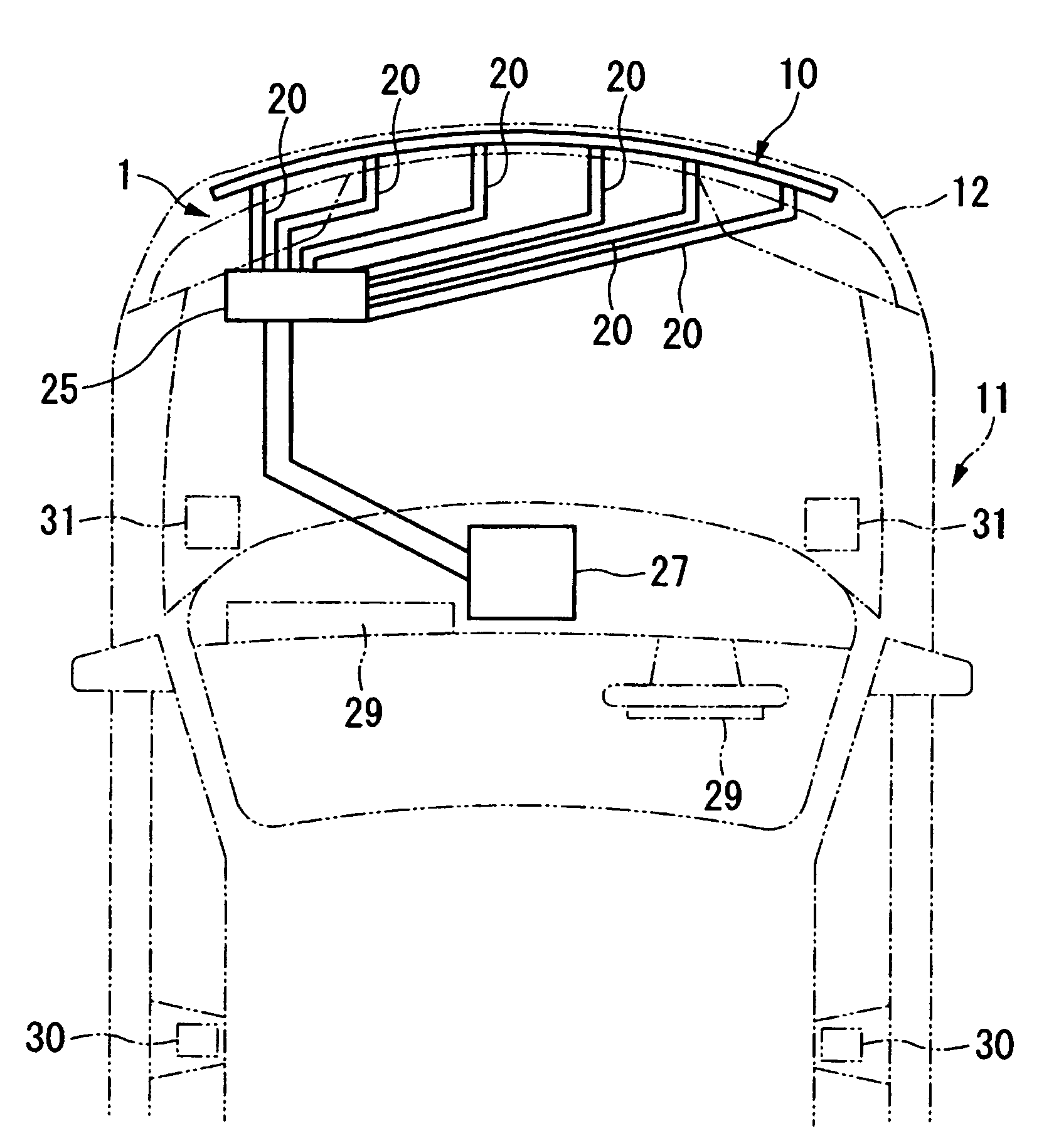

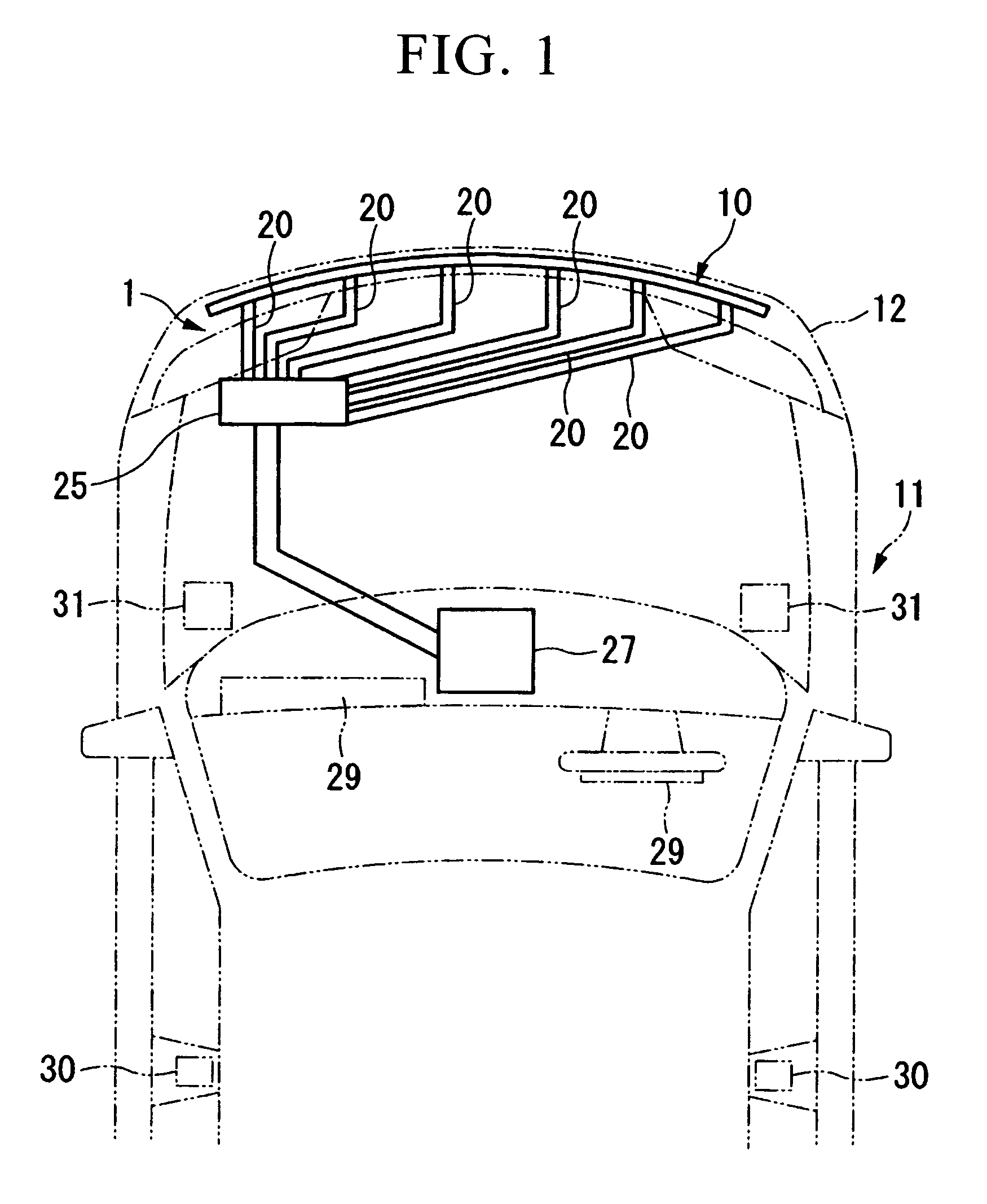

Collision detection sensor for vehicle and collision detection device for vehicle

InactiveUS7304566B2Reduce in quantityReduce manufacturing costAcceleration measurement using interia forcesPedestrian/occupant safety arrangementElectricityCollision detection

A collision detection sensor for a vehicle of the present invention includes a single piezoelectric film which is flat, plural pairs of electrodes which sandwich the piezoelectric film and measure voltages between the electrodes, and spaces provided between the plural pairs of electrodes.

Owner:HONDA MOTOR CO LTD

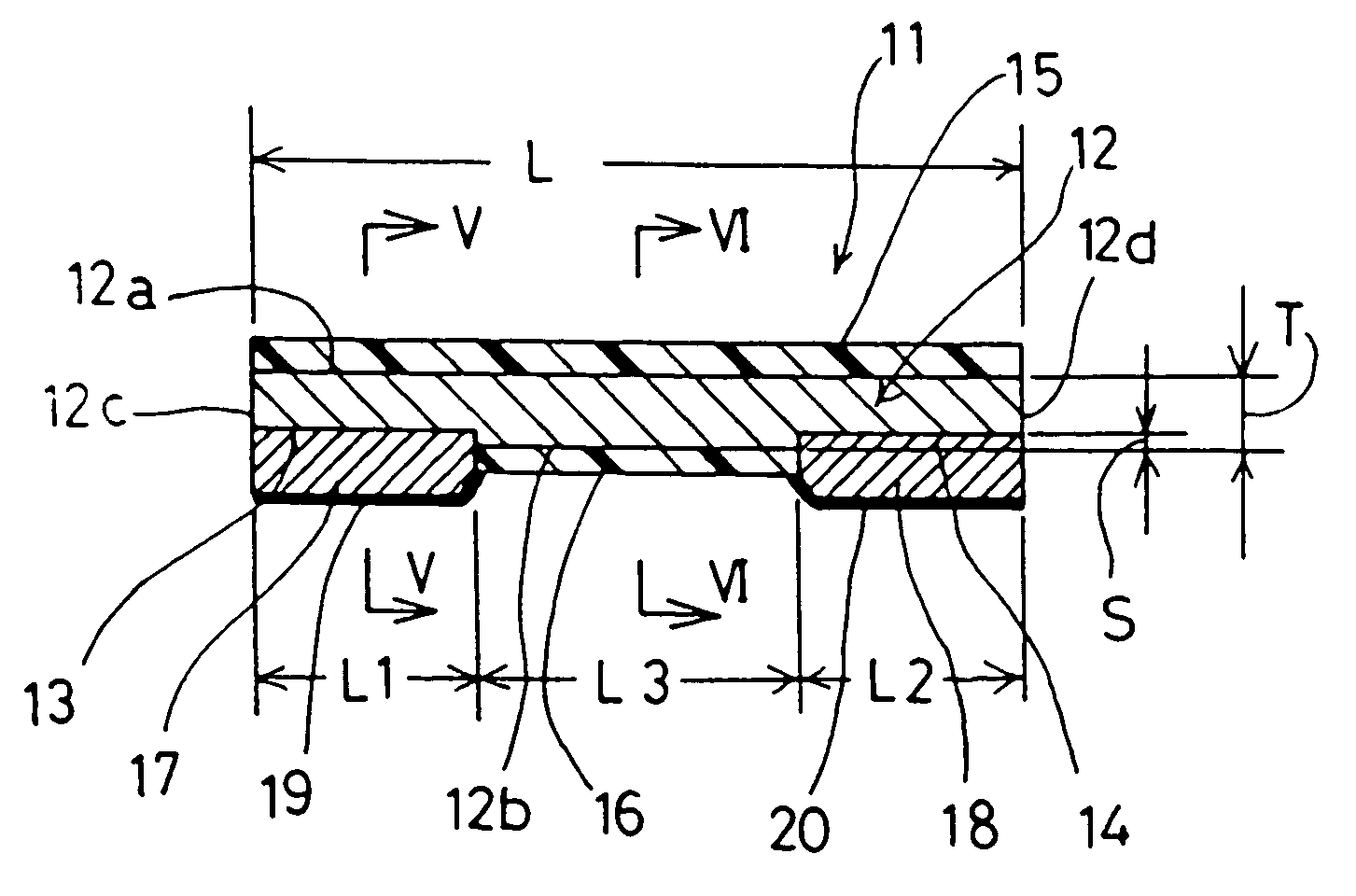

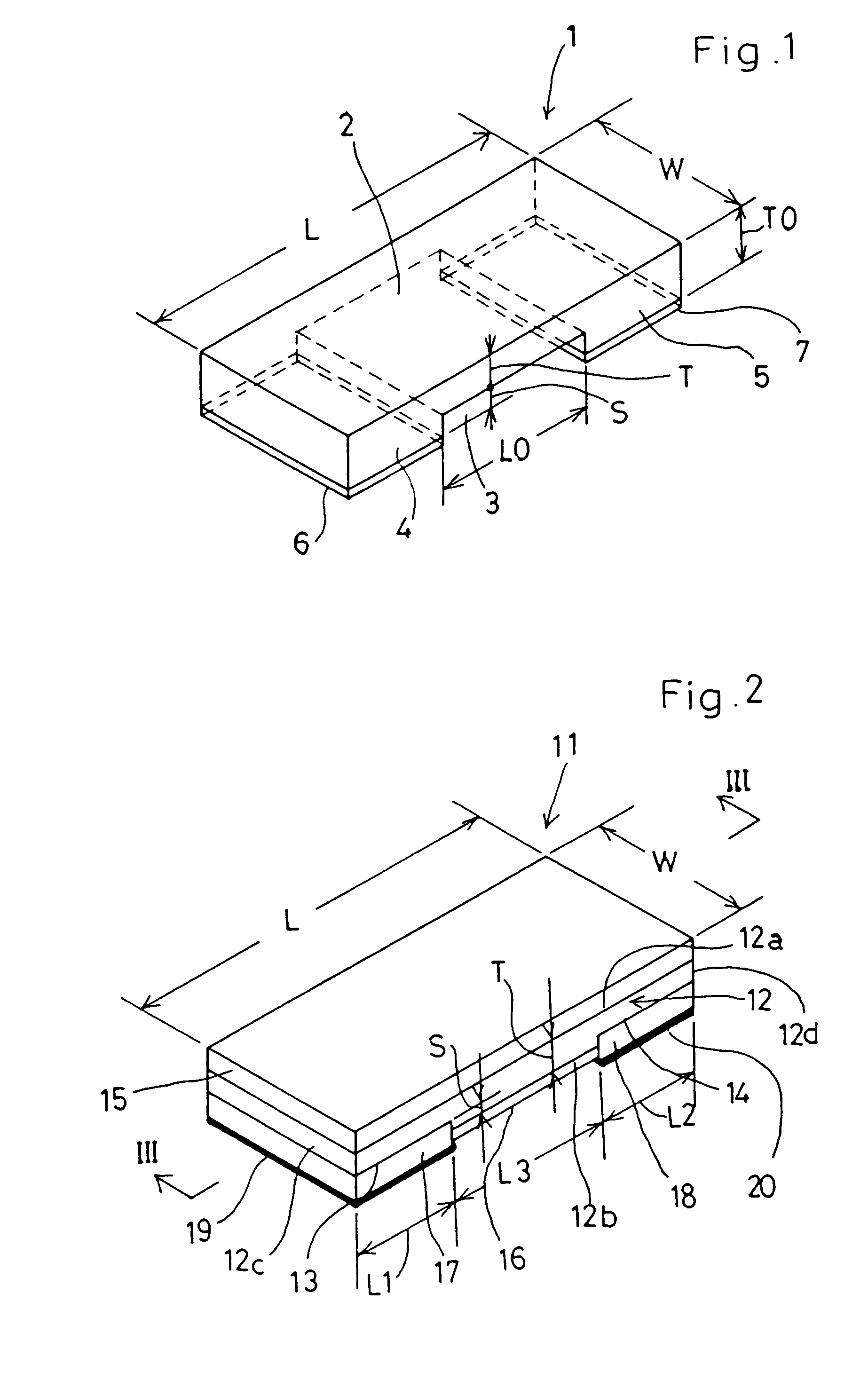

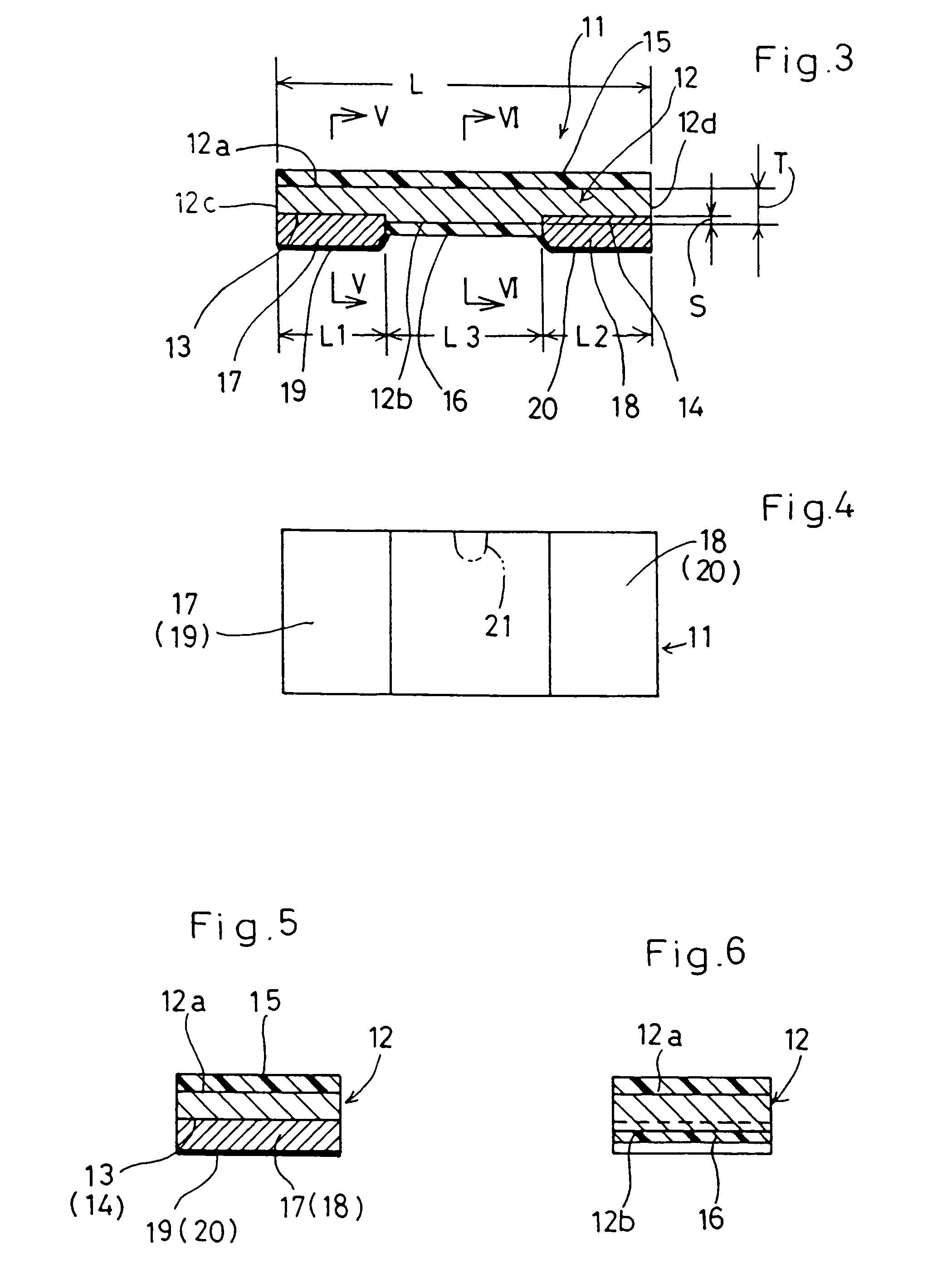

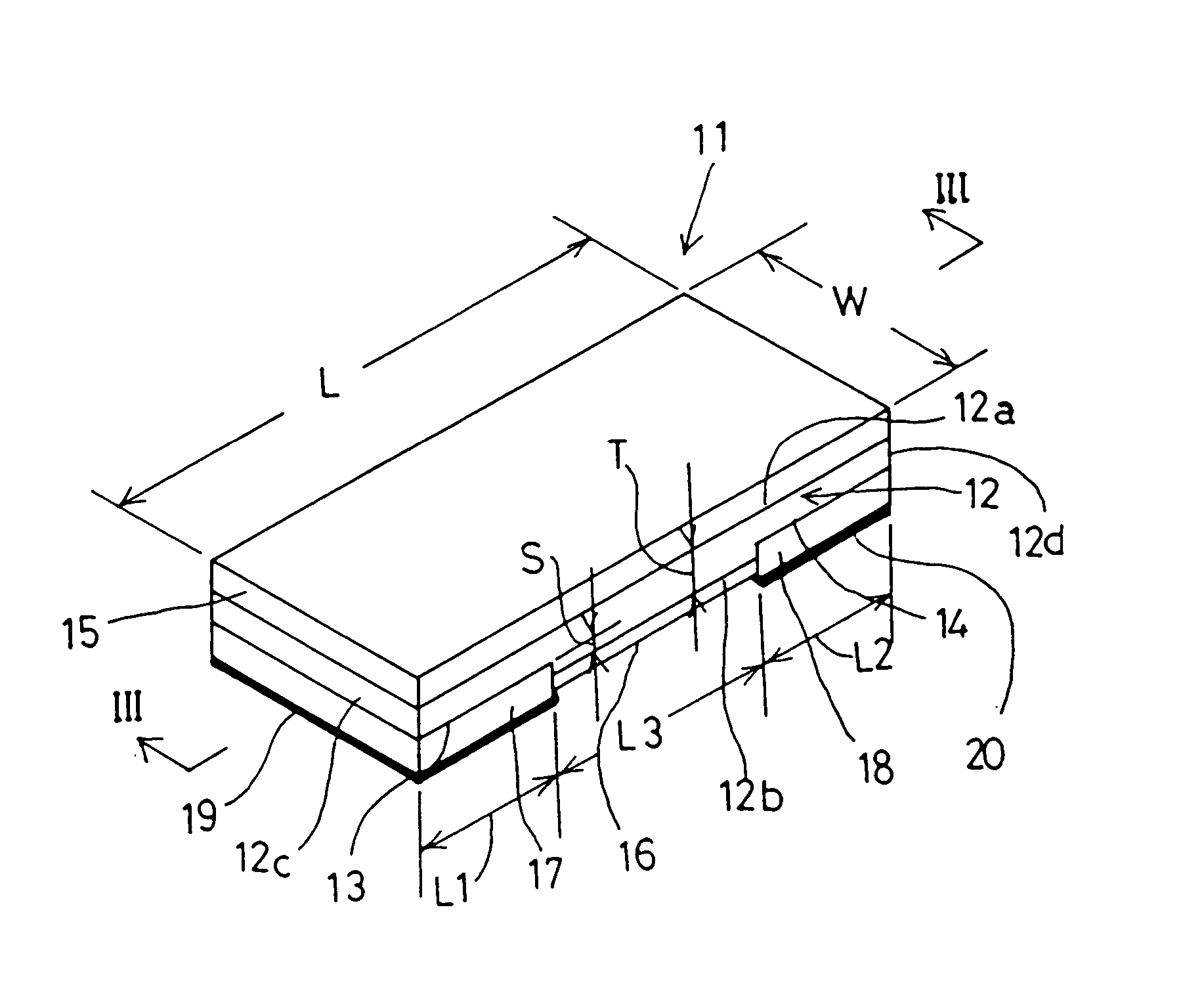

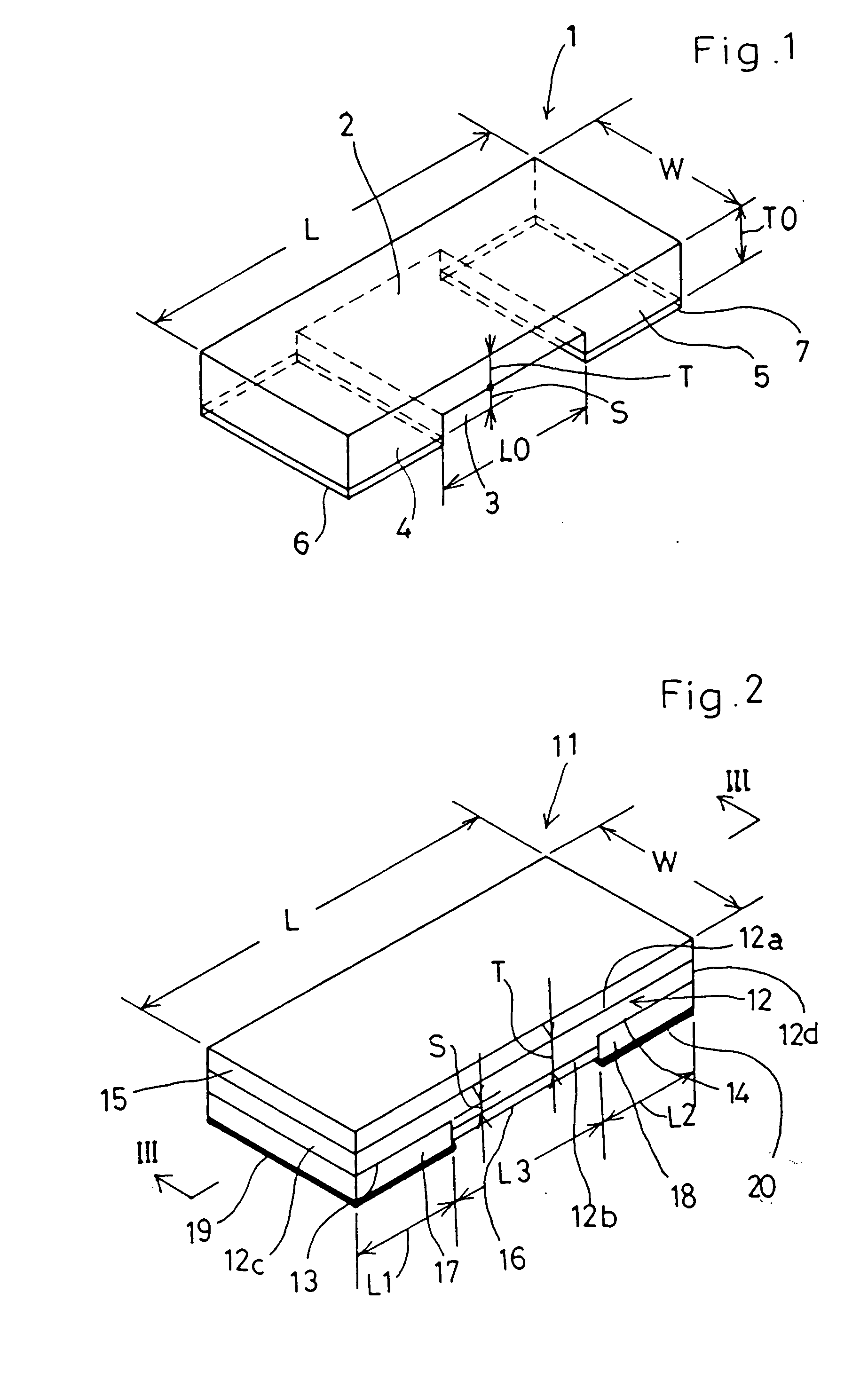

Chip resistor having low resistance and method of making the same

InactiveUS7221254B2Increase connection heightReduce the overall heightResistor chip manufactureResistor detailsLow resistanceMetal

A resistor, including a resistive element made of a metal plate, has a low resistance resulting from connection terminal electrodes formed on both ends of the lower surface of the resistive element. The object thereof is to achieve weight reduction and lower costs by reducing the height of the resistor. To achieve the above object, the ends of the lower surface of the resistive element are provided with recesses for accommodating the connection terminal electrodes, while at least the intermediate area of the lower surface of the resistive element between the connection terminal electrodes is covered with an insulator. Alternatively, a recess may be formed in the middle of the lower surface of the resistive element for using the ends of the lower surface as a pair of connection terminal electrodes, the recess being internally covered with an insulator.

Owner:ROHM CO LTD

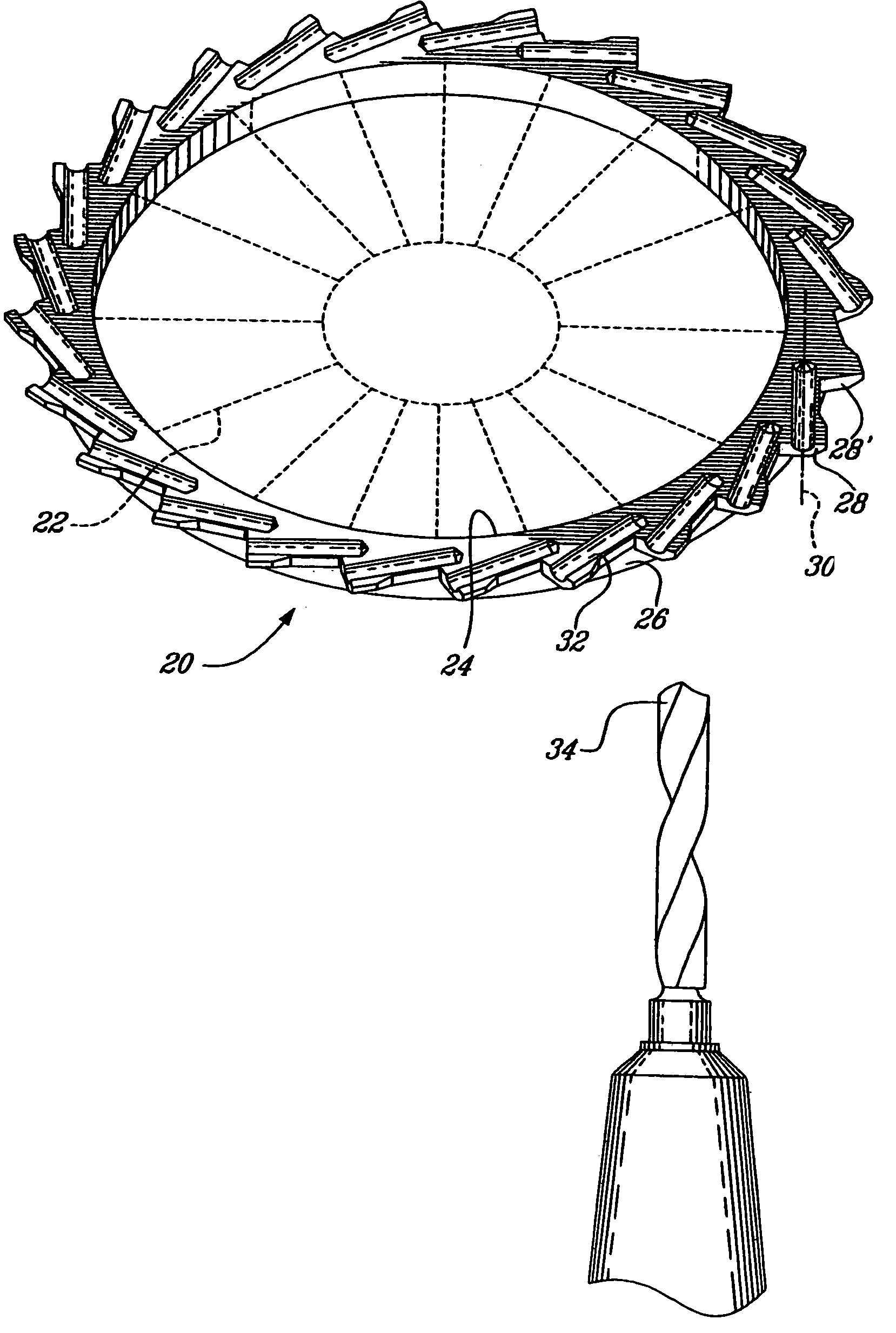

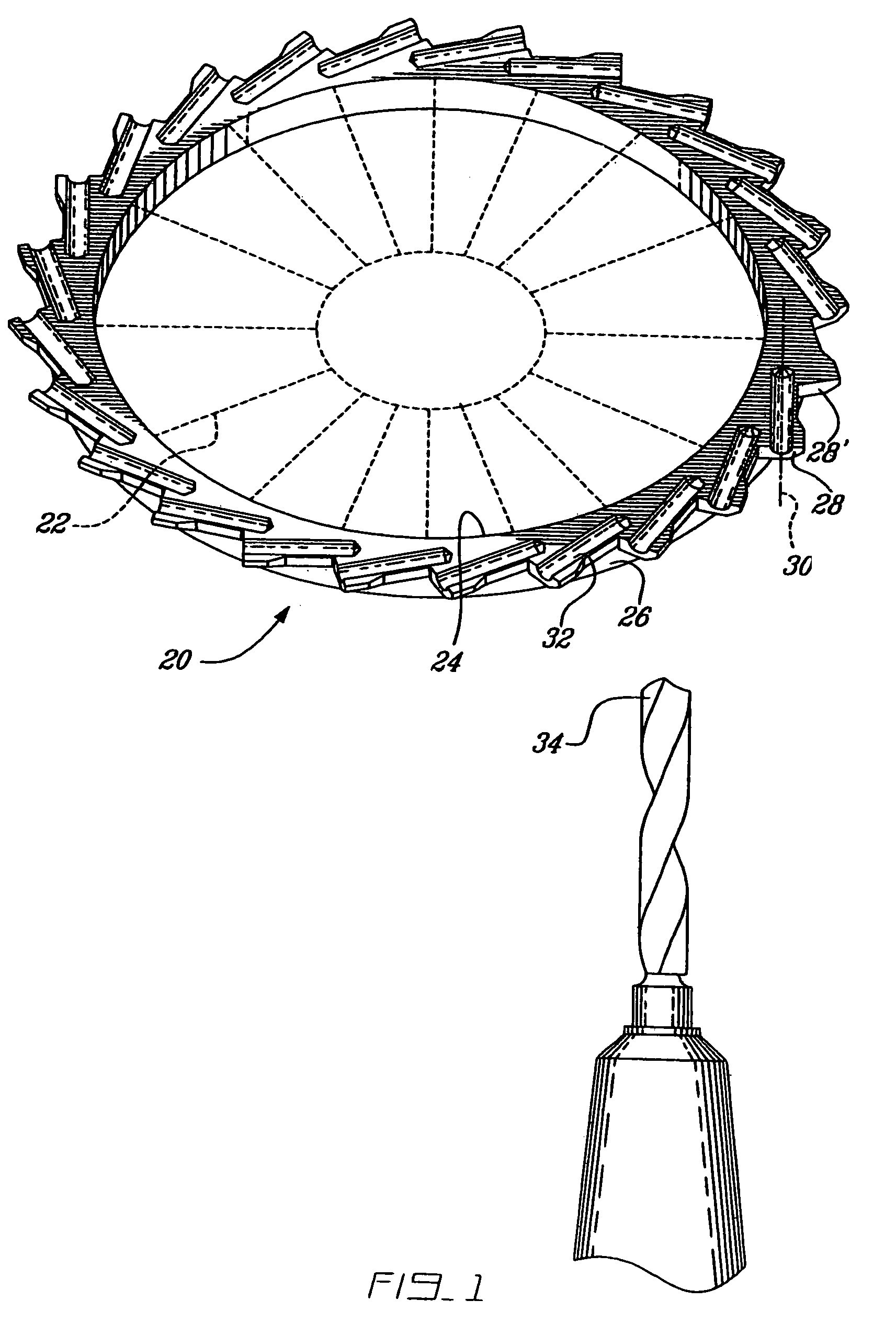

Method of making a gas turbine engine diffuser

InactiveUS7114255B2Minimizes tool deflectionMinimize deflectionEngine manufacturePump componentsTurbineGas turbines

Owner:PRATT & WHITNEY CANADA CORP

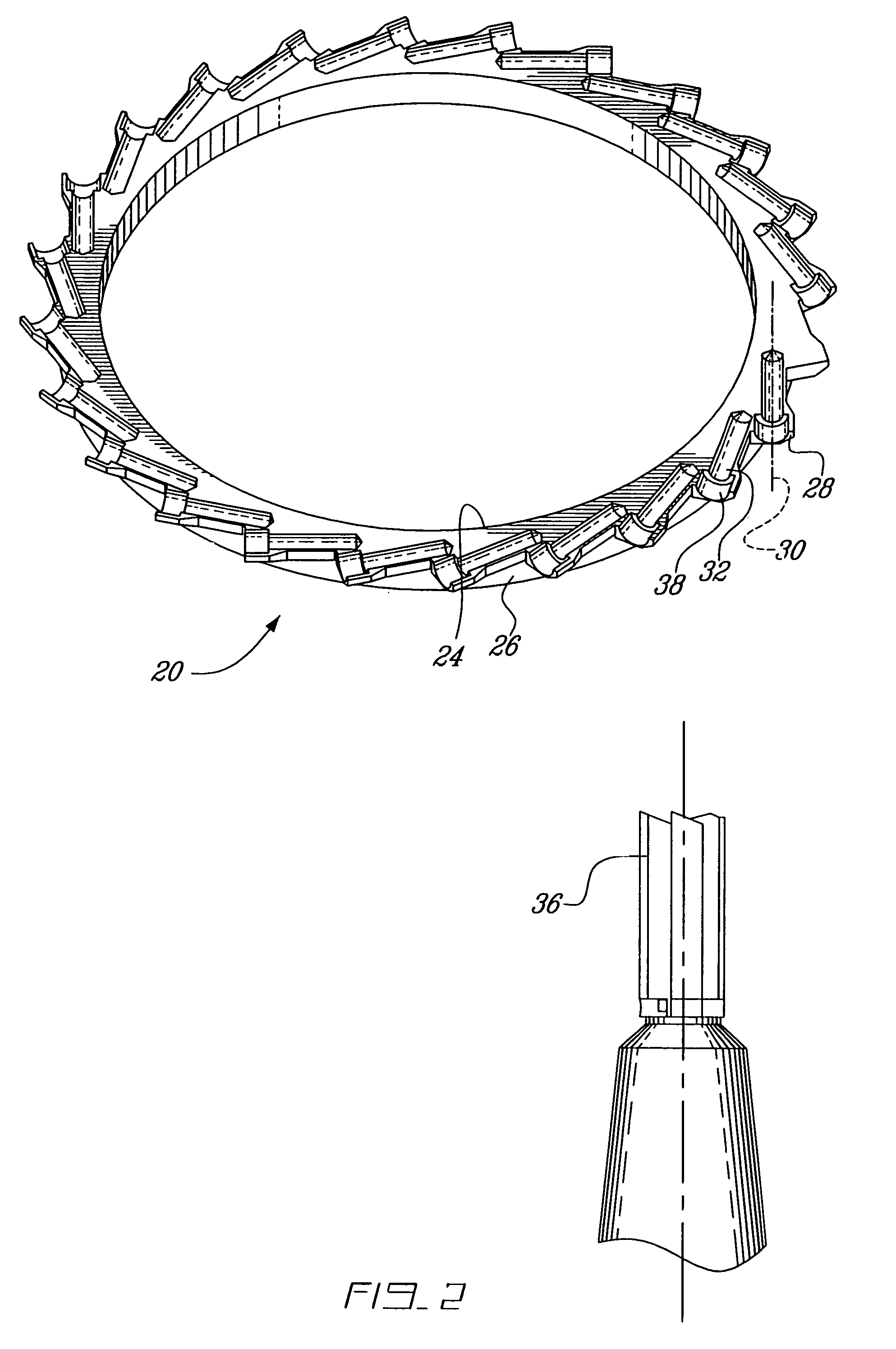

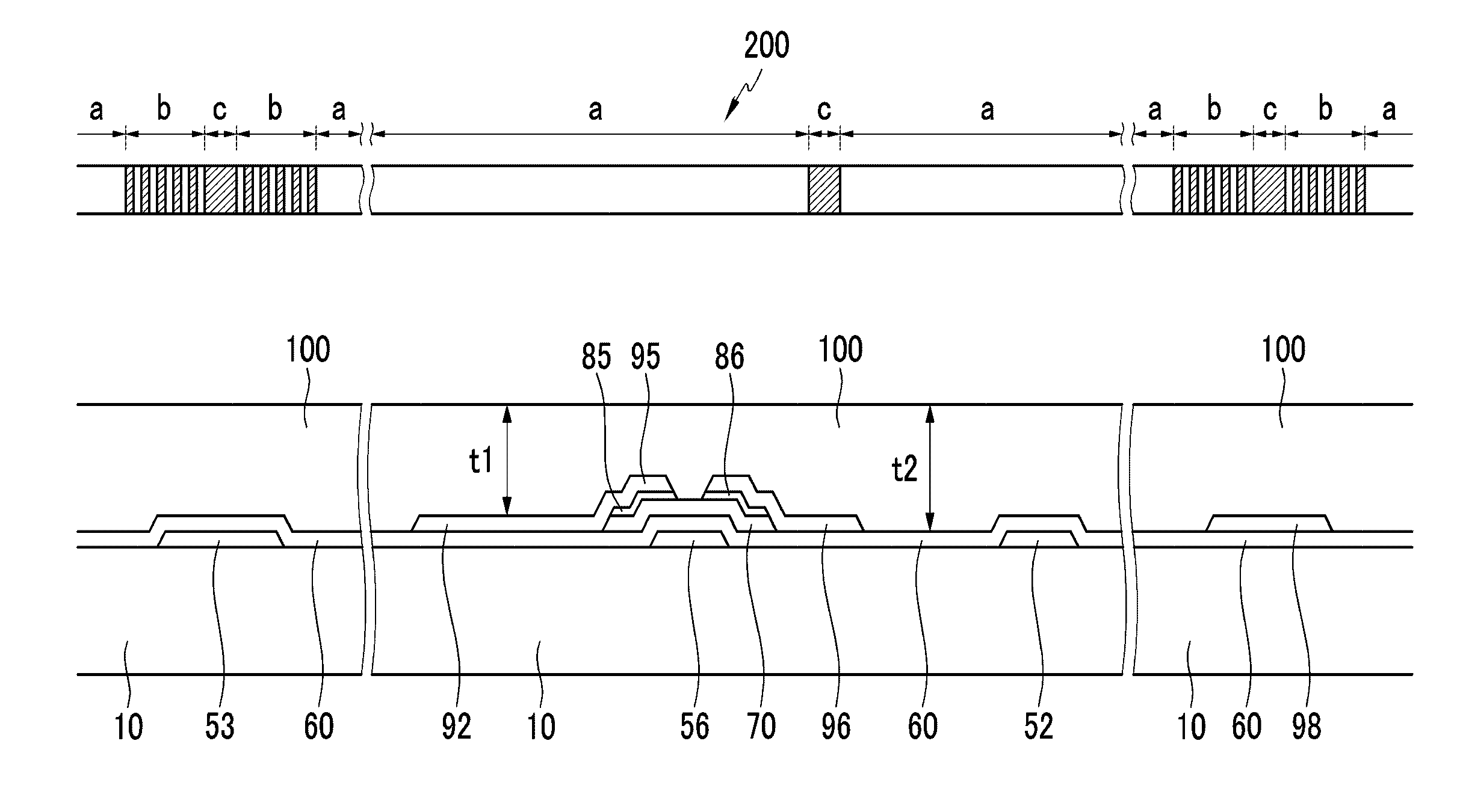

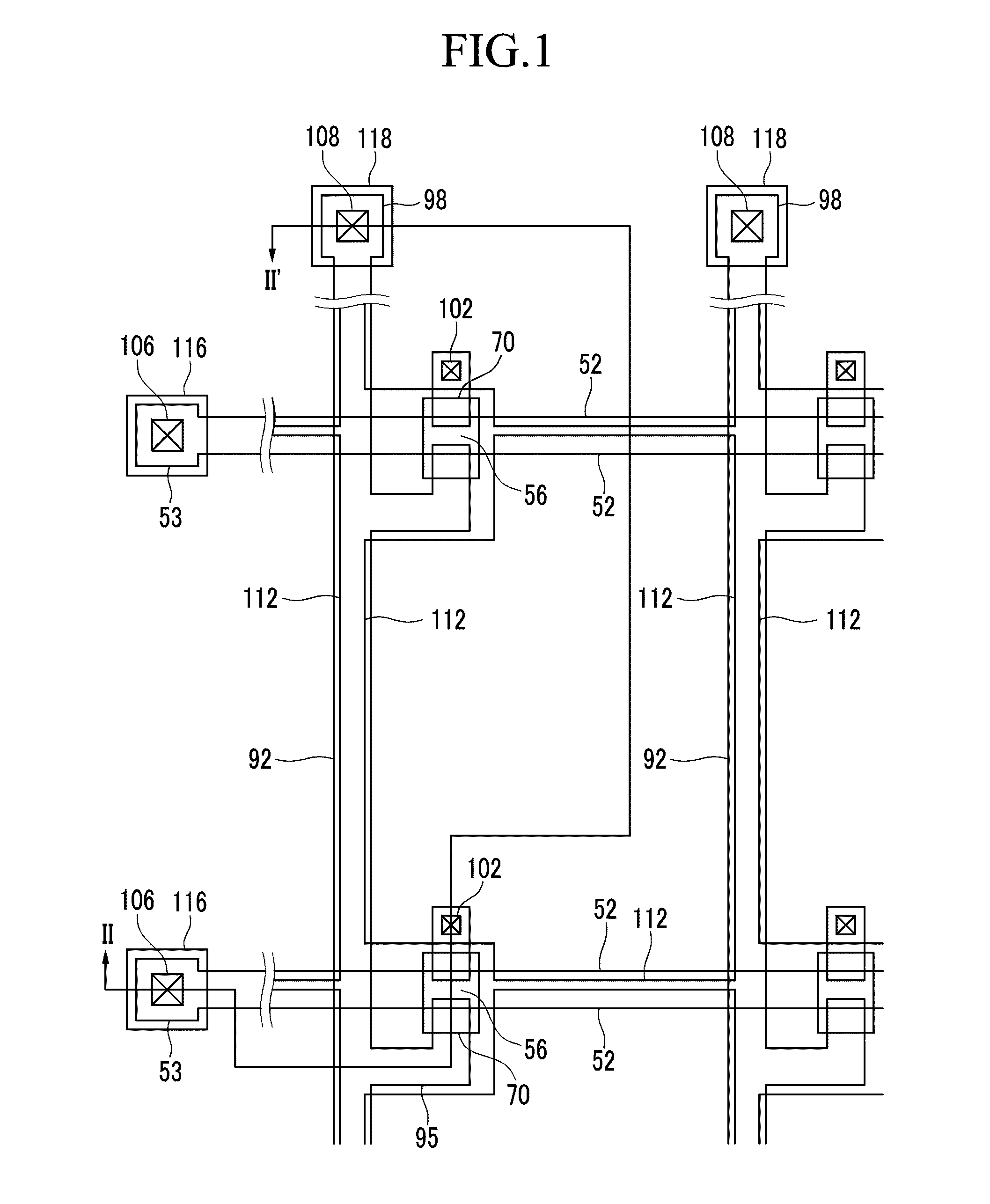

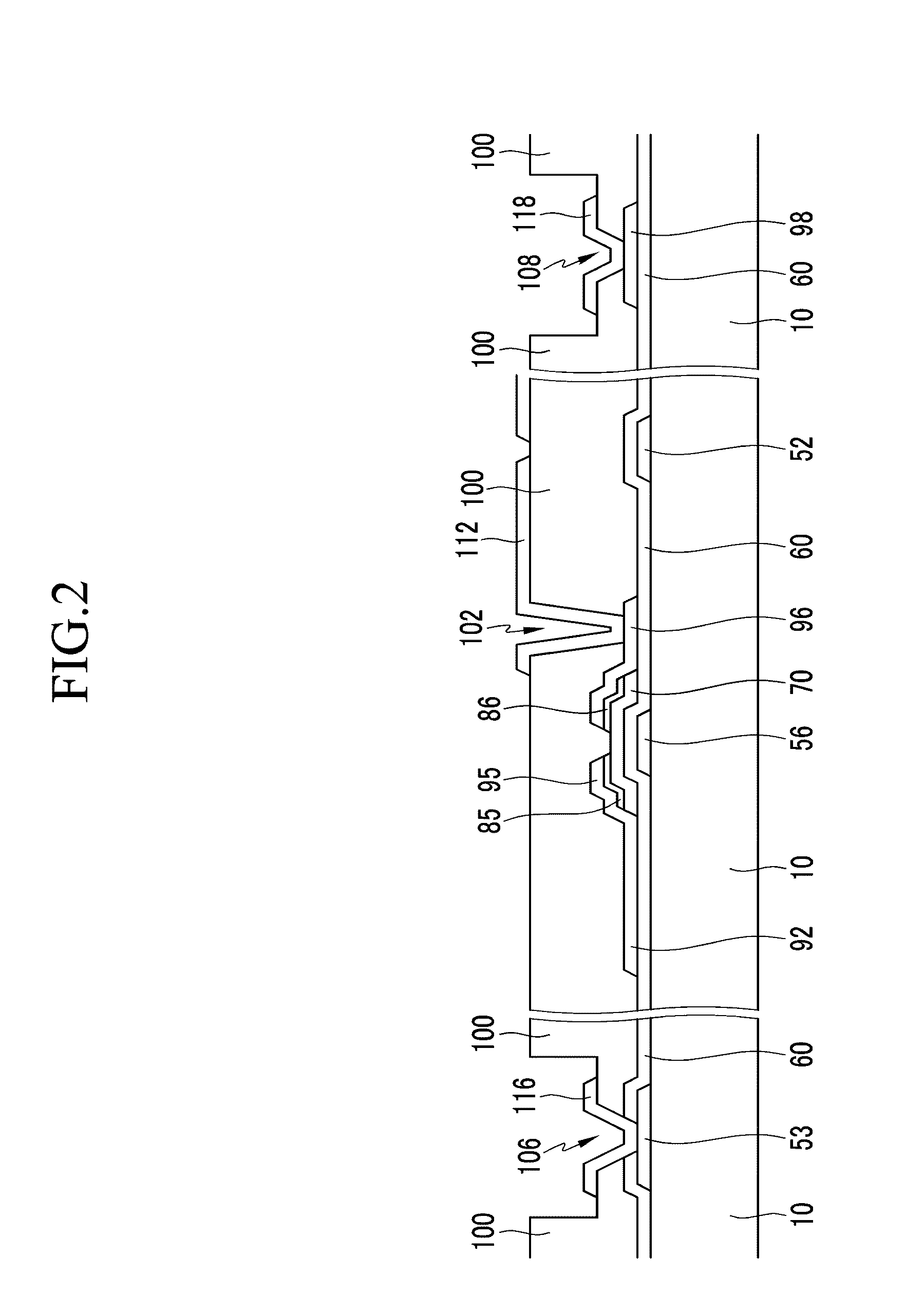

Method for manufacturing a thin film transistor array panel

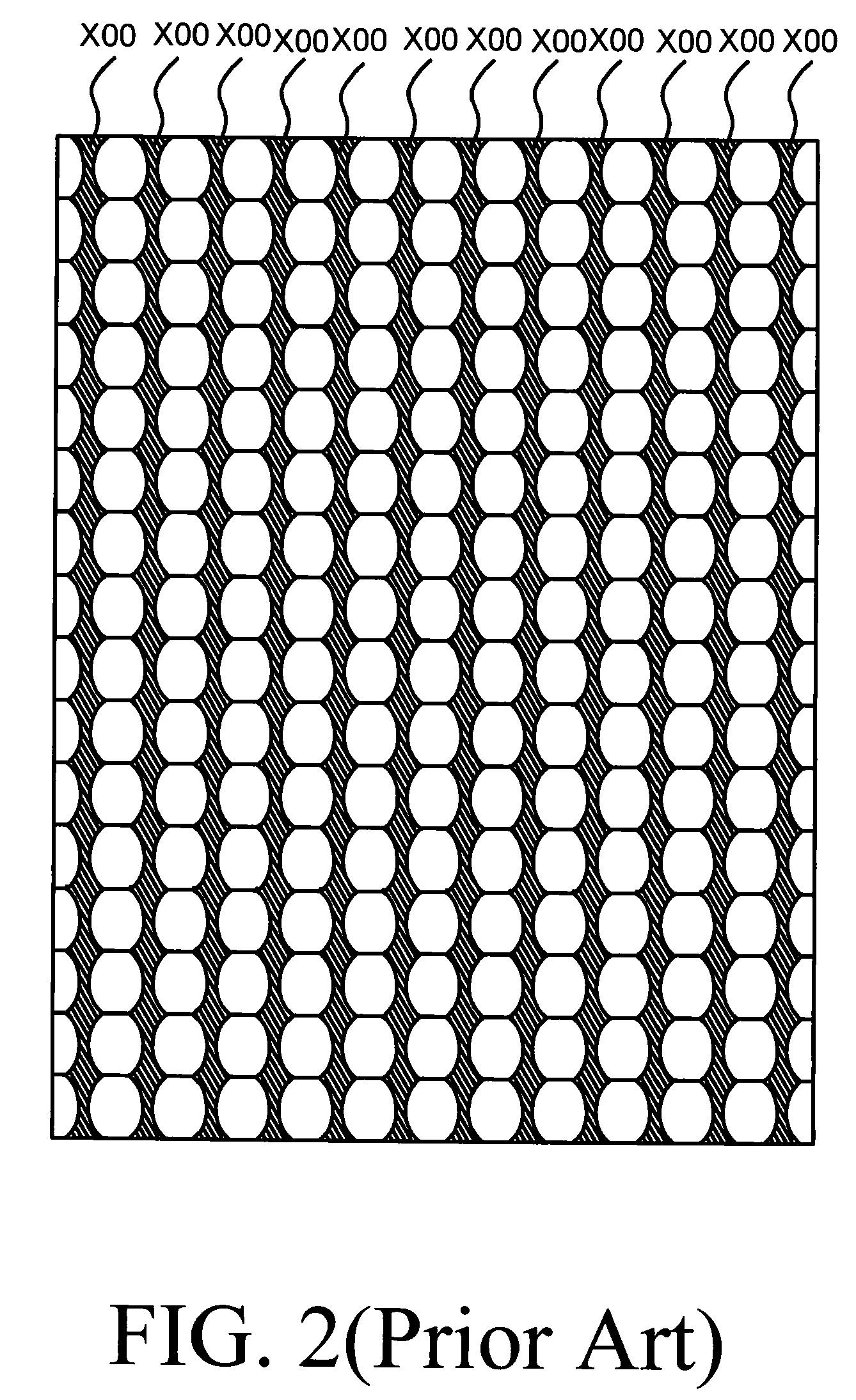

InactiveUS20110177639A1CohesionFurther manufacturing costSolid-state devicesSemiconductor/solid-state device manufacturingLine widthImage resolution

A thin film transistor display panel includes gate wiring formed on an insulation substrate and including gate lines, and gate electrodes and gate pads connected to the gate lines; a gate insulation layer covering the gate wiring; a semiconductor pattern formed over the gate insulation layer; data wiring formed over the gate insulation layer or the semiconductor pattern and including source electrodes, drain electrodes, and data pads; a protection layer including a Nega-PR type of organic insulating layer formed all over the semiconductor pattern and the data wiring, wherein the thickness of the Nega-PR type of organic insulating layer in both the gate and data pad regions is smaller than in the other regions; and a pixel electrode connected to the drain electrode. When exposing the Nega-PR type of passivation layer in the pad region during a photolithography process, a photomask having a lattice pattern made of a metal such as Cr that has a line width of less than the resolution of a light exposer is used. Thus, the resulting post-etch height of the passivation layer can be selectively controlled so as to provide reduced effective thickness in the pad regions.

Owner:SAMSUNG DISPLAY CO LTD

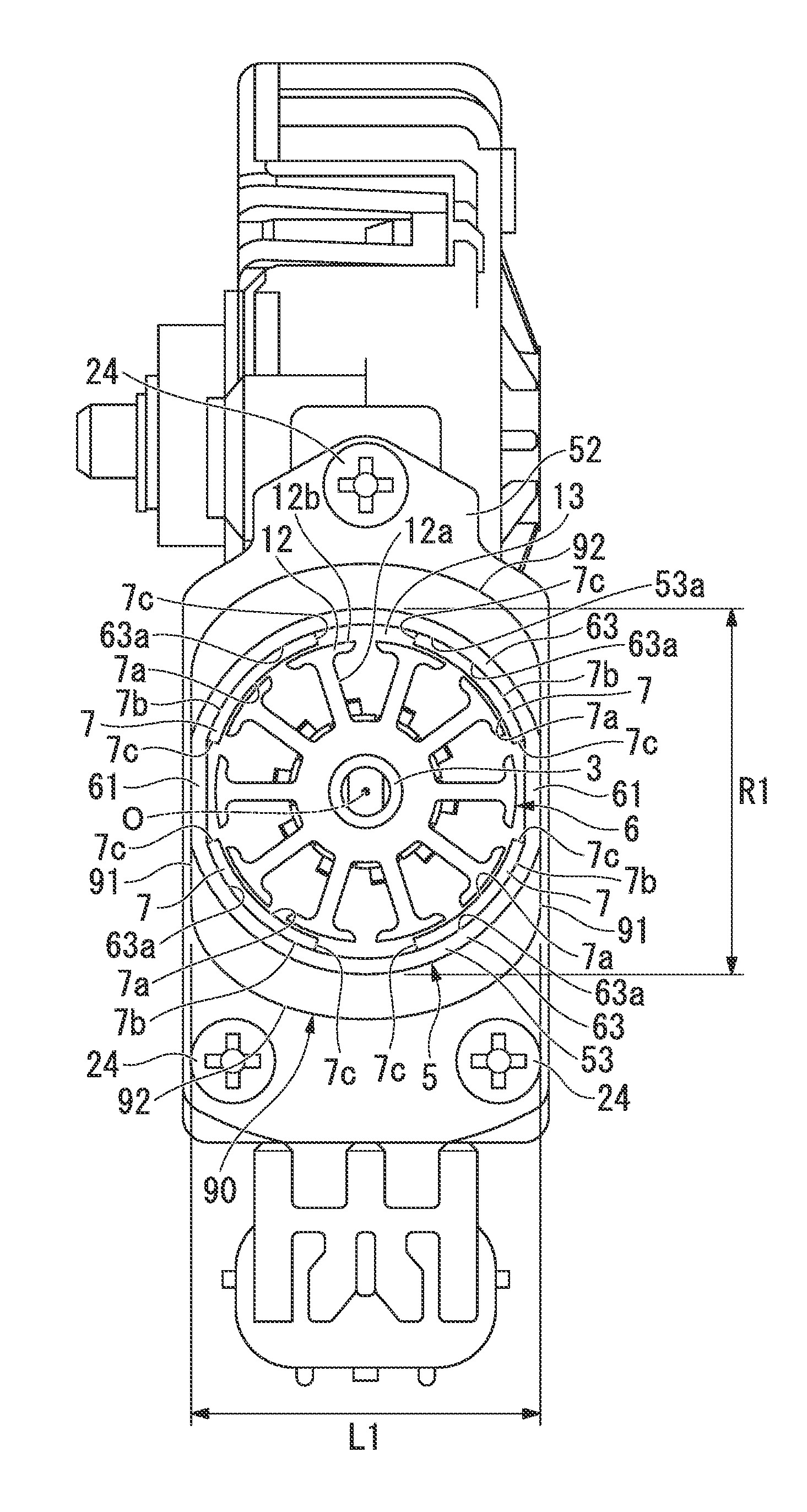

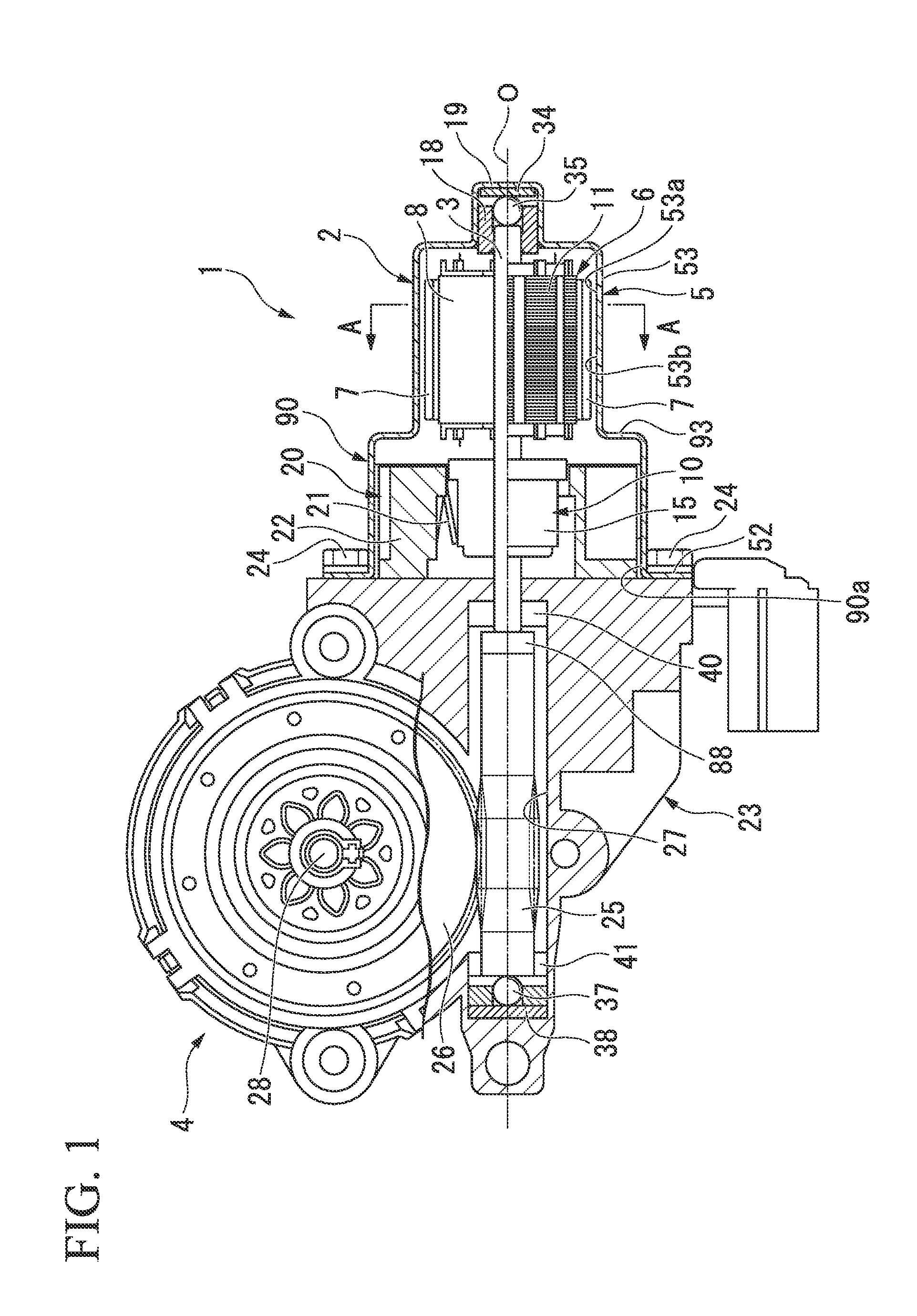

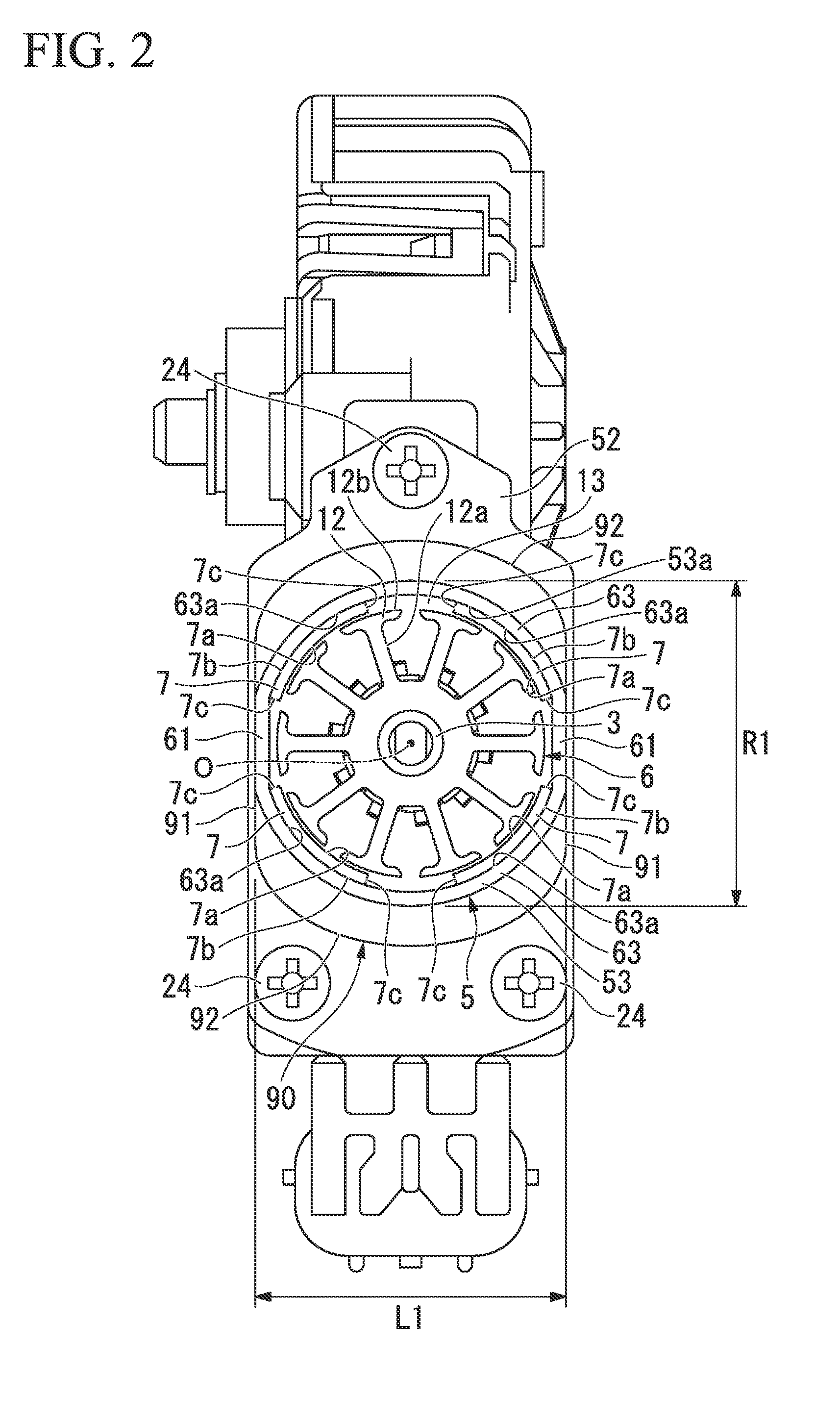

Electric motor

ActiveUS20150130329A1Small sizeImprove balanceMagnetic circuit rotating partsMagnetic circuit stationary partsMagnetElectric motor

An electric motor includes a yoke having a cylindrical section, two pairs of permanent magnets disposed at an inner circumferential surface of the cylindrical section to oppose each other, and an armature rotatably supported further inside in a radial direction than the permanent magnets, wherein at least a pair of first flat sections opposing each other in the radial direction are formed at the cylindrical section, and the permanent magnets are disposed at positions distant from the first flat sections.

Owner:MITSUBA CORP

Chip resistor having low resistance and its producing method

InactiveUS20050225424A1Increase connection heightReduce the overall heightResistor chip manufactureResistors adapted for applying terminalsEngineeringLow resistance

A resistor, including a resistive element made of a metal plate, has a low resistance resulting from connection terminal electrodes formed on both ends of the lower surface of the resistive element. The object thereof is to achieve weight reduction by reducing the height and also to achieve lower costs. To attain the above object, the ends of the lower surface of the resistive element are provided with recesses for accommodating the connection terminal electrodes, while at least the intermediate area of the lower surface of the resistive element between the connection terminal electrodes is covered with an insulator. Alternatively, a recess may be formed in the middle of the lower surface of the resistive element for using the ends of the lower surface as a pair of connection terminal electrodes, the recess being internally covered with an insulator.

Owner:ROHM CO LTD

Oven controlled crystal oscillator for high stability

InactiveUS20050082377A1Easy to operateLarge thicknessDomestic cooling apparatusLighting and heating apparatusTemperature controlHeat sensitive

To provide a highly stable crystal oscillator having increased thermal efficiency. The highly stable crystal oscillator comprises; a thermostat mainframe which maintains the temperature of a crystal resonator including a resonator container for sealing a crystal piece constant, an oscillating element which constitutes an oscillation circuit together with said crystal resonator, a temperature control element which controls the temperature inside of said thermostat mainframe, and a circuit board mounted with said thermostat mainframe, said oscillating element, and said temperature control element. The construction is such that a heat generating chip resistor and a highly heat sensitive element having a higher temperature dependency, among said oscillating element and said temperature control element, are arranged on one principal plane of said circuit board, and said heat generating chip resistor, said highly heat sensitive element, and said thermostat mainframe are directly heat bonded by a thermo-conductive material.

Owner:NIHON DEMPA KOGYO CO LTD

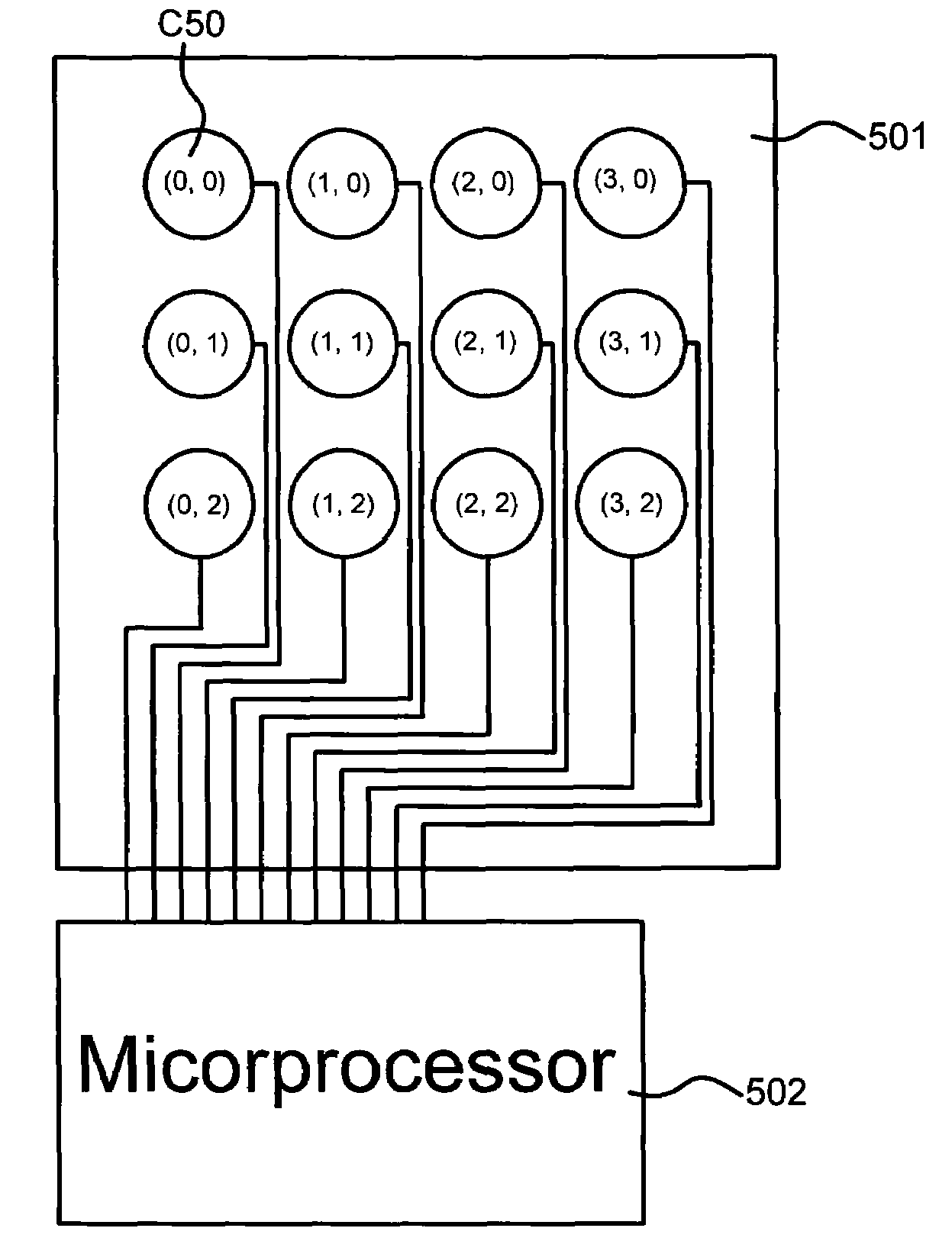

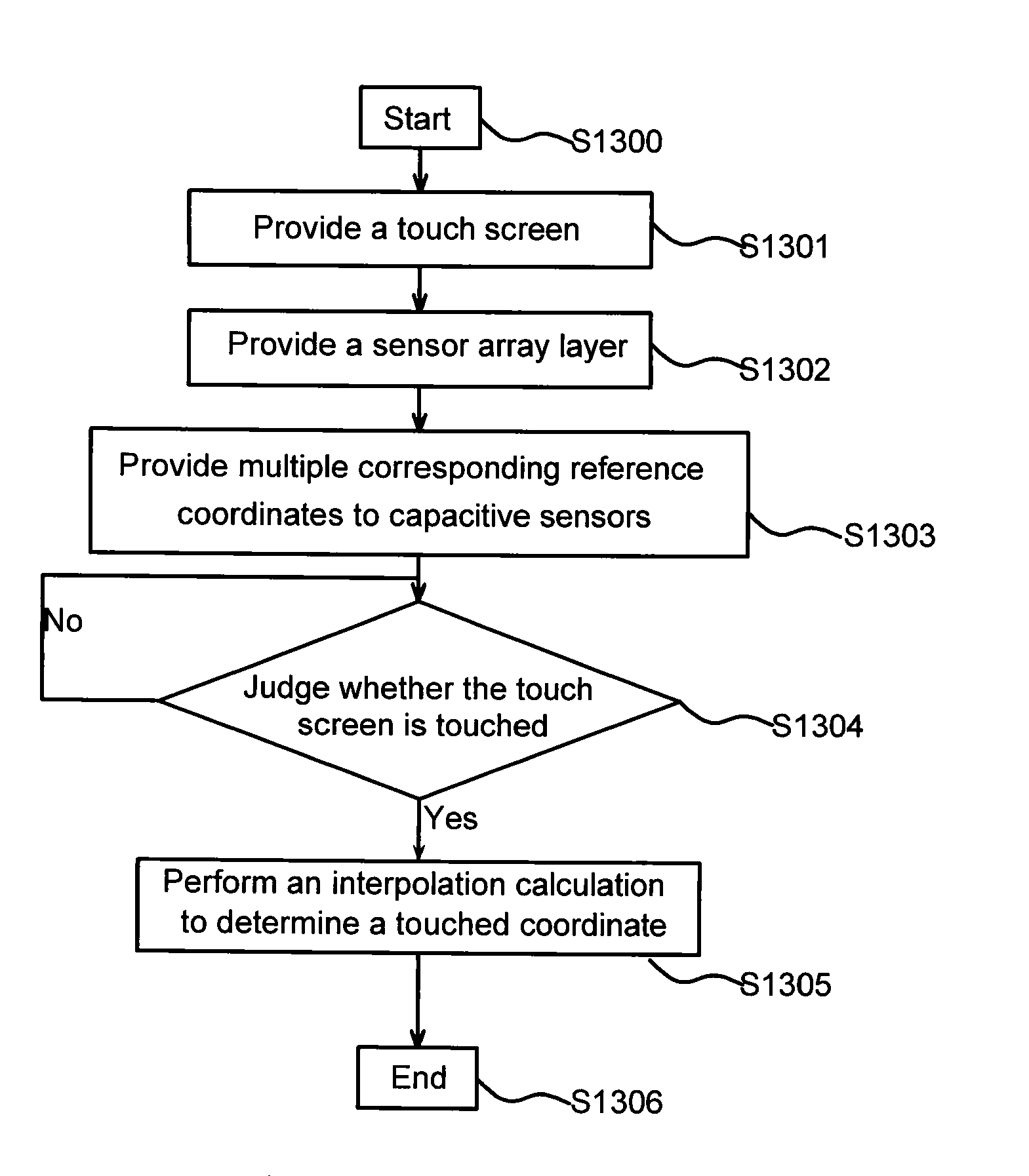

Touch screen and method for positioning coordinate

InactiveUS8462127B2High resolutionReduce manufacturing costInput/output processes for data processingSensor arrayTouchscreen

The present invention relates to a touch screen and a method for positioning a coordinate. The touch screen includes a sensor array layer and a microprocessor. The sensor array layer includes M×N capacitive sensors, wherein M rows of the capacitive sensors are disposed along a first axis, and N columns of the capacitive sensors are disposed along a second axis. The microprocessor includes a plurality of pins correspondingly coupled to the capacitive sensors. When the touch screen is touched to change at least one of sensing values of the capacitive sensors in the sensor array layer, the microprocessor performs an interpolation calculation to determine a touched coordinate according to the sensing values sensed by the capacitive sensors.

Owner:ELAN MICROELECTRONICS CORPORATION

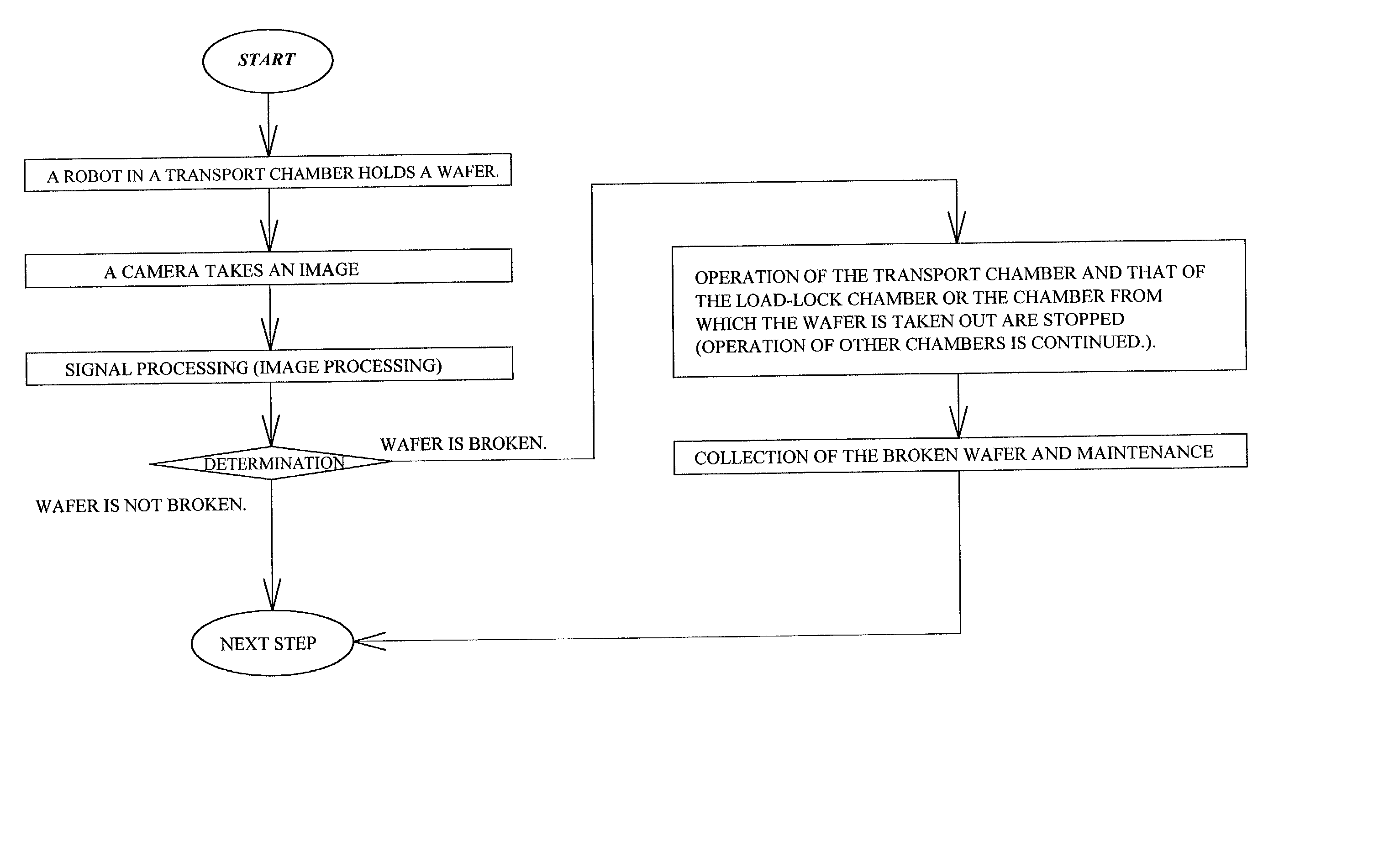

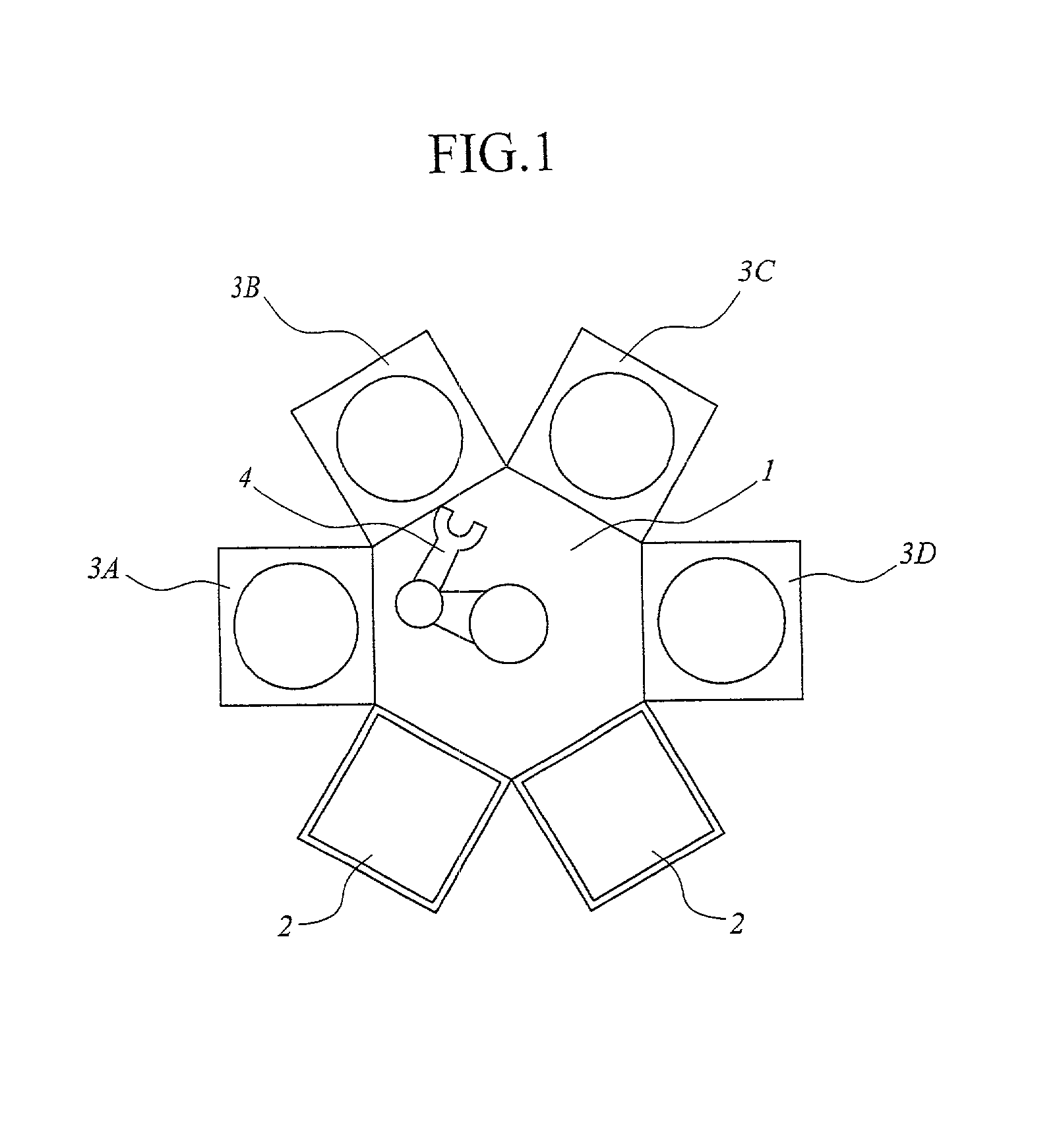

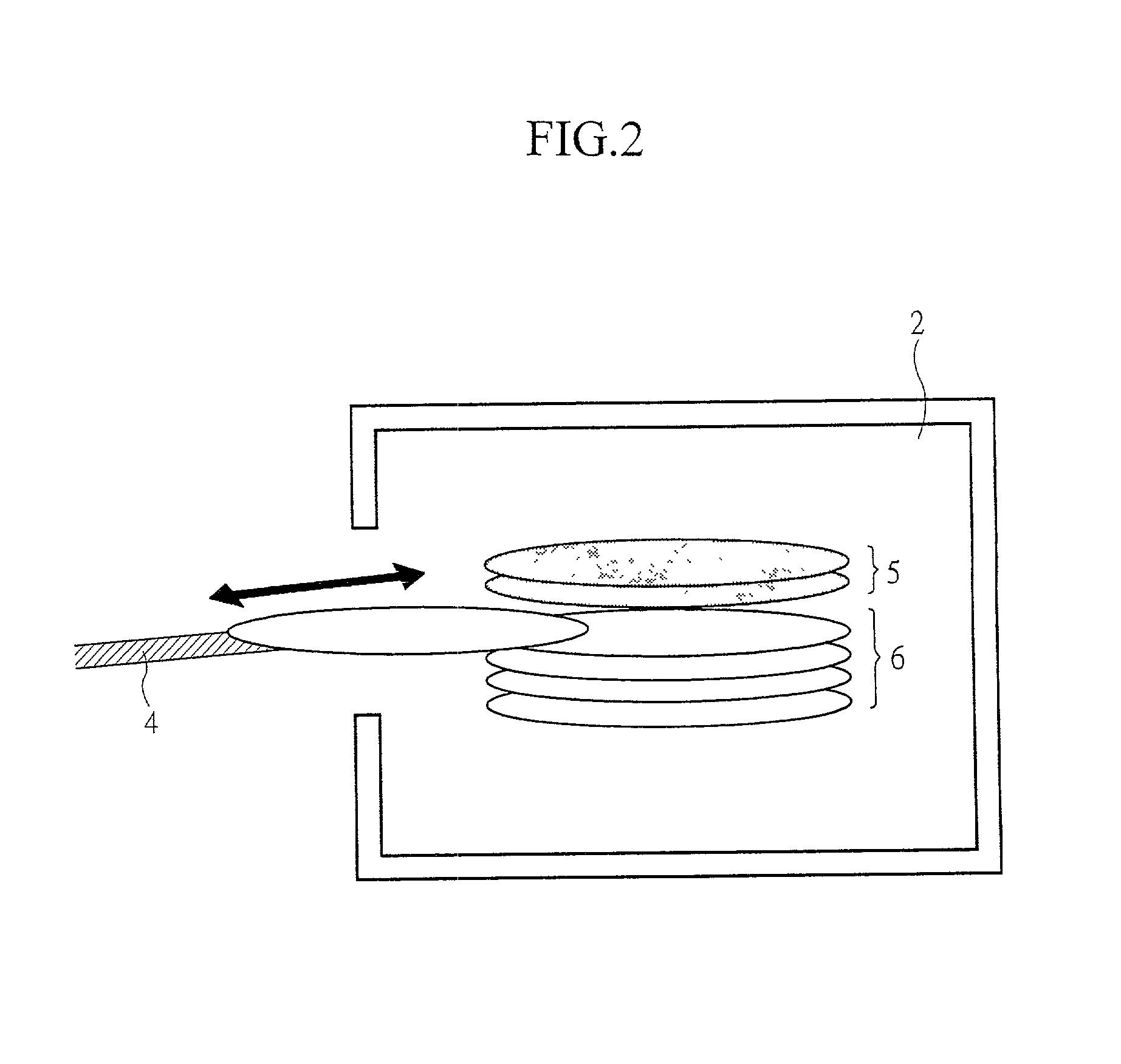

Method of manufacturing semiconductor integrated circuit device and semiconductor manufacturing apparatus

InactiveUS20020127852A1Increase manufacturing costIncrease of cost per waferSemiconductor/solid-state device testing/measurementVacuum evaporation coatingWaferingManufactured apparatus

Disclosed is a technique capable of suppressing the damage of a semiconductor manufacturing apparatus due to the breakage or the crack to the minimum by surely detecting the breakage or the crack on a part of a wafer in a semiconductor manufacturing apparatus of a multi-chamber system. An entire image of a wafer is photographed by a camera in each time when the wafer is processed, and the photographed image is processed by a discrimination unit, thereby determining the presence of the breakage or the crack on the wafer. When the breakage or the crack is detected, an error signal is transmitted from the discrimination unit to a computer that controls the semiconductor manufacturing apparatus, and the operations of the process chamber and the transport chamber used immediately before the detection of the breakage or the crack on the wafer are stopped.

Owner:RENESAS TECH CORP

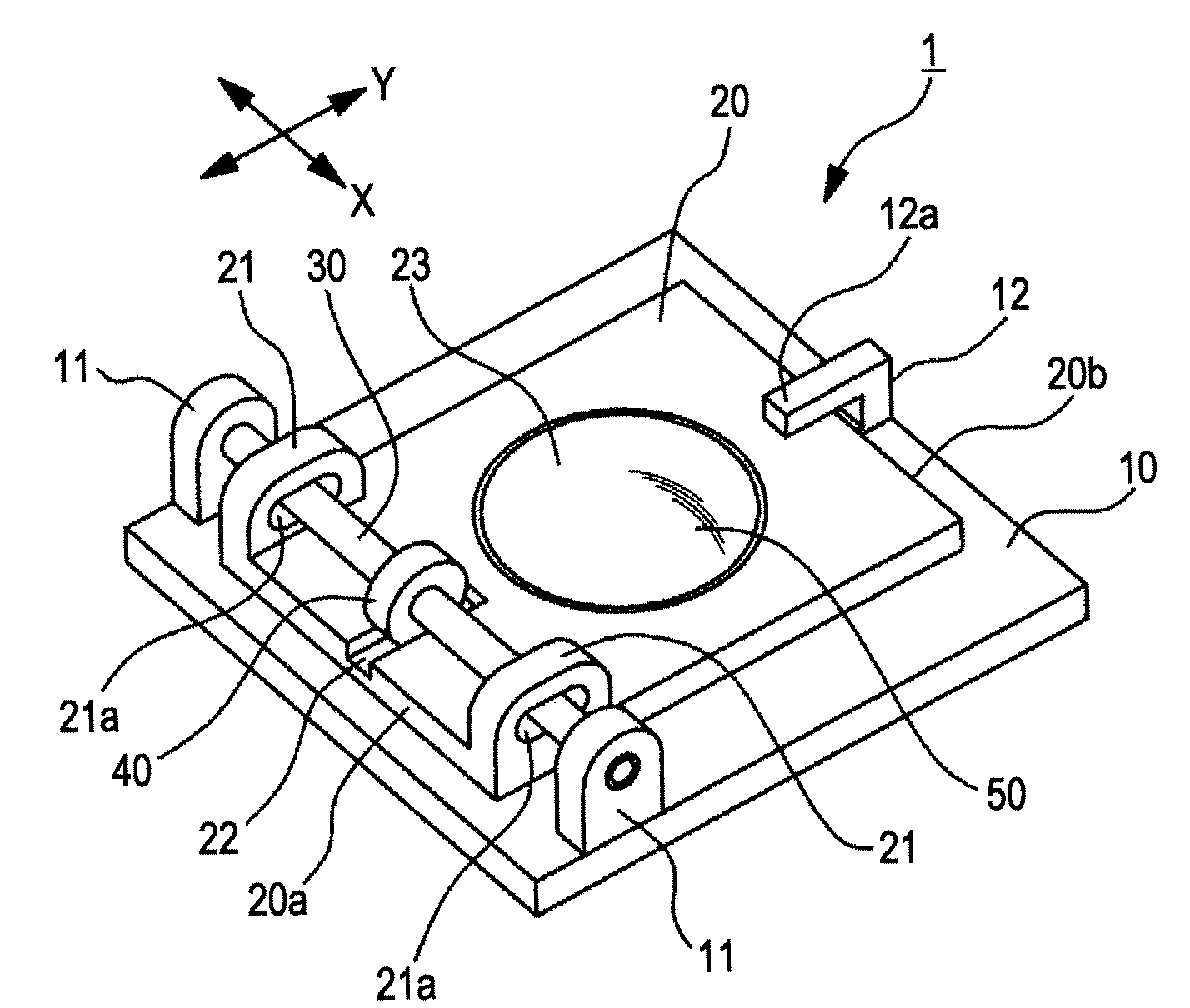

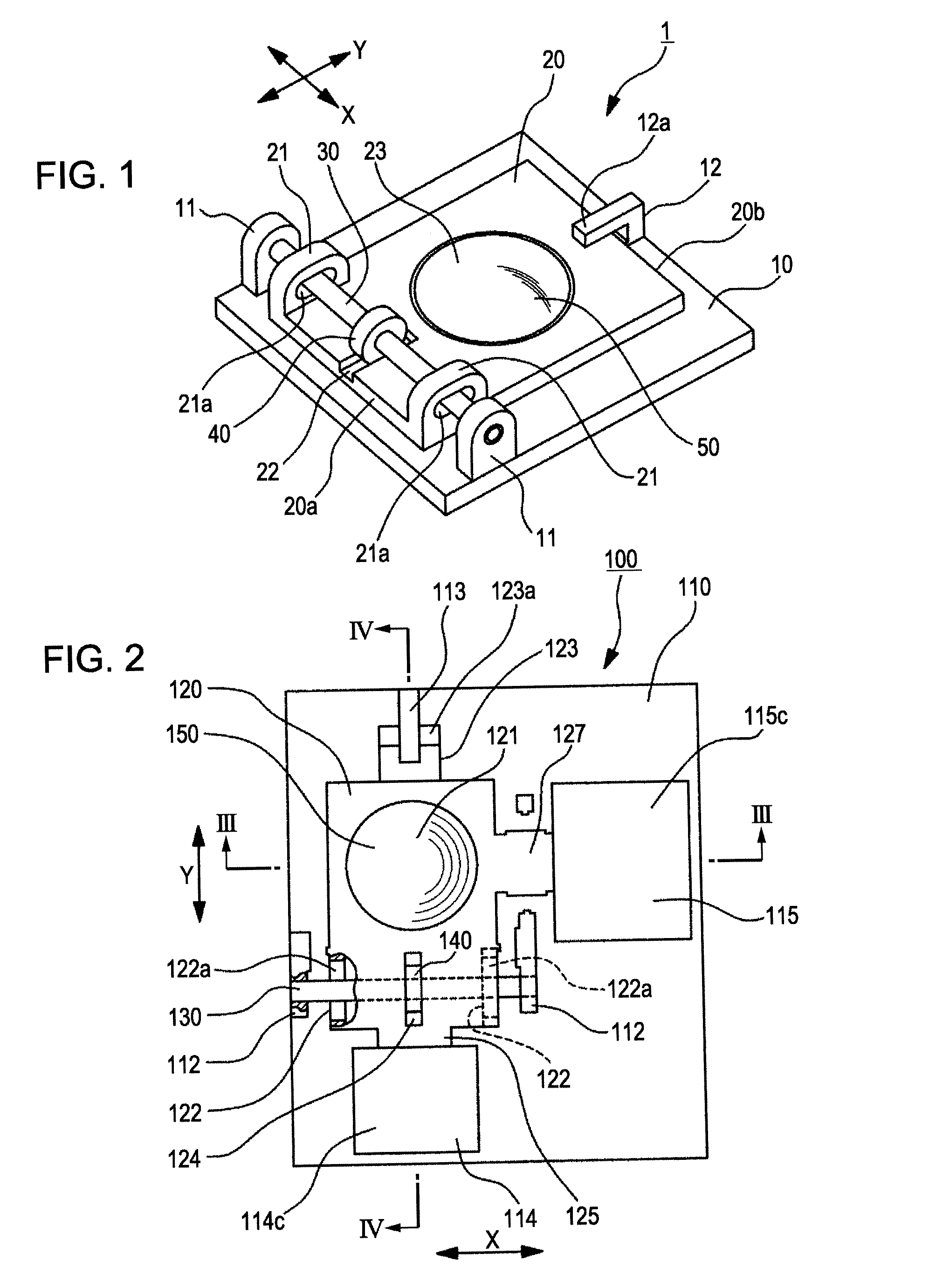

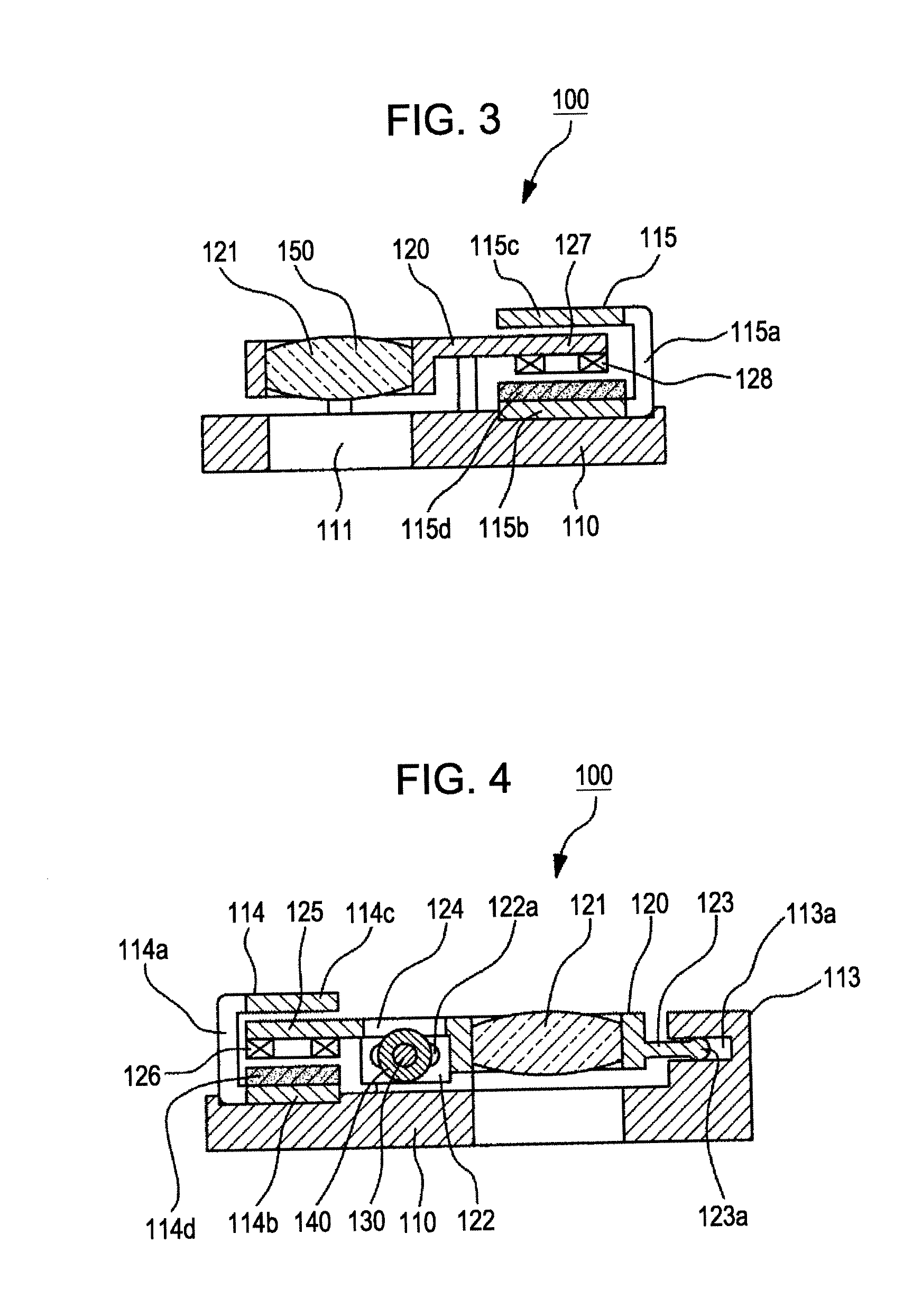

Image stabilization mechanism and image pickup apparatus

InactiveUS20080055571A1Prevent rollingSimple structureTelevision system detailsProjector focusing arrangementOptical axisImage stabilization

An image stabilization mechanism moves a movable lens or an imager in first and second directions perpendicular to each other and perpendicular to a light axis of the lens or an incident light axis of the imager. The mechanism includes a support member for supporting the movable lens or imager, a base member, a guide shaft secured to the base member and extending in the first direction, where the guide shaft is disposed in an elongate hole formed in the support member in a slidable manner in the first and second directions, an anti-rolling member fitted into the guide shaft in a slidable manner in its axis direction and engaged with the support member in a slidable manner in the second direction so as to prevent rolling of the support member about the light axis, and two drivers for moving the support member independently in the first and second directions.

Owner:SONY CORP

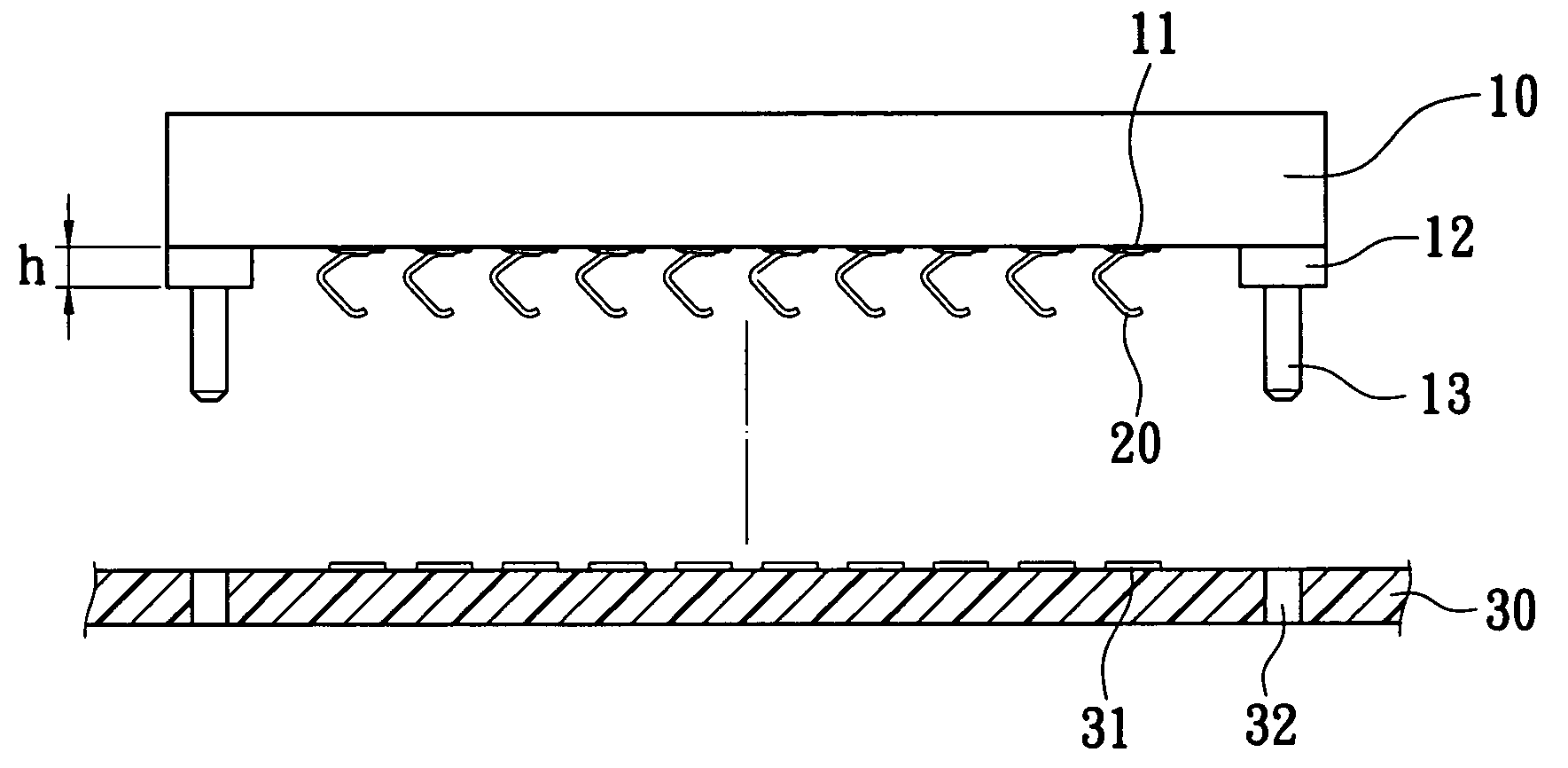

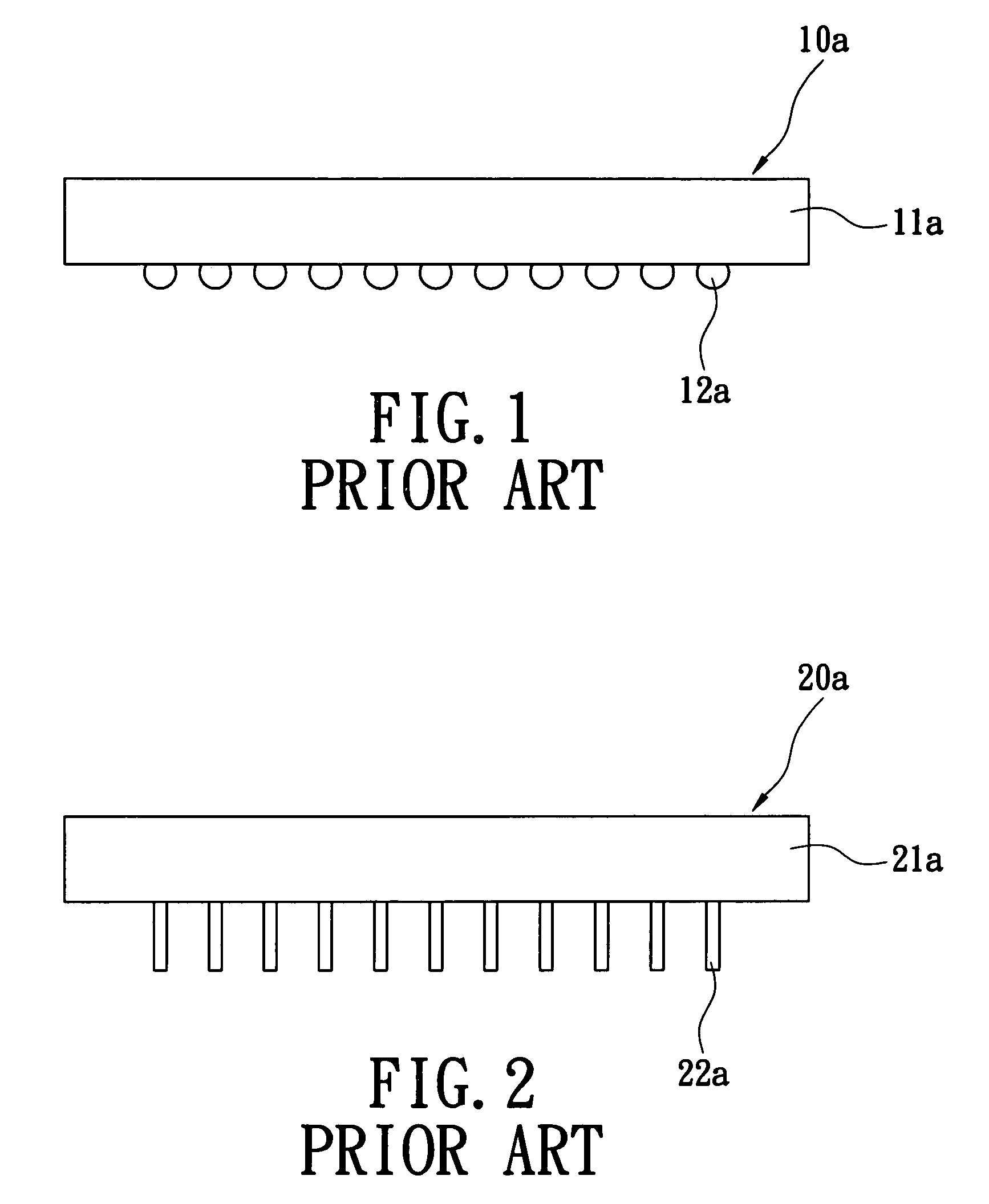

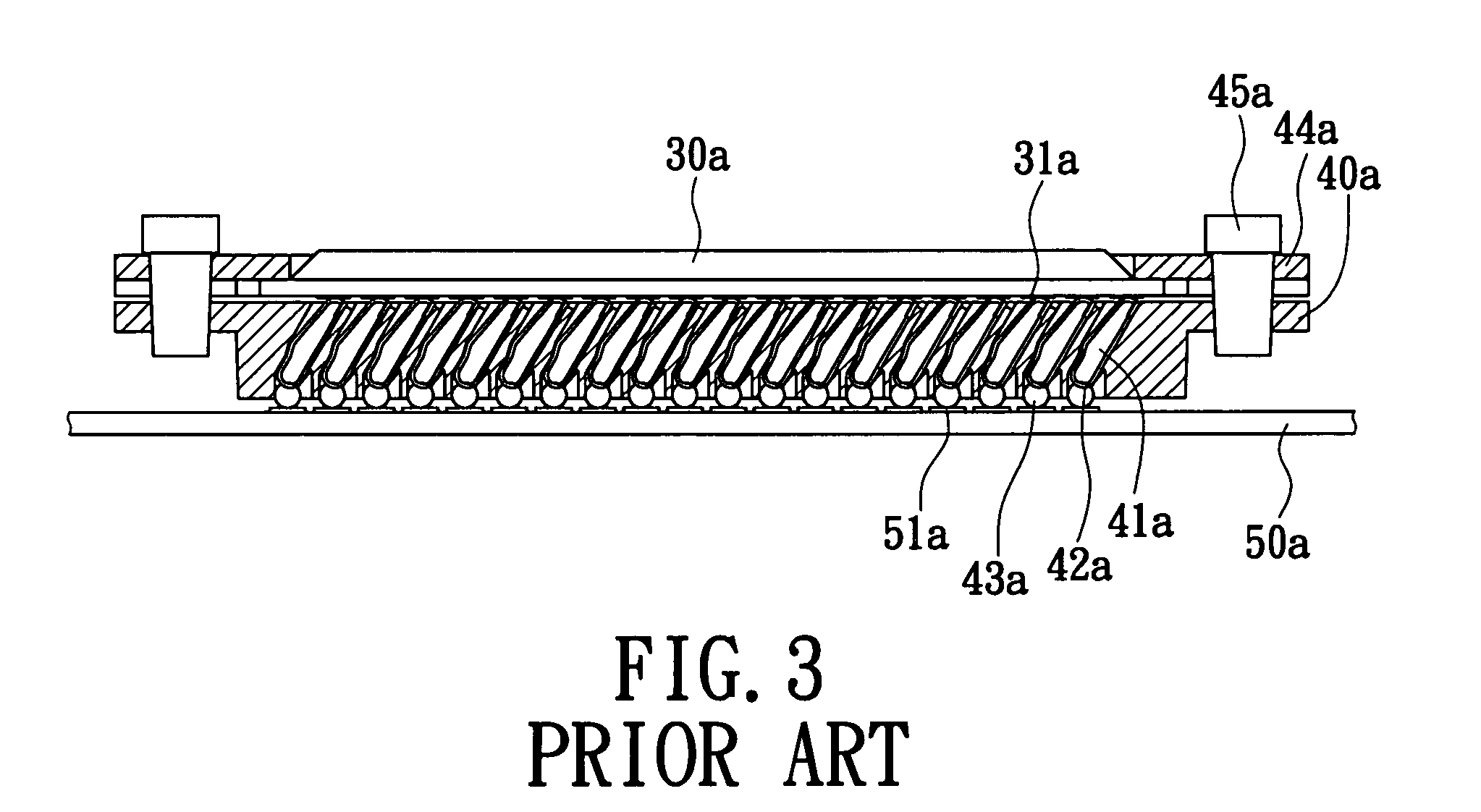

IC module assembly

ActiveUS7057295B2Low costReduce stepsPrinted circuit assemblingSemiconductor/solid-state device detailsEngineeringElectrical and Electronics engineering

An IC module assembly includes an IC module including a plurality of pads disposed on a bottom thereof, a plurality of resilient members respectively soldering to the pads, and a PCB having a plurality of conductive patterns arranged on a top thereof and corresponding to the resilient members respectively, whereby the IC module electrically connects the PCB by the resilient members abutting against the conductive patterns of the PCB.

Owner:JU TED

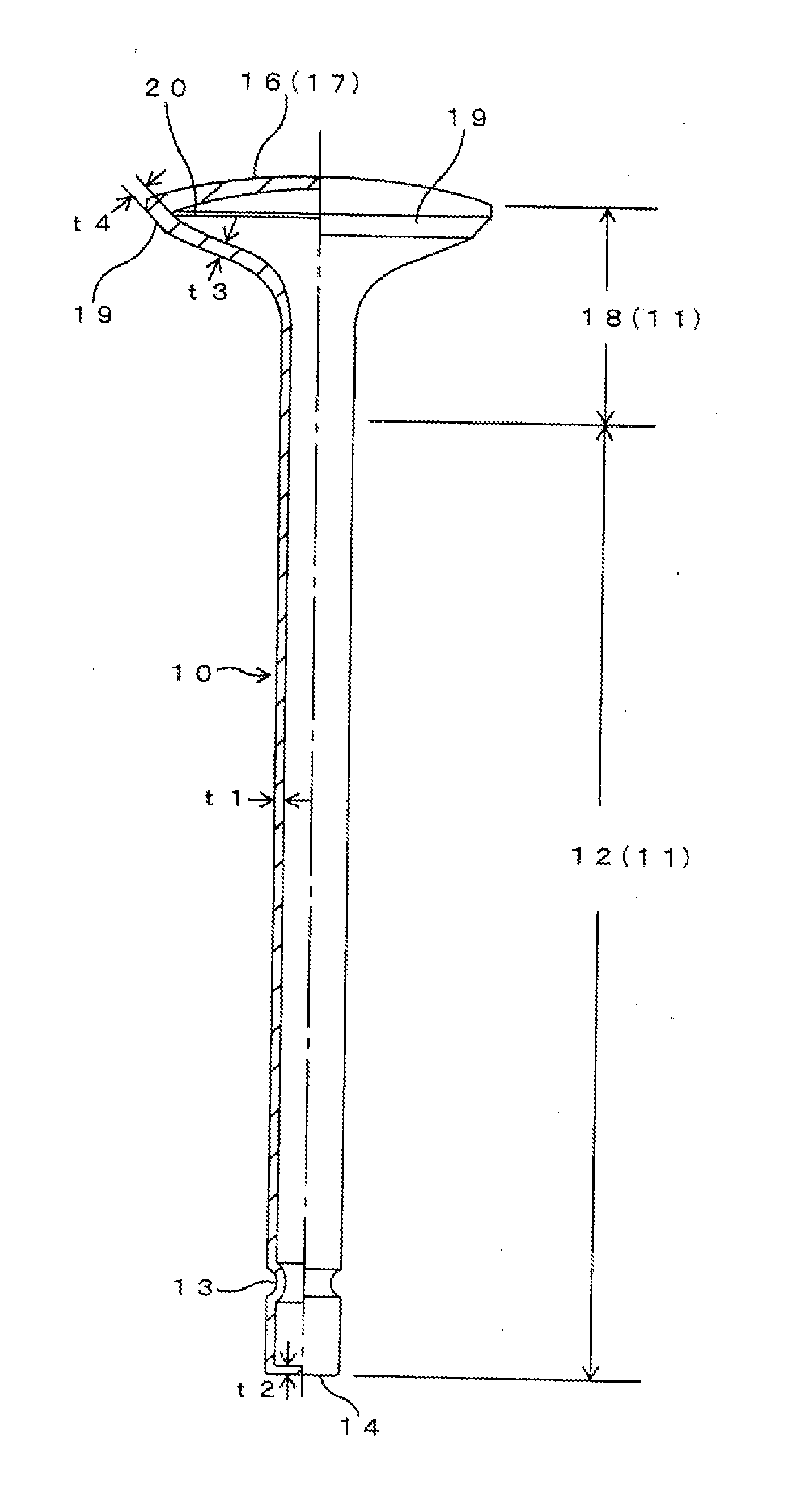

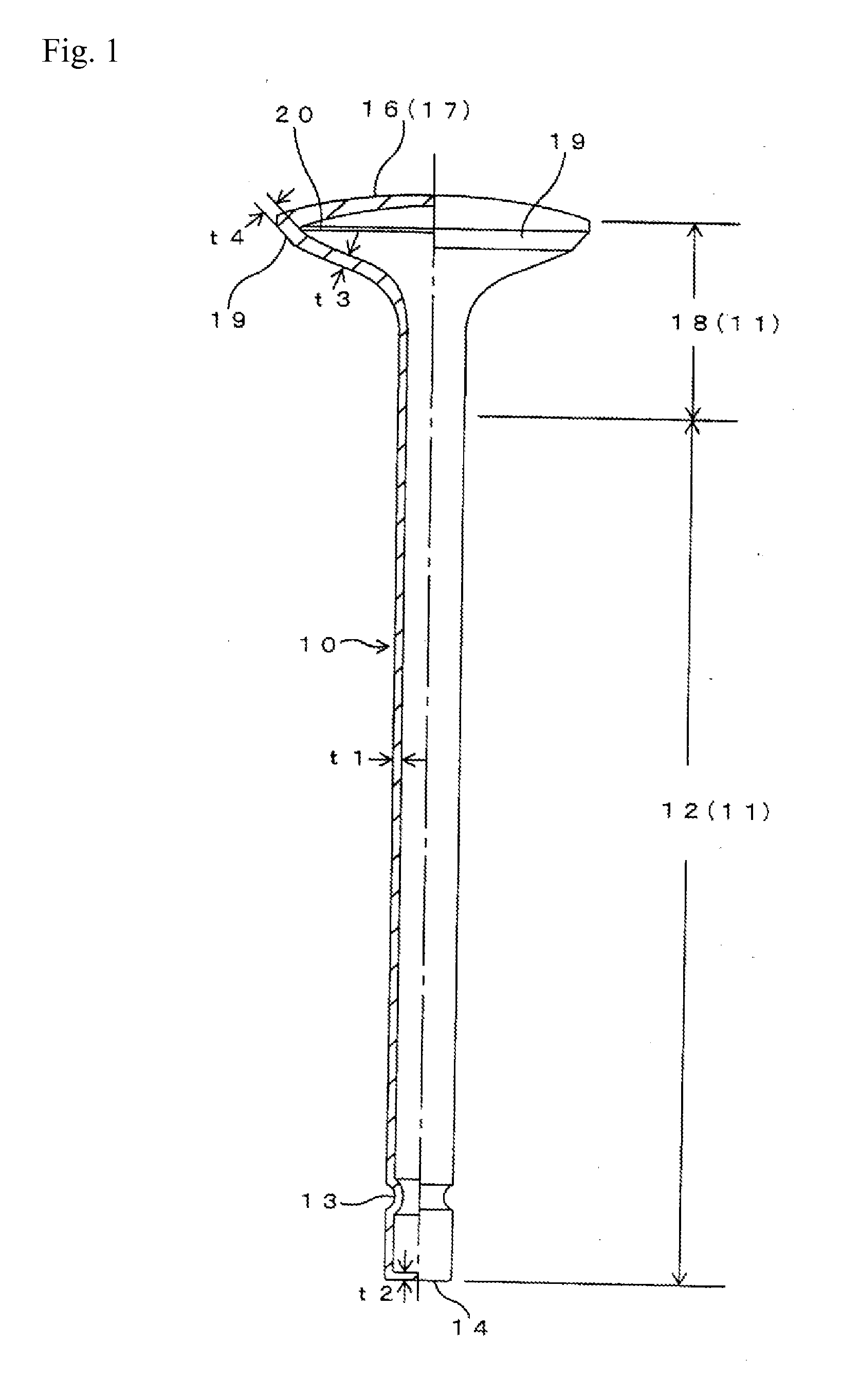

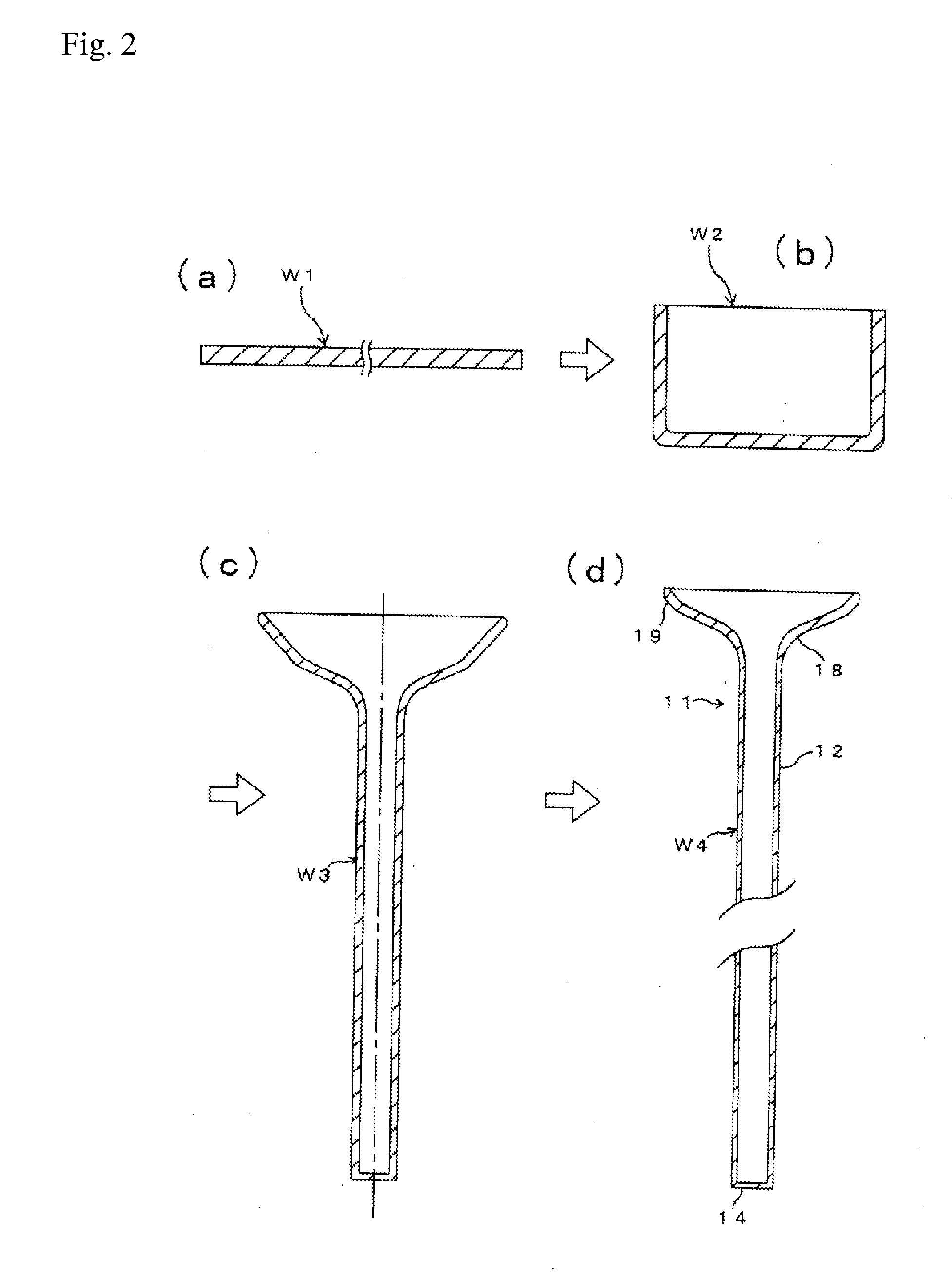

Hollow poppet valve and method of manufacturing the same

ActiveUS20110186000A1CharacteristicCost-effectiveSoldering apparatusMachines/enginesAbutmentEngineering

A hollow poppet valve has a stem portion provided at one end thereof with a tip portion; a cap portion; and a flared fillet portion formed between the stem portion and the cap portion, wherein at least a part of the stem portion that connects to the fillet portion is a thin hollow cylindrical member, and the cap member is welded to the fillet portion. The cap member is thin and has an arcuate axial cross section. It is laser-beam welded to the seat-abutment portion formed at the open end of the fillet portion such that a weld bead is formed along the inner periphery of the interface of the mated ends of the members. The weld bead adds an extra weld depth to the weld, which increases the modulus of section of the welded regions of the cap member and the fillet portion and enhances their welding strength.

Owner:NITTAN VALVE CO LTD

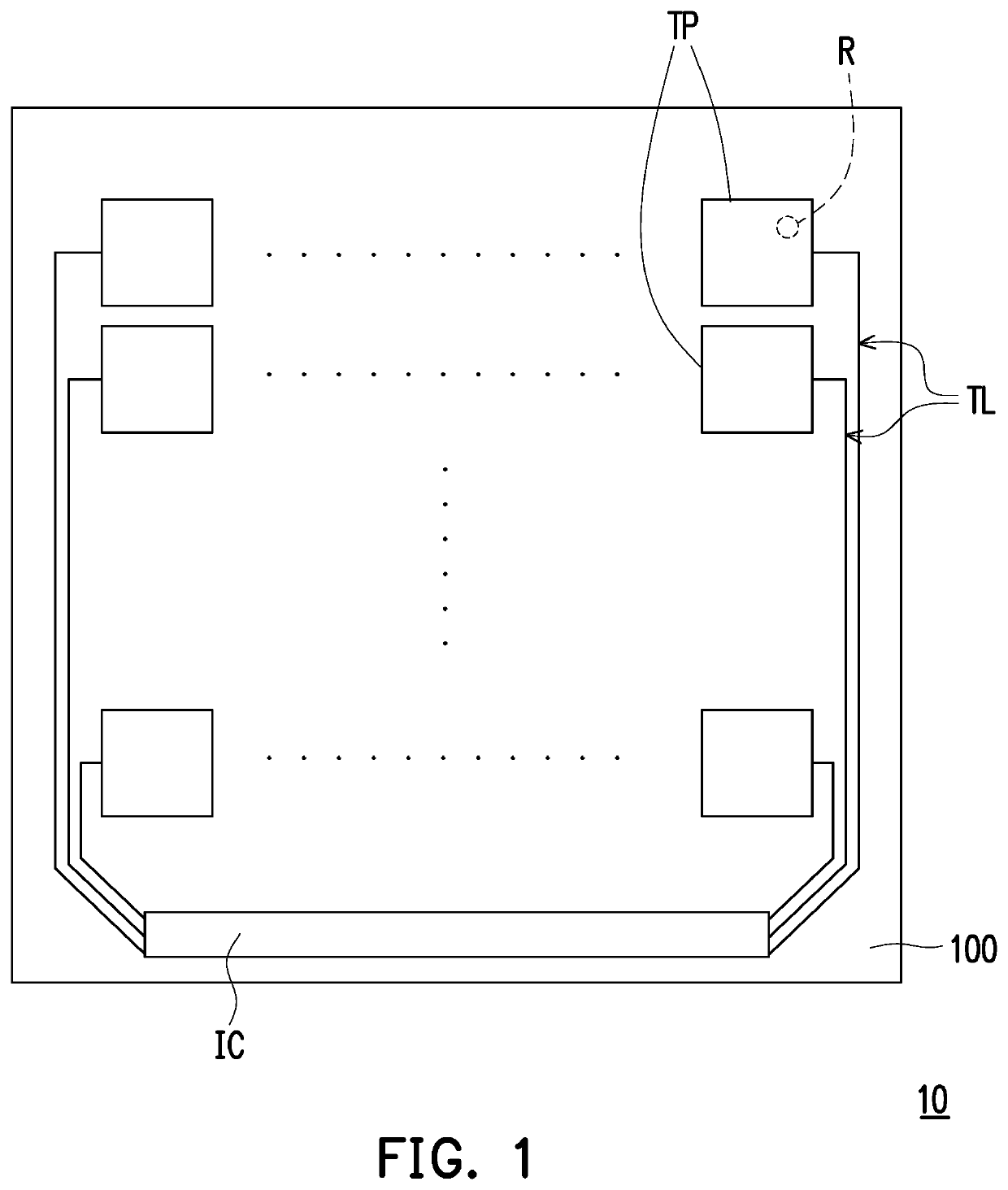

Touch screen and method for positioning coordinate

InactiveUS20100033449A1High resolutionReduce manufacturing costInput/output processes for data processingSensor arrayEngineering

The present invention relates to a touch screen and a method for positioning a coordinate. The touch screen includes a sensor array layer and a microprocessor. The sensor array layer includes M×N capacitive sensors, wherein M rows of the capacitive sensors are disposed along a first axis, and N columns of the capacitive sensors are disposed along a second axis. The microprocessor includes a plurality of pins correspondingly coupled to the capacitive sensors. When the touch screen is touched to change at least one of sensing values of the capacitive sensors in the sensor array layer, the microprocessor performs an interpolation calculation to determine a touched coordinate according to the sensing values sensed by the capacitive sensors.

Owner:ELAN MICROELECTRONICS CORPORATION

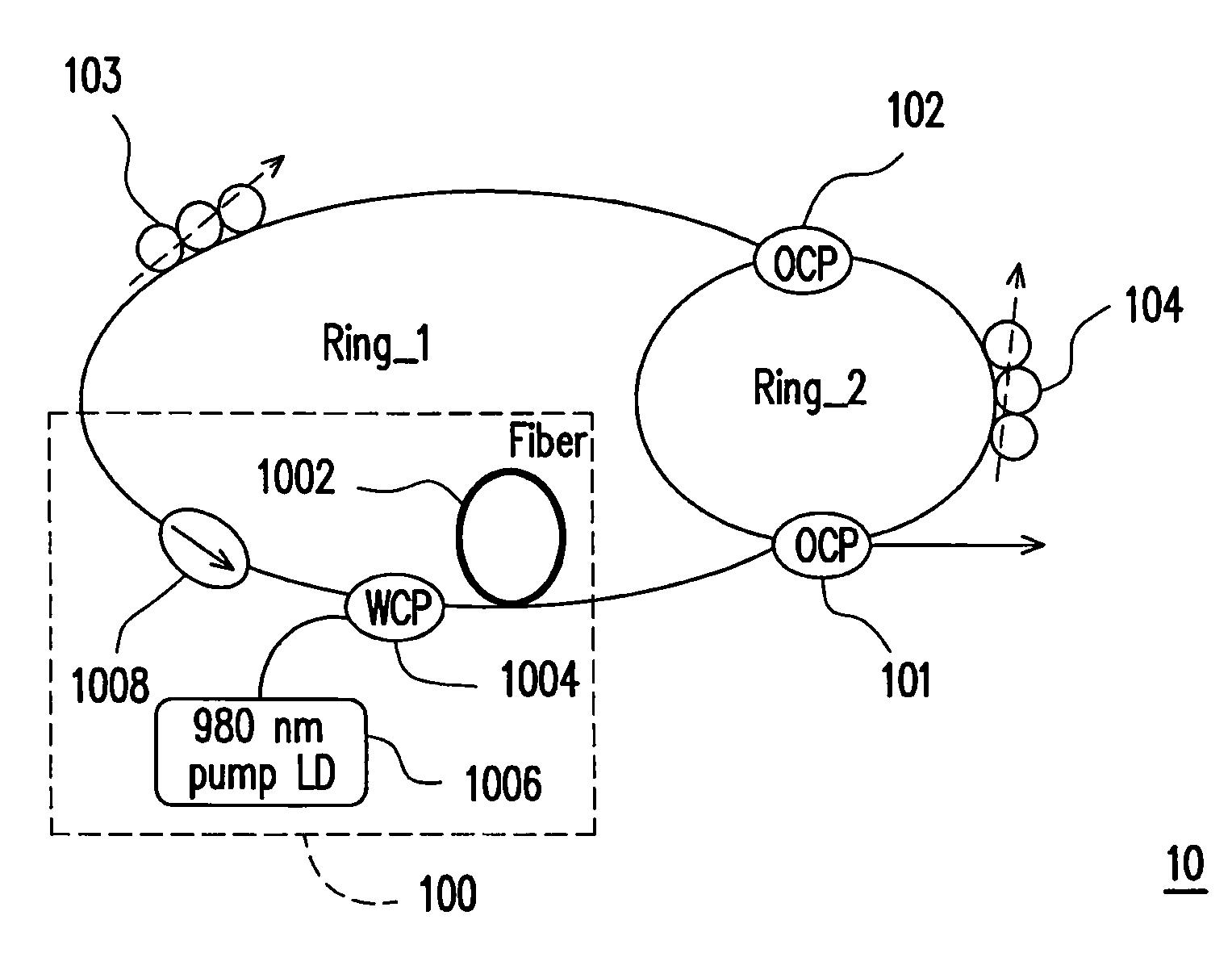

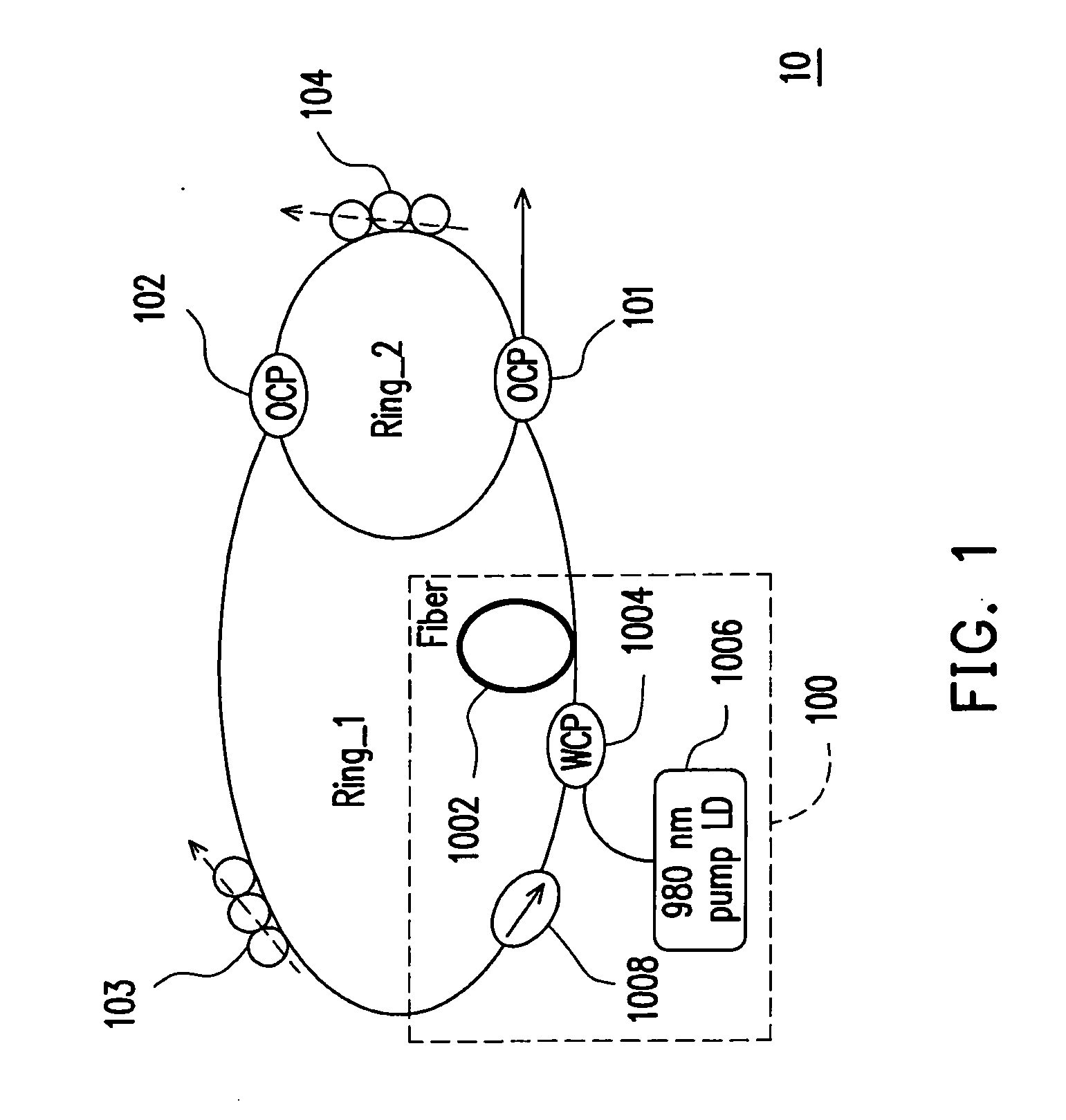

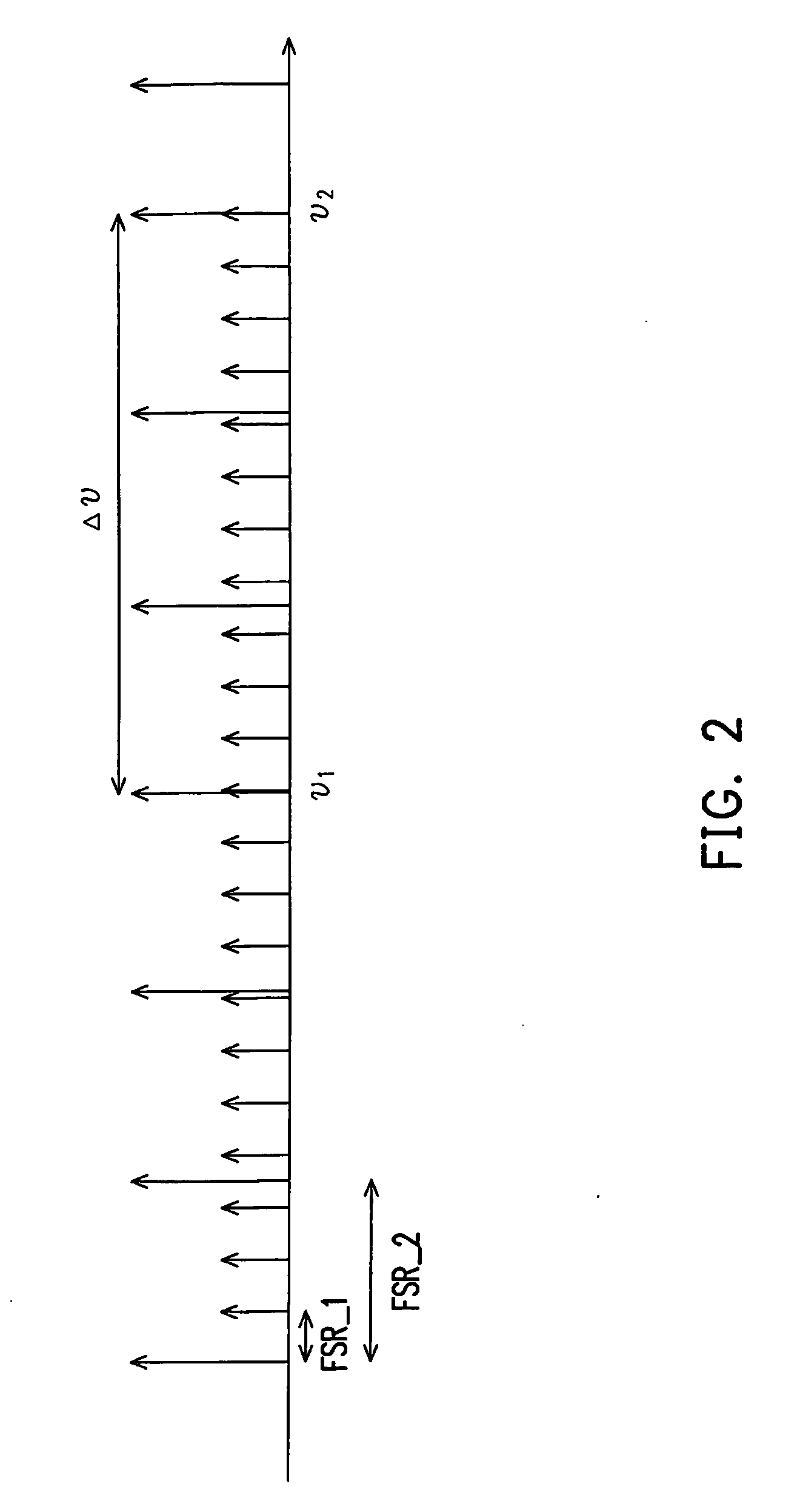

Fiber ring laser

InactiveUS20090086787A1Reduce manufacturing costFurther manufacturing costLaser using scattering effectsRing laserOptical coupler

A fiber ring laser is provided, which includes an optic amplifier, a first optical coupler (OCP), a second OCP, a first fiber ring, a second fiber ring, a first polarization controller (PC), and a second PC. The first fiber ring is coupled to the optic amplifier, the first and the second OCPs. The second fiber ring is coupled to the first and the second OCPs. The optic amplifier amplifies a first laser beam with a specified wavelength range. The first fiber ring receives the first laser beam. The first and the second fiber rings respectively provide a first and a second resonant cavities. The first and the second PCs respectively control polarization states of the first and second resonant cavities. The first laser beam resonates in the first and the second resonant cavities to generate a second laser beam with a first and a second wavelengths.

Owner:IND TECH RES INST

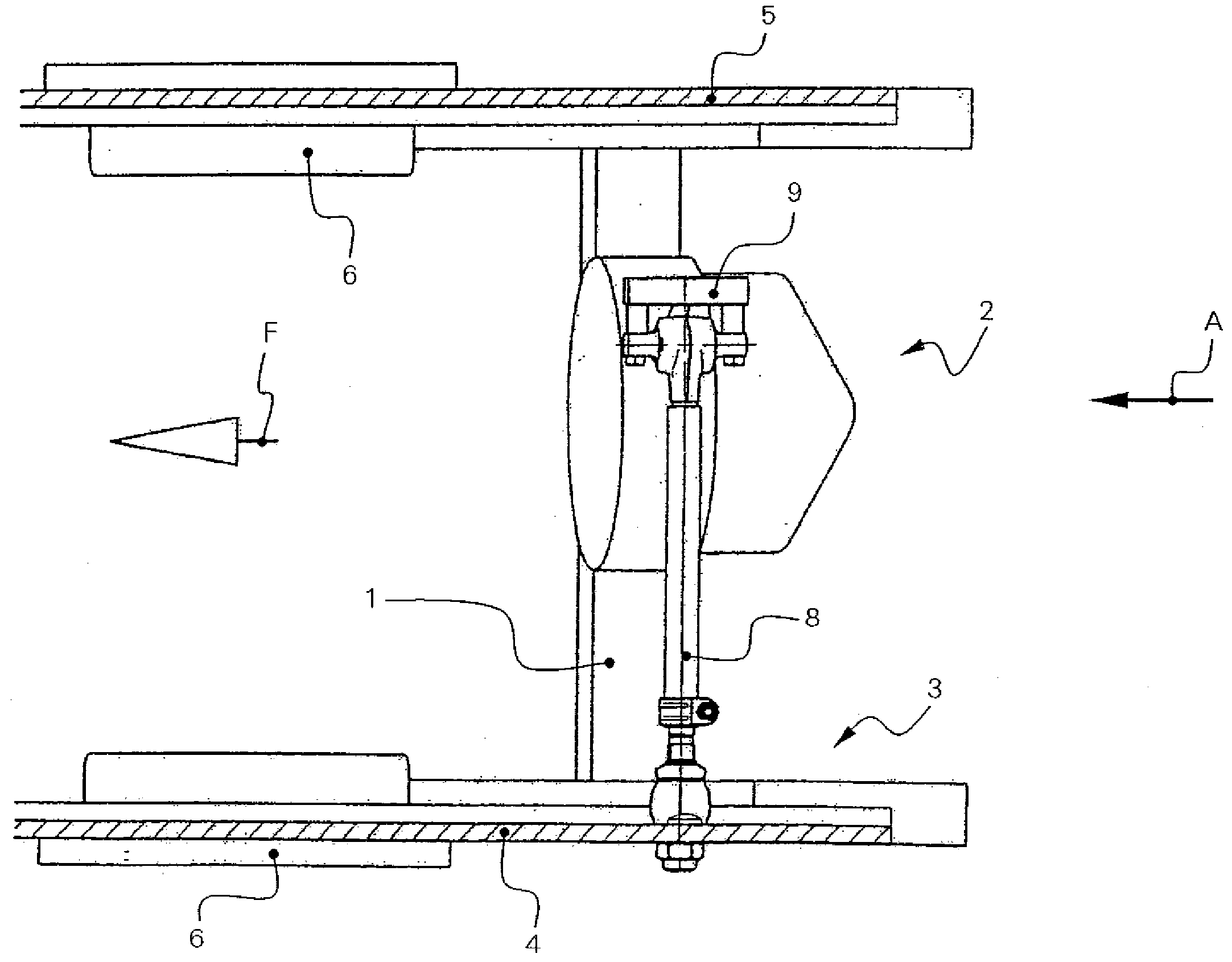

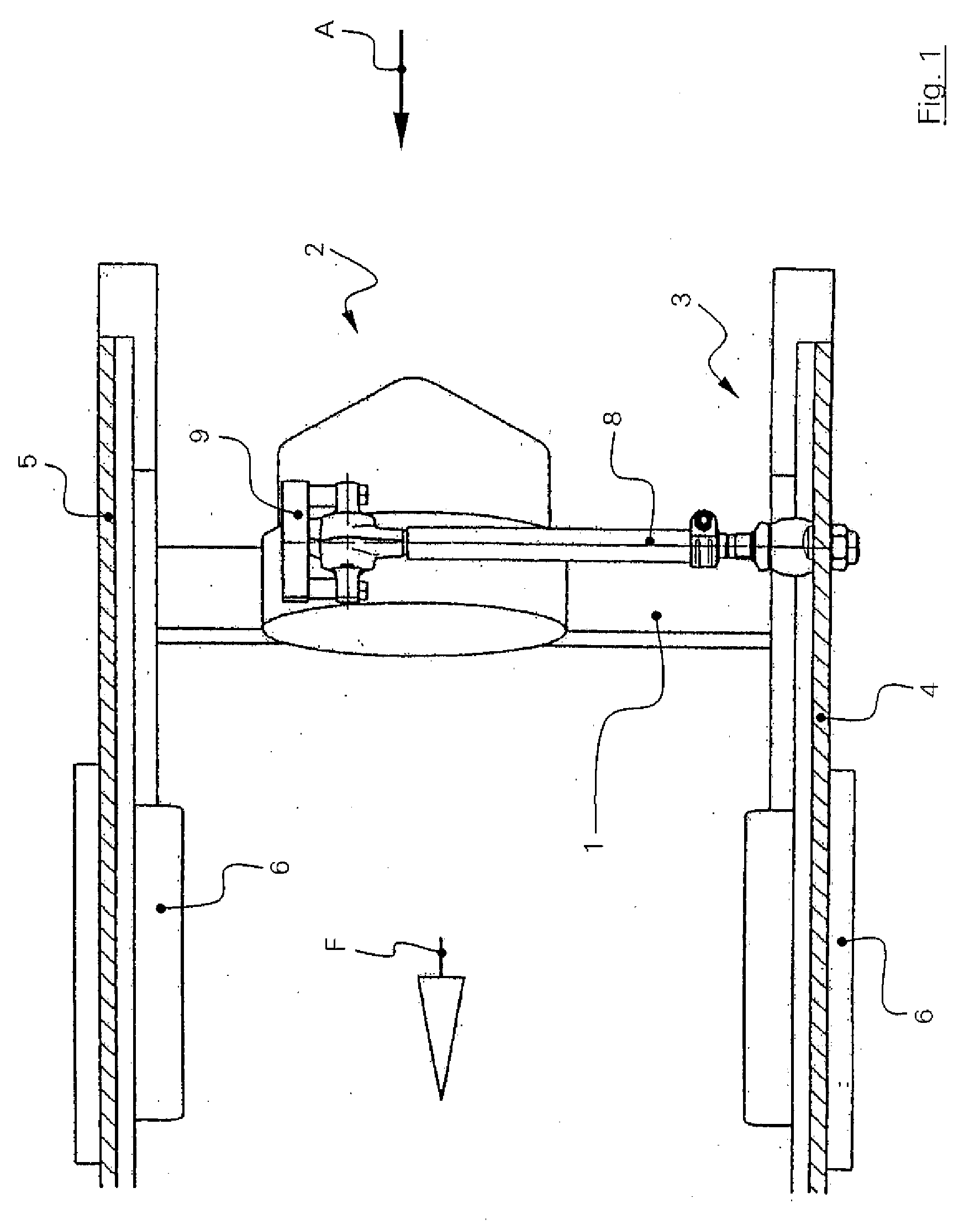

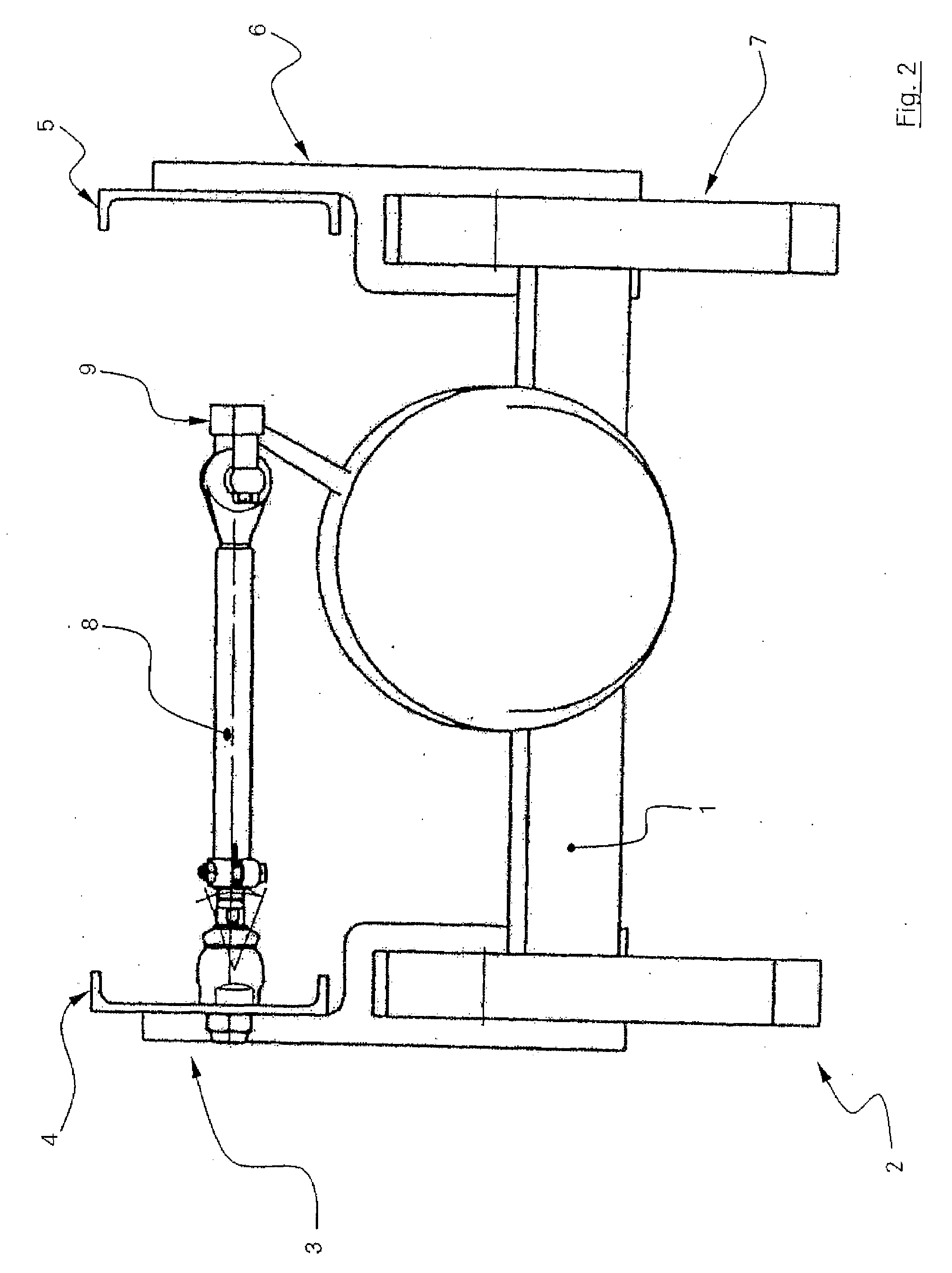

Motor Vehicle

InactiveUS20090001680A1Simple designReduces weight and number of componentResilient suspensionsPivoted suspension armsMobile vehicleAxial joints

A motor vehicle, especially a utility vehicle, with a vehicle chassis (3) as well as with a rear axle arrangement (2) having a rigid axle (1). A Panhard rod (8) for supporting lateral forces or a control arm for supporting longitudinal forces is arranged between the vehicle chassis (3) and the rigid axle (1). The motor vehicle has the Panhard rod (8), which is directly articulated to the vehicle chassis (3) with an axial joint (11) in a pivotingly movable manner or by a control arm. The Panhard rod (8) is articulated to the rigid axle directly with an axial joint (11) in a pivotingly movable manner.

Owner:ZF FRIEDRICHSHAFEN AG

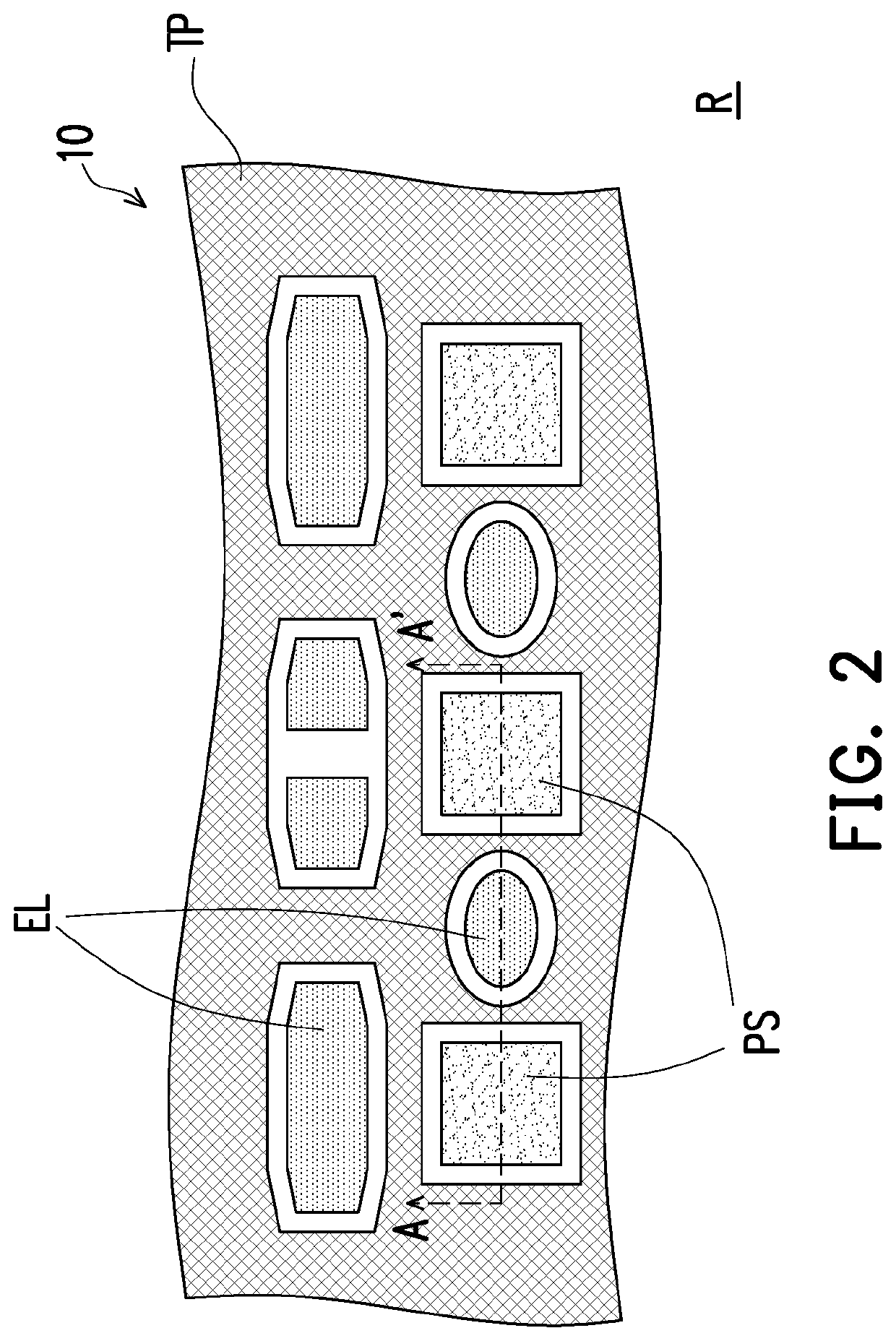

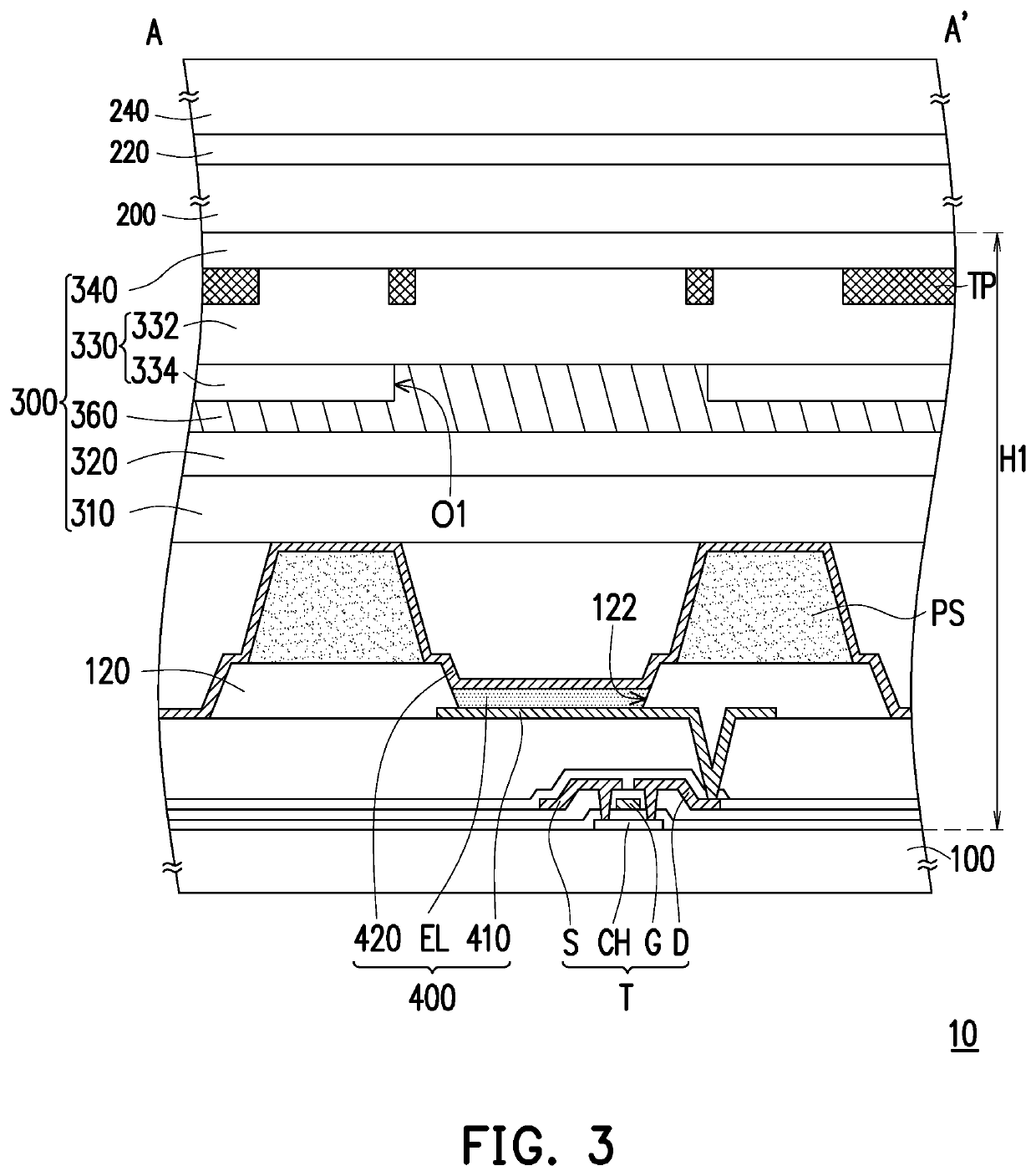

Anti-reflective integrated touch display panel

ActiveUS20200057520A1Increase flexibilityReduce disturbing noiseSolid-state devicesSemiconductor/solid-state device manufacturingSilicon oxideStrontium oxide

An anti-reflective integrated touch display panel includes an anti-reflective structure and touch electrodes. The anti-reflective structure includes a first insulating layer, a second insulating layer disposed on the first insulating layer, a conducting layer disposed on the second insulating layer, a third insulating layer disposed on the second insulating layer, and a fourth insulating layer disposed on the third insulating layer. The first insulating layer includes silicon oxide or silicon nitride, and has a thickness of 0.1 to 2 micrometers. The second insulating layer includes silicon oxide or strontium oxide, and has a thickness of 0.001 to 0.1 micrometer. The conducting layer includes molybdenum, and has a thickness of 0.01 to 0.05 micrometer. The fourth insulating layer includes silicon nitride, and has a thickness of 0.001 to 0.3 micrometer. The touch electrodes are disposed between the third insulating layer and the fourth insulating layer.

Owner:AU OPTRONICS CORP

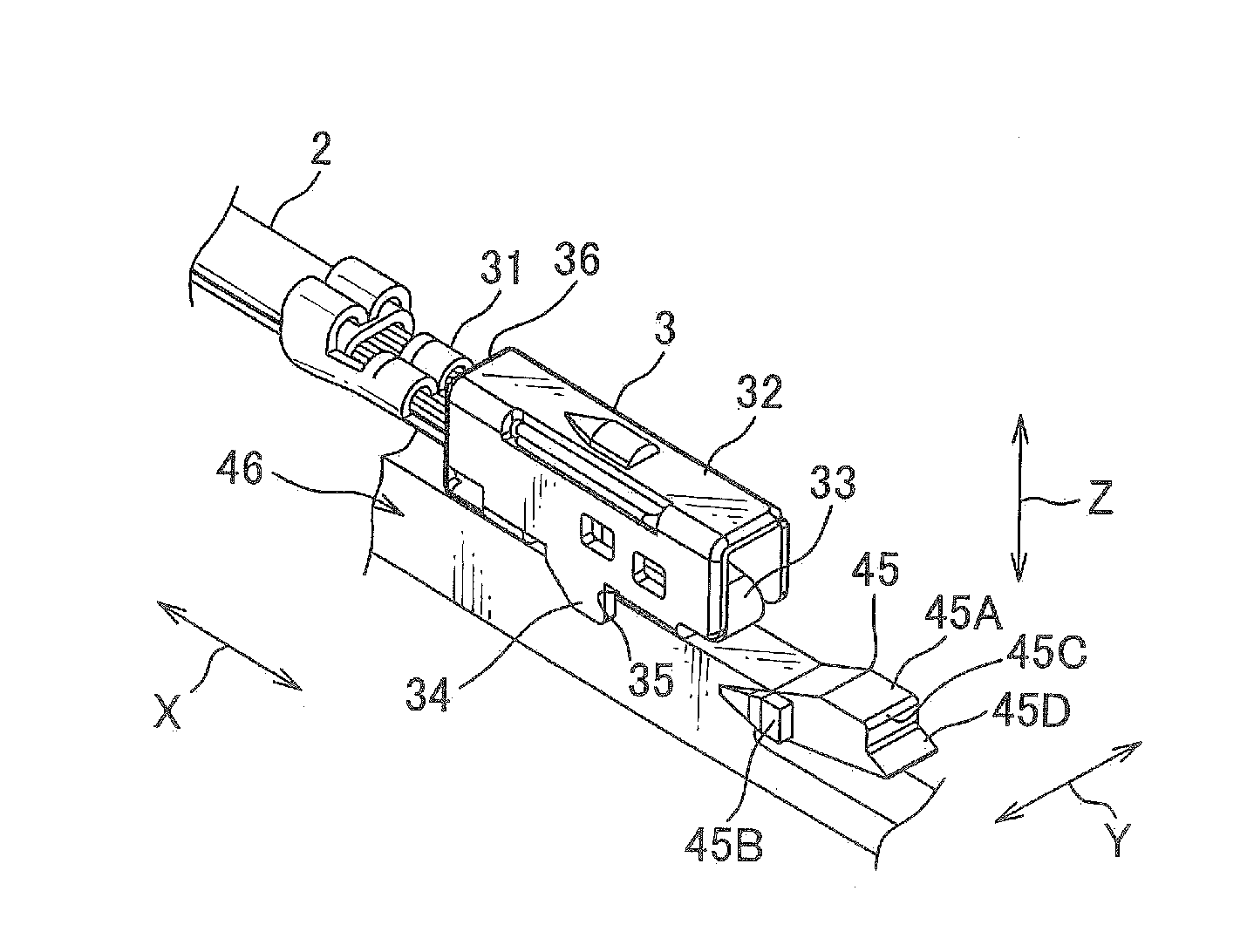

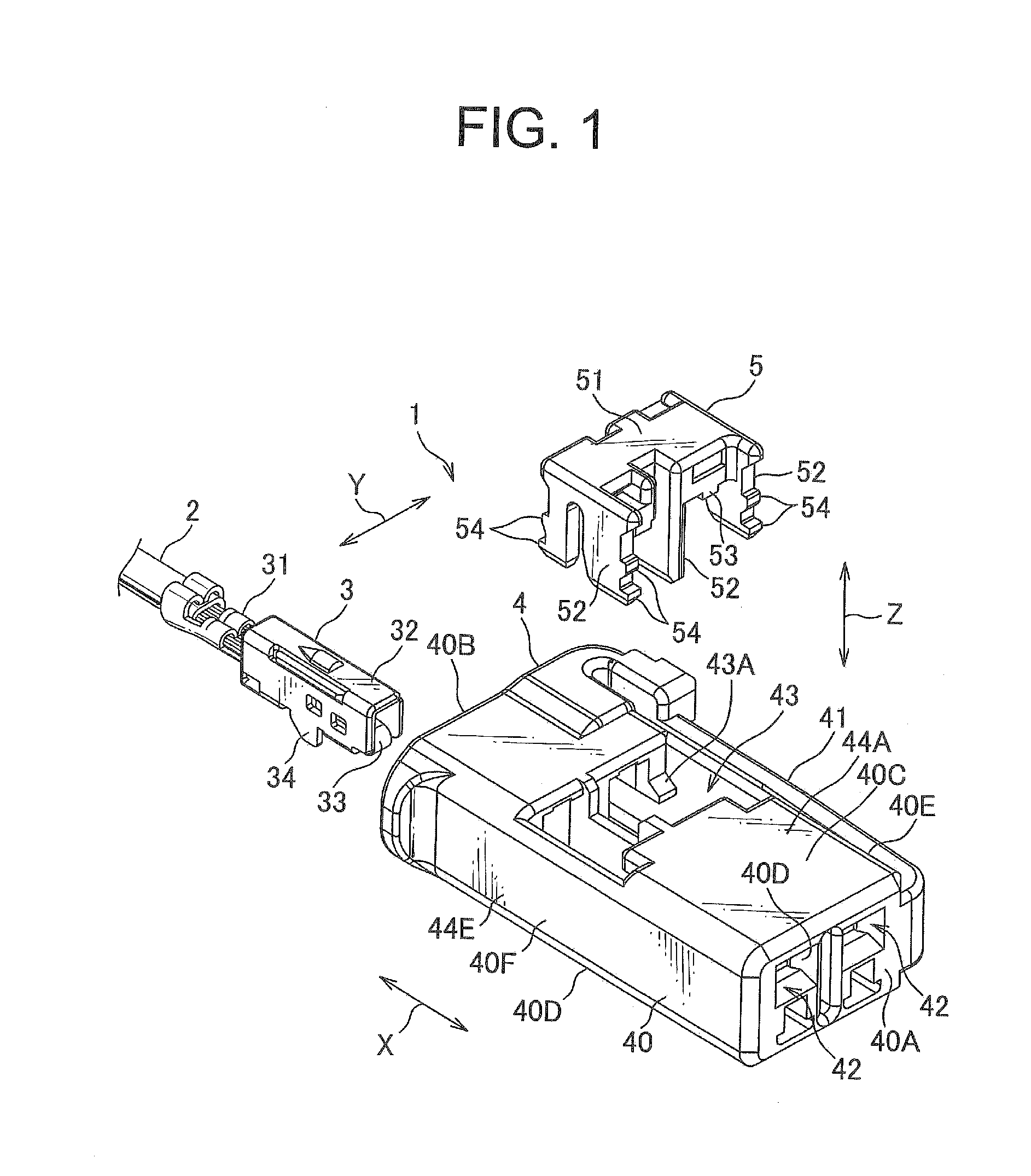

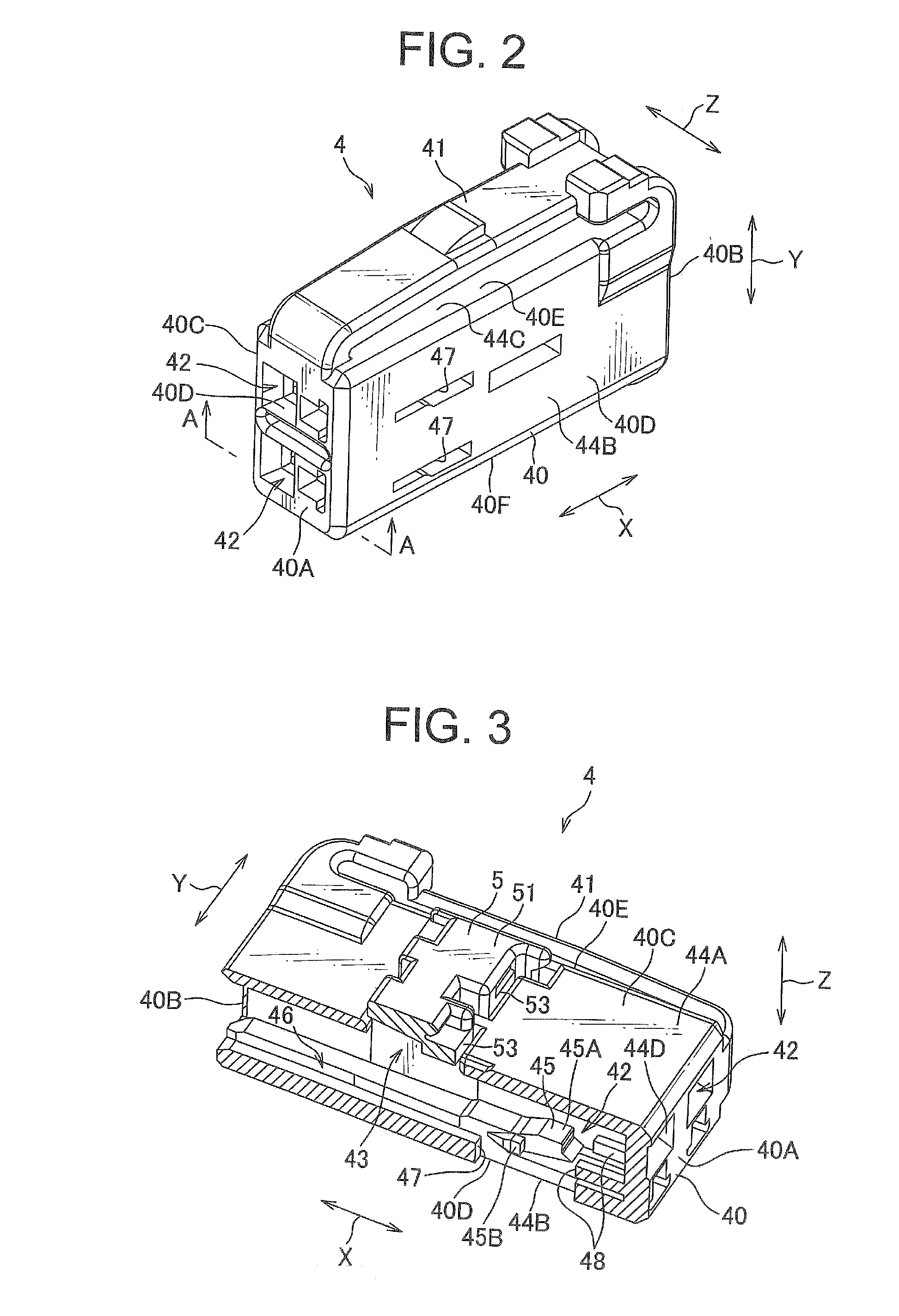

Connector and method of making the same

ActiveUS20140256196A1Decrease manufacturing costIncrease latch forceContact member assembly/disassemblyCoupling device detailsMechanical engineering

There is provided a connector and a method for making the connector preventing escape of a terminal fitting by improving latch force for the terminal fitting over a wide variety of products without inducing upsize or manufacturing cost. The connector comprises a connector housing including a terminal fitting and a terminal housing accommodating the terminal fitting, in which the connector housing includes a wall composing one inner face of the terminal housing, and a latch part latching the terminal fitting, the latch part including a latch arm having a tip extending from a base end disposed the inner face of the wall toward a back side in an insertion direction of the terminal fitting, a latch projection projecting from the latch arm in a direction intersecting the insertion direction.

Owner:YAZAKI CORP

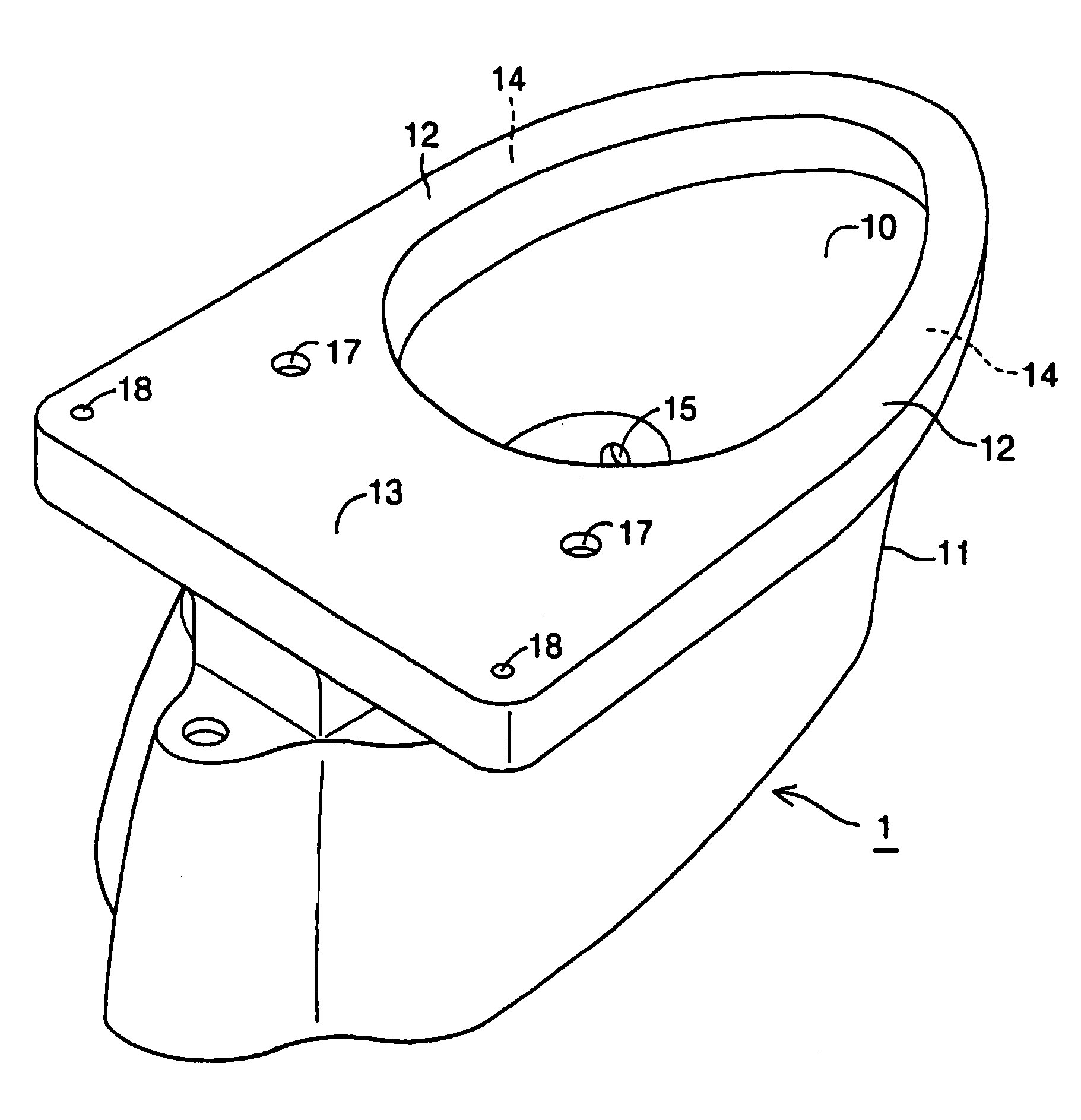

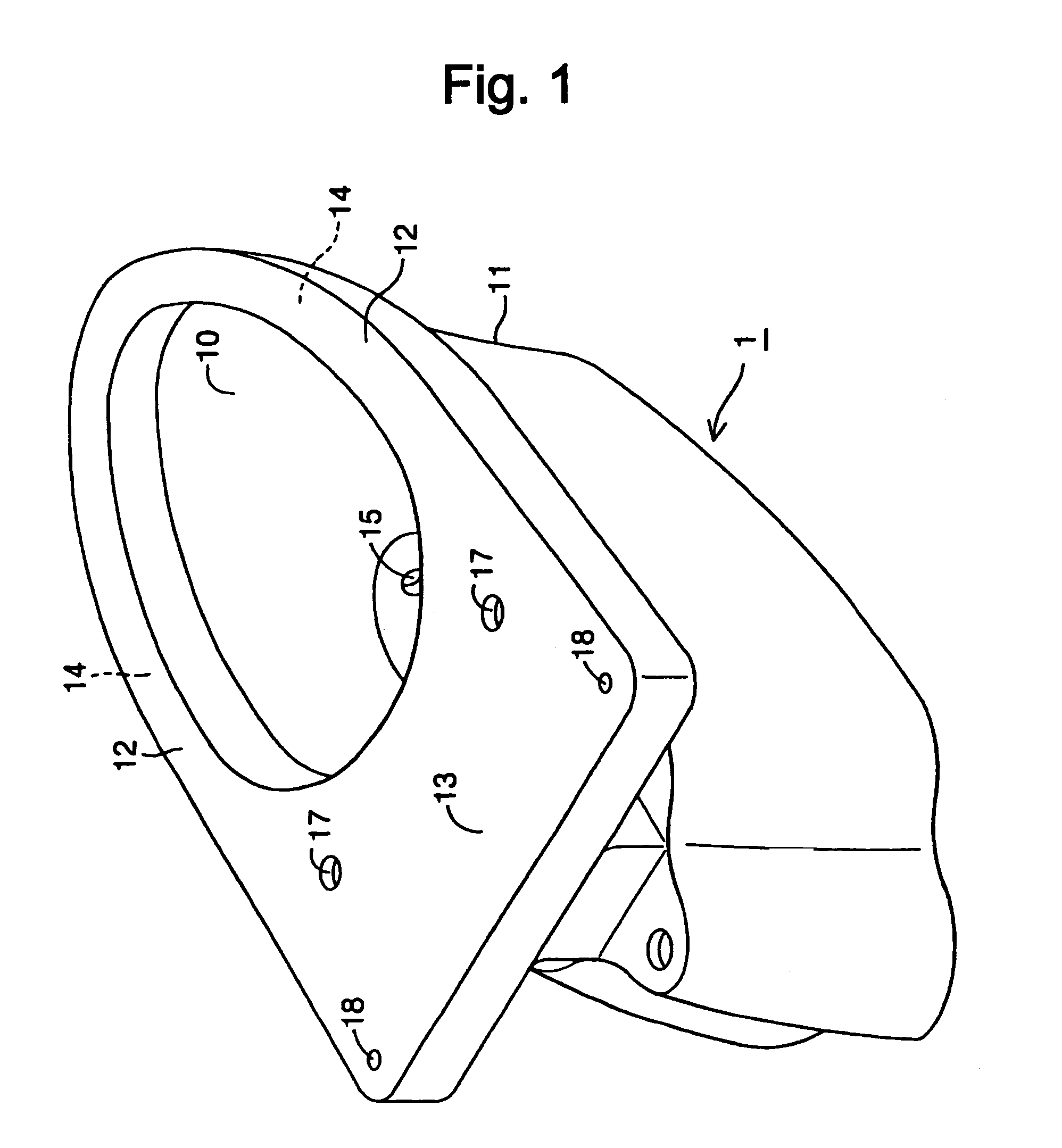

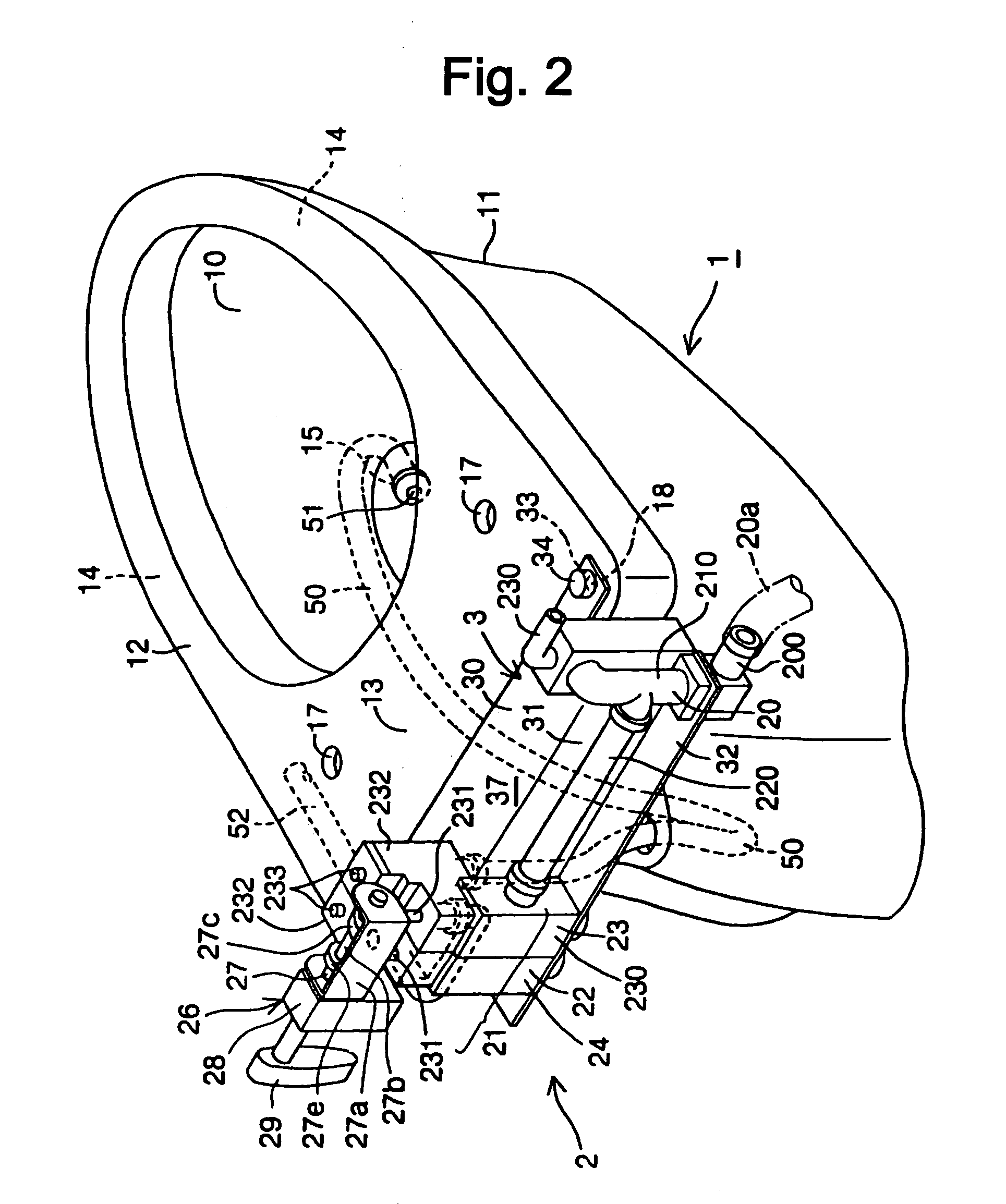

Tankless toilet, western-style flush toilet, part washing device and spud for flush toilet

InactiveUS7036159B2Efficient mass productionReduce manufacturing costUrinalsWater closetsAtmospheric airEngineering

The present invention provides a tankless toilet which can realize the reduction of the manufacturing cost without deteriorating the washing ability of water in the inside of a rim channel. The western-style toilet body includes the rim channel which is formed in the inside of a rim and is capable of washing a toilet bowl with water, and a rim water guide passage which is concealed in a rear wall face of the western-style toilet body and is connected to the rim channel from behind. Further, a through hole which is communicated with the rim water guide passage is formed in the rear wall face of the western-style toilet body. A spud is engaged in the inside of the through hole. The rim conduit is communicated with the rim channel by a water supply passage of the spud without passing the rim water guide passage, while an atmosphere communication hole of a water supply device is communicated with the rim water guide passage by means of a water discharge passage of the spud through a tube.

Owner:LIXIL CORP

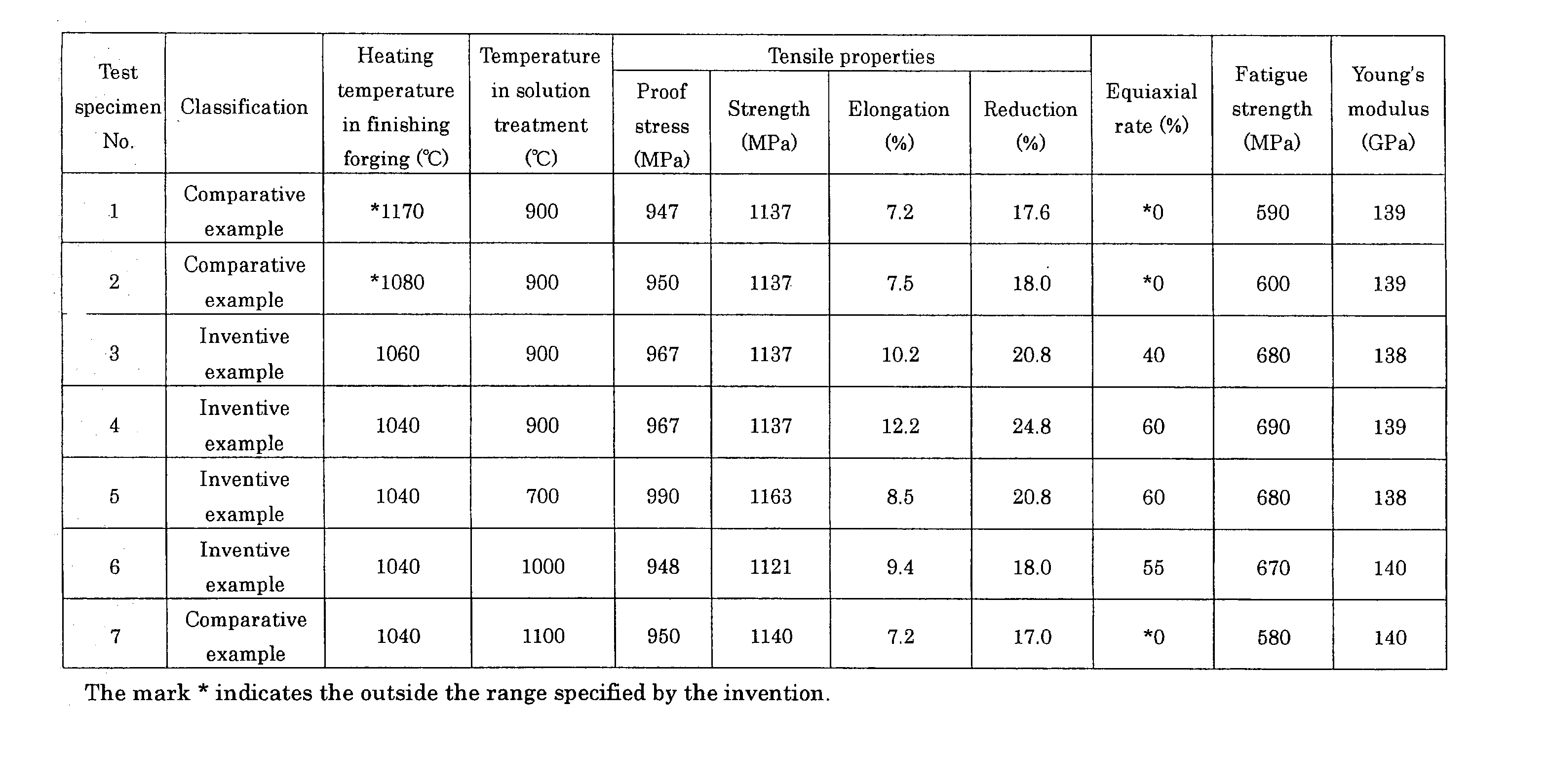

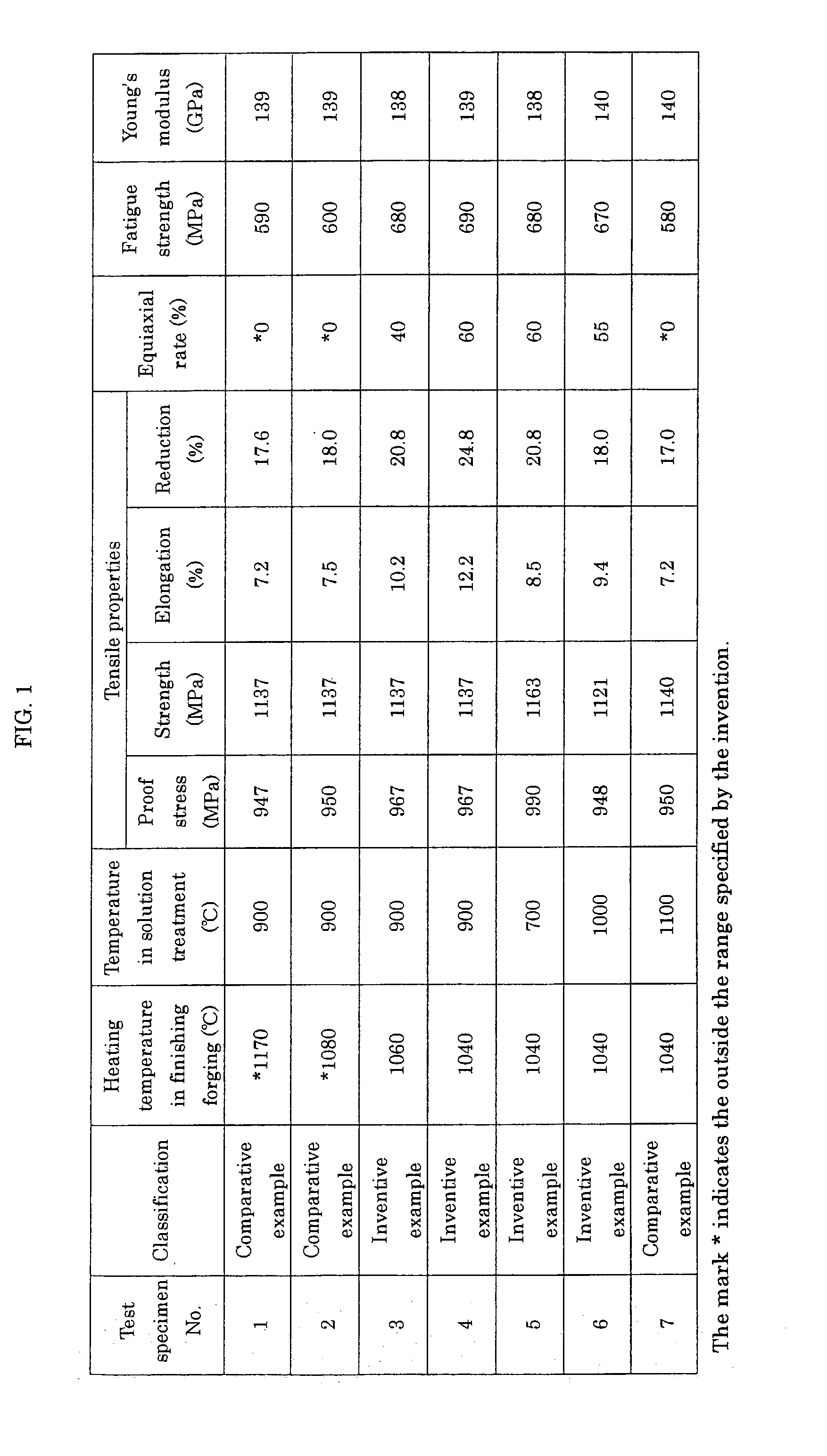

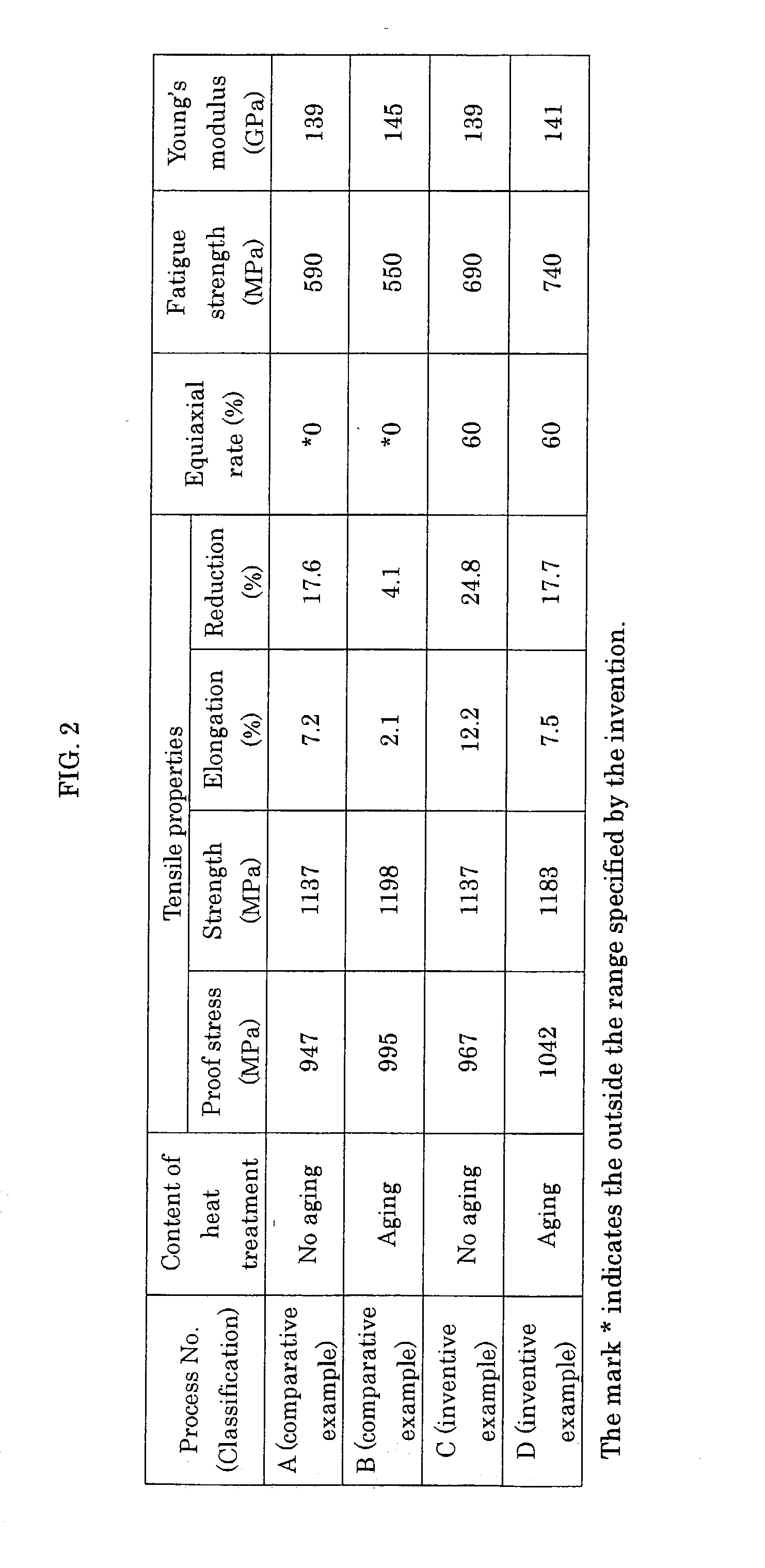

Titanium alloy having high ductility, fatigue strength and rigidity and method of manufacturing same

A titanium alloy is provided wherein metal boride is uniformly crystallized and / or precipitated in the matrix. The heating temperature in the finishing hot working is set smaller than the beta transus temperature by not less than 10° C., thereby causing the matrix to include an equiaxial alpha structure in a rate of not less than 40 vol %. This titanium alloy has excellent properties, i.e., high rigidity, ductility and fatigue strength, which are all required for structural components, and therefore can be widely applied to a mechanical component such as an engine of an automobile, a structural component in an aircraft as well as a component for a high speed rail vehicle.

Owner:SUMITOMO METAL IND LTD +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com