Patents

Literature

56results about How to "Limit current" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

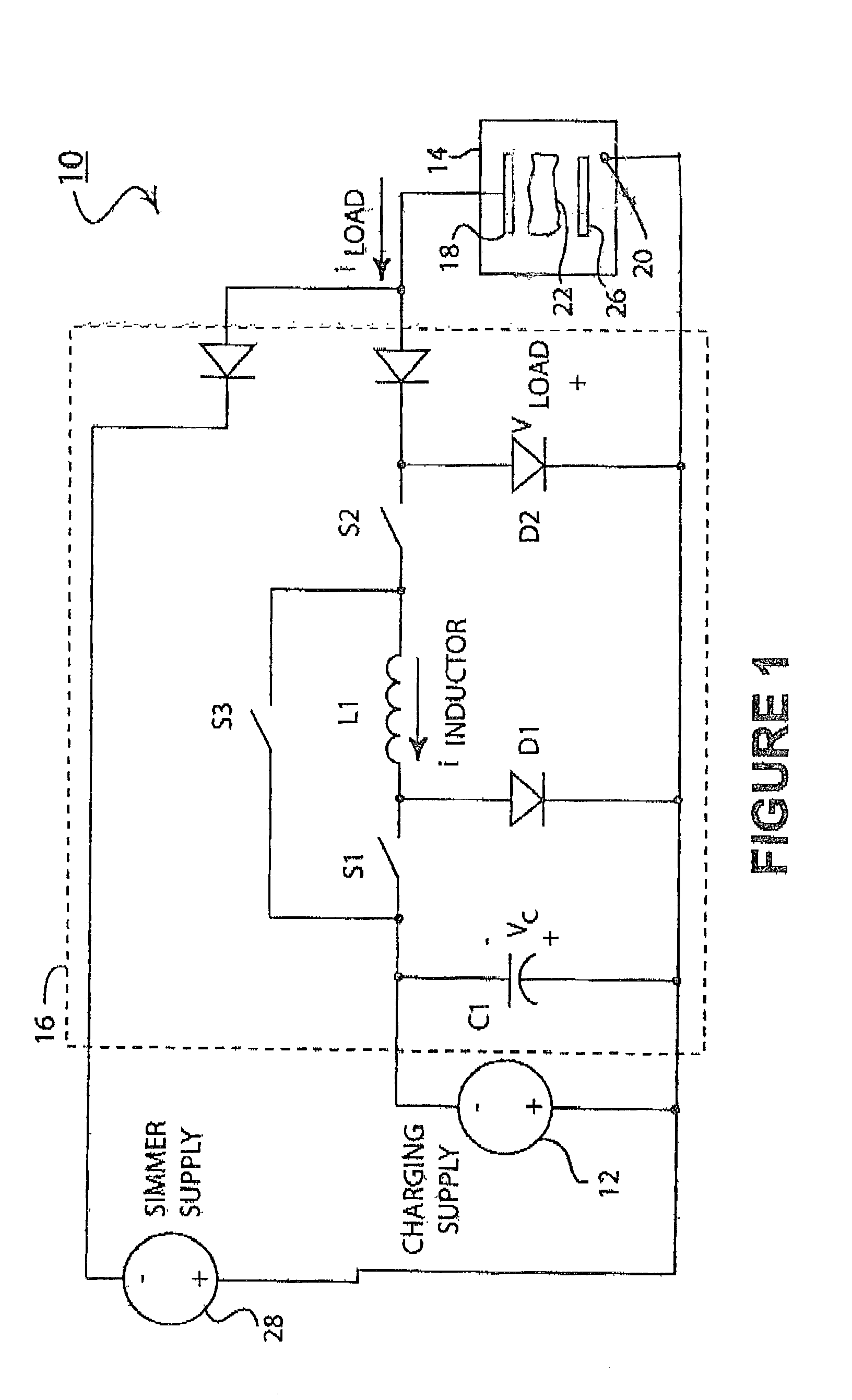

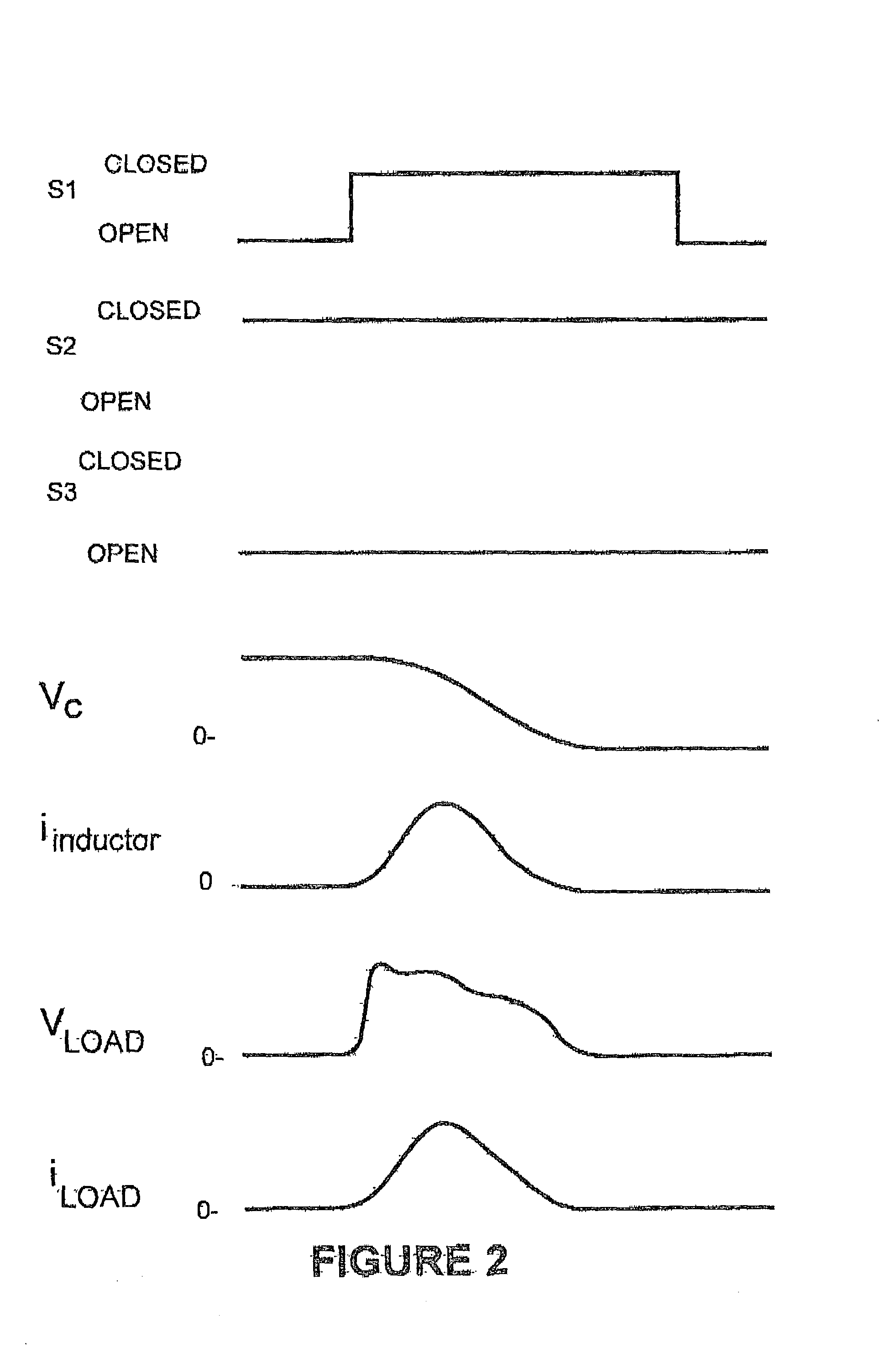

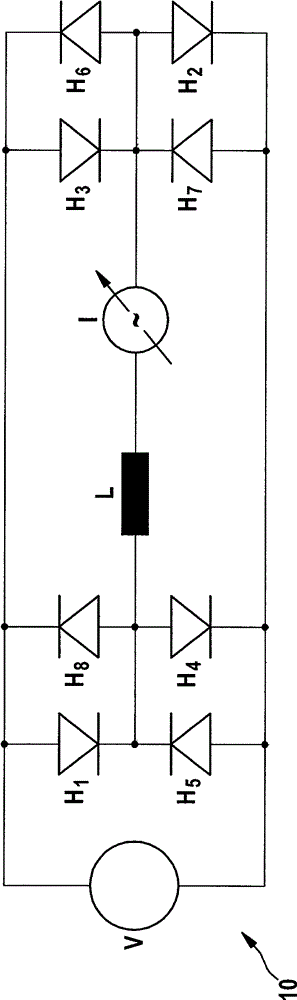

High peak power plasma pulsed supply with arc handling

InactiveUS6808607B2Efficient handling capabilityLimit currentCellsElectric discharge tubesVoltage pulseHigh peak

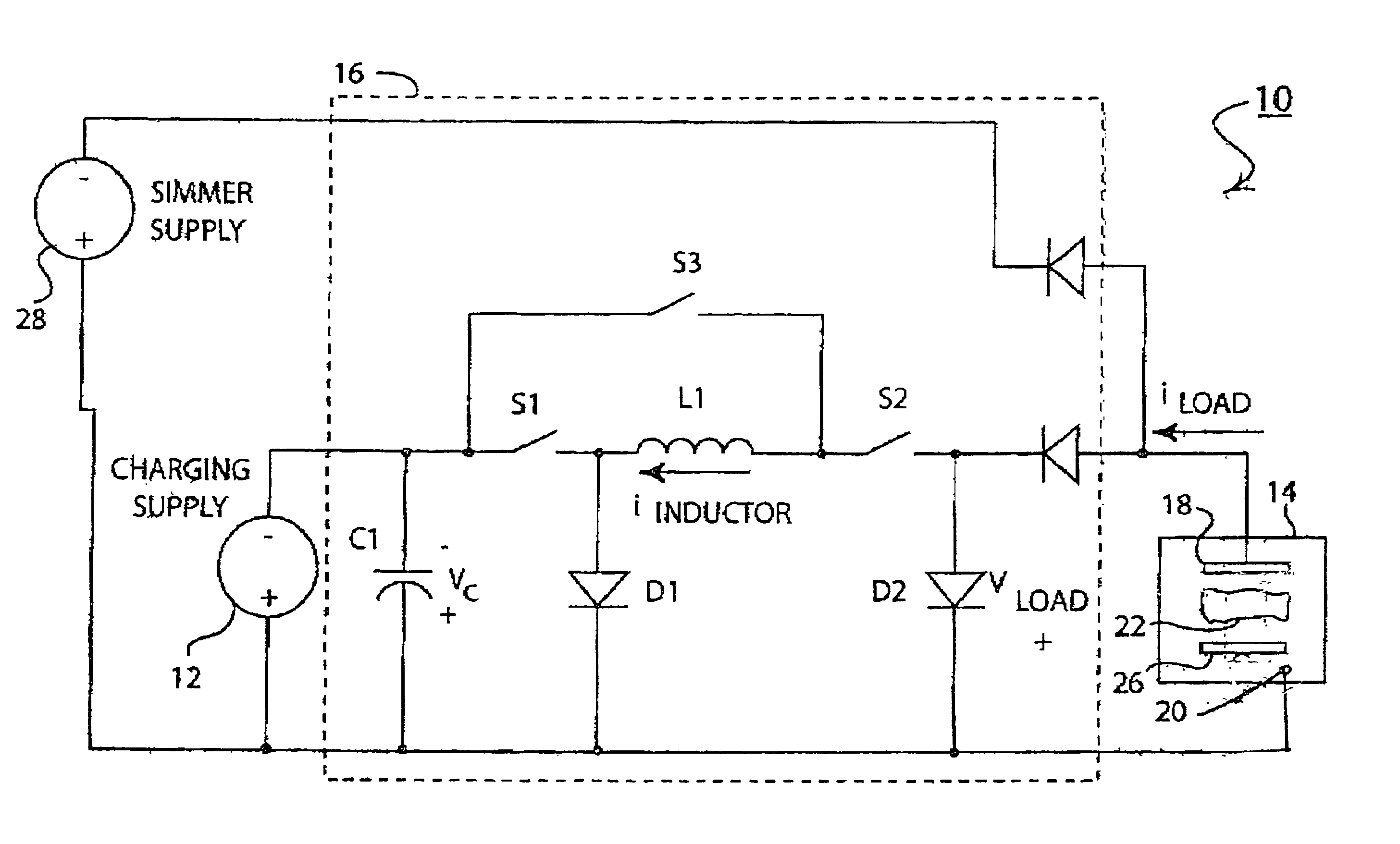

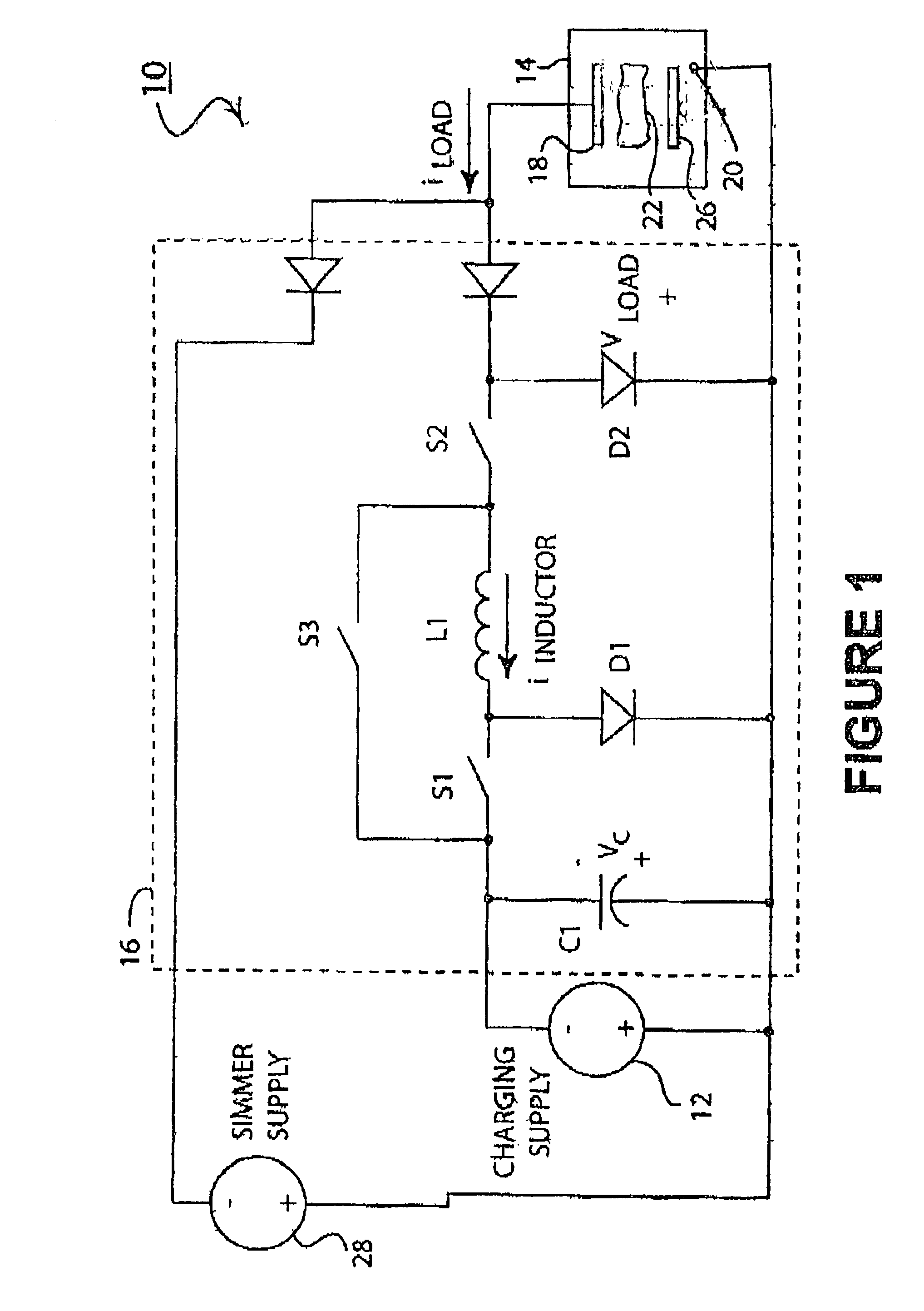

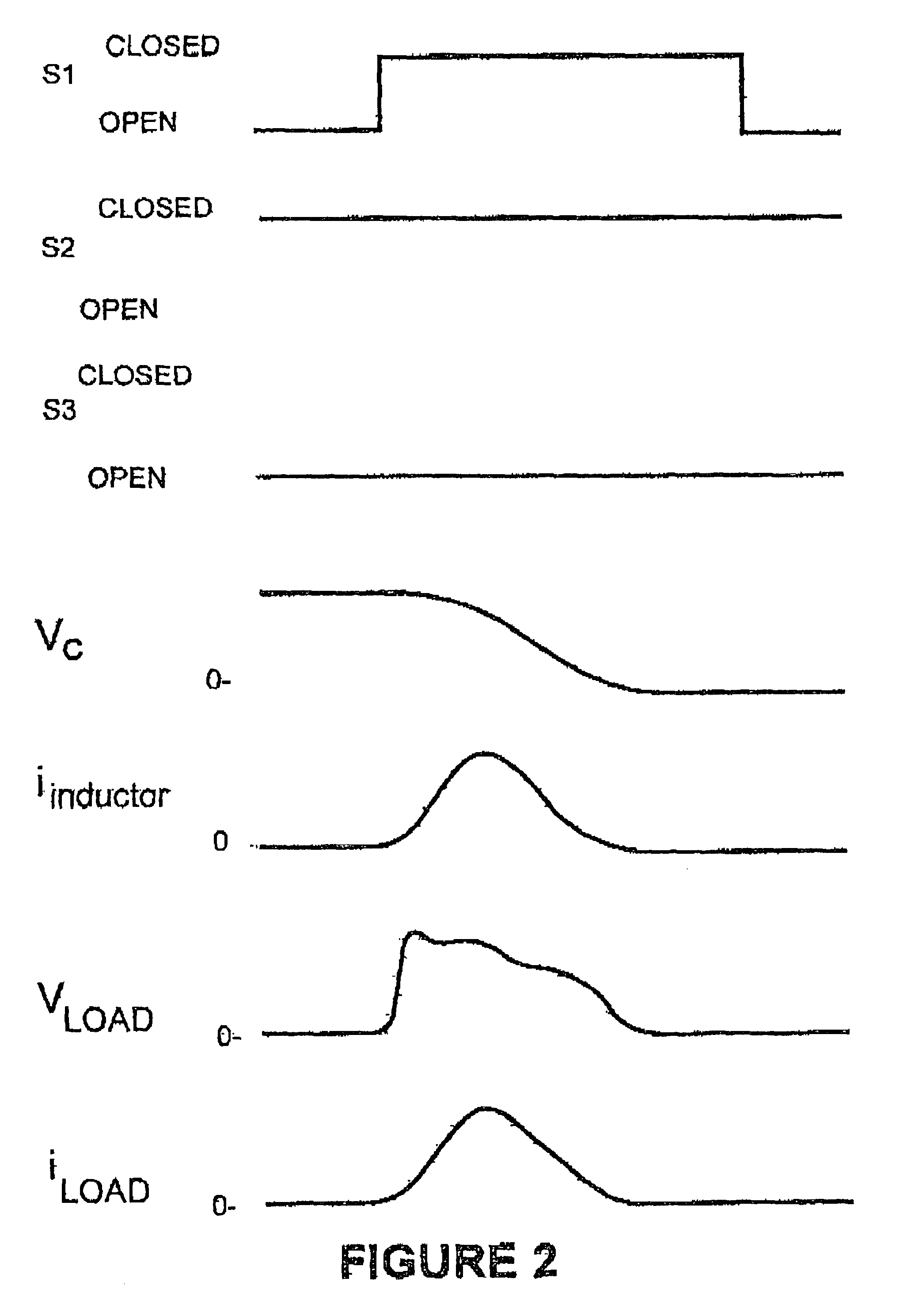

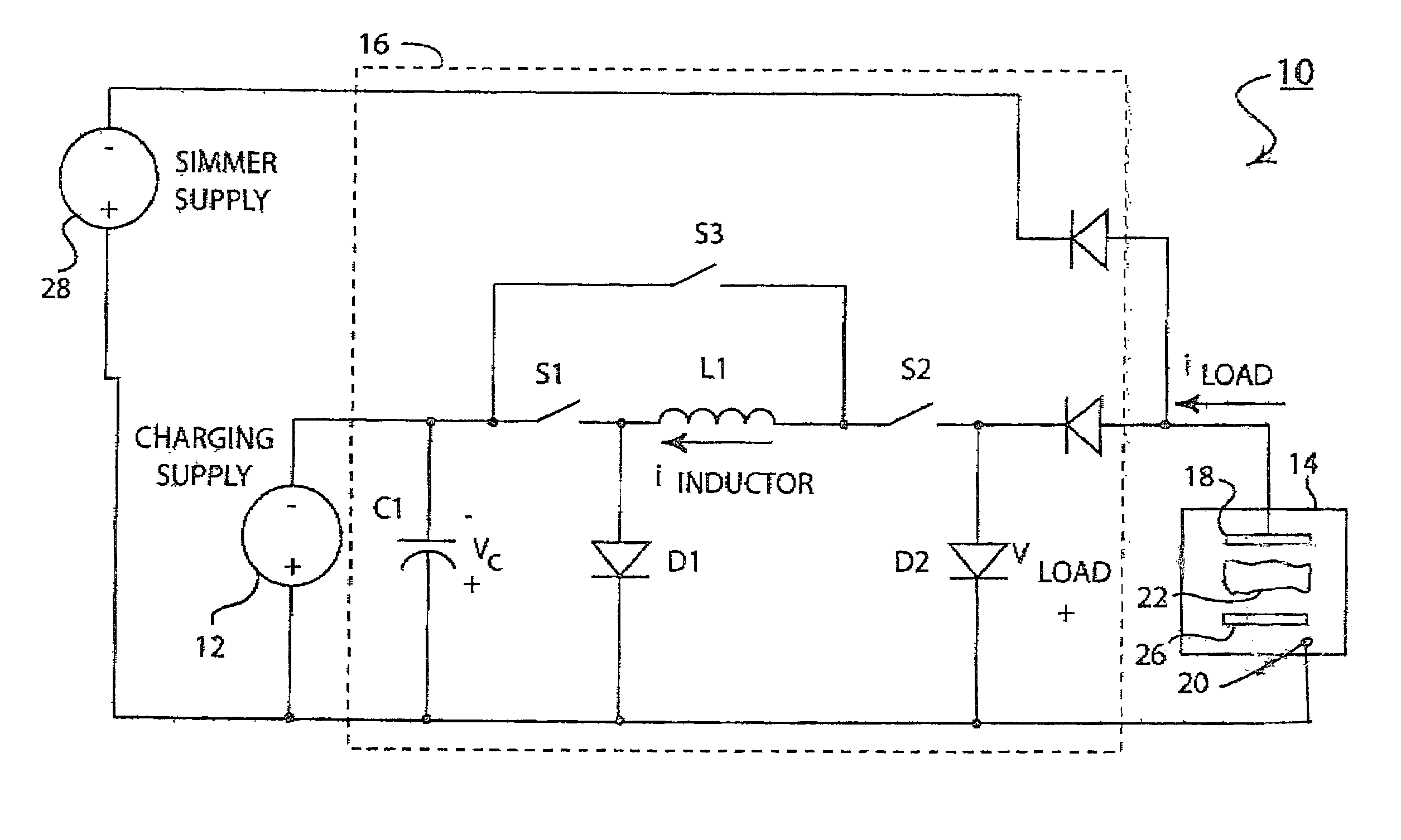

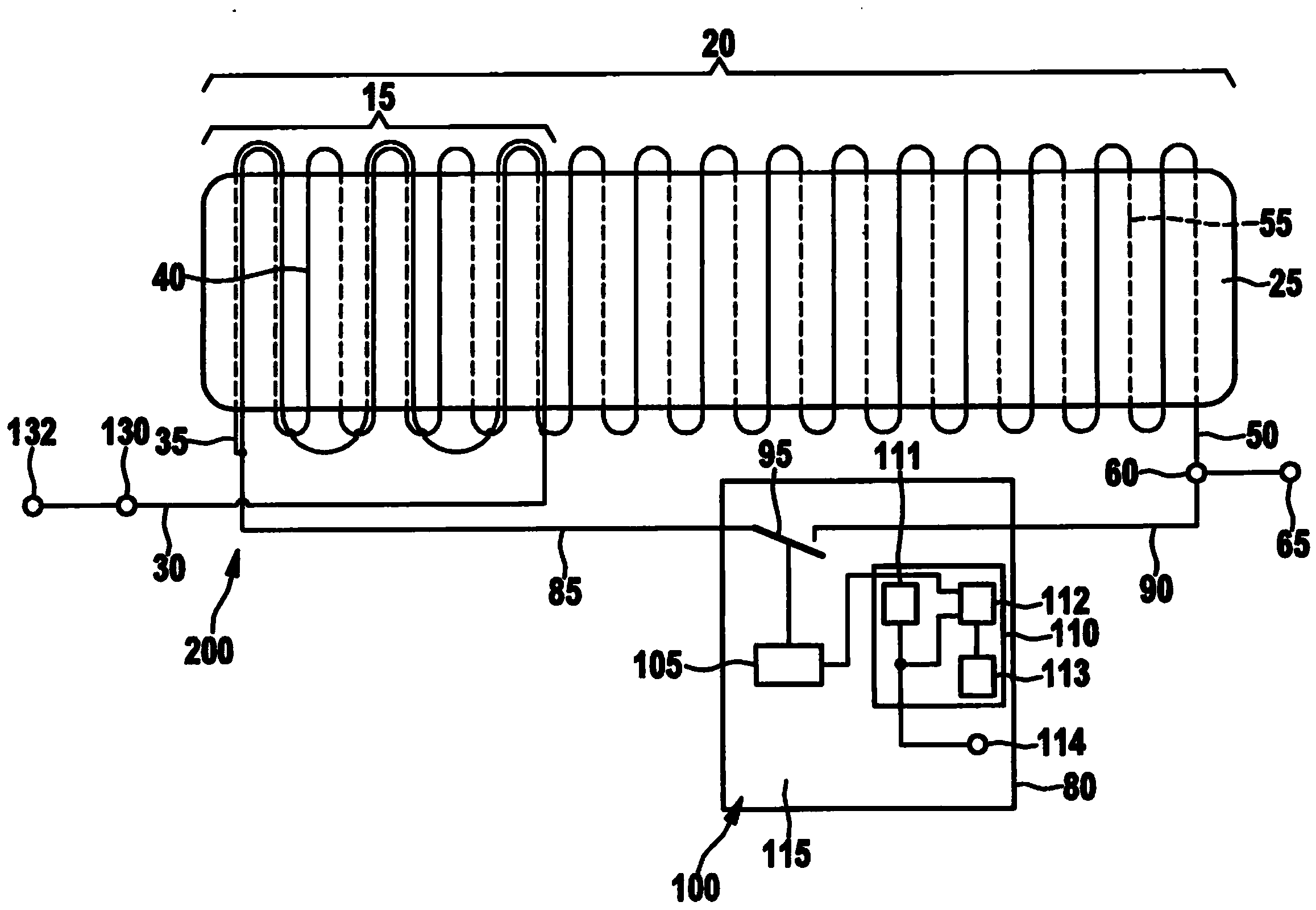

There is provided by this invention novel magnetron sputtering apparatus that is generally comprised of a pulsed dc power supply capable of delivering peak powers of 0.1 megaWatts to several megaWatts with a peak power density greater than 1 kW / cm2. The power supply has a pulsing circuit comprised of an energy storage capacitor and serially connected inductor with a switching means for disconnecting the pulsing circuit from the plasma and recycling the inductor energy back to the energy storage capacitor at the detection of an arc condition. The energy storage capacitor and the serially connected inductor provide an impedance match to the plasma, limits the current rate of rise and peak magnitude in the event of an arc, and shapes the voltage pulses to the plasma.

Owner:ADVANCED ENERGY IND INC

High peak power plasma pulsed supply with arc handling

InactiveUS20040055881A1Efficient handling capabilityLimit currentCellsElectric discharge tubesVoltage pulsePulsed DC

There is provided by this invention novel magnetron sputtering apparatus that is generally comprised of a pulsed dc power supply capable of delivering peak powers of 0.1 megaWatts to several megaWatts with a peak power density greater than 1 kW / cm2. The power supply has a pulsing circuit comprised of an energy storage capacitor and serially connected inductor with a switching means for disconnecting the pulsing circuit from the plasma and recycling the inductor energy back to the energy storage capacitor at the detection of an arc condition. The energy storage capacitor and the serially connected inductor provide an impedance match to the plasma, limits the current rate of rise and peak magnitude in the event of an arc, and shapes the voltage pulses to the plasma.

Owner:ADVANCED ENERGY INDS

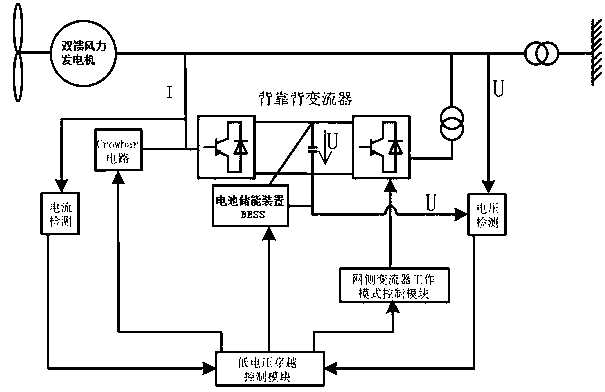

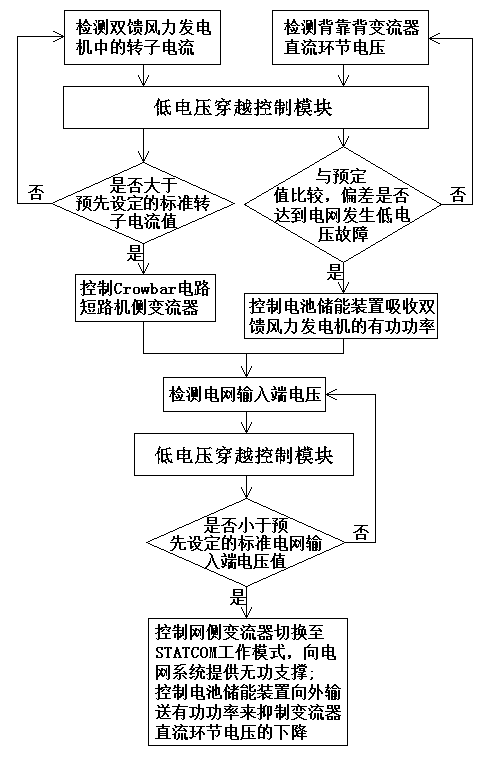

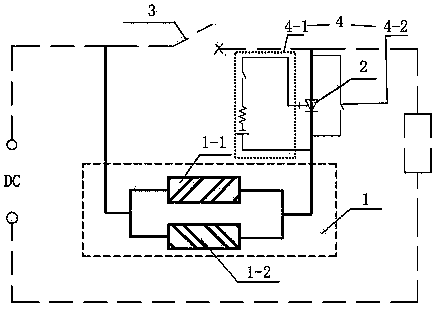

Double-fed wind driven generator system and low-voltage through control method

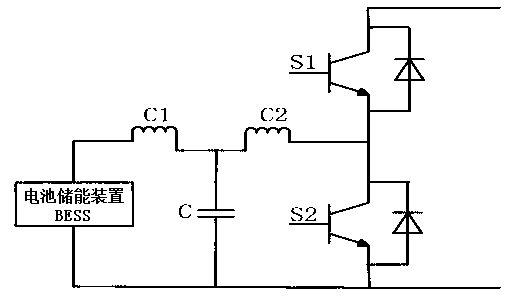

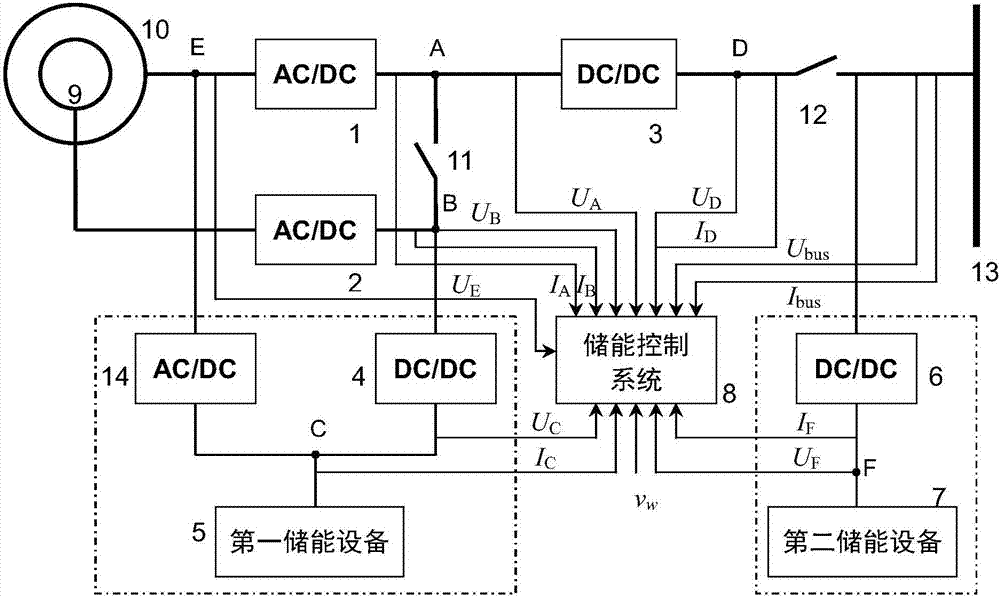

InactiveCN103078349AAvoid chargingSmooth output power fluctuationSingle network parallel feeding arrangementsEnergy storageElectricityElectrical battery

The invention relates to a double-fed wind driven generator system and a low-voltage through control method. According to the double-fed wind driven generator and the low-voltage through control method on the basis of a Crowbar circuit and a battery energy storage device, the low-voltage through capability can be effectively improved under the condition of large-range voltage drop, the double-fed wind driven generator system can be still kept to be connected with a power grid, and the stability of a wind power system is improved.

Owner:HOHAI UNIV

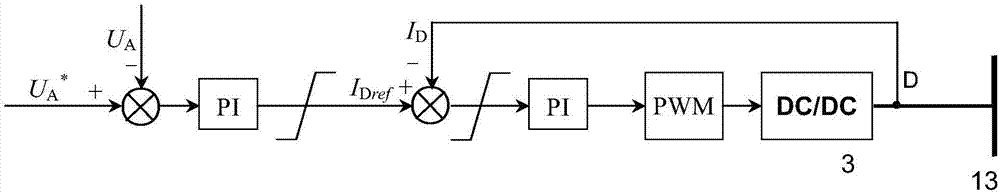

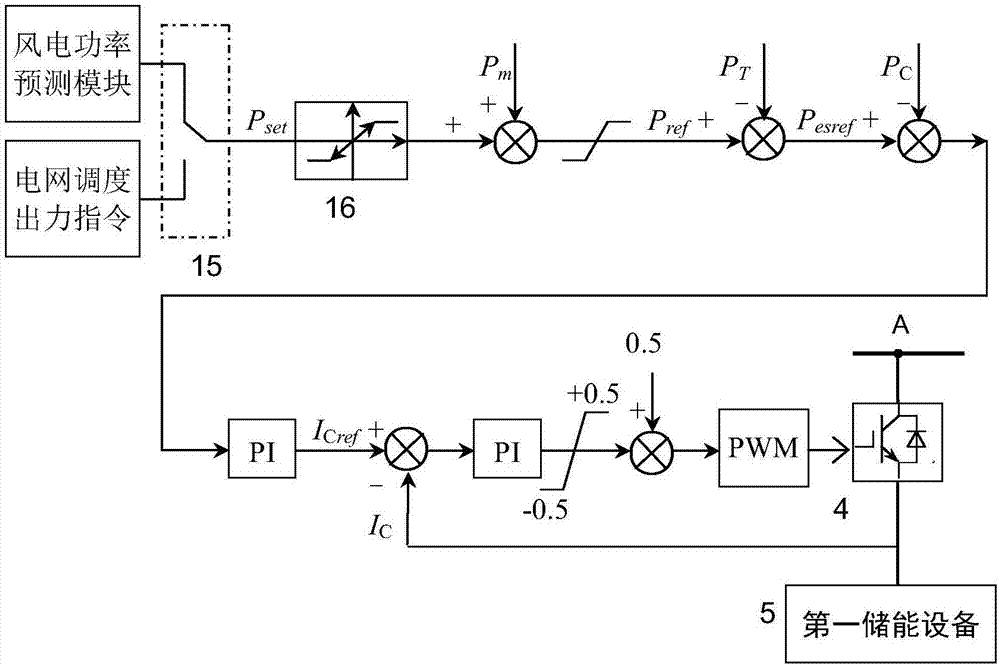

Power fluctuation and malfunction control system and method of direct-current-transmission double-fed wind turbine set

ActiveCN107482653AReduce output powerLimit currentSingle network parallel feeding arrangementsEnergy storageOvervoltageConstant power

The invention relates to a power fluctuation and malfunction control system and method of a direct-current-transmission double-fed wind turbine set, and belongs to the field of wind power. The system includes a double-fed power generator, a stator-side converter, a rotor-side converter, a net-side direct-current converter and an energy storage system. According to the method, firstly, the energy storage system supplies power to the rotator-side converter to achieve inverse conversion; secondly, after a draught fan is enabled, the stator-side converter conducts rectification boosting, the net-side direct-current converter conducts constant power control and controls the energy storage system to charge and discharge electricity to achieve power fluctuation suppression; if voltage drop occurs to a power network, the net-side direct-current converter conducts constant direct voltage control, and the rotator-side converter and the energy storage system run in a voltage drop malfunction control mode; if overvoltage occurs to the power network, the energy storage system conducts voltage clamp on the power network; if the network is disconnected, the net-side direct-current converter conducts constant direct voltage control, the rotator-side converter makes the output power of the power generator turn to zero; and finally, the net-side direct-current converter is switched off. The power fluctuation and malfunction control system and method of the direct-current-transmission double-fed wind turbine set are conducive to usage of the double-fed wind turbine set in a flexible direct current transmission system.

Owner:QUFU NORMAL UNIV

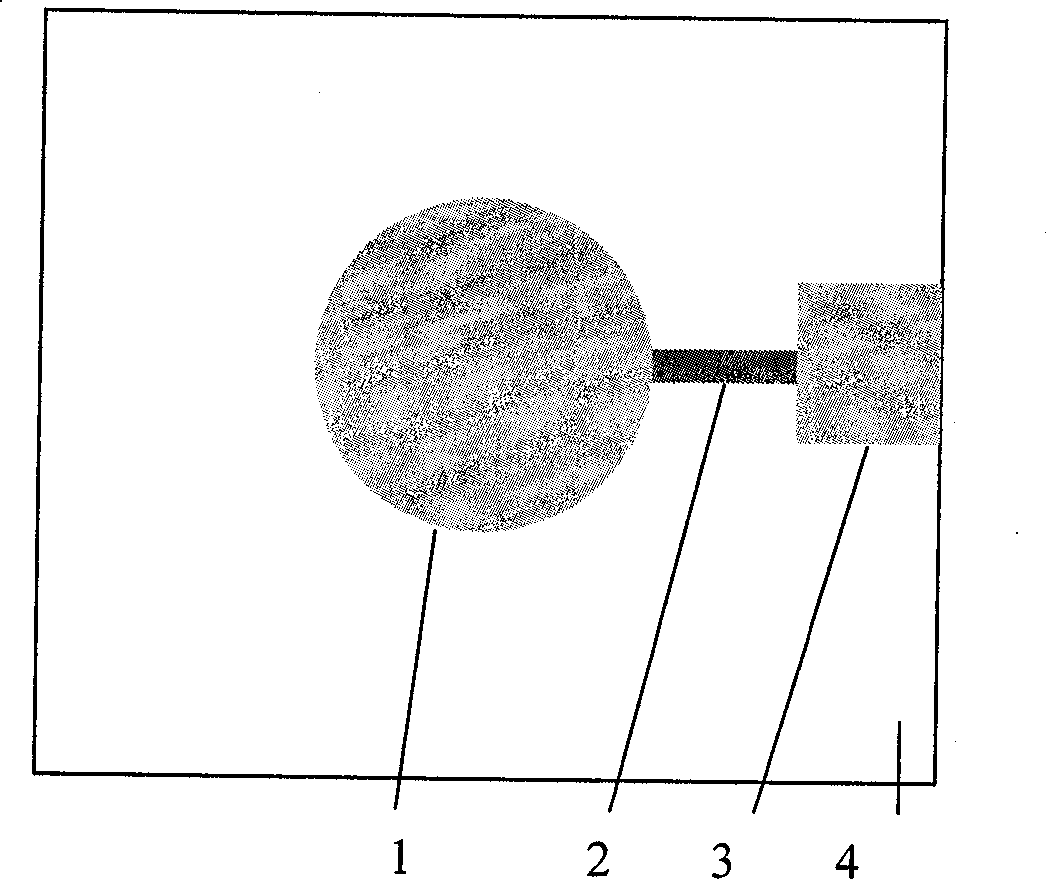

Emitting laser for etching top end non-doping intrinsic layer asymmetric metal membrane vertical cavity surface

InactiveCN101202420AAvoid recombinationReduce compoundingLaser detailsLaser active region structureVertical-cavity surface-emitting laserLaser array

The invention relates to an etching apex non-doped intrinsic layer asymmetrical metal film vertical cavity surface emitting laser and a preparation method thereof. The invention comprises a Bragg reflector, a high resistive layer, an electrode, a substrate and a quantum well active region. The upper surface is etched with a round metal reflection film, a metal film lead, a contact layer of the metal film and an upper electrode and the upper electrode; the lower surface of the substrate is provided with the round metal reflection film, a lower surface metal film lead and a lower surface electrode. By introducing the non-doped intrinsic layer to etch the current aperture and combining the upper surface with the substrate surface to etch a metal film asymmetrical structure in order to implement the restriction to current and optical field, the invention has the efficacies of the electrode and the reflector of the metal film, simplifies a vertical cavity emitting laser array integration process, reduces the logarithm of distributed Bragg reflector, restricts the diffusion area of the current, improves the photoelectric coupling efficiency of injected current, avoids proton bombardment or respective oxidation process and is beneficial for integration as the intrinsic high-resistive layer and a chip implement the grown in one operation.

Owner:HEBEI UNIV OF TECH

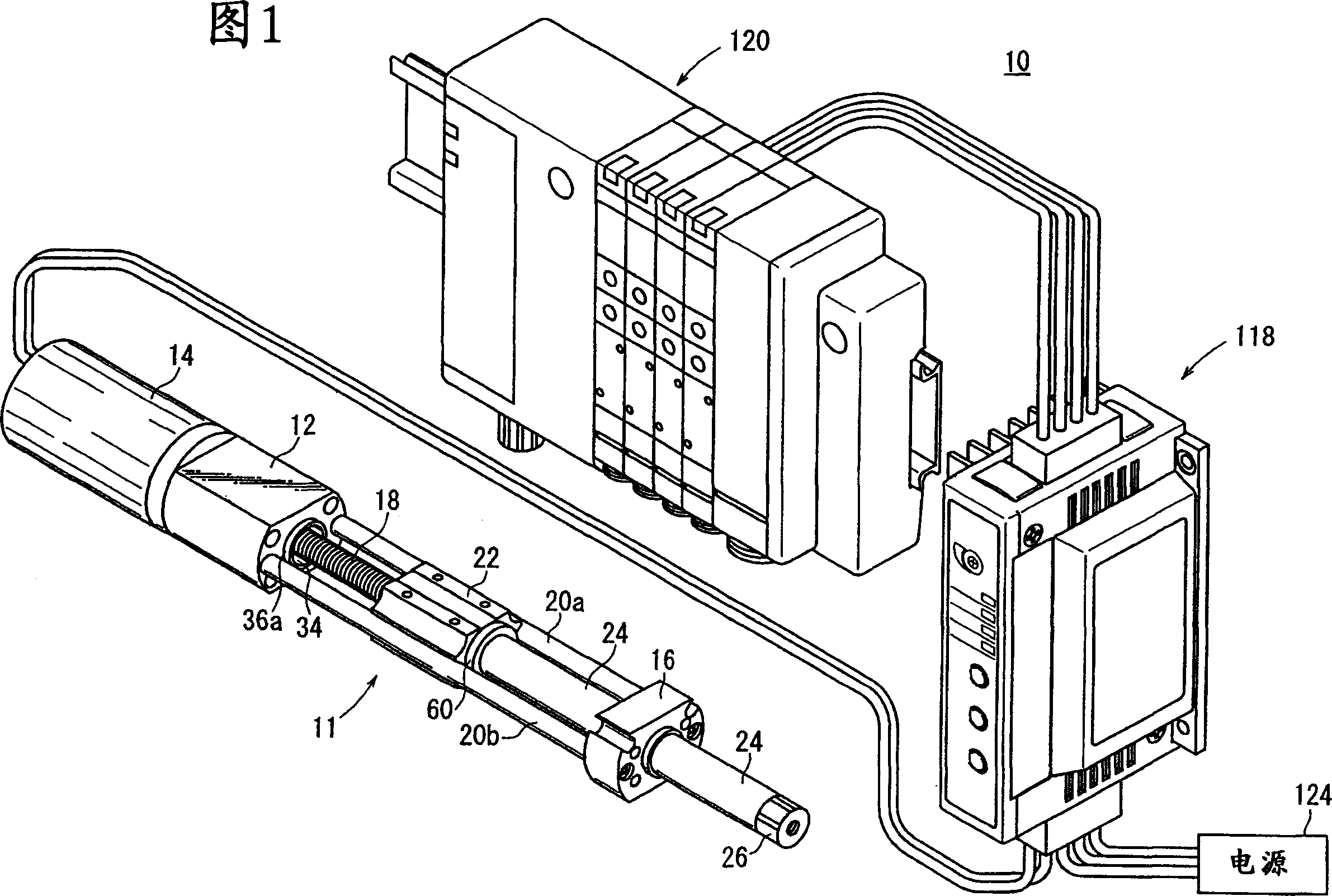

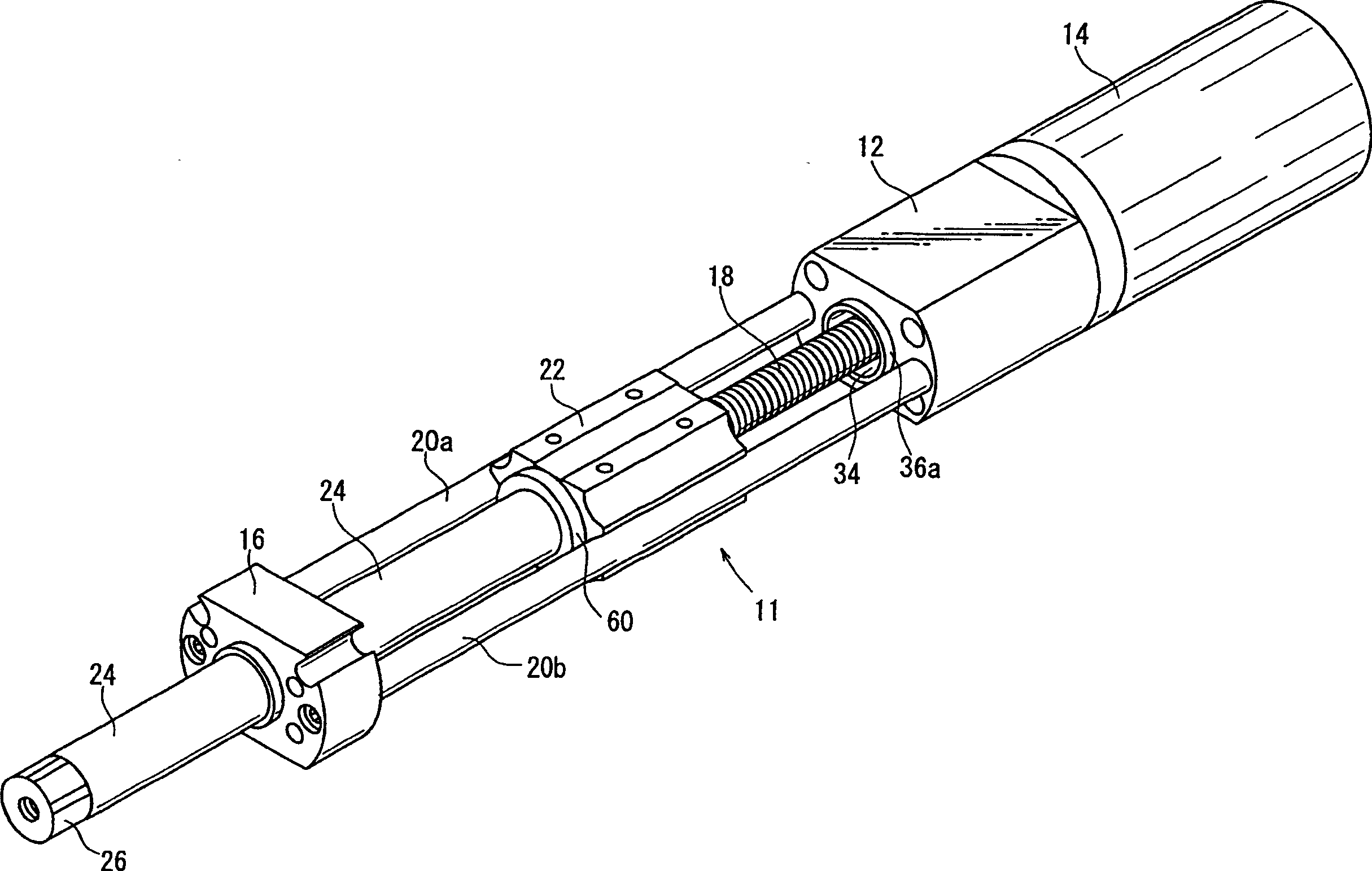

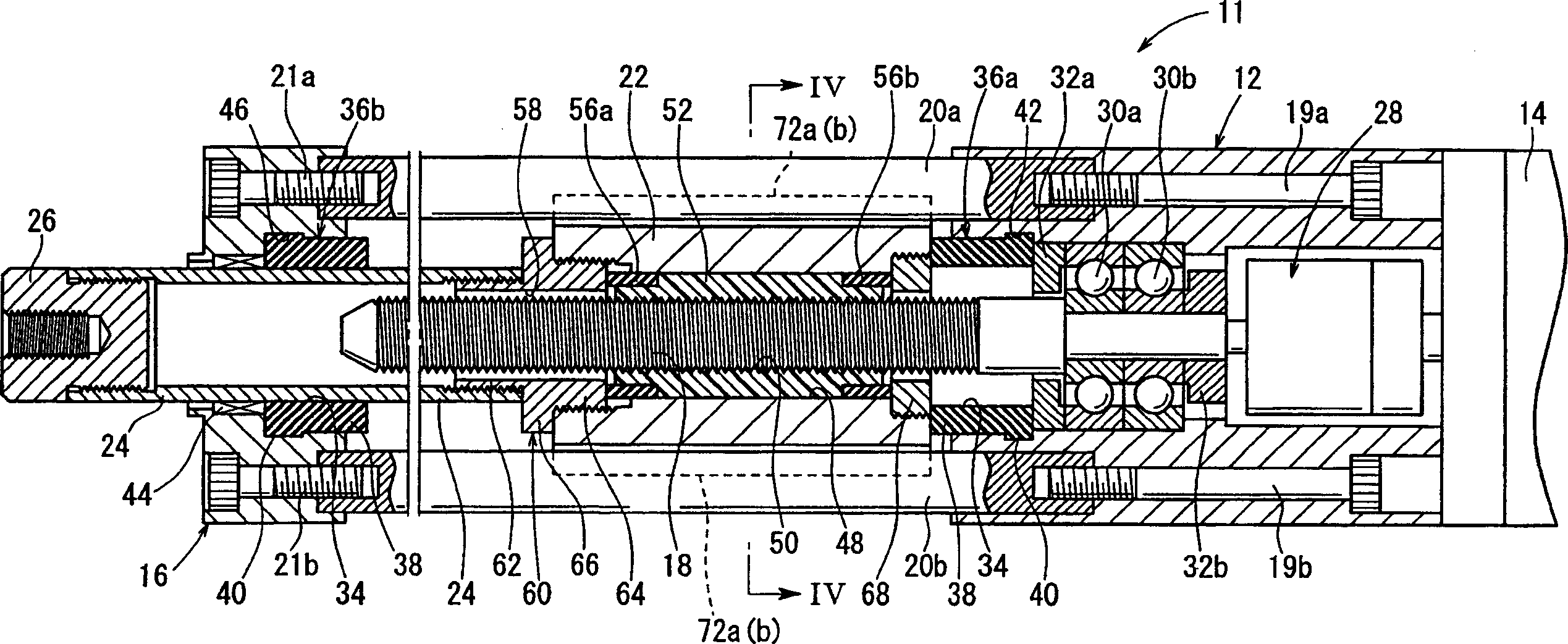

Actuator control system

ActiveCN1796823AGuaranteed durabilityLimit currentNon-rotating vibration suppressionSingle motor speed/torque controlControl systemActuator

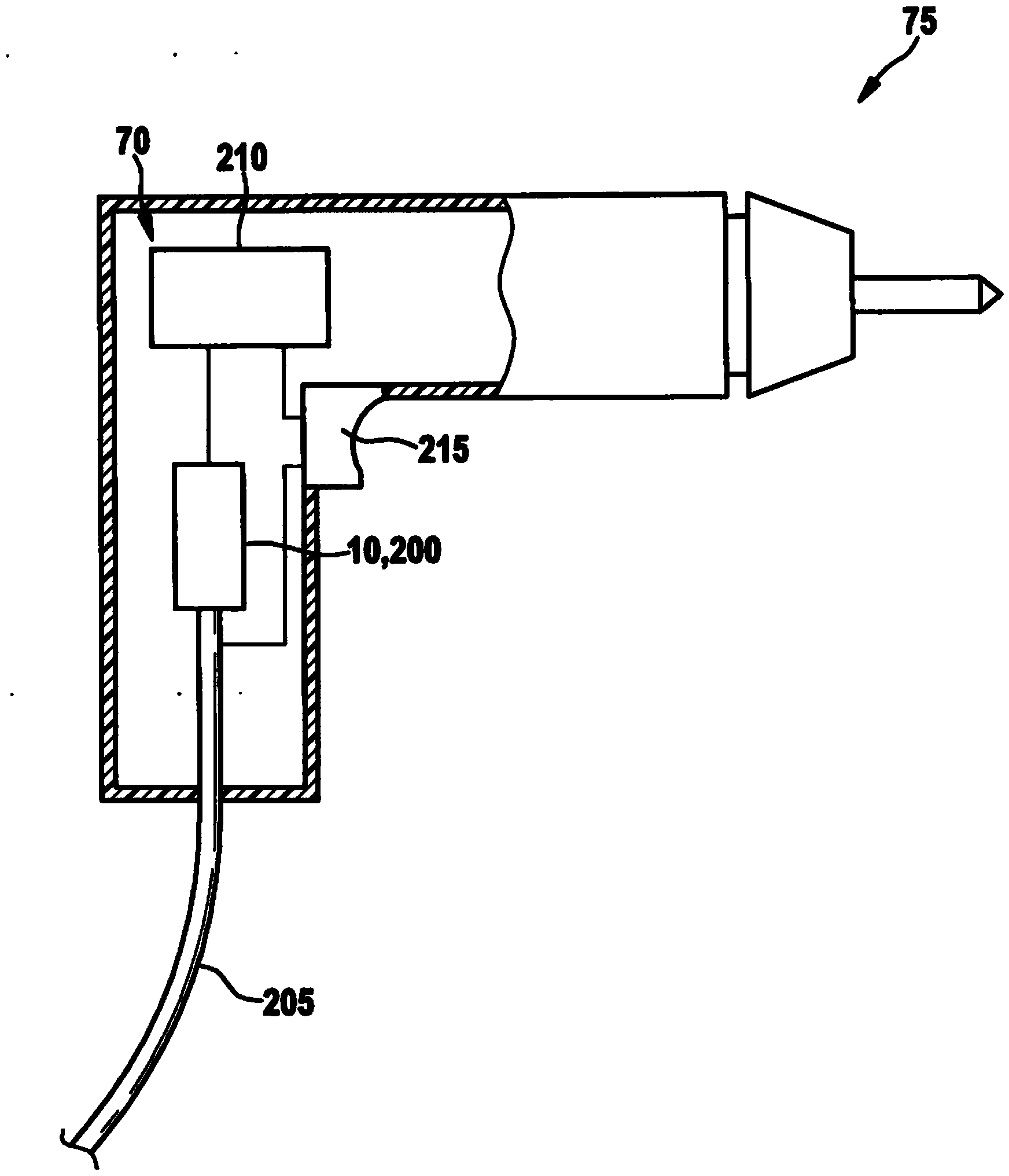

An actuator control system comprises an electric actuator, a driver, and a controller. The electric actuator is provided with a buffering mechanism which absorbs impact applied to a piston rod. The buffering mechanism includes piston dampers which absorb impact applied to a piston, a first end damper which is provided at an end of a housing facing the piston, and a second end damper which is provided on a rod cover separated from the housing by a predetermined distance.

Owner:SMC CORP

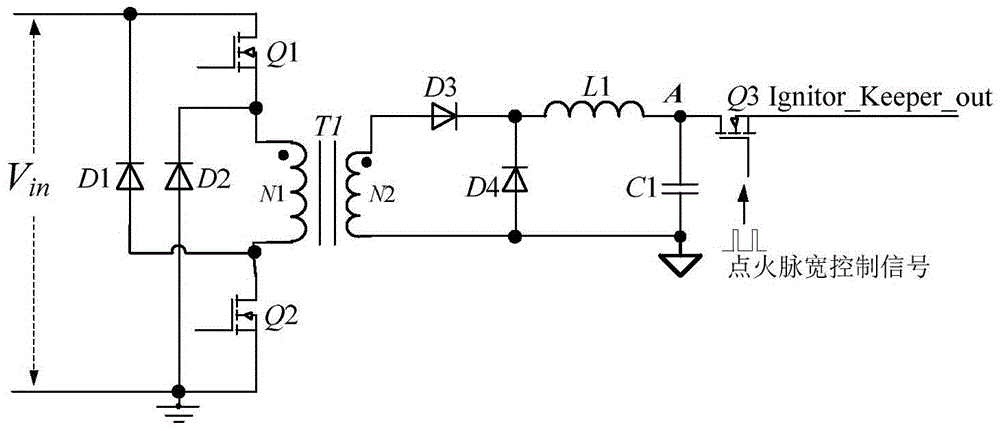

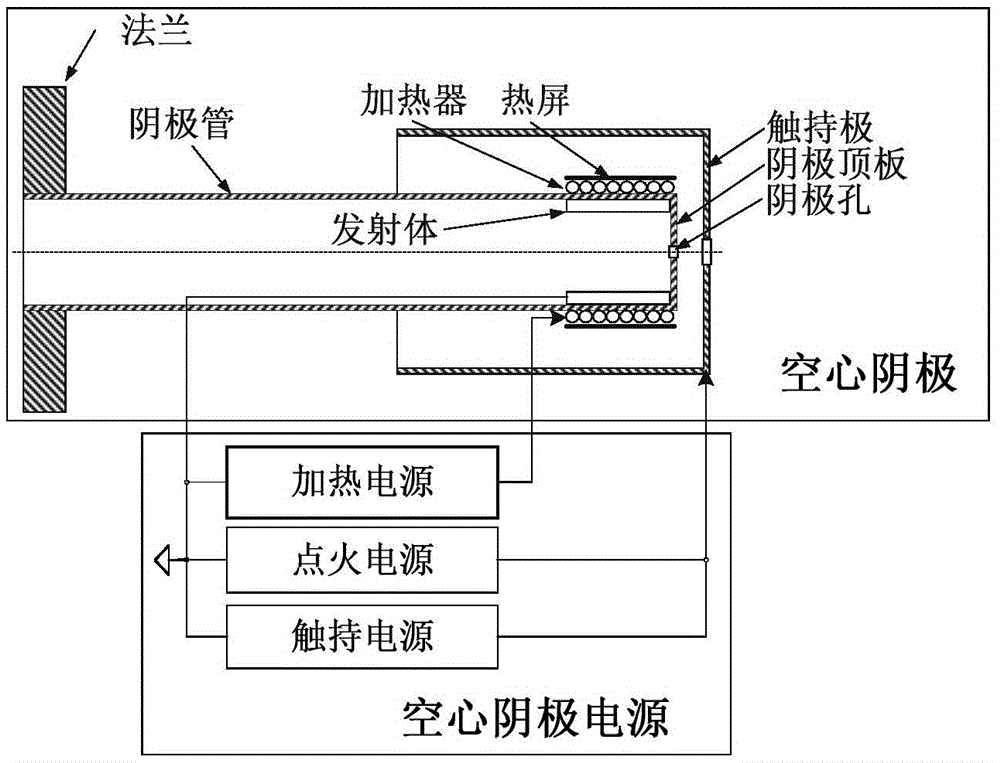

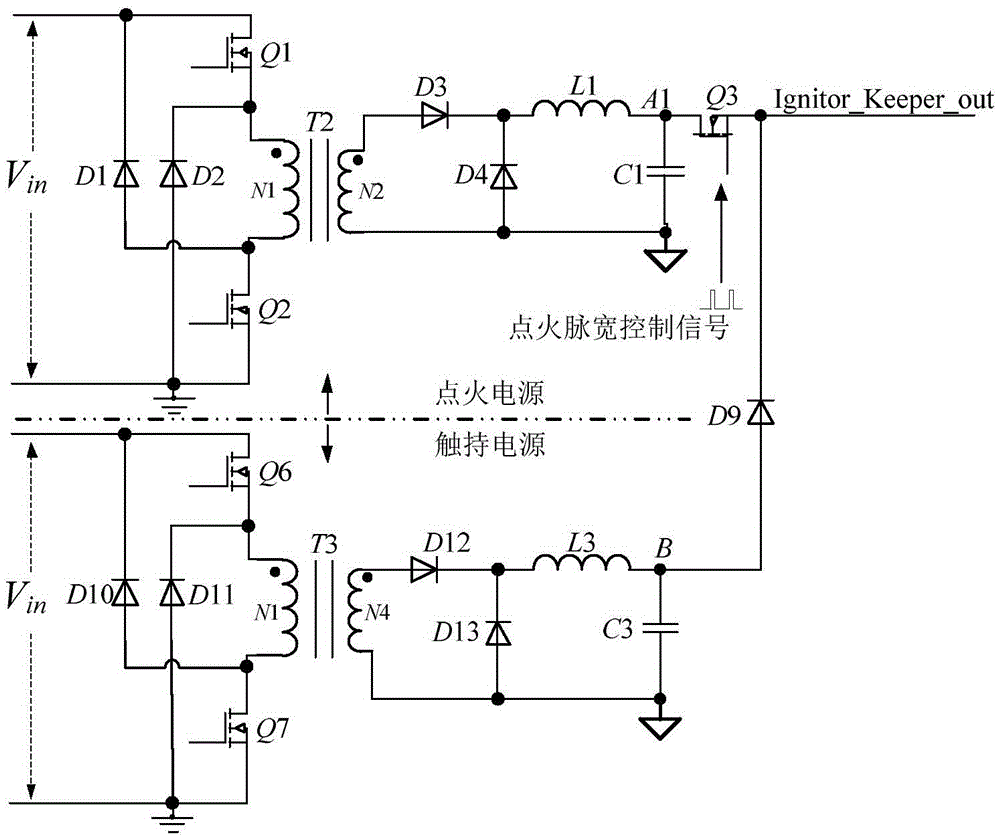

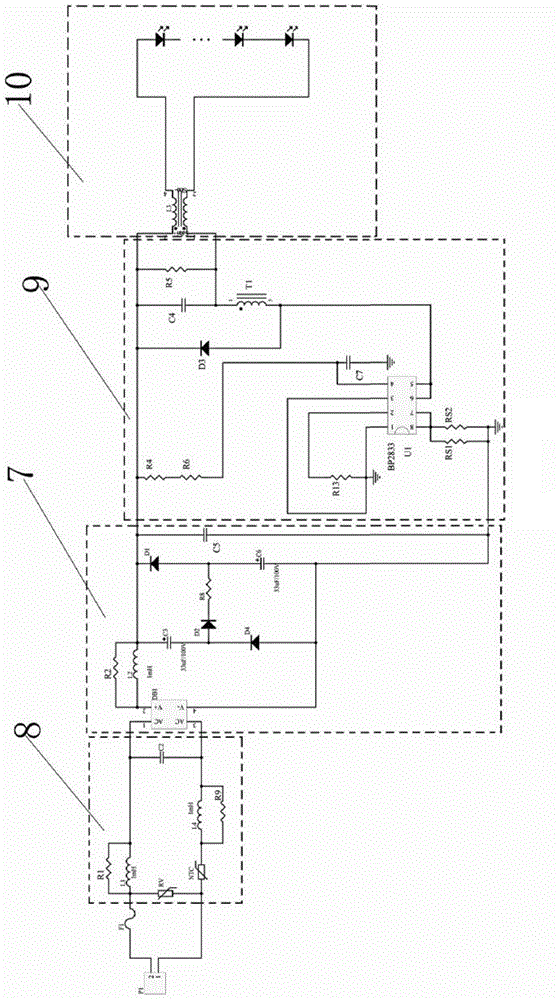

Hollow cathode power converter and control system thereof

ActiveCN105553298AExtend your lifeImprove power densityAc-dc conversionPulse duration/width modulationLoop controlControl system

The invention provides a hollow cathode power converter and a control system thereof. The hollow cathode power converter comprises a main transformer primary side circuit and a main transformer auxiliary side rectifying and wave-filtering circuit; the output voltage of the main transformer auxiliary side rectifying and wave-filtering circuit is sampled to form voltage closed-loop control, and the output current of the main transformer auxiliary side rectifying and wave-filtering circuit is sampled to form output current closed-loop control; before the ignition of a hollow cathode is successful, a holding electrode and reference ground present high impedance, and a current closed-loop does not work; when the ignition of the hollow cathode is successful, the impedance of the holding electrode is decreased until the output voltage of the main transformer auxiliary side rectifying and wave-filtering circuit is dragged to be lower than a second set value so as to judge that the ignition of the hollow cathode is successful; and when the voltage of the holding electrode is decreased to be lower than the maximum limiting voltage of a holding power supply, closed-loop control is carried out on the output current of the main transformer auxiliary side rectifying and wave-filtering circuit. A heating power supply, an ignition power supply and the holding power supply are coupled to obtain a main converter, so that the power density is high, and the dynamic response is improved.

Owner:SHENZHEN ACAD OF AEROSPACE TECH

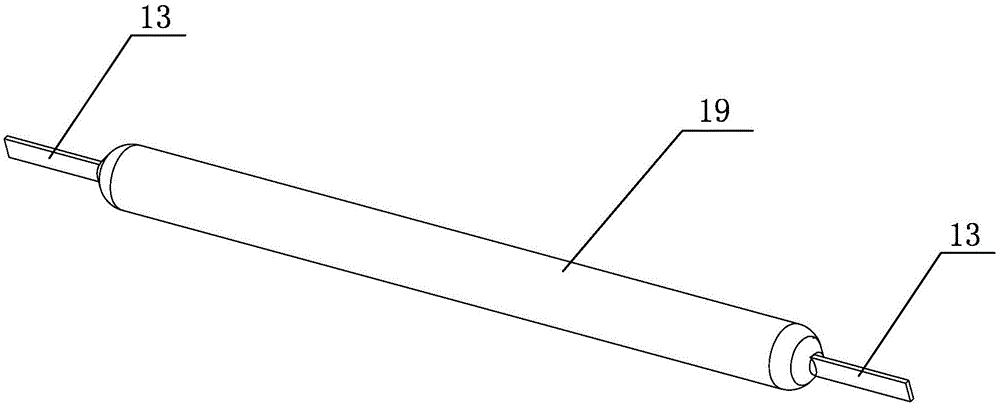

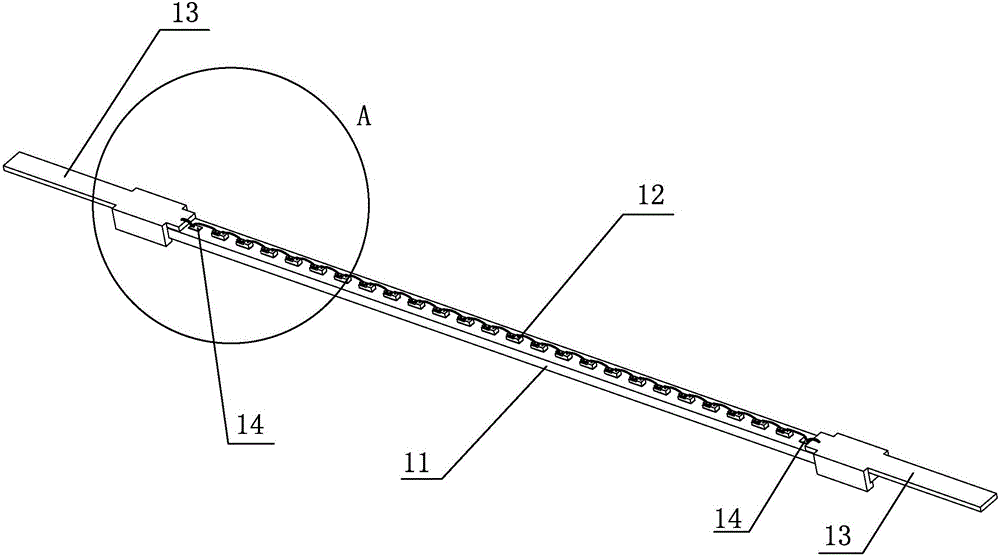

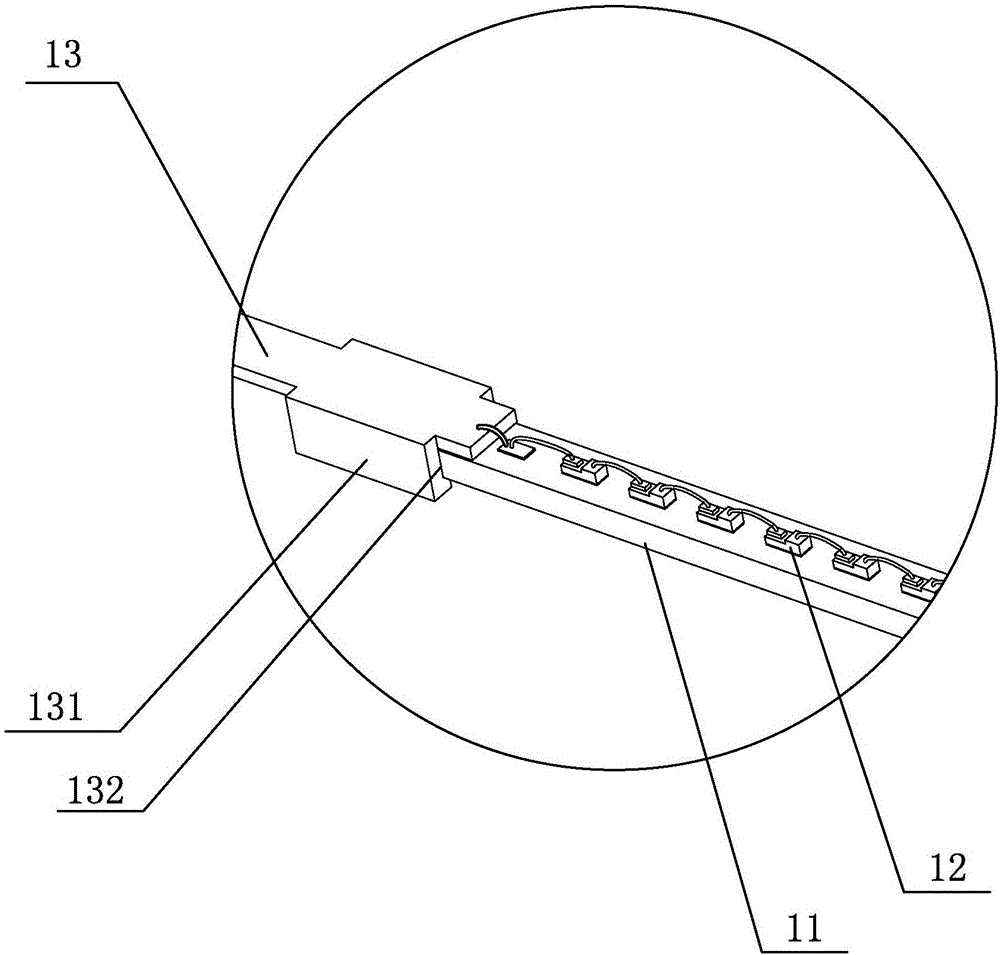

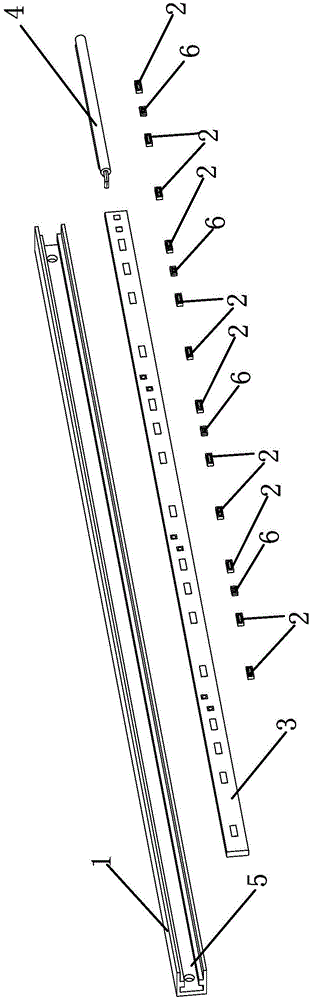

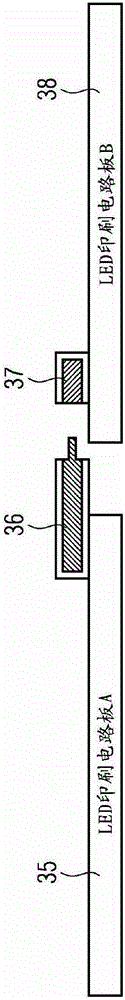

LED light-emitting lamp filament and LED bulb adopting same

InactiveCN106151905AAvoid breakingLimit currentElongate light sourcesElectric circuit arrangementsMetal stripsFluorescence

The invention discloses an LED light-emitting lamp filament and an LED bulb adopting the same. The LED light-emitting lamp filament comprises a strip-shaped substrate and multiple LED chips arranged on the strip-shaped substrate. The two ends of the strip-shaped substrate are each provided with a metal strip-shaped electrode. The multiple LED chips are connected in series to form an LED light source. Multiple electronic devices having one of the conductive function, the current-limiting function and the protection function are arranged at the position, close to one of the ends, on the strip-shaped substrate or the position, close to each of the ends, on the strip-shaped substrate. The metal strip-shaped electrodes, the electronic devices and the LED light source are connected through a wire. The periphery of the strip-shaped substrate, the periphery of the LED light source, the periphery of each electronic device and the periphery of the connection position between the strip-shaped substrate and each metal strip-shaped electrode are coated with fluorescent rubber. The LED light-emitting lamp filament and the LED bulb adopting the same have the beneficial effects that according to different properties of the electronic devices, the connection wire of the LED light source and the metal strip-shaped electrodes can be prevented from rupture; or a current of the LED light-emitting lamp filament can be prevented from overcurrent; or the LED light-emitting lamp filament can be free from influence of overvoltage and overcurrent; or when the LED light-emitting lamp filament is overheated, the heat emitting phenomenon is reduced.

Owner:ZHEJIANG SUNSHINE MEIJIA LIGHTING CO LTD

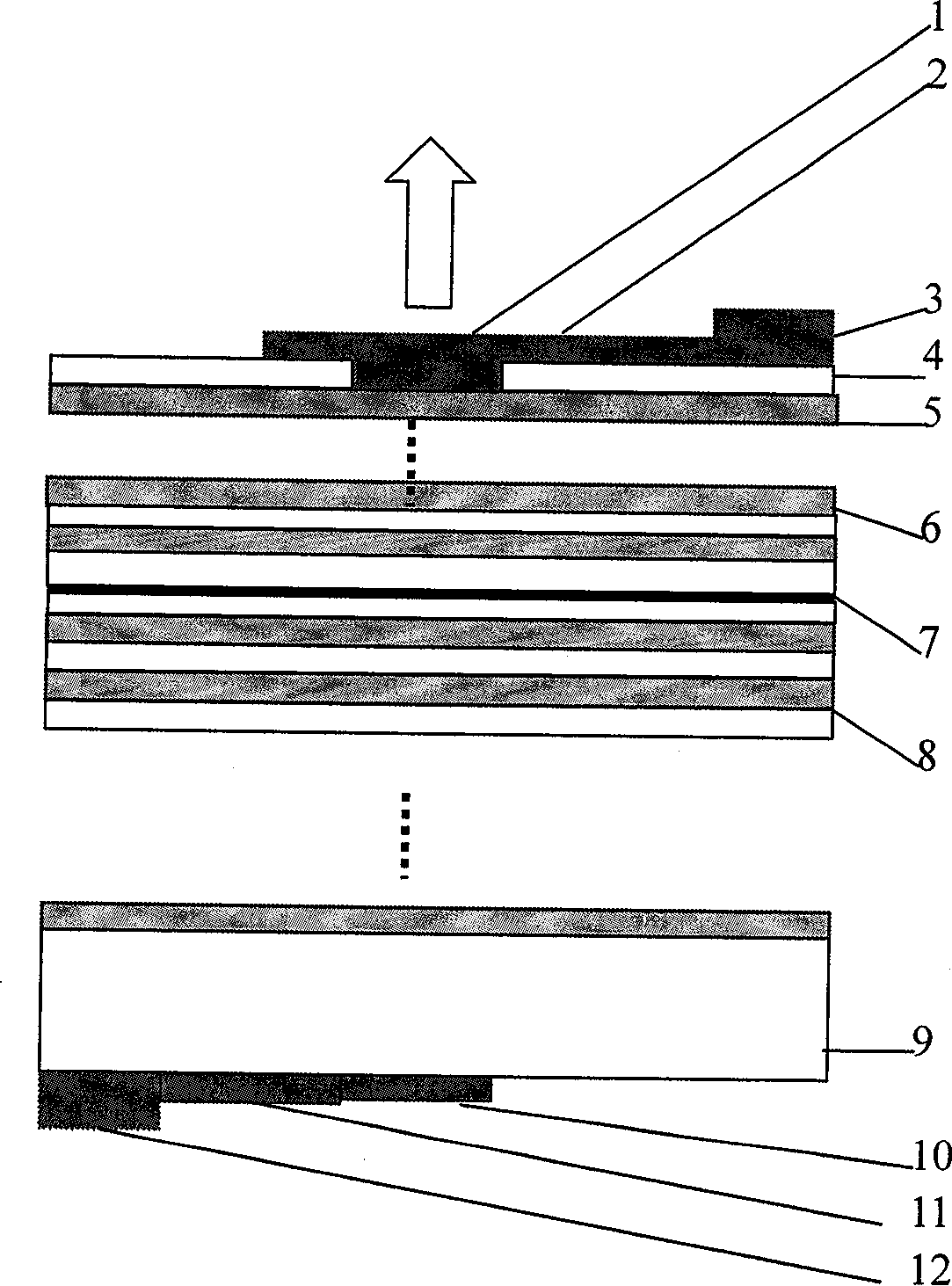

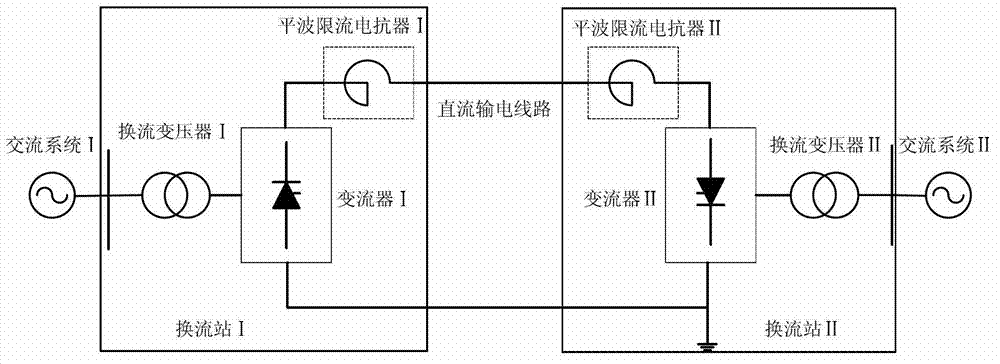

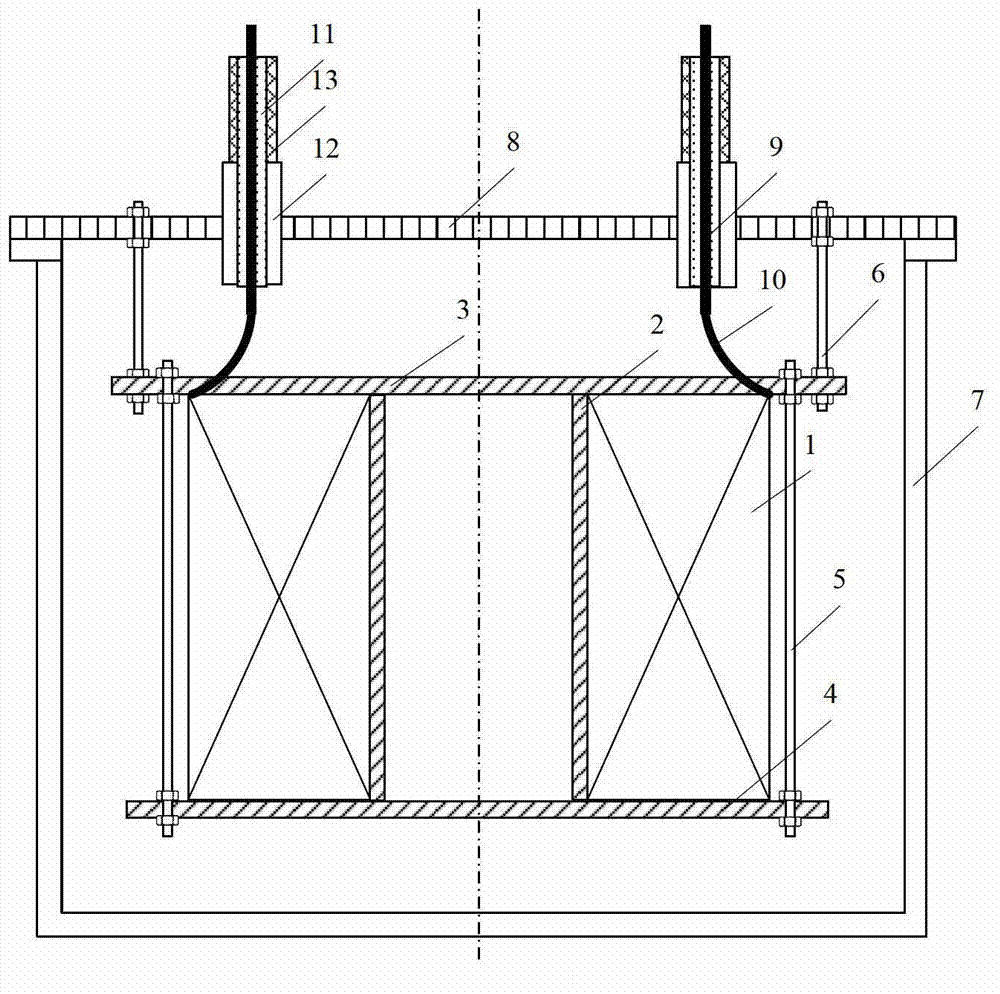

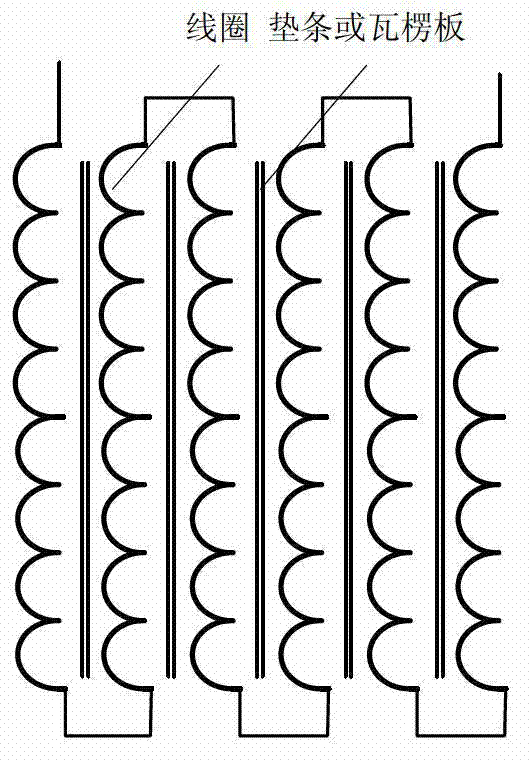

Superconductivity flat wave current limiting reactor applicable to high-voltage direct-current transmission

InactiveCN102789883AReduce energy consumptionImprove breaking capacityTransformersFixed transformers or mutual inductancesInsulation layerTransition line

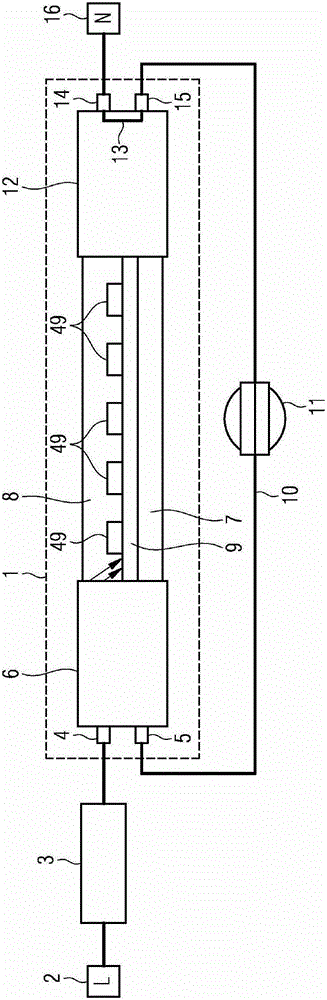

Provided is a superconductivity flat wave current limiting reactor applicable to high-voltage direct-current transmission. A superconducting magnet composed of a superconducting coil (1), a coil frame (2), a coil upper supporting plate (3), a coil lower supporting plate (4) and a coil fastening screw (5) is arranged inside a low-temperature dewar device composed of a low-temperature dewar drum (7) and a low-temperature dewar upper cover plate (8). The superconducting magnet is cooled through direct evaporating of liquid nitrogen or cooled through the liquid nitrogen added into a refrigerator. The superconducting magnet is installed with the low-temperature dewar upper cover plate (8) through a pull rod (6). The superconducting magnet and a transition line (10) are connected with a direct current power grid through a current lead wire (9). A sleeve heat preservation layer (11), a sleeve low-temperature insulation layer (12) and a sleeve normal-temperature insulation layer (13) are arranged outside the current lead wire (9), good insulation is guaranteed, and heat leakage is reduced. The superconductivity flat wave current limiting reactor has no loss and only a flat wave effect is obtained when the direct current power grid works normally. When the direct current power grid is short-circuited, resistance of the reactor is increased fast, and short-circuit current is restrained to certain level.

Owner:INST OF ELECTRICAL ENG CHINESE ACAD OF SCI

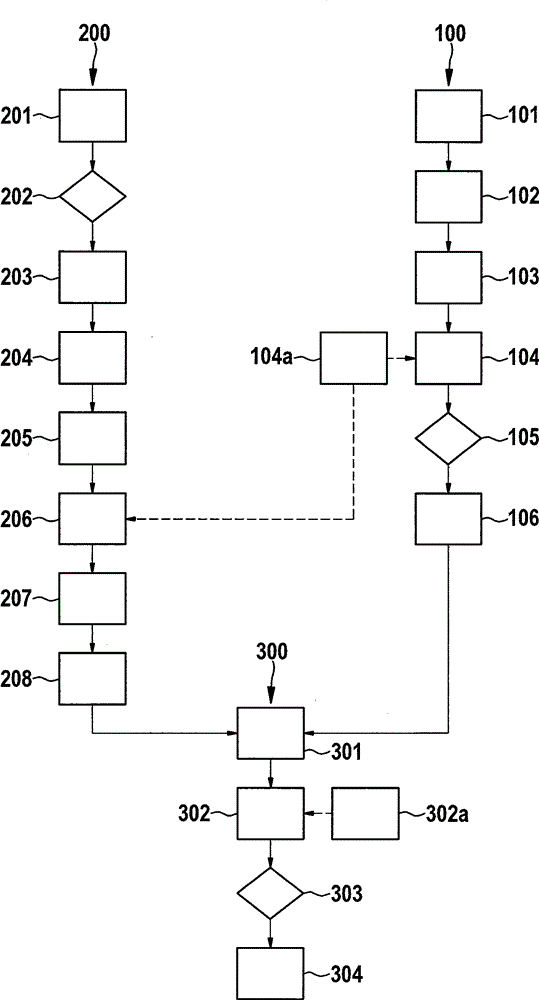

A method for determining a thermal impedance of a semiconductor device

InactiveCN104465316ALow costMonitoring the welding sectionSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsPower semiconductor deviceVoltage drop

The invention relates to a method for determining a thermal impedance of a semiconductor device, wherein the semiconductor device is energized with a warm-up current (101, 201), a power loss of the semiconductor device is determined, a voltage drop dependent on a temperature of the semiconductor device is detected on the semiconductor device (103, 205), the temperature of the semiconductor device over time is determined as a warm-up curve (104, 207), and the thermal impedance of the semiconductor device is determined as a quotient of the determined temperature and the determined power loss (106, 208).

Owner:ROBERT BOSCH GMBH +1

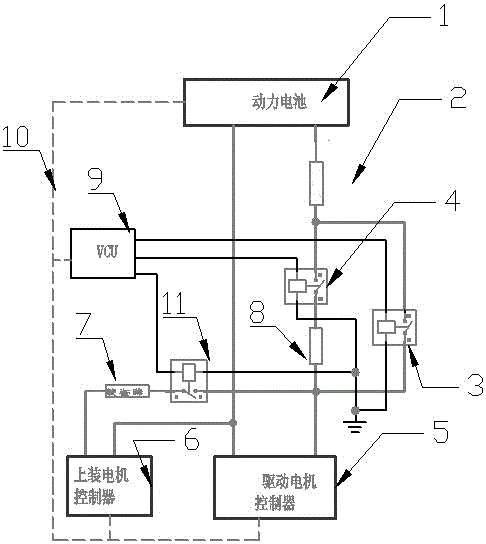

Power distribution control circuit of vehicle-mounted motor controller of electric vehicle and control method of control circuit

ActiveCN106004495ATroubleshooting Power-Up Current Pulse IssuesSolving Current Pulse ProblemsElectric devicesElectric vehicle charging technologyDistribution controlElectrical battery

The invention discloses a power distribution control circuit of a vehicle-mounted motor controller of an electric vehicle and a control method of the control circuit. The control circuit comprises a power battery, a complete vehicle logic unit, the vehicle-mounted motor controller, a drive motor controller, a power-on buffer circuit, a CAN bus and a vehicle-mounted electric control switch, wherein the complete vehicle logic unit is connected with the power battery, the vehicle-mounted motor controller and the drive motor controller, connected with a first electric control switch and a second electric control switch through low-tension control wires and then grounded; a negative electrode of the battery is connected to the vehicle-mounted motor controller and the drive motor controller; a positive electrode of the battery is connected with a parallel circuit formed by the power-on buffer circuit and the second electrical control switch and then connected to the drive motor controller and the vehicle-mounted motor controller. Multiple motor controllers share one power-on buffer circuit through specific control logic, a relay is used among the motor controllers for power distribution control, normal demands are met, and electrical safety can also be guaranteed.

Owner:CHENGDU RAJA NEW ENERGY AUTOMOTIVE TECH CO LTD

Current open circuit arc extinguishing device and method based on nonlinear resistor

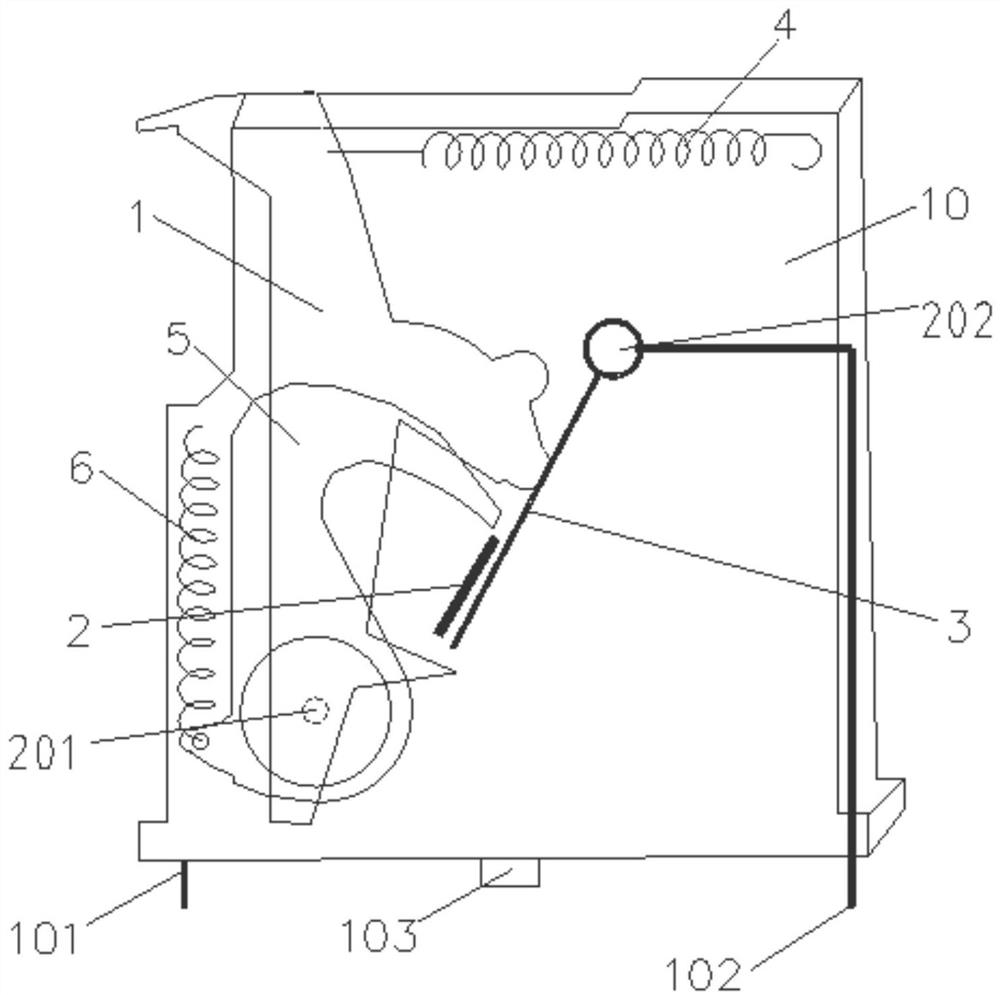

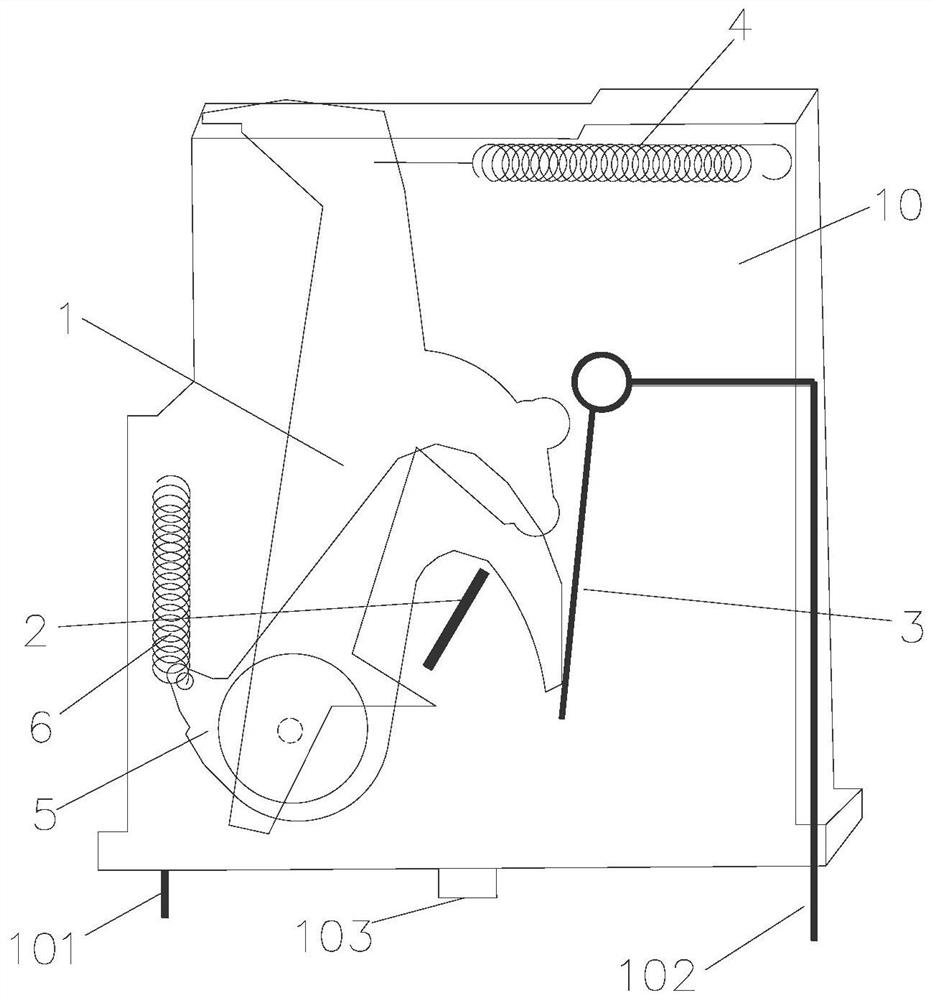

InactiveCN104241058AImprove breaking capacityExtended service lifeCircuit-breaking switch detailsNonlinear resistorEngineering

The invention provides a current open circuit arc extinguishing device and method based on a nonlinear resistor. The problems that according to an existing arc extinguishing device of a circuit breaker, when high-current breaking happens, due to the low arc extinguishing capability, strong electric arcs are generated, and the service life of the circuit breaker is shortened, and even a contact is burnt out are solved. According to the direct-current circuit breaker arc extinguishing device designed based on the characteristics of the nonlinear resistor, the electric arc of the direct-current circuit breaker in the breaking process is reduced through shunting of the circuit and the current limiting capability of the nonlinear resistor. The aims of improving the breaking capacity of the circuit breaker and prolonging the service life of the circuit breaker are achieved.

Owner:JIANGSU JIANGCHENG ELECTRIC

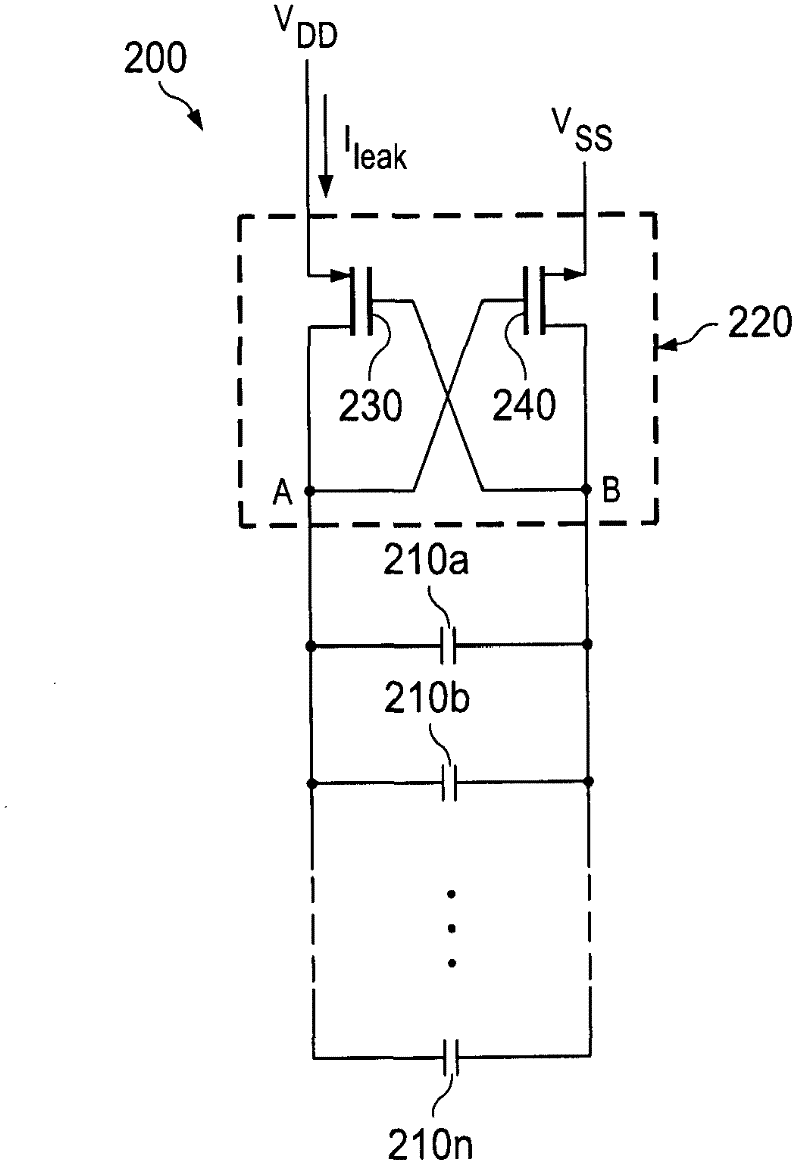

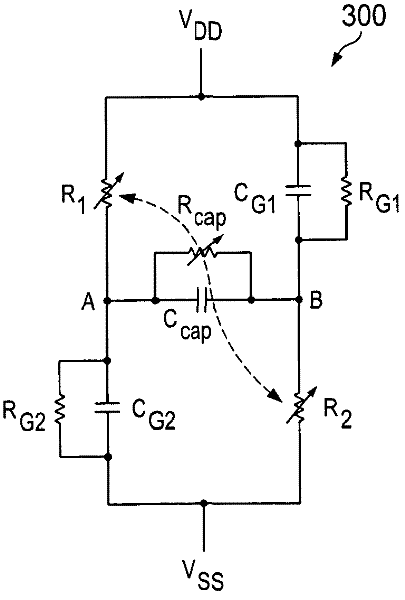

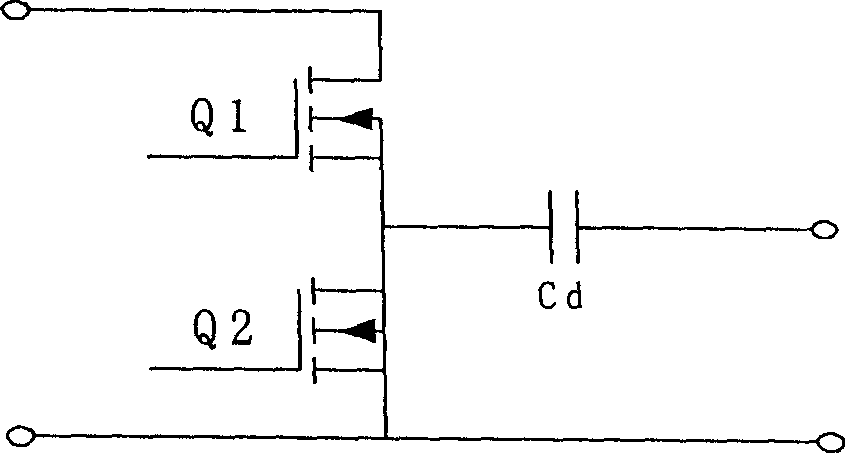

Defectivity-immune technique of implementing MIM-based decoupling capacitors

ActiveCN102339824AReduce Power NoiseLimit currentSemiconductor/solid-state device detailsSolid-state devicesIntegrated circuitEngineering

The invention relates to a defectivity-immune technique of implementing MIM-based decoupling capacitors. An integrated circuit power supply decoupling circuit includes a capacitor and a protection circuit. The capacitor has a first terminal and a second terminal. The protection circuit includes a first transistor having a first conduction path, and a second transistor having a second conduction path. One terminal of the first conduction path is connected to the first terminal of the capacitor, and another terminal of the first conduction path is connected to a first power supply rail. One terminal of the second conduction path is connected to the second terminal of the capacitor, and another terminal of the second conduction path is connected to a second power supply rail.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Bar-type lamp

ActiveCN104456247AImprove cooling effectLimit currentPoint-like light sourceLighting support devicesElectrical resistance and conductanceEngineering

A bar-type lamp comprises an outer shell, LED light sources, an LED substrate and a power wire. The outer shell is an integrally-formed bar-type sectional material and provided with sliding grooves; every three LED light sources and one resistor are connected in series to form a light emitting unit, multiple light emitting units and a control circuit of the bar-type lamp are arranged on the LED substrate, and the LED substrate is arranged in the sliding grooves; a copper plate and an aluminum alloy plate are arranged on the LED substrate and attached to a whole through high-pressure forming. According to the LED substrate of the bar-type lamp, the copper plate and the aluminum alloy plate are attached to a whole through high-pressure forming, aluminum alloy has good cooling performance due to the synergistic effect of specific components and contents of the aluminum alloy plate, the resistors are arranged in the light emitting units to limit current flowing through LED lamp bodies so that voltage at the LED lamp body ends can not be too large, cooling performance is further improved, and the service life of the LED lamp bodies is guaranteed.

Owner:江苏盐新汽车产业投资发展集团有限公司

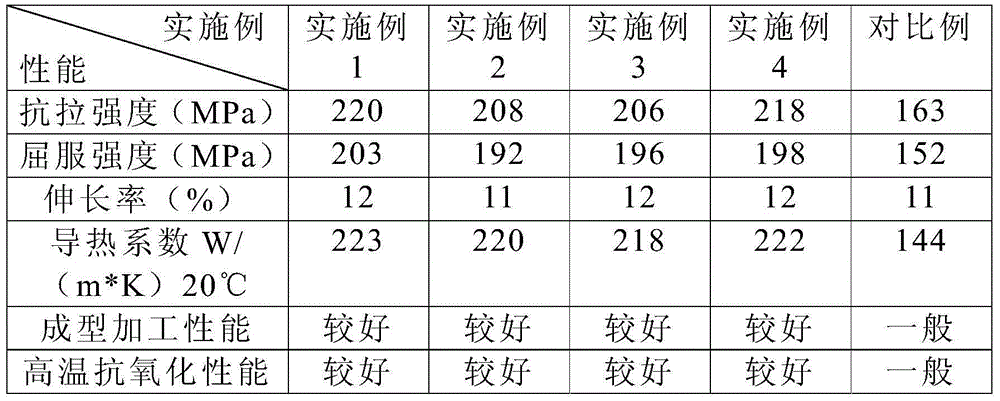

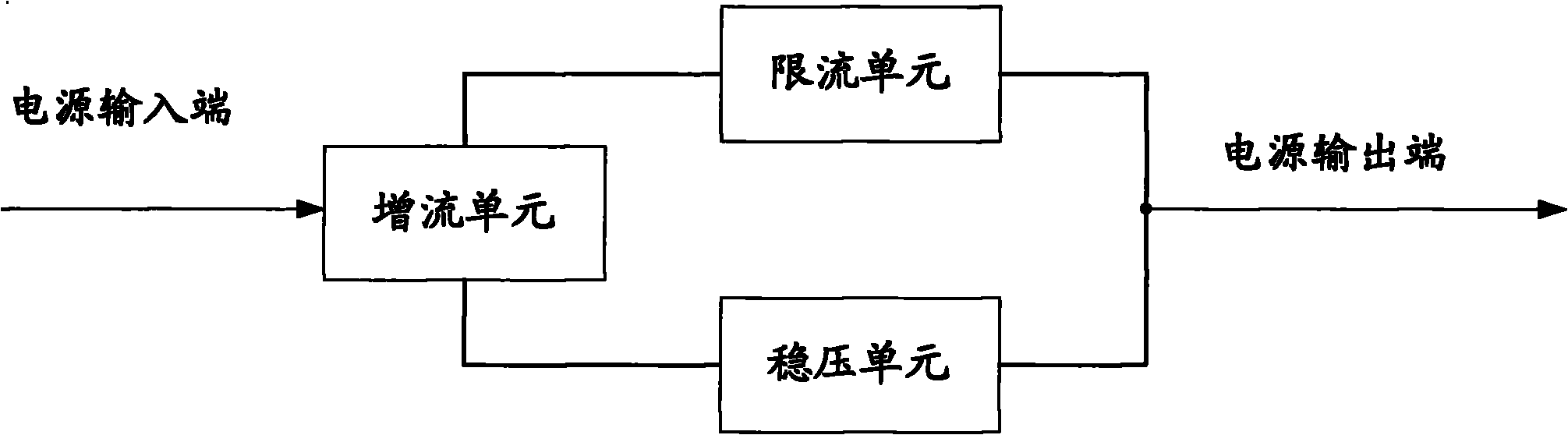

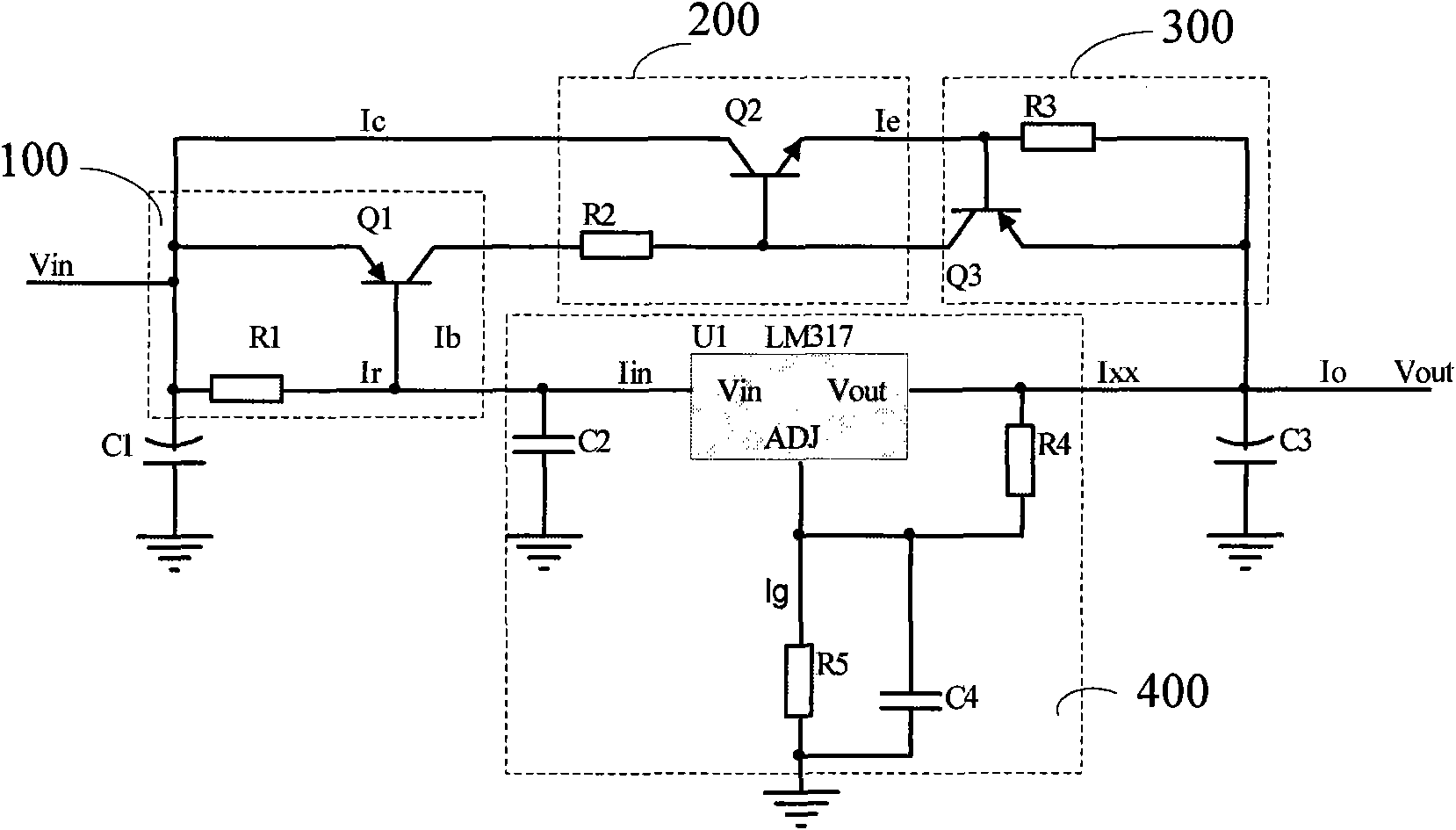

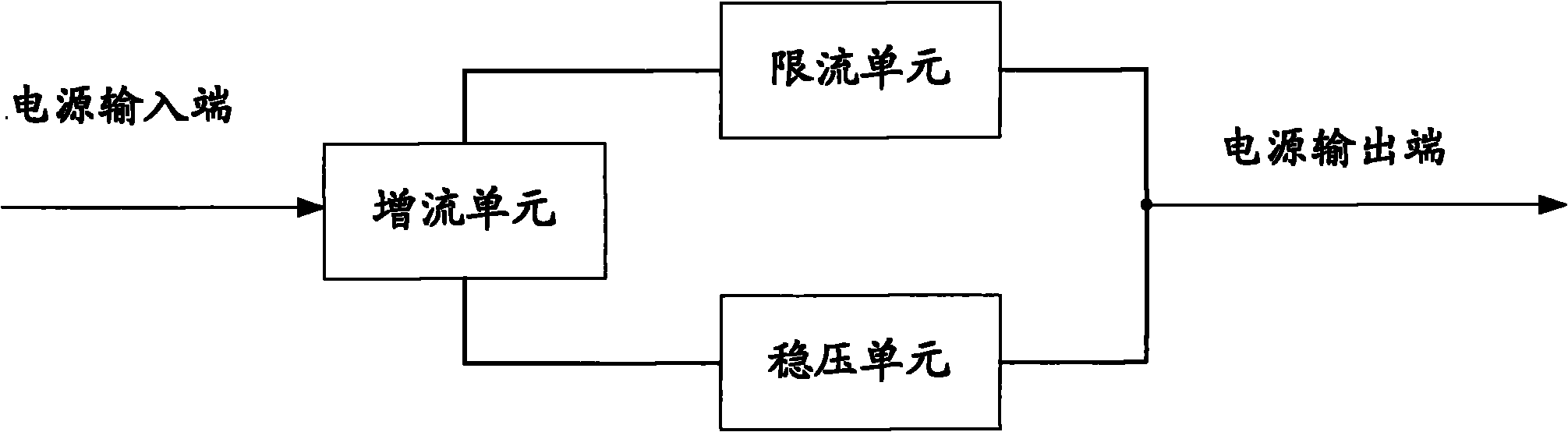

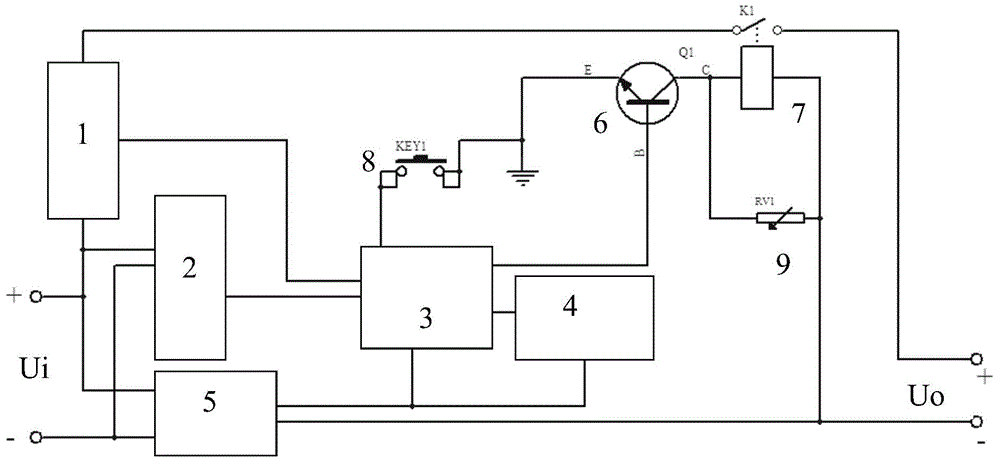

Current increasing and voltage stabilizing circuit with current limiting function

The invention relates to a current increasing and voltage stabilizing circuit with a current limiting function, comprising a current increasing unit used for increasing and outputting a current, a current limiting unit used for limiting overlarge current output by the current increasing unit and a voltage stabilizing unit used for supplying stable output voltage to voltage output by the current increasing unit and the current limiting unit, wherein the input end of the current increasing unit is electrically connected with a power input end of the current increasing and voltage stabilizing circuit, the output end of the current increasing unit is connected with the input end of the current limiting unit, the output end of the current limiting unit is electrically connected with the output end of the voltage stabilizing unit, and the point in which the output end of the current limiting unit is electrically connected with the output end of the voltage stabilizing unit is electrically connected with the power input end of the current increasing and voltage stabilizing circuit. The current increasing and voltage stabilizing circuit with the current limiting function limits the current of the current increasing and voltage stabilizing circuit by adopting the current limiting unit and the voltage stabilizing unit, thereby avoiding that the current is too large to damage the voltage stabilizing unit.

Owner:OCEANS KING LIGHTING SCI&TECH CO LTD +1

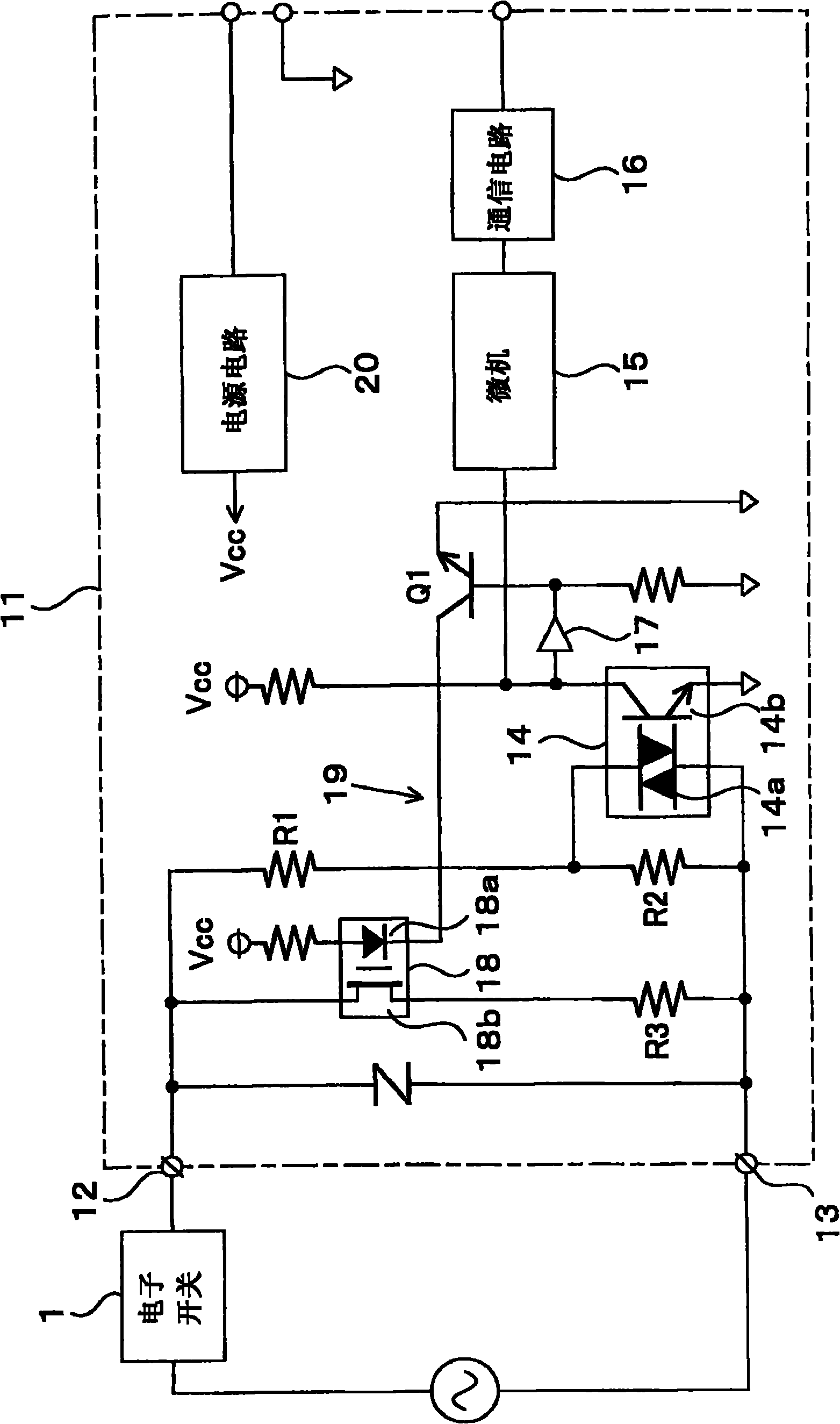

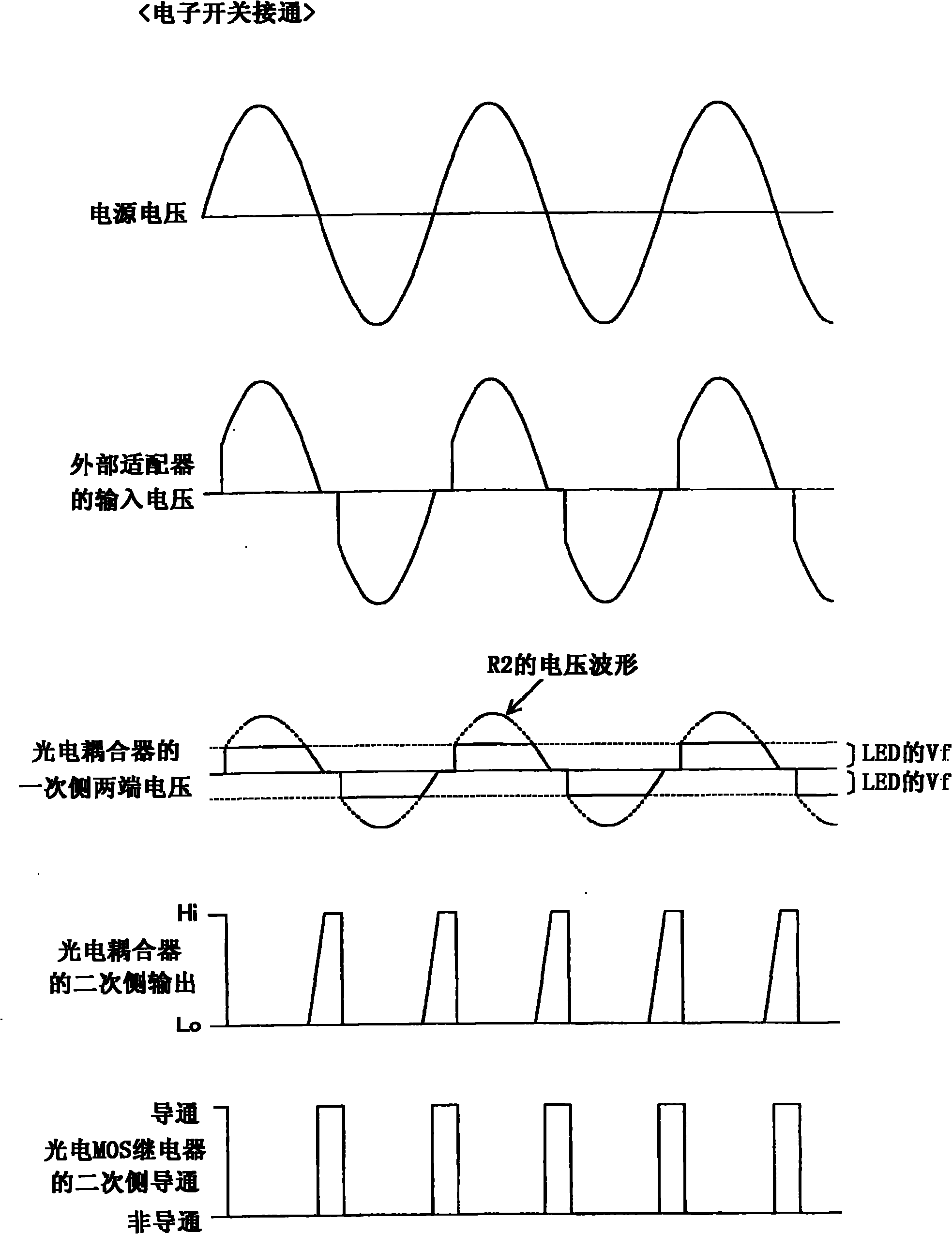

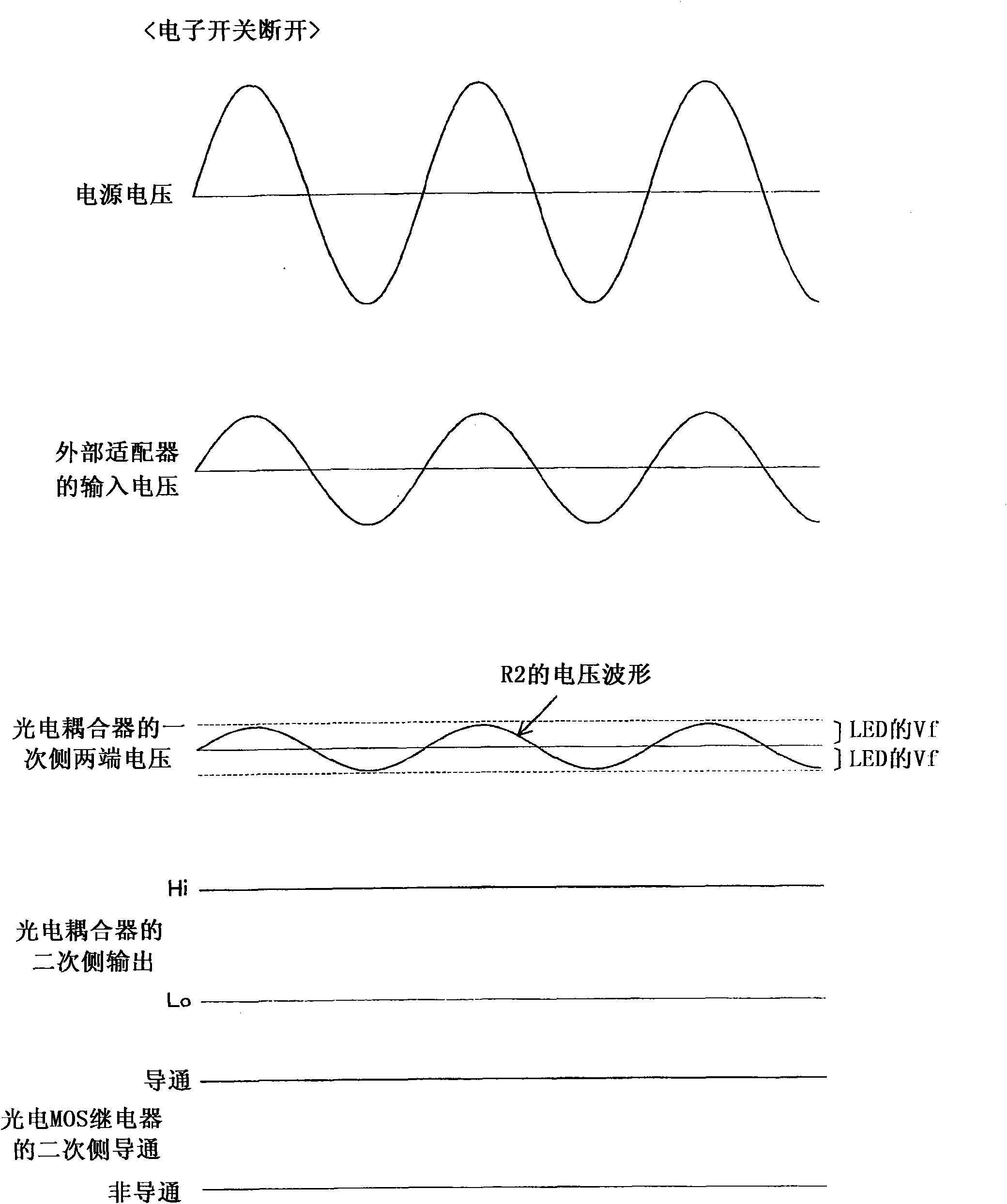

Outer adapter

InactiveCN102457247ASuppress power consumptionMonitor on/off statusMultiple-port networksCircuit interrupters testingPower consumptionInput impedance

An outer adapter can feasibly detect switching on / off state of a two-wire type electronic switch through a circuit with little power consumption. The outer adapter (11) is provided with two input terminals (12,13) which are connected with an electronic switch (1). Voltage dividing resistors (R1,R2) perform voltage dividing on input voltage. According to the voltage over two ends of the voltage dividing resistor (R2), a photoelectric coupler (14) detects the switching on / off state of the electronic switch (1). An impedance adjusting circuit (19) is provided with the following components: an adjusting resistor (R3) which is equipped between the input terminals (12,13), a transistor (Q1) which responds to output of the photoelectric coupler (14) and switches to switch on / off the adjusting resistor (R3), and a photoelectric MOS relay (18). Input impedance of the adapter (11) is adjusted to a relatively high value at a contact conduction state of the electronic switch (1), and is adjusted to a relatively low value at a contact non-conduction state.

Owner:KAWAMURA ELECTRIC INC

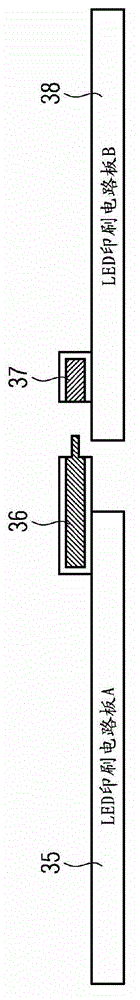

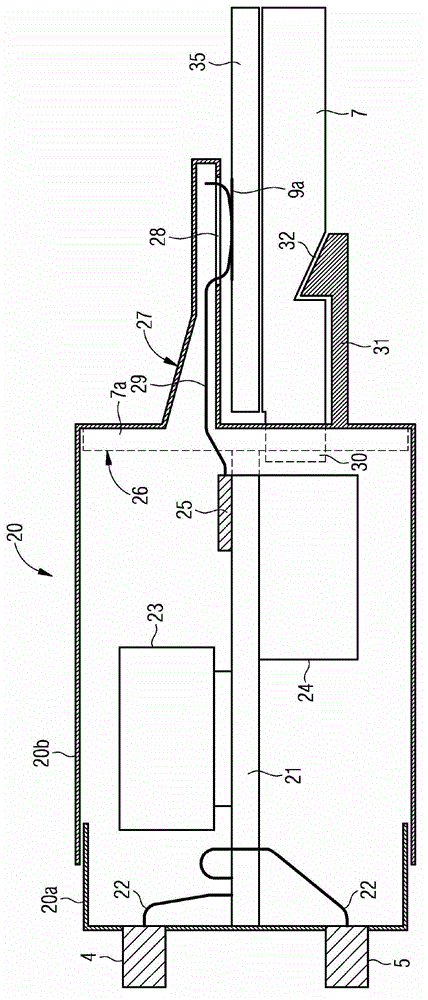

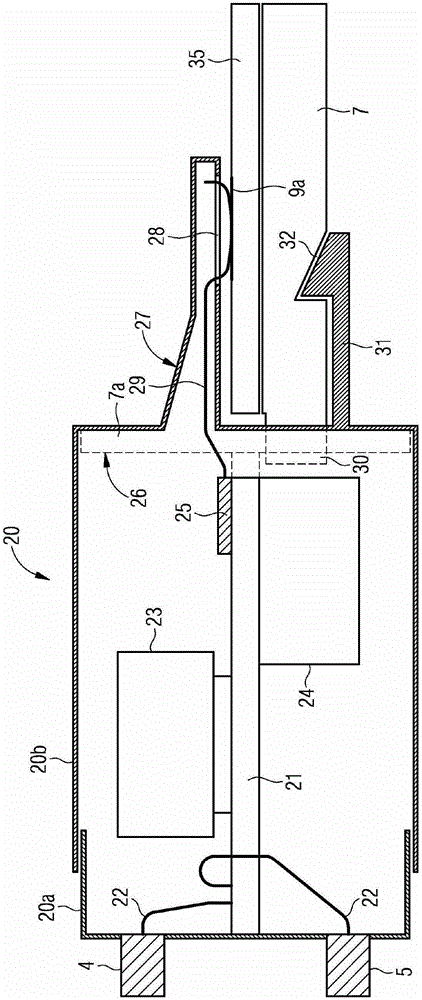

Led lamp

ActiveCN103069216AEasy to fixAvoid damageElectrically conductive connectionsPoint-like light sourceConductive materialsEngineering

The invention relates to an LED lamp having a converter and an arrangement, connected to the converter, of light-emitting diodes arranged on at least one printed circuit board. The converter is arranged in a multi-part, latchable housing which completely surrounds the converter and is made of electrically non-conductive material.

Owner:LEDVANCE GMBH

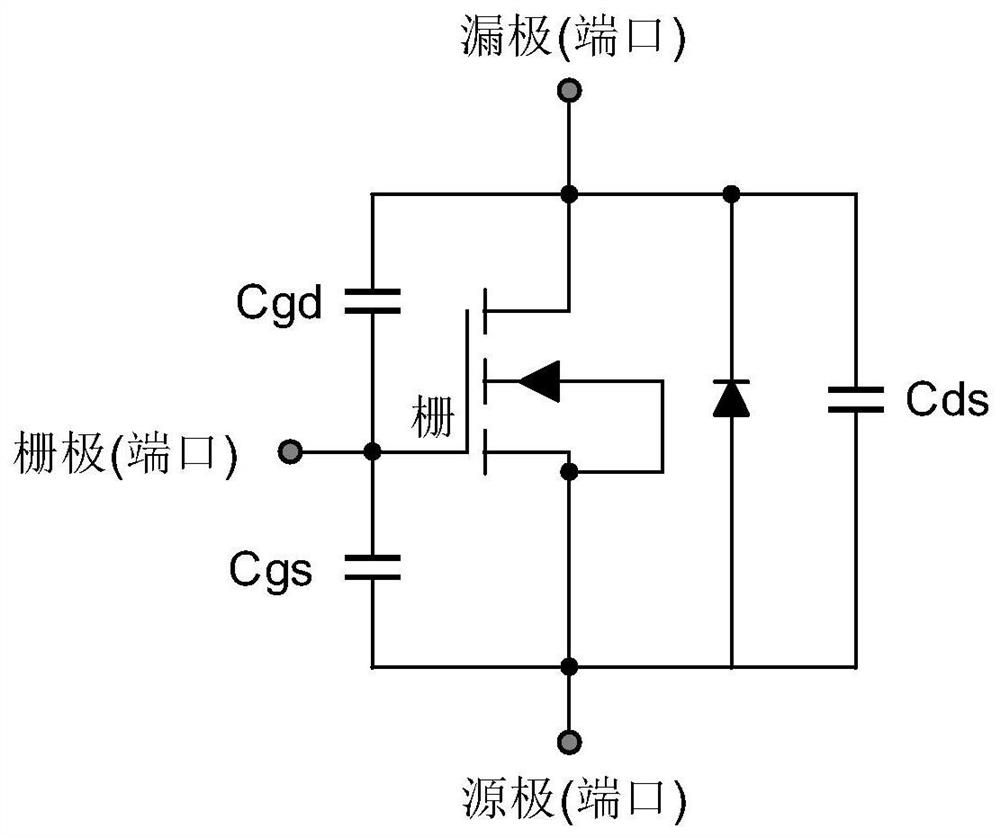

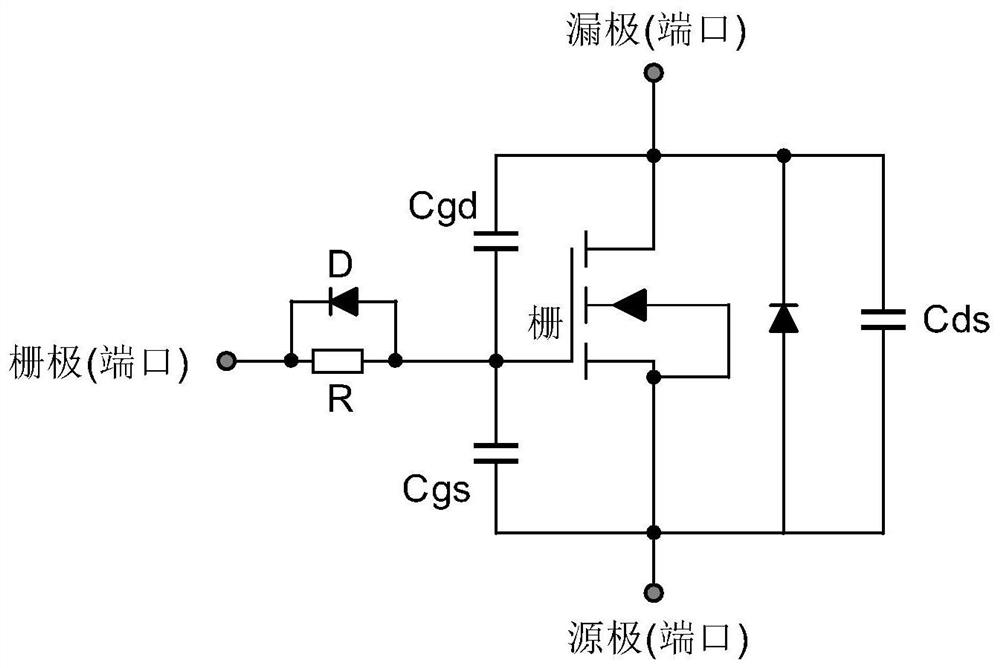

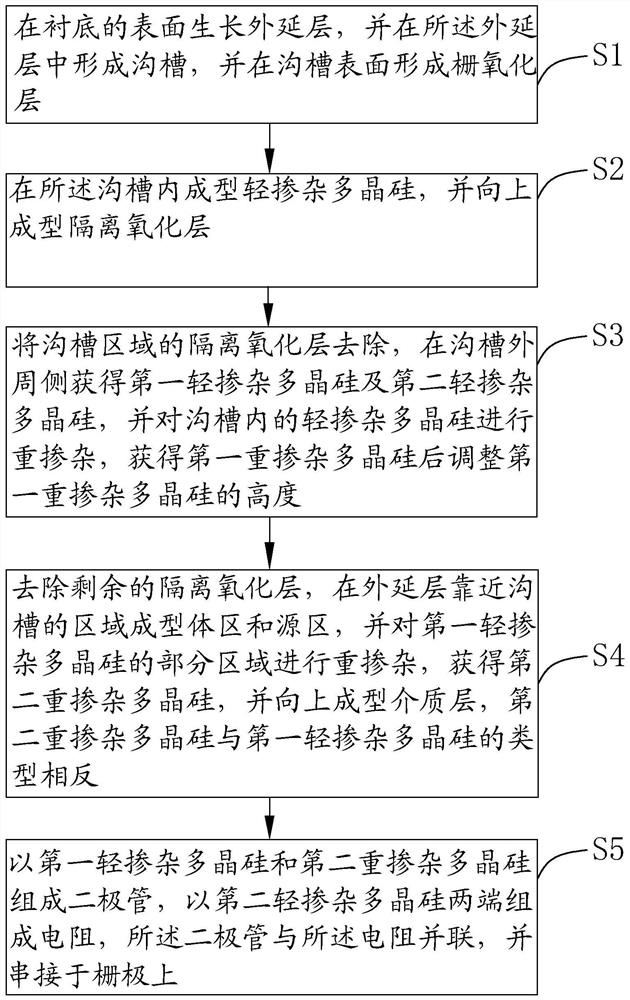

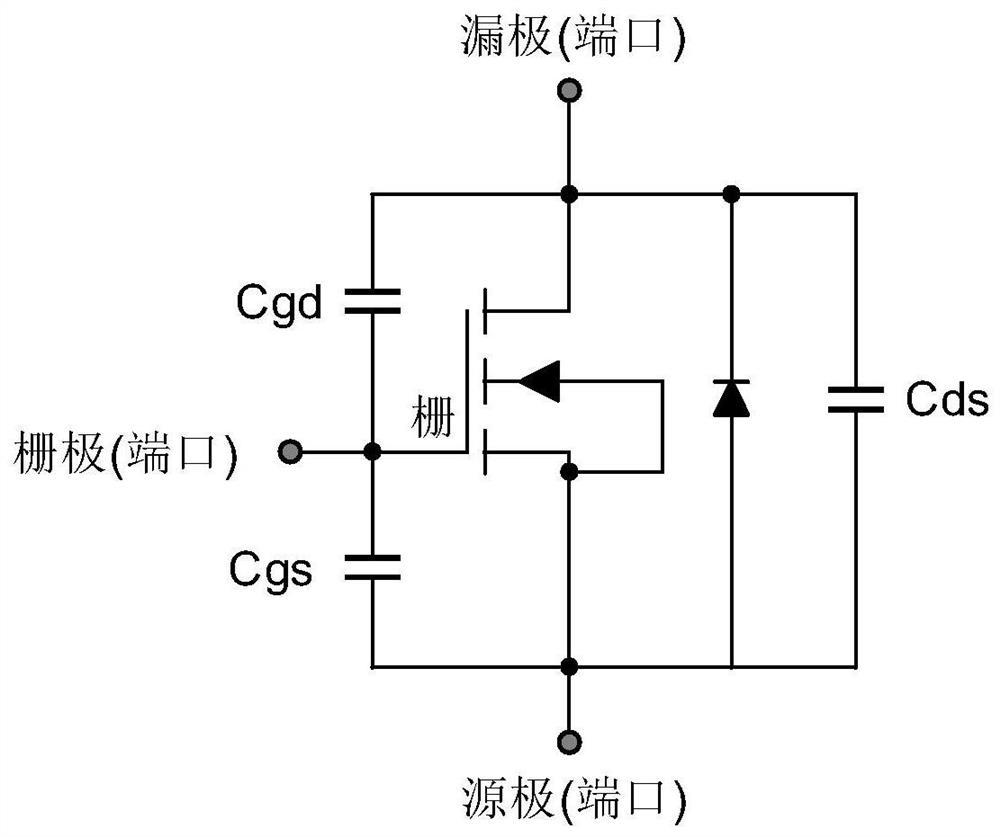

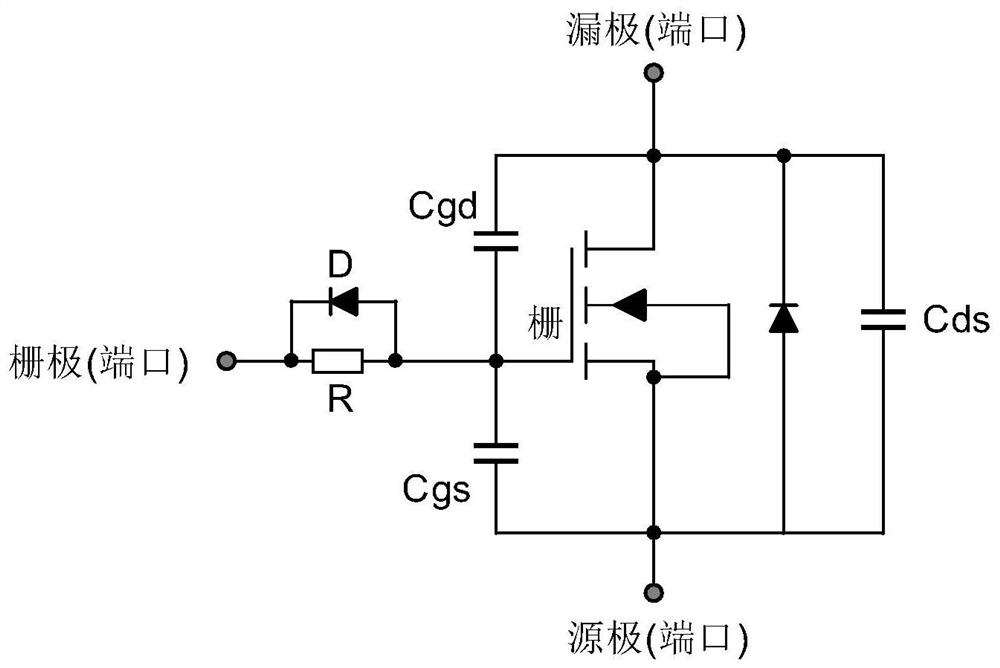

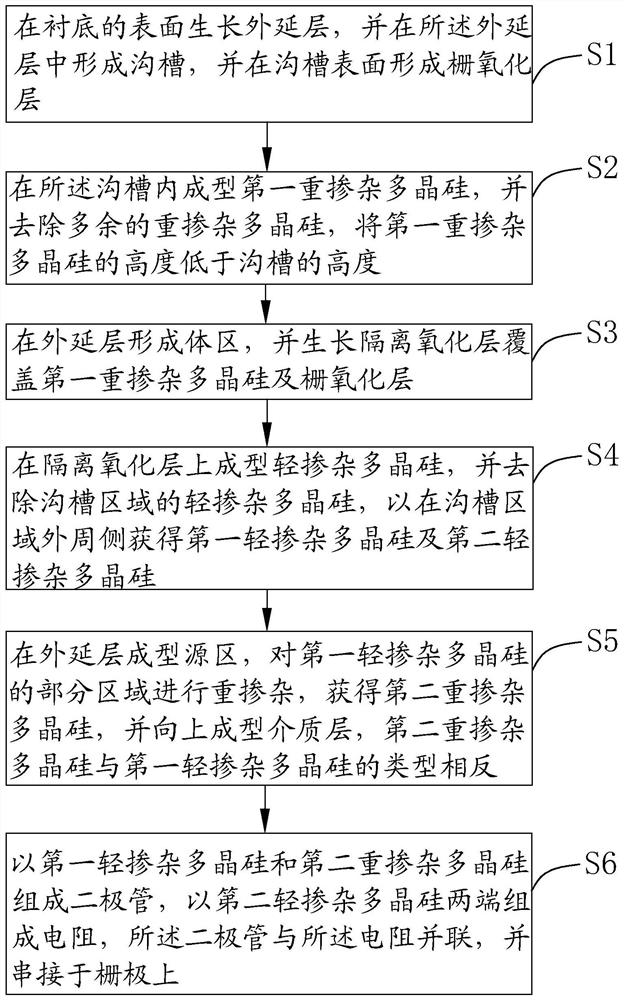

MOSFET chip manufacturing process for improving grid characteristics

PendingCN113764407AAchieve protectionImprove discharge efficiencyTransistorSolid-state devicesMOSFETEngineering

The invention discloses an MOSFET chip manufacturing process for improving grid characteristics, which comprises the following steps: removing an isolation oxide layer in a groove region, obtaining first lightly-doped polycrystalline silicon and second lightly-doped polycrystalline silicon on the peripheral side of a groove, heavily doping the lightly-doped polycrystalline silicon in the groove, obtaining first heavily-doped polycrystalline silicon, and removing the residual isolation oxide layer in a body forming region and a source region, close to the groove, of the epitaxial layer; carrying out heavy doping on part of the region of the first lightly-doped polycrystalline silicon, and obtaining second heavy-doped polycrystalline silicon; forming a dielectric layer upwards, wherein the type of the second heavy-doped polycrystalline silicon is opposite to that of the first lightly-doped polycrystalline silicon; and forming a diode by the first lightly doped polycrystalline silicon and the second heavily doped polycrystalline silicon, forming a resistor by two ends of the second lightly doped polycrystalline silicon, and connecting the diode with the resistor in parallel to be connected to the grid electrode in series. The polycrystalline silicon resistor and the polycrystalline silicon diode are integrated in the chip, so that the current flowing through the grid electrode is effectively limited, and the protection on the grid electrode is realized.

Owner:深圳市芯电元科技有限公司

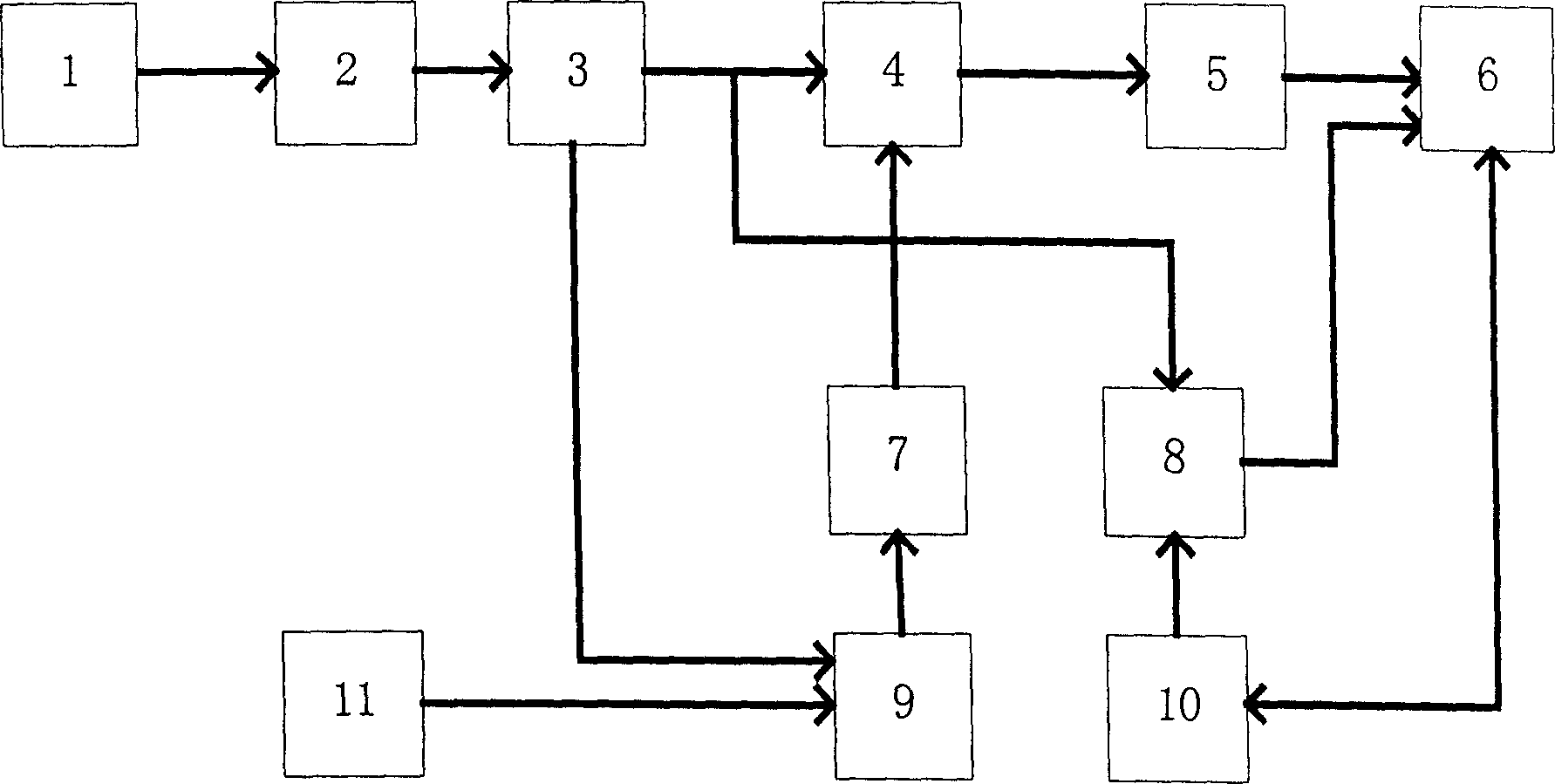

Electronic ballast in use for light tunable gas discharge lamp in high intensity

InactiveCN1874638ALimit currentSo as not to damageElectrical apparatusElectric lighting sourcesEngineeringHigh intensity

The invention comprises: a main circuit comprised of a low-pass filer rectifying circuit, a power factor calibrating circuit, a bridge type inverter circuit and a filtering resonance circuit; and a control circuit composed of an insulation drive circuit, a starting circuit, a frequency regulating circuit, a start control circuit, and a light changes controlling circuit; setting a capacitor at the output of the inductor in said filter resonance circuit in order to limit the current passing through the switch tube in the bridge type inverter circuit at the time of starting the high intensity gas discharge lamp.

Owner:ZHEJIANG UNIV

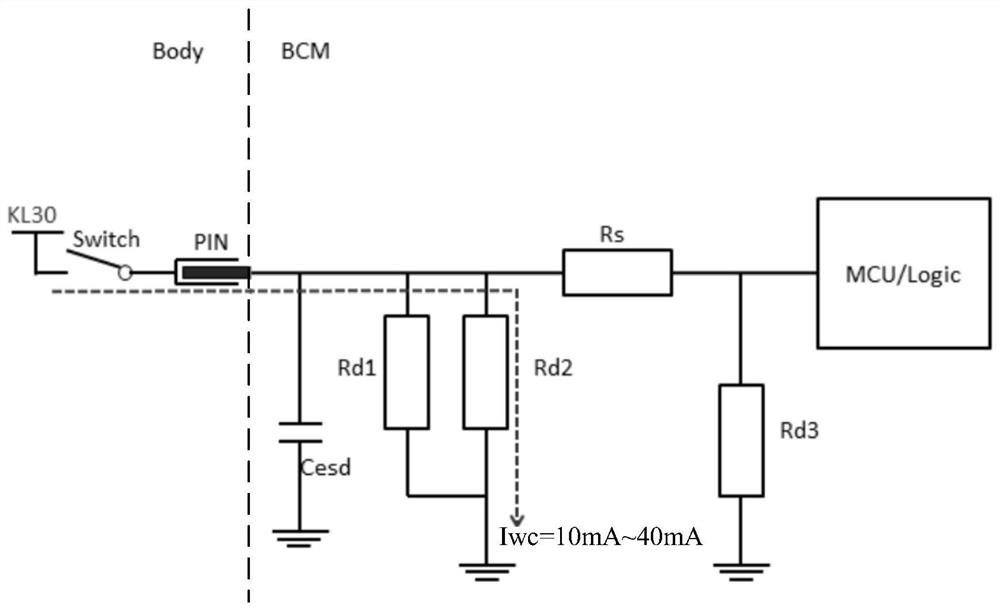

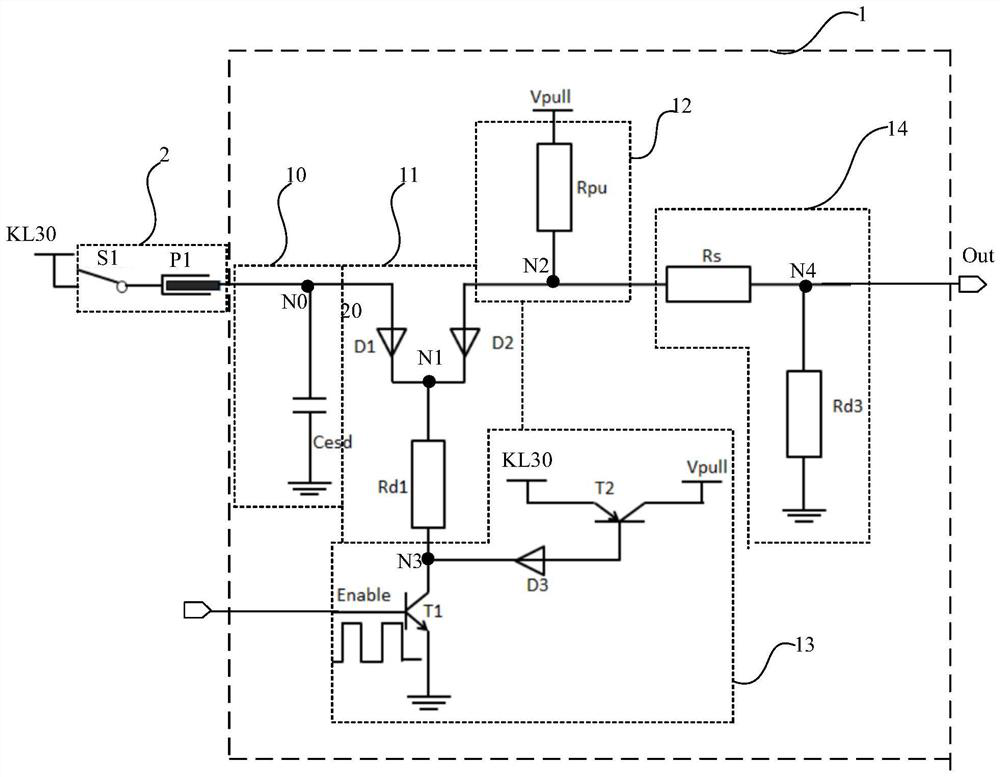

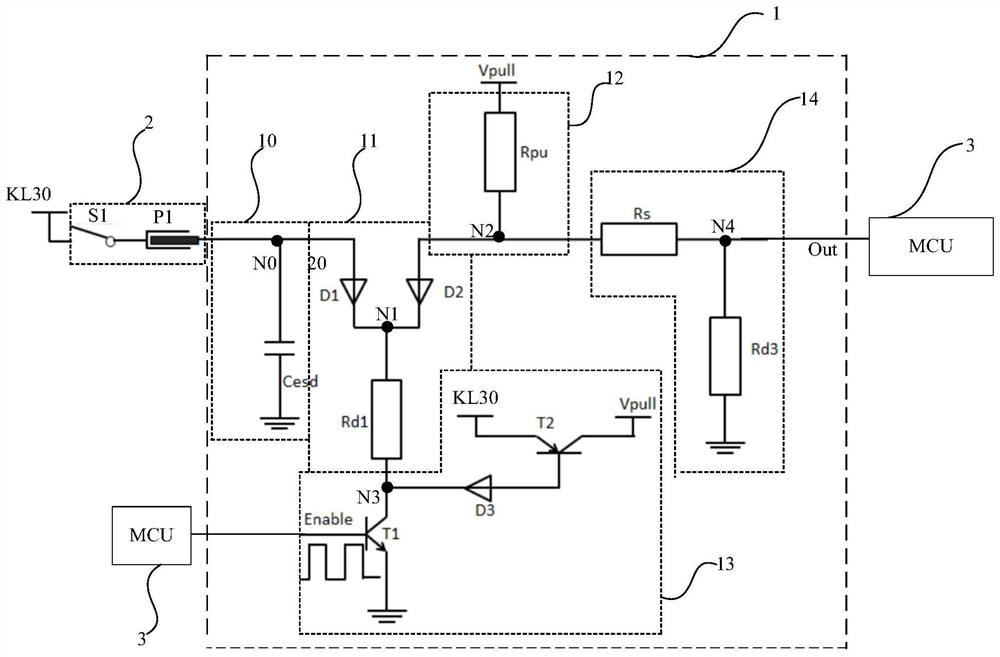

Highly effective signal circuit, control system and electrical equipment

The invention provides a highly effective signal circuit, a control system and electrical equipment, and the highly effective signal circuit is connected to an external power supply through a contactswitch, and comprises a wet current configuration module, a pull-up module, a periodic control module, and a current-limiting voltage-dividing module. The wet current configuration module can periodically configure corresponding wet current for the contact switch under the control of the periodic module. The highly effective signal circuit is simple in structure, low in cost and easy to implement,and by adopting a periodic control strategy, under some conditions that the contact switch is closed, the periodic control module controls the wet current configured by the wet current configurationmodule not to form a loop, so that the reliability of the circuit is improved. Therefore, the problem that the electric quantity of the external power supply is greatly consumed when the contact switch is forgotten to be disconnected for a long time is solved, the electric quantity flowing through the contact switch is greatly reduced, and the energy-saving purpose is achieved.

Owner:UNITED AUTOMOTIVE ELECTRONICS SYST

Direct-current switch

InactiveCN104538254ALimit currentEasy to separateCurrent/voltage measurementRelaysComputer moduleVoltage sensor

The invention relates to a direct-current switch comprising a relay and a relay control module. The relay control module comprises an MCU which is in control connection with a coil of the relay and is sampling connection with a current sensor and a voltage sensor. The current sensor is used for measuring the current flowing through a contact loop of the relay, and the voltage sensor is used for measuring the input voltage of the direct-current switch. The current state and voltage state of the direct-current switch can be visually monitored in real time, so that the operating state of the direct-current switch can be known visually, and furthermore, the power consumption can be calculated based on the voltage and current values.

Owner:XUJI GRP +3

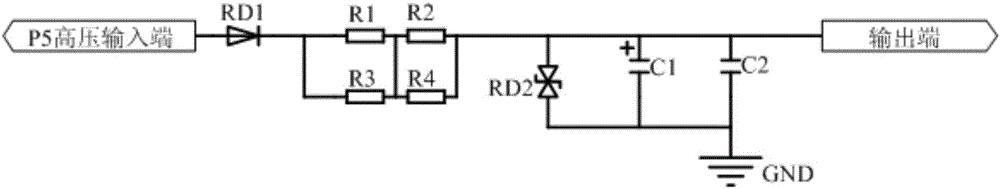

Simple low-cost on-vehicle low-power power supply protecting circuit

InactiveCN105846410ALow costSimple structureEmergency protective arrangements for limiting excess voltage/currentCapacitanceZener diode

A simple low-cost vehicle-mounted low-power power supply protection circuit belongs to the field of automotive circuit control. The invention aims to solve the problems existing in the P5 test of automotive electronic devices. The present invention includes voltage stabilizing diode RD1, bidirectional voltage stabilizing diode RD2, resistors R1-R4, electrolytic capacitor C1 and capacitor C2; the anode of voltage stabilizing diode RD1 is used as the high voltage input end of P5; the cathode of voltage stabilizing diode RD1 is connected to one end of resistor R1 at the same time and one end of resistor R3, the other end of resistor R1 is simultaneously connected to one end of resistor R2, the other end of resistor R3 and one end of resistor R4; the other end of resistor R2 is connected to the other end of resistor R4, one end of bidirectional voltage regulator diode RD2, The anode of the electrolytic capacitor C1 and one end of the capacitor C2 serve as the output end of the protection circuit; the other end of the bidirectional voltage regulator diode RD2 is simultaneously connected to the negative electrode of the electrolytic capacitor C1 and the other end of the capacitor C2, and is grounded.

Owner:AEROSPACE HI TECH HLDG GROUP

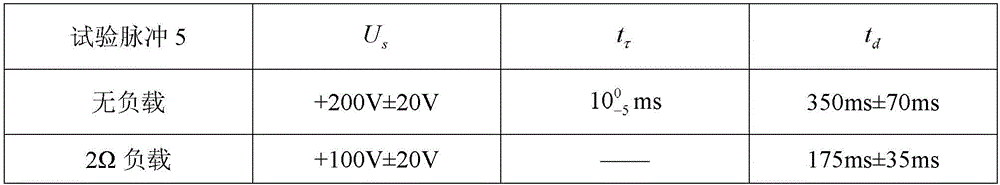

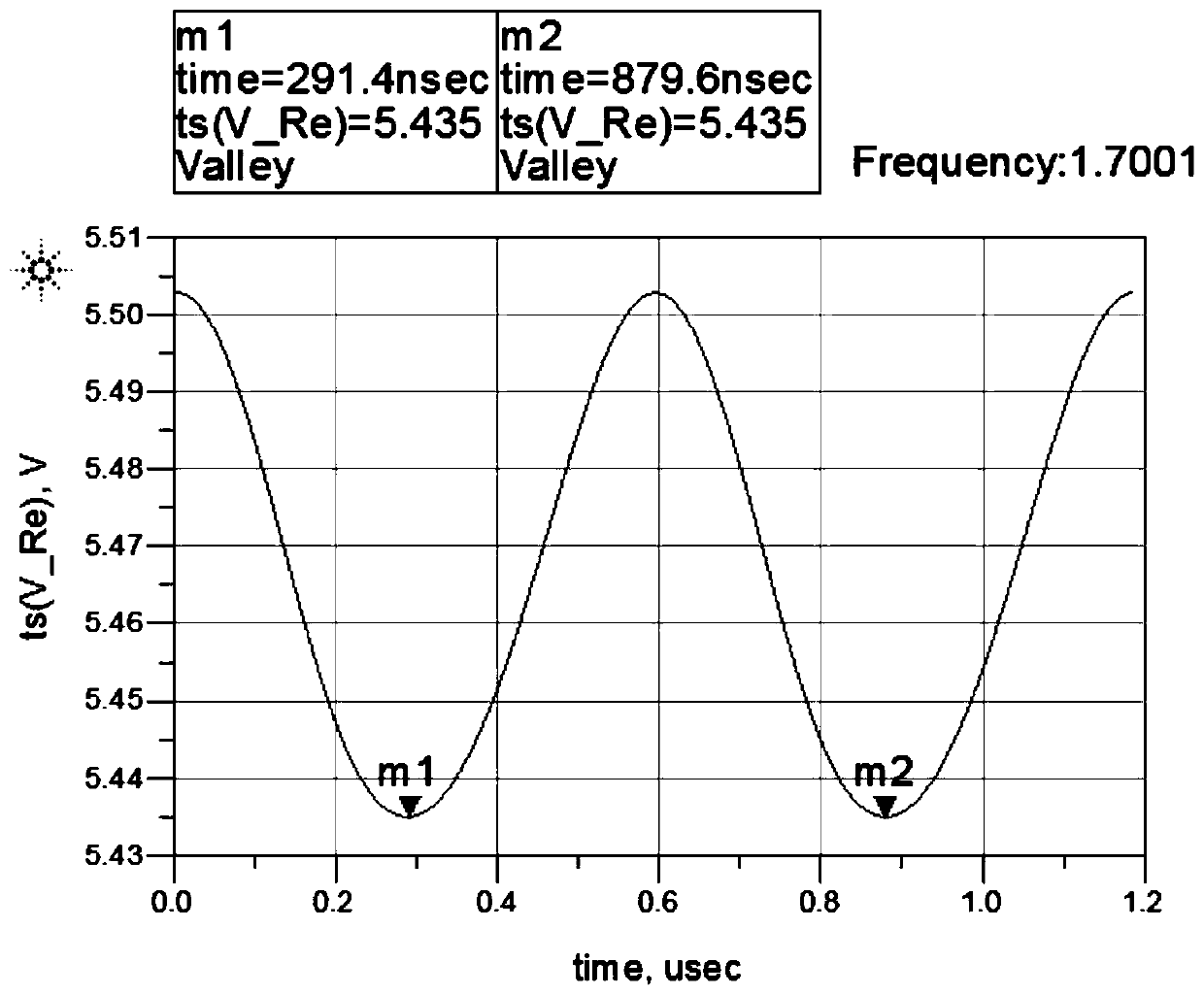

Frequency tracking circuit of CMUT resonant biochemical sensor

ActiveCN110221123ALow working voltageAchieve outputMultiple-port networksFrequency measurement arrangementCapacitanceLow voltage

The invention discloses a frequency tracking circuit of a CMUT resonant biochemical sensor, and the circuit comprises a bias network, an impedance matching network, a CMUTs network, a load capacitancenetwork and a BJT amplification feedback network, wherein the bias network provides DC voltage for the CMUTs and avoids current overload; the impedance matching network tunes to make the CMUTs form aseries-parallel resonant region; and positive feedback of an oscillating signal is formed based on the BJT and the load capacitance network to realize real-time output of the oscillating signal of the CMUTs parallel resonance point. The frequency tracking circuit provided by the invention enables the CMUTs to form a series-parallel resonant region at a low voltage, and the resonant circuit is simple and convenient, the starting time is microsecond, and the CMUTs resonant frequency can be output in real time, which is of great significance for portable and real-time detection applications based on CMUTs resonant biochemical sensors.

Owner:XI AN JIAOTONG UNIV

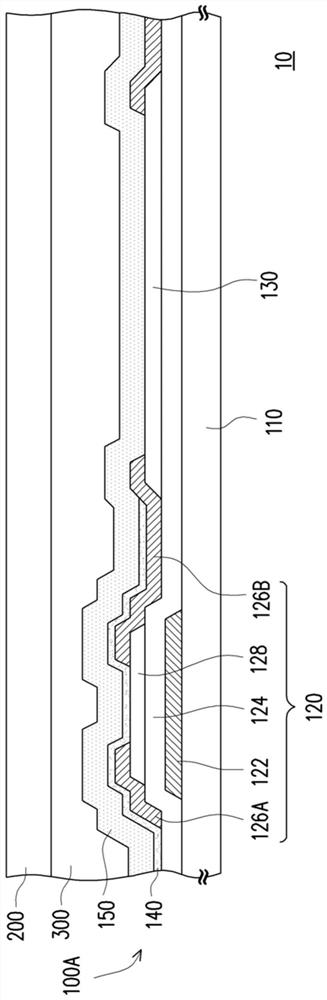

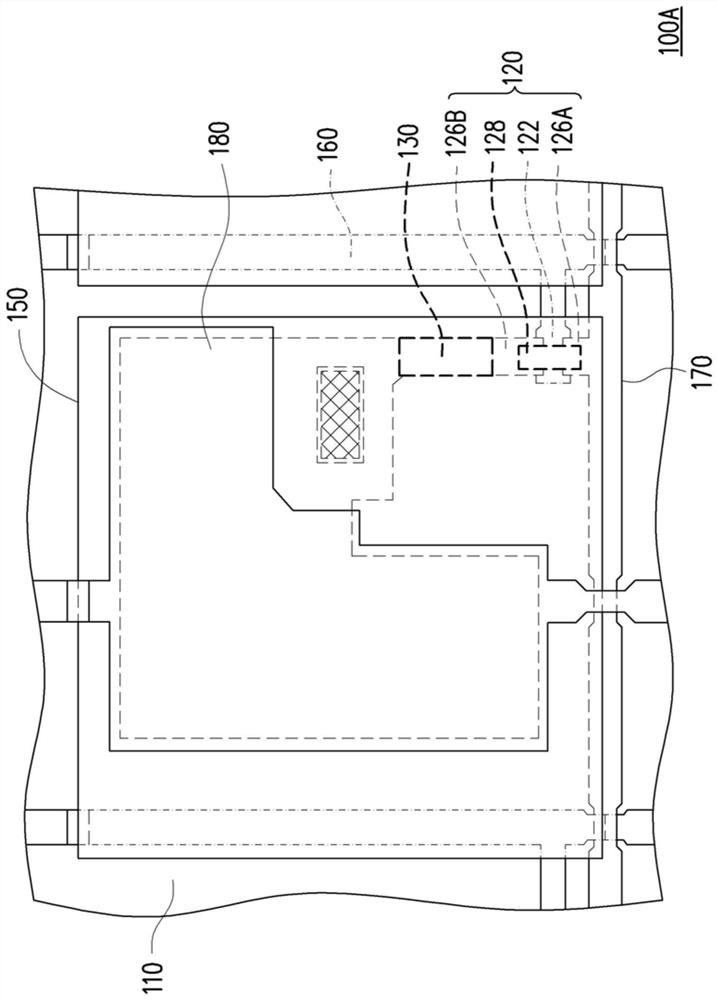

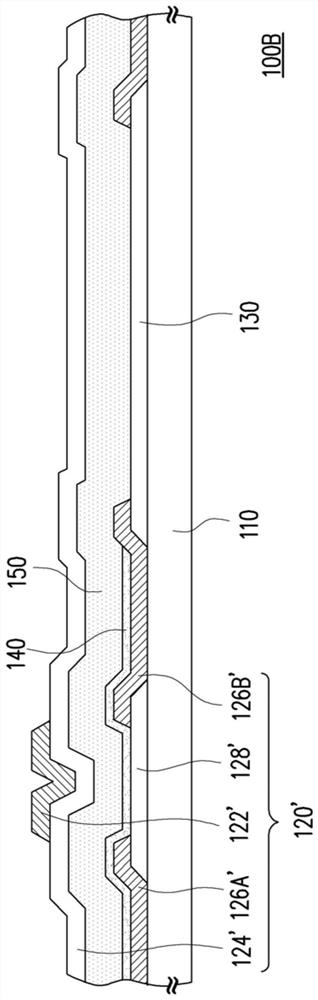

Drive substrate and display device

ActiveCN109698204BAvoid burning active componentsMinimize parasitic capacitanceSolid-state devicesNon-linear opticsDisplay deviceSemiconductor

The invention provides a driving substrate and a display device. The driving substrate includes a substrate, at least one active element, a resistor, a first protection layer and a second protection layer. The active element with the oxide semiconductor layer and the resistor coupled to the active element are disposed on the substrate. The first protection layer covers the active device, wherein a part of the first protection layer directly contacts the oxide semiconductor layer so that the oxide semiconductor layer has a first conductivity. The second protection layer covers the first protection layer and the resistor, wherein a part of the second protection layer directly contacts the resistor so that the resistor has a second conductivity. The first conductivity is different from the second conductivity.

Owner:E INK HLDG INC

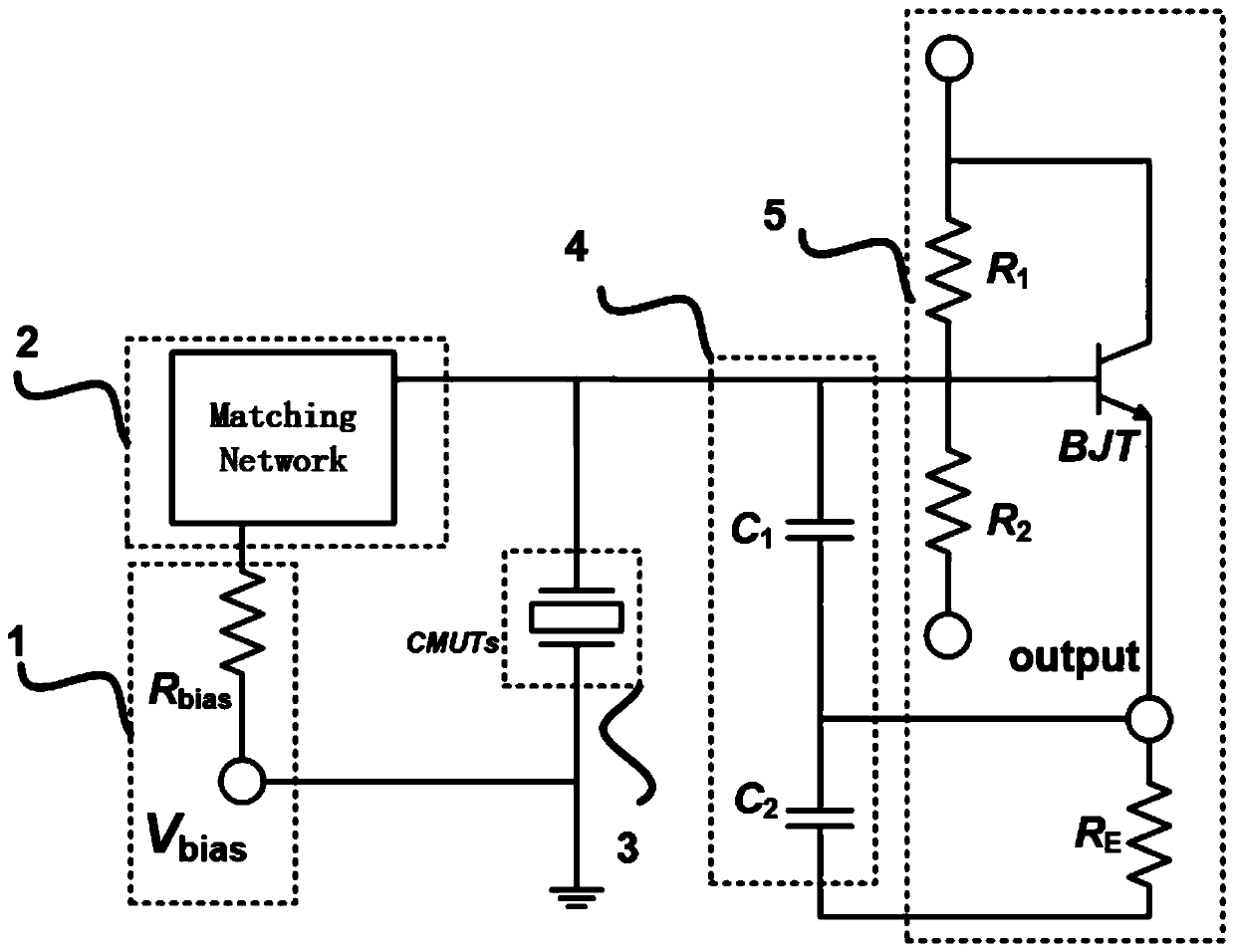

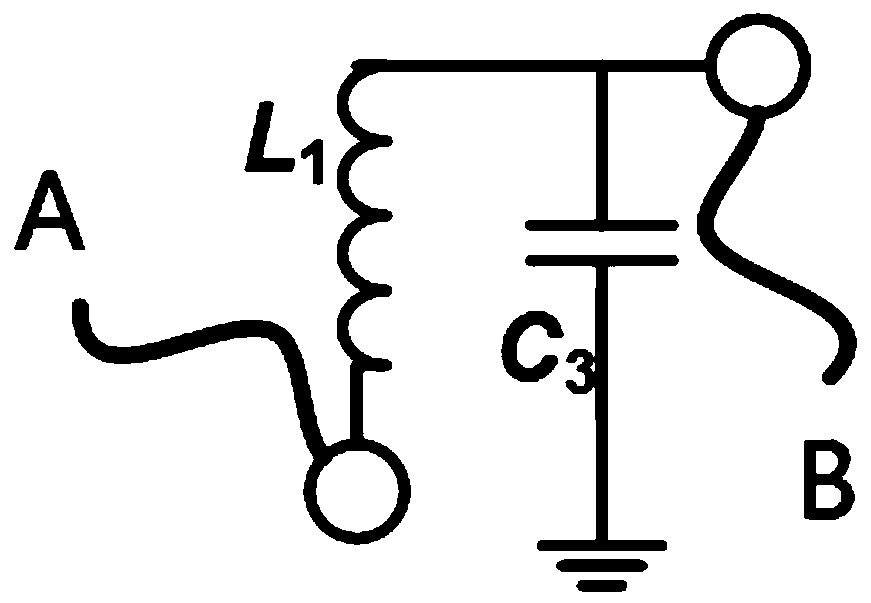

Surge protection device comprising Y-shaped pressure-sensitive chip, and distribution box

PendingCN112003256ADelay the rapid hyperthermia processLimit currentEmergency protective arrangements for limiting excess voltage/currentProtective switch operating/release mechanismsElectric power systemHemt circuits

The invention provides a surge protection device comprising a Y-shaped pressure-sensitive chip, and a distribution box. The surge protection device comprising the Y-shaped pressure-sensitive chip comprises an insulated fixing seat, the Y-shaped pressure-sensitive chip, a first electrode and a second electrode, wherein the first electrode and the second electrode are used for being connected with an external circuit, the Y-shaped pressure-sensitive chip is fixed on the fixing seat, the Y-shaped pressure-sensitive chip comprises an electrode A, an electrode B, an electrode C, a first piezoresistor chip and a second piezoresistor chip, the first piezoresistor chip is located between the electrode A and the electrode B, the second piezoresistor chip is located between the electrode A and the electrode C, the electrode B is electrically connected with the second electrode, and the electrode C is electrically connected with the first electrode. The surge protection device comprising the Y-shaped pressure-sensitive chip, and the distribution box can be used in a direct current system and an unconventional 690 VAC and above power system, and the safety performance is higher.

Owner:广东立信防雷科技有限公司

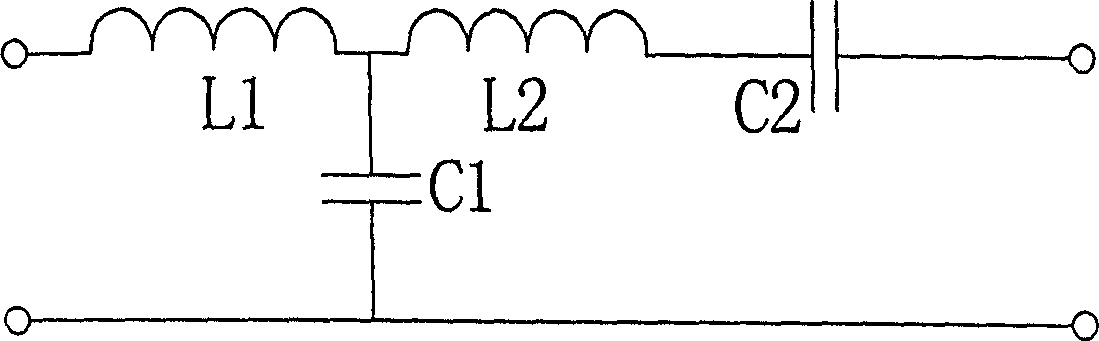

An electrical device and electric device therewith

ActiveCN104240923AImprove electromagnetic compatibilityLimit currentTransformers/inductances coils/windings/connectionsVariable inductancesElectricityEngineering

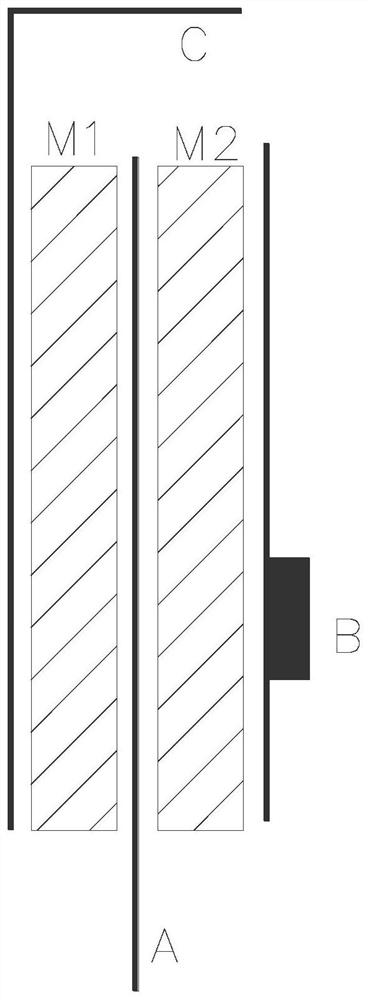

The invention relates to an electrical component and an electrical device therewith, wherein the electrical component includes a first coil 15, a second coil 20 and a switch element 80 includes, with the first coil 15 has a first input 30 and a first output 35, wherein the second coil 20 has a second input 45 and a second output 50, wherein the first input 30 to an electric power source is connectable, the second output 50 is connected to a consumer 70, wherein the second input 45 and second outputs 50 are connected one another via the switching element 80, wherein the first output 35 is connected to the second input 45, the first coil 15 is formed; increasing an electromagnetic tolerance of the load 70 and the second coil 20 is formed to limit a current to the load 70, the switching element 80 is formed, in the closed position substantially completely bridge the second coil 20 and in the open state a substantially to ensure full flow of electric current through the second coil 20.

Owner:ROBERT BOSCH GMBH

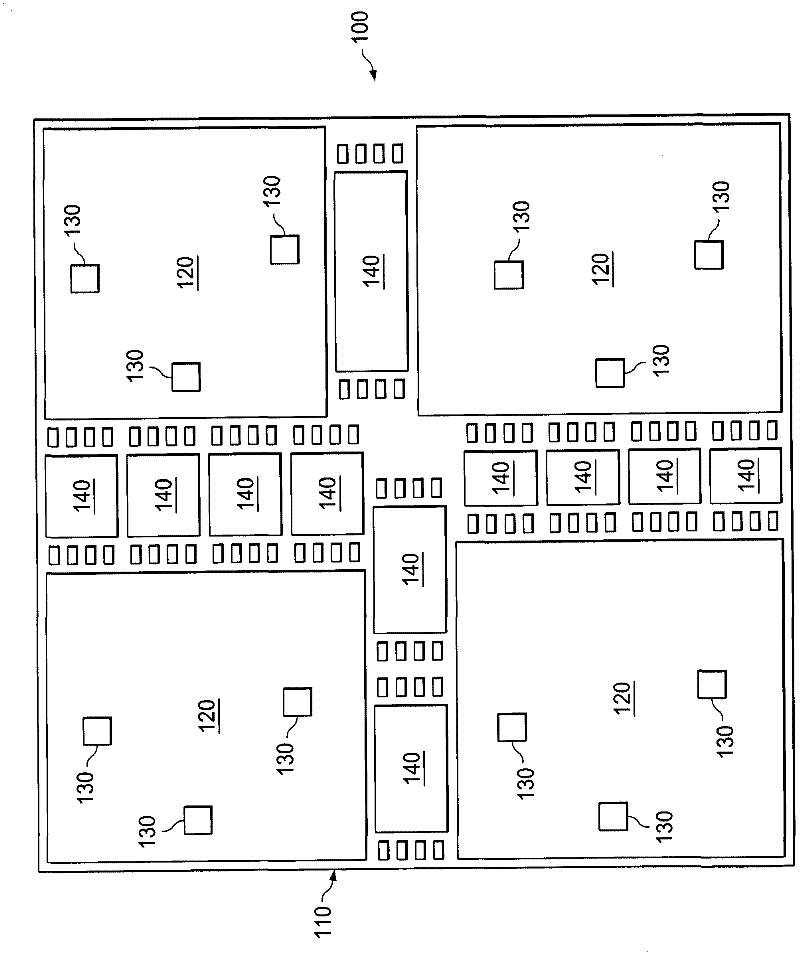

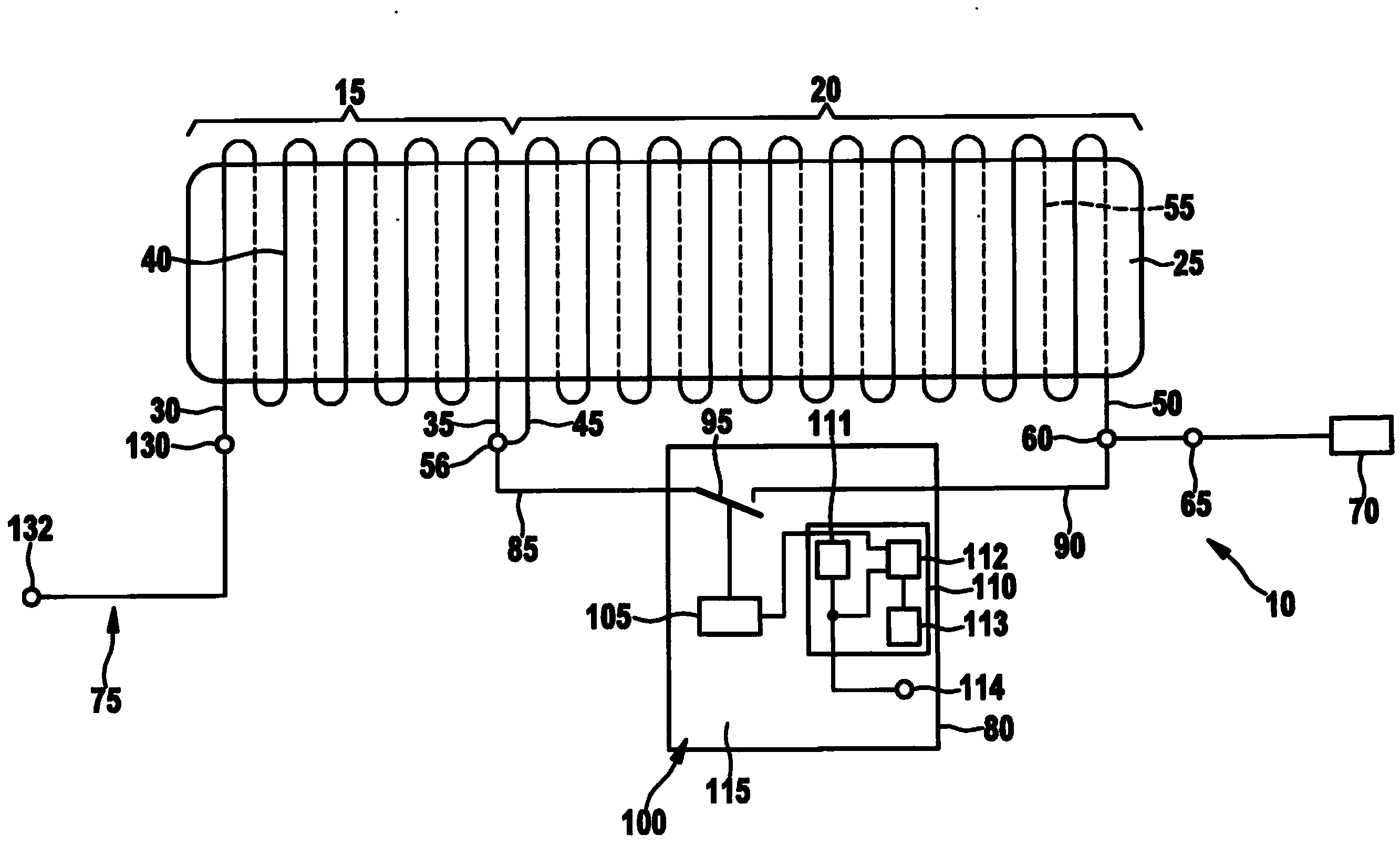

Device for intrinsically safe redundant current supply of field devices

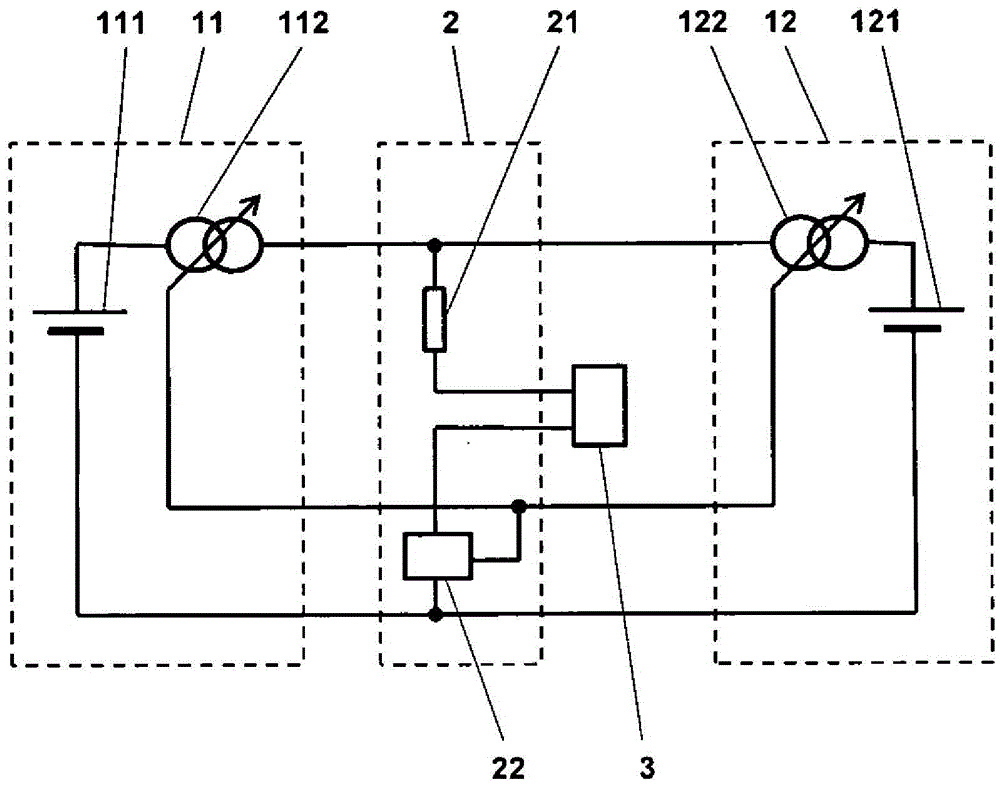

ActiveCN105468066ALimit connectionLimit currentDc source parallel operationConstant-current supply dc circuitElectrical resistance and conductanceCurrent limiting

A device is provided for intrinsically safe redundant current supply of field devices (3) with a common current-limiting resistor (21) in the mesh of the field device and with redundant current supply units (11, 12). In the system, a current sensor (22) can be provided in the mesh of the field device, the output signal of whichis connected to devices for controlling current or active current limiters (112,122) in the redundant current supply units.

Owner:ABB (SCHWEIZ) AG

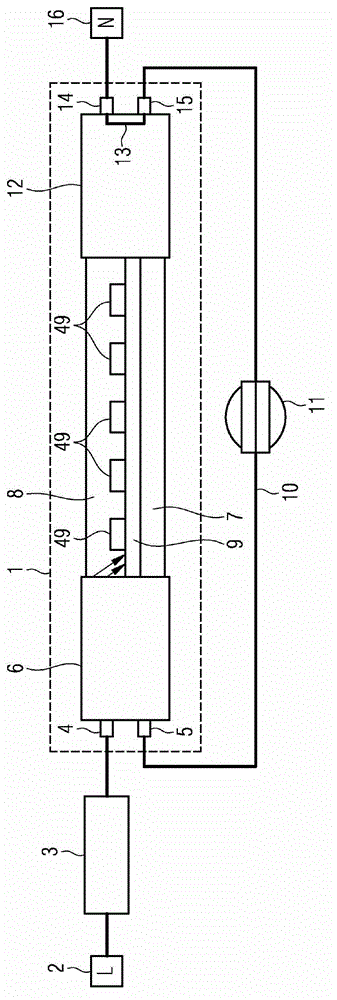

led lights

ActiveCN103069216BEasy to fixAvoid damagePoint-like light sourceElectrical apparatusConductive materialsLED lamp

The invention relates to an LED lamp (1) having a converter (6) and means connected to the converter of light-emitting diodes (8, 49) arranged on at least one printed circuit board (9) . The transducer is arranged in a multi-piece lockable housing (20) made of non-conductive material that completely surrounds the transducer.

Owner:LEDVANCE GMBH

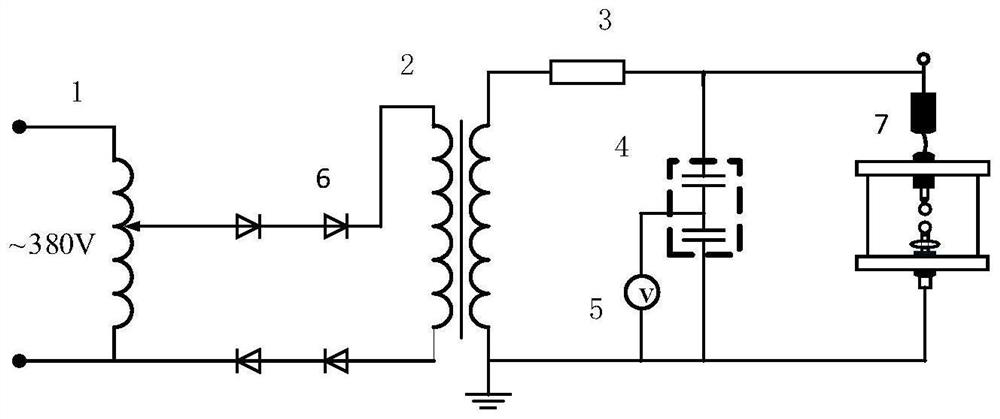

Gas discharge comprehensive experiment platform

InactiveCN113092958ALimit currentSatisfy withstand voltageTesting dielectric strengthCapacitanceCapacitive voltage divider

The invention relates to a gas discharge comprehensive experiment platform, which comprises an induction voltage regulator, a corona-free test transformer, a protection impedance, a capacitive voltage divider, a voltmeter, a gas insulation performance test device and a constant current diode. Compared with a traditional gas discharge comprehensive test platform, constant-current diodes are additionally arranged on the voltage regulator side, the constant-current diodes are used for limiting current in a circuit, and meanwhile the overall withstand voltage value of the circuit is met in the mode that the constant-current diodes are connected in series.

Owner:WUHAN UNIV +2

A mosfet chip manufacturing method for improving gate characteristics

ActiveCN113643982BAchieve protectionImprove discharge efficiencyTransistorSemiconductor/solid-state device manufacturingMOSFETEngineering

The invention discloses a MOSFET chip manufacturing method for improving gate characteristics, including forming lightly doped polysilicon on the isolation oxide layer, and removing the lightly doped polysilicon in the groove area, so as to obtain the first light Doped polysilicon and the second lightly doped polysilicon, in the source region of the epitaxial layer, heavily doped a part of the first lightly doped polysilicon to obtain the second heavily doped polysilicon, and formed a dielectric layer upwards, the second heavily doped polysilicon The type of doped polysilicon is opposite to that of the first lightly doped polysilicon, and the first lightly doped polysilicon and the second heavily doped polysilicon form a diode, and the two ends of the second lightly doped polysilicon form a resistor, the diode and the The resistors are connected in parallel and connected in series with the grid. The polysilicon resistor and polysilicon diode are integrated inside the chip, which can effectively limit the current flowing through the gate, so as to realize the protection of the gate.

Owner:深圳市芯电元科技有限公司