Patents

Literature

75 results about "Dielectric capacitance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Every dielectric material has a dielectric constant. A capacitor has a capacitance proportional to the area of the plates divided by the distance between the plates times the dielectric constant. Therefore a material with a higher dielectric constant will give proportionally more capacitance.

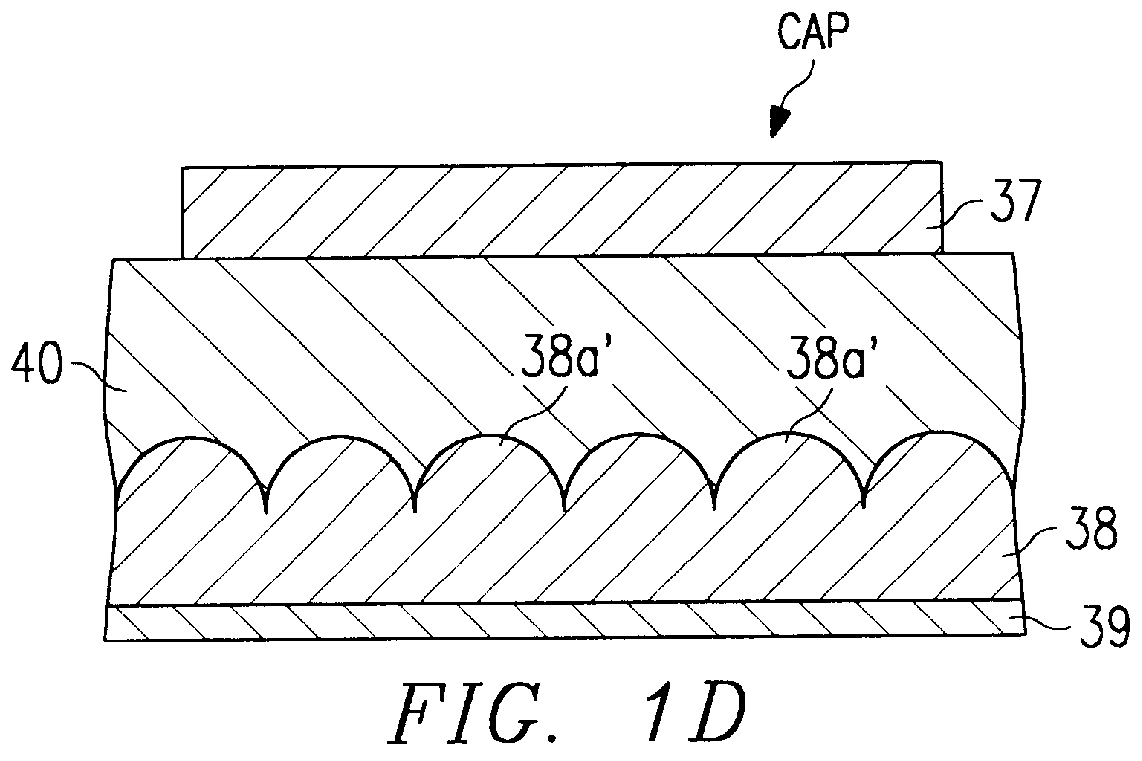

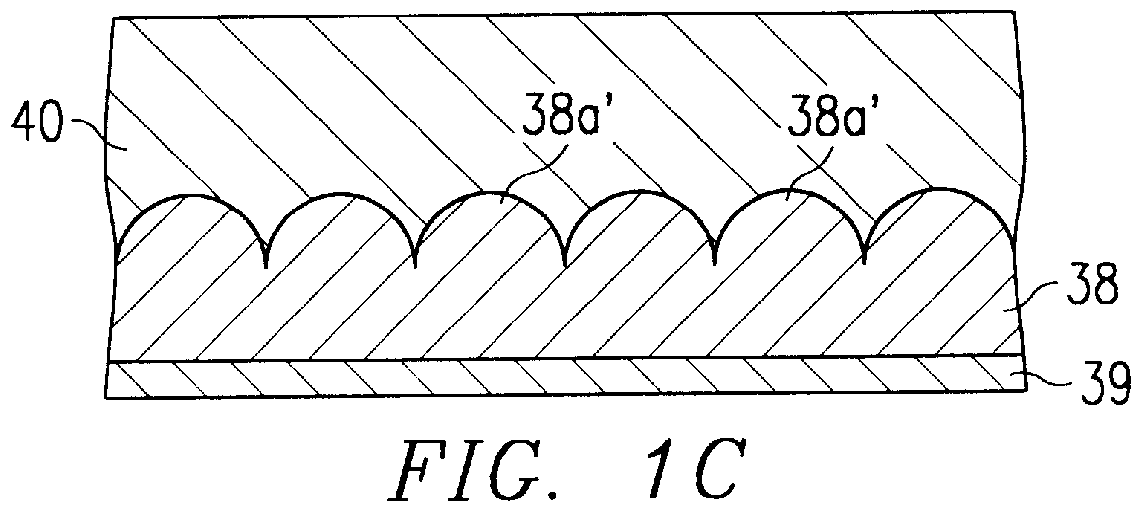

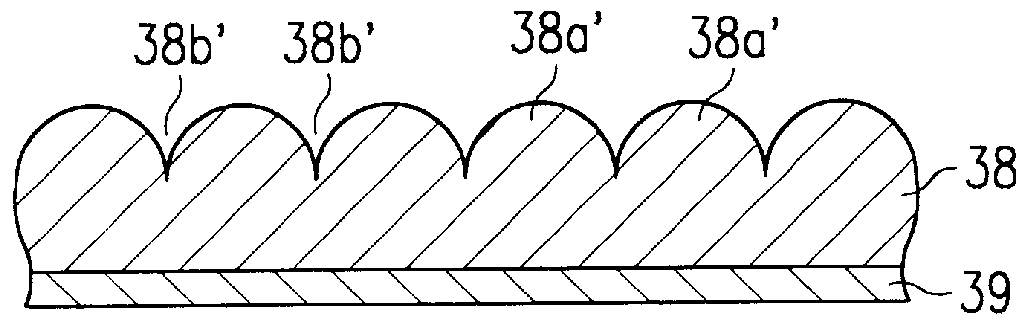

Method for manufacturing dielectric capacitor, dielectric memory device

InactiveUS6033953AReduce leakage currentImprove flatnessTransistorThin/thick film capacitorElectrolysisCapacitor

A dielectric capacitor is provided which has a reduced leakage current. The surface of a first electrode (38) of the capacitor is electropolished and a dielectric film (40) and a second electrode (37) are successively laminated on it. The convex parts pointed end (38a) existing on the surface of the first electrode is very finely polished uniformly by dissolving according to electropolishing, a spherical curved surface in which the radius of curvature has been enlarged is formed, and the surface of the first electrode is flattened. Therefore, concentration of electrolysis can be prevented during the operation at the interface of the first electrode and the dielectric film, and the leakage current can be reduced considerably.

Owner:TEXAS INSTR INC

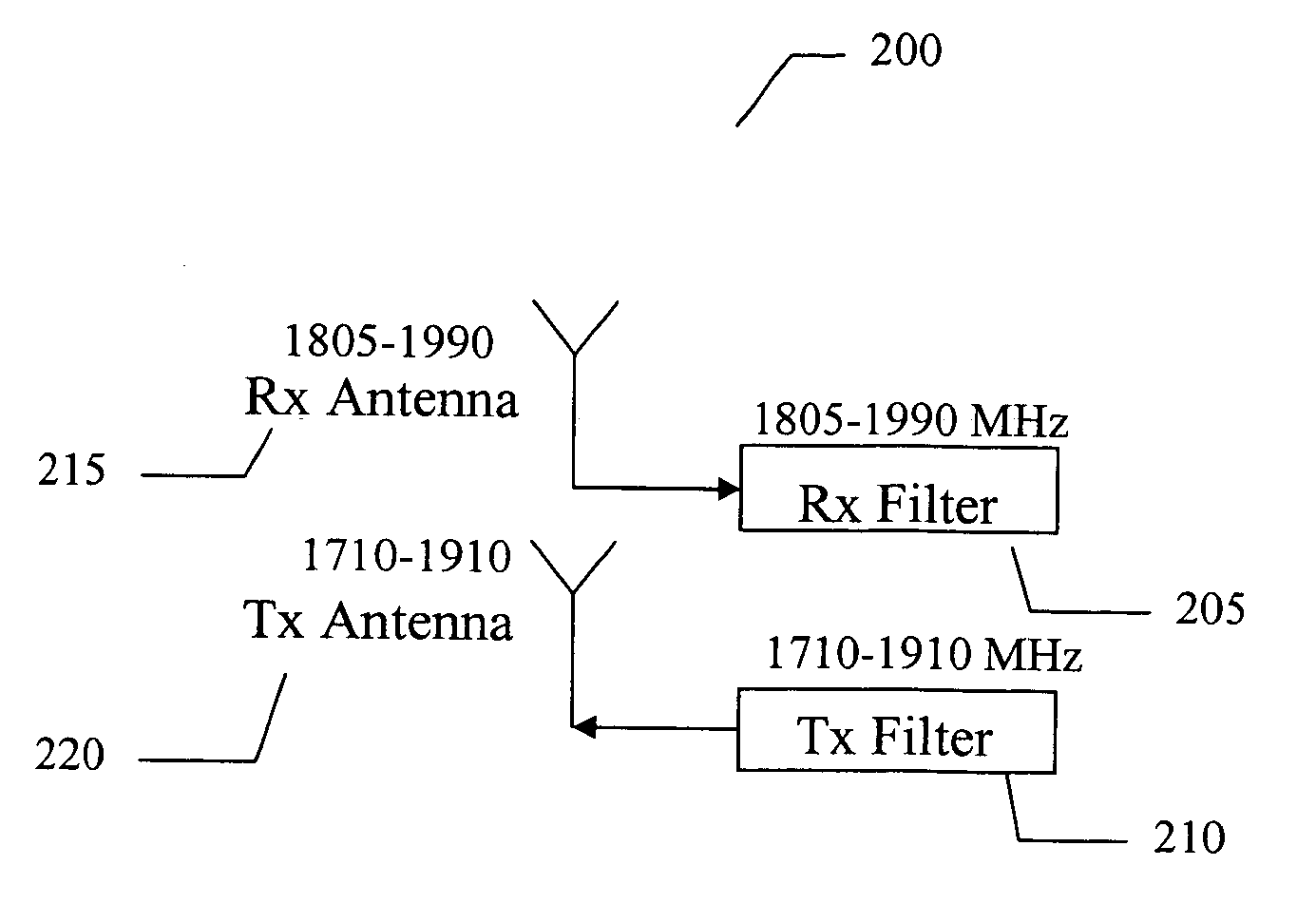

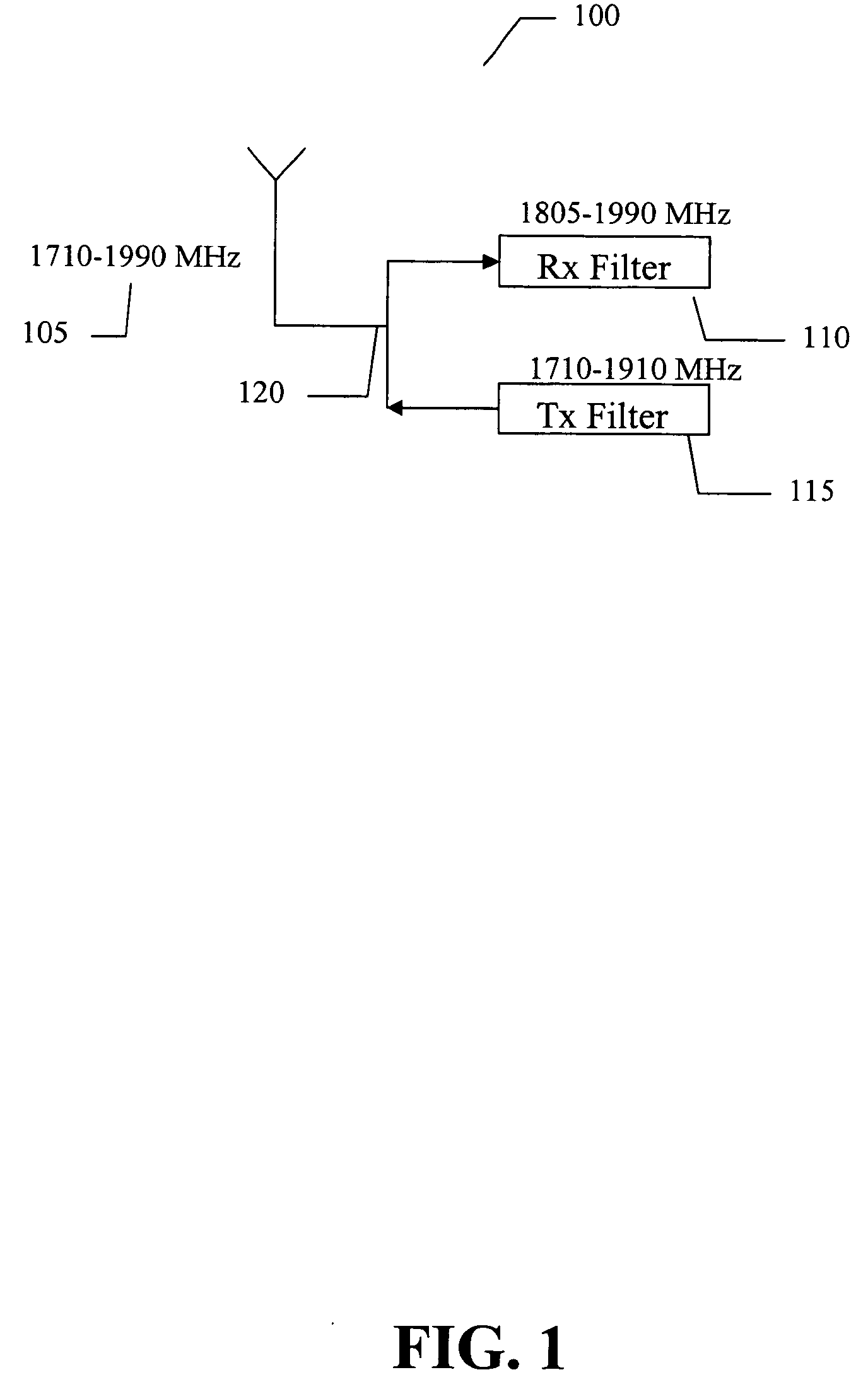

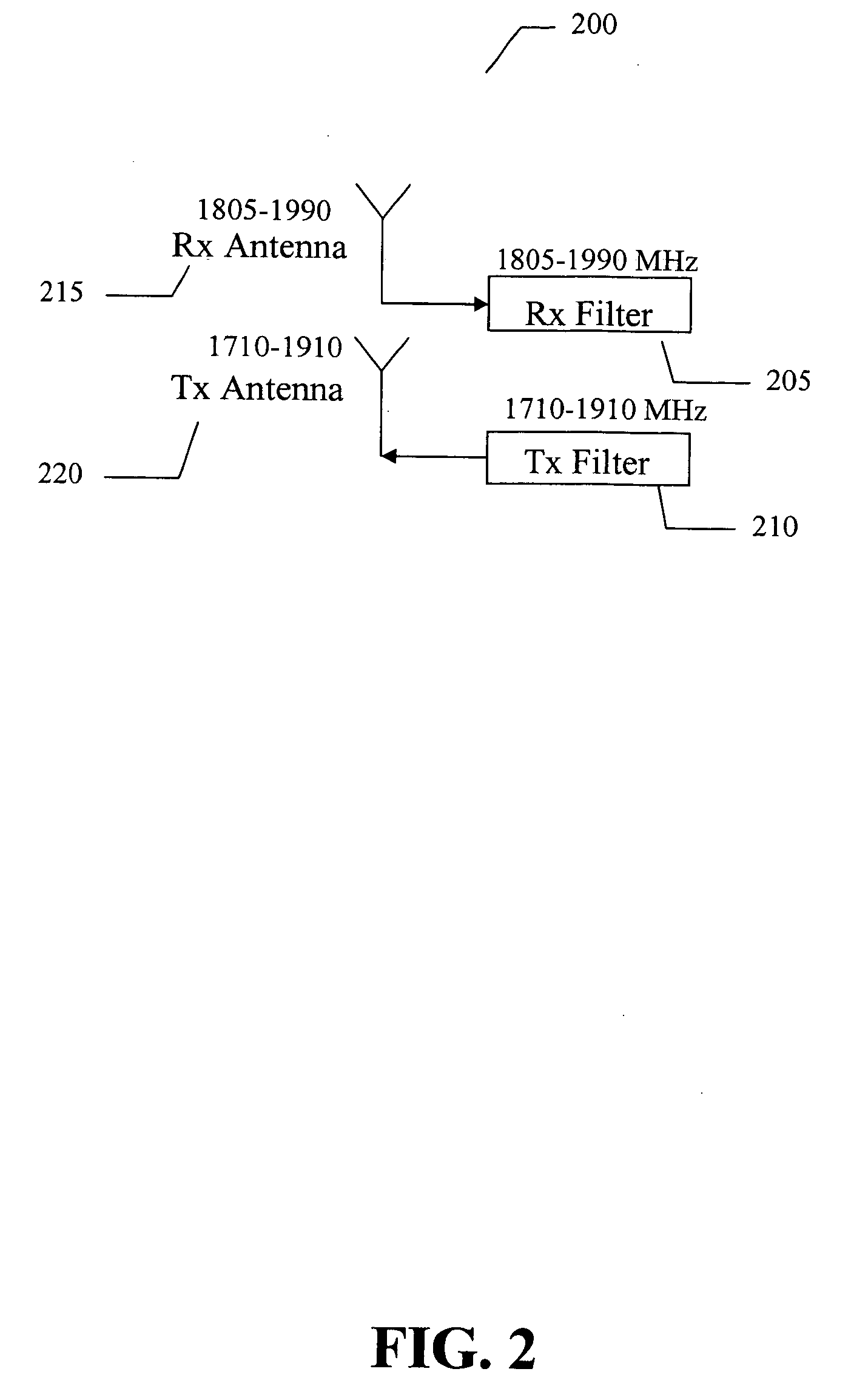

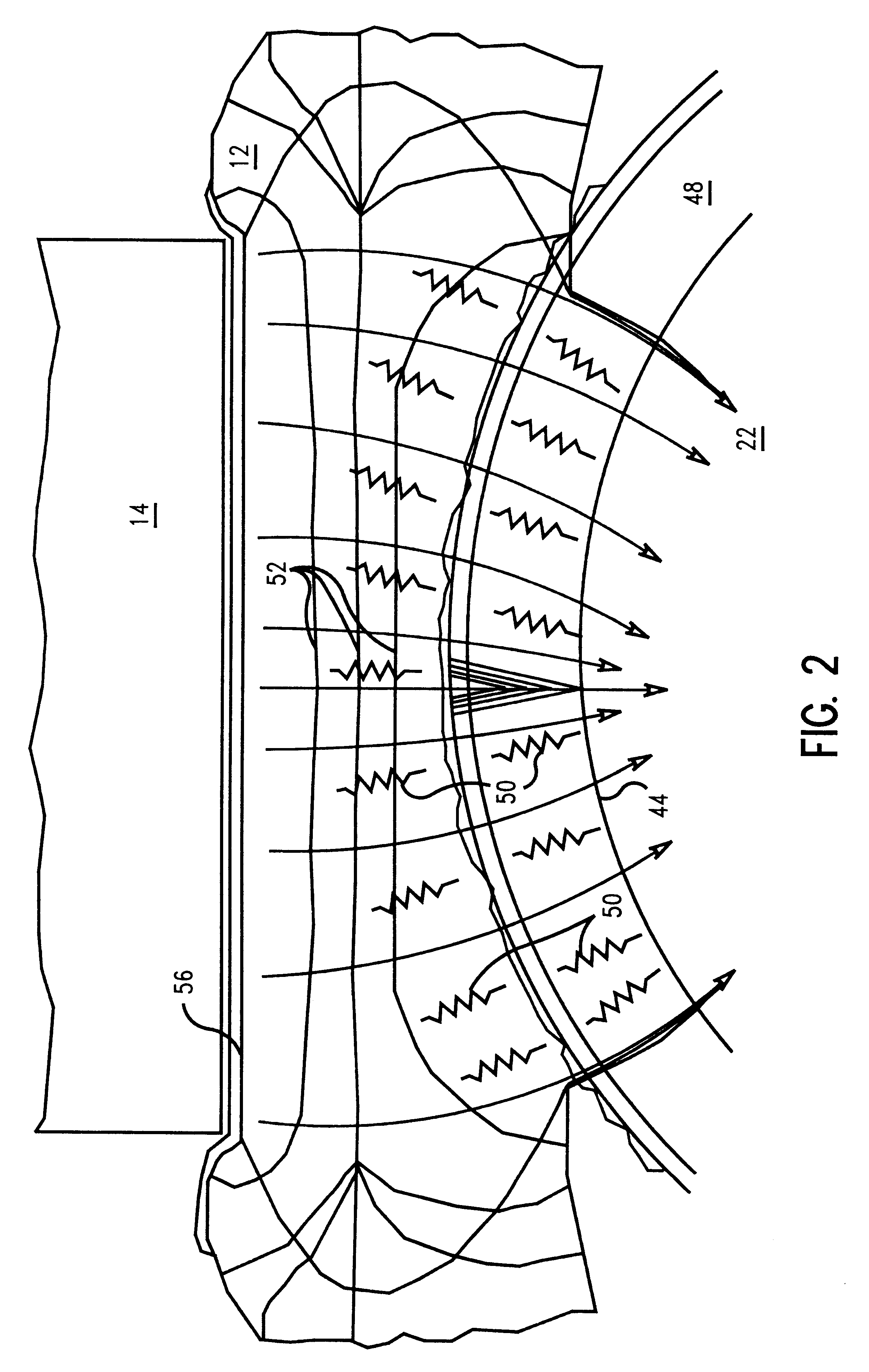

Apparatus and method capable of utilizing a tunable antenna-duplexer combination

An embodiment of the present invention provides an apparatus, an apparatus, comprising a tunable duplexer incorporating at least two separate antennas. The tunable duplexer may be a high-band tunable duplexer or low-band tunable duplexer, although not limited to specific bands. The tunable duplexer may further comprise a transmit filter and a receive filter either of which may be tunable. The tunable duplexer may be made electronically tunable by incorporating an electronically tunable dielectric material and the electronically tunable dielectric material may be Parascan® tunable materials technology. Further, the at least two separate antennas may be made tunable by incorporating voltage-controlled tunable dielectric capacitors placed on at least one antenna package associated with at least one antenna.

Owner:PARATEK MICROWAVE INC

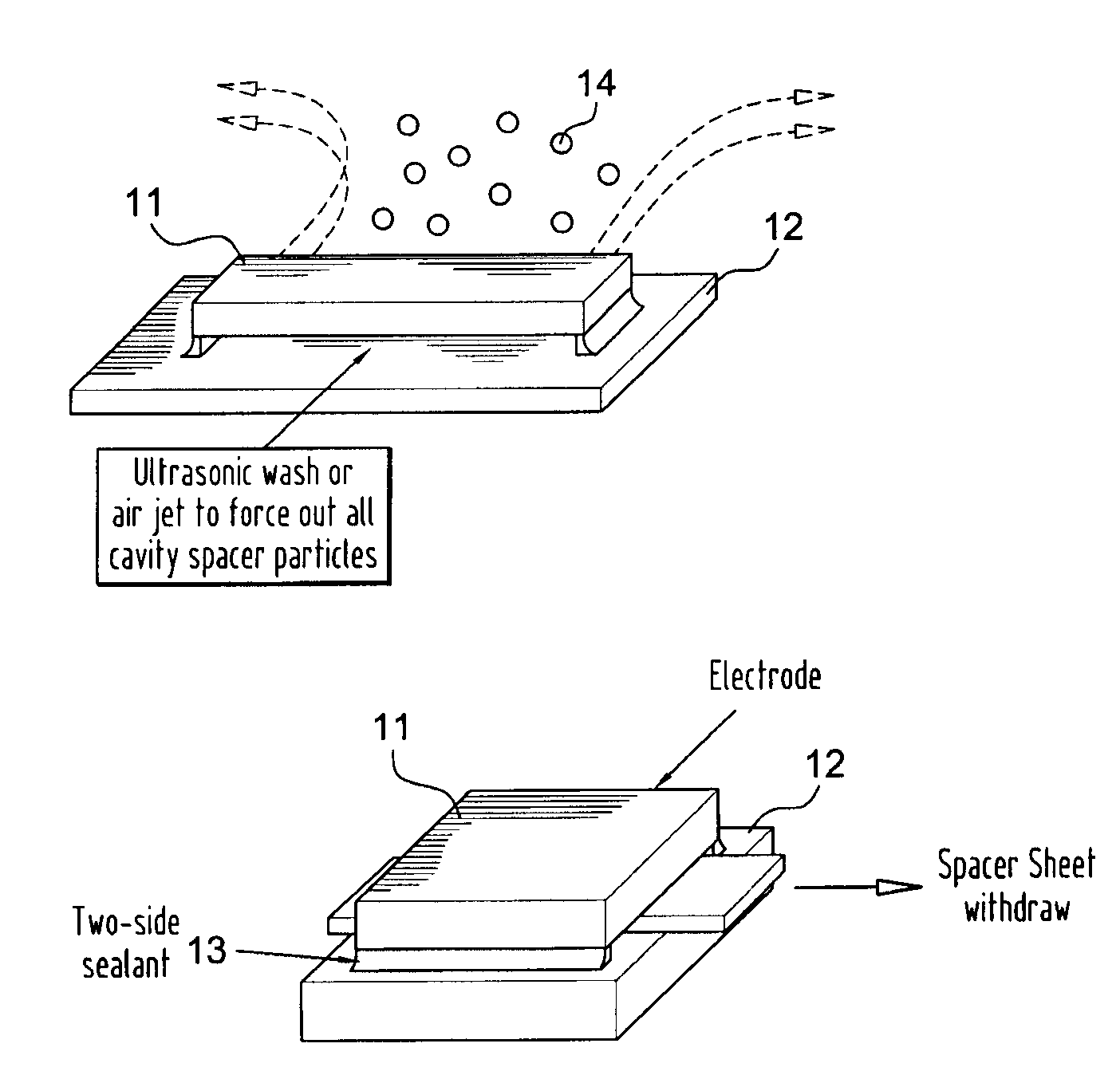

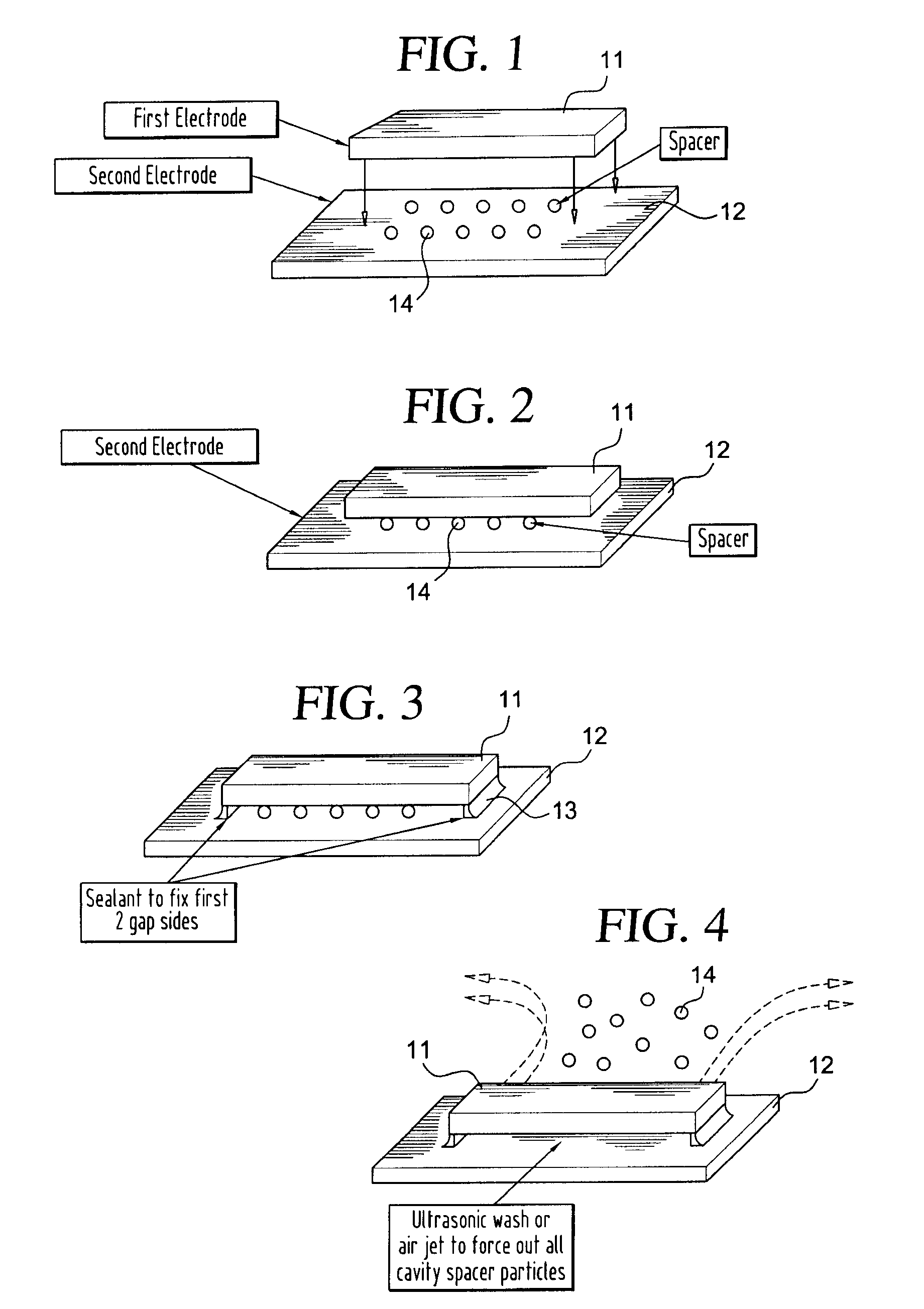

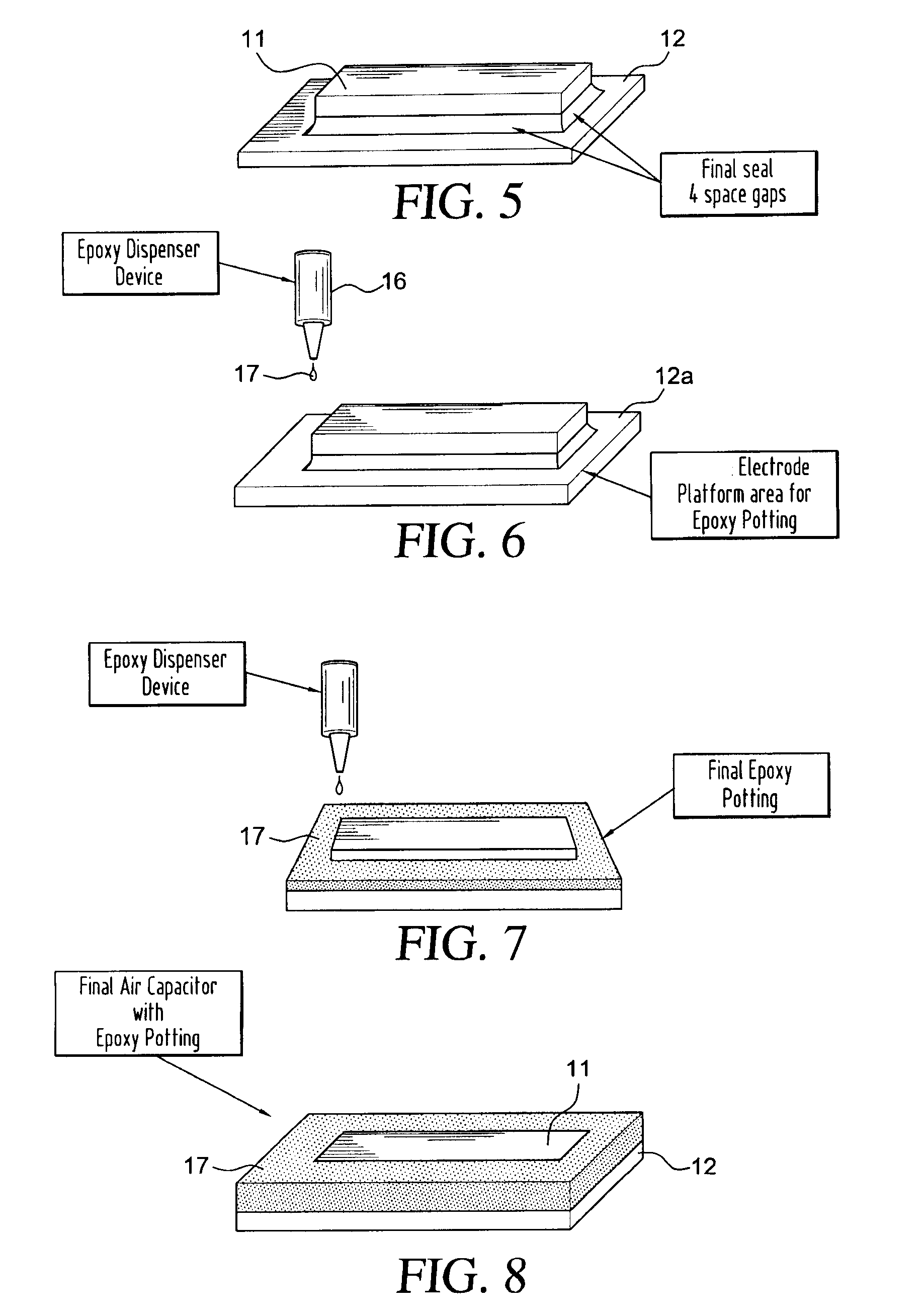

Device and method for making air, gas or vacuum capacitors and other microwave components

ActiveUS7387928B2Free from pollutionFixed capacitor dielectricSemiconductor/solid-state device manufacturingPlanar electrodeMicrowave

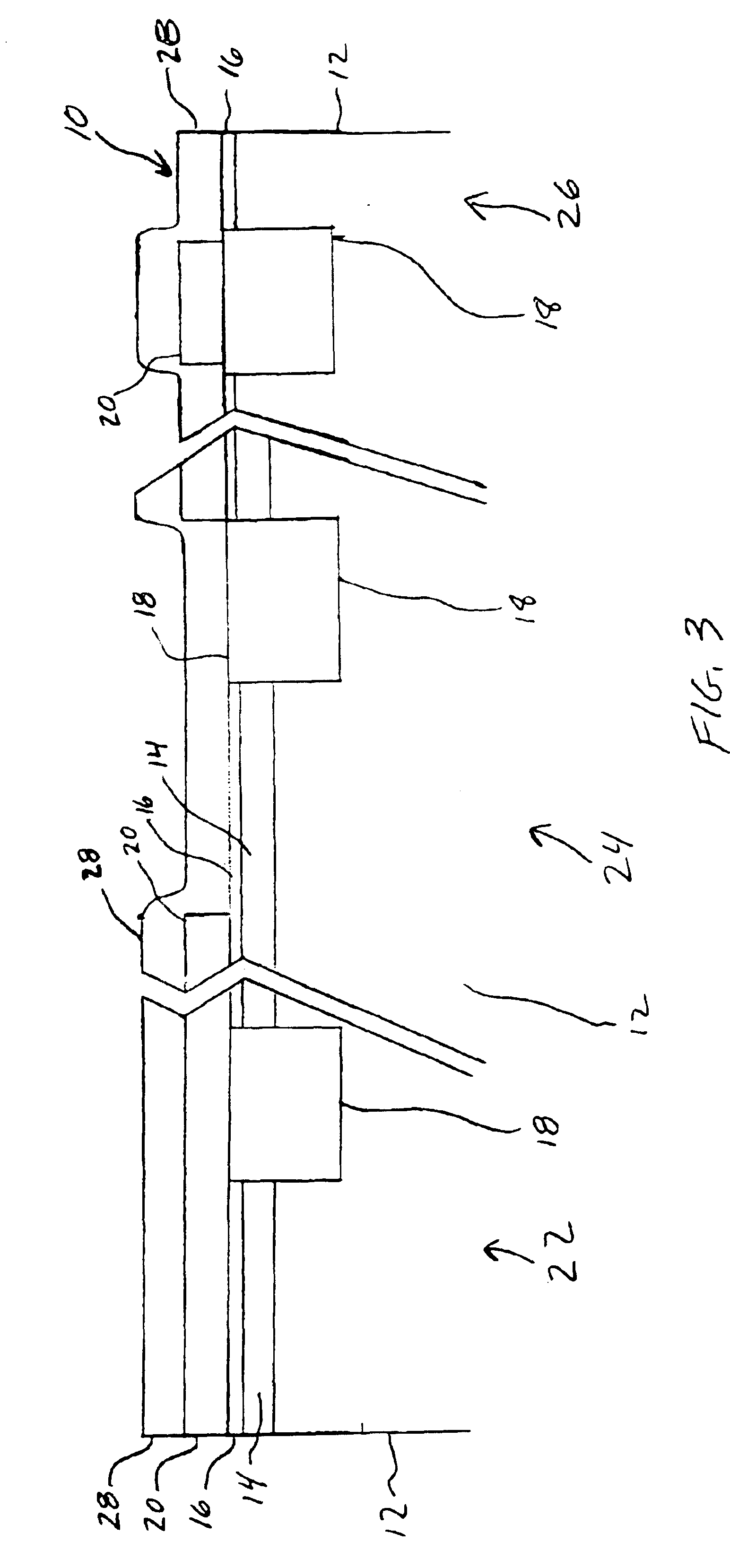

A device and method for making a capacitor and other high frequency and / or microwave components. In particular, an air dielectric capacitor has a first electrode and a second electrode that are spaced apart, planar and each of a different size or area. The first electrode is a smaller, planar electrode that is sealed along its edge with a sealant having a constant dielectric to the second electrode, a larger planar electrode. The dielectric constant of the sealant along the edges of the first electrode is substantially uniform. In addition, an epoxy cover extends around the periphery of the smaller first electrode and is supported along the surface of the larger second electrode.

Owner:DAYEN TECH

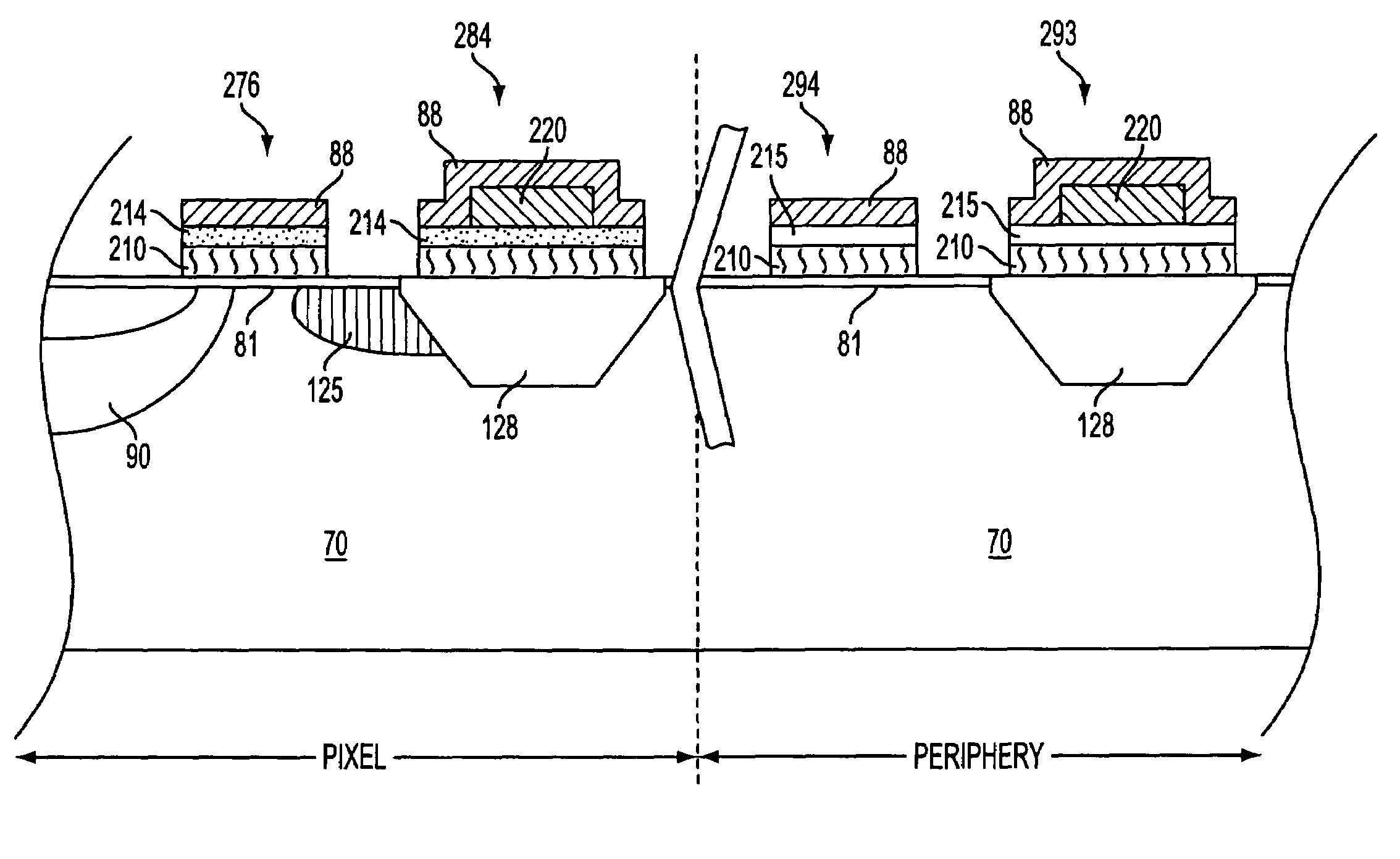

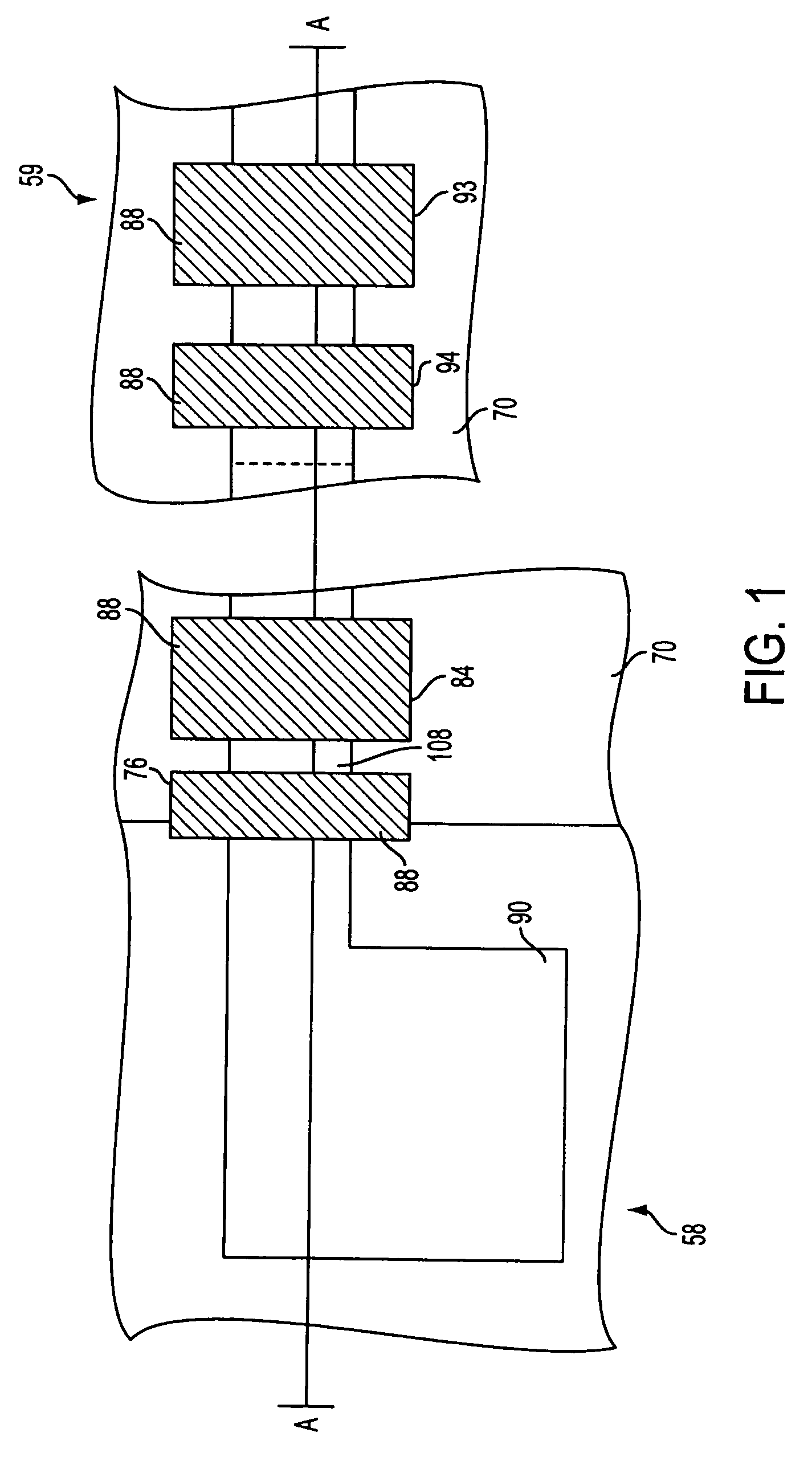

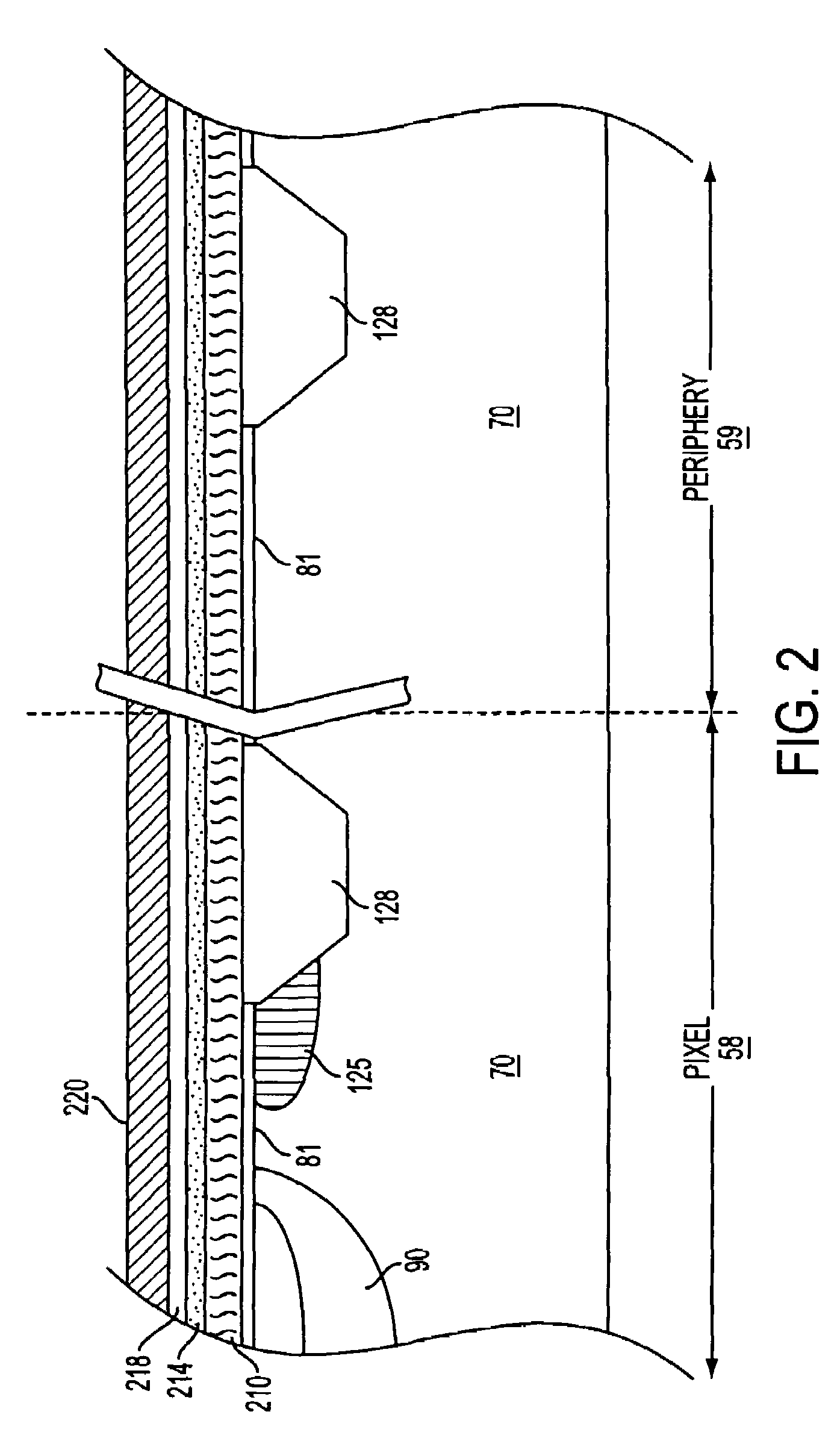

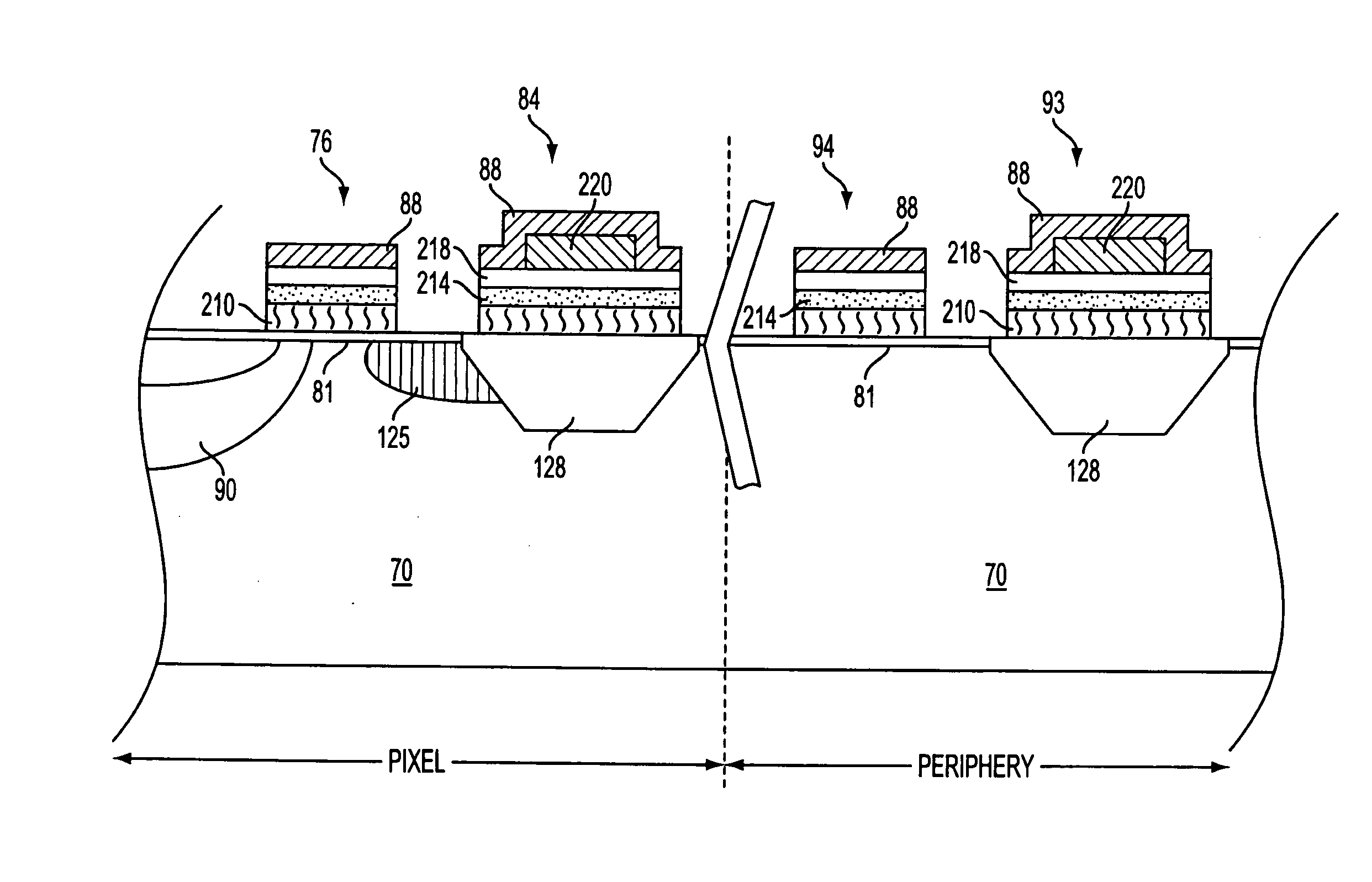

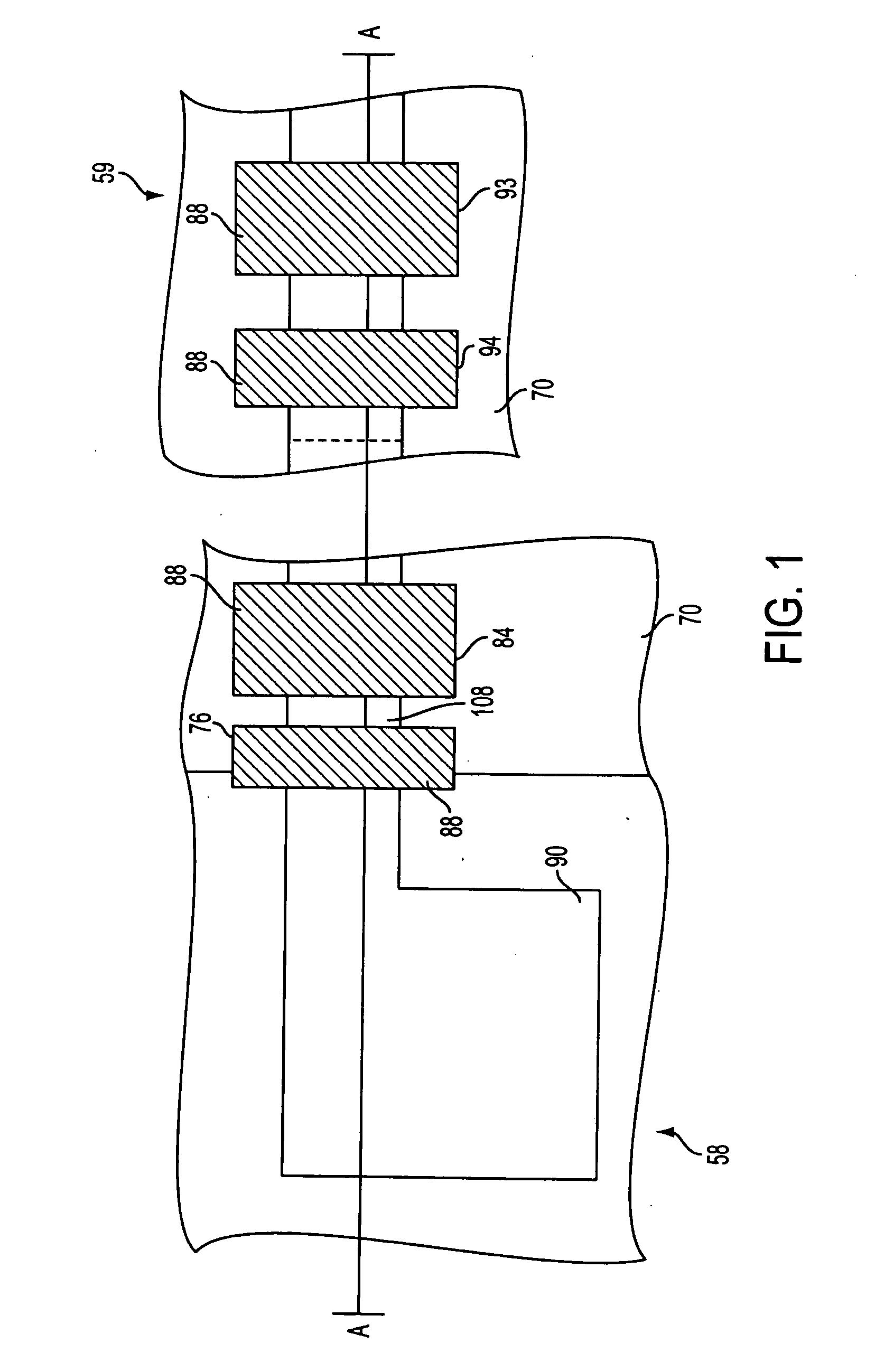

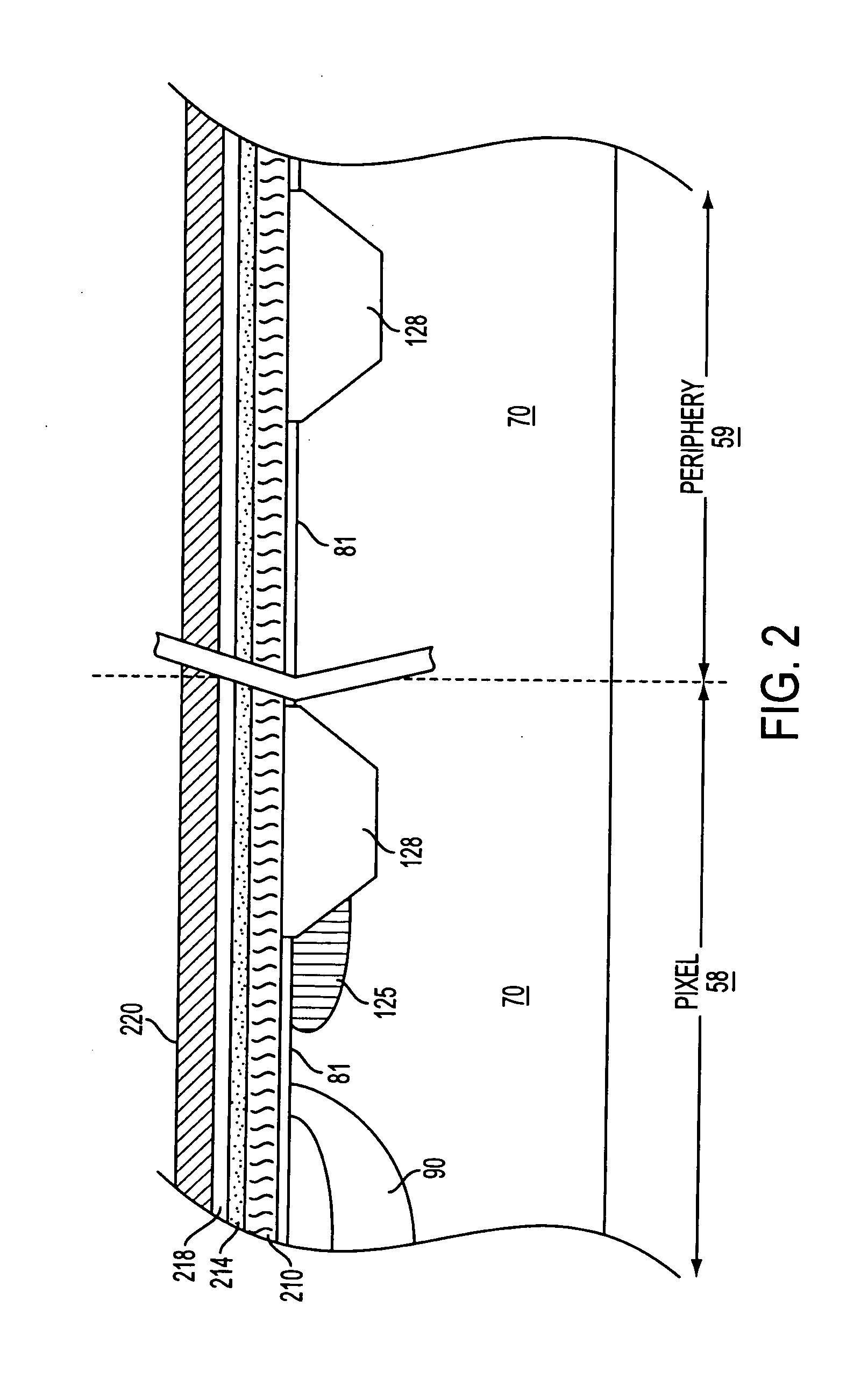

Dual capacitor structure for imagers and method of formation

CMOS and CCD imaging devices comprising different in-pixel capacitors and peripheral capacitors and methods of formation are disclosed. The capacitors used in periphery circuits have different requirements from the capacitors used in the pixel itself. Dual stack capacitors comprising two dielectric layers may be provided to achieve low leakage and high capacitance. A single masking step may be provided such that one region has a dual dielectric capacitor and a second region has a single dielectric capacitor. A different dielectric may also be provided in one region compared to another region wherein the inter-electrode insulator comprises a single dielectric in both regions.

Owner:APTINA IMAGING CORP

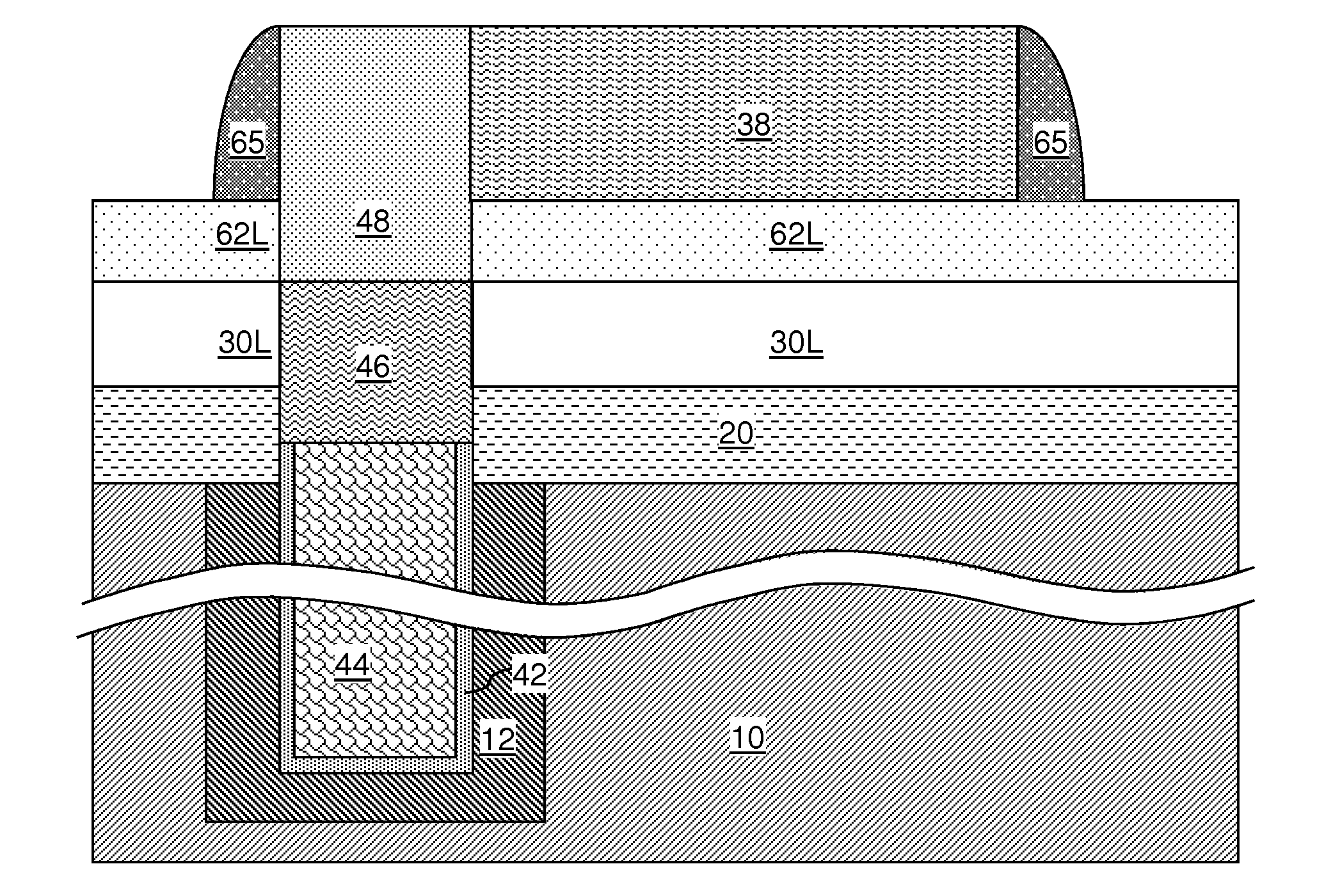

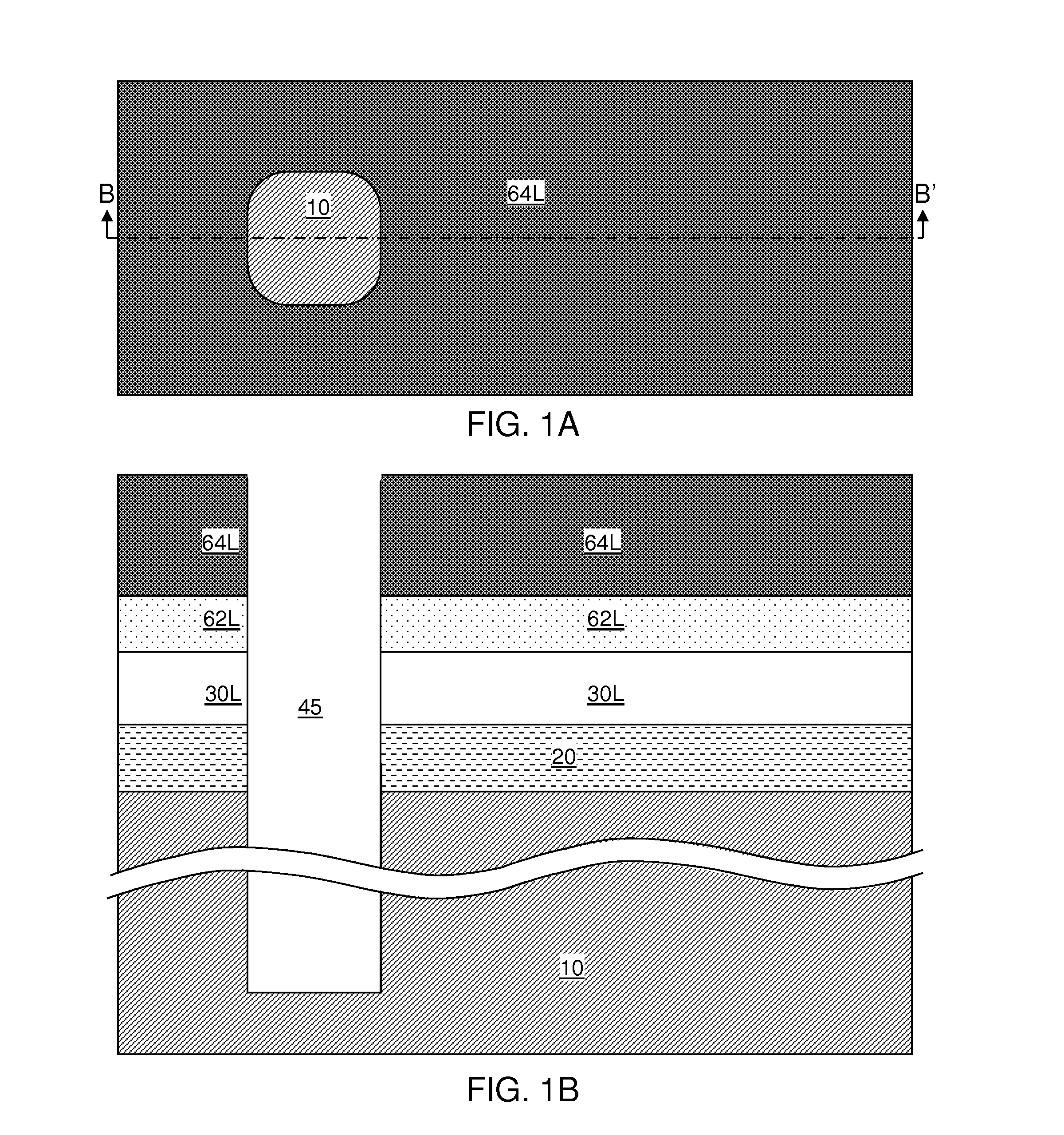

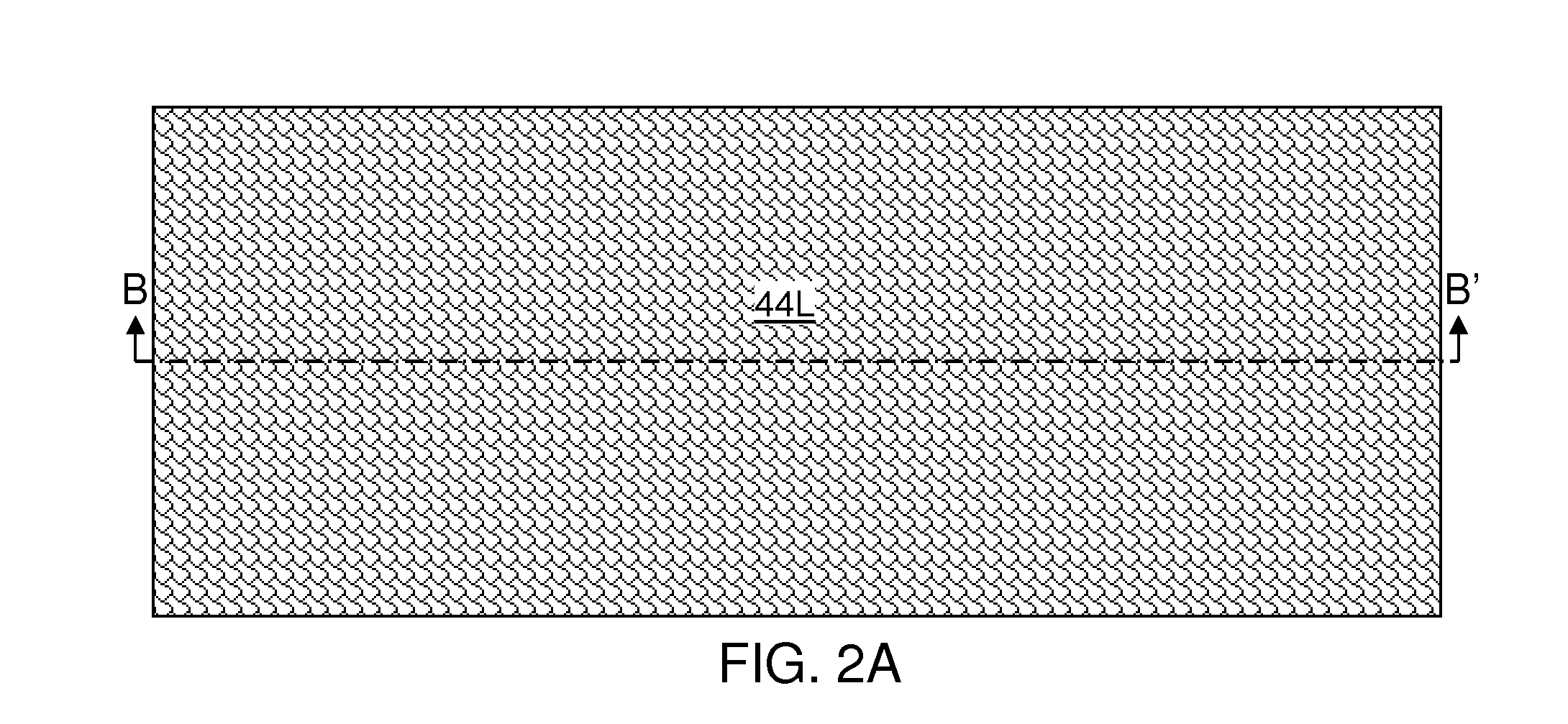

Wrap-around fin for contacting a capacitor strap of a dram

A conductive strap structure in lateral contact with a top semiconductor layer is formed on an inner electrode of a deep trench capacitor. A cavity overlying the conductive strap structure is filled a dielectric material to form a dielectric capacitor cap having a top surface that is coplanar with a topmost surface of an upper pad layer. A semiconductor mandrel in lateral contact with the dielectric capacitor cap is formed. The combination of the dielectric capacitor cap and the semiconductor mandrel is employed as a protruding structure around which a fin-defining spacer is formed. The semiconductor mandrel is removed, and the fin-defining spacer is employed as an etch mask in an etch process that etches a lower pad layer and the top semiconductor layer to form a semiconductor fin that laterally wraps around the conductive strap structure. An access finFET is formed employing two parallel portions of the semiconductor fin.

Owner:GLOBALFOUNDRIES INC

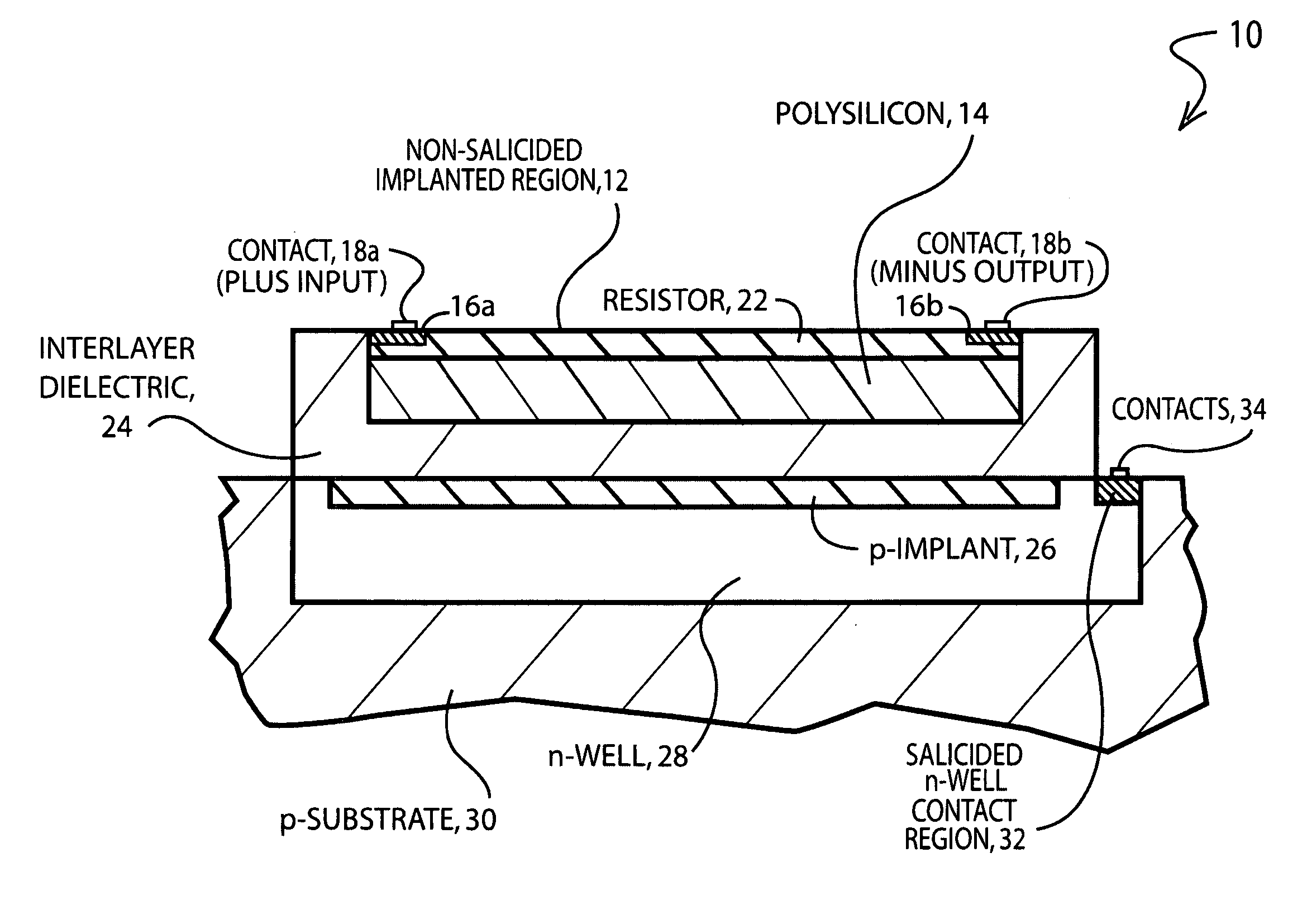

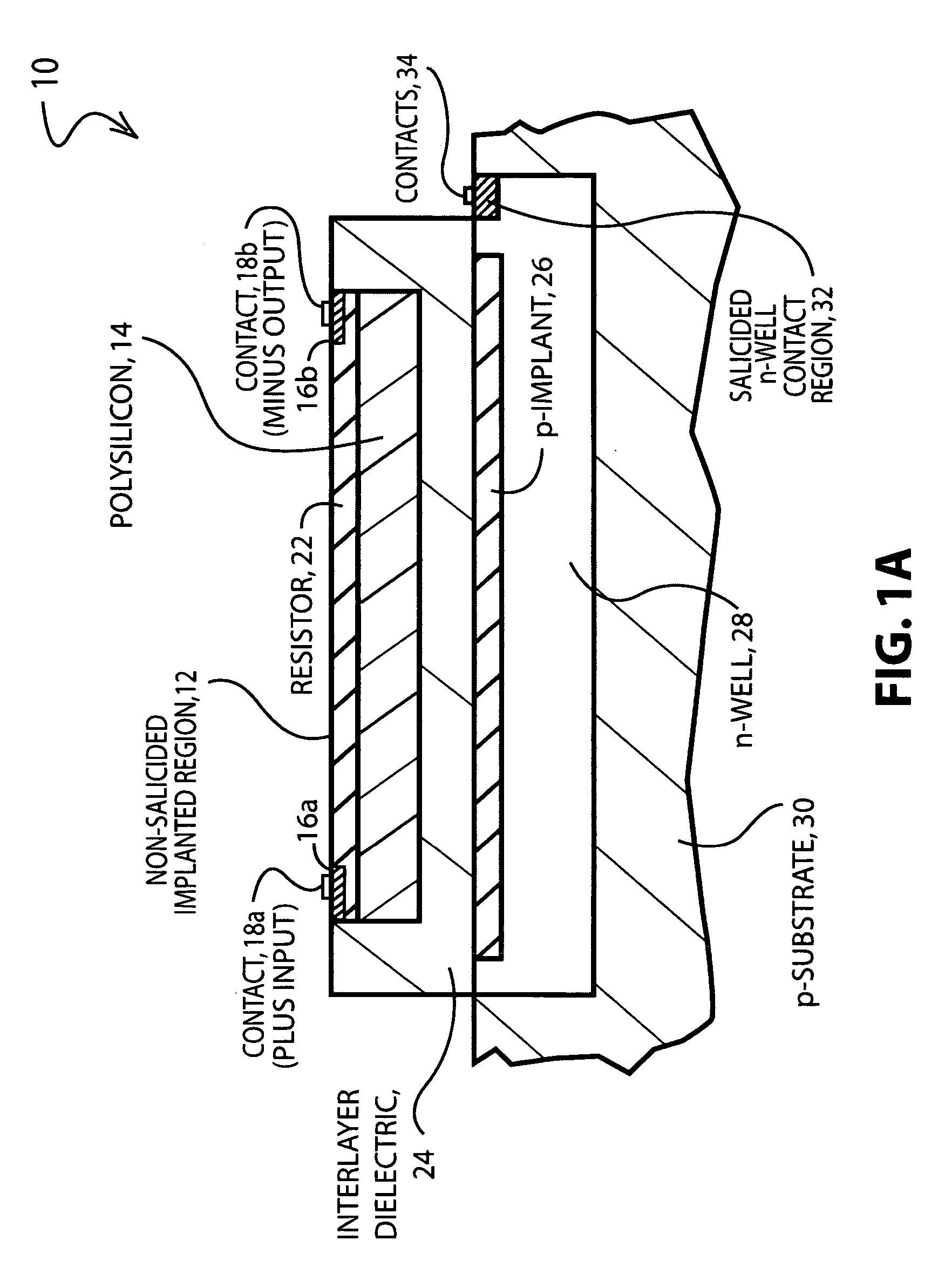

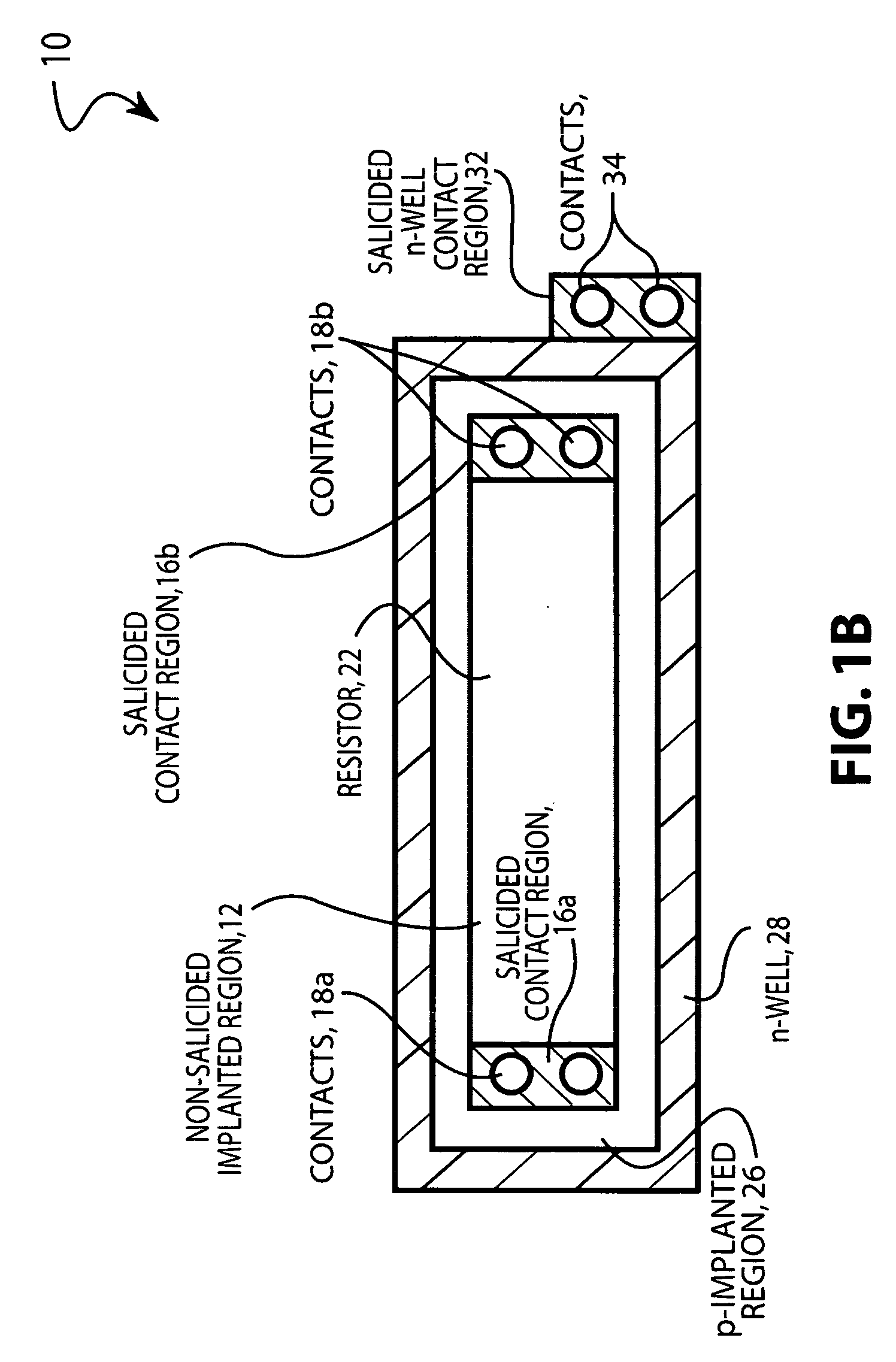

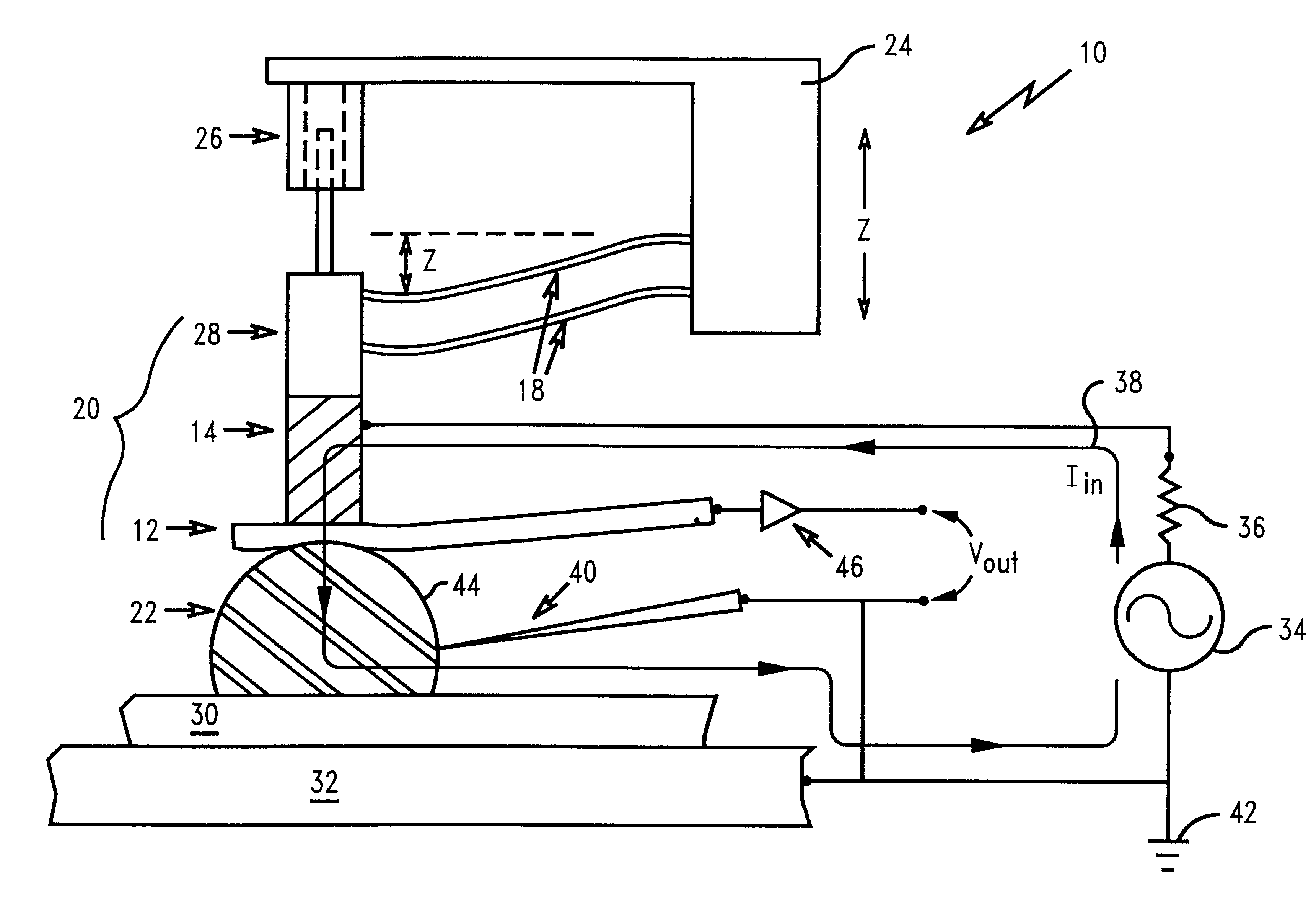

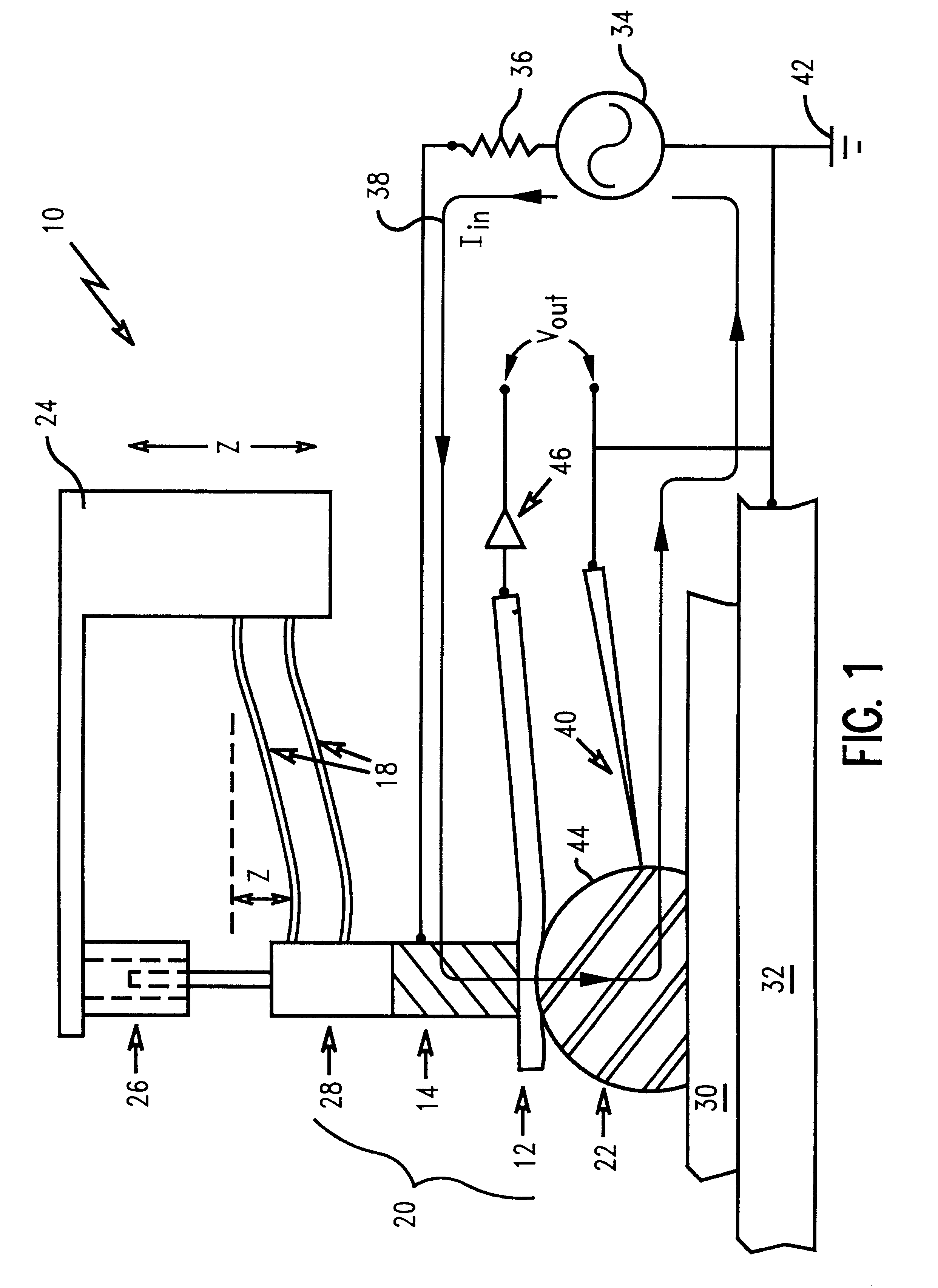

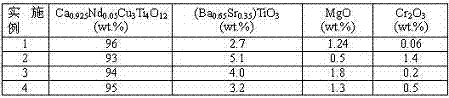

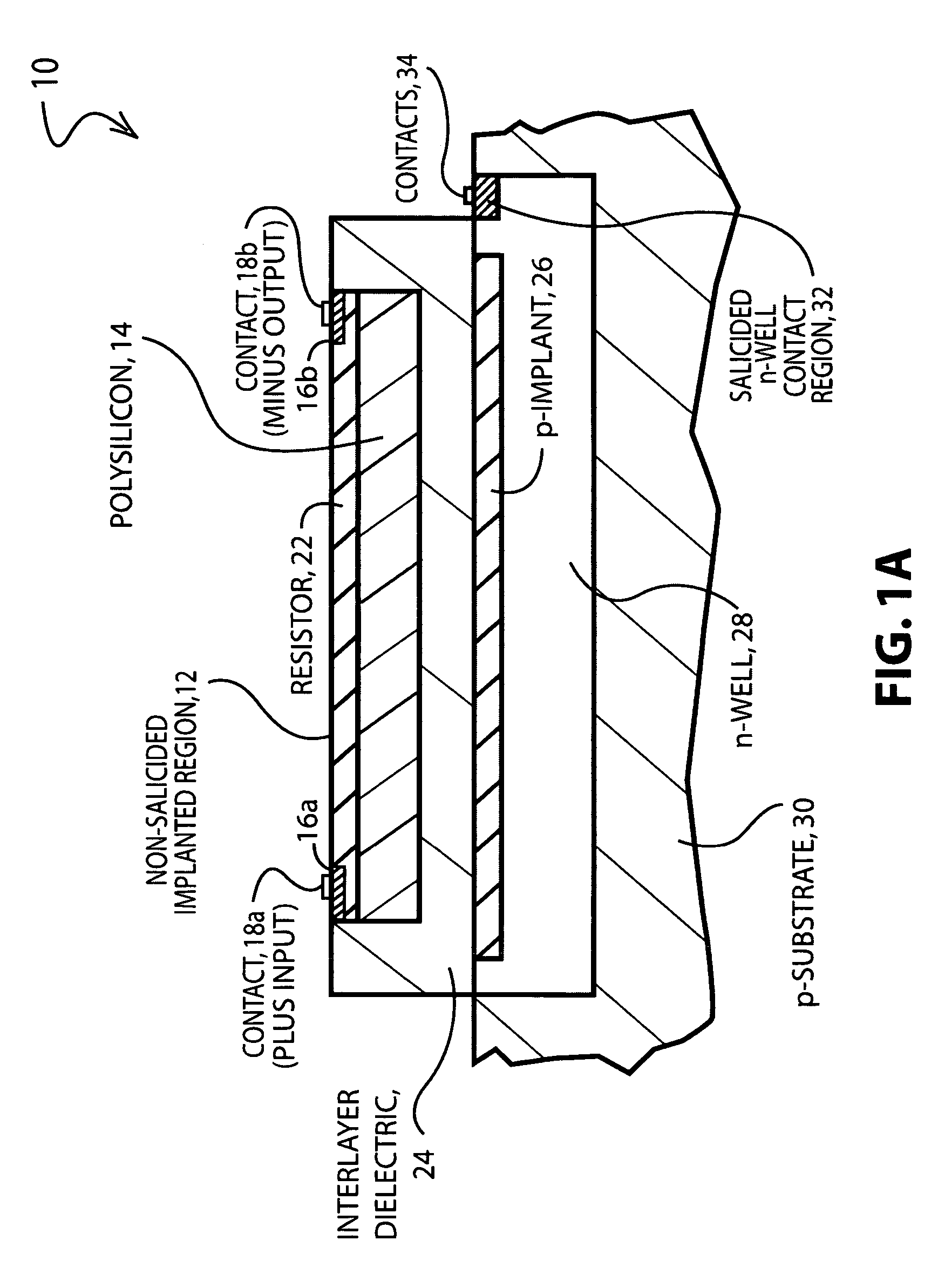

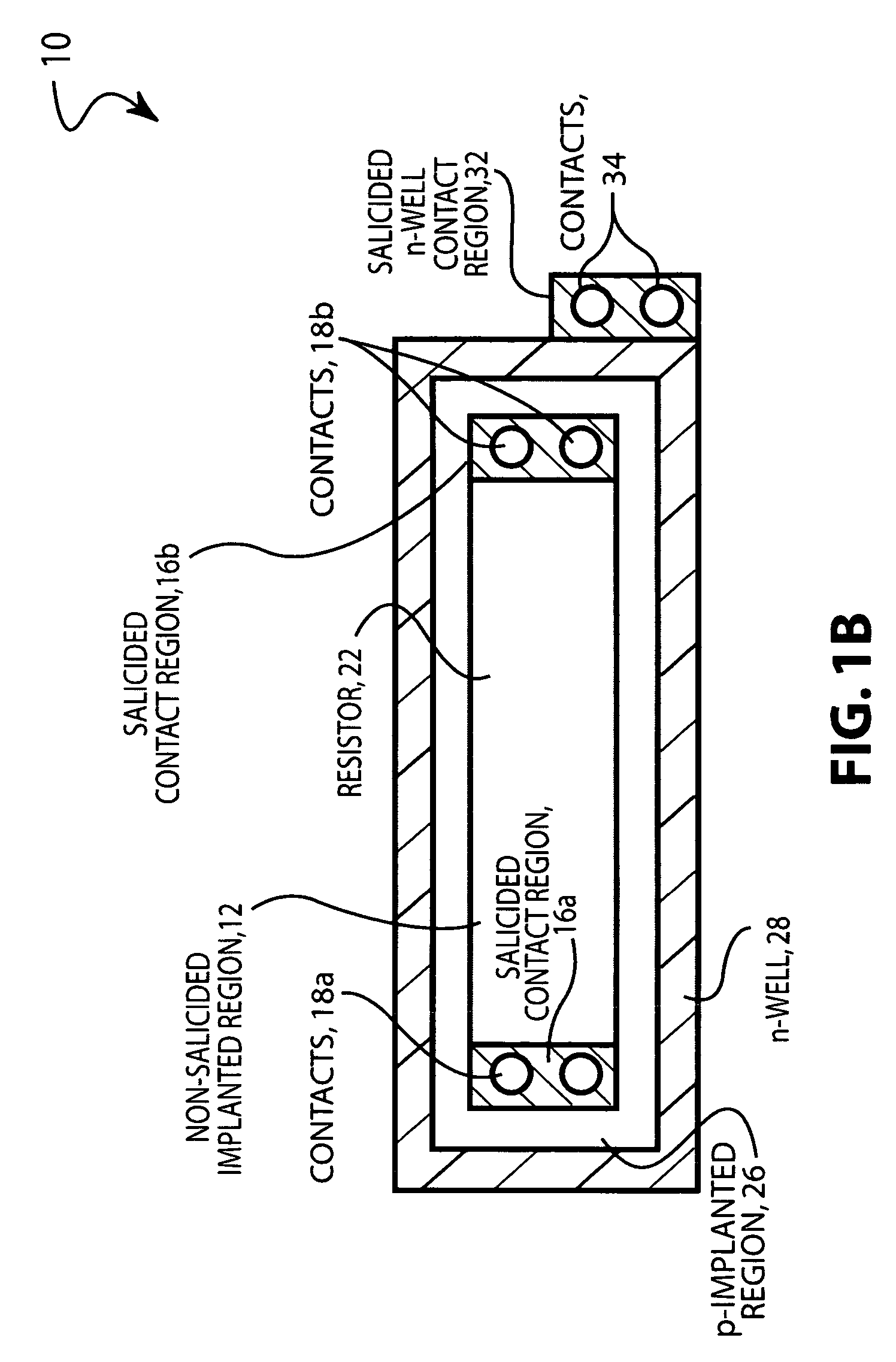

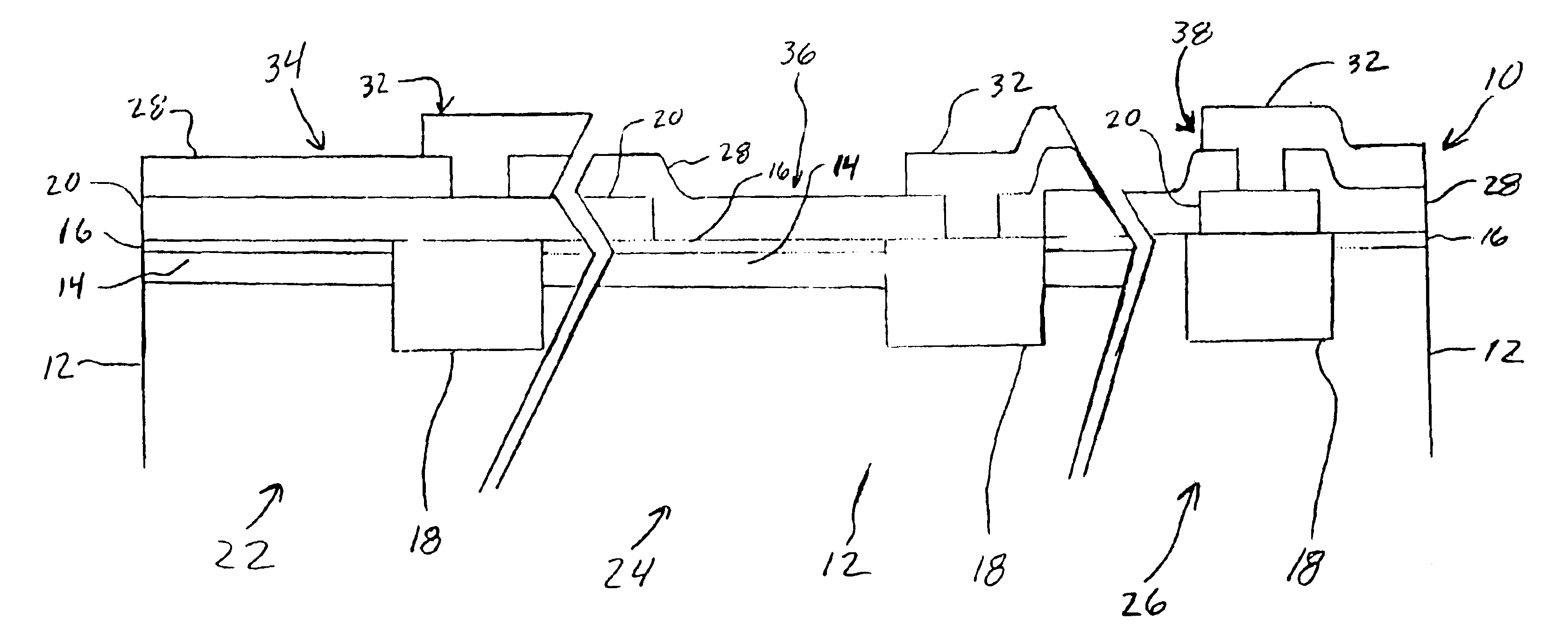

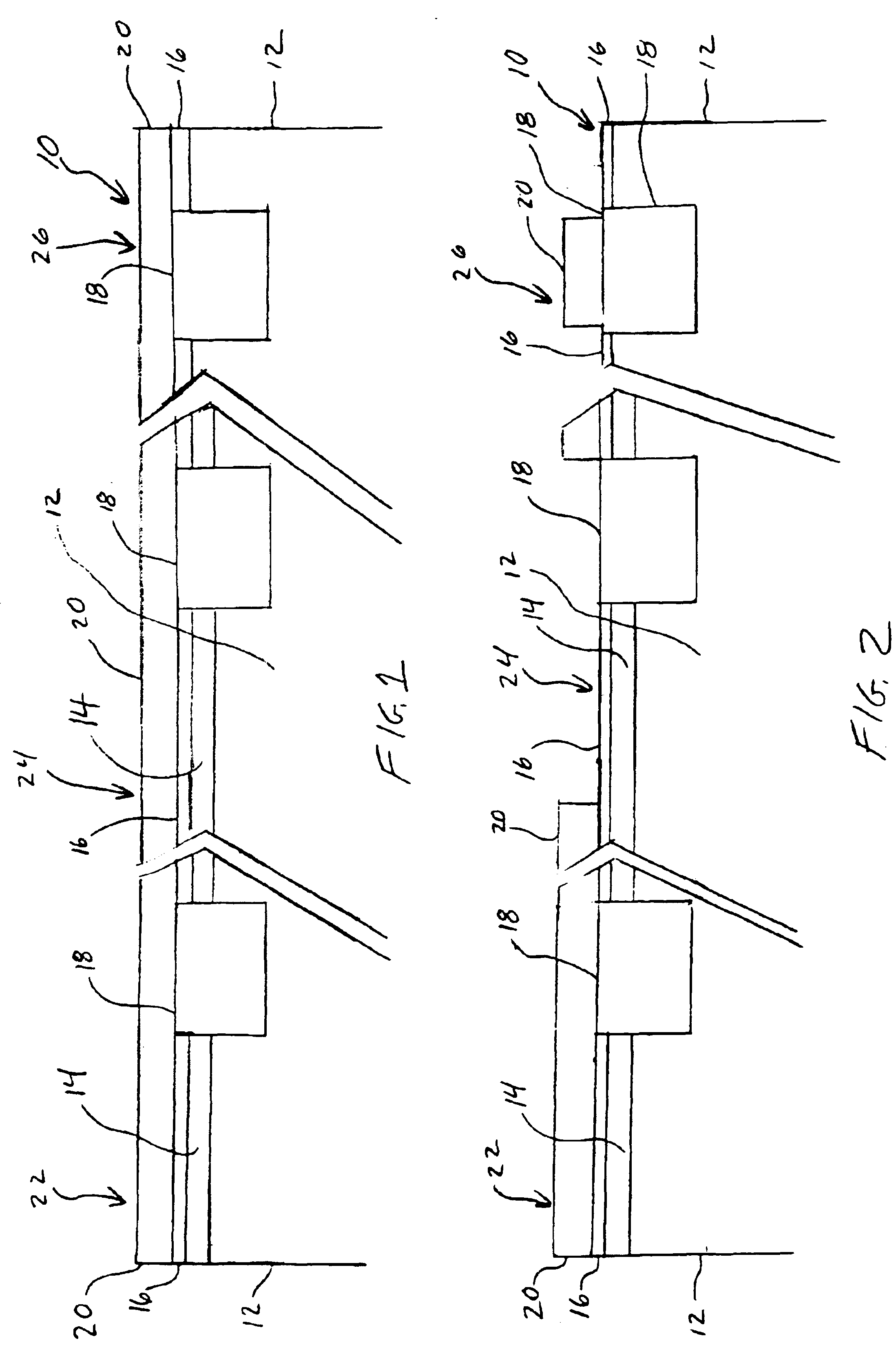

Reduced capacitance resistors

ActiveUS20060118908A1Reduce parasitic capacitanceImproved ac responseSolid-state devicesSemiconductor/solid-state device manufacturingElectrical resistance and conductanceInter layer

A method for reducing the parasitic capacitance in resistors, and a resistor design embodying this method are described. By creating a p-type or an n-type implant inside of an n-well or a p-substrate, respectively, where the n-well or p-substrate is located in a p-substrate or n-substrate, respectively, a capacitively coupled capacitor is formed in series connection with the parasitic inter-layer dielectric capacitance generated when the resistor is fabricated in the dielectric material. The depletion region formed thereby behaves as a series capacitor which reduces the overall capacitance of the assemblage. The n-well or p-substrate can be placed in electrical connection with a ground potential or brought to a chosen voltage to further increase the depletion region and reduce the capacitance of the resistor.

Owner:BELL SEMICON LLC

Method of measuring oxide thickness during semiconductor fabrication

InactiveUS6228665B1TransistorSemiconductor/solid-state device testing/measurementLinear correlationWafer fabrication

A measurement of thickness of a metal oxide layer on a solder ball connection during semiconductor fabrication is demonstrated by an in-situ capacitance measurement of the oxide layer. A linear relationship is shown between the reactance of the metal oxide and its thickness. This linearity is derived empirically, and correlated to Auger Spectroscopy test results for accuracy. The linear relationship demonstrated with these measurements exhibits a linear correlation coefficient, R2, greater than or equal to 0.974. This close, linear relationship allows for accurate testing of the oxide thickness using standard electrical parameter measurements during wafer fabrication.The method requires the determination of an analytical relationship between dielectric thickness and dielectric capacitance; the performance of an in-situ test of the dielectric layer capacitance including measuring the dielectric layer capacitance; and, the calculation of the dielectric layer thickness by using reactance values, calculated from the measured dielectric layer capacitance, as a variable within the analytical relationship.

Owner:IBM CORP

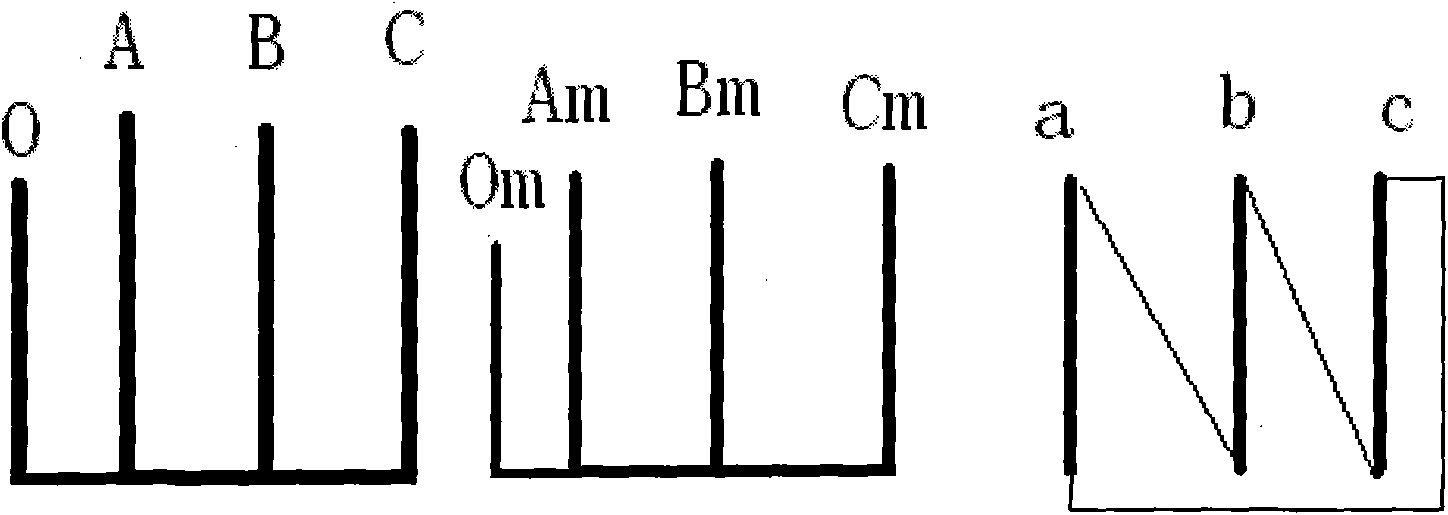

Dielectric-capacitance testing method of deformation degree of transformer winding

InactiveCN101776435AGuaranteed safe operationImprove the quality of workResistance/reactance/impedenceElectrical/magnetic solid deformation measurementQuality of workDielectric loss

The invention provides a dielectric-capacitance testing method of the deformation degree of a transformer winding, belonging to the technical field of test of electric appliance components. The deformation degree of the transformer winding is judged by testing the variation of the dielectric loss and capacitance of the transformer winding. The invention has the advantages that shortage of the prior art is overcome, the deformation degree of the transformer winding is judged by testing the variation of the dielectric loss and capacitance of the transformer winding, the deformation degree of the transformer winding can be accurately judged by an overall dielectric-capacitance method or an interphase dielectric-capacitance method or by complementation and confirmation therebetween so that the repair the operating state of the transformer can be timely and accurately monitored, normal and safe operation of the transformer is ensured, and the working quality and the efficiency of the transformer are improved. The method is particularly suitable for testing the deformation degree of the transformer winding with the voltage of 110kV or above.

Owner:HEBEI ELECTRIC POWER RES INST

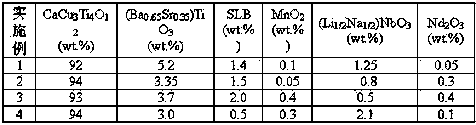

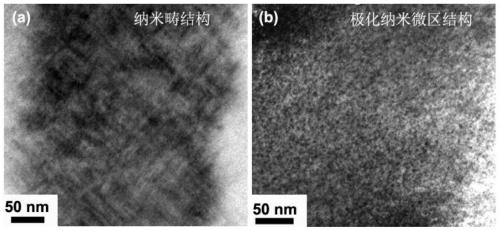

Low temperature sintered giant dielectric ceramic capacitor medium and preparation method thereof

The invention relates to the technical field of inorganic non-metal materials, and particularly discloses a low temperature sintered ceramic capacitor medium with small giant dielectric capacitance temperature change rate and a preparation method thereof. The medium formula comprises the following components: 88 to 96 wt. % of CaCu3Ti4O12, 0.01 to 7.0 wt.% of (Ba0.65Sr0.35) TiO3, 0.01 to 0.6 wt. % of Nd2O3, 0.1 to 4 wt. % of SiO2-Li2O-B2O3 glass powder, 0 to 0.5 wt. % of MnO2, and 0.5 to 4 wt. % of (Li1 / 2Na1 / 2) NbO3, wherein CaCu3Ti4O12, (Ba0.65Sr0.35) TiO3, (Li1 / 2Na1 / 2) NbO3 and SiO2-Li2O-B2O3 glass powder (SLB) are respectively compounded by conventional chemical raw materials through a solid phase method. According to the invention, common chemical raw materials of capacitor ceramic are adopted to prepare the lead-free and cadmium-free ceramic capacitor medium with small giant dielectric capacitance temperature change rate, the sintering temperature of the capacitor ceramic is greatly reduced, and the medium is applicable to the preparation of monolithic ceramic capacitors.

Owner:JIANGSU UNIV

Array of gate dielectric structures to measure gate dielectric thickness and parasitic capacitance

InactiveUS6964875B1Eliminate parasitic capacitanceAccurate measurementSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsGate dielectricParasitic capacitance

Accurate determination of gate dielectric thickness is required to produce high-reliability and high-performance ultra-thin gate dielectric semiconductor devices. Large area gate dielectric capacitors with ultra-thin gate dielectric layers suffer from high gate leakage, which prevents the accurate measurement of gate dielectric thickness. Accurate measurement of gate dielectric thickness of smaller area gate dielectric capacitors is hindered by the relatively large parasitic capacitance of the smaller area capacitors. The formation of first and second dummy structures on a wafer allow the accurate determination of gate dielectric thickness. First and second dummy structures are formed that are substantially similar to the gate dielectric capacitors except that the first dummy structures are formed without the second electrode of the capacitor and the second dummy structures are formed without the first electrode of the capacitor structure. The capacitance, and therefore thickness, of the gate dielectric capacitor is determined by subtracting the parasitic capacitances measured at the first and second dummy structures.

Owner:GLOBALFOUNDRIES INC

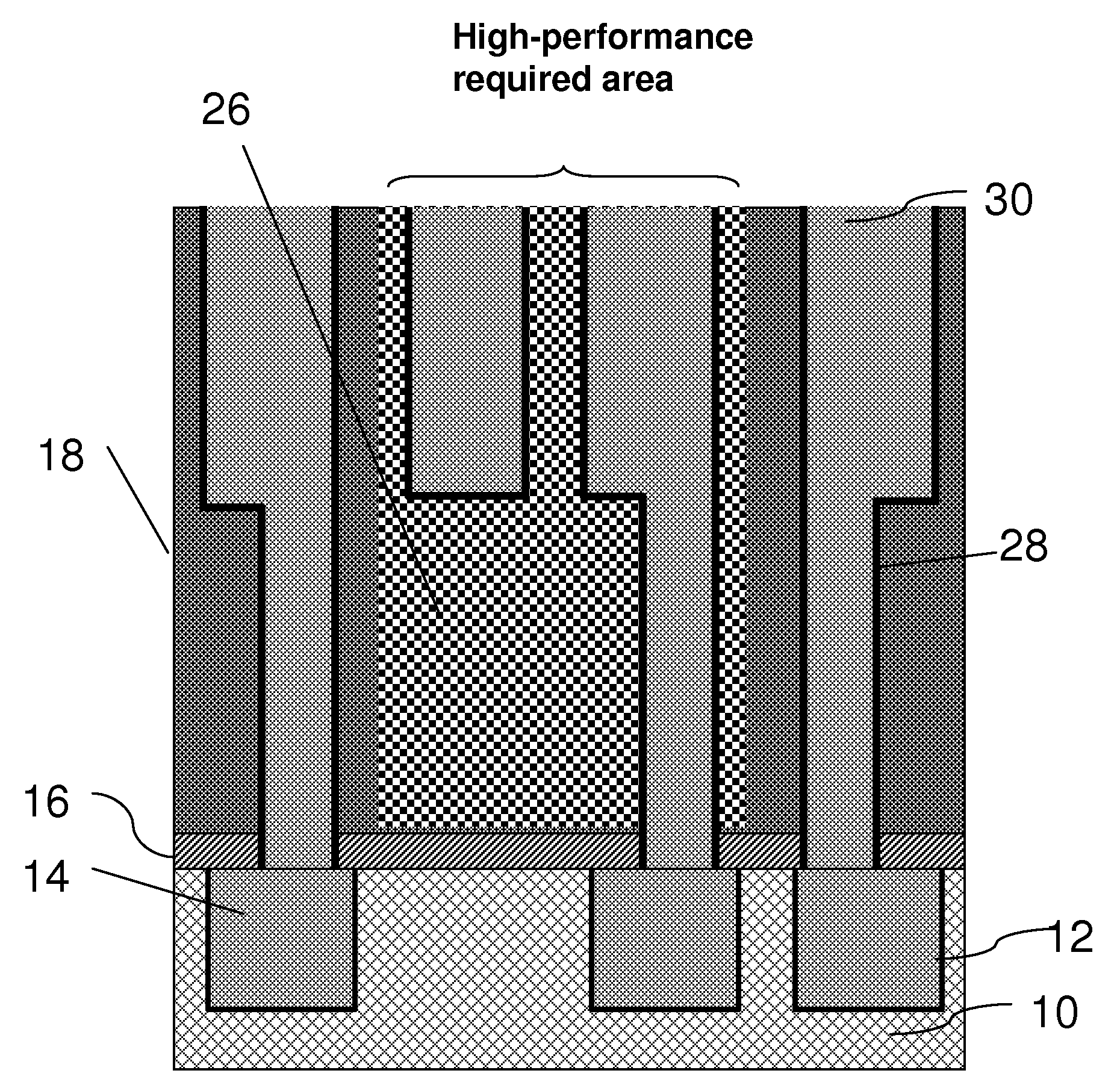

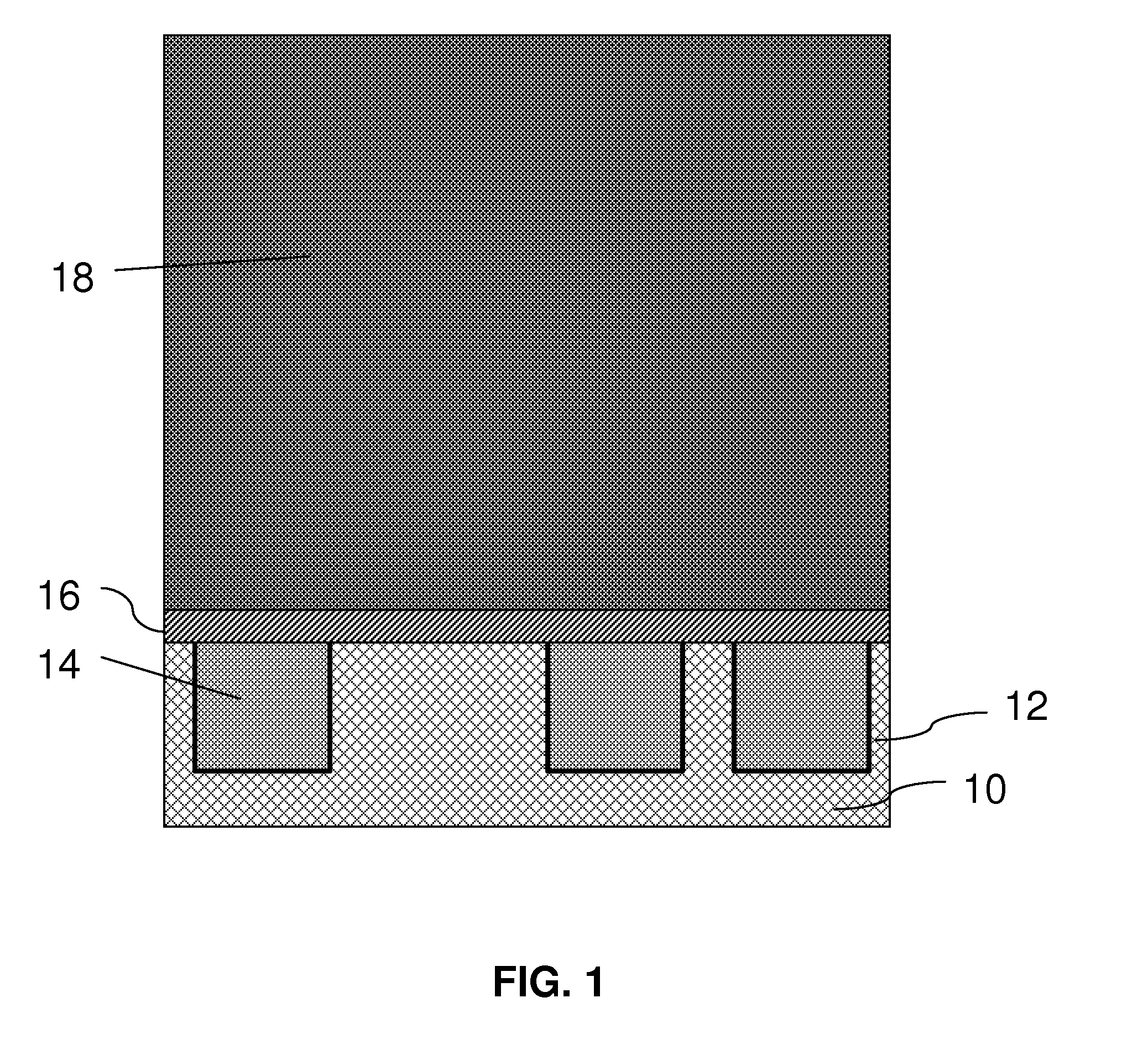

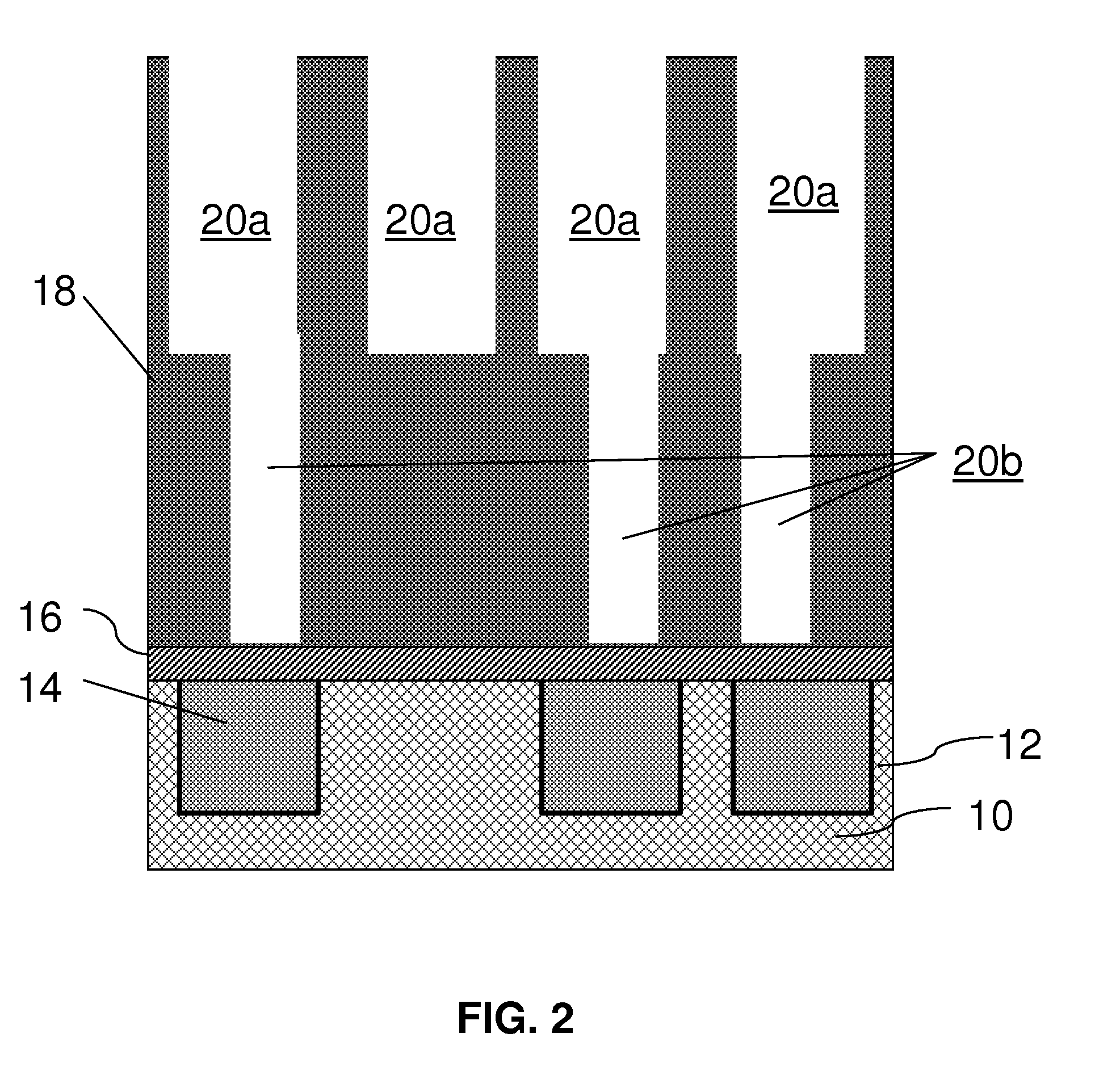

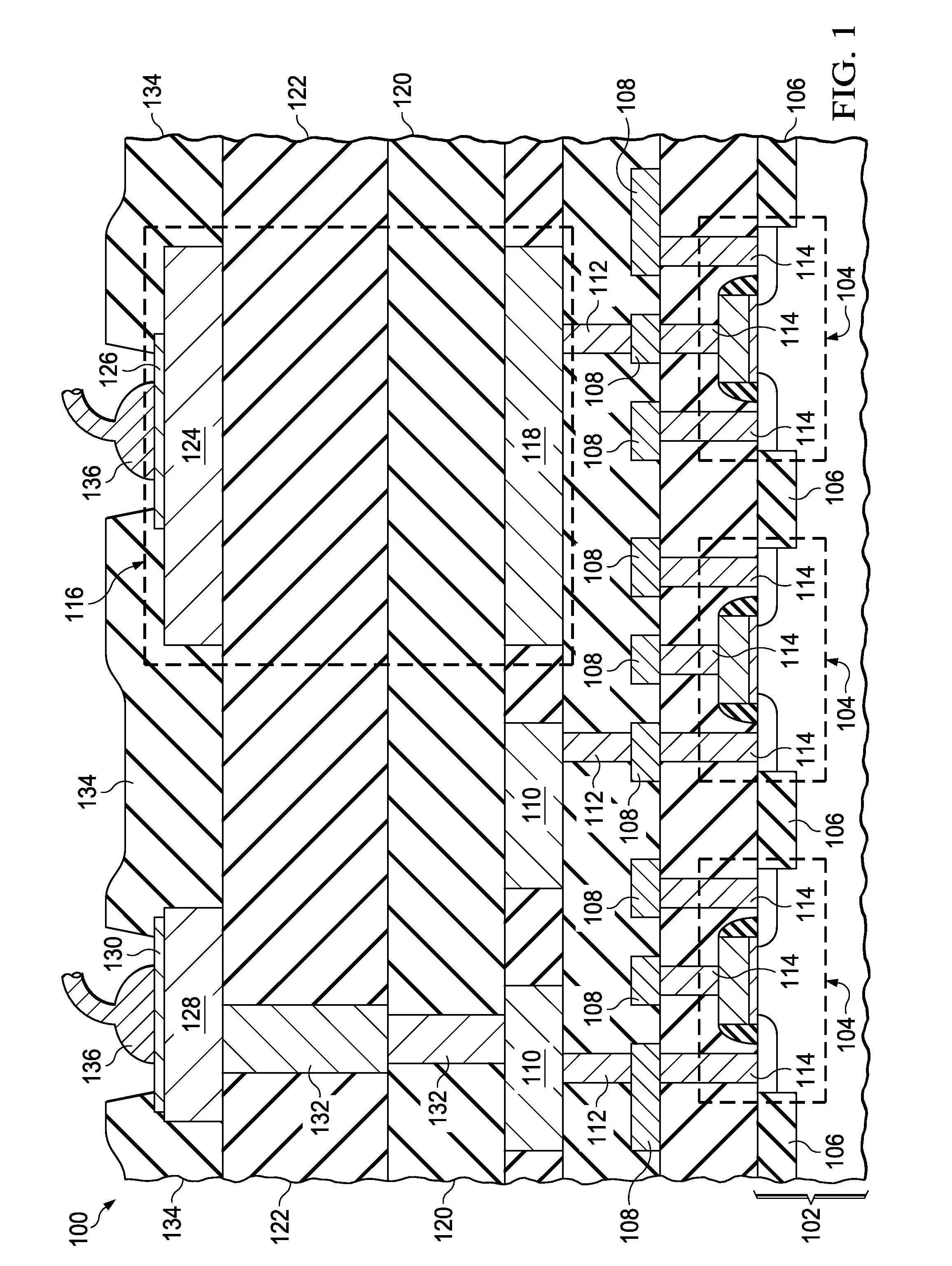

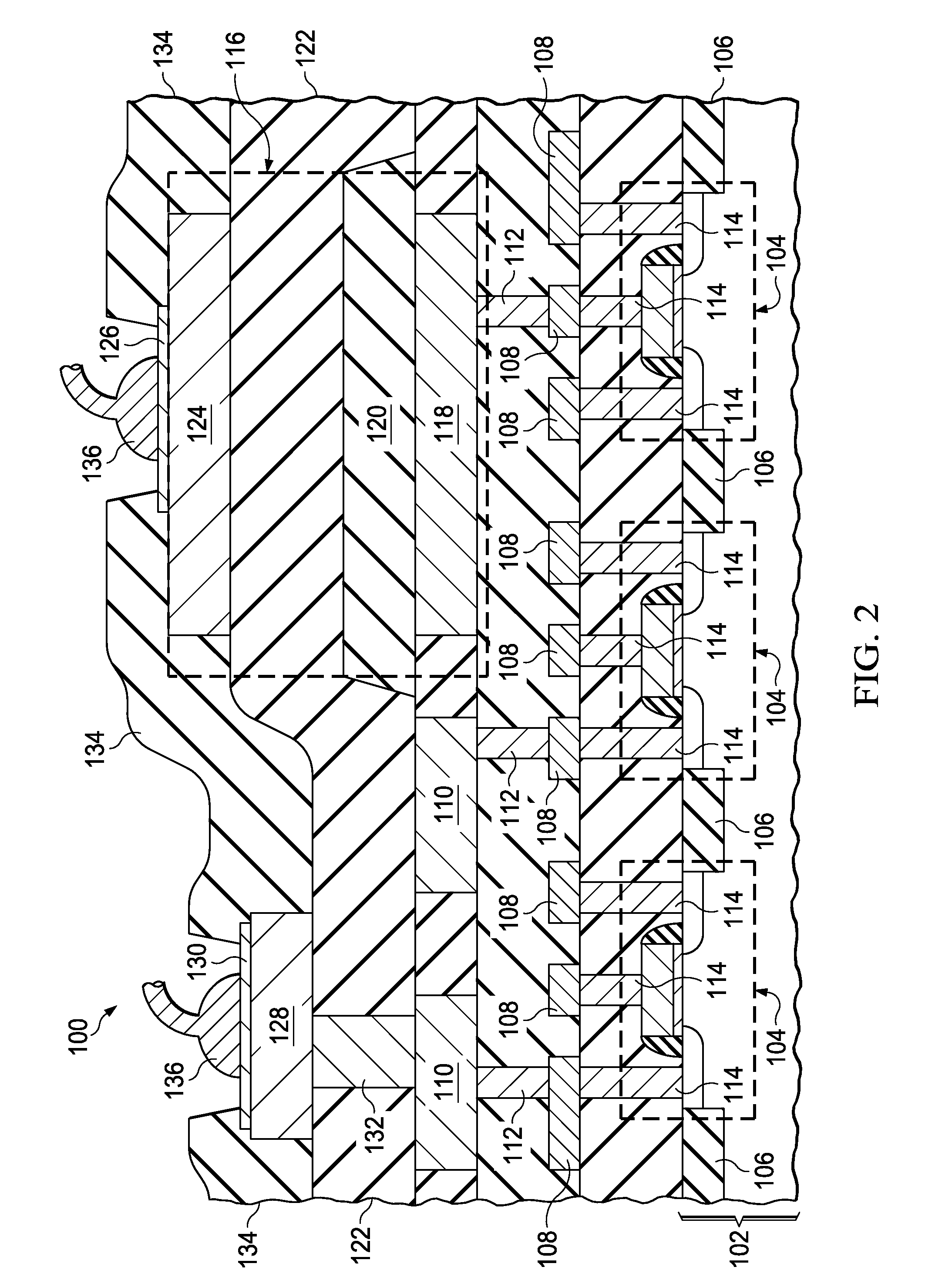

Porous and dense hybrid interconnect structure and method of manufacture

InactiveUS20080122109A1Semiconductor/solid-state device detailsSolid-state devicesSemiconductor structureUltimate tensile strength

A method for manufacturing a structure includes depositing a dense dielectric over the entire wafer, which includes areas that require low dielectric capacitance and areas that require high mechanical strength. The method further includes masking areas of the dense dielectric over the areas that require high mechanical strength and curing unmasked areas of the dense dielectric to burn out porogens inside the dense dielectric and transform the unmasked areas of the dense dielectric to porous dielectric material. A semiconductor structure comprises porous and dense hybrid interconnects for high performance and reliability semiconductor applications.

Owner:IBM CORP

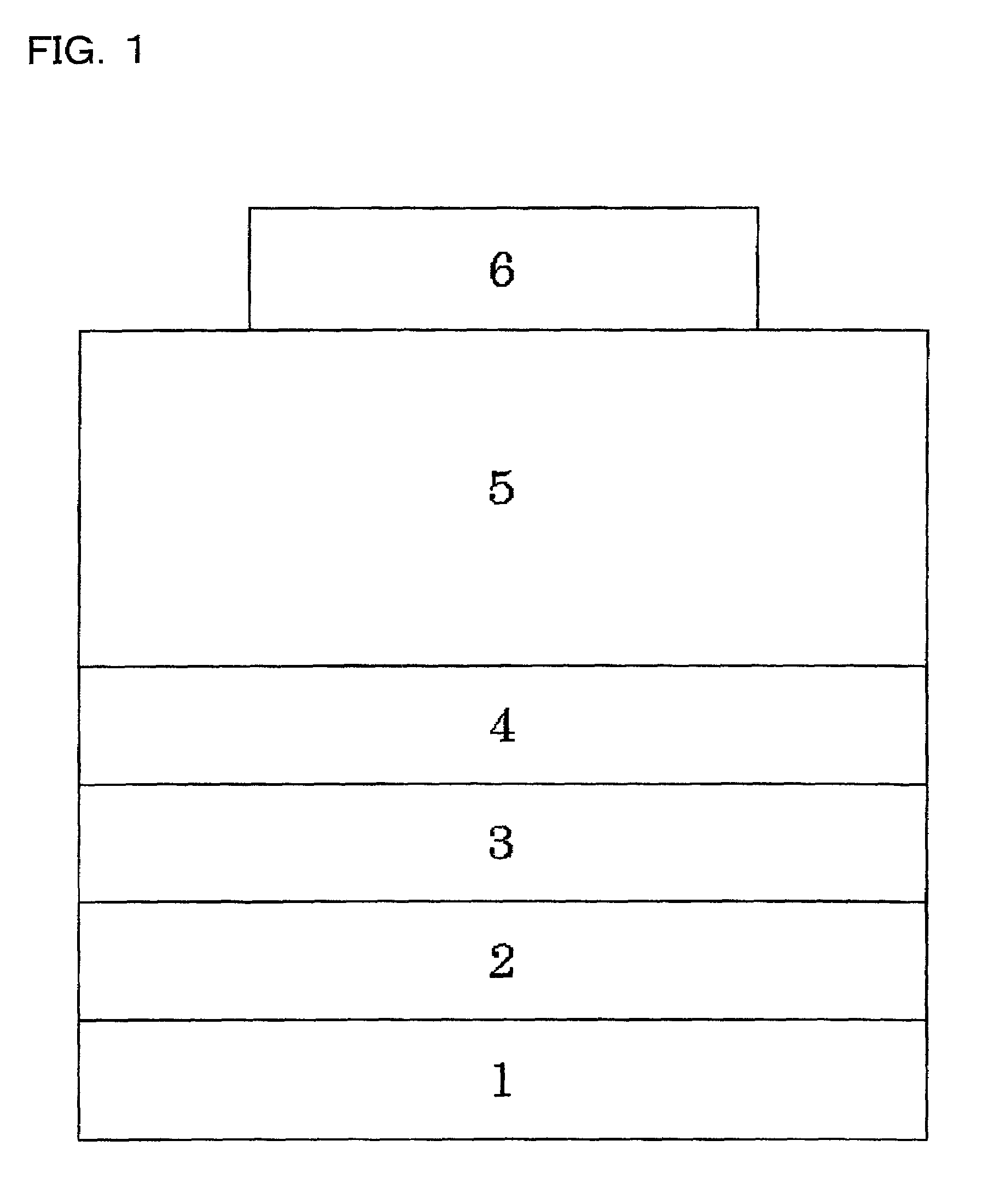

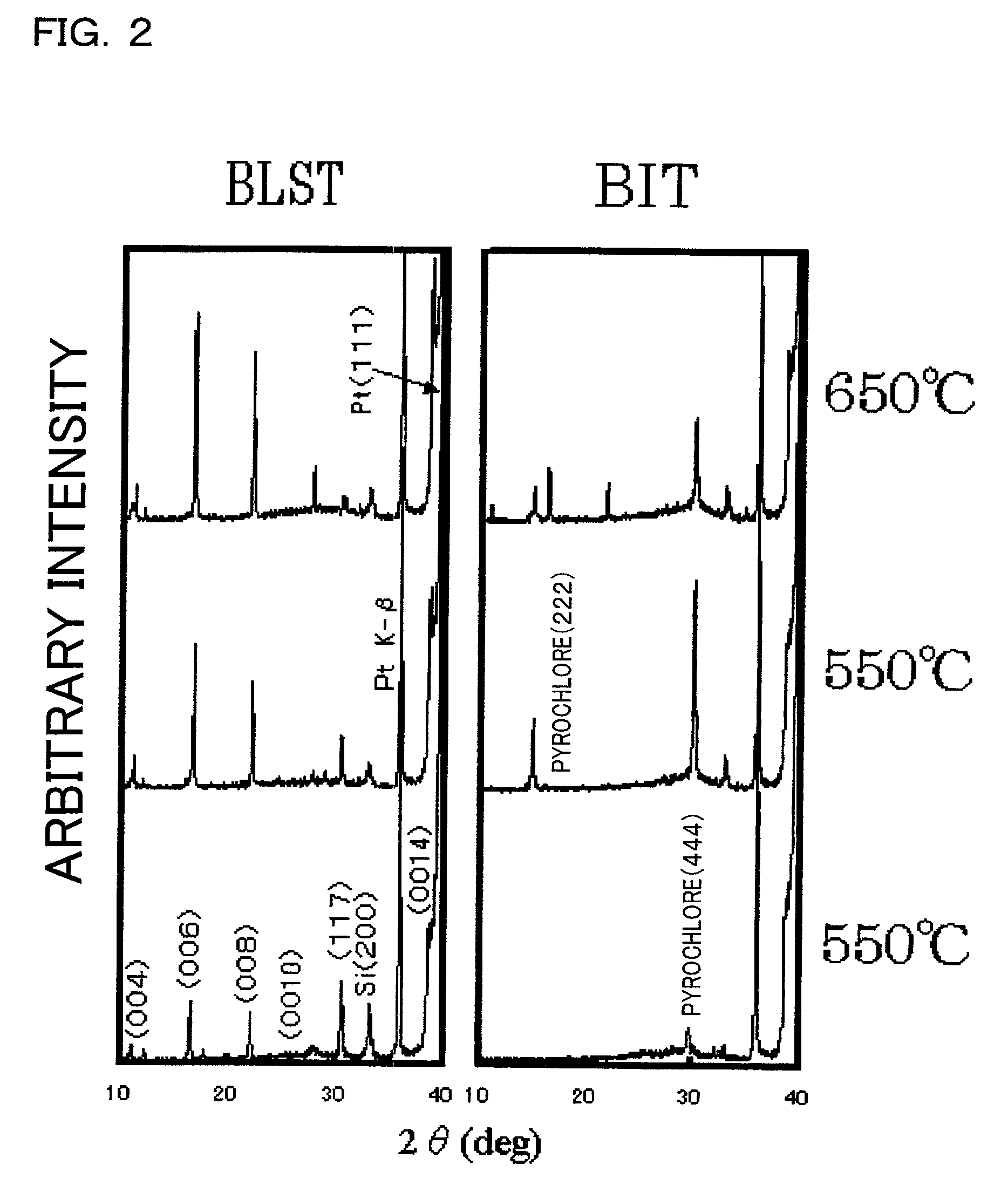

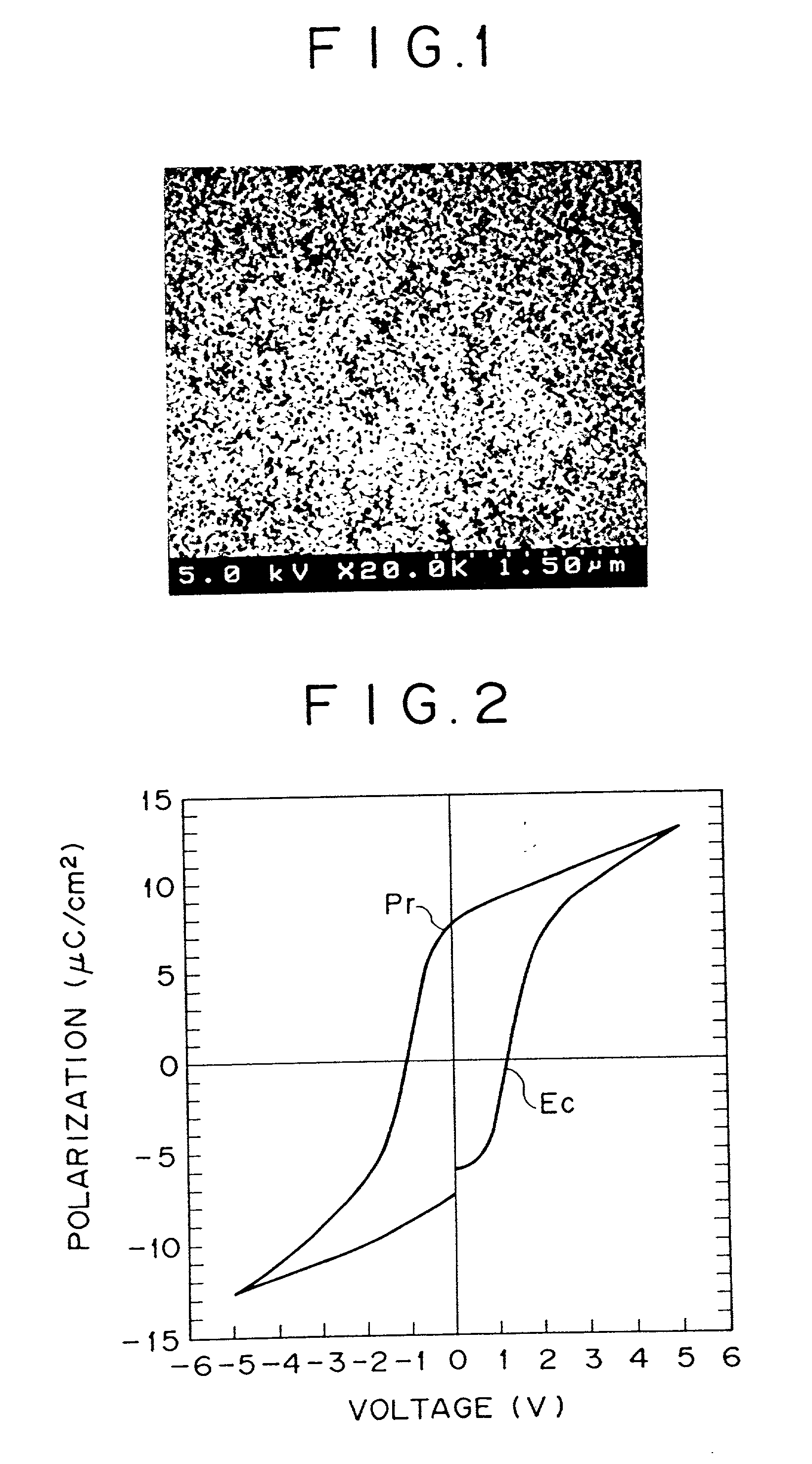

Ceramic and method of manufacturing the same, dielectric capacitor, semiconductor device, and element

InactiveUS7008669B2Reduce crystallizationImprove surface morphologyPiezoelectric/electrostrictive device manufacture/assemblyVacuum evaporation coatingCatalytic effectCeramic

A method of manufacturing a ceramic includes forming a film which includes a complex oxide material having an oxygen octahedral structure and a paraelectric material having a catalytic effect for the complex oxide material in a mixed state, and performing a heat treatment to the film, wherein the paraelectric material is one of a layered catalytic substance which includes Si in the constituent elements and a layered catalytic substance which includes Si and Ge in the constituent elements. The heat treatment includes sintering and post-annealing. At least the post-annealing is performed in a pressurized atmosphere including at least one of oxygen and ozone. A ceramic is a complex oxide having an oxygen octahedral structure, and has Si and Ge in the oxygen octahedral structure.

Owner:SEIKO EPSON CORP

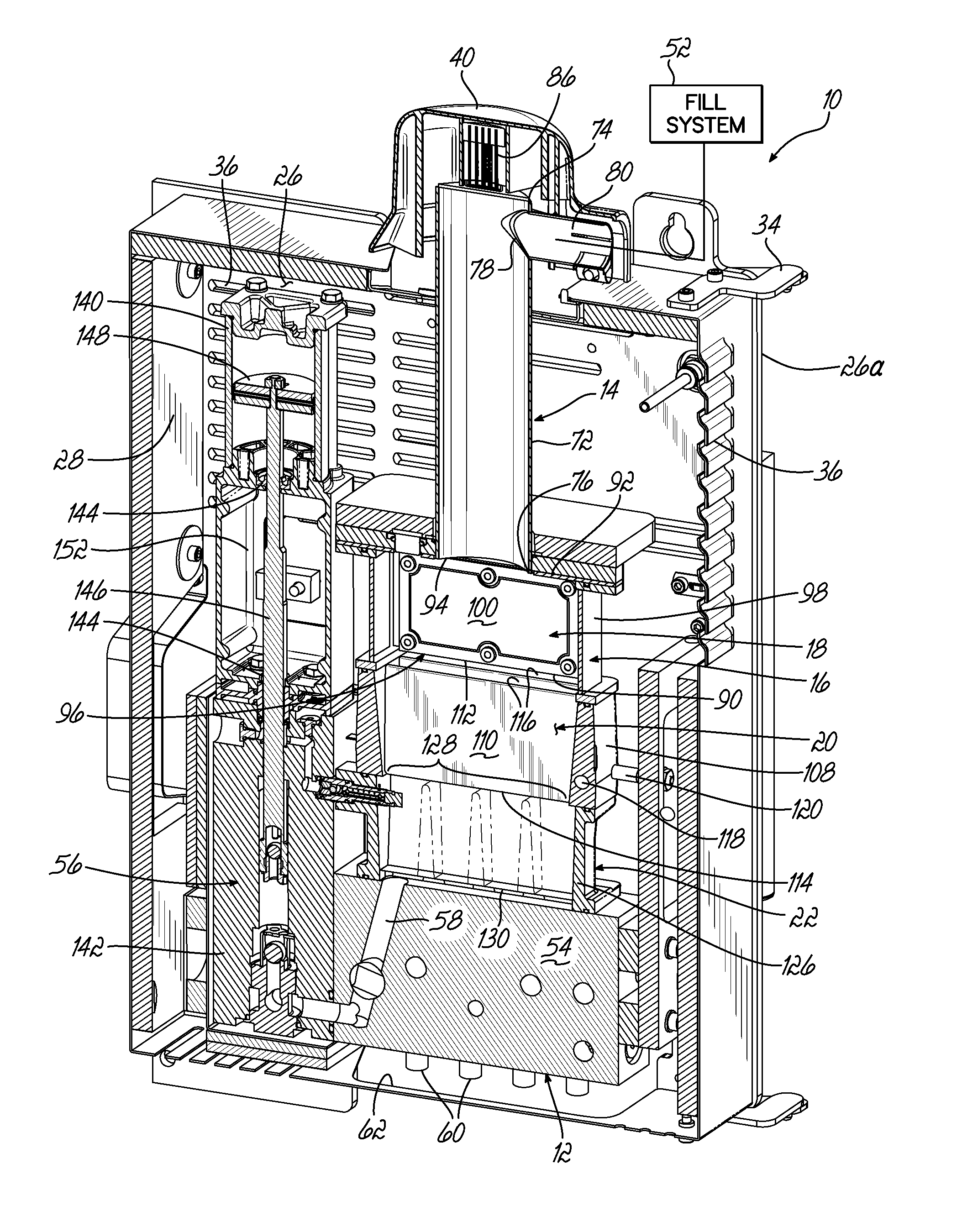

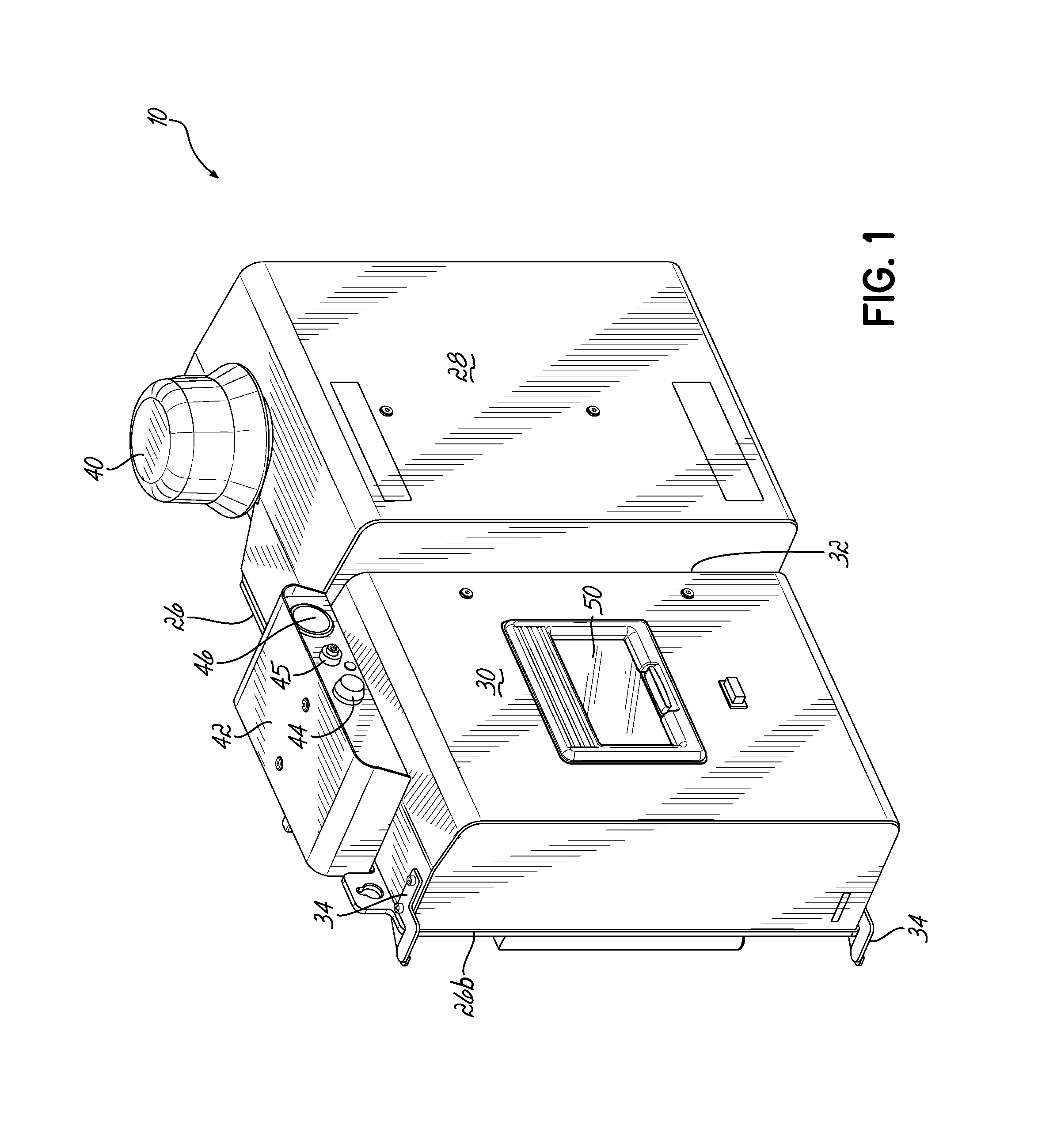

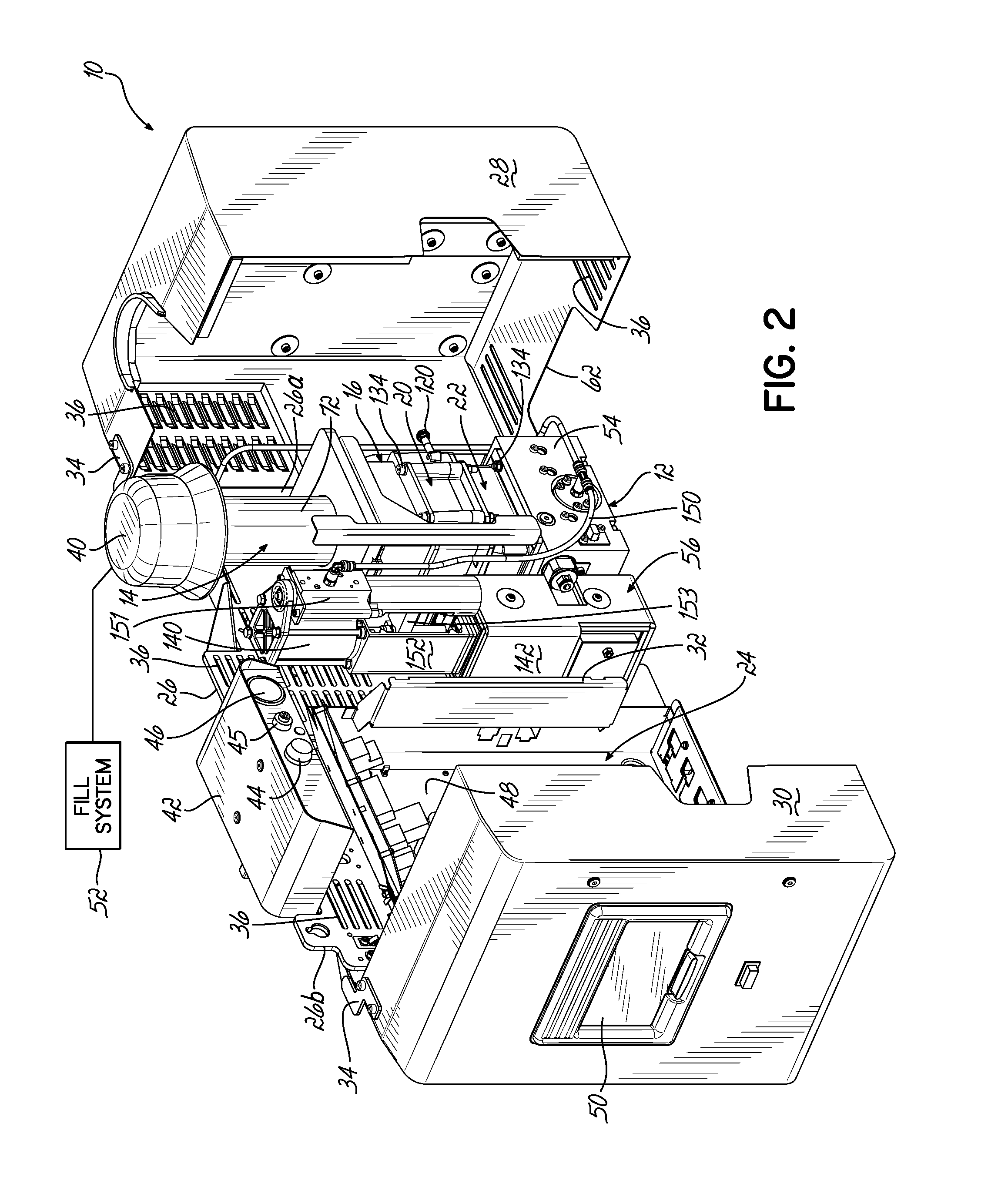

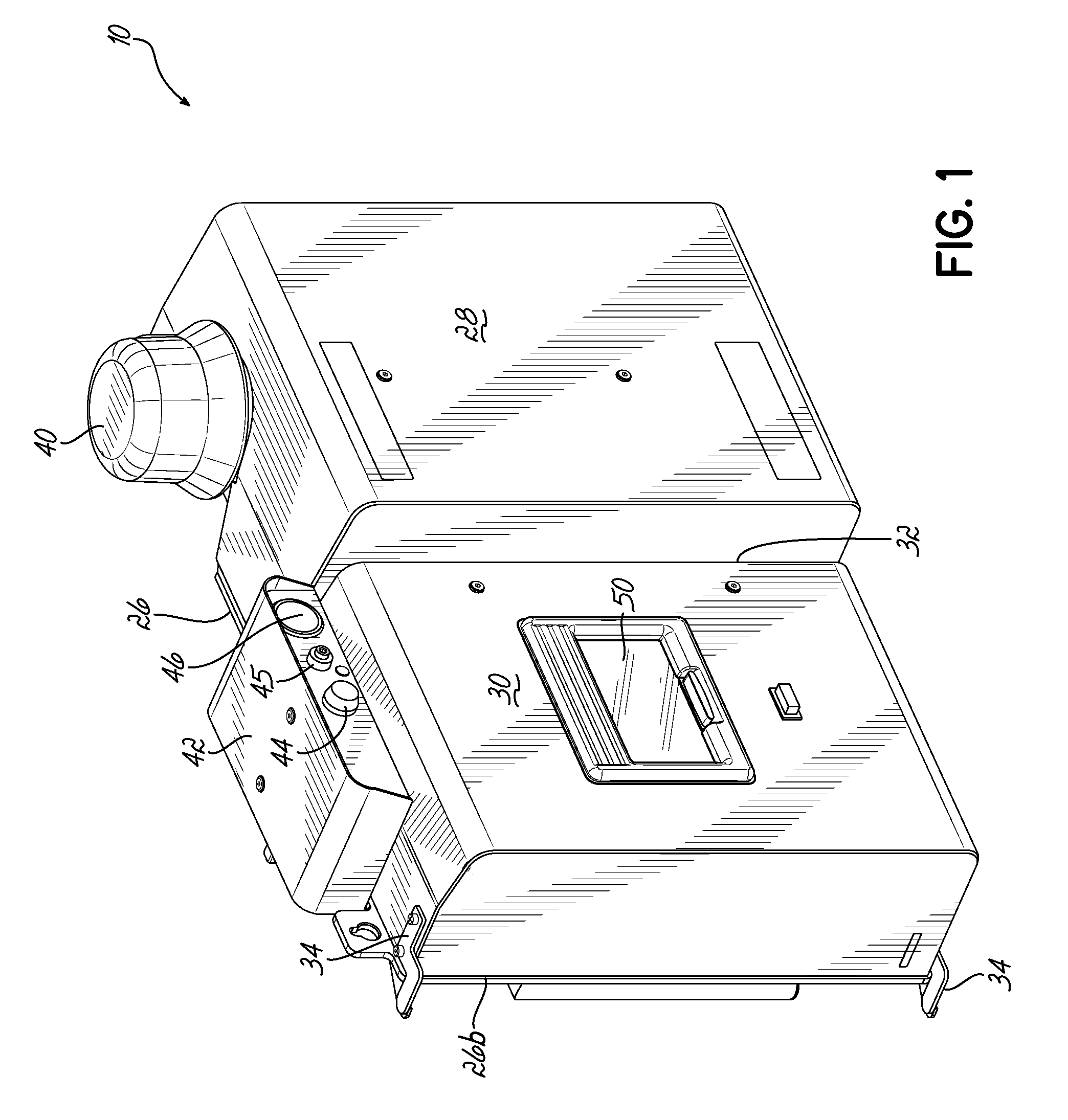

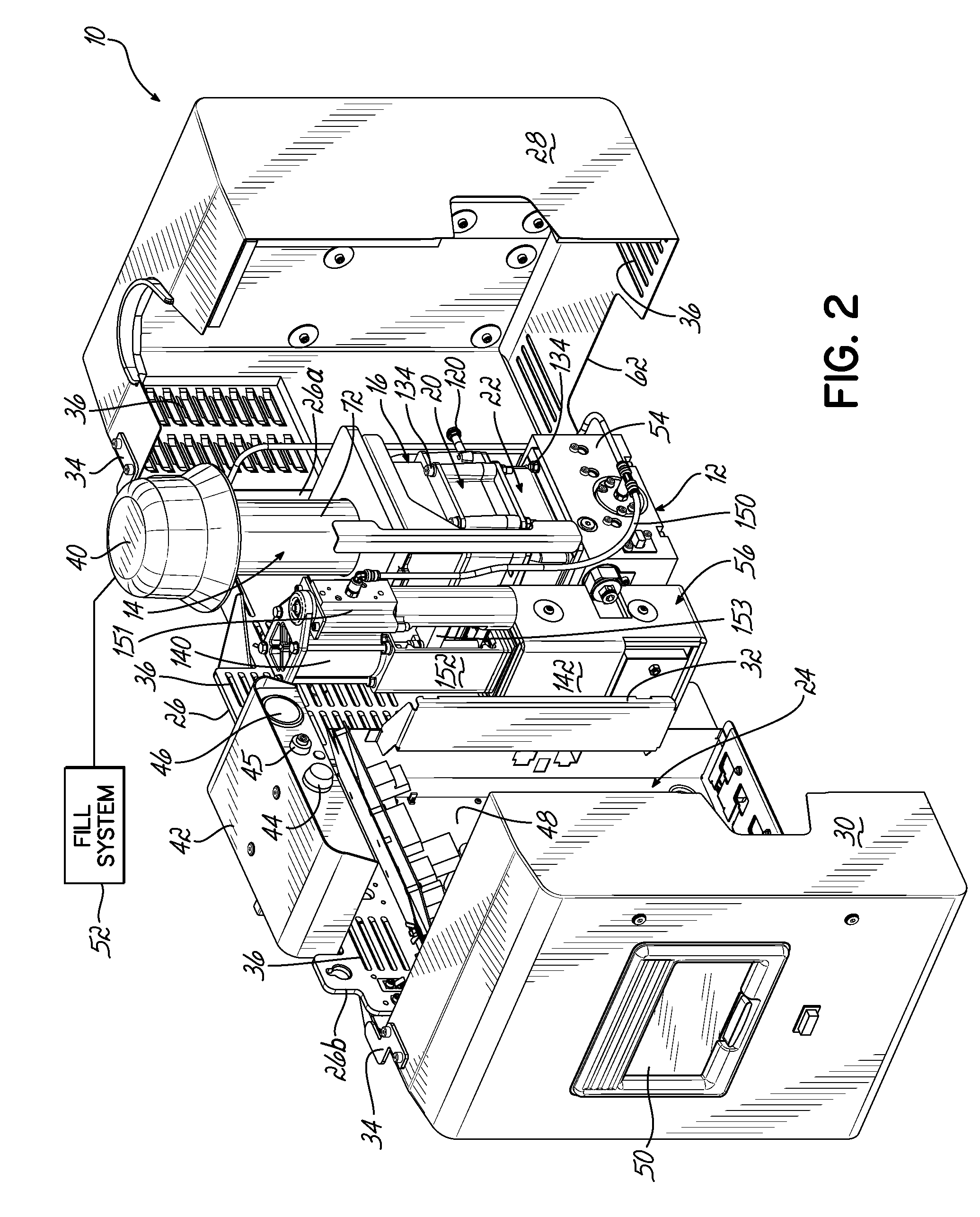

Adhesive dispensing device having optimized reservoir and capacitive level sensor

ActiveUS20140076923A1Fast deliveryAvoid emptyingLiquid surface applicatorsSurgeryAdhesiveControl signal

An adhesive dispensing device includes a heater unit for melting adhesive, a fill system communicating with a receiving space for feeding the heater unit, and a reservoir for receiving melted adhesive from the heater unit. The dispensing device also includes a capacitive level sensor located along a sidewall of the receiving space such that the level of adhesive in the receiving space can be detected by sensing the difference in dielectric capacitance where the adhesive is located compared to where air acts as the dielectric. The size of the driven electrode produces a broader sensing window capable of generating multiple control signals corresponding to different fill levels of adhesive. The receiving space and reservoir are minimized in size so that adhesive is not held at elevated temperatures long enough to char or degrade.

Owner:NORDSON CORP

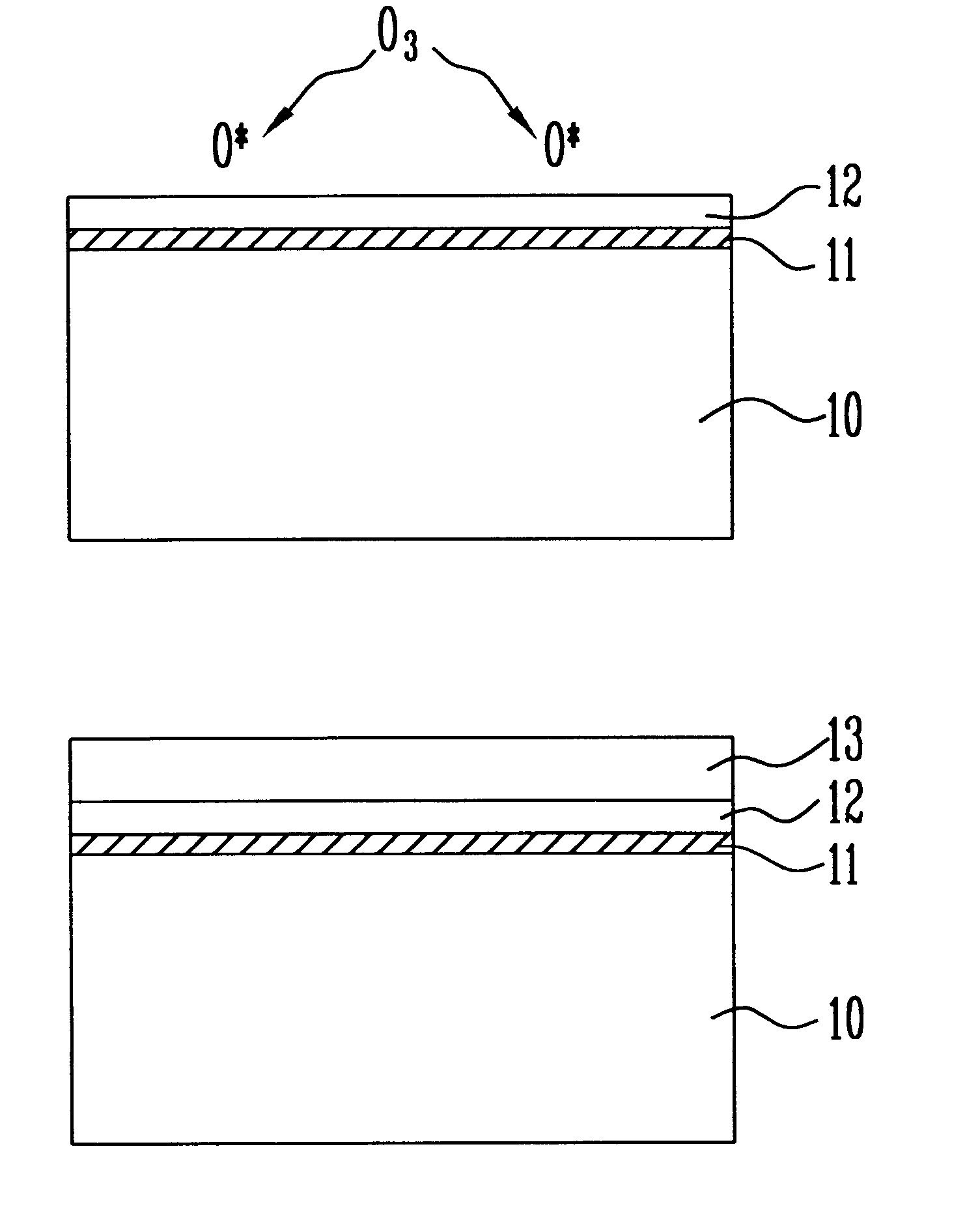

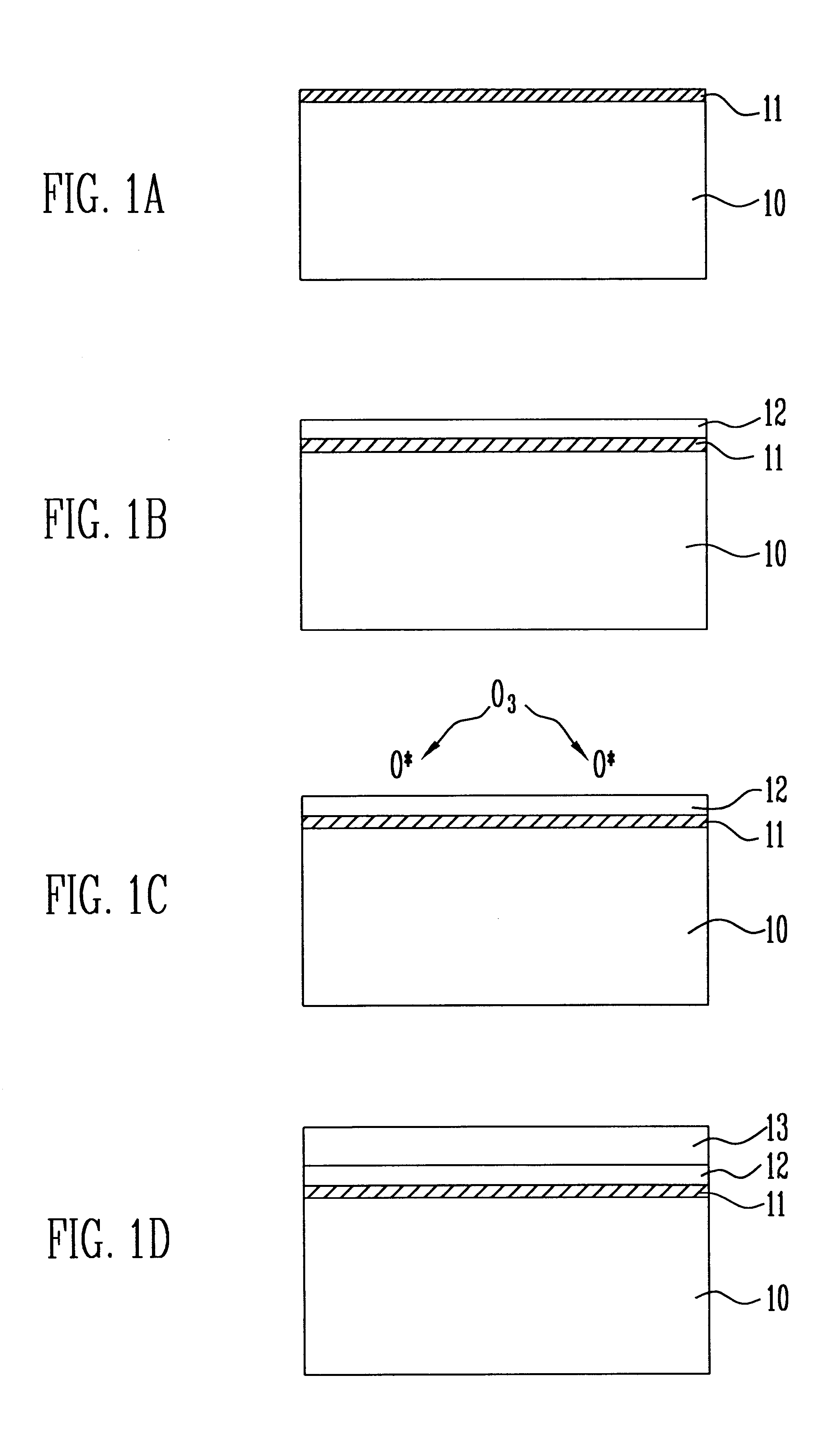

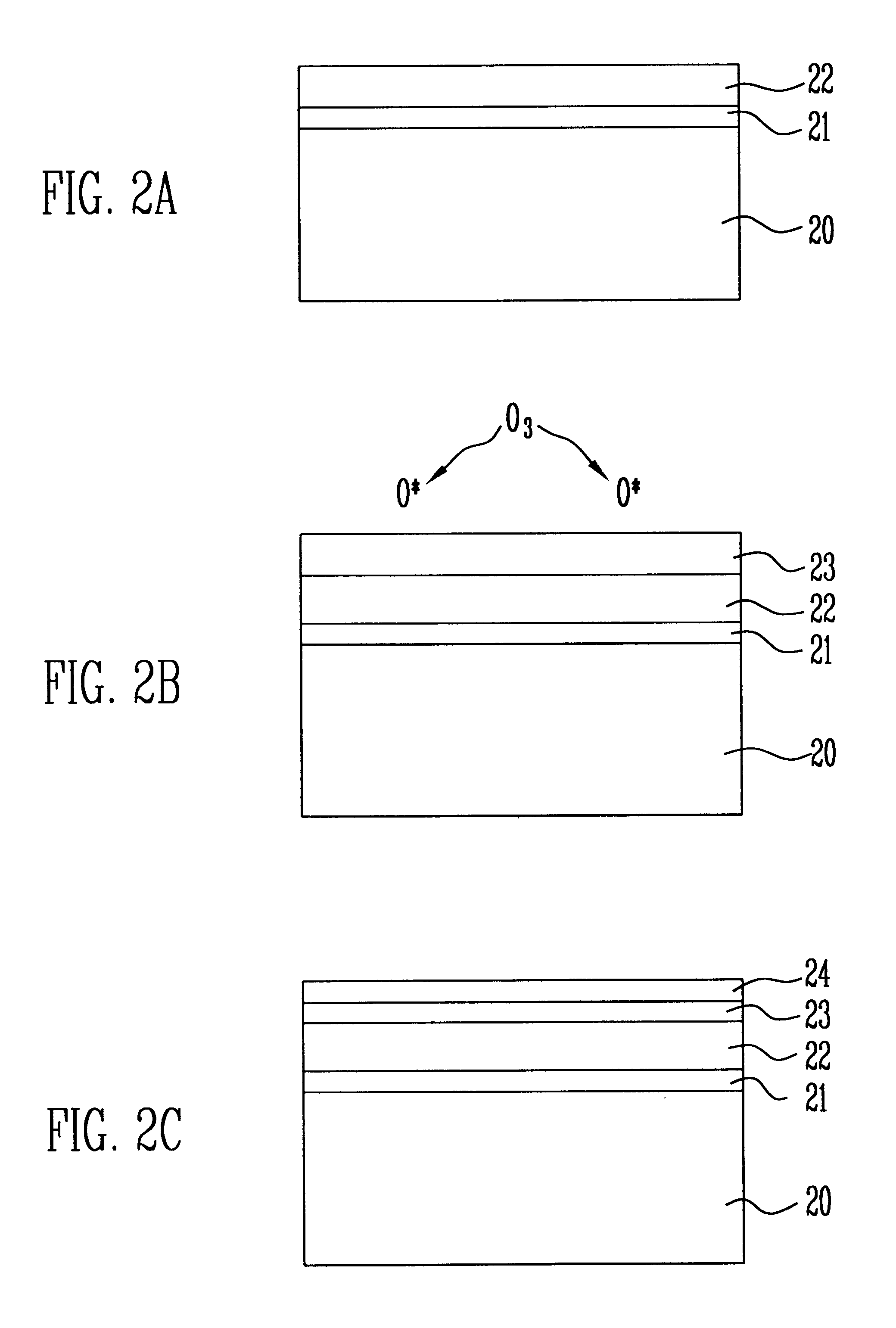

Method of manufacturing a capacitor in a semiconductor device using a high dielectric tantalum oxide or barium strontium titanate material that is treated in an ozone plasma

InactiveUS6329237B1Deterioration of characteristicEfficient removalTransistorSolid-state devicesBarium strontium titanateProcess conditions

There is disclosed a method of making a high dielectric capacitor of a semiconductor device using Ta2O5, BST((Ba1-xSrx)TiO3) etc. of a high dielectric characteristic as a capacitor dielectric film in a very high integrated memory device. The present invention has its object to provide a method of manufacturing a high dielectric capacitor of a semiconductor device, which can effectively remove carbon contained within the thin film after deposition of the BST film and defects of oxygen depletion caused upon deposition of the thin film and which can also remove carbon contained within the thin film after deposition of the tantalum oxide film and defects of oxygen depletion caused upon deposition of the thin film, without further difficult processes or without any deterioration of the electrical characteristic of the capacitor. It employs the technology which is able to effectively removing defects of carbon and oxygen depletion within the thin film, by forming a plasma O3 gas having a good reactivity and by processing the plasma for the BST thin film and tantalum oxide film. Thus, it can extend the lifetime of the activated oxygen of oxygen, which had been a problem in processing a conventional UV-O3, by means of plasma process using O3 gas. Therefore, it can effectively remove defects of carbon and oxygen within the BST thin film and tantalum oxide film without complicating the process or deteriorating the electrical characteristic of the capacitor. The present invention also proposes a detailed process condition, which can optimize the plasma process using O3 gas.

Owner:HYUNDAI ELECTRONICS IND CO LTD

Dual capacitor structure for imagers and method of formation

CMOS and CCD imaging devices comprising different in-pixel capacitors and peripheral capacitors and methods of formation are disclosed. The capacitors used in periphery circuits have different requirements from the capacitors used in the pixel itself. Dual stack capacitors comprising two dielectric layers may be provided to achieve low leakage and high capacitance. A single masking step may be provided such that one region has a dual dielectric capacitor and a second region has a single dielectric capacitor. A different dielectric may also be provided in one region compared to another region wherein the inter-electrode insulator comprises a single dielectric in both regions.

Owner:APTINA IMAGING CORP

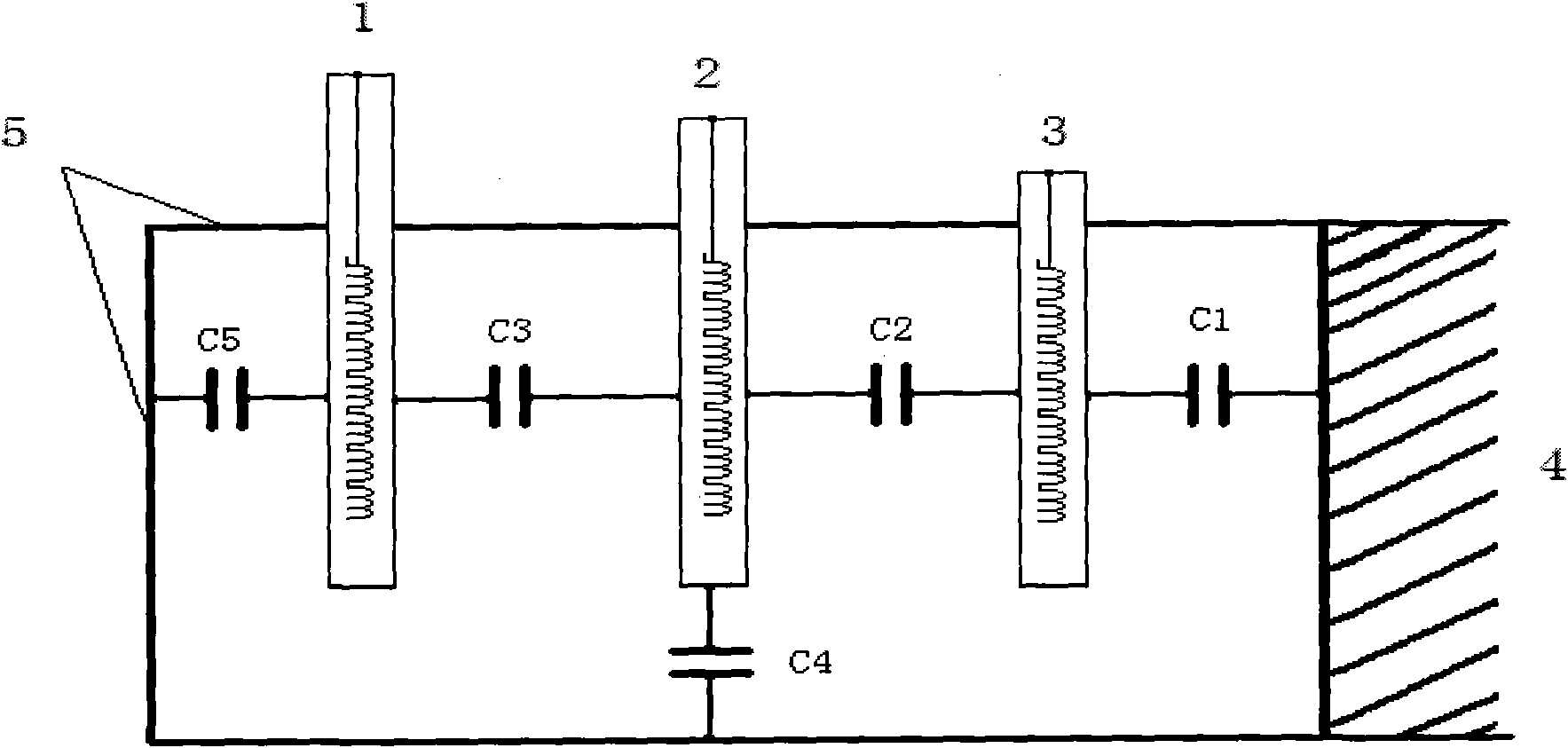

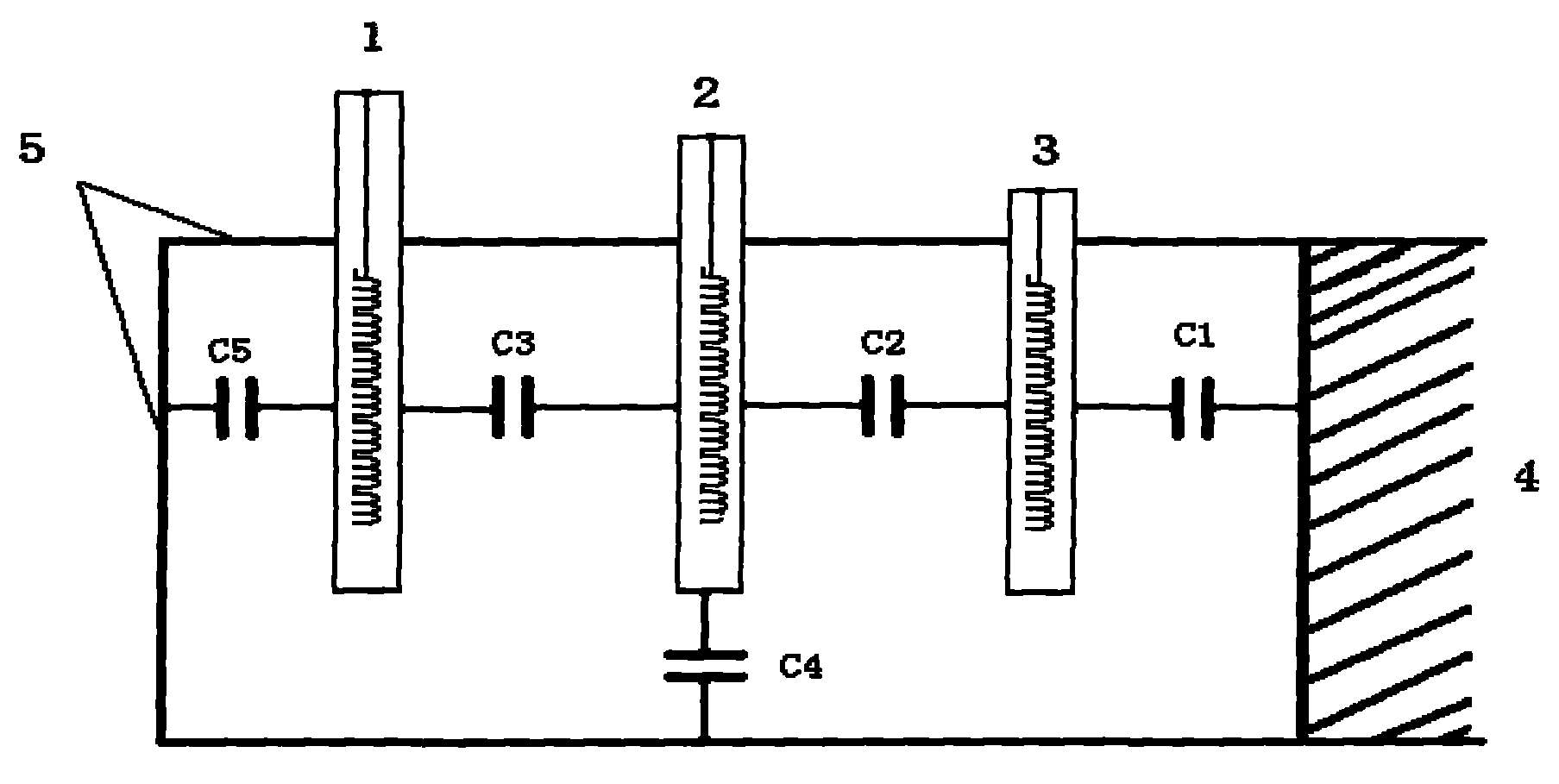

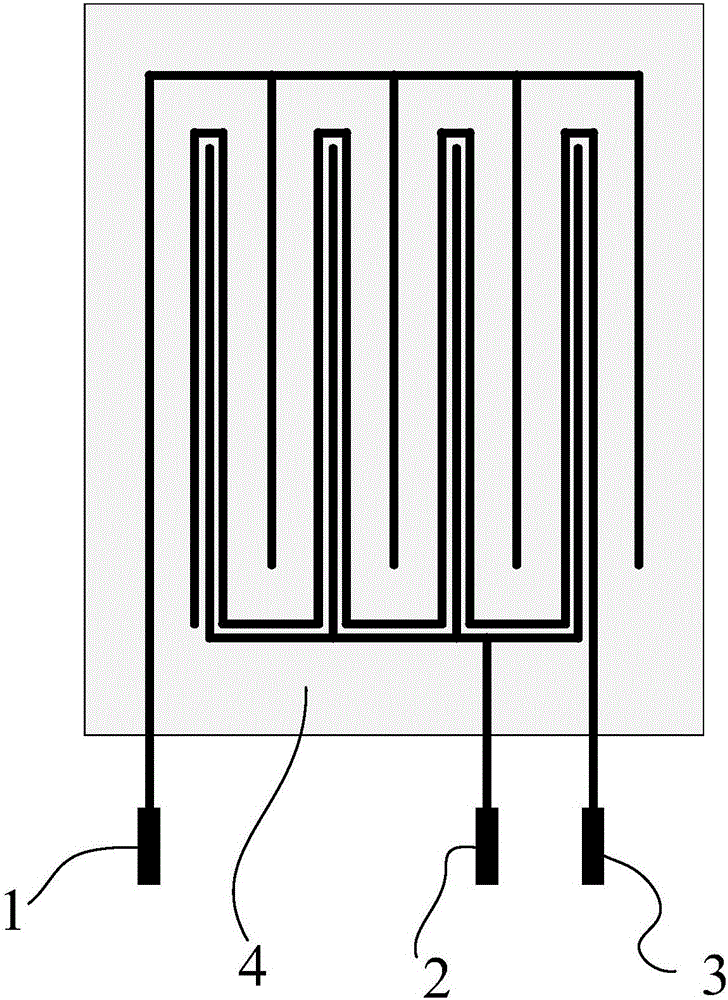

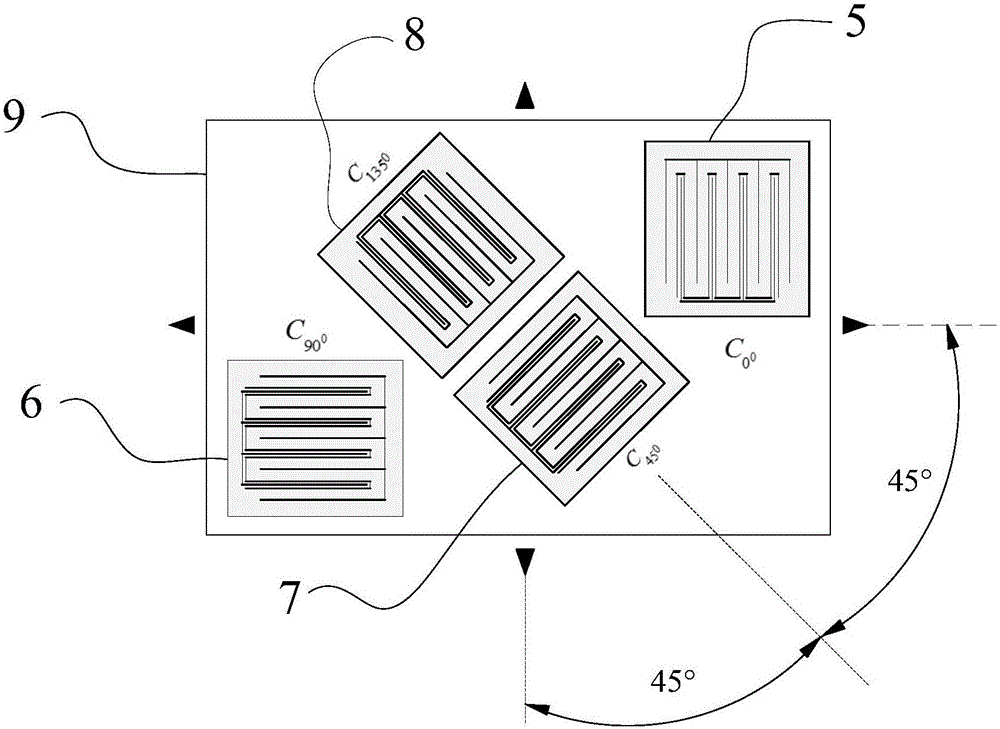

Coplanar capacitor type polymer molecular orientation measuring device and method

ActiveCN106841328AOvercoming detectionOvercome the shortcomings of ambiguous orientationMaterial capacitanceElectricityMeasurement device

The invention discloses a coplanar capacitor type polymer molecular orientation measuring device and method. The measuring device comprises a sensor probe array (10), a capacitance measuring unit (13) and an orientation calculation module (14), wherein the sensor probe array (10) comprises multiple groups of coplanar electrodes; any one group of coplanar electrodes comprises at least two conductive electrodes; the capacitance measuring unit (13) is used for measuring capacitance between any two conductive electrodes in the same coplanar electrode and acquiring multiple groups of capacitance data; and the orientation calculation module (14) is used for calculating molecular orientation of a to-be-measured polymer according to the multiple groups of capacitance data. According to the device and method disclosed by the invention, the molecular orientation of the polymer is measured through the coplanar electrode structure by utilizing anisotropism of dielectric properties of polymer materials, the orientation-dielectric-capacitance relationship is established, and the device and method are applicable to various polymers, belong to nondestructive testing and have the characteristics of high precision, fast response, non-invasive type and the like.

Owner:HUAZHONG UNIV OF SCI & TECH

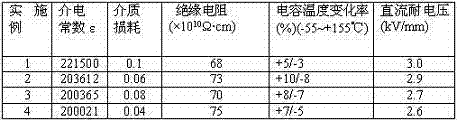

Giant dielectric ceramic capacitor medium as well as preparation method thereof

The invention relates to the technical field of inorganic nonmetal materials and particularly relates to a ceramic capacitor medium with a small giant dielectric capacitance temperature change rate as well as a preparation method thereof. A formula composition of the ceramic capacitor medium comprises the following components: 91wt%-98wt% of Ca0.925Nd0.05Cu3Ti4O12, 0.1wt%-8.0wt% of (Ba0.65Sr0.35)TiO3, 0.1wt%-4wt% of MgO and 0.01wt%-1.8wt% of Cr2O3, wherein the Ca0.925Nd0.05Cu3Ti4O12 and the (Ba0.65Sr0.35)TiO3 are respectively synthesized by adopting conventional chemical materials through a solid-phase method. According to the ceramic capacitor medium and the preparation method thereof disclosed by the invention, the ceramic capacitor medium with the small giant dielectric capacitance temperature change rate, which is lead-free and cadmium-free, is prepared by adopting common chemical materials, namely capacitor ceramic; a sintering temperature of the capacitor ceramic further can be lowered; the medium is suitable for preparing a monolithic ceramic capacitor and a single-layer ceramic chip capacitor.

Owner:JIANGSU UNIV

Reduced capacitance resistors

ActiveUS7242074B2Reduce parasitic capacitanceImprove responseSolid-state devicesSemiconductor/solid-state device manufacturingElectrical resistance and conductanceInter layer

A method for reducing the parasitic capacitance in resistors, and a resistor design embodying this method are described. By creating a p-type or an n-type implant inside of an n-well or a p-substrate, respectively, where the n-well or p-substrate is located in a p-substrate or n-substrate, respectively, a capacitively coupled capacitor is formed in series connection with the parasitic inter-layer dielectric capacitance generated when the resistor is fabricated in the dielectric material. The depletion region formed thereby behaves as a series capacitor which reduces the overall capacitance of the assemblage. The n-well or p-substrate can be placed in electrical connection with a ground potential or brought to a chosen voltage to further increase the depletion region and reduce the capacitance of the resistor.

Owner:BELL SEMICON LLC

Array of gate dielectric structures to measure gate dielectric thickness and parasitic capacitance

InactiveUS6841832B1Eliminate parasitic capacitanceAccurate measurementSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsGate dielectricParasitic capacitance

Accurate determination of gate dielectric thickness is required to produce high-reliability and high-performance ultra-thin gate dielectric semiconductor devices. Large area gate dielectric capacitors with ultra-thin gate dielectric layers suffer from high gate leakage, which prevents the accurate measurement of gate dielectric thickness. Accurate measurement of gate dielectric thickness of smaller area gate dielectric capacitors is hindered by the relatively large parasitic capacitance of the smaller area capacitors. The formation of first and second dummy structures on a wafer allow the accurate determination of gate dielectric thickness. First and second dummy structures are formed that are substantially similar to the gate dielectric capacitors except that the first dummy structures are formed without the second electrode of the capacitor and the second dummy structures are formed without the first electrode of the capacitor structure. The capacitance, and therefore thickness, of the gate dielectric capacitor is determined by subtracting the parasitic capacitances measured at the first and second dummy structures.

Owner:GLOBALFOUNDRIES INC

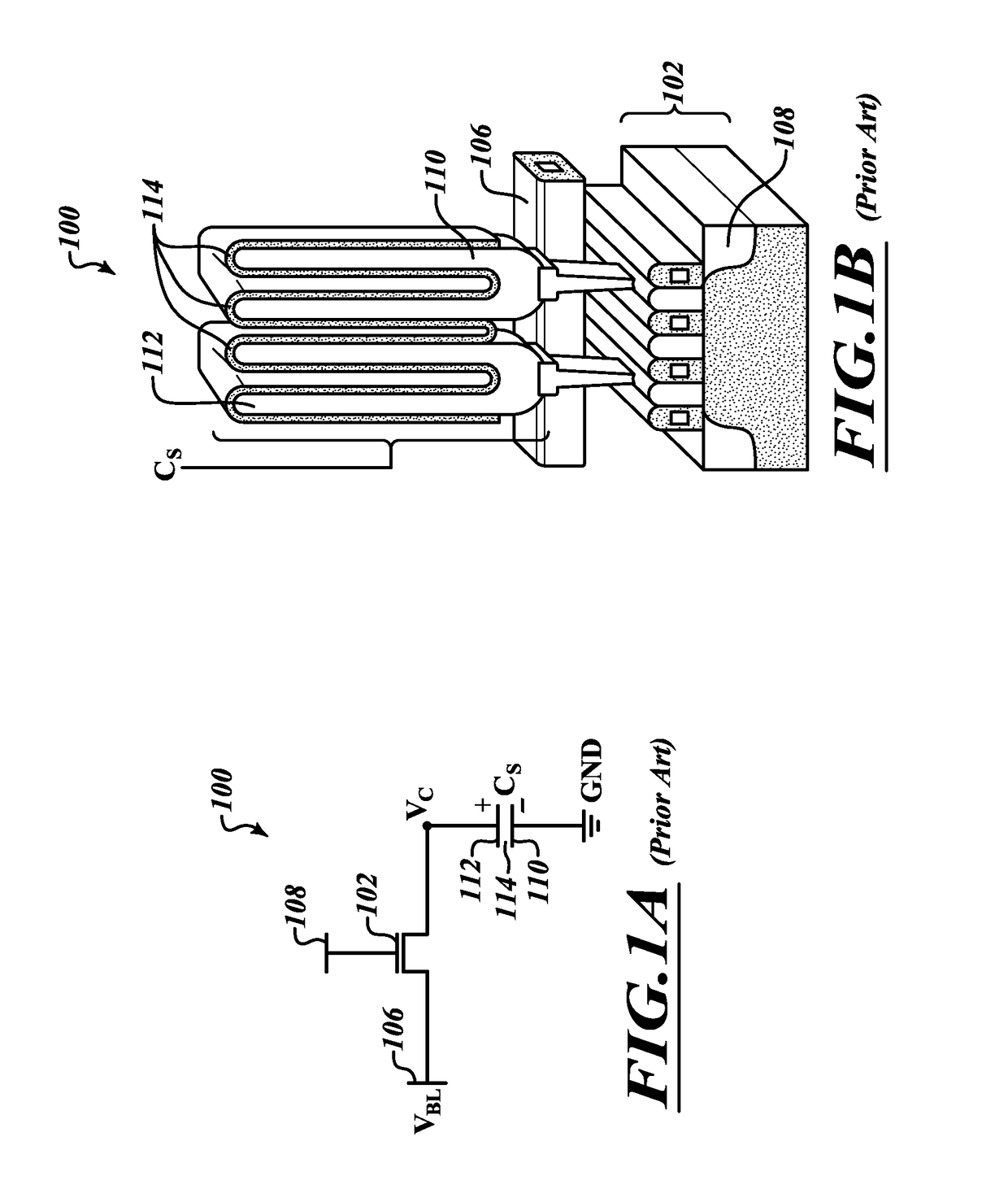

Semiconductor device and method for driving the same

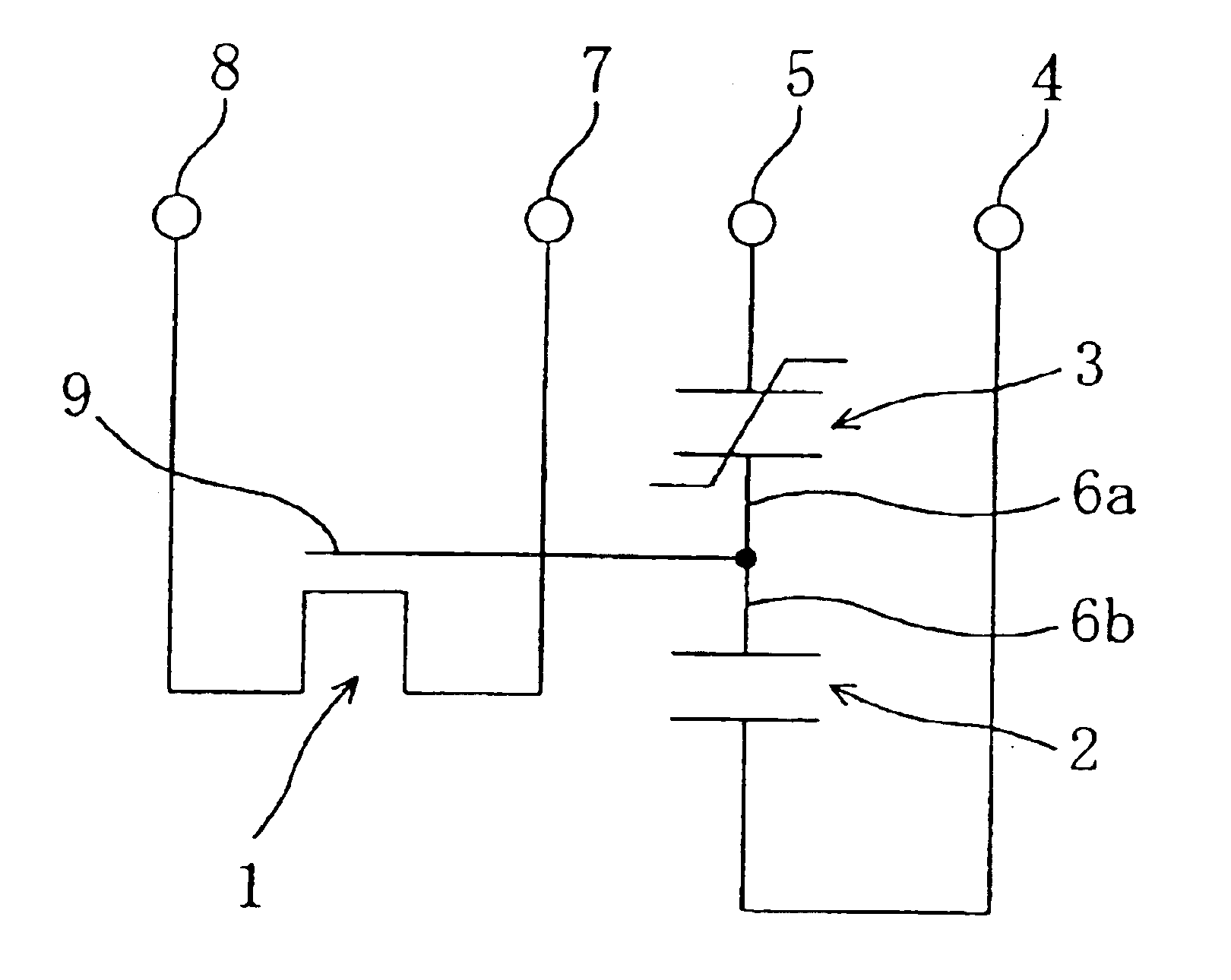

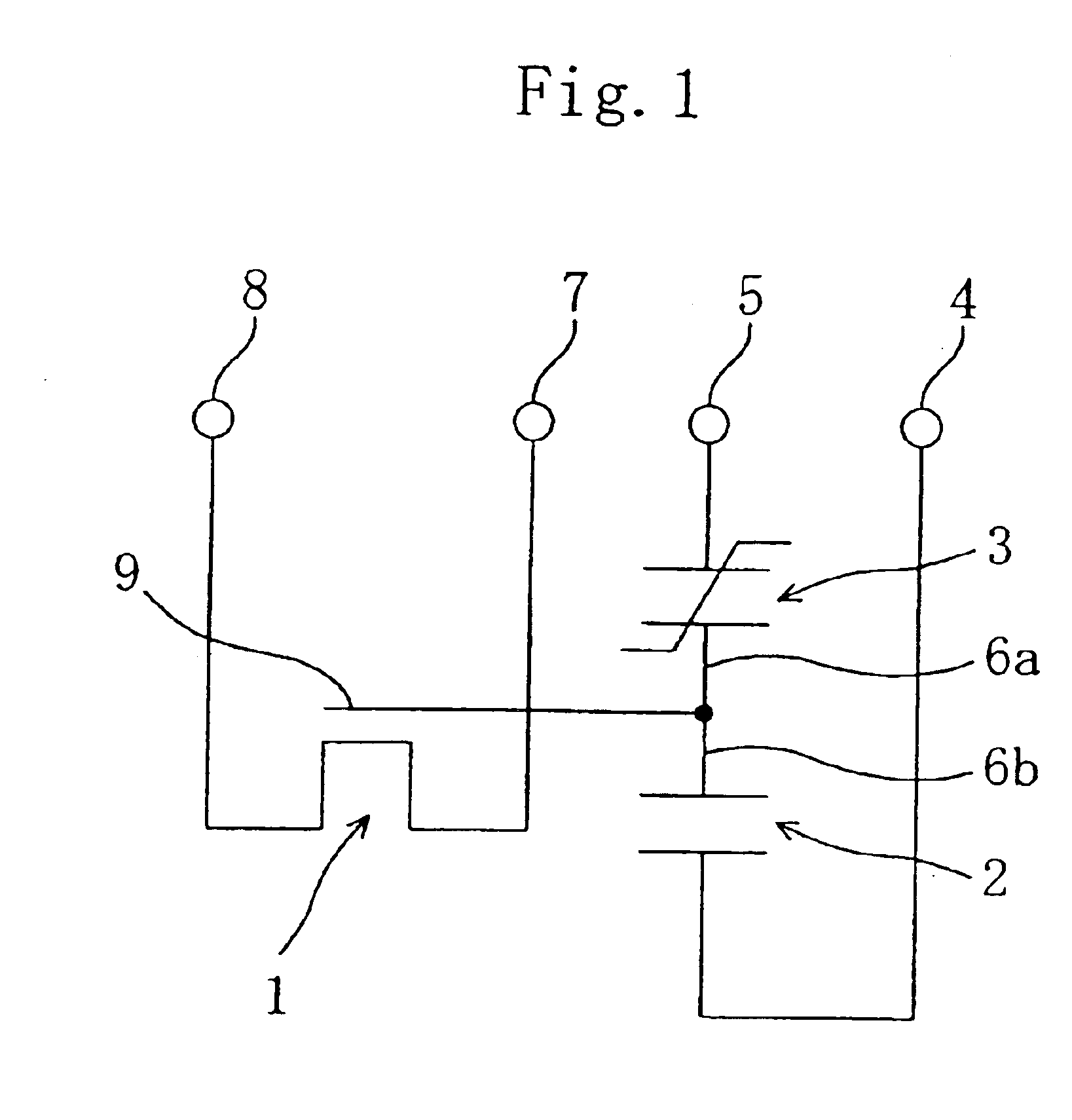

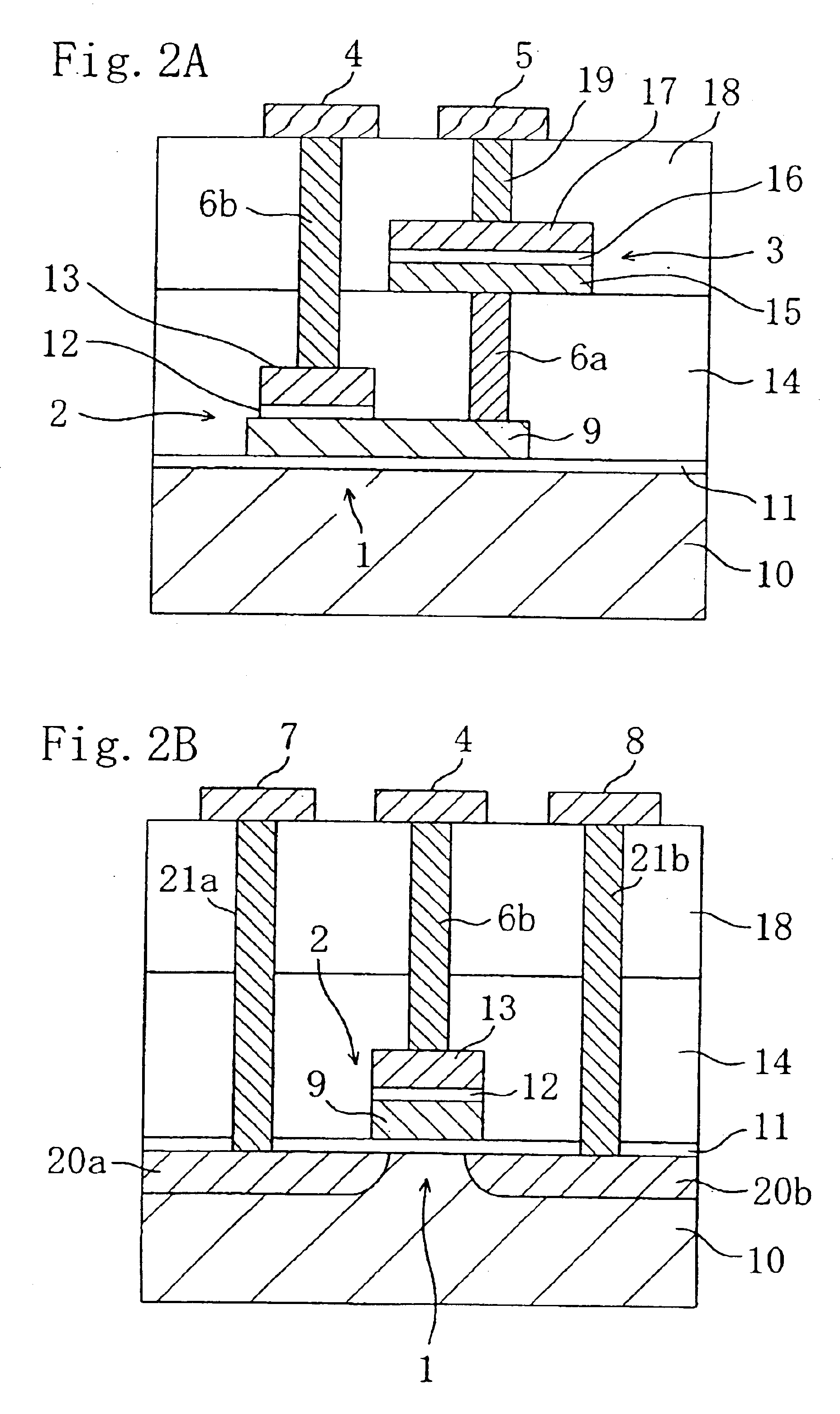

InactiveUS6859381B2Power source voltage can be loweredSimple structureTransistorSolid-state devicesEngineeringSemiconductor

A nonvolatile semiconductor storage element, which is provided with a floating gate electrode, and a dielectric capacitor and a ferroelectric capacitor both connected to the floating gate electrode. By applying voltage between a first polarization voltage supplying terminal and a second polarization voltage supplying terminal, polarization serving as information is generated in the ferroelectric film of the ferroelectric capacitor. Additionally, when a read-out voltage is applied between the ground terminal and the power source voltage terminal that are in connection with the source and drain regions, the MISFET is turned either on or off in correspondence to the state of the charge held in the floating gate electrode, and thus information within the floating gate electrode is read out.

Owner:PANASONIC CORP

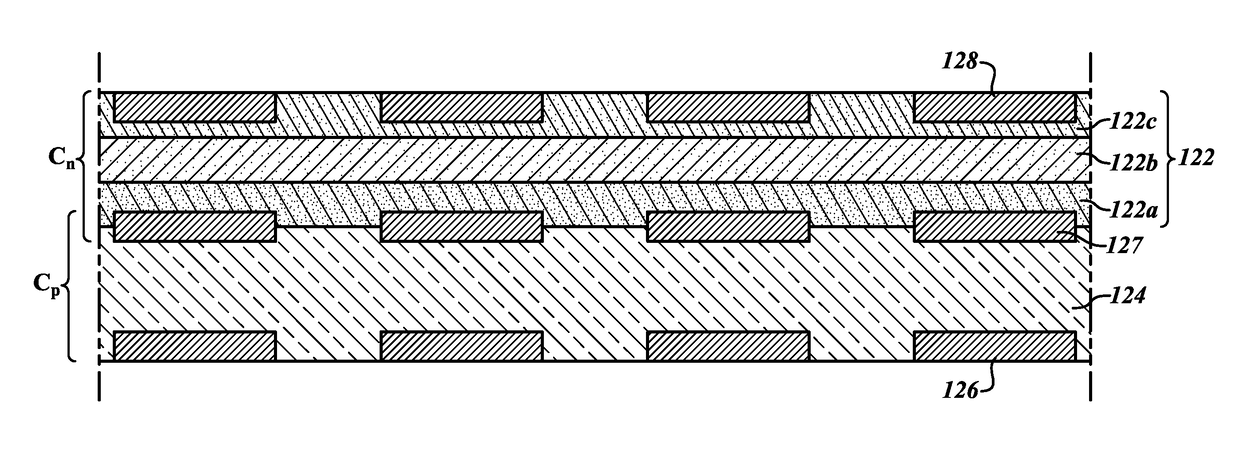

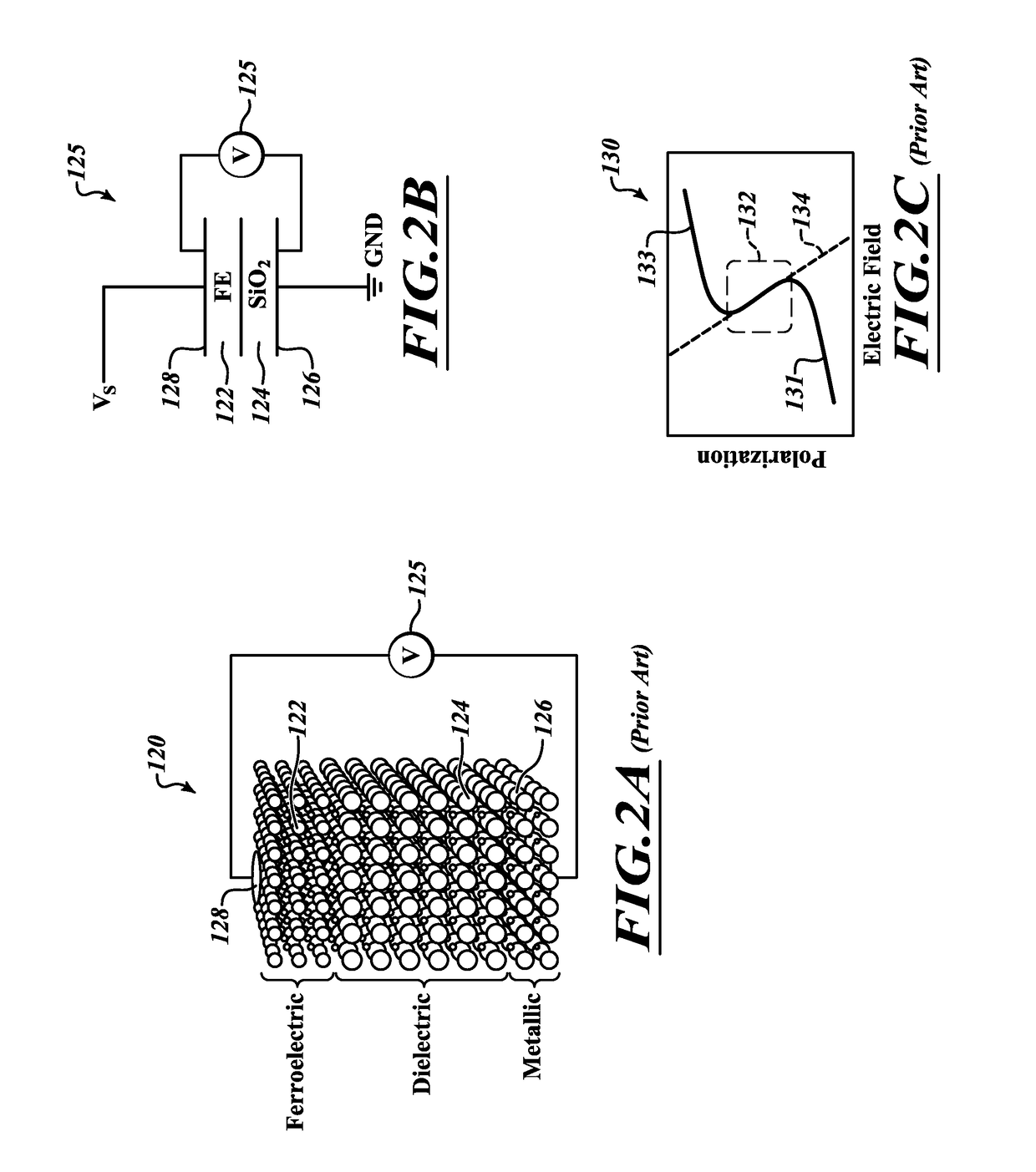

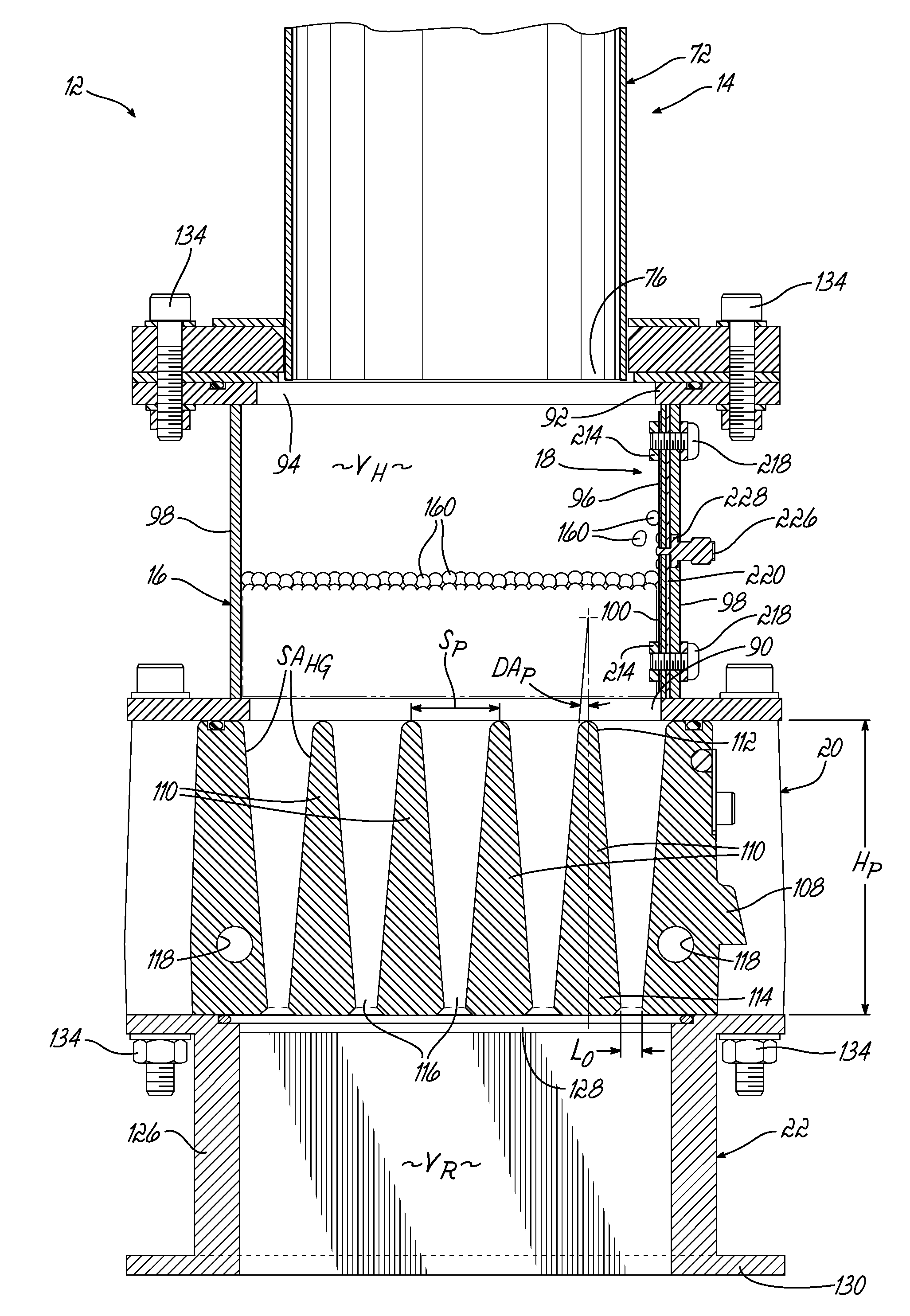

DRAM interconnect structure having ferroelectric capacitors exhibiting negative capacitance

Owner:STMICROELECTRONICS SRL

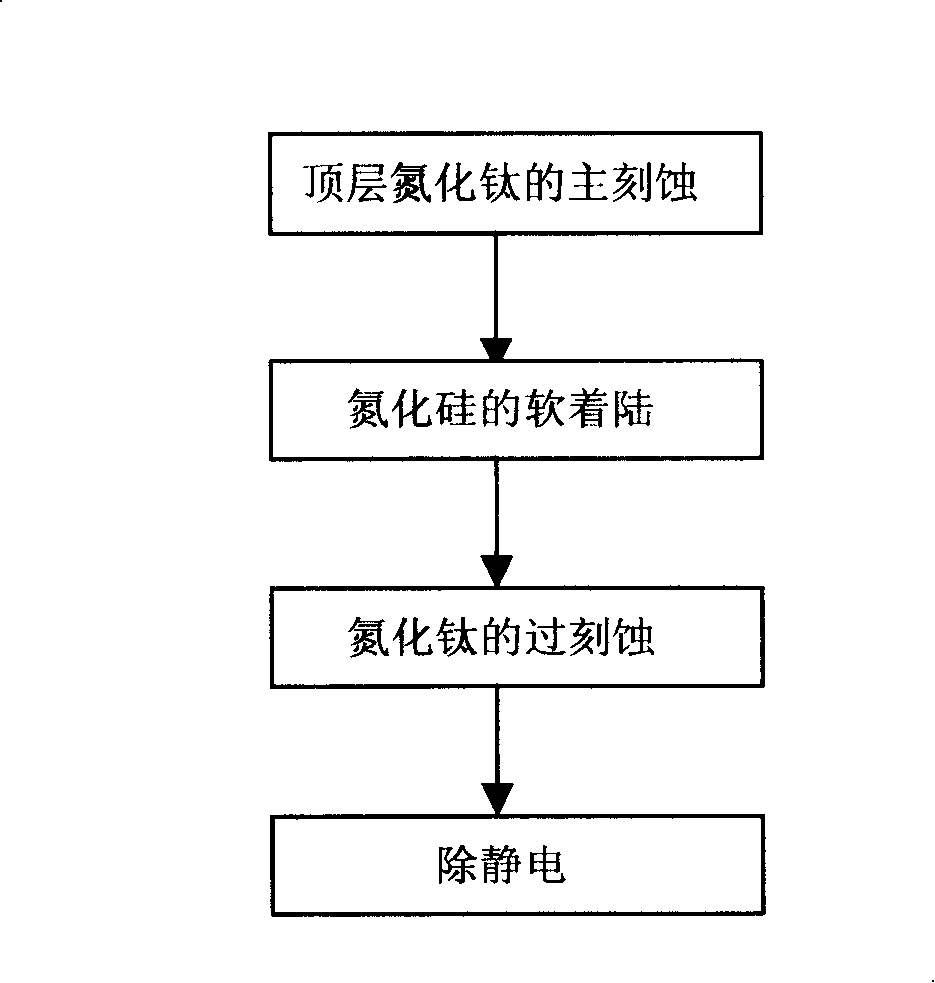

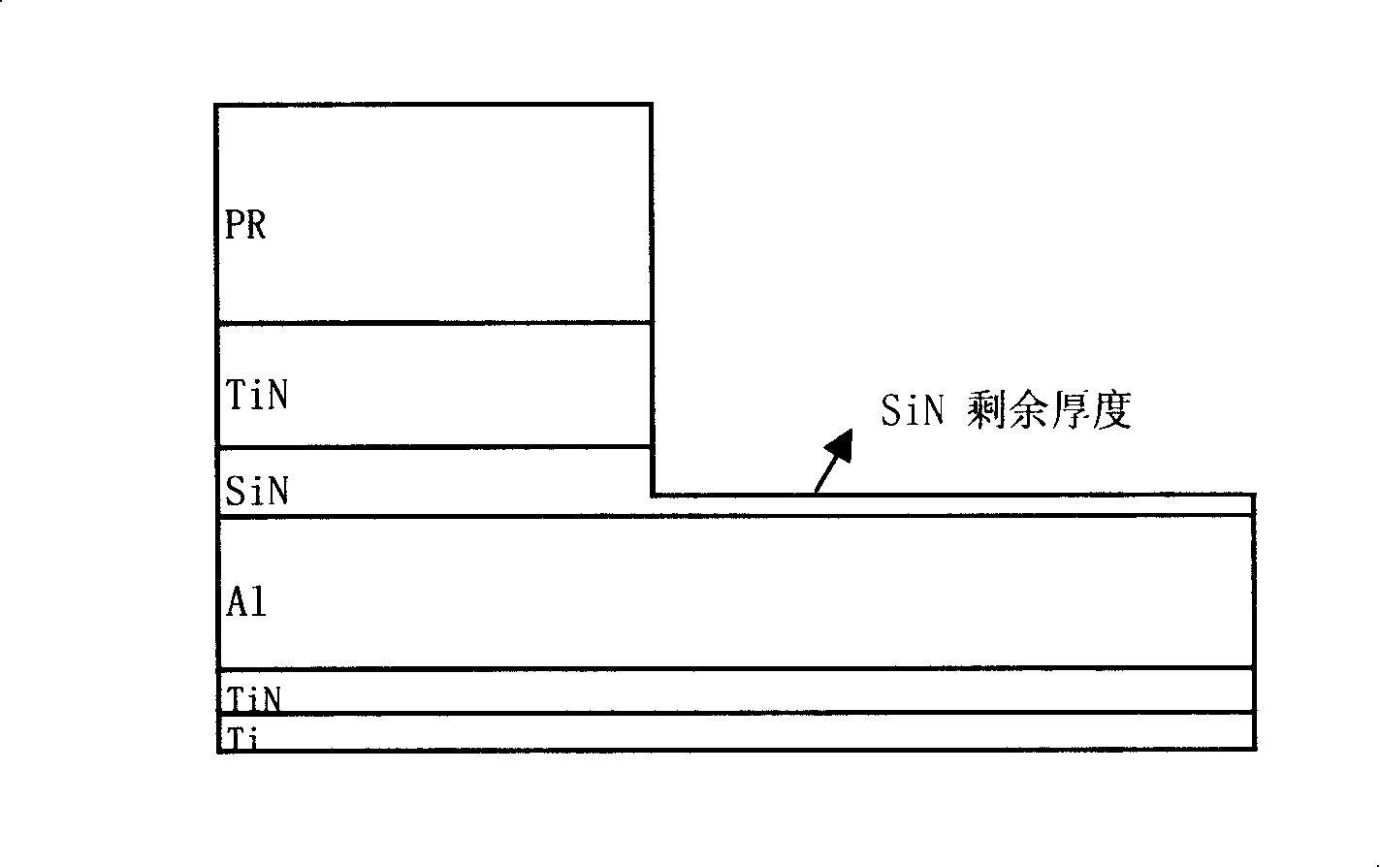

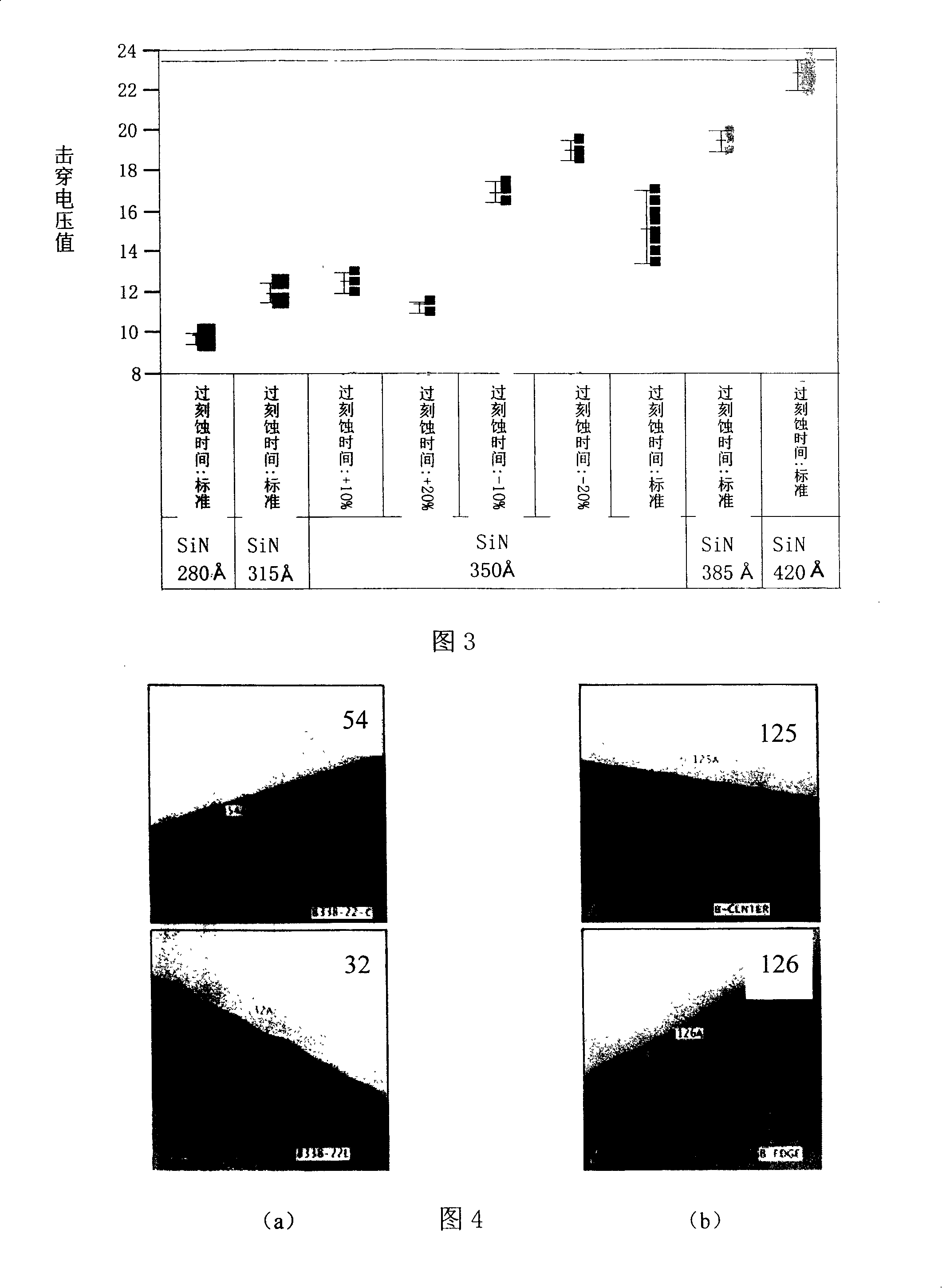

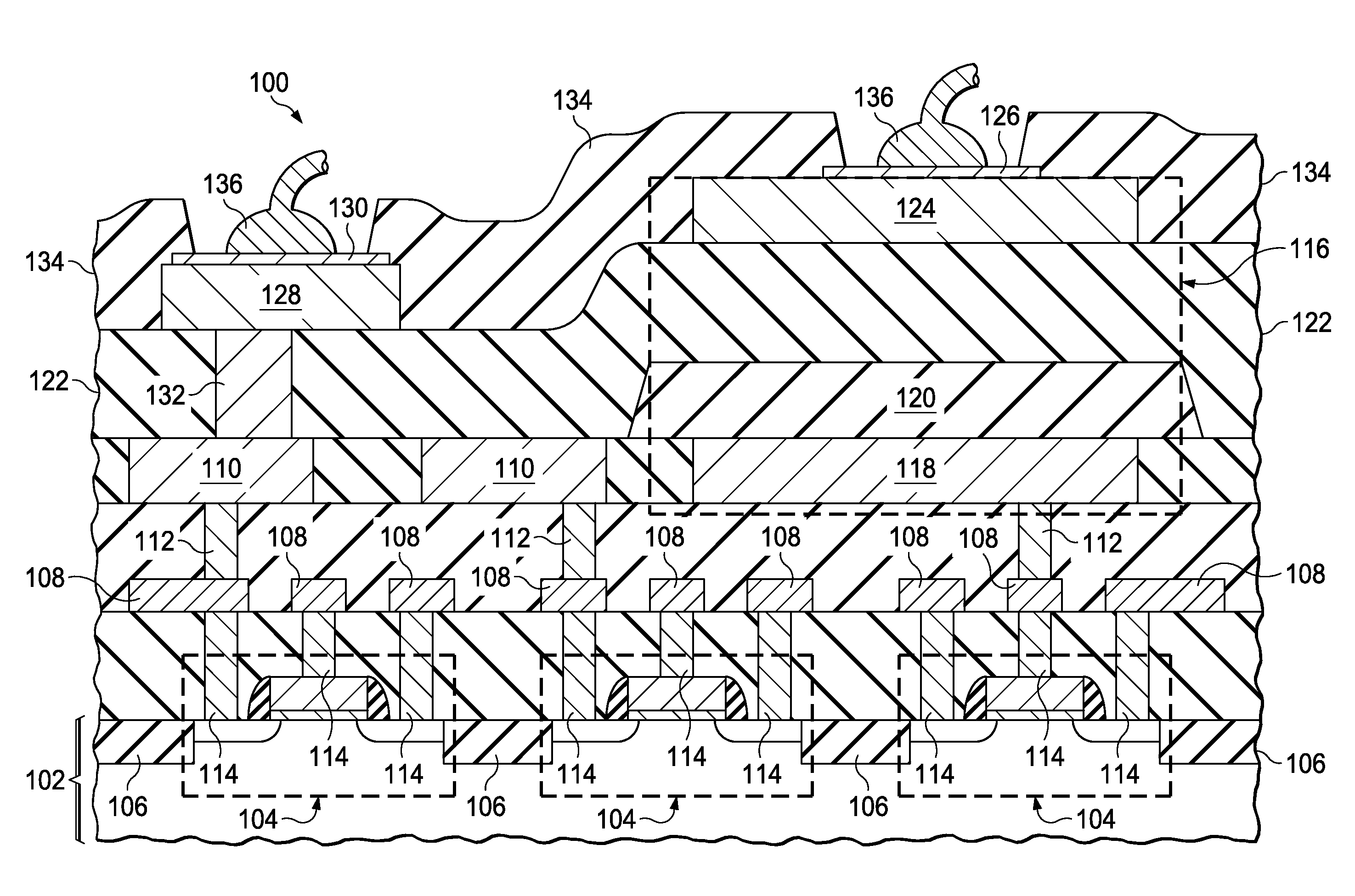

Etching method of radio frequency device thin dielectric substance capacitance

ActiveCN101202217AIncrease remaining thicknessImprove breakdown voltageSemiconductor/solid-state device manufacturingEtchingLow voltage

The invention discloses an etching method used for the thin dielectric capacitance of a radio frequency component. The method includes the following steps: firstly, the main etching of a top-layer titanium nitride is carried out and the etching time is controlled to prevent the etching from contacting a silicon nitride layer; secondly, the soft landing of the silicon nitride is carried out and once the etching end point is reached an instant switching to the next step is done; thirdly, the over etching of the titanium nitride is carried out. The invention can overcome the problem that an excessive etching of the dielectric can result in capacitance breakdown and low voltage.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

High voltage hybrid polymeric-ceramic dielectric capacitor

ActiveUS20150044848A1Fixed capacitor dielectricSemiconductor/solid-state device detailsEngineeringHigh pressure

An integrated circuit includes isolation capacitors which include a silicon dioxide dielectric layer and a polymer dielectric layer over the layer of silicon dioxide. The silicon dioxide dielectric layer and the polymer dielectric layer extend across the integrated circuit. Top plates of the isolation capacitors have bond pads for wire bonds or bump bonds. Bottom plates of the isolation capacitors are connected to components of the integrated circuit. Other bond pads are connected to components in the integrated circuit through vias through the silicon dioxide dielectric layer and the polymer dielectric layer.

Owner:TEXAS INSTR INC

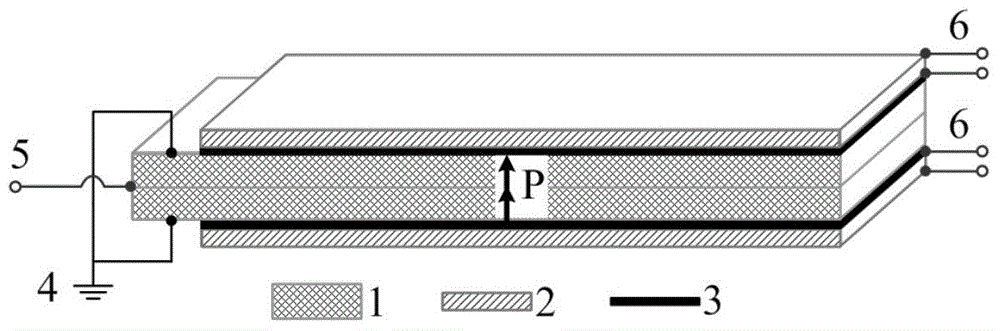

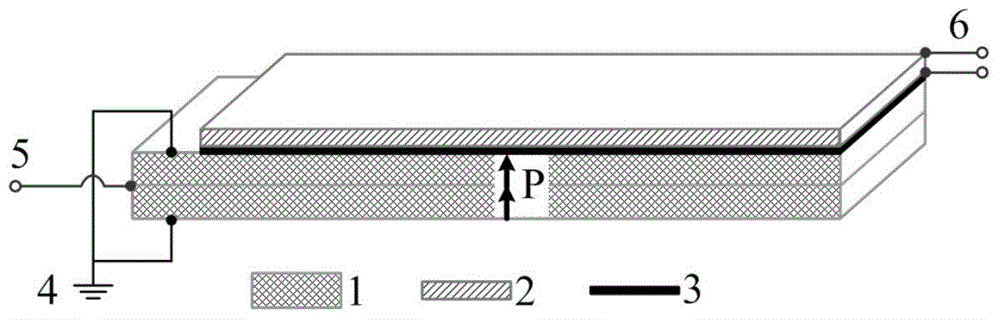

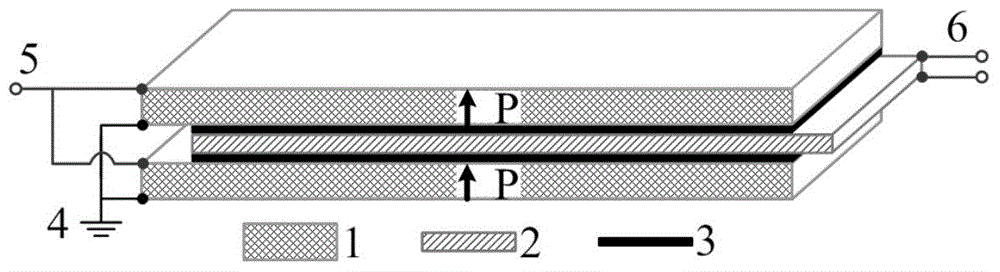

Adjustable and controllable capacitor with layered composite structure, and method of adjusting and controlling dielectric through piezoelectric stress

ActiveCN104882277ARealize regulationOvercoming structural complexityCapacitor with voltage varied dielectricElectricityIntelligent electronic device

The invention discloses an adjustable and controllable capacitor with a layered composite structure, and a method of adjusting and controlling the capacitance of dielectric bodies in a composite structure by applying an electrostatic field and using piezoelectric stress generated through a piezoelectric effect. The adjustable and controllable capacitor comprises ferroelectric piezoelectric patches and ferroelectric dielectric bodies. The ferroelectric piezoelectric patches and the ferroelectric dielectric bodies form multiple layered composite structures by closely bonding or cofiring together. The dielectric bodies are sheet-shaped dielectric bodies to be adjusted and controlled. Under the effect of the electrostatic field, piezoelectric stress or strain generated by the piezoelectric patches is transmitted to the sheet-shaped dielectric bodies to be adjusted and controlled, and the electric interface state of the ferroelectric dielectric bodies is changed under the effect of the outer stress, so the dielectric capacitance can be adjusted and controlled. The capacitor helps to effectively overcome the defects that a conventional adjustable and controllable capacitor is complicated in structure, narrow in adjustable frequency range or the like, has the advantages of being simple in manufacture process, convenient to use and the like, and can be widely applied to the field of adjustable and controllable intelligent electronic devices and equipment.

Owner:PEKING UNIV

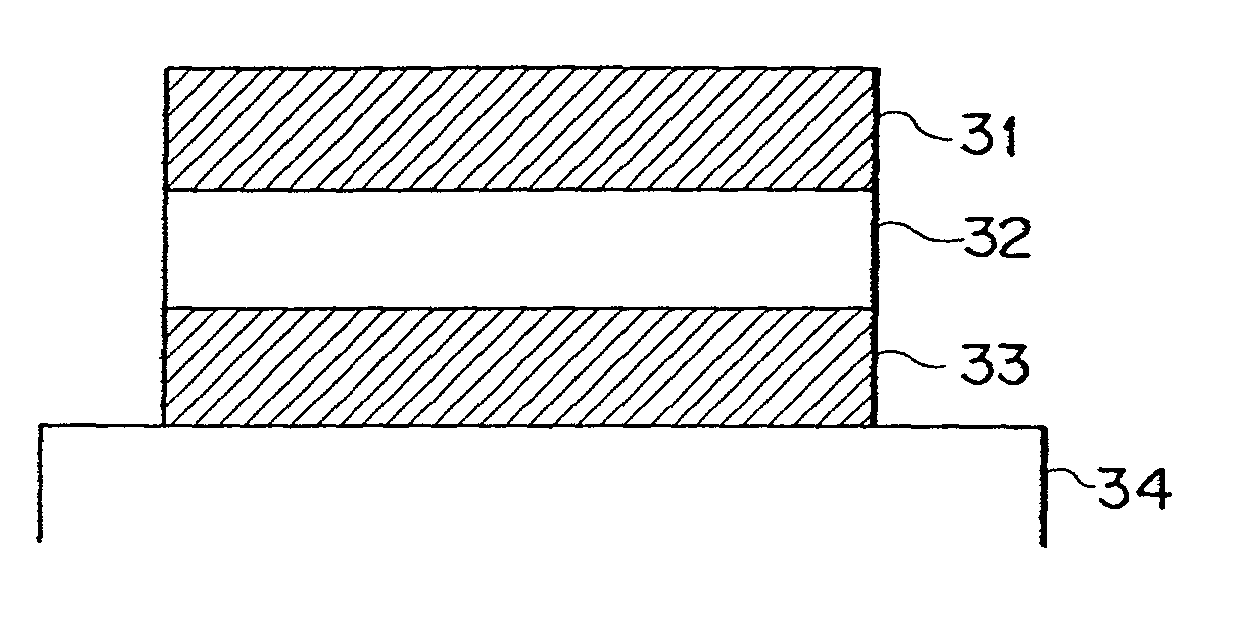

Dielectric capacitor and production process and semiconductor device

InactiveUS20030030967A1Inhibitory responseSolve the lack of functionFixed capacitor dielectricSemiconductor/solid-state device manufacturingSolid reactionSemiconductor

A ferroelectric material readily forms a liquid phase with an alkali metal such as Li, Na, or K (an capacitor of Group Ia) added thereto. The liquid phase reaction takes place at a bottom temperature than the solid-solid reaction. The ferroelectric material crystallizes through the liquid phase reaction. Thus it is possible to crystallize the ferroelectric material without reaction between it and its adjacent electrodes by annealing temperature at 350-500° C. which is bottom than before. Also, a ferroelectric material can be crystallized at a bottom temperature if it is added to Mg or Ca as an alkaline earth capacitor. As in the case of said ferroelectric, a high-dielectric can be crystallized at a bottom temperature (150-450° C.) if it is added to Li, Na, K, Mg, or Ca. The above-mentioned ferroelectric or high-dielectric is formed into a thin film between an top and bottom electrodes so as to produce a ferroelectric capacitor or high-dielectric capacitor.

Owner:NABATAME TOSHIHIDE +3

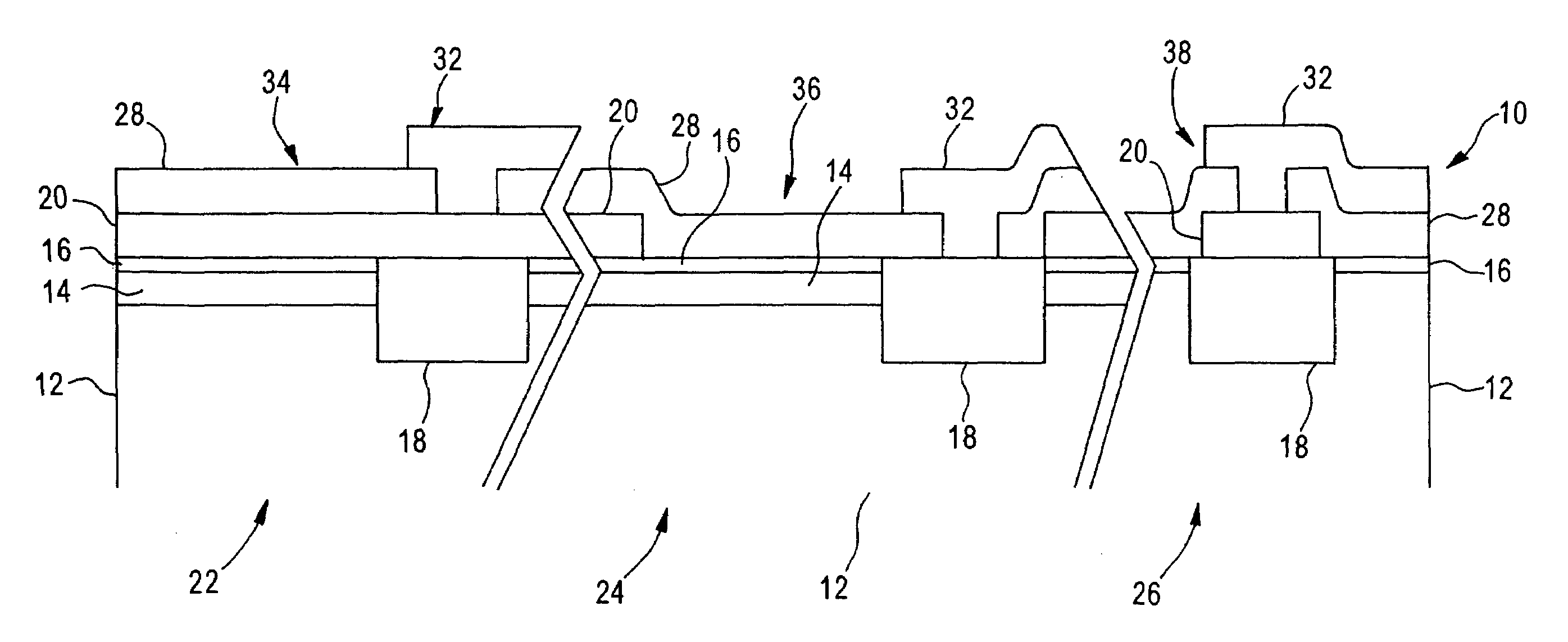

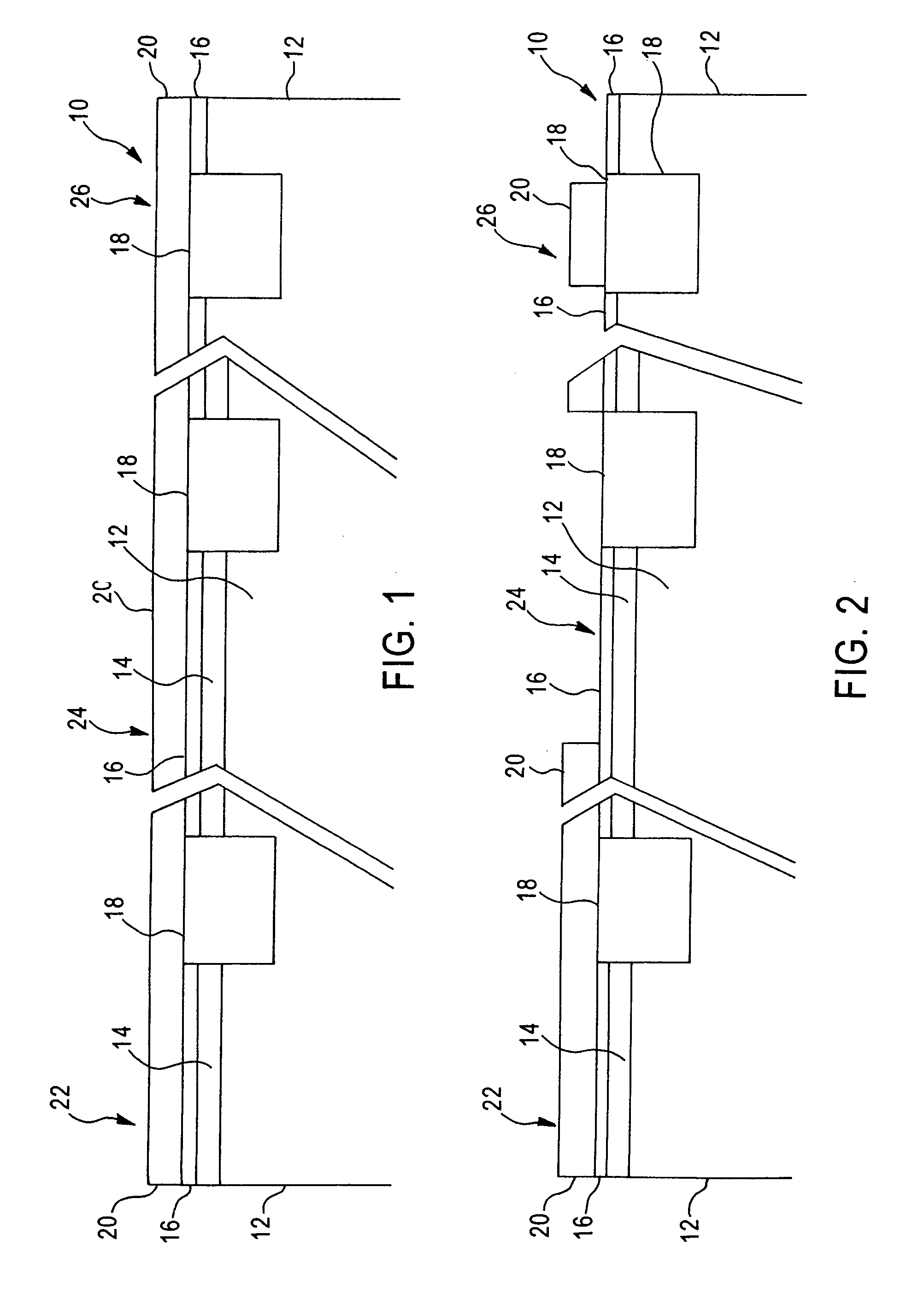

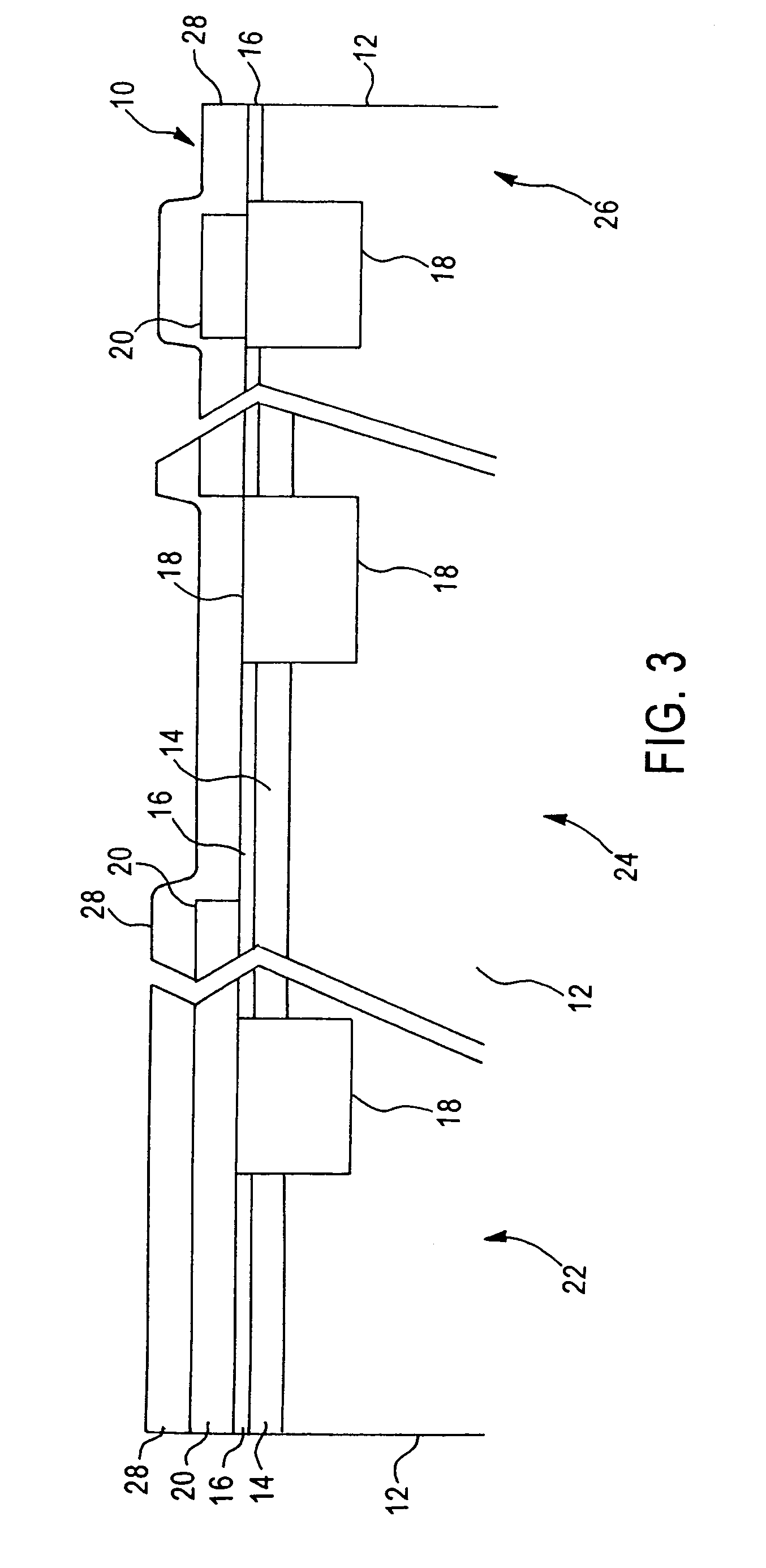

Adhesive dispensing device having optimized reservoir and capacitive level sensor

An adhesive dispensing device includes a heater unit for melting adhesive, a fill system communicating with a receiving space for feeding the heater unit, and a reservoir for receiving melted adhesive from the heater unit. The dispensing device also includes a capacitive level sensor located along a sidewall of the receiving space such that the level of adhesive in the receiving space can be detected by sensing the difference in dielectric capacitance where the adhesive is located compared to where air acts as the dielectric. The size of the driven electrode produces a broader sensing window capable of generating multiple control signals corresponding to different fill levels of adhesive. The receiving space and reservoir are minimized in size so that adhesive is not held at elevated temperatures long enough to char or degrade.

Owner:NORDSON CORP

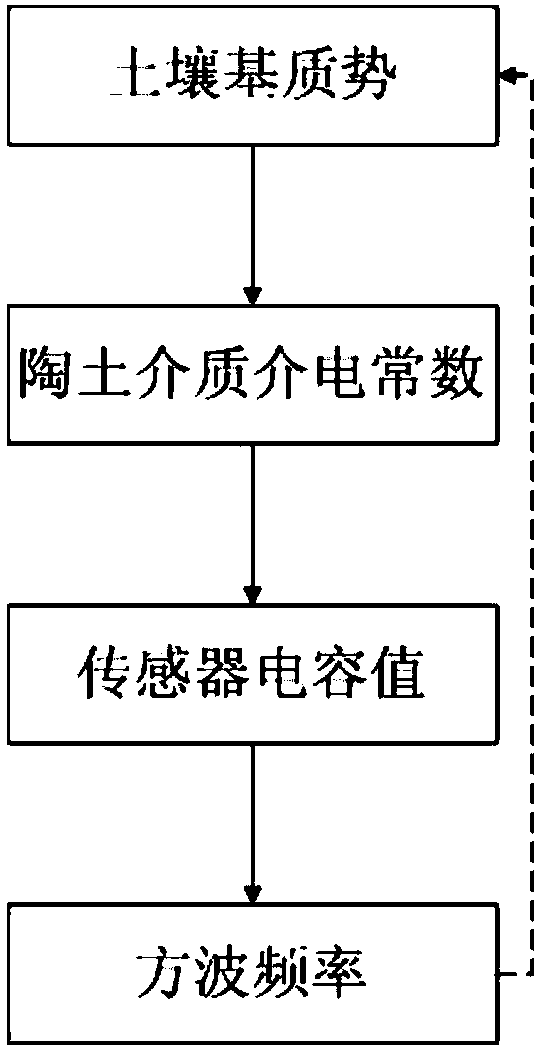

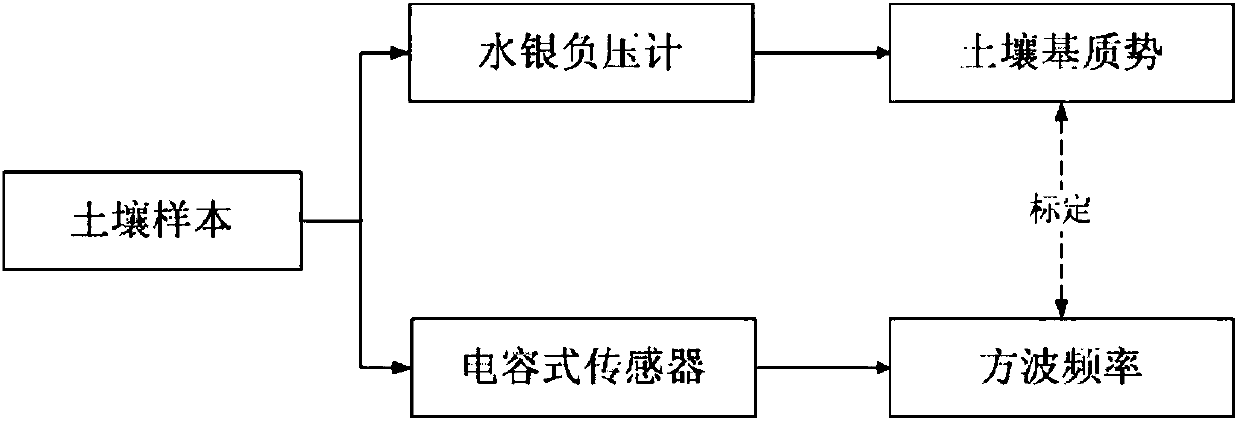

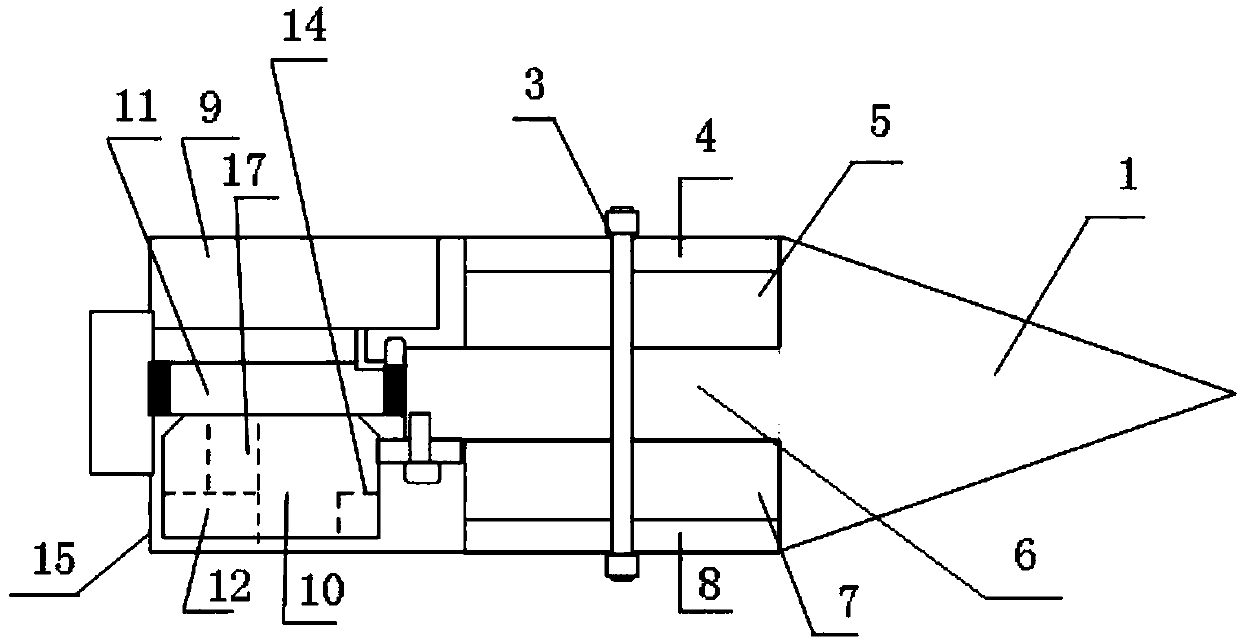

Pottery clay dielectric capacitance type soil matrix potential measurement method

InactiveCN107064243ANo hysteresisGuaranteed accuracyMaterial capacitancePotential measurementSquare waveform

The invention discloses a pottery clay dielectric capacitance type soil matrix potential measurement method and belongs to the technical field of soil matrix potential measurement. The pottery clay dielectric capacitance type soil matrix potential measurement method is characterized by comprising the following steps: converting the variation quantity of soil matrix potential into the variation quantity of measurable capacitance by taking a water-permeable and air-impermeable novel pottery clay material as a capacitance type sensor; converting the variation of the capacitance into the variation of square wave frequency based on a principle of a frequency oscillator; carrying out high-precision measurement on the frequency by applying a direct frequency measurement method; carrying out data fitting to finish the measurement of the soil matrix potential. Compared with the prior art, the sensor based on a capacitance principle has the advantages of high precision, strong anti-interference capability, low learning and utilization cost and the like and is suitable for most soil measurement conditions. The sensor can be used for a long period after being mounted for one time and distributed measurement can be realized; data is processed to obtain space distribution of the soil matrix potential. The method disclosed by the invention provides a novel thought for hydrological researches in China and has very high scientific value.

Owner:WUHAN UNIV

Film as a dielectric in capacitors and process for its production

InactiveUS7079372B2Fixed capacitor electrodesFixed capacitor dielectricVitrificationGlass transition

Owner:BAYER AG

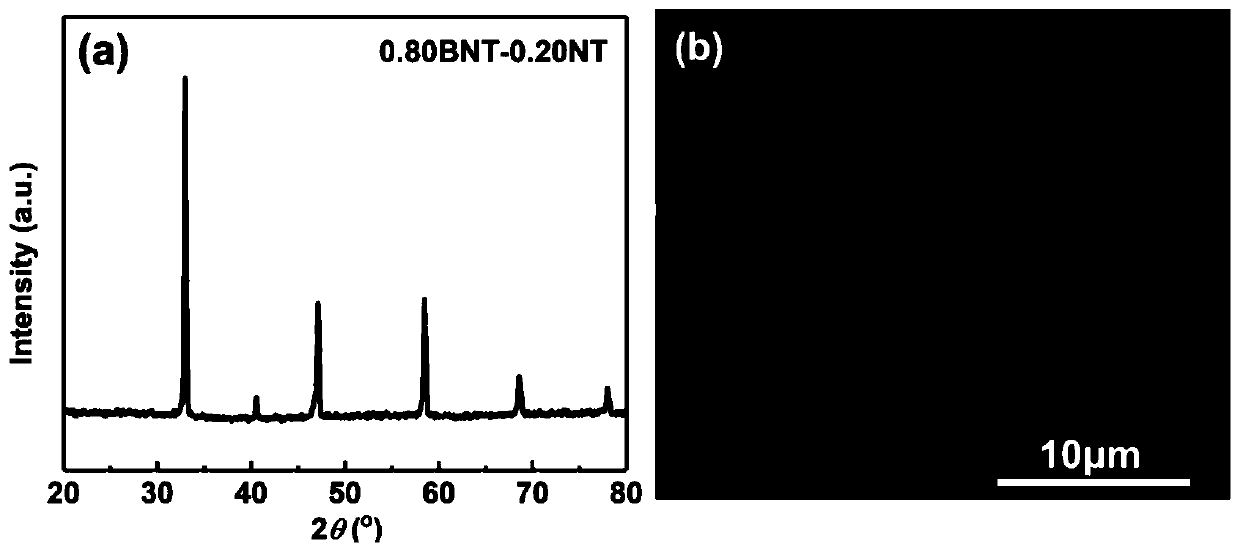

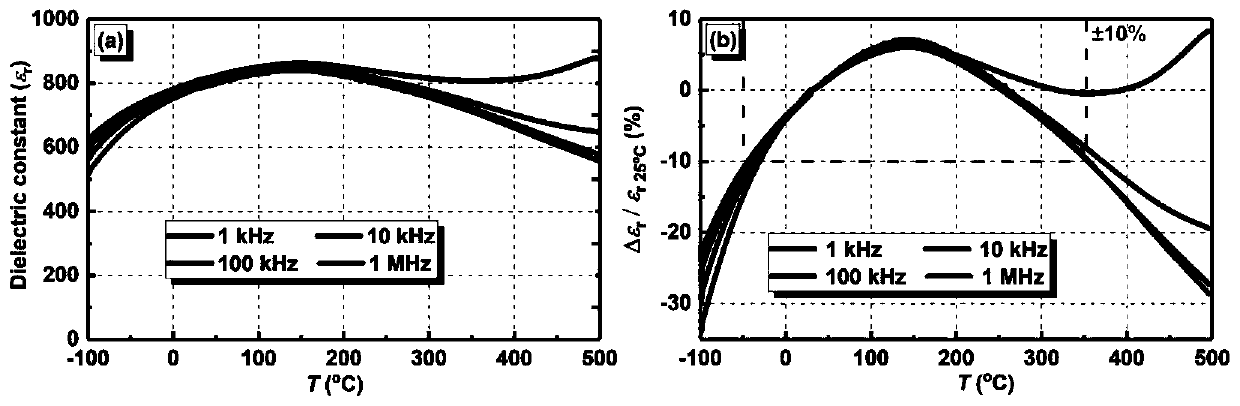

Sodium bismuth titanate-sodium tantanate solid solution ceramic material and preparation method and application thereof

ActiveCN110436920AHigh energy storage densityImprove energy storage efficiencyFixed capacitor dielectricElectricityEnergy storage efficiency

The invention discloses a sodium bismuth titanate-sodium tantanate solid solution ceramic material having wide-temperature stability, and with a general chemical formula of (1-x)Bi<0.5>Na<0.5>TiO<3-x>NaTaO3, with the x being 0.10-0.30. The invention also discloses preparation of the ceramic material and use of the ceramic material in dielectric capacitors. Research found that: under an applied electric field of 38 kV / mm, the ceramic material can achieve a discharge energy density of up to 4.21 J / cm<3>, a storage density of up to 5.41 J / cm<3>, and an energy storage efficiency of up to 77.8%; the ceramic material has excellent temperature stability in dielectric and energy storage performance, namely the dielectric constant fluctuates within a range of less than 10% in the temperature rangeof -50 DEG C to 350 DEG C and the discharge energy density fluctuates within a range of less than 10% in the temperature range of -50 DEG C to 300 DEG. The ceramic material is particularly suitable for high electric fields and high-low temperature dielectric energy storage capacitors.

Owner:CENT SOUTH UNIV

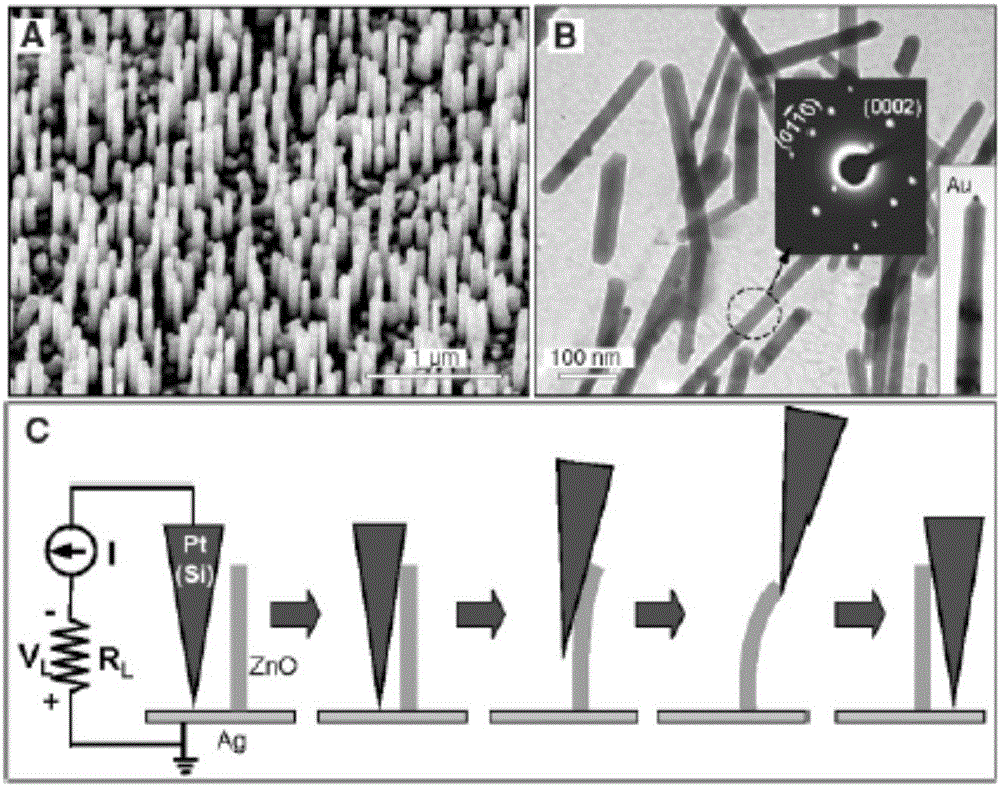

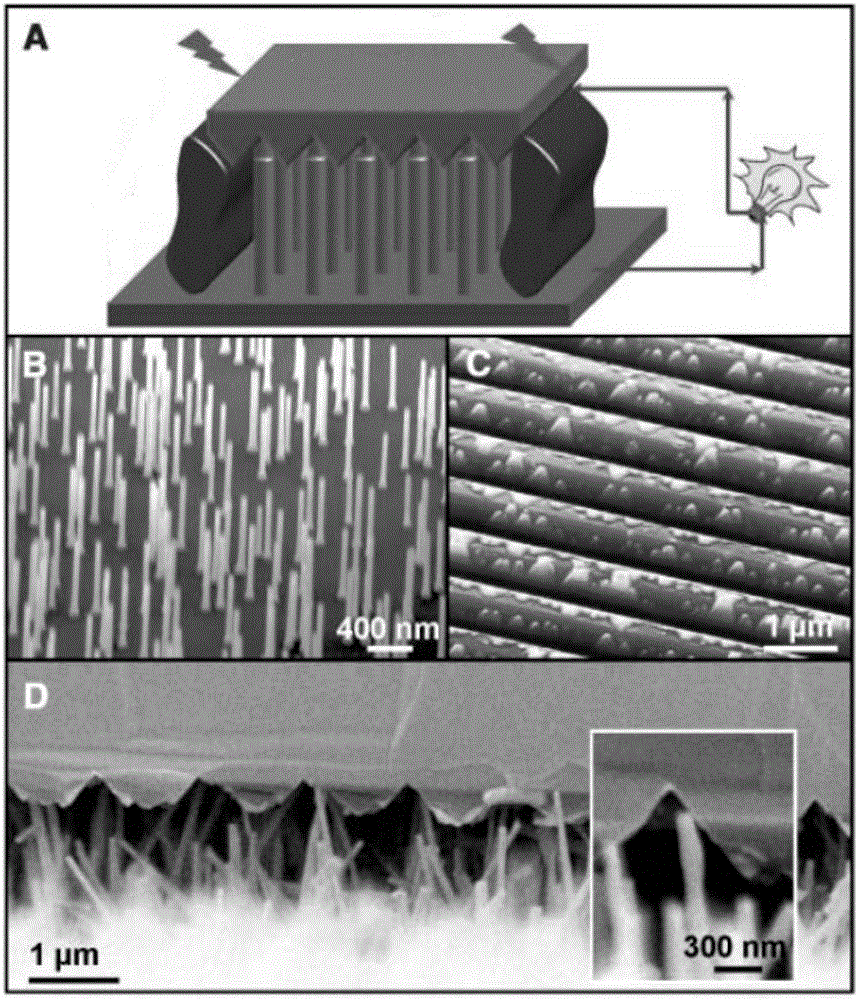

Nanometer piezoelectric micro-energy system

ActiveCN105870318AImprove power generation efficiencyImprove efficiencyPiezoelectric/electrostrictive/magnetostrictive devicesNanogeneratorHigh energy

The invention discloses a nanometer piezoelectric micro-energy system. The nanometer piezoelectric micro-energy system comprises an upper substrate, an upper electrode, a dielectric layer, a lower electrode, a piezoelectric nanometer material and a lower substrate in sequence from top to bottom. The upper substrate, the upper electrode, the dielectric layer and the lower electrode form a dielectric capacitor. The piezoelectric nanometer material is located between the lower substrate and the dielectric capacitor. External force (generated from collected dissipated mechanical energy) is transmitted to the piezoelectric nanometer material and makes the material deform, and then electric energy is generated under the direct piezoelectric effect. The nanometer piezoelectric micro-energy system can reduce leak current, improve the efficiency of a nanometer generator and store the electric energy generated by the nanometer generator, and when needed, the electric energy is continuously and stably output outwards to electric appliances or external storage equipment with higher energy density. Through novel structure design, the nanometer piezoelectric micro-energy system integrates efficient power generation, conversion, storage and output.

Owner:CHONGQING INST OF GREEN & INTELLIGENT TECH CHINESE ACADEMY OF SCI