Patents

Literature

37results about How to "Fabrication cost is increased" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

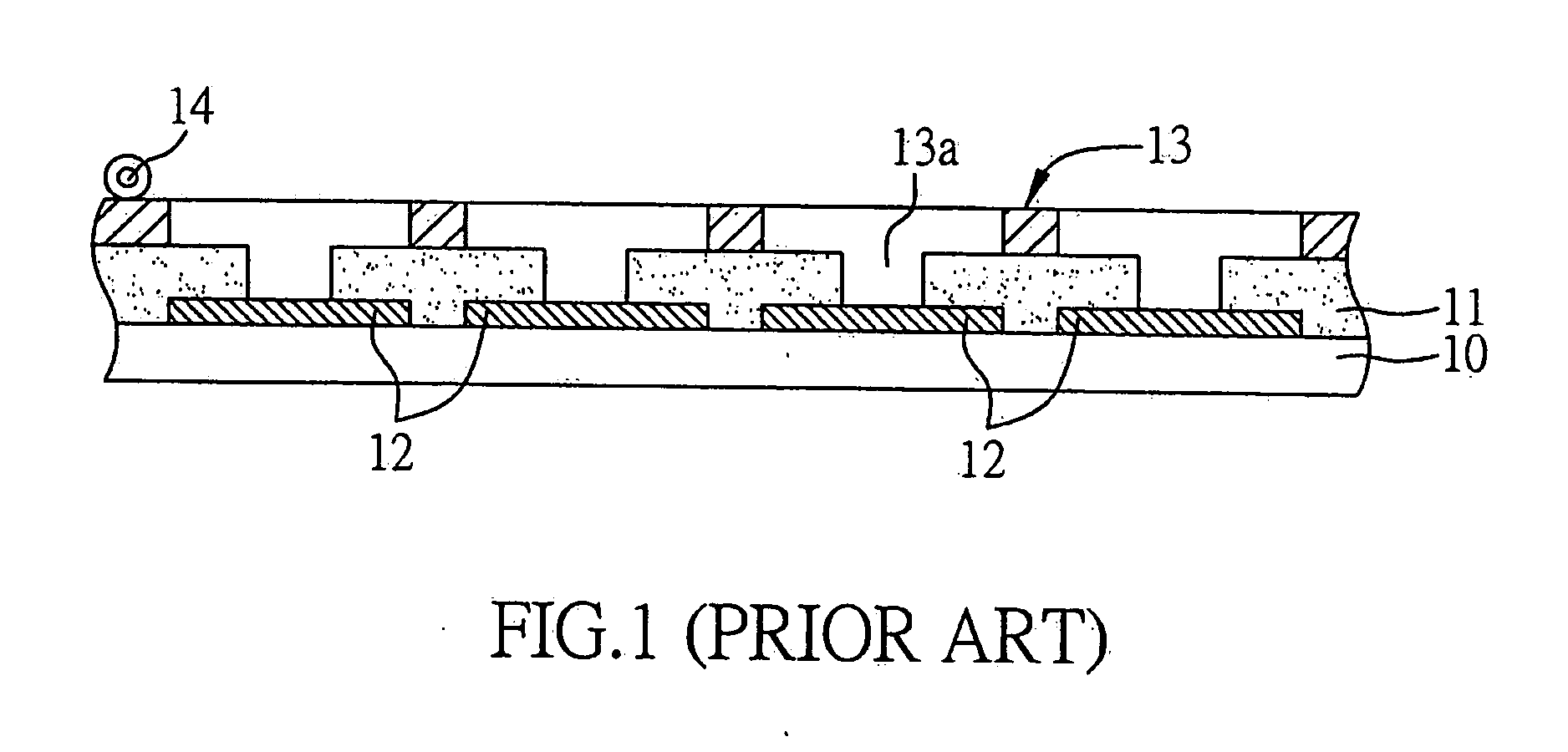

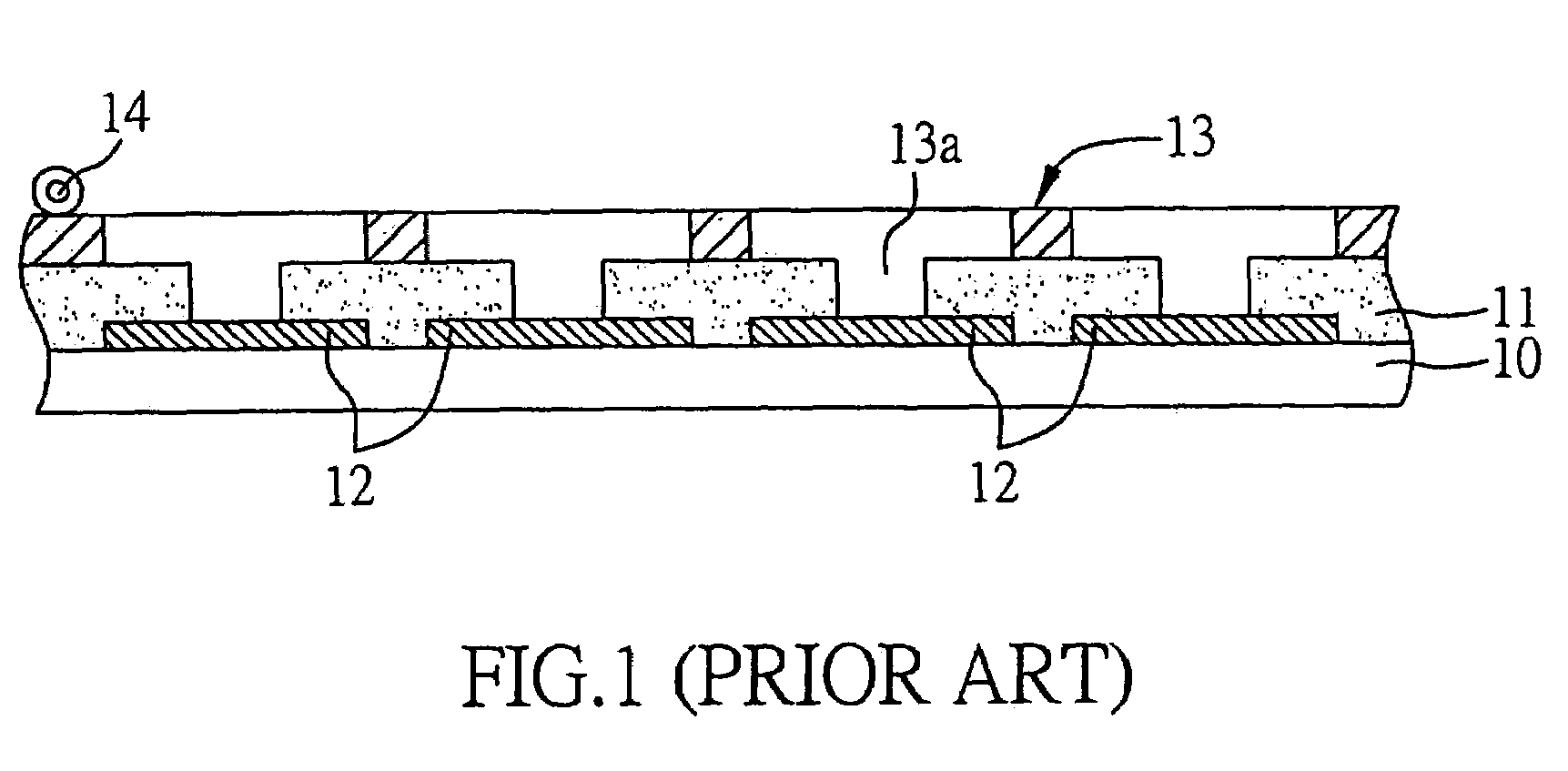

Pre-solder structure on semiconductor package substrate and method for fabricating the same

InactiveUS20050167830A1Pad pitchFabrication cost is increasedPrinted circuit assemblingSemiconductor/solid-state device detailsResistSemiconductor package

A pre-solder structure on a semiconductor package substrate and a method for fabricating the same are proposed. A plurality of conductive pads are formed on the substrate, and a protective layer having a plurality of openings for exposing the conductive pads is formed over the substrate. A conductive seed layer is deposited over the protective layer and openings. A patterned resist layer is formed on the seed layer and has openings corresponding in position to the conductive pads. A plurality of conductive pillars and a solder material are deposited in sequence in each of the openings. The resist layer and the seed layer not covered by the conductive pillars and the solder material are removed. The solder material is subject to a reflow-soldering process to form pre-solder bumps covering the conductive pillars.

Owner:PHOENIX PRECISION TECH CORP

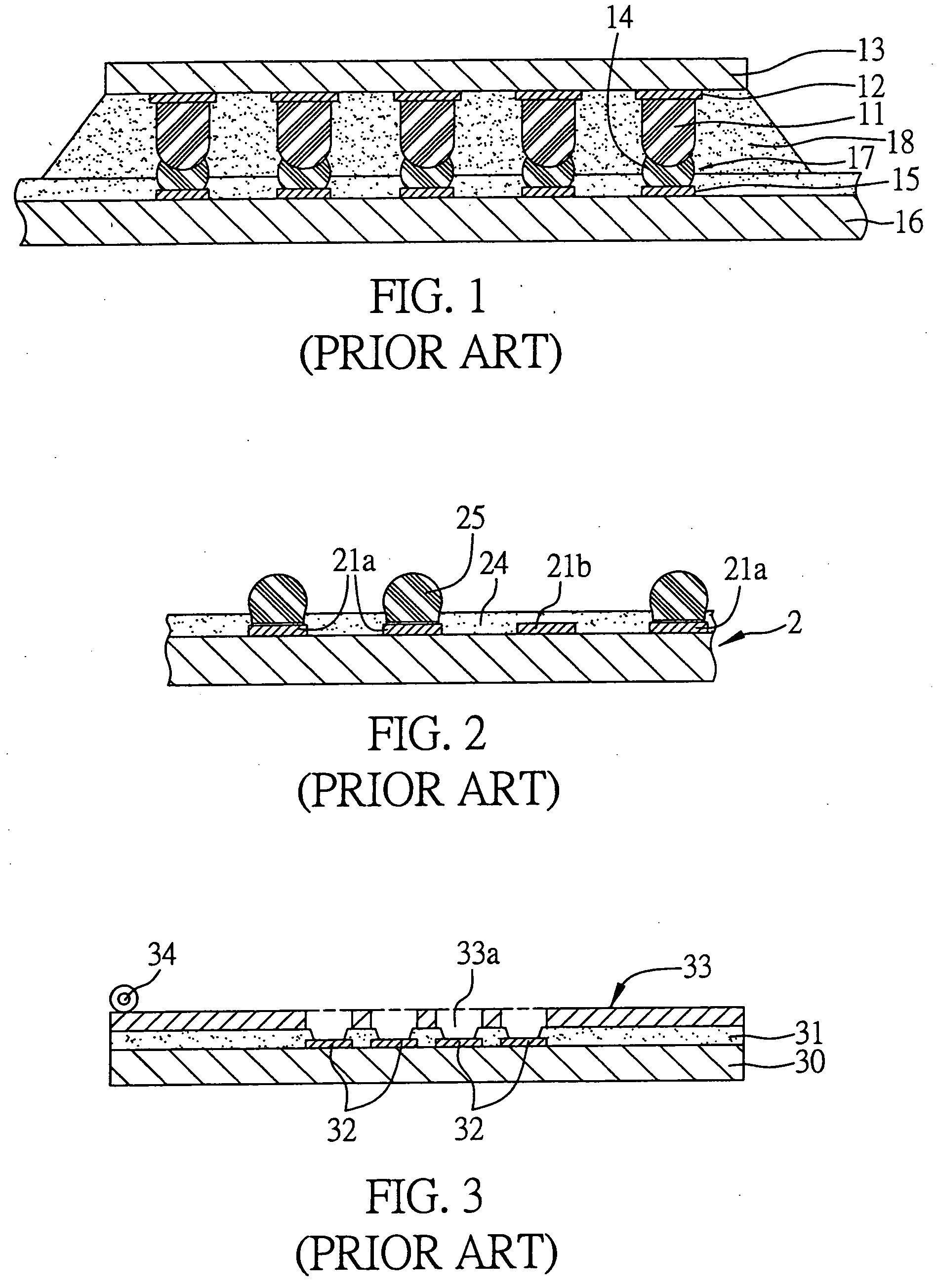

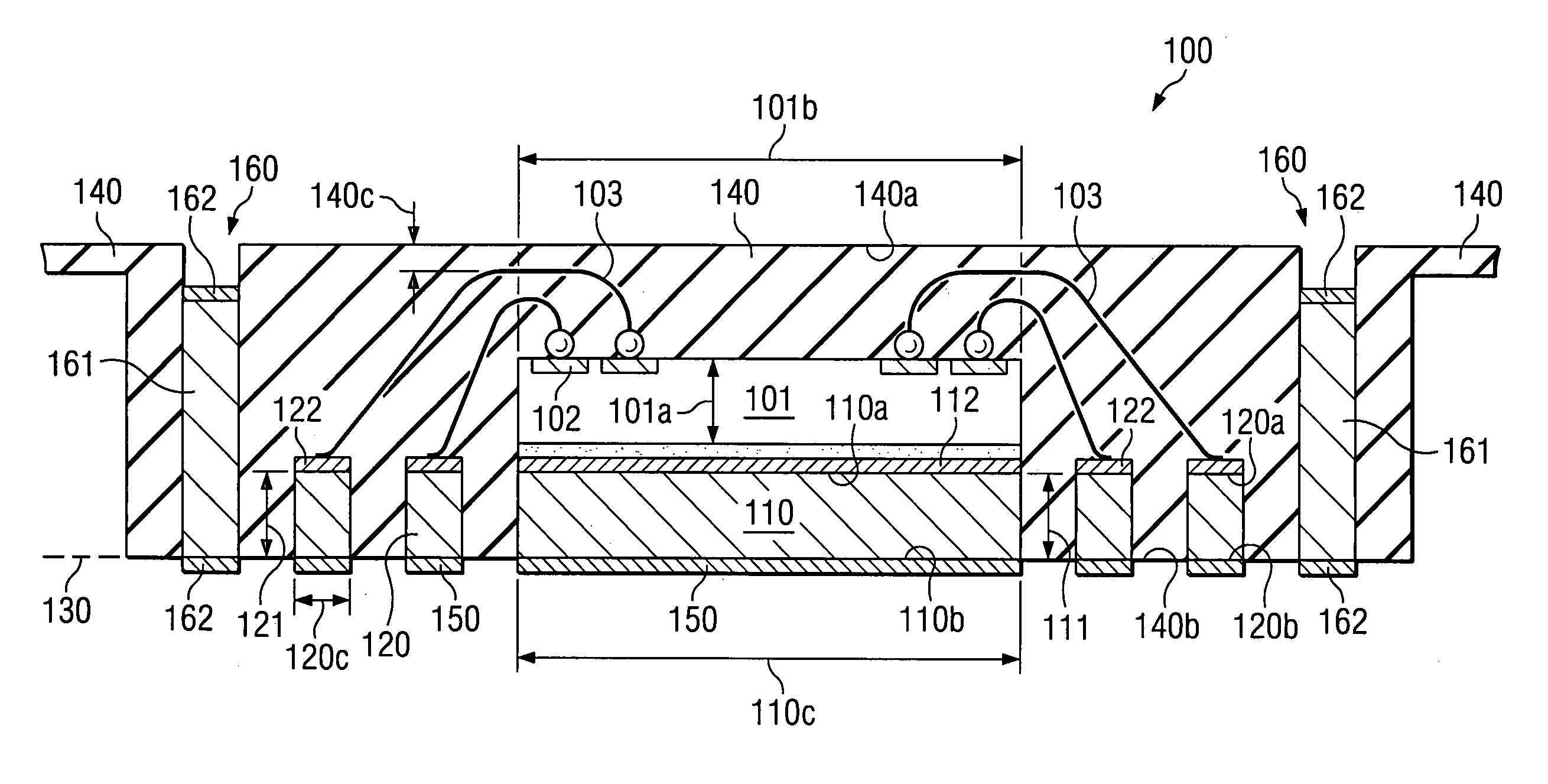

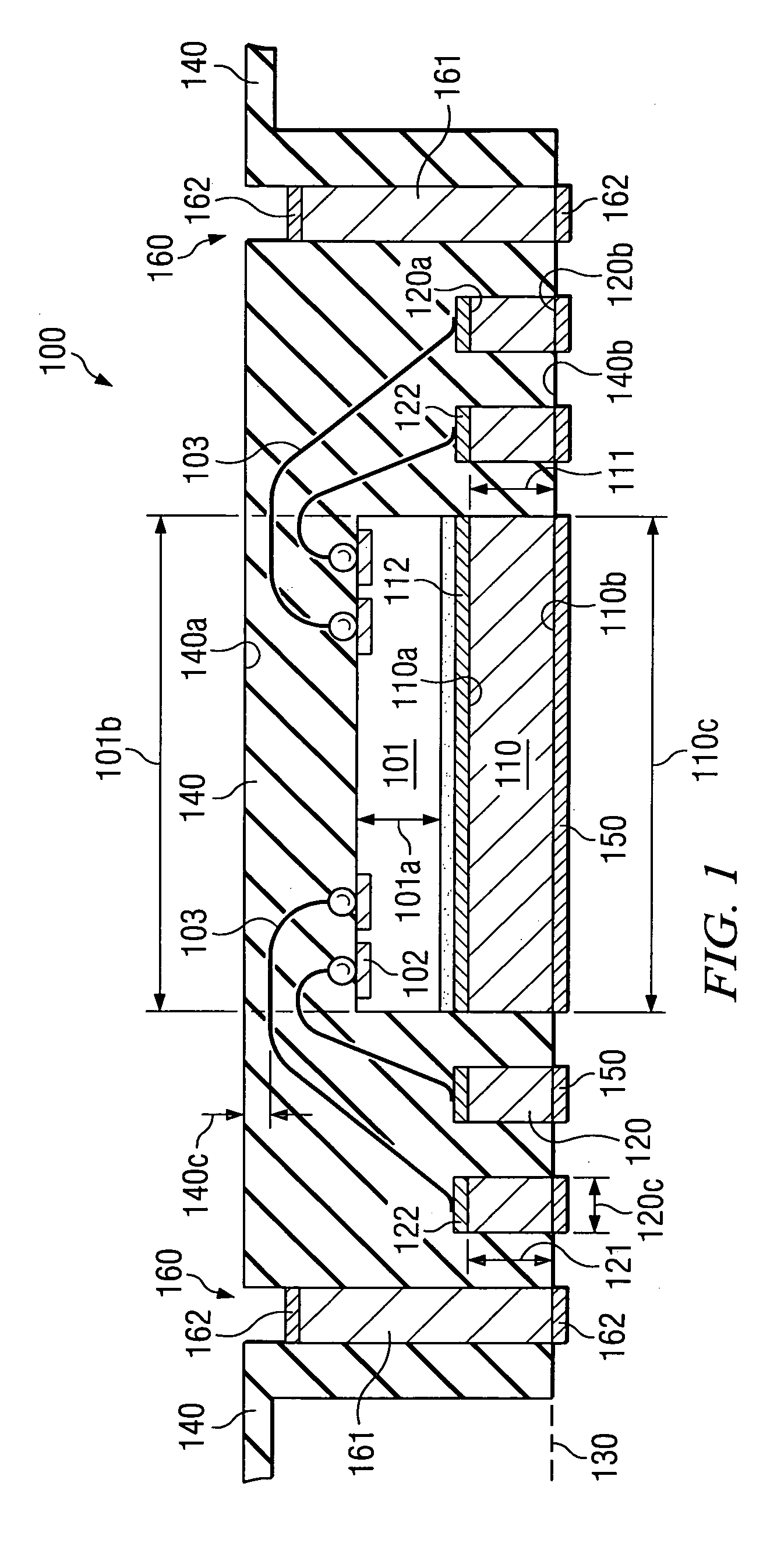

Structure and method of molded QFN device suitable for miniaturization, multiple rows and stacking

ActiveUS20070090524A1Excellent thermal device performanceImprove speed performanceSemiconductor/solid-state device detailsSolid-state devicesLead bondingMiniaturization

A semiconductor device comprising a semiconductor chip (101) assembled on a first copper cuboid (110); the cuboid has sides of a height (111). The device further has a plurality of second copper cuboids (120) suitable for wire bond attachment; the second cuboids have sides of a height (121) substantially equal to the height of the first cuboid. The back surfaces of all cuboids are aligned in a plane (130). Encapsulation compound (140) is adhering to and embedding the chip, the wire bonds, and the sides of all cuboids so that the compound forms a first surface (140b) aligned with the plane of the back cuboid surfaces and a second surface (140a) above the embedded wires. For devices intended for stacking, the devices further comprise a plurality of vias (160) through the encapsulation compound from the first to the second compound surfaces; the vias are filled with copper, and the via locations are matching between the devices-to-be-stacked.

Owner:TEXAS INSTR INC

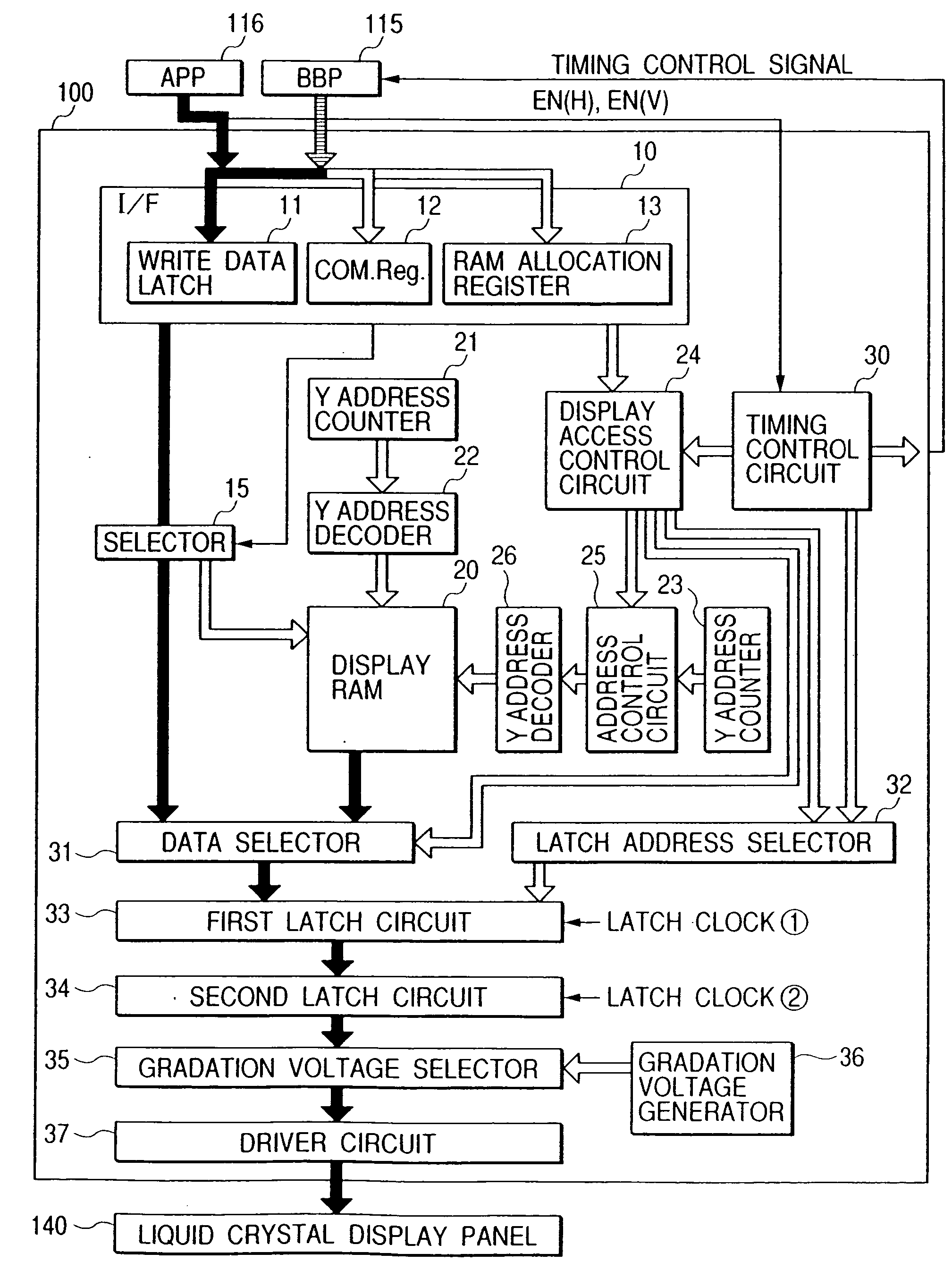

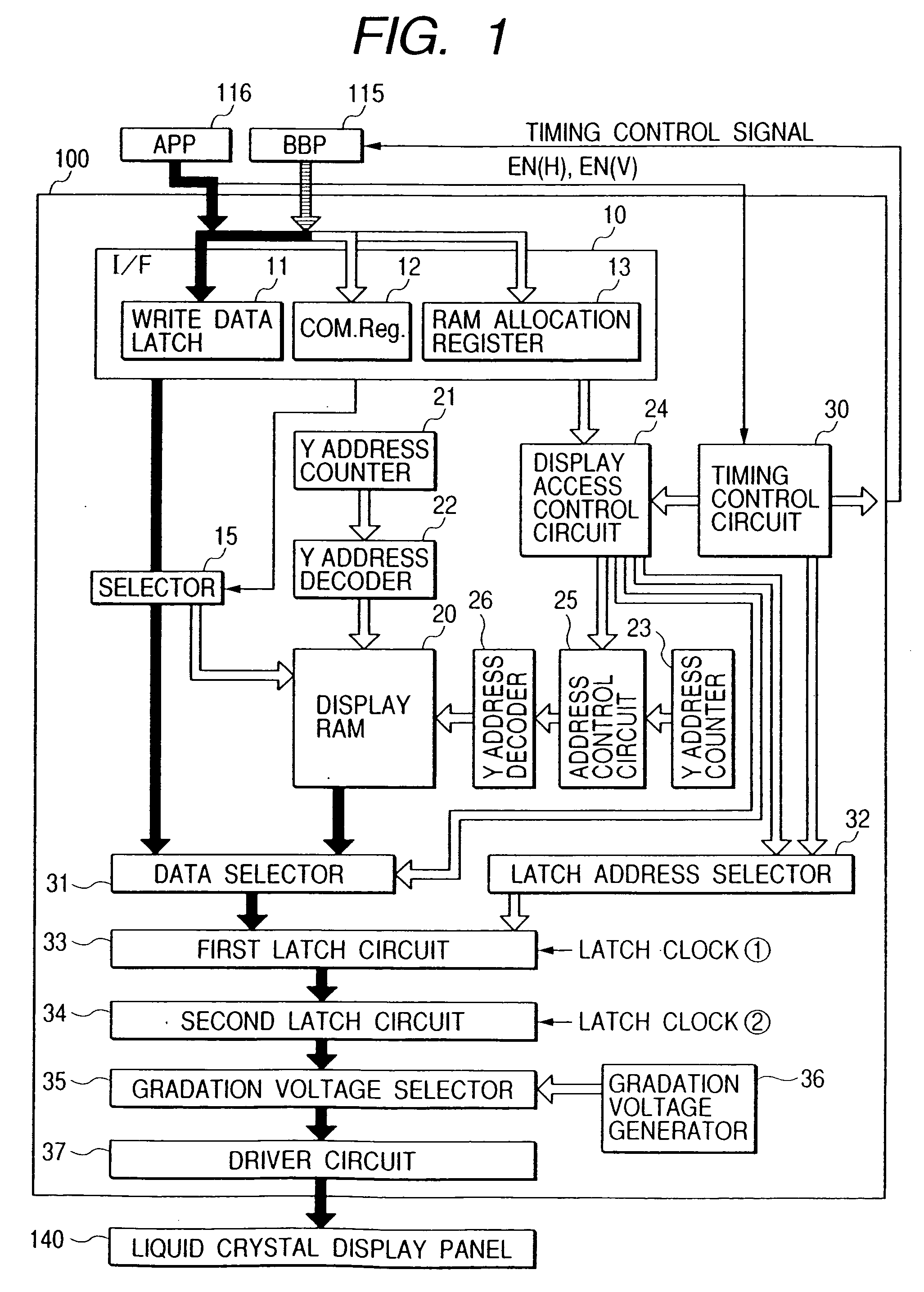

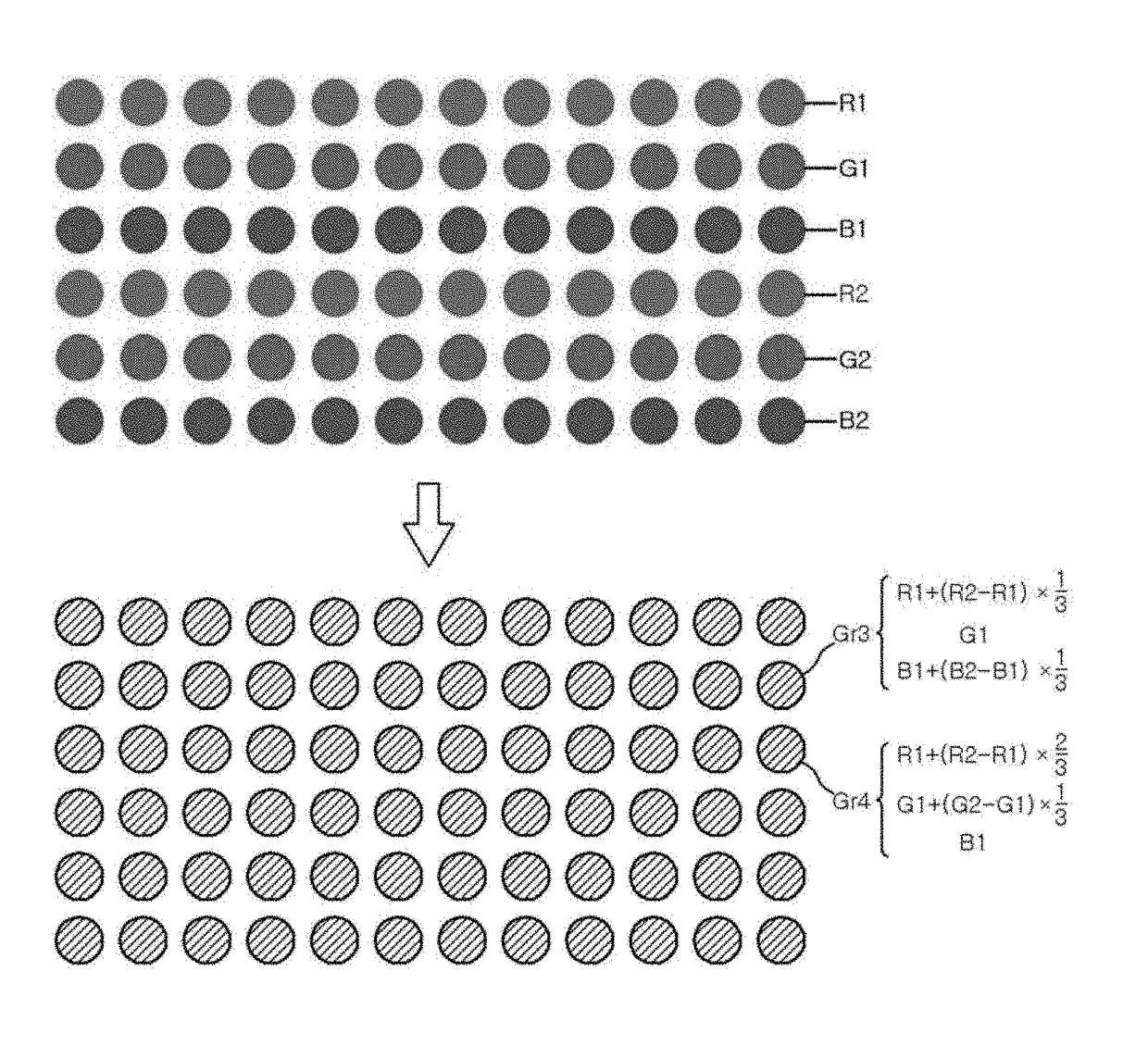

Display driver control circuit and electronic equipment with display device

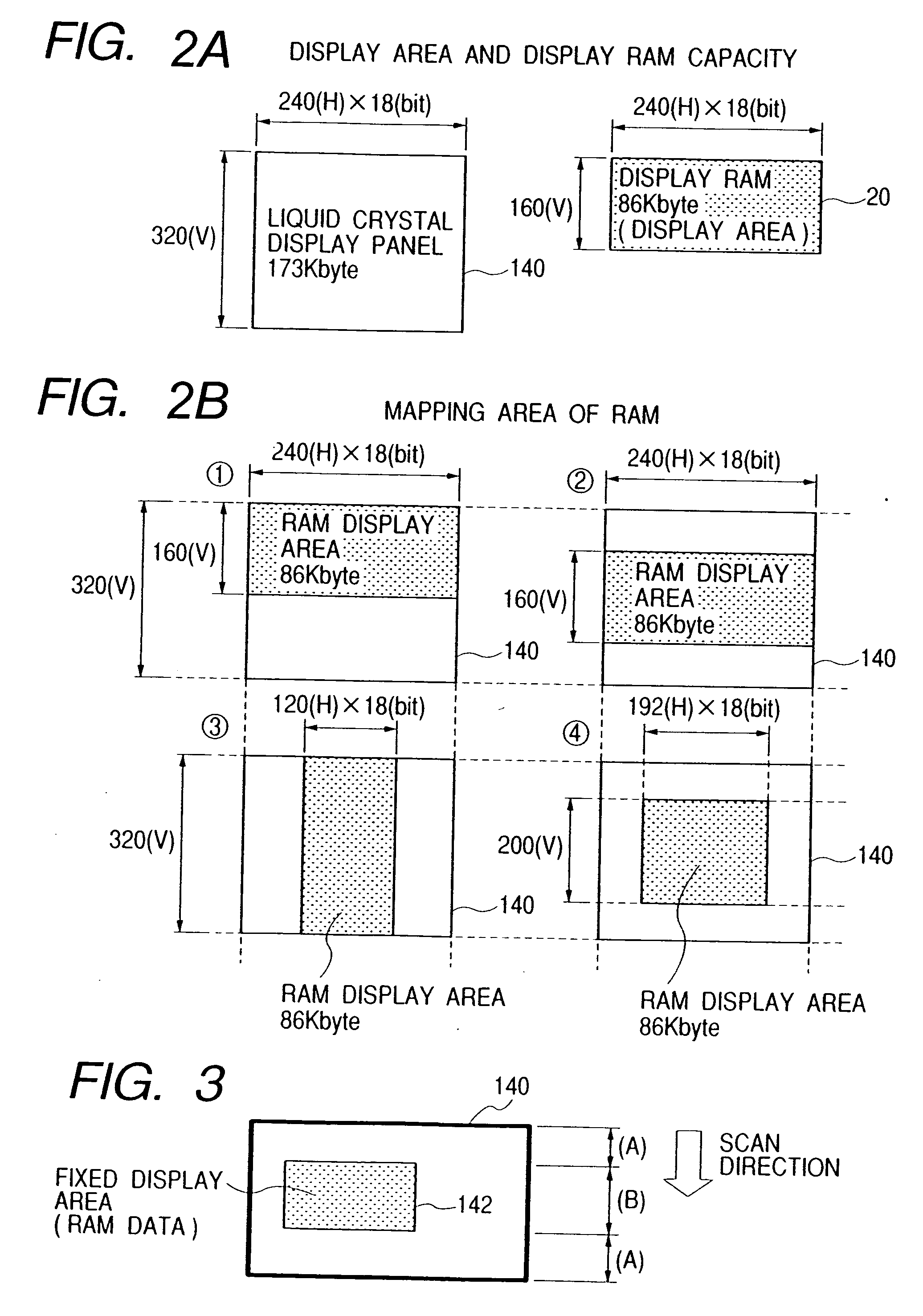

InactiveUS20070035503A1Large capacityNumber of display colors are more and more increasingCathode-ray tube indicatorsControl circuitComputer science

There is provided a display driver control circuit which is just suitable for display drive including display with a small amount of change and display with a large amount of change and can realize saving of chip area and reduction of power consumption and cost. In this display driver control circuit, memory capacity of an internal display memory is set smaller than amount of data of one display picture of a display panel as the drive object, and the display data can be transferred with the system in which externally inputted display data is once stored in the display memory and is then sent of a drive circuit to output a drive signal and with the system in which the display data is sent in direct to the drive circuit by way of no display memory to output a drive signal. Moreover, both transfer methods can be executed on the time division basis.

Owner:KUROKAWA YASUHITO +4

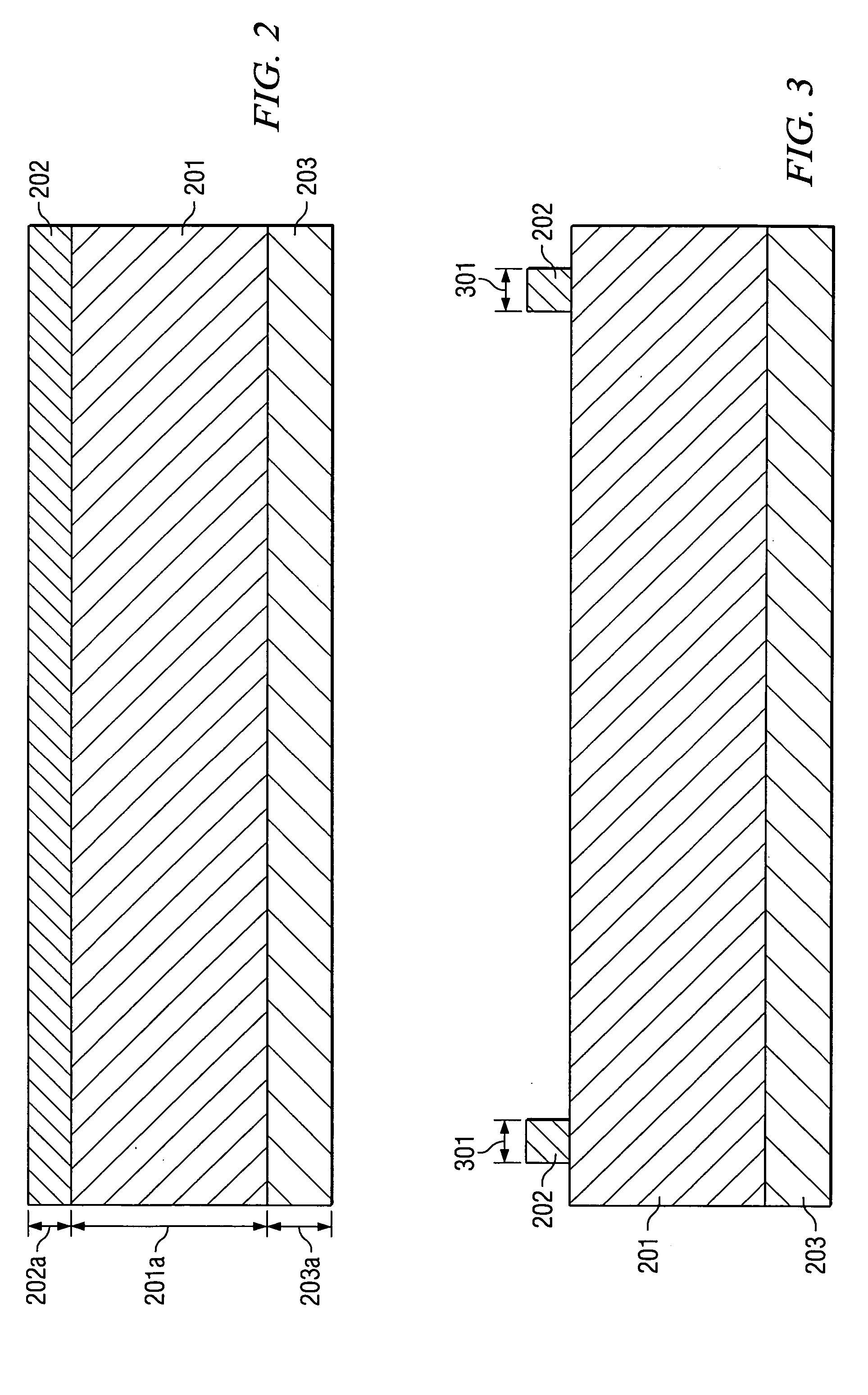

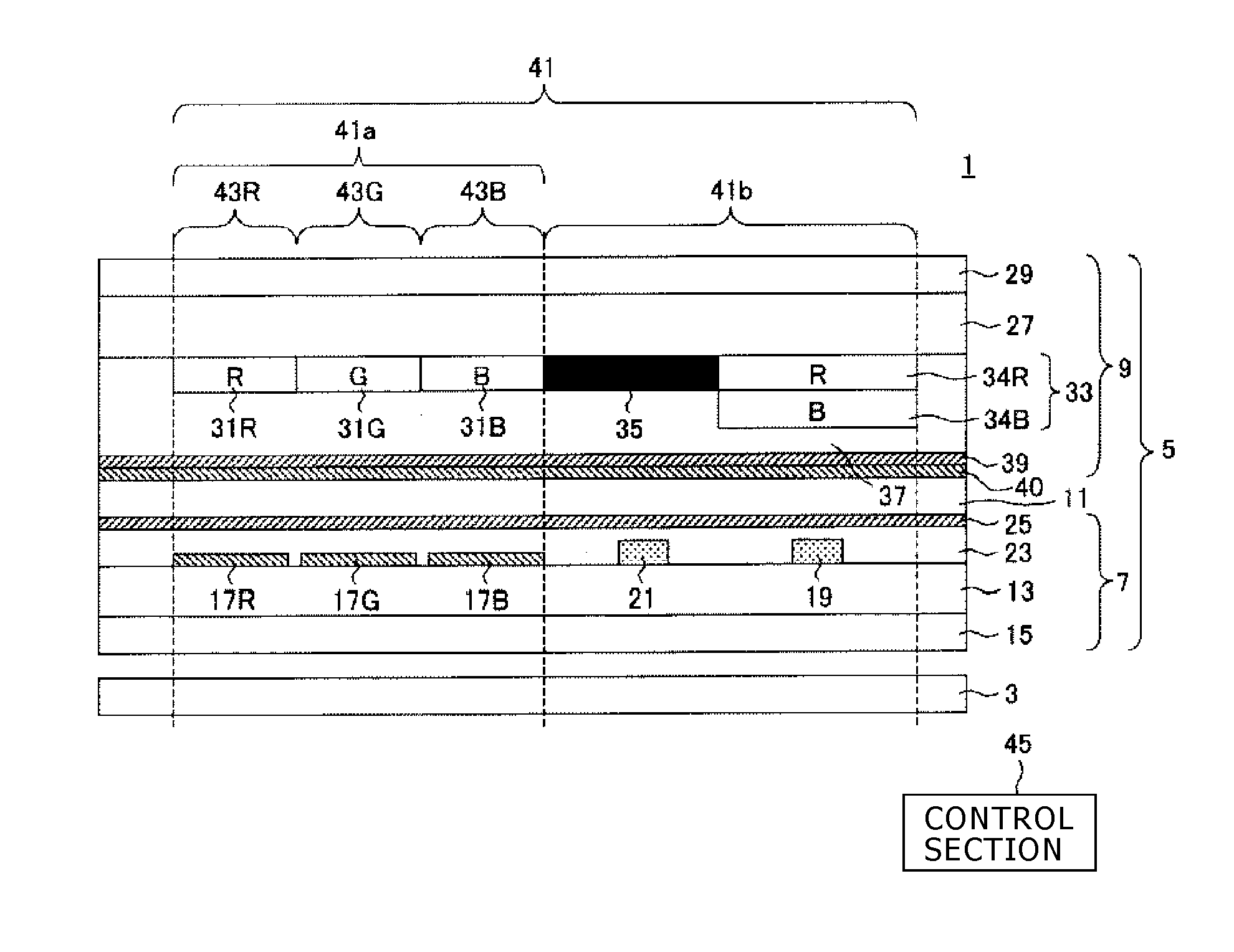

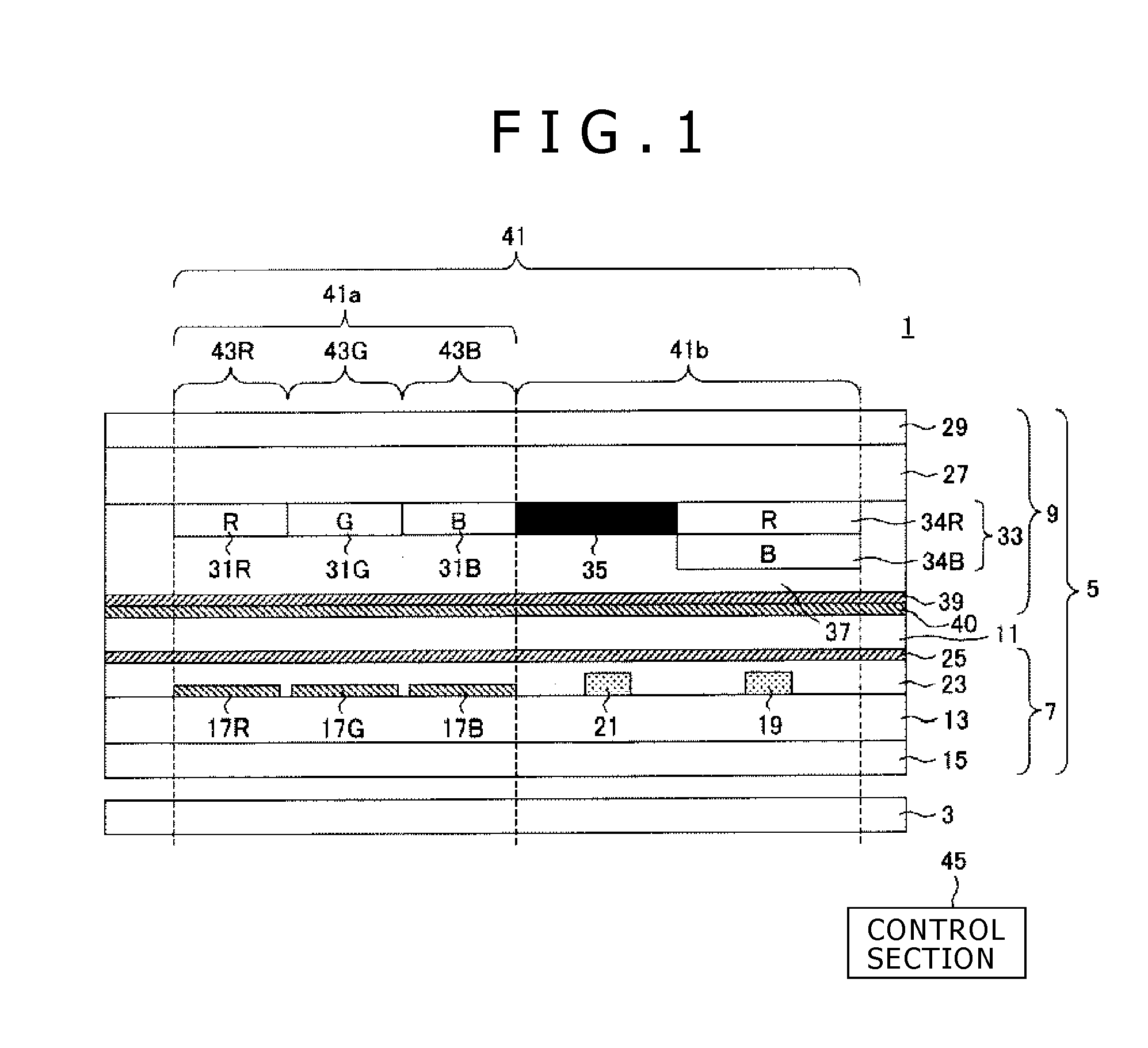

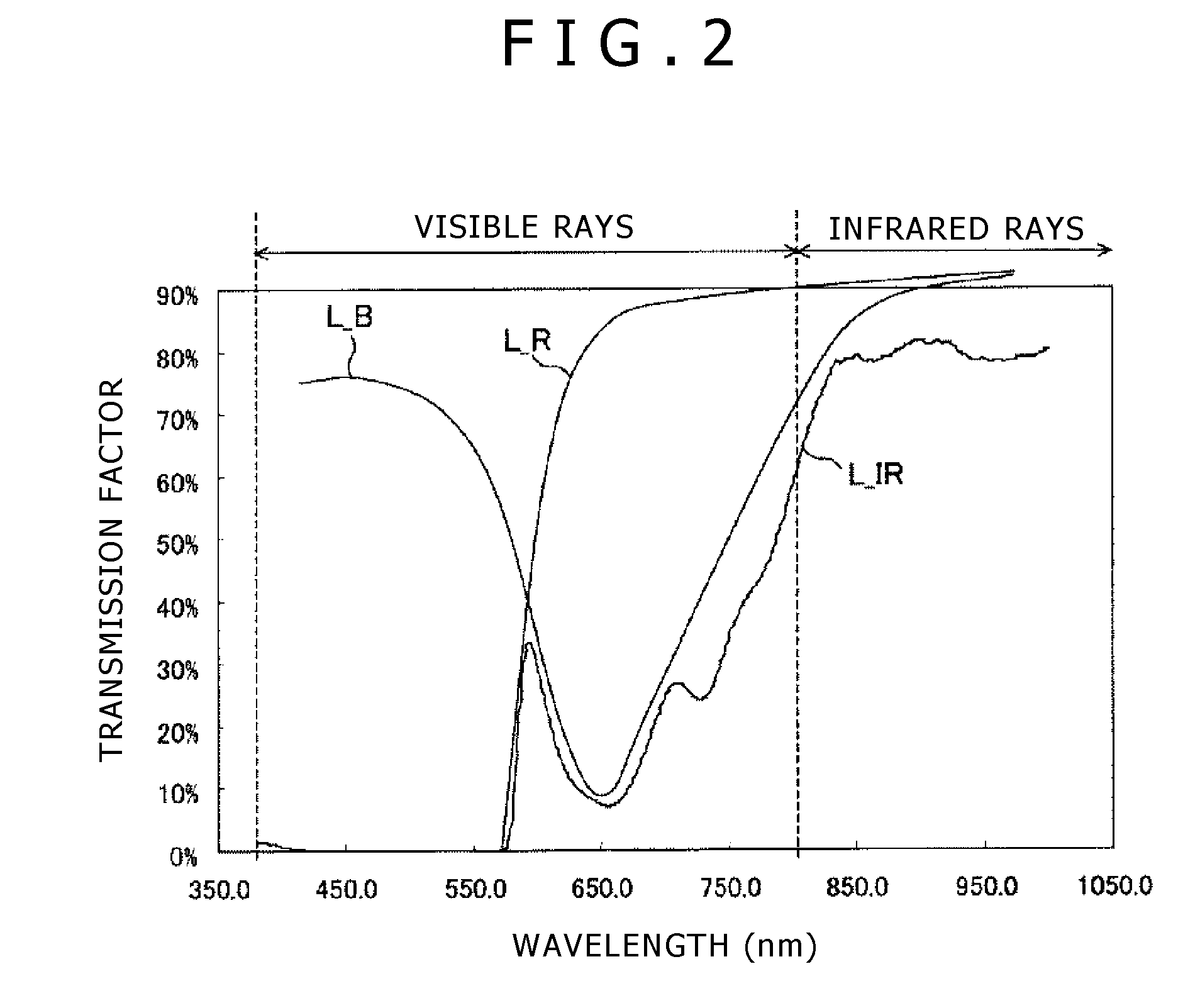

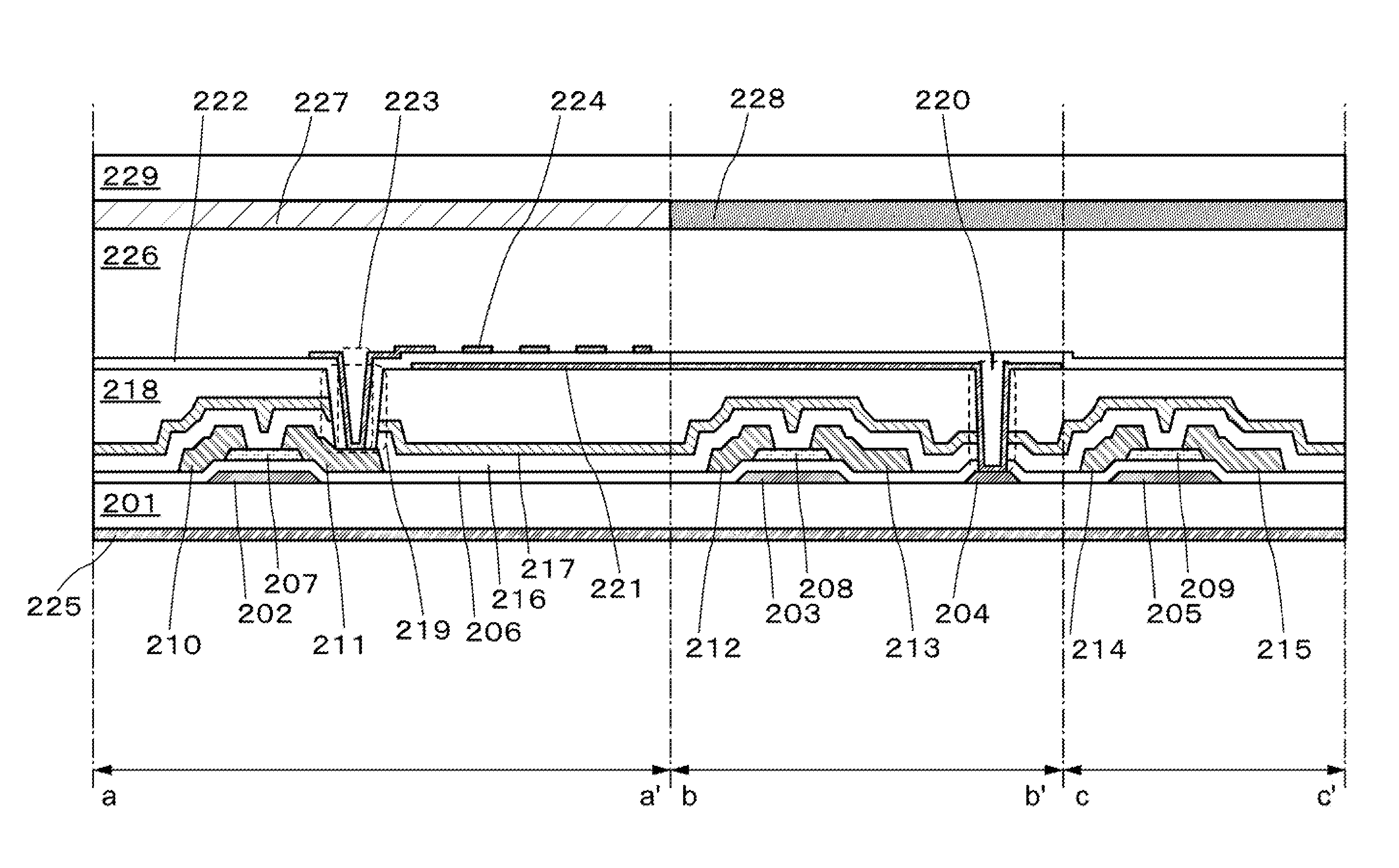

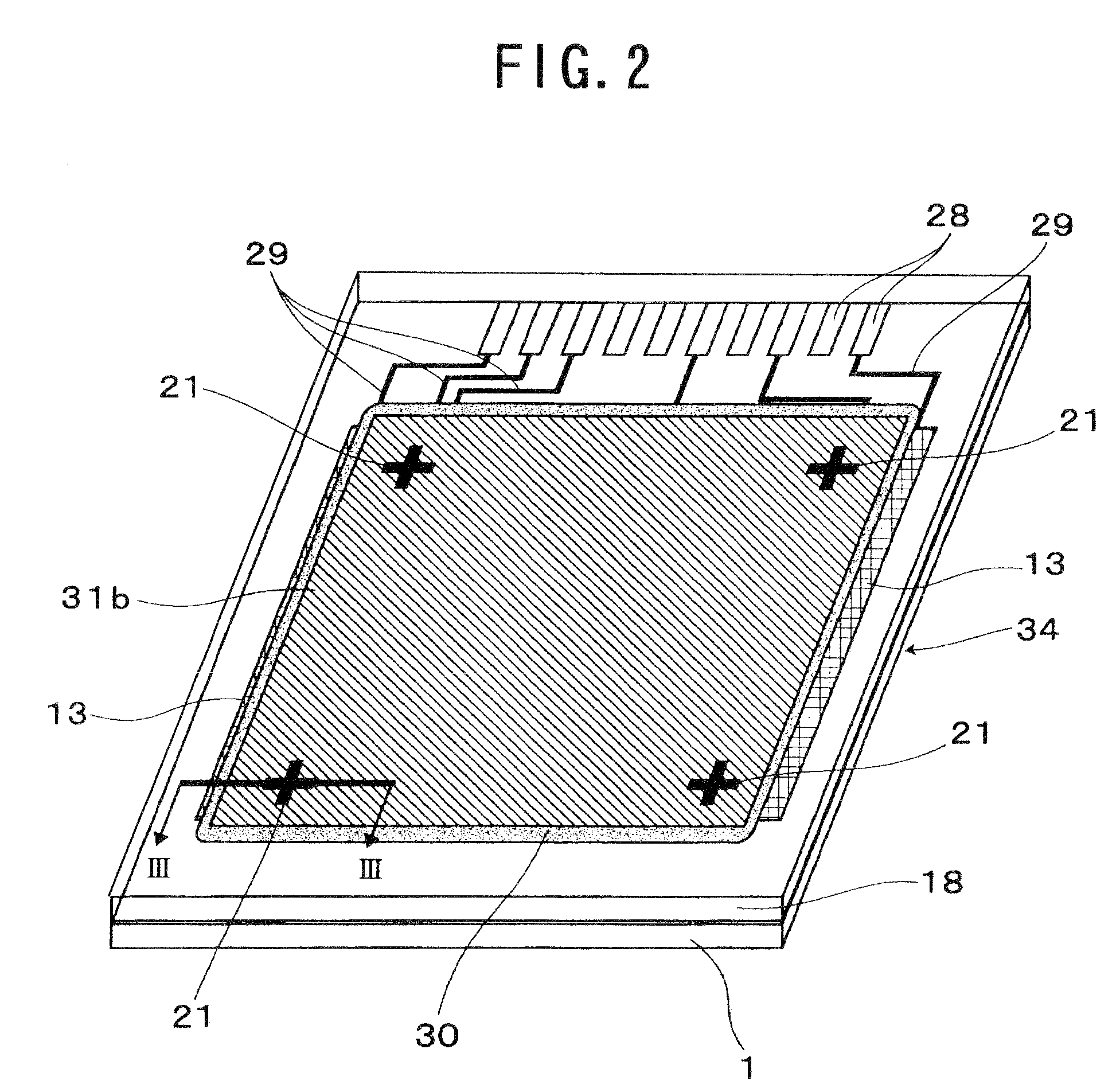

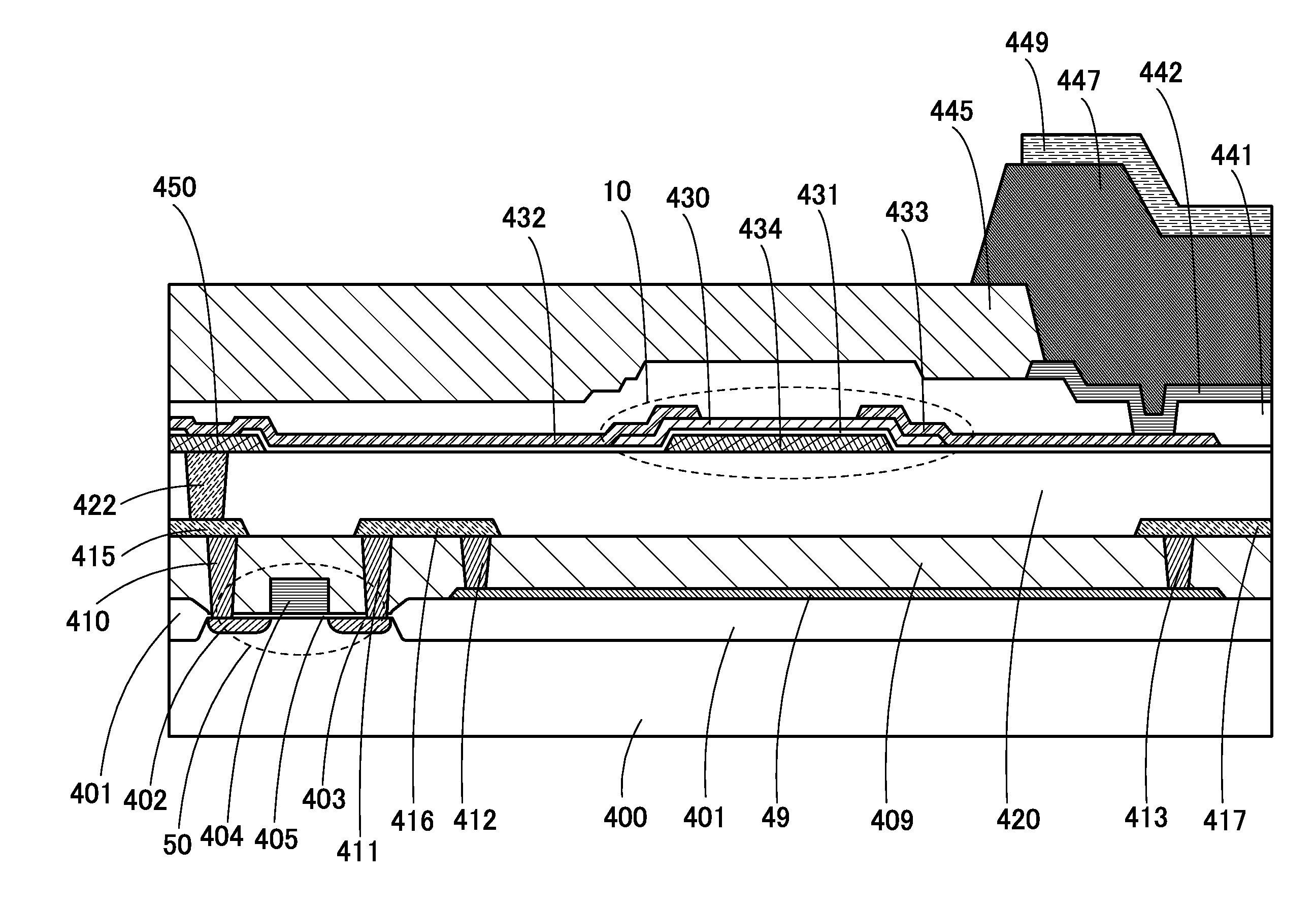

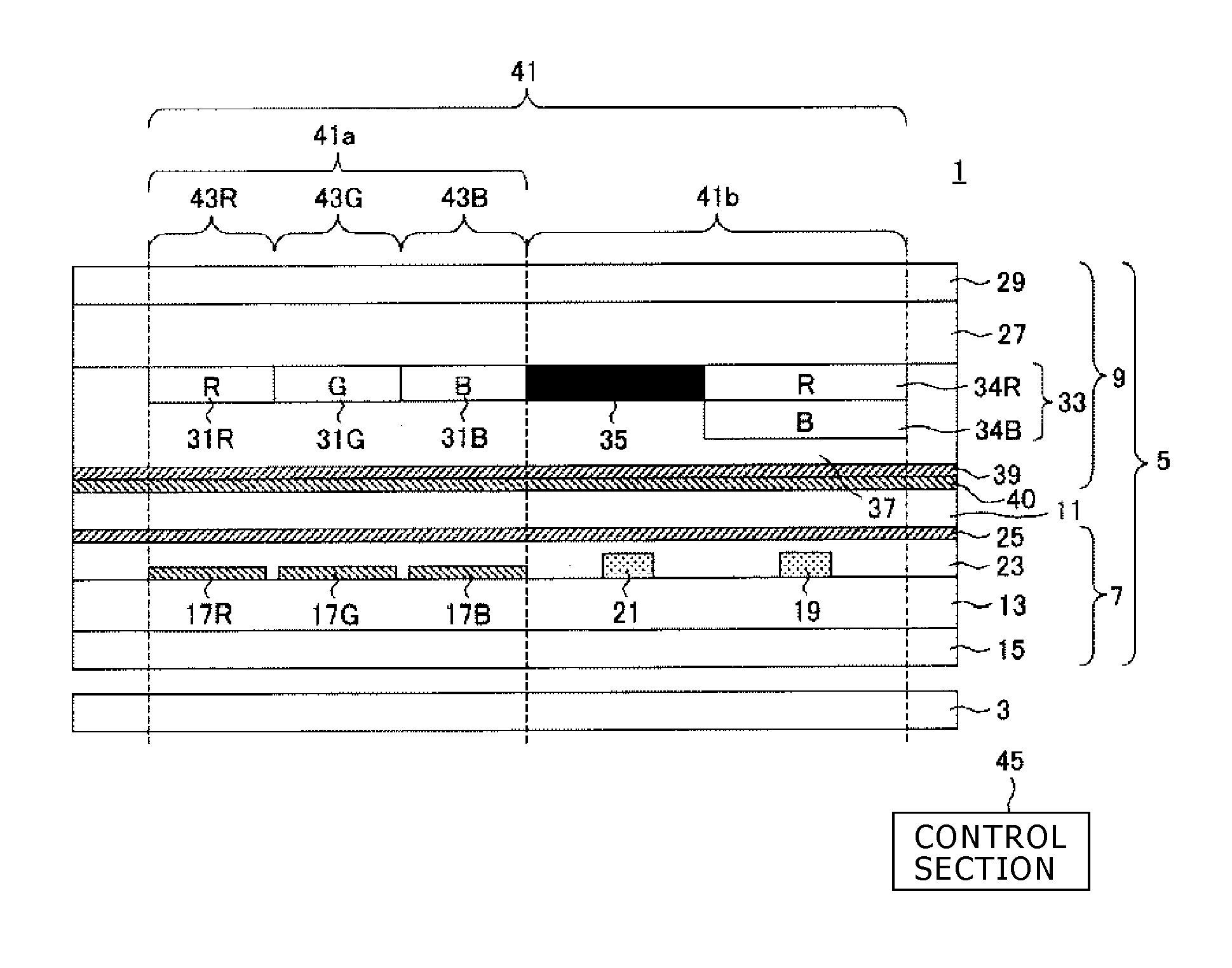

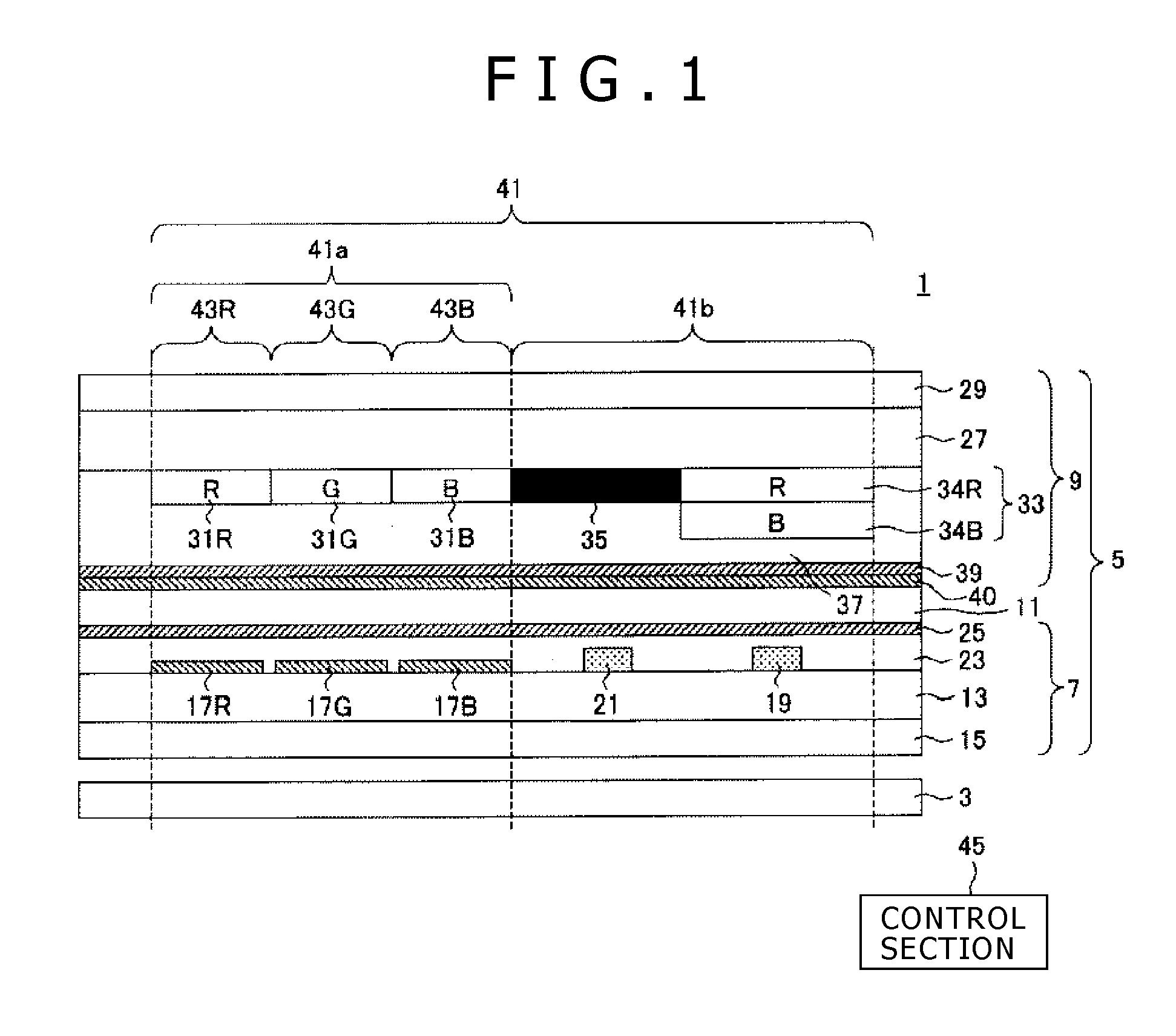

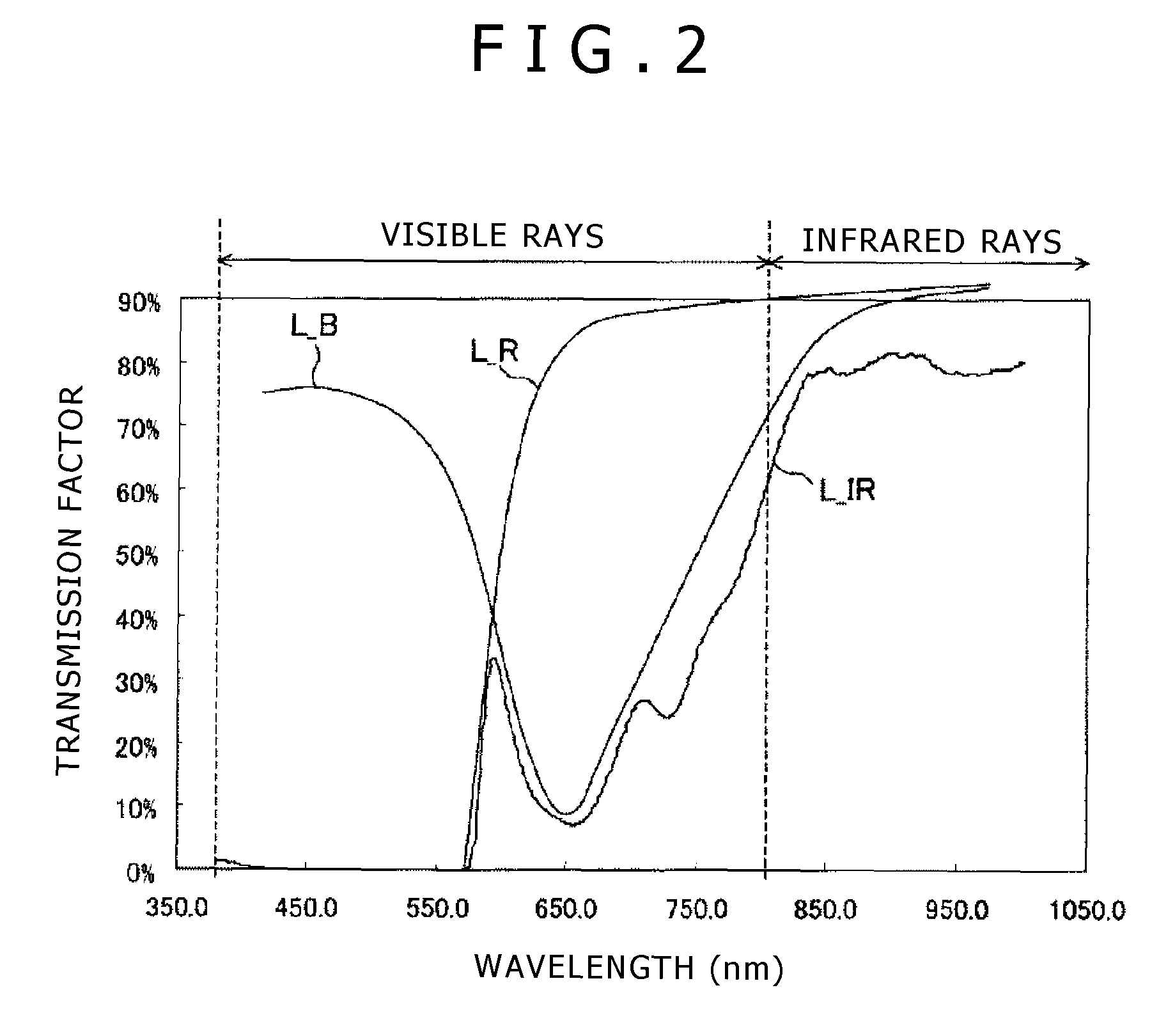

Display apparatus and fabrication method for display apparatus

ActiveUS20100220269A1Simple configurationHigh precisionPhotomechanical exposure apparatusMicrolithography exposure apparatusFilter materialLength wave

A display apparatus is provided which can detect light of a predetermined wavelength with a high degree of accuracy from within light incident from a screen by a simple configuration. The display apparatus includes a CF substrate (9) having a plurality of color filters (31) of different colors for passing light for displaying an image on the screen (55a) and an IR filter (33) provided in a region different from an arrangement region of the color filters of the different colors for passing light incident from the screen (55a), and a main sensor (19) provided on the rear side of the IR filter (33) for detecting light incident from the screen (55a) and passing through the IR filter (33). The IR filter (33) has a laminate of filter materials same as filter materials from which at least two or more ones of the color filters of the different colors are formed respectively.

Owner:JAPAN DISPLAY WEST

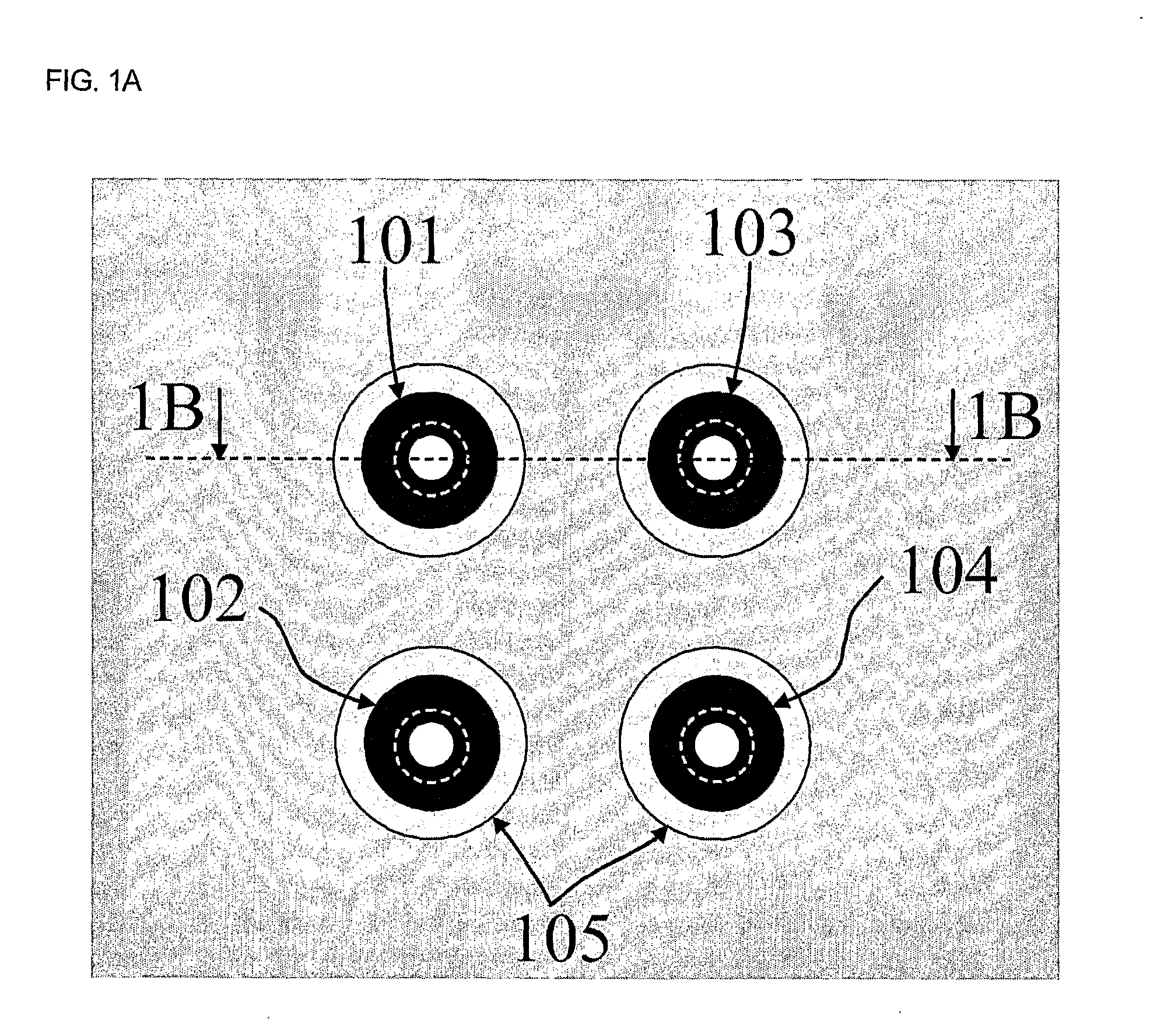

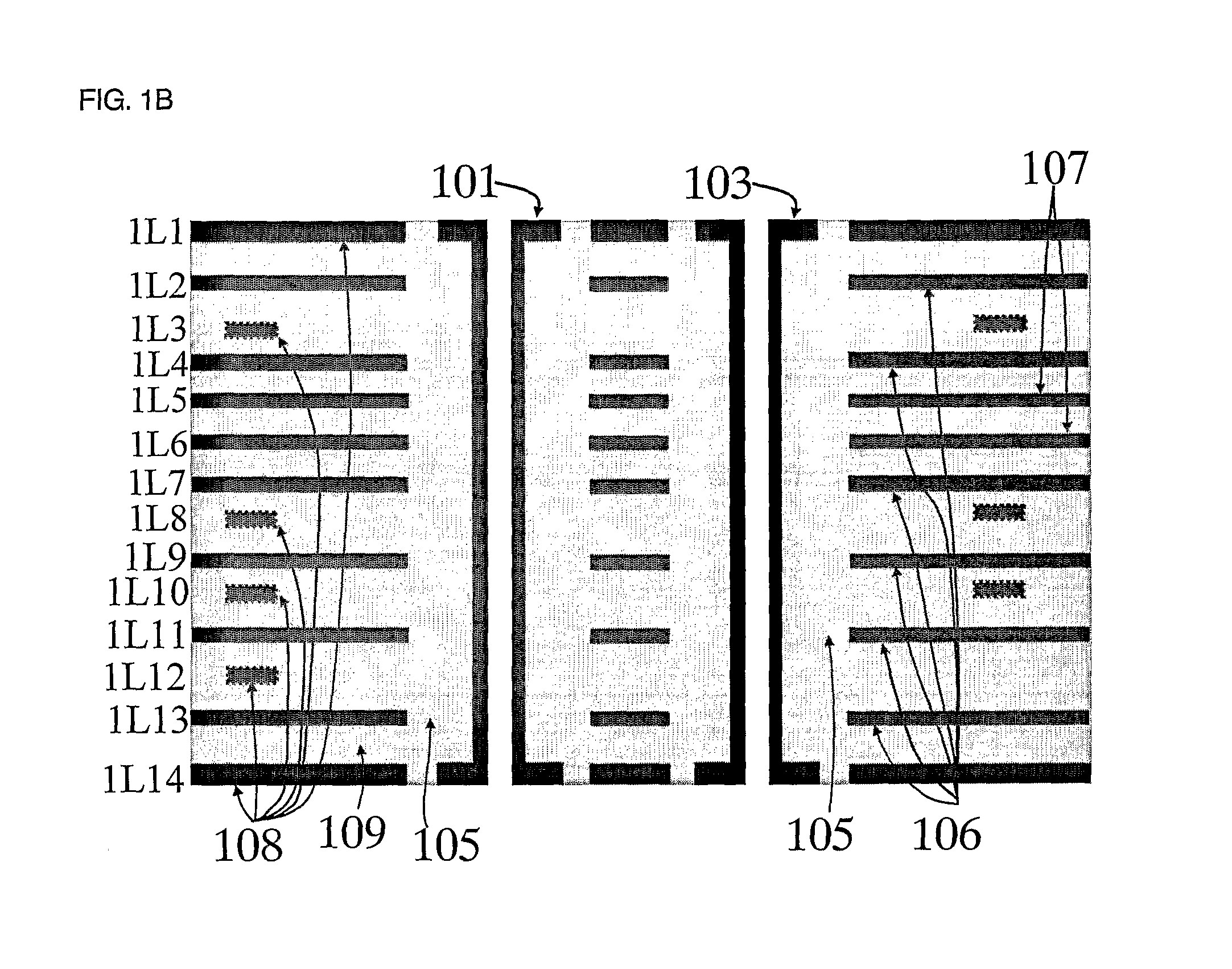

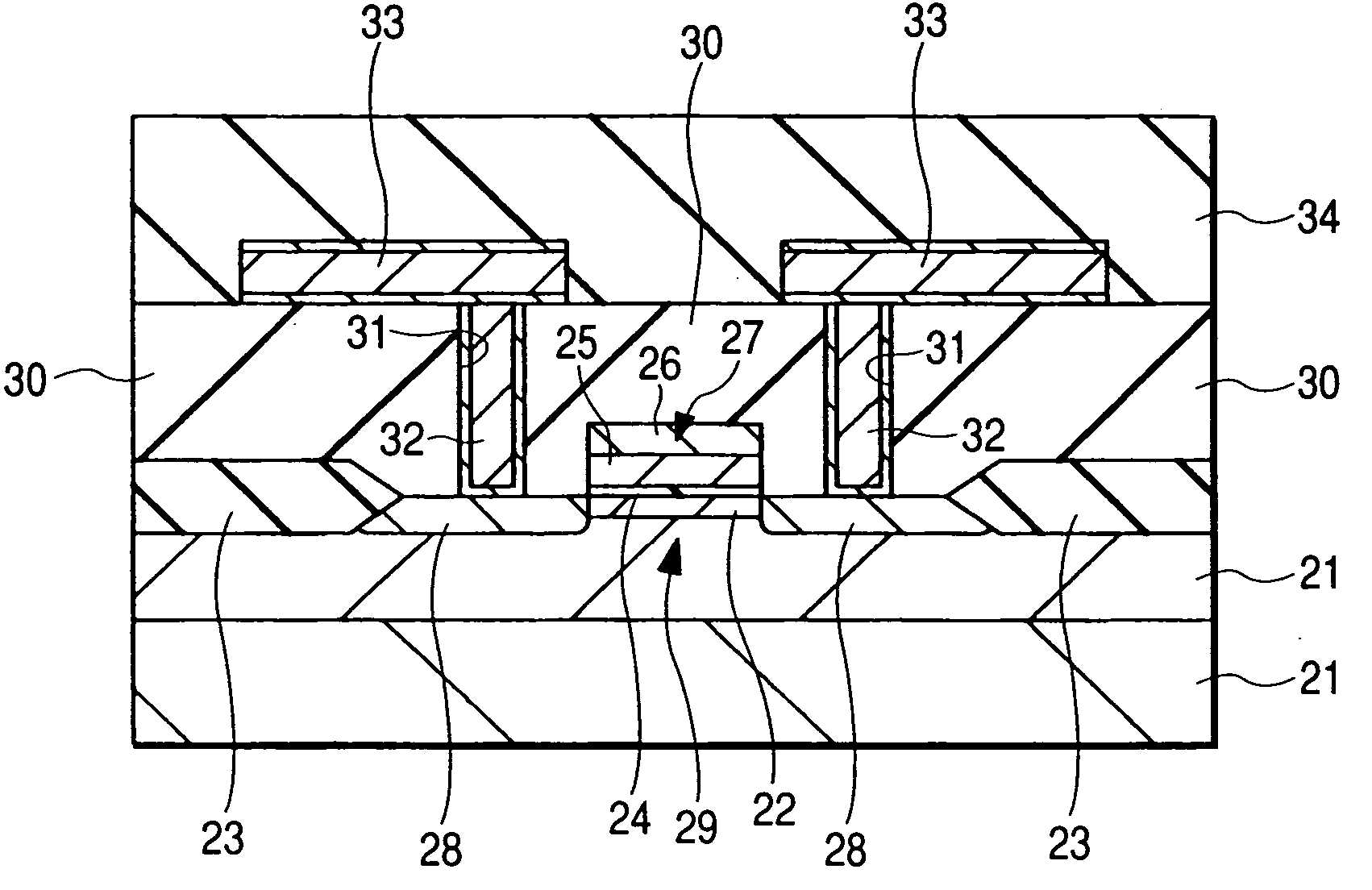

Multilayer substrate

InactiveUS20110203843A1Avoid leakage lossLeakage loss increaseMagnetic/electric field screeningCross-talk/noise/interference reductionCompact dimensionBroadband

To provide more compact dimensions of a via structure formed by signal via pairs and ground vias in multilayer substrate. A multilayer substrate is provided such that the multilayer substrate comprising a high-isolated via cell wherein the high-isolated via cell comprises: two signal via pairs; a shield structure around two signal via pairs consisting of ground vias and ground strips connected to ground vias wherein the shield structure is formed symmetrically in respect to two via pairs to reduce the transformation between mixed modes and also leakage from two signal via pairs; a clearance hole separating signal via pairs from other conductive parts of the multilayer substrate and having predetermined dimensions to provide broadband operation of the high-isolated via cell; and the separating strip disposed symmetrically between said signal via pairs to provide crosstalk reduction between two signal via pairs and common mode decrease.

Owner:NEC CORP

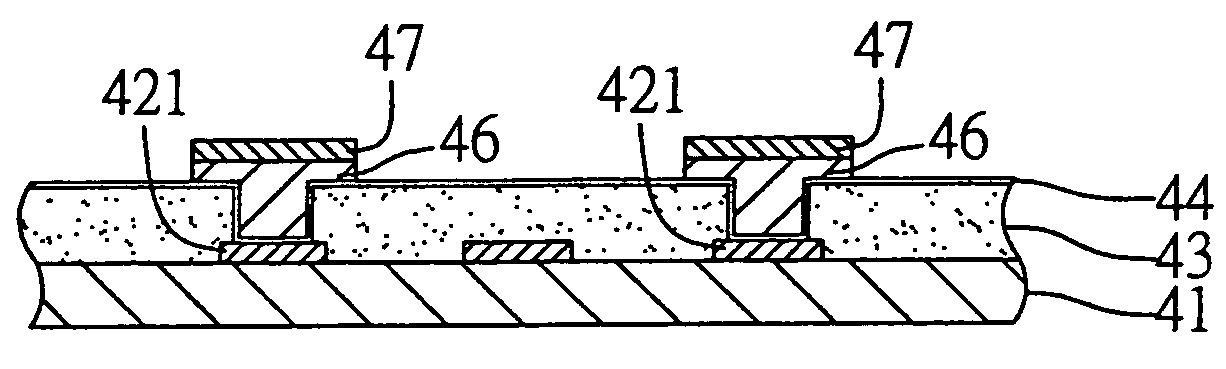

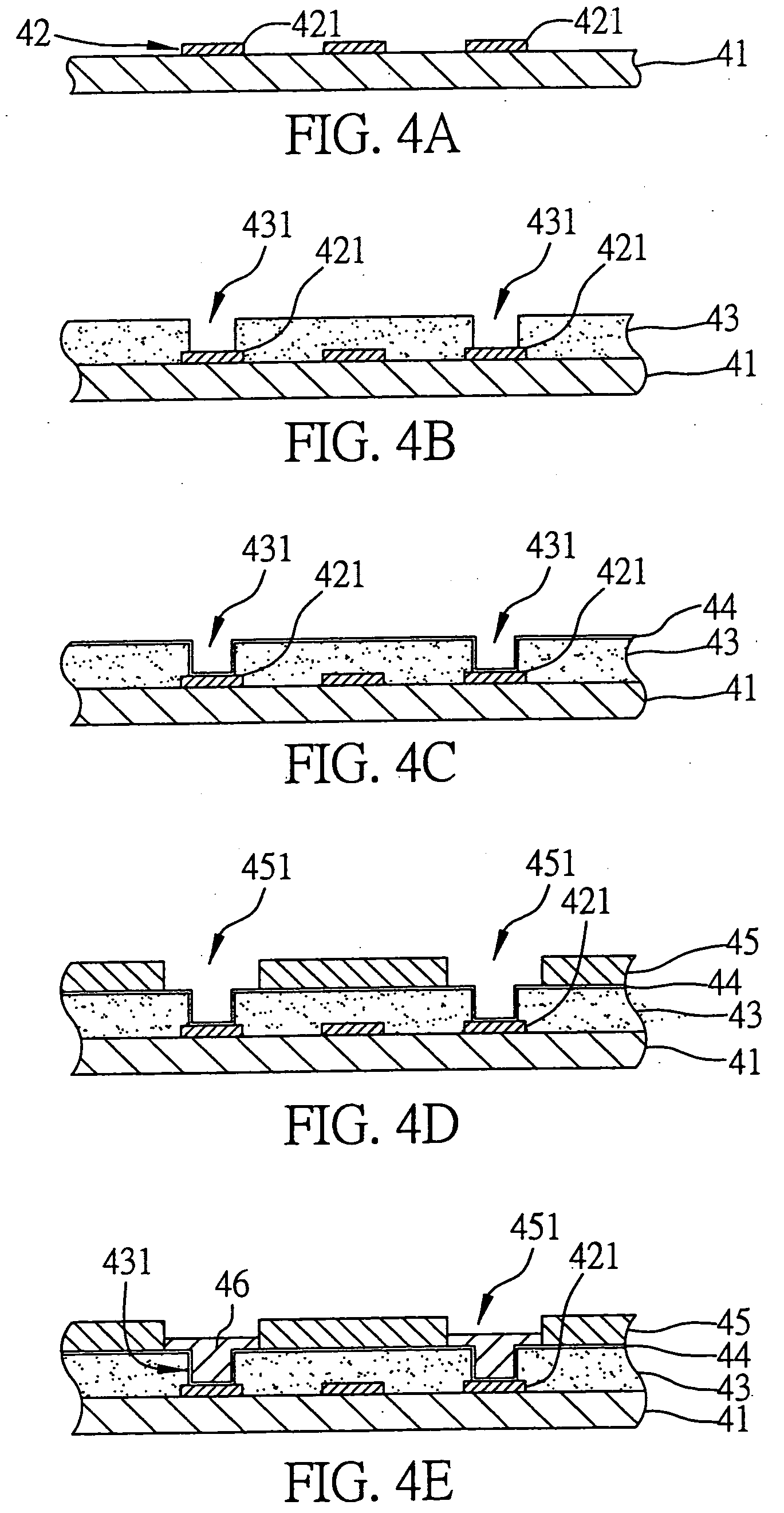

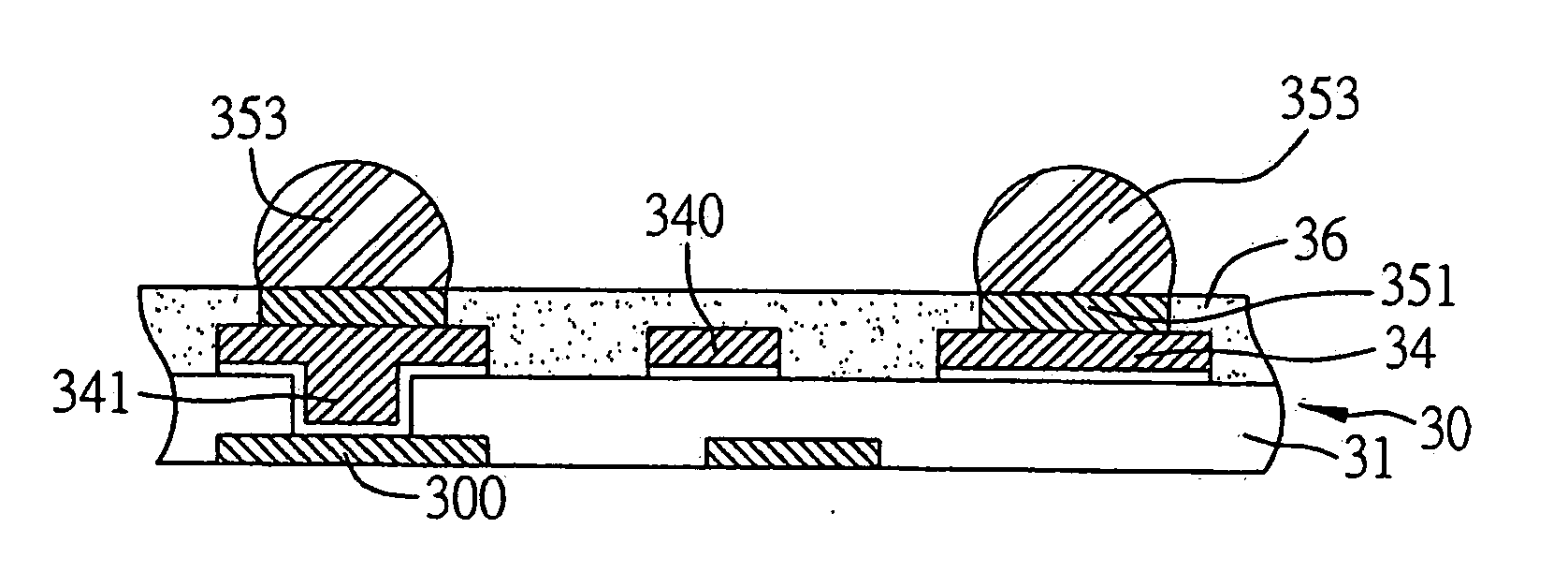

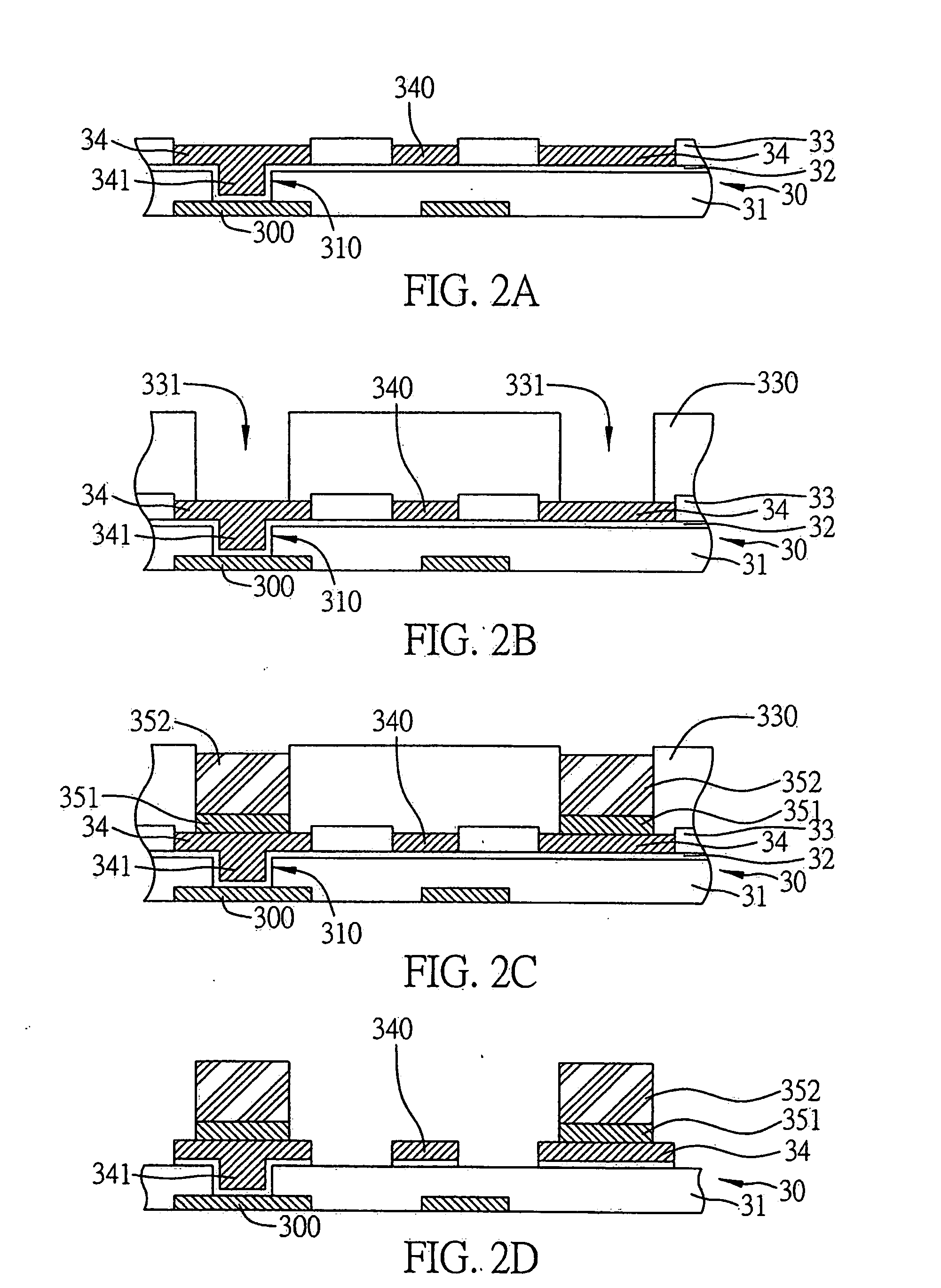

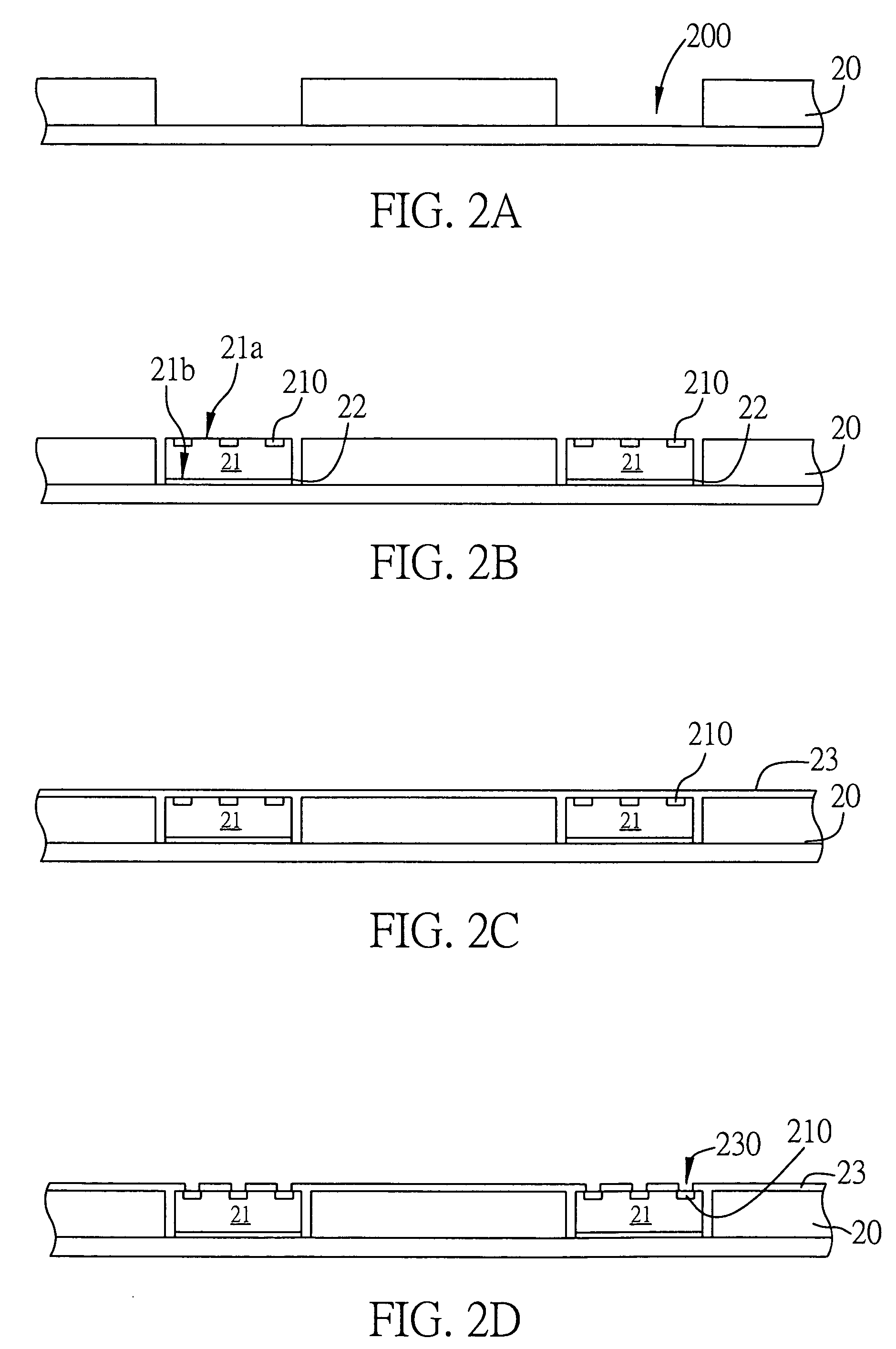

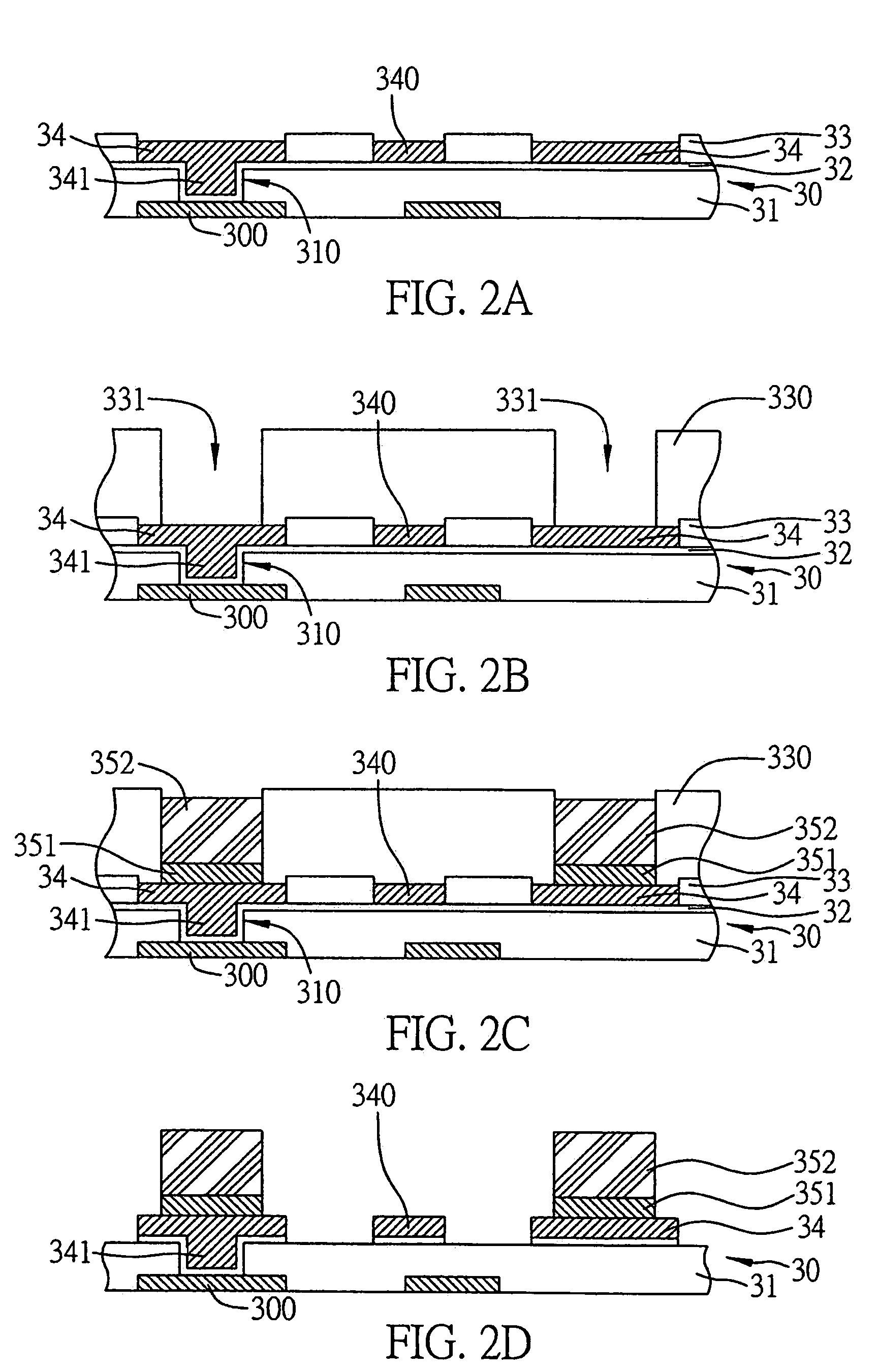

Method for fabricating electrical connection structure of circuit board

ActiveUS20060079081A1Increase bonding strengthAvoidance of alignment problemSemiconductor/solid-state device detailsStacked resist layersResistElectrical connection

A method for fabricating an electrical connection structure of a circuit board is proposed. A patterned resist layer is formed on the circuit board having a plurality of conductive pads, and a plurality of openings is formed in the resist layer to expose the conductive pads. A first conductive material and a second conductive material are successively deposited in the openings of the resist layer and on each of the conductive pads. Then, the resist layer is removed. Subsequently, a protective layer is applied on the circuit board and covers the first and second conductive materials formed on each of the conductive pads. Finally, the protective layer is thinned to expose the second conductive material corresponding in position to each of the conductive pads. Thus, the circuit board can be electrically connected to an external device via the second conductive material.

Owner:PHOENIX PRECISION TECH CORP

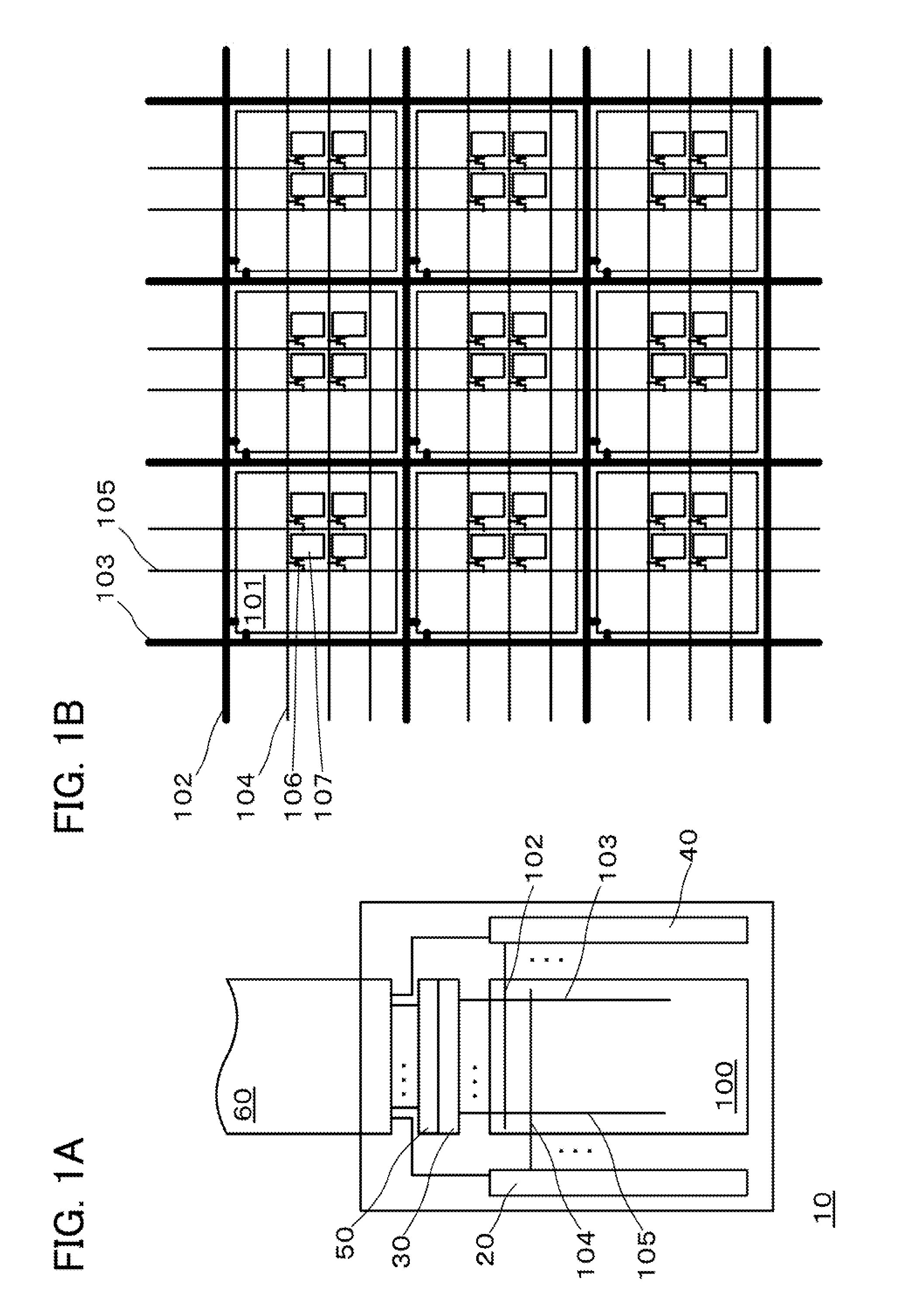

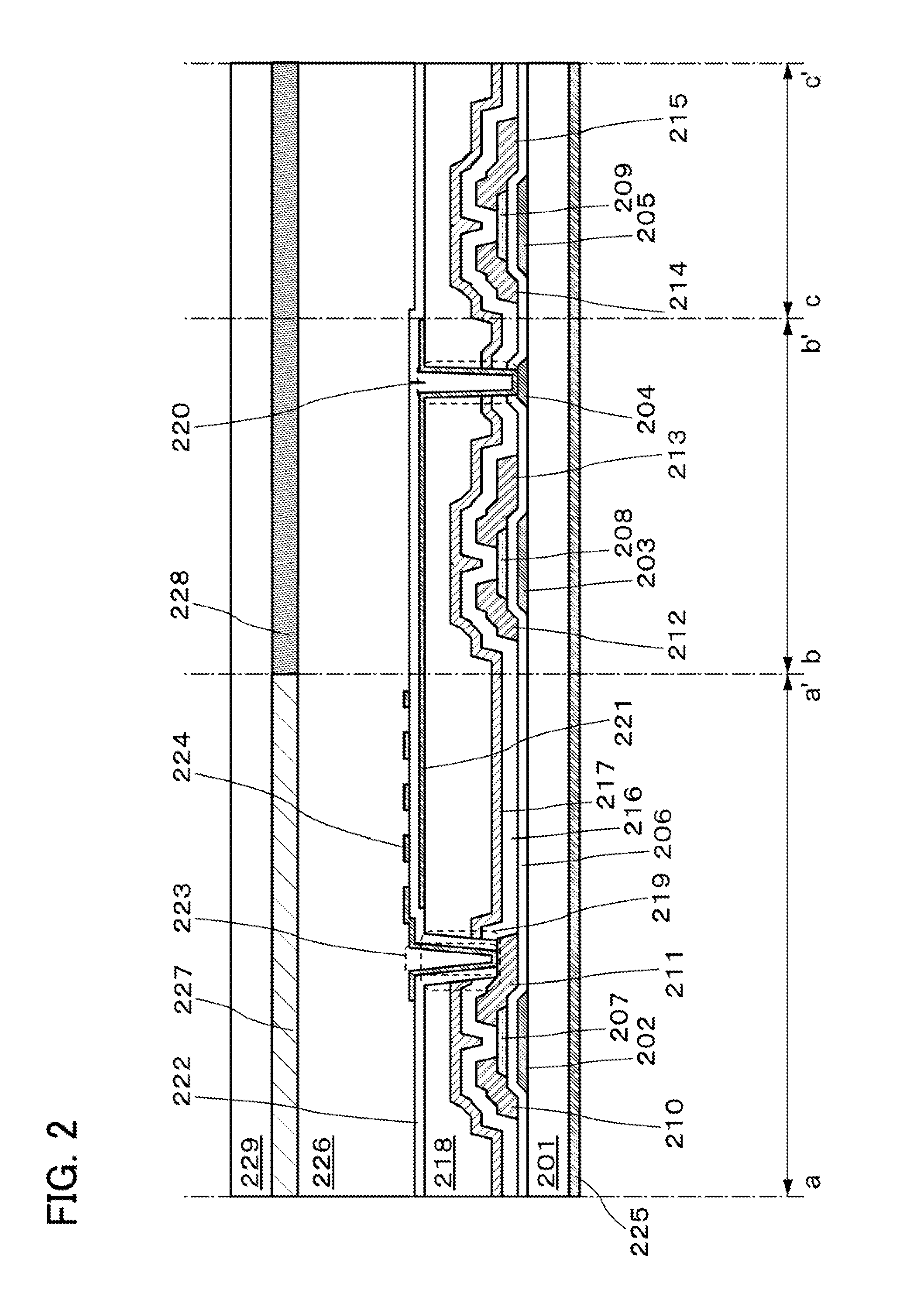

Semiconductor device and display device

InactiveUS20160154263A1Improve display reliabilityWrong input can be reducedTransistorSolid-state devicesPower semiconductor deviceDevice material

An increase in fabricating cost of a display module including a touch sensor is suppressed. A display device which includes a first substrate, a second substrate, and liquid crystal interposed between the first substrate and the second substrate includes a display portion. The display portion includes a sensor unit and a pixel. The sensor unit includes a first transistor, a first conductive film electrically connected to a gate of the first transistor, and a second conductive film. At least part of the first conductive film overlaps with at least part of the second conductive film. The pixel includes a second transistor, and a pixel electrode electrically connected to the second transistor. At least part of the pixel electrode overlaps with at least part of the first conductive film.

Owner:SEMICON ENERGY LAB CO LTD

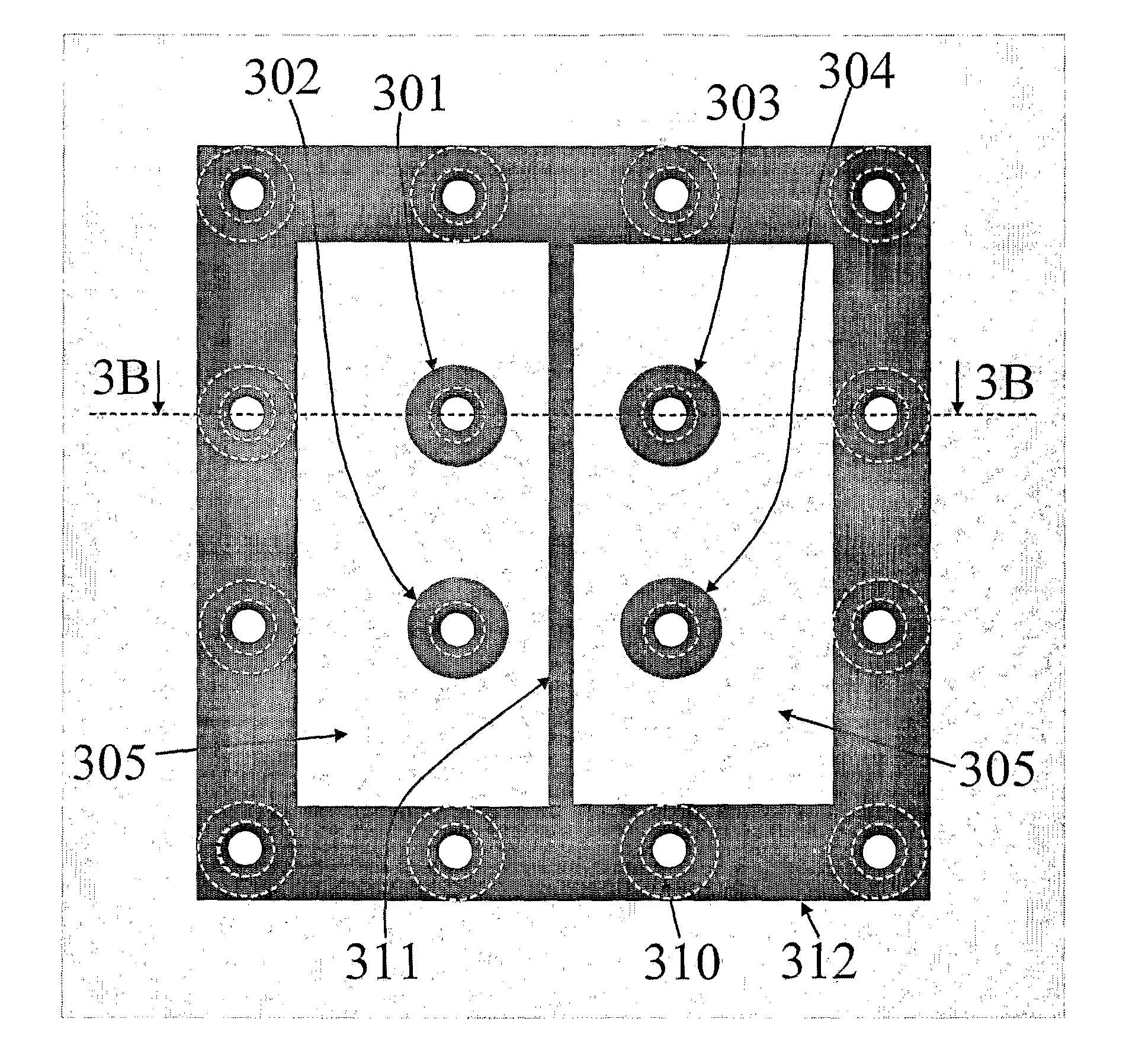

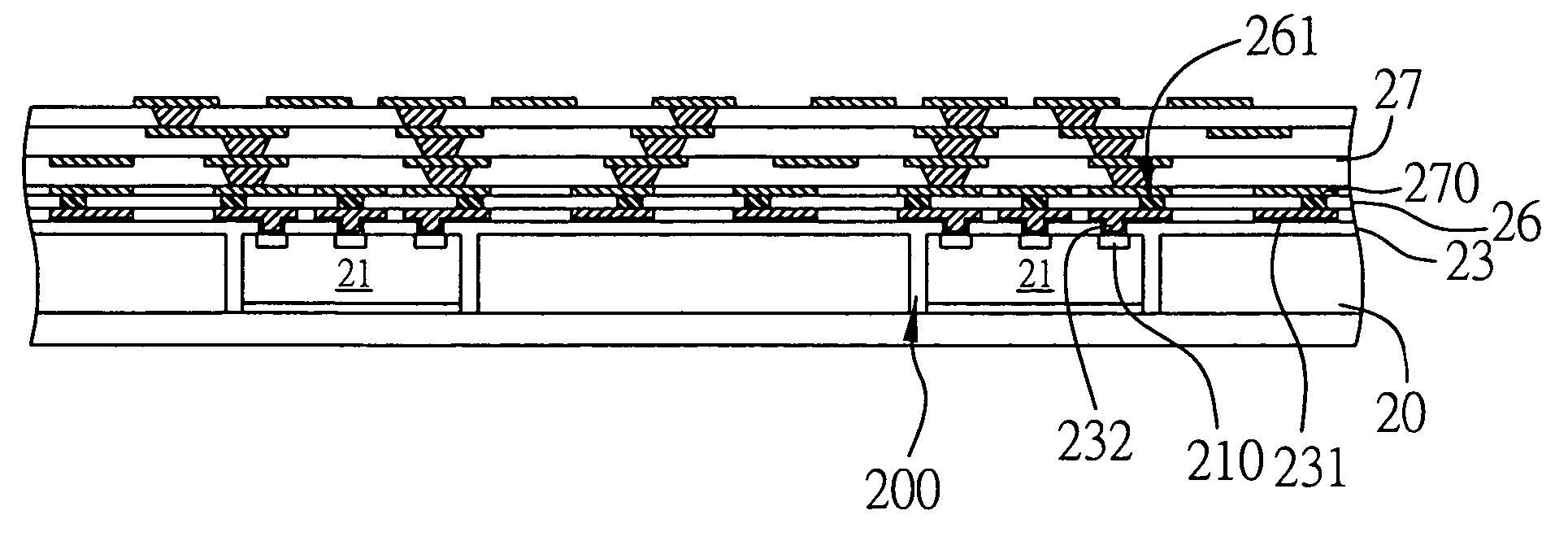

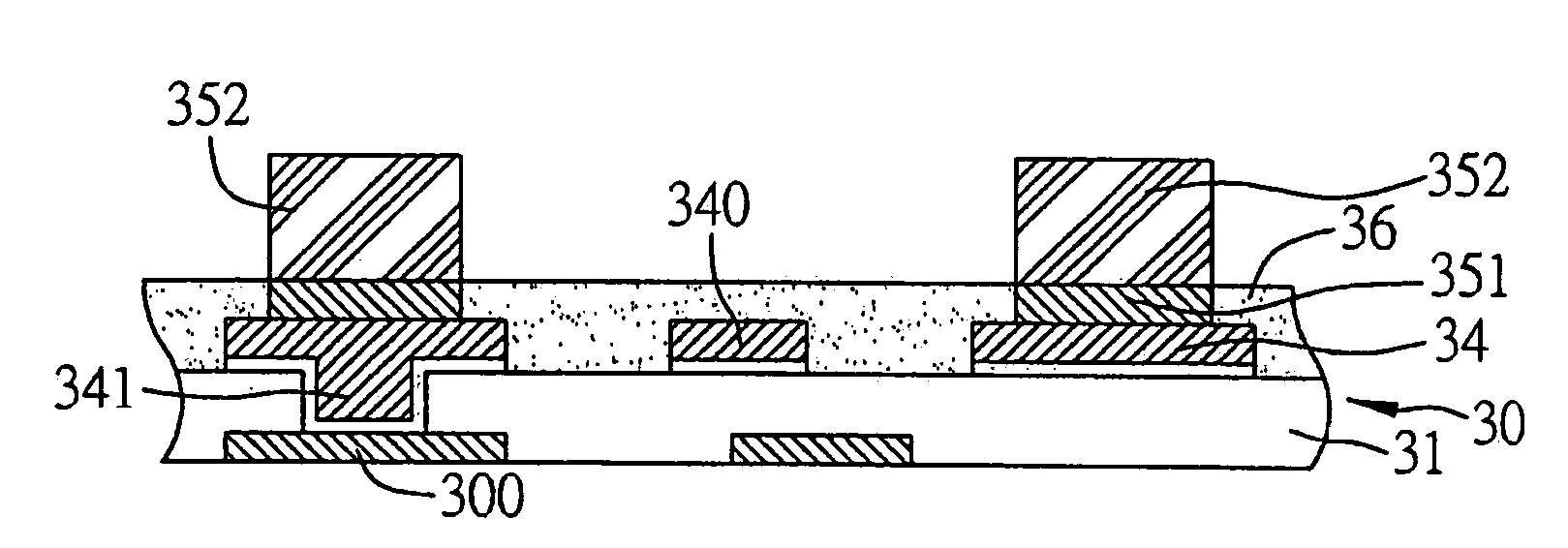

Semiconductor package structure and method for fabricating the same

InactiveUS20060125080A1Avoid lostFabrication cost is increasedSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSemiconductor package

A semiconductor package structure and a method for fabricating the same are proposed. A carrier having at least one cavity is provided. At least one semiconductor chip having electrode pads is mounted in the cavity. A dielectric layer is applied on the carrier and the chip, and has vias for exposing the electrode pads of the chip. A circuit layer and conductive structures are formed on the dielectric layer and in the vias, wherein the conductive structures are electrically connected to the electrode pads of the chip. A conductive adhesive layer having conductive adhesive posts and a circuit board having conductive pads thereon are provided. The circuit board is mounted on the carrier via the conductive adhesive layer. The conductive pads of the circuit board are electrically connected to the circuit layer by the conductive adhesive posts and are further electrically connected to the electrode pads of the chip.

Owner:PHOENIX PRECISION TECH CORP

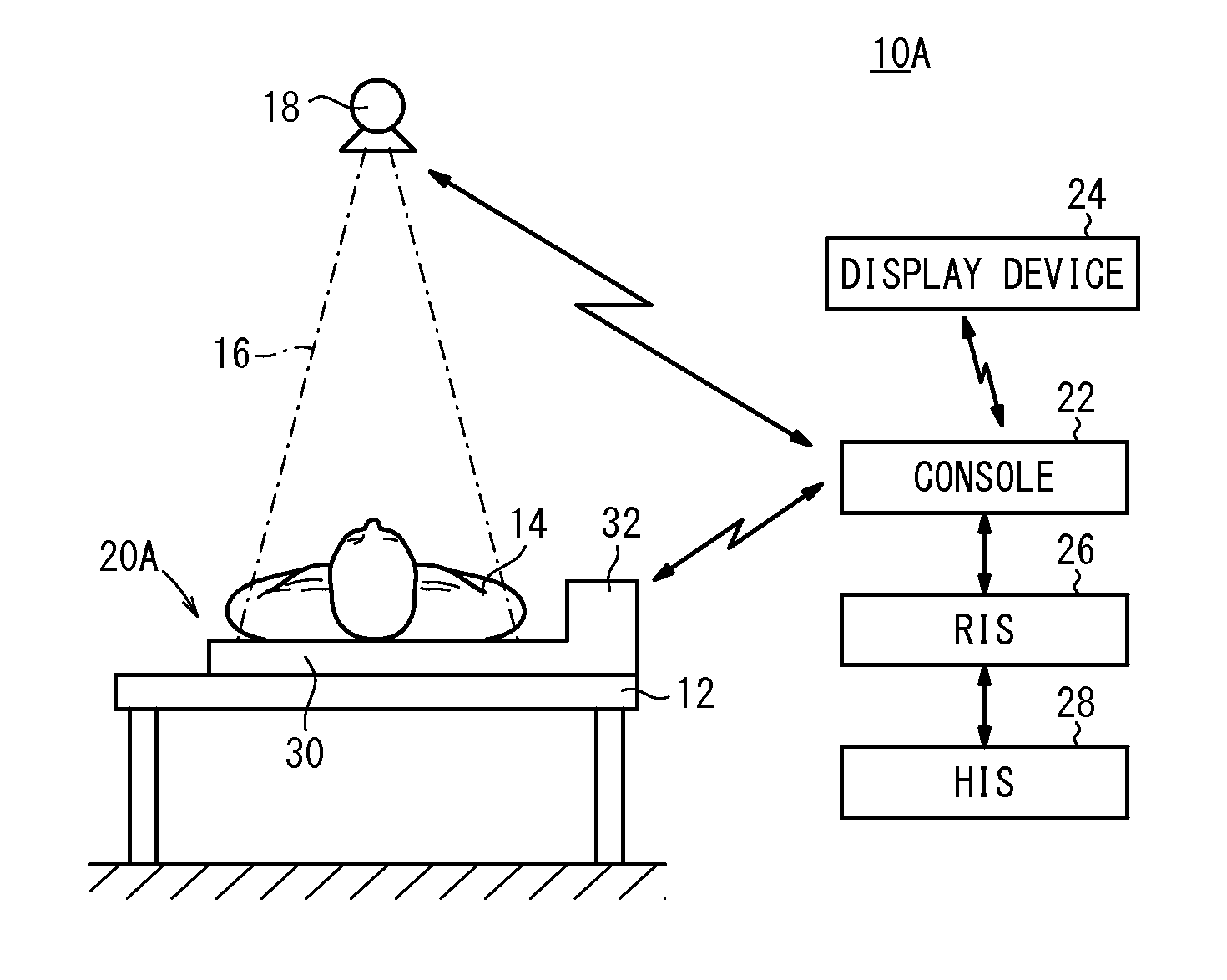

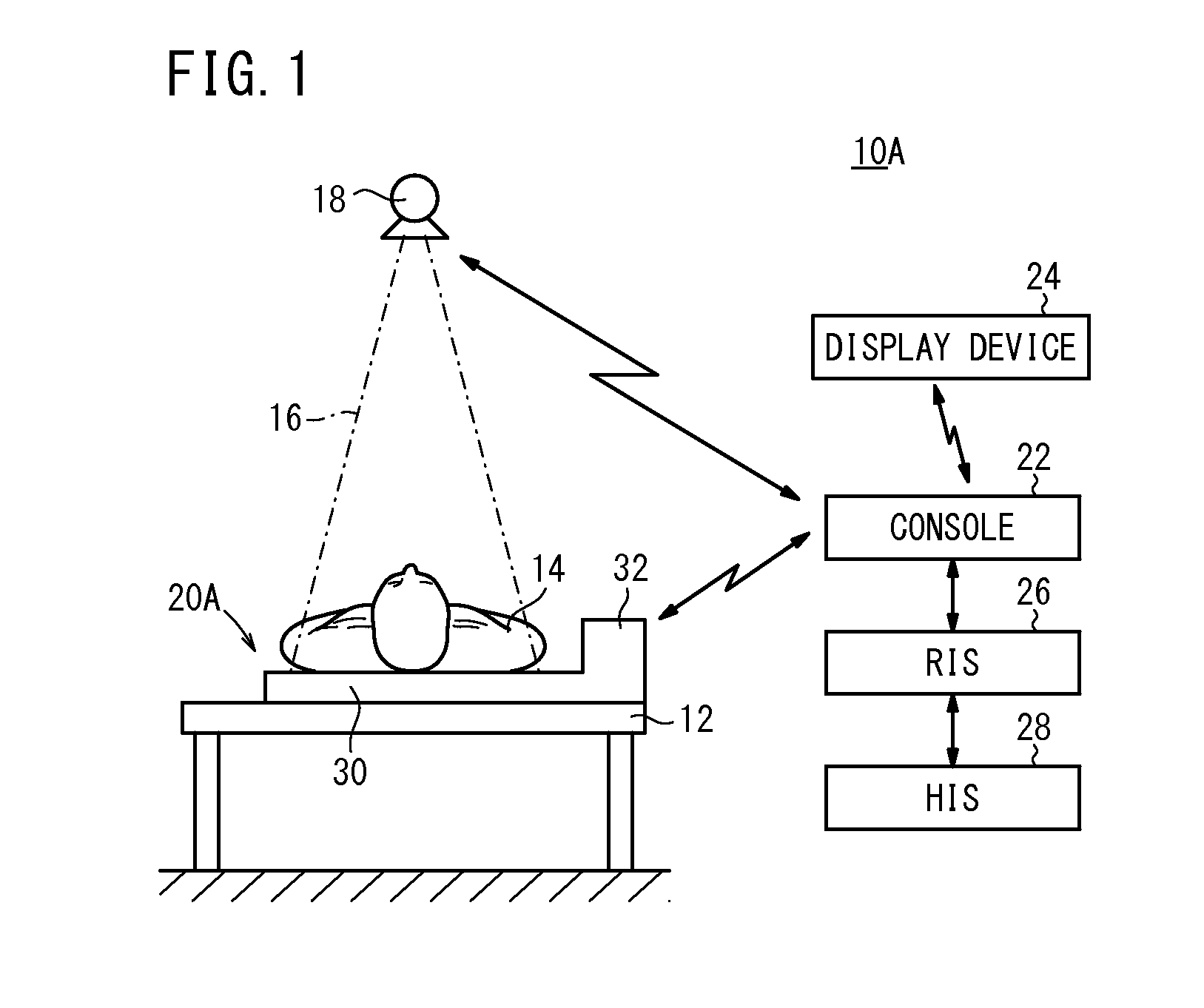

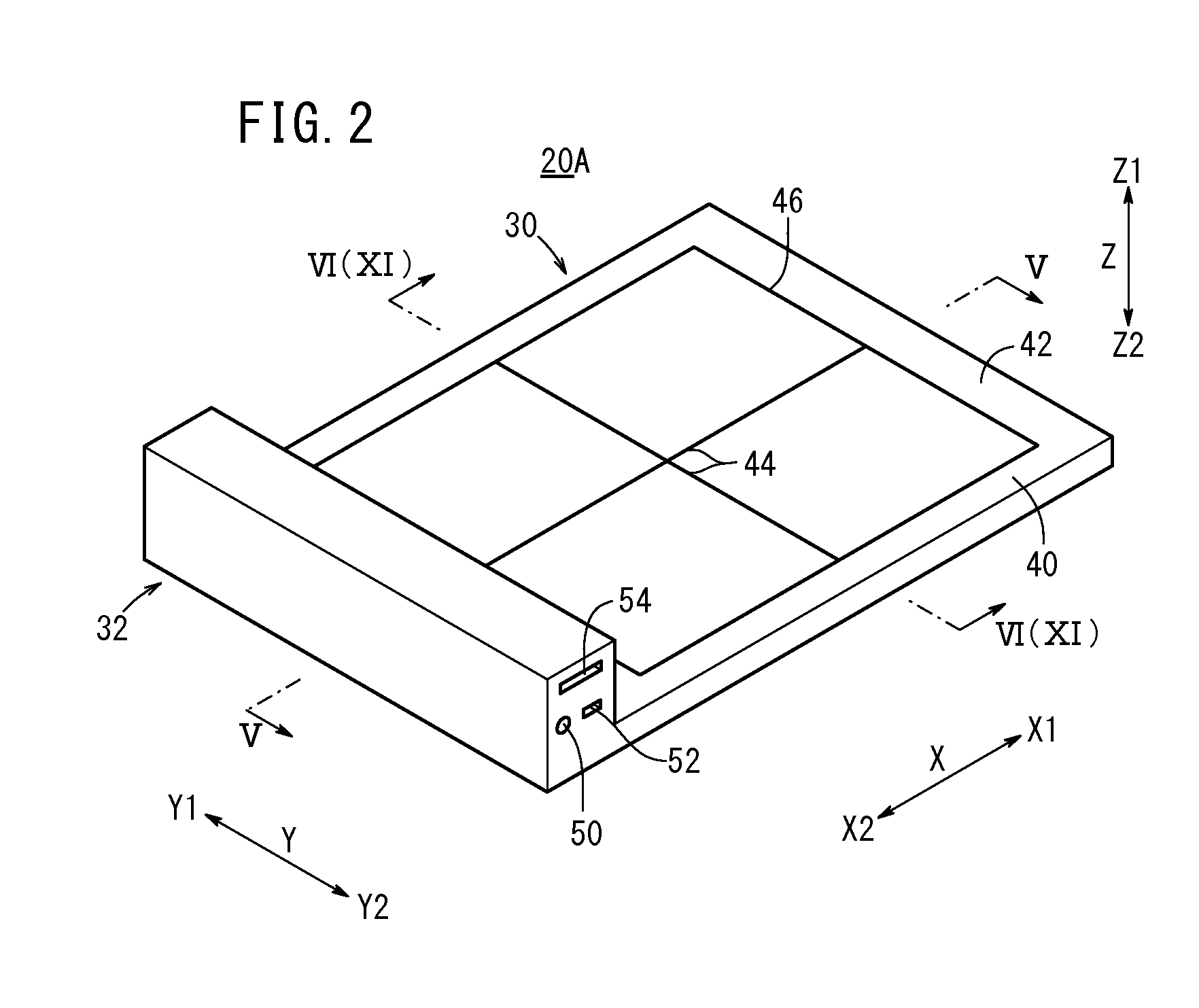

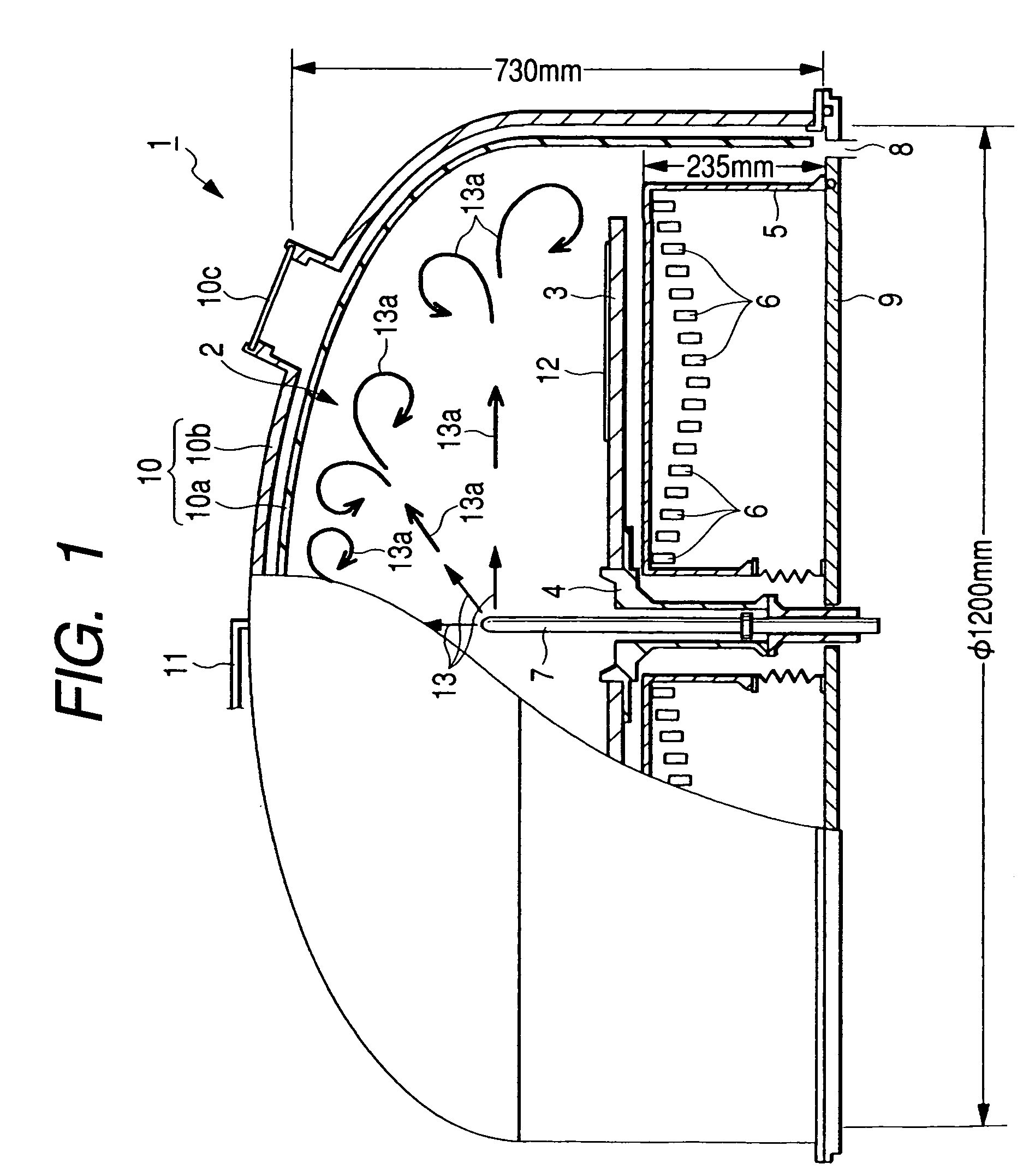

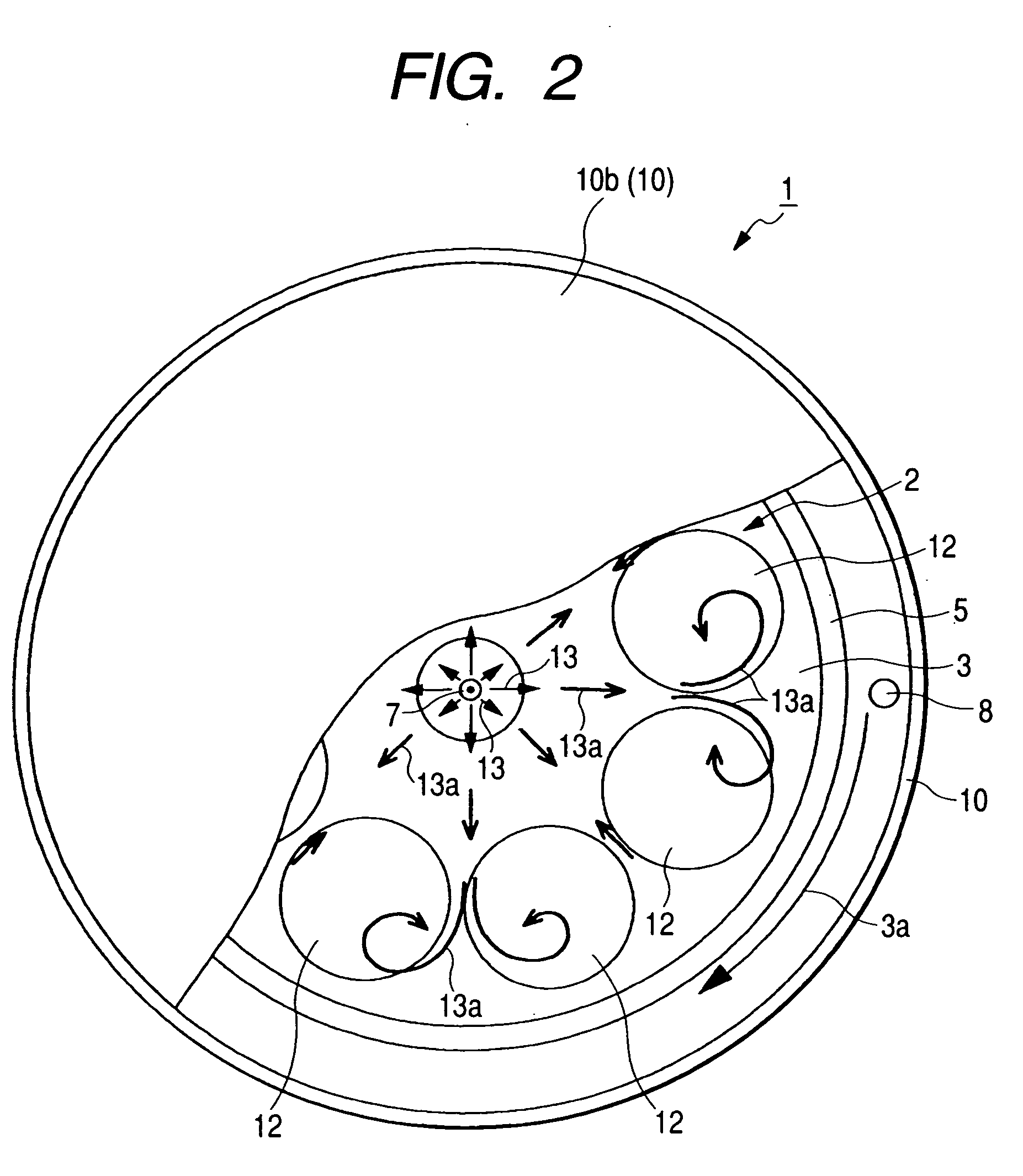

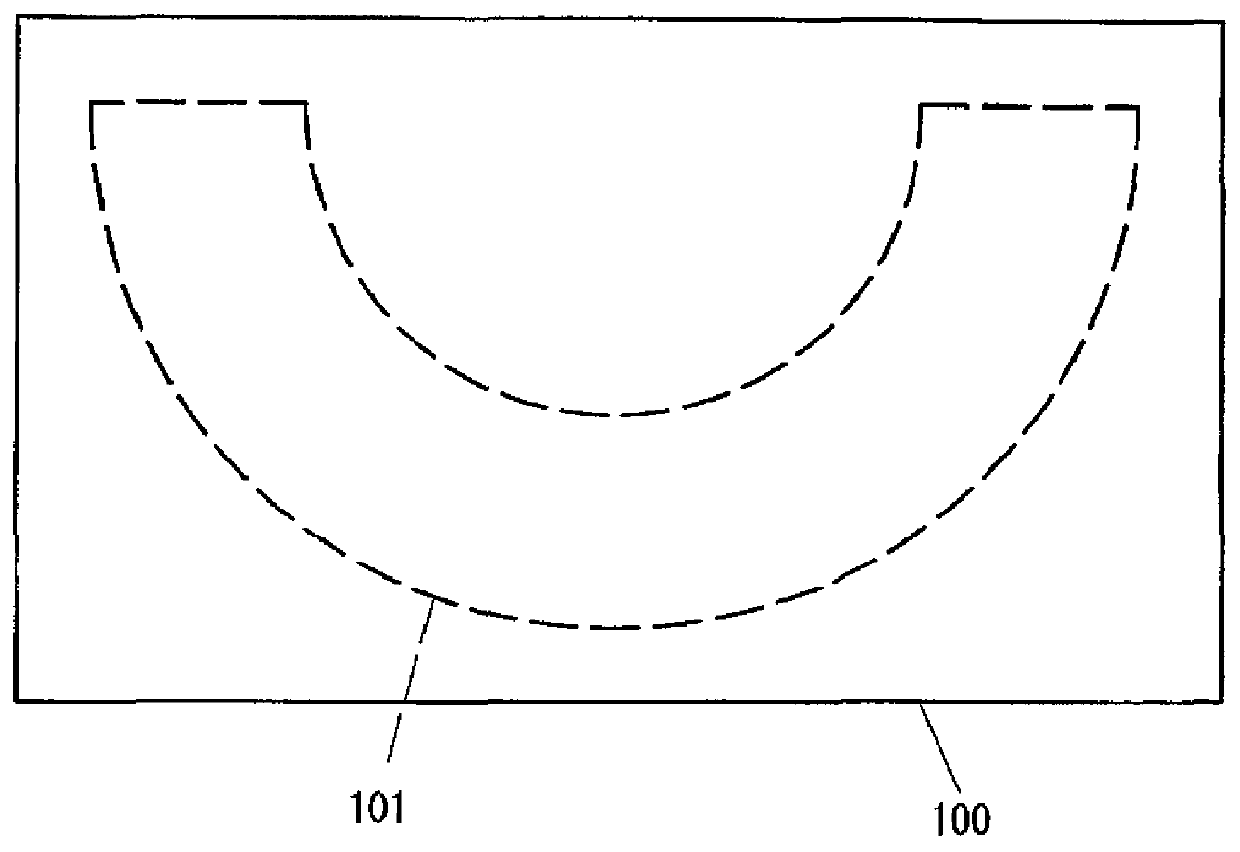

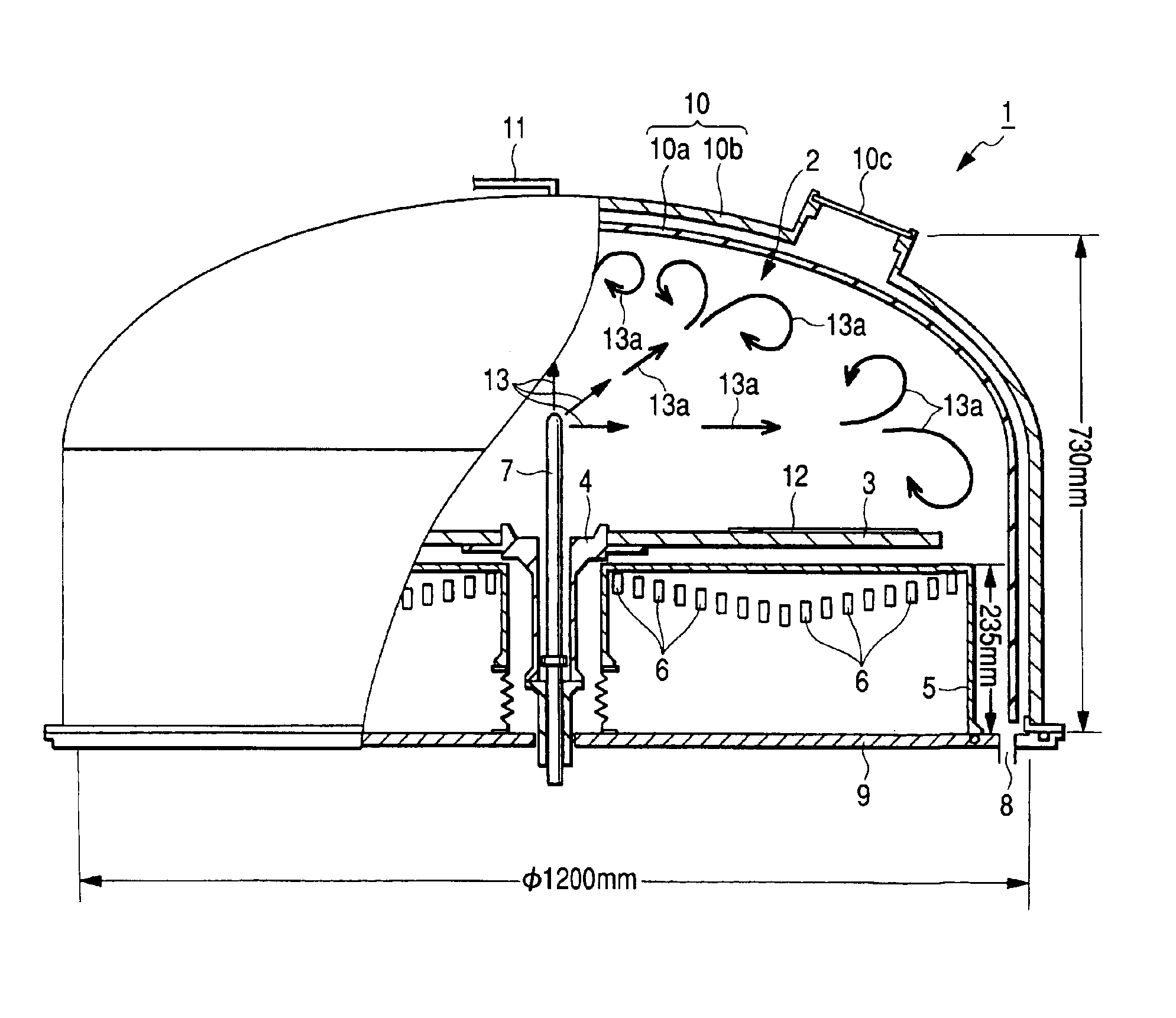

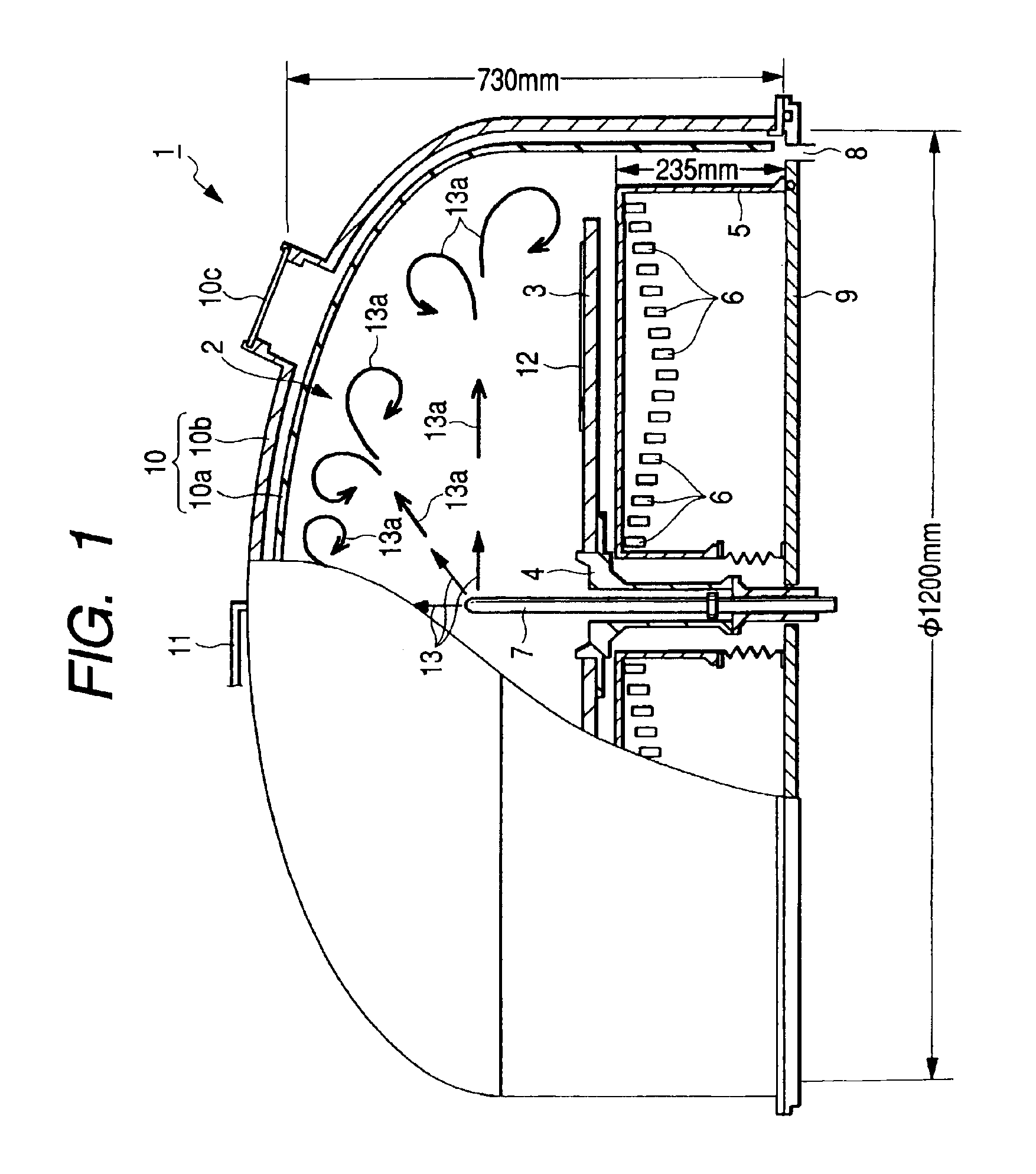

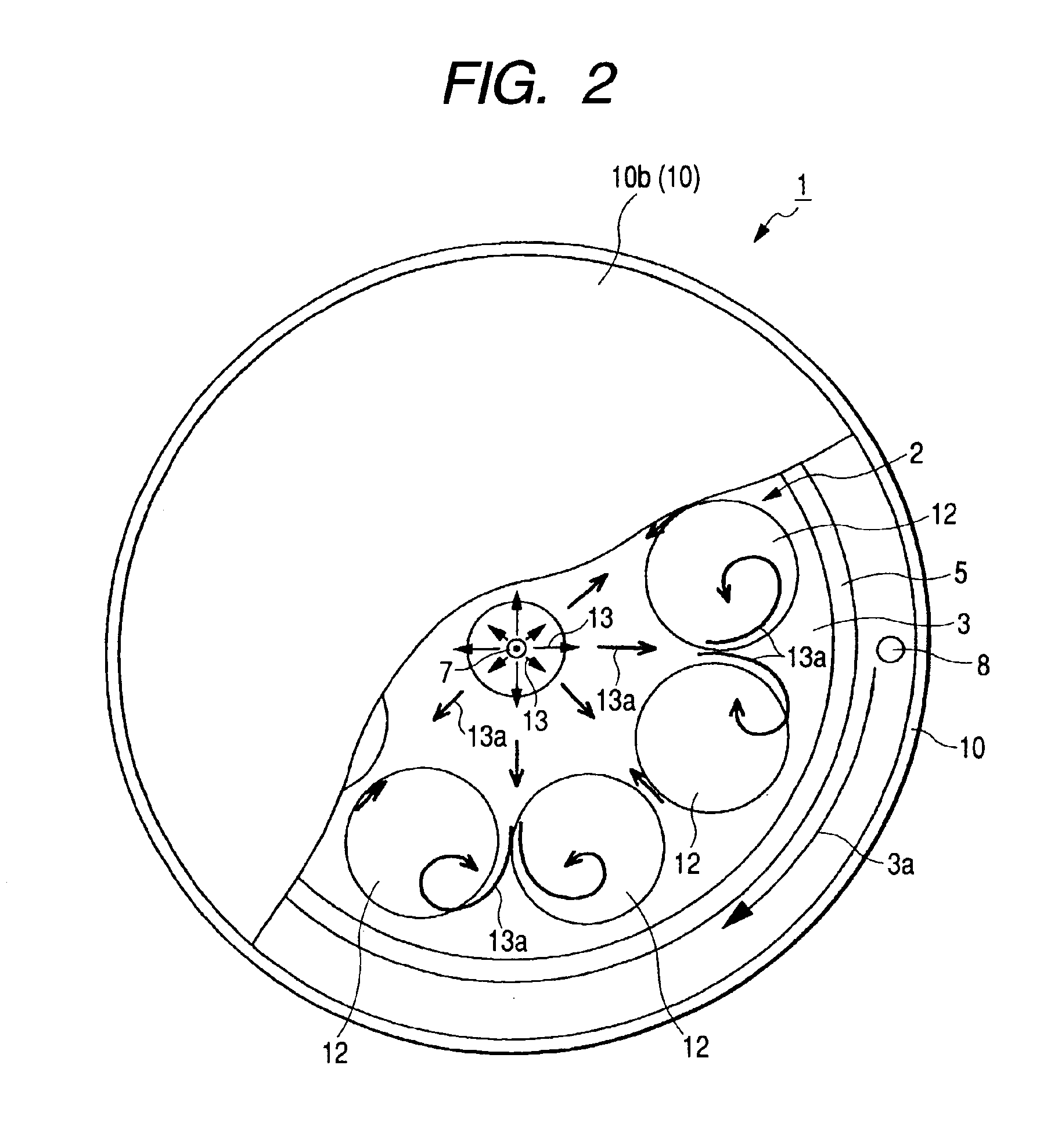

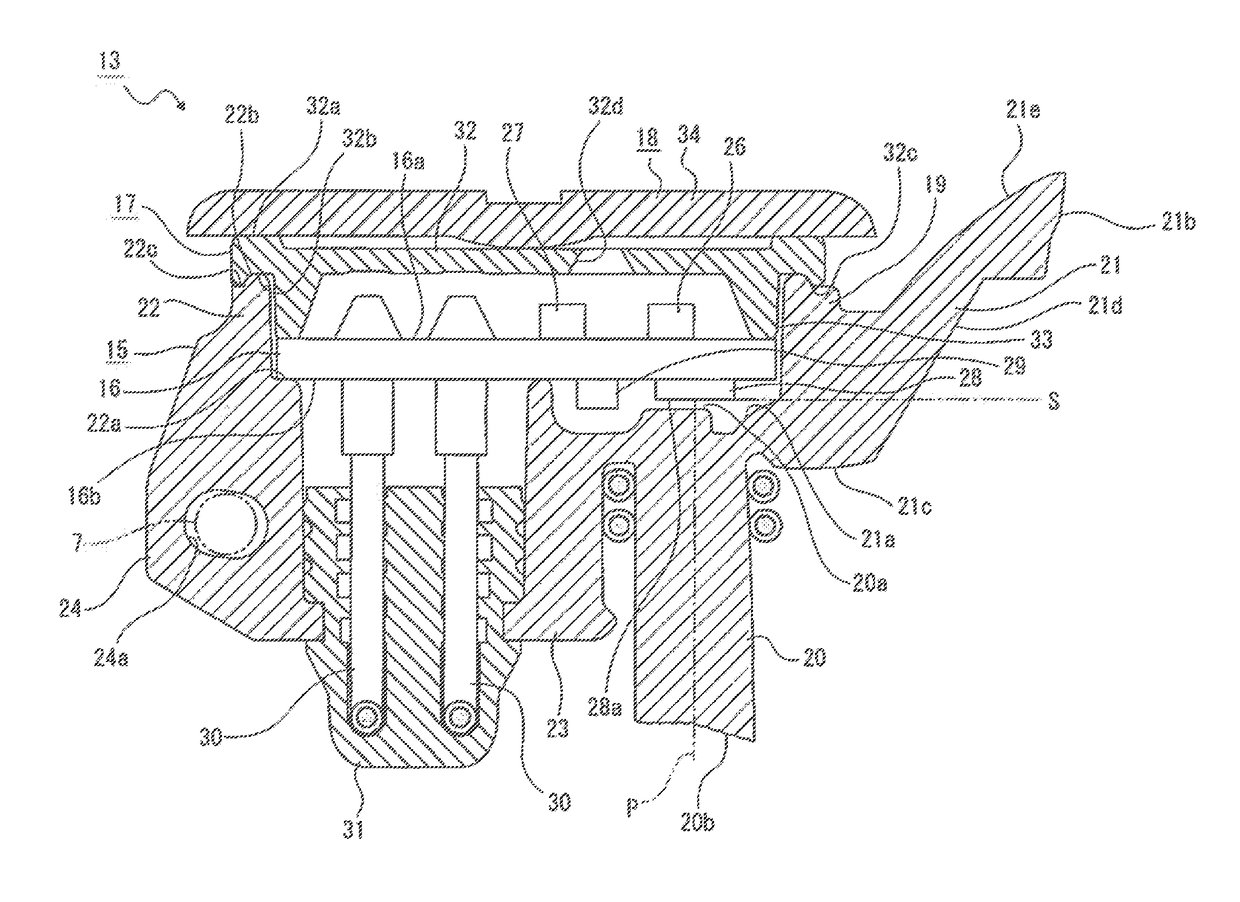

Radiological imaging device

InactiveUS20130092840A1Small weightSmall thicknessMaterial analysis by optical meansRadiation diagnosticsPhotoelectric conversionScintillator

Disclosed is a radiological imaging device which comprises: a radiation conversion panel which is obtained by laminating a scintillator and a photoelectric conversion layer and converts a radiation ray into a radiation image; a base which supports the radiation conversion panel mounted thereon; and a case which houses the radiation conversion panel and the base. The base supports the radiation conversion panel, while deforming the radiation conversion panel into a convex shape with respect to the mounting direction thereof.

Owner:FUJIFILM CORP

Fabrication method of semiconductor device and semiconductor device

InactiveUS20050173705A1Fabrication cost is increasedForming speed of silicon-germanium film is relatively smallPolycrystalline material growthFrom solid stateDevice materialAtmospheric pressure

Gases for film formation are introduced from a plurality of holes provided at a gas nozzle into a processing chamber of a batch-type CVD film-forming apparatus to cause a turbulence of the gases within the processing chamber. In the state where the chamber is kept at a pressure within an atmospheric and quasi-atmospheric pressure region, a silicon-germanium film is epitaxially grown on a semiconductor wafer placed within the processing chamber. Subsequently, a strained silicon film is epitaxially grown on the silicon-germanium film. Thereafter, a semiconductor element is formed in the semiconductor wafer on which the silicon-germanium film and the strained silicon film have been formed, respectively.

Owner:RENESAS TECH CORP +1

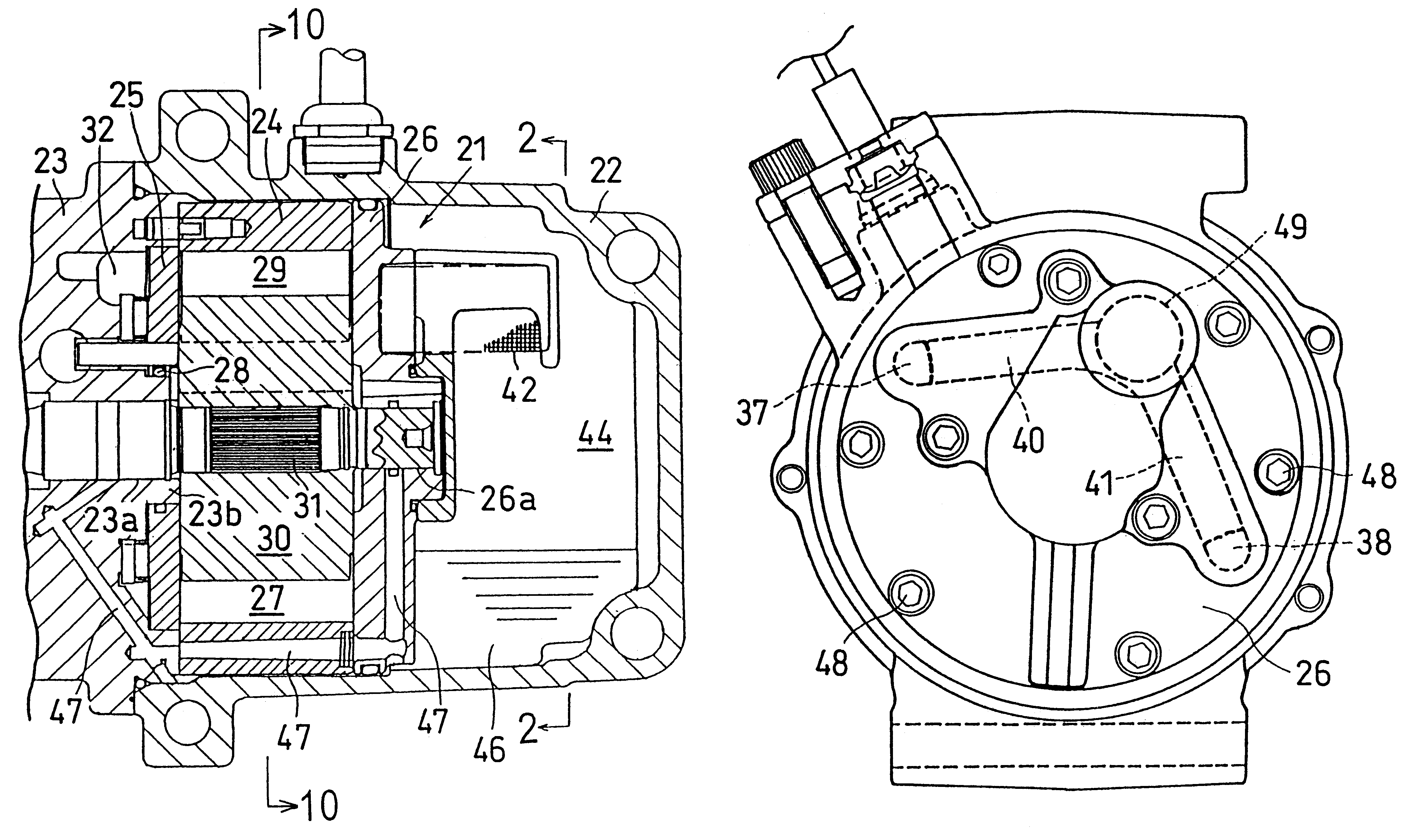

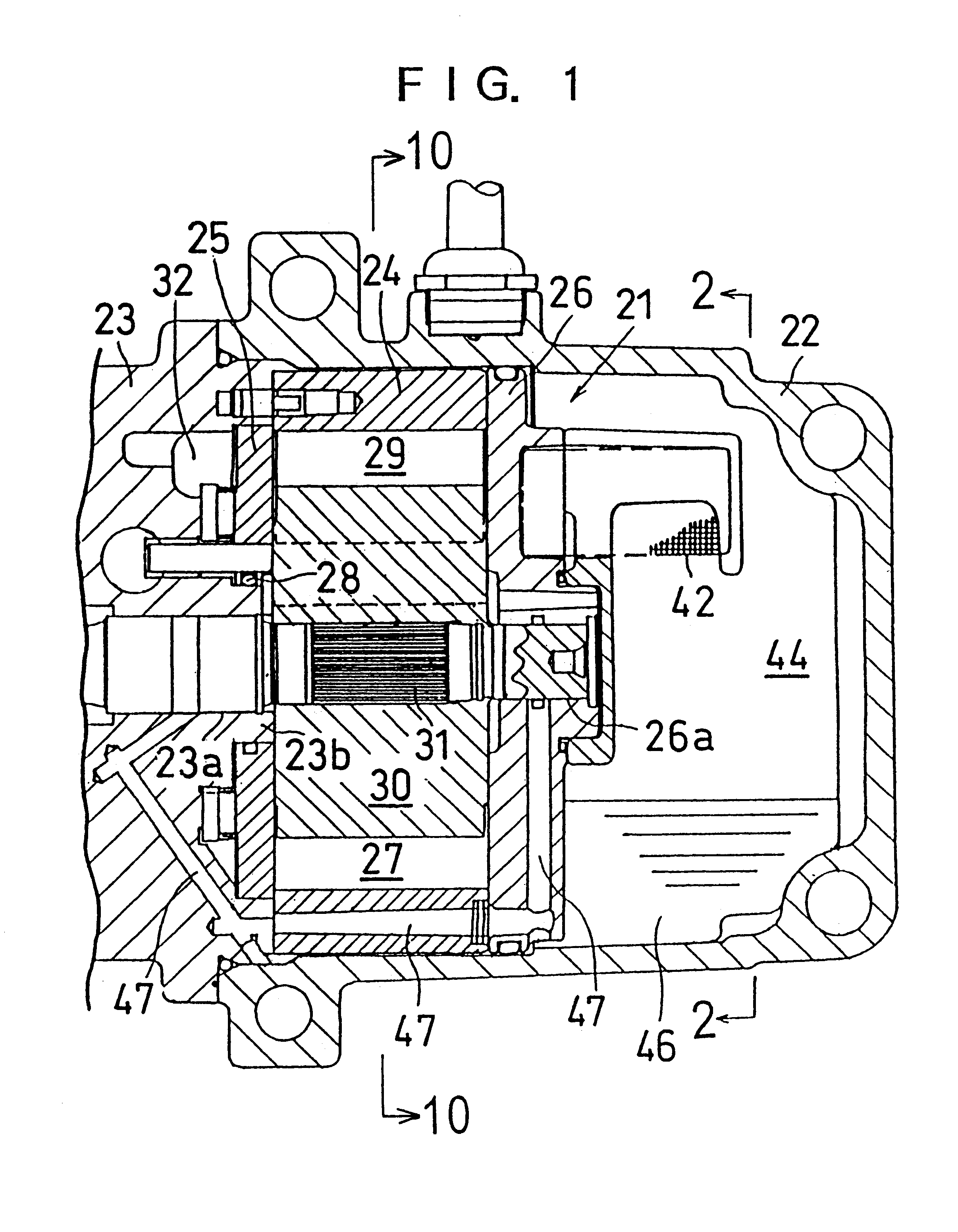

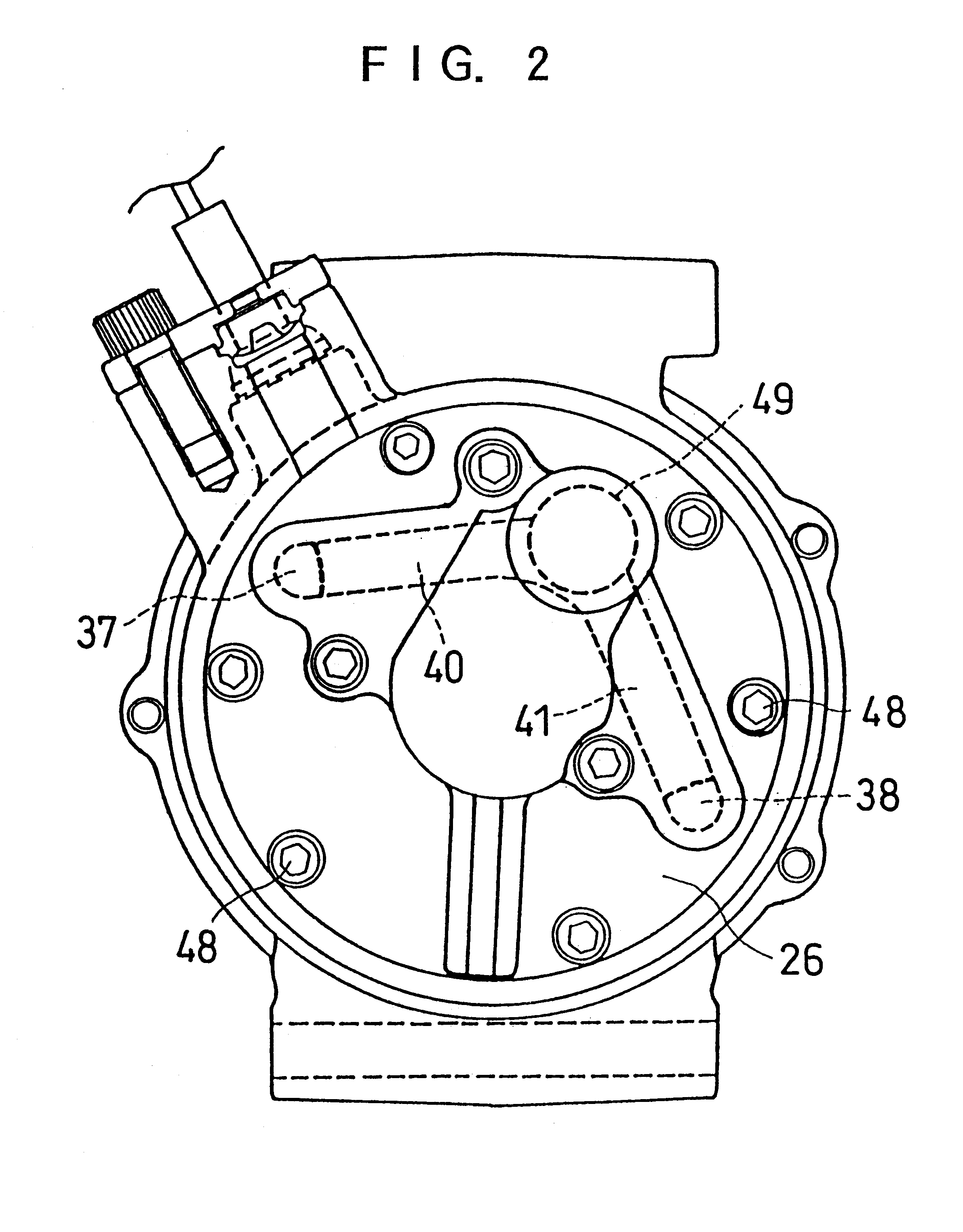

Vane gas compressor having two discharge passages with the same length

InactiveUS6872065B1Increases size of machineReduce noiseOscillating piston enginesRotary piston pumpsGas compressorEngineering

A gas compressor has a cylinder chamber provided with discharge holes. Openings are in communication with the discharge holes, respectively. Discharge passages having the same length are connected with the openings, respectively. The ends of the discharge passages are connected with a common passage. During operation of the cylinder chamber, discharge valves cause the expelled gas to produce pulsations on the upstream side of the two openings. The pulsations are shifted in phase by a half wavelength. Noise due to the pulsations is reduced, because the pulsations of the expelled gas cancel out each other when the gas flows through the common passage.

Owner:CALSONIC COMPRESSOR INC

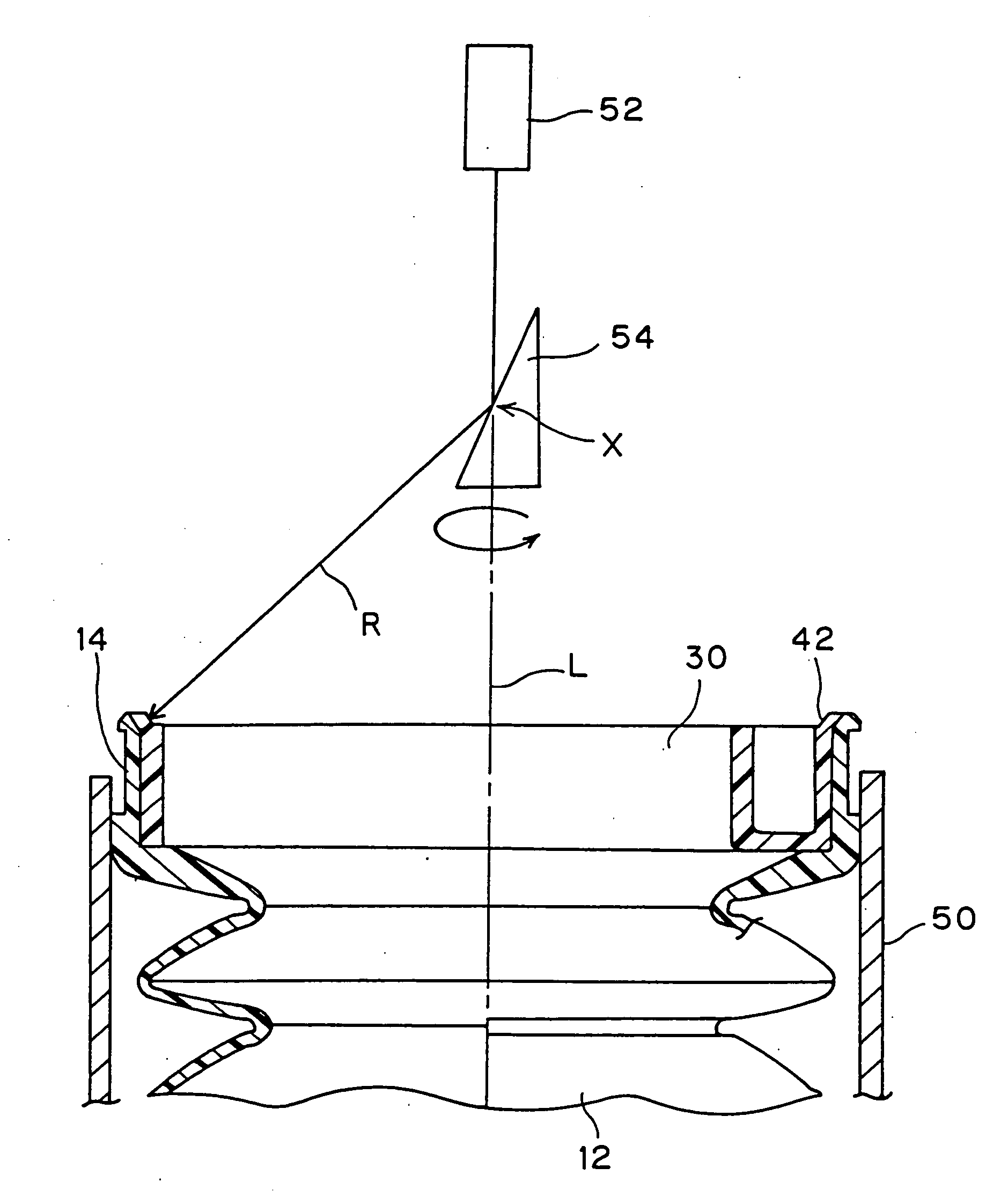

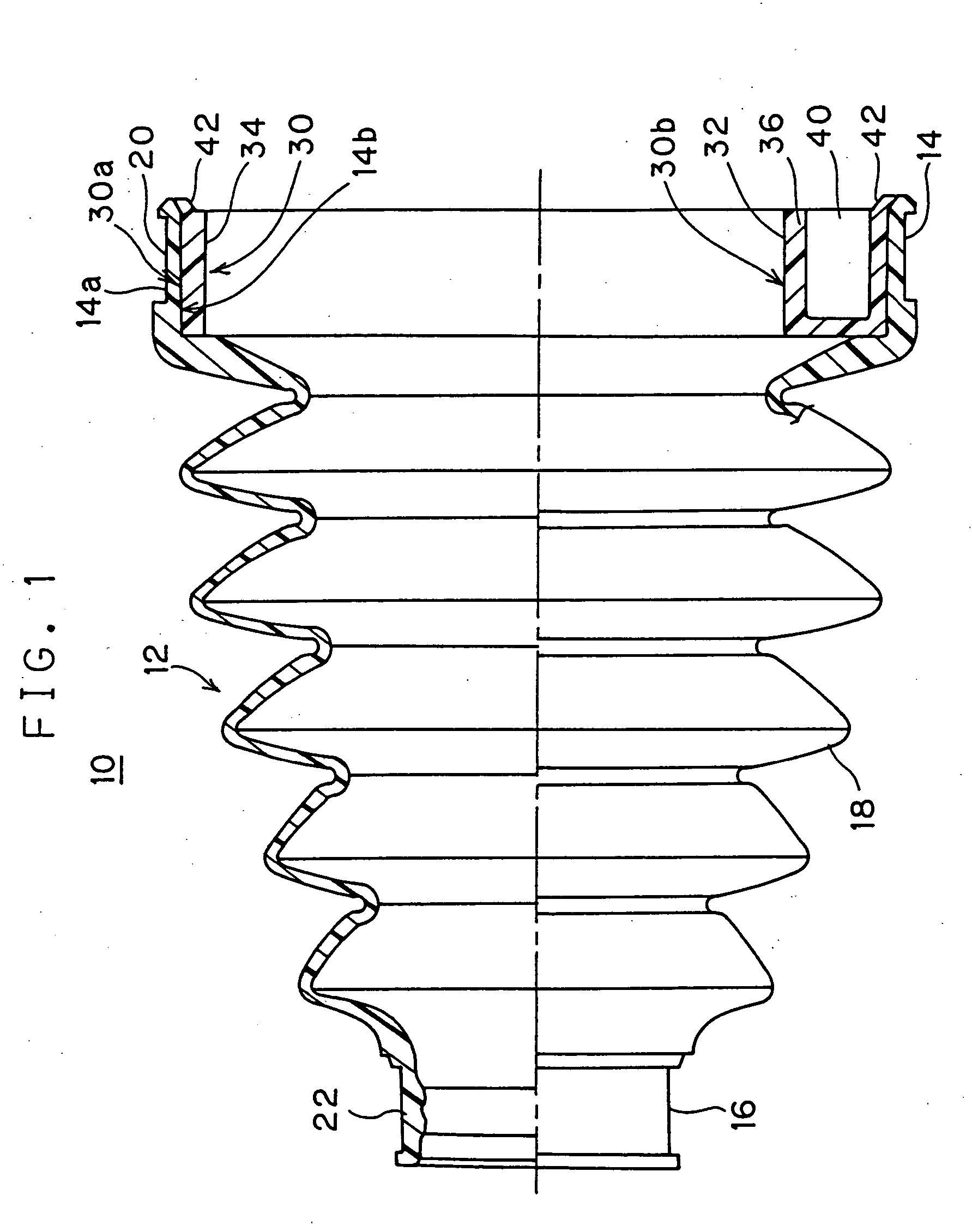

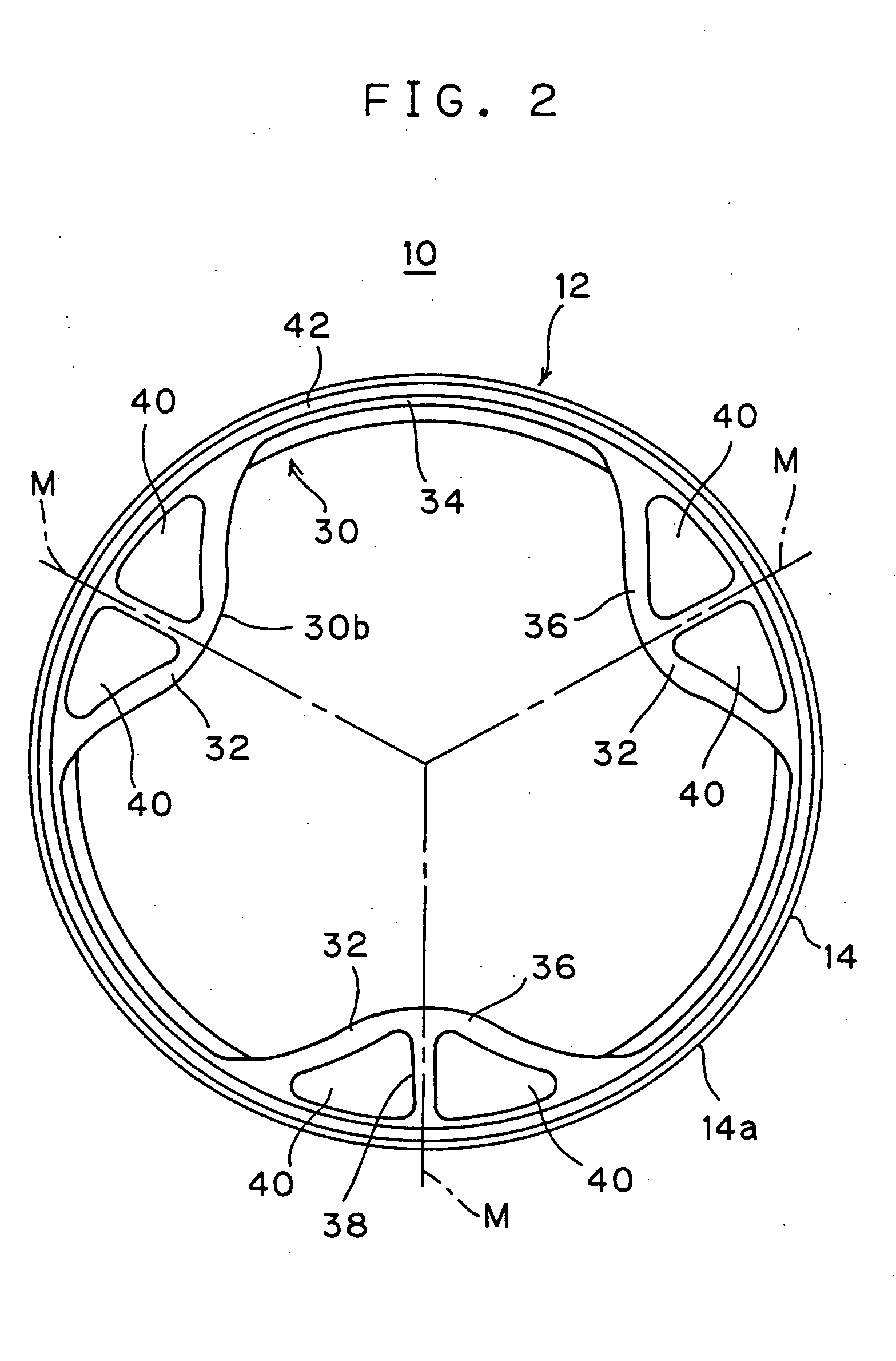

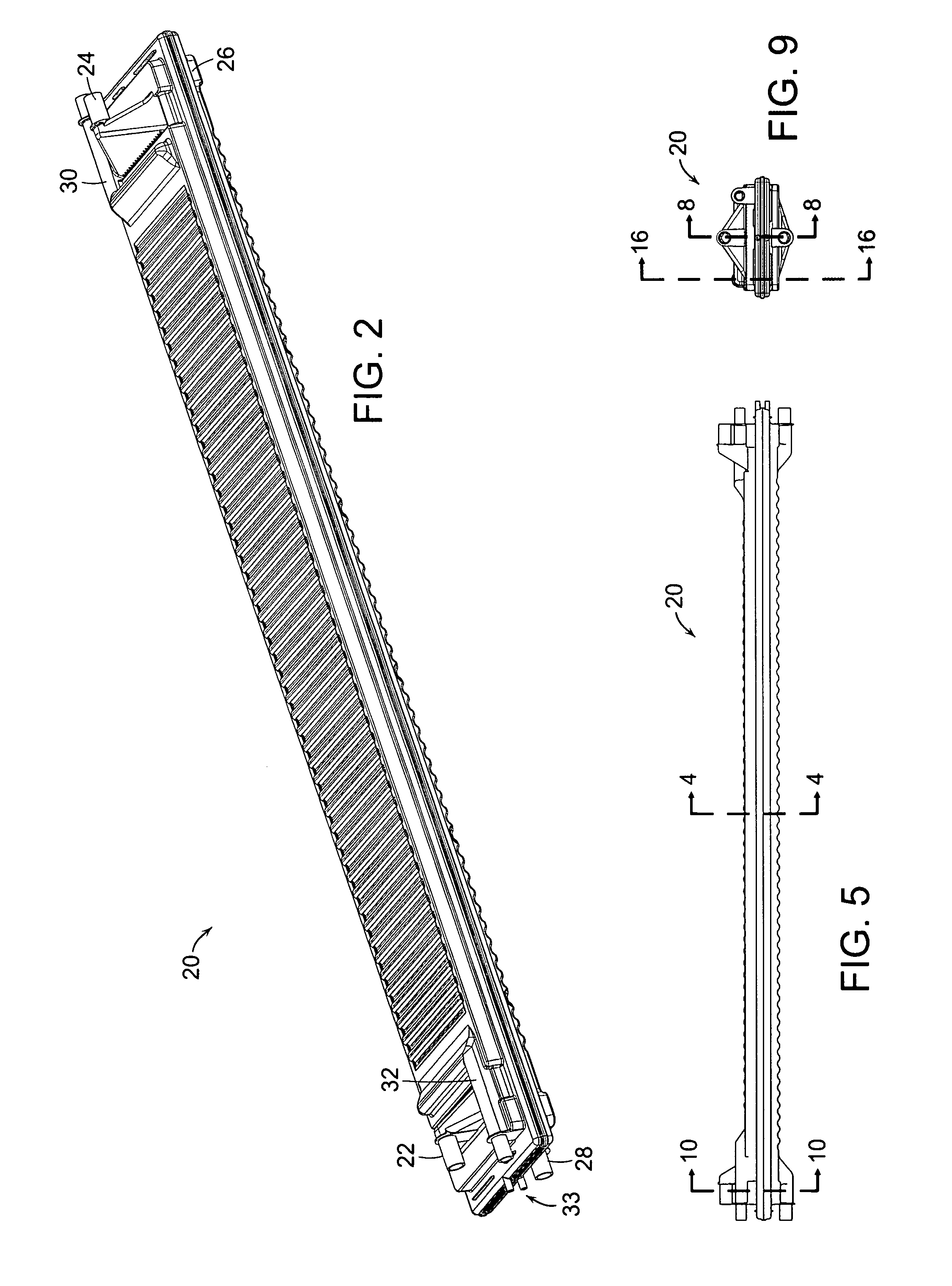

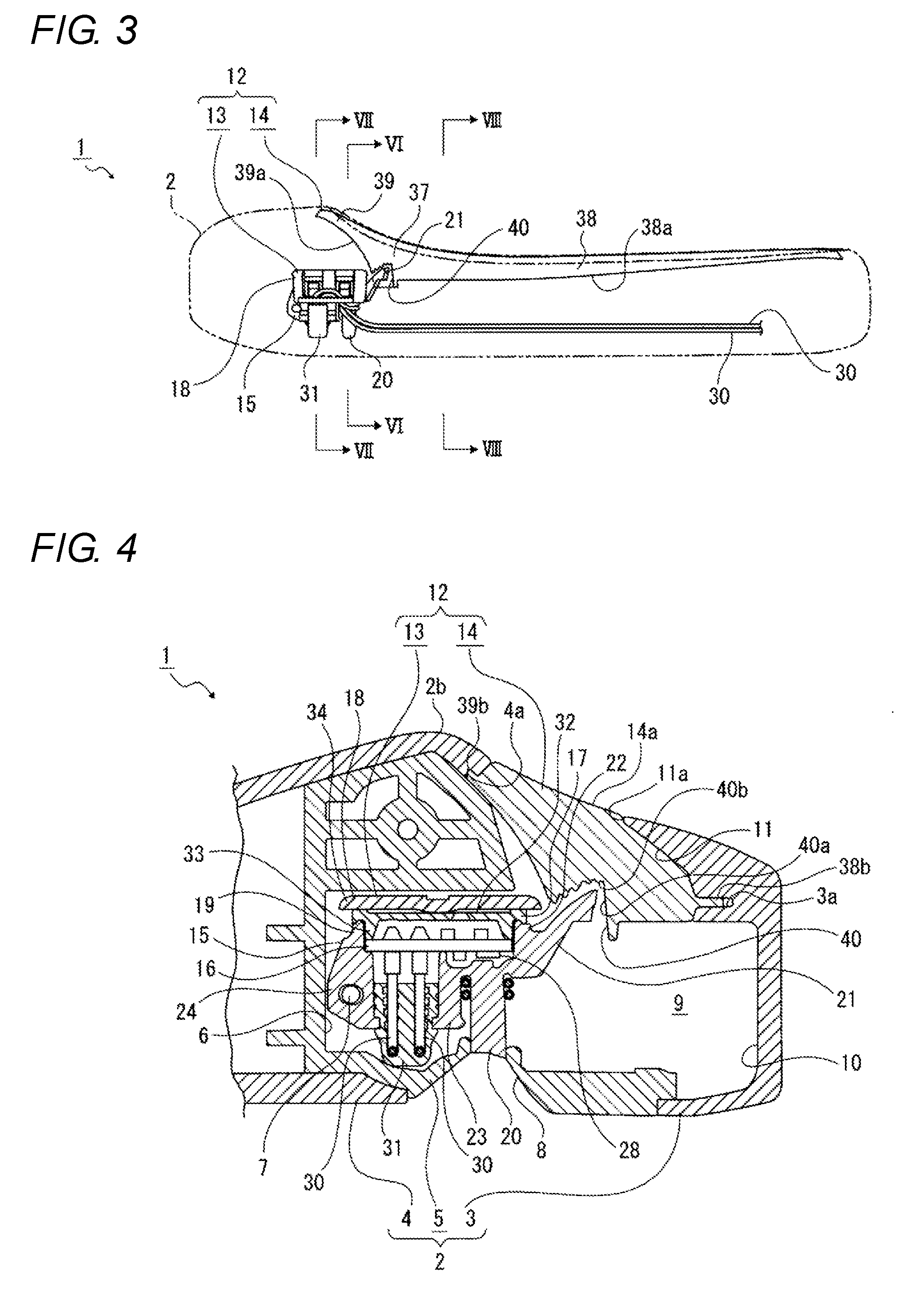

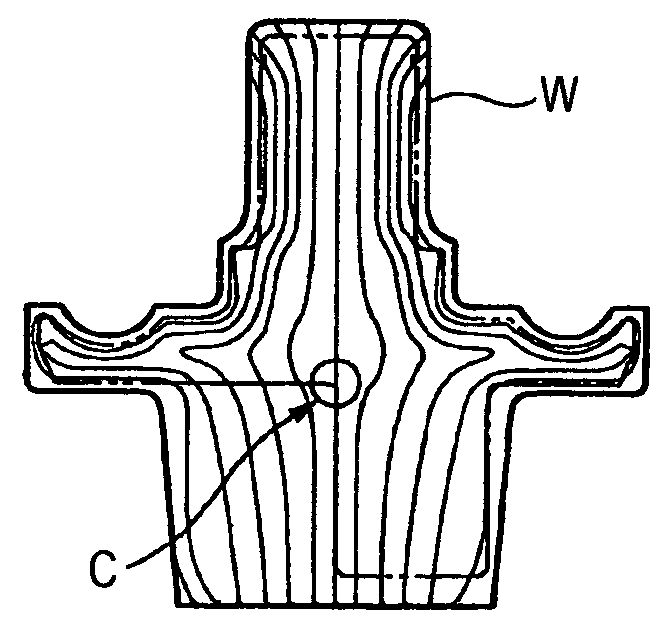

Method of producing resin joint boot

InactiveUS20060086457A1Improve mold precisionImprove sealingYielding couplingLamination ancillary operationsLaserWelding

A method of manufacturing a resin-made joint boot (10) provided with a boot body (12) including a large-diameter tubular part (14), a small-diameter tubular part (16) and a bellows section (18), and a bushing (30) fitted inside the large-diameter tubular part, wherein the boot body and the bushing are separately molded, the bushing is positioned inside the large-diameter tubular part of the boot body, and then, both are integrally fastened by laser welding. The large-diameter tubular part (14) is provided on its internal periphery with an outwardly divergent tilting surface (24) while the bushing (30) is provided with an annular projecting portion (42) to be abuttingly disposed on the tilting surface, and laser (R) is irradiated, penetrating through the annular projecting portion (42) onto the tilting surface (24).

Owner:TOYO TIRE & RUBBER CO LTD

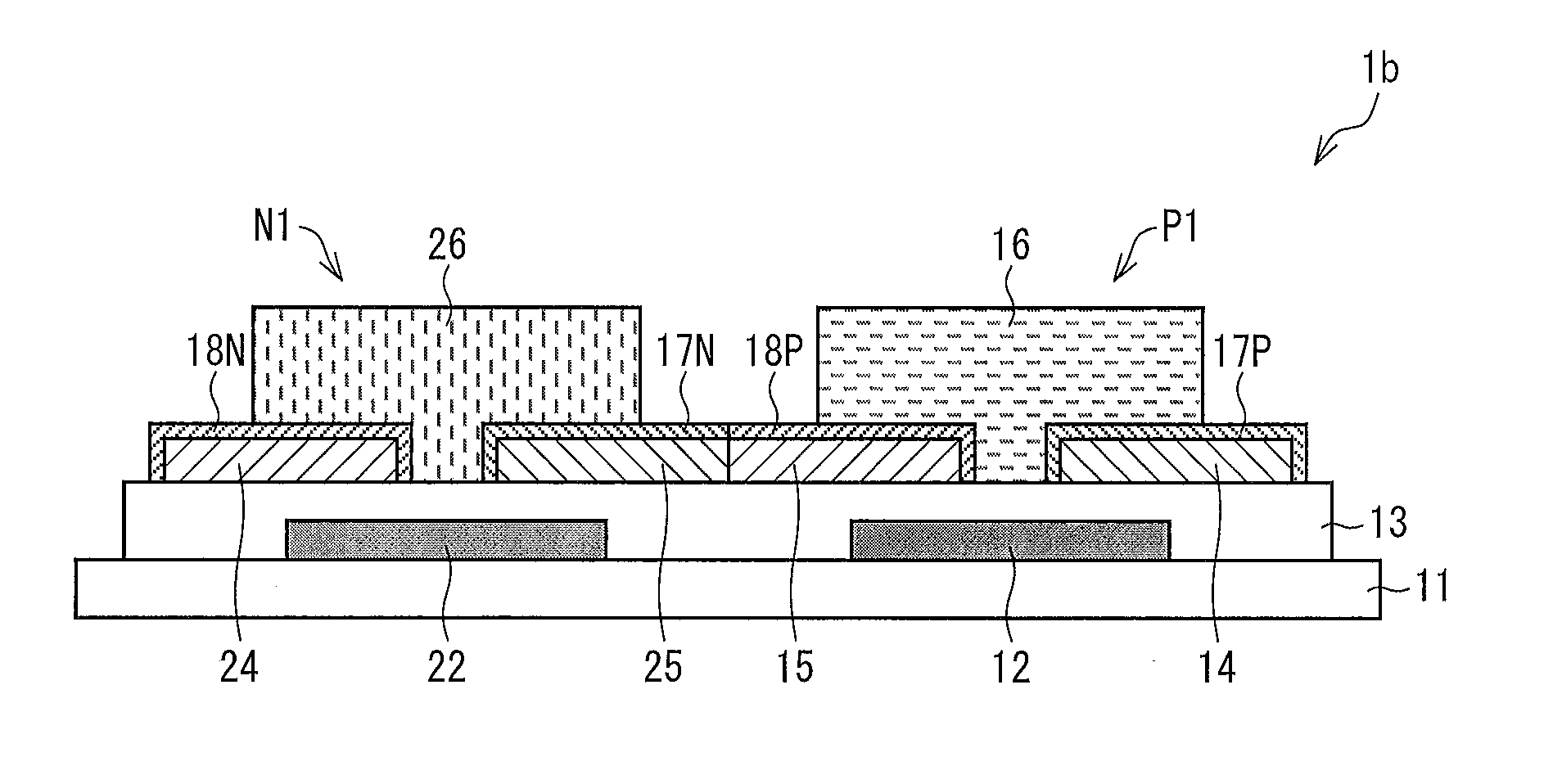

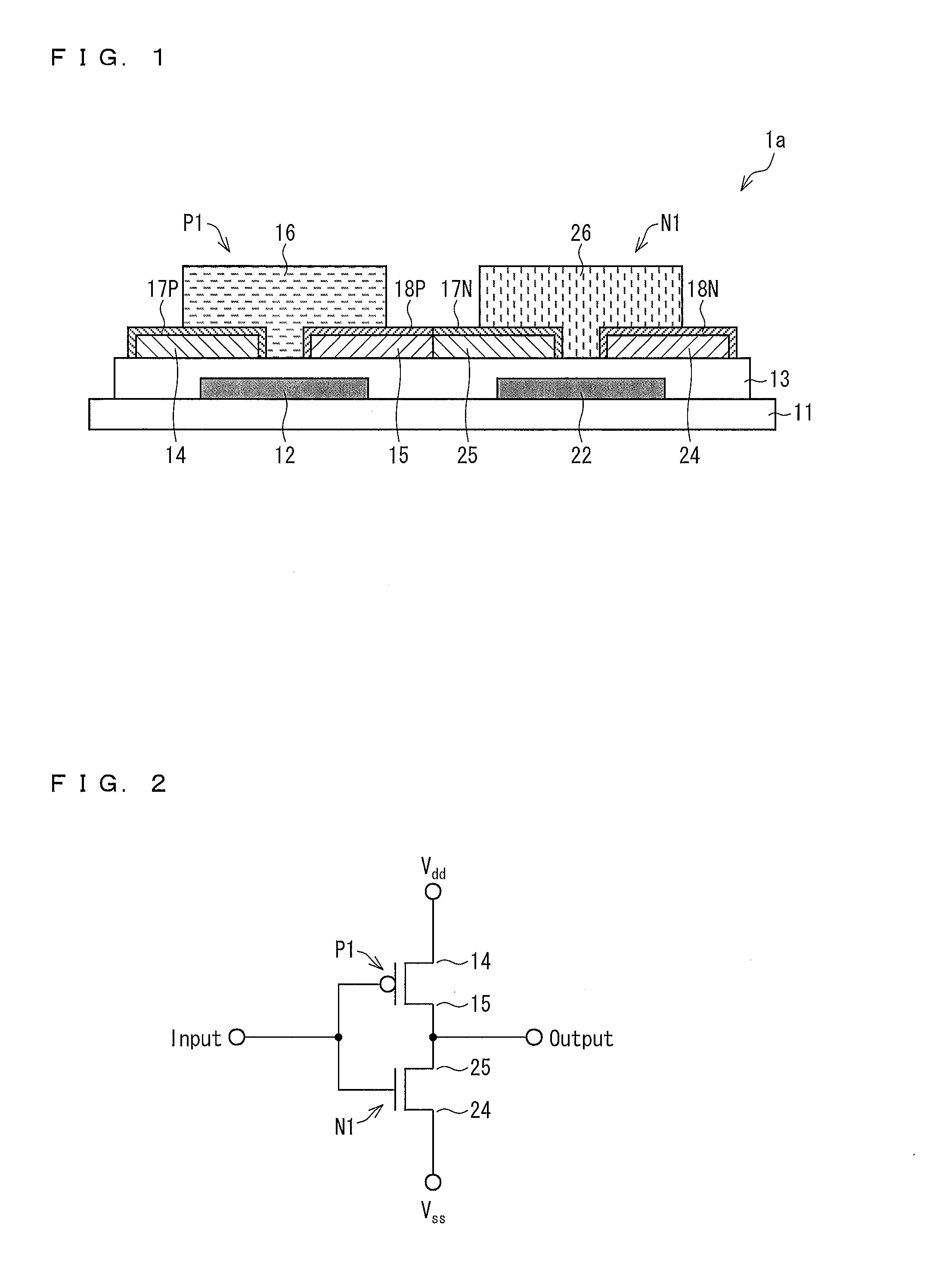

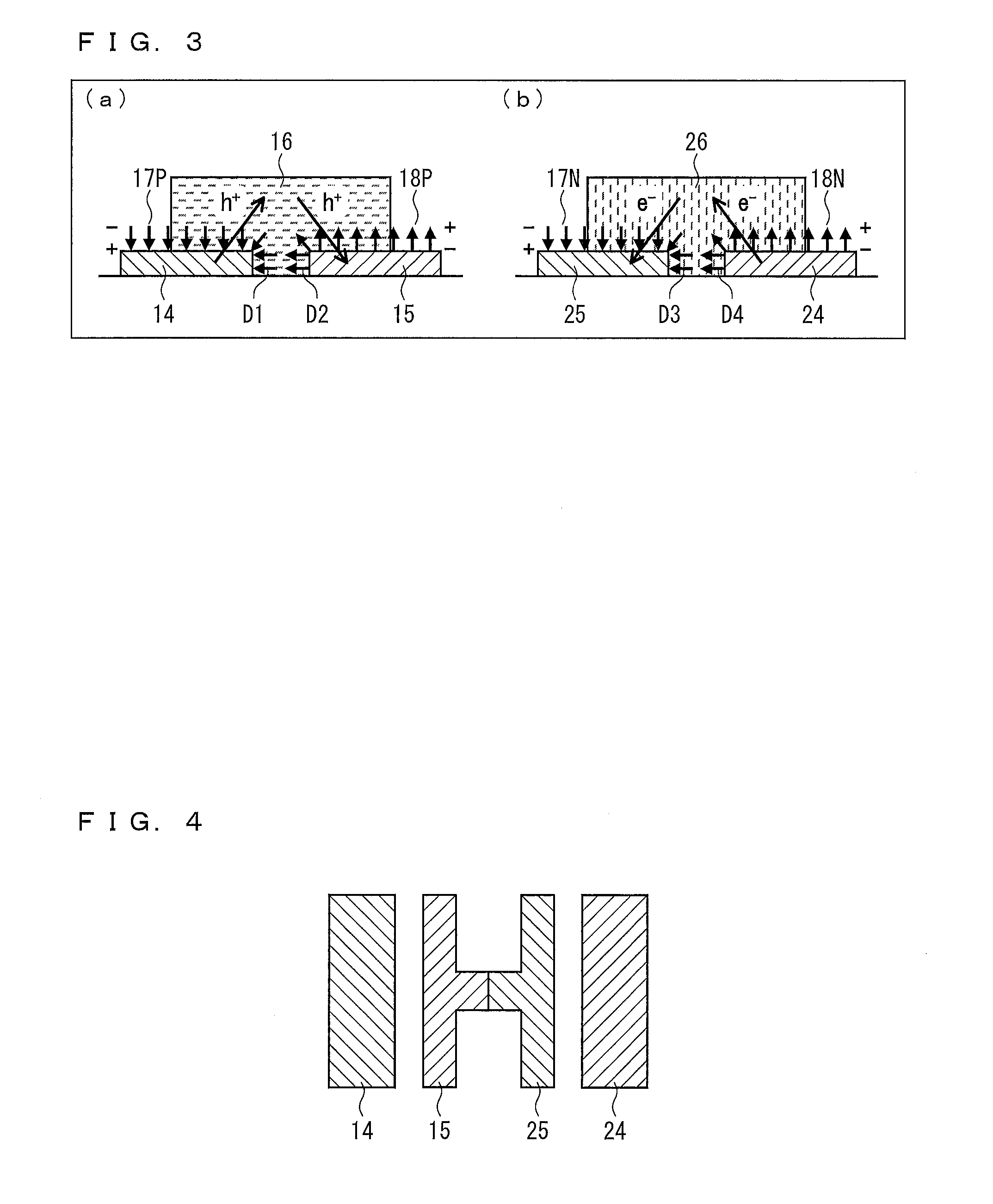

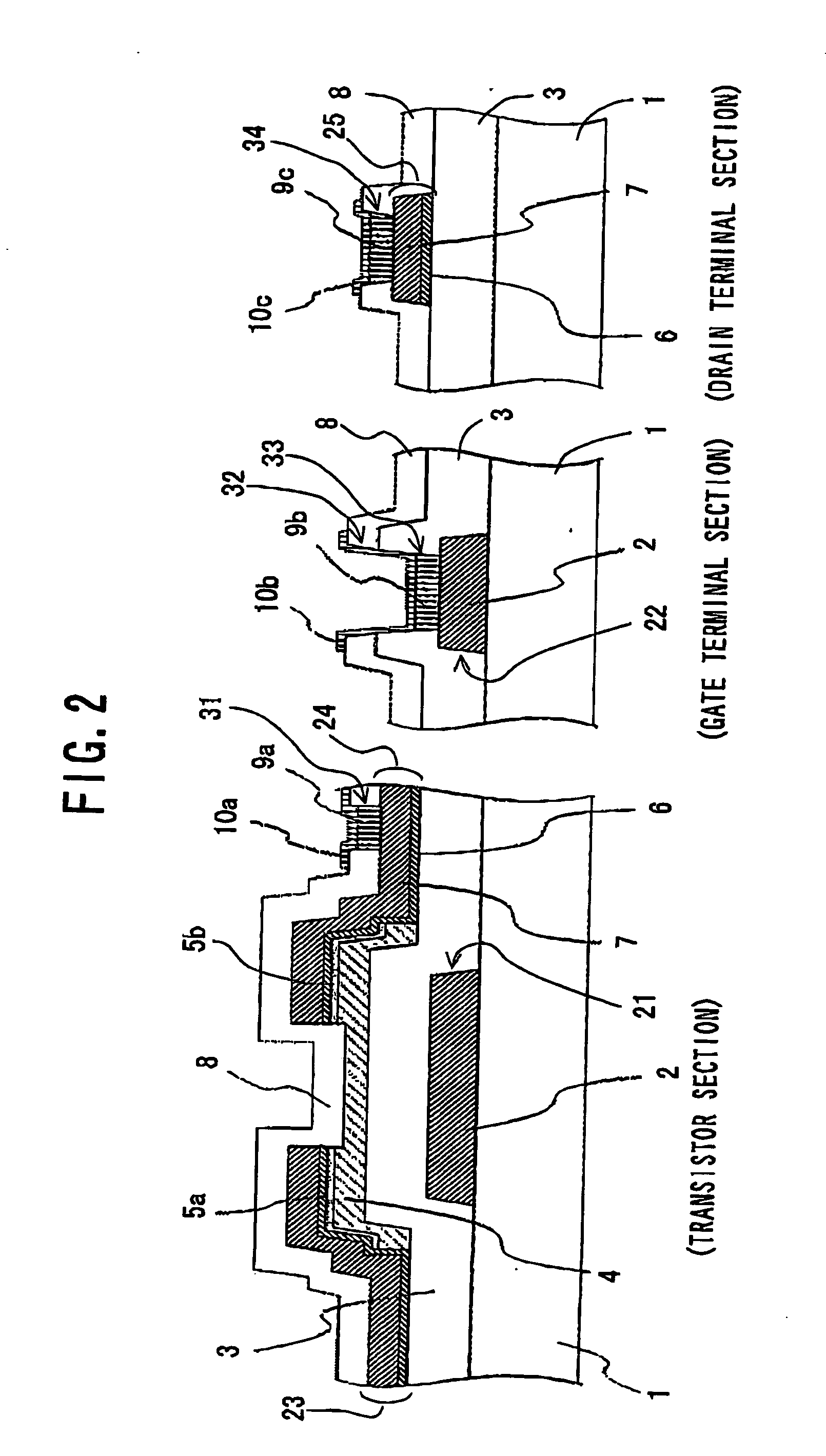

Semiconductor device and method for manufacturing semiconductor device

InactiveUS20120181538A1Prevent increase in fabrication costEnhance electric charge transferTransistorSolid-state devicesSecondary layerOrganic semiconductor

A semiconductor device (1a) which is constituted by organic semiconductors with excellent transistor characteristics and includes: a p-type organic transistor (P1) having a gate electrode (12), a source electrode (14), a drain electrode (15), and a p-type organic semiconductor layer (16); an n-type organic transistor (N1) electrically connected with the p-type organic transistor (P1) and having a gate electrode (22), a source electrode (24), a drain electrode (25), and an n-type organic semiconductor layer (26); first layers for enhancing electric charge transfer, one of the first layers being provided between the source electrode (14) and the organic semiconductor layer (16), the other of the first layers being provided between the drain electrode (25) and the organic semiconductor (26); and second layers for enhancing electric charge transfer and made from a different material from that of the first layers, one of the second layers being provided between the drain electrode (15) and the organic semiconductor layer (16), the other of the second layers being provided between the source electrode (24) and the organic semiconductor layer (26), all of the source electrodes and the drain electrodes being made from a same electrode material.

Owner:SHARP KK

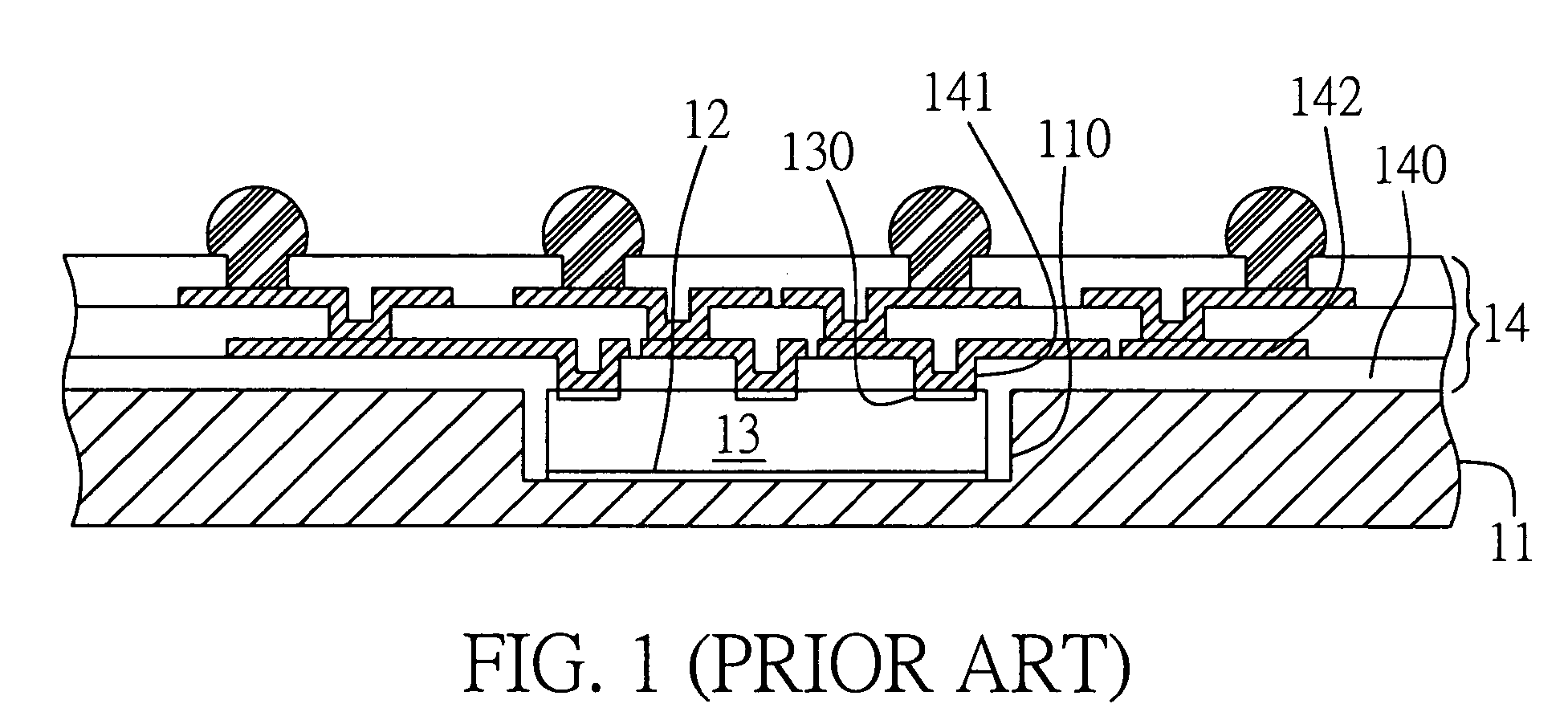

Method for fabricating electrical connection structure of circuit board

ActiveUS7151050B2Reduce material costsShorten production timeSemiconductor/solid-state device detailsPrinted circuit aspectsResistElectrical connection

A method for fabricating an electrical connection structure of a circuit board is proposed. A patterned resist layer is formed on the circuit board having a plurality of conductive pads, and a plurality of openings is formed in the resist layer to expose the conductive pads. A first conductive material and a second conductive material are successively deposited in the openings of the resist layer and on each of the conductive pads. Then, the resist layer is removed. Subsequently, a protective layer is applied on the circuit board and covers the first and second conductive materials formed on each of the conductive pads. Finally, the protective layer is thinned to expose the second conductive material corresponding in position to each of the conductive pads. Thus, the circuit board can be electrically connected to an external device via the second conductive material.

Owner:PHOENIX PRECISION TECH CORP

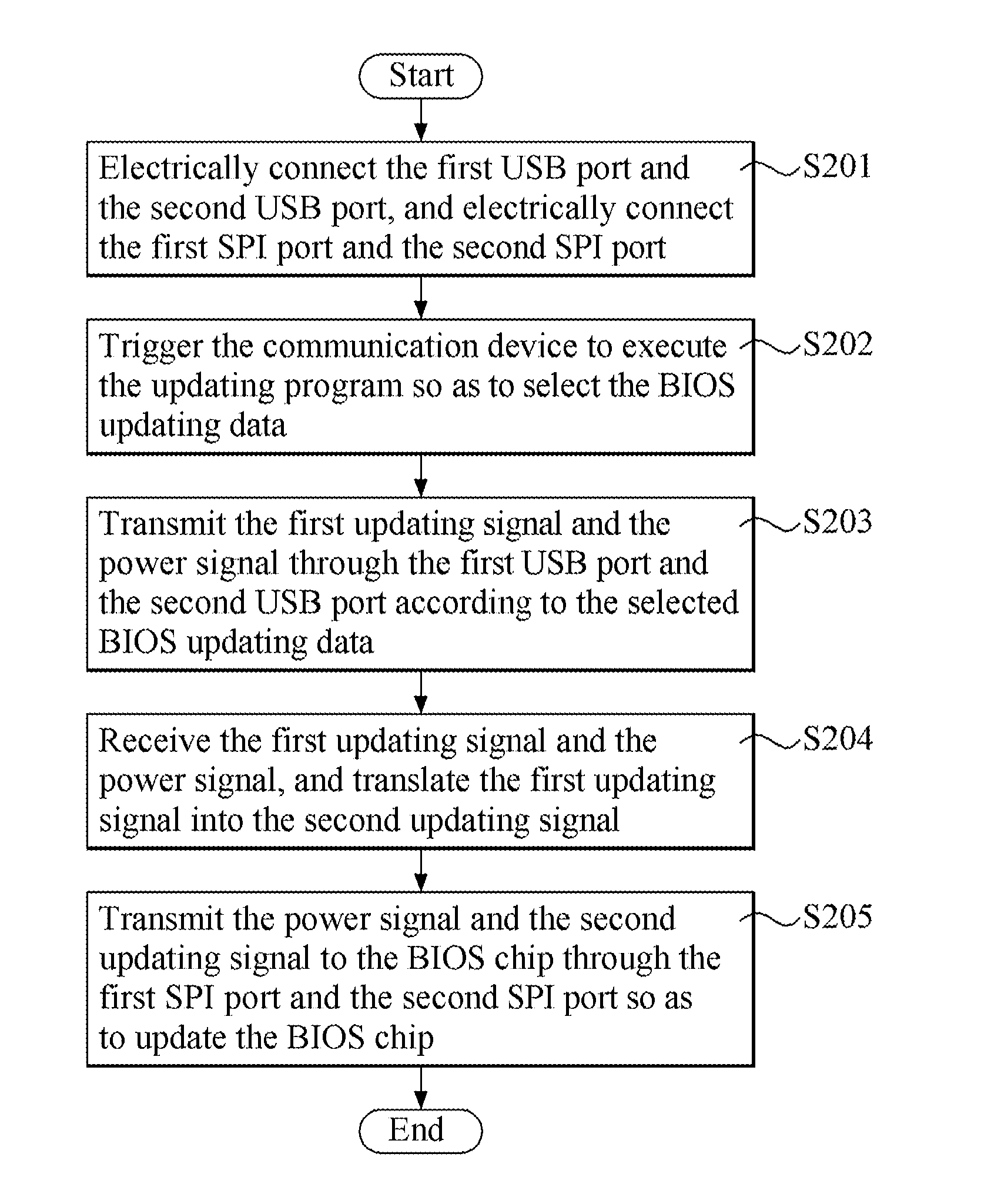

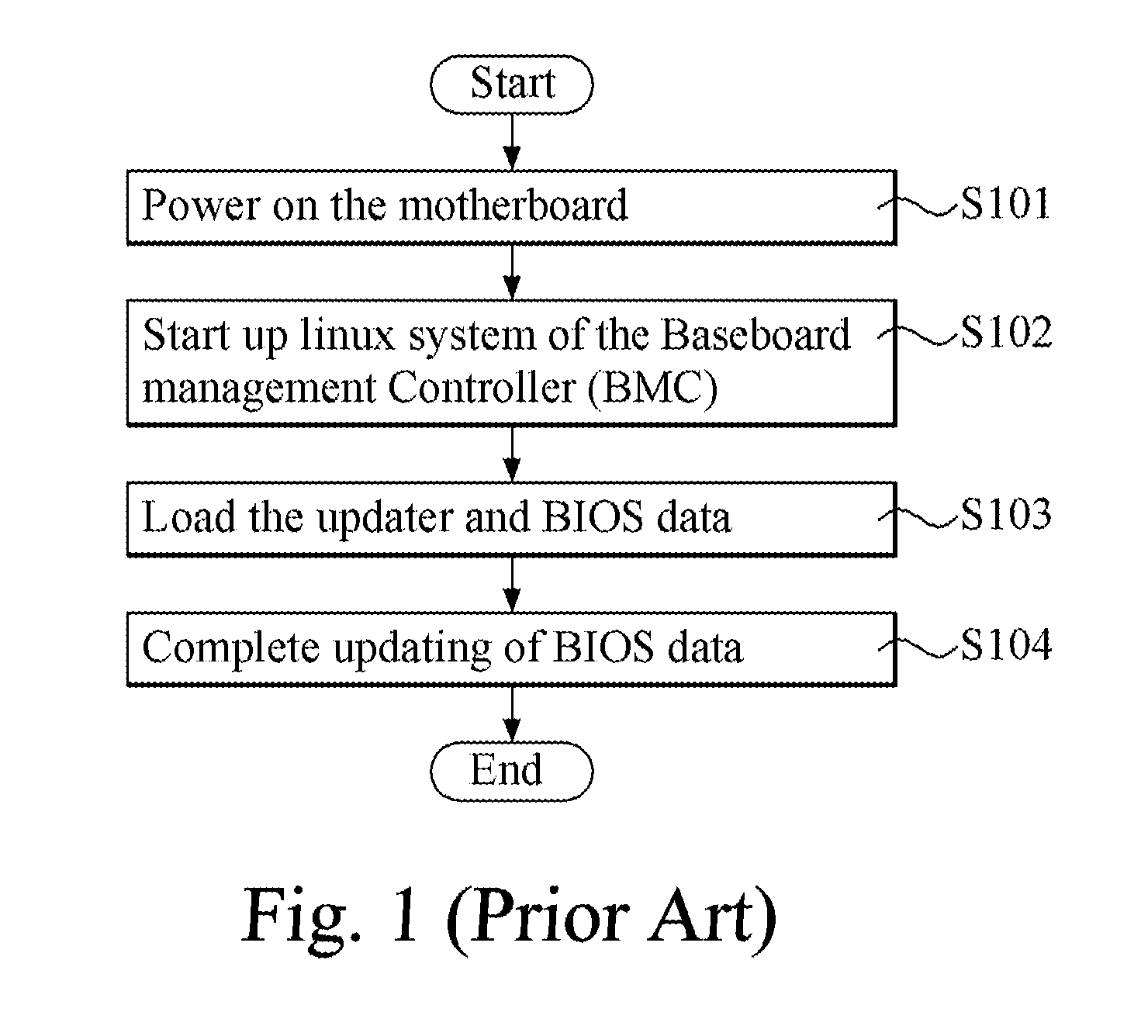

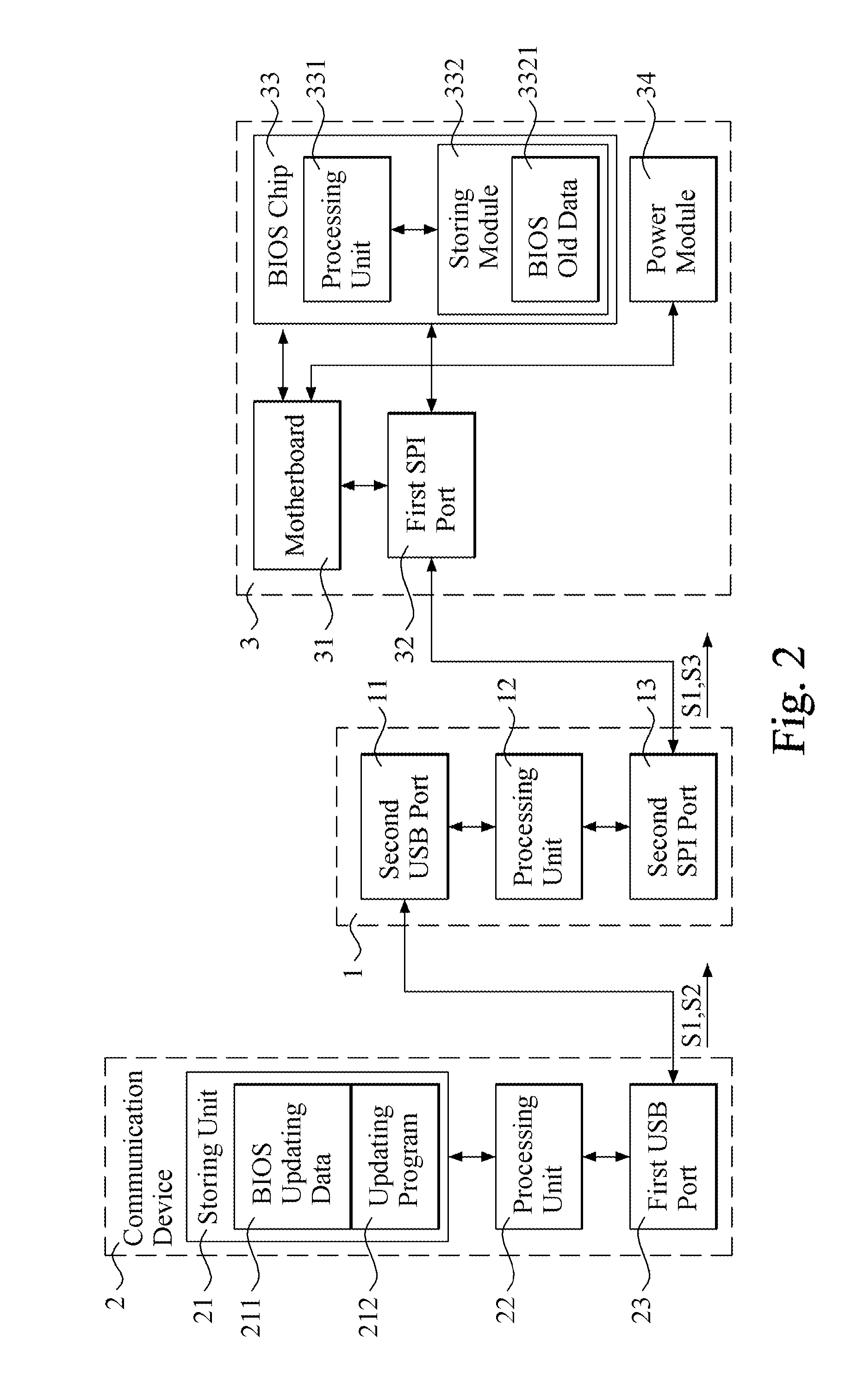

Bridge module for updating basic input/output system and updating method thereof

InactiveUS20160004526A1Fabrication cost is increasedExcessive operating timeVolume/mass flow measurementData resettingElectricityEngineering

A bridge module for updating basic input / output system (BIOS) includes a universal series bus (USB) port and a series peripheral interface bus (SPI) port which are used to connect to a communication device and an electrical device respectively. The communication device stores a BIOS updating data and includes USB port. The electrical device includes a motherboard, a SPI port and a BIOS chip. The SPI port is electrically connected to the motherboard. The BIOS chip is electrically connected to the SPI port and stores a BIOS old data. The method includes the steps of making the bridge module connect to the communication device and the electrical device; and triggering updating process to make the communication device transmit the BIOS updating data to the electrical device through the bridge module to update the electrical device.

Owner:MSI COMP SHENZHEN

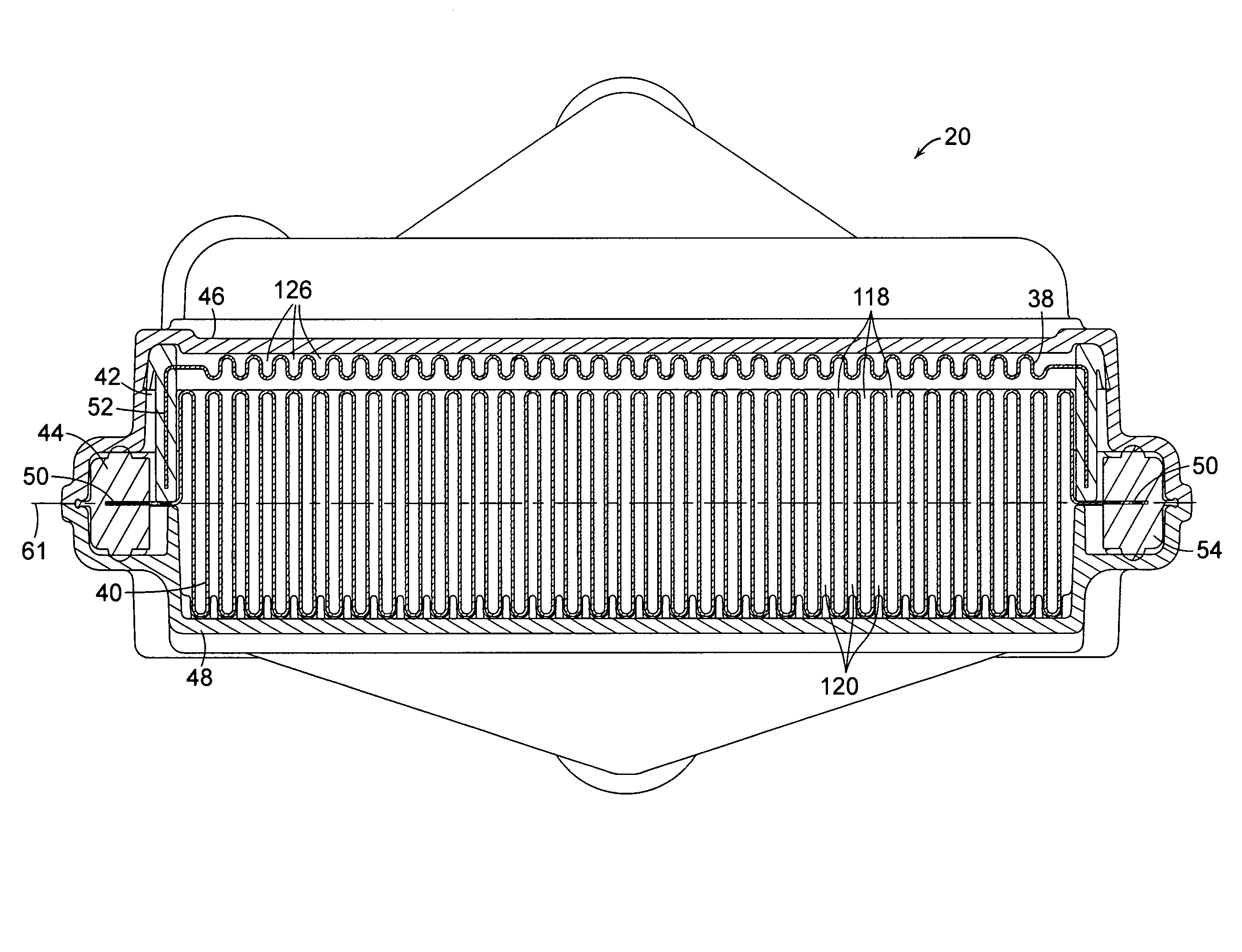

Heat-exchanger sealing

Owner:ZANAQUA TECH

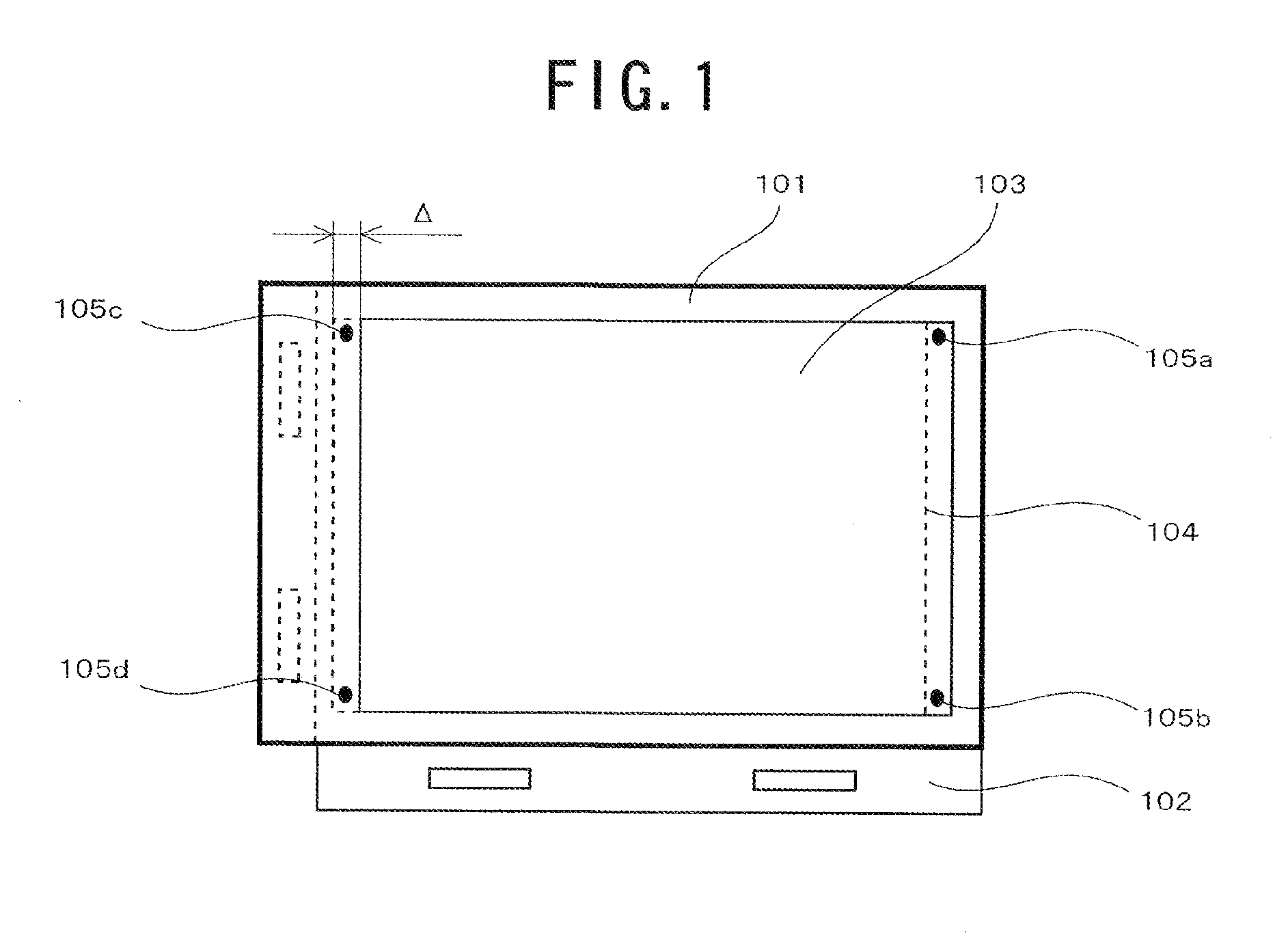

Liquid-crystal display device

ActiveUS20120038857A1High positioning accuracyAvoiding and minimizing enlargementNon-linear opticsEngineeringPolarizer

Owner:NEC LCD TECH CORP

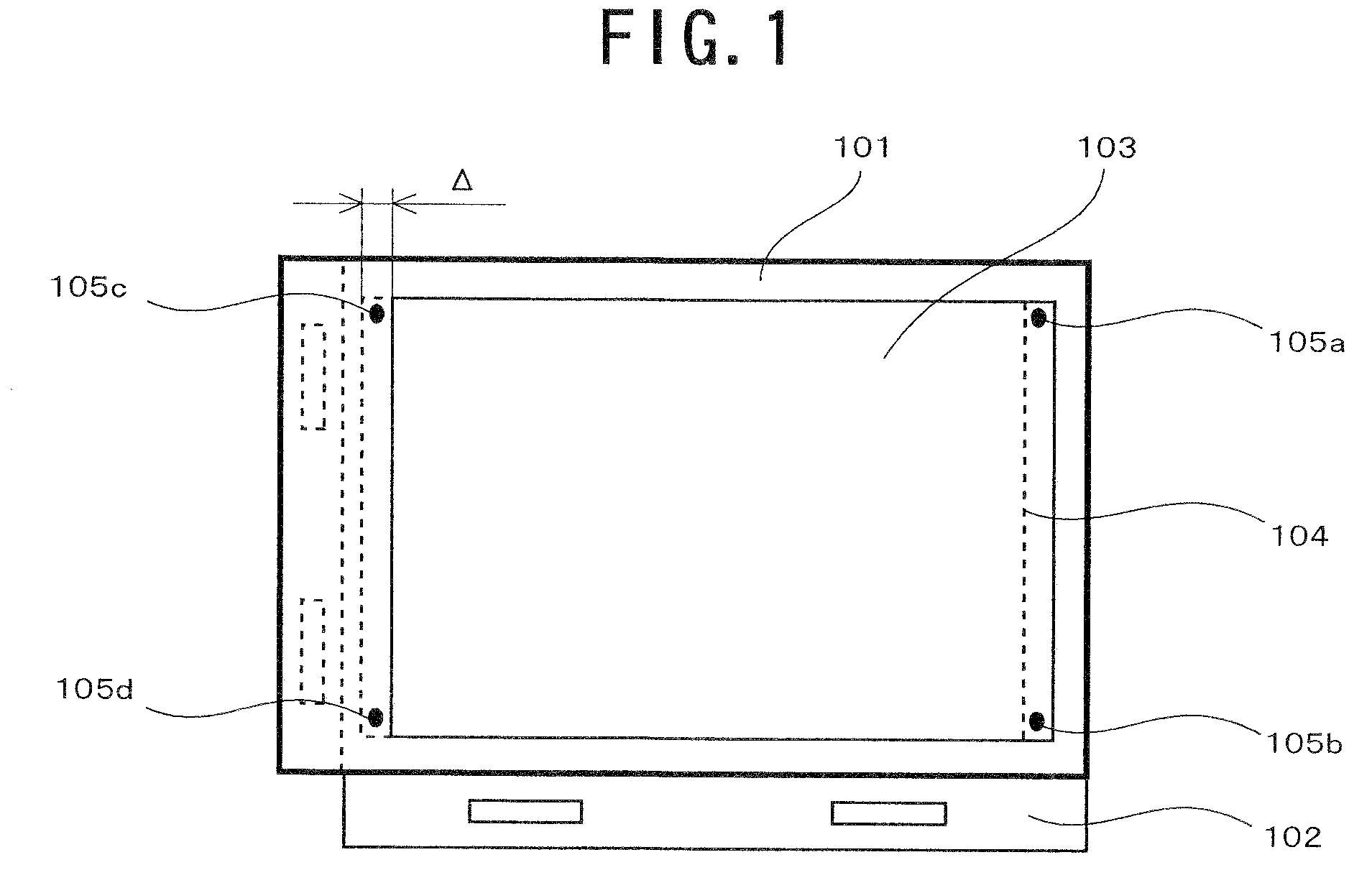

Liquid-crystal display device and method of fabricating the same

InactiveUS20080284958A1High positioning accuracyAvoiding and minimizing enlargementNon-linear opticsEngineeringPolarizer

A liquid-crystal display device makes it possible to attach an optical element to a liquid-crystal display panel with high positional accuracy while avoiding or minimizing the enlargement of the picture-frame region (i.e., the non-display region) induced by the formation of markers on the panel and the increase of the fabrication cost. The panel comprises a main substrate, an opposite substrate, and a liquid crystal enclosed in a gap between the main and opposite substrates, wherein a polarizer plate is attached at least to the opposite substrate. Markers for attaching an optical element to the panel are formed at positions that overlap with the polarizer plate in a non-display region on the main or opposite substrate. Alignment direction regulators regulate the alignment of the liquid crystal molecules to a predetermined direction in the vicinities of the markers, allowing light to pass through at least the opposite substrate.

Owner:NEC LCD TECH CORP

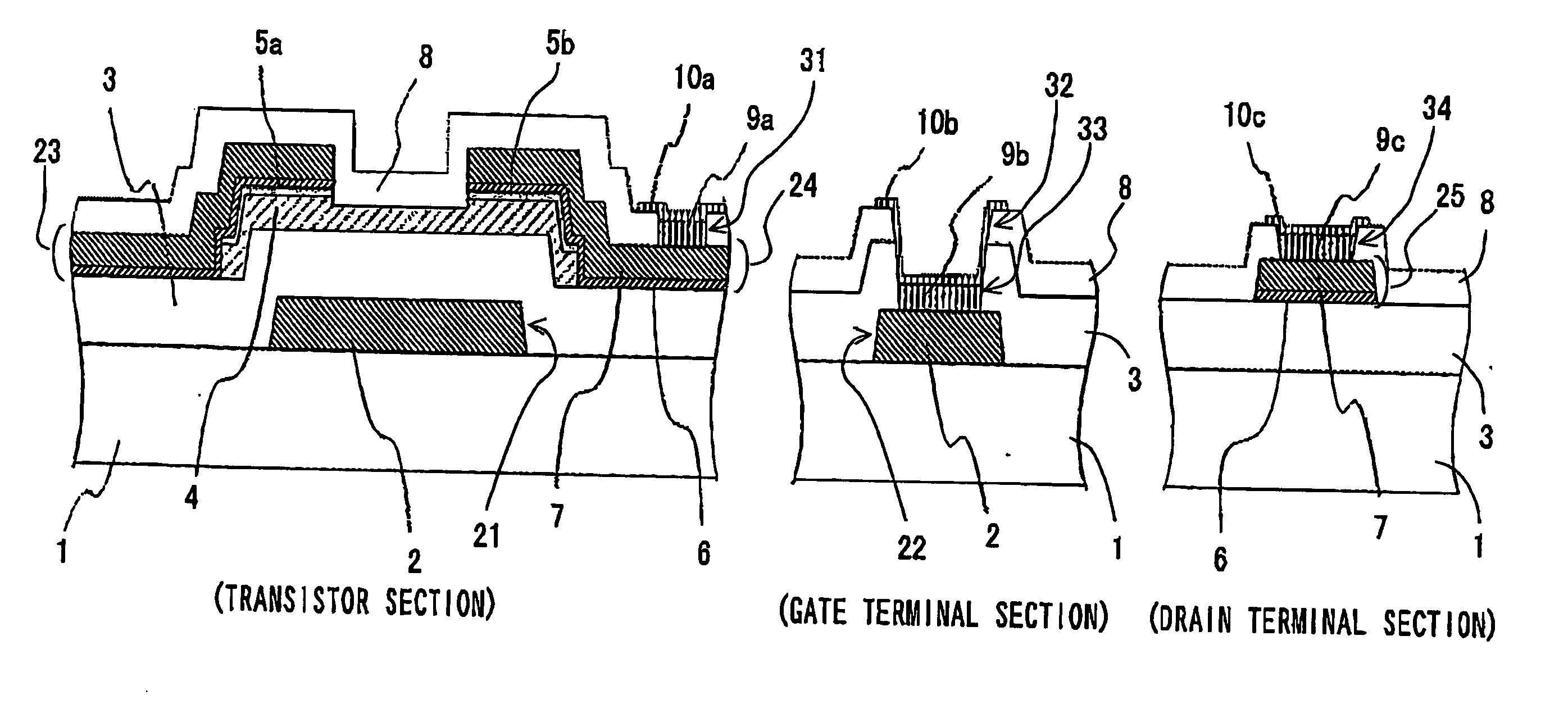

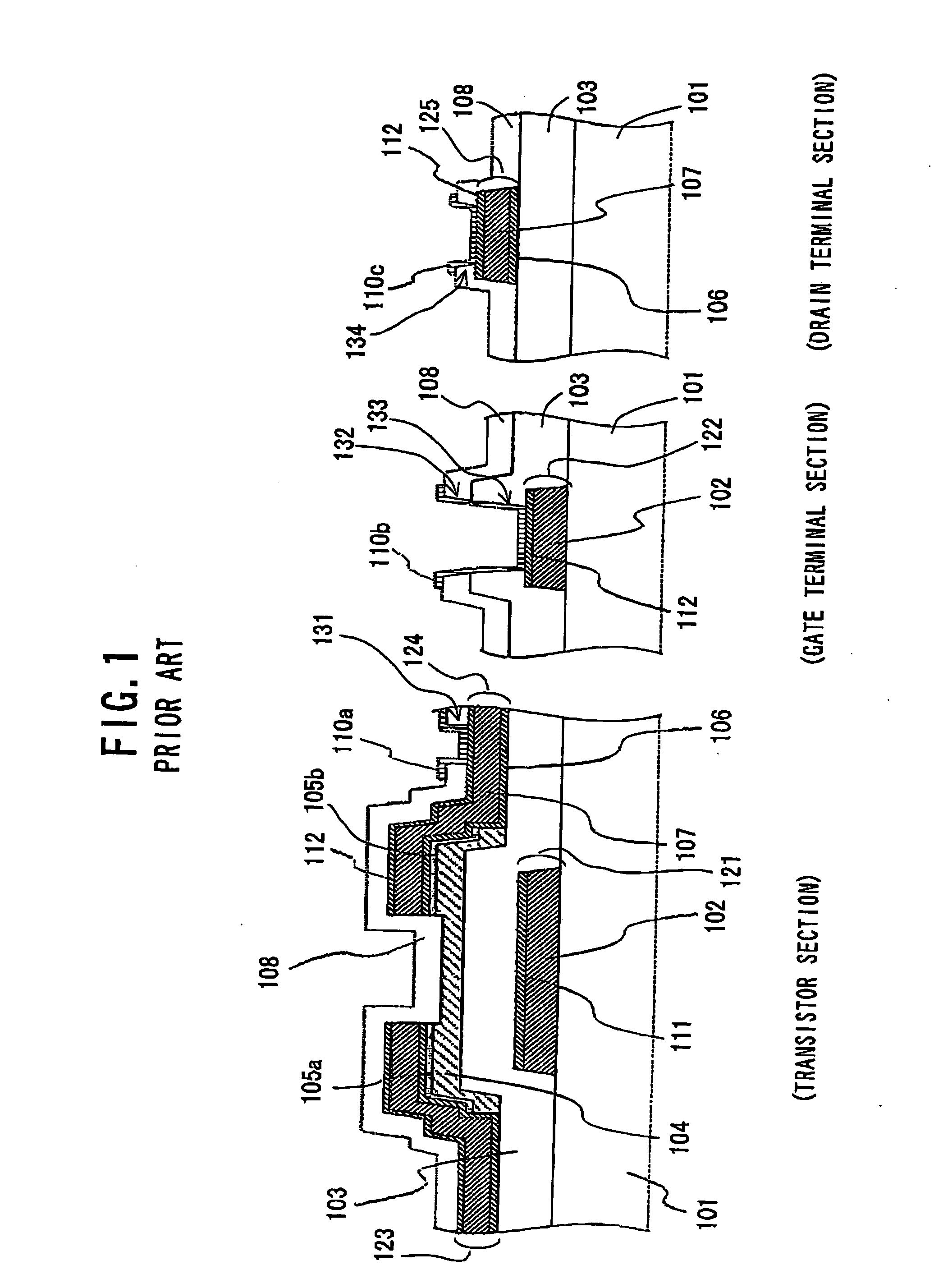

Liquid-crystal display device with thin-film transistors and method of fabricating the same

ActiveUS20070085118A1Decrease productivityFabrication cost is increasedSolid-state devicesNon-linear opticsAlloyConductive materials

A LCD device prevents corrosion of the transparent conductive layers and contact resistance increase without arising the step coverage degradation due to the thickness increase of the interconnection layer, the step coverage degradation due to the formation of undercut portions, and productivity reduction and fabrication cost increase. A first interconnection line comprising a patterned Al or Al alloy layer is disposed on or over an insulating plate. A first insulating layer is formed to cover the first interconnection line to have a contact hole exposing a part of the first interconnection line. A first conductive material made of a plated metal is in contact with the exposed part of the first interconnection line in the contact hole. A first transparent conductive layer is in contact with the first conductive material. The first transparent conductive layer is electrically connected to the first interconnection line by way of the first conductive material.

Owner:VISTA PEAK VENTURES LLC

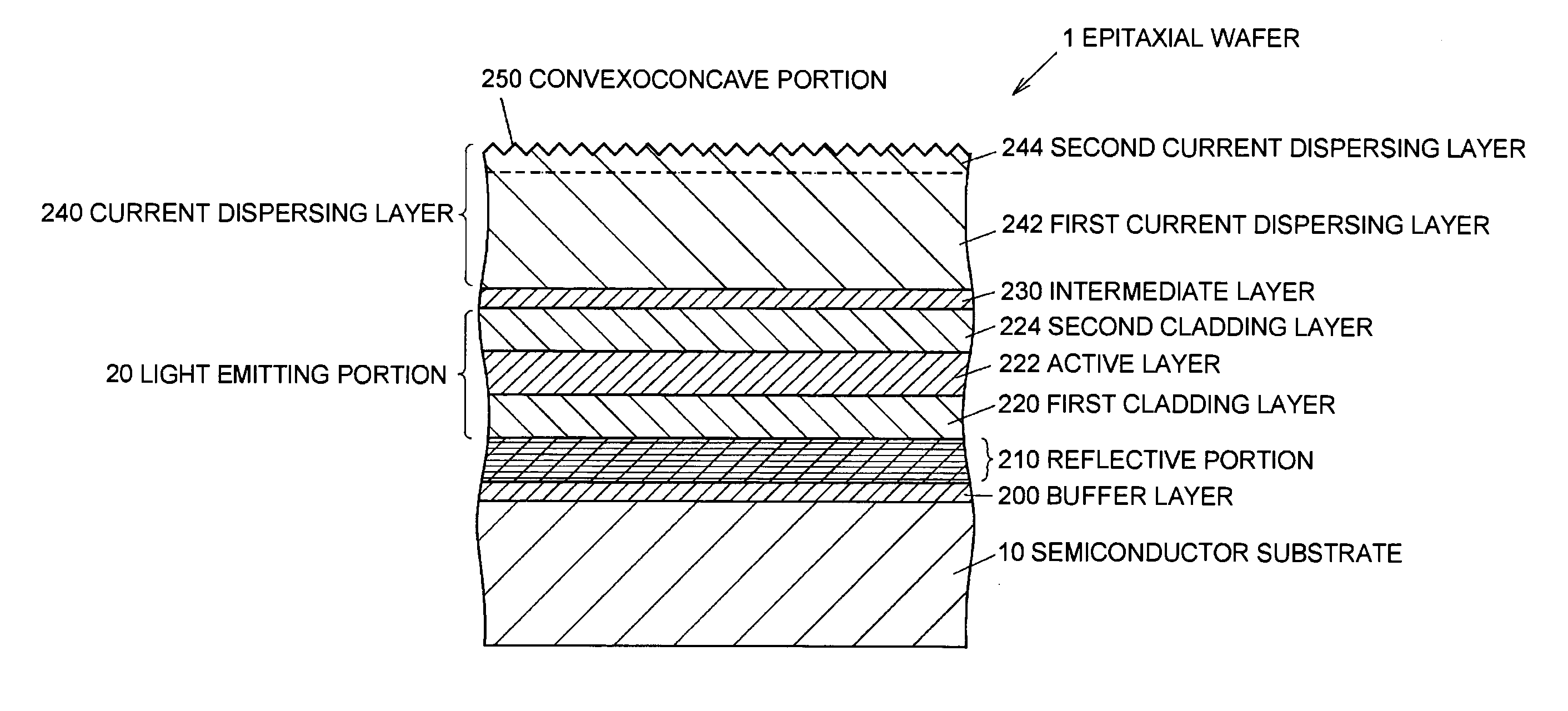

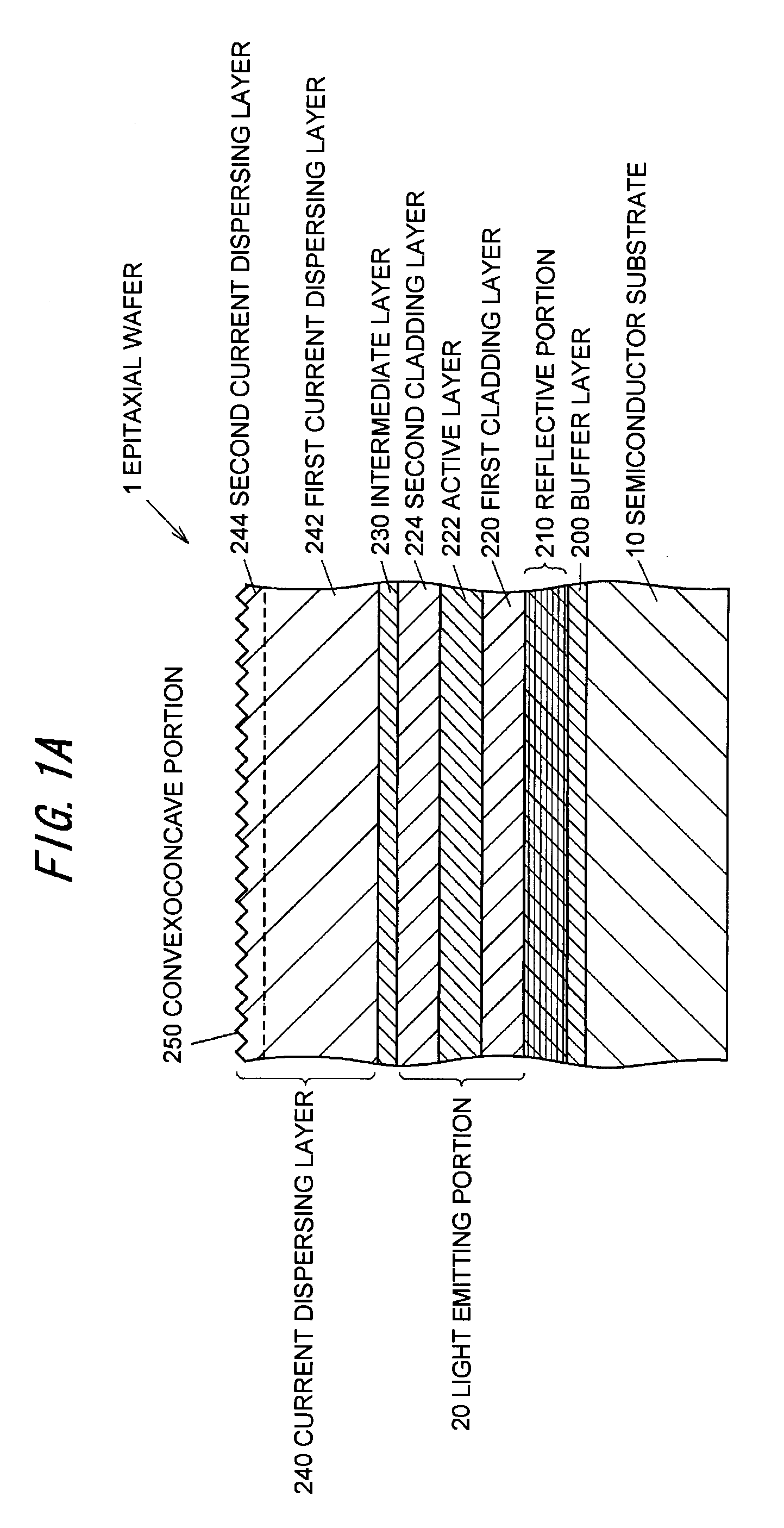

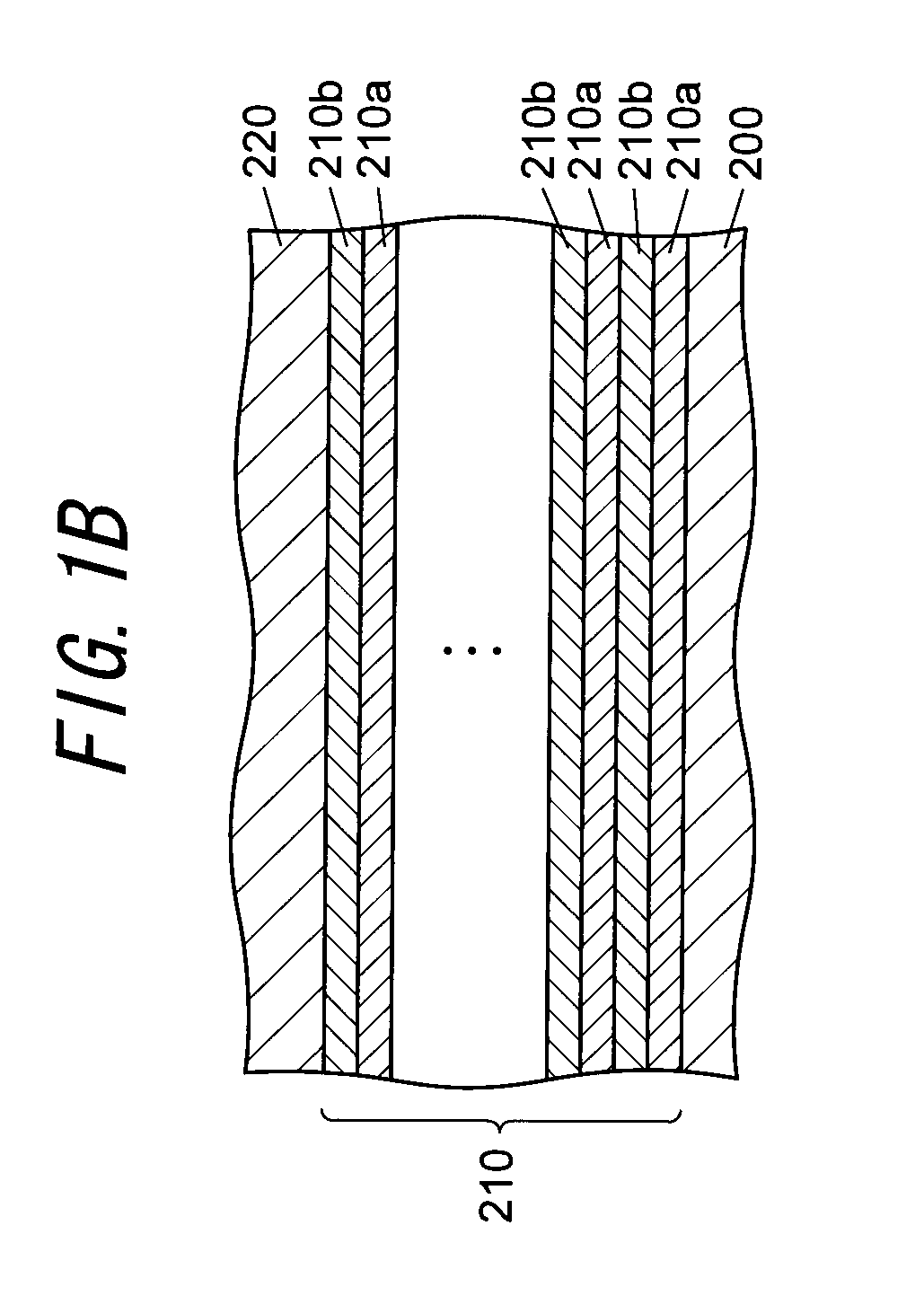

Epitaxial wafer, light-emitting element, method of fabricating epitaxial wafer and method of fabricating light-emitting element

InactiveUS20110057214A1Increase productionLower forward voltageSemiconductor/solid-state device manufacturingSemiconductor devicesWaferingCondensed matter physics

An epitaxial wafer, a light-emitting element, a method of fabricating the epitaxial wafer and a method of fabricating the light-emitting element, which have a high output and a low forward voltage, and can be fabricated without increasing fabricating cost, are provided. The epitaxial wafer is formed with a light-emitting portion, a reflective portion provided between a semiconductor substrate and the light-emitting portion and a current dispersing layer having first and second current dispersing layers, wherein the reflective portion has plural pairs of layers having first and second semiconductor layers wherein the first semiconductor layer has a thickness of TA defined by Equation (1),TA=λp4nA1-(nInsinθnA)2(1)the second semiconductor layer has a thickness of TB defined by Equation (2),TB=λp4nB1-(nInsinθnB)2(2)and the second current dispersing layer has a high carrier density or a high impurity density and is provided with the convexoconcave portion on the surface.

Owner:SUMITOMO CHEM CO LTD

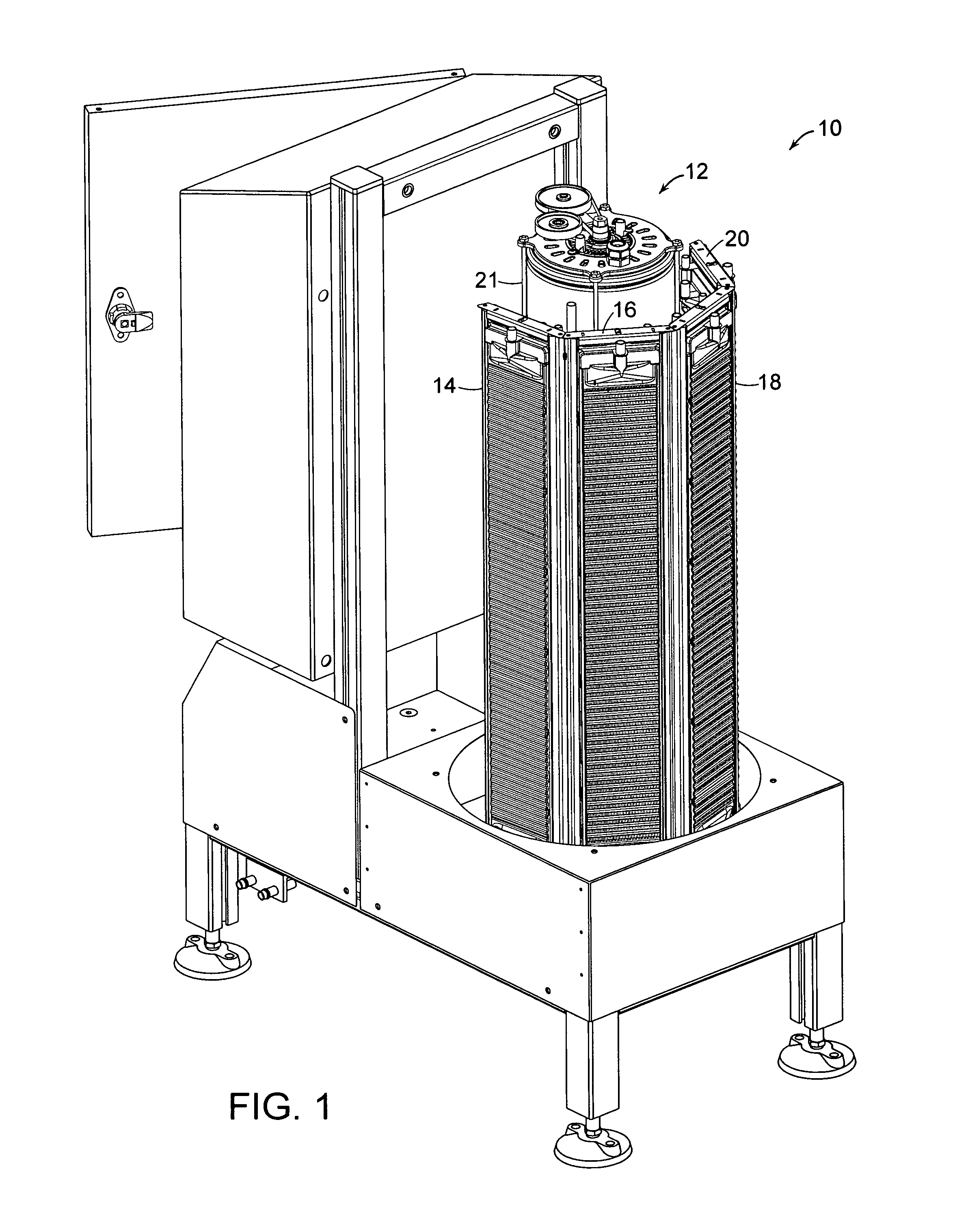

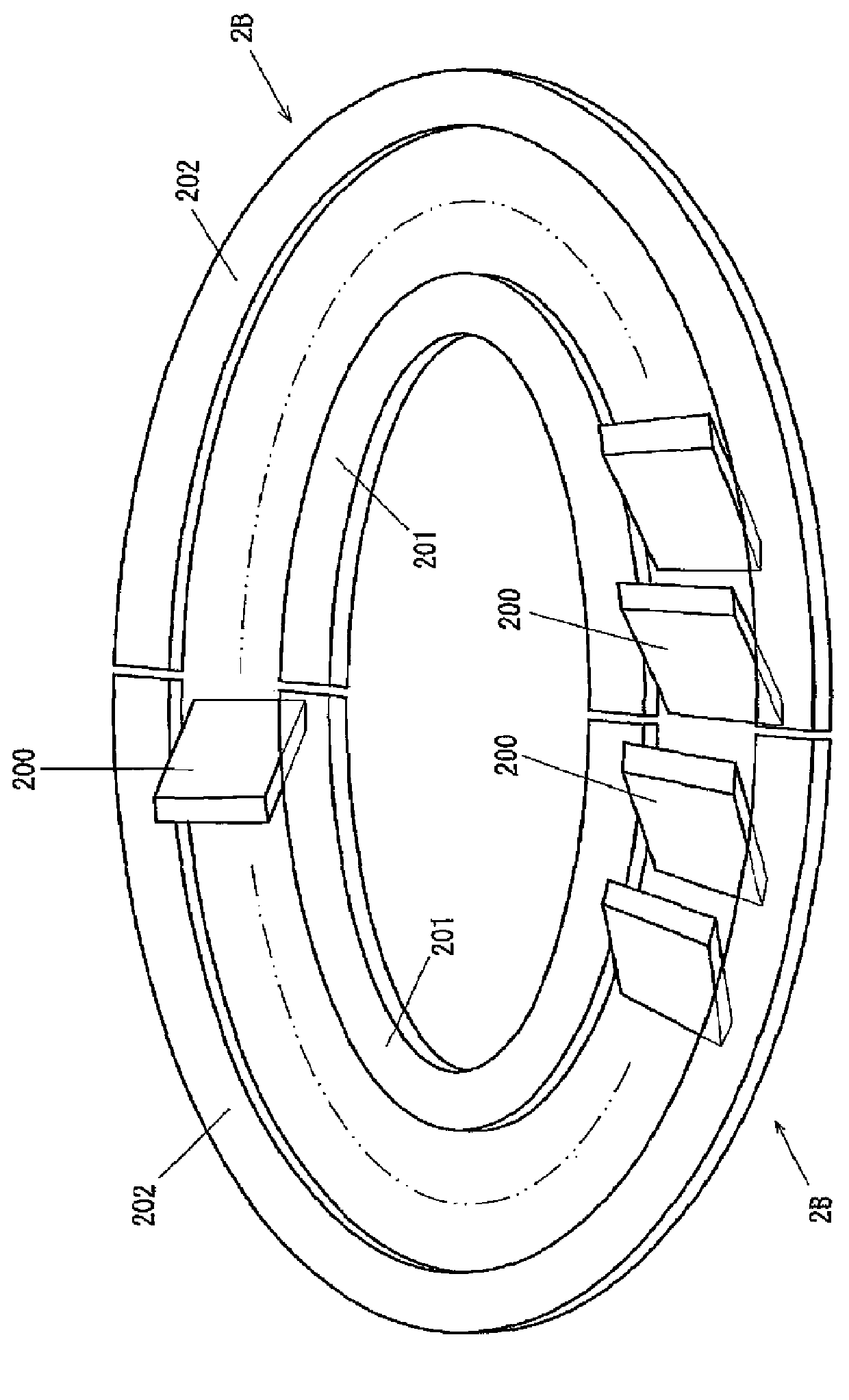

Production method of stator blade and turbo-molecular pump with the stator blade

Disclosed is a method of producing a stator blade for use in a turbo-molecular pump. The method includes subjecting a metal plate to a slitting process to form a blade element having an upstream edge surface and a downstream edge surface, wherein a laser beam is emitted onto the metal plate at an incident angle oblique to a principal surface of the metal plate. Thus, the upstream edge surface and / or the downstream edge surface can be formed to extend obliquely relative to the principal surface of the metal plate, in a simple manner, while eliminating a need for a burr removal operation which would otherwise be necessary in a punching-based slitting process.

Owner:SHIMADZU CORP

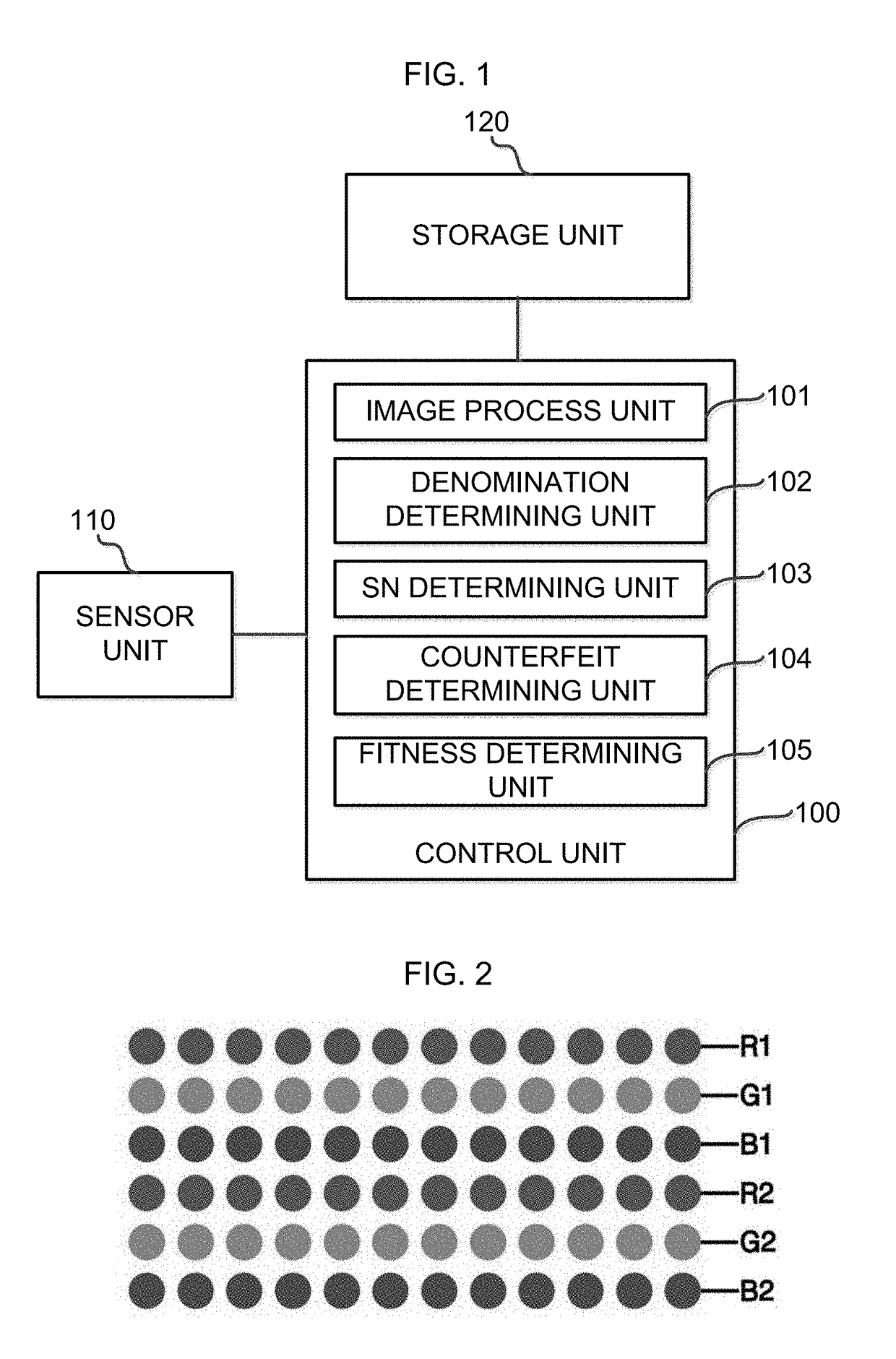

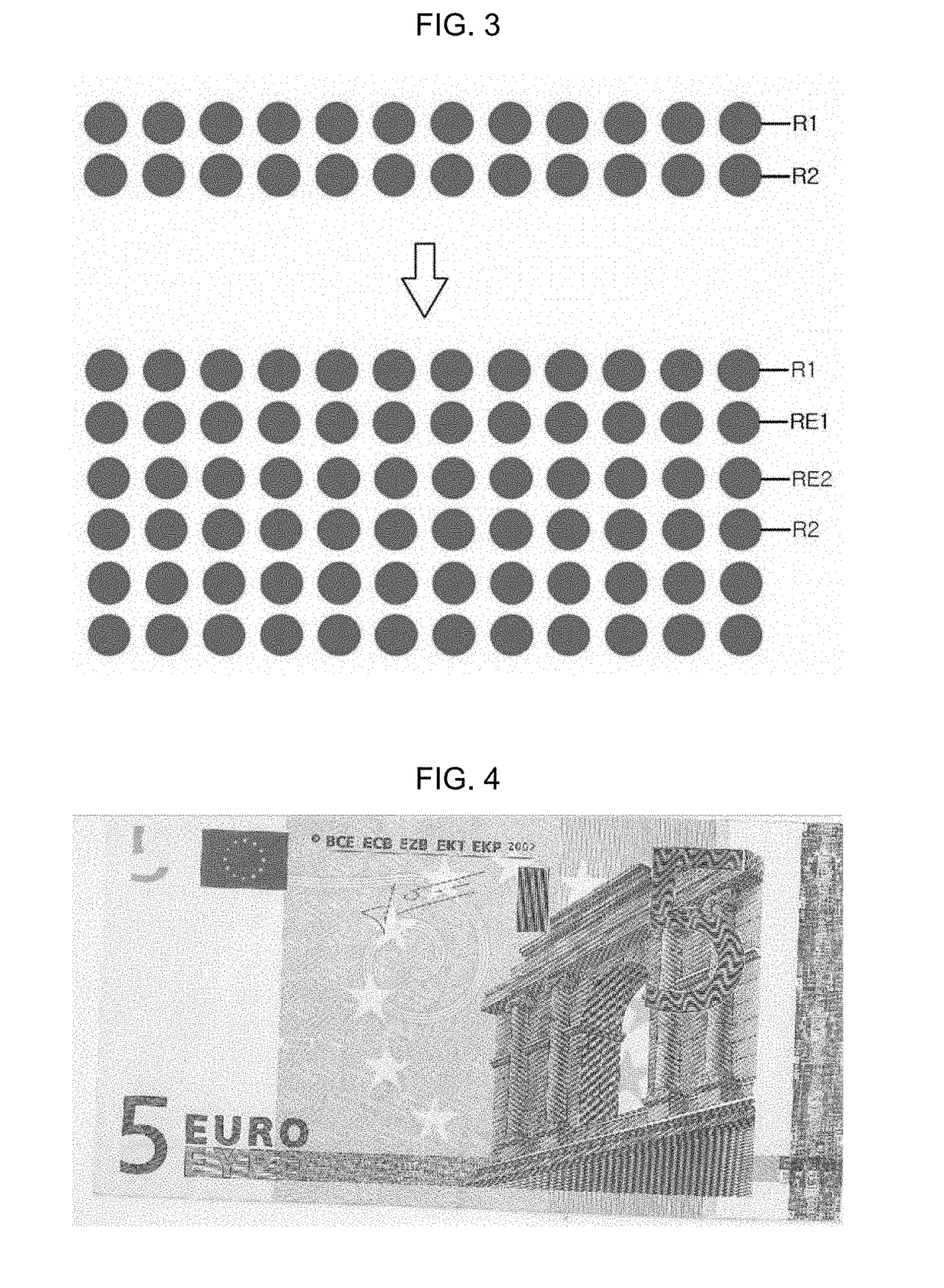

Banknote Processing Apparatus

ActiveUS20170193726A1Improve performanceDecreasing banknote processing speedPaper-money testing devicesColor imageEngineering

A banknote processing apparatus is disclosed. The banknote processing apparatus includes a sensor unit configured to acquire image information of a banknote and project light alternately from red, green, and blue (RGB) light sources onto the banknote, and a control unit configured to (i) acquire per-color image information of the banknote for each RGB color from the image information and (ii) determine at least one of a denomination, an identification mark, an authenticity, and a fitness of the banknote based on the per-color image information.

Owner:KISAN ELECTRONICS

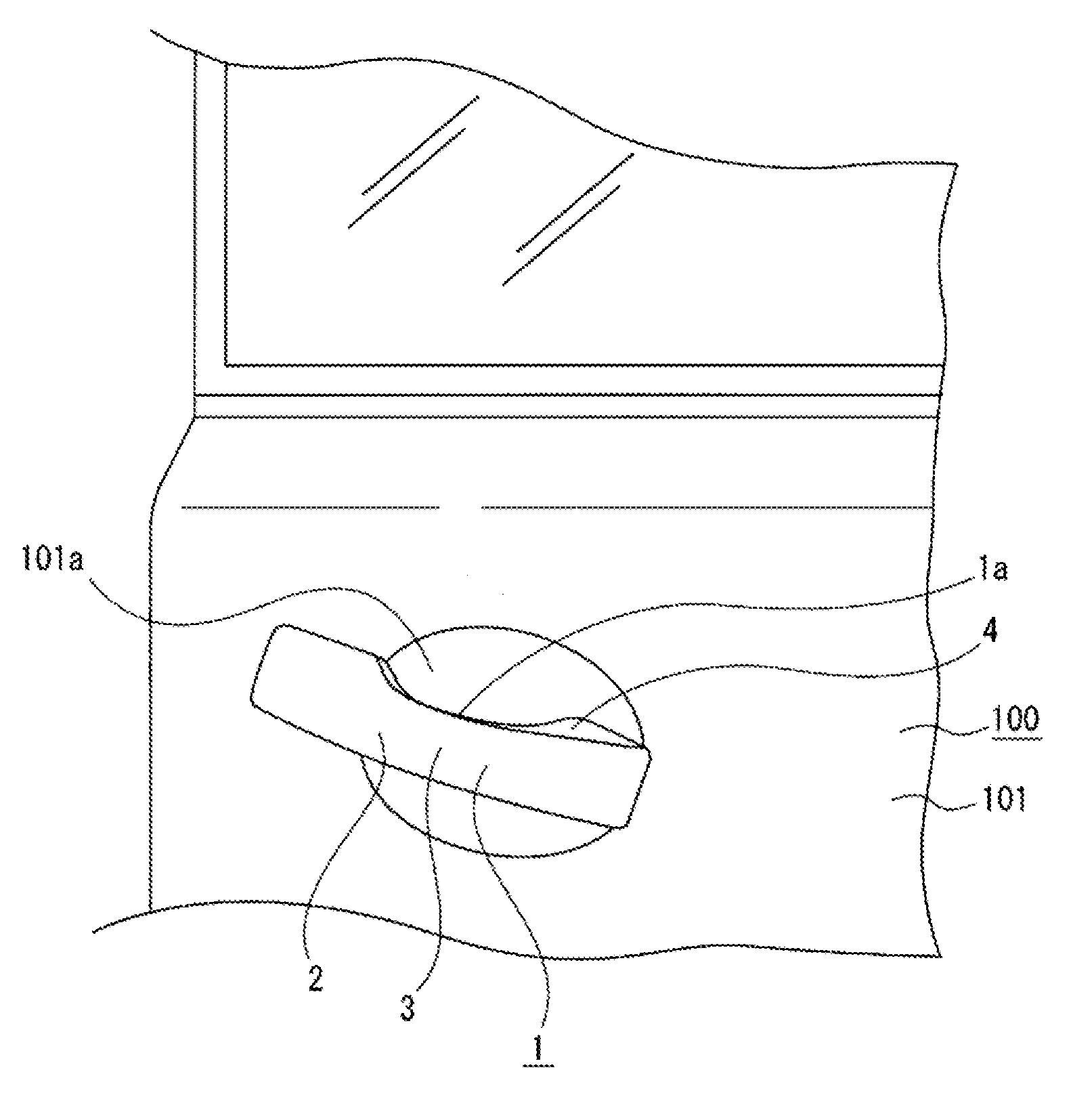

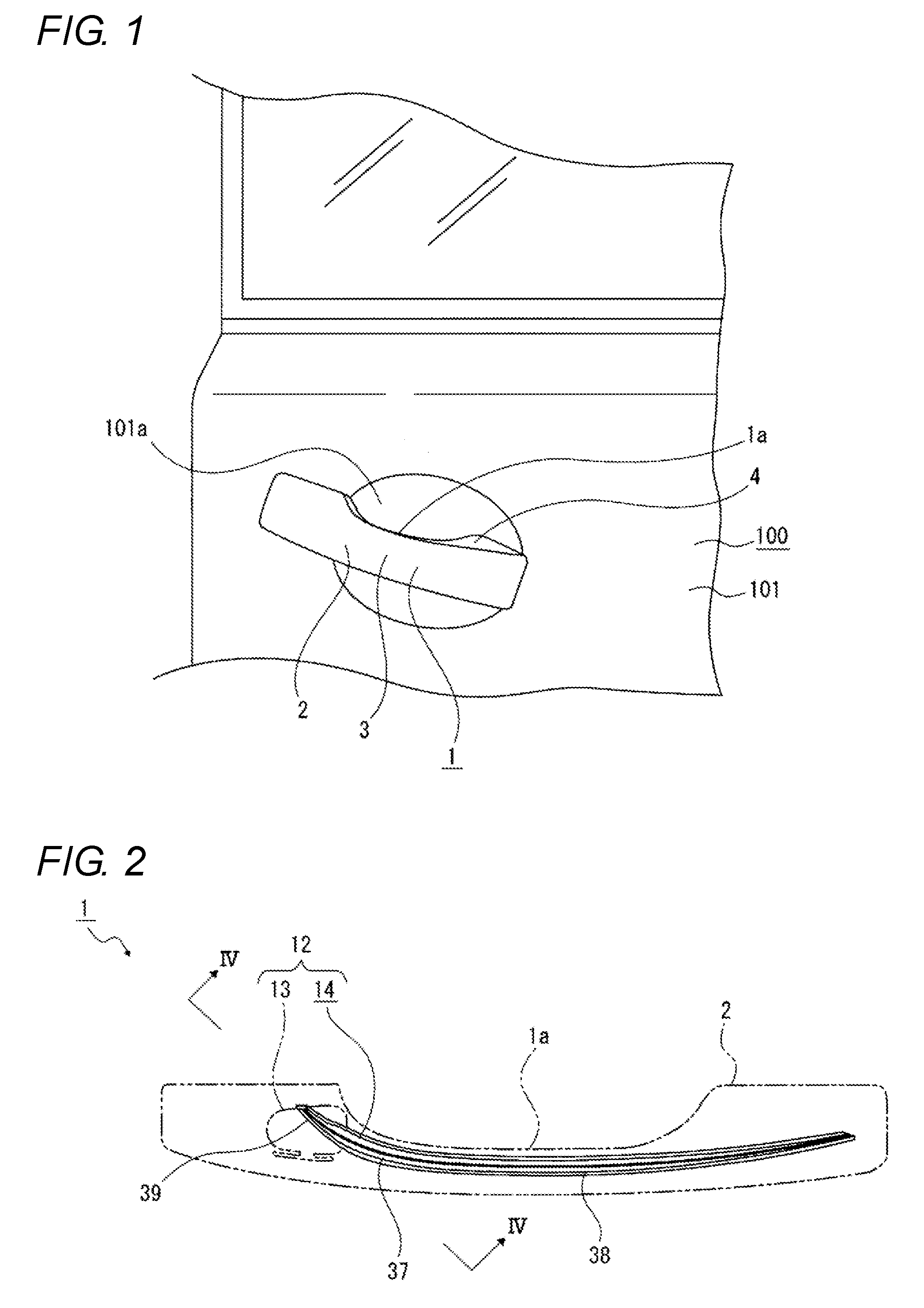

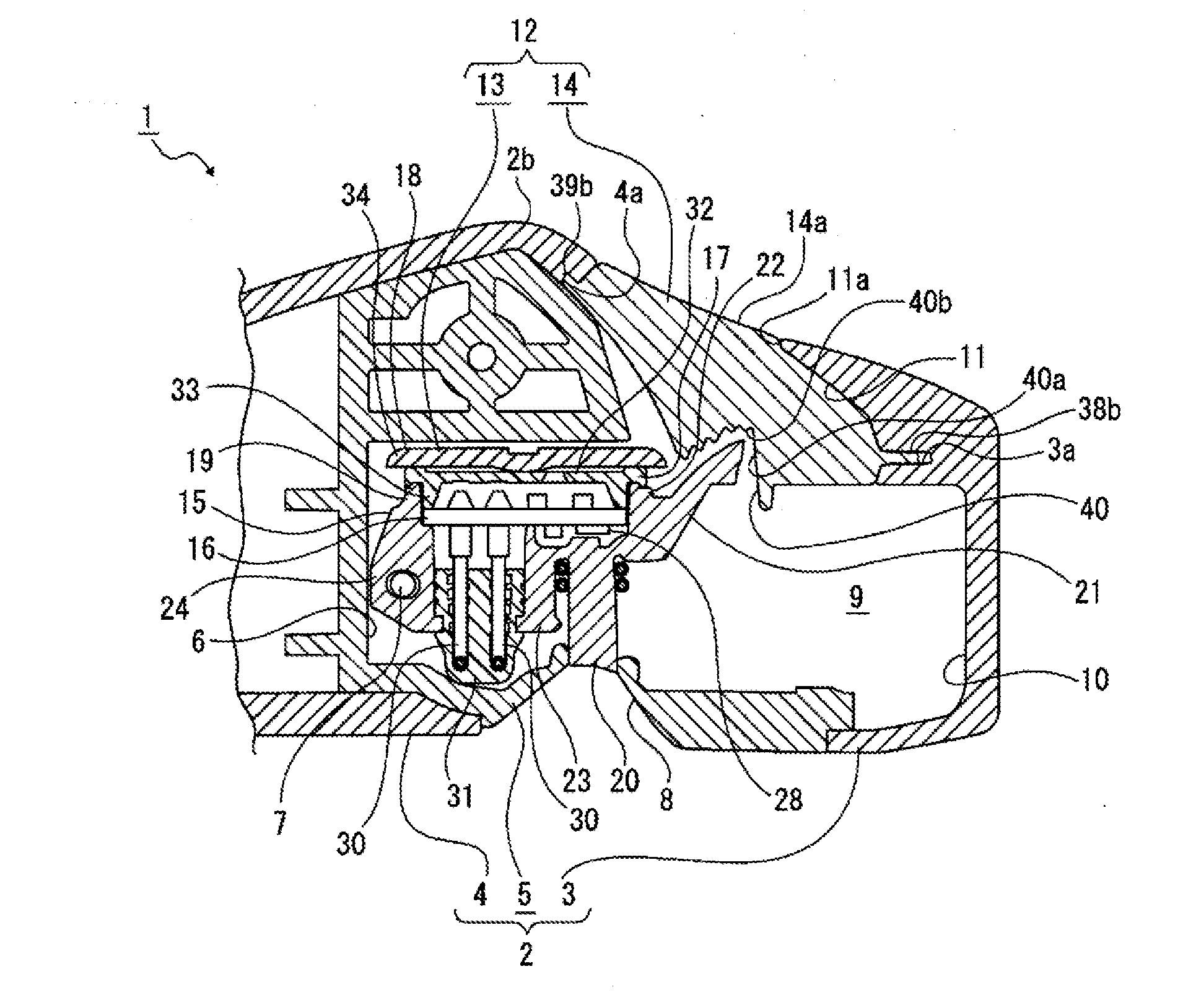

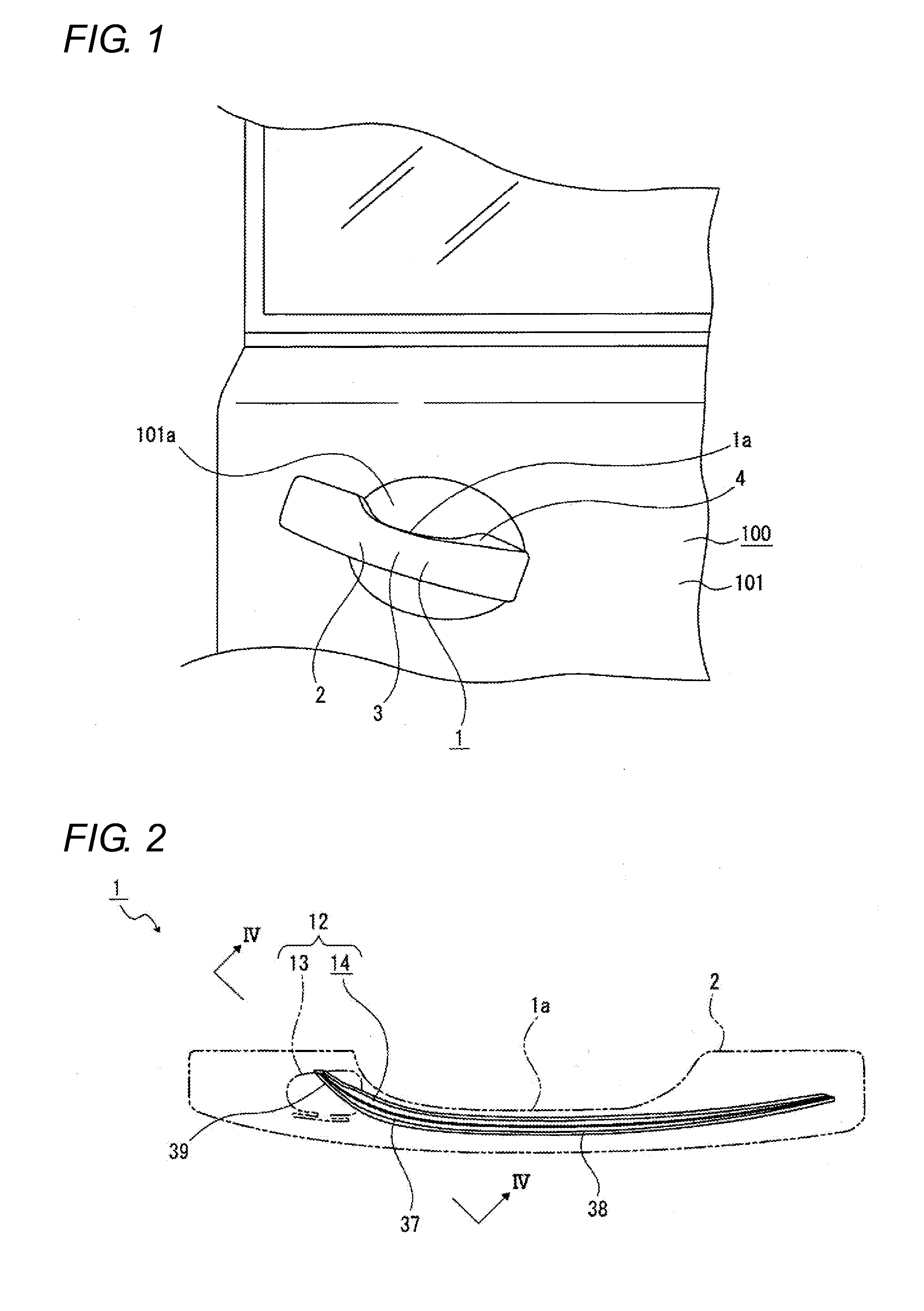

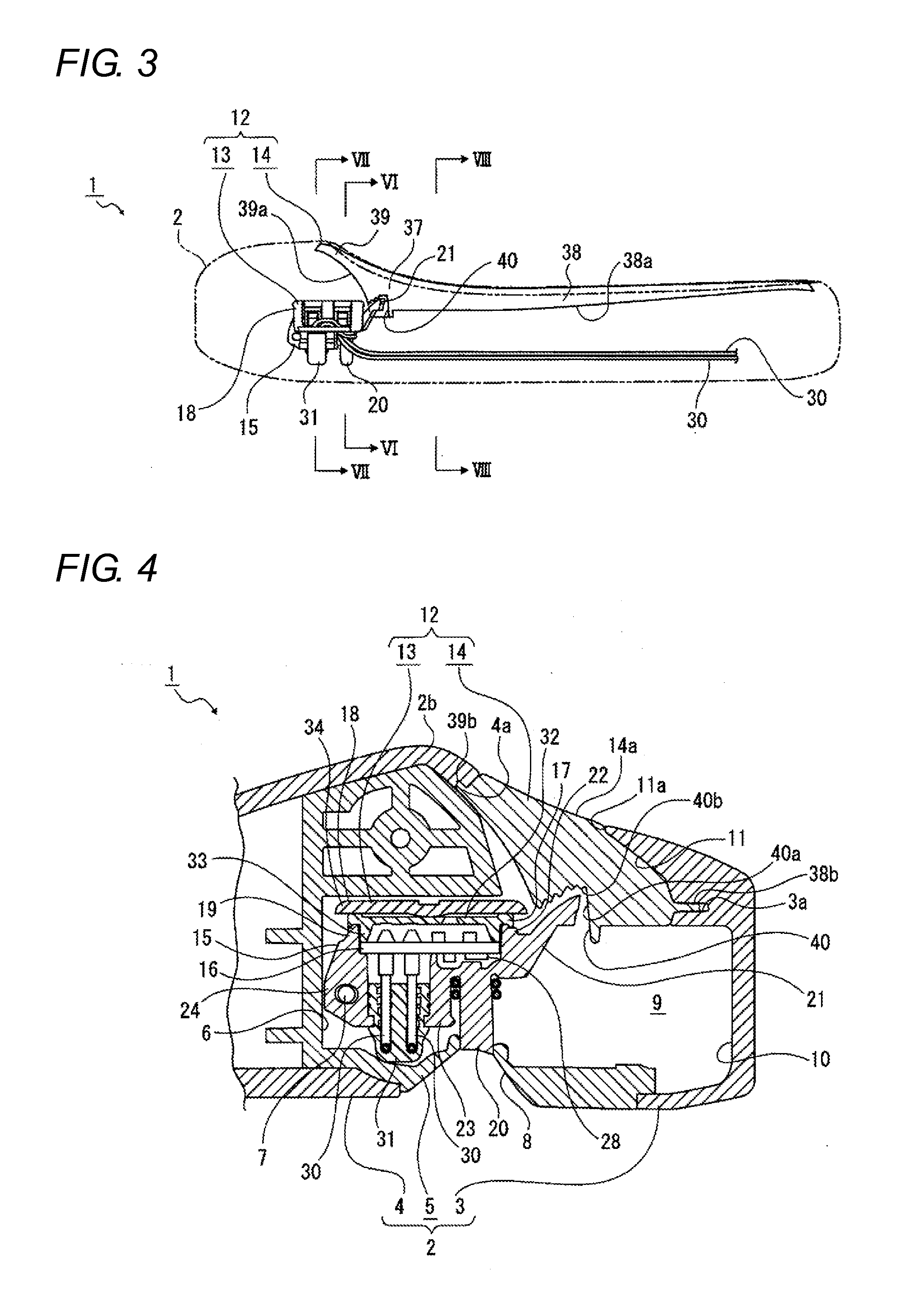

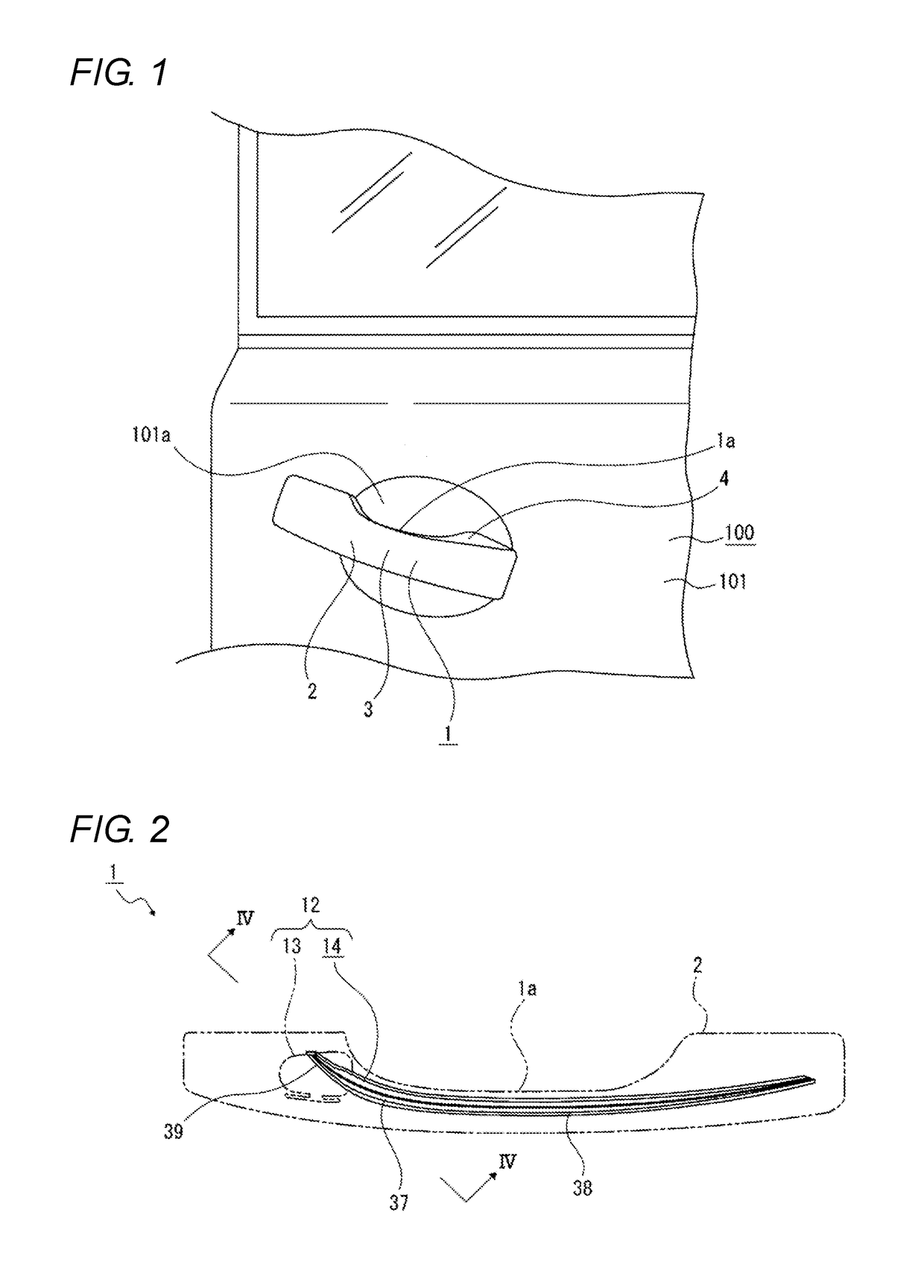

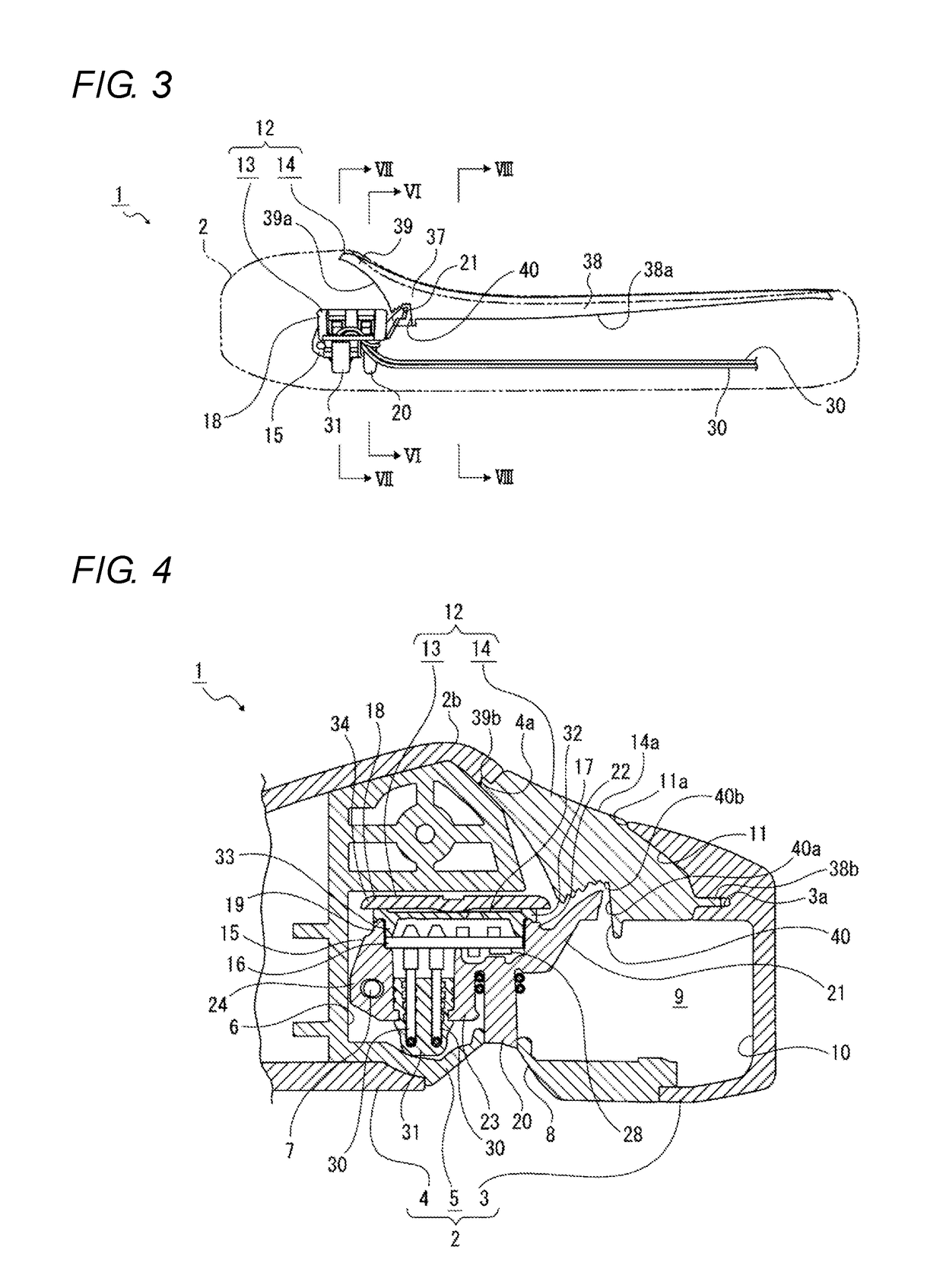

Vehicle lamp

ActiveUS20160297355A1Increase in fabrication costFunction increaseElectric circuit arrangementsOptical signallingLight guideOptoelectronics

A vehicle lamp has a circuit board on which a light emitting element is mounted, a housing for holding the circuit board, a first light guiding lens for guiding part of light emitted from the light emitting element in a predetermined direction, and a second light guiding lens for guiding at least the other part of the light emitted from the light emitting element in the other predetermined direction. The housing, the first light guiding lens and the second light guiding lens are formed integrally.

Owner:KOITO MFG CO LTD

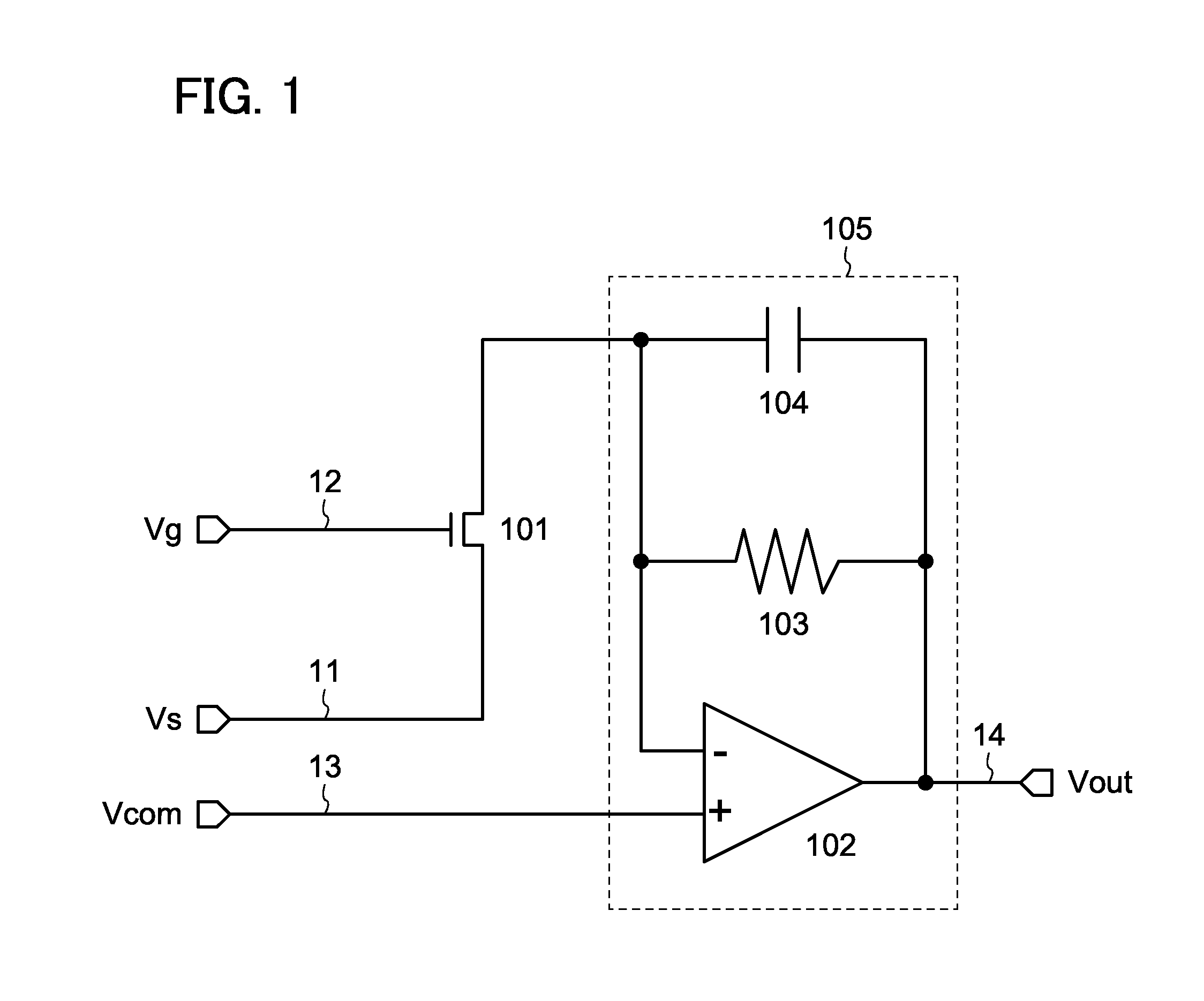

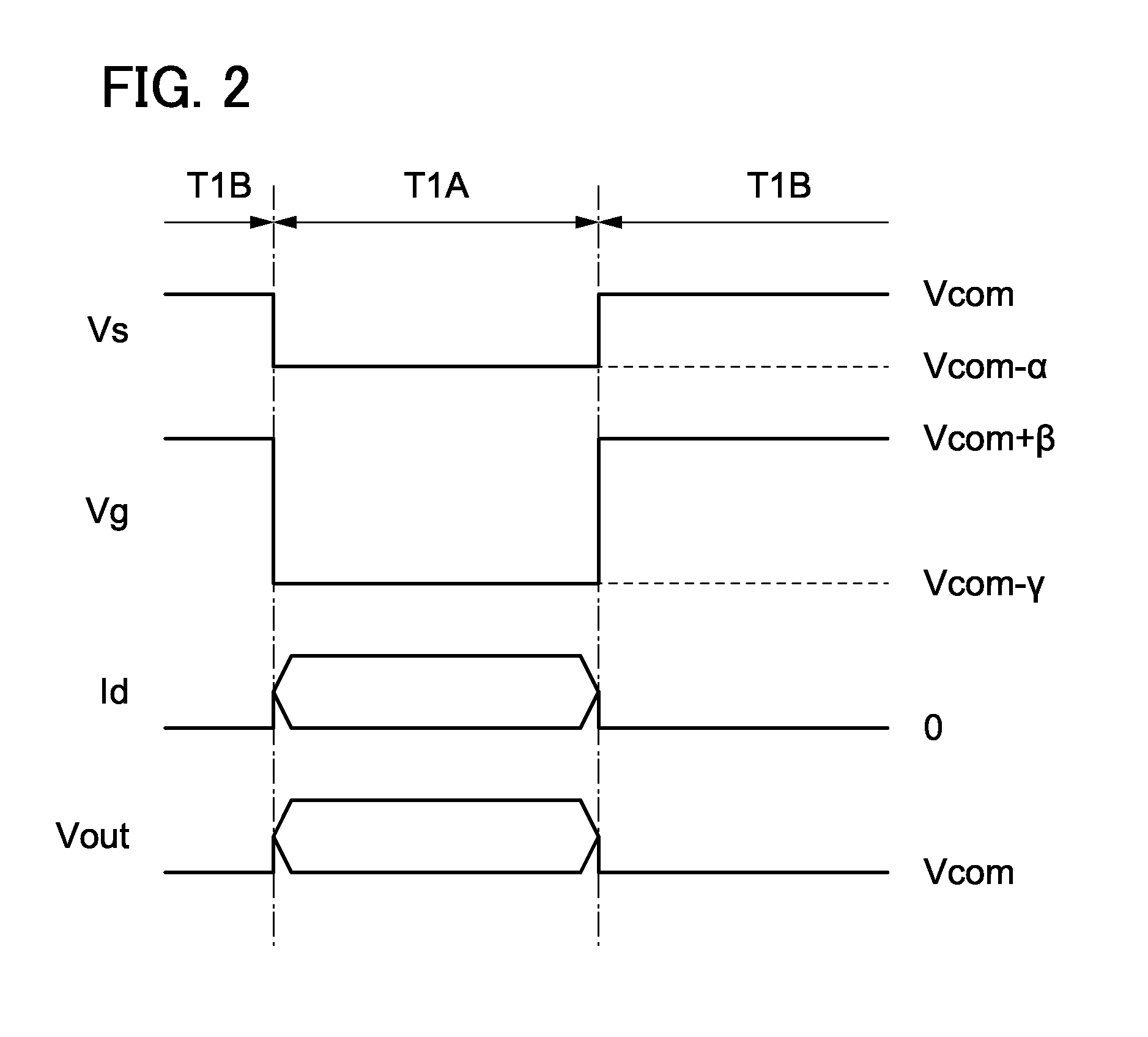

Semiconductor device

ActiveUS20150069386A1Increase the ambient temperature rangeImprove reliabilityTransistorSolid-state devicesPower semiconductor devicePower flow

A sensor circuit with high sensitivity to ultraviolet light. Ultraviolet light is detected using a transistor containing an oxide semiconductor. When the transistor is irradiated with ultraviolet light or light including ultraviolet light, the drain current of the transistor depends on the intensity of the ultraviolet light. Data on the intensity of ultraviolet light is obtained by measuring the drain current of the transistor. Since the band gap of an oxide semiconductor is wider than that of silicon, the sensitivity to light with a wavelength in the ultraviolet region can be increased. Furthermore, an increase in dark current caused by temperature rise in the sensor circuit can be suppressed, resulting in a wider allowable ambient temperature range of the sensor circuit.

Owner:SEMICON ENERGY LAB CO LTD

Vehicle lamp

ActiveUS20160290592A1Improve waterproof performanceImprove work efficiencyPassenger/driving compartment lightingsLight guidesEngineeringLight fixture

Owner:KOITO MFG CO LTD

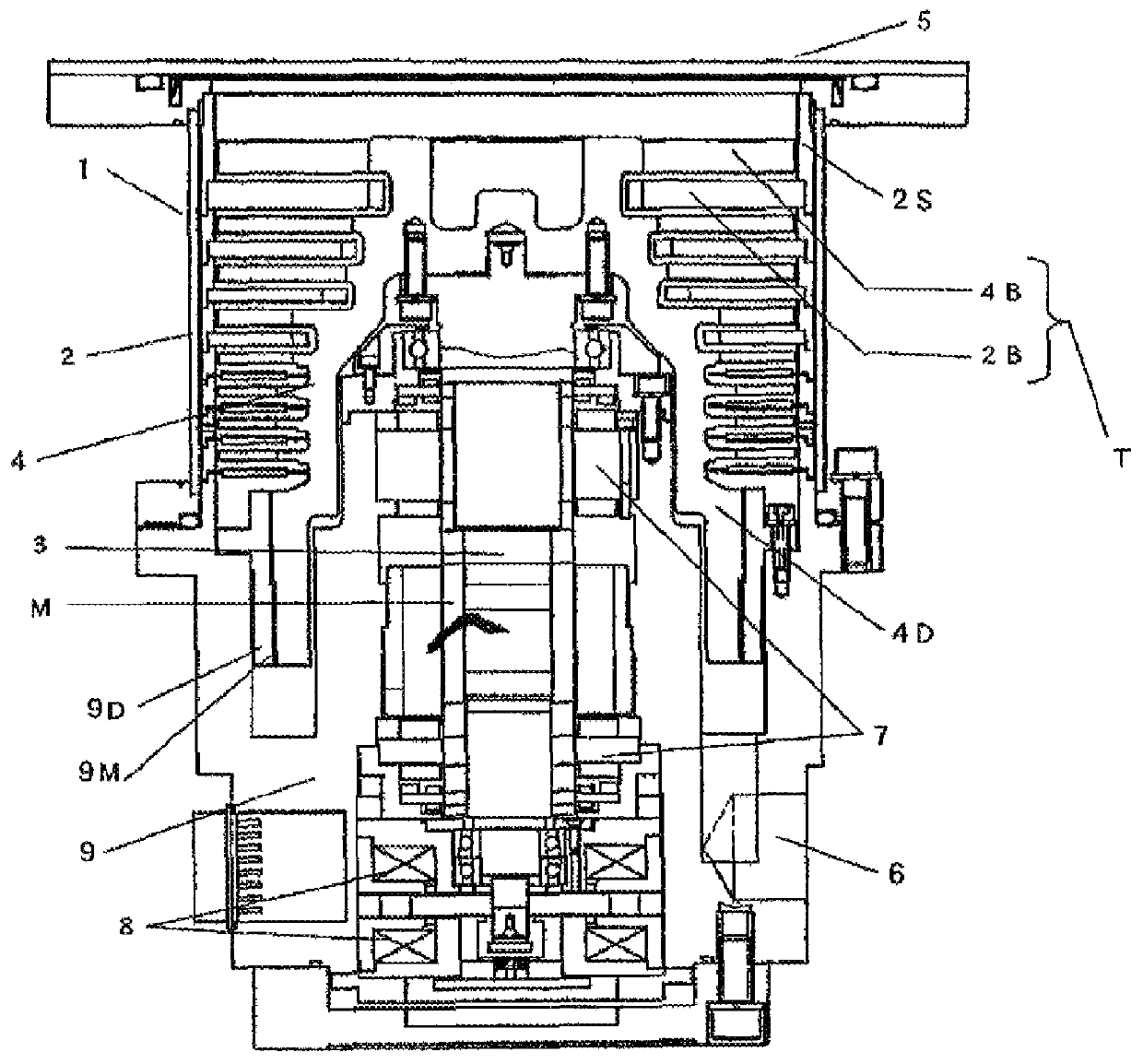

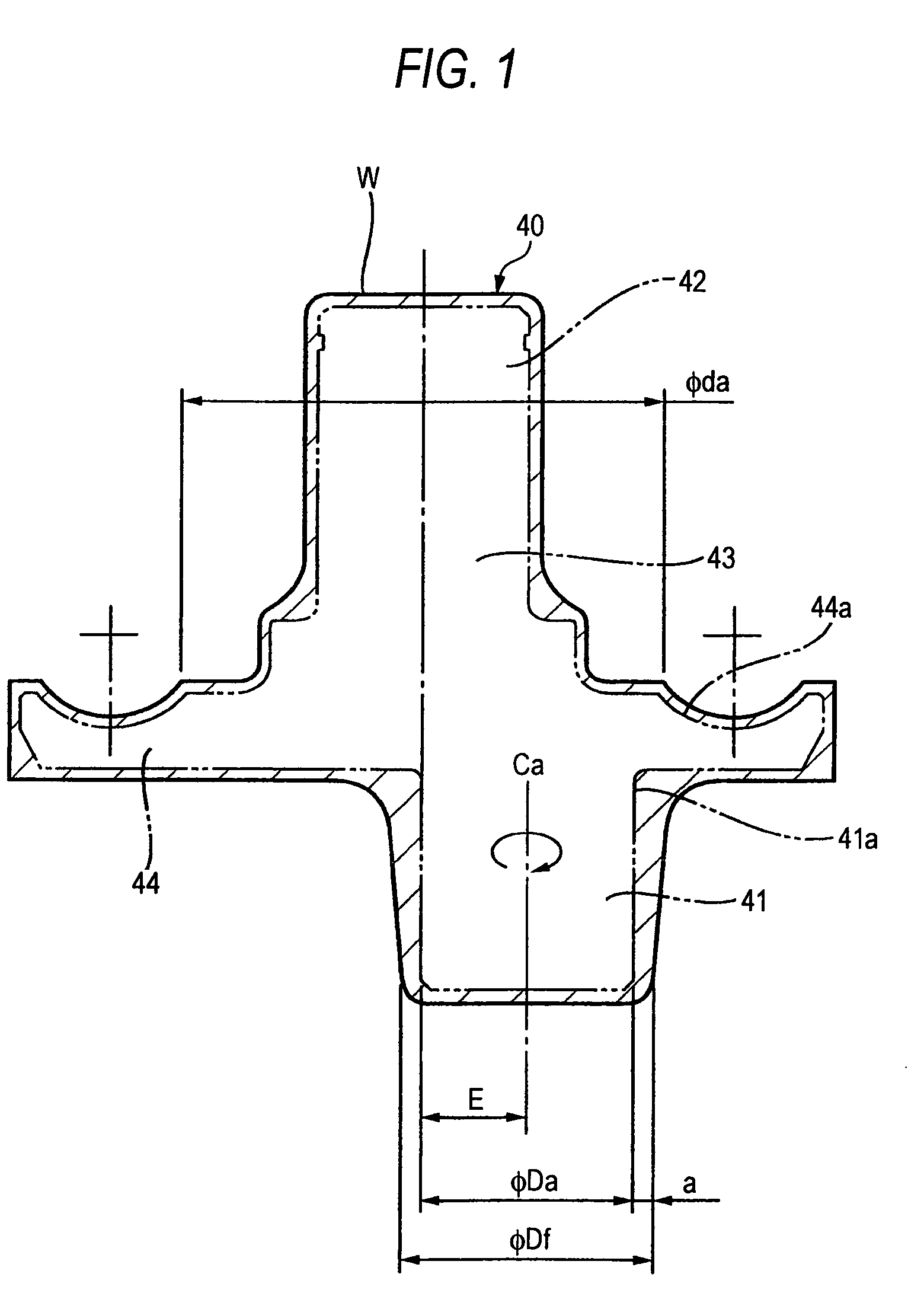

Manufacturing method for variator part of torodidal-type continuously variable transmission, variator part of toroidal-type continuously variable transmission and toroidal-type continuously variable transmission

InactiveUS20050187065A1Low costIncrease in fabrication costRolling contact bearingsMetal-working apparatusVariatorEngineering

A manufacturing method for a variator part of a toroidal-type continuously variable transmission, has the steps of preparing a lower die including a first hole portion and a ring-like projected portion, wherein center lines of the first hole portion and the ring-like projected portion coincide with each other, and an upper die including a second hole portion, wherein a center line of the second hole portion is eccentric from the center line of the first hole portion, mounting a solid material on the lower die so that a center line of the solid material coincides with the center line of the ring-like projected portion, and simultaneously forming the support shaft portion, the outer ring and the pivot shaft portion by pressing the upper die and the lower die so as to approach each other.

Owner:NSK LTD

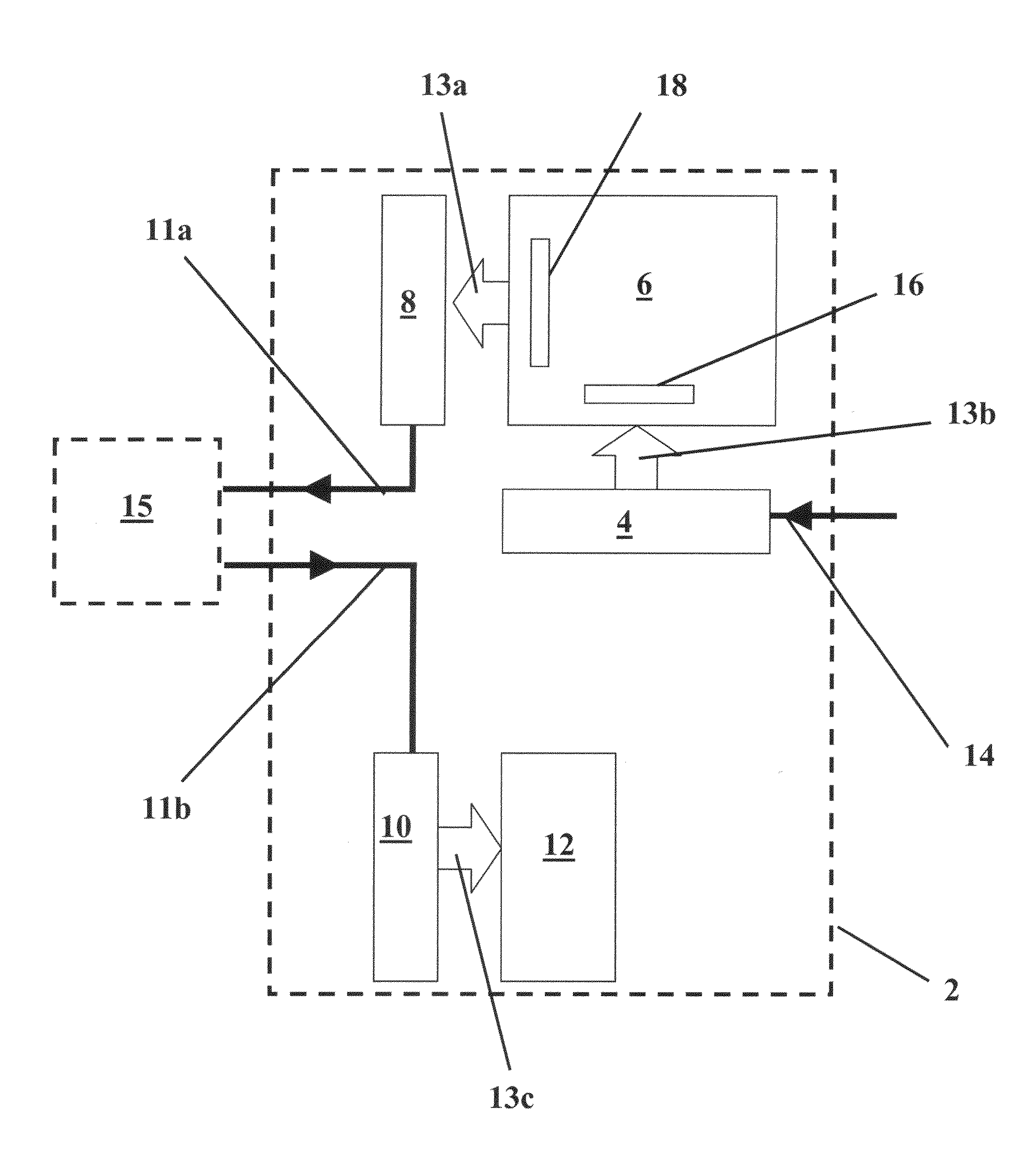

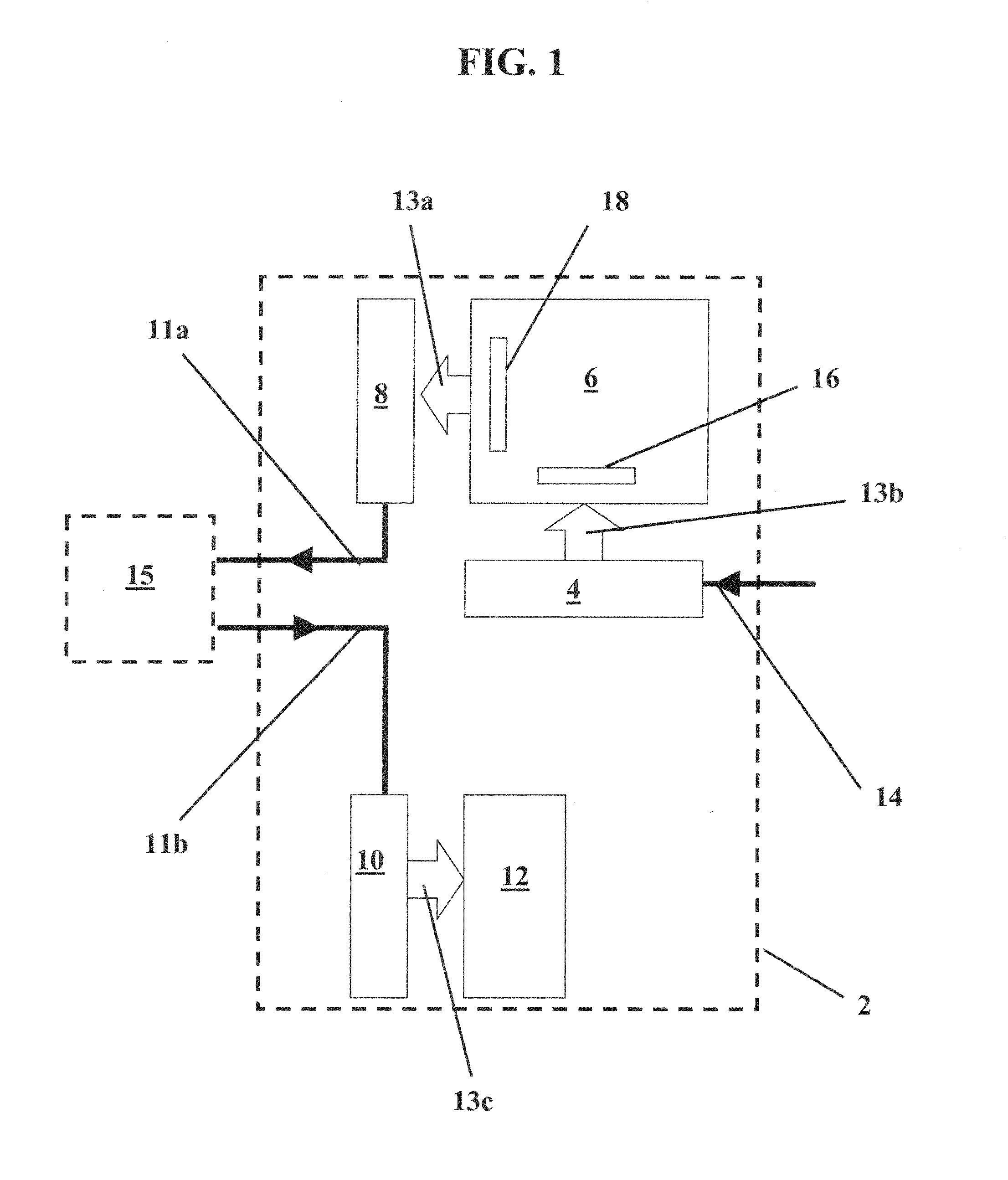

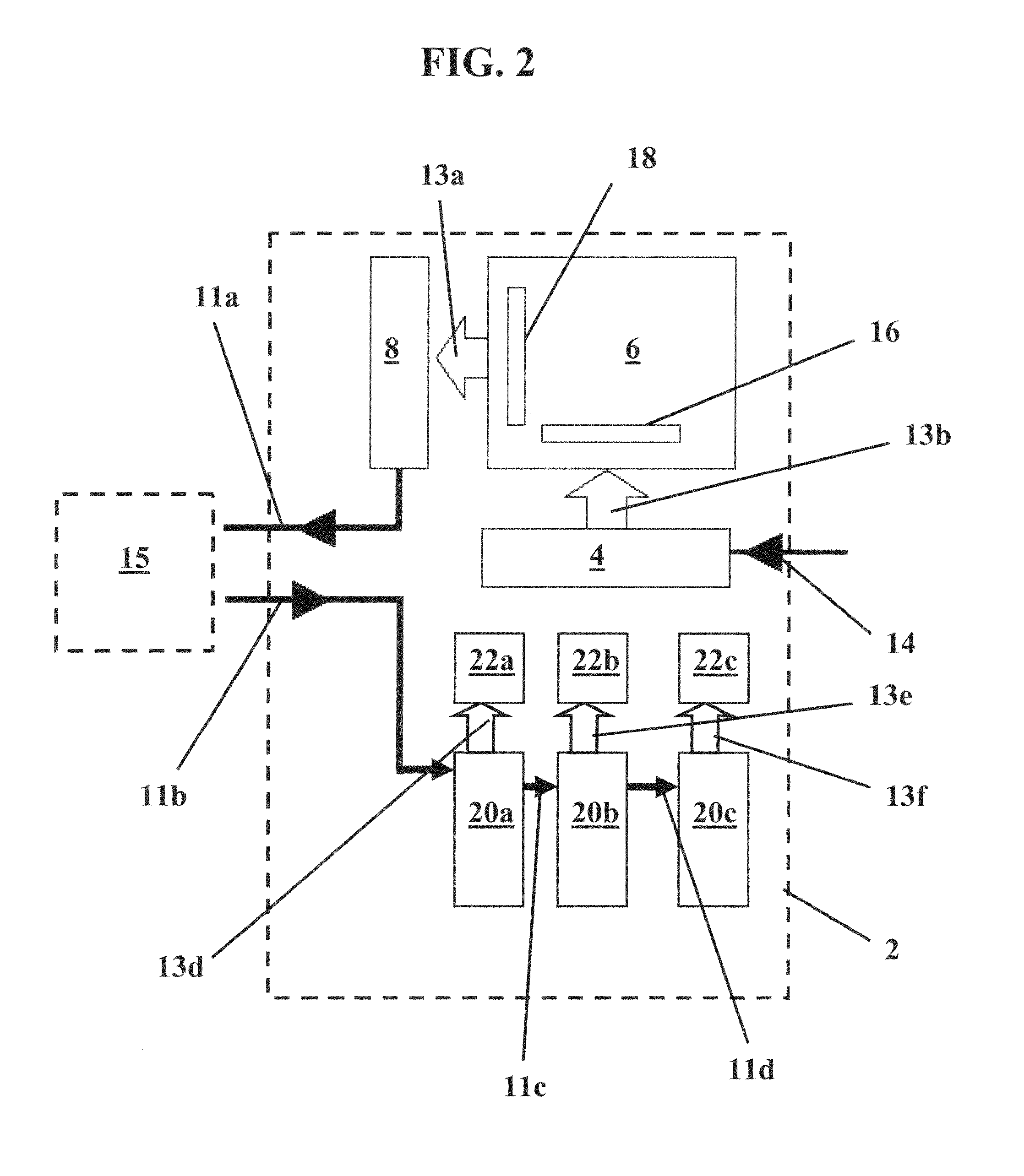

Methods and Apparatuses for Trimming Circuits

InactiveUS20070285105A1Reduce manufacturing costLow costElectrical testingApparatus with stored calibration coefficientsOn boardEngineering

The inventions relate to methods for trimming integrated circuits. Various embodiments include providing a method to trim an integrated circuit wherein trim data is stored in an on-board memory and then sent off of the circuit to be operated on by an external device. Corresponding trim data is then sent back to the integrated circuit in order to potentially modify the function of one or more analog devices along the circuit. Other embodiments include methods for trimming integrated circuits wherein trim data is stored in an on-board memory and retrieved using an on-board sequencer. The retrieved data is used to modify a function of one or more analog devices on the integrated circuit.

Owner:LEXMARK INT INC

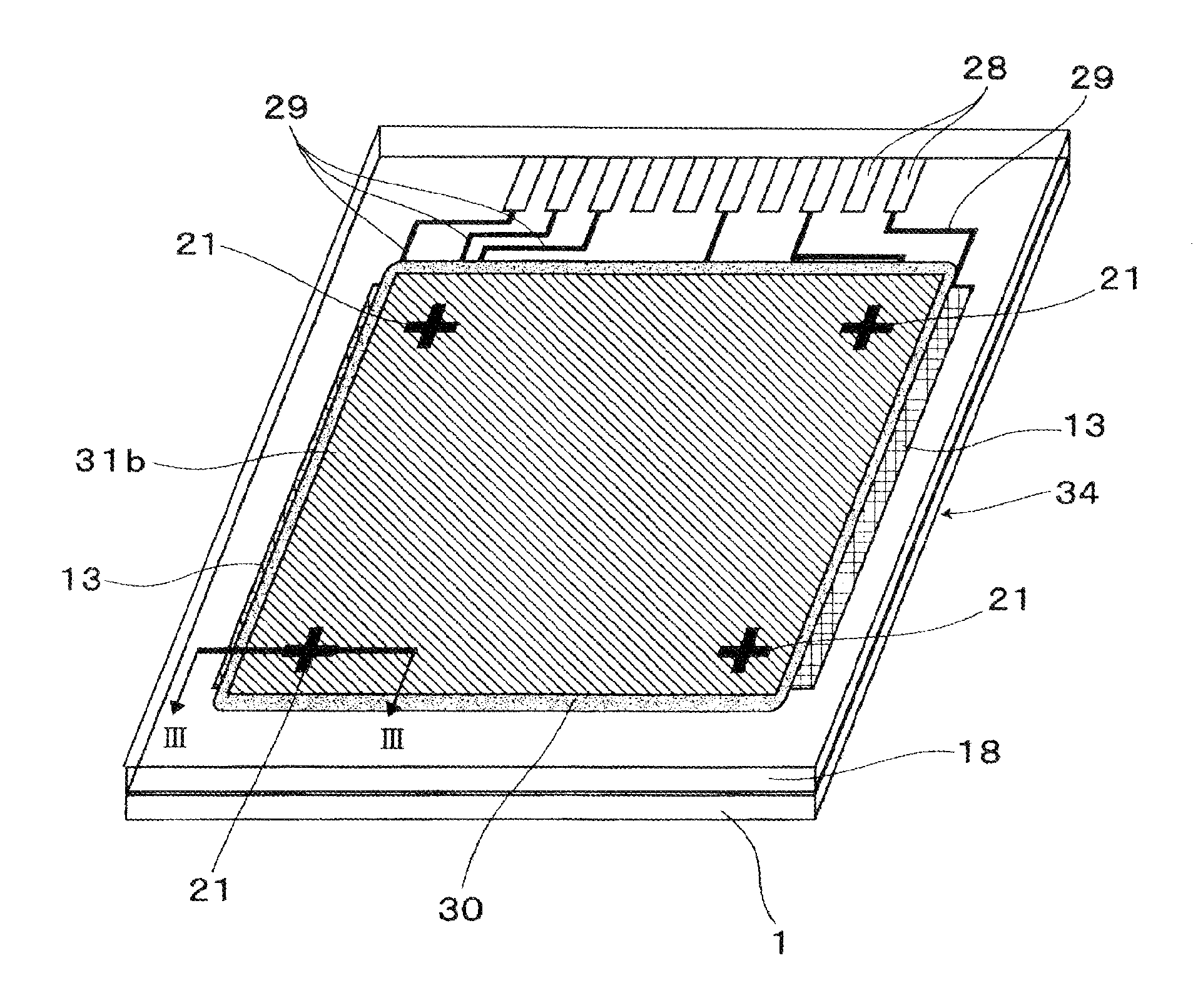

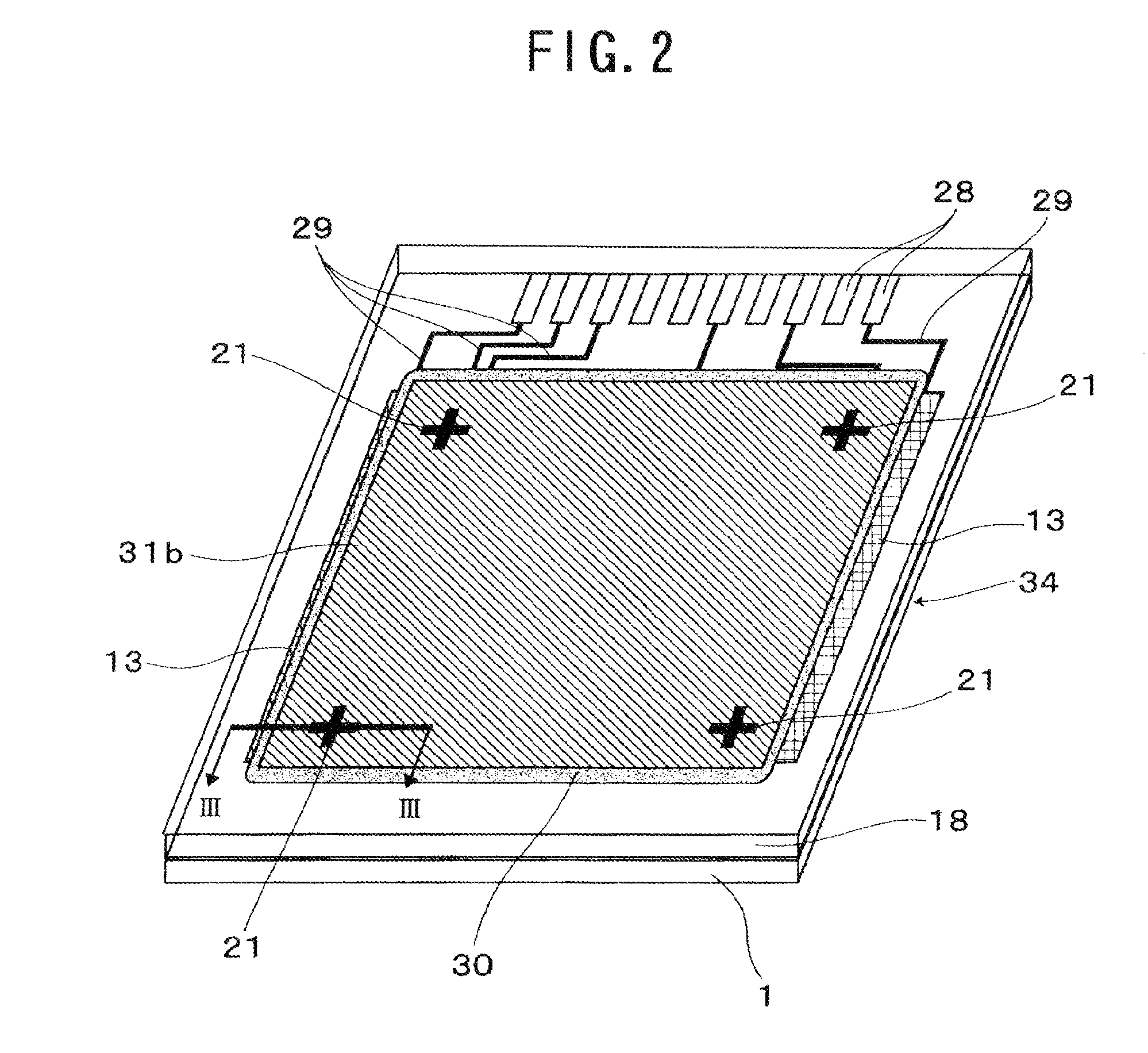

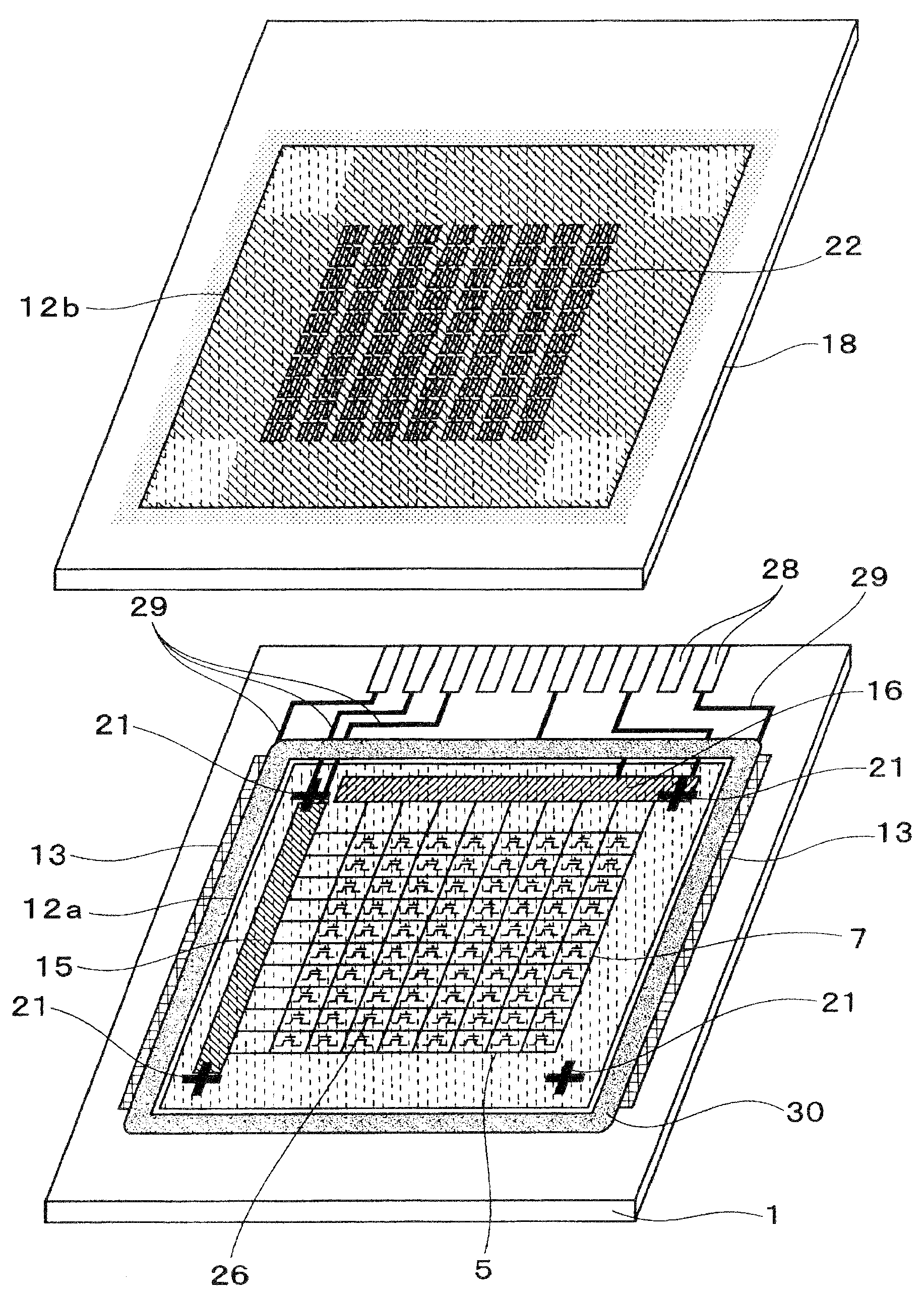

Display apparatus with light detection and fabrication method for display apparatus with light detection

ActiveUS8325298B2Fabrication cost is increasedHigh precisionPhotomechanical apparatusOriginals for photomechanical treatmentEngineeringFilter material

A display apparatus is provided which can detect light of a predetermined wavelength with a high degree of accuracy from within light incident from a screen by a simple configuration. The display apparatus includes a CF substrate (9) having a plurality of color filters (31) of different colors for passing light for displaying an image on the screen (55a) and an IR filter (33) provided in a region different from an arrangement region of the color filters of the different colors for passing light incident from the screen (55a), and a main sensor (19) provided on the rear side of the IR filter (33) for detecting light incident from the screen (55a) and passing through the IR filter (33). The IR filter (33) has a laminate of filter materials same as filter materials from which at least two or more ones of the color filters of the different colors are formed respectively.

Owner:JAPAN DISPLAY WEST

Fabrication method of semiconductor device and semiconductor device

ActiveUS6897129B2Fabrication yield be improveImprove reliabilityPolycrystalline material growthSemiconductor/solid-state device manufacturingStrained siliconSemiconductor

Gases for film formation are introduced from a plurality of holes provided at a gas nozzle into a processing chamber of a batch-type CVD film-forming apparatus to cause a turbulence of the gases within the processing chamber. In the state where the chamber is kept at a pressure within an atmospheric and quasi-atmospheric pressure region, a silicon-germanium film is epitaxially grown on a semiconductor wafer placed within the processing chamber. Subsequently, a strained silicon film is epitaxially grown on the silicon-germanium film. Thereafter, a semiconductor element is formed in the semiconductor wafer on which the silicon-germanium film and the strained silicon film have been formed, respectively.

Owner:RENESAS ELECTRONICS CORP +1

Vehicle lamp with integrally formed housing, first light guiding lens, and second light guiding lens

ActiveUS9987975B2Reduce the numberFunction increaseElectric circuit arrangementsOptical signallingLight guideOptoelectronics

A vehicle lamp has a circuit board on which a light emitting element is mounted, a housing for holding the circuit board, a first light guiding lens for guiding part of light emitted from the light emitting element in a predetermined direction, and a second light guiding lens for guiding at least the other part of the light emitted from the light emitting element in the other predetermined direction. The housing, the first light guiding lens and the second light guiding lens are formed integrally.

Owner:KOITO MFG CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com